Patents

Literature

1498 results about "Phase locked loop circuit" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A phase-locked loop (PLL) is an electronic circuit with a voltage or voltage-driven oscillator that constantly adjusts to match the frequency of an input signal.

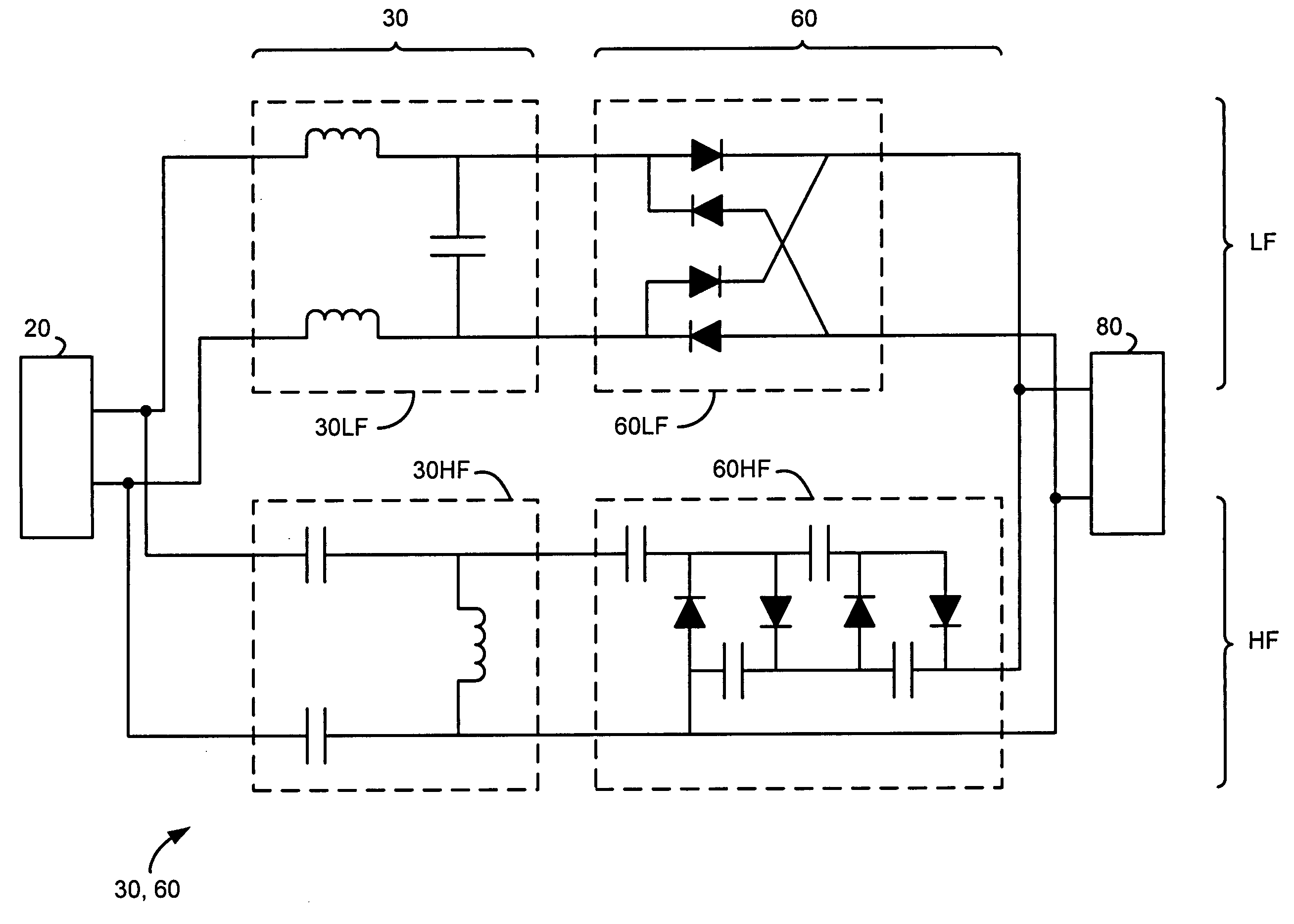

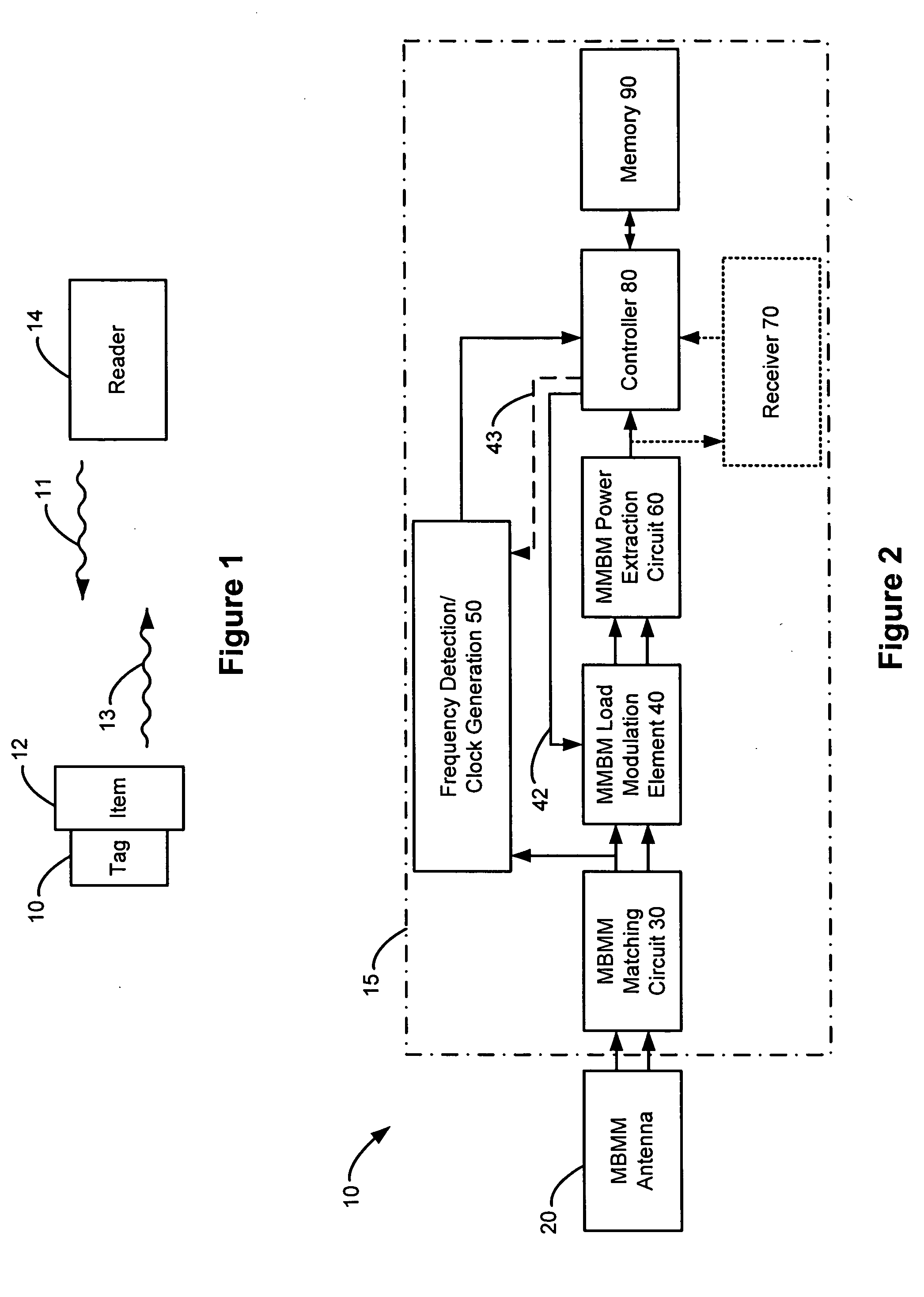

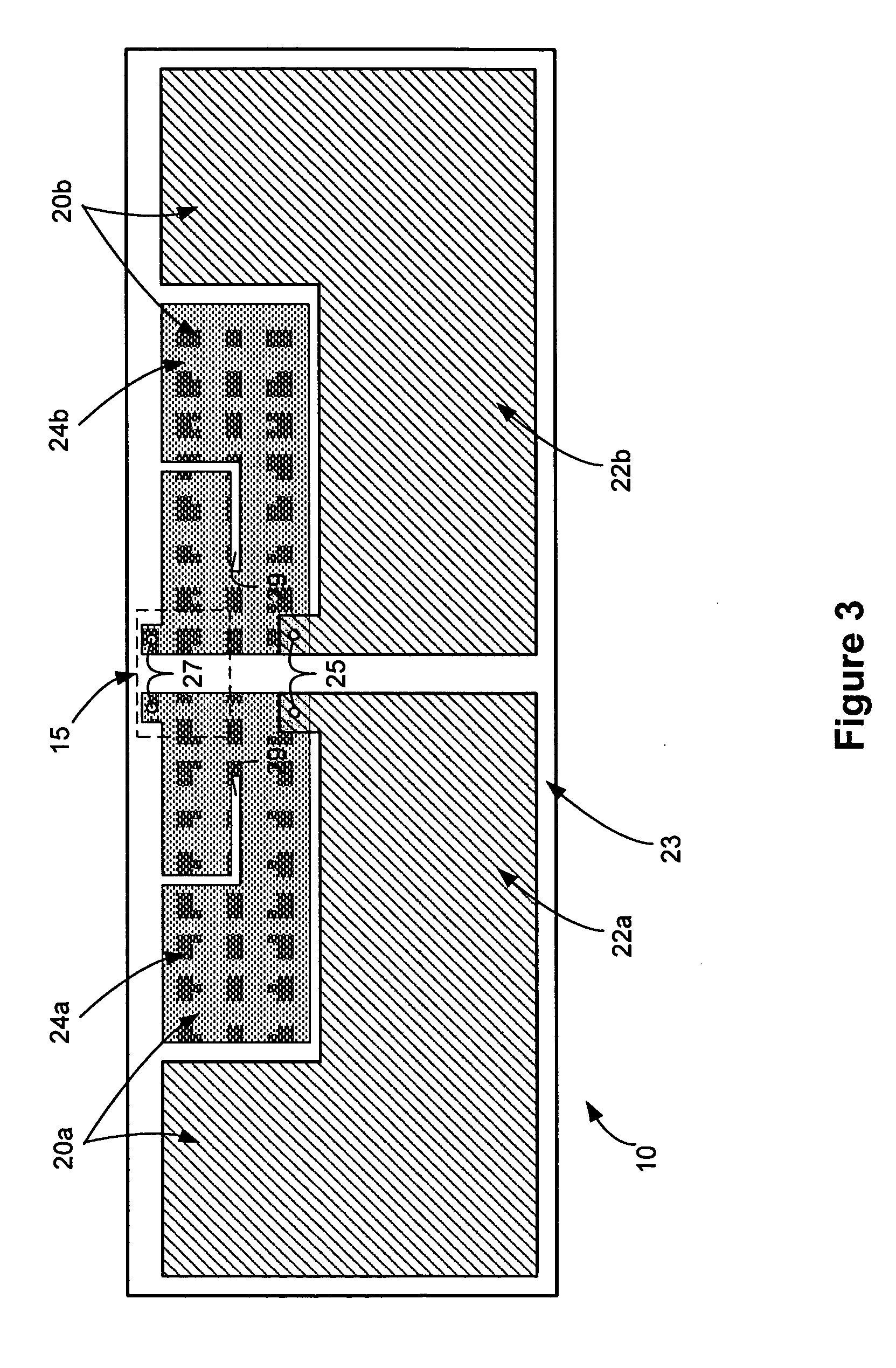

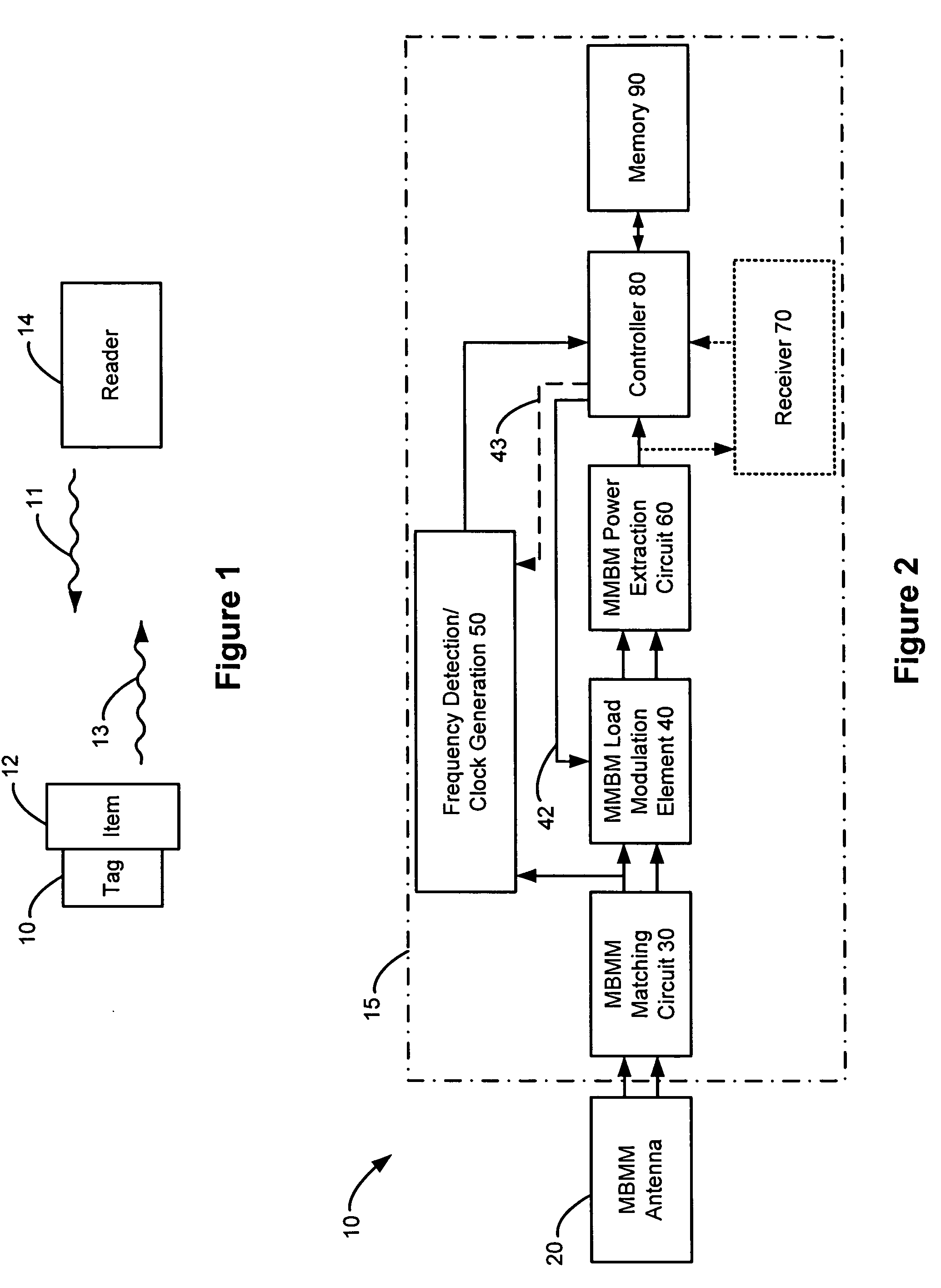

Method and apparatus for multiple frequency RFID tag architecture

ActiveUS20050052283A1Reduce conductivityAntenna arraysSubscribers indirect connectionMulti bandTagged architecture

The present invention provides a multi-band, multi-mode RFID tag that uses a single antenna structure and integrated circuit to provide asset location information at any stage of a supply chain. The unified tag design operates at multiple frequencies (or bands) using the antenna structure, for example, 125 kHz, 13.56 MHz, 915 MHz, and 2.45 GHz, and preferably operates electrostatically (at lower frequencies) and electromagnetically (ay higher frequencies). An on-chip frequency monitor in the integrated circuit automatically determines which frequency is present and derives a local clock for the tag's integrated circuit, which can vary in accordance with the frequency or which can be constant. Alternatively, a phase locked loop circuit can be used to derive a local clock signal modulated into the interrogation signal. On-chip matching and power extraction circuits derive power for the tag from the interrogation signal, which is preferably passive. Additionally, a receiver can receive data from the interrogation signal.

Owner:MOTOROLA SOLUTIONS INC

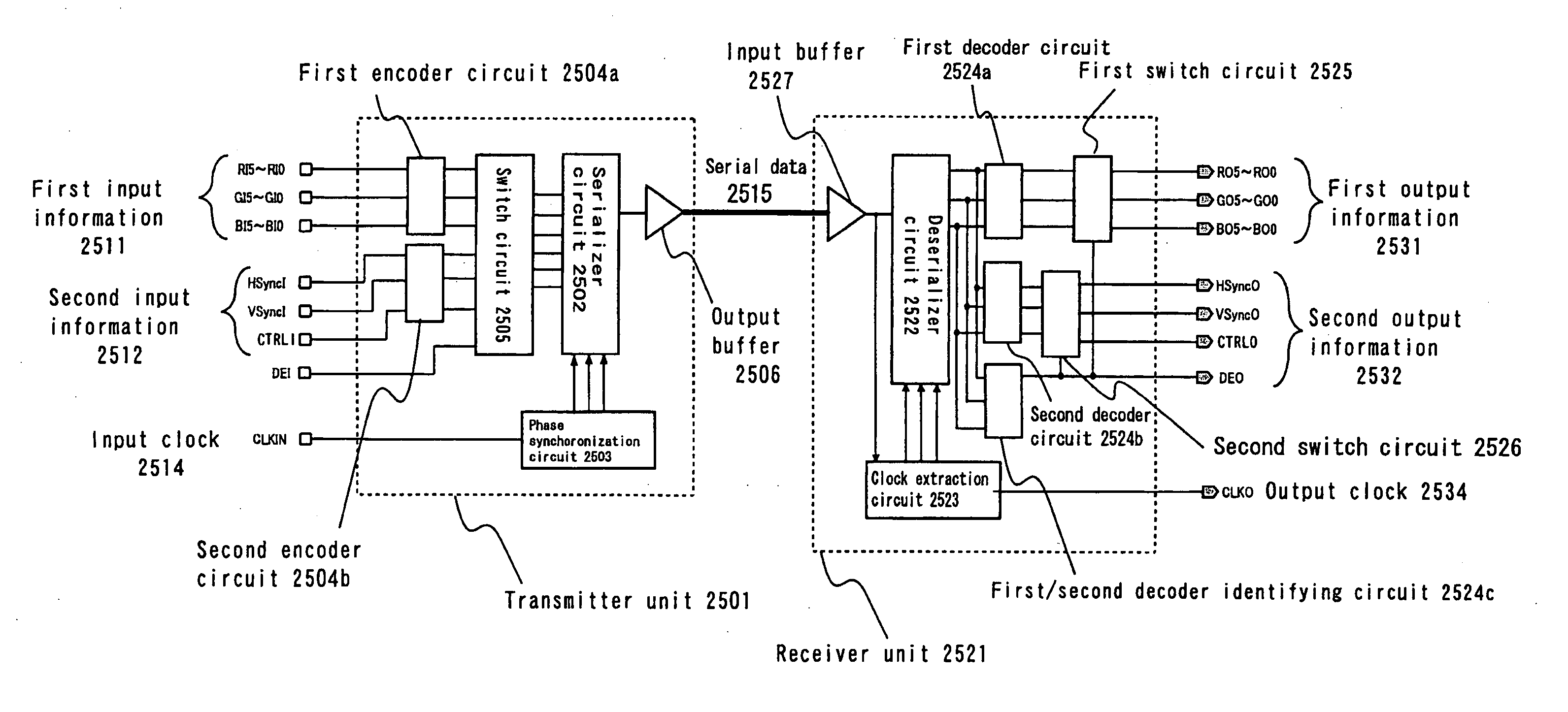

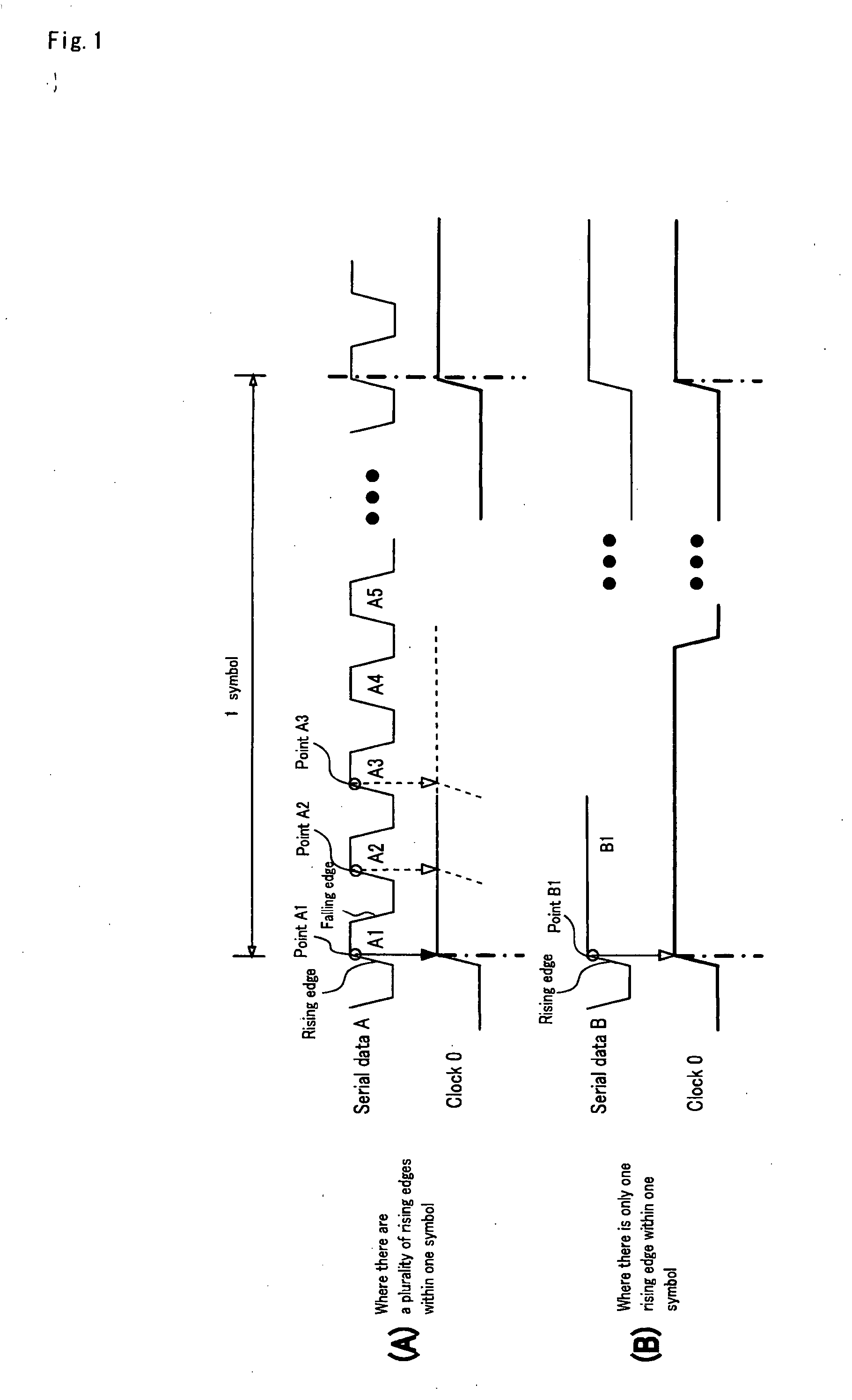

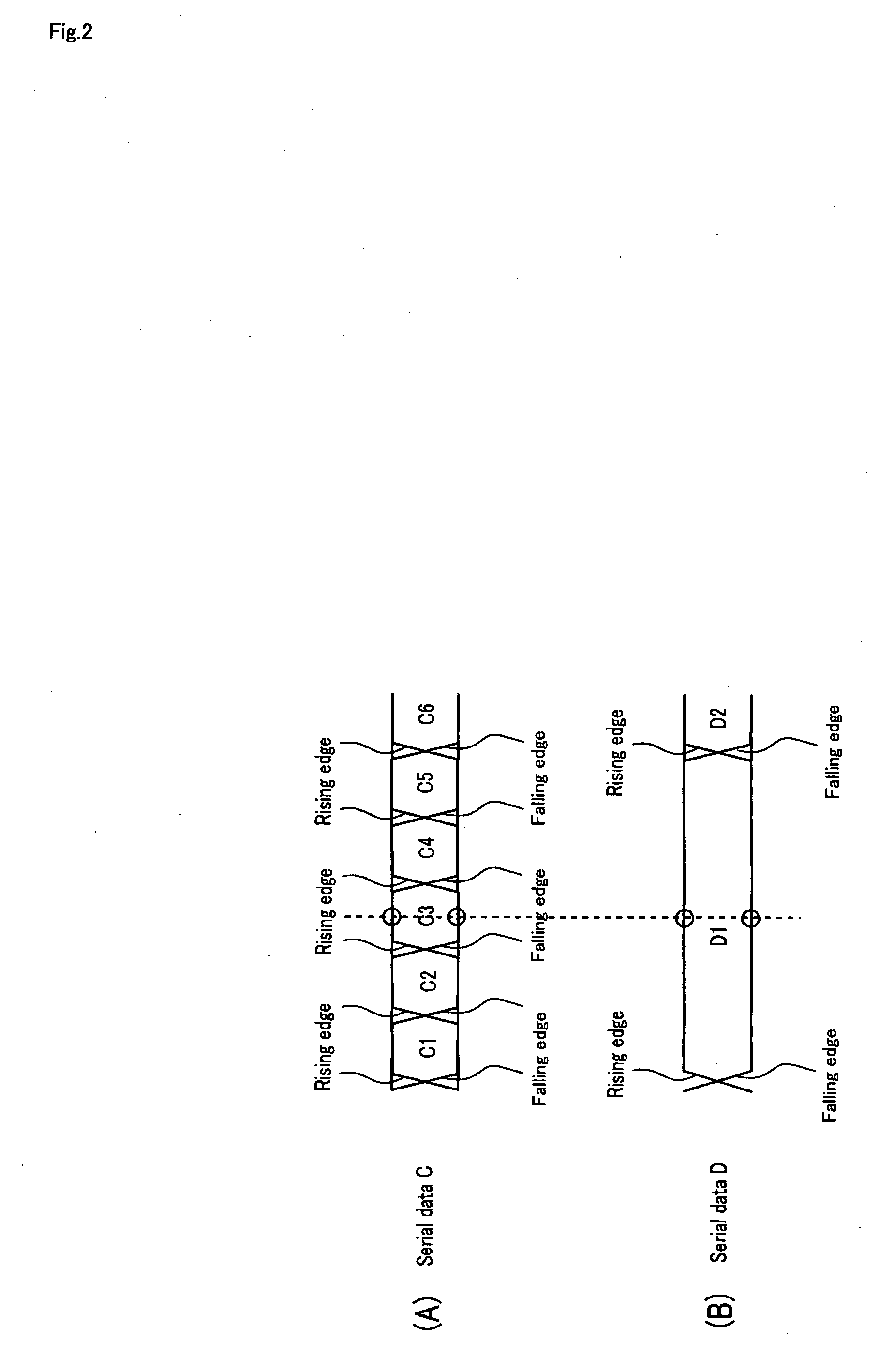

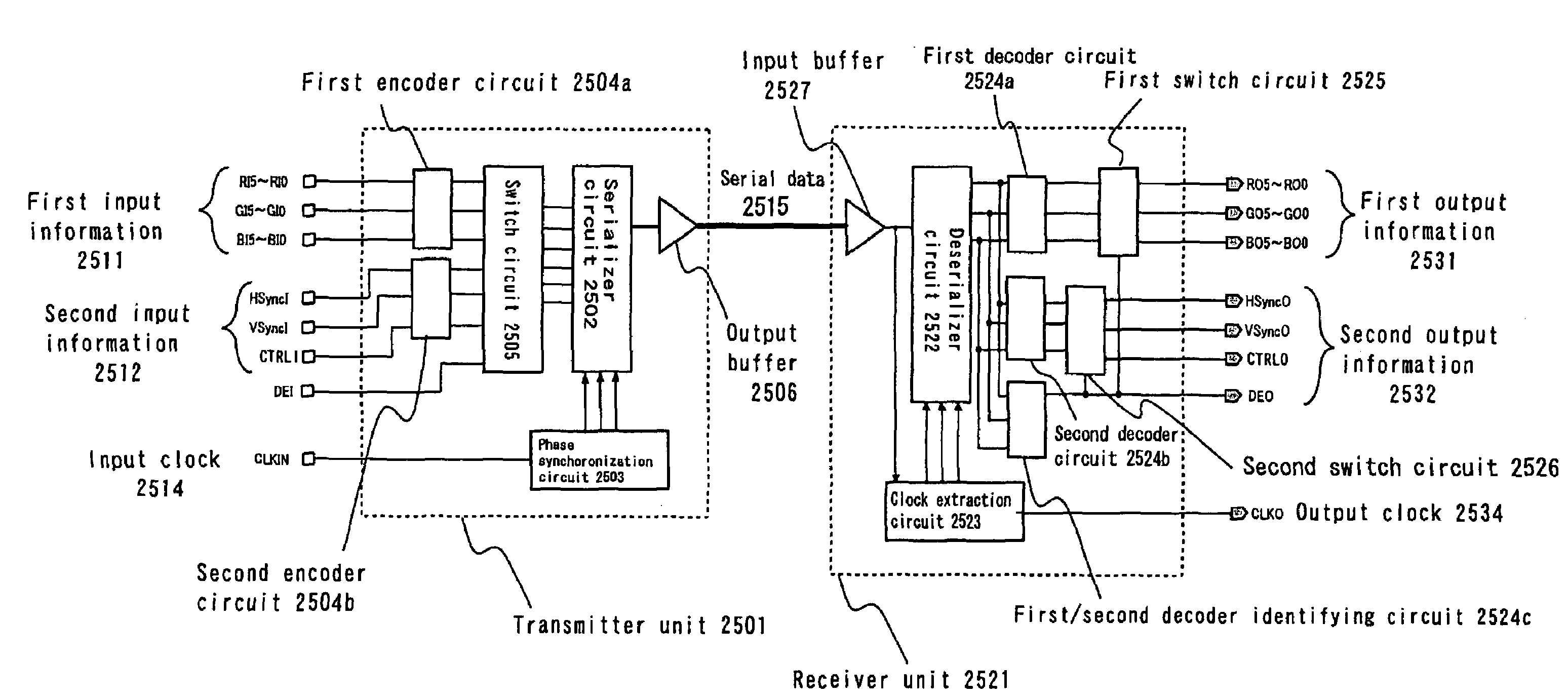

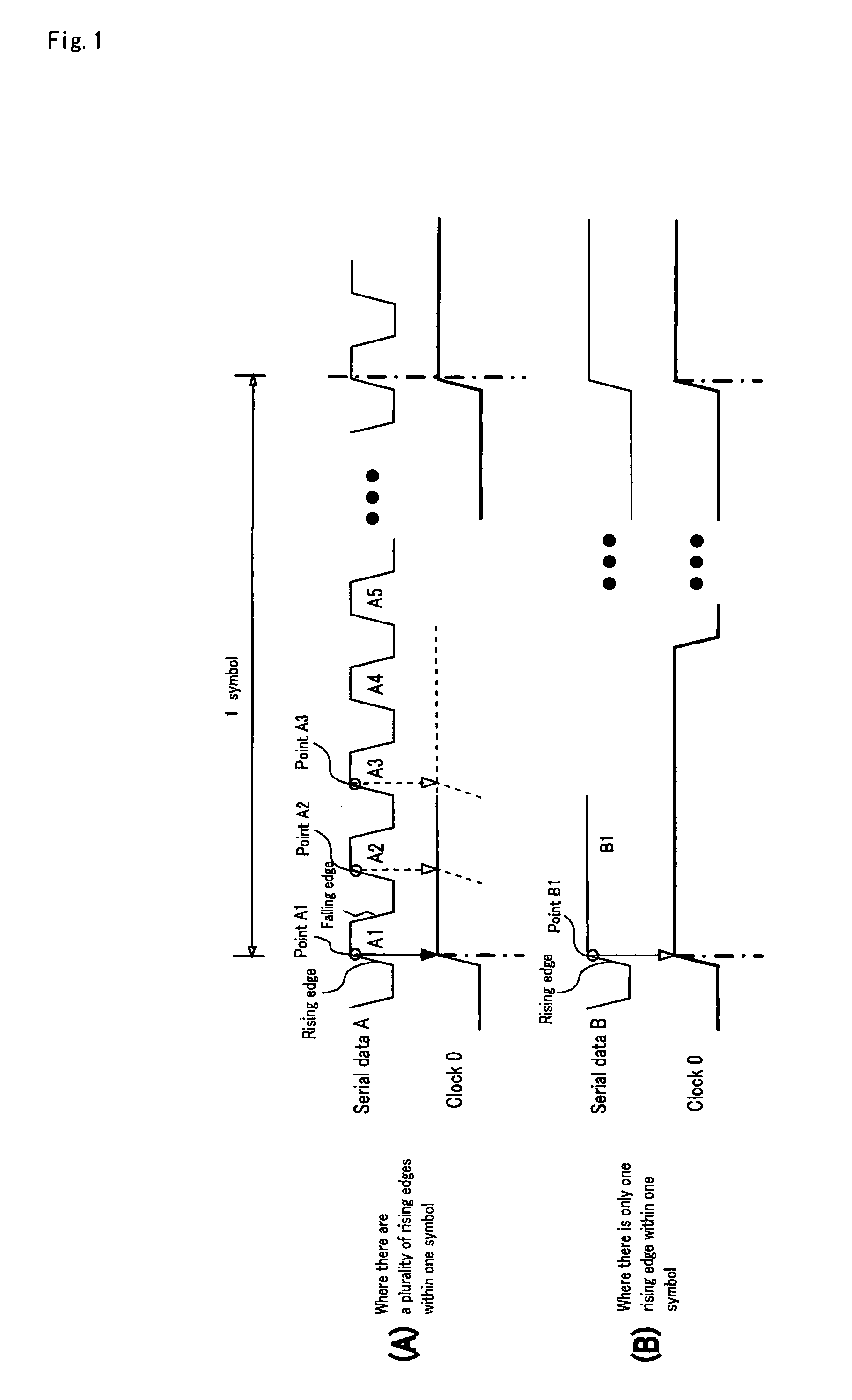

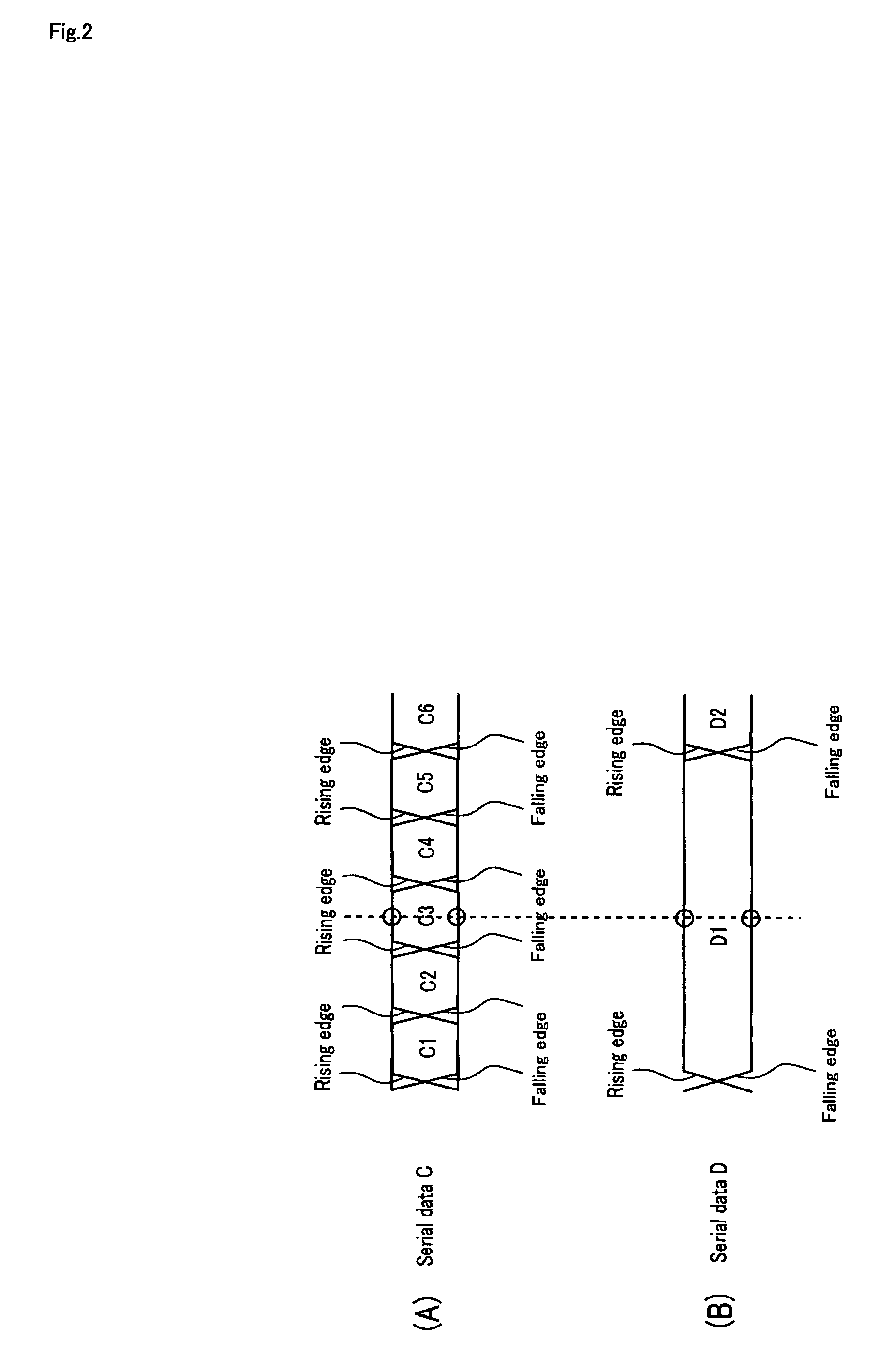

Transmitter circuit, receiver circuit, clock data recovery phase locked loop circuit, data transfer method and data transfer system

ActiveUS20050286643A1Reduce errorsData transmission is stableTelevision system detailsFrequency/rate-modulated pulse demodulationDigital dataPhase locked loop circuit

[Problems] To realize a reliable and stable transfer of digital data that does not require a reference clock and a handshake operation. [Means for Solving the Problem] The present invention provides a digital data transfer method for alternately and periodically transferring first information and second information respectively in a first period and in a second period, wherein: an amount of information of the first information per unit time in the first period is greater than an amount of information of the second information per unit time in the second period; and the second information in the first period is transferred as pulse-width-modulated serial data.

Owner:THINE ELECTRONICS

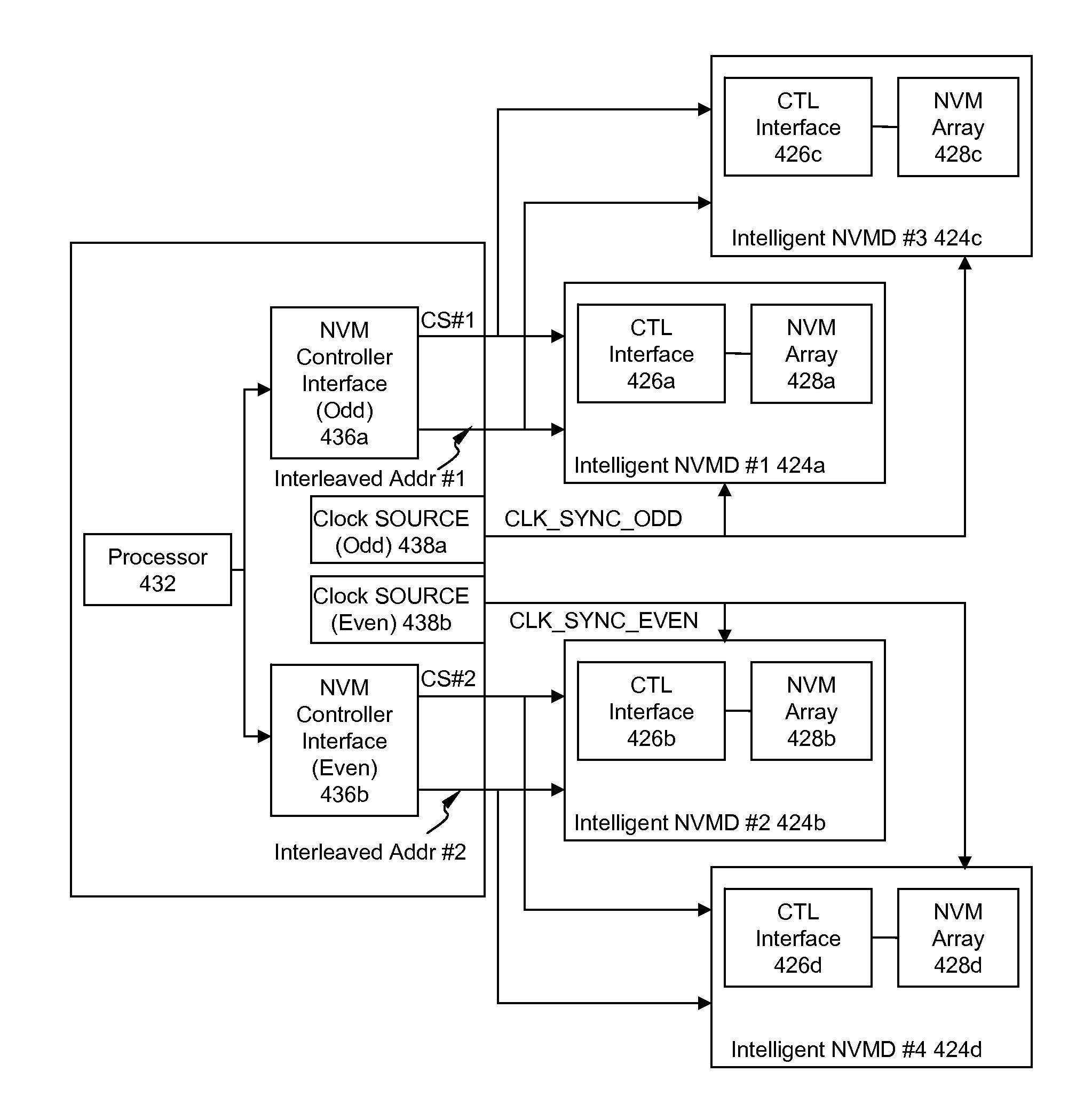

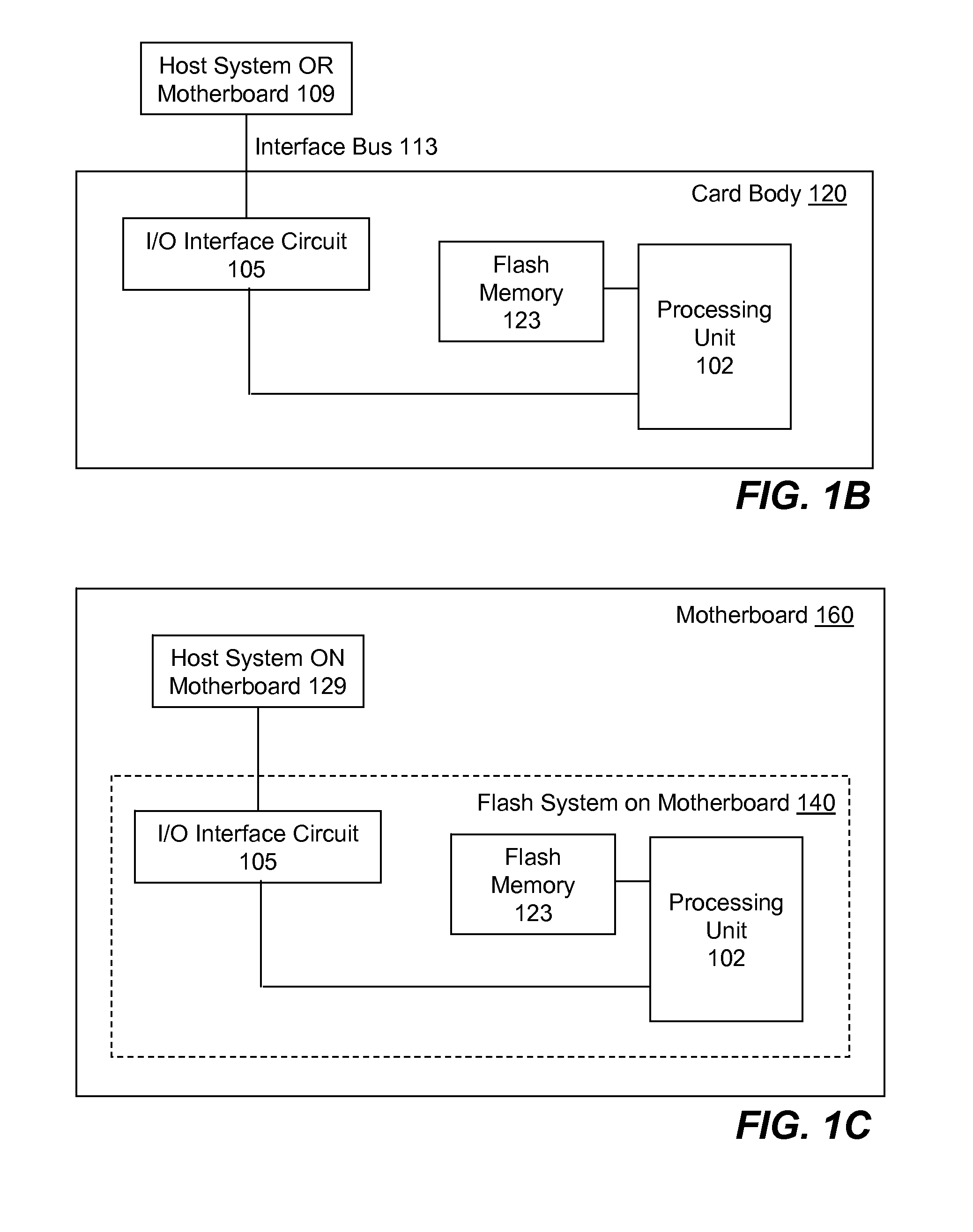

High Performance and Endurance Non-volatile Memory Based Storage Systems

InactiveUS20080320209A1Reduce dataEndurance of the NVM based storage system is increasedMemory architecture accessing/allocationMemory adressing/allocation/relocationPhase locked loop circuitPhysical address

High performance and endurance non-volatile memory (NVM) based storage systems are disclosed. According to one aspect of the present invention, a NVM based storage system comprises at least one intelligent NVM device. Each intelligent NVM device includes a control interface logic and NVM. Logical-to-physical address conversion is performed within the control interface logic, thereby eliminating the need of address conversion in a storage system level controller. In another aspect, a volatile memory buffer together with corresponding volatile memory controller and phase-locked loop circuit is included in a NVM based storage system. The volatile memory buffer is partitioned to two parts: a command queue; and one or more page buffers. The command queue is configured to hold received data transfer commands by the storage protocol interface bridge, while the page buffers are configured to hold data to be transmitted between the host computer and the at least one NVM device.

Owner:SUPER TALENT ELECTRONICS

Transmitter circuit, receiver circuit, clock data recovery phase locked loop circuit, data transfer method and data transfer system

ActiveUS7535957B2Reduce errorsData transmission is stableTelevision system detailsFrequency/rate-modulated pulse demodulationDigital dataPhase locked loop circuit

[Problems] To realize a reliable and stable transfer of digital data that does not require a reference clock and a handshake operation.[Means for Solving the Problem] The present invention provides a digital data transfer method for alternately and periodically transferring first information and second information respectively in a first period and in a second period, wherein: an amount of information of the first information per unit time in the first period is greater than an amount of information of the second information per unit time in the second period; and the second information in the first period is transferred as pulse-width-modulated serial data.

Owner:THINE ELECTRONICS

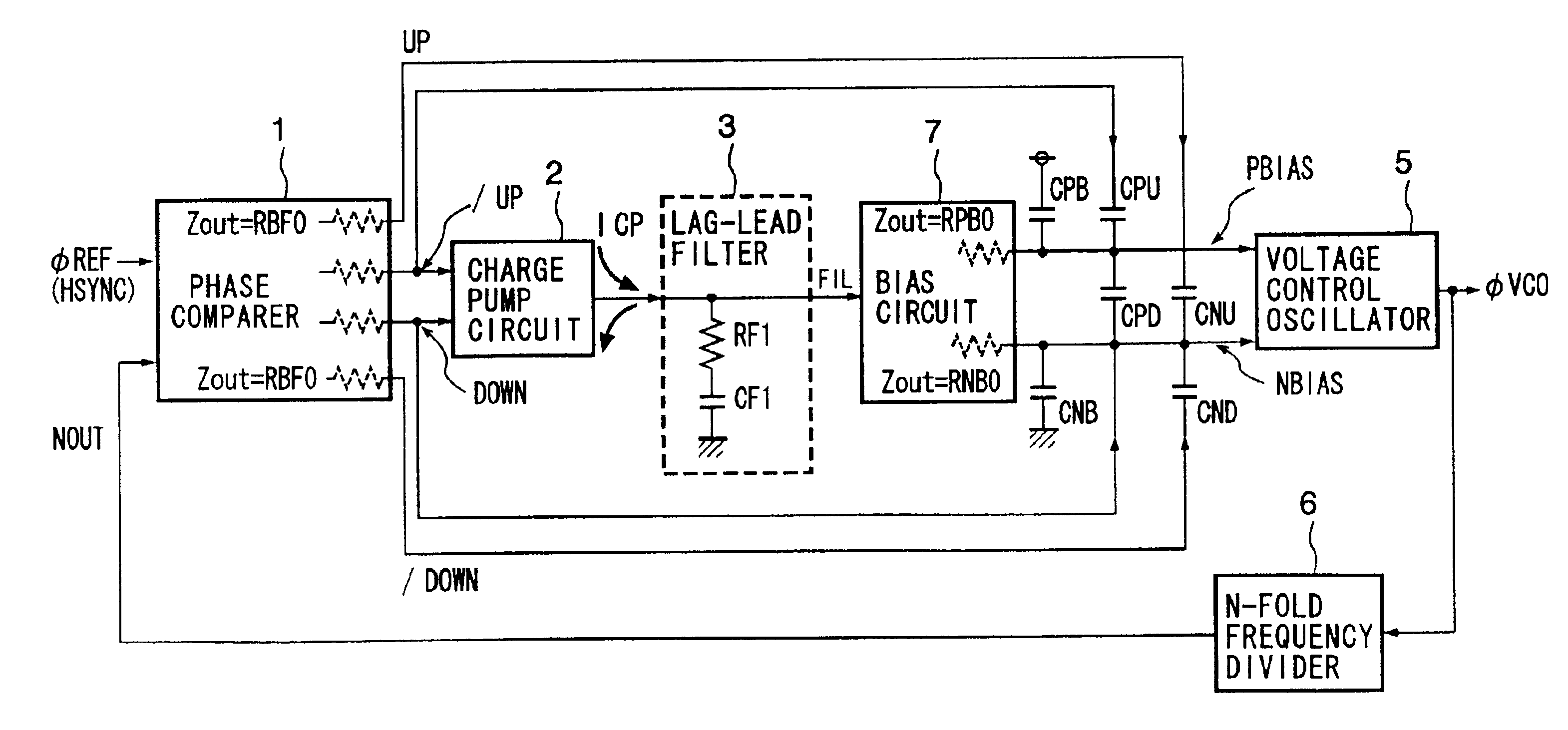

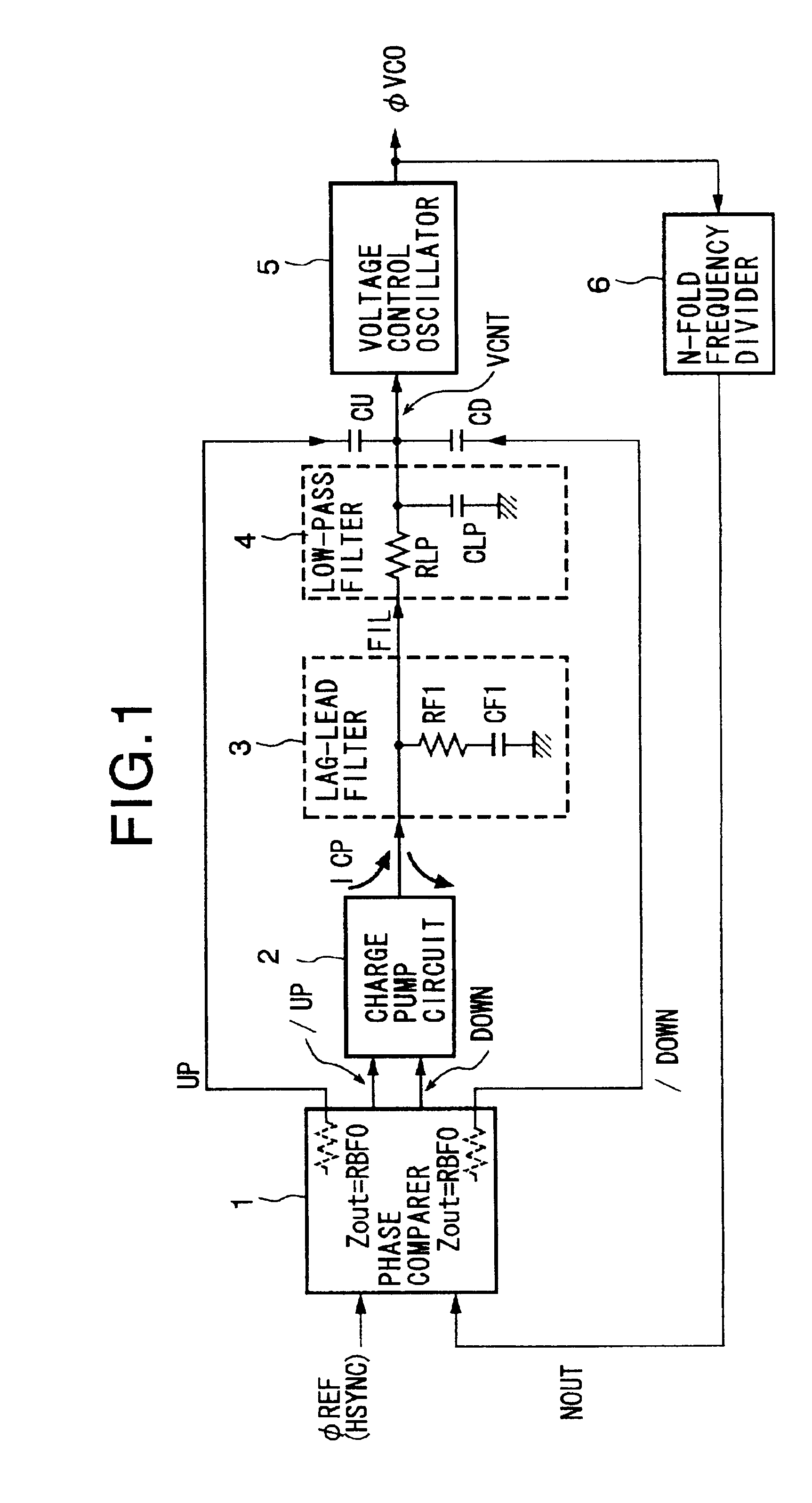

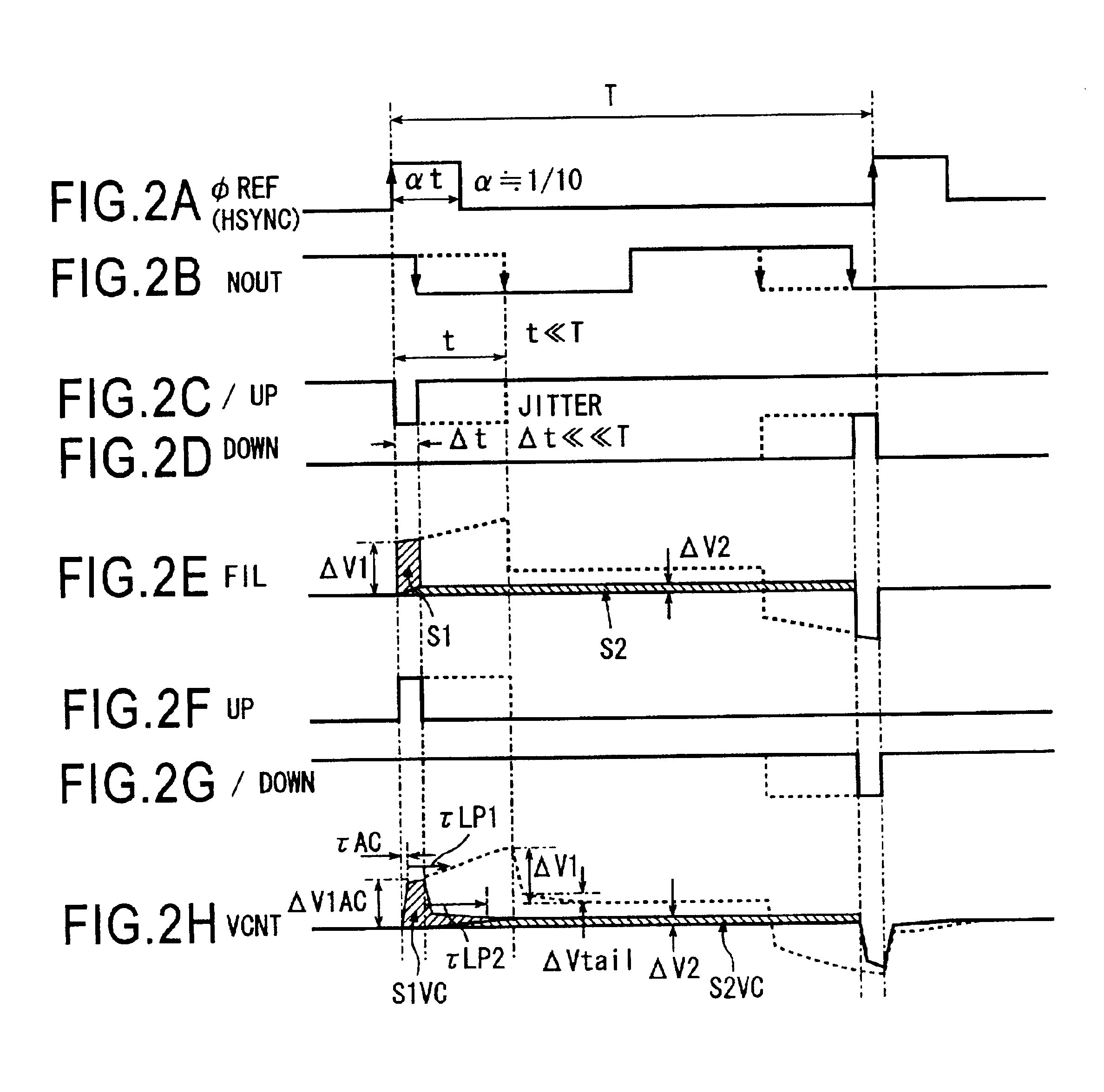

Phase-locked loop circuit and delay-locked loop circuit

InactiveUS6954511B2Reduce changesPulse automatic controlTransmissionPhase locked loop circuitLow-pass filter

A PLL circuit and a DLL circuit able to stabilize a control voltage within a short time after a phase pull-in operation in each cycle of a reference clock. In a phase comparator, the size of a leading phase or a delayed phase of a feedback signal is detected with respect to a reference clock signa, and pulse signals having pulse widths corresponding to the size are output. A current corresponding to the signals is output from a charge pump circuit to a lag-lead filter, and a control voltage obtained by removing noise of the above output is output from a low-pass filter to a voltage-controlled oscillator. Furthermore, through capacitors, pulse signals are superposed on the control voltage, and a sharp waveform is obtained by correcting blunting of the waveform by the low-pass filter. Due to this, the control voltage is stabilized within a short time after a phase pull-in operation in each cycle of the reference clock signal.

Owner:SONY CORP

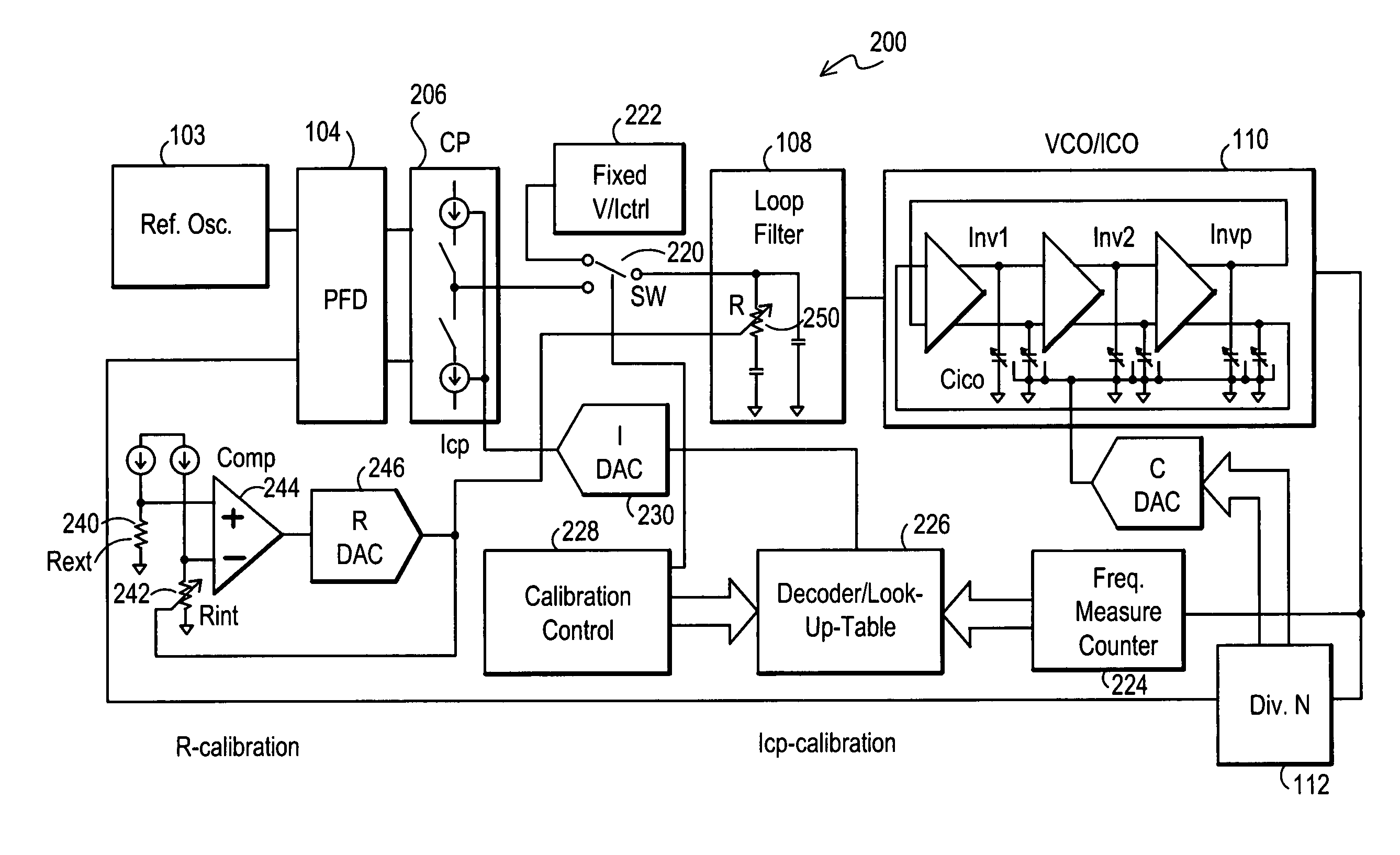

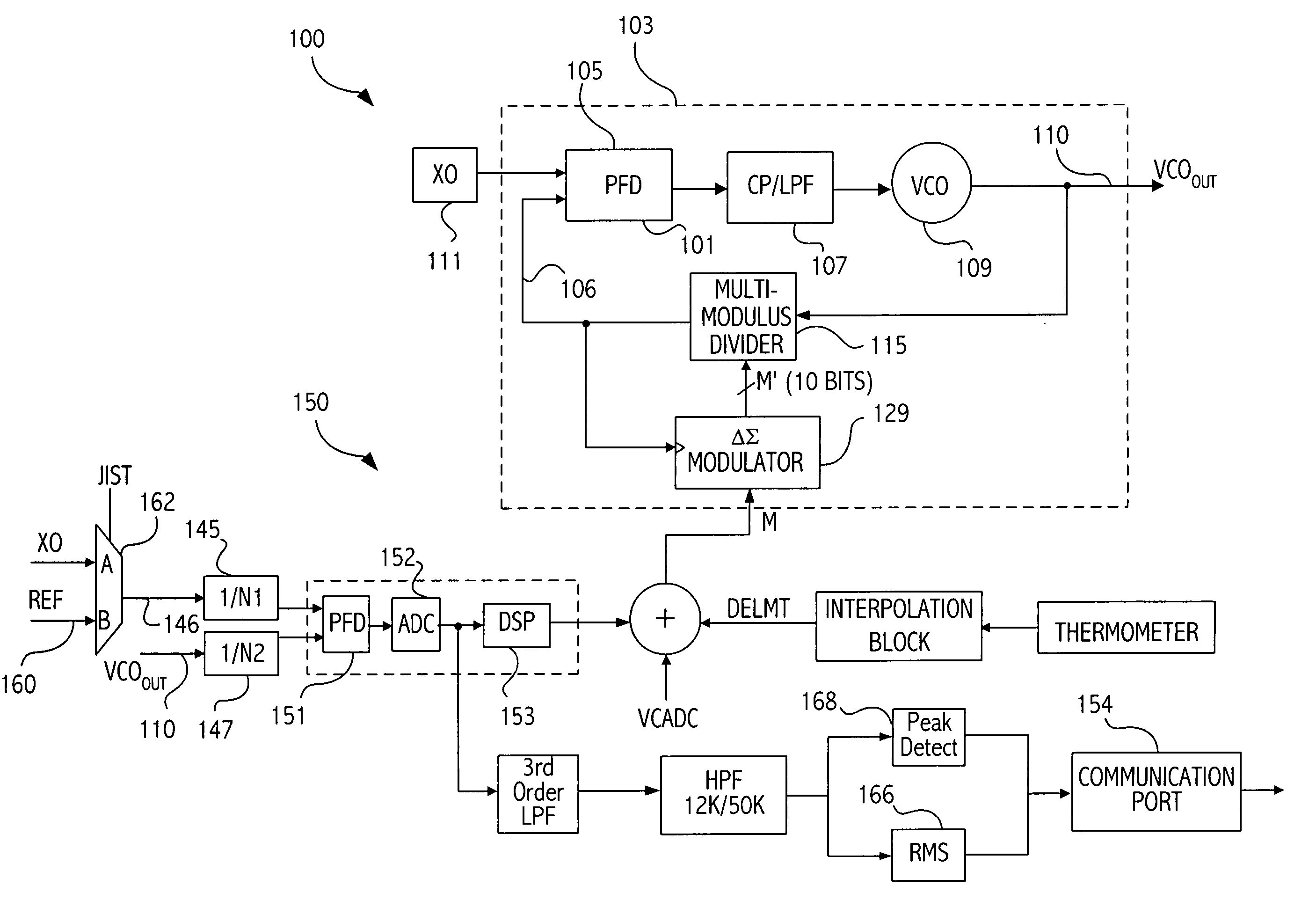

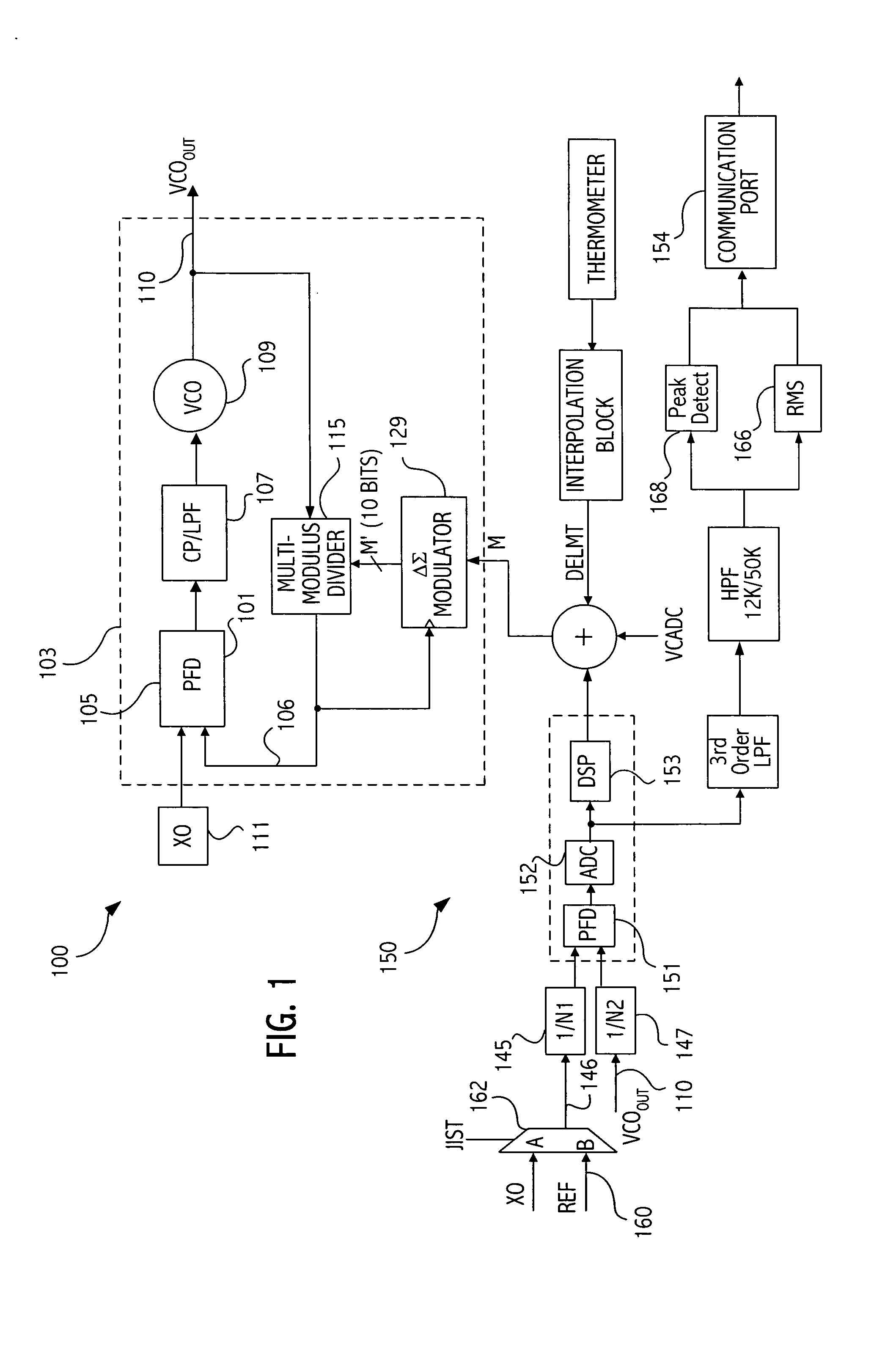

Method and apparatus to achieve a process, temperature and divider modulus independent PLL loop bandwidth and damping factor using open-loop calibration techniques

InactiveUS7095287B2Reduce complexityImprove accuracyPulse automatic controlFrequency analysisDamping factorProportional control

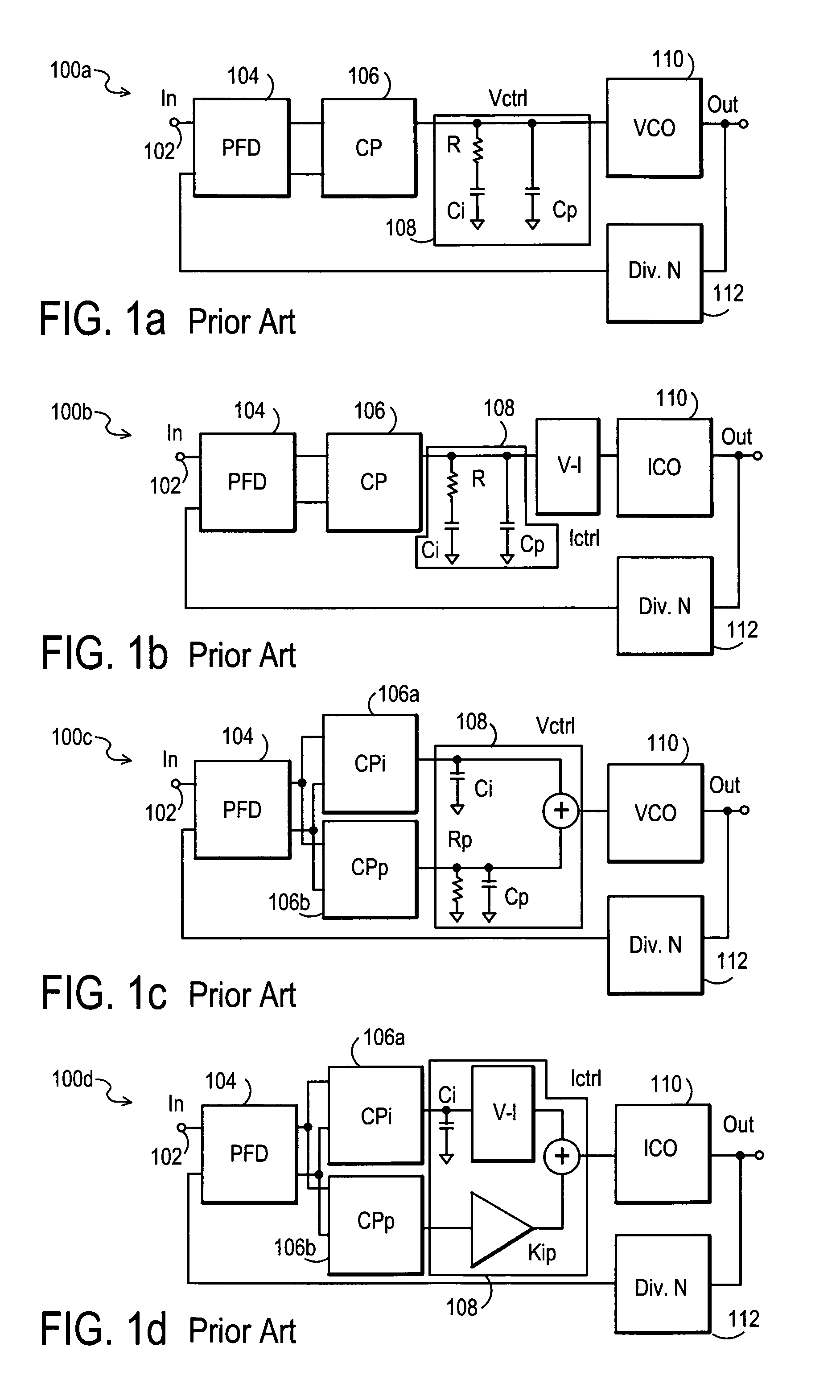

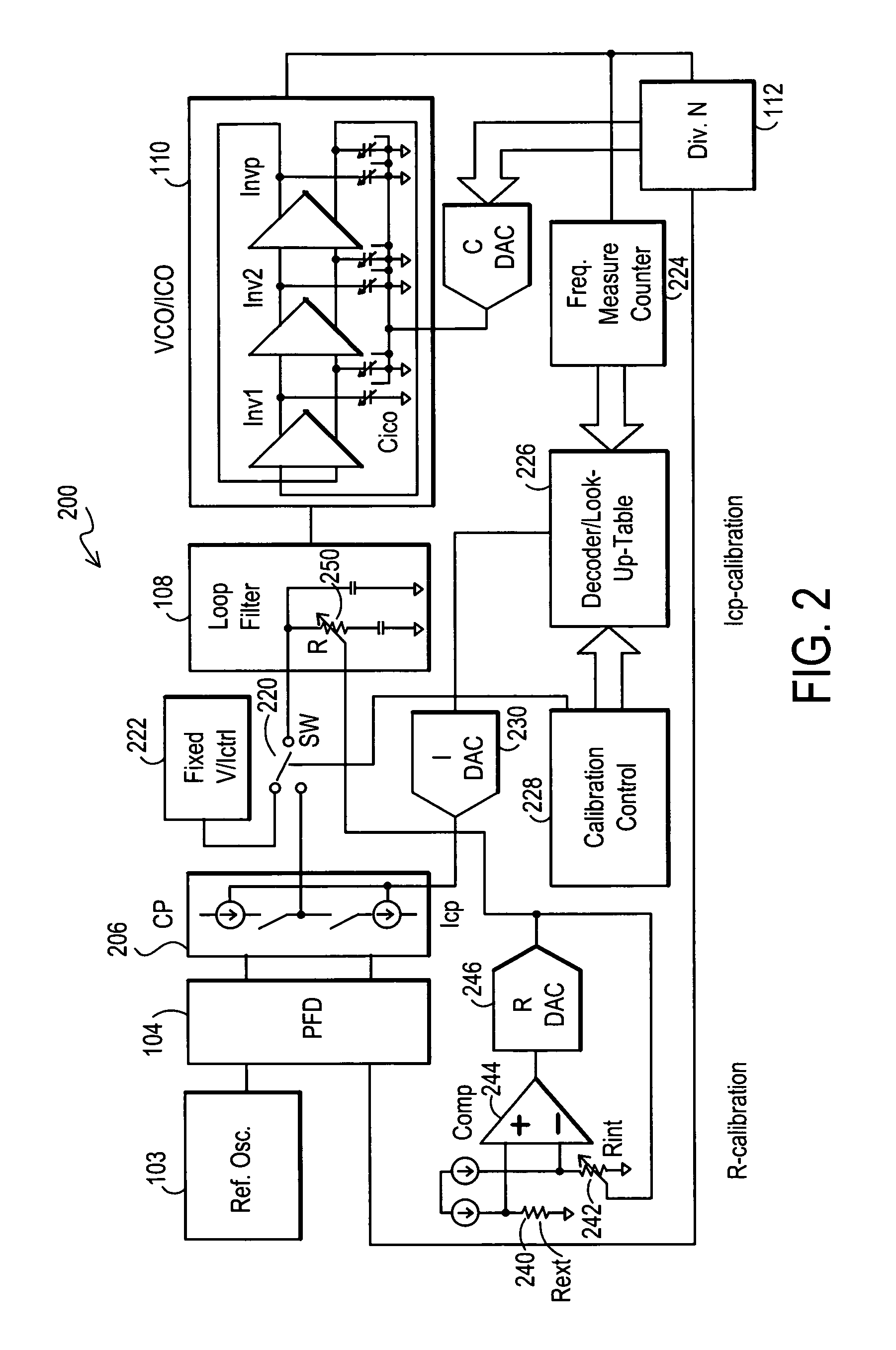

Several open-loop calibration techniques for phase-locked-loop circuits (PLL) that provide a process, temperature and divider modulus independence for the loop bandwidth and damping factor are disclosed. Two categories of open-loop techniques are presented. The first method uses only a single measurement of the output frequency from the oscillator and adjusts a single PLL loop element that performs a simultaneous calibration of both the loop bandwidth and damping factor. The output frequency is measured for a given value of the oscillator control signal and the charge-pump current is adjusted such that it cancels the process variation of the oscillator gain. The second method uses two separate and orthogonal calibration steps, both of them based on the measurement of the output frequency from the oscillator when a known excitation is applied to the open loop signal path. In the first step the loop bandwidth is calibrated by adjusting the charge-pump current based on the measurement of the forward path gain when applying a constant phase shift between the two clocks that go to the phase frequency detector, while the integral path is hold to a constant value. During the second step the damping factor is calibrated by adjusting the value of the integral loop filter capacitor based on the measurement of the oscillator output frequency when excited with a voltage proportional with the integral capacitor value, while the proportional control component is zeroed-out.

Owner:SILICON LAB INC

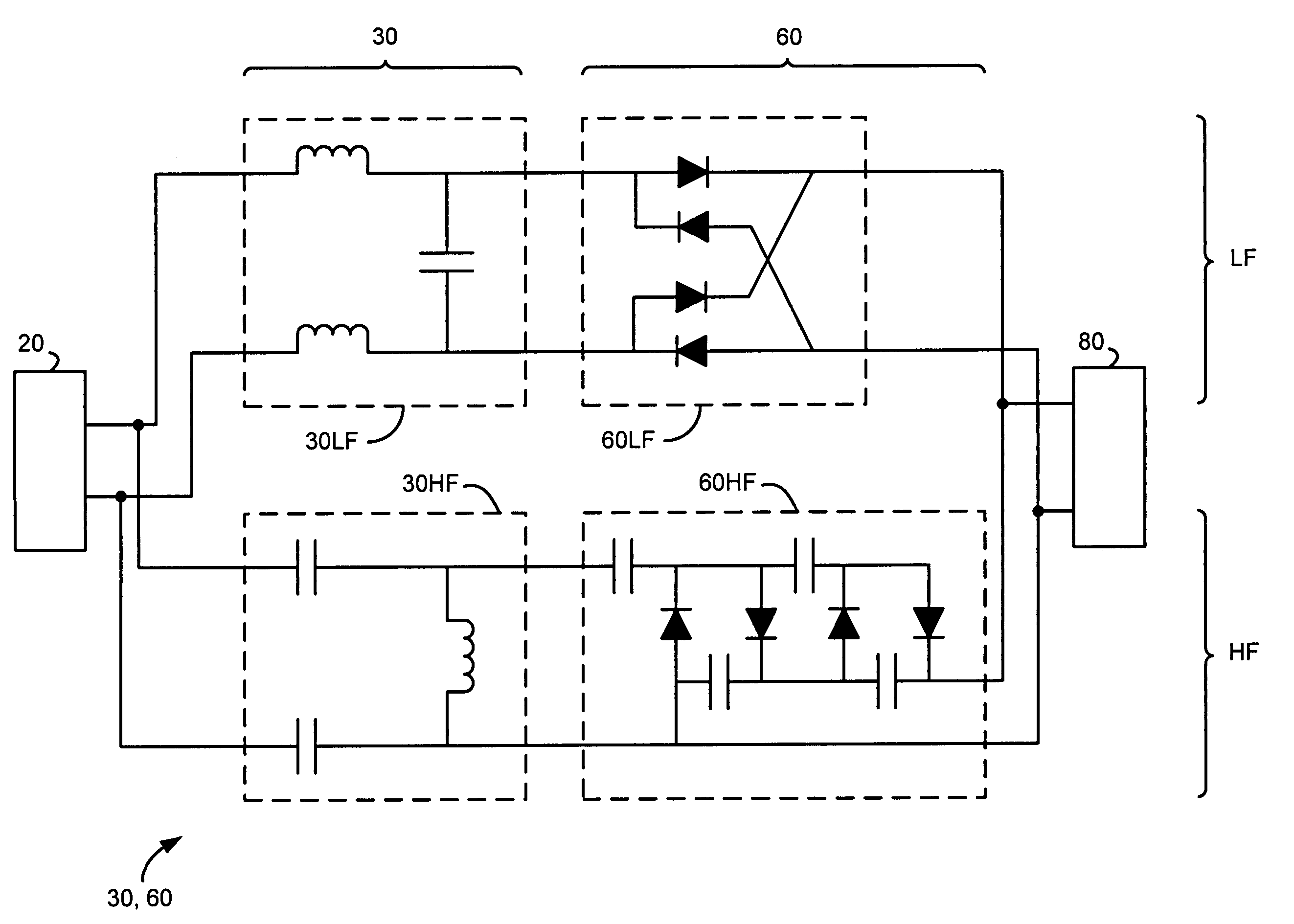

Method and apparatus for multiple frequency RFID tag architecture

The present invention provides a multi-band, multi-mode RFID tag that uses a single antenna structure and integrated circuit to provide asset location information at any stage of a supply chain. The unified tag design operates at multiple frequencies (or bands) using the antenna structure, for example, 125 kHz, 13.56 MHz, 915 MHz, and 2.45 GHz, and preferably operates electrostatically (at lower frequencies) and electromagnetically (ay higher frequencies). An on-chip frequency monitor in the integrated circuit automatically determines which frequency is present and derives a local clock for the tag's integrated circuit, which can vary in accordance with the frequency or which can be constant. Alternatively, a phase locked loop circuit can be used to derive a local clock signal modulated into the interrogation signal. On-chip matching and power extraction circuits derive power for the tag from the interrogation signal, which is preferably passive. Additionally, a receiver can receive data from the interrogation signal.

Owner:MOTOROLA SOLUTIONS INC

Phase lock loop with coarse control loop having frequency lock detector and device including same

ActiveUS7102446B1Improve portabilitySynchronization is simplePulse automatic controlCounting chain pulse countersTransceiverPhase locked loop circuit

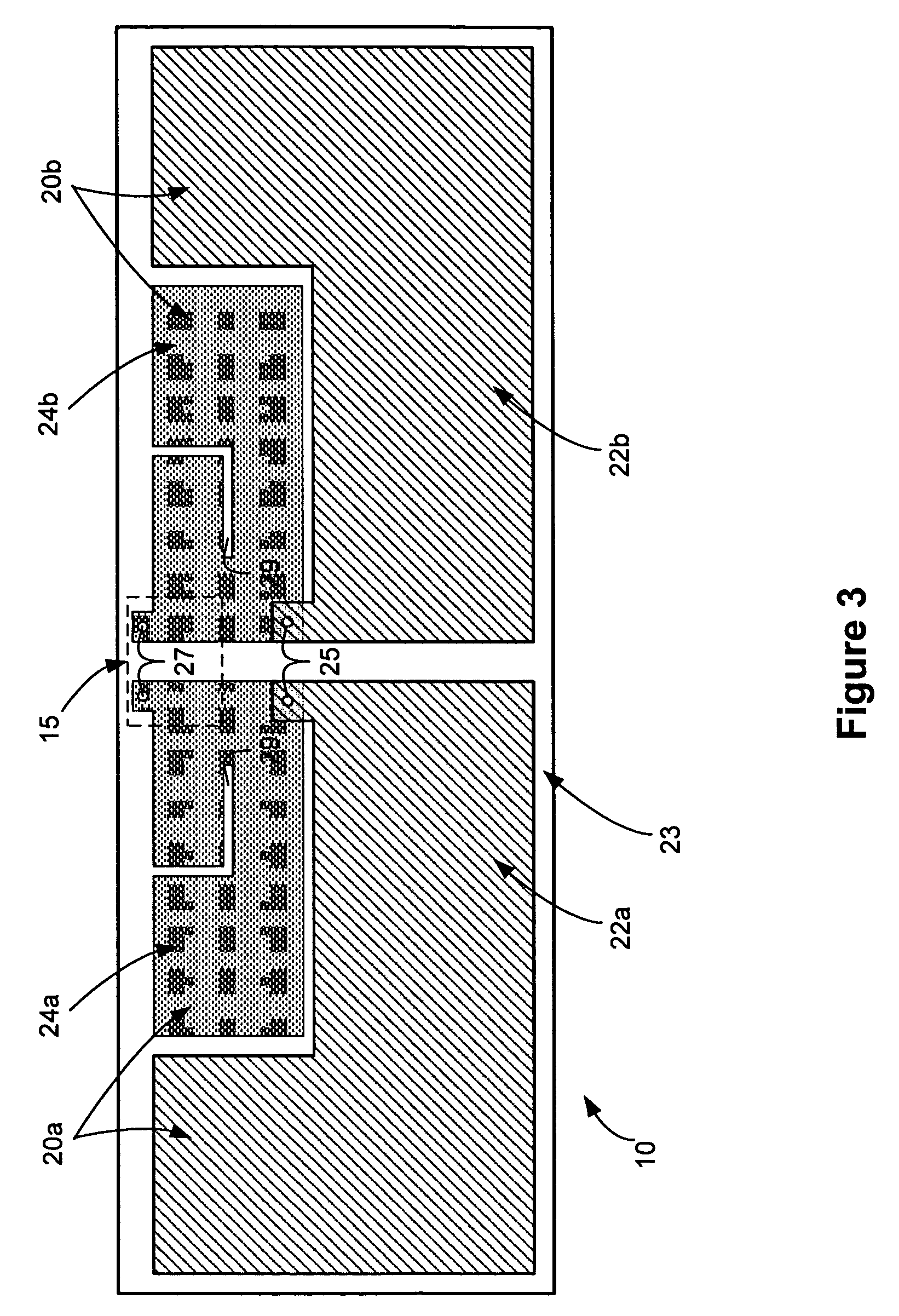

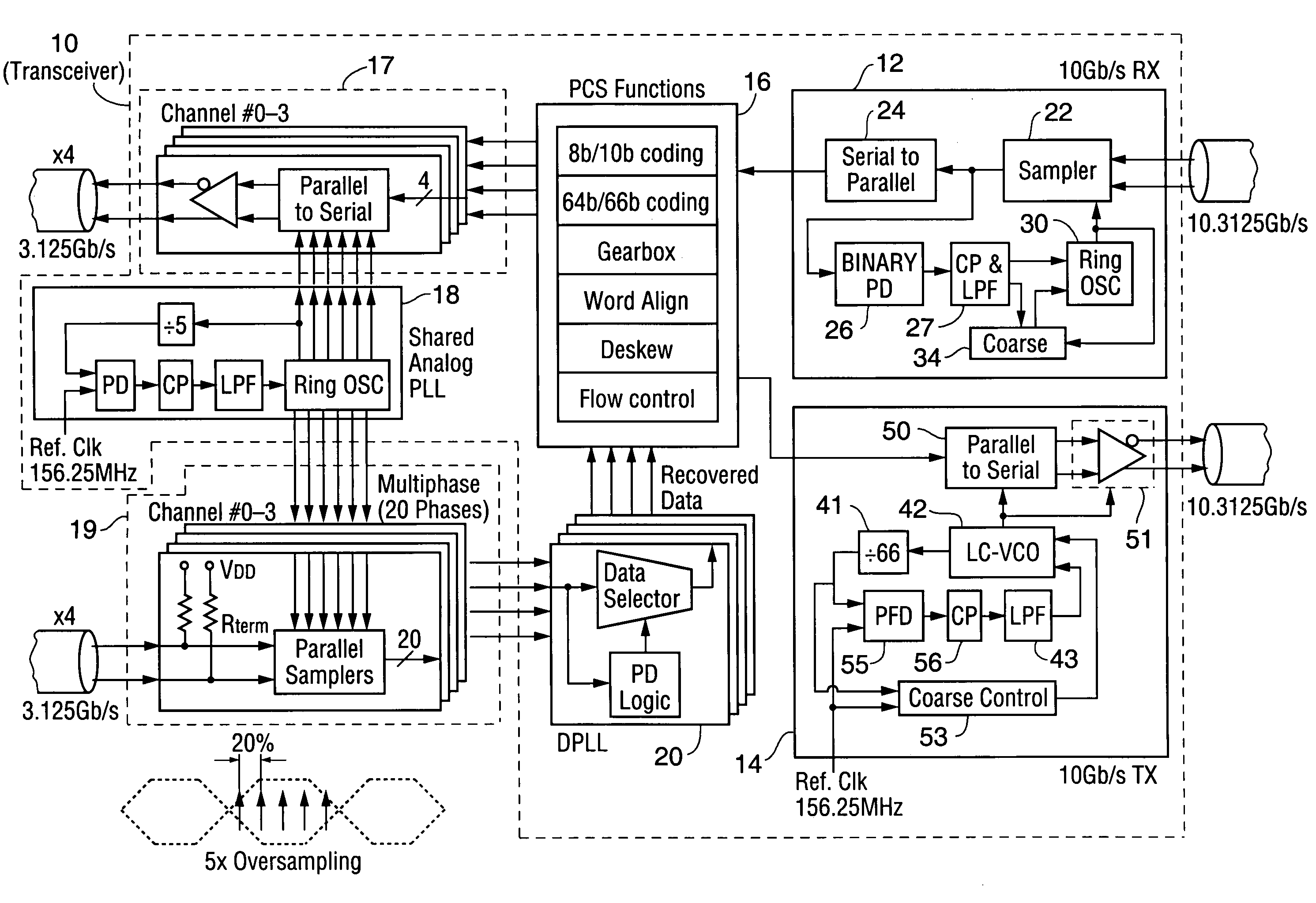

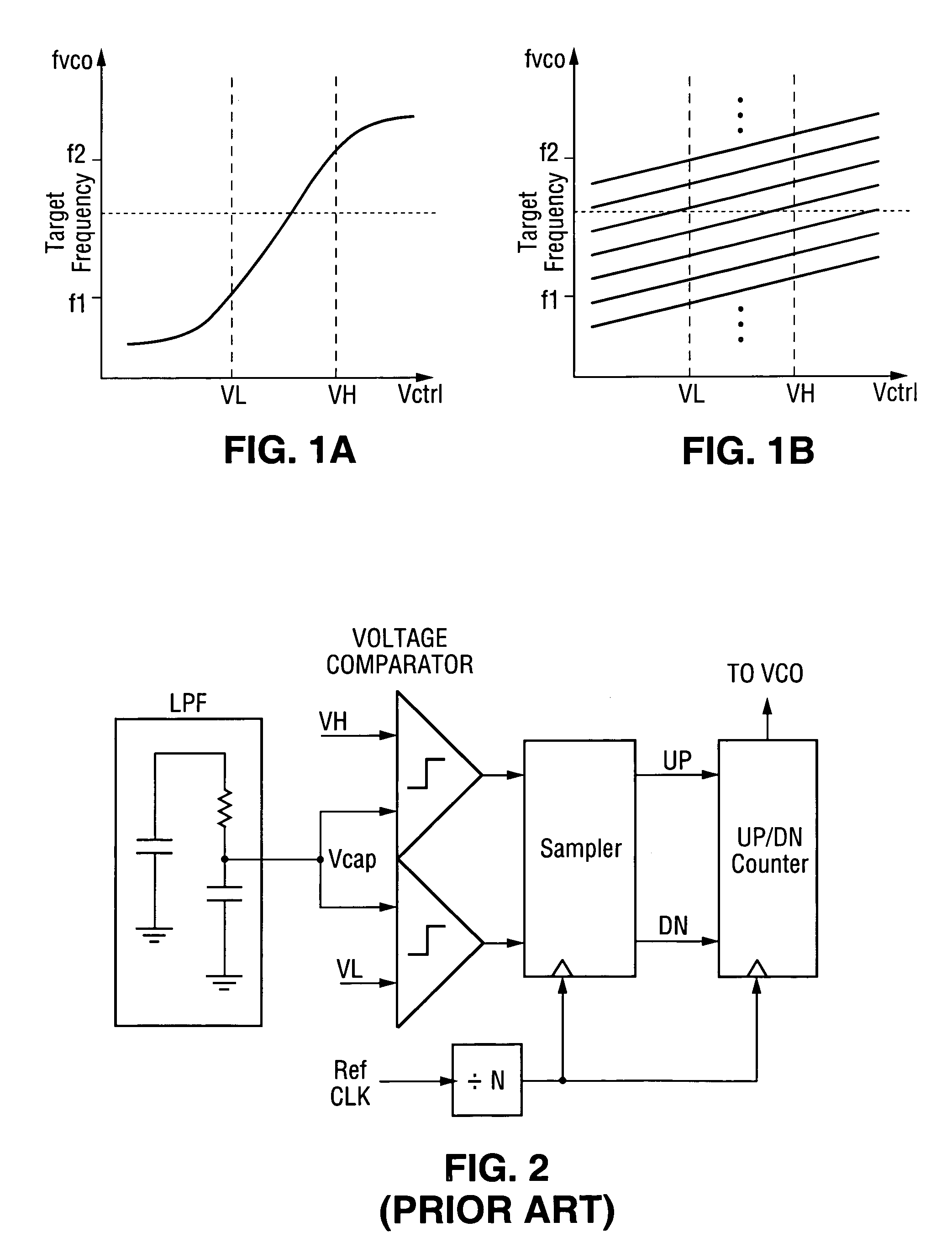

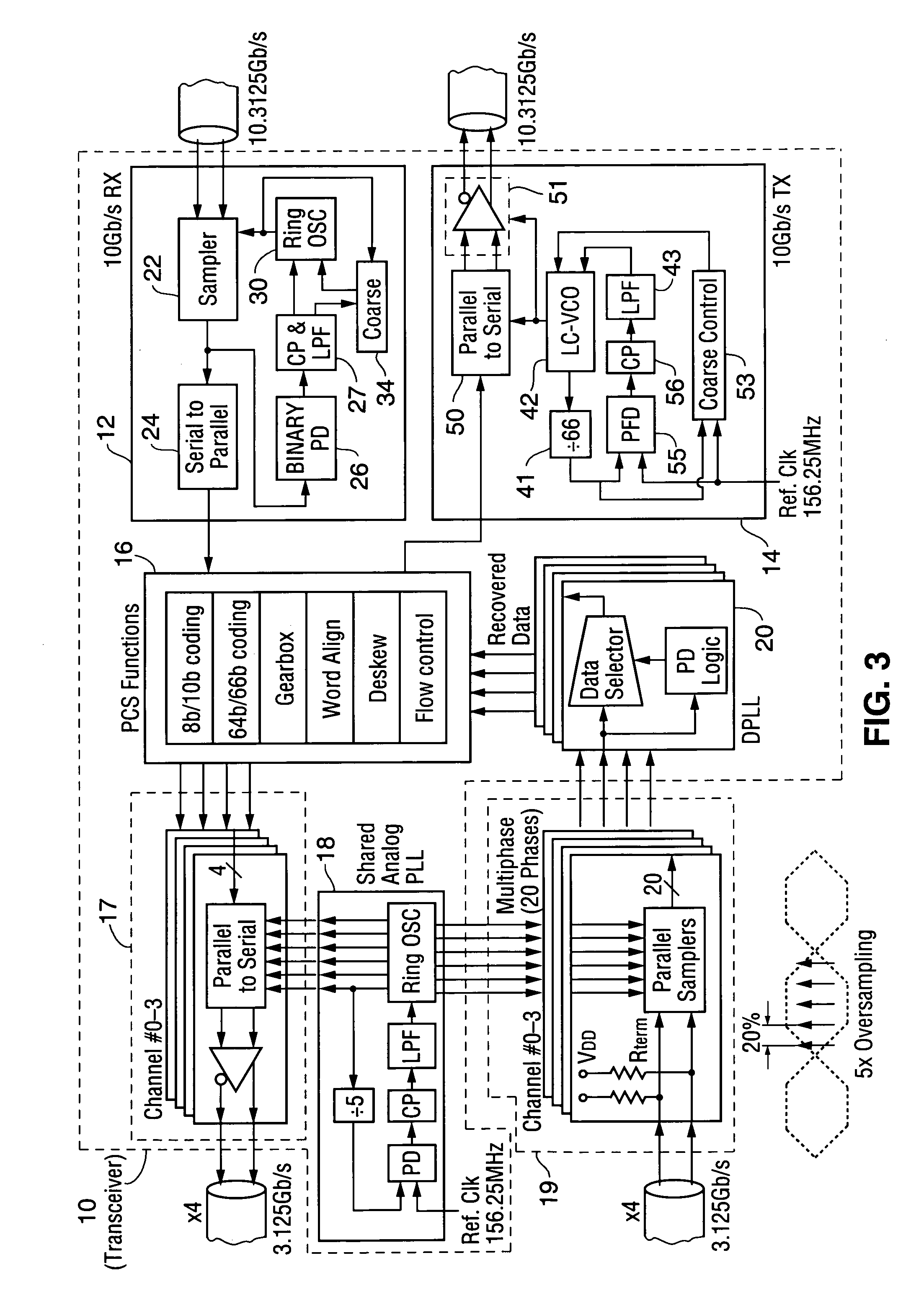

A phase lock loop (PLL) for controlling a sampling clock or other clock, and a data sampling circuit, transceiver, or other device including such a PLL. The PLL includes a multi-range VCO, at least one fine control loop for controlling the VCO, and a coarse control loop for controlling the VCO by changing its frequency-voltage characteristic. The coarse control loop includes a frequency lock detector and voltage range monitoring logic. Typically, the frequency lock detector locks operation of the coarse control loop when the difference between the VCO output clock frequency and a reference frequency decreases to within a predetermined threshold, and the unlocked coarse control loop employs the voltage range monitoring logic to change the VCO frequency-voltage characteristic when the VCO's fine control voltage leaves a predetermined range. Other aspects are a transceiver (including at least two receiver interfaces and a transmitter interface) implementing a clocking scheme employing no more than three PLLs for clock generation, and a transceiver having a multi-layered receiver interface including digital circuitry and a single clock-generating PLL (an analog PLL for generating a multiphase clock to be shared by all layers of the receiver interface). Each receiver interface layer performs blind oversampling on a different received signal using the multiphase clock and the digital circuitry includes multilayered digital phase lock loop circuitry which receives the oversampled data.

Owner:LATTICE SEMICON CORP

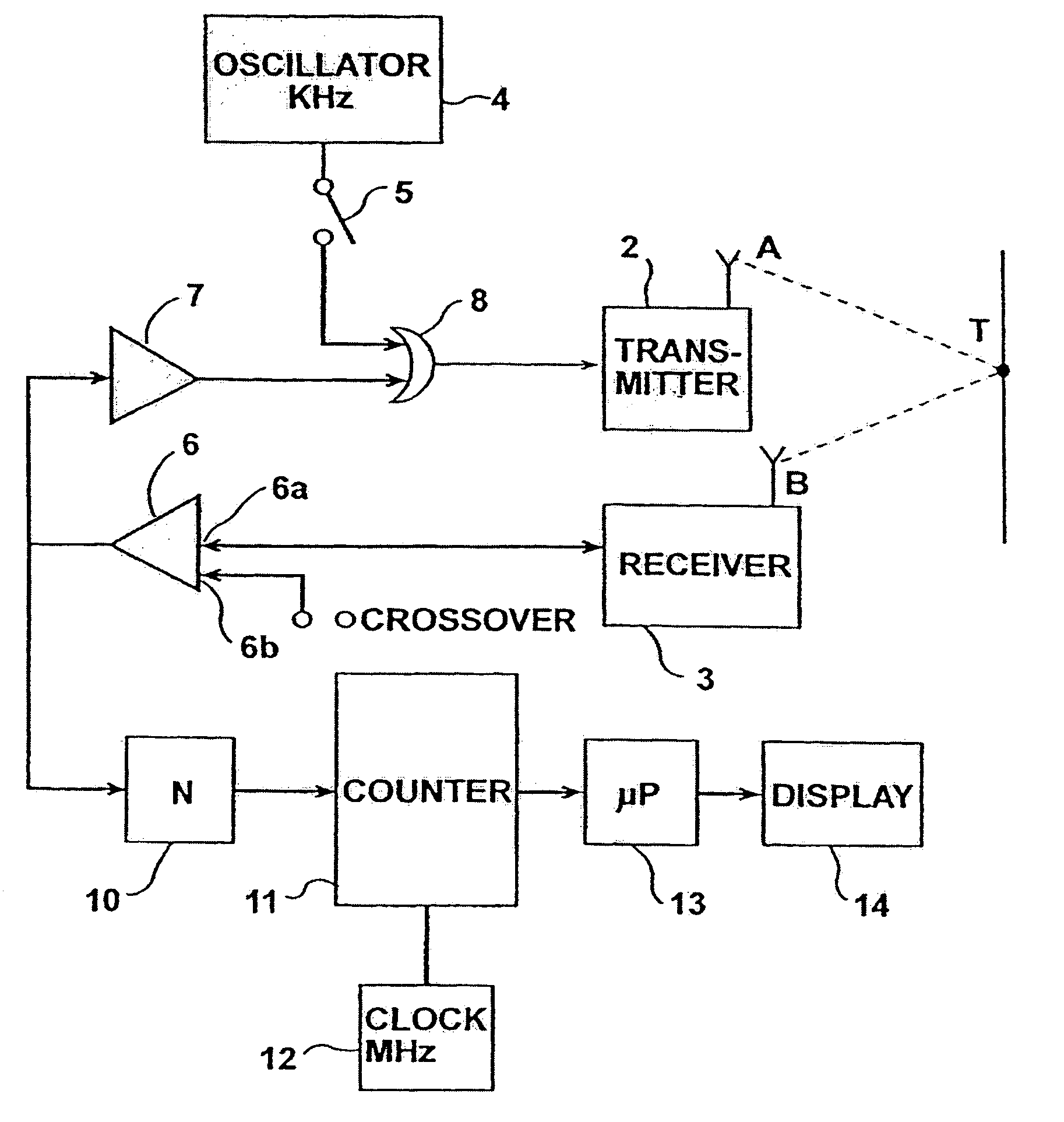

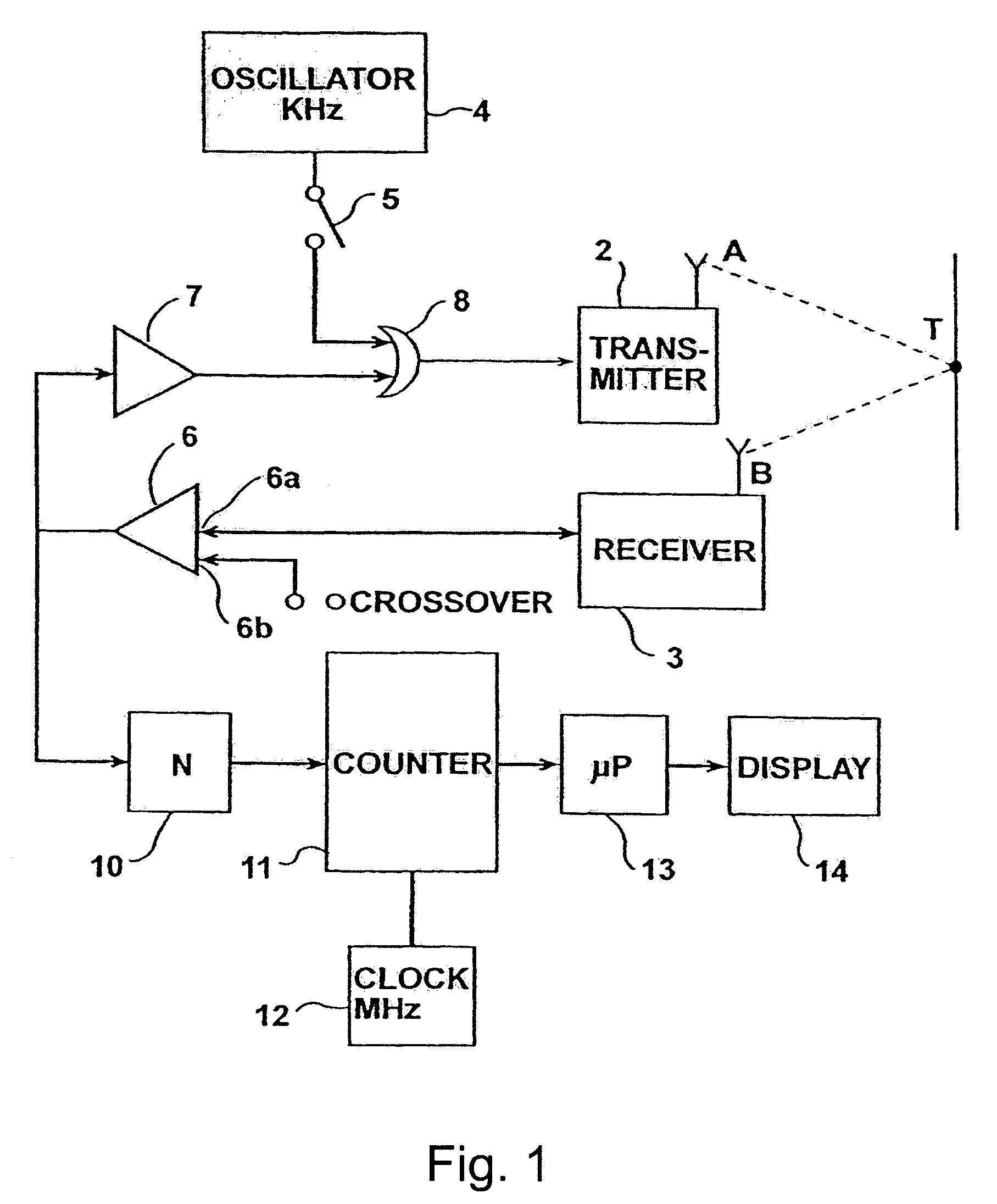

High-precision measuring method and apparatus

InactiveUS7080554B2Vibration measurement in solidsAnalysing fluids using sonic/ultrasonic/infrasonic wavesPhase locked loop circuitTransmission channel

Owner:NEXENSE

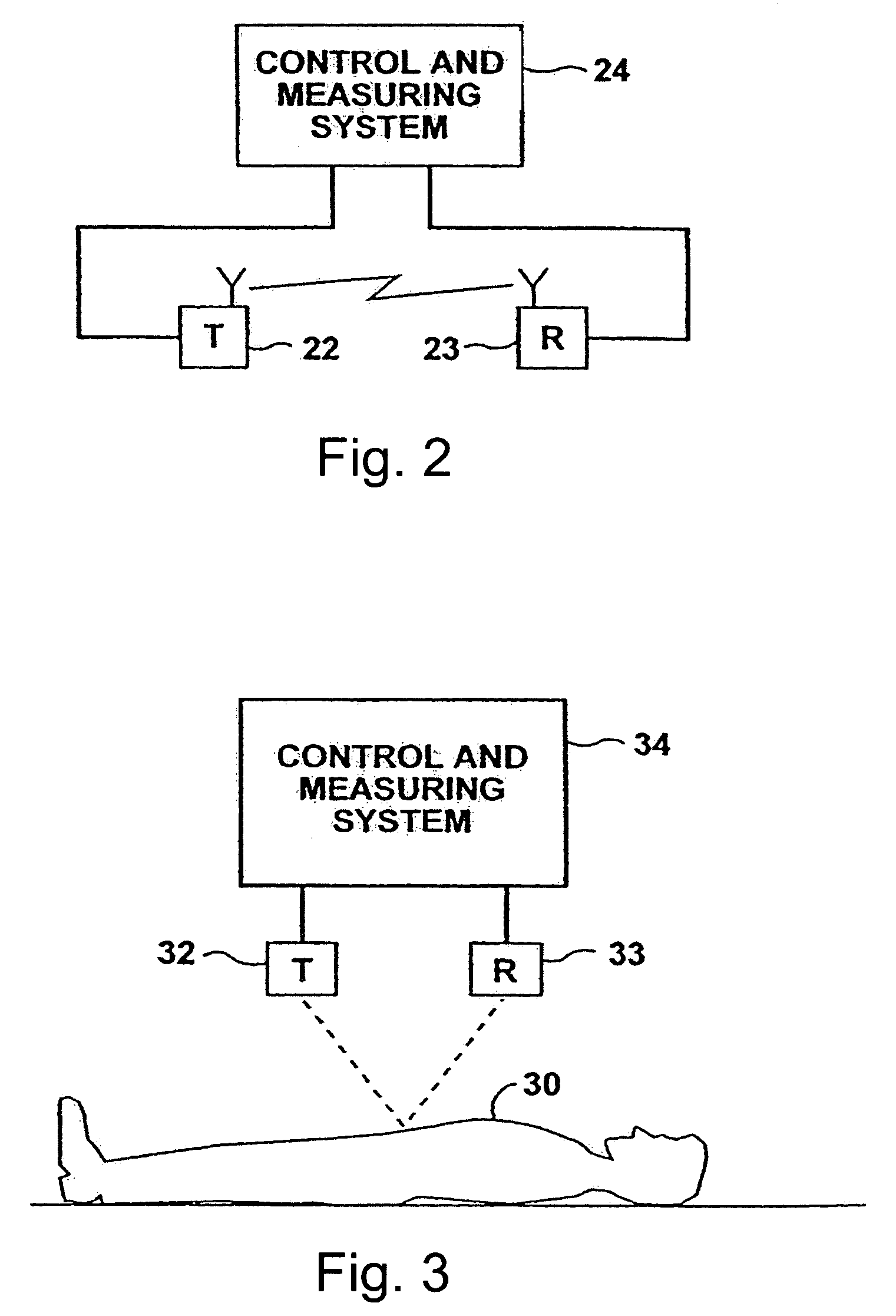

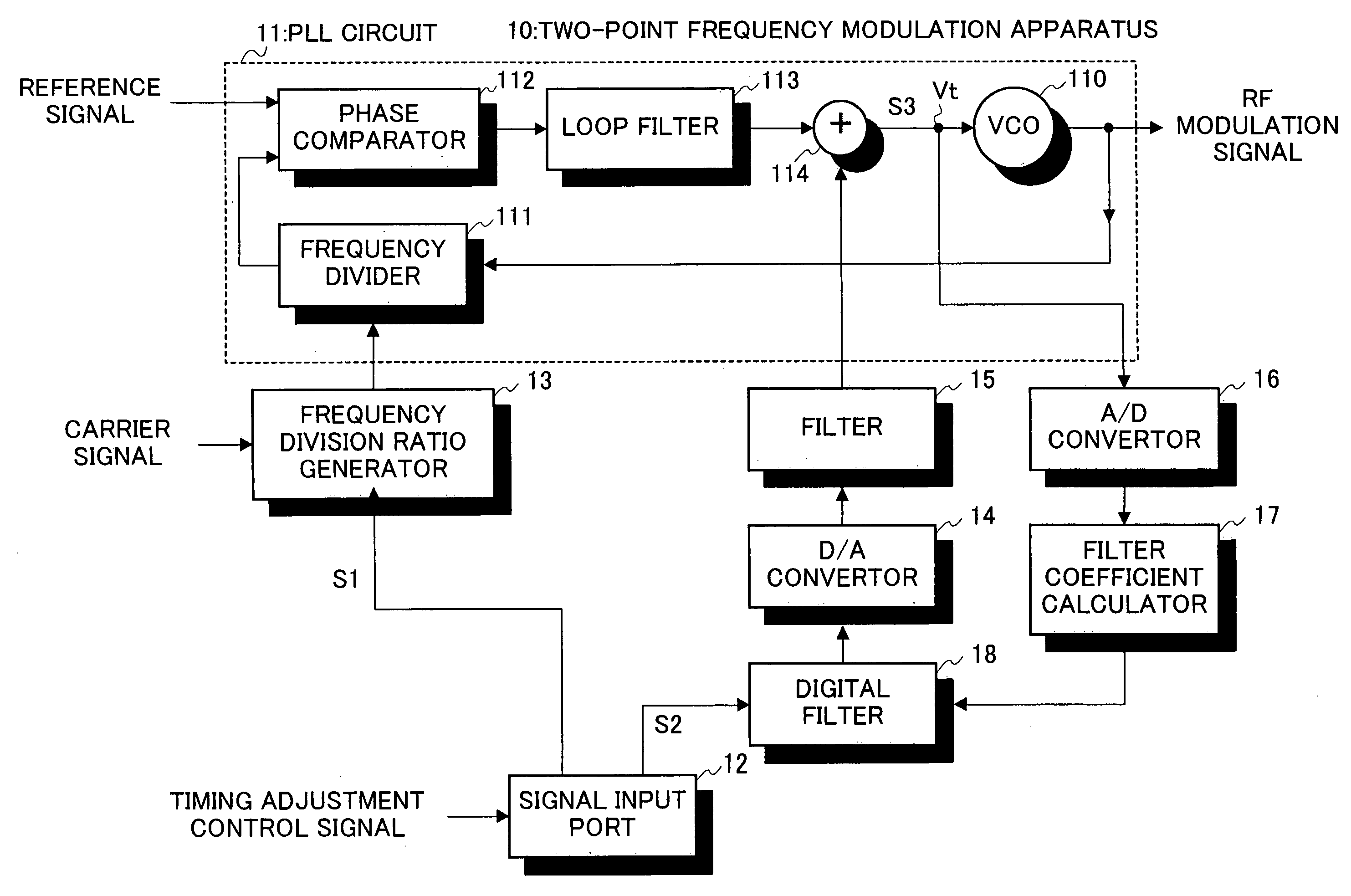

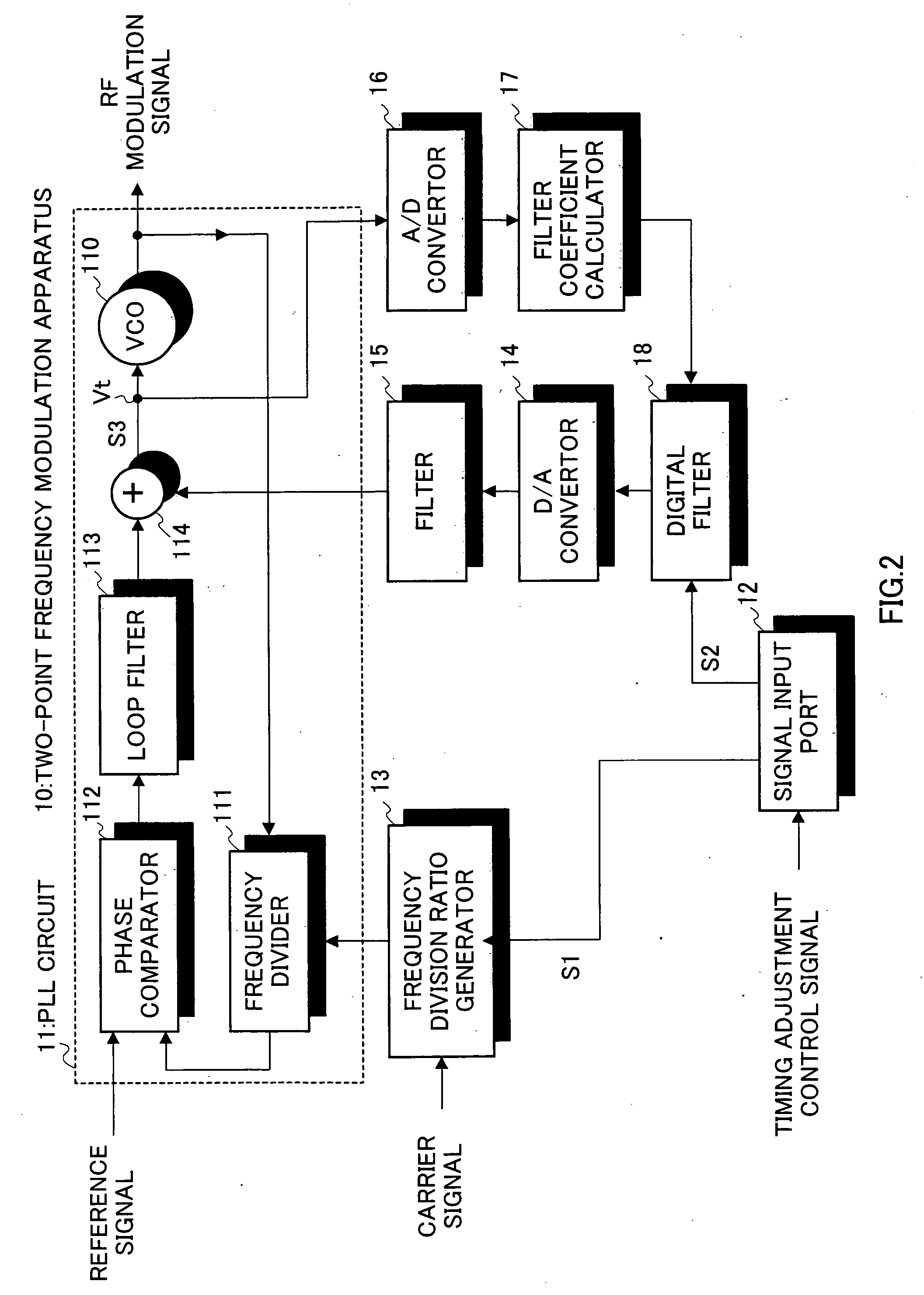

Two-point frequency modulation apparatus, wireless transmitting apparatus, and wireless receiving apparatus

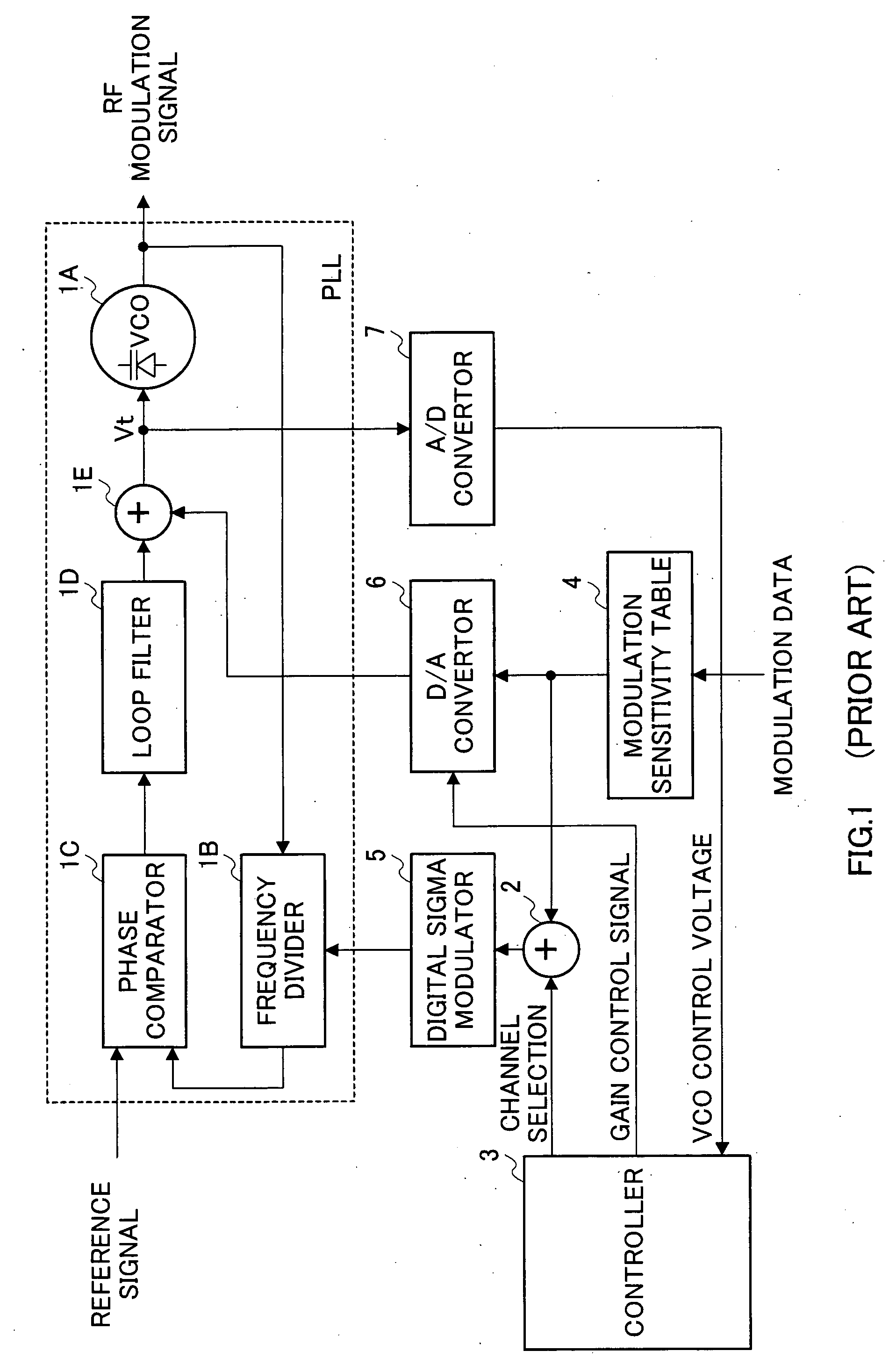

InactiveUS20050232385A1Reduces input timing differenceHigh modulation accuracyPulse automatic controlAngle modulation detailsLoop filterPhase difference

A two-point frequency modulation apparatus is provided that reduces input timing difference and improves modulation accuracy. Two-point frequency modulation apparatus 10 has: PLL circuit 11; frequency division ratio generator 13 that generates the frequency division ratio in frequency divider 111 based on first digital baseband signal S1 and carrier signal; adder 114 that adds second digital baseband signal S2 to the output signal of loop filter 113; a delay index calculator (filter coefficient calculator 17) that calculates the delay index based on the magnitude of change in the amplitude of the output signal of adder 114; and a delay adjuster (digital filter 18) that shifts the phase of one of first digital baseband signal S1 and second digital baseband signal S2 according to the delay index so as to reduce the phase difference.

Owner:PANASONIC CORP

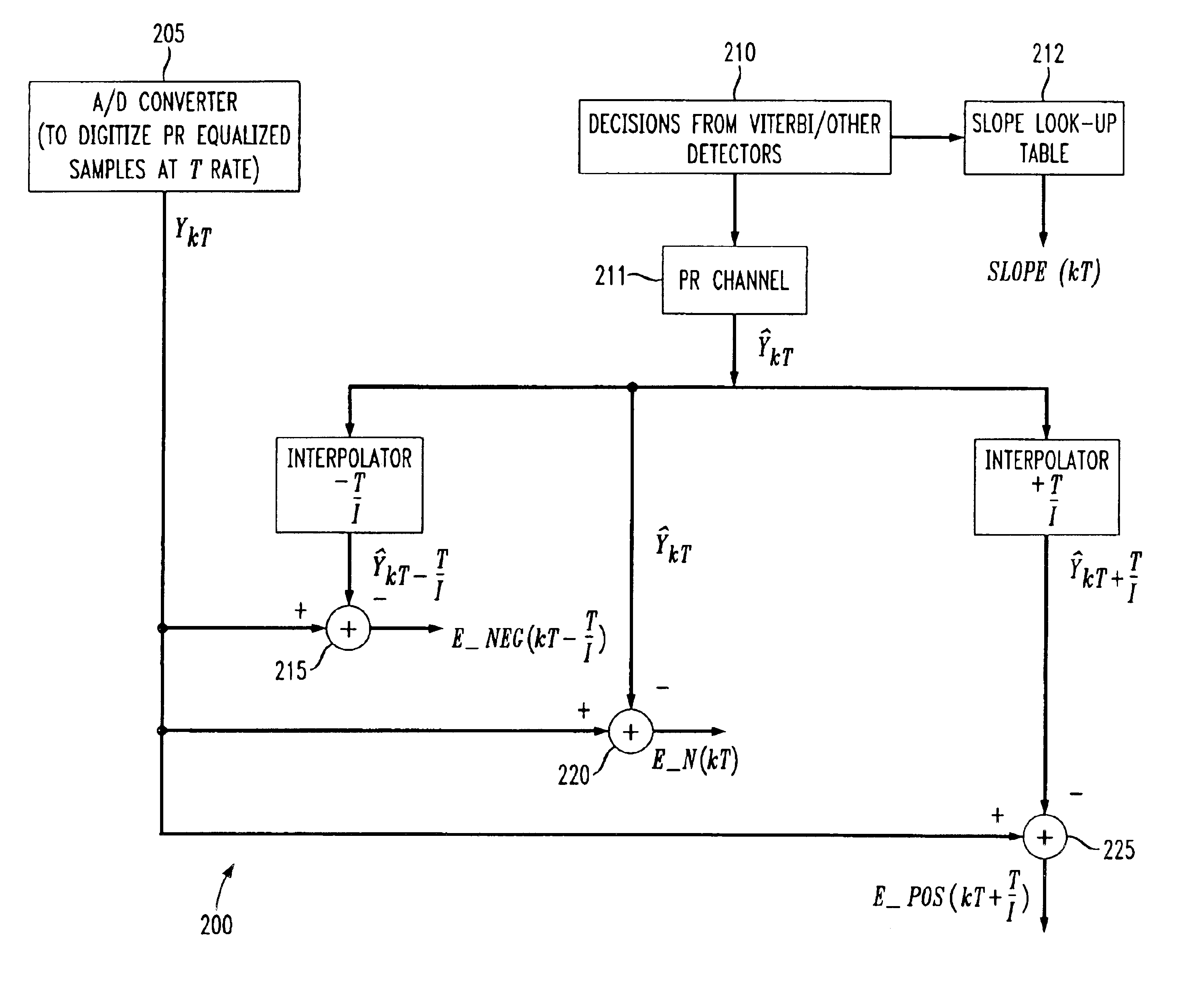

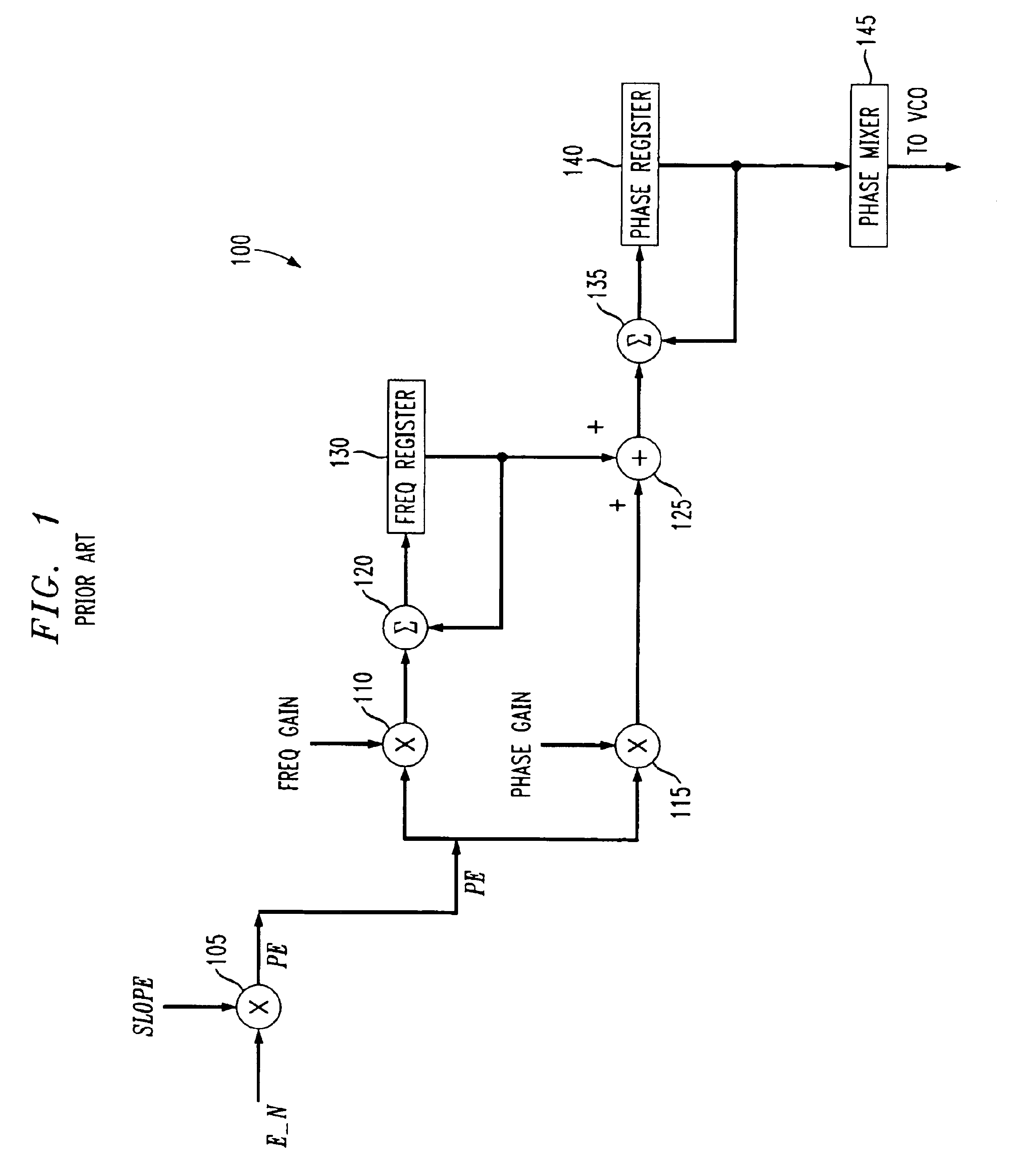

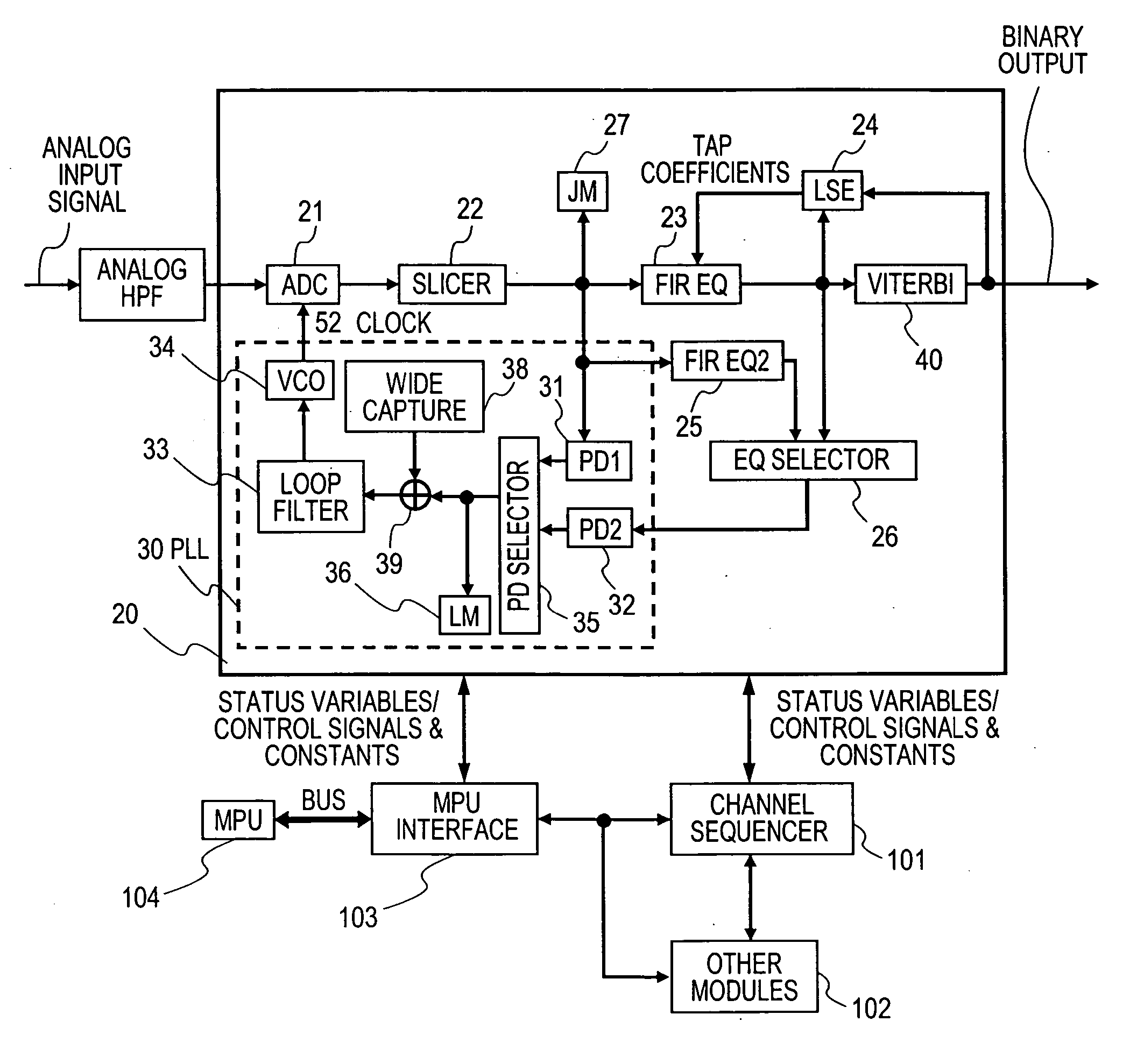

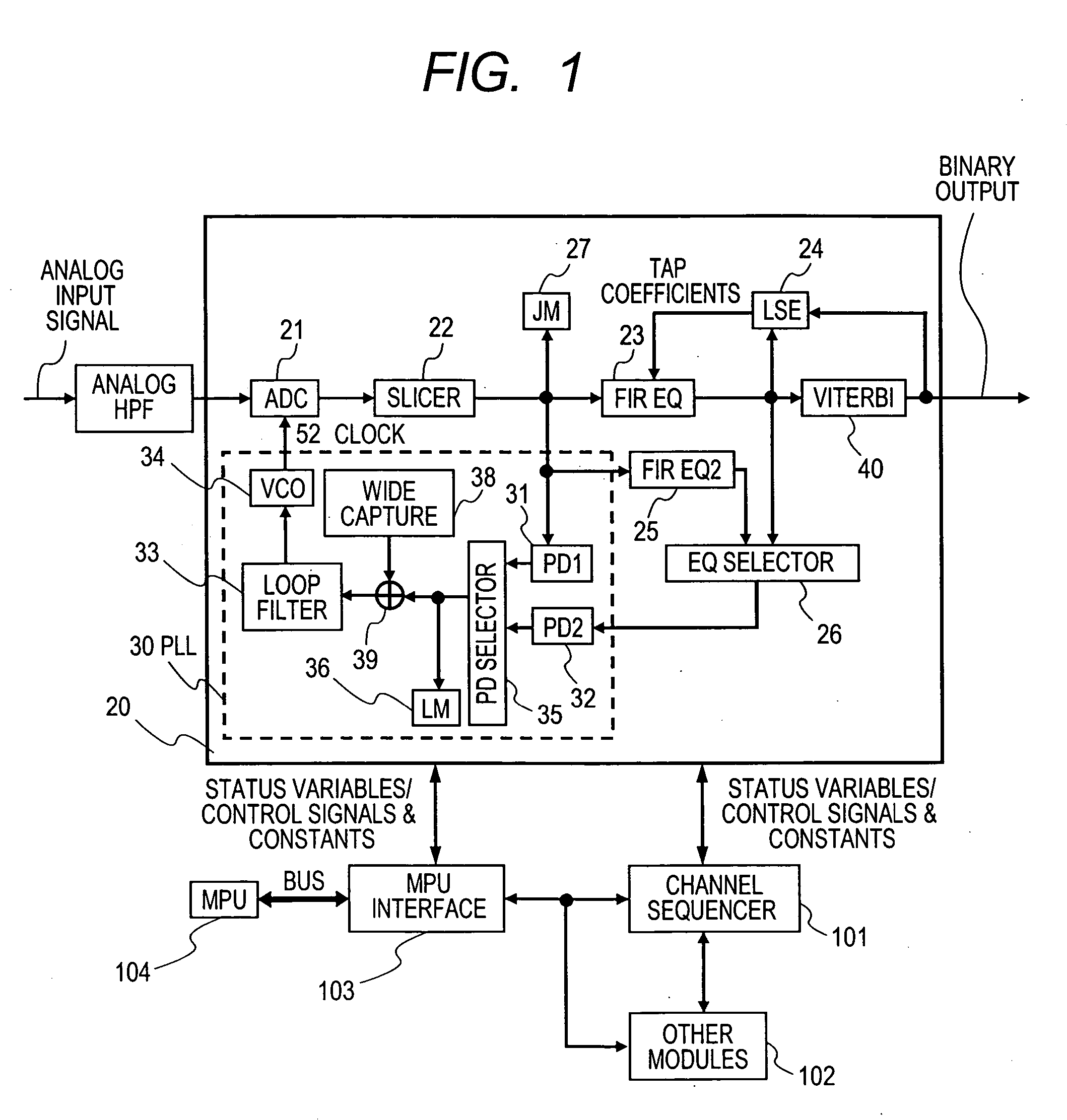

Scheme to improve performance of timing recovery systems for read channels in a disk drive

InactiveUS6856183B2Pulse automatic controlVoltage-current phase anglePhase locked loop circuitEngineering

A digital phase lock loop circuit including an error generation circuit for generating at least three error signals and a phase error adjustment circuit for generating at least one phase error adjustment signal from the at least three error signals. By using at least three error signals, as opposed to just one, the drift in the sampling phase of the recovered clock is easily detected and corrected to reduce burst errors and to improve loss of lock (LOL) performance.

Owner:BROADCOM INT PTE LTD

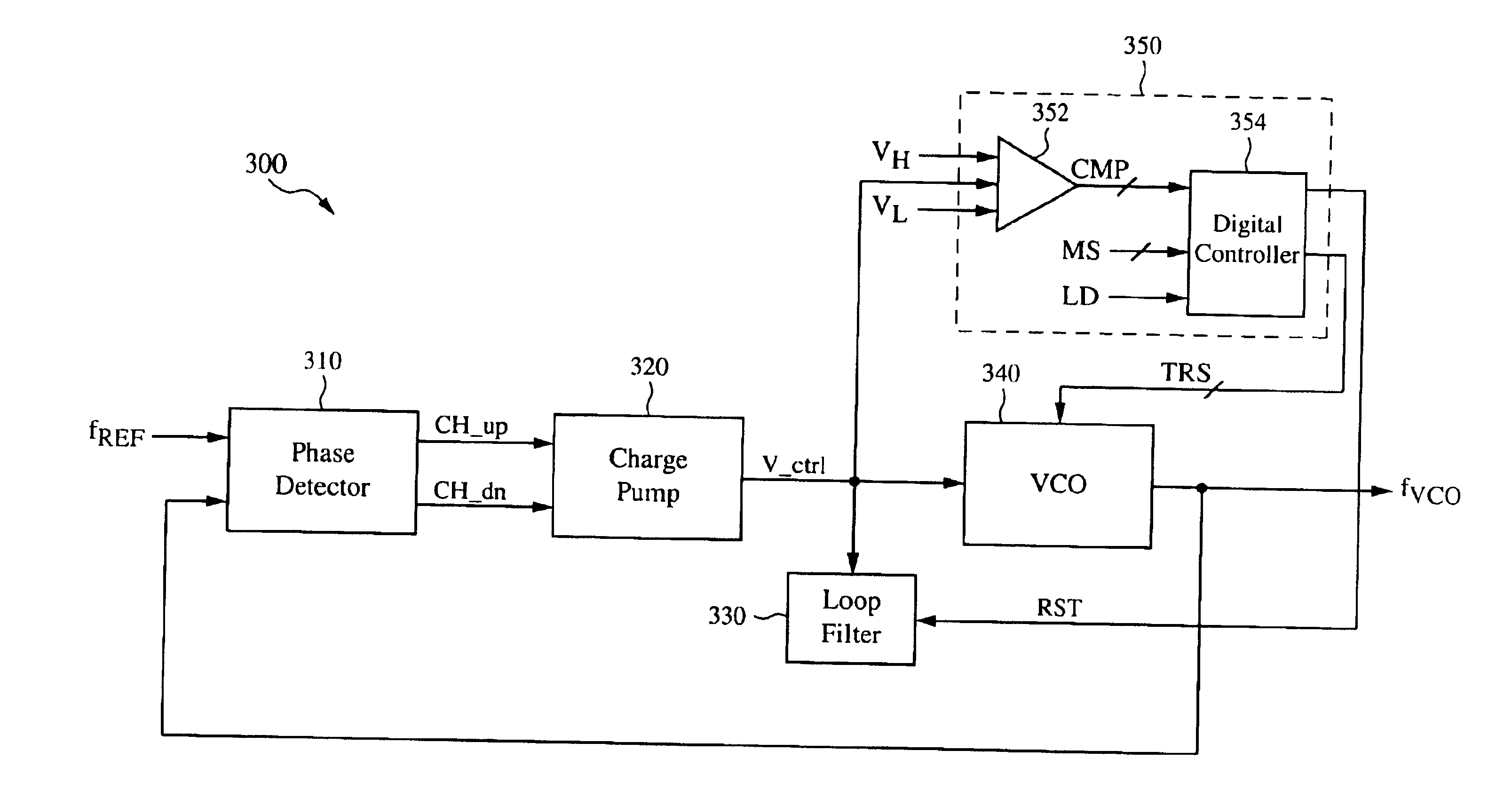

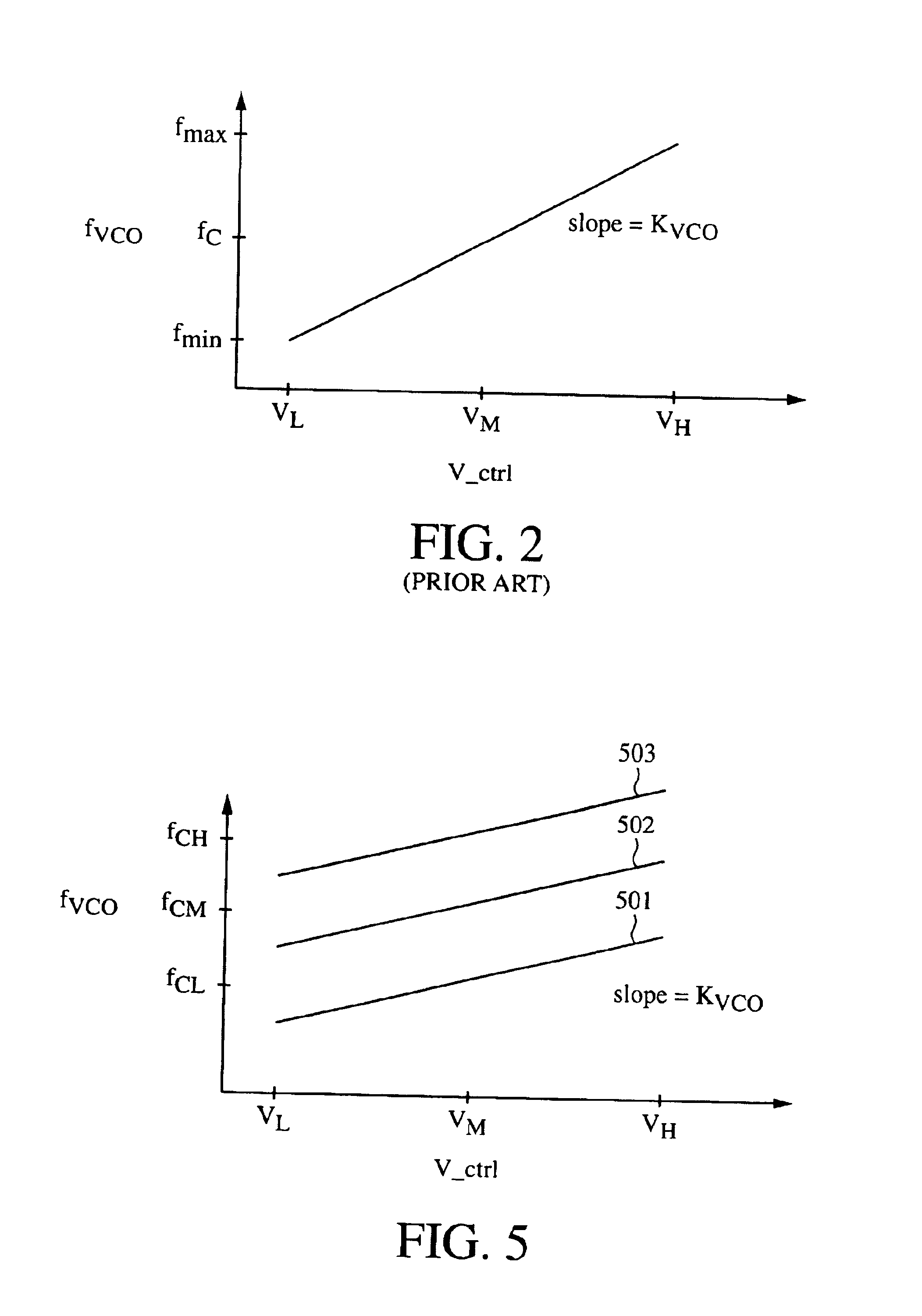

Phase locked loop circuit with self adjusted tuning

A phase-locked loop (PLL) circuit includes a voltage-controlled oscillator (VCO) having a first input to receive a control voltage, one or more second inputs to receive one or more tuning range control signals, and an output to provide an oscillation output signal, a phase detector having inputs to receive the oscillation output signal and a reference signal, a charge pump having an input coupled to the output of the phase detector and having an output to generate the control voltage, a loop filter having an input to receive the control voltage and having a control terminal, and a controller having inputs to receive the control voltage, a high reference voltage, a low reference voltage, and one or more mode signals, and having a first output connected to the control terminal of the loop filter and second outputs to generate the tuning range signals.

Owner:PROMISE TECHNOLOGY

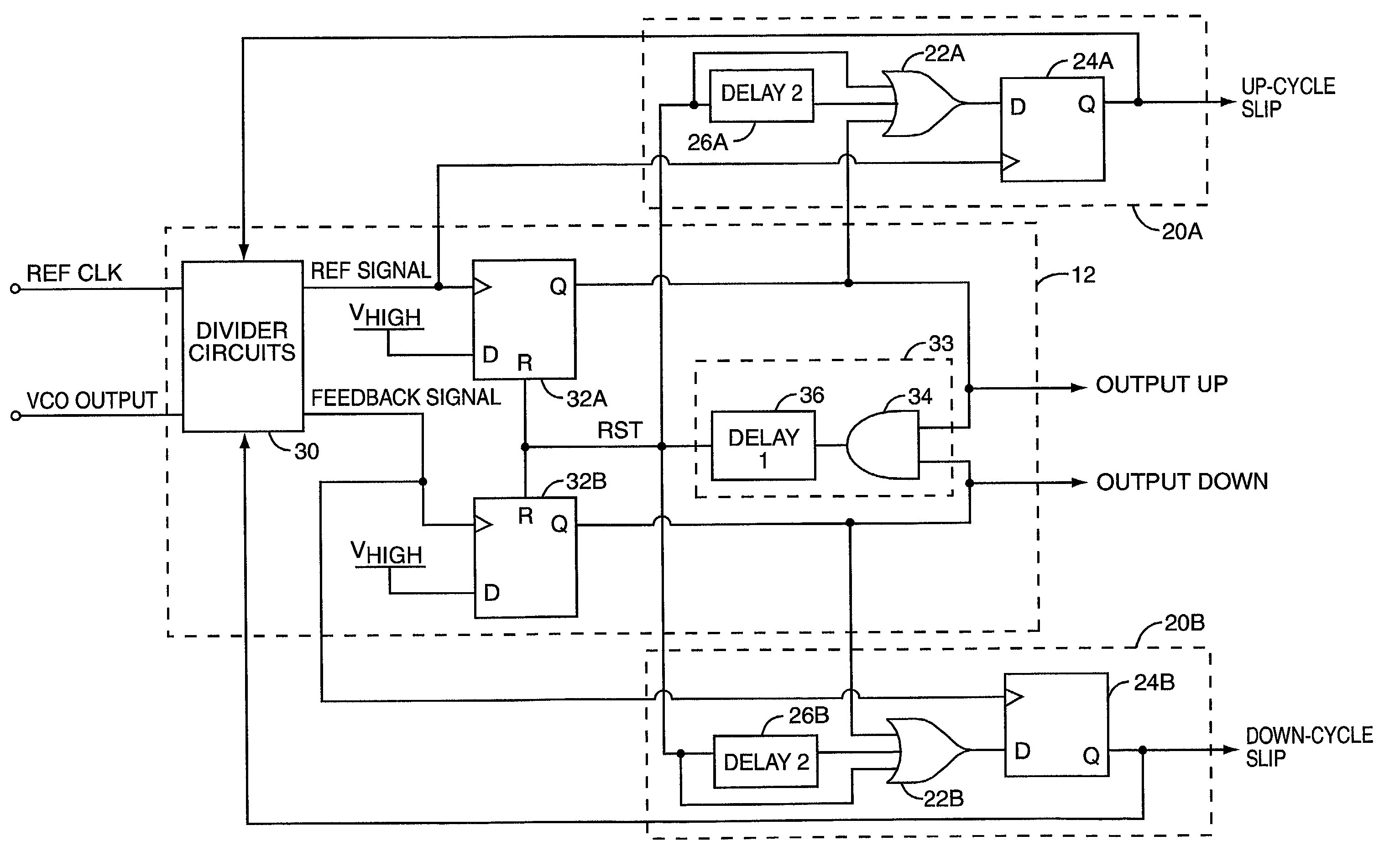

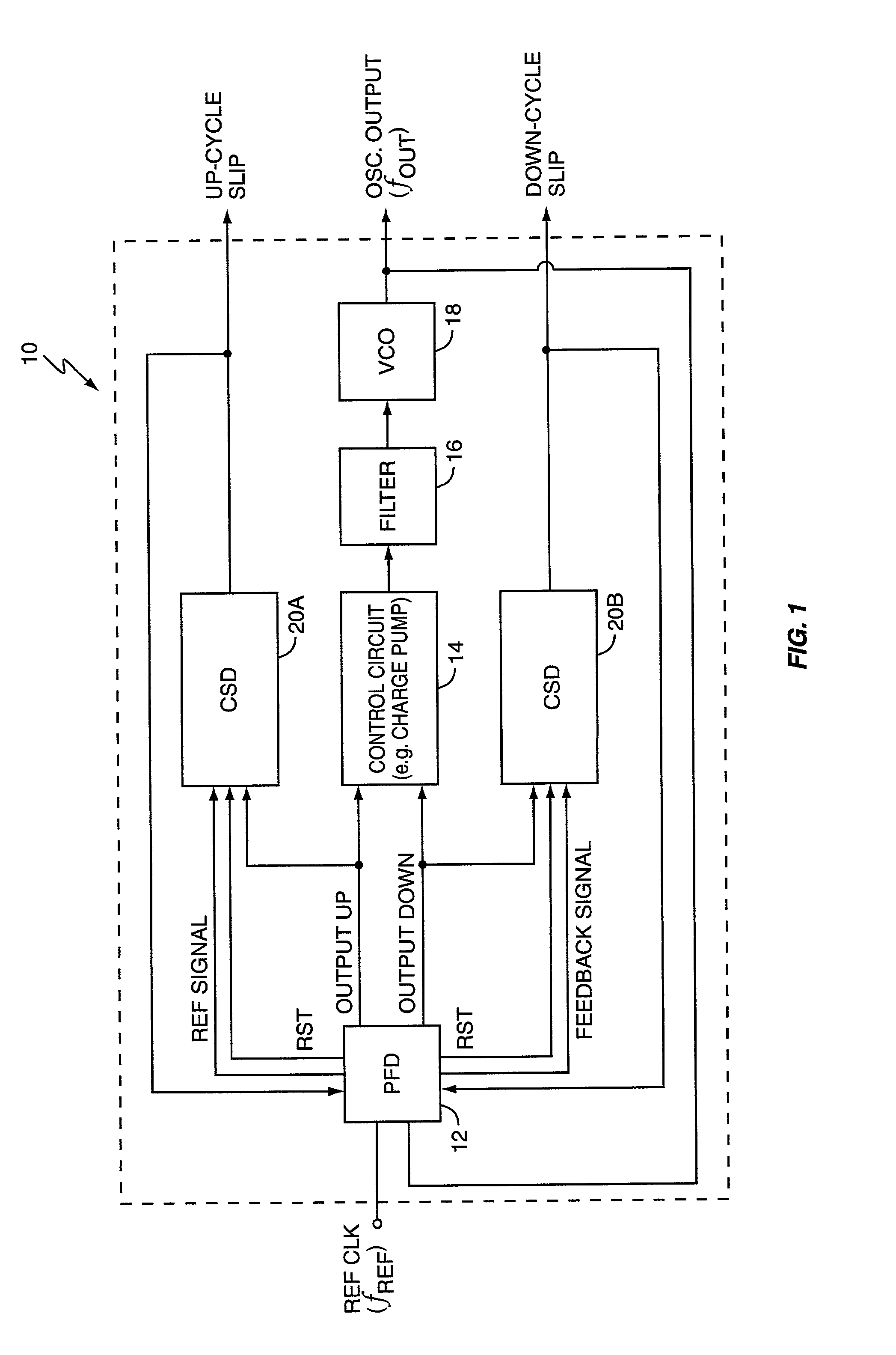

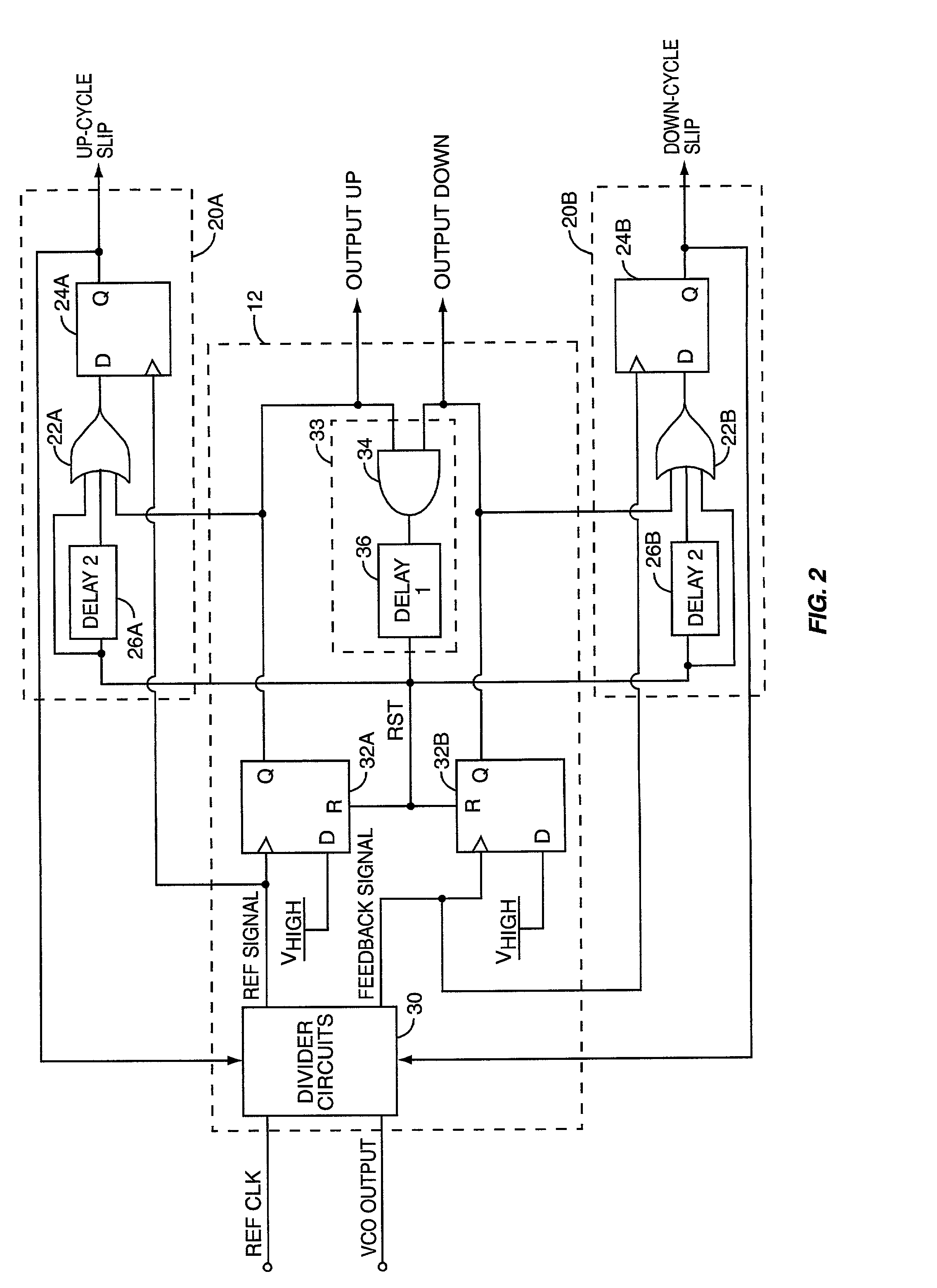

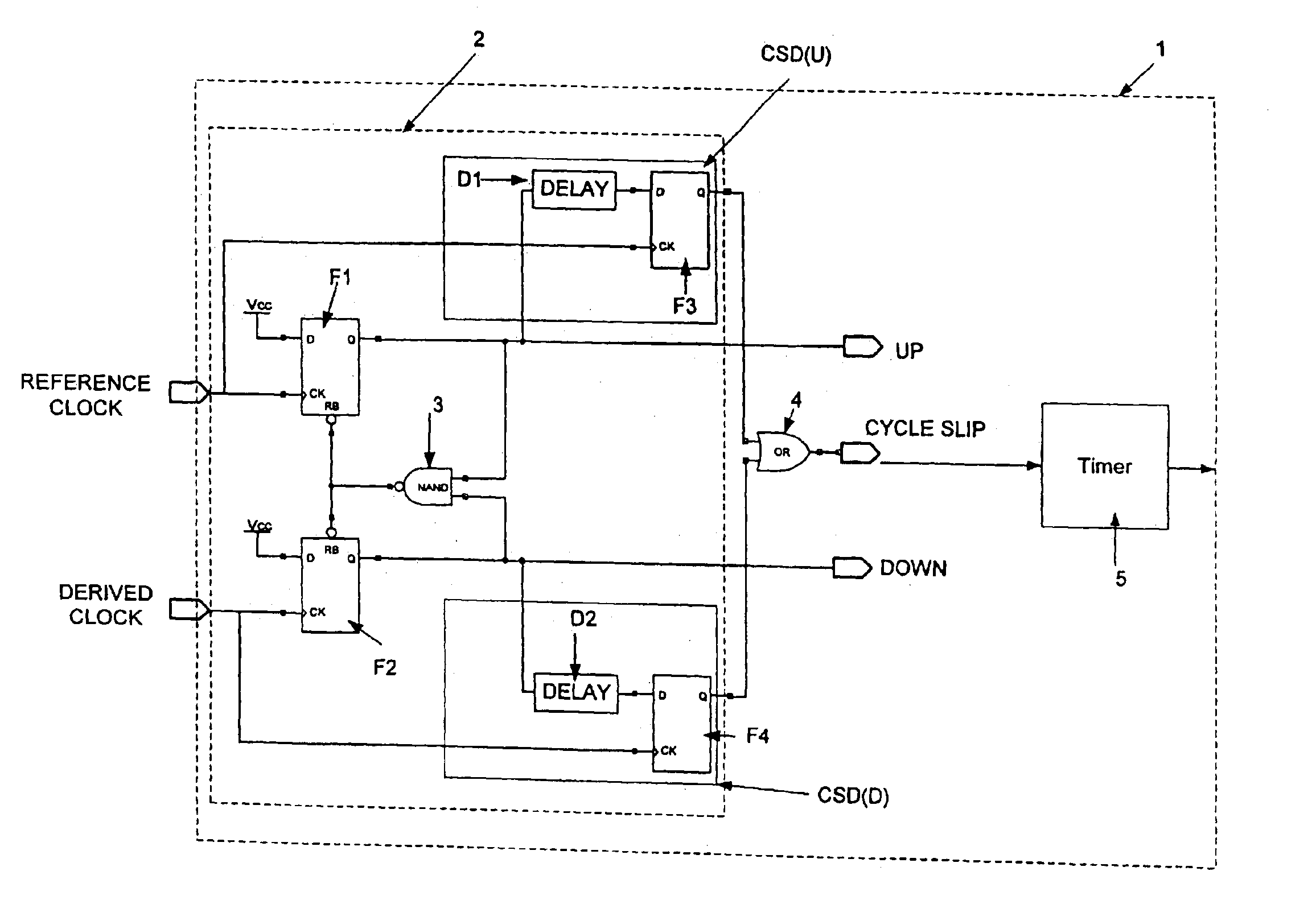

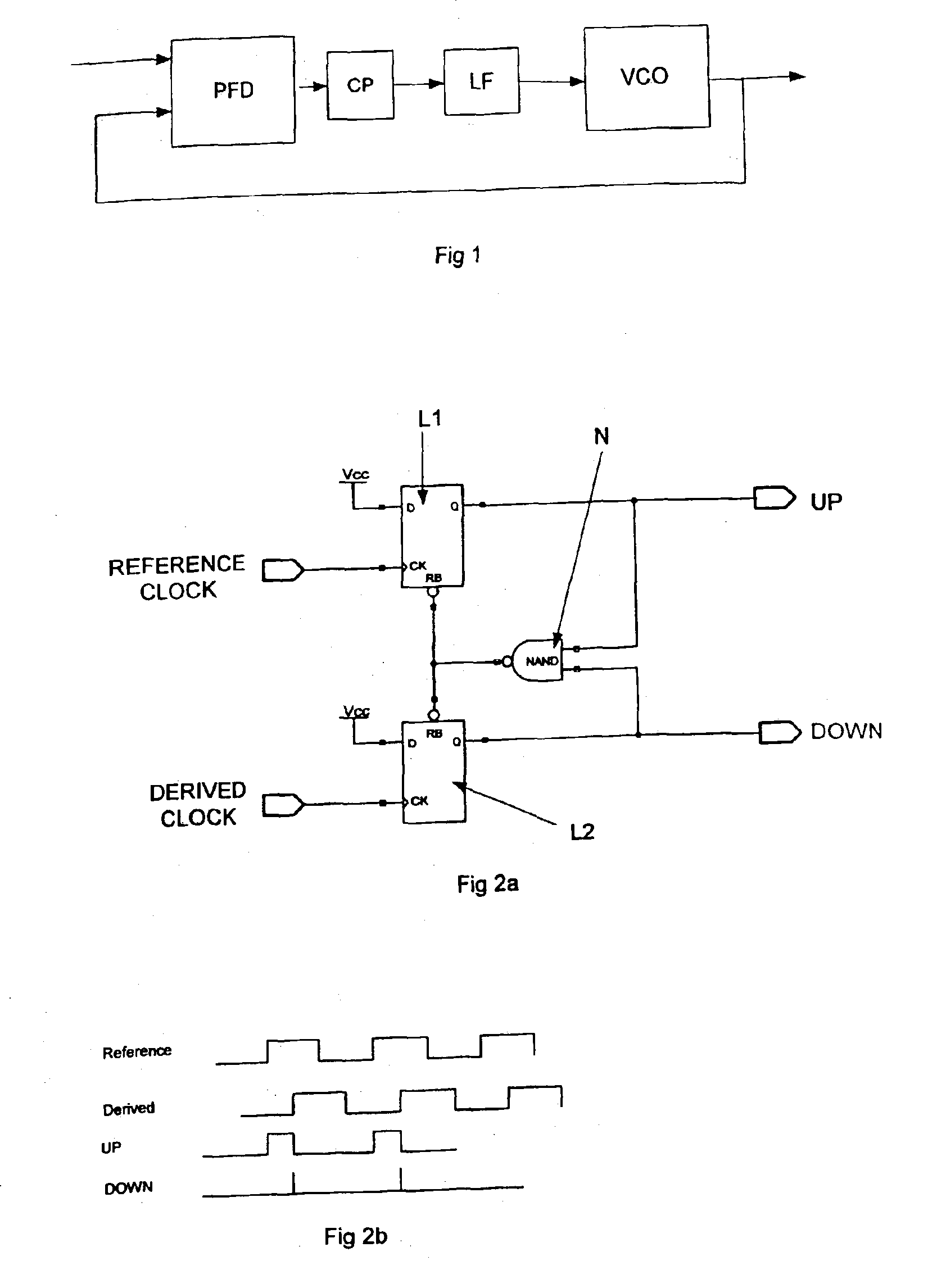

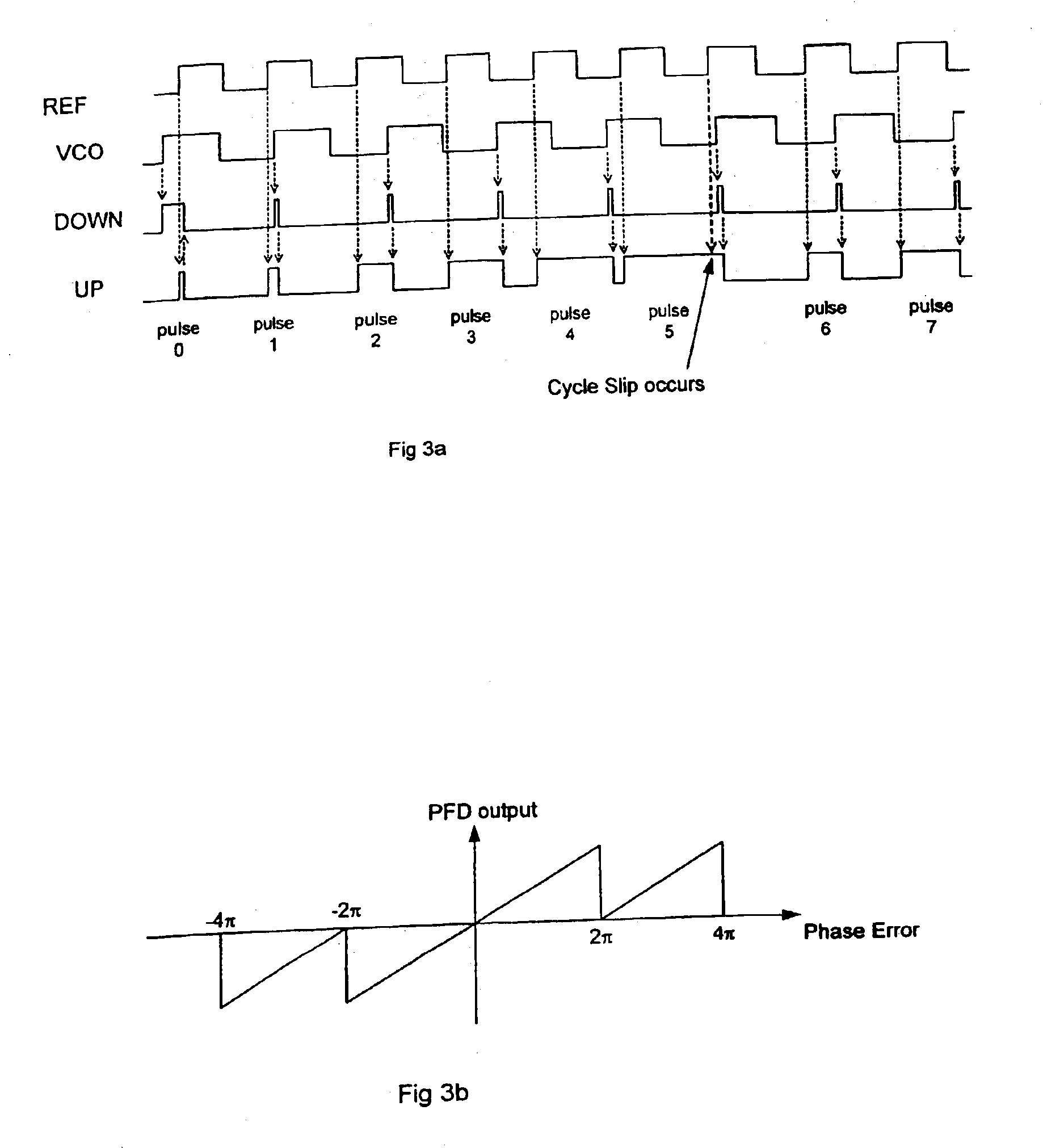

PLL cycle slip detection

InactiveUS7003065B2Pulse automatic controlVoltage-current phase angleControl signalPhase locked loop circuit

A cycle slip detector interfaces with a phase / frequency detector (PFD), such as might be used in a phase-locked loop circuit (PLL), and indicates when cycle slips occur in the PFD. Typically, the PFD generates output control signals as a function of the phase difference between first and second input signals, with the first input signal usually serving as a reference signal against which the PLL adjusts the second input signal. The PFD provides linear phase comparison between its input signals, provided their relative phase difference does not exceed ±2π radians. If one of the two signals leads or lags the other by more than that amount, a cycle slip occurs, and the PFD responds nonlinearly. The cycle slip detector provides logic for detecting and indicating leading and lagging cycle slips as they occur in the PDF, and is typically implemented as a minimal arrangement of logic gates and flip-flops.

Owner:ERICSSON INC

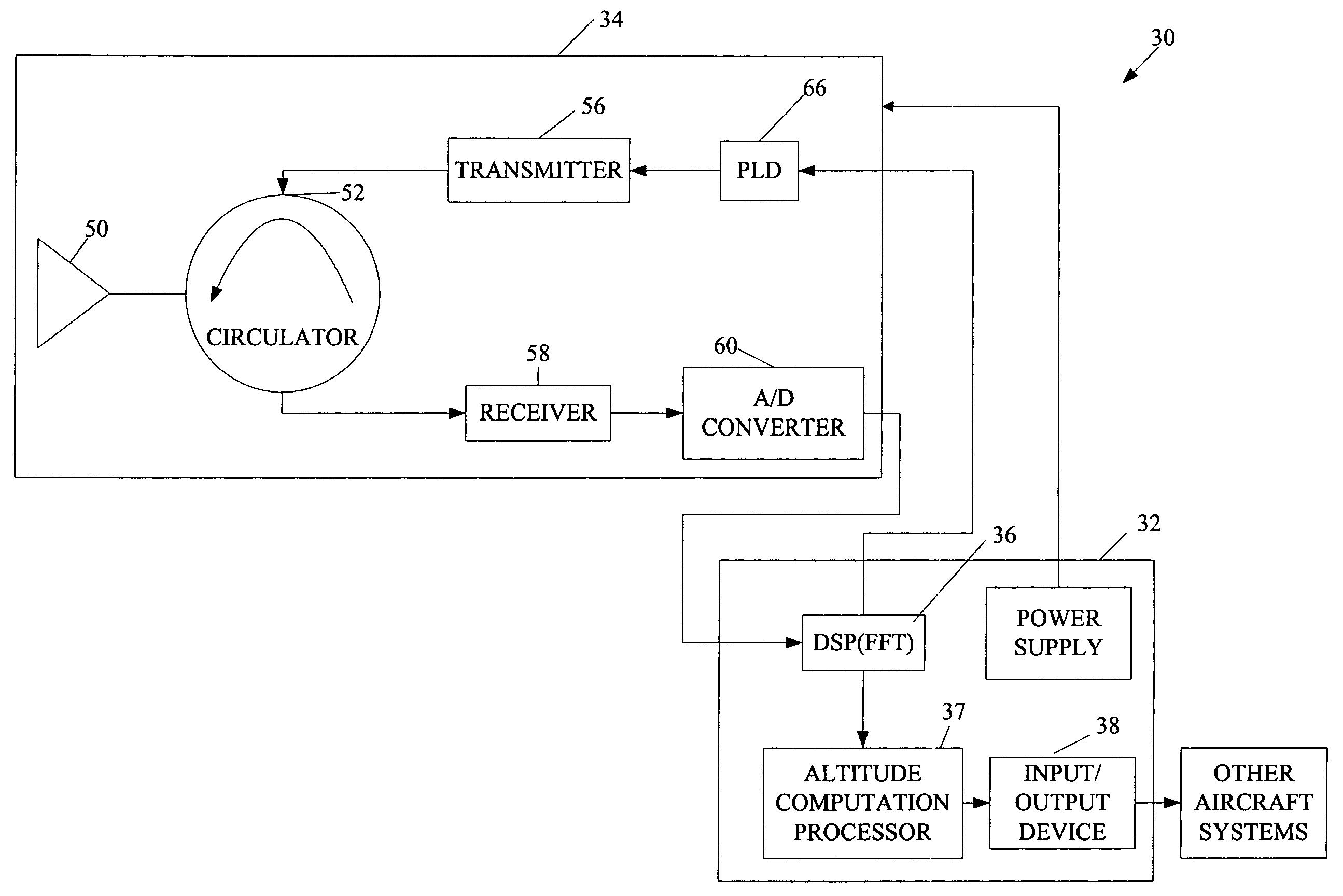

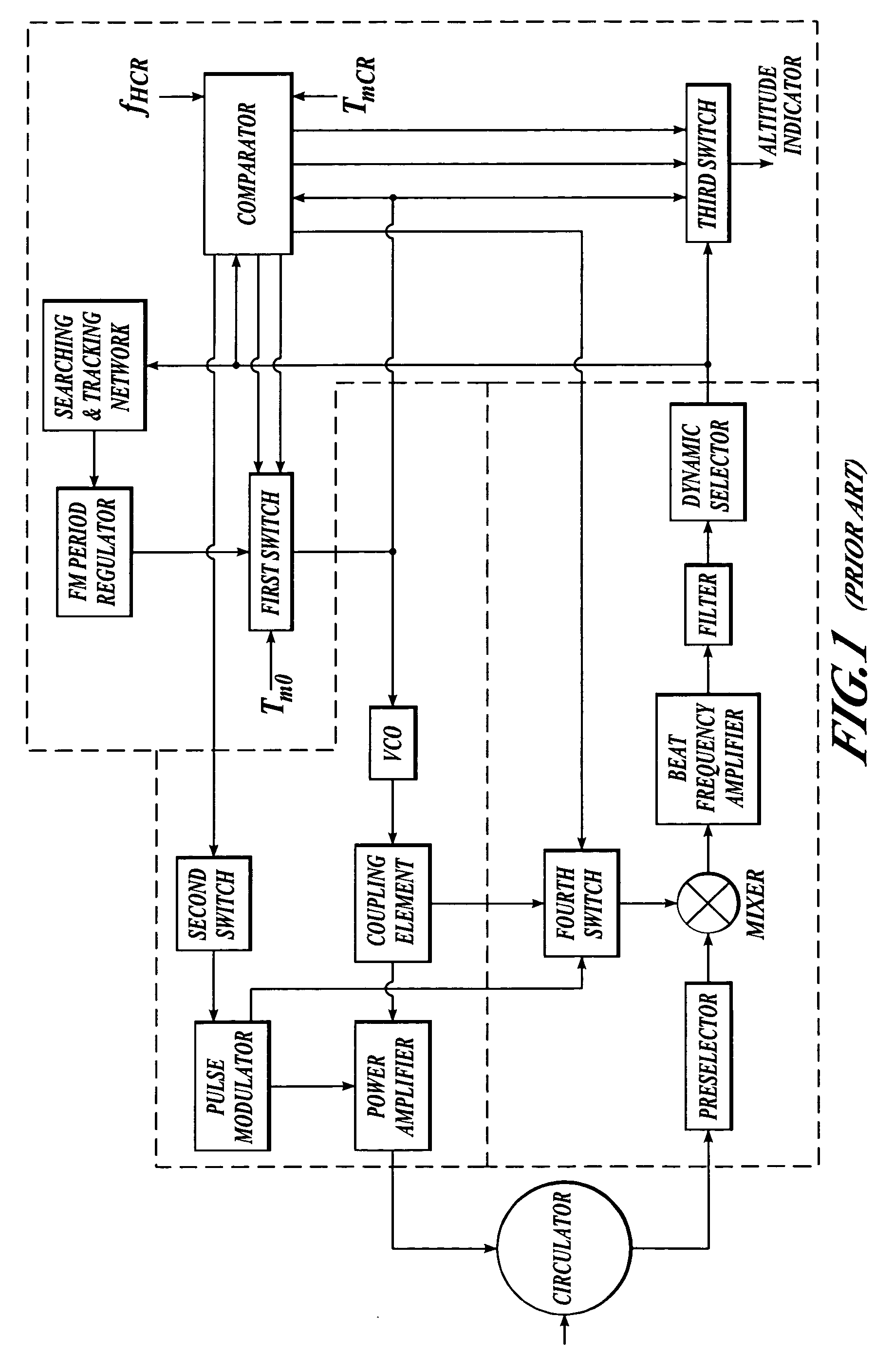

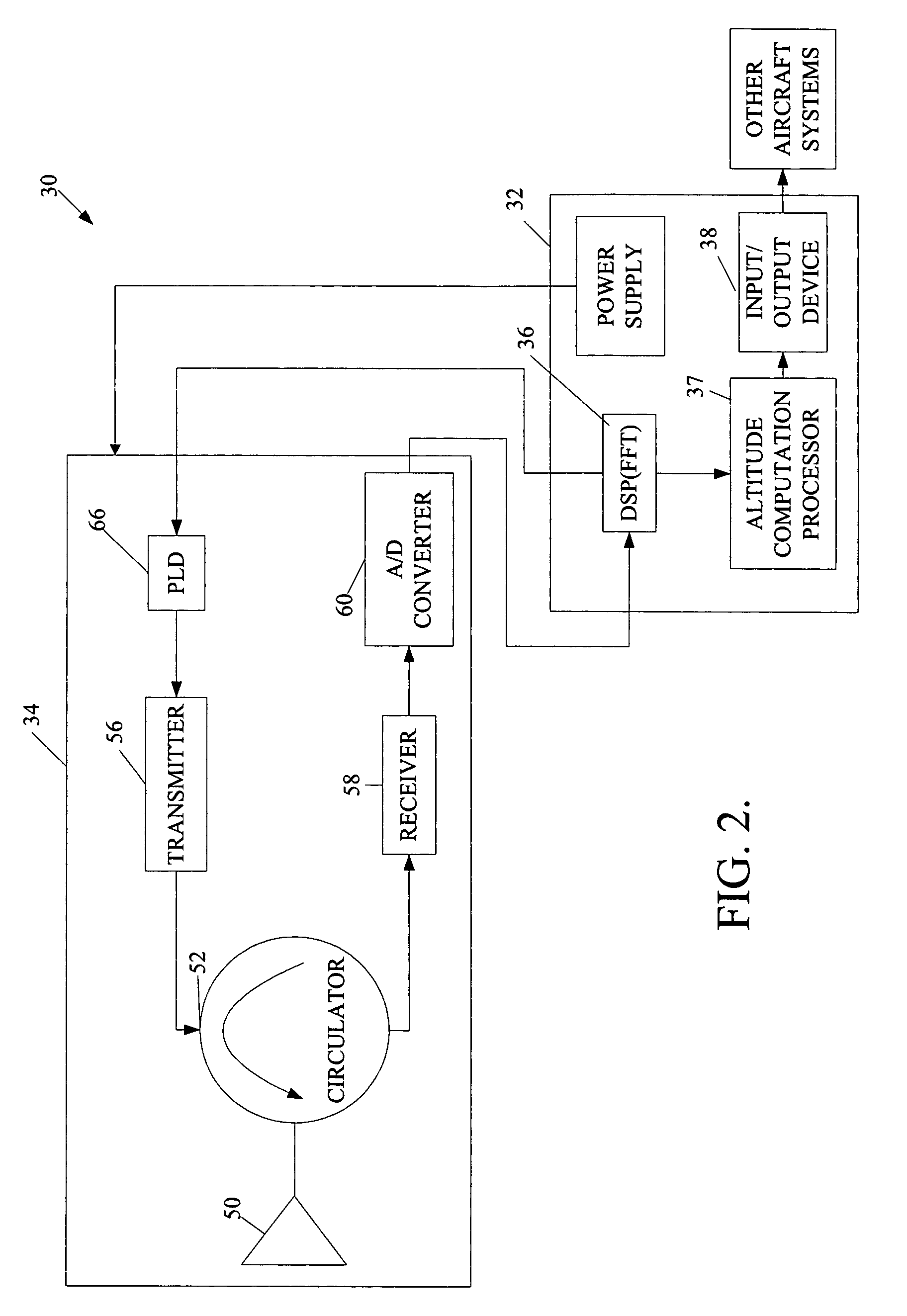

Radar altimeter

ActiveUS7239266B2Constant bandwidthConstant rateRadio wave reradiation/reflectionDigital signal processingPhase locked loop circuit

The present invention provides a radar altimeter system with a closed loop modulation for generating more accurate radar altimeter values. The system includes an antenna, a circulator, a receiver, and a transmitter. The circulator receives or sends a radar signal from / to the antenna. The receiver receives the received radar signal via the circulator. The transmitter generates a radar signal and includes a phase-locked loop circuit for generating the radar signal based on a pre-defined phase signal. The transmitter includes a direct digital synthesizer that generates the phase signal based on a pre-defined clock signal and a control signal. The system includes a digital signal processor and a tail strike warning processor that determine position of a tail of the aircraft relative to ground and present an alert if a warning condition exists based on the determined position of the tail of the aircraft and a predefined threshold.

Owner:HONEYWELL INT INC

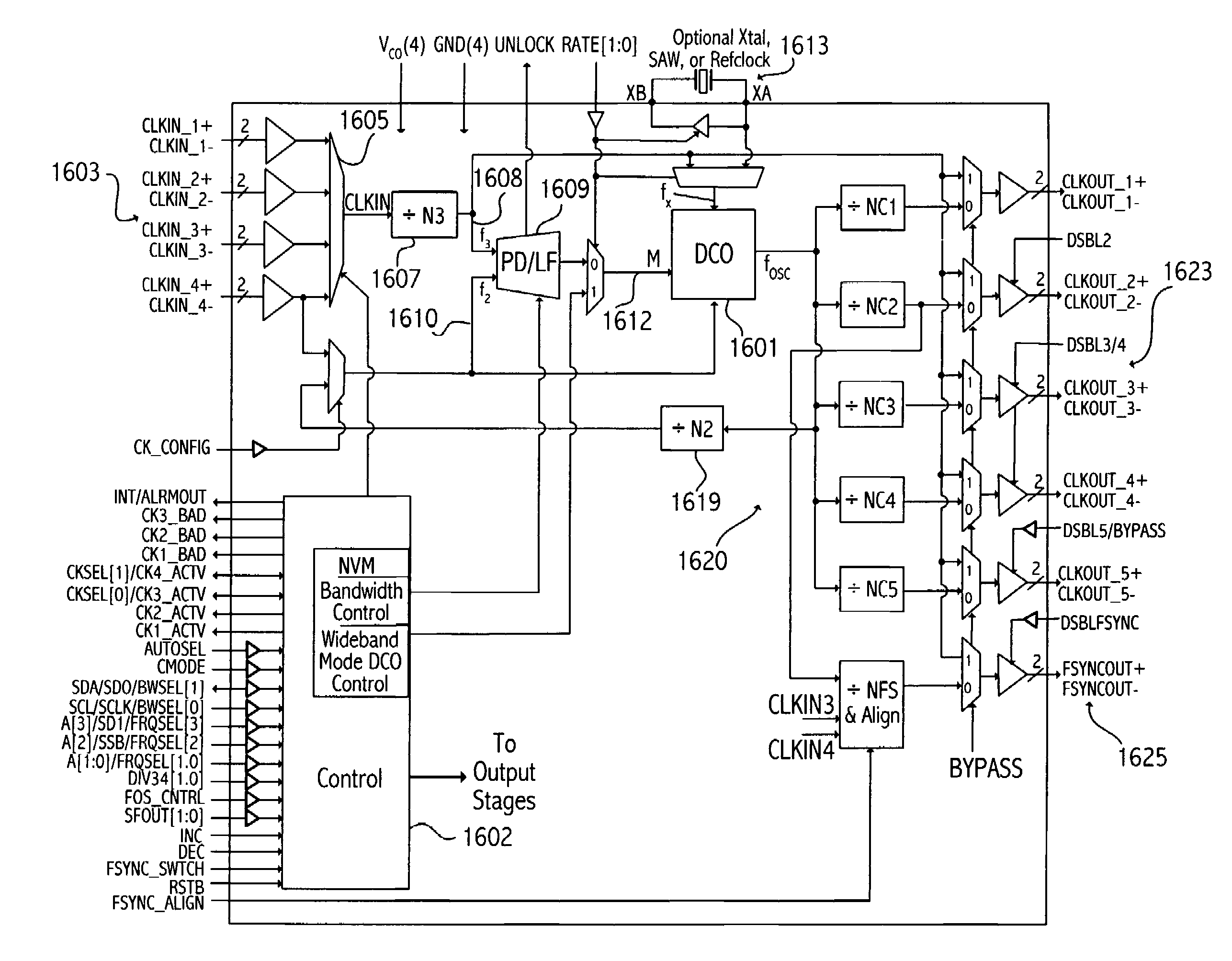

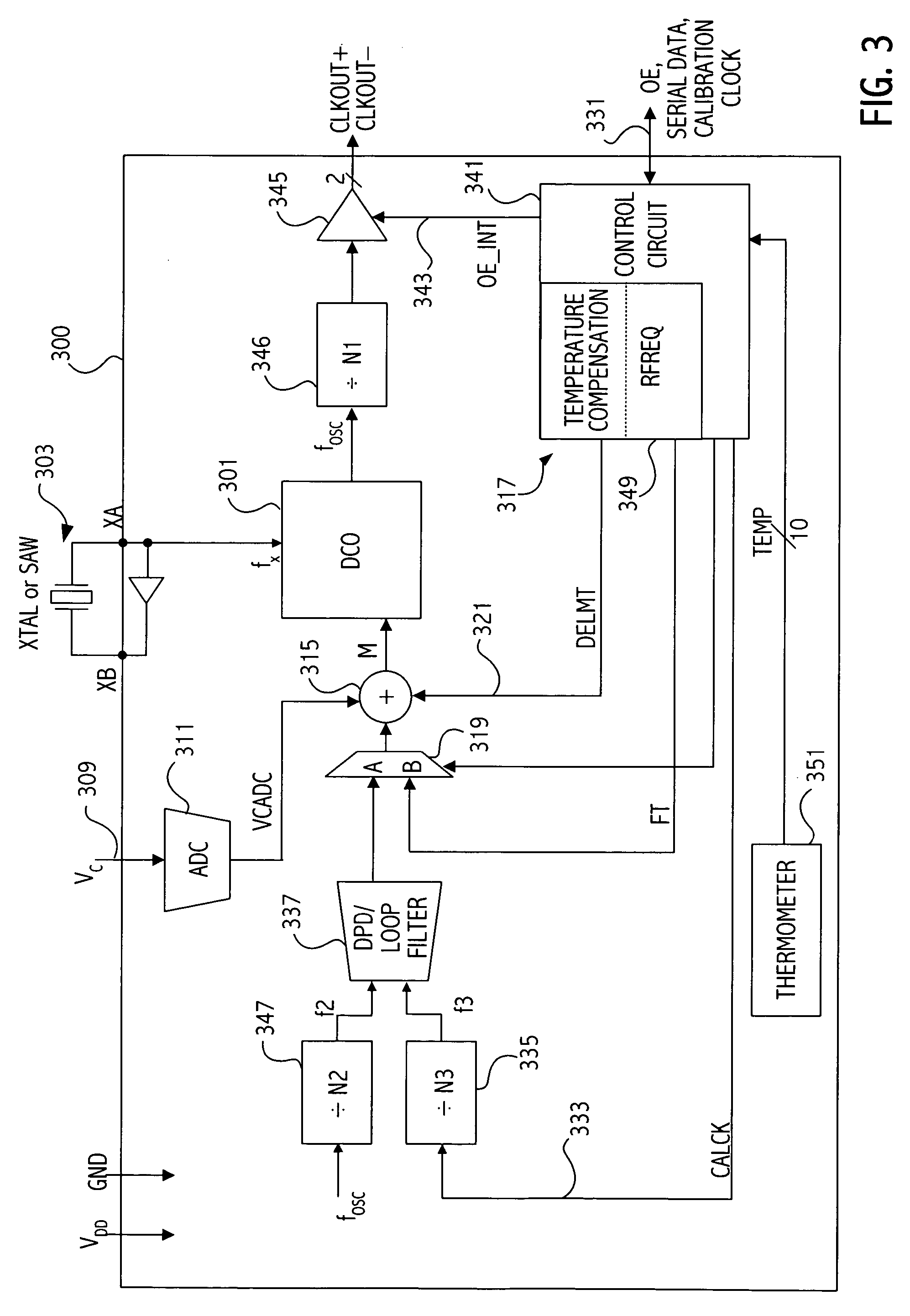

Multi-frequency clock synthesizer

ActiveUS7295077B2Pulse automatic controlOscillations generatorsPhase detectorPhase locked loop circuit

A phase-locked loop (PLL) circuit includes an input for receiving a timing reference signal, a phase detector circuit coupled to receive the timing reference signal, a controllable oscillator circuit controlled according to an output of the phase detector circuit, and a feedback divider circuit having an output coupled to the phase detector and an input coupled to the controllable oscillator circuit. The phase-locked loop circuit is coupled to output one of a plurality of output signals having an arbitrary frequency relationship to each other according to a frequency selection mechanism, the frequency selection mechanism including one or more input terminals coupled to control a divide ratio of the feedback divider circuit. The frequency selection mechanism selects one of a plurality of stored values. The selected stored value controls, at least in part, a divide ratio of the feedback divider circuit, thereby providing a pin programmable device capable of selecting among output frequencies having an arbitrary relationship to each other.

Owner:SKYWORKS SOLUTIONS INC

Phase/frequency detector and phase lock loop circuit

ActiveUS6856202B2Avoid the needHigh frequencyPulse automatic controlVoltage-current phase angleDetector circuitsControl signal

The present invention relates to cycle slip detectors for phase and frequency detectors (PFD) and to lock detectors for phase lock loop (PLL) circuits. The present invention provides a cycle slip detector circuit for use with a phase and frequency detector circuit having first and second signal inputs, and arranged to provide first and second PLL control signal outputs responsive to clock edges in the first and second input signals respectively; the cycle slip detector circuit comprising: means for determining a cycle slip between said input signals by determining when a delayed output signal coincides with a respective input signal.

Owner:CIRRUS LOGIC INC

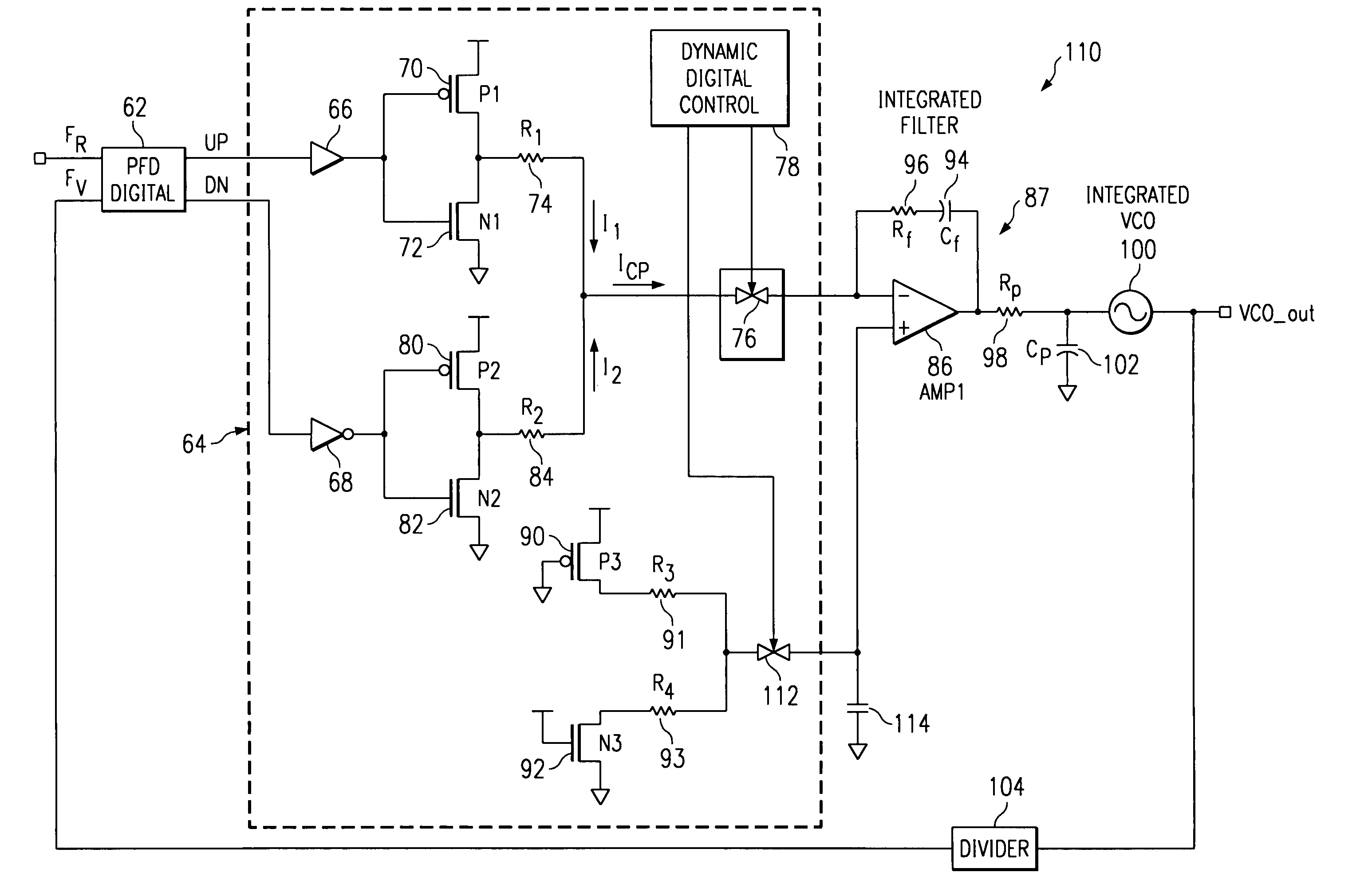

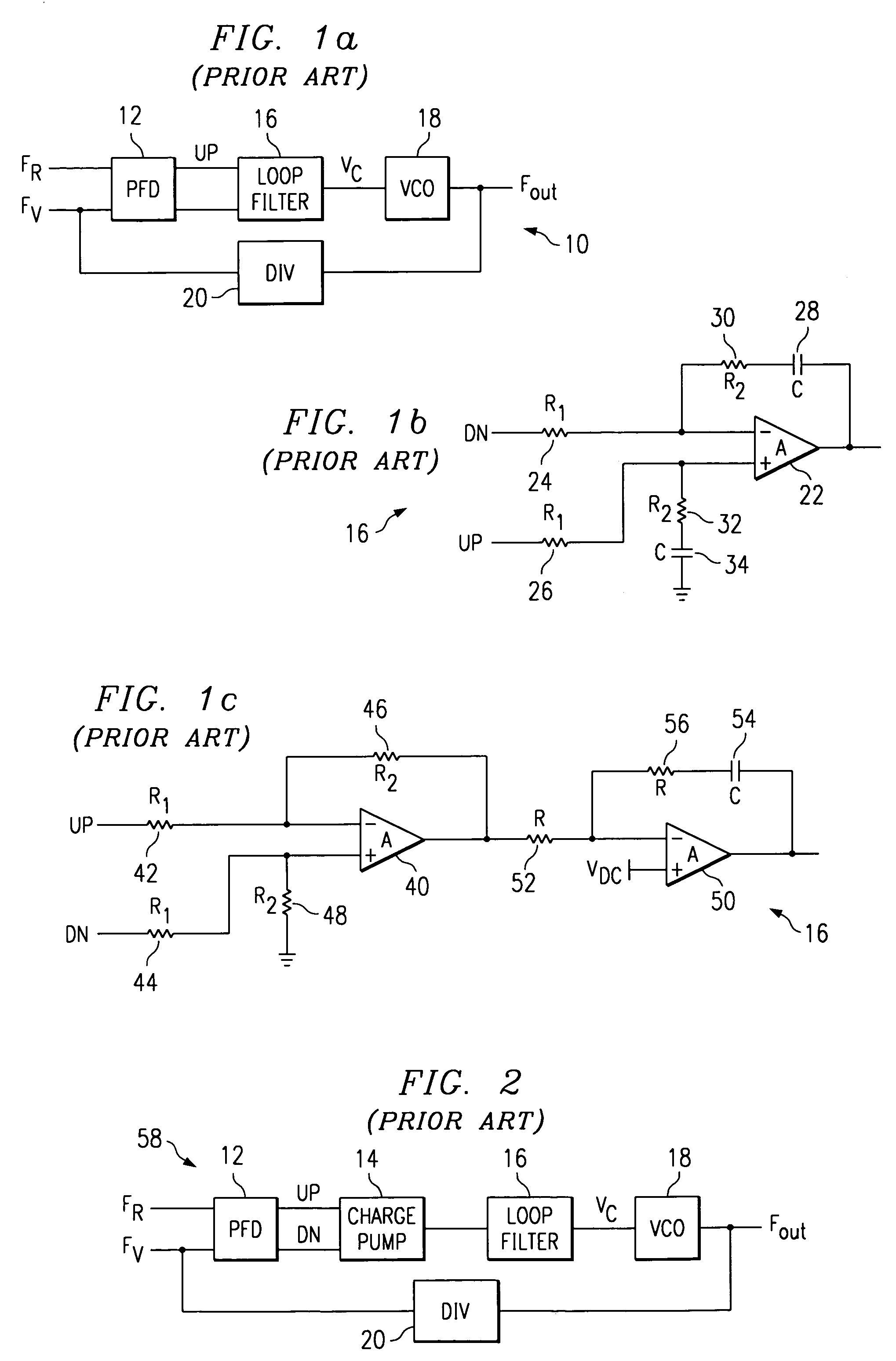

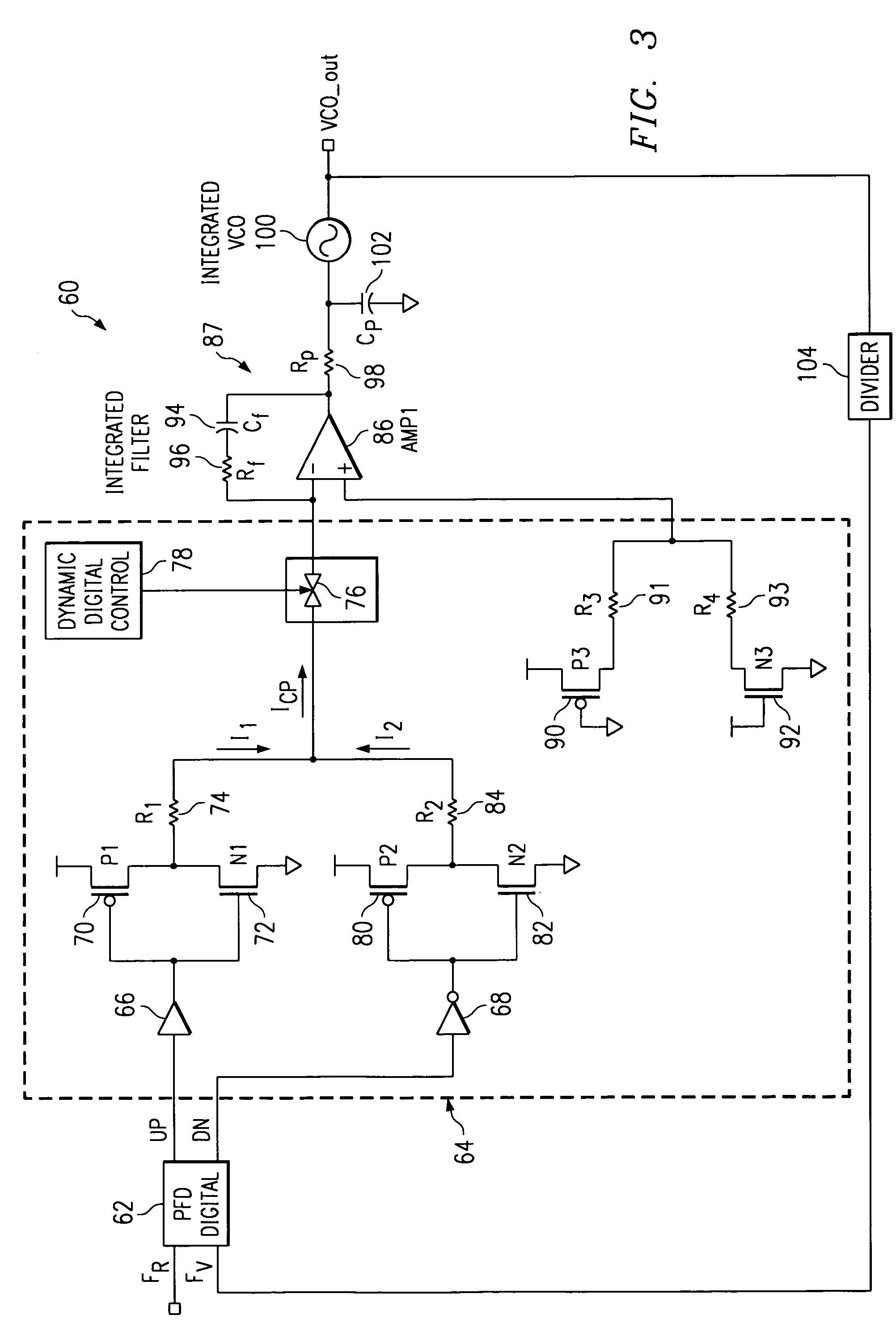

Charge pump phase locked loop with improved power supply rejection

ActiveUS6963233B2Improve power supply rejection ratioVoltage variationPulse automatic controlElectric variable regulationPhase detectorElectricity

A phase lock loop circuit (60) has a phase frequency detector (62), a charge pump (64), an active filter (87) and a voltage-controlled oscillator (100). The phase detector generates signals responsive to reference signal FR and VCO output signal FV. A charge pump generates a voltage at the input of a first transmission gate (76) according to the values of the phase detector signals. A predetermined voltage is generated at the input of a second transmission gate (112). When the transmission gates (76, 110) are closed (low impedance) the charge pump may sink or source current to the inverting input of the operational amplifier (86) of the active filter 86 and the predetermined voltage is applied to the non-inverting input. When the transmission gates are open (high impedance state) the inverting input is electrically isolated from the node and the non-inverting output is isolated from the power supply.

Owner:TEXAS INSTR INC

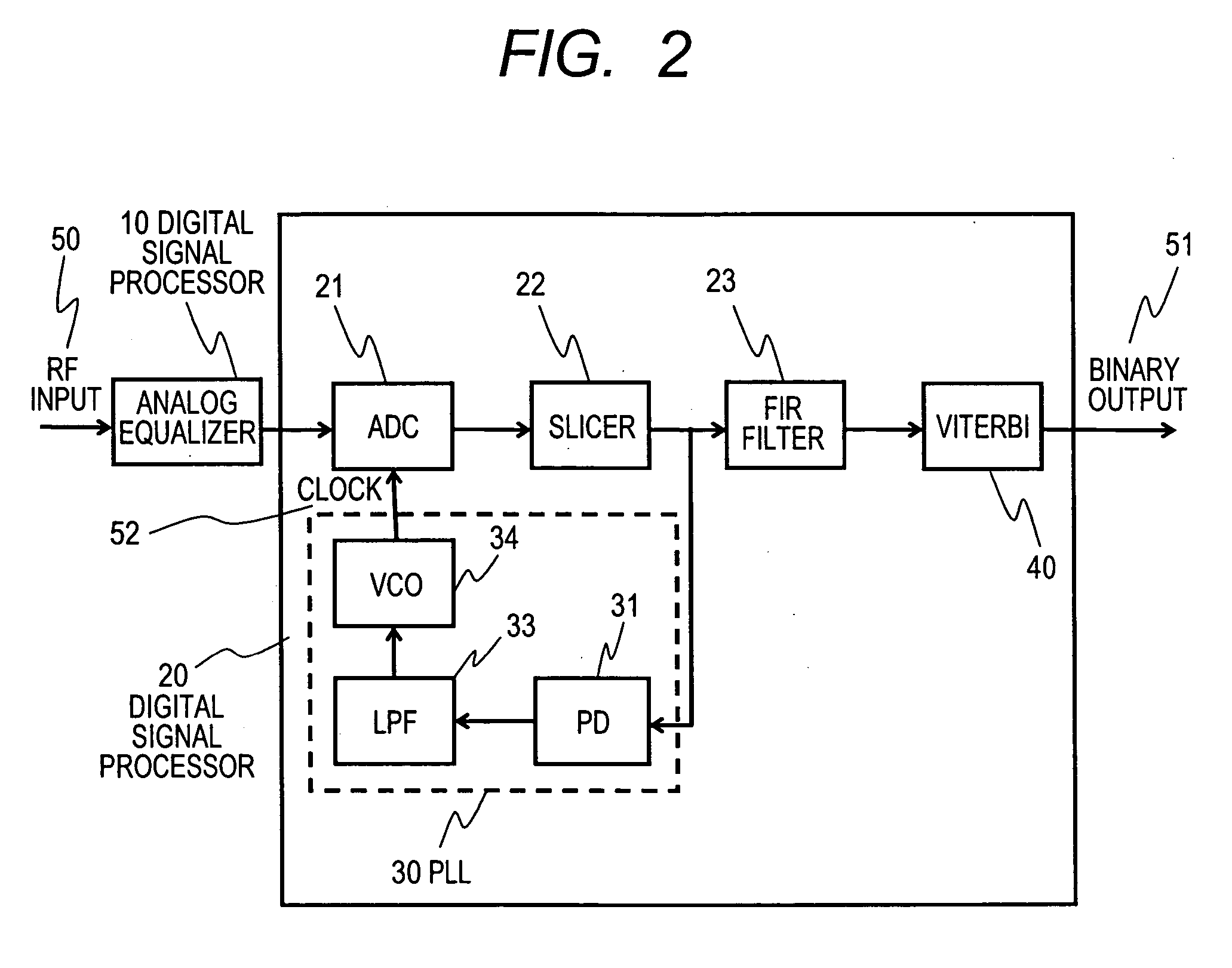

Information read device and read signal processing circuit

ActiveUS20060280240A1High error rateSatisfied with the effectMultiple-port networksFilamentary/web record carriersSignal processing circuitsSignal-to-noise ratio (imaging)

An optical disk read signal processing system for Blu-ray disc systems to ensure stable phase-locked locked operation even with a low signal-to-noise ratio. This system changes a loop configuration of a phase lock loop circuit according to the operating state, and utilizes a FIR equalizer for phase detection. This system attains a low error rate even when the signal-to-noise ratio of an input signal is low, and avoids pulse edges with low phase detection accuracy or signal pulse streams with a high possibility of being mistakenly detected as an edge in conventional methods, and also supports diverse types of input signals.

Owner:HITACHI CONSUMER ELECTRONICS CORP

Jitter self test

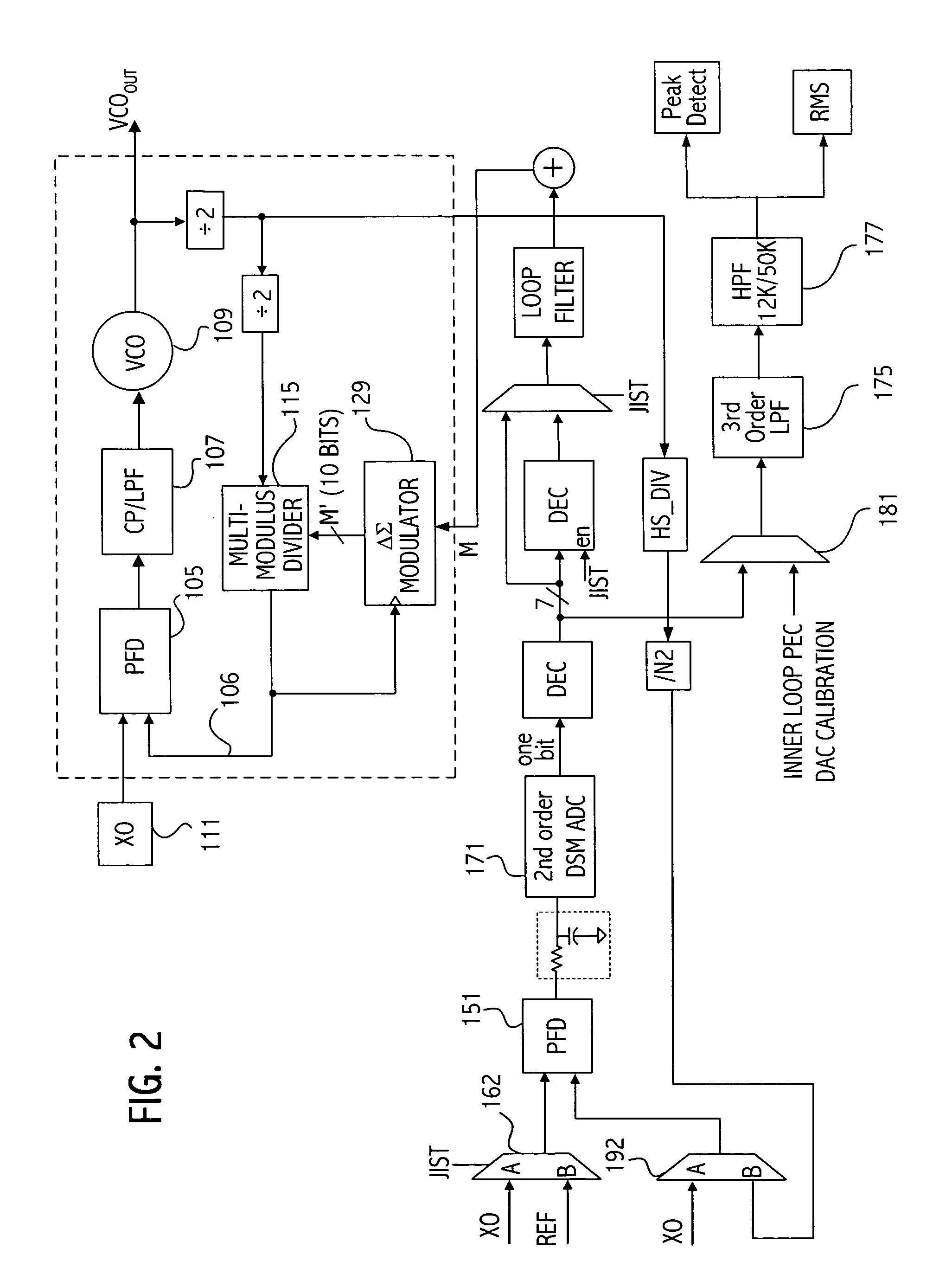

Jitter is measured by receiving a first reference signal at a first phase-locked loop (PLL) circuit and generating at an output of the first phase-locked loop circuit an output signal based at least in part on the first reference signal, the output signal including a jitter component to be measured. A signal corresponding to the output signal and a signal corresponding to the first reference signal are compared in a phase detector of a second phase-locked loop circuit. A value corresponding to an output of the comparison is stored that includes information indicative of the measured jitter component.

Owner:SILICON LAB INC

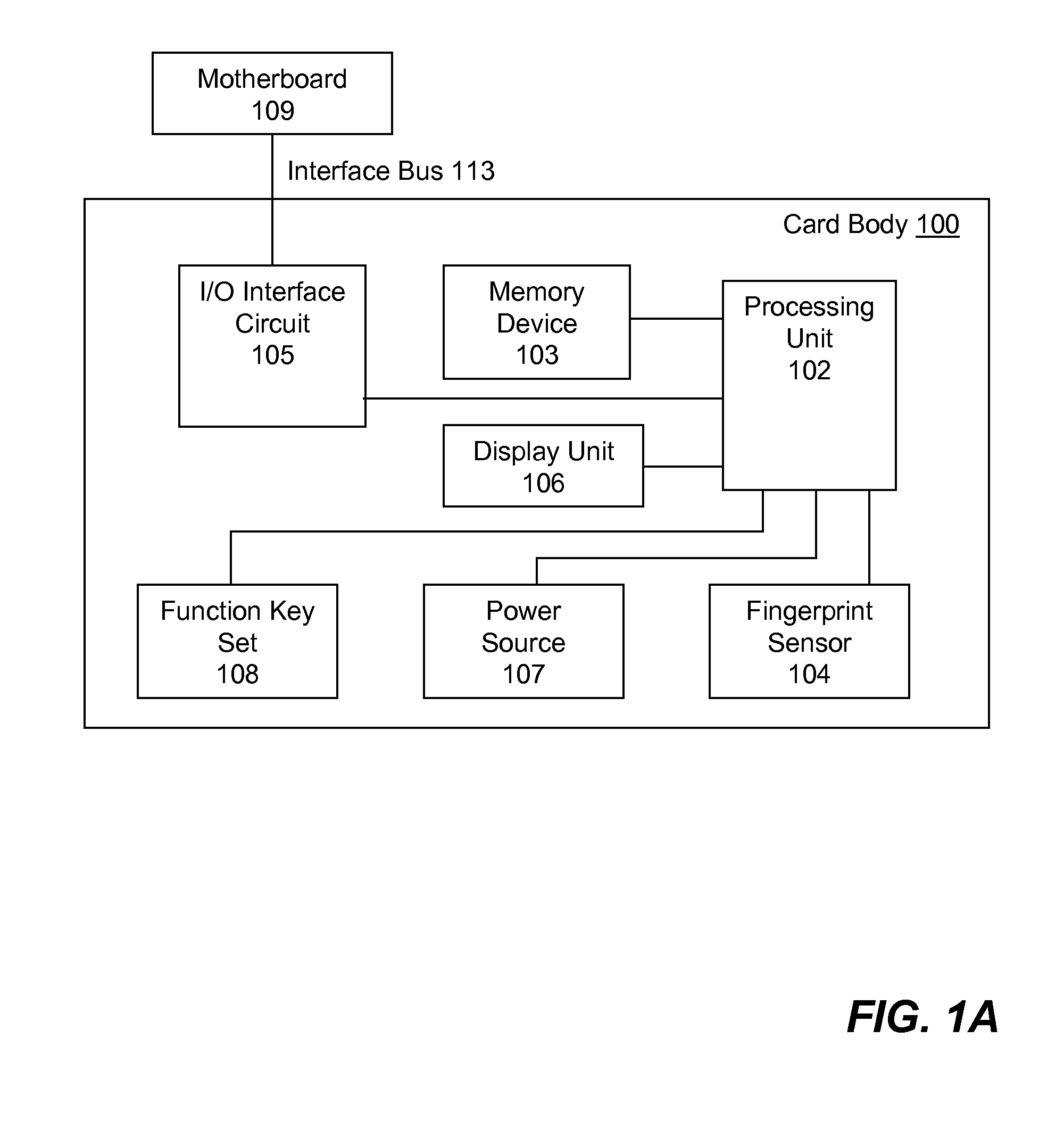

Low power digital phase lock loop circuit

ActiveUS20110273210A1Increase power usageSufficient powerPulse automatic controlAngle demodulation by phase difference detectionPhase locked loop circuitClock rate

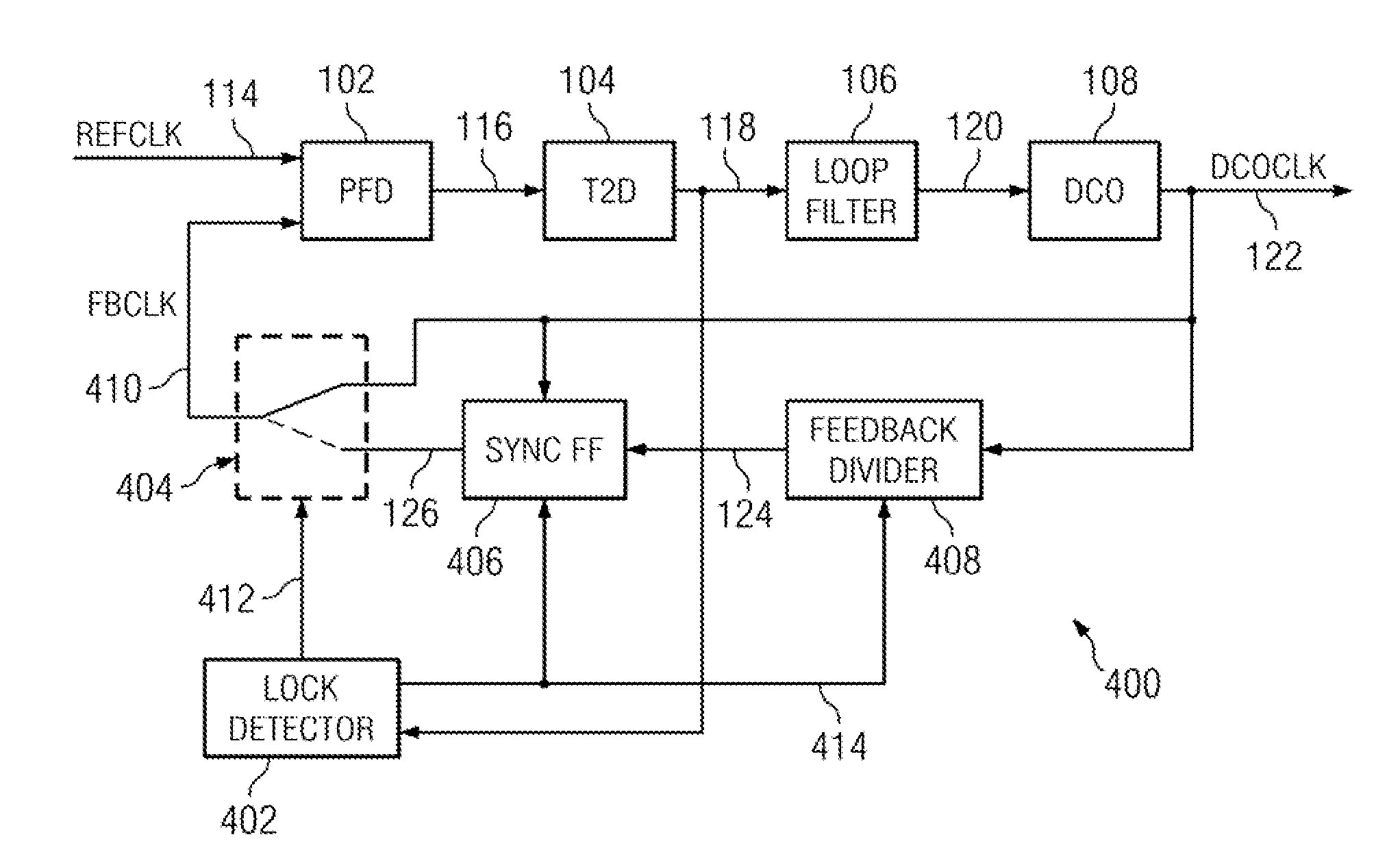

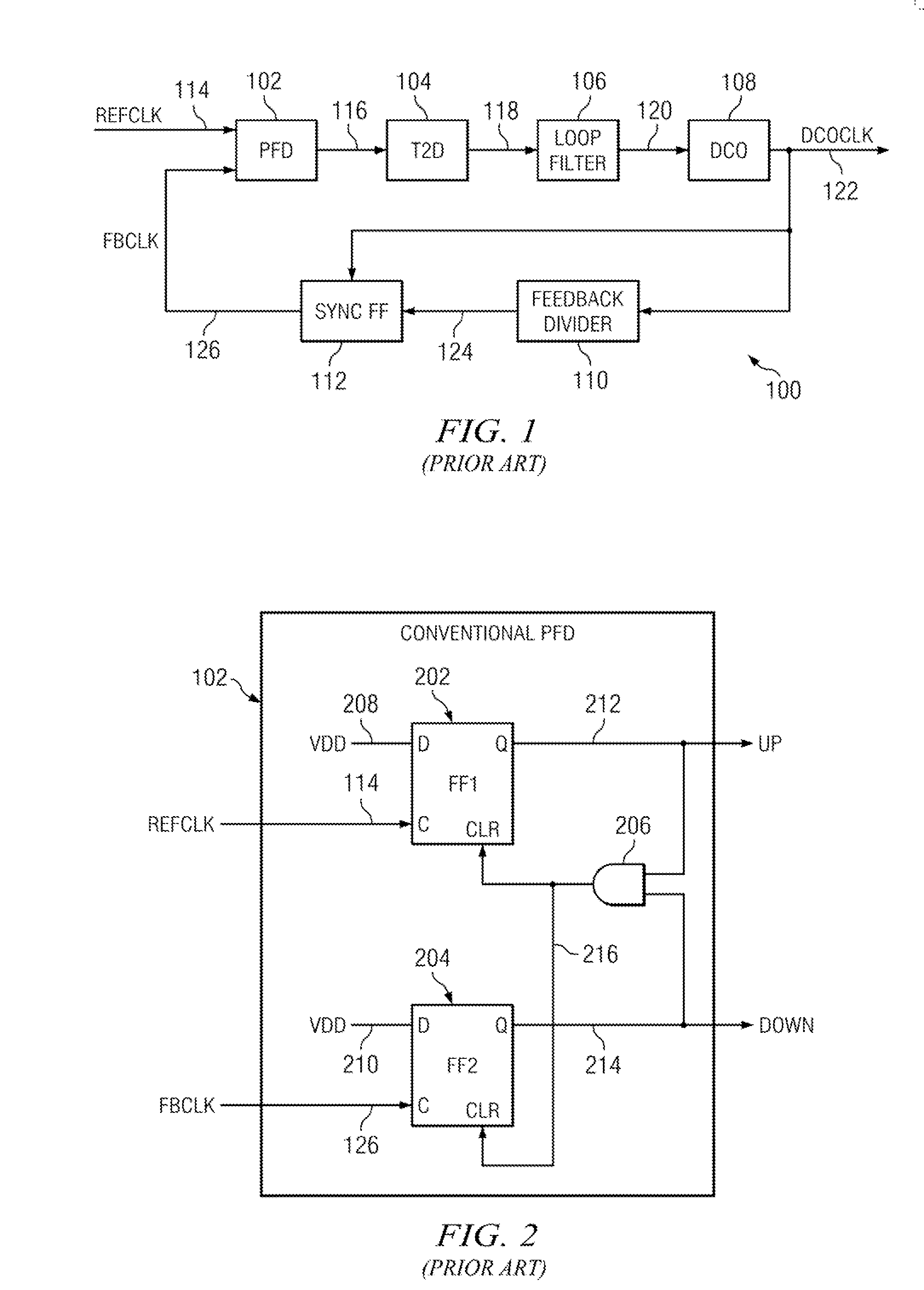

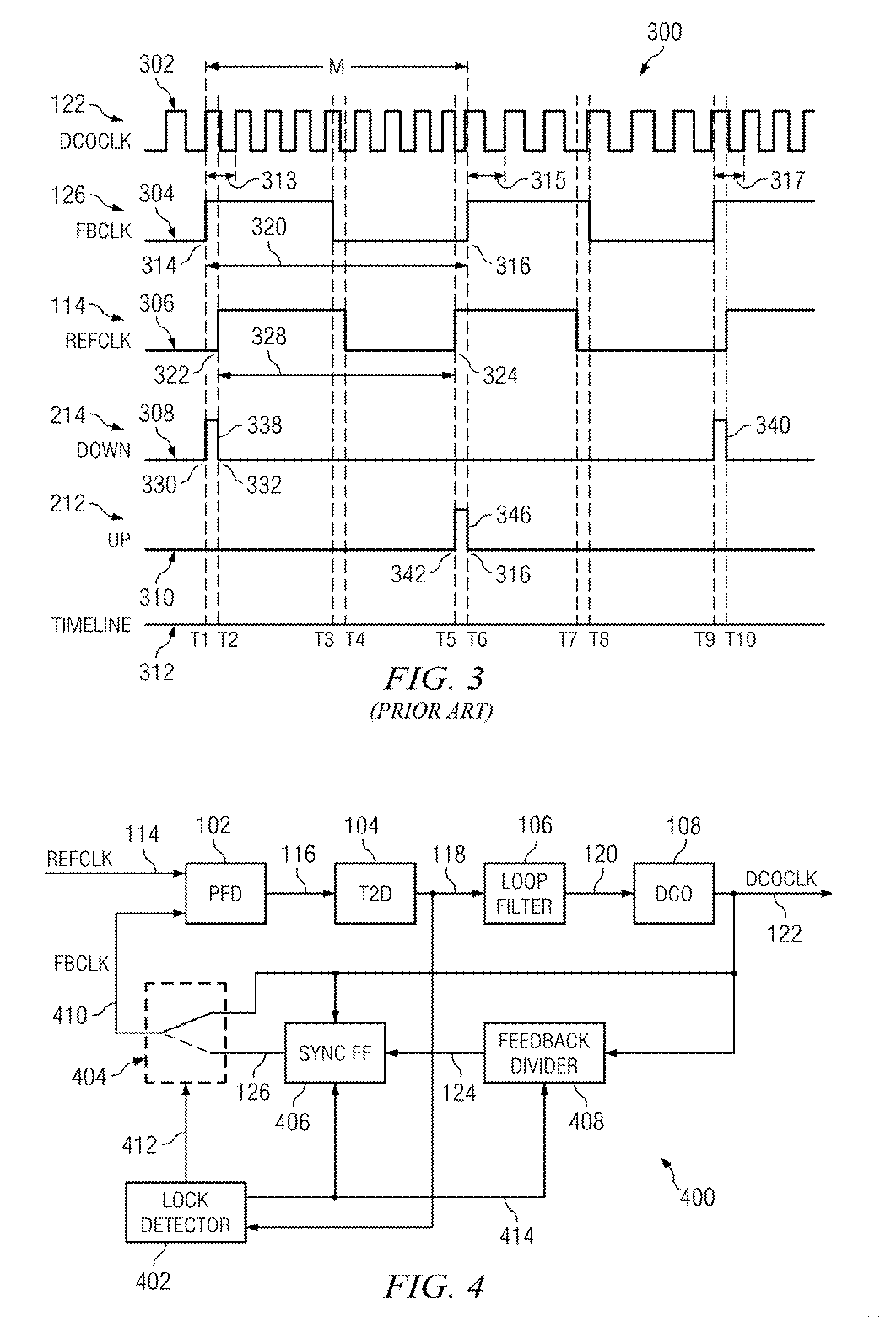

A digital phase lock loop circuit, where under certain conditions the phase error is derived from phase comparison between a reference clock edge and the next oscillator clock edge rather than a feedback clock edge. This technique can be used to significantly reduce digital phase lock loop circuit power by disabling feedback divider and sync FF once initial frequency lock is established, provided phase jitter of digital phase lock loop circuit is low enough so that there is no cycle slip. This technique can also be used to multiply the effective reference clock frequency of digital phase lock loop circuits to increases the loop bandwidth, thus reducing the phase noise. Both the applications of this technique can be combined in some circuits.

Owner:TEXAS INSTR INC

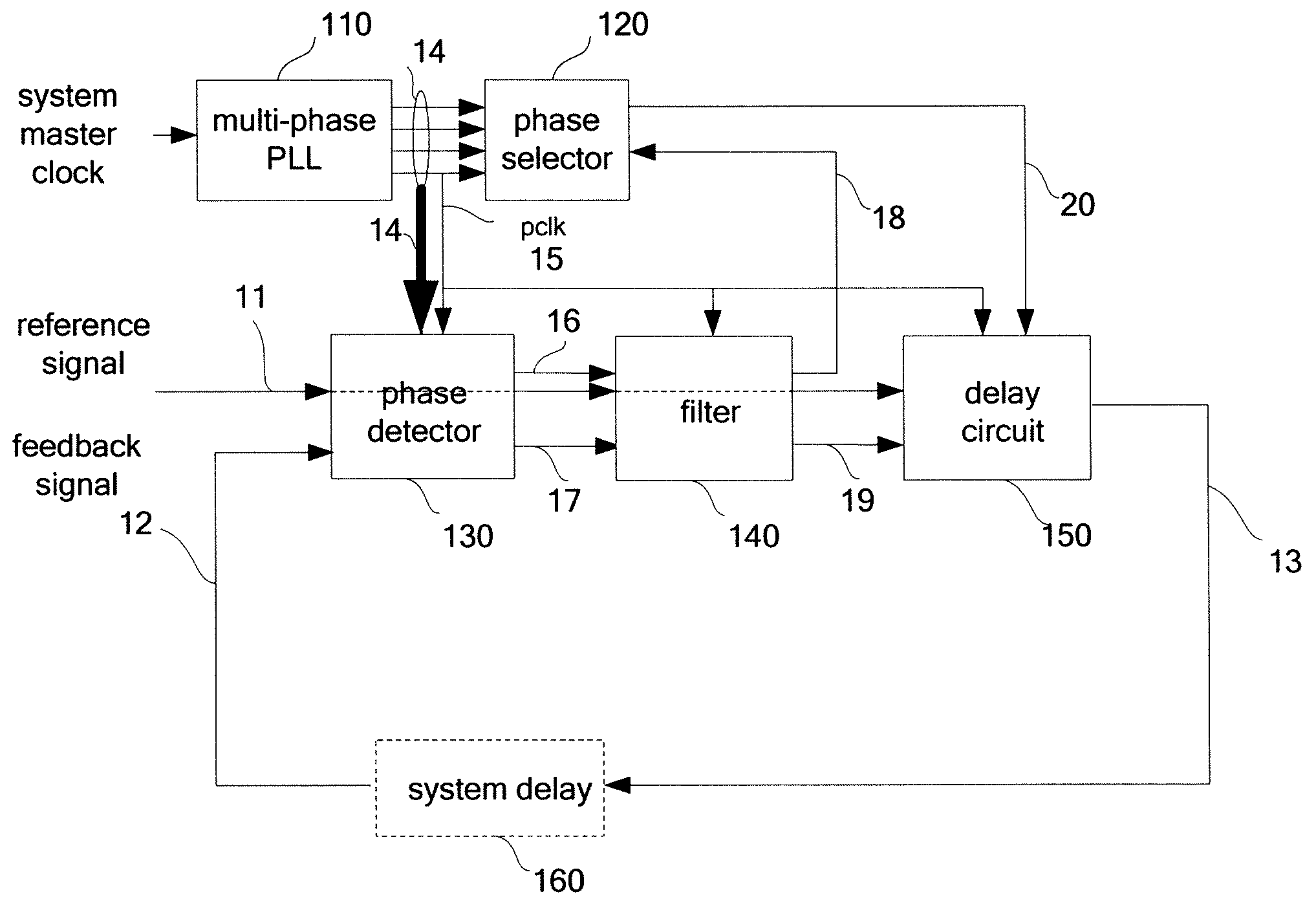

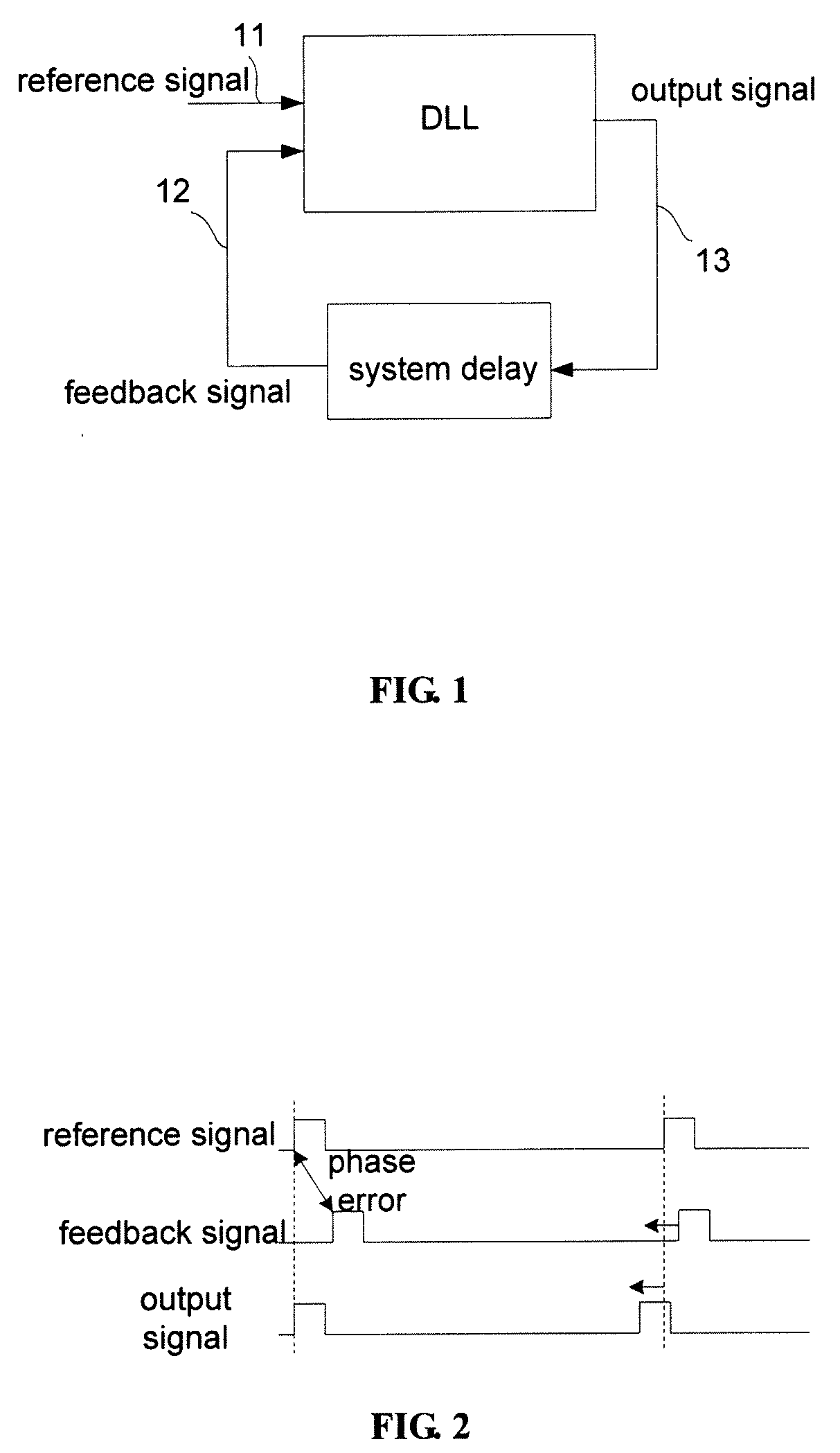

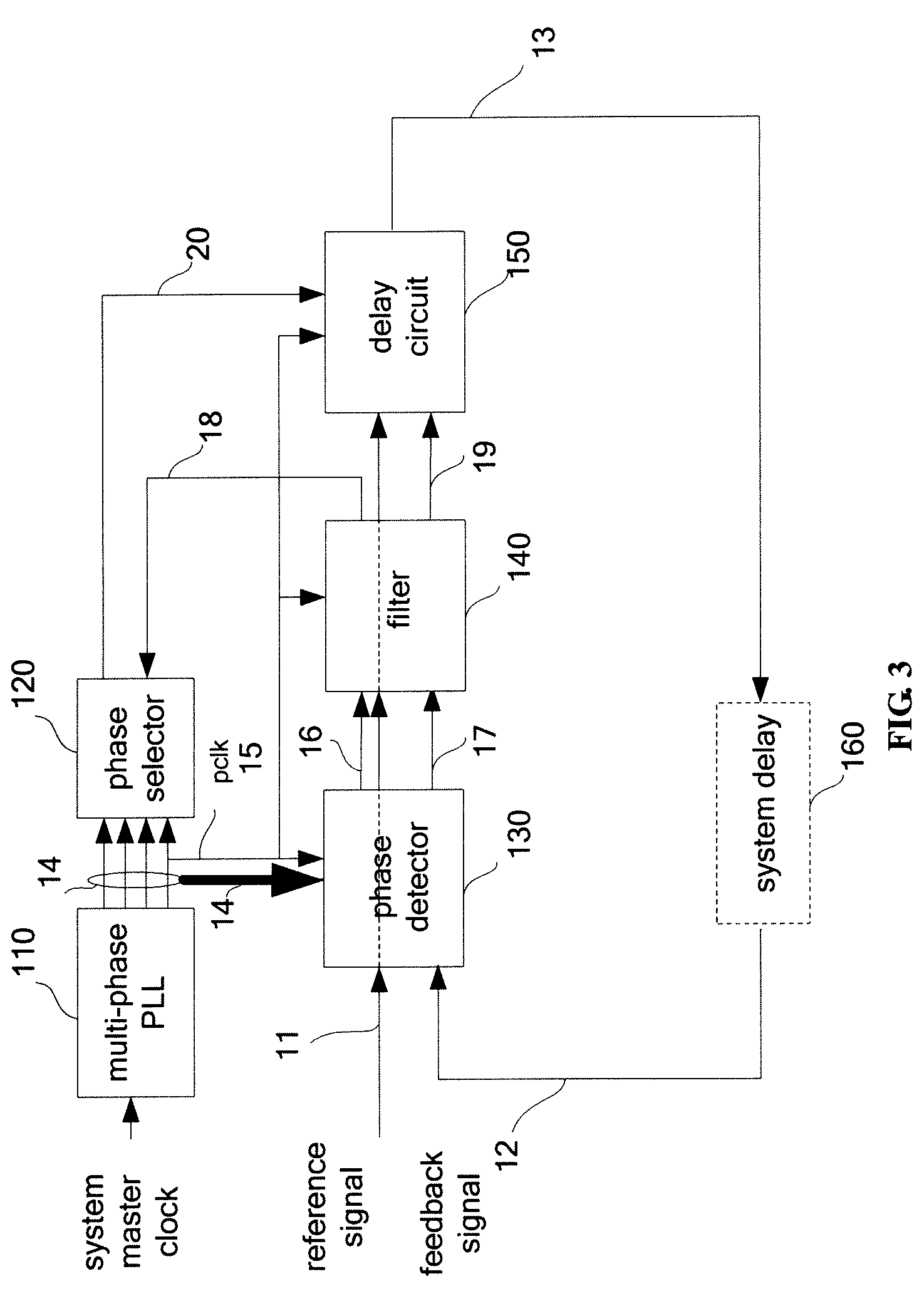

Semi-Digital Delay Locked Loop Circuit and Method

ActiveUS20090243679A1High resolutionSmall DLL jitterTelevision system detailsPulse automatic controlPhase detectorPhase locked loop circuit

A scalable DLL (delay locked loop) circuit that has a calibration mechanism to auto tune locking precision. The delay locked loop circuit includes a multi-phase phase locked loop circuit for generating a plurality of phase signals according to a system clock, wherein one of the phase signals is a pixel clock; a phase detector for detecting an integral phase error and a fractional phase error between a reference signal and a feedback signal according to the pixel clock; a phase selector for selecting one of the phase signals according to the fractional phase error; and a delay circuit for shifting the phase of the reference signal according to the integral phase error and the selected phase signal to generate an output signal.

Owner:XUESHAN TECH INC

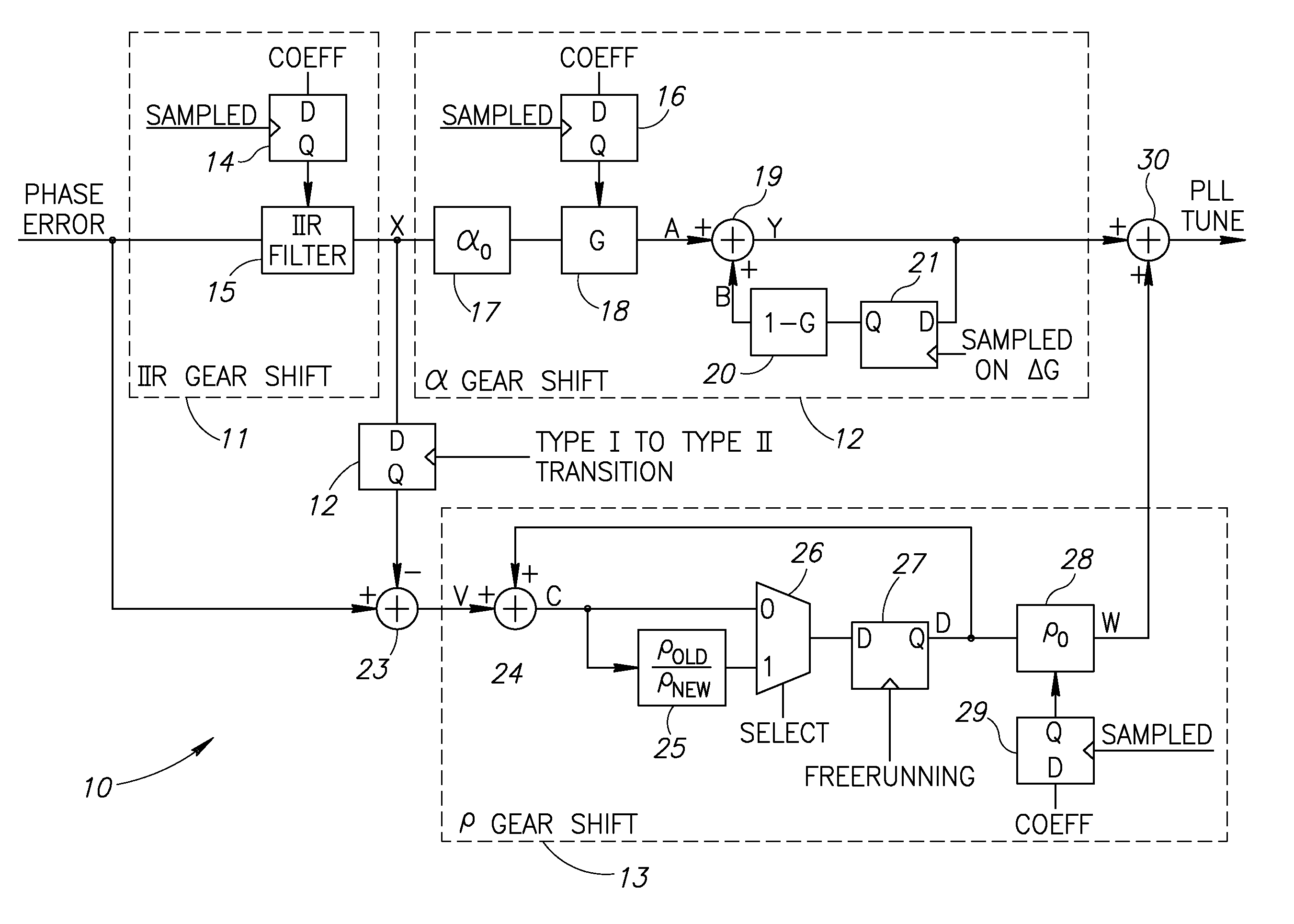

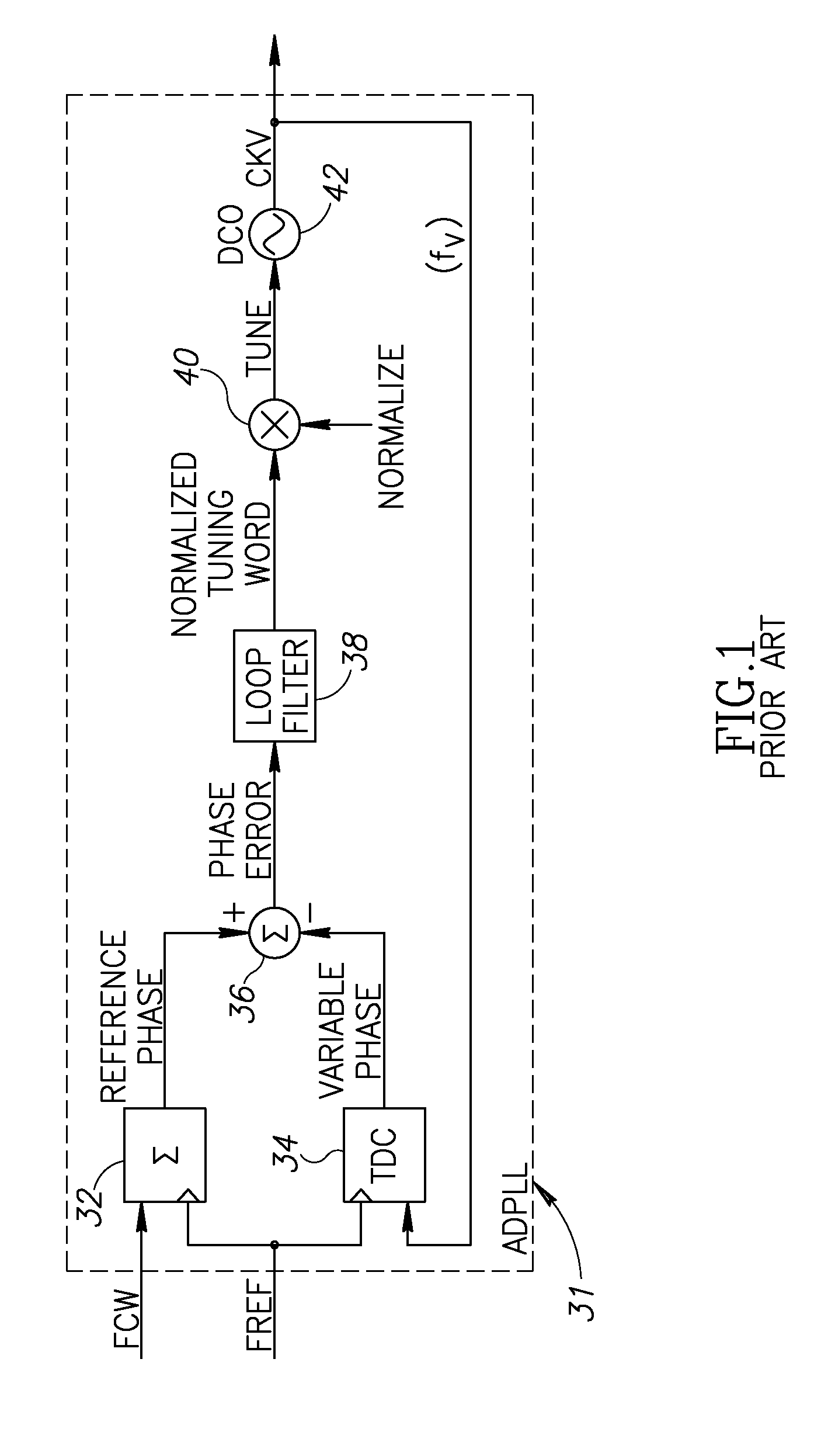

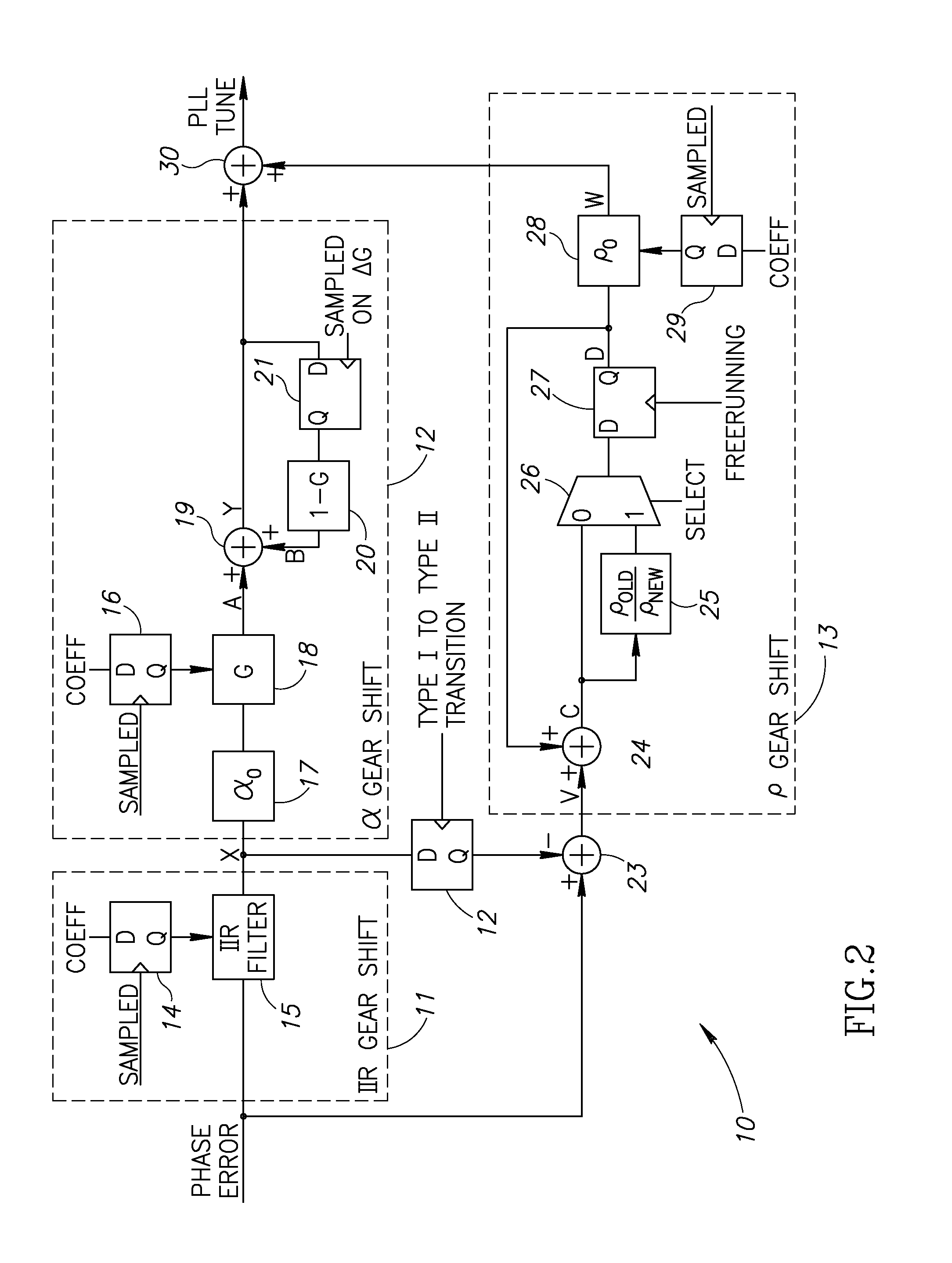

Continuous reversible gear shifting mechanism

ActiveUS20070085622A1High bandwidthLoop gain can be increasedPulse automatic controlOscillations generatorsPhase locked loop circuitLoop bandwidth

A novel gear shifting mechanism operative to adjust the loop gain of a phase locked loop (PLL) circuit in a continuous and reversible manner. The loop gain can be increased to widen the bandwidth of the loop and can also be decreased to narrow the loop bandwidth. The mechanism incorporates an α gear shift circuit, a p gear shift circuit and an optional IIR gear shift circuit. The α gear shift circuit comprises a infinite impulse response (IIR) filtering which enables hitless operation of the PLL loop at the occurrence of gear shift events. The α gear shift circuit comprises an accumulator whose output is multiplied by the gain value ρ. The invention enables multiple gear shifts in either positive or negative direction to be achieved by configuring the loop gain variables α and ρ which may be accomplished in software.

Owner:TEXAS INSTR INC

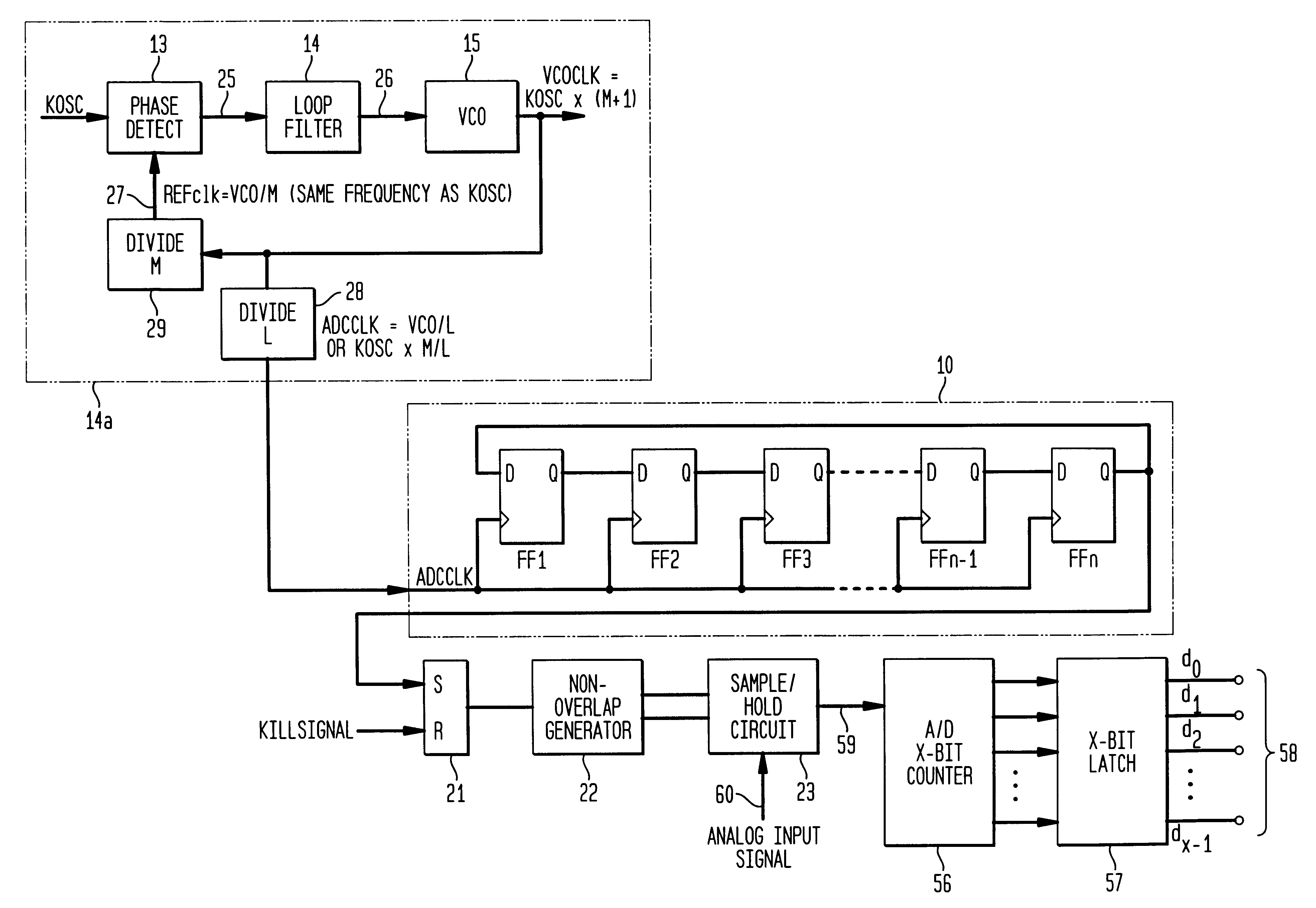

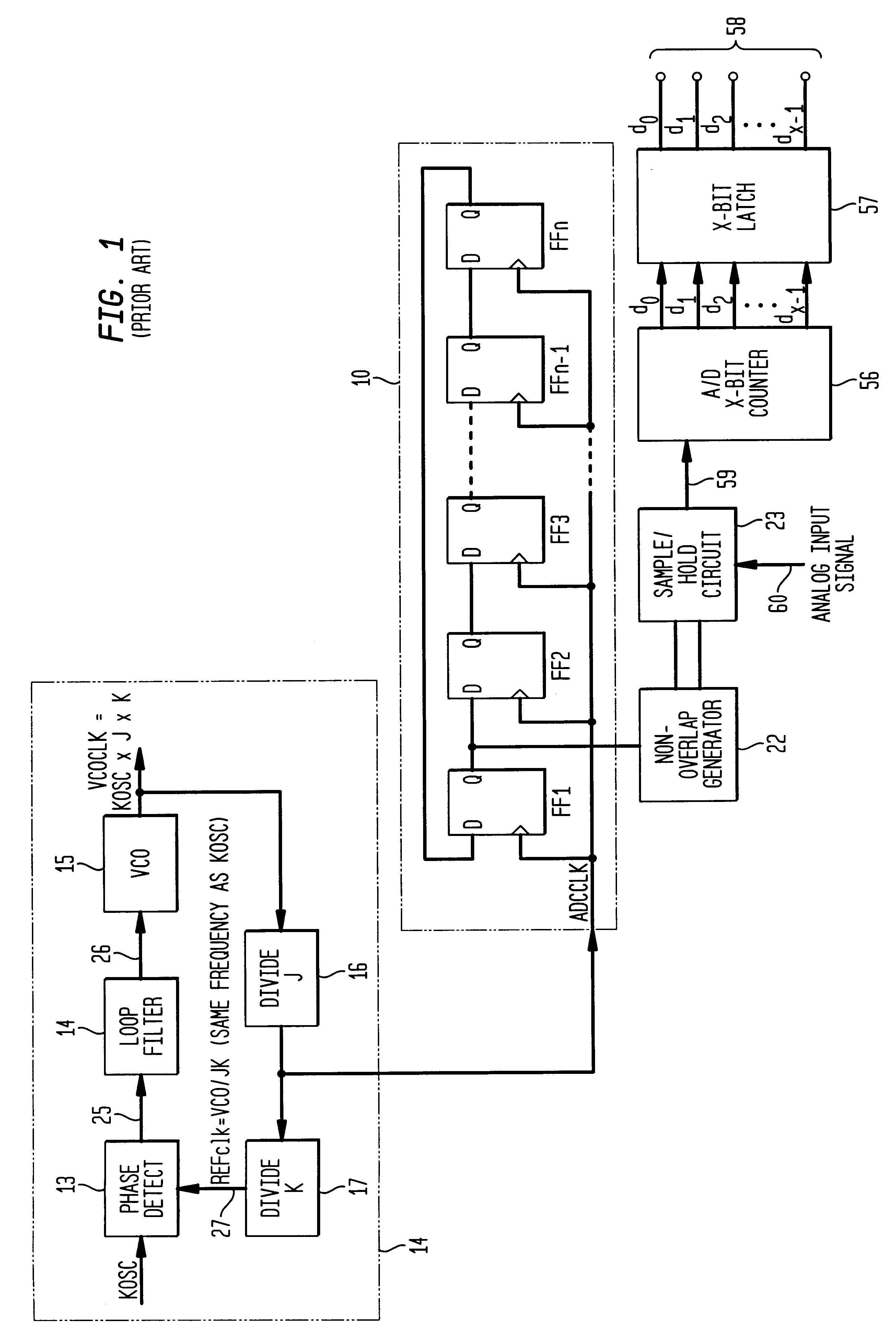

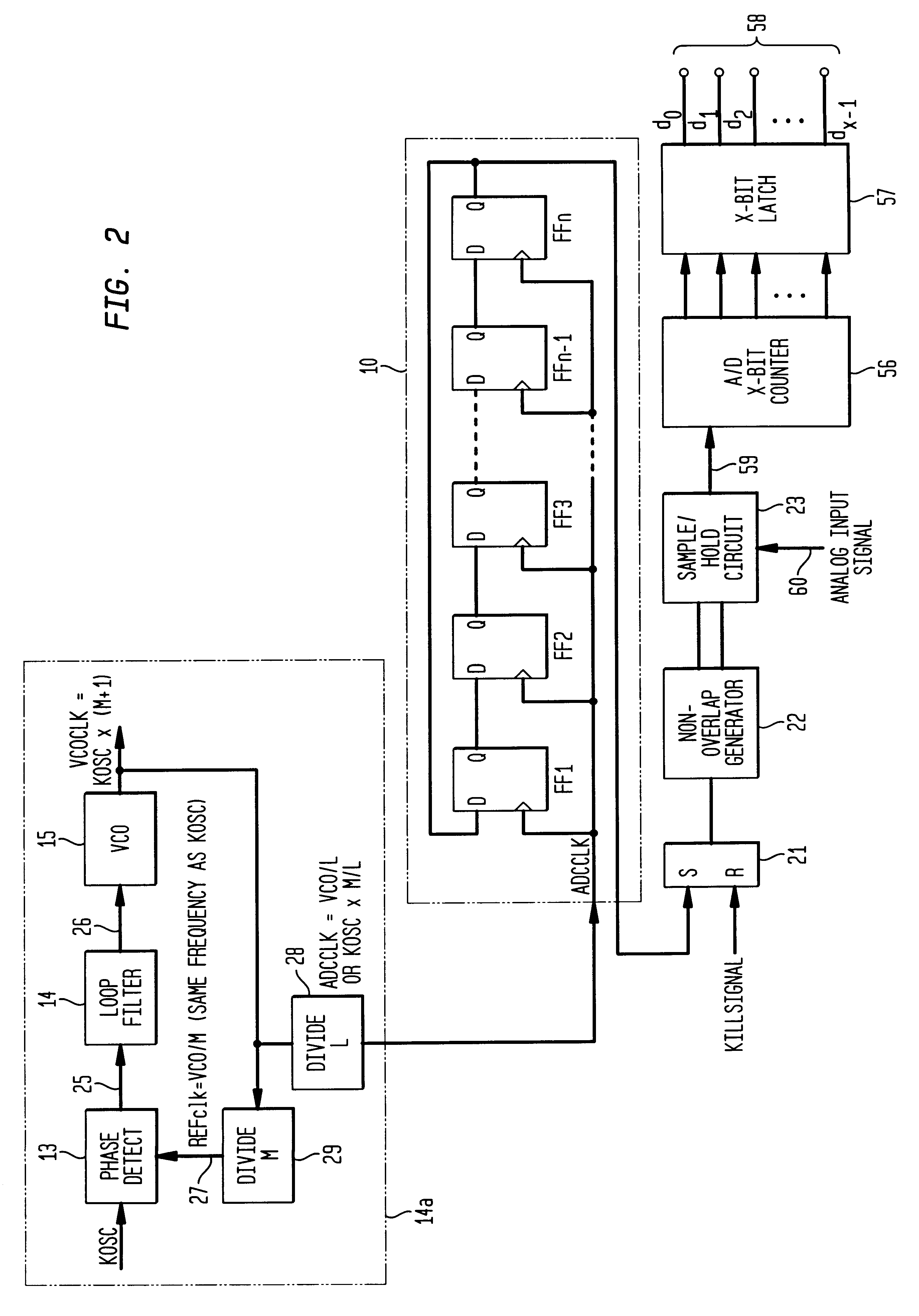

Clocking technique for reducing sampling noise in an analog-to-digital converter

InactiveUS6232905B1Low costHigh resolutionElectric signal transmission systemsAnalogue-digital convertersLeading edgeDigital down converter

A method and apparatus are disclosed for improving the operation of an analog-to-digital converter ("ADC"). A separate "clean" oscillator clock is to be used in combination with a "noisy" ADC clock being regulated by a phase-locked-loop (PLL) circuit. The "noisy" ADC clock drives the digital control logic and also turns on the sample signal for the purpose of sampling. The second clock, which has a substantially fixed (i.e., "clean") frequency is used to generate a short pulse, the leading edge of which turns off the sample signal, thereby providing an improved sampling process with greater resolution. The interaction of the two clocks is controlled with digital logic circuitry.

Owner:LUCENT TECH INC

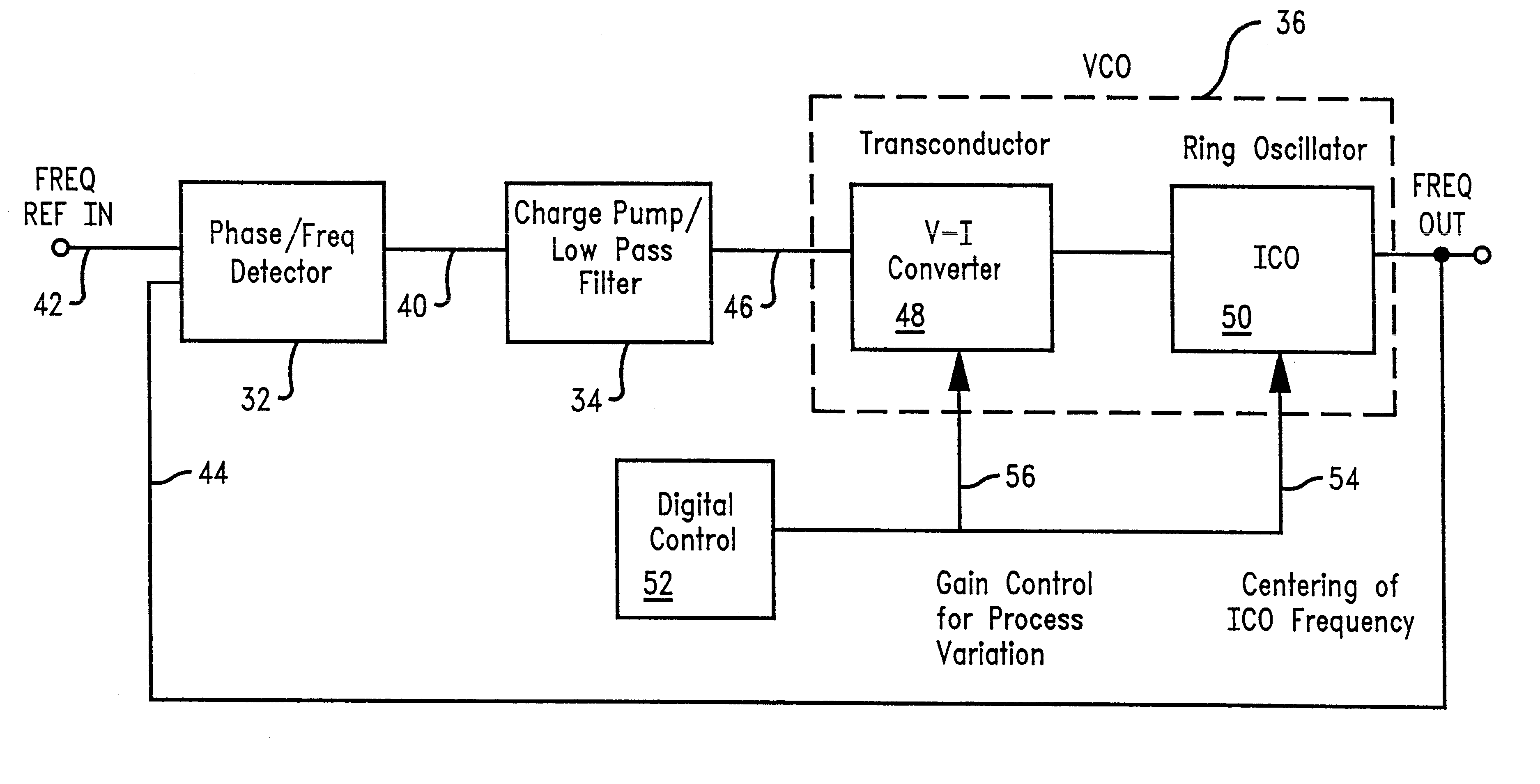

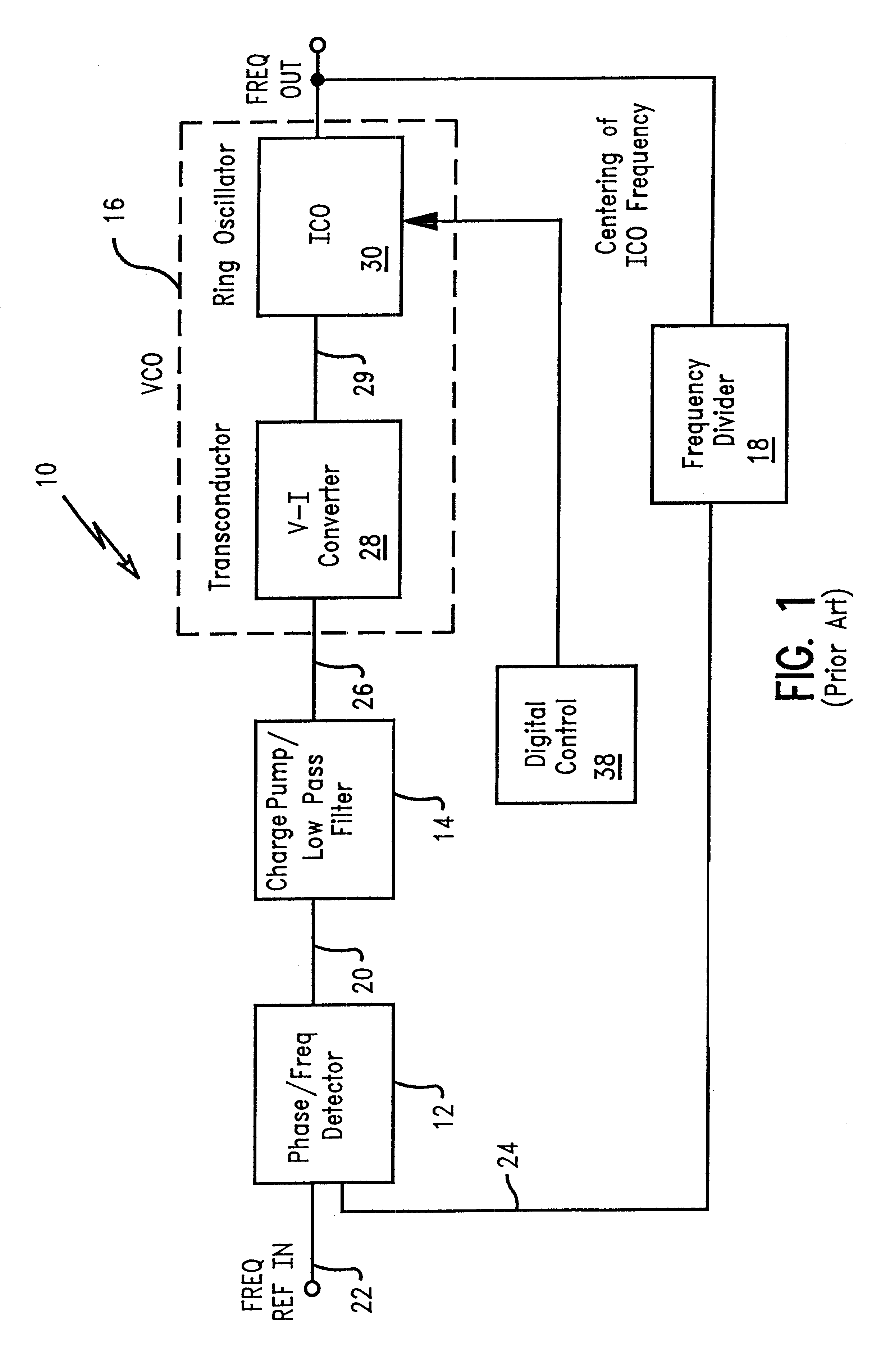

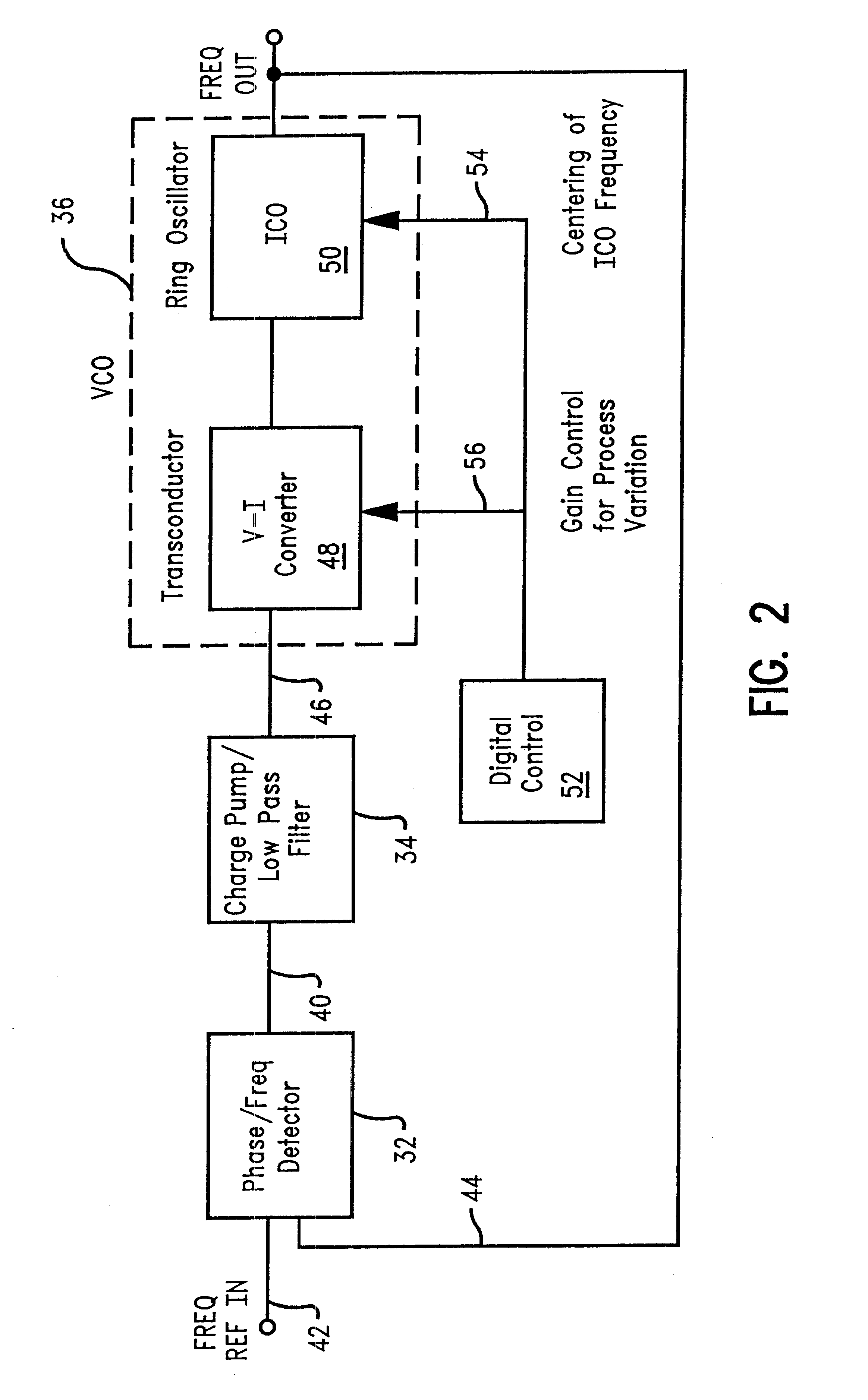

Linear voltage controlled oscillator transconductor with gain compensation

InactiveUS6466100B2More of the gainLess of the gainPulse automatic controlPulse generation by logic circuitsPhase locked loop circuitLow-pass filter

A voltage controlled oscillator of a phase locked loop circuit having digitally controlled gain compensation. The digital control circuitry provides binary logic input to the voltage controlled oscillator for a digitally controlled variable resistance circuit, a digitally controlled variable current transconductor circuit, or differential transistor pairs having mirrored circuitry for adjusting the V-I gain. The latter configuration requires the voltage controlled oscillator to incorporate a source-coupled differential pair which is driven by a low pass filter capacitor output voltage, and connected to load transistors; a current source and a current mirror for generating a tail current; individual banks of transistors to mirror the load transistor currents; a digital-to-analog converter with control lines outputted there from, the digital-to-analog converter used to increase the amount of current allowed to flow to the transconductor output, the current being digitally increased and decreased corresponding to an amount of current pulled from the current source, and mirroring the current through at least one transistor mirror circuit.

Owner:MARVELL ASIA PTE LTD

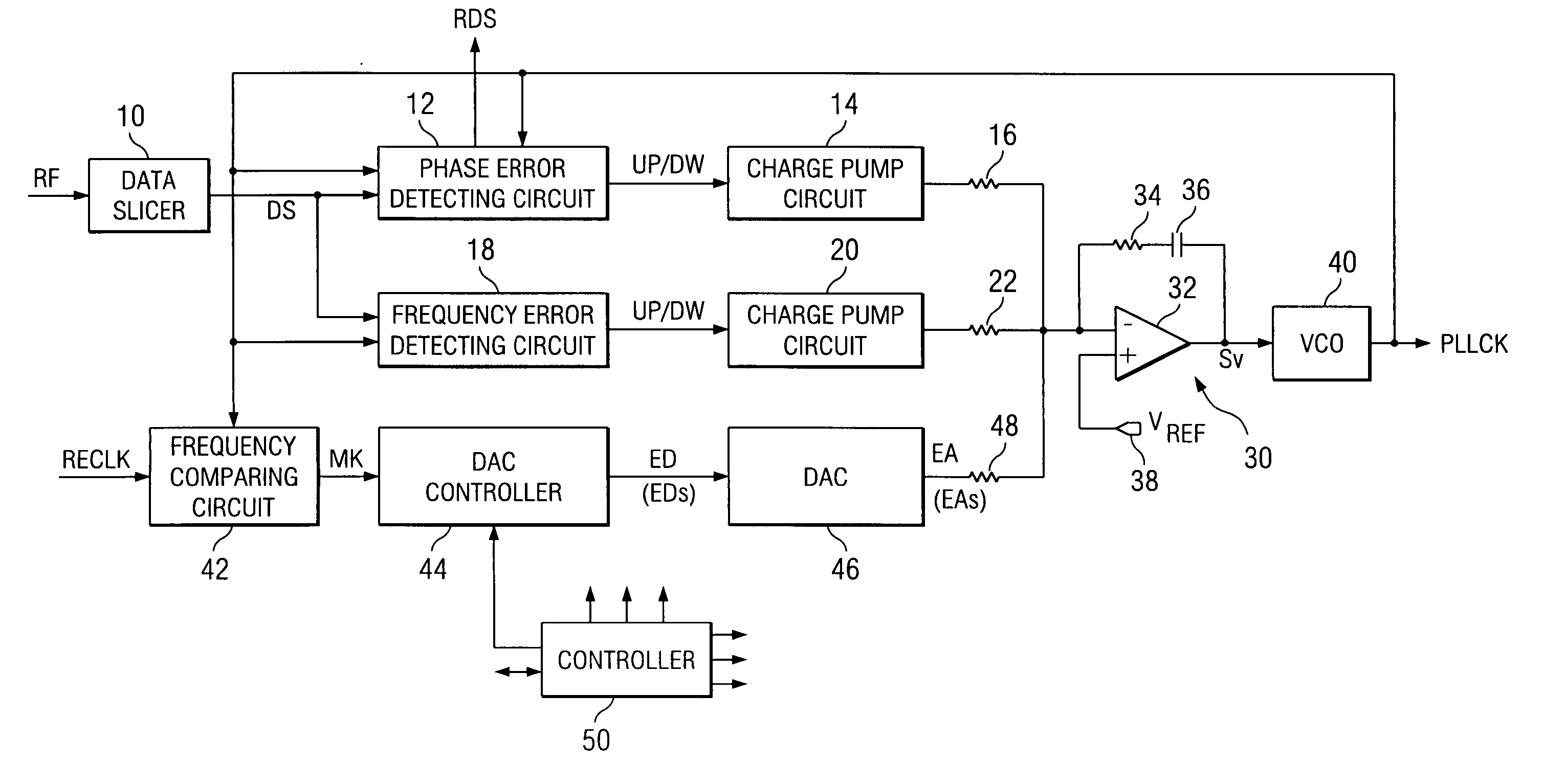

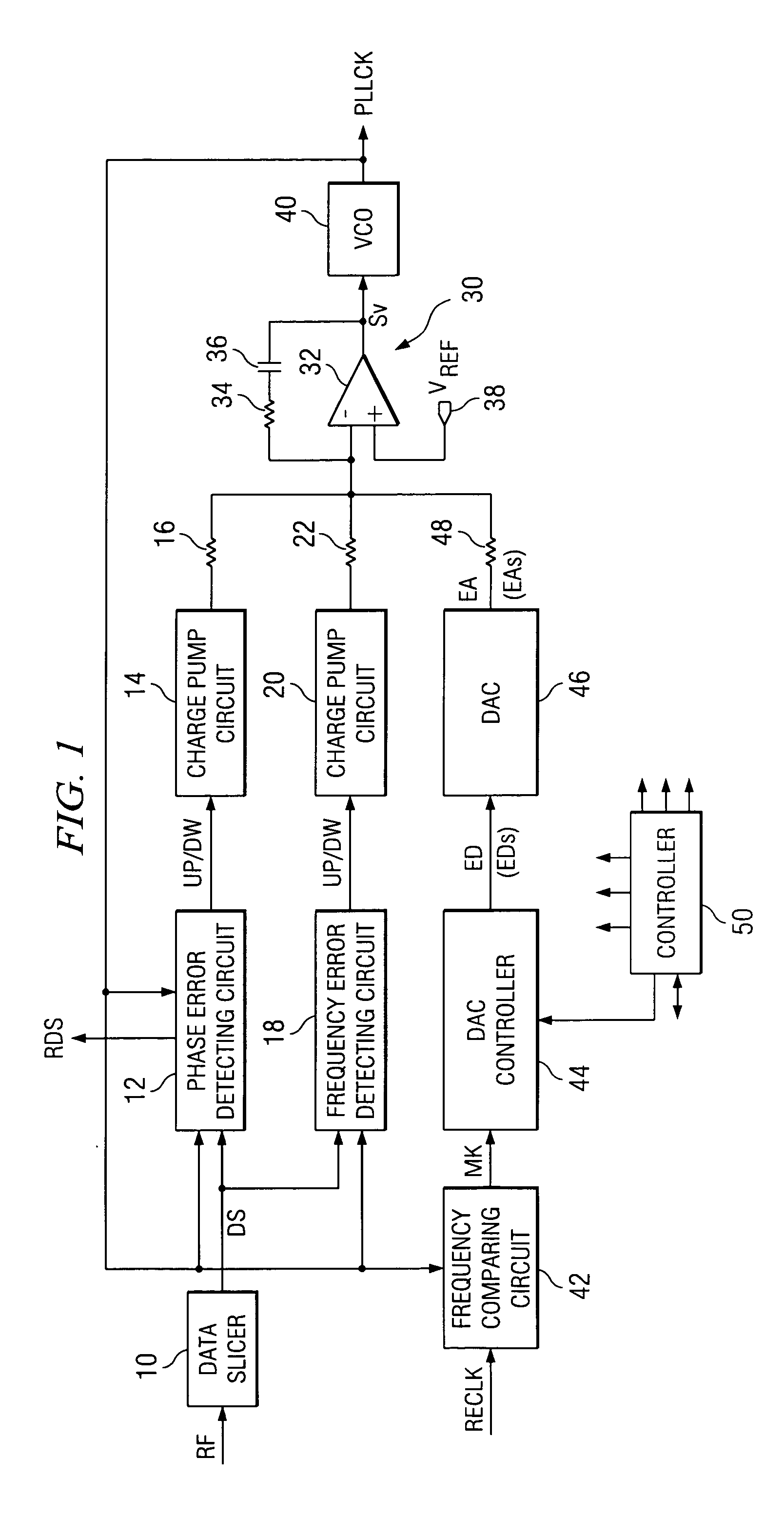

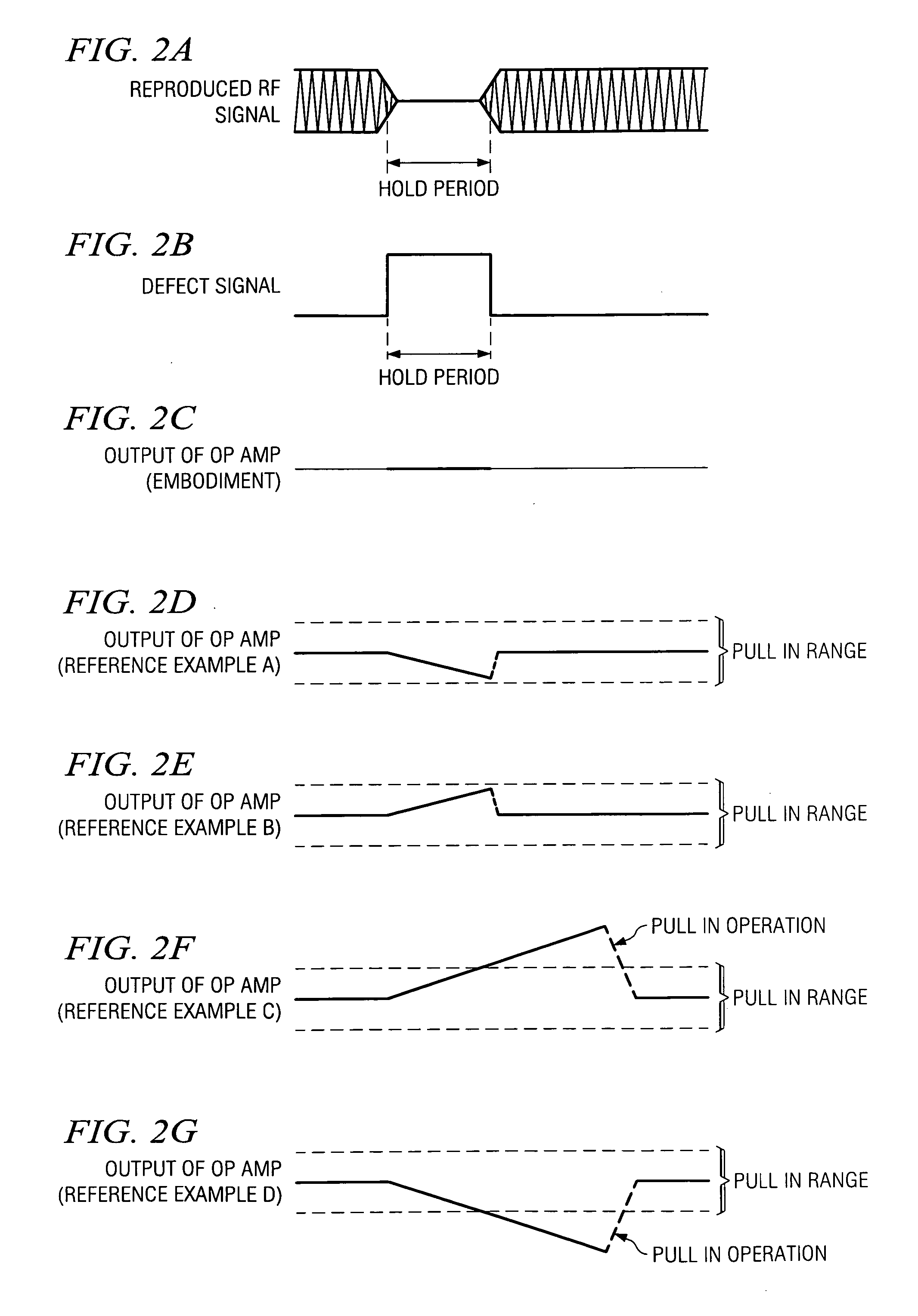

Phase-locked loop circuit

ActiveUS20060114069A1Improve measurement resolutionAccurate resolutionPulse automatic controlAngle demodulation by phase difference detectionLoop filterPhase locked loop circuit

A phase locked loop (PLL) circuit automatically corrects the offset of the analog (especially active type) loop filter to improve the stability and precision of the locked clock or frequency signals. In addition to the general PLL circuit configuration having active type loop filter (30), the PLL circuit also has a frequency comparing circuit (42), a DAC controller (44) and a DAC (digital-to-analog converter) (46). In an offset measurement mode, the outputs of phase error detecting circuit (12, 14) and frequency error detecting circuit (18, 20) are cut, respectively, to establish locking in offset measurement locked loop (42, 44, 45, 30, 40). In this case, offset correction code (EDs) are identified and held. In normal mode, DAC controller (44) has offset correction code (ED) input to DAC (46), and DAC (46) sends offset correction signal (EAs) to loop filter (30).

Owner:TEXAS INSTR INC

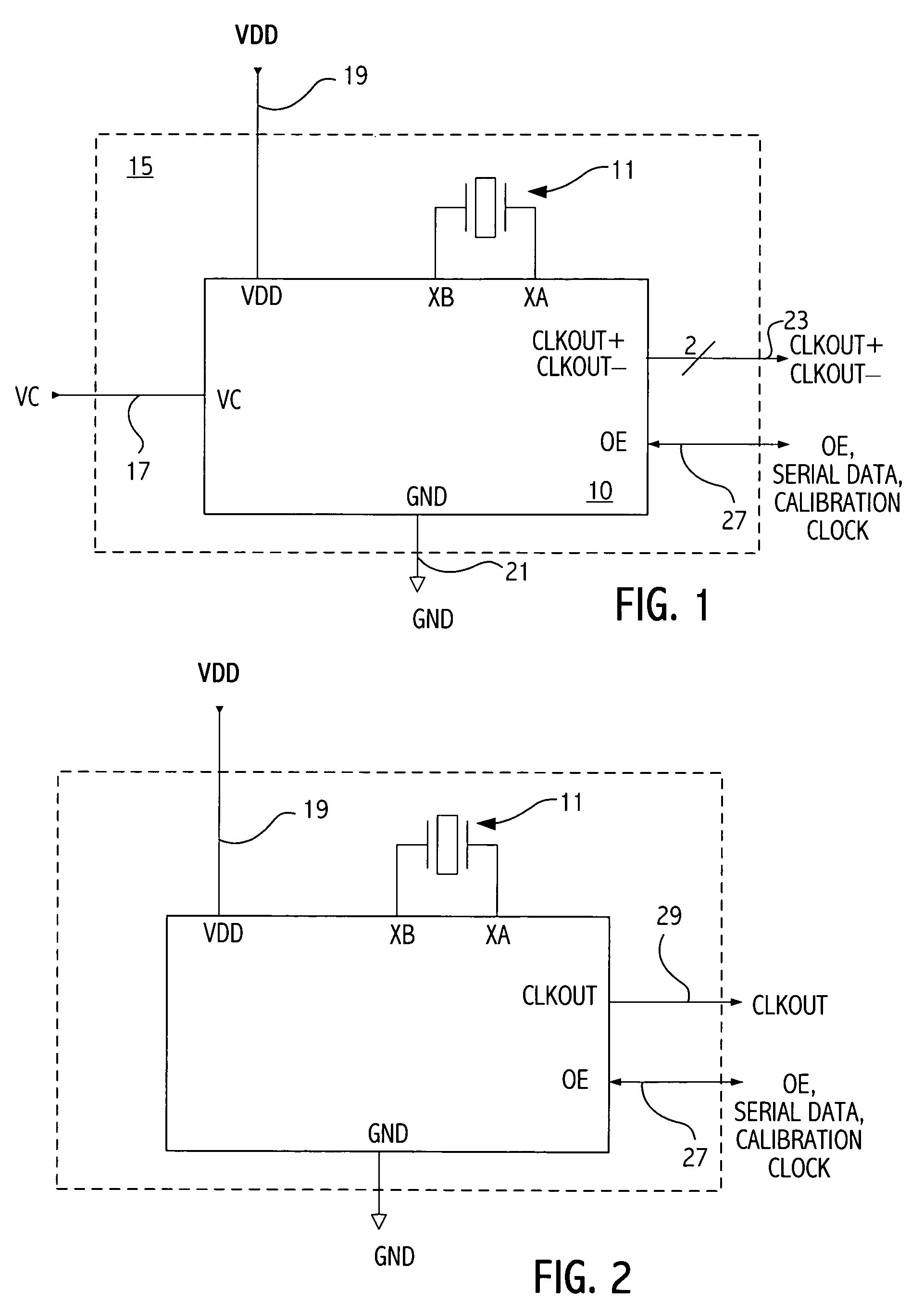

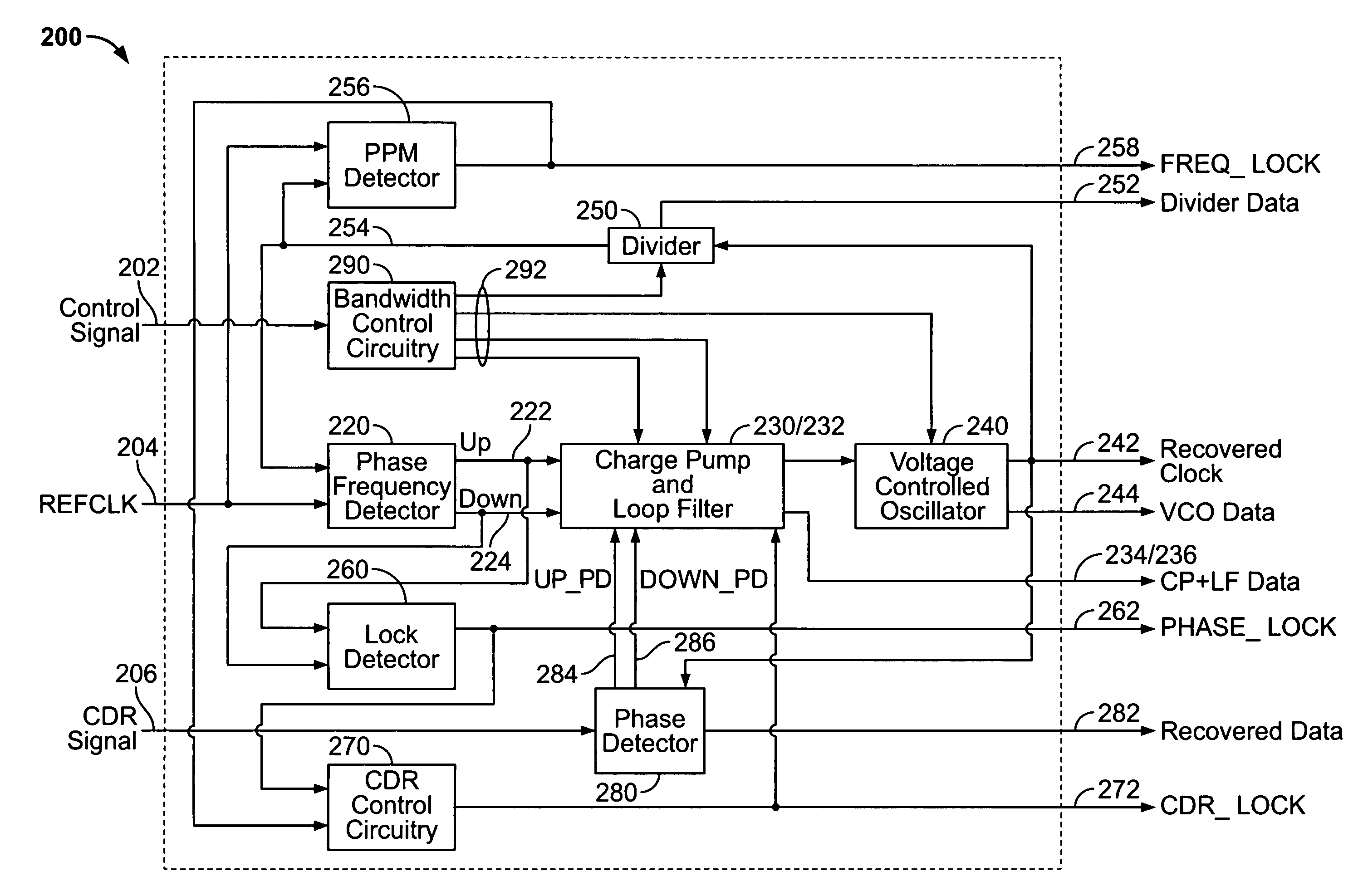

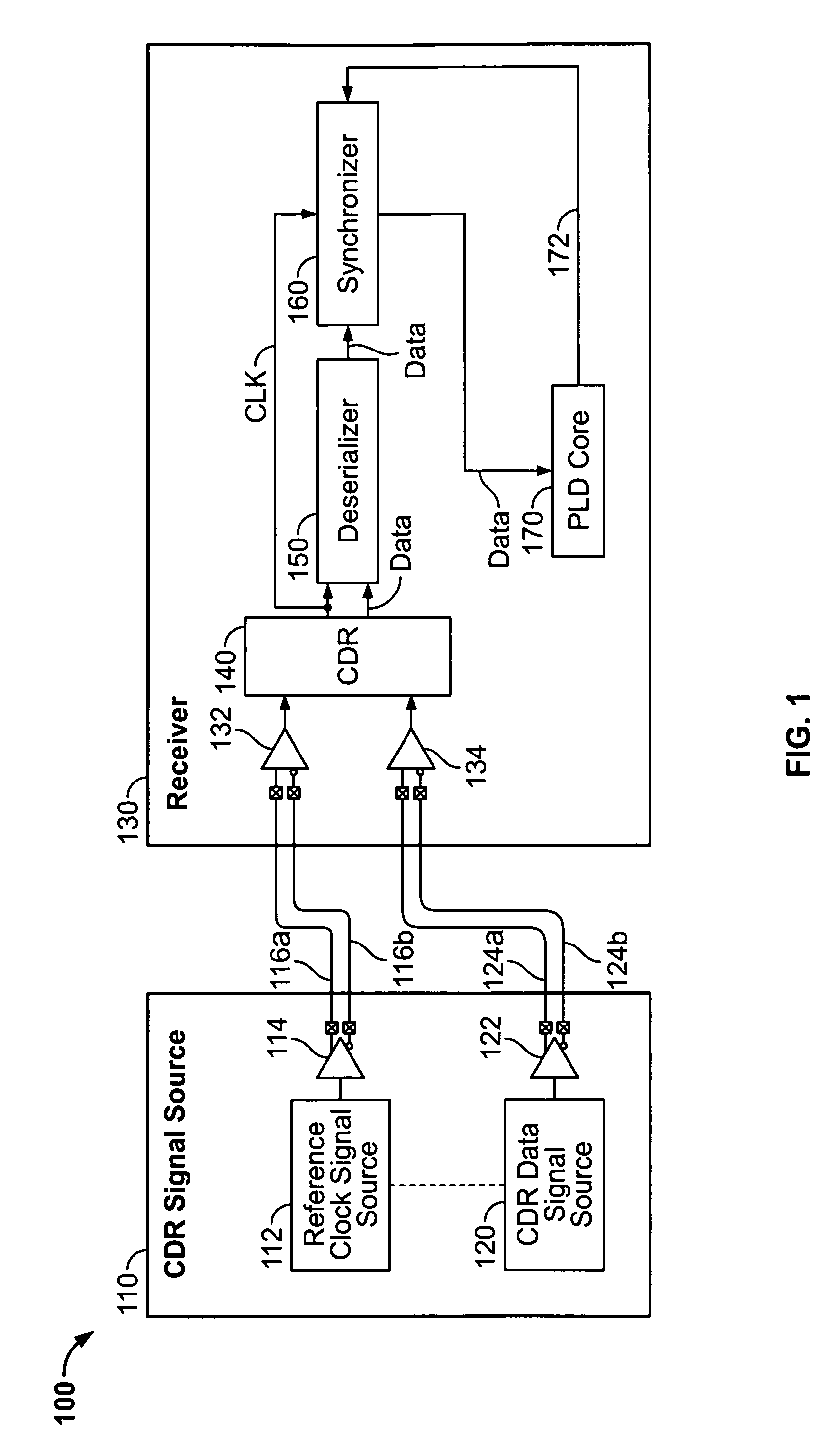

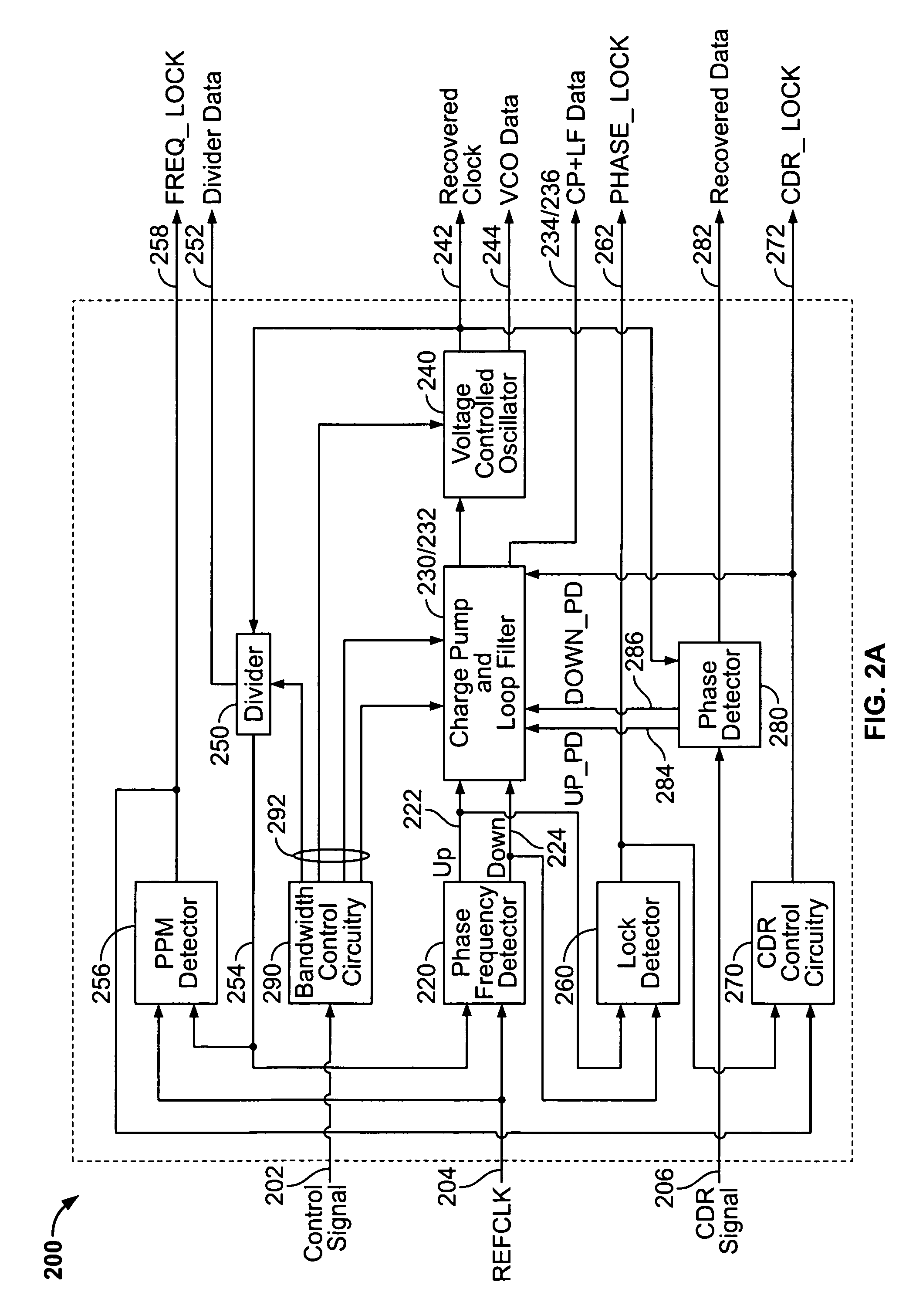

Clock data recovery circuitry and phase locked loop circuitry with dynamically adjustable bandwidths

InactiveUS7149914B1Synchronisation information channelsPulse automatic controlPhase locked loop circuitUser input

Clock data recovery (CDR) circuitry or phase locked loop (PLL) circuitry can be provided with a dynamically adjustable bandwidth. One CDR circuit or PLL circuit can be provided to support multiple systems or protocols, multiple parameter requirements for a given system or protocol, and changes in the input frequency or data rate within a given system or protocol. The parameters can include jitter (e.g., jitter tolerance, jitter transfer, jitter generation), source of dominant noise, and lock time. Control signals can be used to dynamically adjust the bandwidth of the CDR circuitry or PLL circuitry while the circuitry is processing data. The control signals can be set by a PLD, by a processor, by circuitry external to the PLD, or by user input.

Owner:ALTERA CORP

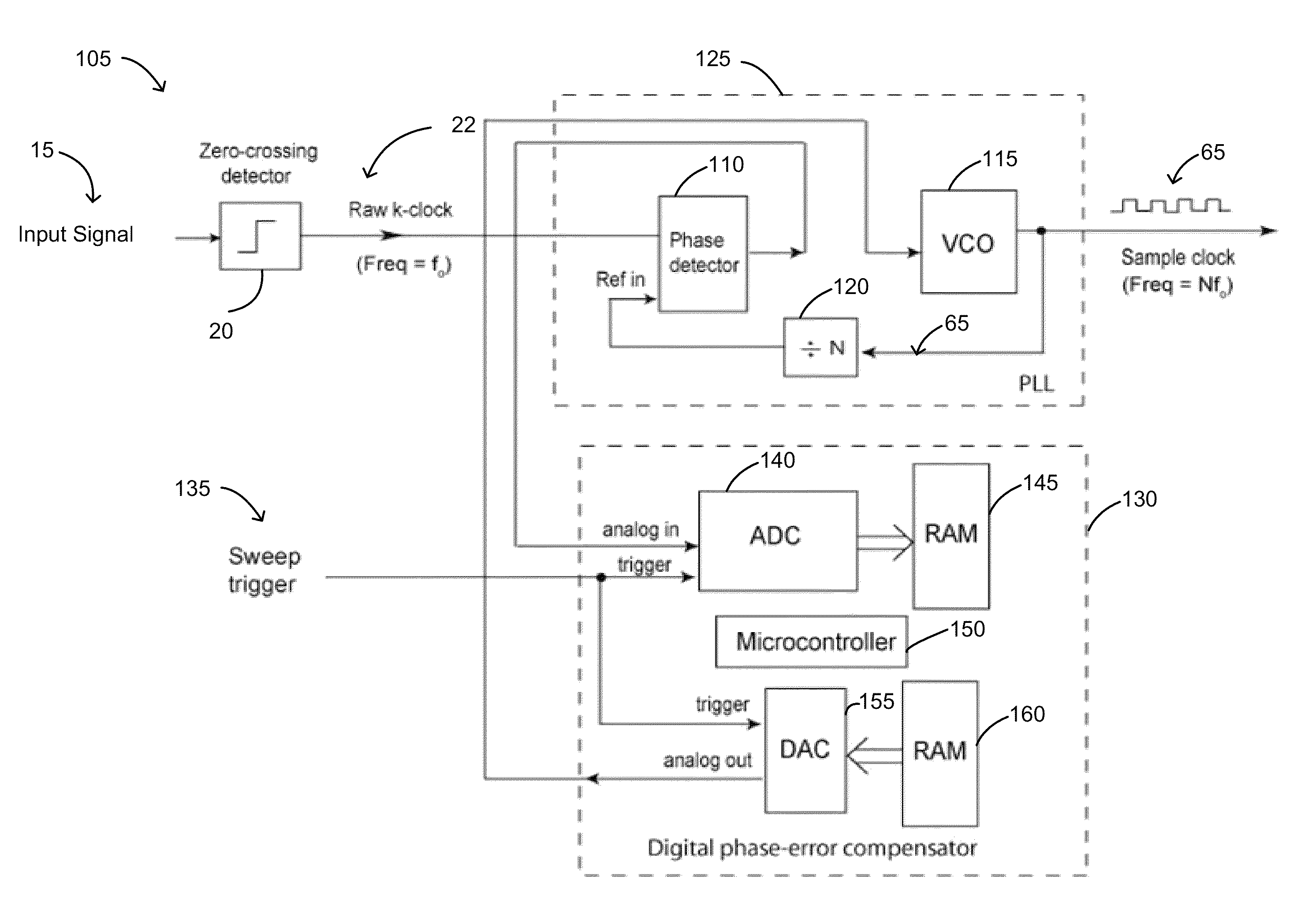

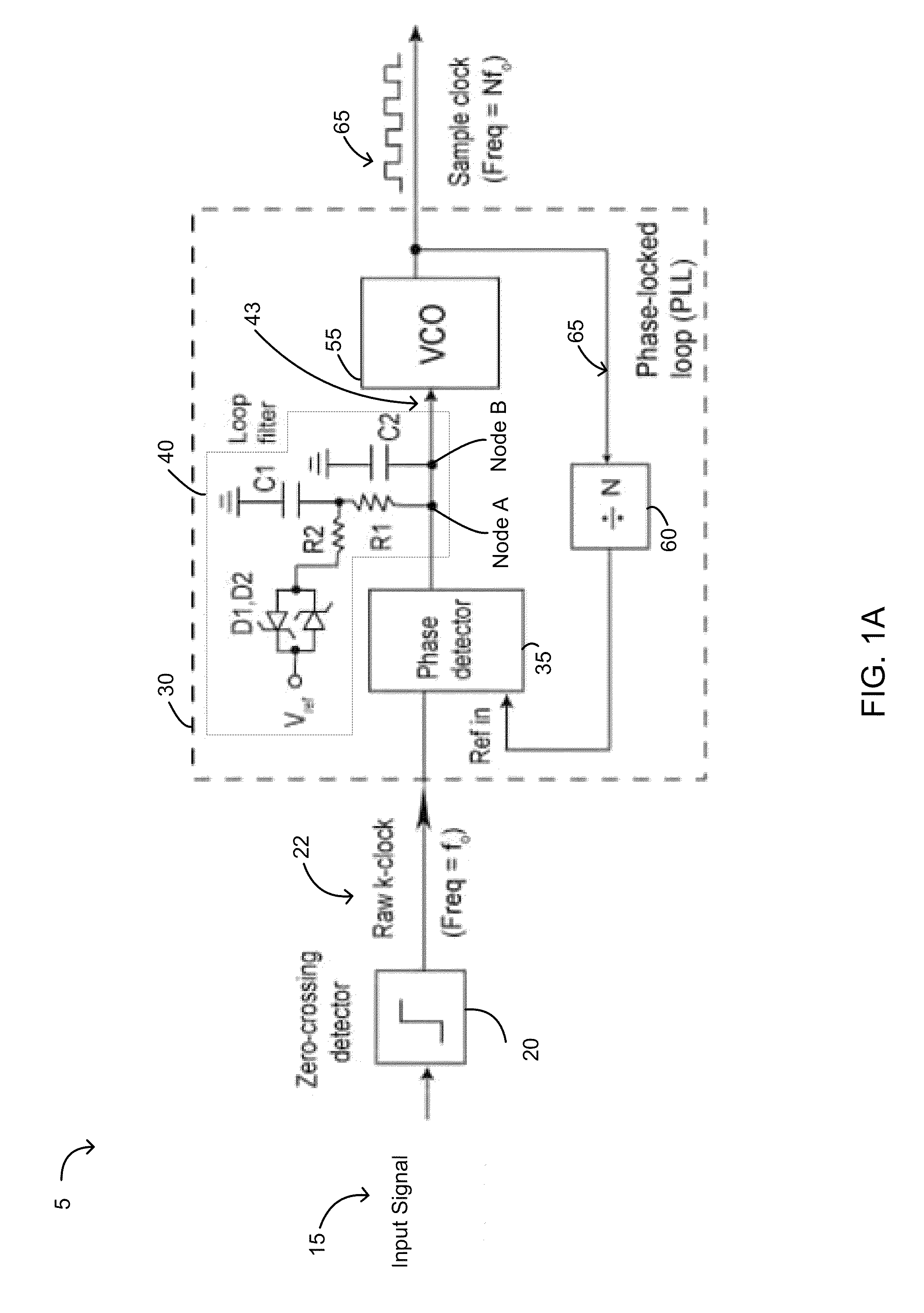

Phase-lock loop-based clocking system, methods and apparatus

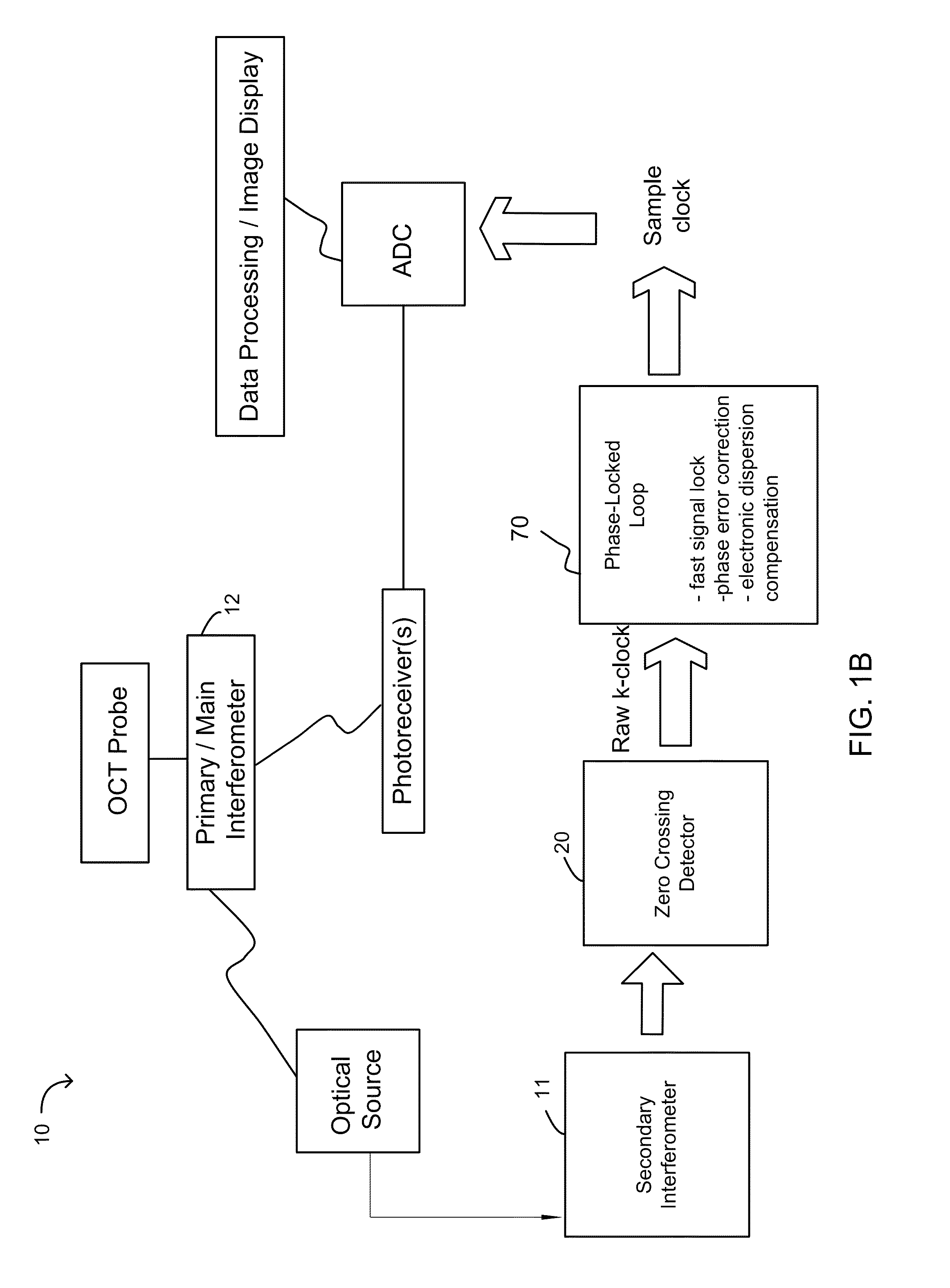

In part, the invention relates to an optical coherence tomography system that includes one or more phased-locked loop circuits. In one embodiment, the phased-locked loop circuit includes a phase detector, a loop filter, and a voltage controlled oscillator wherein the phased-locked loop circuit is configured to generate a sample clock. The optical coherence tomography system can include an analog to digital converter having a sample clock input, an interferometric signal input, and a sample data output, the analog to digital converter configured to receive the sample clock and sample OCT data in response thereto. In one embodiment, the phased-locked loop circuit is configured to lock on a first signal in less than or equal to about 1 microseconds.

Owner:LIGHTLAB IMAGING

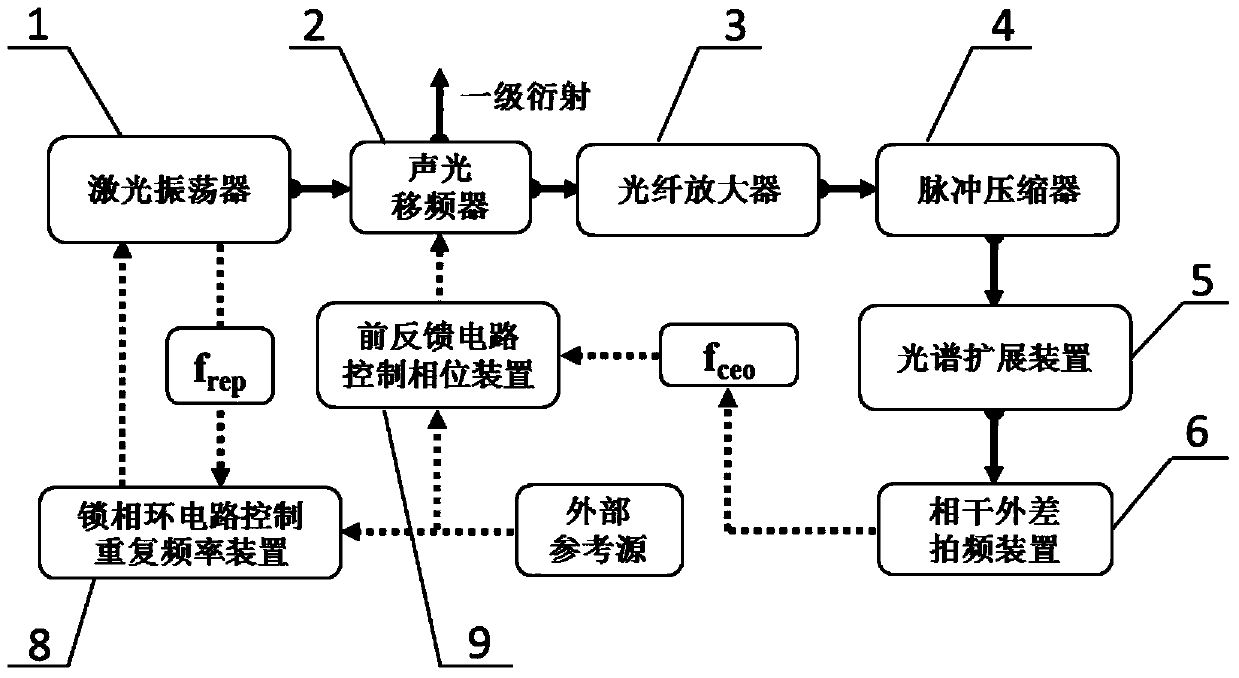

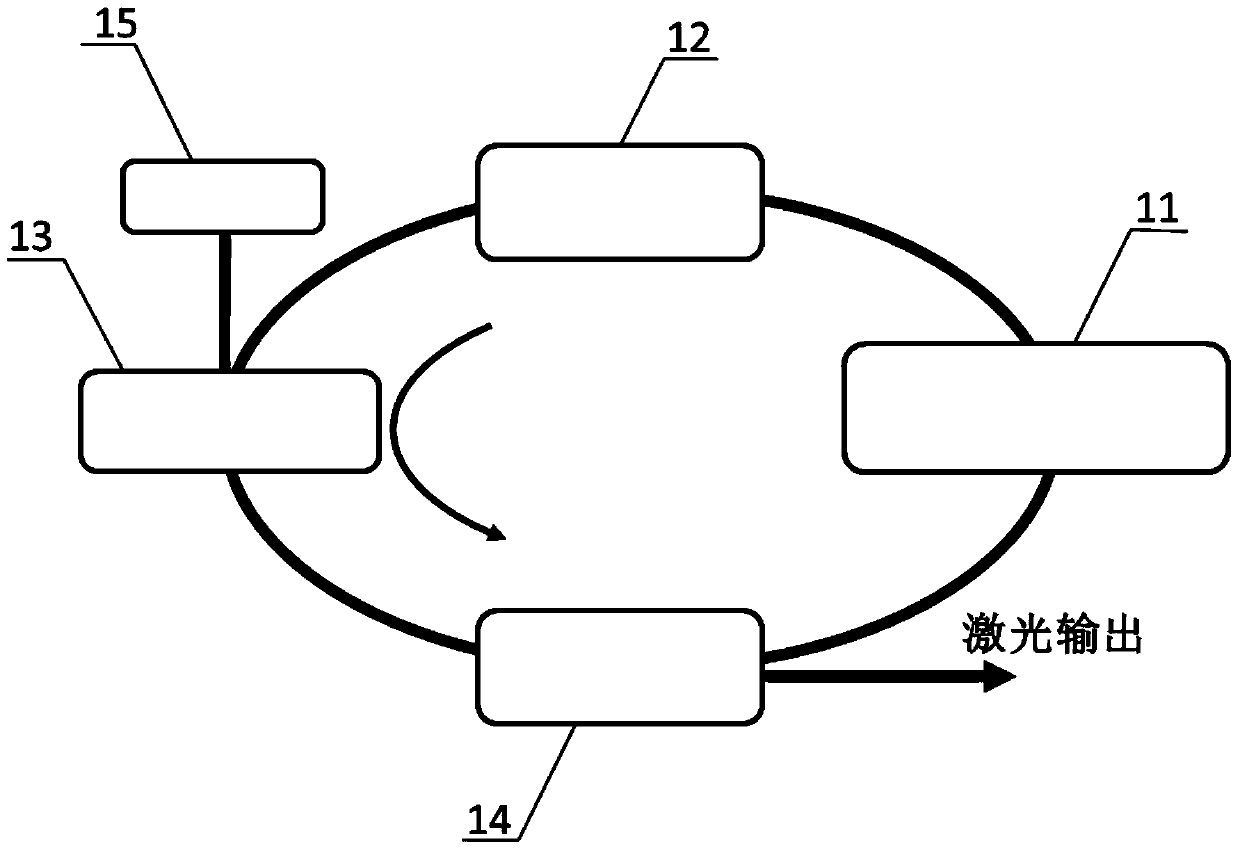

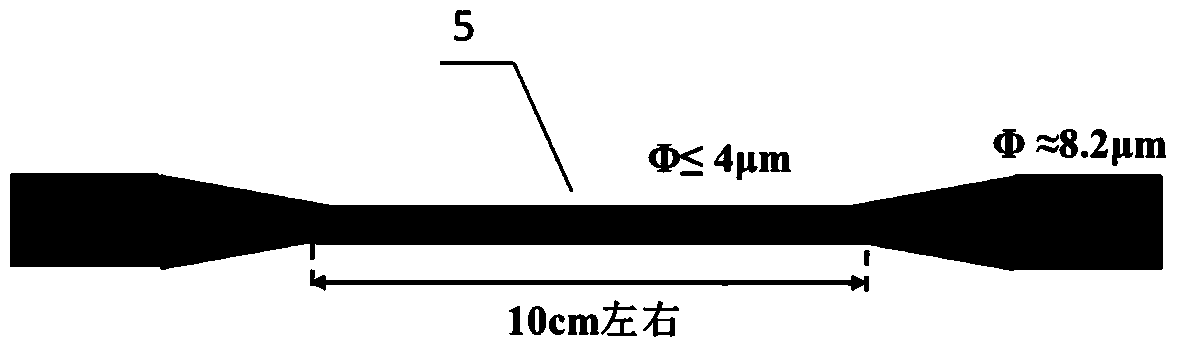

Low noise fiber laser frequency combs device with controllable carrier envelope phase shift frequency

ActiveCN103633537AImprove stabilityCarrier envelope phase shift frequency precise controlOptical resonator shape and constructionActive medium shape and constructionLow noisePhase locked loop circuit

The application provides a low noise fiber laser frequency combs device with controllable carrier envelope phase shift frequency. The low noise fiber laser frequency combs device with controllable carrier envelope phase shift frequency comprises an optical path structure and a circuit structure, wherein the optical path structure comprises an oscillator, an acousto-optic frequency shifter, an optical fiber amplifier, a pulse compressor, an optical fiber spread spectrum device and a coherent heterodyne beat device; and the circuit structure comprises a feed-forward circuit control phase device and a phase-locked loop circuit control repetition frequency device. The fiber laser oscillator can ensure long-time operation of a system, so that the stability of the system is superior to that of a system adopting a solid laser oscillator; through the technologies of optimizing intracavity net dispersion of the fiber oscillator, introducing an inner cavity modulator in the oscillator, adopting the feed-forward acousto-optic frequency shifter, and the like, the low noise fiber laser frequency combs device can be realized; and meanwhile, due to the application of the acousto-optic frequency shifter, the carrier envelope phase shift frequency of the optical frequency combs can be accurately regulated, so that the optical frequency combs device with precise phase position regulation and secular stability is provided for realizing applications such as optical frequency standard, attosecond science and non-linear optics.

Owner:INST OF PHYSICS - CHINESE ACAD OF SCI

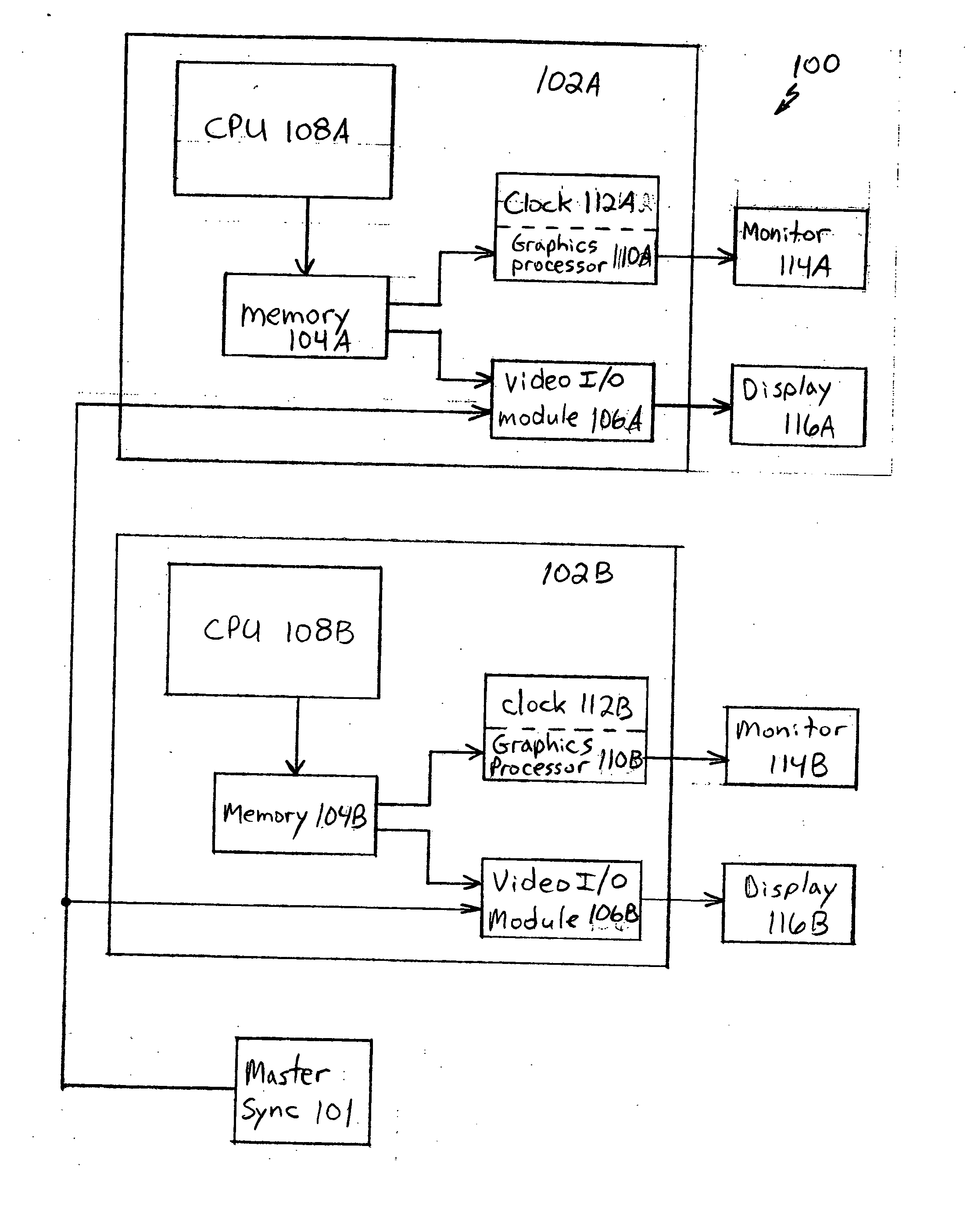

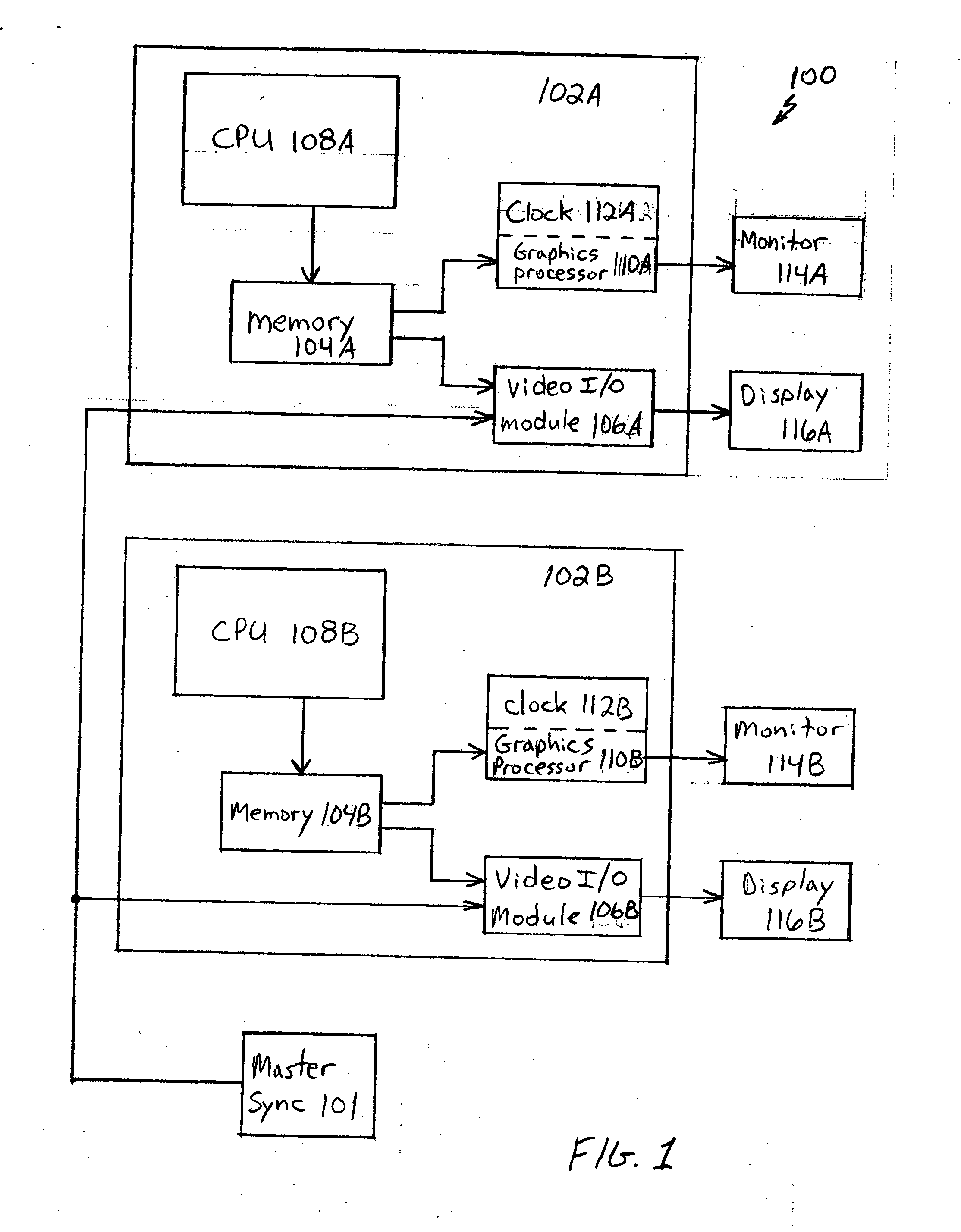

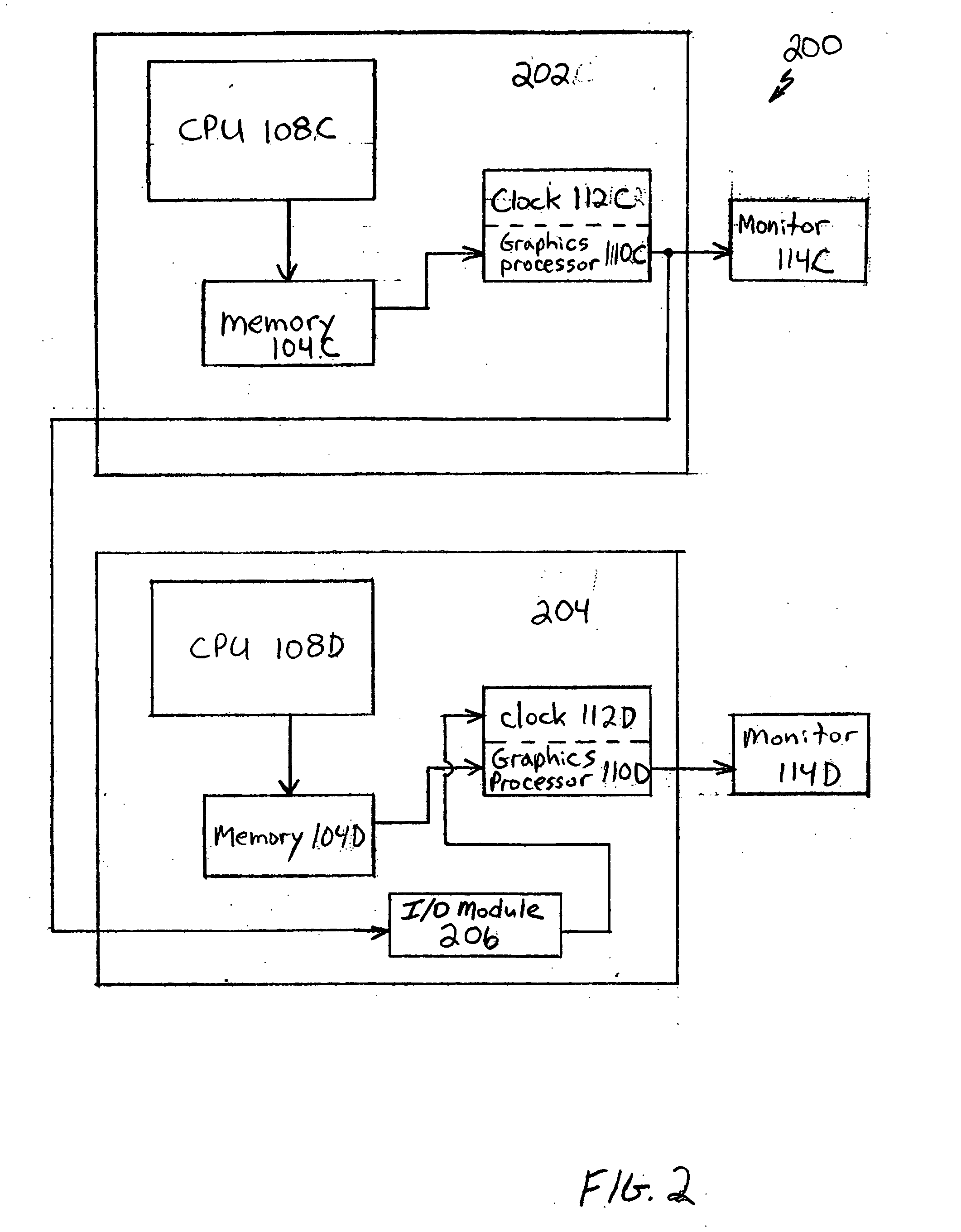

System for synchronizing display of images in a multi-display computer system

InactiveUS20050093854A1Frequency/rate-modulated pulse demodulationCathode-ray tube indicatorsData synchronizationComputer graphics (images)

An image display system synchronizes the display of images on a plurality of display devices. The system includes a first computer system generating a first signal representing first image data to be displayed on a first display device, a second computer system generating a second signal representing second image data to be displayed on a second display device, and means for synchronizing the first and second image data. The synchronizing means includes a phase-locked loop circuit having a digital rate controller. The digital rate controller allows programmable control of the speed of the phase-locked loop.

Owner:RPX CORP +1

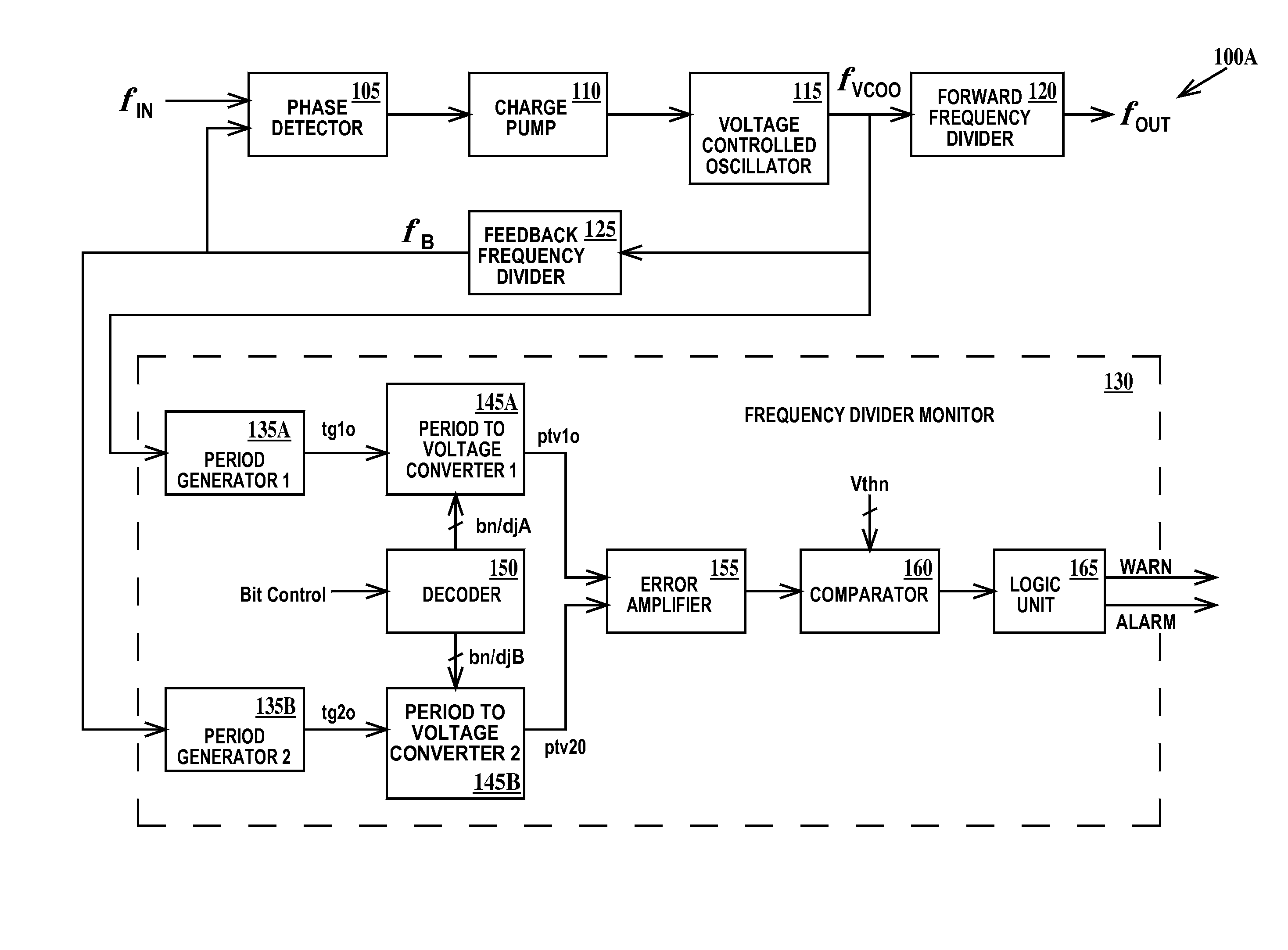

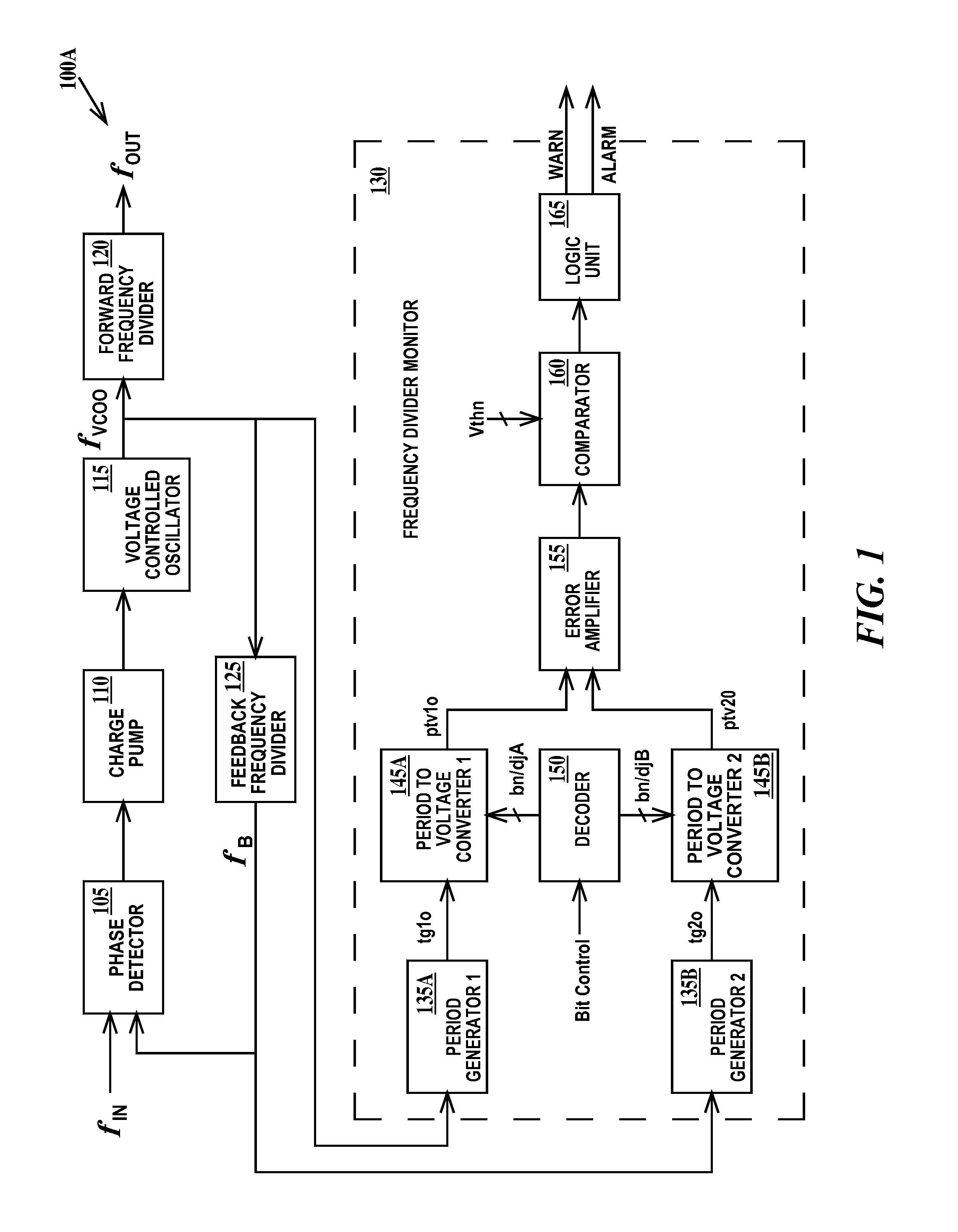

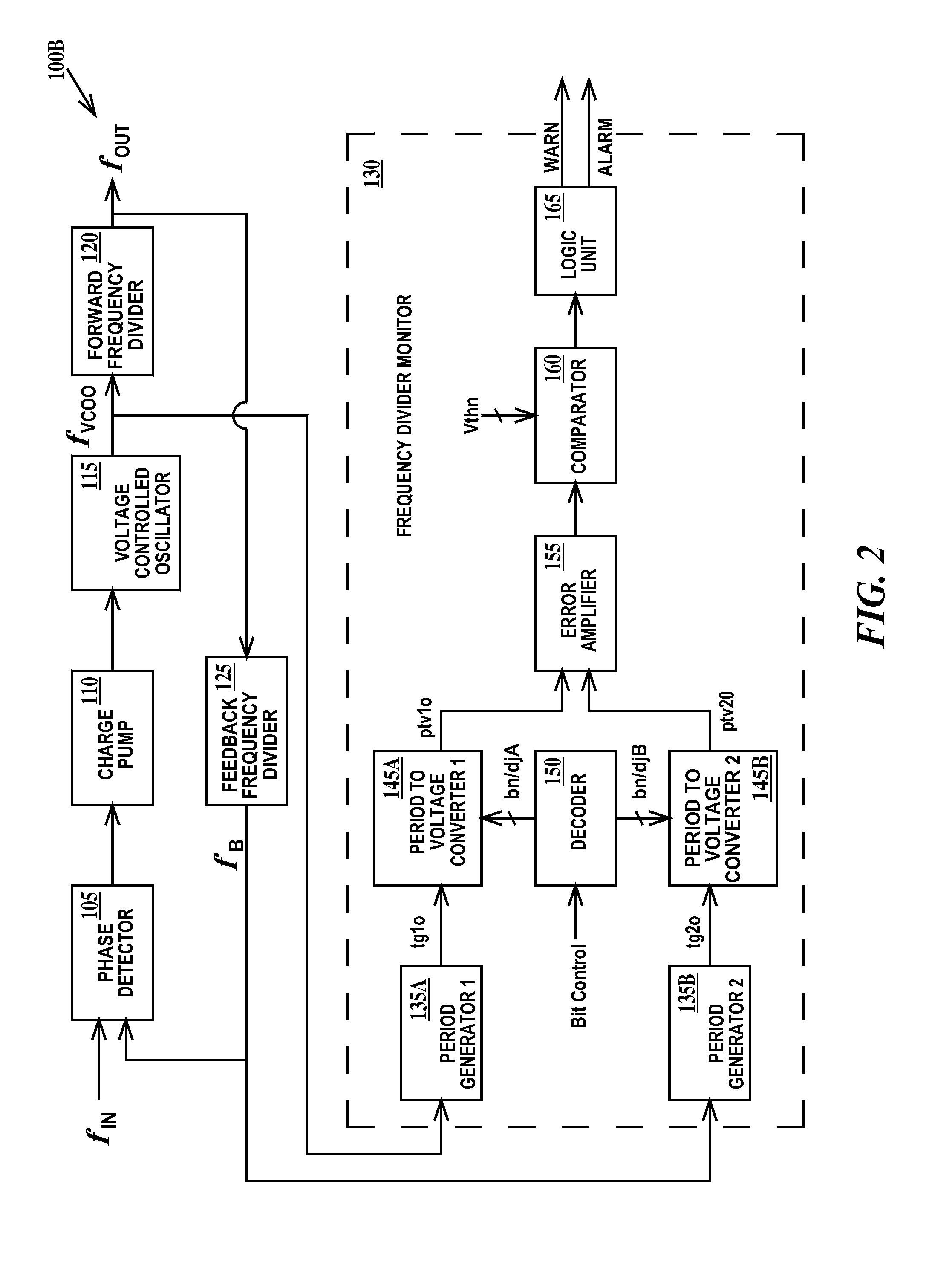

Frequency divider monitor of phase lock loop

Owner:FENG KAI +1