Patents

Literature

389 results about "Lock time" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

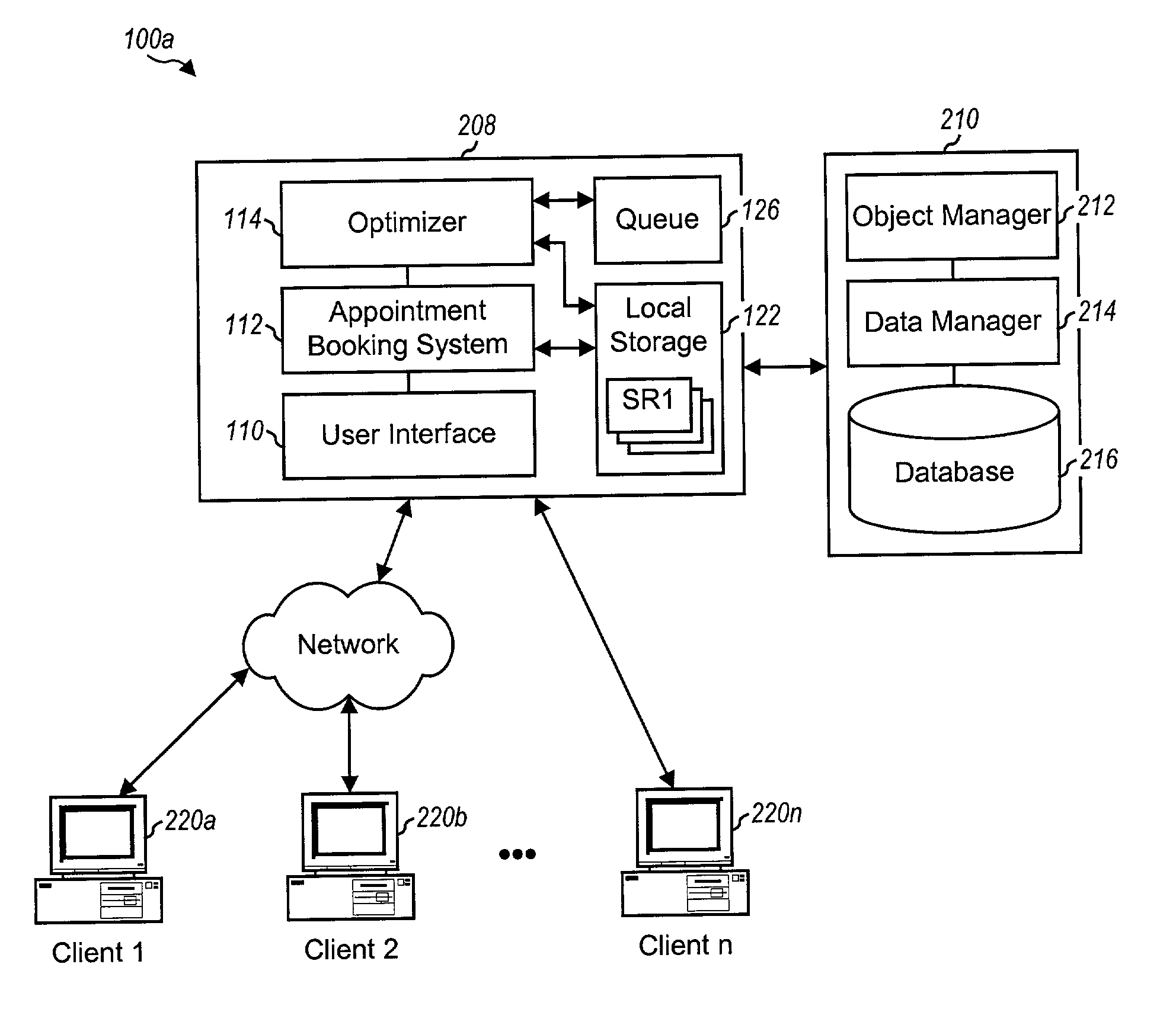

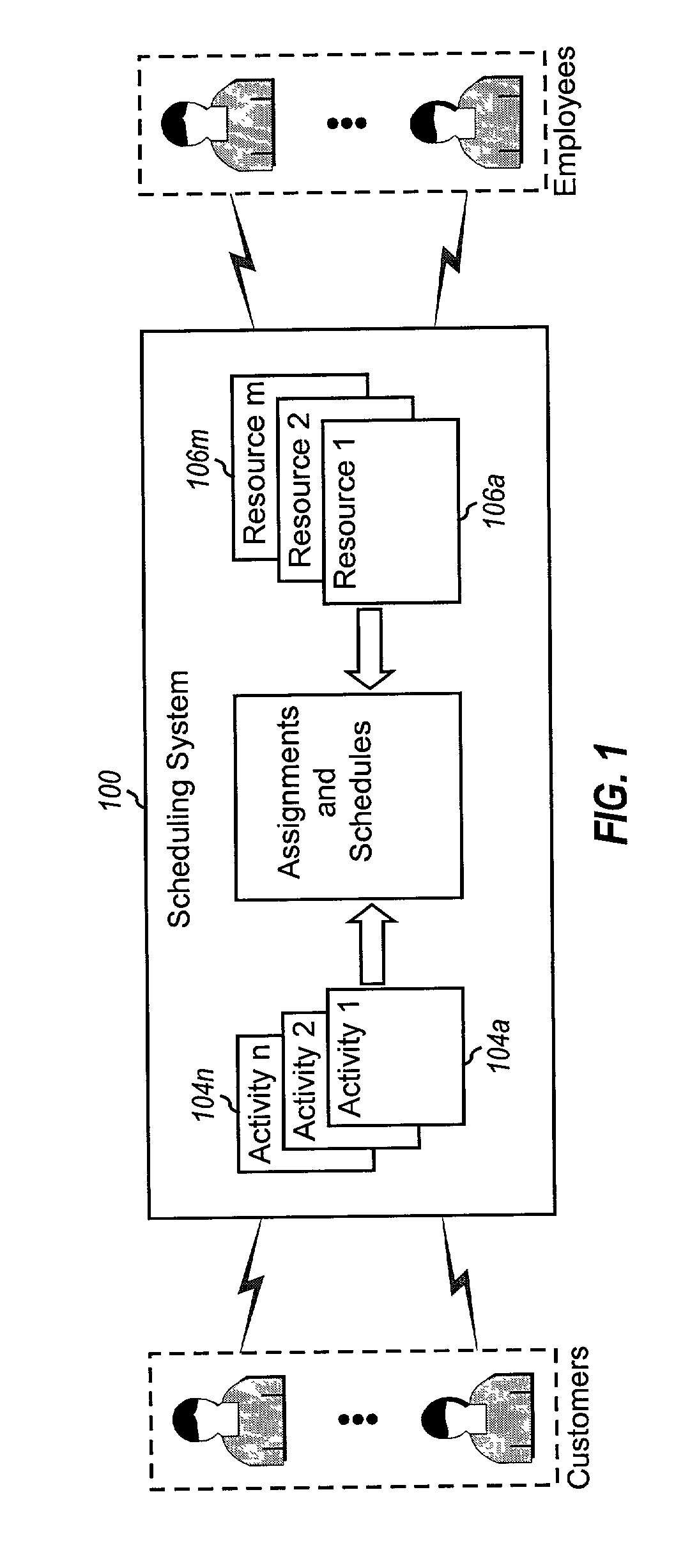

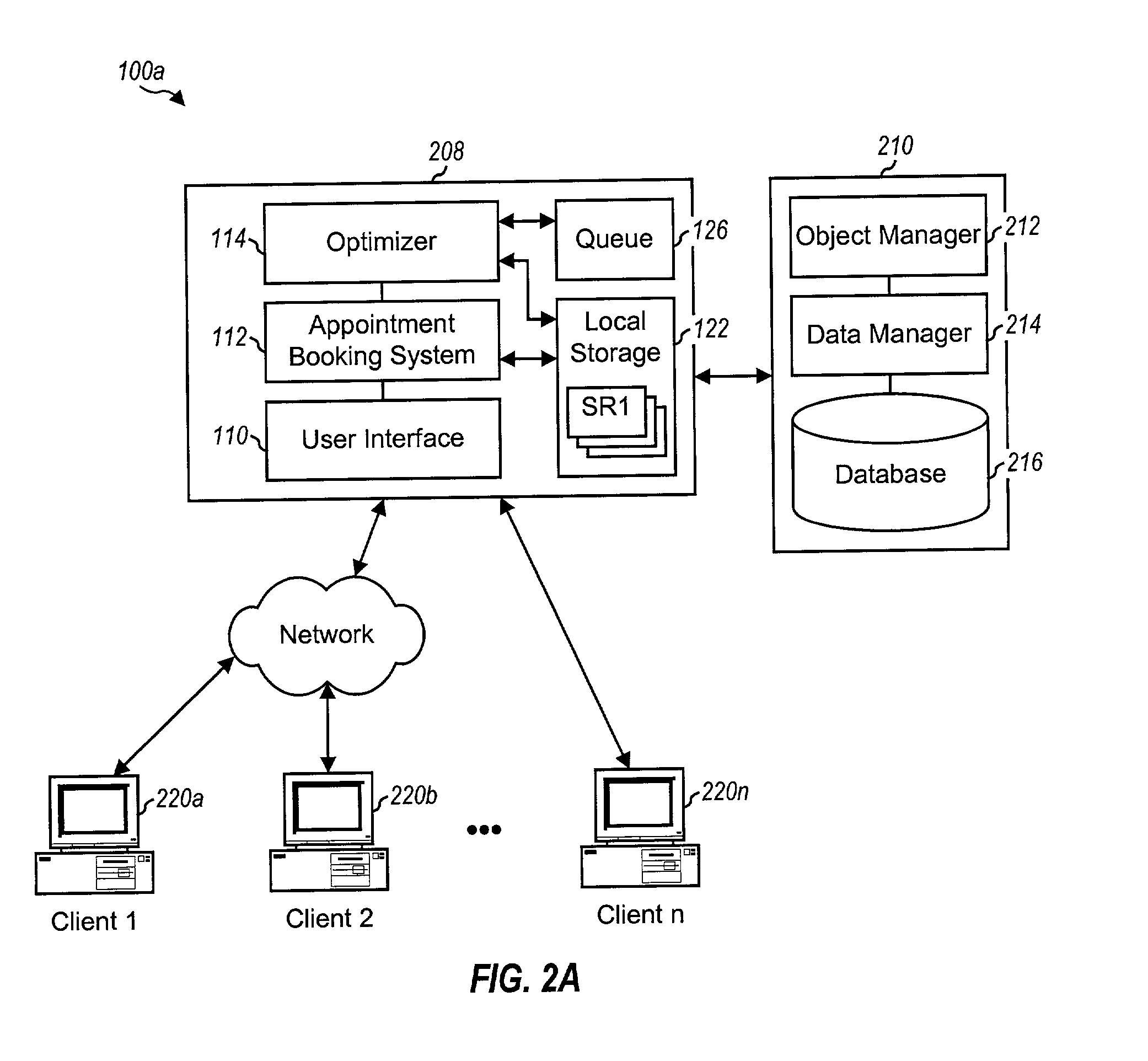

Method and system for scheduling activities

ActiveUS20070208604A1Efficiently schedule activityOptimize schedulingDigital computer detailsElectric digital data processingLock timeReal-time computing

Owner:SIEBEL SYST INC

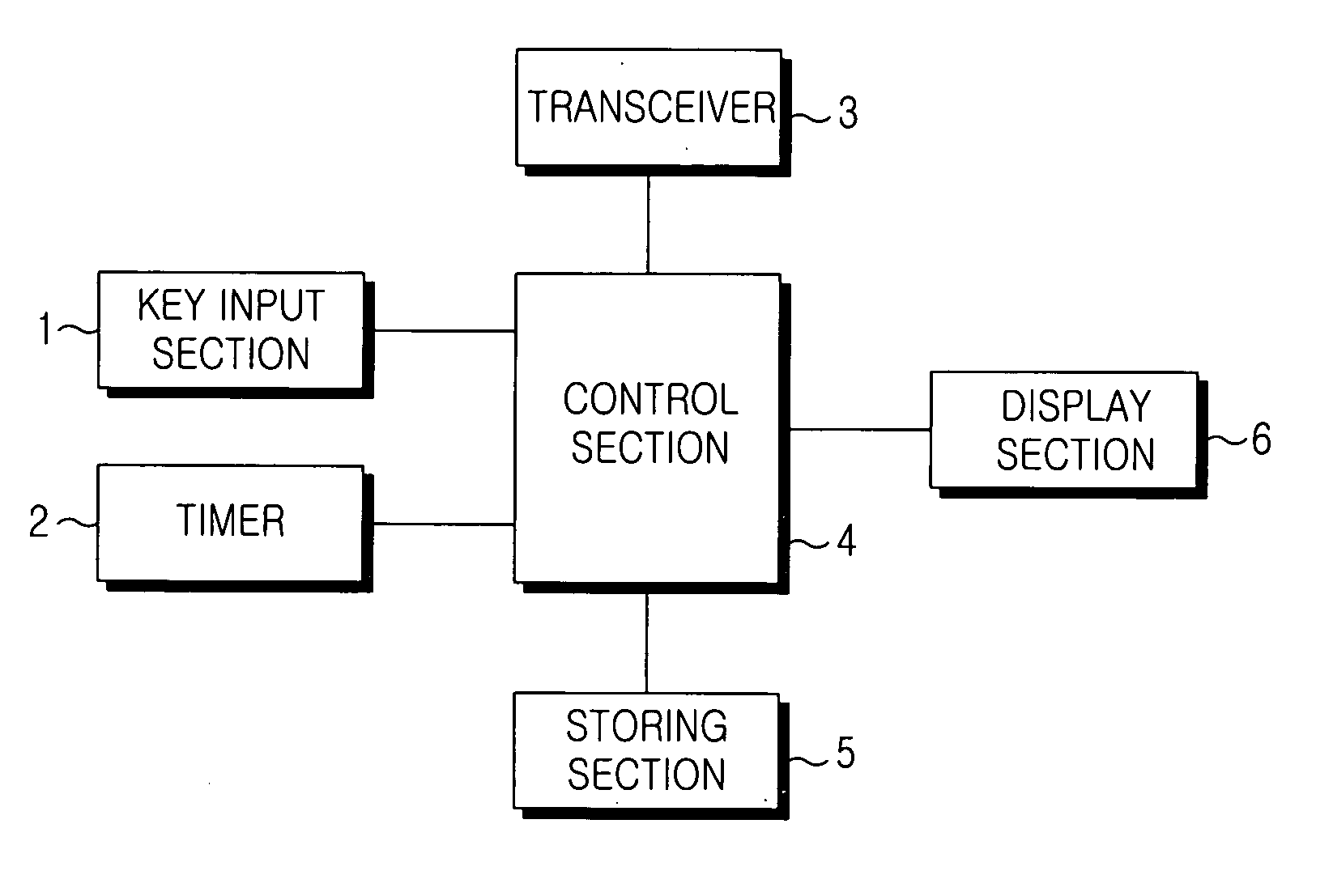

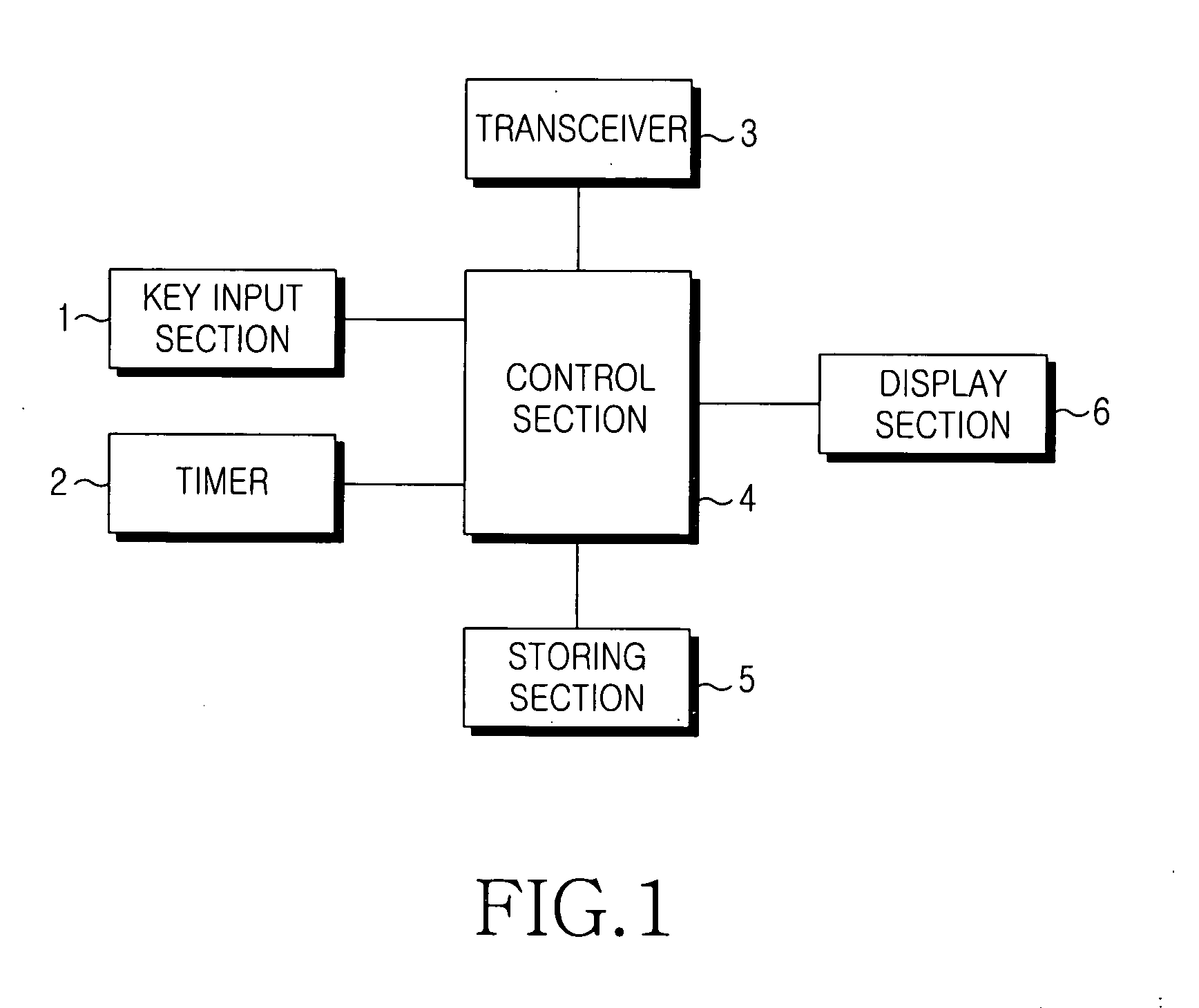

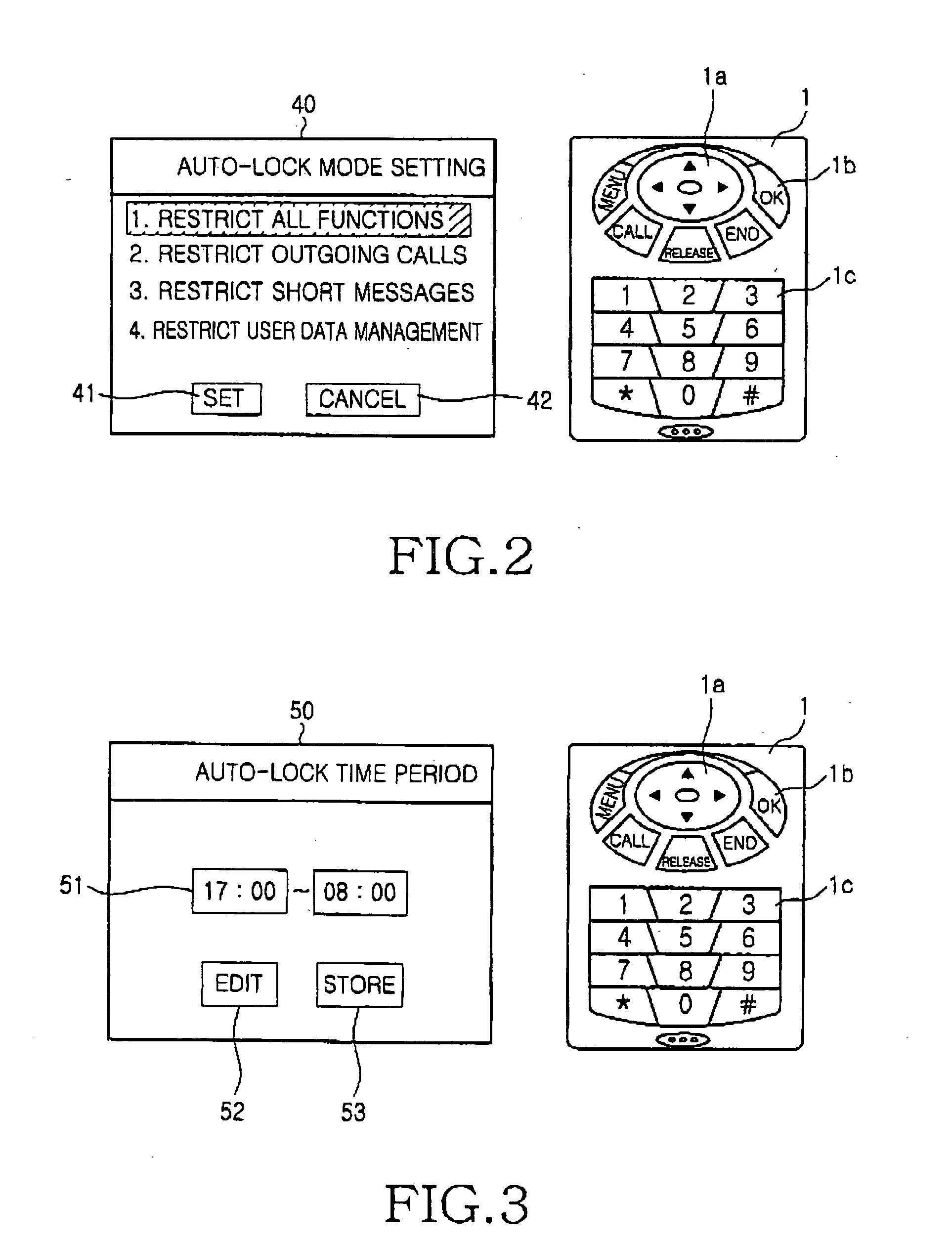

Mobile terminal and method for auto-locking thereof

InactiveUS20050154935A1Prevent illegal useAutomatically locking a mobile terminalUnauthorised/fraudulent call preventionDigital data processing detailsTime segmentComputer science

Disclosed is a method for automatically locking a mobile terminal having functions, such as incoming and outgoing calls. The method includes the steps of setting an auto-lock time period to restrict the use of one or more predetermined functions; activating an auto-lock mode to restrict the use of the predetermined functions during the auto-lock time period; and inactivating the auto-lock mode after the auto-lock time period. The auto-lock mode for automatically locking functions of the mobile terminal can be set to be activated only during specified time or during all other times of the day according to the spatial and temporal patterns of the user's daily routine.

Owner:SAMSUNG ELECTRONICS CO LTD

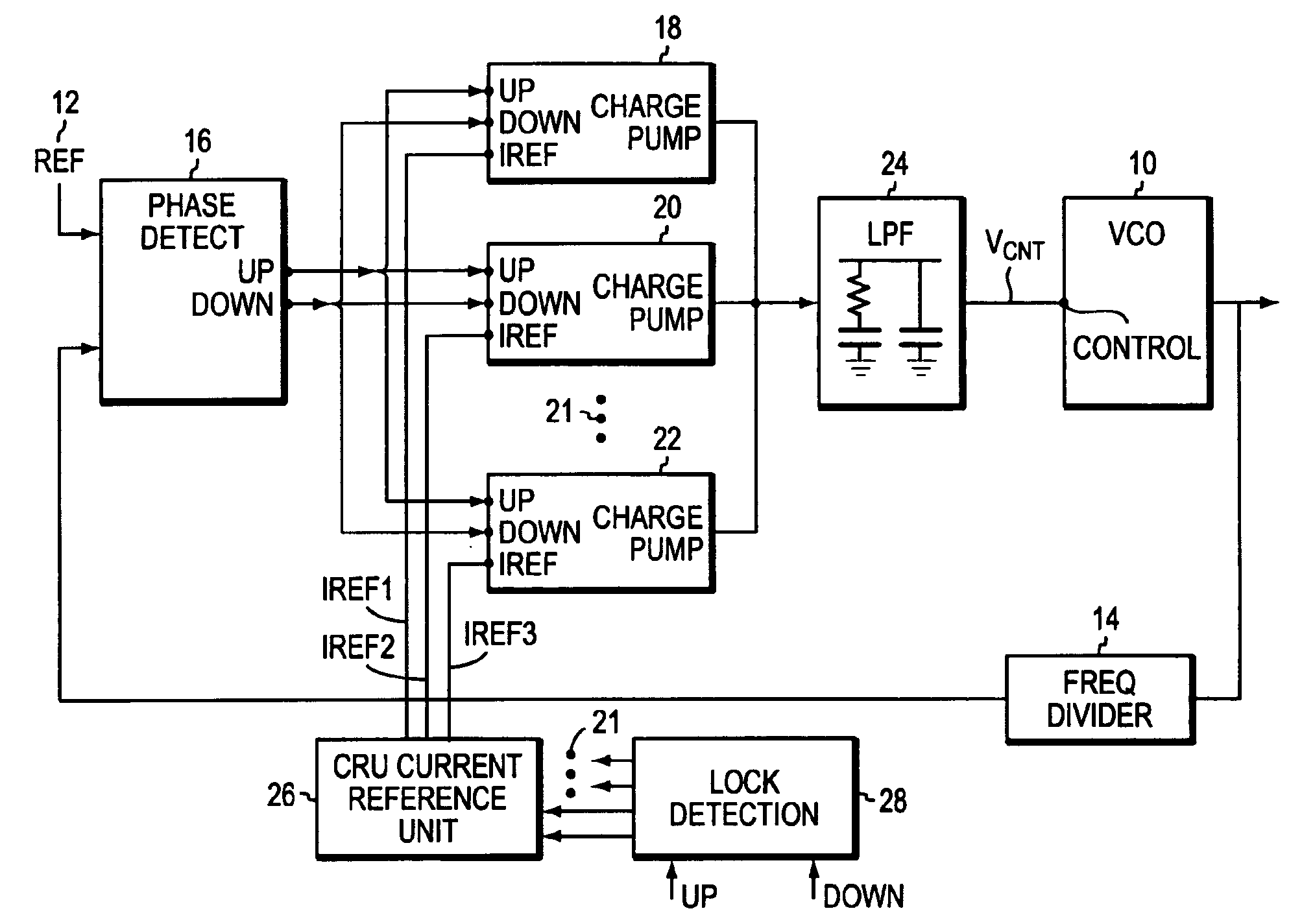

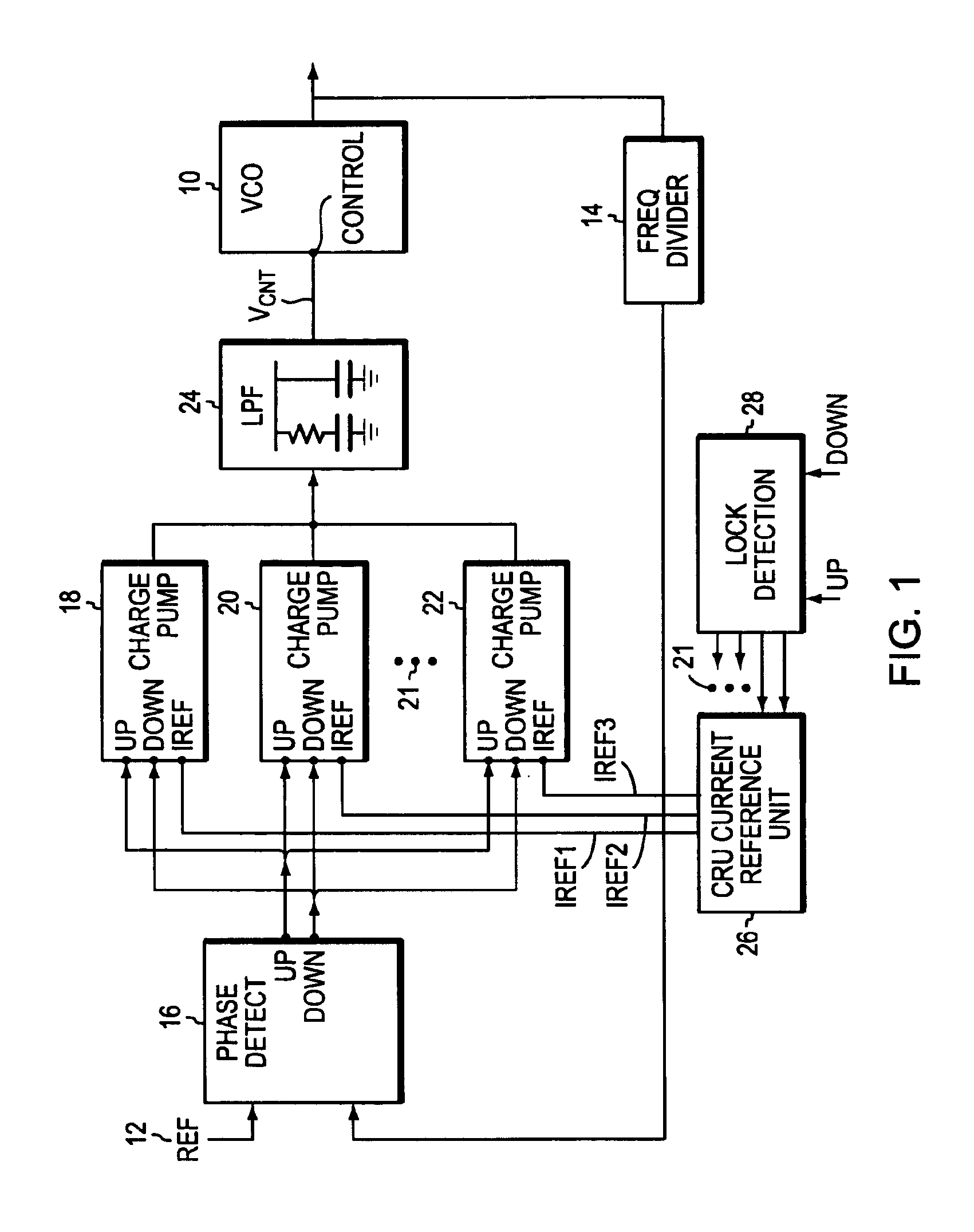

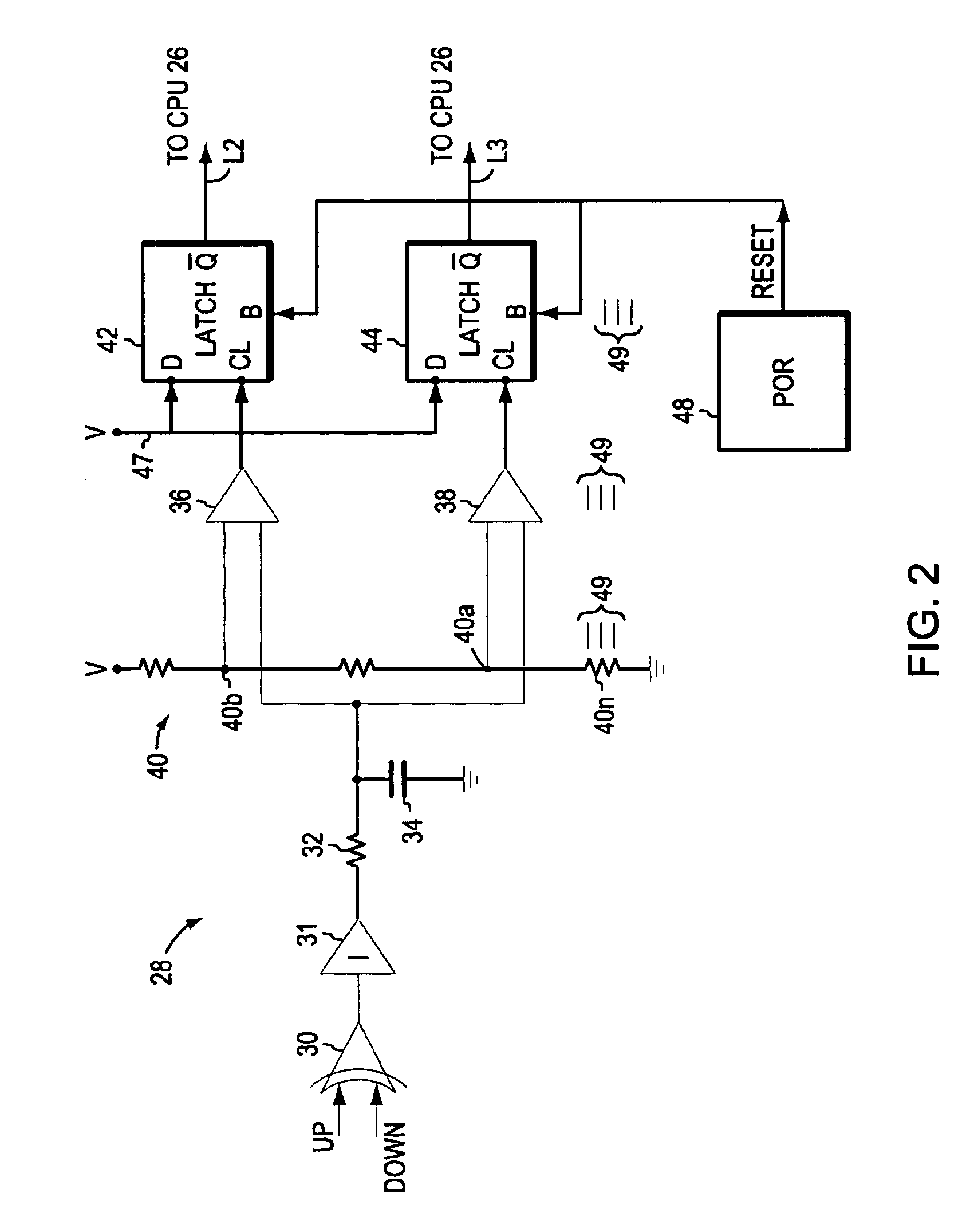

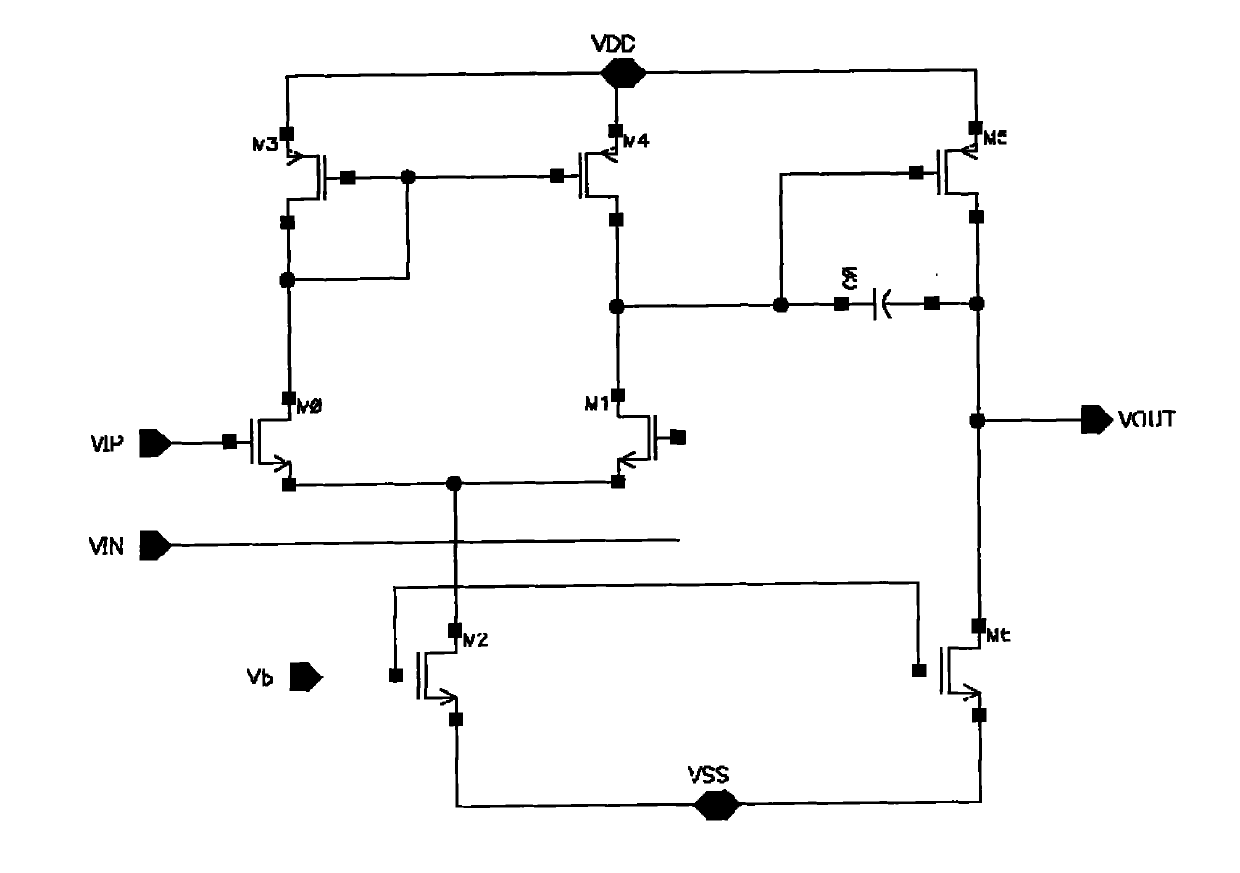

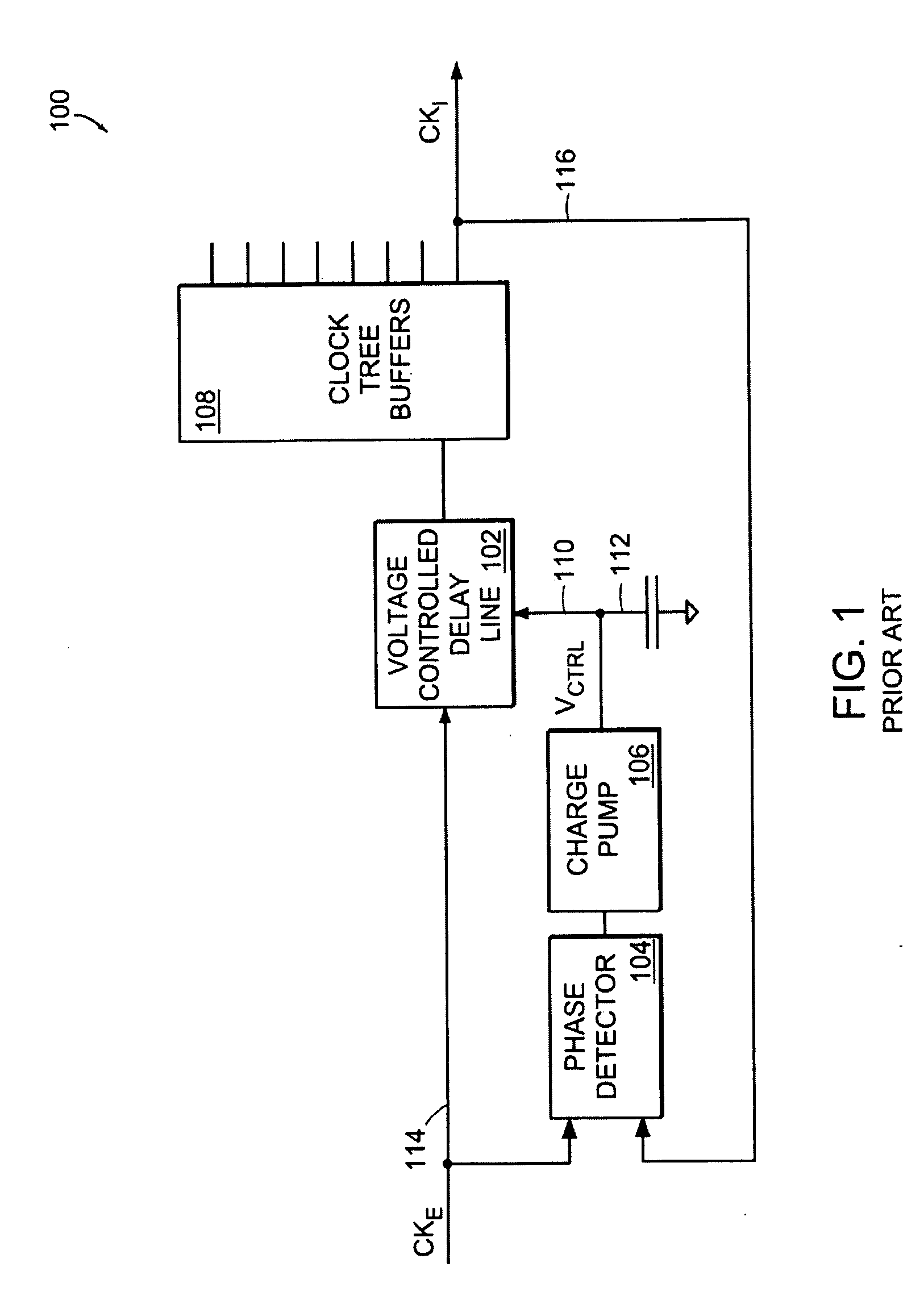

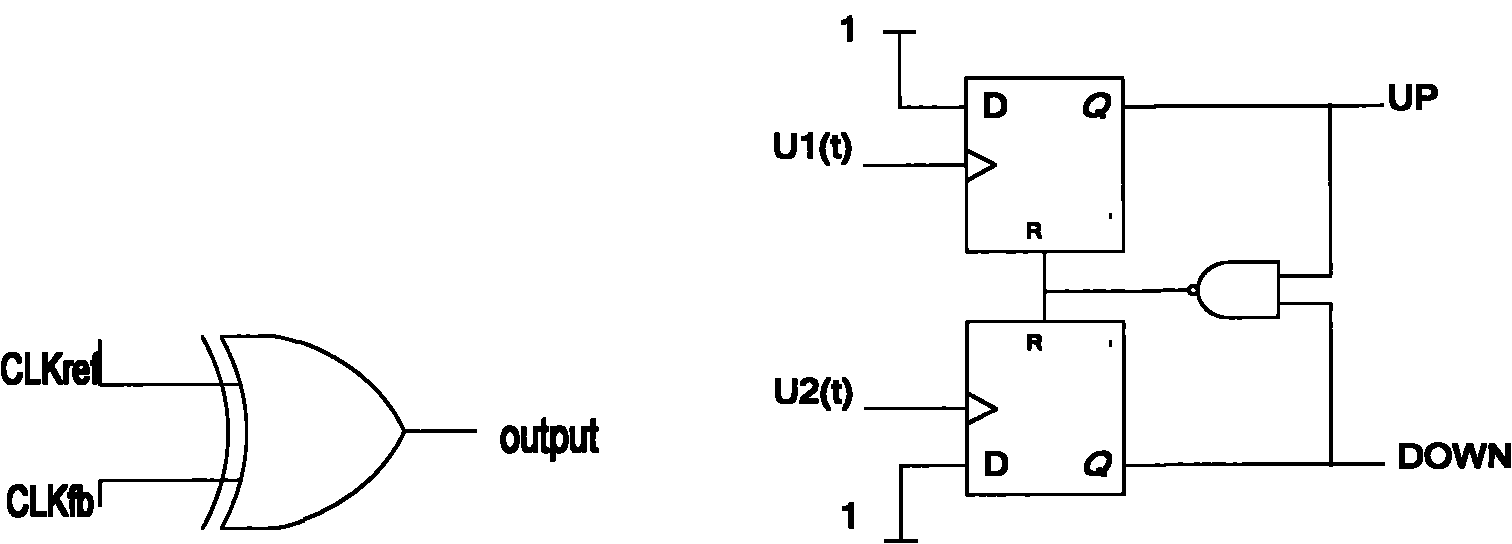

Circuitry to reduce PLL lock acquisition time

ActiveUS6940356B2Decrease frequency/phase errorFast frequencyPulse automatic controlOscillator tubesPhase detectorSwitched current

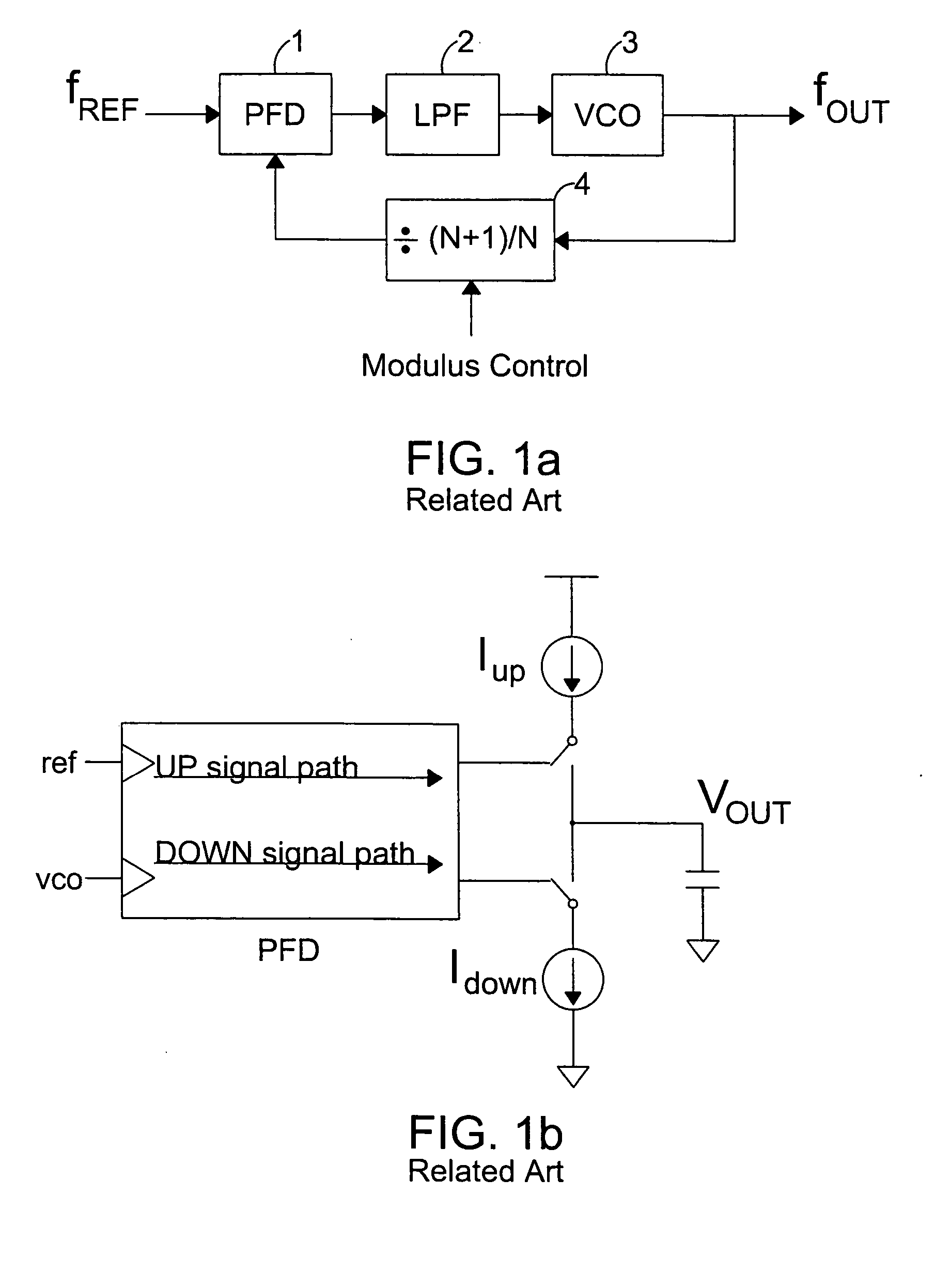

A phase locked loop, PLL, is described with multiple parallel charge pumps that are selectively disabled as phase lock is approached. A lock detection circuit is described that enabled reference currents to be fed to the parallel charge pumps. The error signal from a phase detector is arranged as UP and a DOWN signals that are averaged in the lock detector. When the average error is large, all the reference currents feed the charge pumps that provide a high loop gain to reduce the lock time. As the lock becomes closer selective reference currents are disabled to reduce loop gain so that a smooth transition to lock is made. Selectively switching currents into a low pass filter that usually follows a charge pump in a PLL circuit automatically reduces switching noise by the operation of the low pass filter.

Owner:SEMICON COMPONENTS IND LLC

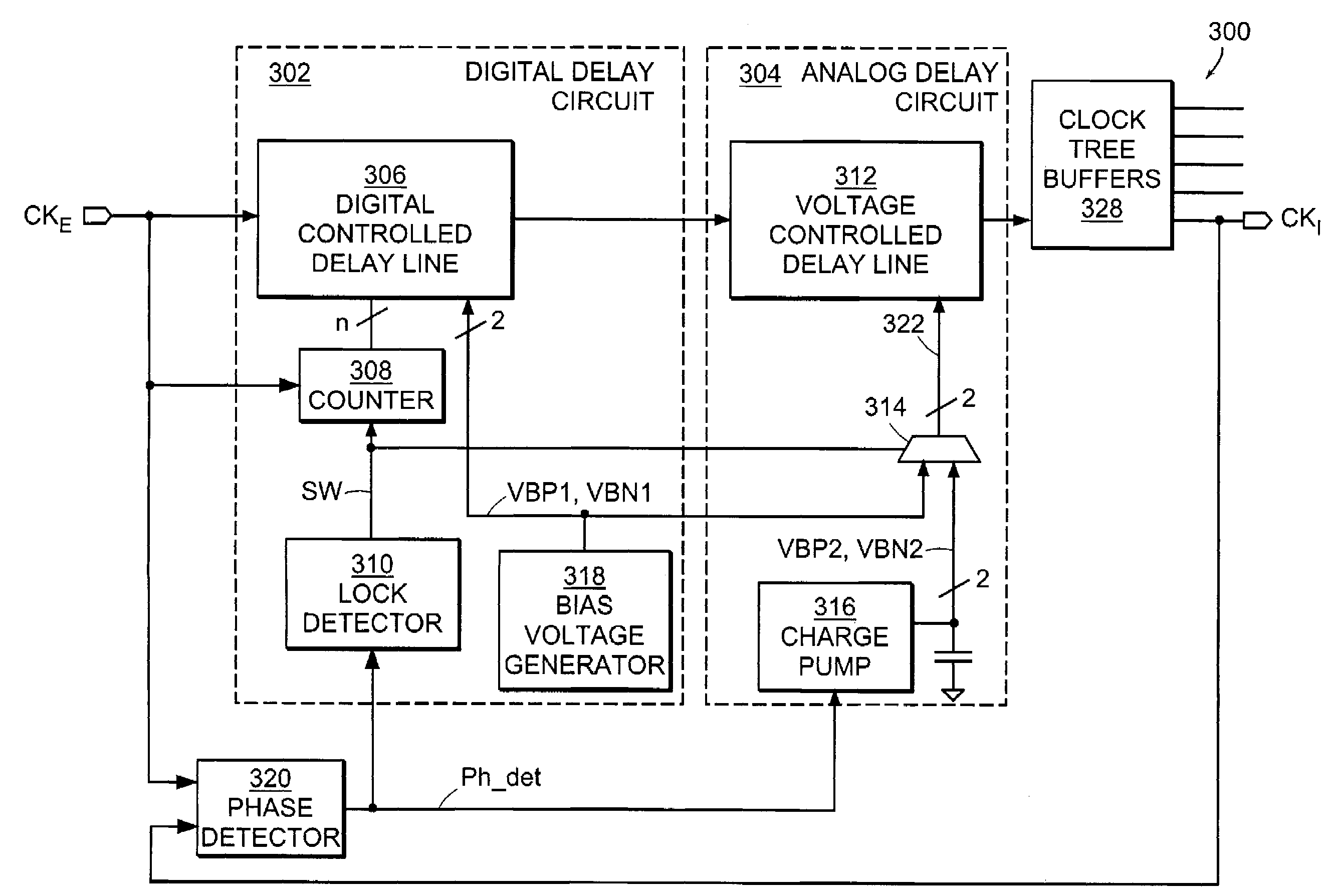

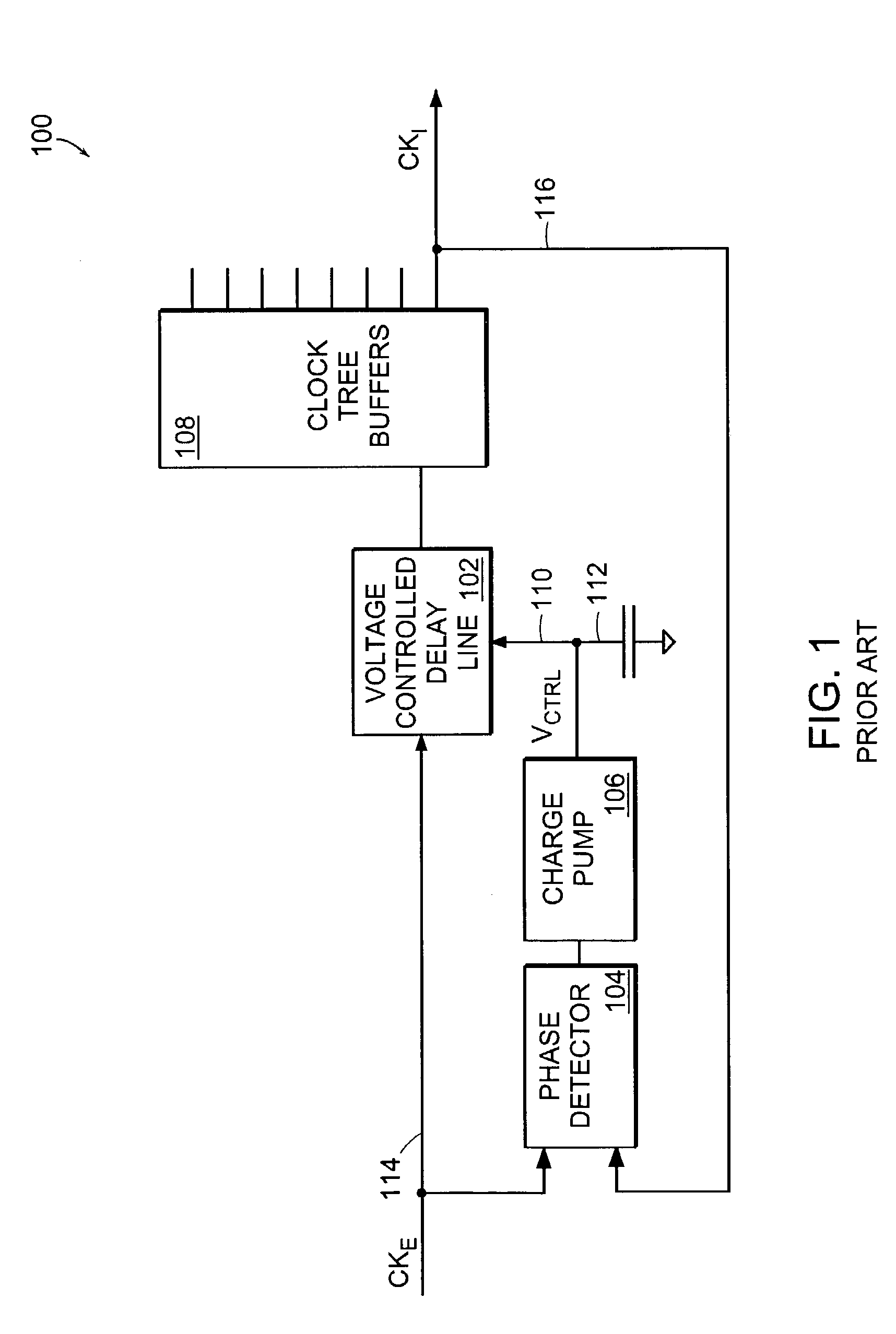

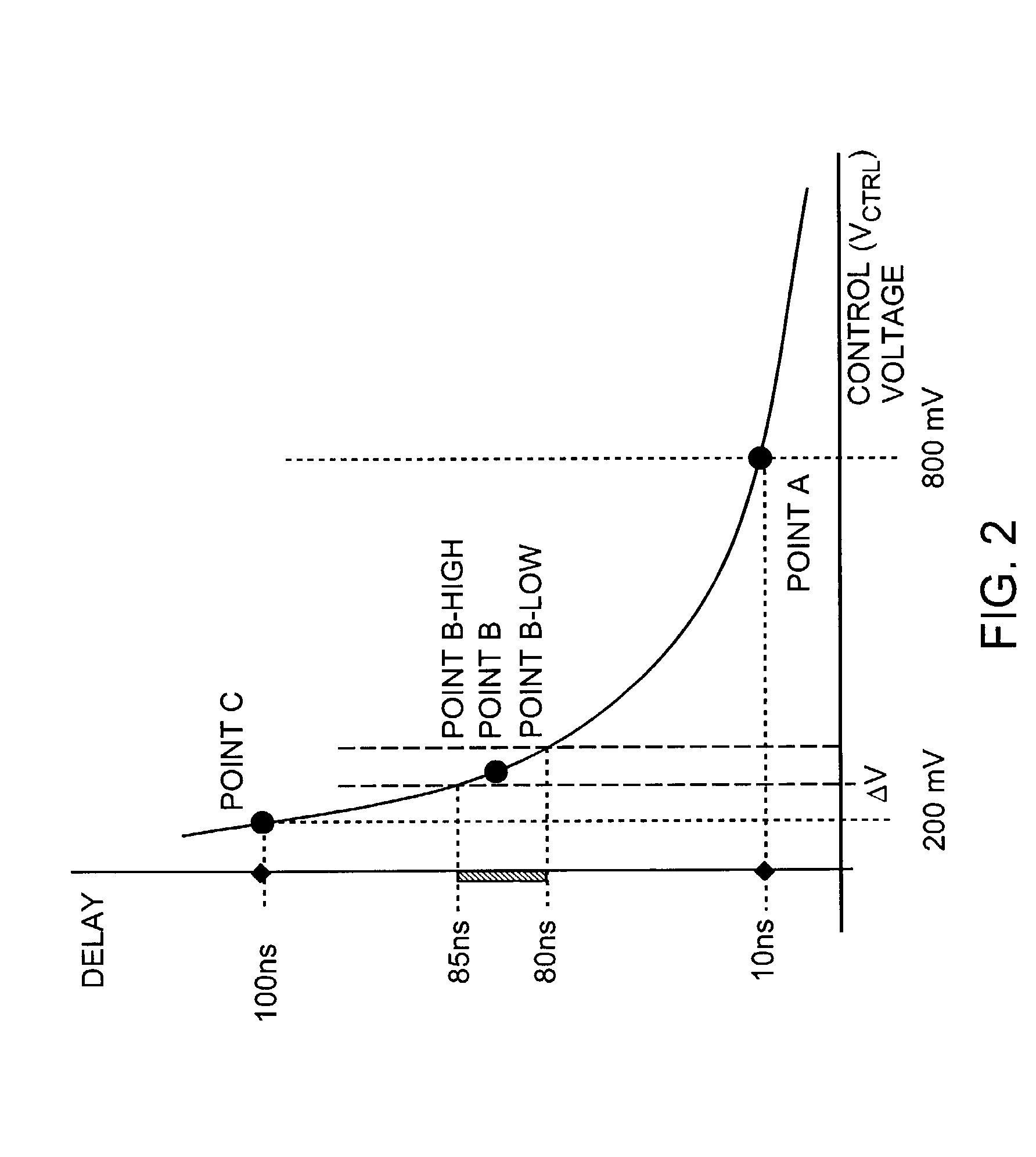

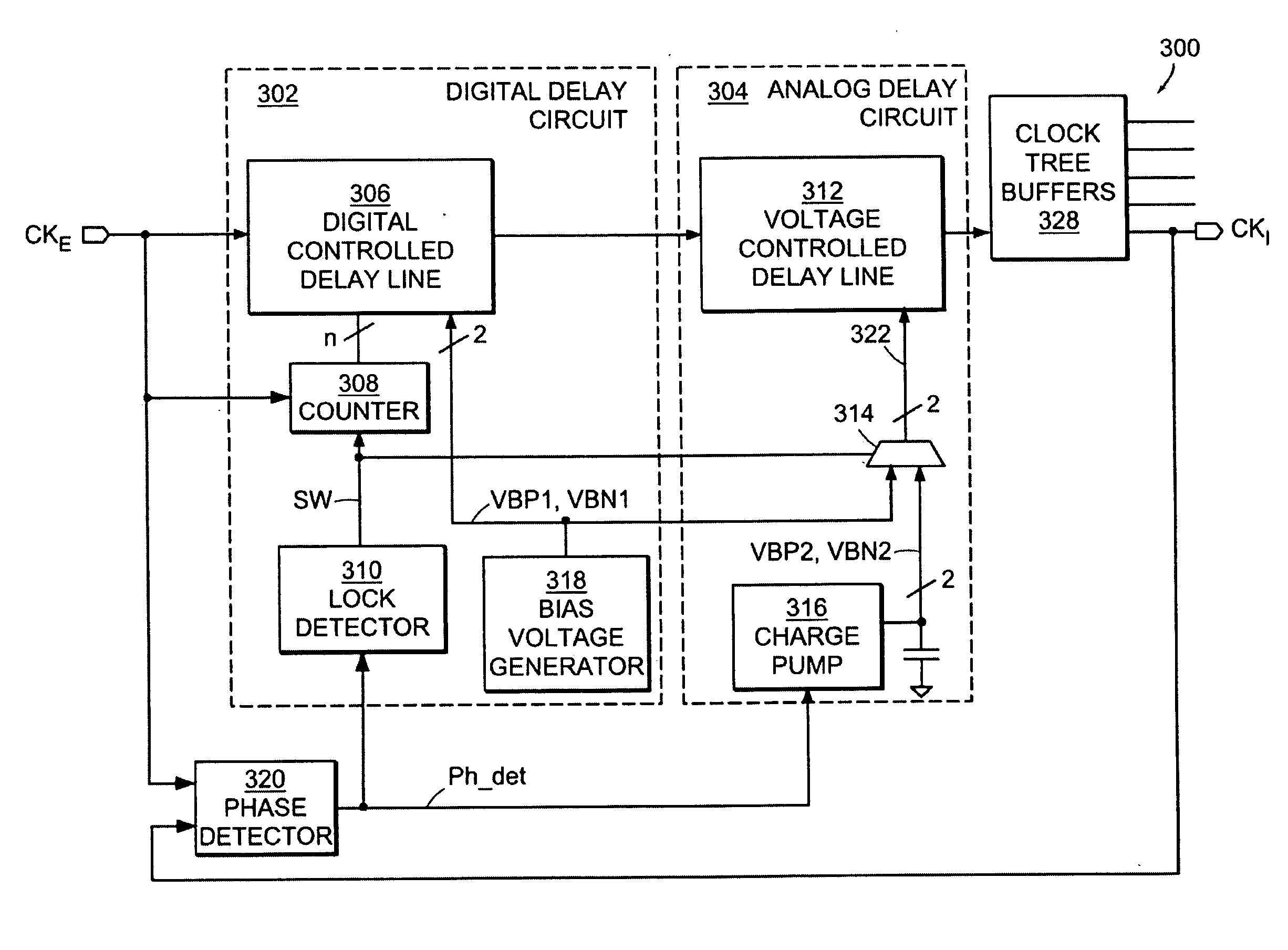

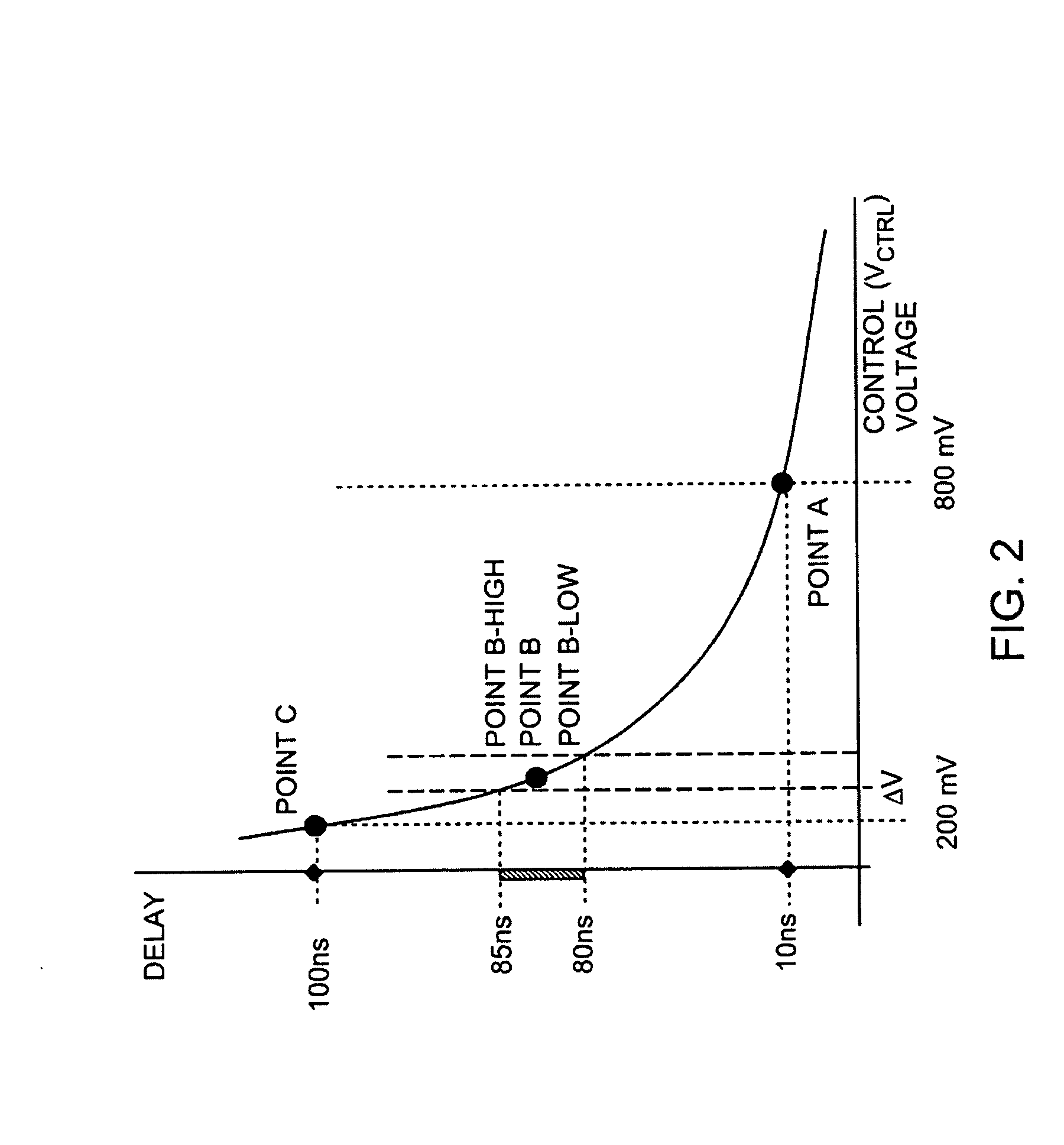

Wide frequency range delay locked loop

ActiveUS7336752B2Improve accuracyImprove stabilityPulse automatic controlAngle demodulation by phase difference detectionDelay-locked loopSilicon

A delay locked loop operates over a wide range of frequencies and has high accuracy, small silicon area usage, low power consumption and a short lock time. The DLL combines an analog domain and a digital domain. The digital domain is responsible for initial lock and operational point stability and is frozen after the lock is reached. The analog domain is responsible for normal operation after lock is reached and provides high accuracy using smaller silicon area and low power.

Owner:MOSAID TECH

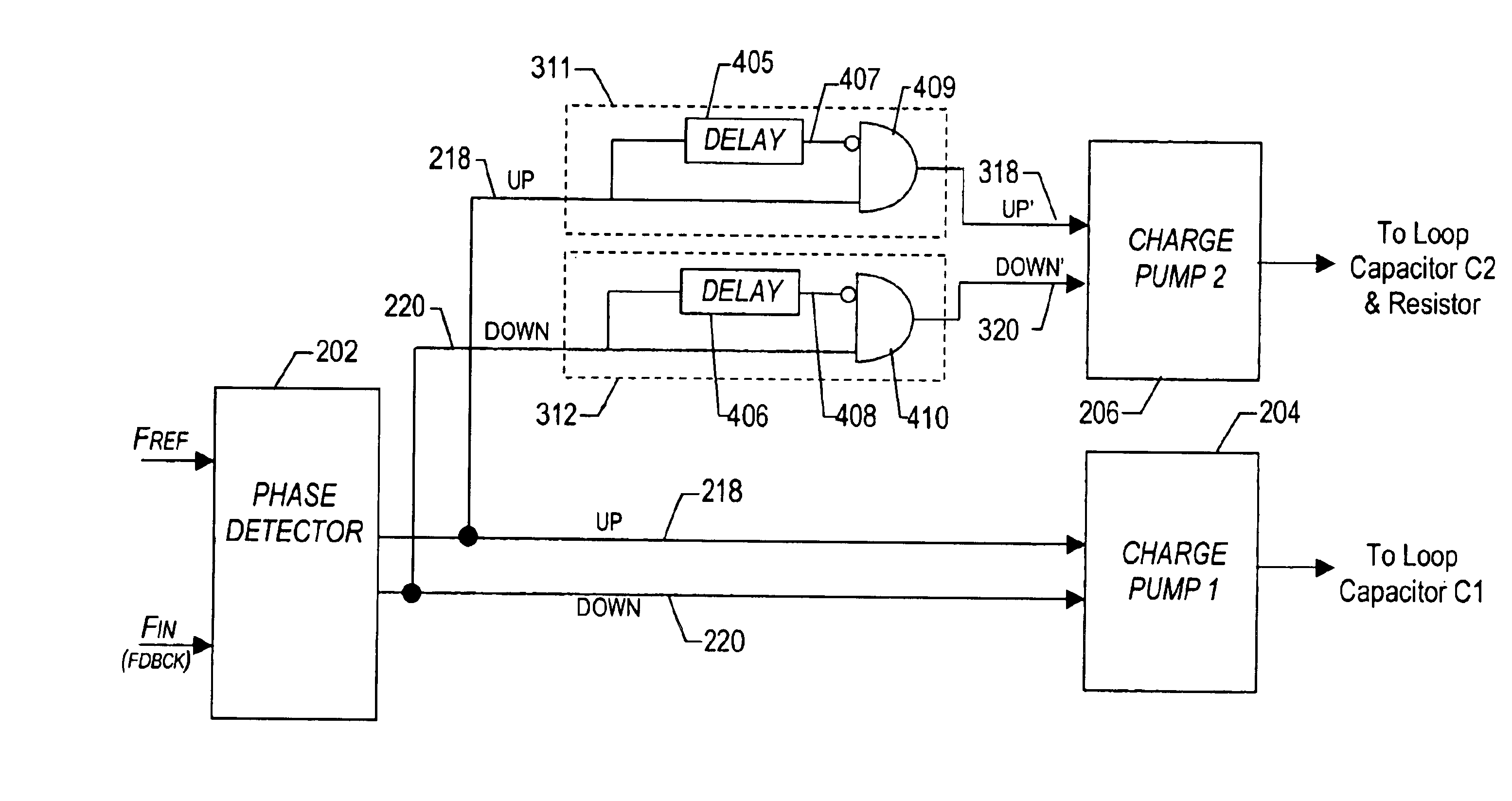

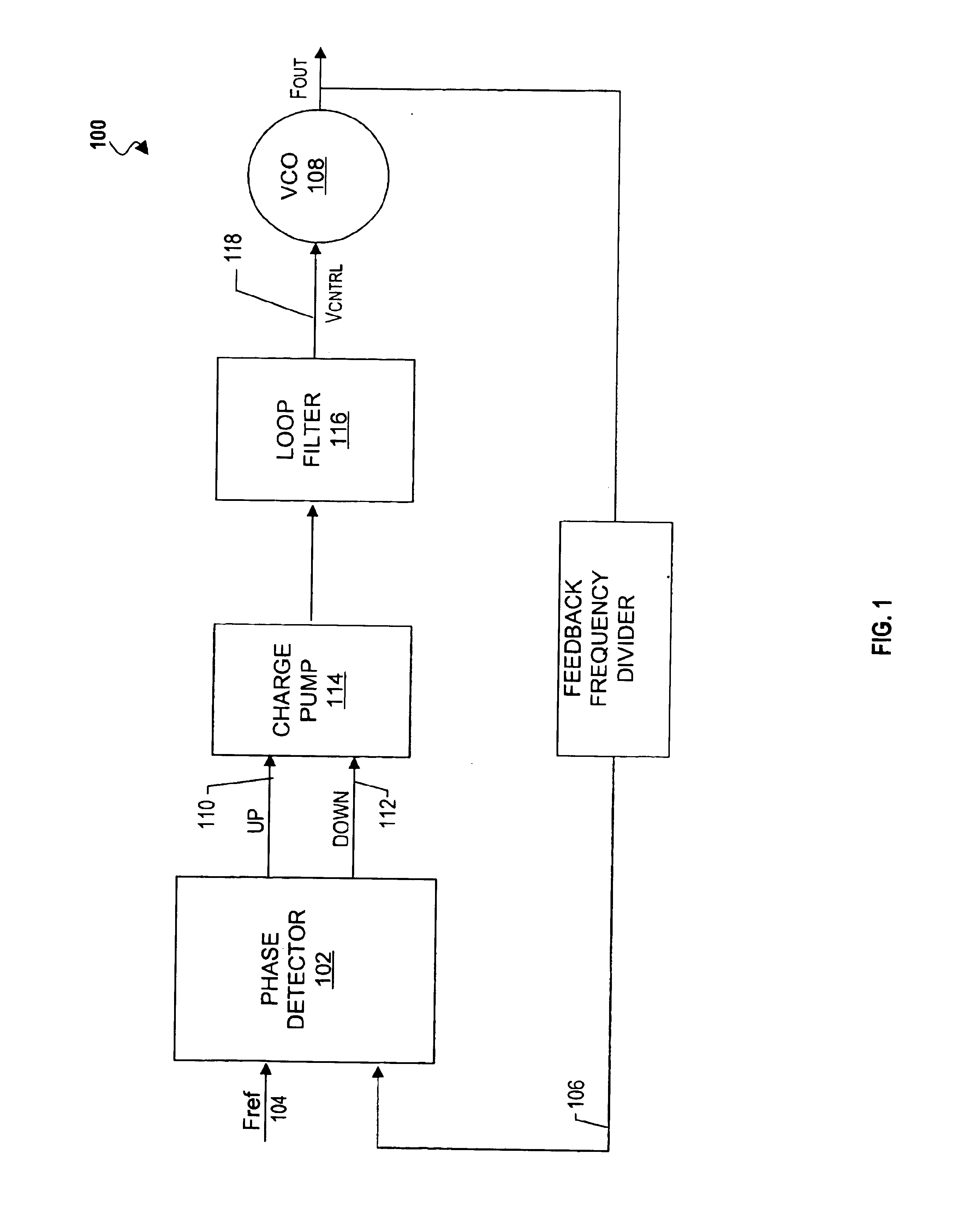

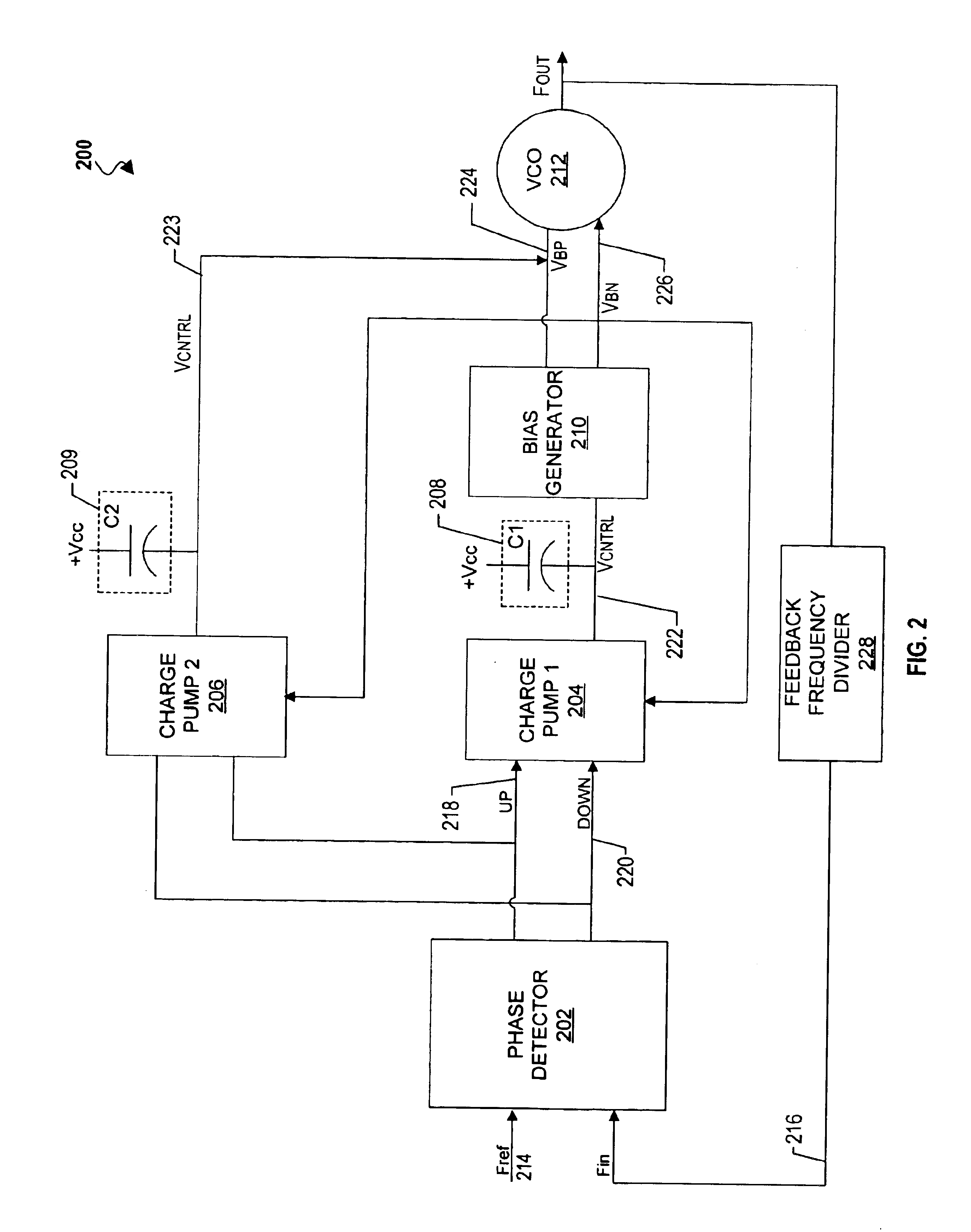

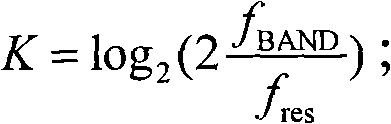

Method and apparatus for reducing lock time in dual charge-pump phase-locked loops

InactiveUS6937075B2Pulse automatic controlAngle demodulation by phase difference detectionPhase detectorControl signal

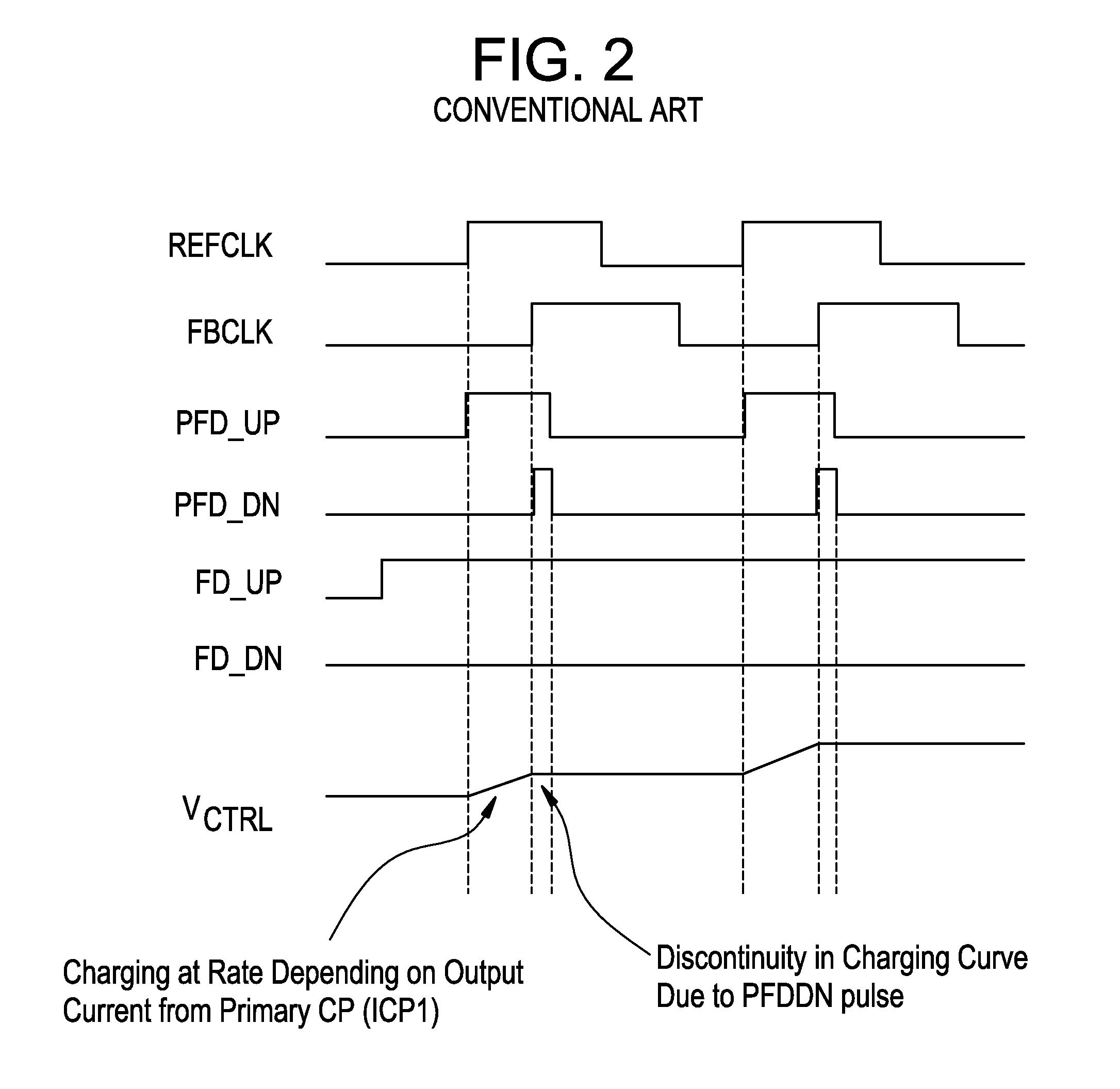

A phase-locked loop includes a phase detector to measure a phase offset between a reference clock signal and a feedback clock signal, and to generate first and second output control signals having a pulse width corresponding to the phase offset. The phase locked loop further includes a first pulse width control circuit coupled to the phase detector to reduce the pulse width of the first output control signal producing a first modified output control signal, a second pulse width control circuit coupled to the phase detector to reduce the pulse width of the second output control signal producing a second modified output control signal, a first charge pump coupled to the phase detector to provide a first charge signal responsive to the first and second output control signals, and a second charge pump coupled to the first and second pulse width control circuits to provide a second charge signal responsive to the first and second modified output control signals.

Owner:INTEL CORP

Phase-locked loop and automatic frequency calibration circuit thereof and phase-locked loop self-tuning locking method

InactiveCN101951259ASpeed up lock timeGuaranteed robustnessPulse automatic controlSelf-tuningLock time

The invention discloses a phase-locked loop and an automatic frequency calibration circuit thereof. The phase-locked loop comprises a phase / frequency detector, a charge pump, a filter, a voltage-controlled oscillator (VCO) and a first frequency divider which are connected in sequence, wherein the phase-locked loop further comprises the automatic frequency calibration circuit; the automatic frequency calibration circuit reduces the oscillation frequency CKV of the VCO when the oscillation frequency CKV of the VCO after undergoing frequency division by the first frequency divider is higher than the reference frequency CKR, and increases the oscillation frequency CKV of the VCO when the oscillation frequency CKV of the VCO is lower than the reference frequency CKR; and a precharging circuit A0 is connected at the input end of the filter and carries out precharging when AFC carries out searching. The phase-locked loop has the rapid self-tuning locking function and ensures the VCO to carry out coarse tuning automatically to approach the final tuning coil, thus reducing the locking time of the phase-locked loop.

Owner:SHANGHAI NATLINEAR ELECTRONICS CO LTD

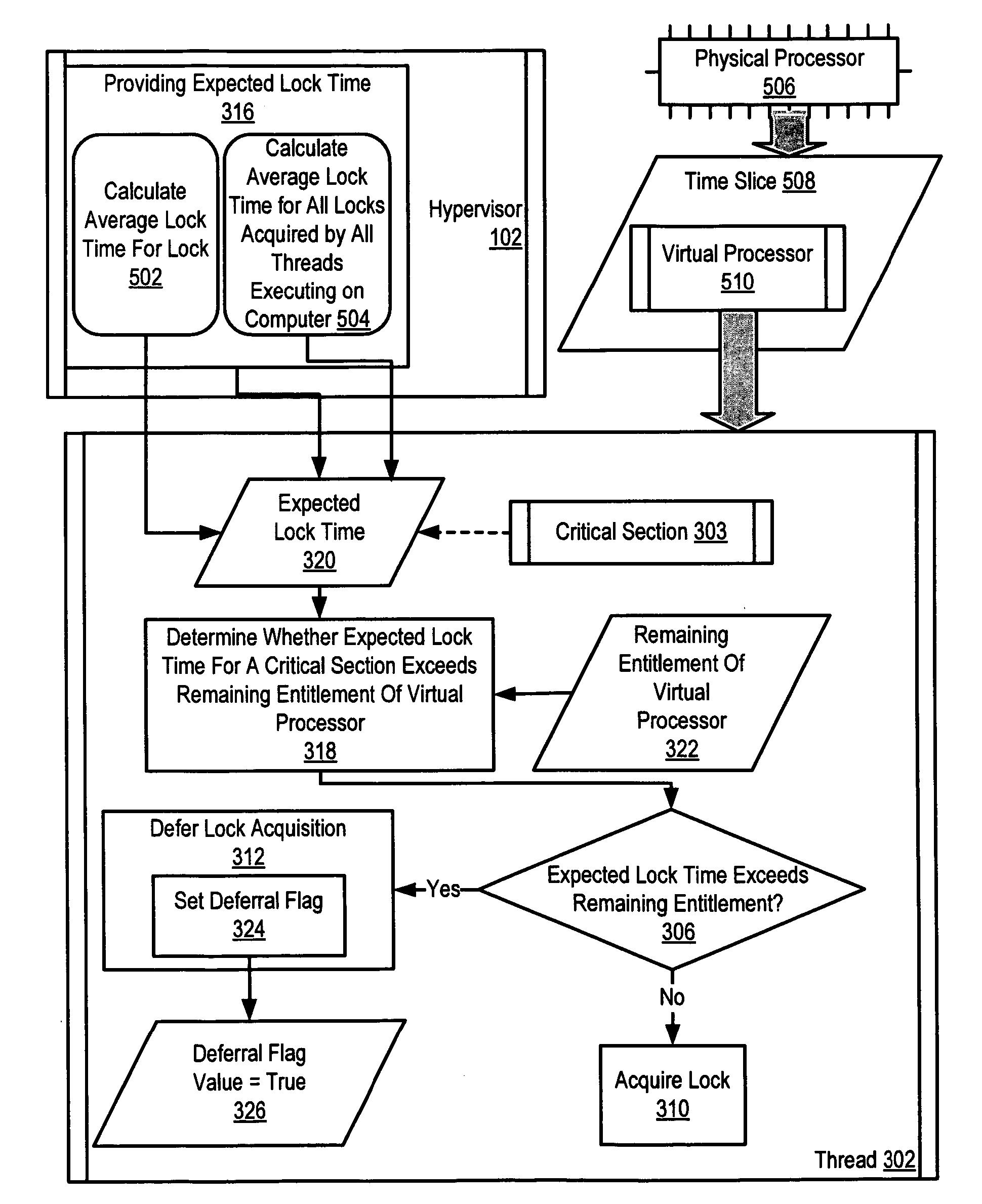

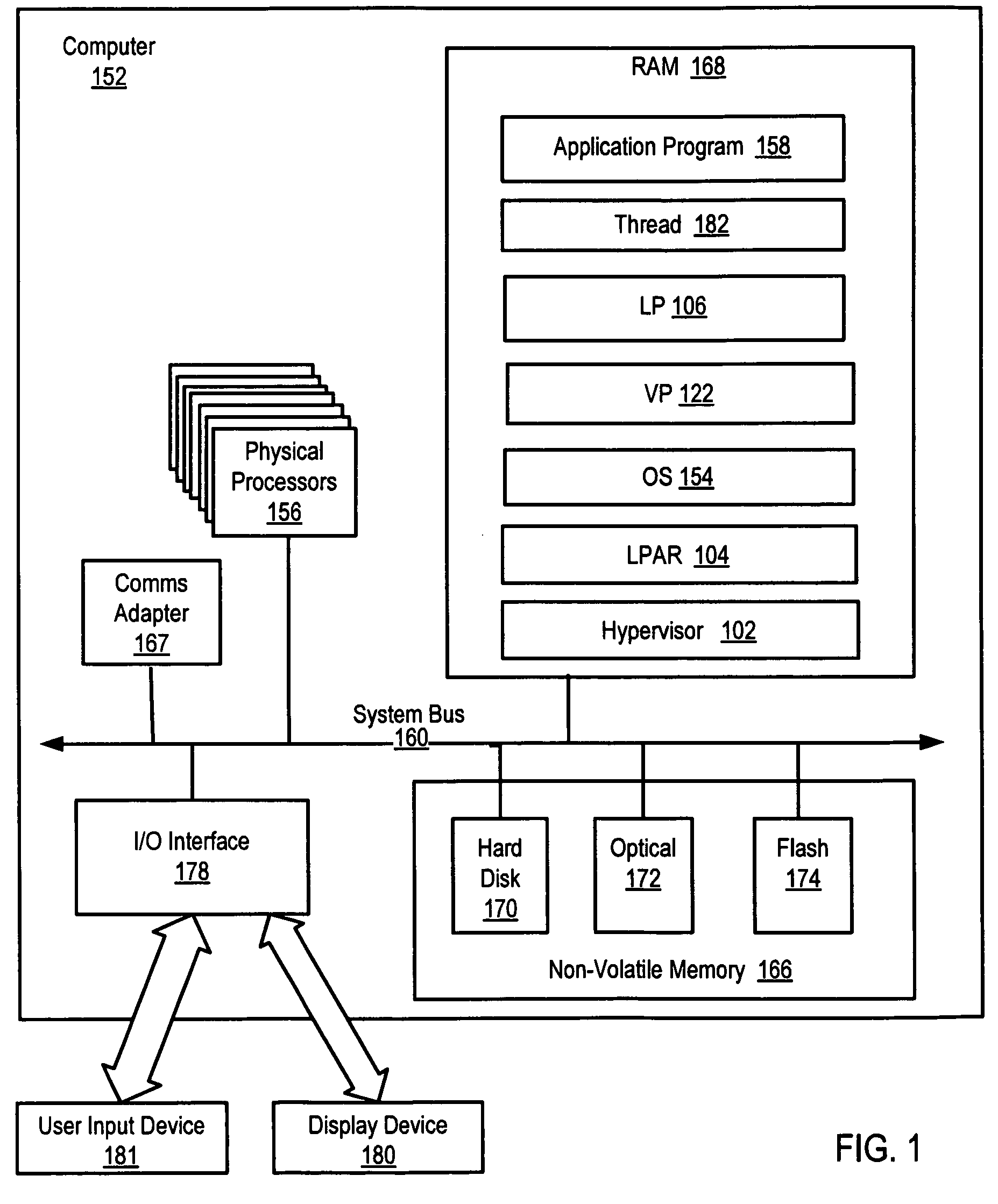

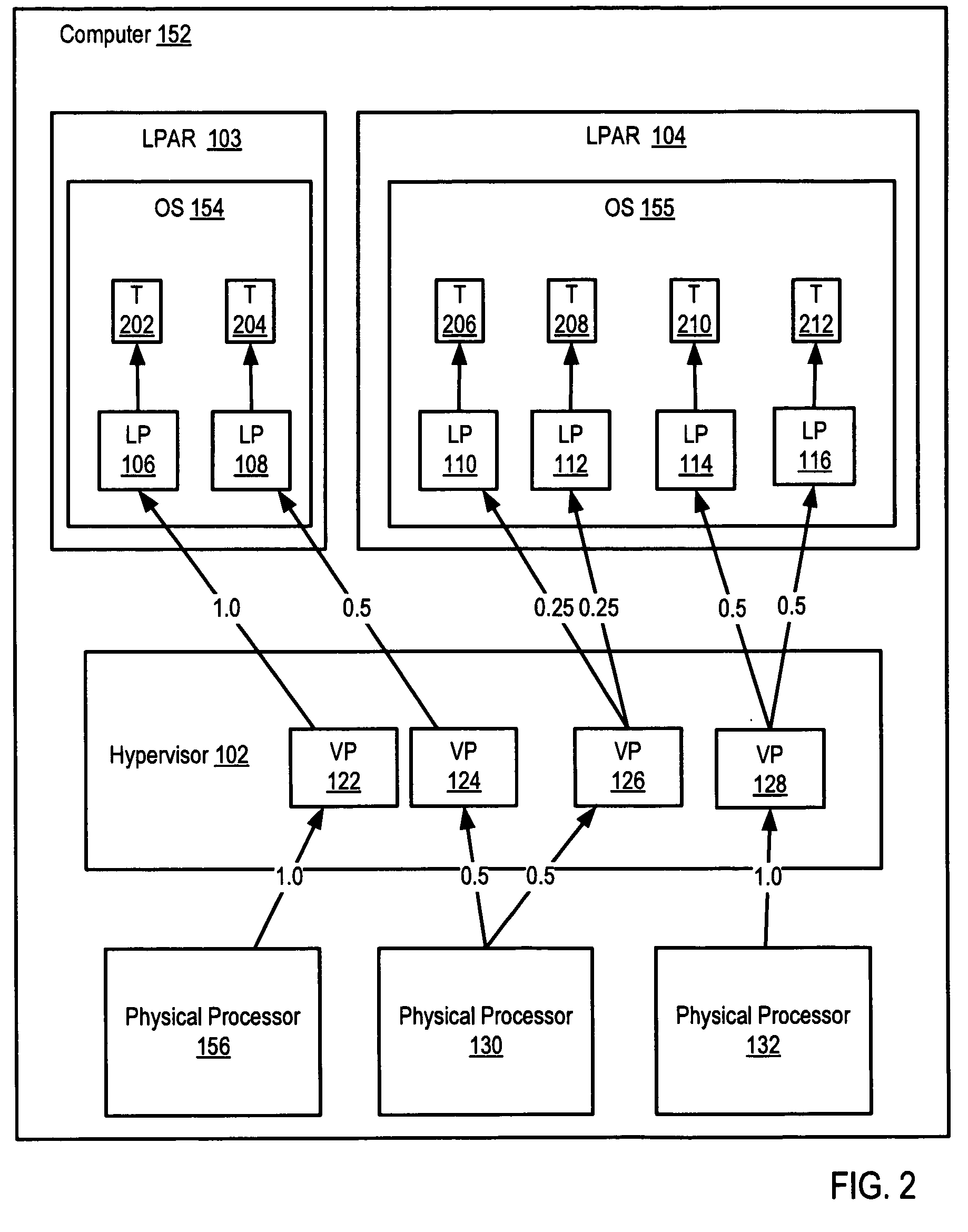

Administration of locks for critical sections of computer programs in a computer that supports a multiplicity of logical partitions

InactiveUS20060277551A1Multiprogramming arrangementsSoftware simulation/interpretation/emulationCritical sectionPhysics processing unit

Administration of locks for critical sections of computer programs in a computer that supports a multiplicity of logical partitions that include determining by a thread executing on a virtual processor executing in a time slice on a physical processor whether an expected lock time for a critical section of the thread exceeds a remaining entitlement of the virtual processor in the time slice and deferring acquisition of a lock if the expected lock time exceeds the remaining entitlement.

Owner:IBM CORP

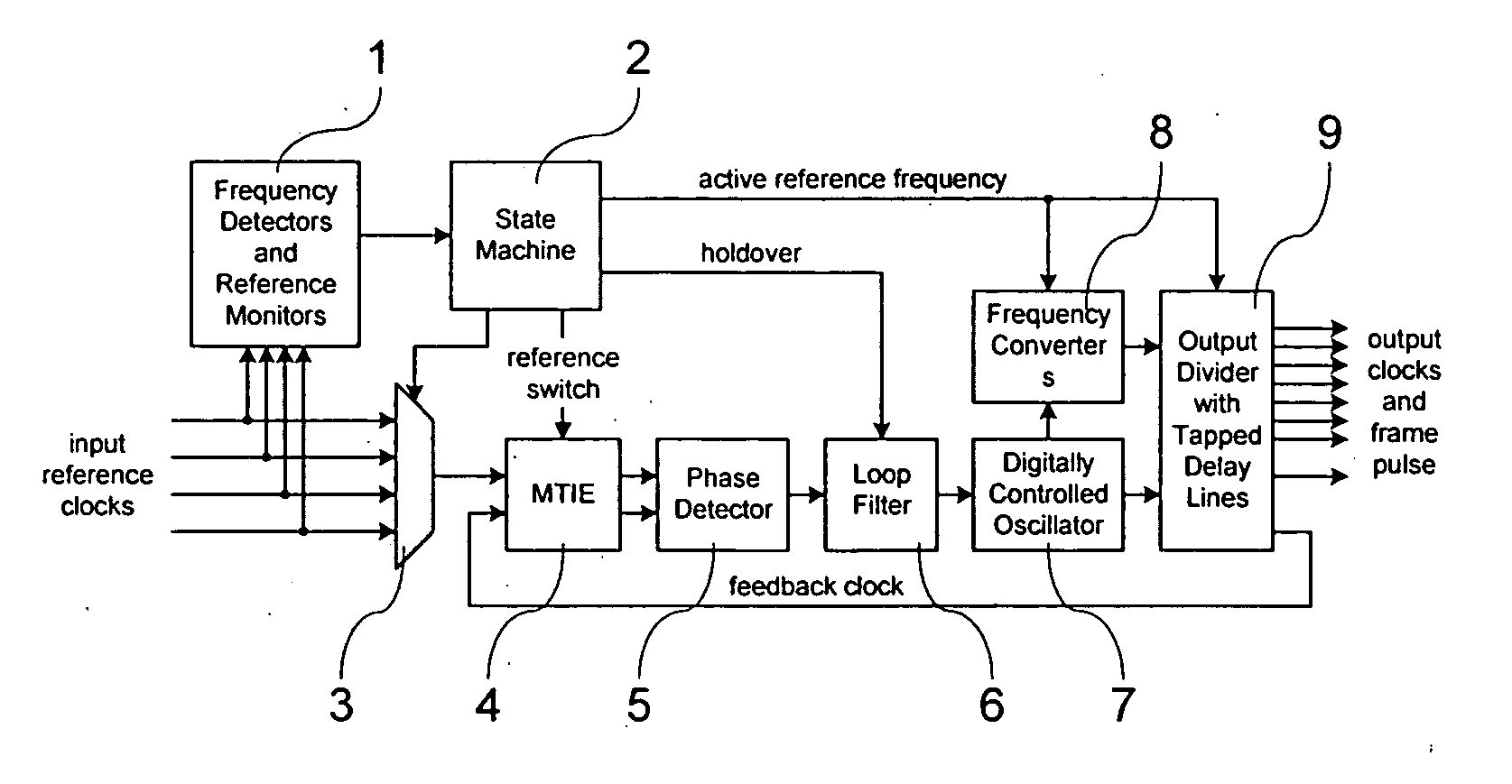

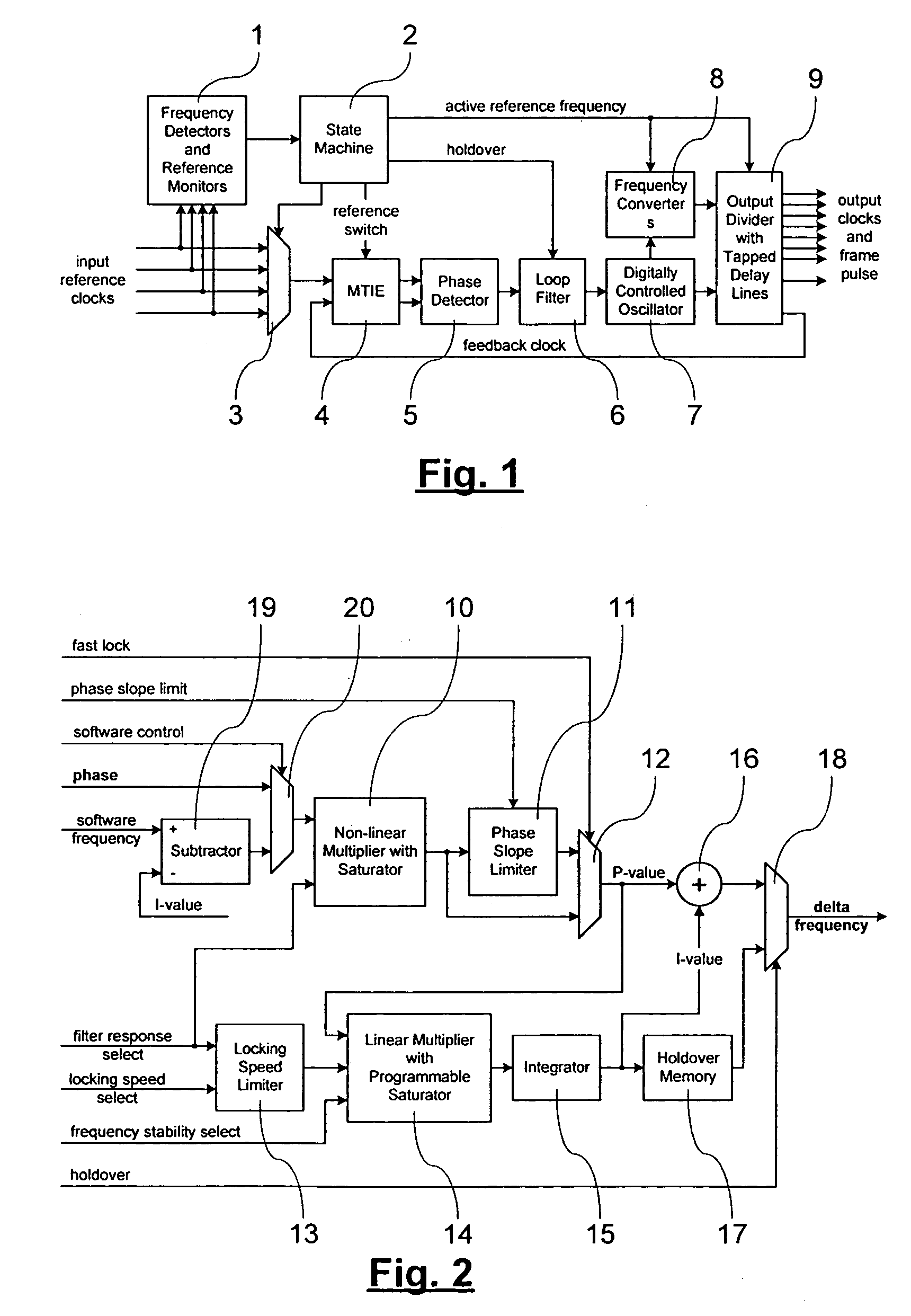

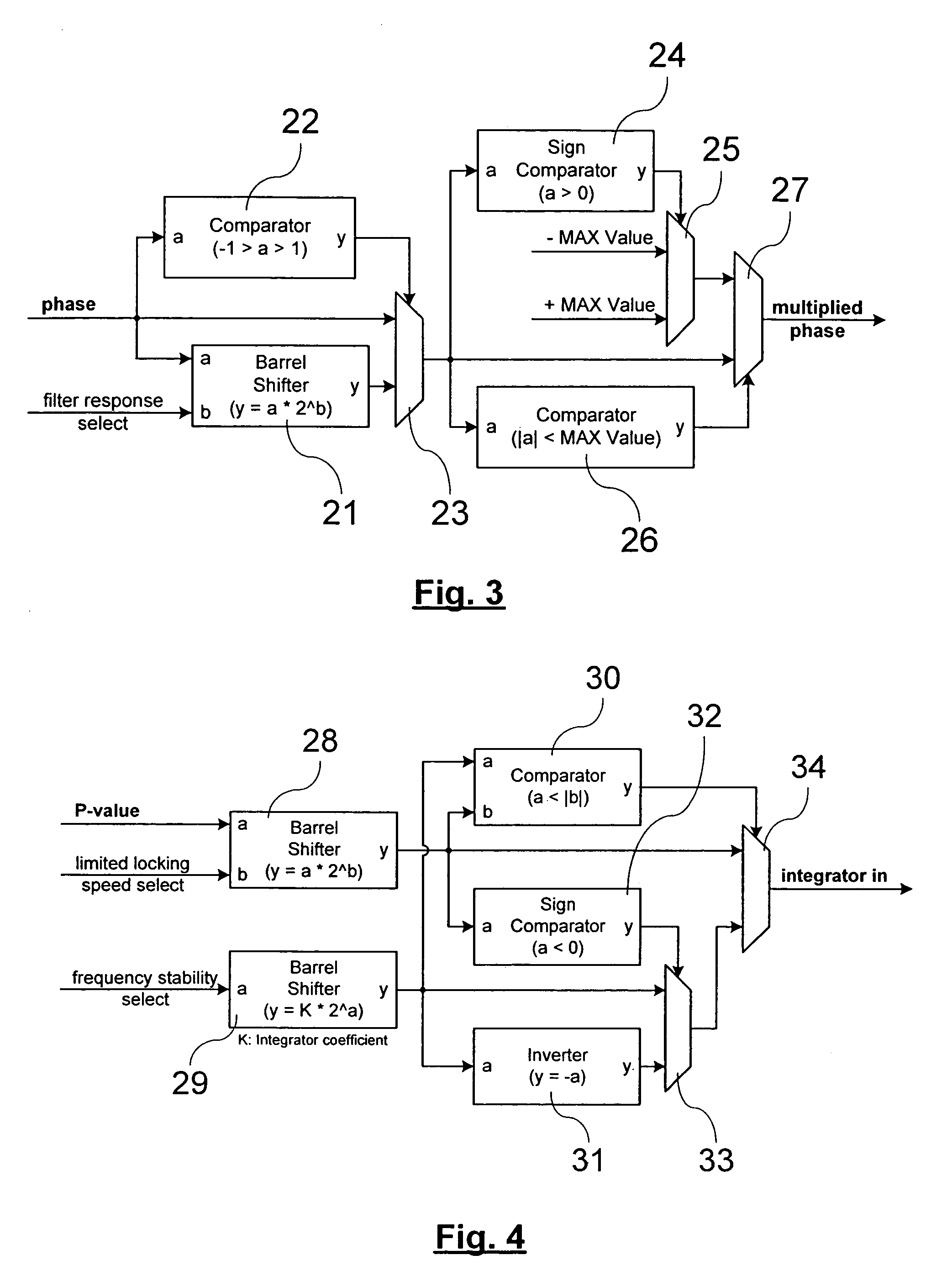

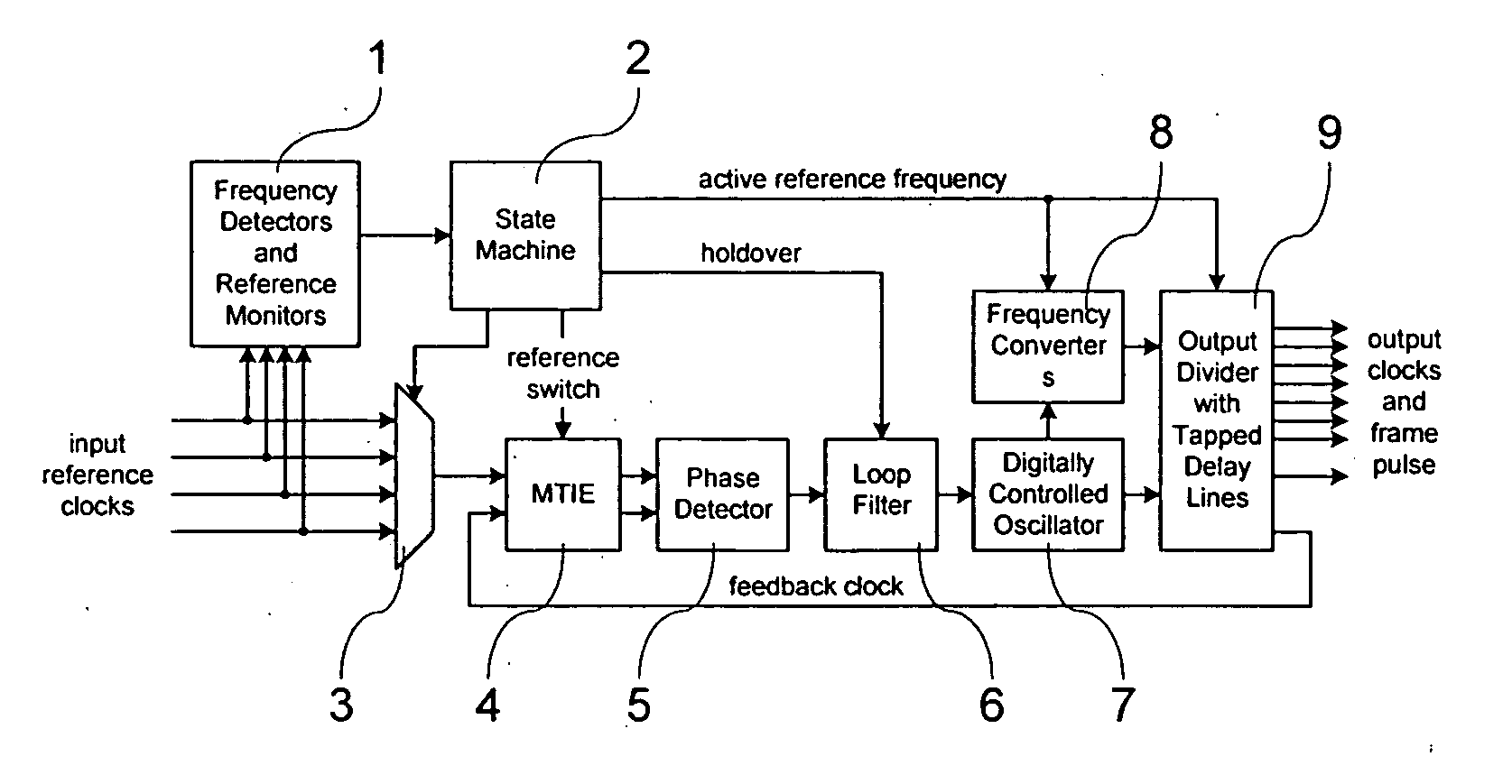

Digital phase locked loop with selectable normal or fast-locking capability

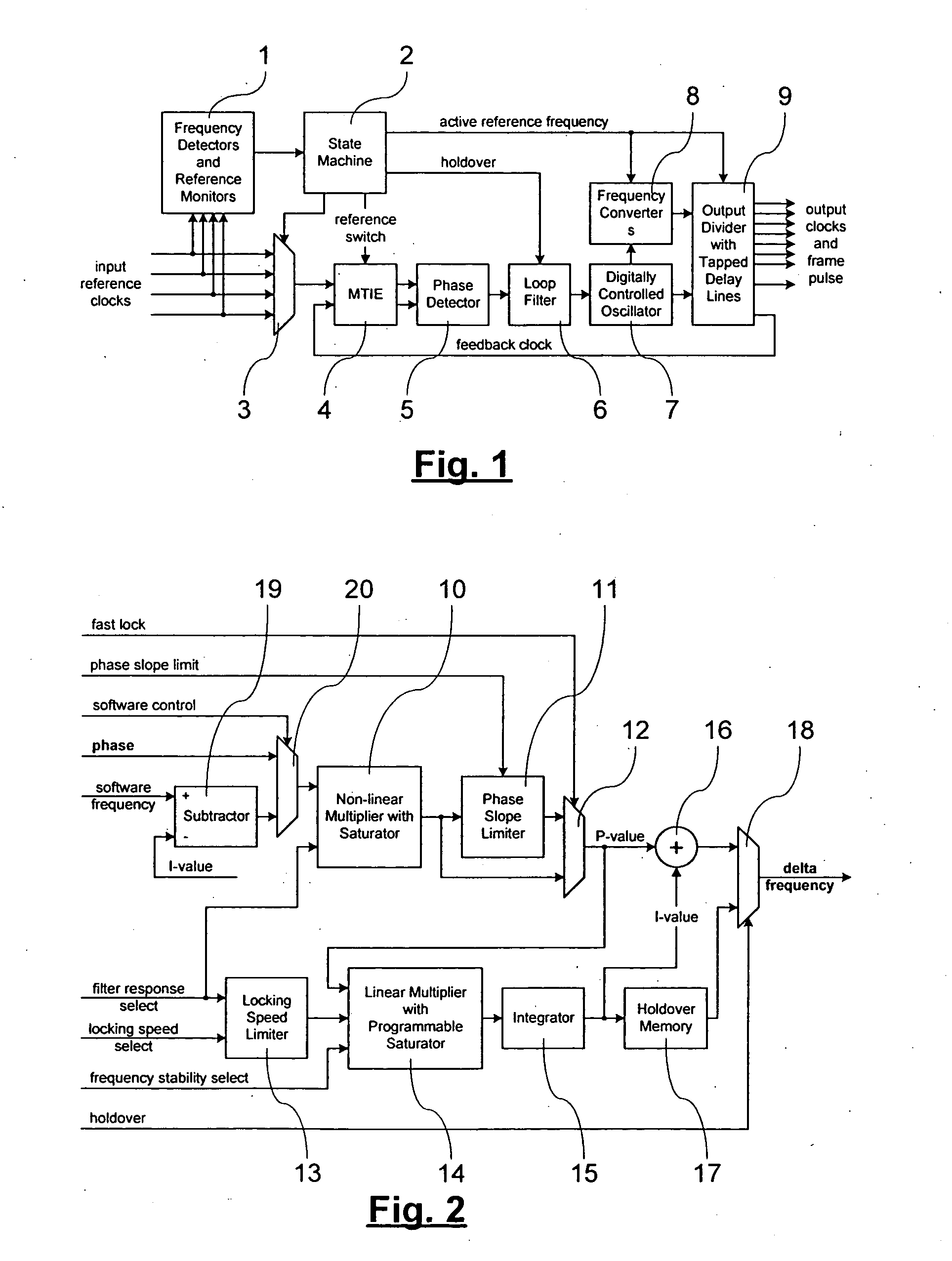

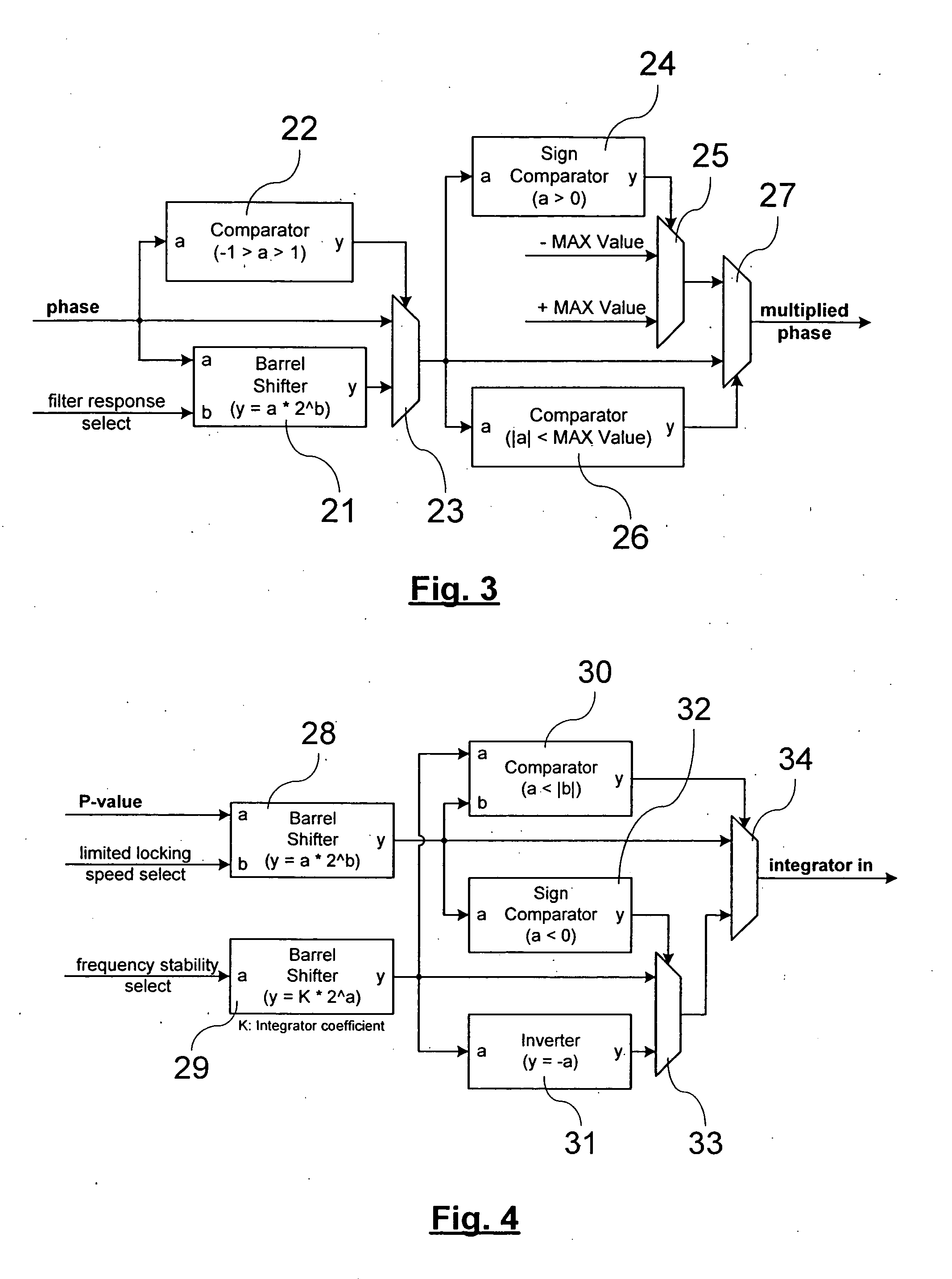

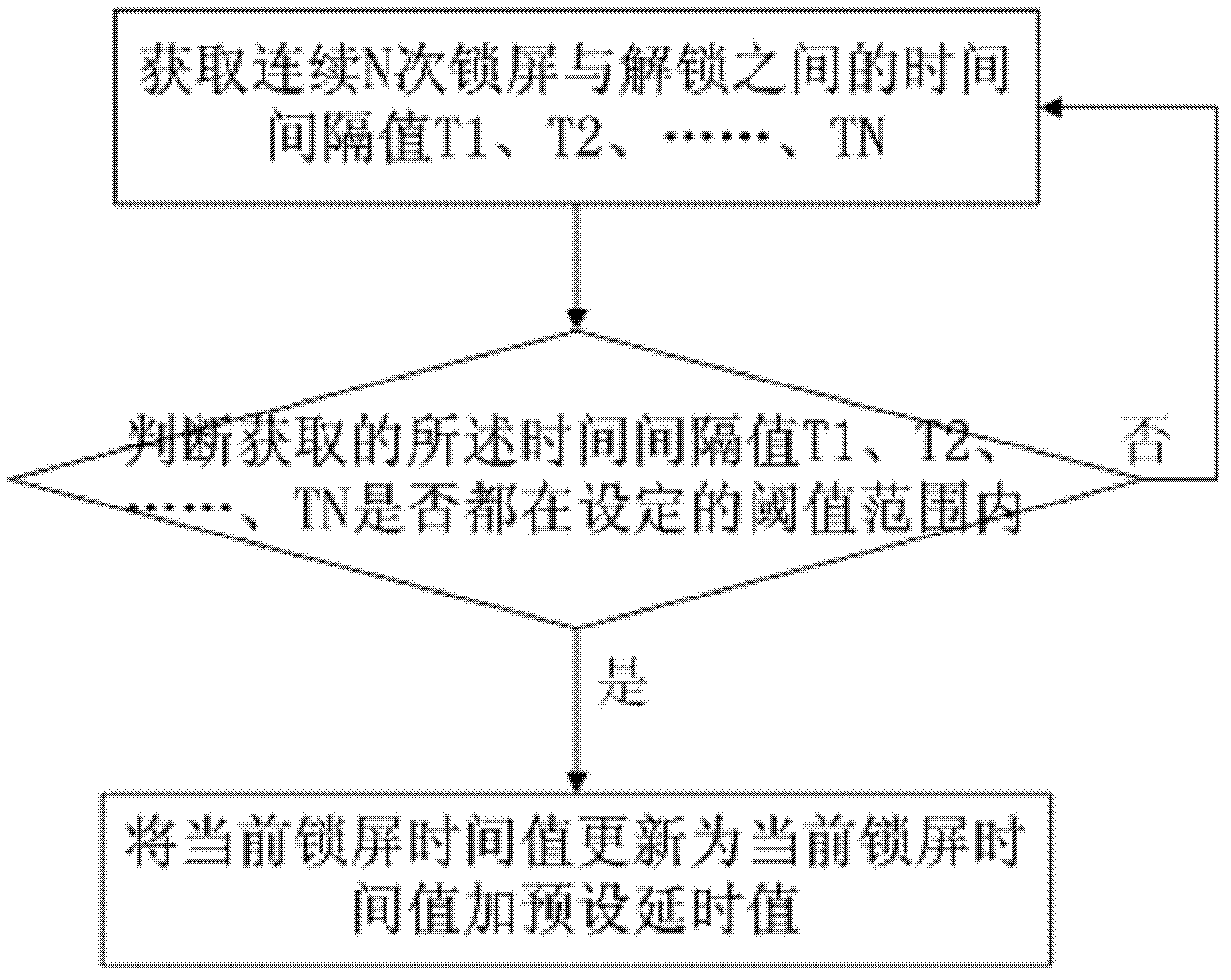

A digital phase locked loop with fast locking capability includes a digitally controlled oscillator for producing an output signal phase locked to an input reference clock, a phase detector for measuring the phase difference between said input reference clock and a feedback clock, and a loop filter for producing a control signal for the digitally controlled oscillator The loop filter includes a proportional circuit for developing a first signal proportional to said phase difference, an integrator for developing a second integrated signal from said first signal, an adder for adding said first and second signals to develop said control signal, and a weighting circuit, preferably a linear multiplier, for selectively adding extra weight to the first signal at an input to the integrator to shorten the locking time of the phase locked loop in a fast locking mode and to rapidly achieve a stable frequency in holdover mode.

Owner:ZARLINK SEMICON LTD

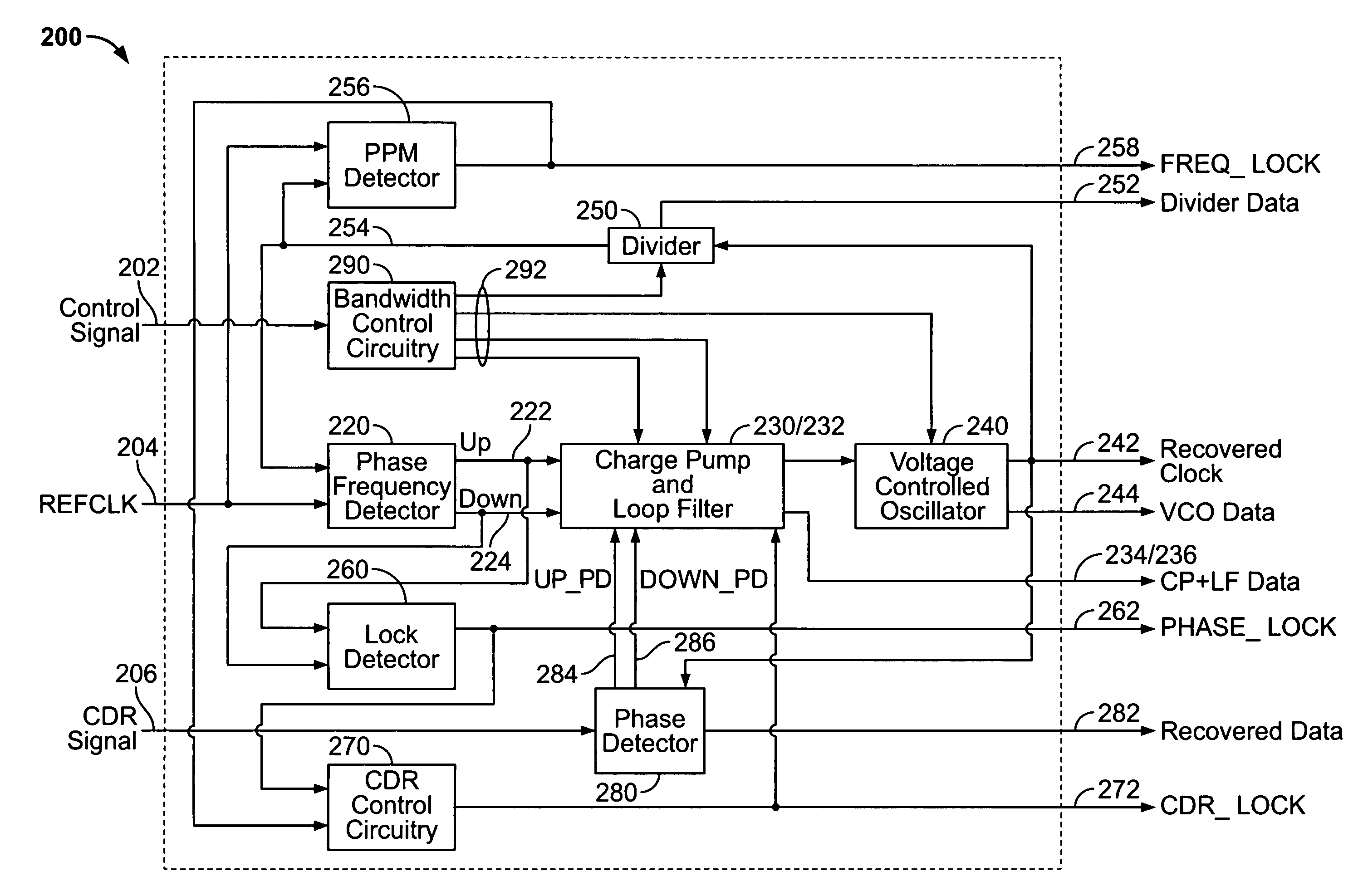

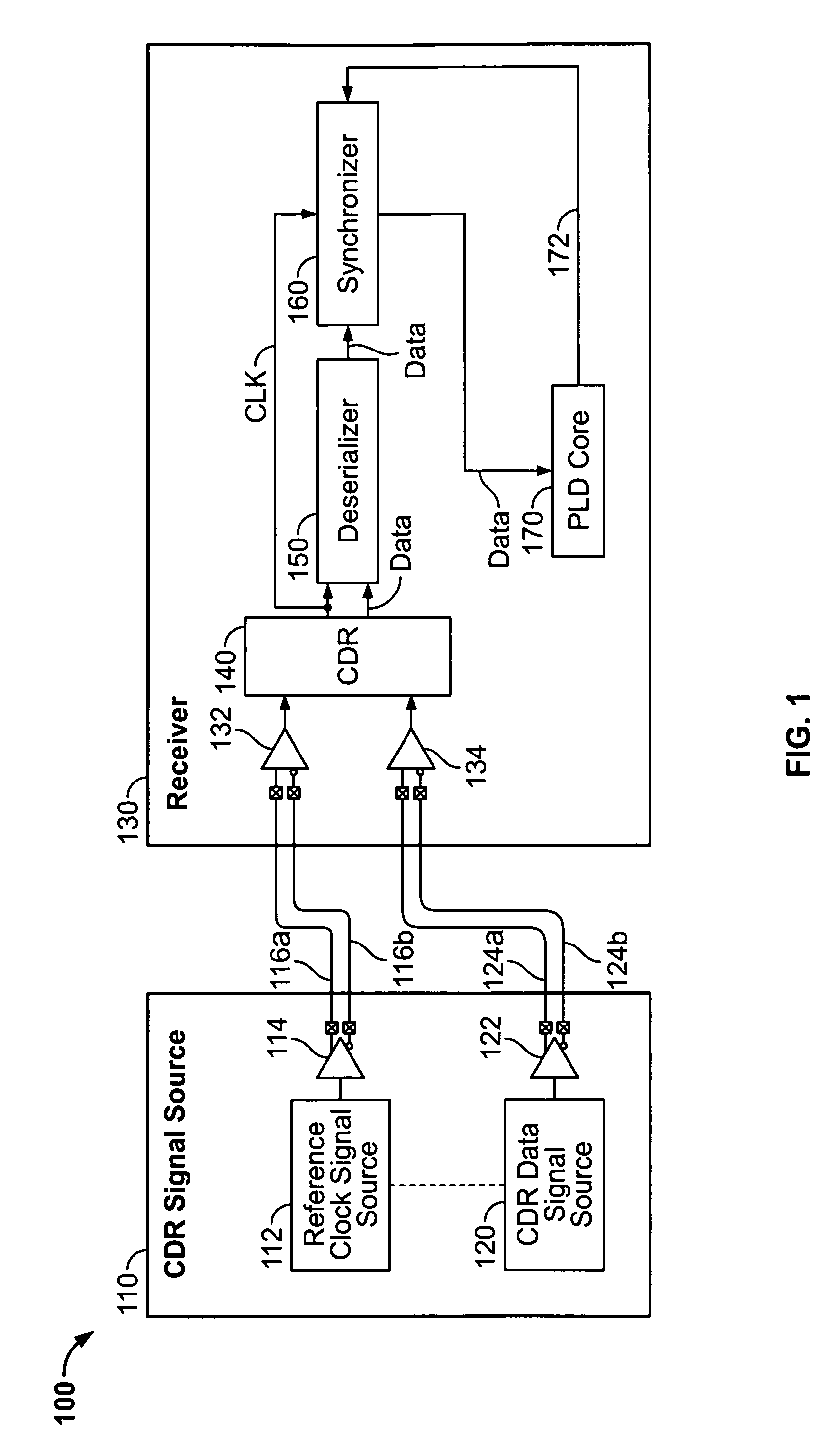

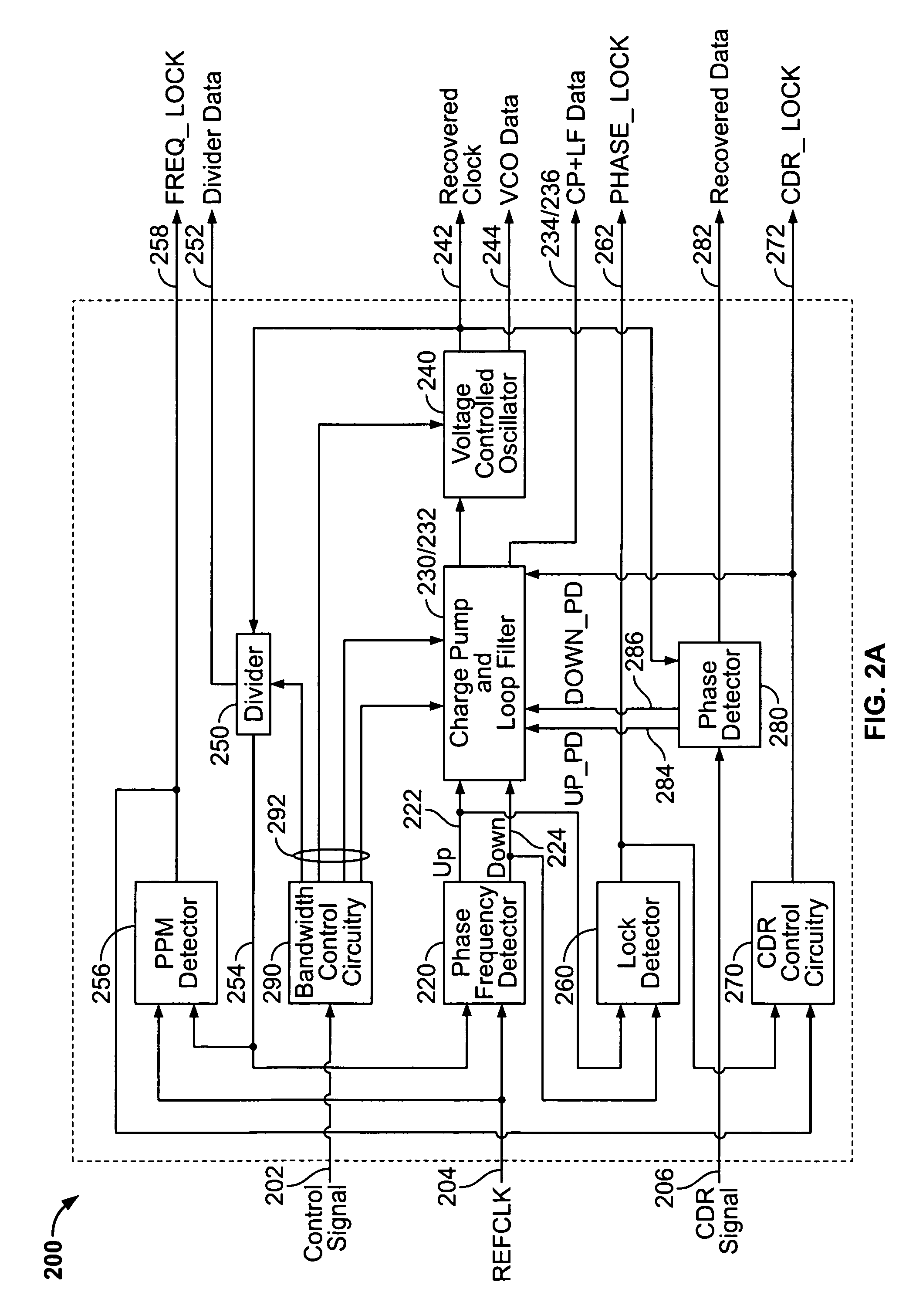

Clock data recovery circuitry and phase locked loop circuitry with dynamically adjustable bandwidths

InactiveUS7149914B1Synchronisation information channelsPulse automatic controlPhase locked loop circuitUser input

Clock data recovery (CDR) circuitry or phase locked loop (PLL) circuitry can be provided with a dynamically adjustable bandwidth. One CDR circuit or PLL circuit can be provided to support multiple systems or protocols, multiple parameter requirements for a given system or protocol, and changes in the input frequency or data rate within a given system or protocol. The parameters can include jitter (e.g., jitter tolerance, jitter transfer, jitter generation), source of dominant noise, and lock time. Control signals can be used to dynamically adjust the bandwidth of the CDR circuitry or PLL circuitry while the circuitry is processing data. The control signals can be set by a PLD, by a processor, by circuitry external to the PLD, or by user input.

Owner:ALTERA CORP

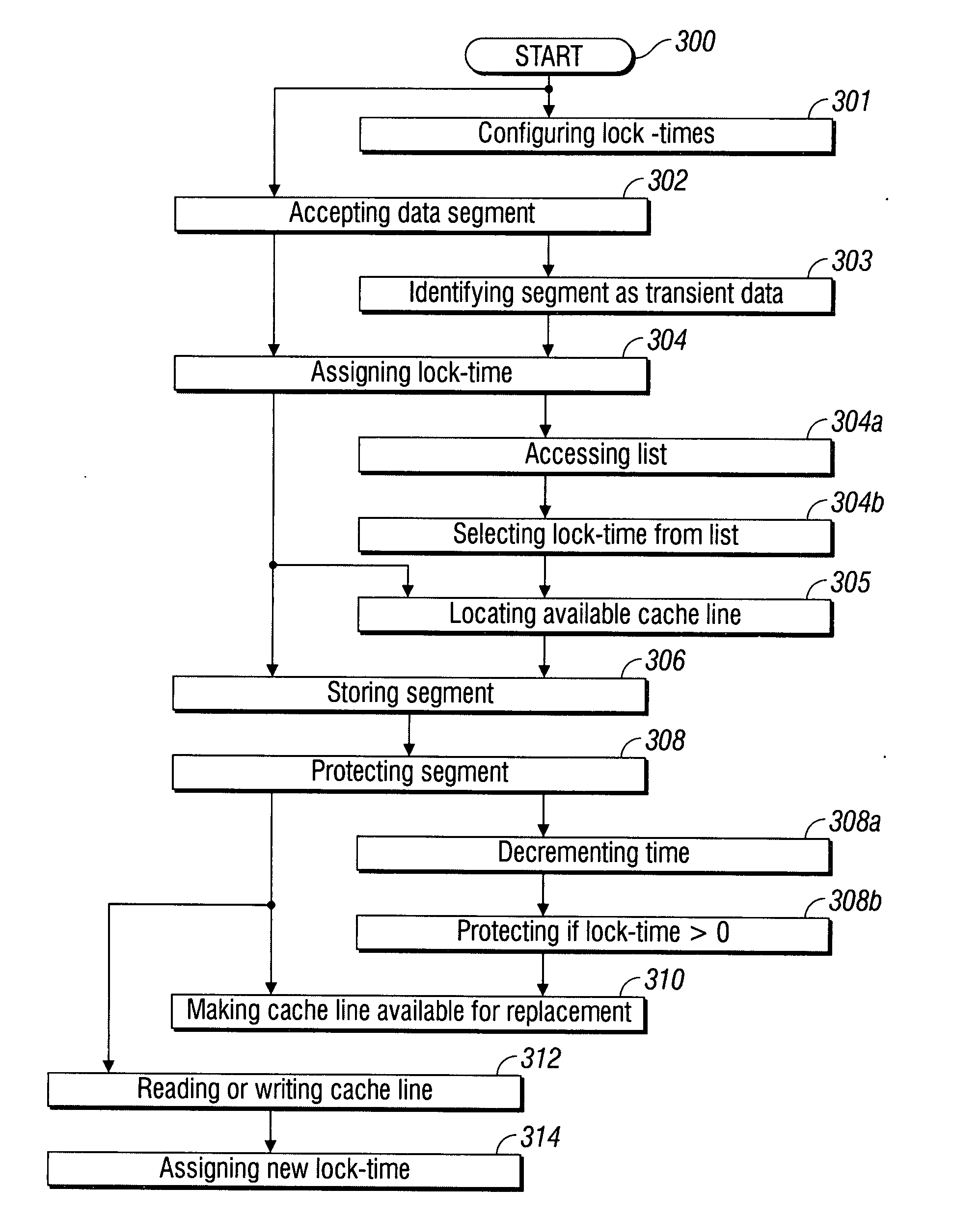

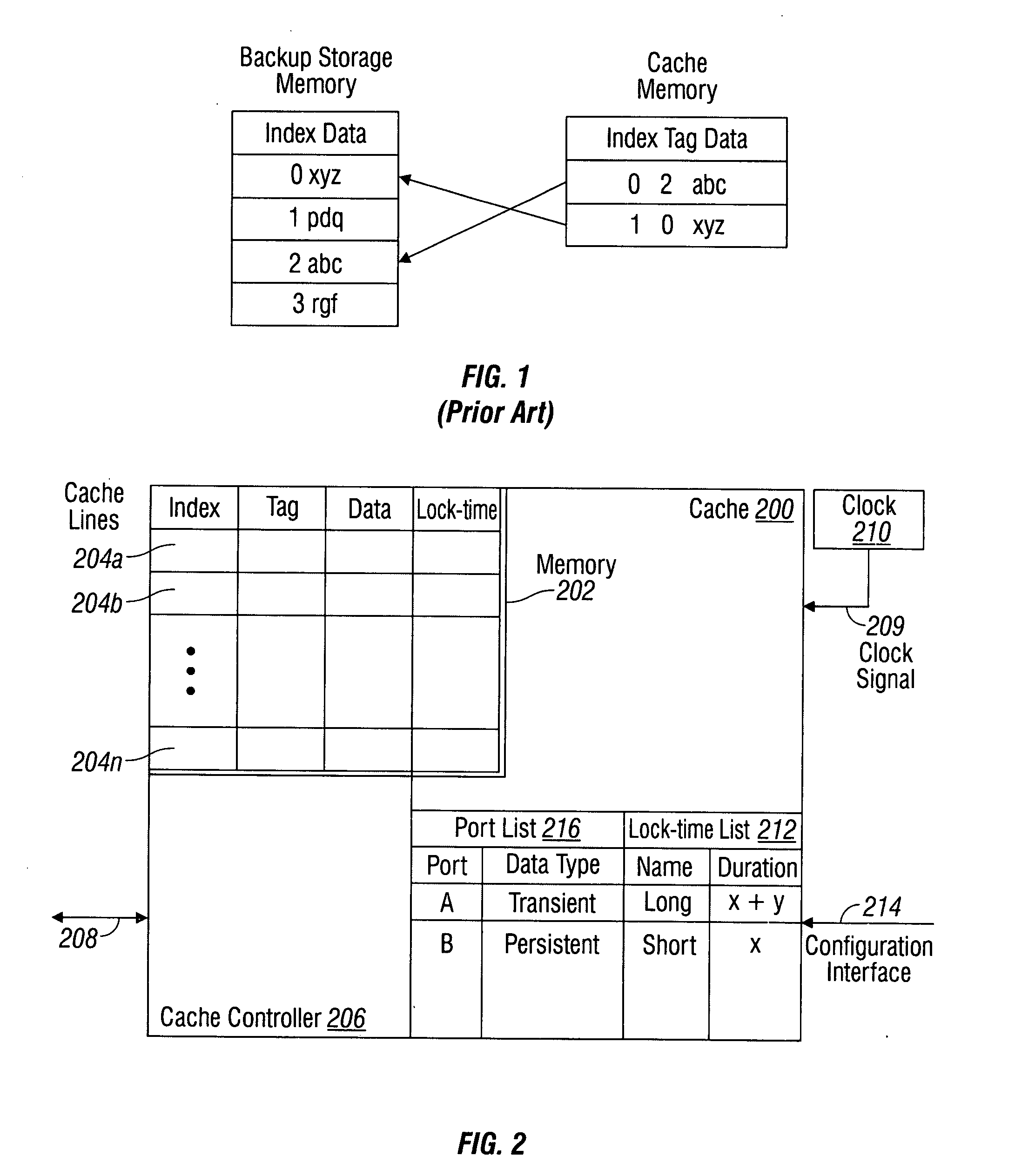

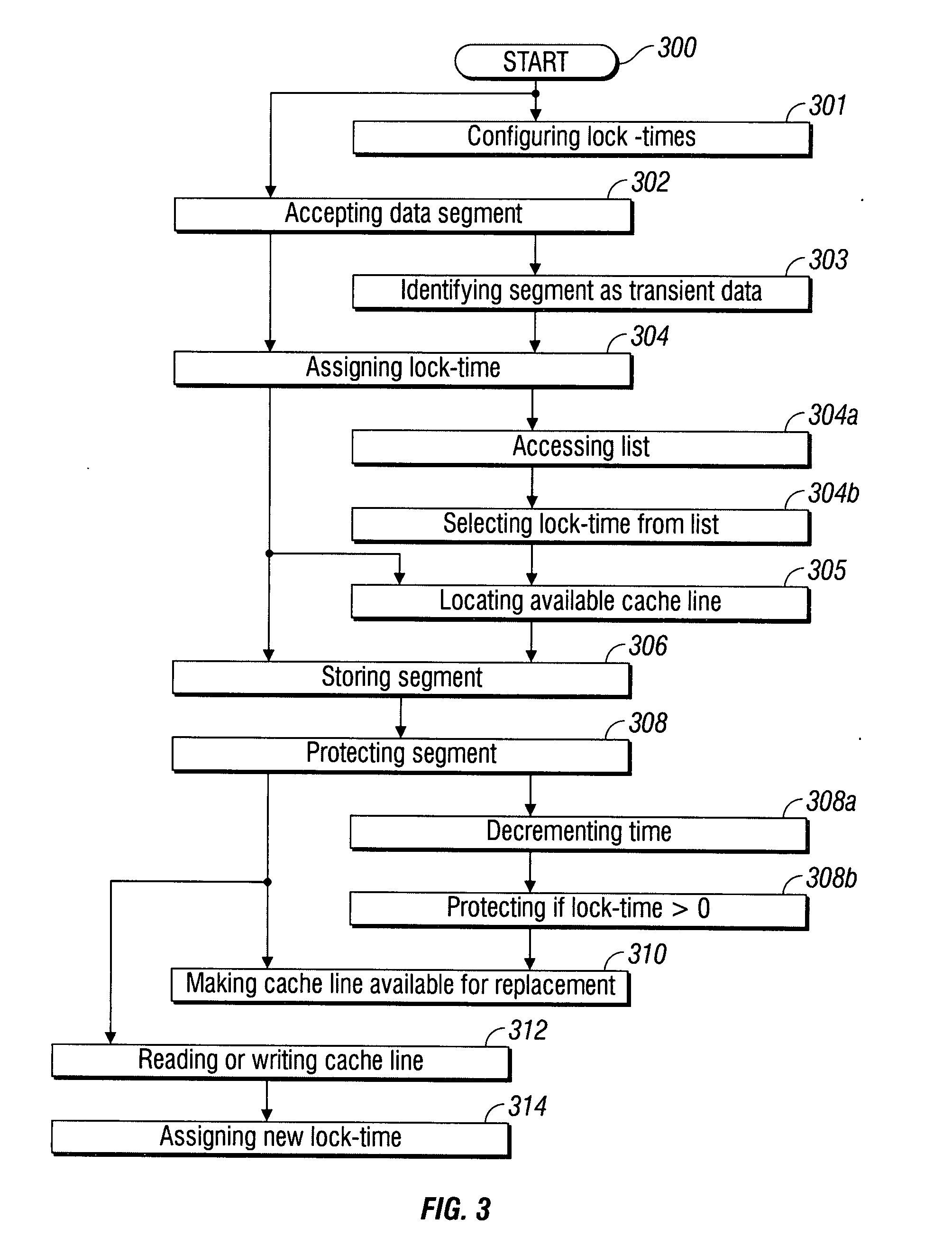

Time-based cache control

InactiveUS20090037660A1Improve performanceSimplifies cache managementMemory systemsParallel computingLock time

A time-based system and method are provided for controlling the management of cache memory. The method accepts a segment of data, and assigns a cache lock-time with a time duration to the segment. If a cache line is available, the segment is stored (in cache). The method protects the segment stored in the cache line from replacement until the expiration of the lock-time. Upon the expiration of the lock-time, the cache line is automatically made available for replacement. An available cache line is located by determining that the cache line is empty, or by determining that the cache line is available for a replacement segment. In one aspect, the cache lock-time is assigned to the segment by accessing a list with a plurality of lock-times having a corresponding plurality of time duration, and selecting from the list. In another aspect, the lock-time durations are configurable by the user.

Owner:APPLIED MICRO CIRCUITS CORPORATION

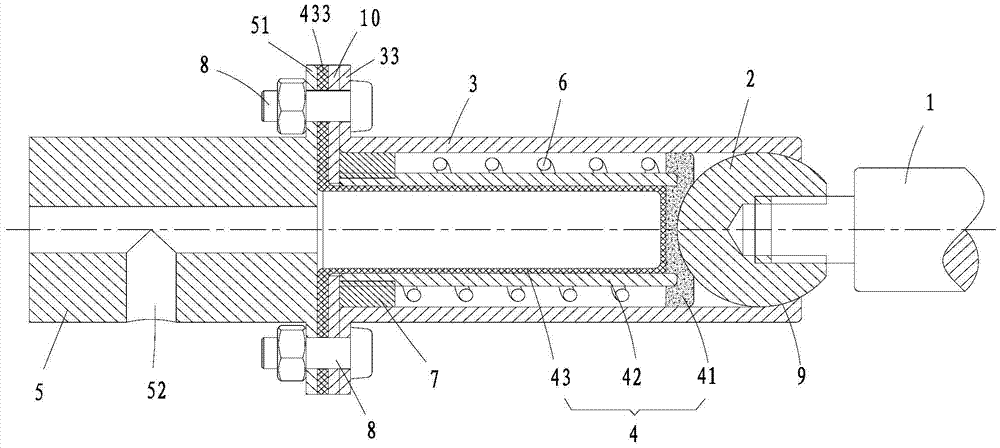

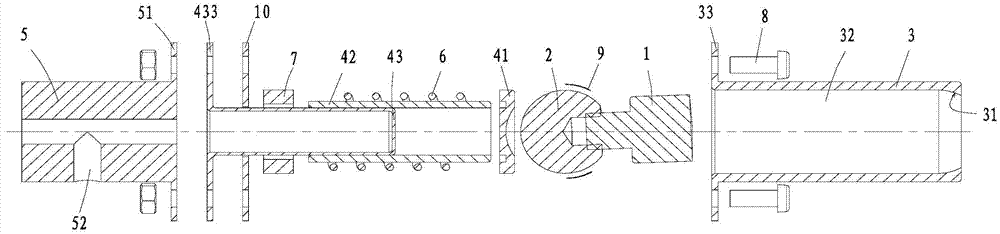

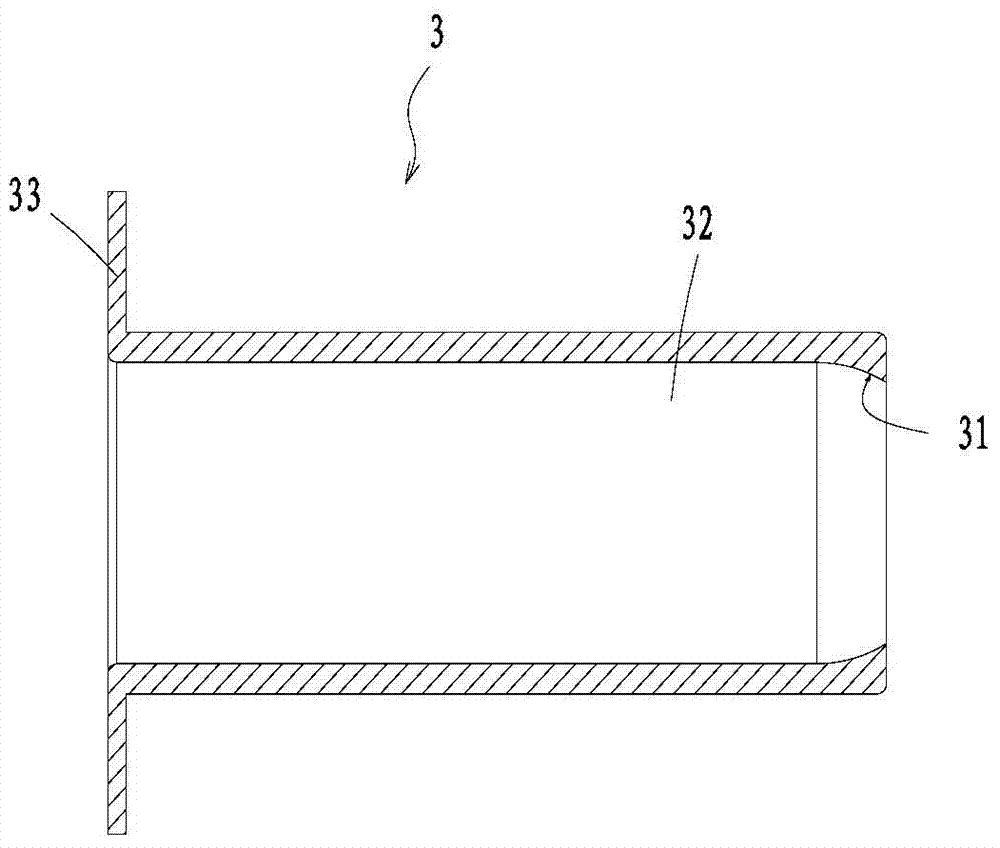

Ball joint locking method and device

ActiveCN103610555AAchieve instant multi-point lockAchieve isolationJointsOperating tablesEngineeringSacroiliac joint

The invention provides a ball joint locking method and a locking device designed according to the method. A ball head of a ball joint is sleeved with a connecting sleeve which can be movably locked with the ball head or be in a release state with the ball head. An abutting assembly connected with a hydraulic system is arranged in a position corresponding to a matching position of the ball head and the connecting sleeve at locking time. Under the action of pressure oil provided by the hydraulic system, the abutting assembly is forced to instantly press the outer surface of the ball head and enables the ball head to abut against the position matched with the connecting sleeve at the same time, so that the abutting assembly and the connecting sleeve lock the ball head in a multipoint mode. When pressure is released, the abutting assembly and the connecting sleeve can restore to original positions automatically, so that the locking state and the release state of the ball joint can be switched quickly. According to the ball joint locking method and the locking device, the characteristics that the hydraulic system is small in inertia and quick in response are fully utilized, so that that the device have the advantages of being simple in structure, reliable in locking, and good in effect, and can ensure rigid connection and bear certain load moment at the same time. Moreover, locking devices can be connected in series through the same oil path for utilization in one product.

Owner:SHENZHEN INST OF ADVANCED TECH CHINESE ACAD OF SCI

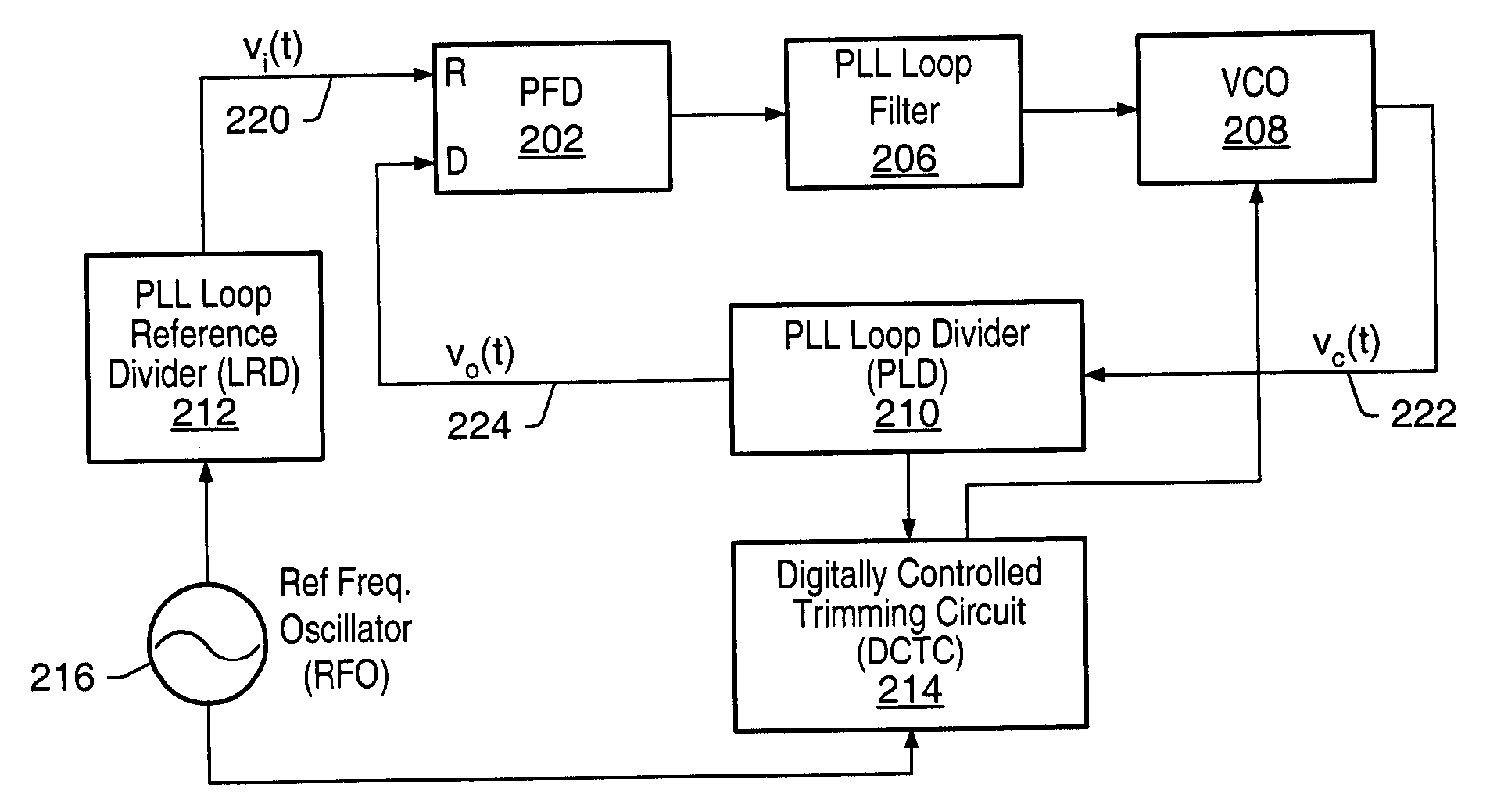

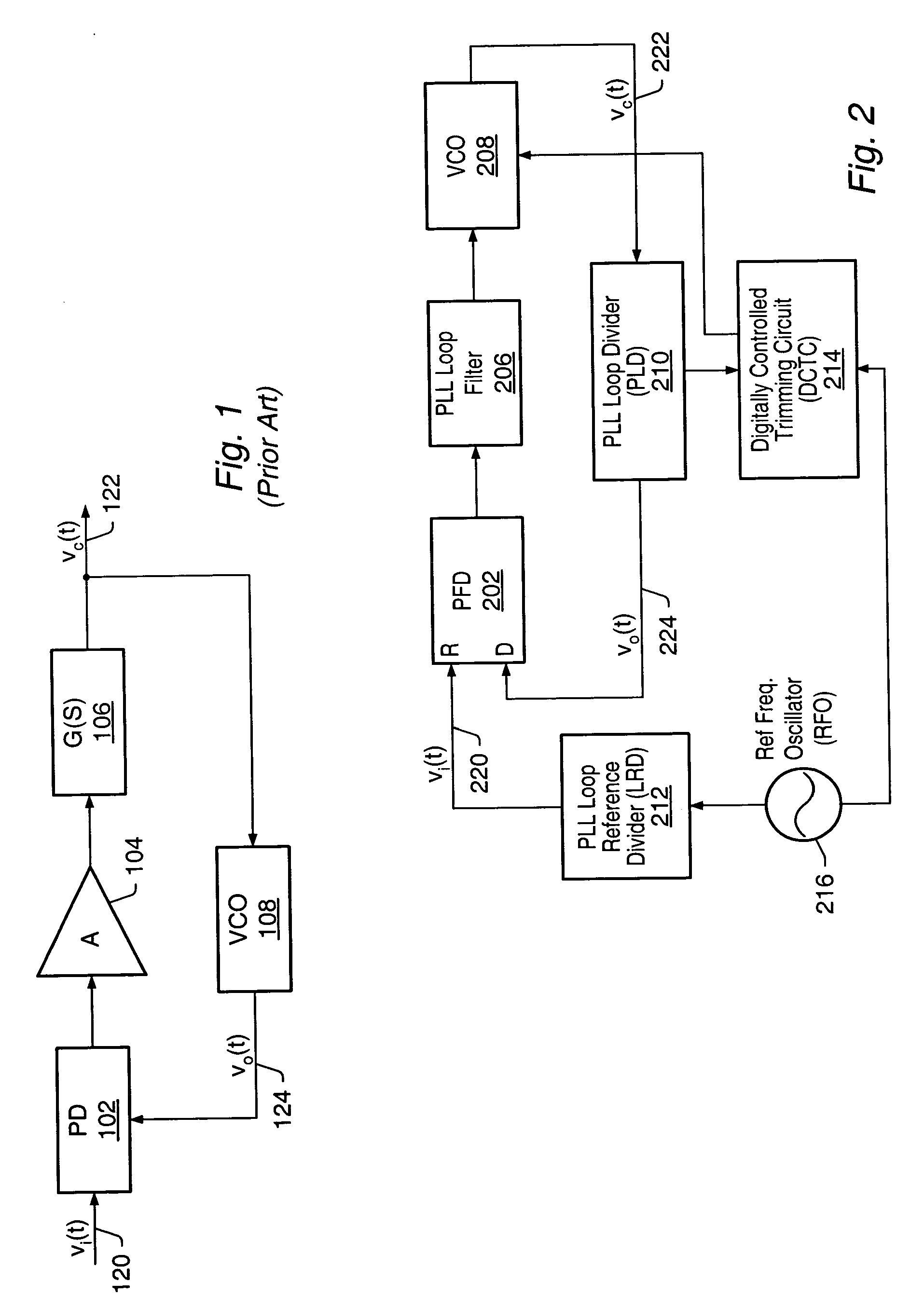

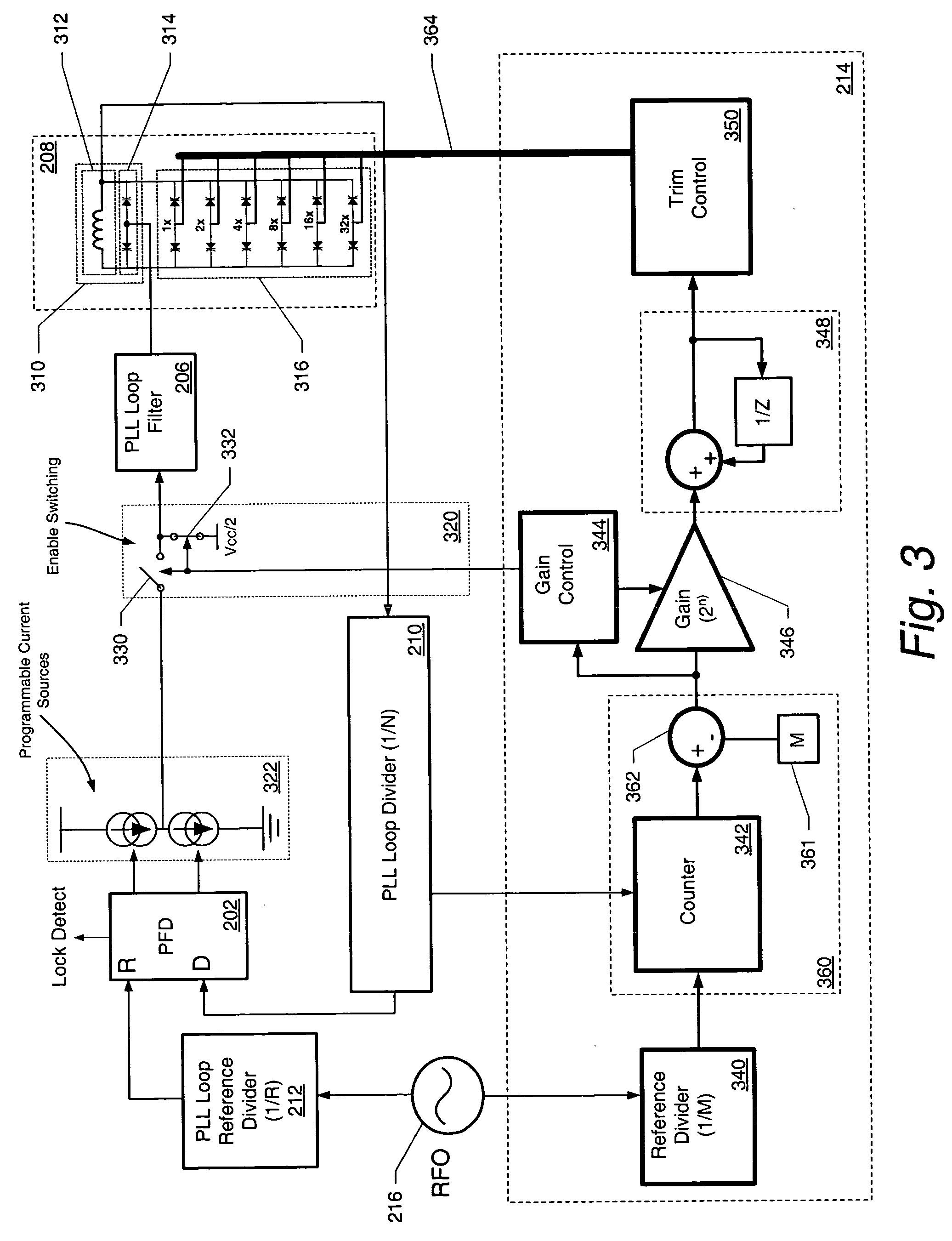

All digital PLL trimming circuit

InactiveUS20050046452A1Shorten lock timeFrequency differencePulse automatic controlPhase detectorClock recovery

In one set of embodiments, the invention comprises a system and method for automatically trimming the center frequency of a VCO in a PLL. The trimming may be performed by a digitally controlled trimming circuit, which may be operated to modify a gain of the VCO and may be used as part of a clock recovery architecture or as part of a high-end PLL. It may also be used by itself in low-end PLLs. In one embodiment, a second loop based solely on the frequency difference between a reference frequency and a divided output frequency of the VCO is introduced into the PLL loop. This frequency loop may be optimized by the inclusion of a gain control stage, which may lower the locking time. A control module may also be introduced to delay the deployment of the phase detector until the frequency loop has fully converged, that is until trimming has been completed, thus preventing the two loops from interfering with each other and compromising each other's performance.

Owner:MICROCHIP TECH INC

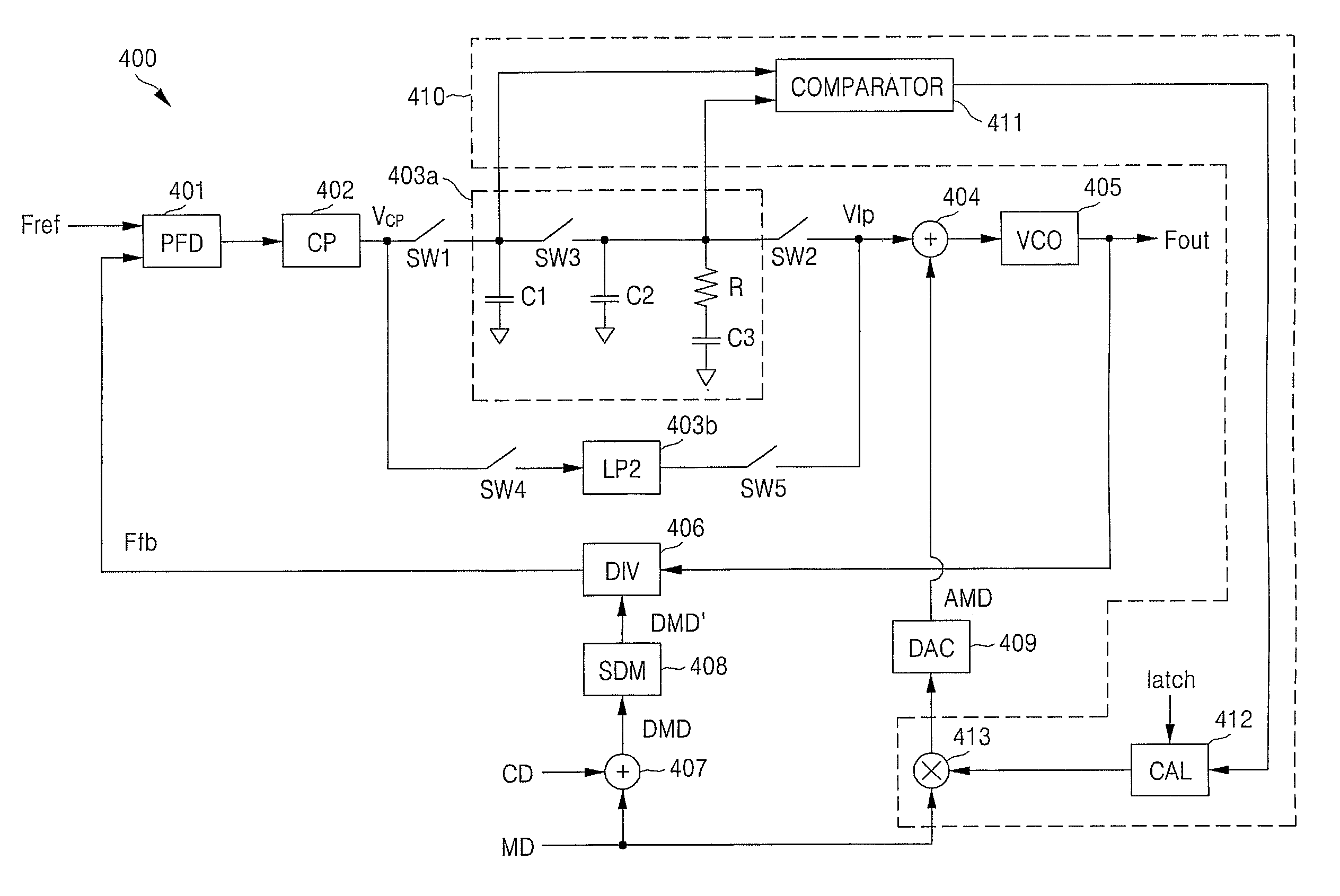

Phase locked loop circuit performing two point modulation and gain calibration method thereof

InactiveUS20090153254A1Shorten lock timeWide bandwidthPulse automatic controlAngle modulationLoop filterPhase locked loop circuit

A PLL circuit for two point modulation includes a first loop filter, a second loop filter, a plurality of switching devices, and a calibration module. The first loop filter filters an output voltage of a charge pump during a gain calibration operation. The second loop filter filters the output voltage of the charge pump during a normal operation. The first loop filter has a bandwidth wider than that of the second loop filter to perform a fast calibration by reducing a lock time. The operation of the first loop filter, the operation of the second loop filter, and the opening of the first loop filter are determined by the switching operations of the switching devices. The calibration module adjusts a gain of analog modulation data based on a frequency error accumulated in the first loop filter after the first loop filter is open during the gain calibration operation.

Owner:SAMSUNG ELECTRONICS CO LTD

Fast lock circuit for a phase lock loop

InactiveUS7728675B1Increase volumeSlow chargingPulse automatic controlOscillator tubesLoop filterDetector circuits

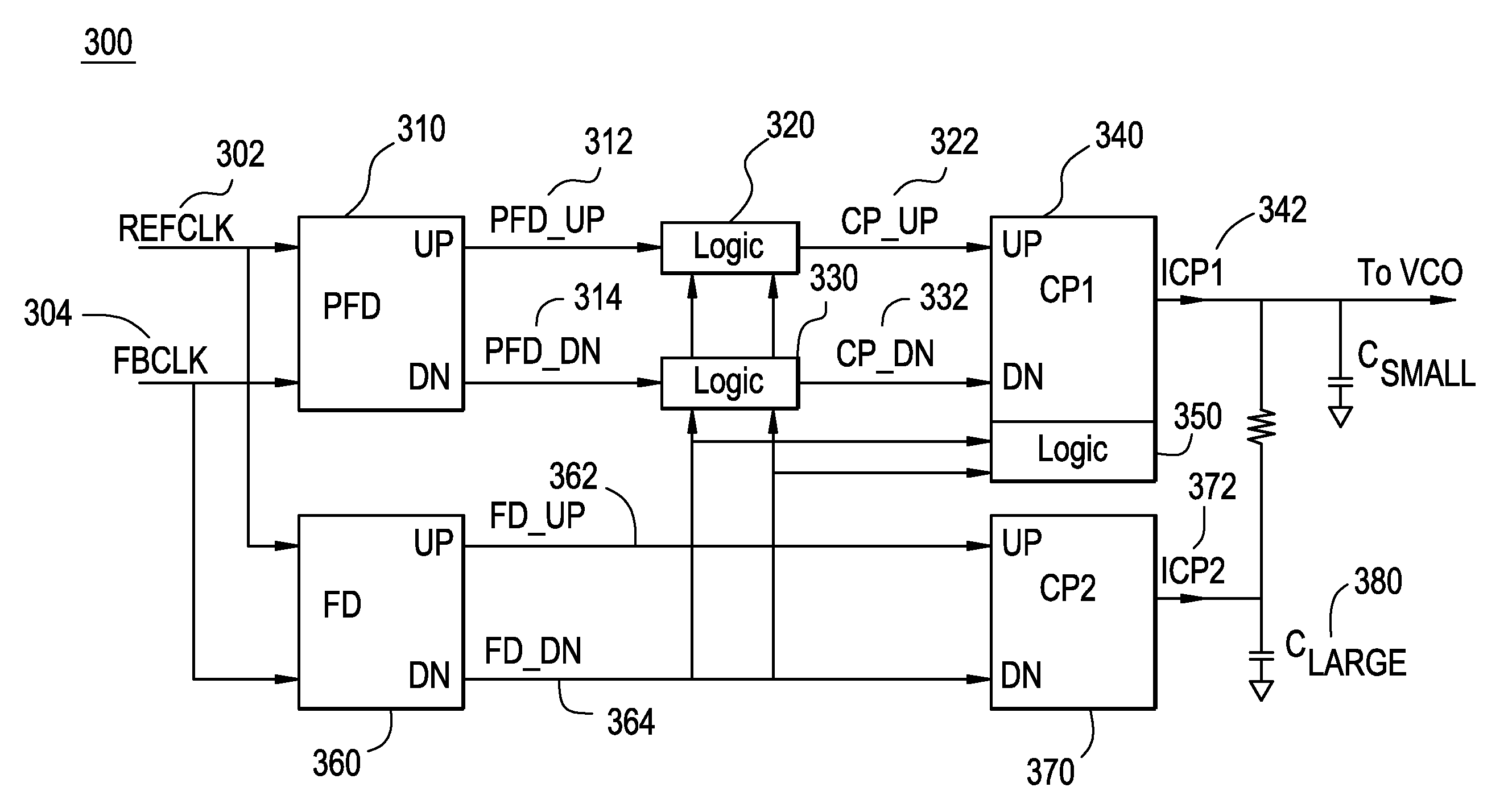

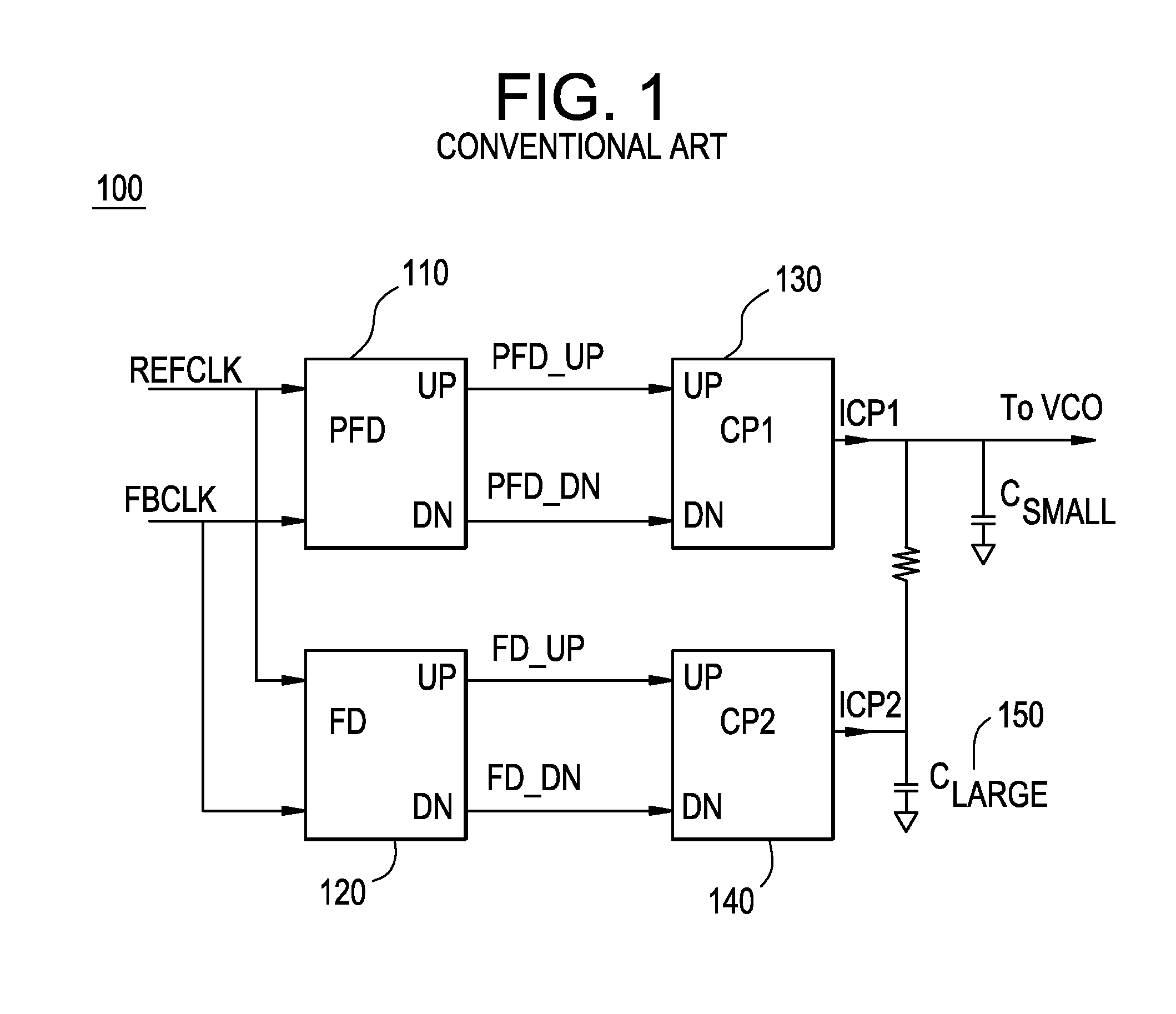

A fast lock circuit for phase lock loop comprising a frequency detector, a phase frequency detector, a logic unit and a corresponding charge pump for the frequency and the phase frequency detectors. Embodiments of the present invention use the logic unit to relay signals from the phase frequency detector circuit to the charge pump when the PLL is in lock. The logic circuit relay signals from the frequency detector circuit before the PLL is in lock. As a result, a constant current is supplied to a large loop filter capacitor before lock. In one embodiment, additional logic circuit may be used to maximize the output current. Therefore, using the logic circuit to supply constant current charges the large loop filter capacitor continuously and avoids a slow down in charging the large loop filter. Accordingly, current is no longer wasted and the lock time is improved.

Owner:MONTEREY RES LLC

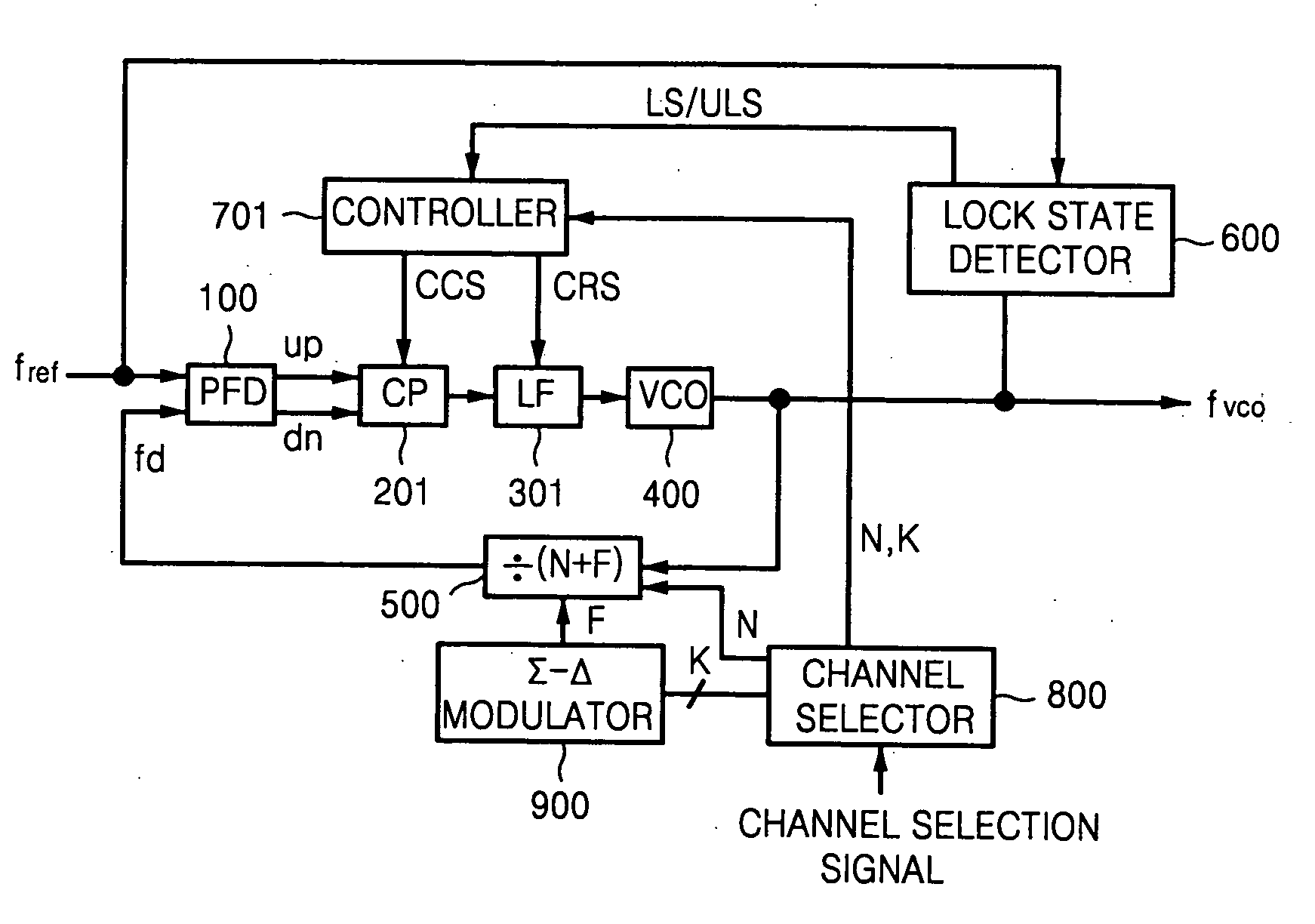

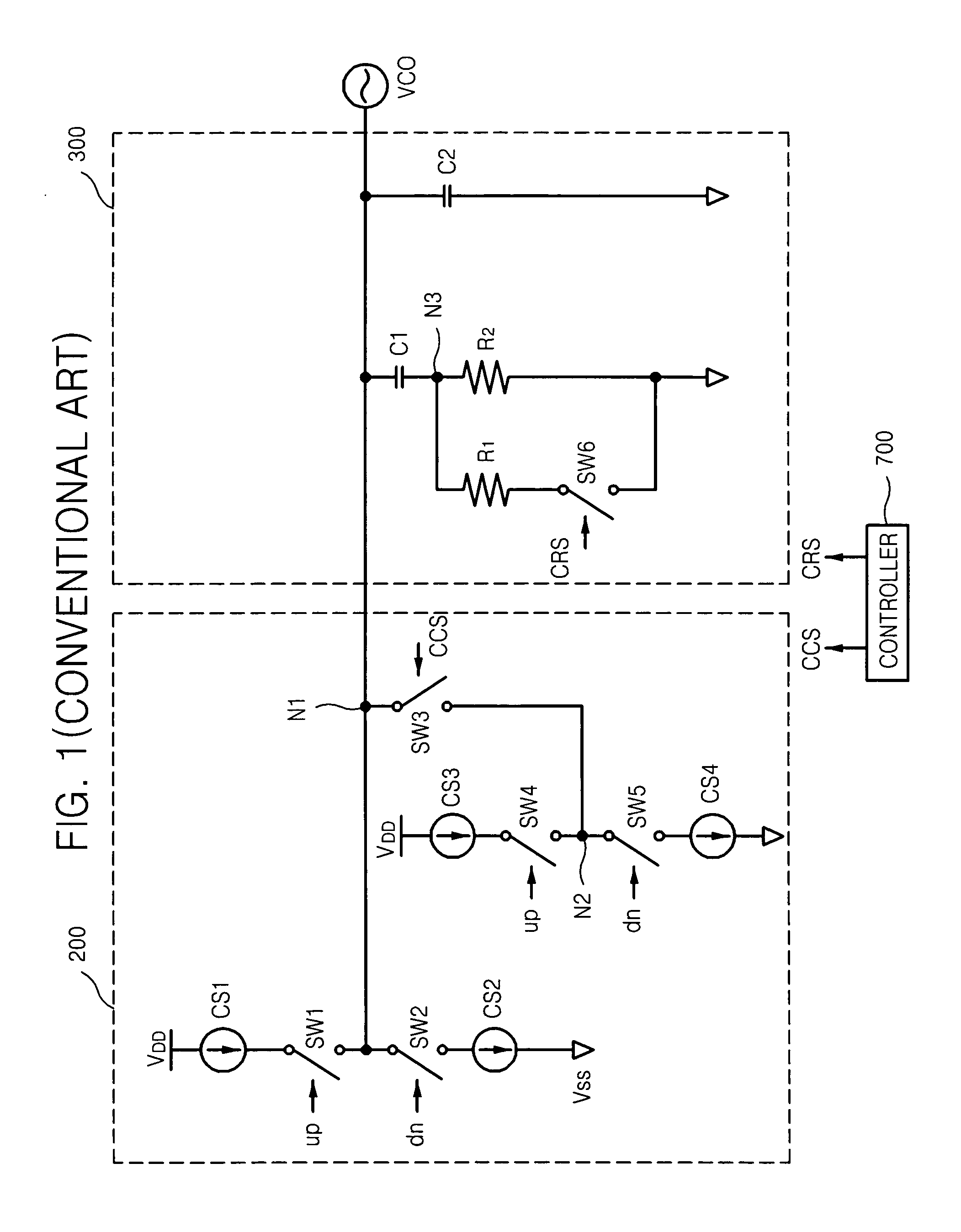

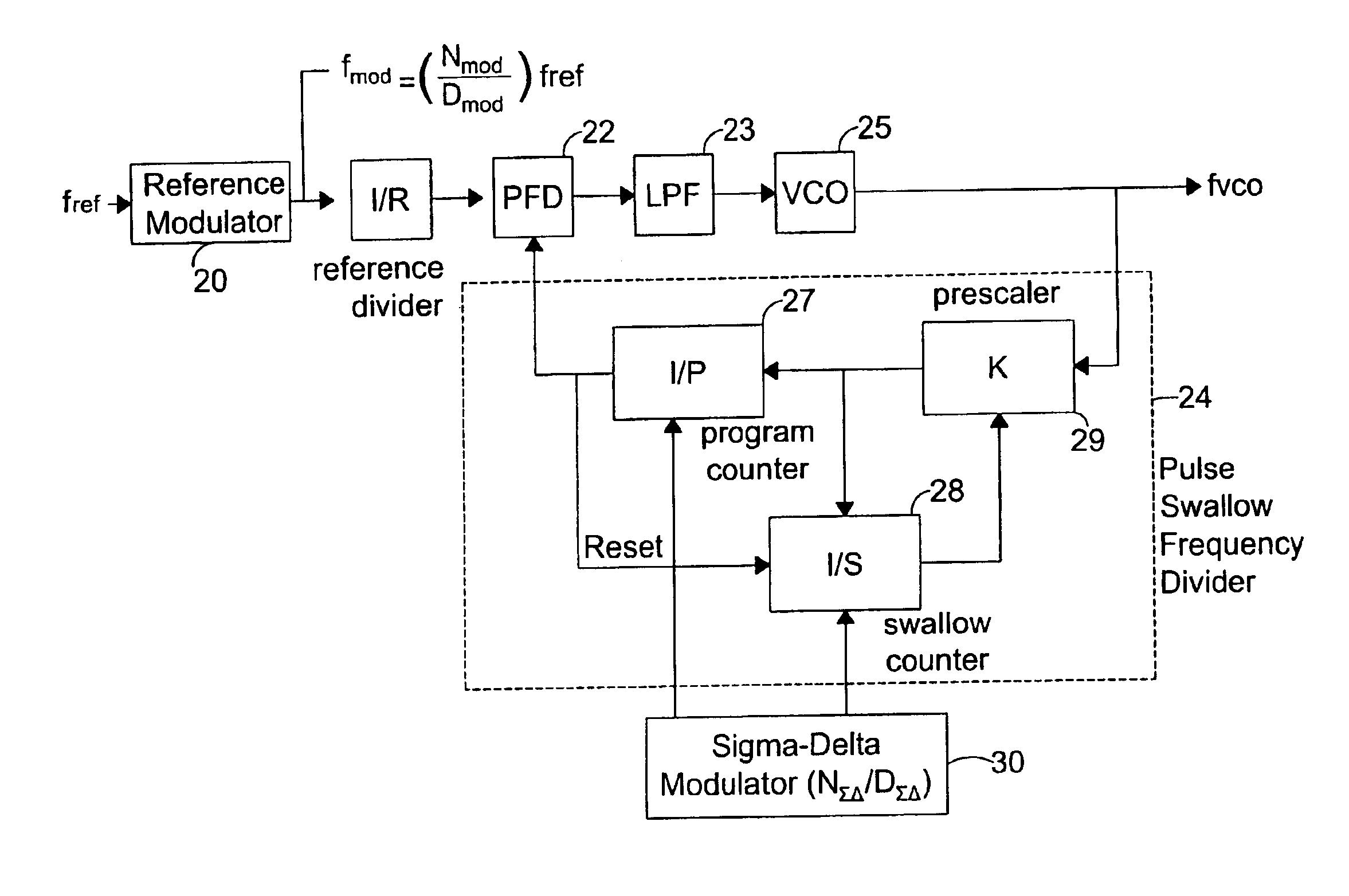

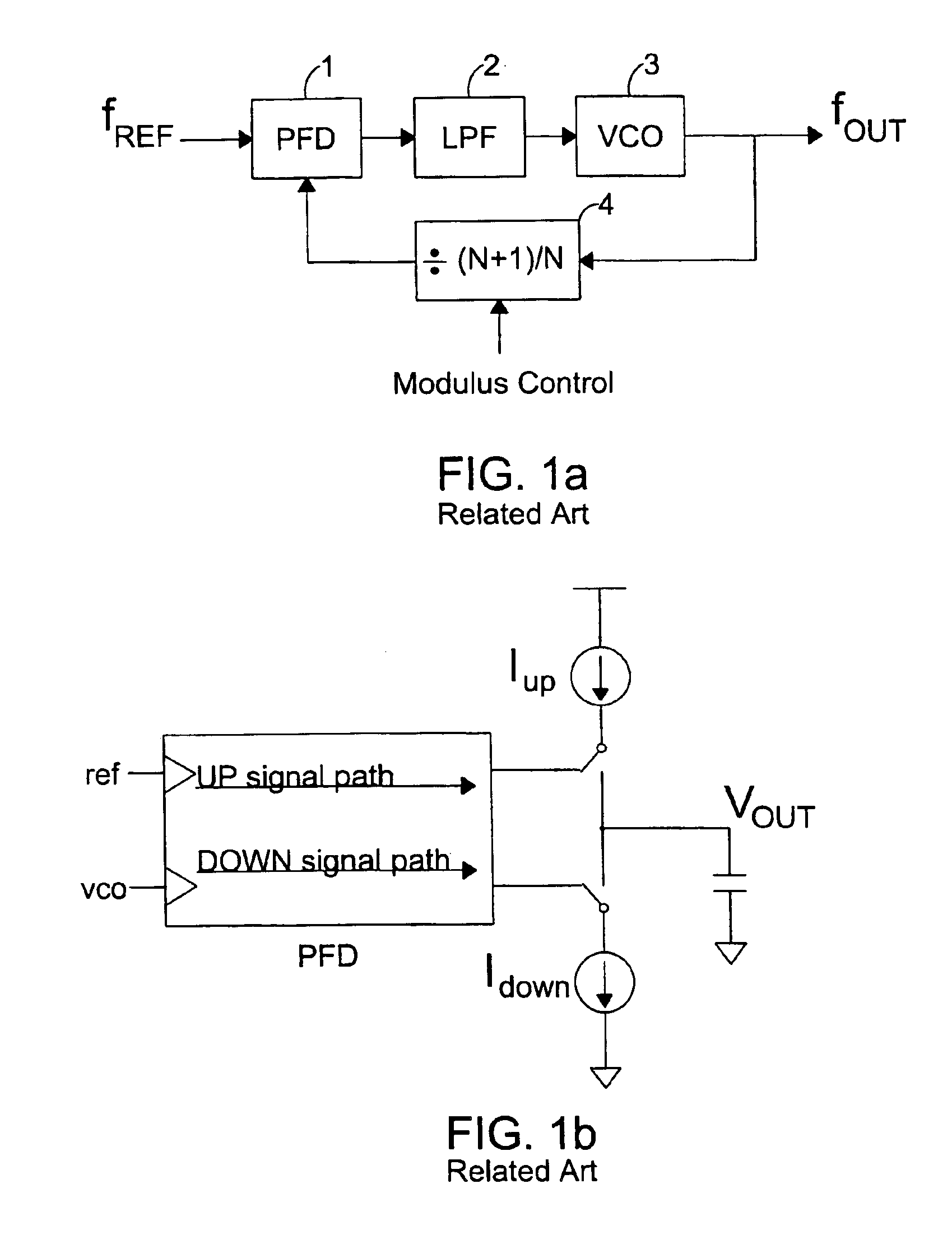

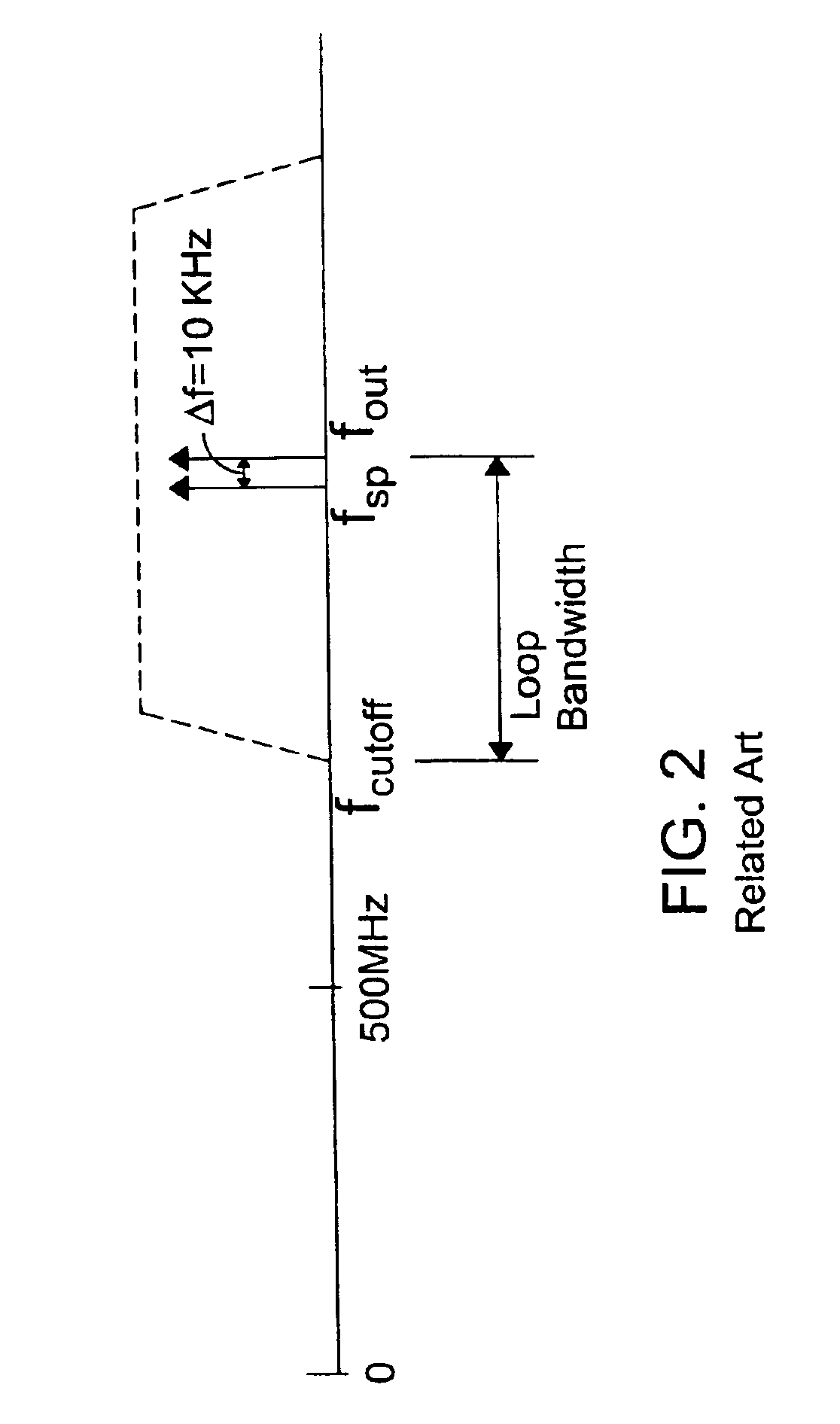

System and method for suppressing noise in a phase-locked loop circuit

ActiveUS20040085103A1Pulse automatic controlCounting chain pulse countersSignal-to-noise ratio (imaging)Phase locked loop circuit

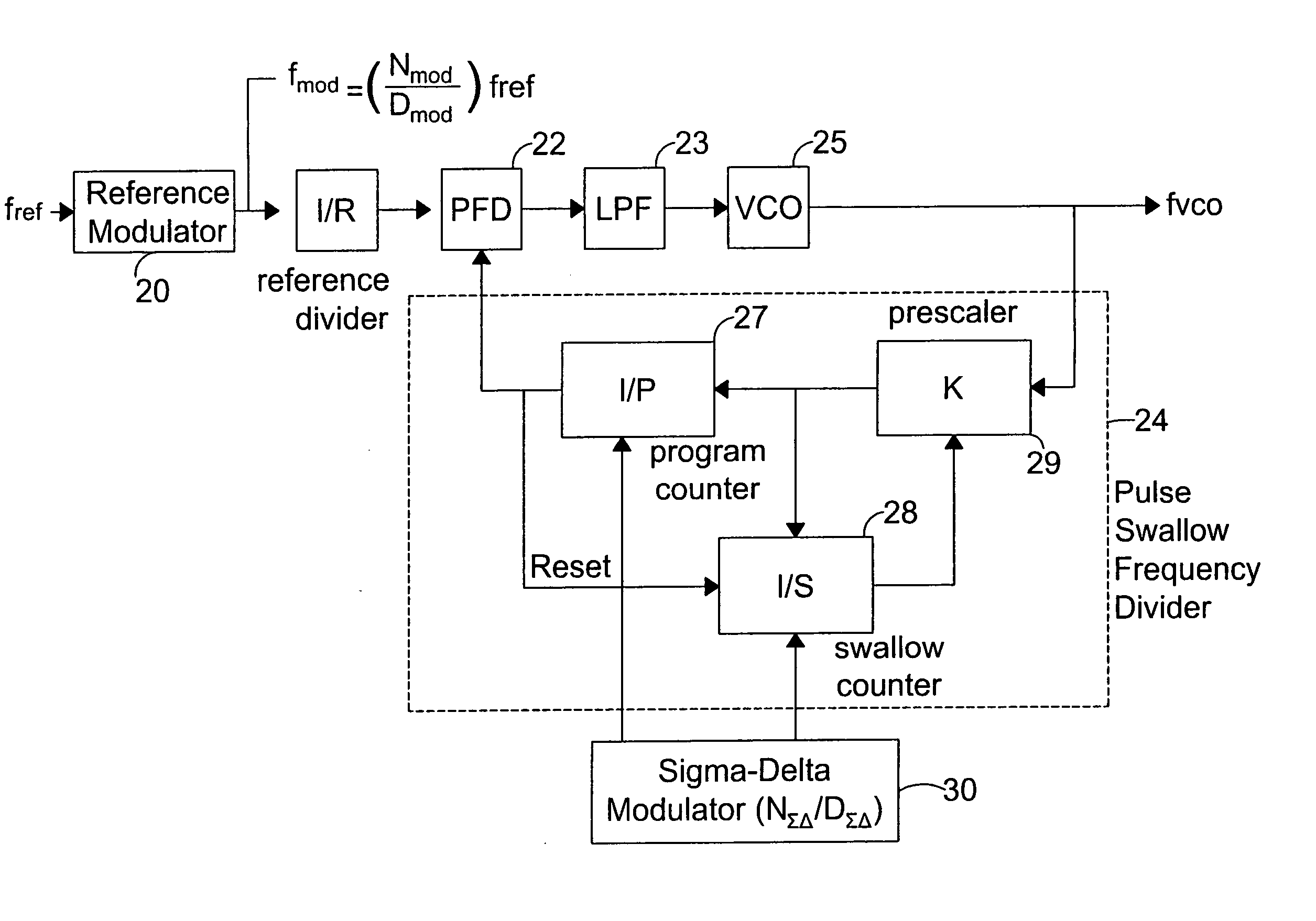

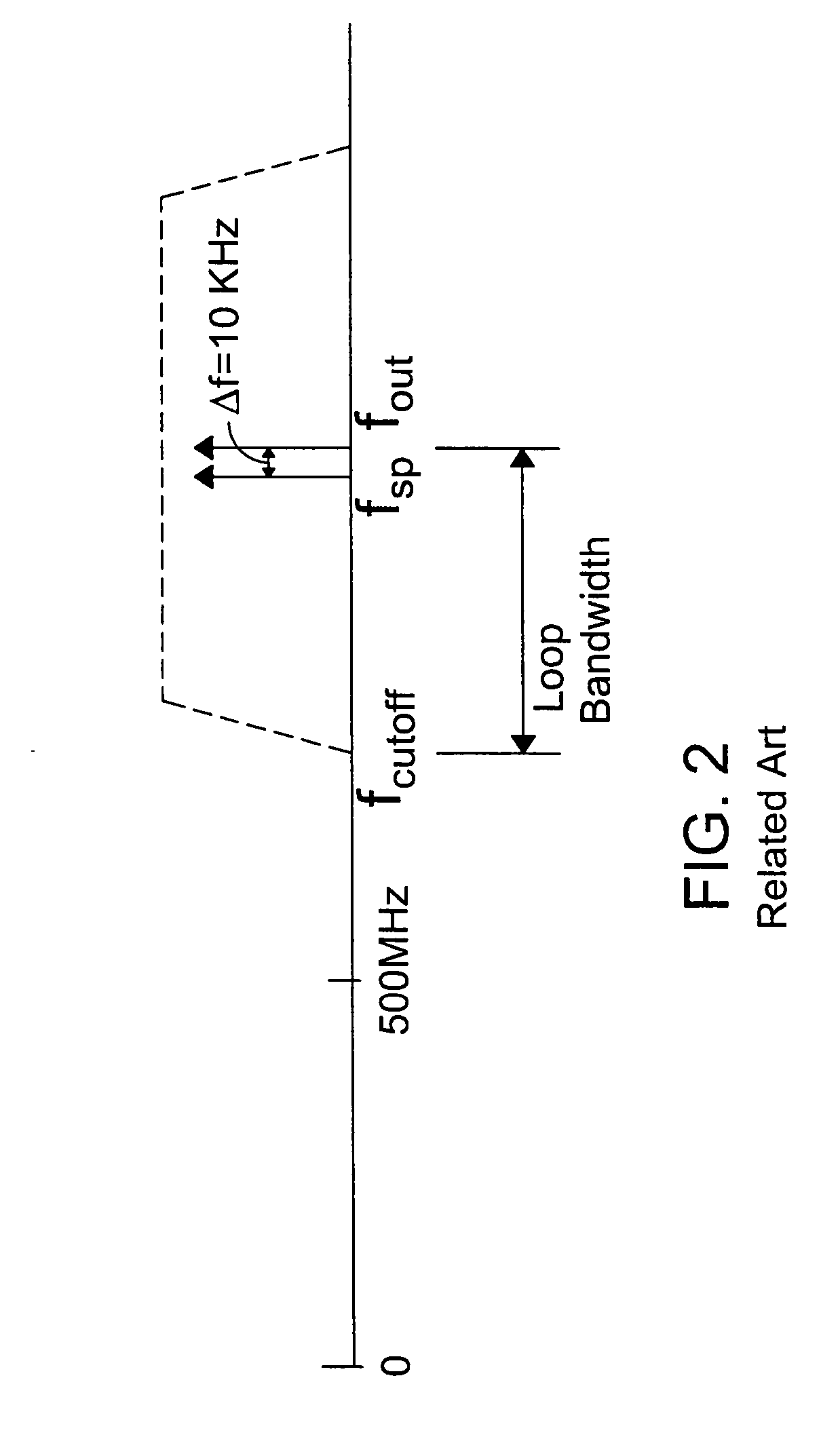

A system and method for improving the signal-to-noise ratio of a frequency generator suppresses phase noise and noise generated from mismatches in the internal generator circuits. This is accomplished using a modulation scheme which shifts spurious noise signals outside the loop bandwidth of the generator. When shifted in this manner, the noise signals maybe removed entirely or to any desired degree using, for example, a filter located along the signal path of the generator. In one embodiment, a Sigma-Delta modulator controls the value of a pulse-swallow frequency divider situated along a feedback path of a phase-locked loop to achieve a desired level of noise suppression. In another embodiment, a reference signal input into a phase-locked loop is modulated to effect noise suppression. In another embodiment, the foregoing forms of modulation are combined to accomplish the desired frequency shift. Through these modulation techniques, the signal-to-noise ratio of the frequency generator may be substantially improved while simultaneously achieving faster lock times.

Owner:GCT SEMICONDUCTOR INC

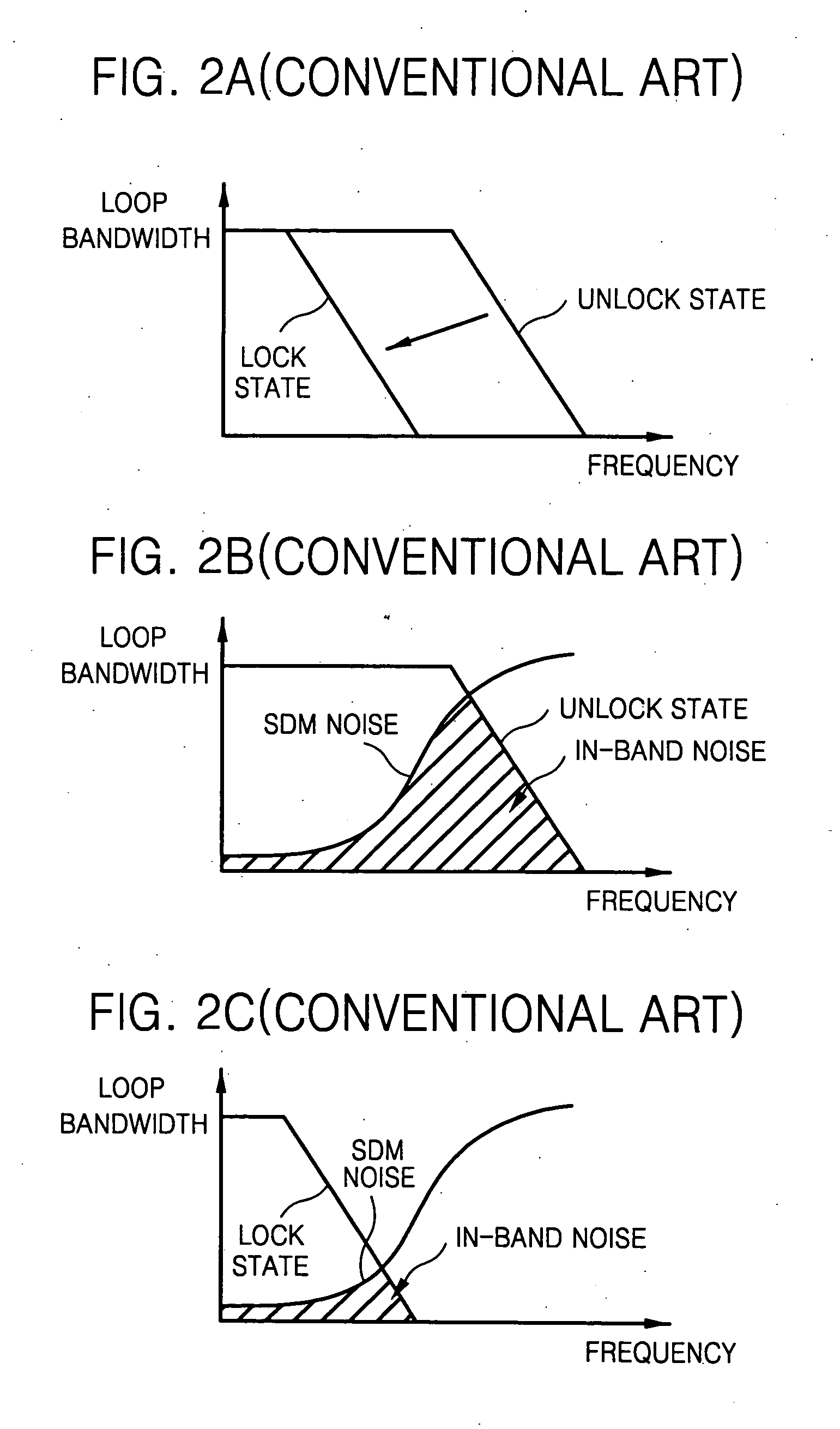

Sigma-delta fractional-N PLL with reduced frequency error

ActiveUS20070164829A1Reduce frequencyImprove the immunityPulse automatic controlOscillator tubesLoop filterLow noise

A sigma-delta fractional-N phase locked loop has faster lock time with increased charge pump current and decreased loop filter resistance in the unlock state. On the other hand, the sigma-delta fractional-N phase locked loop has lower noise susceptibility and lower frequency error with gradual decrease in charge pump current and gradual increase in loop filter resistance, in the lock state.

Owner:SAMSUNG ELECTRONICS CO LTD

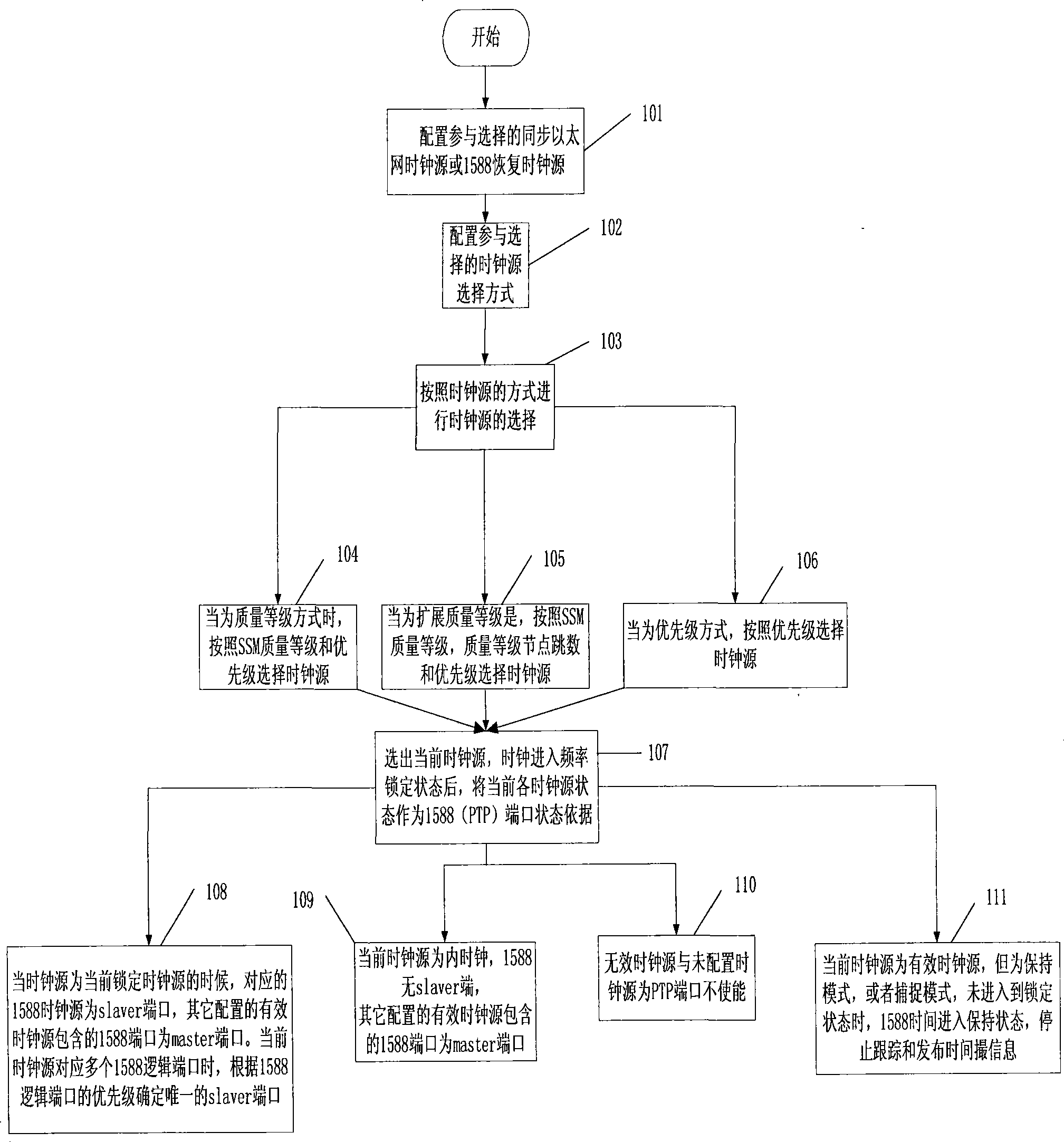

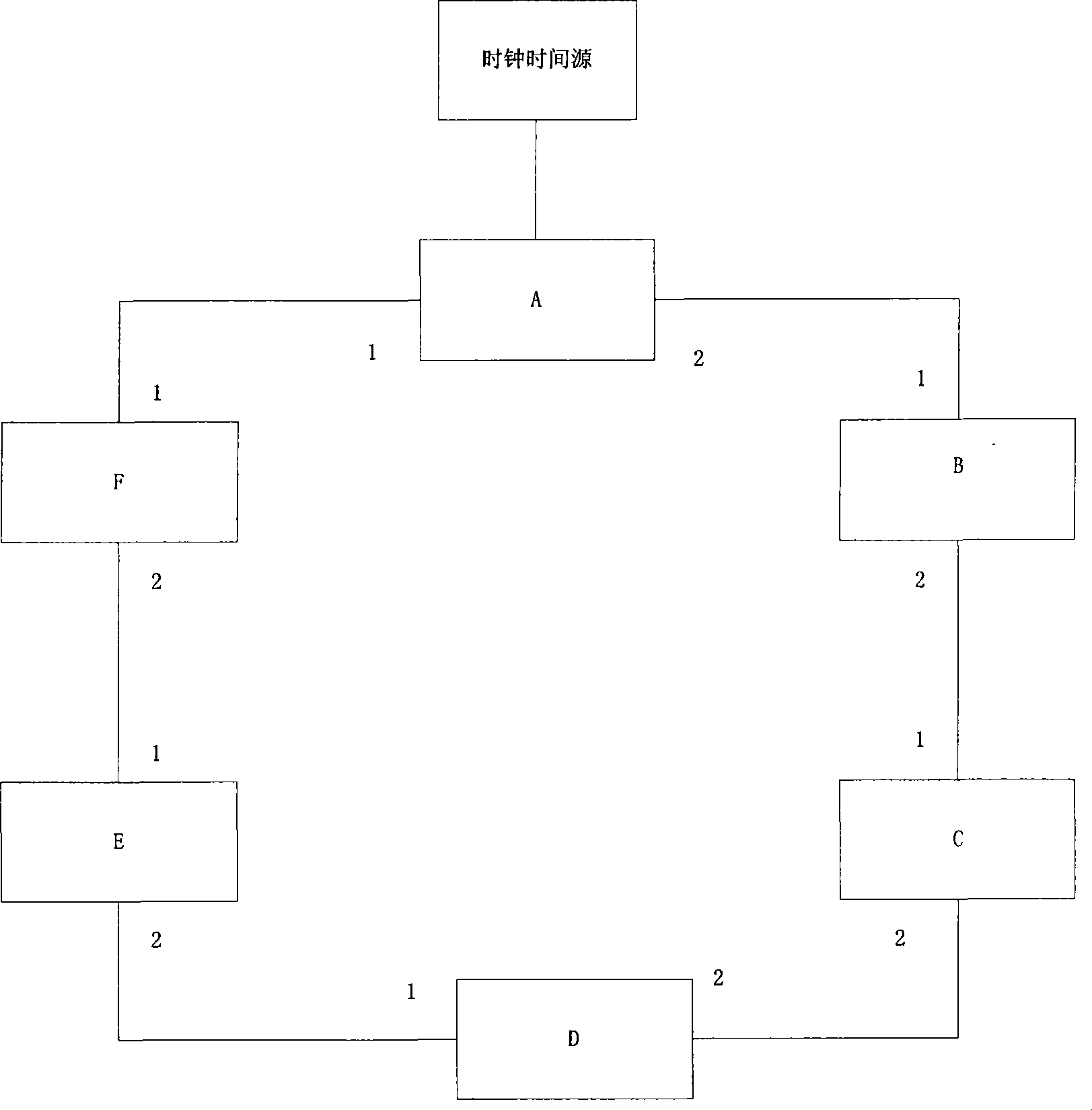

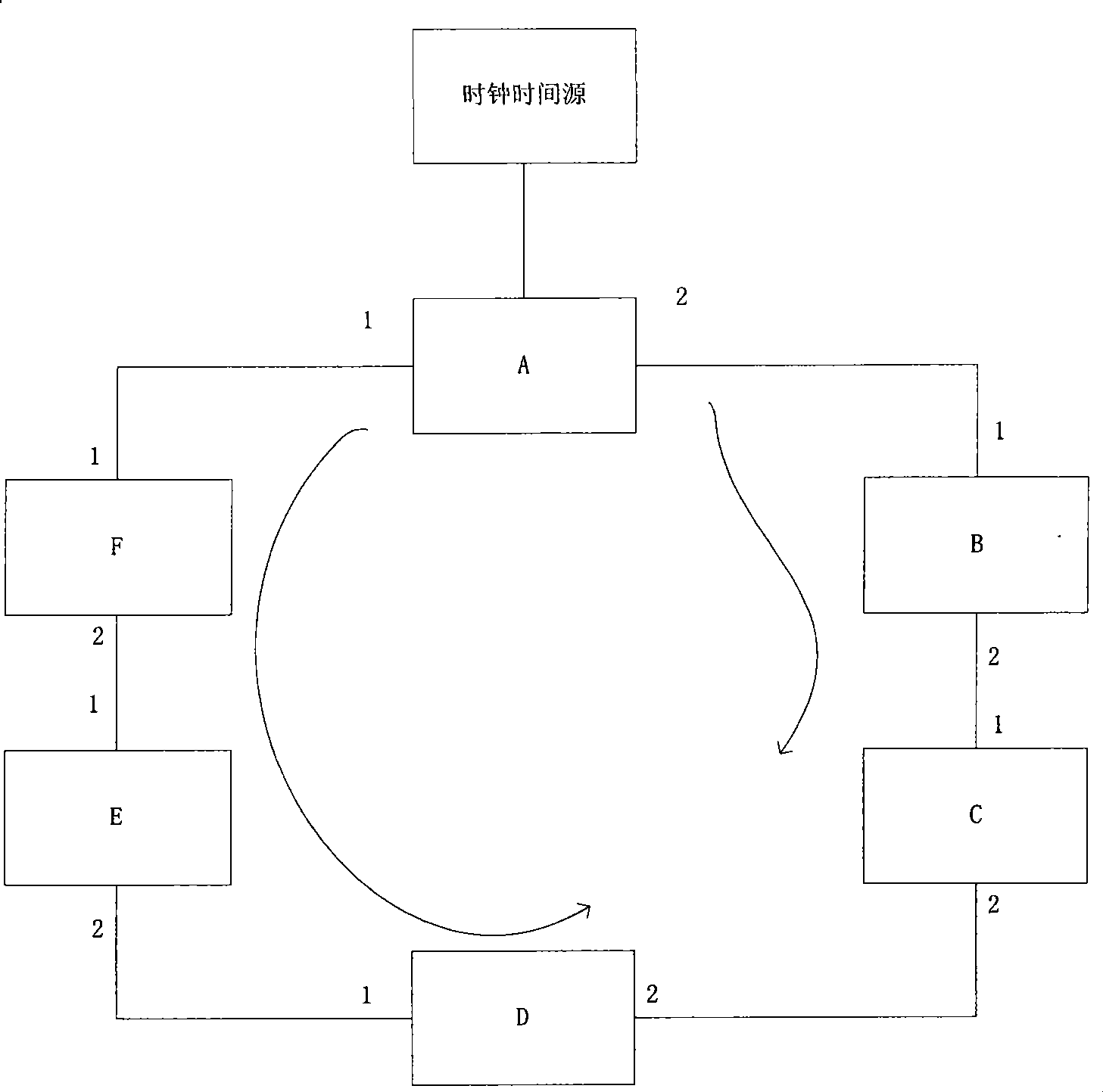

Method and system for transferring protection time in synchronous network

ActiveCN101465707AImprove stabilityReduce mistakesSynchronisation arrangementTime-division multiplexTime errorTime Protocol

The invention discloses a method and a system for protecting time transfer in synchronization network; a corresponding module is added to the prior art to use time synchronization frequency of the synchronization network as the basis of time synchronization protocol, so the network is ensured to synchronously lock clock signal; a synchronization network clock source which participates in selection is configured, and the clock source selection mode is configured; current clock source is selected according to the selection mode, and the frequency state of the current clock source is synchronously locked; the current clock source state is used as state basis of accurate time protocol port to sequentially lock time of element location nodes in the synchronization network. The corresponding module is added to the prior art to use time synchronization frequency of the synchronization network as the basis of time synchronization protocol, so the time transfer error in element location nodes is greatly reduced, and the time error in large scale networking is reduced, and the stability of synchronization network is improved in the switching process of clock sources.

Owner:ZTE CORP

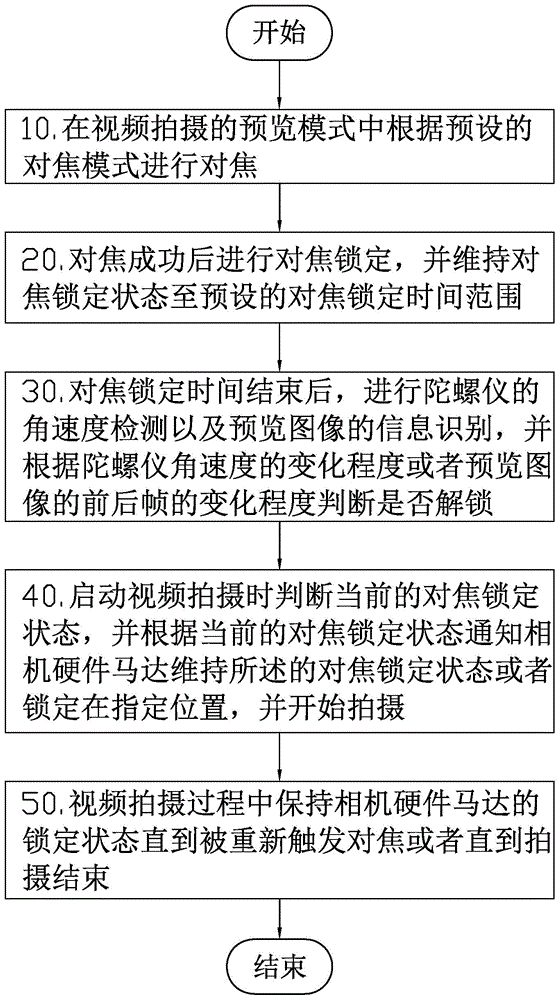

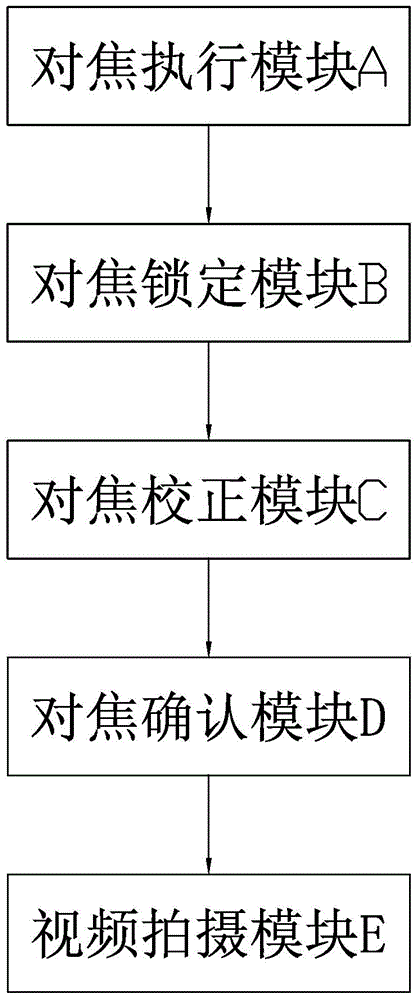

Focusing locking method and system for video shooting

ActiveCN104954695AReduce jitterImprove collection effectTelevision system detailsColor television detailsTime rangeGyroscope

The invention discloses a focusing locking method and system for video shooting. The method comprises steps as follows: focusing is performed according to a preset focusing mode in a preview mode of video shooting, focusing locking is performed after focusing success, the focusing locking state is kept within a preset focusing locking time range, after the focusing locking time is up, detection of the angular velocity of a gyroscope and information identification of a preview image are performed, whether unlocking is performed or not is judged according to the change degree of the angular velocity of the gyroscope or the change degree of front and back frames of the preview image, the current focusing locking state is judged when video shooting is started, a camera hardware motor is informed of keeping of the focusing locking state or locking in a designated position for shooting according to the current focusing locking state, and the locking state of the camera hardware motor is kept in the video shooting process until focusing retriggering or shooting completion. Therefore, the problem of recording focusing displacement caused by repeated focusing is effectively solved, and the video capture effect is improved.

Owner:XIAMEN MEITUZHIJIA TECH

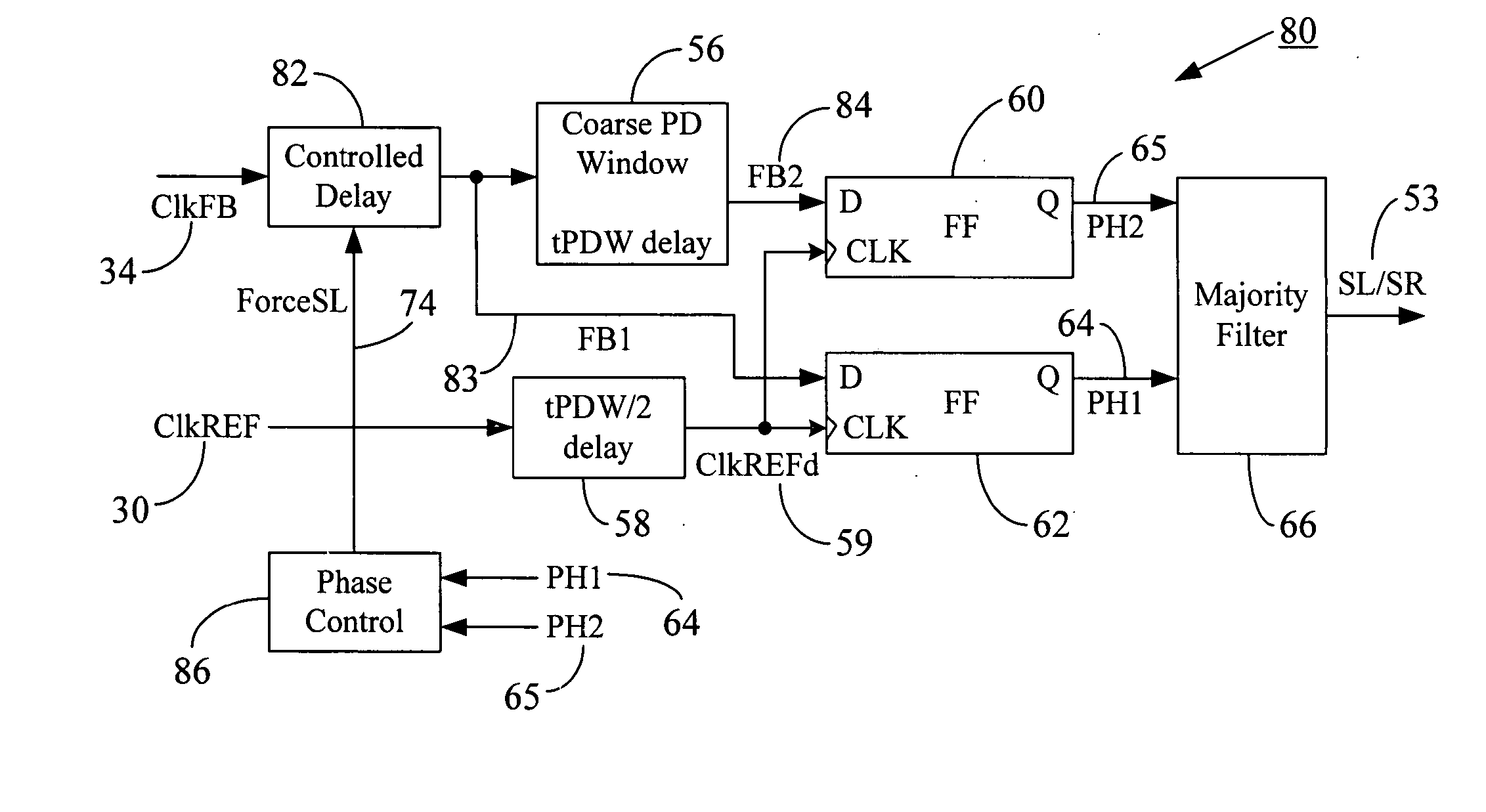

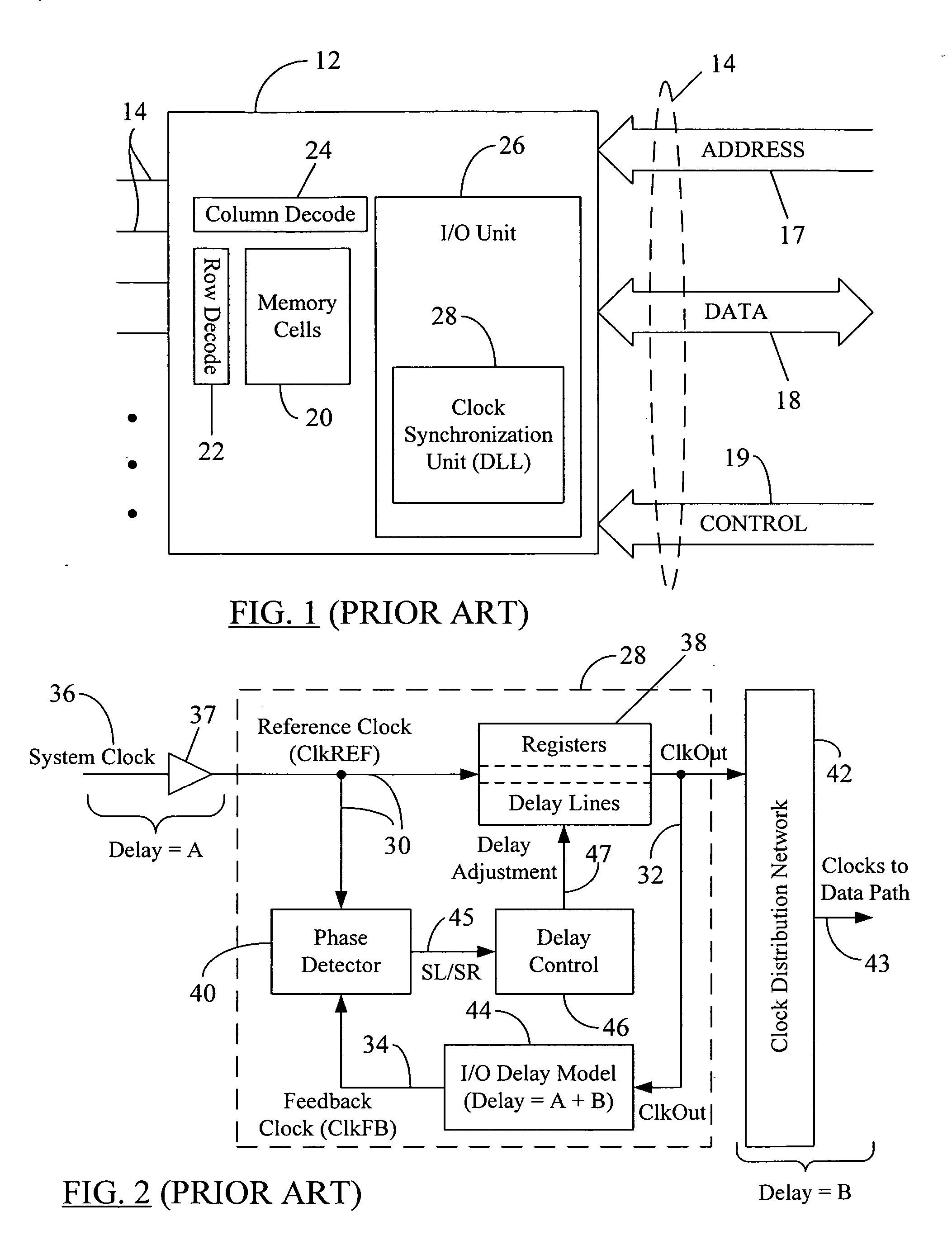

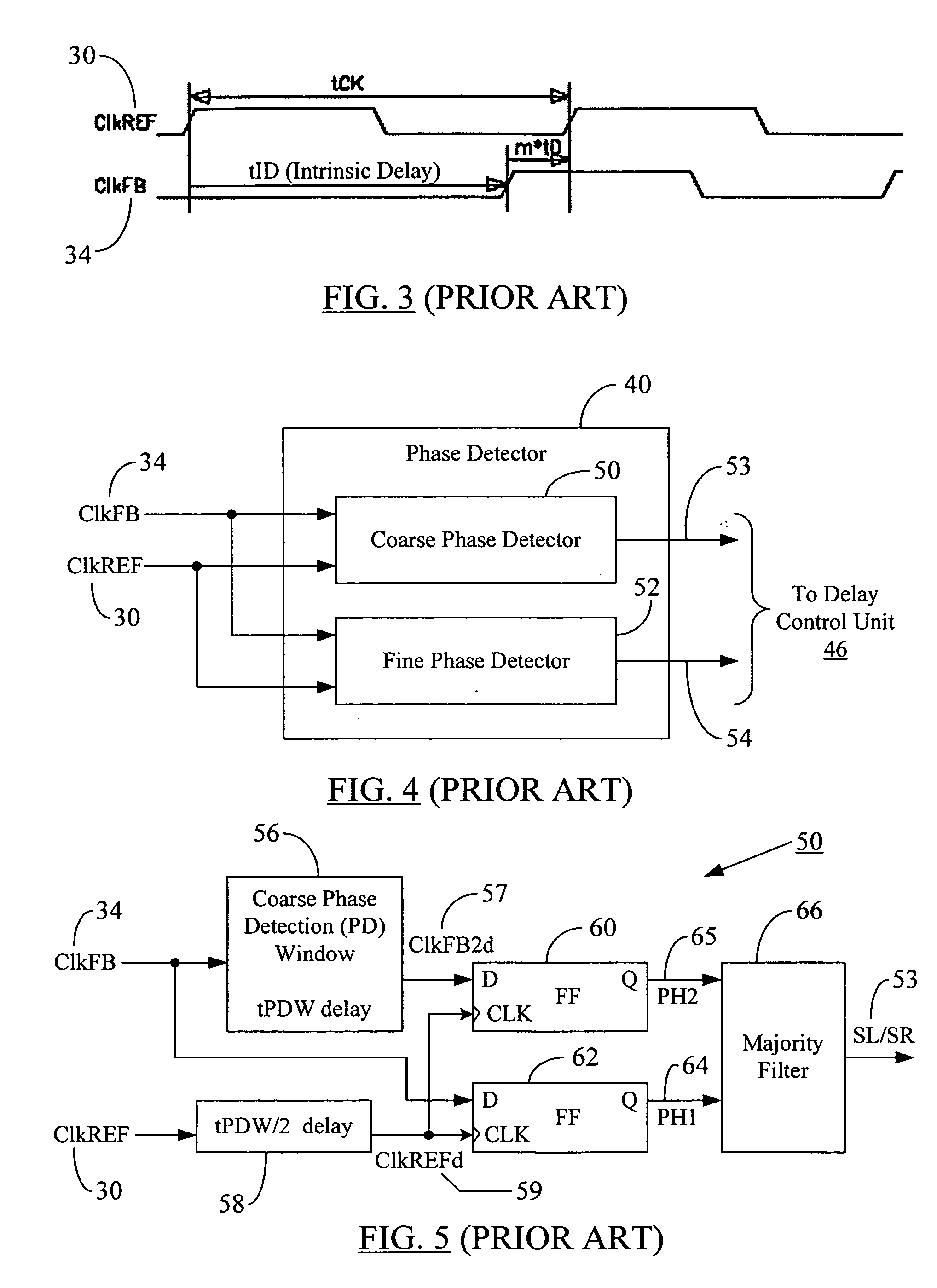

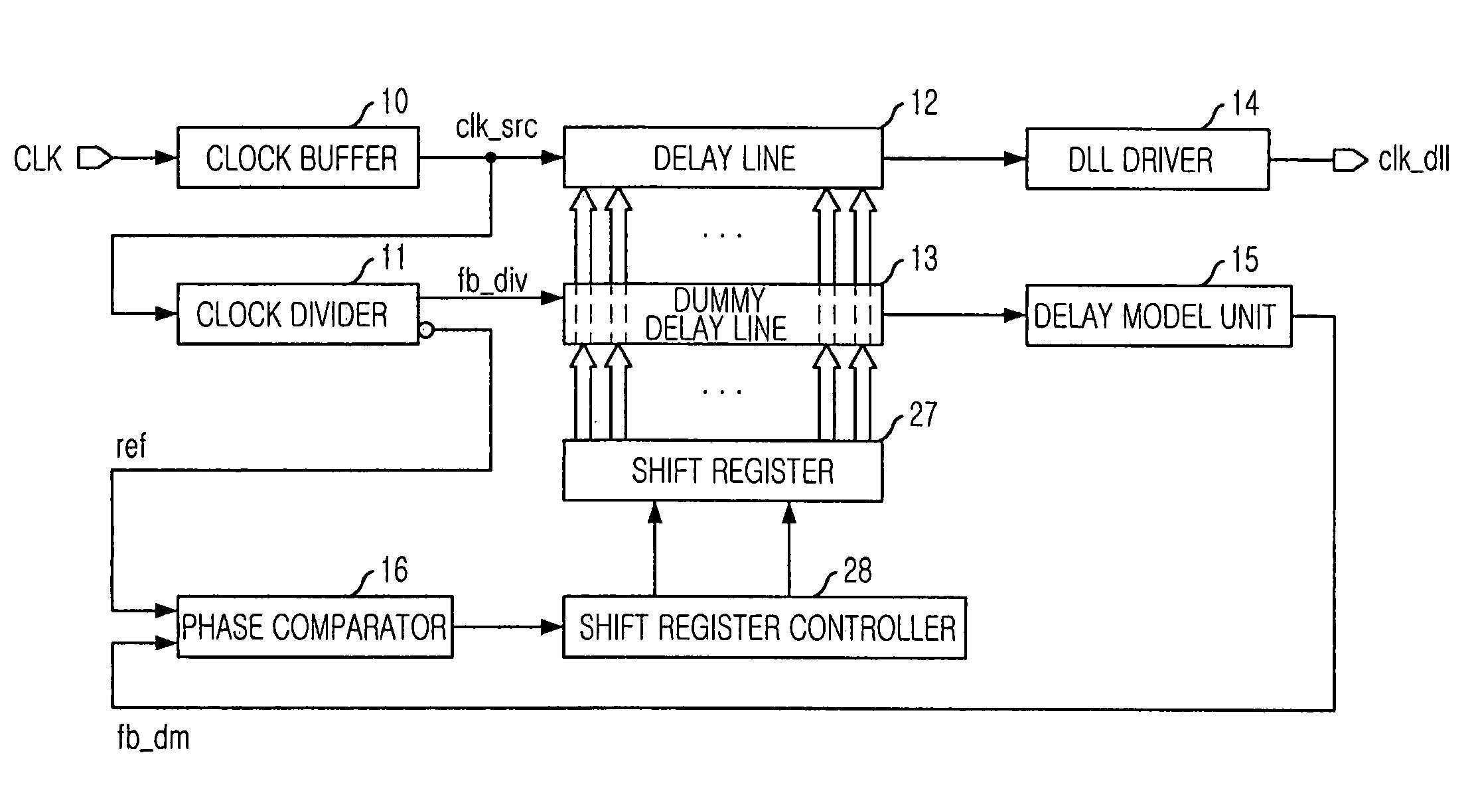

DLL phase detection using advanced phase equal

ActiveUS20050262373A1Faster DLL locking timeFast locking timePulse automatic controlError detection/correctionPhase detectorDelay-locked loop

A system and method are disclosed to generate and terminate clock shift modes during initialization of a synchronous circuit (e.g., a delay-locked loop or DLL). Upon initialization, the DLL is entered into a ForceSL (Force Shift Left) mode and an On1x mode (i.e., left shifting on each clock cycle). The feedback clock that tracks the phase of the reference clock (which, in turn, is derived from the system clock) is initially delayed in a coarse phase detector prior to applying it to the coarse phase detection window. Two delayed versions of the feedback clock are sampled by the reference clock to generate a pair of phase information signals, which are then used to establish an advanced phase equal (APHEQ) signal. The APHEQ signal advances onset of the PHEQ (phase equalization) phase and is used to terminate the ForceSL and On1x modes, thereby preventing wrong ForceSL exit due to clock jitter or feedback path overshooting during On1x exit. The avoidance of wrong ForceSL exit and On1x overshooting problems further results in faster DLL locking time.

Owner:MICRON TECH INC

Digital phase locked loop with selectable normal or fast-locking capability

ActiveUS20050258908A1Fast outputPulse automatic controlTime-division multiplexPhase detectorLoop filter

A digital phase locked loop with fast locking capability includes a digitally controlled oscillator for producing an output signal phase locked to an input reference clock, a phase detector for measuring the phase difference between said input reference clock and a feedback clock, and a loop filter for producing a control signal for the digitally controlled oscillator The loop filter includes a proportional circuit for developing a first signal proportional to said phase difference, an integrator for developing a second integrated signal from said first signal, an adder for adding said first and second signals to develop said control signal, and a weighting circuit, preferably a linear multiplier, for selectively adding extra weight to the first signal at an input to the integrator to shorten the locking time of the phase locked loop in a fast locking mode and to rapidly achieve a stable frequency in holdover mode.

Owner:ZARLINK SEMICON LTD

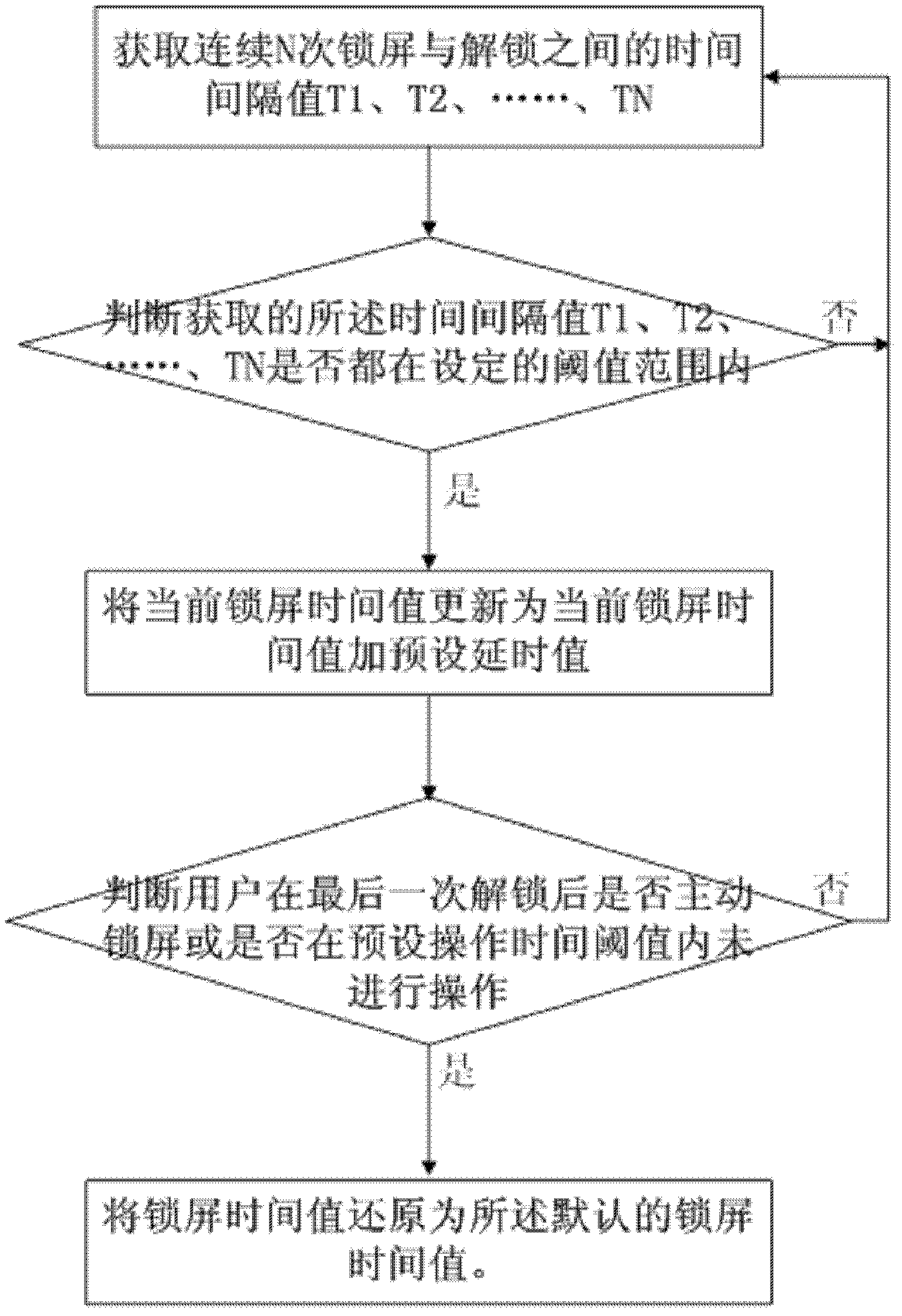

Method and device for adjusting screen locking time as well as electronic terminal

ActiveCN102662816AReduce unlock operationsImprove satisfactionPower managementUnauthorised/fraudulent call preventionDelayed timeLock time

The invention discloses a method and a device for adjusting screen locking time as well as an electronic terminal. The method comprises the following steps: obtaining values T1, T2, ..., TN of time intervals between continuous N times of screen locking and screen unlocking; and updating the current screen locking time value to the sum of the current screen locking time value plus a predetermined delay time value when judging that the obtained values T1, T2, ..., TN of time intervals are all within a given threshold value range, i.e., the method and the device can be used for monitoring the use conditions of terminal automatic screen locking and user unlocking in real time, judging whether the current screen locking time is appropriate according to the time intervals between continuous N times of screen locking and screen unlocking under the current use environment and conditions, and if not, automatically updating the current screen locking time value to the sum of the current screen locking time value plus the predetermined delay time value, so that the aim of dynamically adjusting the screen locking time according to the current use environment and conditions is achieved, and therefore the screen unlocking operations and screen locking setting of users are effectively reduced and the satisfaction degree of user experience is improved.

Owner:ZTE CORP

System and method for suppressing noise in a phase-locked loop circuit

InactiveUS6952125B2Suppress noiseShorten lock timePulse automatic controlCounting chain pulse countersSignal-to-noise ratio (imaging)Phase locked loop circuit

A system and method for improving the signal-to-noise ratio of a frequency generator suppresses phase noise and noise generated from mismatches in the internal generator circuits. This is accomplished using a modulation scheme which shifts spurious noise signals outside the loop bandwidth of the generator. When shifted in this manner, the noise signals maybe removed entirely or to any desired degree using, for example, a filter located along the signal path of the generator. In one embodiment, a Sigma-Delta modulator controls the value of a pulse-swallow frequency divider situated along a feedback path of a phase-locked loop to achieve a desired level of noise suppression. In another embodiment, a reference signal input into a phase-locked loop is modulated to effect noise suppression. In another embodiment, the foregoing forms of modulation are combined to accomplish the desired frequency shift. Through these modulation techniques, the signal-to-noise ratio of the frequency generator may be substantially improved while simultaneously achieving faster lock times.

Owner:GCT SEMICONDUCTOR INC

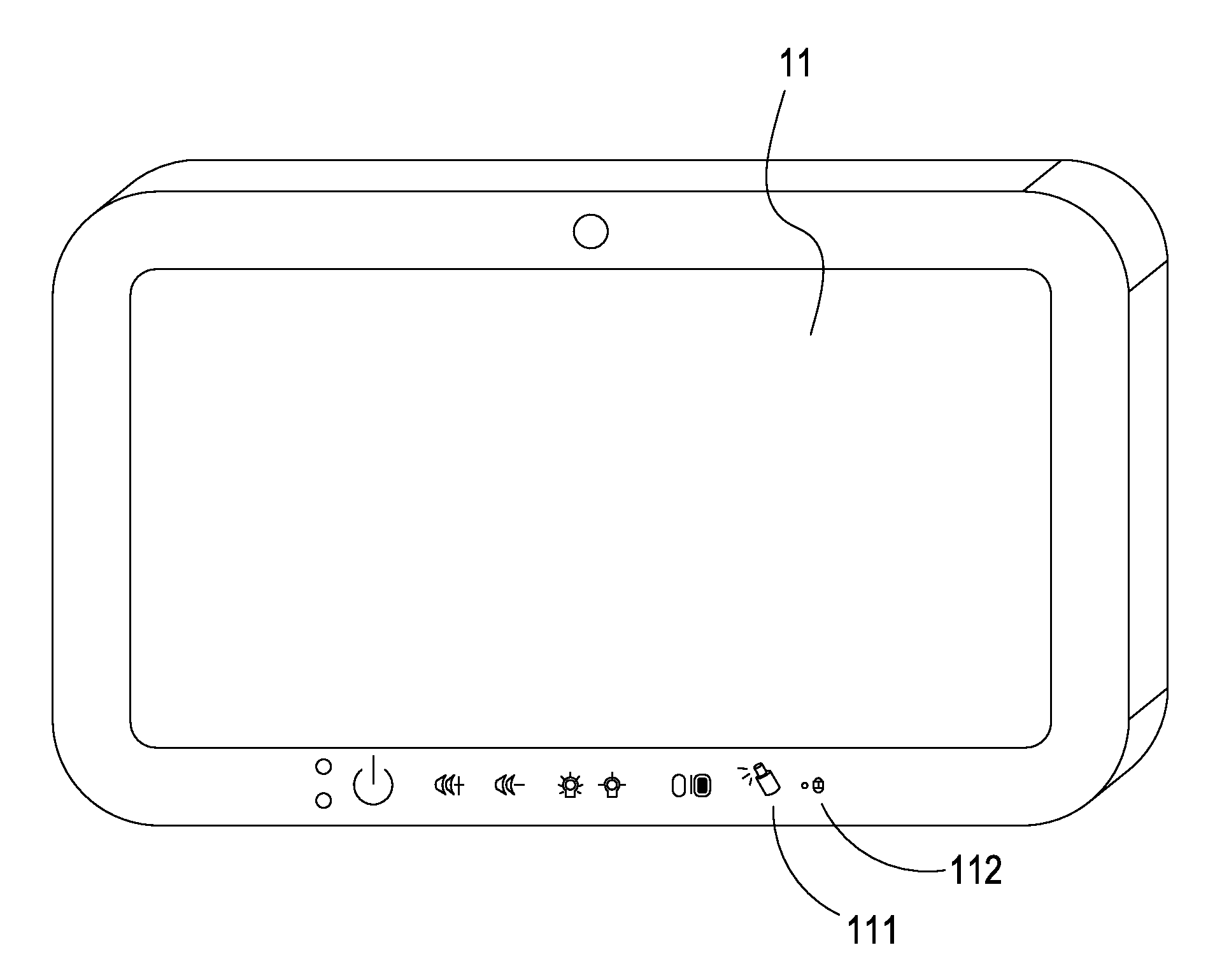

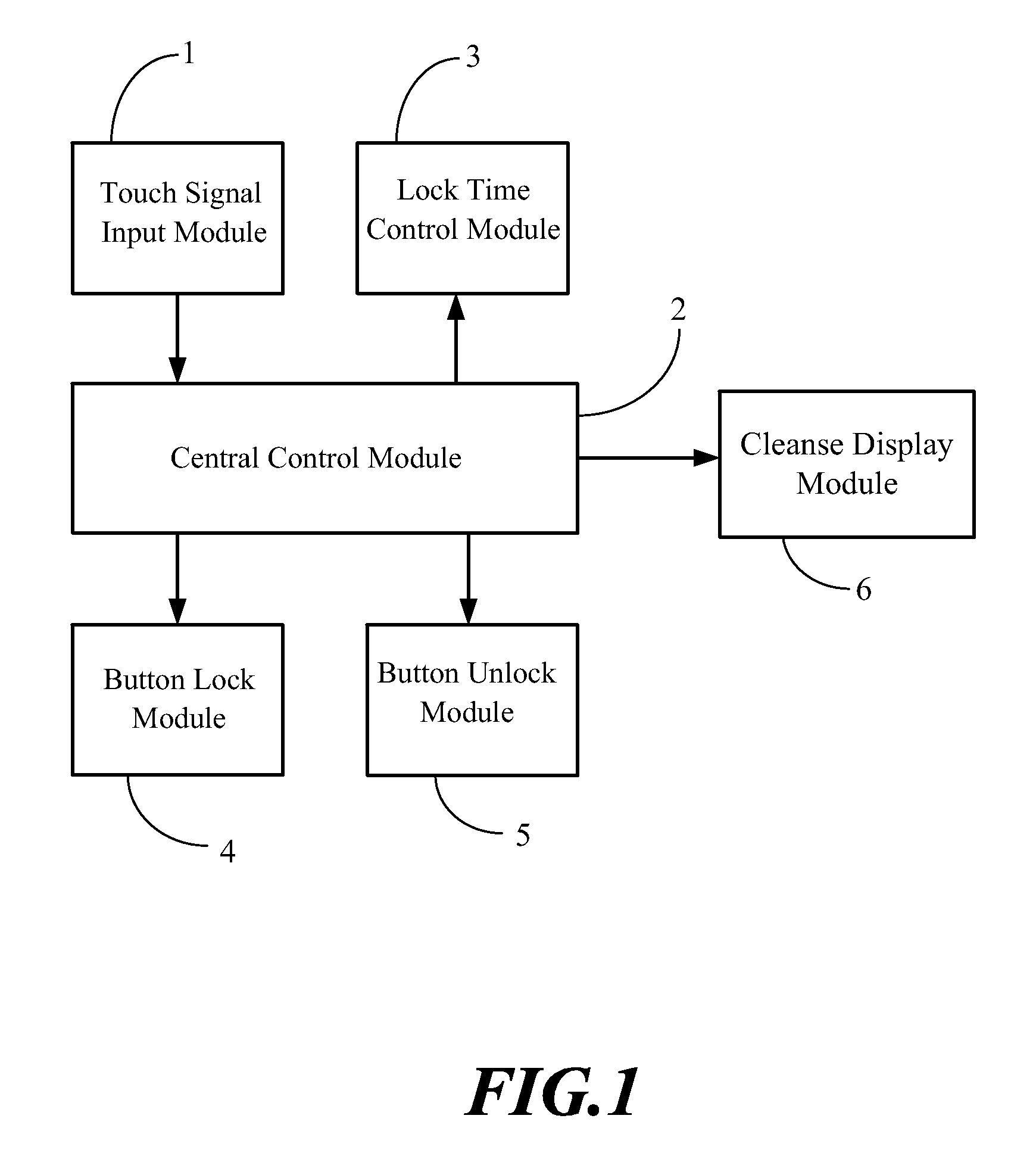

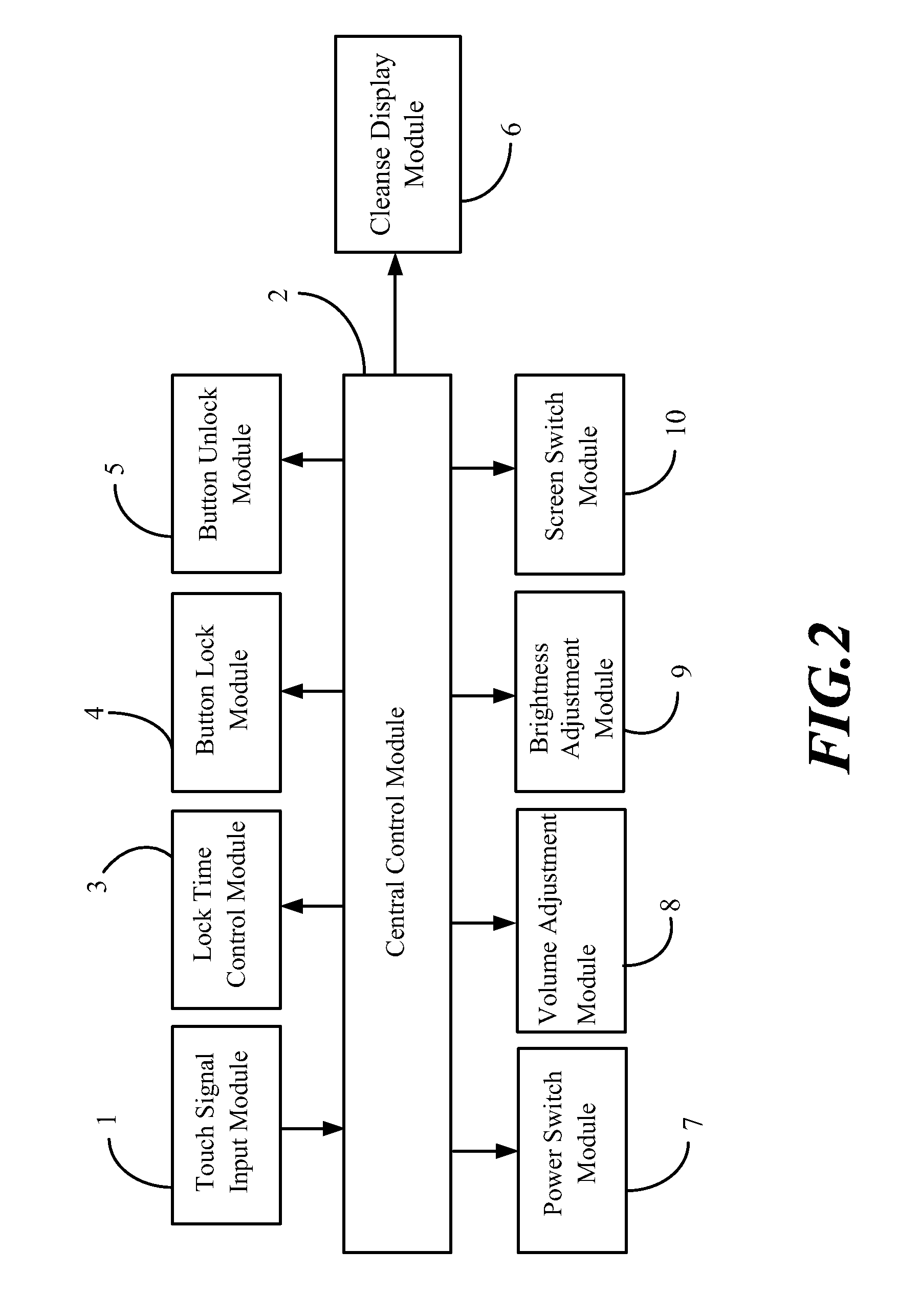

Button control system for medical touch screen and method thereof

InactiveUS20120084728A1Preventing erroneously touching touchFacilitating to perform cleanse process efficientlyInput/output processes for data processingControl systemEngineering

A button control system for medical touch screen and method thereof comprises a central control module, a touch signal input module, a lock time control module, a button lock module, a button unlock module and a cleanse display module, wherein the central control module determines the signal inputted by the touch signal input module, and selects to control the button lock module or the button unlock module thereby locking or unlocking a touch button; furthermore, the lock time control module is configured to set up the lock time for the touch button so as to preset the lock time of the touch button as cleansing the touch screen by the user, and after pressing down the cleanse touch button on the touch screen, it allows to control to lock or unlock other touch buttons and also to effectively prevent the occurrence of the situation where the screen button is erroneously touched as performing the cleanse process.

Owner:WINCOMM CORP

Wide frequency range delay locked loop

InactiveUS20080089459A1Improve accuracyImprove stabilityPulse automatic controlAngle demodulation by phase difference detectionDelay-locked loopSilicon

A delay locked loop operates over a wide range of frequencies and has high accuracy, small silicon area usage, low power consumption and a short lock time. The DLL combines an analog domain and a digital domain. The digital domain is responsible for initial lock and operational point stability and is frozen after the lock is reached. The analog domain is responsible for normal operation after lock is reached and provides high accuracy using smaller silicon area and low power.

Owner:MOSAID TECH

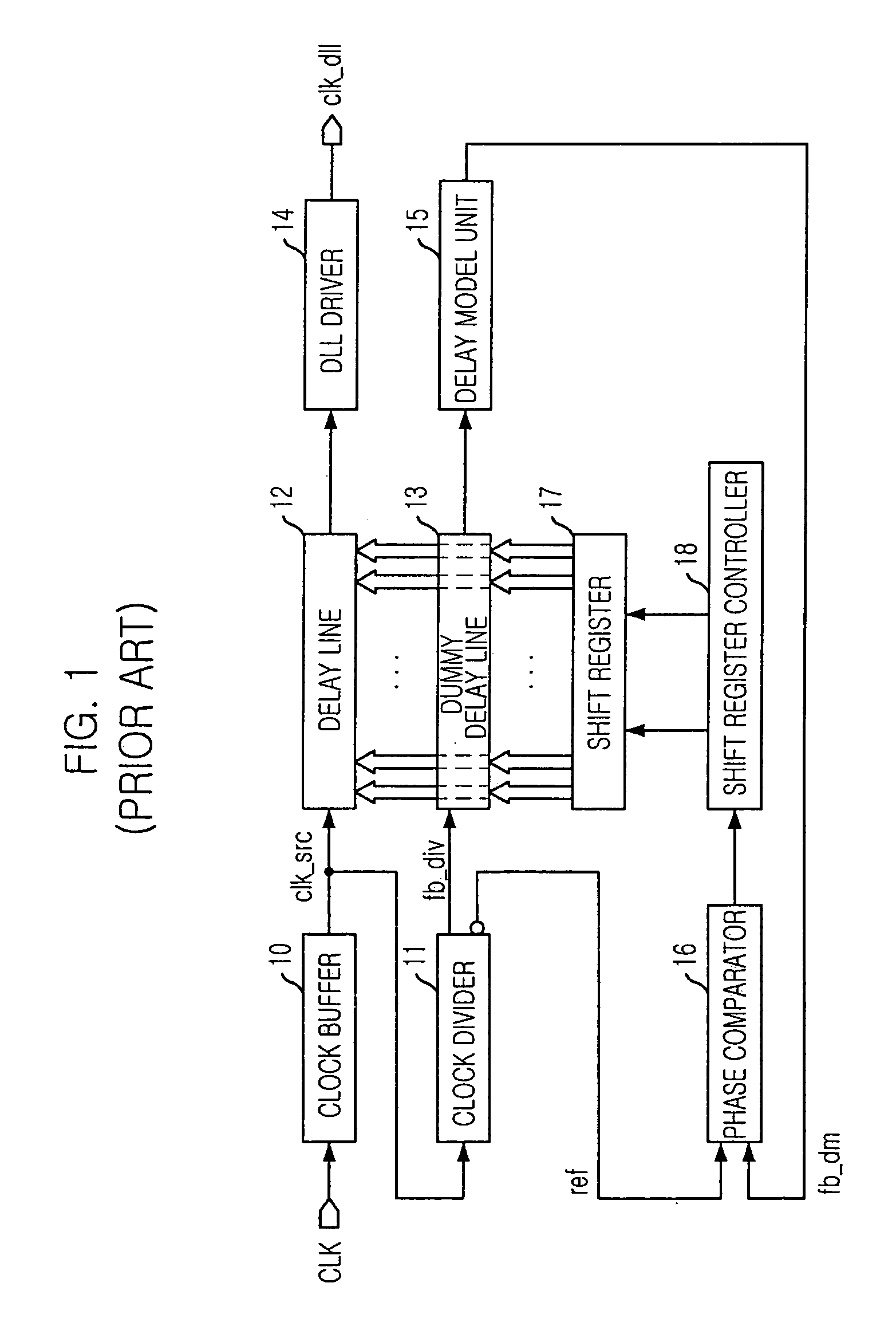

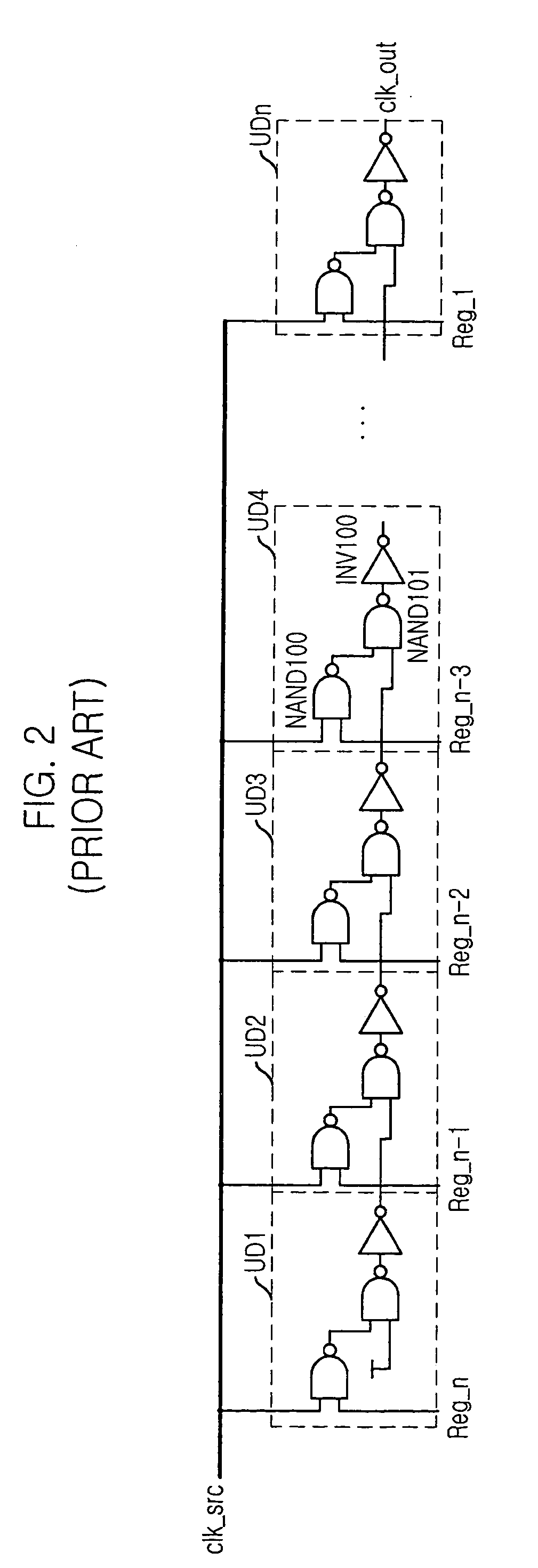

Register controlled delay locked loop with reduced delay locking time

ActiveUS7098712B2Minimize timePulse automatic controlDigital storageProcessor registerControl signal

A register controlled delay locked loop includes a clock generation unit which receives an external clock signal for generating a source clock signal by buffering the external clock signal and for generating a delay monitoring clock signal and a reference clock signal by diving the source clock signal by a natural number; a delay line control unit which receives the reference clock signal and a feed-backed clock signal for generating a normal shift control signal and an acceleration shift control signal based on a result of a comparison between phases of the reference clock signal and the feed-backed clock signal; a delay line unit which receives the source clock signal for generating a delay locked clock signal by delaying the source clock signal according to a delay amount of the delay line unit determined by the normal shift control signal and the acceleration shift control signal; and a delay model unit for estimating a delay amount generated while the external clock signal is passed to a data output pin to generate the feed-backed clock signal, wherein an absolute delay amount based on the acceleration shift control signal is larger than that based on the normal shift control signal.

Owner:SK HYNIX INC

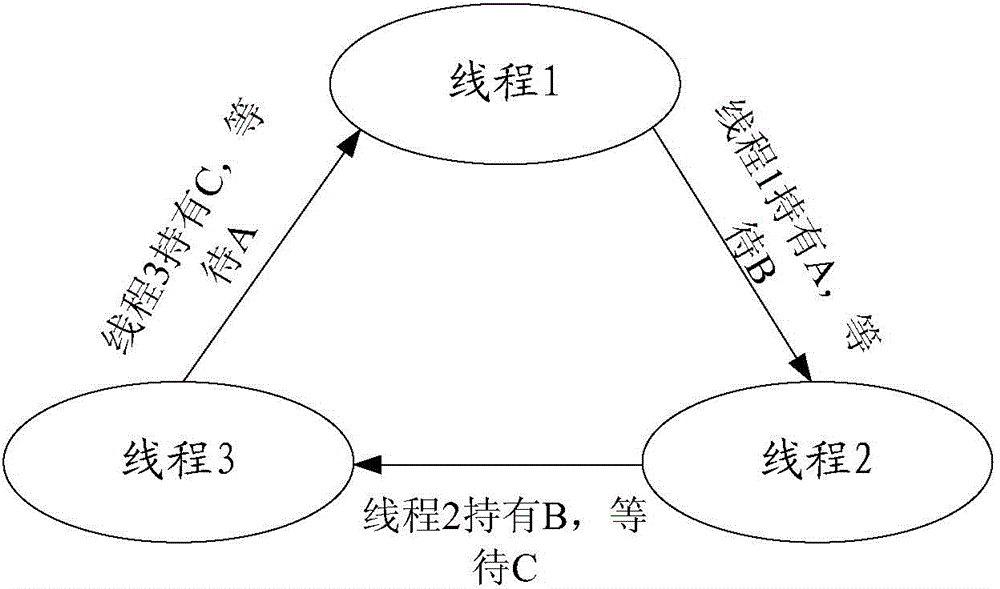

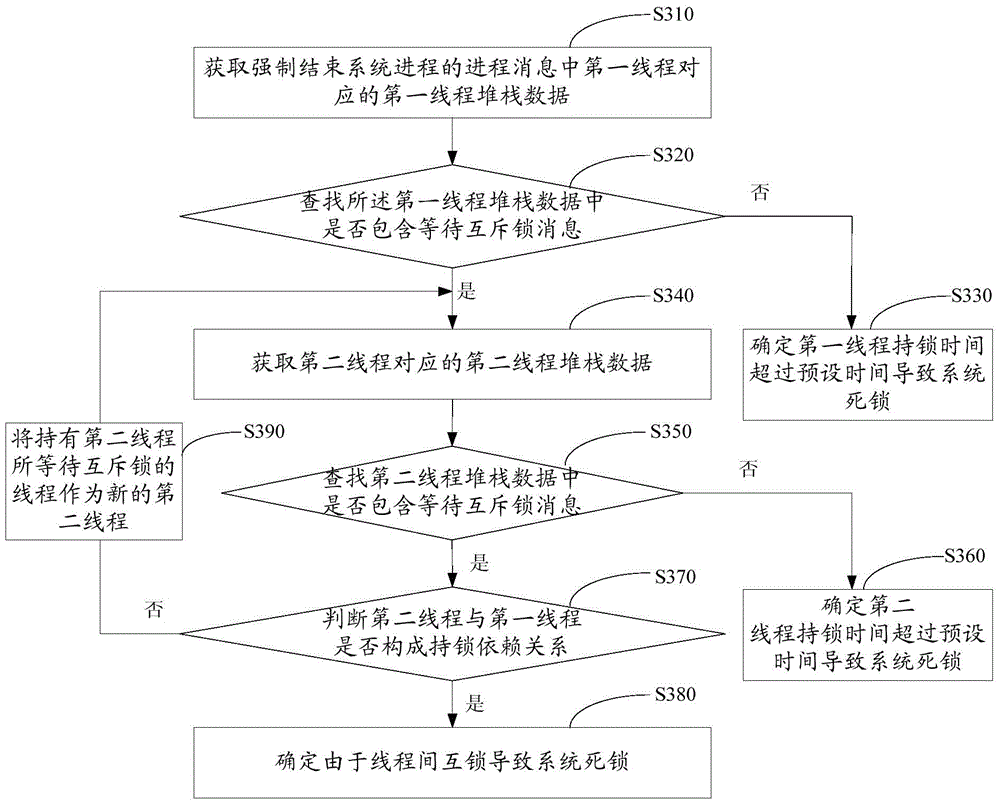

System restarting reason detection method, device and terminal equipment

ActiveCN103942113AQuick fixEfficient determinationFault responseMultiprogramming arrangementsTerminal equipmentComputer science

The embodiment of the invention discloses a system restarting reason detection method, device and terminal equipment. The system restarting reason detection method includes the steps that after an intelligent terminal is restarted, firstly, a system journal file needs to be obtained, then whether the system journal file contains process information for ending a system process compulsively or not is found out, when the process information for ending the system process compulsively is contained, related thread stack data are obtained, and the reason for system deadlock is obtained according to the thread stack data; when the reason for system deadlock is interlocking between threads, the interlocked threads are determined; when the reason for system deadlock is that the lock time of the threads exceeds a preset time, the threads with the lock time exceeding the preset time are determined. Consequently, after the intelligent terminal is restarted, whether restarting is caused by system deadlock or not can be detected rapidly, if restarting is caused by system deadlock, deadlock threads can be determined rapidly, research personnel do not need to analyze system messages one by one, and therefore the speed is high, and the efficiency is high.

Owner:XIAOMI INC

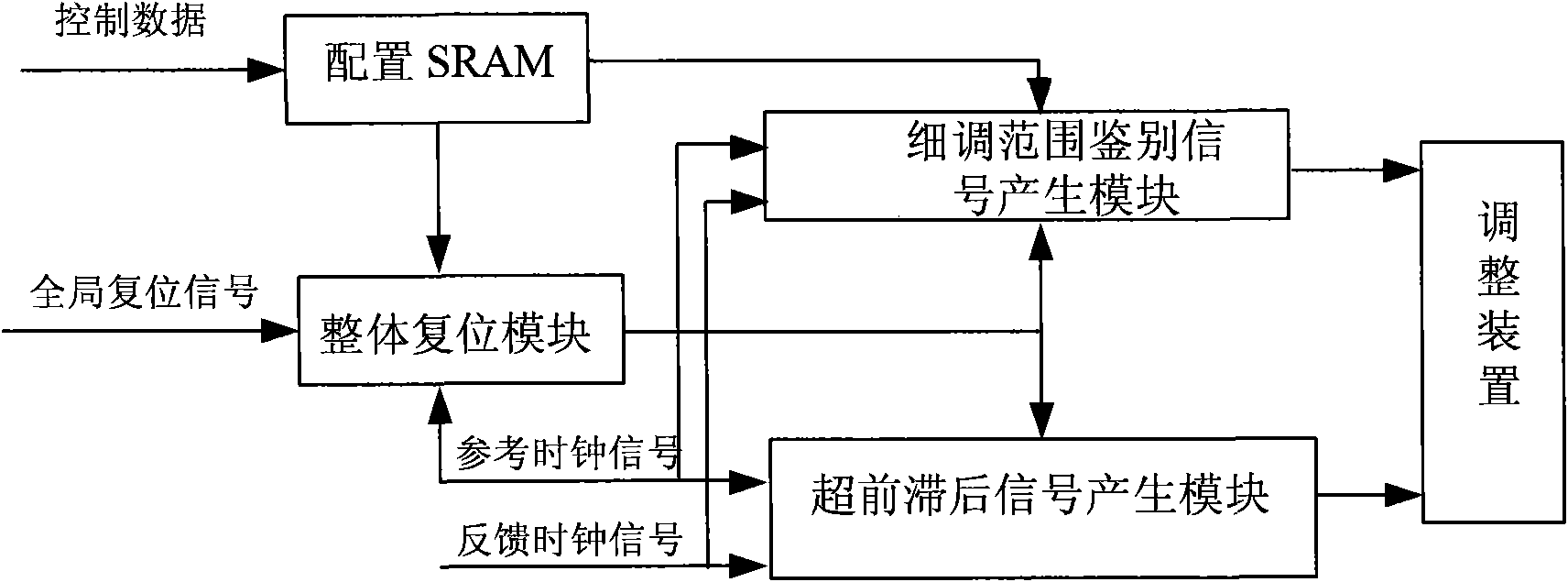

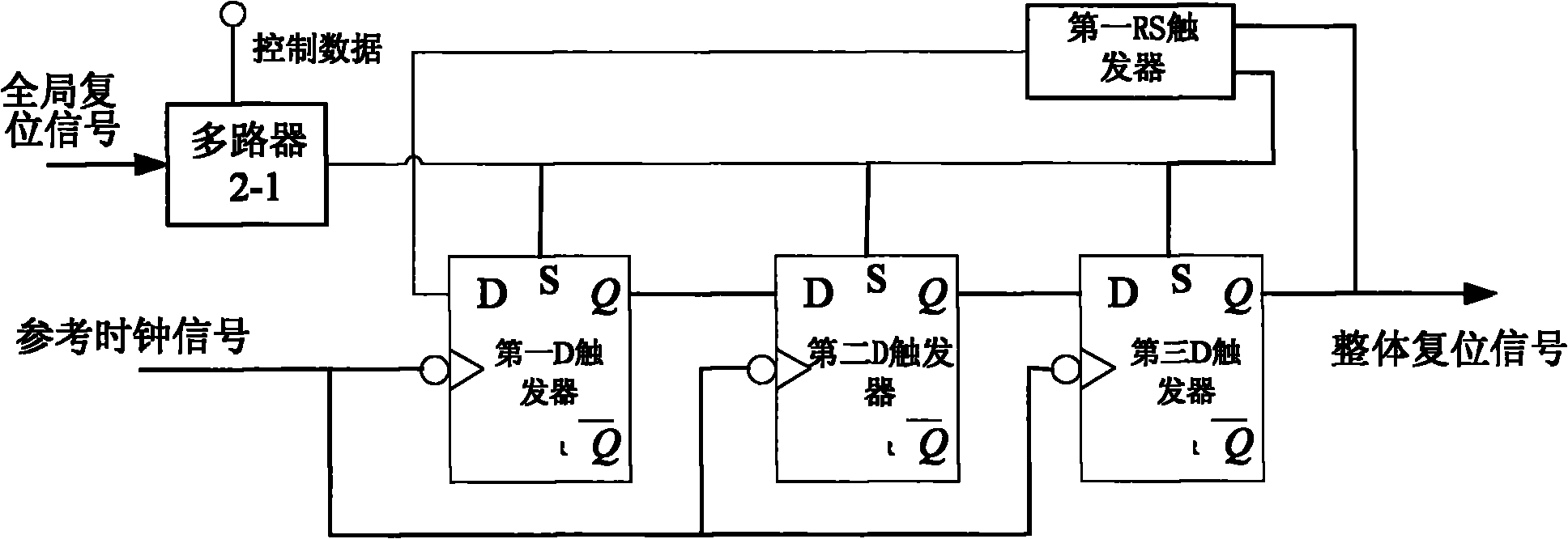

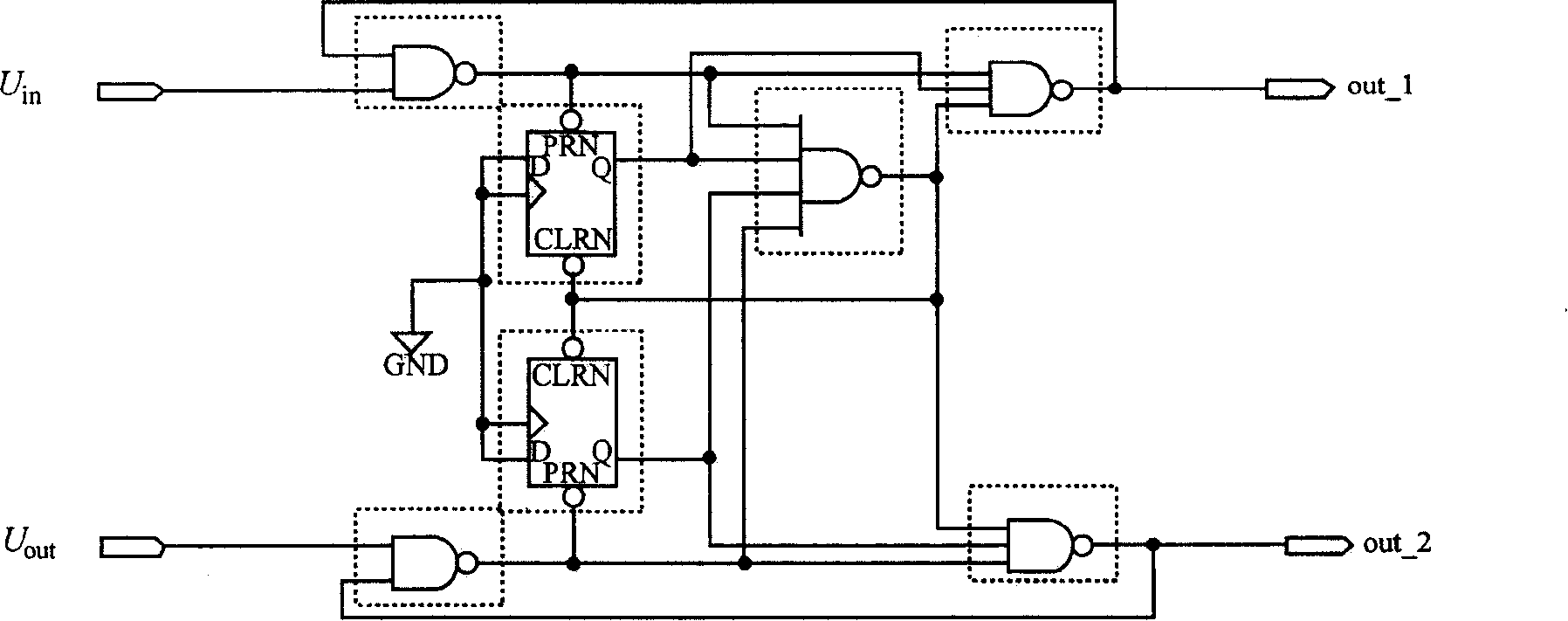

Configurable phase discriminator for time-delay locking ring

ActiveCN101789784AAdjust lock timeImprove controllabilityPulse automatic controlDiscriminatorPhase detector

The invention relates to a configurable phase discriminator for a time-delay locking ring, which comprises a configurable SRAM, an integral resetting module, an advanced-lagged signal generating module and a fine adjusting range identification signal generating module. Data in the embedded configurable SRAM is changed and different phase discriminating precisions are set according to different application requirements, so as to realize the controllability of fine and rough adjusting; meanwhile, as the embedded configurable SRAM controls different starting moments of fine adjusting, the structure of hardware does not need to be changed in the using process and the locking time of a loop circuit can be adjusted only by changing a code stream in the SRAM according to the requirements. In addition, the advanced-lagged signal generating module which is composed of two D triggers and three RS triggers is used for sampling and outputting two input clock signals and judging whether the two input clock signals are advanced or lagged; the fine adjusting range identification signal generating module which is composed of a nand gate and two pulse generating circuits is used not only for judging whether the phase difference of the two clocks reaches the set fine adjusting range, but also for controlling the starting time of fine adjusting by controlling the pulse generating width.

Owner:BEIJING MXTRONICS CORP +1

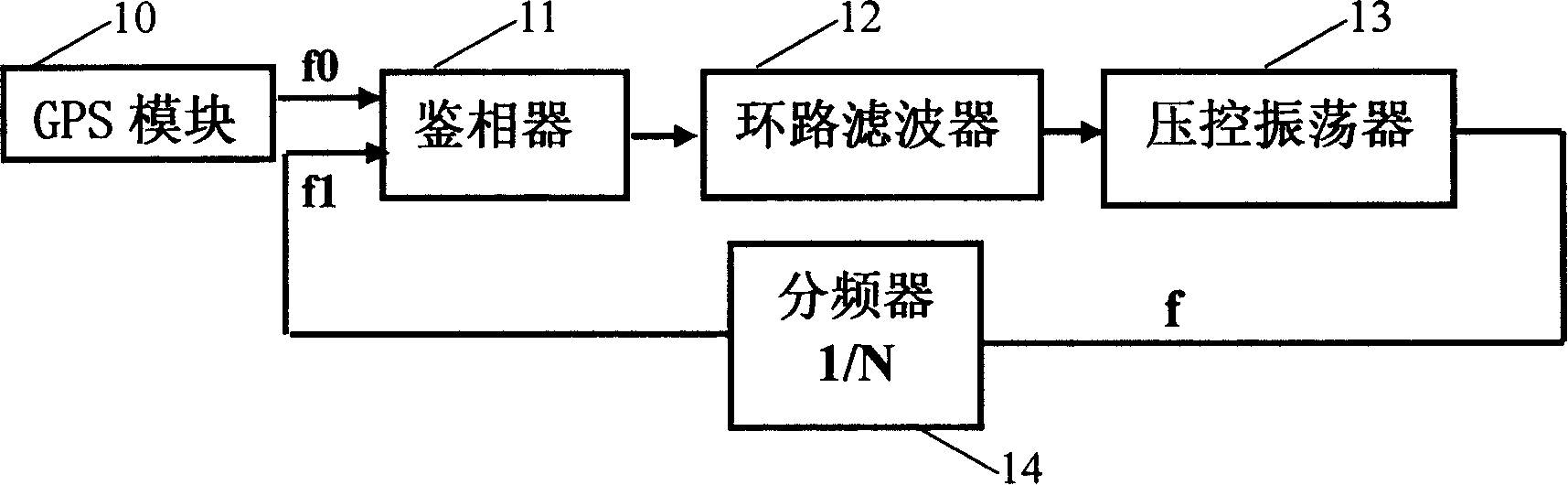

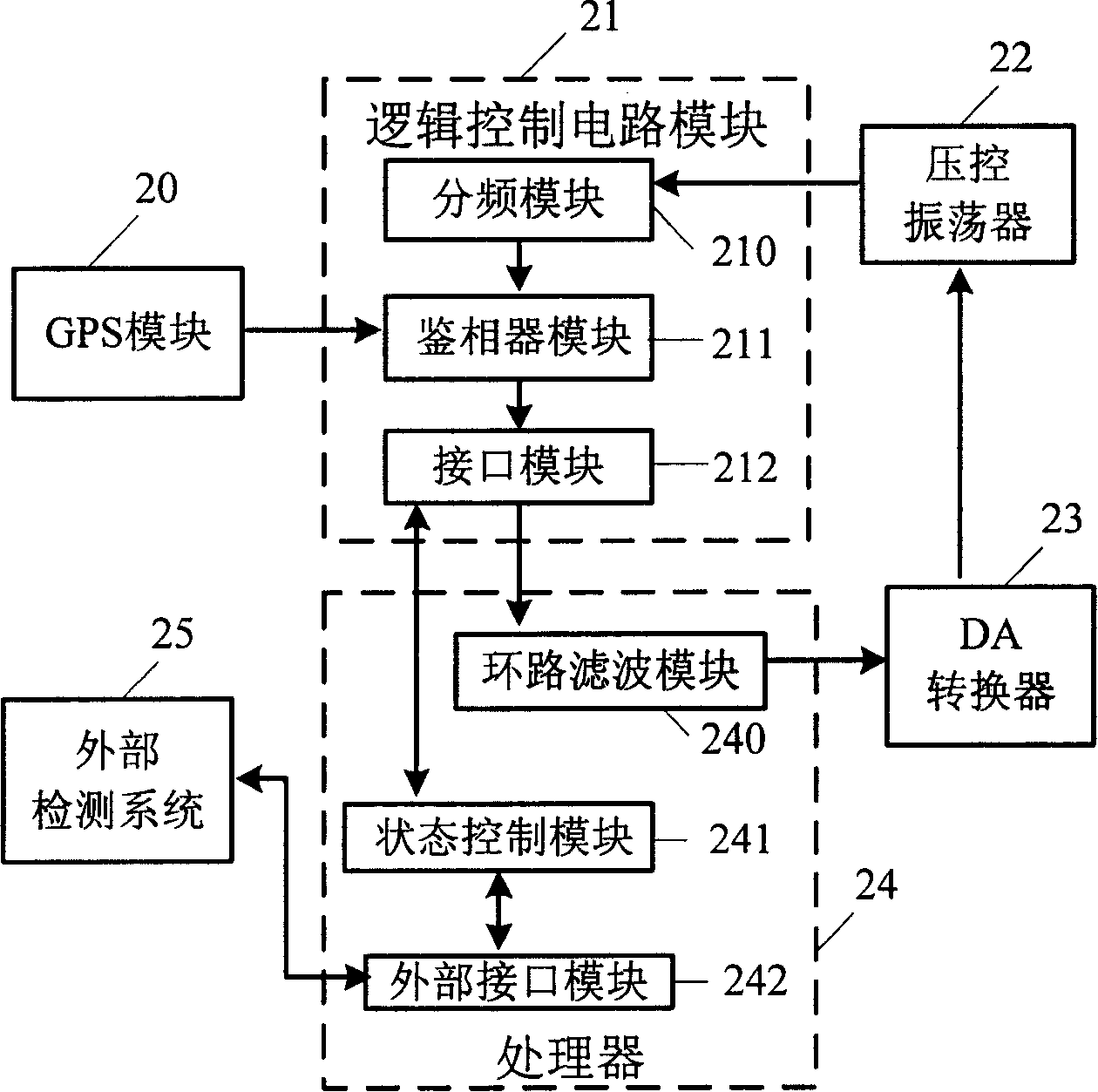

Clock phase-locked method to extract synchronous clock of global positioning system and clock phase-locked loop

ActiveCN101179371AQuick lockLow costPulse automatic controlBeacon systems using radio wavesGlobal Positioning SystemClock phase

The invention discloses a synchronous clock phase-locking method for extracting synchronous clock of global positioning system. The invention is used for capturing test signals from global positioning system module with a output frequency ranging of 500Hz to 1MHz, capturing compared clock signals synchronous with the local clock signals, detecting phase of the test signals and the compared clock signals, and adjusting the frequency of local clock signal according to the phase detection results so that the compared clock signals are synchronous with the test signals. By adopting the method, the clock phase-locking ring disclosed by the invention can quickly lock the synchronous clock of the global positioning system. The invention adopts the high-frequency clock signals as the reference clock, thereby reducing the difficulty in designing the frequency division circuit, shortening the phase-locking time of the clock phase-locking ring and saving a large quantity of hardware resources.

Owner:DATANG MOBILE COMM EQUIP CO LTD

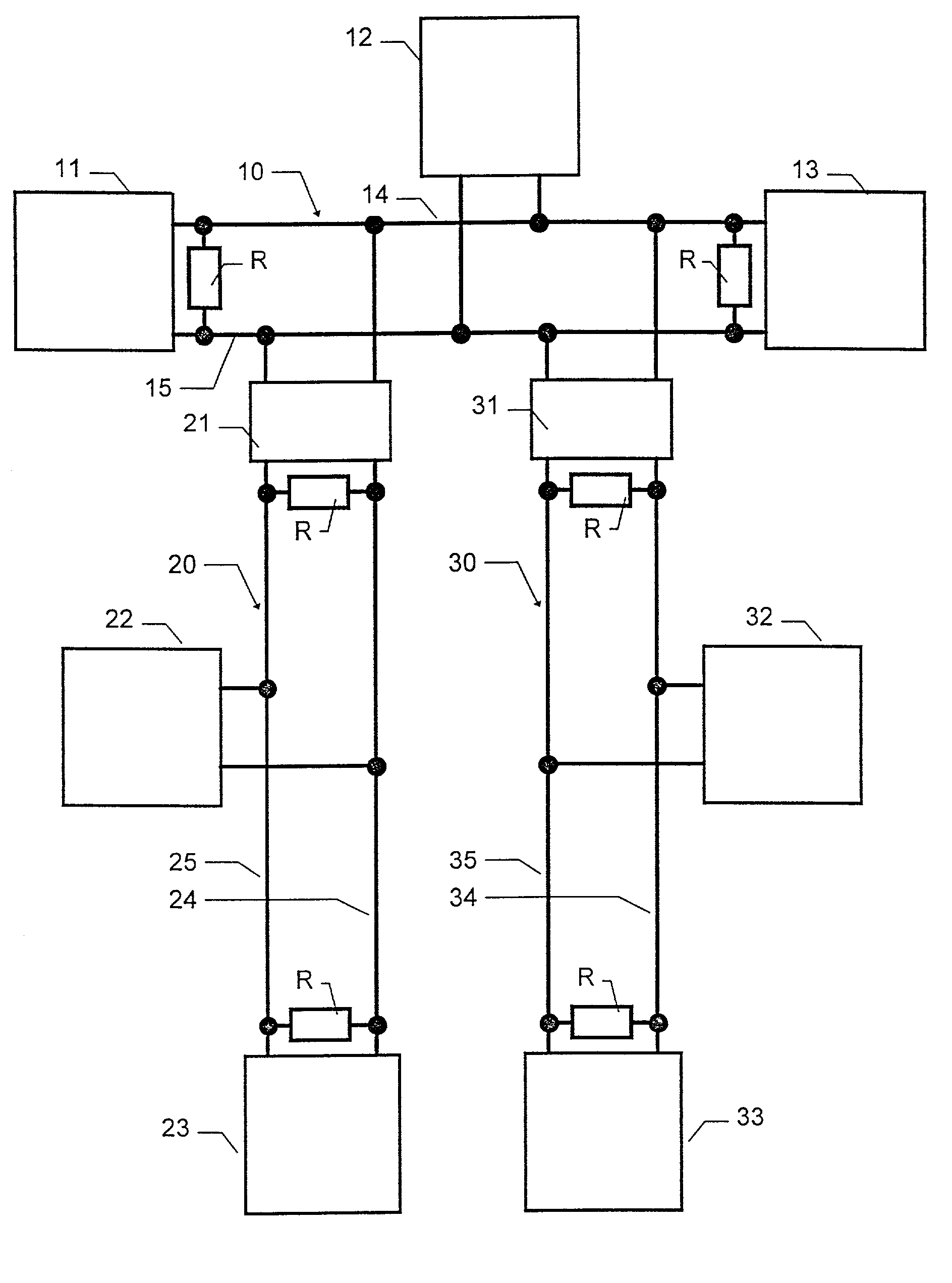

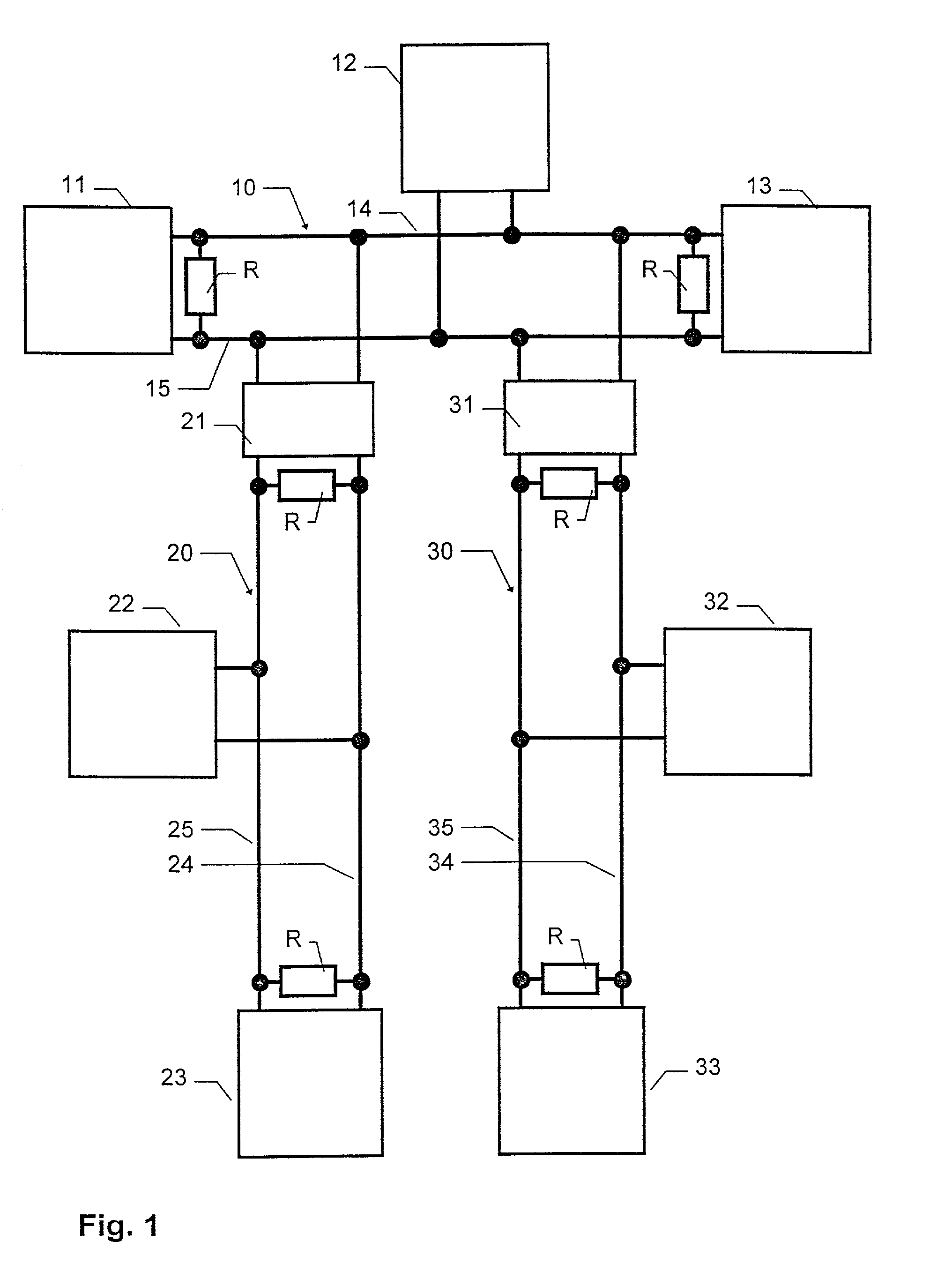

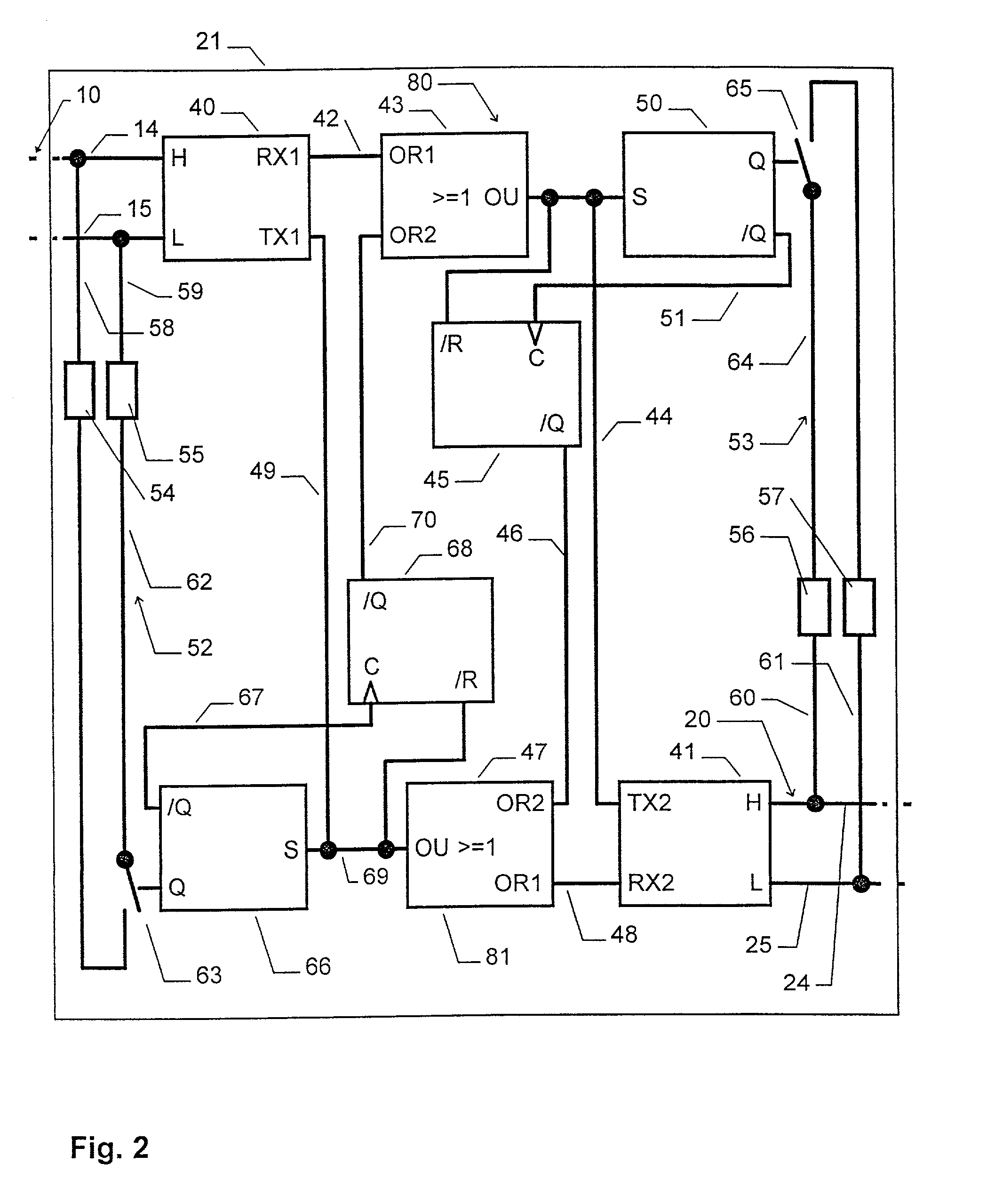

Bus repeater

InactiveUS20030074511A1Compact designExtended waiting timeFrequency-division multiplex detailsRepeater/relay circuitsPulse sequenceLock time

A bus-repeater for coupling at least one first bus with a second bus, by way of which data may be transmitted in the form of serial digital signal pulse sequences and including at least one first and a second transmit-receive means, with which the first and, respectively, the second bus may be coupled and by way of which the bus-repeater may transmit signal pulse sequences, received via the first bus on the second bus, and vice versa. In accordance with the invention the bus-repeater comprises locking means, which during transmission of a signal pulse received from the first bus to the second bus lock transmission by the bus-repeater of signal pulses, received from the second bus, via the first bus for a transmission locking time and vice versa.

Owner:FESTO AG & CO KG

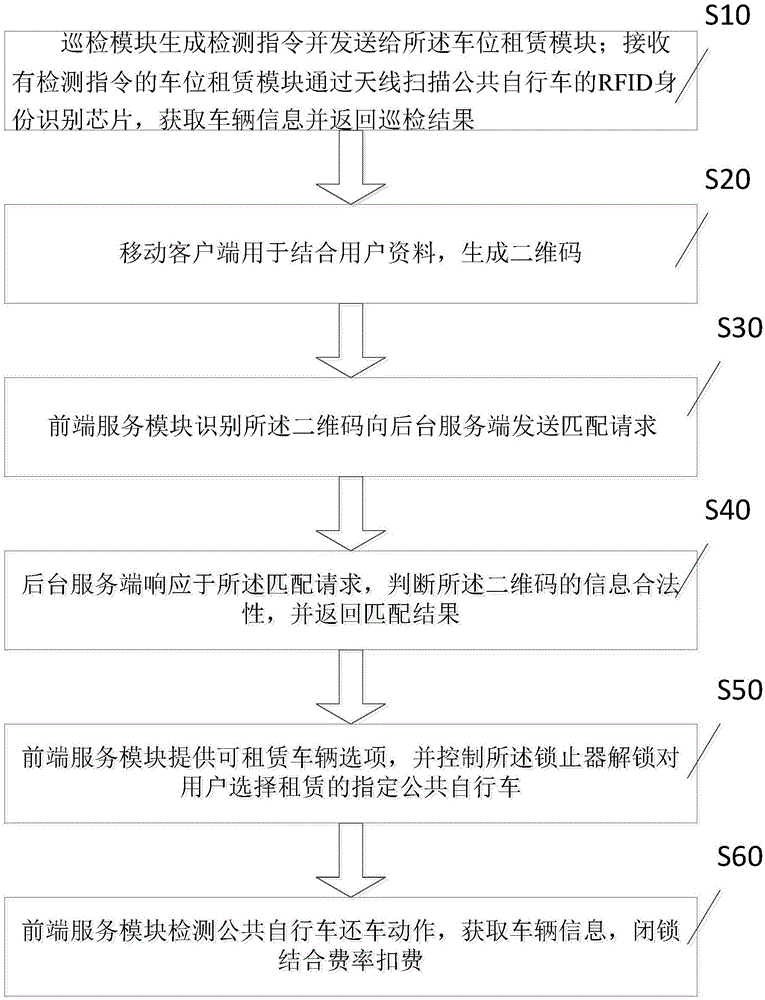

Public bicycle renting method achieved by scanning two-dimensional code

InactiveCN105976531AReduce cumbersomeImprove experienceTicket-issuing apparatusCo-operative working arrangementsComputer hardwareComputer module

The invention discloses a public bicycle renting method achieved by scanning a two-dimensional code. The method includes the following steps that S20, a mobile client generates the two-dimensional code through user data; S30, a front-end service module recognizes the two-dimensional code and sends a matching request to a background server; S40, the background server responds to the matching request, information legality of the two-dimensional code is judged, and a matching result is returned; S50, the front-end service module provides rentable bicycle options, and a lock is controlled to unlock a specific public bicycle selected by a user to rent; S60, the front-end service module detects a public bicycle vehicle return action to obtain bicycle information, and fee is charged according to locking time and rate. Bicycle renting is achieved by scanning the two-dimensional code through the front-end service module, complexity caused by card application is reduced, and user experience is improved. The defect that IC cards in different cities are not uniform or unified is overcome, the bicycle can be rented by means of the two-dimensional code, and great convenience is brought to foreign visitors.

Owner:HANGZHOU GST TECH