Patents

Literature

283 results about "Left shifting" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The term “left shift” means that a particular population of cells is “shifted” towards more immature precursors (meaning that there are more immature precursors present than you would normally see).

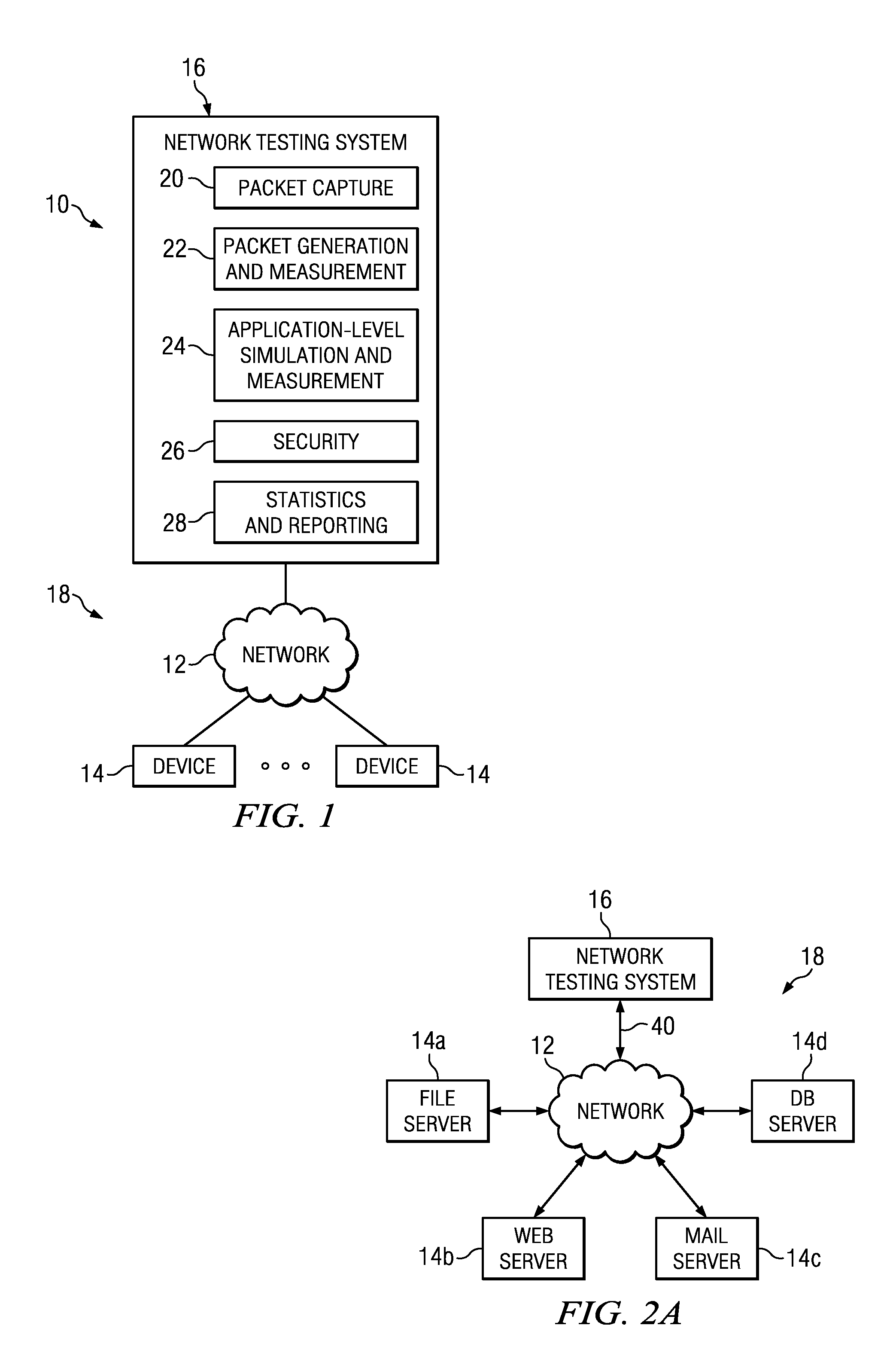

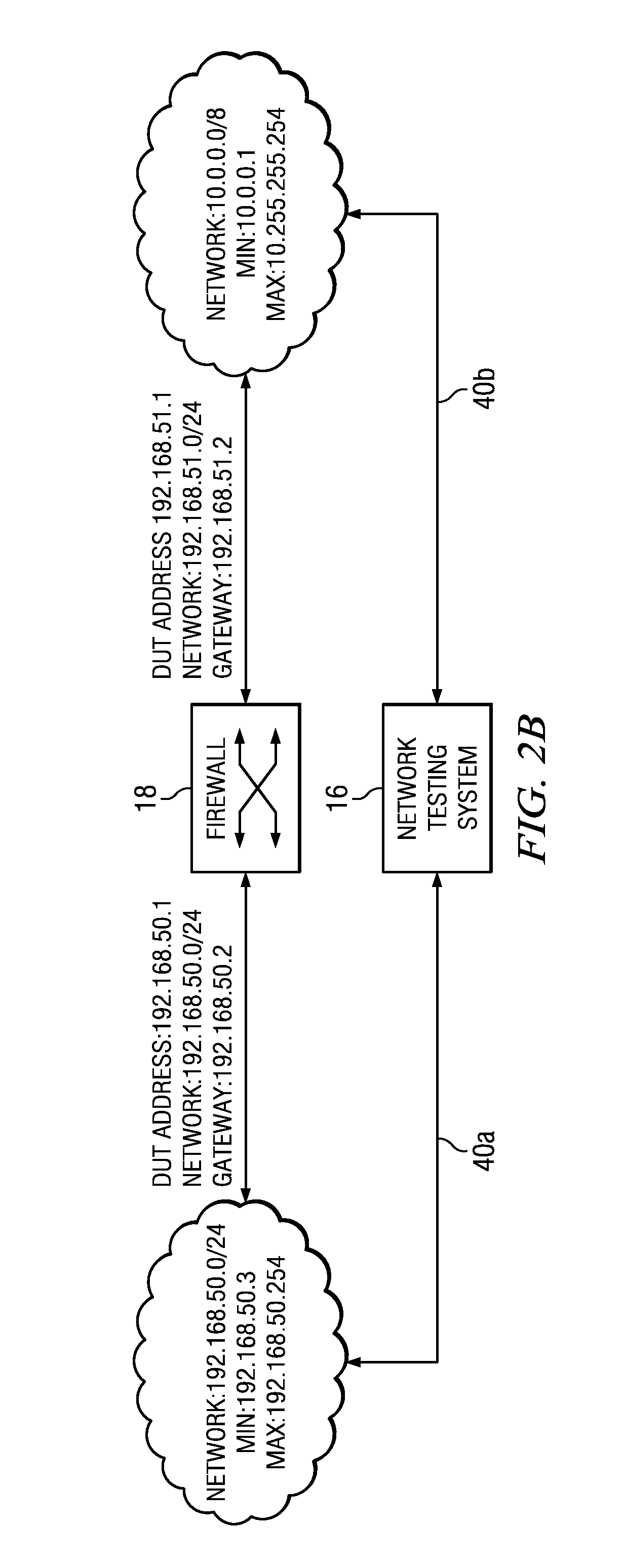

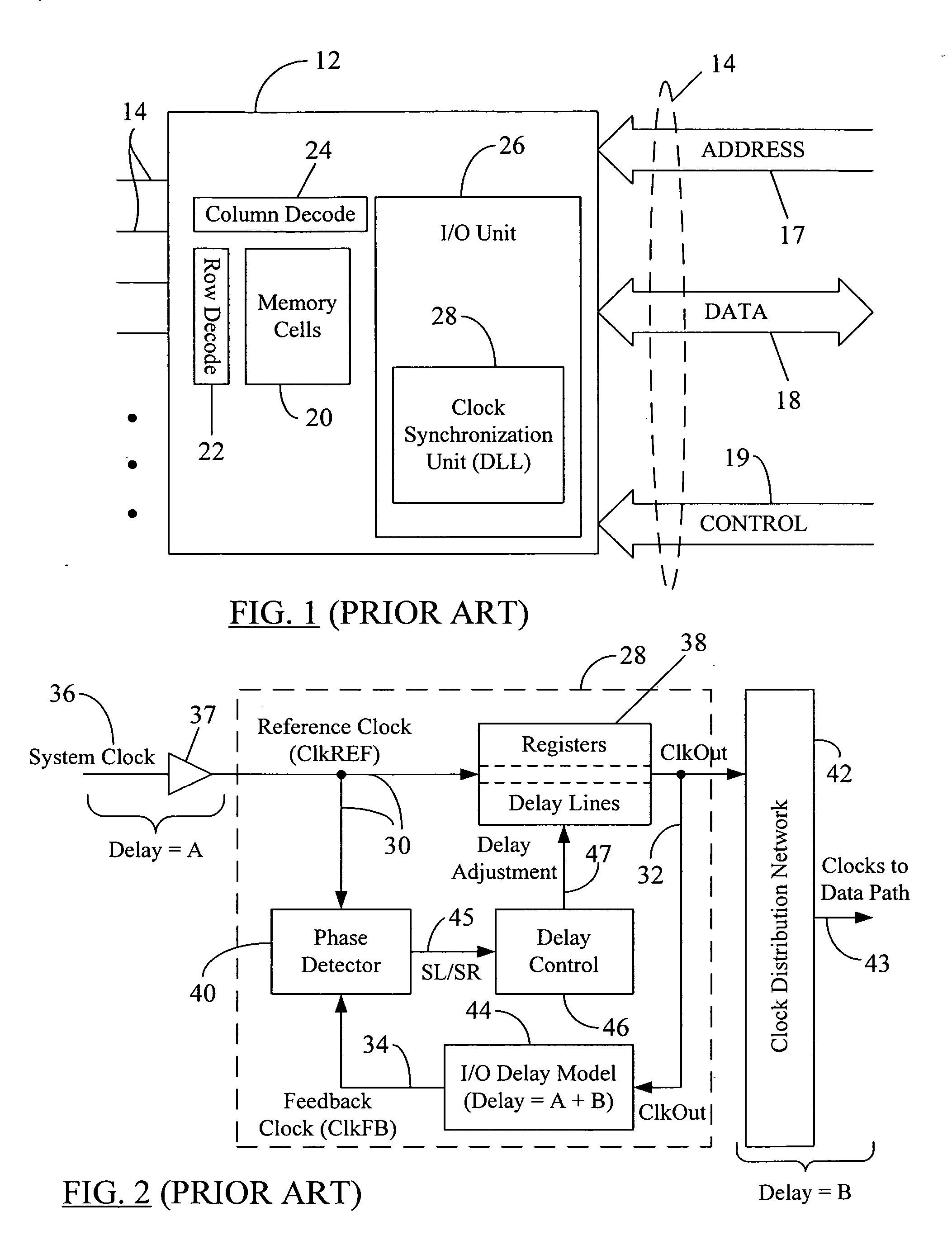

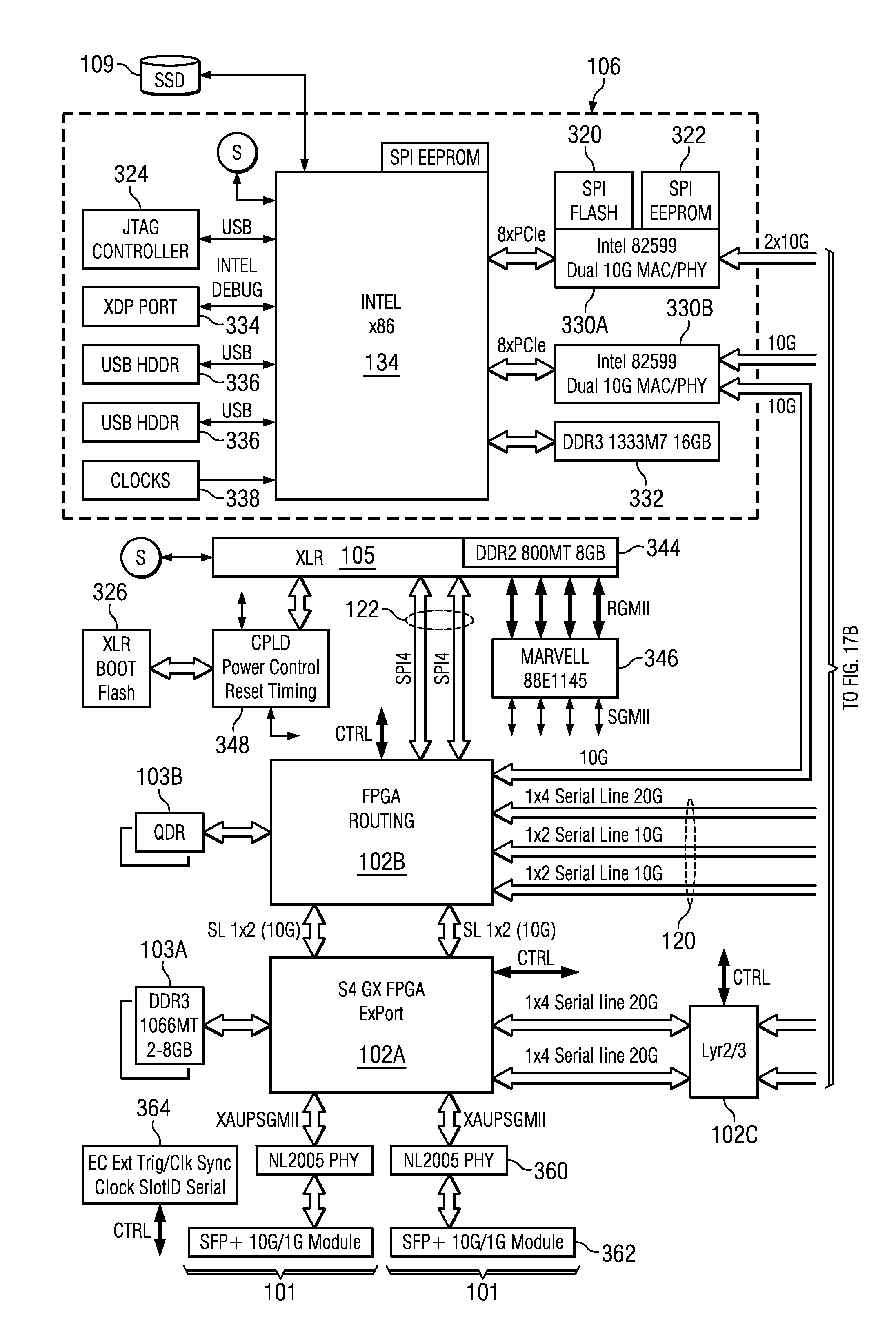

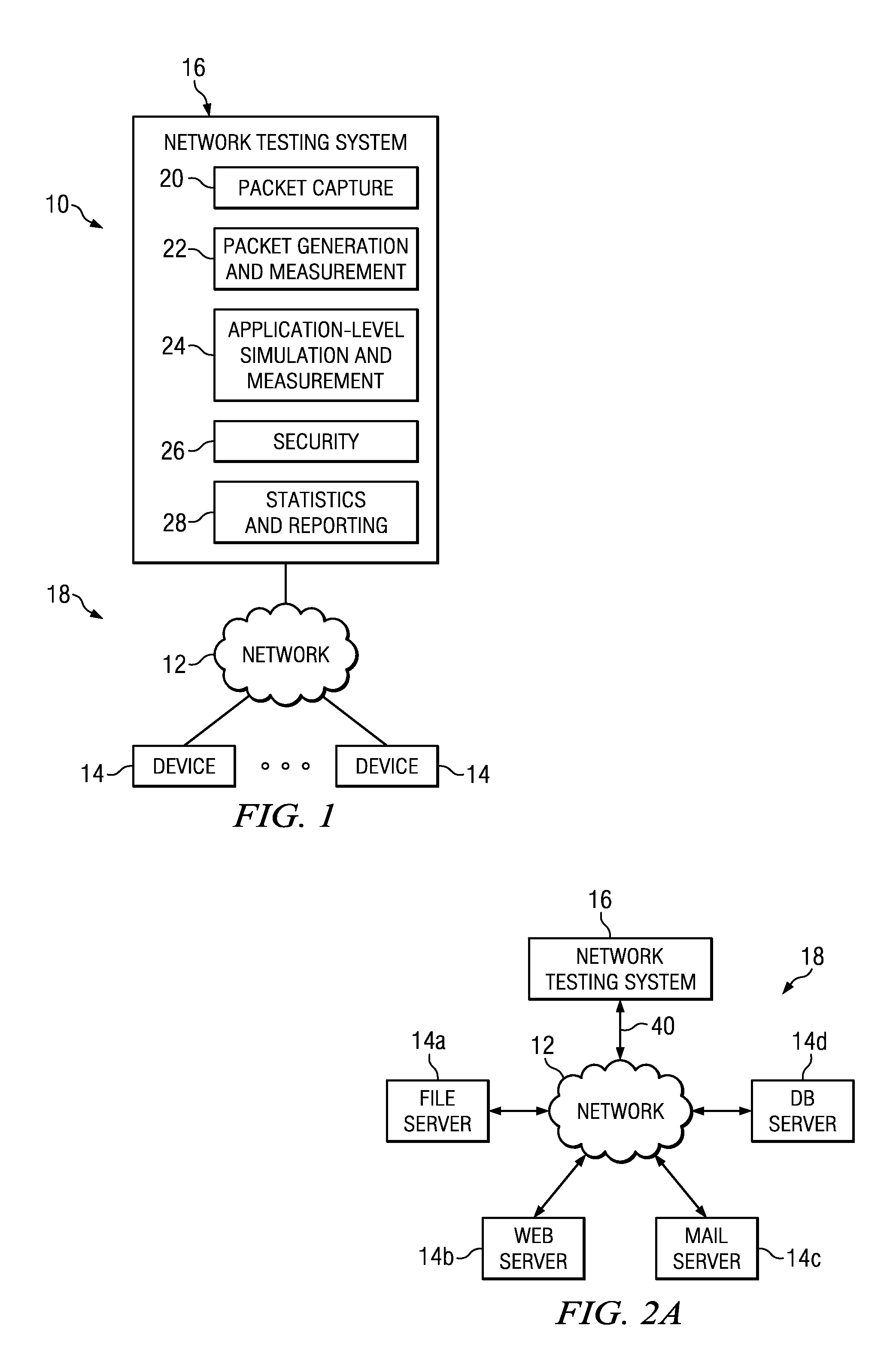

Systems and methods for efficient memory access

InactiveUS20130346719A1Memory architecture accessing/allocationMemory adressing/allocation/relocationProcessing coreProcessor register

A computer-implemented method of accessing data comprises resetting the value of a register of a first processing core of a multi-core processor, copying the bits of a compressed pointer into the lowest order bits of the register, left shifting the register a predetermined number of bits, and executing on the first processing core a first instruction referencing memory at a virtual address specified by the register.

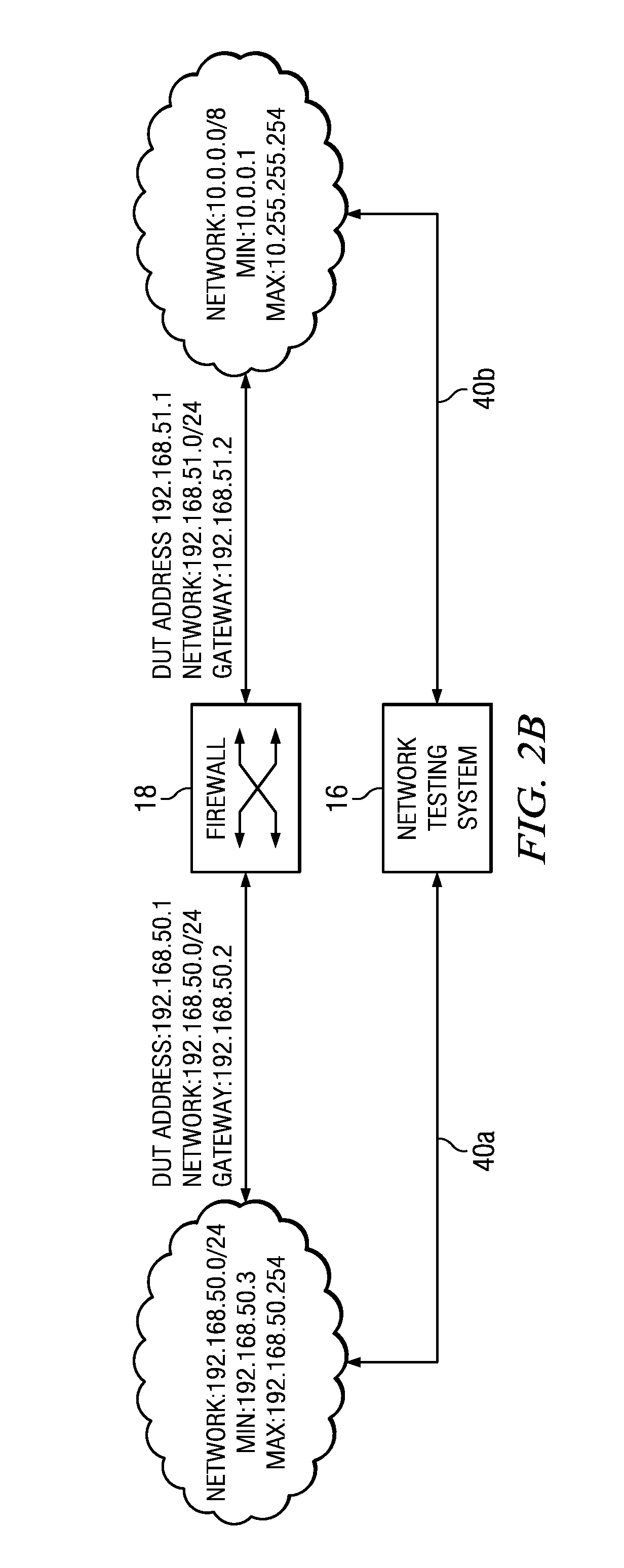

Owner:KEYSIGHT TECH SINGAPORE (SALES) PTE LTD

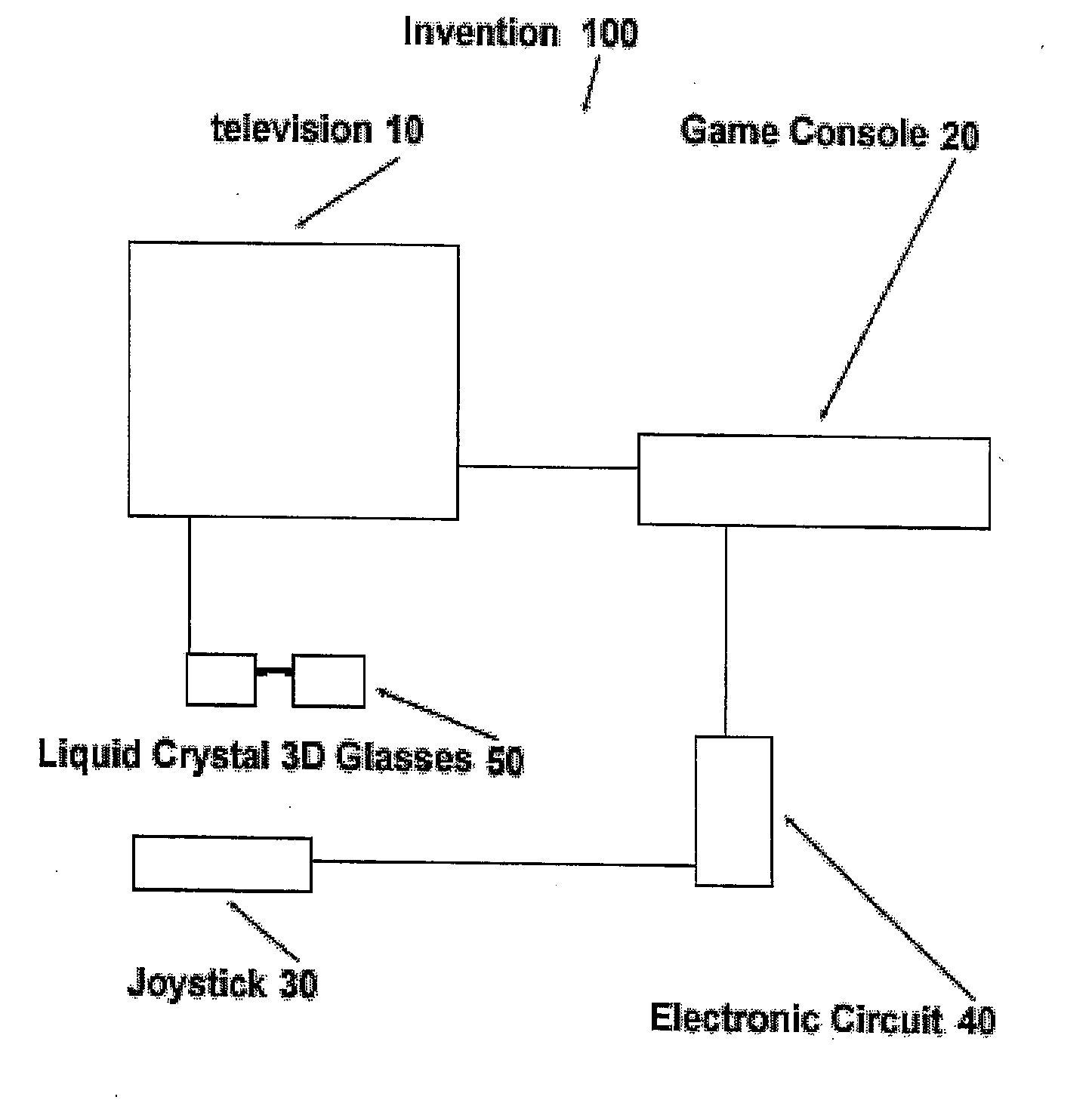

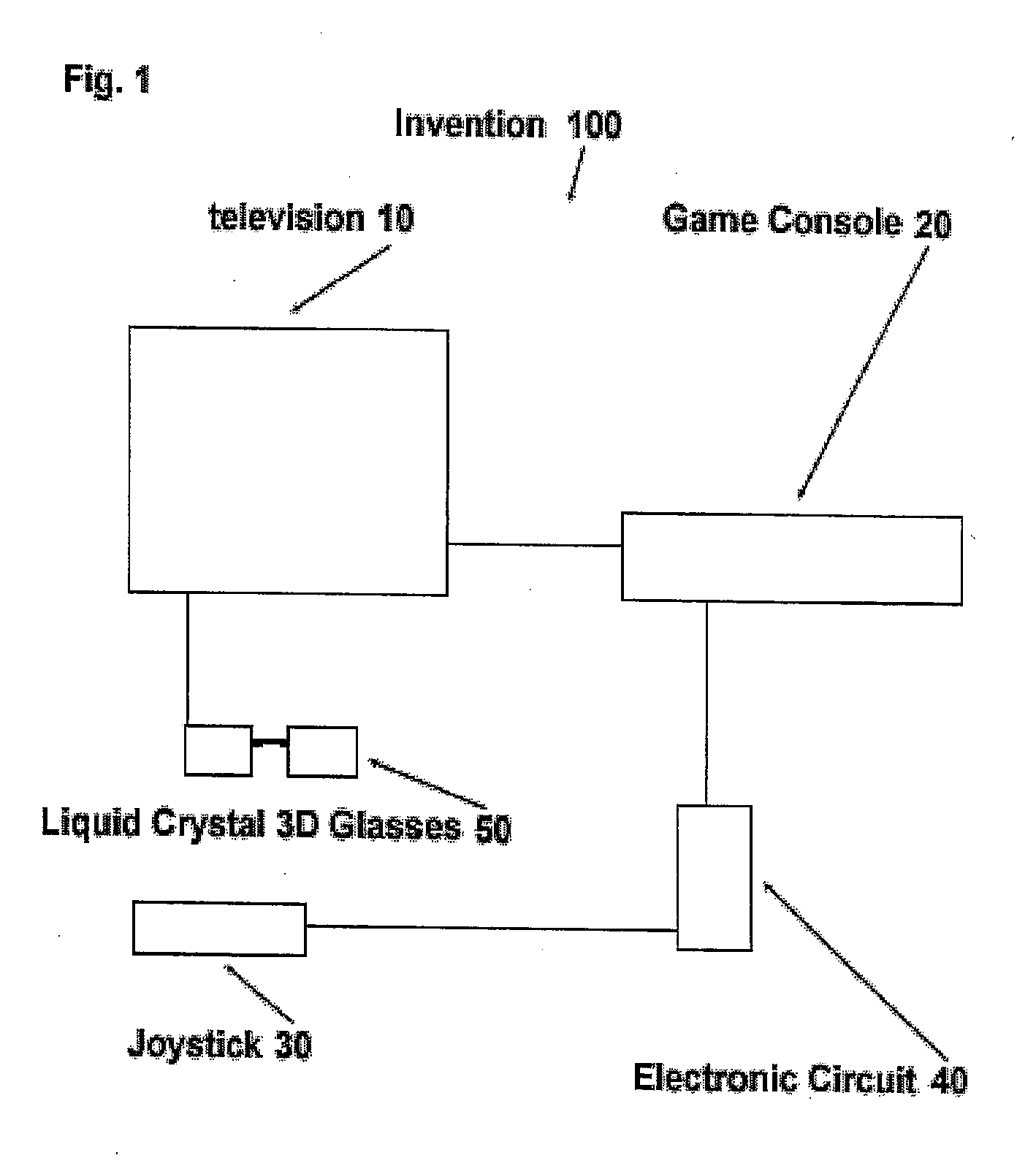

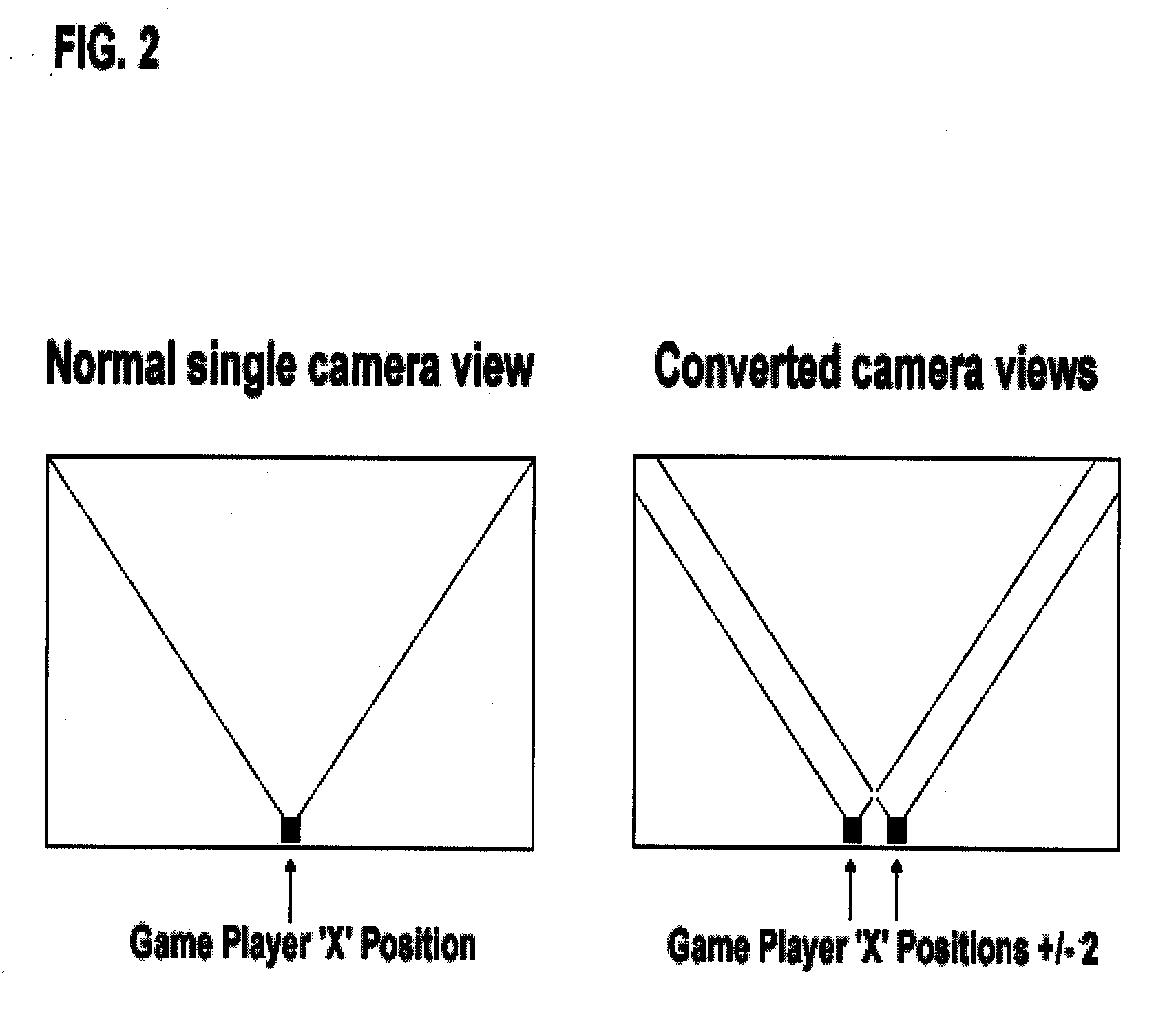

Three dimensional image generator

A method and apparatus for producing a stereoscopic 3D image in a video game being displayed on a television or video monitor. The game player look-at position is shifted laterally to the left and right of the actual player look-at position during alternating vertical refresh cycles. A pair of liquid crystal glasses may be synchronized to the vertical refresh cycle such that a player wearing the glasses alternately sees the left-shifted image and the right-shifted image, producing a stereoscopic 3D image.

Owner:SPLITFISH

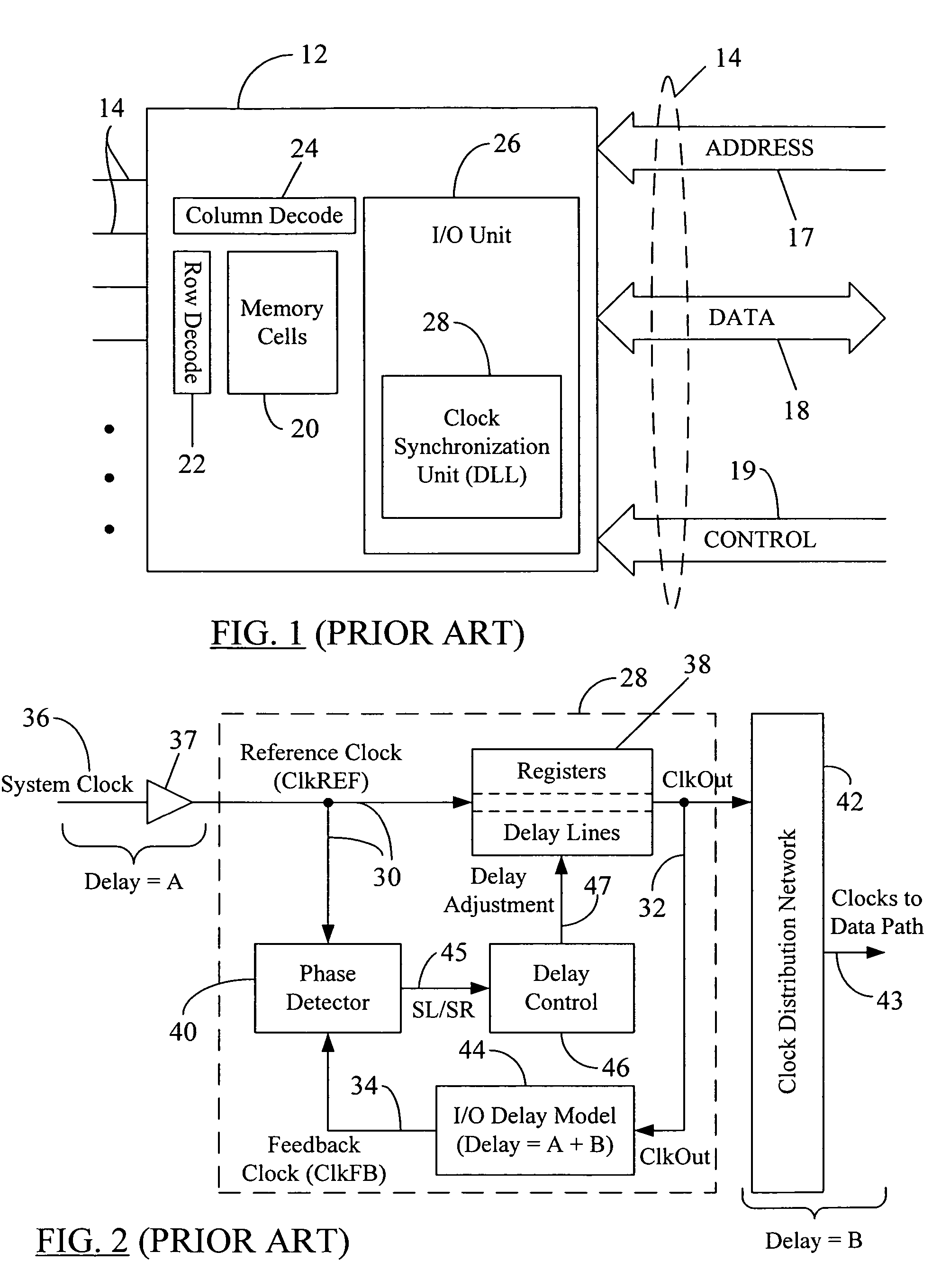

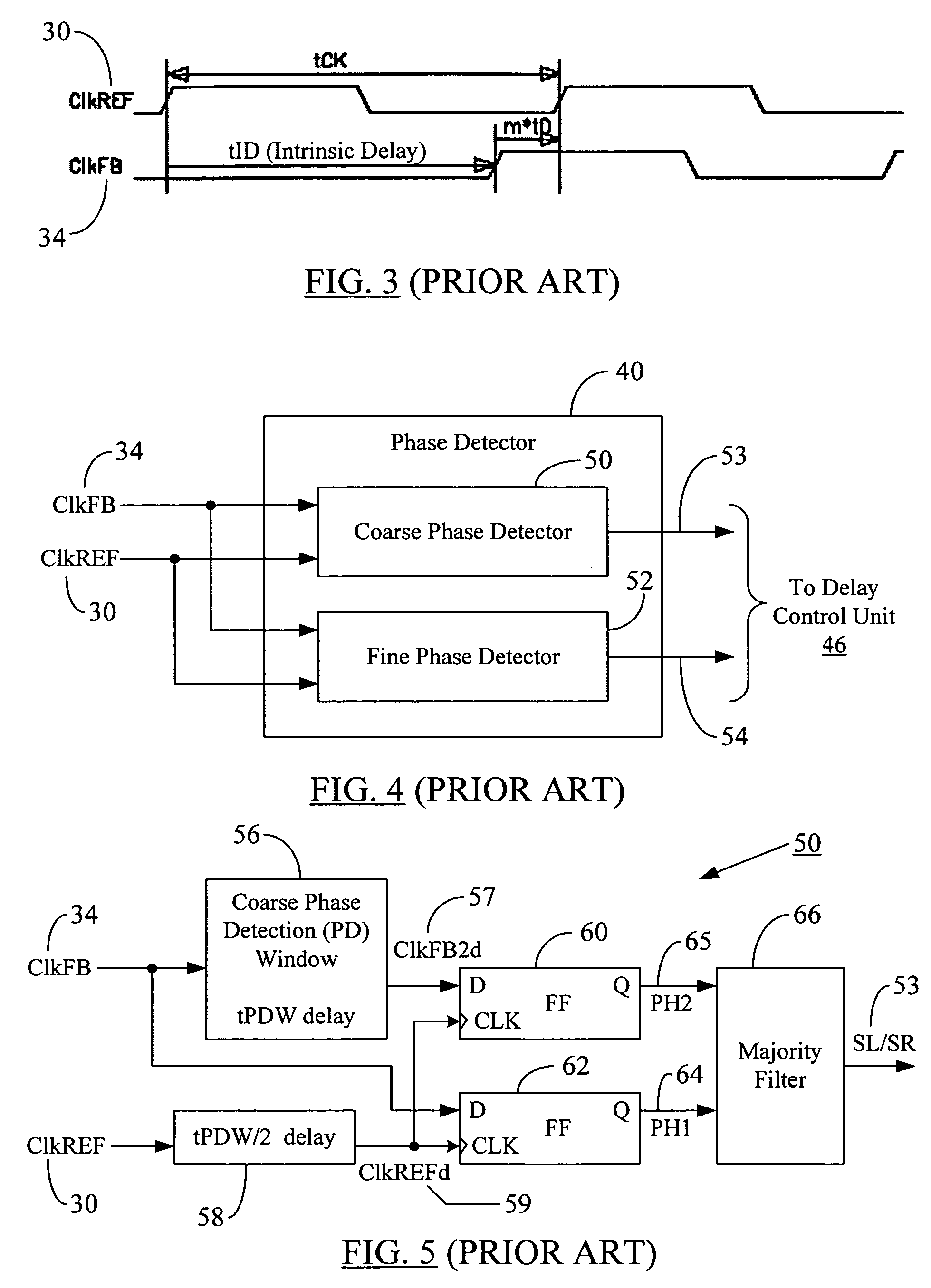

DLL phase detection using advanced phase equal

ActiveUS20050262373A1Faster DLL locking timeFast locking timePulse automatic controlError detection/correctionPhase detectorDelay-locked loop

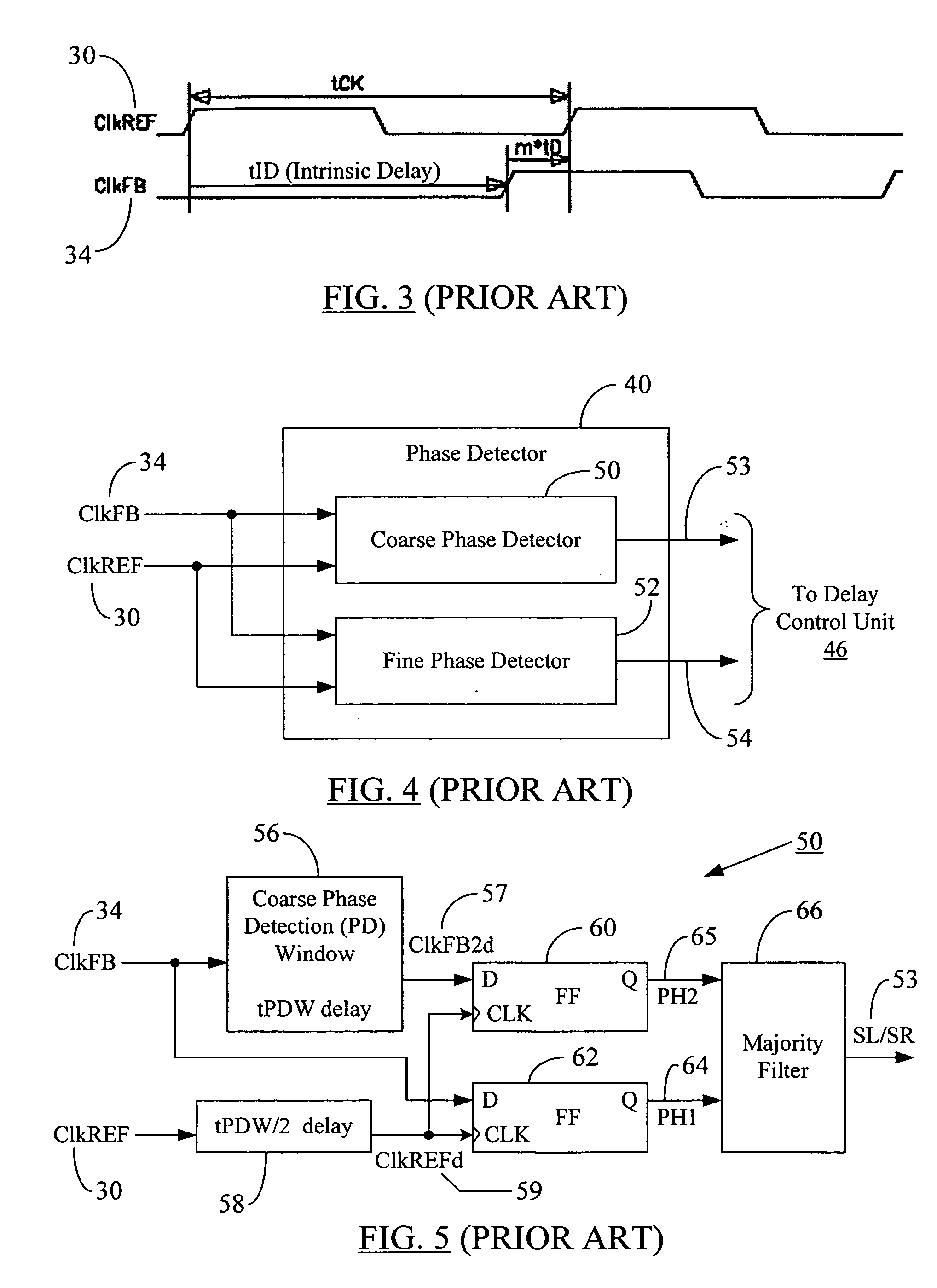

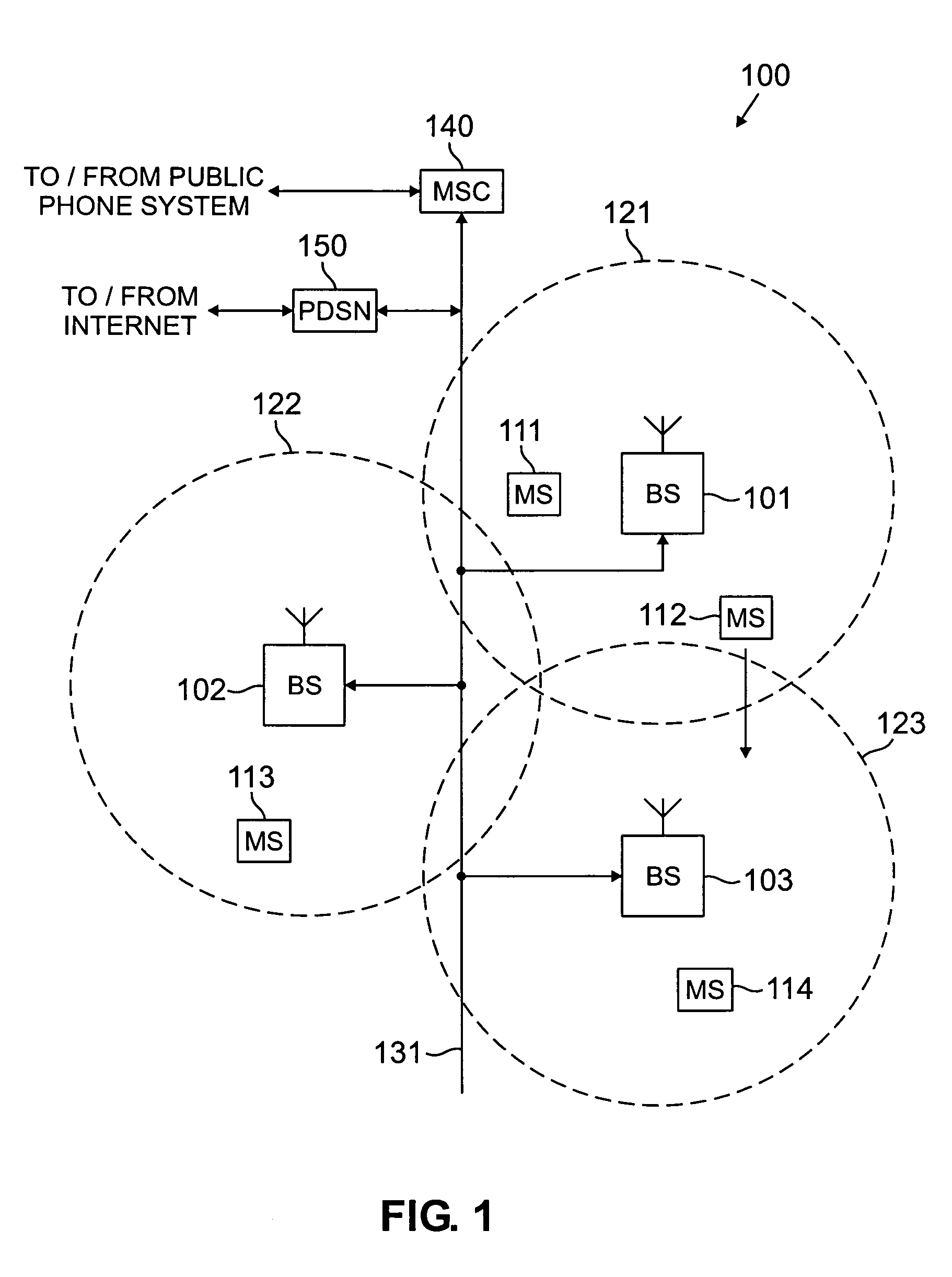

A system and method are disclosed to generate and terminate clock shift modes during initialization of a synchronous circuit (e.g., a delay-locked loop or DLL). Upon initialization, the DLL is entered into a ForceSL (Force Shift Left) mode and an On1x mode (i.e., left shifting on each clock cycle). The feedback clock that tracks the phase of the reference clock (which, in turn, is derived from the system clock) is initially delayed in a coarse phase detector prior to applying it to the coarse phase detection window. Two delayed versions of the feedback clock are sampled by the reference clock to generate a pair of phase information signals, which are then used to establish an advanced phase equal (APHEQ) signal. The APHEQ signal advances onset of the PHEQ (phase equalization) phase and is used to terminate the ForceSL and On1x modes, thereby preventing wrong ForceSL exit due to clock jitter or feedback path overshooting during On1x exit. The avoidance of wrong ForceSL exit and On1x overshooting problems further results in faster DLL locking time.

Owner:MICRON TECH INC

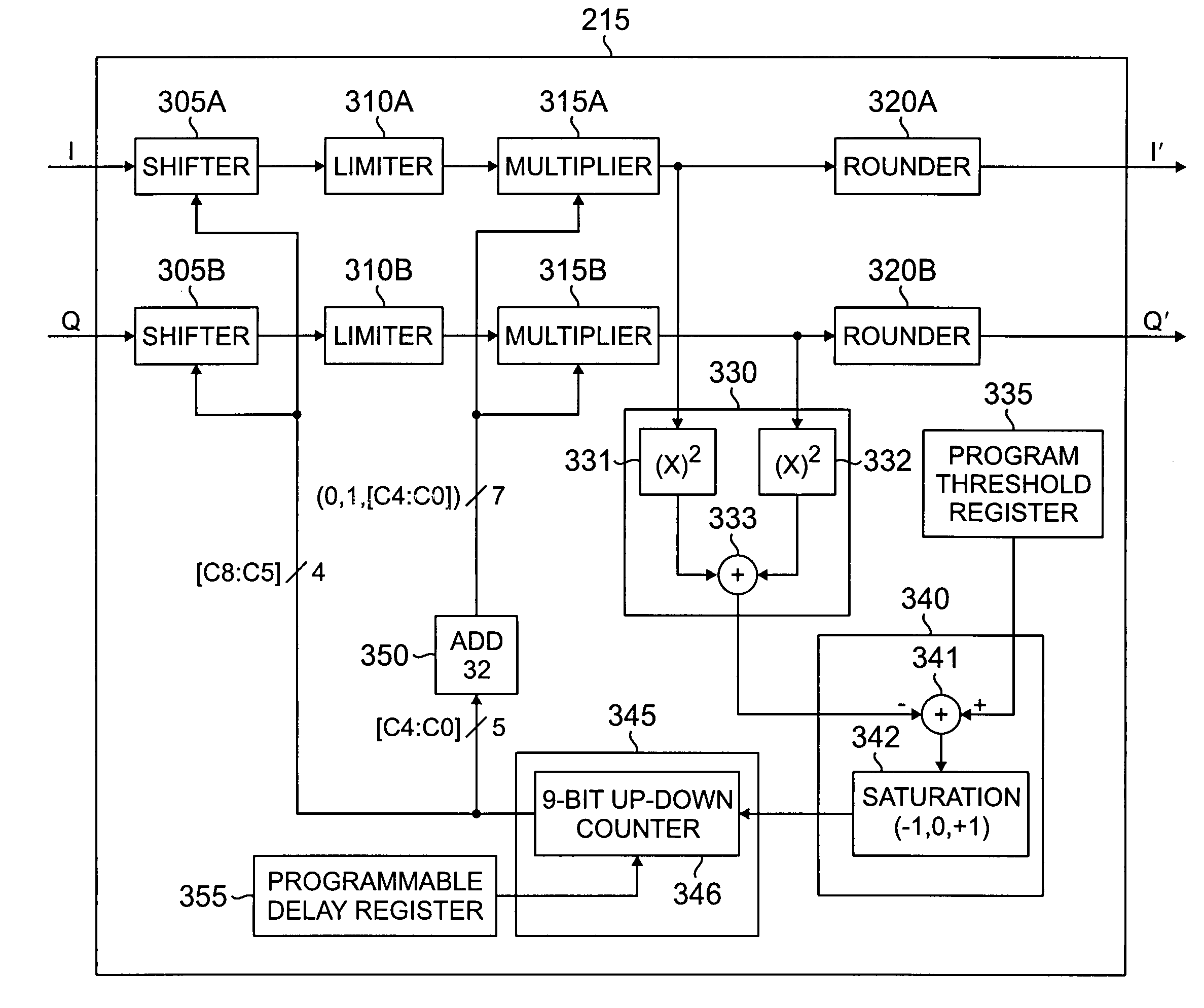

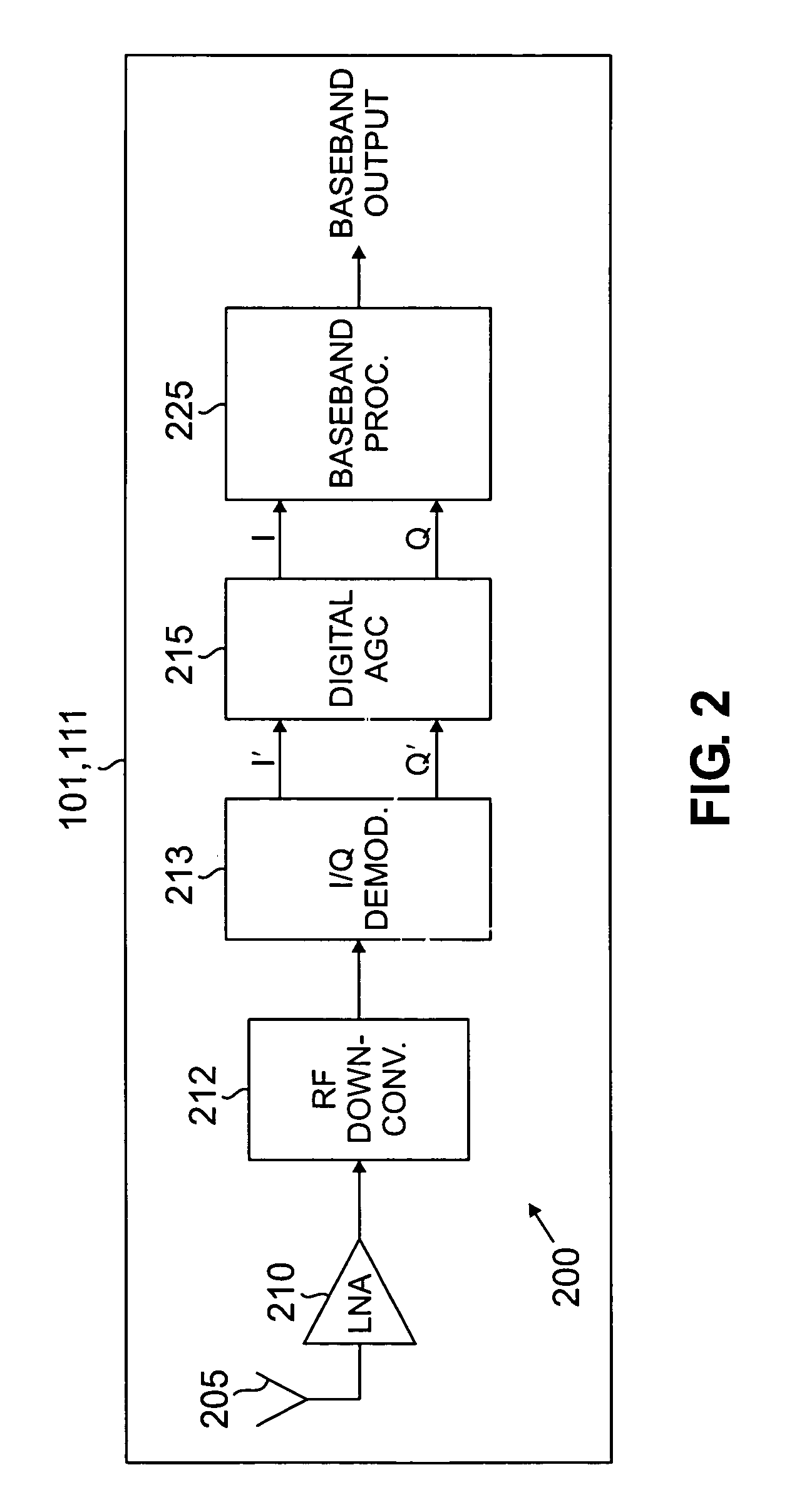

Fully digital AGC circuit with wide dynamic range and method of operation

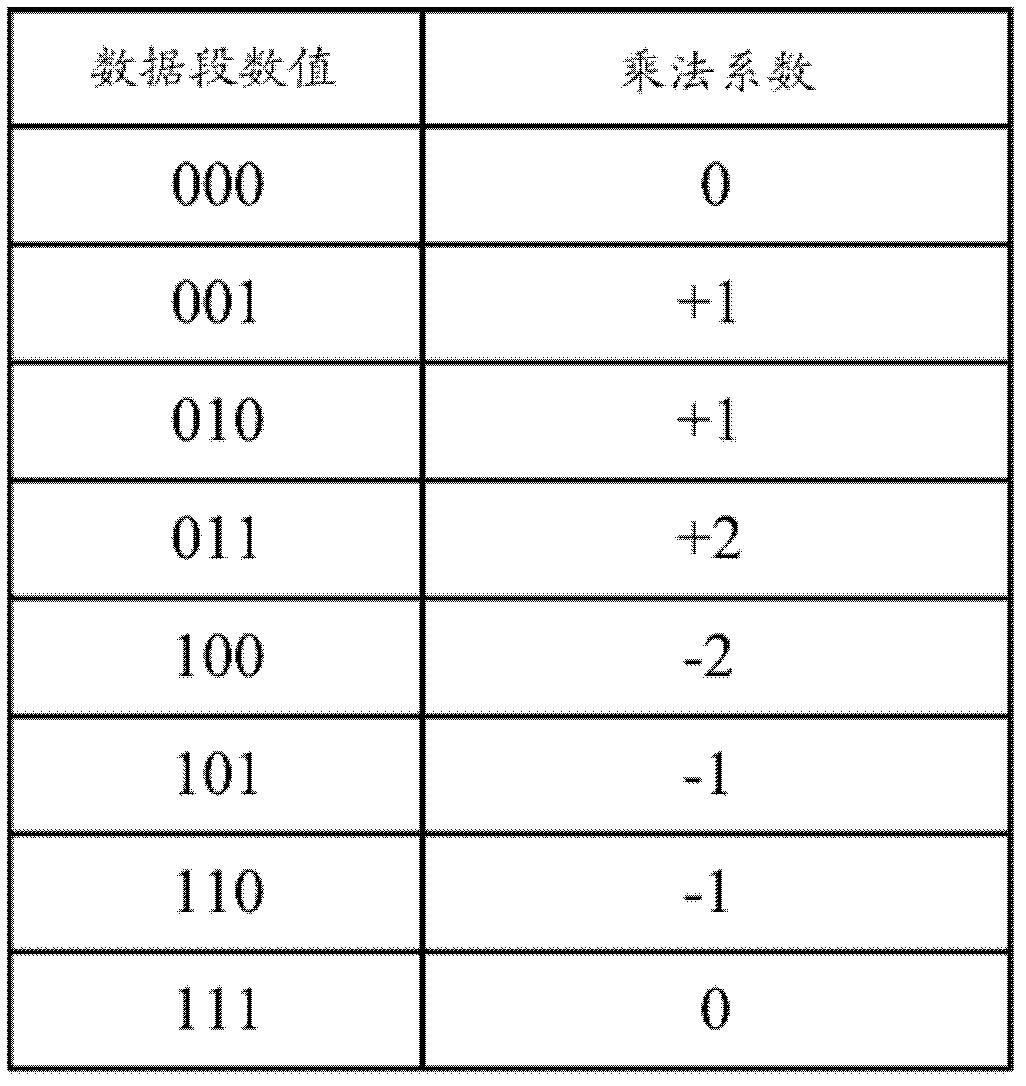

InactiveUS7031409B2MinimizesEasy to implementAmplitude-modulated carrier systemsRadio transmissionBinary multiplierEngineering

A digital automatic gain control (AGC) circuit for use in a radio frequency (RF) receiver. The AGC circuit comprises: 1) a first shifter for receiving an in-phase signal as a first series of X-bit samples and left-shifting each X-bit sample by a number of bits determined by a coarse scaling factor; 2) a first limiter for receiving the D most significant bits of the output of the first shifter and outputting a subset of the D most significant bits of the first shifter output; 3) a first multiplier for multiplying the subset of the D most significant bits of the first shifter output by a fine scaling factor to produce a first M-bit product; and 4) a gain adjustment circuit for comparing a power signal derived from the first M-bit product to a maximum threshold value and generating the coarse scaling factor and the fine scaling factor.

Owner:SAMSUNG ELECTRONICS CO LTD

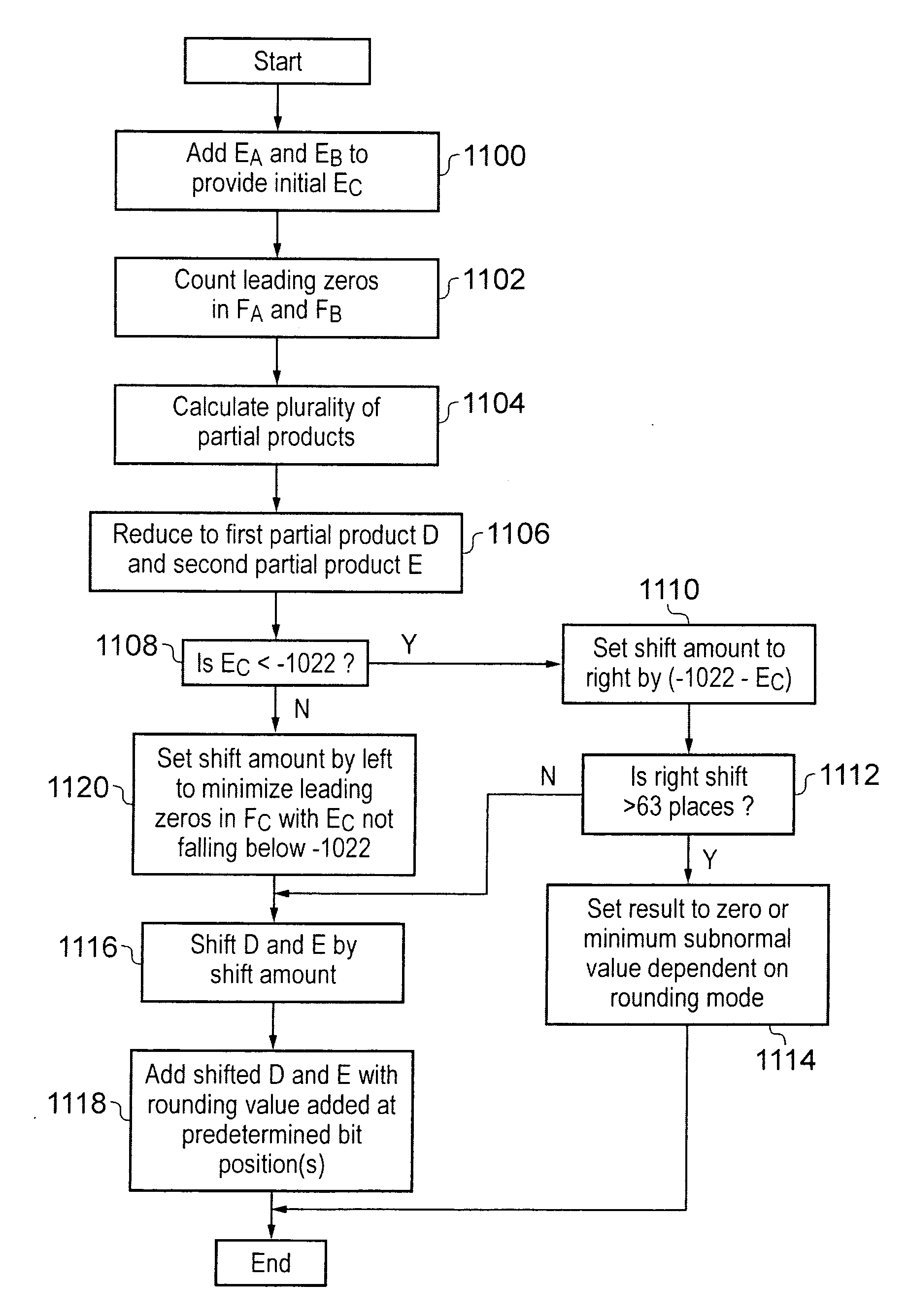

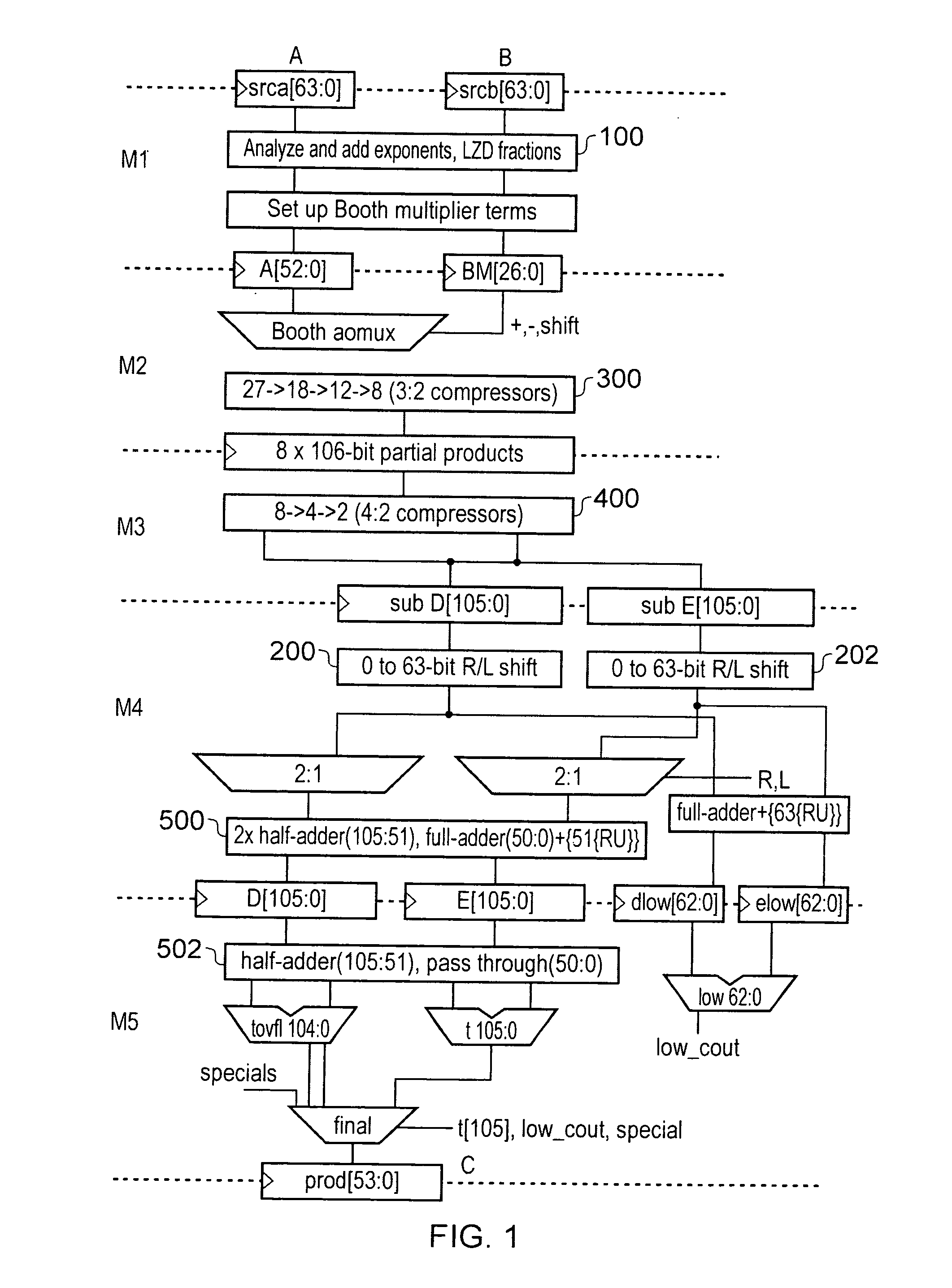

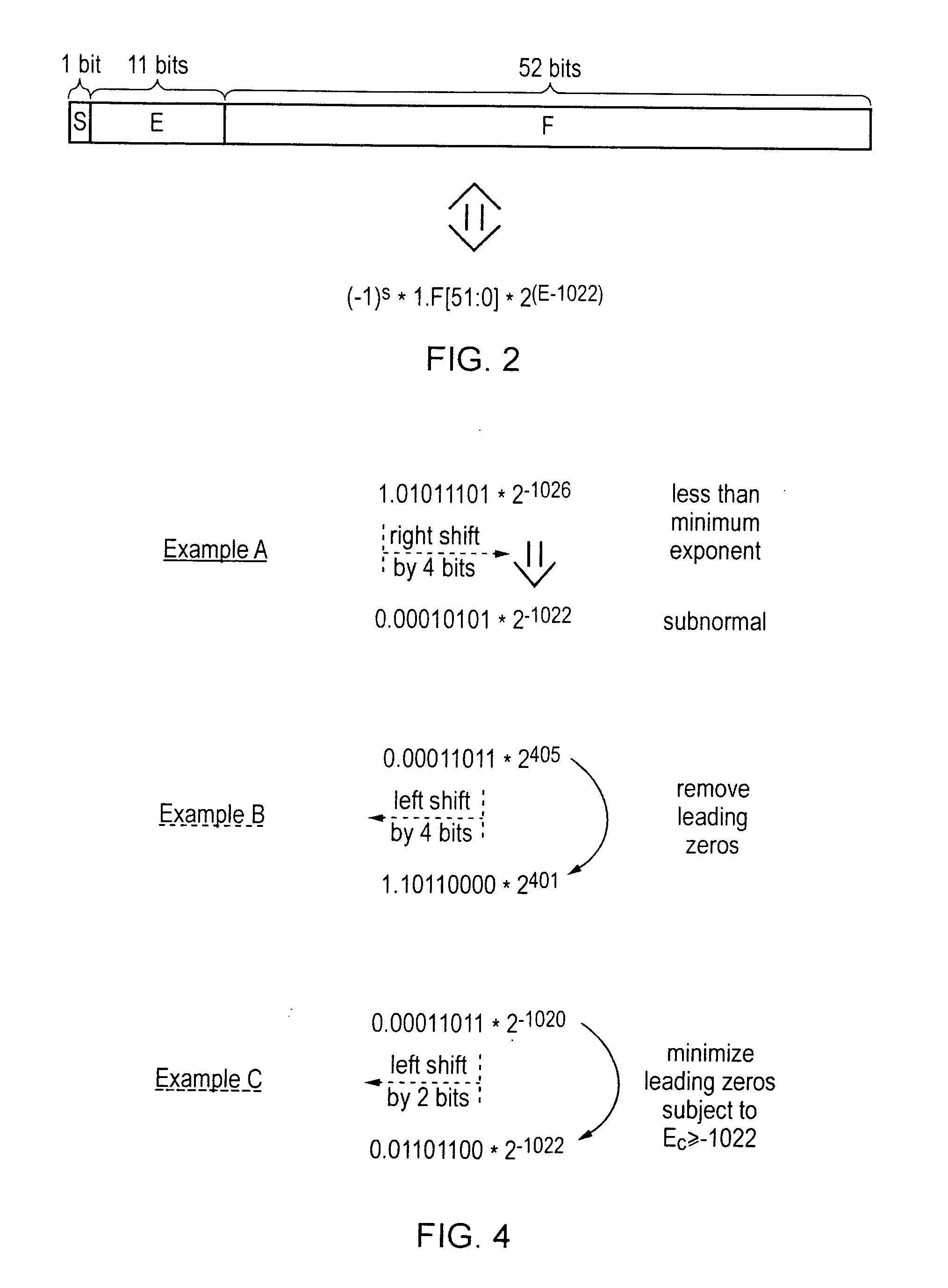

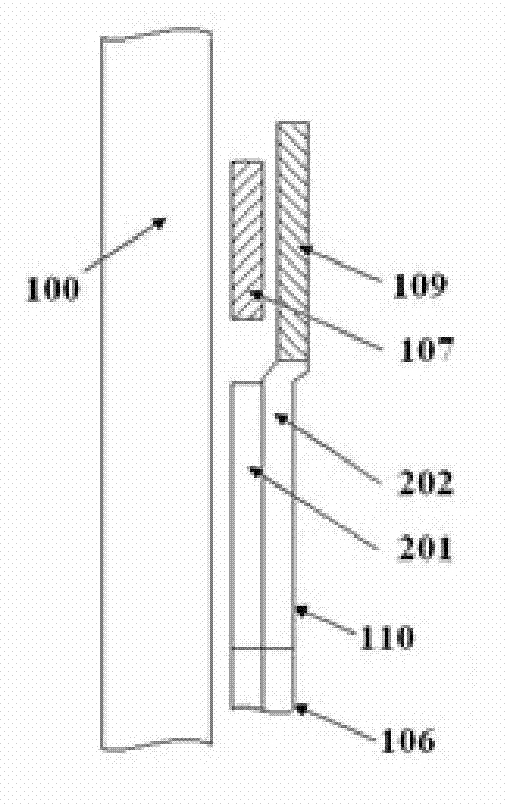

Floating point multiplier with partial product shifting circuitry for result alignment

ActiveUS20110106868A1Minimize the numberReduce delaysDigital computer detailsData conversionRight shiftOperand

A floating point multiplier includes a data path in which a plurality of partial products are calculated and then reduced to a first partial product and a second partial product. Shift amount determining circuitry 100 analyses the exponents of the input operands A and B as well as counting the leading zeros in the fractional portions of these operands to determine an amount of left shift or right shift to be applied by shifting circuitry 200, 202 within the multiplier data path. This shift amount is applied so as to align the partial products so that when they are added they will produce the result C without requiring this to be further shifted. Furthermore, shifting the partial products to the correct alignment in this way in advance of adding these partial products permits injection rounding combined with the adding of the partial products to be employed for cases including subnormal values.

Owner:ARM LTD

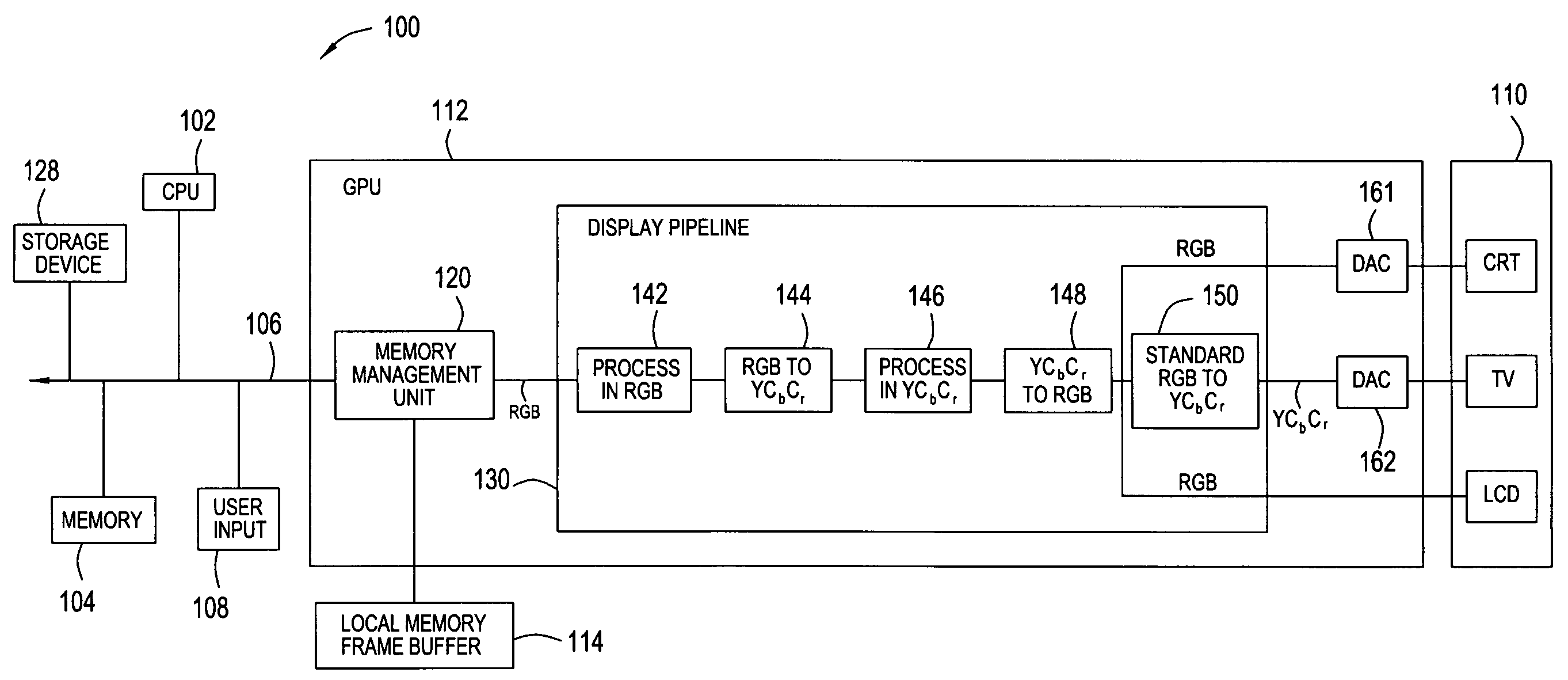

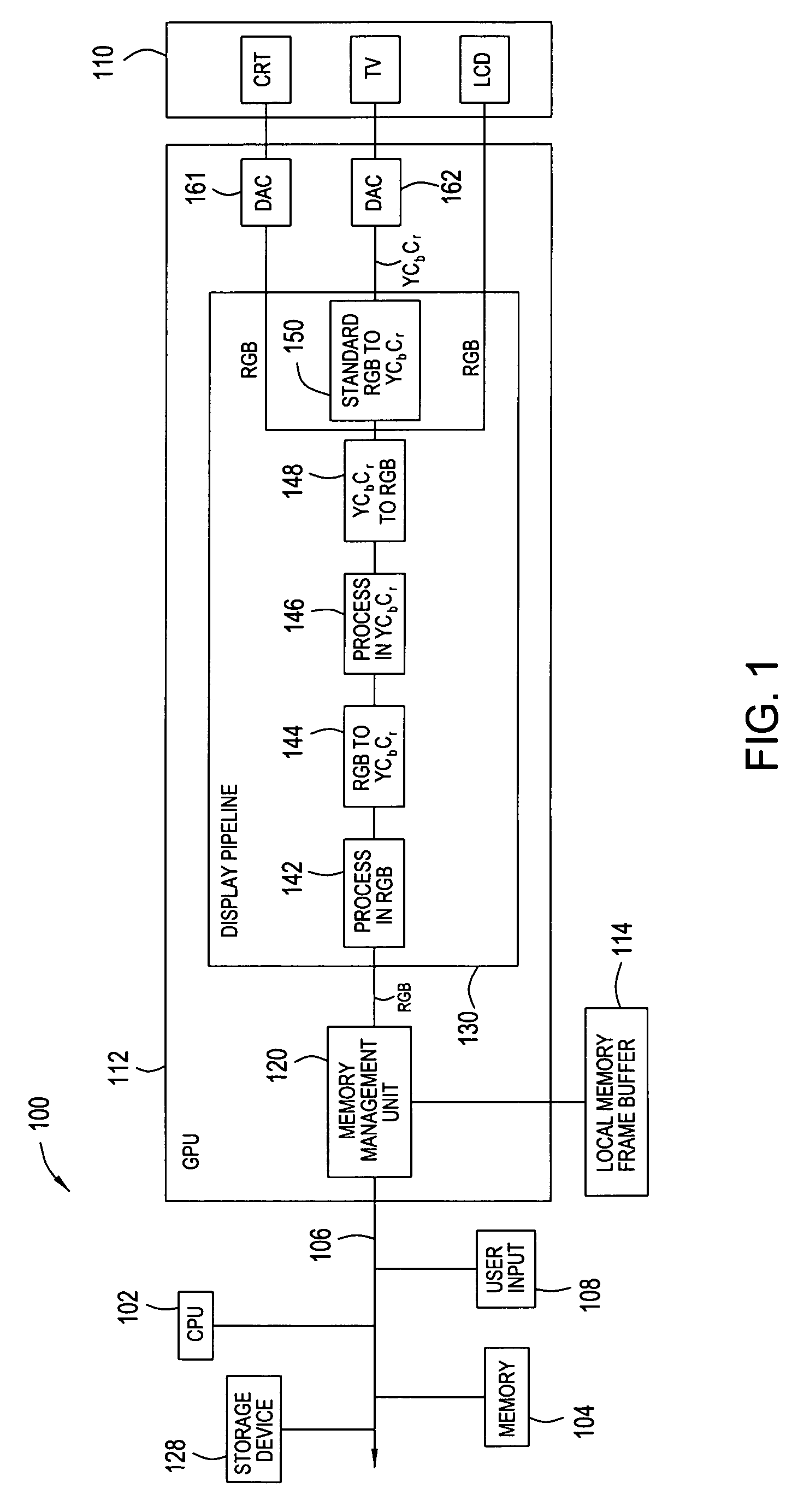

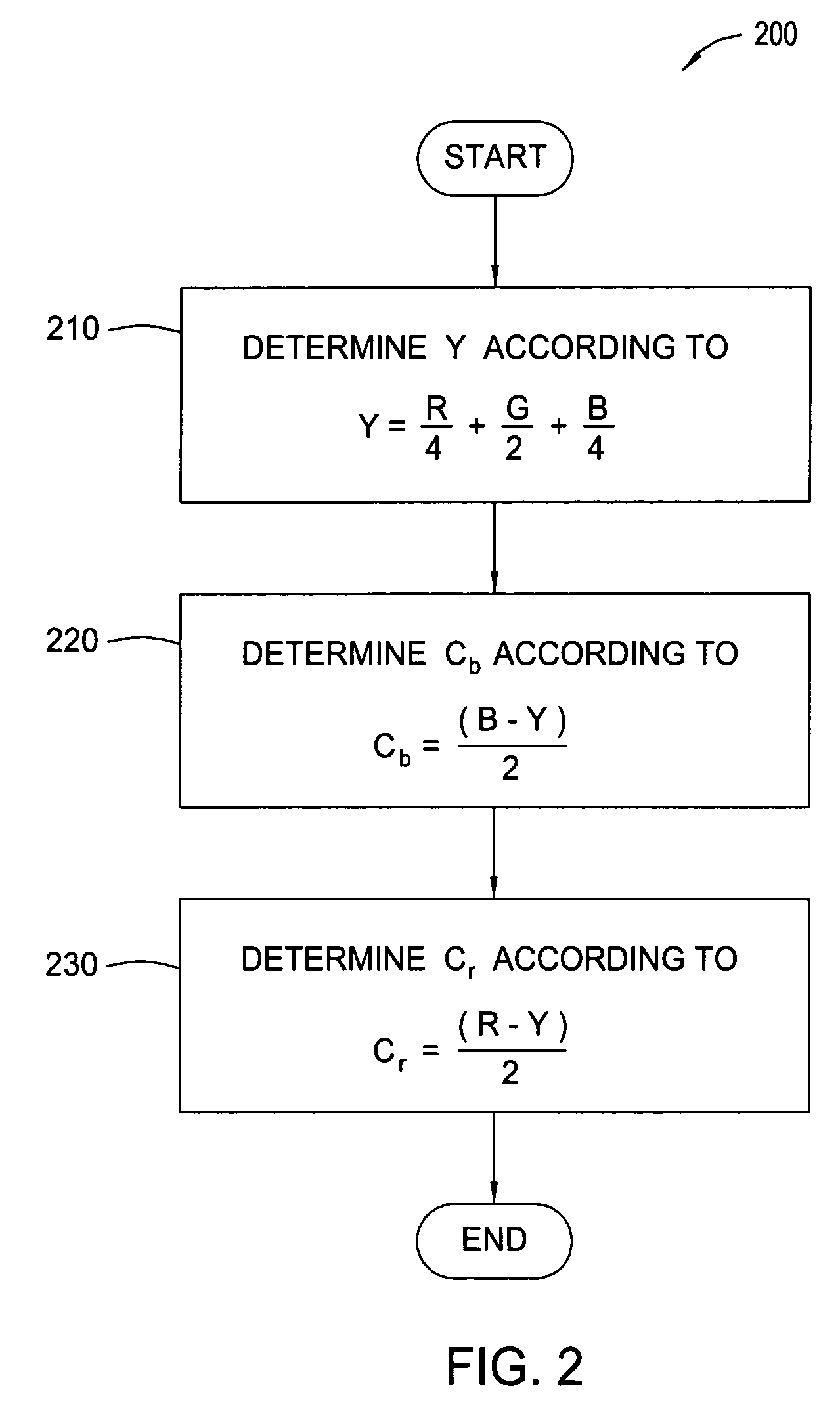

Minimalist color space converters for optimizing image processing operations

ActiveUS7050065B1Low costSimple processCathode-ray tube indicatorsPictoral communicationGraphicsImaging processing

An apparatus for graphics processing unit, which includes a memory for storing pixel data in a red, green and blue (RGB) color space and a display pipeline. The display pipeline includes an RGB color space to a luminance color, blue color difference and red color difference (YCbCr) color space converter module configured to convert the pixel data from the RGB color space to the YCbCr color space. The RGB to YCbCr color space converter module generates a luminance color component (Y) of the pixel data by adding ¼ of a red color (R) component of the pixel data to ½ of a green color (G) component of the pixel data and ¼ of a blue color (B) component of the pixel data. The luminance color component (Y) of the pixel data may be determined by left shifting the green color (G) component of the pixel data by one bit, adding the result to the red color (R) component of the pixel data and the blue color (B) component of the pixel data, and right shifting the sum by two bits.

Owner:NVIDIA CORP

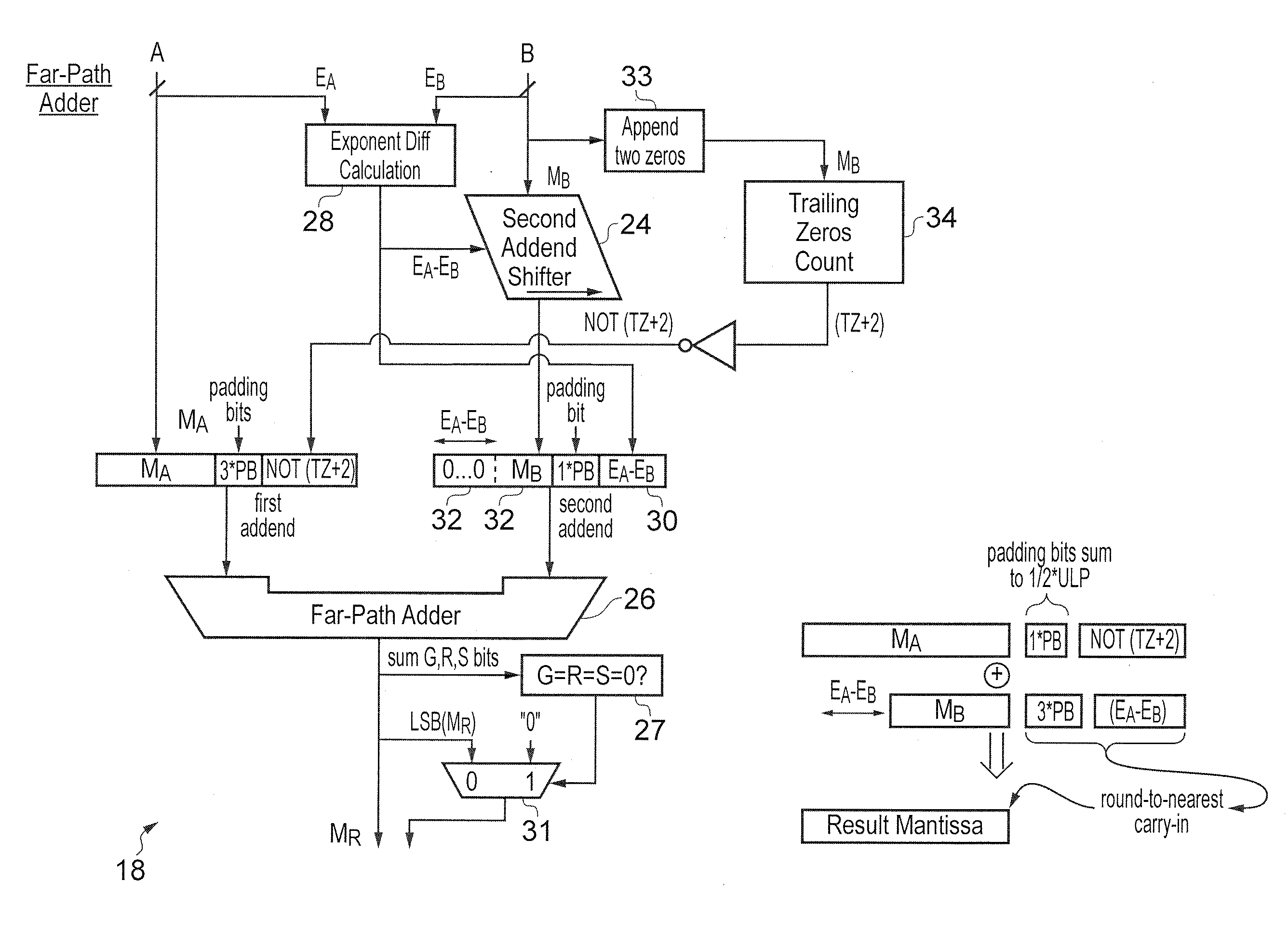

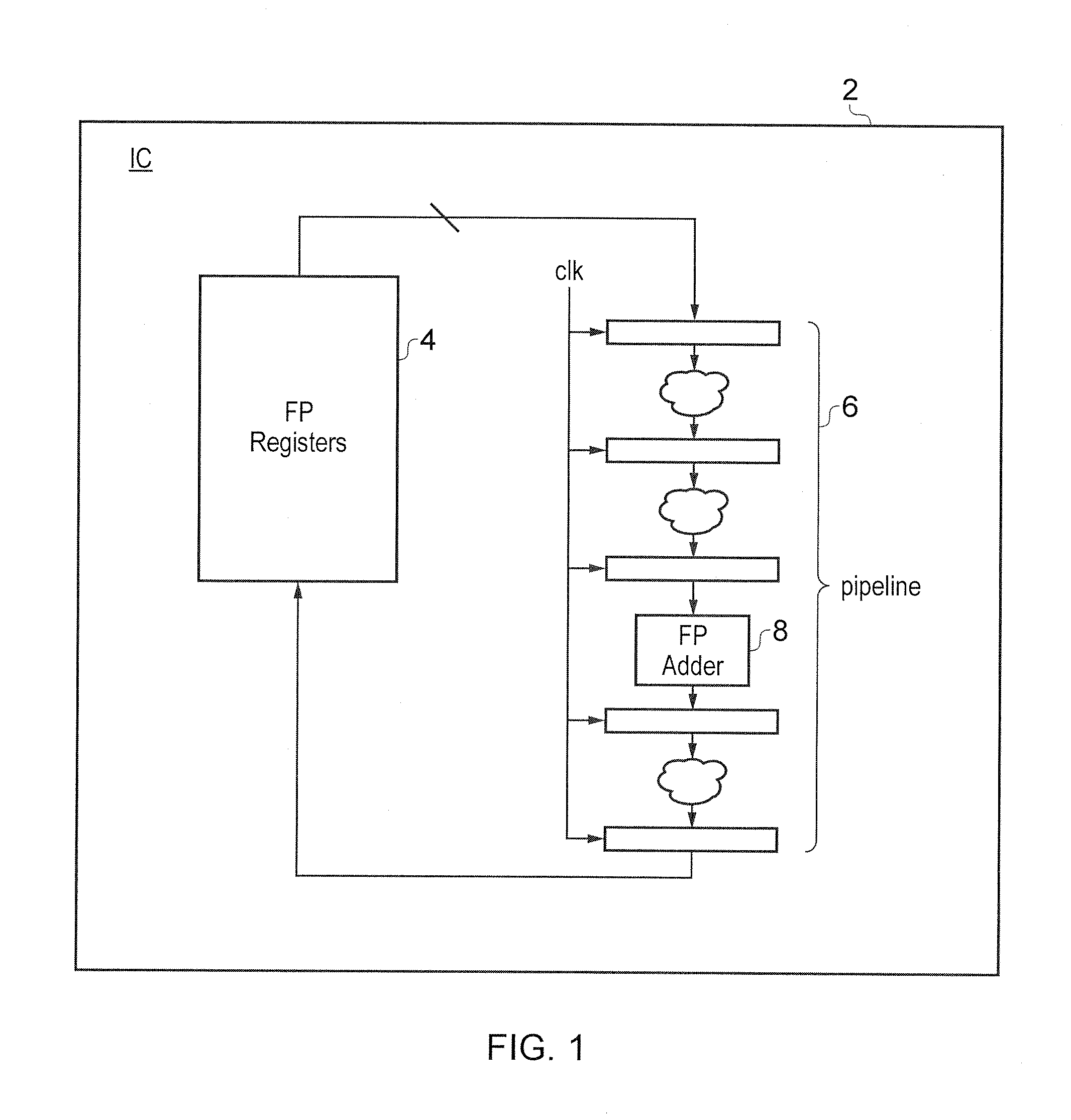

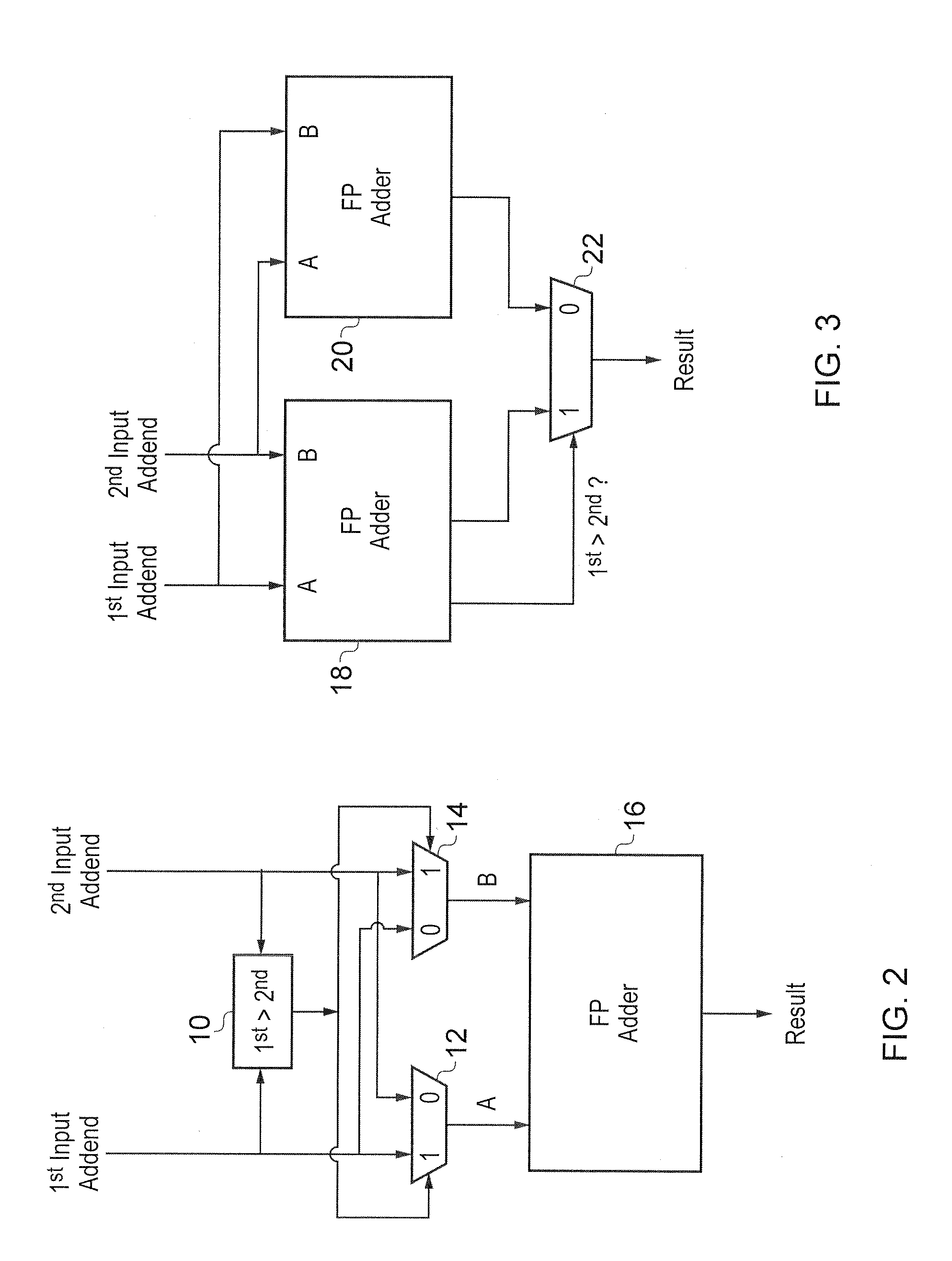

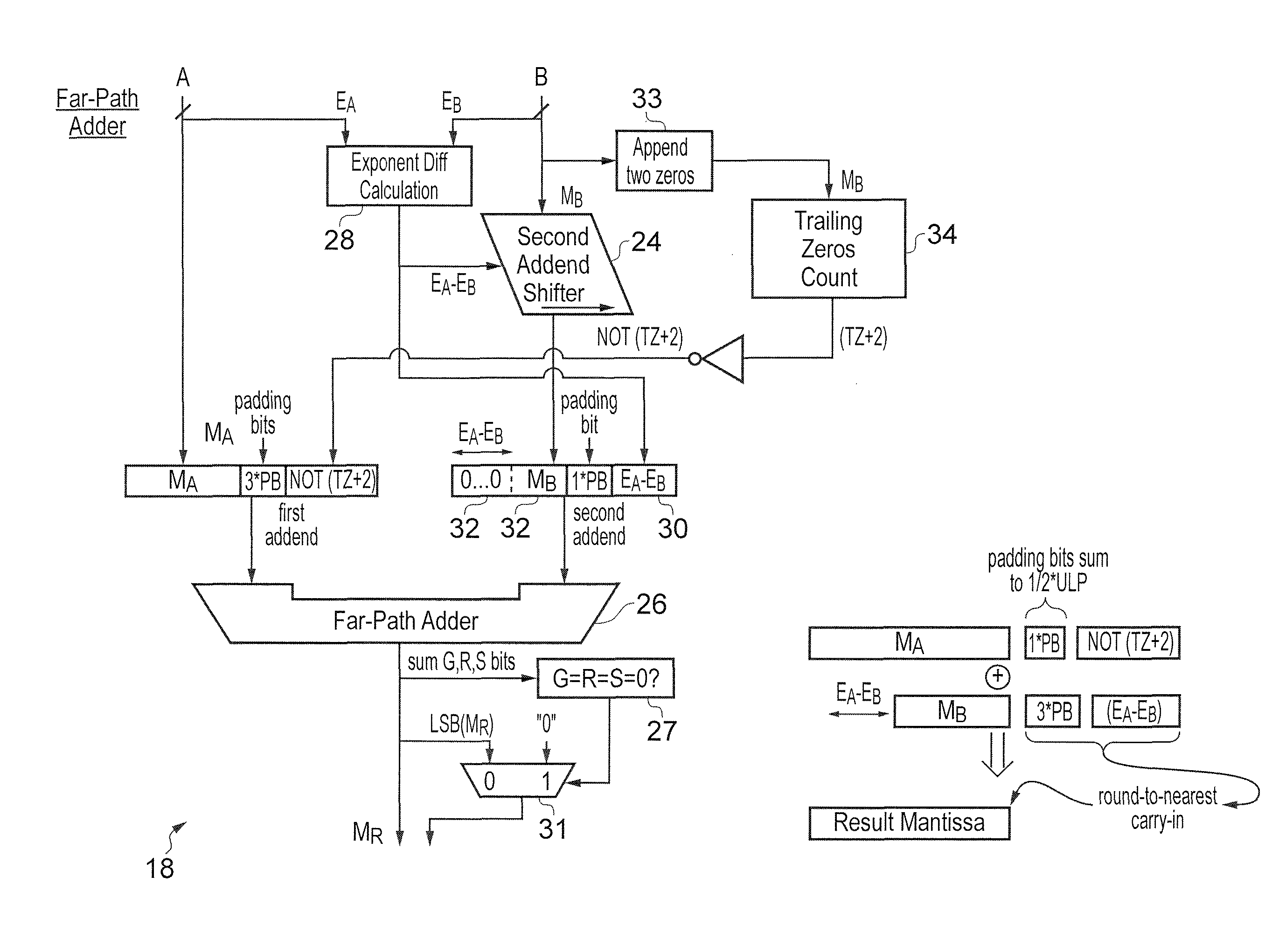

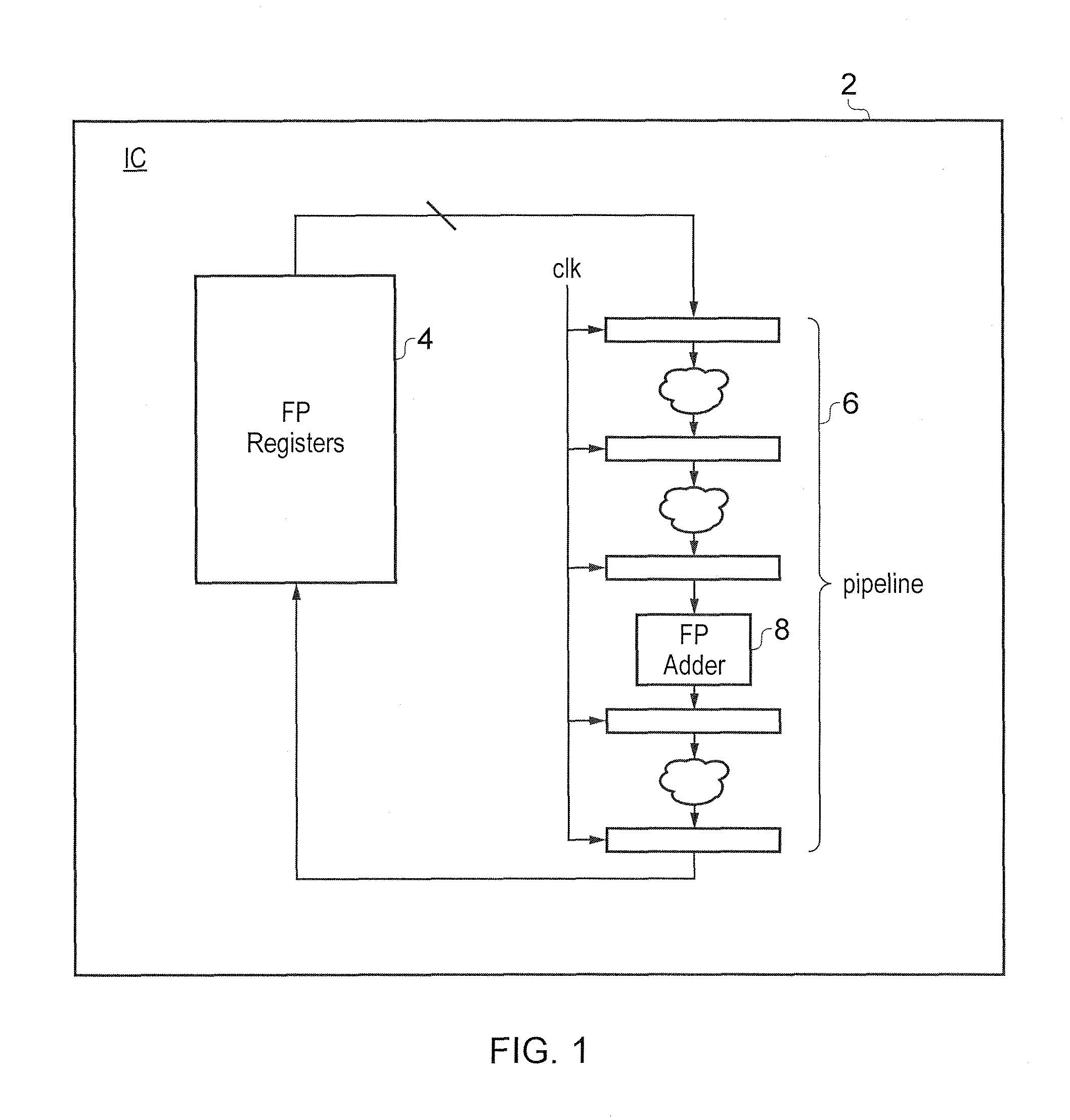

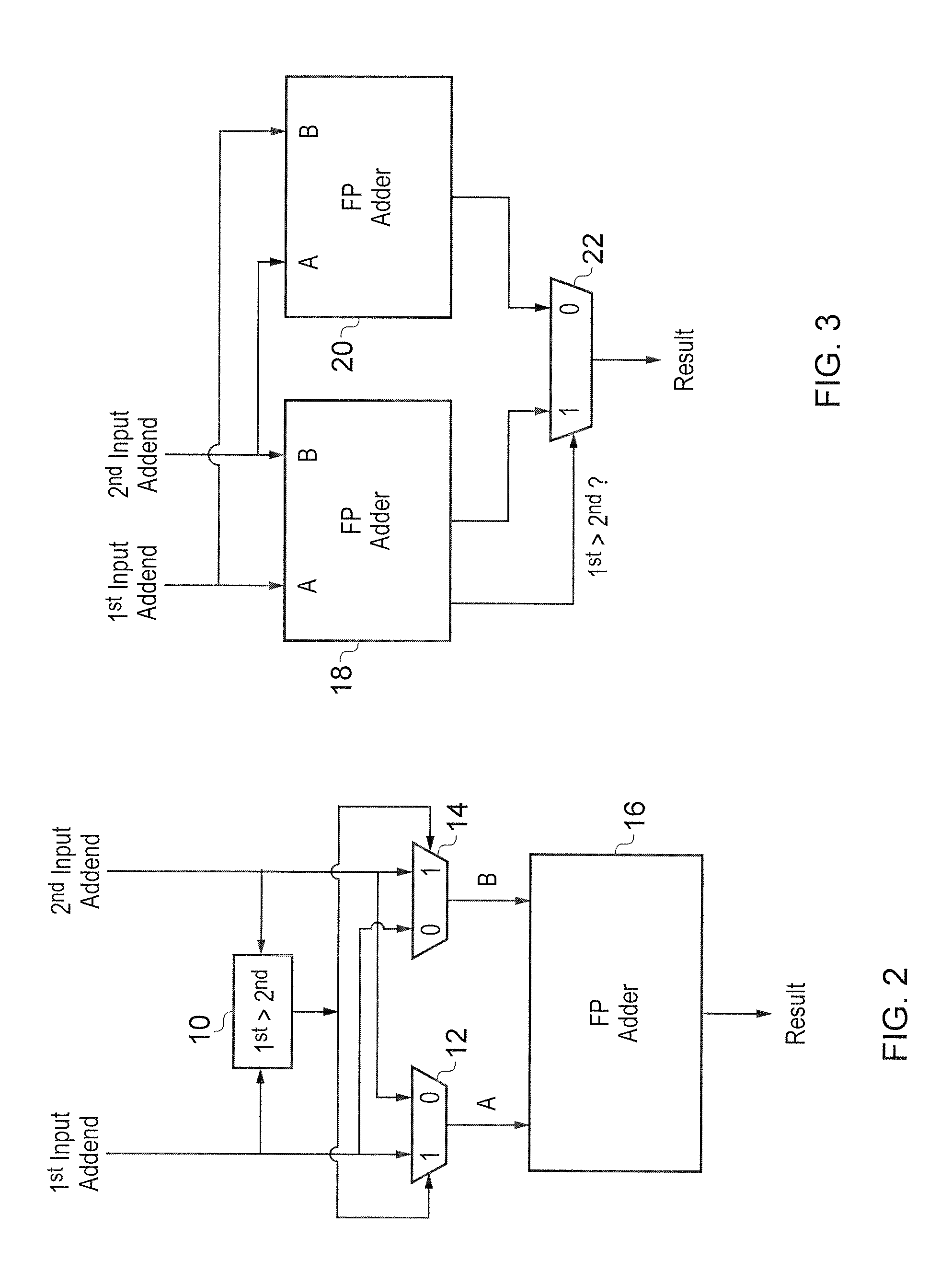

Floating-point adder

ActiveUS20130007084A1Lower latencyMaintain balanceComputations using contact-making devicesComputer architectureOperand

Floating point adder circuitry 16, 18, 20 is provided with far-path circuitry 18 and near-path circuitry 20. The far-path circuitry utilises a count of trailing zeros TZ and a difference in the input operand exponents to form respective suffix values which are concatenated with the mantissas of the input addends and serve when summed to generate a carry out taking the place of a conventionally calculated sticky bit. Within the near-path, minimum value circuitry 46 is used to calculate the lower of a leading zeros count of the intermediate mantissa produced in a subtraction and the larger of the input operand exponent values such that a left shift applied to the intermediate mantissa value is not able to produce a invalid floating point result due to applying a left shift to remove leading zeros that is too larger and accordingly corresponds to an exponent which cannot be validly represented.

Owner:ARM LTD

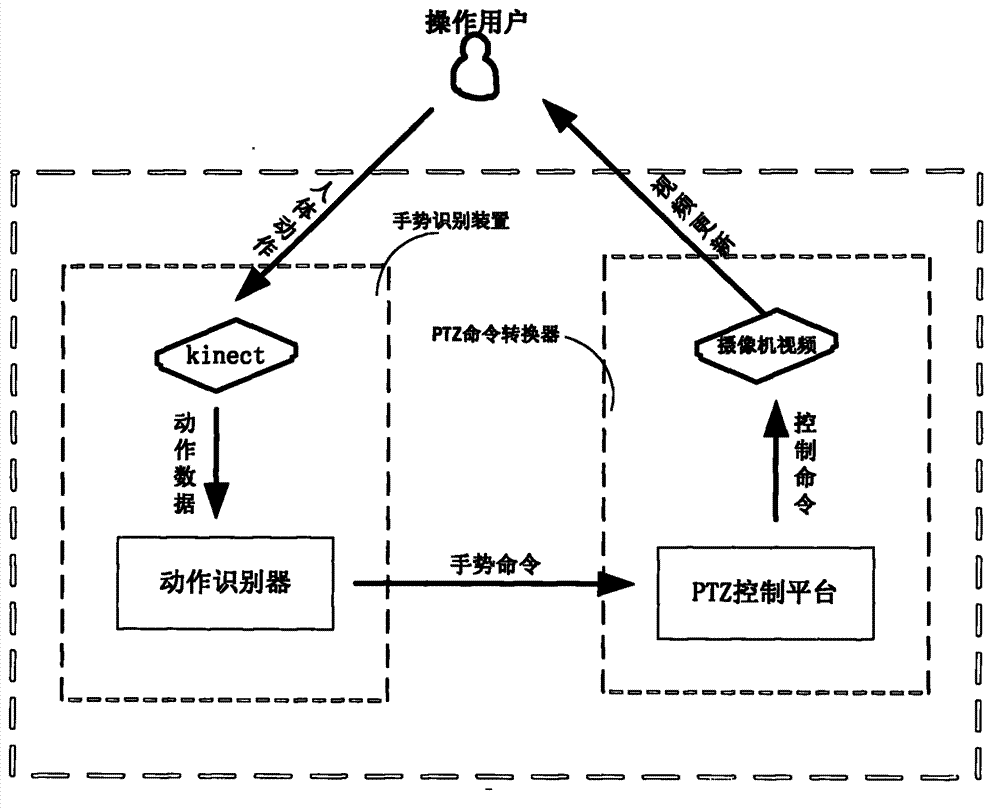

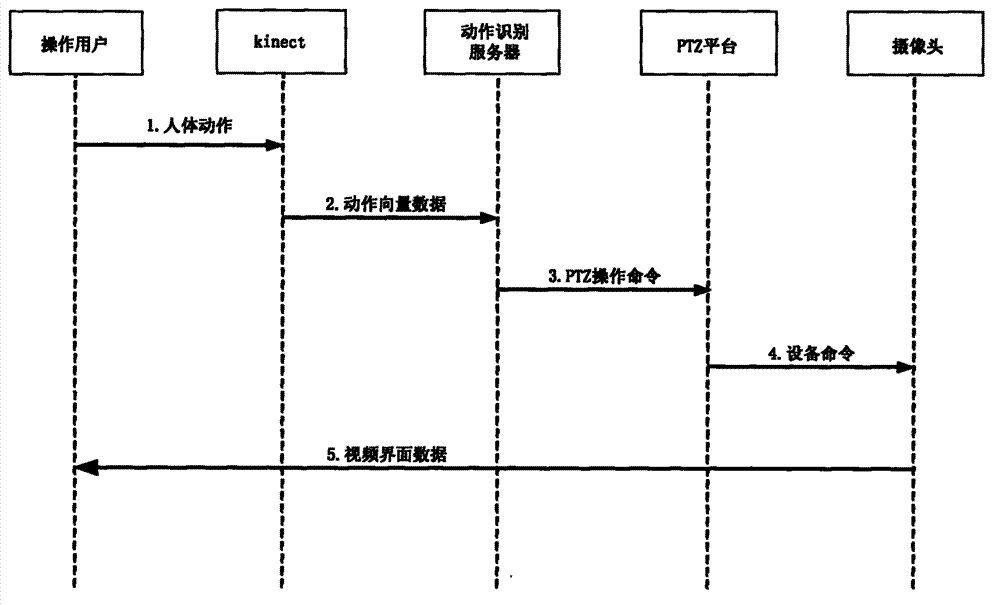

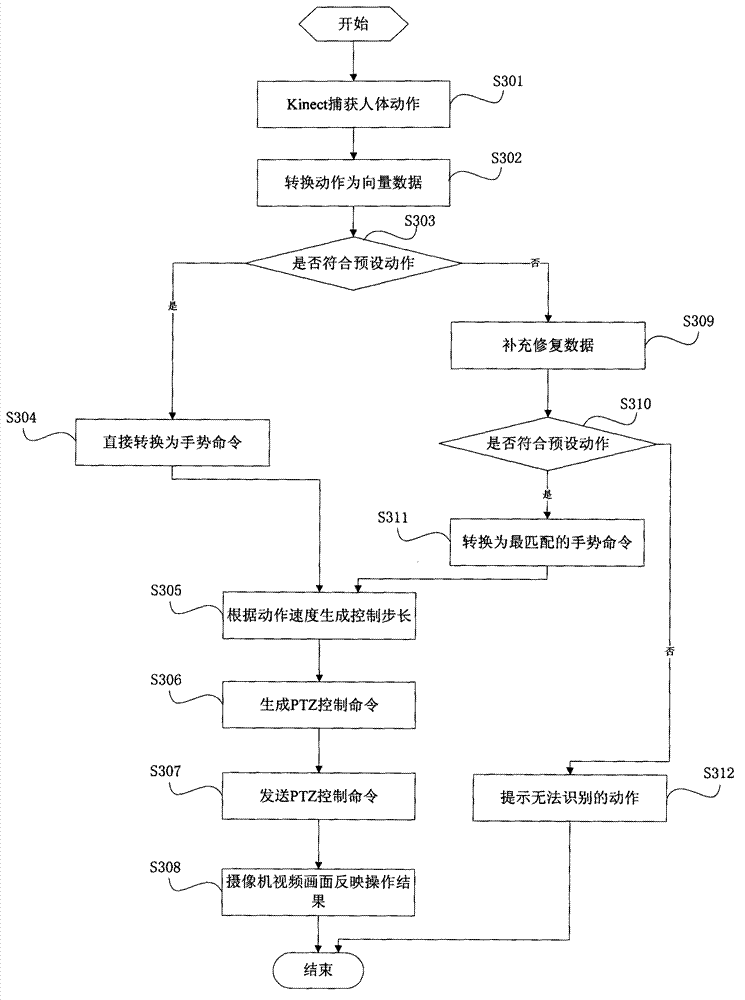

Method, device and system of pan tilt zoom (PTZ) control of video camera based on kinect

InactiveCN103118227AInput/output for user-computer interactionTelevision system detailsVideo monitoringPan tilt zoom

The invention discloses a method, a device and a system of pan tilt zoom (PTZ) control of a video camera based on kinect. PTZ control of the video camera for security and protection monitoring can be achieved through human movements, complex operation interfaces are not required, and PTA control of the video camera is operated simply and conveniently through a video monitoring system. The method, the device and the system comprise that the human movements are caught through the kinect, human movement vector quantity data are input into behavior identification software, after corresponding data optimization, data conversion and behavior judgment, the human movements are converted into PTZ control commands of the monitoring video camera, the PTZ control commands include upward shift, downward shift, left shift, right shift, picture enlargement, picture shrink, preset position switchover, windshield wiper starting and the like, the control commands are sent to the video camera to conduct PTZ control, the video executes corresponding movements, and operation results are displayed in real time through real-time video frames.

Owner:PCI TECH GRP CO LTD

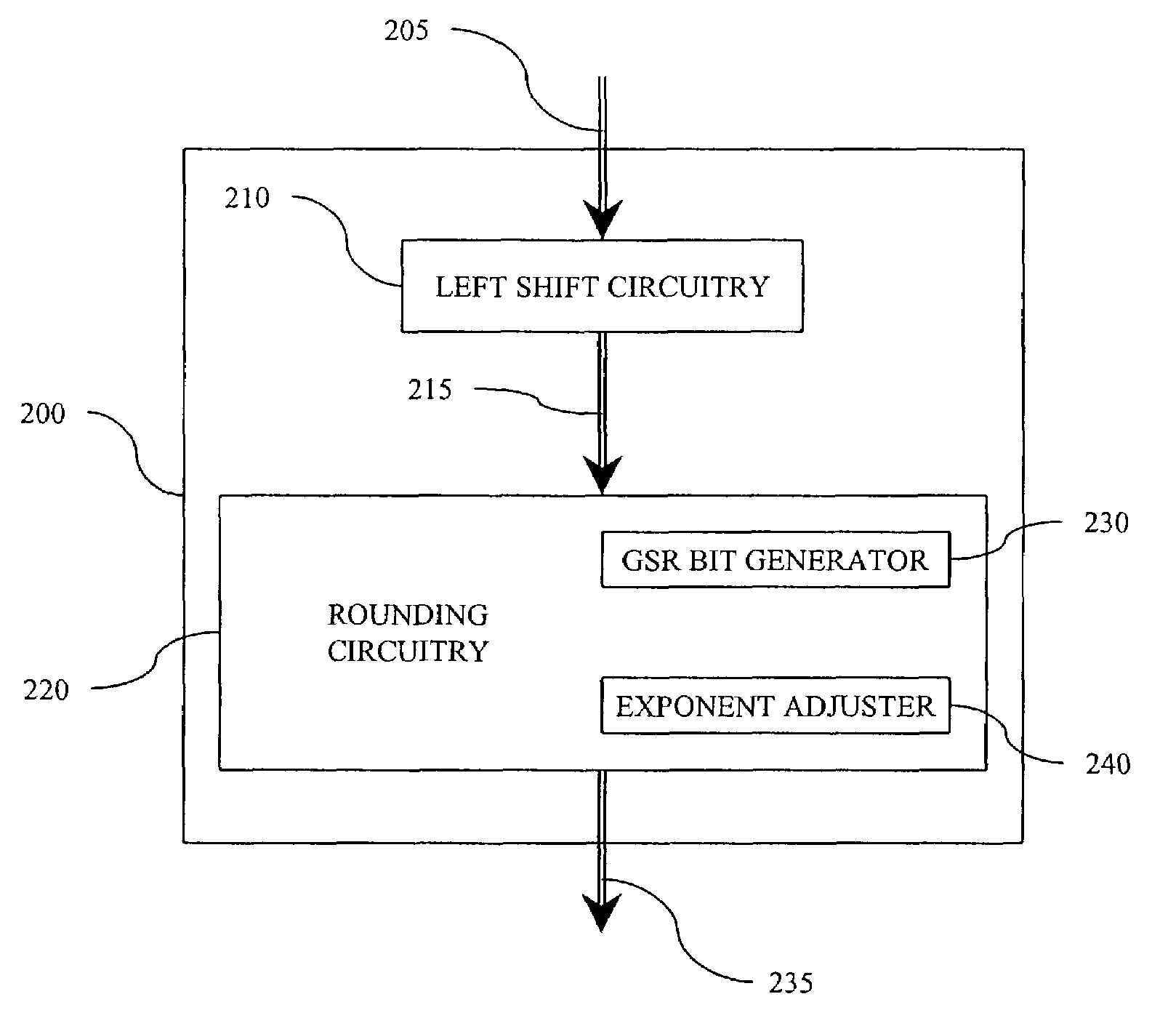

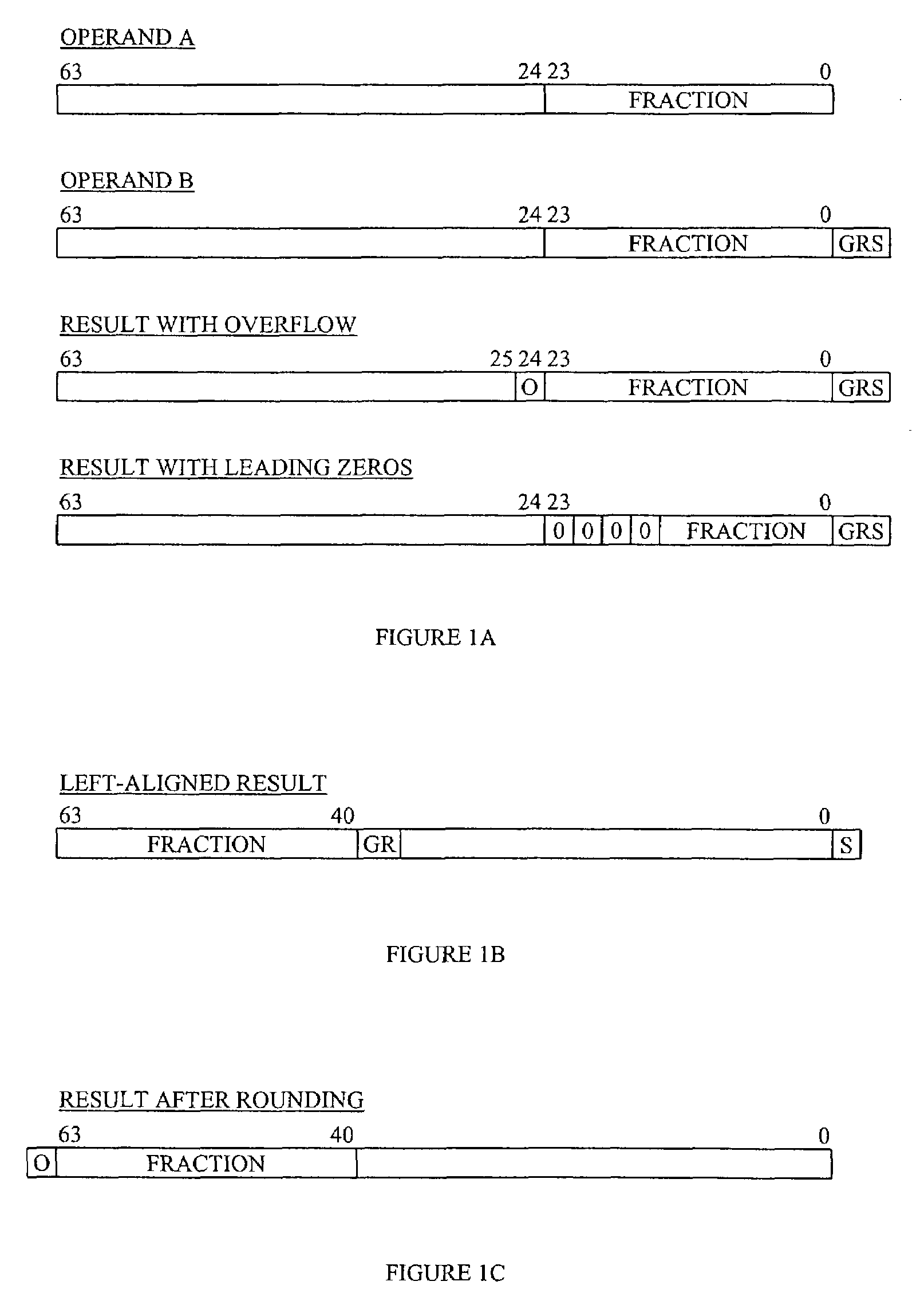

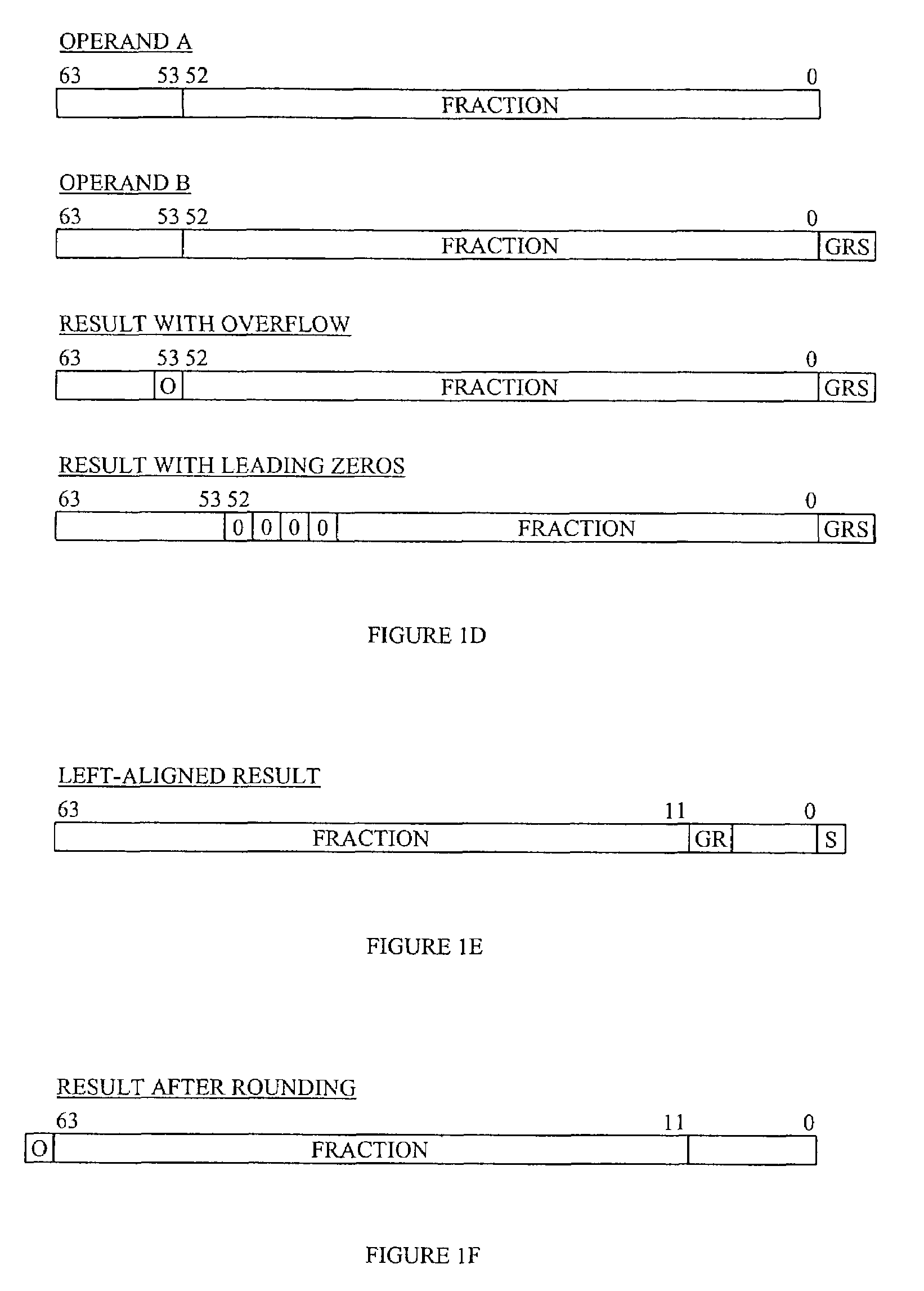

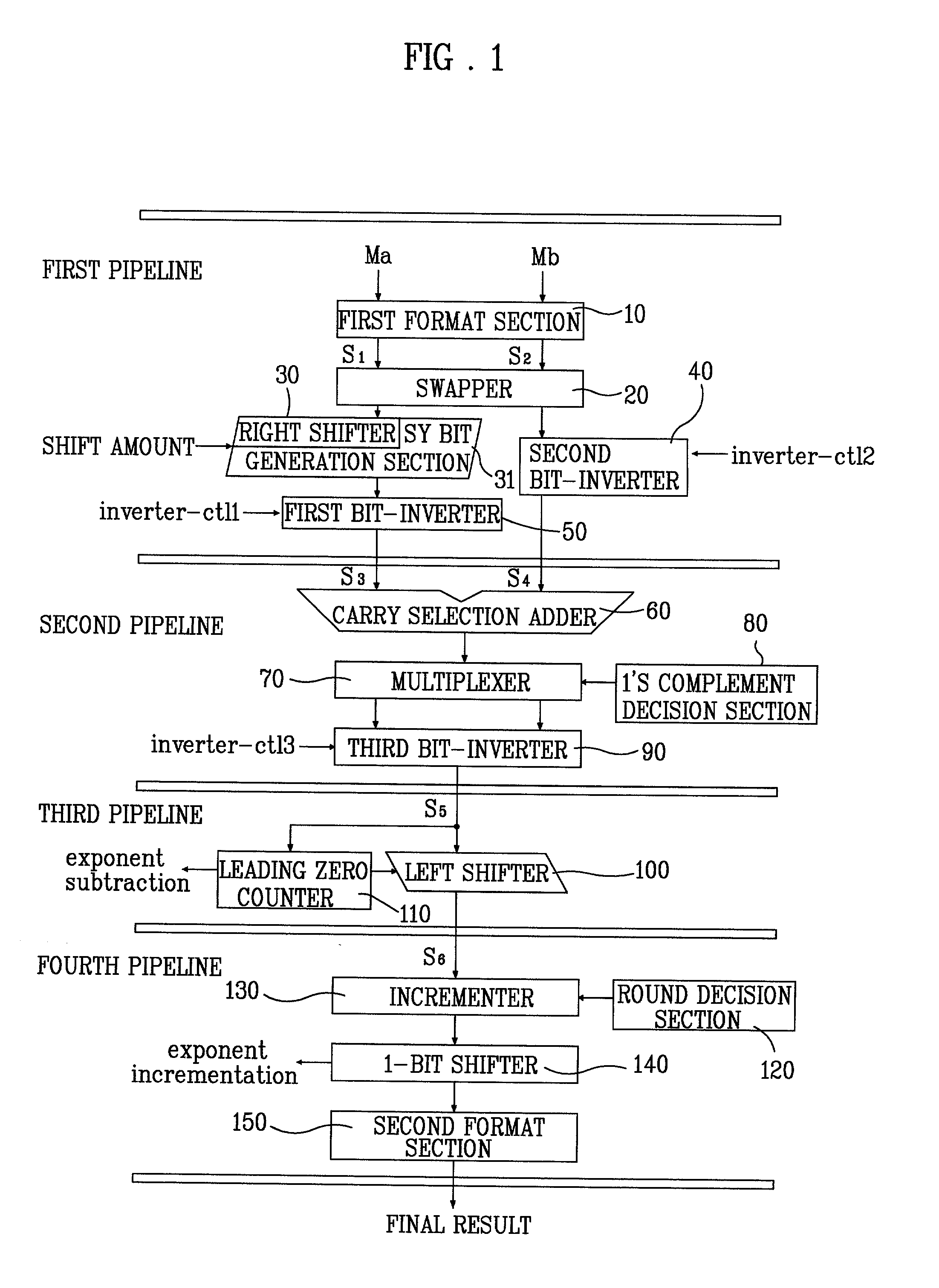

Circuit and method for normalizing and rounding floating-point results and processor incorporating the circuit or the method

InactiveUS7062525B1Reduce complexityData conversionComputation using denominational number representationFloating-point unitDatapath

For use in a floating-point unit that supports floating-point formats having fractional parts of varying widths and employs a datapath wider than the fractional parts, a circuit and method for normalizing and rounding floating-point results and processor incorporating the circuit or the method. In one embodiment, the circuit includes: (1) left-shift circuitry for aligning a fractional part of the floating-point result with a most significant bit of the datapath and irrespective of a width of the fractional part to yield a shifted fractional part and (2) rounding circuitry, coupled to the shift circuitry, that rounds the shifted fractional part.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

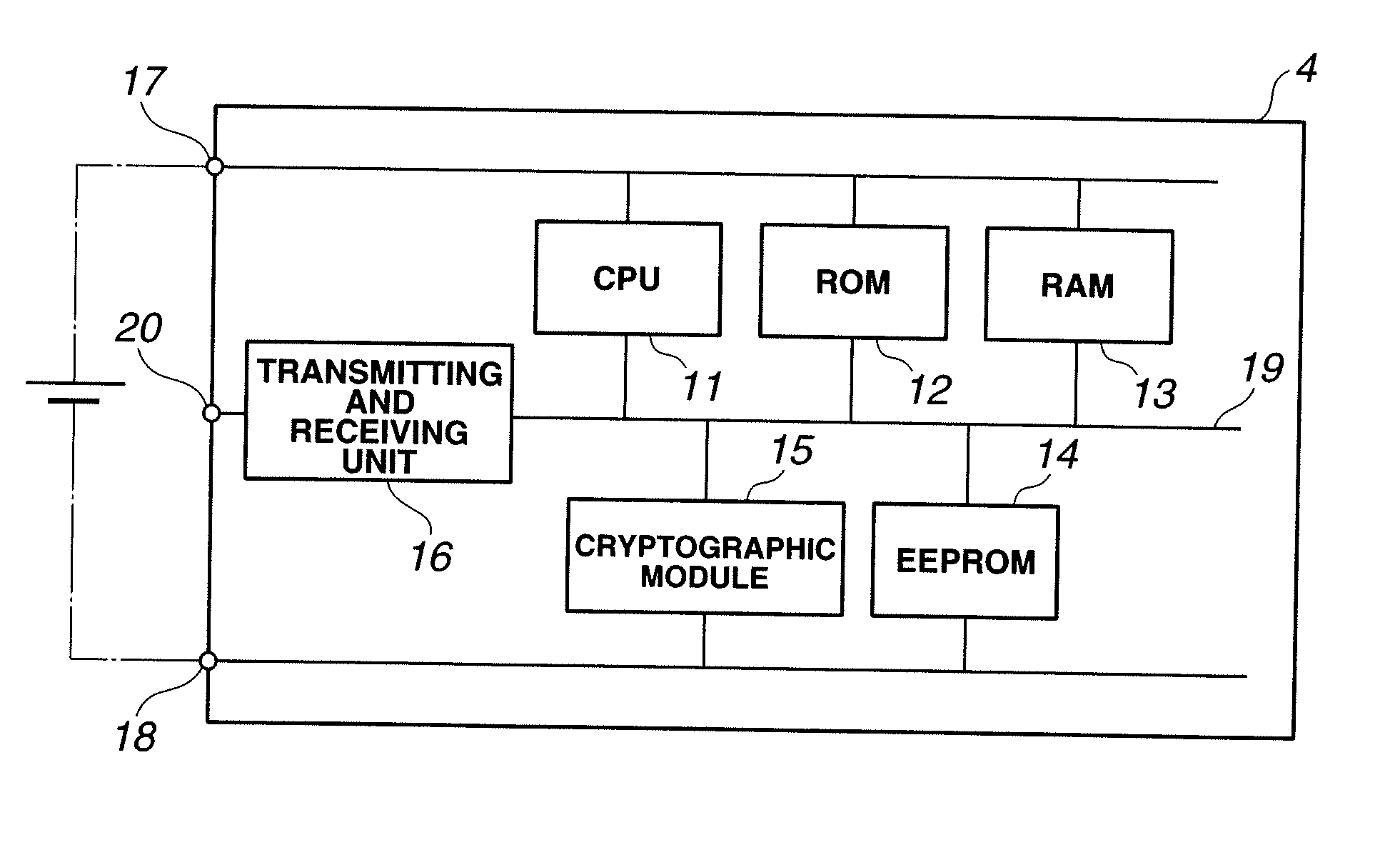

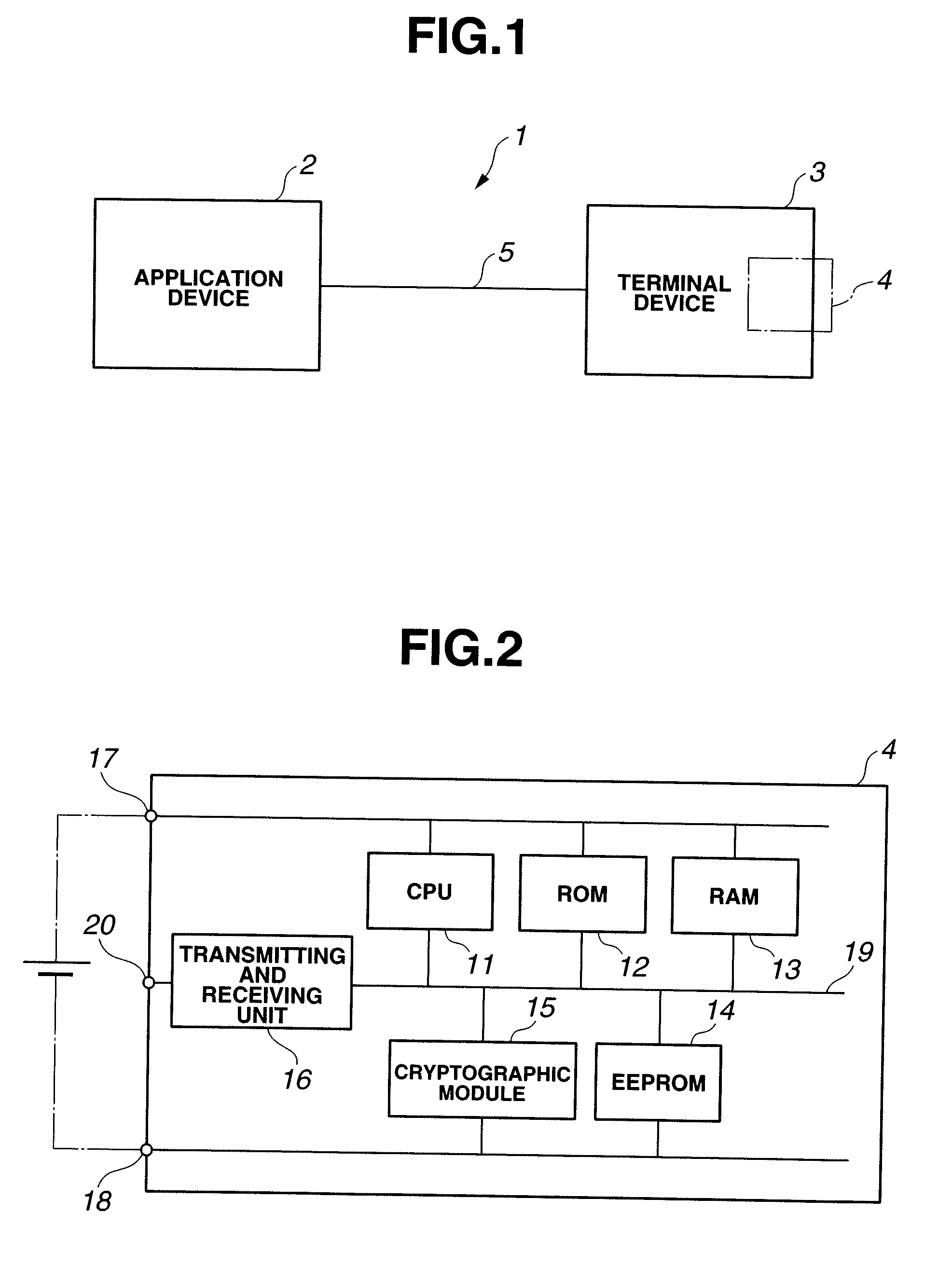

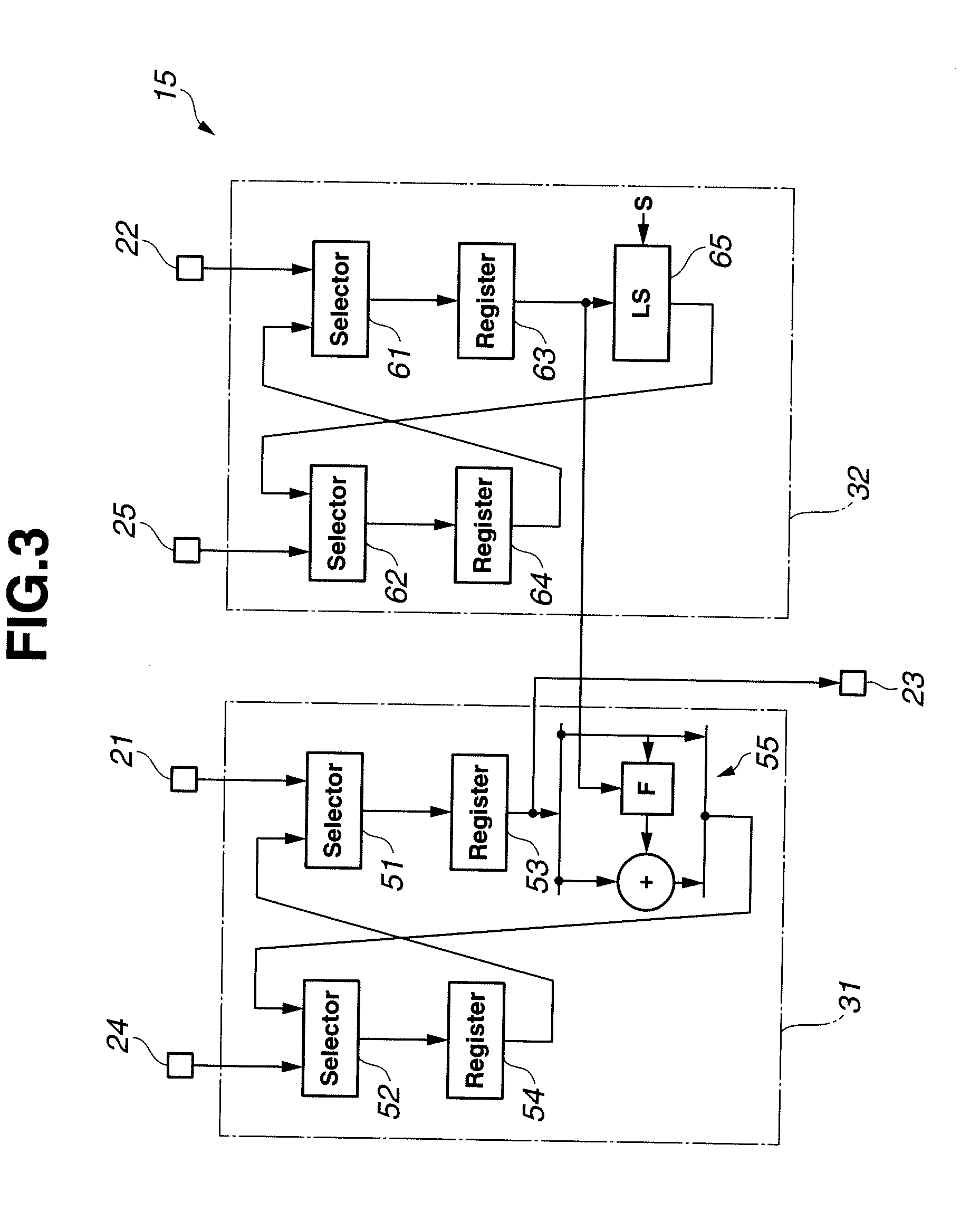

Cryptographic module and IC card

ActiveUS20080056488A1Error detection/correctionVolume/mass flow measurementComputer hardwareProcessor register

Owner:KK TOSHIBA

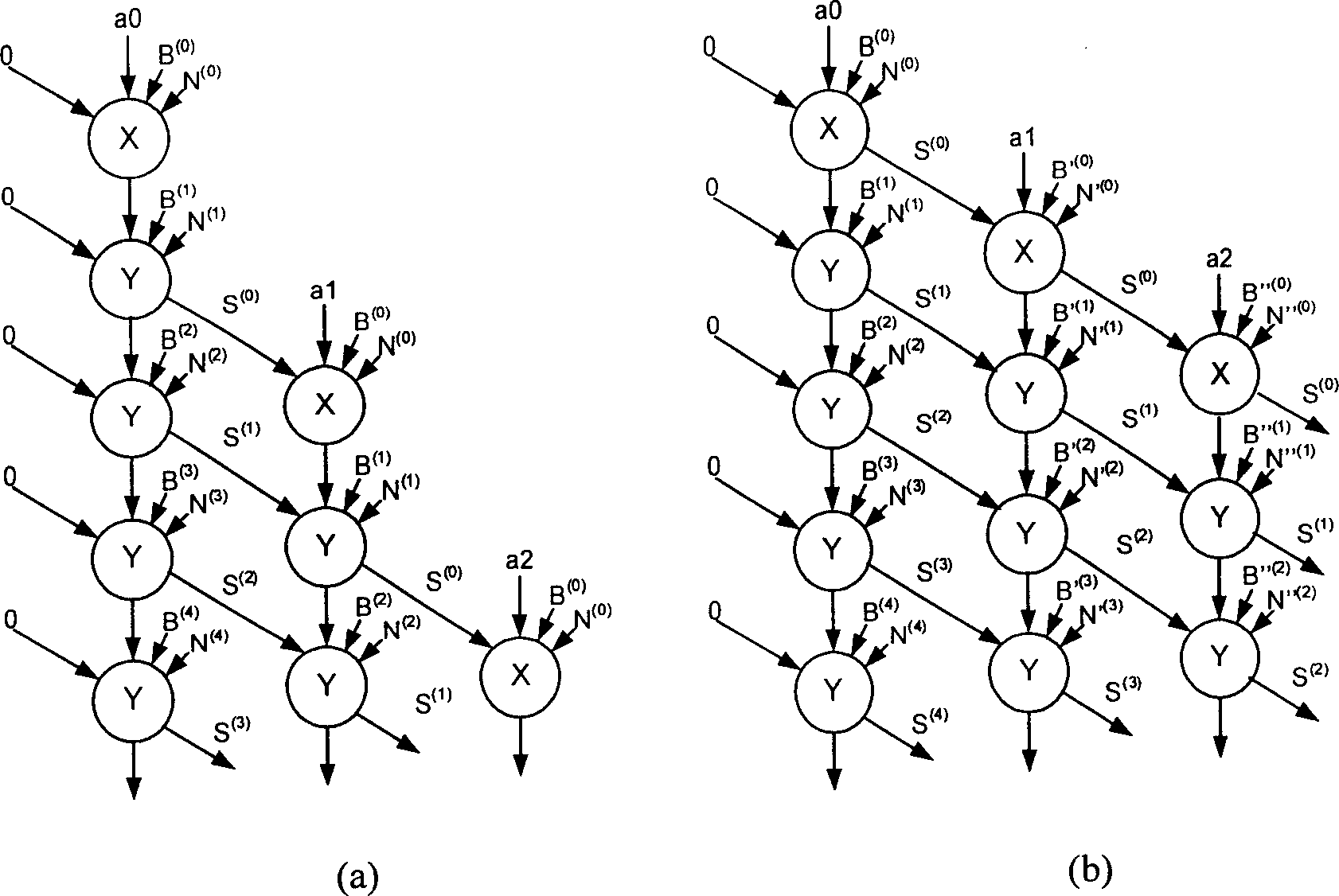

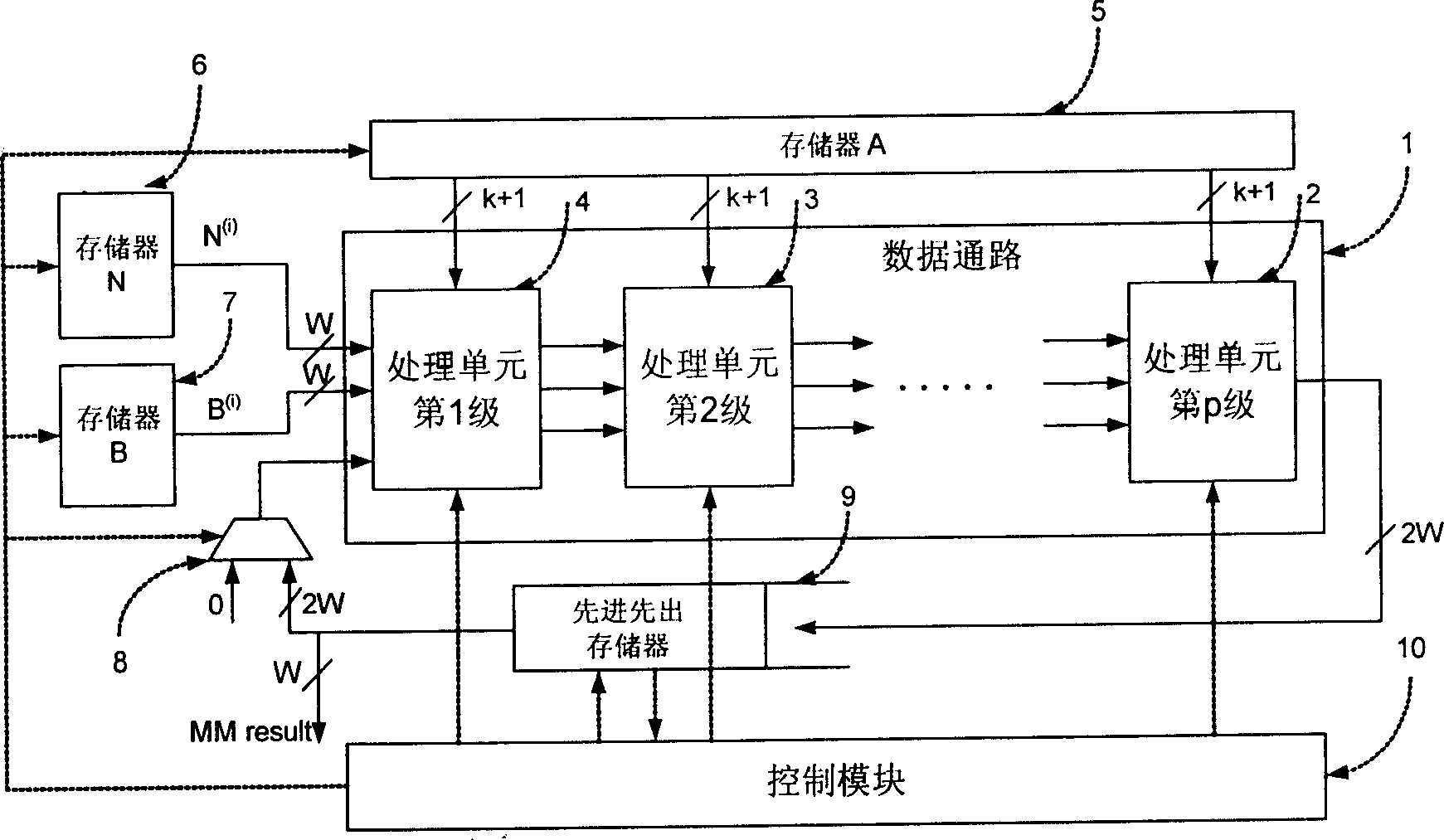

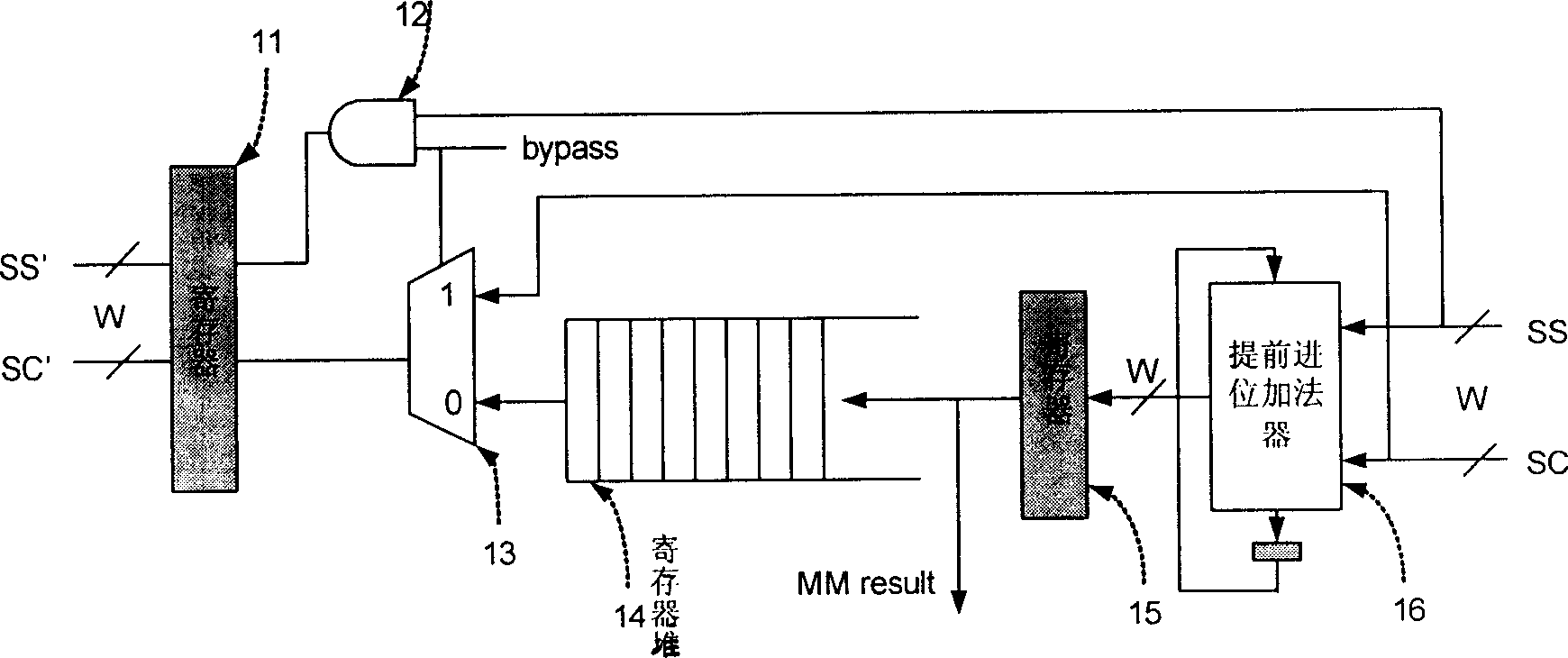

Extensible high-radix Montgomery's modular multiplication algorithm and circuit structure thereof

InactiveCN1731345AHigh speedReduce overheadComputations using residue arithmeticMontgomery reductionAnalog multiplier

The invention relates to an extended high base Montgomery analog multiplying algorithm and the circuit structure in the field of integrated circuit technology. It improves multiply characters high base Montgomery analog multiplying algorithm, wherein each step dose left shift operation to the batch N and the multiplicand B but not to the result S so that the delay between the two data path lines can de reduced from two clock weeks to one clock week. The circuit structure comprises: three storages used to store A, B and N operation numbers, a line type data path module which is formed by first stage to p stage processing units, a control module used to control the entire analog multiplier computing course and first-in first-out storage.

Owner:上海微科集成电路有限公司 +1

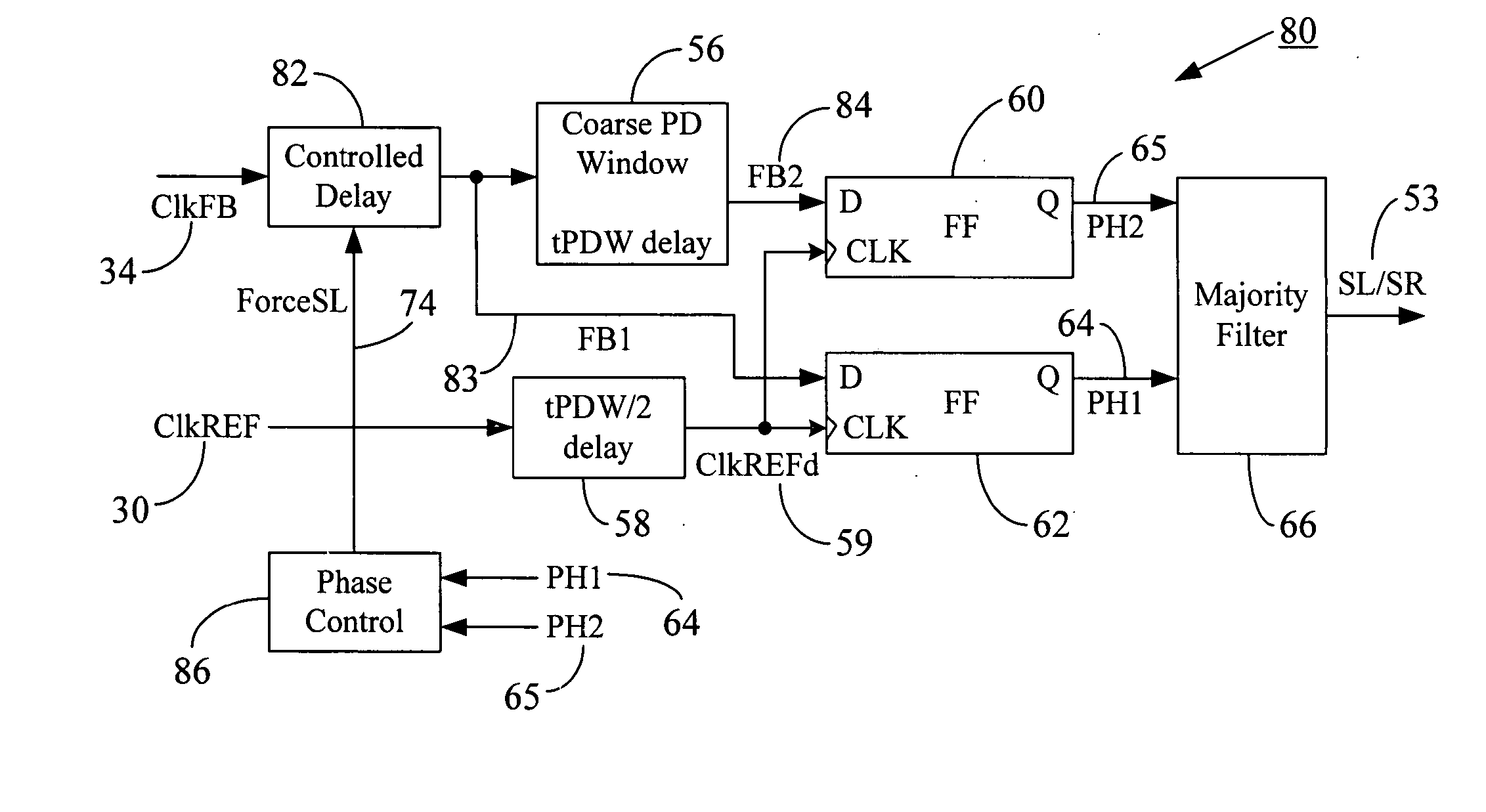

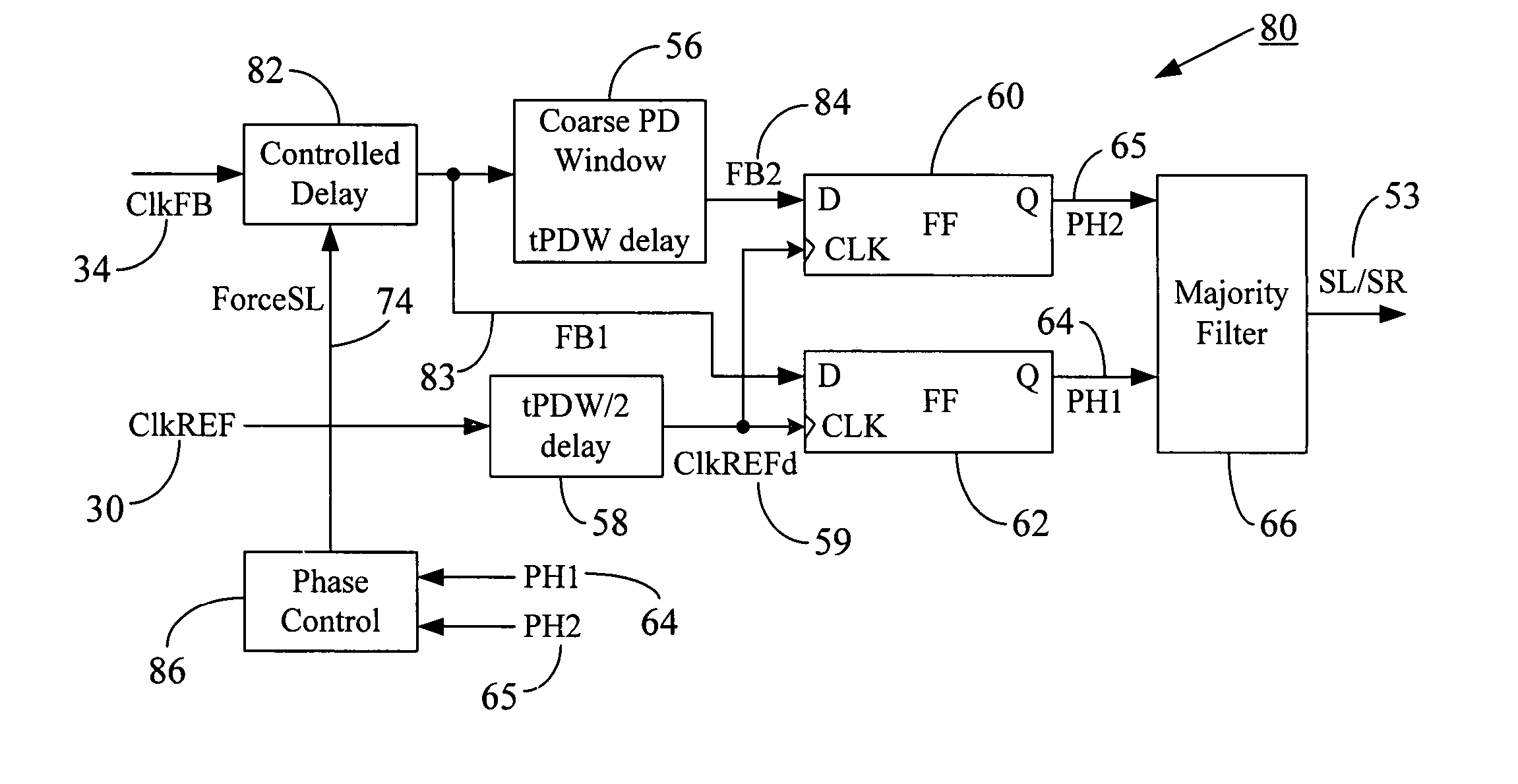

DLL phase detection using advanced phase equalization

ActiveUS7421606B2Fast locking timePulse automatic controlError detection/correctionPhase detectorDelay-locked loop

A system and method are disclosed to generate and terminate clock shift modes during initialization of a synchronous circuit (e.g., a delay-locked loop or DLL). Upon initialization, the DLL is entered into a ForceSL (Force Shift Left) mode and an On1x mode (i.e., left shifting on each clock cycle). The feedback clock that tracks the phase of the reference clock (which, in turn, is derived from the system clock) is initially delayed in a coarse phase detector prior to applying it to the coarse phase detection window. Two delayed versions of the feedback clock are sampled by the reference clock to generate a pair of phase information signals, which are then used to establish an advanced phase equal (APHEQ) signal. The APHEQ signal advances onset of the PHEQ (phase equalization) phase and is used to terminate the ForceSL and On1x modes, thereby preventing wrong ForceSL exit due to clock jitter or feedback path overshooting during On1x exit. The avoidance of wrong ForceSL exit and On1x overshooting problems further results in faster DLL locking time.

Owner:MICRON TECH INC

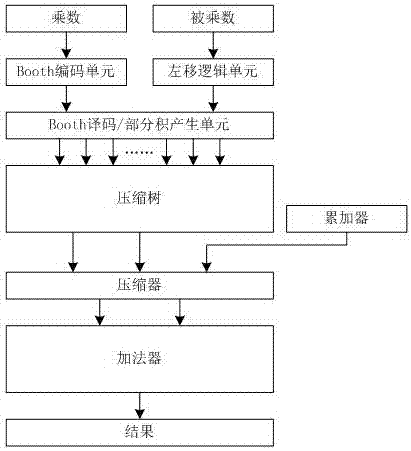

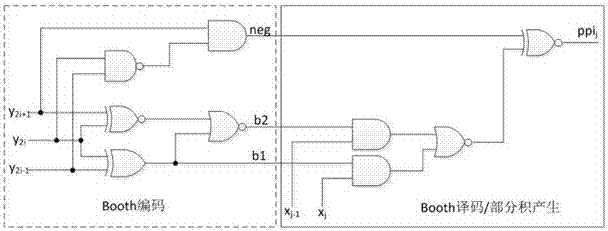

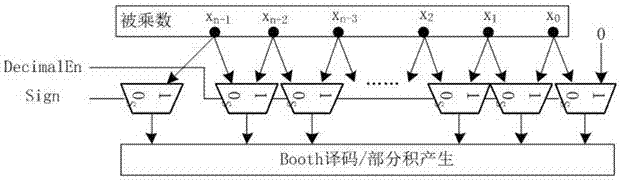

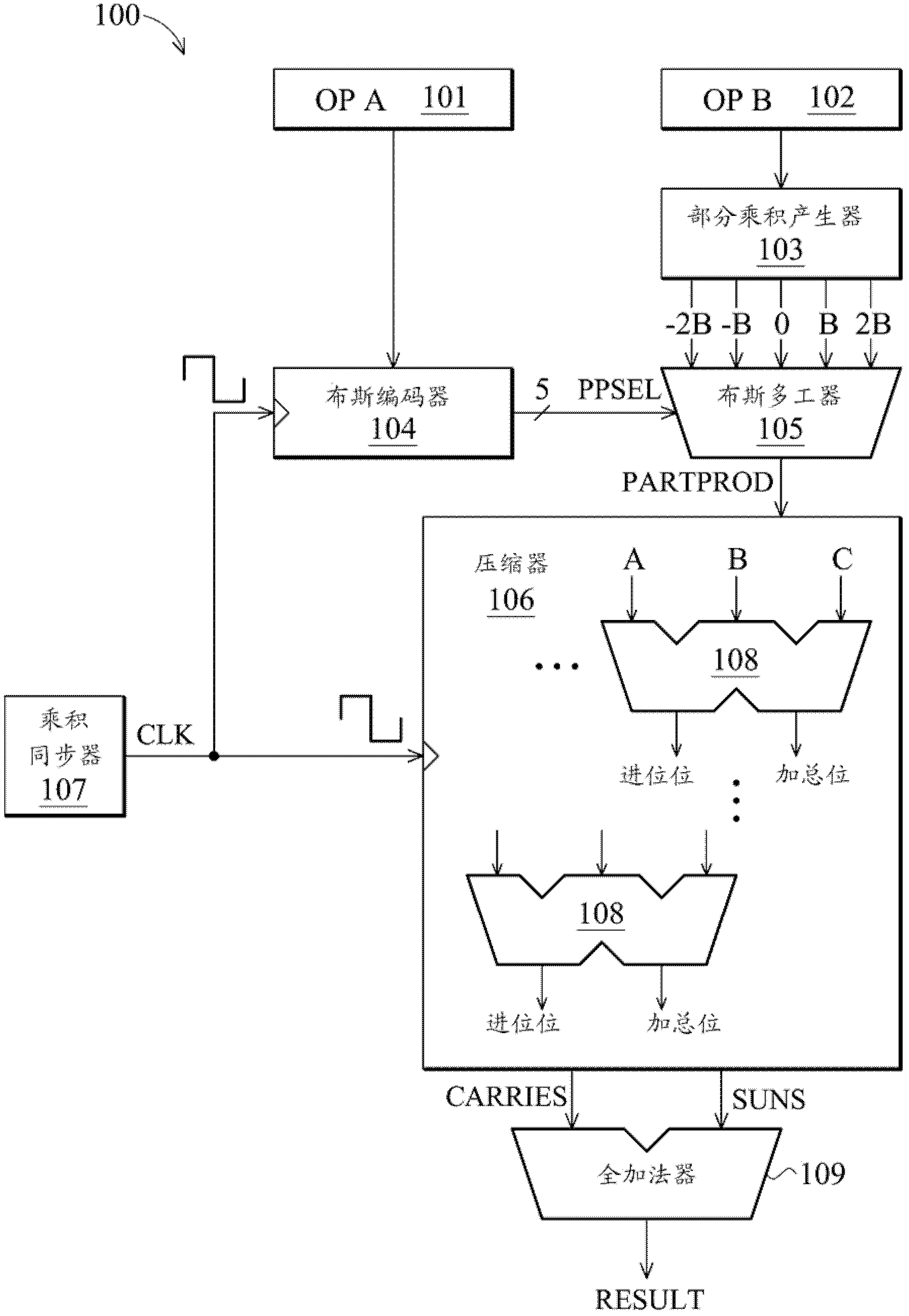

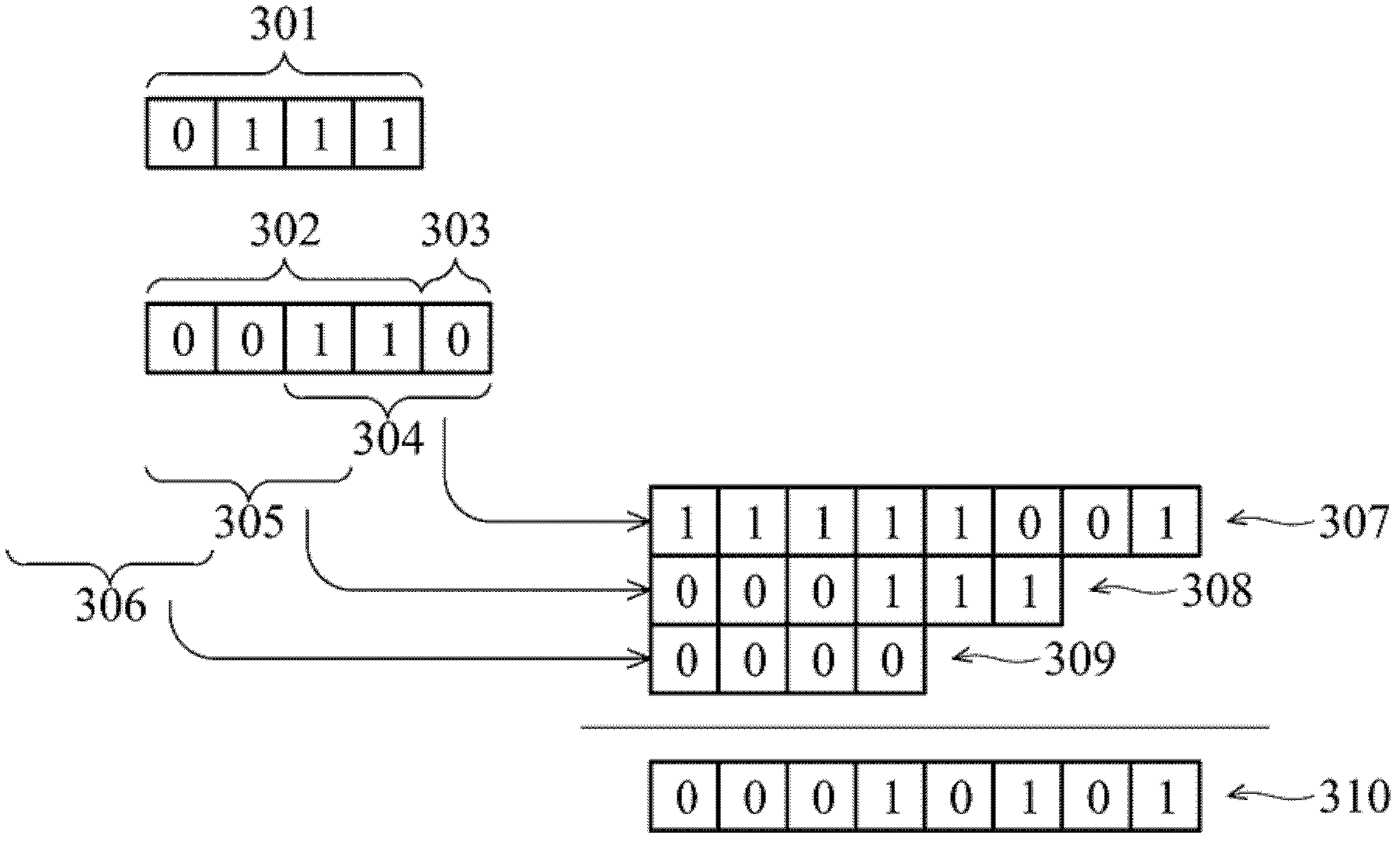

Fixed-point multiplying accumulator

InactiveCN106897046ALower latencyGuaranteed performanceDigital data processing detailsTime delaysComputer science

The invention discloses a fixed-point multiplying accumulator, which comprises a Booth coding unit, a left shift logic unit, a Booth decoding / partial product generation unit, a compression tree, a compressor and a summator, wherein the Booth coding unit is used for coding a multiplier; the left shift logic unit is used for enabling a multiplicand to leftwards shift for one bit to carry out lower-bit zero filling when the multiplicand is a decimal; the Booth decoding / partial product generation unit is used for generating partial products; the compression tree is used for compressing the partial products and outputting two piece of compressed data; the compressor is used for compressing data provided by the accumulator and the compression tree; and the summator is used for carrying out an addition operation on the data output by the compressor to output a result. By use of the fixed-point multiplying accumulator, fixed point integer / decimal multiplication, multiply-accumulation / subtraction functions and overflow judgment functions are realized, the time delay of a multiply-accumulator is not increased, and the performance of a processor is guaranteed.

Owner:青岛专用集成电路设计工程技术研究中心

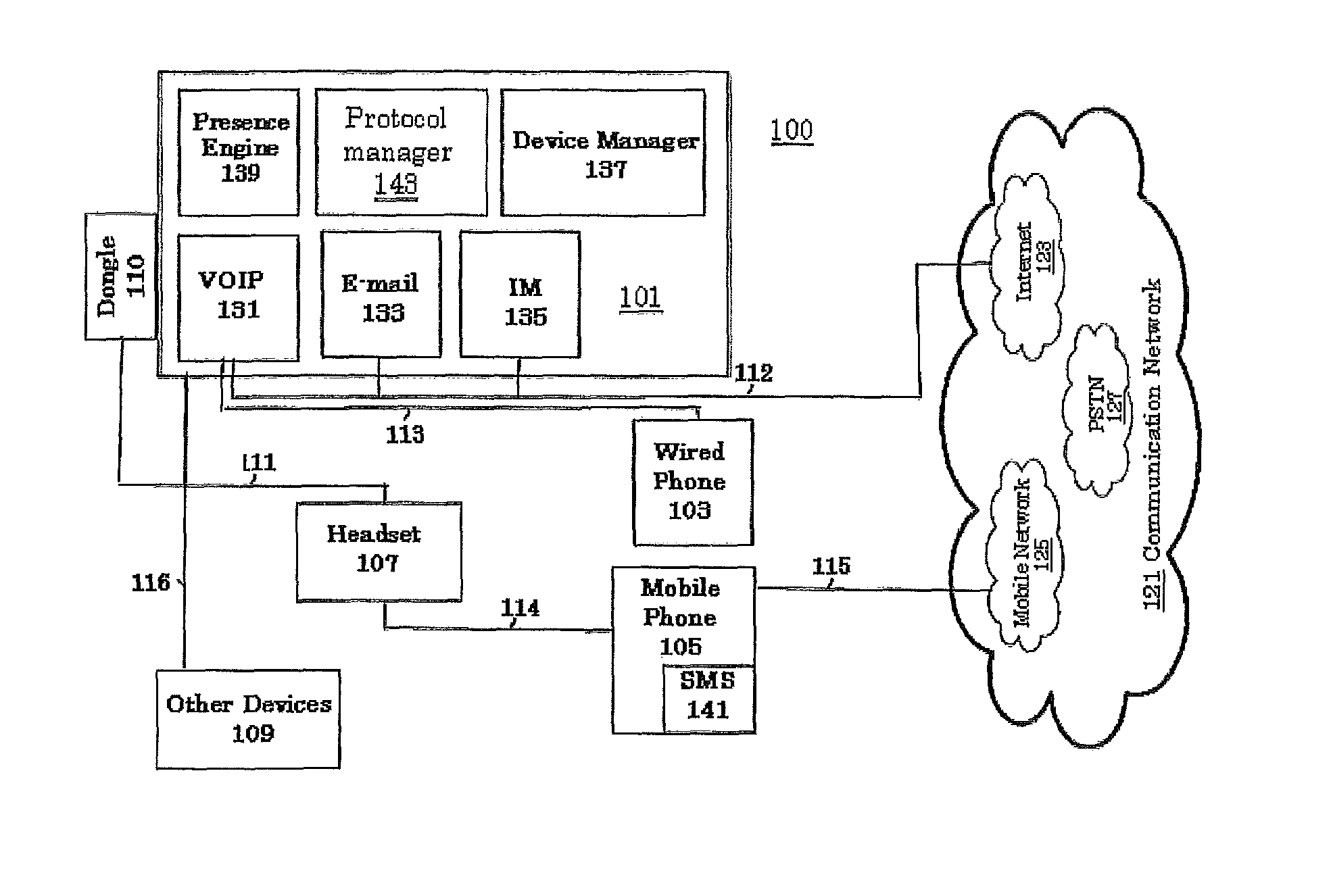

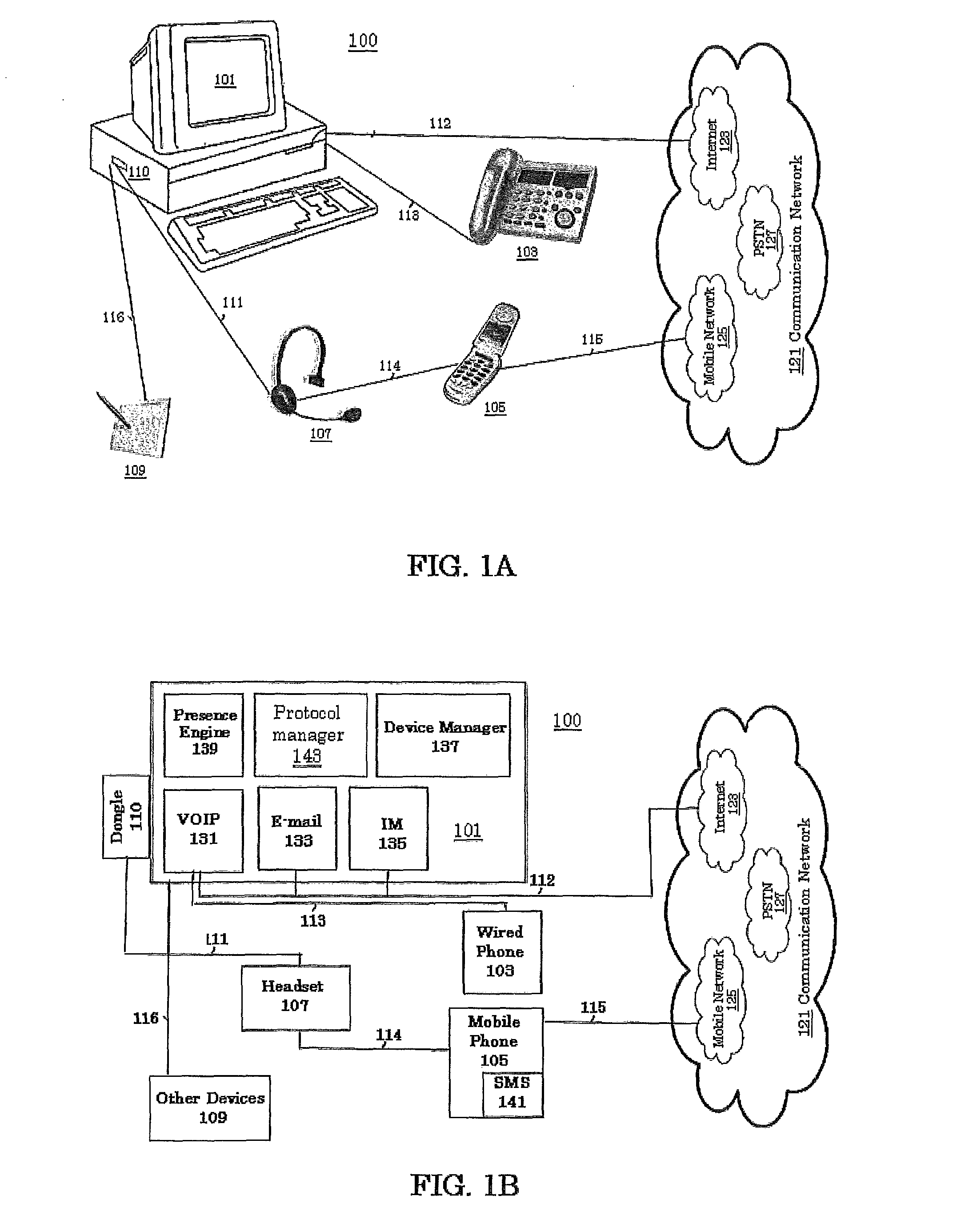

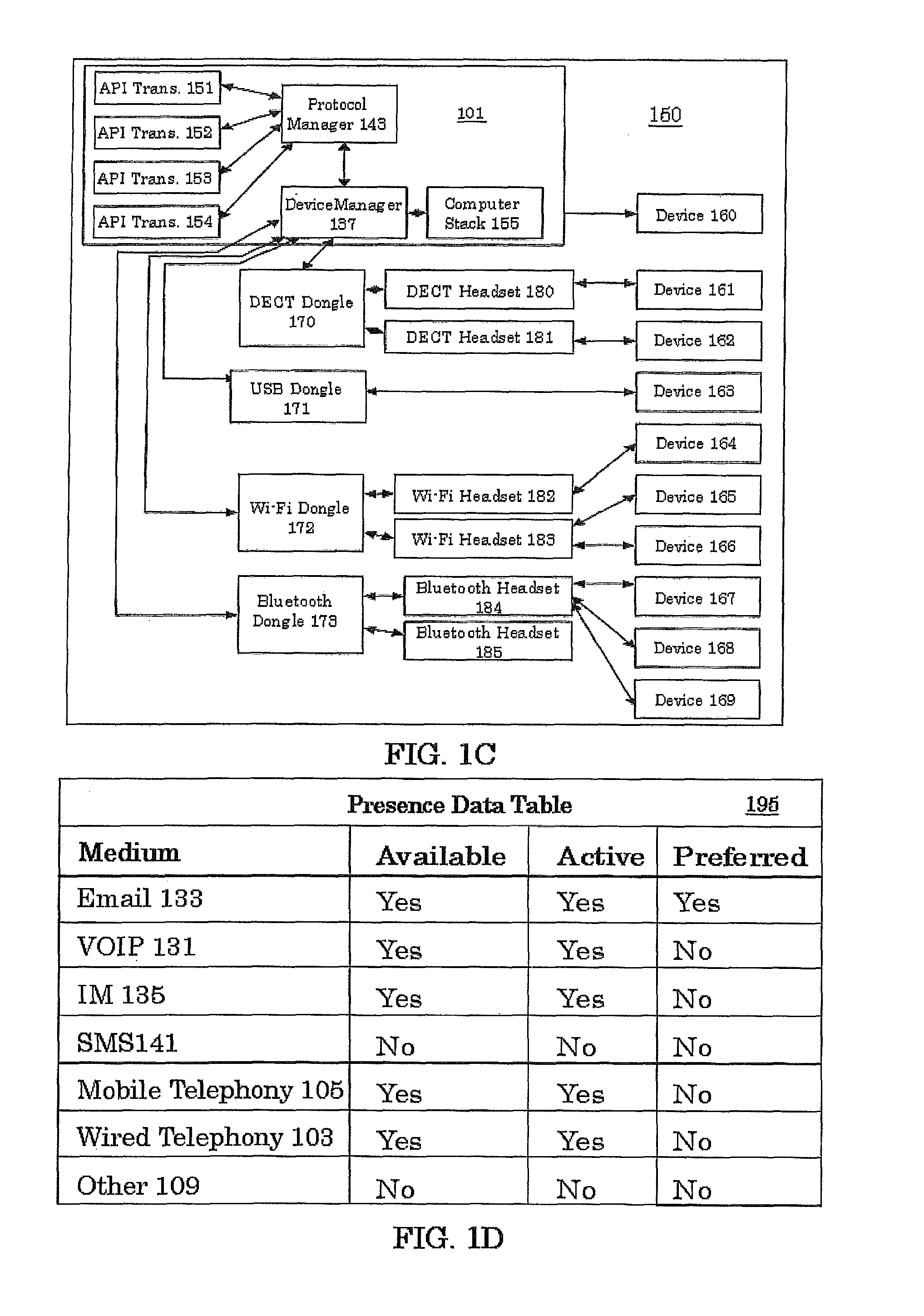

Conneciton Device and Protocol

ActiveUS20120005281A1Service provisioningInterprogram communicationComputer hardwareNetwork Communication Protocols

A common communications protocol is described among devices in a unified communications network. Native devices receive upstream commands and forward them to downstream devices without interpreting the commands. The native devices reformat commands intended for mapped devices in the unified communications network. The common communications protocol calls for left shifting address fields for transmitted commands until the command arrives at its intended destination.

Owner:PLANTRONICS

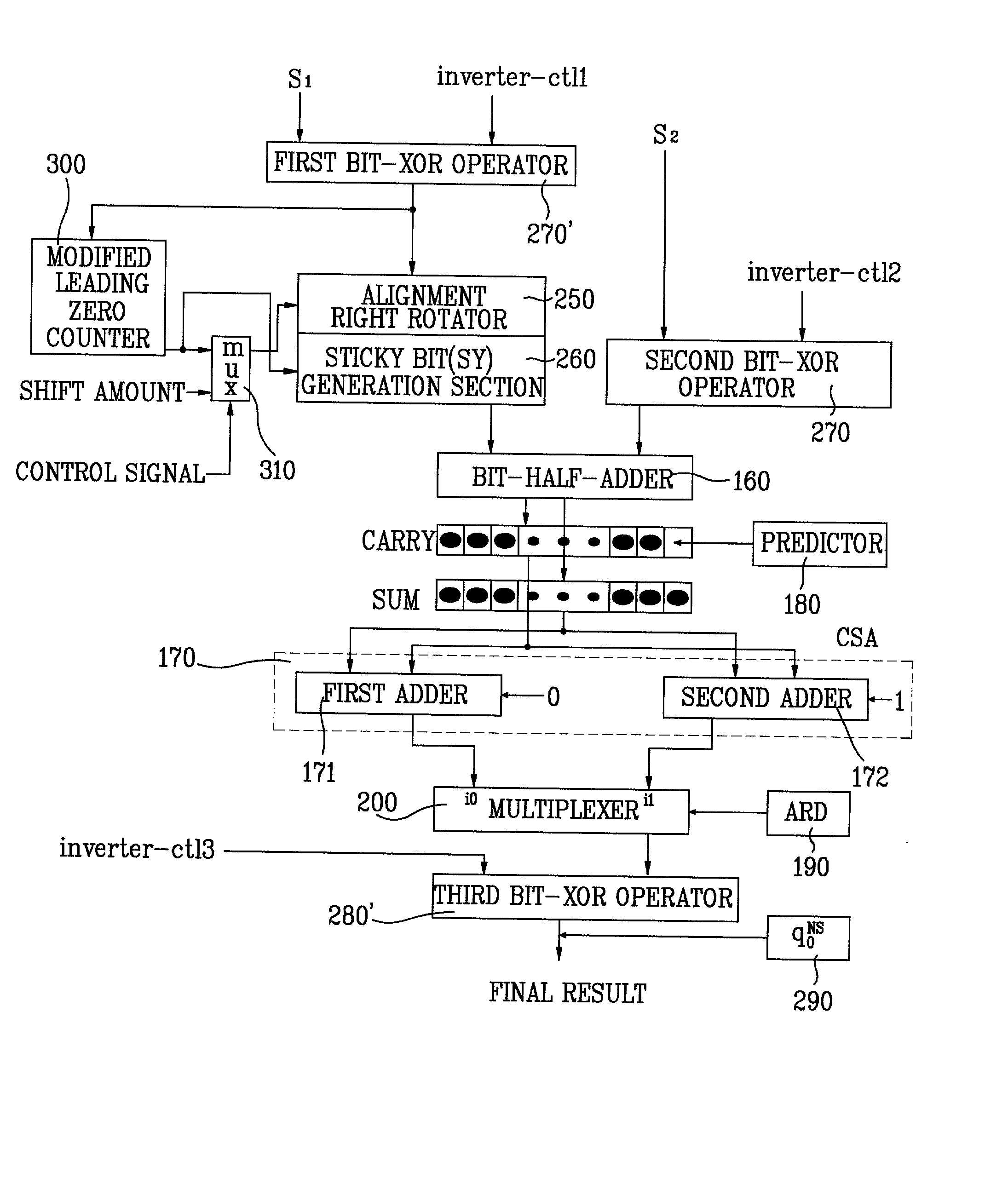

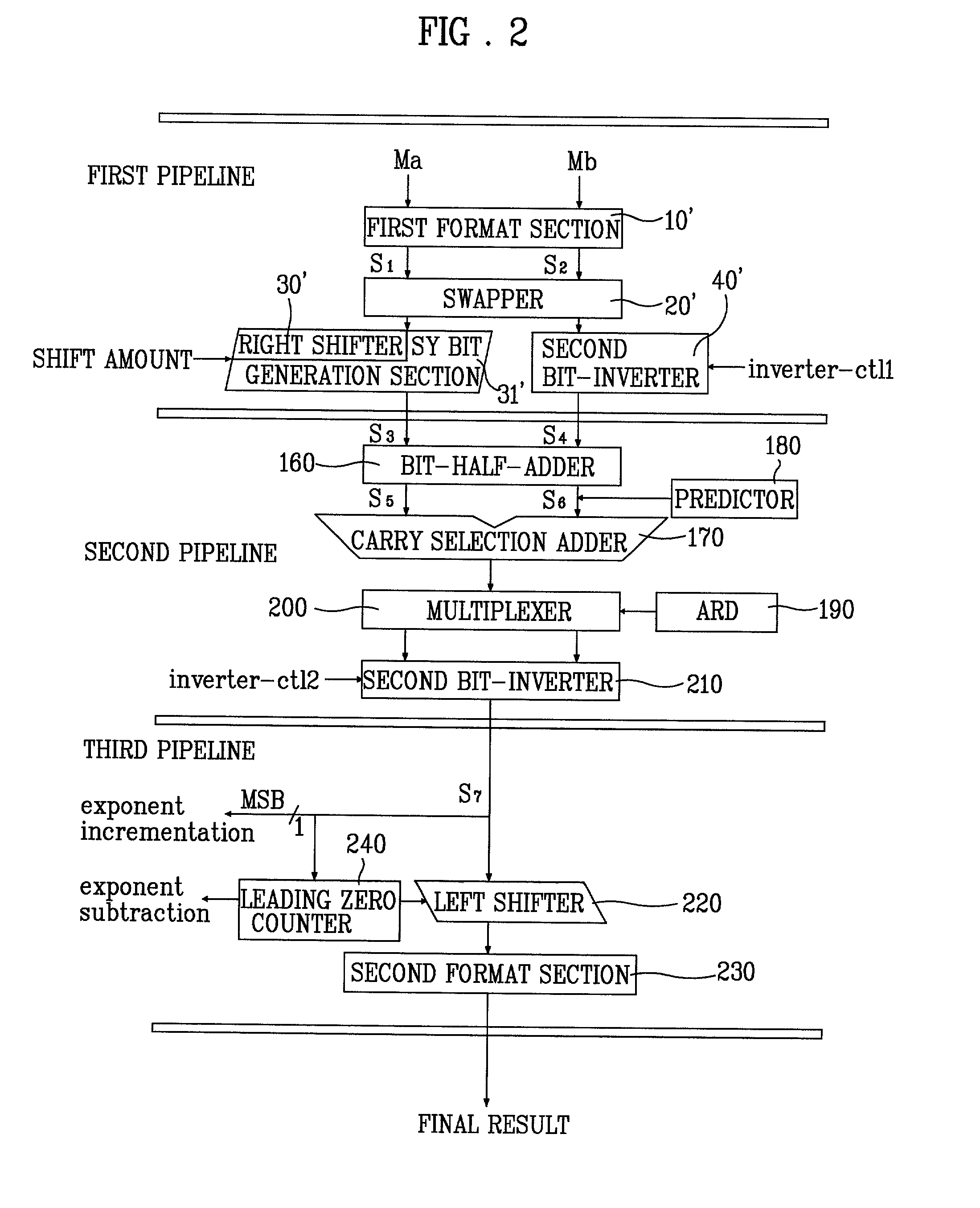

Apparatus and method of performing addition and rounding operation in parallel for floating-point arithmetic logical unit

InactiveUS20020129075A1Computations using contact-making devicesComputation using non-contact making devicesArithmetic logic unitRight shift

A floating-point ALU that performs an IEEE rounding and an addition in parallel in a simultaneous rounding method (SRM) type floating-point adder. The floating-point ALU includes an alignment / normalization section for bypassing or inverting a first fraction part and a second fraction part, performing an alignment by performing a right shift as much as a value obtained from an exponent part or performing a normalization through a left shift by calculating a leading zero with respect to the first fraction part, and obtaining a guard bit (G), round bit (R), and sticky bit (Sy); and an addition and rounding operation section for performing a addition and rounding with respect to the first fraction part and second fraction part outputted through the alignment / normalization section. According to the floating-point ALU, the processing time and the hardware size can be reduced, and the hardware of the SRM can be used as it is.

Owner:YONSEI UNIVERSITY

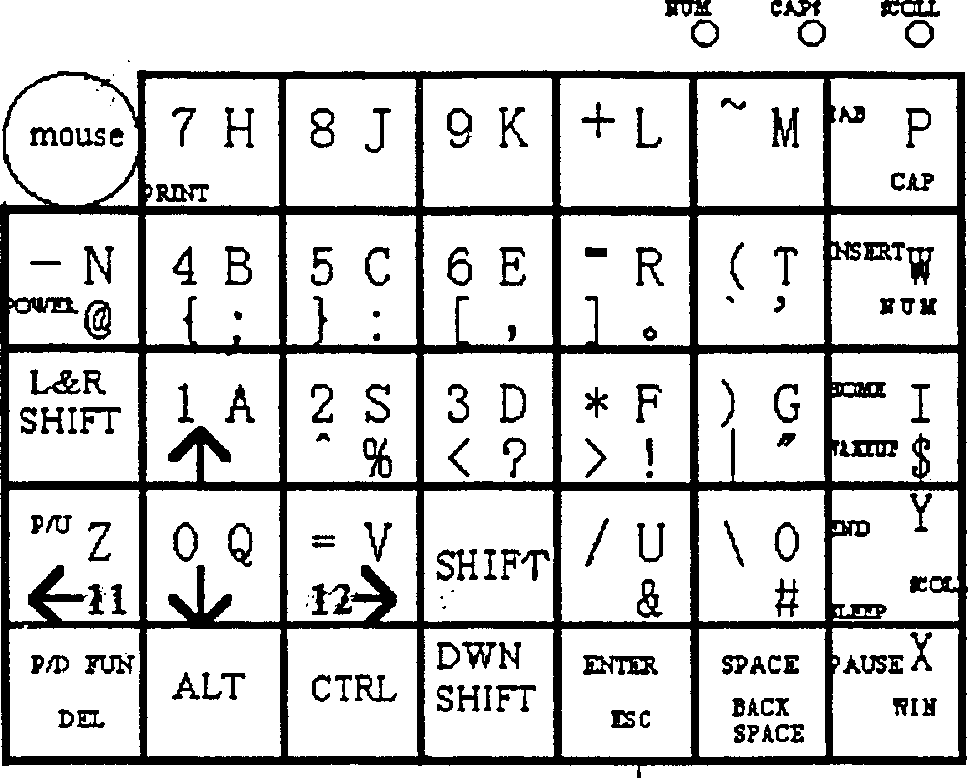

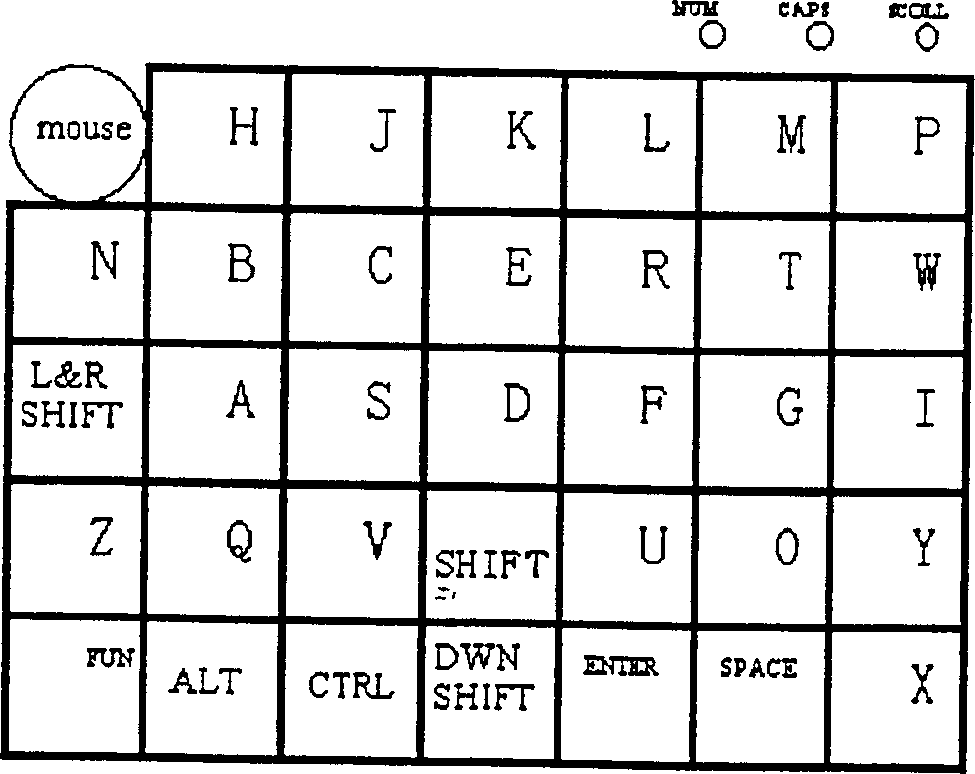

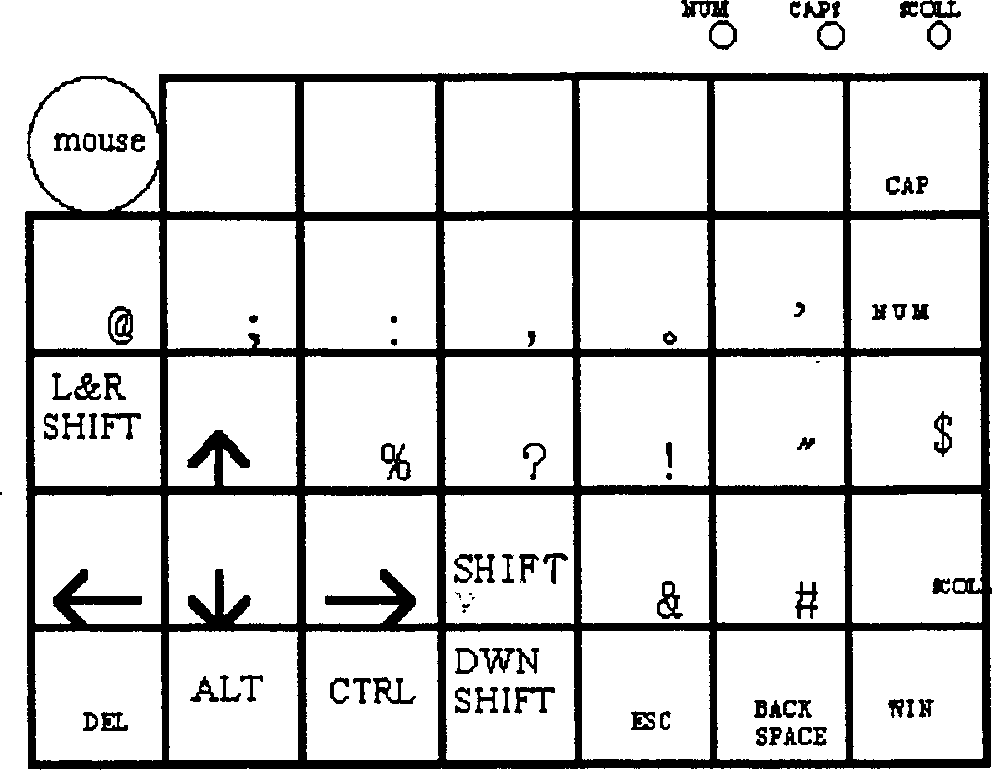

Single-hand operated keyboard and its input method

InactiveCN1403903AReasonable number of keysReasonable settingInput/output processes for data processingDown shiftingLeft shifting

The present invention provides single-hand operated keyboard and its input method and consists of code scanning circuit, signal transmission interface, base plate and keys. The keyboard features at most 48 keys including letter keys, switching keys and special function keys. The switching keys include one available SHIFT key, one L&SHIFT key for left shift and one DWNSHIFT key for down shift. Each key is divided into four areas including the I or default area, the II or down key area, the III or left area and the IV or down left area. The keyboard is suitable for single-handed operation and meets the requirement of development in computer.

Owner:冯文生

Floating-point adder

ActiveUS9009208B2Lower latencyLittle countComputations using contact-making devicesComputer architectureOperand

Floating point adder circuitry 16, 18, 20 is provided with far-path circuitry 18 and near-path circuitry 20. The far-path circuitry utilises a count of trailing zeros TZ and a difference in the input operand exponents to form respective suffix values which are concatenated with the mantissas of the input addends and serve when summed to generate a carry out taking the place of a conventionally calculated sticky bit. Within the near-path, minimum value circuitry 46 is used to calculate the lower of a leading zeros count of the intermediate mantissa produced in a subtraction and the larger of the input operand exponent values such that a left shift applied to the intermediate mantissa value is not able to produce a invalid floating point result due to applying a left shift to remove leading zeros that is too larger and accordingly corresponds to an exponent which cannot be validly represented.

Owner:ARM LTD

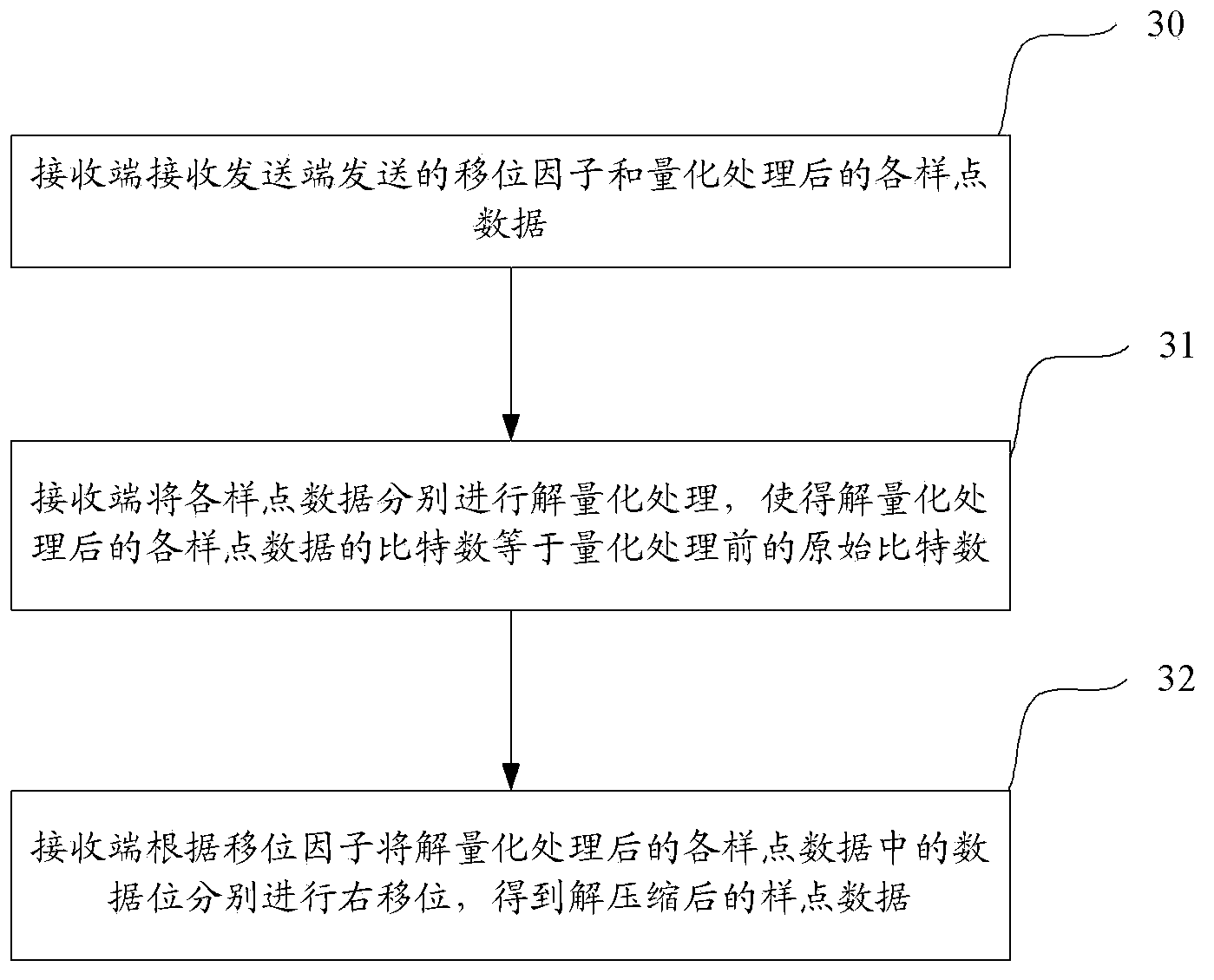

Data compression transmitting and decompression method and apparatus

InactiveCN103634273AEasy to compressModulated-carrier systemsPolarisation/directional diversityData compressionRight shift

An embodiment of the invention discloses a data compression transmitting and decompression method and an apparatus, relates to the field of wireless communication, and is used for optimizing a data compression scheme. In the method, a transmitting terminal divides data to be transmitted into packets, and as for each packet: a shift factor is determined according to a highest order bit of sampling point data of the largest value after a sign bit is removed in the packet, and left shift is conducted respectively for data bits of the sampling point data in the packet according to the shift factor; quantization processing is carried out respectively for the sampling point data after the left shift, so that the number of bits of the sampling point data after the quantization processing is equal to the target number of bits of compression; and the shift factor and the sampling point data after the quantization processing are transmitted to the receiving terminal, the receiving terminal carries out de-quantization processing respectively for the sampling point data, right shift is conducted respectively for the data in the sampling point data after the de-quantization processing according to the shift factor, and decompressed sampling point data are obtained. According to the invention, the performance of the data compression is optimized.

Owner:CHINA ACAD OF TELECOMM TECH

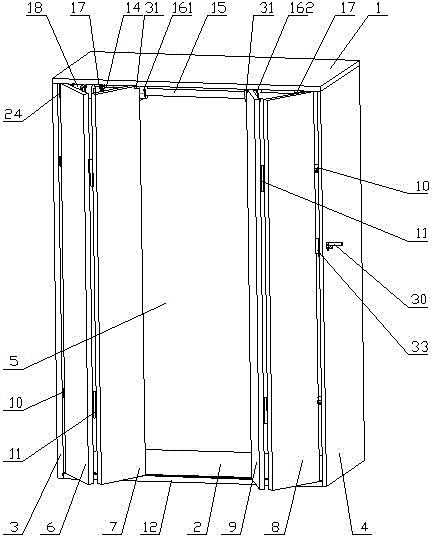

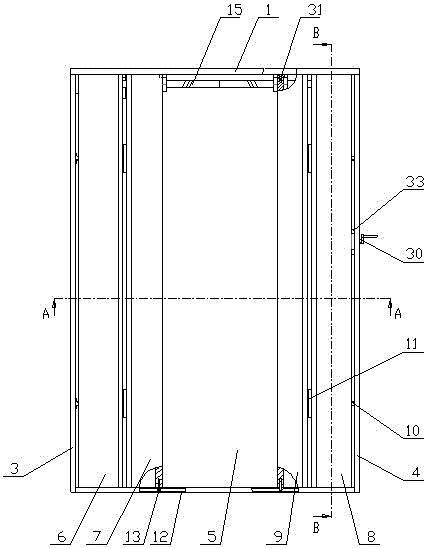

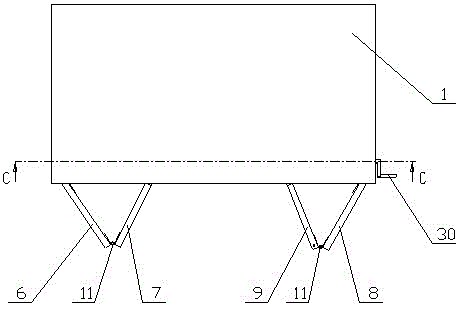

Electric flat-opening push-pull type multiple door wardrobe

InactiveCN105971465ASimple structureRealize automatic opening and closing of doorsWardrobesPower-operated mechanismElectromagnetic clutchElectric drive

The invention discloses an electric flat-opening push-pull multi-door wardrobe, which comprises a cabinet body composed of a top board, a bottom board, a left side board, a right side board and a rear side board, and a left rotating cabinet connected with the left side board of the cabinet body through a hinge. The door, the left translation cabinet door connected with the left rotation cabinet door through the hinge, the right rotation cabinet door connected with the right panel of the cabinet body through the hinge, the right translation cabinet door connected with the right rotation cabinet door through the hinge, fixed on the cabinet The guide rail of the bottom plate of the body, the guide rail pulleys fixed on the guide rails on the left and right translation cabinet doors, and the guide rail pulleys fixed on the cabinet body are composed of motor, lead screw, timing belt, timing pulley, screw nut and electromagnetic clutch. The cabinet door electric drive system and the cabinet door manual drive system composed of synchronous belt pulley, synchronous belt, handle, synchronous belt wheel shaft and synchronous belt wheel seat. The electric side-opening push-pull multi-door wardrobe of the present invention has a simple structure, has the characteristics of sliding doors and flat-hung doors, can realize automatic door opening and closing, and can be manually operated when the power is off.

Owner:张冬明

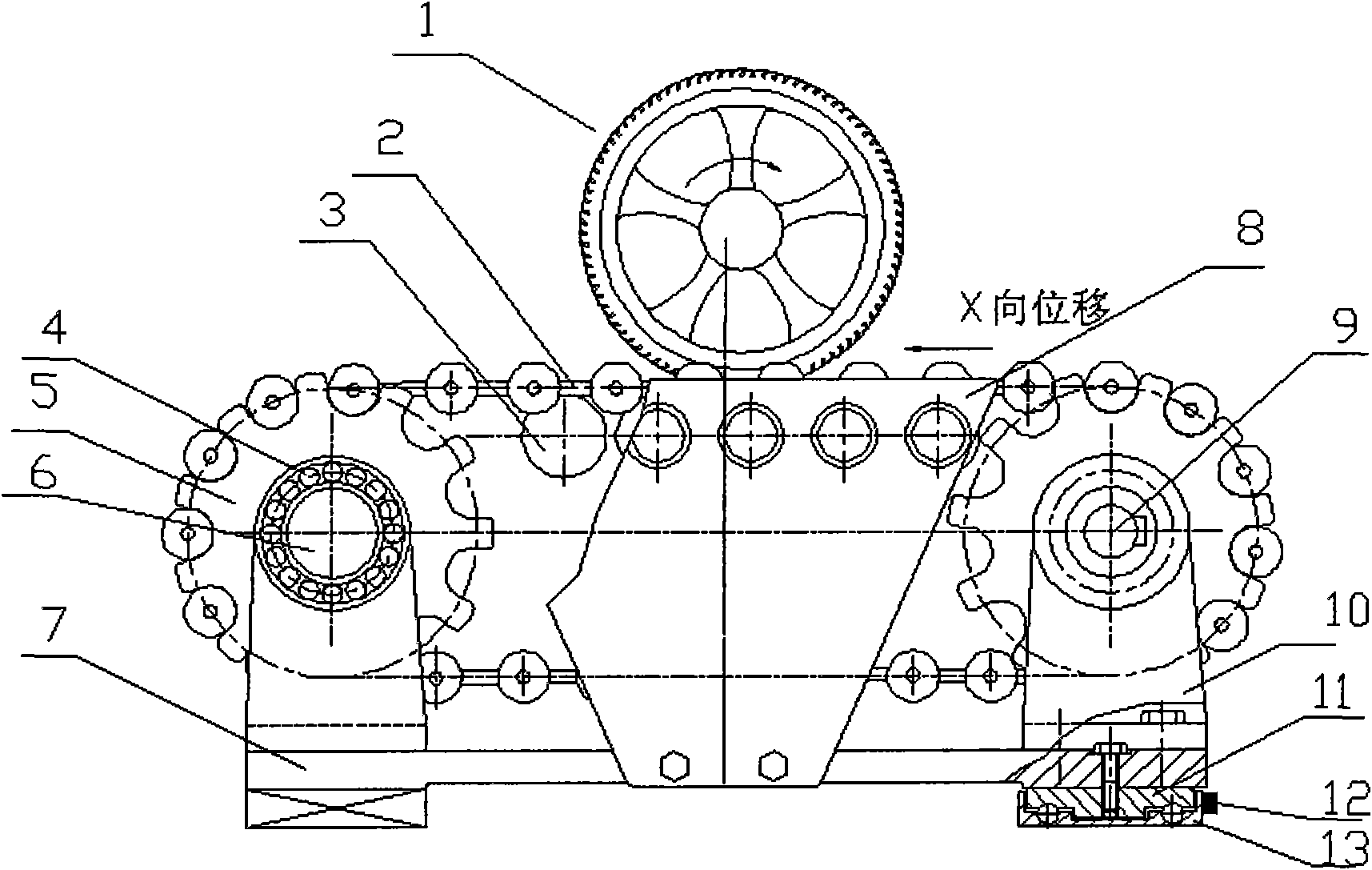

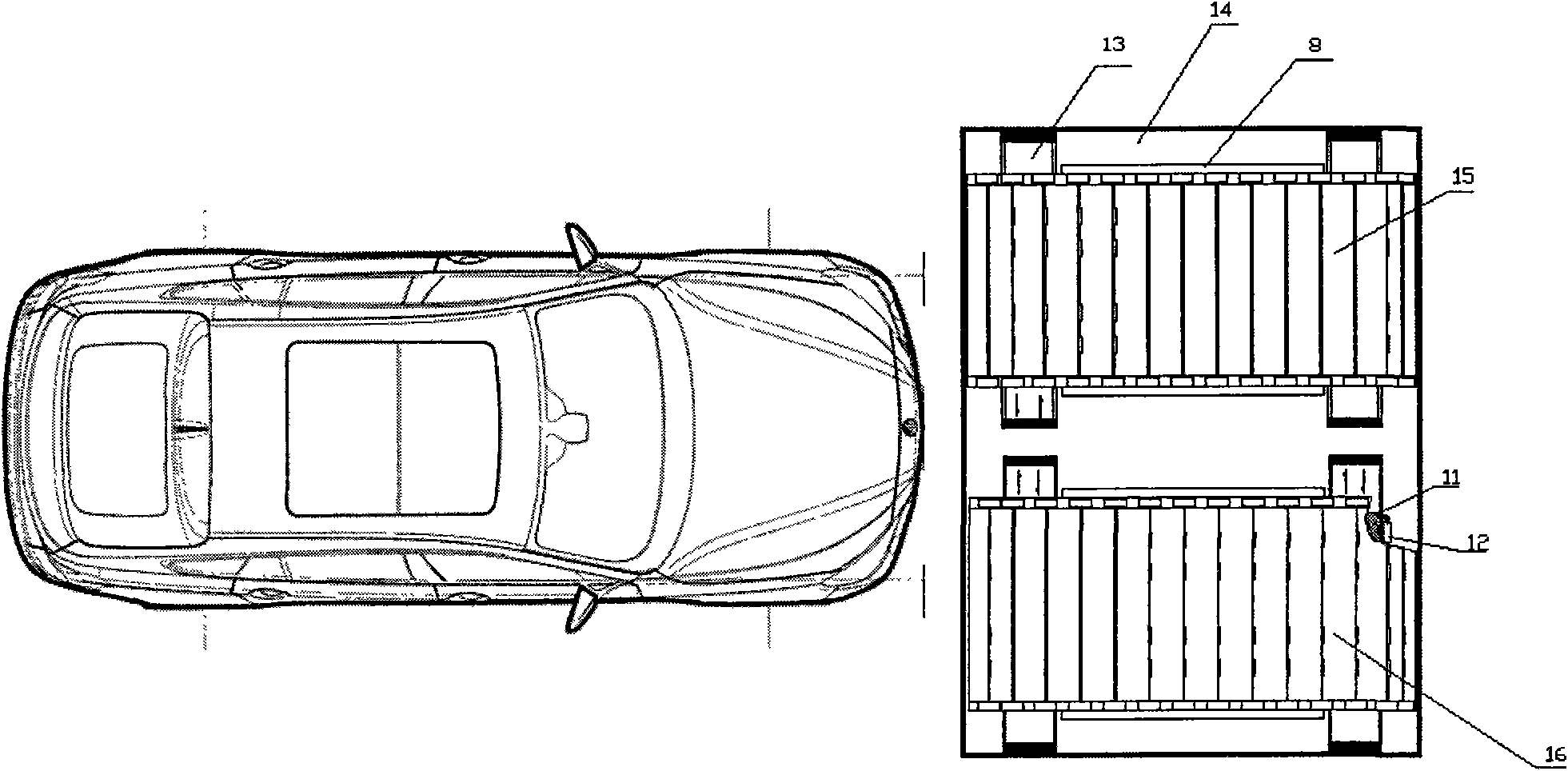

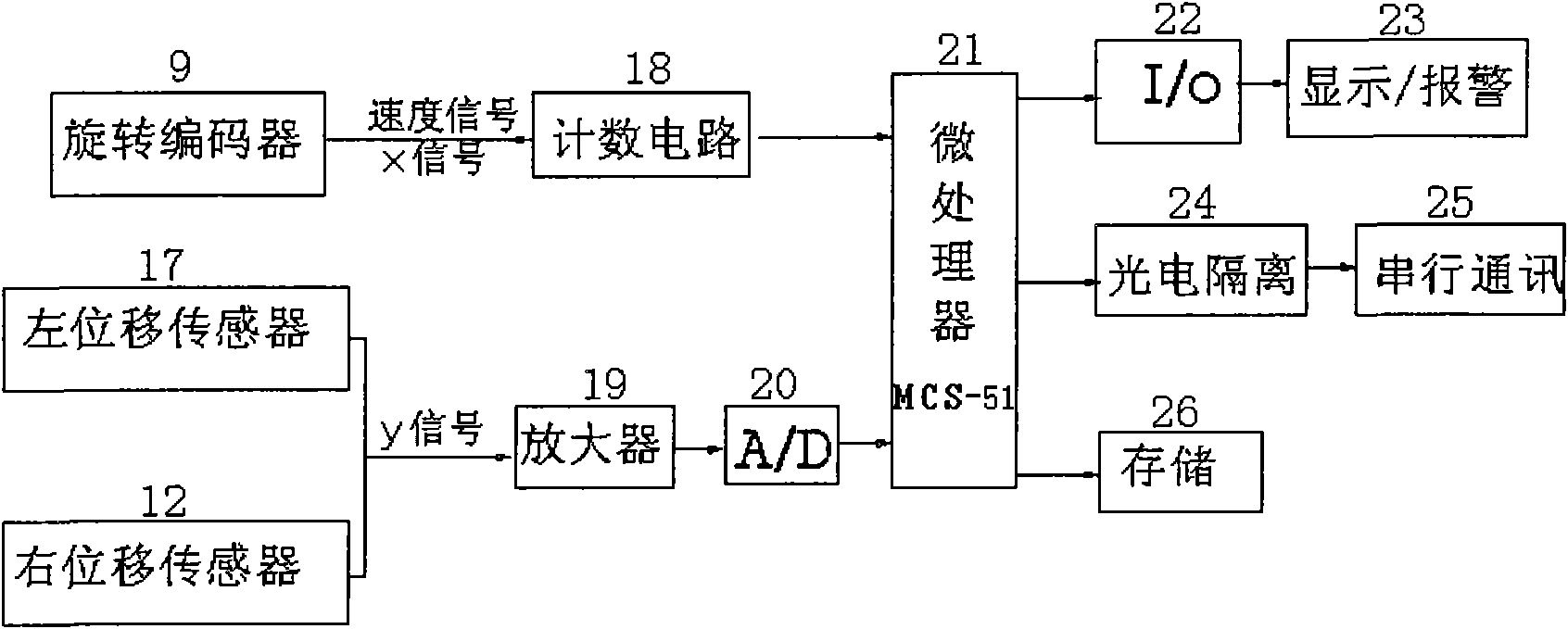

Automobile sideslip detector and method for detecting sideslip

InactiveCN101592557AThe test result is reasonableIn line with actual operating conditionsUsing electrical meansVehicle wheel testingBall bearingAudio power amplifier

The invention discloses an automobile sideslip detector and a method for detecting sideslip. The automobile sideslip detector consists of a mechanical part and an electric part, wherein chain wheels of the mechanical part are fixed on a chain wheel shaft, and a plane link plate and two chain wheels form chain drive connection; a base plate is arranged on a sliding plate, the sliding plate is connected with a plate type linear guide rail through a ball bearing, and the sliding plate can reciprocate on the plate type guide rail transversely; a left-shift sensor and a right-shift sensor of the electric part are connected with an amplifier respectively, and the amplifier is connected with a microprocessor through an A / D converter; a rotary encoder is connected with the microprocessor through a counting circuit; and a rotating shaft of the rotary encoder and the chain wheel shaft are arranged coaxially, and the fixed parts of the left-shift sensor and the right-shift sensor are arranged on the plate type linear guide rail. The sideslip detector amplifies the detection running distance X of a detected automobile so that the detection is more accurate, and can measure sideslip values at different speeds and different loads for accurately matching suspension fork positional parameters of a front steering wheel.

Owner:SOUTH CHINA UNIV OF TECH

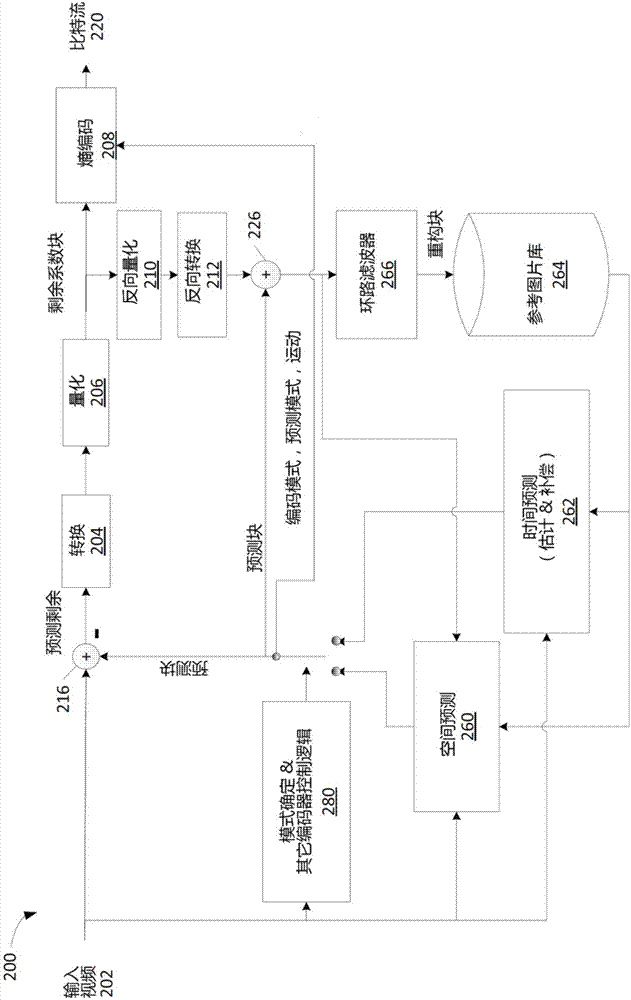

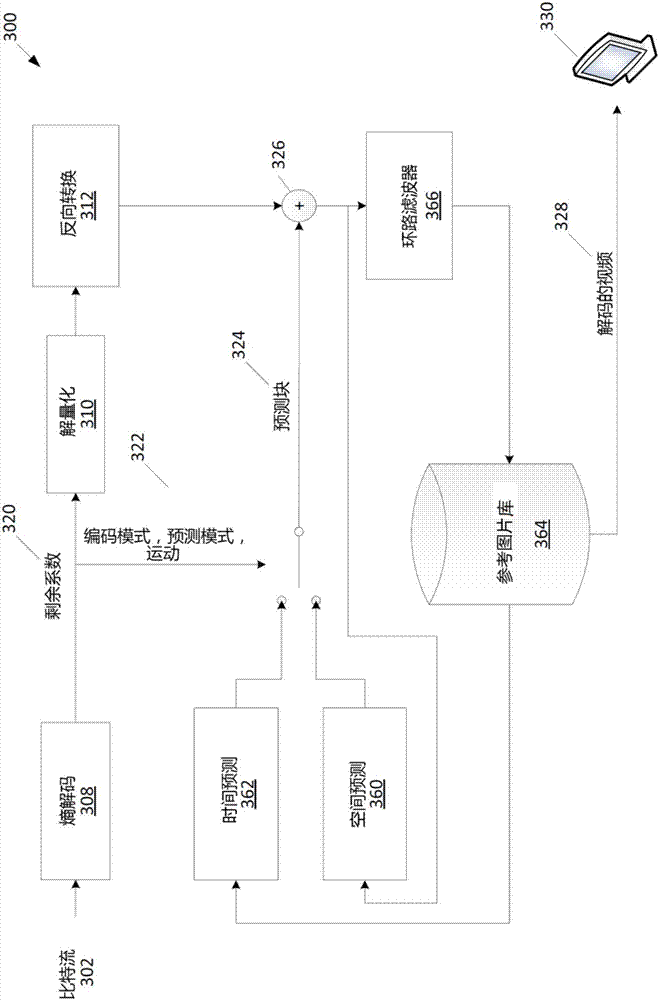

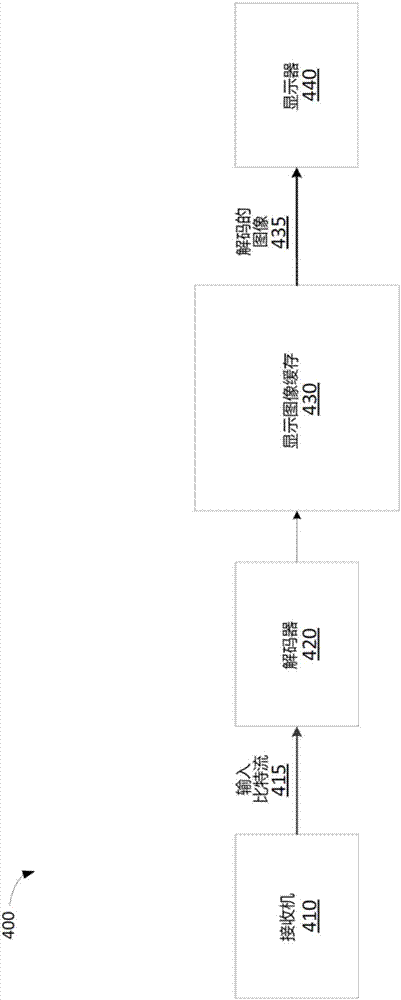

Escape color coding for palette coding mode

Systems, methods, and instrumentalities are disclosed for escape color coding for palette coding mode. A video bitstream may be received. The video bitstream may comprise a quantization parameter (QP) and / or a quantized escape color value that corresponds to an escape color pixel. A scaled escape color value may be generated by scaling the quantized escape color value by a scaling factor. A left- shift parameter may be determined based on the QP. A left-shifted escape color value may be generated by left-shifting the scaled escape color value based on the left-shift parameter. A right-shifted escape color value may be generated by right-shifting the left-shifted escape color value based on a constant parameter. A reconstructed escape color value may be determined based on the right-shifted escape color value. The device may decode the video bitstream based on the reconstructed escape color value.

Owner:VID SCALE INC

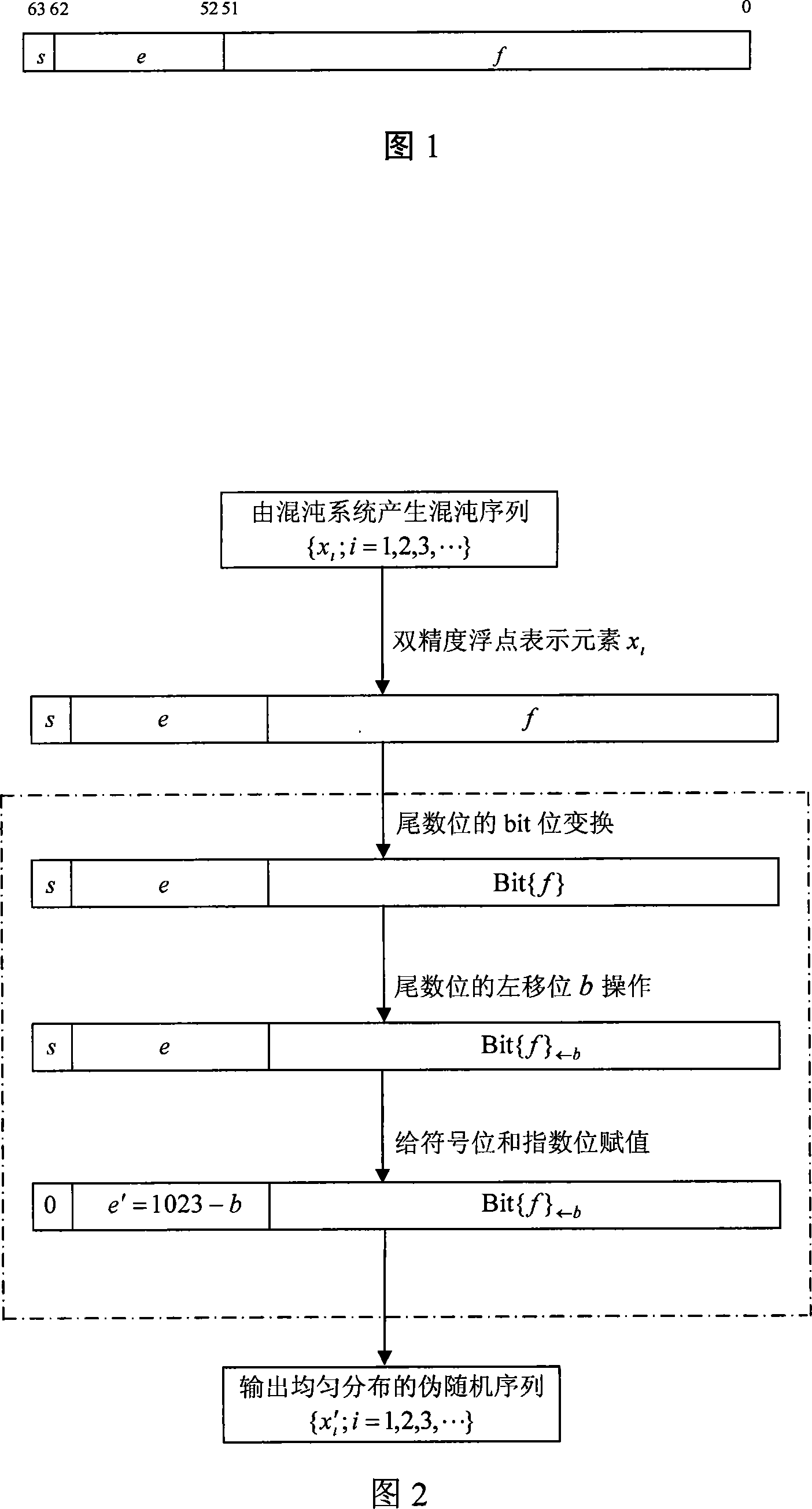

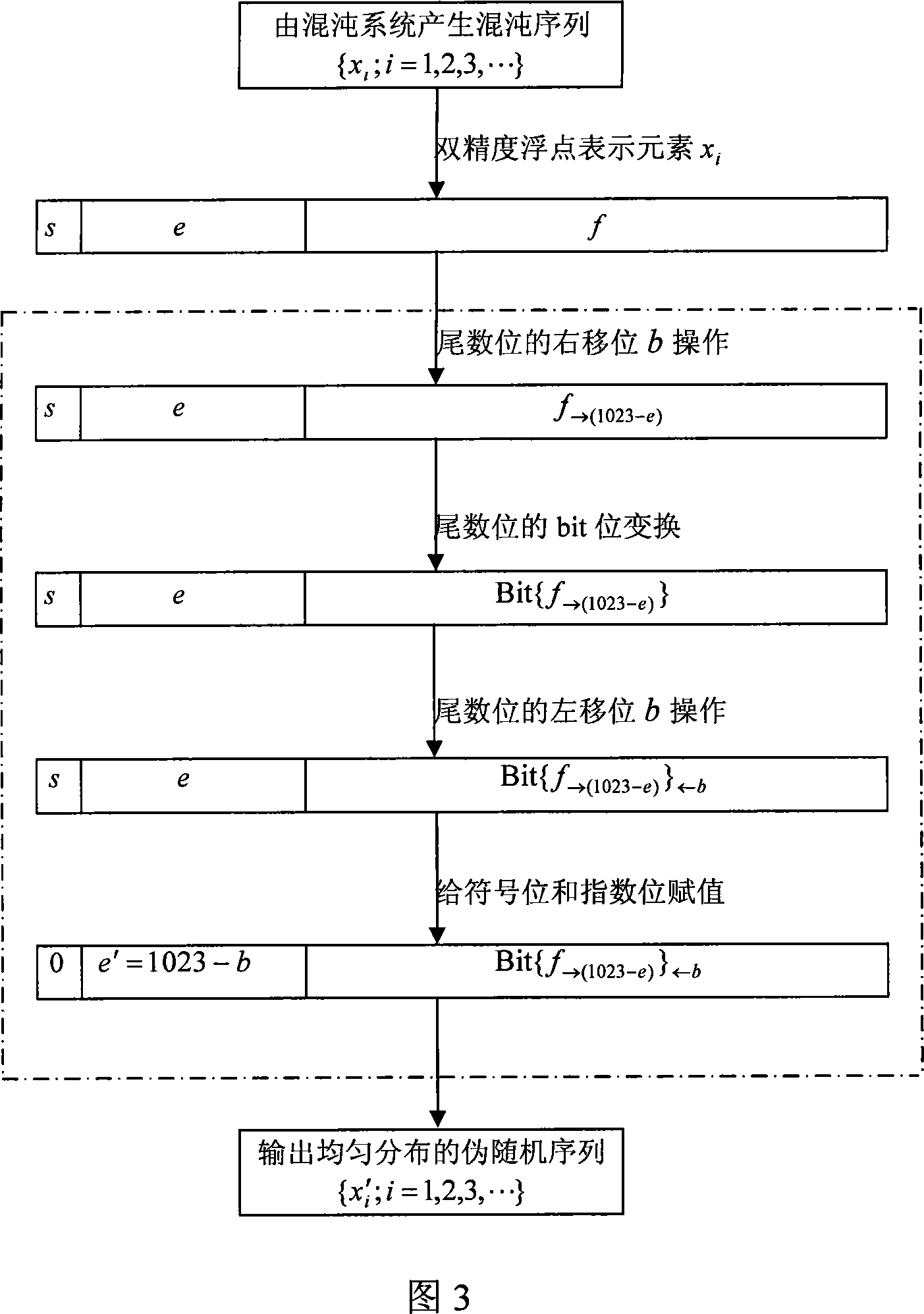

A method to obtain uniform distributed pseudo random sequence in random chaos system

InactiveCN101217360AEvenly distributedEasy to implementSecret communicationSecuring communicationRight shiftSign bit

The invention discloses a pseudo-random sequence even obtaining method from an arbitrary chaotic system. The invention comprises the following steps: for an arbitrary solid pattern chaotic sequence from a chaotic map system or a chaotic differential dynamic system, if the field of definitions of the chaotic sequence is (-1, 1), a real number converter carries on right shift b operations successively to the mantissas of each element in the arbitrary solid pattern chaotic sequence, switches the bit position of mantissa and carries on left shift b operations to the mantissas; the sign bit is endowed with a value '0' and an asynchronous exponential bit is endowed with a value '1023-b' to obtain an even-distributed pseudo-random sequence; or the real number converter switches the position of bit successively of the mantissas of each element in the arbitrary solid pattern chaotic sequence, carries on left shift b operations to the mantissas; the sign bit is endowed with a value '0' and an asynchronous exponential bit is endowed with a value '1023-b' to obtain the even-distributed pseudo-random sequence. The invention can obtain good-homogeneity pseudorandom number from an arbitrary chaotic system, in particular to be convenient for the realization of digital system.

Owner:CENT SOUTH UNIV

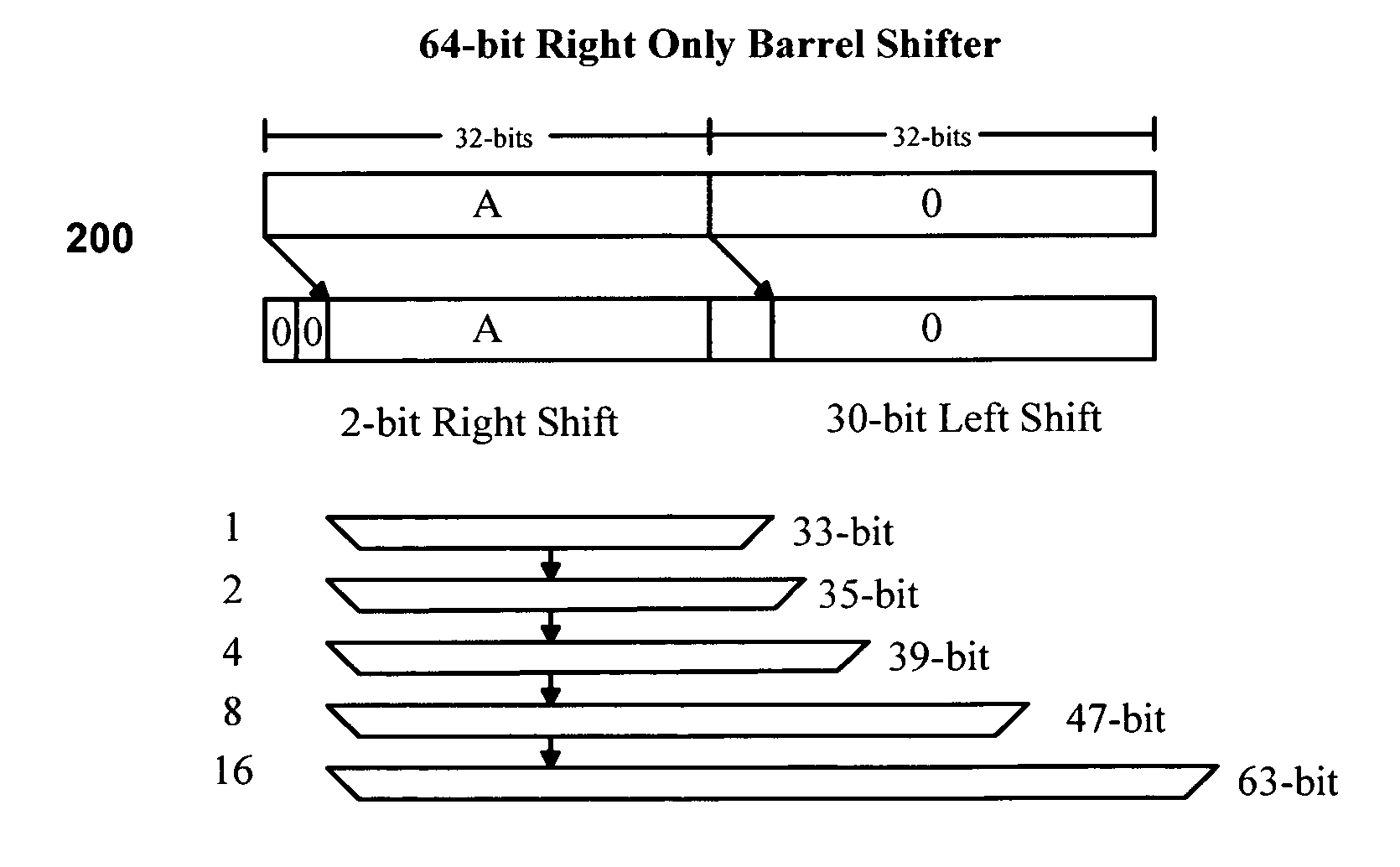

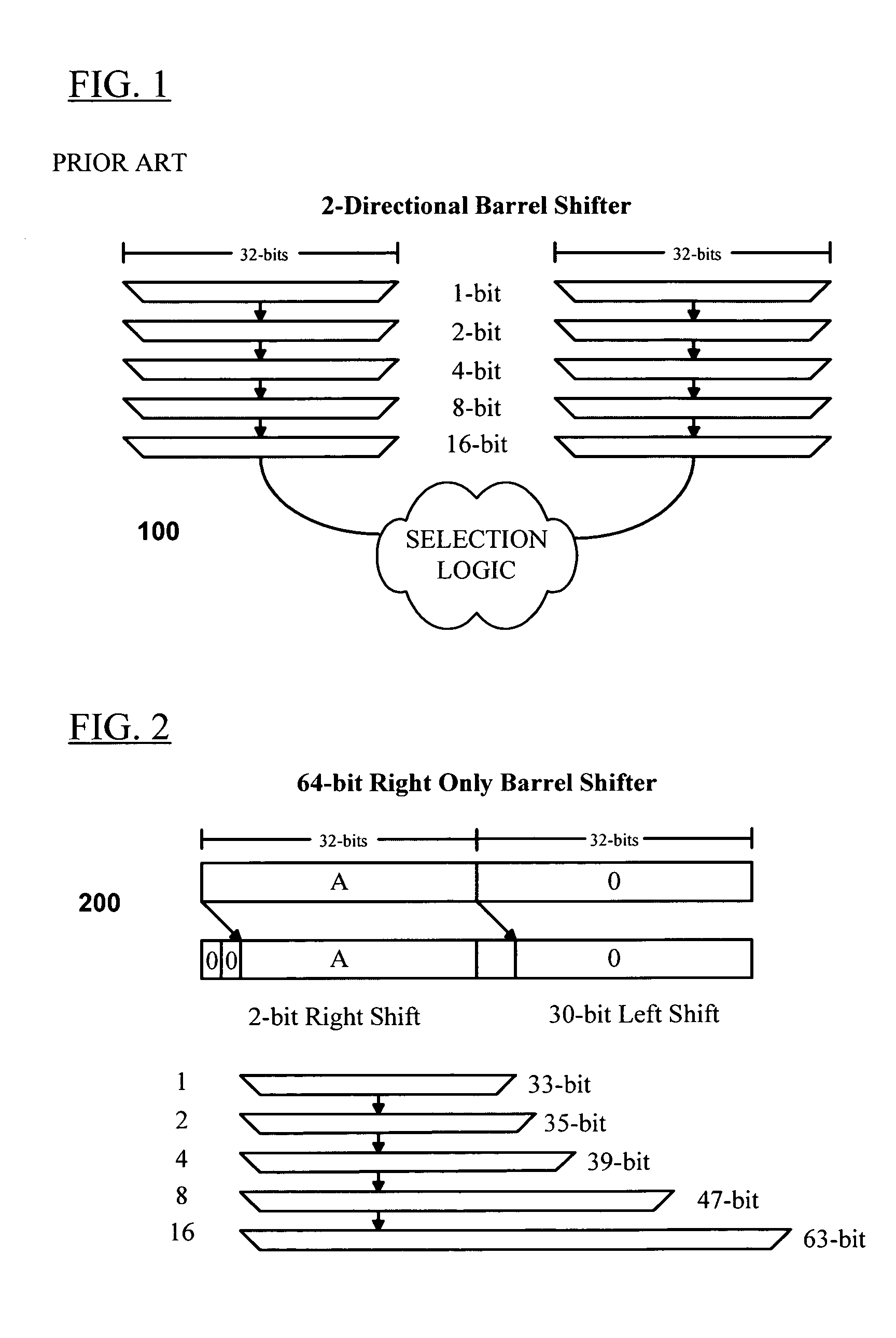

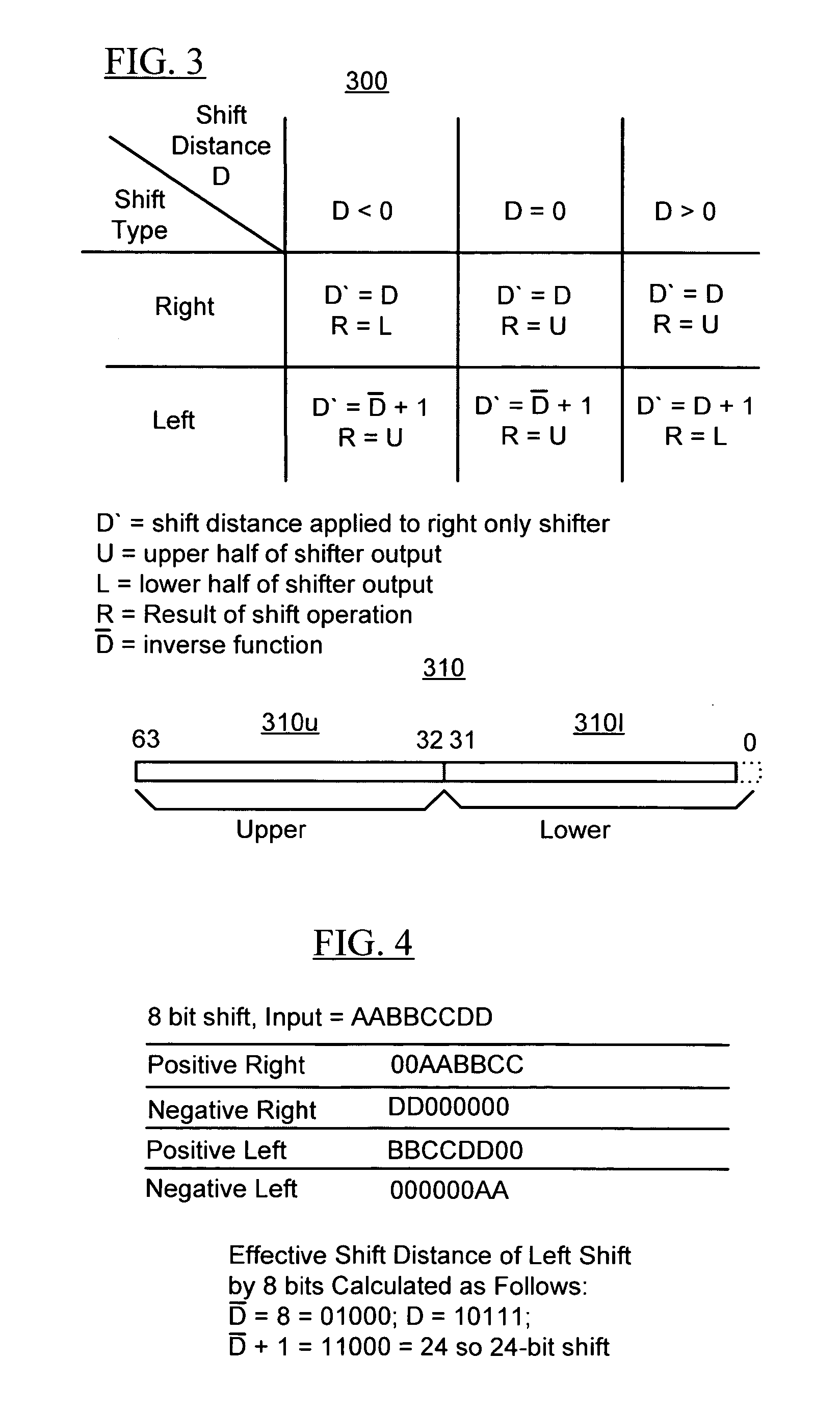

Barrel shifter for a microprocessor

InactiveUS20050289323A1Reduce power consumptionImprove performanceEnergy efficient ICTError detection/correctionRight shiftMultiplexer

A 2N bit right only barrel shifter for a microprocessor comprising upper and lower N bit shifter portions. A N bit input is put in the upper portion. An X bit right shift of the N bit number yields the results in the N bit upper portion and the result of an N-X bit left shift in the lower portion. The N bit shifter is comprised of a Log2N stage multiplexer where in each successive stage of the multiplexer adds 2x additional bits where x increments from 0 to (Log2N-1).

Owner:ARC INT LTD

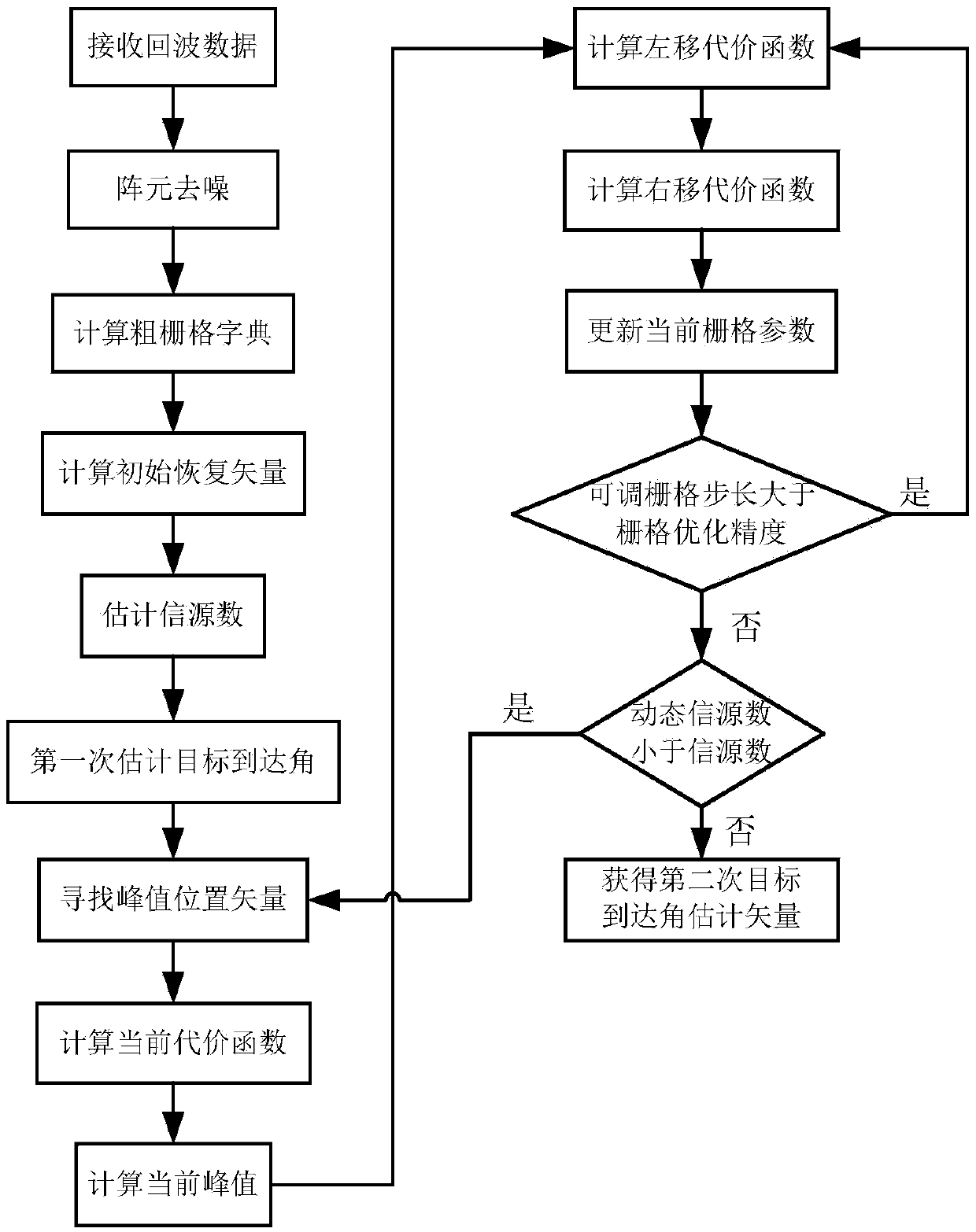

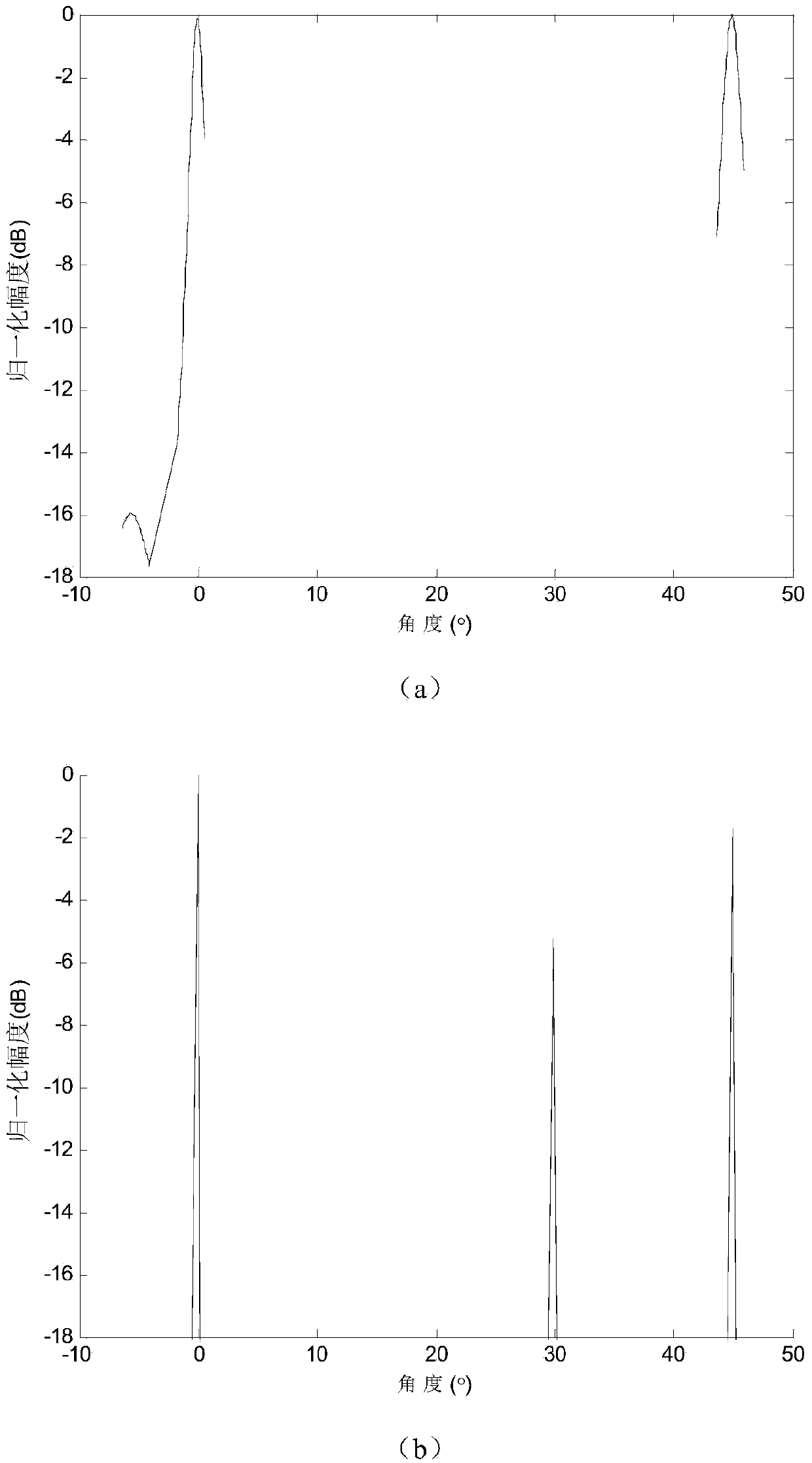

Grid offset optimization object DOA (Direction of Arrival) estimation method based on source number estimation

ActiveCN105334488AOvercome the problem of estimated performance degradation or even failureOvercome the rank deficit problemRadio wave direction/deviation determination systemsEstimation methodsRight shift

The invention discloses a grid offset optimization object DOA (Direction of Arrival) estimation method based on source number estimation. The grid offset optimization object DOA estimation method based on source number estimation mainly solves the problem that the prior art is low the DOA estimation performance when the source number is unknown and the sample is small and under the coherent source situation. The implementation process of the method comprises: utilizing array element denoising to perform denoising processing for the received data so as to acquire a data observation vector; solving the peak value for the recovery vector acquired through calculation so as to estimate the source number and the primary target DOA; calculating the current peak value and the current cost function; calculating and comparing the left shift cost function value and the right shift cost function value to update the current grid parameter; and not stopping the angle estimation until the adjustable grid step length satisfies the grid precision and the dynamic source number is greater than the estimated source number, and obtaining the secondary DOA estimation vector. The grid offset optimization object DOA estimation method based on source number estimation realizes high-precision DOA estimation for sparse multi targets when the source number is unknown and the sample is small and under the coherent source situation.

Owner:XIDIAN UNIV

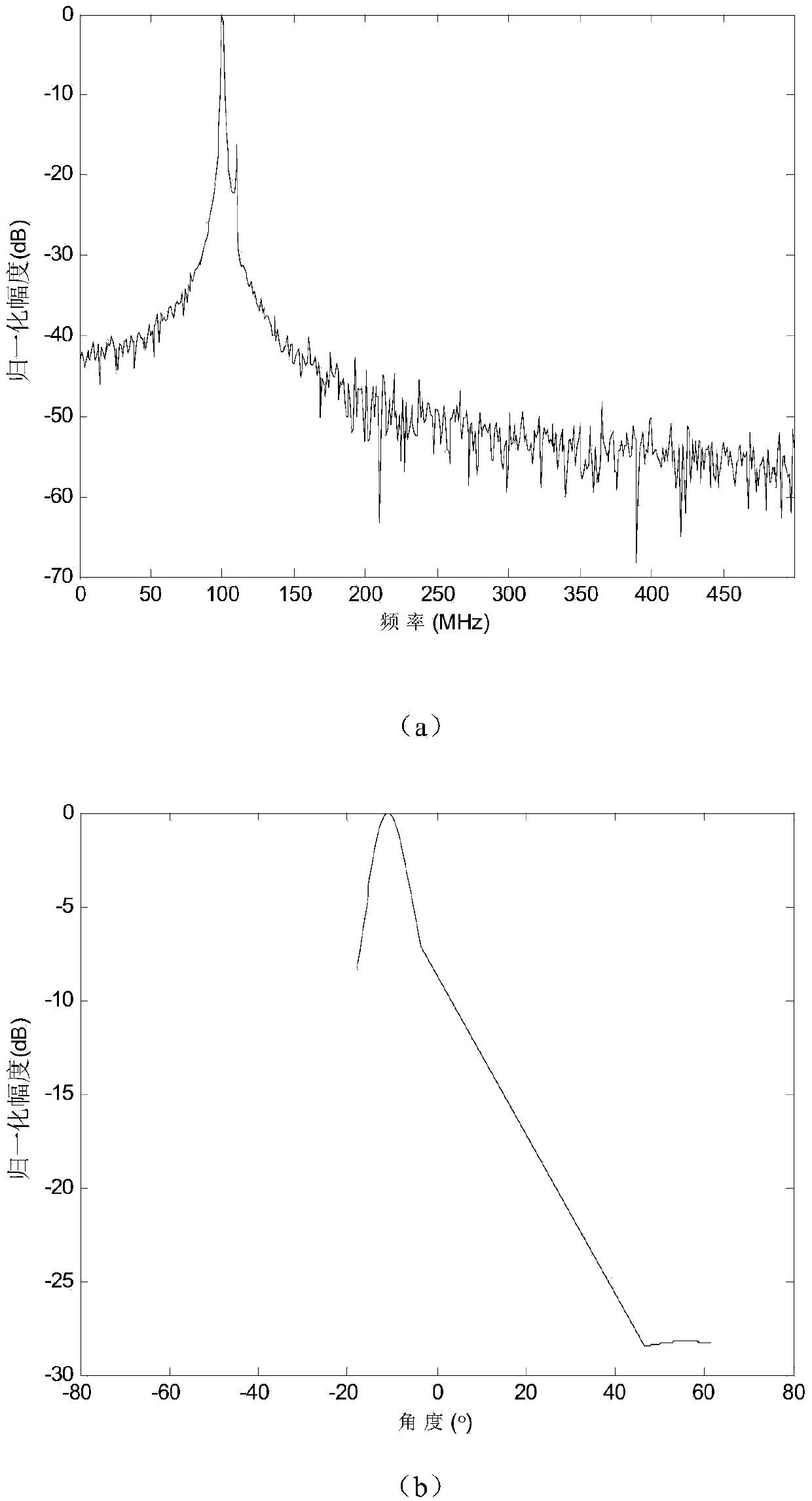

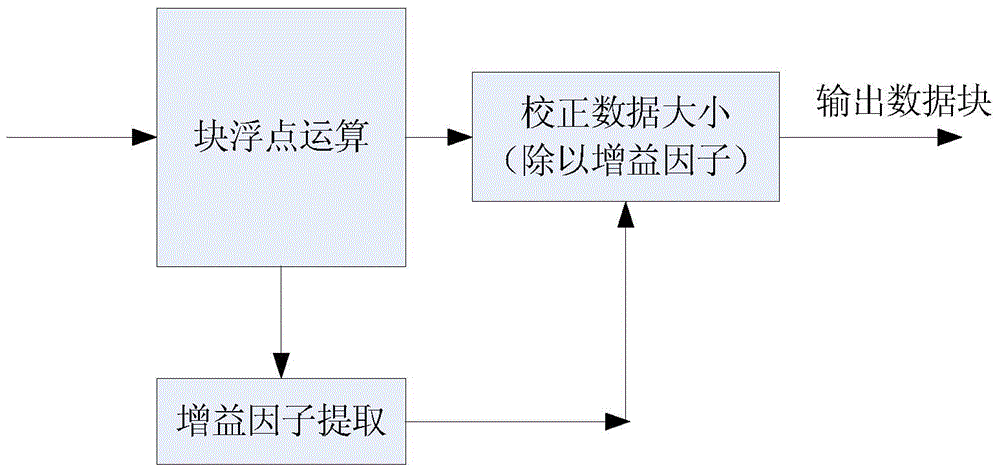

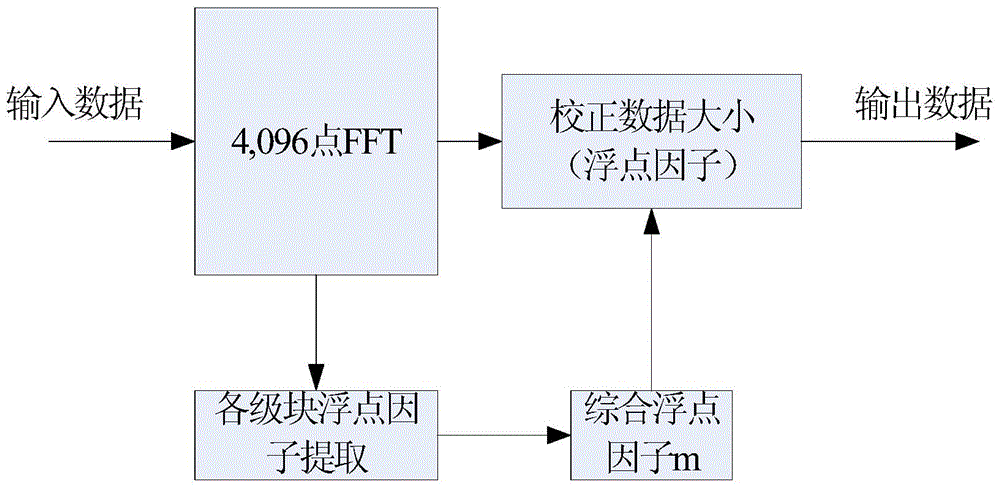

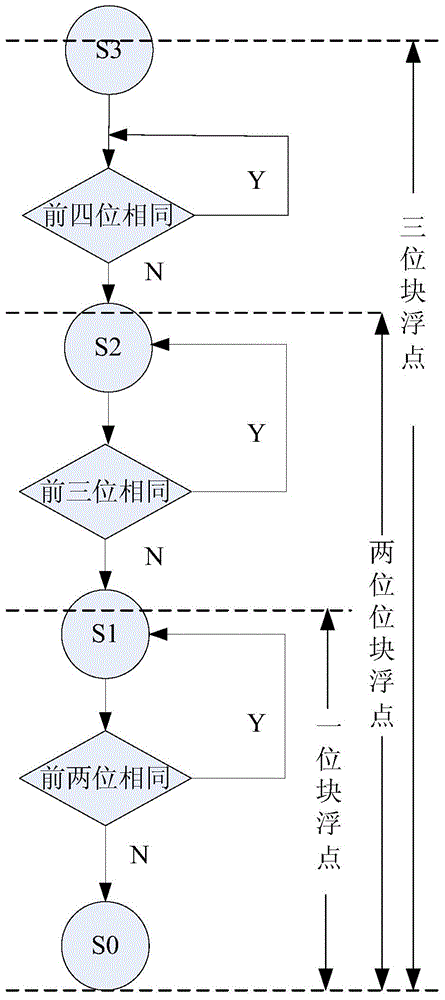

Floating point calculation method based on FPGA

ActiveCN104679719ASolve conflictsImprove the efficiency of floating-point operationsComplex mathematical operationsRight shiftParallel computing

The invention provides a floating point calculation method based on a FPGA. The method comprises the steps of processing a group of data which is identical in index and different in mantissa and used as a data block, expressing the data in calculation by adopting a fixed point format, adjusting the data precision by virtue of left shifting, right shifting the data to avoid the overflow error in the fixed point calculation, and dividing result data by a preset gain to obtain correct data after the calculation is ended. By adopting the floating point calculation method, the contradiction between a fixed point algorithm and a floating point algorithm is solved, the floating point calculation efficiency is improved, and the cost is reduced.

Owner:南京晶达微电子科技有限公司

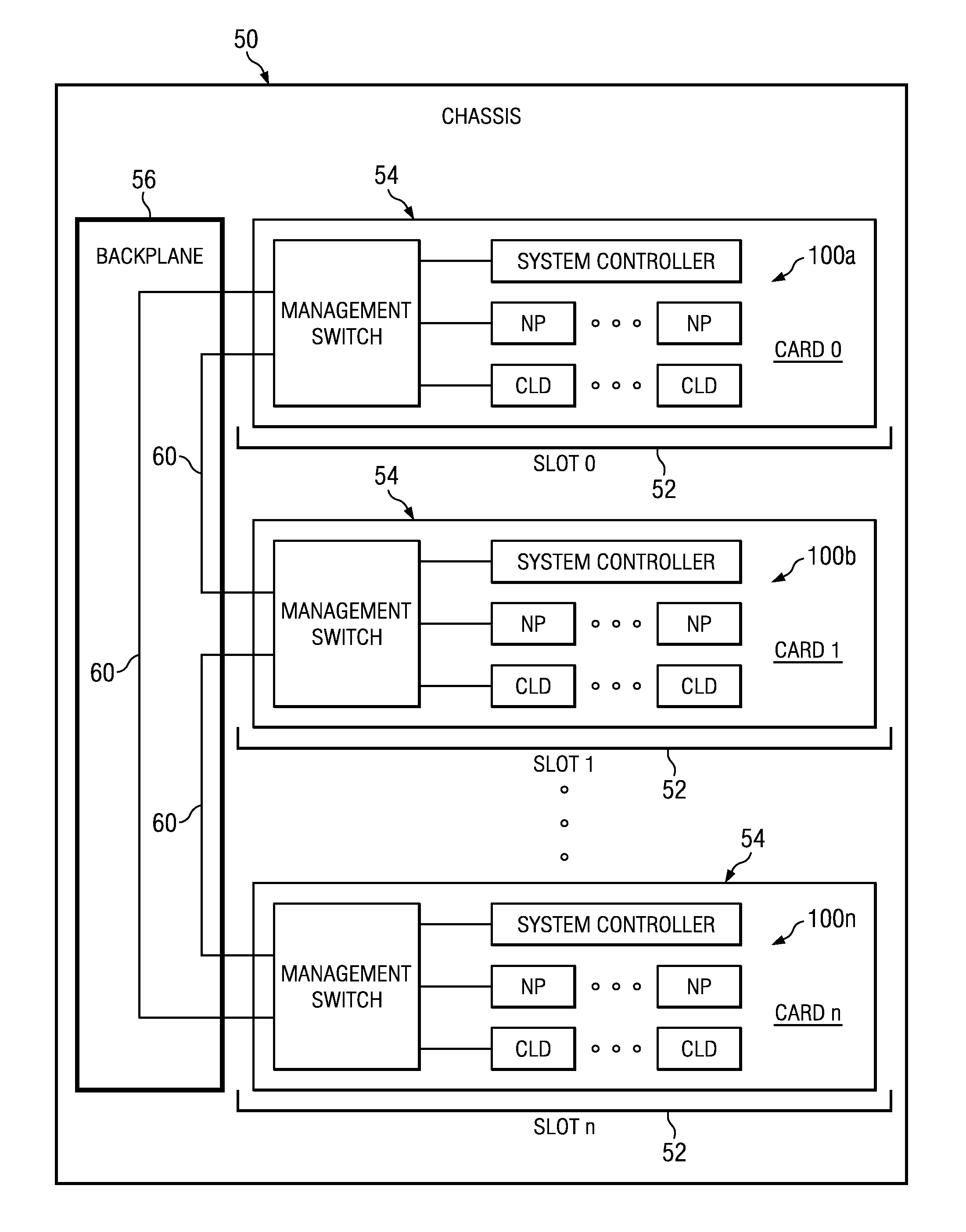

Systems and methods for efficient memory access

InactiveUS9075735B2Memory architecture accessing/allocationEnergy efficient ICTProcessing coreProcessor register

A computer-implemented method of accessing data comprises resetting the value of a register of a first processing core of a multi-core processor, copying the bits of a compressed pointer into the lowest order bits of the register, left shifting the register a predetermined number of bits, and executing on the first processing core a first instruction referencing memory at a virtual address specified by the register.

Owner:KEYSIGHT TECH SINGAPORE (SALES) PTE LTD

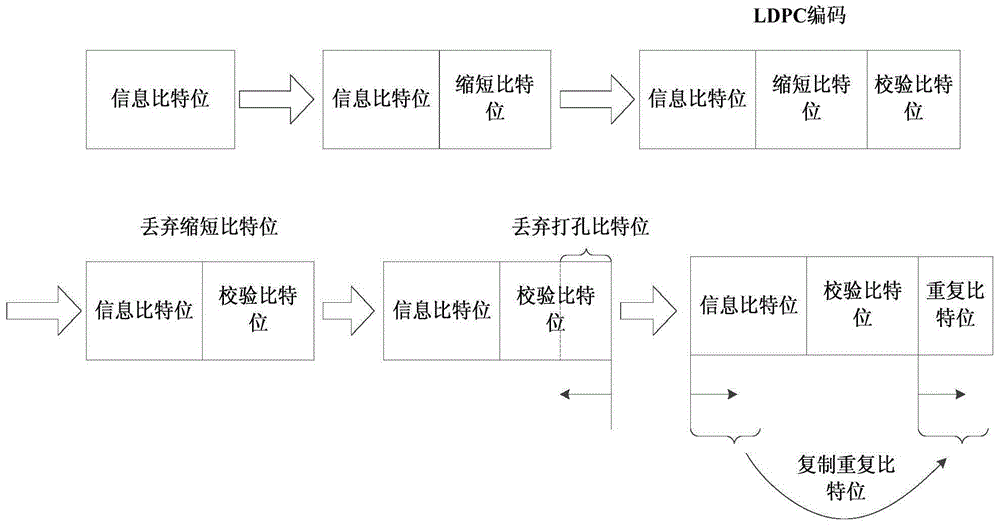

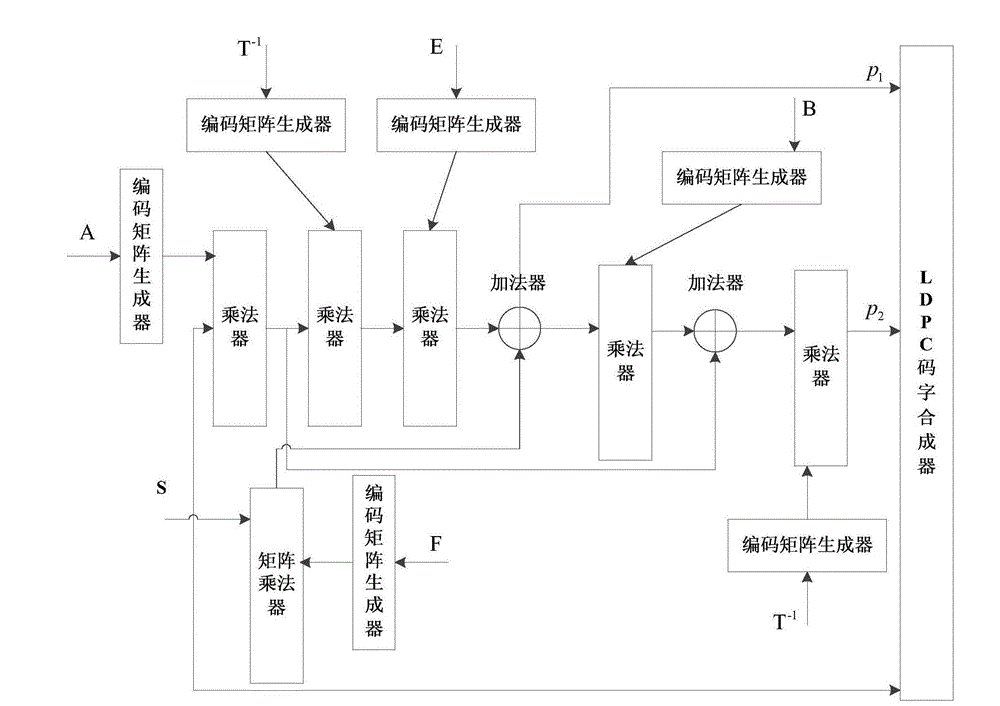

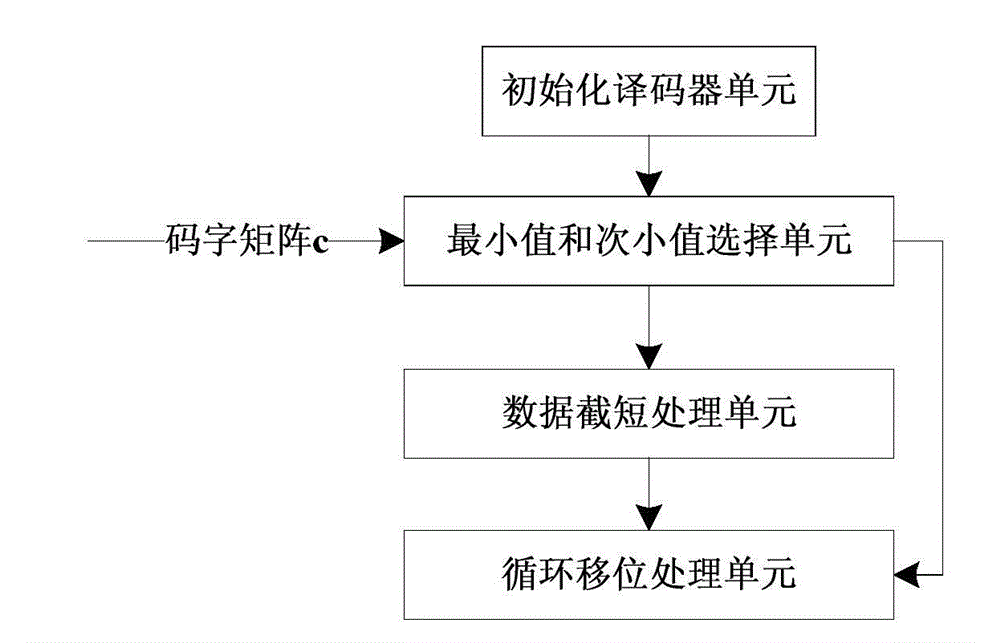

Universal processor-based LDPC (Low Density Parity Check) encoding and decoding method

ActiveCN104617959AImprove the speed of encoding and decodingError correction/detection using multiple parity bitsDecoding methodsData stream

The invention discloses an LDPC (Low Density Parity Check) encoding method. The method comprises the following steps: determining vectors p1 and p2 and obtaining an encoding result vector, wherein multiplication processing of any matrix and any vector during determination of the vectors p1 and p2 comprises the steps of taking each row of any matrix as a thread, multiplying the corresponding row of the matrix by any vector and constituting the multiplication results of all rows into a result vector; the multiplication operation of any row of any matrix by any vector comprises the steps of determining a vector starting position corresponding to each element j of the ith row of the matrix, performing left shift on data of length Z-Ai, j from a starting position in any vector through a single-instruction multiple-data stream mode, shifting the data of length Ai, j in front of the starting position to the space after the data subjected to left shift to obtain a vector shift result corresponding to the element j and adding the vector shift result of each element. Through the method, the encoding speed can be improved in a universal processor by using multi-thread and SIMD (Single Instruction Multiple Data) processing.

Owner:BEIJING UNIV OF POSTS & TELECOMM

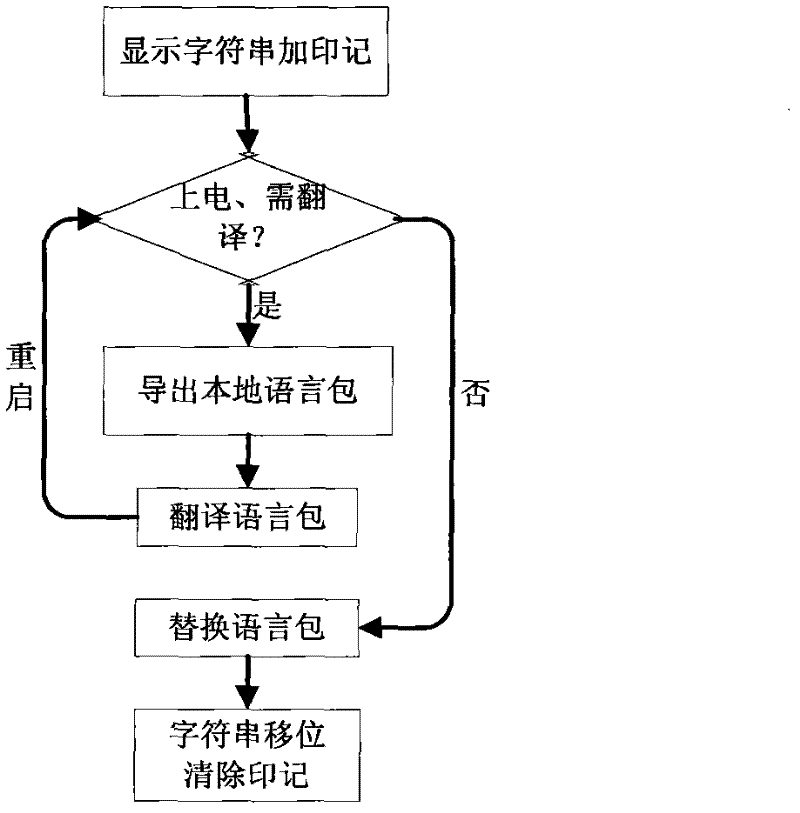

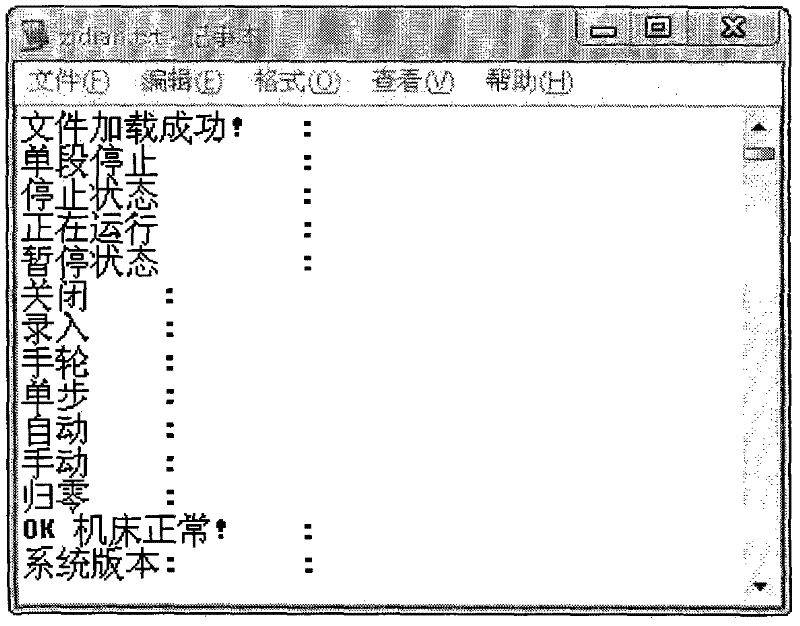

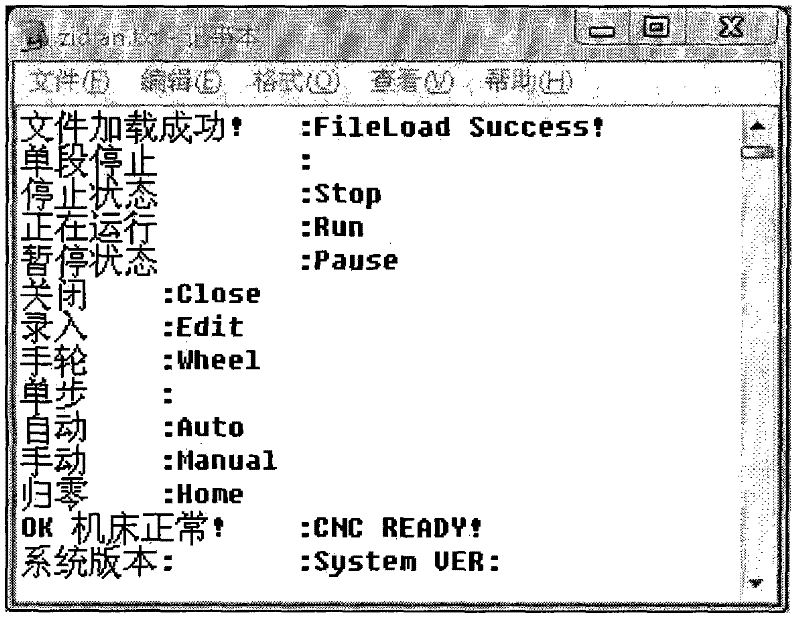

Multi-language translation device and translation method of system text

The invention discloses a multi-language translation device and a translation method of a system text. The device comprises a character string stamping unit, a translation judgment / local language package exporting unit, a translation language package unit, a replacing language package unit, a shifting processing unit and a file memory. The method comprises: stamping a displayed character string when writing a source program, and compiling; exporting the local language package and translating the local language package into corresponding sentences if system electrification detection needs to be translated; copying the sentences to the file memory of the system after translation, replacing the character string which needs to be translated in an execution program as translated character string in the system file memory, and carrying out left shifting processing to remove the stamp; keeping running the system normally and displaying that the character string is updated. With the invention, a system developer does not need to carry out translation or compile the source program for each language singly, and a product user can change the text displayed on a system interface randomly according to work demand or favor of oneself.

Owner:ADTECH SHENZHEN TECH

No-carry multiplication device and processing method thereof

The invention provides a no-carry multiplication device and a processing method thereof. The device includes a no-carry pre-format unit, a Booth encoder, a reducer, a left shift device and an XOR gate. The no-carry pre-format unit receives a multiplier operand and formats the multiplier operand into multiple parts. The Booth encoder receives and judges the parts, and selects multiple first part product of a multiplicand operand. By using the parts, multiple second part product of the multiplicand operand can be avoided to select. The second part product causes carry bit. The reducer couples with the Booth encoder. The first part product is totalized through a plurality of carry storage summators. The carry storage summators generate a plurality of totaling bits and a plurality of carry bits. The carry storage summators are arranged in a Wallace tree architecture. When a no-carry multiplying is in execution, the carry bits can not be enabled. The left shift device couples with the reducer and shifts output of the reducer at least one bit. The XOR gate couples with the reducer and the left shift device for XOR operation and generates a no-carry multiplication result.

Owner:VIA TECH INC

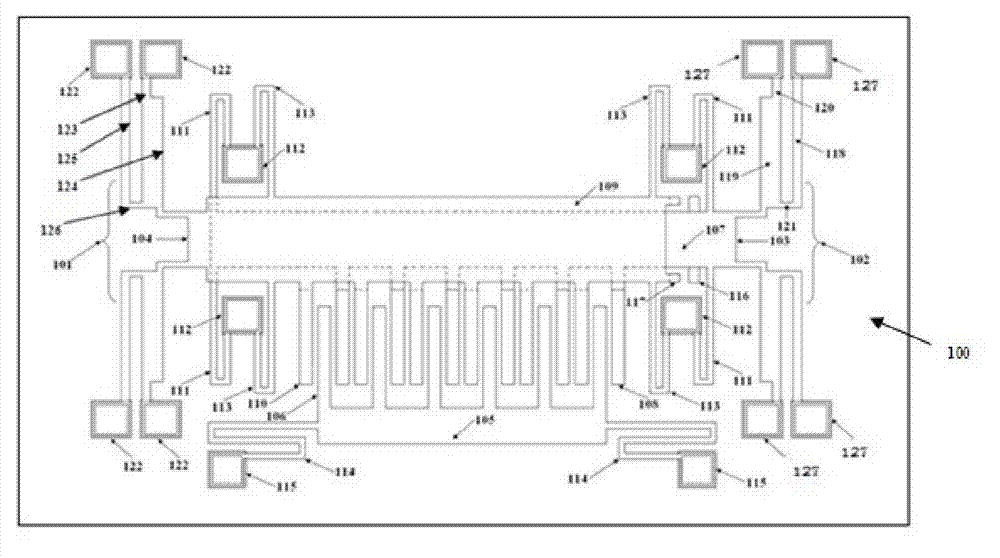

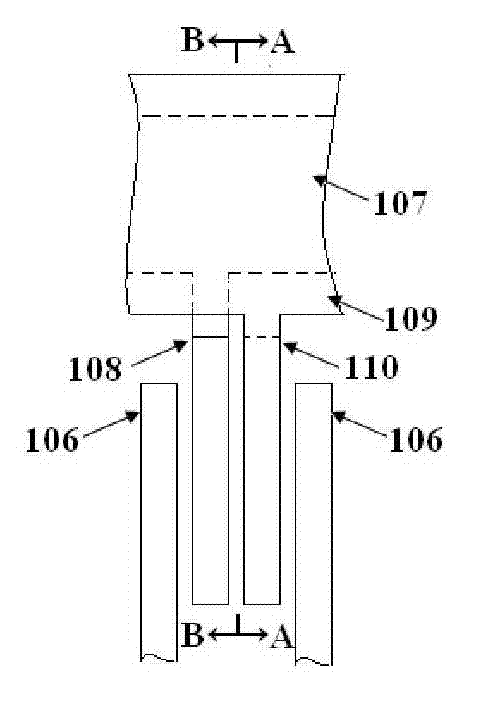

Electro-thermal-driven micro-electro-mechanical comb tooth mechanism for regulating variable intervals of teeth

InactiveCN102951593AAchieving AMIncrease the sensor detection signal amplitudePiezoelectric/electrostrictive devicesFlexible microstructural devicesElectrothermal actuatorRight shift

The invention discloses an electro-thermal-driven micro-electro-mechanical comb tooth mechanism for regulating variable intervals of teeth. The electro-thermal-driven micro-electro-mechanical comb tooth mechanism comprises a left-shift electrothermal actuator, a right-shift electrothermal actuator, a fixed tooth, a moving tooth, four first anchor regions and an insulating substrate, wherein the fixed tooth consists of a left-shift fixed tooth and a right-shift fixed tooth; the left-shift electrothermal actuator is connected with one end of the left-shift fixed tooth, and the two ends of the left-shift fixed tooth are respectively connected to the first anchor regions; the right-shift electrothermal actuator is connected with one end of the right-shift fixed tooth, and the two ends of the right-shift fixed tooth are respectively connected to the first anchor regions; the left-shift fixed tooth comprises a first wide beam, a left-shift comb tooth and four first folding beams; the right-shift fixed tooth comprises a first wide beam, a right-shift comb tooth and four second folding beams; the moving tooth comprises a quality block, a moving tooth comb tooth, two second anchor regions and two third folding beams; and a left-shift stop block is arranged on the first wide beam, and a right-shift stop block is arranged on the second wide beam. Under the driving of an electrothermal driving force, the micro-electro-mechanical comb tooth mechanism regulates the intervals of the teeth to enable a signal generated by micro-electro-mechanical vibration to be strong.

Owner:SOUTHEAST UNIV