Patents

Literature

807results about "Computations using contact-making devices" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

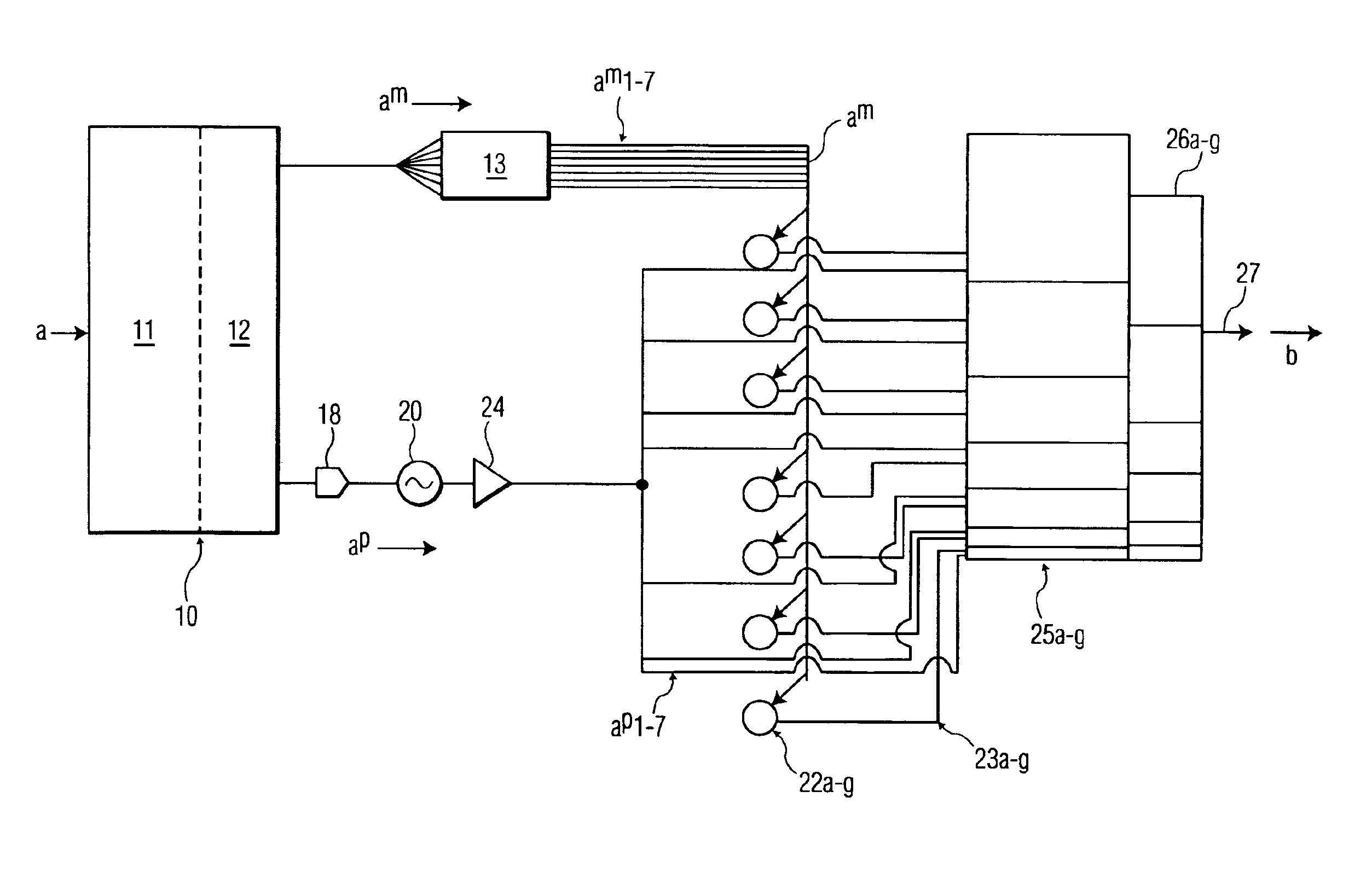

Encoded information reading terminal with micro-electromechanical radio frequency front end

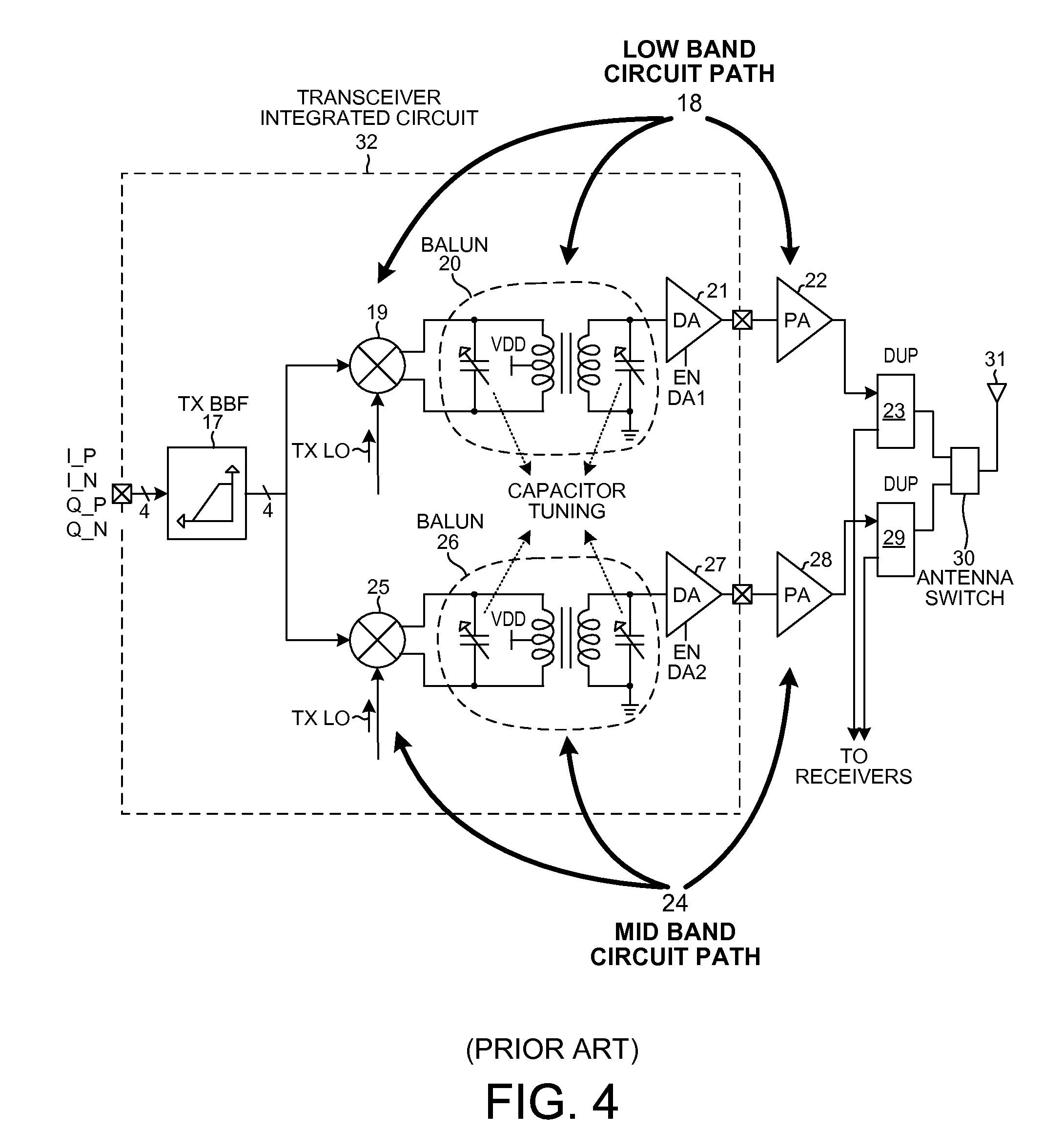

ActiveUS8779898B2Multiplex system selection arrangementsComputations using contact-making devicesMulti bandRF front end

Owner:HAND HELD PRODS

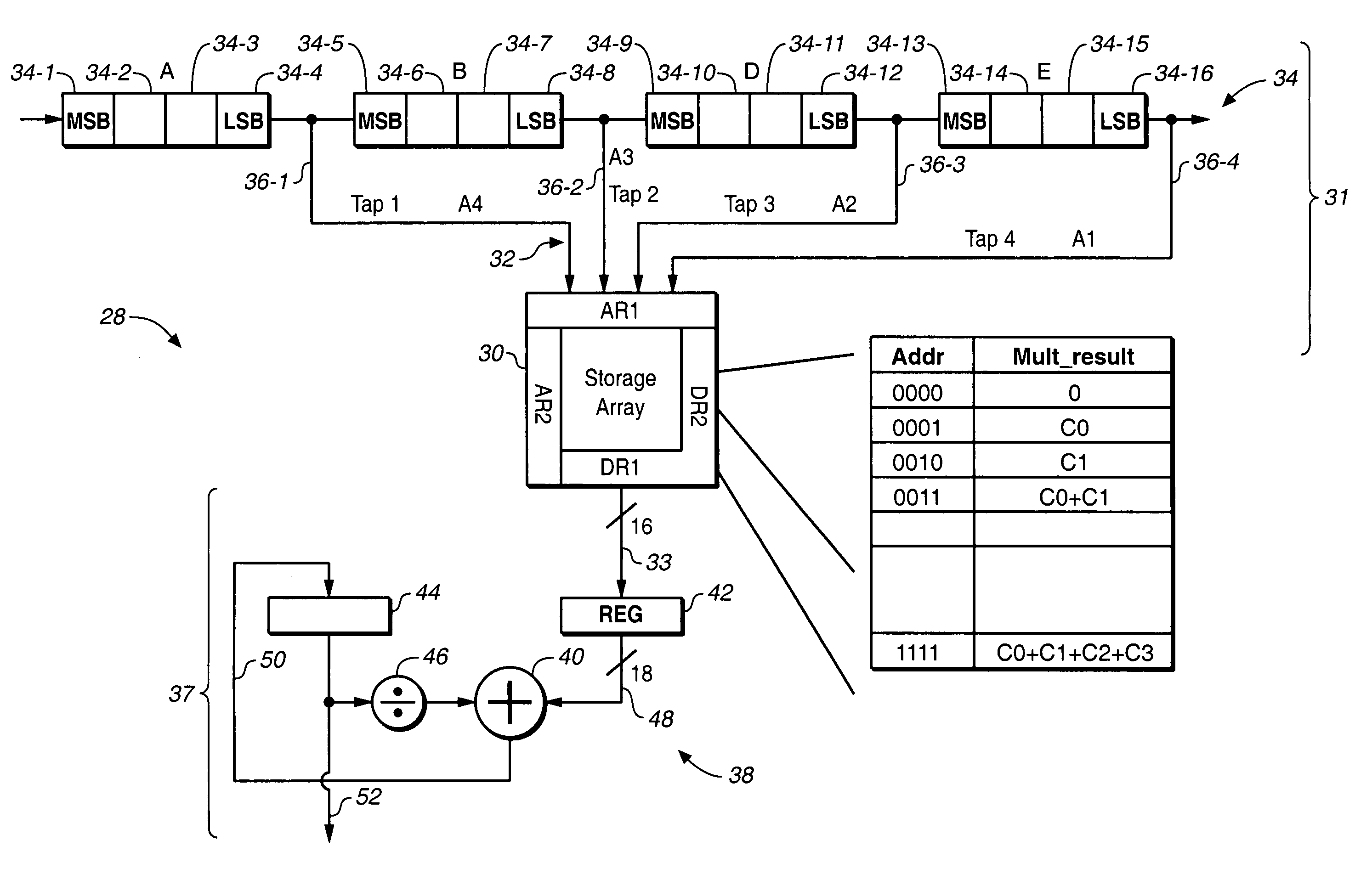

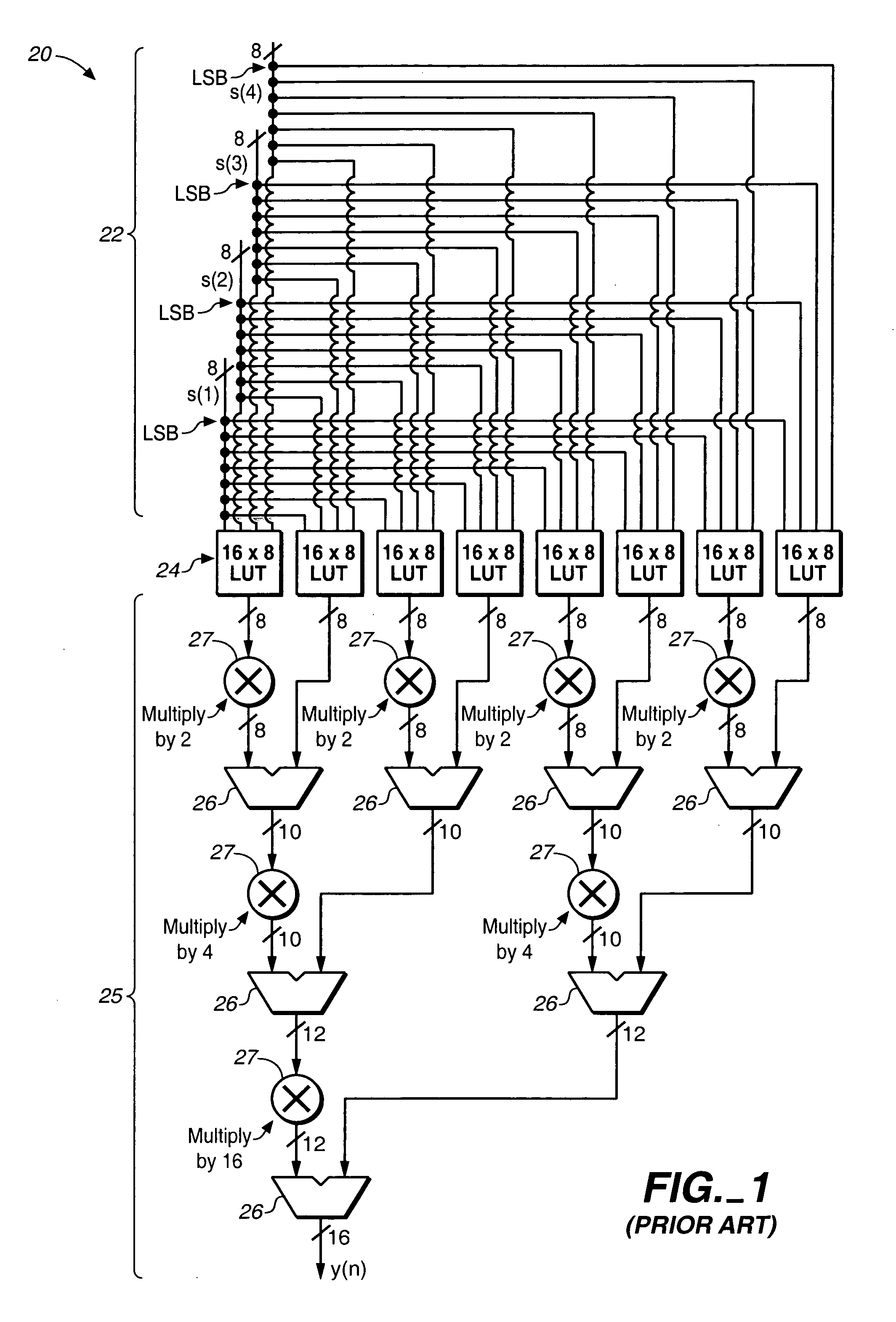

Variable fixed multipliers using memory blocks

InactiveUS6943579B1Computations using contact-making devicesComputation using non-contact making devicesProgrammable logic deviceOperand

A programmable logic device includes at least one RAM block generating a first multi-bit calculation result which may, but does not necessarily, involve a multiplication of two operands. A shift operation is driven by a second multi-bit calculation result shifts the second multi-bit calculation result by at least one bit to generate a shifted second multi-bit calculation result. A multi-bit adder coupled to the at least one RAM block adds the shifted second multi-bit calculation result to the first multi-bit calculation result.

Owner:ALTERA CORP

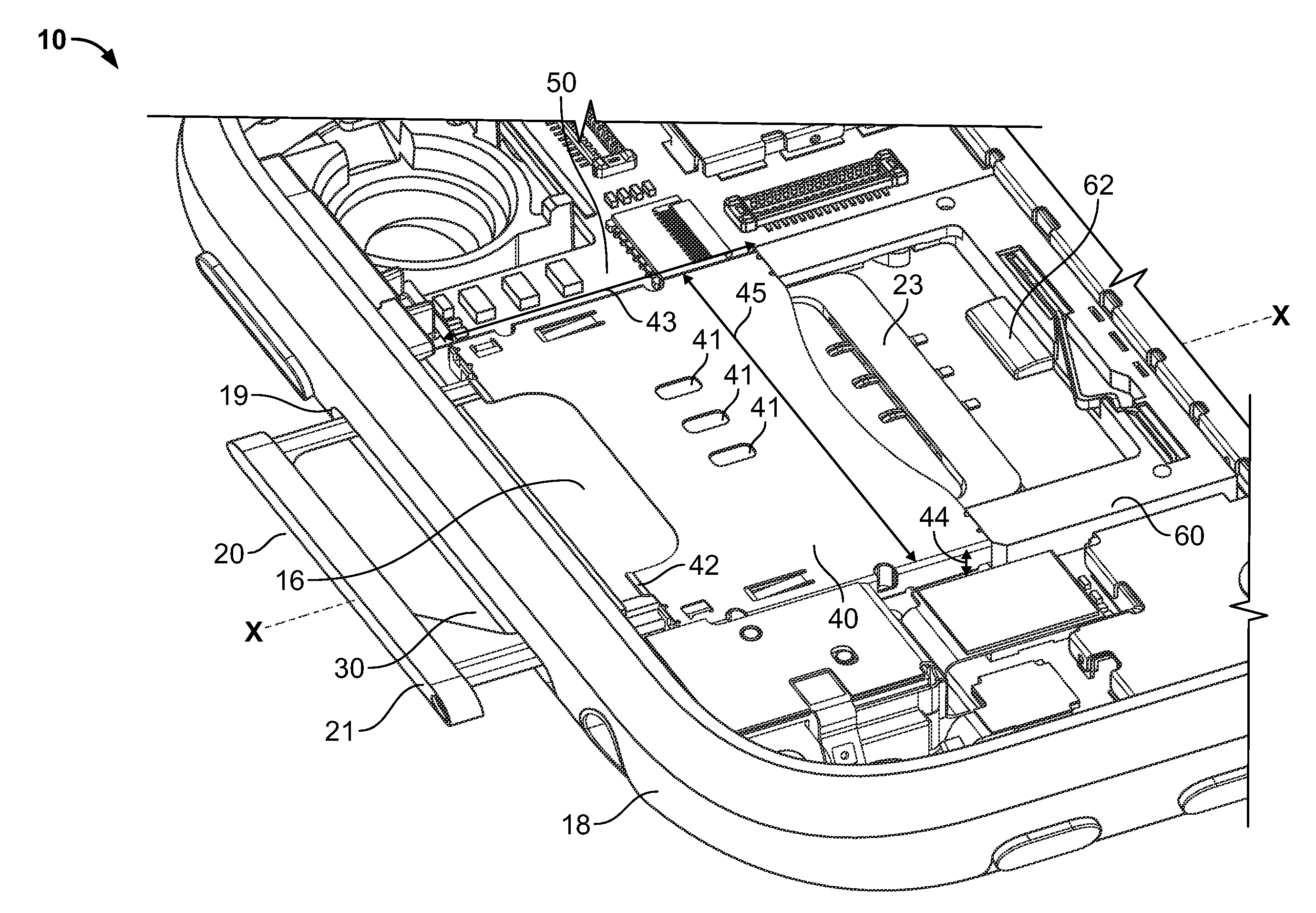

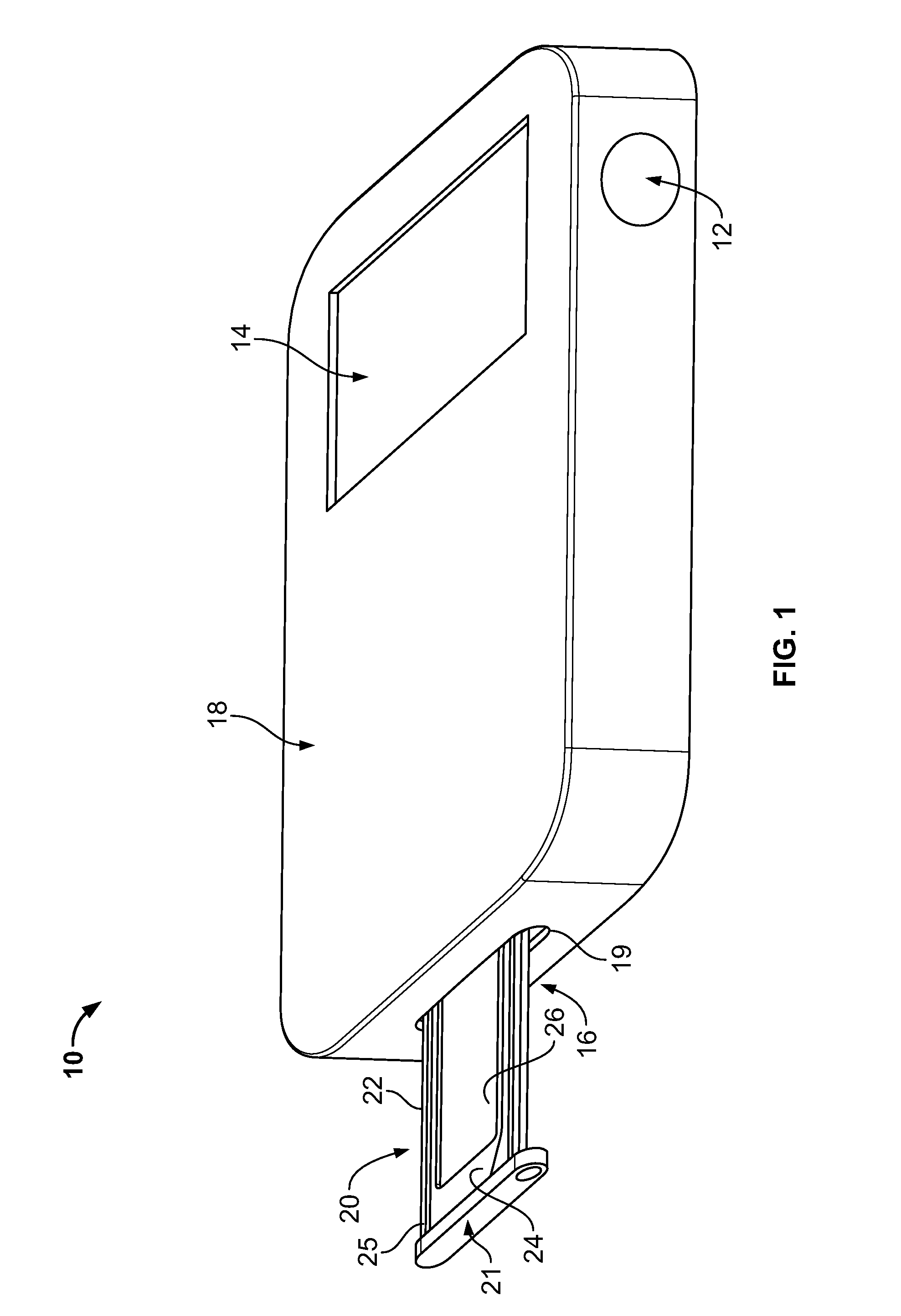

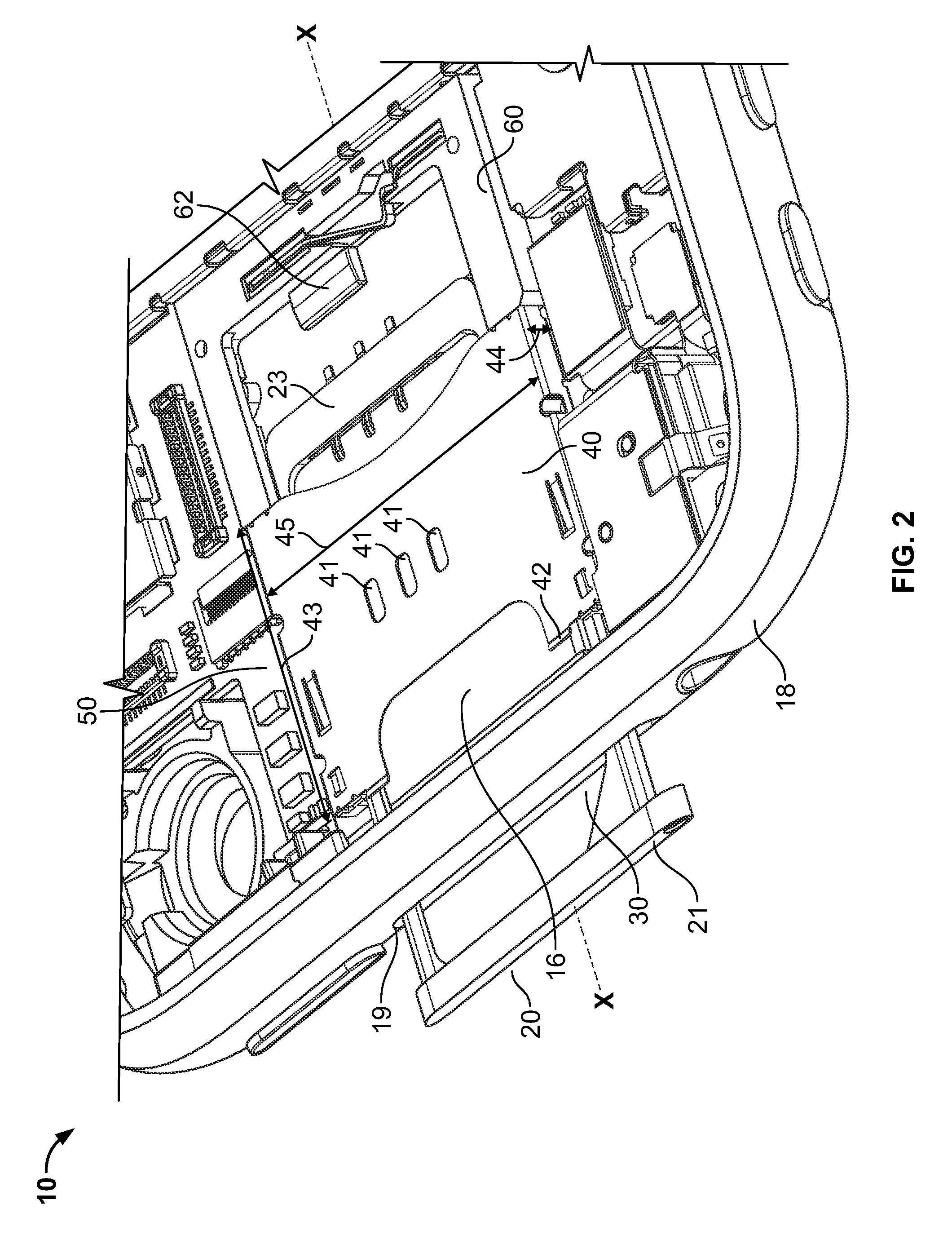

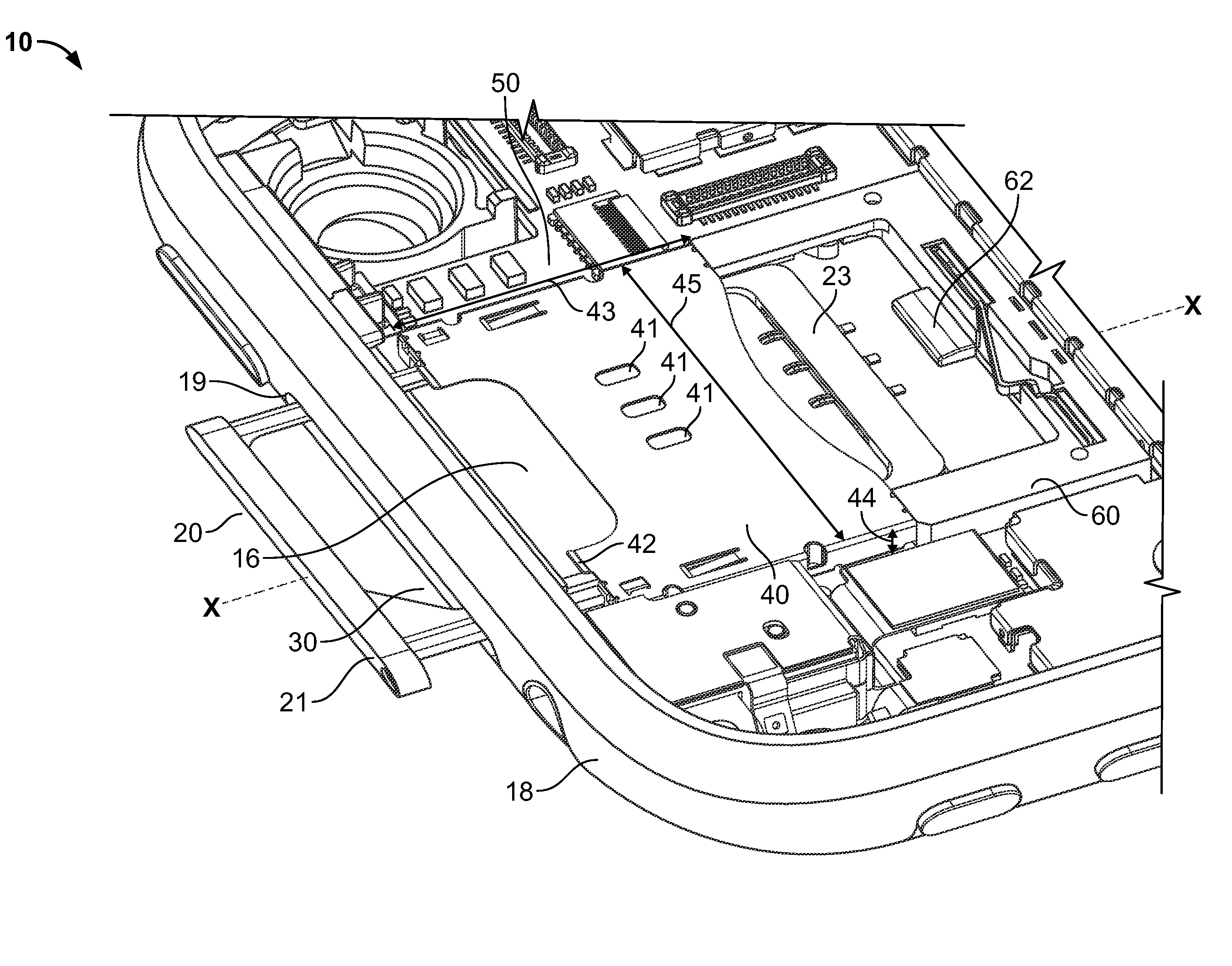

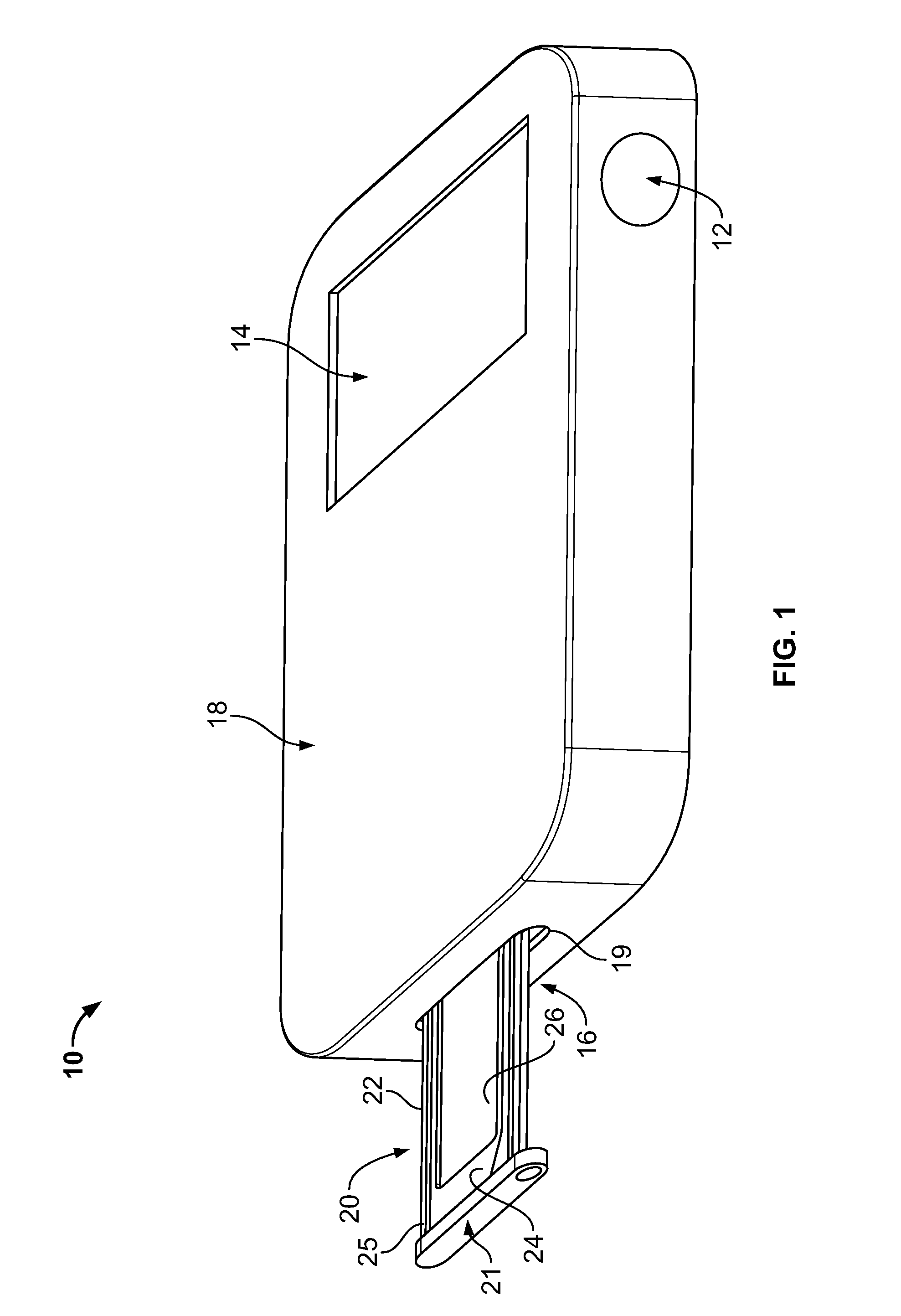

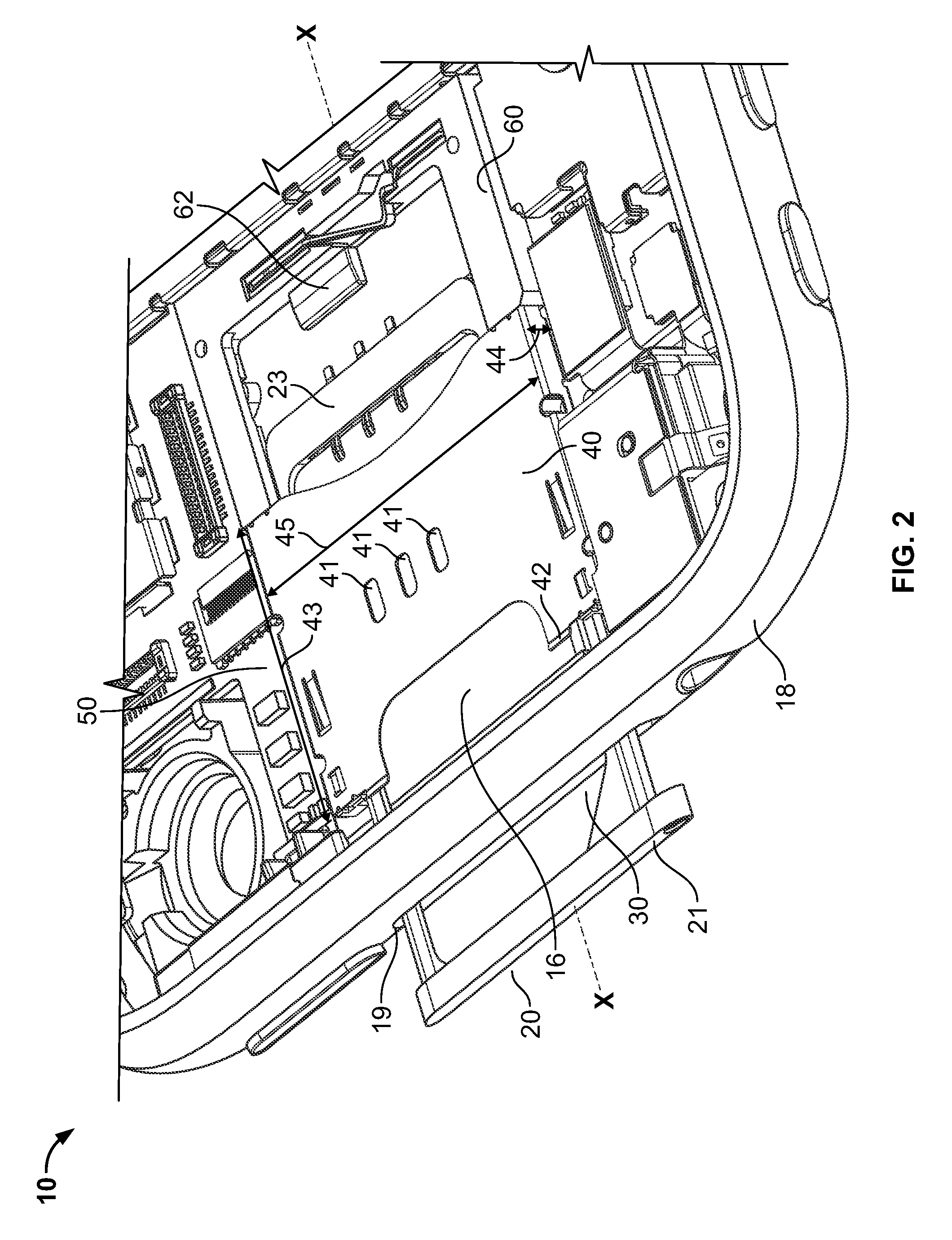

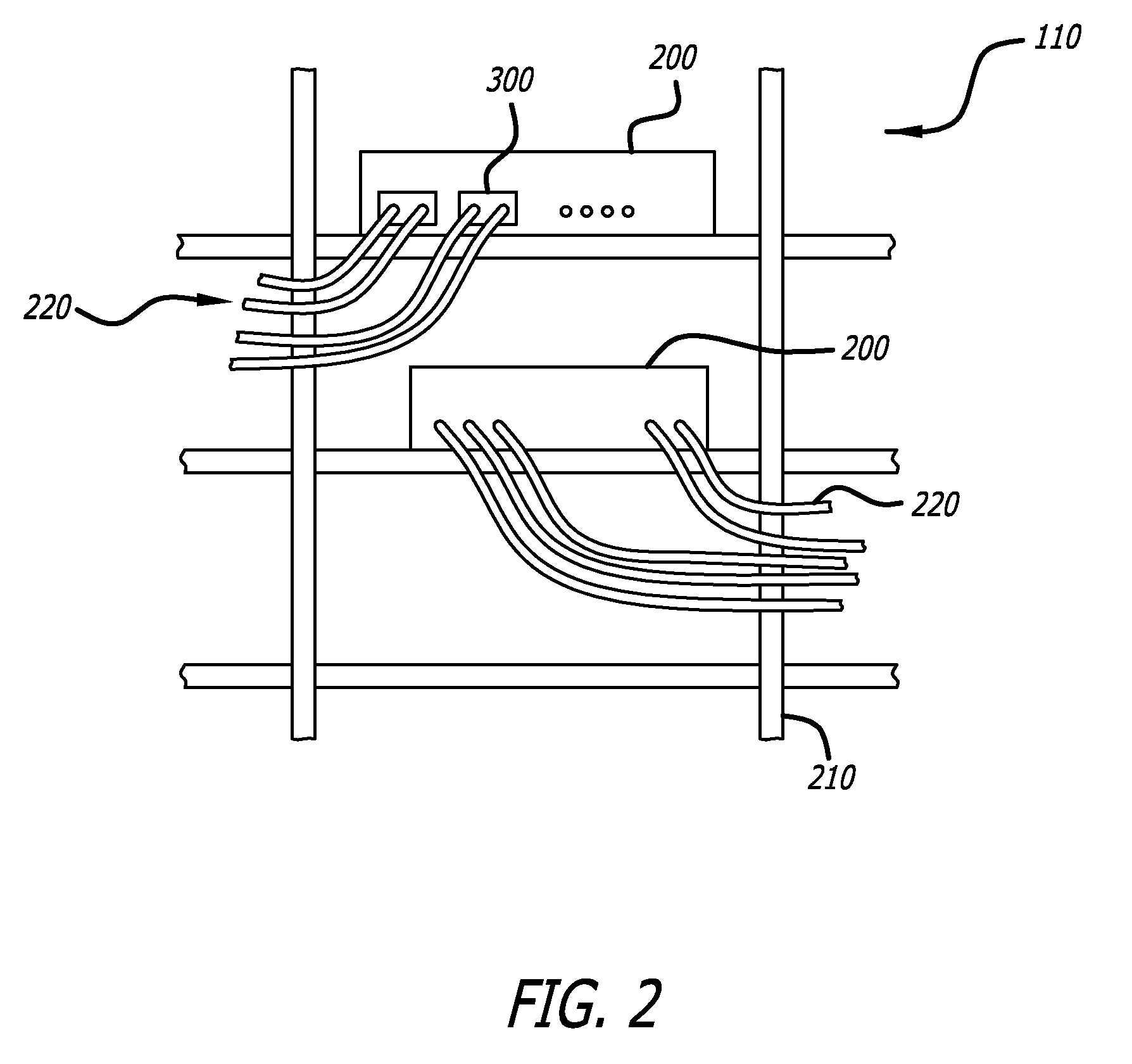

Compact ejectable component assemblies in electronic devices

ActiveUS20090267677A1Computations using contact-making devicesDevices with card reading facilityDetentBiomedical engineering

Electronic devices are provided with ejectable component assemblies. The ejectable component assembly may include a tray that can be loaded with one or more removable modules, wafers coupled to circuit boards, cages and retaining plates to assist in retaining the tray within the assembly. The ejectable component assembly may include springs operative to engage detents in the tray to retain the tray in the assembly. The ejectable component assembly may include a tray ejector mechanism for ejecting the tray from the assembly.

Owner:APPLE INC

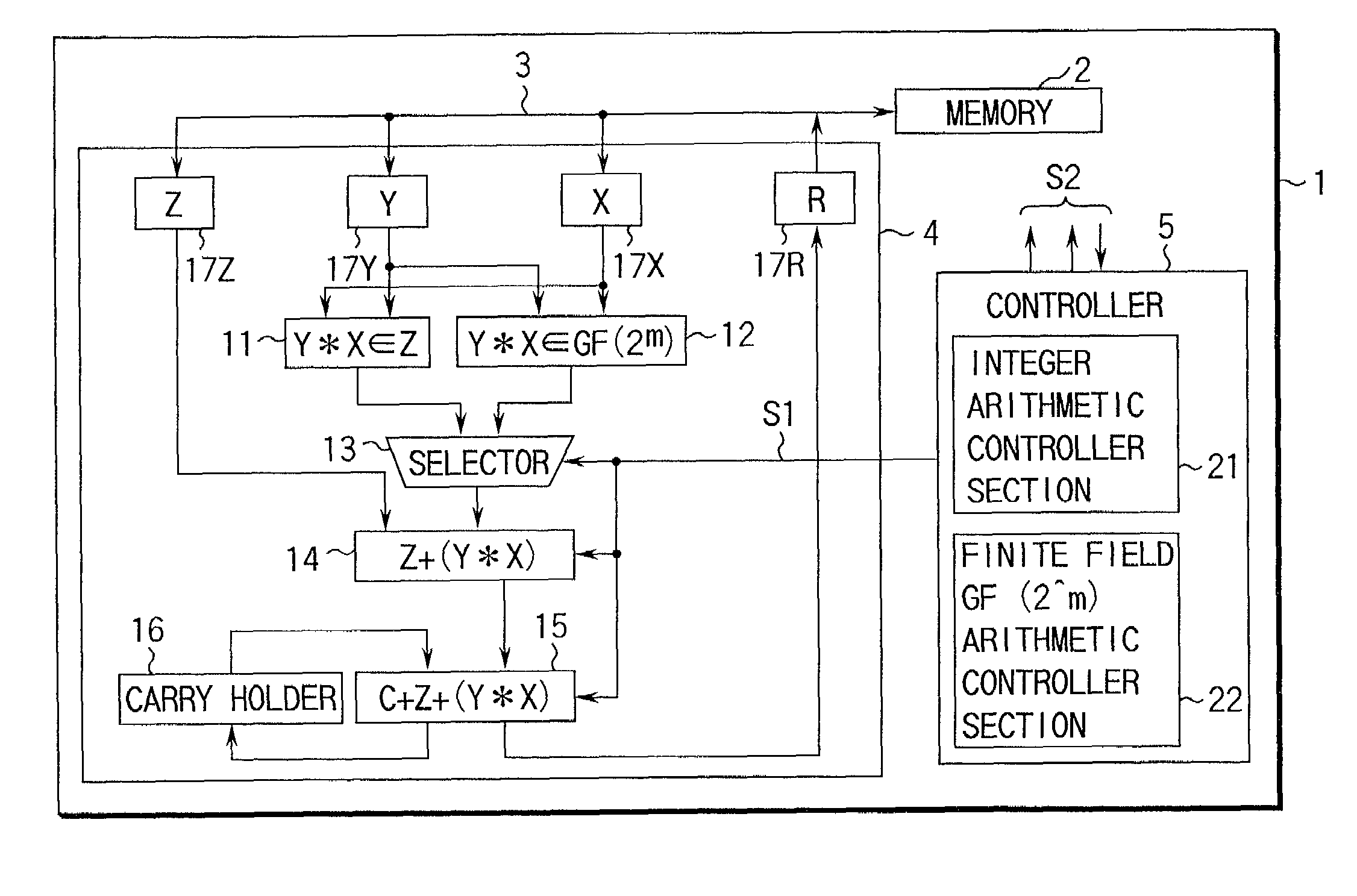

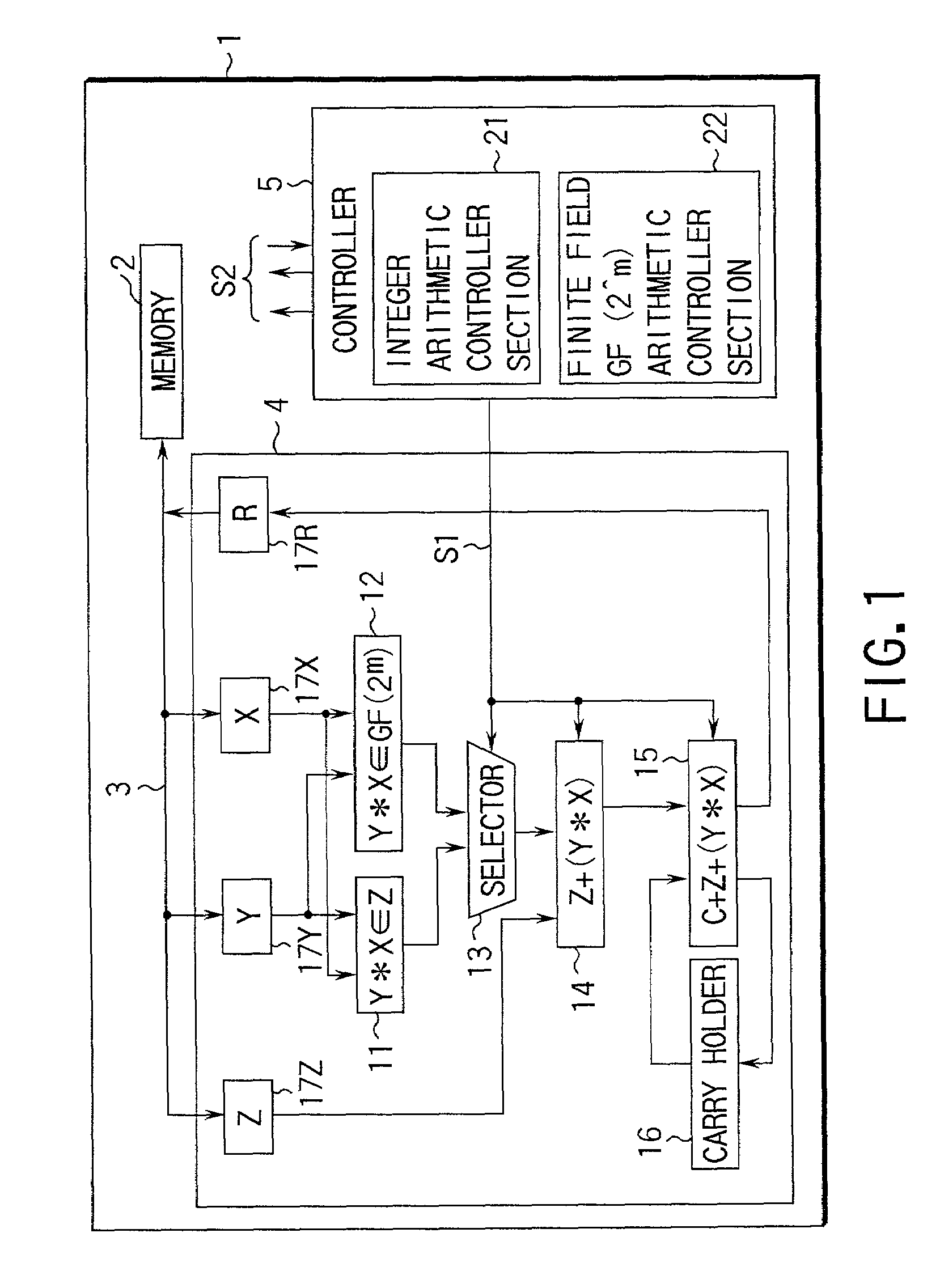

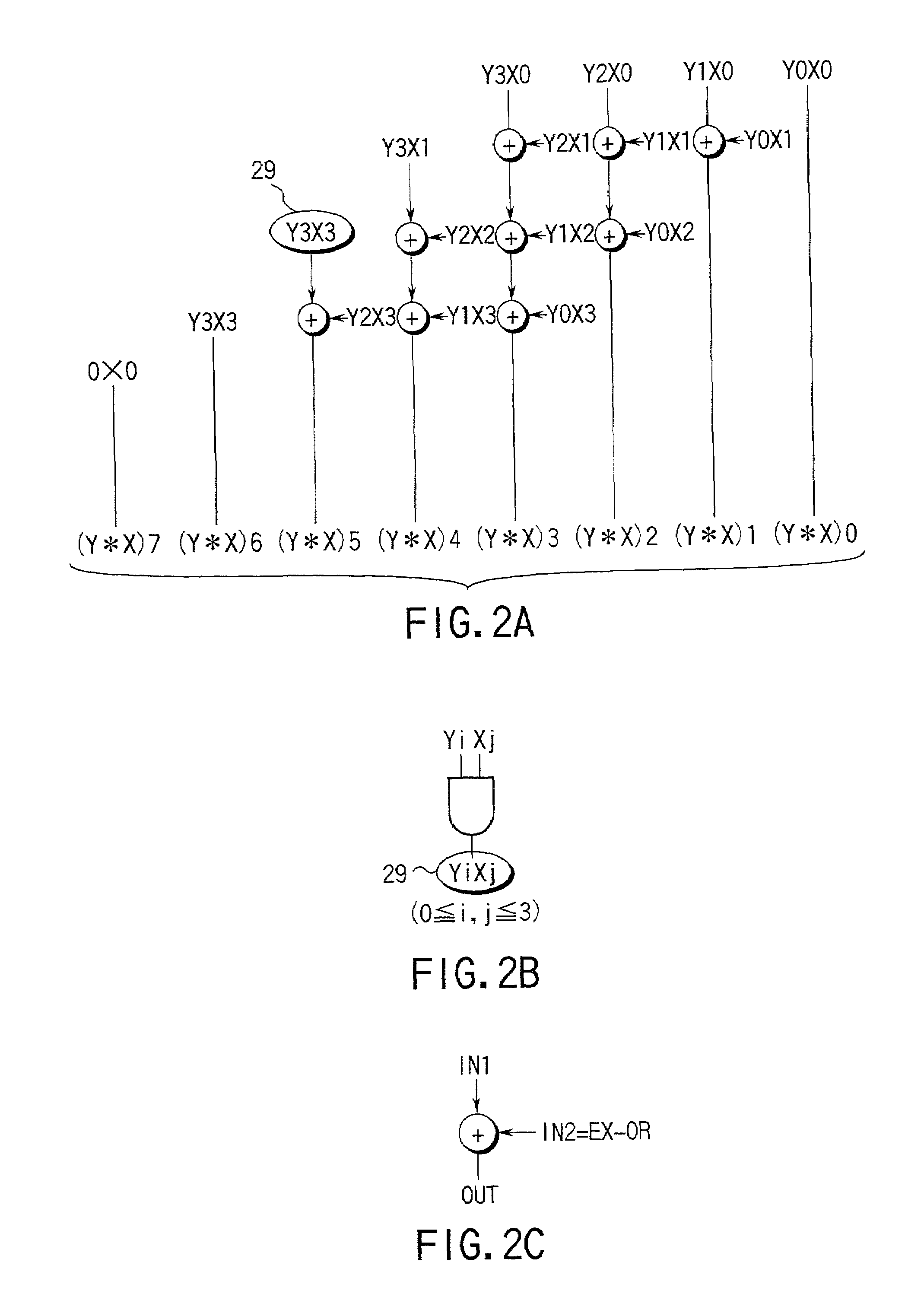

Arithmetic method and apparatus and crypto processing apparatus for performing multiple types of cryptography

InactiveUS7277540B1Computations using contact-making devicesDigital computer detailsComputer scienceArithmetic circuits

An arithmetic apparatus for performing a long product-sum operation includes an integer unit arithmetic circuit, a finite field GF(2^m) based unit arithmetic circuit logically adjacent to the integer unit arithmetic circuit, a selector for selecting the integer unit arithmetic circuit or the finite field GF(2^m) based unit arithmetic circuit, and an adder circuit which has a buffer for storing interim result data, adds the interim result data to the result data obtained by one of the integer unit arithmetic circuit and the finite field GF(2^m) based unit arithmetic circuit which is selected by the selector, propagates a carry in an integer unit arithmetic operation, and propagates no carry in a finite field GF(2^m) based unit arithmetic operation.

Owner:KK TOSHIBA

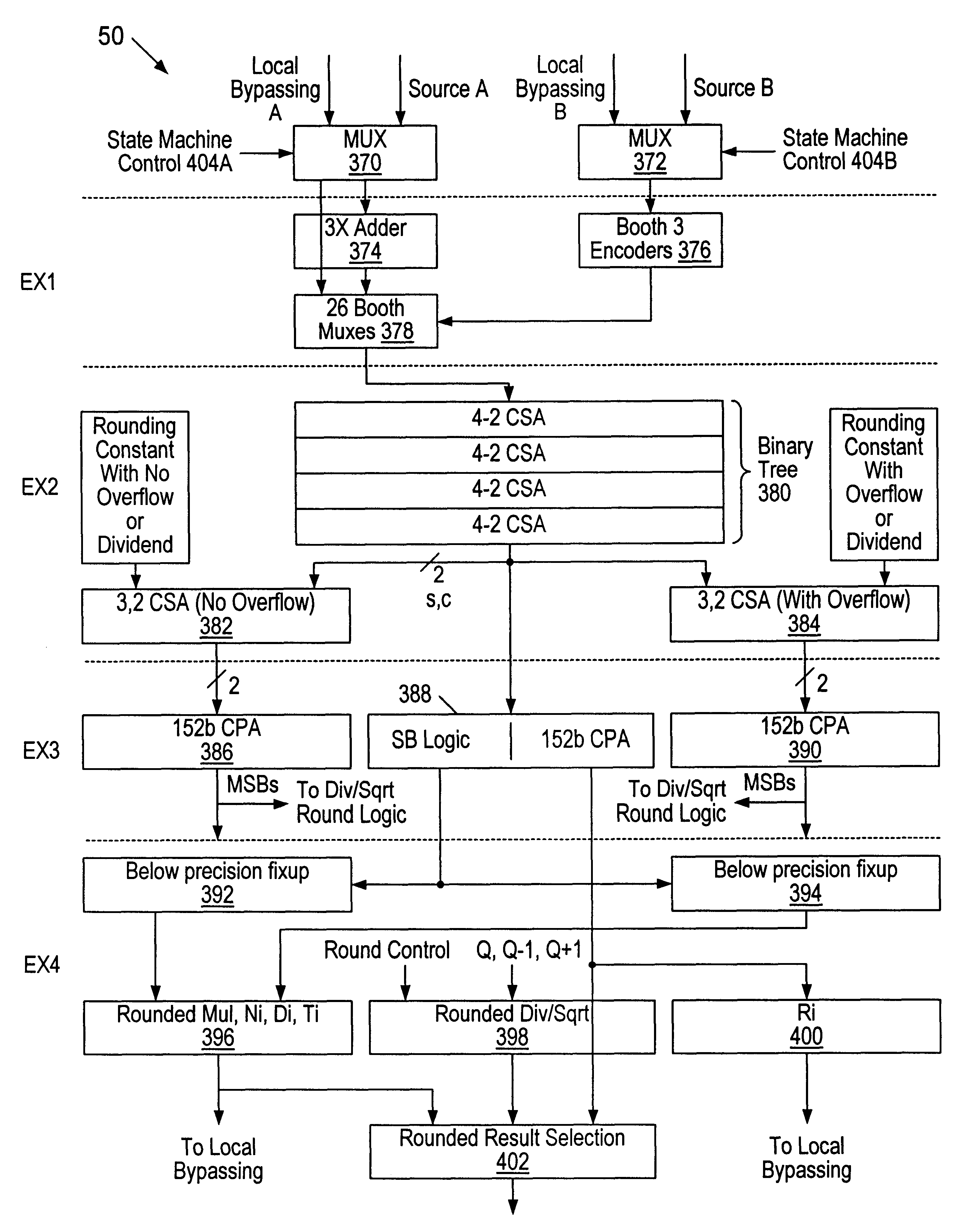

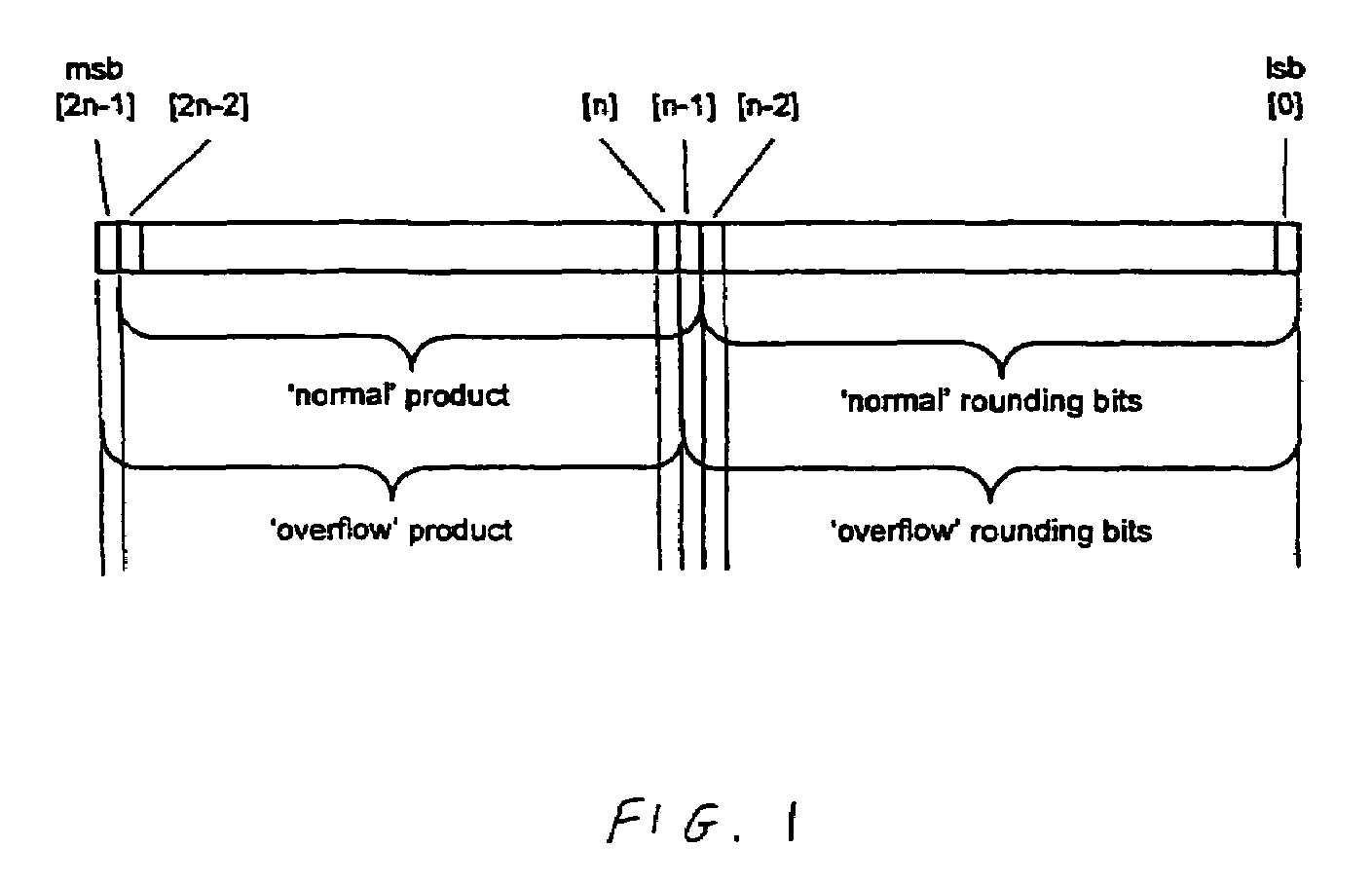

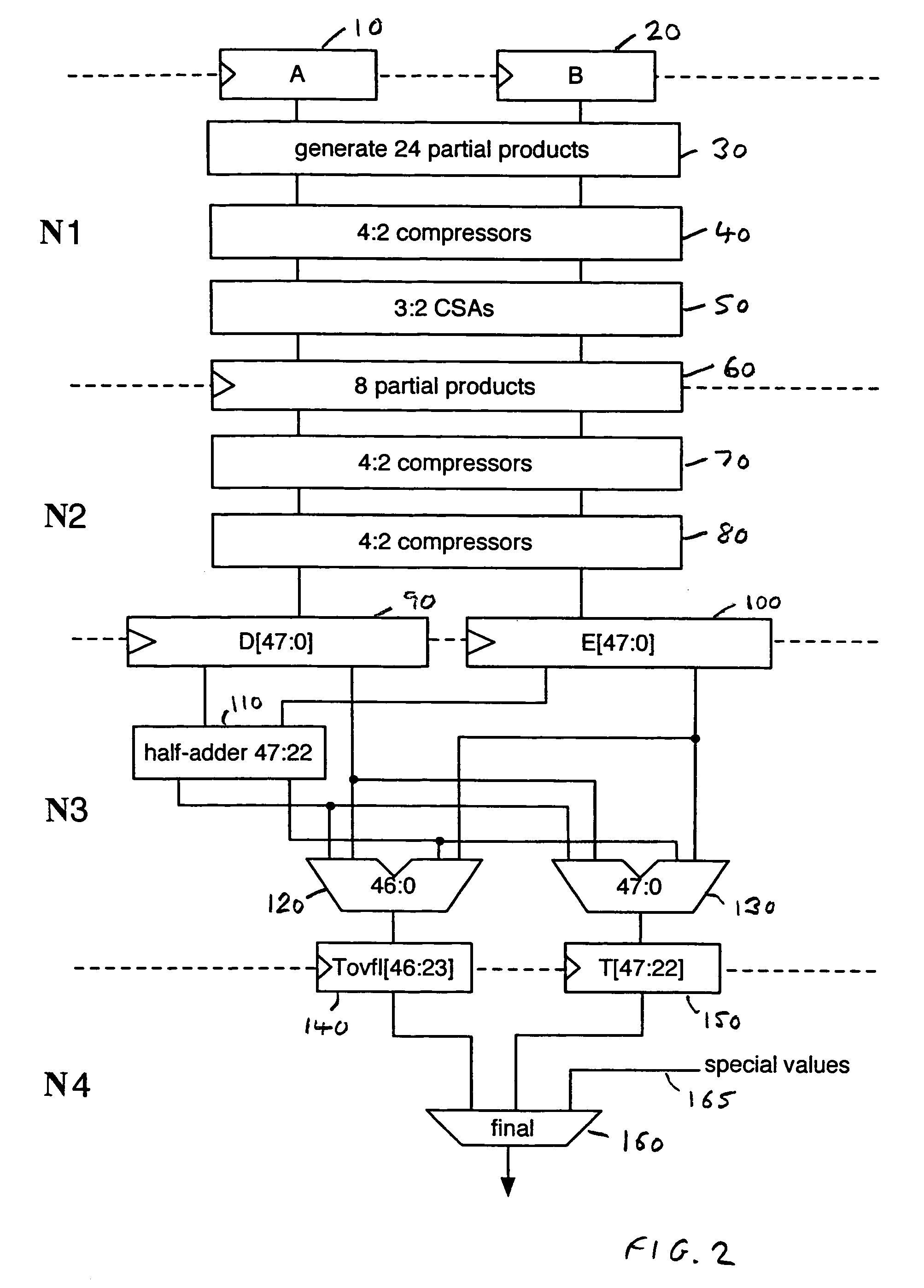

Shared FP and SIMD 3D multiplier

InactiveUS6490607B1Computations using contact-making devicesRuntime instruction translationComputerized systemTheoretical computer science

A multiplier configured to perform multiplication of both scalar floating point values (XxY) and packed floating point values (i.e., X1xY1 and X2xY2). In addition, the multiplier may be configured to calculate XxY-Z. The multiplier comprises selection logic for selecting source operands, a partial product generator, an adder tree, and two or more adders configured to sum the results from the adder tree to achieve a final result. The multiplier may also be configured to perform iterative multiplication operations to implement such arithmetical operations such as division and square root. The multiplier may be configured to generate two versions of the final result, one assuming there is an overflow, and another assuming there is not an overflow. A computer system and method for performing multiplication are also disclosed.

Owner:ADVANCED SILICON TECH

Compact ejectable component assemblies in electronic devices

ActiveUS8462514B2Devices with card reading facilityComputations using contact-making devicesBiomedical engineering

Electronic devices are provided with ejectable component assemblies. The ejectable component assembly may include a tray that can be loaded with one or more removable modules, wafers coupled to circuit boards, cages and retaining plates to assist in retaining the tray within the assembly. The ejectable component assembly may include springs operative to engage detents in the tray to retain the tray in the assembly. The ejectable component assembly may include a tray ejector mechanism for ejecting the tray from the assembly.

Owner:APPLE INC

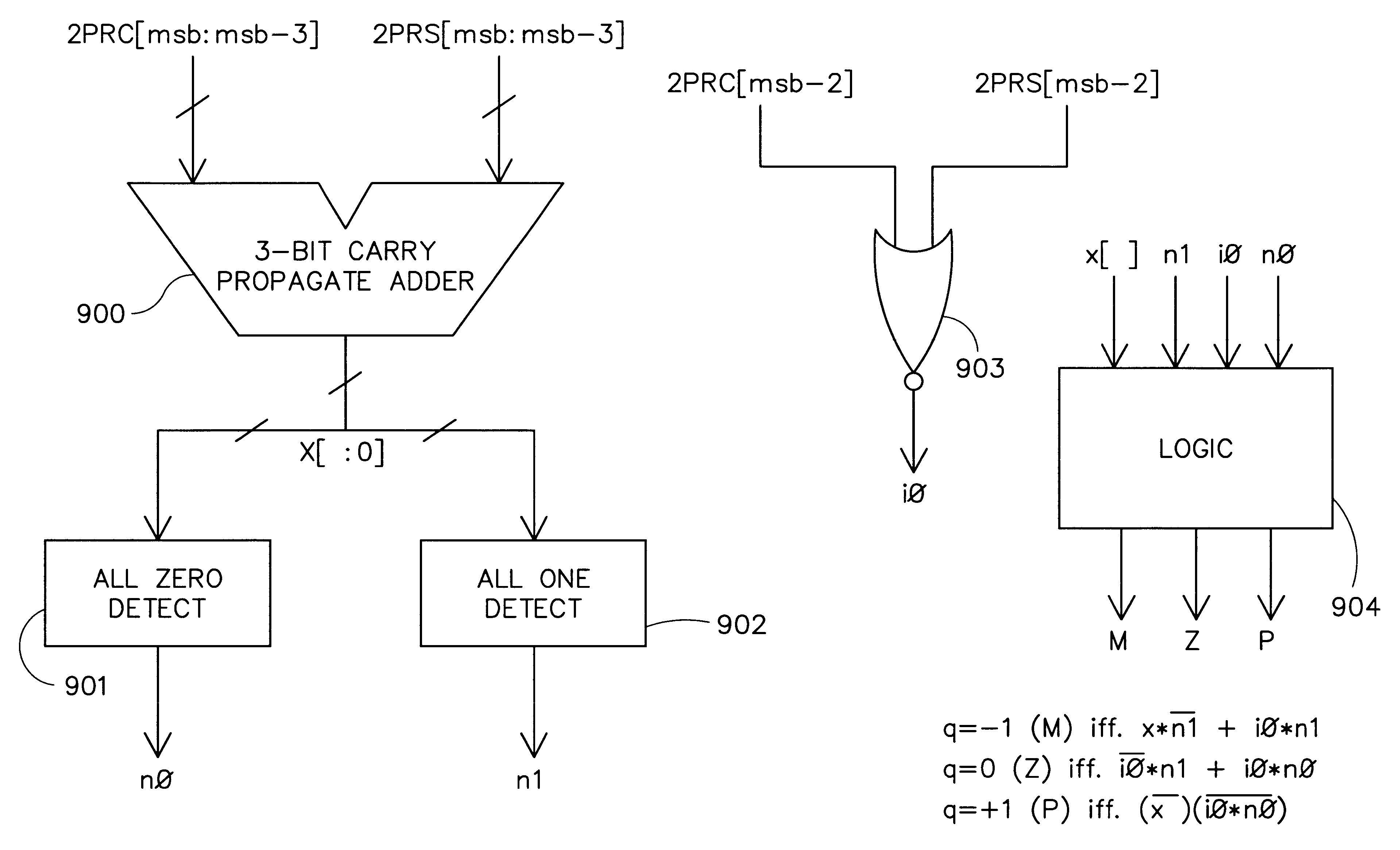

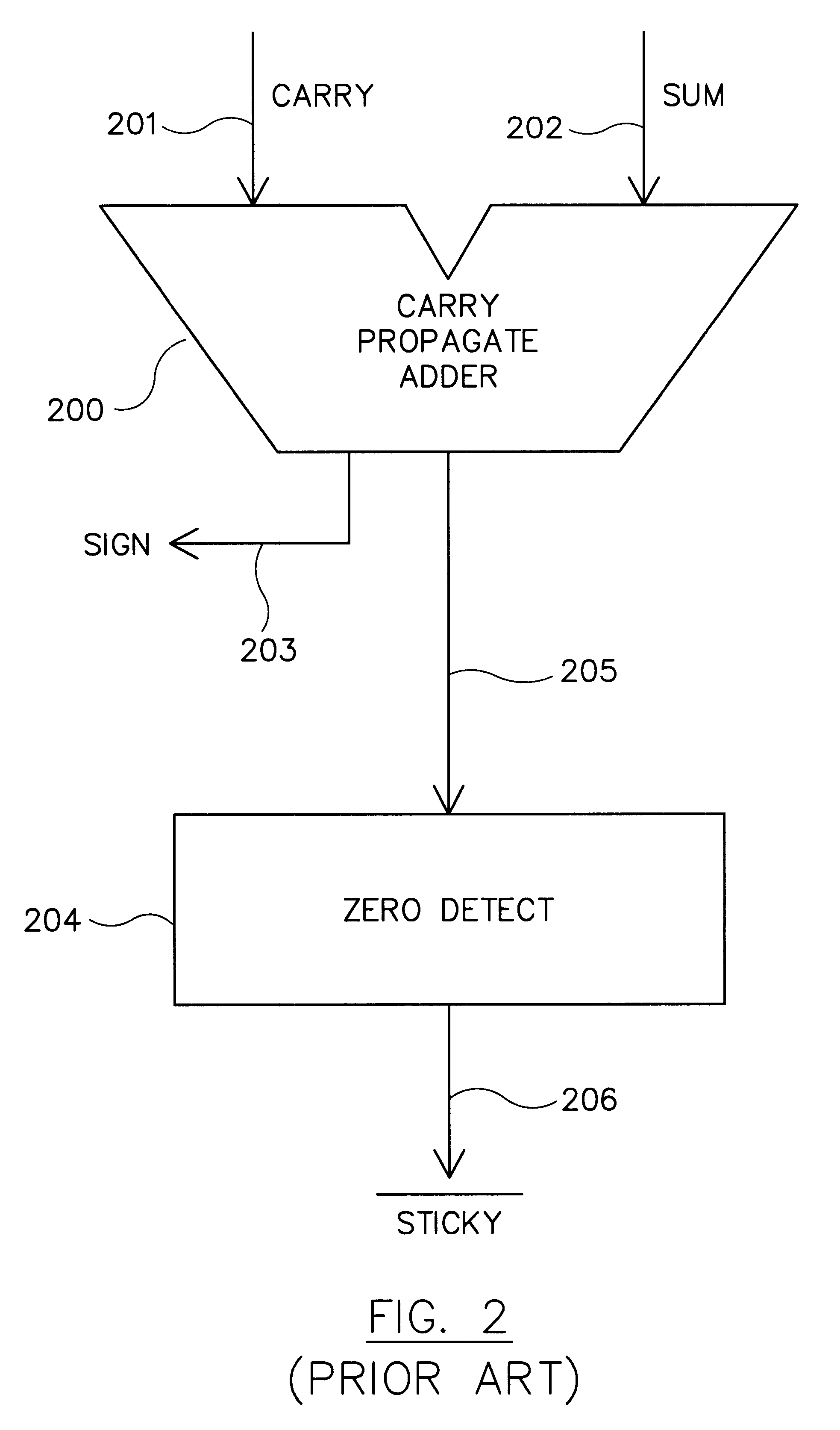

Quotient digit selection logic for floating point division/square root

InactiveUS6594681B1Computations using contact-making devicesComputation using non-contact making devicesCarry propagationAlgorithm

Quotient digit selection logic using a three-bit carry propagate adder is presented. An enhanced quotient digit selection function prevents the working partial remainder from becoming negative if the result is exact. The enhanced quotient digit selection logic chooses a quotient digit of zero instead of a quotient digit of one when the actual partial remainder is zero. Using a four bit estimated partial remainder where the upper four bits are zero, a possible carry propagation into fourth most significant bit is detected. This can be accomplished by looking at the fourth most significant sum and carry bits of the redundant partial remainder. If they are both zero, then a carry propagation out of that bit position into the least significant position of the estimated partial remainder is not possible, and a quotient digit of zero is chosen. This provides a one cycle savings since negative partial remainders no longer need to be restored before calculating the sticky bit. Extra hardware is eliminated because it is no longer necessary to provide any extra mechanism for restoring the preliminary final partial remainder. Latency is improved because no additional cycle time is required to restore negative preliminary partial remainders. In an alternative embodiment, where the upper three bits of the estimated partial remainder are ones while the fourth most significant bit is zero, a quotient digit of negative one is chosen. This alternative embodiment allows correct exact results in all rounding modes including rounding toward plus or minus infinity.

Owner:ORACLE INT CORP

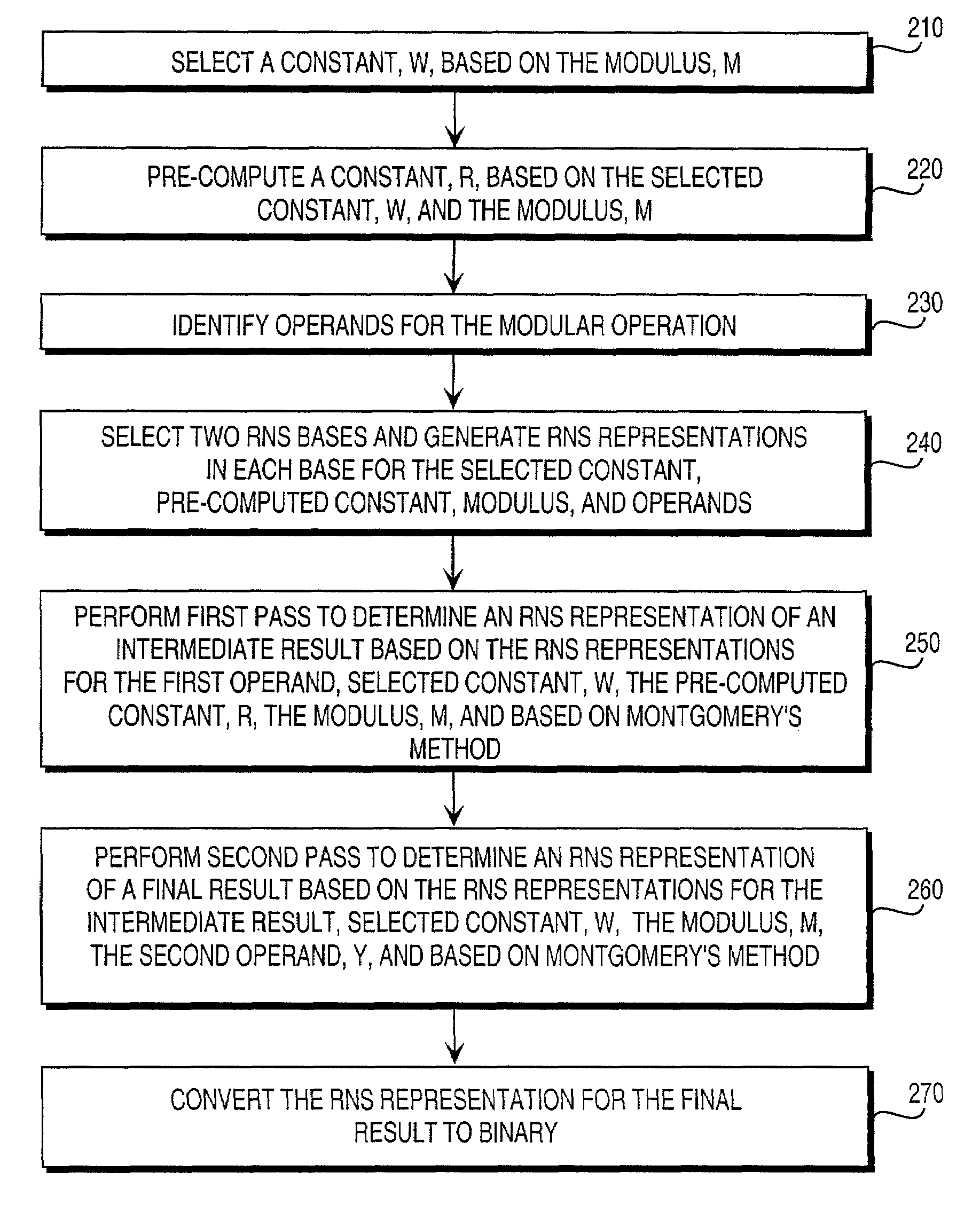

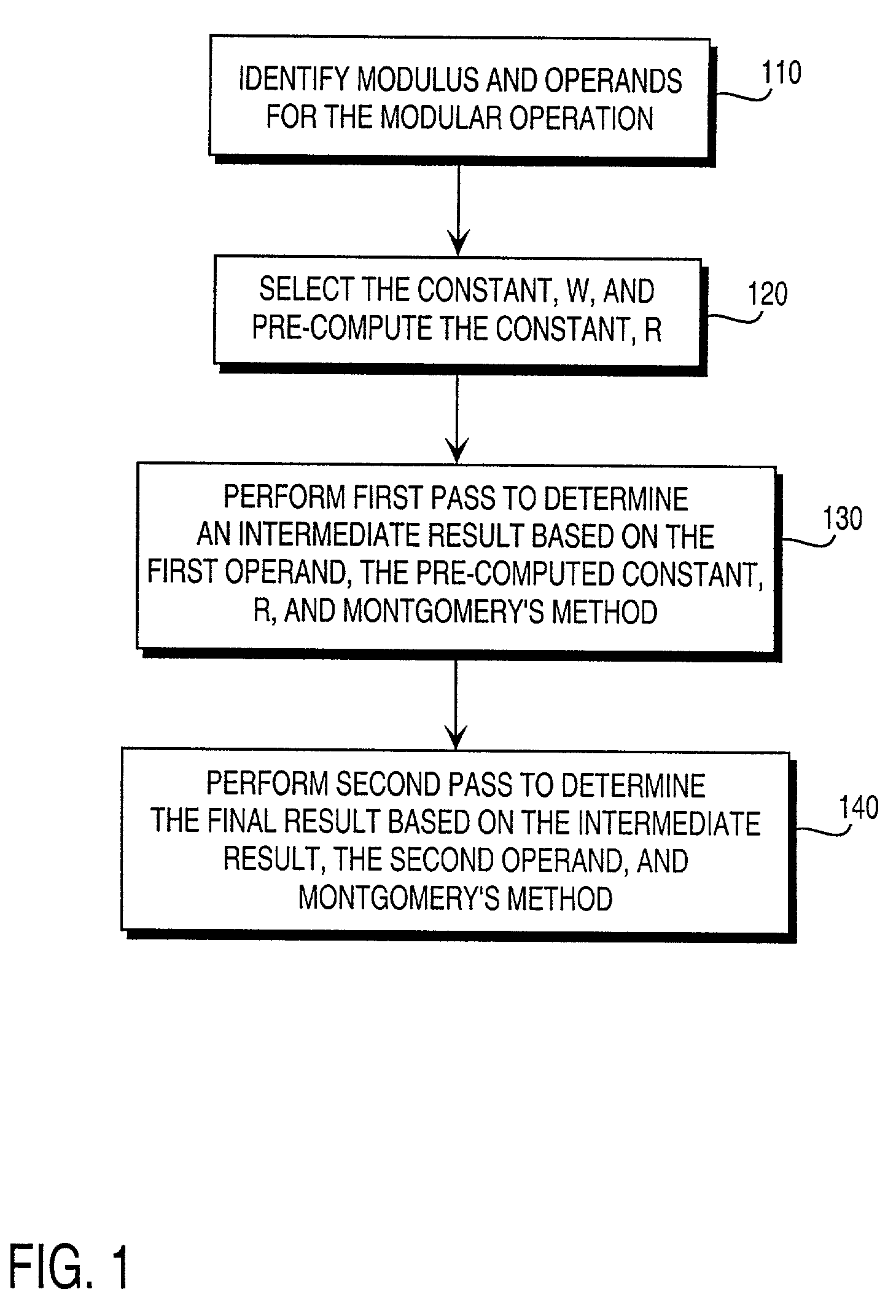

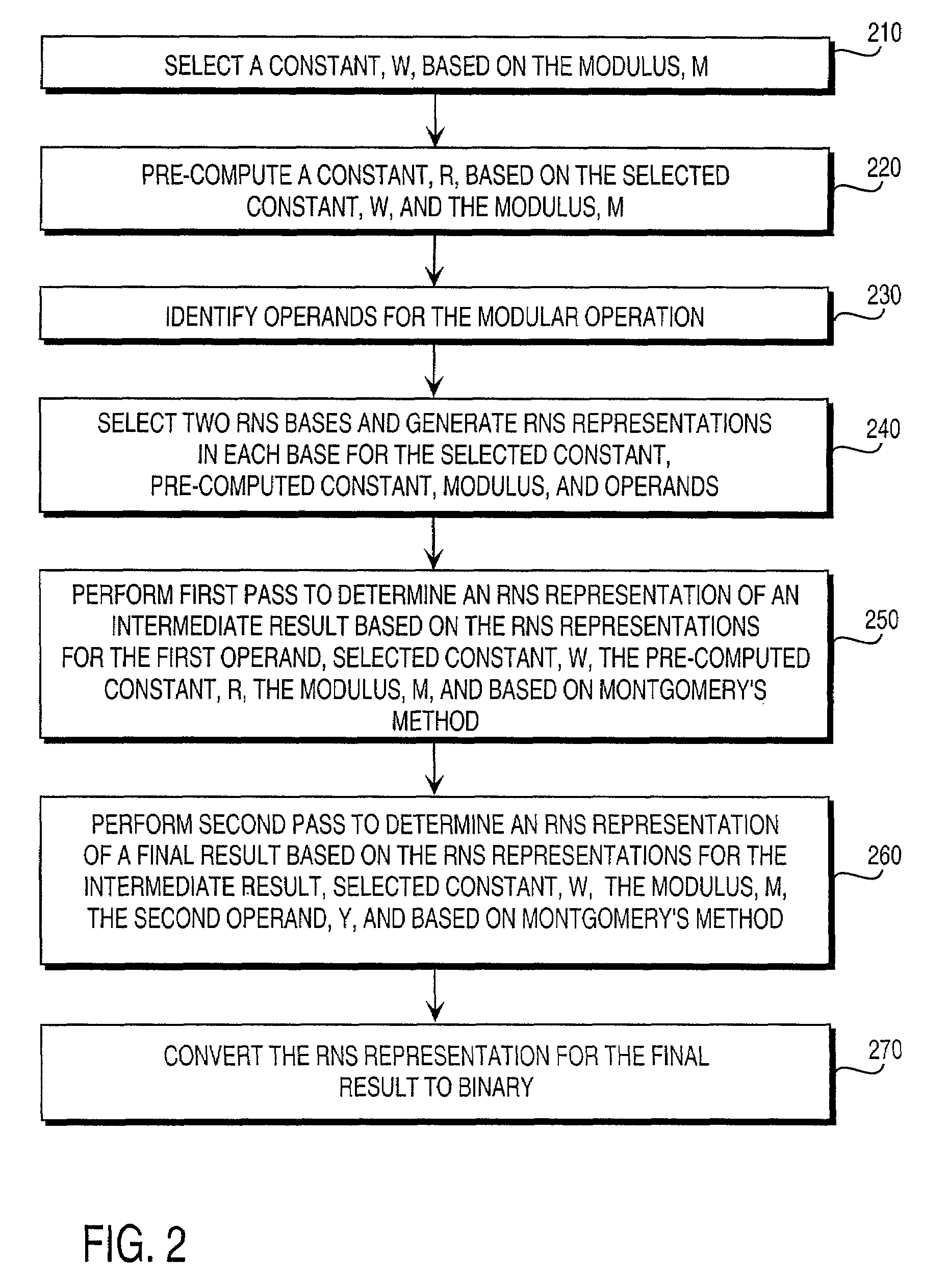

Residue number system based pre-computation and dual-pass arithmetic modular operation approach to implement encryption protocols efficiently in electronic integrated circuits

InactiveUS7027598B1Computations using contact-making devicesComputation using non-contact making devicesProcessor registerModularity

A pre-computation and dual-pass modular operation approach to implement encryption protocols efficiently in electronic integrated circuits is disclosed. An encrypted electronic message is received and another electronic message generated based on the encryption protocol. Two passes of Montgomery's method are used for a modular operation that is associated with the encryption protocol along with pre-computation of a constant based on a modulus. The modular operation may be a modular multiplication or a modular exponentiation. Modular arithmetic may be performed using the residue number system (RNS) and two RNS bases with conversions between the two RNS bases. A minimal number of register files are used for the computations along with an array of multiplier circuits and an array of modular reduction circuits. The approach described allows for high throughput for large encryption keys with a relatively small number of logical gates.

Owner:CISCO TECH INC

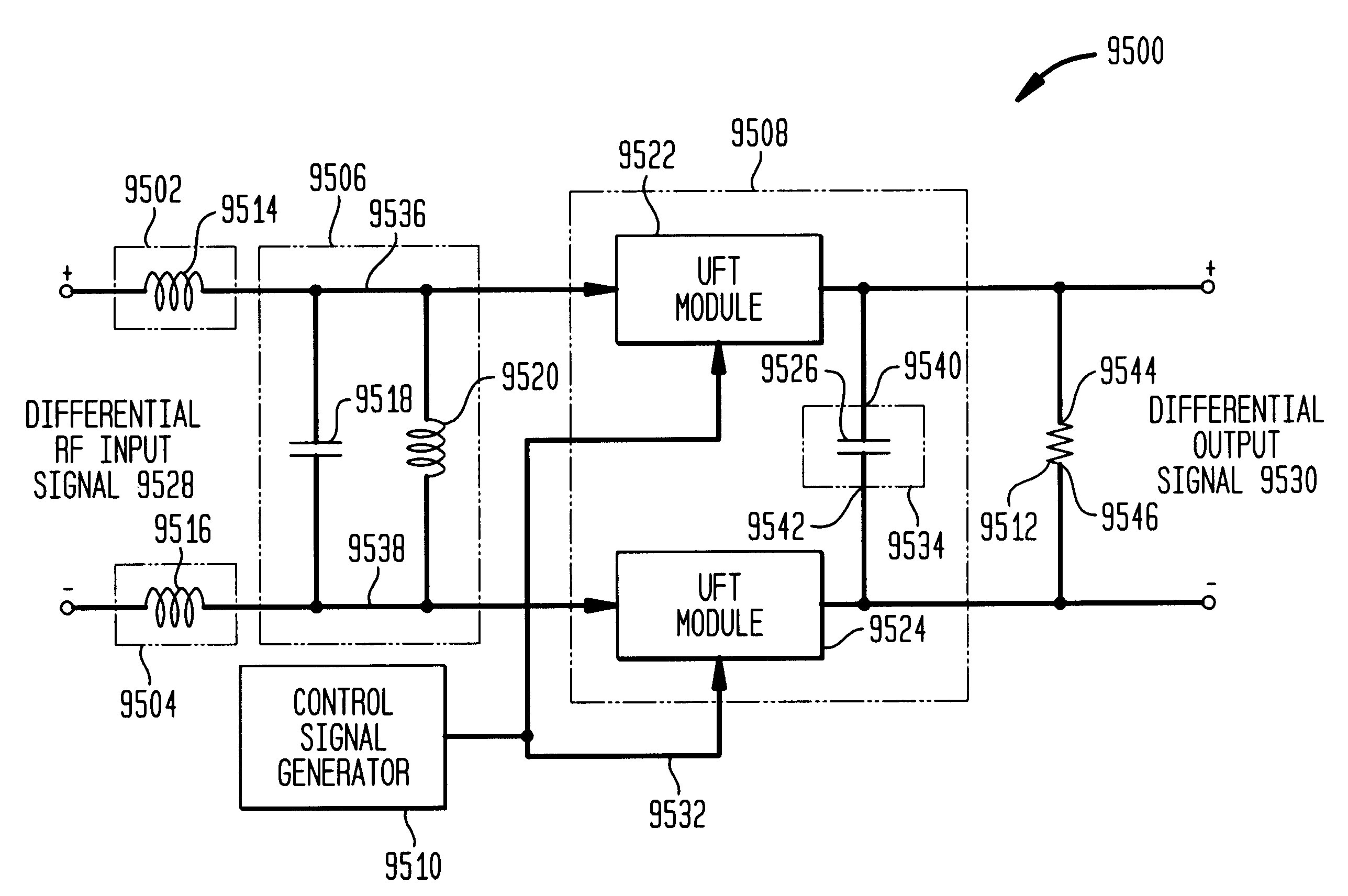

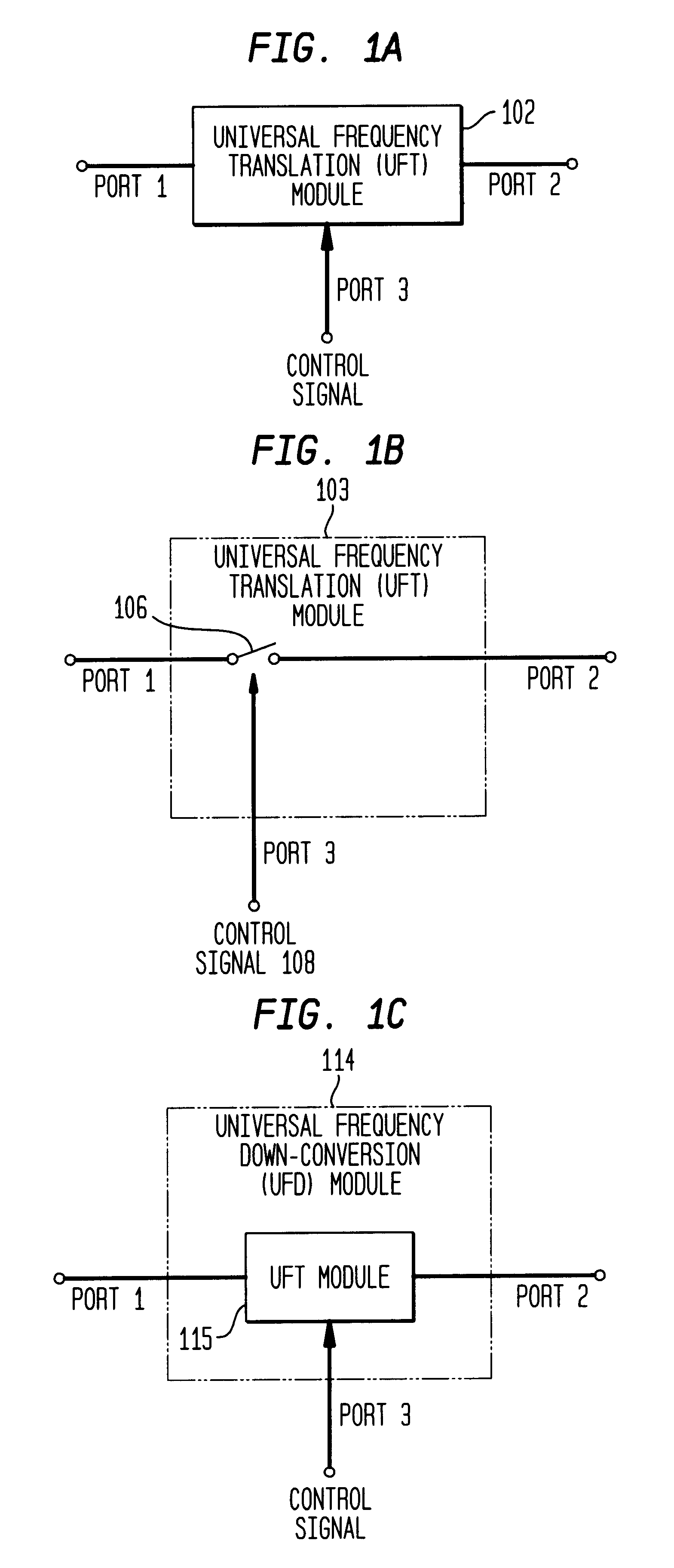

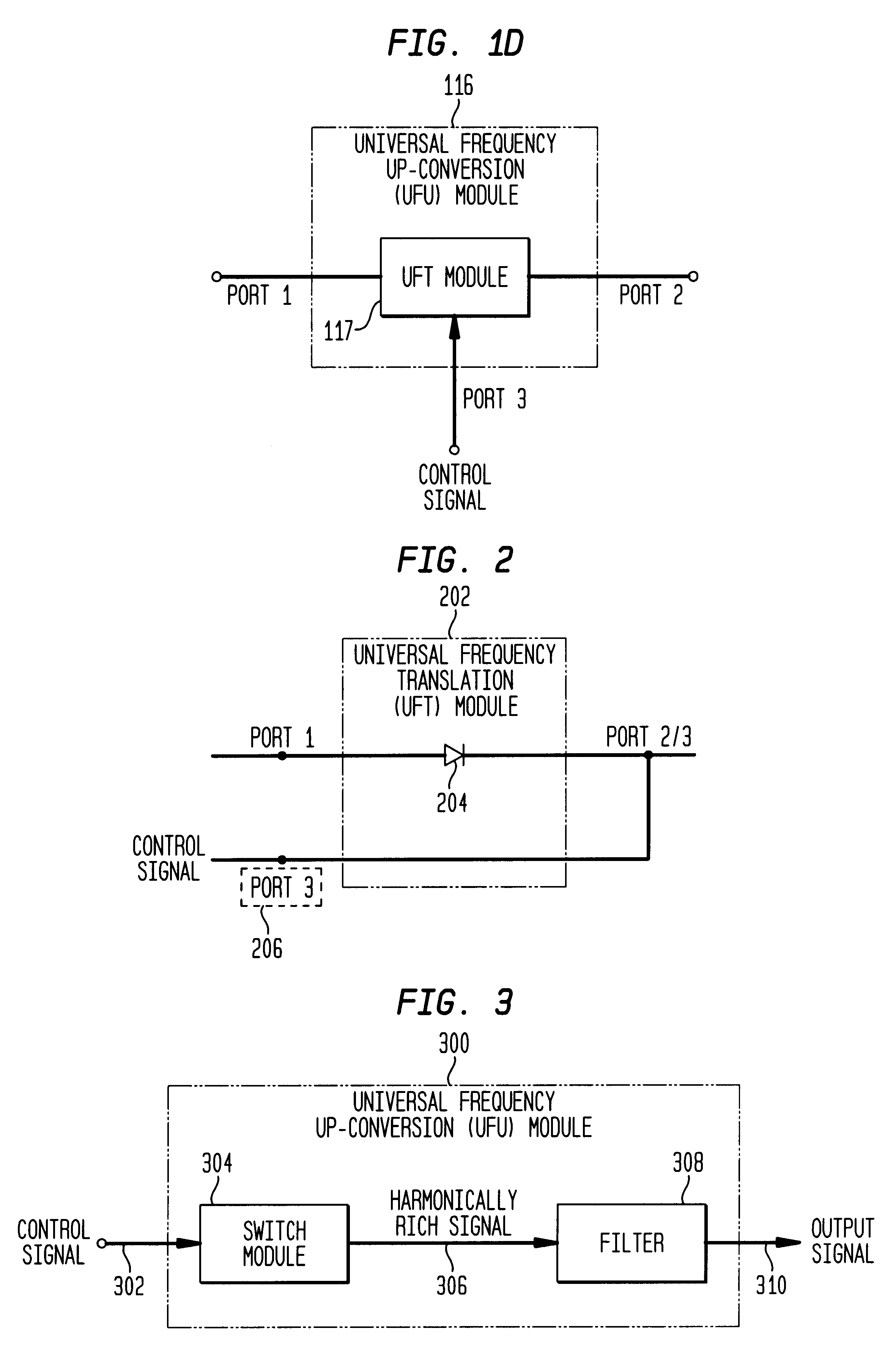

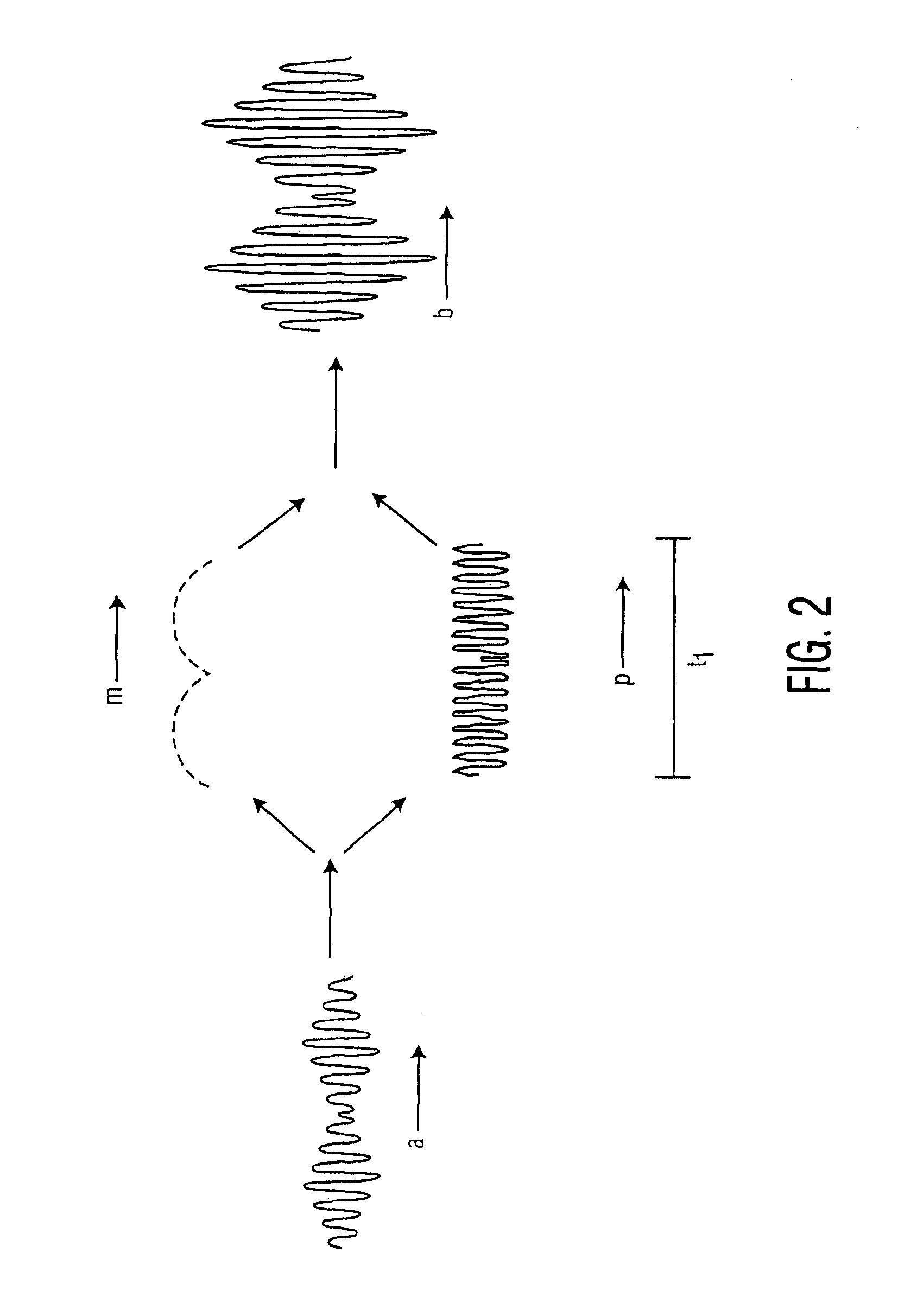

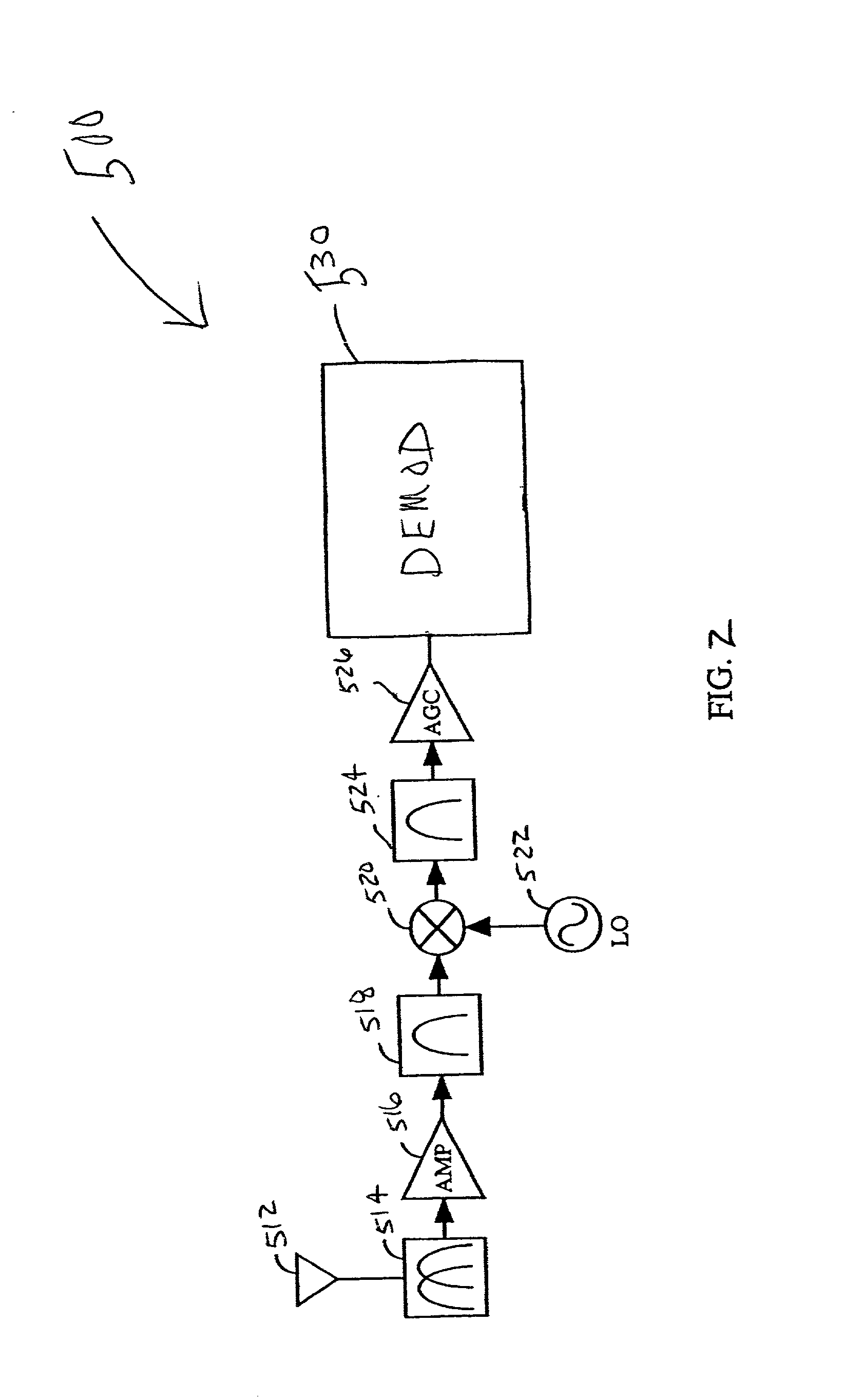

Differential frequency down-conversion using techniques of universal frequency translation technology

InactiveUS6963734B2Reduce voltageImprove dynamic rangeModulation transferenceComputations using contact-making devicesEngineeringDynamic range

Methods, systems, and apparatuses for down-converting an electromagnetic (EM) signal by aliasing the EM signal, and applications thereof are described herein. Reducing or eliminating DC offset voltages and re-radiation generated when down-converting an electromagnetic (EM) signal is also described herein. Down-converting a signal and improving receiver dynamic range is also described herein.

Owner:PARKER VISION INC

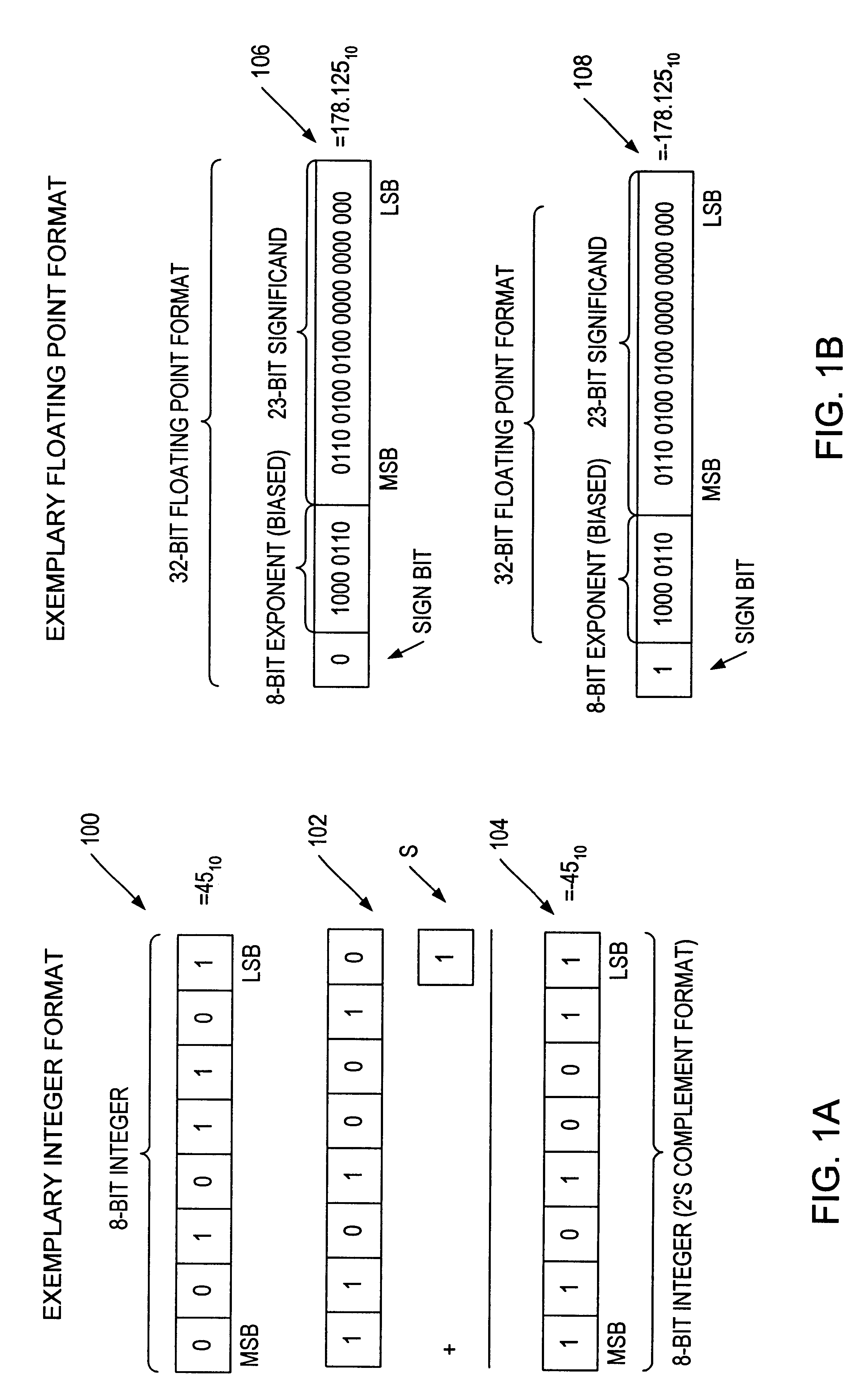

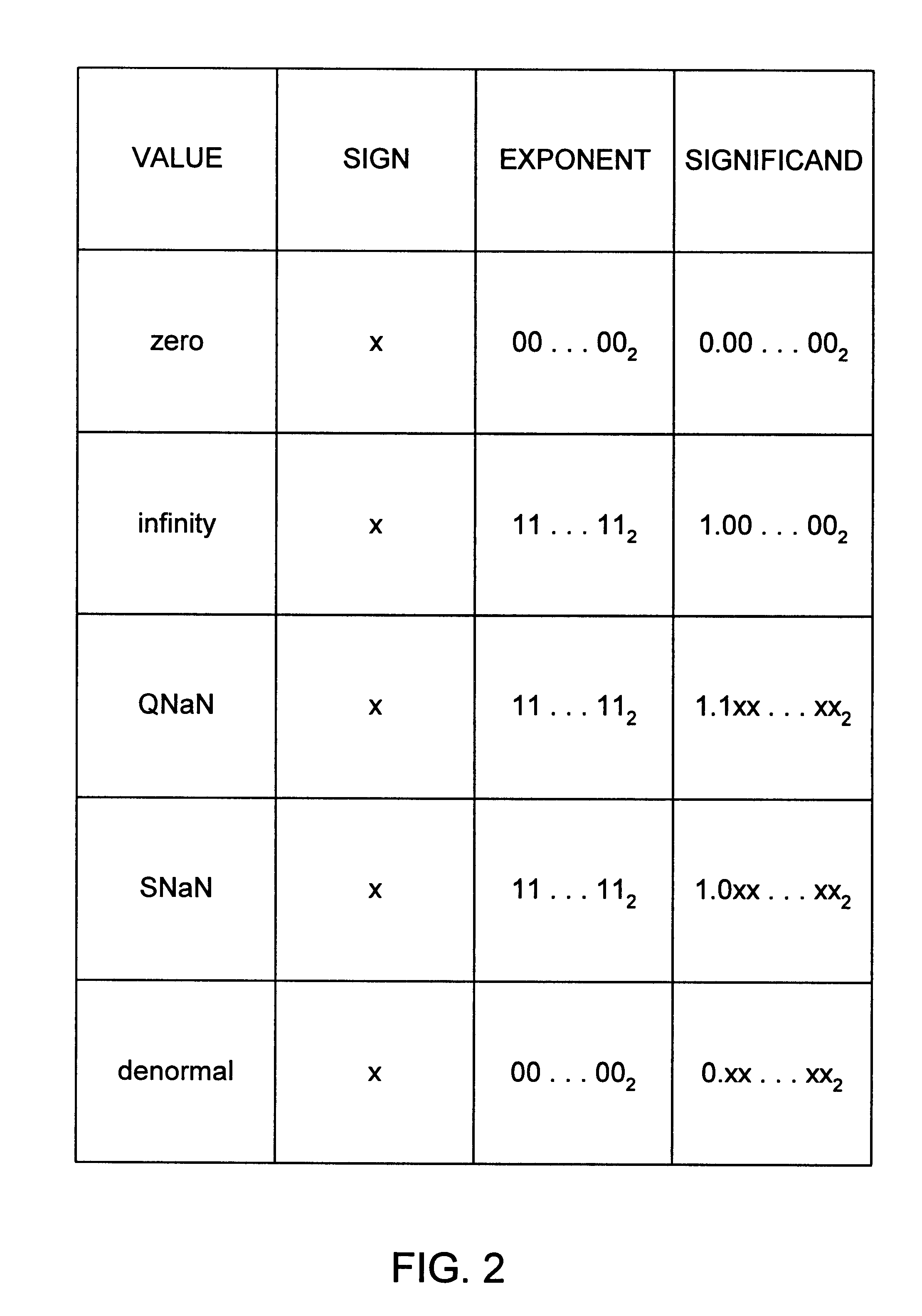

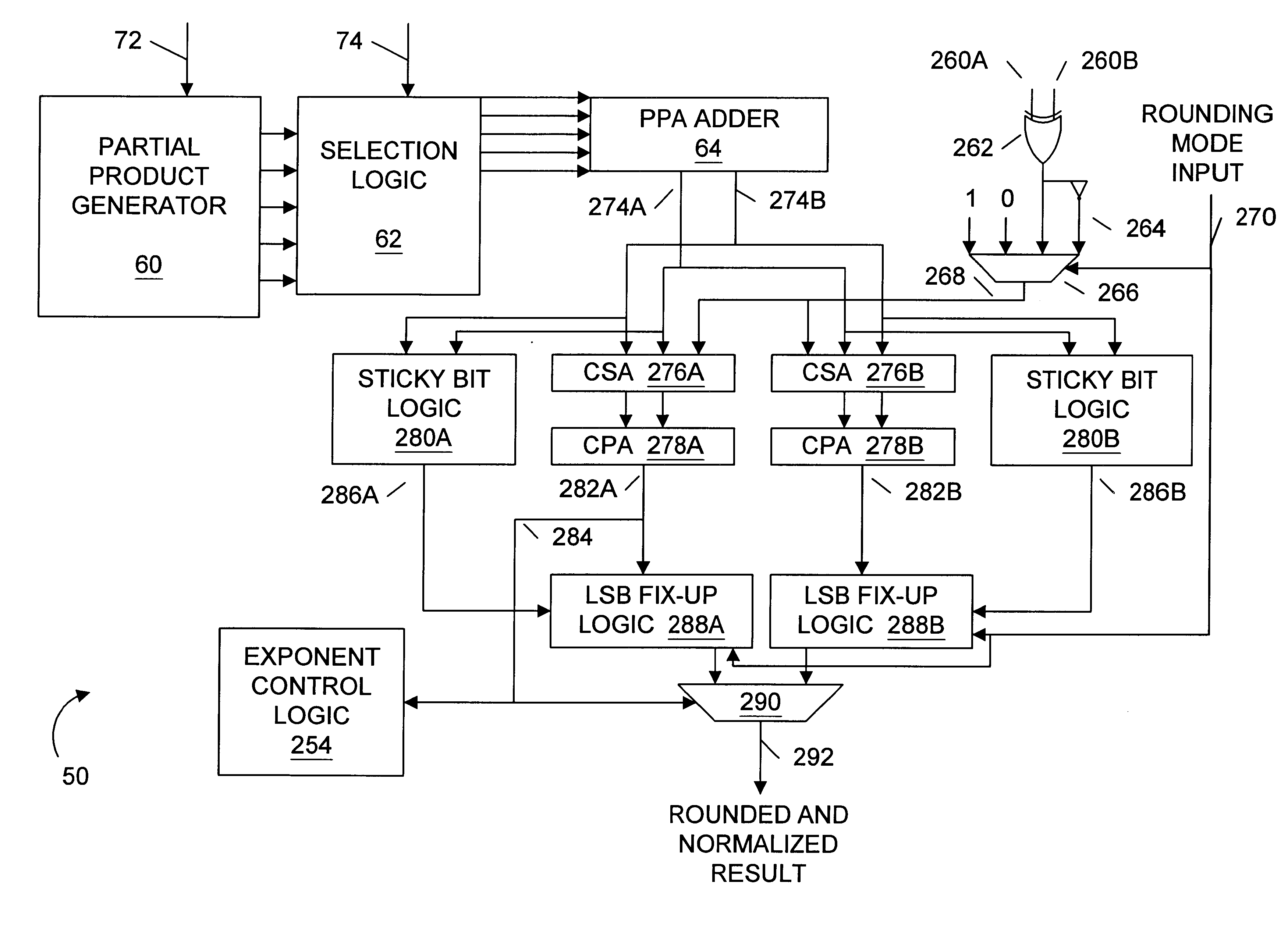

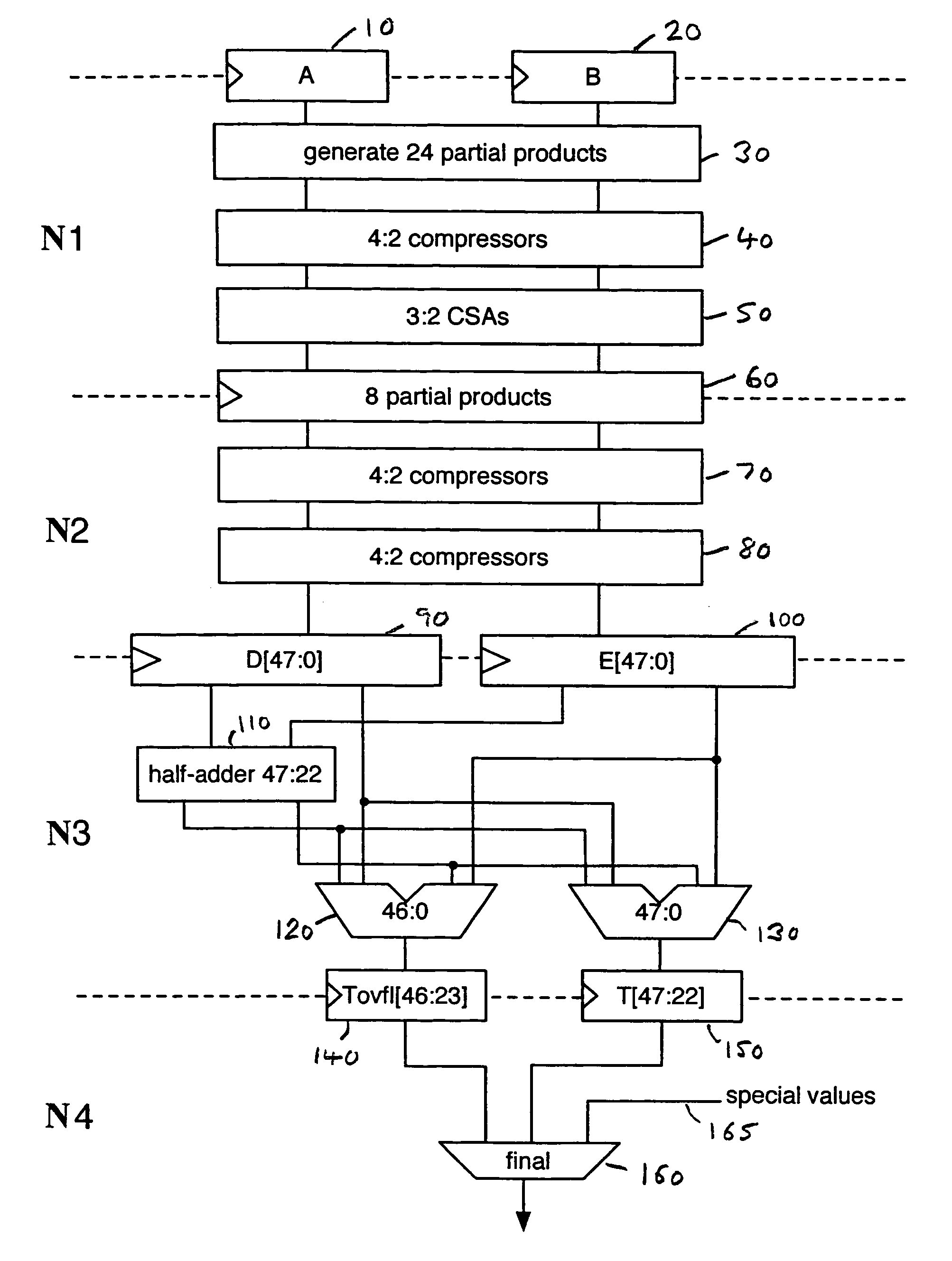

Method and apparatus for rounding and normalizing results within a multiplier

InactiveUS6269384B1Computations using contact-making devicesRuntime instruction translationRoundingControl signal

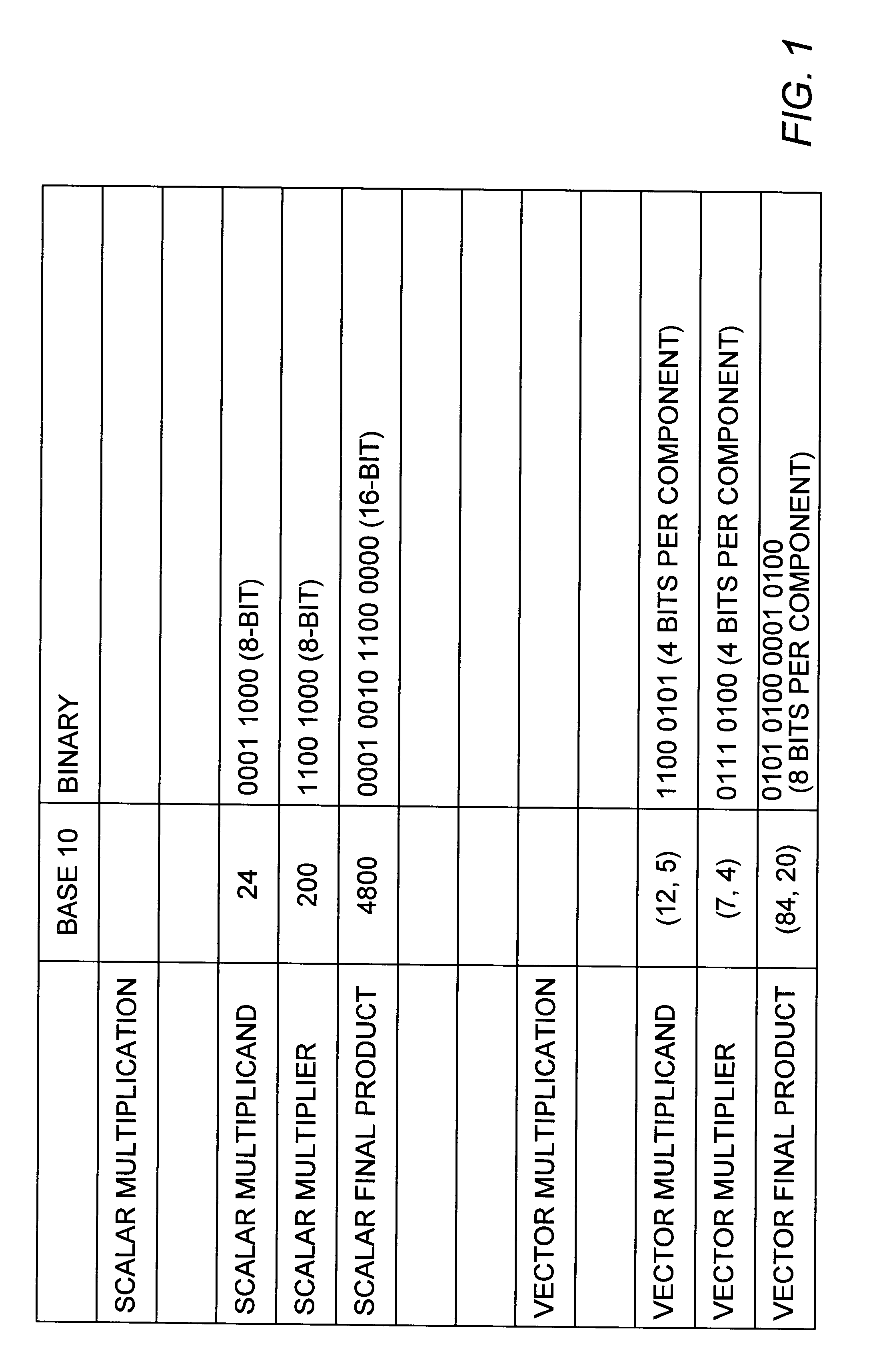

A multiplier capable of performing signed and unsigned scalar and vector multiplication is disclosed. The multiplier is configured to receive signed or unsigned multiplier and multiplicand operands in scalar or packed vector form. An effective sign for the multiplier and multiplicand operands may be calculated based upon each operand's most significant bit and a control signal. The effective signs may then be used to create and select a number of partial products according to Booth's algorithm. Once the partial products have been created and selected, they may be summed and the results may be output. The results may be signed or unsigned, and may represent vector or scalar quantities. When a vector multiplication is performed, the multiplier may be configured to generate and select partial products so as to effectively isolate the multiplication process for each pair of vector components. The multiplier may also be configured to sum the products of the vector components to form the vector dot product. The final product may be output in segments so as to require fewer bus lines. The segments may be rounded by adding a rounding constant. Rounding and normalization may be performed in two paths, one assuming an overflow will occur, the other assuming no overflow will occur.

Owner:ADVANCED MICRO DEVICES INC

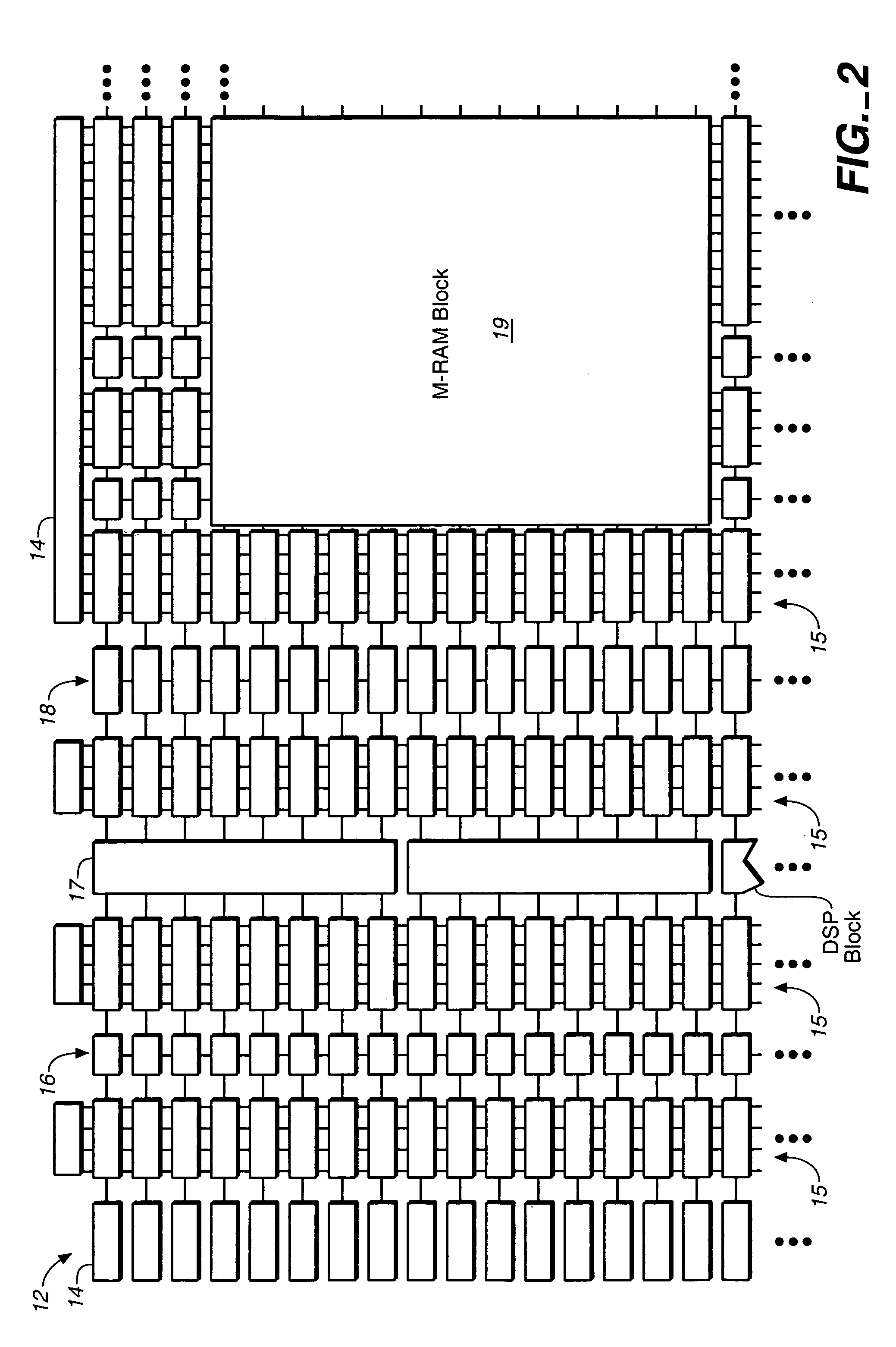

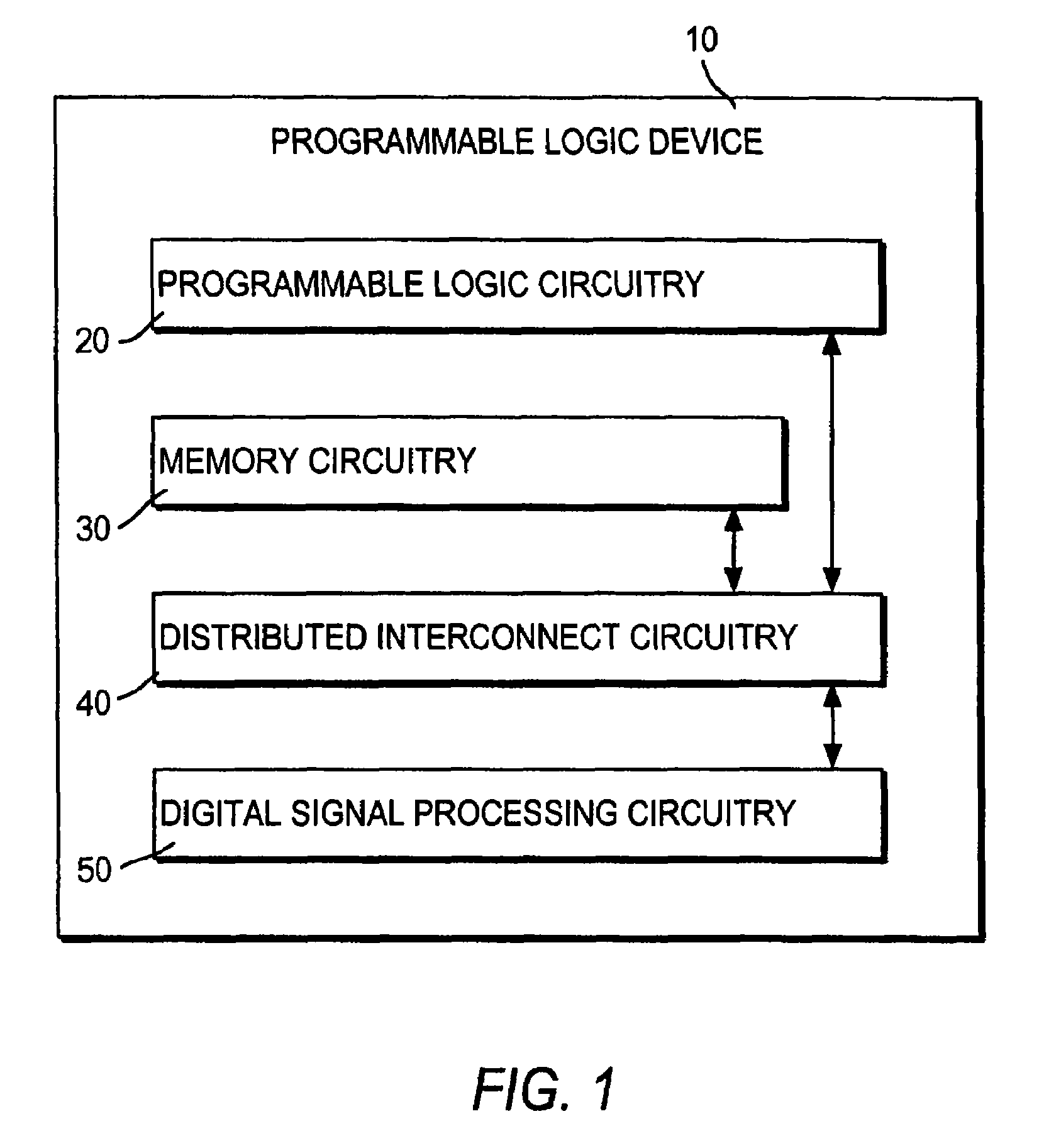

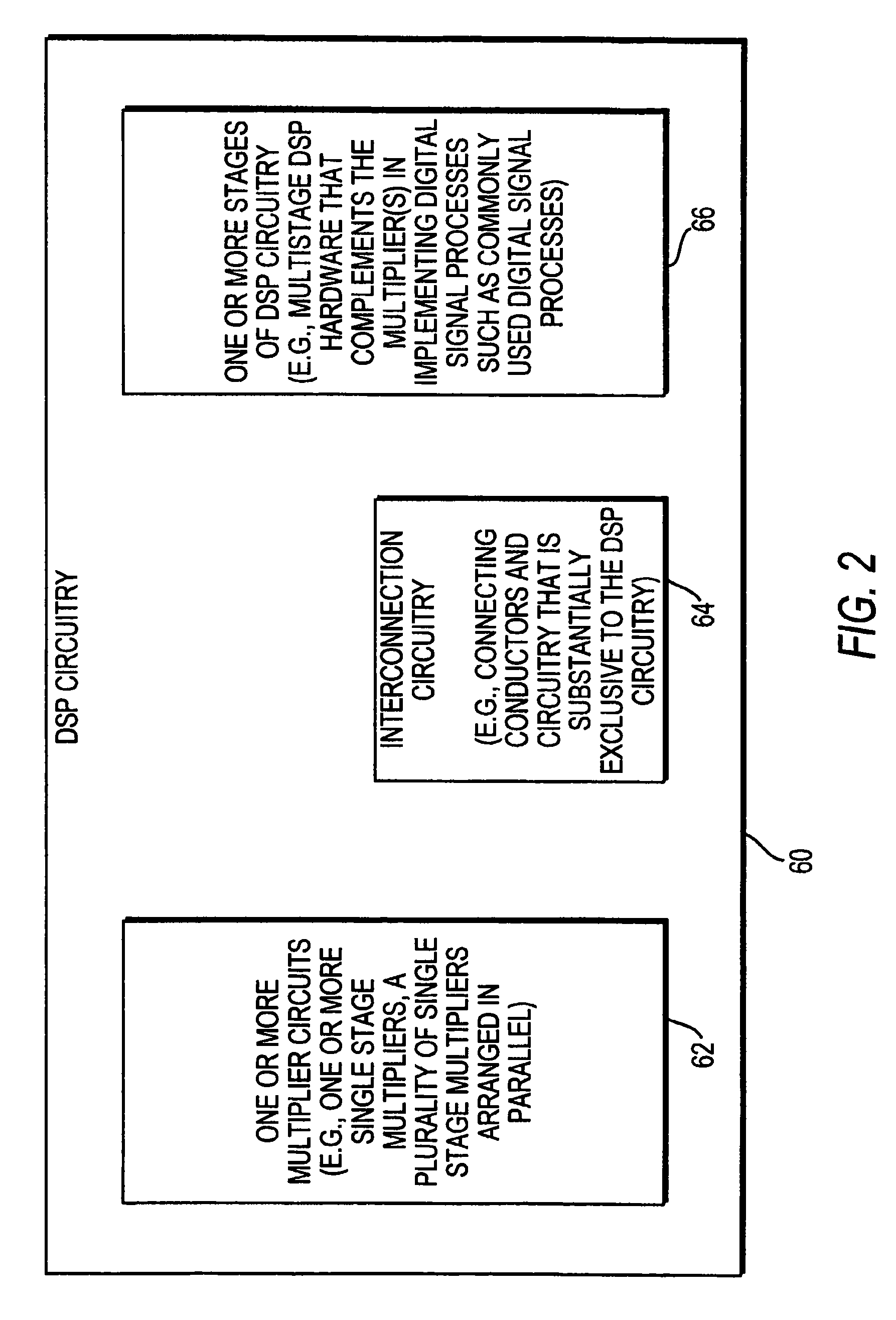

Devices and methods with programmable logic and digital signal processing regions

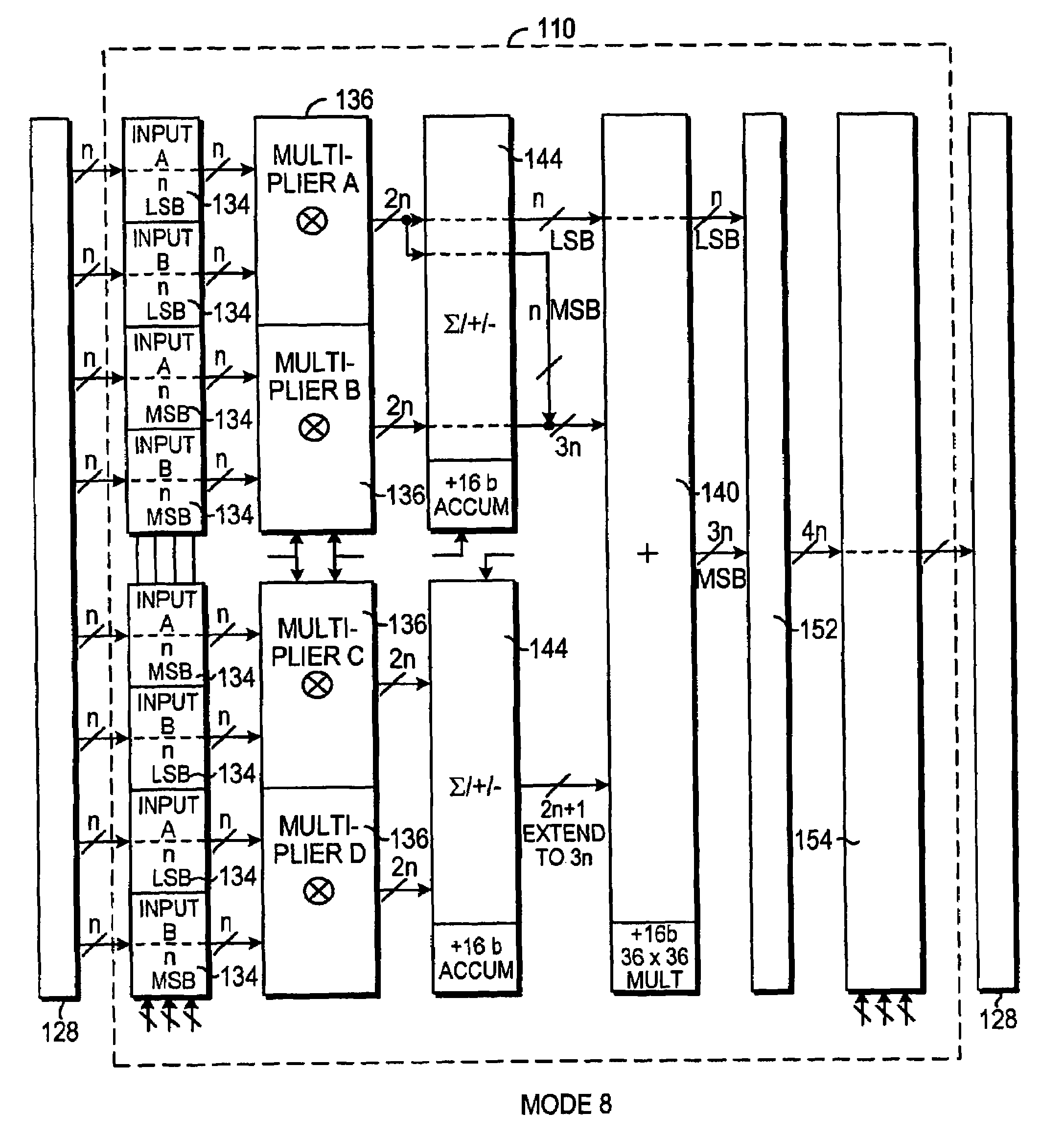

InactiveUS7346644B1High speedImprove latencyComputations using contact-making devicesComputation using non-contact making devicesGeneral purposeDigital signal processing

A programmable logic integrated circuit device (“PLD”) includes programmable logic and a dedicated (i.e., at least partly hard-wired) digital signal processing region for performing or at least helping to perform digital signal processing tasks that are unduly inefficient to implement in the more general-purpose programmable logic and / or that, if implemented in the programmable logic, would operate unacceptably or at least undesirably slowly. The digital signal processing region may include multiple digital signal processing stages. The digital signal processing region may include a multiplier stage and one or more stages that can operate in combination with the multiplier stage. The digital signal processing region has a plurality of modes such as for providing multiply-and-accumulate operation, multiply-and-add operation, etc.

Owner:ALTERA CORP

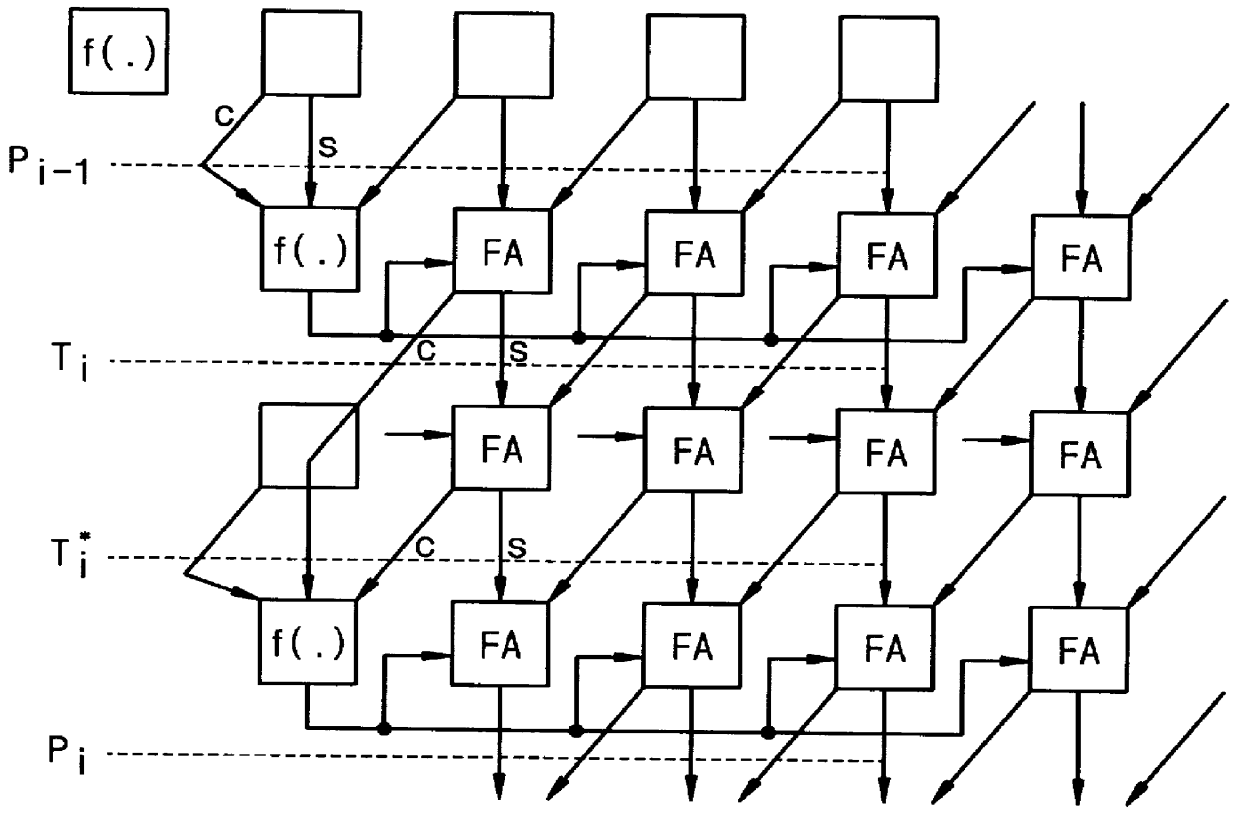

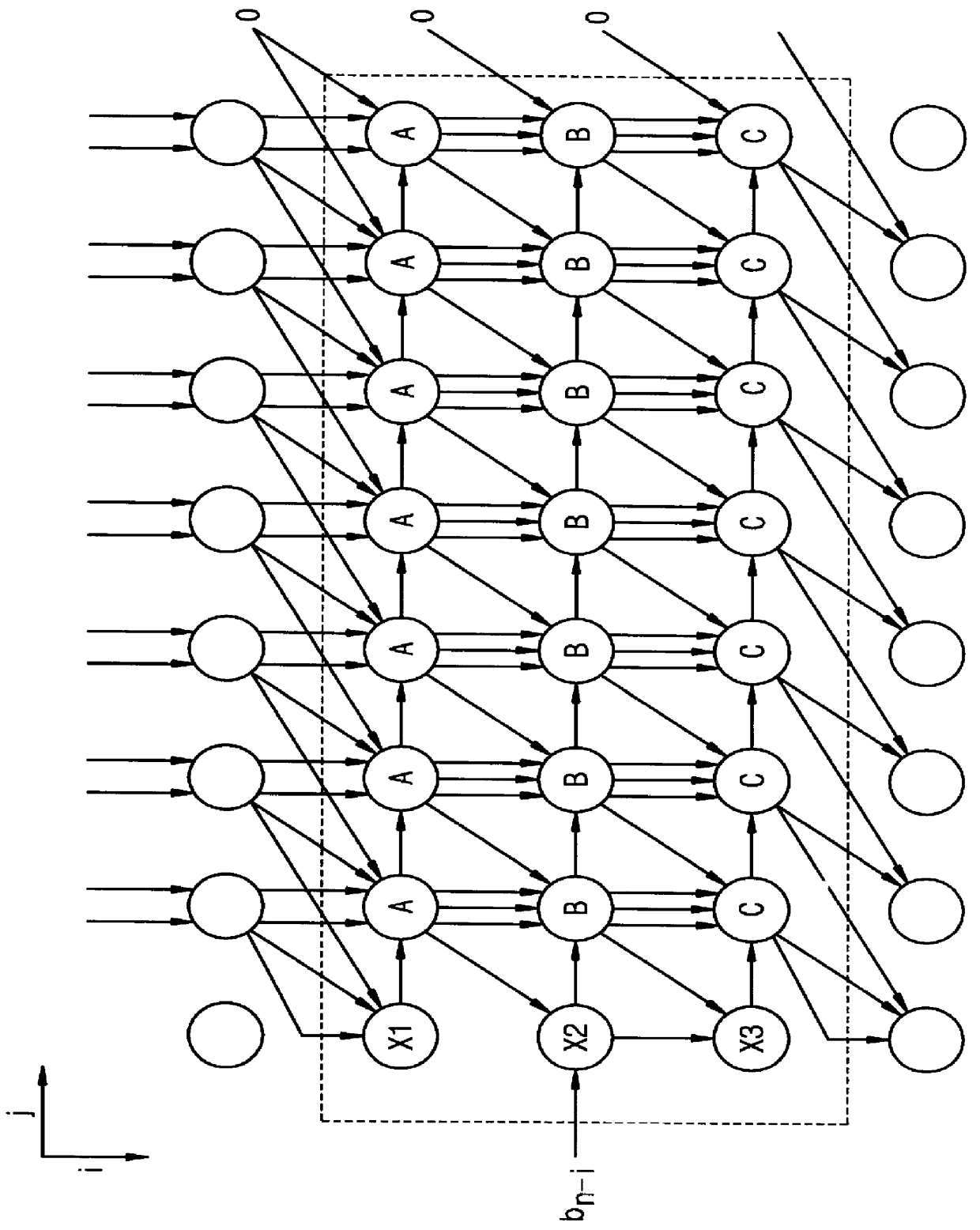

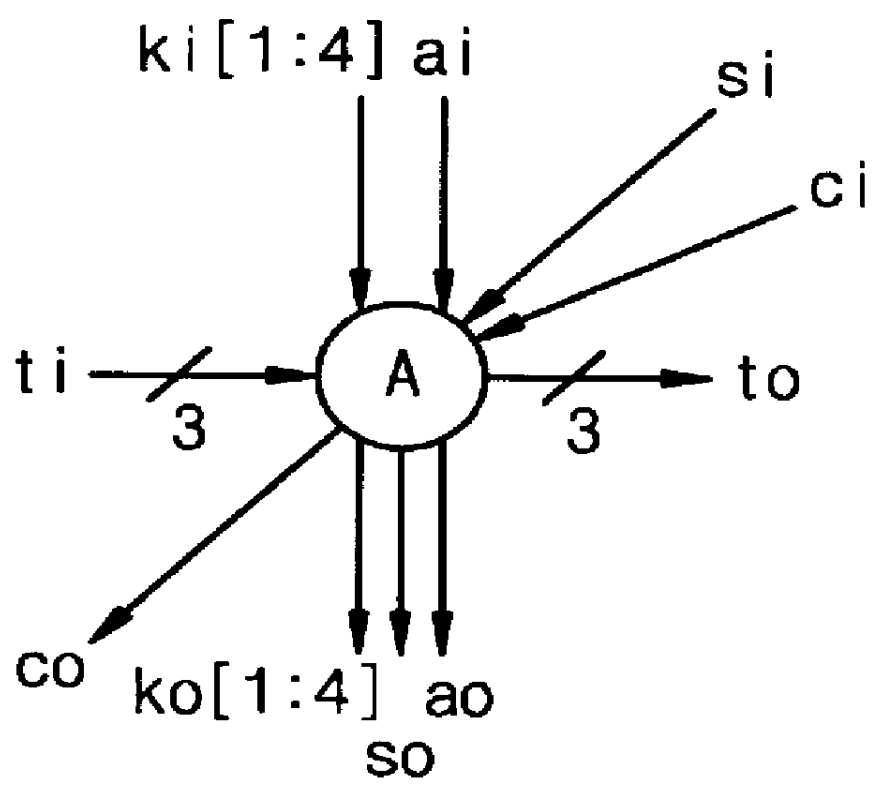

Device and method for modular multiplication

InactiveUS6151393AEasy mappingImprove performanceComputations using contact-making devicesComputation using non-contact making devicesEngineeringFine grain

A method and apparatus are disclosed for performing modular multiplication. Modular multiplication in accordance with the present invention includes precalculating a 2's complement of a given modulus and multiples of the 2's complement and calculating a total magnitude of end-around carries during the modular multiplication. The calculated multiples are selected depending on the total magnitude of the end-around carries, and the selected multiples are added. The disclosure includes array structures in accordance with the present invention. The invention includes an algorithm designed for Rivest-Shamir-Adelman (RSA) cryptography and based on the familiar iterative Homer's rule, but uses precalculated complements of the modulus. The problem of deciding which multiples of the modulus to subtract in intermediate iteration stages has been simplified using simple look-up of precalculated complement numbers, thus allowing a finer-grain pipeline. Regularity and local connections make the algorithm suitable for high-performance array implementation in FPGA's (field programmable gate arrays) or deep submicron VLSI's.

Owner:SAMSUNG ELECTRONICS CO LTD

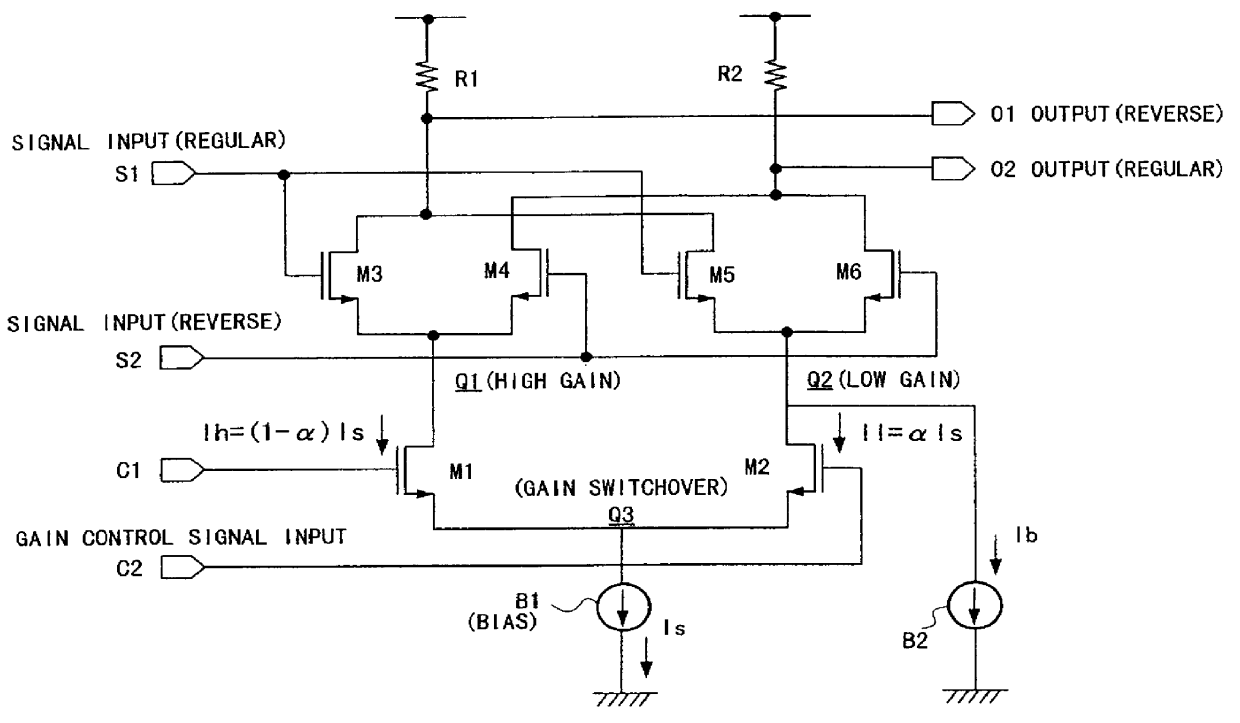

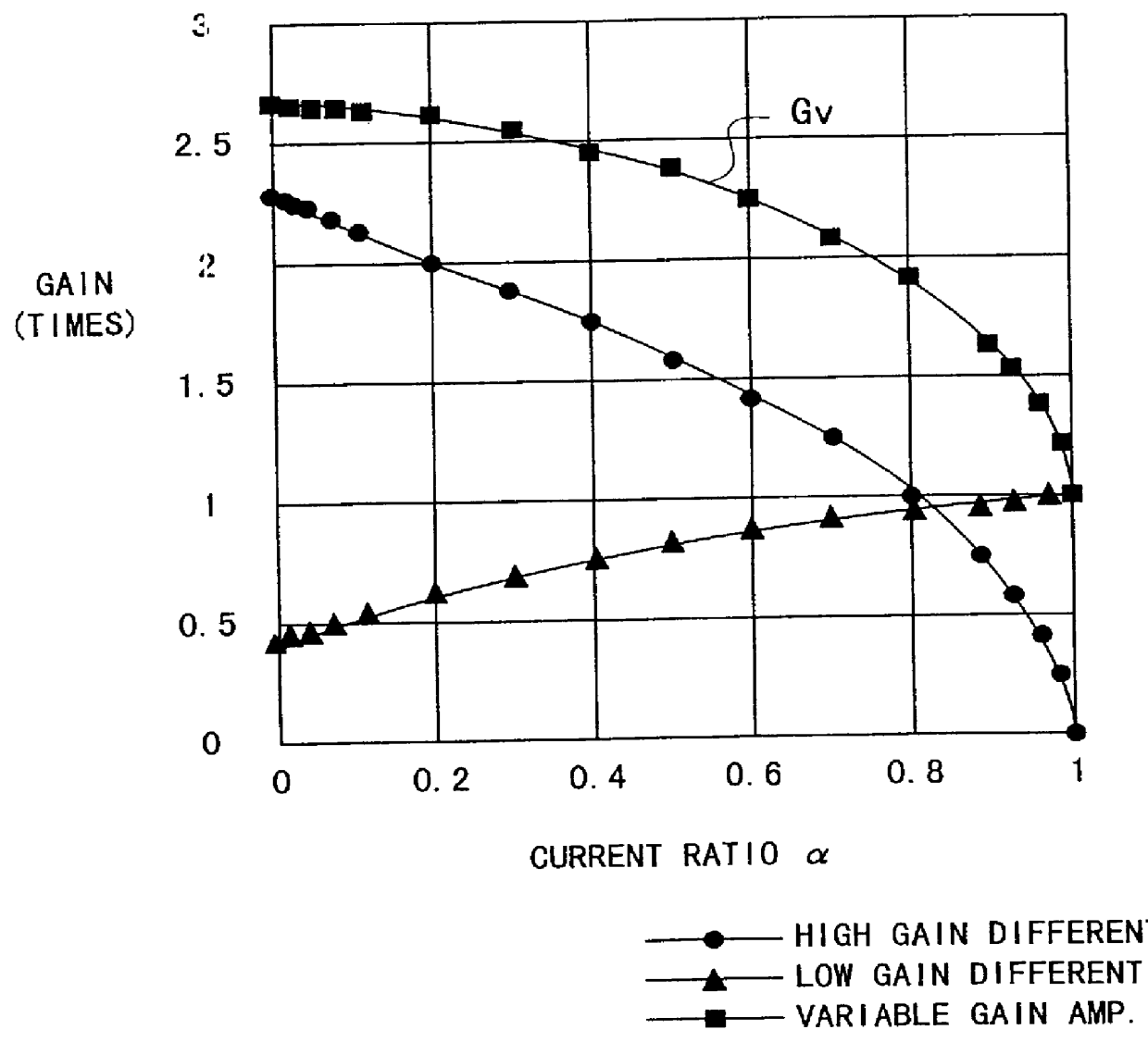

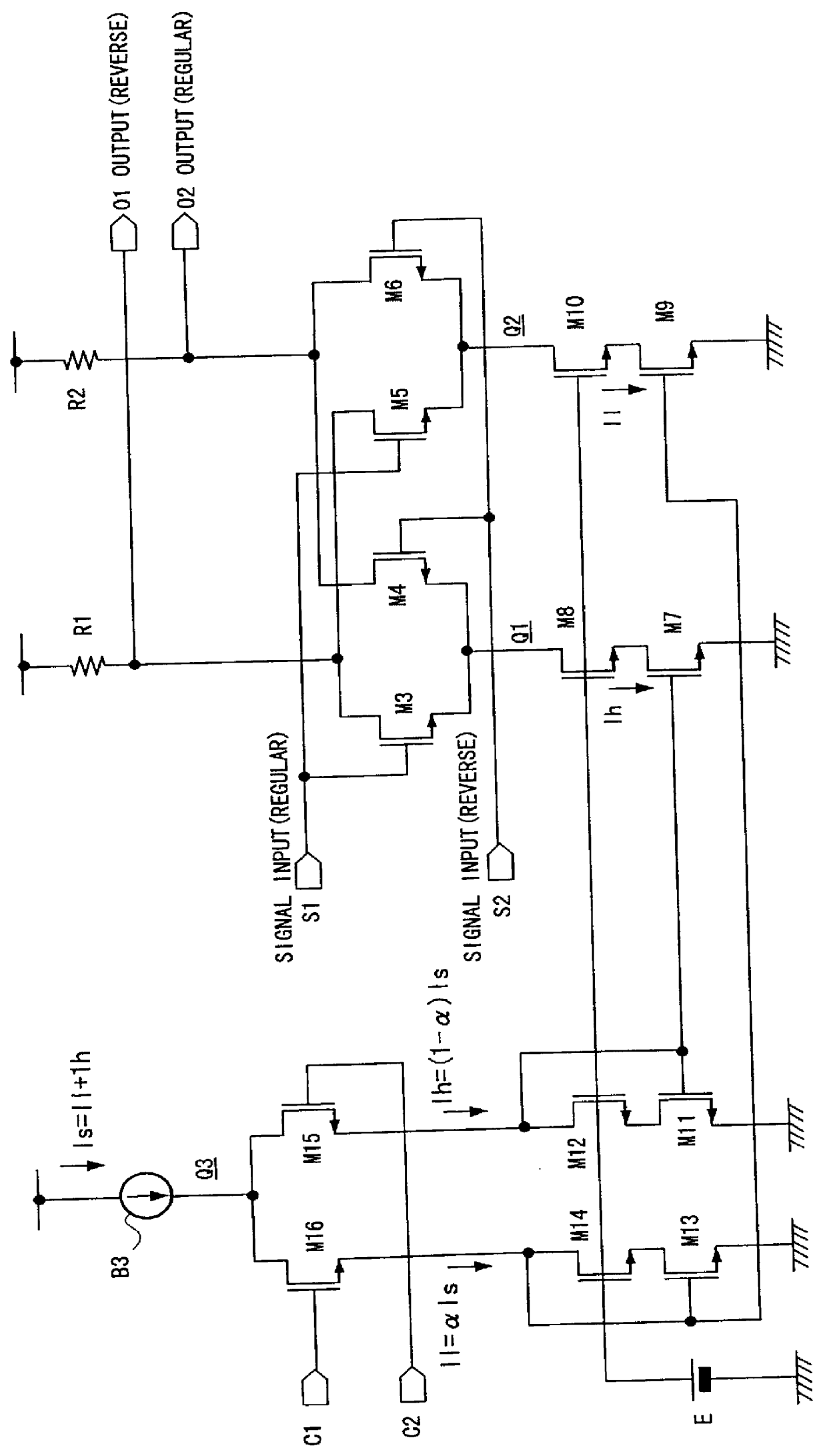

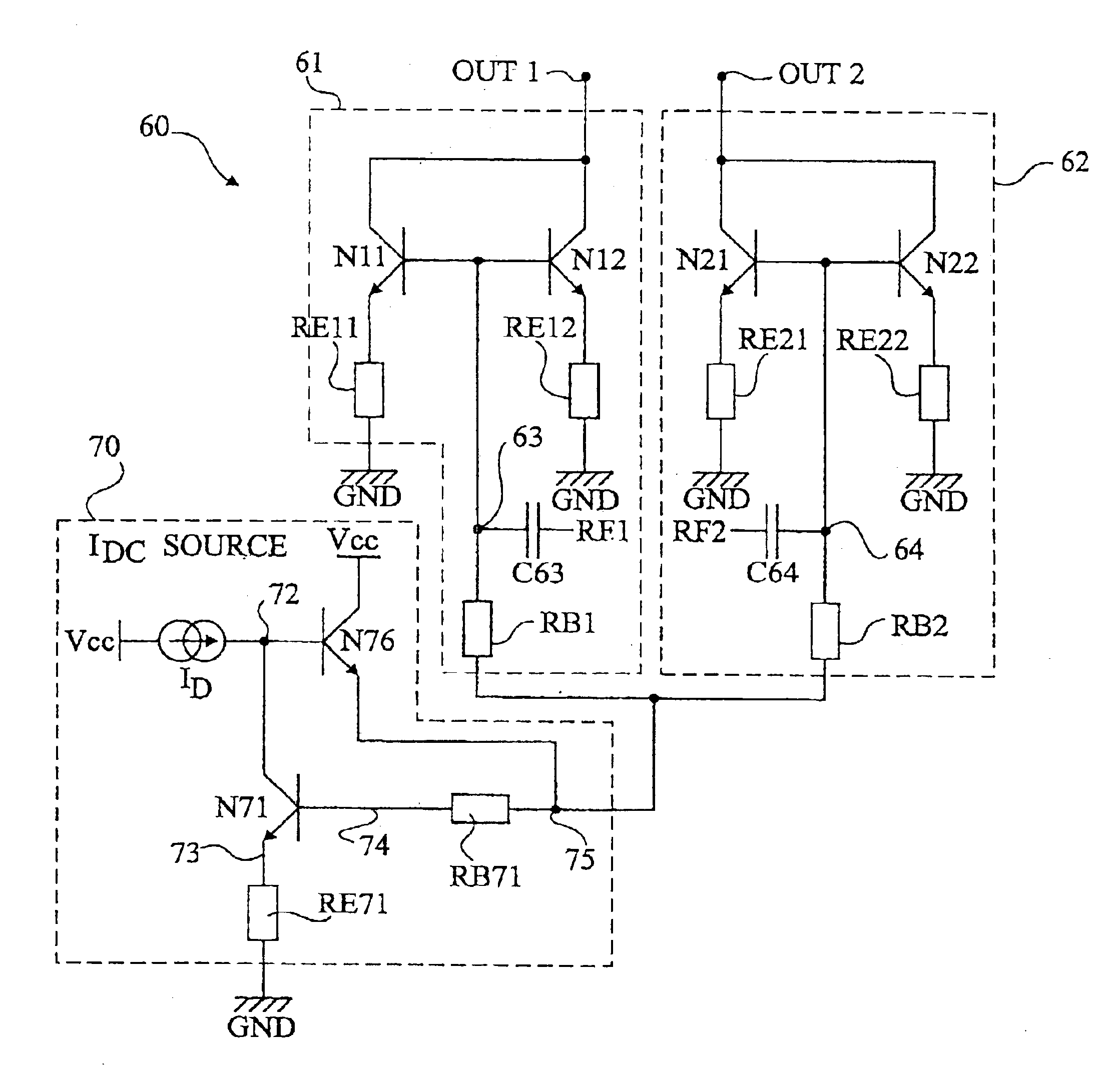

Variable gain amplifier

InactiveUS6163215AComputations using contact-making devicesGain controlAudio power amplifierVariable-gain amplifier

In a variable gain amplifier controlling a gain by using differential amplifiers with a gain control signal, a gain switchover differential amplifier or a bias circuit which composes a current mirror with the gain switchover differential amplifier is connected between a high and a low gain differential amplifier for the same bias current which are mutually connected to share load resistances for the same output polarity and a bias current source common to both of the differential amplifiers, to perform switchover operations of the high and the low differential amplifier by a gain control signal, and a current source which flows a fixed offset current through at least the low one of the high and the low differential amplifier is provided.

Owner:FUJITSU LTD

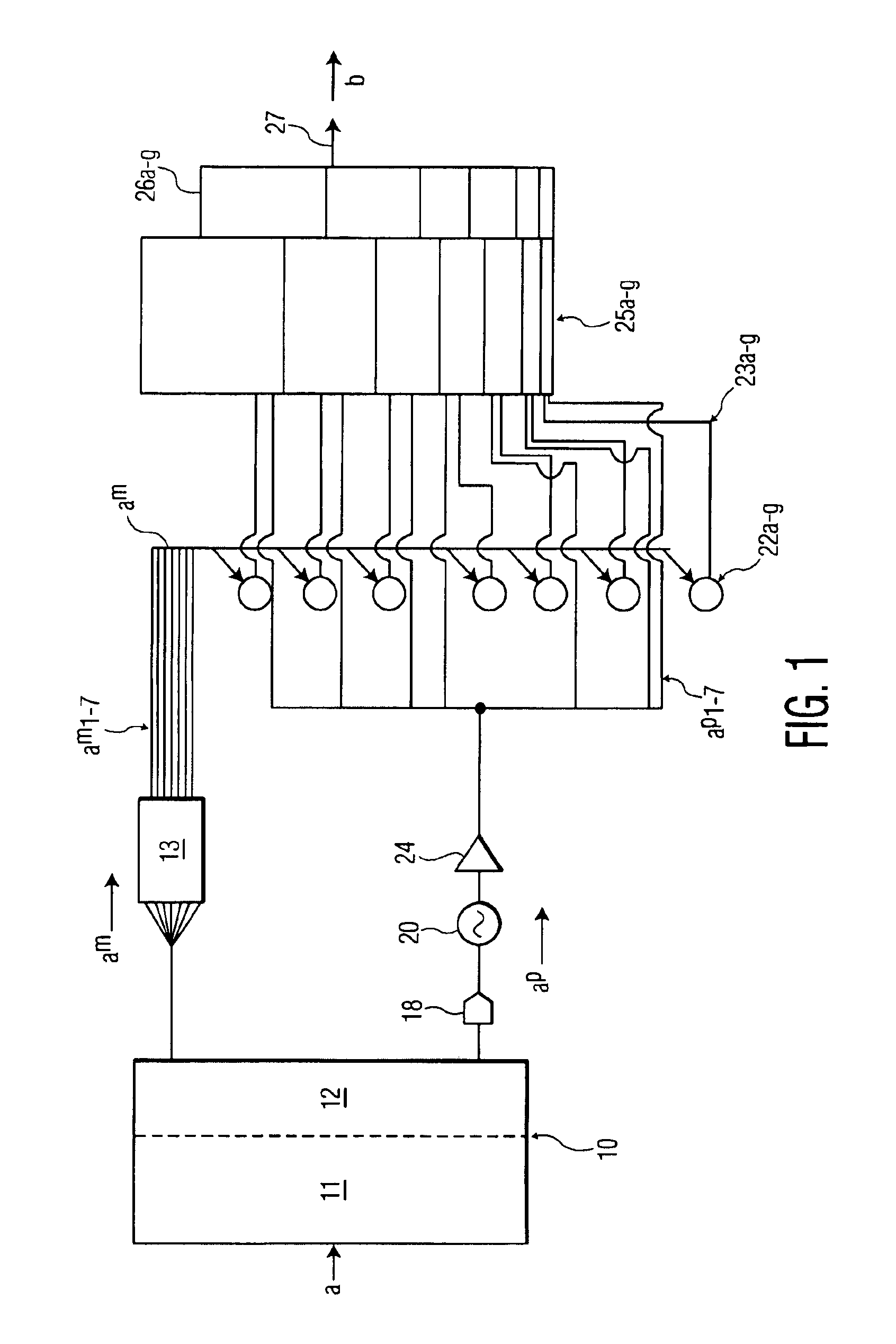

Apparatus, methods and articles of manufacture for electromagnetic processing

Apparatus, methods and articles of manufacture are shown for modifying electromagnetic waves. Through using various wave characteristics such as amplitude to regulate a current source, a current is output that may be used in any number of ways, such as driving an antenna or other load.

Owner:NORTH SOUTH HLDG

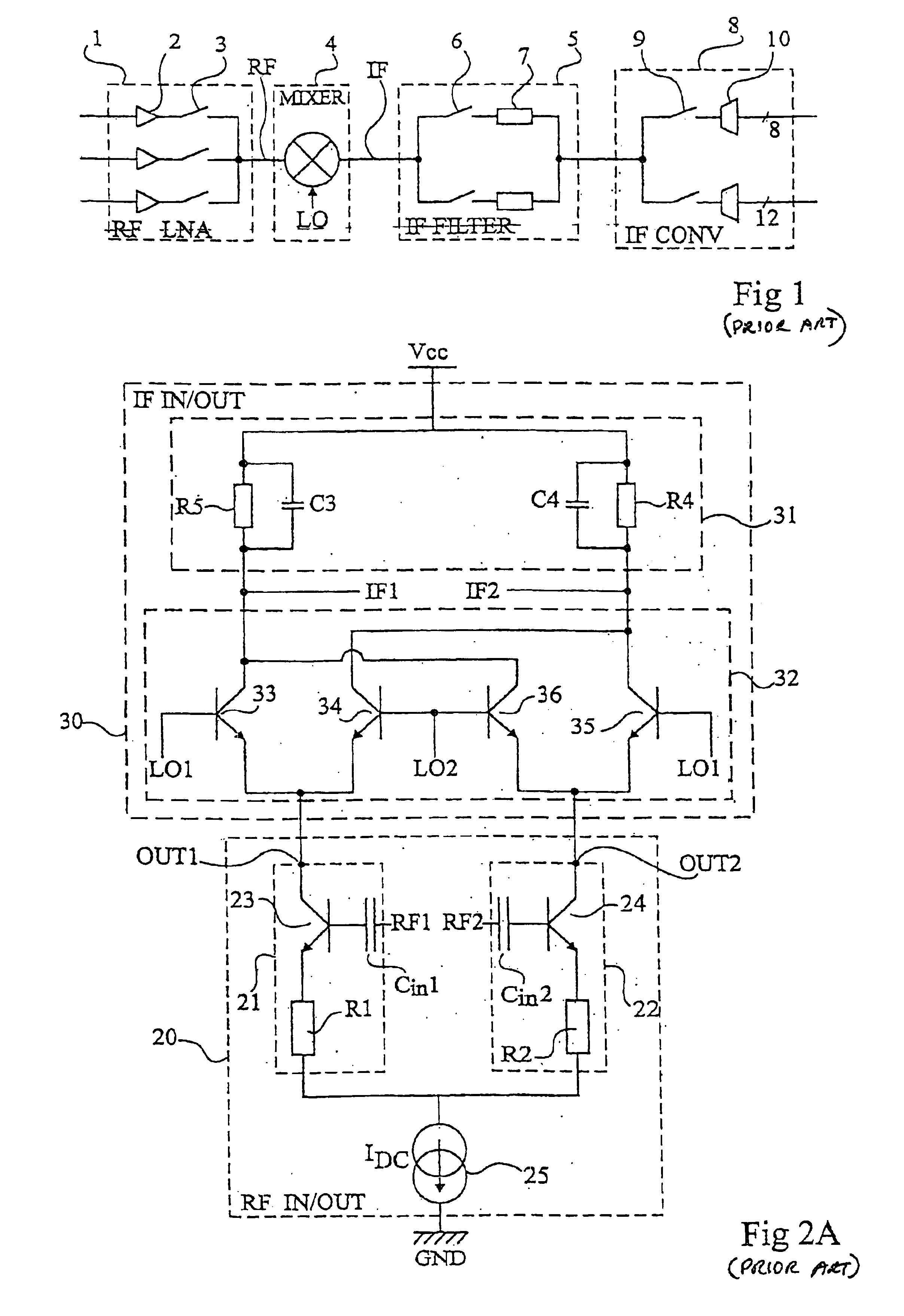

Class AB differential mixer

InactiveUS6882194B2Reduce power consumptionModulation transference by semiconductor devices with minimum 2 electrodesModulation transference balanced arrangementsLow voltageReference line

A differential mixer including at least two input / output stages, each stage including two identical branches, each branch of one of the two stages including at least two bipolar transistors the bases of which define a first pair of input / output terminals of the stage and are connected to a same D.C. current source individually by a respective isolating resistor; the collectors of which define a second pair of input / output terminals of the stage which forms a pair of input / output terminals of another stage of the mixer; and the emitters of which are individually connected to a low voltage reference line by a respective degenerative impedance.

Owner:STMICROELECTRONICS SRL

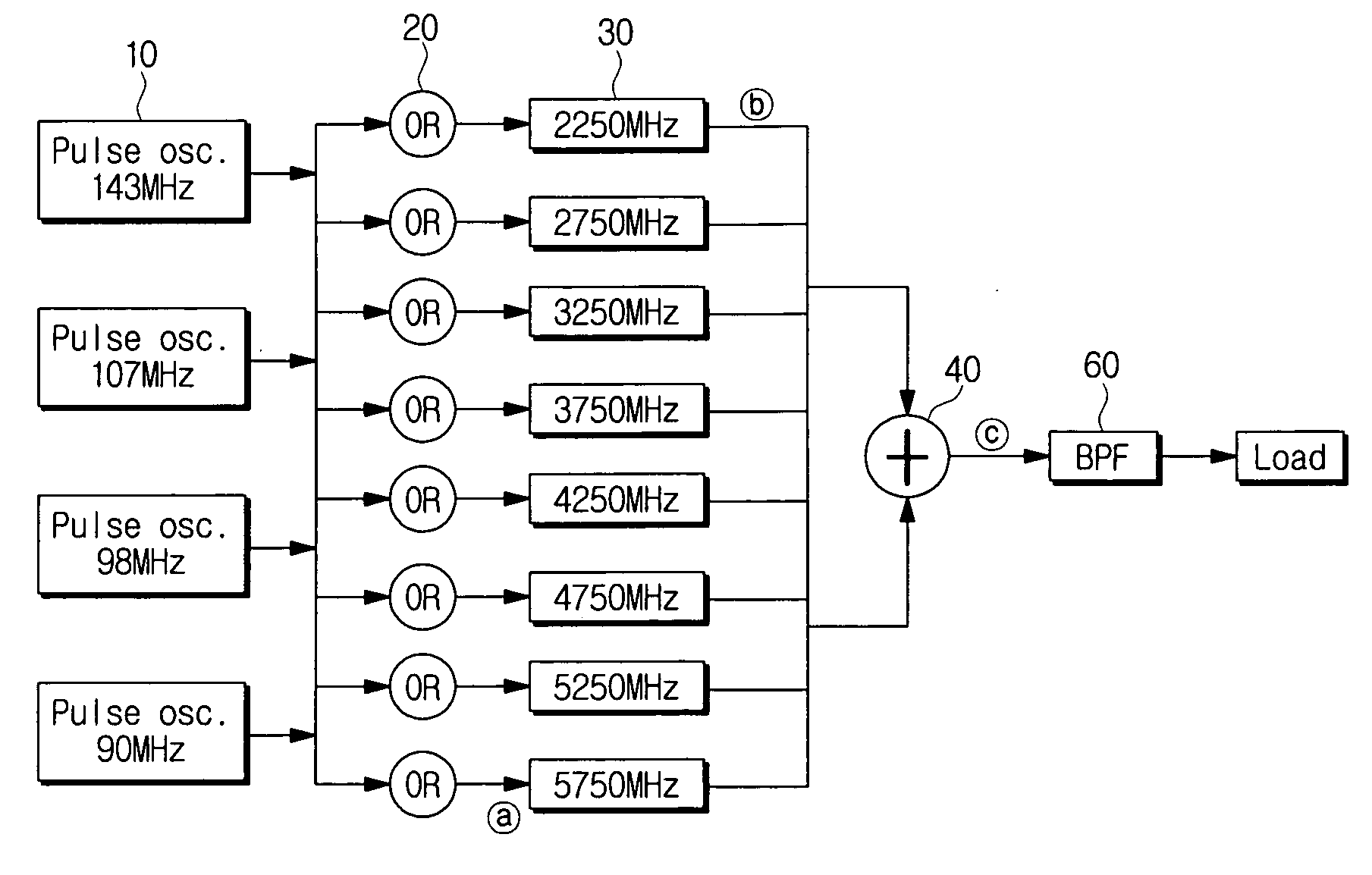

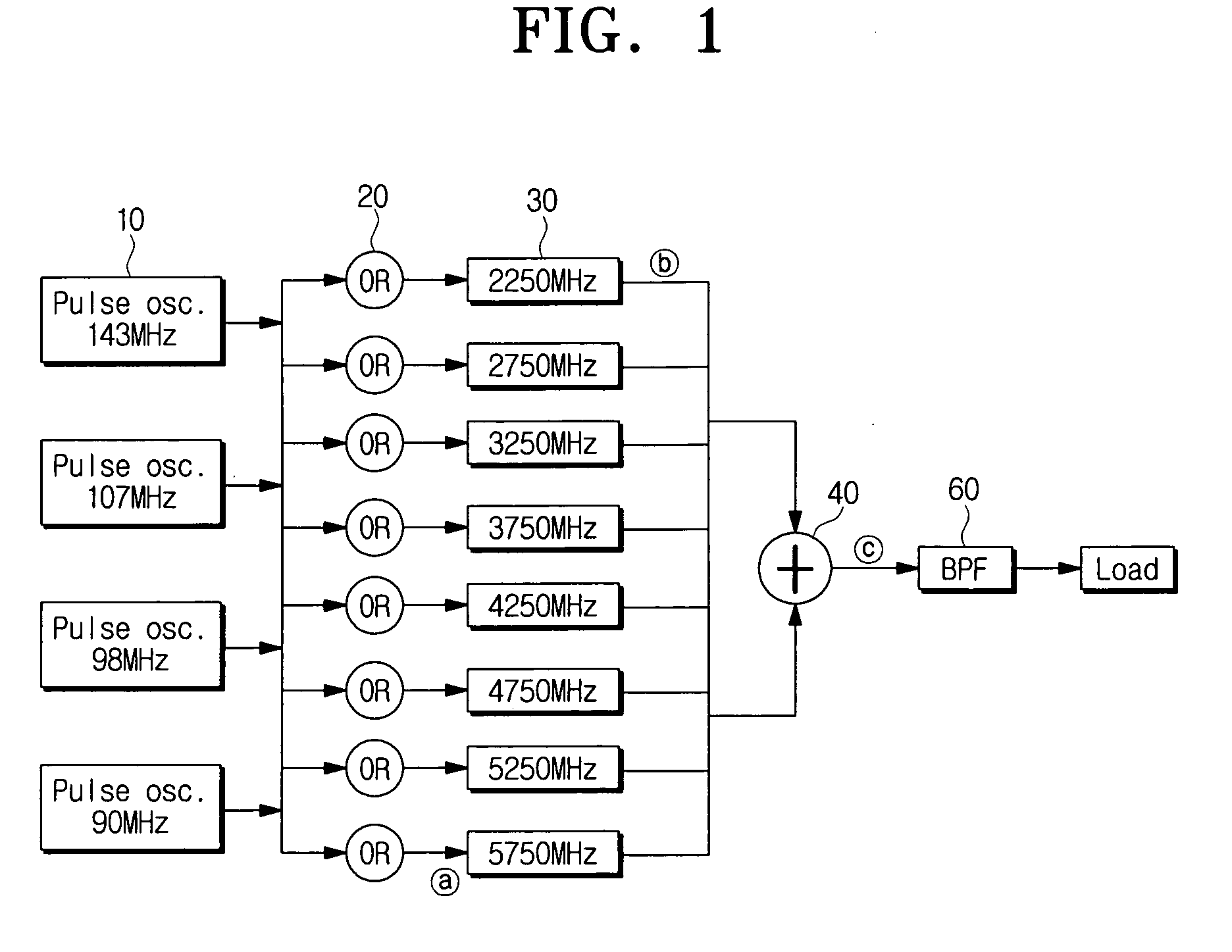

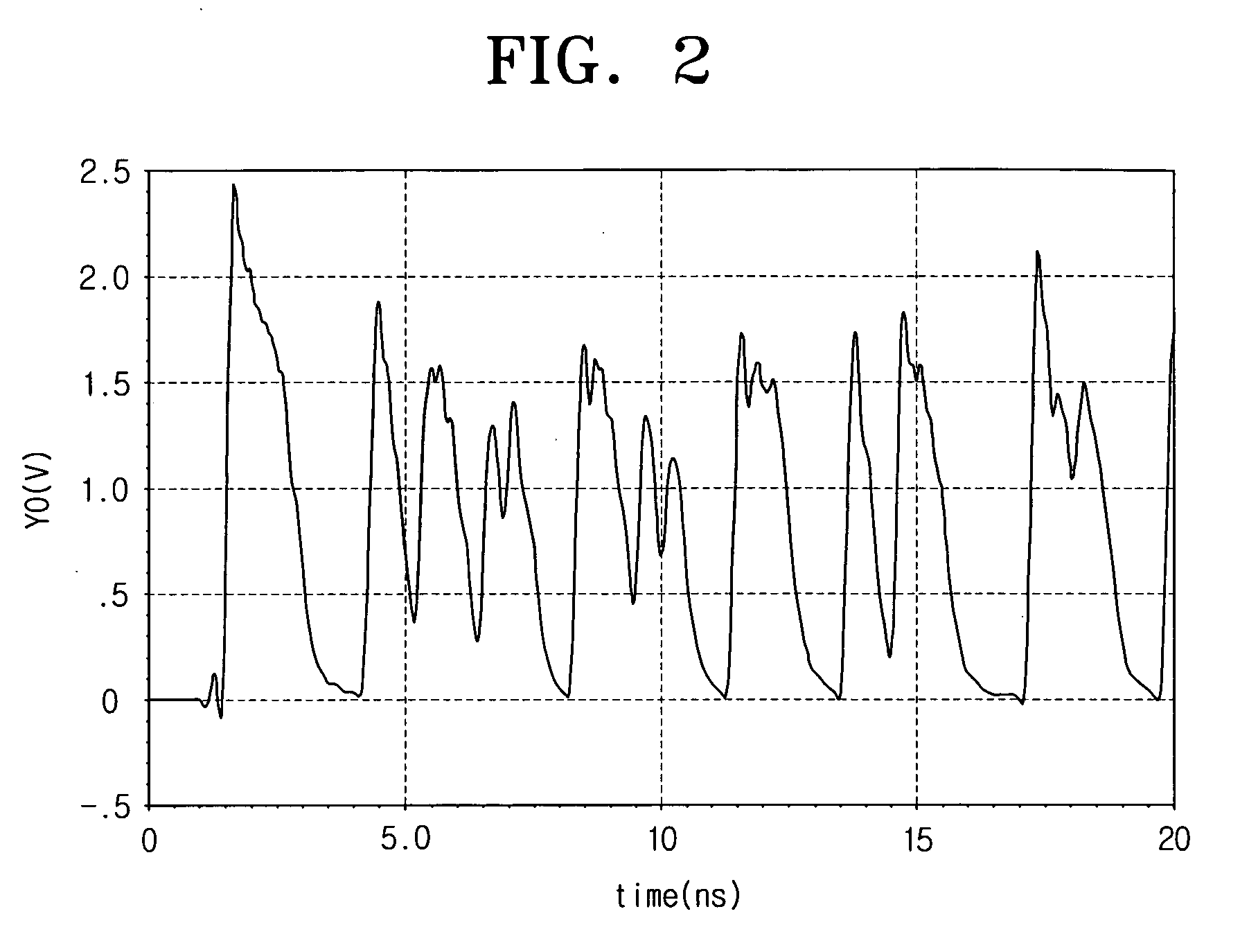

Adjustable chaotic signal generator using pulse modulation for ultra wideband (UWB) communications and chaotic signal generating method thereof

ActiveUS20070121945A1Computations using contact-making devicesModulated-carrier systemsUltra-widebandLocal oscillator

An adjustable chaotic signal generator using pulse modulation for UWB communications, and a chaotic signal generating method thereof are provided. The chaotic signal generator for UWB communications includes a plurality of pulse generators which generates pulses of different frequencies; at least one combiner which combines the pulses generated at the pulse generators; and a plurality of local oscillators which receives signals from the combiner, respectively, and generates a chaotic signal by increasing the received signals to different frequency bands. Accordingly, a plurality of users can conduct the radio communications in a specific wireless communication range at the same time by generating the chaotic signal that can be split to the multiple channels. Also, the chaotic signal generator is structured using devices integratable on an integrated circuit.

Owner:SAMSUNG ELECTRONICS CO LTD

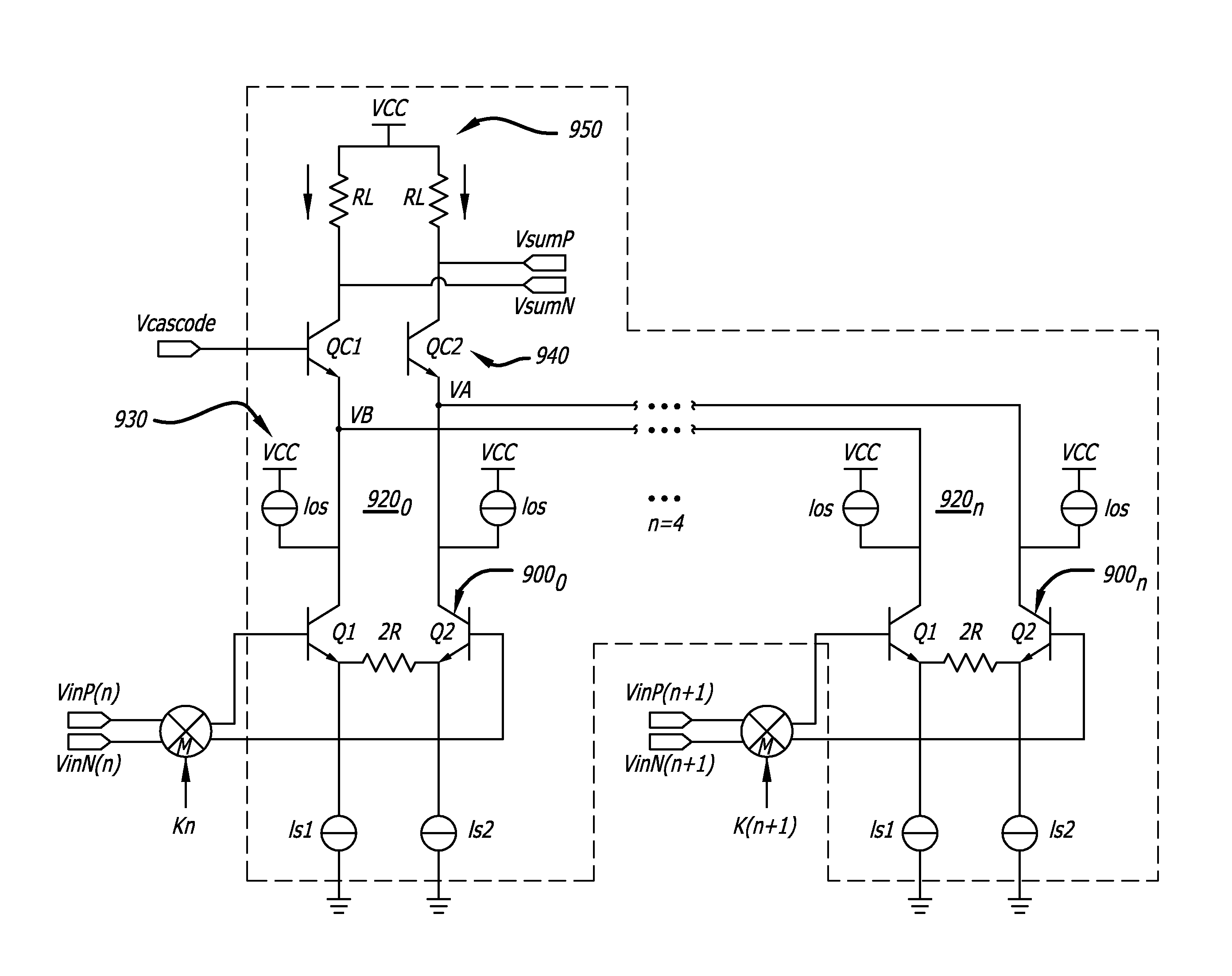

Analog finite impulse response filter

ActiveUS20100271107A1Transversal filtersComputations using contact-making devicesParasitic capacitanceEngineering

According to one embodiment of the invention, a programmable finite impulse response (FIR) filter is implemented with differential isolation circuits to isolate parasitic capacitance from attenuating an output signal at both a first and second differential output terminals of the FIR filter. The FIR includes a summing circuit that provides operational advantages to the FIR filter.

Owner:LUMENTUM OPERATIONS LLC

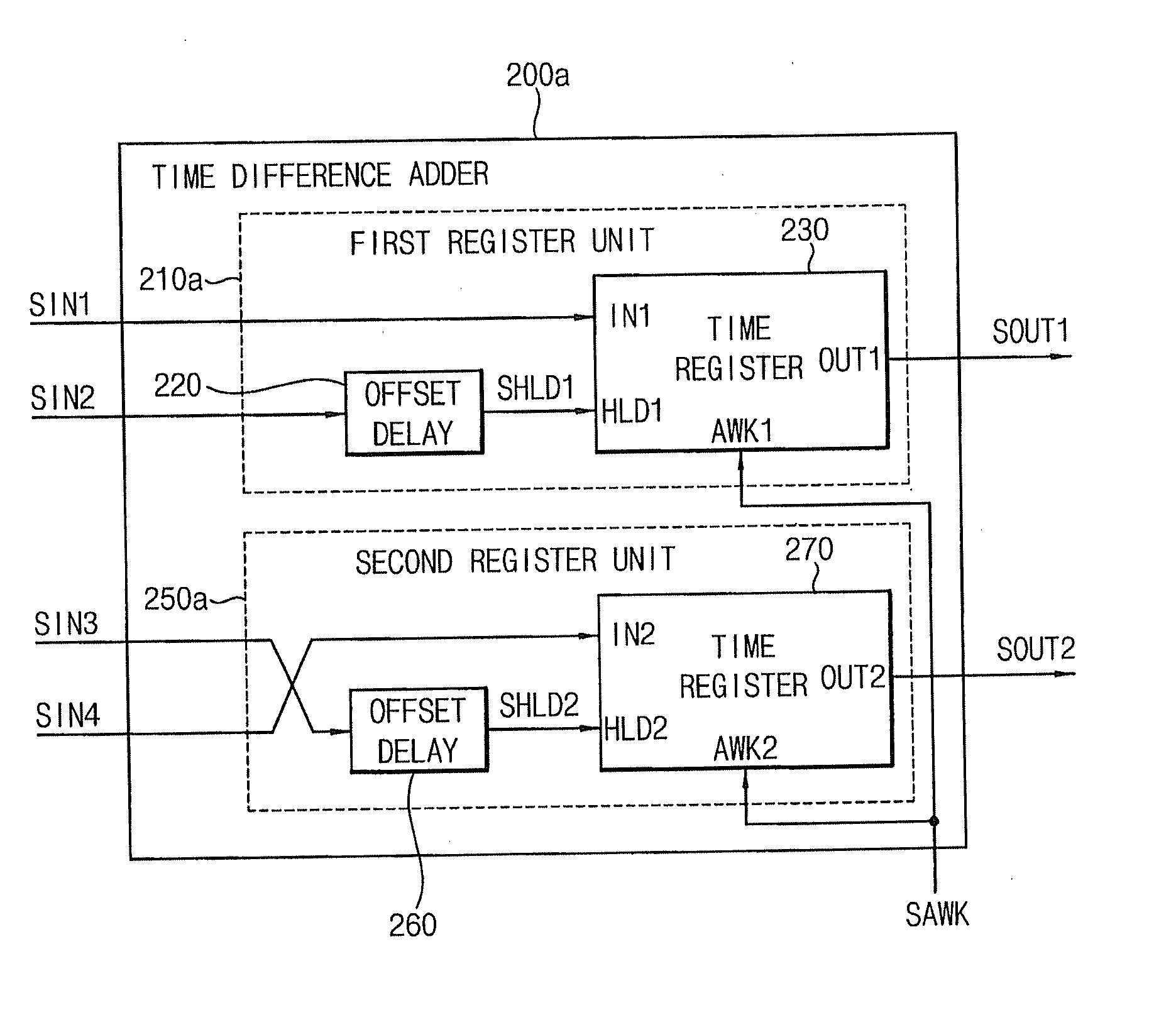

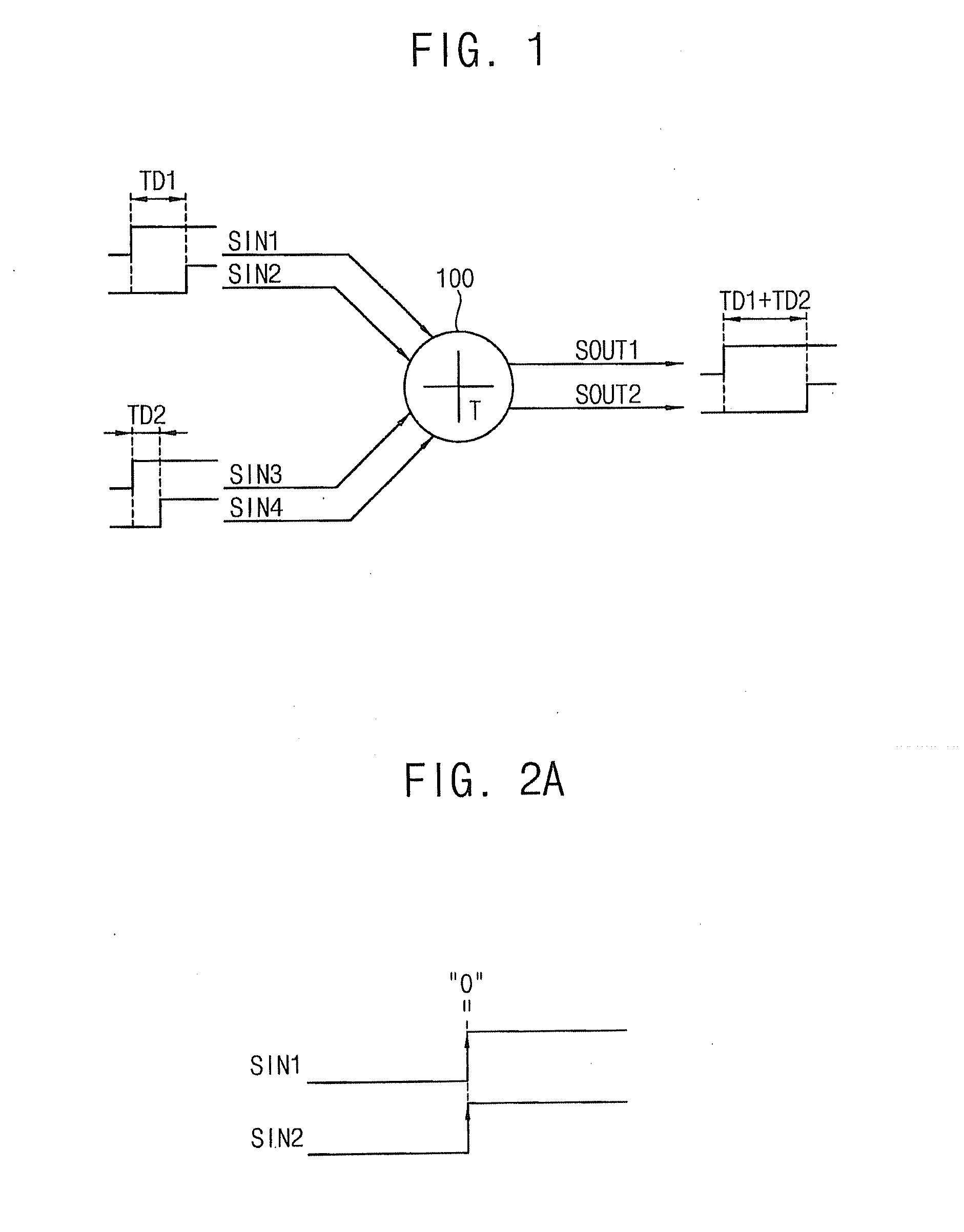

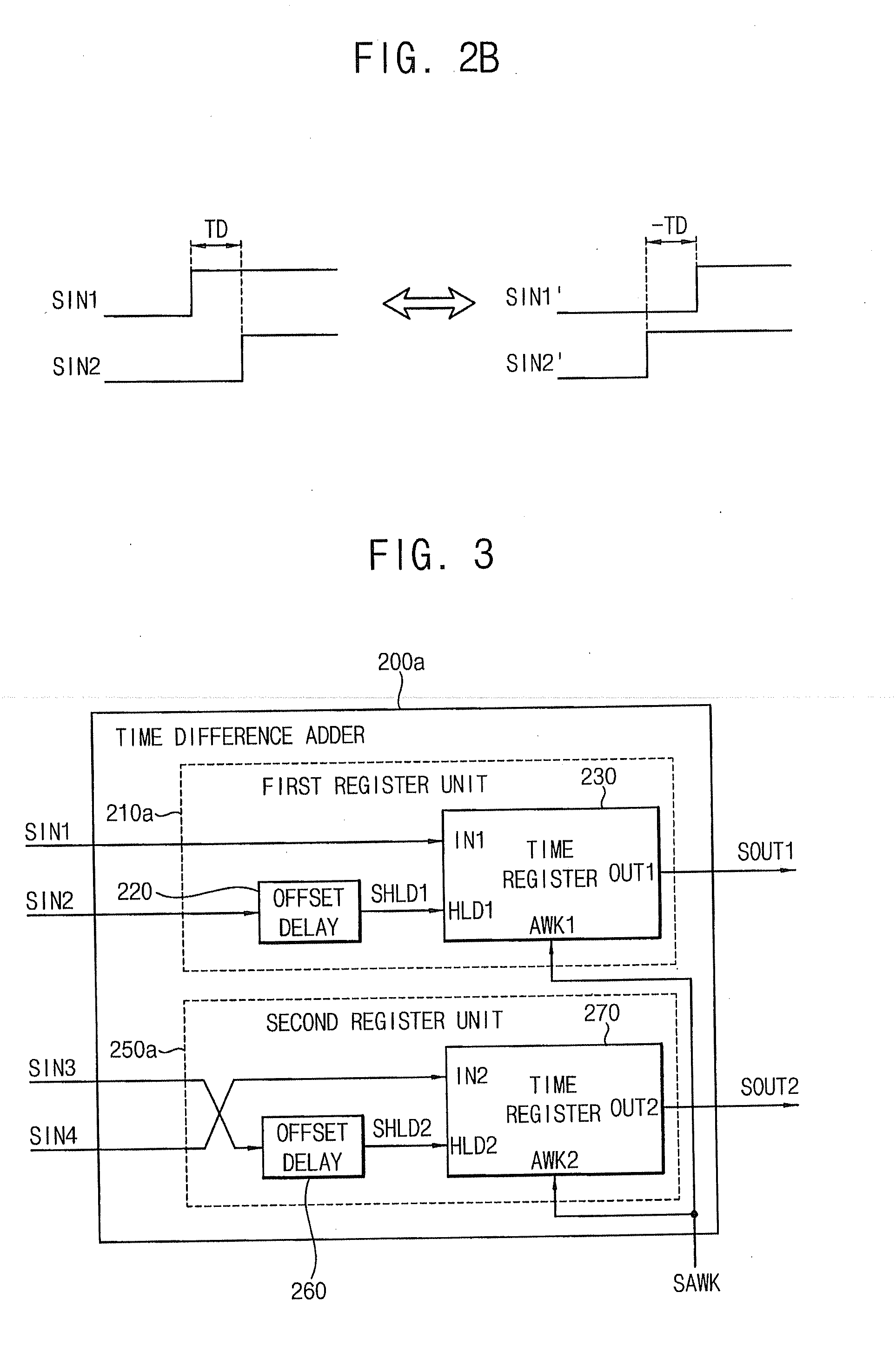

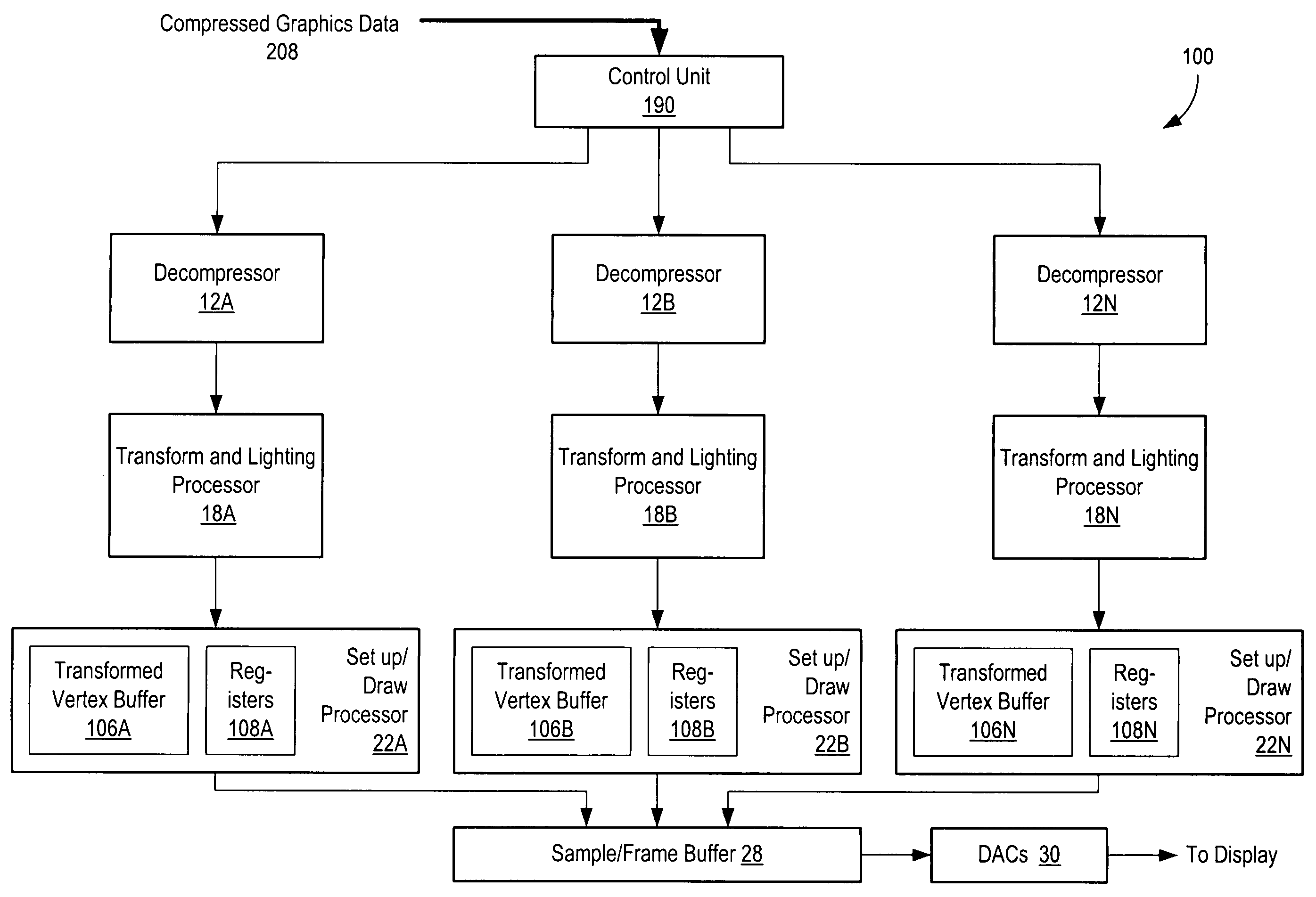

Time difference adders, time difference accumulators, sigma-delta time-to-digital converters, digital phase locked loops and temperature sensors

ActiveUS20120306553A1Computations using contact-making devicesPulse automatic controlDigital down converterProcessor register

A time difference adder included in a system-on-chip (SOC) includes a first register unit and a second register unit. The first register unit is configured to receive first and second input signals having a first time difference, and generate a first output signal in response to a first signal. The second register unit is configured to receive third and fourth input signals having a second time difference, and generate a second output signal having a third time difference with respect to the first output signal in response to the first signal. The third time difference corresponds to a sum of the first time difference and the second time difference.

Owner:SAMSUNG ELECTRONICS CO LTD

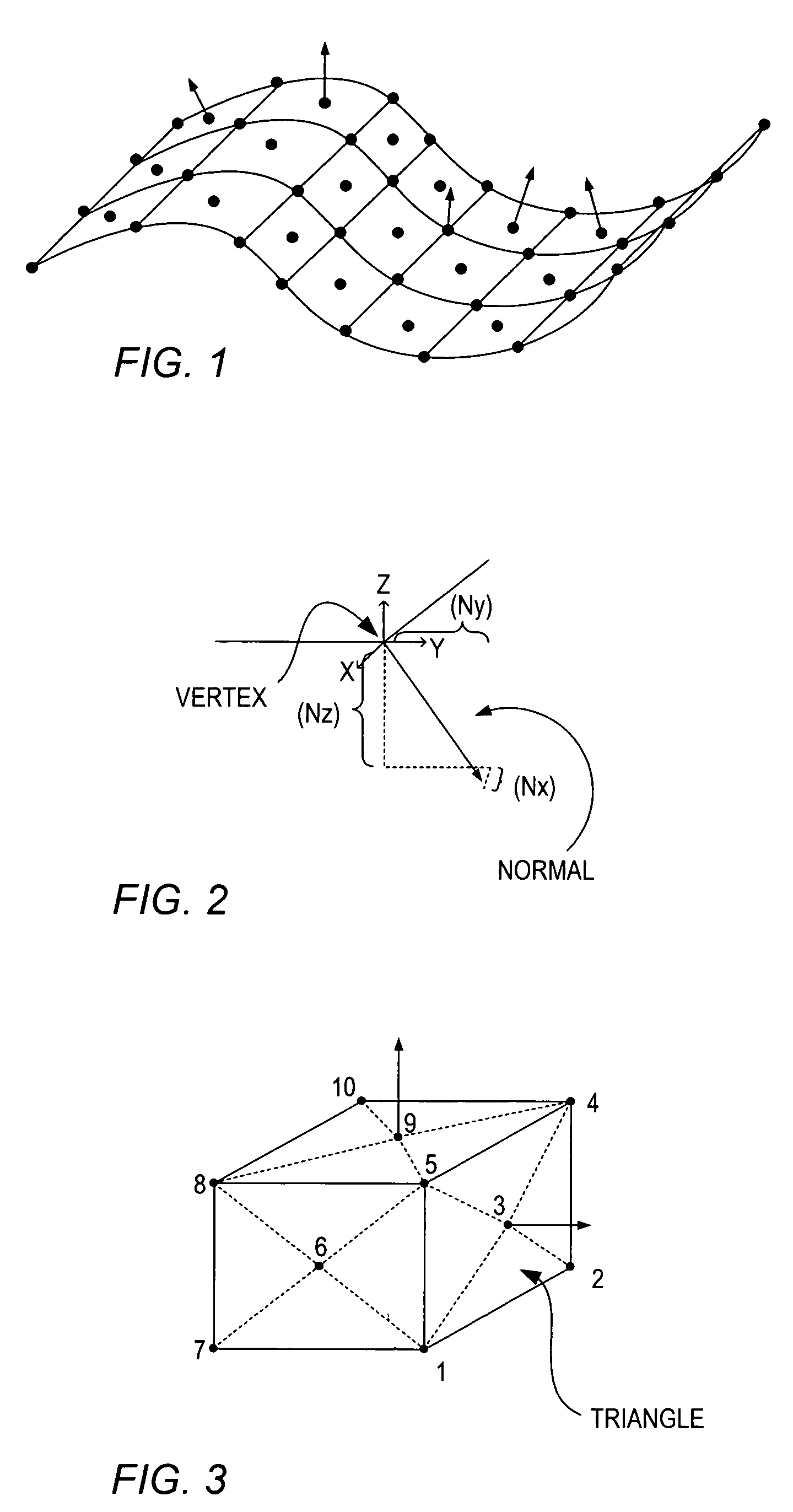

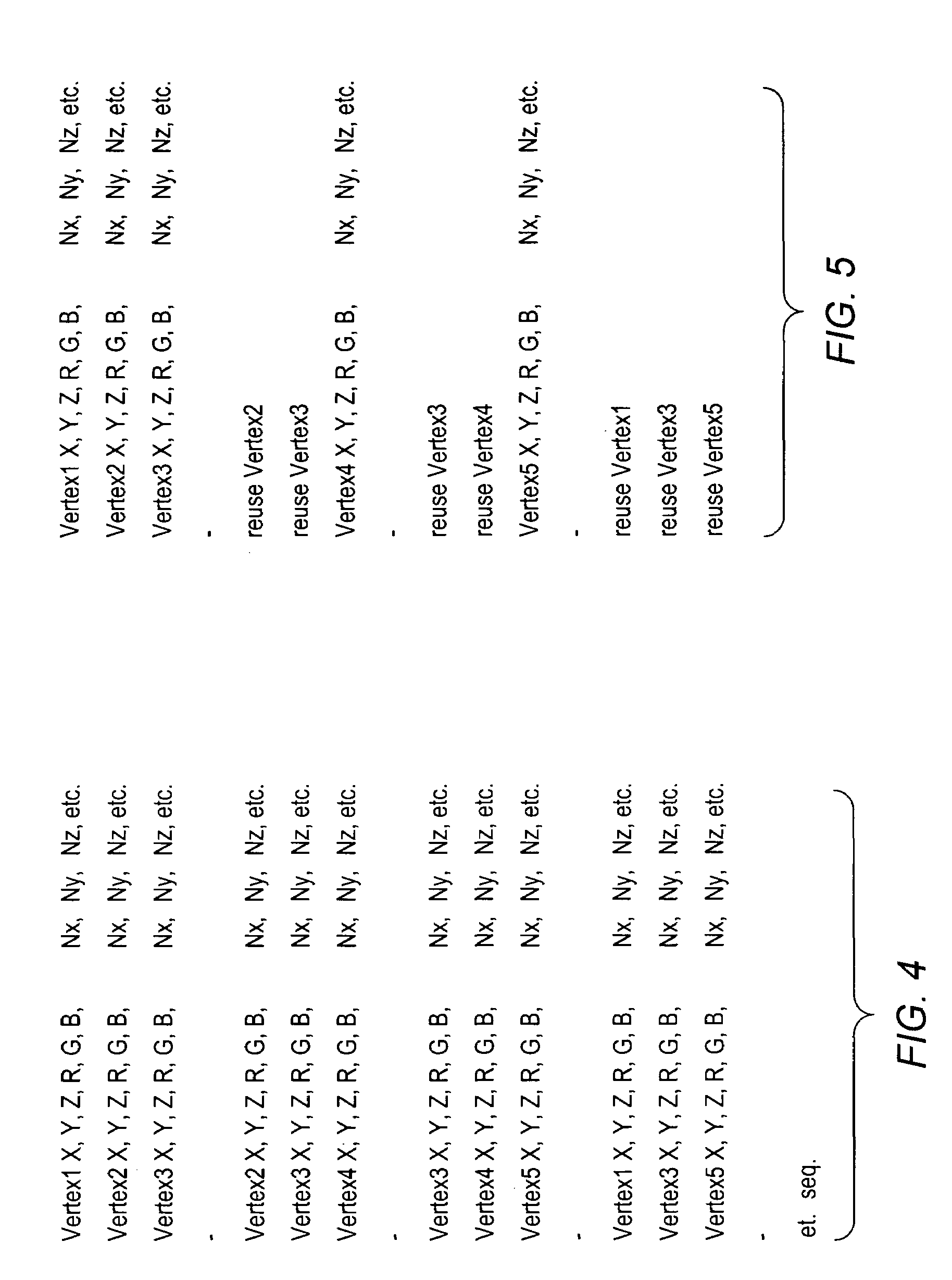

Graphics system with just-in-time decompression of compressed graphics data

InactiveUS7071935B1Improve efficiencyReduce loadComputations using contact-making devicesDigital computer detailsGraphicsGeometric primitive

A graphics system and method for increasing efficiency of decompressing blocks of compressed geometry data and reducing redundant transformation and lighting calculations is disclosed. Multiple decompression pipelines are used to increases the decompression speed. A control unit receives blocks of compressed geometry data information and selectively routes them to a plurality of decompression pipelines. Each decompression pipeline is configured to decompress the blocks into a set of vertices. The reduction in redundant calculations is accomplished by delaying the formation of geometric primitives until after transformation and lighting has been performed on the vertices. Transformation and / or lighting are performed independently on a vertex-by-vertex basis without reference to which geometric primitives the vertices belong to. After transformation and or lighting, geometric primitives may be formed utilizing previously generated connectivity information. The connectivity information may include mesh buffer references, vertex tags, or other types of information.

Owner:ORACLE INT CORP

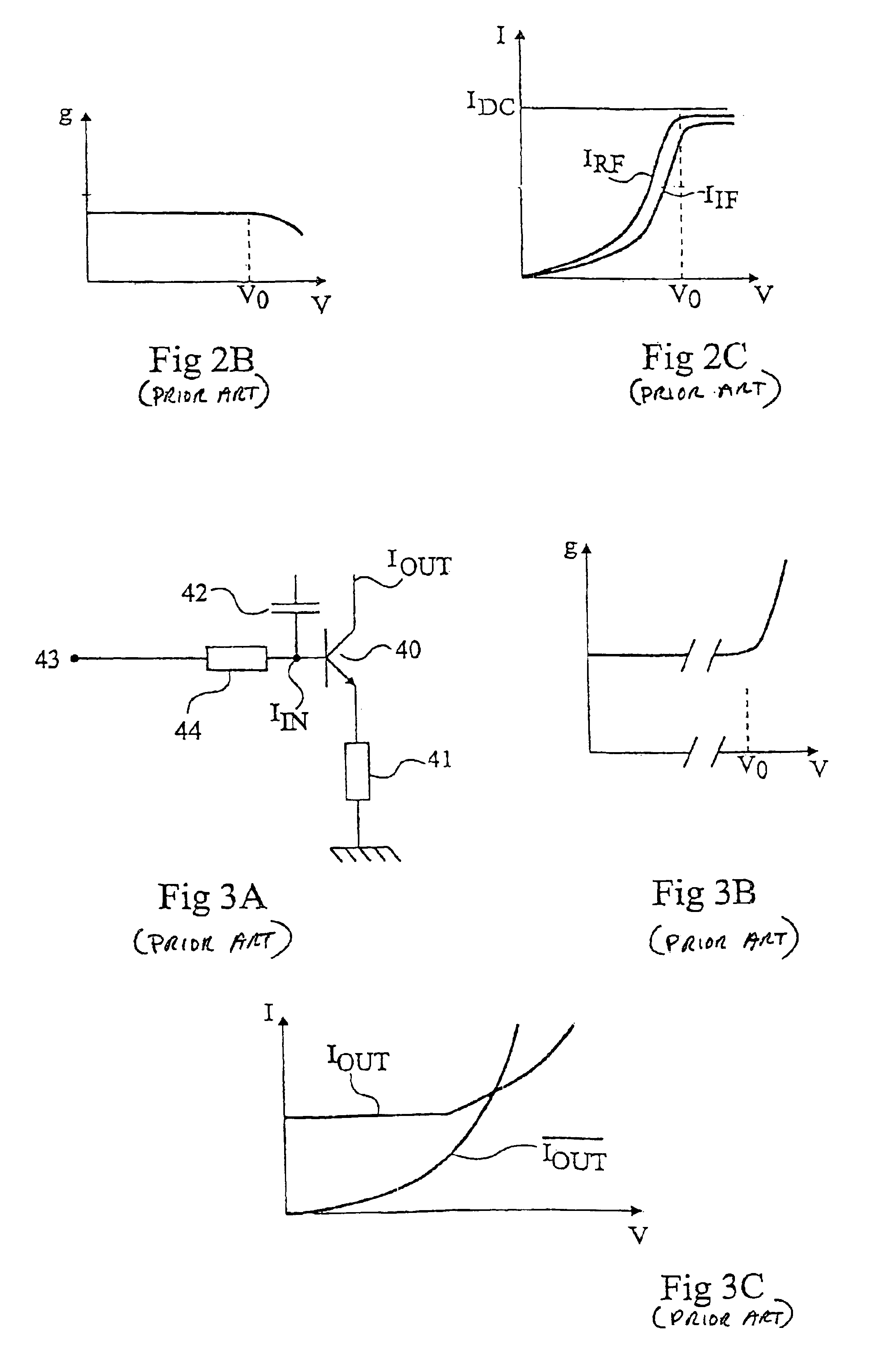

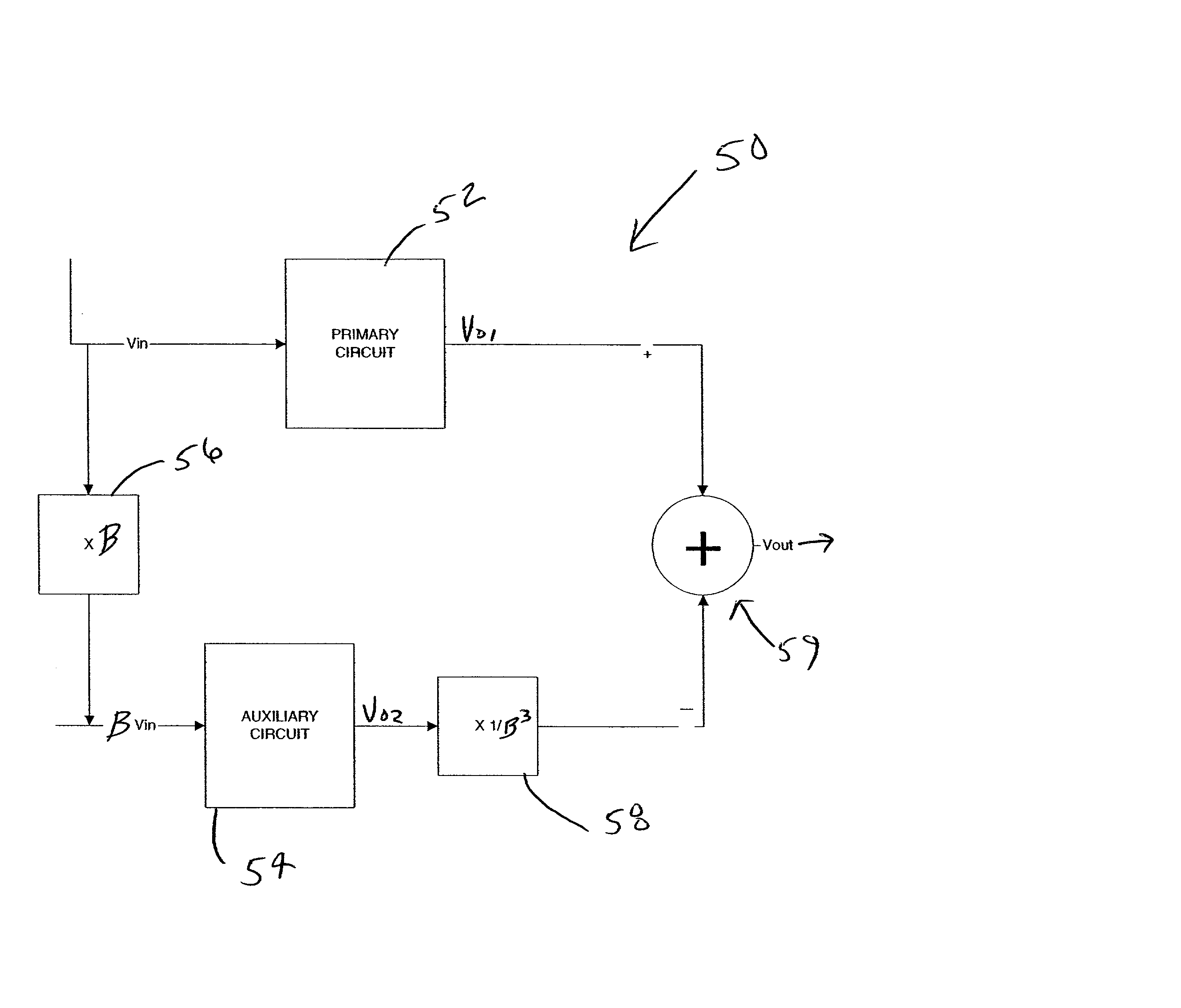

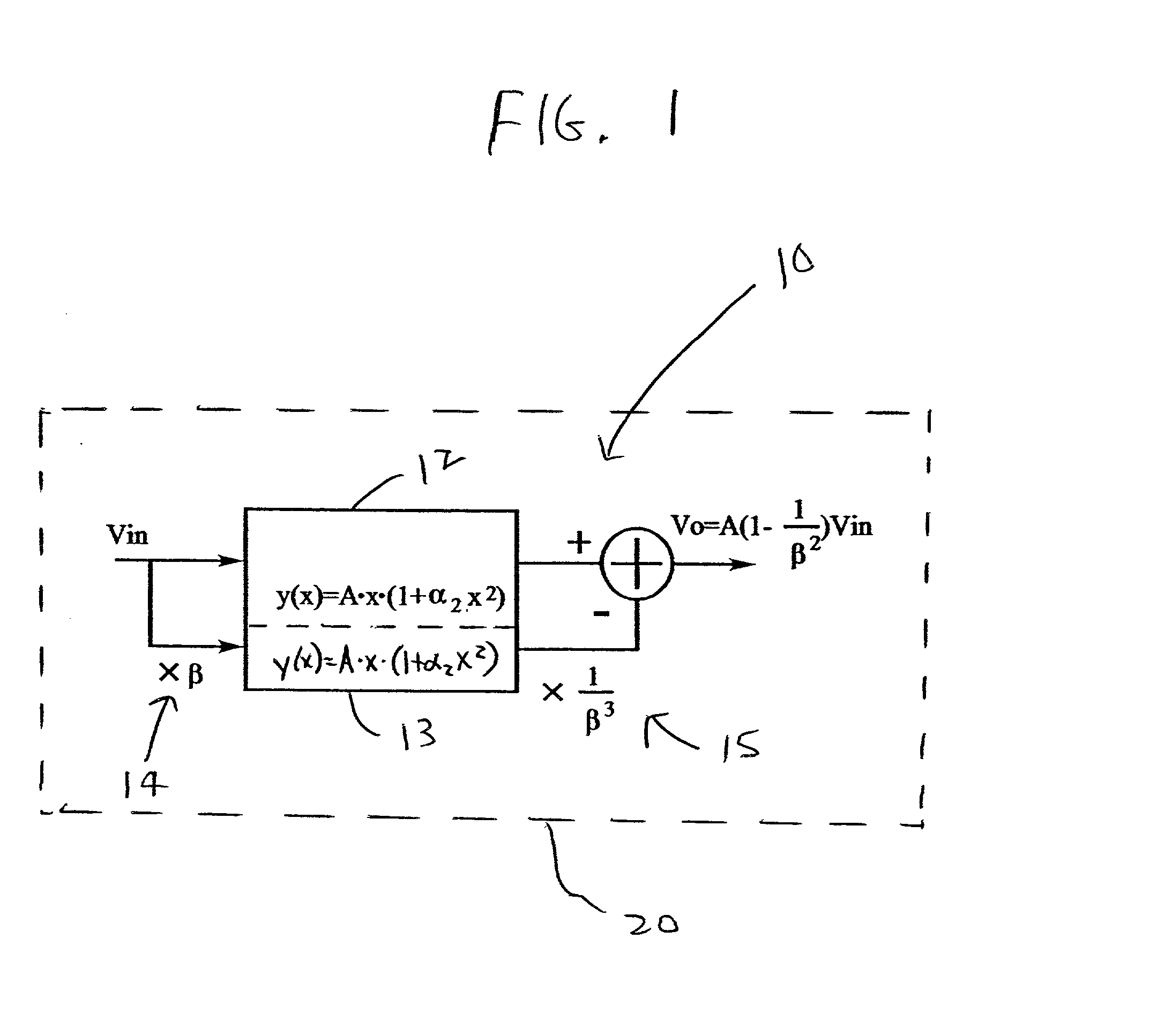

High linearity circuits and methods regarding same

InactiveUS20020126767A1Improve linearitySufficient gainAmplifier modifications to reduce non-linear distortionComputations using contact-making devicesHarmonicLinearity

Circuits and methods that improve linearity with use of cancellation of at least a portion, and preferably, substantially all of, at least one significant harmonic from the output of a primary circuit, e.g., the 3.sup.rd harmonic, using the output of a substantially functionally identical auxiliary circuit.

Owner:RGT UNIV OF MINNESOTA

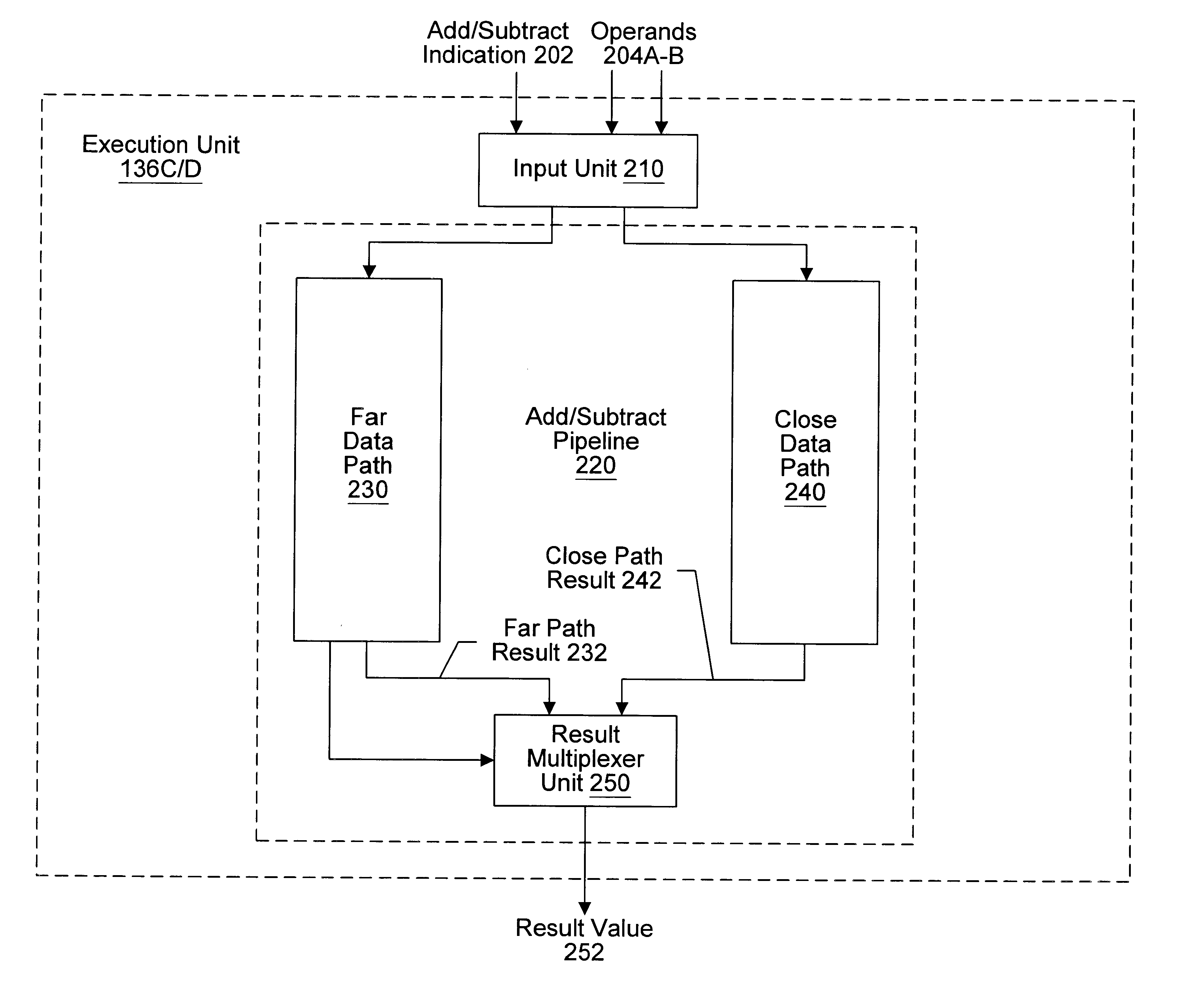

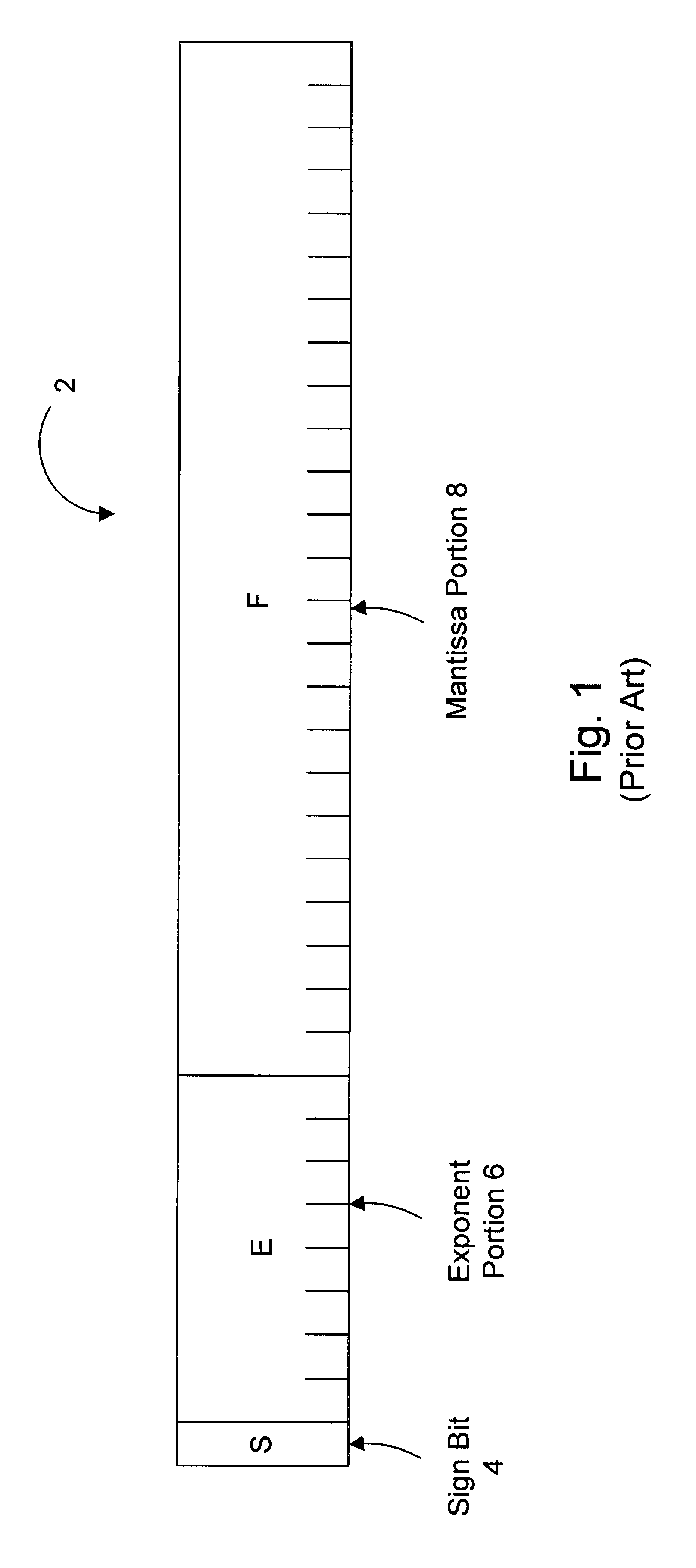

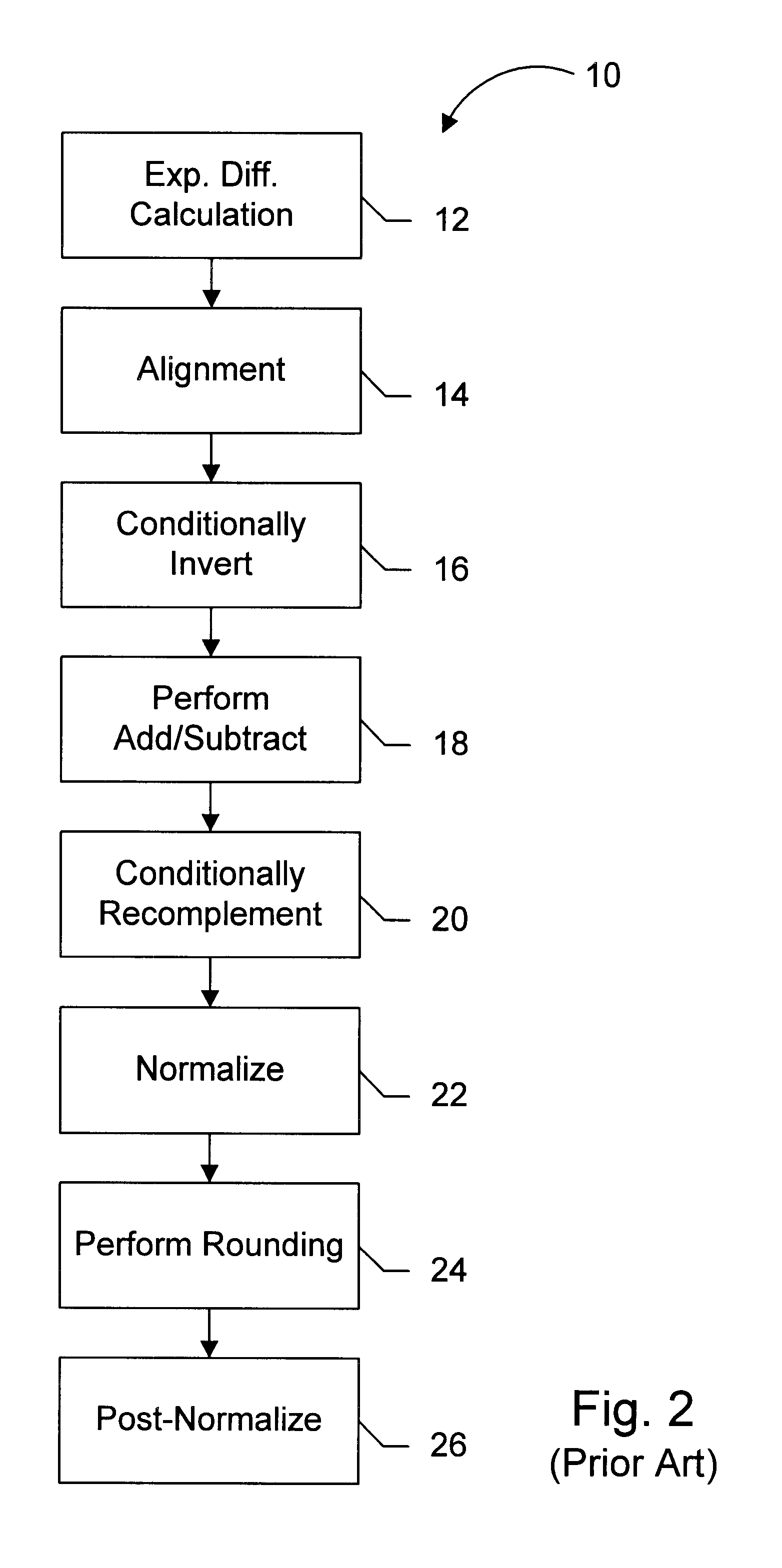

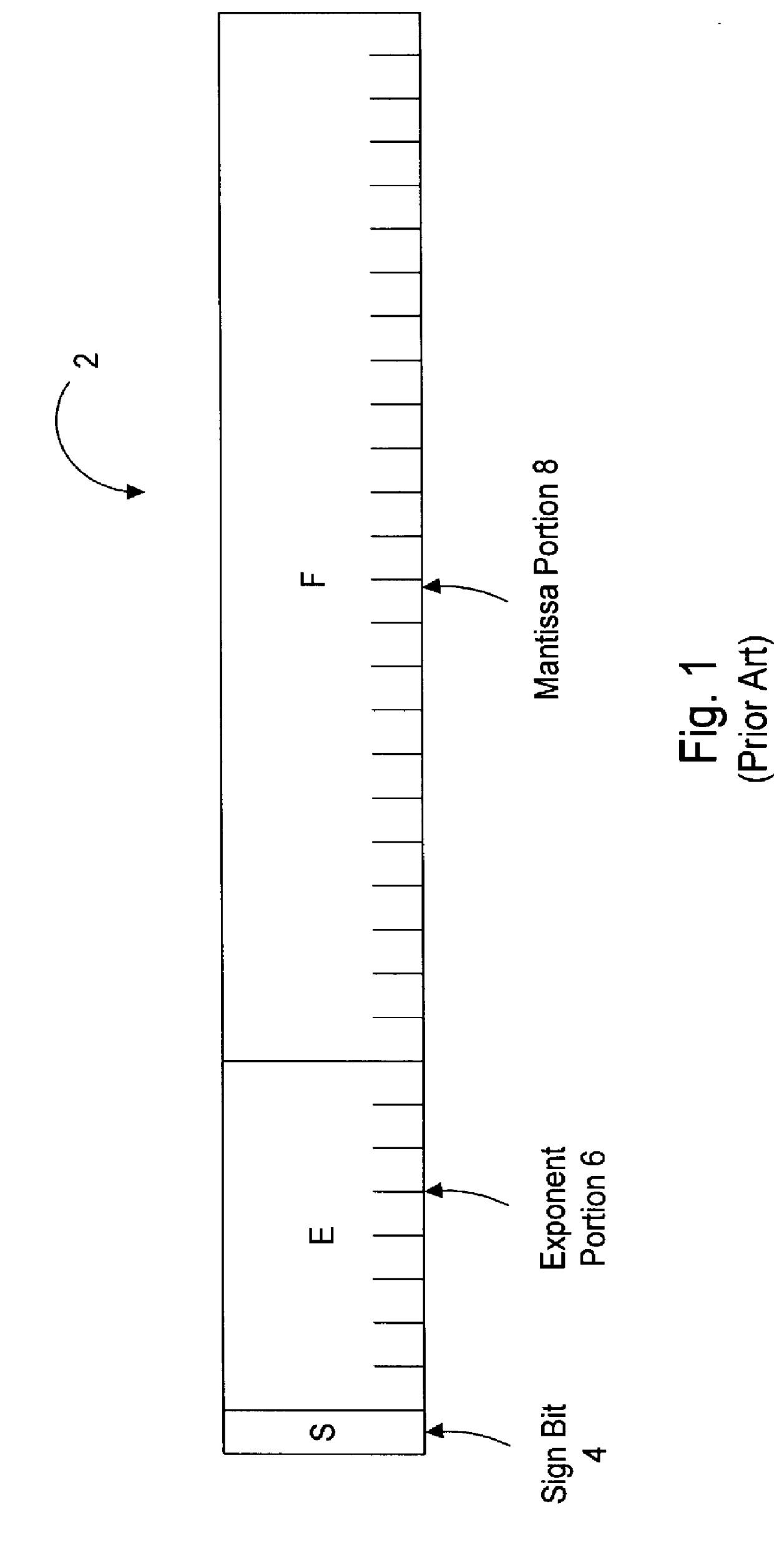

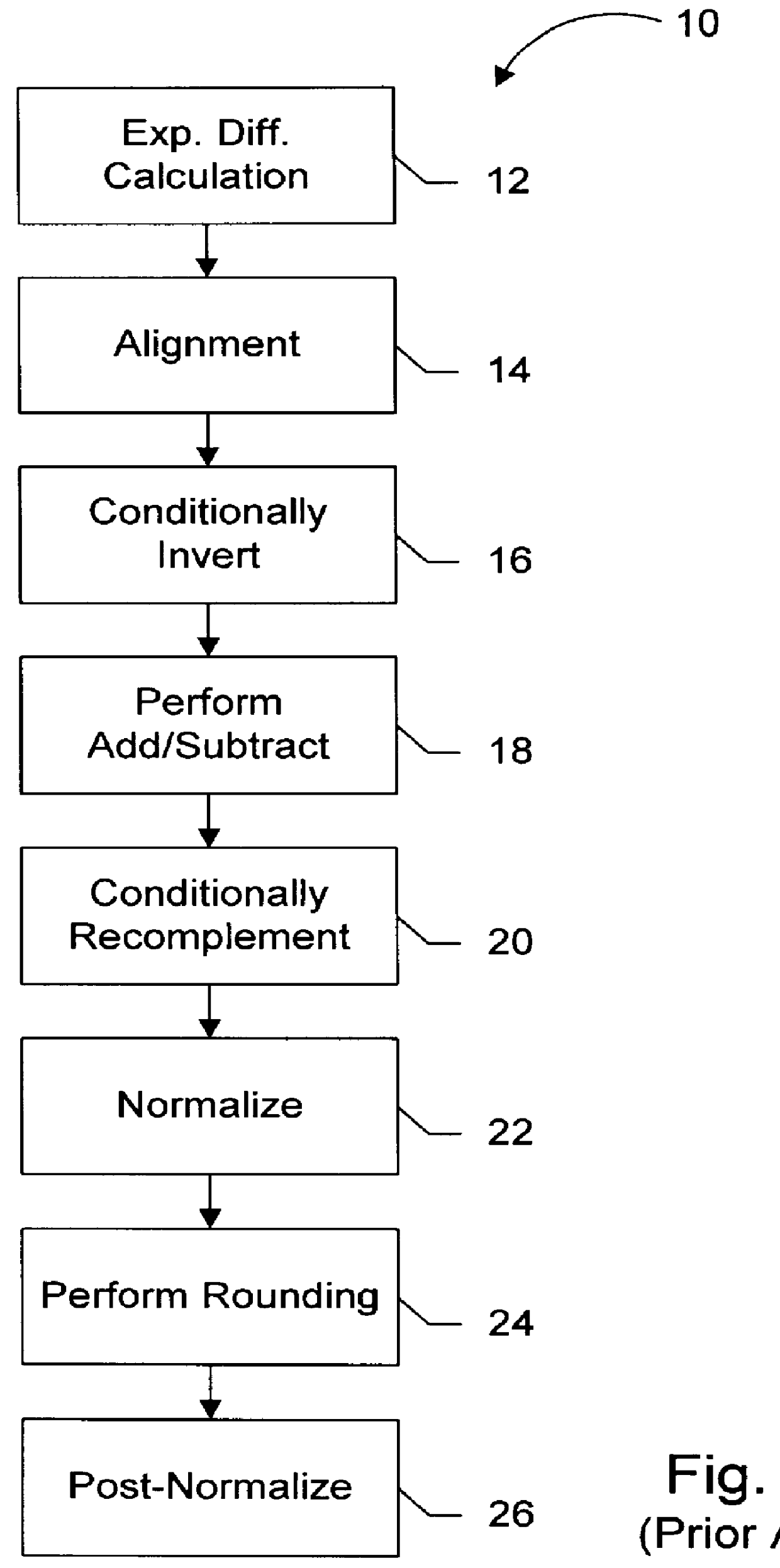

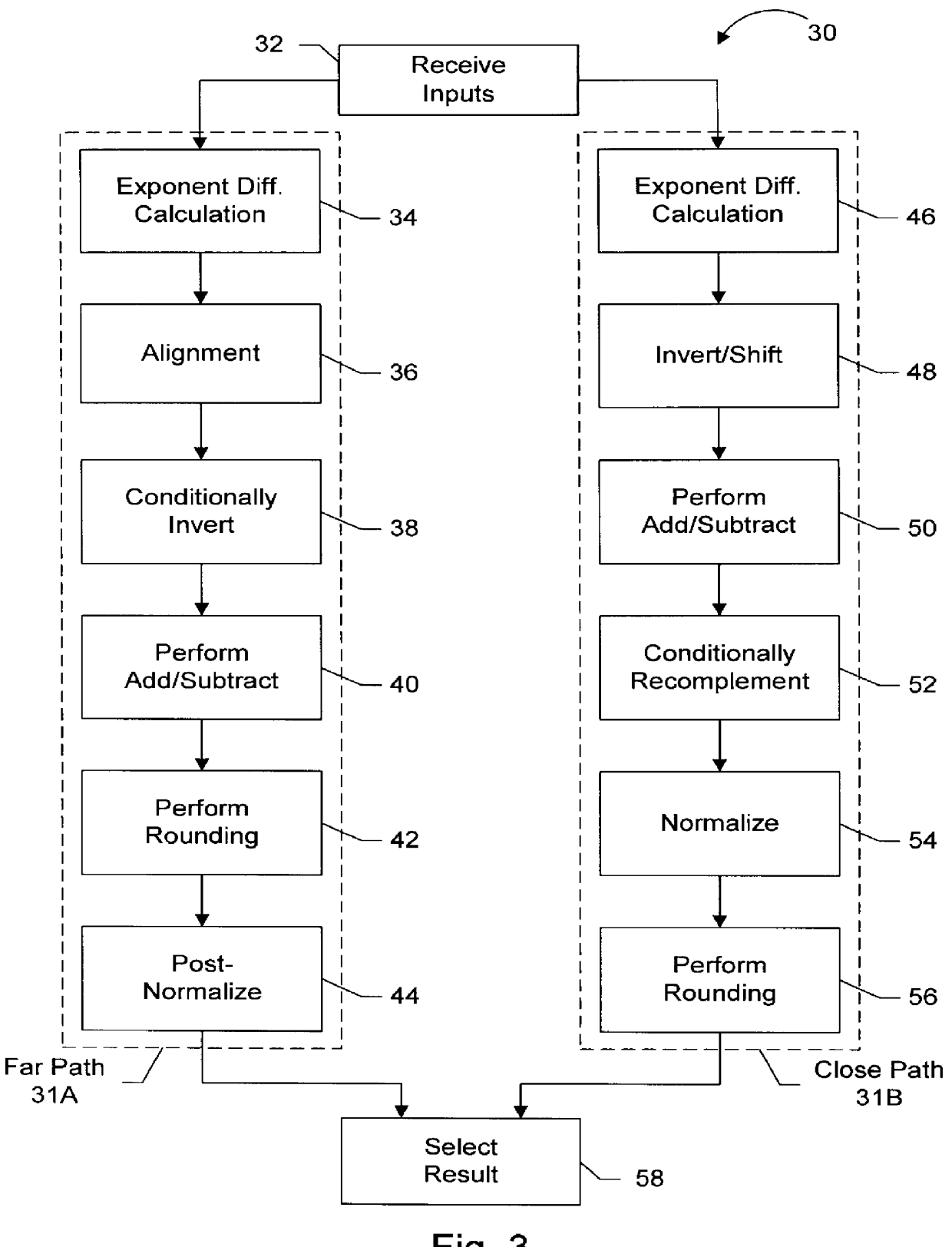

Floating point addition pipeline including extreme value, comparison and accumulate functions

InactiveUS6397239B2Computations using contact-making devicesComputation using non-contact making devicesPathPingExecution unit

A multimedia execution unit configured to perform vectored floating point and integer instructions. The execution unit may include an add / subtract pipeline having far and close data paths. The far path is configured to handle effective addition operations and effective subtraction operations for operands having an absolute exponent difference greater than one. The close path is configured to handle effective subtraction operations for operands having an absolute exponent difference less than or equal to one. The close path is configured to generate two output values, wherein one output value is the first input operand plus an inverted version of the second input operand, while the second output value is equal to the first output value plus one. Selection of the first or second output value in the close path effectuates the round-to-nearest operation for the output of the adder.

Owner:GLOBALFOUNDRIES INC

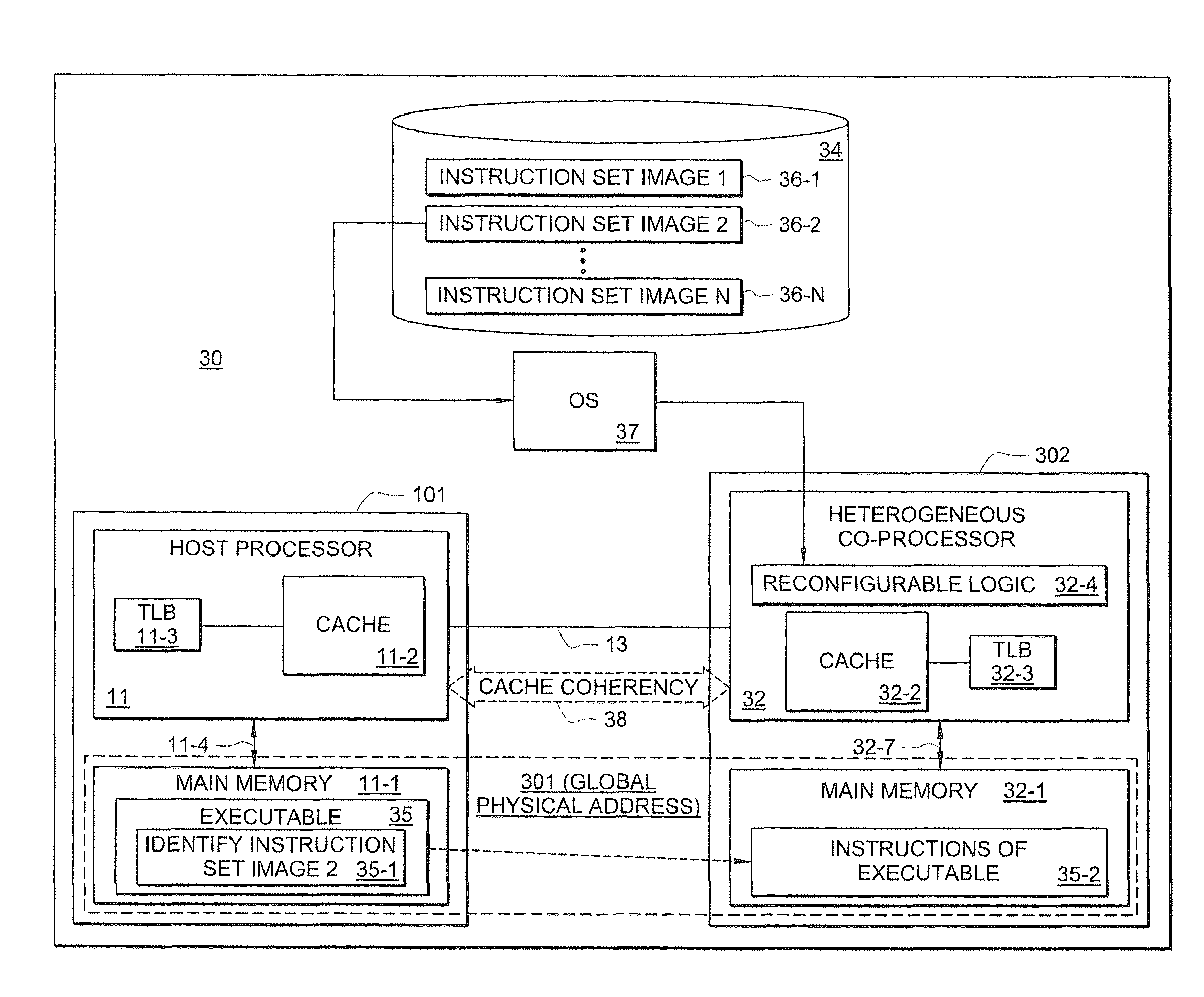

Dispatch mechanism for dispatching instructions from a host processor to a co-processor

ActiveUS8122229B2Computations using contact-making devicesMemory adressing/allocation/relocationMaster processorInstruction set

A dispatch mechanism is provided for dispatching instructions of an executable from a host processor to a heterogeneous co-processor. According to certain embodiments, cache coherency is maintained between the host processor and the heterogeneous co-processor, and such cache coherency is leveraged for dispatching instructions of an executable that are to be processed by the co-processor. For instance, in certain embodiments, a designated portion of memory (e.g., “UCB”) is utilized, wherein a host processor may place information in such UCB and the co-processor can retrieve information from the UCB (and vice-versa). The UCB may thus be used to dispatch instructions of an executable for processing by the co-processor. In certain embodiments, the co-processor may comprise dynamically reconfigurable logic which enables the co-processor's instruction set to be dynamically changed, and the dispatching operation may identify one of a plurality of predefined instruction sets to be loaded onto the co-processor.

Owner:MICRON TECH INC

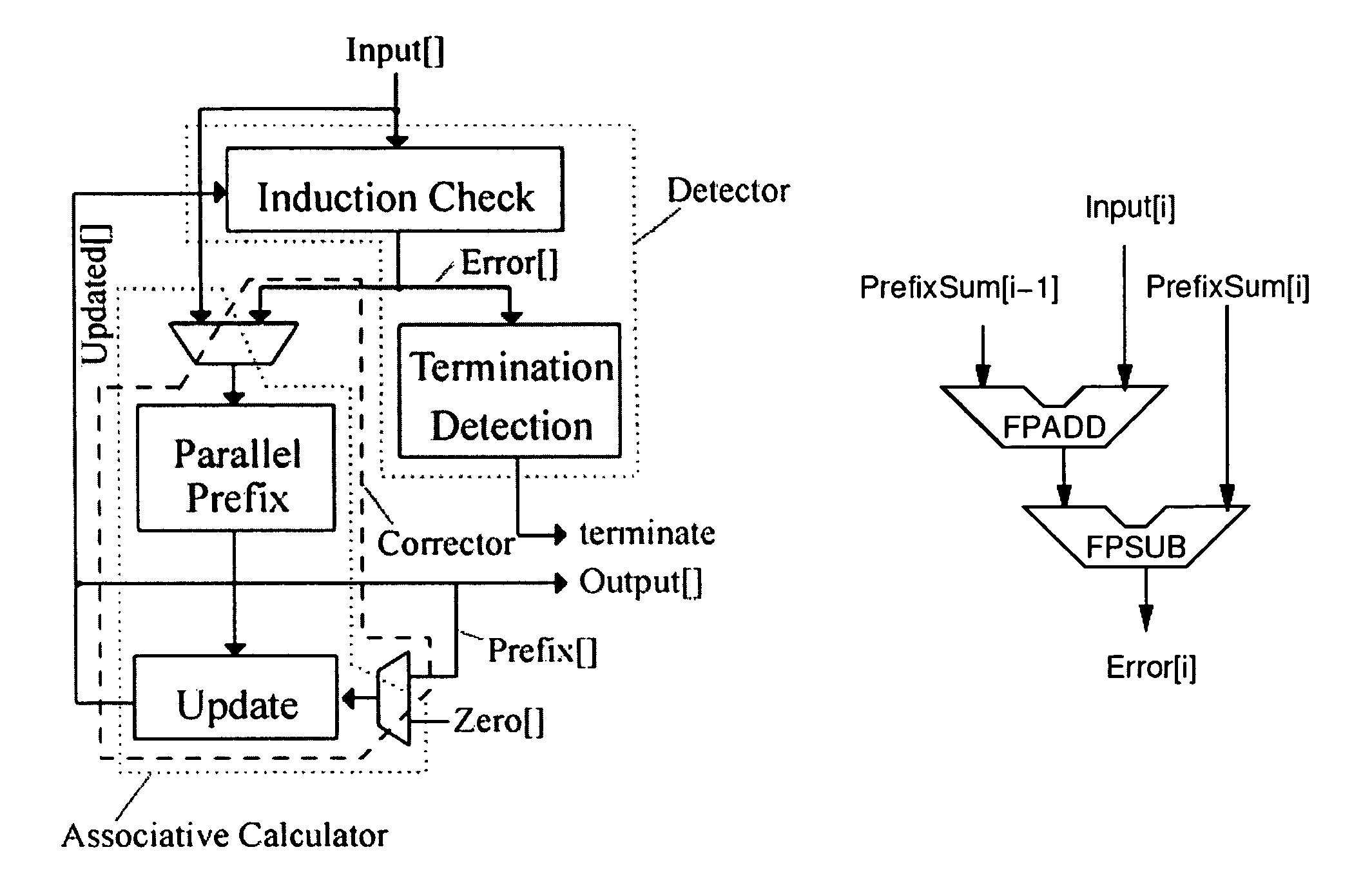

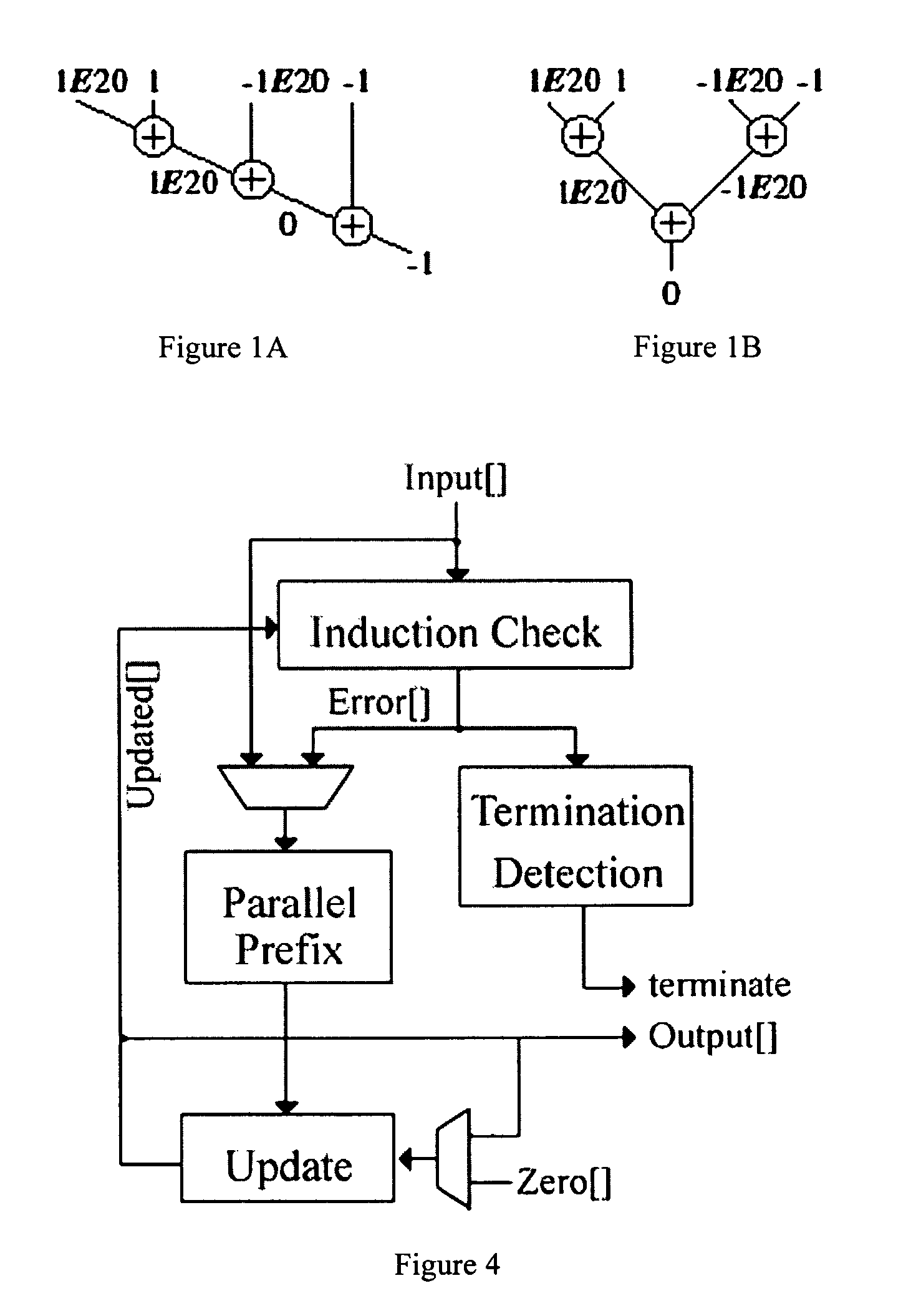

Method and a circuit using an associative calculator for calculating a sequence of non-associative operations

An apparatus and method that use an associative calculator for calculating a sequence of non-associative operations on a set of input data, comprising: using the associative calculator to calculate from the set of input data an evaluated value of each operation of said sequence as if the non-associative operations were associative operations; detecting if some of the evaluated values are erroneous; if there are erroneous evaluated values, correcting the erroneous evaluated values; and if there are no erroneous evaluated value, outputting as the result of the sequence of non-associative operations the evaluated value of the last operation of the sequence.

Owner:CALIFORNIA INST OF TECH

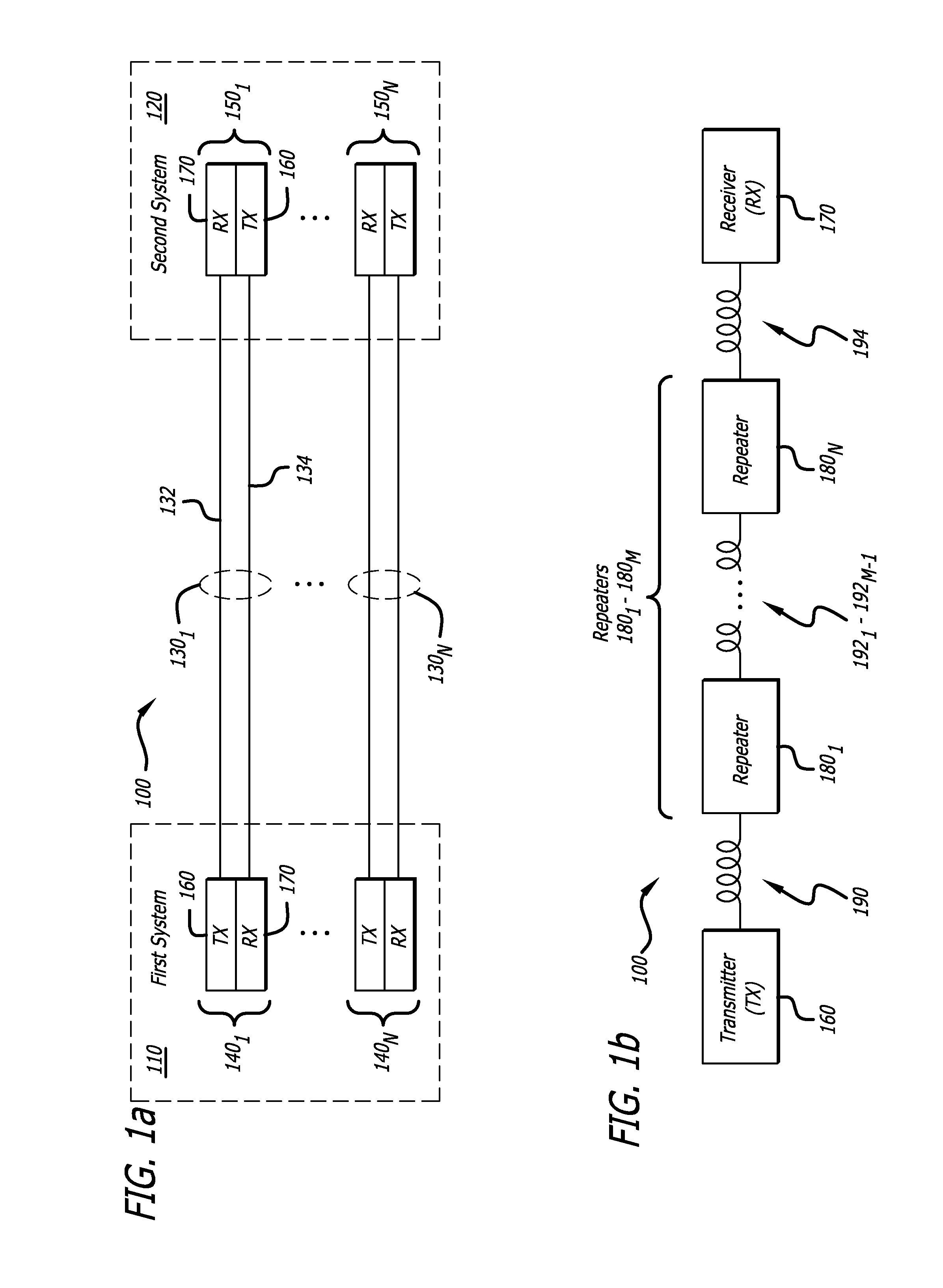

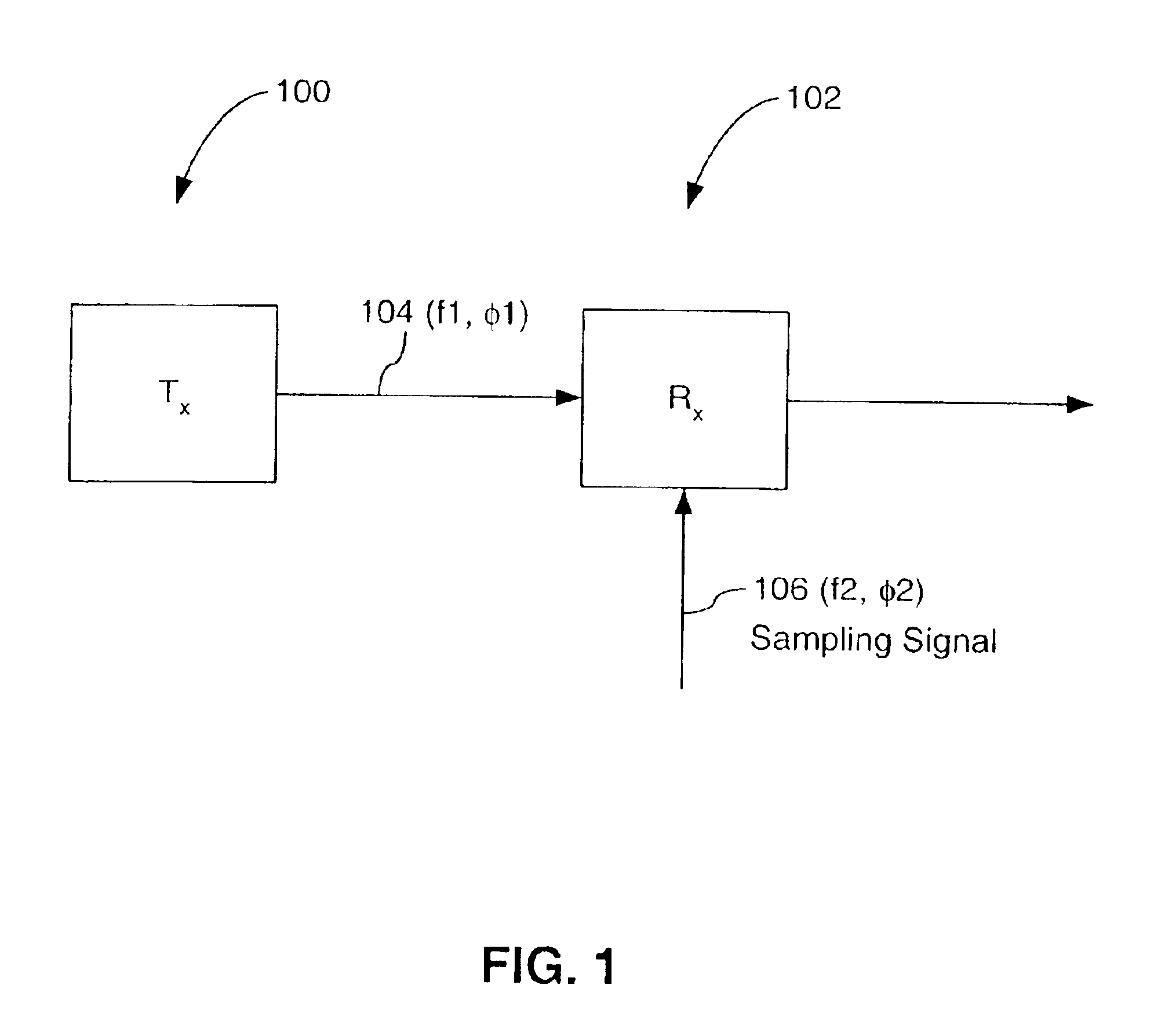

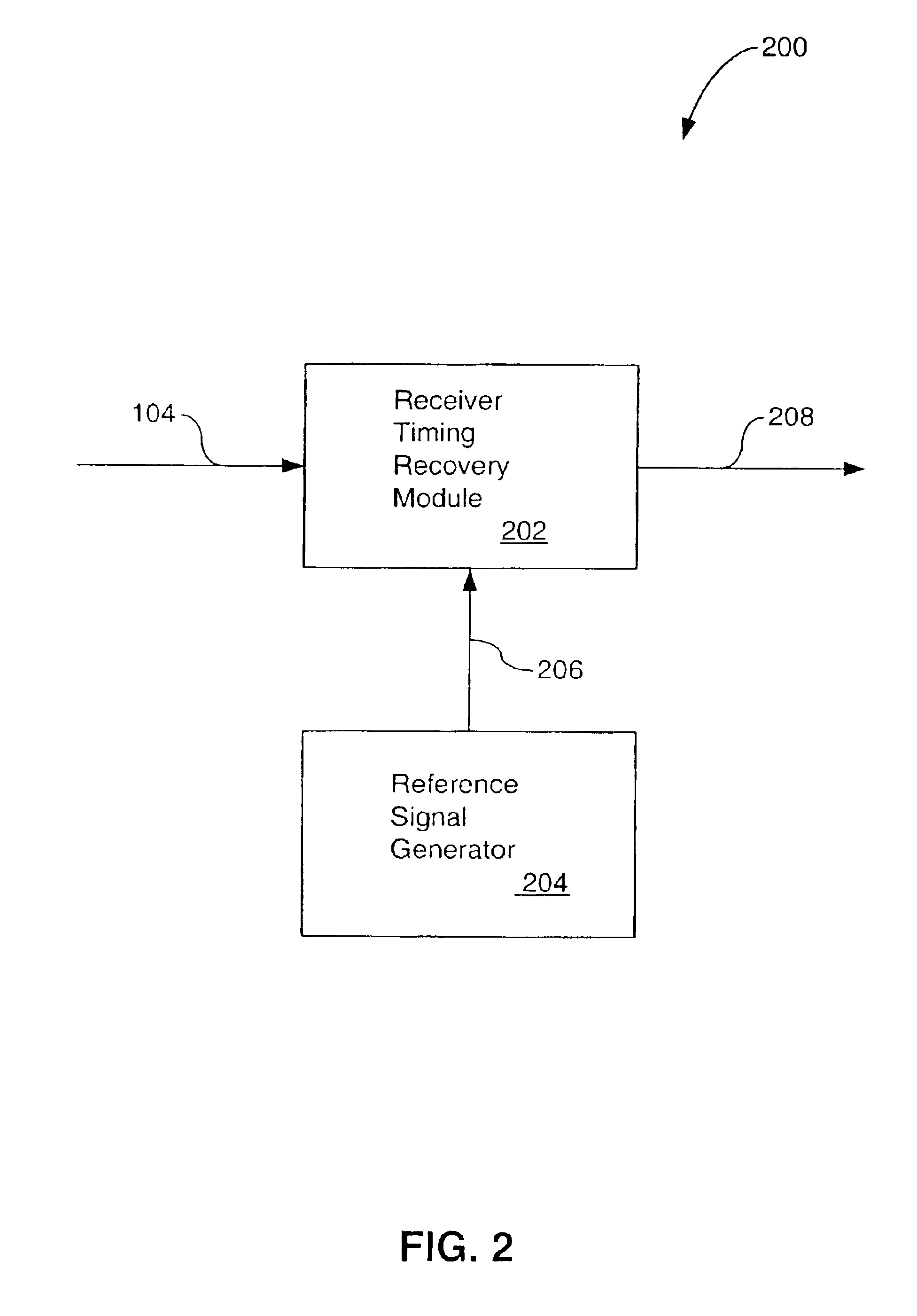

Phase interpolator device and method

InactiveUS6791388B2Reduce frequency offsetComputations using contact-making devicesPulse automatic controlTransceiverGigabit

A high-speed serial data transceiver includes multiple receivers and transmitters for receiving and transmitting multiple analog, serial data signals at multi-gigabit-per-second data rates. Each receiver includes a timing recovery system for tracking a phase and a frequency of the serial data signal associated with the receiver. The timing recovery system includes a phase interpolator responsive to phase control signals and a set of reference signals having different predetermined phases. The phase interpolator derives a sampling signal, having an interpolated phase, to sample the serial data signal. The timing recovery system in each receiver independently phase-aligns and frequency synchronizes the sampling signal to the serial data signal associated with the receiver. A receiver can include multiple paths for sampling a received, serial data signal in accordance with multiple time-staggered sampling signals, each having an interpolated phase.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

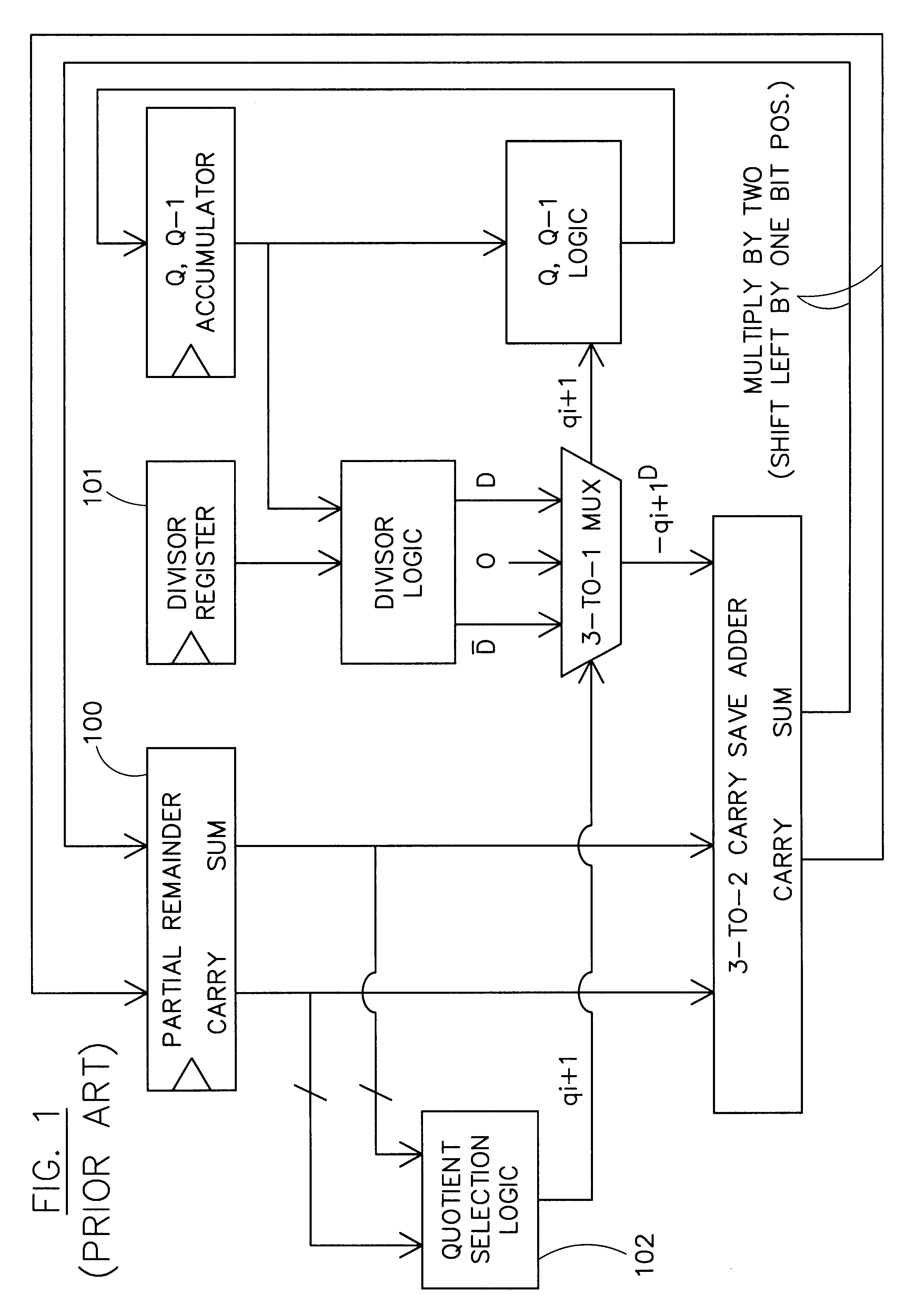

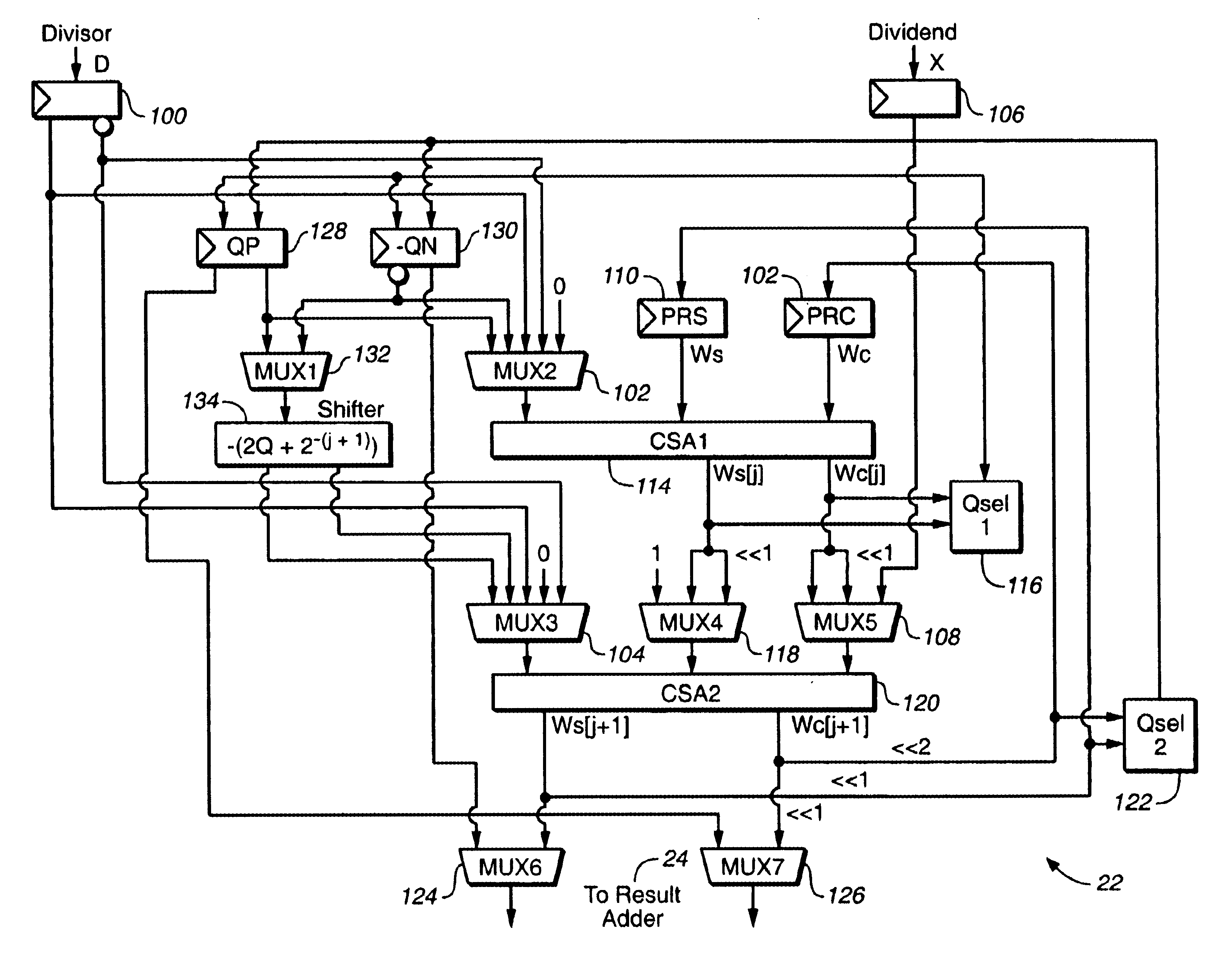

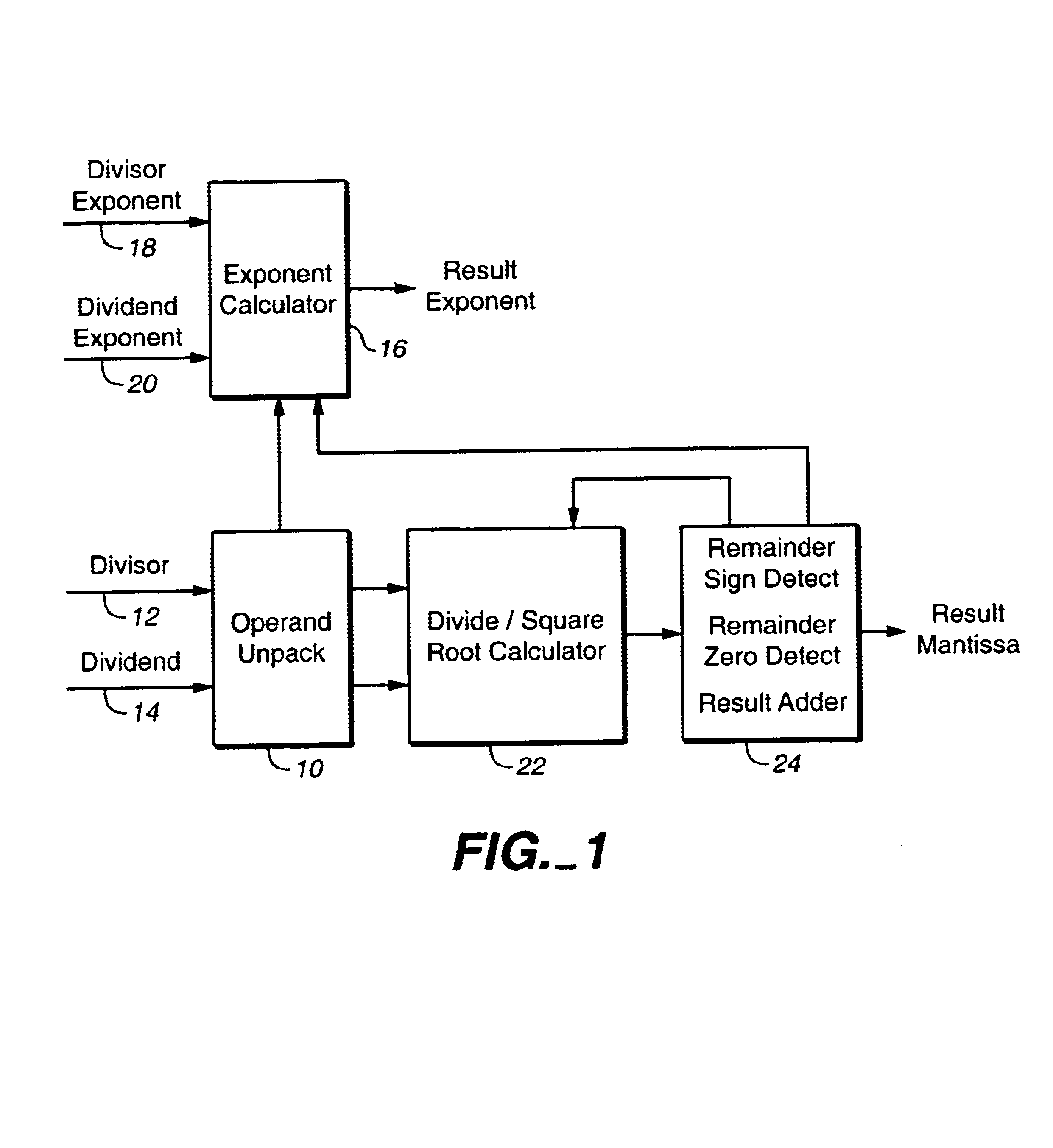

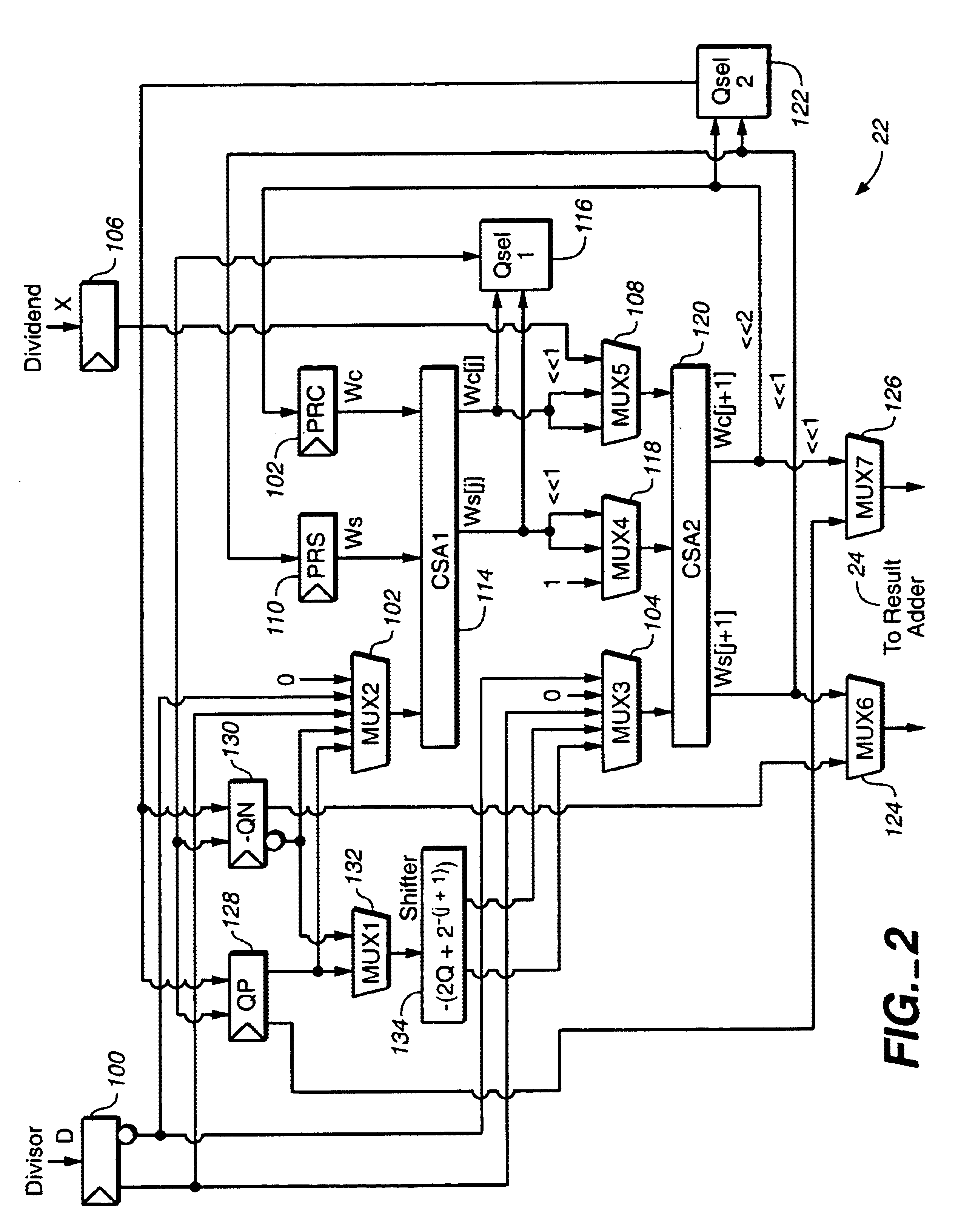

Floating point divide and square root processor

An iterative mantissa calculator calculates a quotient mantissa for a divide mode or a result mantissa for a square-root mode. The calculator includes at least first and second summing devices. In the divide mode, each summing device calculates a respective estimated partial remainder W[j+1] for the next iteration, j+1, as 2*W[j]−Sj+1*D, where W[j] is the estimated partial remainder for the current iteration calculated during the prior iteration, Sj+1 is the quotient bit estimated for the next iteration, and D is the respective divisor bit. The estimated quotient bit for the next iteration is selected based on the calculated partial remainder. In the square-root mode, the first summing device calculates 2W[j]−2S[j]Sj+1, where W[j] is the estimated partial remainder and Sj+1 is the estimated result generated during the current iteration, j. A shift register shifts the value of the estimated result, Sj+1, to generate −Sj+12·2−(j+1), which is summed with the result from the first summing device to generate the estimated partial remainder for the square root mode.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

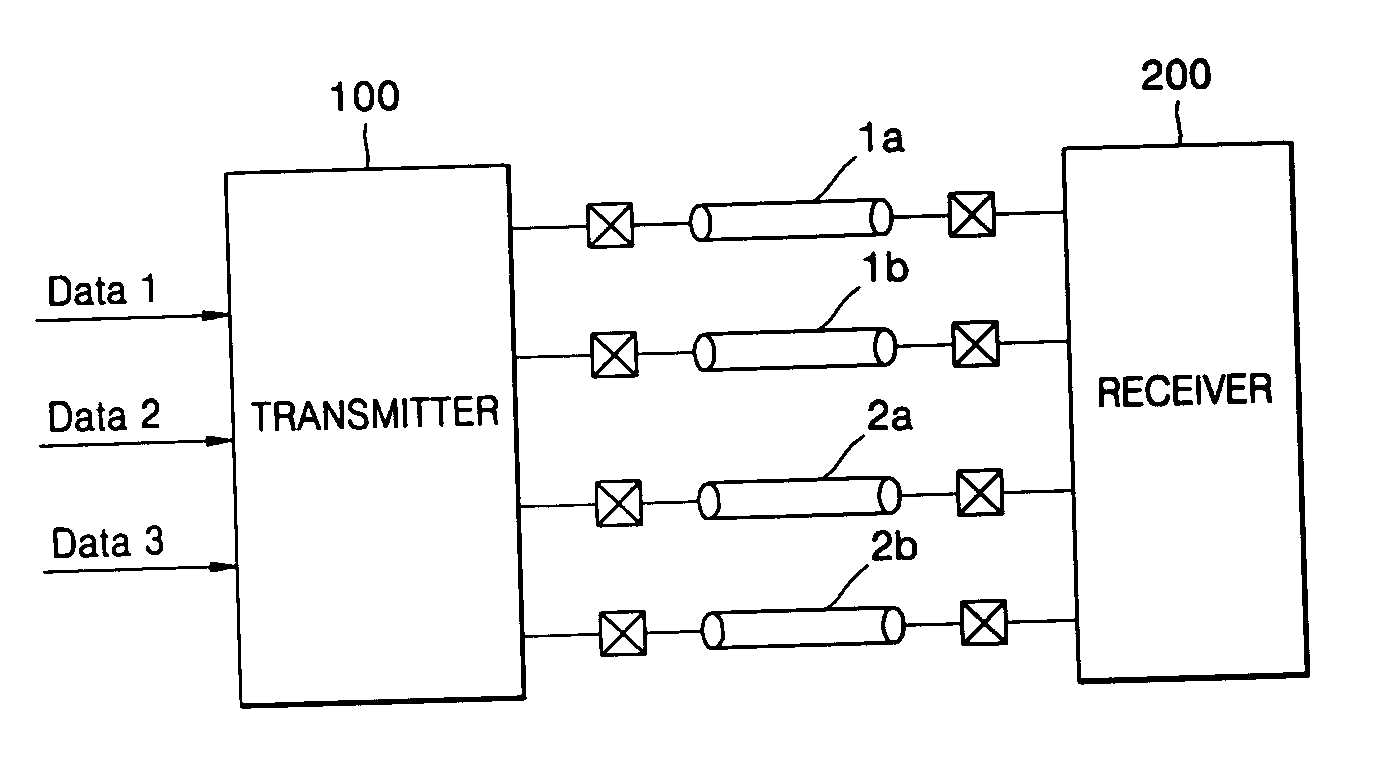

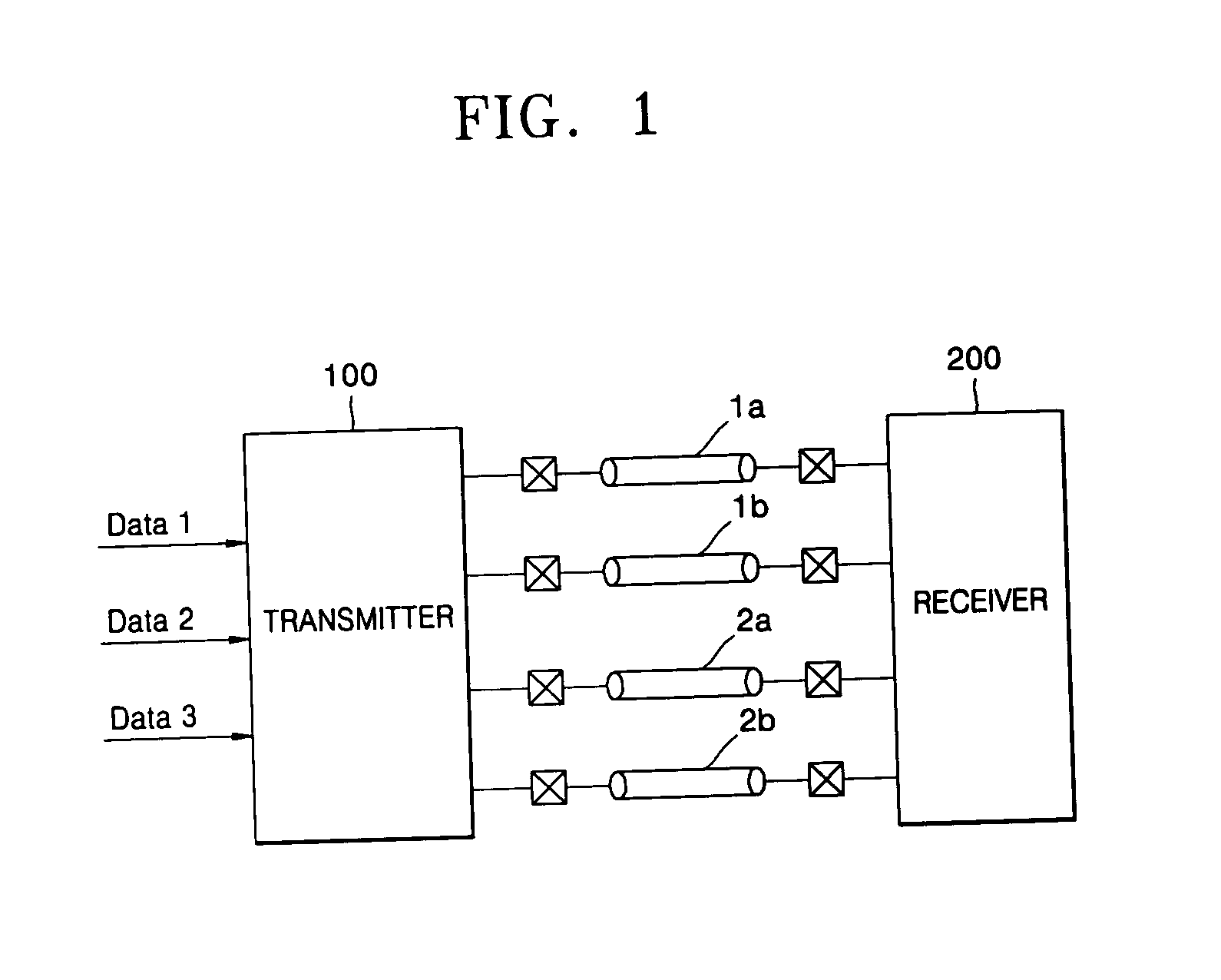

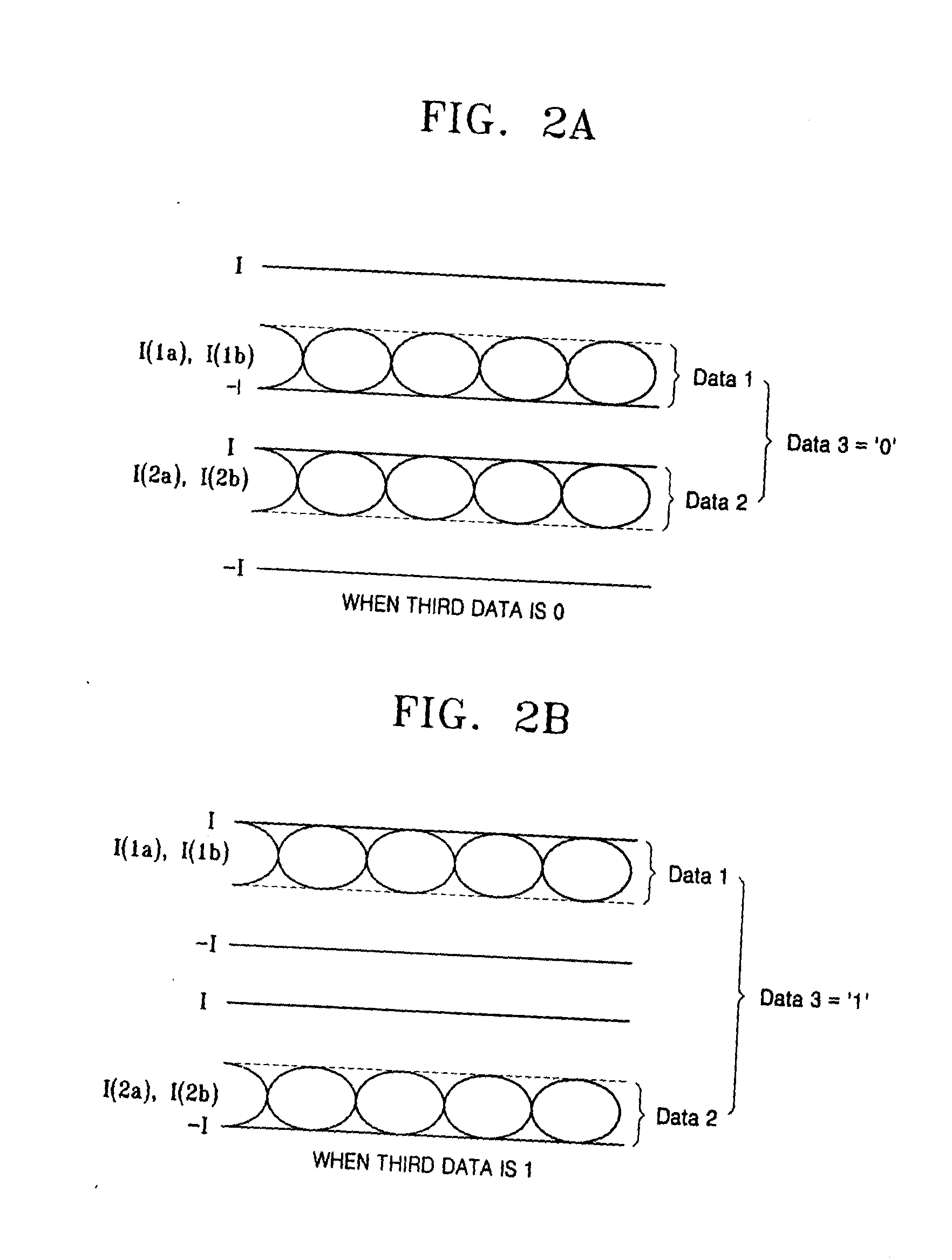

Current mode differential transmission method and system for transmitting three units of data using four signal lines

InactiveUS20060013331A1Reduce in quantityChannel dividing arrangementsComputations using contact-making devicesDifferential transmissionEngineering

Provided are a current mode differential transmission method and system for differentially transmitting three units of data using four signal lines. The method includes: dividing the four signal lines 1a, 1b, 2a and 2b into two pairs of signal lines 1a / 1b and 2a / 2b, and differentially transmitting respective data (first data and second data) via the two pairs of signal lines 1a / 1b and 2a / 2b; and transmitting the other data (third data) by differentially changing common mode currents of the two pairs of signal lines 1a / 1b and 2a / 2b.

Owner:POSTECH ACAD IND FOUND

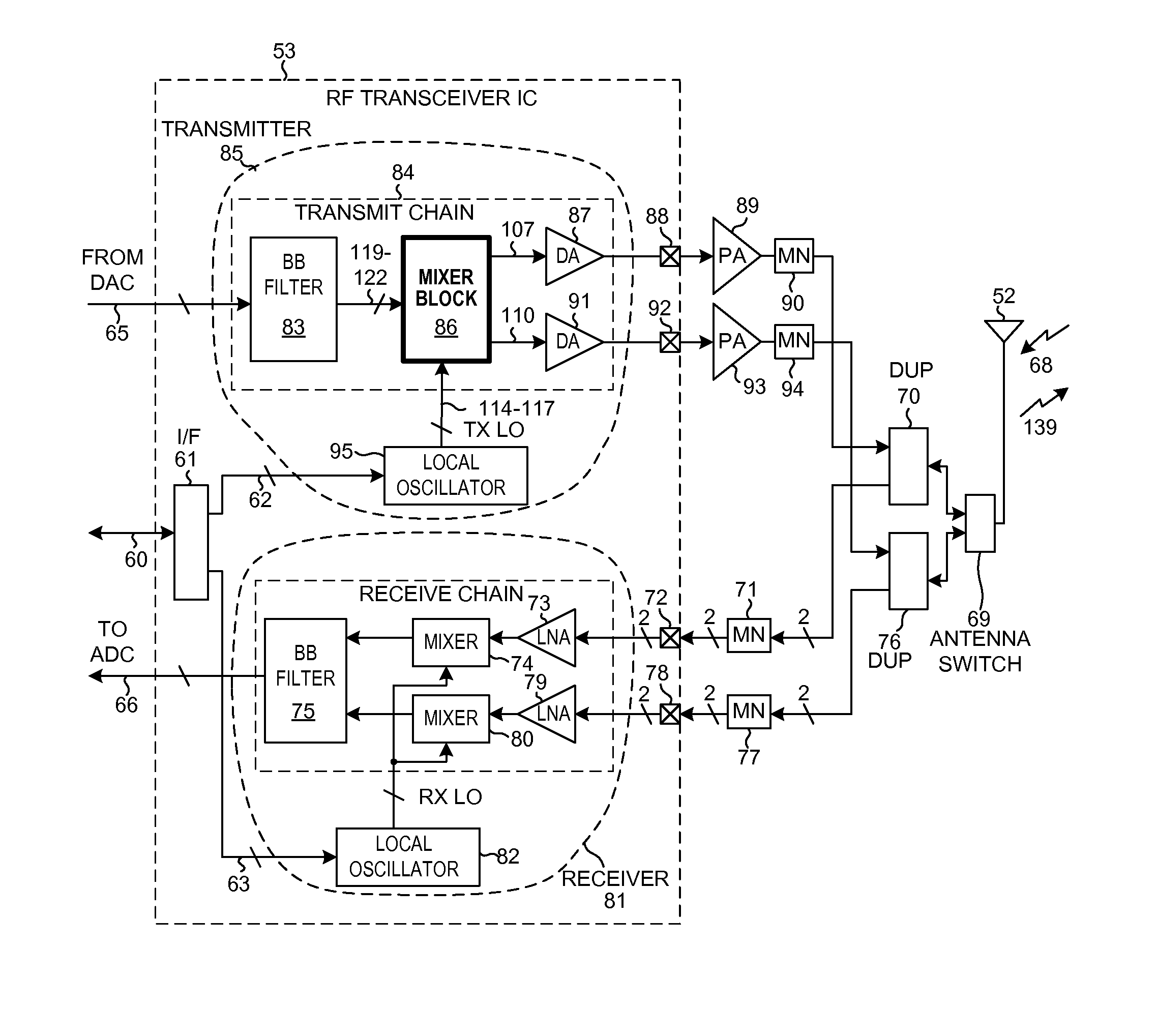

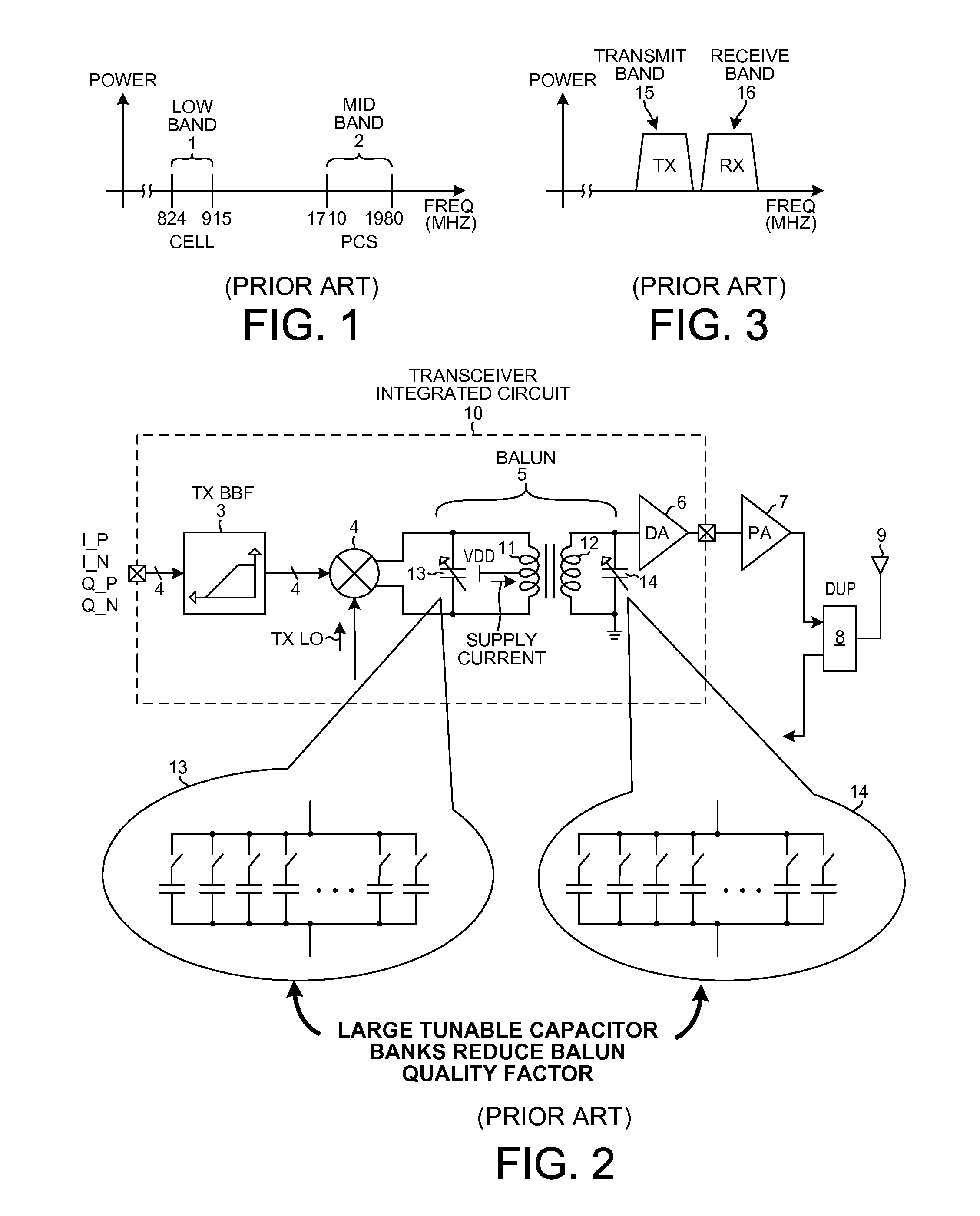

Wideband balun having a single primary and multiple secondaries

ActiveUS20120013387A1Reduce power consumptionPerformance requirementMultiple-port networksModulation transferenceWideband balunAudio power amplifier

An RF transmitter capable of transmitting over a wide range of frequencies includes a mixer, a wideband high-Q balun, a first driver amplifier and a second driver amplifier. The balun has a single primary winding and two secondary windings. A differential output of the mixer is coupled to the primary winding. A first of the two secondary windings is coupled to drive the first driver amplifier. A second of the two secondary windings is coupled to drive the second driver amplifier. One driver amplifier is used when transmitting at lower frequencies whereas the other driver amplifier is used when transmitting at higher frequencies. By appropriate sizing of the inductances of the secondary windings and by switching out one of the secondary windings at certain times, the balun is tunable to operate over the wide frequency range while having a high quality factor Q, thereby facilitating reduced power consumption while simultaneously meeting performance requirements.

Owner:QUALCOMM INC

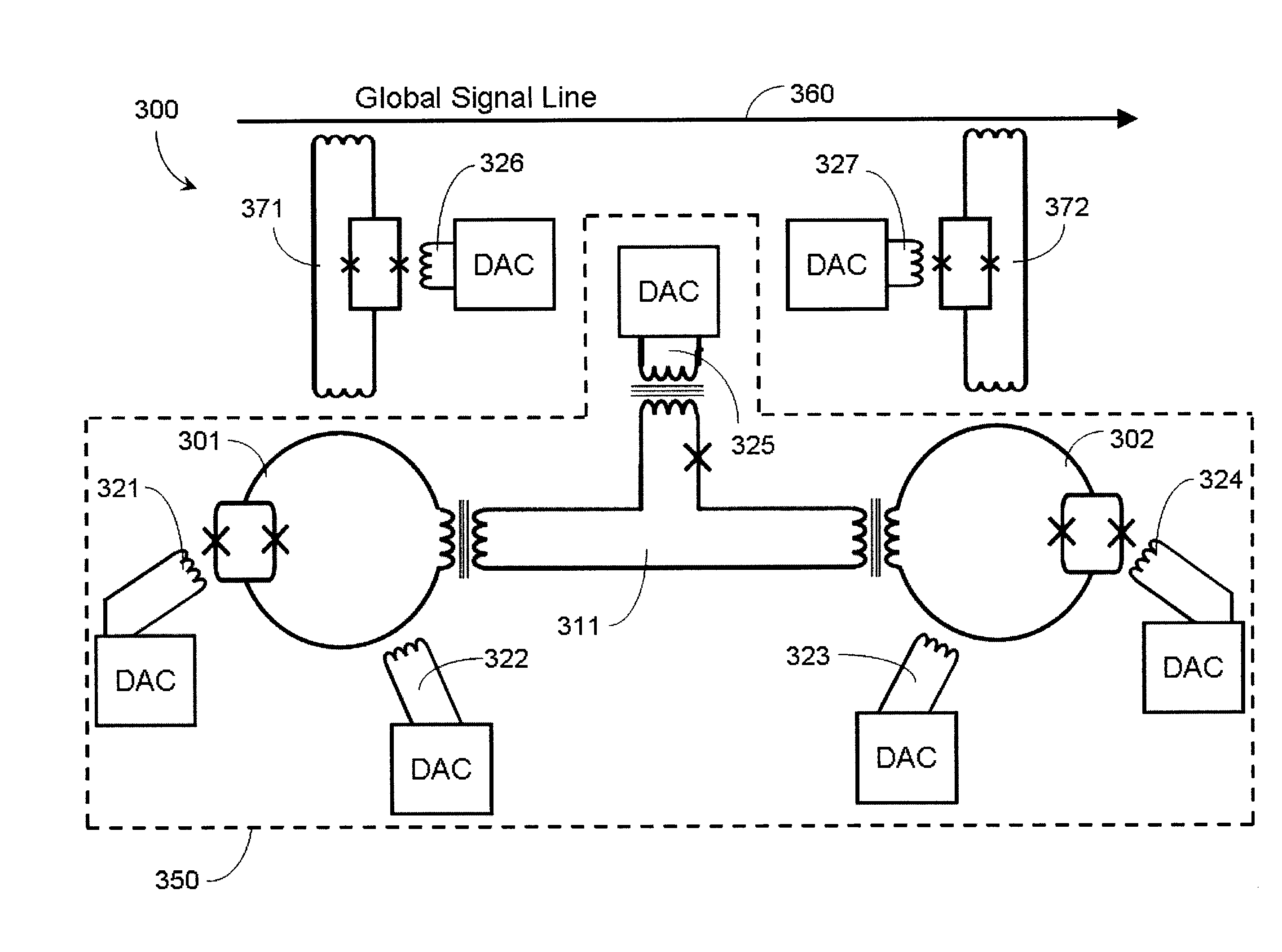

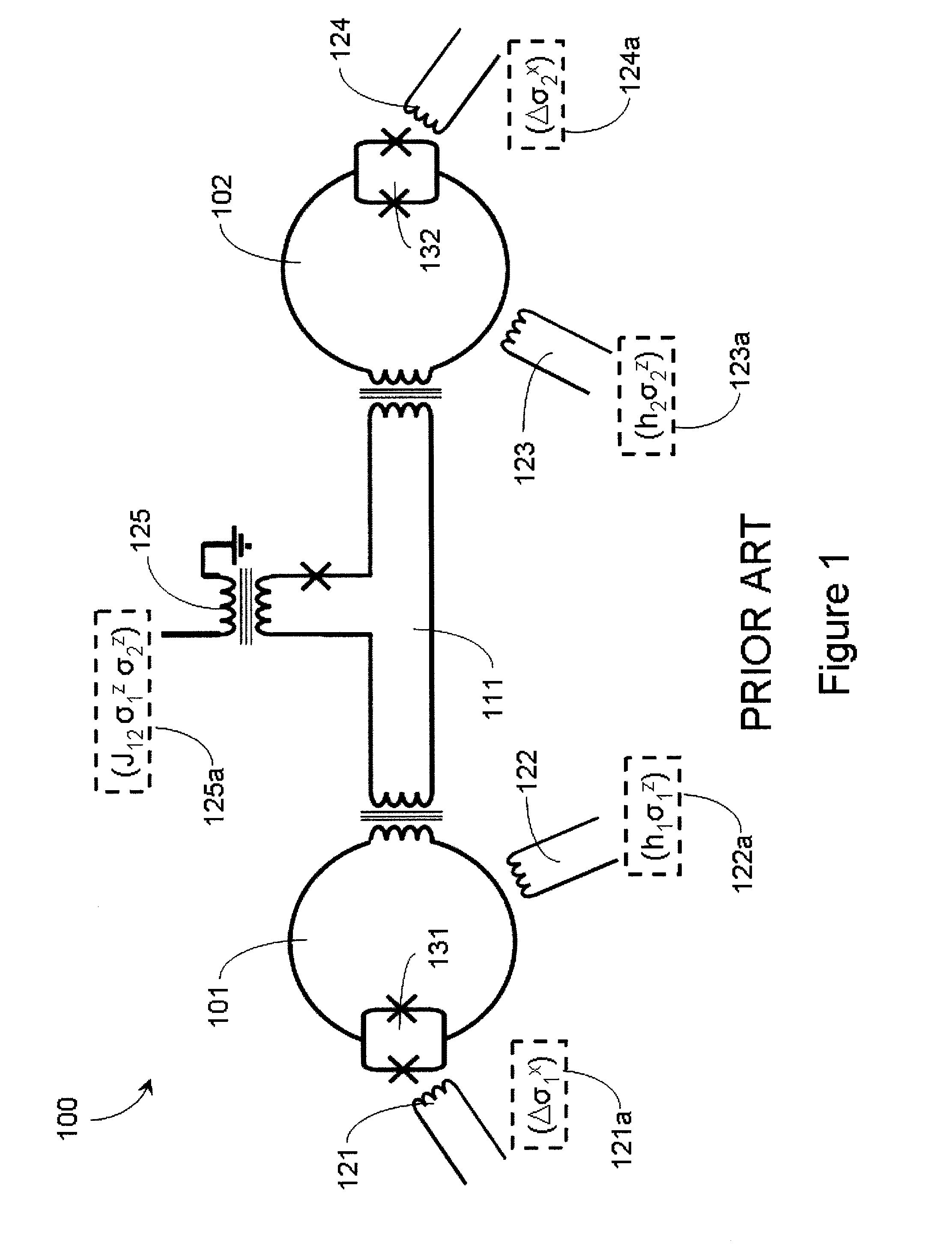

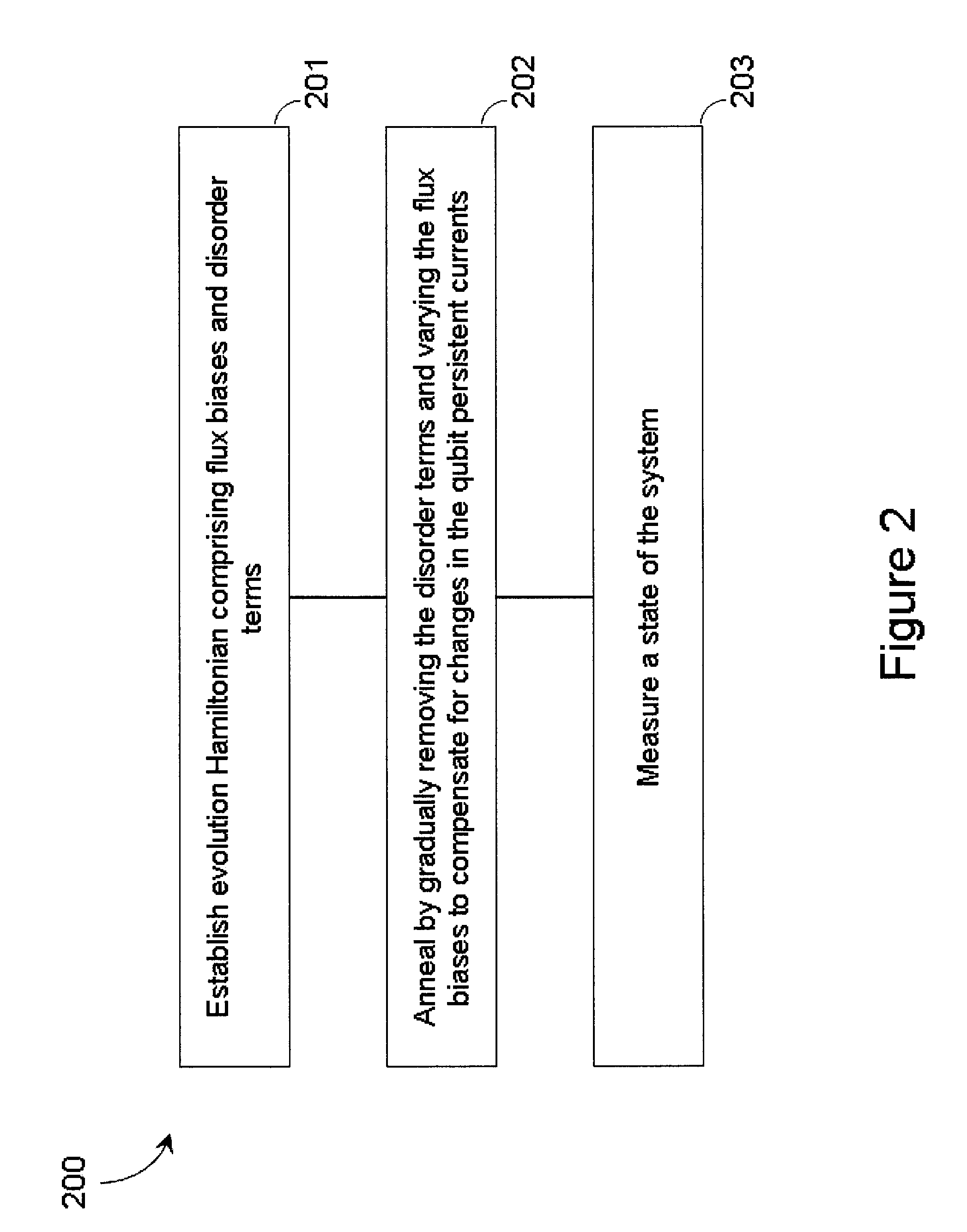

Systems, methods, and apparatus for calibrating, controlling, and operating a quantum processor

Quantum annealing may include applying and gradually removing disorder terms to qubits of a quantum processor, for example superconducting flux qubits of a superconducting quantum processor. A problem Hamiltonian may be established by applying control signals to the qubits, an evolution Hamiltonian established by applying disorder terms, and annealing by gradually removing the disorder terms. Change in persistent current in the qubits may be compensated. Multipliers may mediate coupling between various qubits and a global signal line, for example by applying respective scaling factors. Two global signal lines may be arranged in an interdigitated pattern to couple to respective qubits of a communicatively coupled pair of qubits. Pairs of qubits may be communicatively isolated and used to measure a response of one another to defined signals.

Owner:D WAVE SYSTEMS INC

Floating point arithmetic unit including an efficient close data path

InactiveUS6094668AComputations using contact-making devicesRuntime instruction translationMultiplexerExecution unit

An execution unit configured to execute vectored floating point and integer instructions. The execution unit may include an add / subtract pipeline having far and close data paths. The far data path is configured to handle effective addition operations, as well as effective subtraction operations for operands having an absolute exponent difference greater than one. The close data path is configured to handle effective subtraction operations for operands having an absolute exponent difference less than or equal to one. The close data path includes an adder unit configured to generate a first and second output value. The first output value is equal to the first input operand plus an inverted version of the second input operand, while the second output value is equal to the first output value plus one. The two output values are conveyed to a multiplexer unit, which selects one of the output values as a preliminary subtraction result based on a final selection signal received from a selection unit. The selection unit generates the final selection signal from a plurality of preliminary selection signals based on the carry in signal to the most significant bit of the first adder output value. Selection of the first or second output value in the close data path effectuates the round-to-nearest operation.

Owner:ADVANCED SILICON TECH

Data processing apparatus and method for performing floating point multiplication

ActiveUS7668896B2Efficient detectionAvoid the needComputations using contact-making devicesComputation using non-contact making devicesLeast significant bitFloating point multiplication

The first and second n-bit significands are multiplied producing a pair of 2n-bit vectors, and half adder logic produces a corresponding plurality of carry and sum bits. A product exponent is checked for correspondence with a predetermined exponent value. A sum operation generates a first result equivalent to the addition of the pair of 2n-bit vectors. First adder logic uses corresponding m carry and sum bits, the least significant of them carry bits being replaced with the increment value prior to the first adder logic performing the first sum operation. Second adder logic performs a second sum operation and uses the corresponding m−1 carry and sum bits replacing the least significant m−1 carry bits with the rounding increment value prior to the second adder logic second sum operation. The n-bit result is derived from either the first rounded result, the second rounded result or a predetermined result value.

Owner:ARM LTD

Popular searches

Simultaneous aerial operations Radio transmission Sensing record carriers Subscribers indirect connection Electric signalling details Burglar alarm by hand-portable articles removal Antenna details Logic circuits using elementary logic circuit components Conveying record carriers Computing operations for multiplication/division