Patents

Literature

199results about "Transversal filters" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

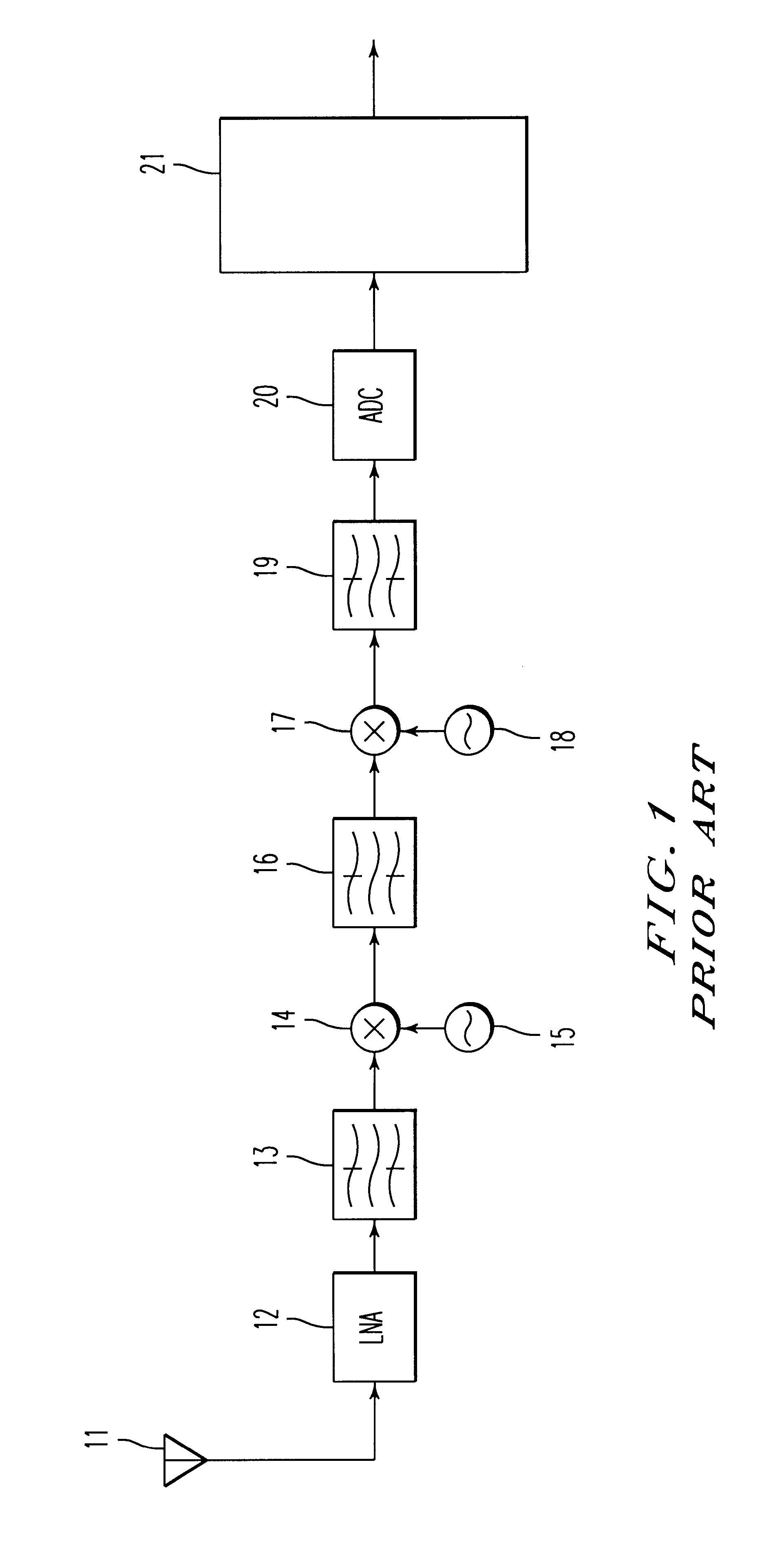

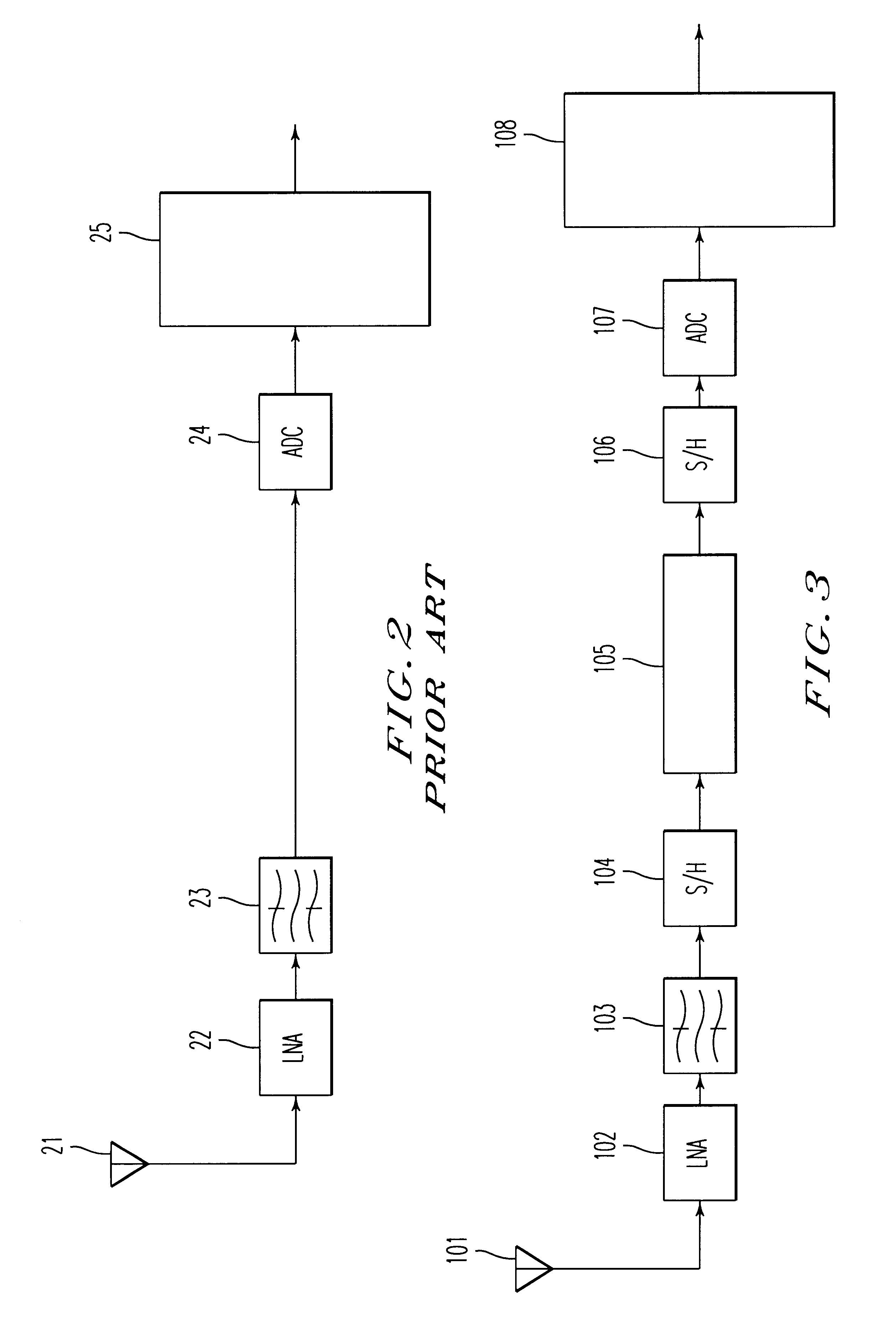

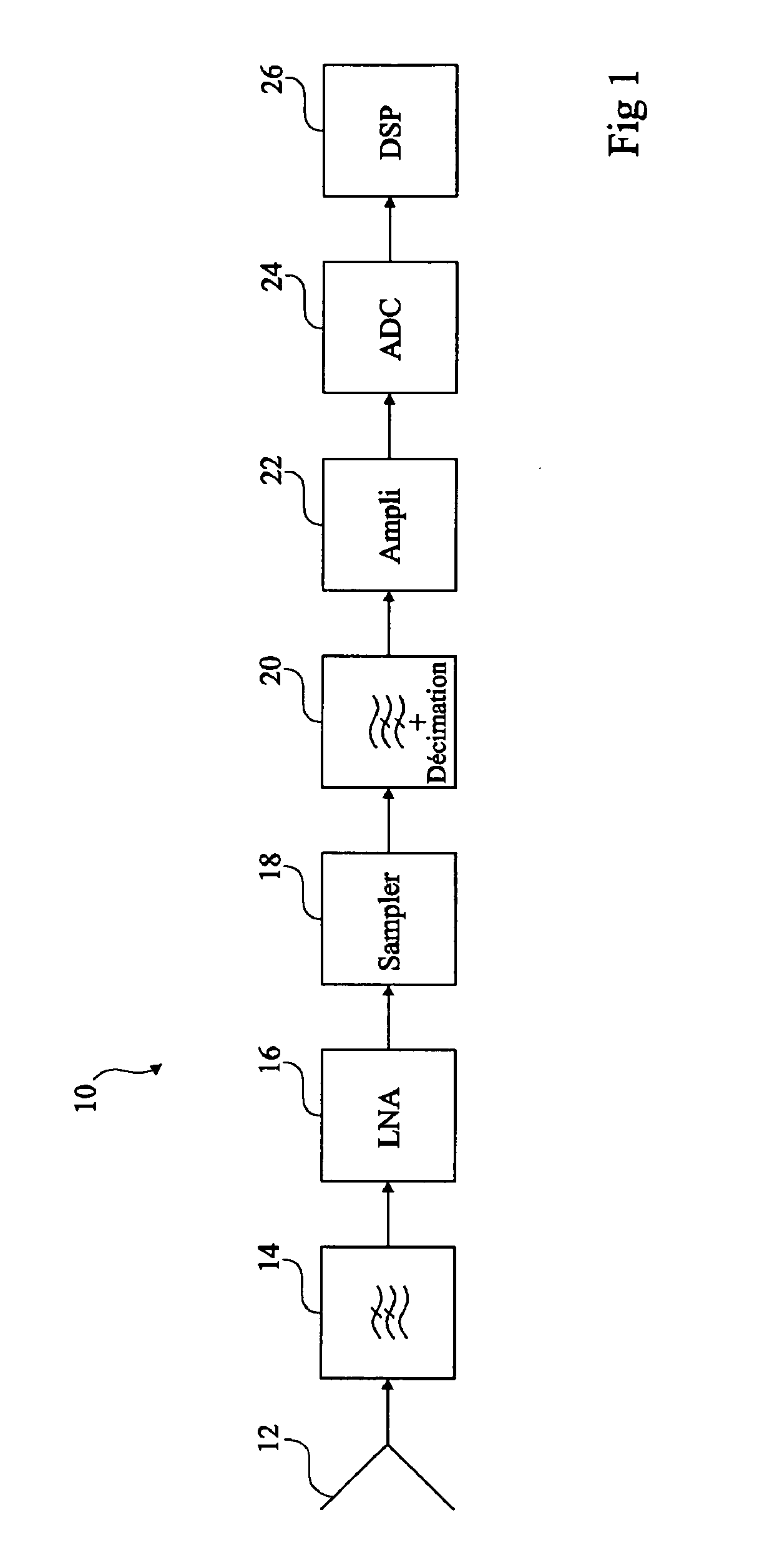

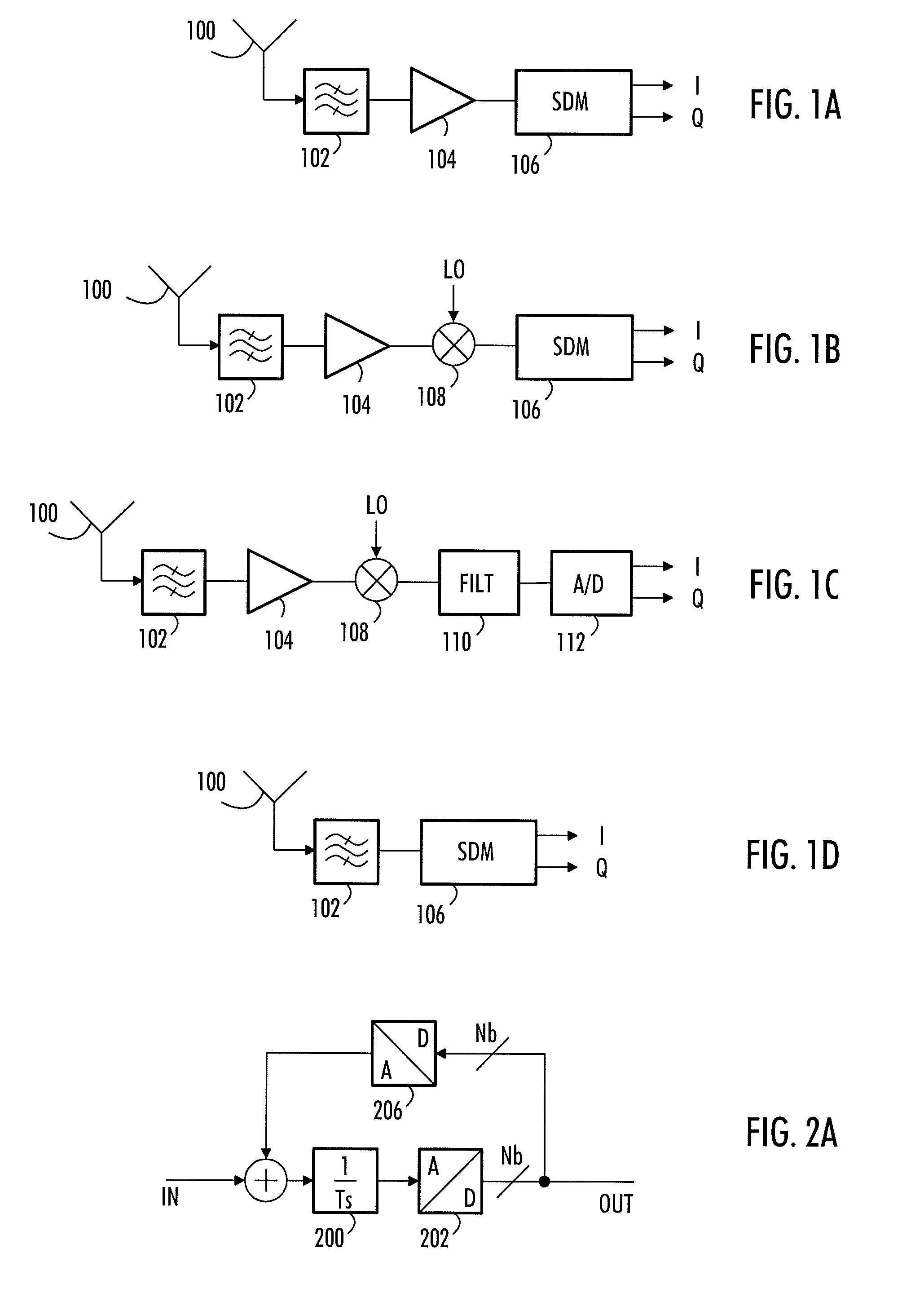

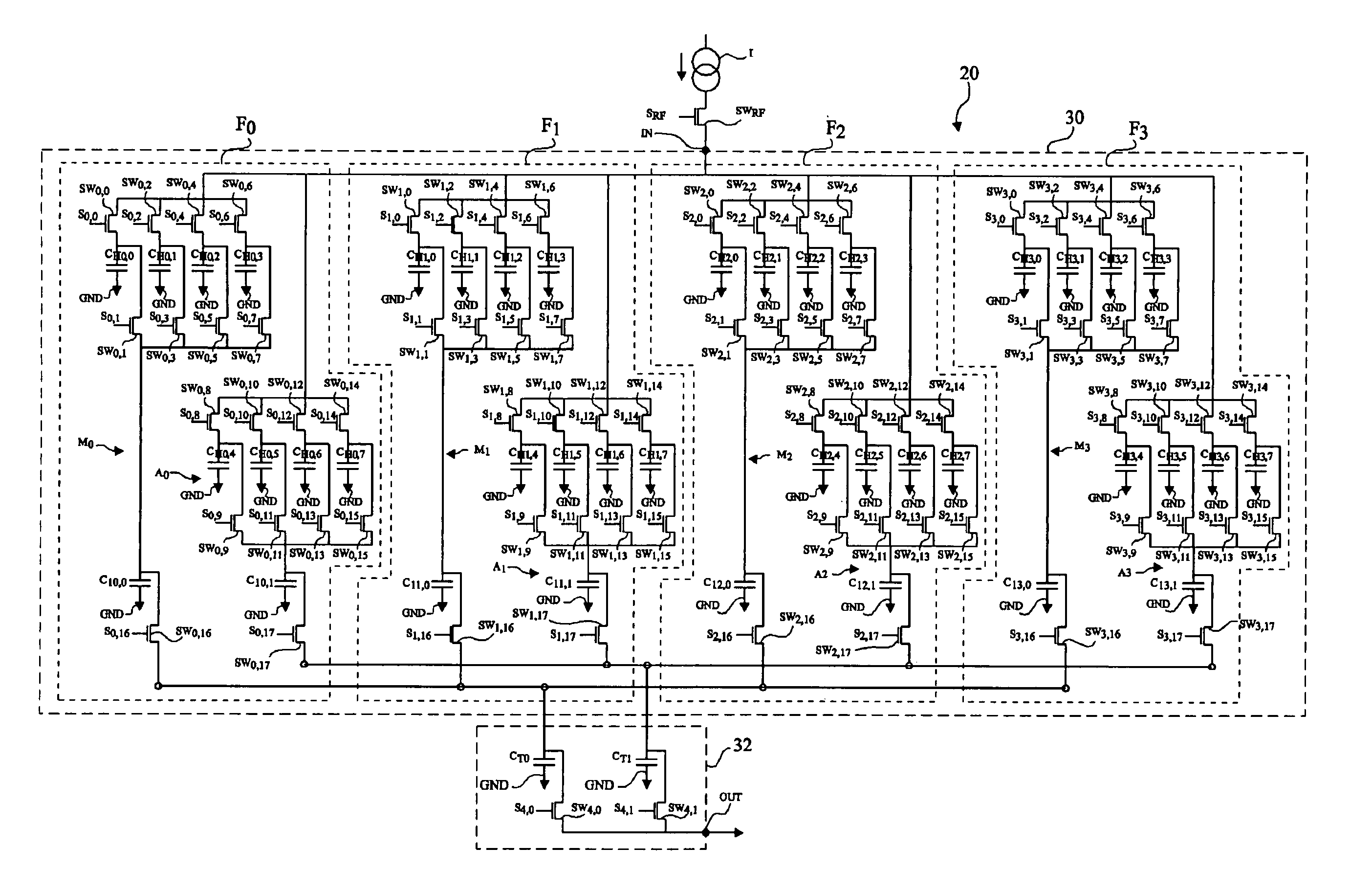

Sampling system

A sampling system arranged such that a modulated signal received by an antenna and input via a low noise amplifier and a band-pass filter is sampled at a sampling frequency higher than the signal band of the modulated signal by a first sample and hold circuit and is input to an analog decimation filter to remove a frequency component which may turn out to be aliasing noise. The output of the analog decimation filter is sampled with a sampling frequency lower than the sampling frequency of the first sample and hold circuit by a second sample and hold circuit and is digitized by an A / D converter to be demodulated by a demodulator. The sampling system which can convert the modulated signal into a low frequency without using the highly precision mixer circuit or a filter having sharp characteristics may be provided by constructing as described above.

Owner:KK TOSHIBA

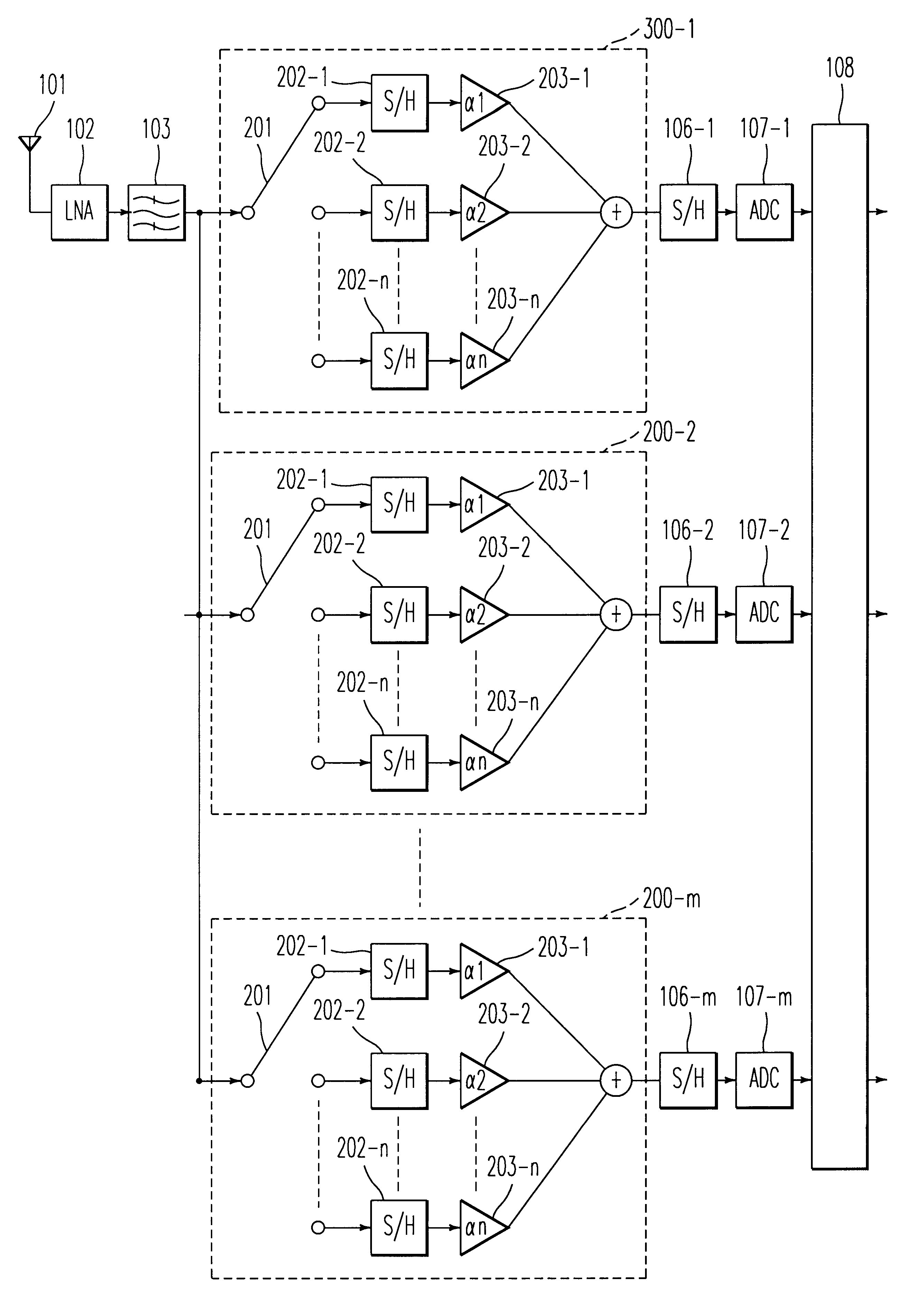

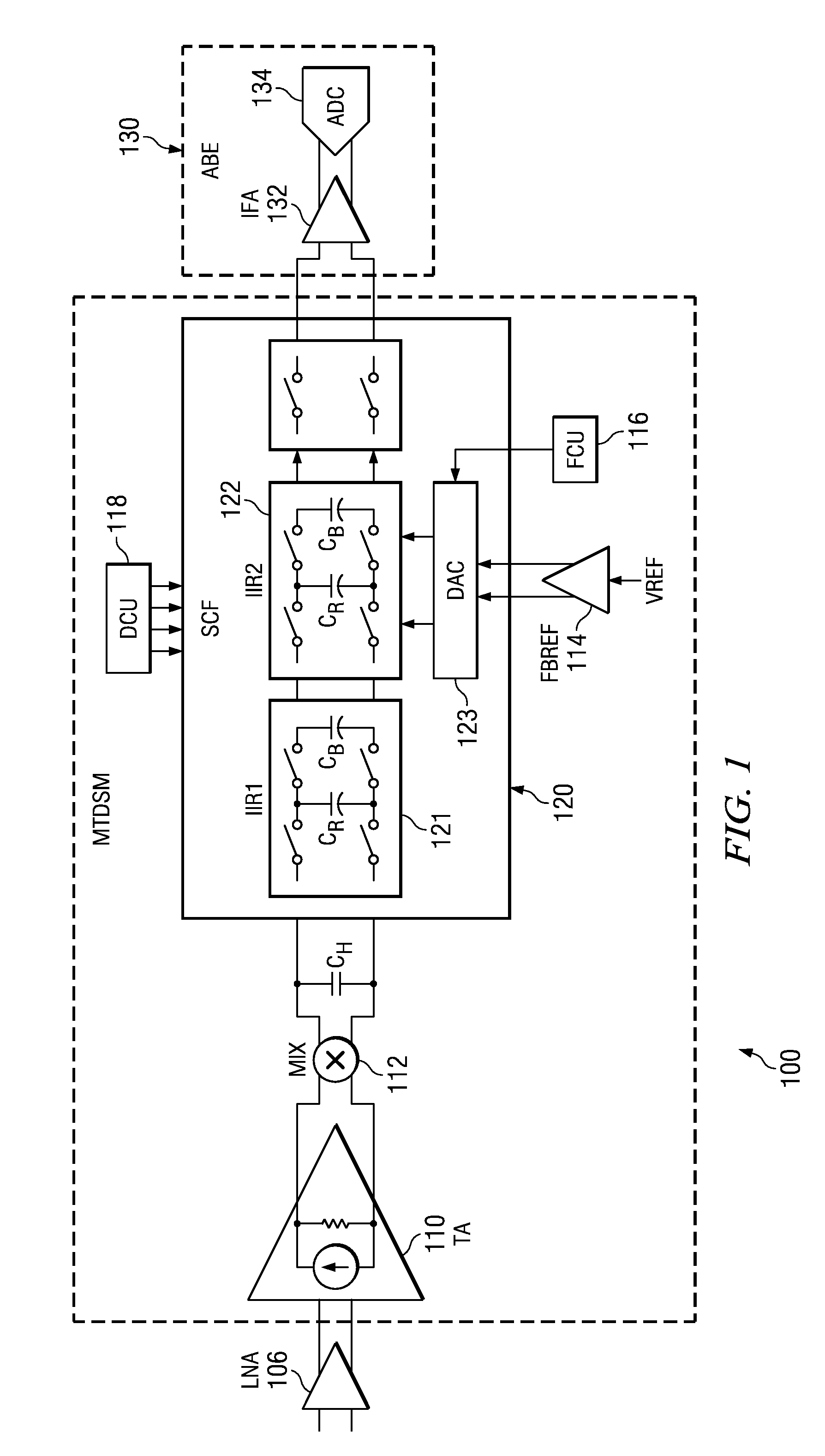

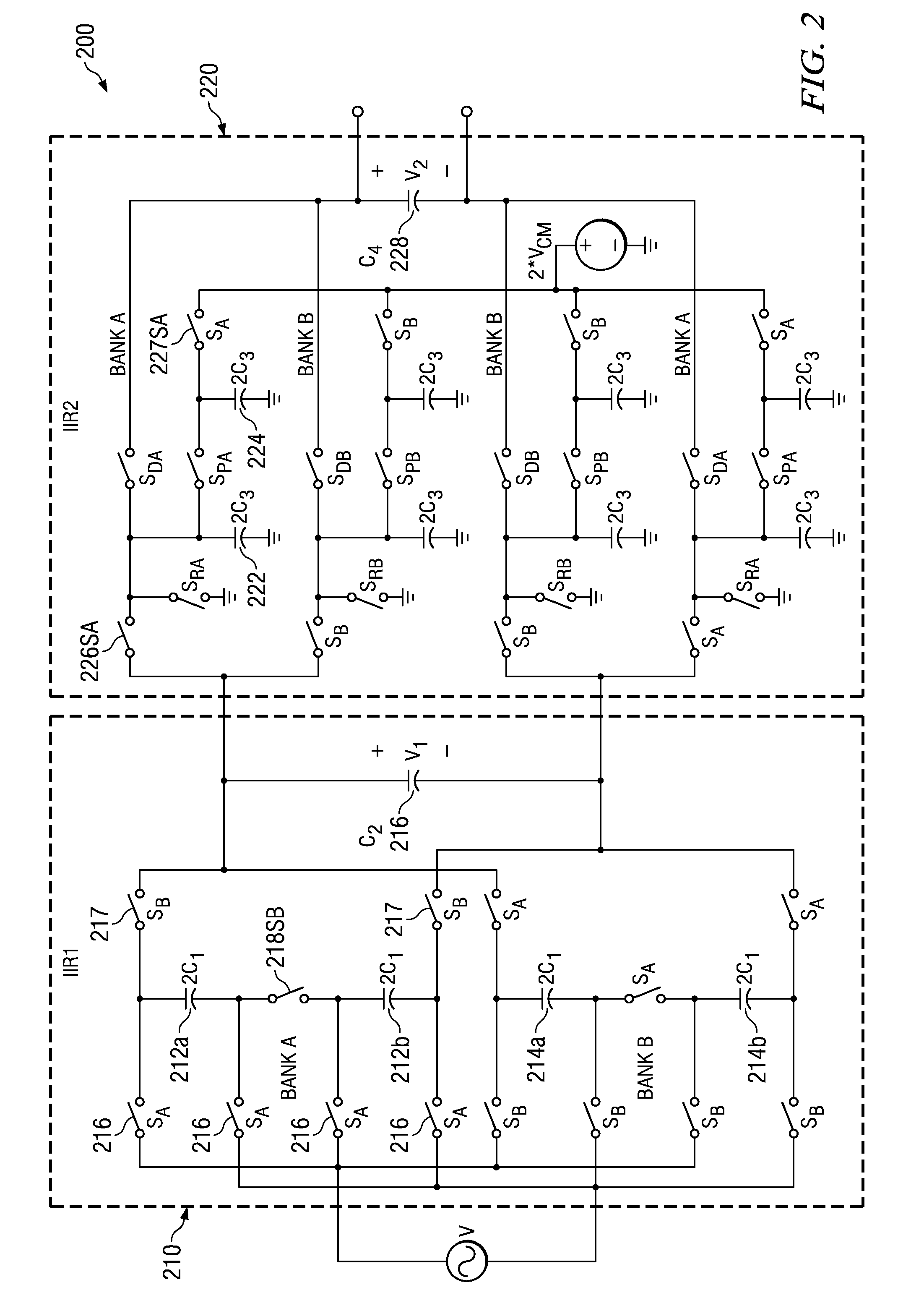

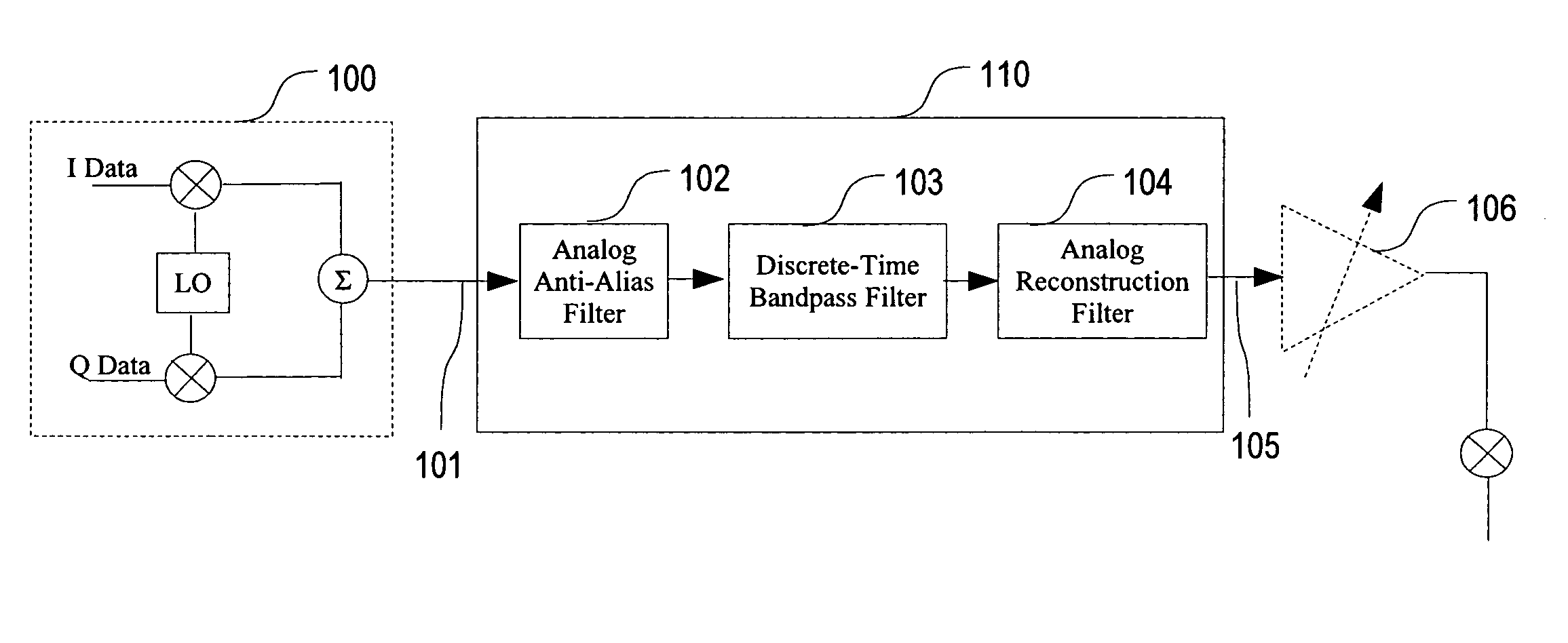

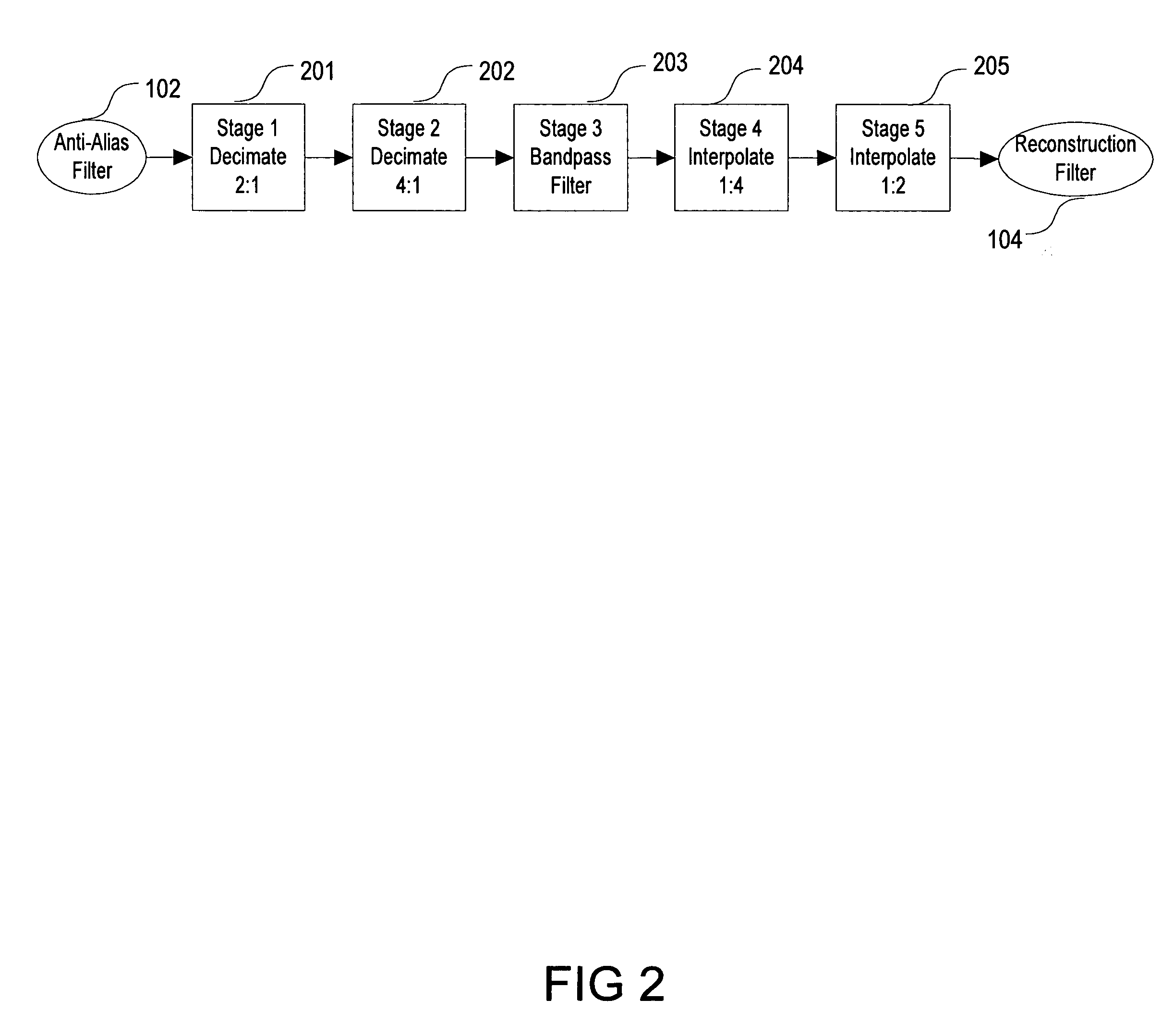

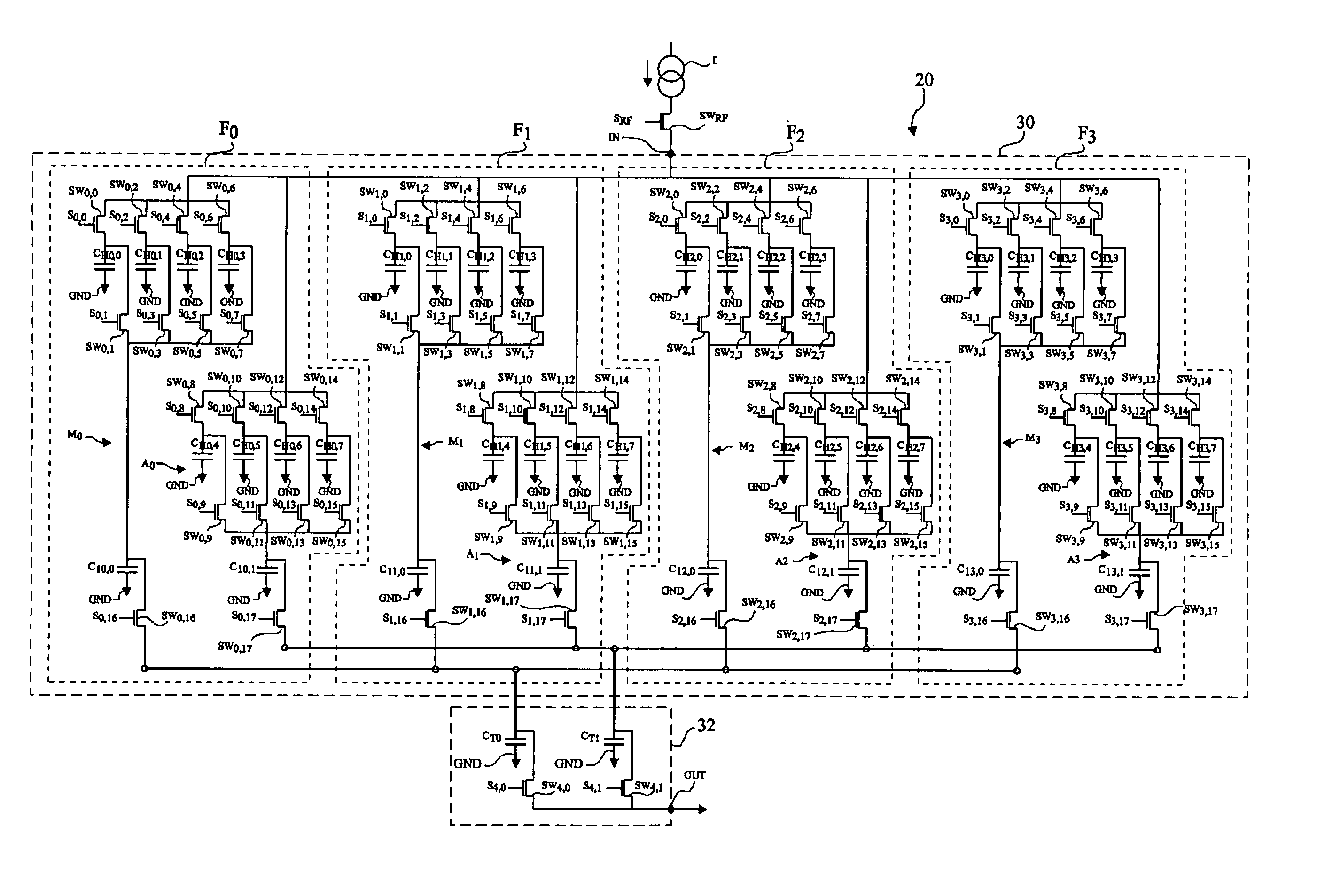

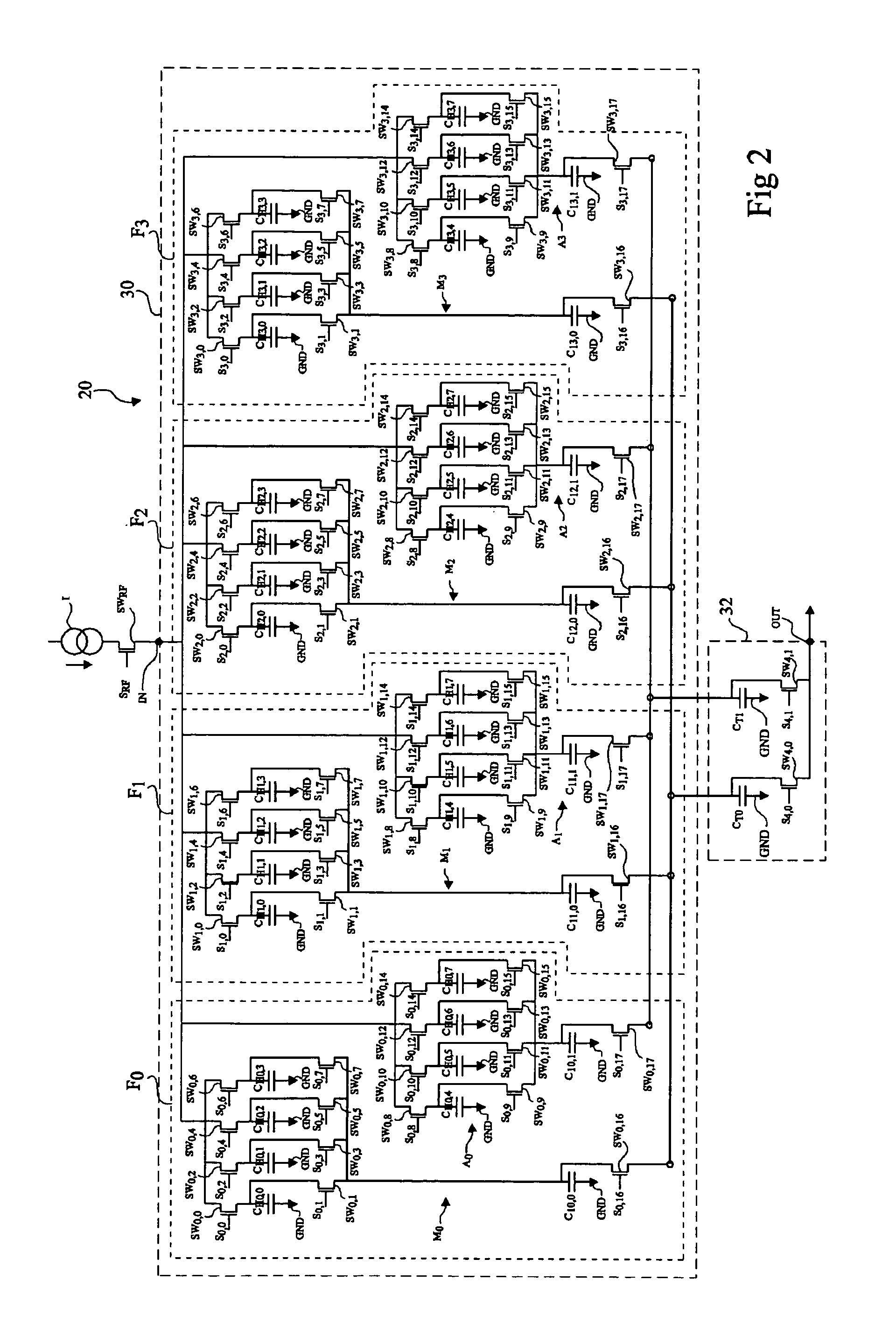

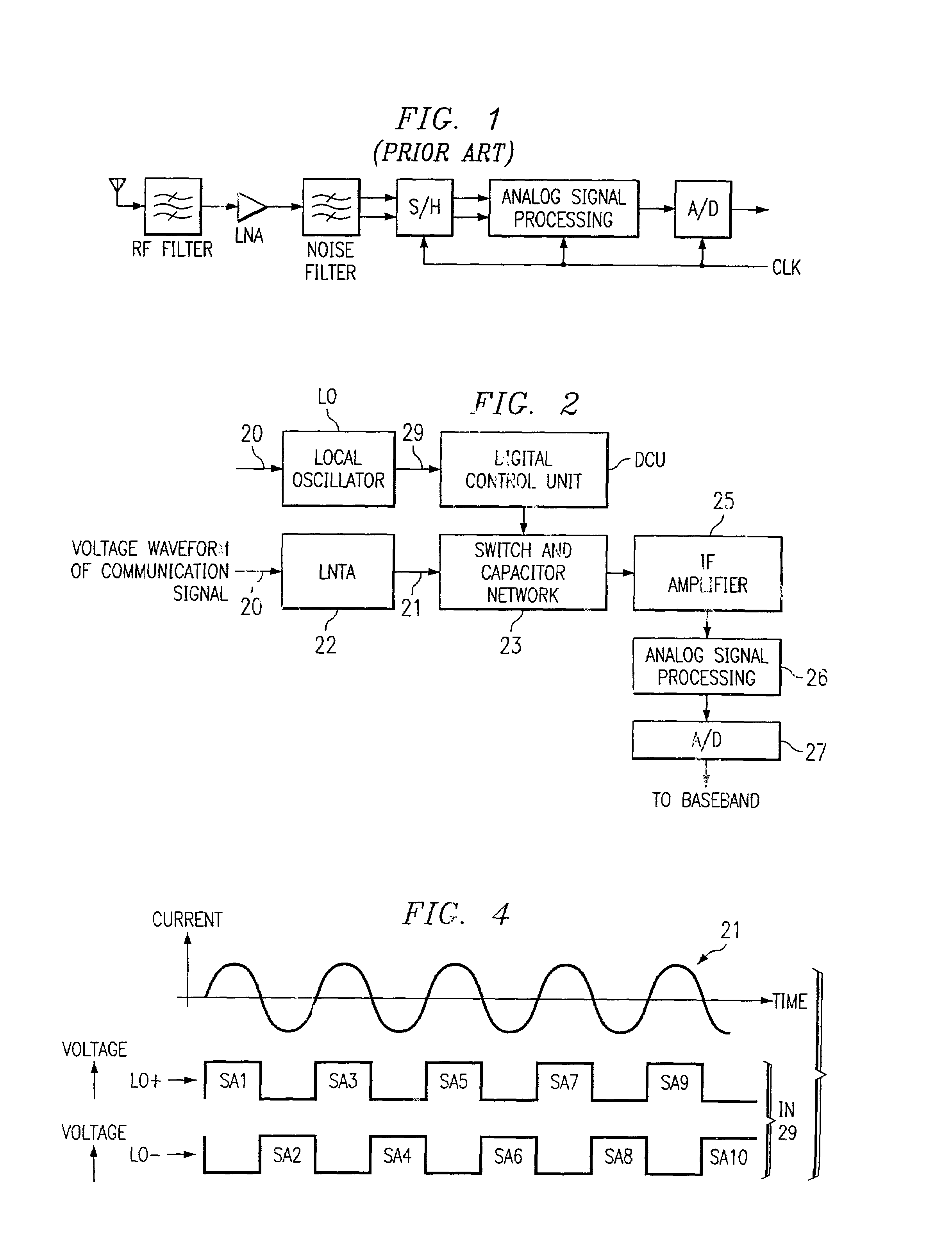

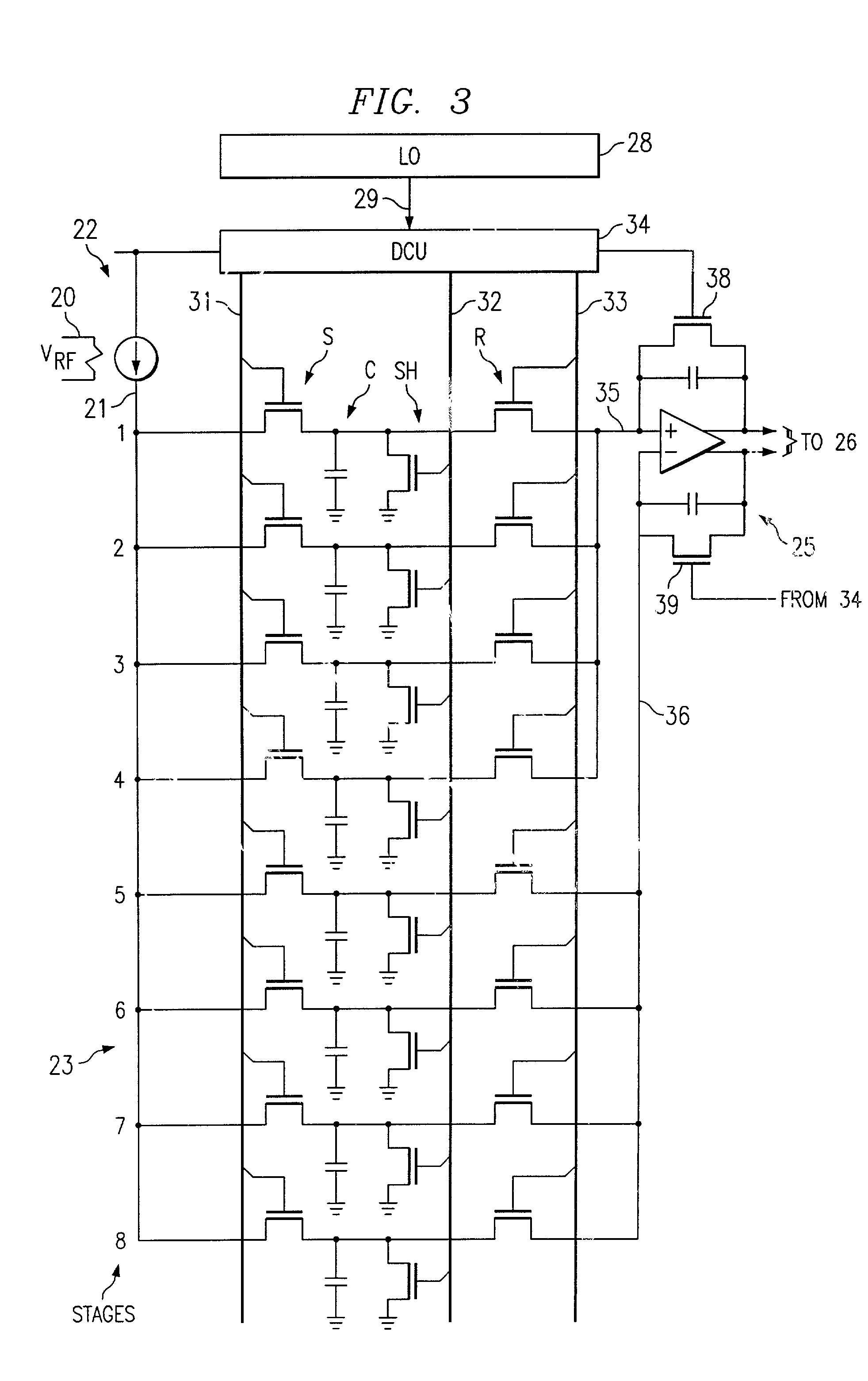

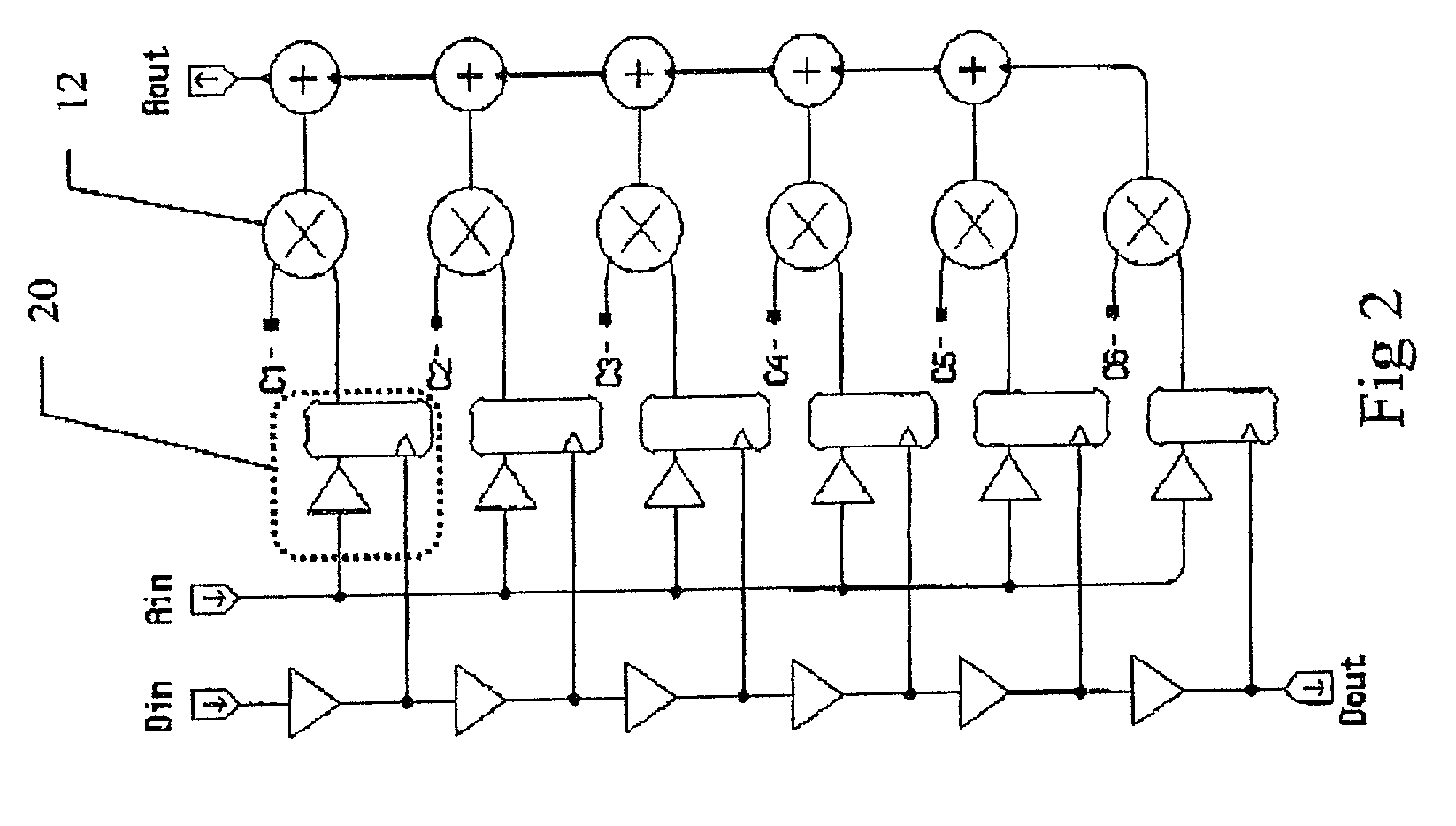

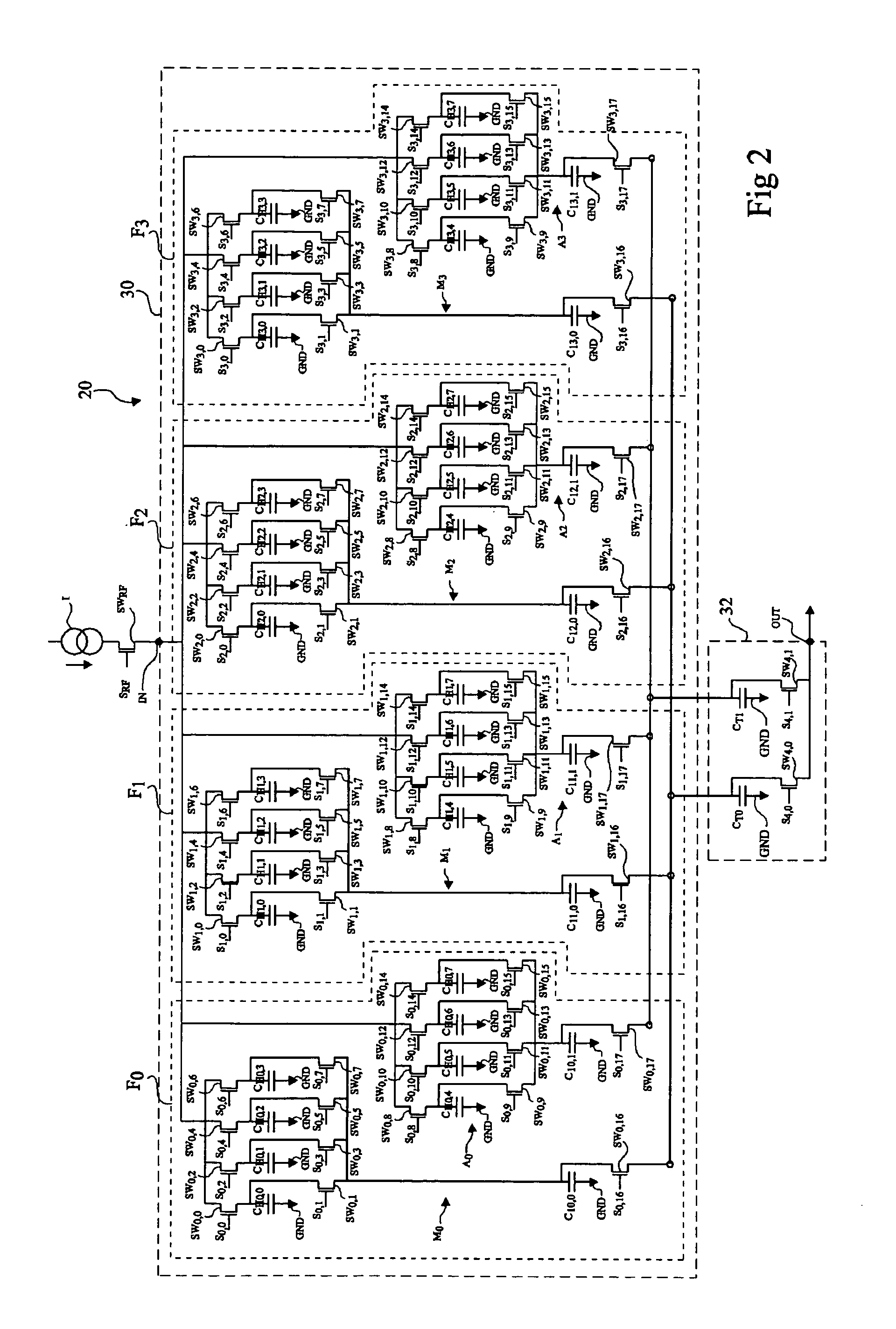

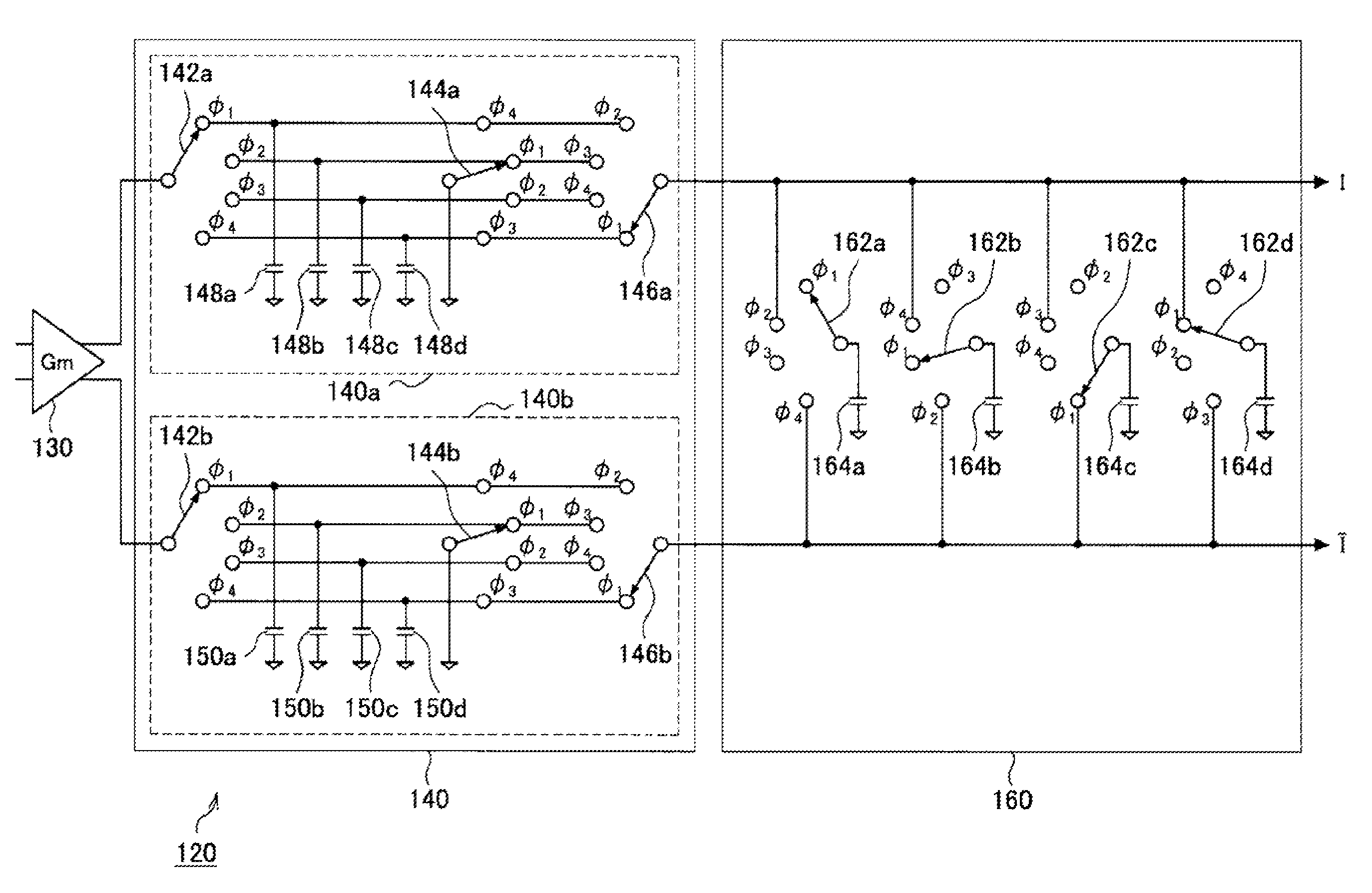

Multi-Tap Direct Sub-sampling Mixing System for Wireless Receivers

ActiveUS20090002066A1Transversal filtersSwitched capacitor networksHybrid systemAudio power amplifier

A multi-tap direct sub-sampling mixing system for wireless receivers is provided with a dynamically configurable passive switched capacitor filter. A front end amplifier is connected to receive a signal. The passive switched capacitor filter is connected to receive the amplified signal and has an output for providing a filtered signal. The switched capacitor filter has at least two sections that are each operable as a pole, wherein a first section of the at least two sections has sets of at least two stacked capacitors interconnected with a set of switches operable to amplify in input voltage provided to an input of the first section in response to operation of the set of switches; and a back end section connected to the output of the switched capacitor filter to receive the filtered signal.

Owner:TEXAS INSTR INC

Analog finite impulse response filter

ActiveUS20100271107A1Transversal filtersComputations using contact-making devicesParasitic capacitanceEngineering

According to one embodiment of the invention, a programmable finite impulse response (FIR) filter is implemented with differential isolation circuits to isolate parasitic capacitance from attenuating an output signal at both a first and second differential output terminals of the FIR filter. The FIR includes a summing circuit that provides operational advantages to the FIR filter.

Owner:LUMENTUM OPERATIONS LLC

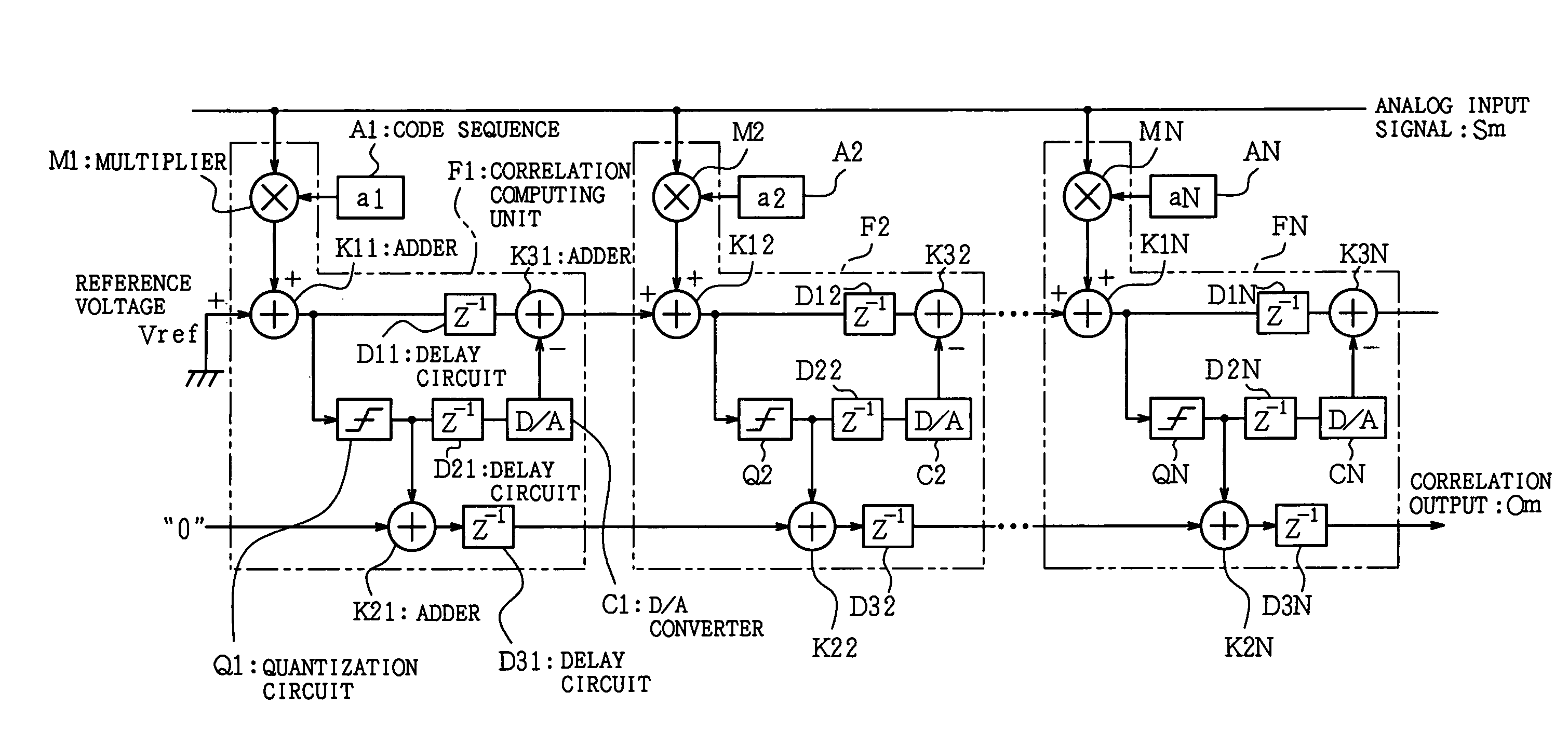

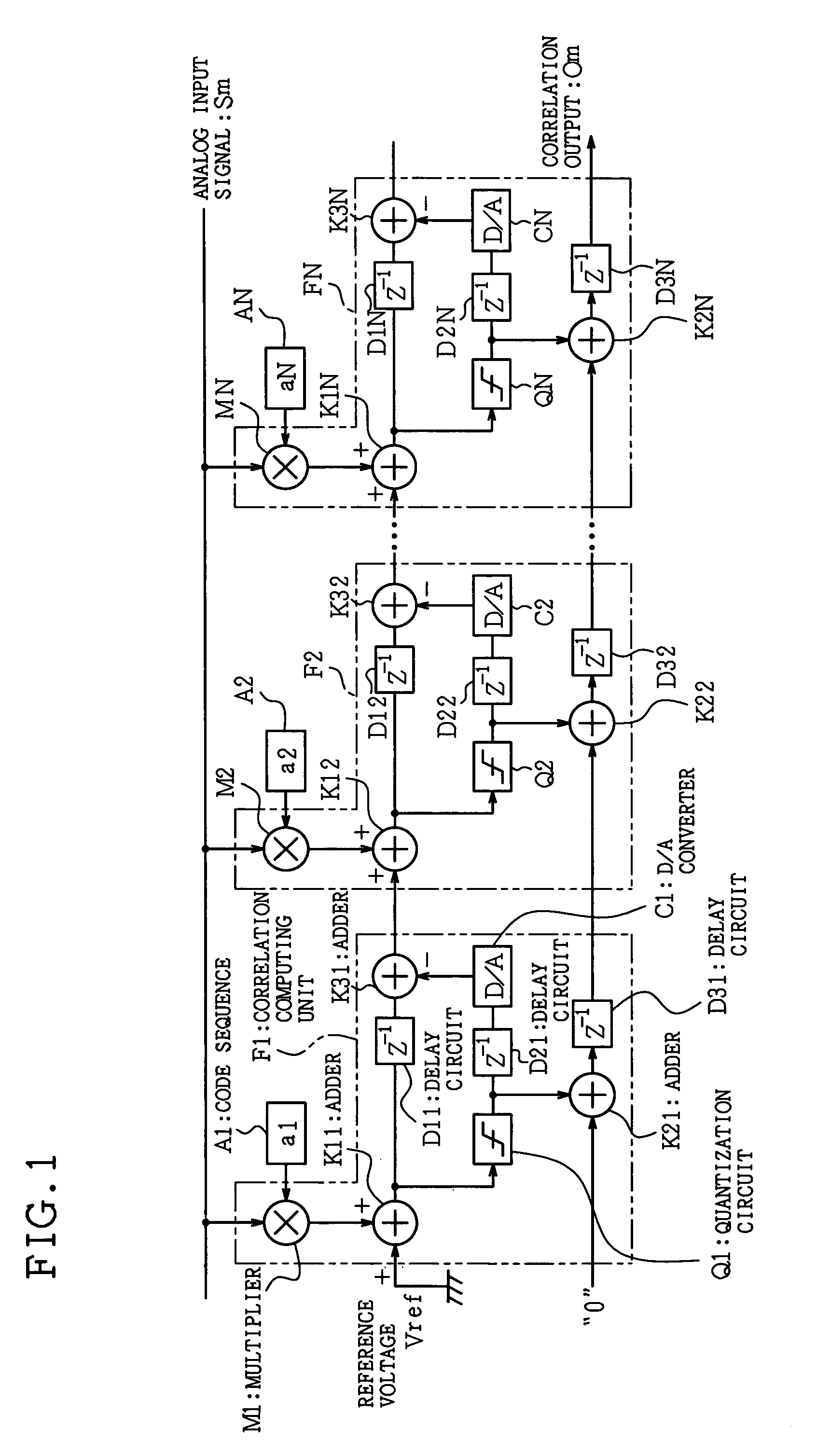

Filter circuit

InactiveUS6983011B1Reduce circuit sizeReduce power consumptionMultiple-port networksPower saving provisionsComputer scienceDynamic range

In a filter circuit of the present invention, a partial quantization value is computed by a quantization circuit according to a spread code and others in a unit at an arbitrary stage, where an integrating value is increased. The partial quantization value is successively added by an adder formed by a counter and is transmitted to a unit of the following stage. In an adder of the following stage, an analog residual is computed by subtracting an analog converted value of the partial quantization value, that is obtained by a D / A converter, from the integrating value so as to suppress an increase in the analog cumulative value. With this arrangement, the cumulative value is increased according to an increase in the number of taps, so that an analog adder can reduce power consumption, which is caused by expansion of a dynamic range at the following stage.

Owner:SHARP KK

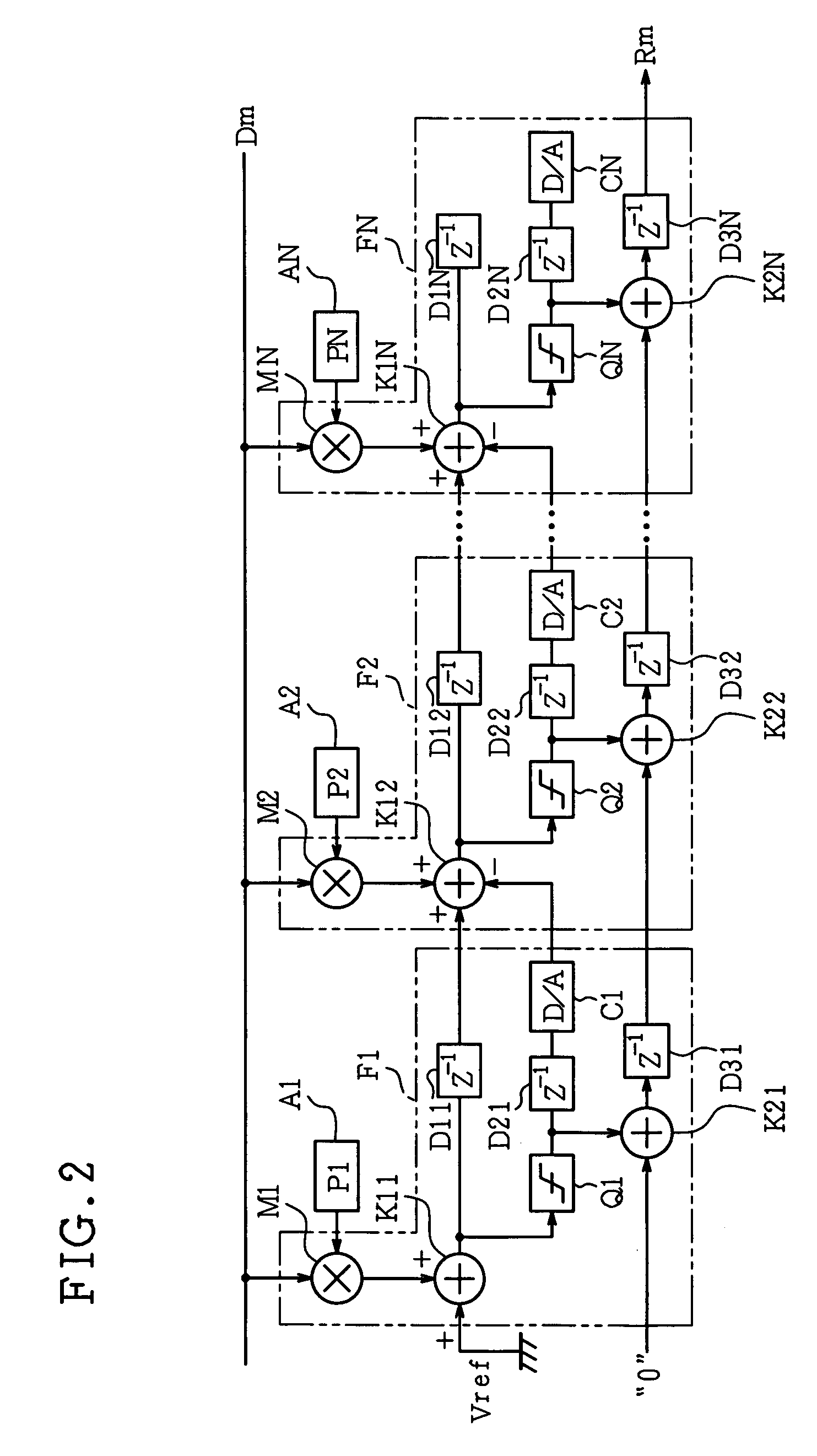

Digital/Analogue conversion apparatus

ActiveUS20090110217A1Reduce out-of-band quantization noiseSignificantly increases in-band noise (Transversal filtersDigitally weighted transducing elementsImage resolutionAnalog signal

A digital / analog conversion apparatus for converting a digital signal into an analog signal. The digital / analog conversion apparatus can generate a high-quality analog signal, even when elements configuring the digital / analog conversion apparatus have variance, with high resolution and a small circuit size. The data conversion apparatus is provided with a first data converter for reducing the number of bits of an input signal, a second data converter for converting the format of the first output signal, and a third data converter for conversion into a code which corresponds to the history of the output from the second data converter.

Owner:TRIGENCE SEMICONDUCTOR INC

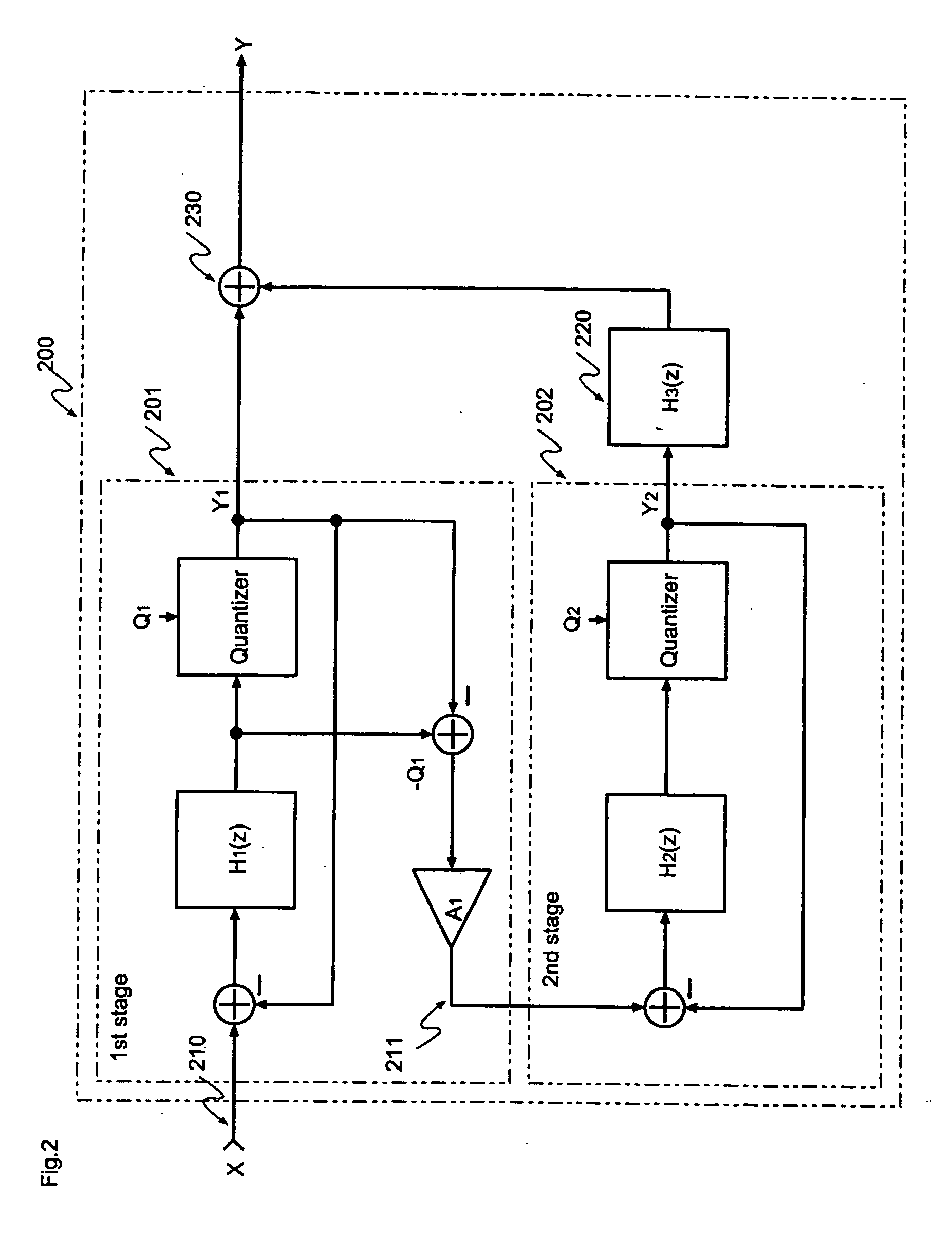

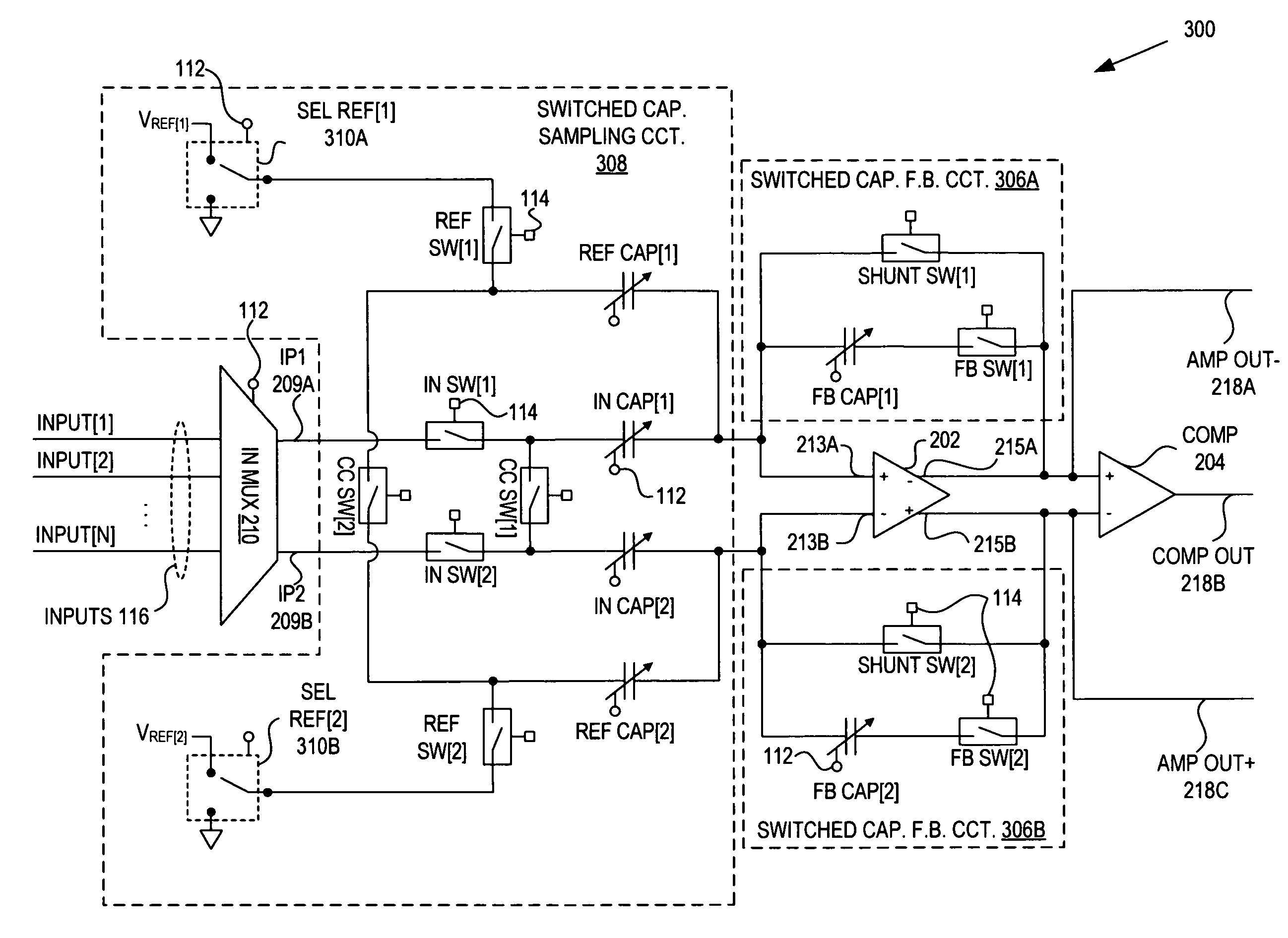

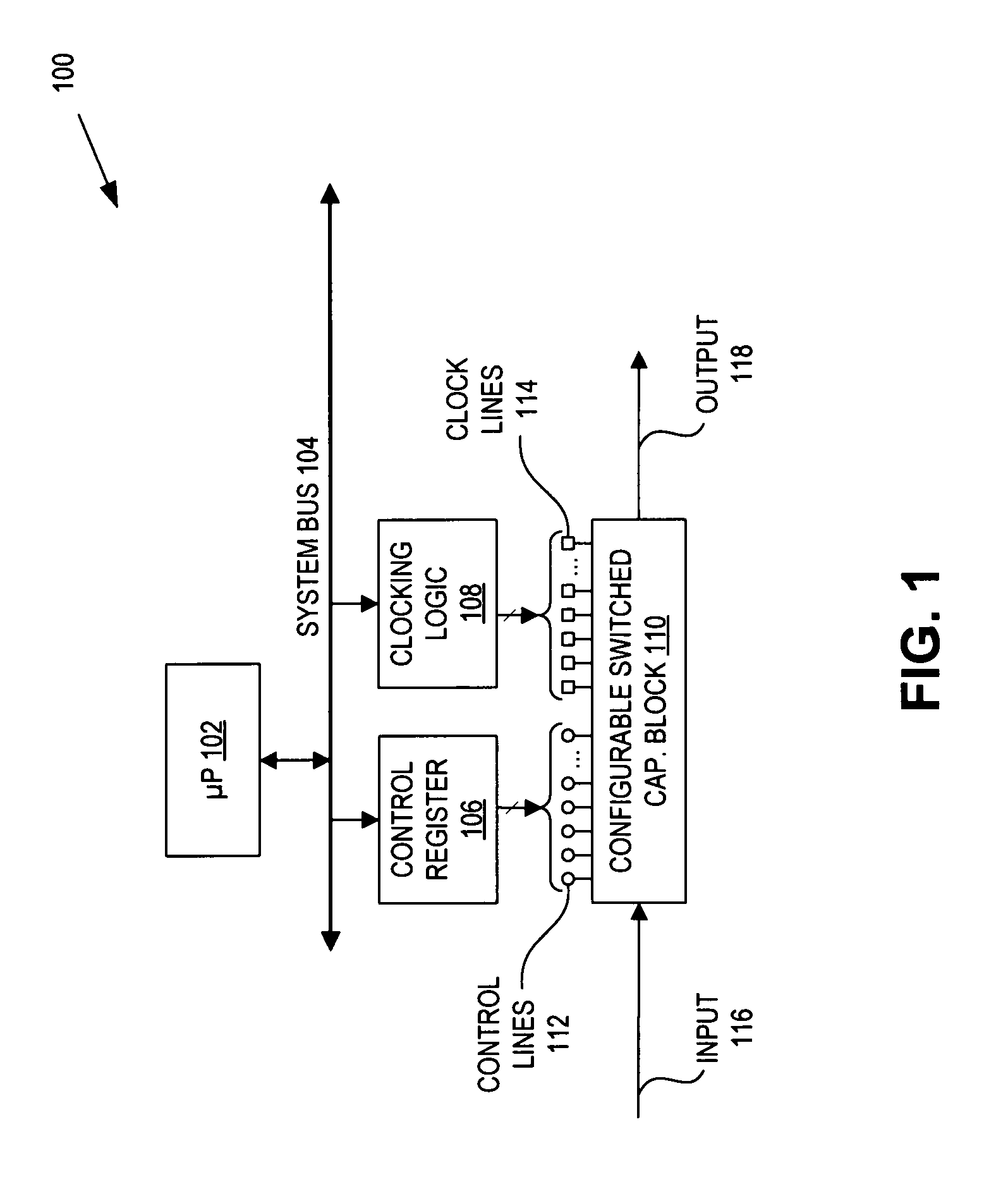

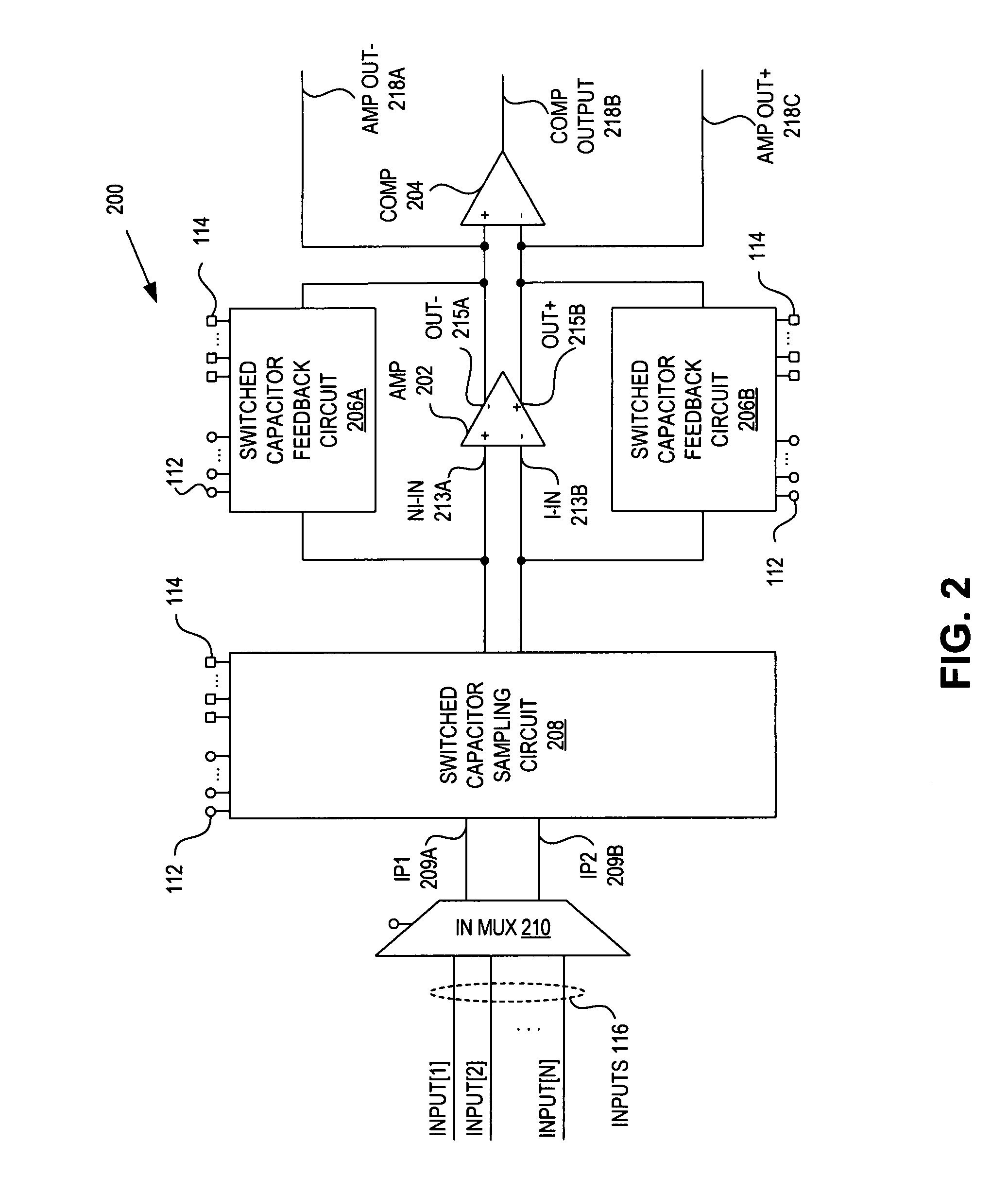

Configurable switched capacitor block

ActiveUS7679422B1Computing operations for integral formationElectric signal transmission systemsAudio power amplifierFeedback circuits

A configurable switched capacitor block includes a switched-capacitor (SC) sampling circuit, a fully differential amplifier, an SC feedback circuit, and a comparator. The SC sampling circuit is coupled to receive an input signal and to selectively generate a sampled signal to a differential input of the amplifier. The SC feedback circuit is coupled between the differential inputs and the differential outputs of the amplifier to selectively control a feedback of the amplifier. The comparator is coupled to the differential outputs of the amplifier to generate an output signal. The configurable switched capacitor block has multiple modes of operation which are selectable by programming the SC sampling circuit and the SC feedback circuit.

Owner:CYPRESS SEMICON CORP

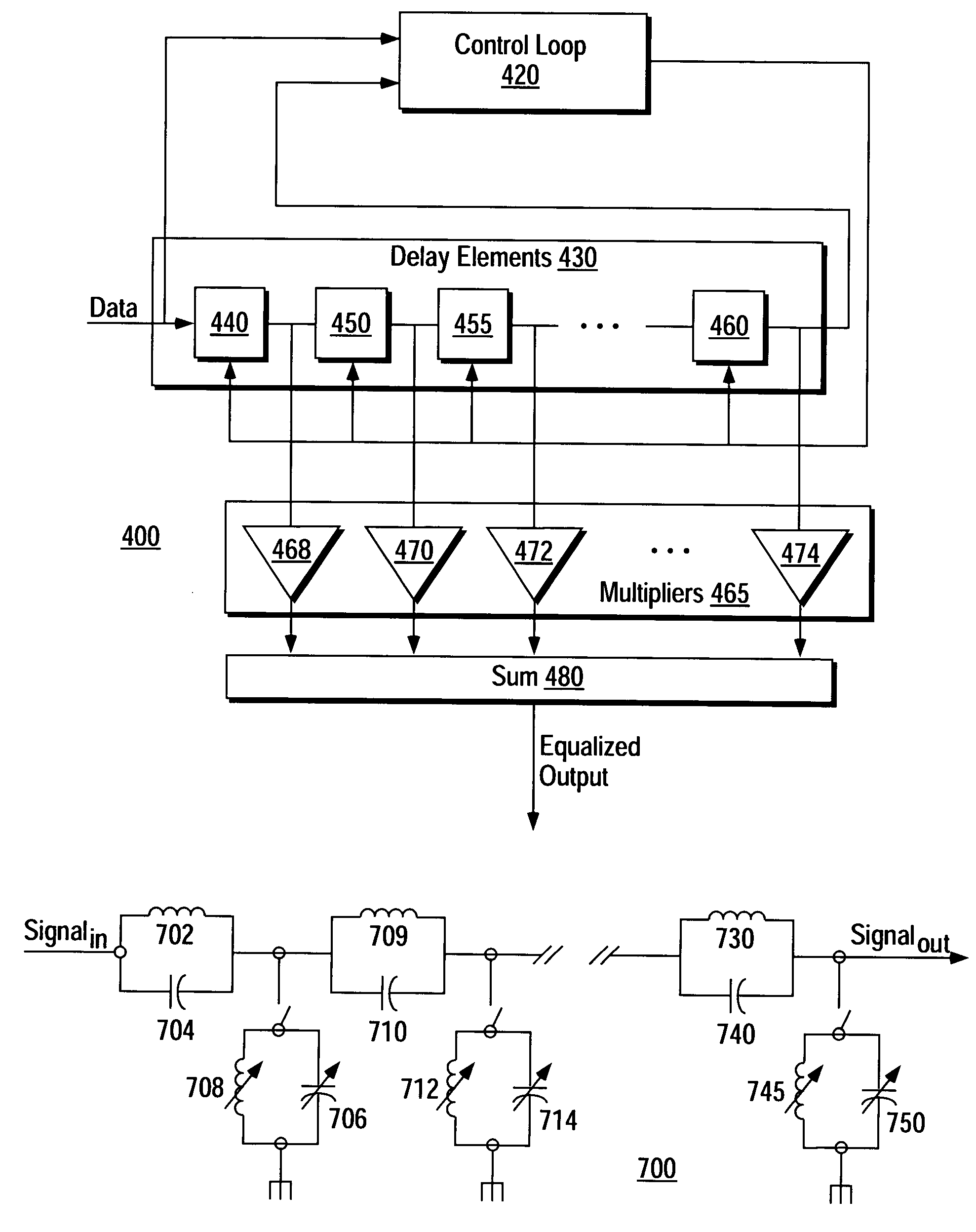

Adaptive equalization with group delay

InactiveUS20060146926A1Reduce impactReduces undesired interactionMultiple-port networksTransversal filtersEqualizationControl theory

Methods, apparatuses, and systems are presented for performing adaptive equalization involving receiving a signal originating from a channel associated with inter-symbol interference, filtering the signal using a filter having a plurality of adjustable tap weights to produce a filtered signal, and adaptively updating each of the plurality of adjustable tap weights to a new value to reduce effects of inter-symbol interference, wherein each of the plurality of adjustable tap weights is adaptively updated to take into account a constraint relating to a measure of error in the filtered signal and a constraint relating to group delay associated with the filter. Each of the plurality of adjustable tap weights may be adaptively updated to drive group delay associated with the filter toward a target group delay.

Owner:MICROSEMI STORAGE SOLUTIONS

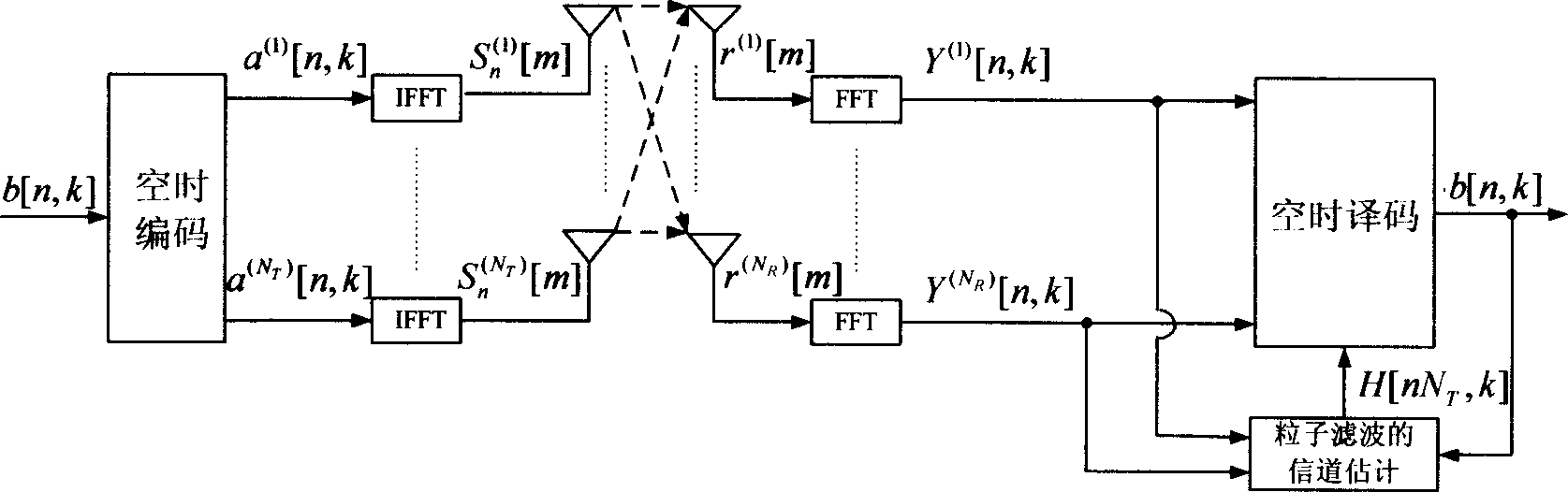

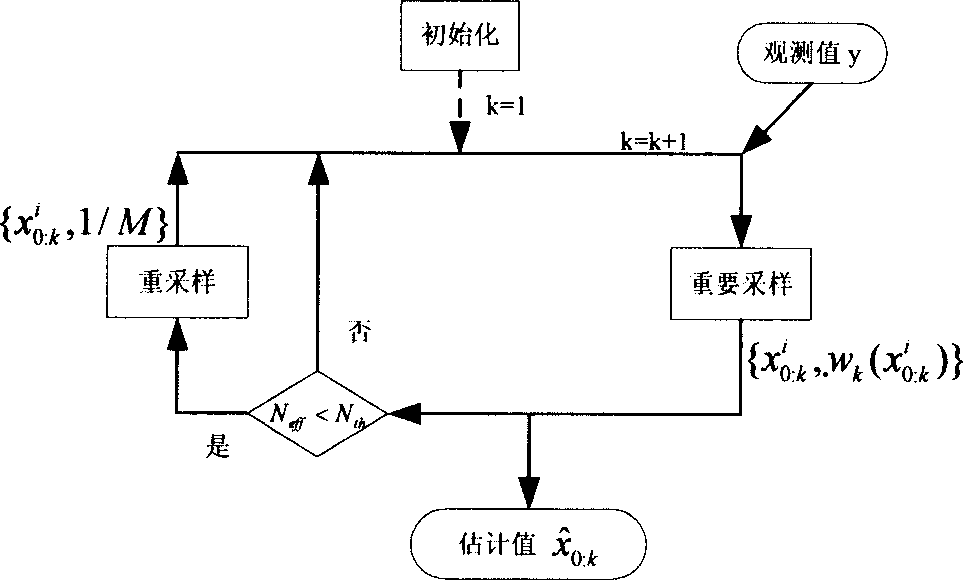

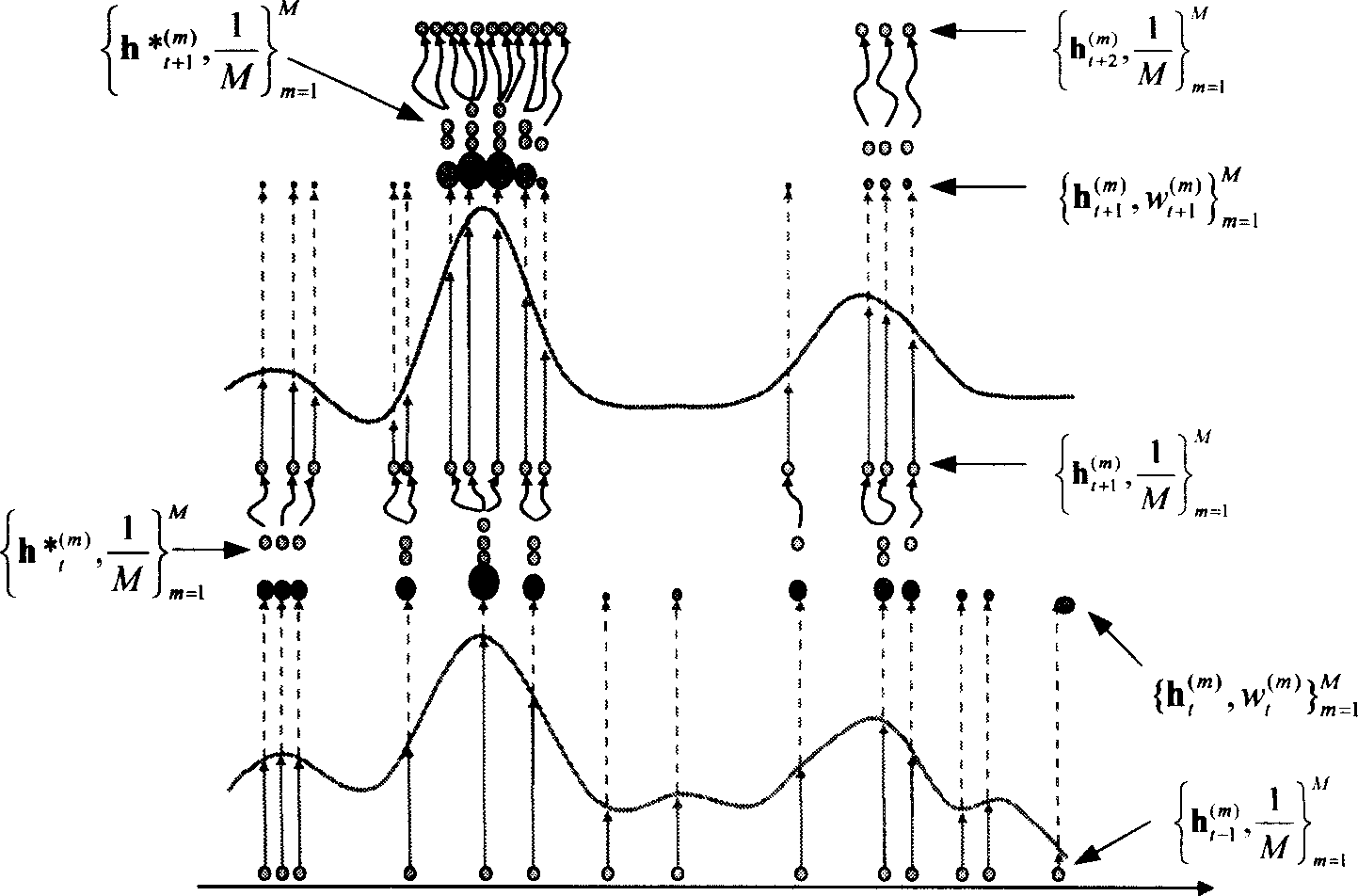

Channel estimation method based on particle filtering

InactiveCN1866763ASimplified Computational ComplexityEstimated performance is robustTransversal filtersModulated-carrier systemsCurrent channelFiltration

The invention discloses a channel estimation method of corpuscle filtration in the radio transmission domain, which comprises the following steps: estimating least square of channel according to known pilot information; getting initial value which is estimated by the pilot channel; installing particle range and particle amount; giving out initial weight of every particle; using likelihood function to calculate likelihood function value of weight value of every particle according to signal which is received by pick-up antenna; normalizating likelihood function value of every particle; getting normalizated weight value of every particle; using Bayes's theory to get probability distribution function value of current channel value; resampling particle according to judgement condition; transforming current particle to next pilot area; getting channel estimated value of all pilot areas; carrying out interpolation algorism; getting channel estimated value of all transmitted data symbol; finishing channel information estimation. The invention has moderate property and strong anti-noise ability.

Owner:SHANGHAI JIAO TONG UNIV +1

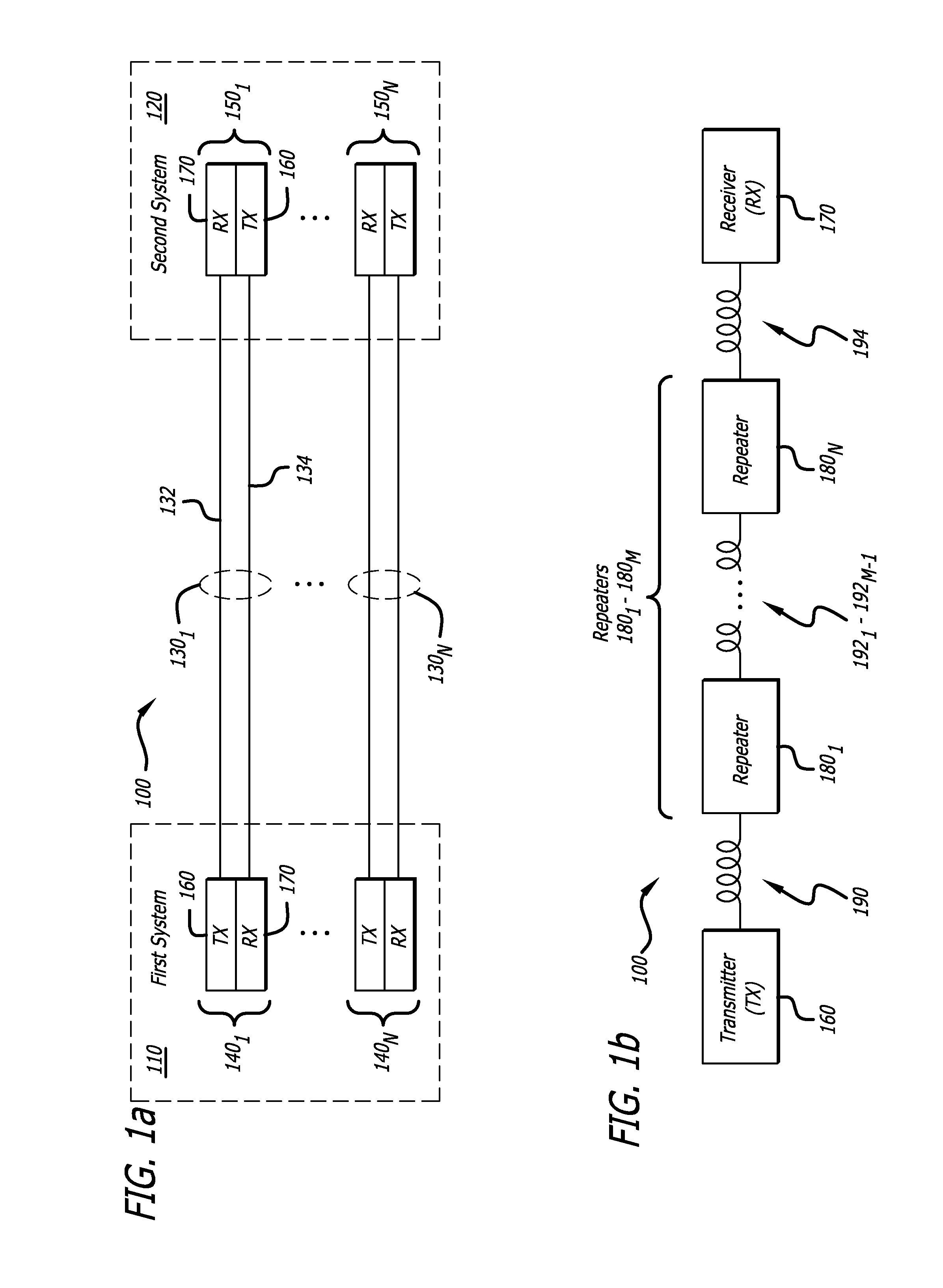

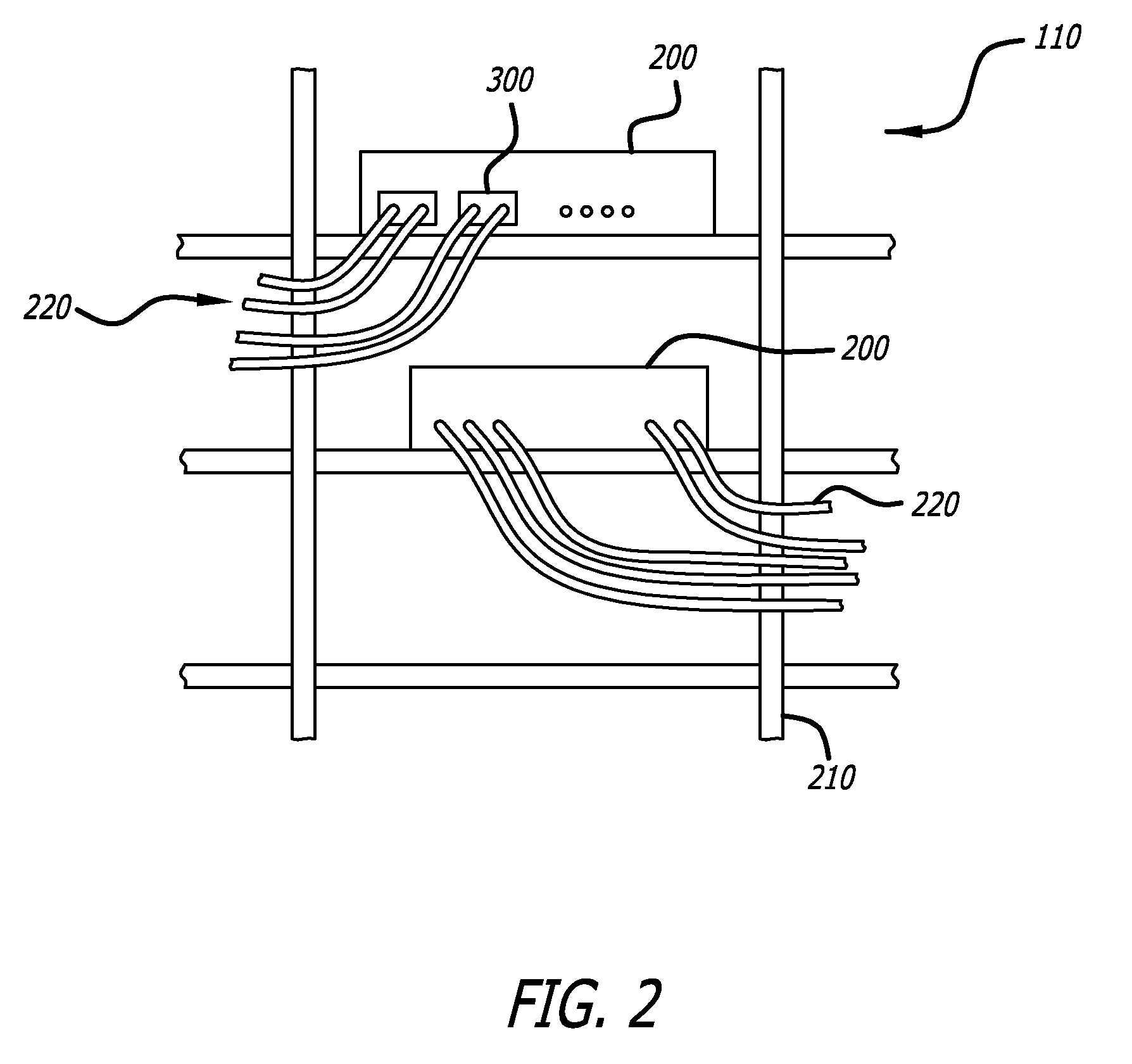

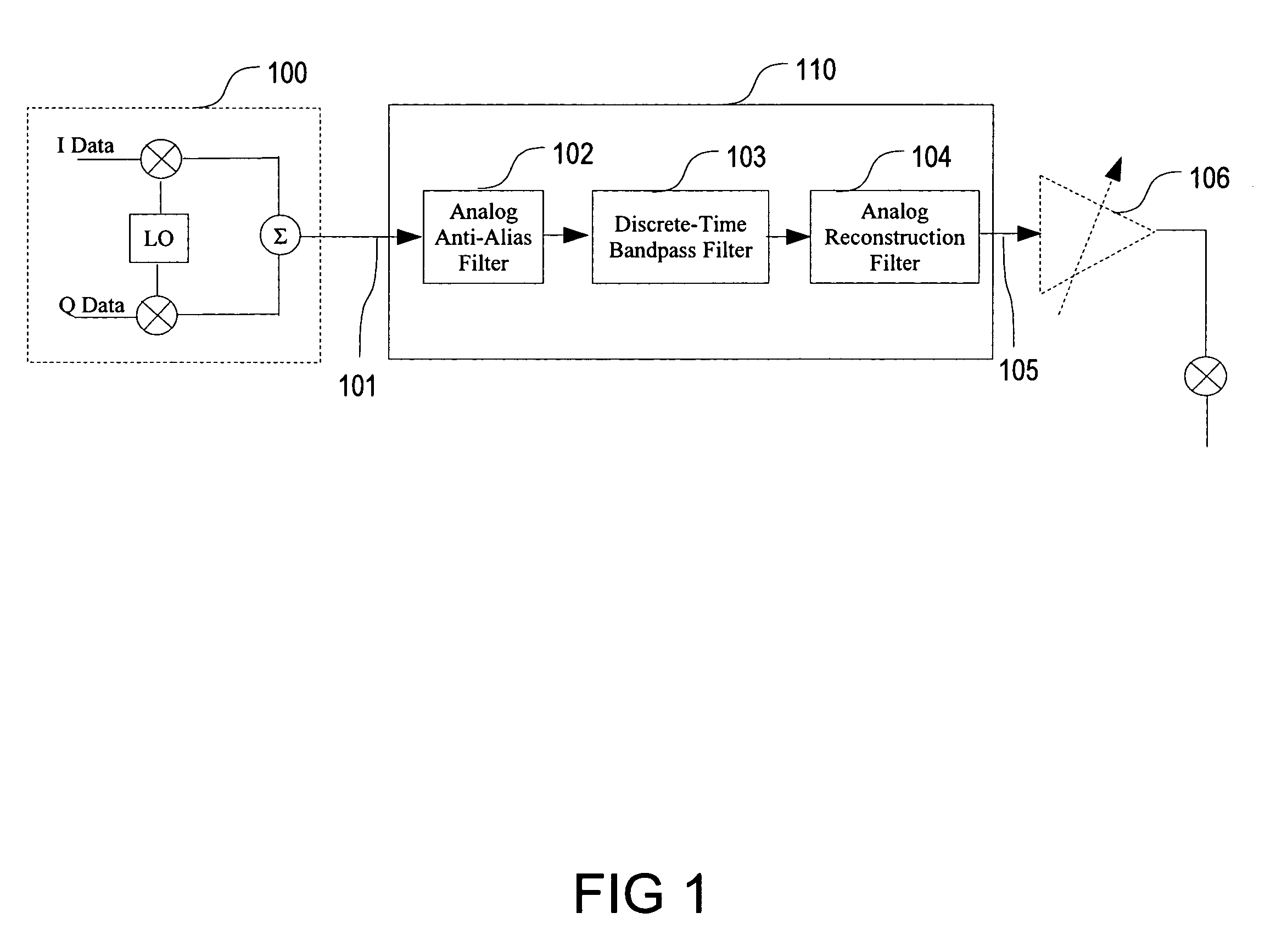

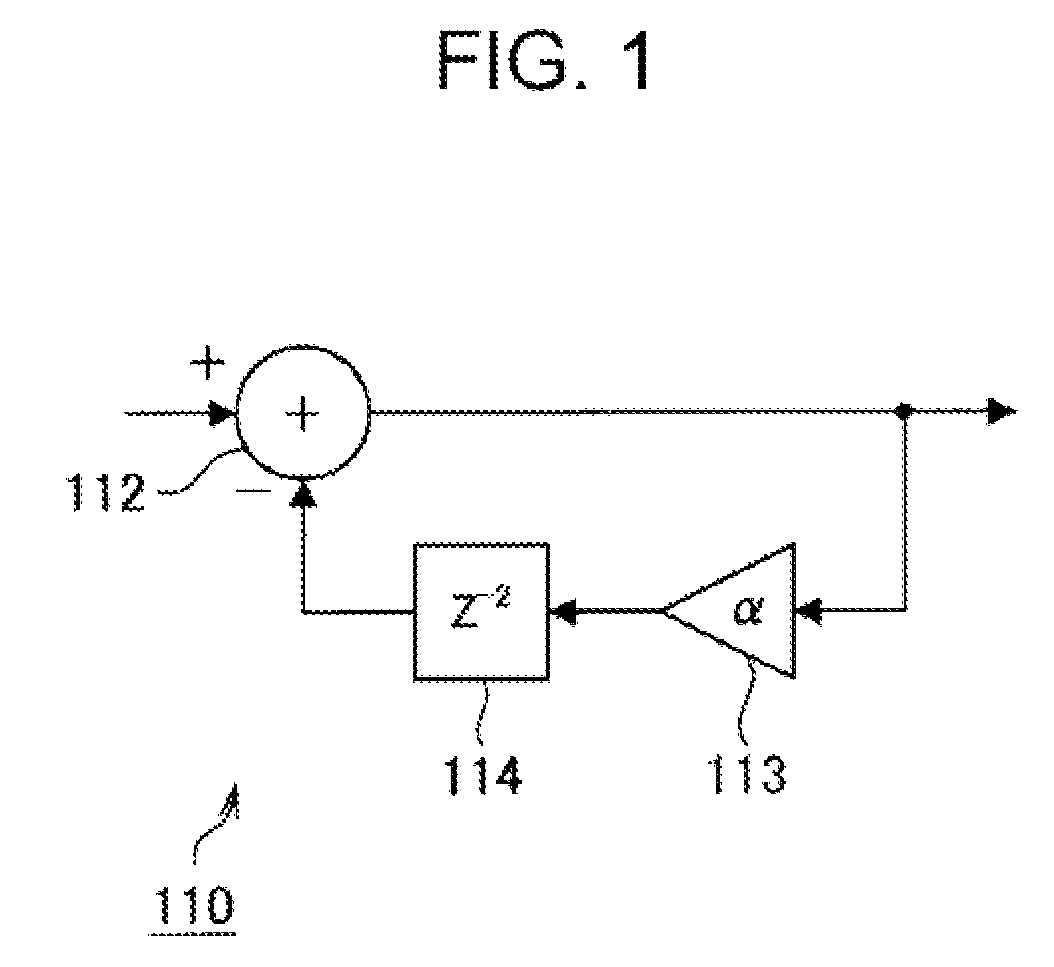

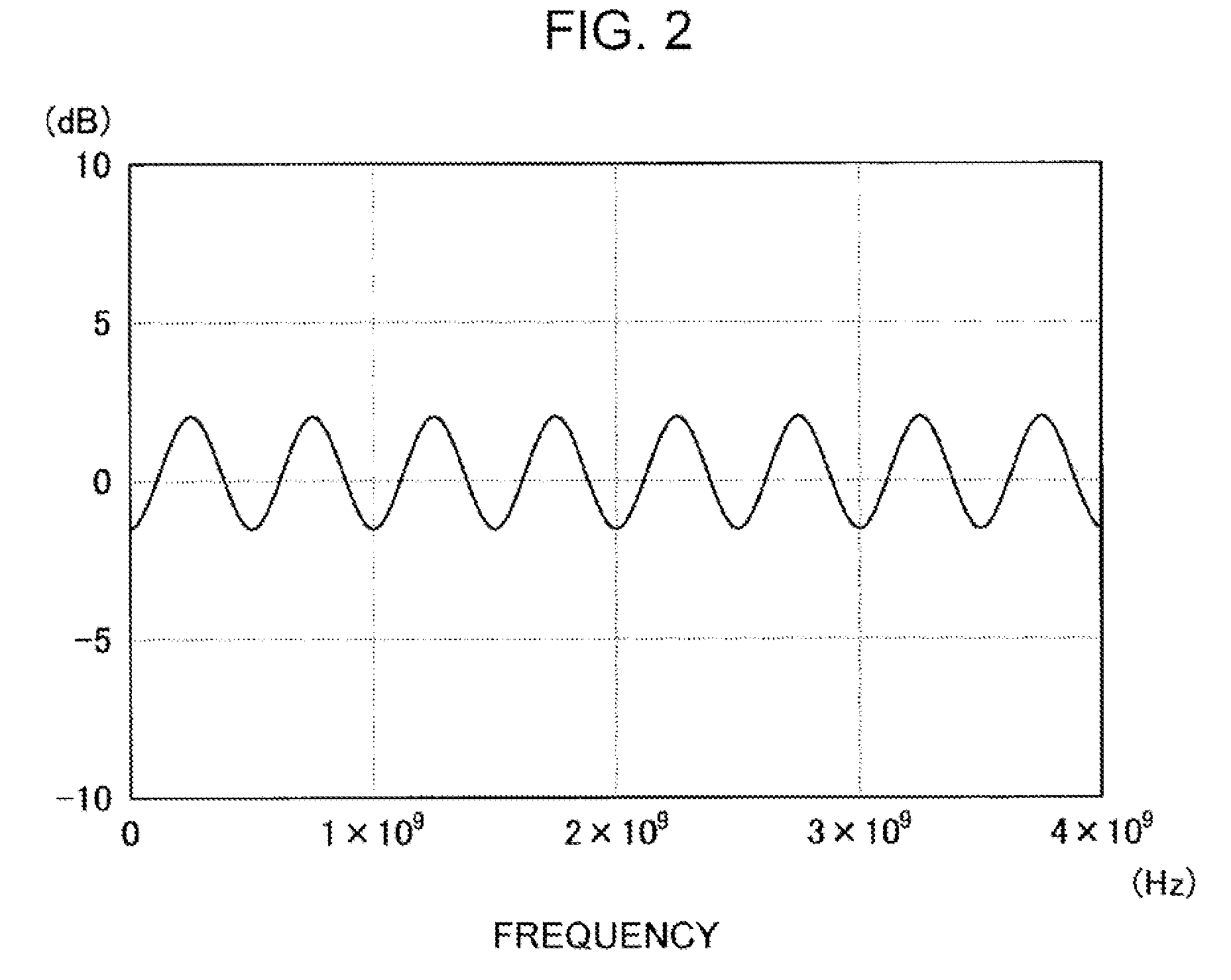

Physical layer repeater with discrete time filter for all-digital detection and delay generation

InactiveUS8078100B2Improve performanceQuick checkTransversal filtersDigital technique networkBandpass filteringCommunications system

A discrete time bandpass filter element (103) having multiple stages (201, 202, 203, 204, 205) for use in a time division duplex radio protocol communications system including an automatic gain control. Discrete time bandpass filter is used to generate delay and can replace SAW filters in a wireless frequency translating repeater.

Owner:QUALCOMM INC

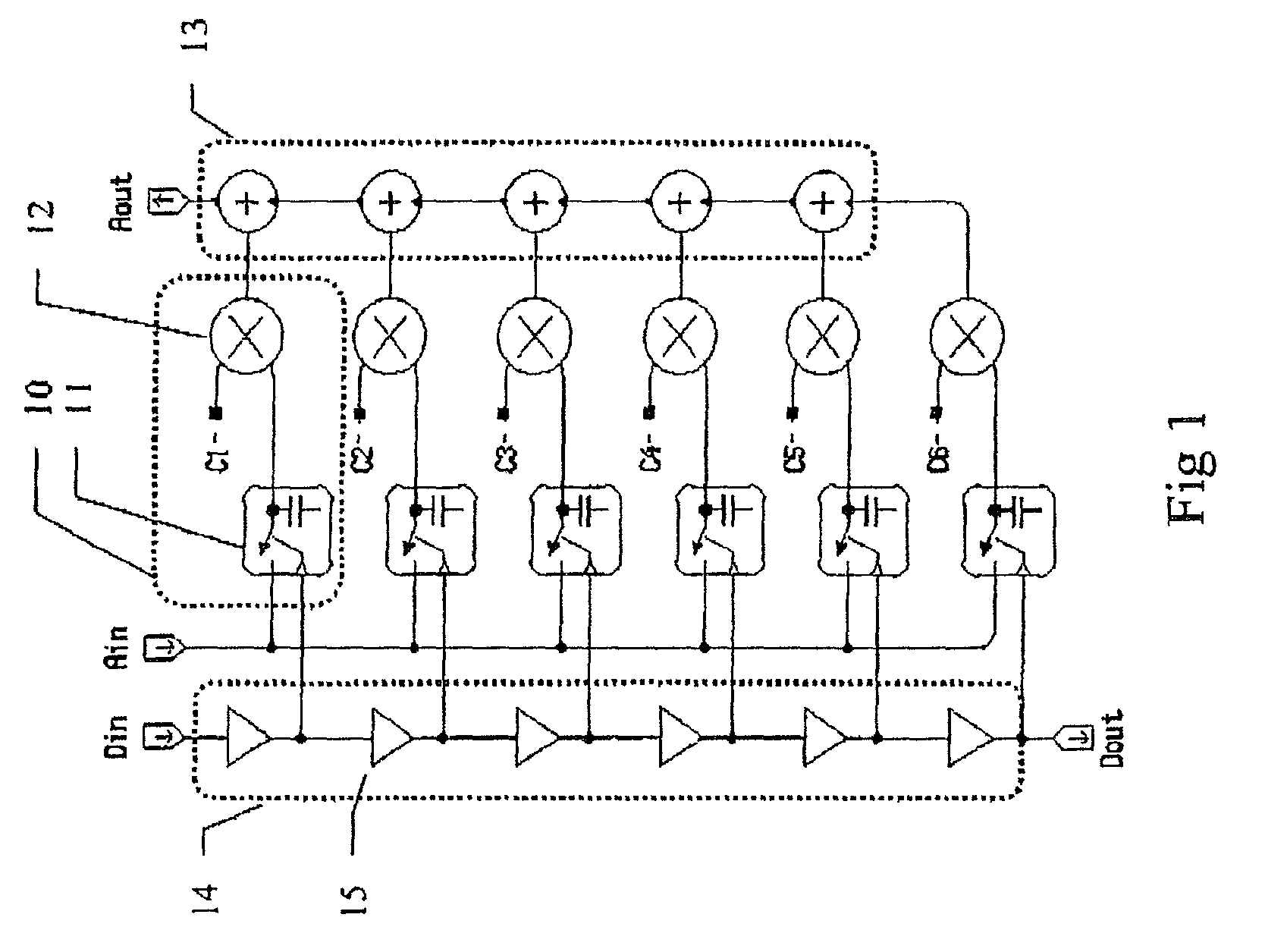

Analog filter with passive components for discrete time signals

InactiveUS7539721B2Well formedTransversal filtersOscillations generatorsClock rateDiscrete-time signal

A filter intended to receive a discrete time signal at a sampling clock frequency, comprising a determined number, greater than 2, of filtering units, each filtering unit comprising head capacitors in a number equal to the determined number, assembled in parallel between an input terminal and the terminal of an integration capacitor; and means for connecting, in successive clock cycles in a number equal to the determined number, successively each head capacitor to the input terminal, and for then simultaneously connecting the head capacitors to the integration capacitor, and in which the successive clock cycles during which the head capacitors of a filtering unit are connected to the input terminal are offset by one clock cycle from one filtering unit to the next one.

Owner:ST ERICSSON SA

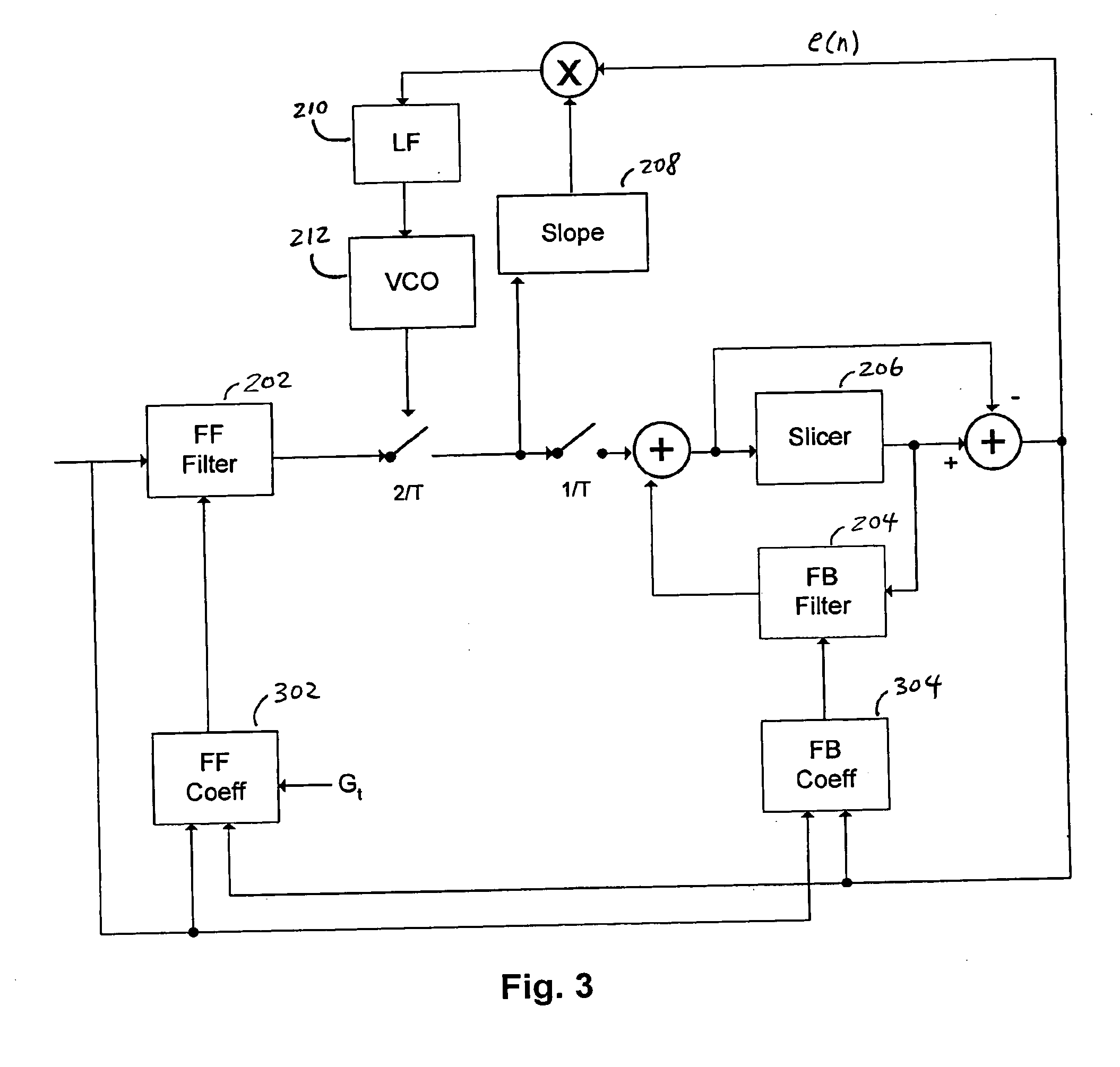

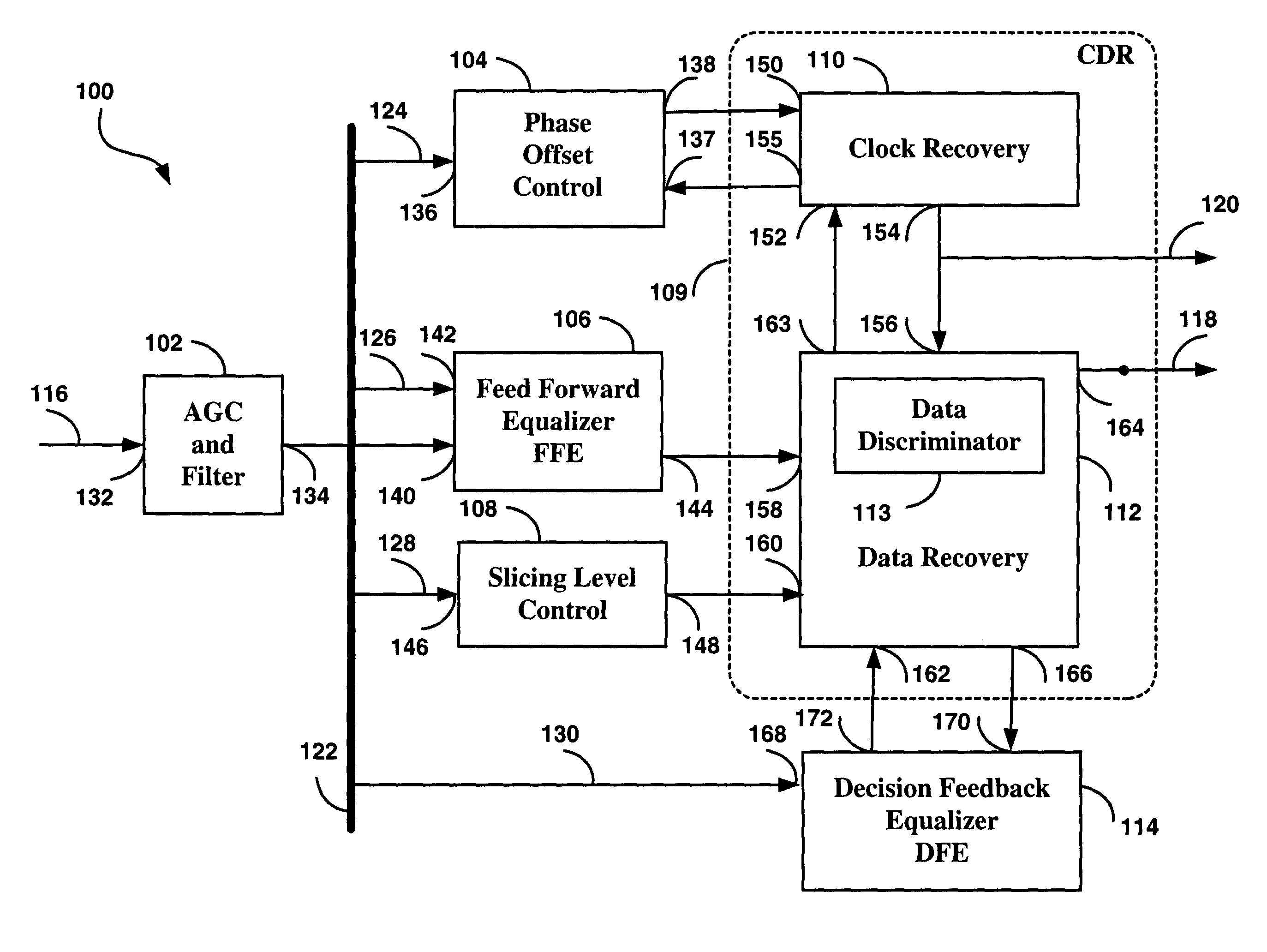

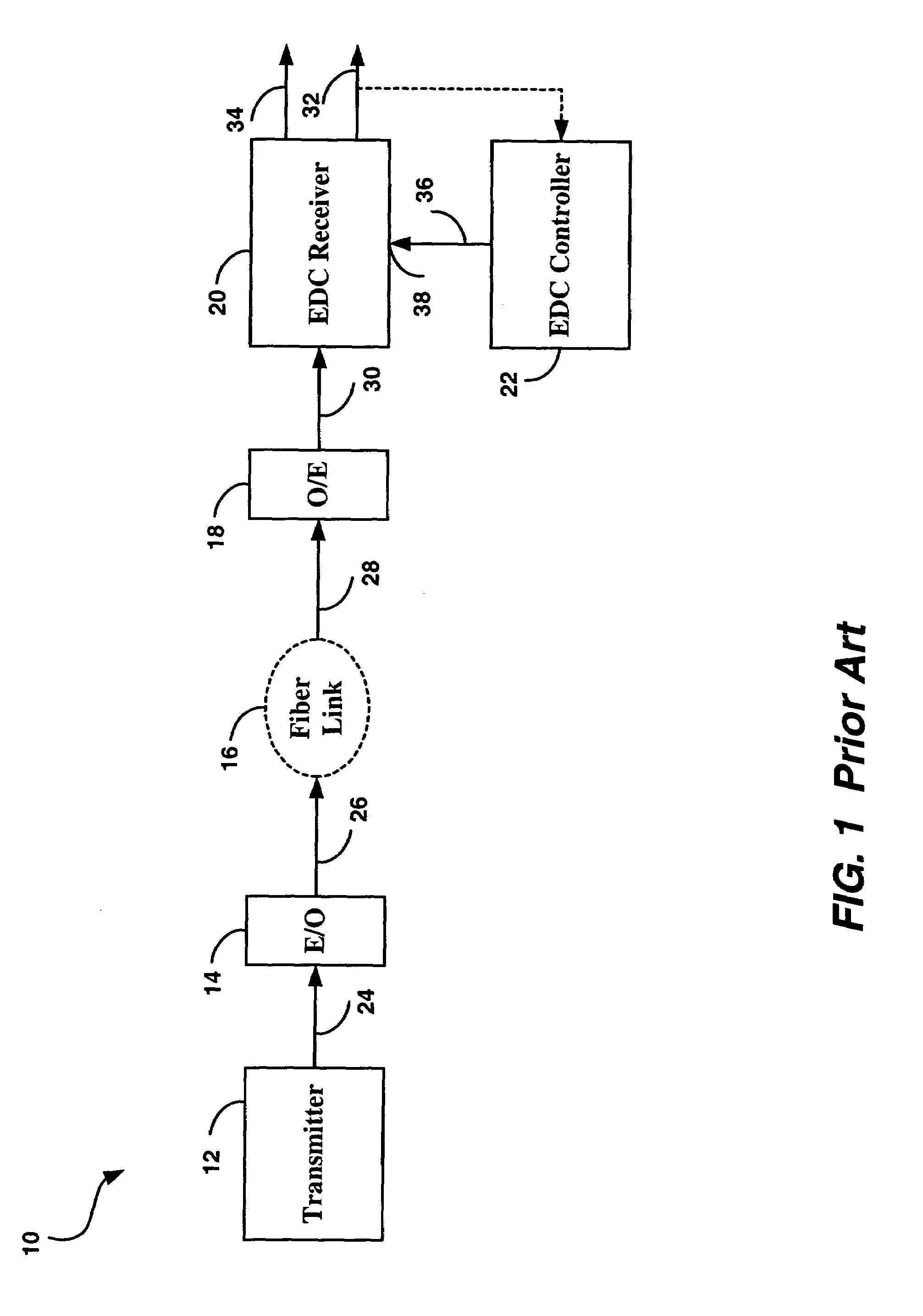

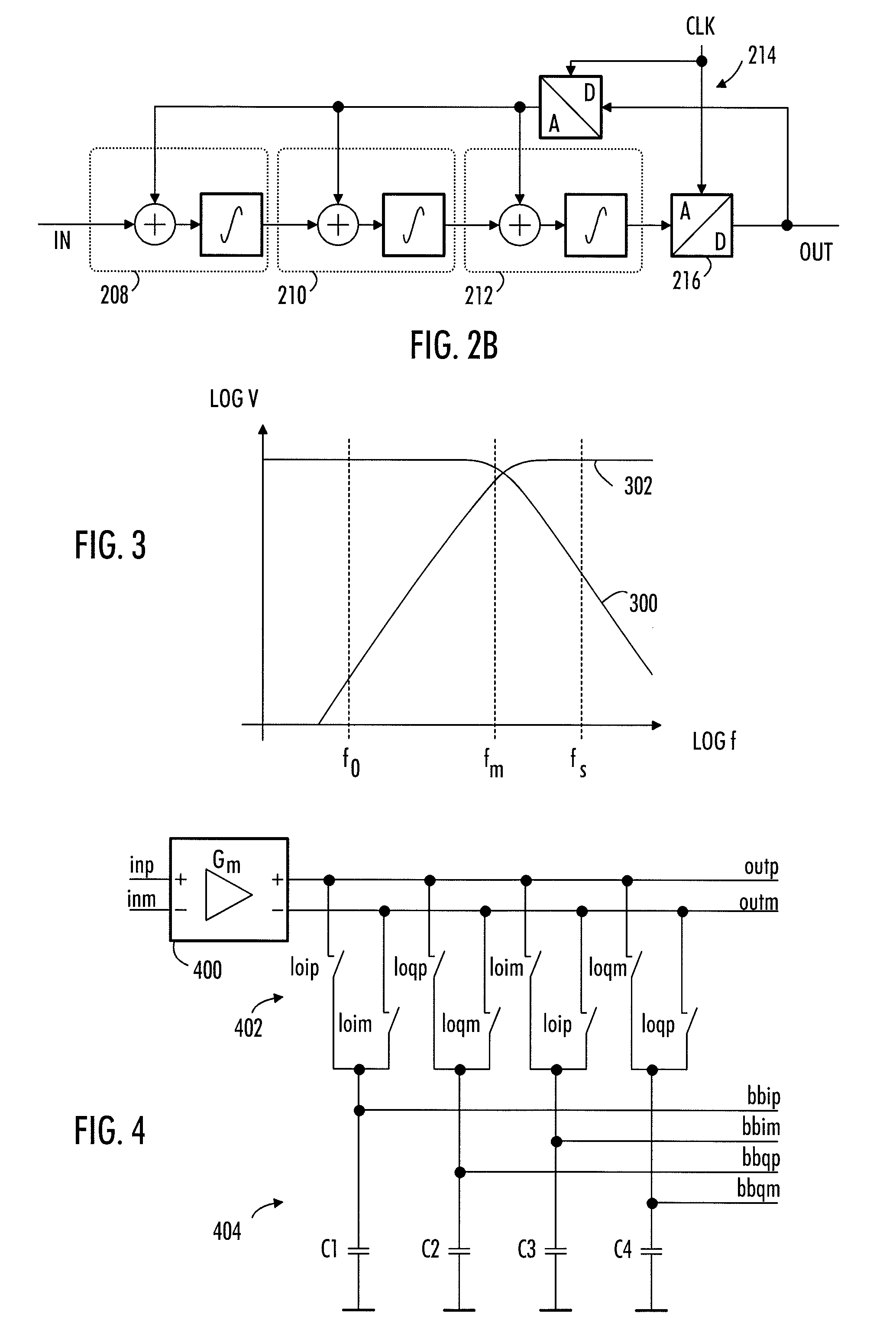

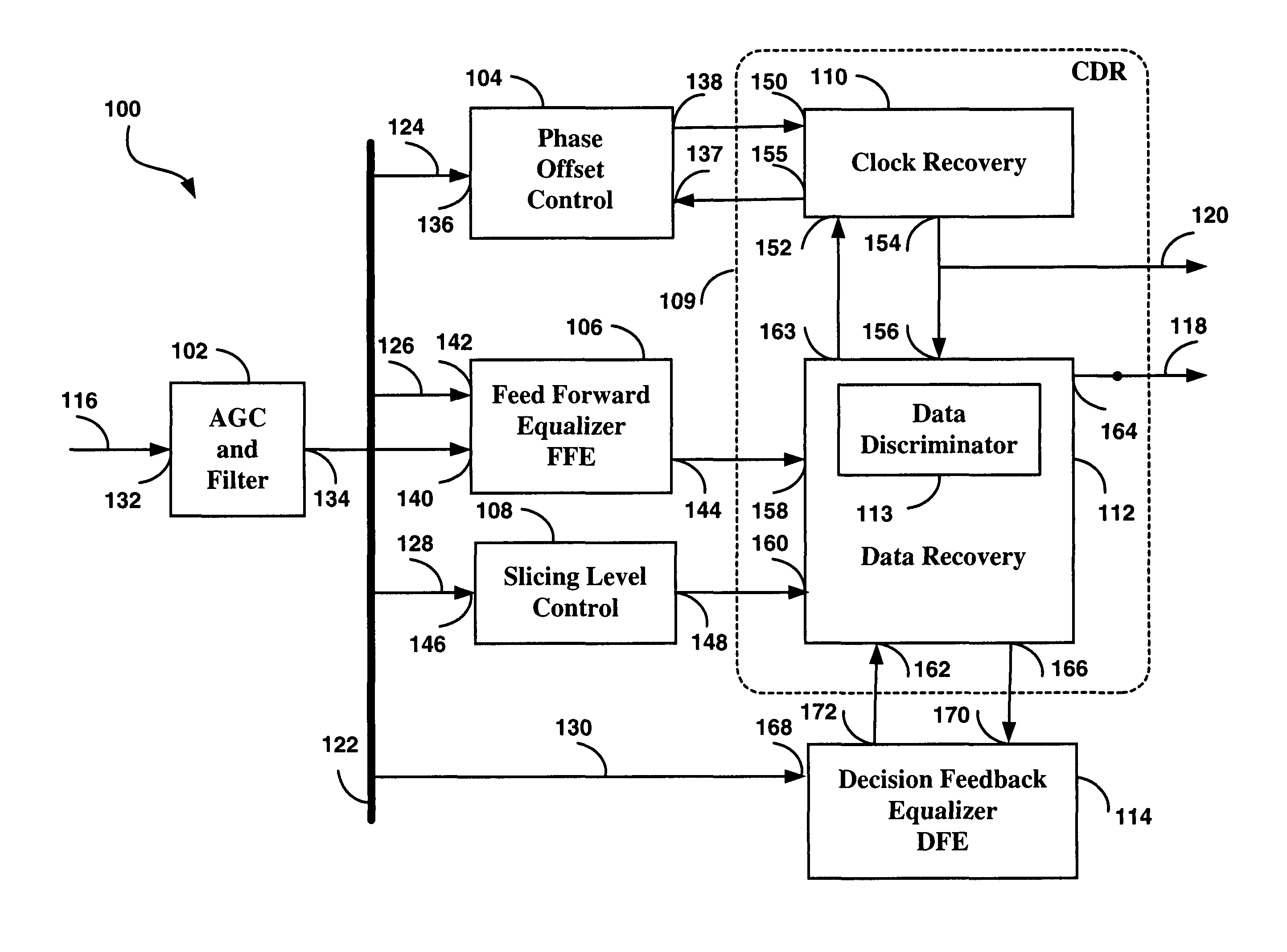

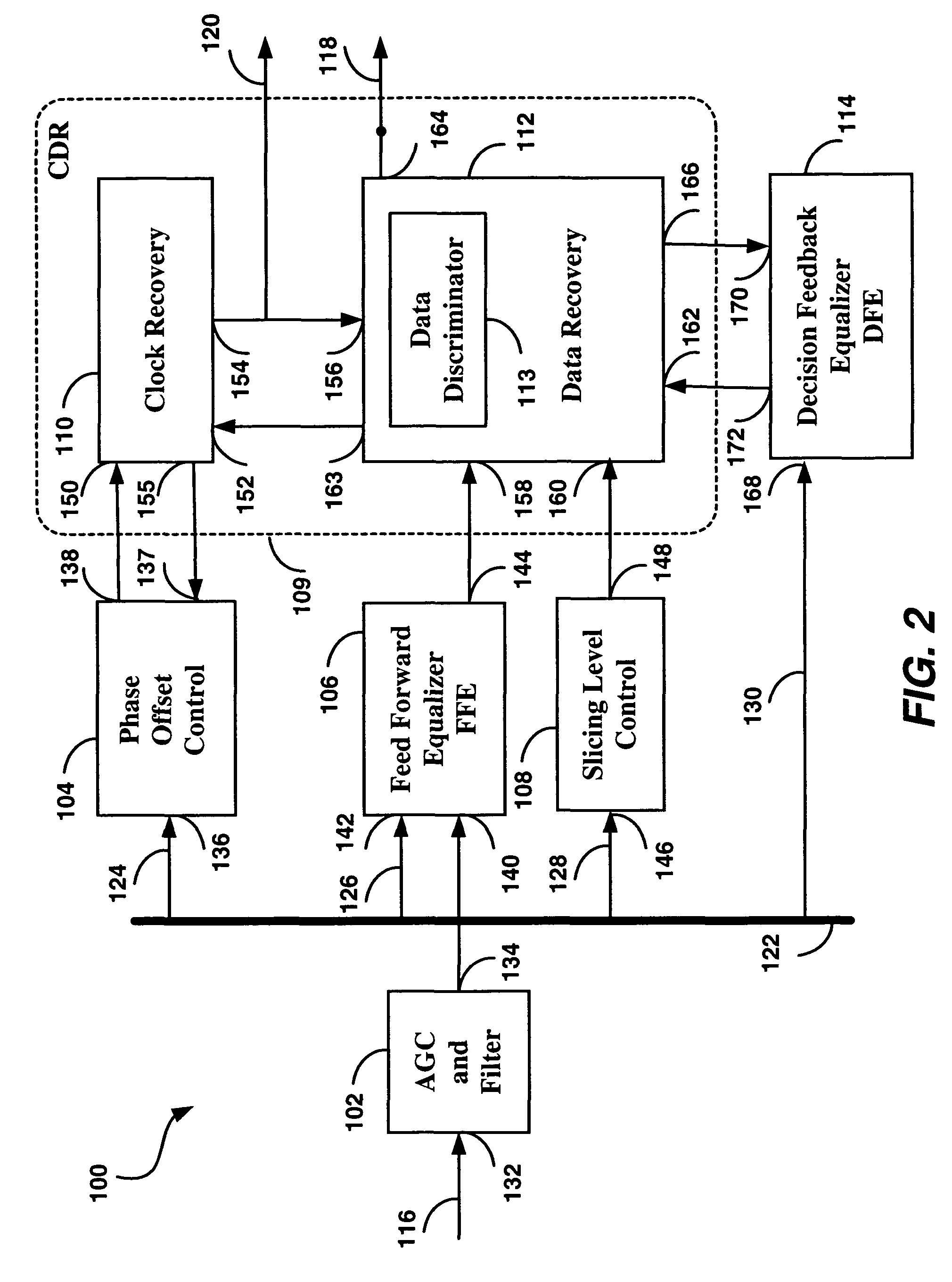

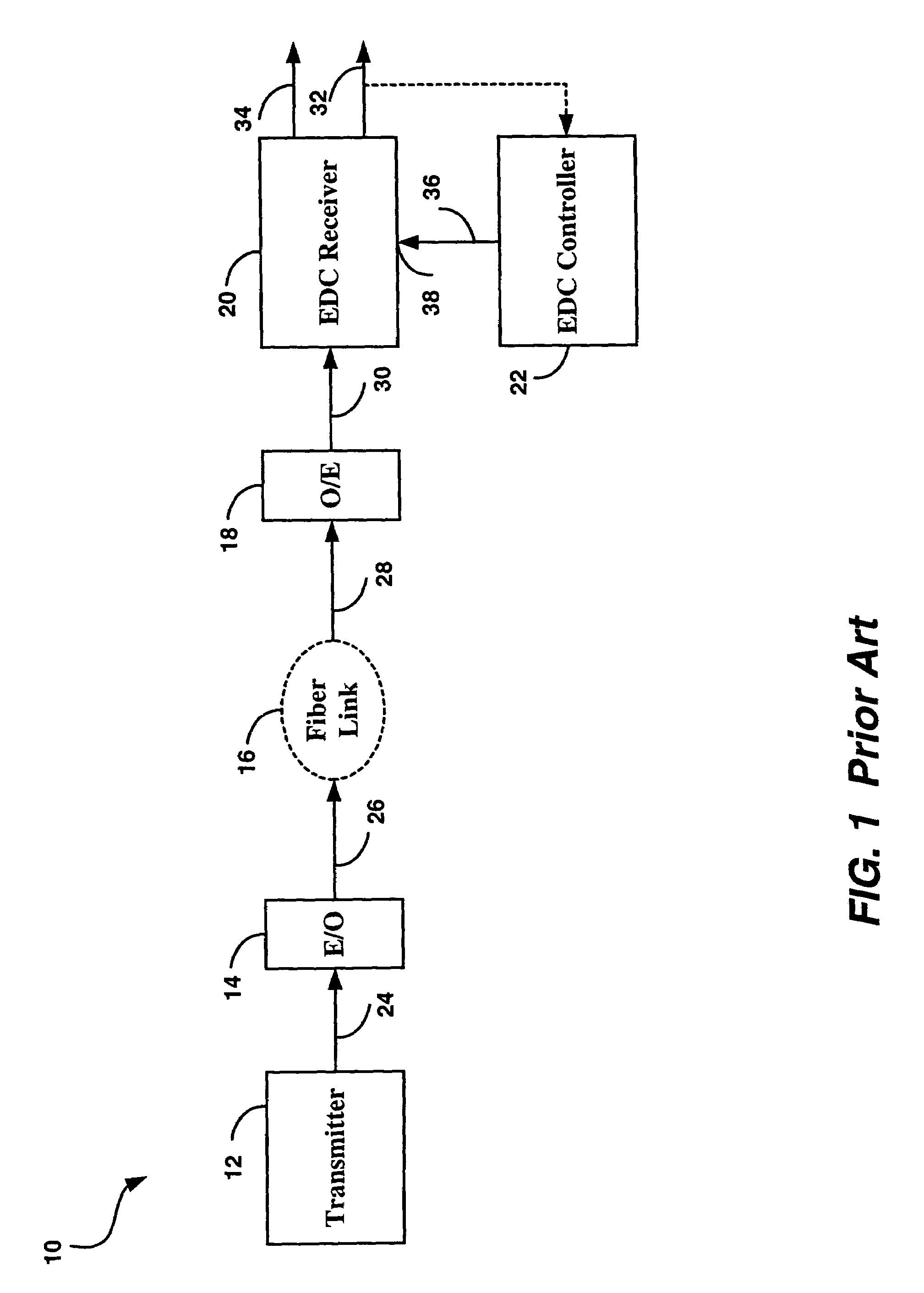

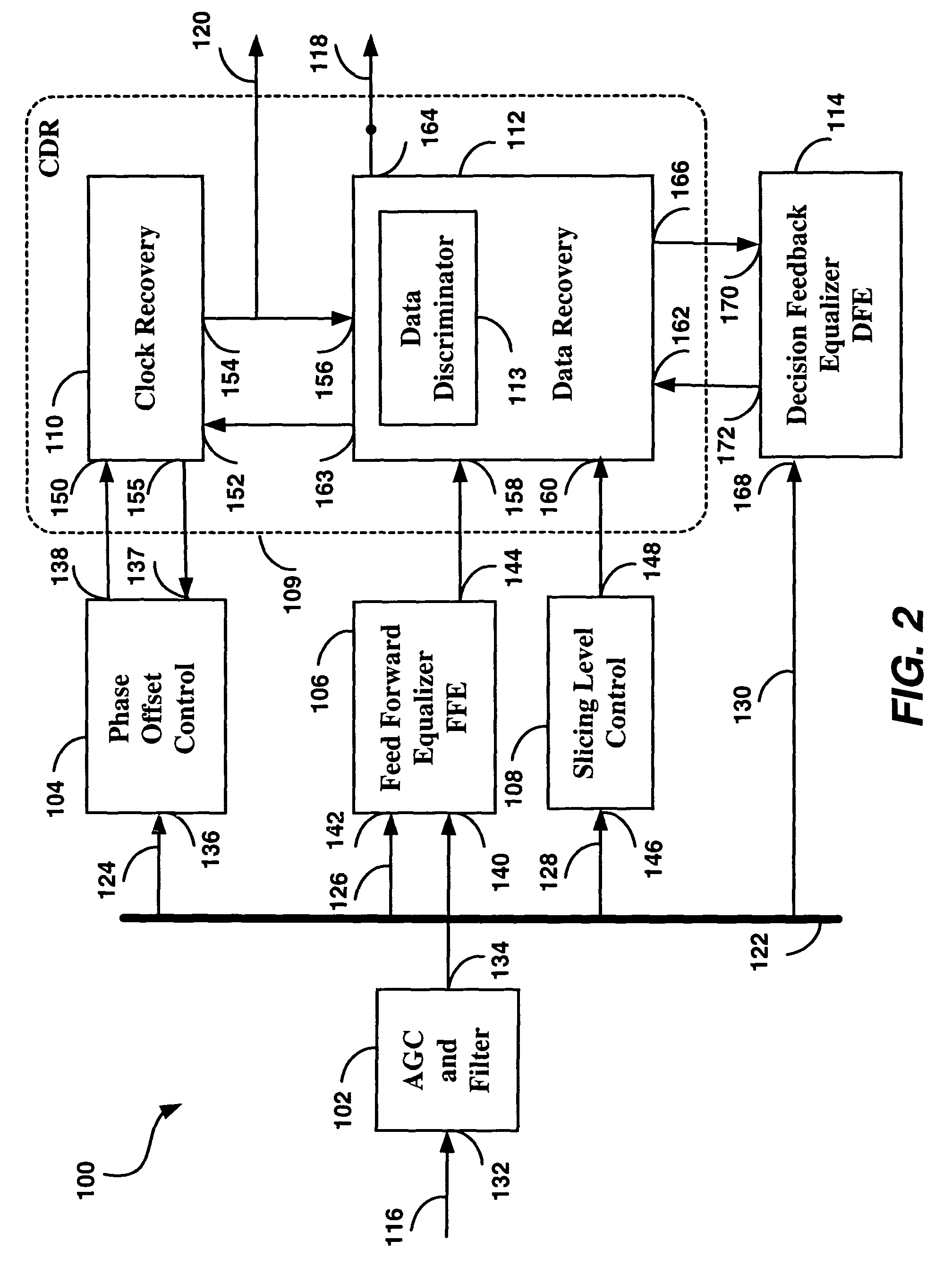

Differential receiver circuit with electronic dispersion compensation

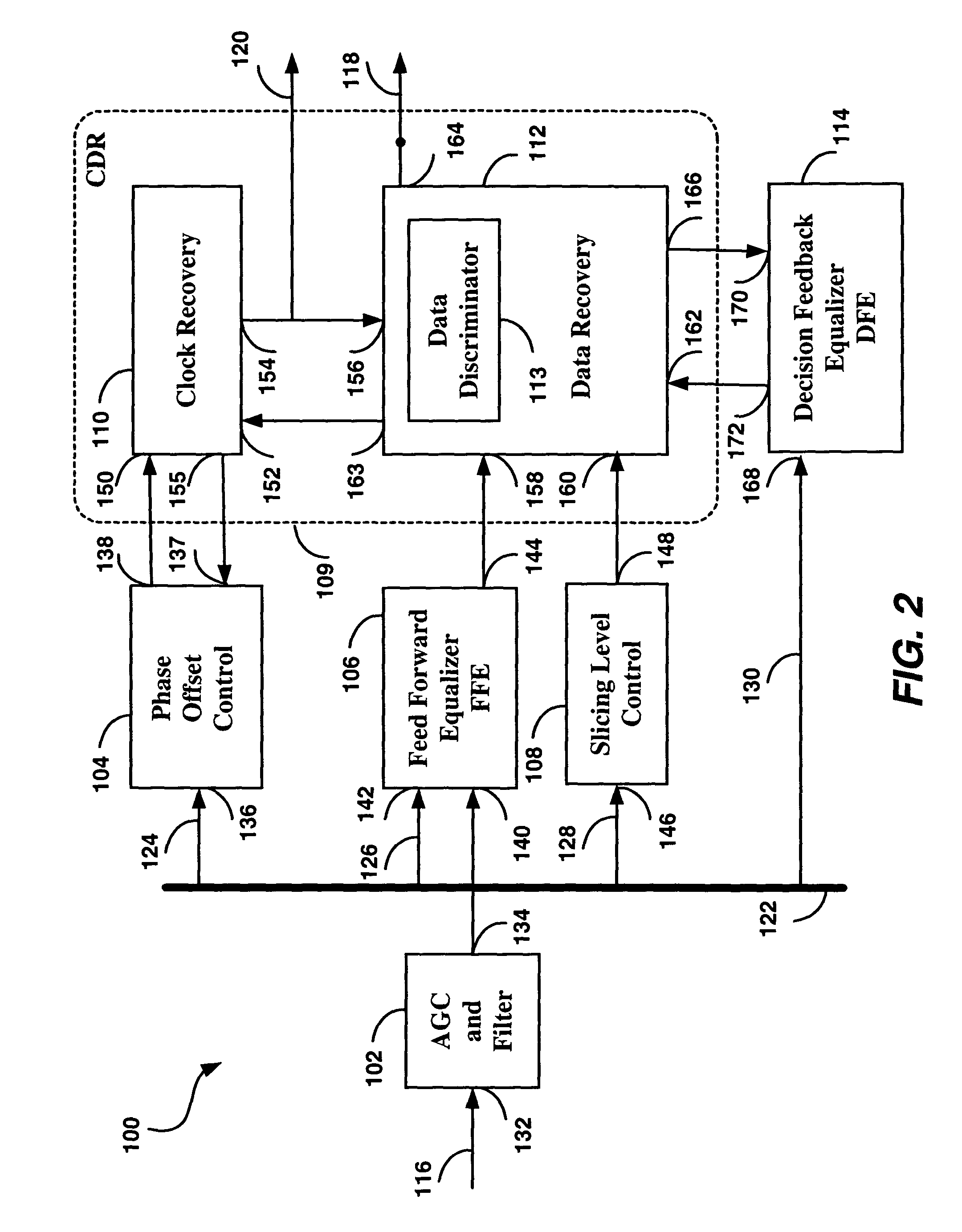

The invention describes a number of differential, balanced high-speed circuits that permit the design of a receiver with Electronic Dispersion Compensation (EDC) on a single semiconductor substrate, including the functions of an analog Fast Forward Equalizer (FFE), a Clock and Data Recovery, a Decision Feedback Equalizer (DFE), enhanced by additional circuits that permit control of the slicing level to compensate for pulse distortion, and control of the phase offset to set the optimal eye sampling time when a distorted signal is received. To provide the utmost speed of operation, all circuits including the phase locked loop, operate as differential circuits which include a number of improvements in the design of the charge pump, the decision feedback equalizer, the slicing level control, and others.

Owner:MACOM CONNECTIVITY SOLUTIONS LLC

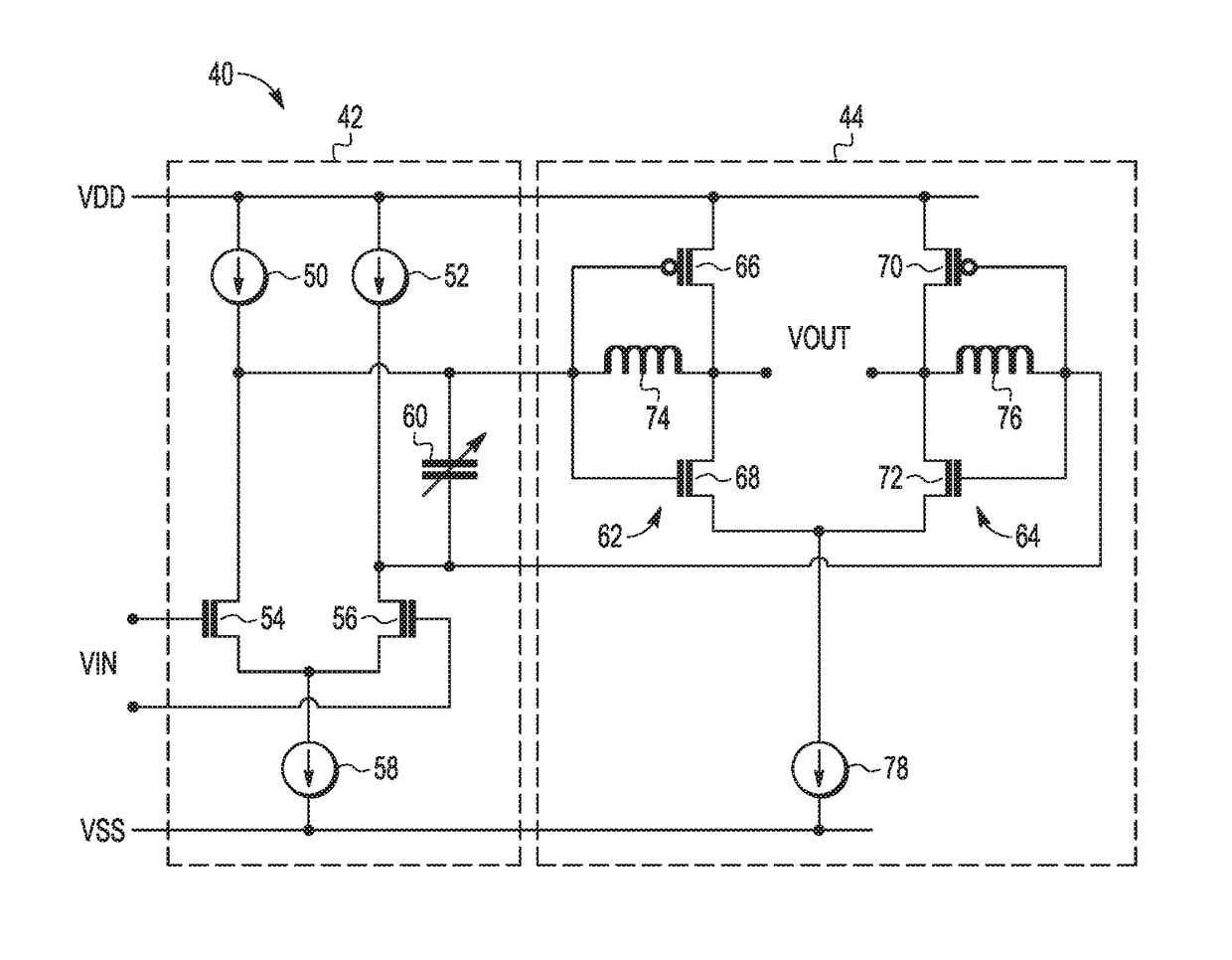

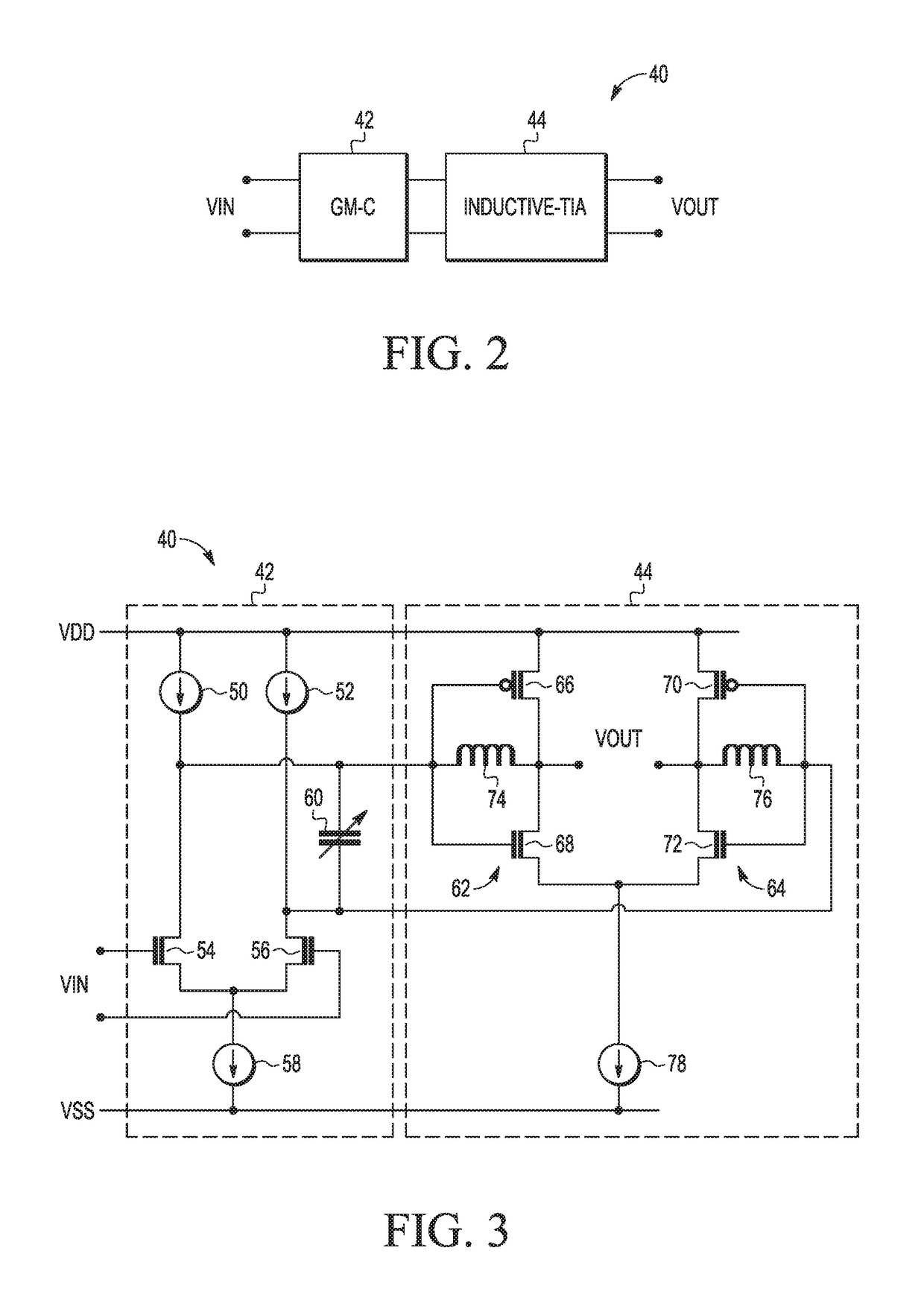

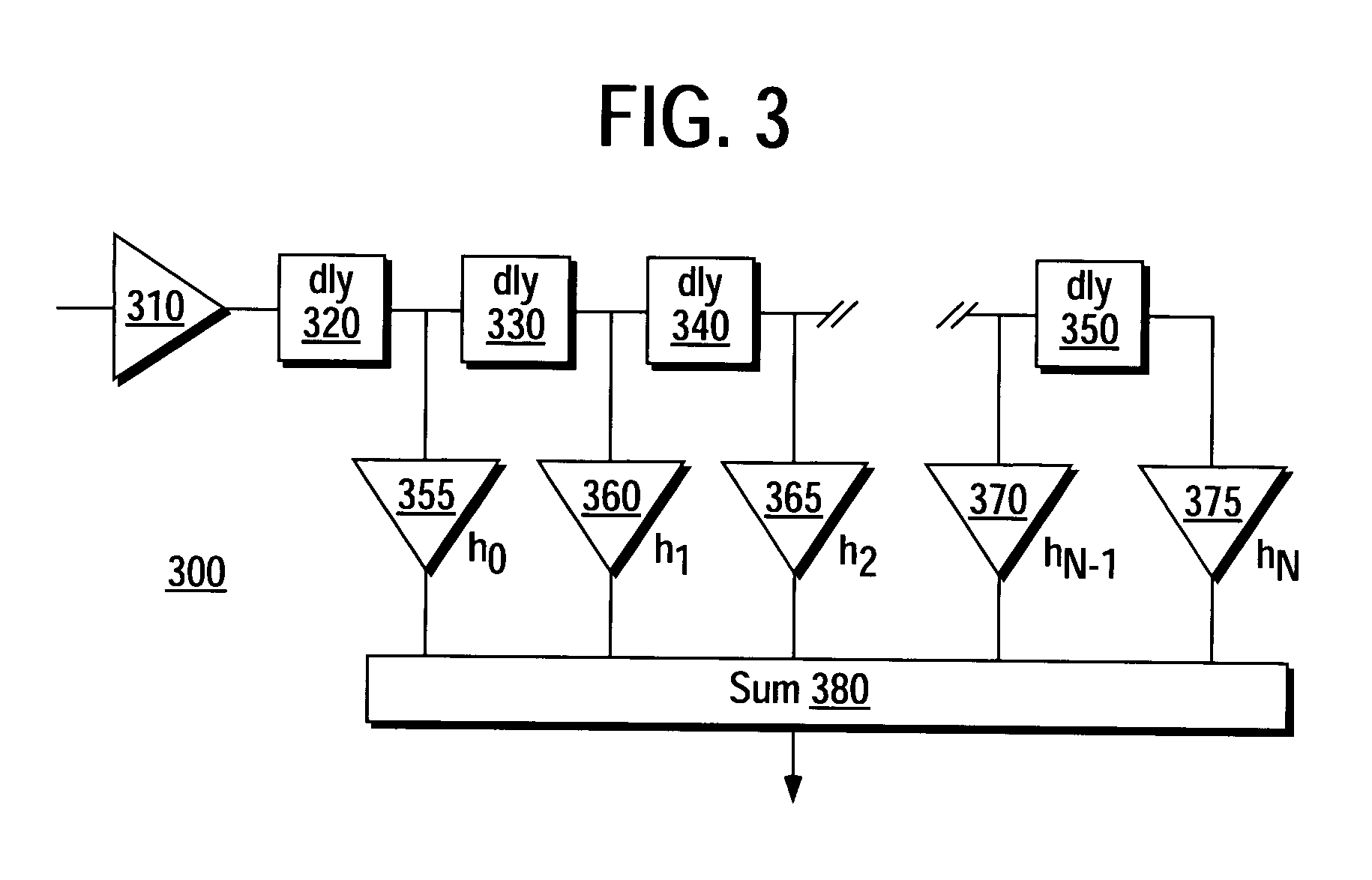

Analog delay cell and tapped delay line comprising the analog delay cell

An analog delay cell is provided that includes a transconductance-capacitance stage and an inductive transimpedance amplifier stage that provides an all-pass transfer function. In another embodiment, an adaptive analog delay cell including a transconductance (gm) plus capacitance (C) stage and an inductive-capacitance transimpedance amplifier (TIA) stage with digitally programmable phase-shift is provided. The adaptive analog delay cell increases the phase-shift by incorporating an LC network in the feedback path of the transimpedance stage. The disclosed analog delay cells can be used to provide delays in a tapped delay line. Also, the disclosed analog delay cells may be used to perform the multiplier and summation functions of a tapped delay line in addition to providing the delays. In another embodiment, the transimpedance amplifier stage includes an inductive-capacitive transimpedance amplifier stage.

Owner:NXP USA INC

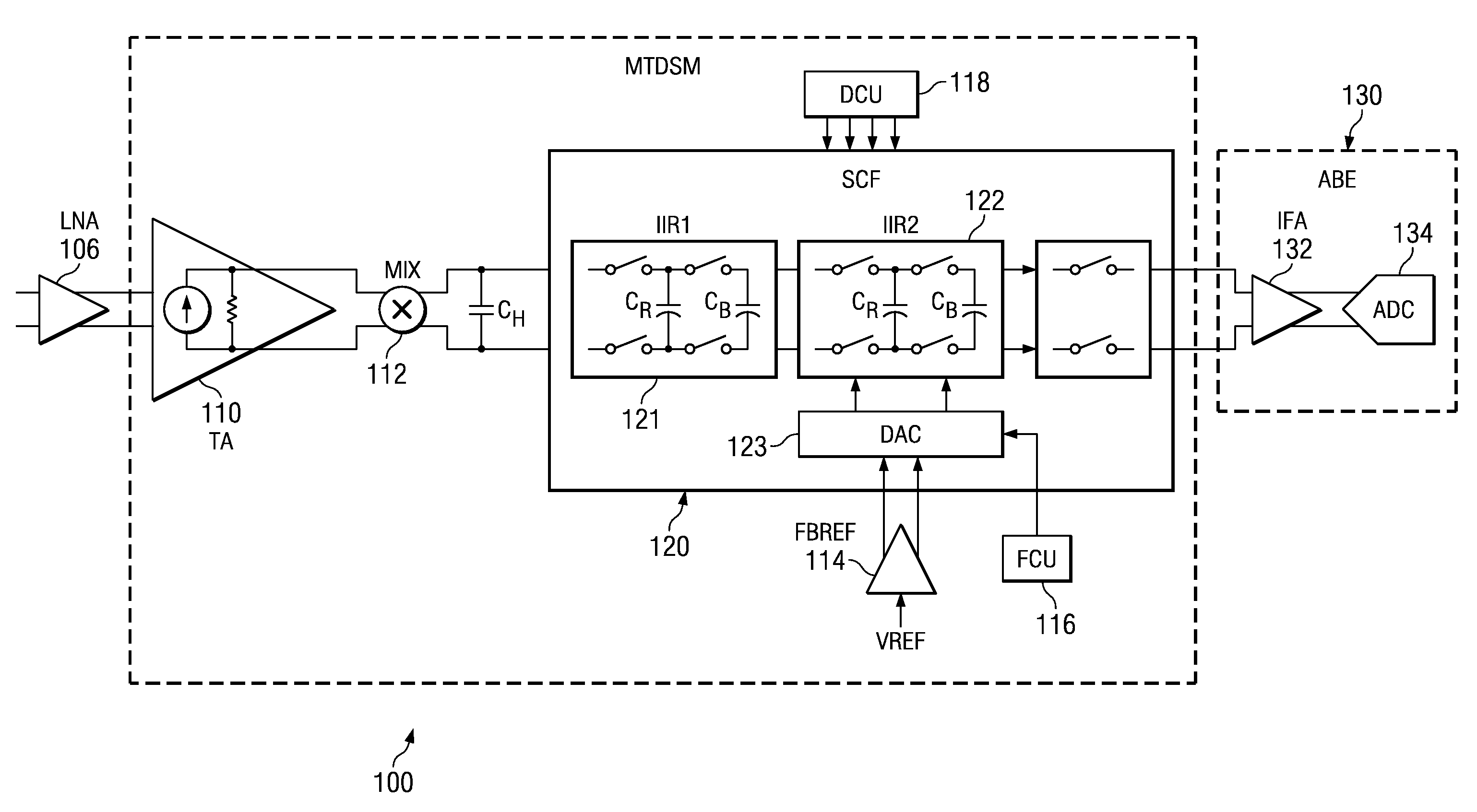

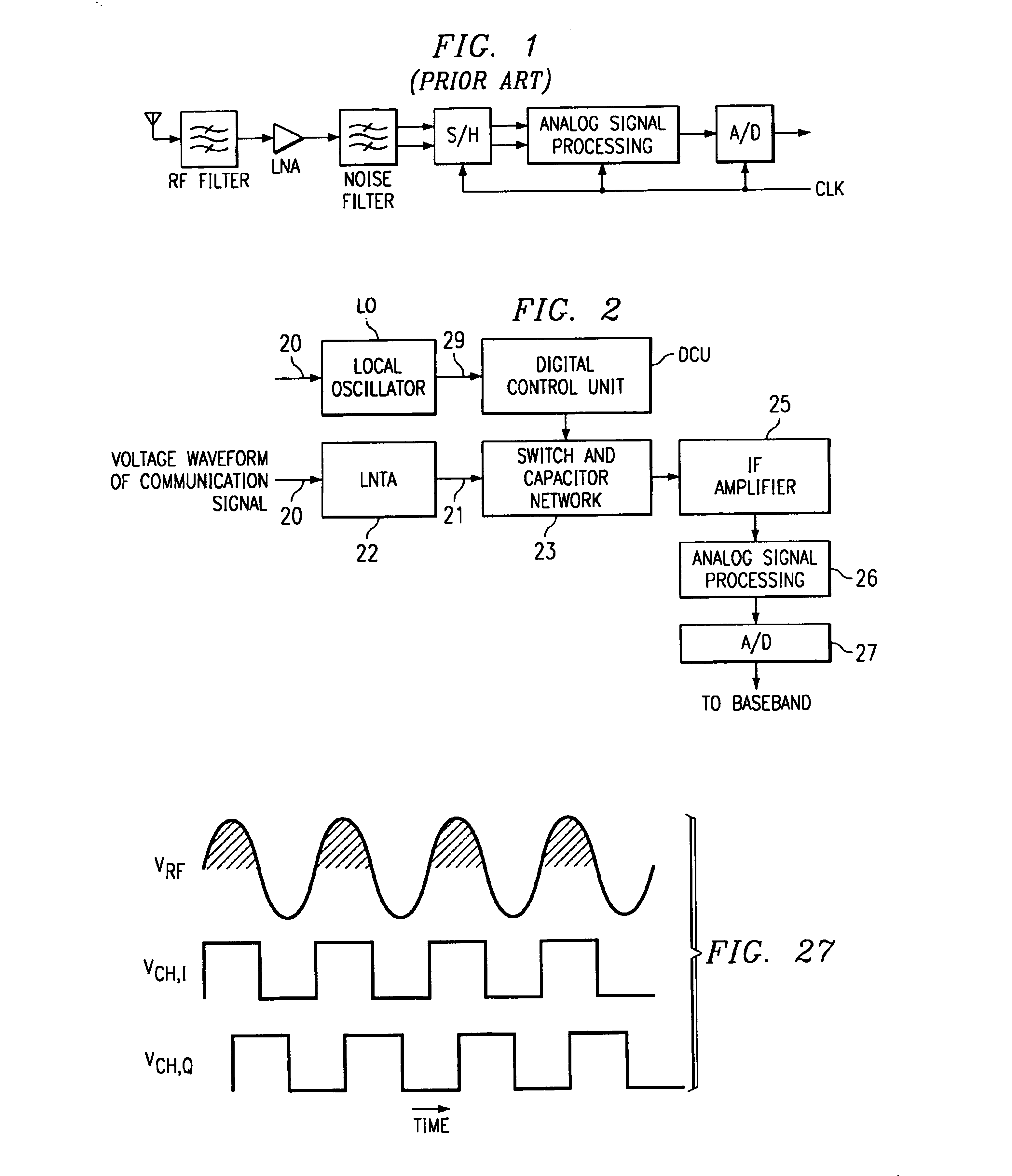

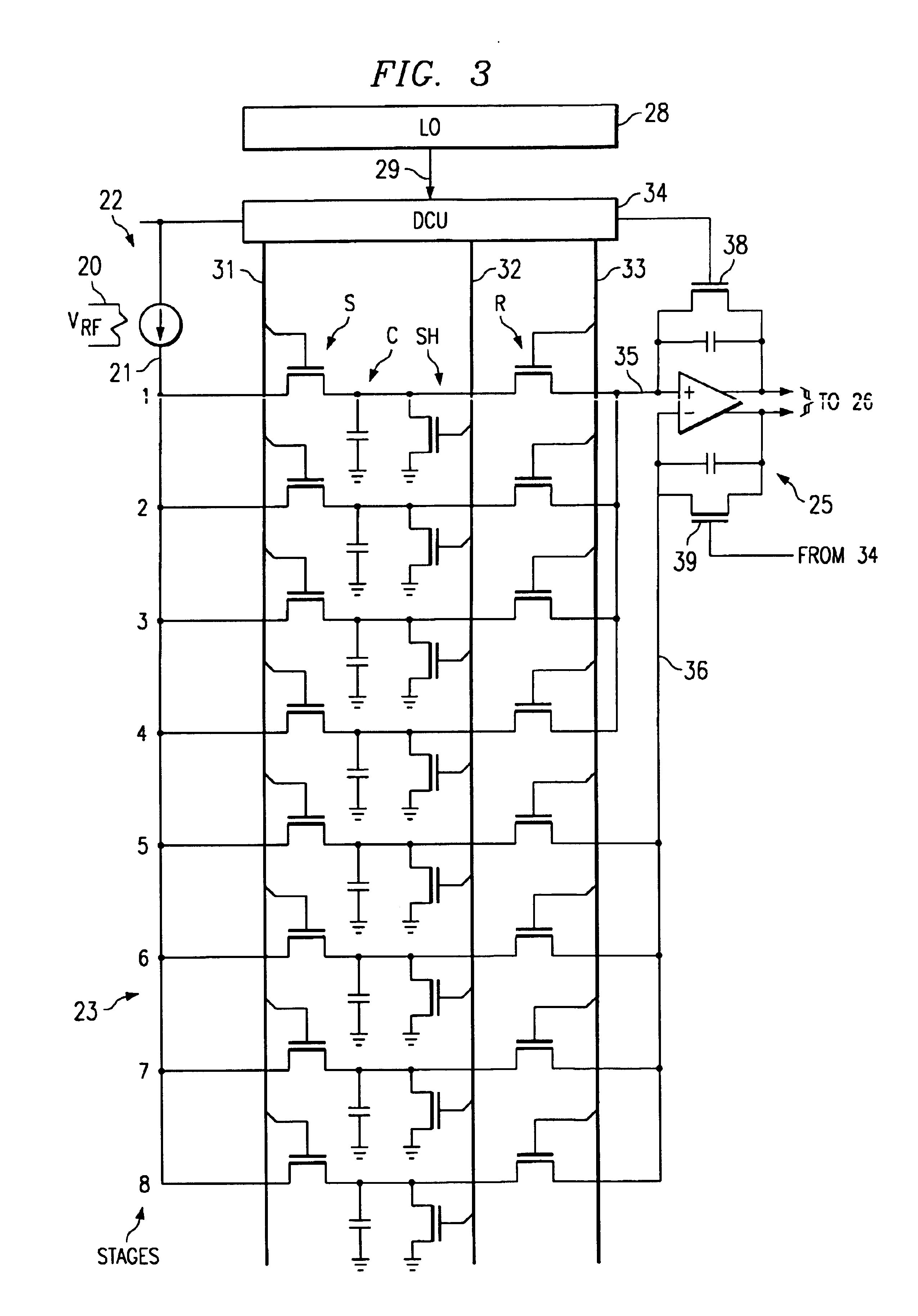

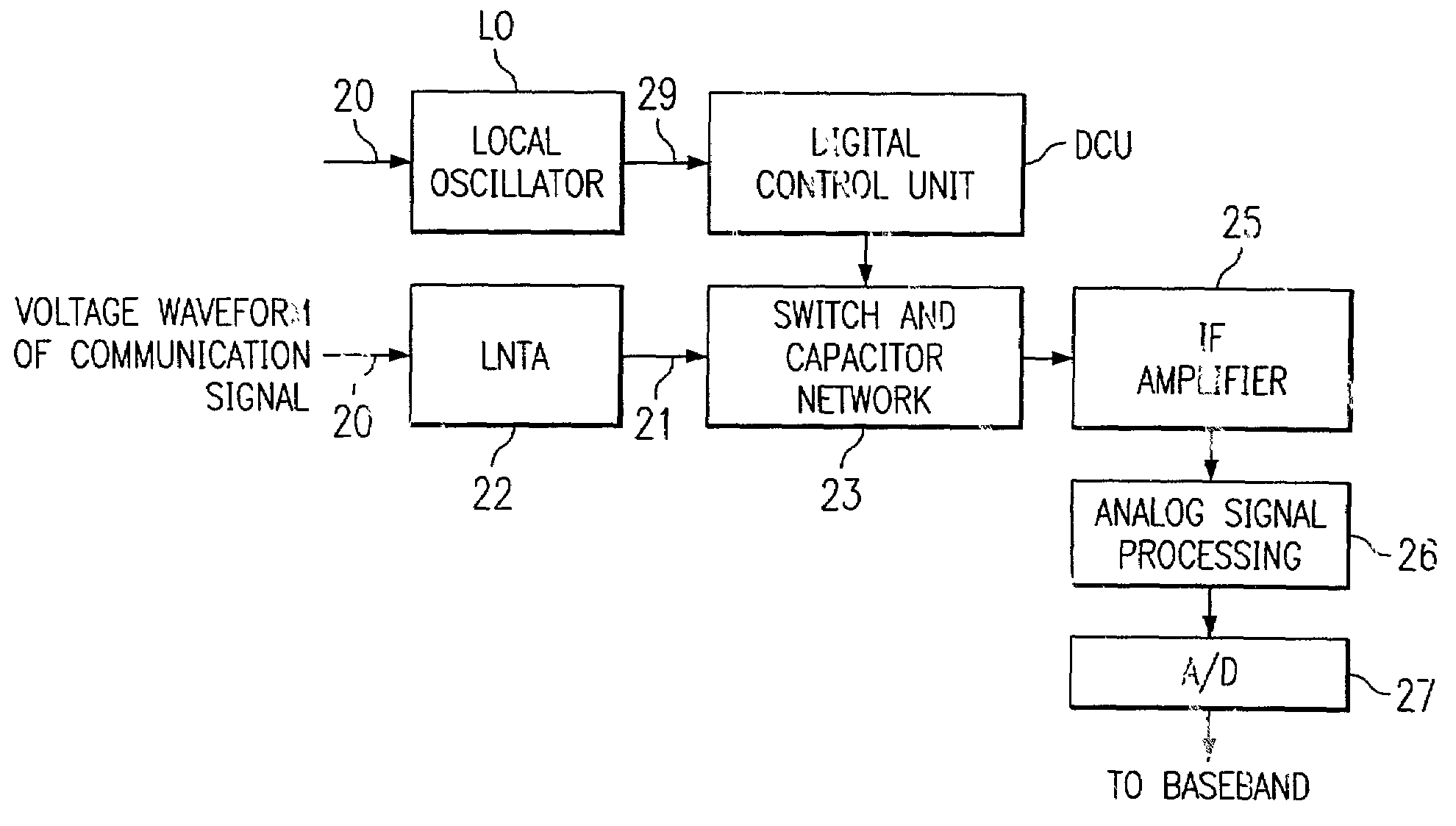

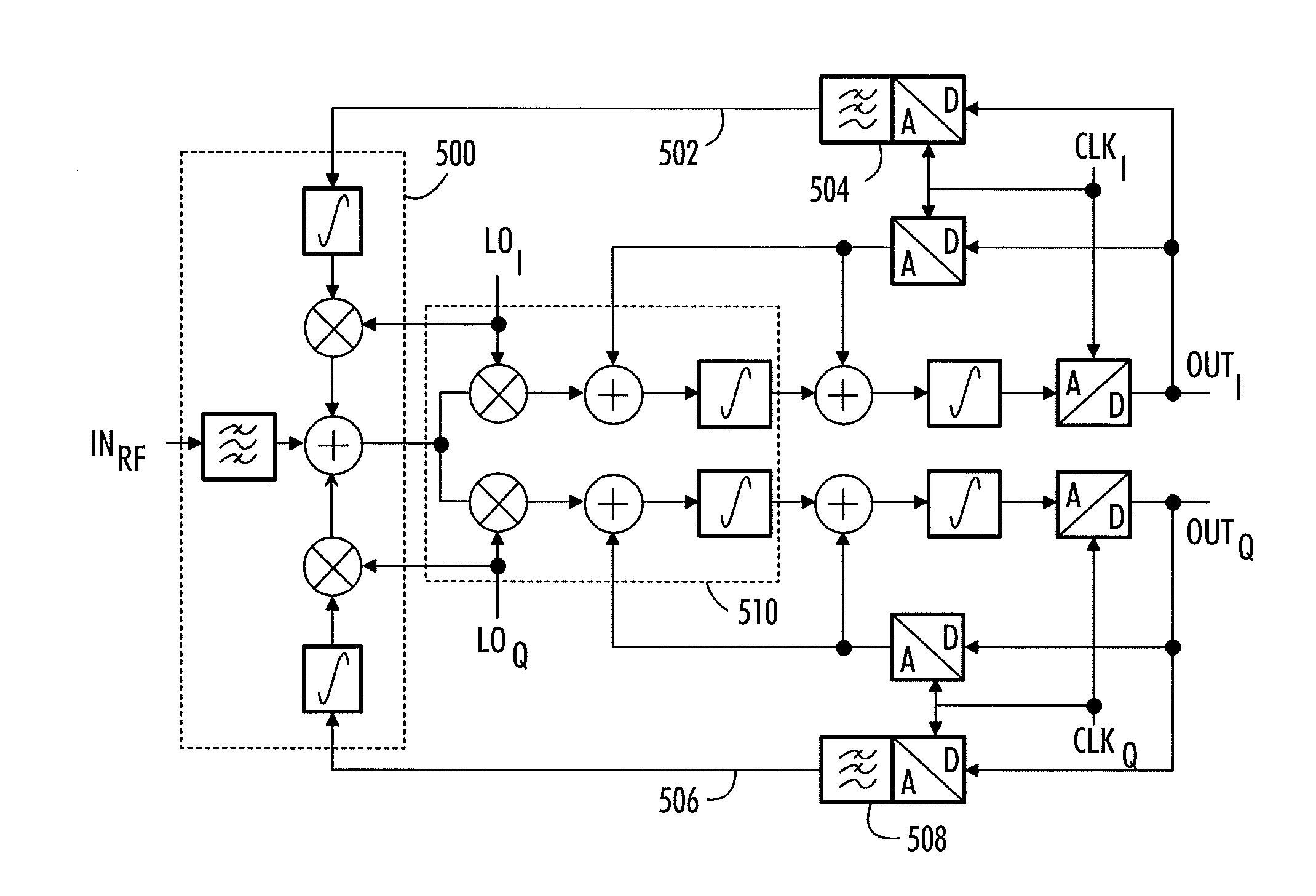

Subsampling communication receiver architecture with relaxed IFA readout timing

A first periodic voltage waveform (20) is downconverted into a second periodic voltage waveform (35, 36). A plurality of temporally distinct samples (SA1, SA2, . . . ) respectively indicative of areas under corresponding fractional-cycles of the first voltage waveform are obtained. The samples are combined to produce the second voltage waveform, and are also manipulated to implement a filtering operation such that the second voltage waveform represents a downconverted, filtered version of the first voltage waveform. The second waveform is driven by an amplifier stage (25), and the second waveform can be advantageously constructed so as to permit the amplifier stage to perform internal resets, offset corrections and other ancillary amplifier stage adjustments without losing information in the first waveform.

Owner:TEXAS INSTR INC

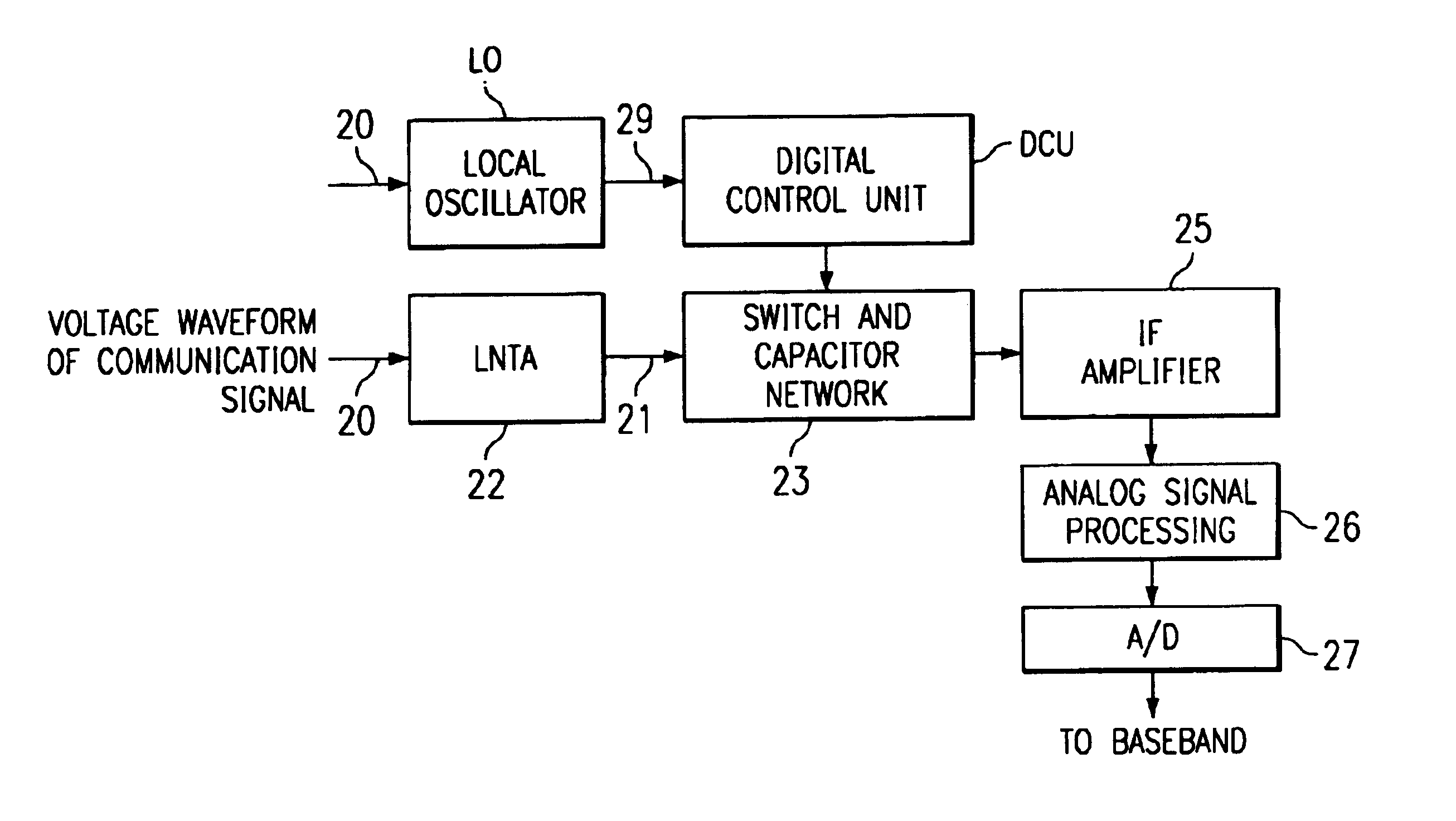

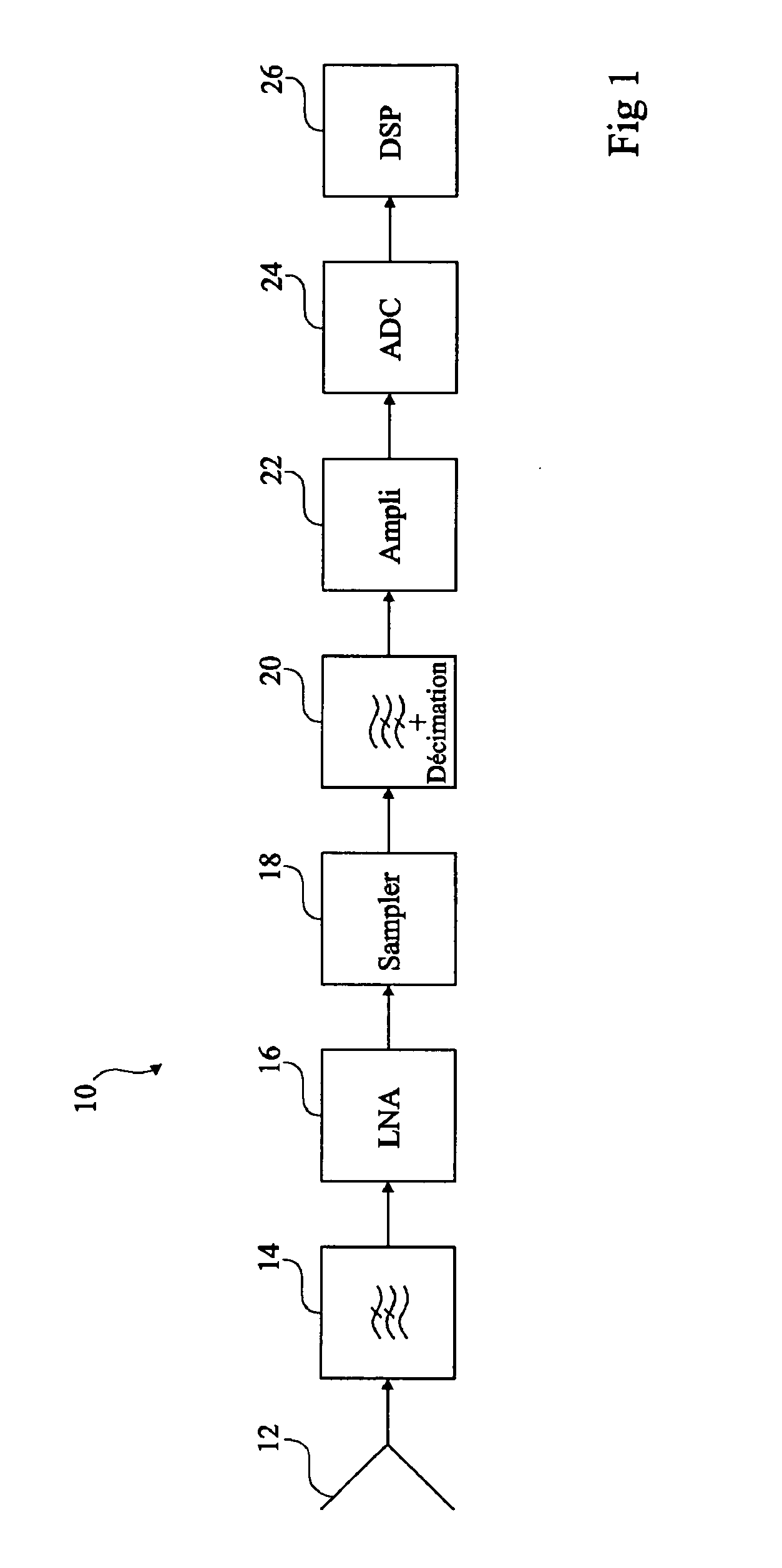

Digitally controlled analog RF filtering in subsampling communication receiver architecture

A first periodic voltage waveform (20) is downconverted into a second periodic voltage waveform (35, 36). A plurality of temporally distinct samples (SA1, SA2, . . . ) respectively indicative of areas under corresponding half-cycles of the first voltage waveform are obtained. The samples are combined to produce the second voltage waveform, and are also manipulated to implement a filtering operation such that the second voltage waveform represents a downconverted, filtered version of the first voltage waveform.

Owner:TEXAS INSTR INC

Apparatus comprising frequency selective circuit and method

ActiveUS20100097258A1Improve frequency selectivityImprove Noise PerformanceElectric signal transmission systemsTransversal filtersBandpass filteringAnalog signal

An apparatus, having as an input an analog signal, is provided. The apparatus comprises a first circuit comprising an impedance transferring circuit configured to band pass filter the input signal, obtaining a filtered signal; the impedance transferring circuit comprising: a transconductance amplifier (1102), and a switching arrangement (1106, 1108) and an impedance circuit (404) connected in series, the switching arrangement being configured to switch the impedance of the impedance circuit of the impedance transferring circuit from base band to the frequency of the input signal. The apparatus further comprises a second circuit (1112) configured to perform down mixing to the filtered signal obtaining a base band signal and a feedback loop connecting the base band signal to the switching arrangement (1114, 1116) and the impedance circuit, the signal of the feedback loop configured to control the properties of the first circuit.

Owner:WSOU INVESTMENTS LLC

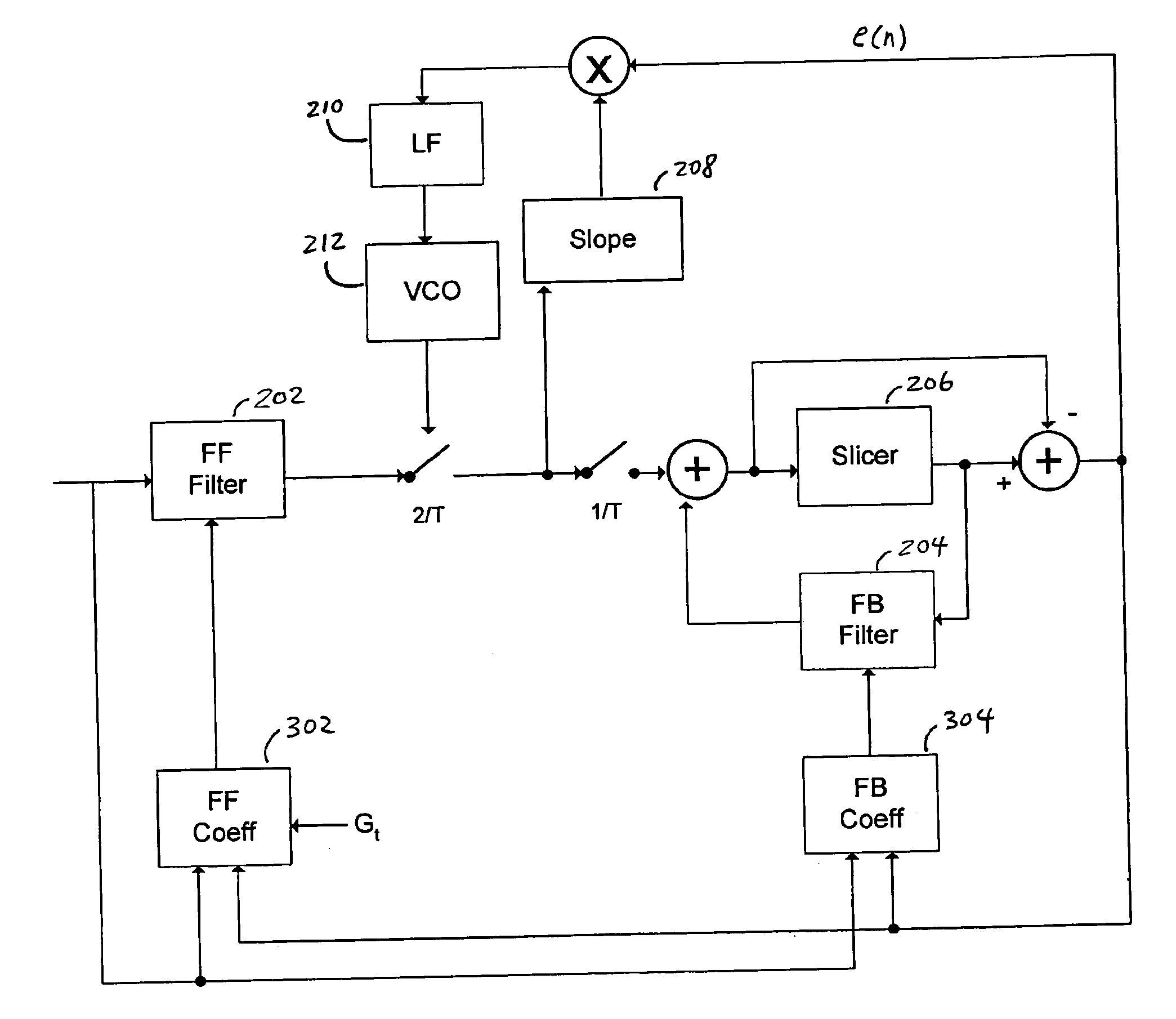

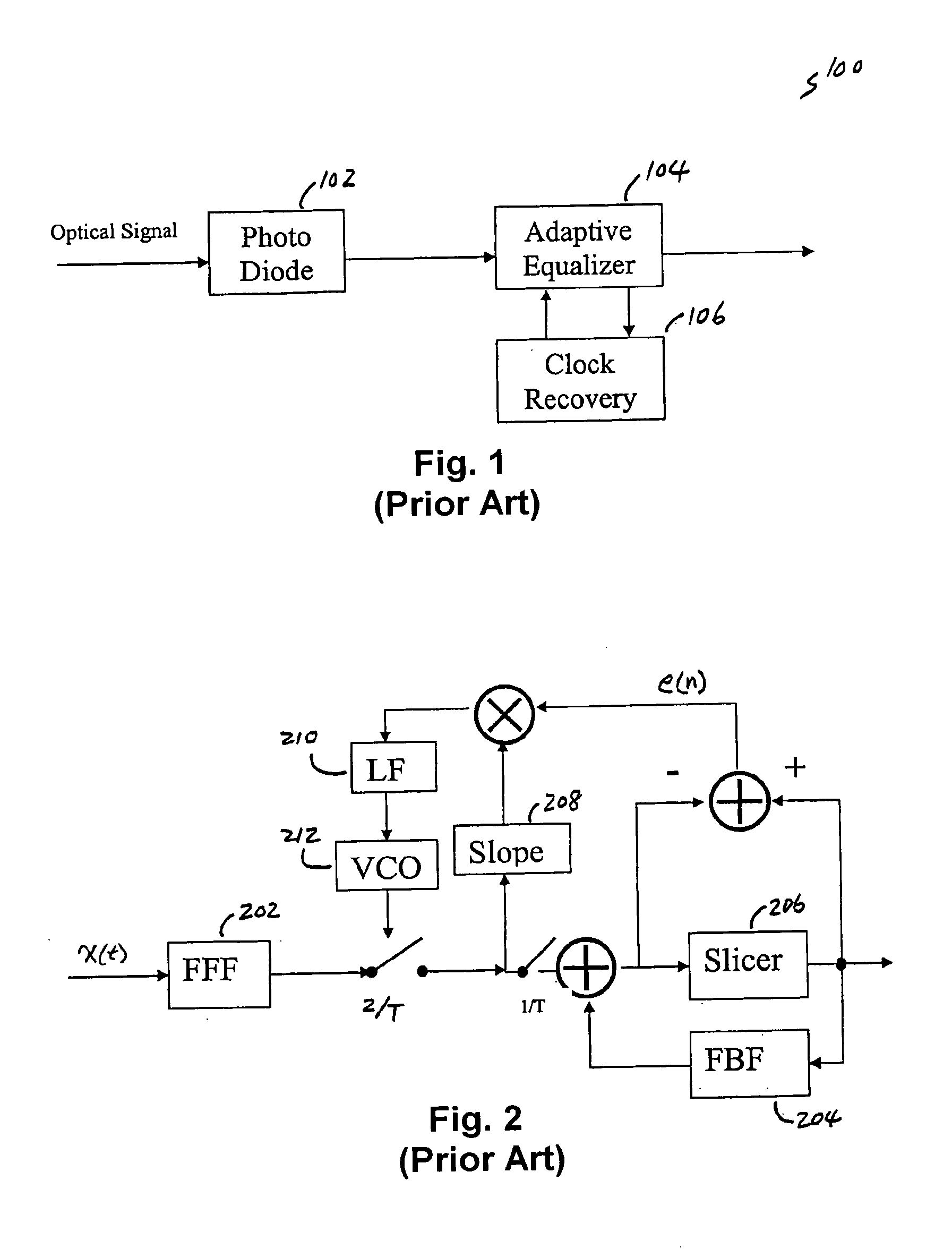

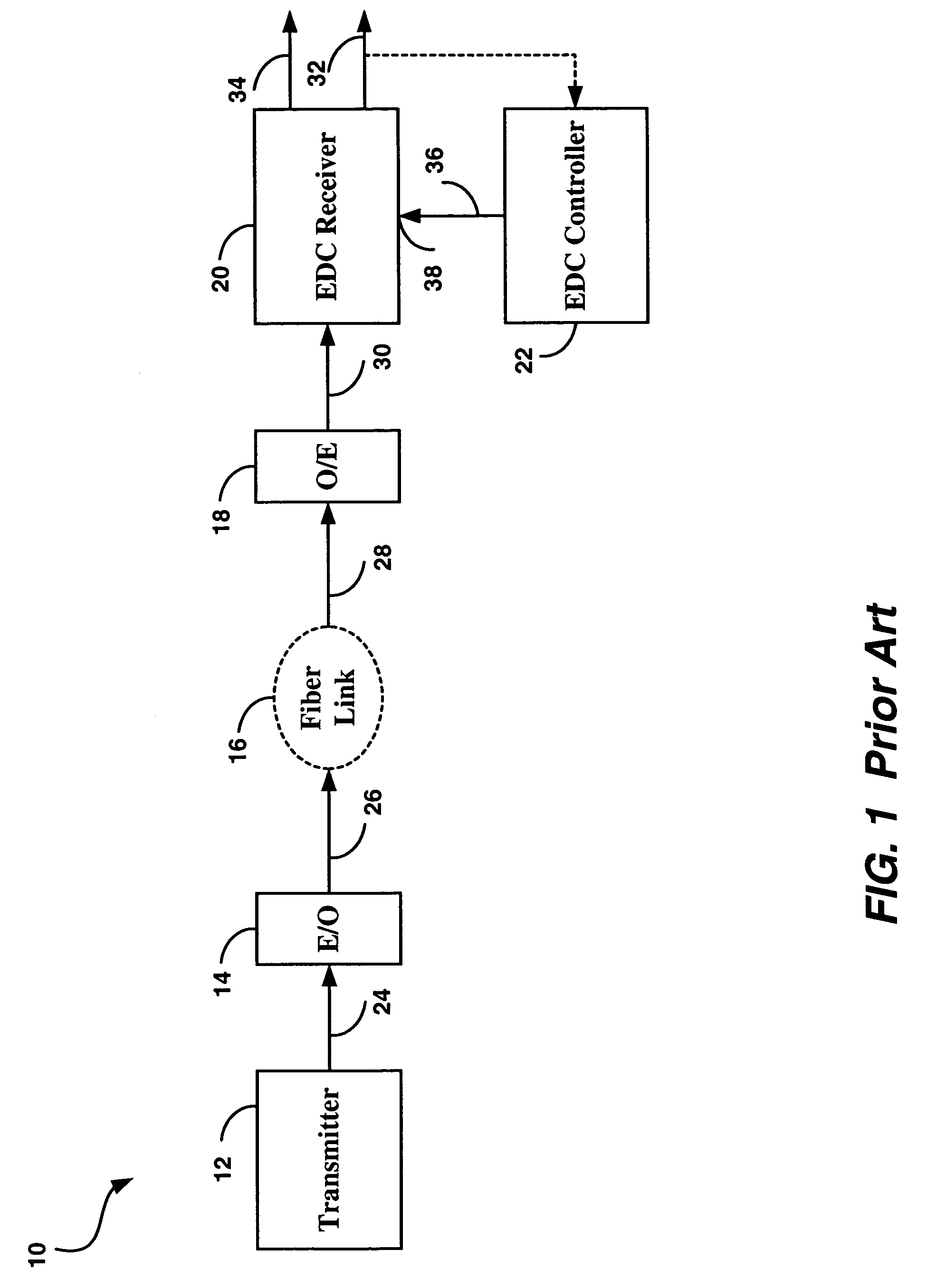

High speed circuits for electronic dispersion compensation

ActiveUS7184478B2Avoid and minimize shortcomingMultiple-port networksTransversal filtersSemiconductorDispersion compensation

The invention describes a number of differential, balanced high-speed circuits that permit the design of a receiver with Electronic Dispersion Compensation (EDC) on a single semiconductor substrate, including the functions of an analog Fast Forward Equalizer (FFE), a Clock and Data Recovery, a Decision Feedback Equalizer (DFE), enhanced by additional circuits that permit control of the slicing level to compensate for pulse distortion, and control of the phase offset to set the optimal eye sampling time when a distorted signal is received. To provide the high speed of operation, all circuits including the phase locked loop, operate as differential circuits, which include a number of improvements in the design of the charge pump, the decision feedback equalizer, the slicing level control, and others.

Owner:MACOM CONNECTIVITY SOLUTIONS LLC

Digital/analogue conversion apparatus

ActiveUS8423165B2Reduce quantization noiseImprove noiseTransversal filtersDigitally weighted transducing elementsImage resolutionEngineering

A digital / analog conversion apparatus for converting a digital signal into an analog signal. The digital / analog conversion apparatus can generate a high-quality analog signal, even when elements configuring the digital / analog conversion apparatus have variance, with high resolution and a small circuit size. The data conversion apparatus is provided with a first data converter for reducing the number of bits of an input signal, a second data converter for converting the format of the first output signal, and a third data converter for conversion into a code which corresponds to the history of the output from the second data converter.

Owner:TRIGENCE SEMICONDUCTOR INC

Differential receiver circuit with electronic dispersion compensation for optical communications systems

ActiveUS7321621B2Multiple-port networksTransversal filtersCommunications systemOptical communication

The invention describes a number of differential, balanced high-speed circuits that permit the design of a receiver with Electronic Dispersion Compensation (EDC) on a single semiconductor substrate, including the functions of an analog Fast Forward Equalizer (FFE), a Clock and Data Recovery, a Decision Feedback Equalizer (DFE), enhanced by additional circuits that permit control of the slicing level to compensate for pulse distortion, and control of the phase offset to set the optimal eye sampling time when a distorted signal is received. To provide the utmost speed of operation, all circuits including the phase locked loop, operate as differential circuits which include a number of improvements in the design of the charge pump, the decision feedback equalizer, the slicing level control, and others.

Owner:MACOM CONNECTIVITY SOLUTIONS LLC

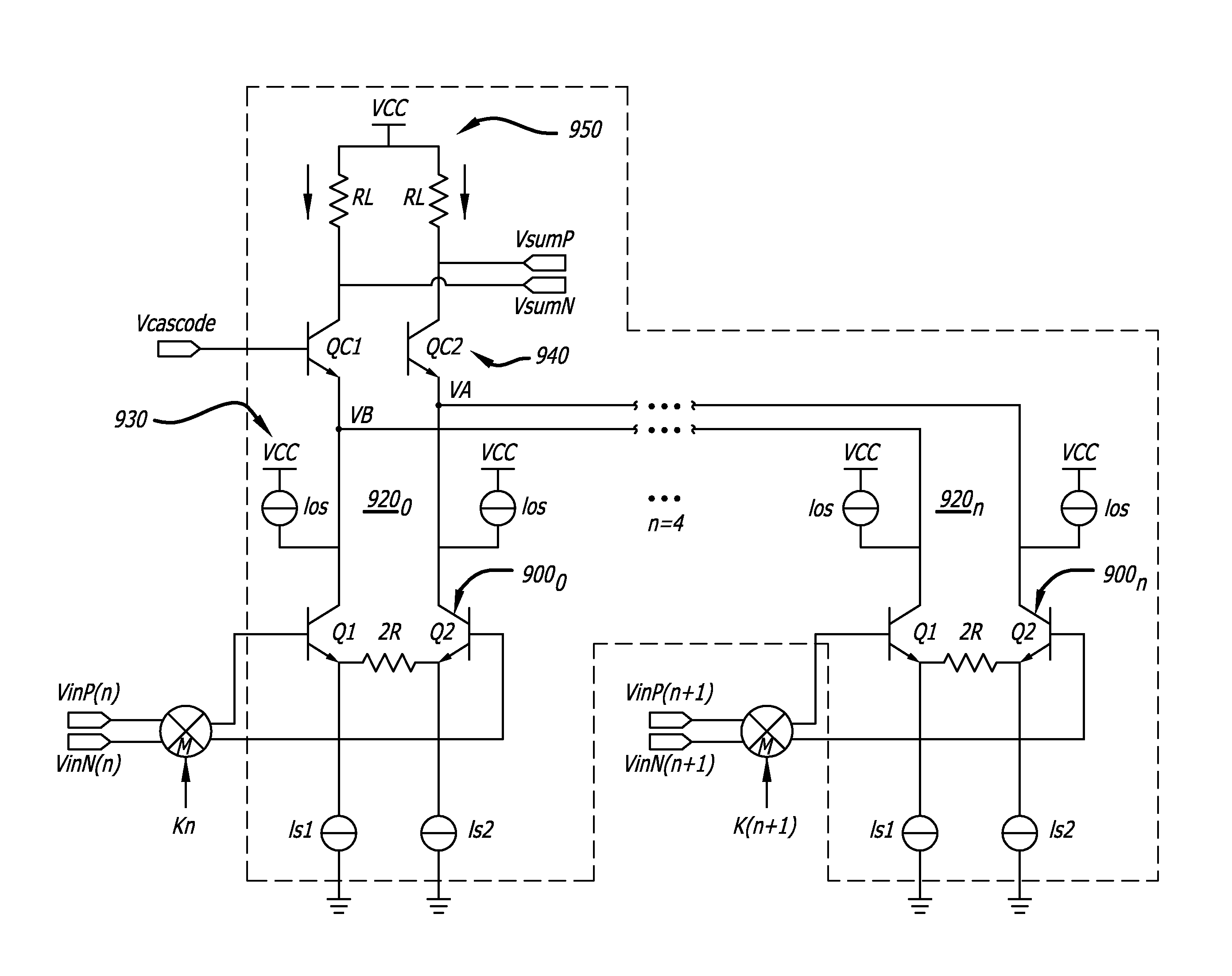

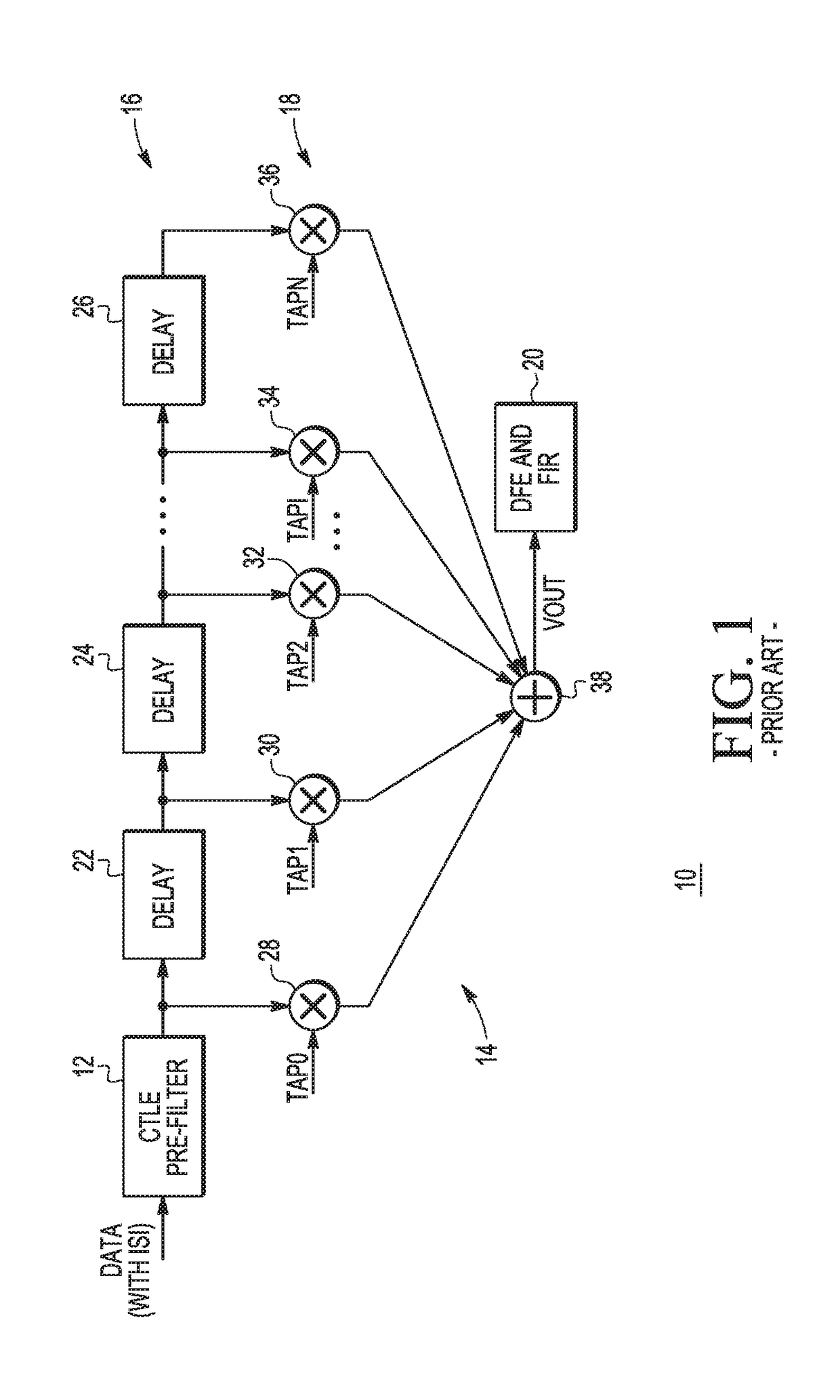

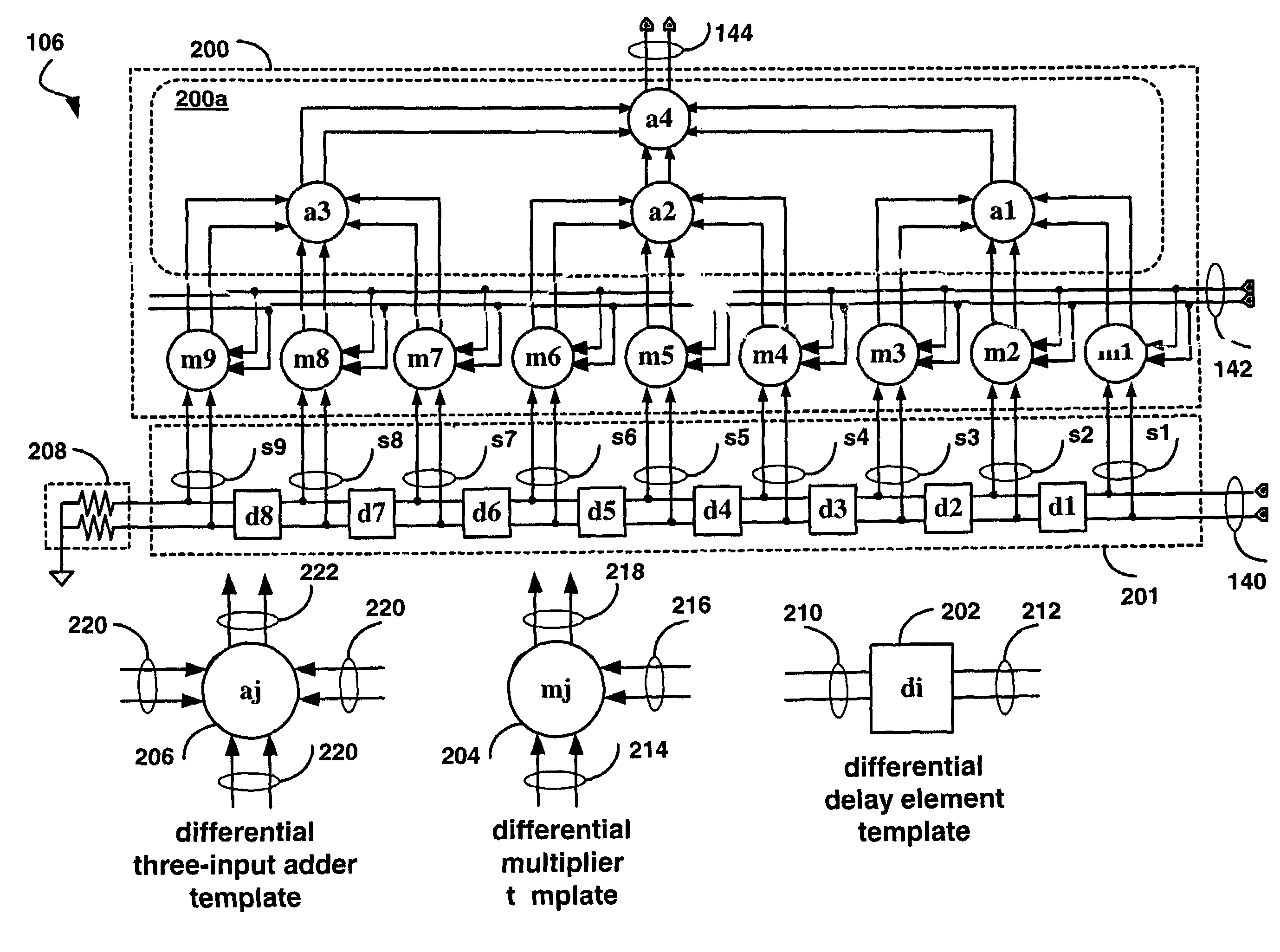

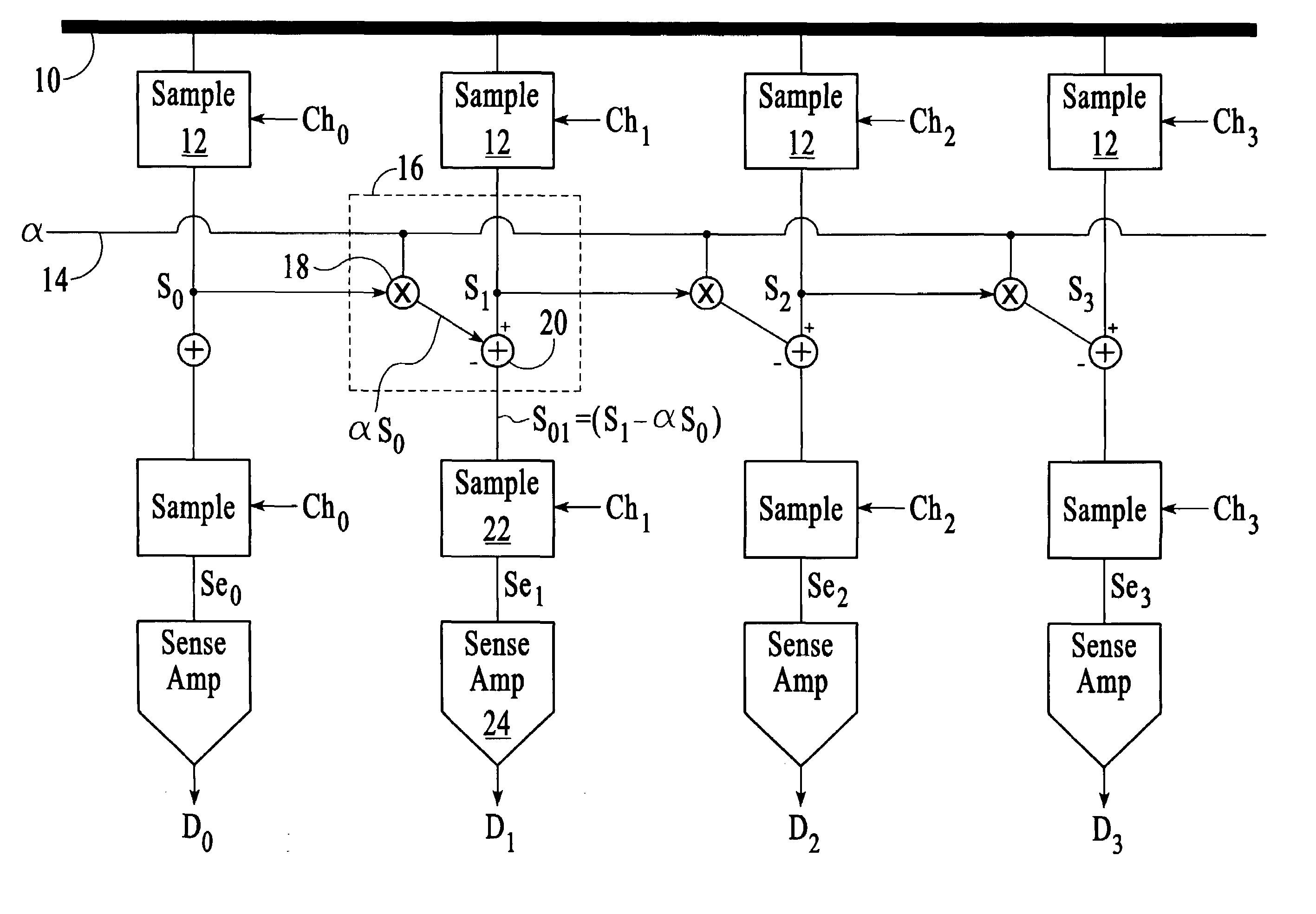

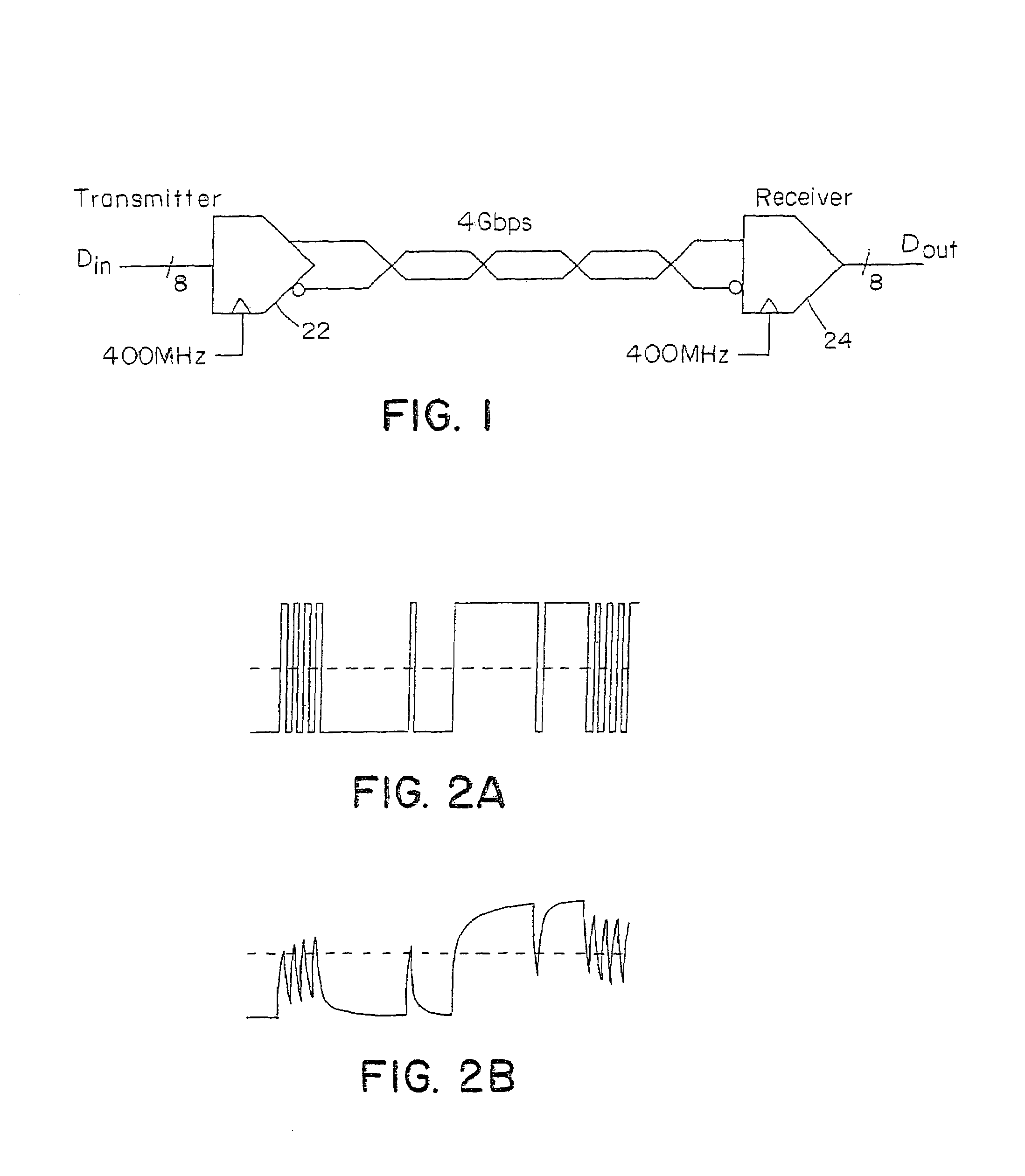

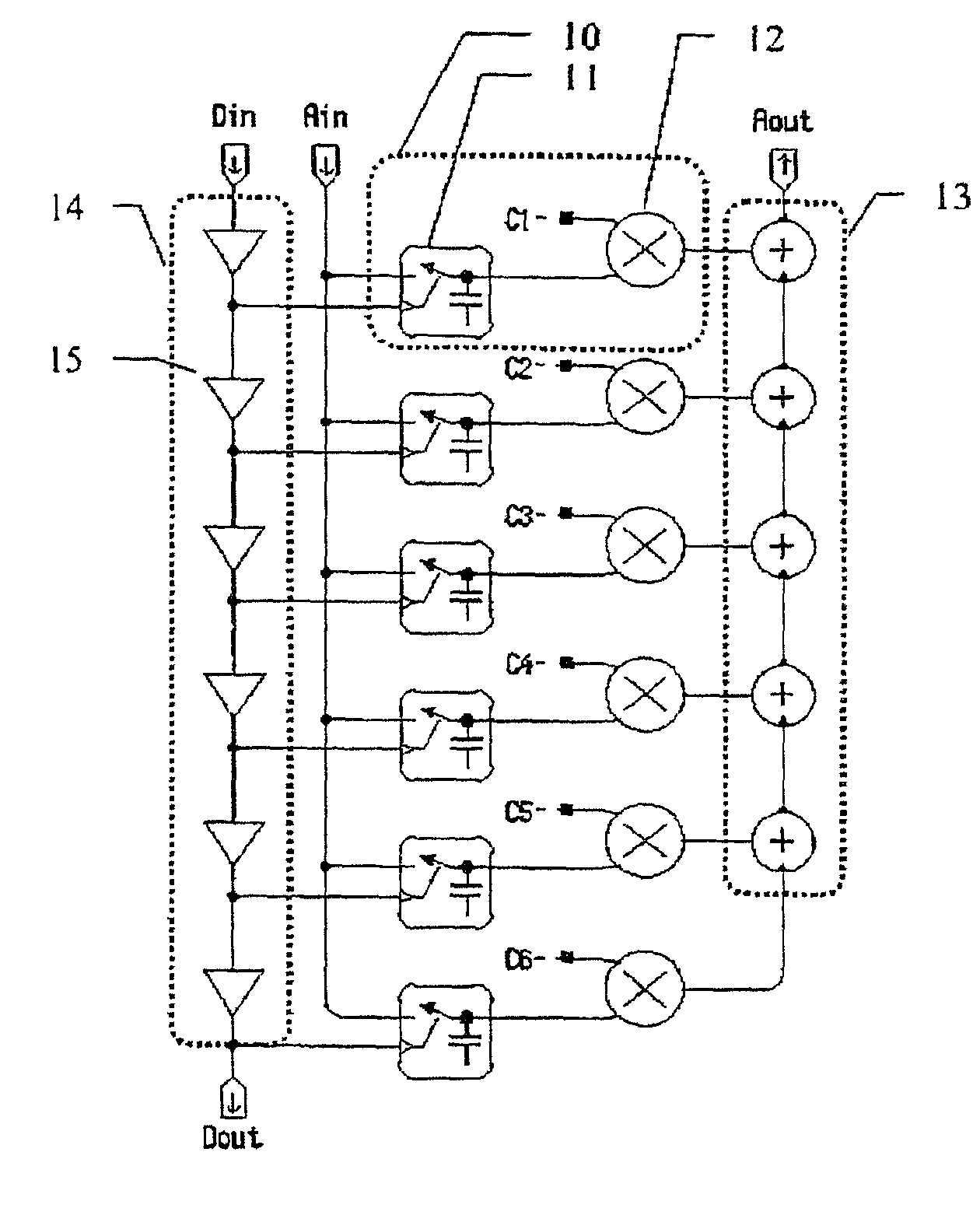

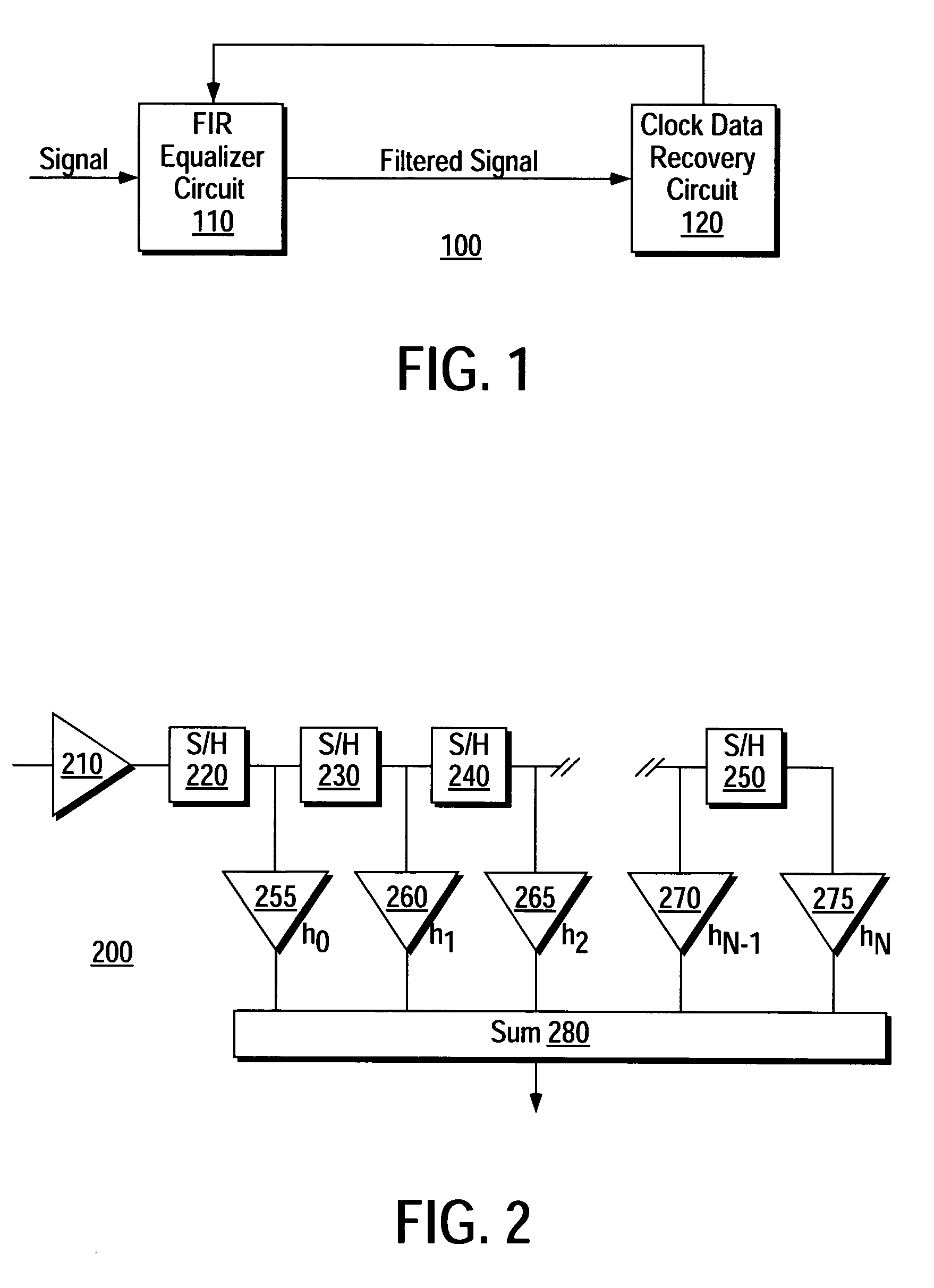

Analog N-tap FIR receiver equalizer

An equalizer includes plural samplers for sampling an incoming input data stream according to plural phases of a sampling clock, each sampler producing a data sample. Operating in the analog domain, a multi-tap finite impulse response (FIR) filter weights the data samples and combines the weighted data samples to produce a filtered data bit. The filtered data bits thus form an equalized output data stream. The equalizer can compensate for characteristics of a communications channel, such as low-pass characteristics. The channel may carry high-speed, e.g., multi-gigabit per second, traffic.

Owner:THE BOARD OF TRUSTEES OF THE LELAND STANFORD JUNIOR UNIV +1

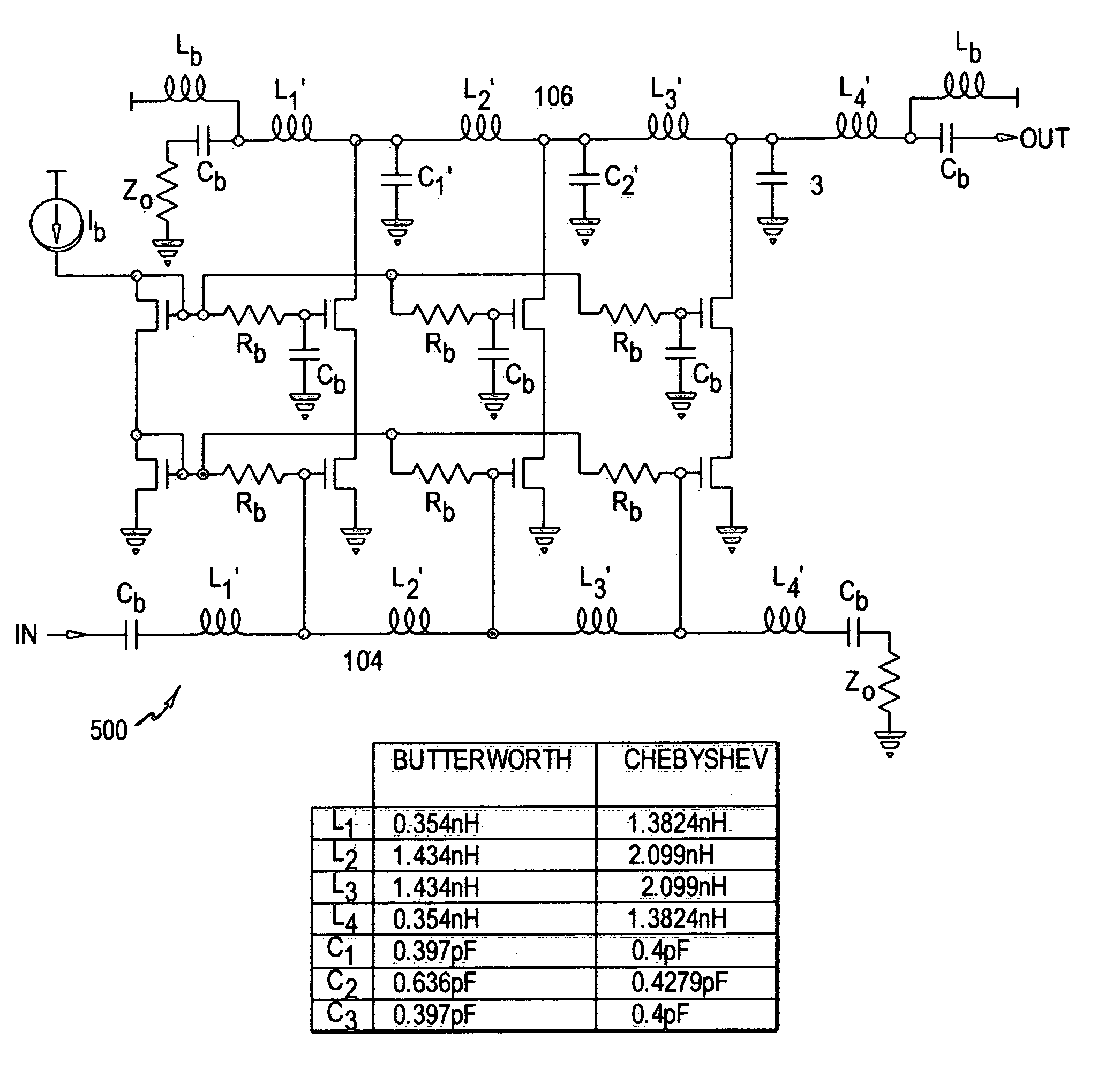

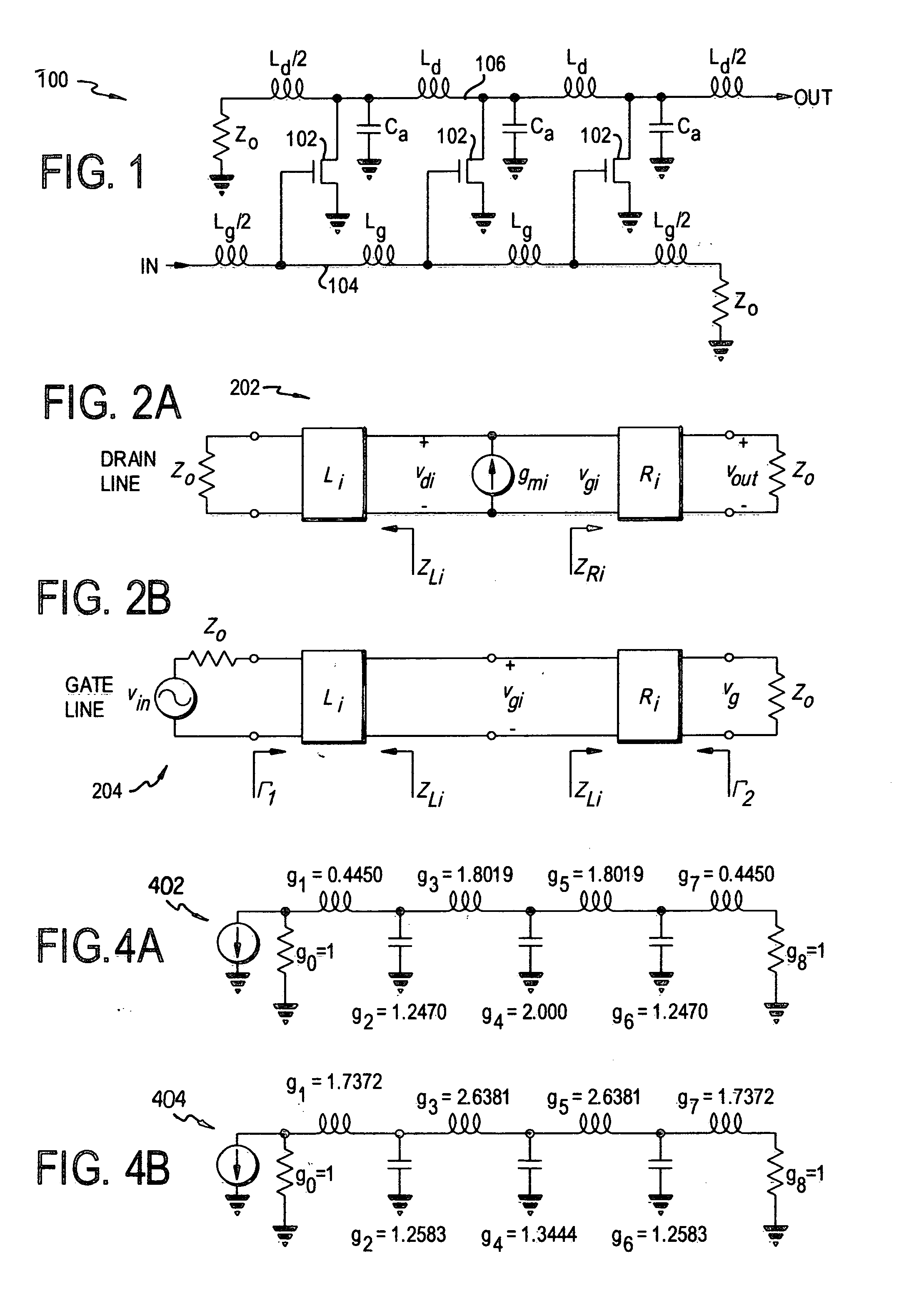

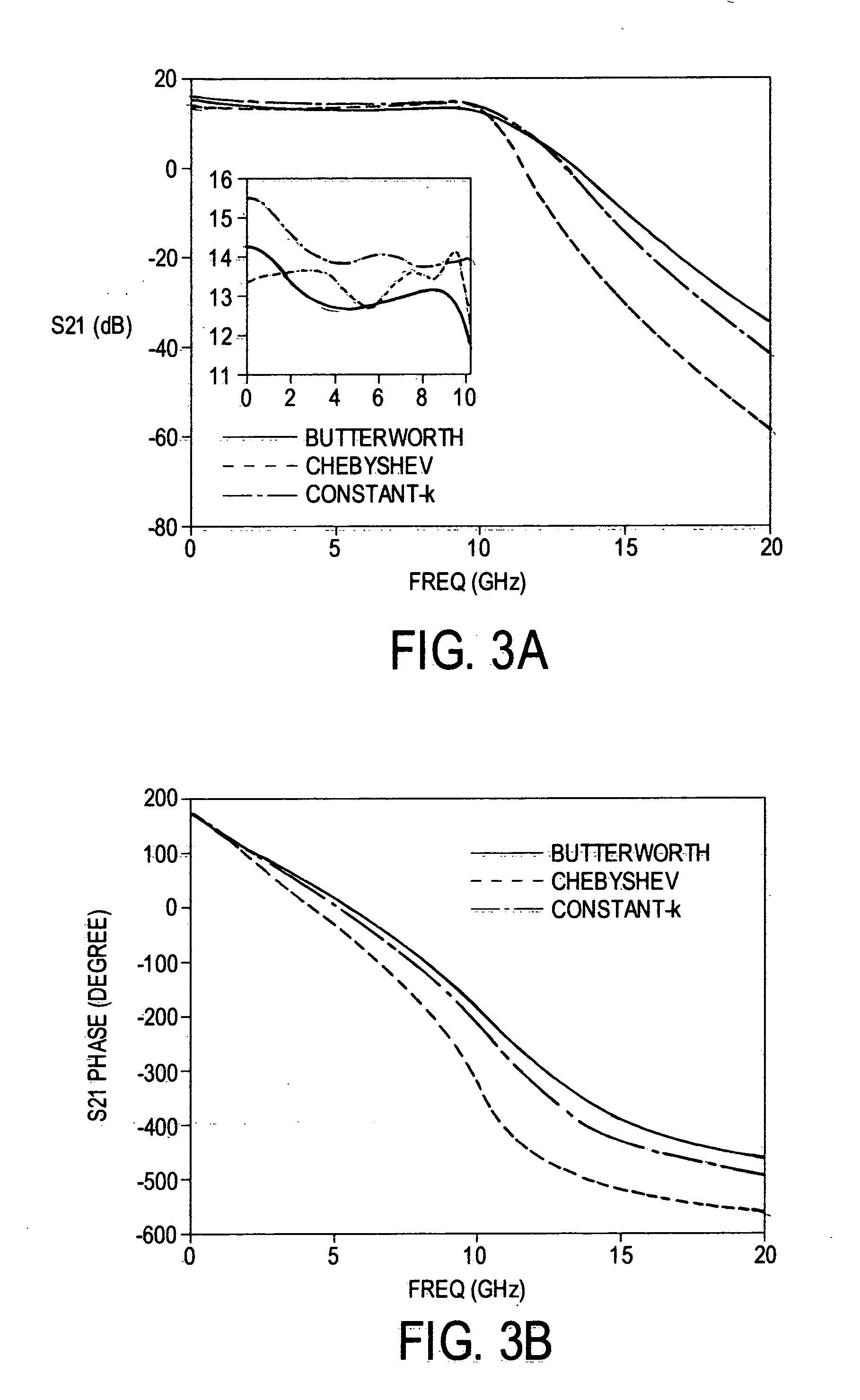

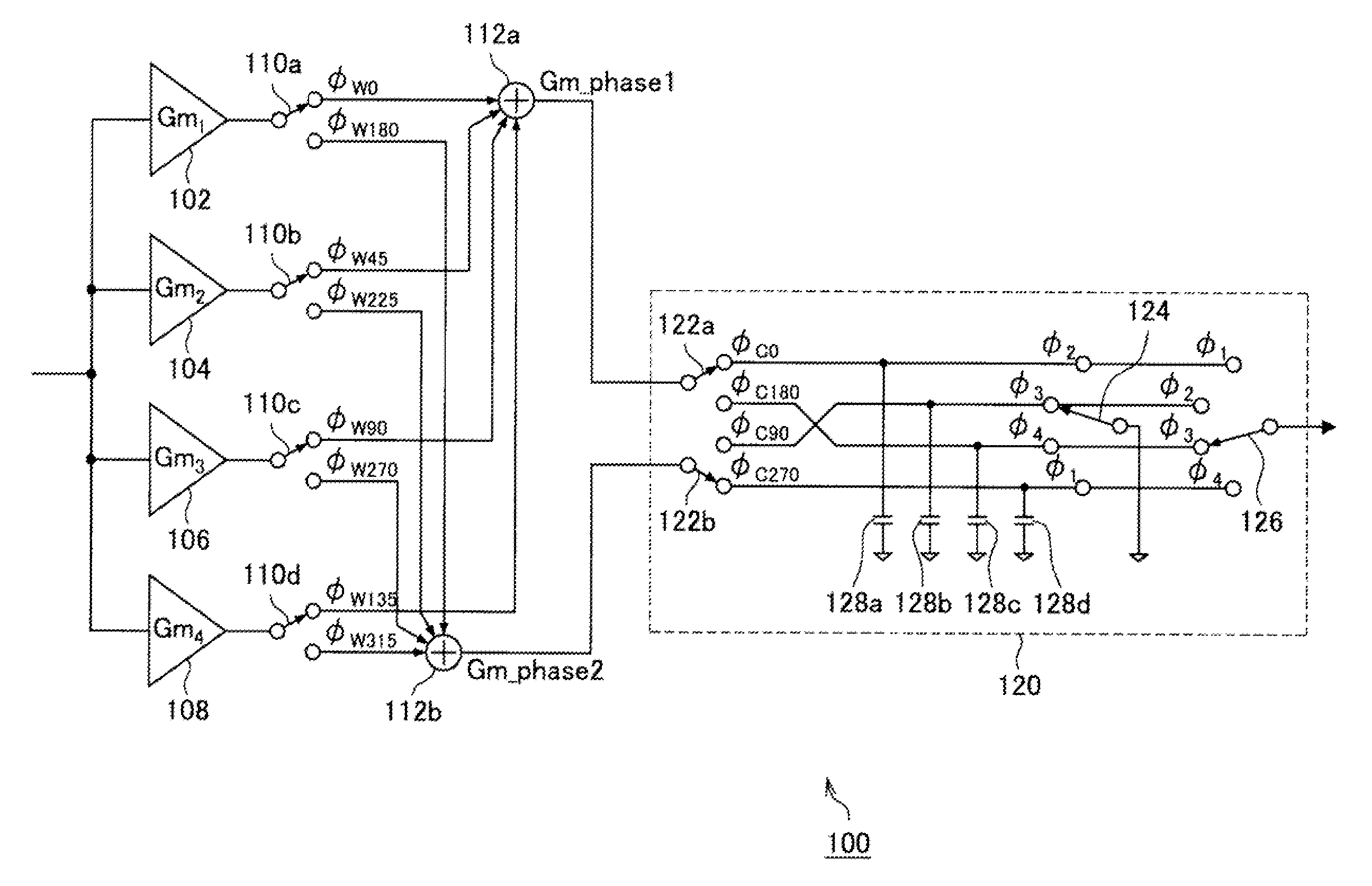

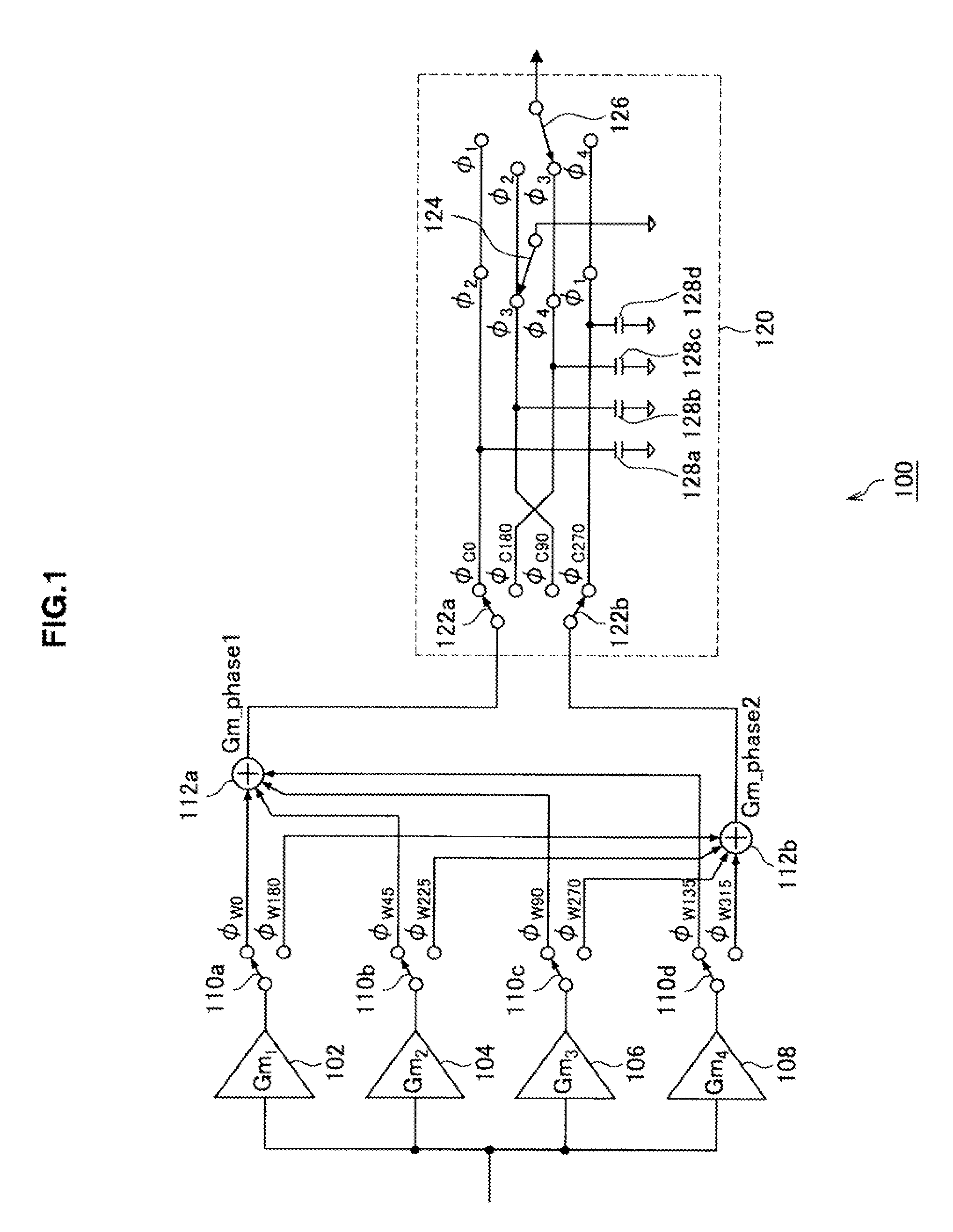

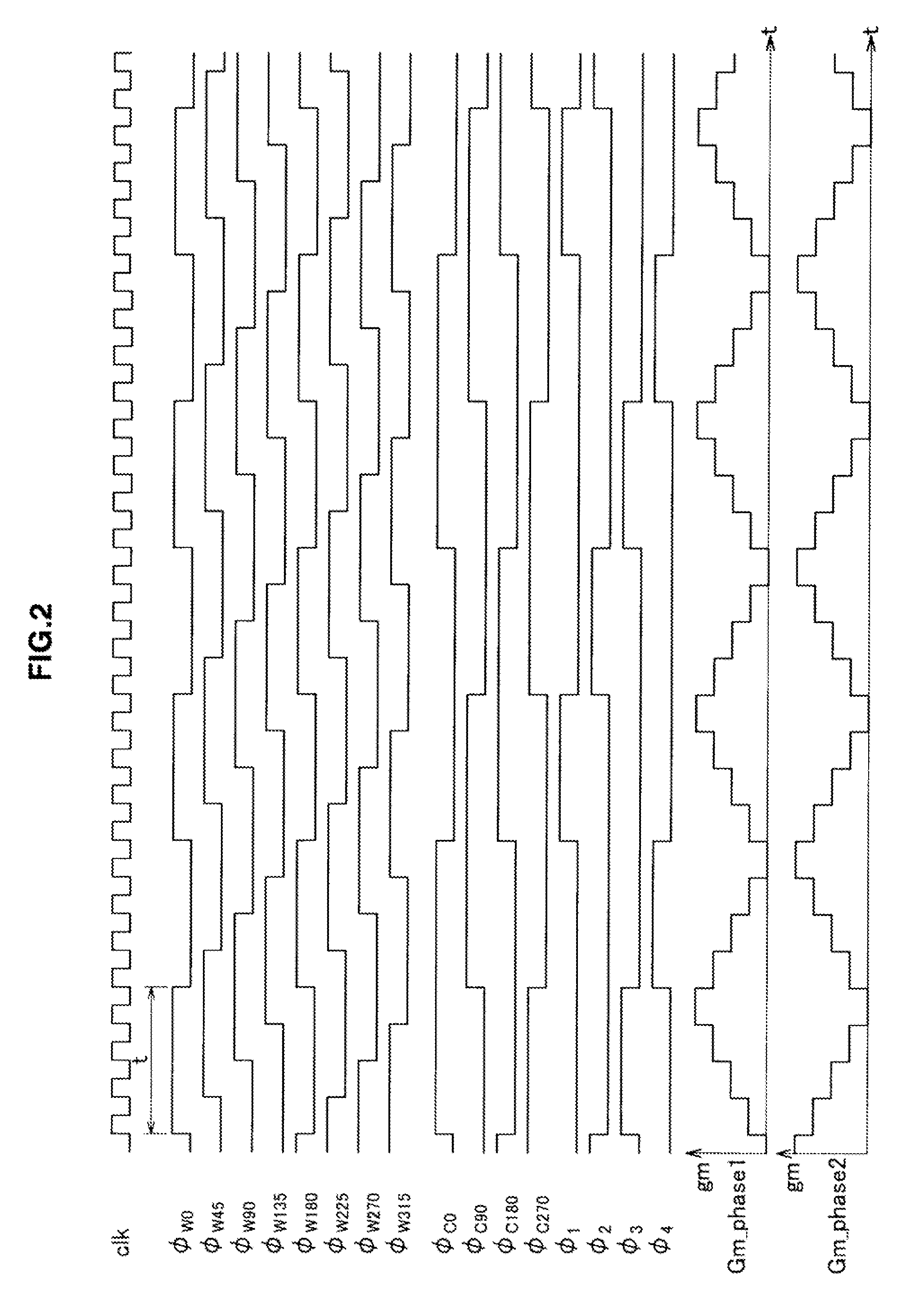

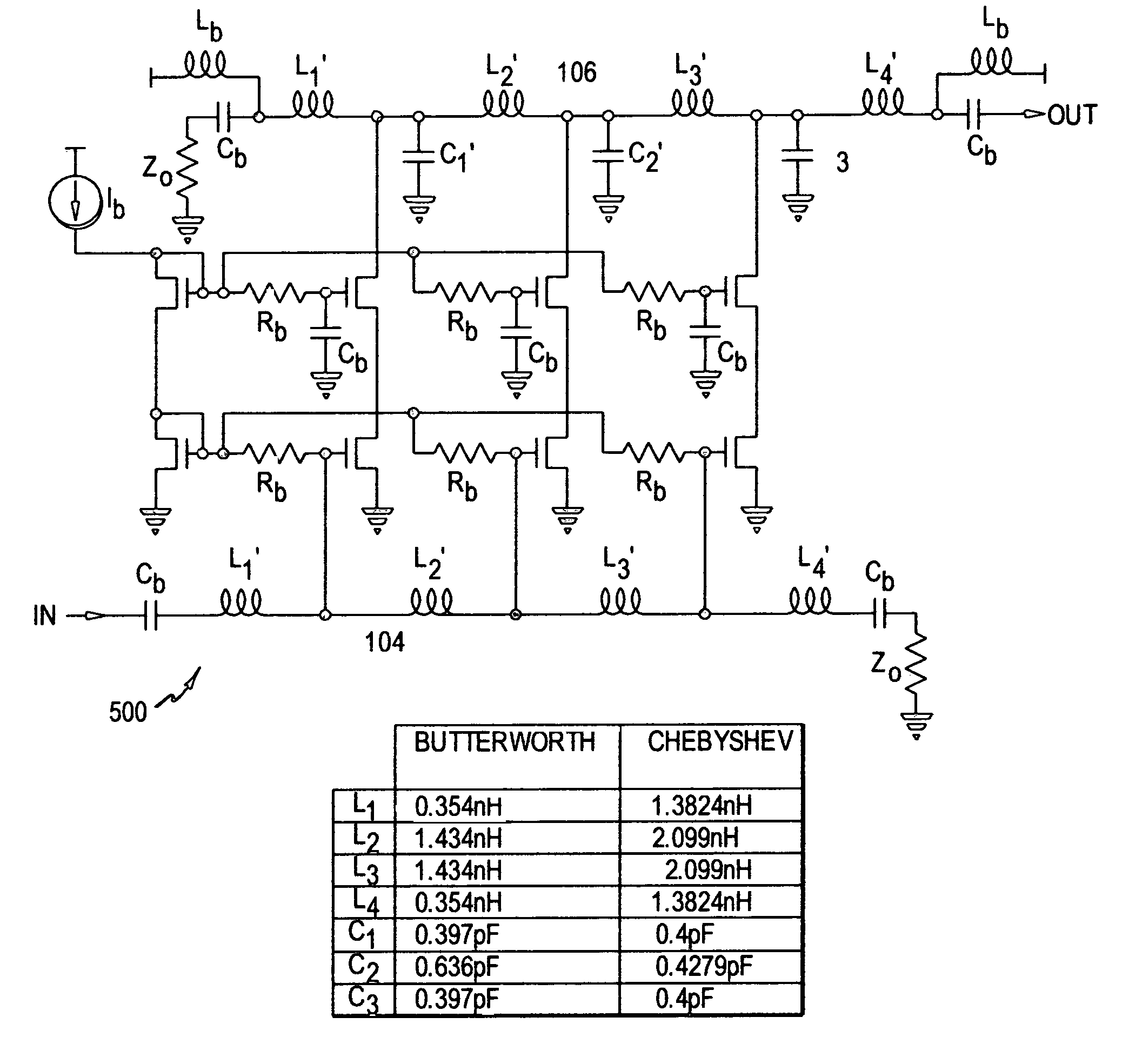

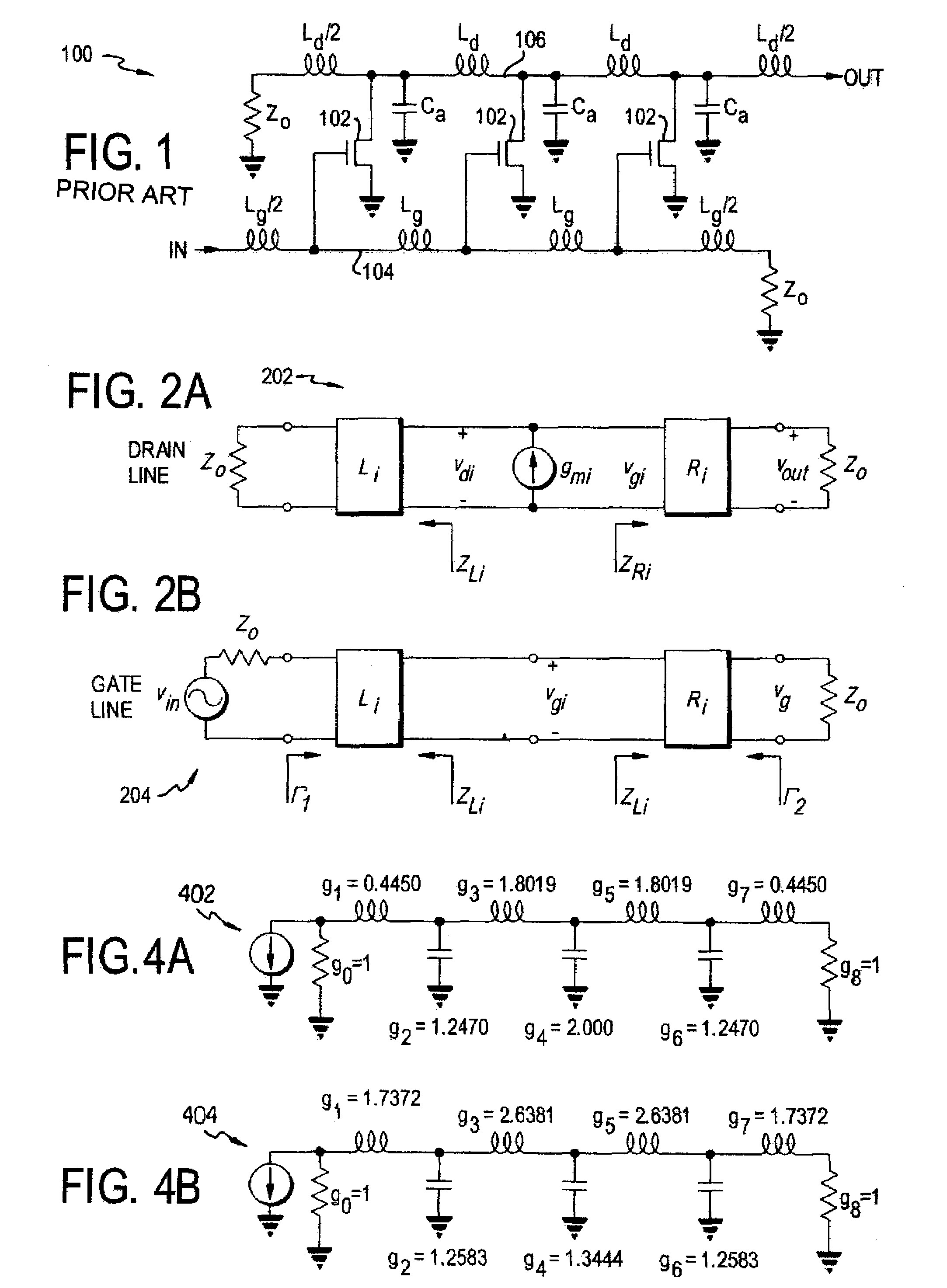

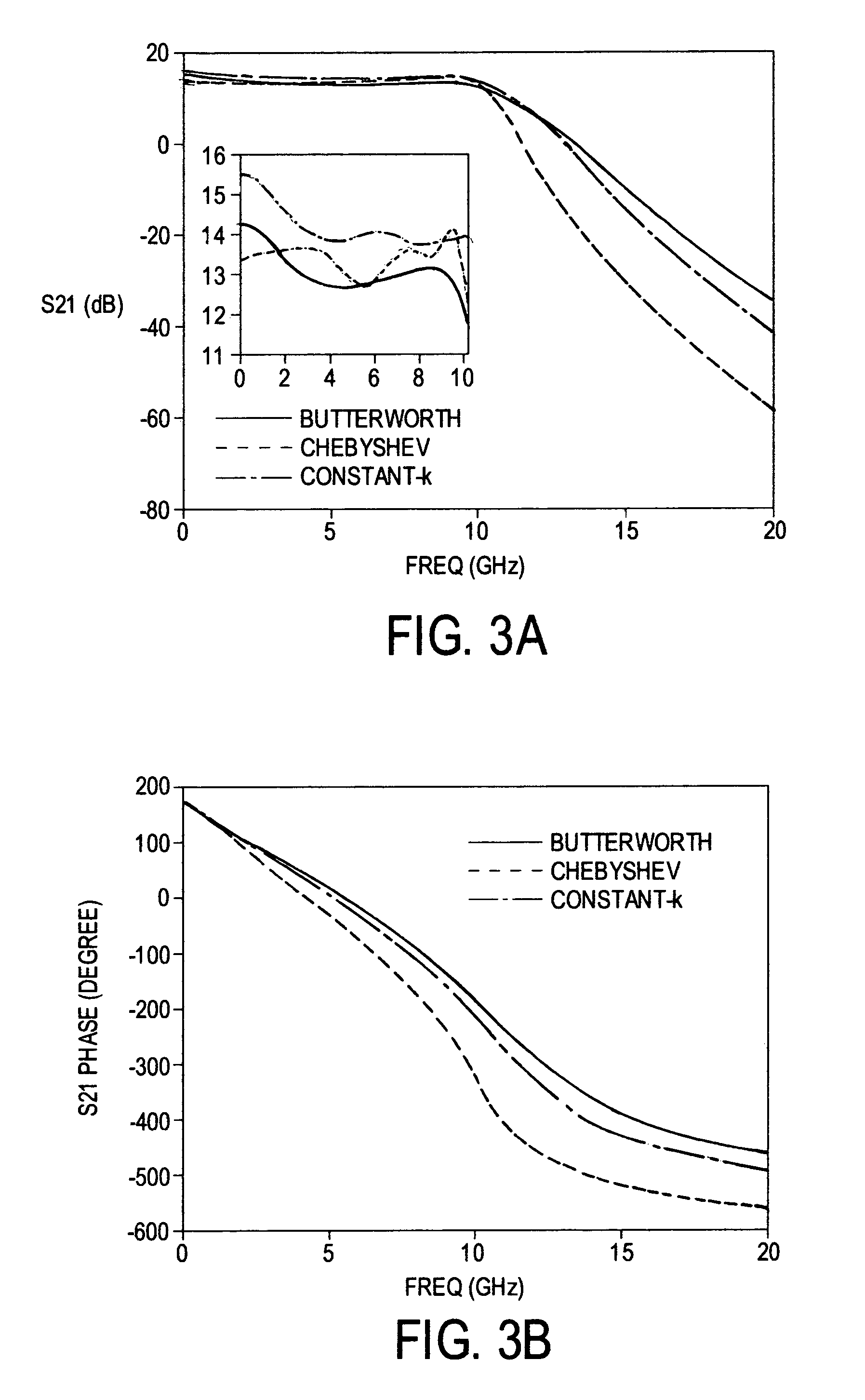

Distributed amplifier with built-in filtering functions

ActiveUS20070182481A1Easy to controlTransversal filtersAmplifier combinationsUltra-widebandTransceiver

A distributed amplifier uses non-uniform filtering structures to provide better control over pass-band and stop-band characteristics. The various sections can have different tap coefficients. A notch filter can be implemented for interference suppression or pulse shaping in an ultra-wideband transceiver.

Owner:UNIVERSITY OF ROCHESTER

Charge Domain Filter Device

InactiveUS20080007326A1Pass efficientlyTransversal filtersSwitched capacitor networksImpulse responseCapacitor

There is provided a charge domain filter device including a plurality of transconductors each of which converts an input voltage to a current and outputs the current and a filter unit that filters output signals from said plurality of transconductors by repeatedly charging and discharging a plurality of capacitors, wherein an impulse response of the charge domain filter device is obtained through convolution of a first impulse corresponding to a charge time length over which said capacitors are charged and a second impulse corresponding to each of said plurality of transconductors.

Owner:SONY CORP

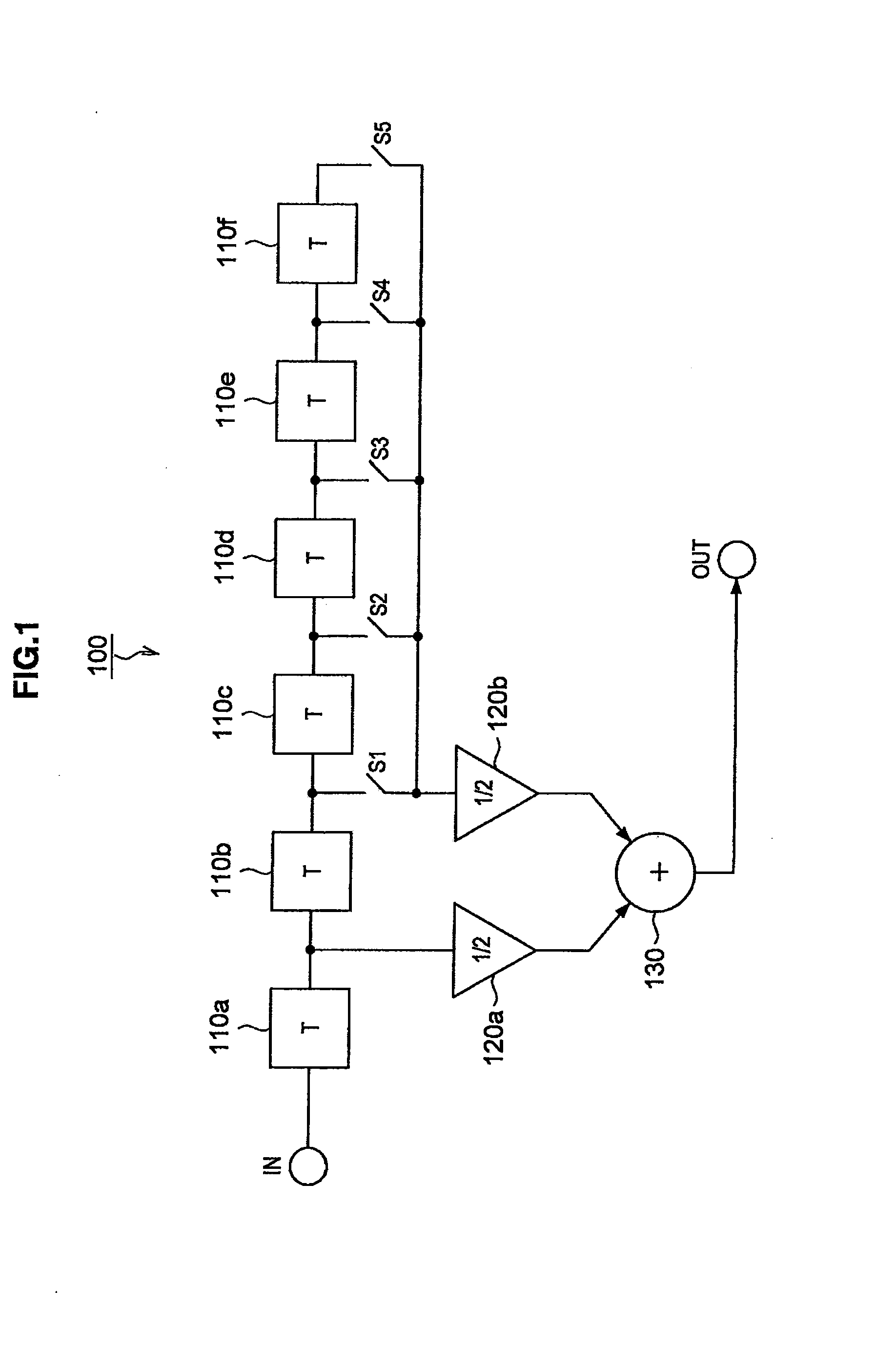

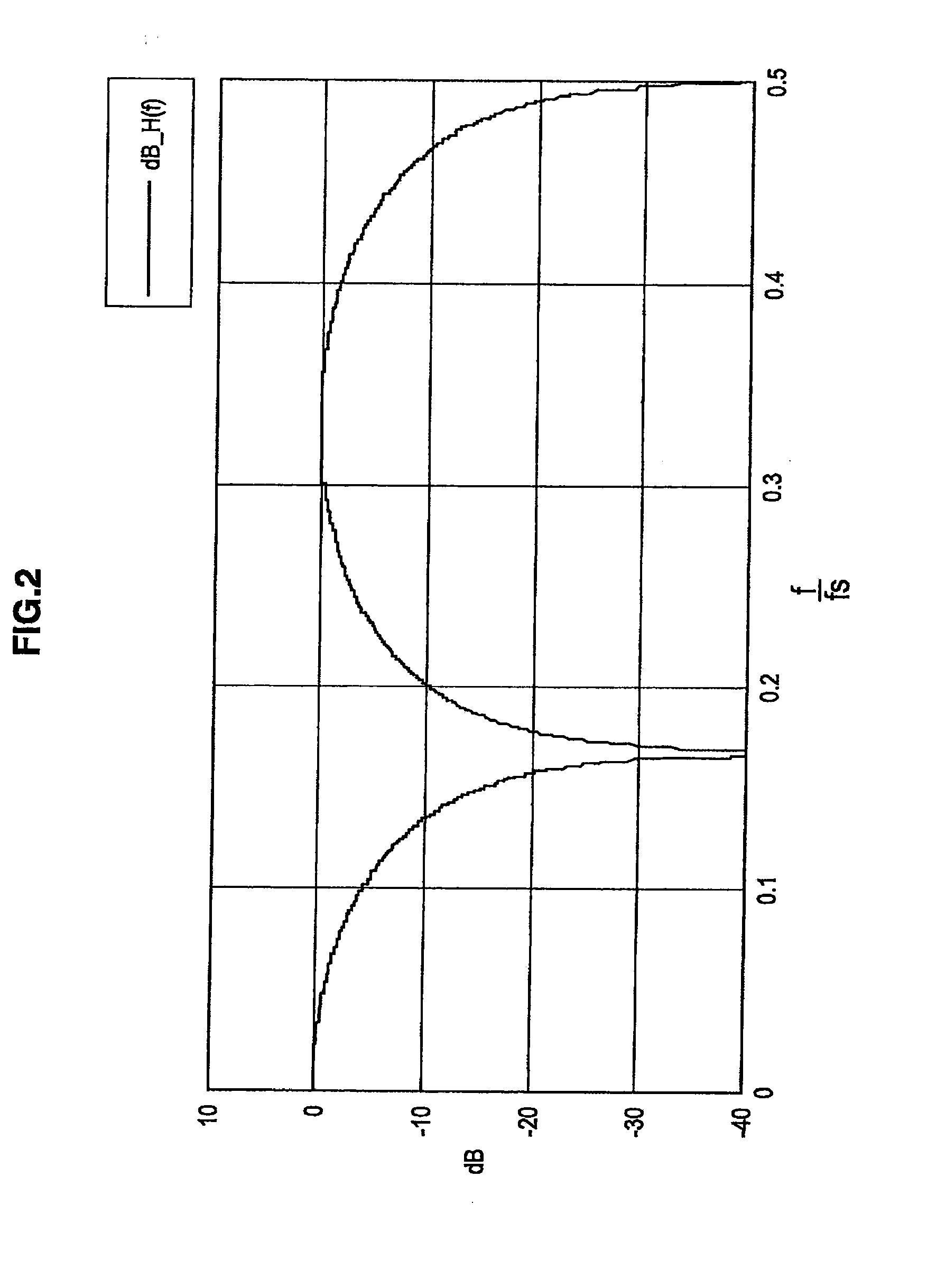

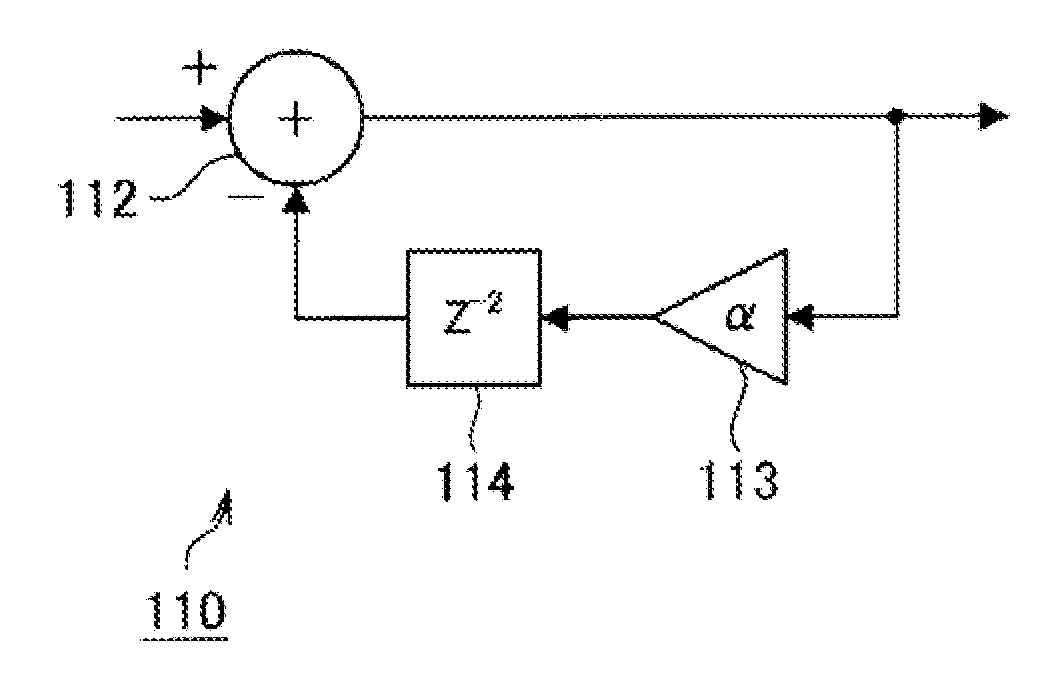

High speed filter

ActiveUS7028070B2Frequency efficiencyReduce the burden onComputing operations for integral formationTransversal filtersBinary multiplierAnalog signal

An electronic filter operates as a correlator that provides a discrete approximation of an analog signal. The analog to digital conversion is integrated directly approximation calculation. An array of sample and hold circuits or single bit comparators provide outputs to a series of multipliers, the other input of which is a coefficient value of a Fourier series approximation of the desired frequency response. Each of the sample and hold circuits samples sequentially in time and holds its sample until the next cycle. Thus the sample point rotates in time through the array and each new sample is multiplied by a different coefficient. The output of the multipliers is summed for evaluation.

Owner:ESS TECHNOLOGY

Analog filter with passive components for discrete time signals

InactiveUS20060071707A1Well formedTransversal filtersOscillations generatorsDiscrete-time signalControl theory

A filter intended to receive a discrete time signal at a sampling dock frequency, comprising a determined number, greater than 2, of filtering units, each filtering unit comprising head capacitors in a number equal to the determined number, assembled in parallel between an input terminal and the terminal of an integration capacitor; and means for connecting, in successive dock cycles in a number equal to the determined number, successively each head capacitor to the input terminal, and for then simultaneously connecting the head capacitors to the integration capacitor, and in which the successive dock cycles during which the head capacitors of a filtering unit are connected to the input terminal are offset by one dock cycle from one filtering unit to the next one.

Owner:ST ERICSSON SA

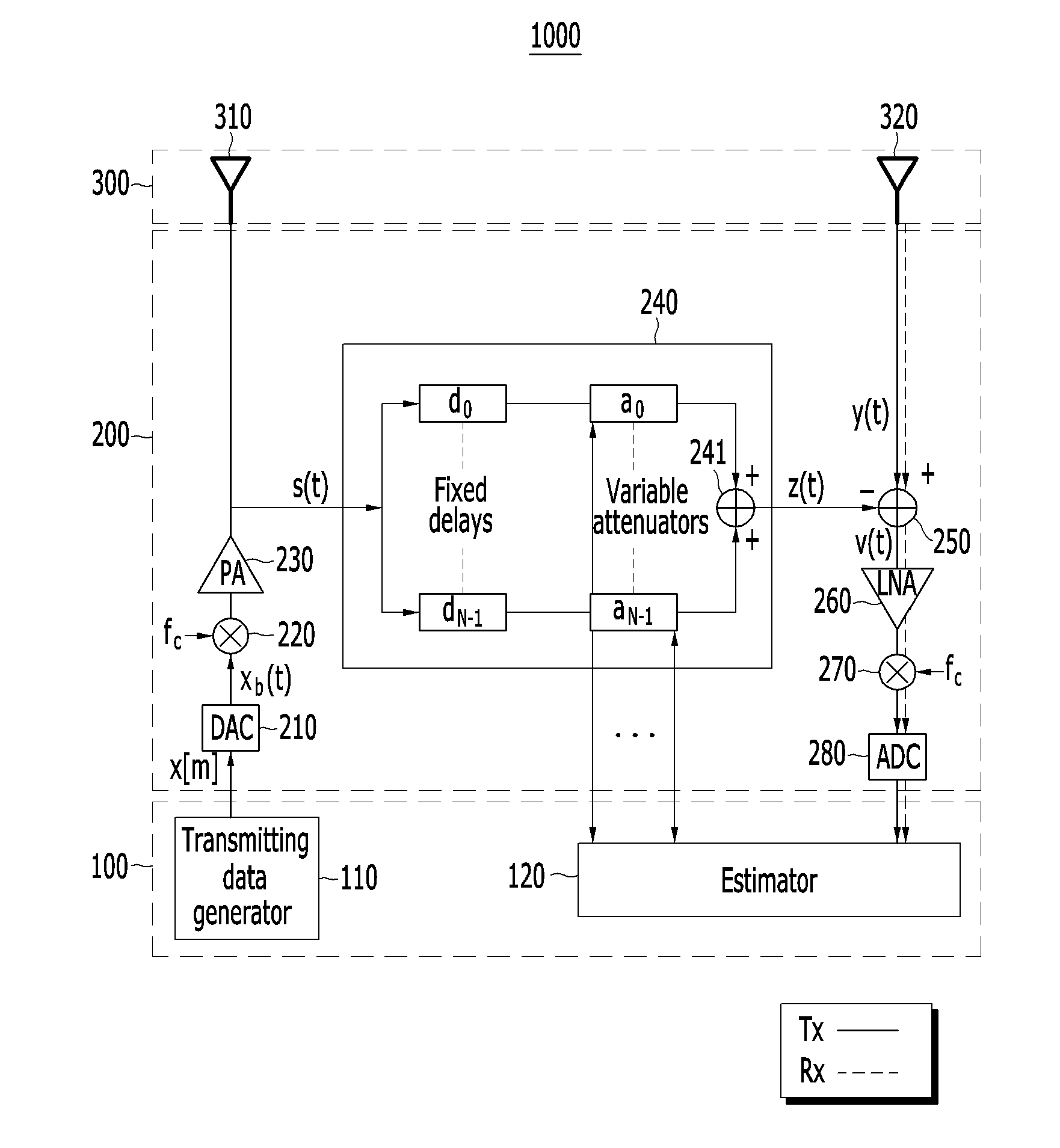

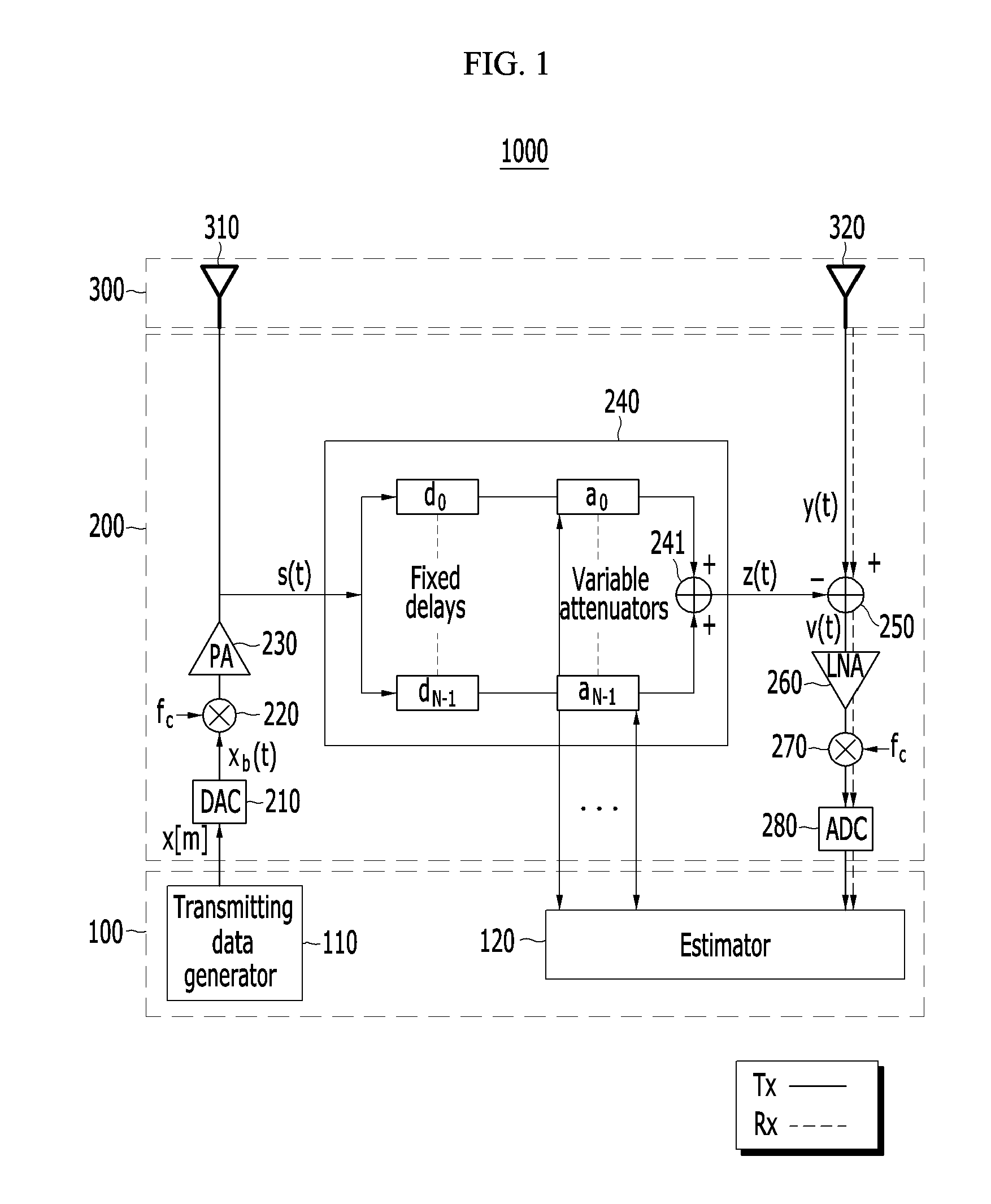

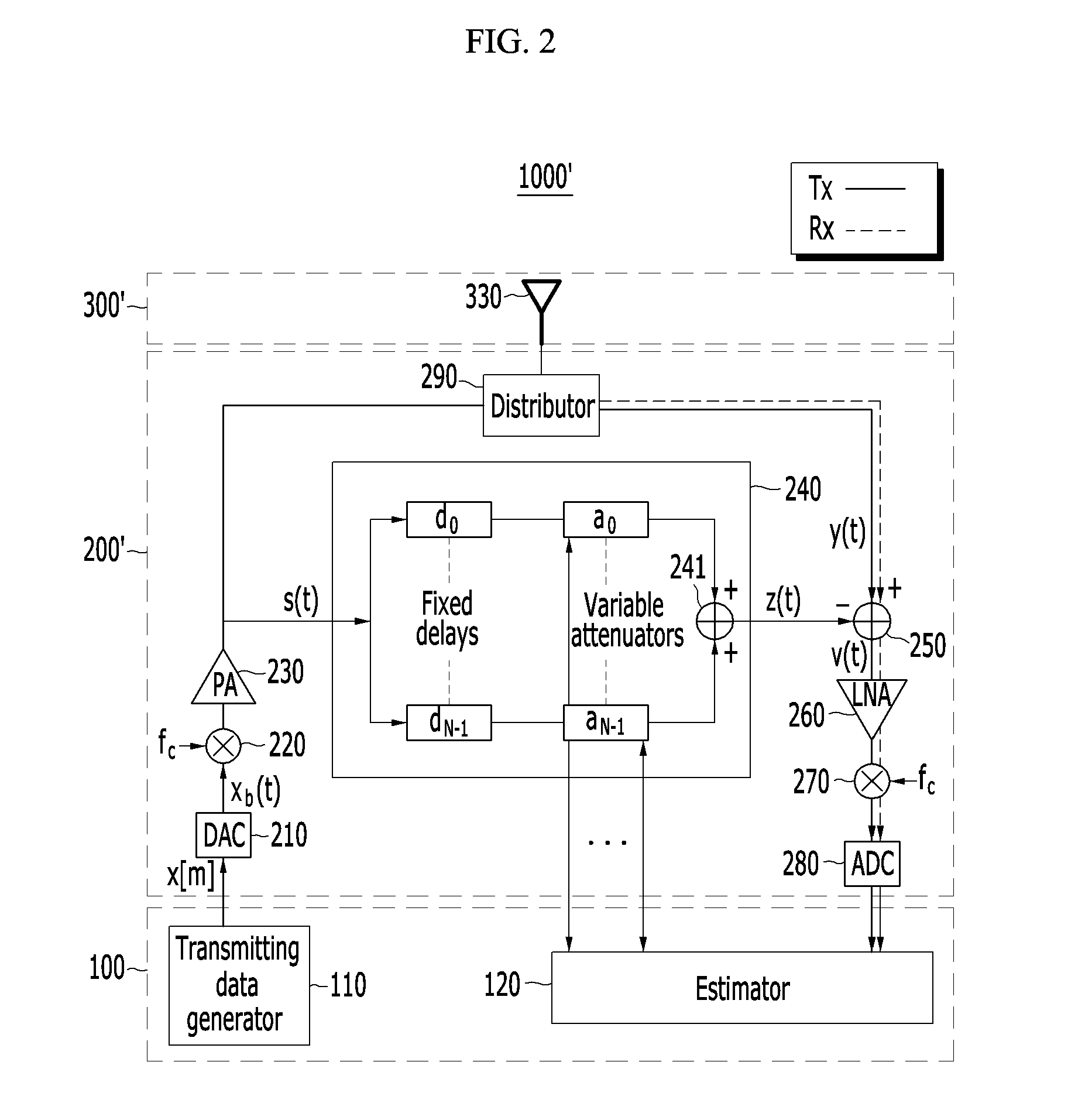

Method and apparatus for tuning finite impulse response filter in in-band full duplex transceiver

ActiveUS20160380799A1High SIC gainAdapt quicklyTransversal filtersTransmission control/equalisingUltrasound attenuationTransceiver

A method and an apparatus for tuning an FIR filter in an in-band full duplex transceiver. The method for tuning an FIR filter may include: setting attenuation of the FIR filter to be a first value and then estimating input information of the FIR filter; estimating a delta response using the estimated input information of the FIR filter; and updating the attenuation of the FIR filter to a second value using the estimated delta response.

Owner:ELECTRONICS & TELECOMM RES INST

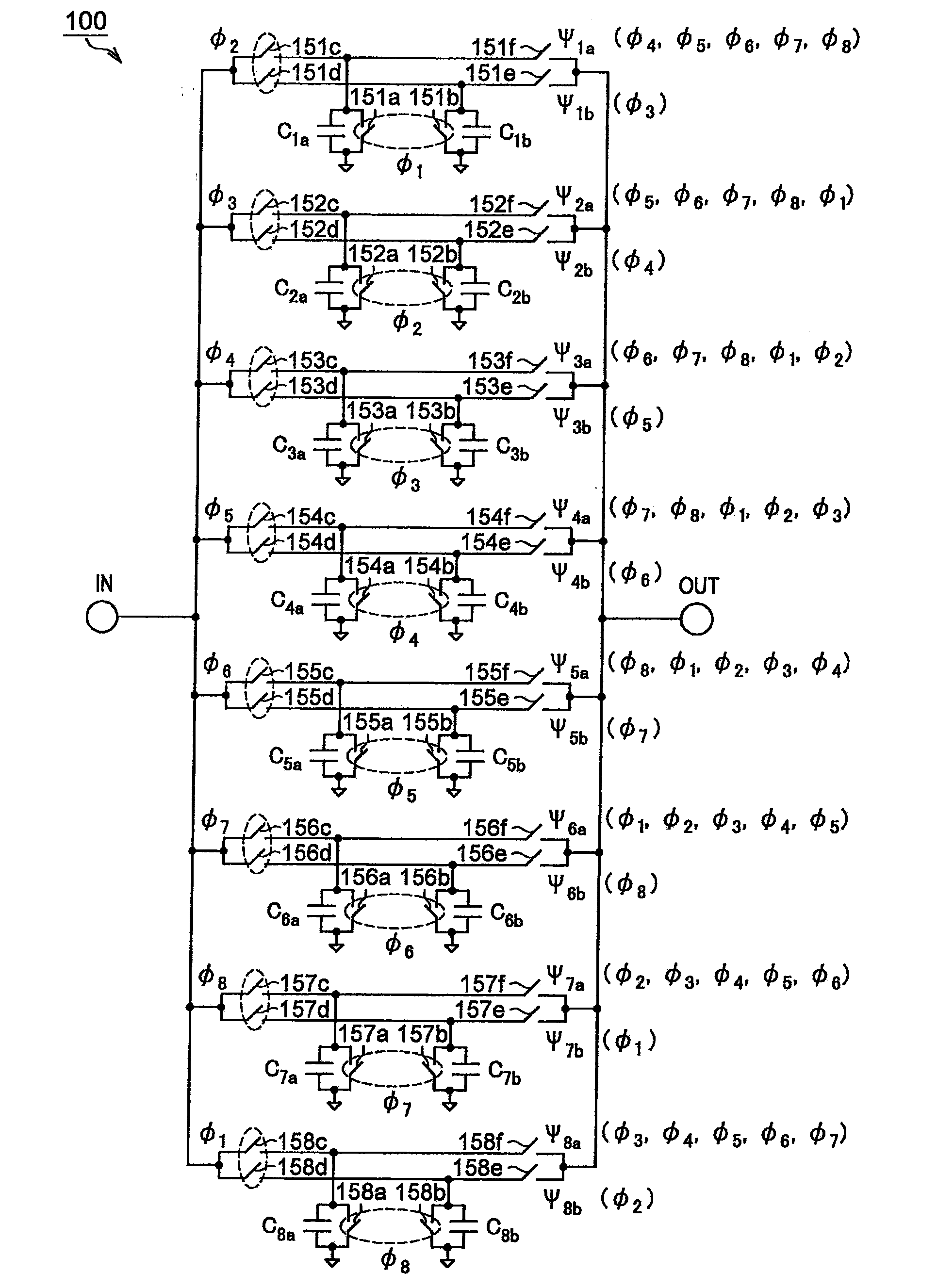

Charge Domain Filter Circuit

InactiveUS20090134938A1Reconfigurable filter characteristicsReduce power consumptionMultiple-port networksTransversal filtersCapacitanceEngineering

A charge domain filter circuit includes a first signal output portion, at least one second signal output, portion, a third signal output portion, and an adder portion. The first signal output portion outputs a first signal that is sampled at a specified time interval. Each second signal, output portion outputs a second signal that is sampled after a specified delay after the first signal is sampled. Where a plurality of the second signal output portions is included, the second signals are sampled in succession. The third signal output portion outputs a third signal that is sampled after a specified delay after the last second signal is sampled. The adder portion adds the first, second, and third signals together and outputs the result. The capacitance ratio of the sampling capacitors in the first signal output portion and the second signal output portion is one of continuously or discretely varied.

Owner:SONY CORP

Charge Domain Filter Device

InactiveUS20080088389A1Reduce power consumptionMultiple-port networksTransversal filtersBandpass filteringSinc filter

A charge domain filter device includes a SINC filter with a frequency characteristic expressed by a SINC function, and a bandpass filter connected to an output end of the SINC filter and having a frequency characteristic with a particular center frequency.

Owner:SONY CORP

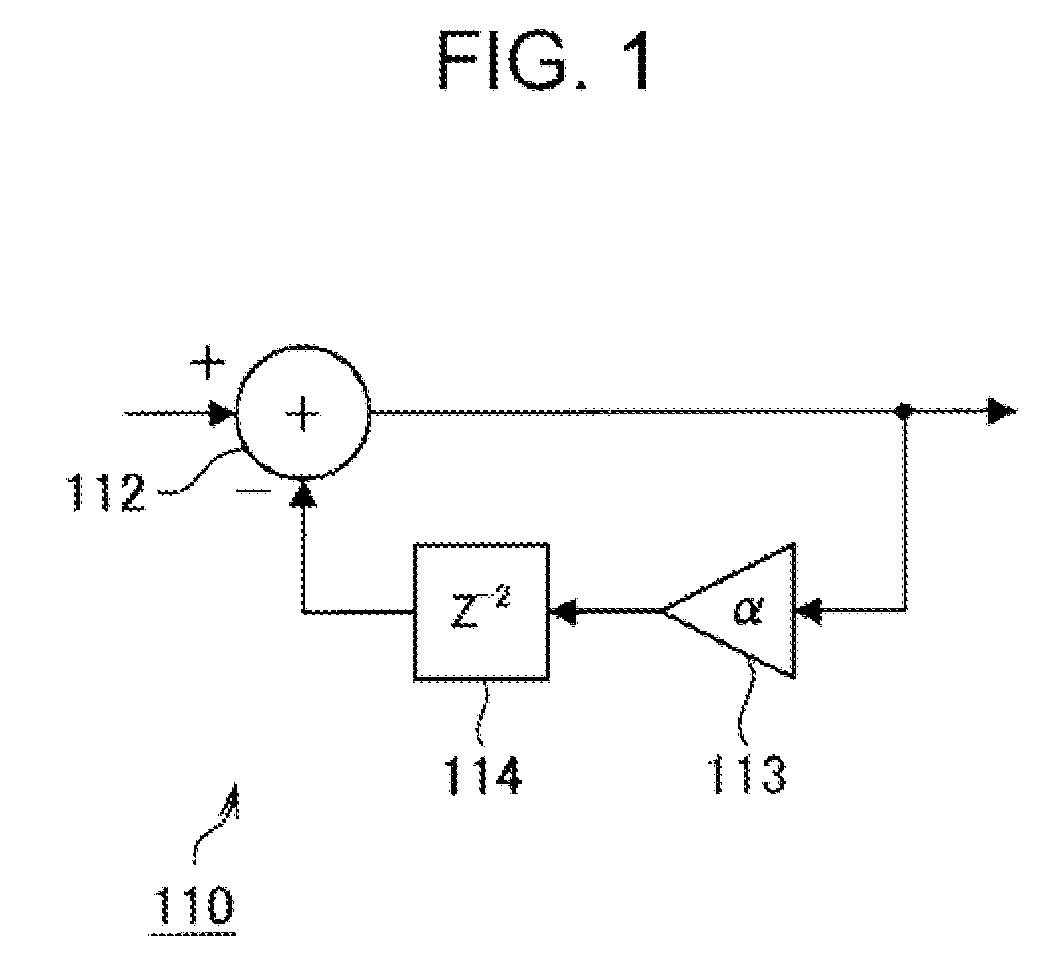

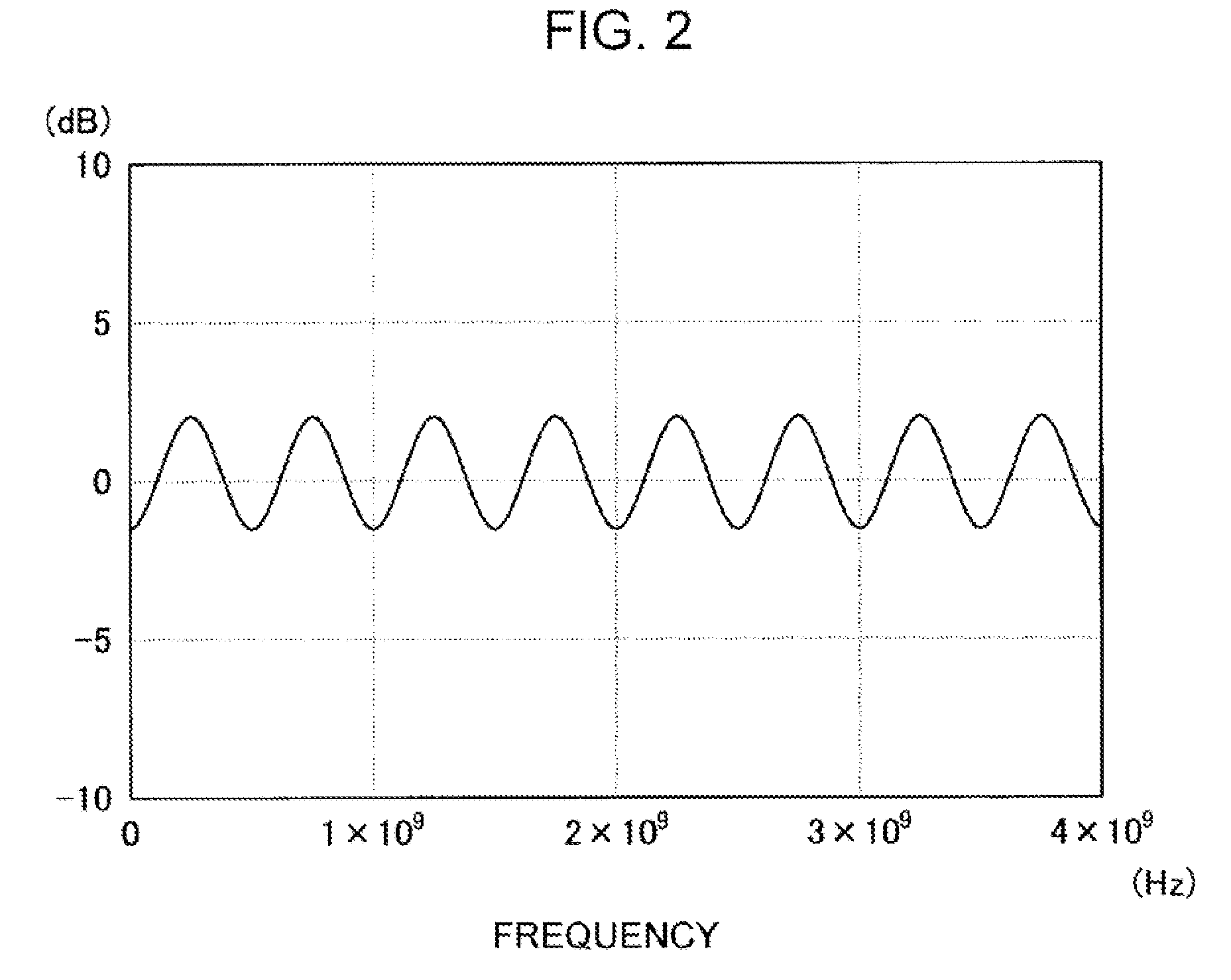

Tuned continuous time delay FIR equalizer

An analog finite impulse response (“FIR”) filter generates a continuous time output using a chain of tunable delay elements. The tunable delay elements generate a time delay in an input signal. A calibration circuit, consisting of a control loop, tunes the delay elements to provide precision in the time delay response of the delay elements. The control loop generates a delay adjustment, based on the period of reference signals, and the phase adjustment is used to tune the parameters of the delay elements. The tunable delay elements may comprise any combination of transmission lines, lumped elements and semi-lumped elements.

Owner:AVAGO TECH INT SALES PTE LTD

Distributed amplifier with built-in filtering functions

A distributed amplifier uses non-uniform filtering structures to provide better control over pass-band and stop-band characteristics. The various sections can have different tap coefficients. A notch filter can be implemented for interference suppression or pulse shaping in an ultra-wideband transceiver.

Owner:UNIVERSITY OF ROCHESTER

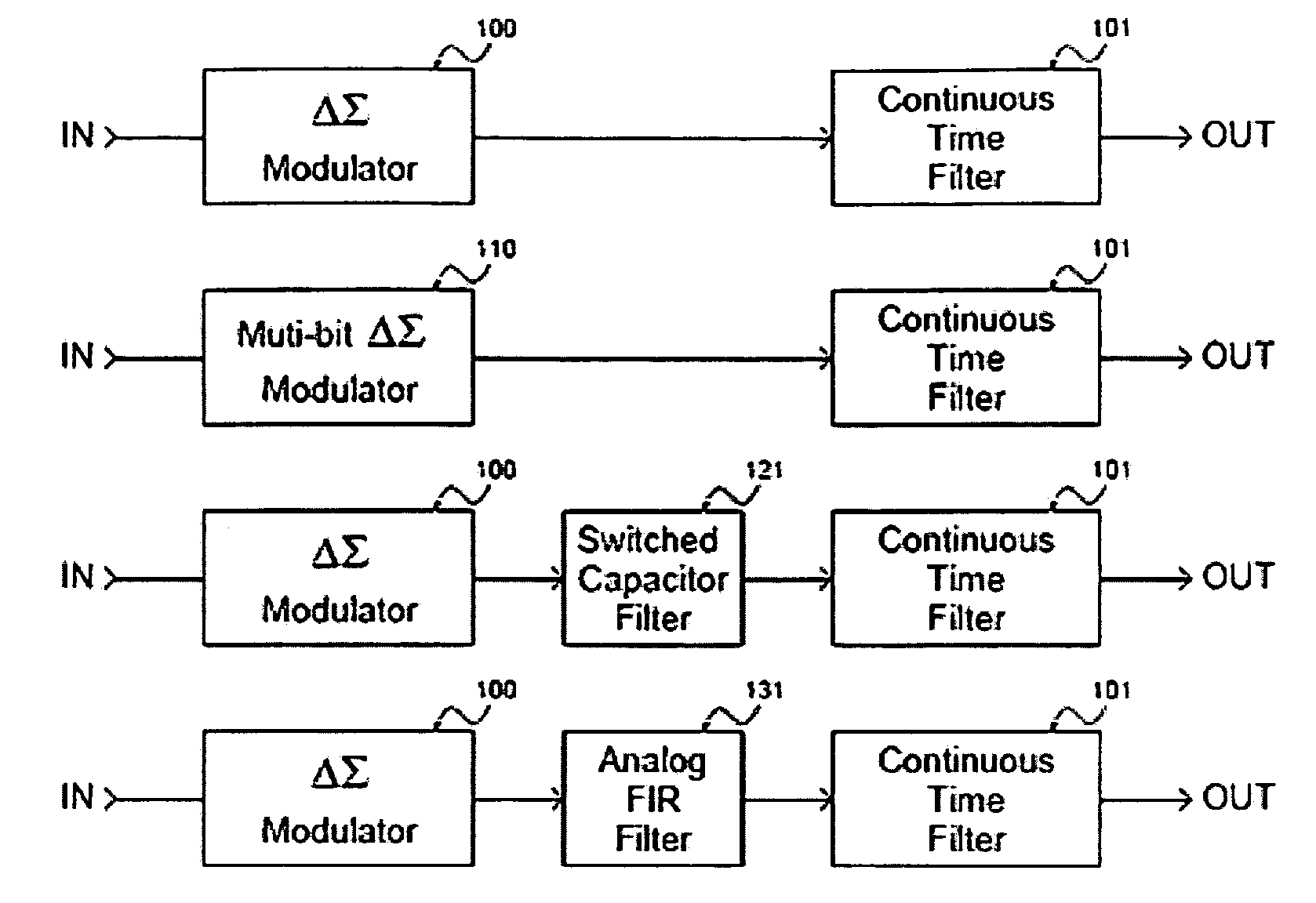

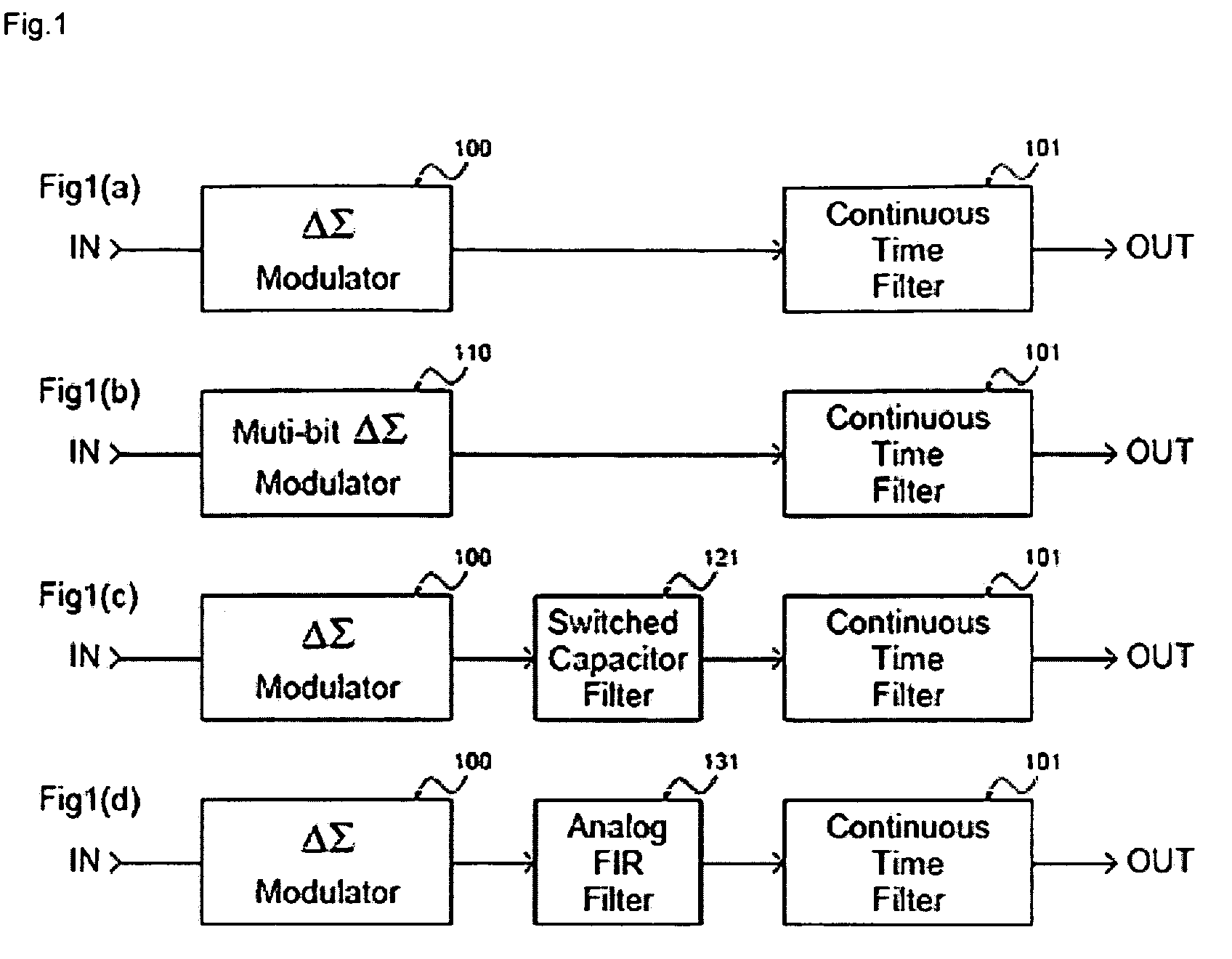

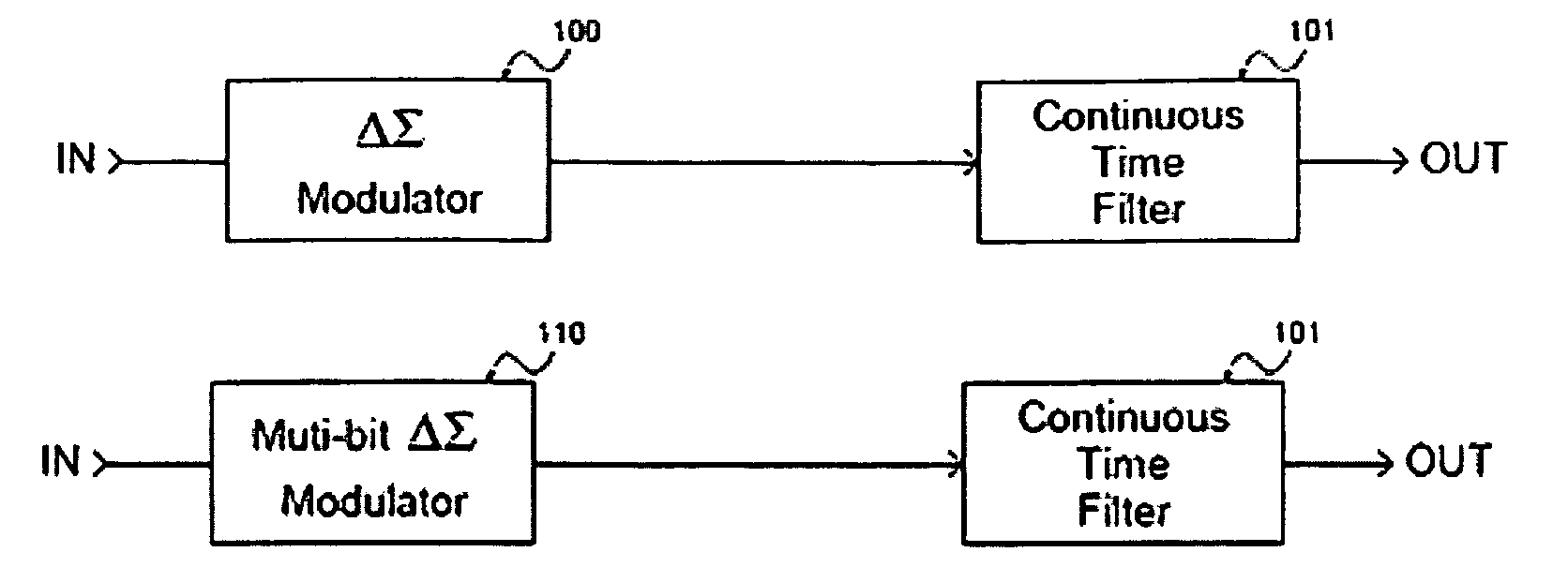

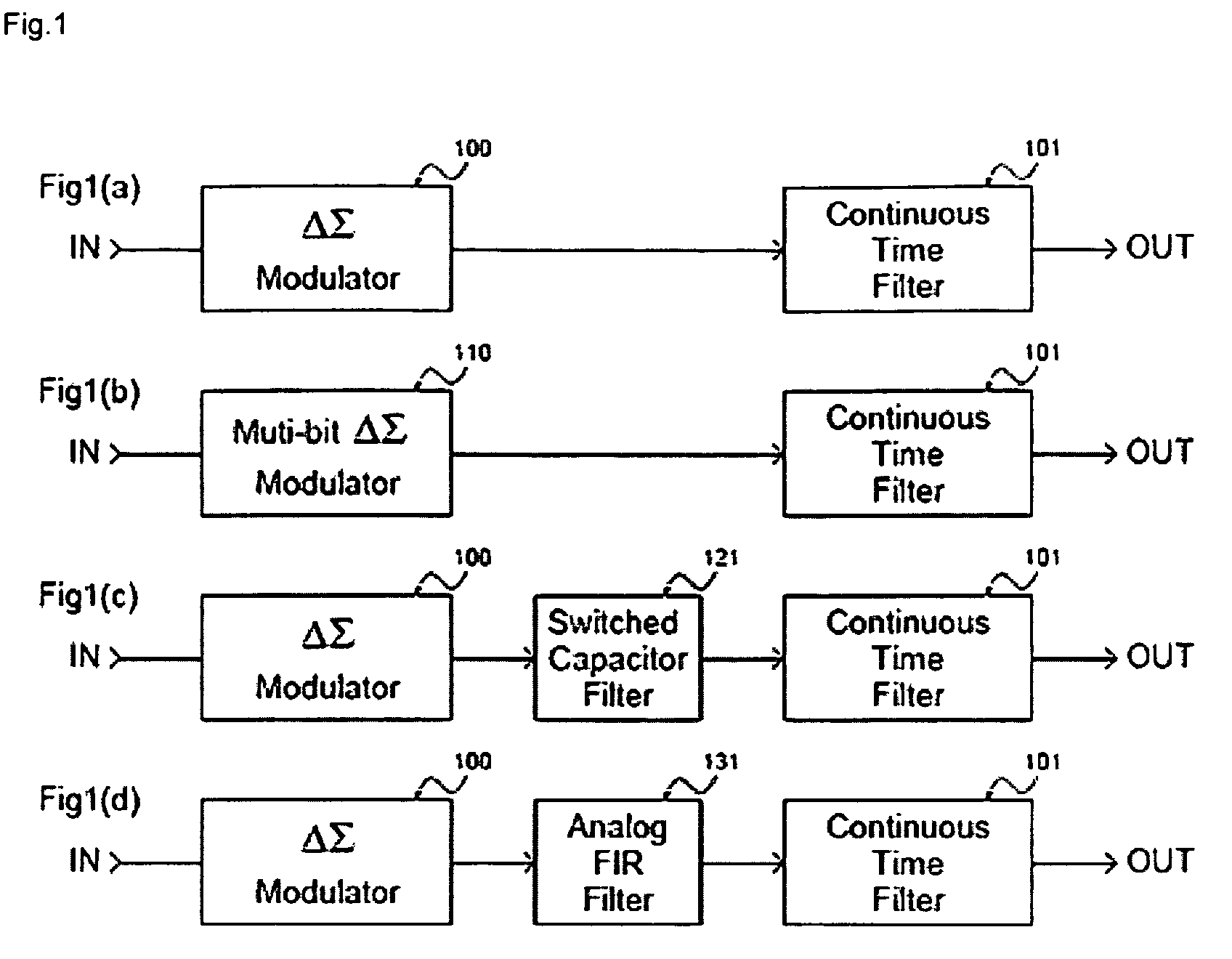

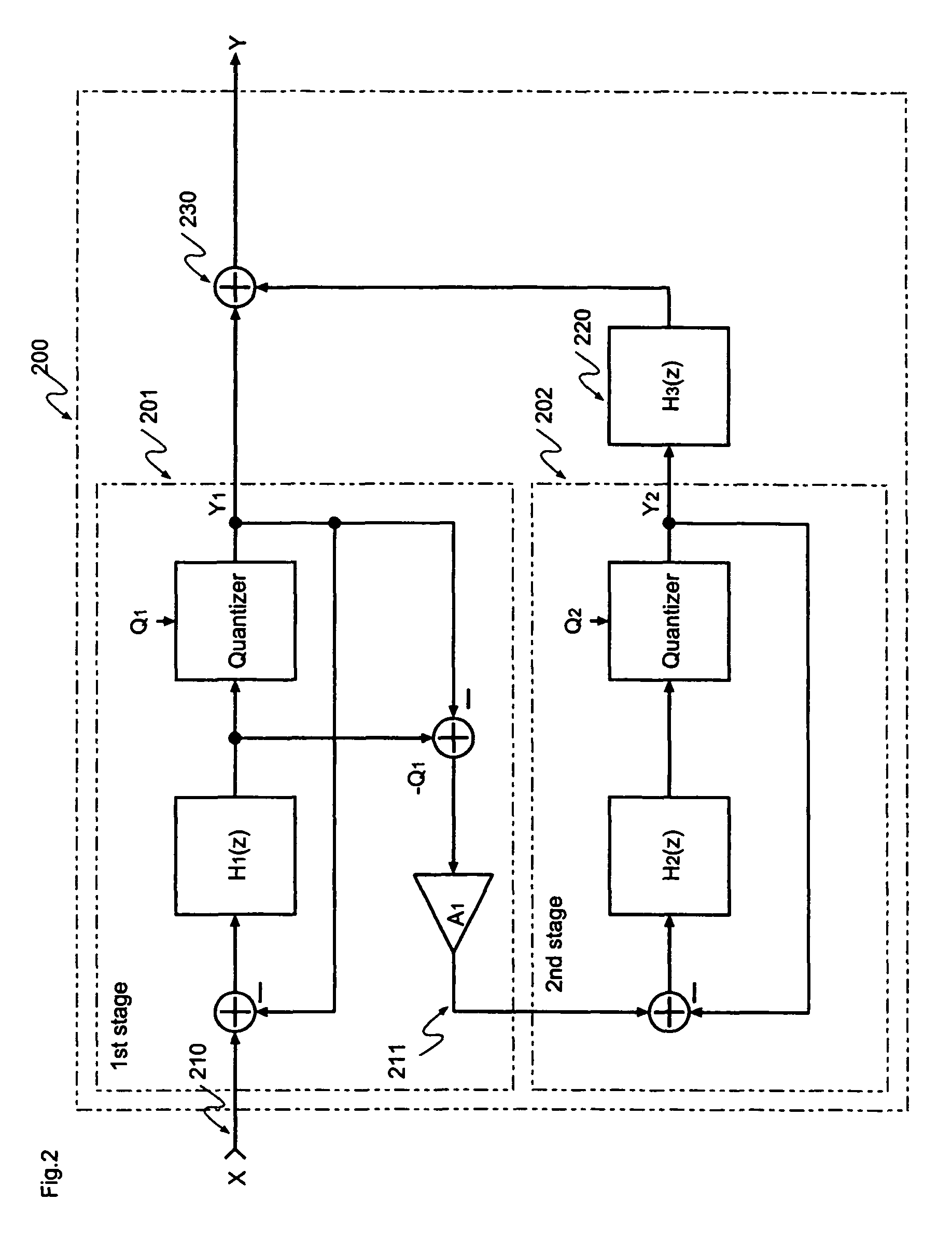

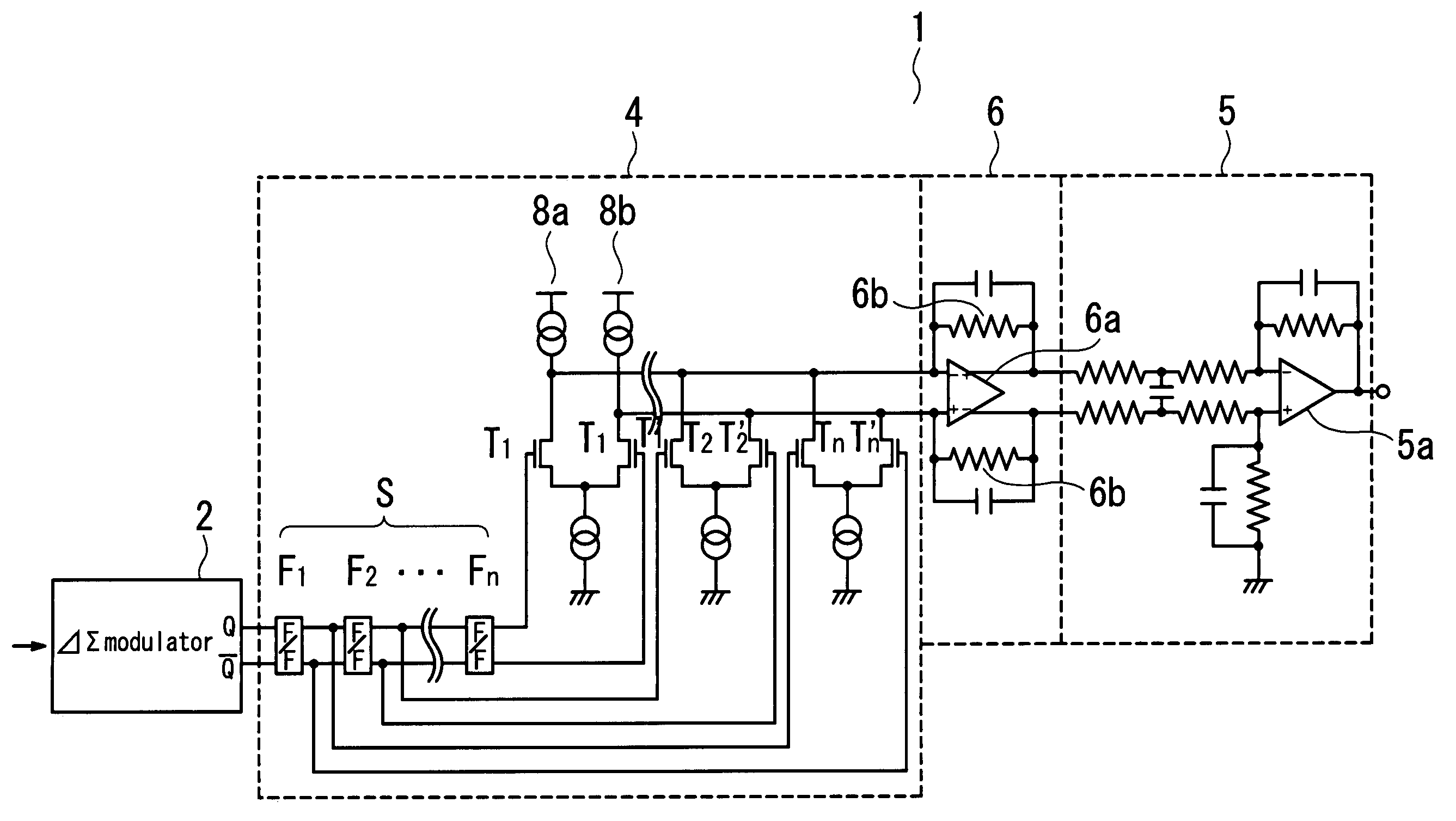

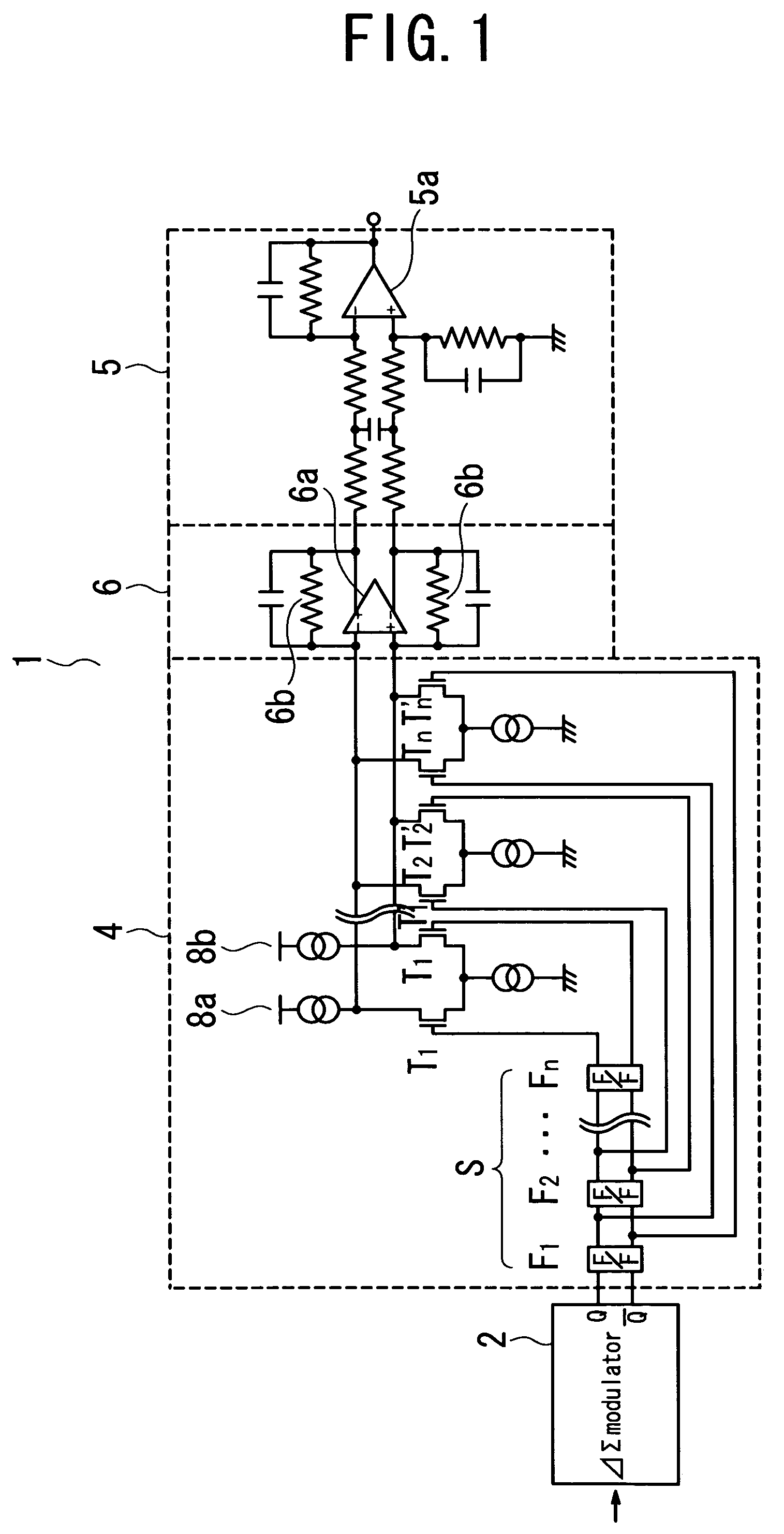

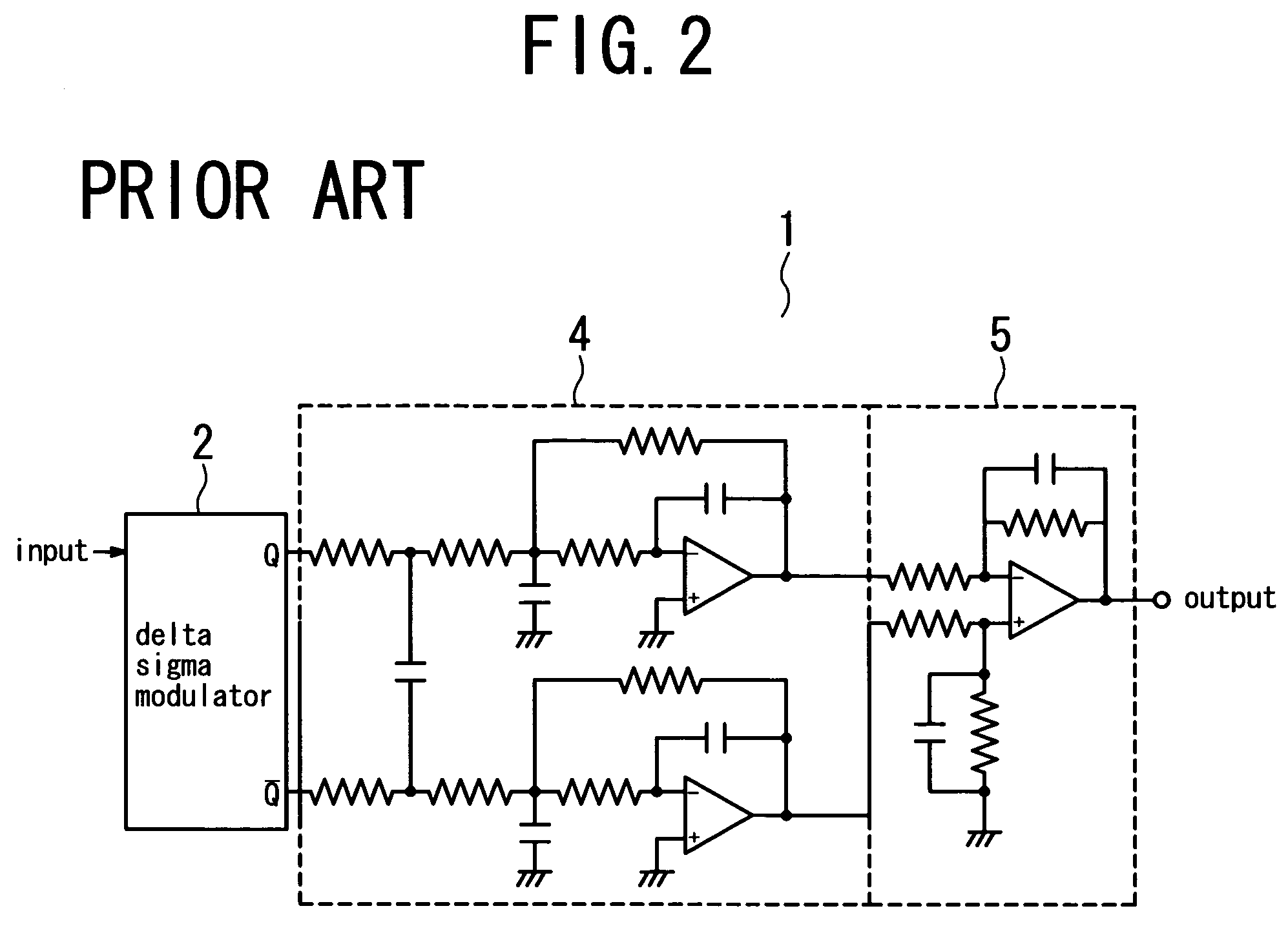

Output filter for delta sigma modulator and digital signal processor provided with the same

InactiveUS7256720B2Reduce resistanceReduce thermal noiseElectric signal transmission systemsTransversal filtersShift registerEngineering

The invention intends to reduce noises by resistors in an output filter for a delta sigma modulator. The output filter uses an FIR filter with constant current sources as the current source, extracts output data of the delta sigma modulator from each taps of a shift register, controls MOS transistors by the extracted delayed signals, attains currents weighted according to the FIR filter coefficients corresponding to the number of the taps from the constant current sources, adds the currents attained, and performs the current-to-voltage conversion of the currents thus attained by feedback resistors of a full differential operational amplifier.

Owner:ROHM CO LTD

Charge domain filter device

InactiveUS7636012B2Reduce power consumptionMultiple-port networksTransversal filtersBandpass filteringSinc filter

A charge domain filter device includes a SINC filter with a frequency characteristic expressed by a SINC function, and a bandpass filter connected to an output end of the SINC filter and having a frequency characteristic with a particular center frequency.

Owner:SONY CORP