Patents

Literature

362results about "Computing operations for integral formation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Method of determining the derivative of an input signal

InactiveUS20050256919A1Eliminate Phase Delay IssuesSimple methodComputing operations for integral formationComputing operations for integration/differentiationChemistry

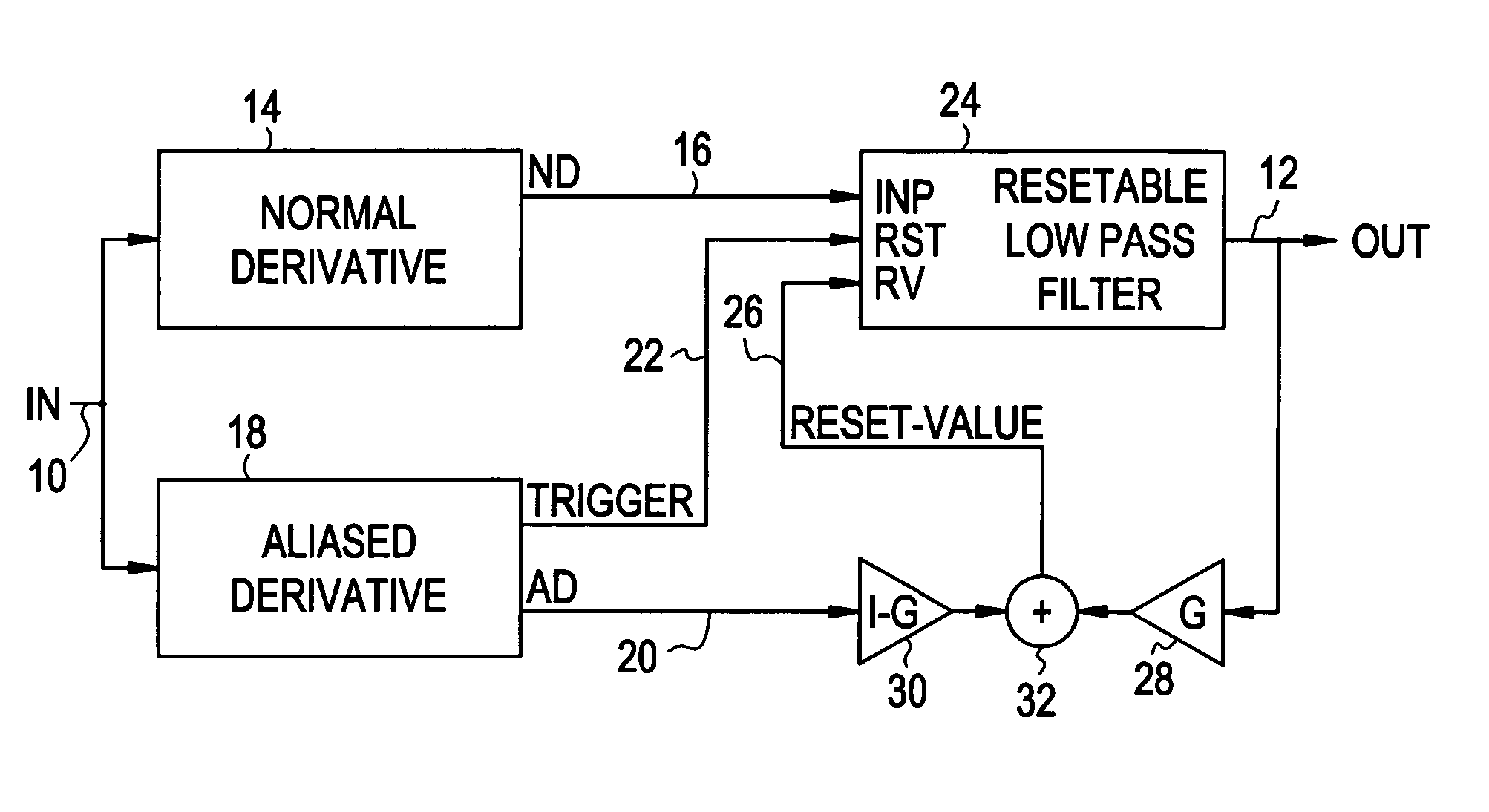

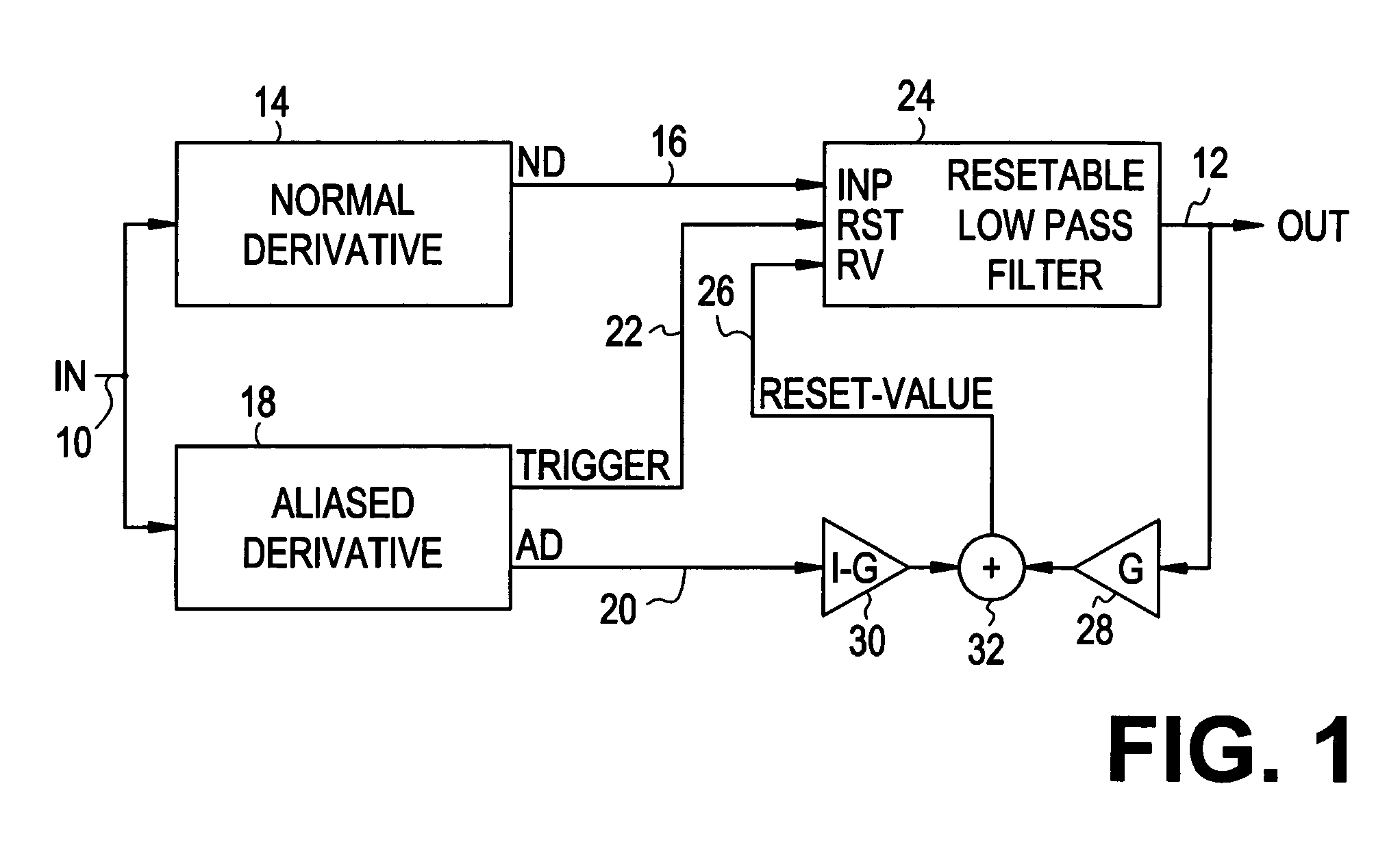

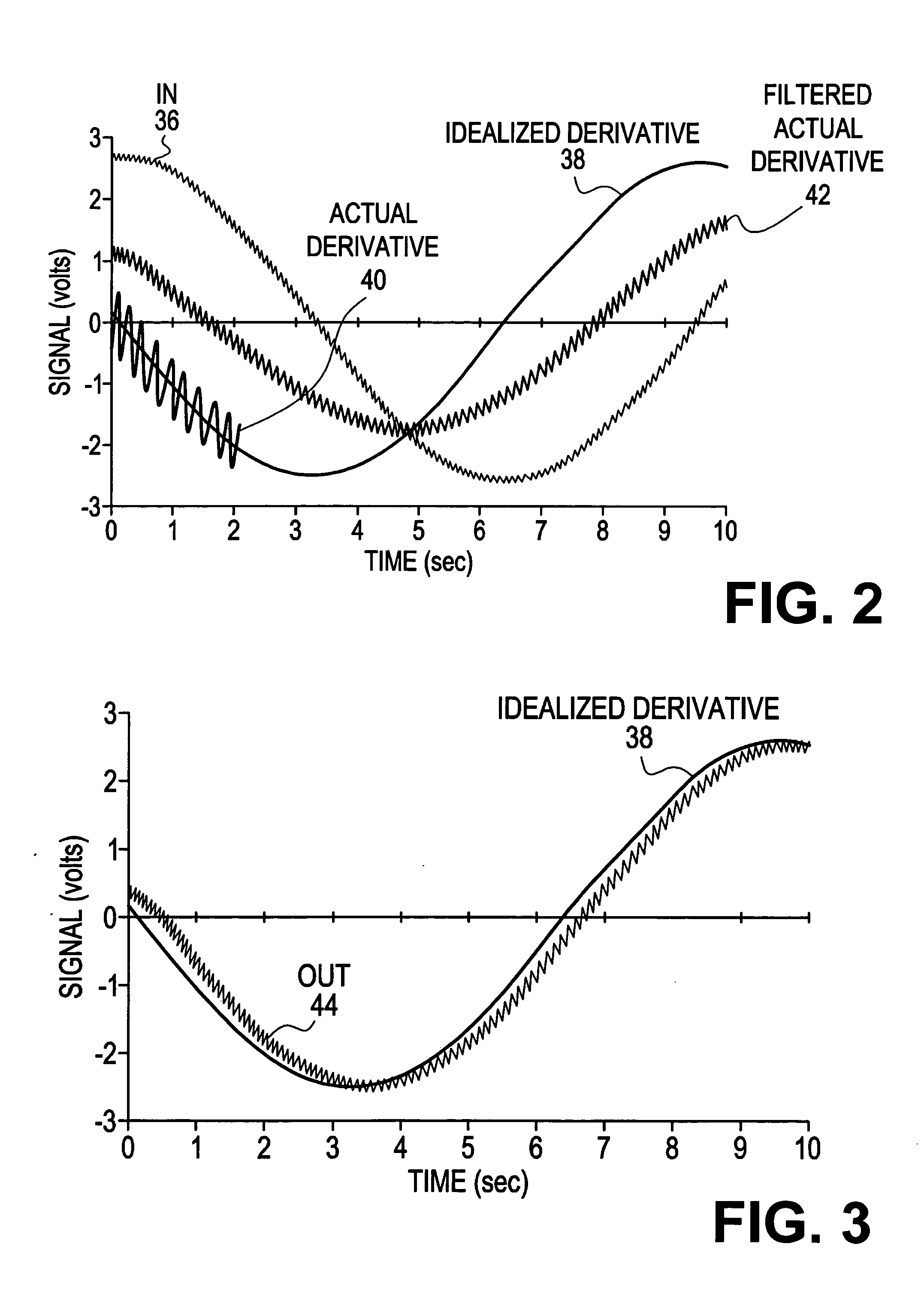

The derivative of a noise-containing input signal is determined by using an aliased derivative to periodically reset a filtered version of a normally determined derivative. The aliased derivative is calculated using a slower update or sampling rate than the normally determined derivative, and the filtered version of the normally determined derivative is reset to a reset value at each update of the aliased derivative. The reset value is based on a weighted sum of the aliased derivative and the filter output. The periodically reset filter output closely follows an idealized derivative of the input signal, substantially eliminating the phase delay introduced by conventional filtering.

Owner:GM GLOBAL TECH OPERATIONS LLC

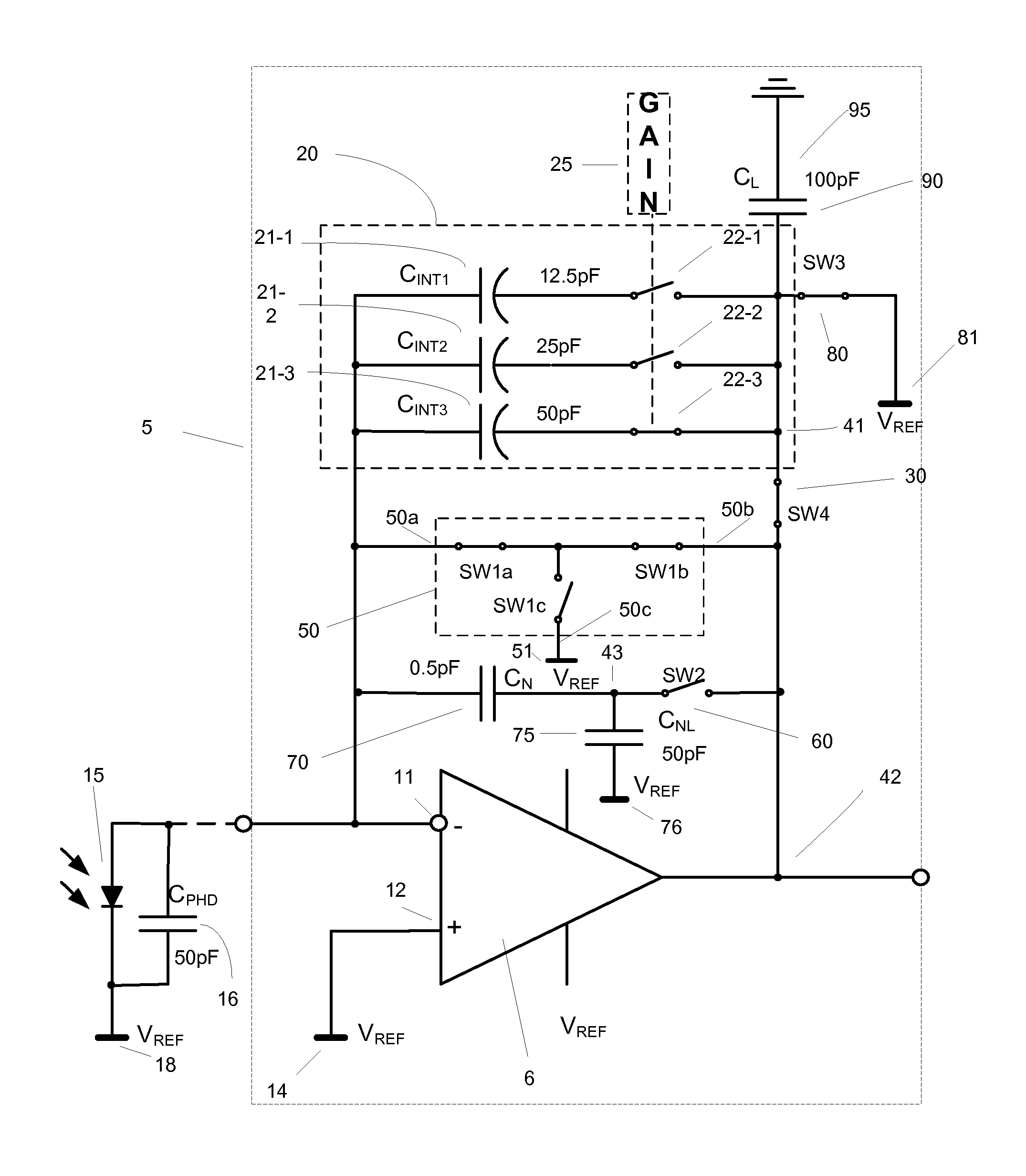

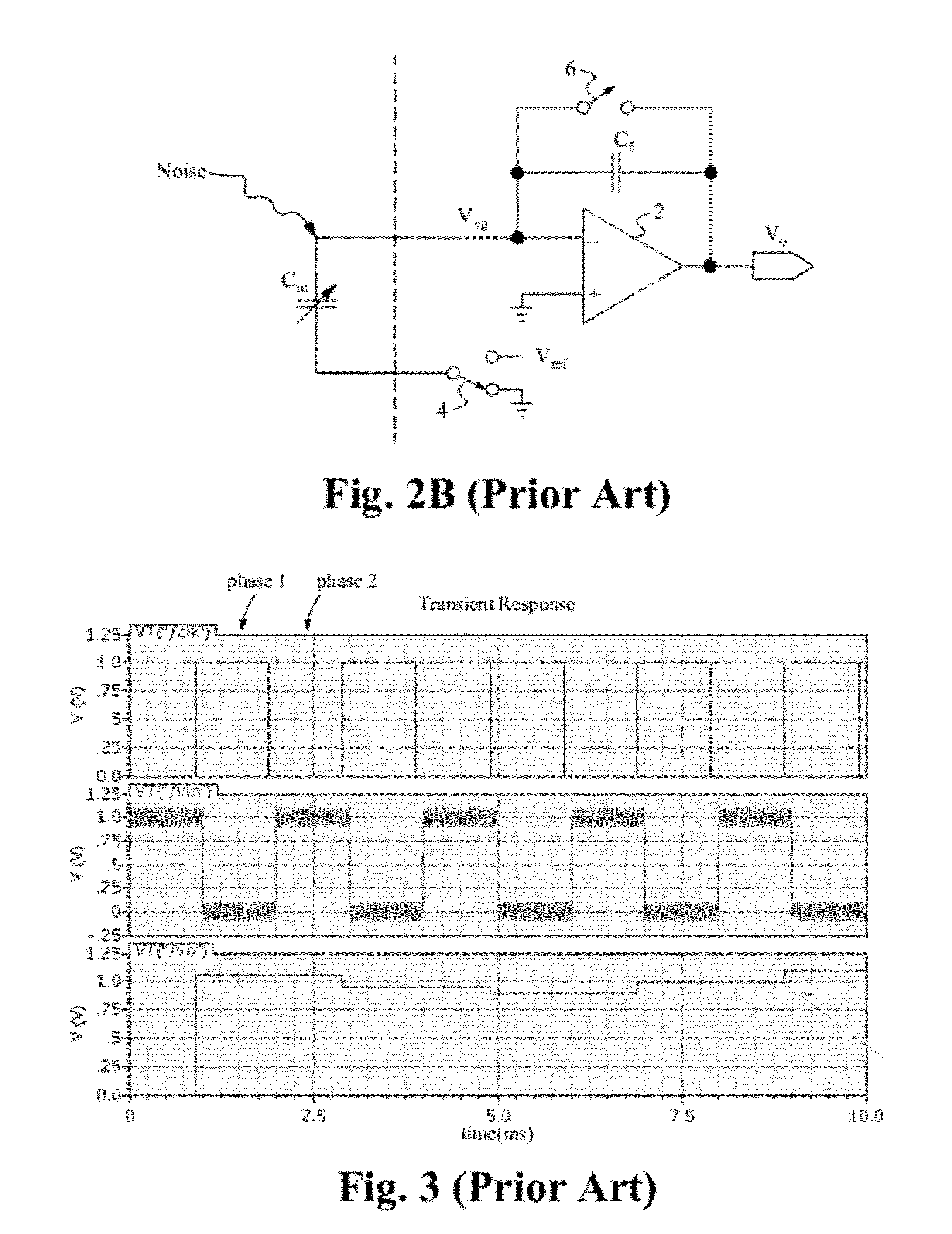

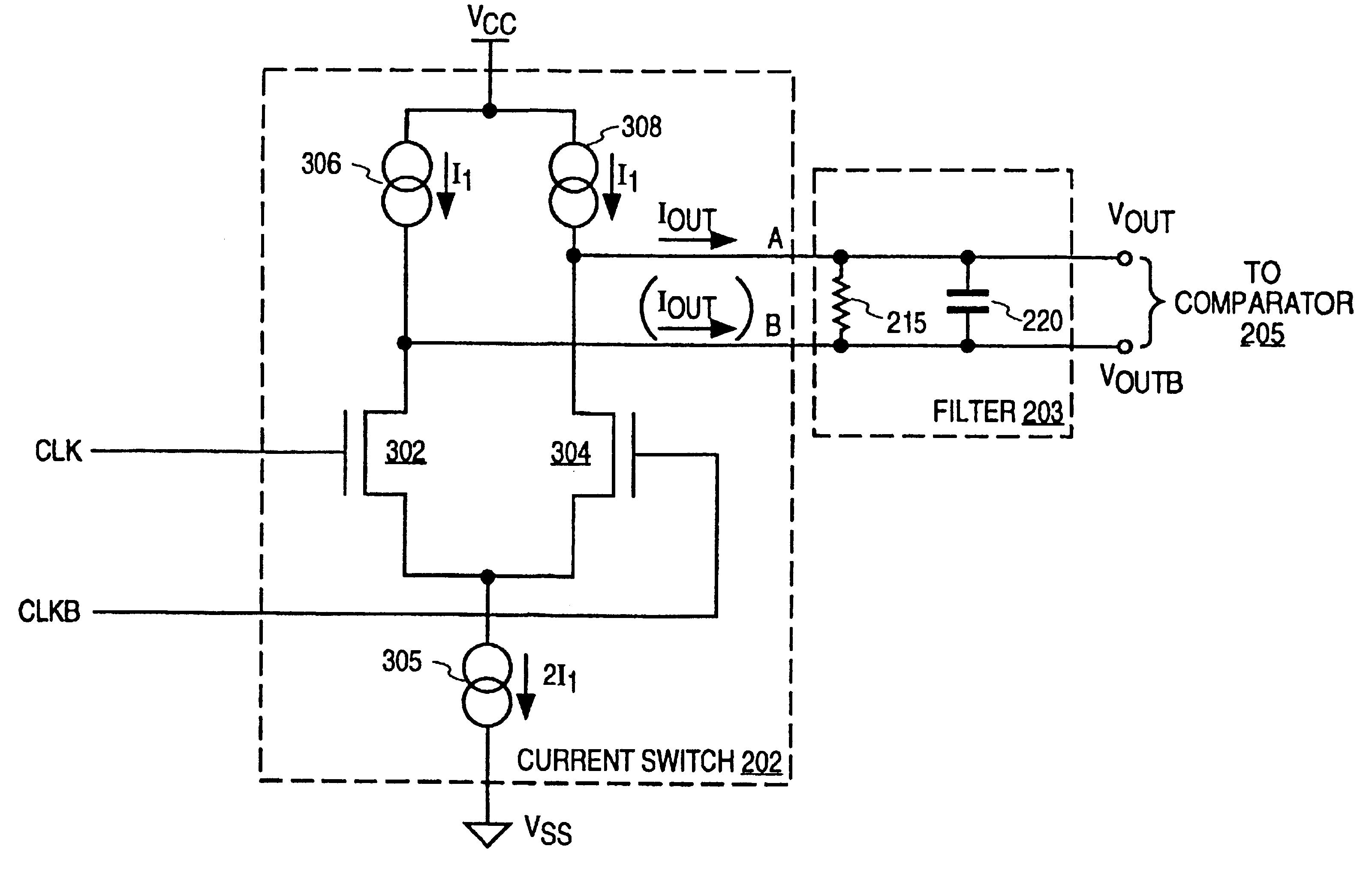

Calibration of integrated circuit time constants

InactiveUS6842710B1Computing operations for integral formationComputing operations for integration/differentiationRC time constantVoltage reference

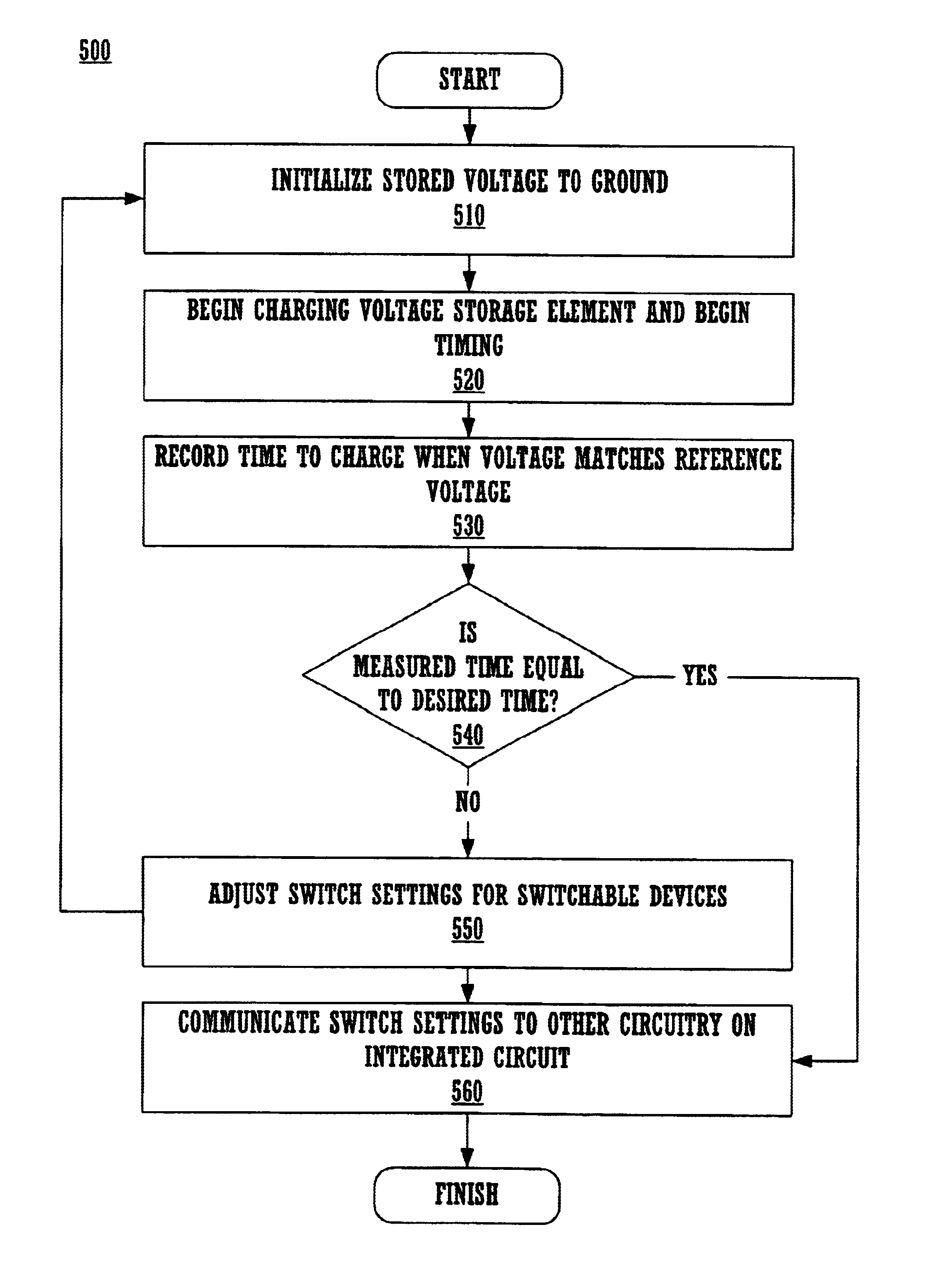

A method and system for calibrating a time constant within an integrated circuit. A voltage storage element is charged, and the time required to achieve a reference voltage on the storage element is measured. The measured time is compared to a desired time. It necessary, an adjustable impedance is modified to change the charging time, and the cycle may be repeated until the charging time matches the desired time. In this novel manner, an actual RC time constant, as rendered in a particular integrated circuit, is measured and potentially adjusted to match a desired time constant. Advantageously, configuration information of the adjustable impedance may be communicated to other circuitry within the integrated circuit to enable such circuitry to implement the same RC time constant in analog signal processing. Consequently, embodiments of the present invention overcome incidences of wide tolerance in passive components implemented in integrated circuits. Beneficially, no external test equipment is required.

Owner:TAMIRAS PER PTE LTD LLC

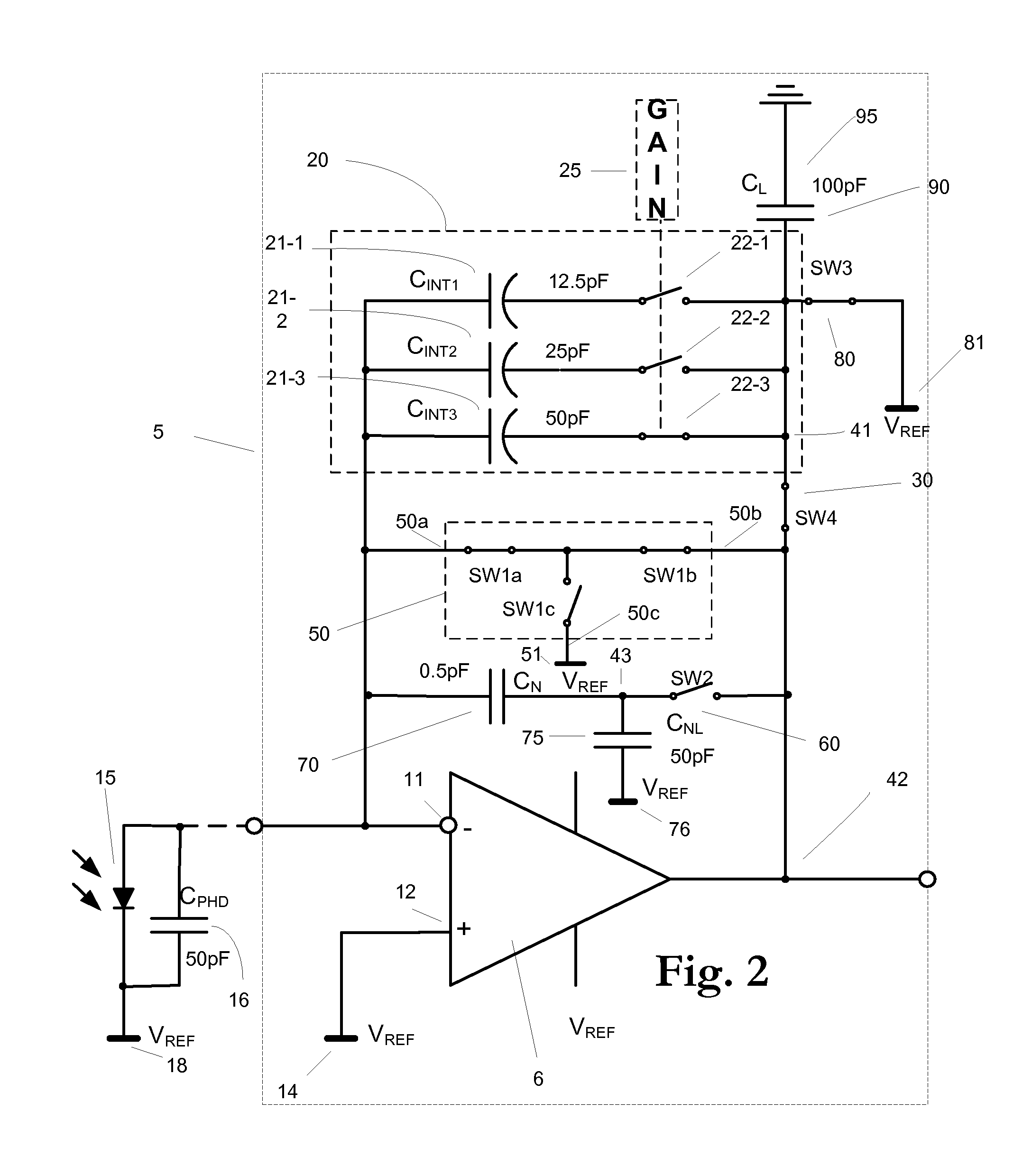

Apparatus for current-to-voltage integration for current-to-digital converter

InactiveUS20090273386A1Reduce charge injectionReduce demandComputing operations for integral formationComputing operations for integration/differentiationDigital down converterIntegrator

Owner:CUSTOM ONE DESIGN

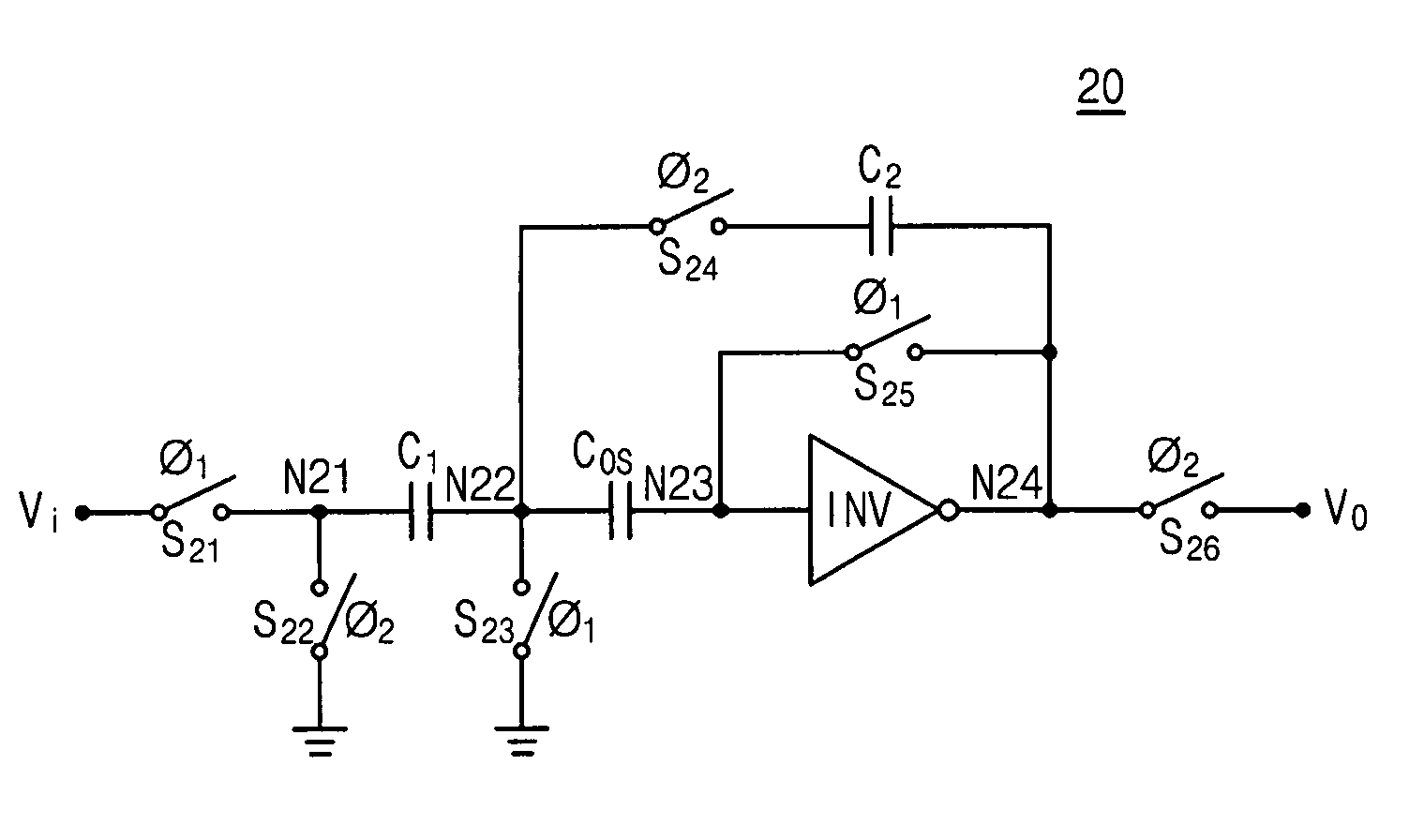

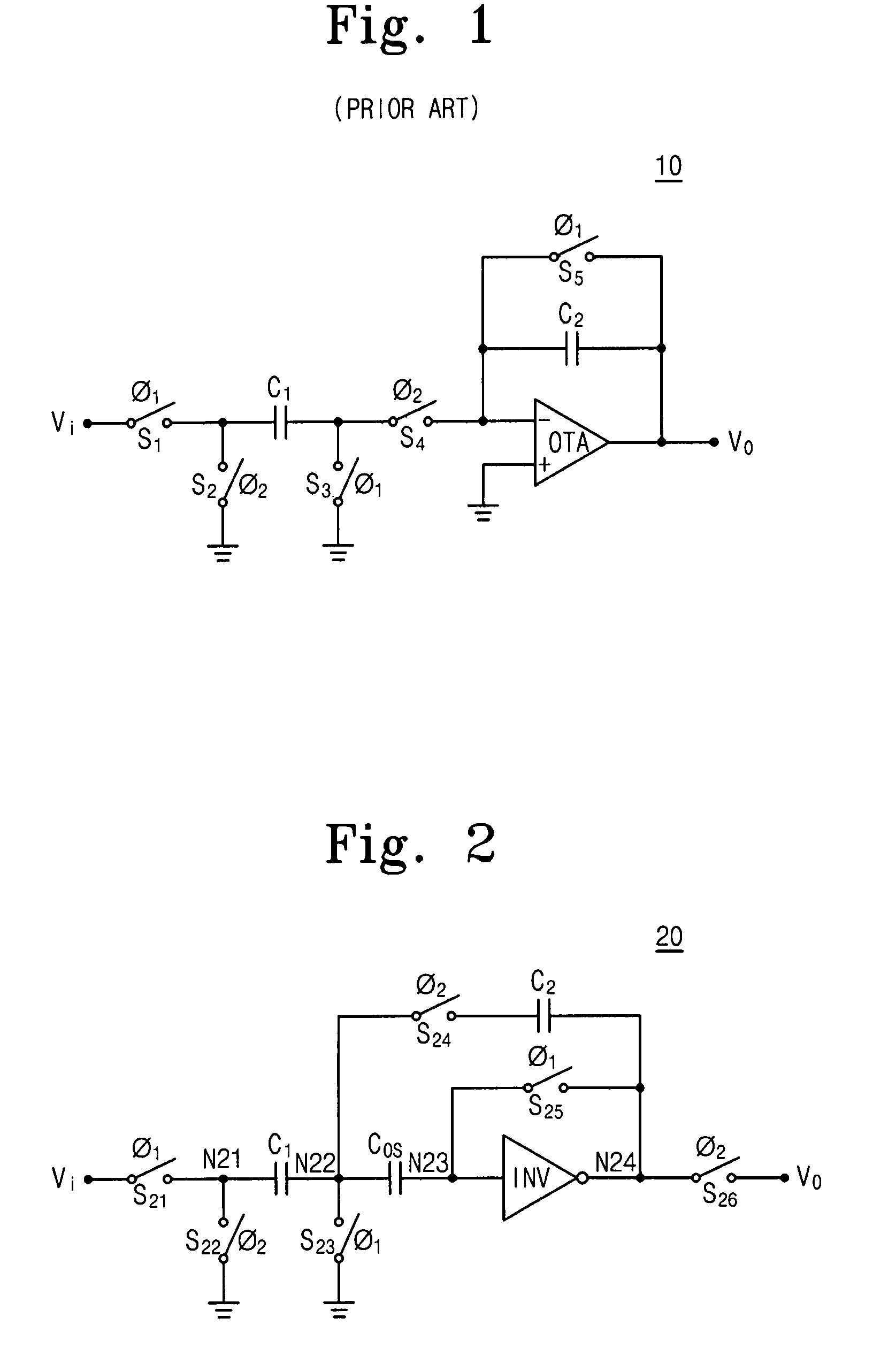

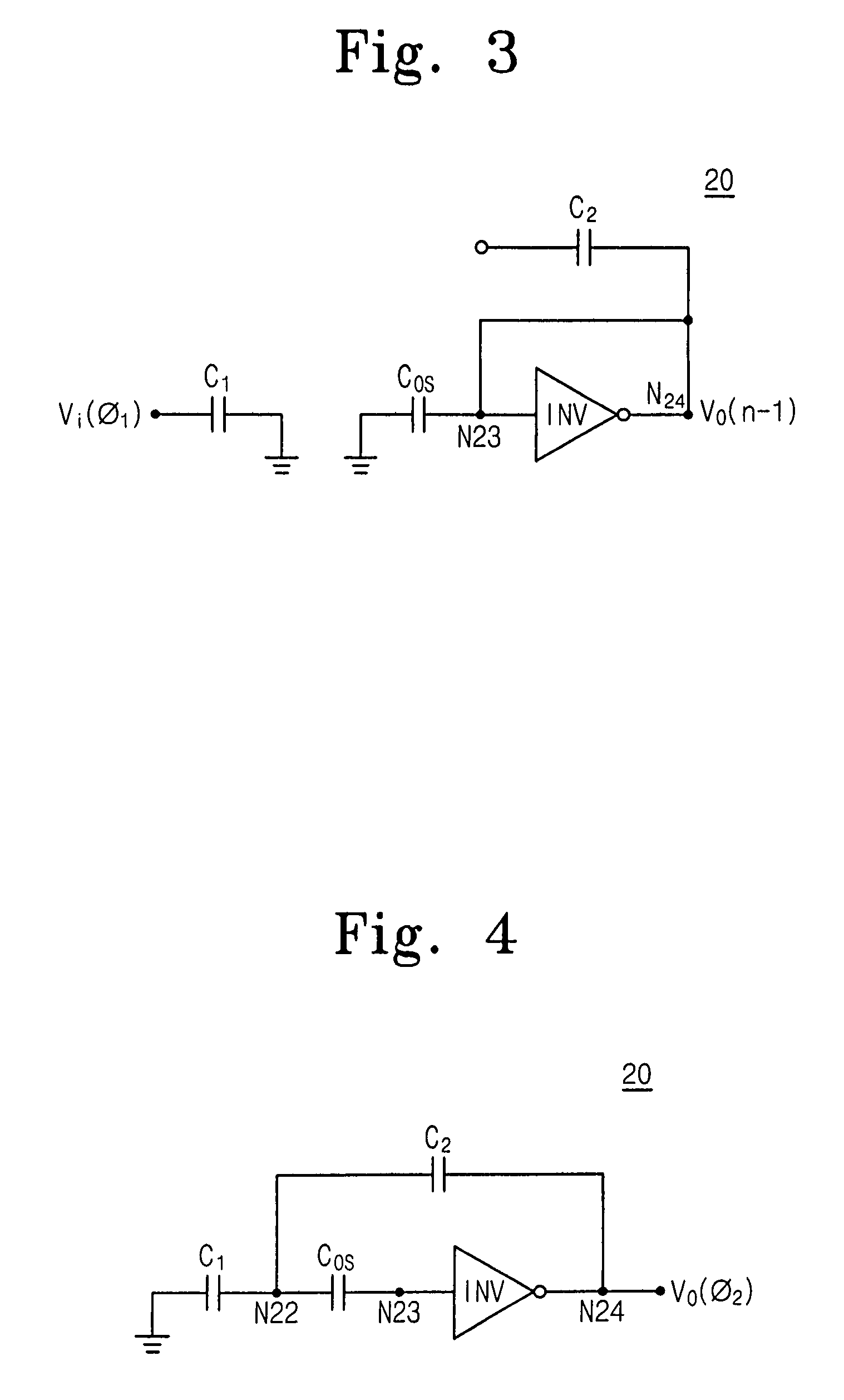

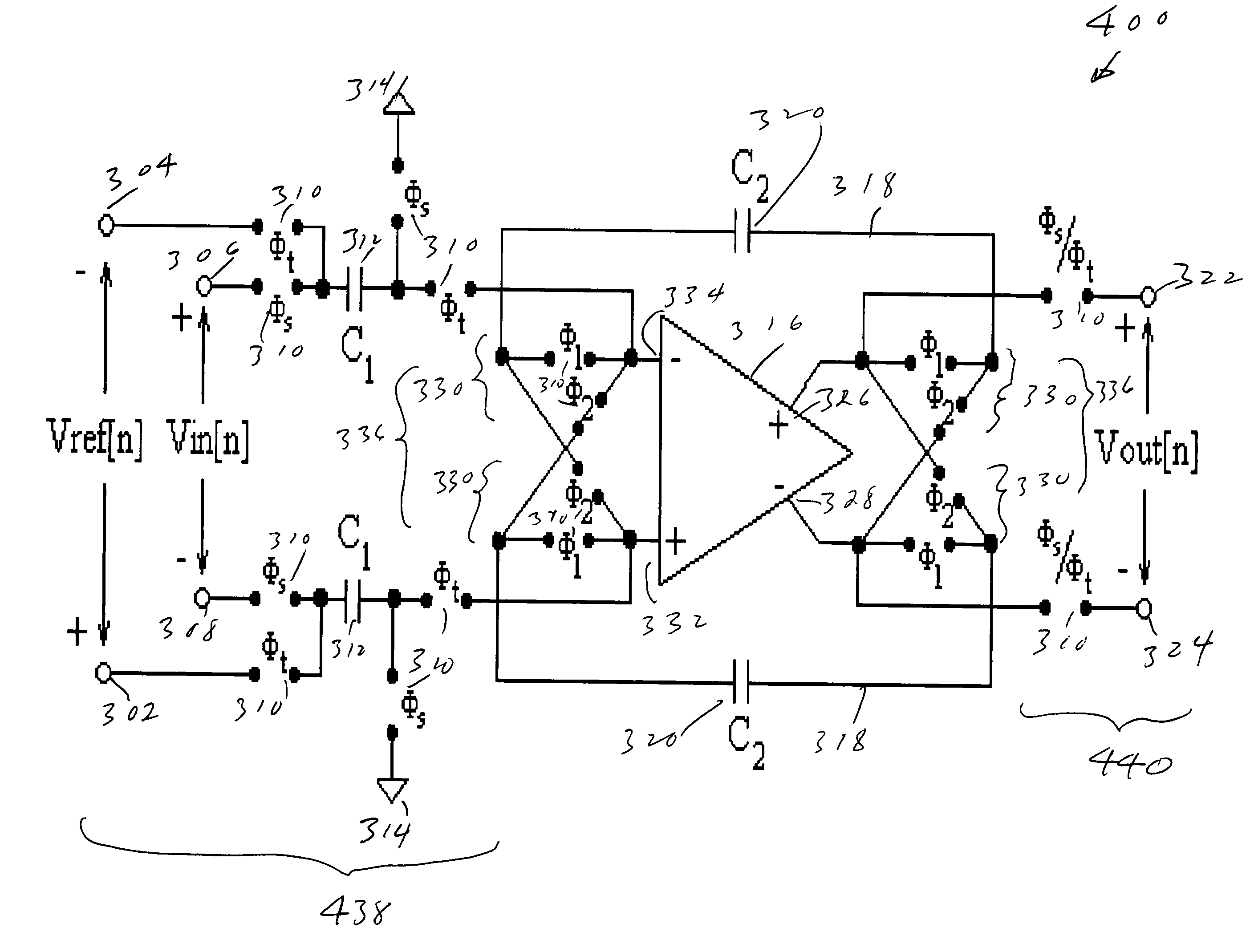

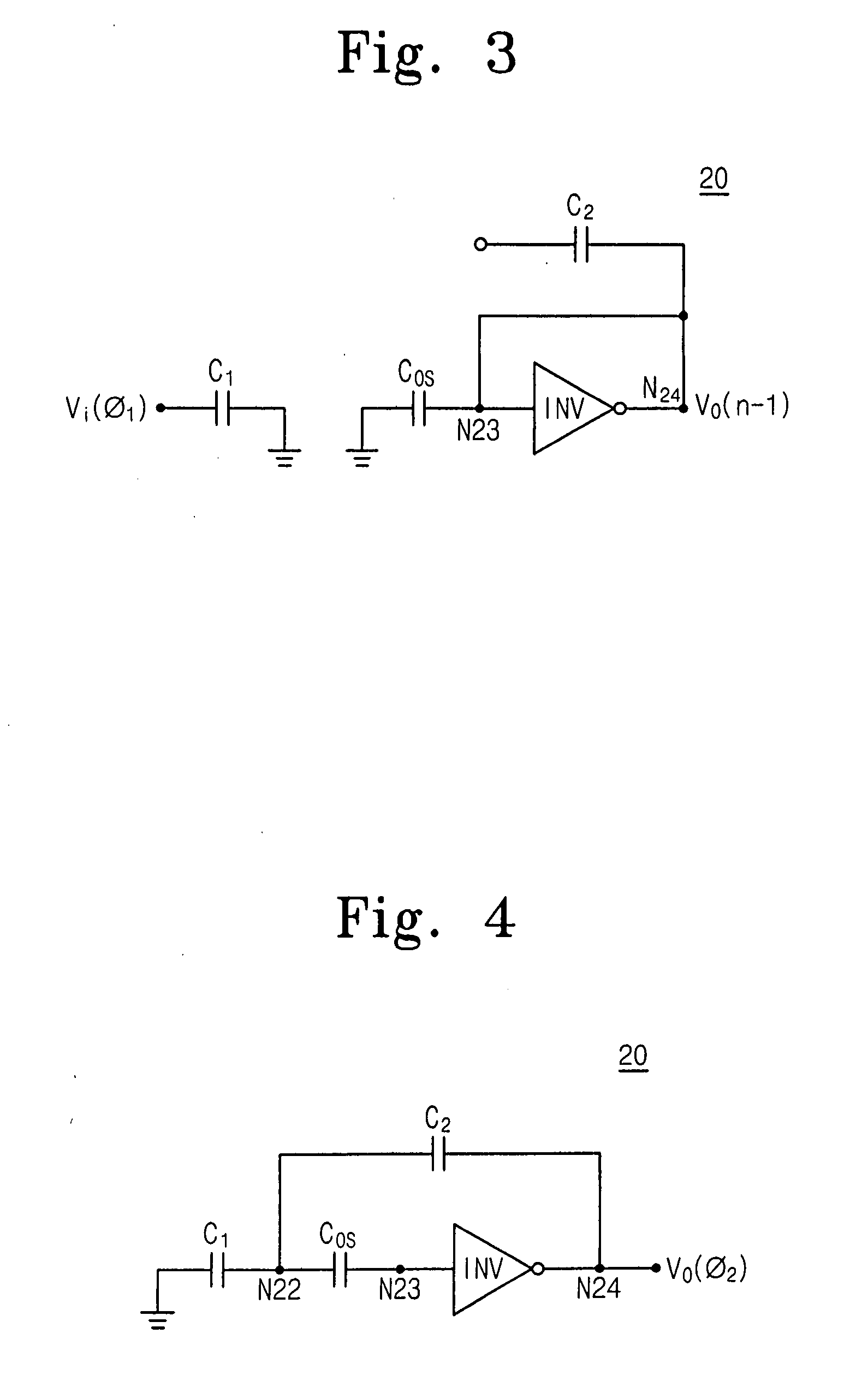

Switched capacitor circuit with inverting amplifier and offset unit

ActiveUS7800427B2Reduce power consumptionReduce circuit areaAmplifier modifications to reduce non-linear distortionComputing operations for integral formationCapacitanceAudio power amplifier

A switched capacitor circuit includes an amplifier, a charging unit, an offset unit, and an integrating unit. The charging unit is coupled between an input node and a first node, and is for accumulating charge corresponding to an input signal during a sampling mode. The offset unit is coupled between the first node and an input of the amplifier, and is for maintaining the first node to be a virtual ground during an integrating mode. The integrating unit is coupled between the first node and an output of the amplifier, and is for receiving charge from the charging unit during the integrating mode.

Owner:SAMSUNG ELECTRONICS CO LTD +1

Methods and apparatus for calibrating output voltage levels associated with current-integrating summing amplifier

InactiveUS20080187037A1Simple technologyComputing operations for integral formationMultiple-port networksIntegratorVoltage reference

Methods and apparatus are disclosed for calibrating summing amplifiers based on current integration. For example, apparatus for calibrating output voltage levels of a current-integrating summing amplifier includes the following components. A duplicate integrator circuit is provided, wherein the duplicate integrator circuit replicates an integrator circuit of the current-integrating summing amplifier. A comparing circuit, coupled to the duplicate integrator circuit, is provided for comparing at least one output voltage level generated by the duplicate integrator circuit with a reference voltage level. A feedback loop circuit, coupled to the comparing circuit and the duplicate integrator circuit, is provided for adjusting at least one bias signal of the duplicate integrator circuit so that the output voltage level generated by the duplicate integrator circuit matches the reference voltage level, wherein the bias signal is applied to the integrator circuit of the current-integrating summing amplifier thereby calibrating output signal components due to multiple input signals of the current-integrating summing amplifier.

Owner:GLOBALFOUNDRIES US INC

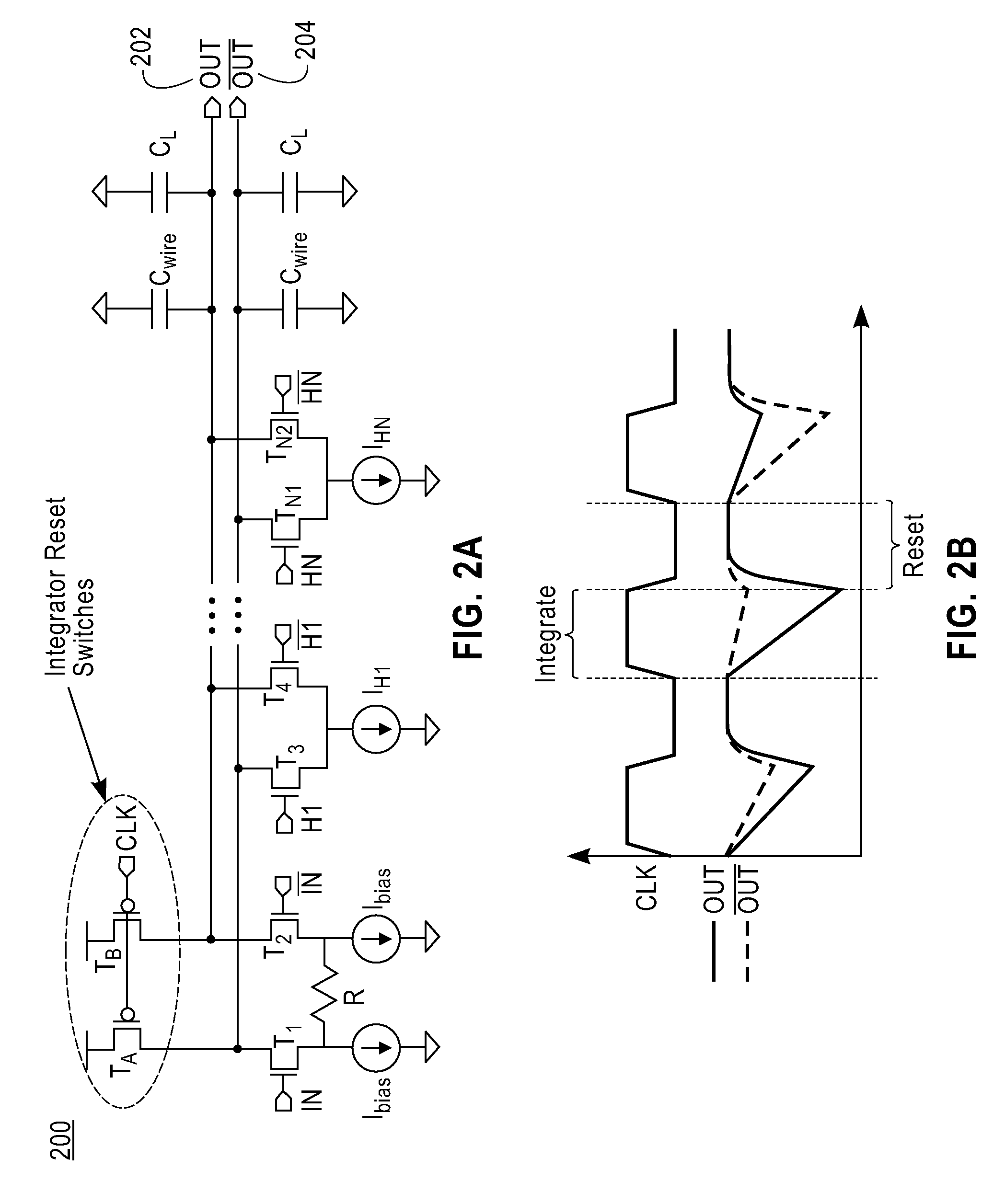

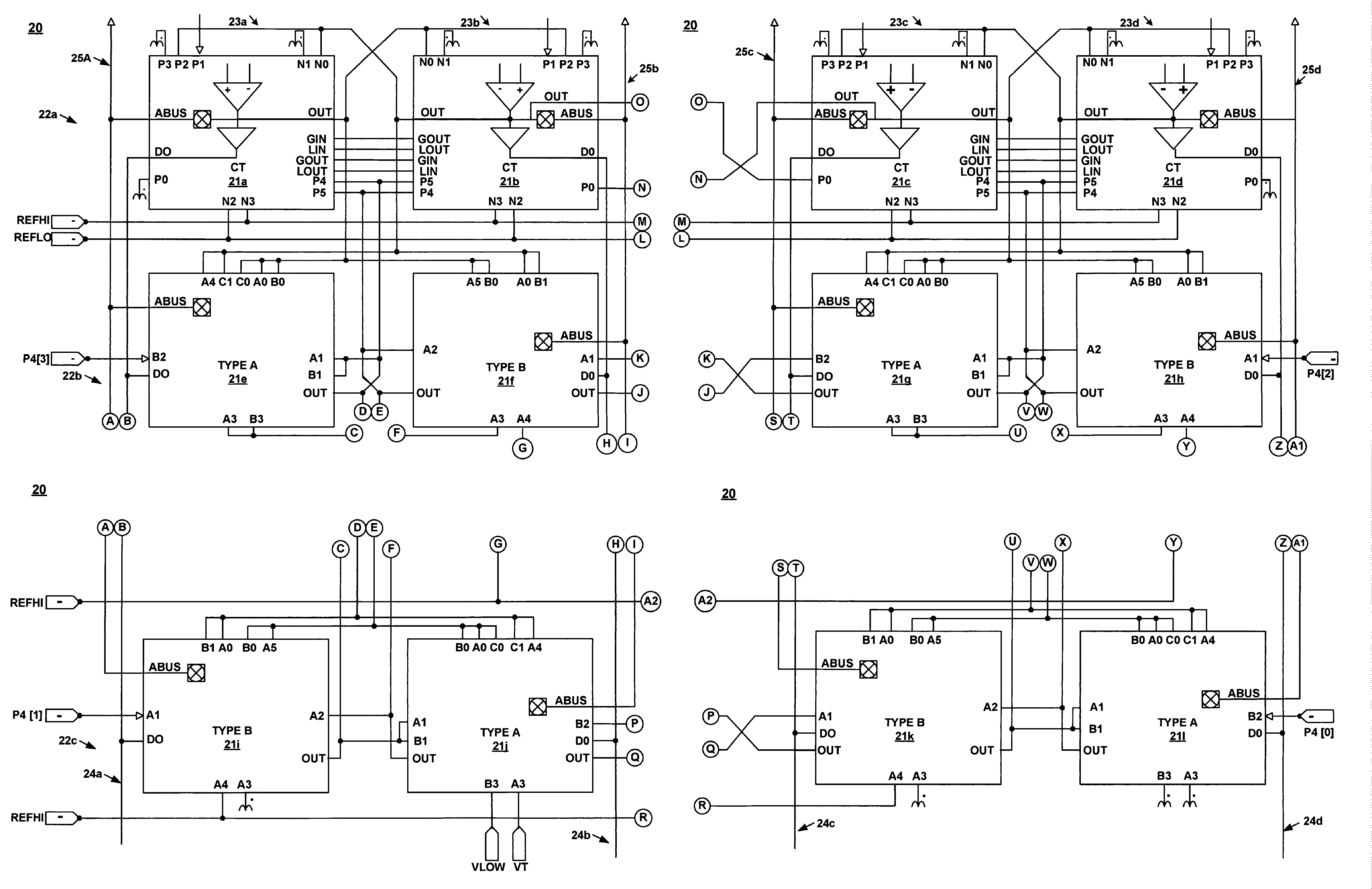

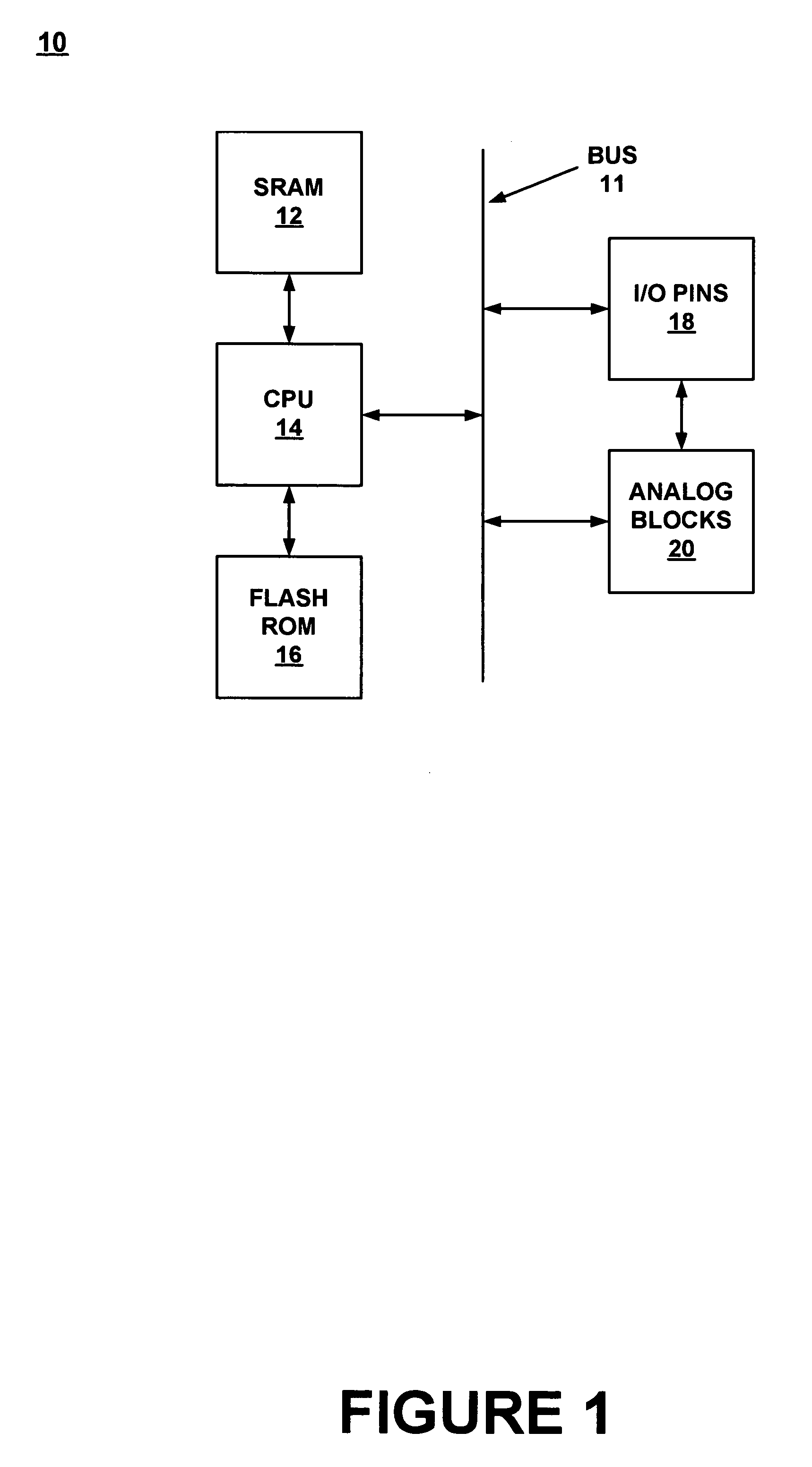

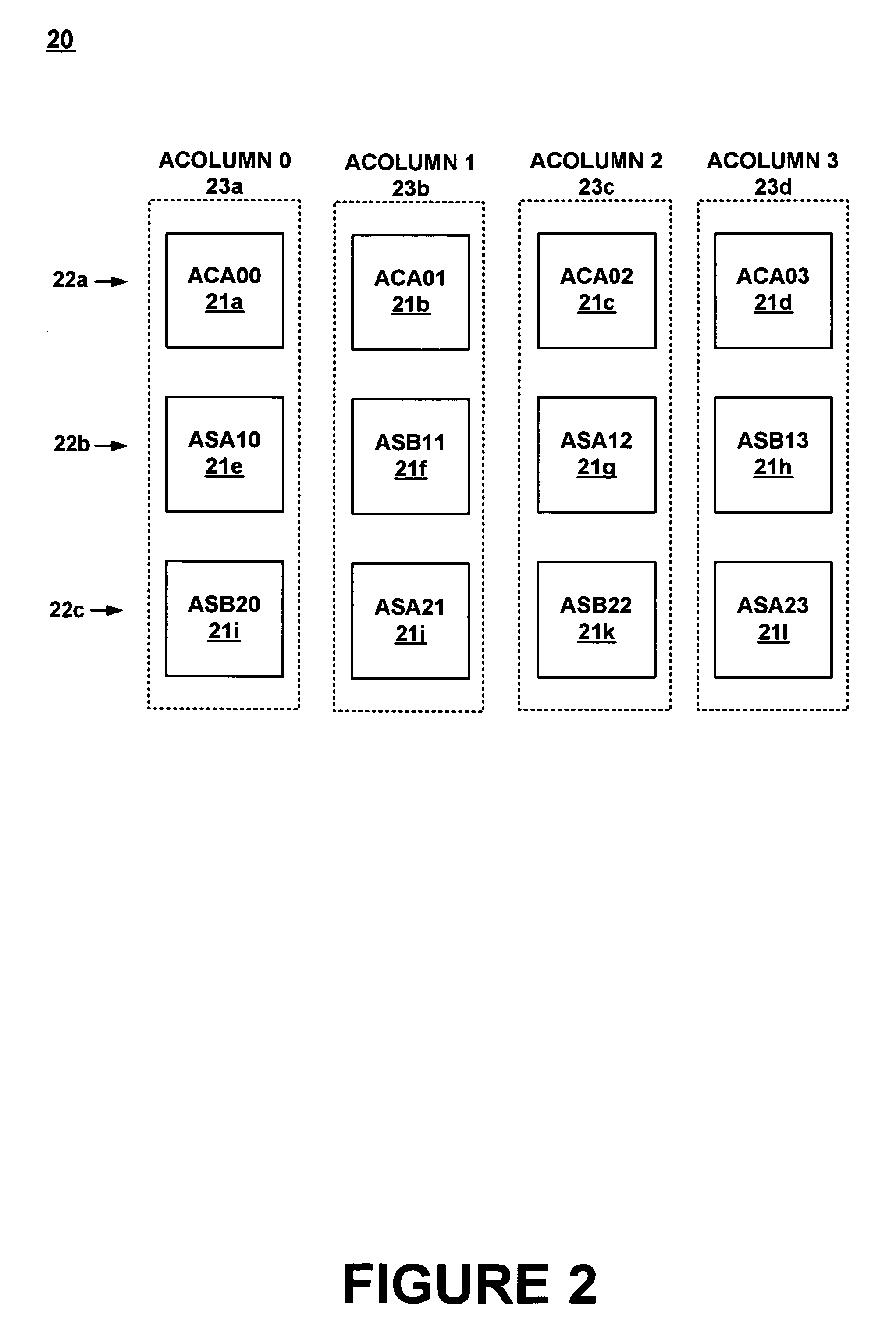

Method for synchronizing and resetting clock signals supplied to multiple programmable analog blocks

InactiveUS6967511B1Efficiently usLow costComputing operations for integral formationComputing operations for integration/differentiationA domainComputer science

A method for establishing frequency and phase alignment of clock signals across a domain of analog blocks coupled in a single integrated circuit. Different analog functions are implemented by selectively and electrically coupling different combinations of analog blocks. The analog blocks may be arrayed in a number of columns. A synchronized clock signal is supplied to all of the analog blocks in a combination of blocks, even when the blocks are in different columns. The frequency of the clock signal can be changed dynamically depending on the analog function to be achieved.

Owner:CYPRESS SEMICON CORP

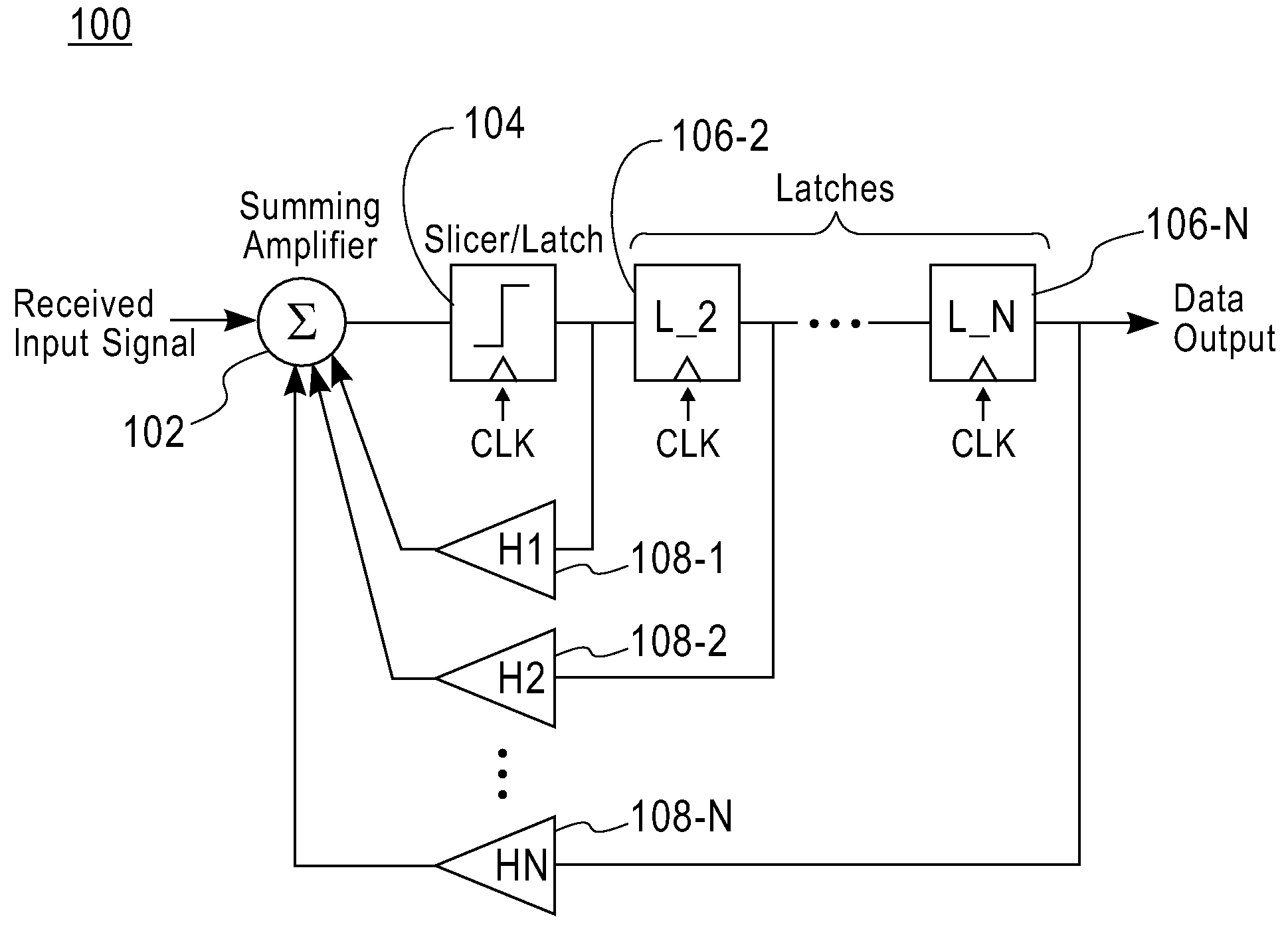

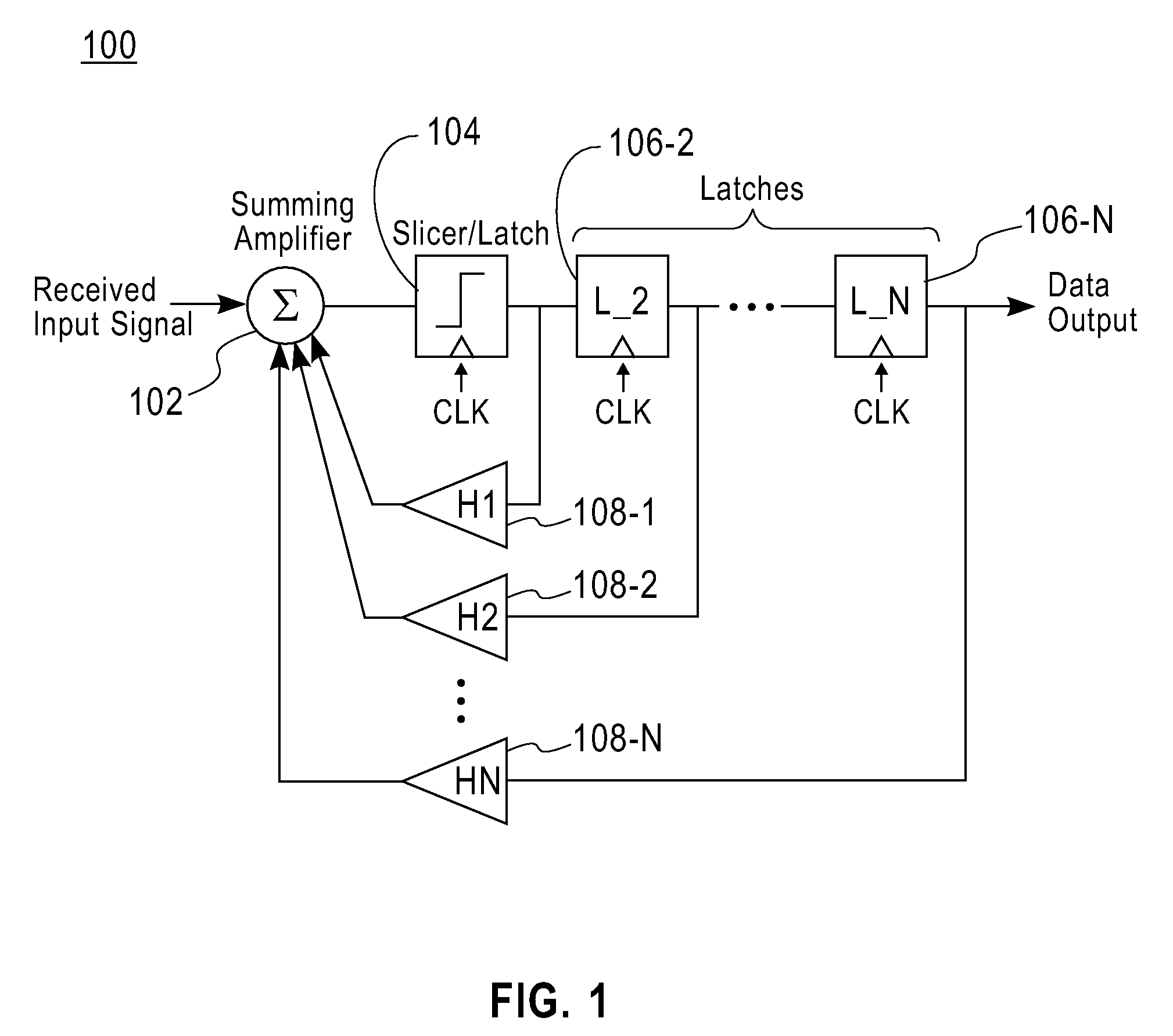

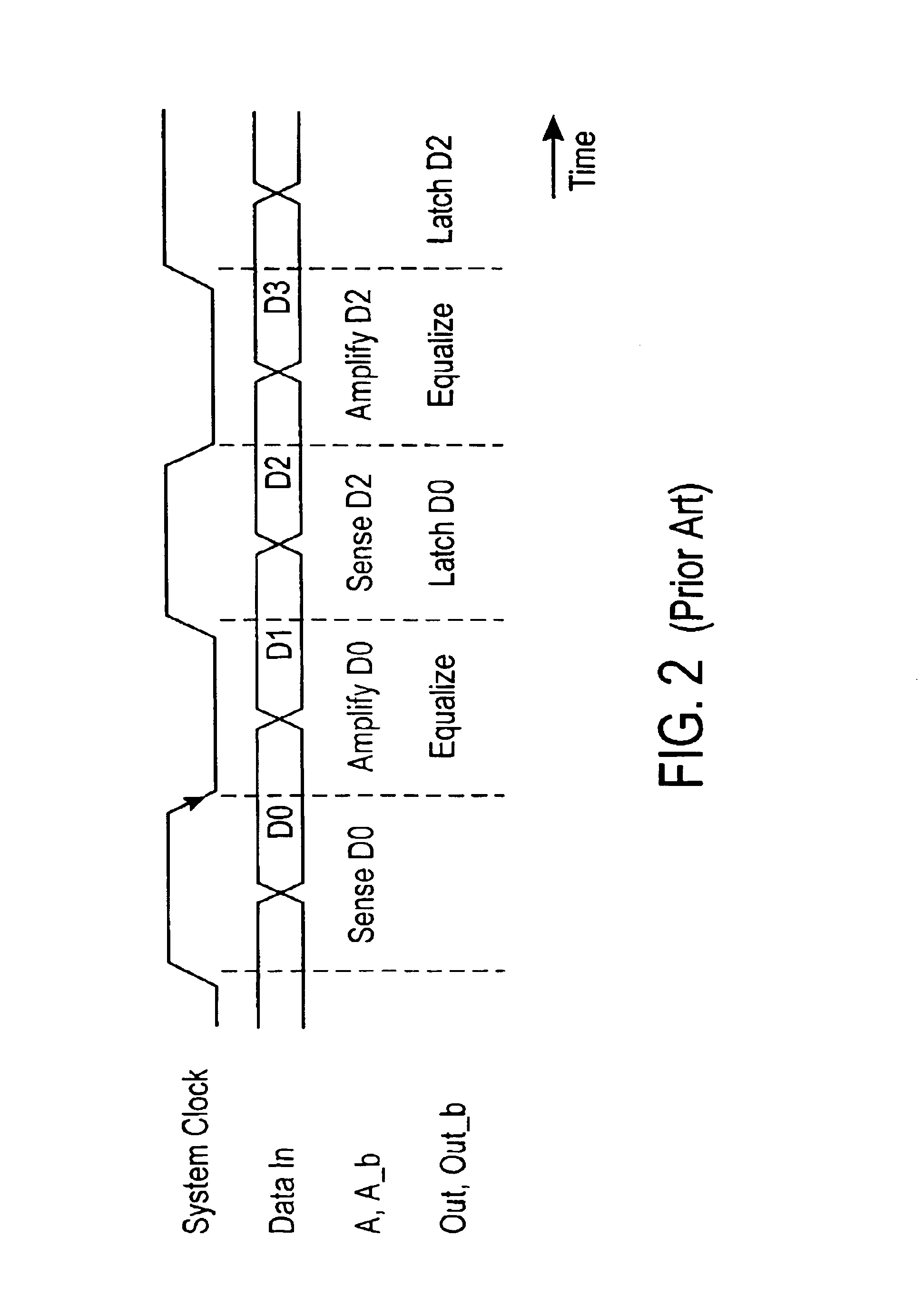

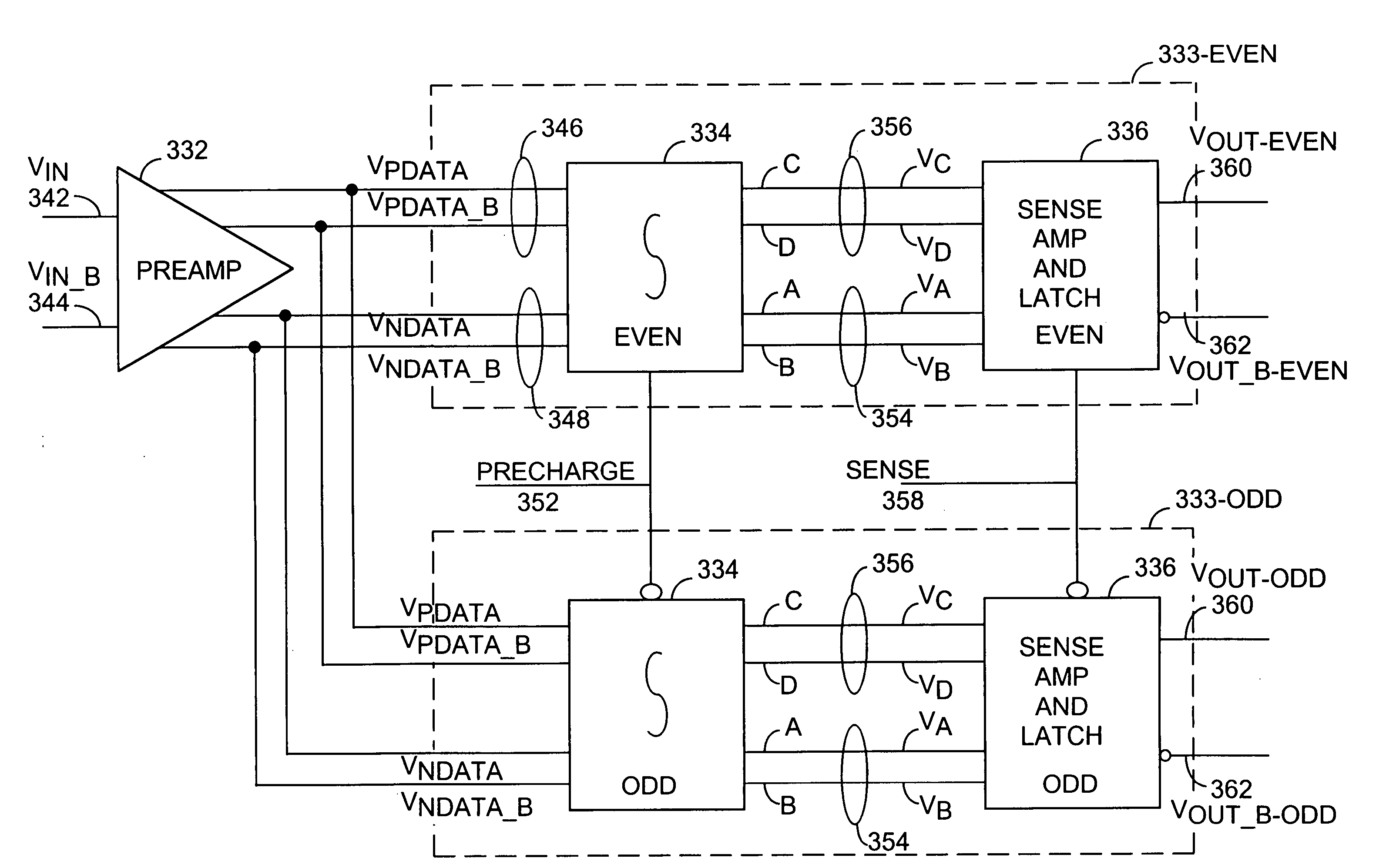

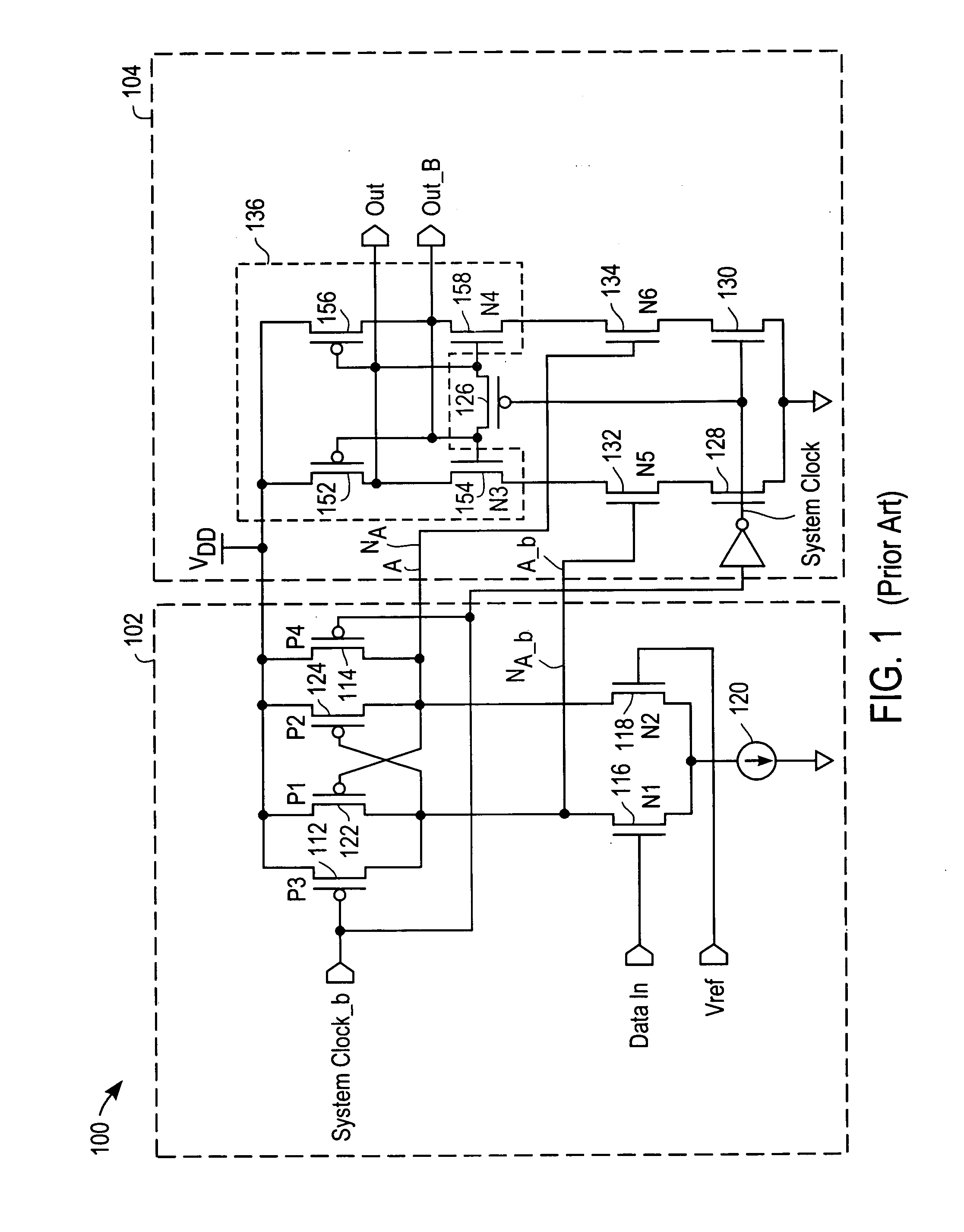

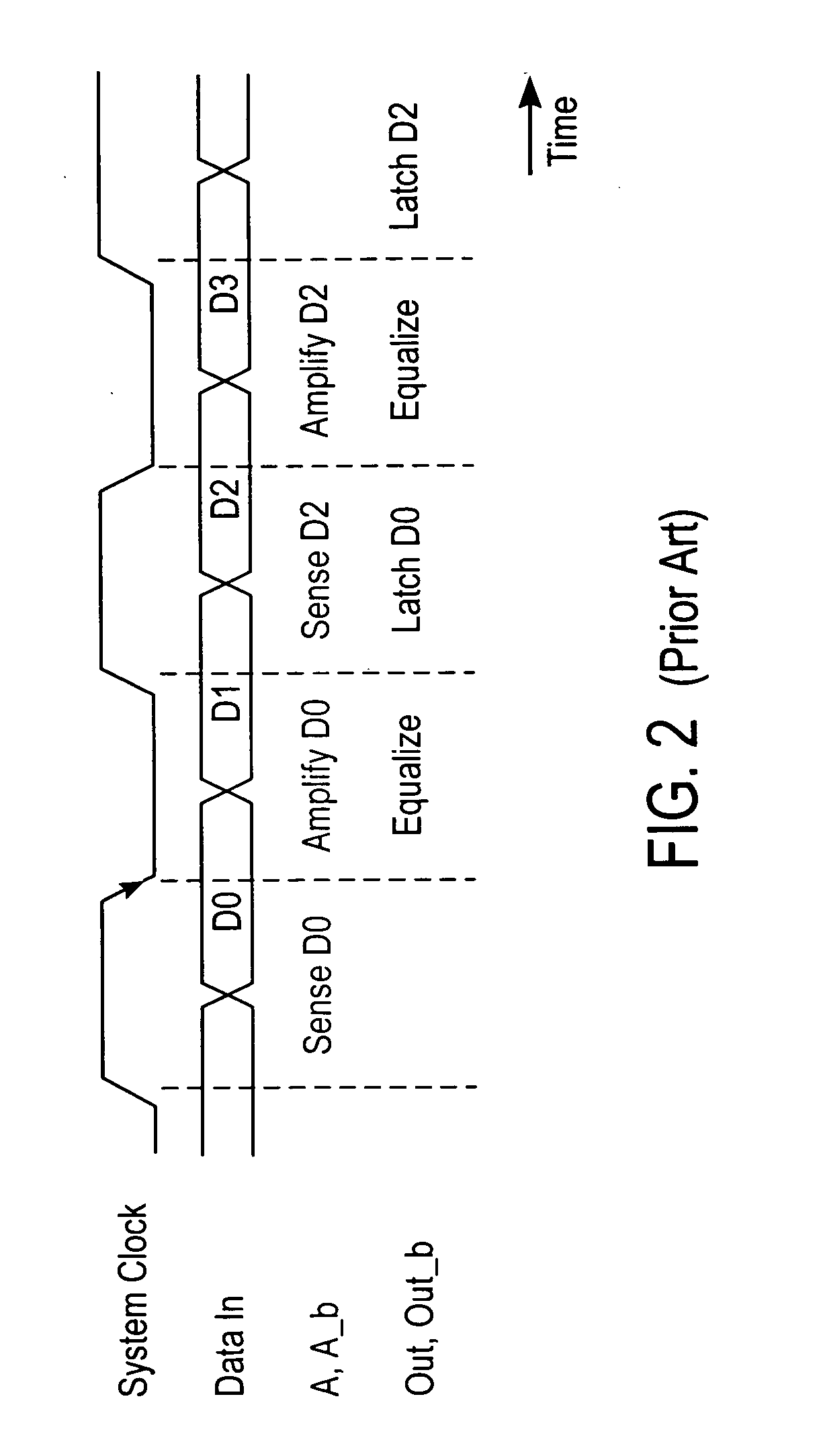

Method and apparatus for receiving high speed signals with low latency

InactiveUS6965262B2Reduces input-to-output latencyReduce static power consumptionDigital differential analysersDigital storageIntegratorAudio power amplifier

An apparatus and method for receiving high-speed signals having a wide common-mode range with low input-to-output latency. In one embodiment, the receiver includes an integrator to accumulate charge in accordance with an input signal during an integration time interval to produce an output voltage. A sense amplifier samples and converts the output voltage of the integrator to a logic signal; and a latch stores the logic signal. In an alternate embodiment, a preamplifier conditions the input signal prior to being integrated. In another embodiment using multiple receivers, circuitry is added to the receiver to compensate for timing errors associated with the distribution of the timing signals. In yet another embodiment, the integrator is coupled to an equalization circuit that compensates for intersymbol interference. In another embodiment, another circuit compensates for accumulated voltage offset errors in the integrator.

Owner:RAMBUS INC

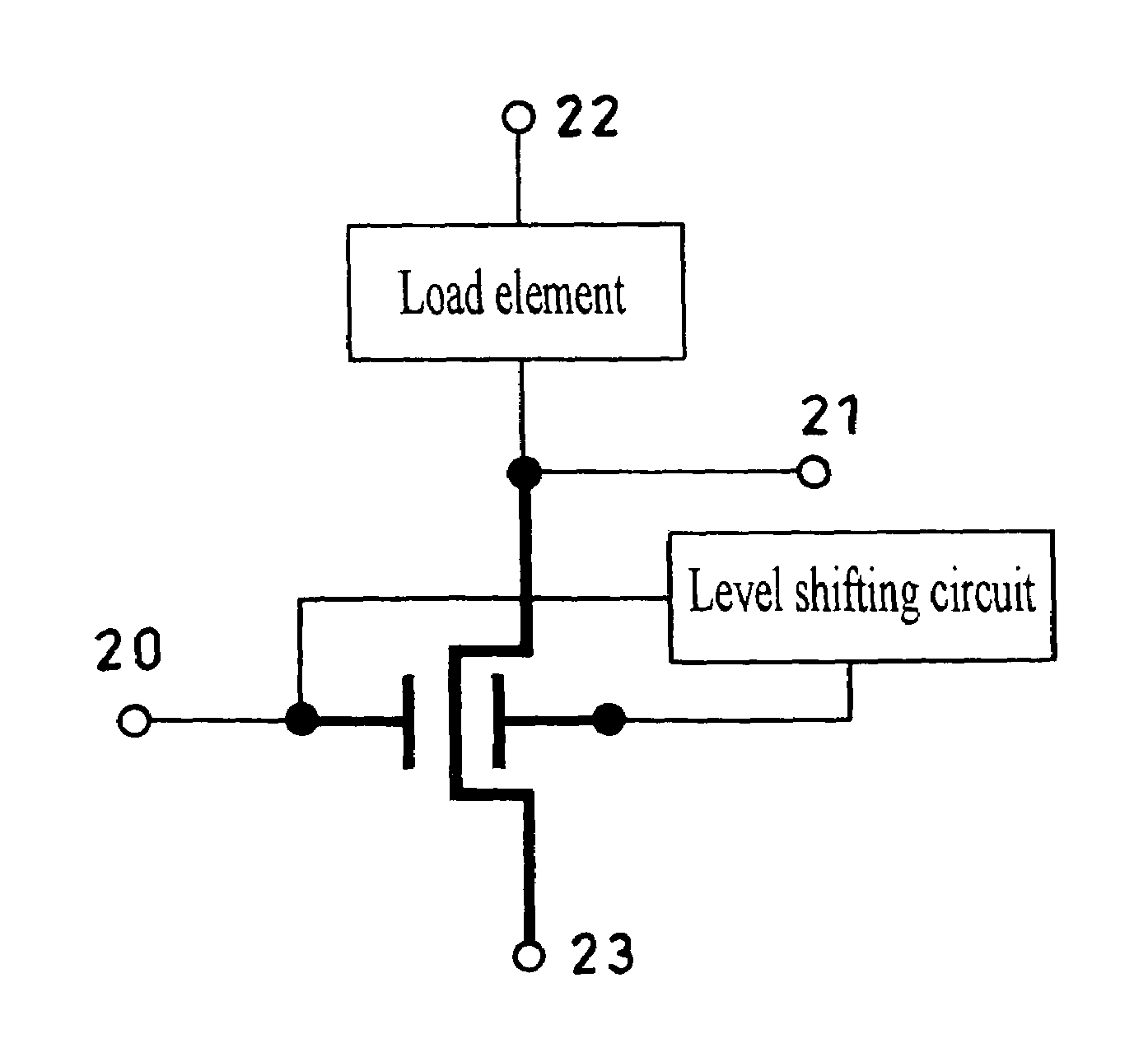

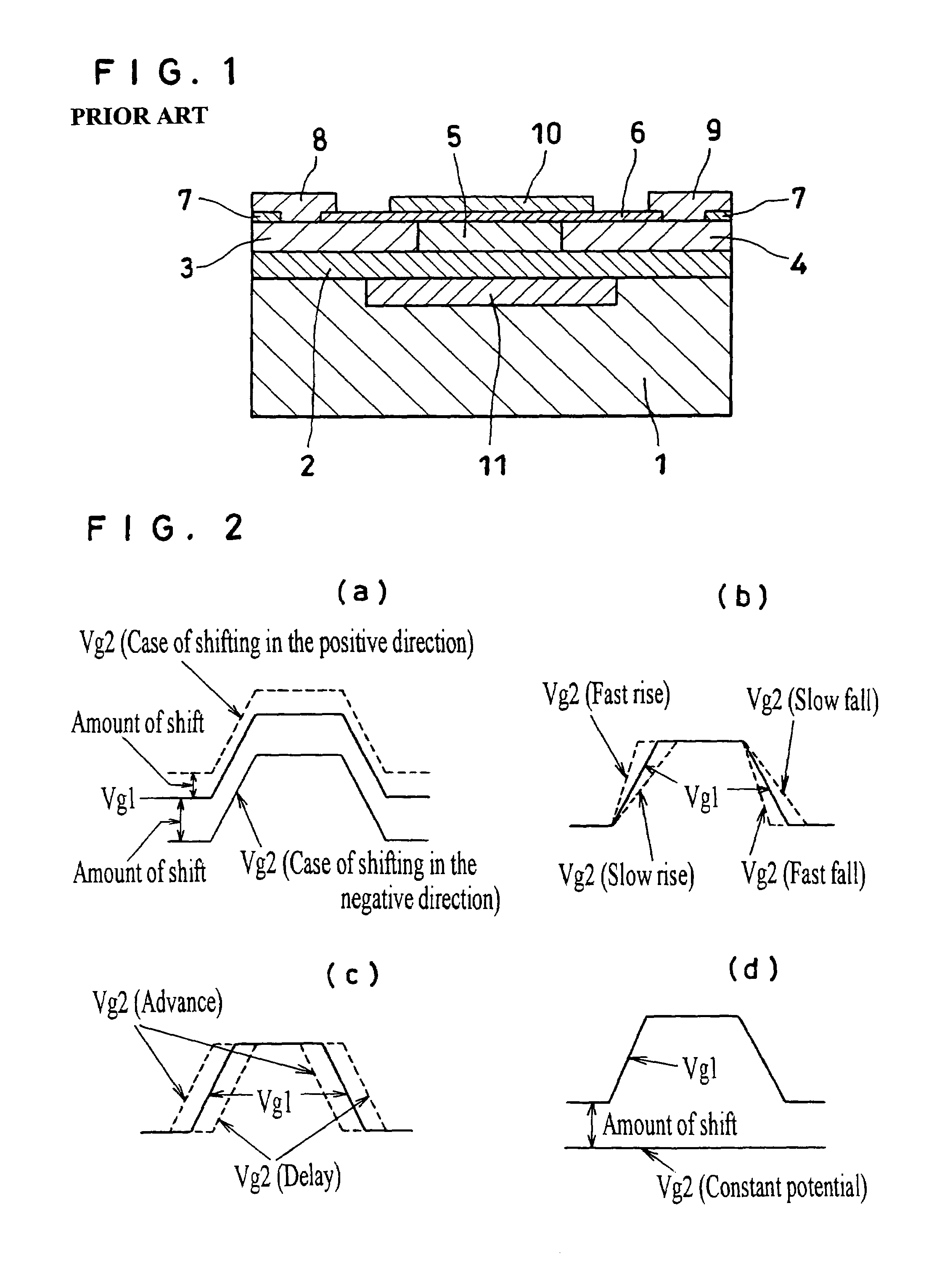

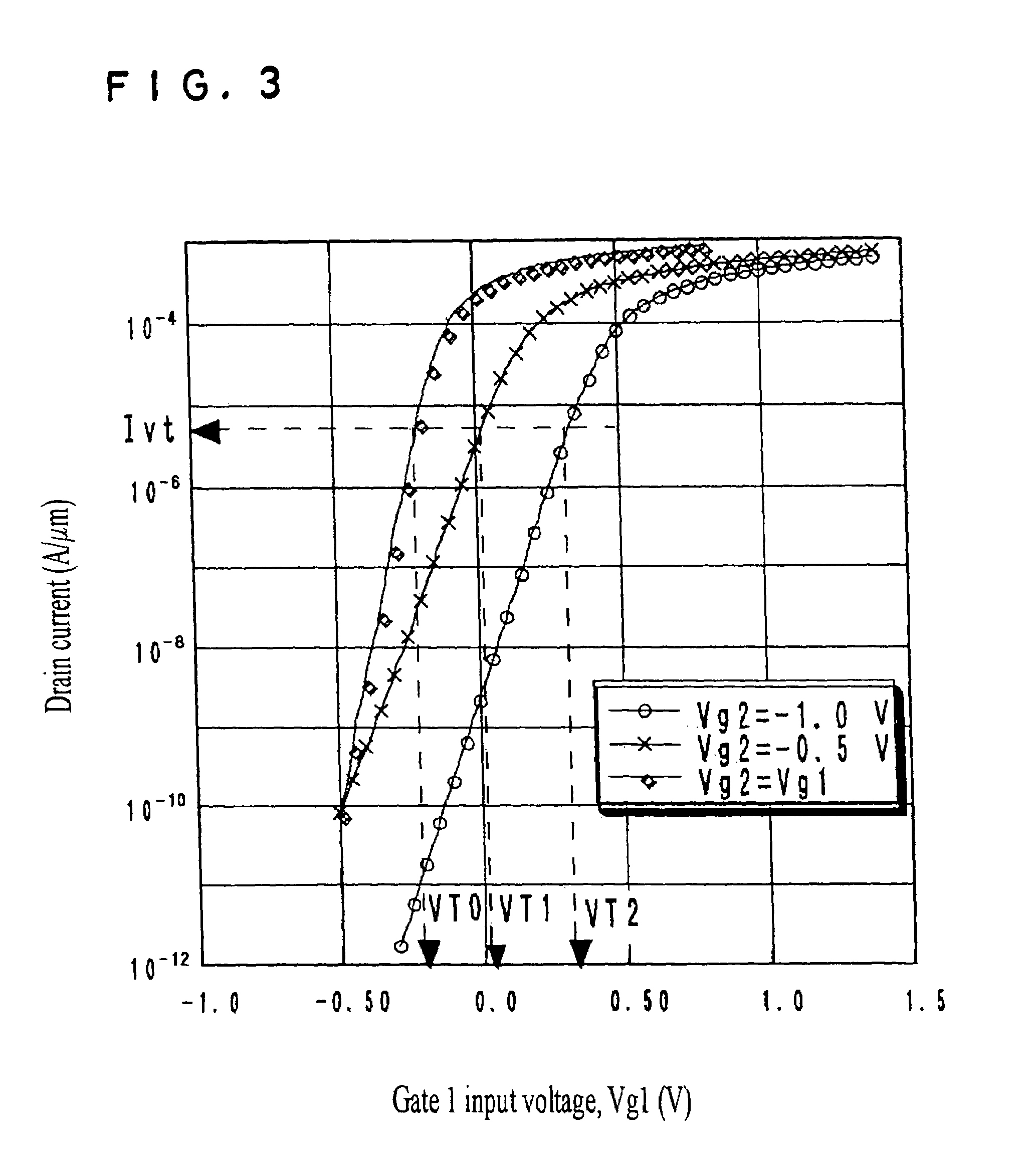

Method for application of gating signal in insulated double gate FET

In an insulated double gate FET, the threshold voltage during the operation of a transient response thereof is enabled to be arbitrarily and accurately controlled by a method that includes applying a first input signal intended to perform an ordinary logic operation to one of the gate electrodes thereof and applying, in response to this signal, a second signal that has a signal-level temporal-change direction as the first input signal and has at least one of the low level and the high level thereof shifted by a predetermined magnitude or endowed with a predetermined time difference or has the time slower or faster signal level change of the signal to the other gate electrode.

Owner:NAT INST OF ADVANCED IND SCI & TECH

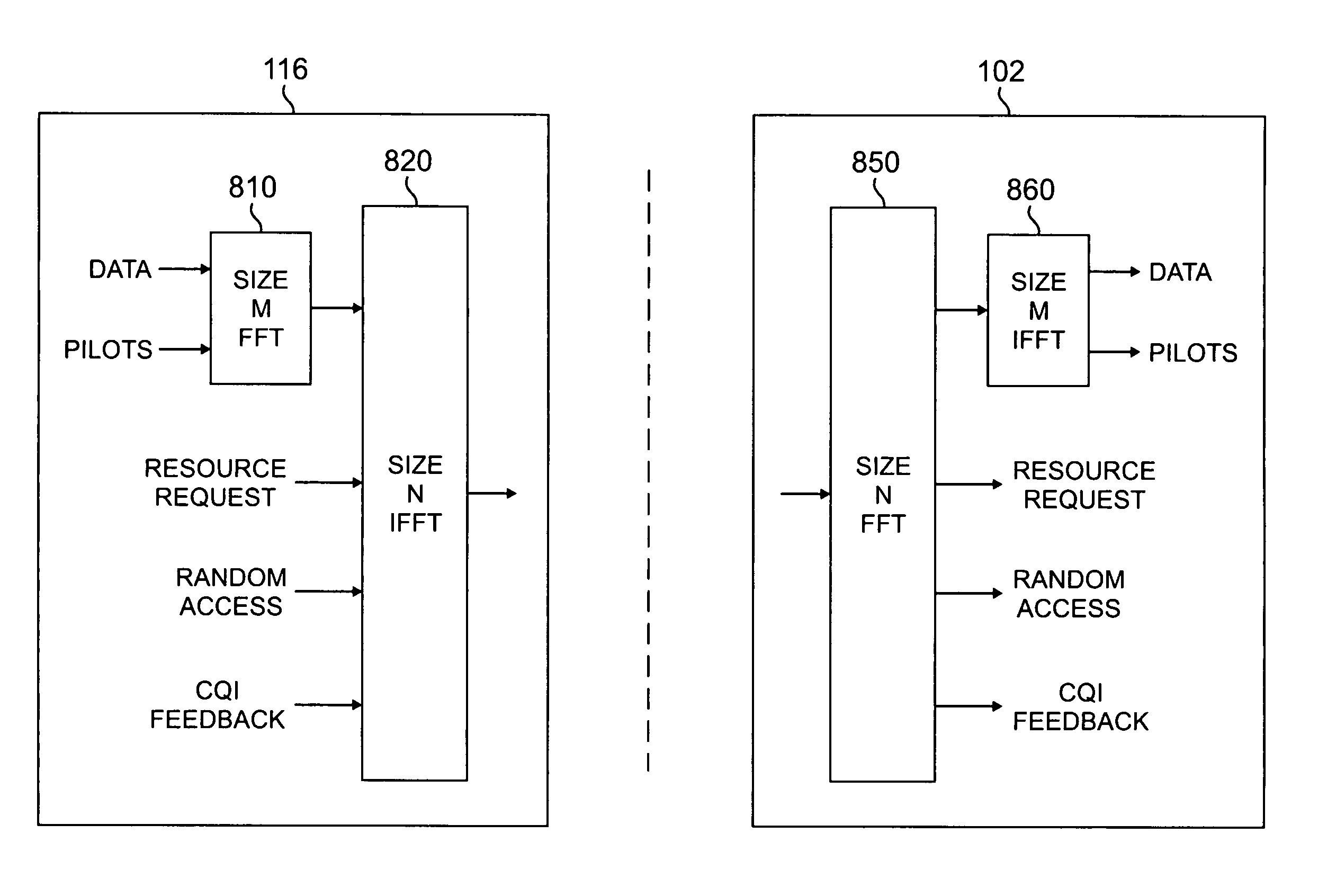

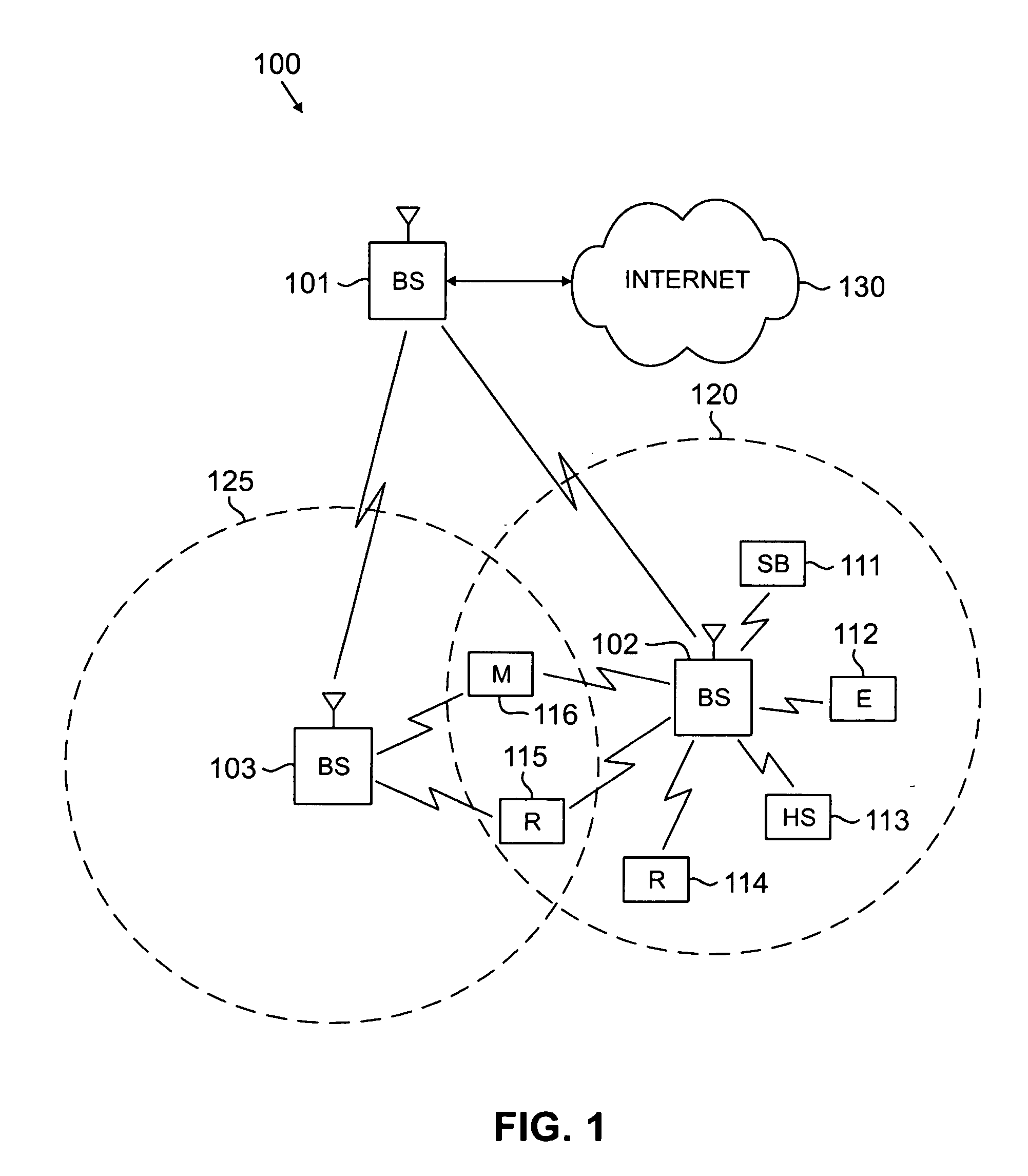

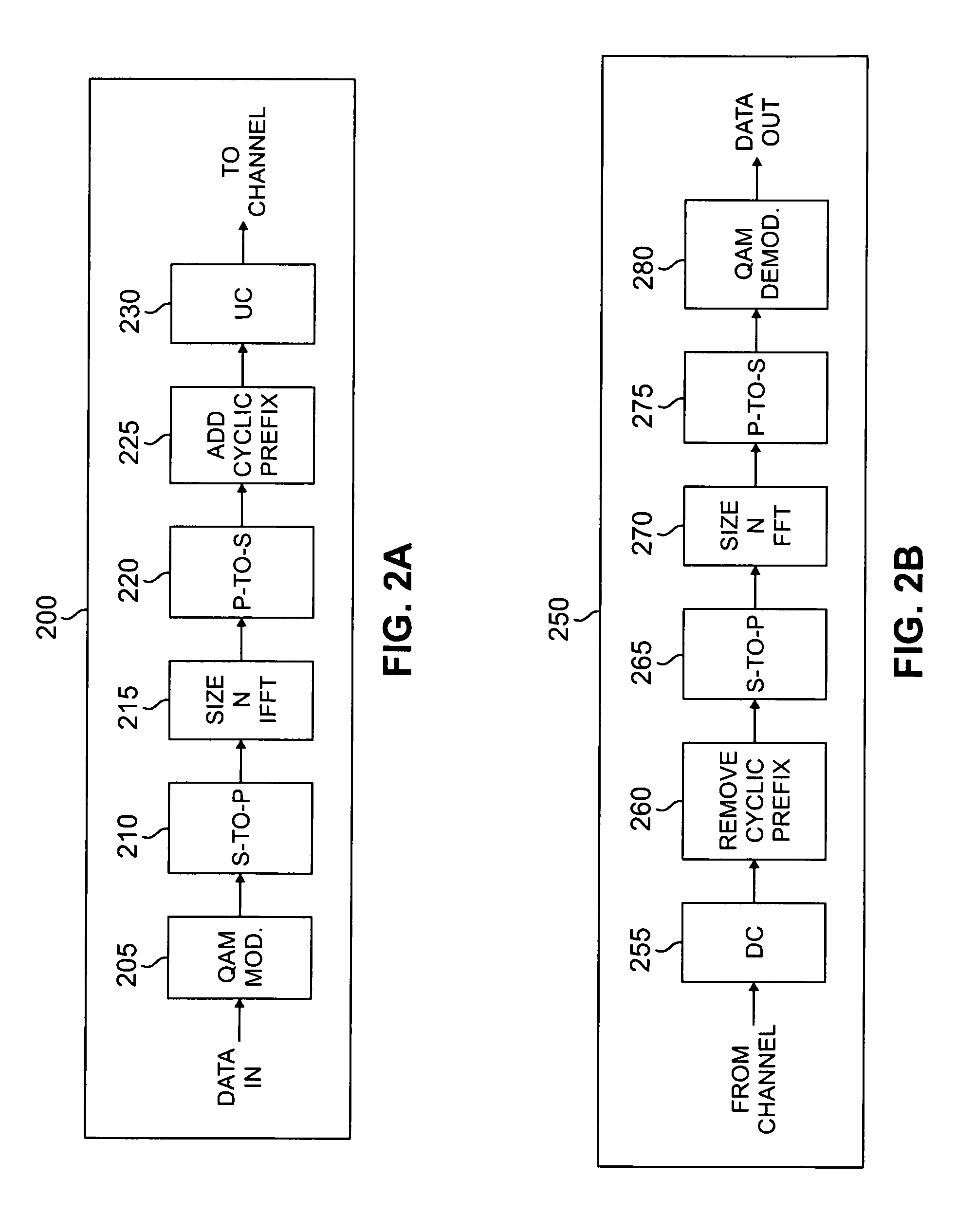

Apparatus and method for FT pre-coding of data to reduce PAPR in a multi-carrier wireless network

ActiveUS20060227888A1Low average power ratioMultiple-port networksComputing operations for integral formationTime domainMulti carrier

A subscriber station for use in a wireless network capable of communicating according to a multi-carrier protocol, such as OFDM or OFDMA. The subscriber station comprises a size M Fourier Transform (FFT or DFT) block for receiving input symbols and generating M FT pre-coded outputs and a size N inverse Fourier Transform (IFFT or IDFT) block capable of receiving N inputs, where the N inputs include the M FT pre-coded outputs from the size M FT block. The size N IFT block generates N outputs to be transmitted to a base station of the wireless network. The input symbols comprise user data traffic to be transmitted to the base station. The size N IFT block also receives signaling and control information on at least some of N-M inputs. The FT pre-coding generates a time-domain signal that has a relatively lower peak-to-average power ratio (PAPR).

Owner:HUAWEI TECH CO LTD

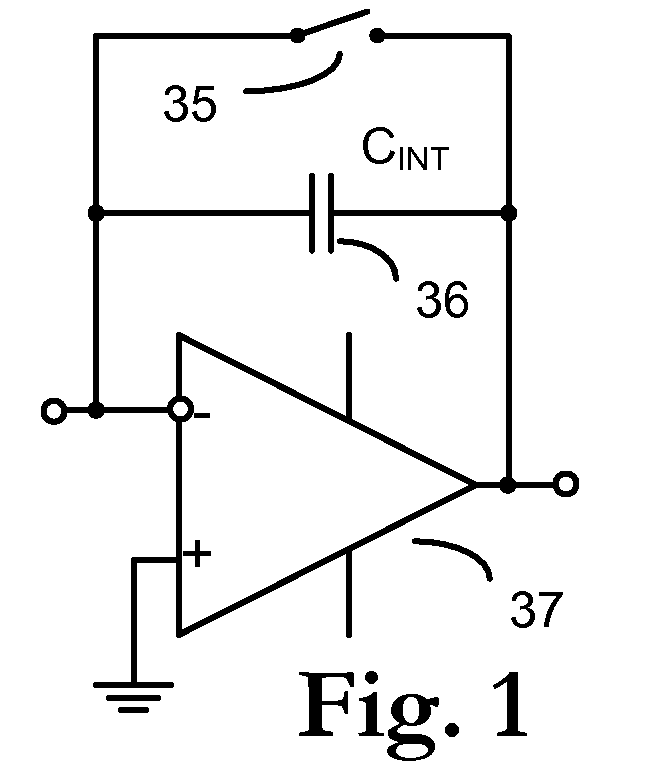

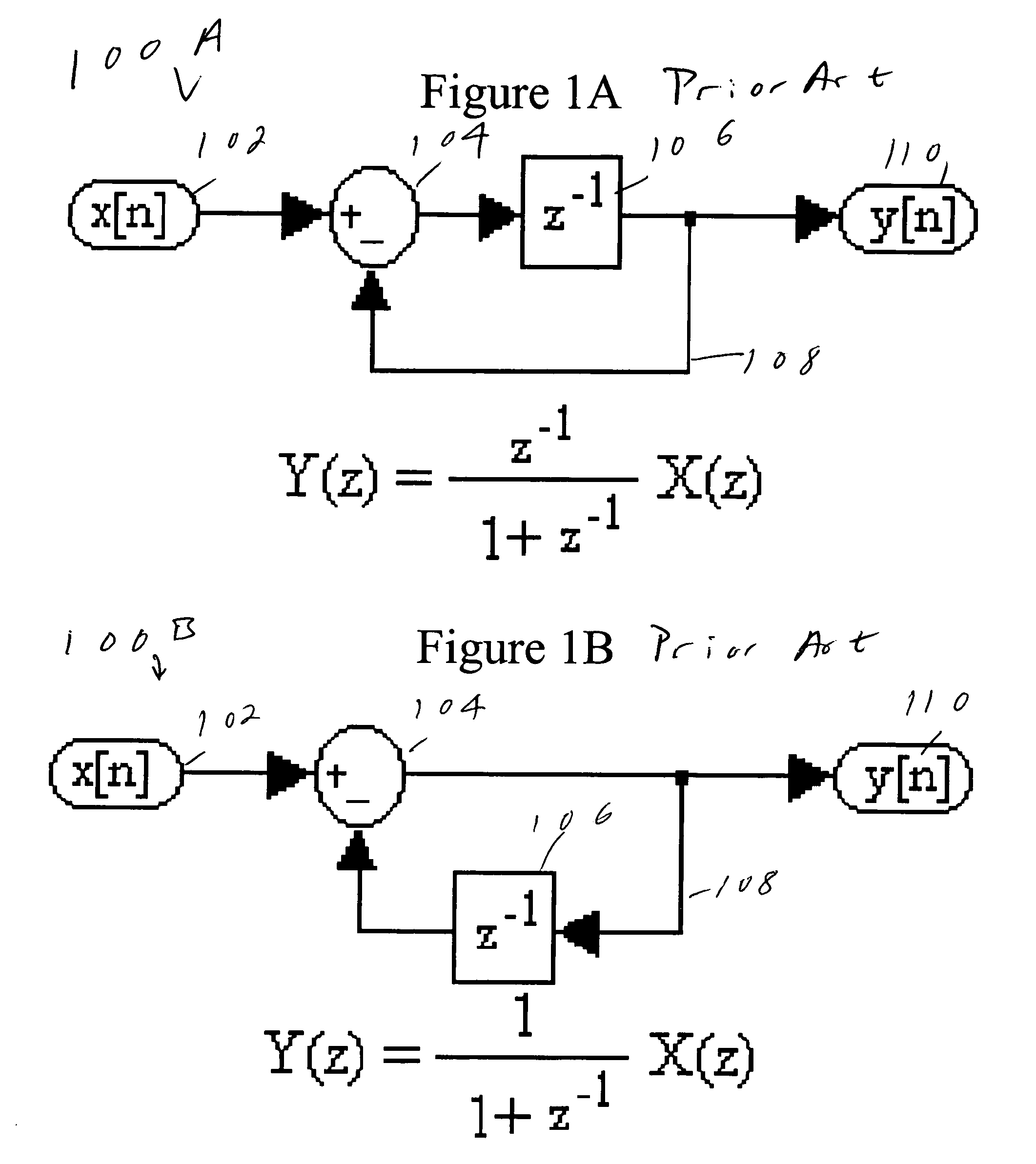

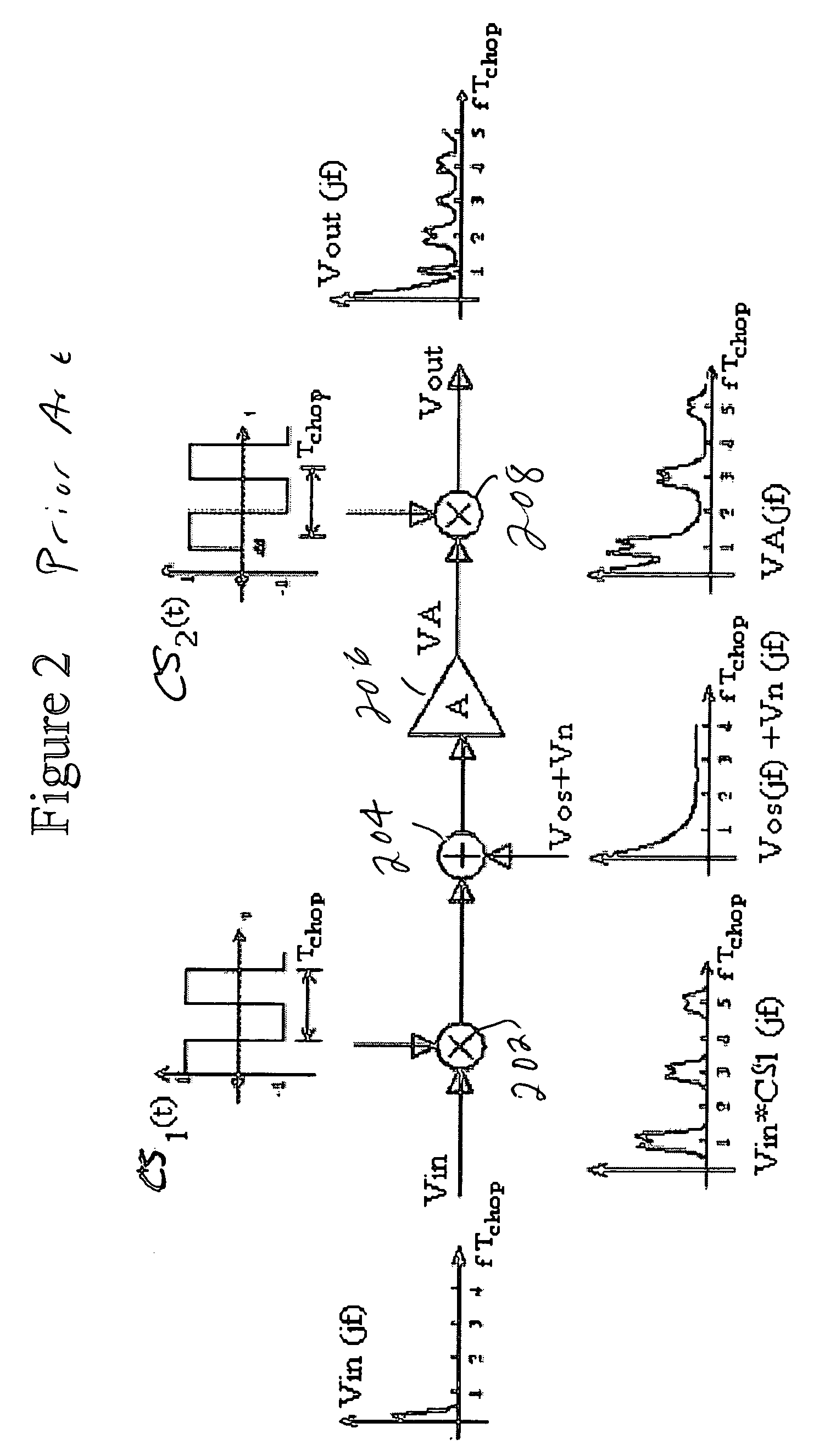

Switched-capacitor high-pass mirrored integrator

InactiveUS7038532B1Improve noise characteristicsComputing operations for integral formationComputing operations for integration/differentiationCapacitanceAudio power amplifier

In a high-pass (mirrored) integrator structure that employs chopper modulation, the input and output of the mirrored integrator are connected to the input and output ports of the operational amplifier, bypassing the chopper stabilization modulators. The mirrored integrator can be used in sigma-delta analog-to-digital converters.

Owner:UNIVERSITY OF ROCHESTER

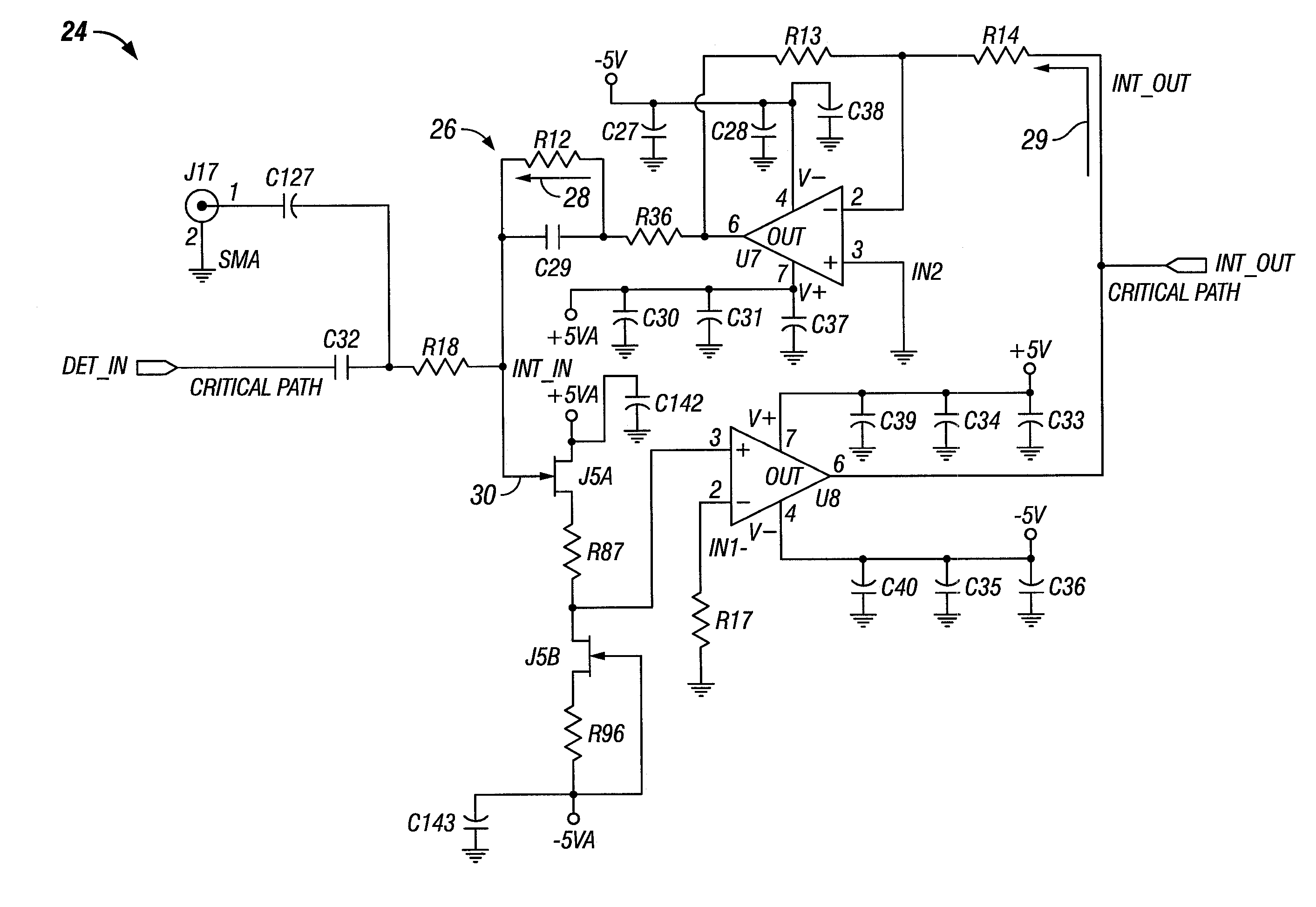

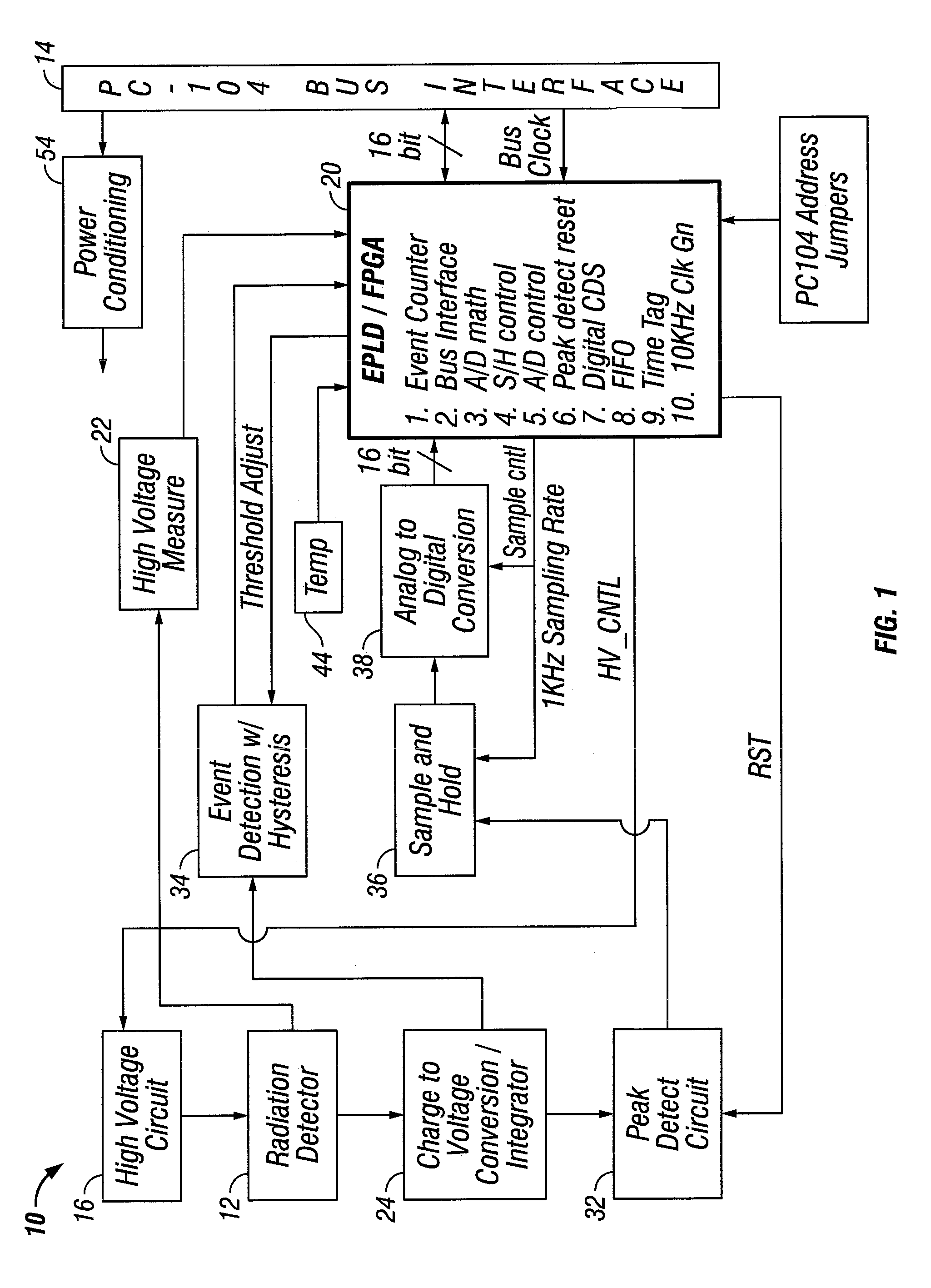

Integrator circuitry for single channel radiation detector

InactiveUS7411198B1Wide dynamic rangeComputing operations for integral formationComputing operations for integration/differentiationIntegratorAudio power amplifier

Input circuitry is provided for a high voltage operated radiation detector to receive pulses from the detector having a rise time in the range of from about one nanosecond to about ten nanoseconds. An integrator circuit, which utilizes current feedback, receives the incoming charge from the radiation detector and creates voltage by integrating across a small capacitor. The integrator utilizes an amplifier which closely follows the voltage across the capacitor to produce an integrator output pulse with a peak value which may be used to determine the energy which produced the pulse. The pulse width of the output is stretched to approximately 50 to 300 nanoseconds for use by subsequent circuits which may then use amplifiers with lower slew rates.

Owner:NASA

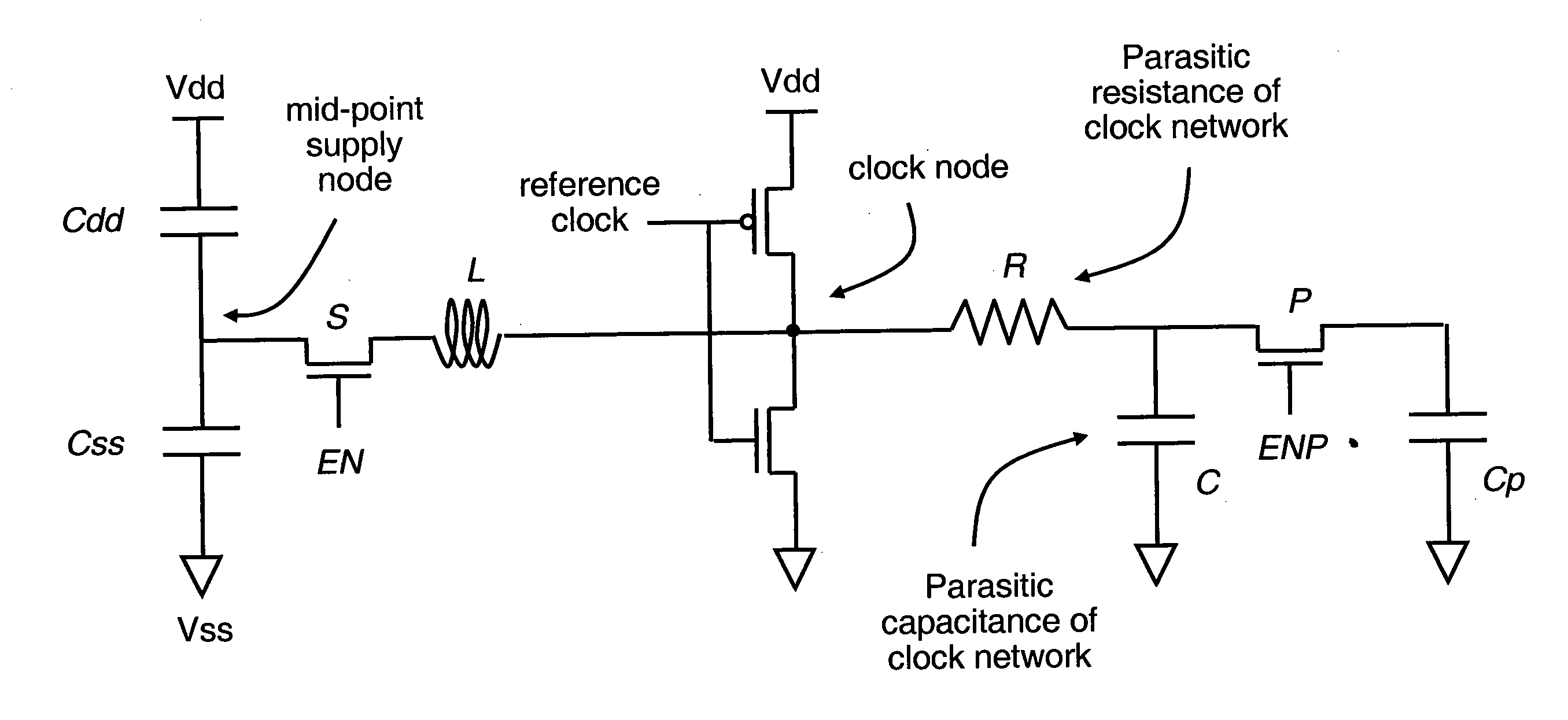

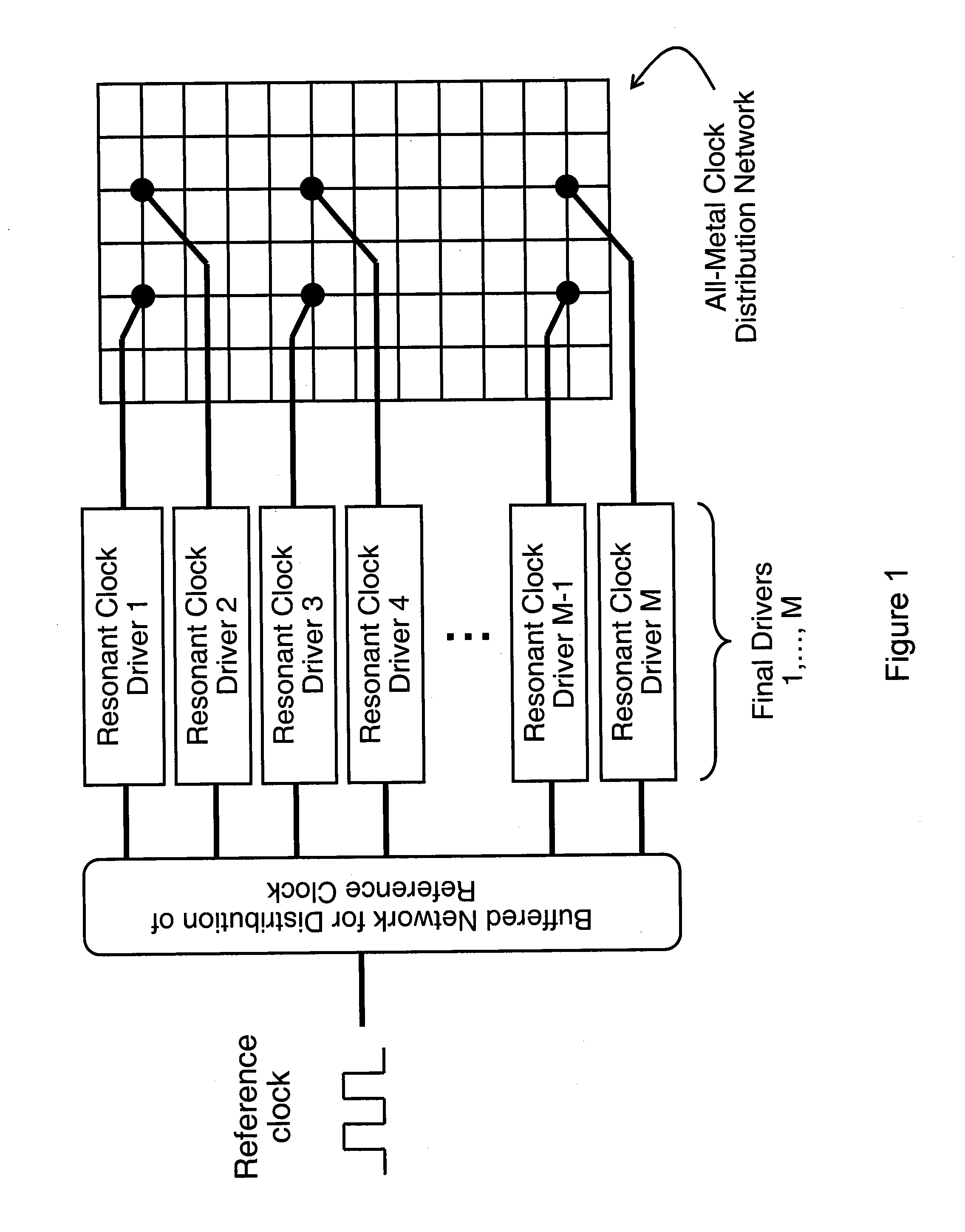

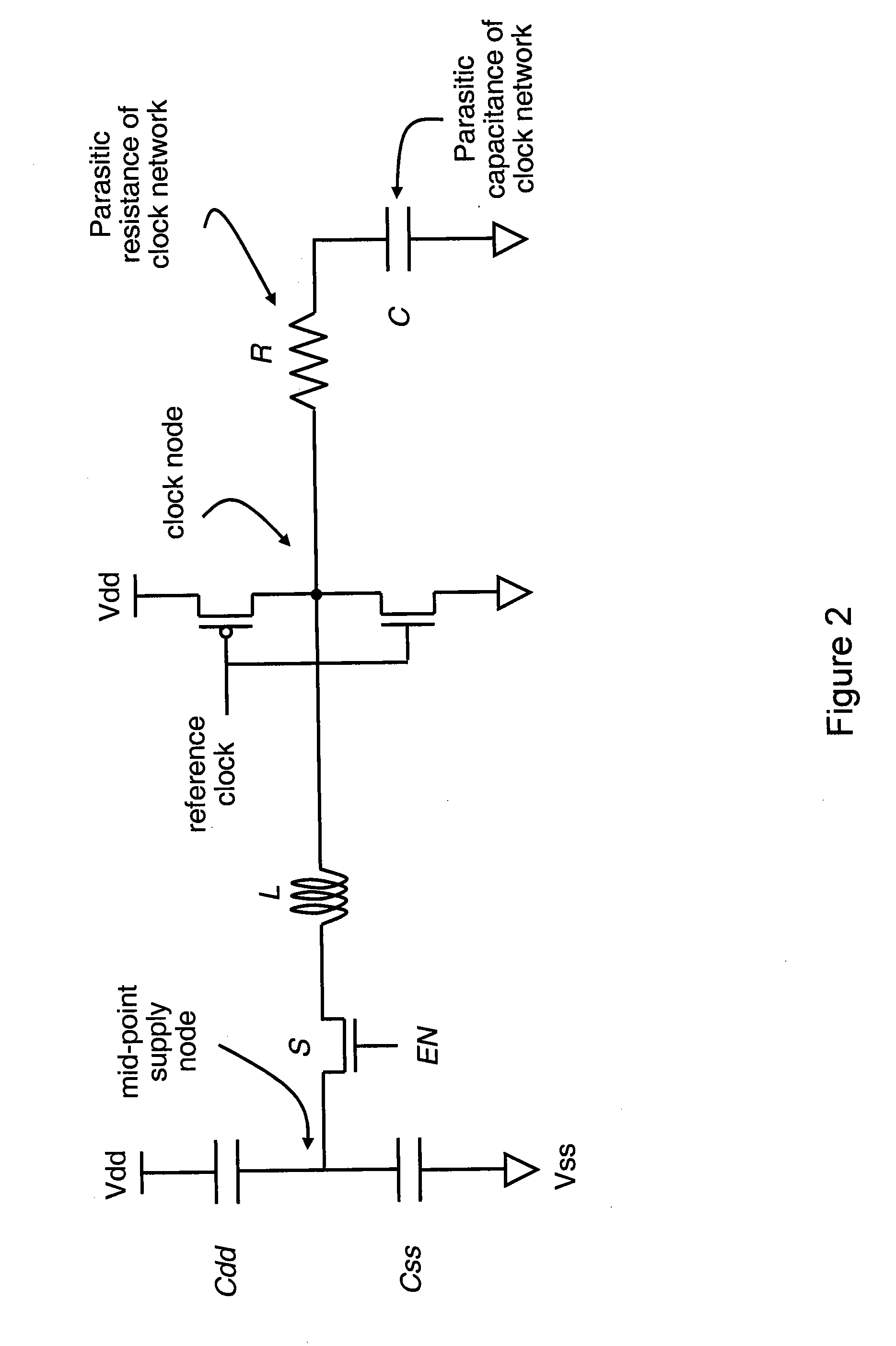

Architecture for adjusting natural frequency in resonant clock distribution networks

ActiveUS20110090018A1Run energy savingReduce overheadComputing operations for integral formationComputing operations for integration/differentiationSemiconductorDistribution networks

An inductor architecture for resonant clock distribution networks is proposed. This architecture allows for the adjustment of the natural frequency of a resonant clock distribution network, so that it achieves energy-efficient operation at multiple clock frequencies. The proposed architecture is primarily targeted at the design of integrated inductors and exhibits relatively low area overheads. Such an architecture is generally applicable to semiconductor devices with multiple clock frequencies, and high-performance and low-power clocking requirements such as microprocessors, ASICs, and SOCs. Moreover, it is applicable to the binning of semiconductor devices according to achievable performance levels.

Owner:CYCLOS SEMICON

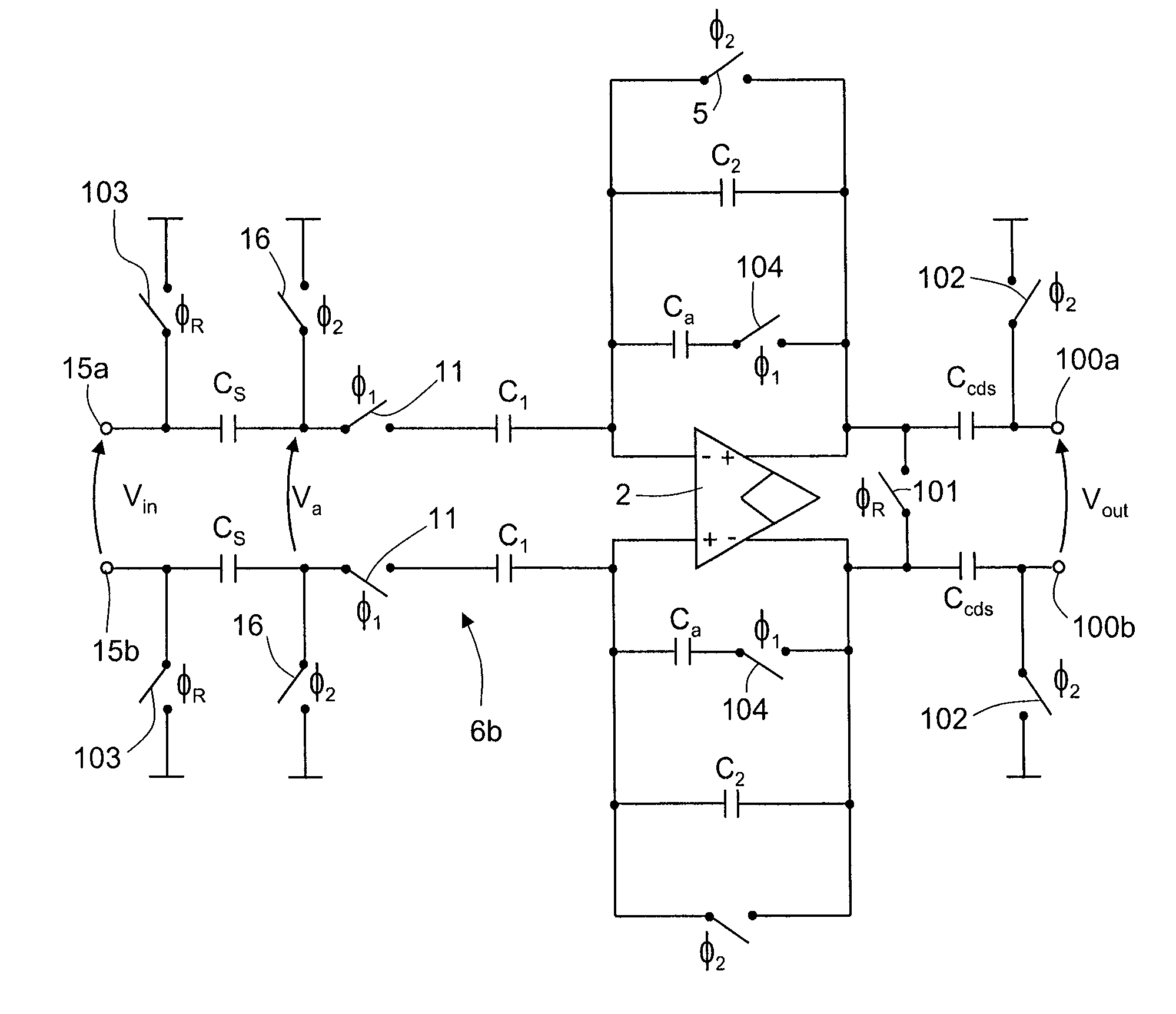

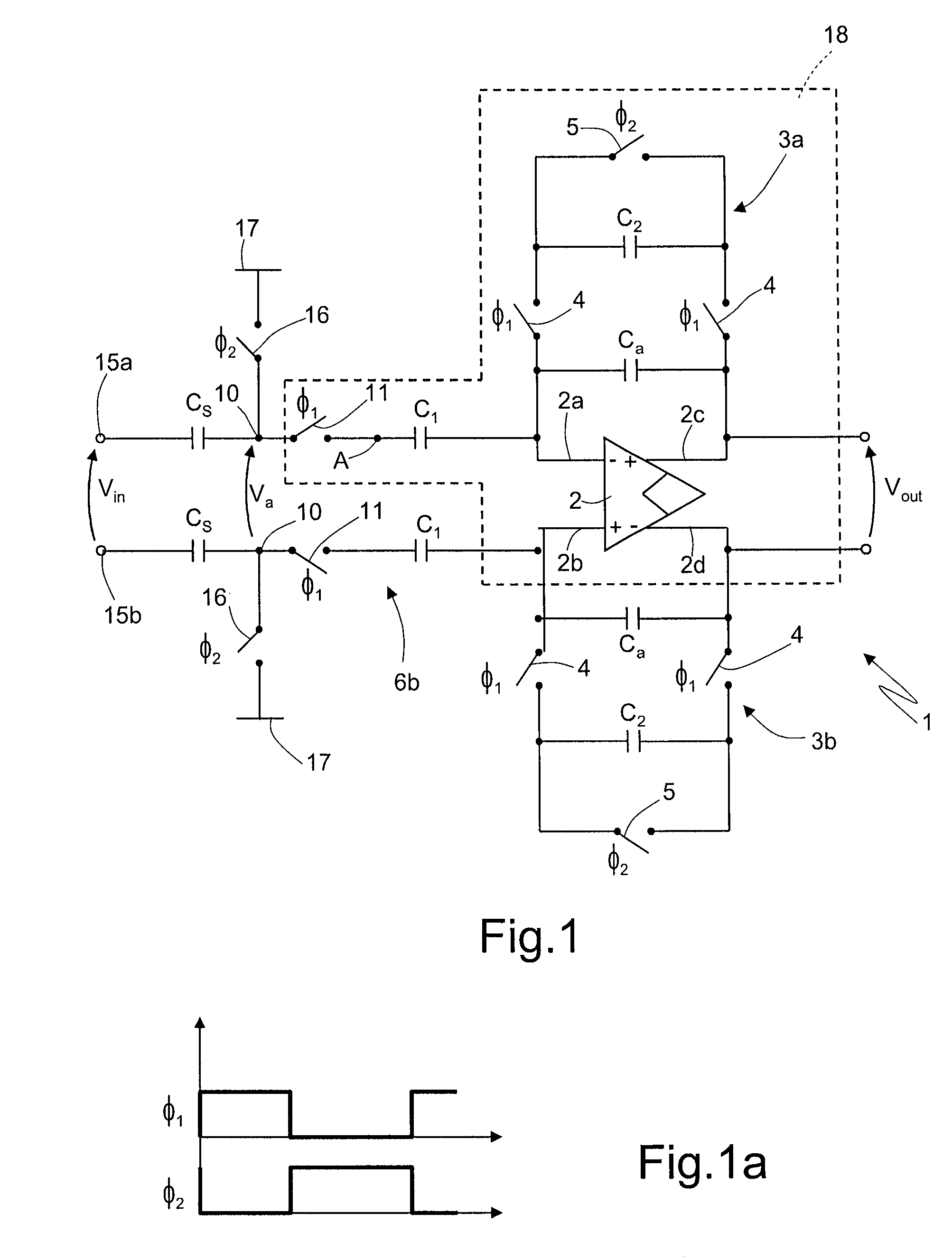

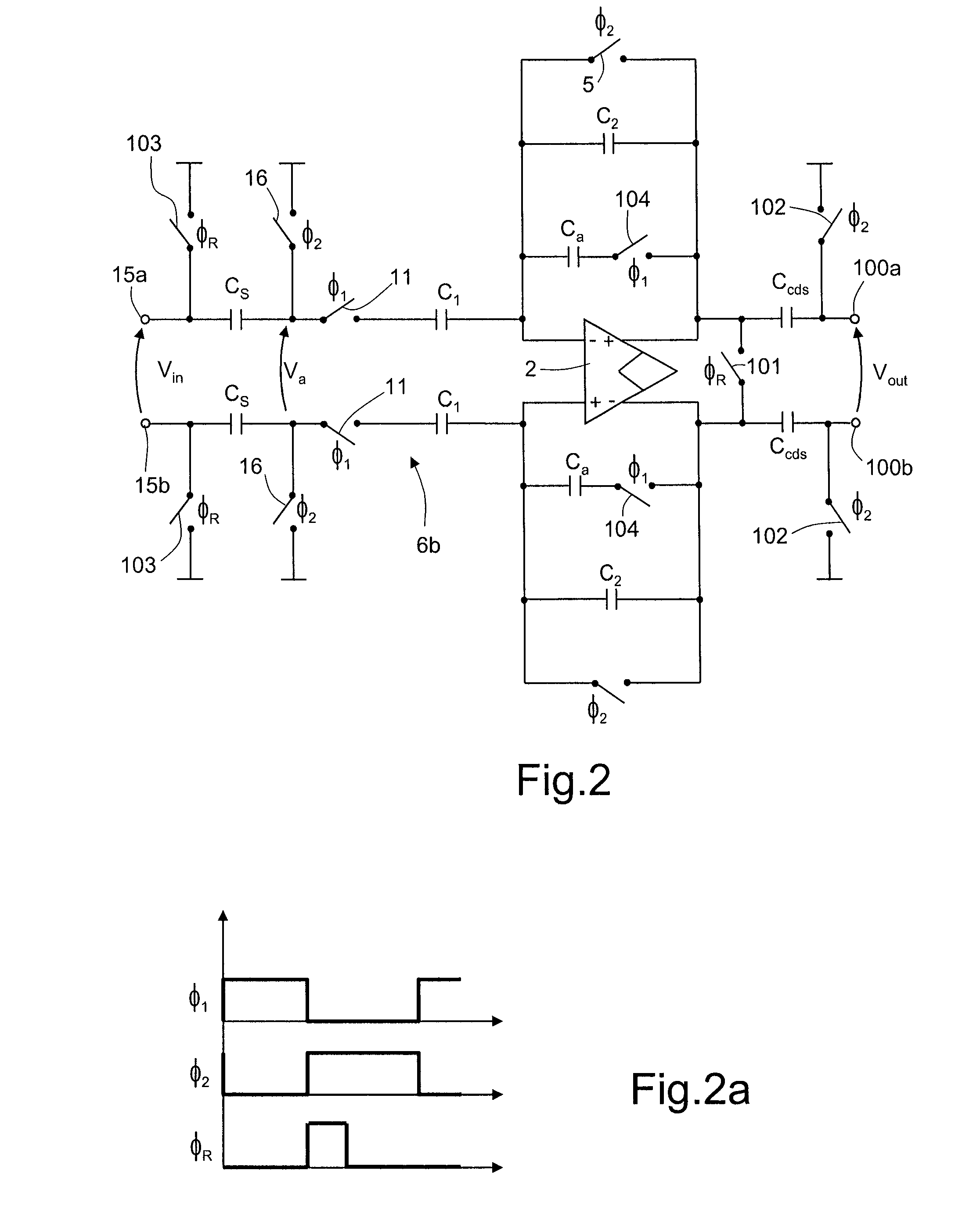

Switched-capacitor band-pass filter of a discrete-time type, in particular for cancelling offset and low-frequency noise of switched-capacitor stages

ActiveUS8497746B2Eliminate offsetReduce flicker noiseComputing operations for integral formationMultiple-port networksCapacitanceAudio power amplifier

A band-pass filter made up by an operational amplifier and by an input circuit. The input circuit is formed by a capacitive filtering element, connected to the input of the operational amplifier; a coupling switch, coupled between an input node and the capacitive filtering element; a capacitive sampling element, coupled between the input of the filter and the input node; and a sampling switch, coupled between the input node and a reference-potential line. The coupling switch and the input sampling switch close in phase opposition according to a succession of undesired components sampling and sensing steps, so that the capacitive sampling element forms a sampler for sampling the undesired component in the undesired components sampling step, in the absence of the component of interest, and forms a subtractor of the undesired components from the input signal in the sensing step.

Owner:STMICROELECTRONICS SRL

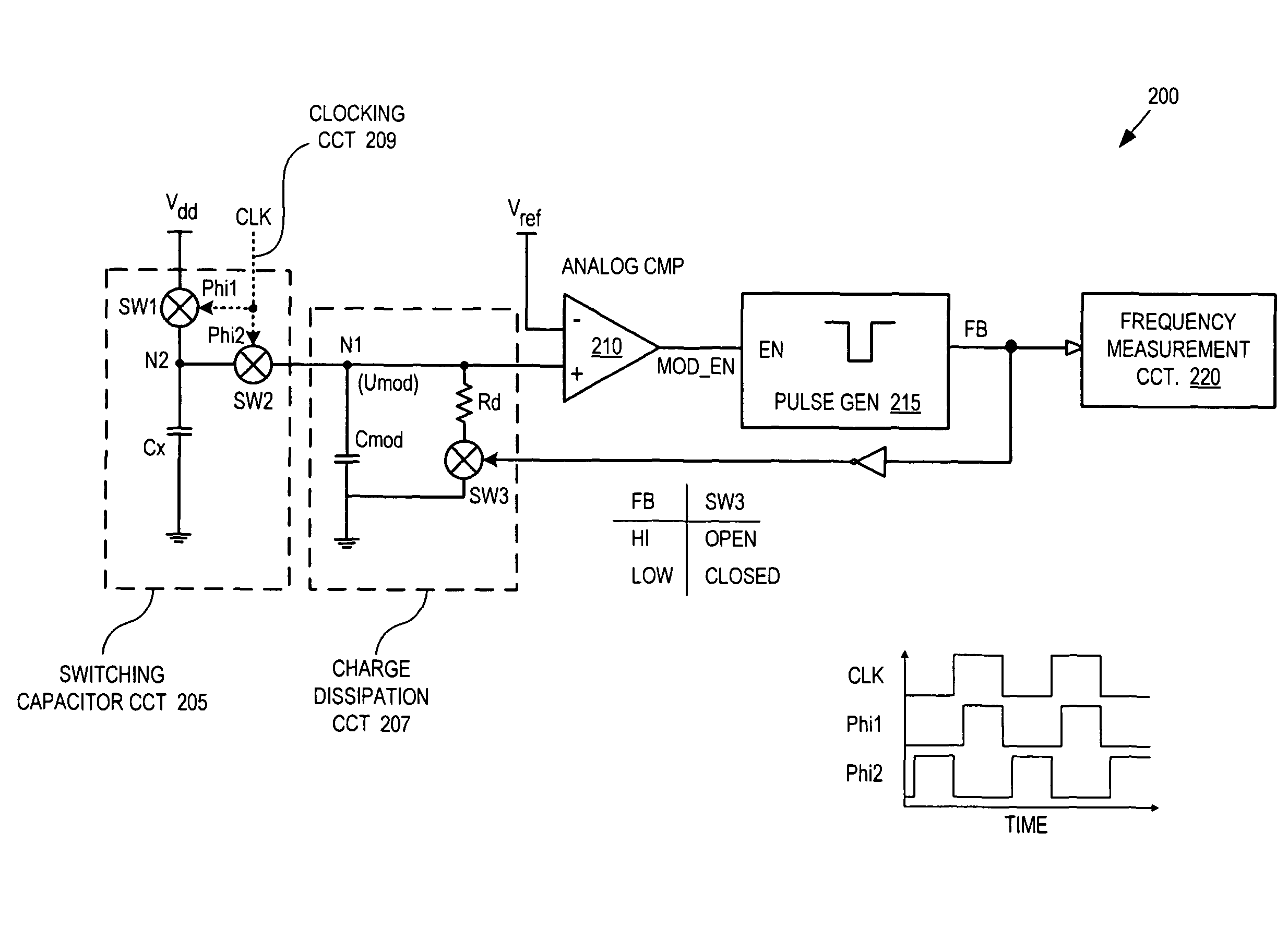

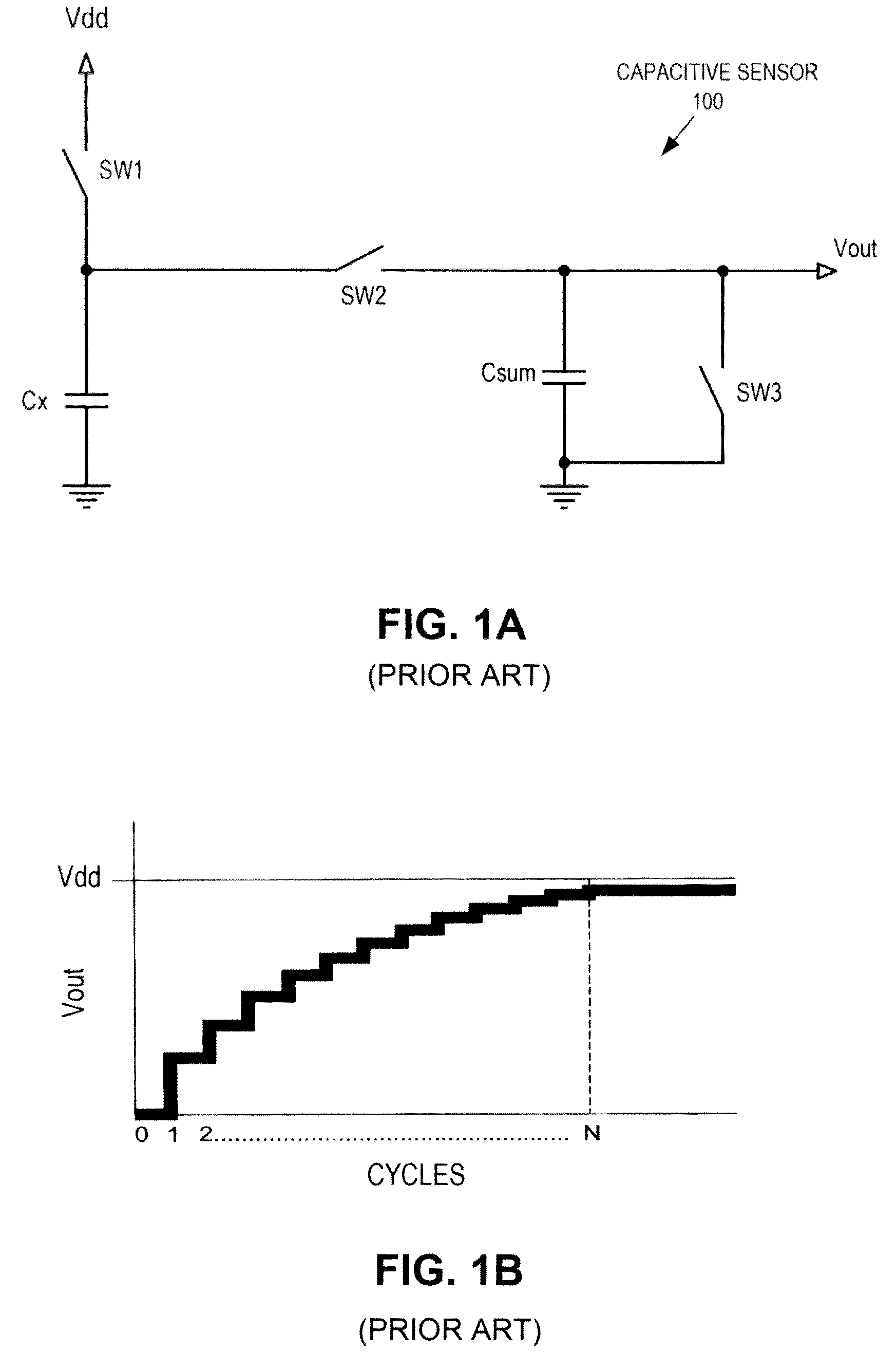

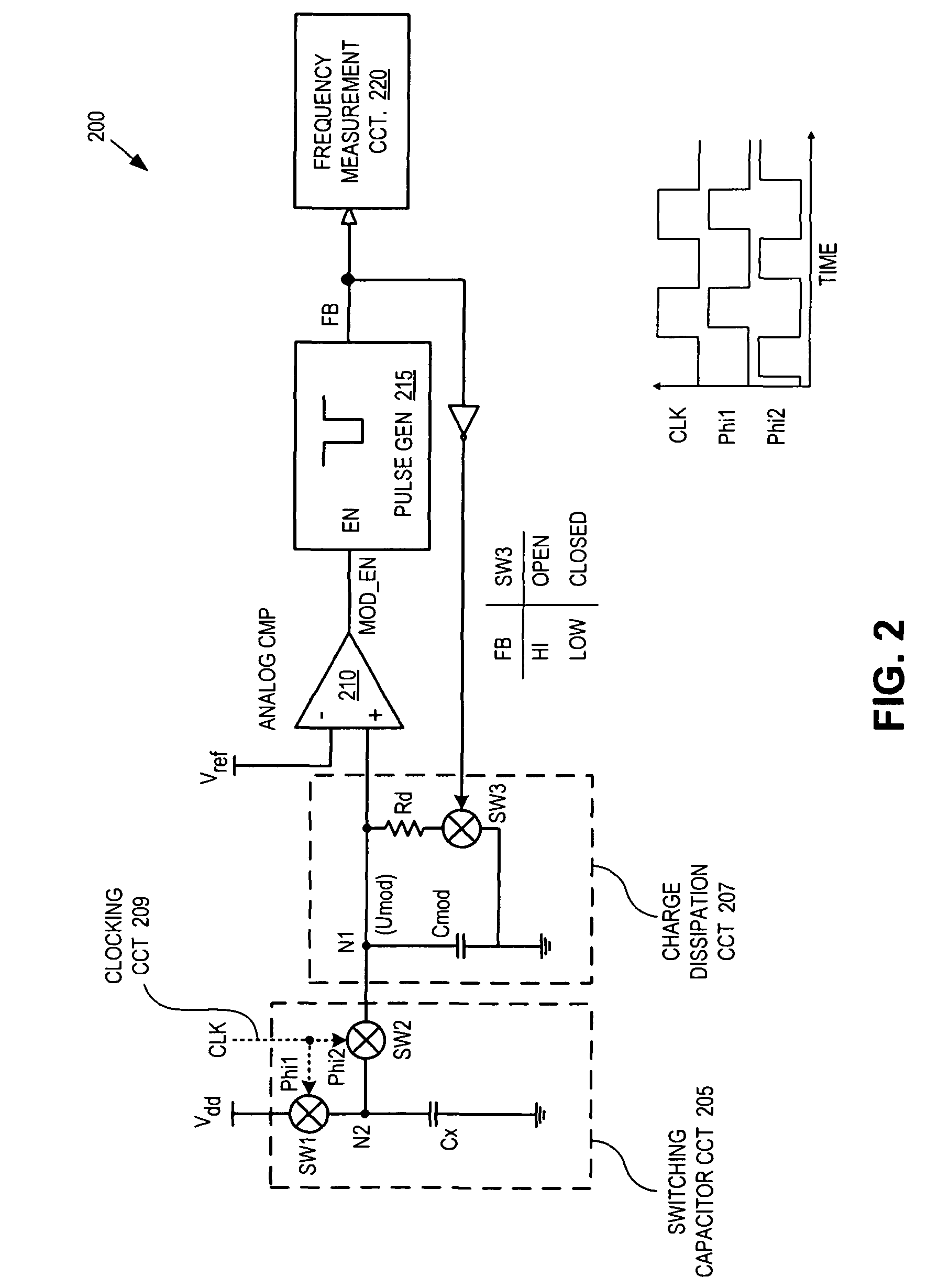

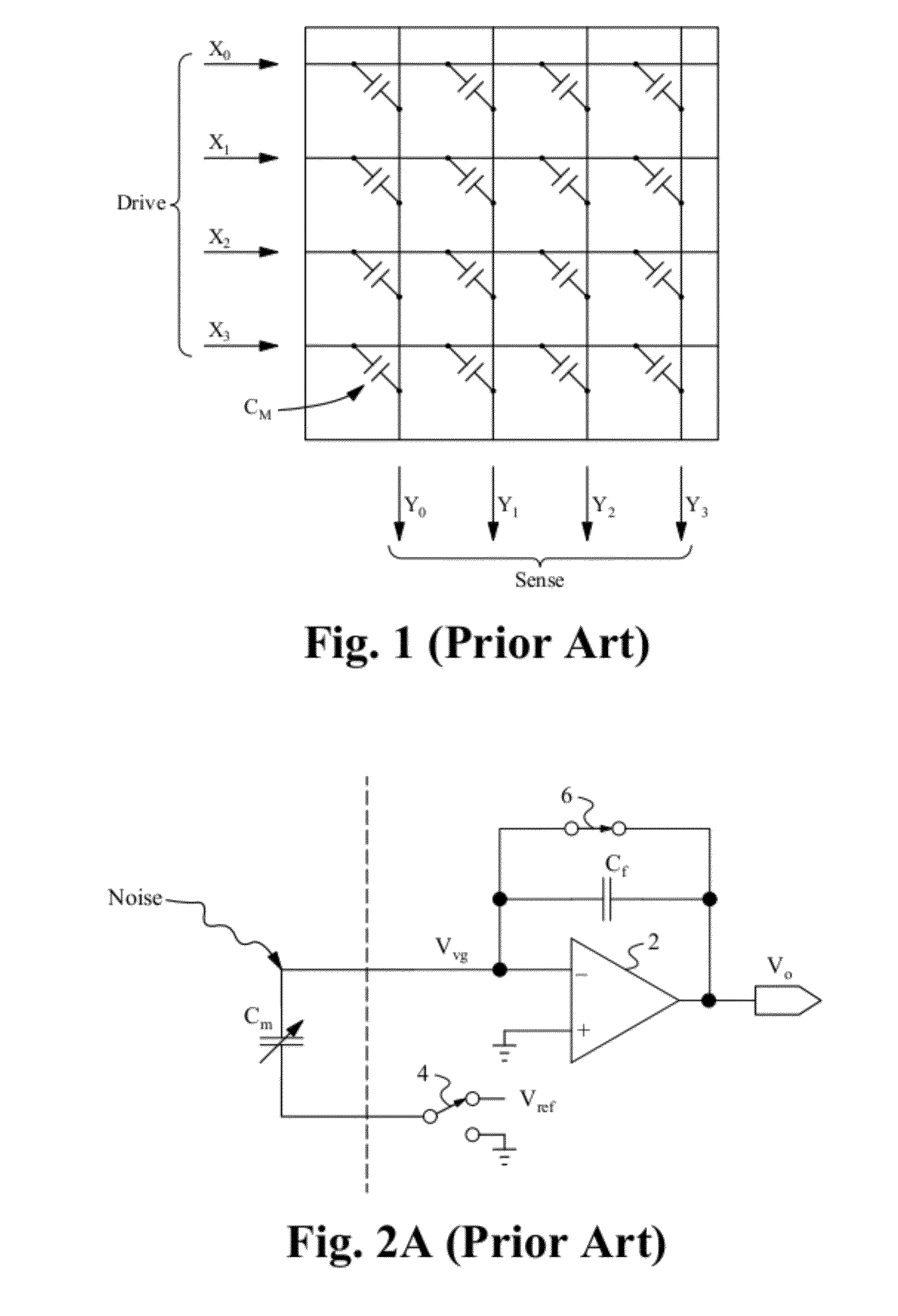

Capacitance to frequency converter

ActiveUS8169238B1Computing operations for integral formationComputing operations for integration/differentiationCapacitanceFrequency changer

A capacitance to frequency converter includes a switching capacitor circuit, a charge dissipation circuit, a comparator, and a signal generator. The switching capacitor circuit charges a sensing capacitor and transfers charge from the sensing capacitor to a circuit node of the charge dissipation circuit. The comparator is coupled to the charge dissipation circuit to compare a potential at the circuit node to a reference voltage. The signal generator is coupled to an output of the comparator and to the charge dissipation circuit. The signal generator is responsive to the output of the comparator to generate a signal fed back to control the charge dissipation circuit. A frequency of the signal is proportional to a capacitance of the sensing capacitor.

Owner:CYPRESS SEMICON CORP

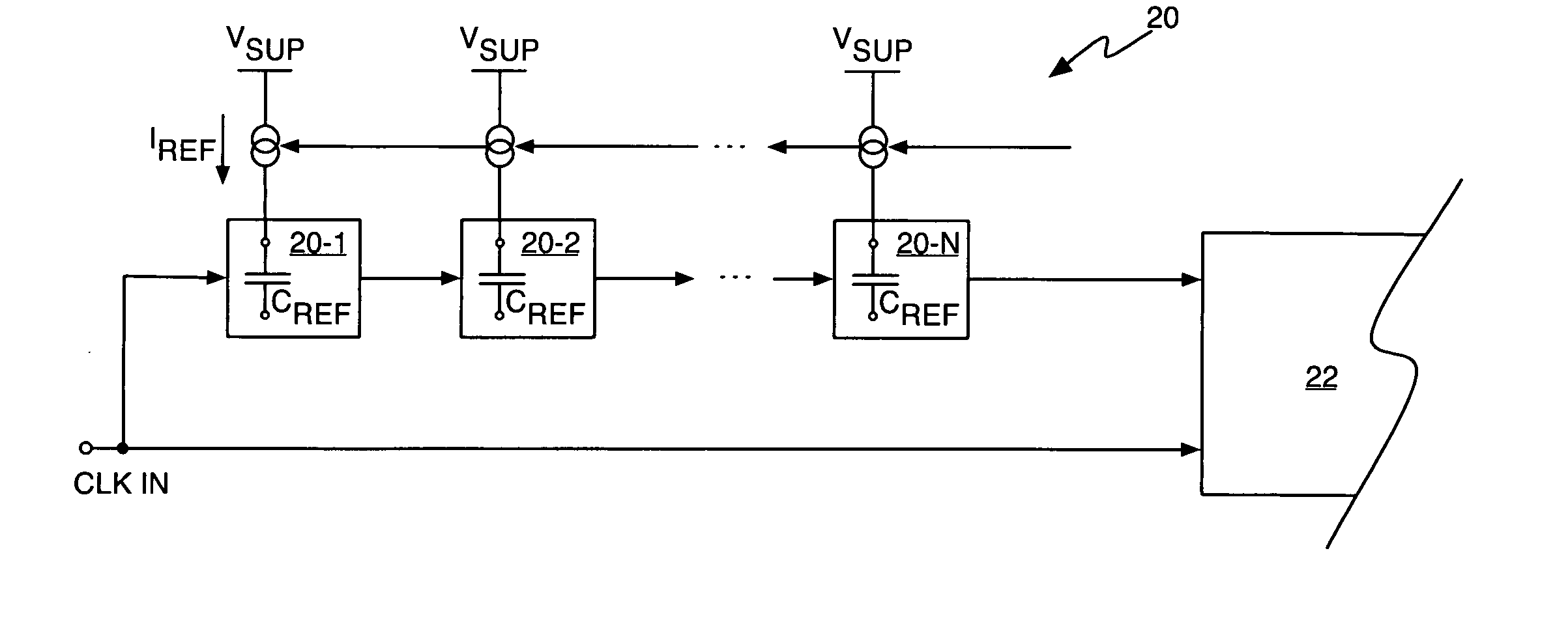

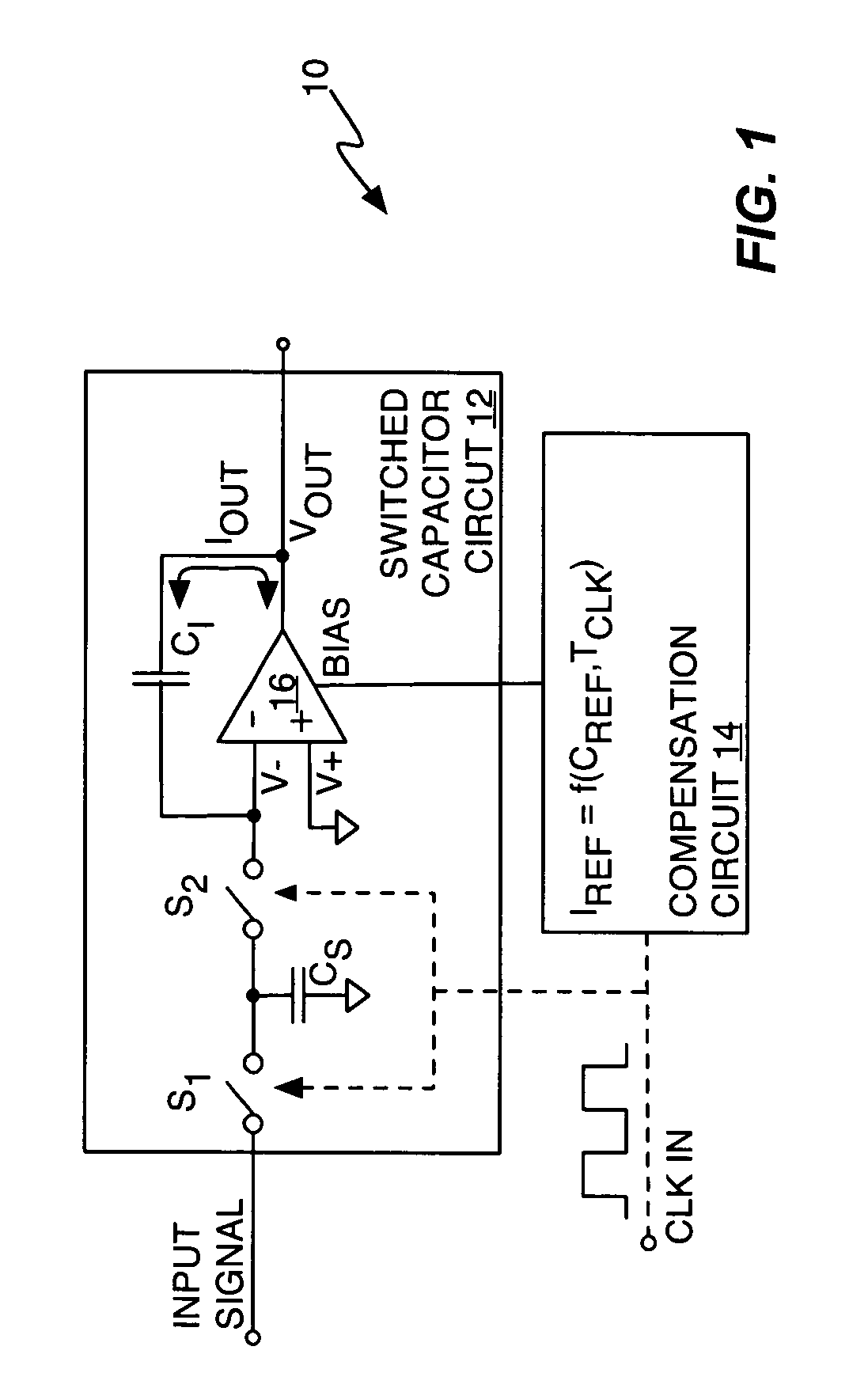

Switched capacitor circuit compensation apparatus and method

ActiveUS20050140422A1Easy to useIncrease currentElectric analogue storesDigital differential analysersCapacitanceLoop control

A compensated switched capacitor circuit comprises a switched capacitor circuit and a compensation circuit. The compensation circuit generates a reference current that varies under closed loop control to maintain a targeted slew rate for charging a reference capacitor that is determined by the input clock frequency. The switched capacitor circuit's output amplifier is configured such that its output current varies in proportion to the reference current. Thus, by configuring the reference capacitor to track the effective capacitance of the switched capacitor circuit, the settling time of the switched capacitor circuit may be made relatively insensitive to the value of and changes in the effective capacitance over a range of clock frequencies. The compensation circuit may include a clock reconditioning circuit to ensure that the switched capacitor circuit is clocked at a desired duty cycle.

Owner:TELEFON AB LM ERICSSON (PUBL)

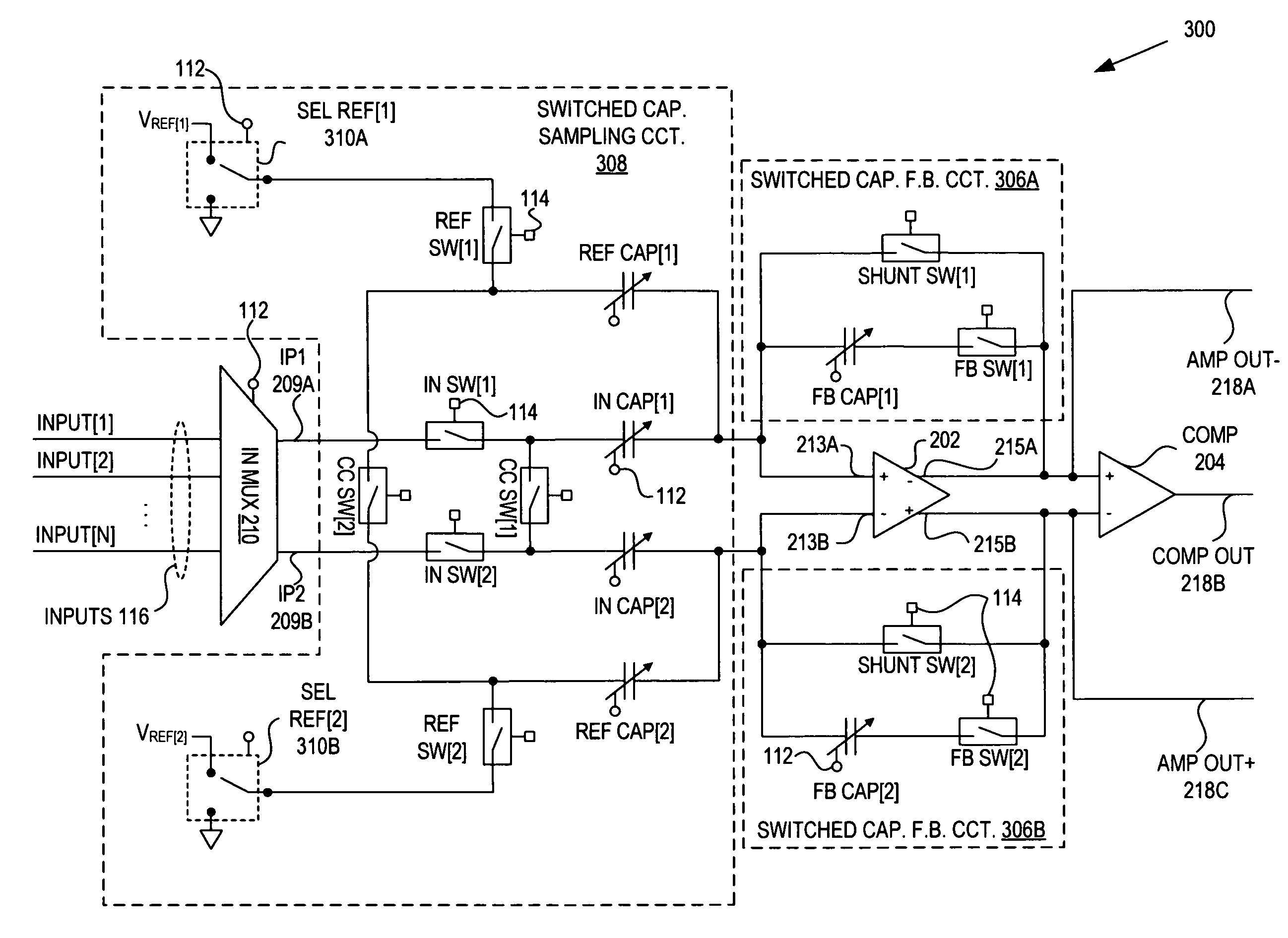

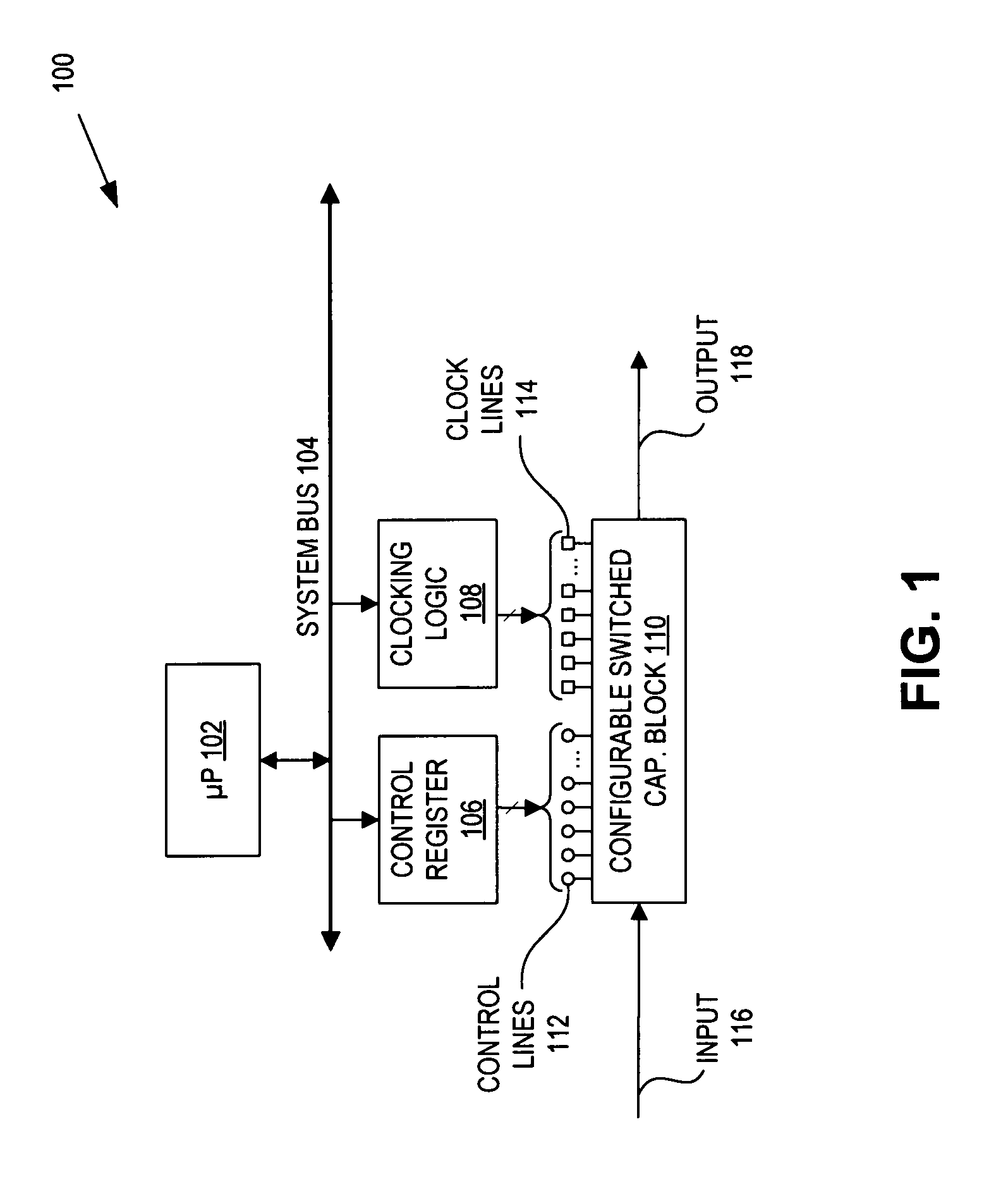

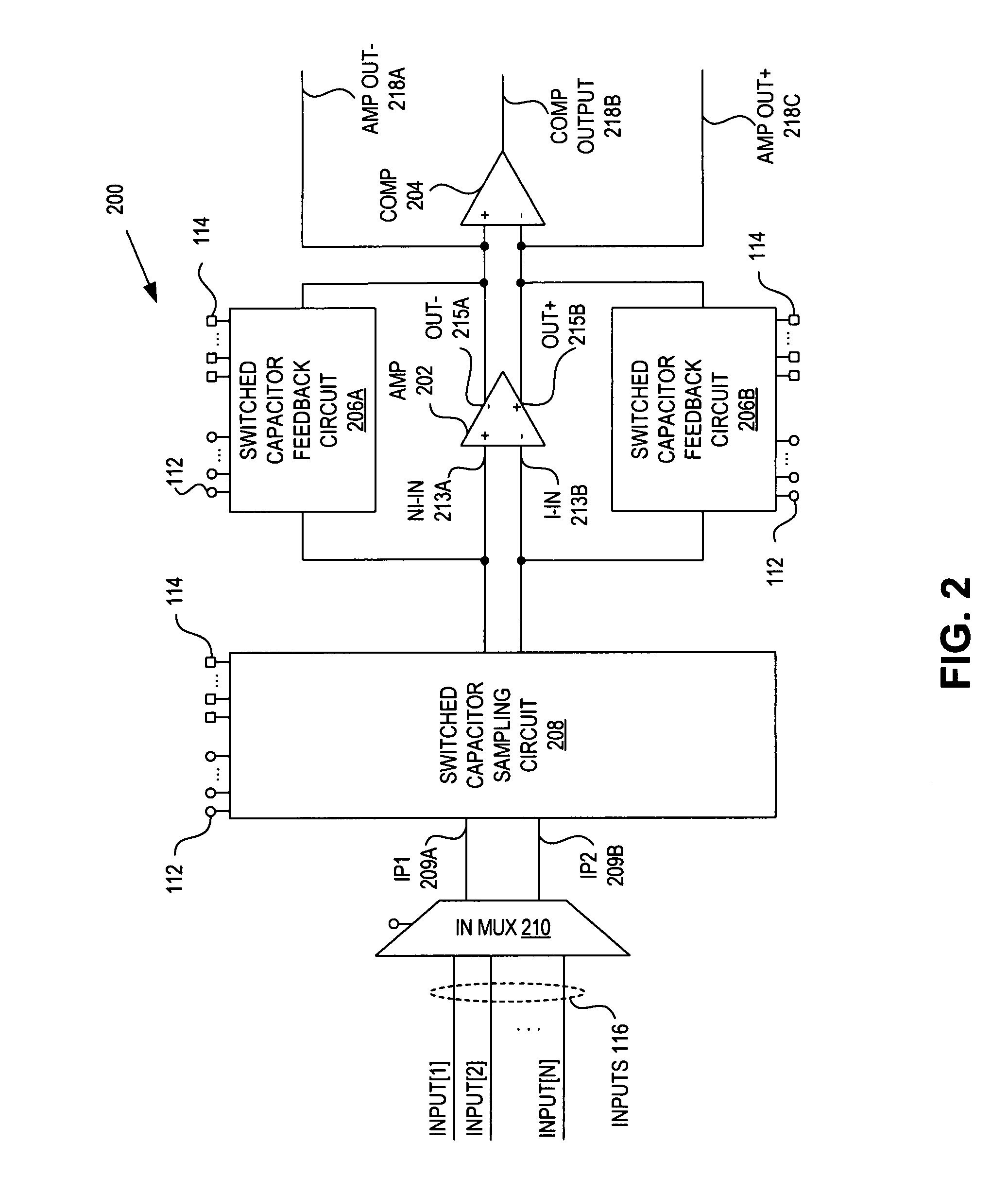

Configurable switched capacitor block

ActiveUS7679422B1Computing operations for integral formationElectric signal transmission systemsAudio power amplifierFeedback circuits

A configurable switched capacitor block includes a switched-capacitor (SC) sampling circuit, a fully differential amplifier, an SC feedback circuit, and a comparator. The SC sampling circuit is coupled to receive an input signal and to selectively generate a sampled signal to a differential input of the amplifier. The SC feedback circuit is coupled between the differential inputs and the differential outputs of the amplifier to selectively control a feedback of the amplifier. The comparator is coupled to the differential outputs of the amplifier to generate an output signal. The configurable switched capacitor block has multiple modes of operation which are selectable by programming the SC sampling circuit and the SC feedback circuit.

Owner:CYPRESS SEMICON CORP

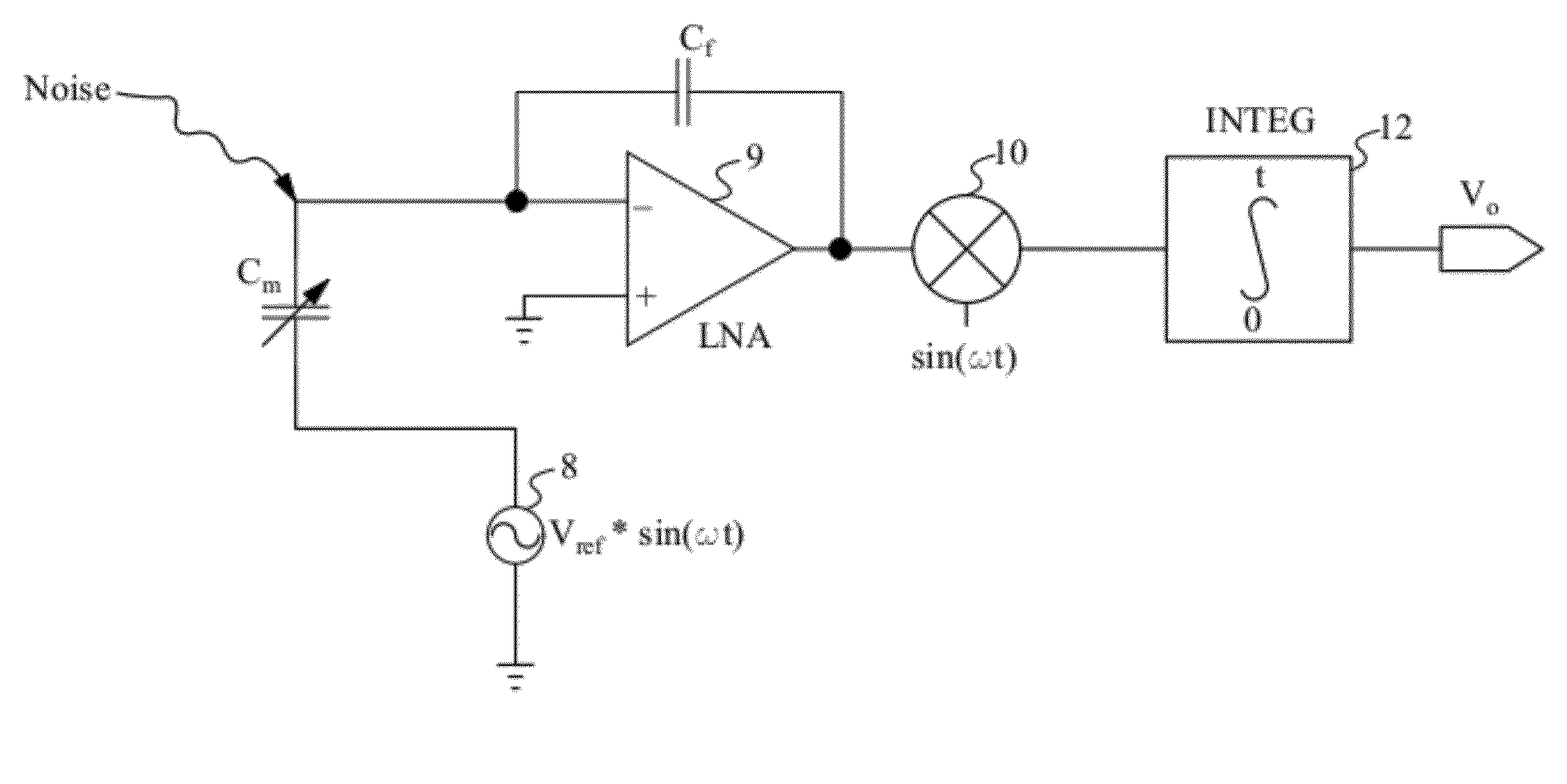

Calibration for mixed-signal integrator architecture

ActiveUS20120218020A1Decreases integrated output voltageIncrease costComputing operations for integral formationComputing operations for integration/differentiationIntegratorDisplay device

A mixed signal correlator utilizes coherent detection within a capacitance measurement application. In some applications, the mixed signal correlator is used to measure capacitance of a touch screen display. An external capacitor whose capacitance is measured is kept small for improved sensitivity and can be used for a variety of applications having varied integration periods for measurement. The external capacitor is kept small and can be used for varied applications by adjusting the output voltage within a range that is less than the supply voltage, and maintaining a count of the adjustments to later reconstruct an actual output voltage for the integration period. An output is a weighted sum of an analog integrator output and a digital counter output.

Owner:QUALCOMM INC

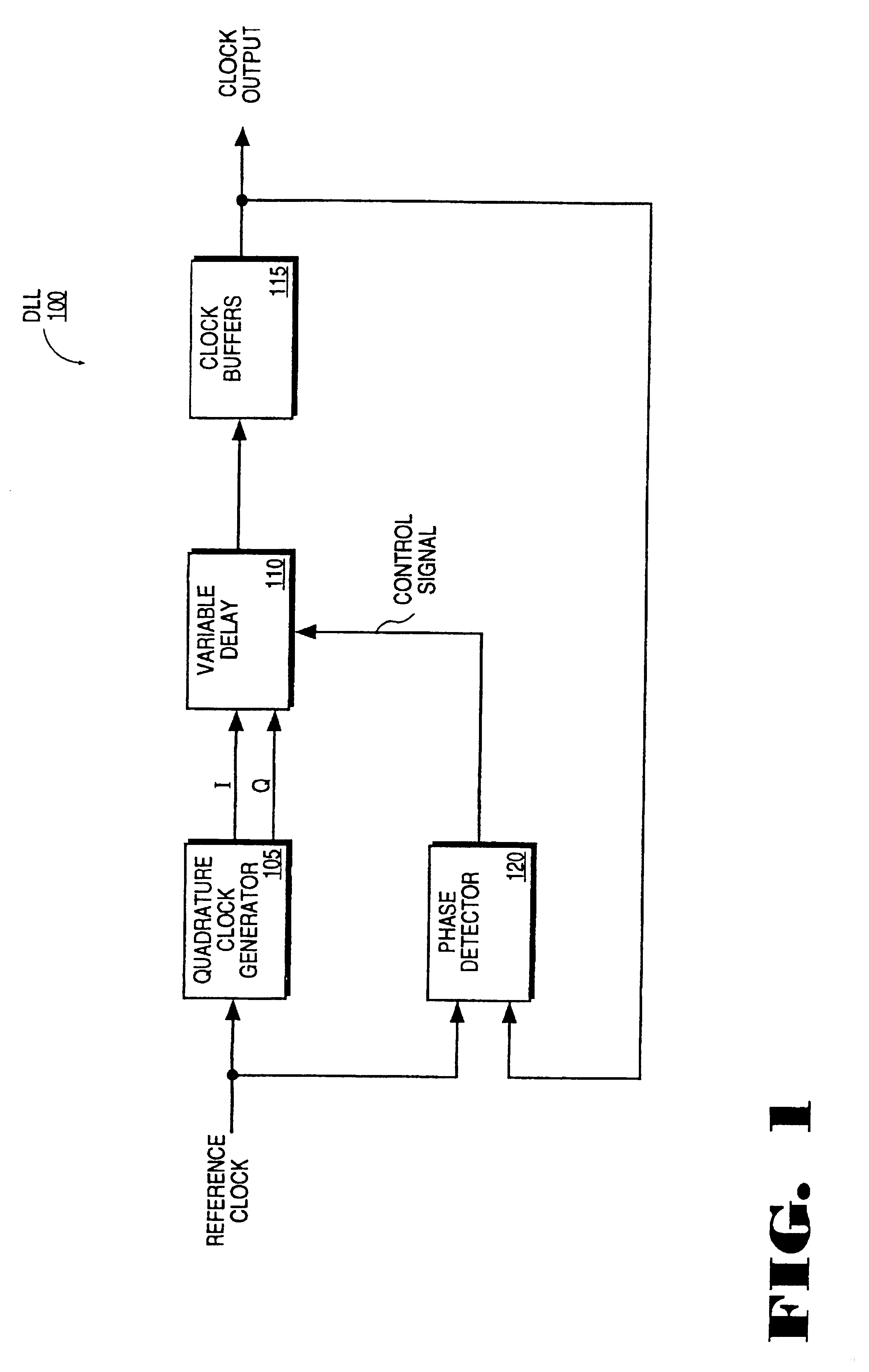

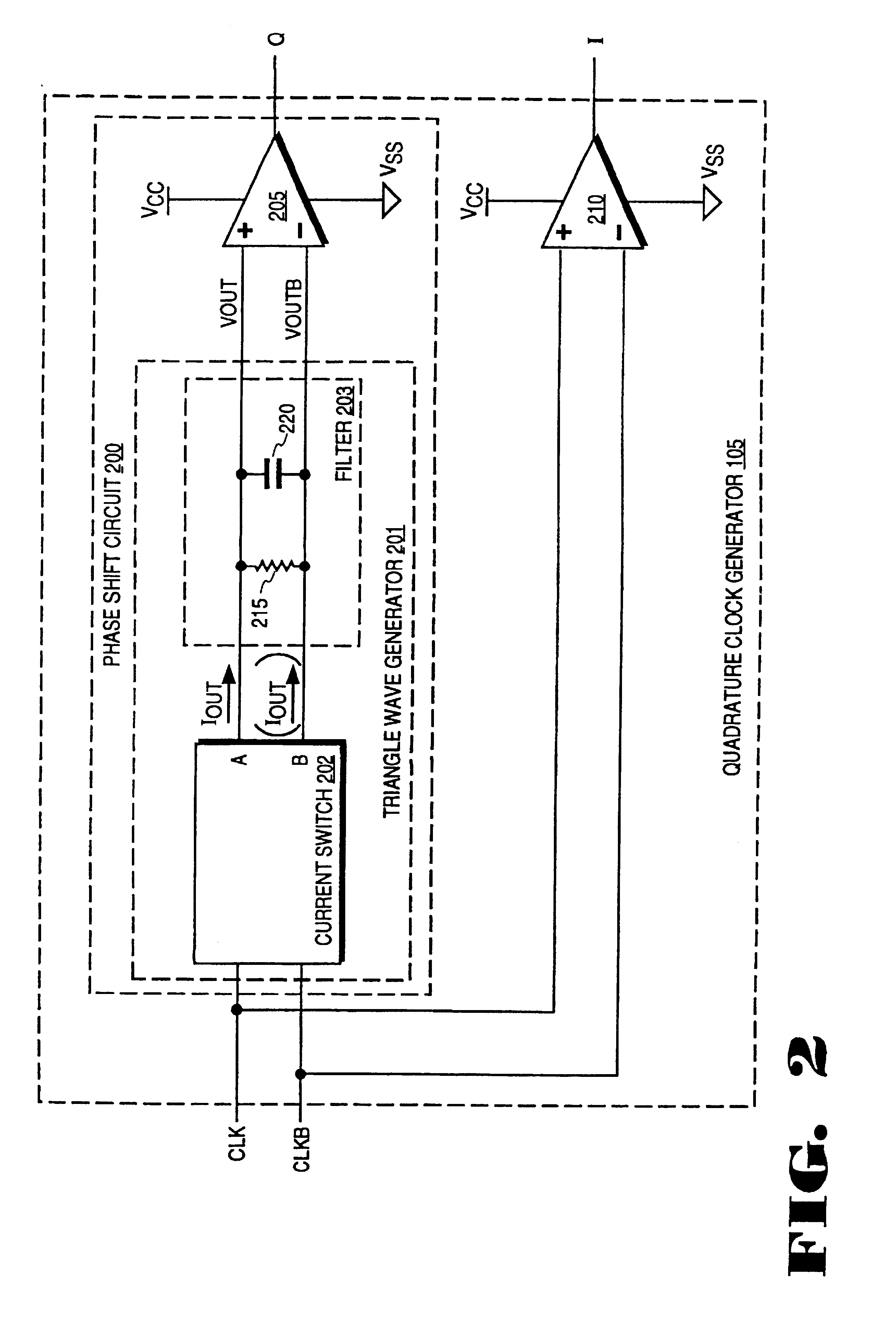

At frequency phase shifting circuit for use in a quadrature clock generator

InactiveUSRE37452E1Enhance the shake effectComputing operations for integral formationComputing operations for integration/differentiationPhase shiftedClock generator

A phase shifting circuit that may be used as part of a quadrature clock generator. The phase shifting circuit comprises a triangle wave generator coupled to receive an input reference signal. The triangle wave generator outputs a pair of complementary triangle wave signals in response to the input reference signal. A comparator having a pair of inputs is coupled to receive the pair of complementary triangle wave signals. The comparator outputs an output signal having a predetermined phase relationship with the input reference signal in response to a comparison between the pair of complementary triangle wave signals.

Owner:RAMBUS INC

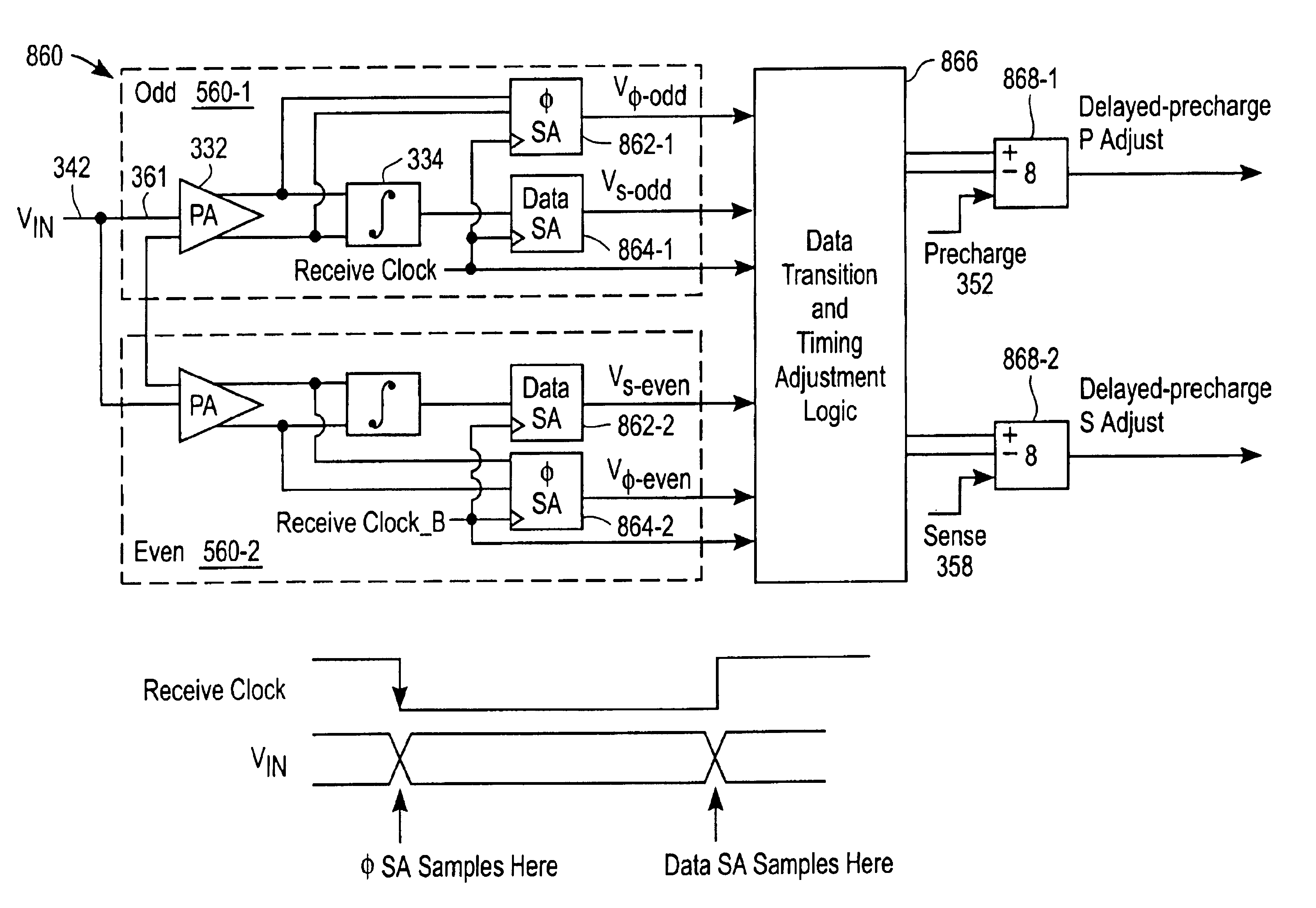

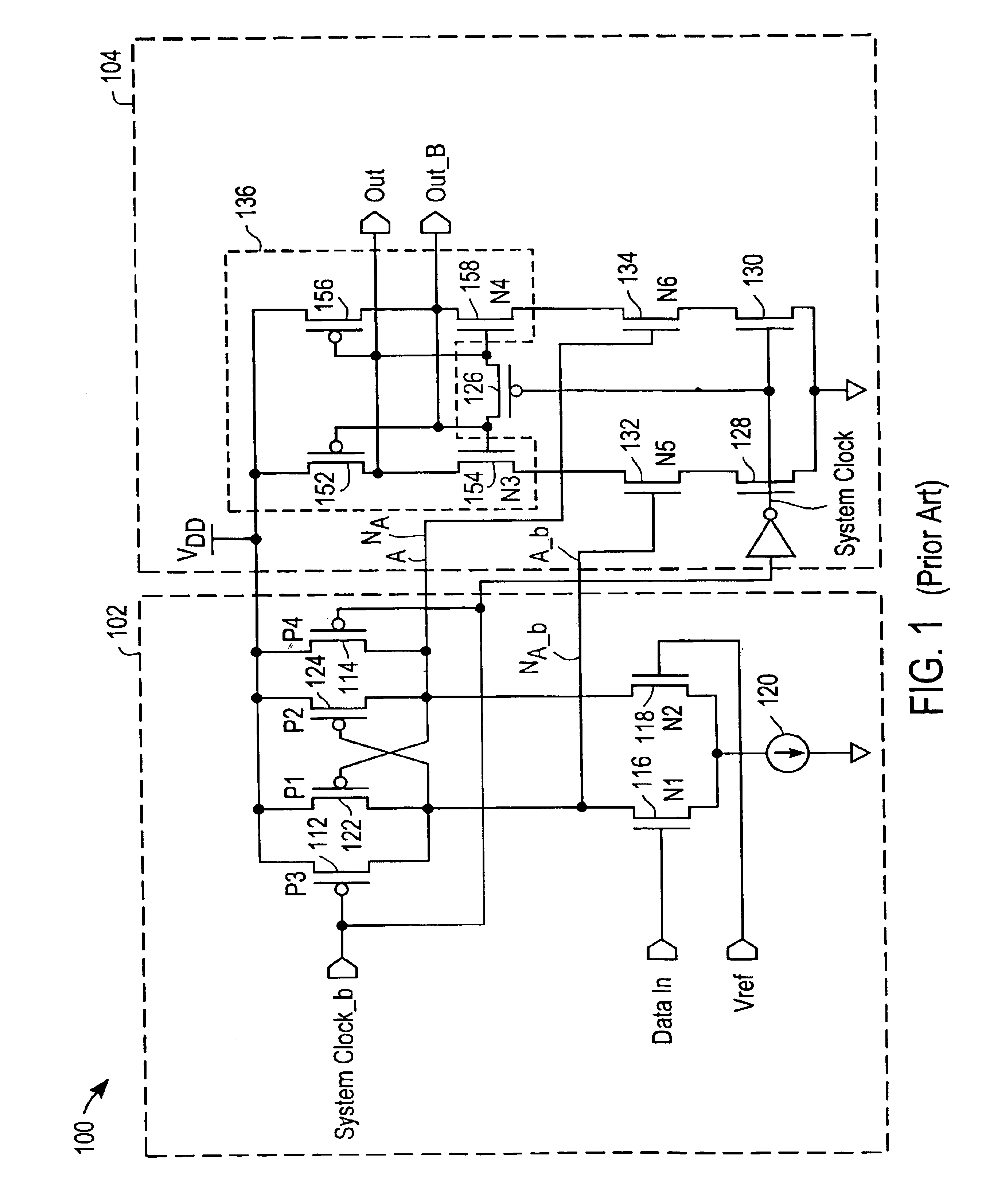

Method and apparatus for receiving high speed signals with low latency

InactiveUS20060061405A1Reduce signal delayDigital differential analysersDigital storageIntegratorAudio power amplifier

An apparatus and method for receiving high-speed signals having a wide common-mode range with low input-to-output latency. In one embodiment, the receiver includes an integrator to accumulate charge in accordance with an input signal during an integration time interval to produce an output voltage. A sense amplifier samples and converts the output voltage of the integrator to a logic signal; and a latch stores the logic signal. In an alternate embodiment, a preamplifier conditions the input signal prior to being integrated. In another embodiment using multiple receivers, circuitry is added to the receiver to compensate for timing errors associated with the distribution of the timing signals. In yet another embodiment, the integrator is coupled to an equalization circuit that compensates for intersymbol interference. In another embodiment, another circuit compensates for accumulated voltage offset errors in the integrator.

Owner:RAMBUS INC

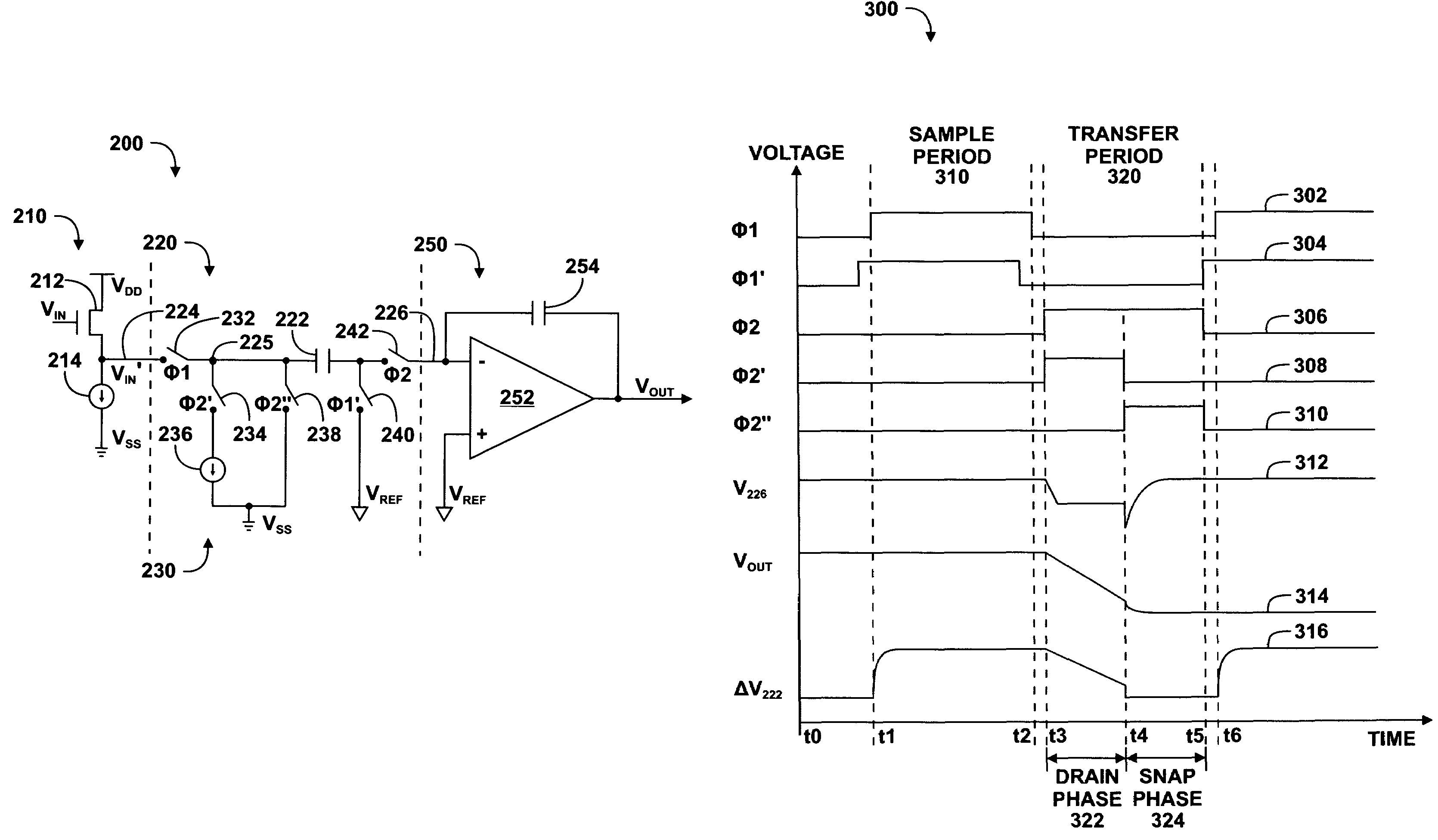

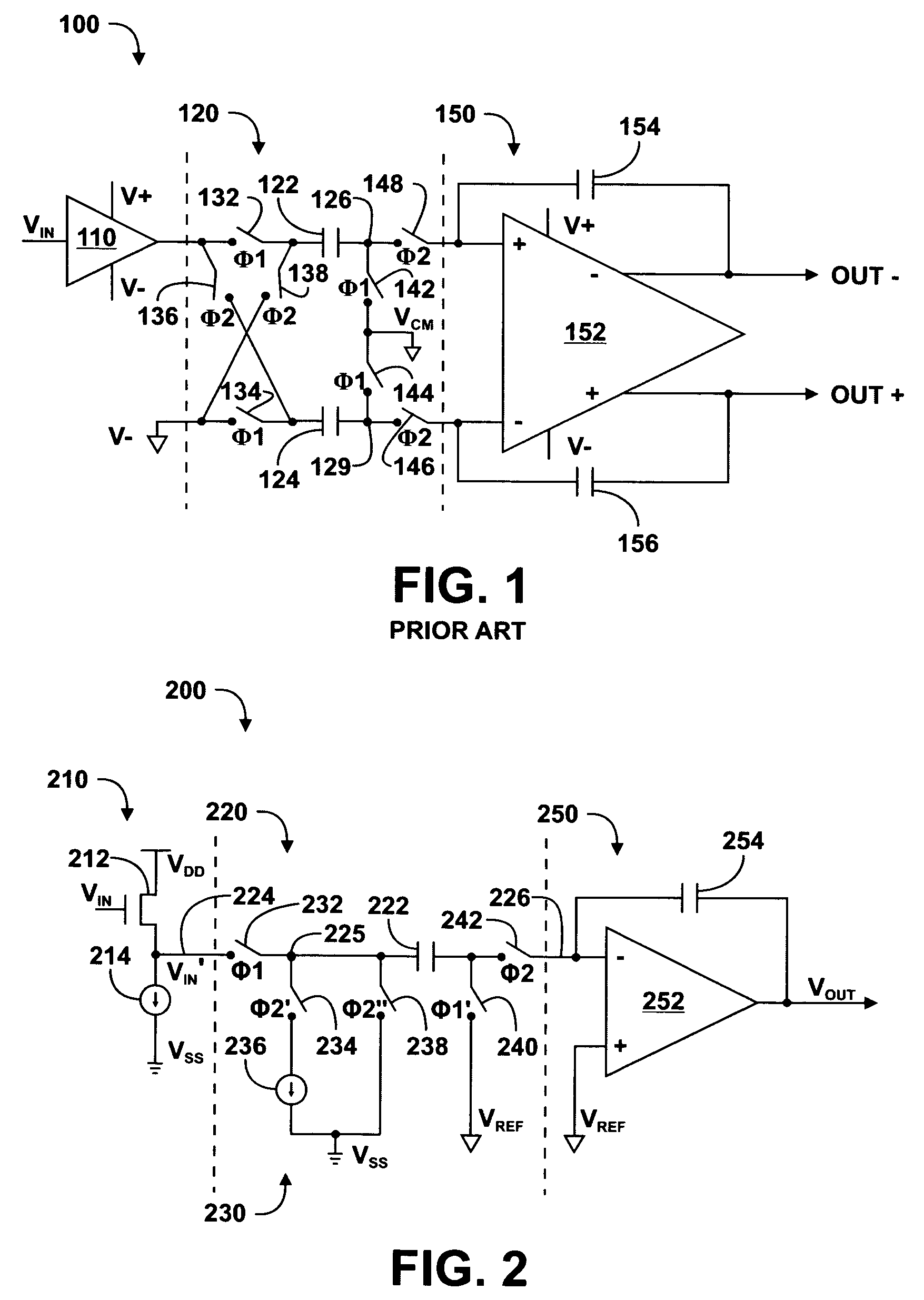

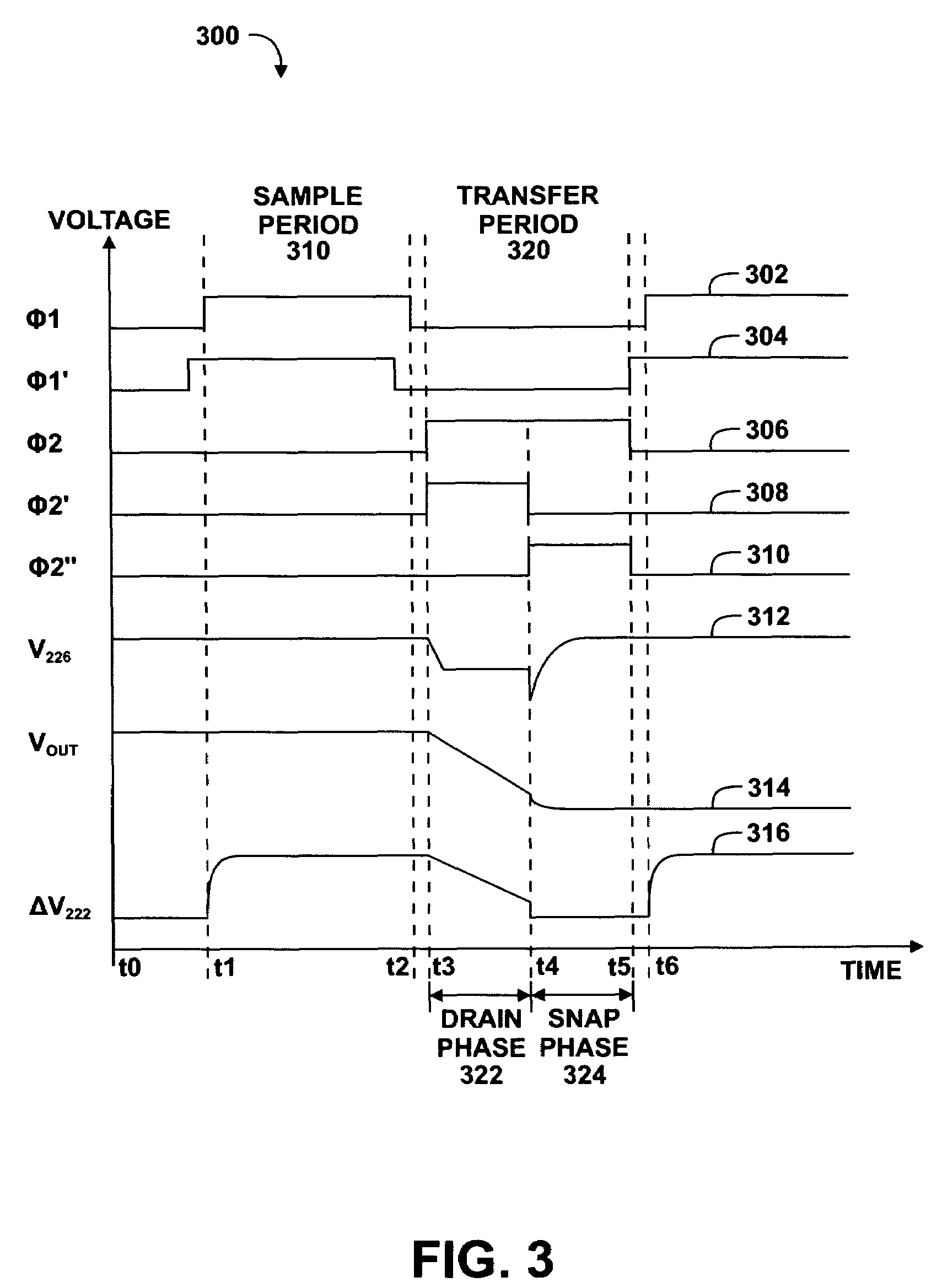

Switched capacitor input circuit and method therefor

InactiveUS7157956B2Computing operations for integral formationComputing operations for integration/differentiationIntegratorEngineering

A switched capacitor input circuit (200) includes an input buffer (210), a switched capacitor sampler circuit (220), and an integrator (250). The input buffer (210) has an input terminal for receiving an input voltage, and an output terminal. The switched capacitor sampler circuit (220) has an input terminal coupled to the output terminal of the input buffer (210), and an output terminal. The switched capacitor sampler circuit (220) includes a capacitor (222) and stores a charge proportional a voltage at the output terminal of the input buffer (210) in the capacitor (222) during a sample period, and transfers the charge from the capacitor (222) to the output terminal thereof during a transfer period subsequent to the sample period in a plurality of charge portions corresponding to a like plurality of phases of the transfer period. The integrator (250) has an input terminal coupled to the output terminal of the switched capacitor sampler circuit, and an output terminal for providing an output voltage signal.

Owner:SILICON LAB INC

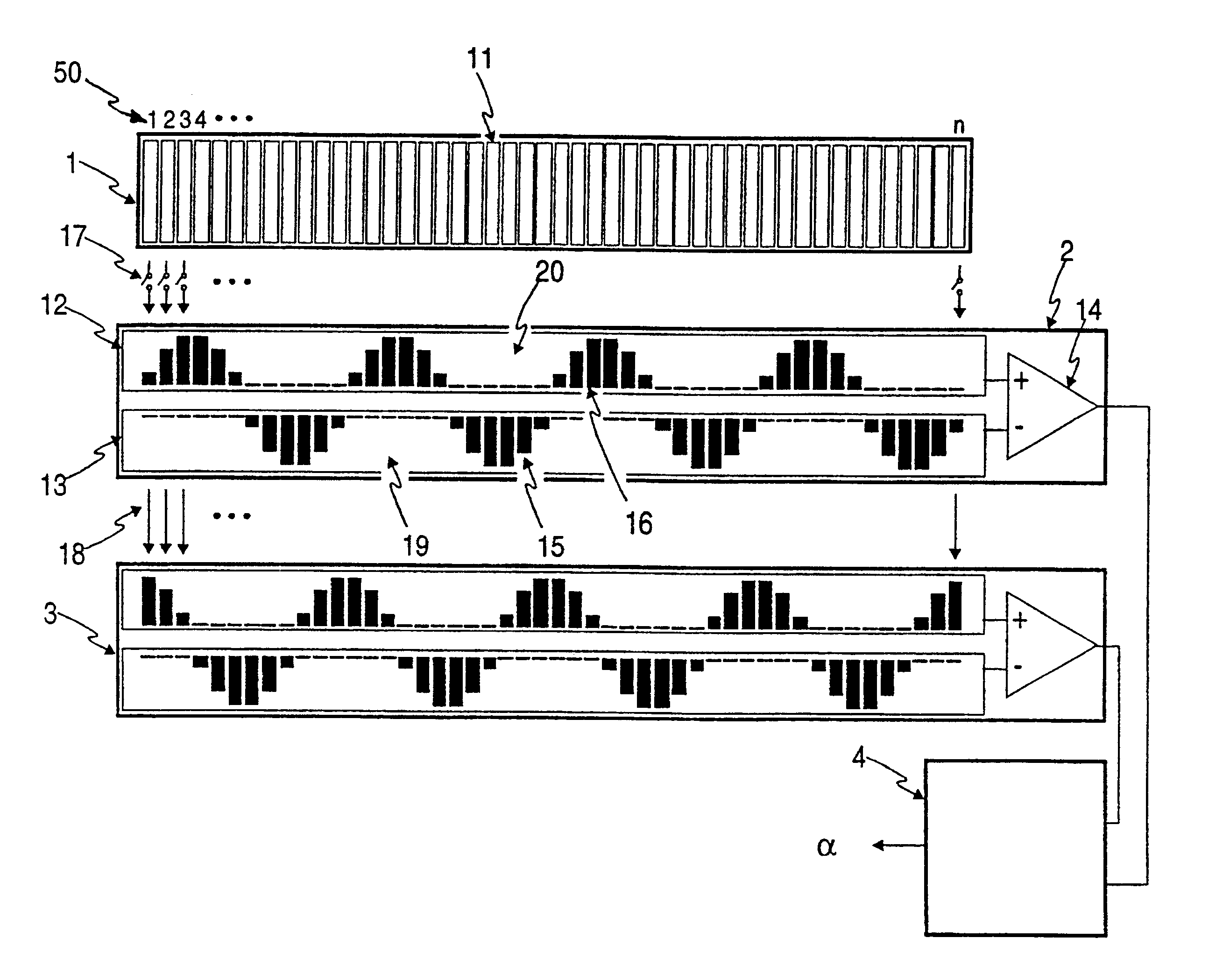

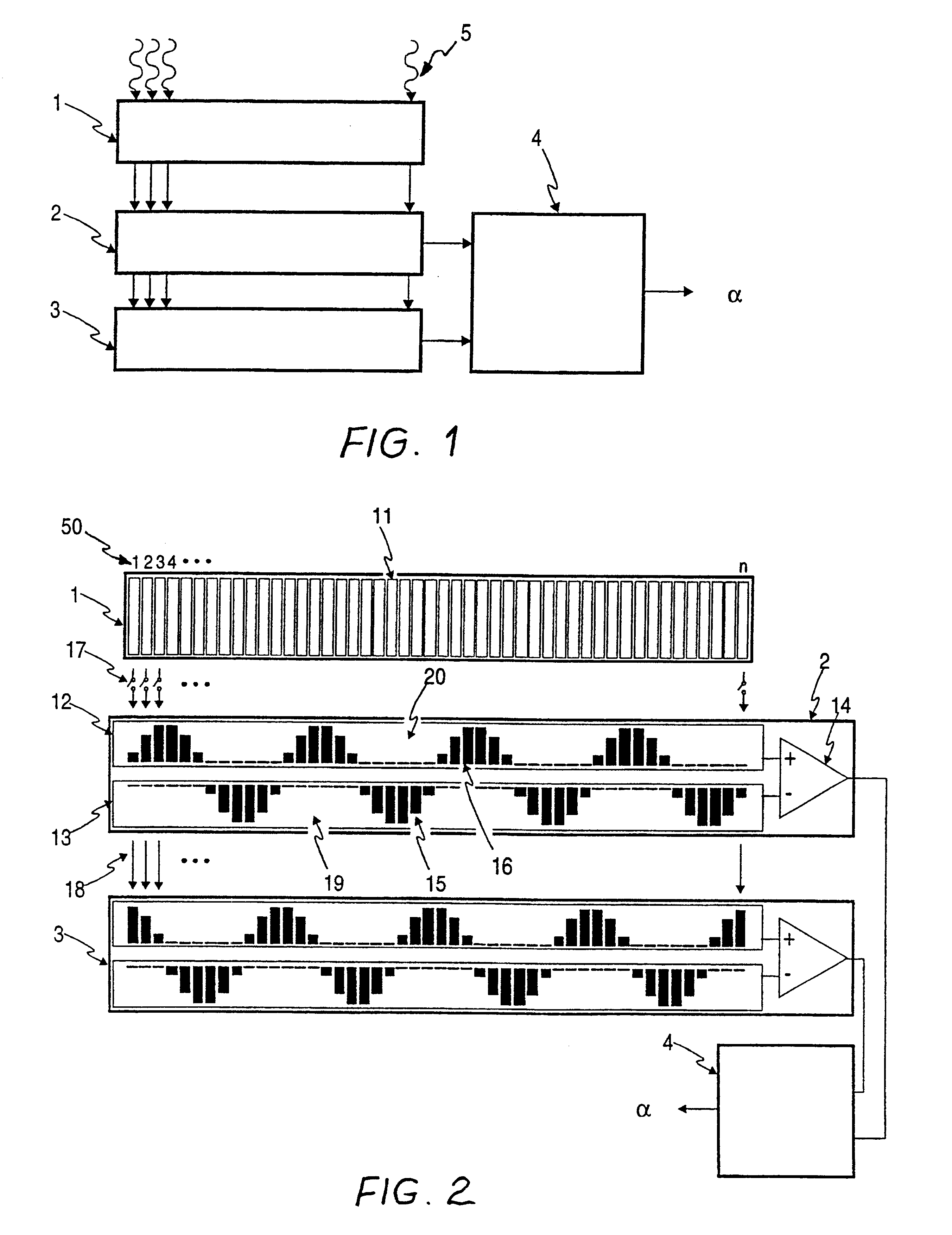

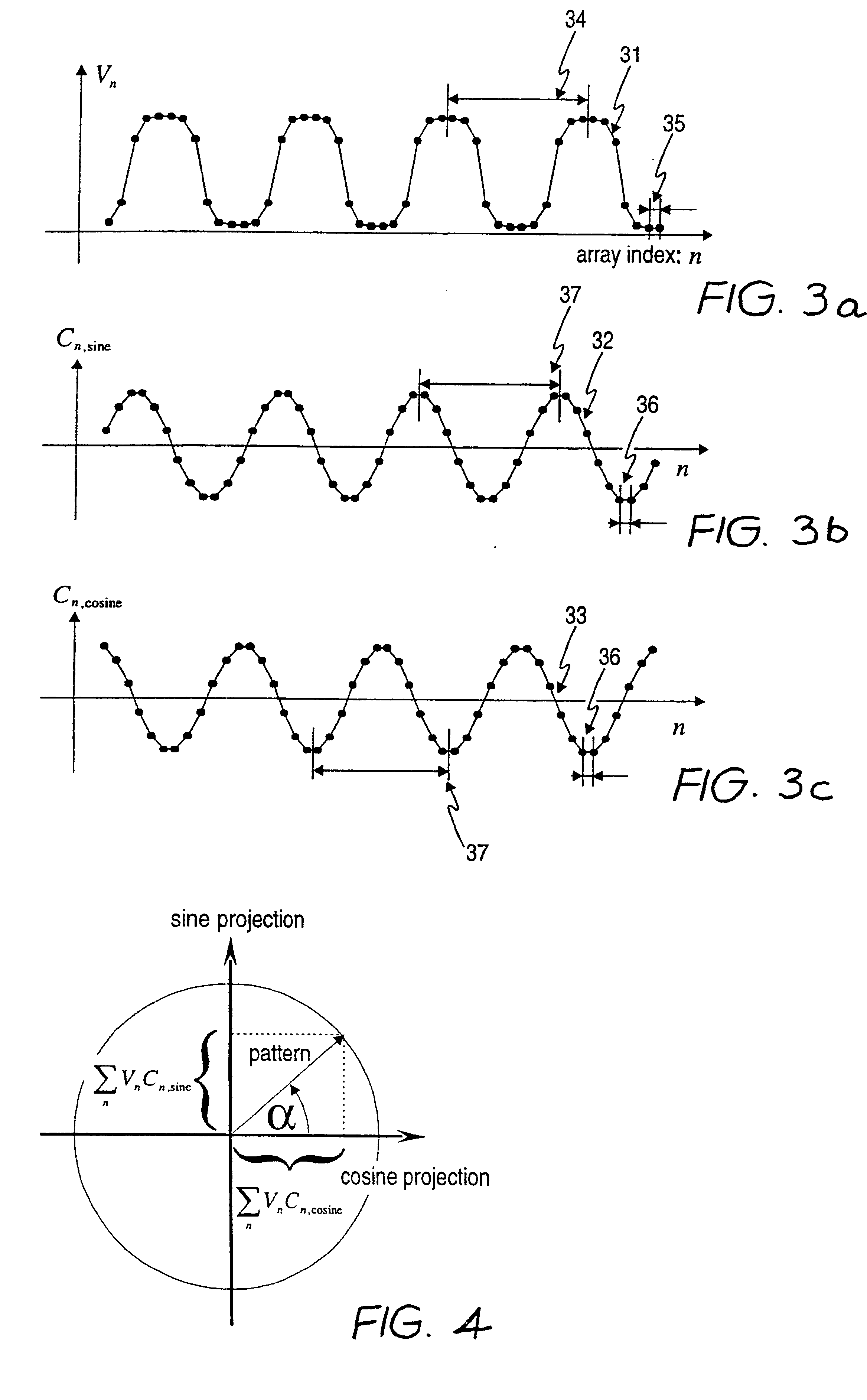

Position sensor and circuit for optical encoder

InactiveUS6528783B1Computing operations for integral formationElectric signal transmission systemsPhysicsPhase shifted

An electronic circuit for measuring the position of a spatially periodic intensity pattern of incident radiation includes an array of detectors (1); two or more correlator units (2, 3) each having arrays of capacitors (12, 13) connected to a buffer (14); and a phase angle computing unit (4). The pitch of the array of detectors (1) is smaller than the pitch of the incident intensity pattern so that the latter is oversampled, yielding high accuracy. The detector outputs (17) are weighted by respective fixed capacitance values (15, 16) which vary periodically along arrays of capacitors (12, 13), and a weighted sum of outputs for each correlator unit (2, 3) is output at its respective buffer (14). The capacitance values (15, 16) of respective correlator units (2, 3) are mutually offset by a predetermined phase shift. The analog computation using capacitor arrays (12, 13) is fast and energy efficient, and can be implemented as a VLSI circuit.

Owner:BISHOP INNOVATION PTY LTD

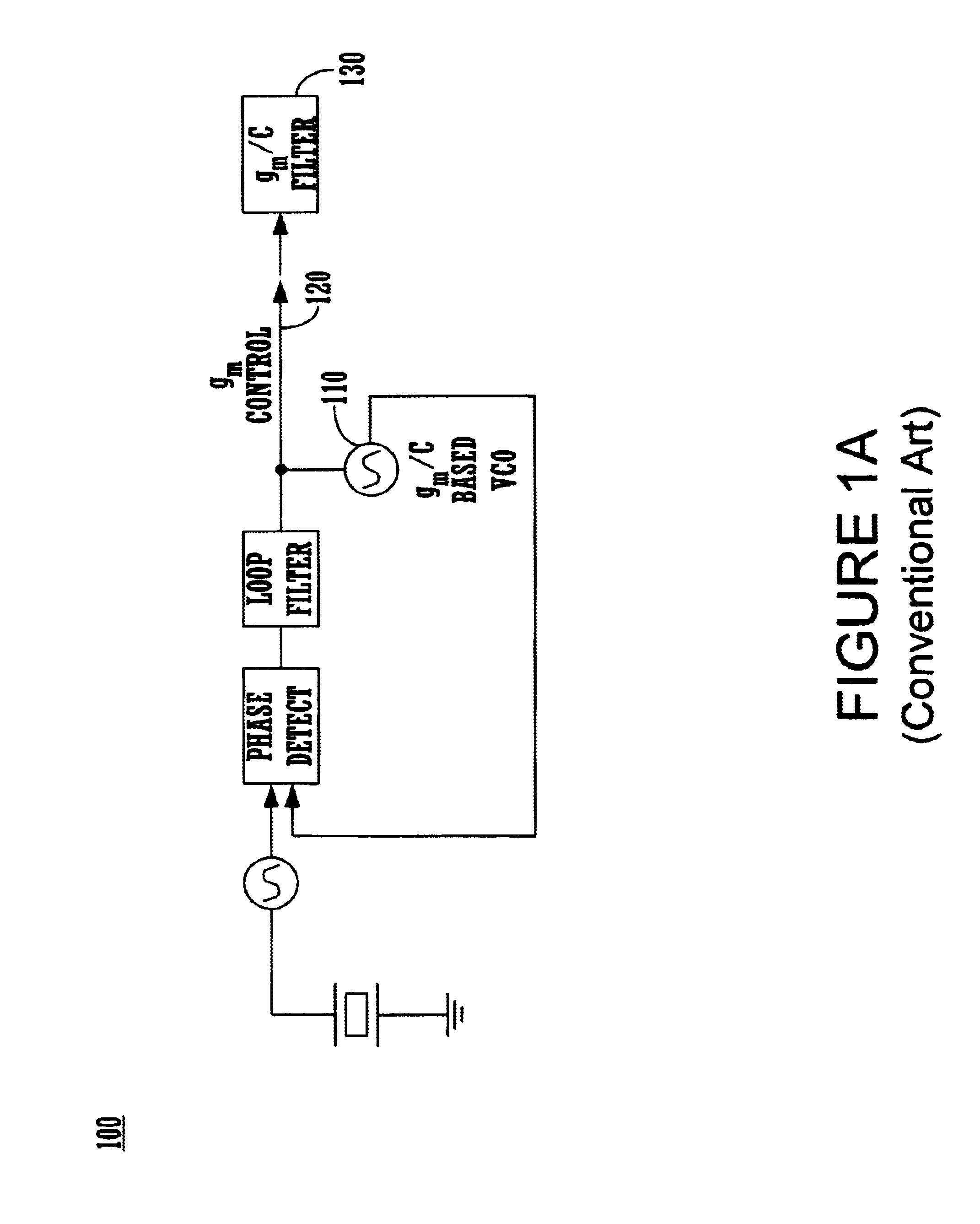

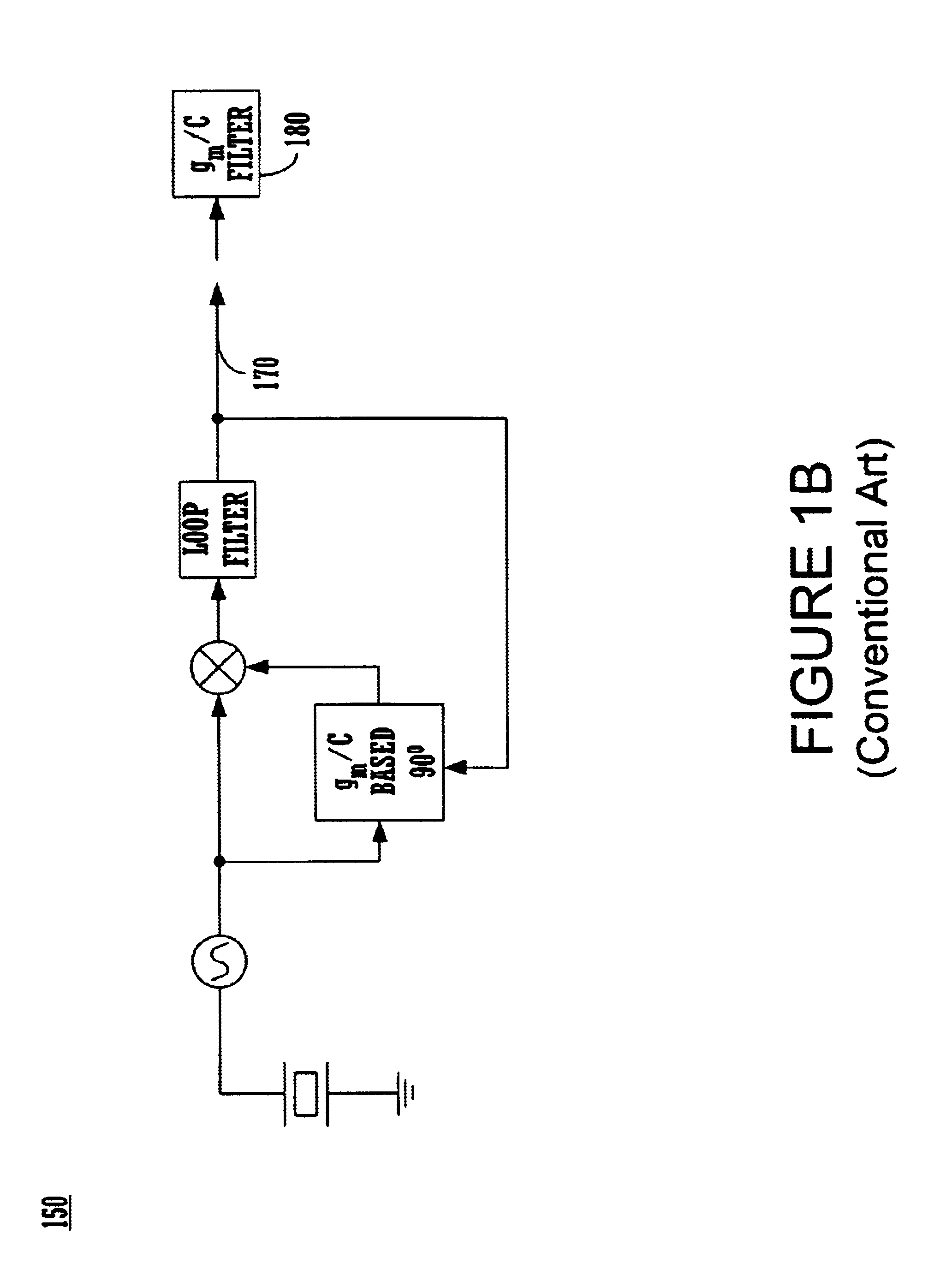

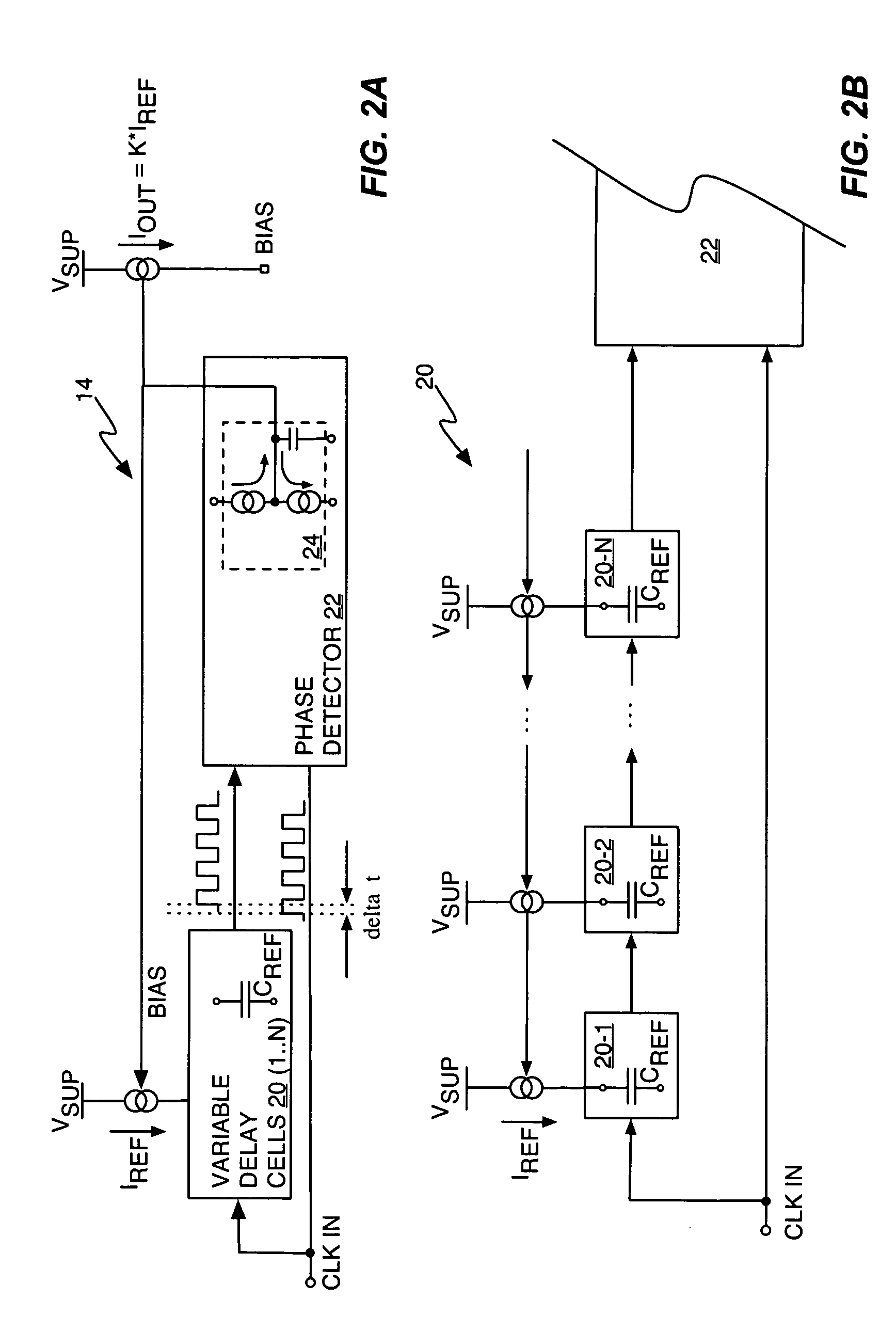

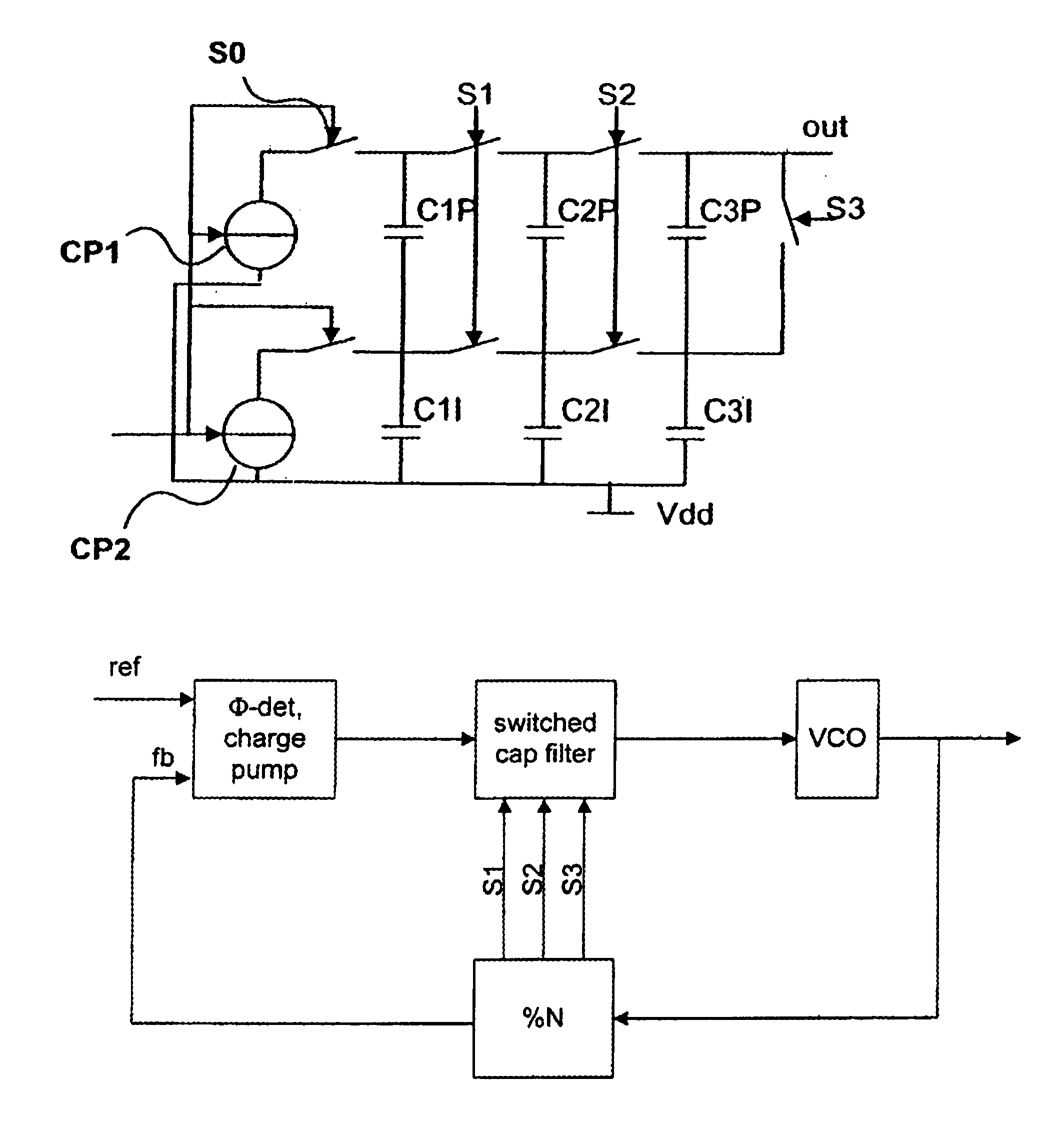

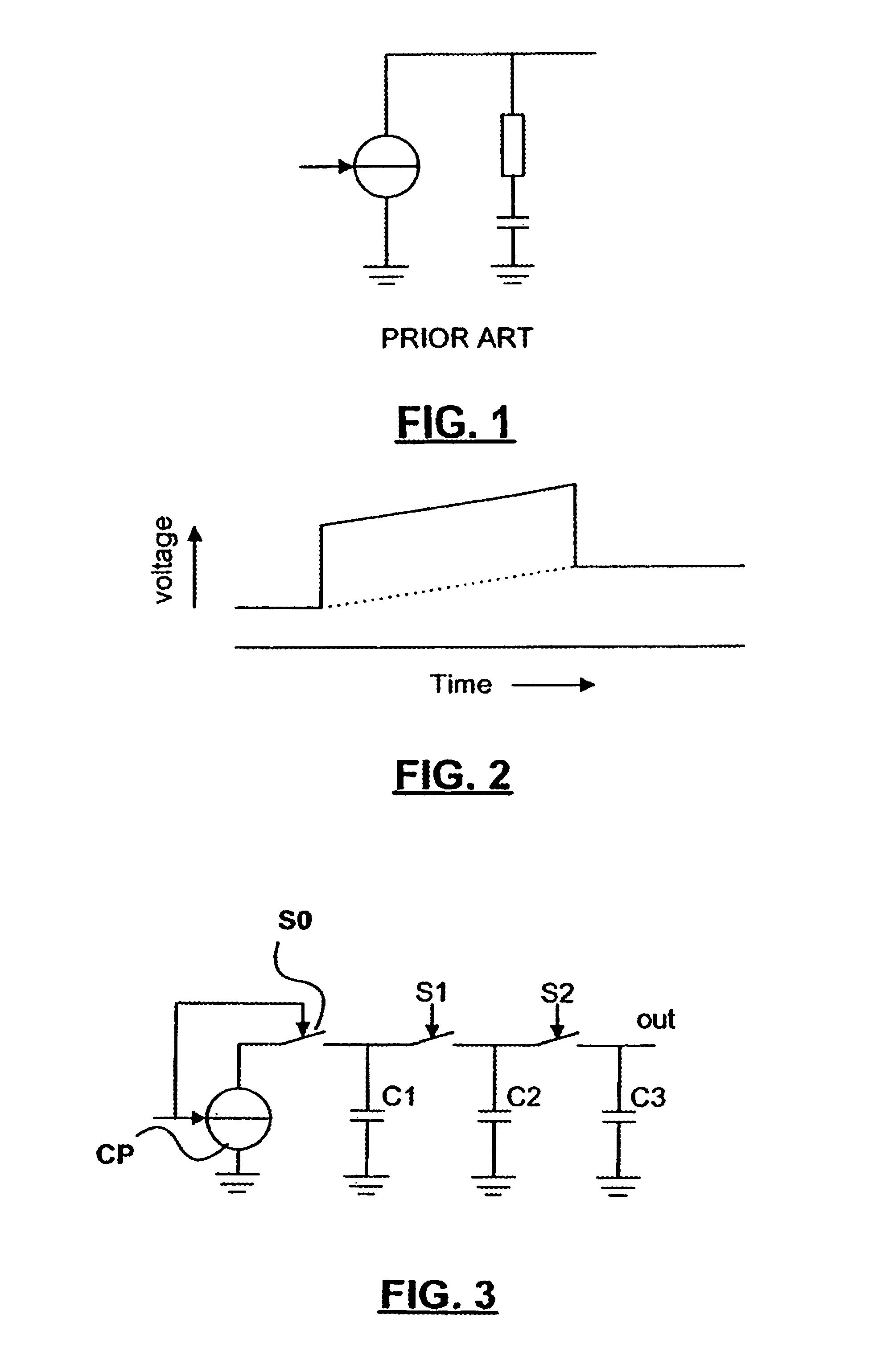

Analog PLL with switched capacitor resampling filter

InactiveUS7078946B2Reduce noiseComputing operations for integral formationComputing operations for integration/differentiationSwitched capacitorPhase-locked loop

A resampler filter for use in an analog phase-locked loop has a charge pump and one or more switched capacitors switched by signals derived from a voltage controlled oscillator in the phase locked loop.

Owner:ZARLINK SEMICON LTD

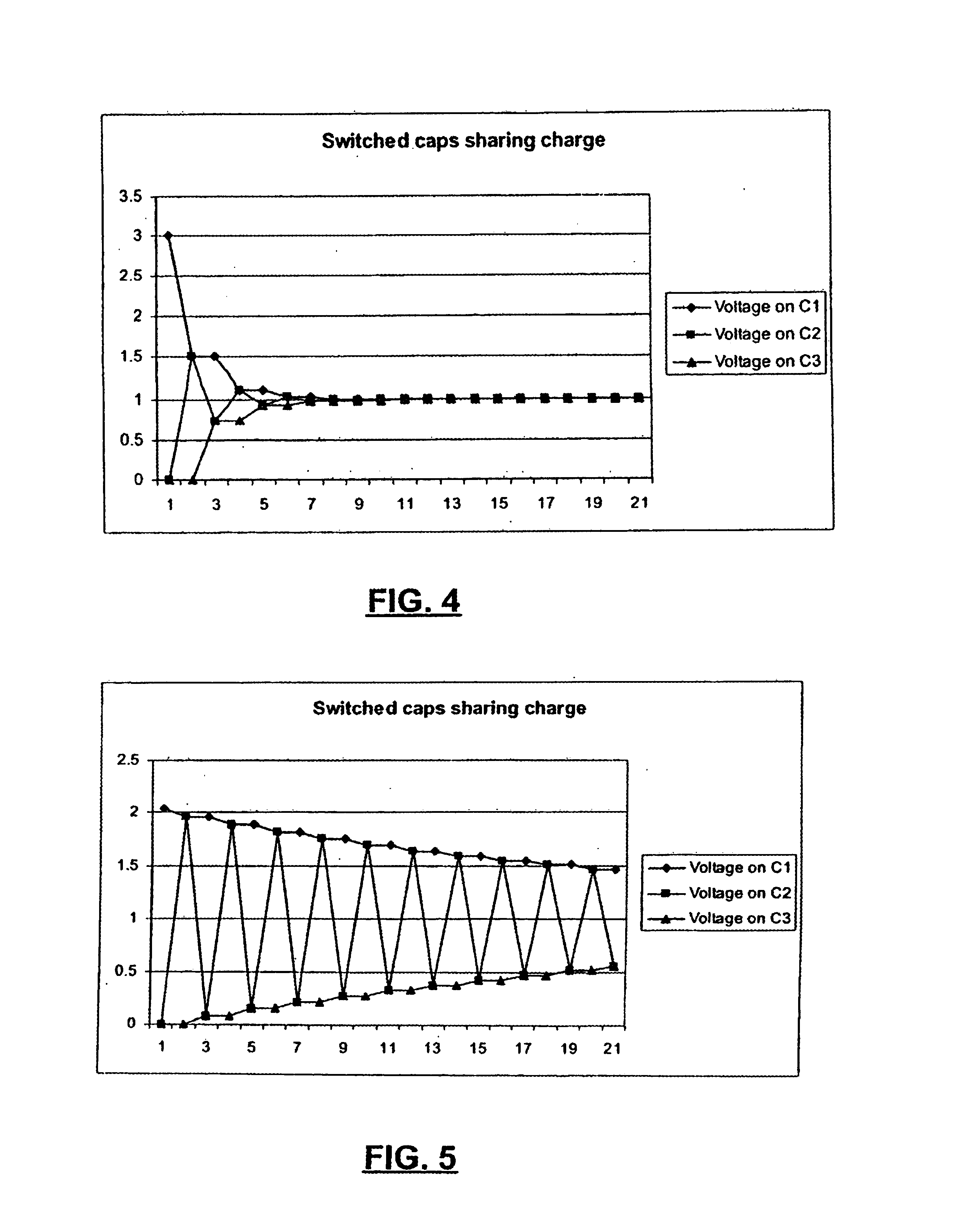

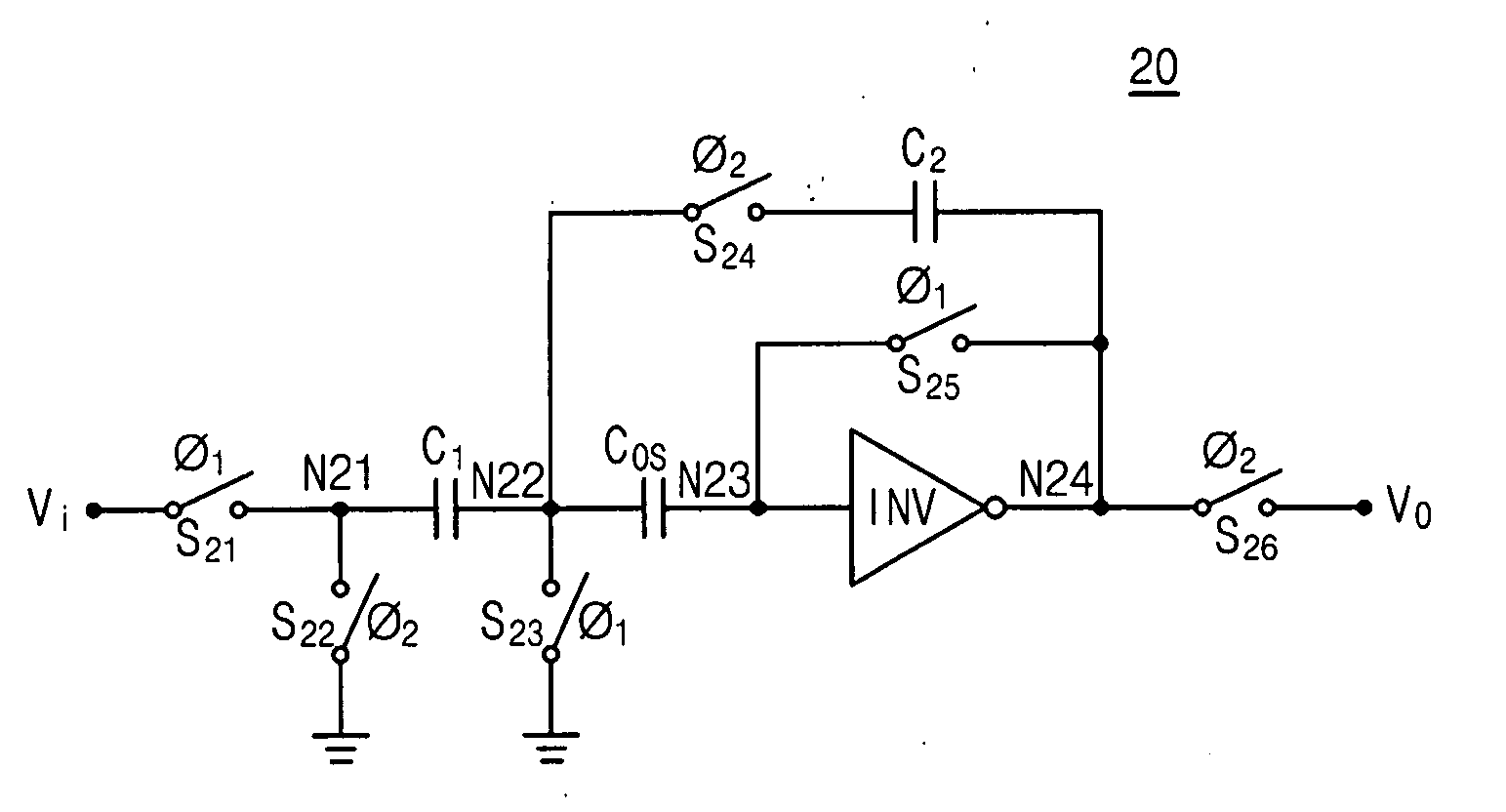

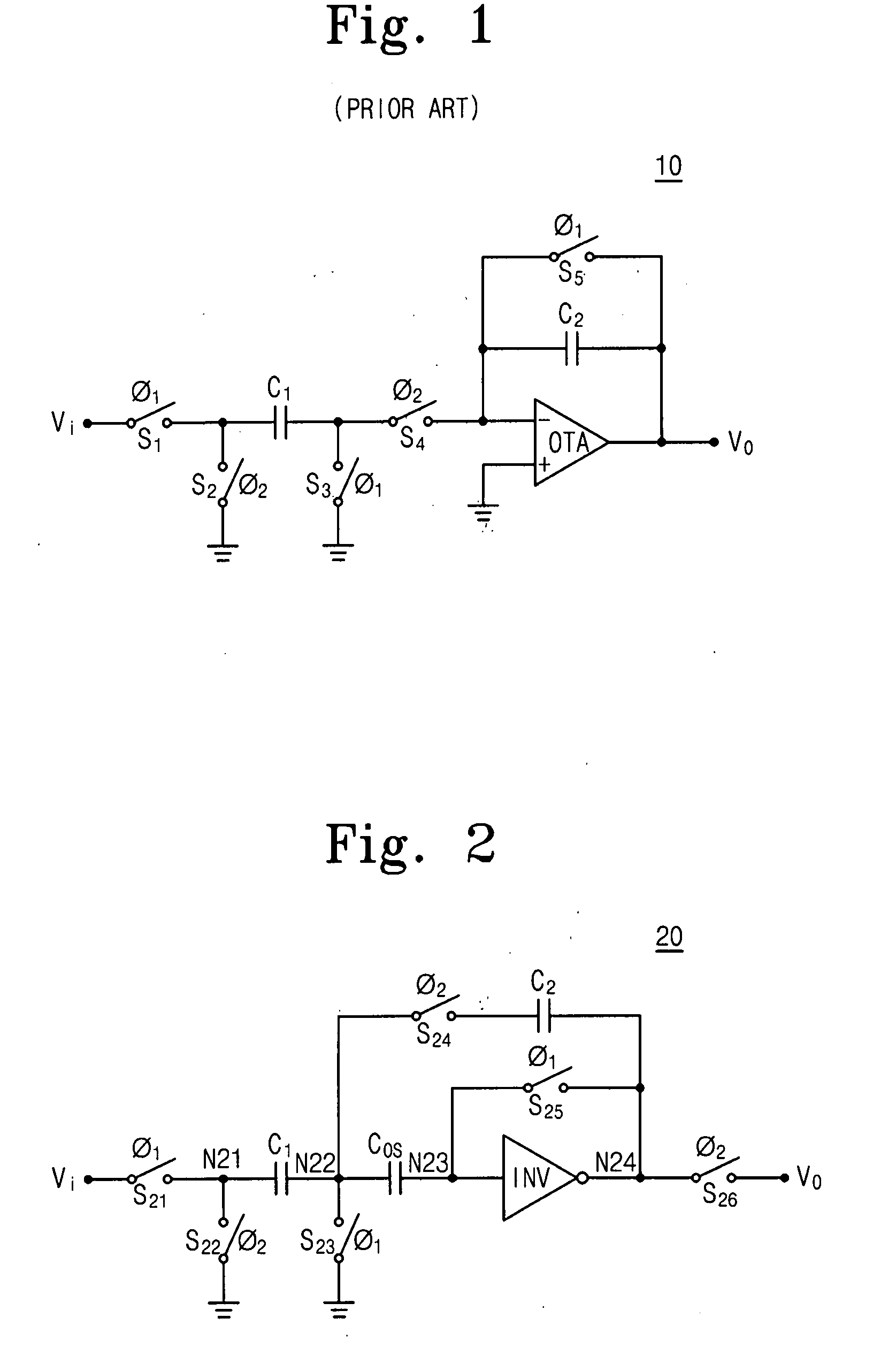

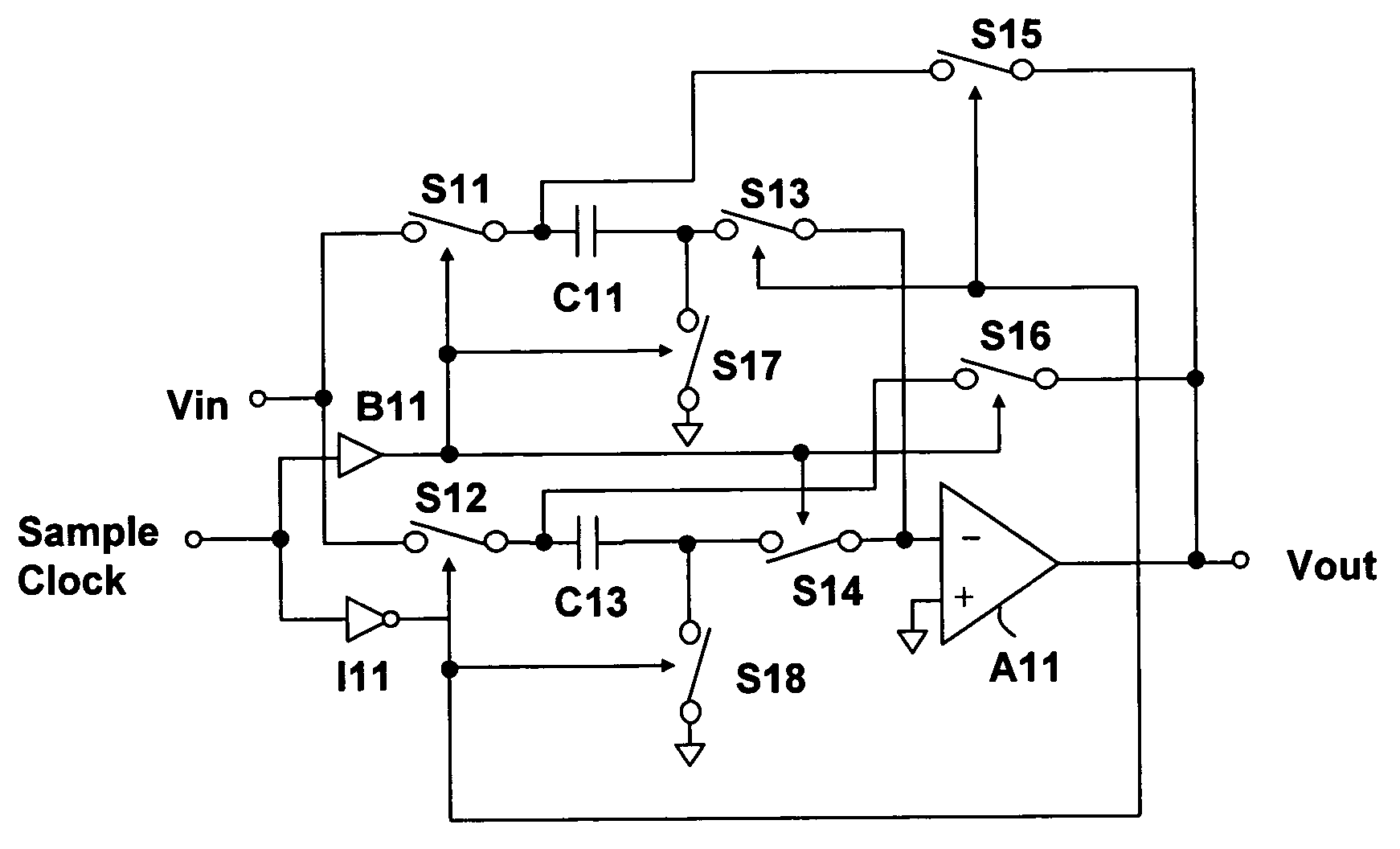

Switched capacitor circuit with inverting amplifier and offset unit

ActiveUS20080116966A1Reduce power consumptionReduce circuit areaComputing operations for integral formationAmplifier modifications to reduce non-linear distortionAudio power amplifierSample Mode

A switched capacitor circuit includes an amplifier, a charging unit, an offset unit, and an integrating unit. The charging unit is coupled between an input node and a first node, and is for accumulating charge corresponding to an input signal during a sampling mode. The offset unit is coupled between the first node and an input of the amplifier, and is for maintaining the first node to be a virtual ground during an integrating mode. The integrating unit is coupled between the first node and an output of the amplifier, and is for receiving charge from the charging unit during the integrating mode.

Owner:SAMSUNG ELECTRONICS CO LTD +1

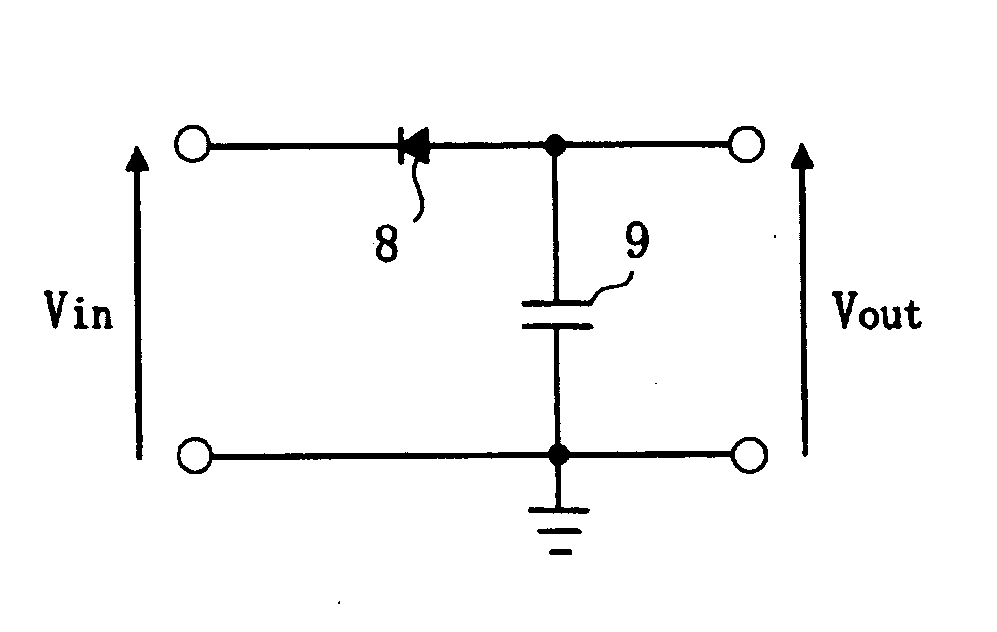

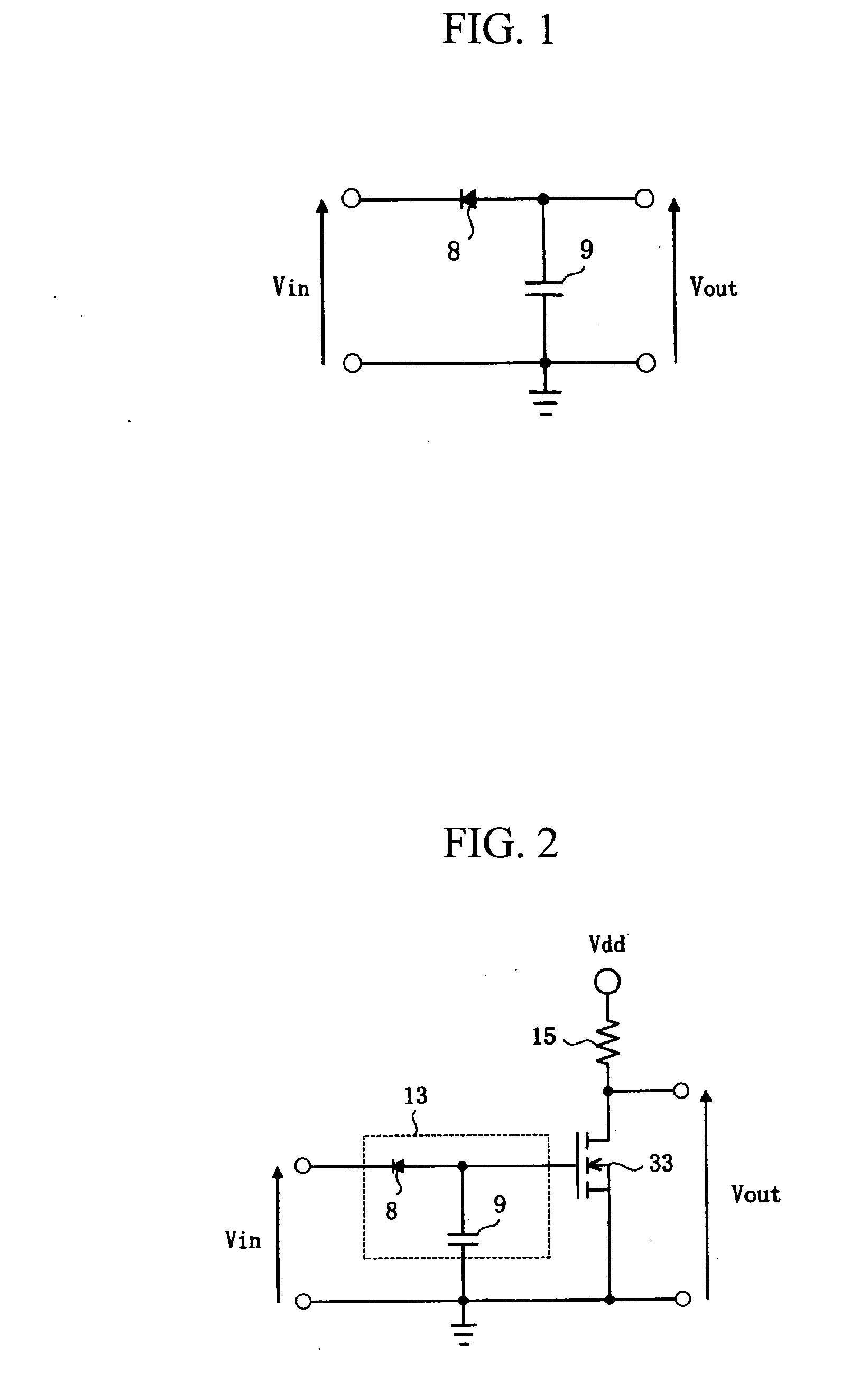

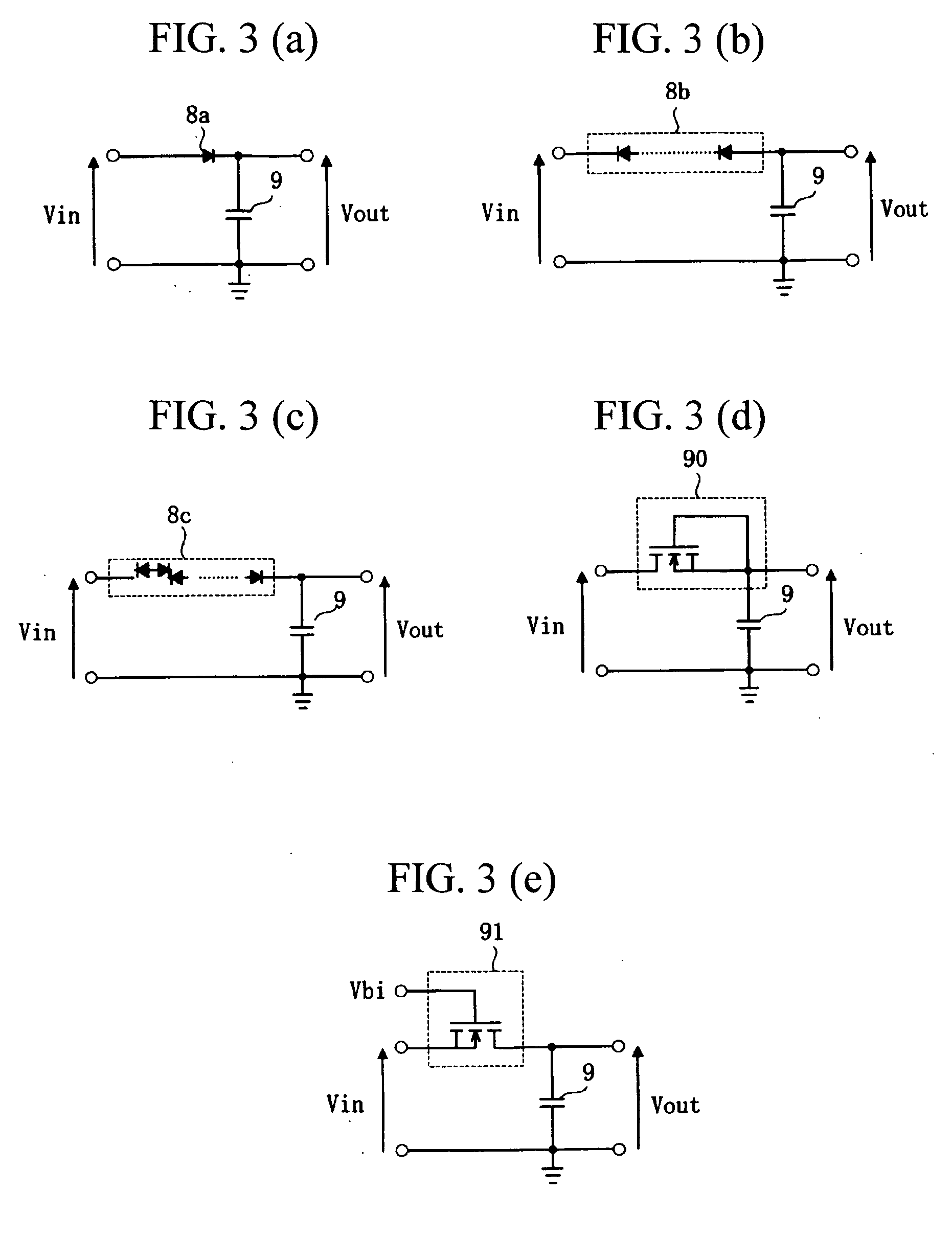

Integration circuit, decrement circuit, and semiconductor devices

InactiveUS20060022609A1Reduce areaSmall sizeComputing operations for integral formationComputing operations for integration/differentiationMOSFETPower flow

Owner:RENESAS ELECTRONICS CORP

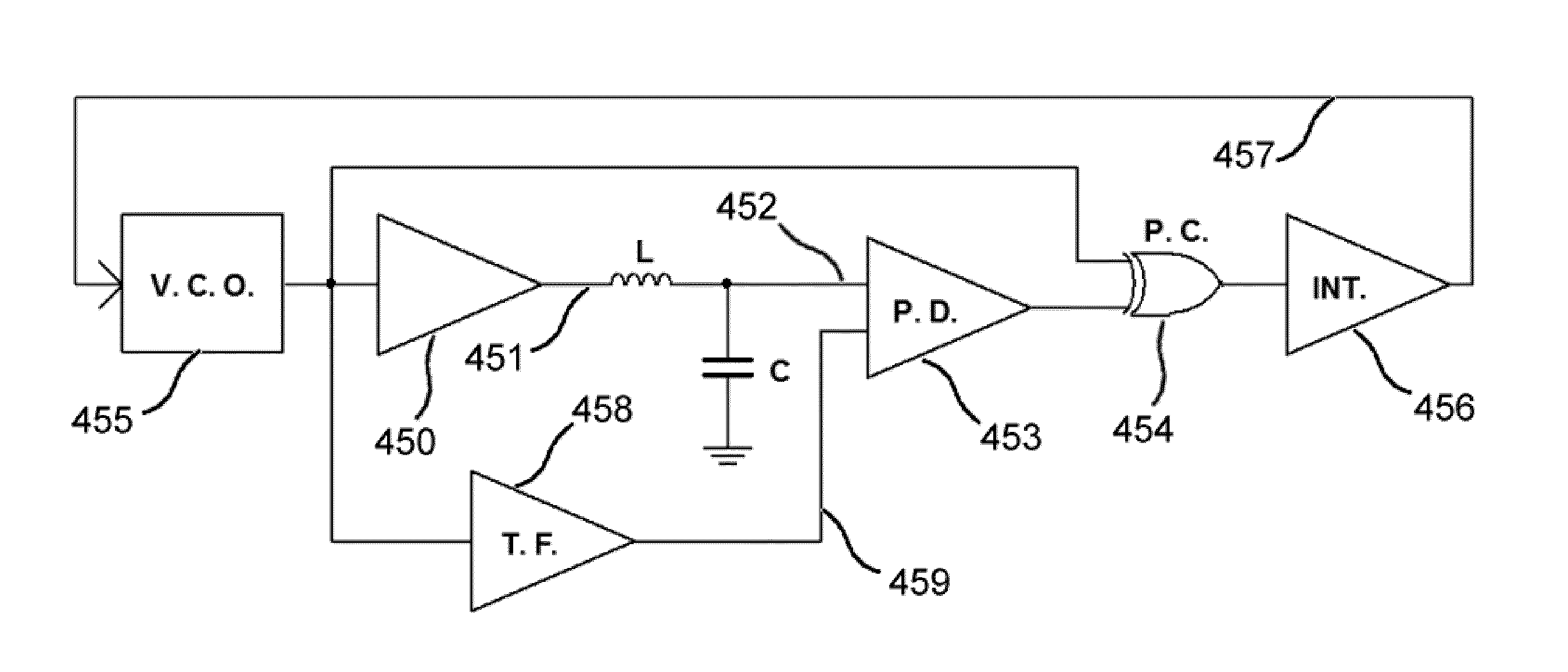

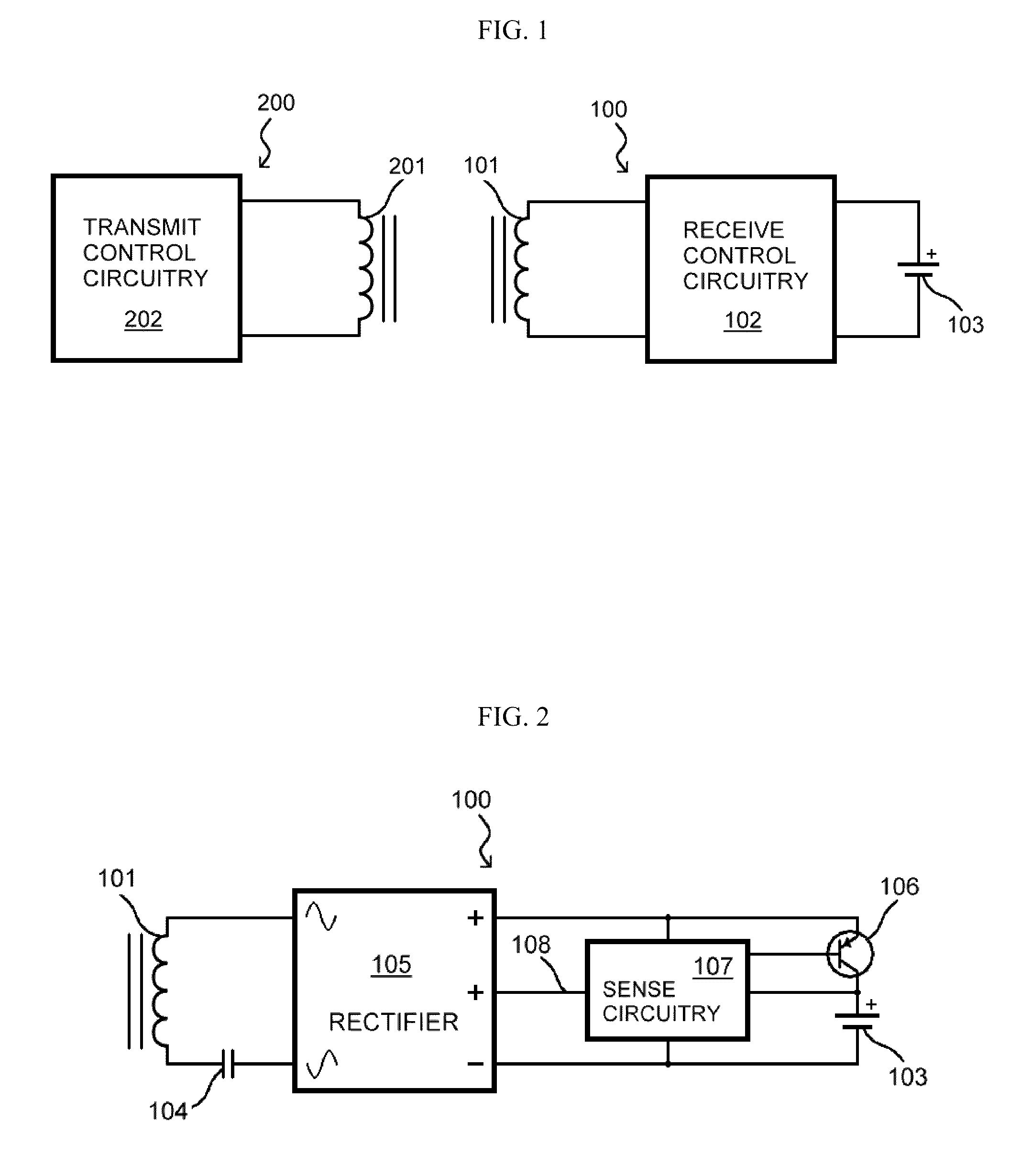

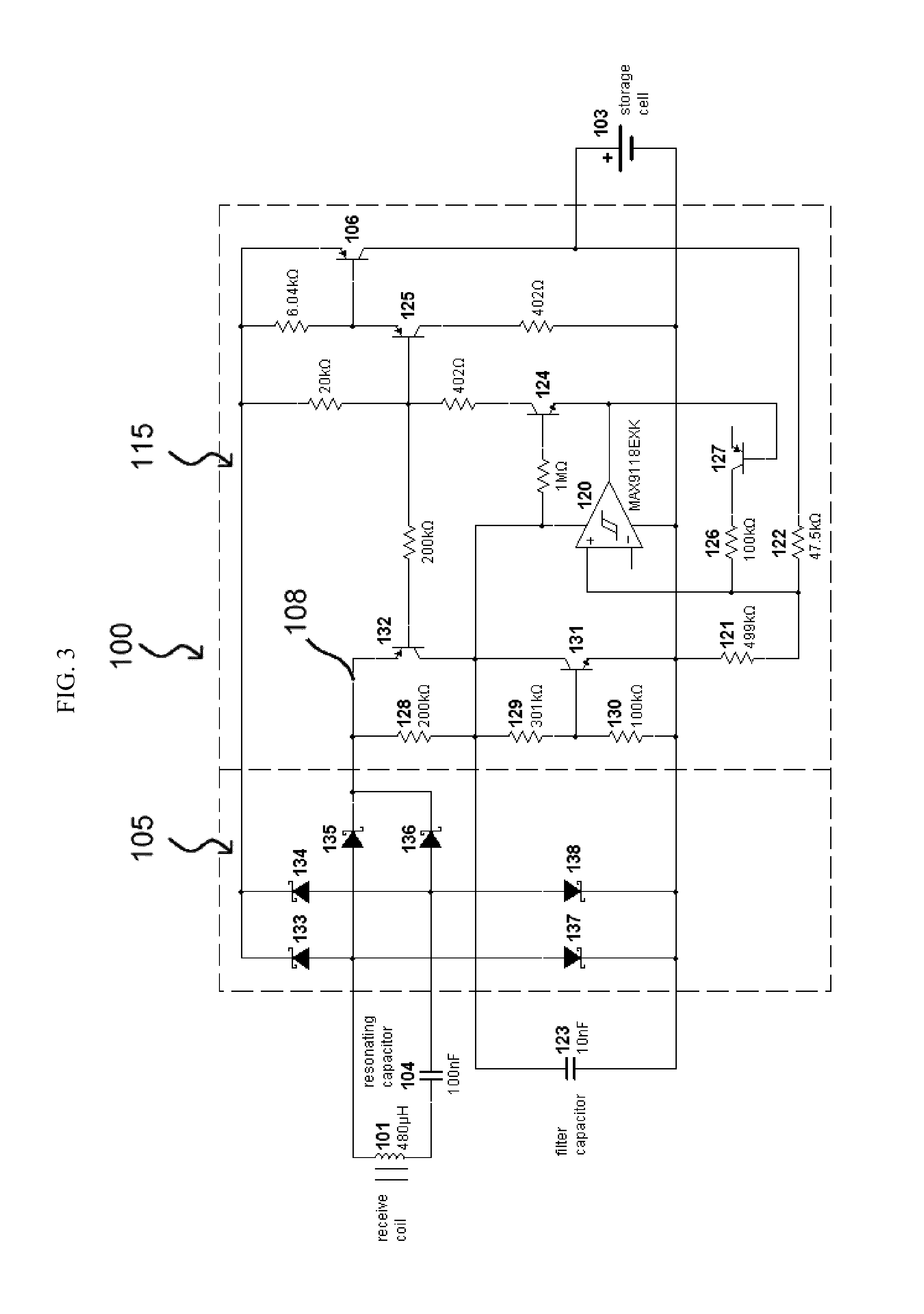

Systems and methods for maintaining a drive signal to a resonant circuit at a resonant frequency

ActiveUS8022775B2Computing operations for integral formationBatteries circuit arrangementsPhase detectorPhase difference

Systems and methods for maintaining a drive signal to a resonant circuit at a resonant frequency are provided. A system for maintaining a drive signal to a resonant circuit at a resonant frequency can include: an oscillator configured to provide an output to a phase comparator and a drive circuit, the drive circuit configured to provide a drive signal to a resonant circuit; a phase detector configured to receive a filtered version of the drive signal from the resonant circuit and provide a phase-indicating signal to the phase comparator; and the phase comparator, wherein the phase comparator is configured to provide a signal based on the phase difference between the oscillator output and the phase-indicating signal, wherein the signal from the phase comparator is used to control the frequency of the oscillator such that the phase difference converges to a fixed value.

Owner:ETYMOTIC RES

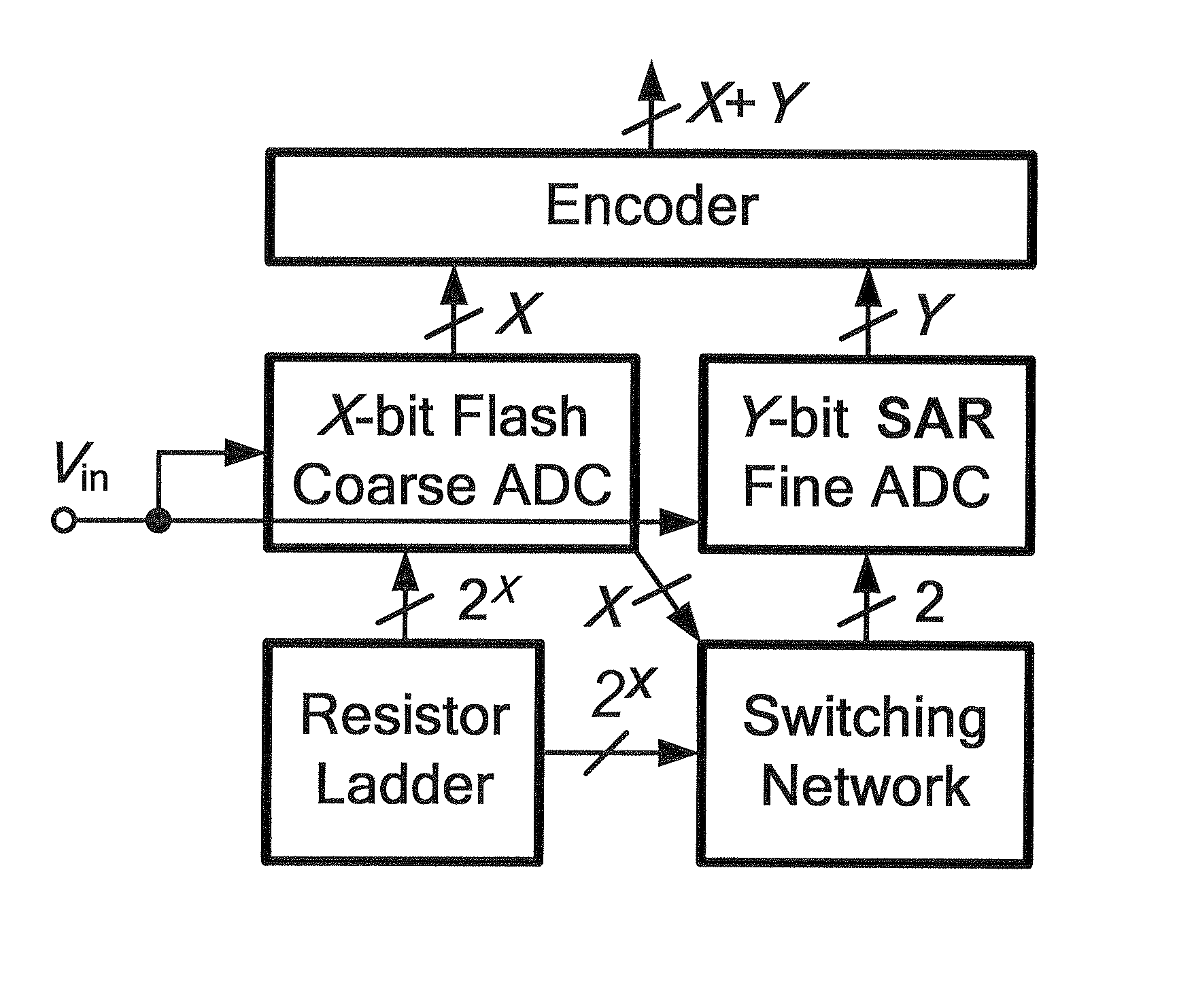

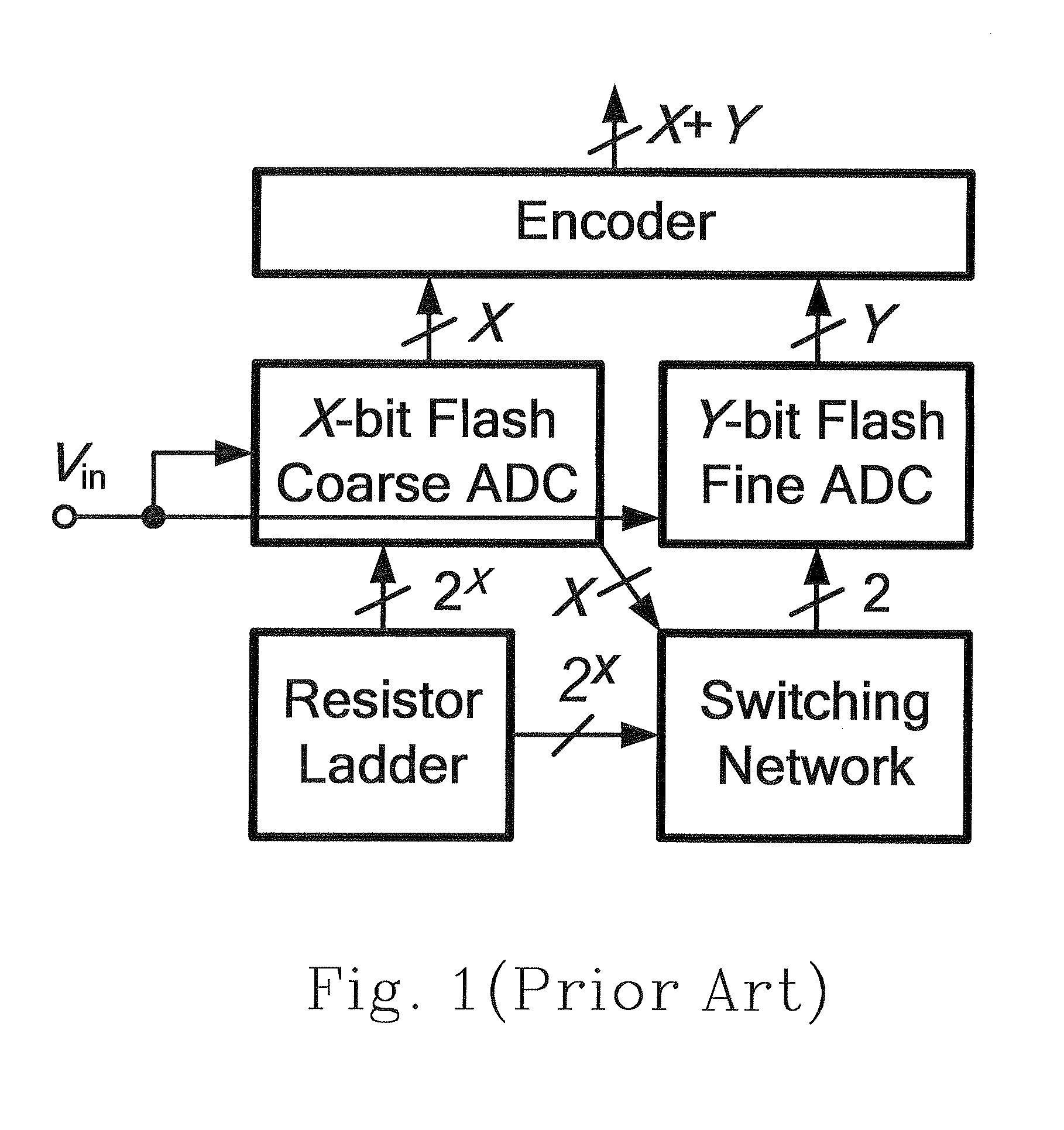

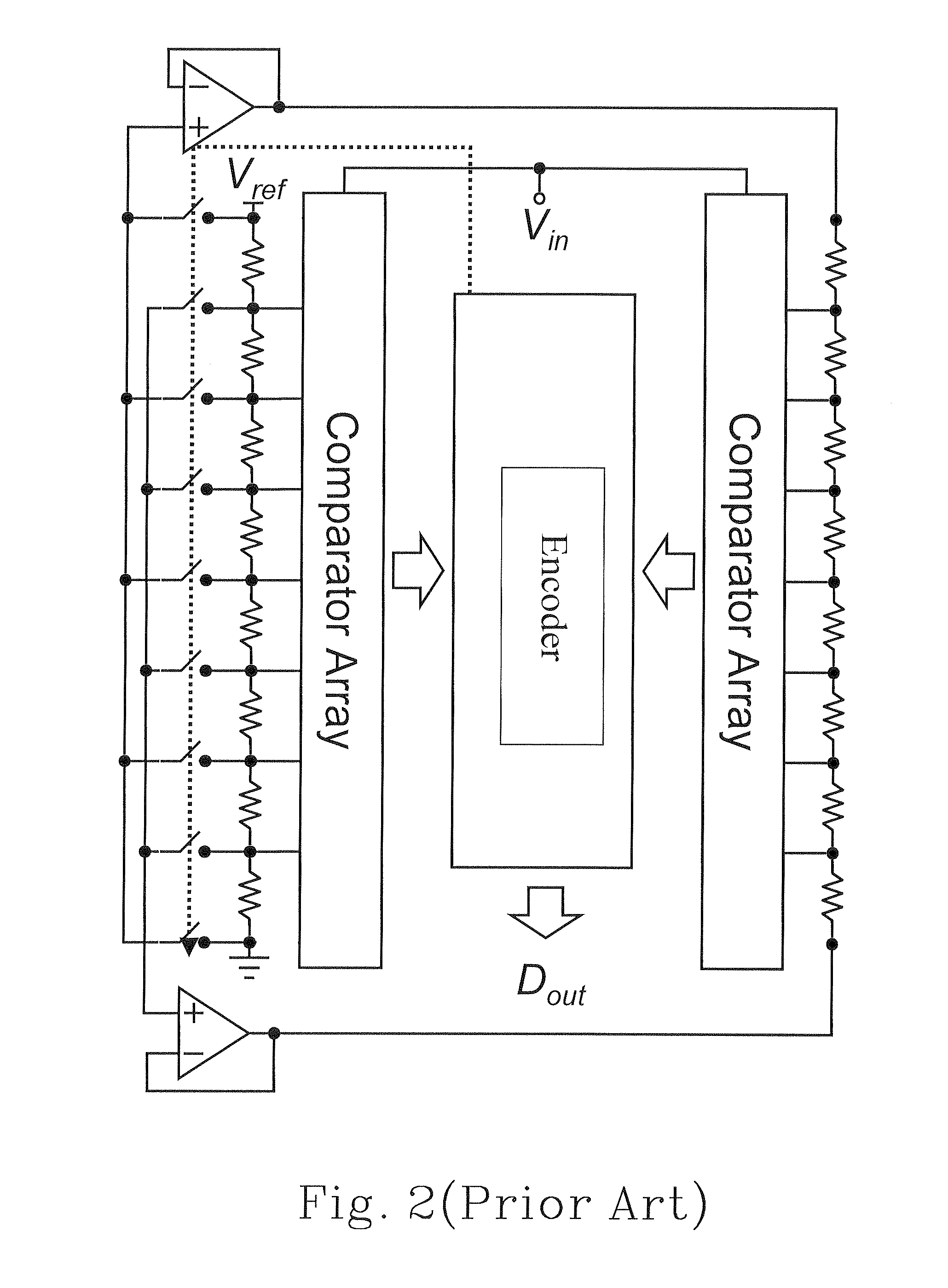

Subrange analog-to-digital converter and method thereof

InactiveUS20120154193A1Improves differential non-linearity (DNL)Fast sampling speedComputing operations for integral formationElectric signal transmission systemsDigital down converterEngineering

The configurations and adjusting method of a subrange analog-to-digital converter (ADC) are provided. The provided subrange ADC includes a X.5-bit flash ADC, a Y-bit SAR ADC and a (X+Y)-bit segmented capacitive digital-to-analog converter (DAC).

Owner:NAT CHENG KUNG UNIV

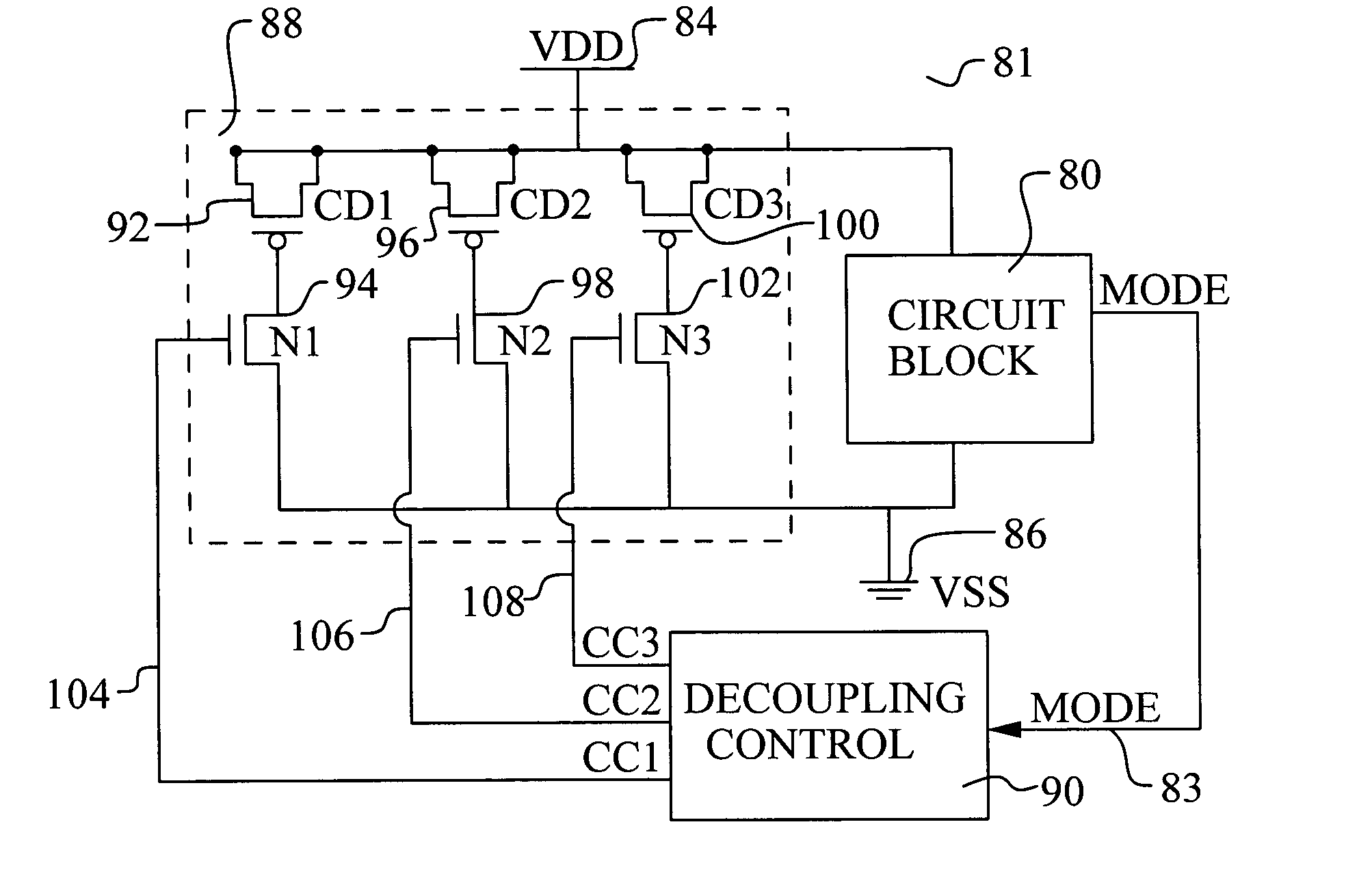

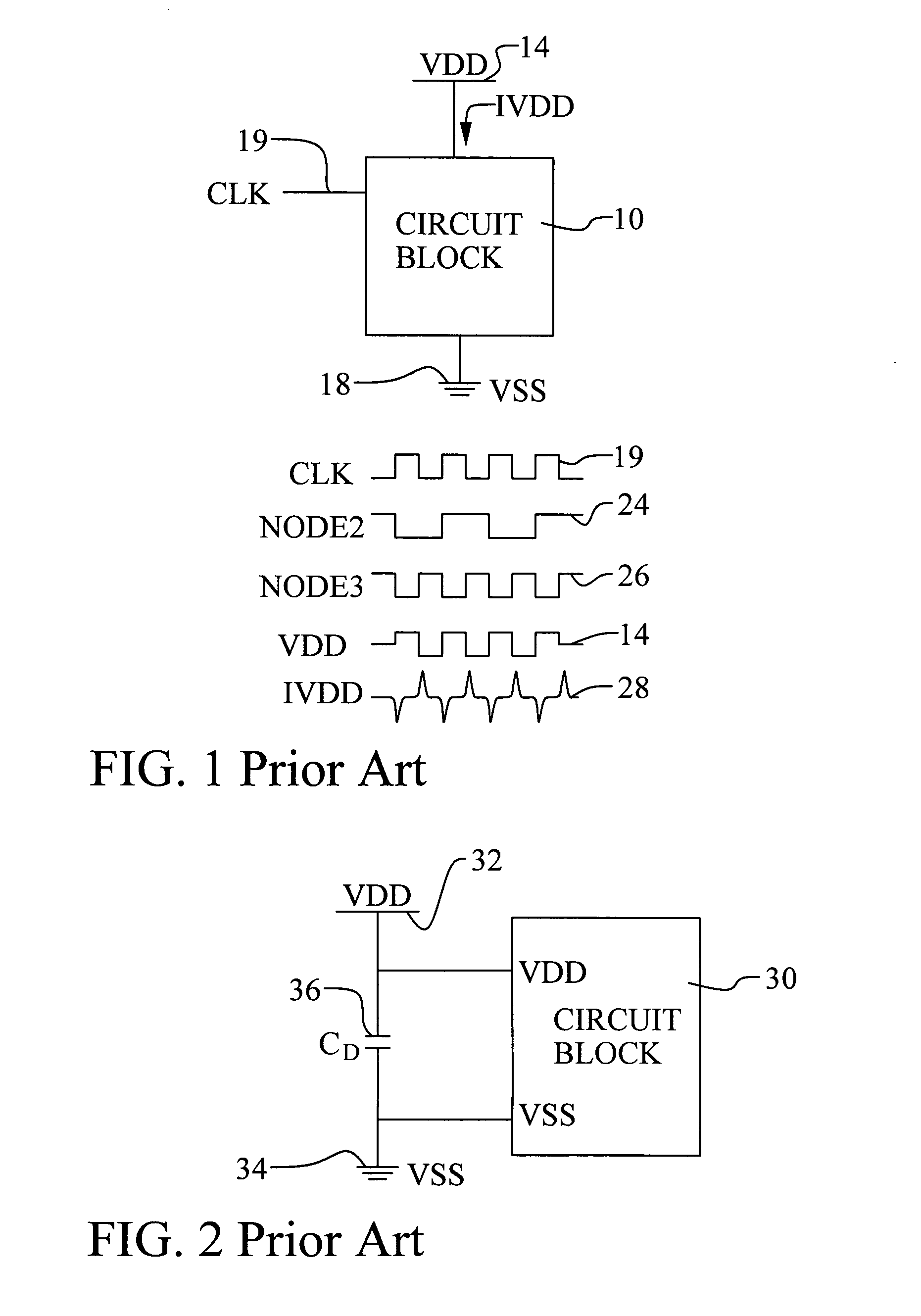

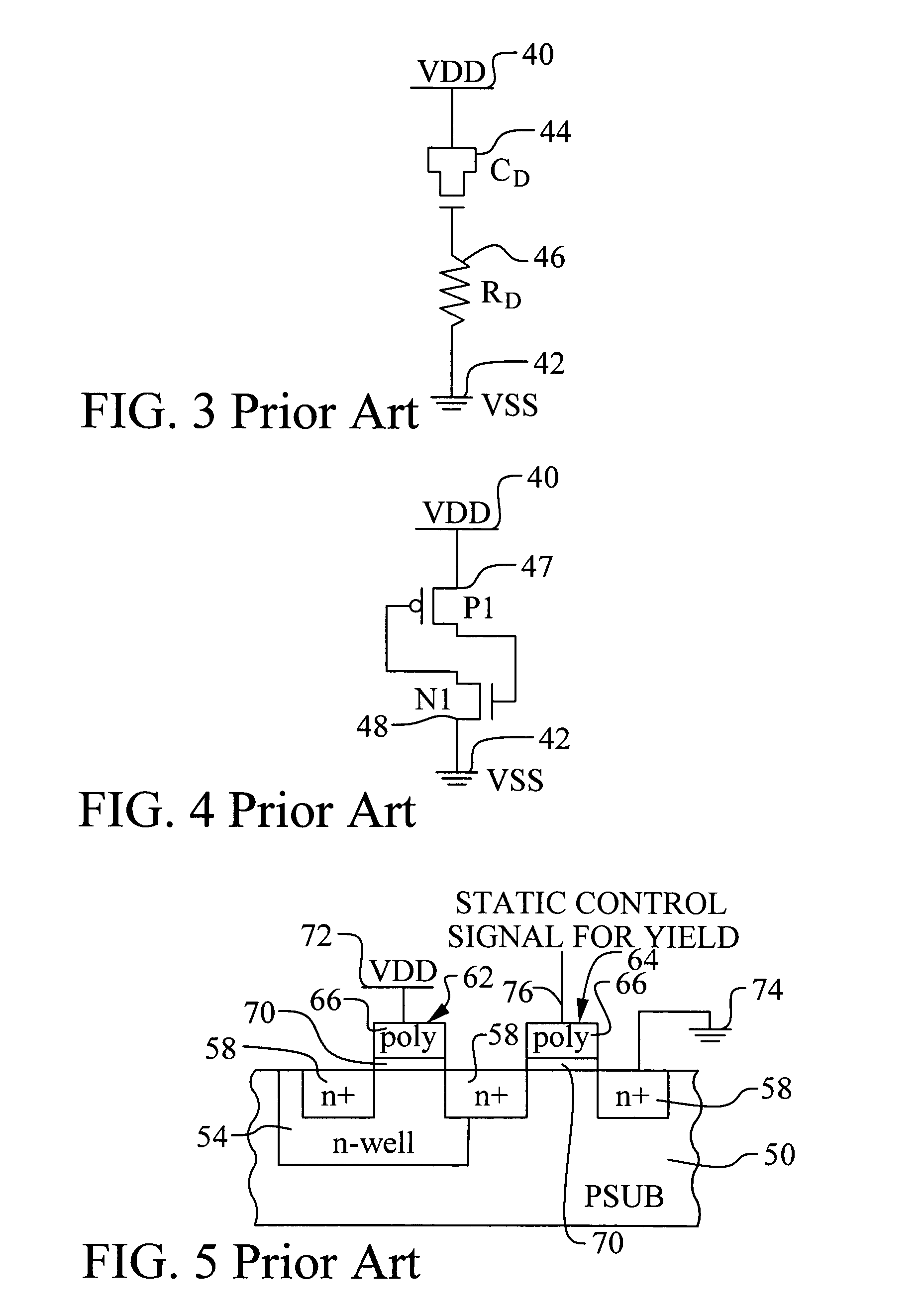

Dynamically adjustable decoupling capacitance to reduce gate leakage current

InactiveUS20050062523A1Reduce switching noiseCurrent is limitedComputing operations for integral formationComputing operations for integration/differentiationCapacitanceGate leakage current

A new method to reduce switching noise on an integrated circuit device is achieved. The method comprises providing an integrated circuit device comprising a power supply, a ground, and a plurality of switchable capacitors. Each switchable capacitor is connected from the power supply to ground. The operating mode of the integrated circuit device is tracked. An optimal capacitance value is selected based on the operating mode. A set of switchable capacitors from the plurality of switchable capacitors is selected to thereby connect the optimal capacitance value from the power supply to ground.

Owner:TAIWAN SEMICON MFG CO LTD

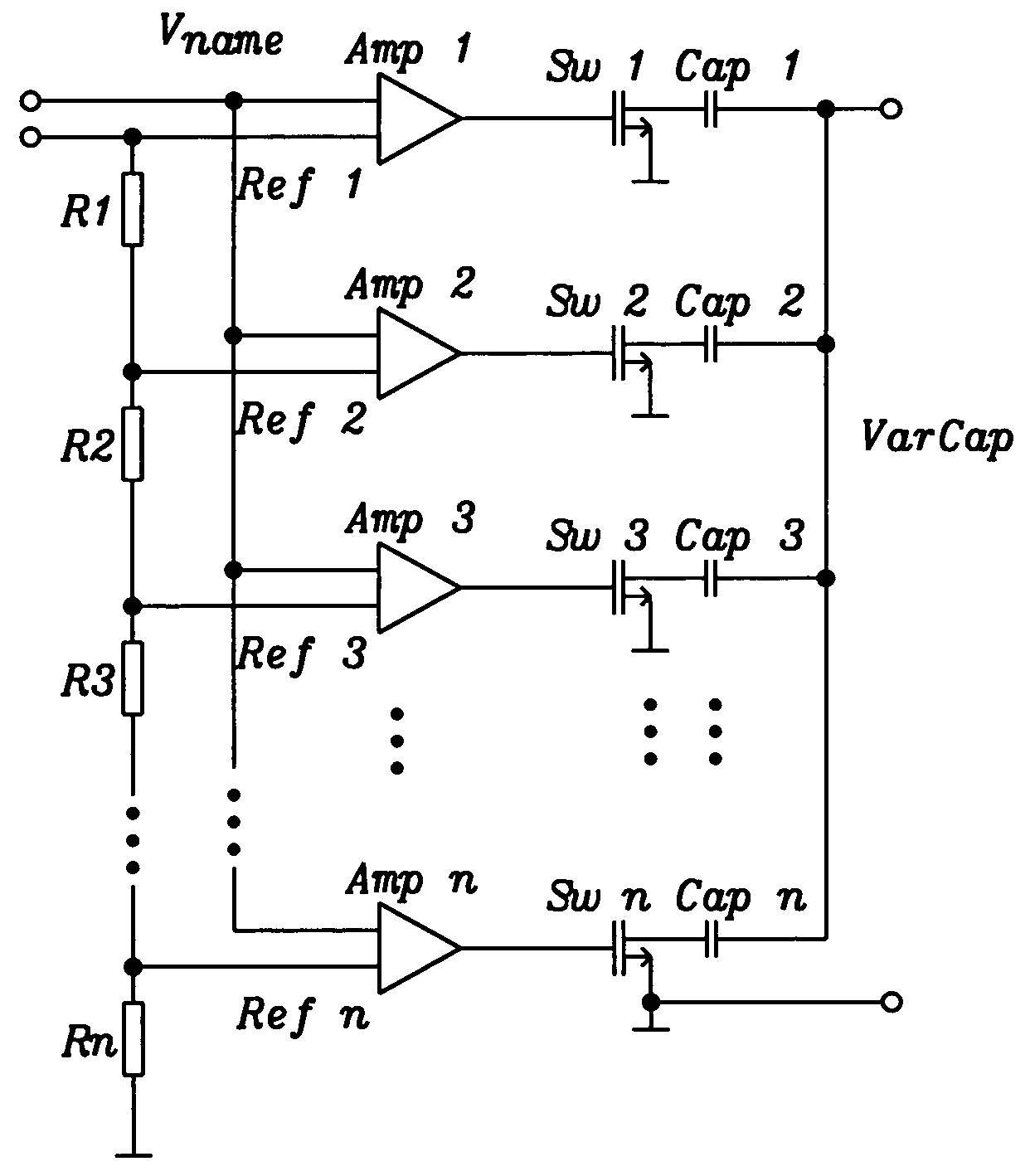

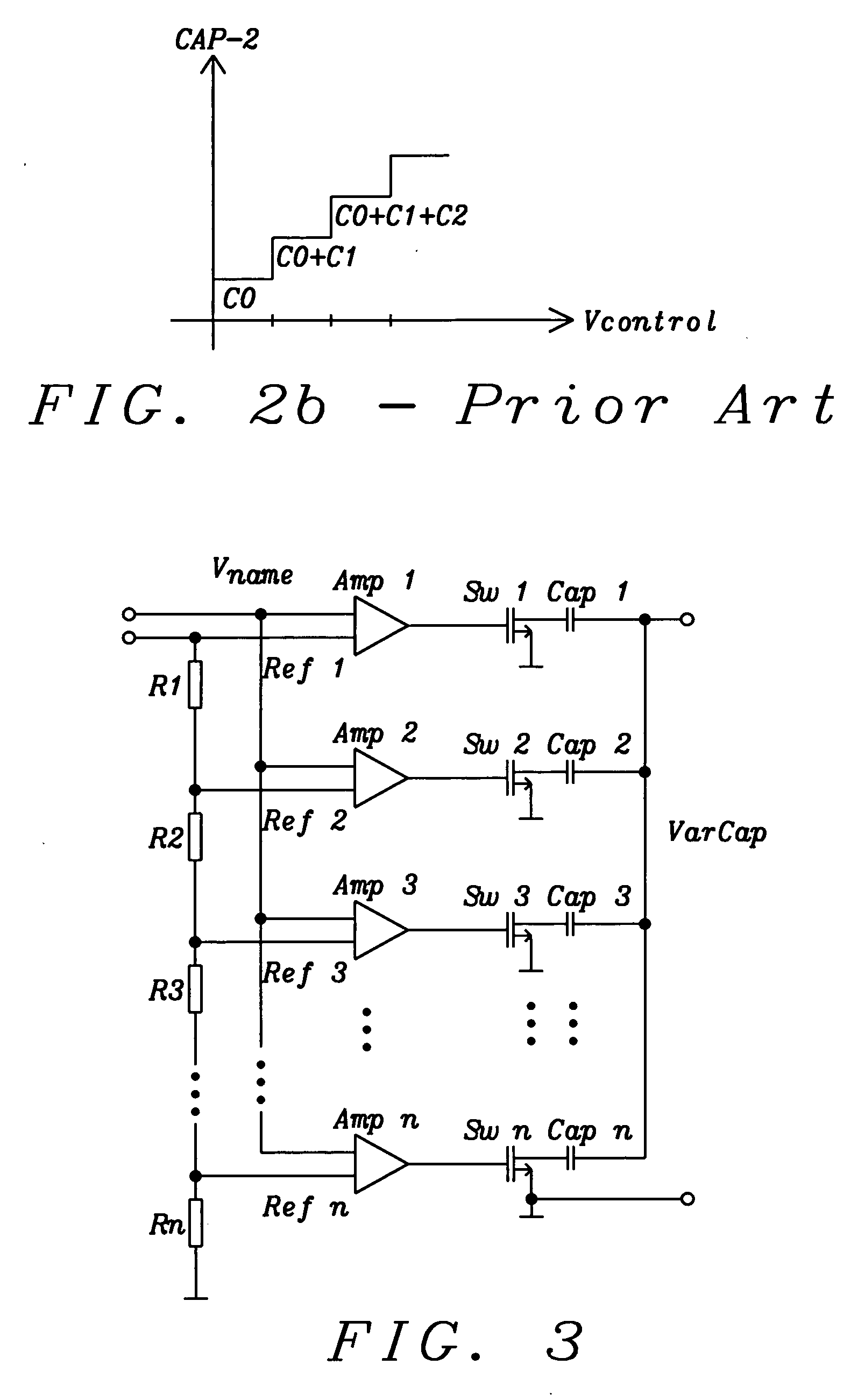

High Q linear controlled variable capacitor using translinear amplifier

InactiveUS20050151575A1Many degrees of freedomMinimize impactComputing operations for integral formationComputing operations for integration/differentiationQ factorLinear control

A voltage controlled variable capacitor, formed of a larger number of fixed capacitor segments and a corresponding number of switching elements, uses translinear amplifiers to control each switching element. Each translinear amplifier linearly switches from the fully off to the fully on state; a minimum number of switching stages (ideally only one) is in the mode-of-change at any one time with a minimum overlap. The arrangement achieves a nearly linear change of capacitance at linear tuning voltage change, while resulting in high Q-factor due to the low RDSon and high RDSoff of the fully switched stages. The invention eliminates temperature and voltage dependencies of other solutions like varactor diodes.

Owner:DIALOG SEMICONDUCTOR

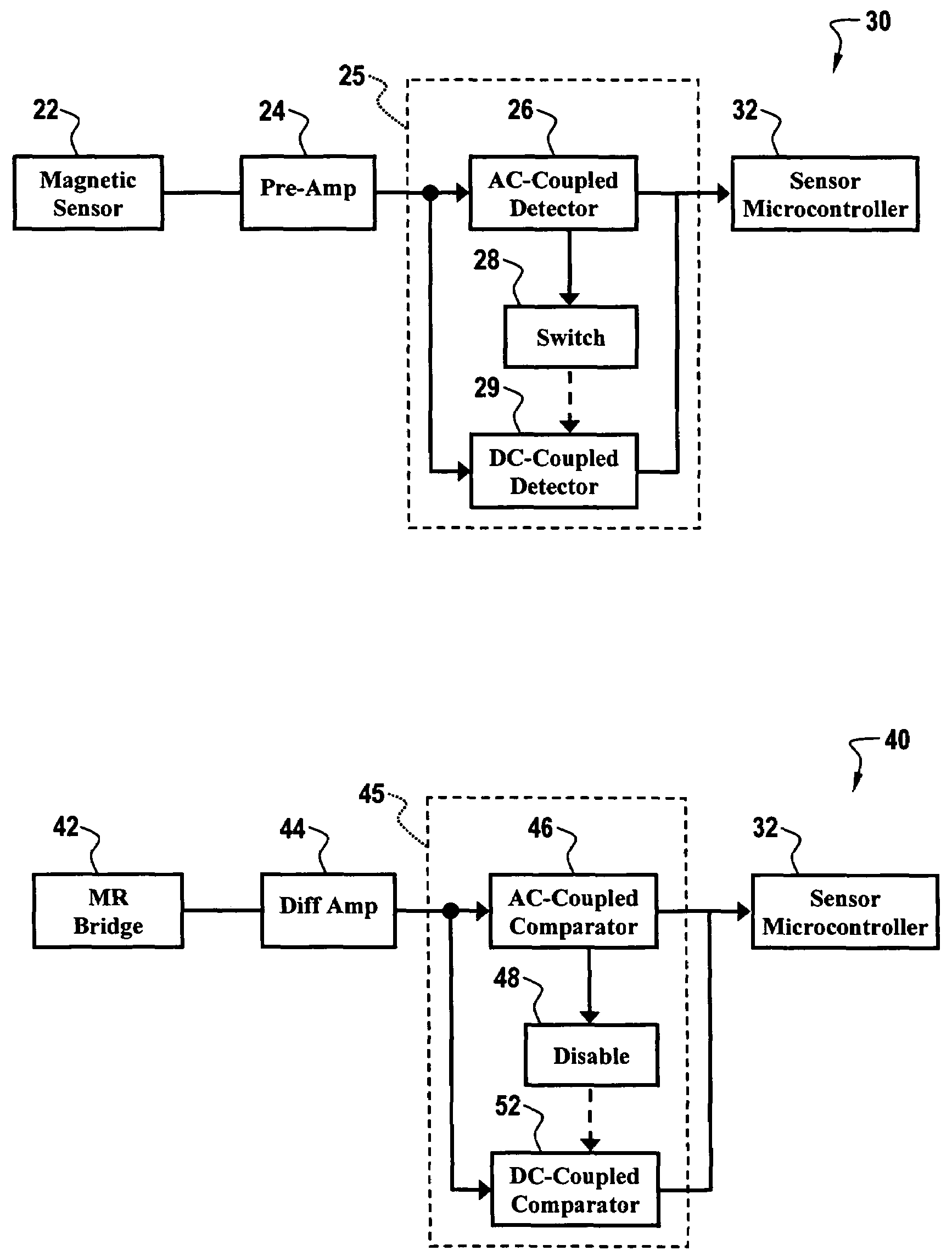

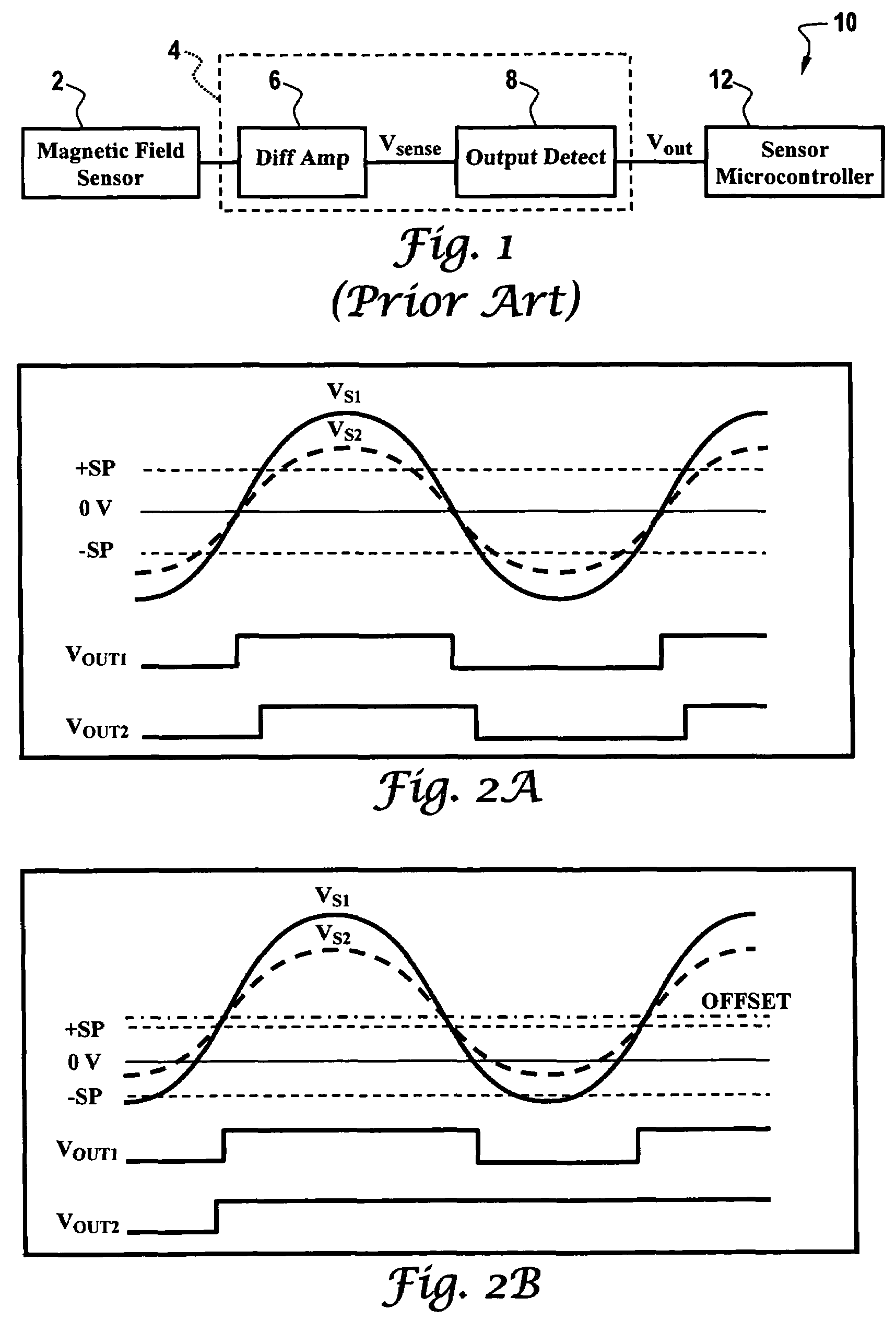

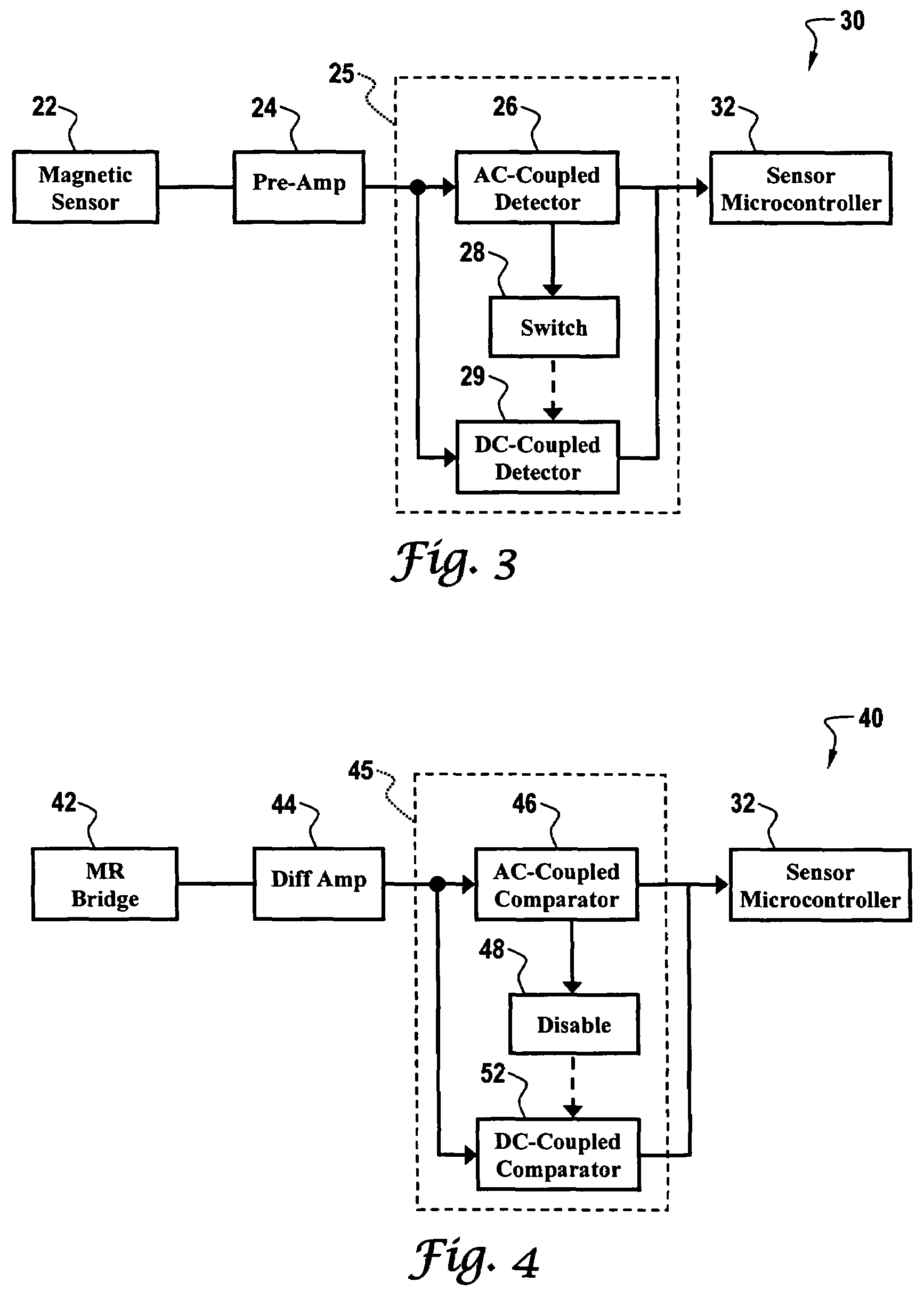

Sensor signal conditioning circuit

InactiveUS7391204B2Computing operations for integral formationComputing operations for integration/differentiationSignal conditioning circuitsEngineering

A sensor signal conditioning circuit and sensor system incorporating the same. In one embodiment, the signal conditioning circuit includes a DC-coupled detector that converts a sensor signal into a discrete level signal. An AC-coupled detector having a dynamic DC threshold input also converts the sensor signal into a discrete level signal and has a startup delay associated with the dynamic DC threshold input. The signal conditioning circuit further includes a device that inhibits the DC-coupled detector responsive to the dynamic DC threshold input reaching a specified threshold voltage level such that the AC-coupled detector provides the detected output during steady-state sensor operation.

Owner:HONEYWELL INT INC

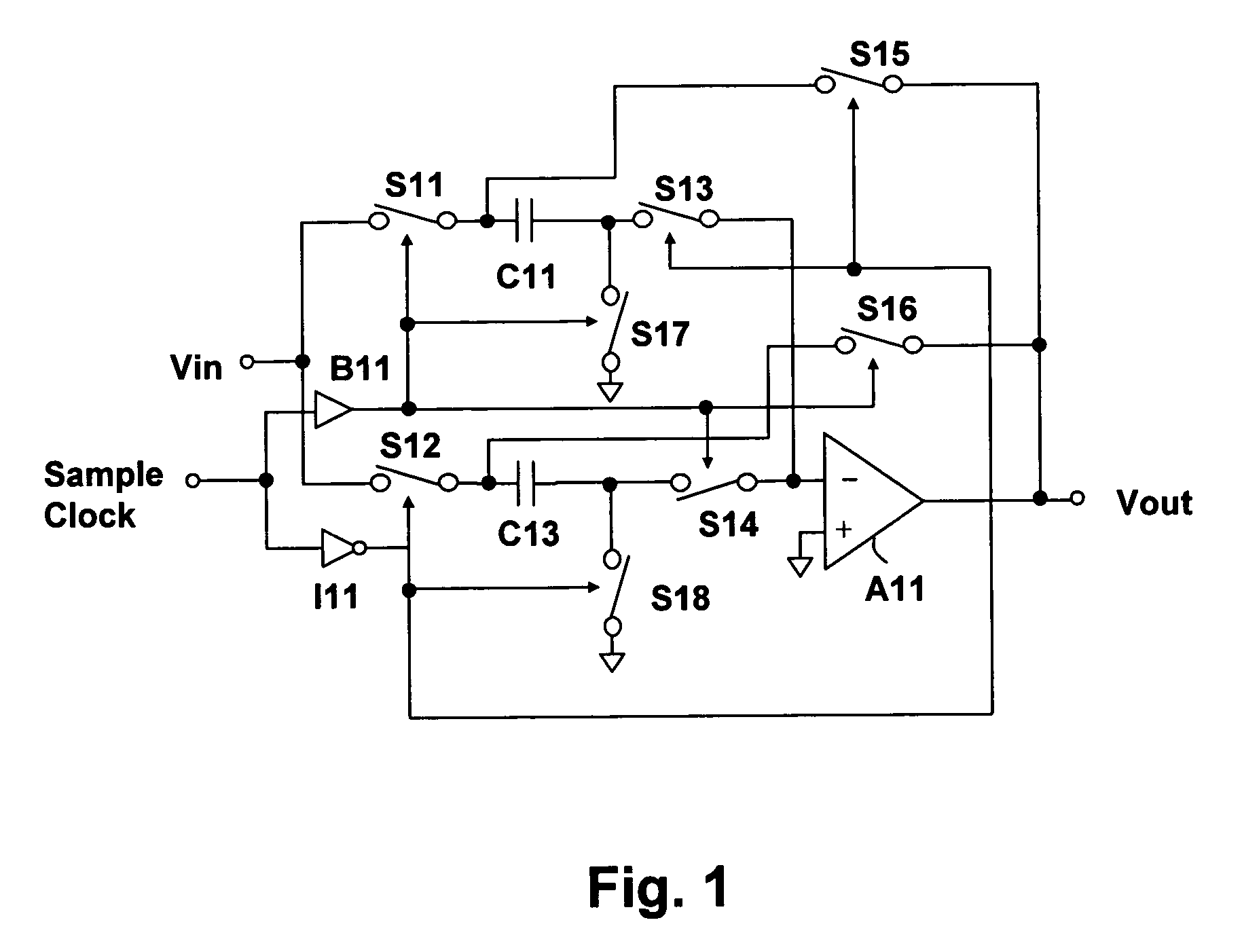

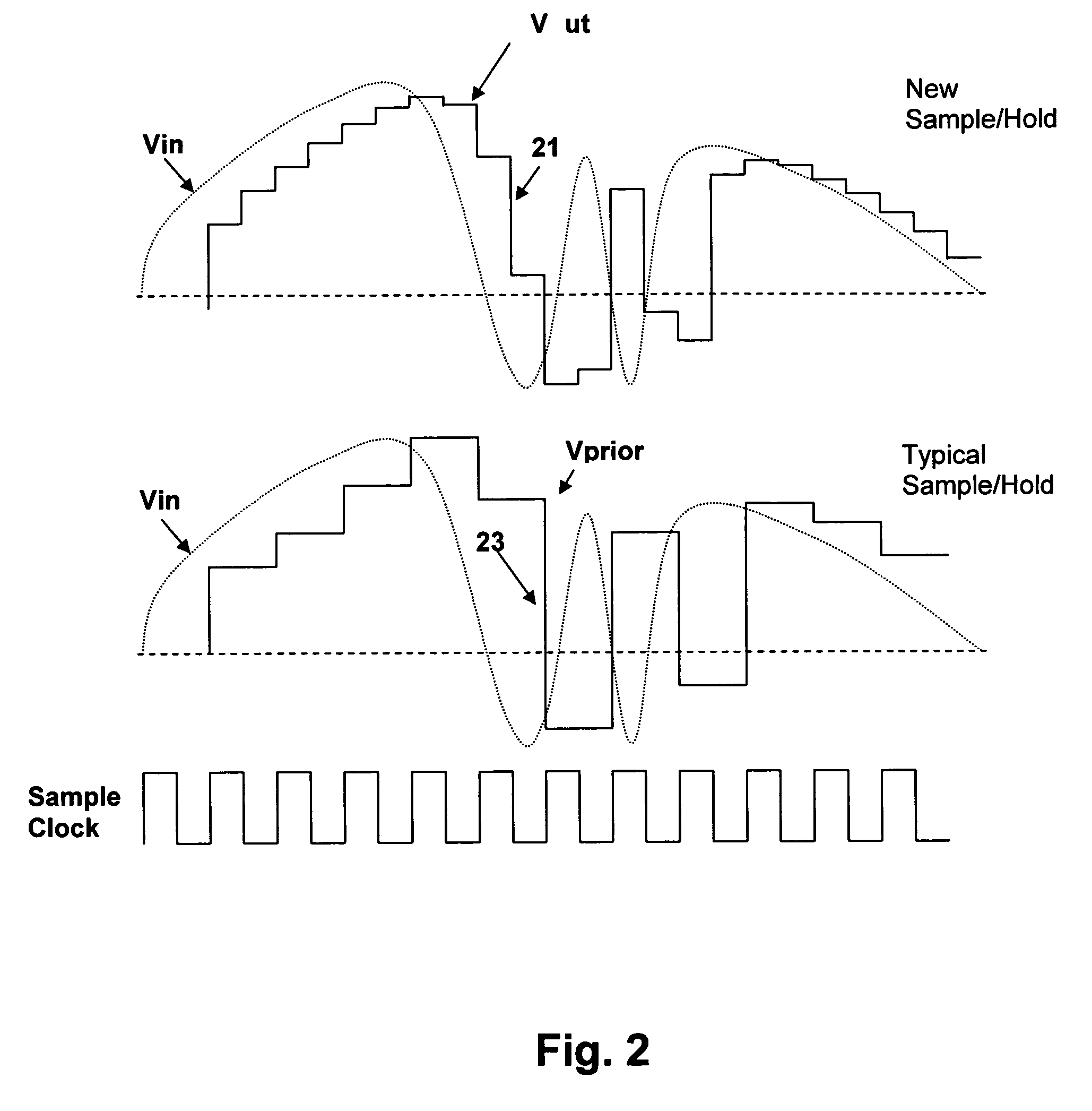

Switched-capacitor sample/hold having reduced amplifier slew-rate and settling time requirements

ActiveUS20050073351A1Lower conversion rateReduce errorsAnalogue/digital conversionComputing operations for integral formationCapacitanceNegative feedback

A switched-capacitor sample / hold circuit and method having reduced slew-rate and settling time requirements provides for lower-cost and / or lower-power implementation of sample / hold circuits and / or reduced error due to amplifier characteristics. The switched-capacitor sample / hold circuit incorporates a pair of capacitors that are alternatively and mutually-exclusively switched between an input sample position and an amplifier hold position, providing a dual sampled amplifier output signal that has reduced transitions at each sample interval. An alternative embodiment of the sample / hold circuit incorporates a fully-differential amplifier having a differential input and a differential output. Four capacitors are employed forming two of the dual sampled switched-capacitor circuits, one in each negative feedback path (inverted output to non-inverting input, non-inverted output to inverting input) of the amplifier. The two dual sampled switched-capacitor circuits are referenced to each other, providing fully differential operation and cancellation of error due to charge injection.

Owner:MICROCHIP TECH INC

Popular searches

Measurement arrangements for variable Acceleration measurement Mitigation of undesired influences Computation using denominational number representation Resistance/reactance/impedence Electronic circuit testing Frequency selective two-port networks Special data processing applications Tunable filters Switched capacitor networks