Patents

Literature

736 results about "Charge injection" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Also, you can have another matched FET placed to pull a comparable amount of charge off the node. Another context for charge injection is charge injected into the substrate. Thus charge can then make its way to other circuits and provide a source of crosstalk between them.

Organic electroluminescent device and method for manufacturing the same

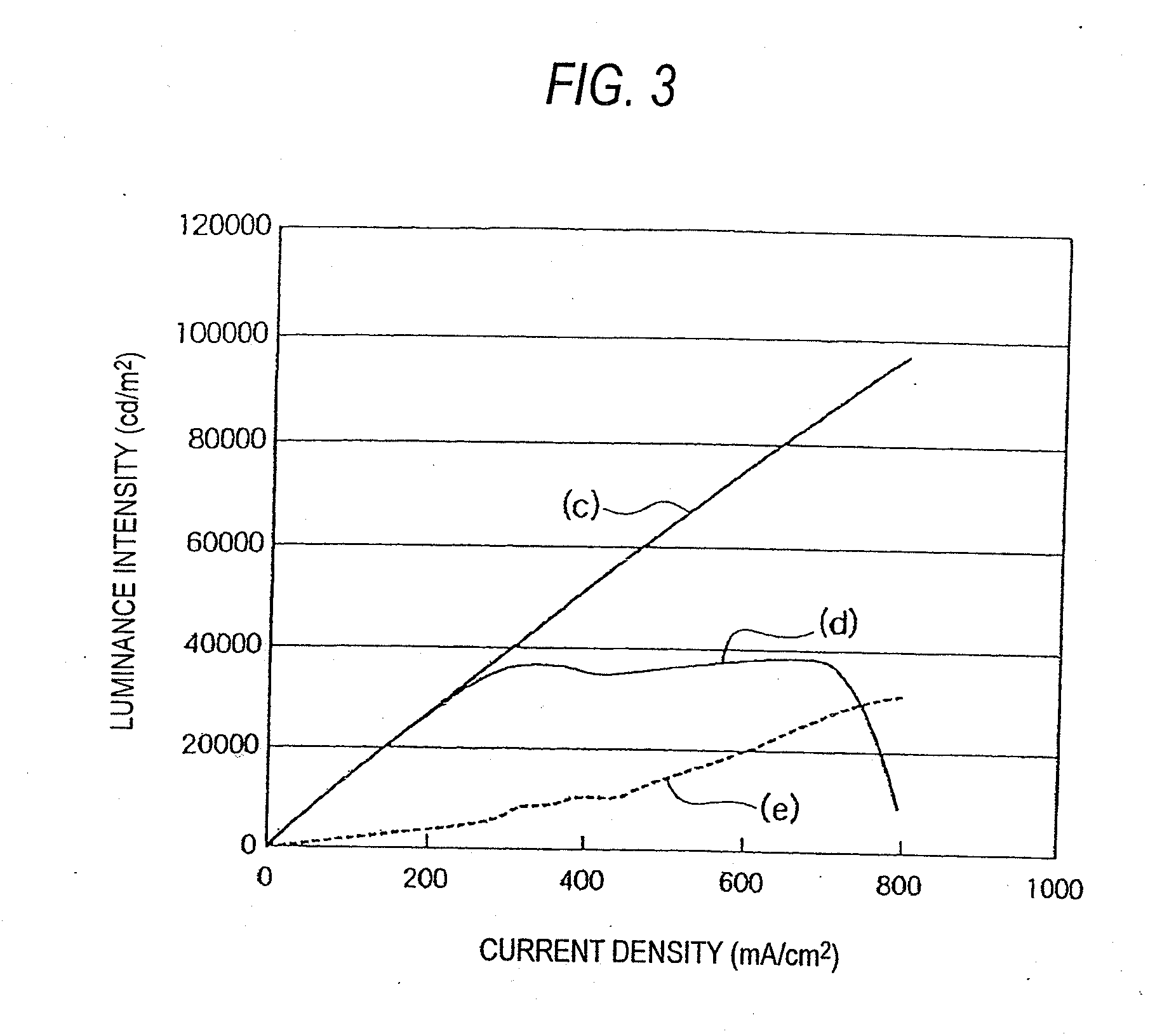

InactiveUS20050170208A1Maintain good propertiesEasy to manufactureDischarge tube luminescnet screensElectroluminescent light sourcesCharge injectionOrganic solvent

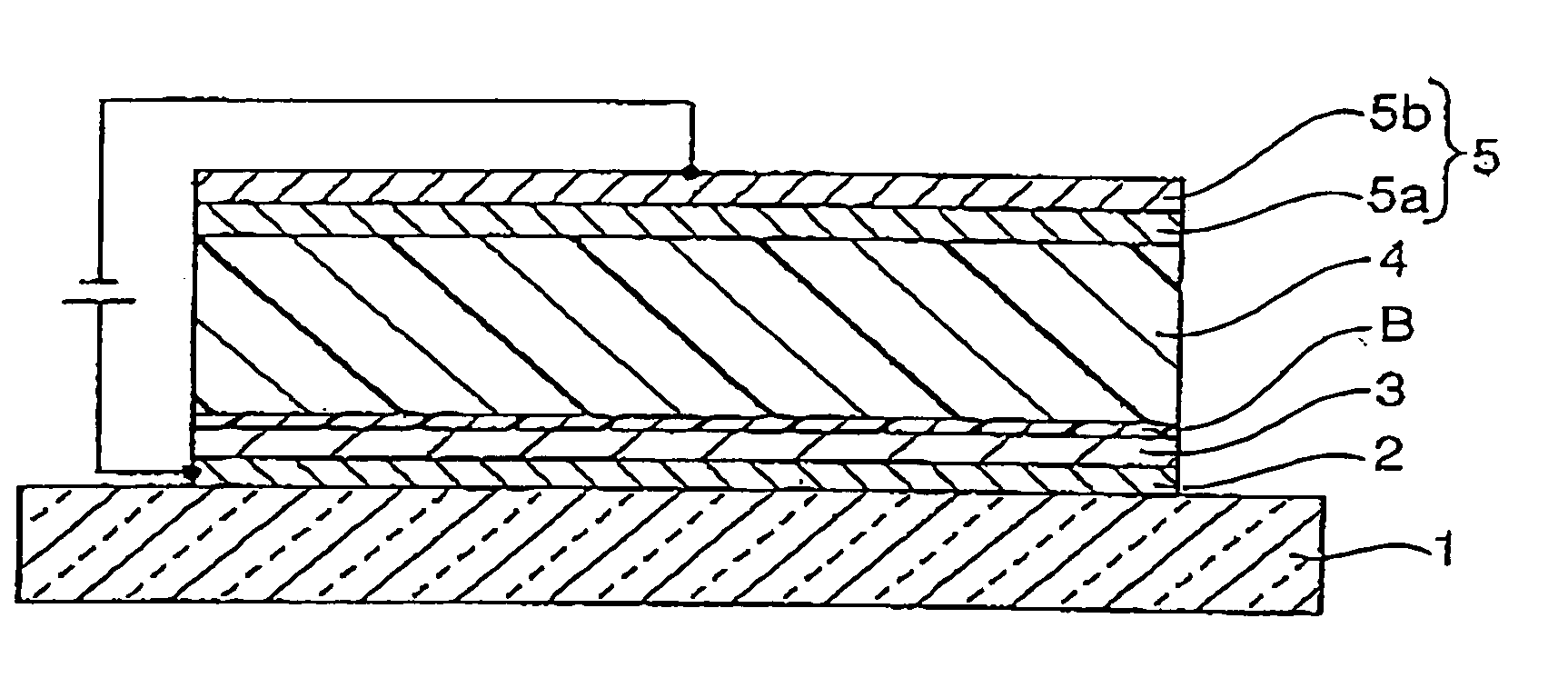

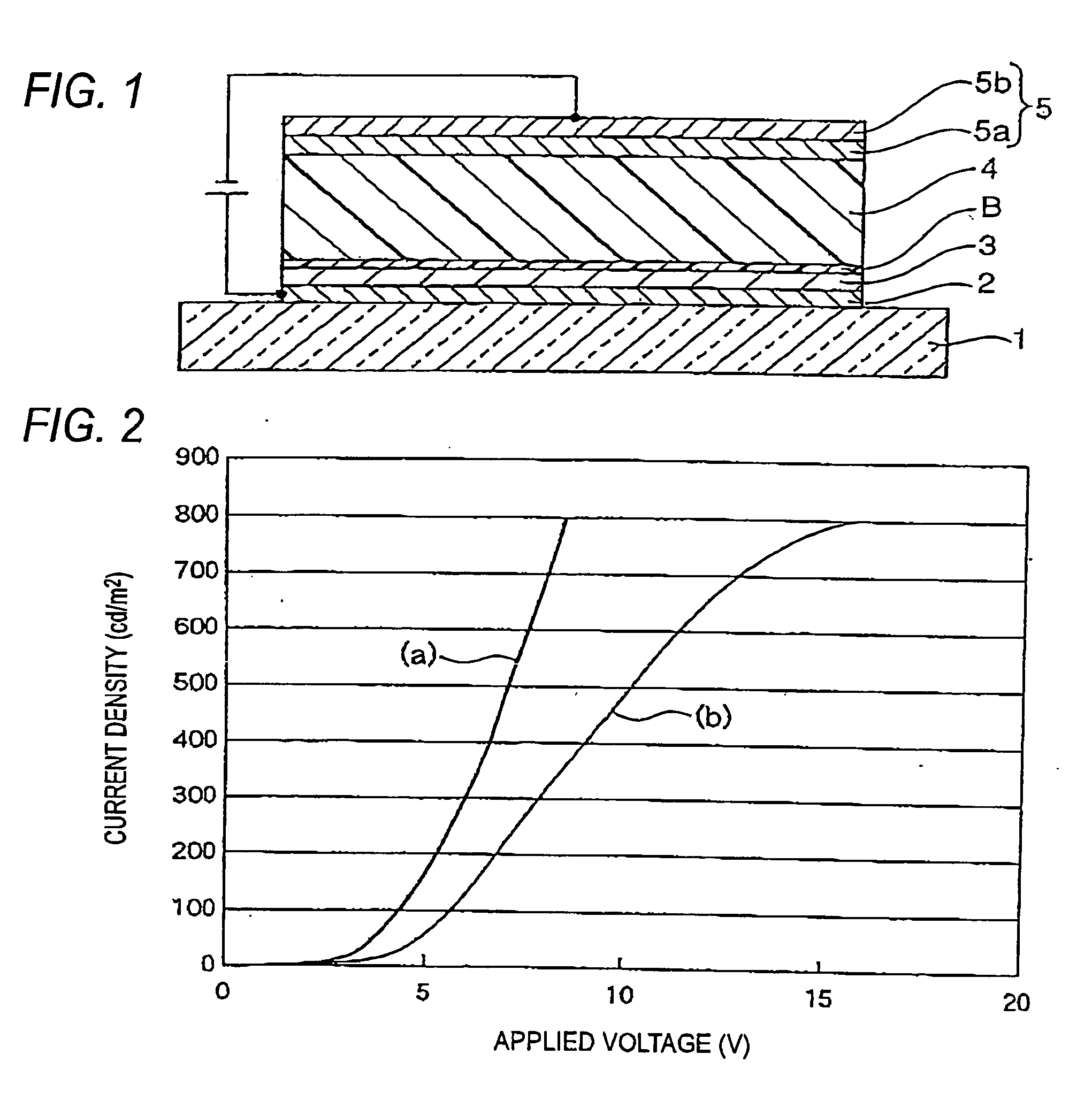

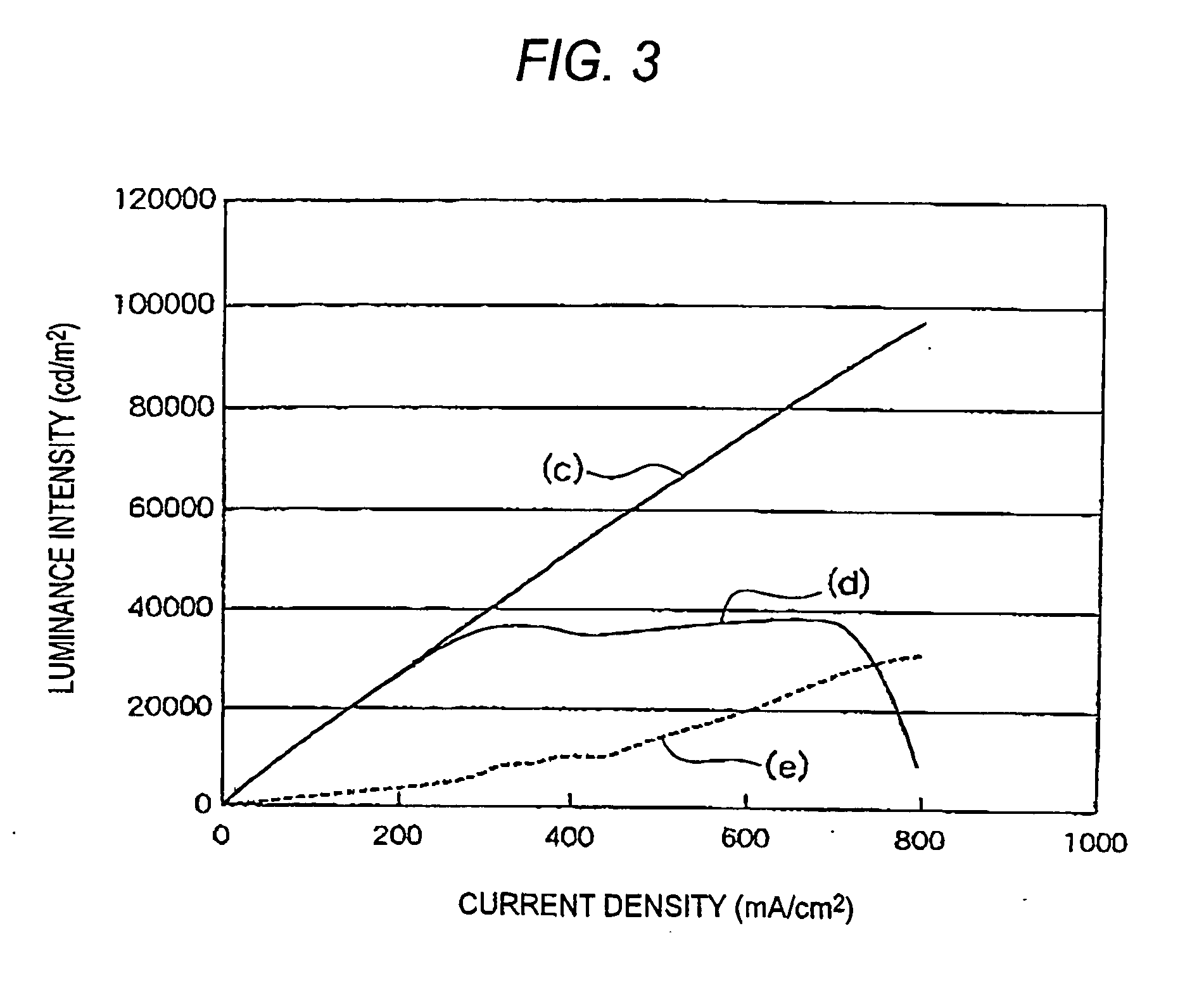

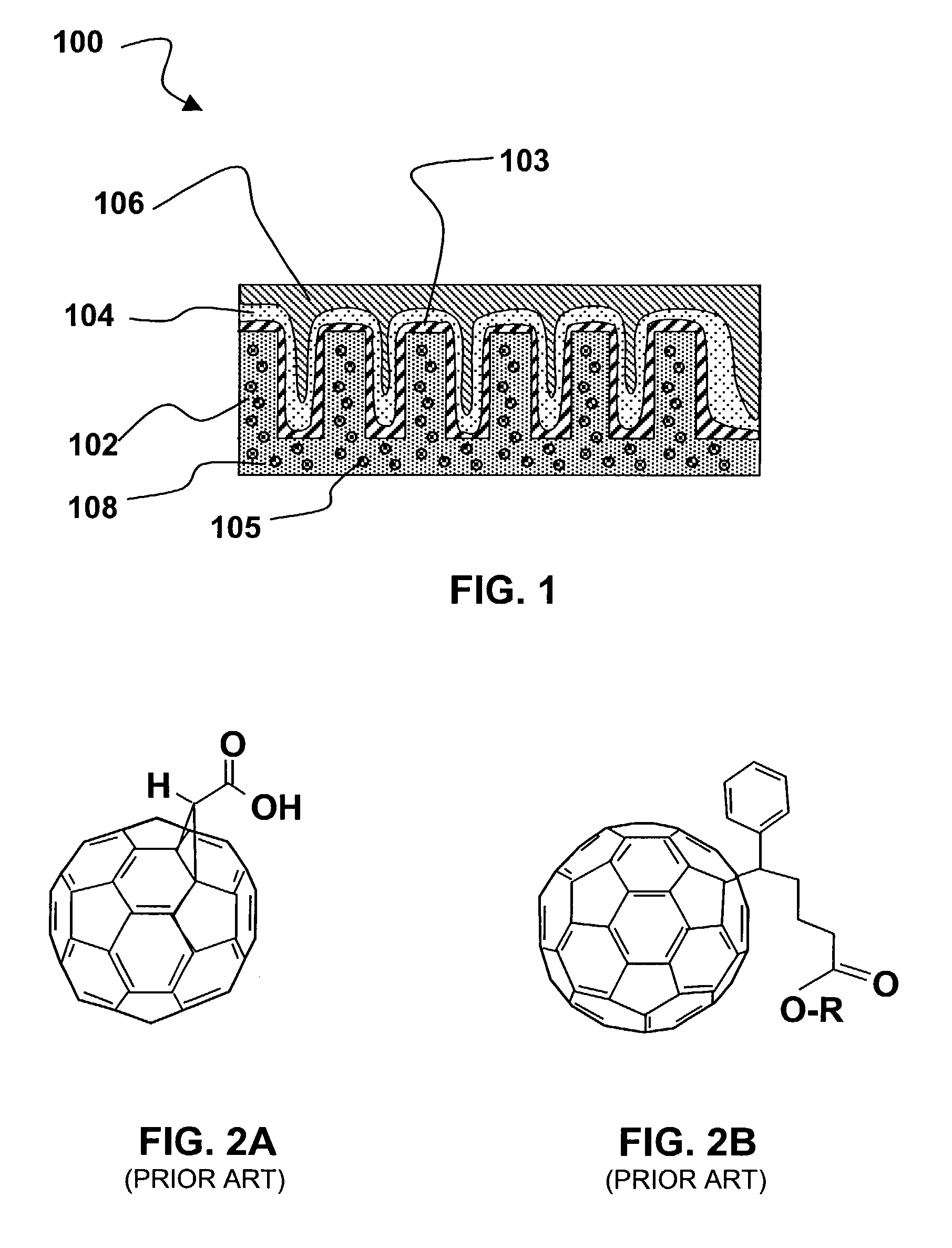

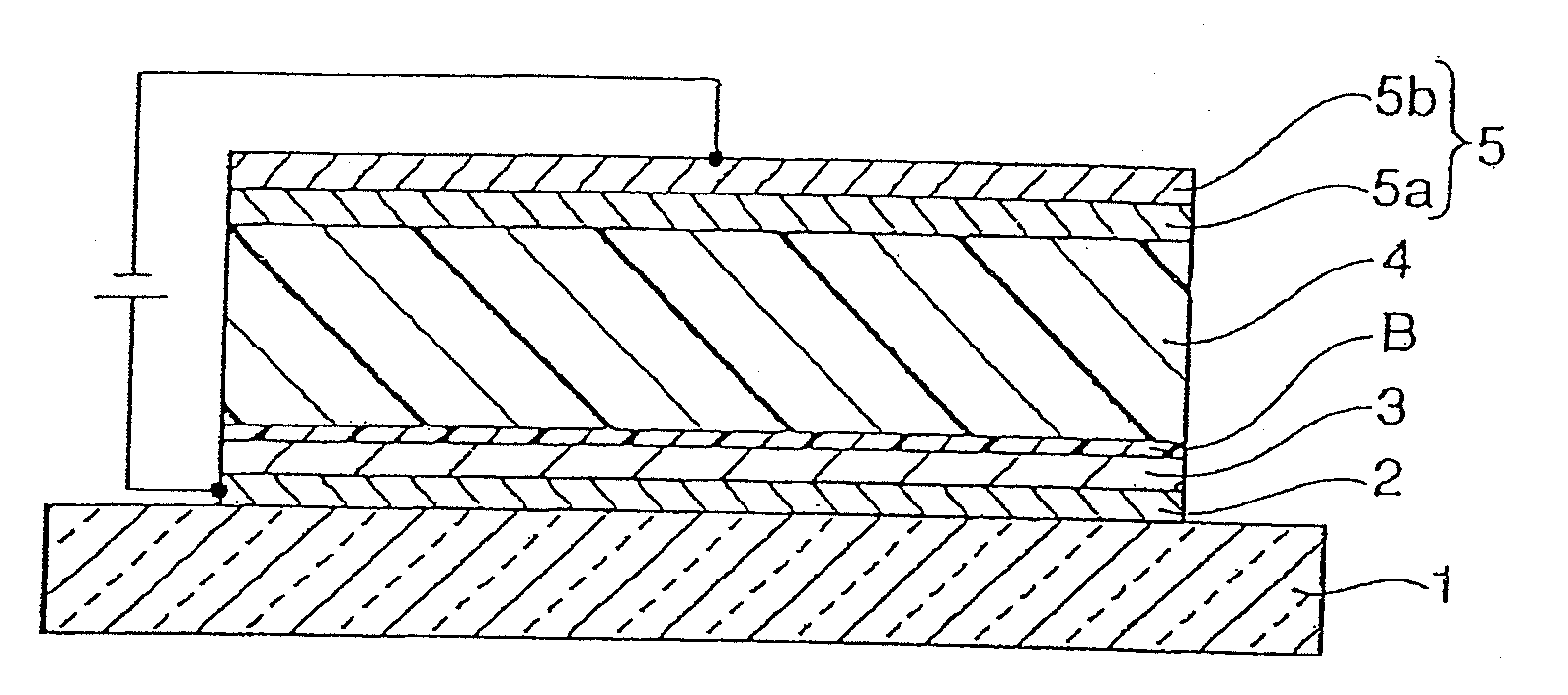

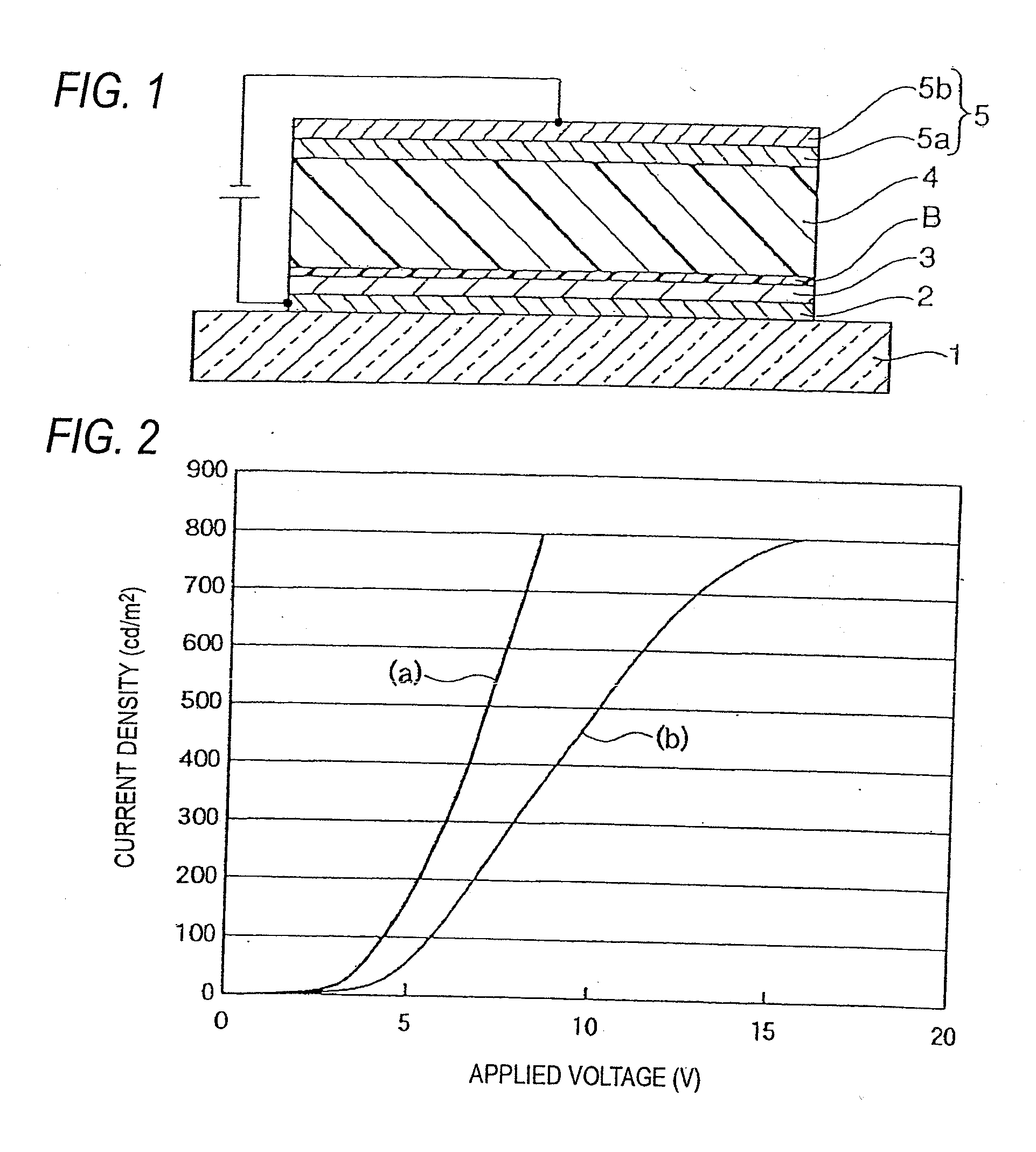

An organic EL device which drives over a wide range from low brightness to high brightness for light source applications, operates stably over a wide range of brightness and has excellent life property is provided. The device comprises at least one pair of electrodes 2 and 5, and a plurality of functional layers disposed between the electrodes 2 and 5, the functional layers comprising a layer 4 having the light emitting function, which is composed of at least one polymeric material and contains an organic solvent and a charge injection layer 3 composed of at least one inorganic material.

Owner:JOLED INC

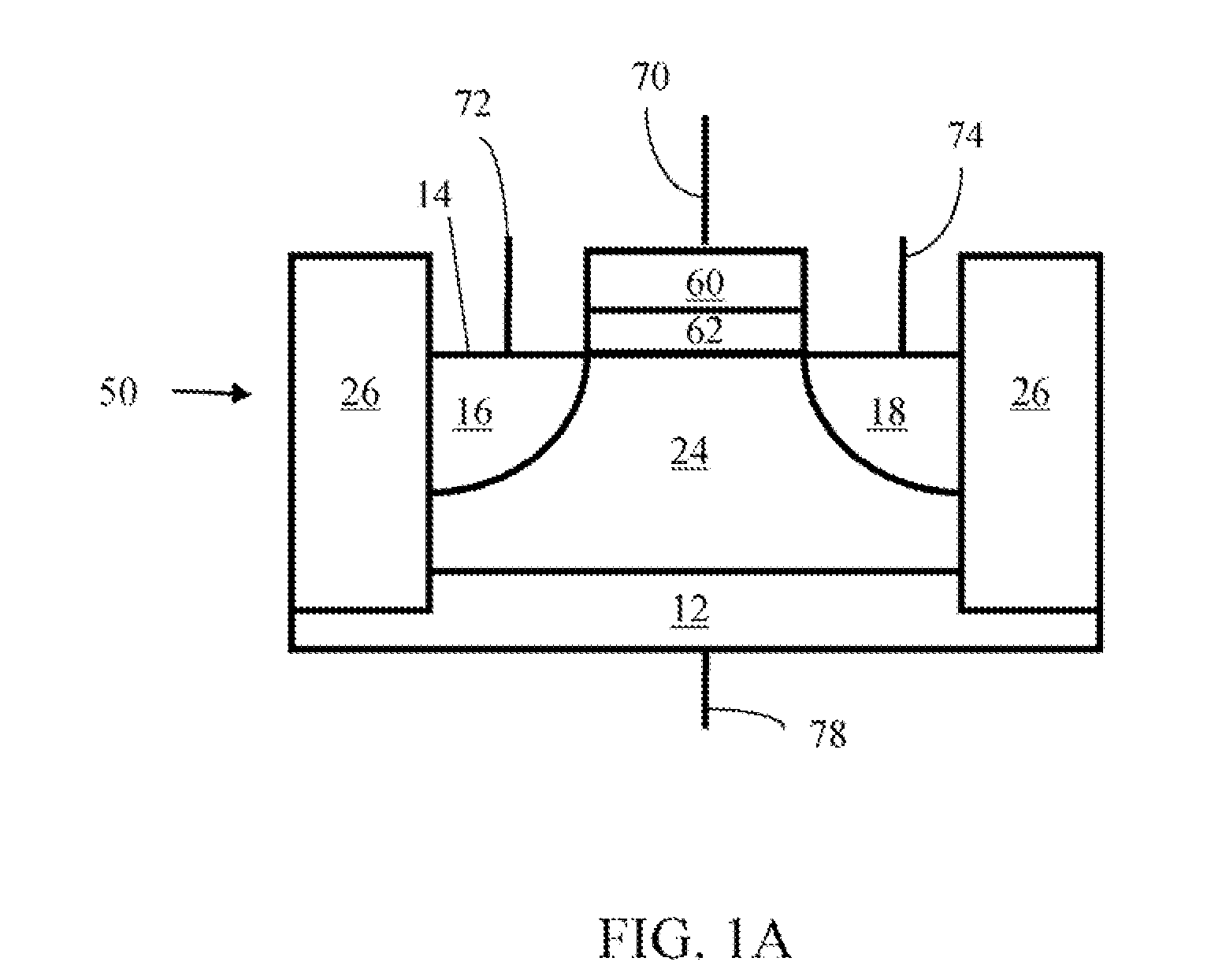

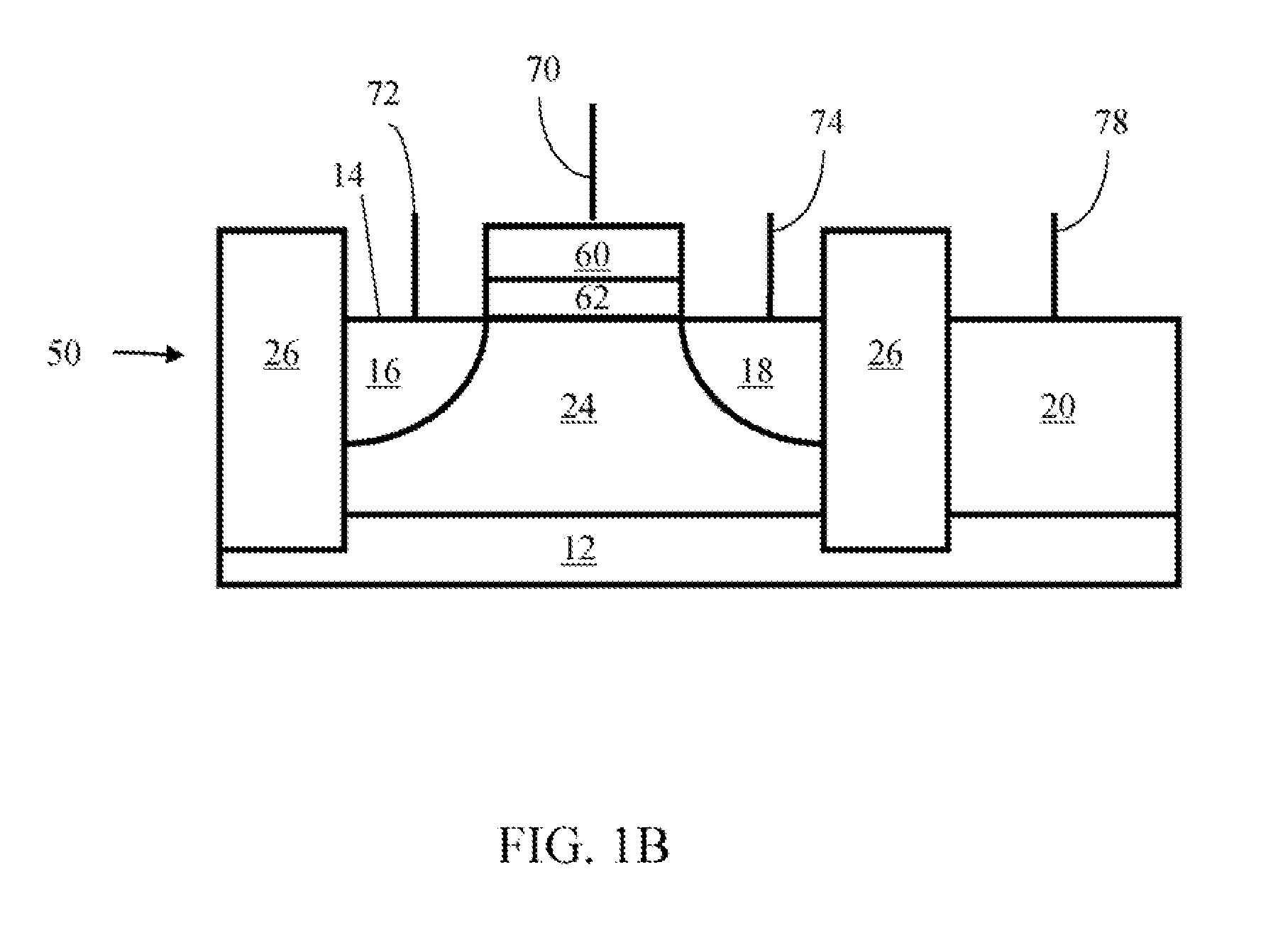

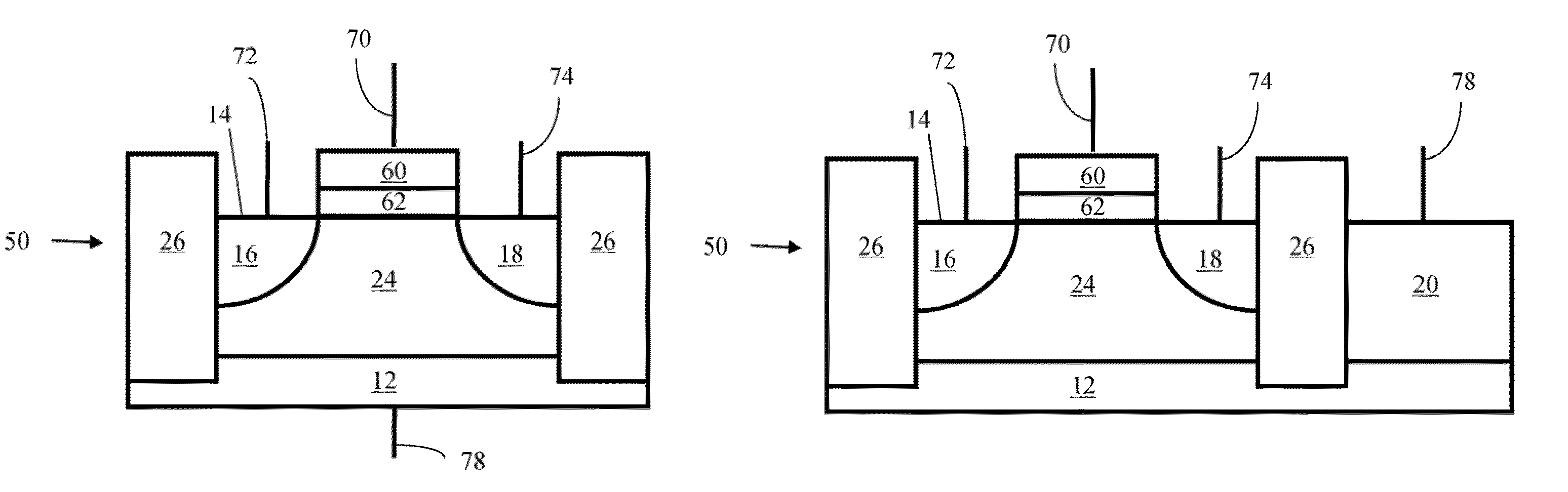

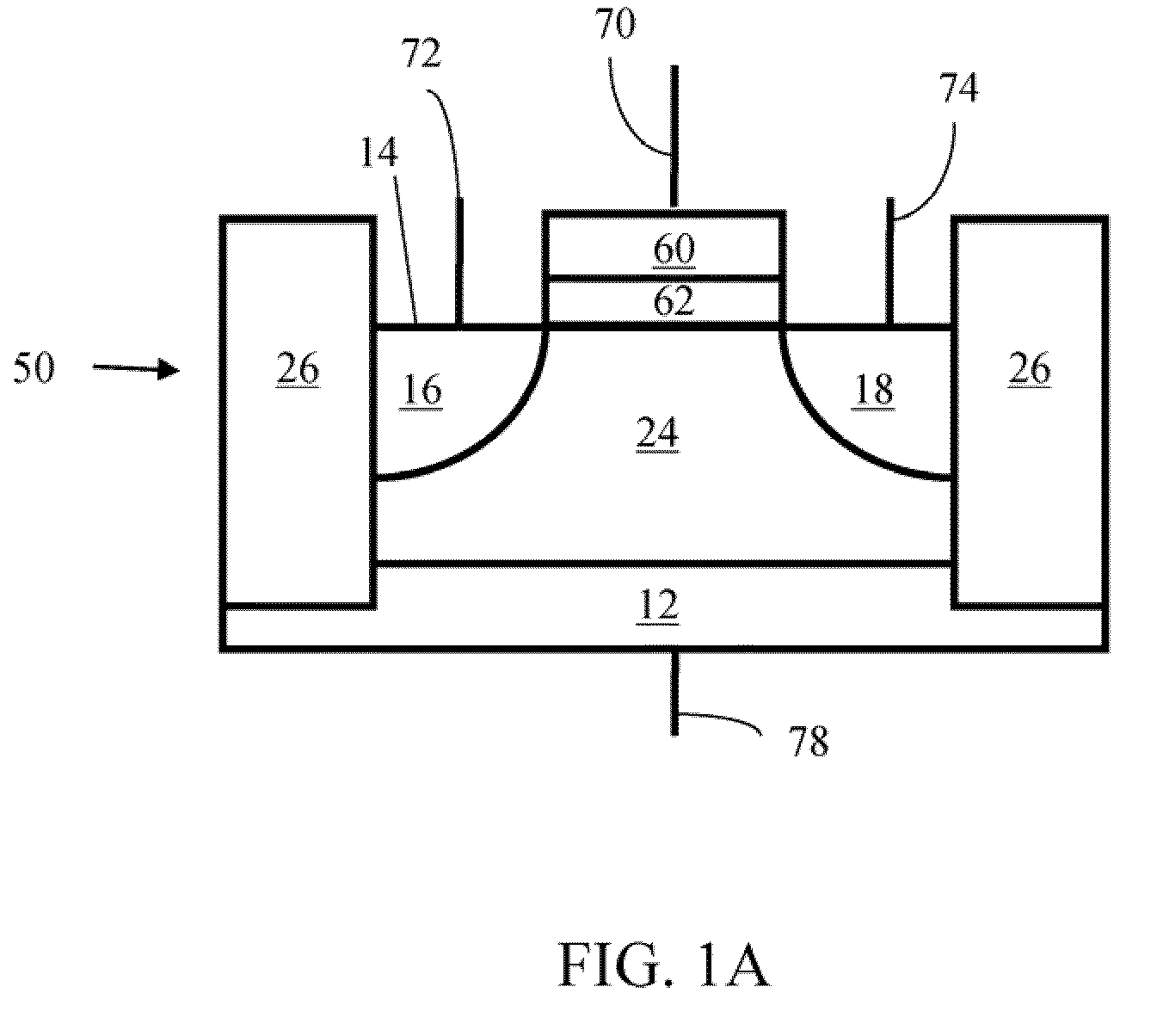

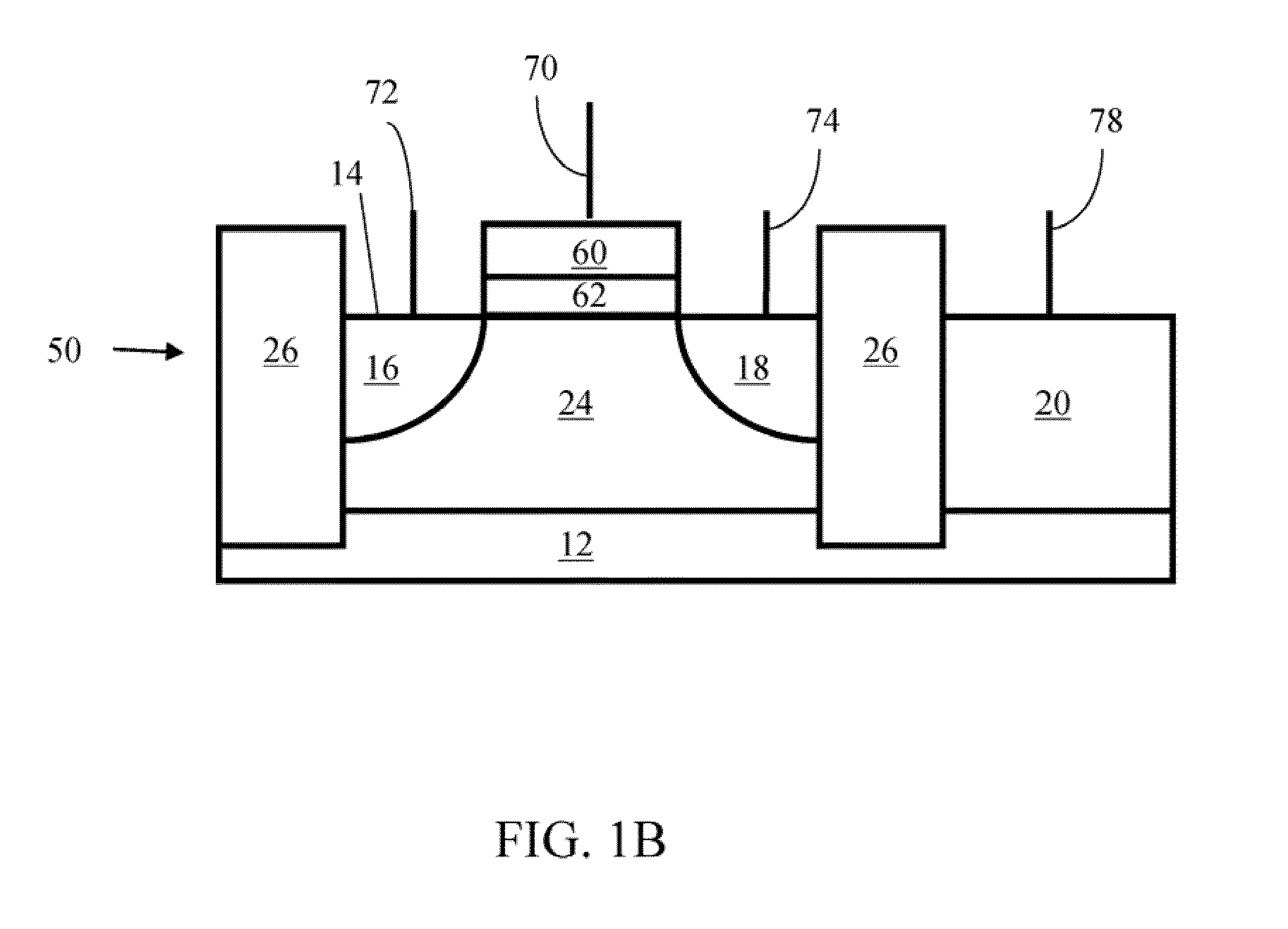

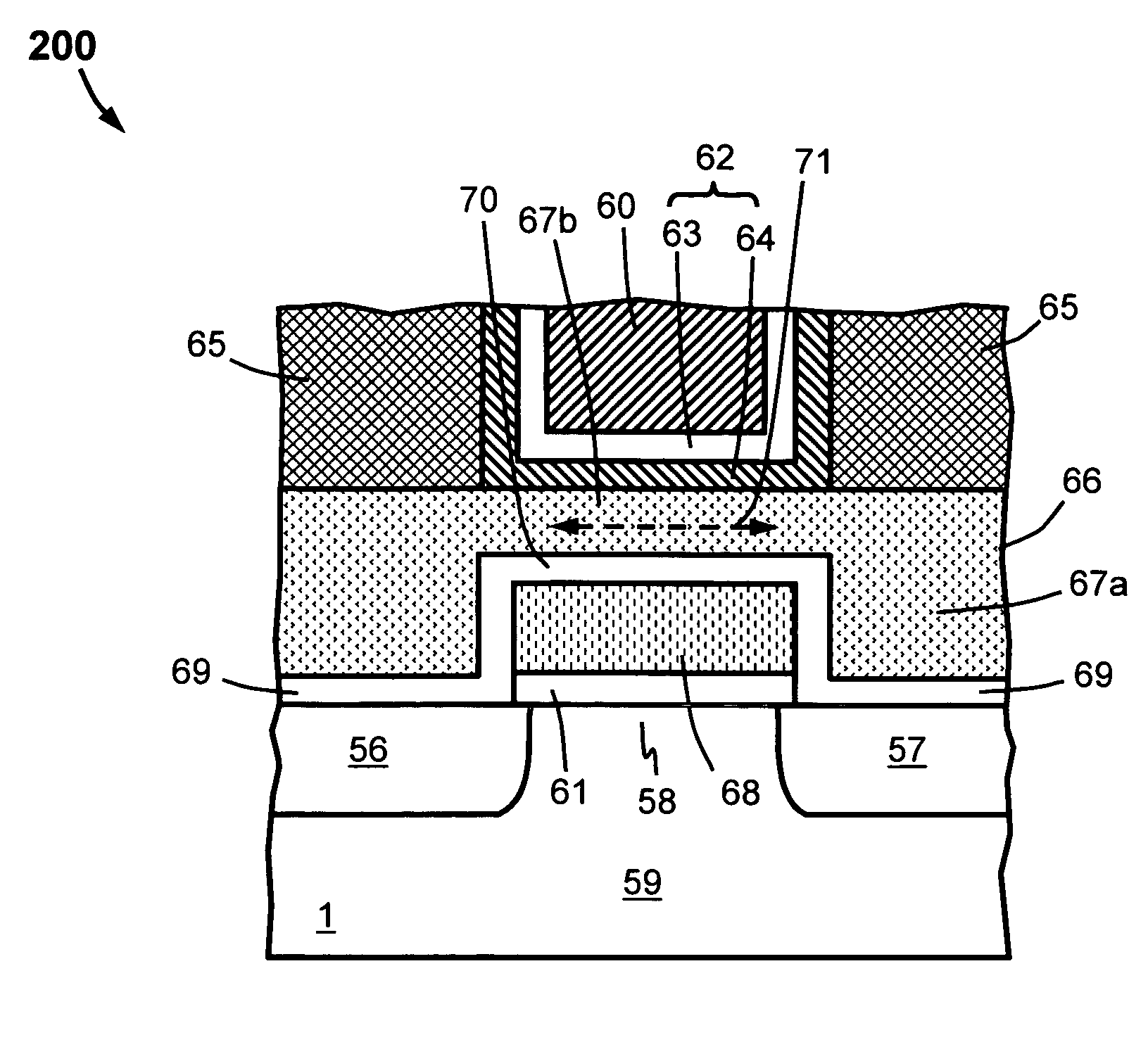

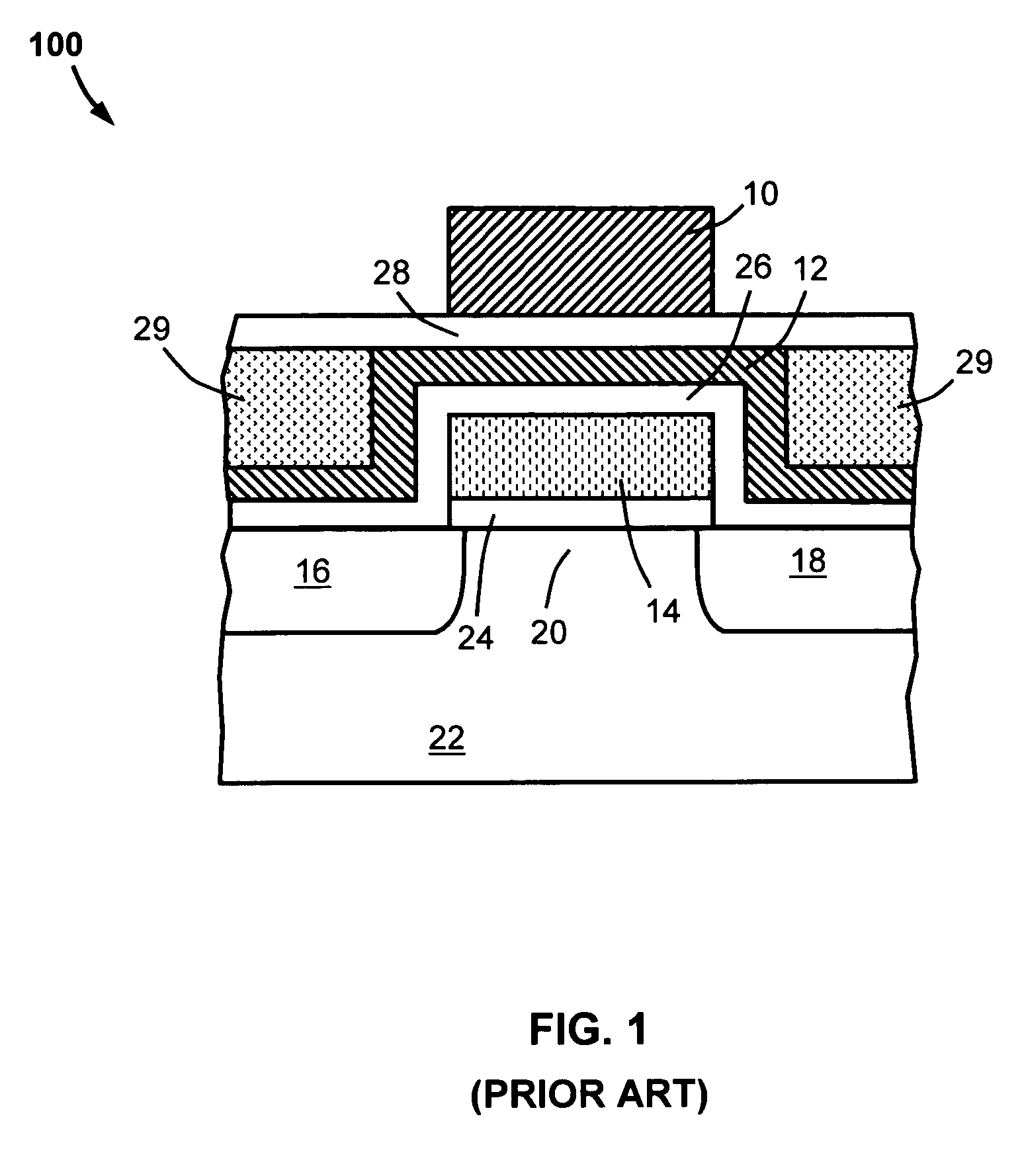

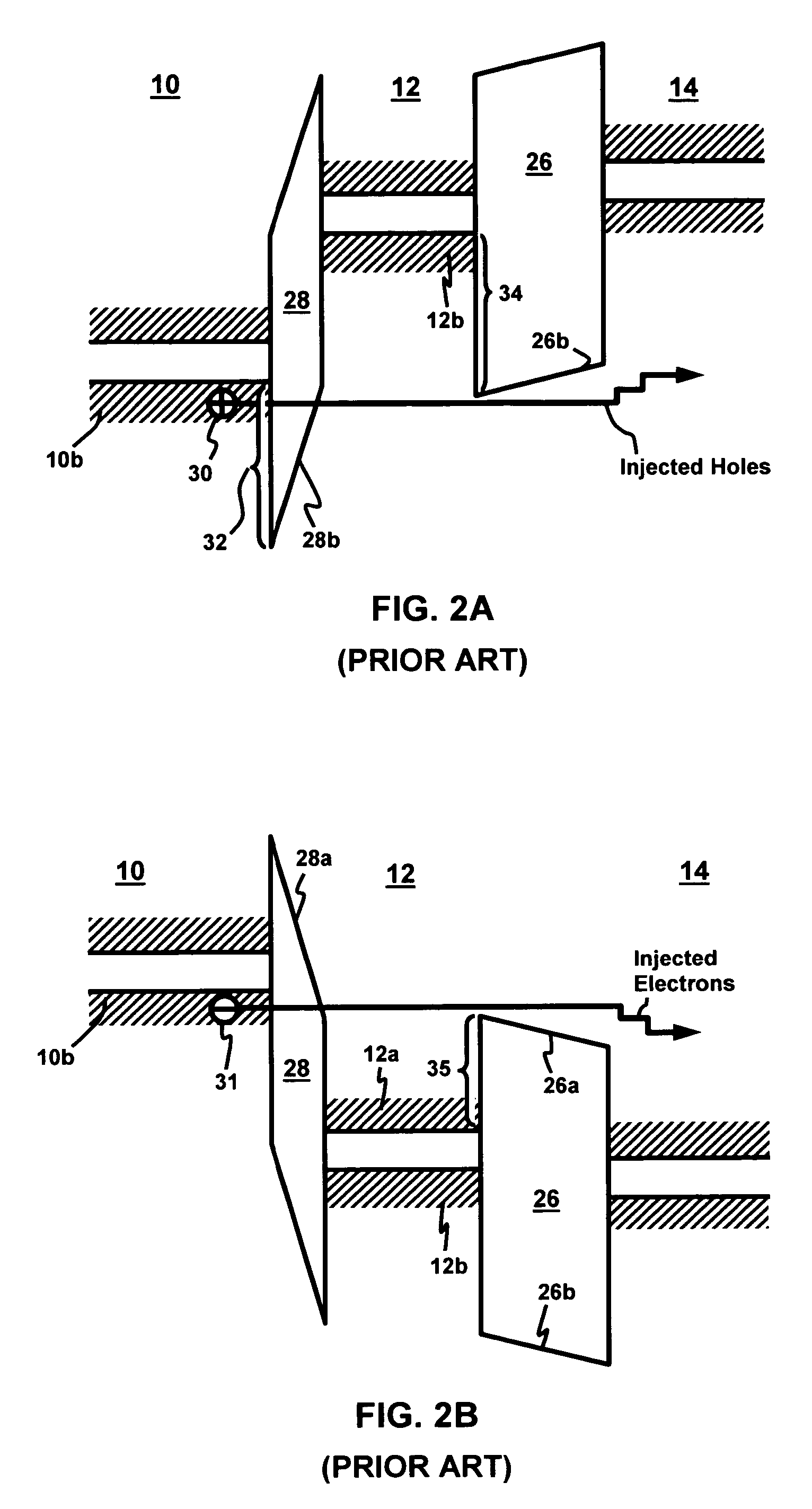

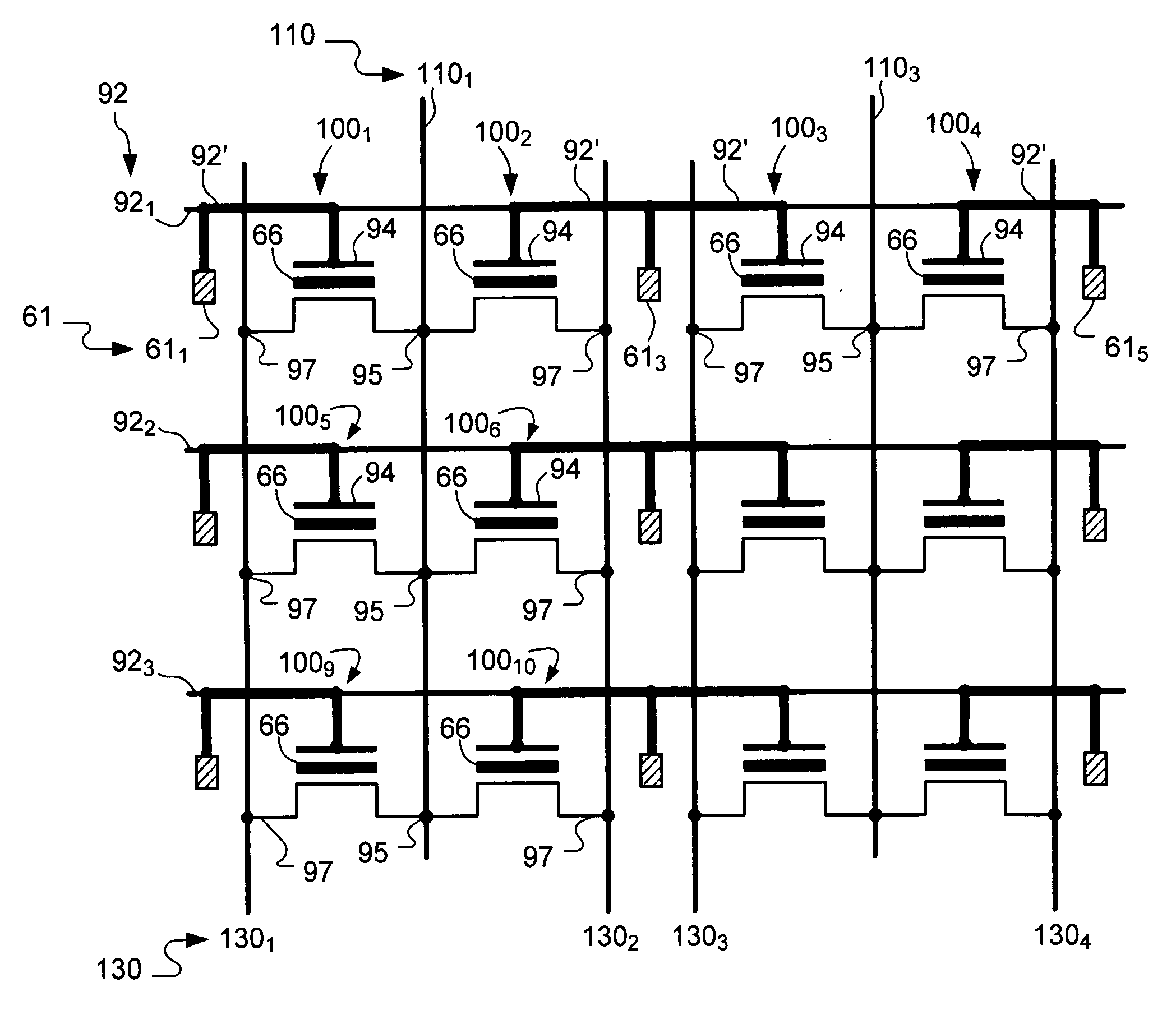

Semiconductor memory having electrically floating body transistor

ActiveUS20120012915A1Large memory windowLarger memory windowTransistorSolid-state devicesCharge injectionBack bias

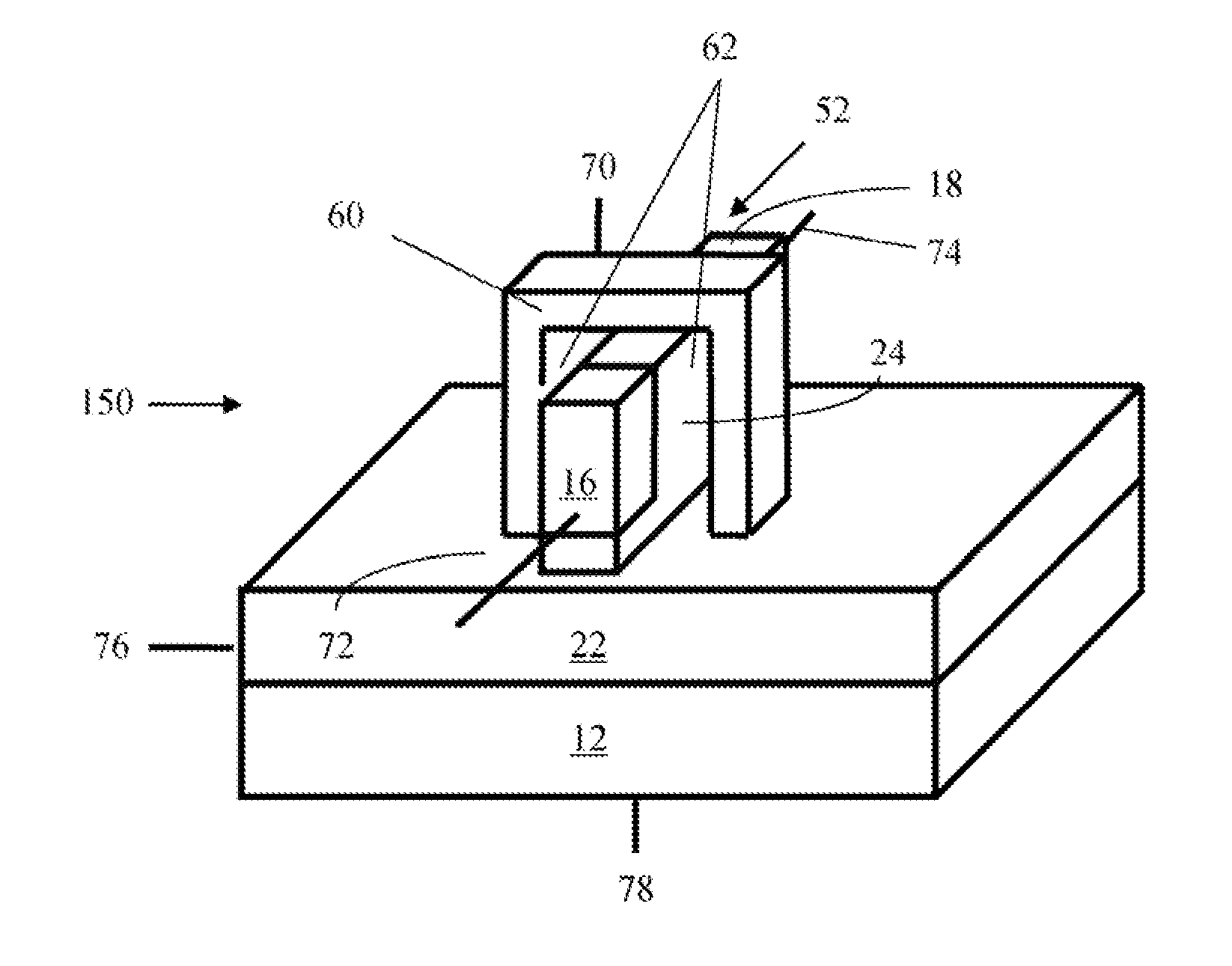

A semiconductor memory cell includes a floating body region configured to be charged to a level indicative of a state of the memory cell; a first region in electrical contact with said floating body region; a second region in electrical contact with said floating body region and spaced apart from said first region; a gate positioned between said first and second regions; and a back-bias region configured to inject charge into or extract charge out of said floating body region to maintain said state of the memory cell. Application of back bias to the back bias region offsets charge leakage out of the floating body and performs a holding operation on the cell. The cell may be a multi-level cell. Arrays of memory cells are disclosed for making a memory device.

Owner:ZENO SEMICON

Semiconductor memory having electrically floating body transistor

A semiconductor memory cell includes a floating body region configured to be charged to a level indicative of a state of the memory cell; a first region in electrical contact with said floating body region; a second region in electrical contact with said floating body region and spaced apart from said first region; a gate positioned between said first and second regions; and a back-bias region configured to inject charge into or extract charge out of said floating body region to maintain said state of the memory cell. Application of back bias to the back bias region offsets charge leakage out of the floating body and performs a holding operation on the cell. The cell may be a multi-level cell. Arrays of memory cells are disclosed for making a memory device.

Owner:ZENO SEMICON

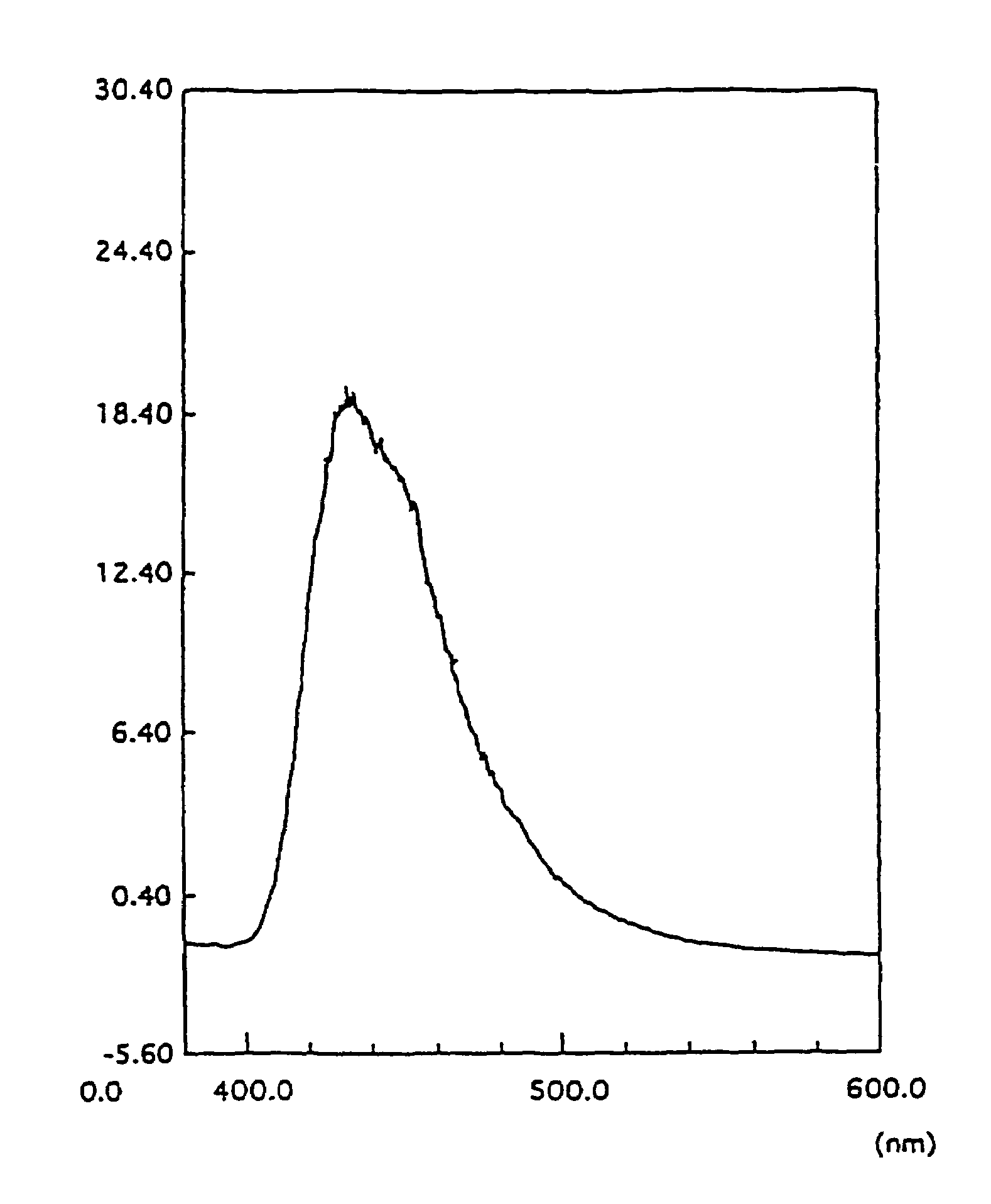

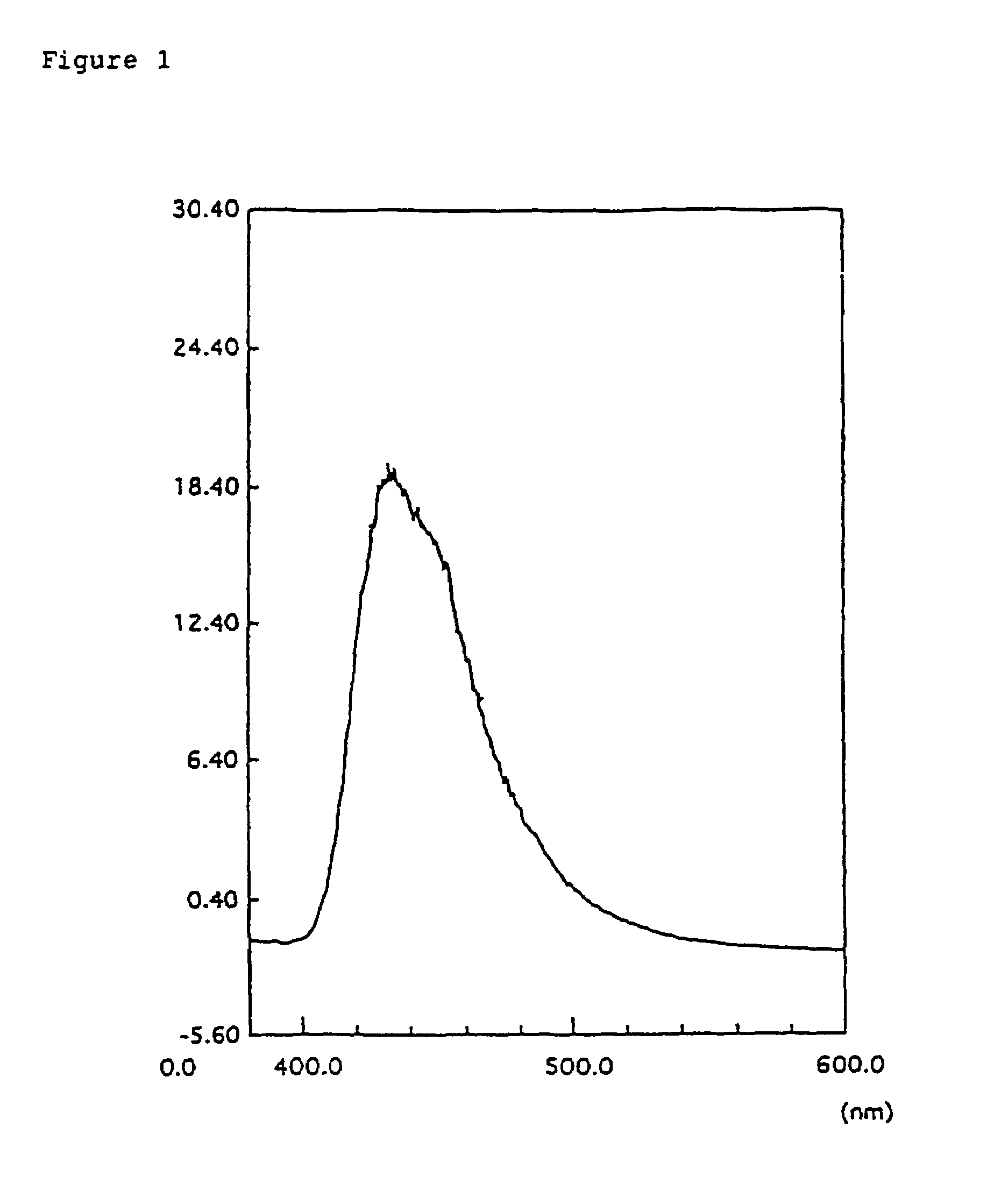

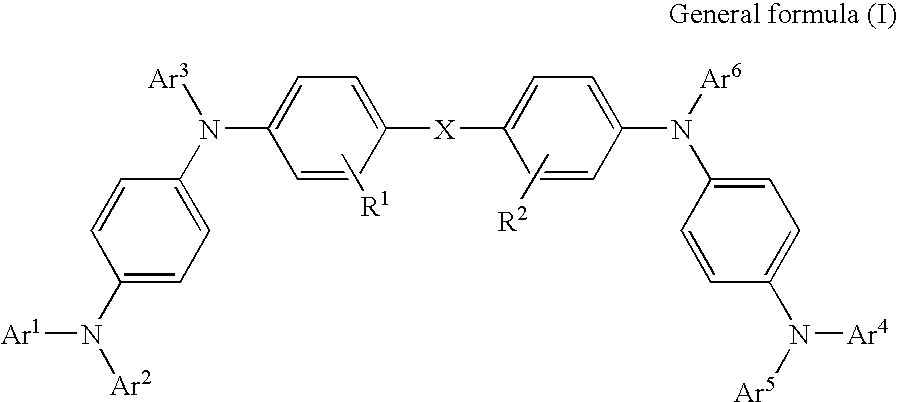

Organic electroluminescence device and phenylenediamine derivative

InactiveUS7399537B2Reduce the driving voltageSmall ionization potentialOrganic chemistryDischarge tube luminescnet screensElectron holeCharge injection

The invention is to provide an organic EL device having a long life time that can reduce the driving voltage of the organic EL device, and to provide a material having a small ionization potential and exhibiting a large hole mobility by using as a layer or a zone. The organic electroluminescence device comprises a pair of electrodes and an organic light emitting layer sandwiched in the electrodes, characterized in that a hole transporting zone provided between the electrodes comprises the phenylenediamine derivative represented by the specific structural formulae, and the phenylenediamine derivative has a hole mobility of 10−4 cm2 / V·s or more upon using as a layer or a zone, with the organic light emitting layer containing a charge injection auxiliary.

Owner:IDEMITSU KOSAN CO LTD

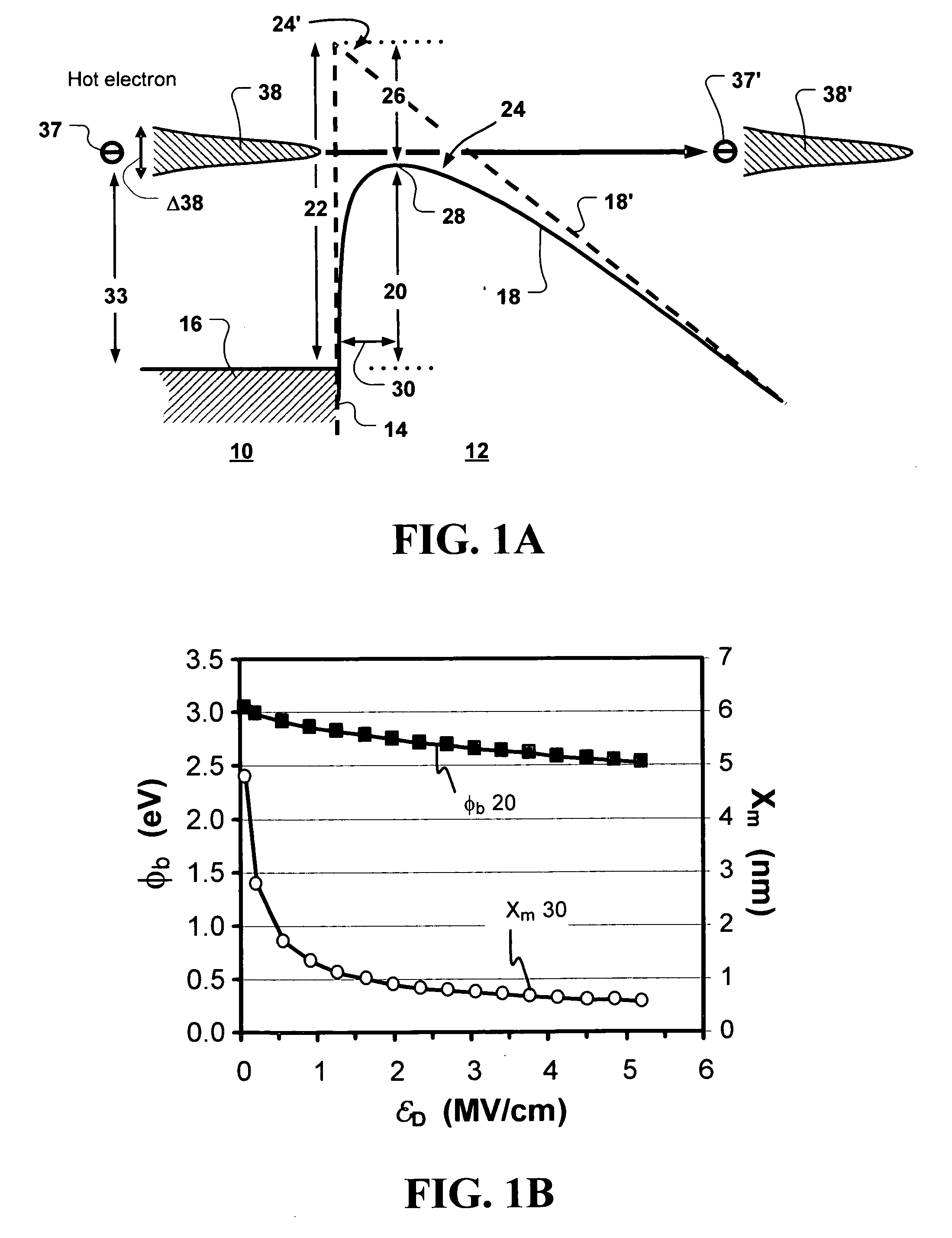

Method and apparatus for nonvolatile memory

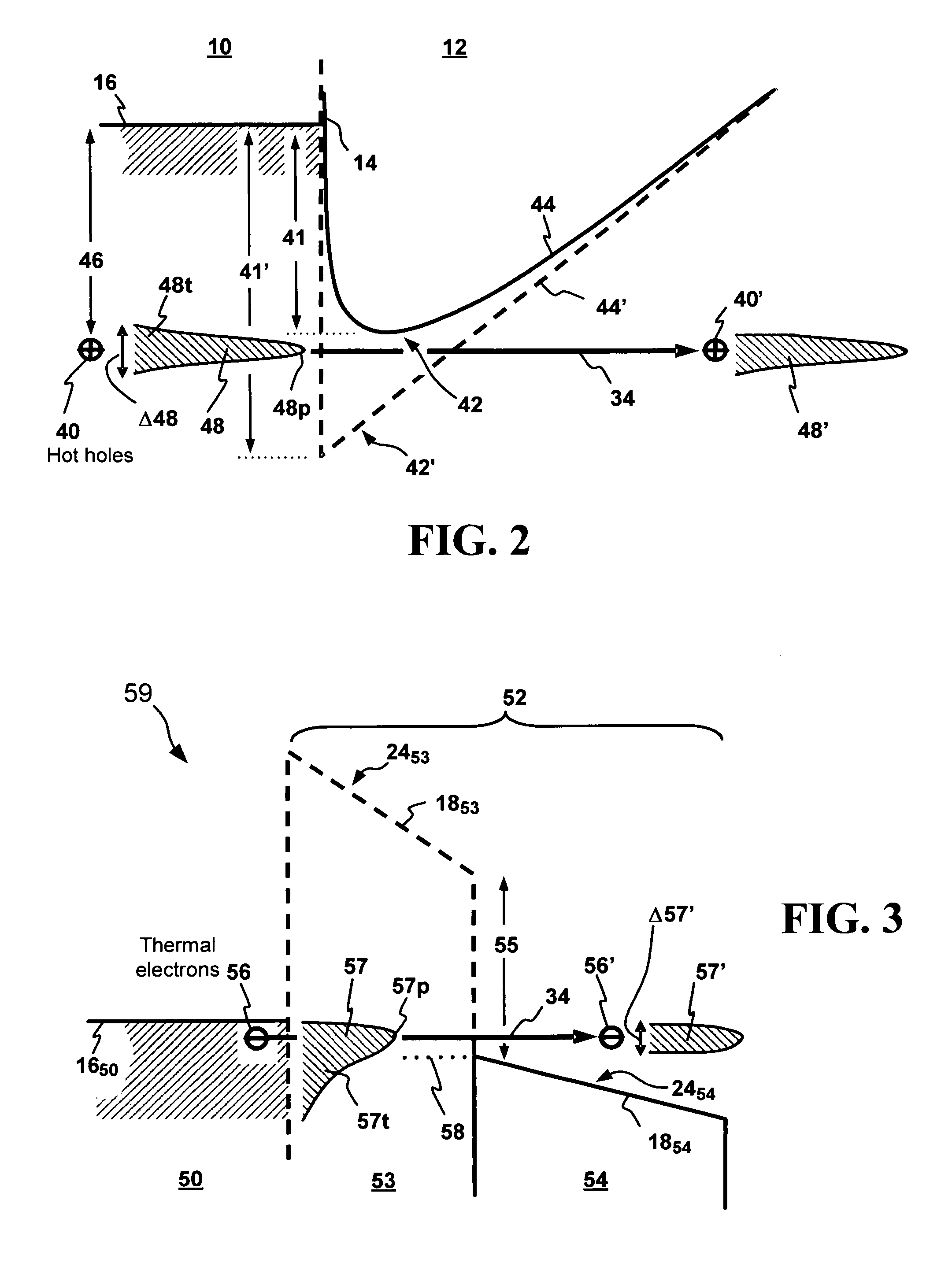

Method and apparatus on charges injection using piezo-ballistic-charges injection mechanism are provided for nonvolatile memory device. The device has a strain source, an injection filter, a tunneling gate, a ballistic gate, a charge storage region, a source, and a drain with a channel defined between the source and drain. The strain source permits piezo-effect in ballistic charges transport to enable the piezo-ballistic-charges injection mechanism. The injection filter permits transporting of charge carriers of one polarity type from the tunneling gate through the blocking material and the ballistic gate to the charge storage region while blocking the transport of charge carriers of an opposite polarity from the ballistic gate to the tunneling gate. The present invention further provides an energy band engineering method permitting the memory device be operated without suffering from disturbs, from dielectric breakdown, from impact ionization, and from undesirable RC effects.

Owner:MARVELL ASIA PTE LTD

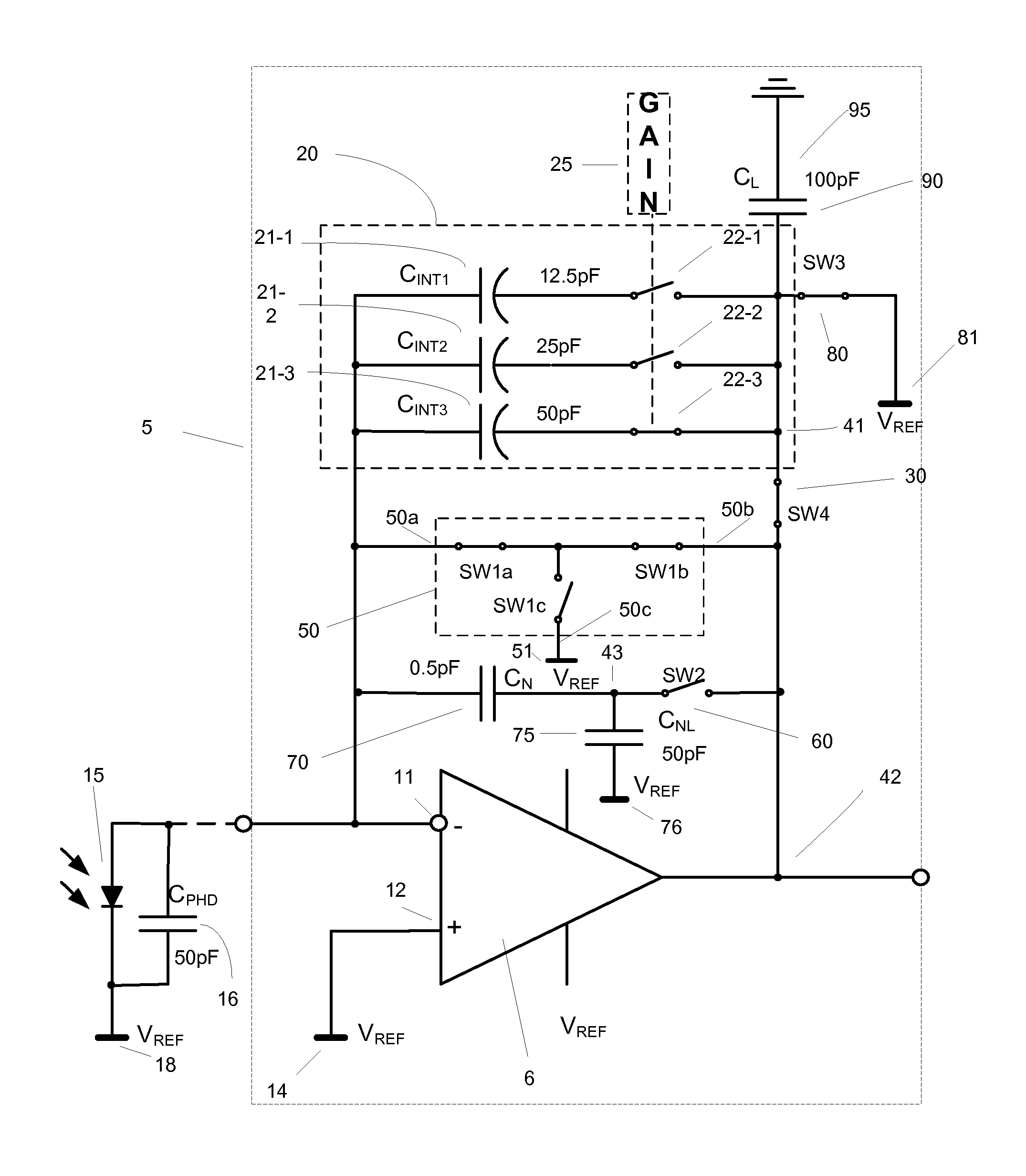

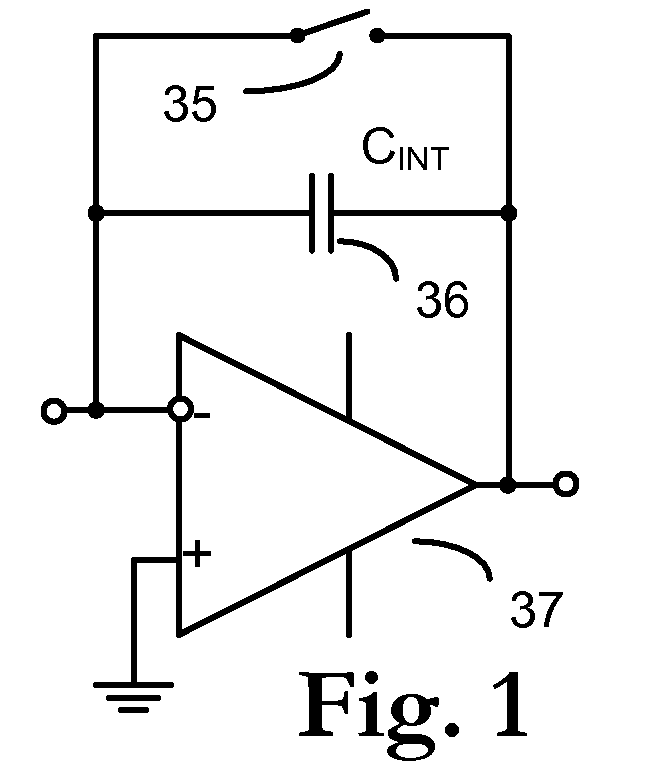

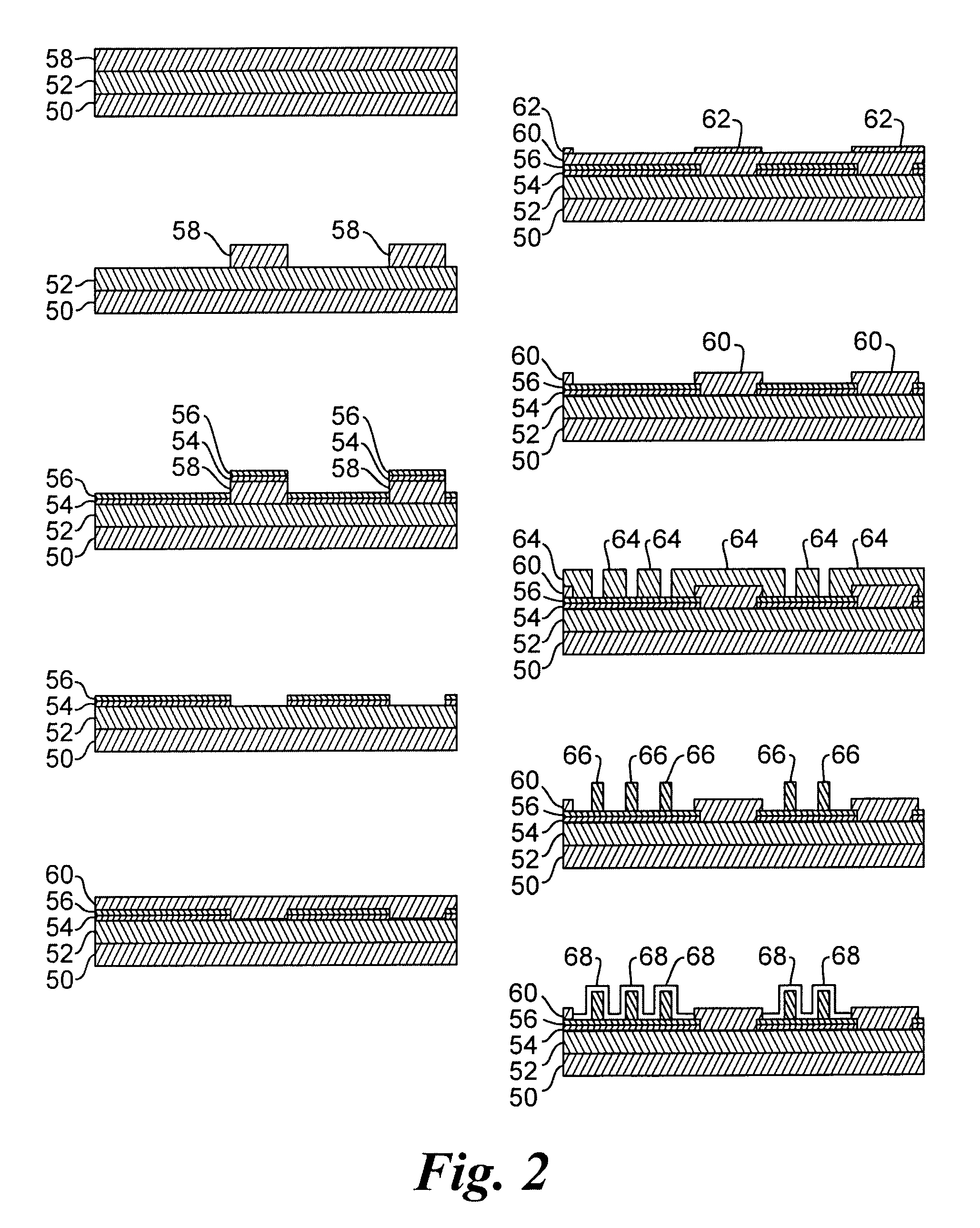

Apparatus for current-to-voltage integration for current-to-digital converter

InactiveUS20090273386A1Reduce charge injectionReduce demandComputing operations for integral formationComputing operations for integration/differentiationDigital down converterIntegrator

Owner:CUSTOM ONE DESIGN

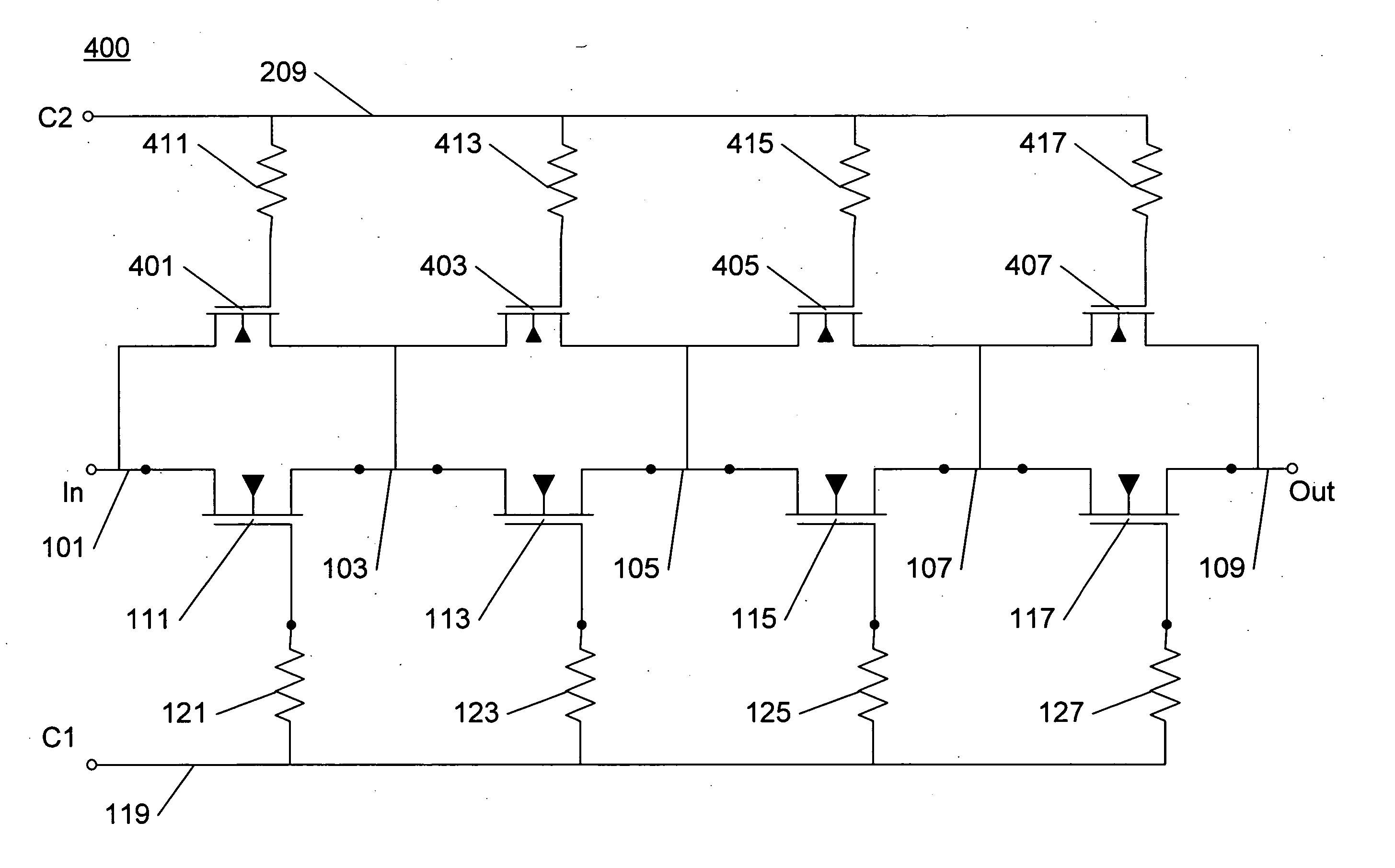

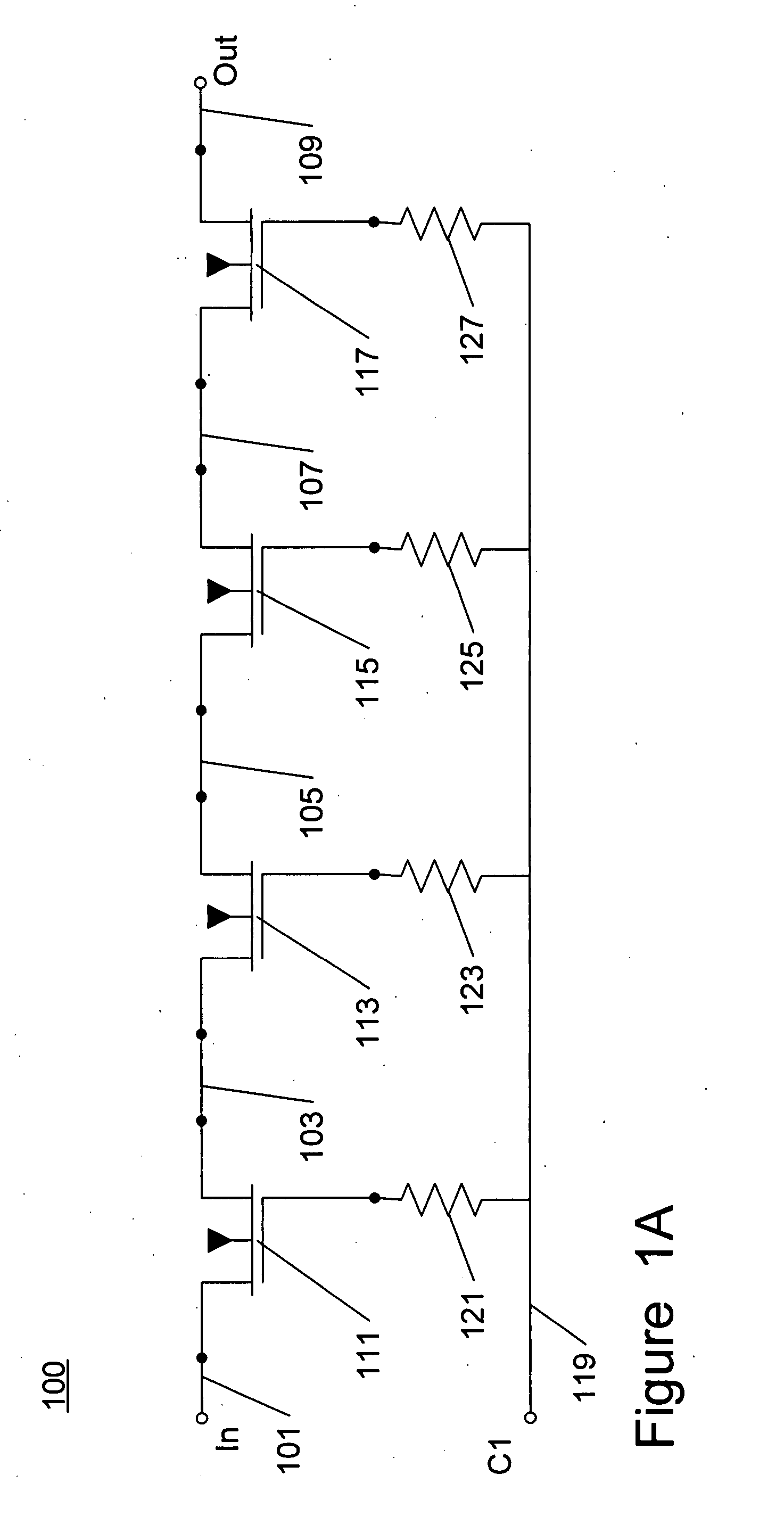

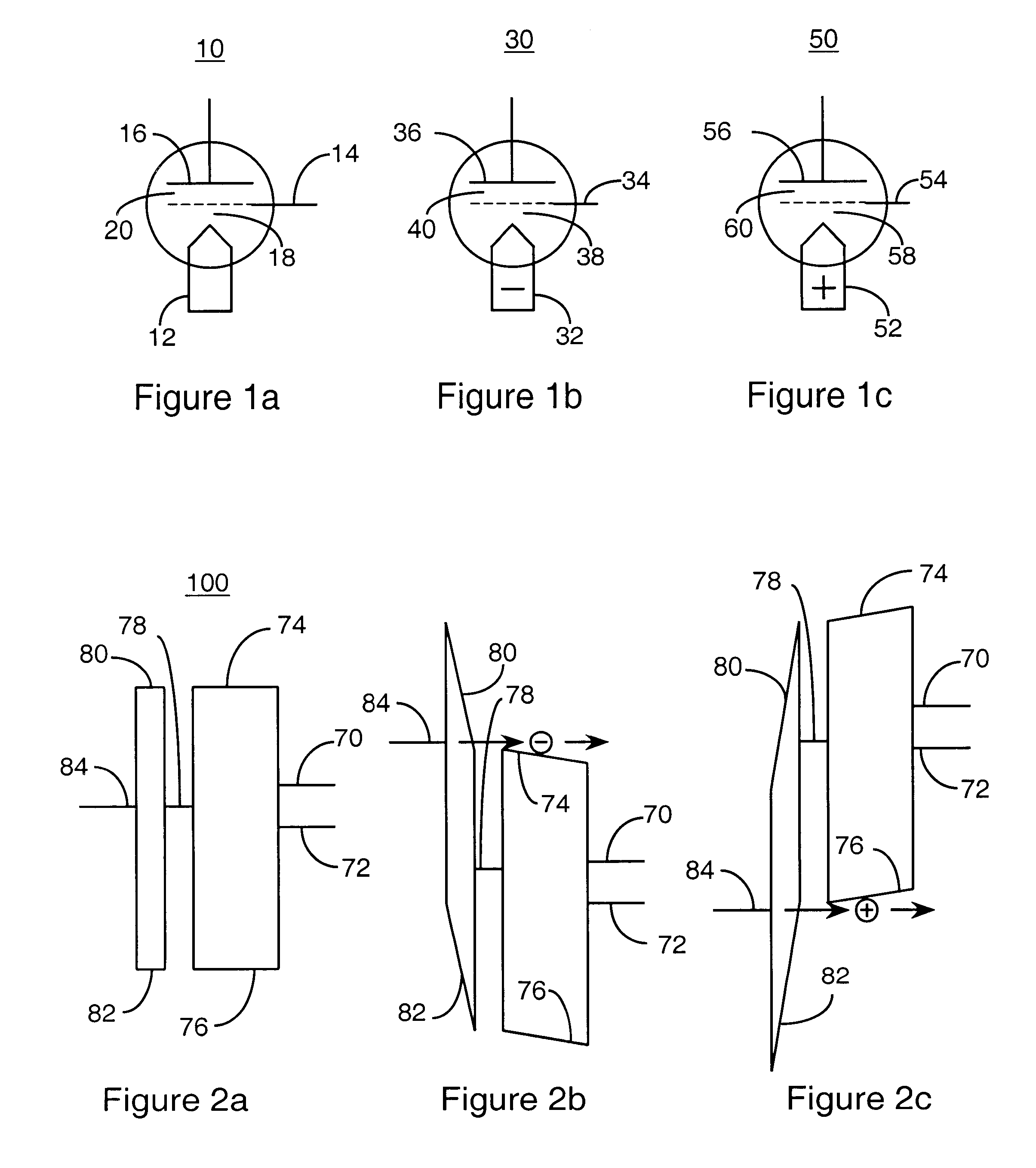

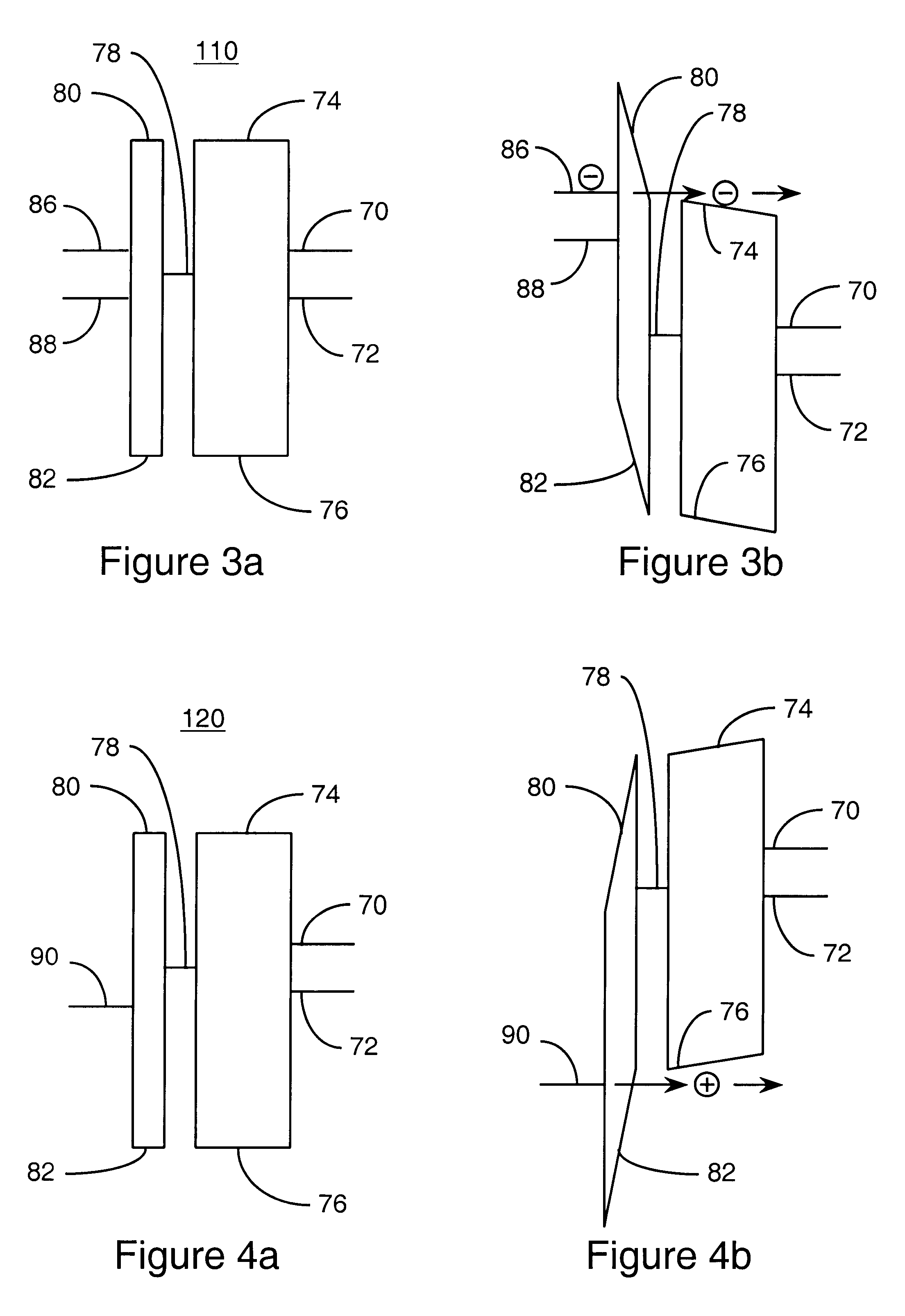

Circuit and method for controlling charge injection in radio frequency switches

A circuit and method for controlling charge injection in a circuit are disclosed. In one embodiment, the circuit and method are employed in a semiconductor-on-insulator (SOI) Radio Frequency (RF) switch. In one embodiment, an SOI RF switch comprises a plurality of switching transistors coupled in series, referred to as “stacked” transistors, and implemented as a monolithic integrated circuit on an SOI substrate. Charge injection control elements are coupled to receive injected charge from resistively-isolated nodes located between the switching transistors, and to convey the injected charge to at least one node that is not resistively-isolated. In one embodiment, the charge injection control elements comprise resistors. In another embodiment, the charge injection control elements comprise transistors. A method for controlling charge injection in a switch circuit is disclosed whereby injected charge is generated at resistively-isolated nodes between series coupled switching transistors, and the injected charge is conveyed to at least one node of the switch circuit that is not resistively-isolated.

Owner:PEREGRINE SEMICONDUCTOR

Charge pump circuit

InactiveUS6535051B2Pulse automatic controlElectric variable regulationCharge injectionControl signal

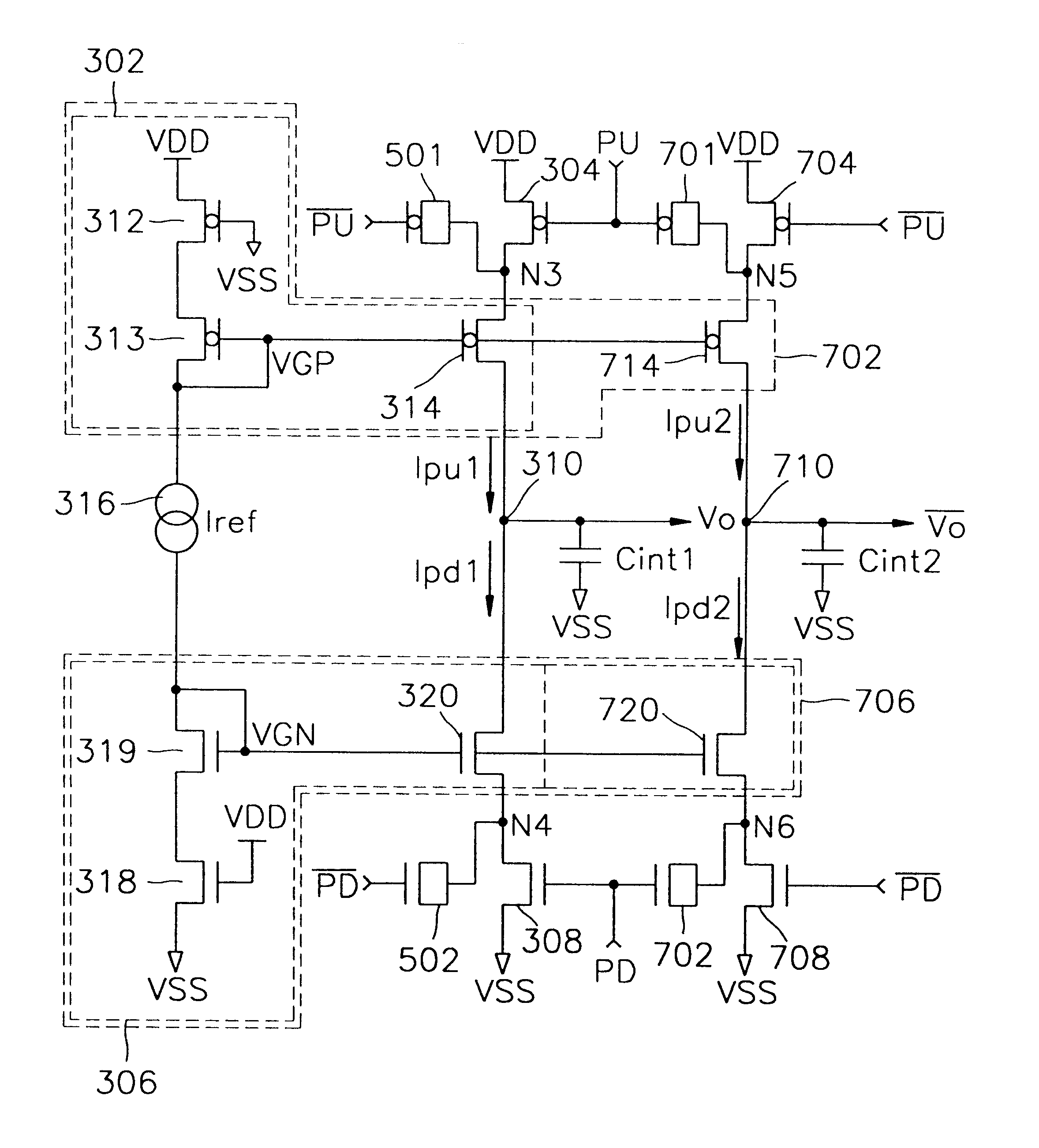

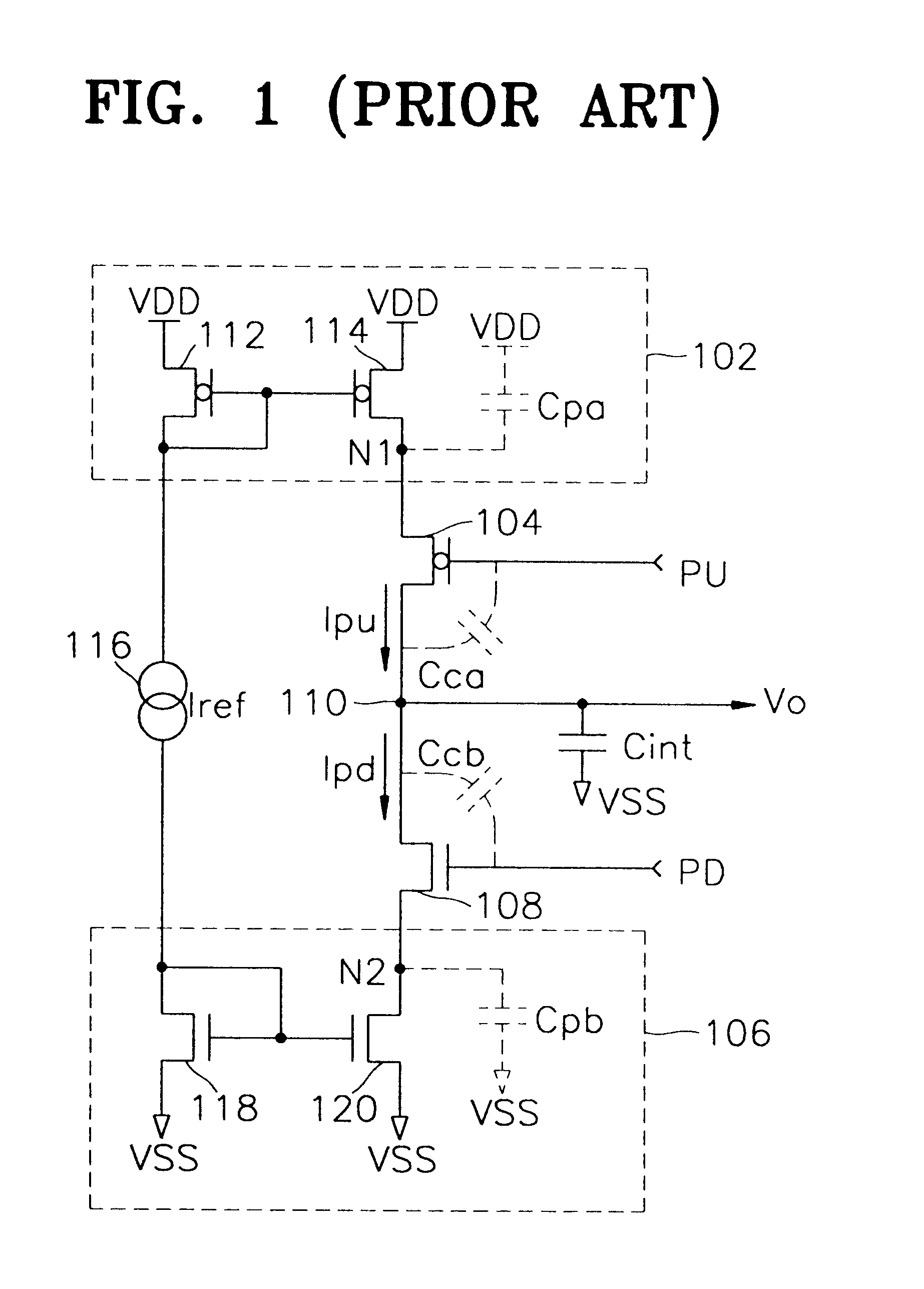

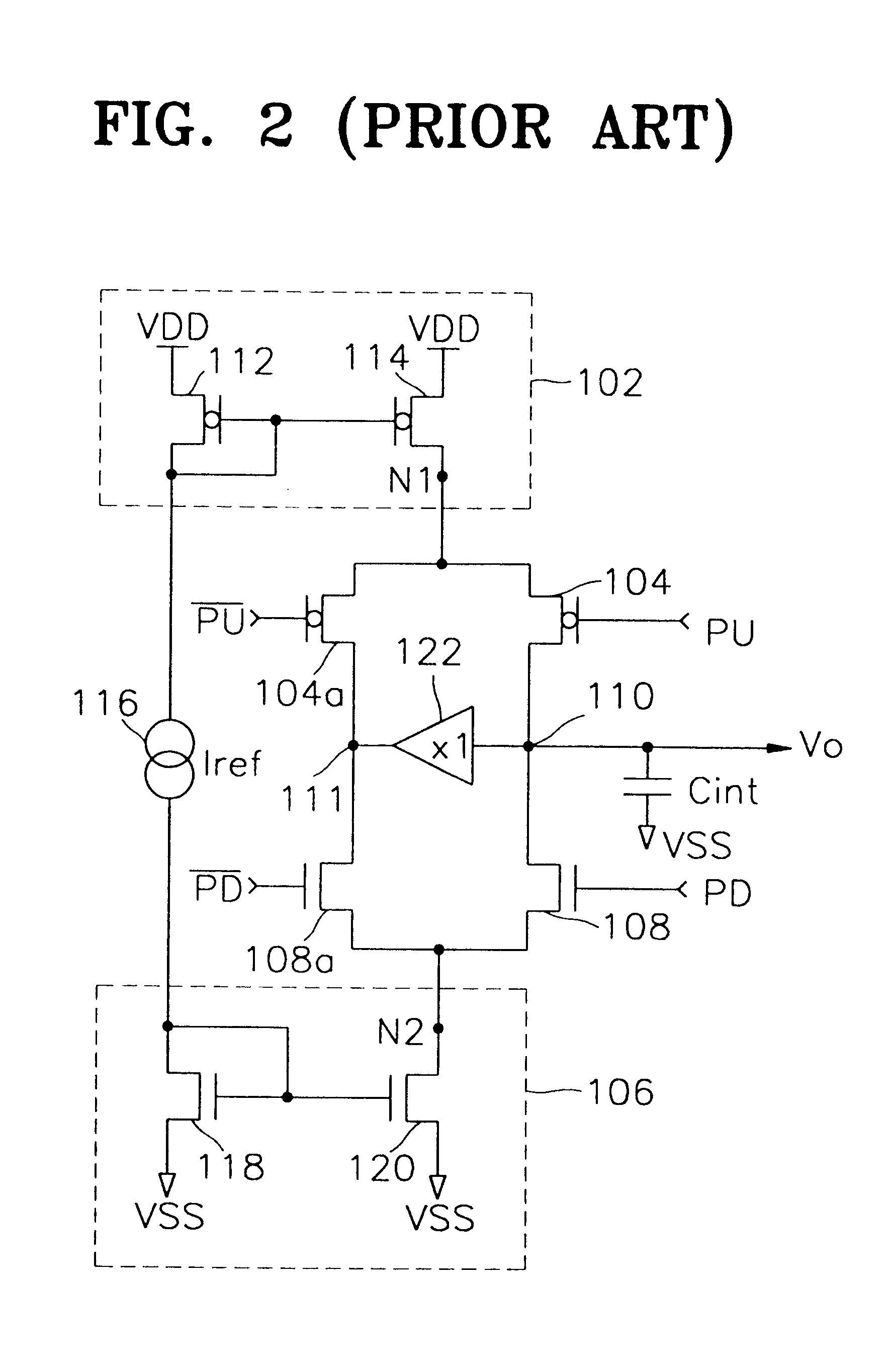

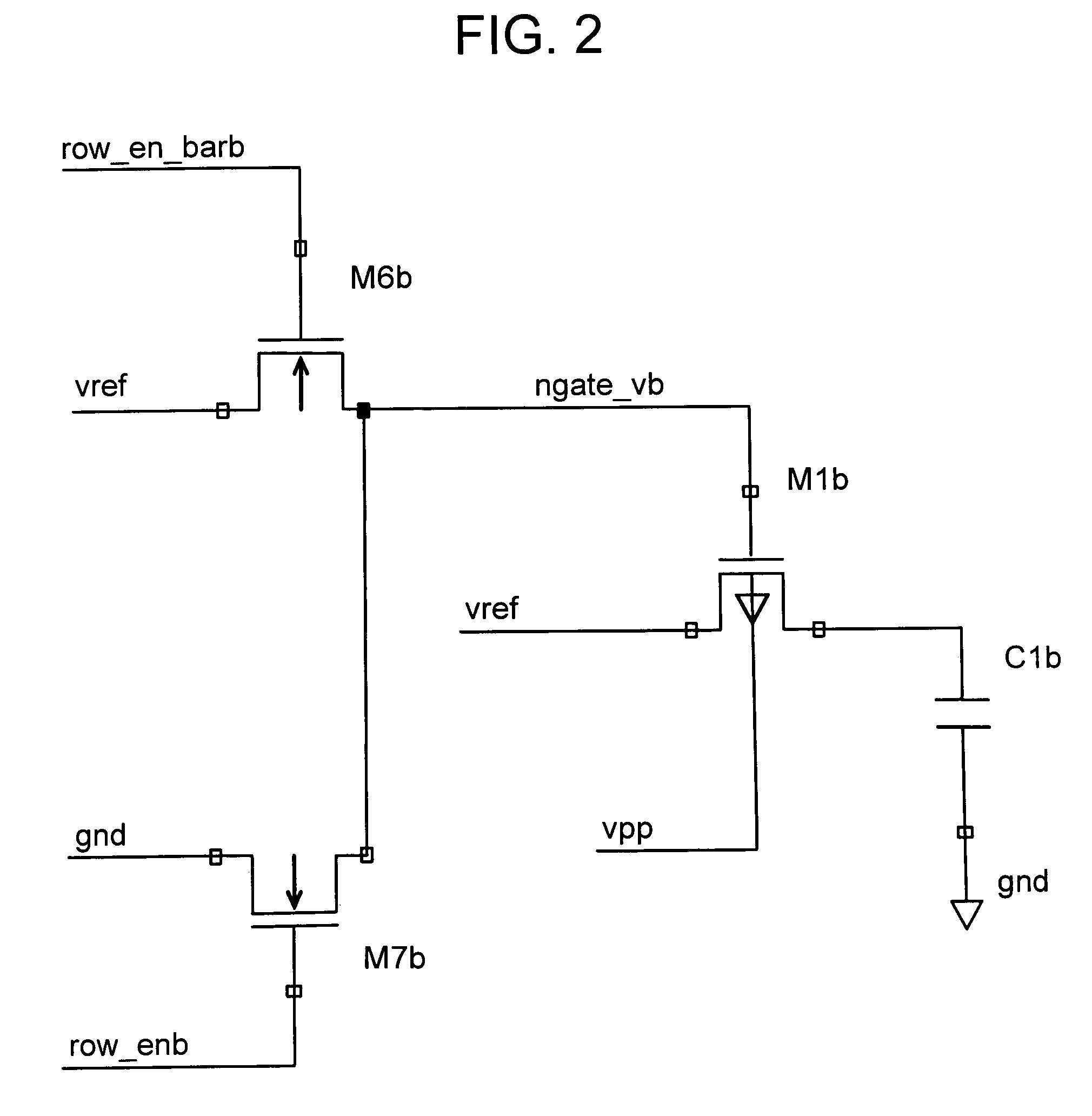

A charge pump circuit capable of preventing coupling and charge injection without increasing a layout area and power consumption is provided. The charge pump circuit includes a pull-up current source, a pull-down current source, a first switching device, and a second switching device. The pull-up current source sources pump-up current to the output node. The pull-down current source includes a current mirror and sinks pump-down current from the output node. In particular, the first switching device is connected between a supply voltage node and the pull-up current source and is switched in response to a pump-up control signal. The second switching device is connected between the second current source and a ground voltage node and is switched in response to a pump-down control signal. The current pump circuit may further include a first dummy capacitor one end of which is connected to a junction between the first switching device and the first current source and a second dummy capacitor one end of which is connected to a junction between the second switching device and the second current source.

Owner:SAMSUNG ELECTRONICS CO LTD

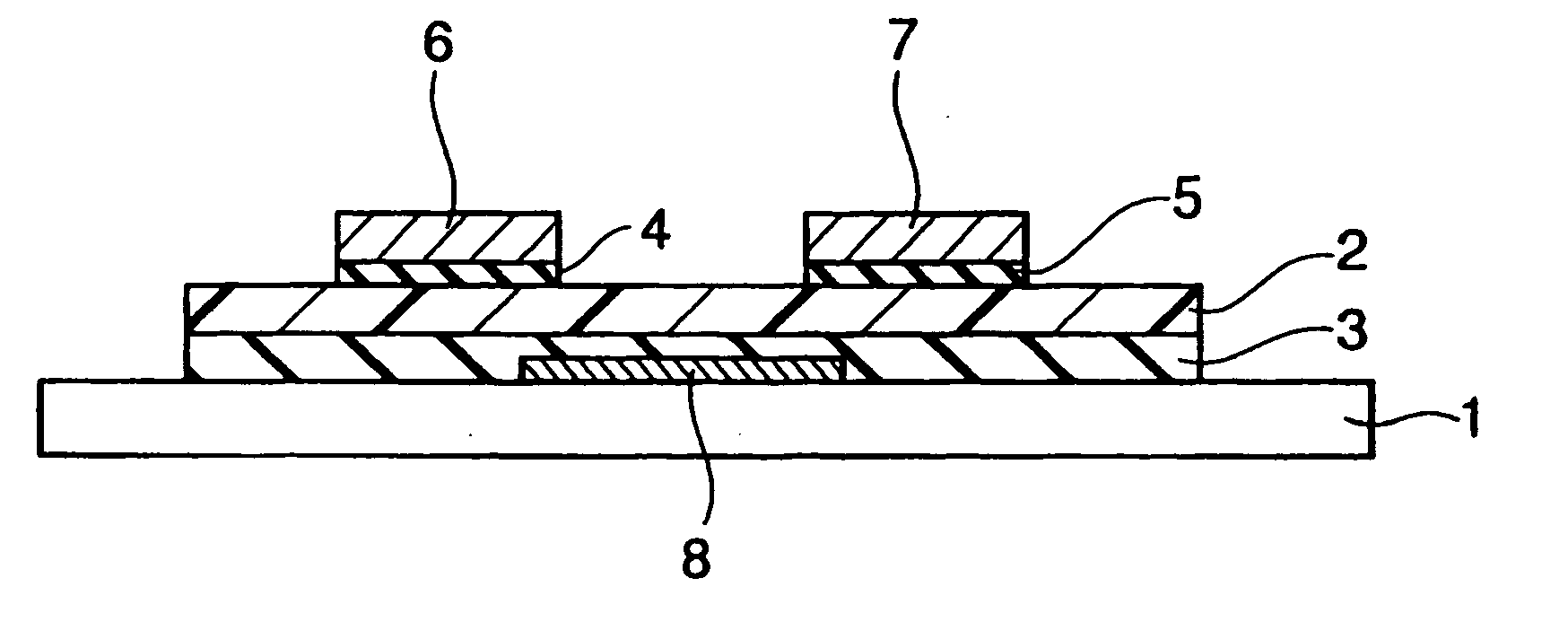

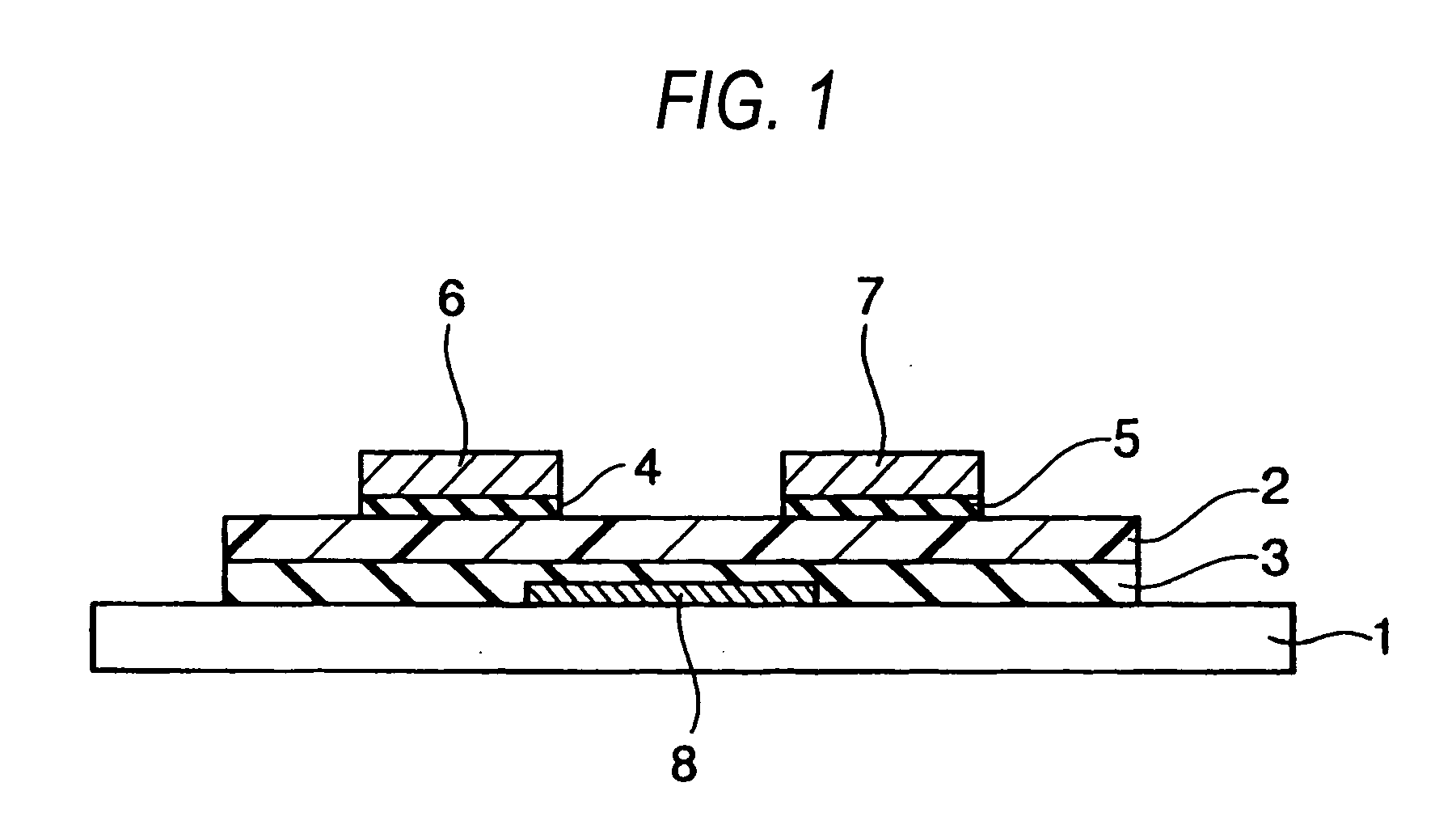

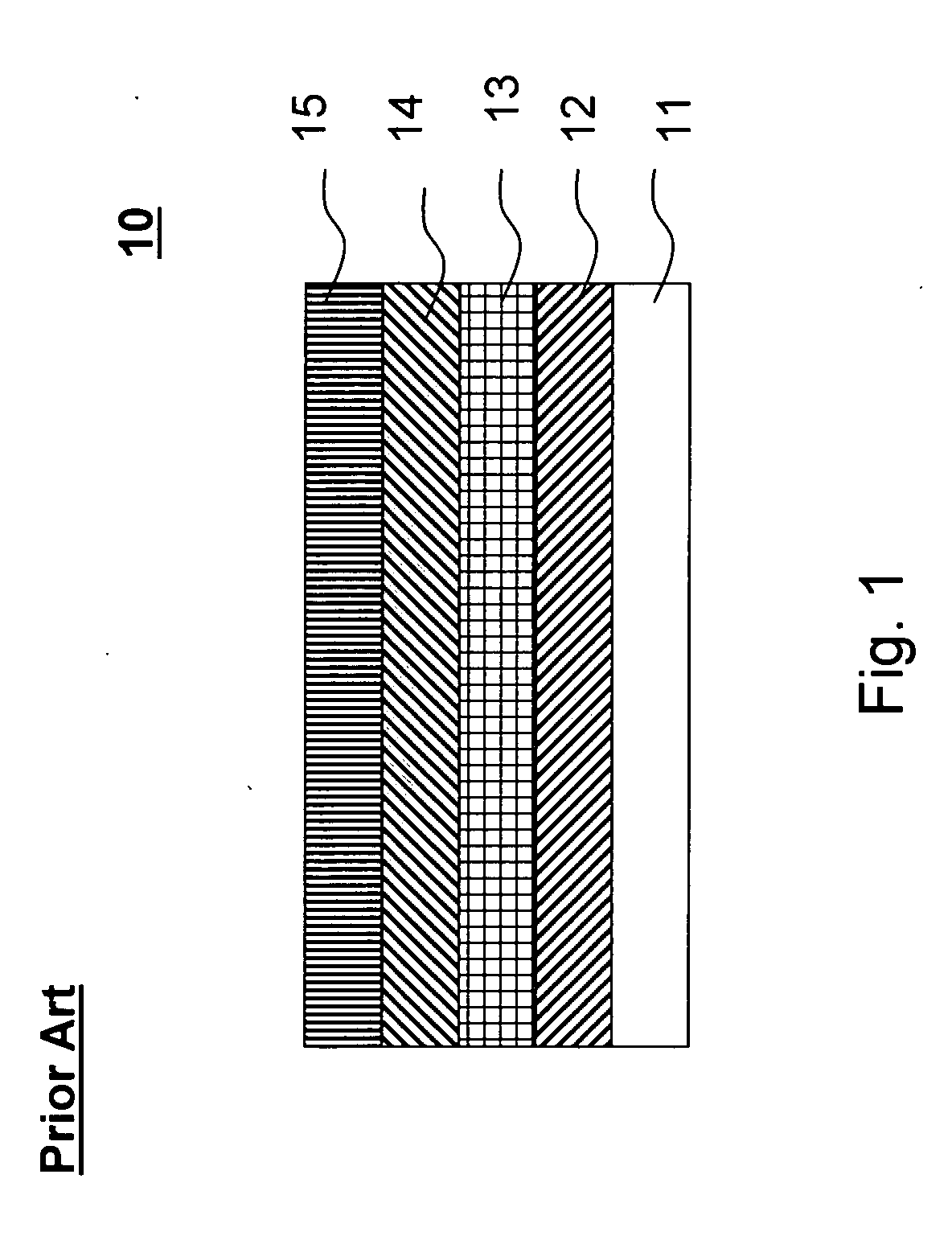

Organic field effect transistor and method of manufacturing the same

InactiveUS20050263756A1Characteristic changeExtend your lifeSolid-state devicesSemiconductor/solid-state device manufacturingCharge injectionContact formation

To provide an organic field effect transistor with stable characteristics and a long life span, an organic field effect transistor includes a gate electrode 8 formed on an organic semiconductor film 2 made of an organic semiconductor material with a gate insulating film 3 interposed therebetween; and a source electrode 6 and a drain electrode 7 provided so as to come in contacts with the organic semiconductor film with the gate electrode 8 interposed therebetween. At least one of the source electrode 6 and the drain electrode 7 is formed in contact with the organic semiconductor film 2 with charge injection layers 4 and 5 made of an inorganic material interposed therebetween.

Owner:PANASONIC CORP

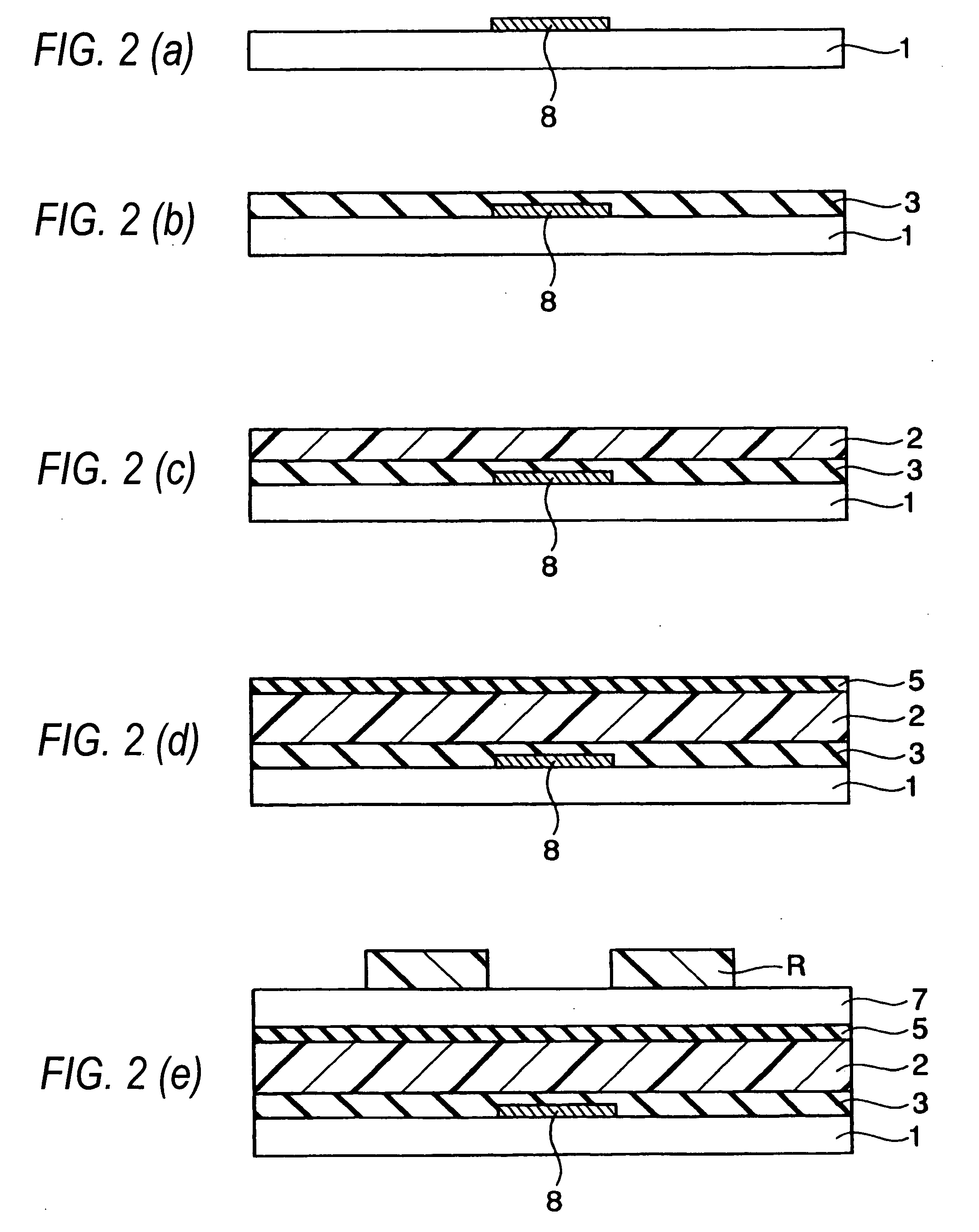

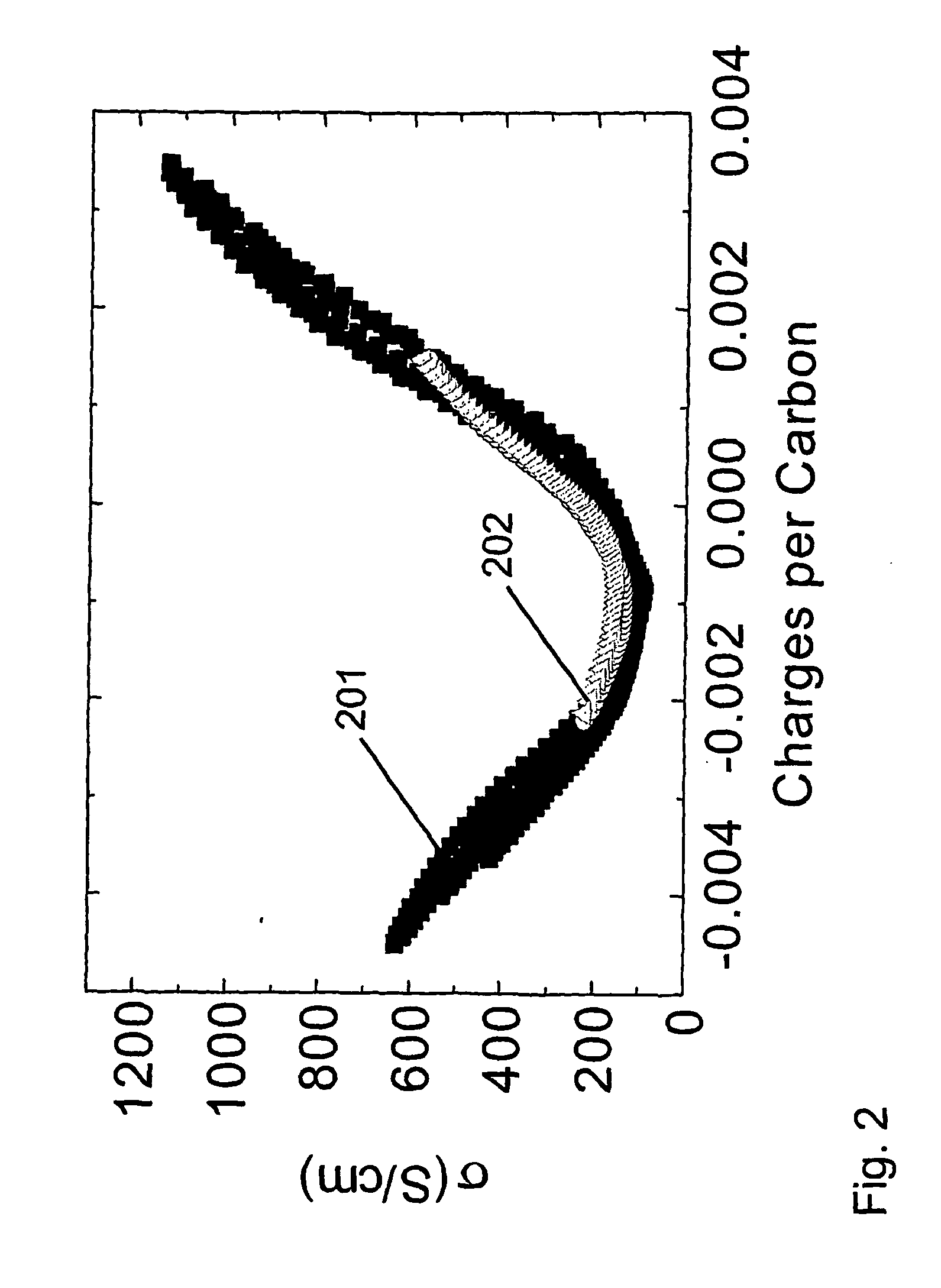

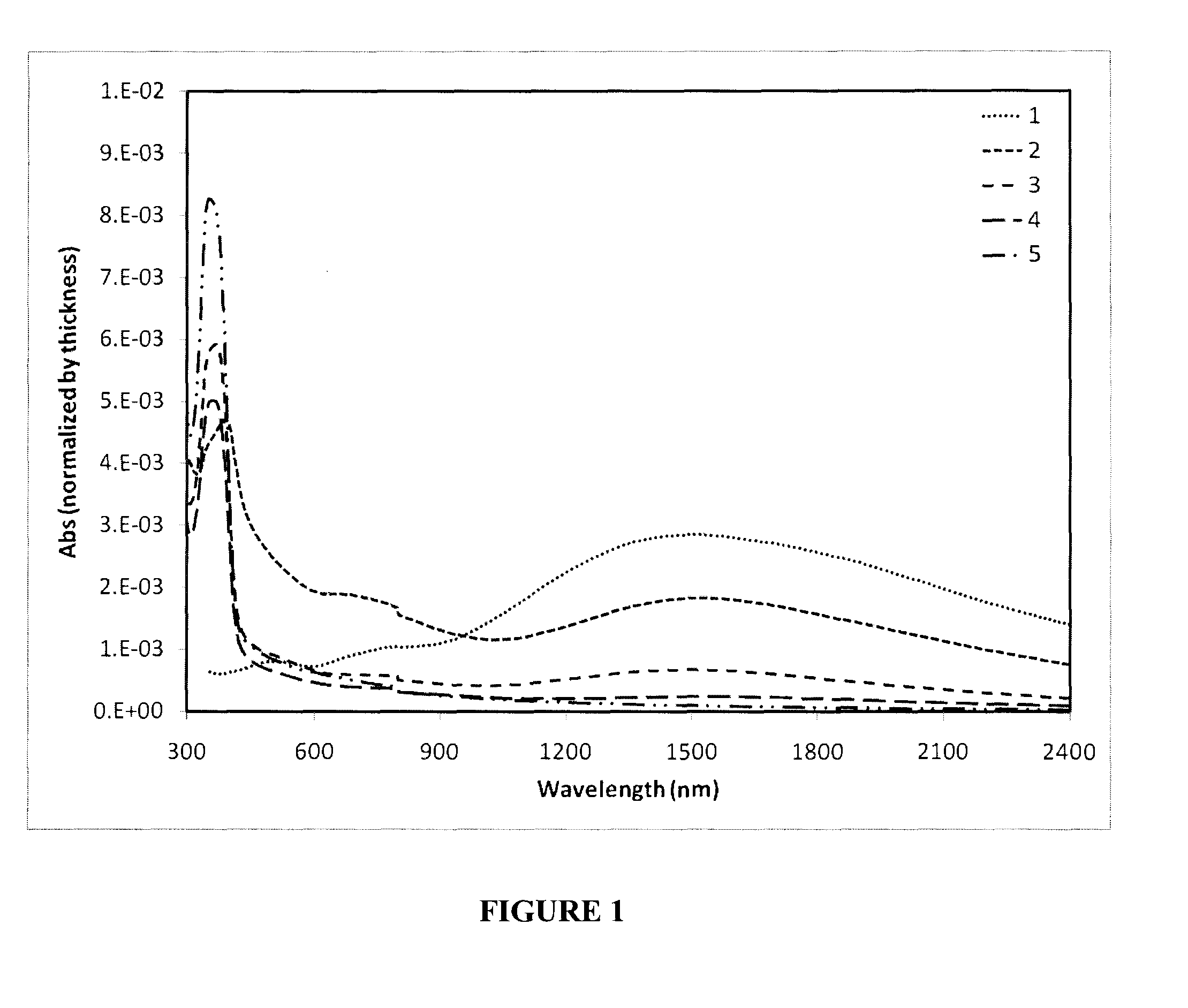

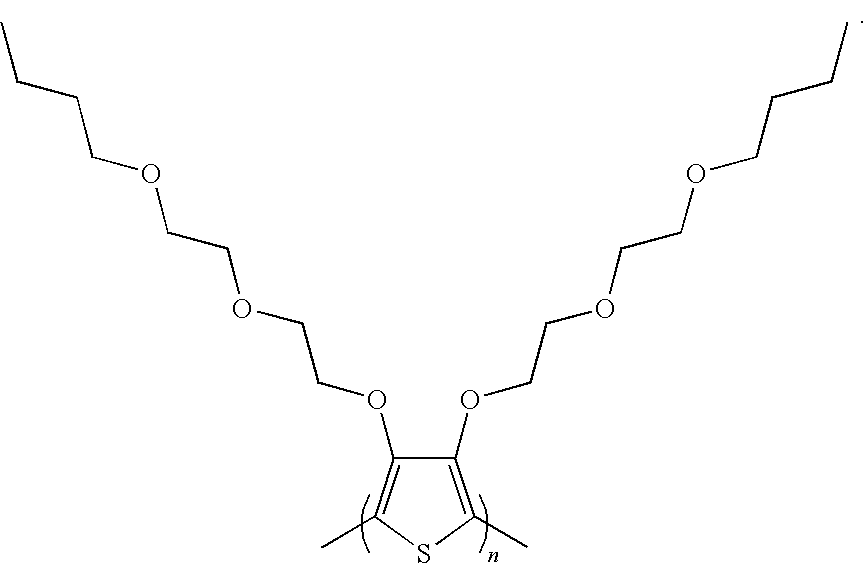

Material and device properties modification by electrochemical charge injection in the absence of contacting electrolyte for either local spatial or final states

InactiveUS20070108068A1Change propertiesMaterial nanotechnologyElectrolysis componentsCharge injectionDevice Properties

In some embodiments, the present invention is directed to processes for the combination of injecting charge in a material electrochemically via non-faradaic (double-layer) charging, and retaining this charge and associated desirable properties changes when the electrolyte is removed. The present invention is also directed to compositions and applications using material property changes that are induced electrochemically by double-layer charging and retained during subsequent electrolyte removal. In some embodiments, the present invention provides reversible processes for electrochemically injecting charge into material that is not in direct contact with an electrolyte. Additionally, in some embodiments, the present invention is directed to devices and other material applications that use properties changes resulting from reversible electrochemical charge injection in the absence of an electrolyte.

Owner:BOARD OF RGT THE UNIV OF TEXAS SYST

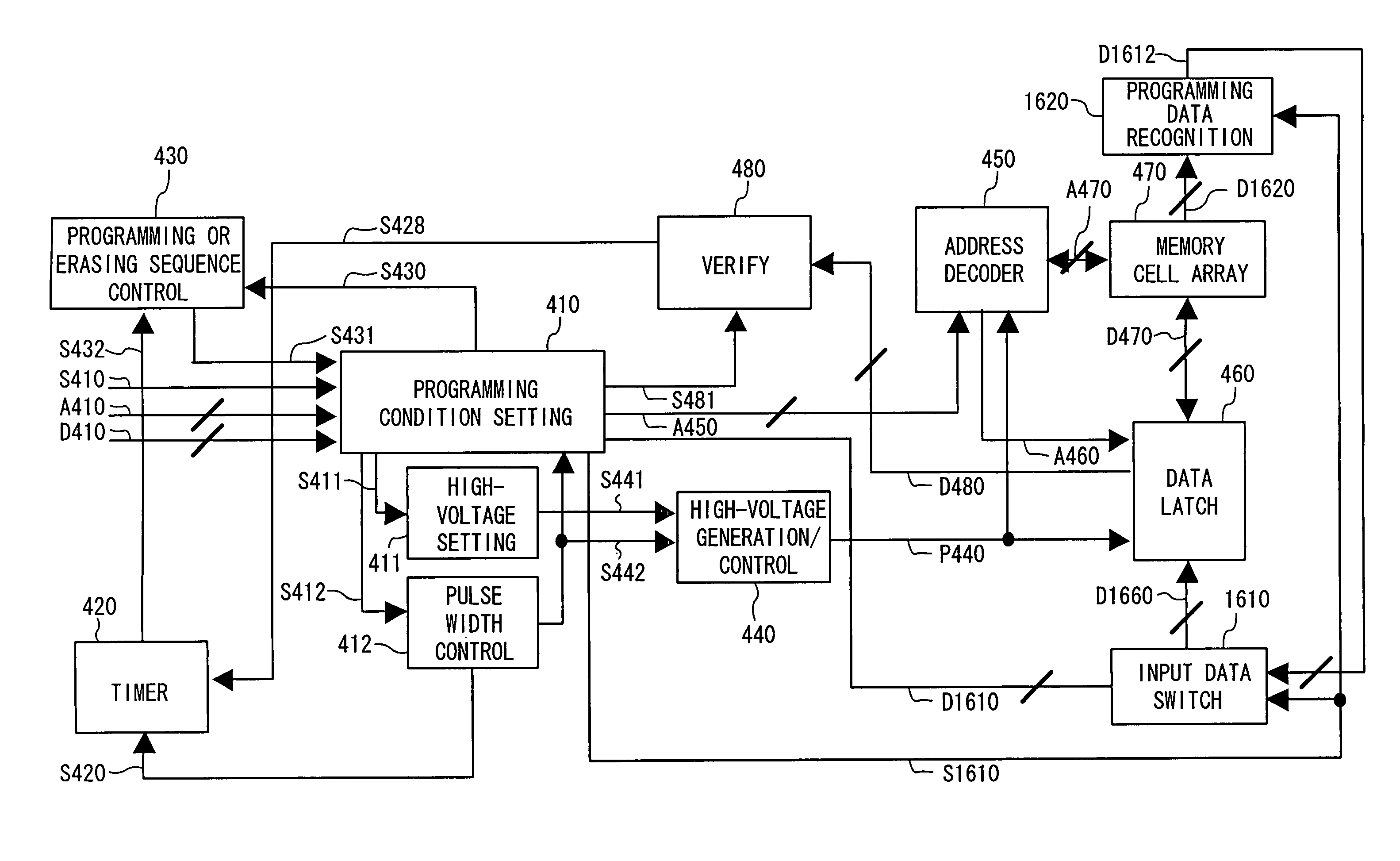

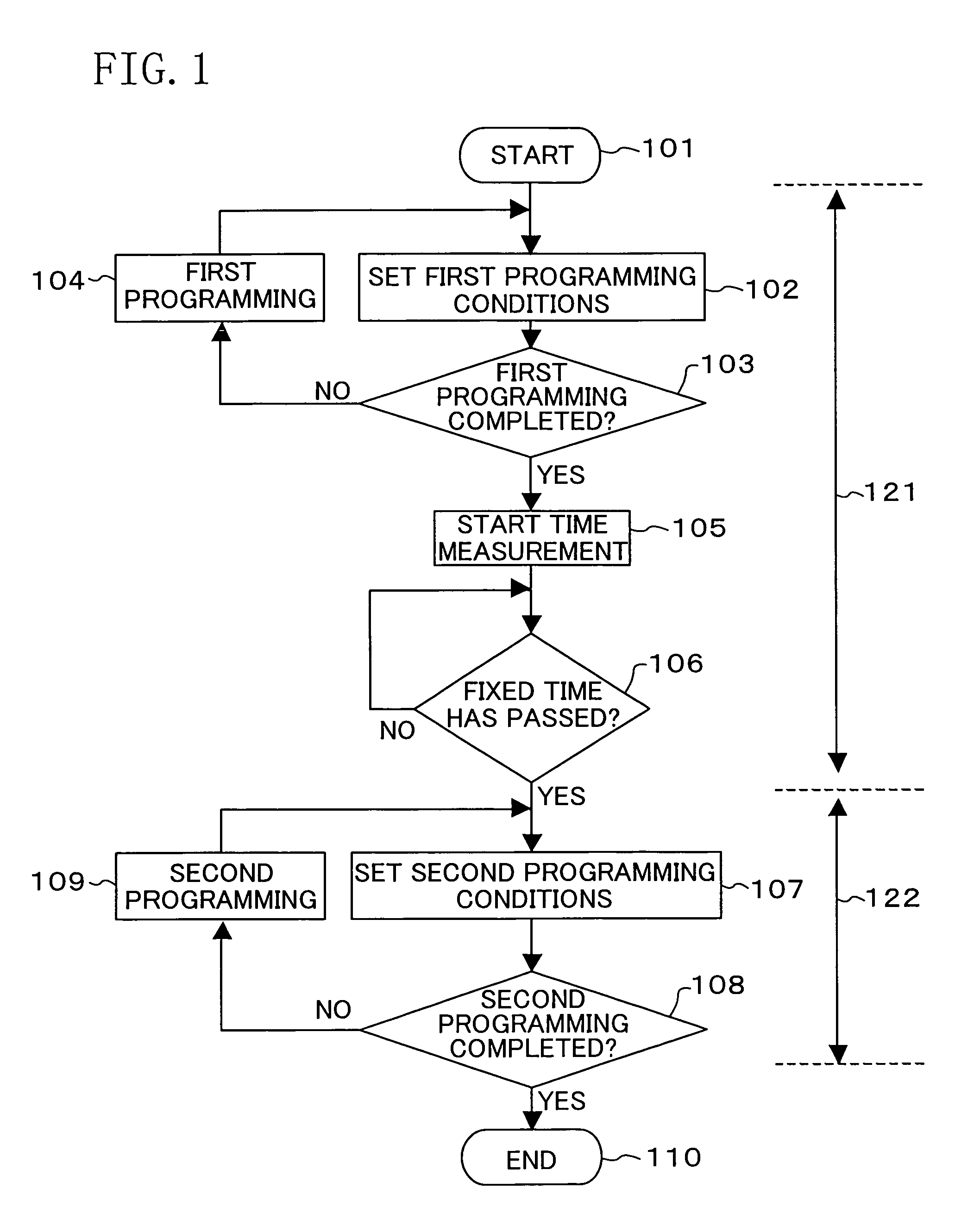

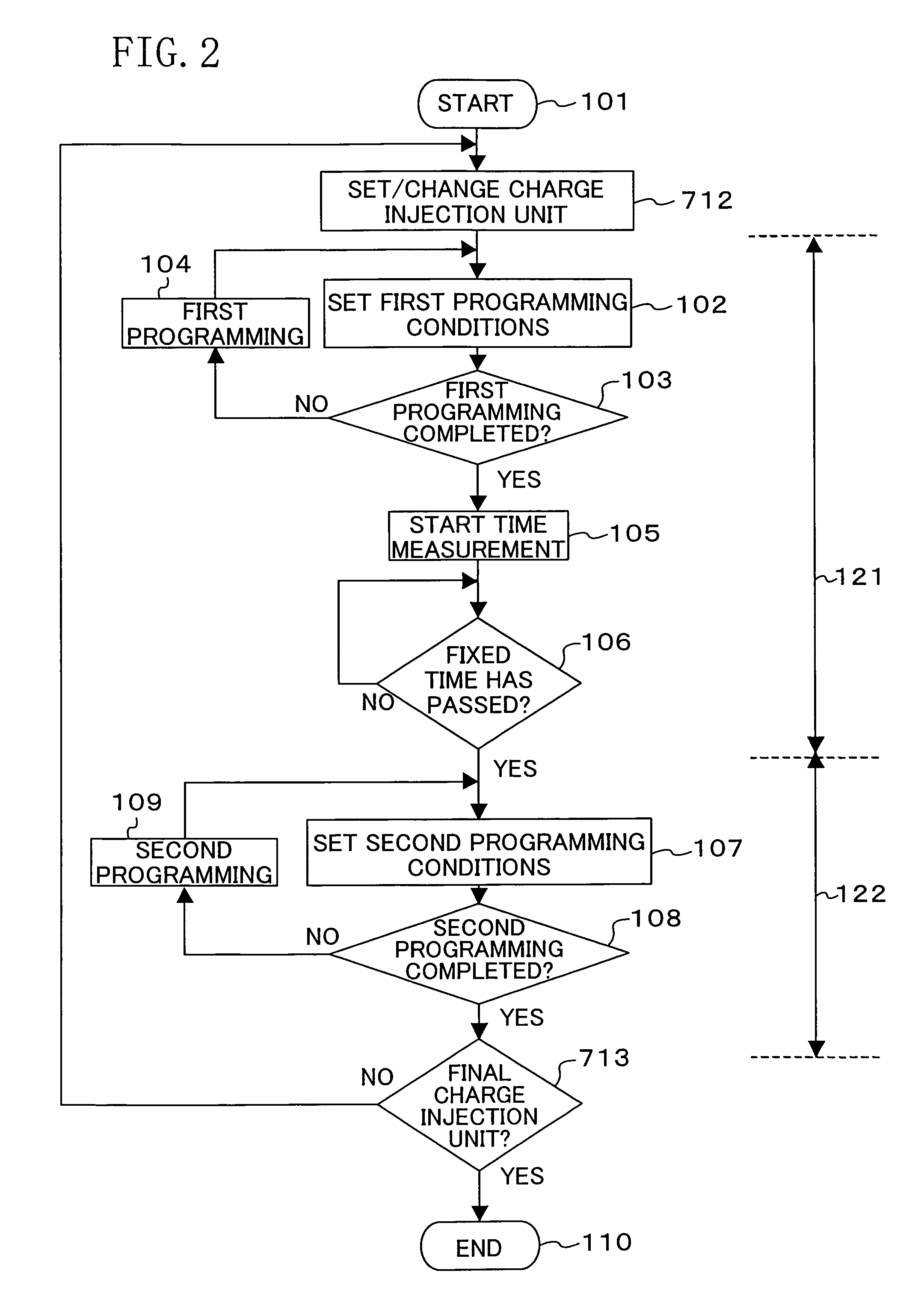

Nonvolatile semiconductor memory device and programming or erasing method therefor

ActiveUS7460410B2Inhibit deteriorationData retentionRead-only memoriesDigital storageCharge injectionCharge loss

In a nonvolatile memory cell having a trap layer, programming or erasing is made in a sequence of first charge injection with a given wait time being secured and second charge injection executed after the first charge injection. Surrounding charge that deteriorates the data retention characteristic is reduced by use of initial variation occurring immediately after programming (charge loss phenomenon due to binding of injected charge with the surrounding charge in an extremely short time), and then the charge loss due to the initial variation is compensated, to thereby improve the data retention characteristic.

Owner:PANASONIC SEMICON SOLUTIONS CO LTD

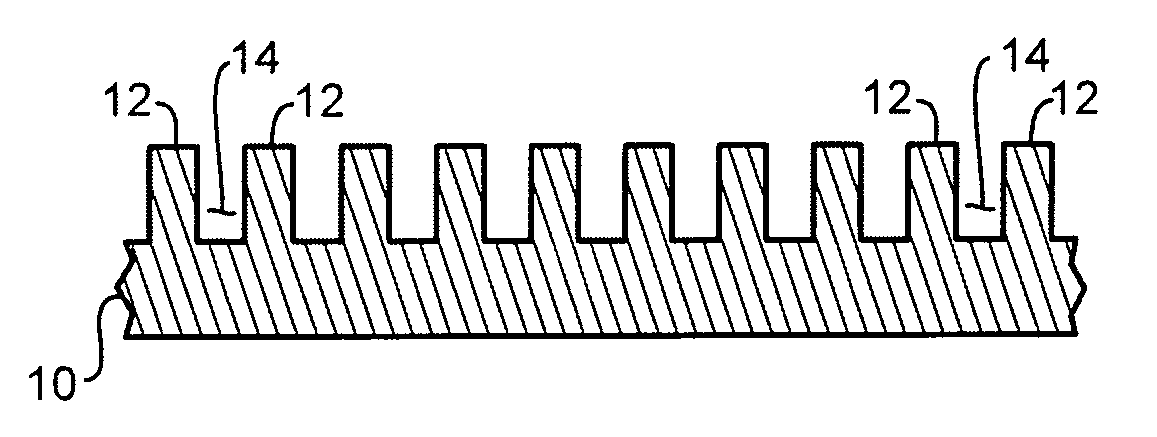

Noble metal electrodes with nanostructures

InactiveUS20080161887A1Increase the effective surface areaImprove the level ofMaterial nanotechnologySpinal electrodesCapacitanceCharge injection

An electrode assembly having homogeneous noble metal or blended alloy nanostructures for enhancement of capacitive charge injection. Applications can include stimulation of the baroreflex, neural stimulation and cardiac stimulation. In one embodiment, a matrix of substantially elongate nanocylinders or nanotubes are configured to deliver electrical charge to a target tissue, conducting charge substantially along the elongate axes of the nanostructures. The configuration enhances the real or effective area of the electrode to promote capacitive charge injection, and entraps solution for more complete recovery of electro-generated species. Certain embodiments may be configured to apply a suction through the electrode for temporary placement of the electrode for mapping the response of the electrode vs. positioning.

Owner:CVRX

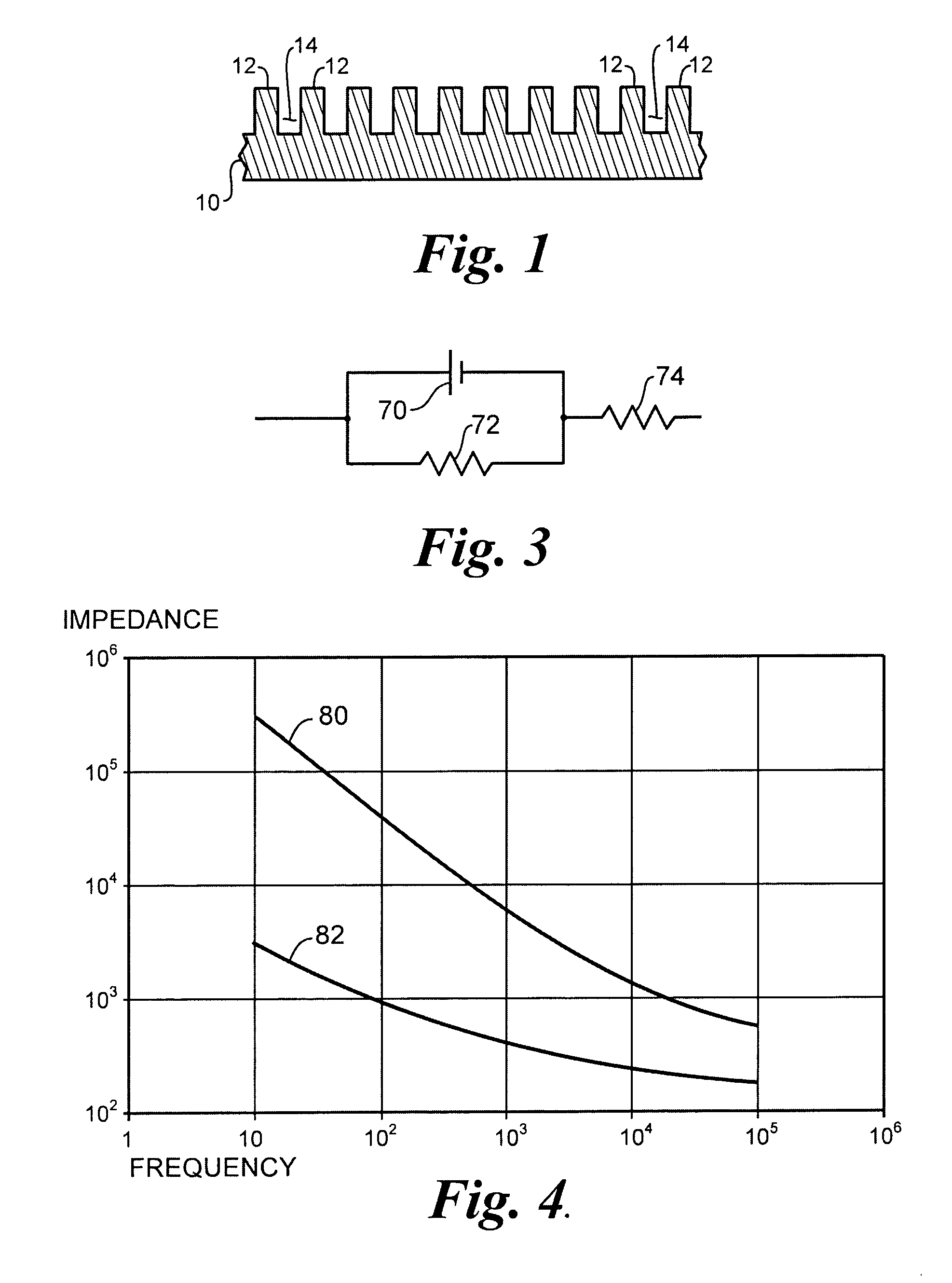

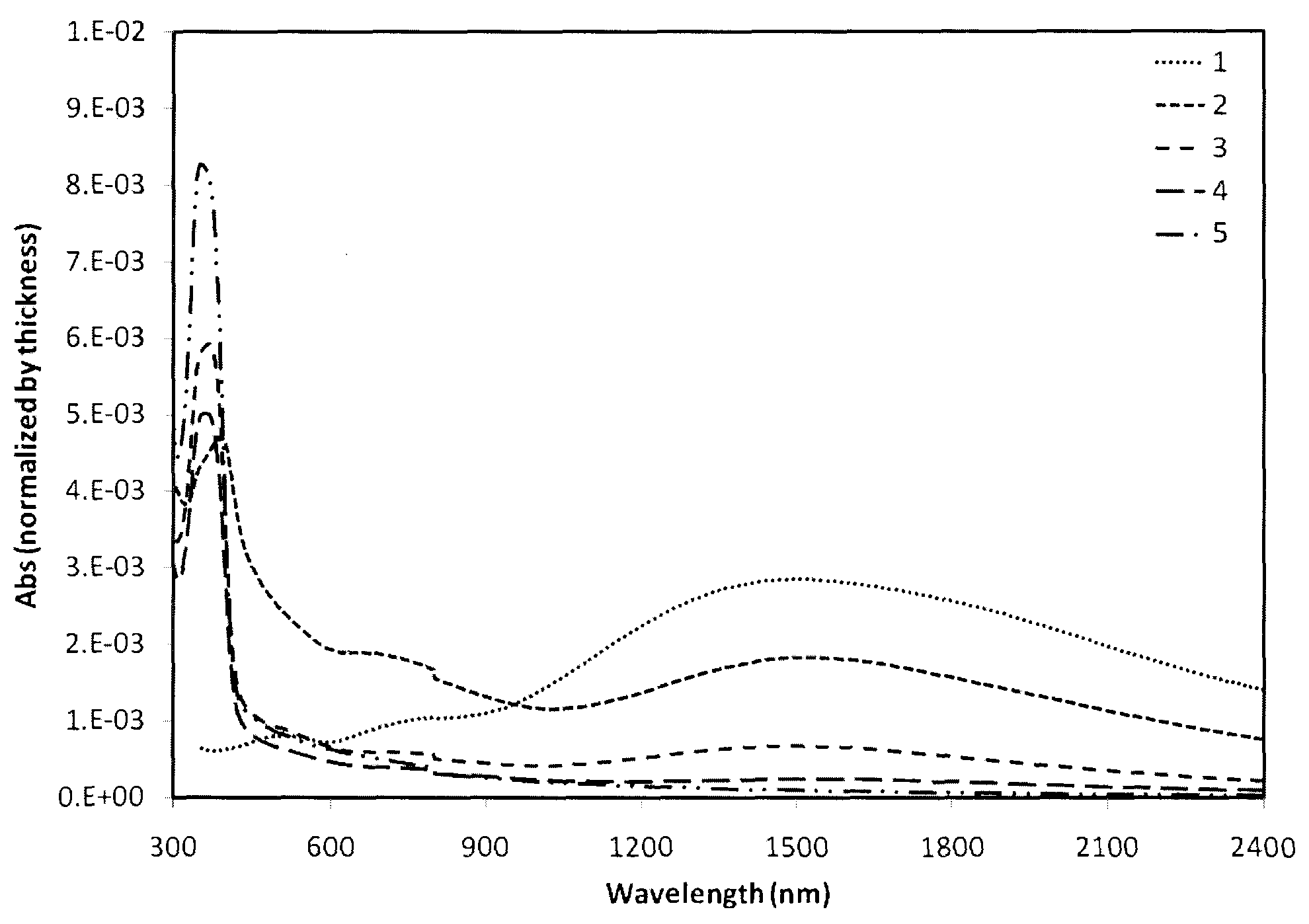

Inter facial architecture for nanostructured optoelectronic devices

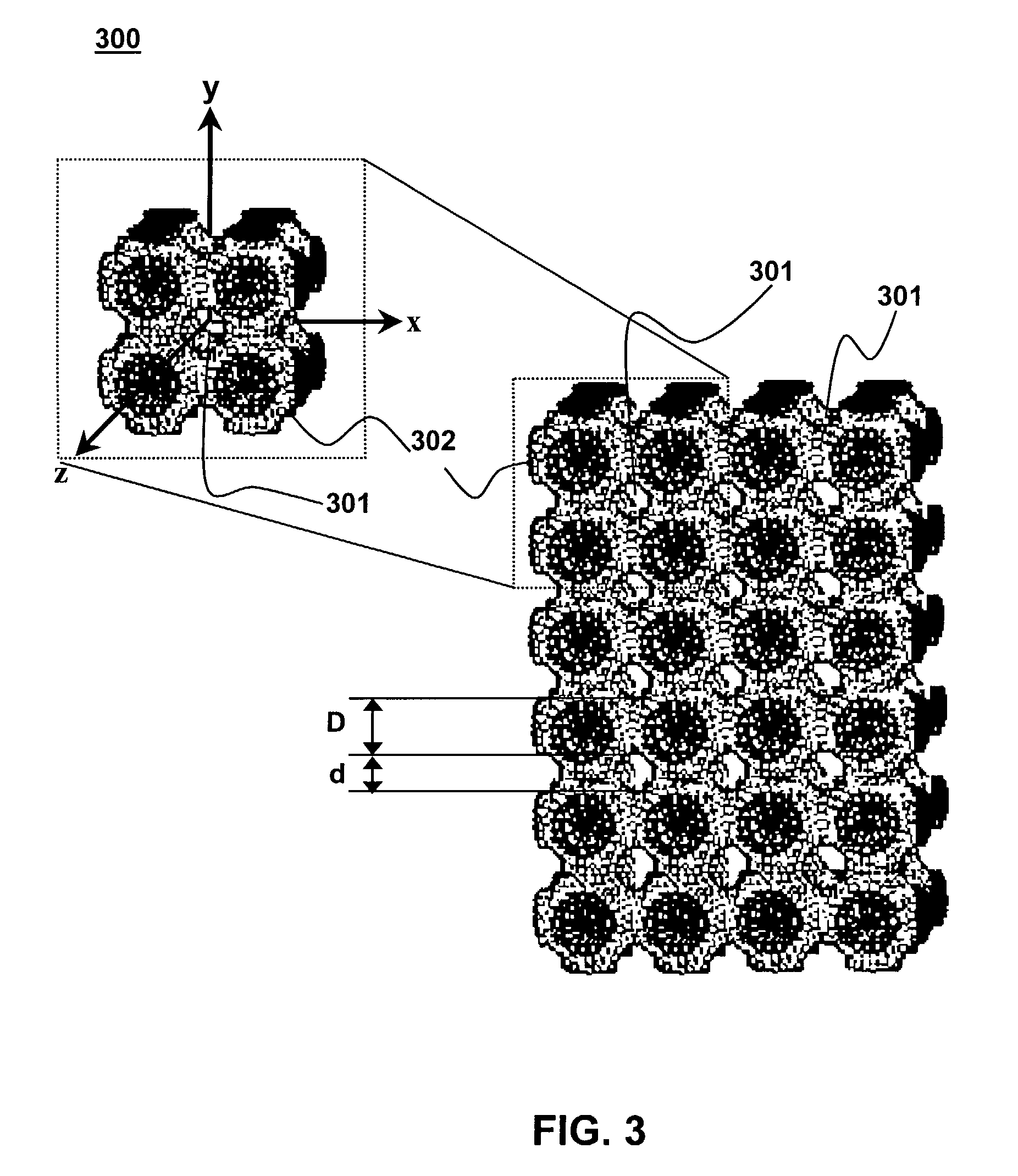

InactiveUS7511217B1Low costImprove equipment efficiencyFinal product manufactureNanoinformaticsCharge injectionFilling materials

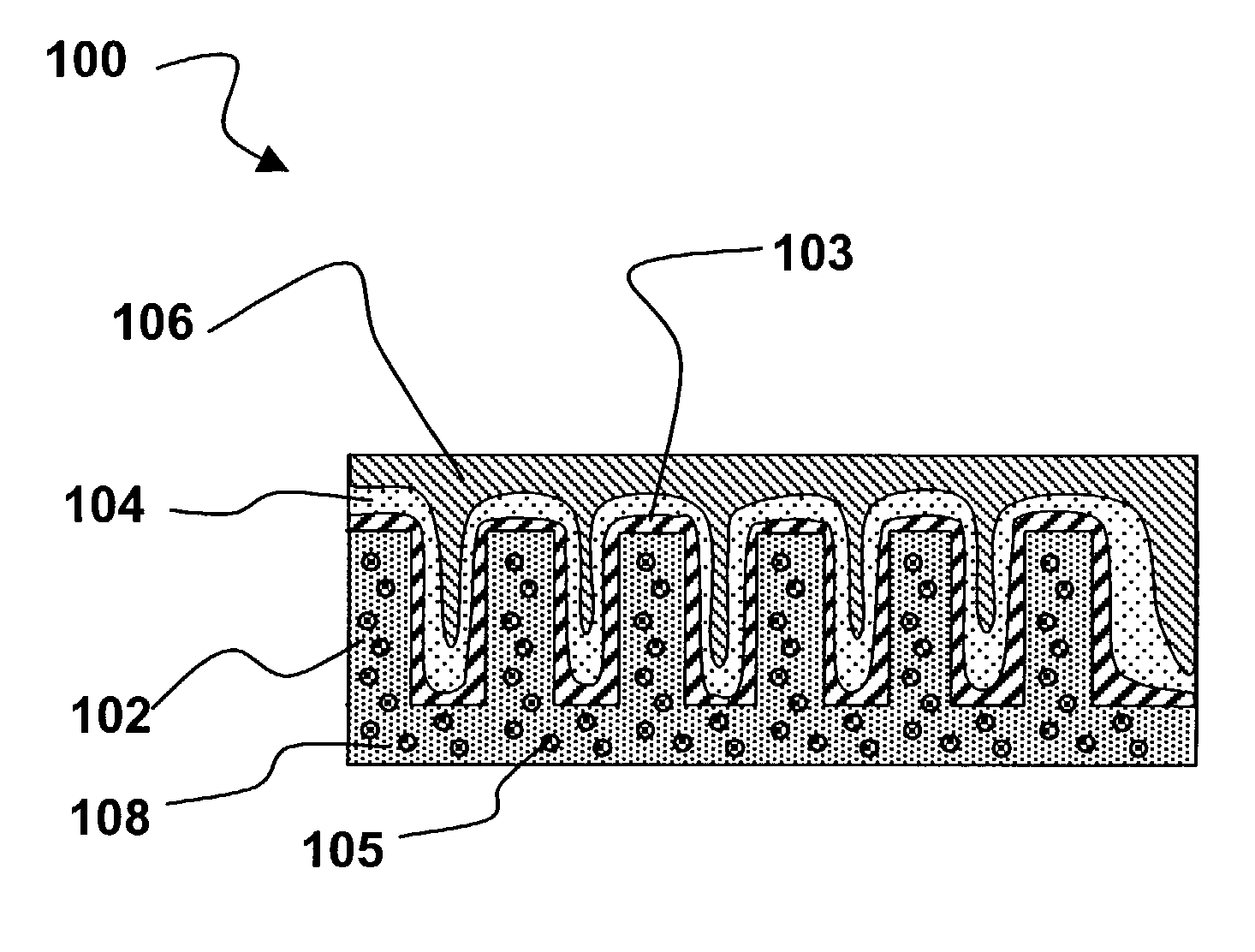

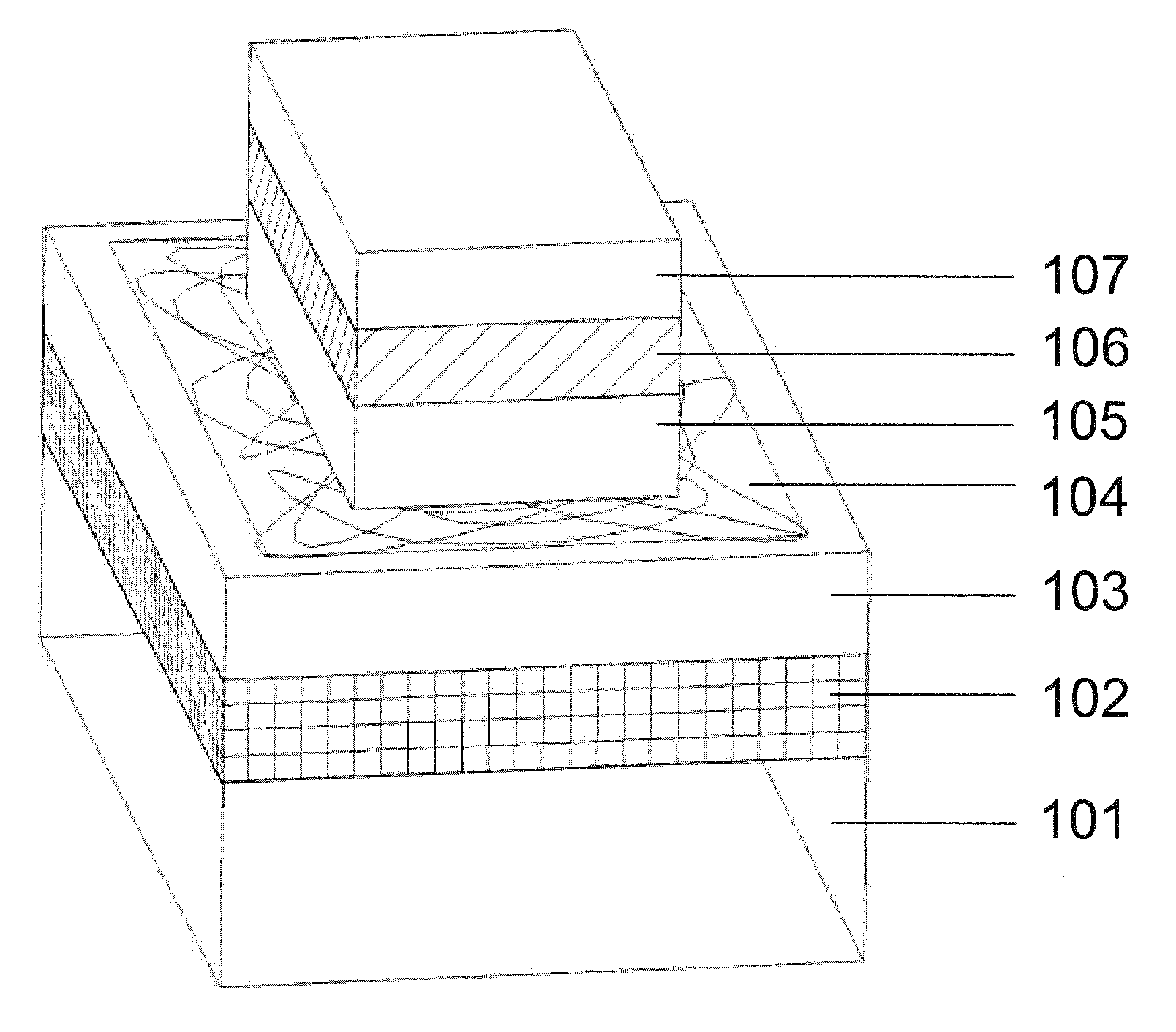

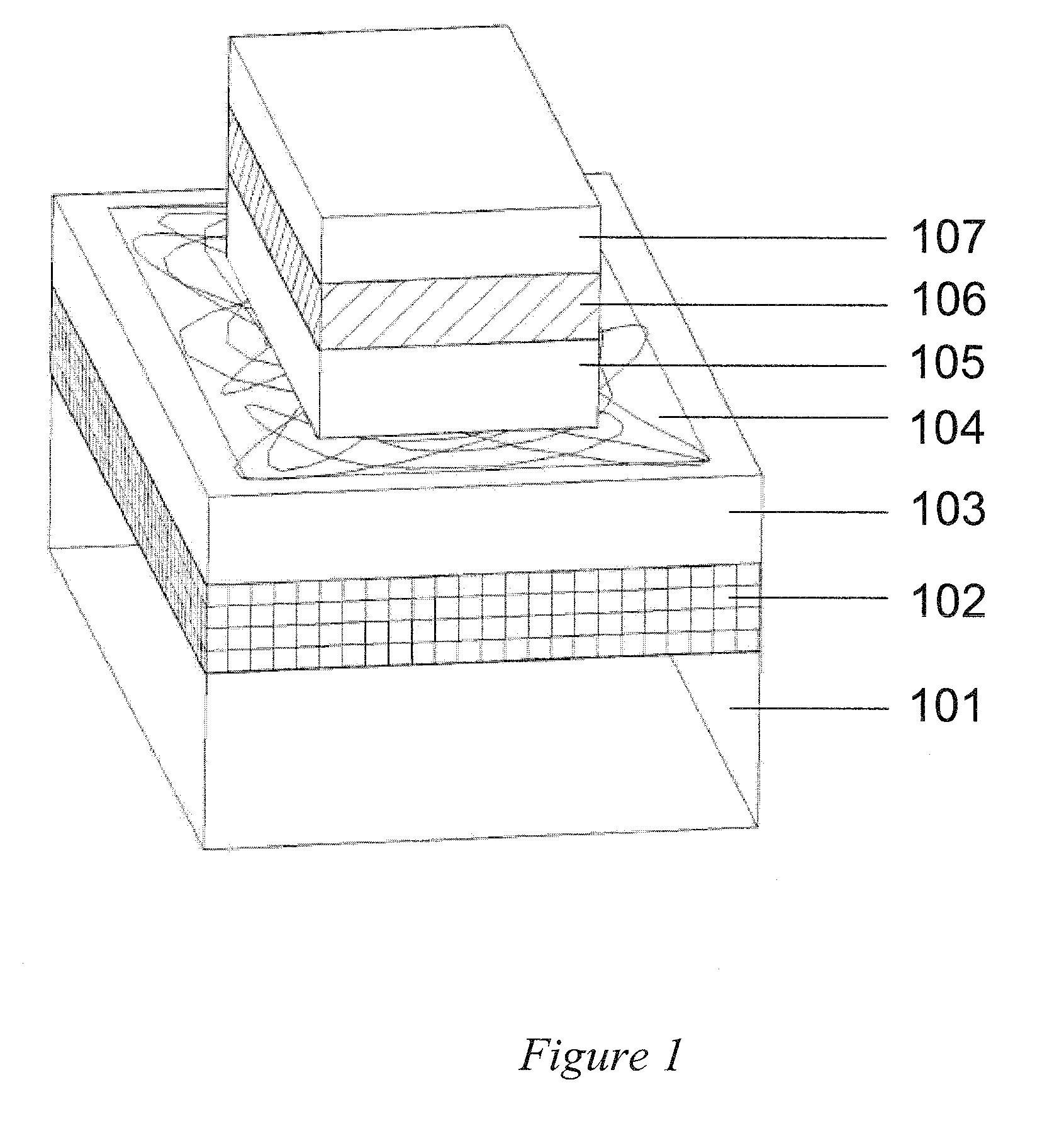

An optoelectronic apparatus, a method for making the apparatus, and the use of the apparatus in an optoelectronic device are disclosed. The apparatus may include an active layer having a nanostructured network layer with a network of regularly spaced structures with spaces between neighboring structures. One or more network-filling materials are disposed in the spaces. At least one of the network-filling materials has complementary charge transfer properties with respect to the nanostructured network layer. An interfacial layer, configured to enhance an efficiency of the active layer, is disposed between the nanostructured network layer and the network-filling materials. The interfacial layer may be configured to provide (a) charge transfer between the two materials that exhibits different rates for forward versus backward transport; (b) differential light absorption to extend a range of wavelengths that the active layer can absorb; or (c) enhanced light absorption, which may be coupled with charge injection.

Owner:AERIS CAPITAL SUSTAINABLE IP

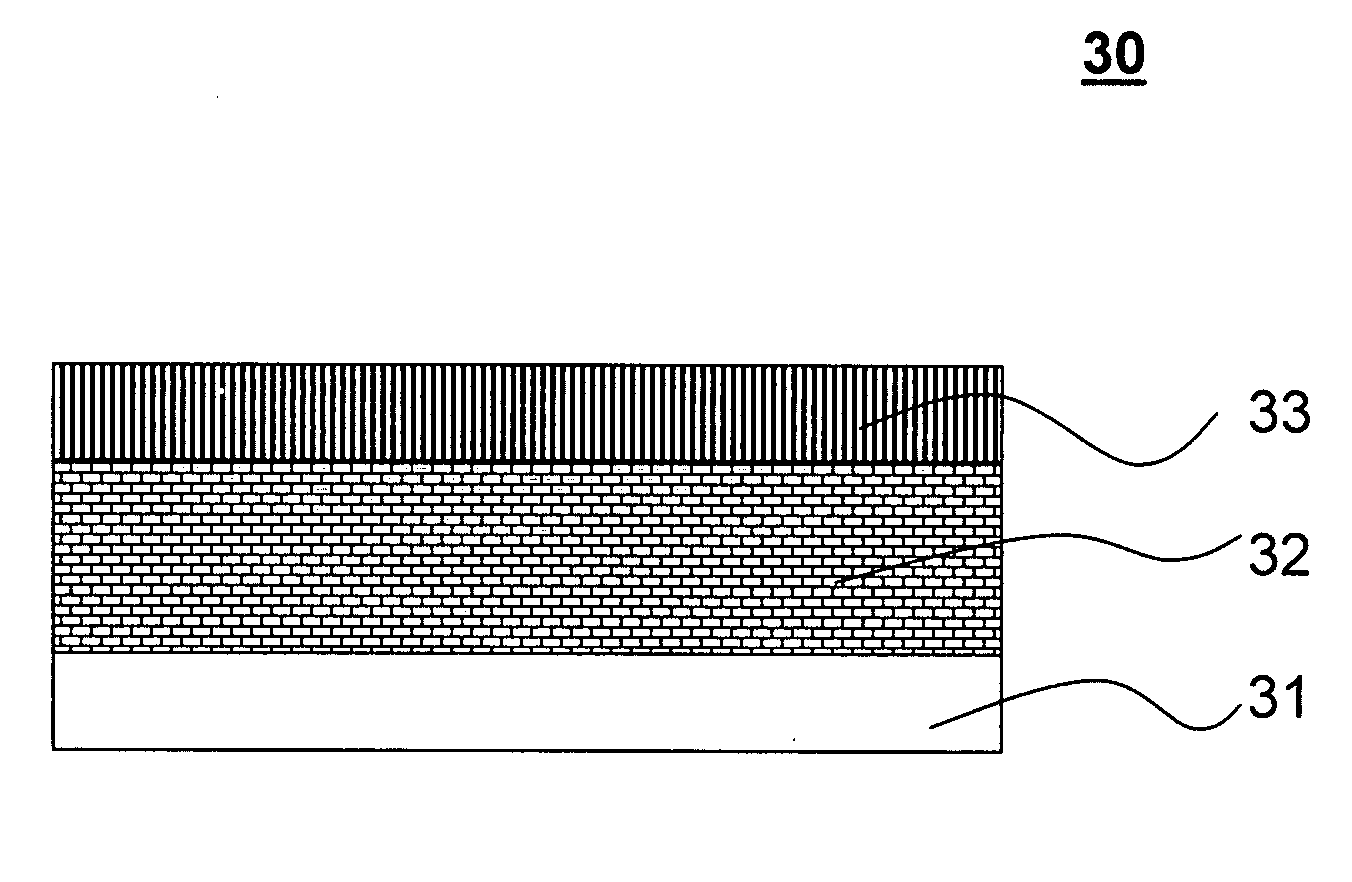

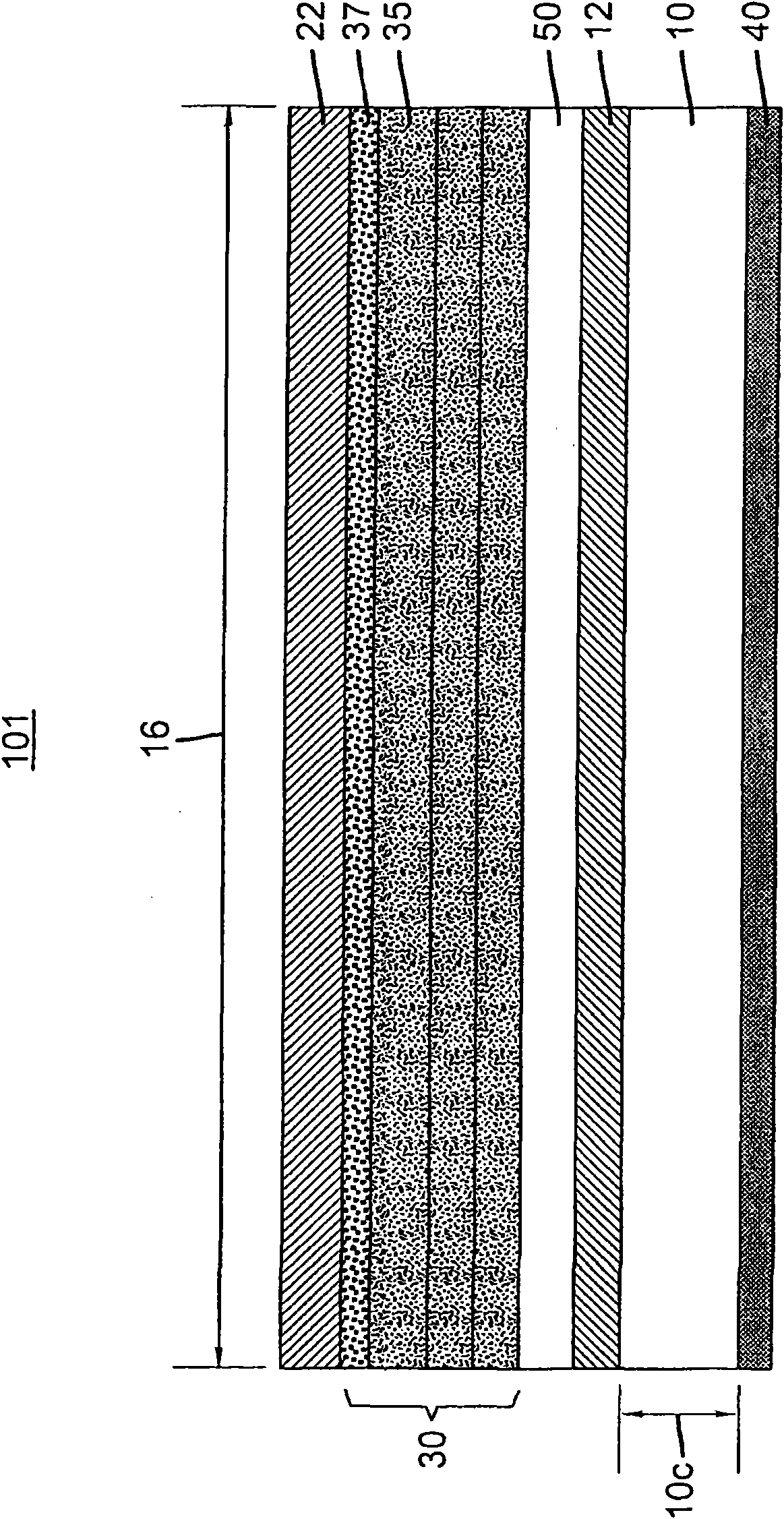

Organic electroluminescent device and method for manufacturing the same

InactiveUS20090160325A1Maintain good propertiesEasy to manufactureDischarge tube luminescnet screensElectroluminescent light sourcesCharge injectionOrganic solvent

An organic EL device which drives over a wide range from low brightness to high brightness for light source applications, operates stably over a wide range of brightness and has excellent life property is provided. The device comprises at least one pair of electrodes 2 and 5, and a plurality of functional layers disposed between the electrodes 2 and 5, the functional layers comprising a layer 4 having the light emitting function, which is composed of at least one polymeric material and contains an organic solvent and a charge injection layer 3 composed of at least one inorganic material.

Owner:PANASONIC CORP

Method and apparatus for injecting charge onto the floating gate of a nonvolatile memory cell

A tunneling charge injector includes a conducting injector electrode, a grid insulator disposed adjacent the conducting injector electrode, a grid electrode disposed adjacent said grid insulator, a retention insulator disposed adjacent said grid electrode, and a floating gate electrode disposed adjacent said retention insulator. In the tunneling charge injector, charge is injected from the conducting injector electrode onto the floating gate. Electrons are injected onto the floating gate when the conducting injector electrode is negatively biased with respect to the grid electrode, and holes are injected onto the floating gate when the conducting injector electrode is positively biased with respect to the grid electrode. The tunneling charge injector is employed in a nonvolatile memory cell having a nonvolatile memory element with a floating gate such as a floating gate MOS transistor. In the nonvolatile memory cell, the floating gate of the tunneling charge injector is coupled to or forms a part of the floating gate of the nonvolatile memory element. The tunneling charge injector is employed to inject charge onto the floating gate of the nonvolatile memory element. A memory device includes an array of nonvolatile memory cells wherein each of the memory cells comprises a nonvolatile memory element with a floating gate such as a floating gate MOS transistor and a tunneling charge injector having a floating gate that is either coupled to the floating gate of the nonvolatile memory element or forms a portion of the floating gate of the nonvolatile memory element.

Owner:JOHN MILLARD & PAMELA ANN CAYWOOD 1989 REVOCABLE LIVING TRUST AGREEMENT THE

High-density array of micro-machined electrodes for neural stimulation

ActiveUS7676274B2High charge injection limitLower impedanceSpinal electrodesHead electrodesCharge injectionHigh density

The present invention is a micro-machined electrode for neural-electronic interfaces which can achieve a ten times lower impedance and higher charge injection limit for a given material and planar area.

Owner:SECOND SIGHT MEDICAL PRODS +1

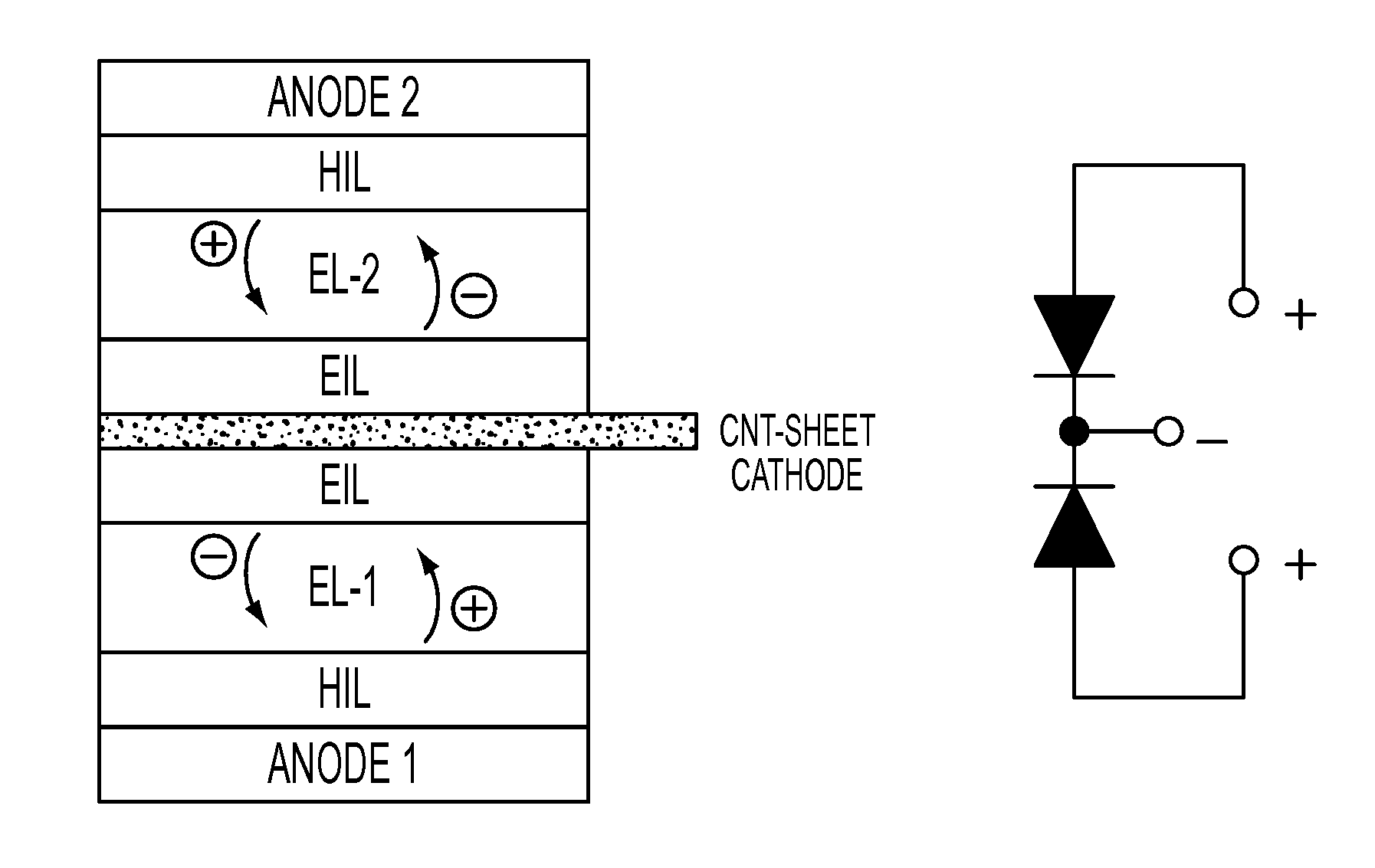

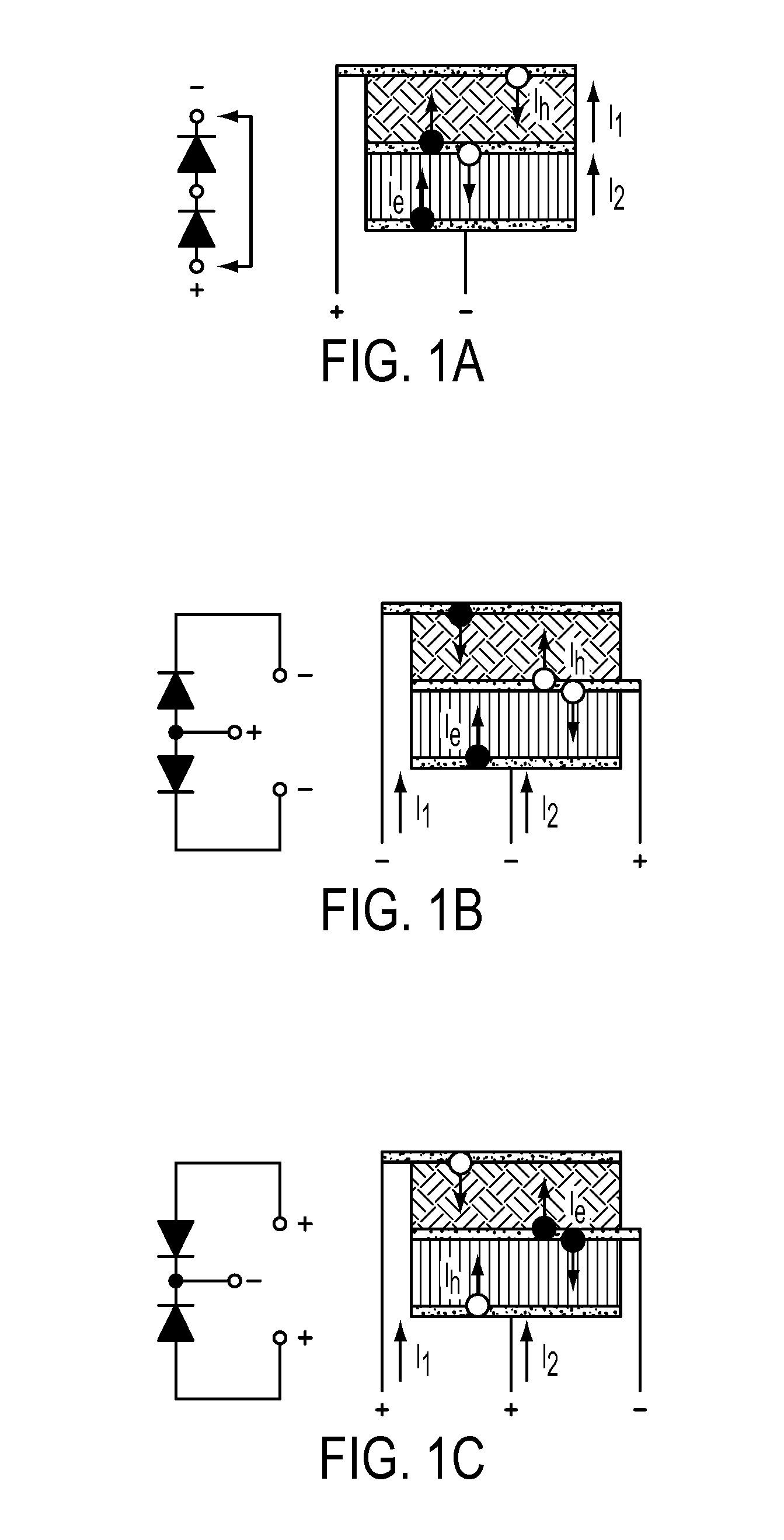

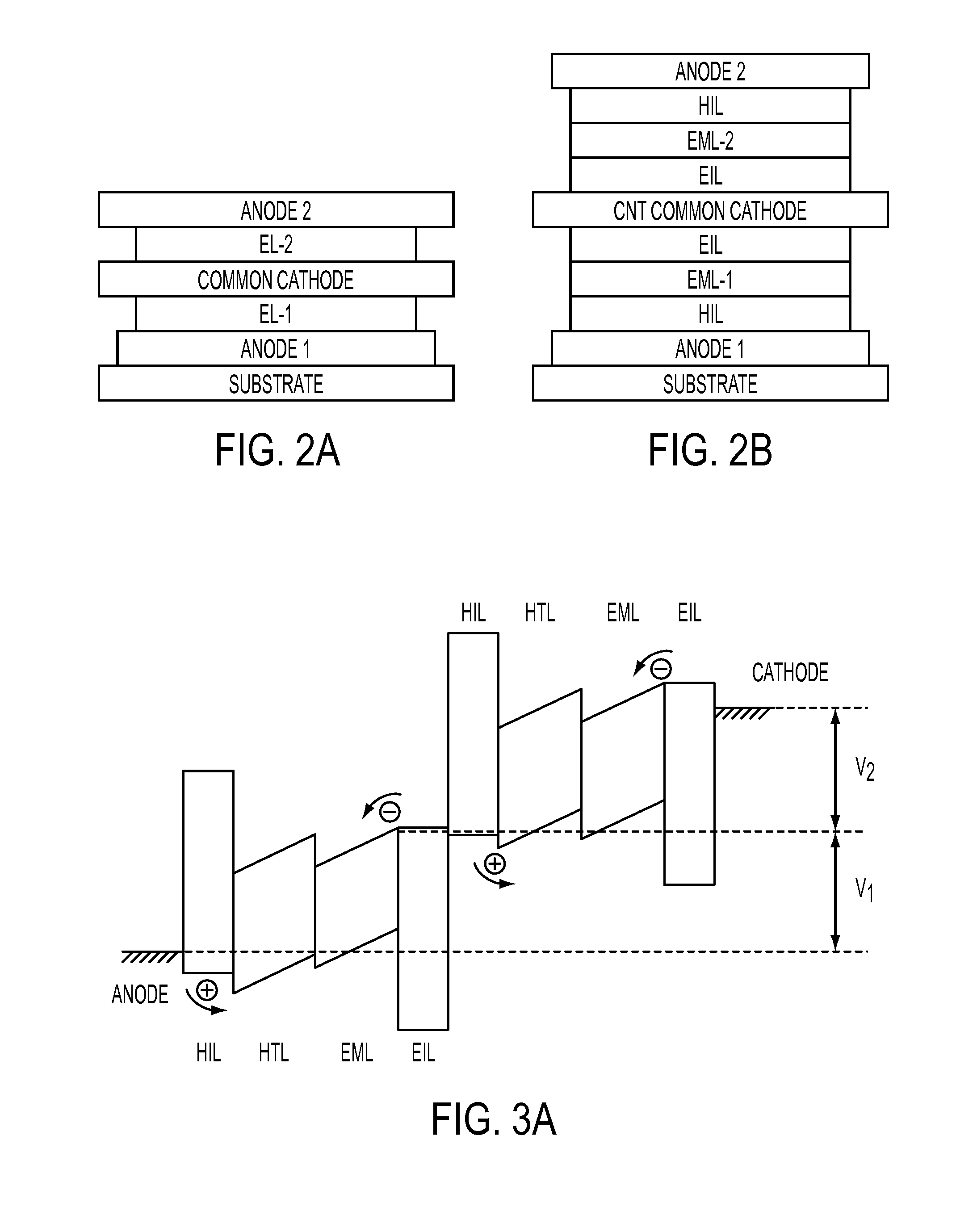

Monolithic parallel multijunction OLED with independent tunable color emission

InactiveUS20130240847A1Improve Charge Injection EfficiencyImprove device performanceSolid-state devicesSemiconductor/solid-state device manufacturingCharge injectionInter layer

A tandem organic light emitting diode (OLED) device comprised of multiple stacked single OLEDs electrically connected in parallel via transparent interlayer is recited herein. Transparent interlayers are coated by charge injection layers in order to enhance the charge injection efficiency and decrease the operation voltage. Transparent nanomaterials, such as carbon nanotube sheets (or graphene, graphene ribbons and similar conductive transparent nano-carbon forms) are used as Interlayers or outer electrodes. Furthermore, functionalization of carbon nanotubes inter layers by n-doping (or p-doping) converts them into common cathode (or common anode), further decreasing operation voltage of tandem. The development of these alternative interconnecting layers comprised of nanomaterials simplifies the process and may be combined with traditional OLED devices. In addition, novel architectures are enabled that allow the parallel connection of the stacked OLEDs into monolithic multi-junction OLED tandems.

Owner:BOARD OF RGT THE UNIV OF TEXAS SYST +1

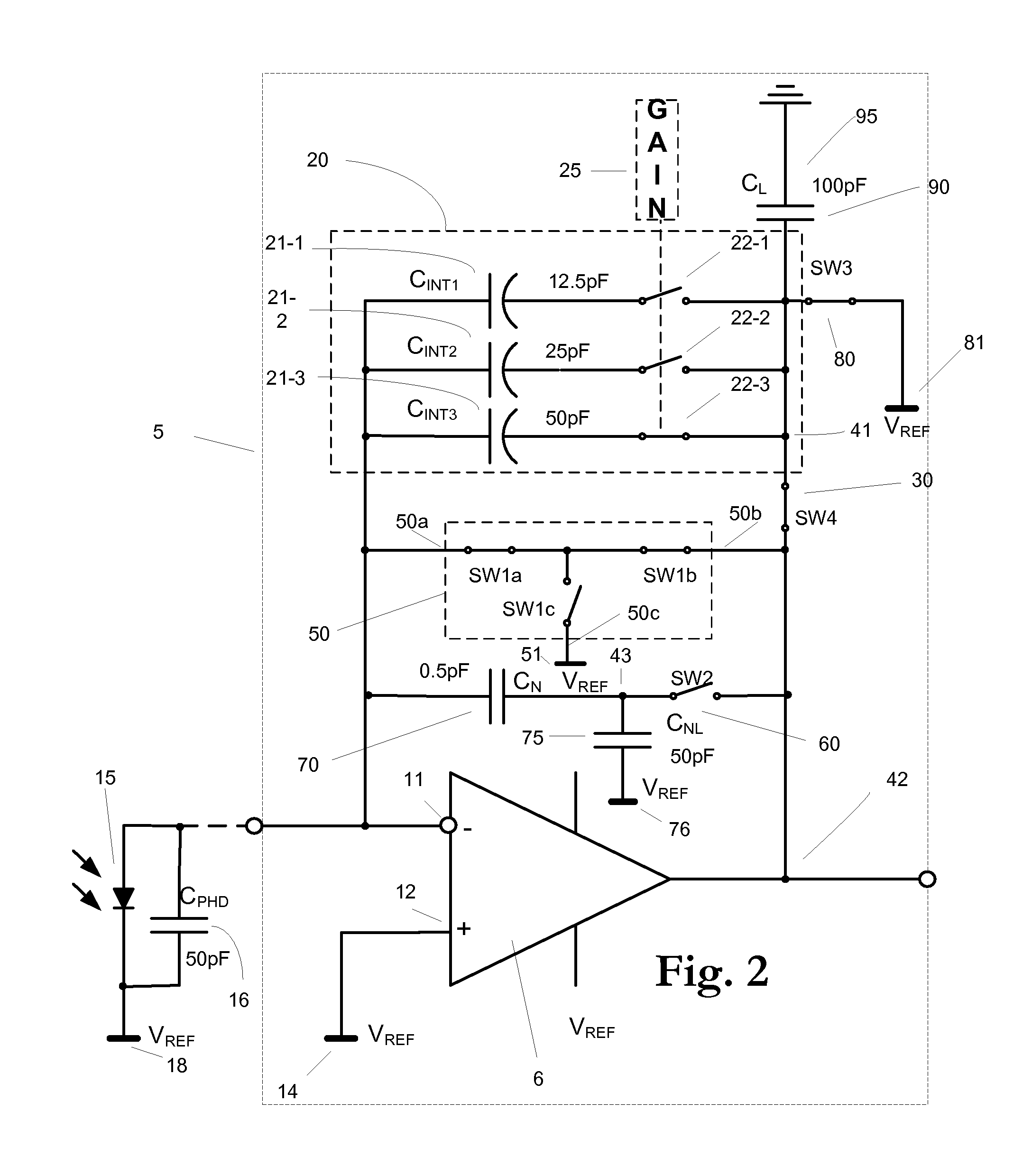

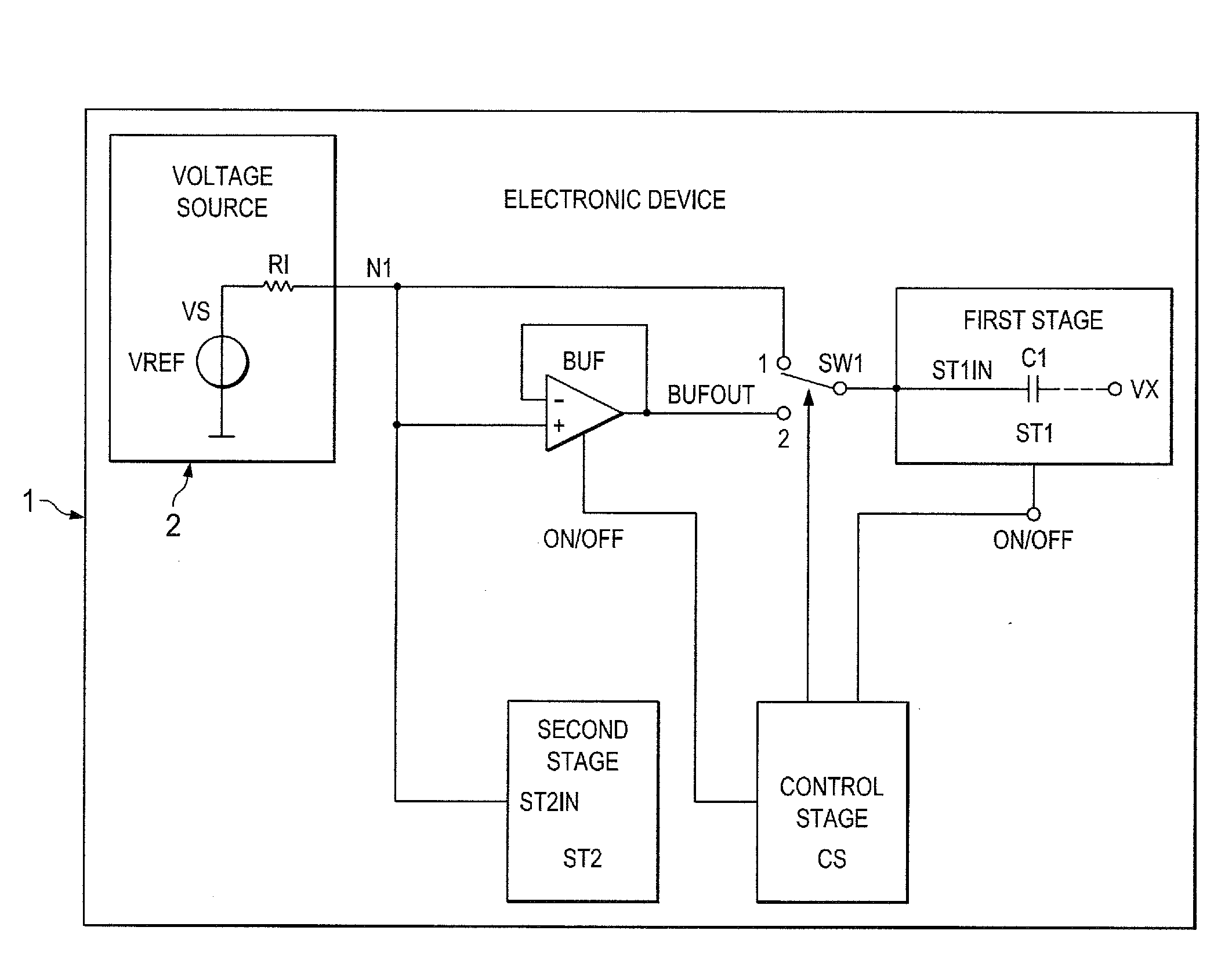

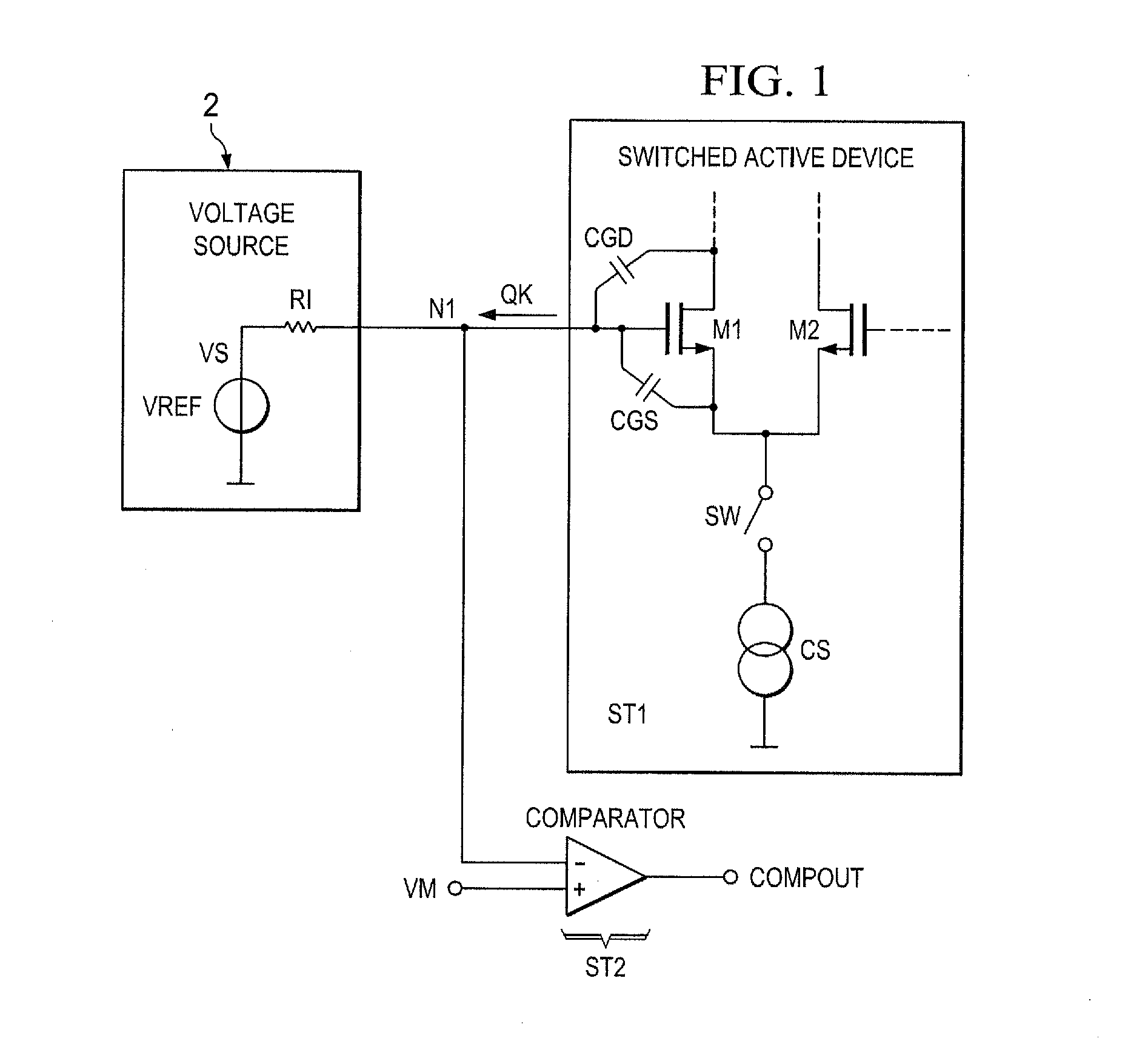

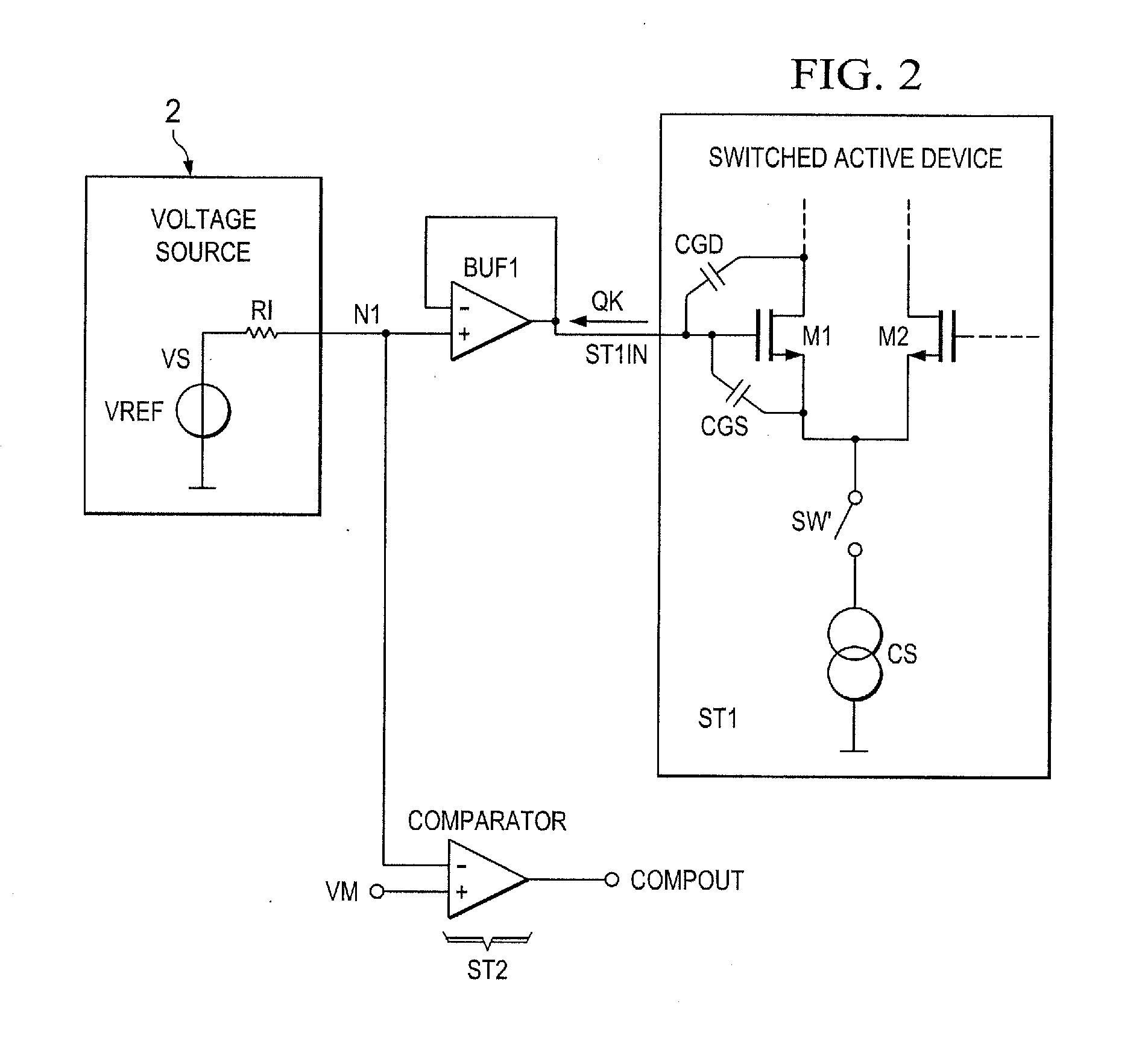

Electronic device and method for kickback noise reduction of switched capacitive loads and method of operating the electronic device

ActiveUS20120092055A1Improve offsetSmall input capacitanceAnalogue/digital conversionPulse automatic controlCapacitanceCharge injection

An electronic device which includes a first stage having an input capacitance, a switch, a buffer and a second stage having an input sensitive to charge injection and / or voltage glitches. An input of the buffer and the input of the second stage are coupled together at a first node which is configured to be coupled to a voltage source for supplying a reference voltage to the input of the first stage having the input capacitance. In a first configuration of the switch, the switch is arranged to either connect the input of the first stage to the first node and to disconnect the input of the first stage from an output of the buffer. In a second configuration of the switch, to connect the input of the first stage to the output of the buffer and to disconnect the input of the first stage from the first node.

Owner:TEXAS INSTR INC

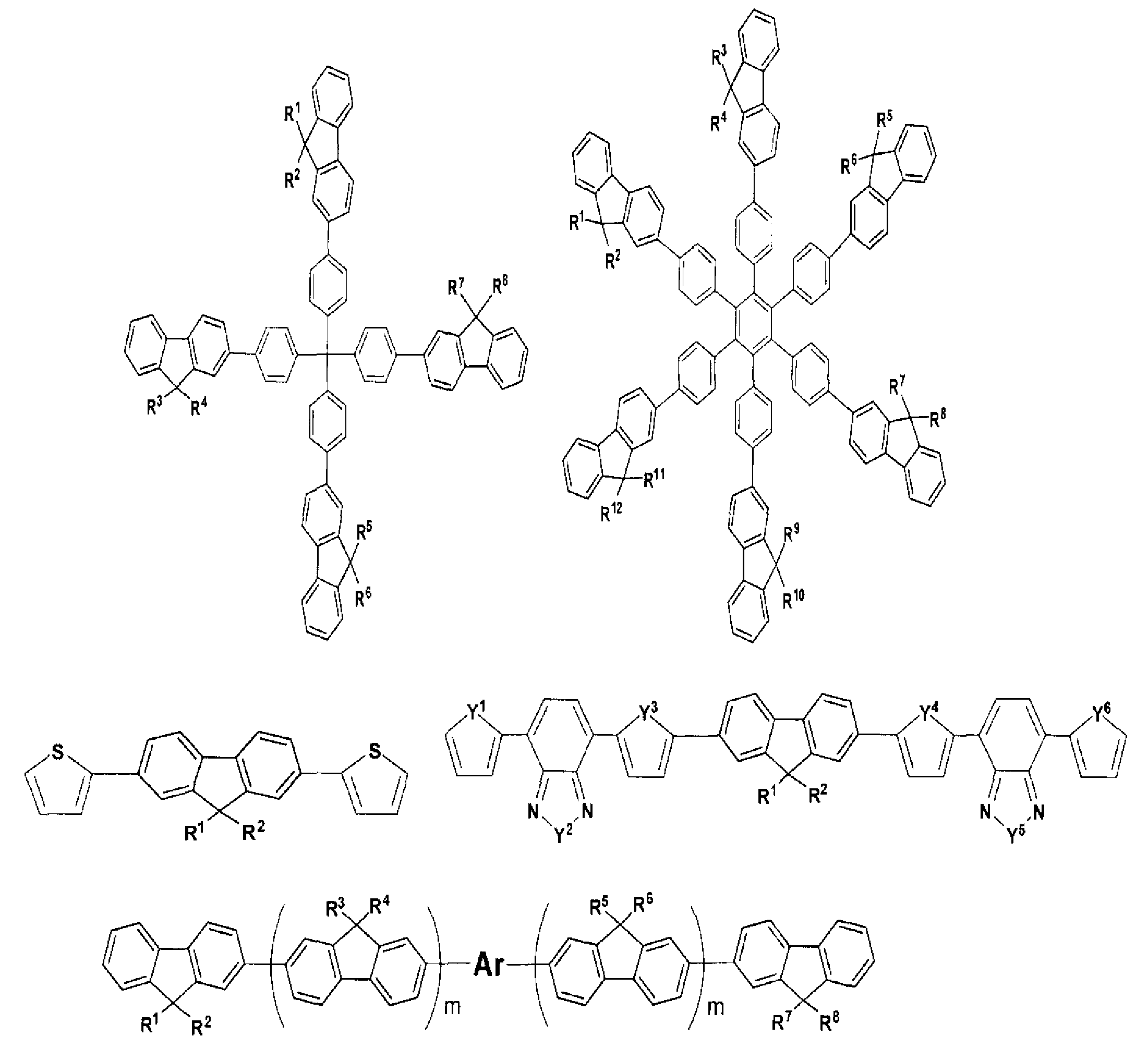

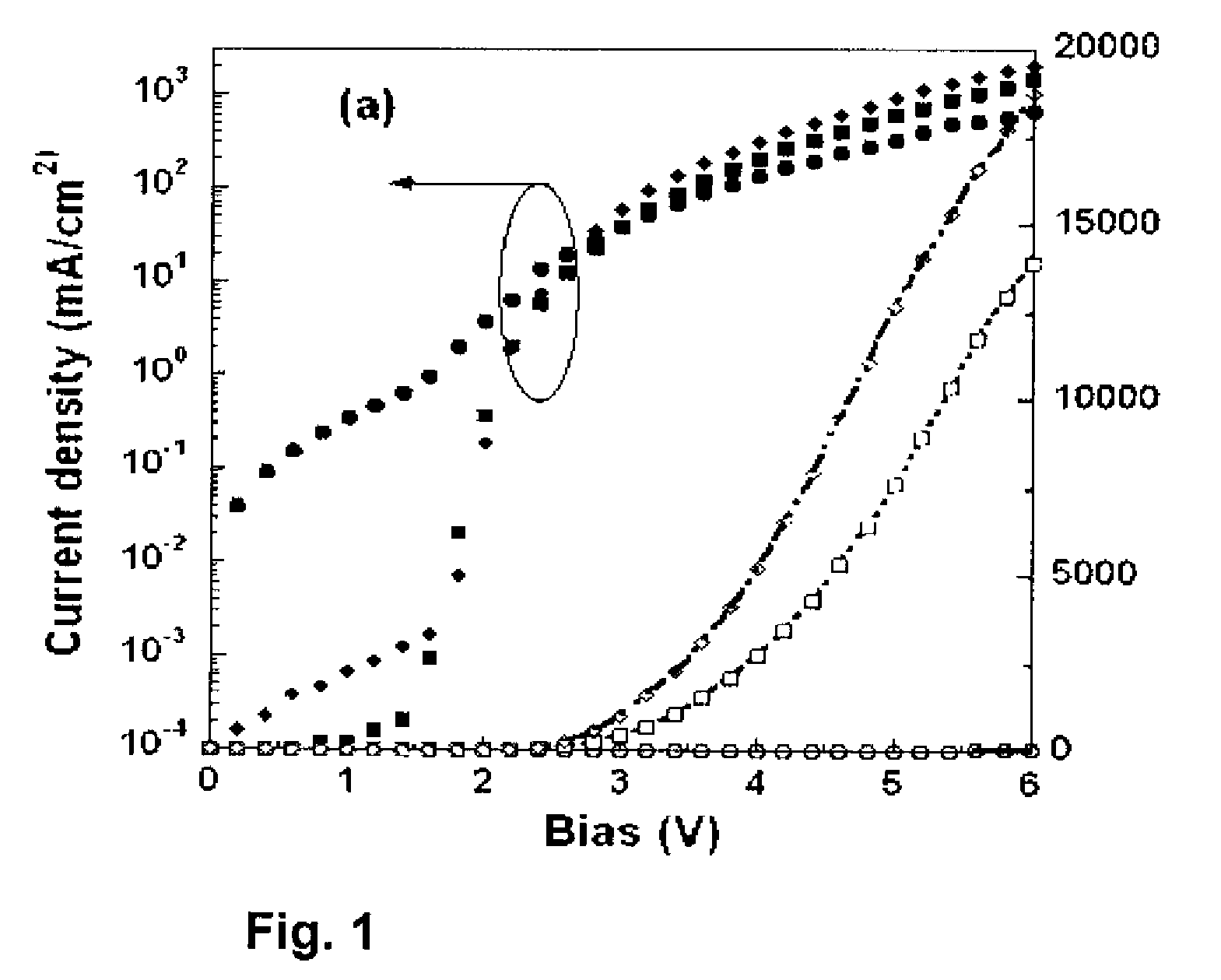

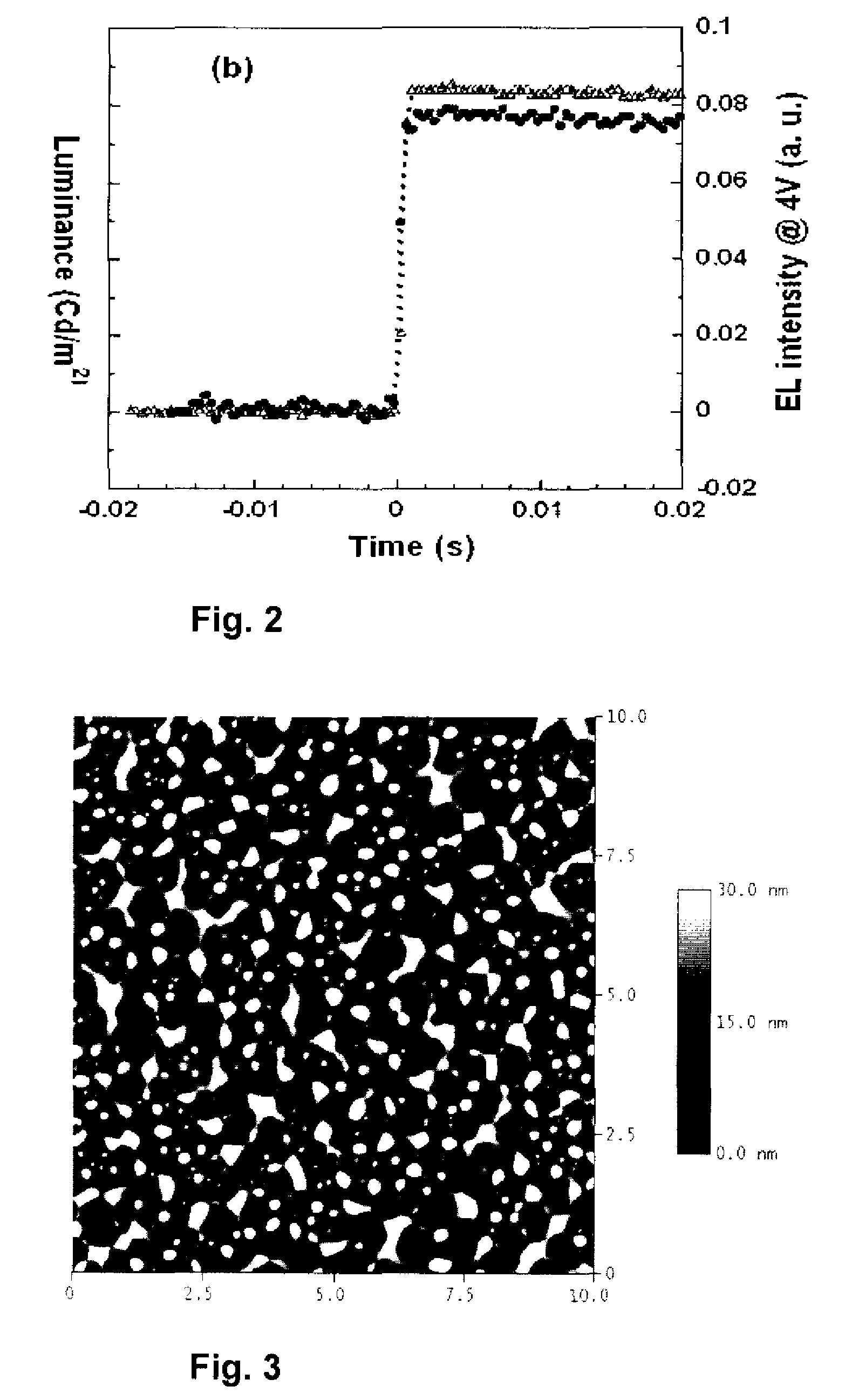

All-in-one organic electroluminescent inks with balanced charge transport properties

InactiveUS20080135804A1Easy to shapeElectroluminescent light sourcesSolid-state devicesCharge injectionFlexible organic light-emitting diode

The present invention discloses all-in-one organic electroluminescent inks for balanced charge injection. When of single layer organic lighting emitting diodes are made from these inks, the charge balance can be readily achieved. By using the invented all-in-one organic electroluminescent inks, both the device structure and the fabrication process are simplified, which will increase the production yield and reduce the production cost in manufacturing such devices. This invention also teaches methods to fabricate single layer all-in-one organic light emitting diodes.

Owner:XIAO STEVEN SHUYONG

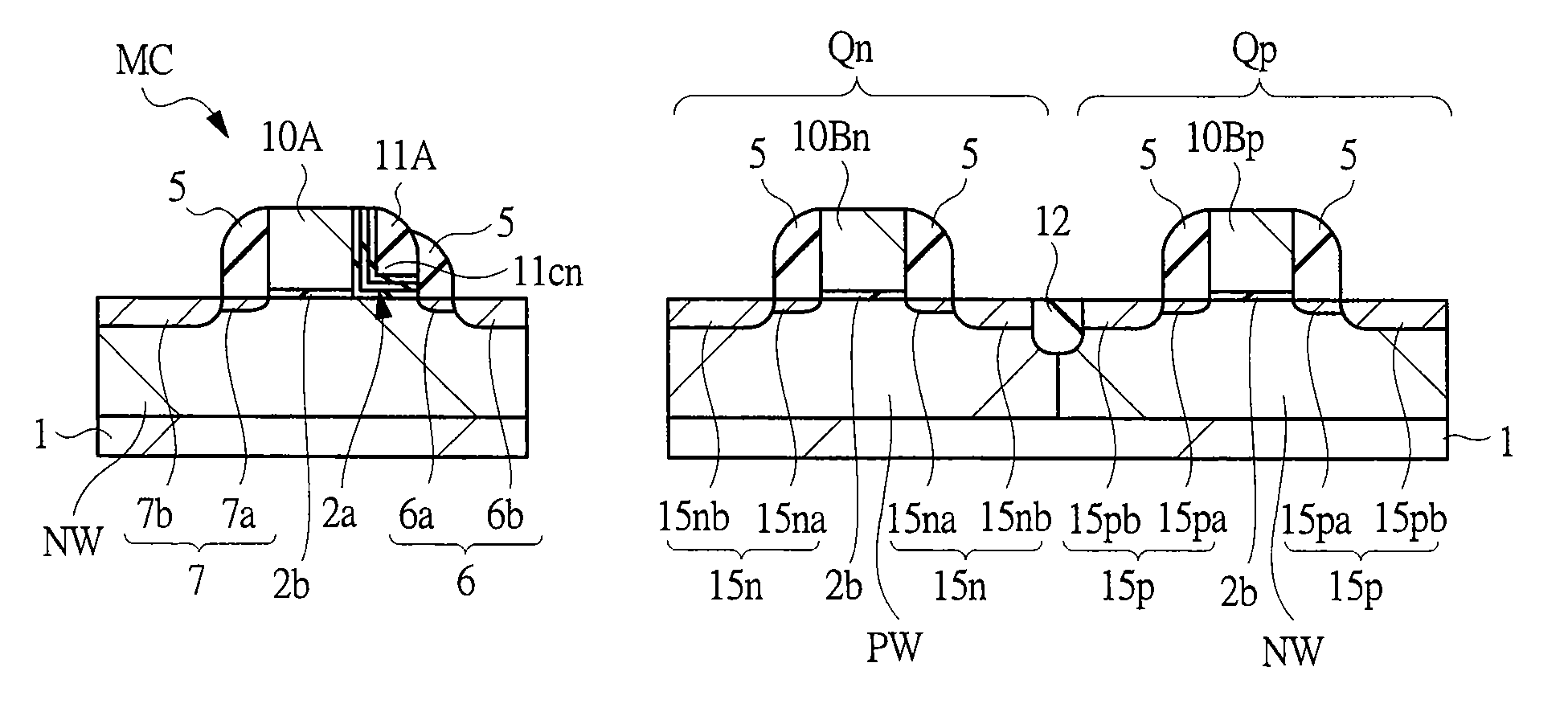

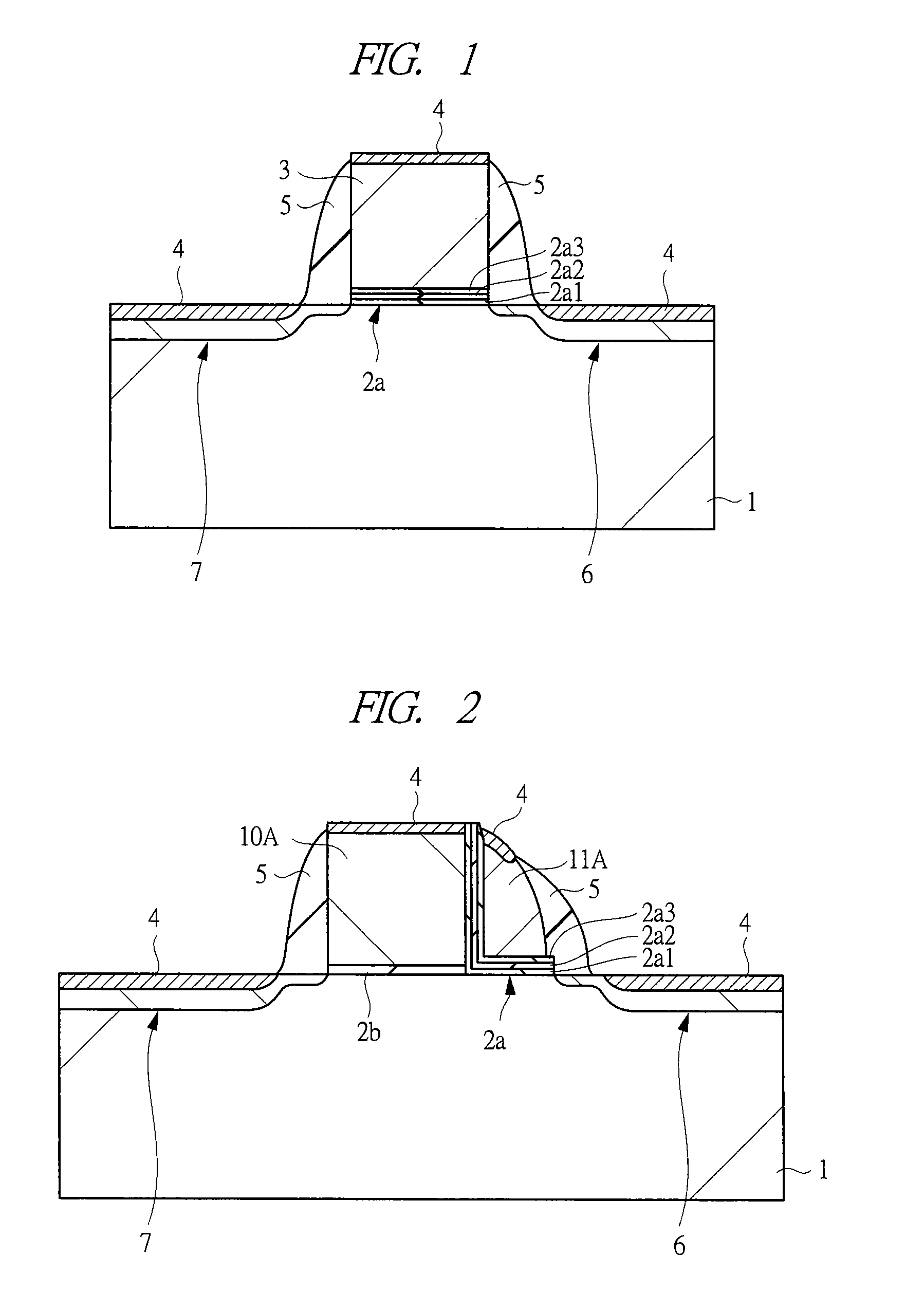

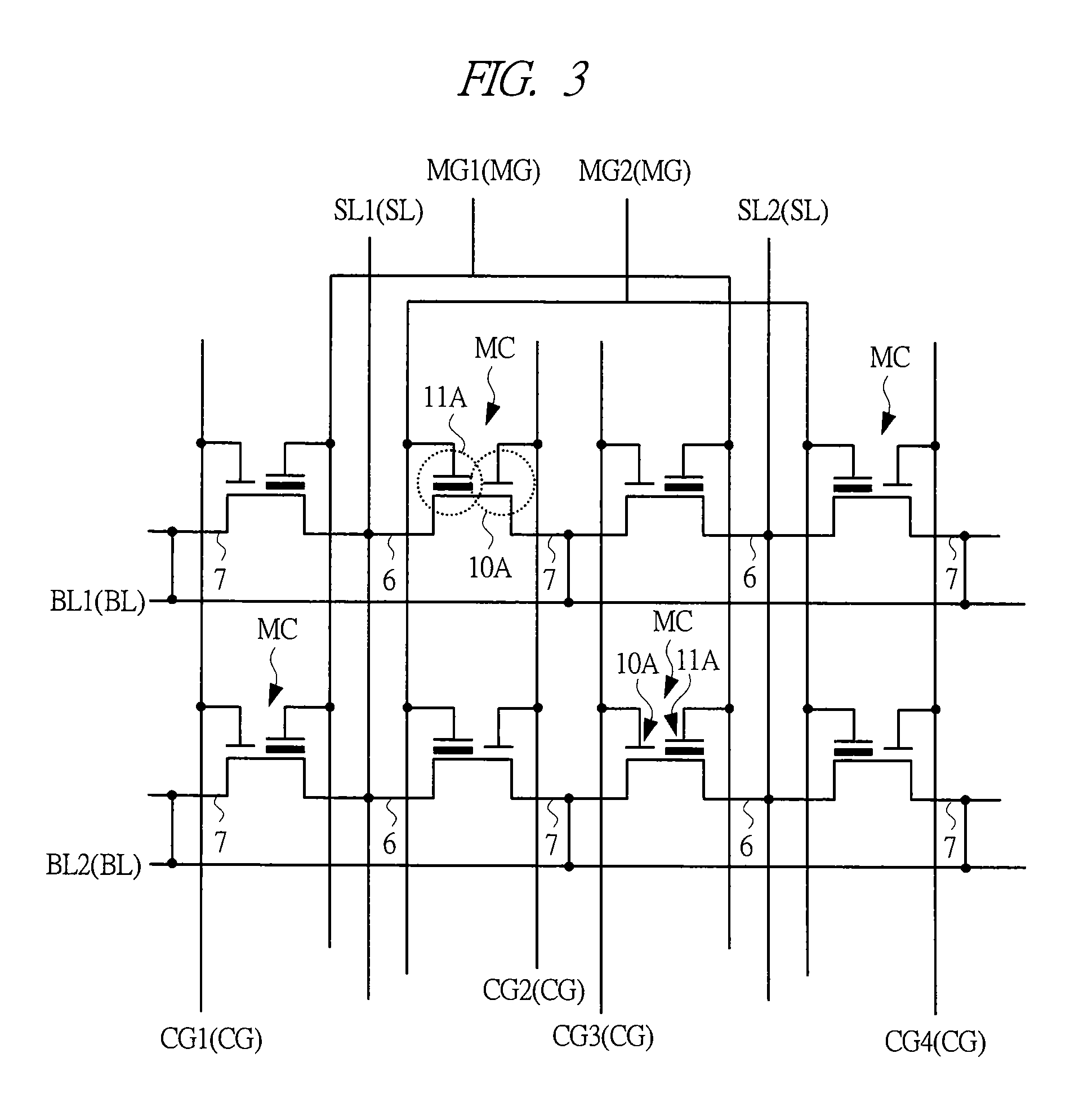

Nonvolatile semiconductor memory devices with charge injection corner

ActiveUS20080290401A1The formation process is simpleImprove injection efficiencySolid-state devicesRead-only memoriesManufacturing cost reductionCharge injection

An erase method where a corner portion on which an electric field concentrates locally is provided on the memory gate electrode, and charges in the memory gate electrode are injected into a charge trap film in a gate dielectric with Fowler-Nordheim tunneling operation is used. Since current consumption at the time of erase can be reduced by the Fowler-Nordheim tunneling, a power supply circuit area of a memory module can be reduced. Since write disturb resistance can be improved, a memory array area can be reduced by adopting a simpler memory array configuration. Owing to both the effects, an area of the memory module can be largely reduced, so that manufacturing cost can be reduced. Further, since charge injection centers of write and erase coincide with each other, so that (program and erase) endurance is improved.

Owner:RENESAS ELECTRONICS CORP

Charge injection and transport layers

ActiveUS20100109000A1Improve device performanceImprove efficiencyConductive materialSolid-state devicesCharge injectionDopant

Compositions for use in hole transporting layers (HTLs) or hole injection layers (HILs) are provided, as well as methods of making the compositions and devices fabricated from the compositions. OLED devices can be made. The compositions comprise at least one conductive conjugated polymer, at least one semiconducting matrix component that is different from the conductive conjugated polymer, and an optional dopant, and are substantially free of an insulating matrix component.

Owner:NISSAN CHEM IND LTD

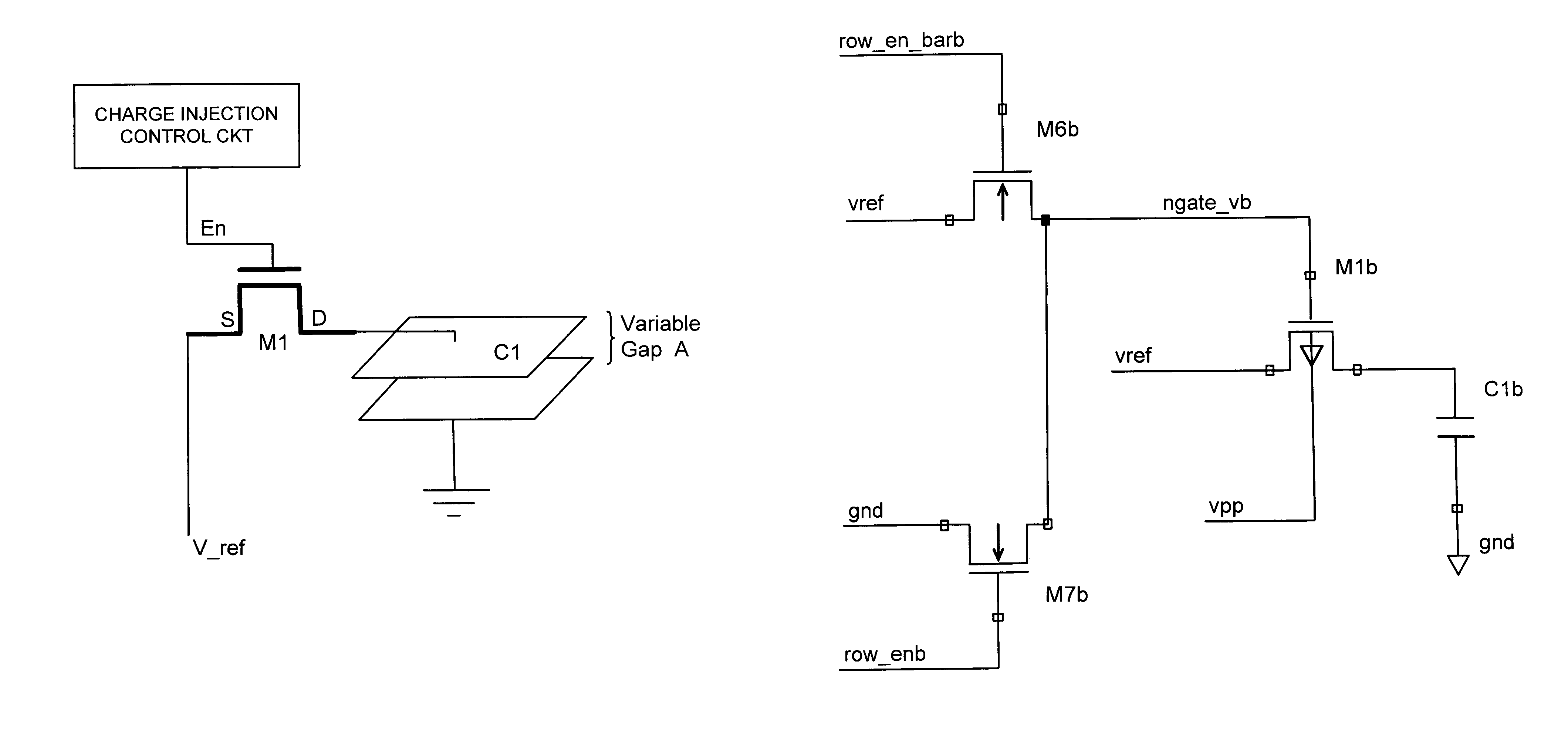

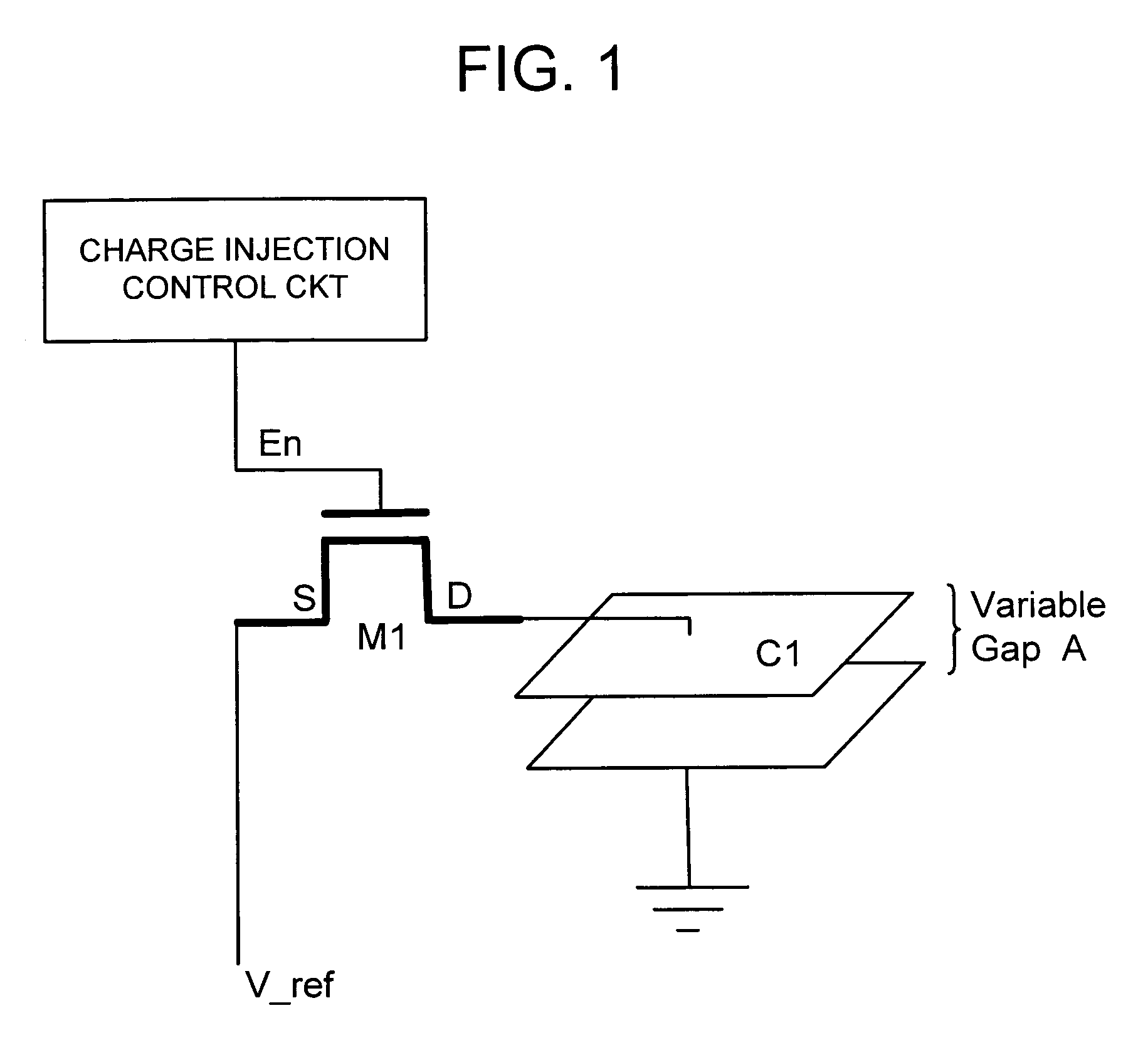

Method and apparatus for reducing charge injection in control of MEMS electrostatic actuator array

InactiveUS6970031B1Pulse automatic controlStatic indicating devicesCharge injectionElectrostatic actuator

A control circuit for a MEMS (Micro-Electro-Mechanical System) has a semiconductor switch which has a source, a drain and a gate, which is associated with a selected one of spatially arranged fixed and movable plates of a variable capacitor, and is arranged to selectively connect the selected one of the fixed and movable plates with a voltage source. A charge injection control circuit is associated with the semiconductor switch and attenuates current injection into the selected one of the fixed and movable plates of the capacitor.

Owner:HEWLETT PACKARD DEV CO LP

Stratified scavenged two-stroke engine

InactiveUS20050139179A1Increase volumeCombustion enginesEngine controllersCharge injectionFour-stroke engine

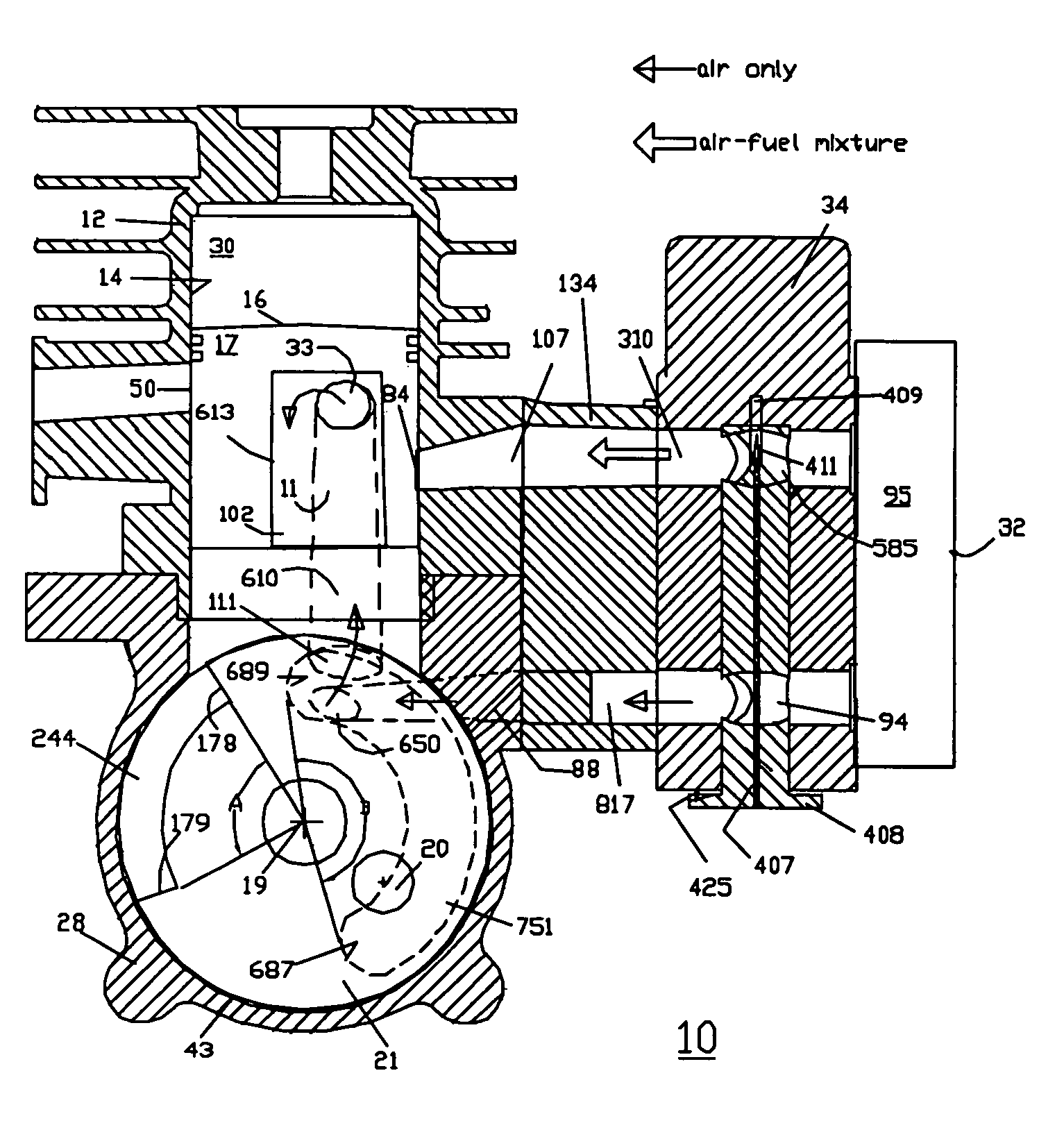

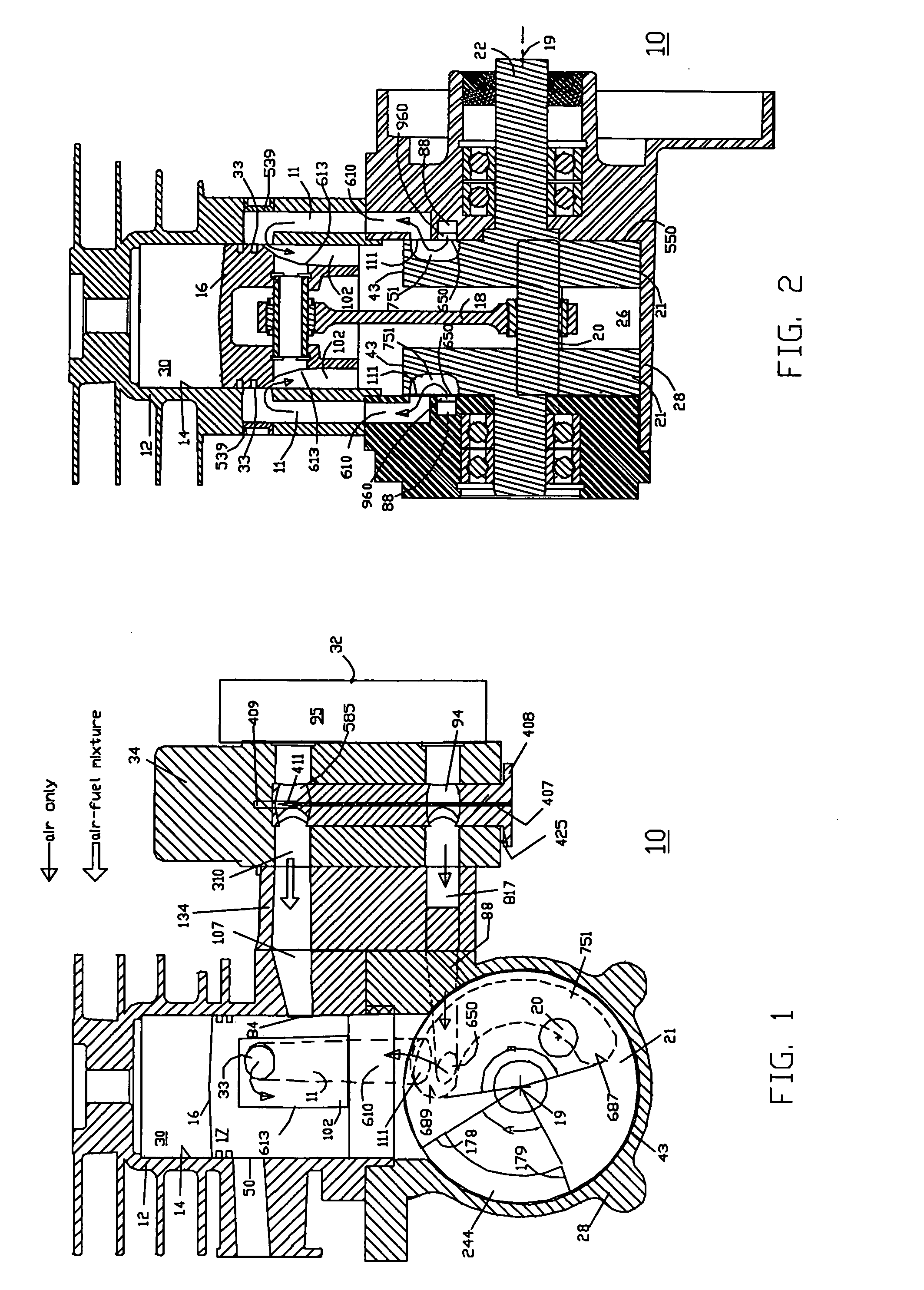

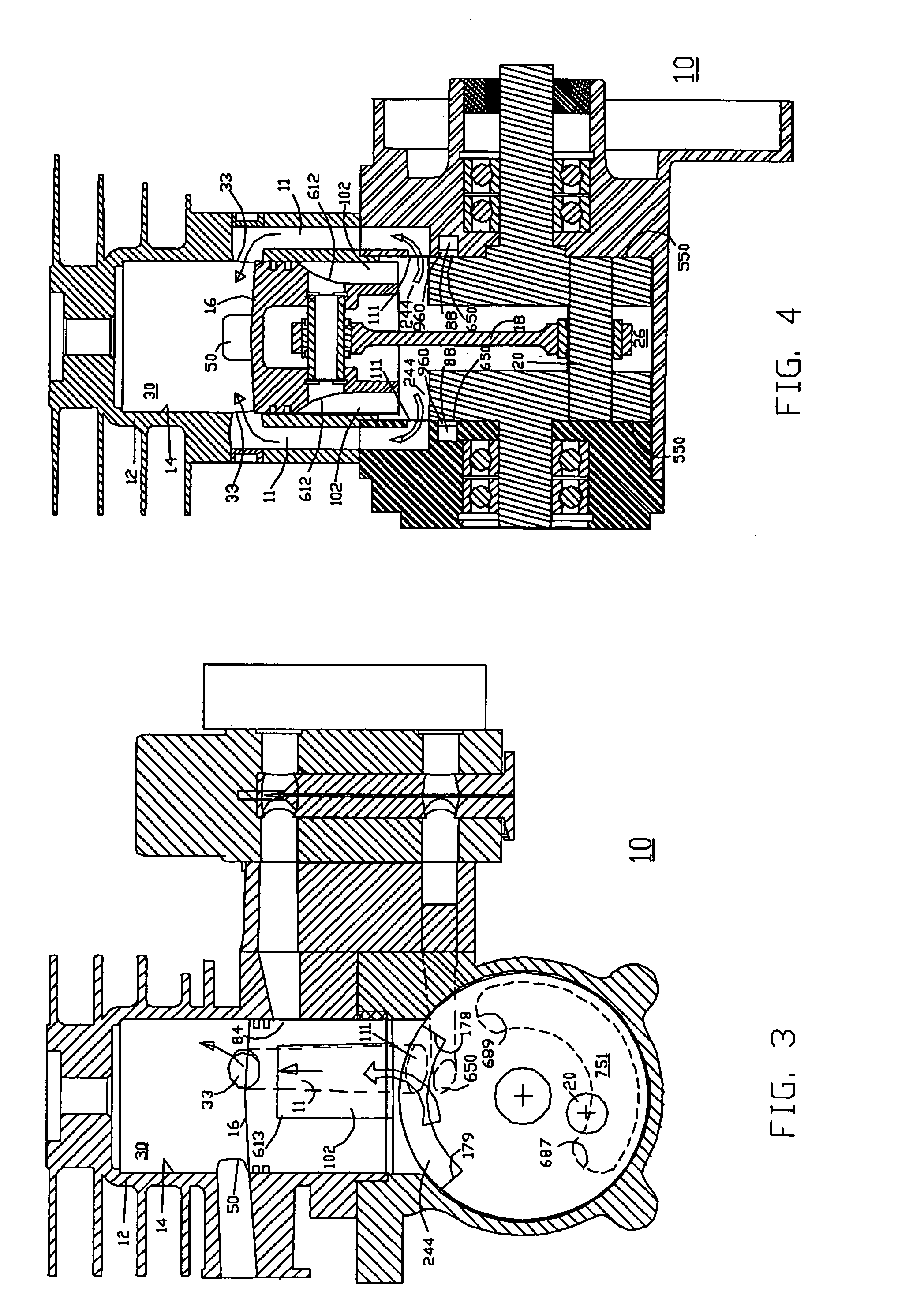

A two-stroke internal combustion engine includes at least one gaseous communication charge passage between a crankcase chamber and a combustion chamber of the engine and a piston to open and close the top end of the passage and a rotary valve to open and close the lower end of the transfer passage. The air inlet port to the transfer passage for stratified scavenging is opened and closed by the crank-web that has passages and cutouts. The rotary valve replaces the one-way reed valve used in stratified scavenged and charged two-stroke engines. The air passes from the lower end of transfer passage to the top end and into the crankcase through the piston passage, alternatively air may also pass through the adjacent transfer passage directly or through a passage in the piston into the crankcase. A two-stroke engine also consists of a charge injection system controlled by the crank web eliminating the one-way valve.

Owner:HOMELITE TECH

Conjugated oligoelectrolyte electron transporting layers

InactiveUS20090230362A1Clear molecular structureGood reproducibilitySilicon organic compoundsElectrolytic capacitorsPolyelectrolyteCharge injection

An organic electronic or an optoelectronic device containing a conjugated oligoelectrolyte. In more particularized embodiments, the conjugated oligoelectrolyte is the charge injection or transport layer. The conjugated oligoelectrolyte can be positively or negatively charged, and used in conjunction in a device with either or high or low work function metal.

Owner:RGT UNIV OF CALIFORNIA

Electroluminescent device having improved light output

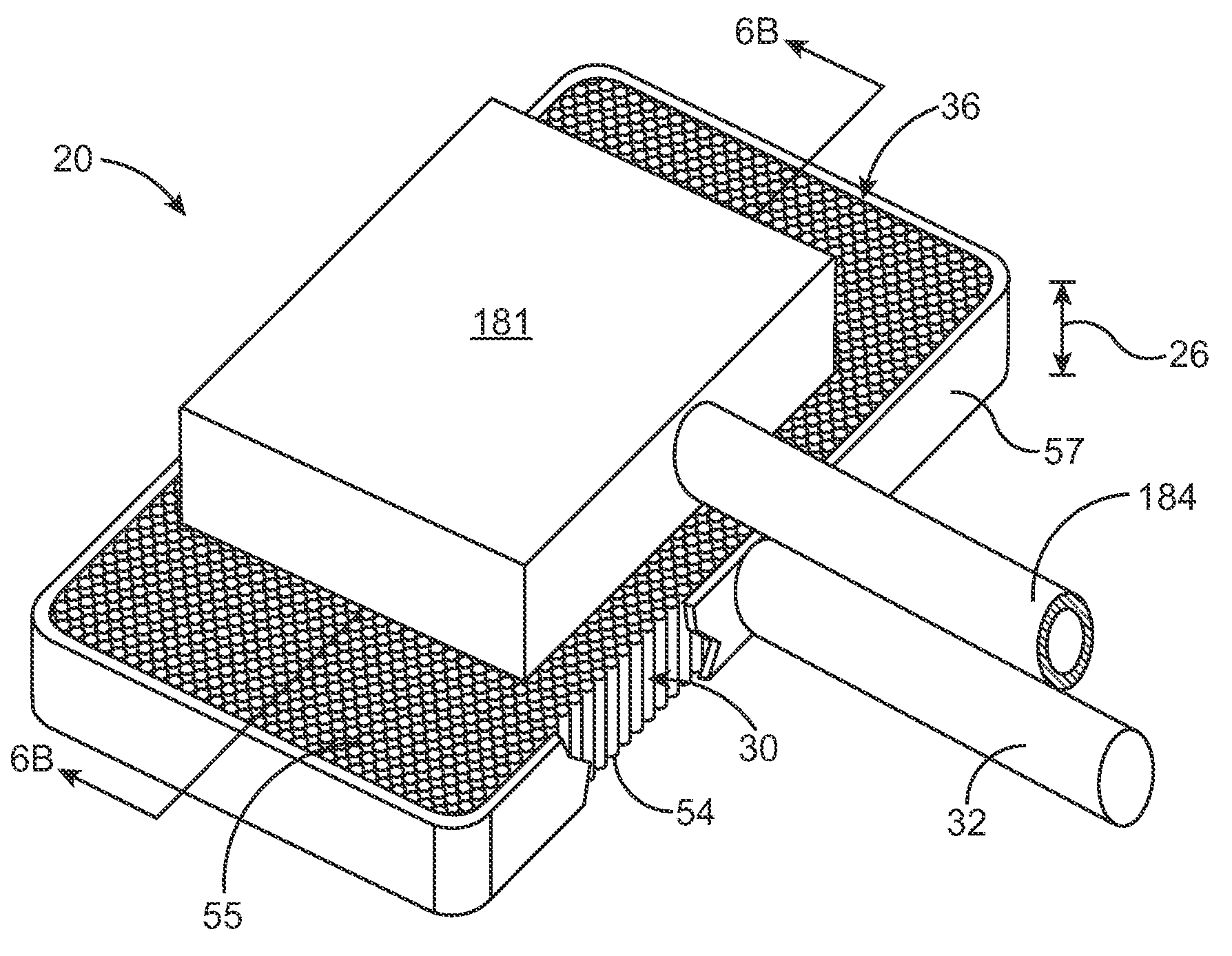

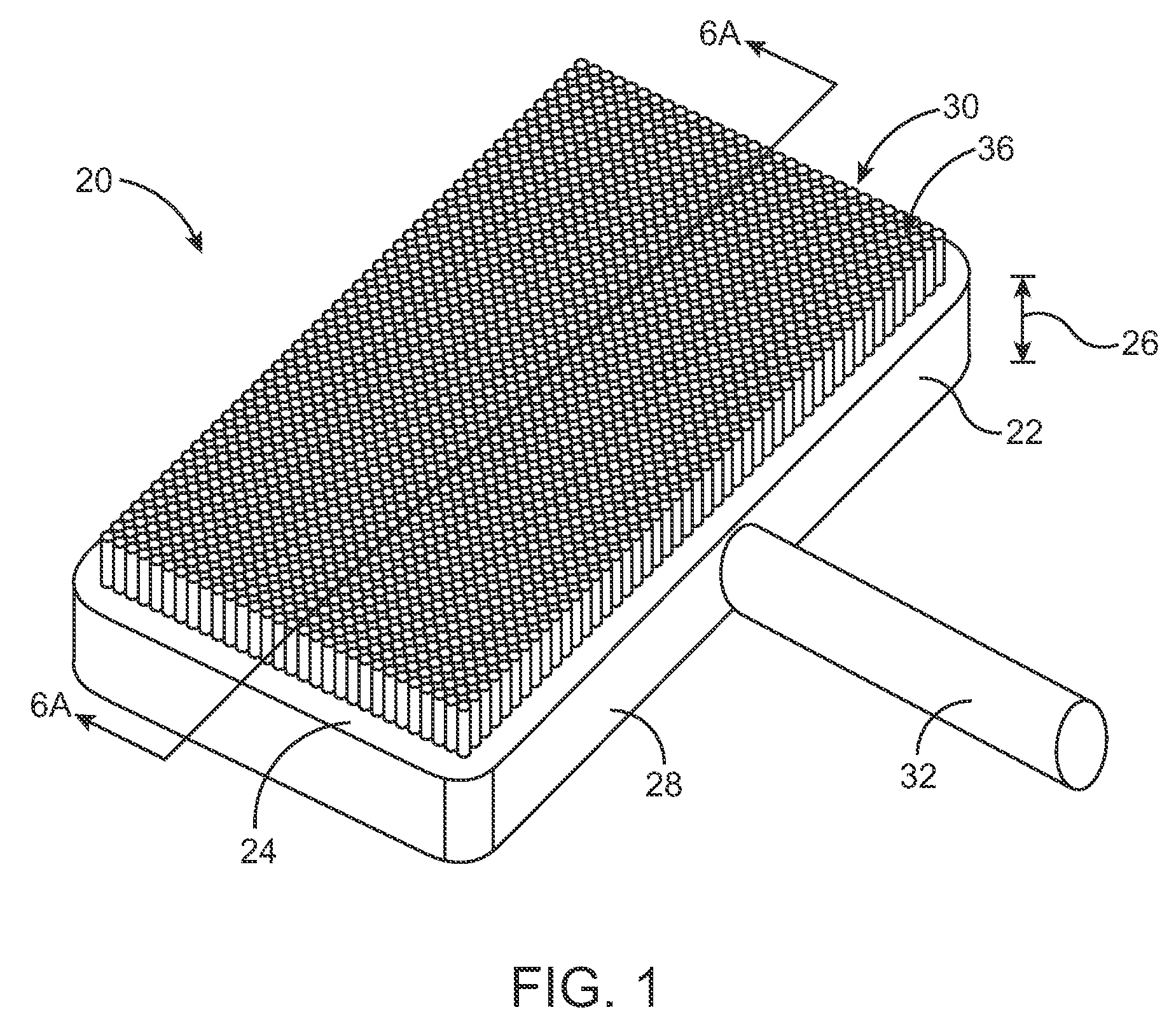

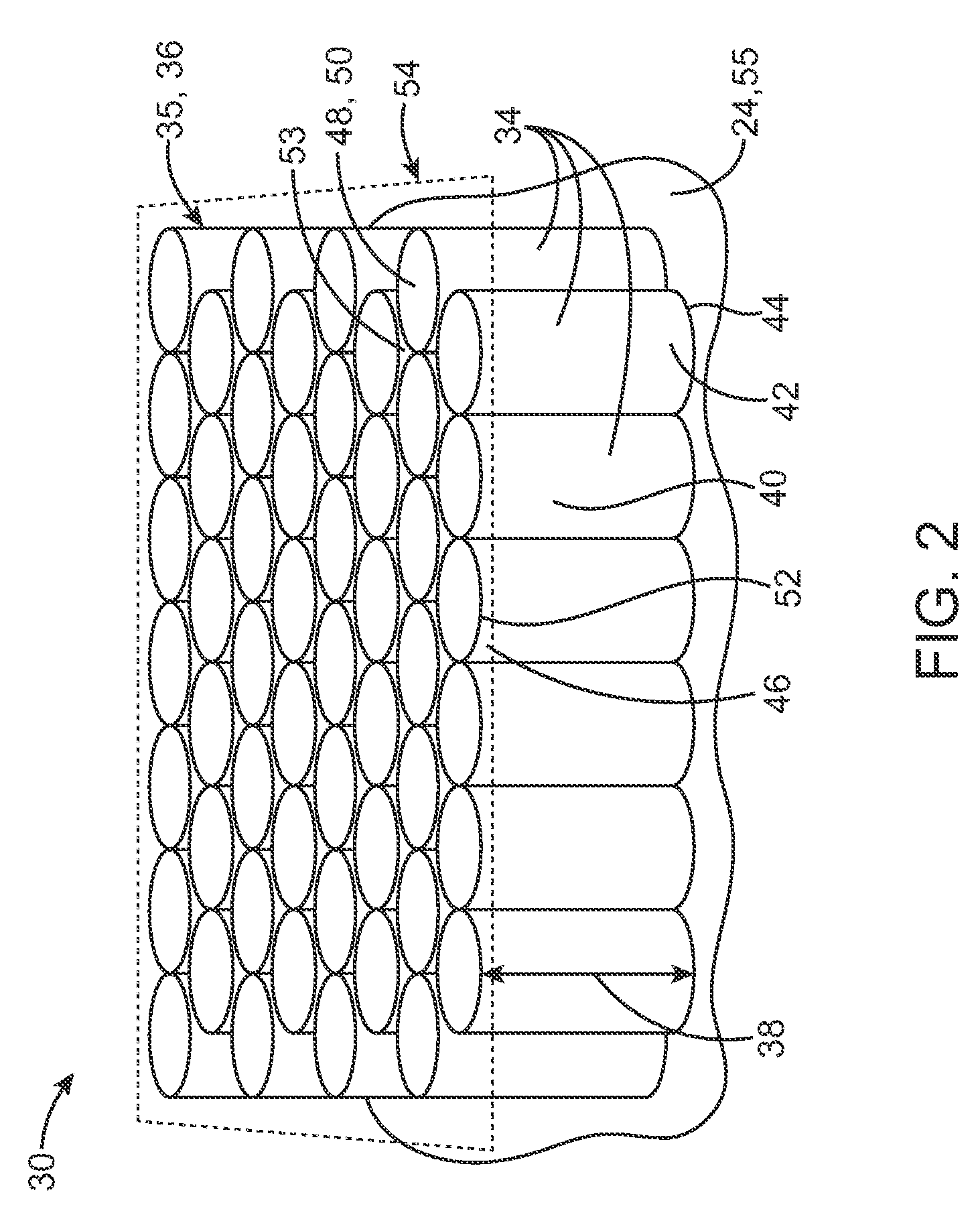

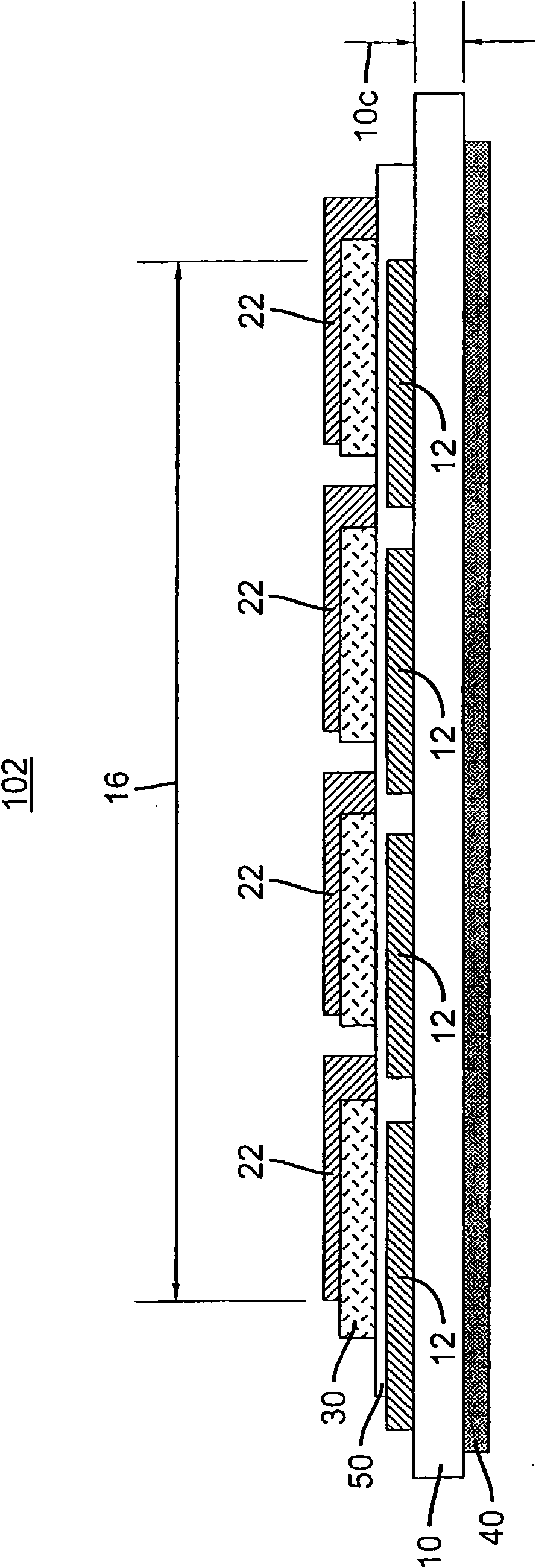

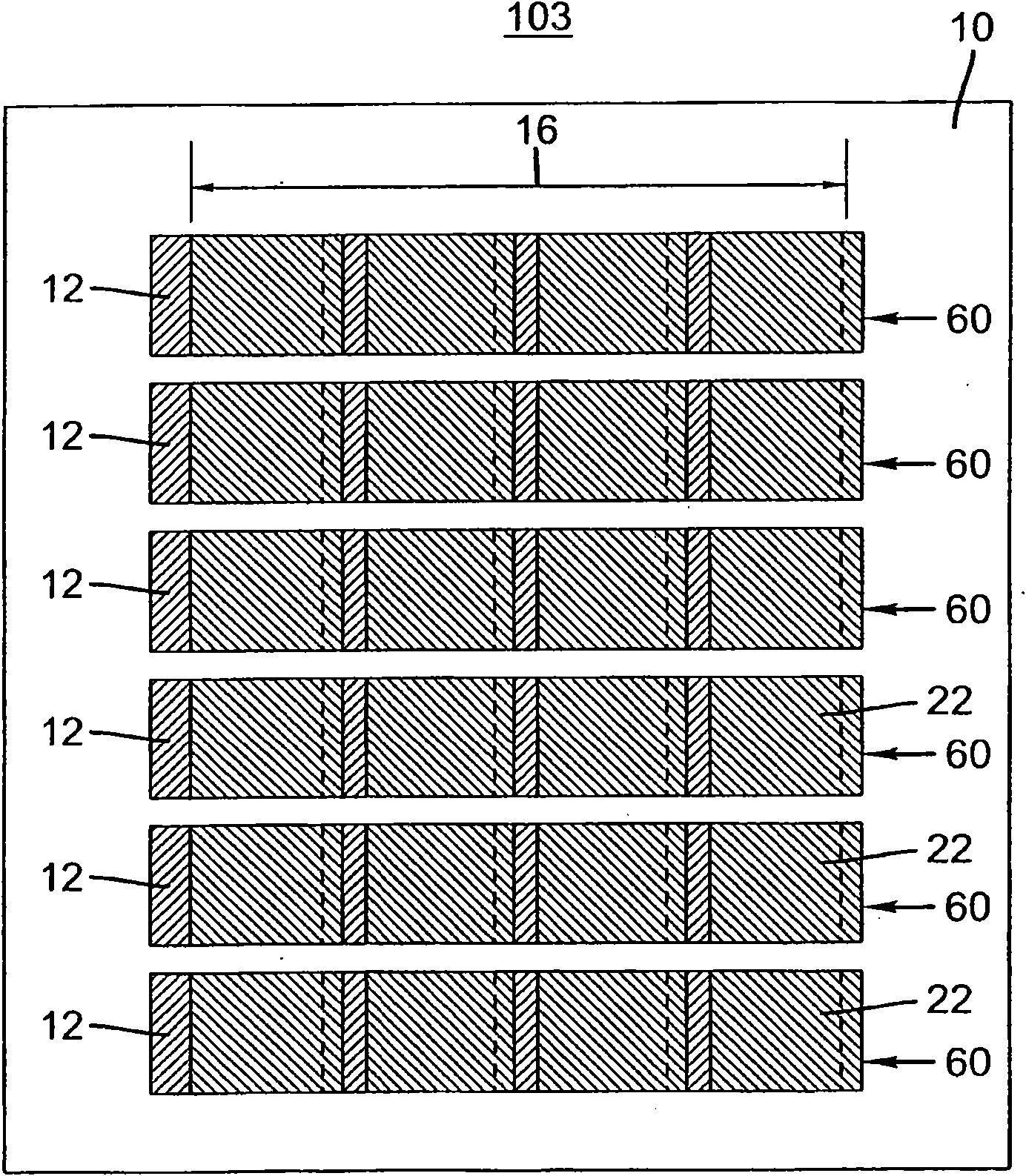

Provided is an OLED device including a transparent substrate having a first surface and a second surface, a transparent electrode layer disposed over the first surface of the substrate, a short reduction layer disposed over the transparent electrode layer, an organic light-emitting element disposed over the short reduction layer and including at least one light-emitting layer and a charge injection layer disposed over the light emitting layer, a reflective electrode layer disposed over the charge injection layer and a light extraction enhancement structure disposed over the first or second surface of the substrate; wherein the short reduction layer is a transparent film having a through-thickness resistivity of 10<-9> to 10<2>ohm cm<2>; wherein the reflective electrode layer includes Ag orAg alloy containing more than 80% of Ag; and the total device size is larger than 10 times the substrate thickness.

Owner:GLOBAL OLED TECH

Nanotube enabled, gate-voltage controlled light emitting diodes

ActiveUS20100237336A1Small increase in lifetime of deviceMaterial nanotechnologyNanoinformaticsElectron injectionField effect

Embodiments of the invention relate to vertical field effect transistor that is a light emitting transistor. The light emitting transistor incorporates a gate electrode for providing a gate field, a first electrode comprising a dilute nanotube network for injecting a charge, a second electrode for injecting a complementary charge, and an electroluminescent semiconductor layer disposed intermediate the nanotube network and the electron injecting layer. The charge injection is modulated by the gate field. The holes and electrons, combine to form photons, thereby causing the electroluminescent semiconductor layer to emit visible light. In other embodiments of the invention a vertical field effect transistor that employs an electrode comprising a conductive material with a low density of states such that the transistors contact barrier modulation comprises barrier height lowering of the Schottky contact between the electrode with a low density of states and the adjacent semiconductor by a Fermi level shift.

Owner:UNIV OF FLORIDA RES FOUNDATION INC

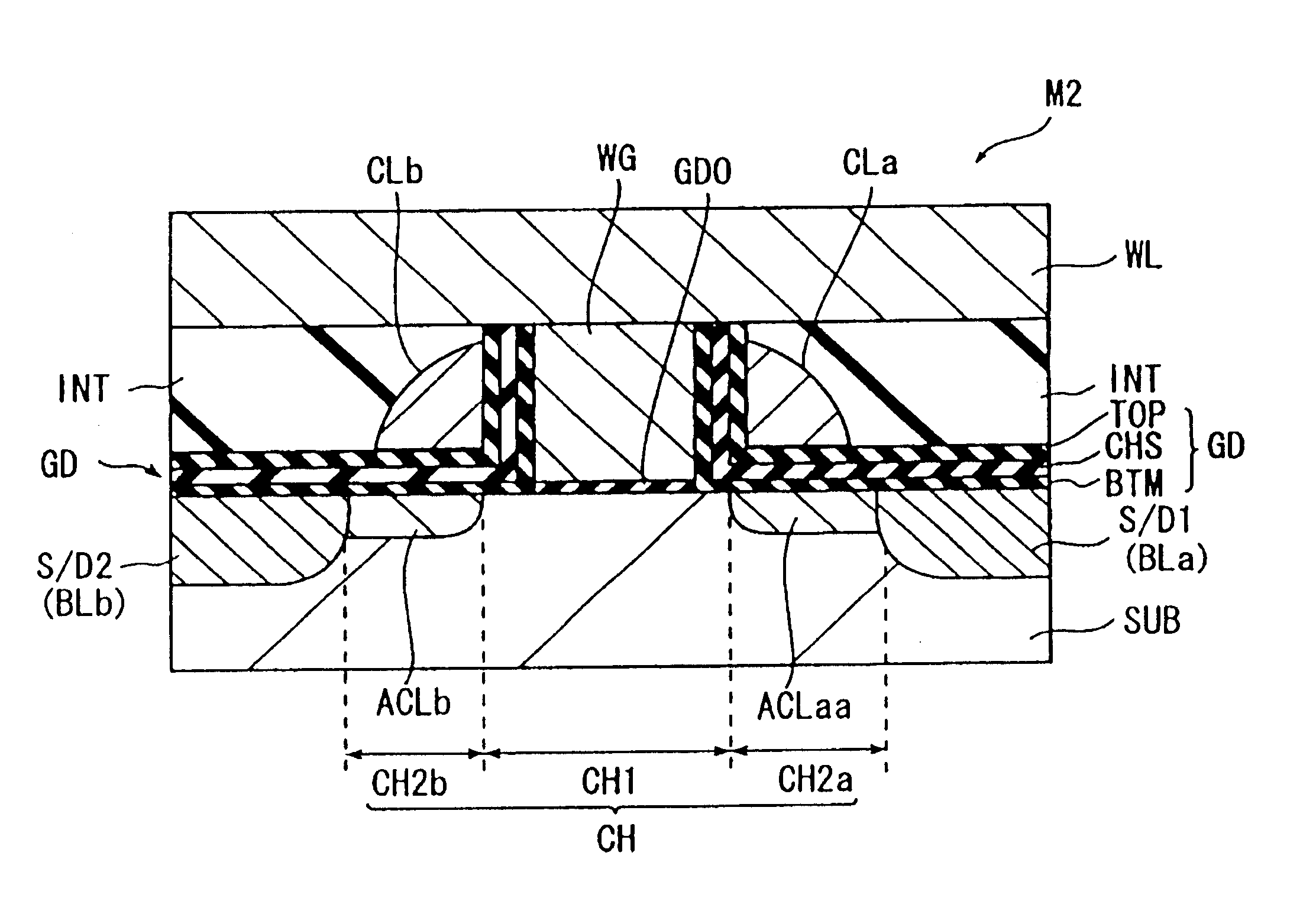

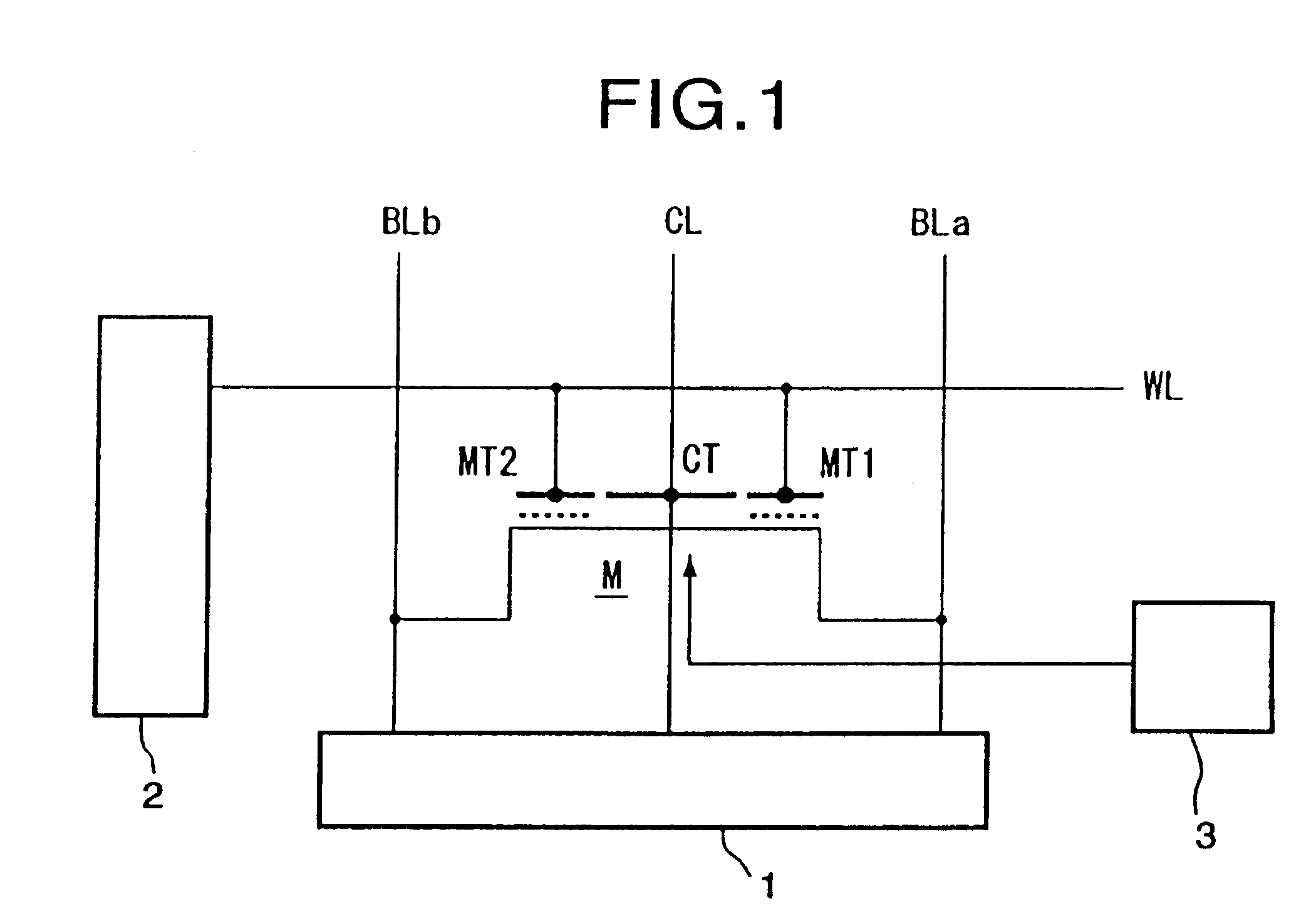

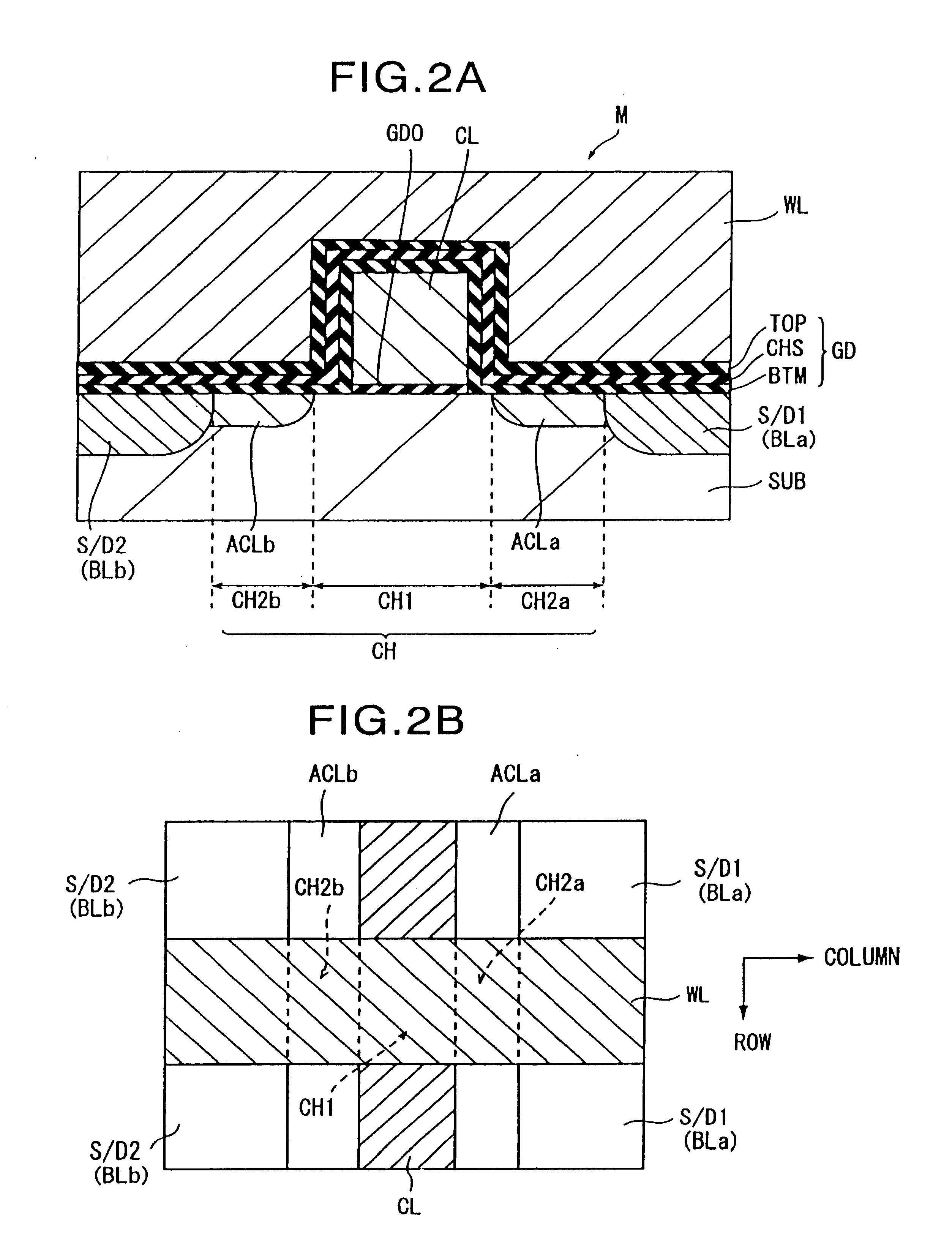

Nonvolatile semiconductor memory device

To propose a new channel structure suitable for high efficiency source side injection, and provide a non-volatile semiconductor memory device and a charge injection method using the same. The non-volatile memory device includes a first conductivity type semiconductor substrate (SUB), a first conductivity type inversion layer-forming region (CH1), second conductivity type accumulation layer-forming regions (ACLa, ACL2b), second conductivity type regions (S / D1, S / D2), an insulating film (GD0) and a first conductive layer (CL) formed on the inversion layer-forming region (CH1). A charge accumulation film (GD) and a second conductive layer (WL) are stacked on an upper surface and side surface of the first conductive layer (CL), an exposure surface of the inversion layer-forming region (CH1), and an upper surface of the accumulation layer-forming regions (ACLa, ACLb) and the second conductivity type regions (S / D1, S / D2). The second conductive layer (WL) is connected to a word line and second conductivity type regions (S / D1, S / D2) are connected to bit lines (Bla, BLb).

Owner:SONY CORP

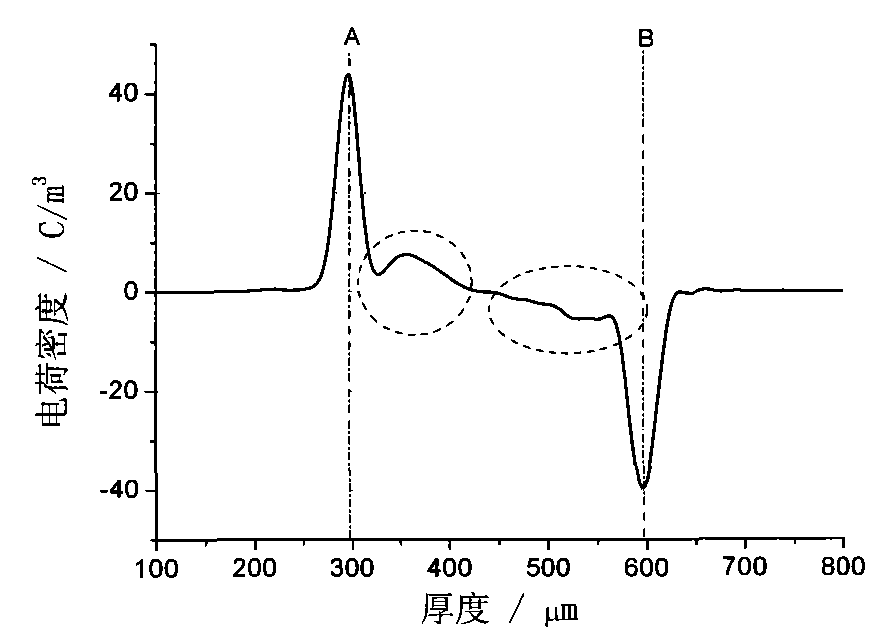

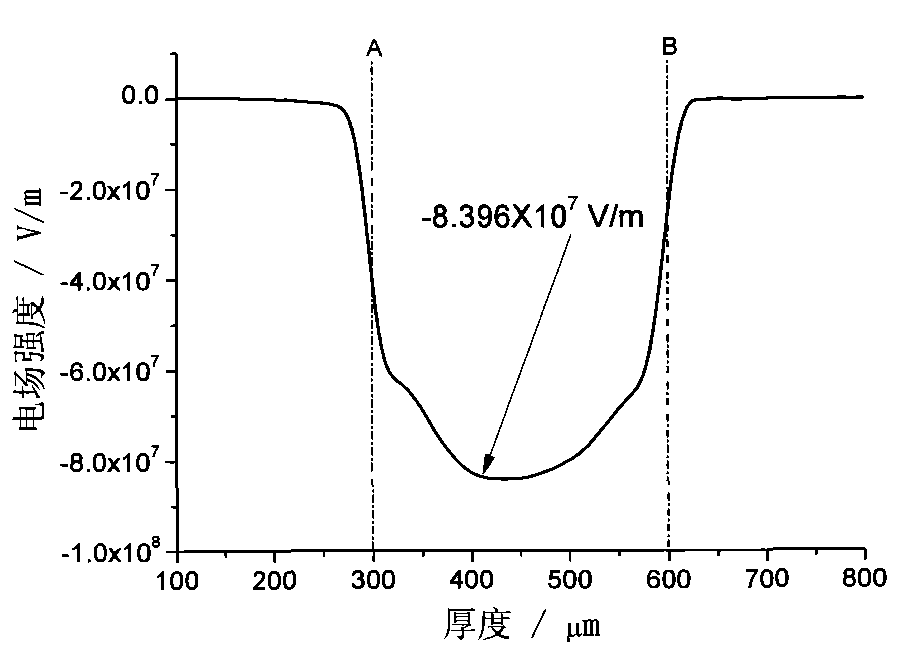

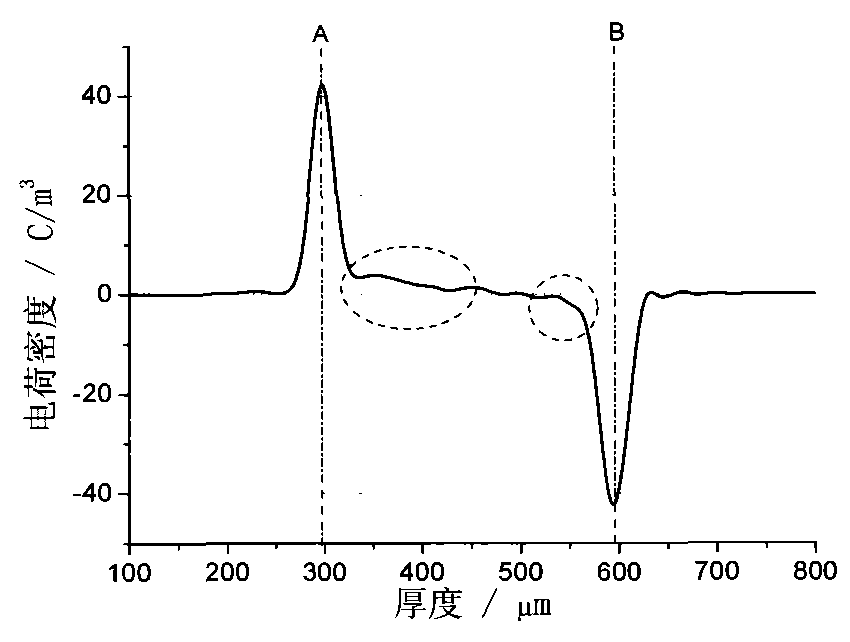

Cable semi-conductive shielding material and preparation method thereof

InactiveCN101585943AAvoid accumulationReduces the effect of increased conductivityPower cables with screens/conductive layersLinear low-density polyethyleneCross linker

The invention provides a cable semi-conductive shielding material which belongs to the field of electric cable fabrication technique and a preparation method thereof, and the components of the material and the content thereof are as follows: ethylene-vinyl acetate copolymer or linear low density polyethylene 100 proportion by weight, black carbon 10-50 proportion by weight, anti-oxidant 0.1-5 proportion by weight as well as cross linker 0.1-5 proportion by weight. The method provided by the invention can effectively inhibit accumulation of space charges in insulation material, and improves electric field threshold value of injected space charge, which reduces insulation material electric conductivity increased effect induced by space charge-limited current (SCLC), and the electric field distortion rate in XLPE is only 14-19% under -60kV / mm extra electric field for 60 minutes.

Owner:SHANGHAI JIAO TONG UNIV

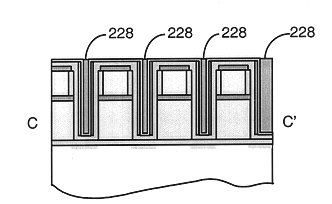

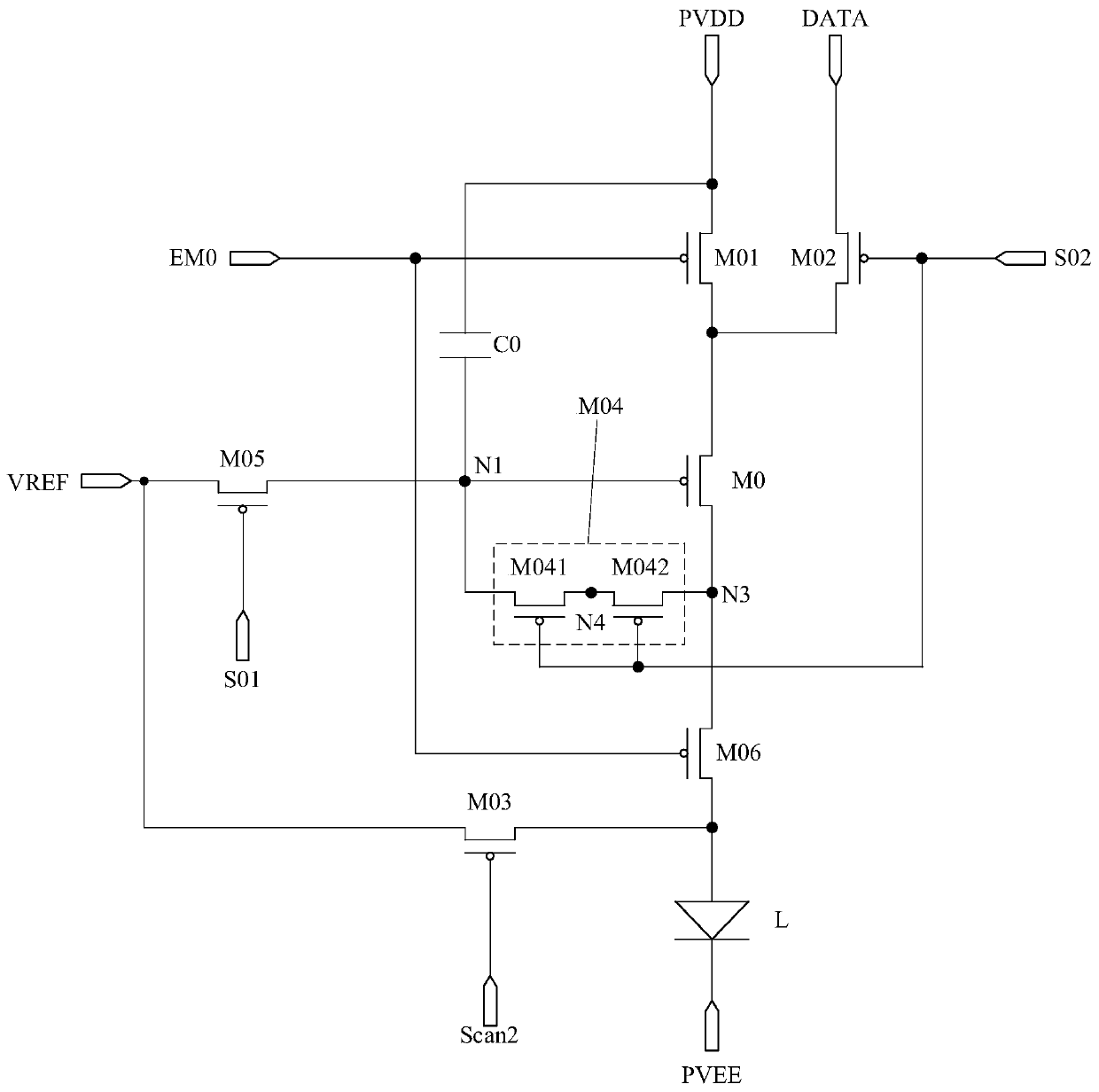

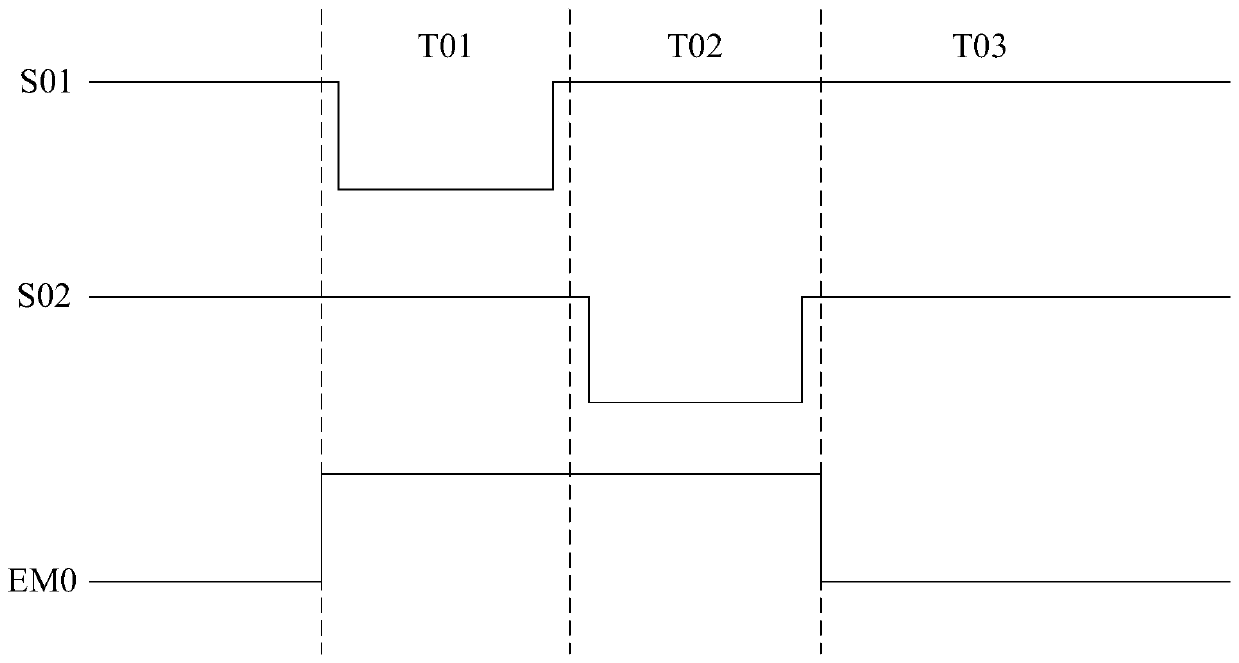

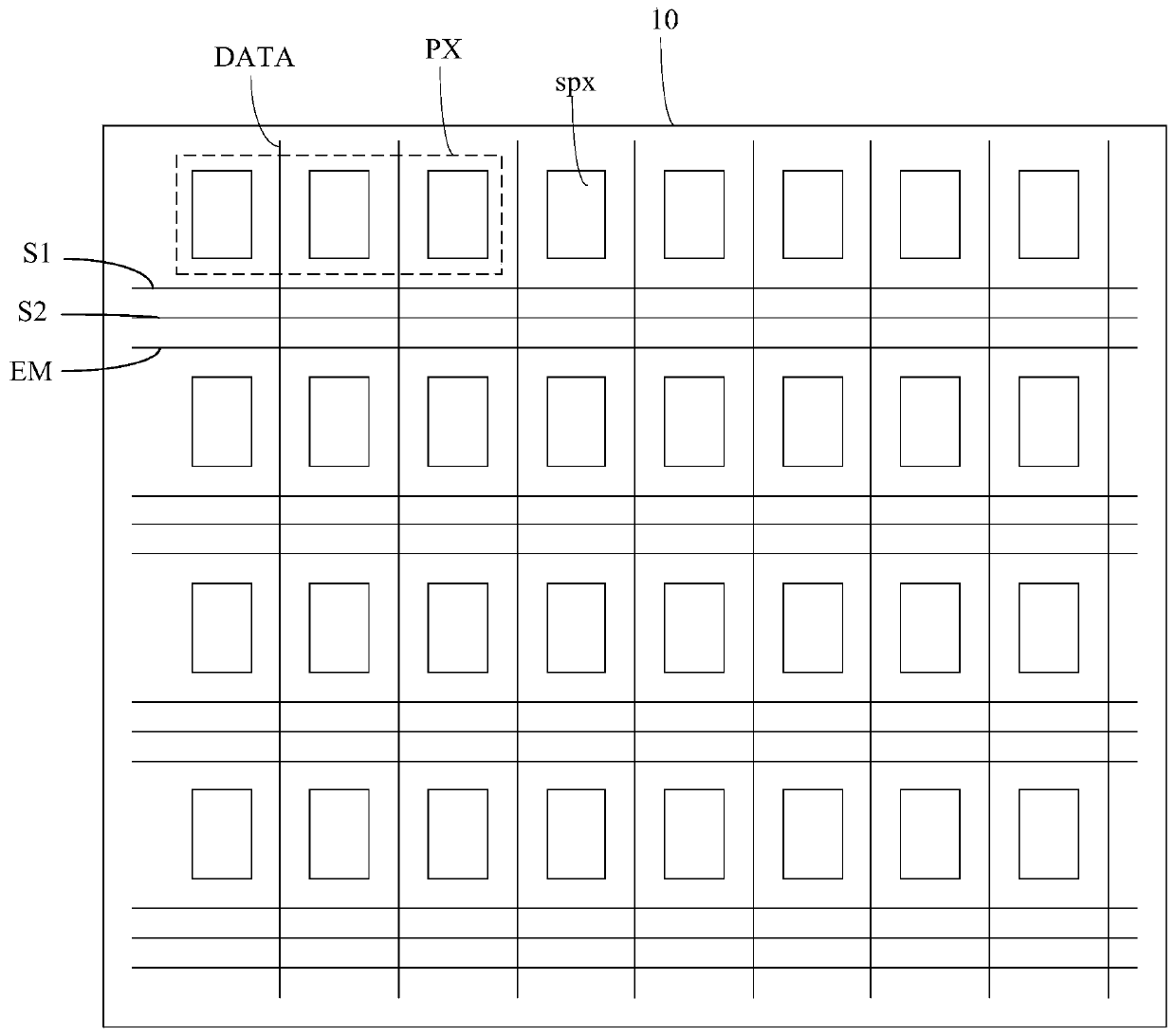

Display panel and display device

ActiveCN110992880AImprove display uniformityStable voltageStatic indicating devicesCapacitanceCharge injection

The invention discloses a display panel and a display device. A threshold compensation circuit comprises a first threshold compensation transistor, a second threshold compensation transistor and a shielding capacitor. Wherein a first threshold compensation transistor and a second threshold compensation transistor are arranged; the length L of the channel region of the transistor can be increased equivalently, and the current I of the transistor is inversely proportional to the length L of the channel region, so that when the length L of the channel region is increased, the current I of the transistor can be reduced, and the quantity of charges flowing into the node N1 from the node N4 can be reduced. Moreover, by arranging the shielding capacitor, the charge of the node N4 can be stored inthe shielding capacitor by utilizing the charge storage effect of the shielding capacitor. Therefore, during signal switching on the scanning signal line, charges of the node N4 can be prevented frombeing injected into the node N1, so that the voltage of the grid electrode of the driving transistor can be kept stable, and the display uniformity of the display panel is improved.

Owner:WUHAN TIANMA MICRO ELECTRONICS CO LTD

Low power electrically alterable nonvolatile memory cells and arrays

Nonvolatile memory cells having a conductor-filter system, a conductor-insulator system, and a charge-injection system are provided. The conductor-filter system provides band-pass filtering function, charge-filtering function, and mass-filtering function to charge-carriers flows. The conductor-insulator system provides Image-Force barrier lowering effect to collect charge-carriers. The charge-injection system includes the conductor-filter system and the conductor-insulator system, wherein the filter of the conductor-filter system contacts the conductor of the conductor-insulator system. Apparatus on cell architecture are provided for the nonvolatile memory cells. Additionally, apparatus on array architectures are provided for constructing the nonvolatile memory cells in memory array. Method on manufacturing such memory cells and array architectures are provided.

Owner:MARVELL ASIA PTE LTD