Patents

Literature

1714results about How to "Improve device performance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

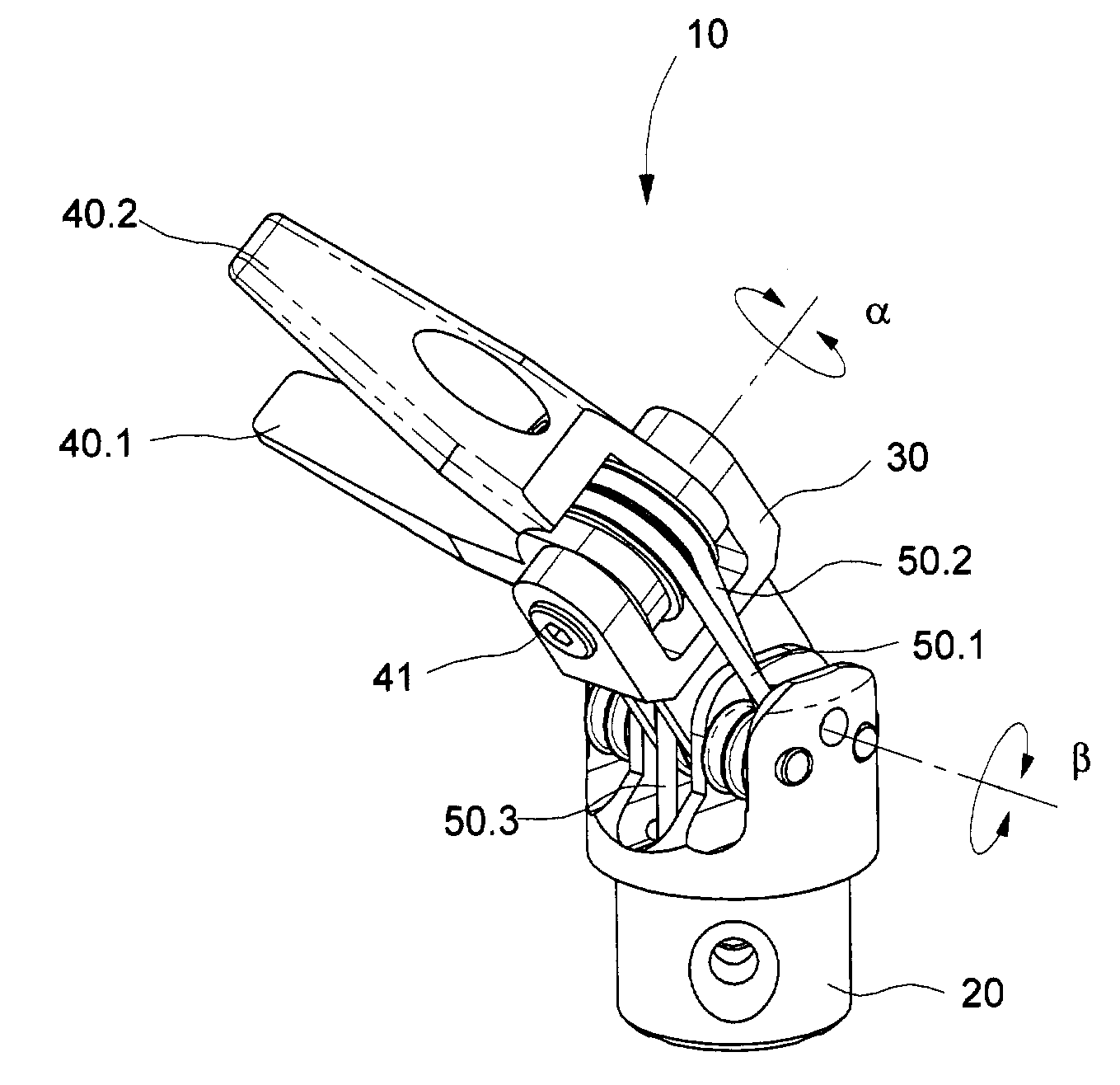

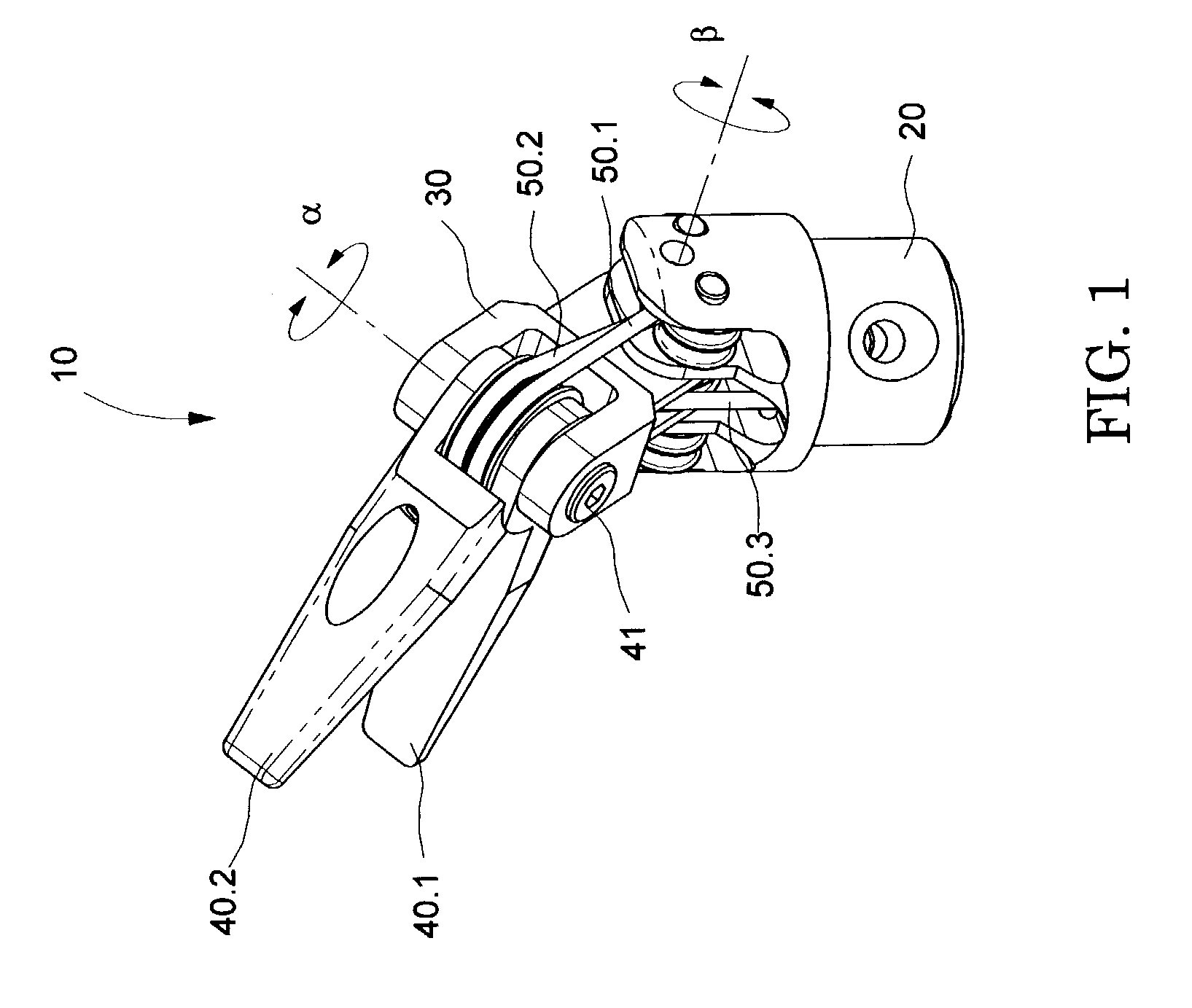

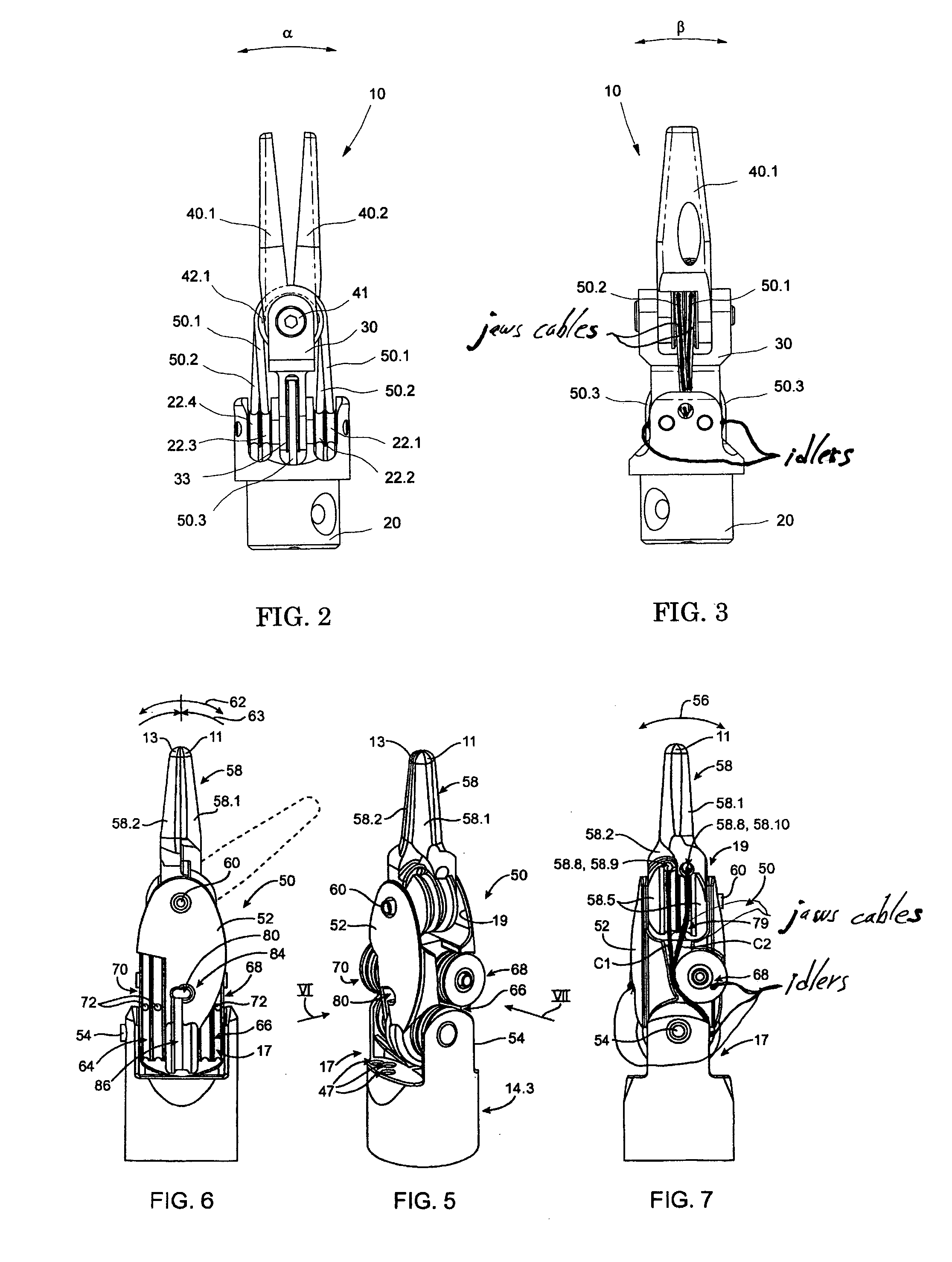

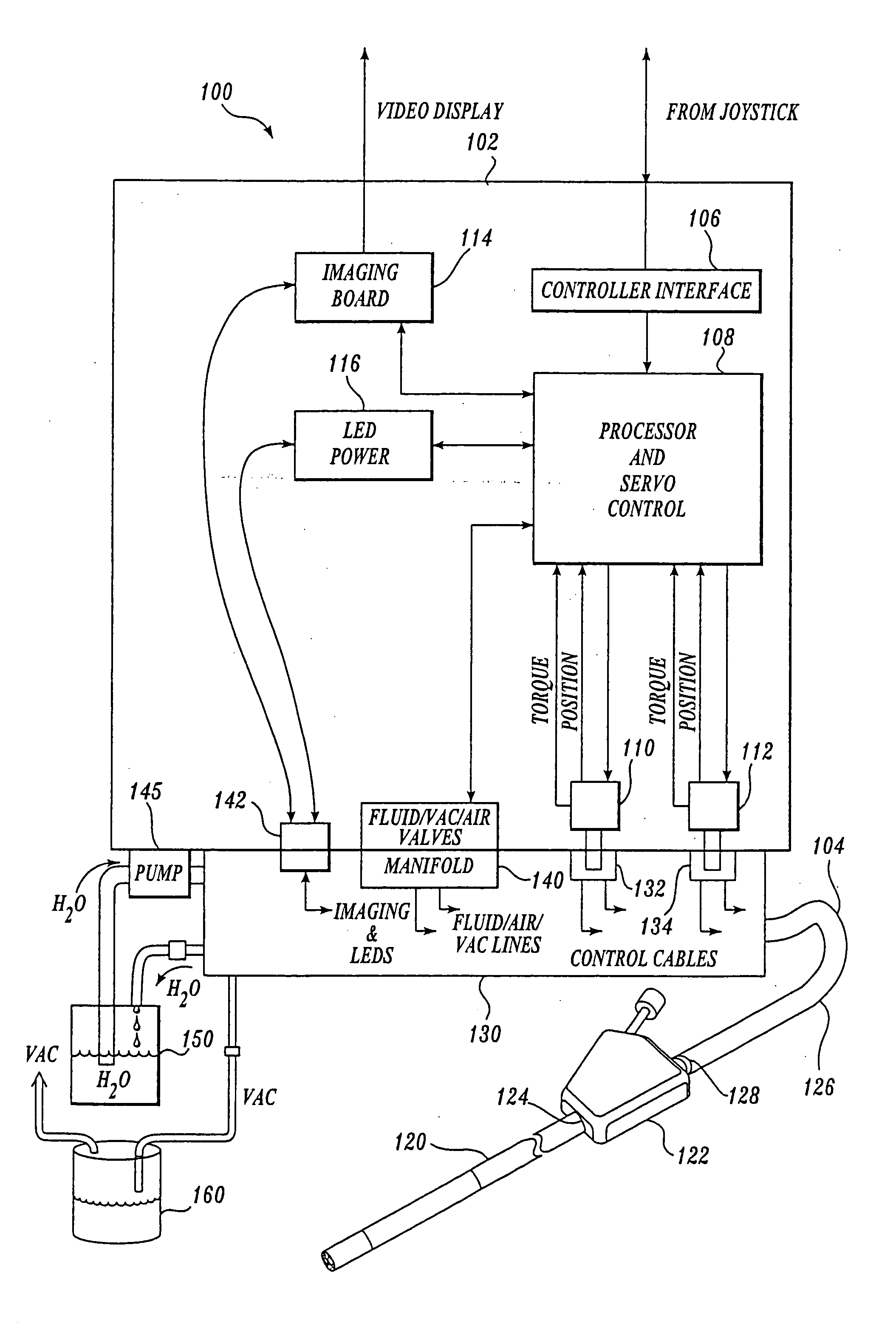

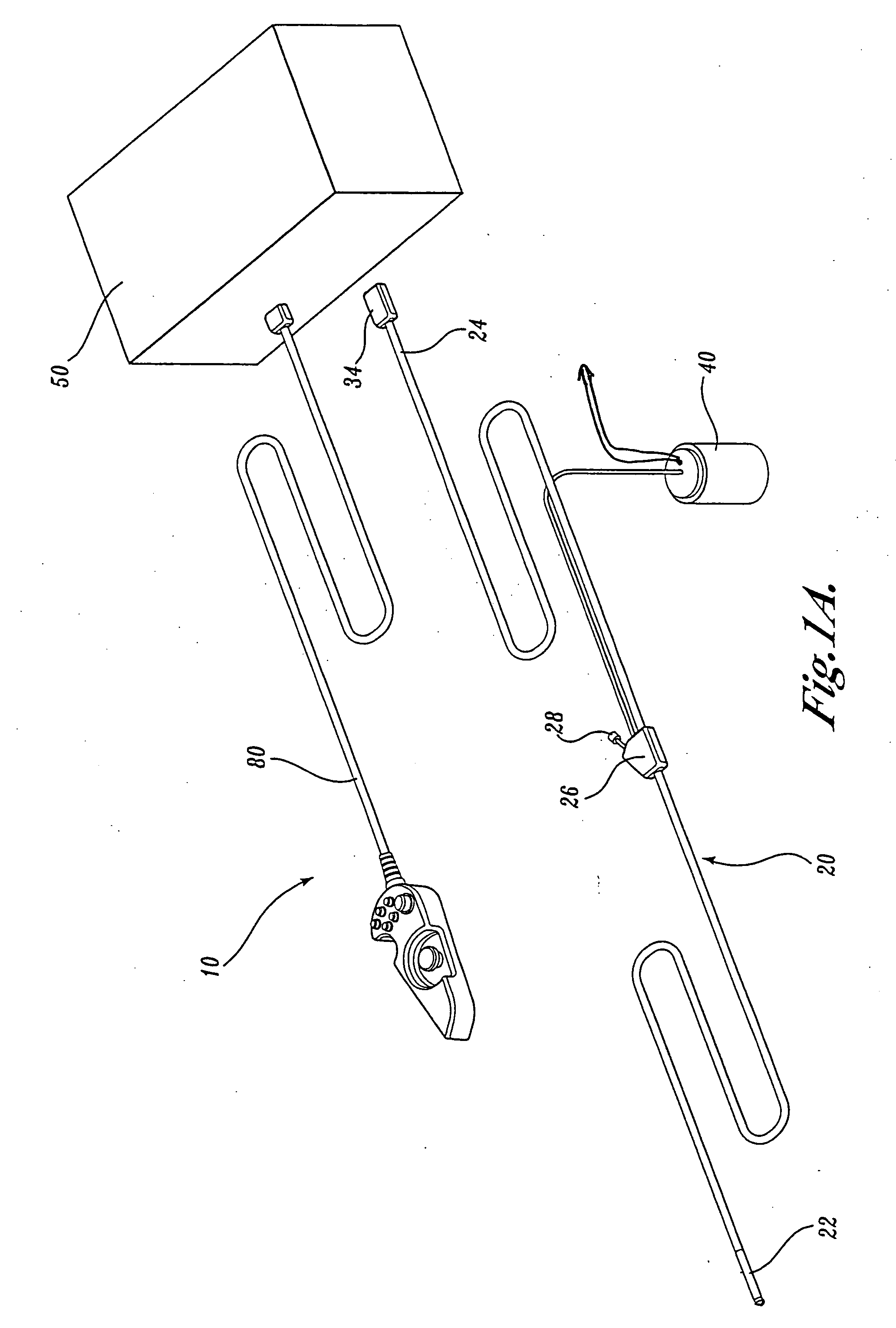

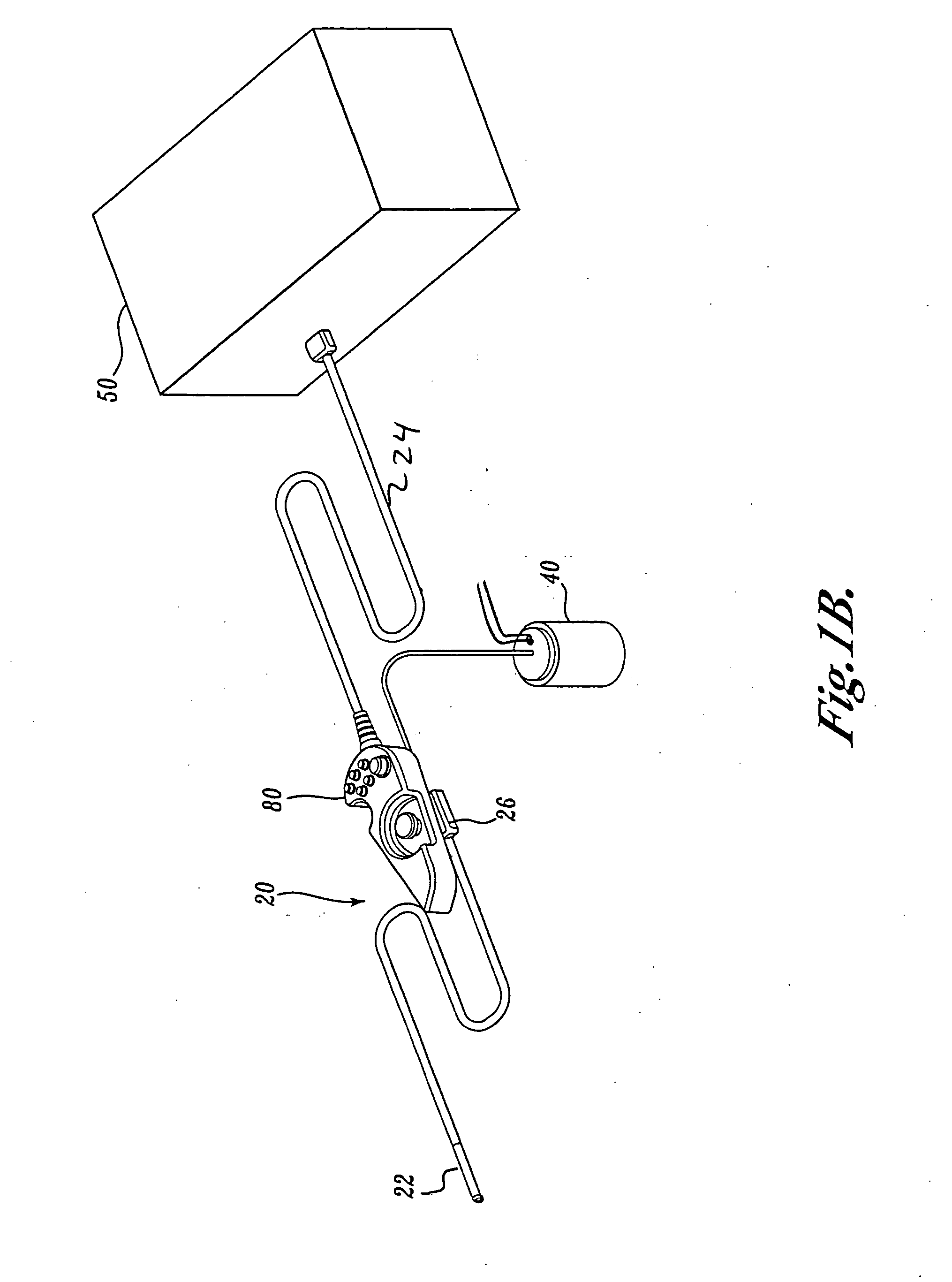

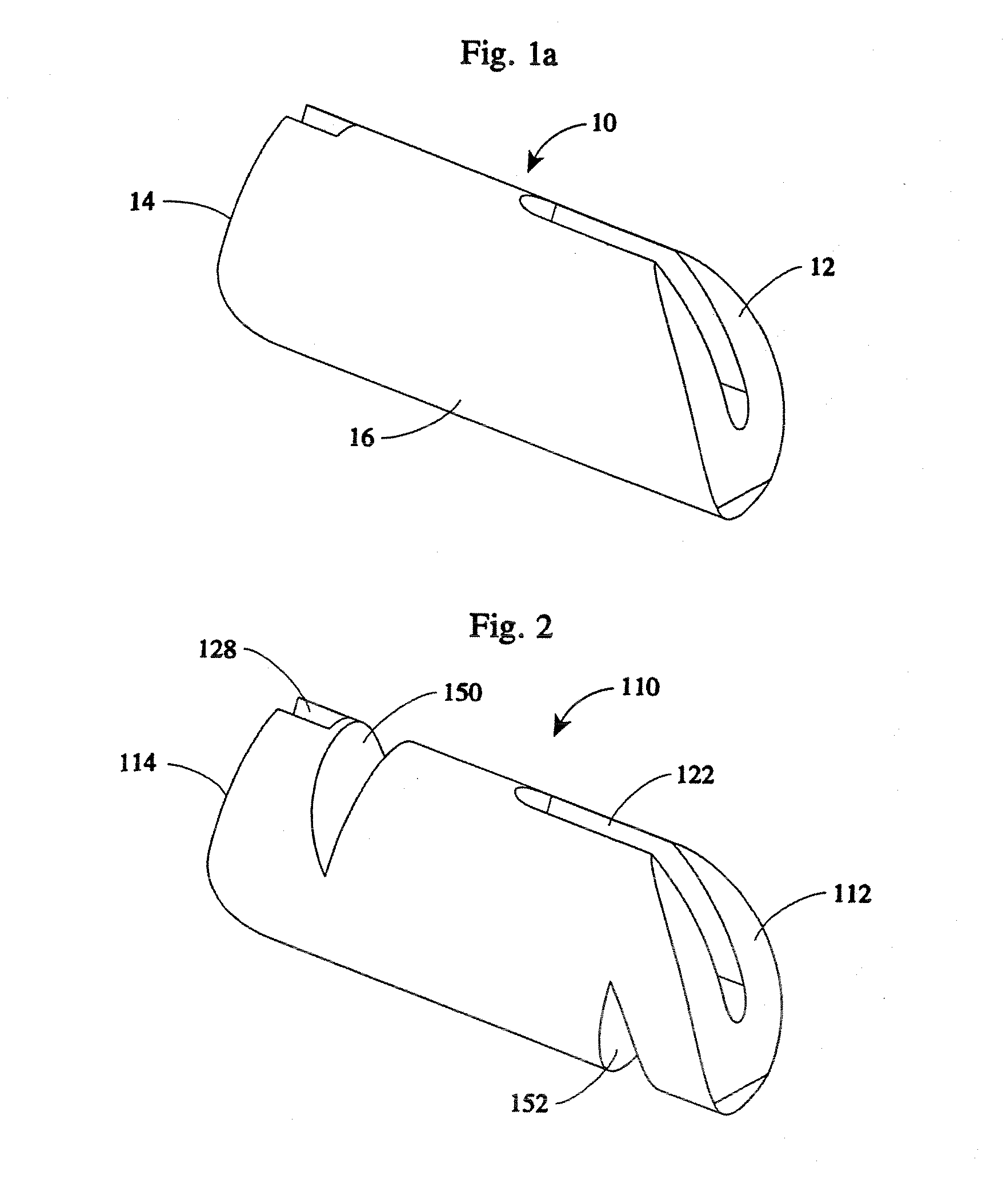

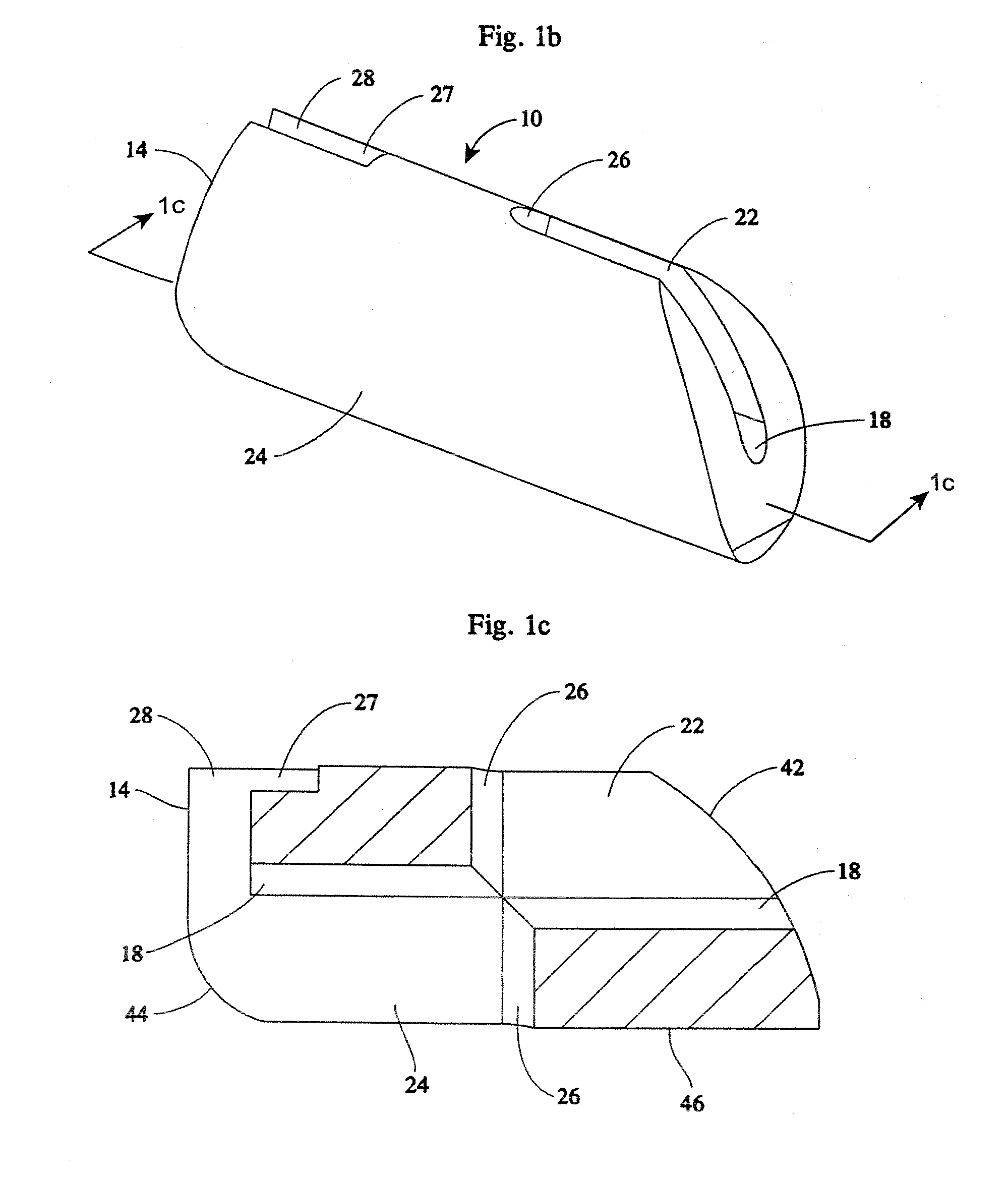

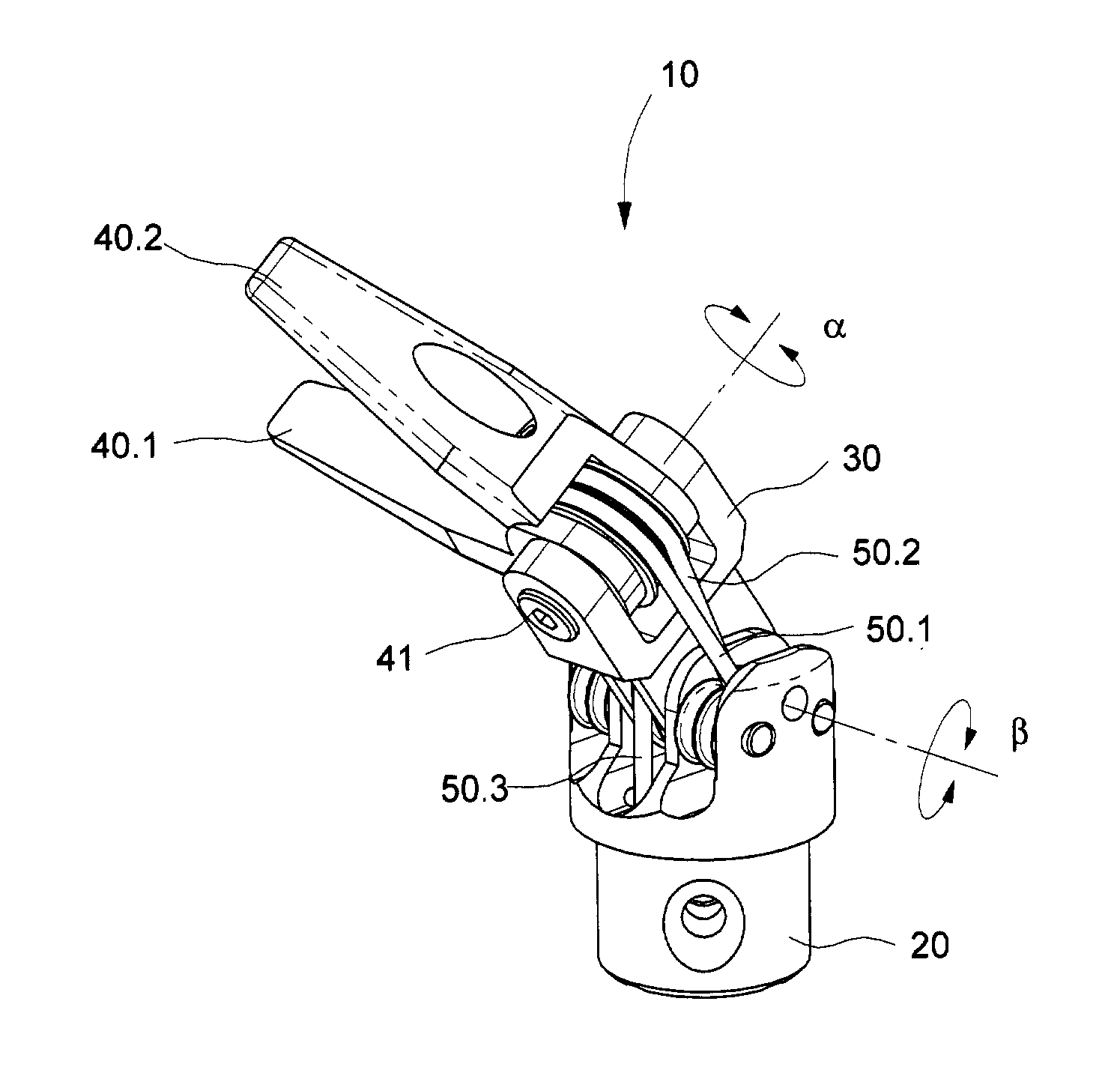

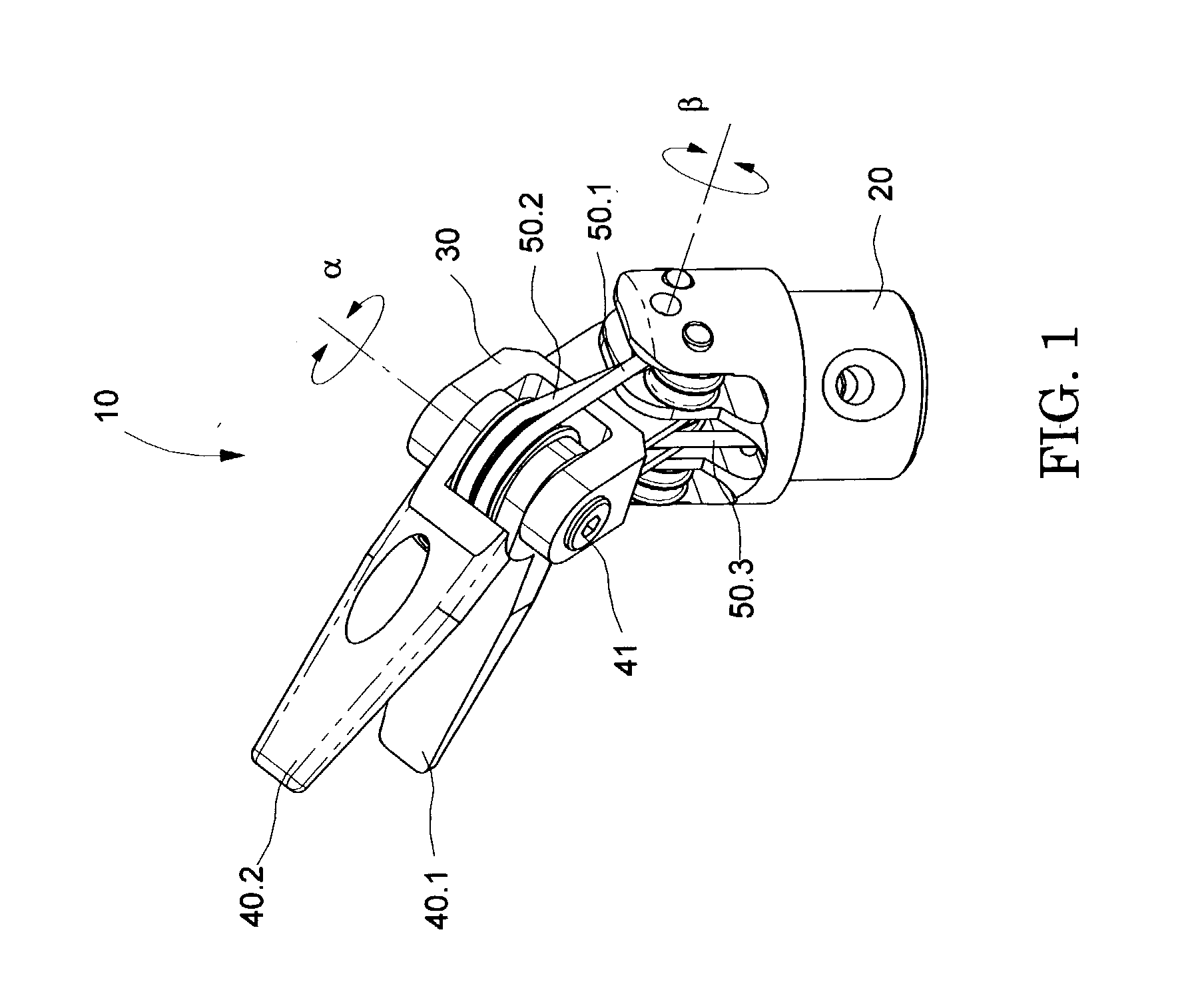

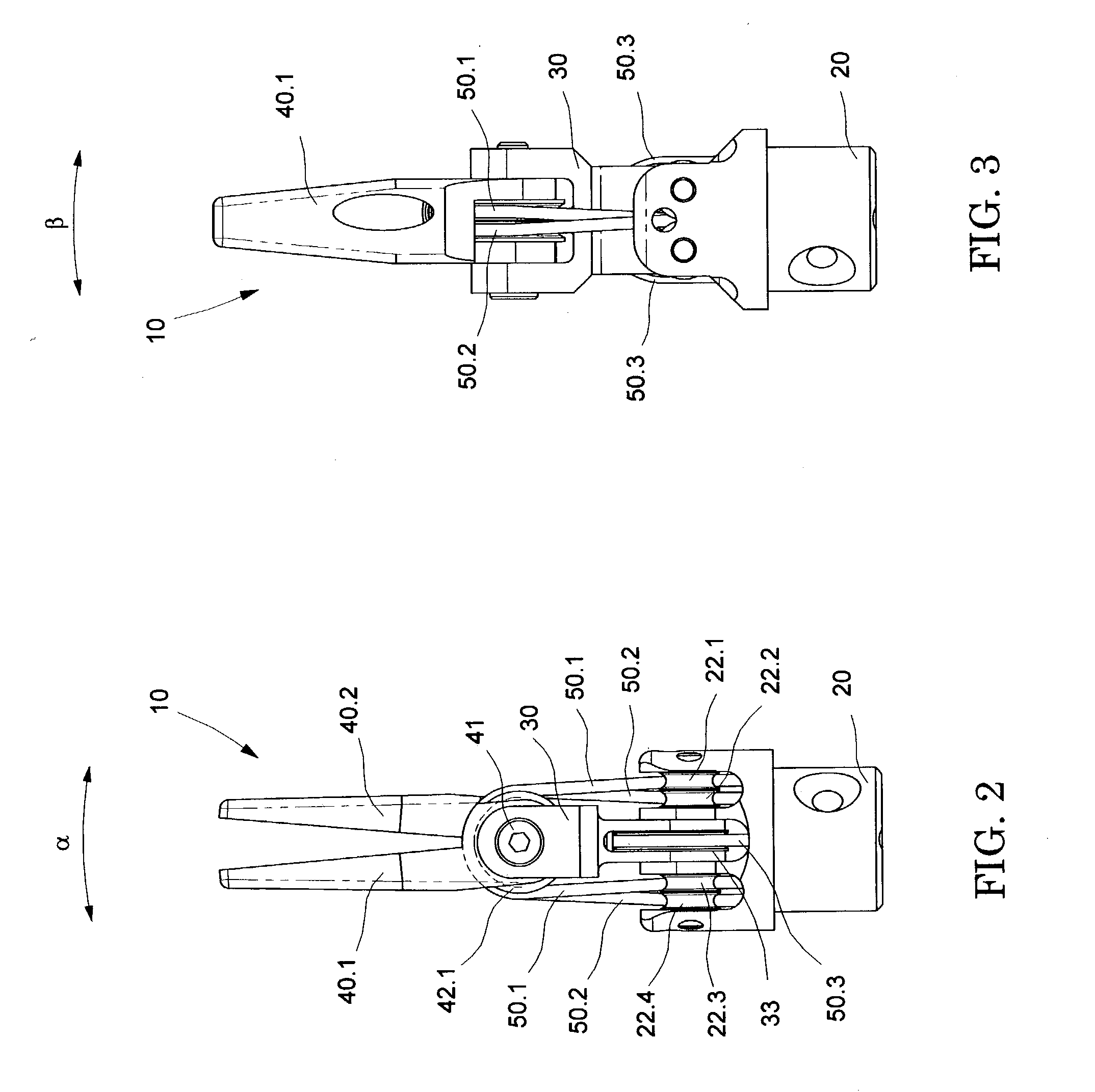

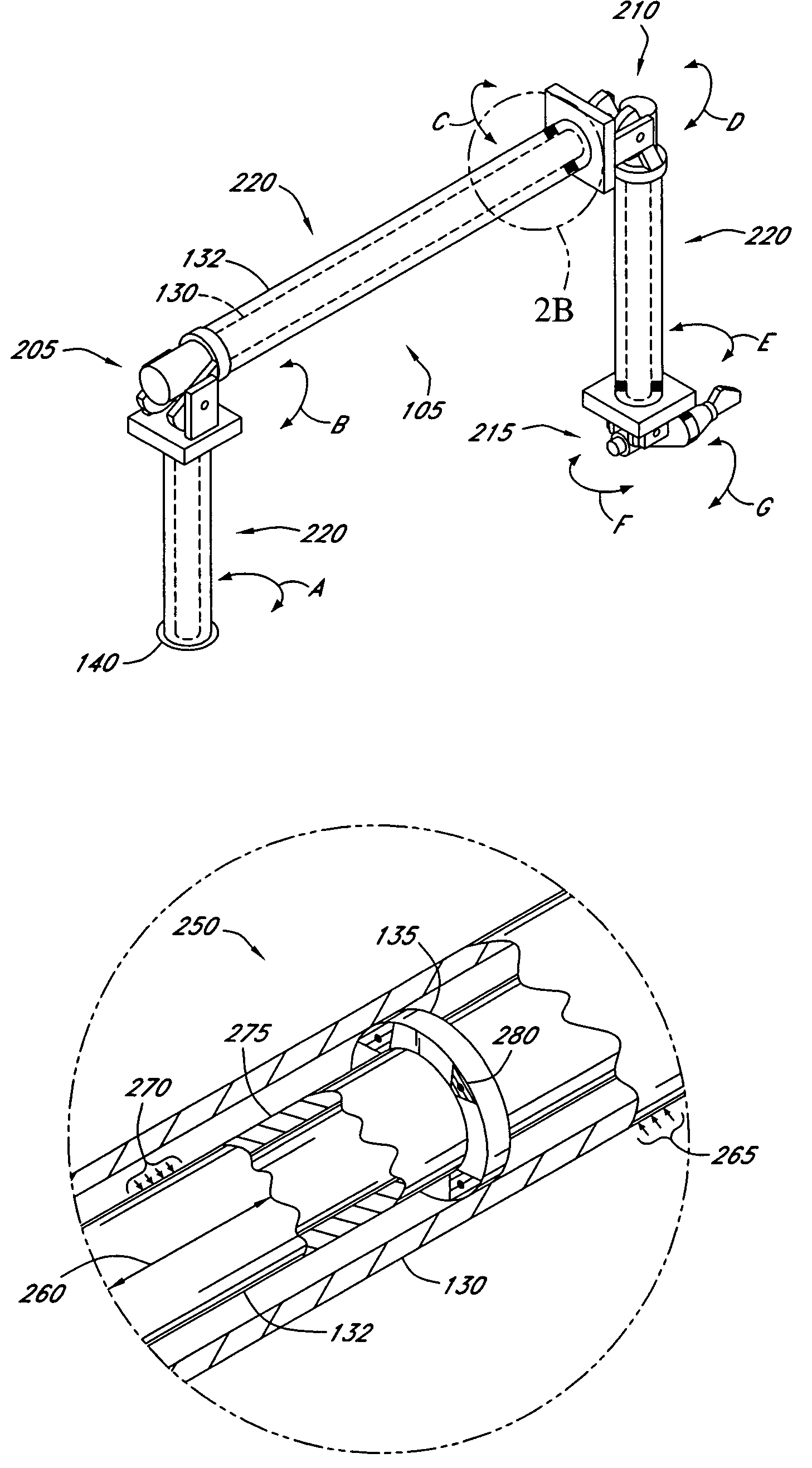

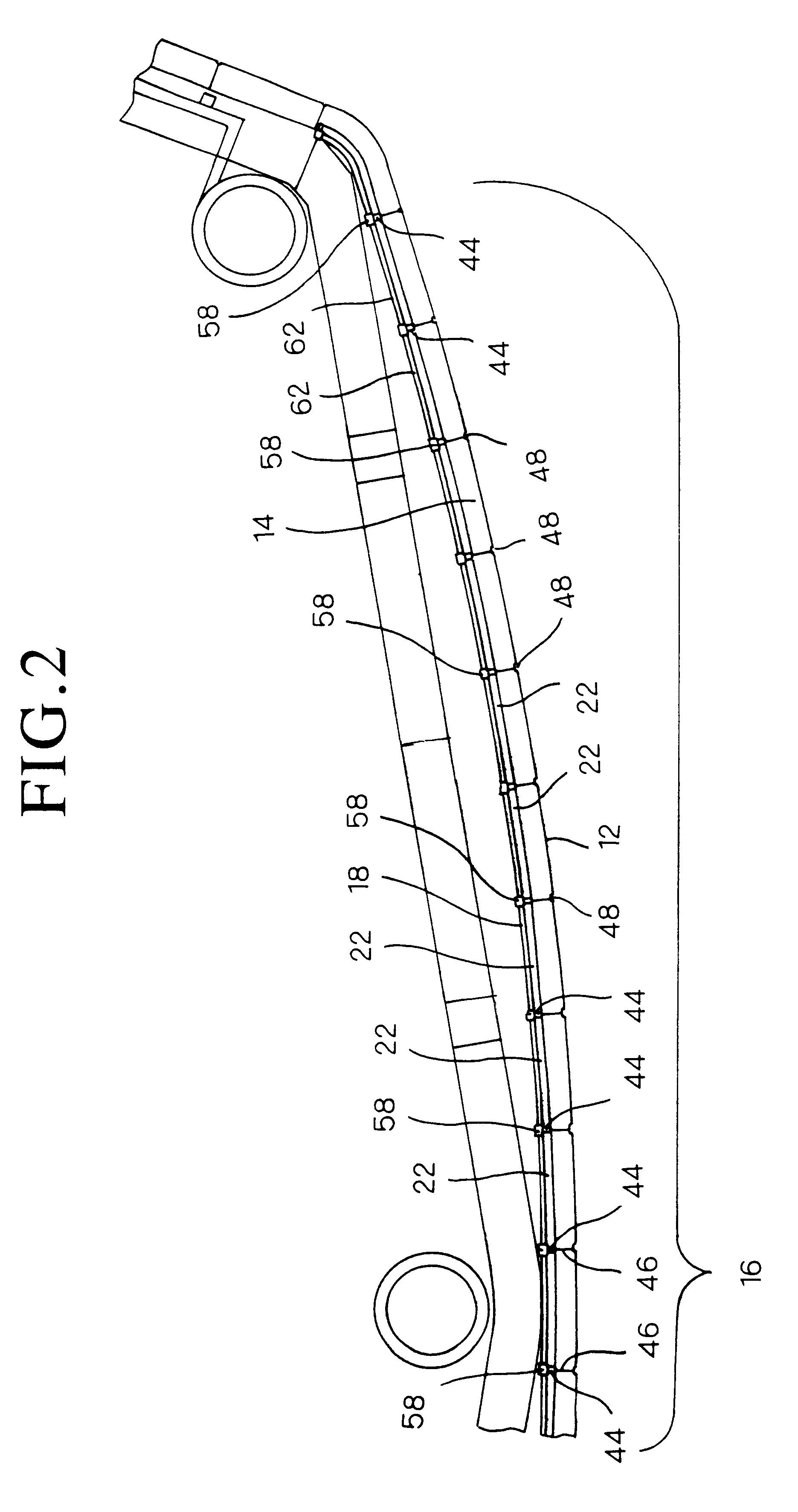

Wrist with decoupled motion transmission

InactiveUS6969385B2Reduce inertiaImprove device performanceMechanical apparatusJointsEngineeringActuator

The present invention is a wrist mechanism and a method for making robotic devices in which the transmission of motion, force and / or torque around a revolute joint can be accomplished without coupling. This construction allows mounting the actuators on the base or lower elements of a mechanism, so that only linkage elements move the end-effector. Thus reducing inertia of the moving elements and increasing performance of the device. The decoupled motion of the end-effector or links is achieved by routing their transmission cables around idler pulleys placed parallel to the joint rotation axis on an optimal position such any stretch on the transmission cable is minimized. In particular, this construction can be use for robotic surgical tools that have two independently driven jaws, decoupled and orthogonal from its articulating wrist. This device may be used in grasping, cutting, suturing or alike operations.

Owner:MOREYRA MANUEL RICARDO

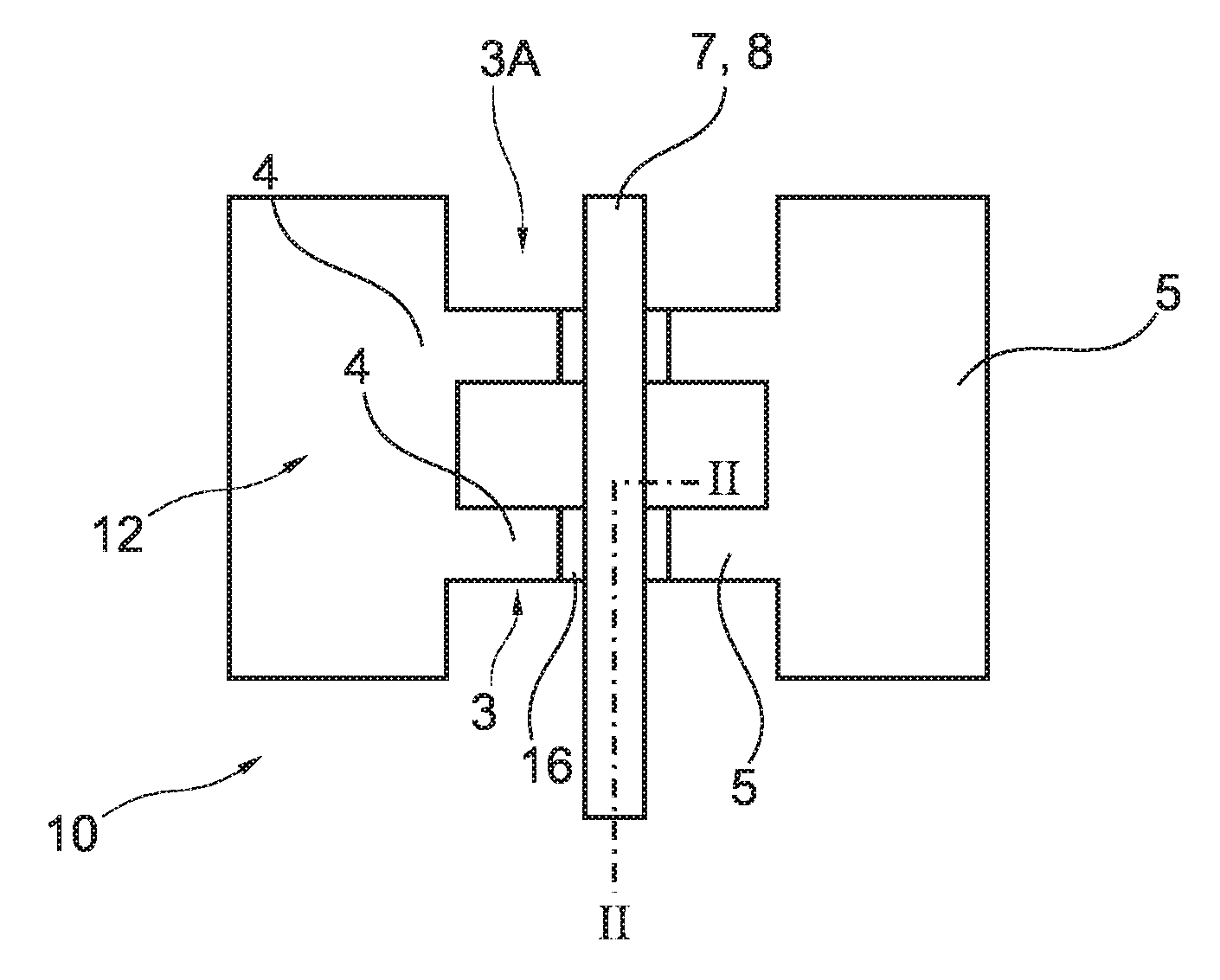

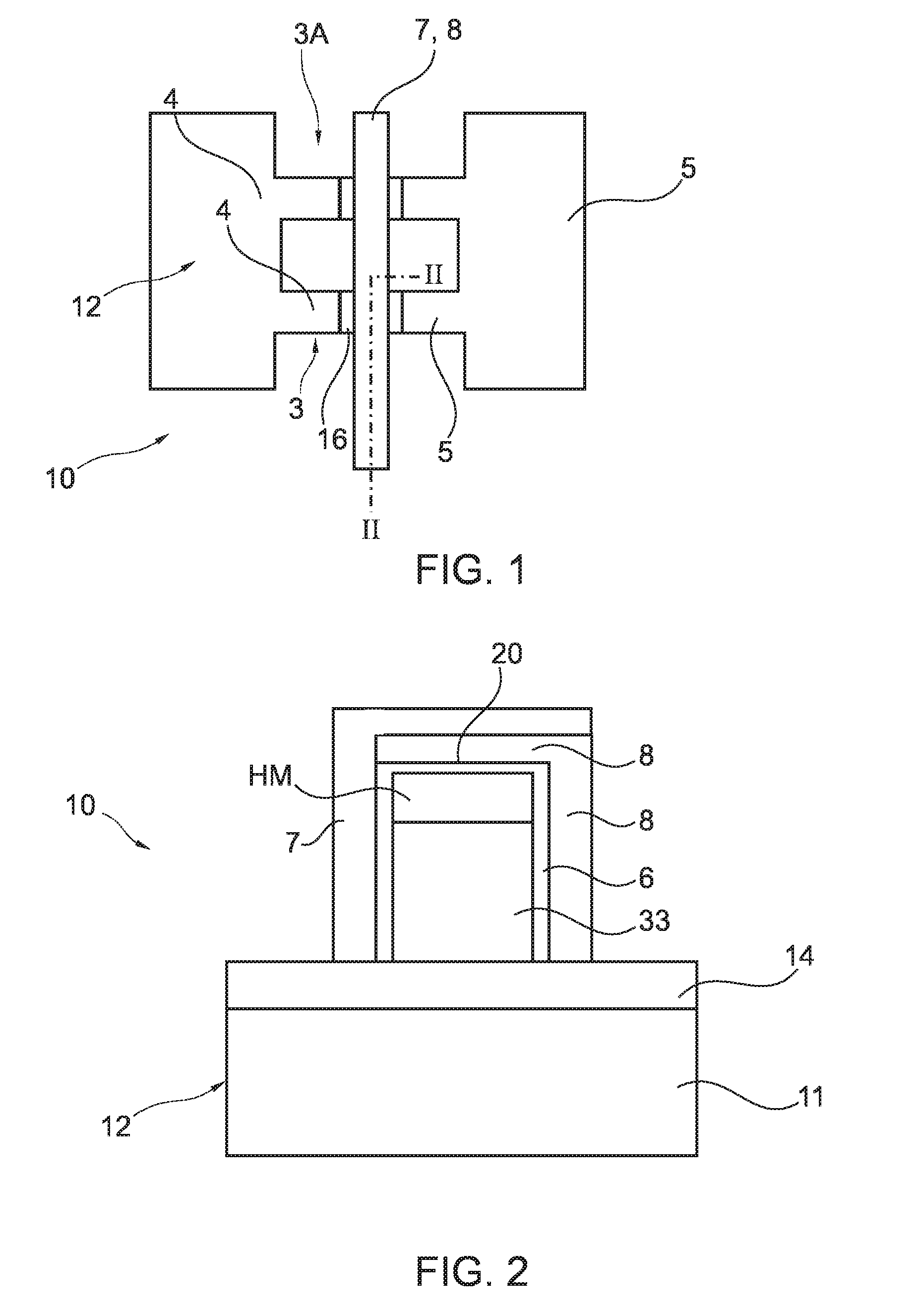

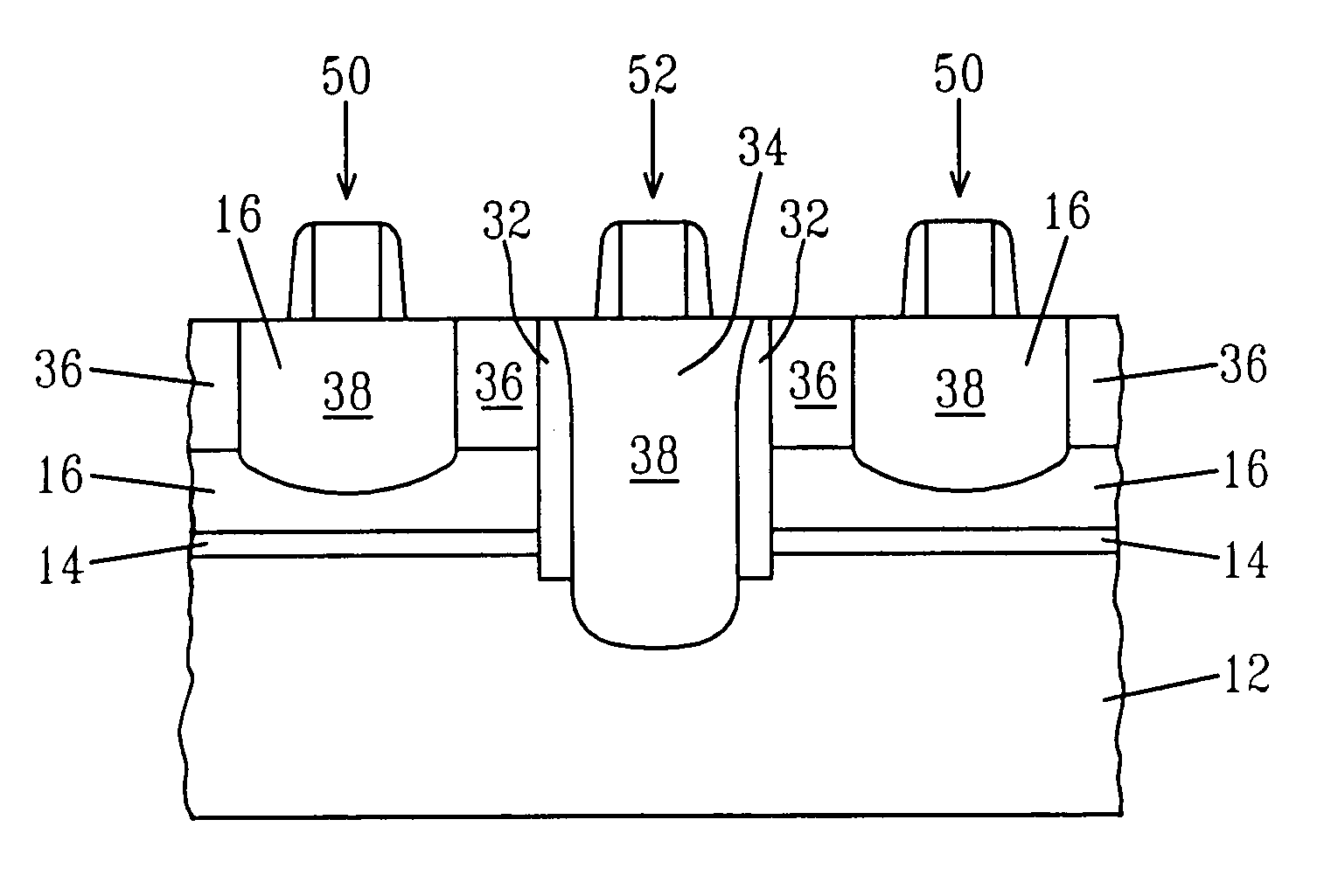

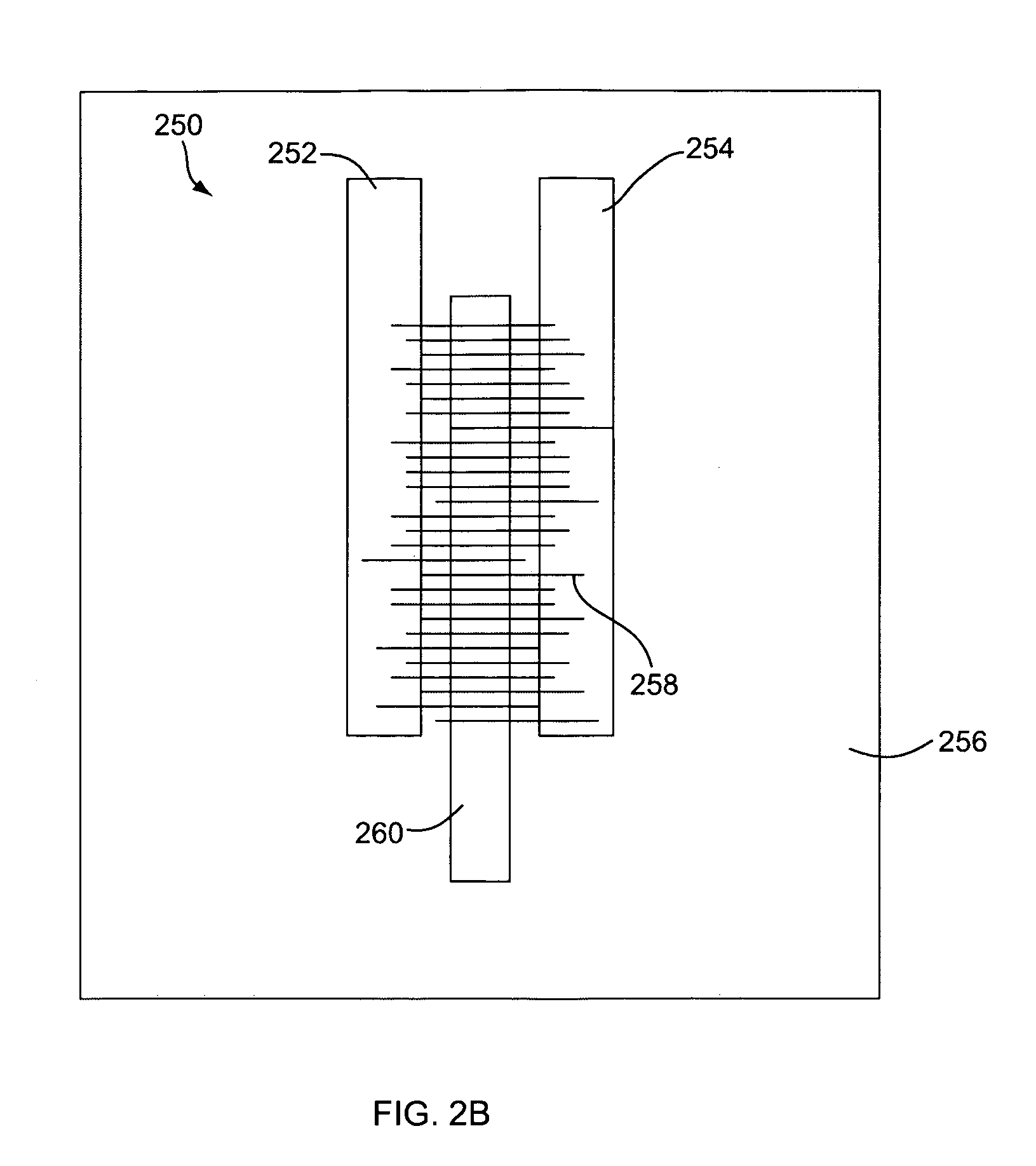

Transistor device and method of manufacturing such a transistor device

ActiveUS20100025766A1Suitable for high-scale integrationImprove device performanceSolid-state devicesSemiconductor/solid-state device manufacturingGate insulatorEngineering

A transistor device (10), the transistor device (10) comprising a substrate (11, 14), a fin (3, 3A) aligned along a horizontal direction on the substrate (11, 14), a first source / drain region (4) of a first type of conductivity in the fin (3, 3A), a second source / drain region (5) of a second type of conductivity in the fin (3, 3A), wherein the first type of conductivity differs from the second type of conductivity, a channel region (33) in the fin (3, 3A) between the first source / drain region (4) and the second source / drain region (5), a gate insulator (6) on the channel region (33), and a gate structure (7, 8) on the gate insulator (6), wherein the sequence of the first source / drain region (4), the channel region (33) and the second source / drain region (5) is aligned along the horizontal direction.

Owner:UNITED MICROELECTRONICS CORP

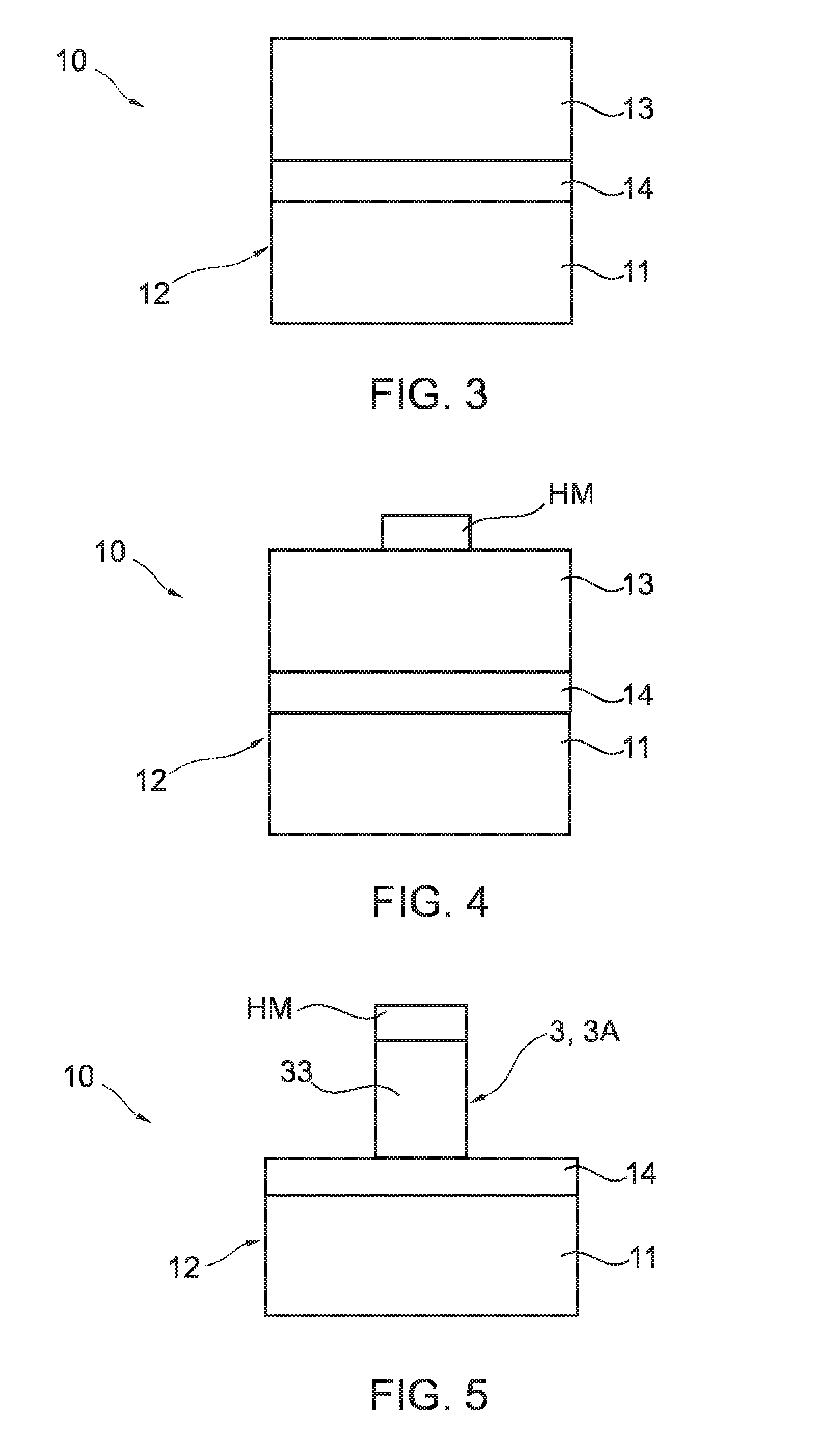

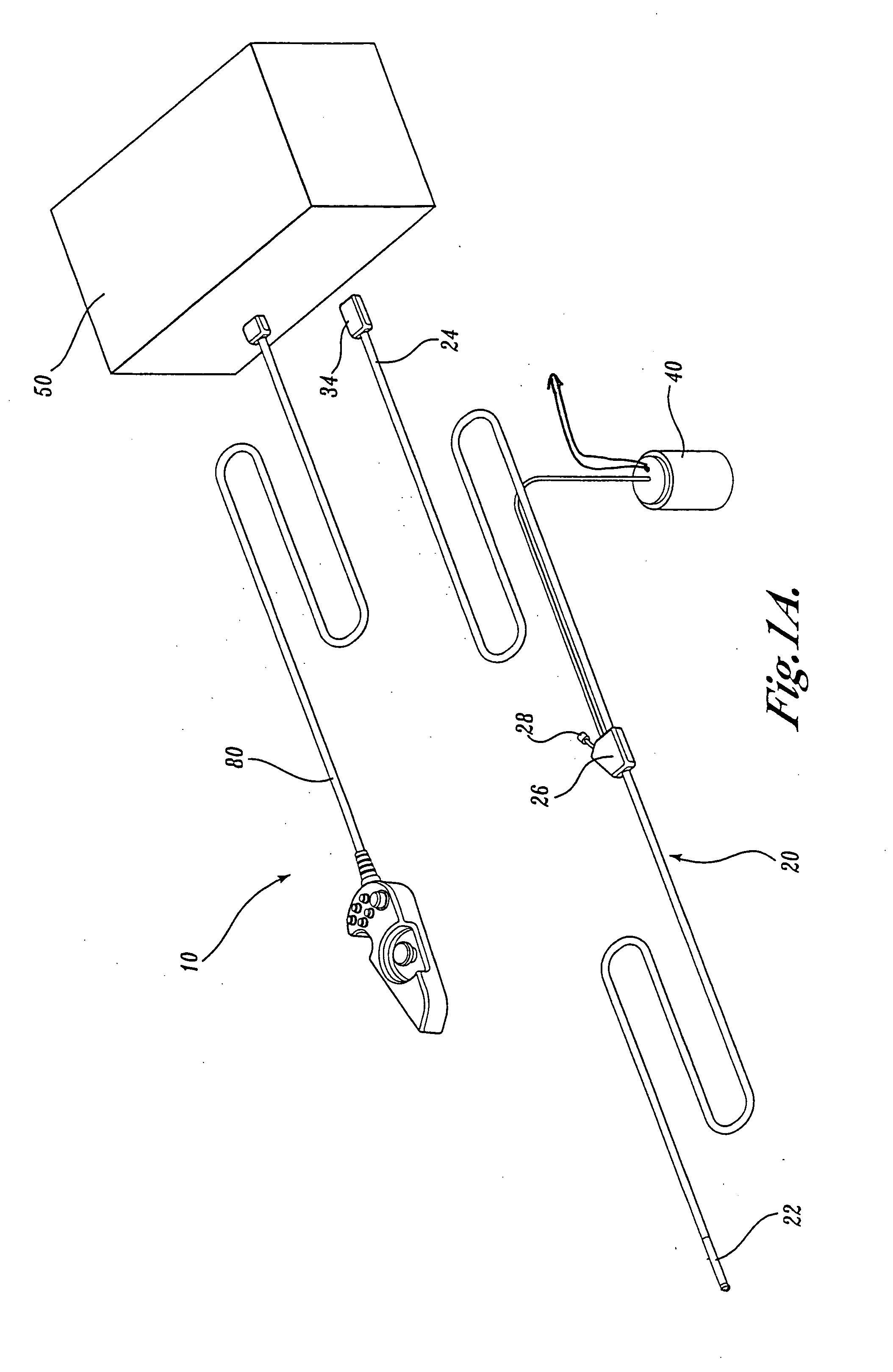

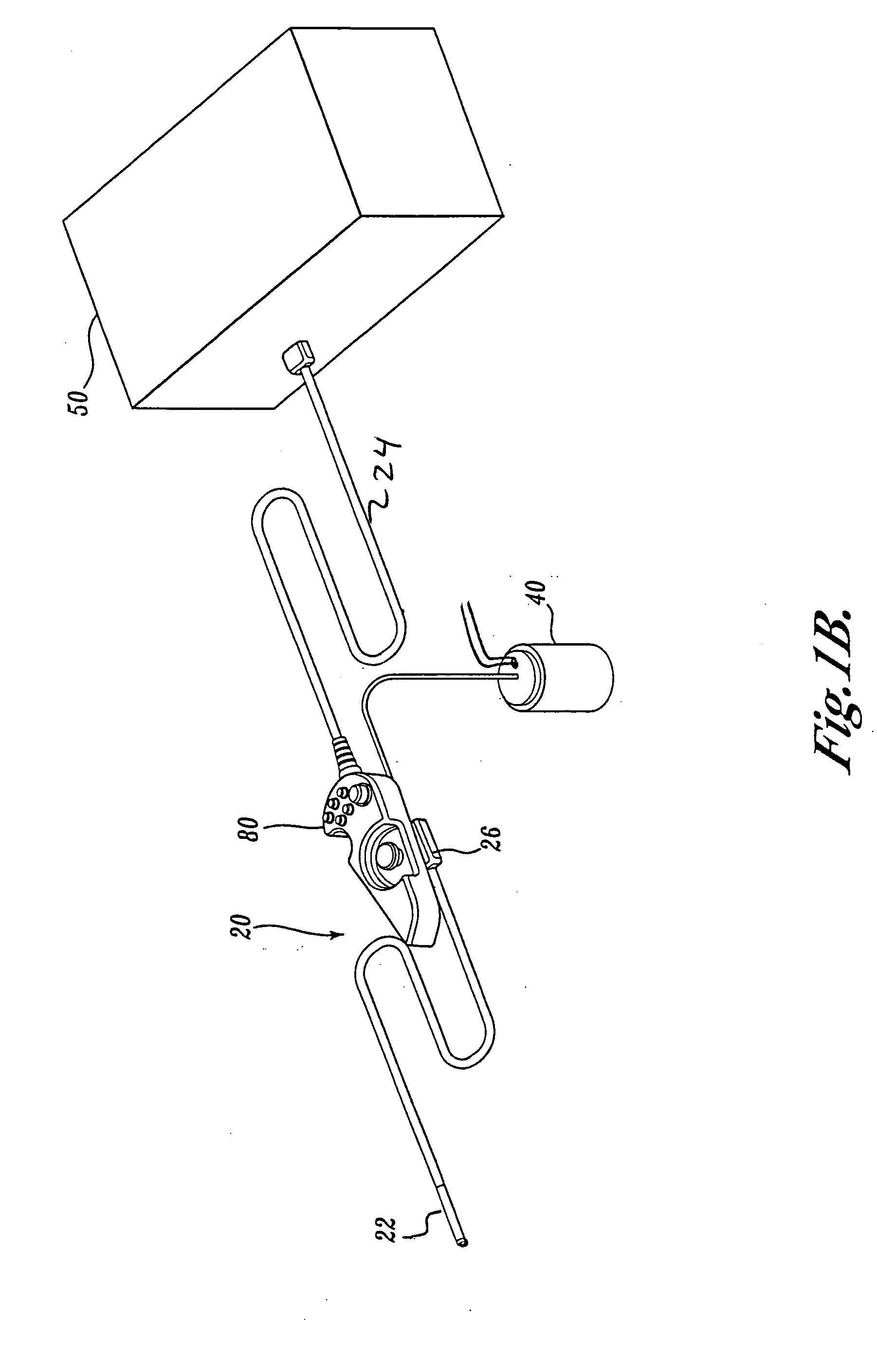

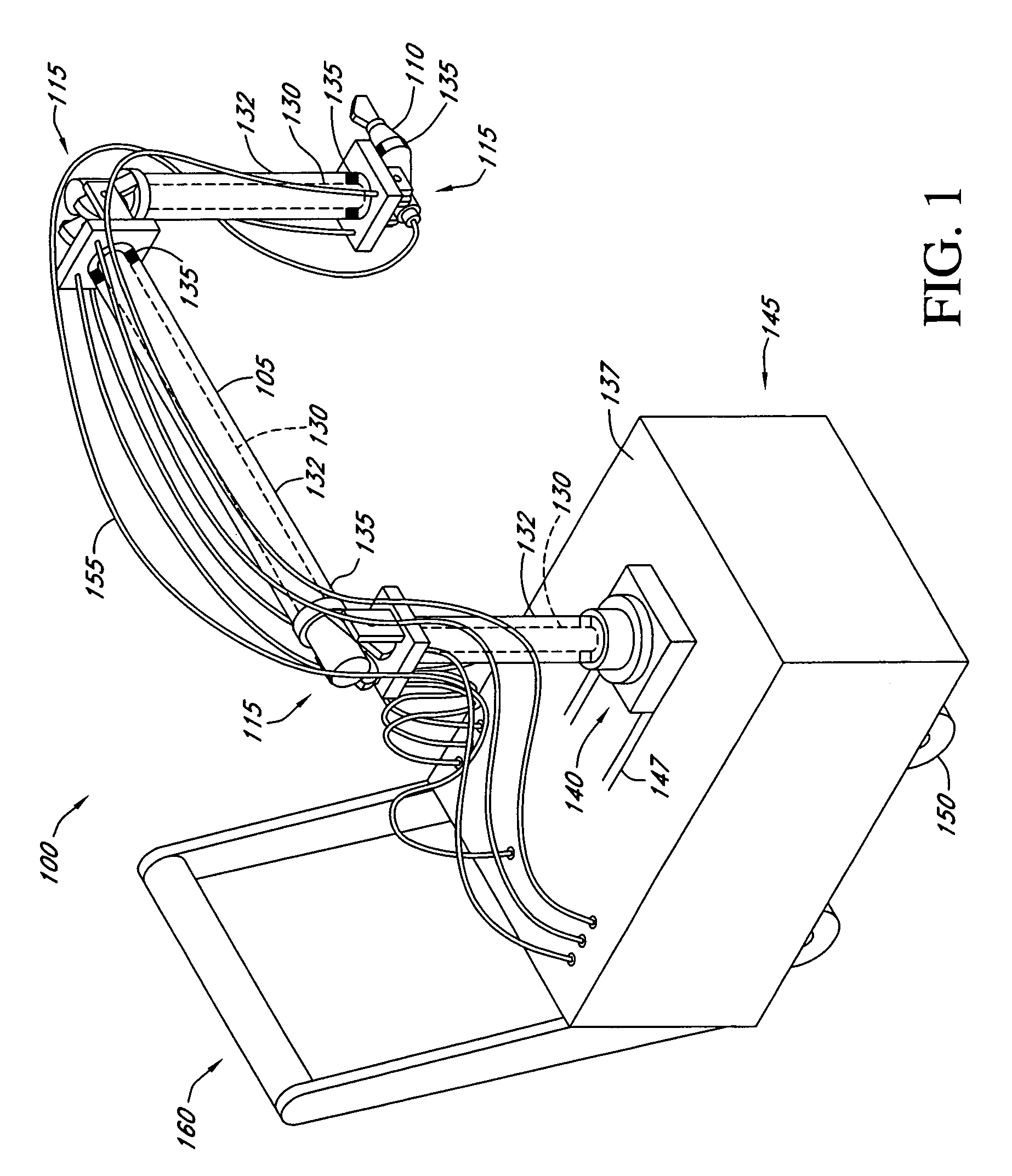

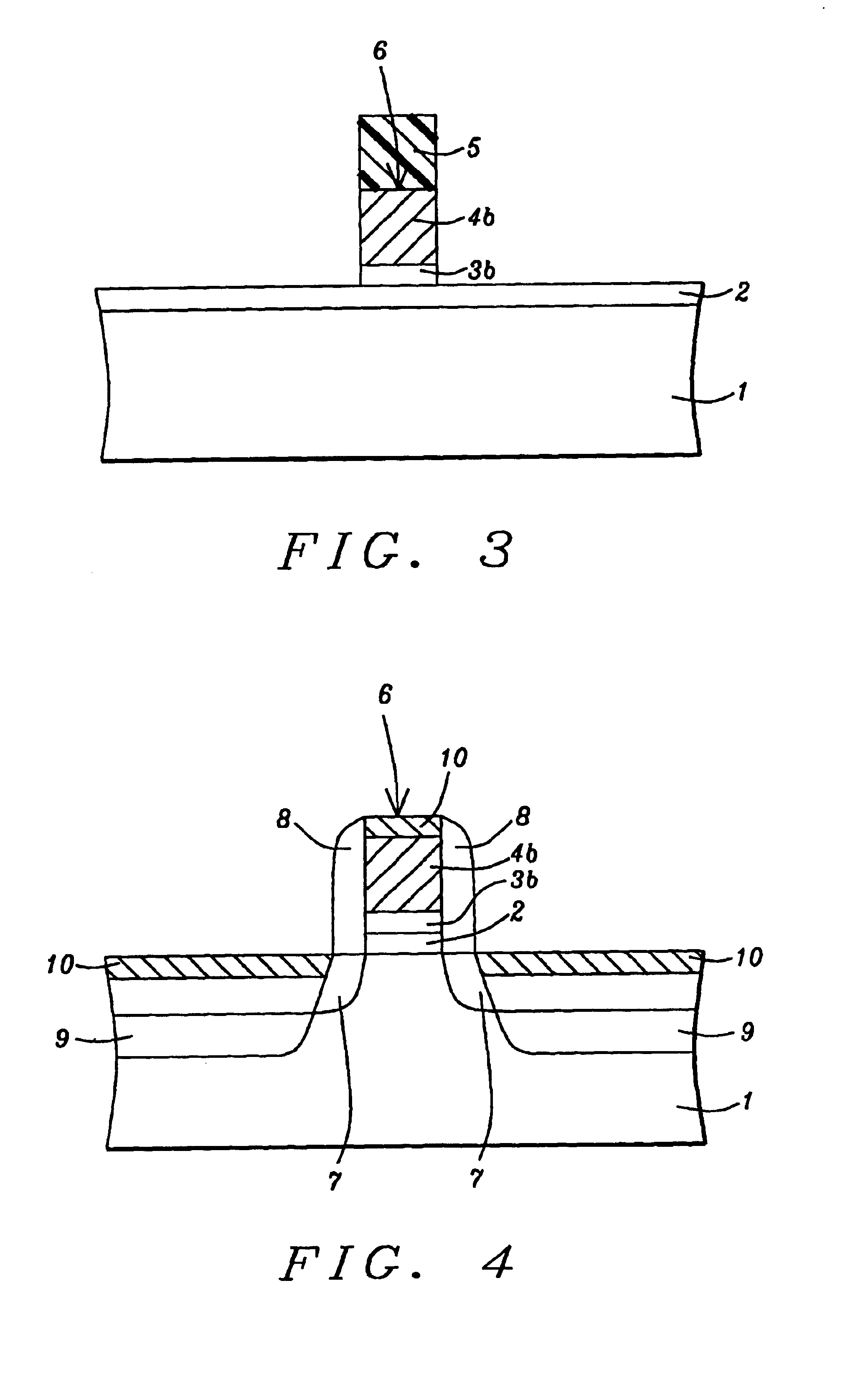

Force feedback control system for video endoscope

ActiveUS20050119527A1Reduce coefficient of frictionImprove device performanceSurgeryEndoscopesFluidicsControl system

A video endoscope system includes a reusable control cabinet and an endoscope that is connectable thereto. The endoscope may be used with a single patient and then disposed. The endoscope includes an illumination mechanism, an image sensor, and an elongate shaft having one or more lumens located therein. An articulation joint at the distal end of the endoscope allows the distal end to be oriented by the actuators in the control cabinet or actuators in a control handle of the endoscope. Fluidics, electrical, navigation, image, display and data entry controls are integrated into the system along with other accessories.

Owner:BOSTON SCI SCIMED INC

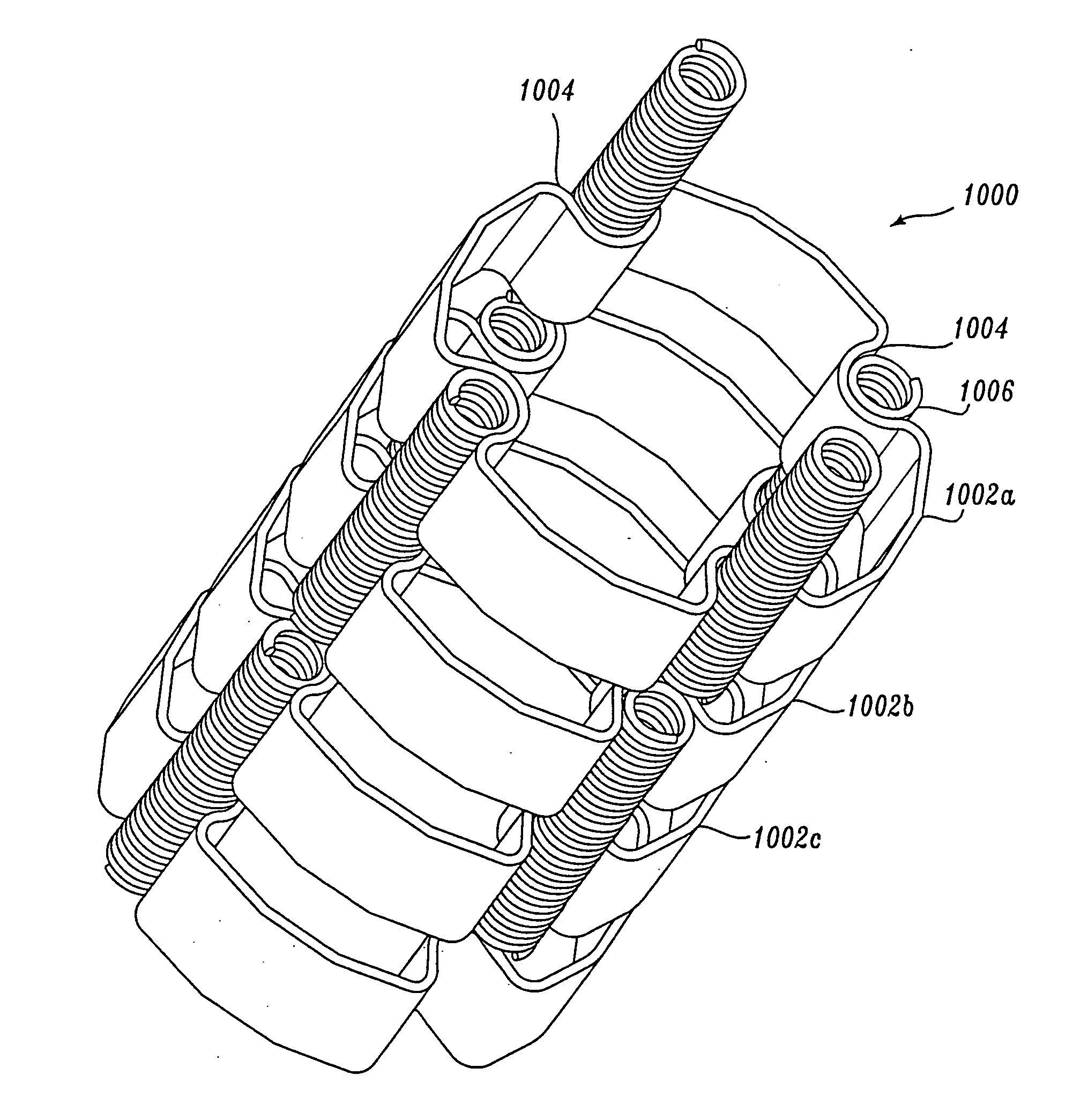

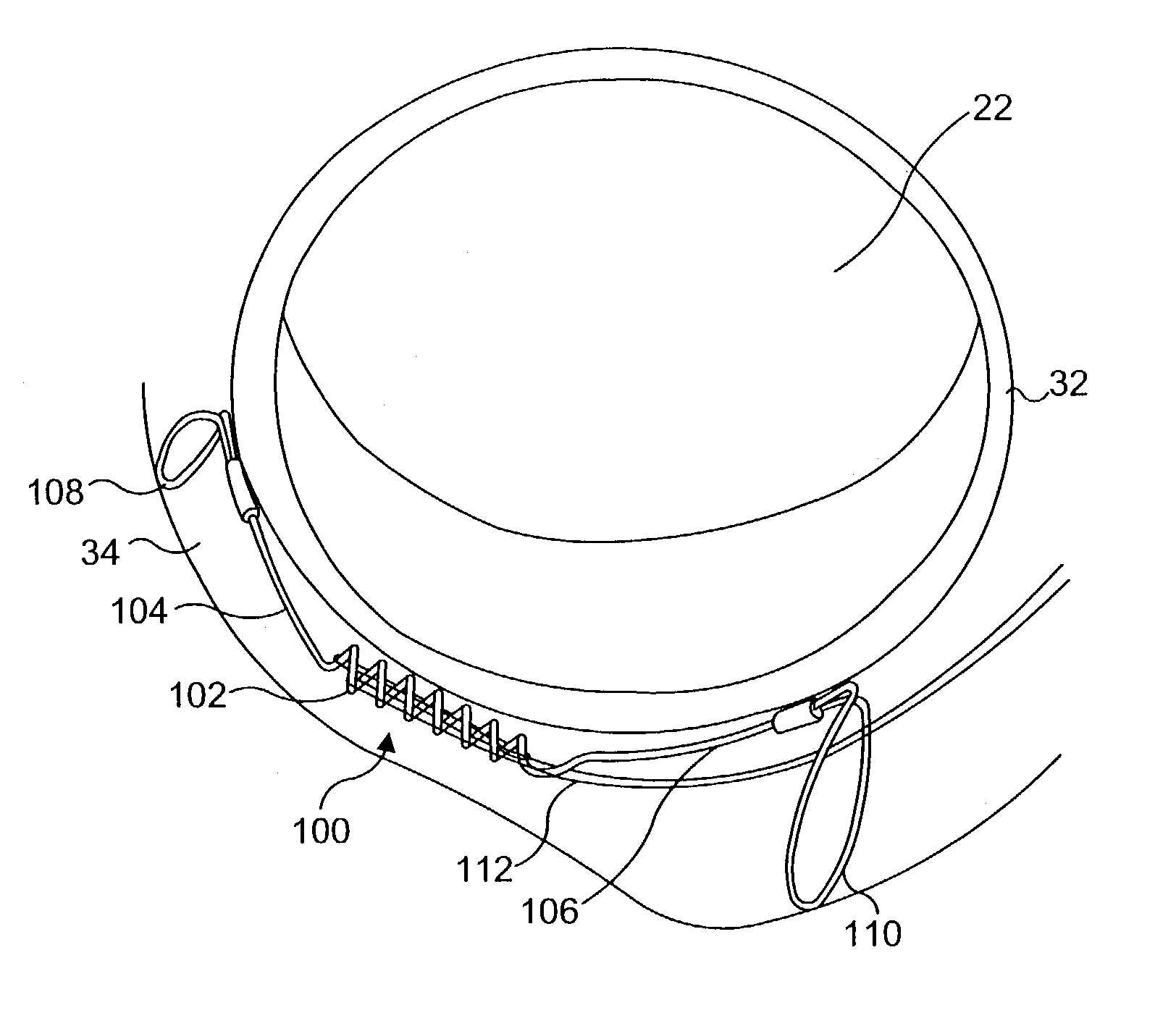

Articulation joint for video endoscope

ActiveUS20050131279A1Reduce coefficient of frictionImprove device performanceSurgeryEndoscopesFluidicsEngineering

A video endoscope system includes a reusable control cabinet and an endoscope that is connectable thereto. The endoscope may be used with a single patient and then disposed. The endoscope includes an illumination mechanism, an image sensor, and an elongate shaft having one or more lumens located therein. An articulation joint at the distal end of the endoscope allows the distal end to be oriented by the actuators in the control cabinet or actuators in a control handle of the endoscope. Fluidics, electrical, navigation, image, display and data entry controls are integrated into the system along with other accessories.

Owner:BOSTON SCI SCIMED INC

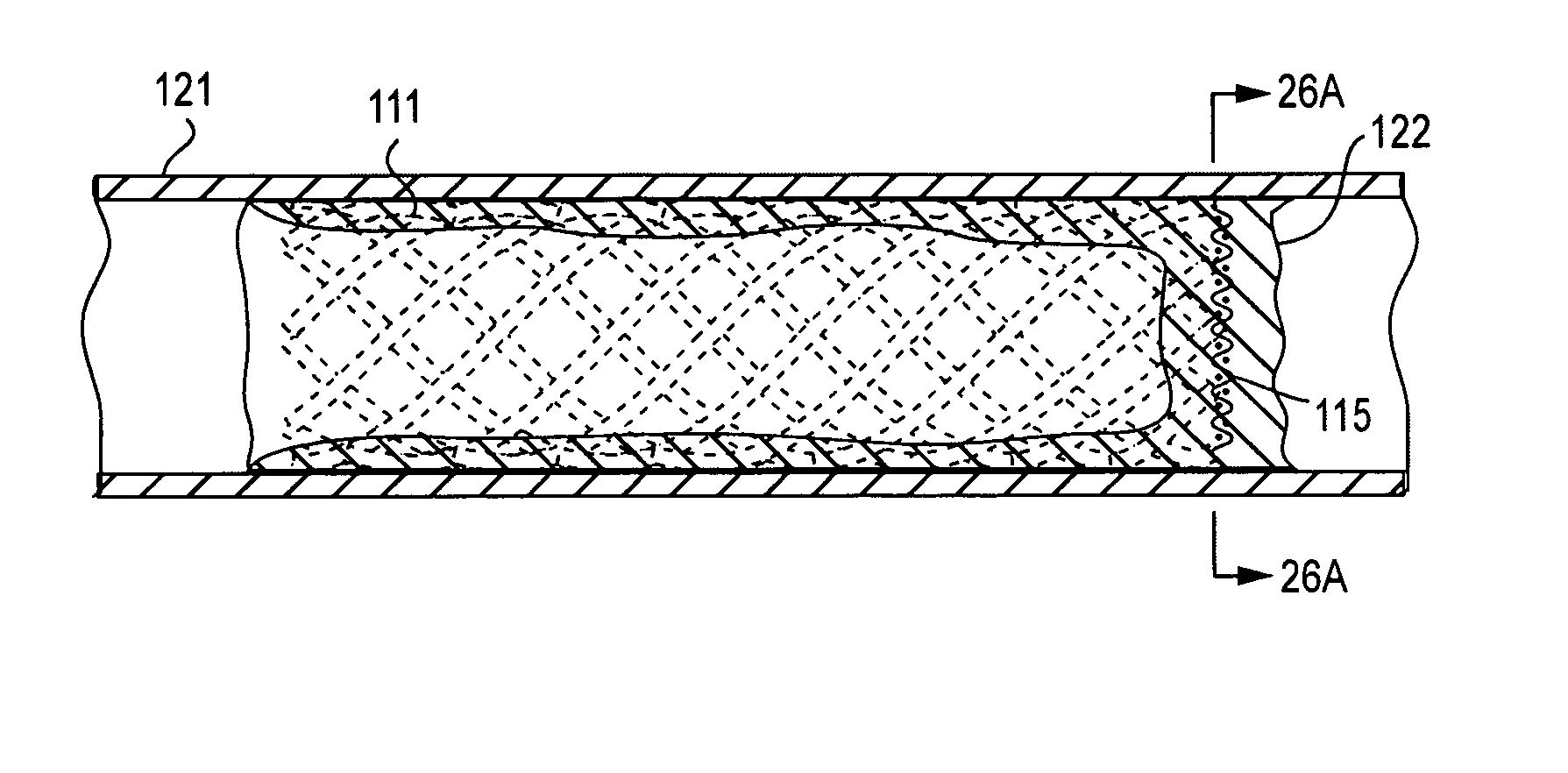

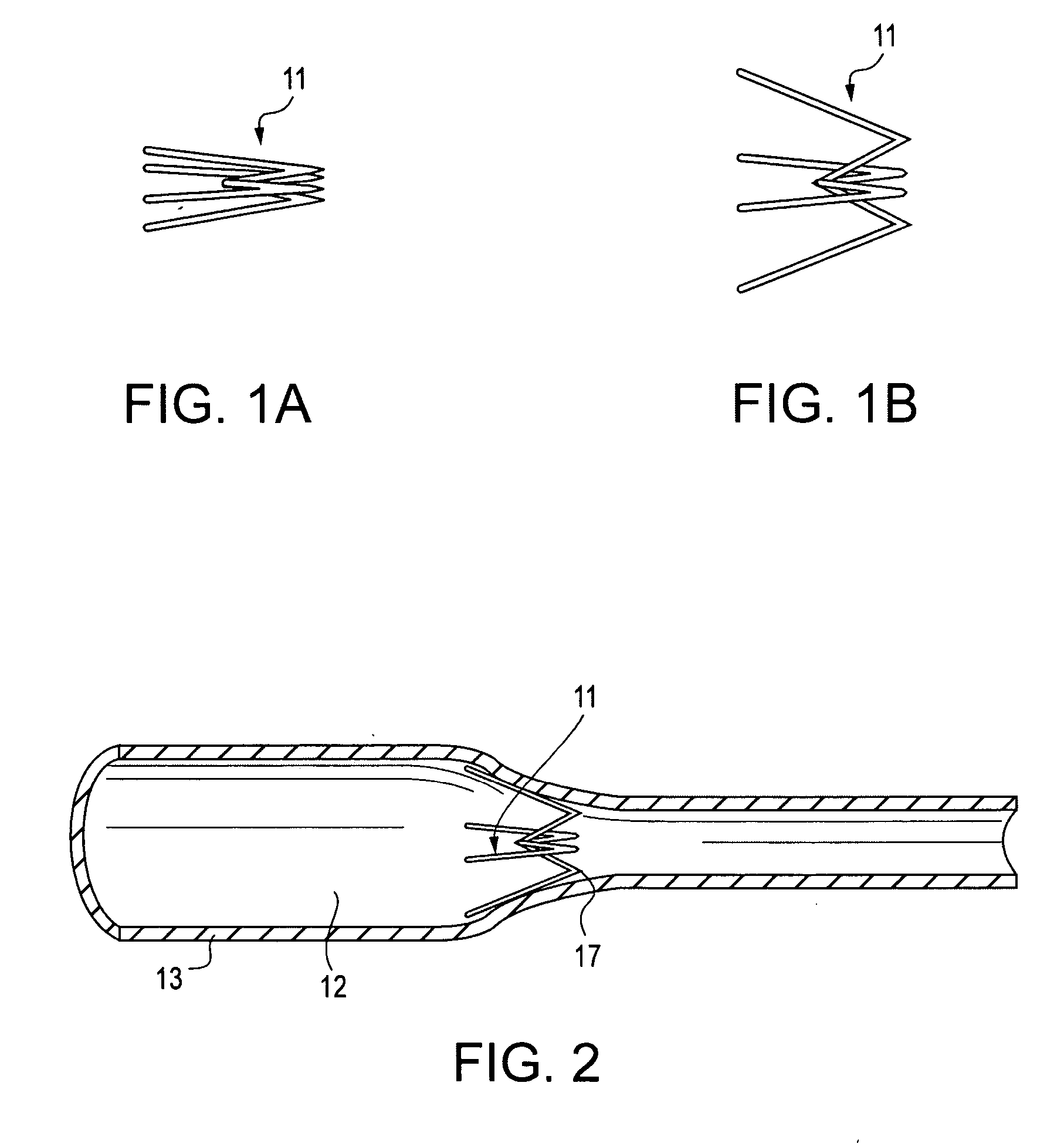

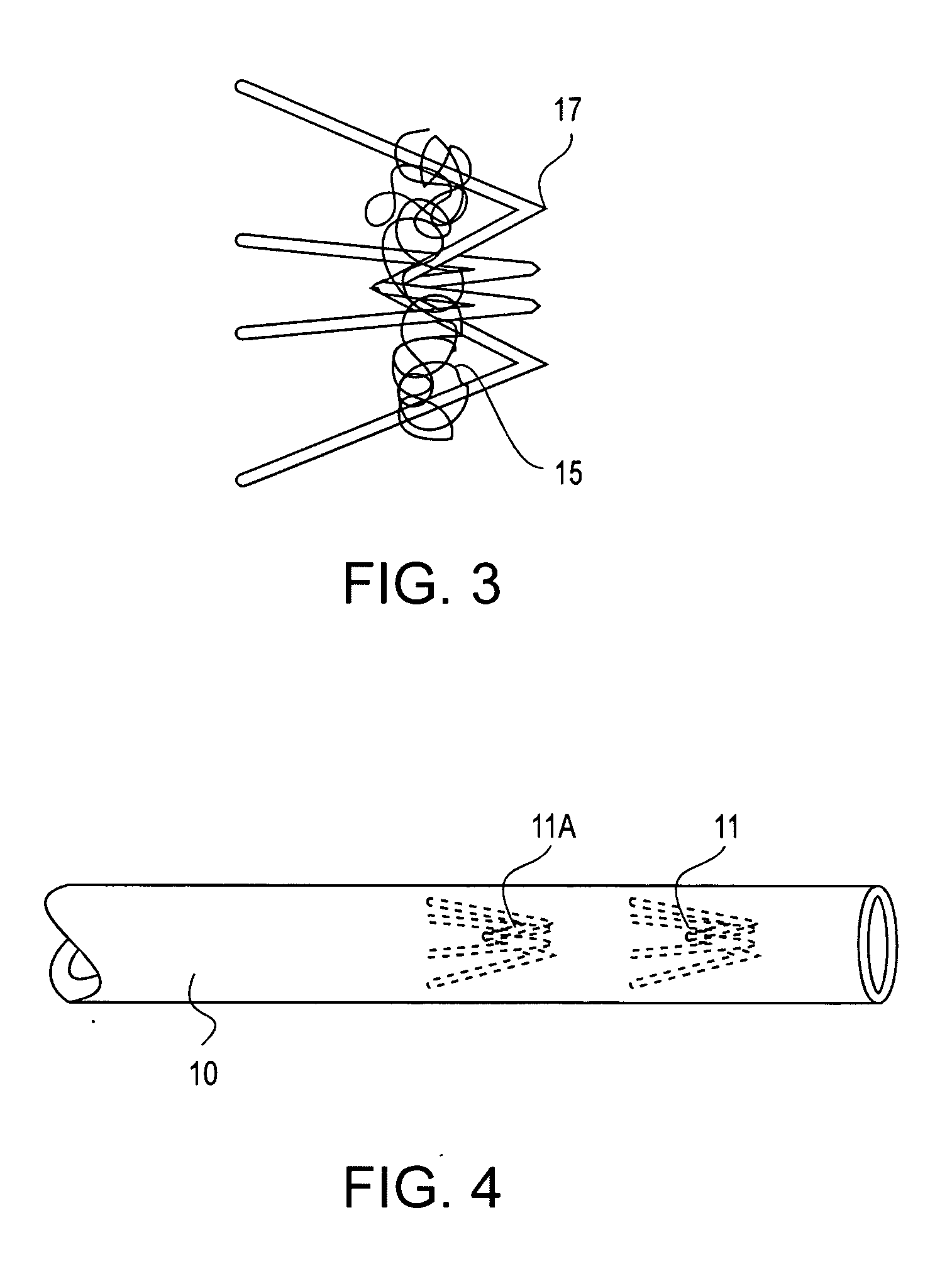

Methods and devices for occluding body lumens and/or enhancing tissue ingrowth

InactiveUS20060009798A1Enhance ingrowthTissue ingrowth is further enhancedStentsFallopian occludersMesh gridEpithelial tissue

The present invention provides devices, methods and systems for the occlusion of various lumens in a body of a patient including devices and methods for enhancing tissue ingrowth, particularly endothelial tissue growth within an occlusive device. The system includes an occlusive device and a delivery device for placing the occlusive device in a body lumen. The occlusive device is generally a tubular member with a mesh member disposed thereon. The occlusive device is configured to be radially expandable along a longitudinal axis of the tubular member and implantable with a delivery catheter such that the occlusive device is in a collapsed state when positioned in the delivery catheter and in an expanded state when positioned in a lumen of a patient. The mesh member of the occlusive device is configured to promote epithelial tissue ingrowth.

Owner:BAYER ESSURE

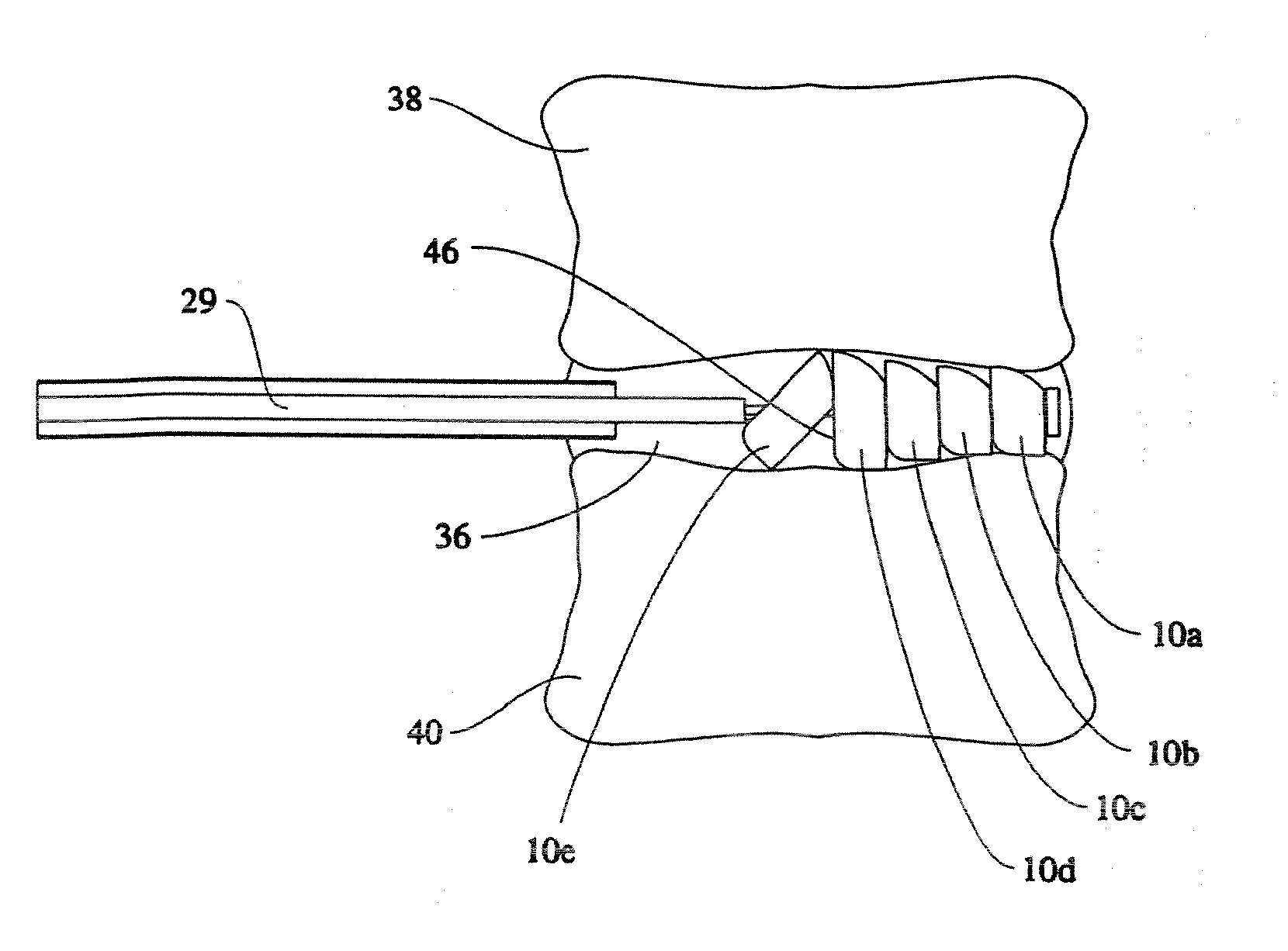

Linked slideable and interlockable rotatable components

InactiveUS20060189999A1Avoid serious distractionsImprove abilitiesBone implantSpinal implantsDistractionPermanent implant

Medical devices having one or more rotatable linkable components or segments, delivered in a first orientation relative to a component guide into a tissue cavity, such as the interbody vertebral space. After delivery, each segment may be rotated to a second, different orientation relative to the component guide, such as into a permanent vertical standing position. The segments achieve maximum distraction of the cavity space such as adjacent vertebra end plates, while using a minimal invasive surgical (MIS) approach. When the segments are tightened in place, the device provides long-term stability. The device can be used as a distraction instrument and / or permanent implant that can be used for interbody fusion, nuclear replacement, or anywhere in the body where a stable distraction of tissue and / or the implantation of material such as a device with an MIS approach is desired.

Owner:MORPHOGENY

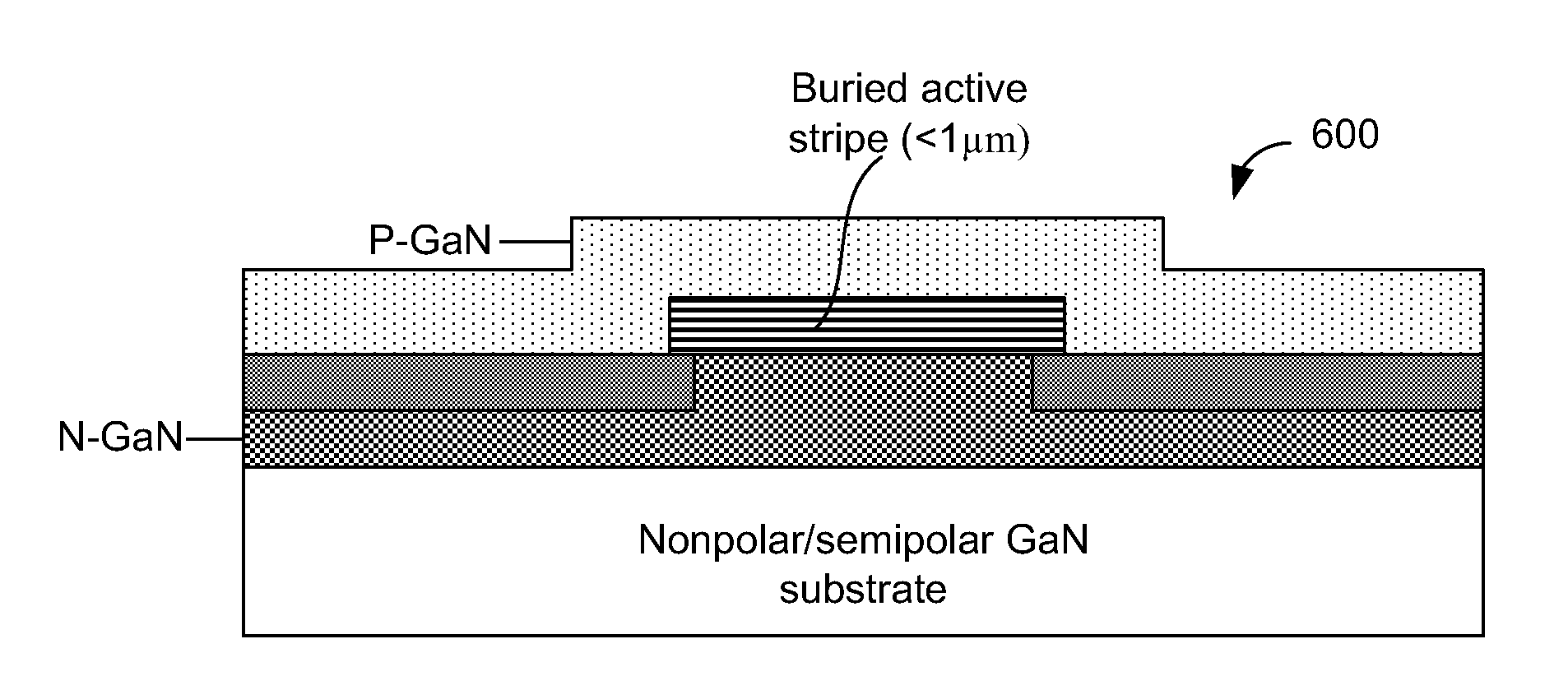

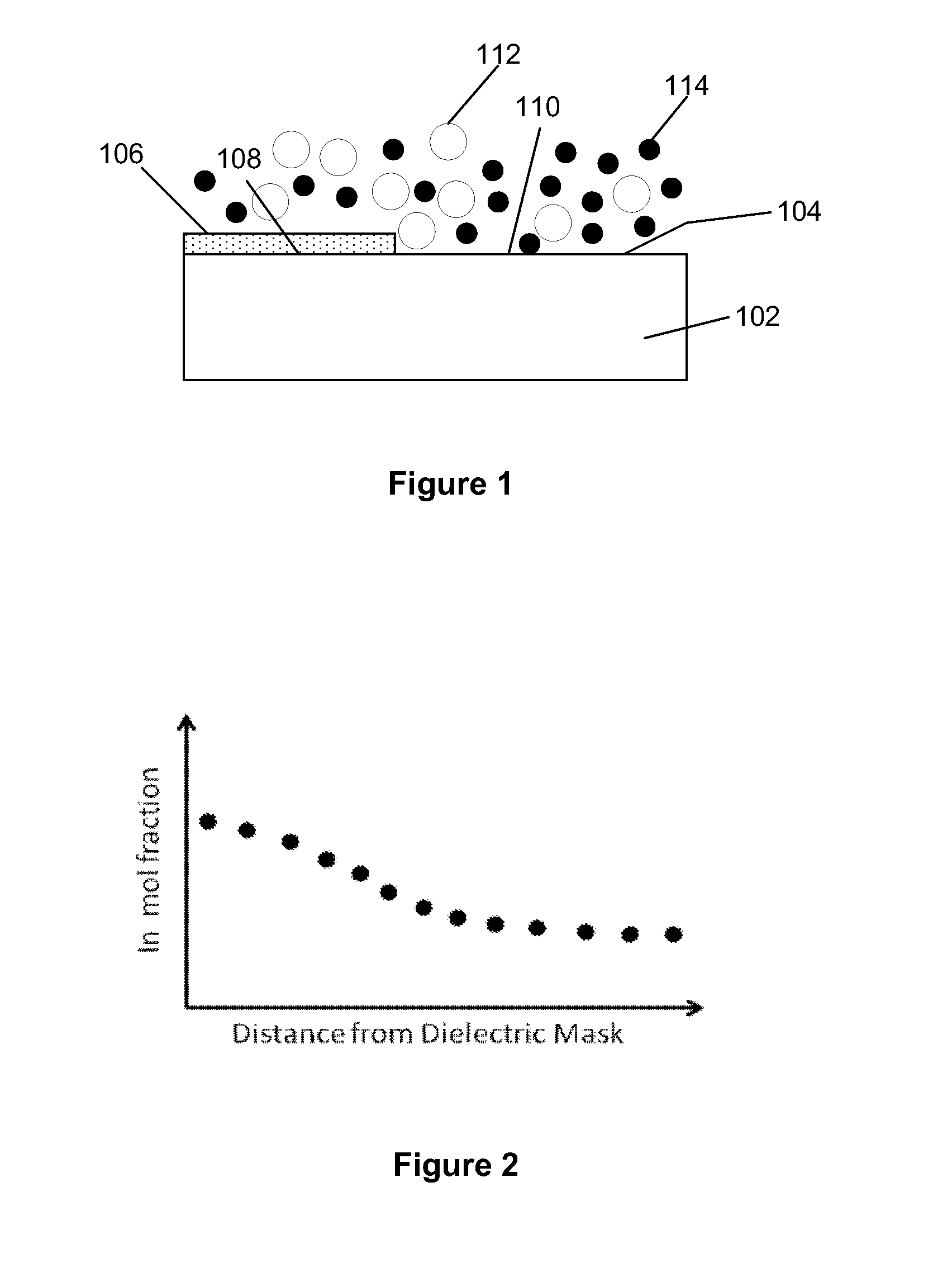

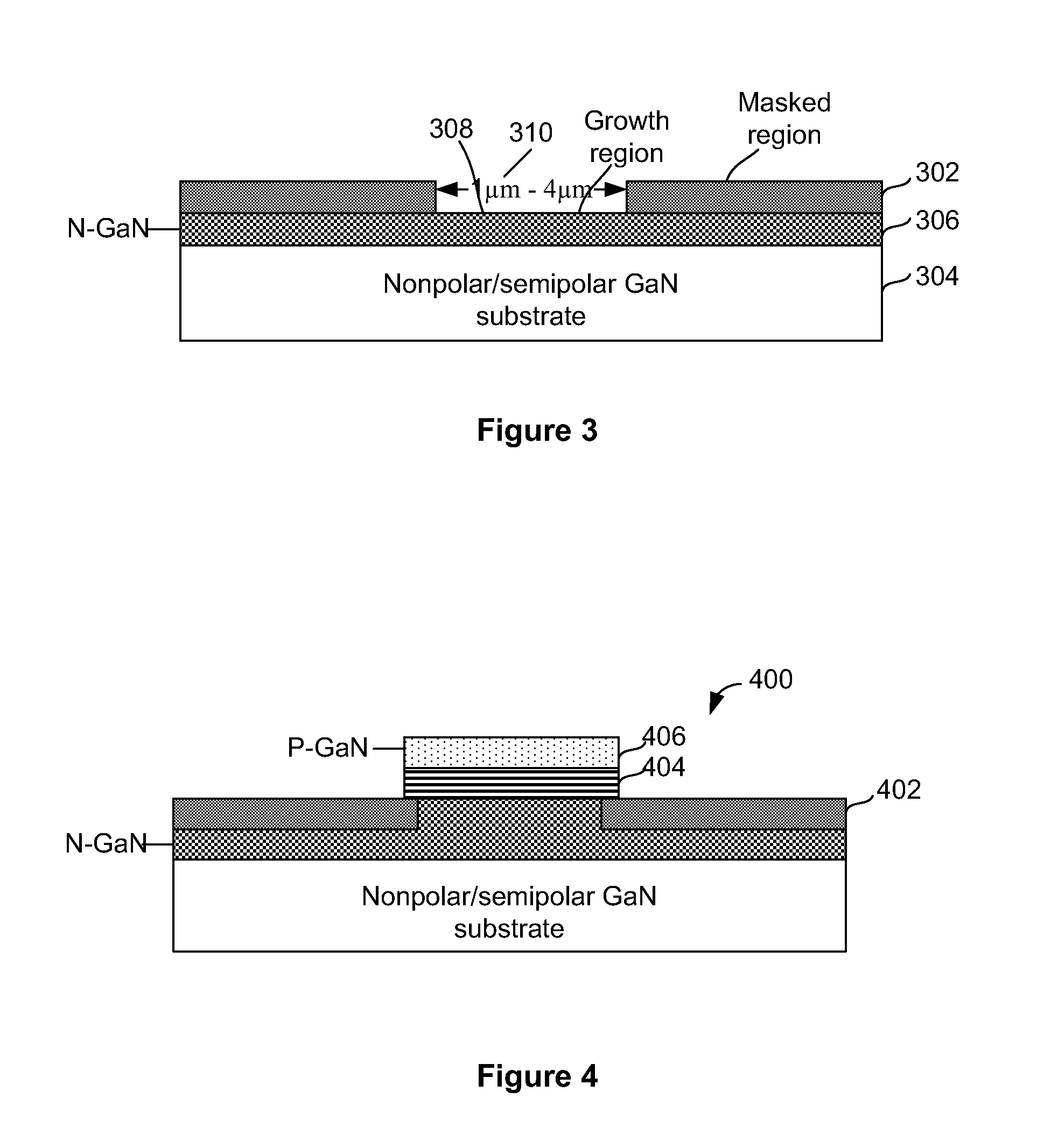

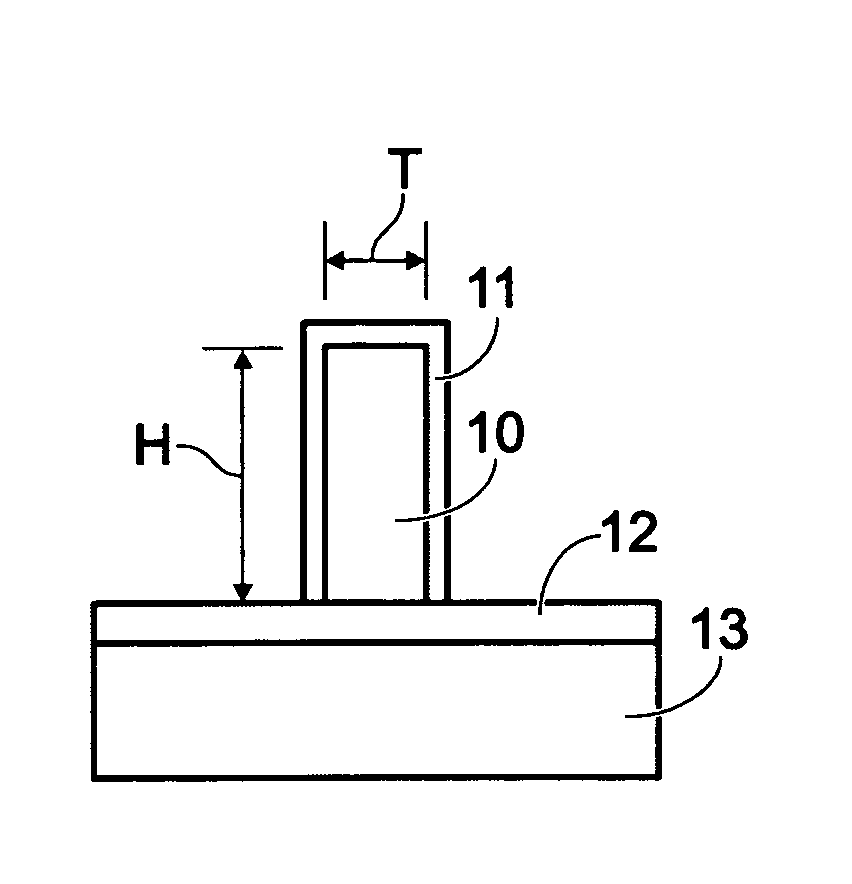

Selective area epitaxy growth method and structure

InactiveUS20090309127A1Improve the level ofSmall sizePolycrystalline material growthNanoinformaticsIndiumPhotoluminescence

A gallium containing crystalline material. The material comprises a bulk semi-polar gallium indium containing crystalline material having a thickness of about 20 nanometers to about 1000 nanometers. The material includes a spatial width dimension of no greater than about 10 microns characterizing the thickness of the bulk semi-polar gallium indium containing crystalline material. The material includes a photoluminescent characteristic of the crystalline material having a first wavelength, which is at least five nanometers greater than a second wavelength, which is derived from an indium gallium containing crystalline material grown on a growth region of greater than about 15 microns.

Owner:SORAA +1

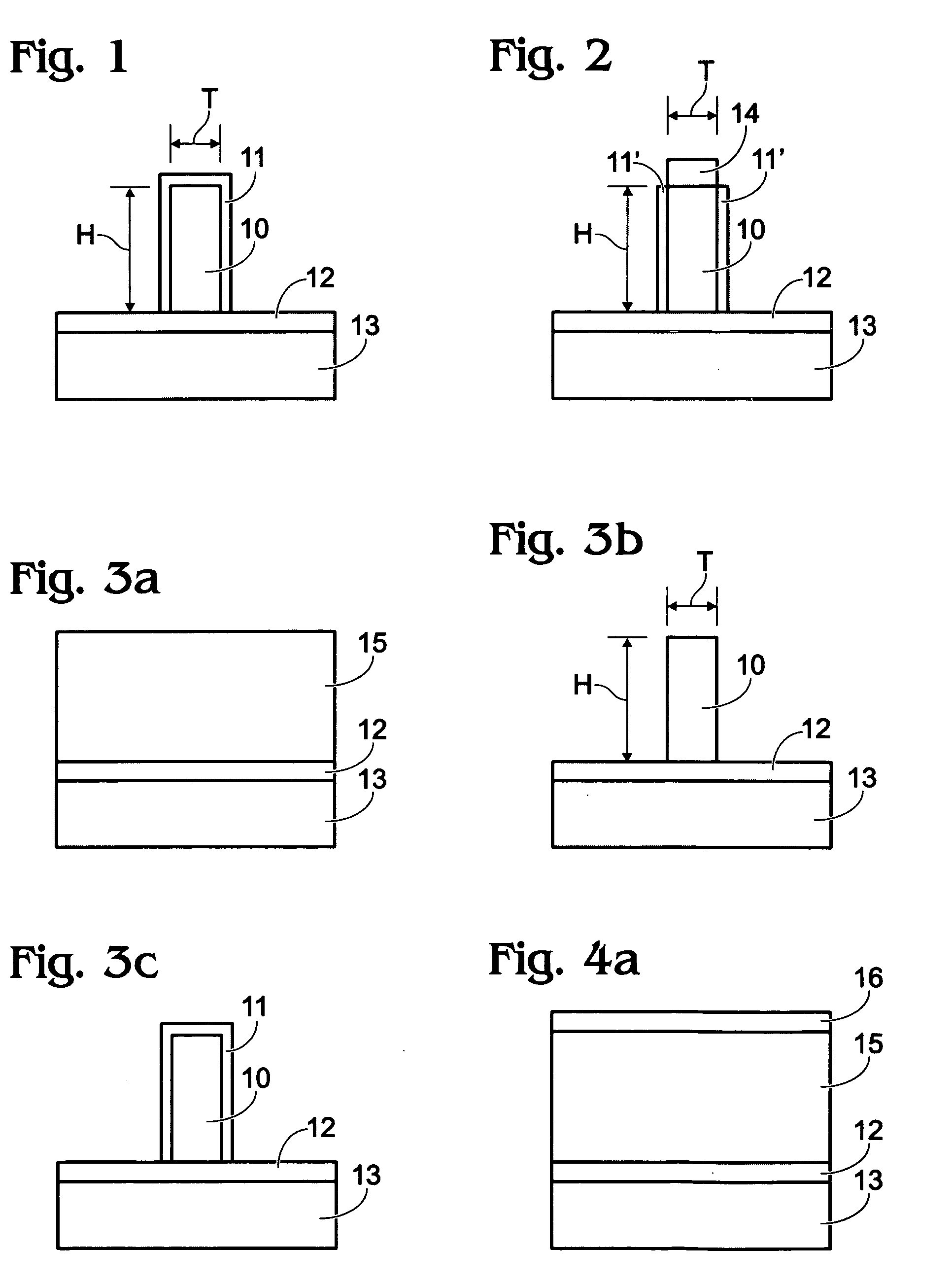

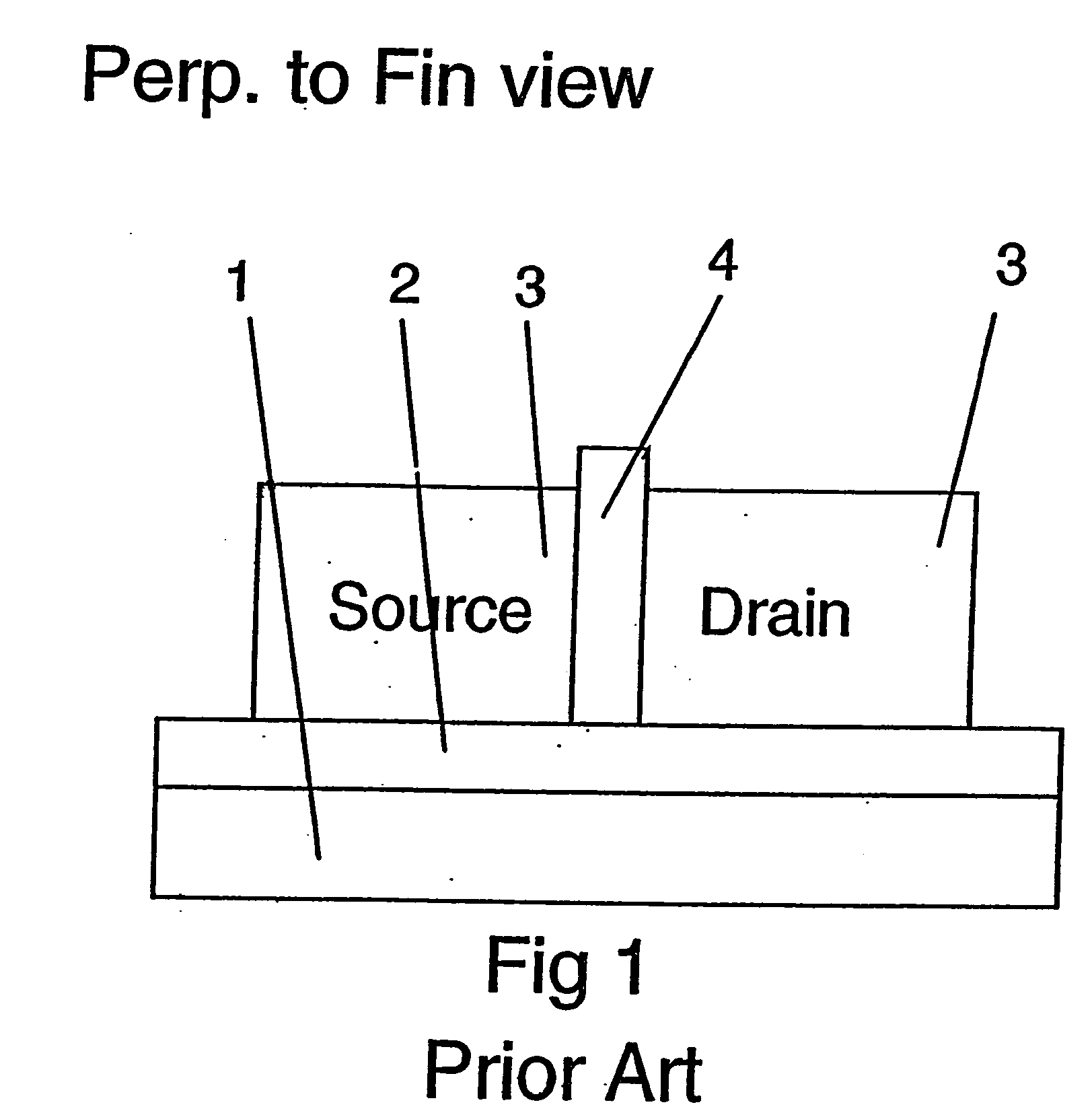

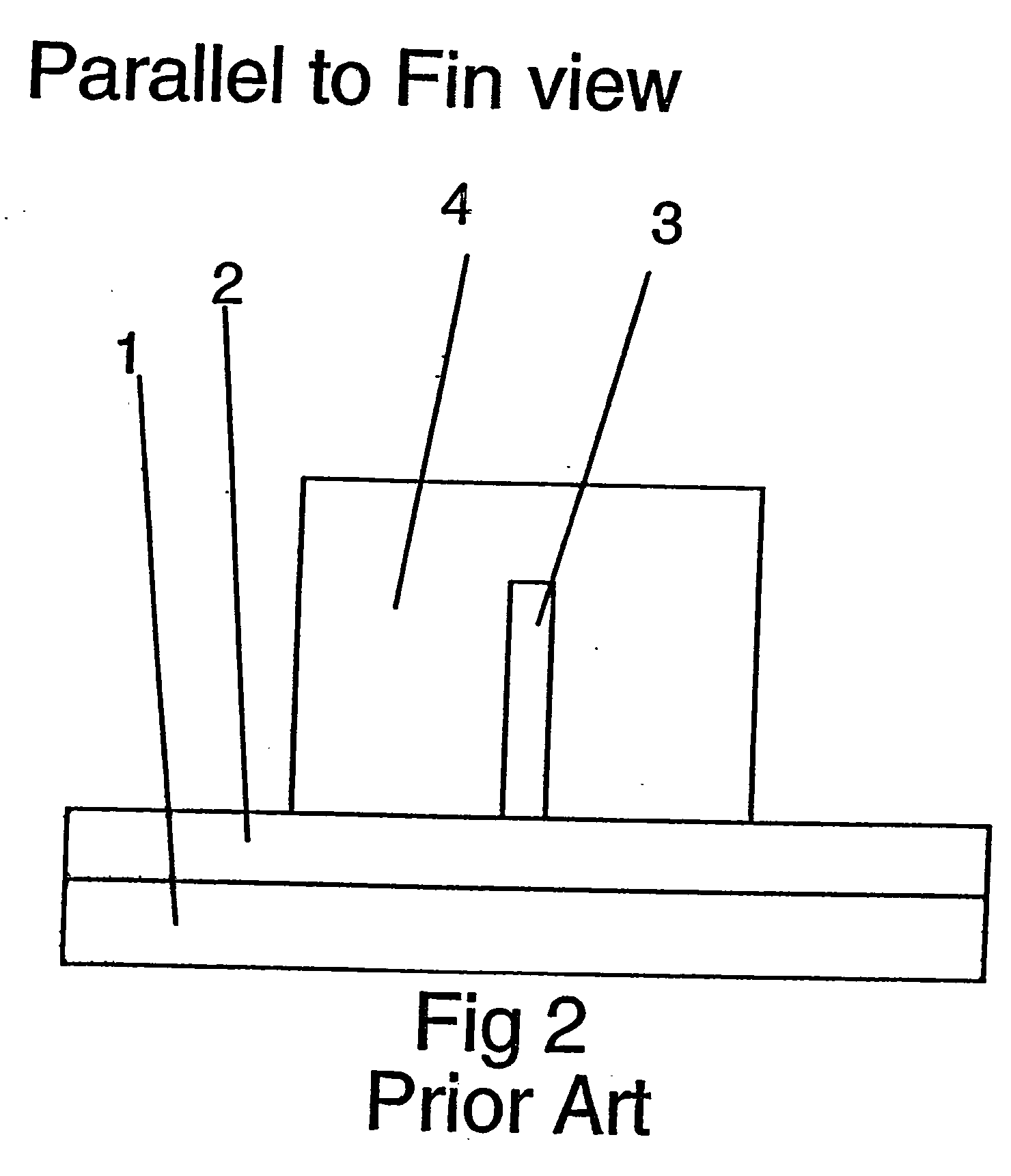

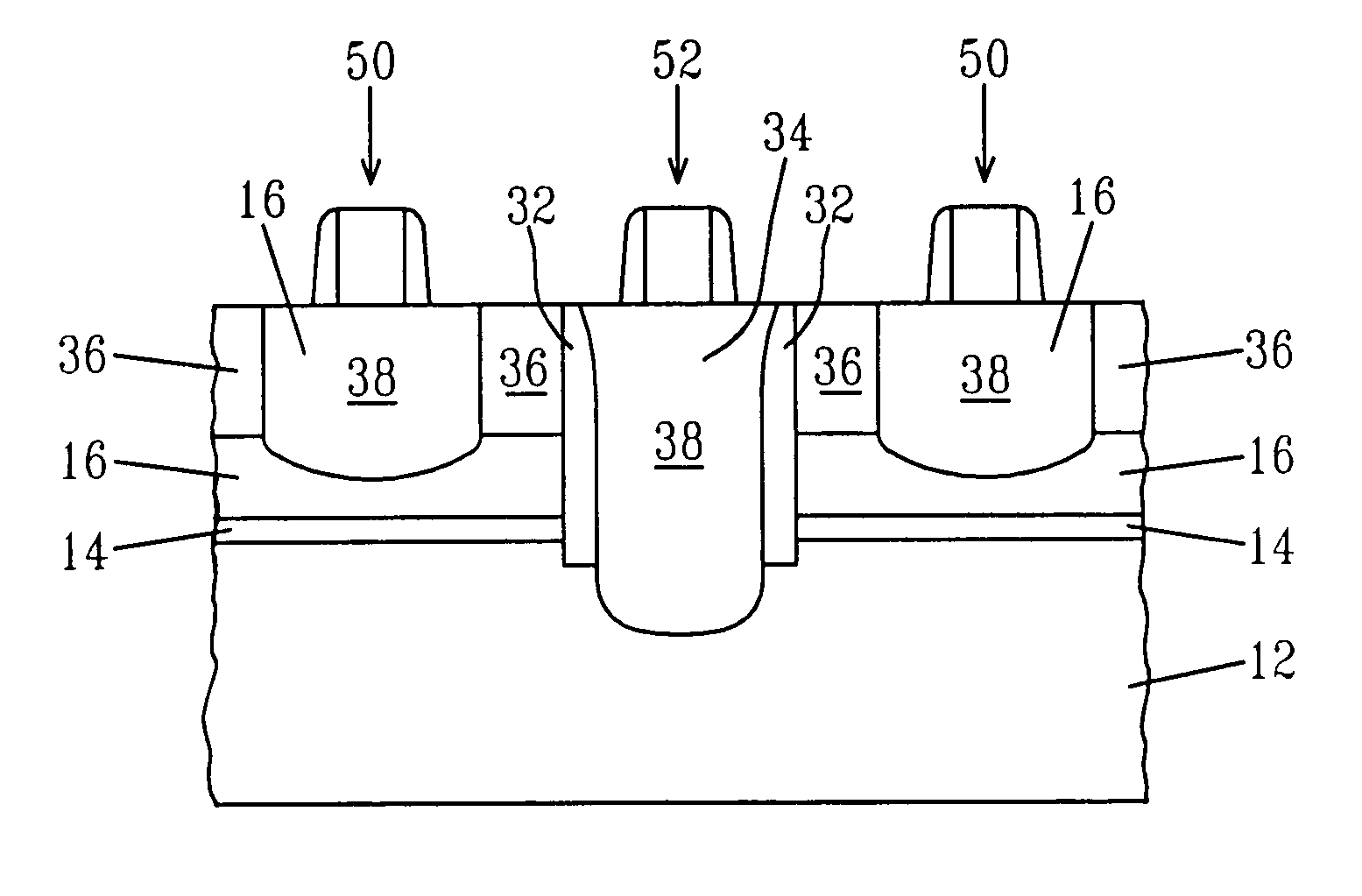

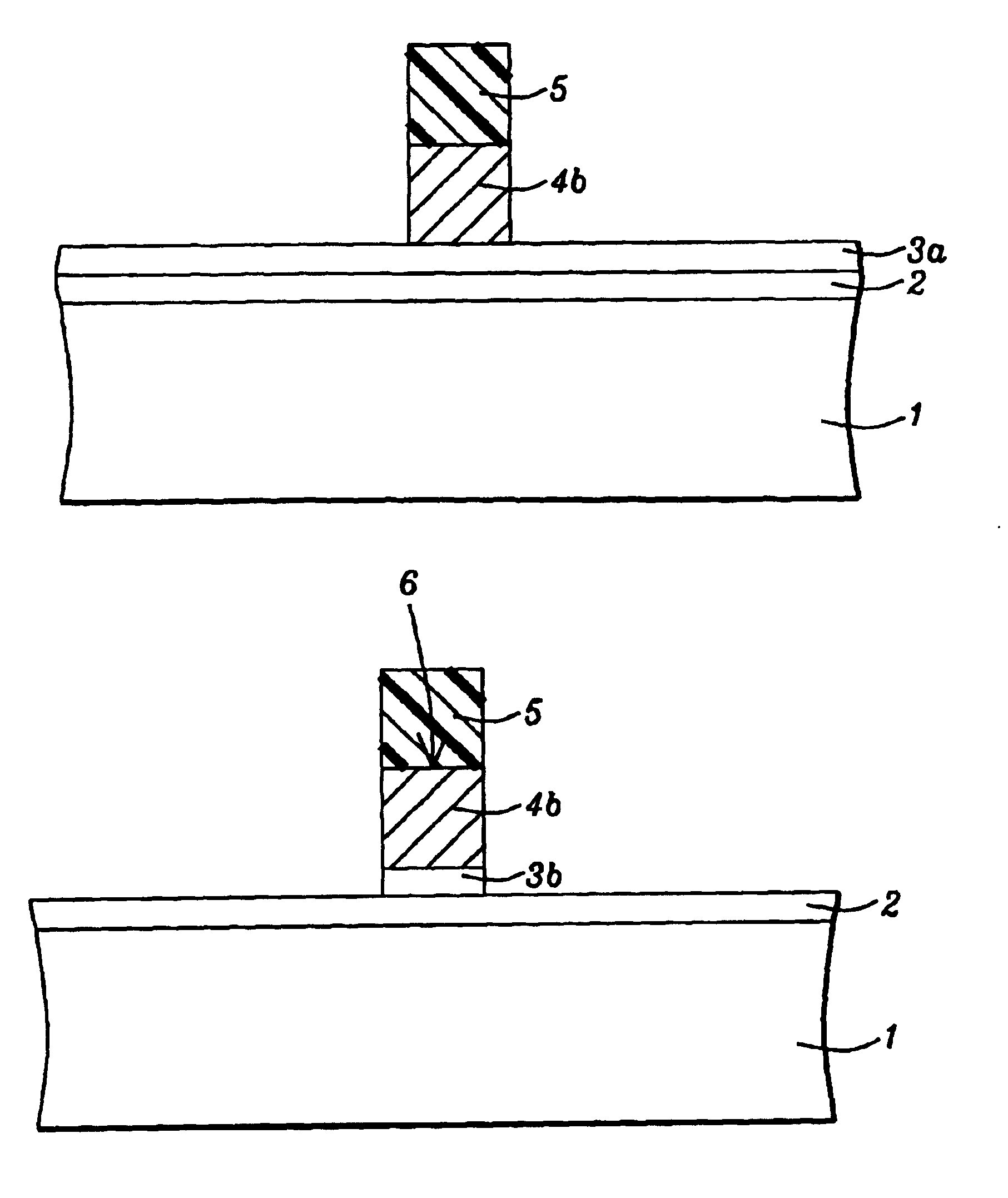

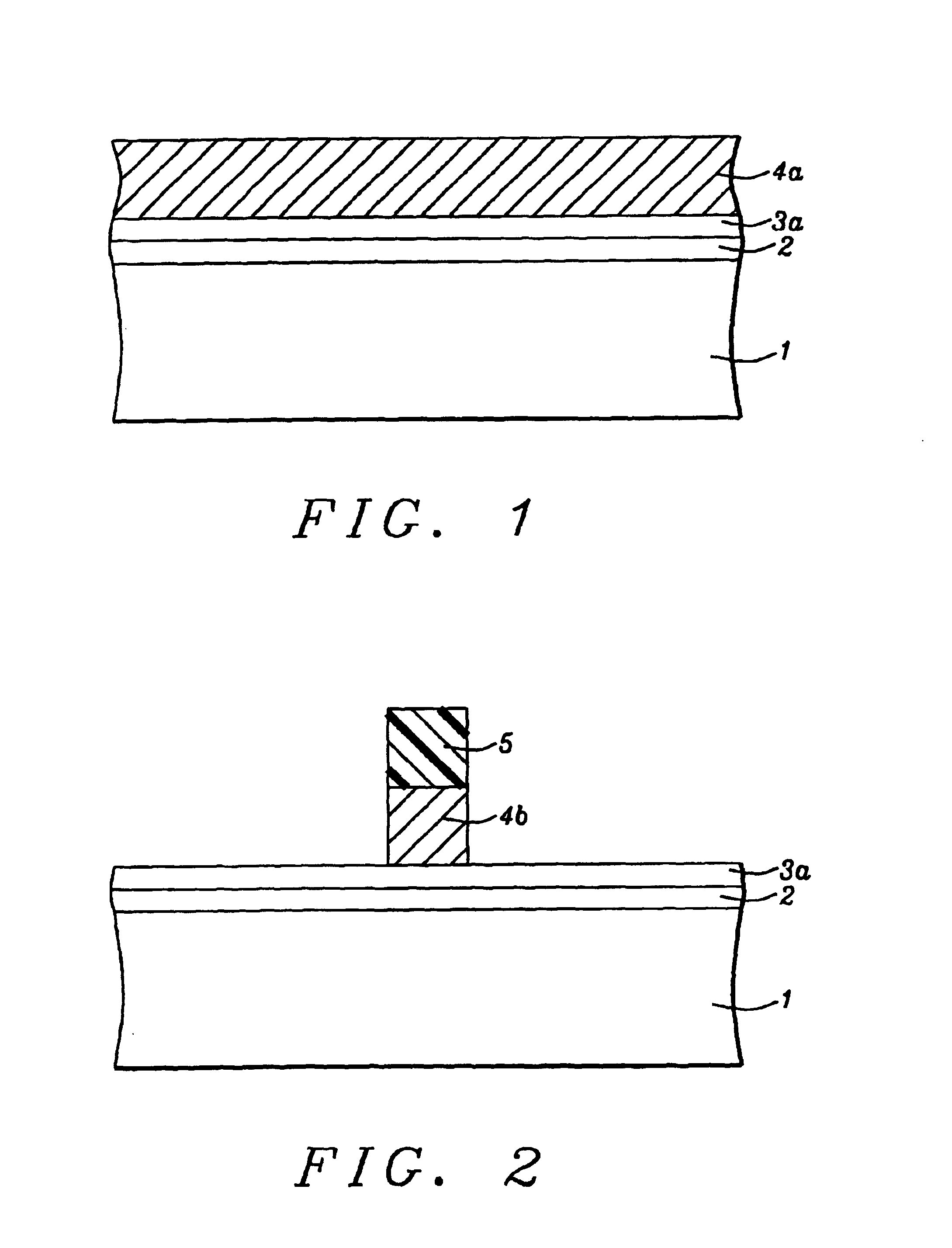

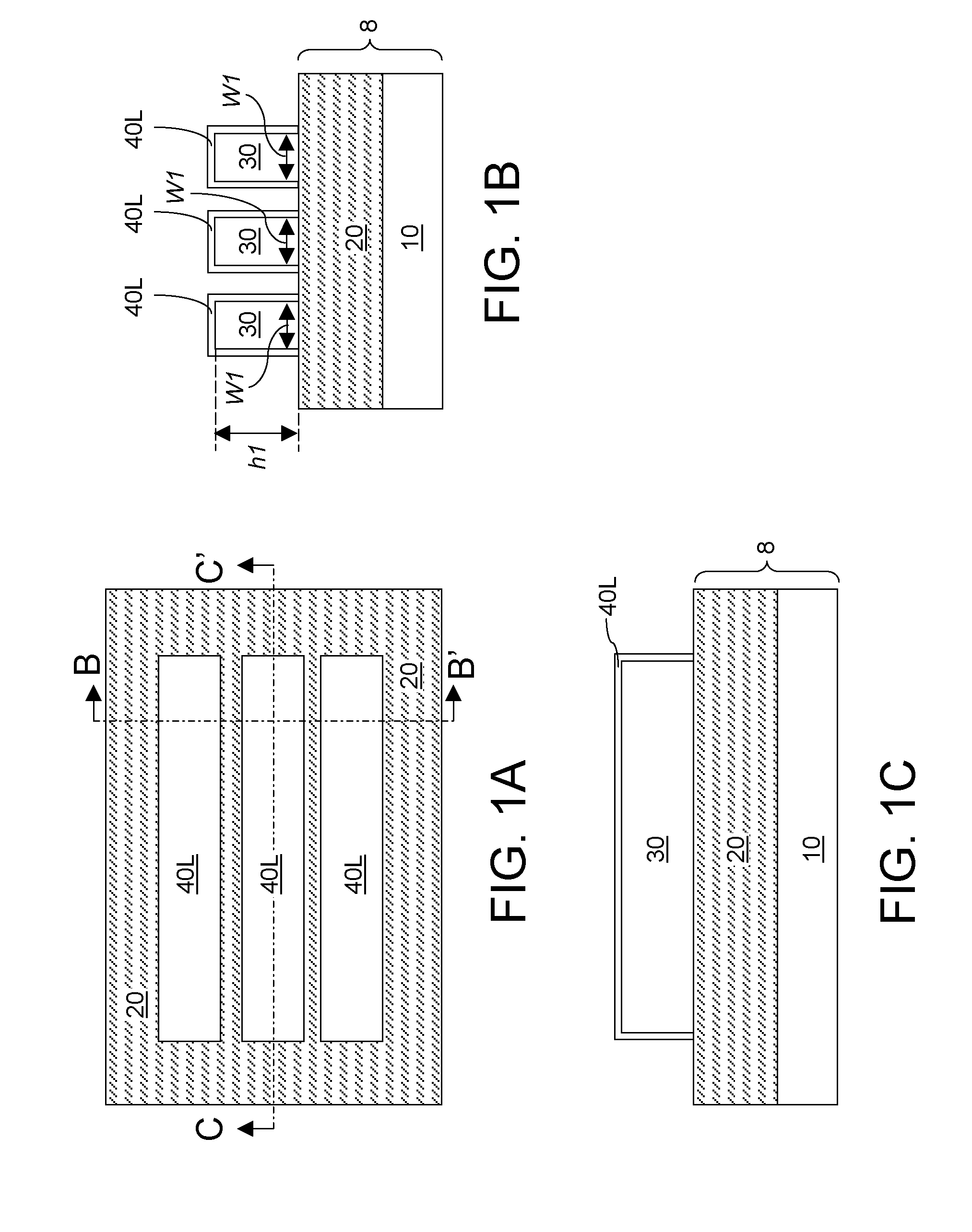

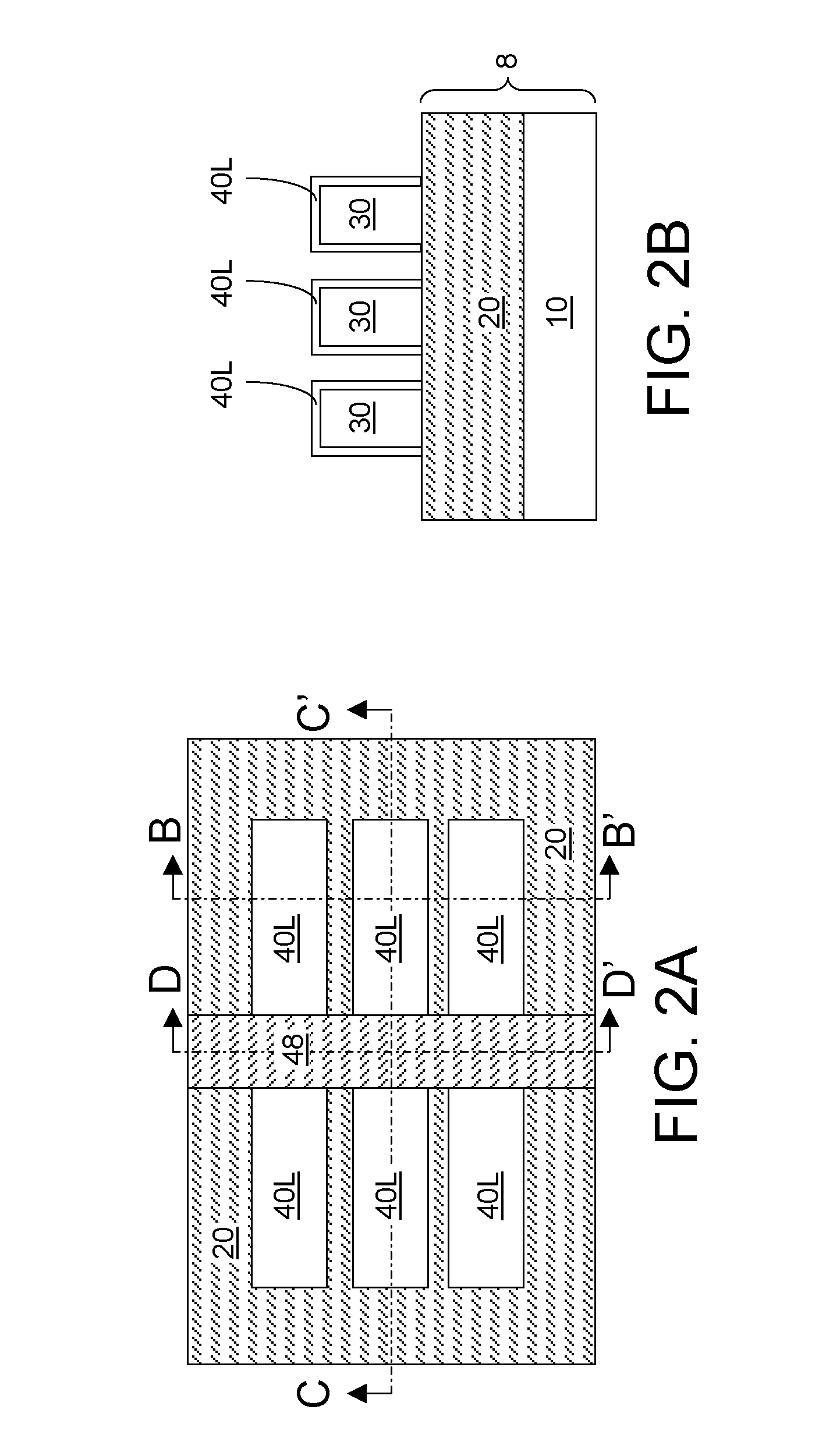

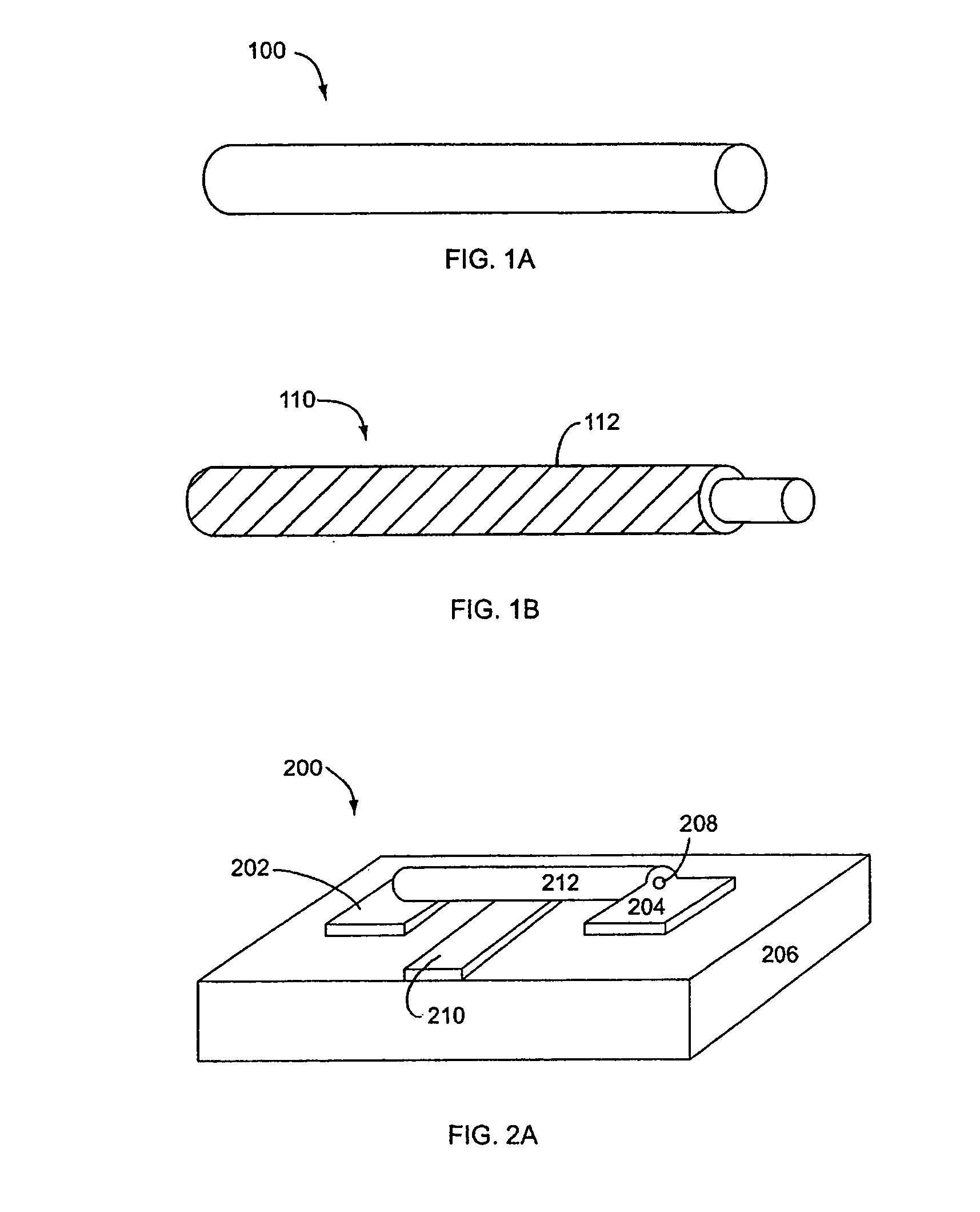

Strained silicon fin structure

InactiveUS20060113522A1Suppression of short channel effectsIncrease currentTransistorSemiconductor/solid-state device manufacturingDriving currentLattice mismatch

Disclosing is a strained silicon finFET device having a strained silicon fin channel in a double gate finFET structure. The disclosed finFET device is a double gate MOSFET consisting of a silicon fin channel controlled by a self-aligned double gate for suppressing short channel effect and enhancing drive current. The silicon fin channel of the disclosed finFET device is a strained silicon fin channel, comprising a strained silicon layer deposited on a seed fin having different lattice constant, for example, a silicon layer deposited on a silicon germanium seed fin, or a carbon doped silicon layer deposited on a silicon seed fin. The lattice mismatch between the silicon layer and the seed fin generates the strained silicon fin channel in the disclosed finFET device to improve hole and electron mobility enhancement, in addition to short channel effect reduction characteristic inherently in a finFET device.

Owner:MICROSOFT TECH LICENSING LLC +1

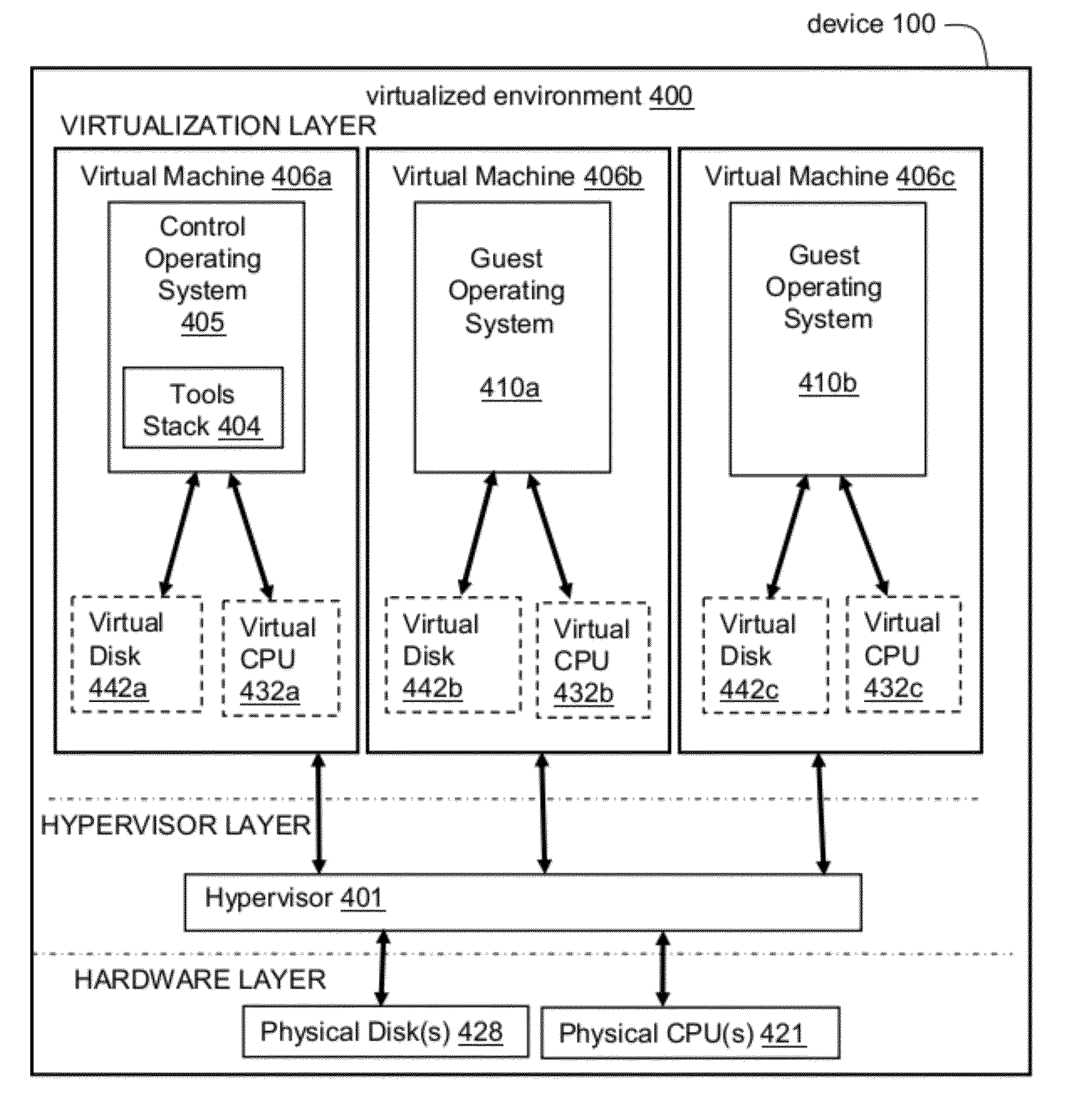

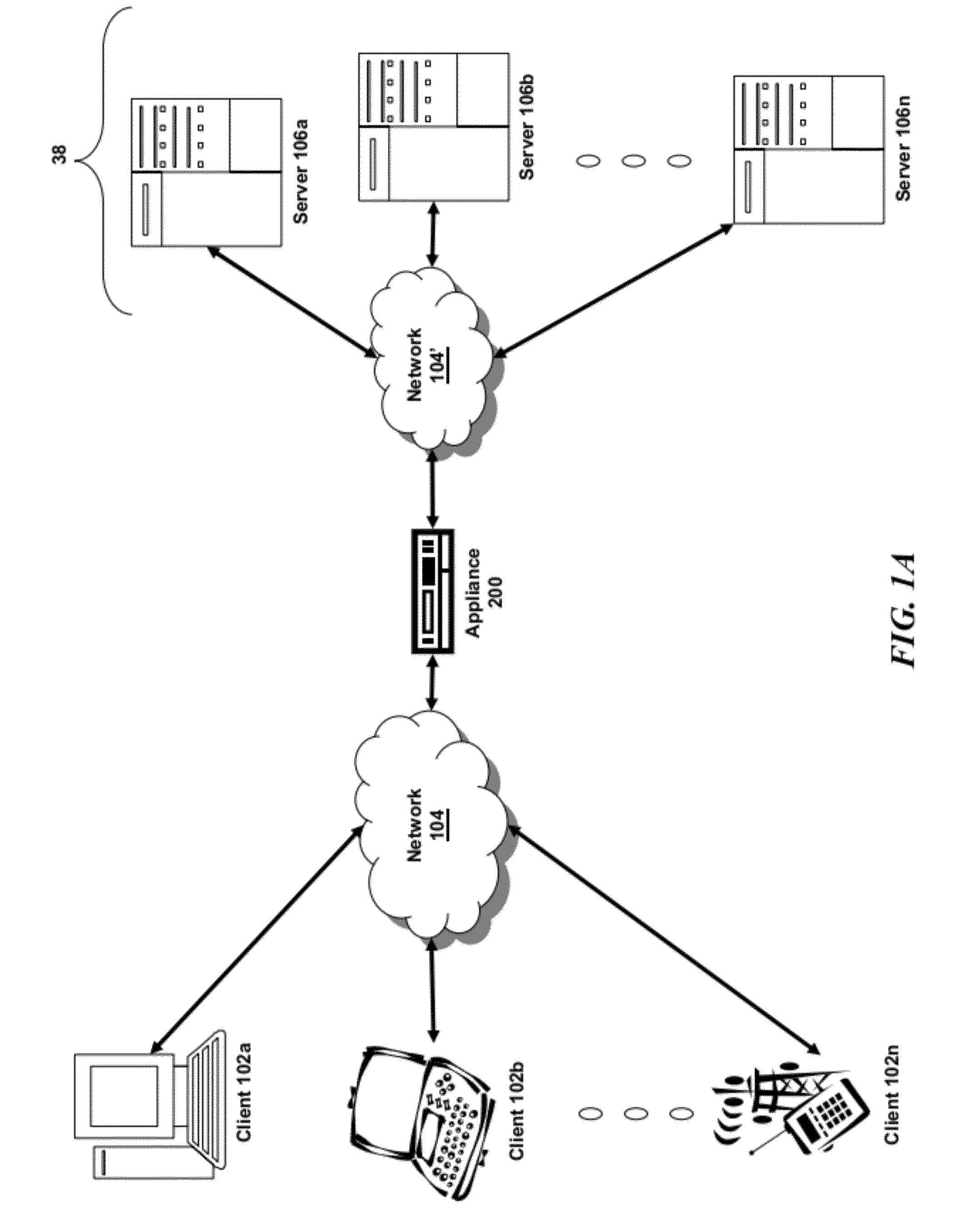

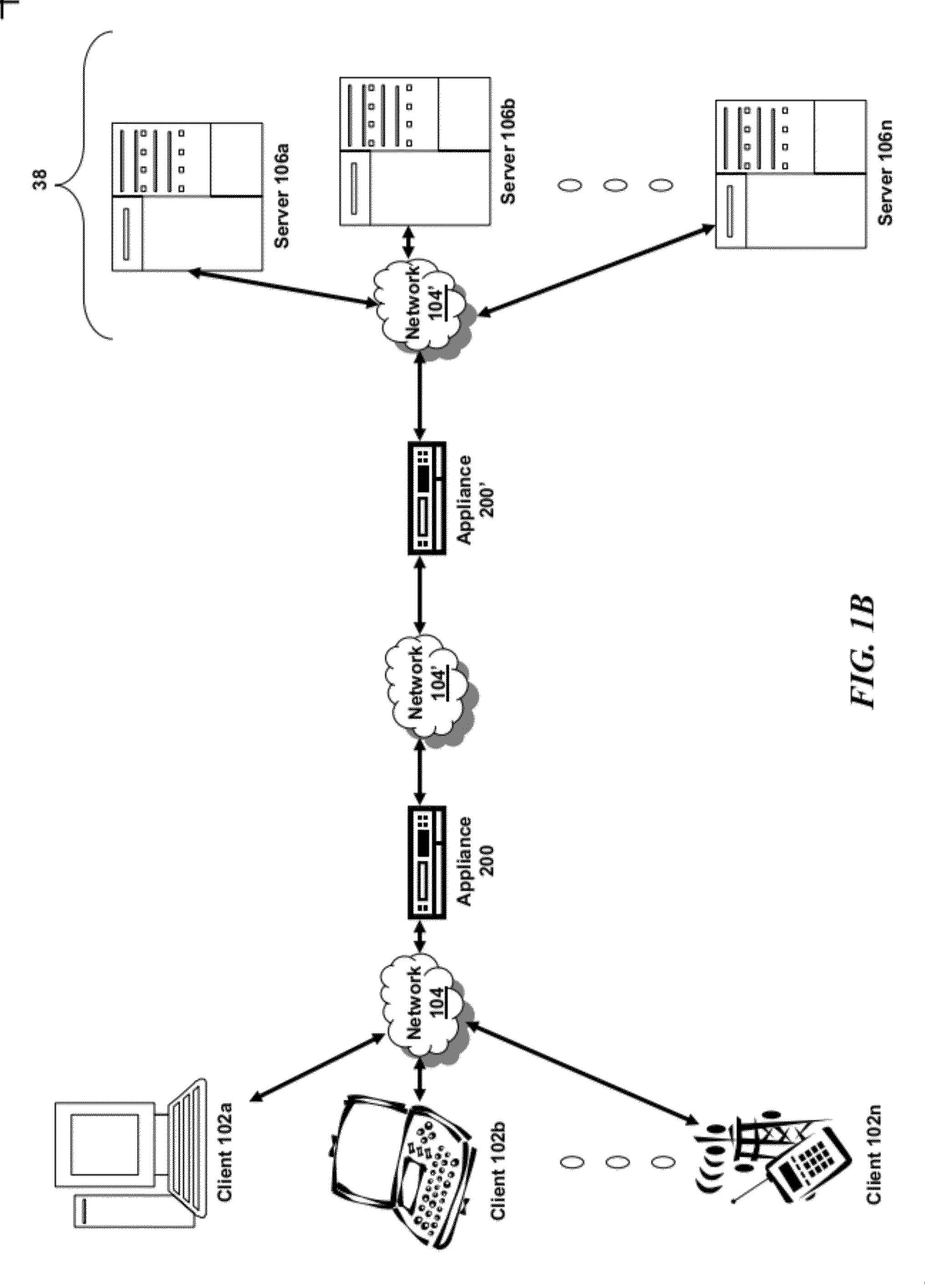

Systems and methods for sr-iov pass-thru via an intermediary device

ActiveUS20120284712A1OptimizationUpgrade and downgrade capacityDigital computer detailsHybrid transportVirtualizationVirtual device

This disclosure describes a system for Single Root I / O Virtualization (SR-IOV) pass-thru for network packet processing via a virtualized environment of a device. The system includes a device comprising a virtualized environment and a plurality of virtual machines having a virtual network interface for receiving and transmitting network packets. A driver for the physical network interface of the device creates a plurality of virtual devices corresponding to the physical network interface, which appear as a Peripheral ComponentInterconnect (PCI) device to the virtualized environment. A virtual device of the plurality of virtual devices is assigned via the virtualized environment to each virtual machine of the plurality of virtual machines. The virtual machine uses the virtual device assigned to the virtual machine, to receive and transmit network packets via the physical network interface of the device.

Owner:CITRIX SYST INC

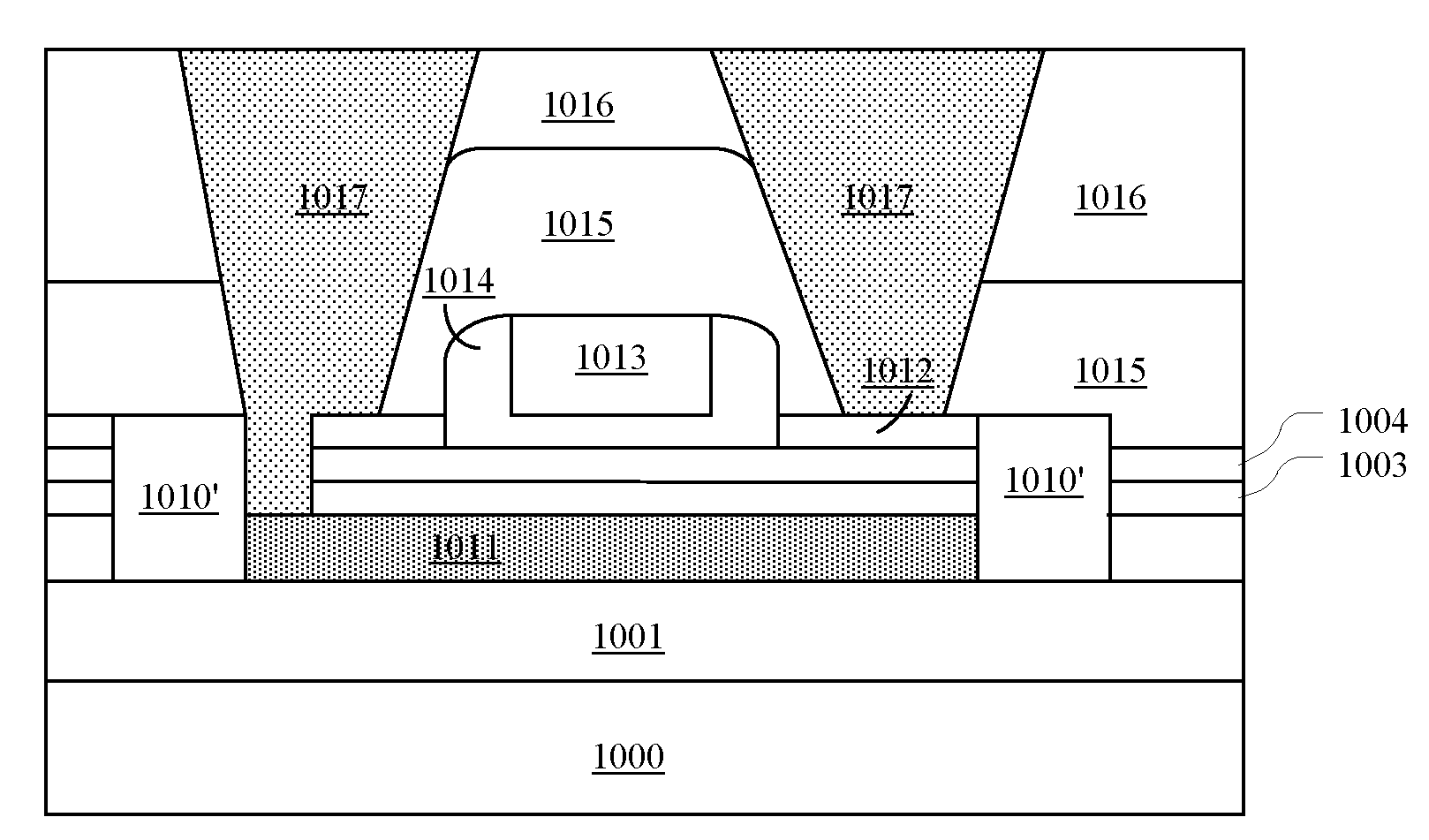

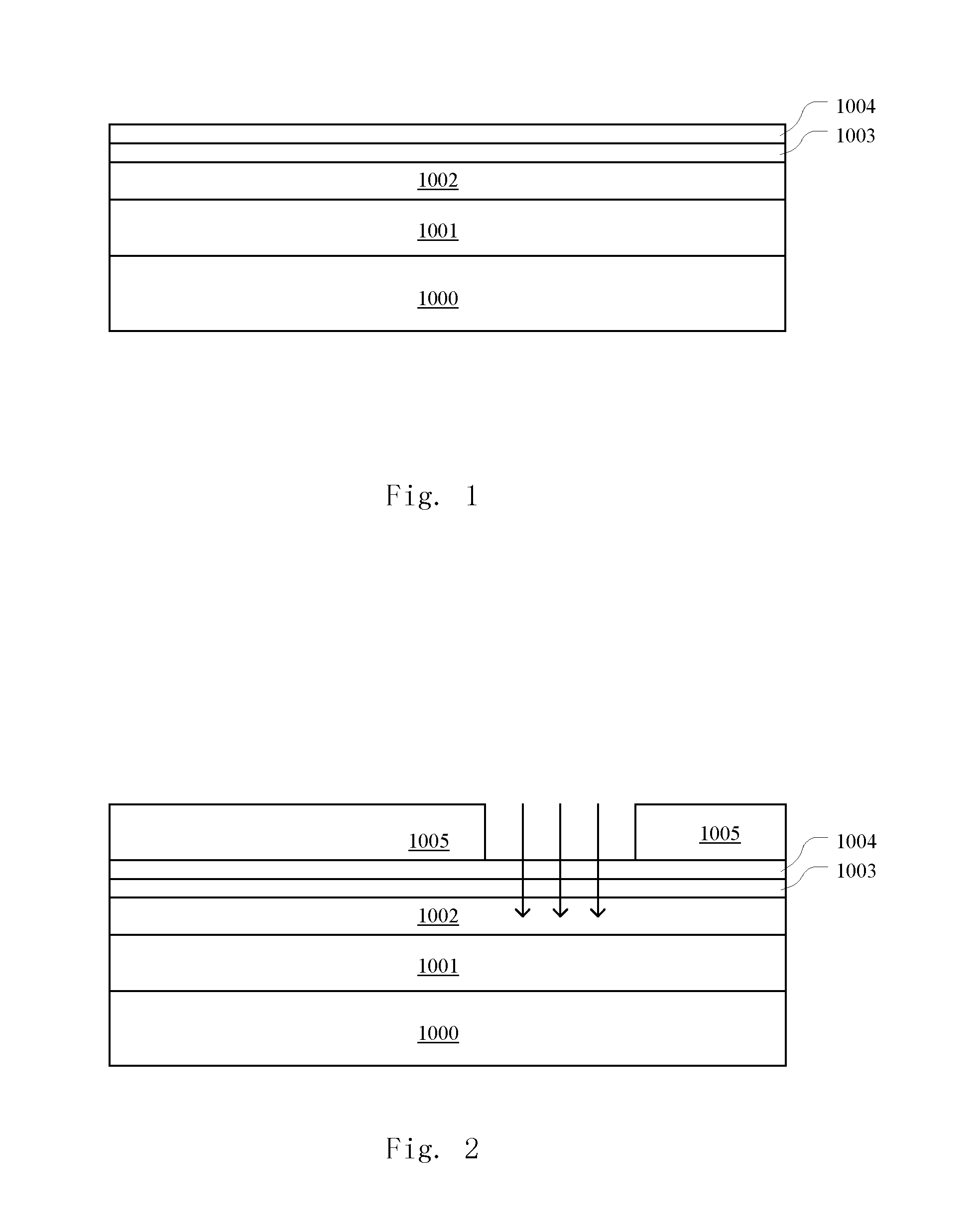

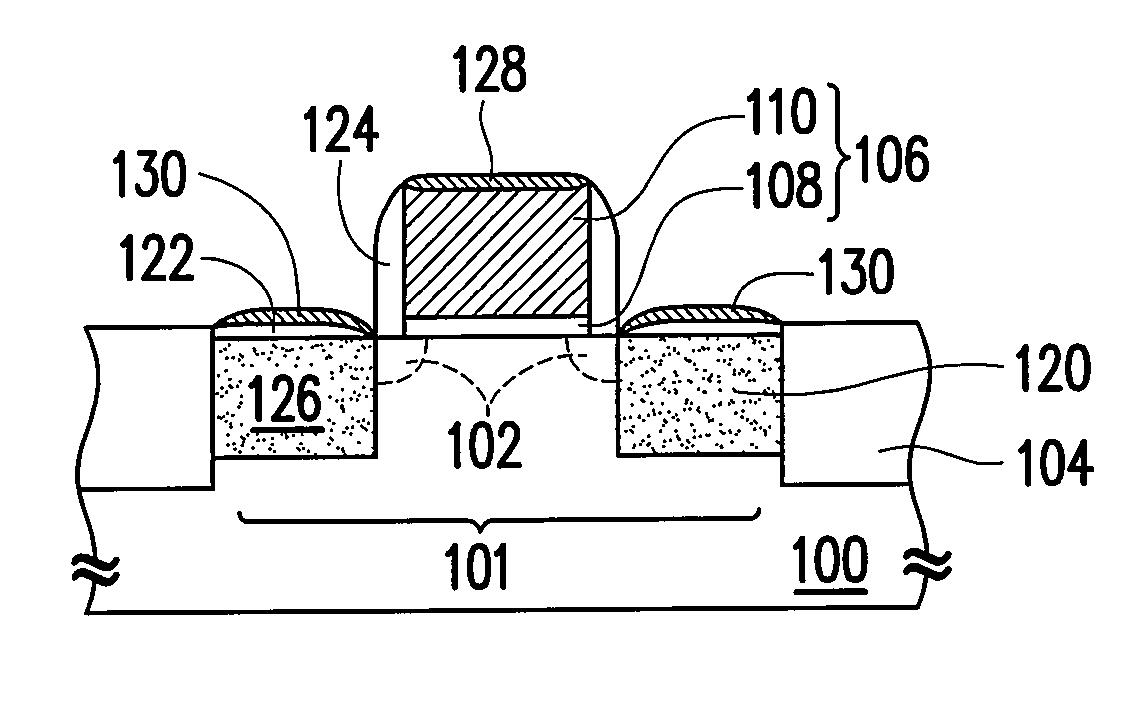

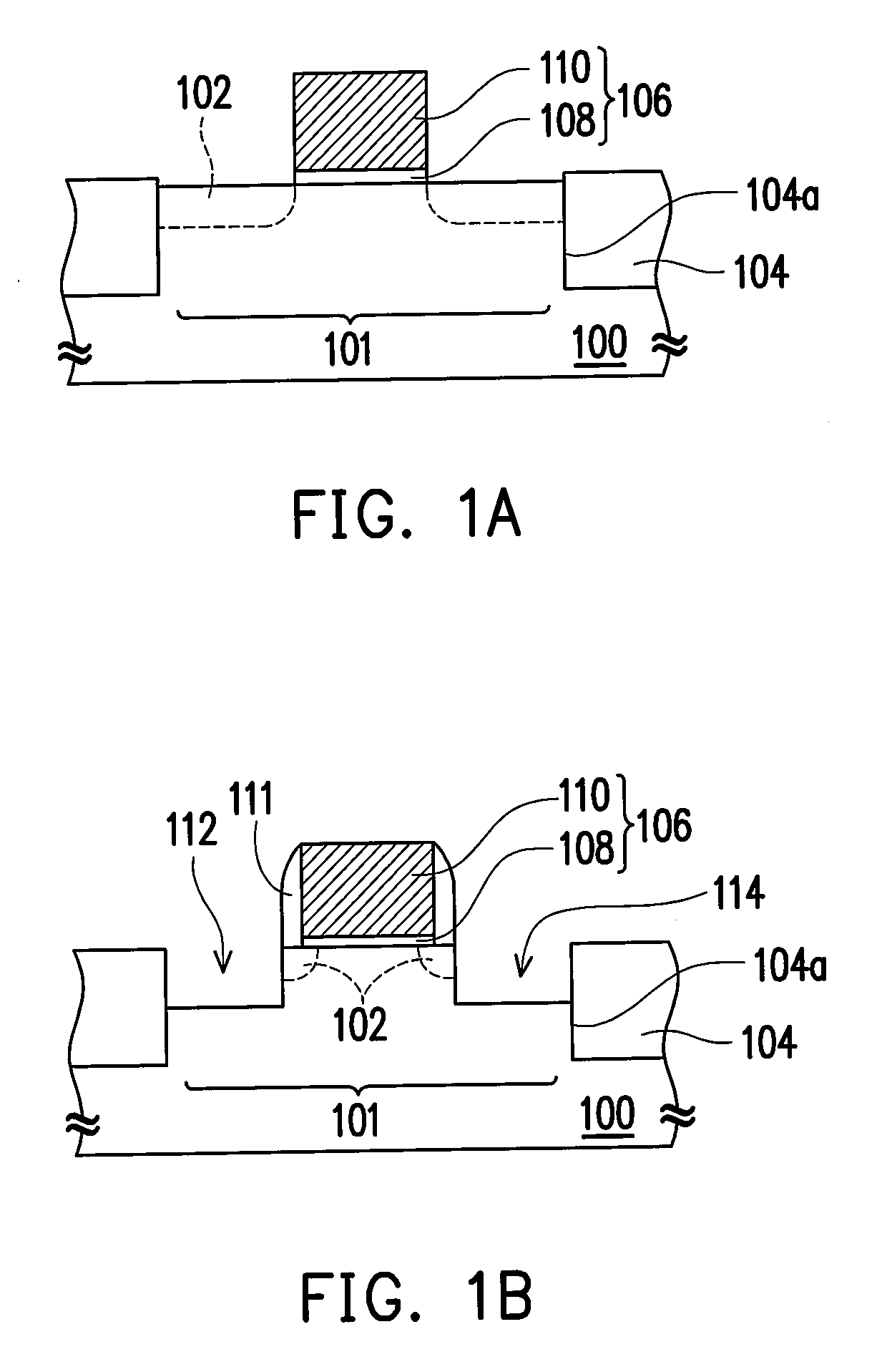

Semiconductor structure and method for manufacturing the same

ActiveUS20120104495A1Simple manufacturing processHighly integratedTransistorSolid-state devicesSemiconductor structureEngineering

The present application discloses a semiconductor structure and a method for manufacturing the same. The semiconductor structure according to the present invention adjusts a threshold voltage with a common contact, which has a portion outside the source or drain region extending to the back-gate region and provides an electrical contact of the source or drain region and the back-gate region, which leads to a simple manufacturing process, an increased integration level and a lowered manufacture cost. Moreover, the asymmetric design of the back-gate structure further increases the threshold voltage and improves the performance of the device.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

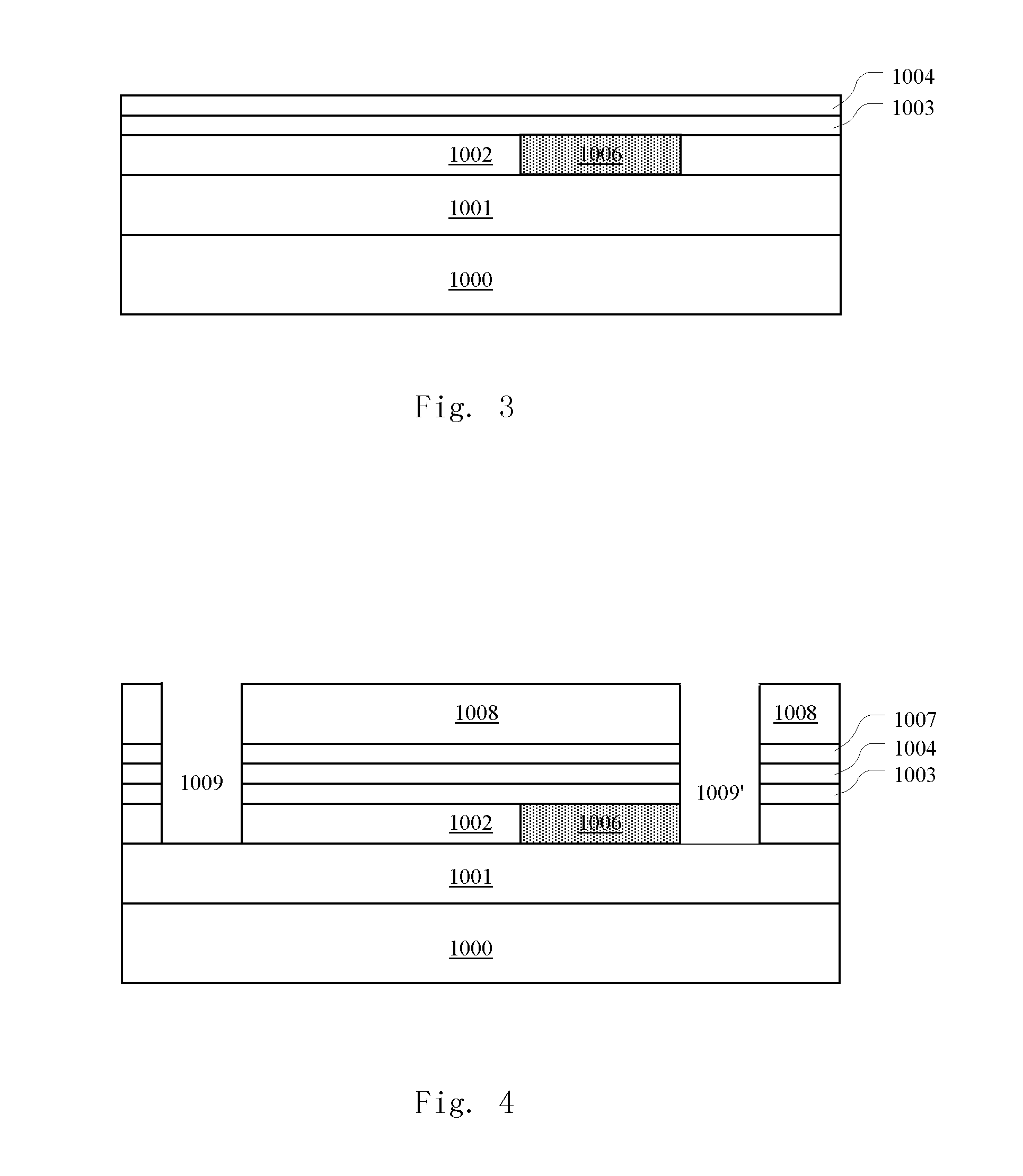

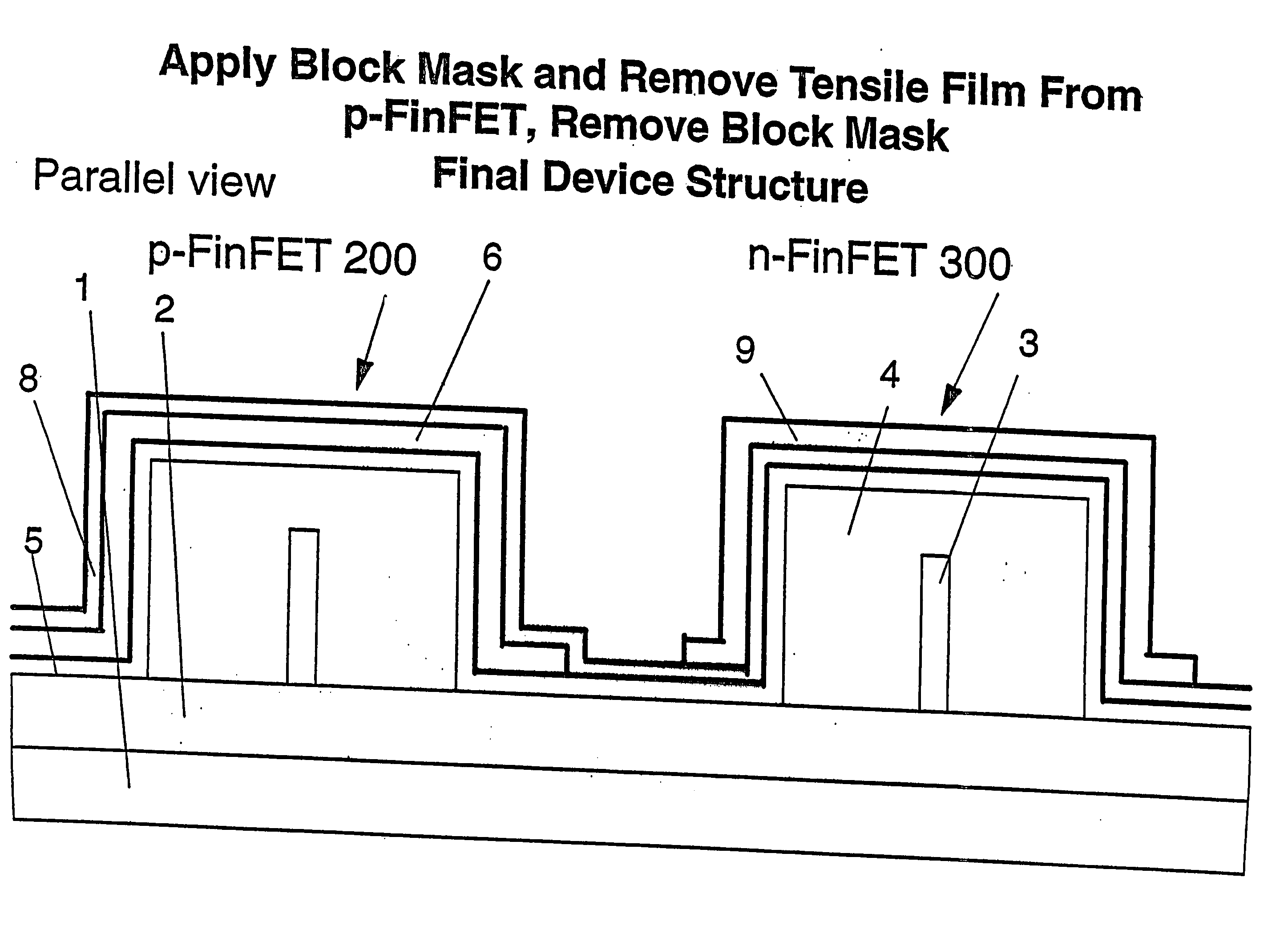

Strained finfet cmos device structures

InactiveUS20060057787A1Improve mobilityImprove device performanceTransistorSolid-state devicesCMOSEngineering

A semiconductor device structure, includes a PMOS device 200 and an NMOS device 300 disposed on a substrate 1,2, the PMOS device including a compressive layer 6 stressing an active region of the PMOS device, the NMOS device including a tensile layer 9 stressing an active region of the NMOS device, wherein the compressive layer includes a first dielectric material, the tensile layer includes a second dielectric material, and the PMOS and NMOS devices are FinFET devices 200, 300.

Owner:GLOBALFOUNDRIES US INC

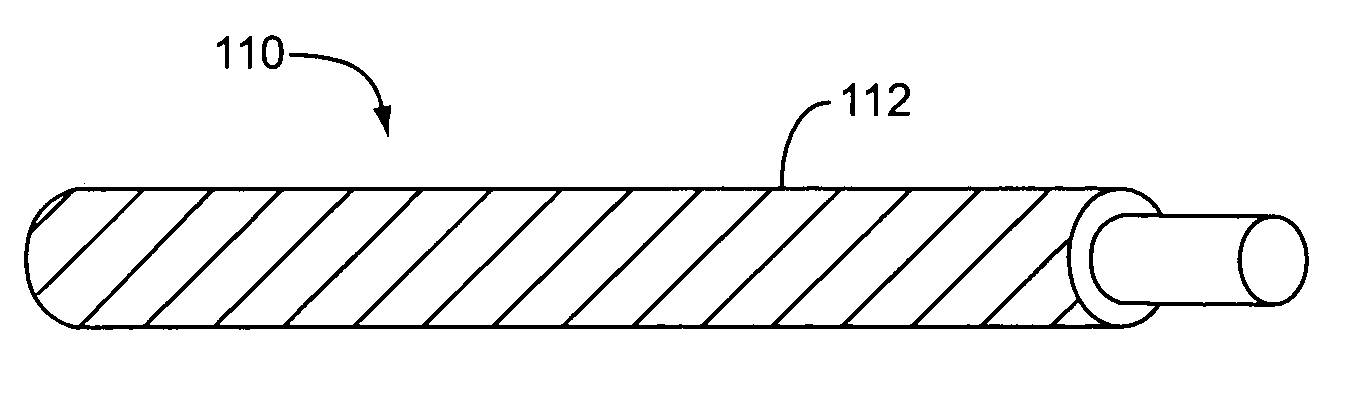

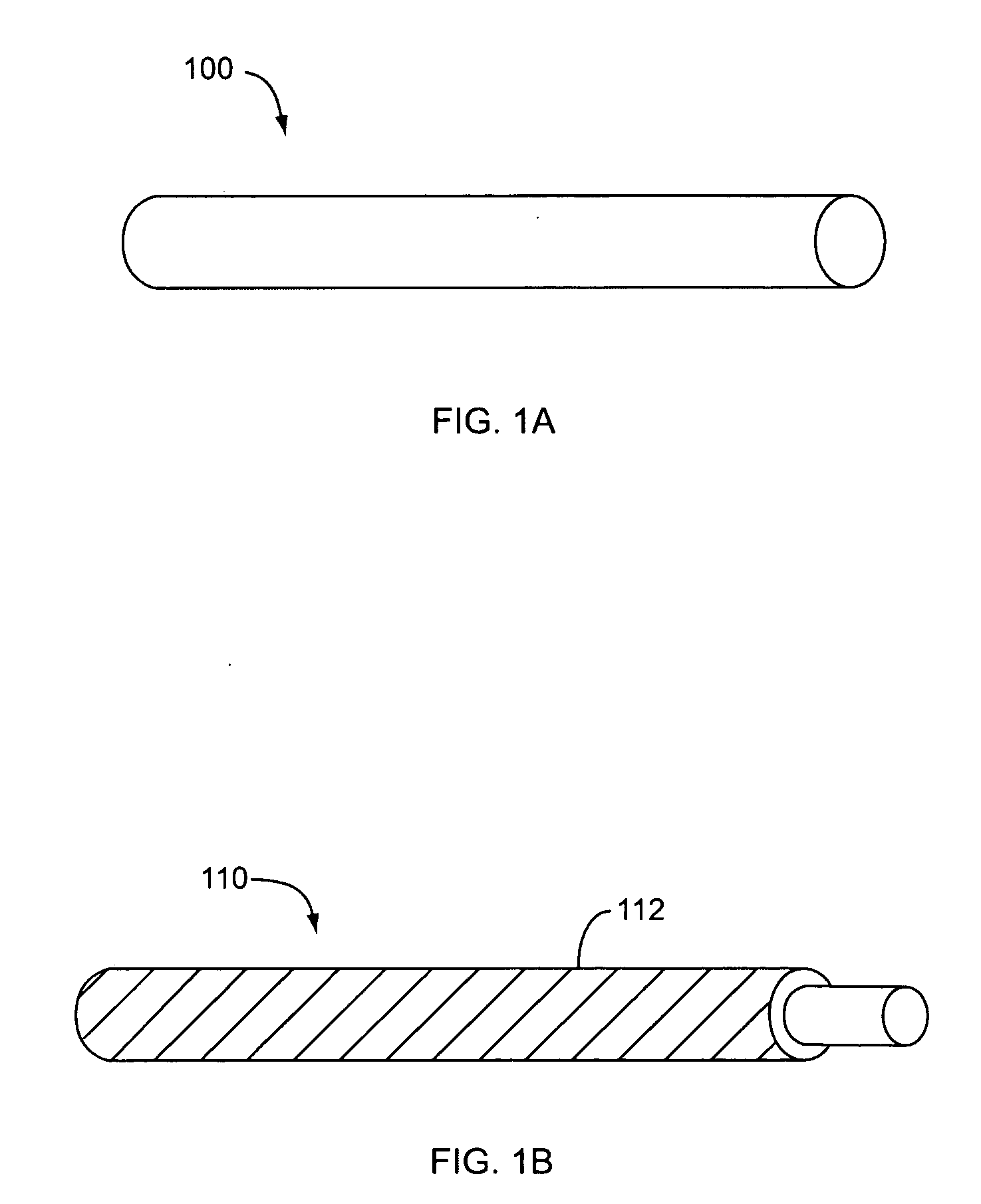

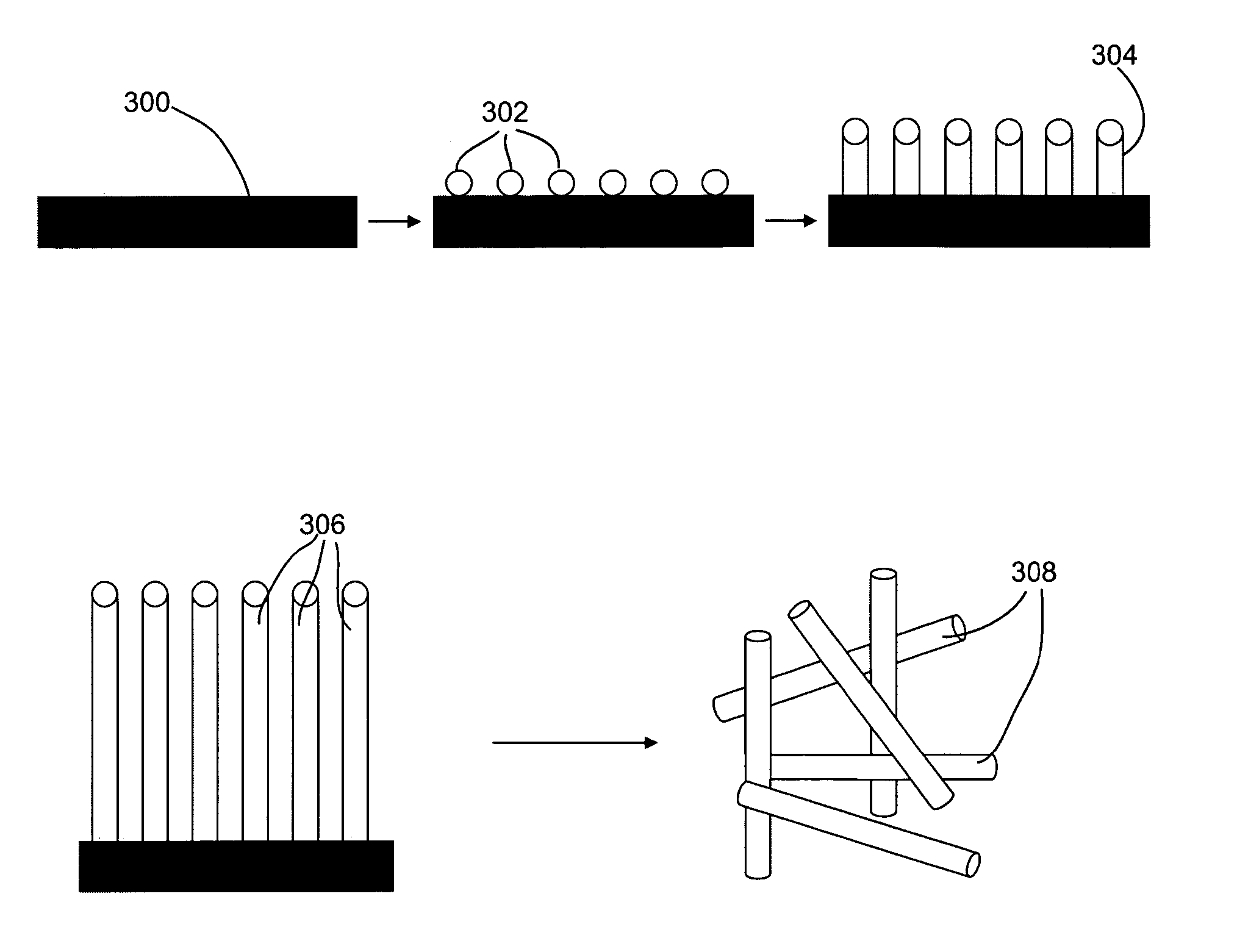

Systems and methods for harvesting and integrating nanowires

ActiveUS20060008942A1Ease of mass productionImprove device performanceLayered productsNanoinformaticsNanowireInk printer

The present invention is directed to methods to harvest, integrate and exploit nanomaterials, and particularly elongated nanowire materials. The invention provides methods for harvesting nanowires that include selectively etching a sacrificial layer placed on a nanowire growth substrate to remove nanowires. The invention also provides methods for integrating nanowires into electronic devices that include placing an outer surface of a cylinder in contact with a fluid suspension of nanowires and rolling the nanowire coated cylinder to deposit nanowires onto a surface. Methods are also provided to deposit nanowires using an ink-jet printer or an aperture to align nanowires. Additional aspects of the invention provide methods for preventing gate shorts in nanowire based transistors. Additional methods for harvesting and integrating nanowires are provided.

Owner:ONED MATERIAL INC

Wrist with decoupled motion transmission

InactiveUS20030208186A1Reduce inertiaImprove device performanceMechanical apparatusDiagnosticsEngineeringActuator

The present invention is a wrist mechanism and a method for making robotic devices in which the transmission of motion, force and / or torque around a revolute joint can be accomplished without coupling. This construction allows mounting the actuators on the base or lower elements of a mechanism, so that only linkage elements move the end-effector. Thus reducing inertia of the moving elements and increasing performance of the device. The decoupled motion of the end-effector or links is achieved by routing their transmission cables around idler pulleys placed parallel to the joint rotation axis on an optimal position such any stretch on the transmission cable is minimized. In particular, this construction can be use for robotic surgical tools that have two independently driven jaws, decoupled and orthogonal from its articulating wrist.

Owner:MOREYRA MANUEL RICARDO

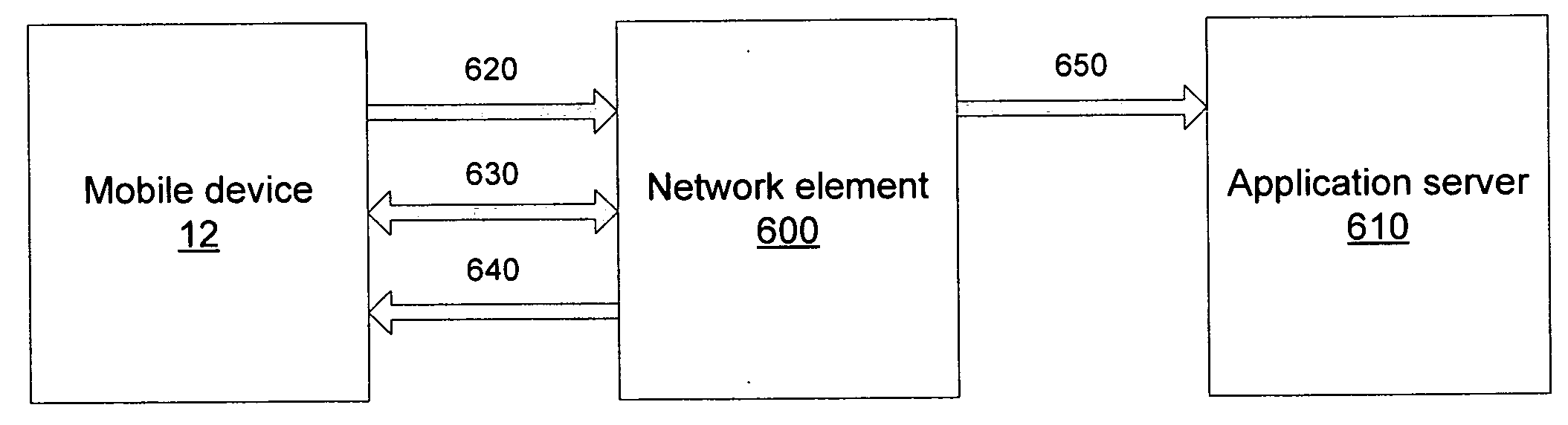

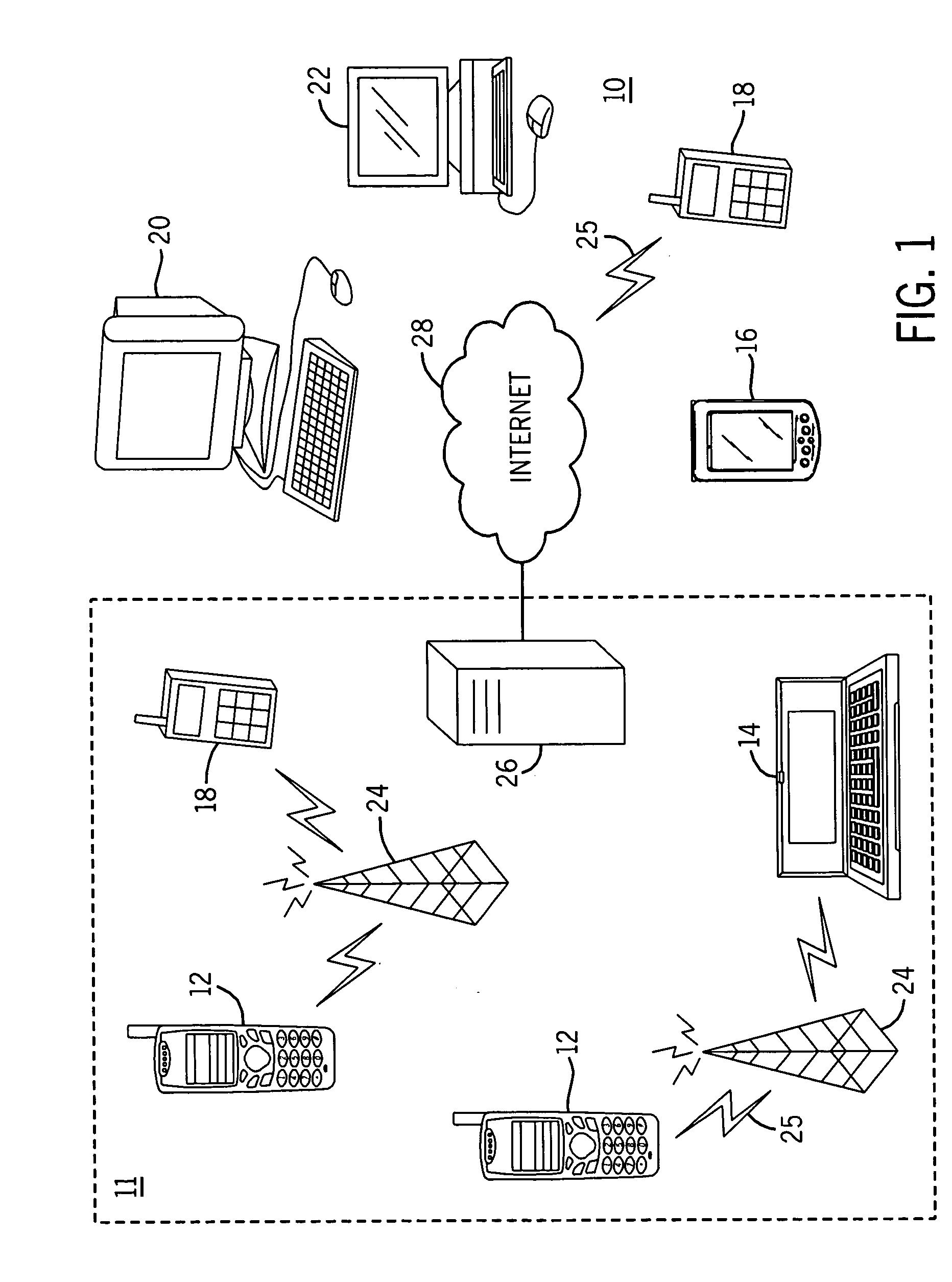

Mobile network optimized method for keeping an application IP connection always on

ActiveUS20080059582A1Reduce the burden onImprove device performanceMultiple digital computer combinationsTransmissionApplication serverApplication programming interface

A system and method of maintaining an always-on application client communication is provided. An application programming interface implemented on a device hosting an always-on application client determines if network-based keep-alive functionality exists in a network where the device operates. If network-based keep-alive functionality exists, a network element is instructed to transmit keep-alive messages to the application server on behalf of the device. The network element can be implemented in or as a variety of existing network elements, e.g., as a GPRS gateway serving node or a standalone keep-alive network element. Alternatively, an application server communicatively connected to the always-on application client may query whether network-based keep-alive functionality exists. If network-based keep-alive functionality exists, the application server negotiates with the always-on application client to determine an application-specific mechanism for implementing the network-based keep-alive functionality. When an application server queries for network-based keep-alive functionality, an application programming interface need not be utilized.

Owner:NOKIA TECHNOLOGLES OY

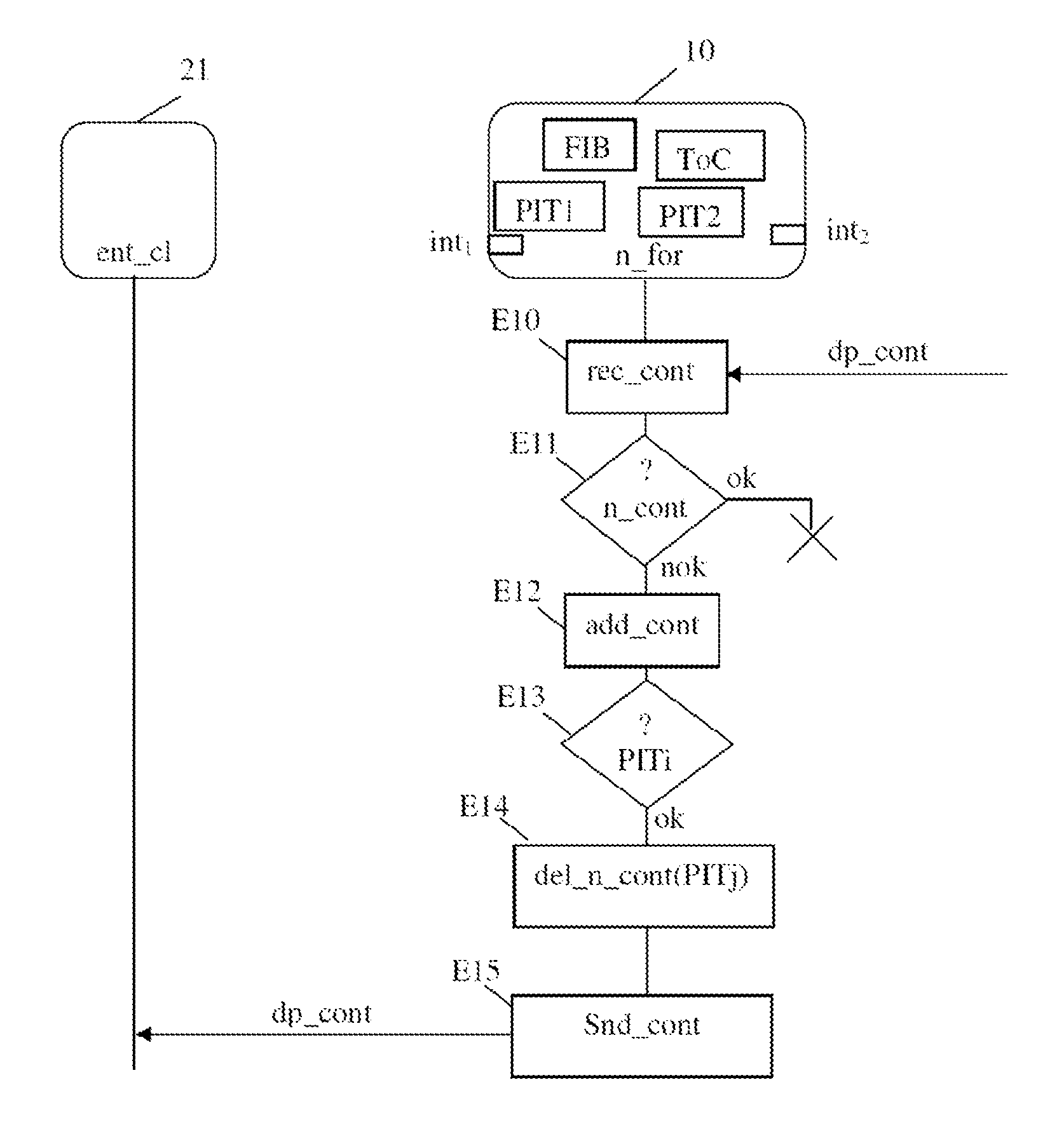

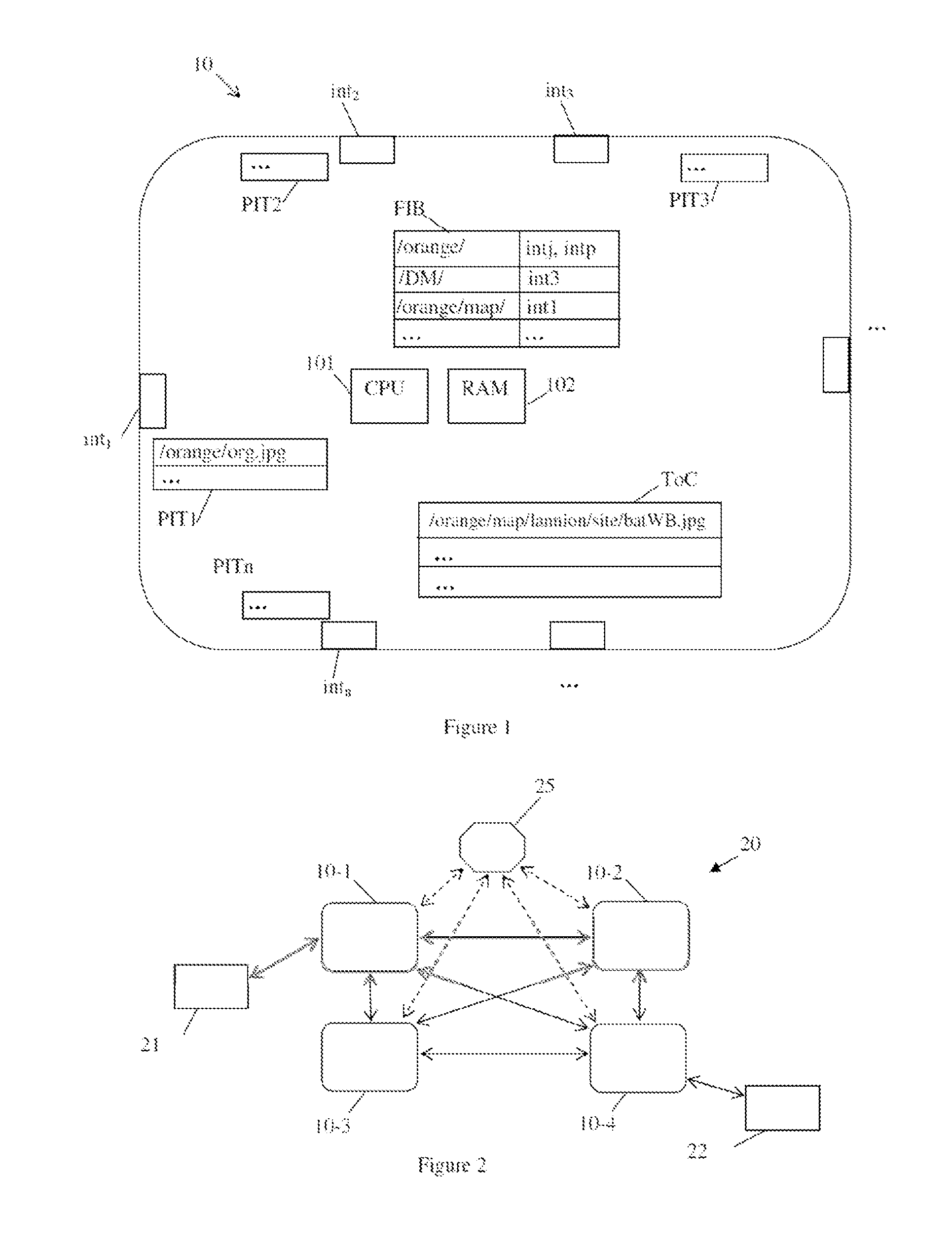

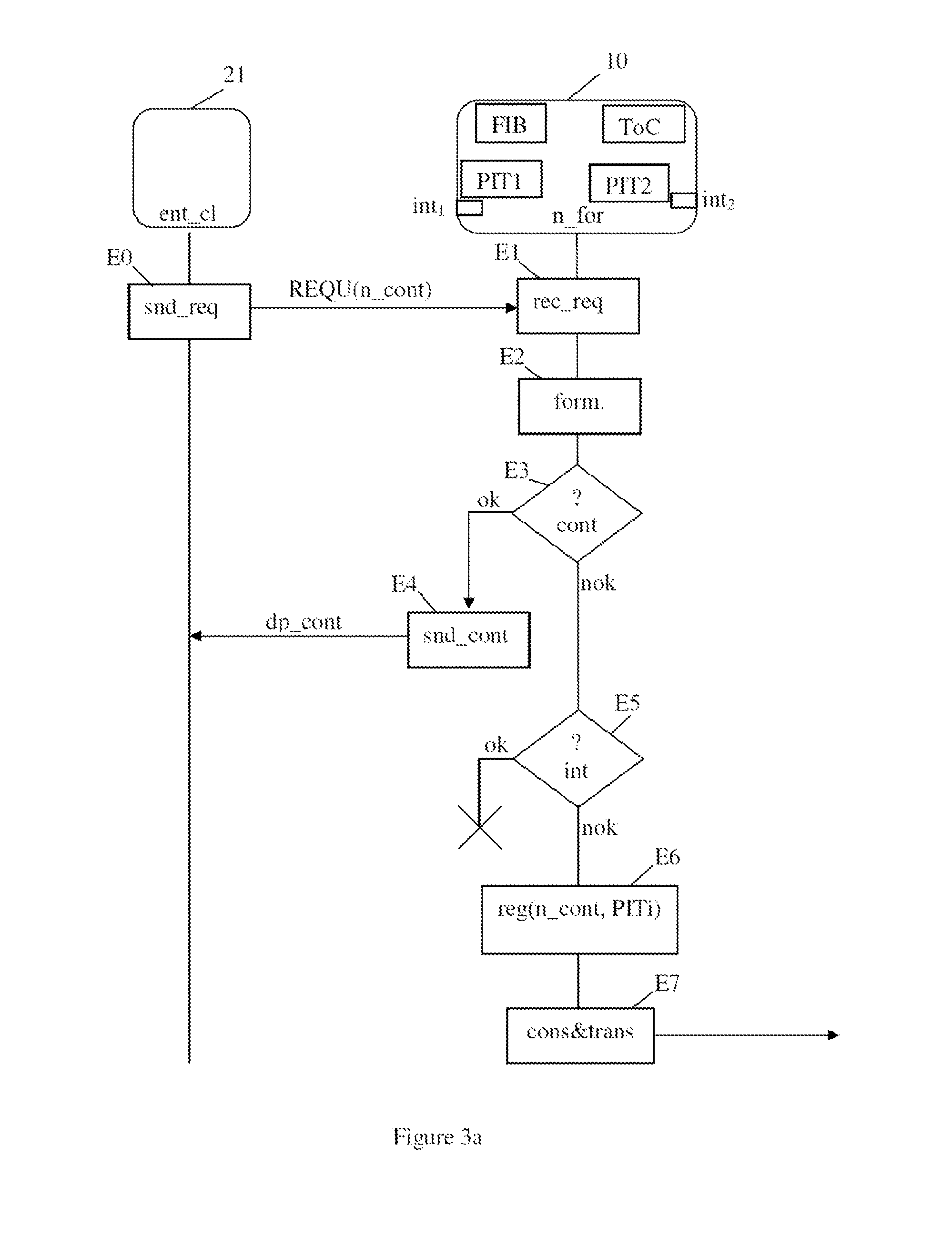

Method for Processing a Request in an Information-Centric Communication Network

ActiveUS20140314093A1Small sizeOptimize processing timeData switching by path configurationRouting tableNetwork packet

A method for processing a request for content by a routing device in a communication network implementing a name-based routing. The device includes plural interfaces to receive a request for content and a data packet associated with a content, and a routing table adapted to determine, based on a content name, at least one interface to route the request. The method includes: receiving the request through a first interface; if the device is not able to provide said data packet, searching for the name of the content in a table of pending requests associated with the first interface; in case the content name does not appear in the table, storing the name of the content in the table; and transmitting the request through at least one second interface, the second interface being determined as a function of the name of the content on the basis of the routing table.

Owner:ORANGE SA (FR)

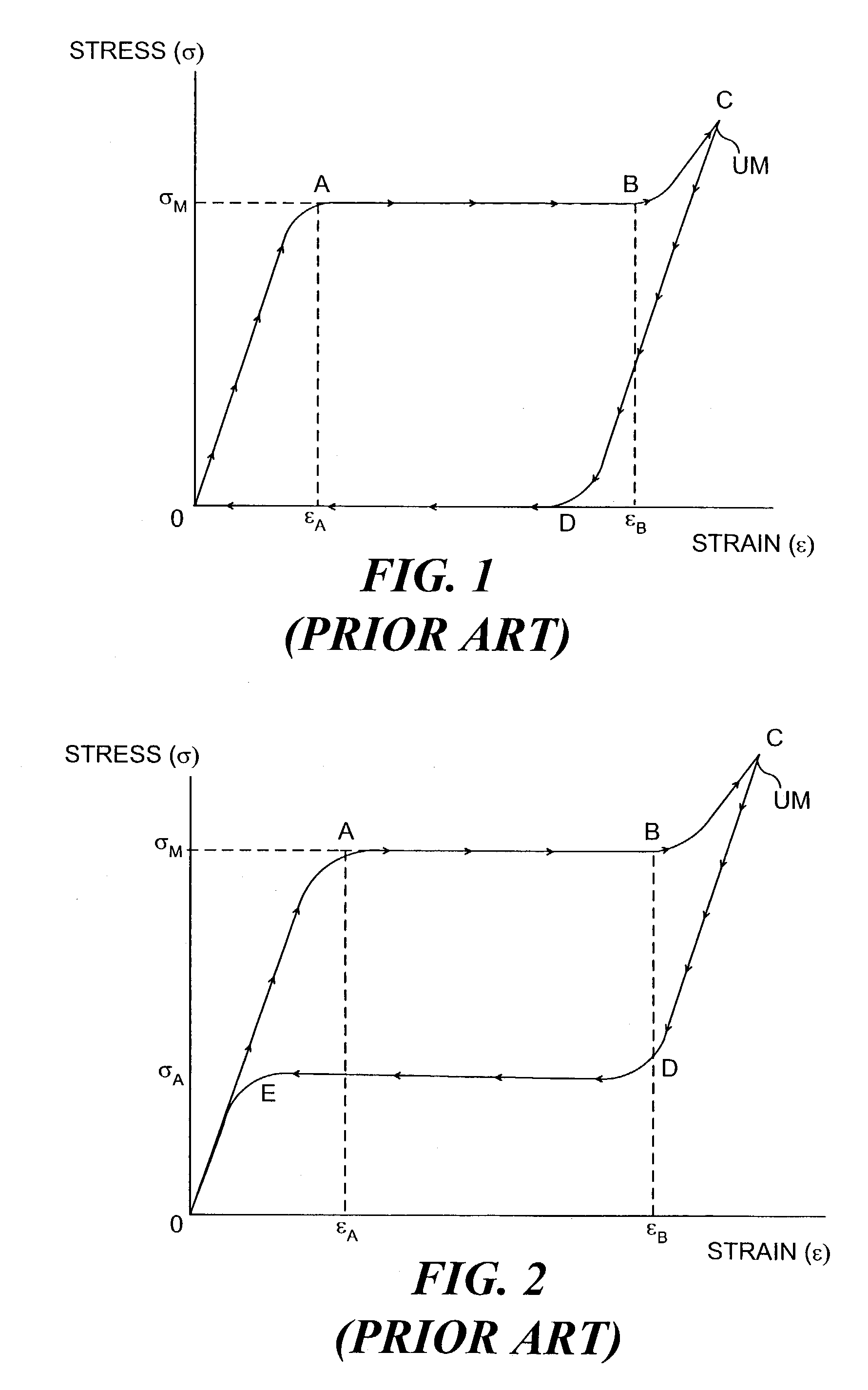

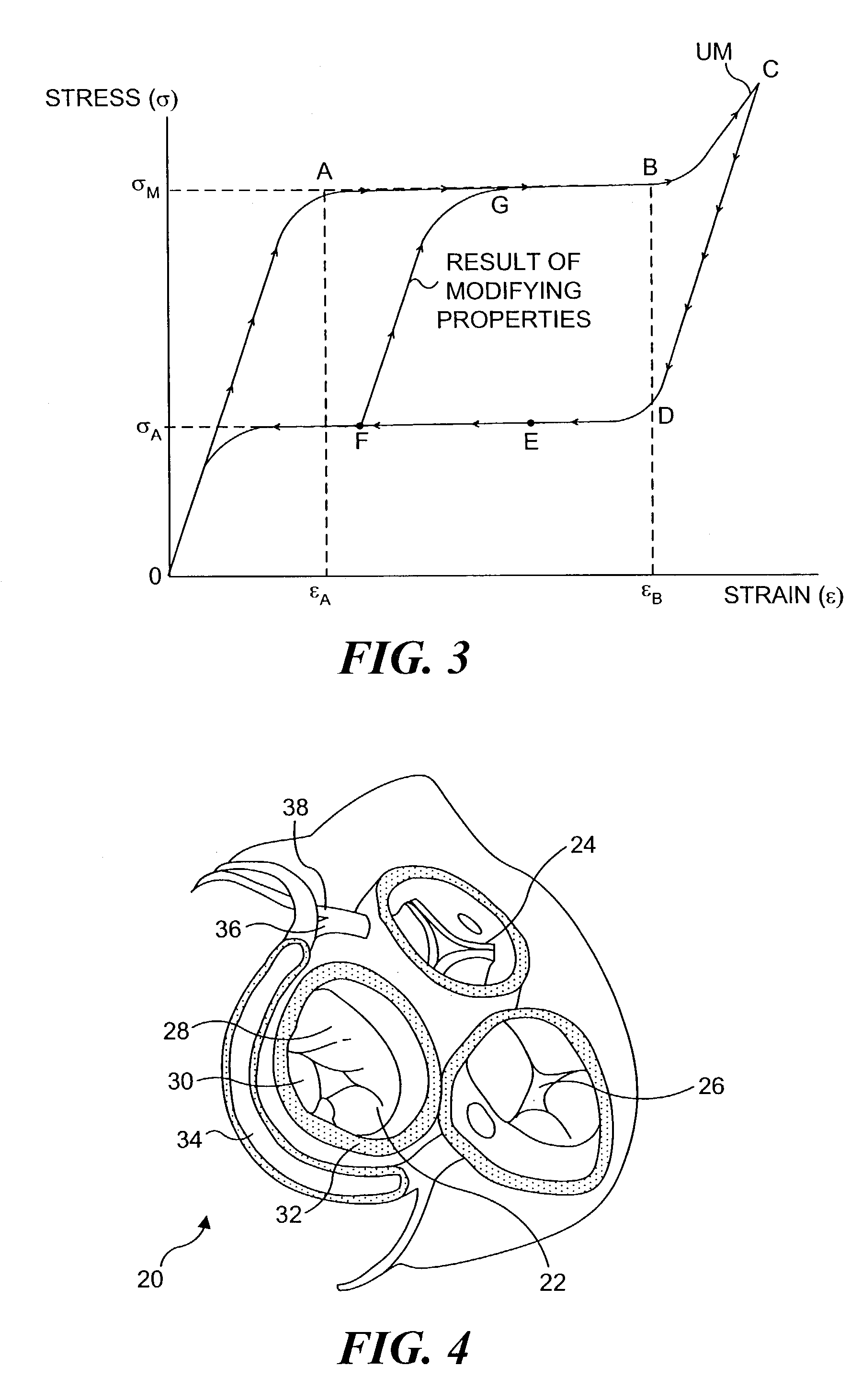

Mitral valve device using conditioned shape memory alloy

A mitral valve annulus reshaping device includes at least a portion that is formed of a biocompatible shape memory alloy SMA having a characteristic temperature, Af, that is preferably below body temperature. The device is constrained in an unstable martensite (UM) state while being introduced through a catheter that passes through the venous system and into the coronary sinus of the heart. The reshaping device is deployed adjacent to the mitral valve annulus of the heart as it is forced from the catheter. When released from the constraint of the catheter, the SMA of the device at least partially converts from the UM state to an austenitic state and attempts to change to a programmed shape that exerts a force on the adjacent tissue and modifies the shape of the annulus. The strain of the SMA can be varied when the device is within the coronary sinus.

Owner:CARDIAC DIMENSIONS

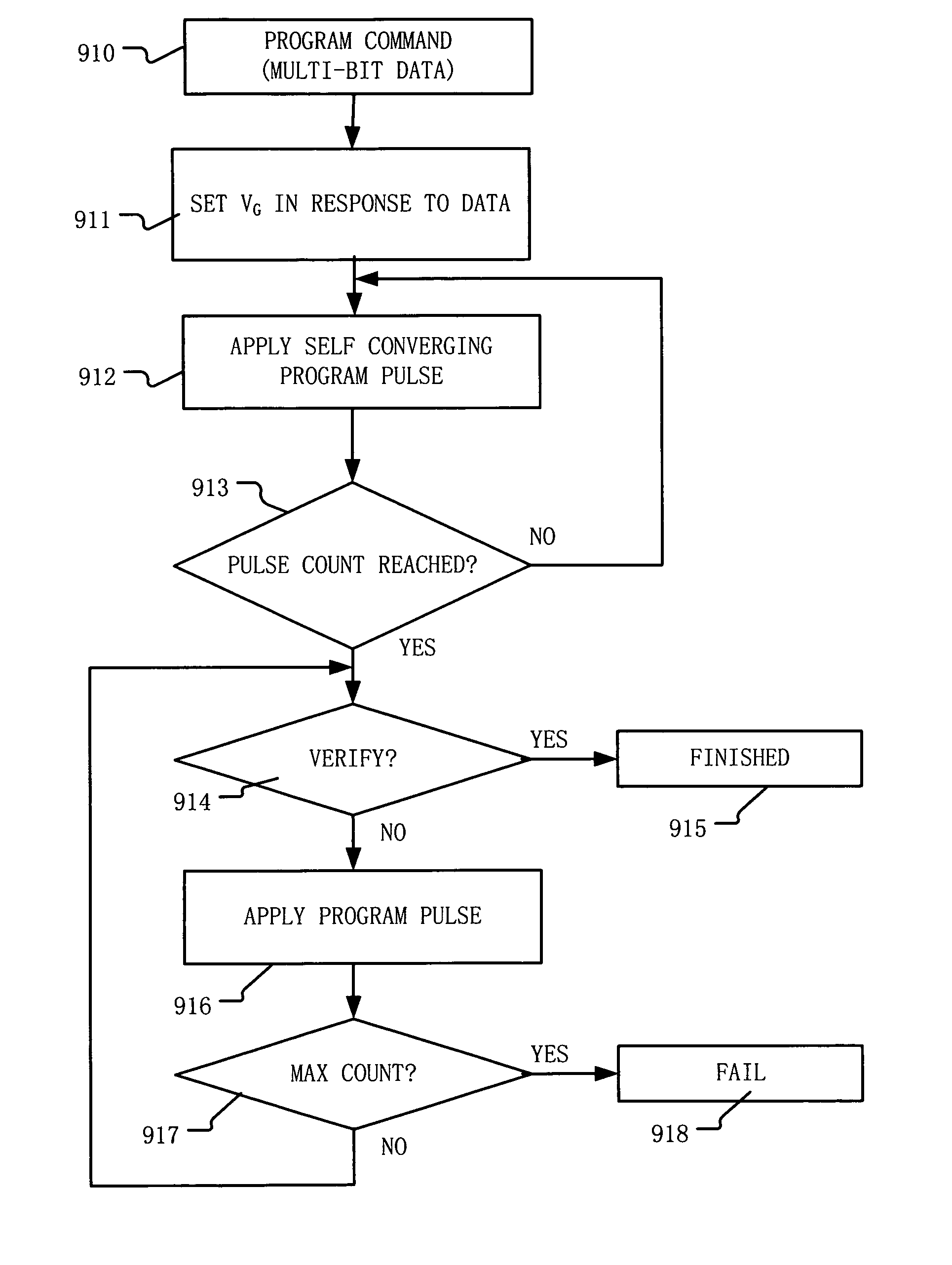

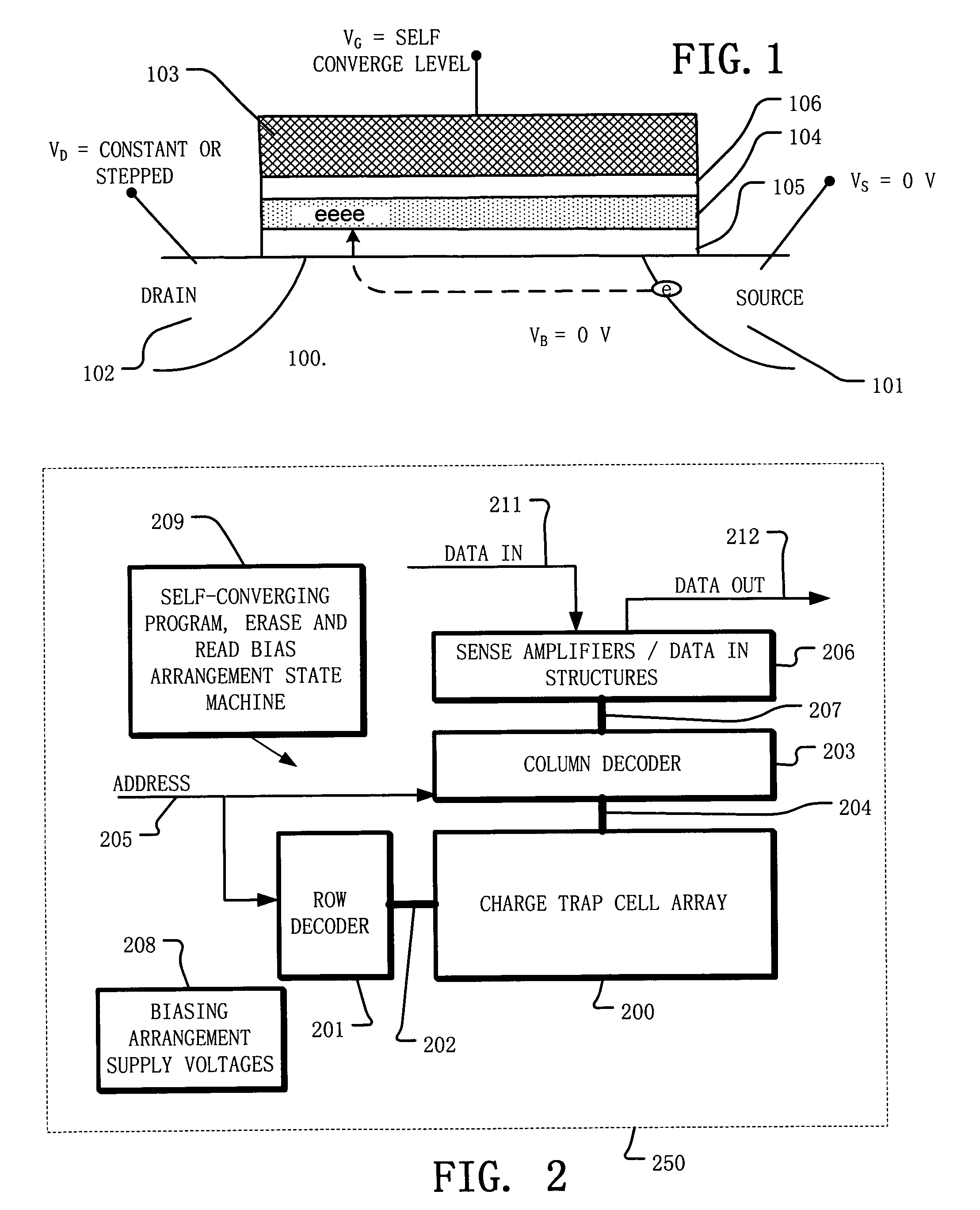

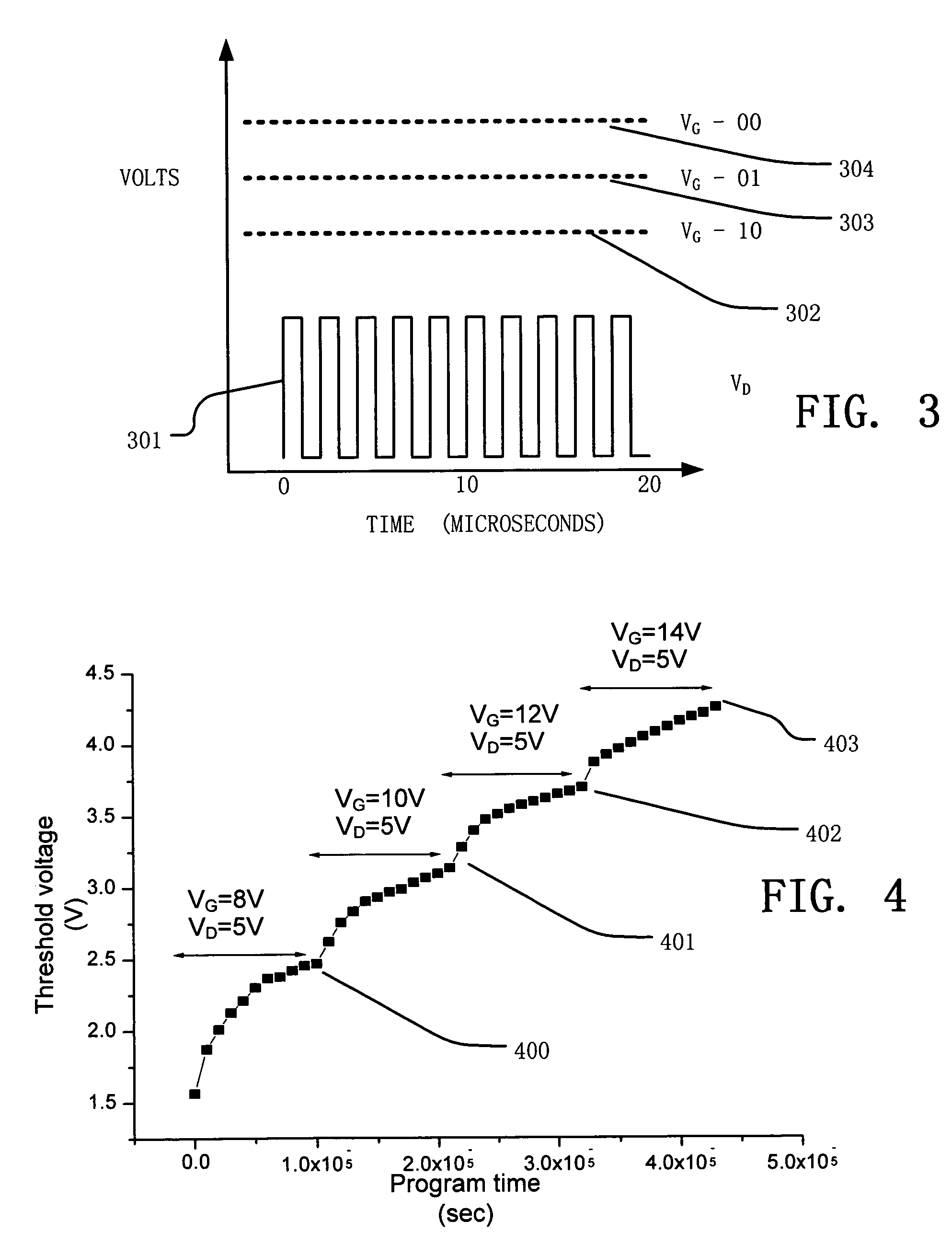

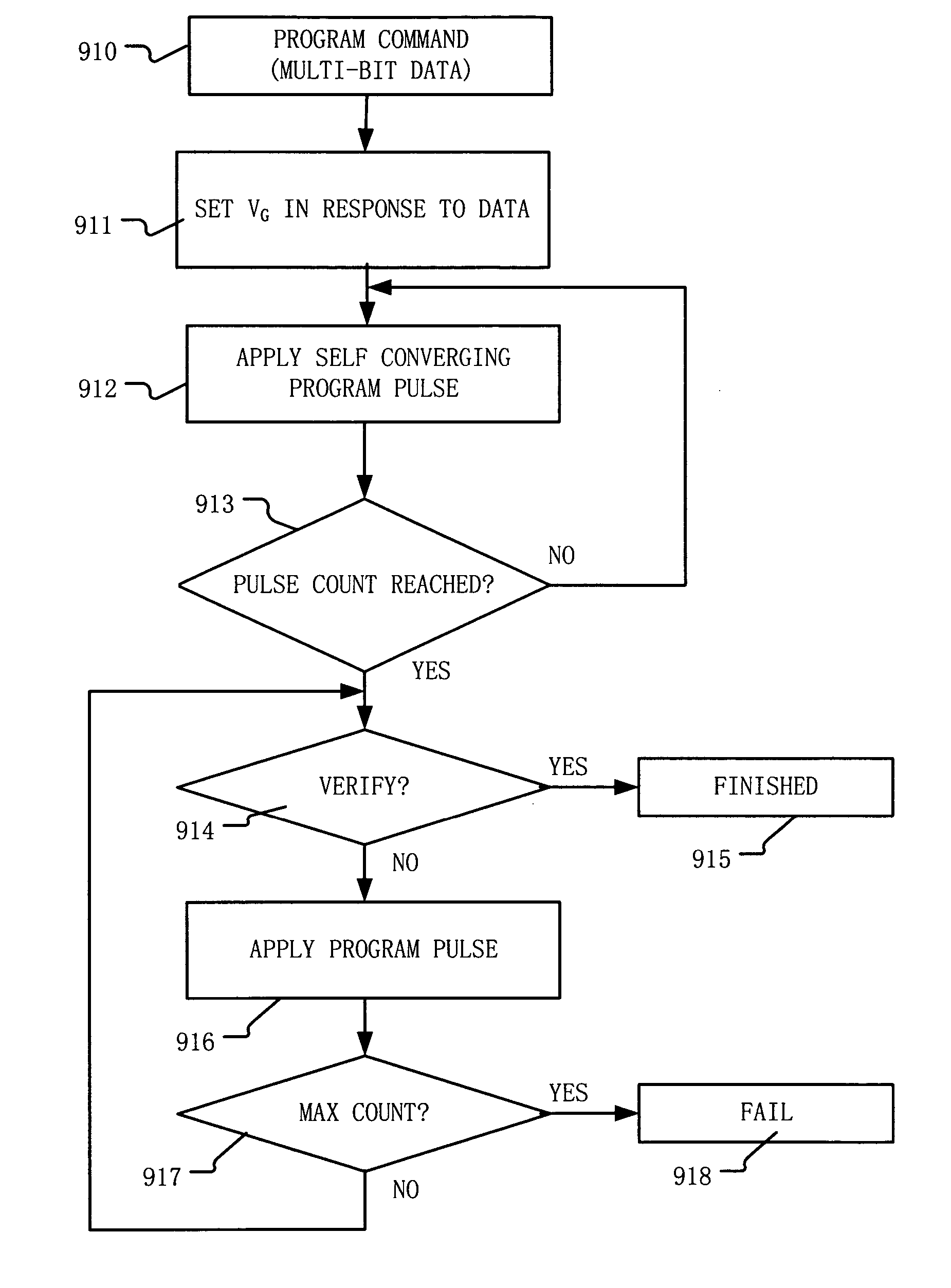

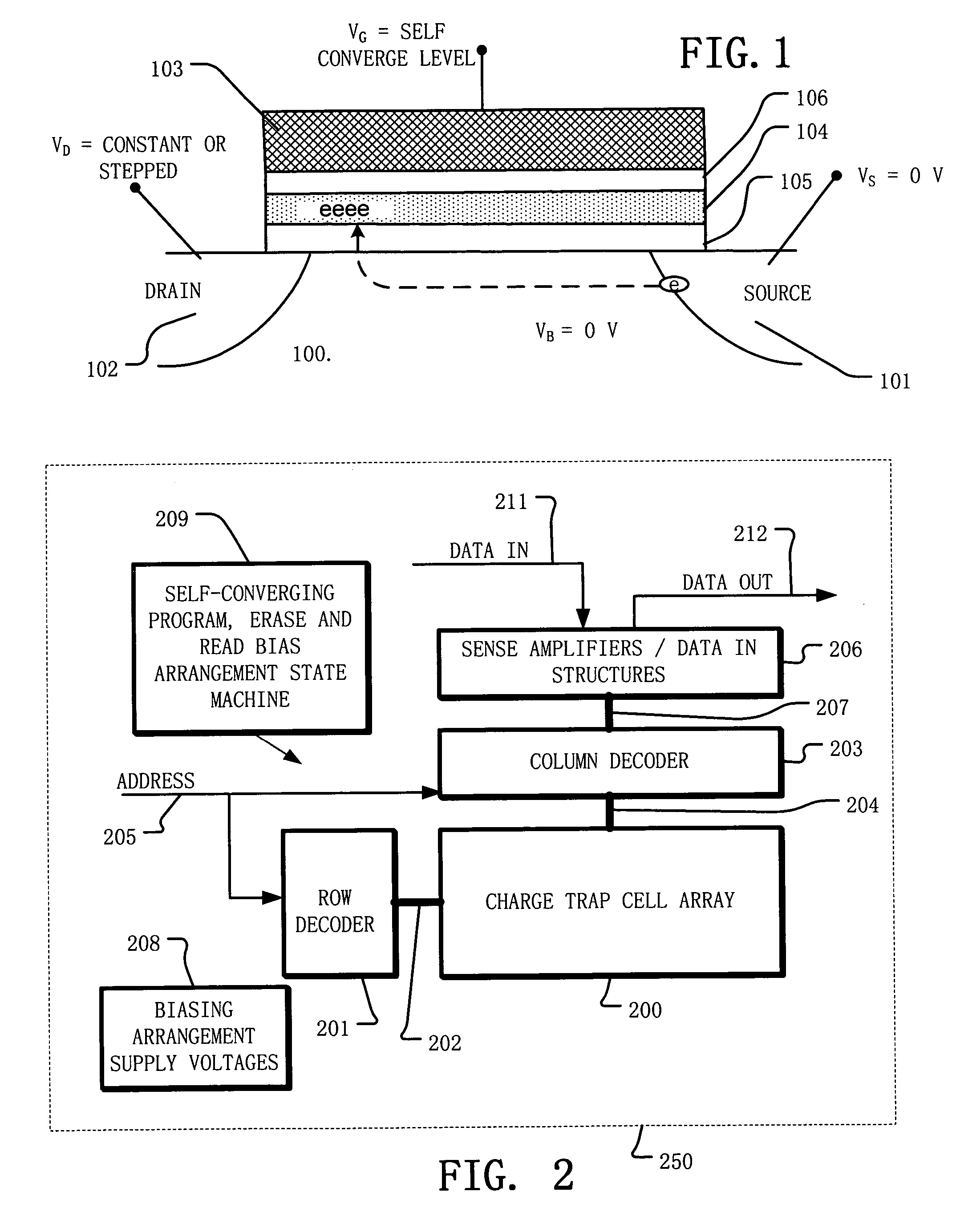

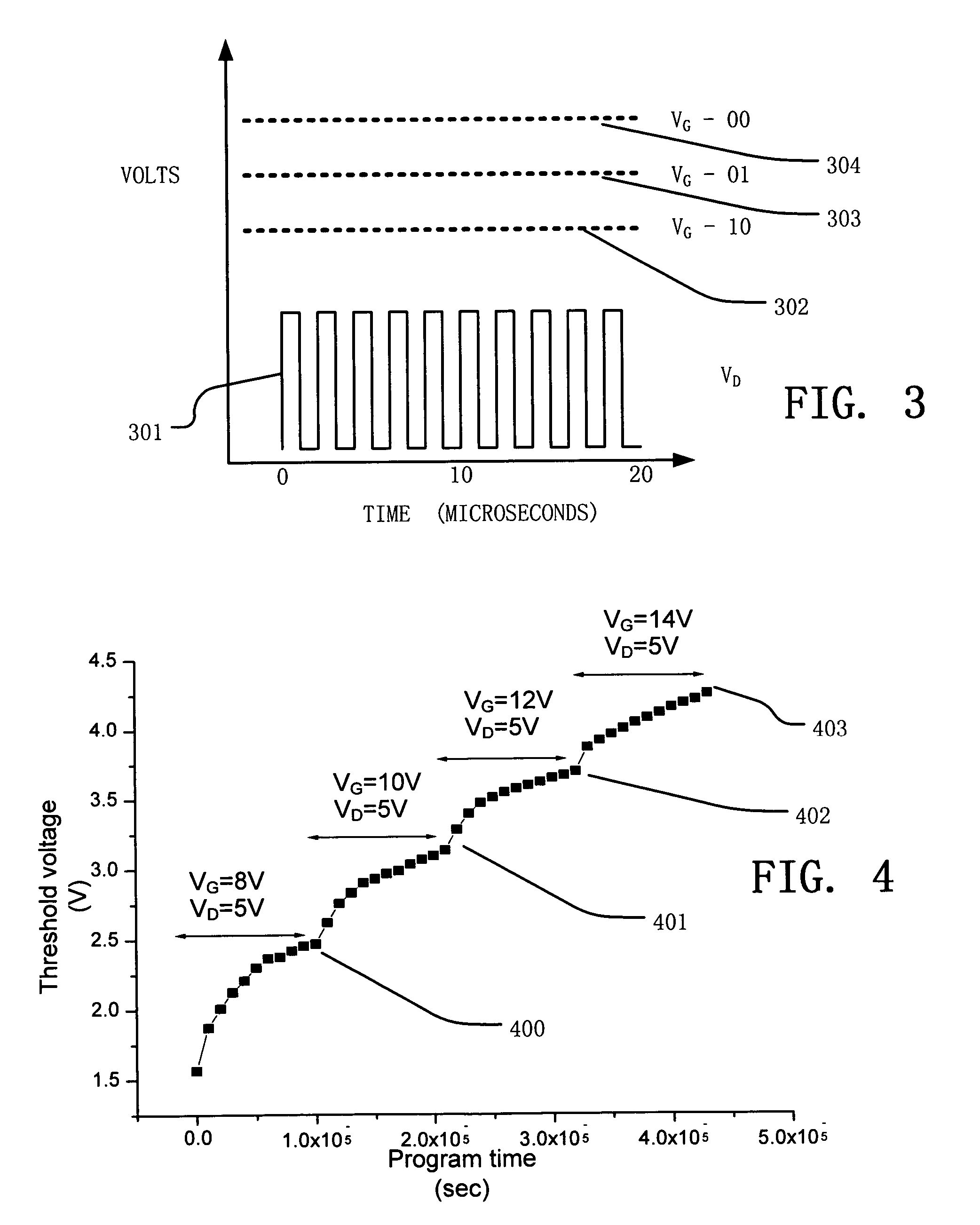

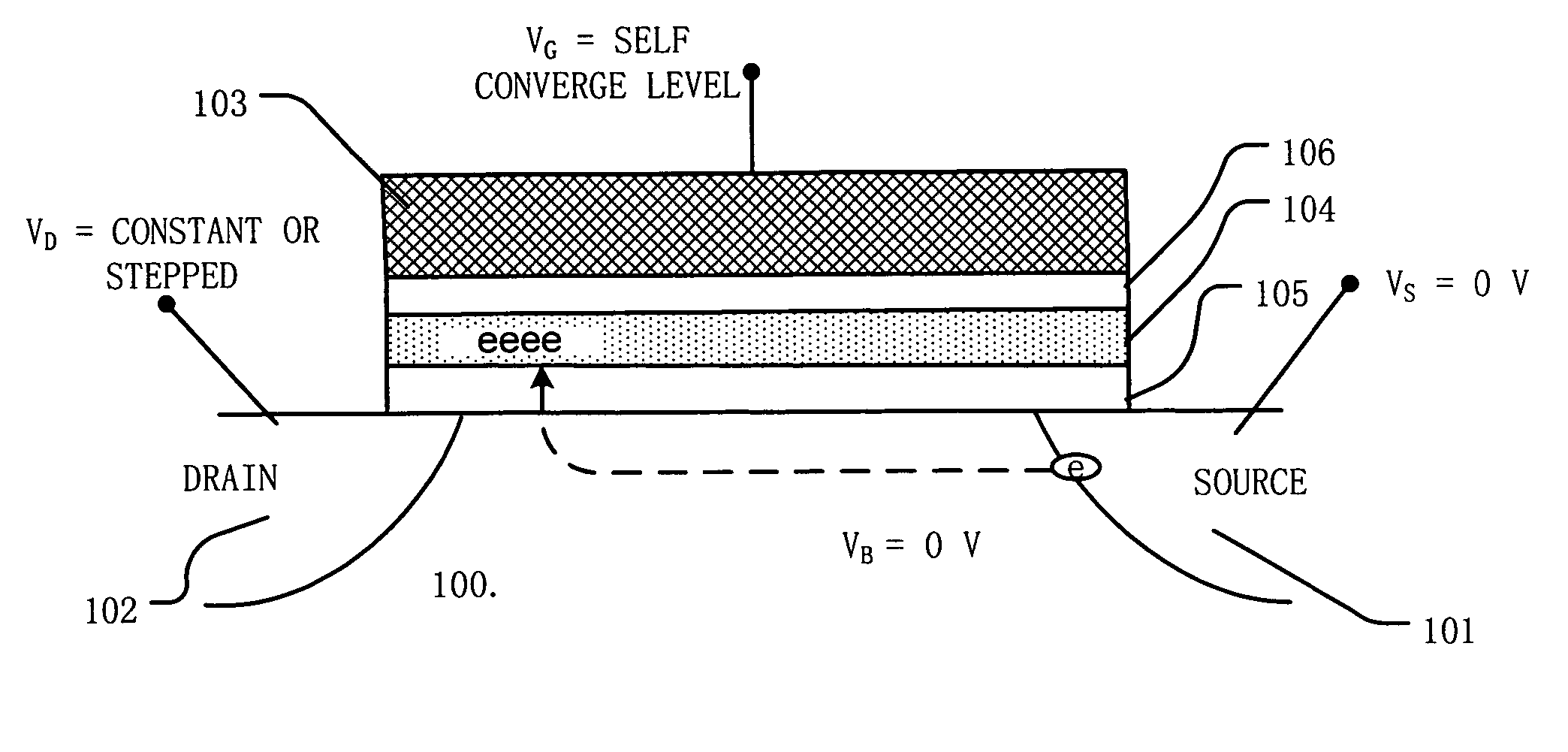

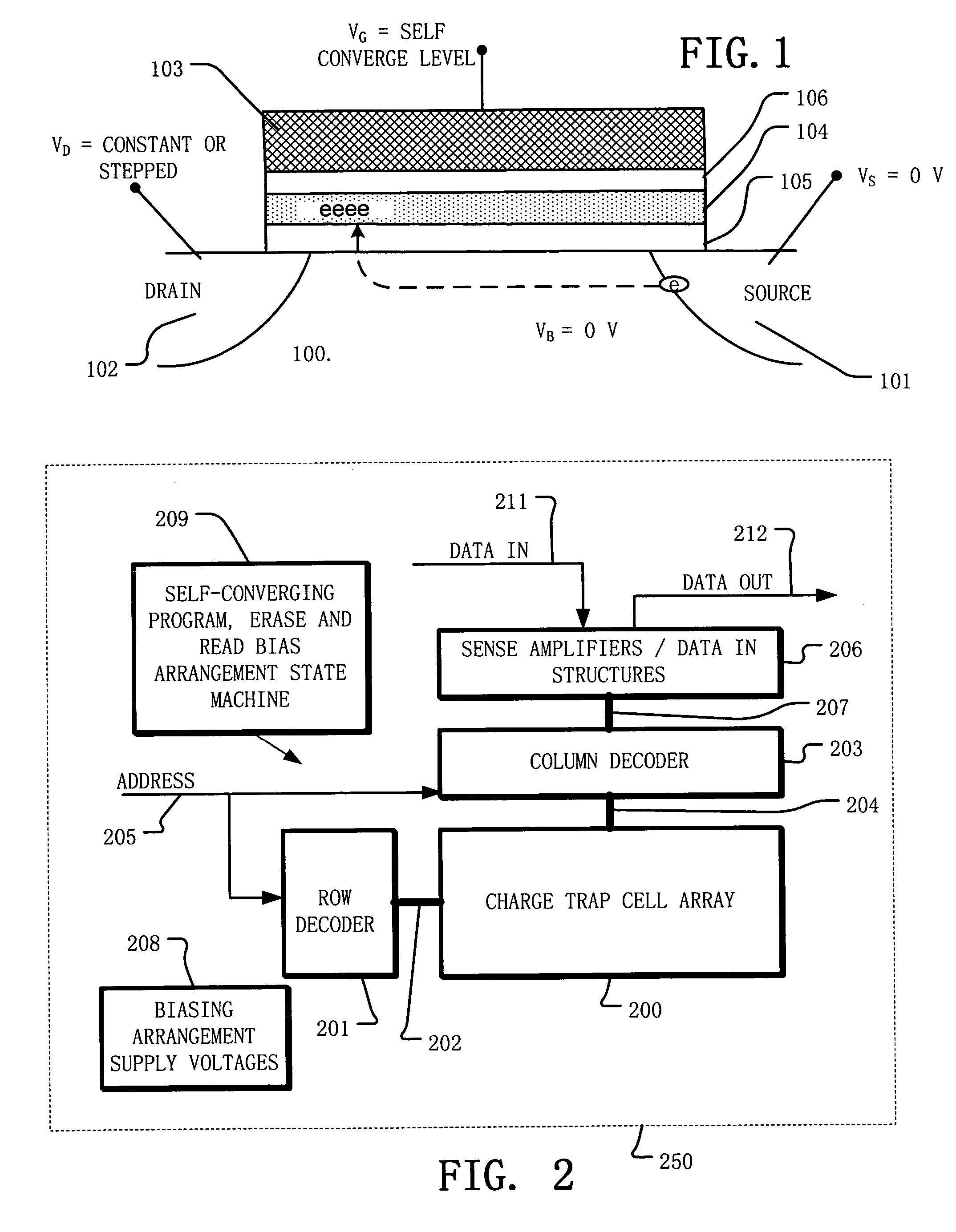

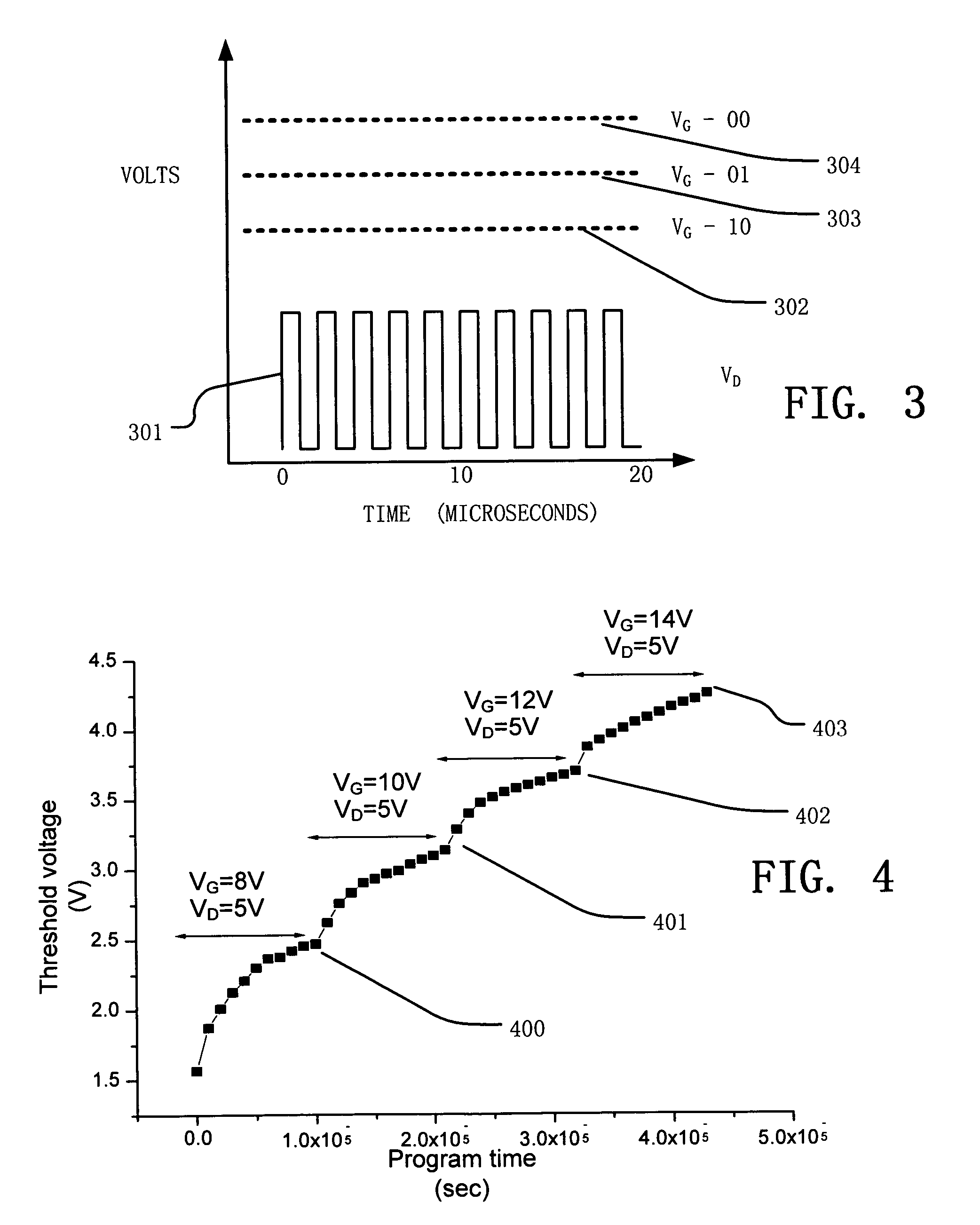

Operation scheme for programming charge trapping non-volatile memory

ActiveUS7151692B2Verify operation is reduced and eliminatedShorten the timeRead-only memoriesDigital storageEngineeringGate voltage

A circuit and method for self-converging programming of a charge storage memory cell, such as NROM or floating gate flash. The method includes determining a data value from one of more than two data values to be stored in the memory cell, and applying a gate voltage to the control gate at one of a predetermined set of gate voltage levels selected in response to the determined data value. Programming parameters are controlled to establish a self-converging threshold state that is determined by the selected gate voltage. In this manner, the threshold voltage converges on a target threshold corresponding with the determined data value for the memory cell. Program verify operations are reduced or eliminated in various embodiments, reducing the overall time required for the program operation, and improving device performance. A second portion of the program operation can include verify operations to improve threshold margins across the array.

Owner:MACRONIX INT CO LTD

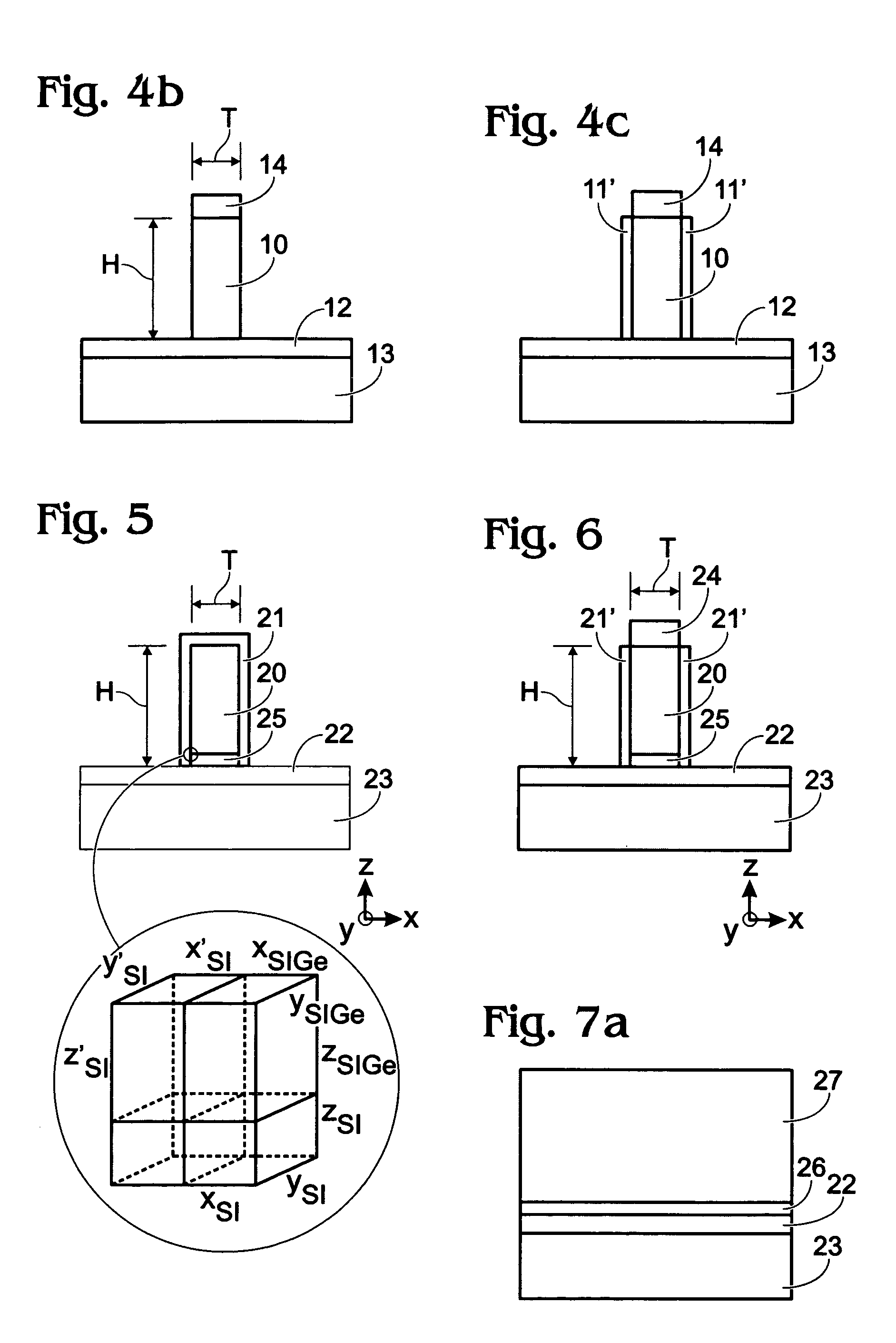

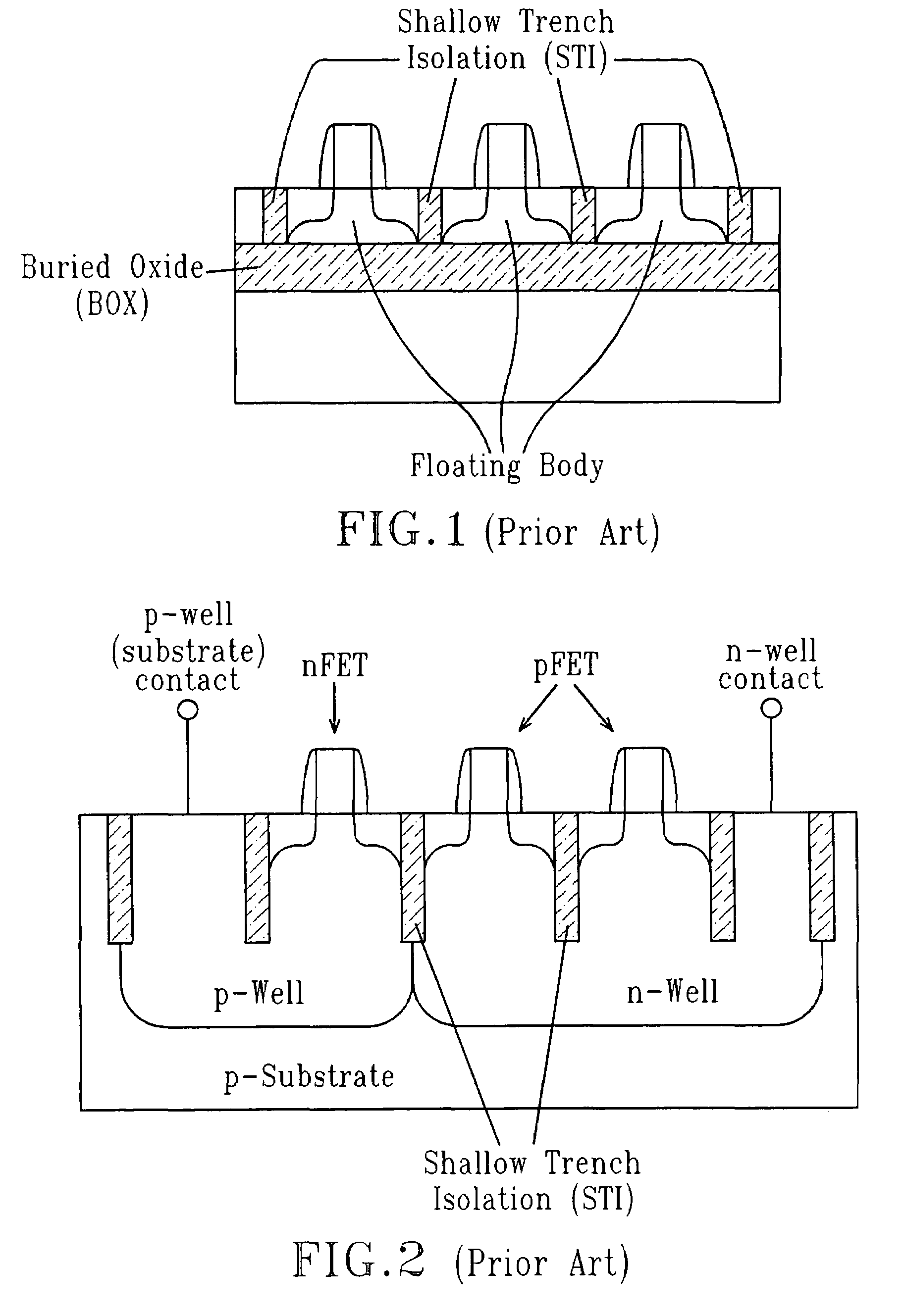

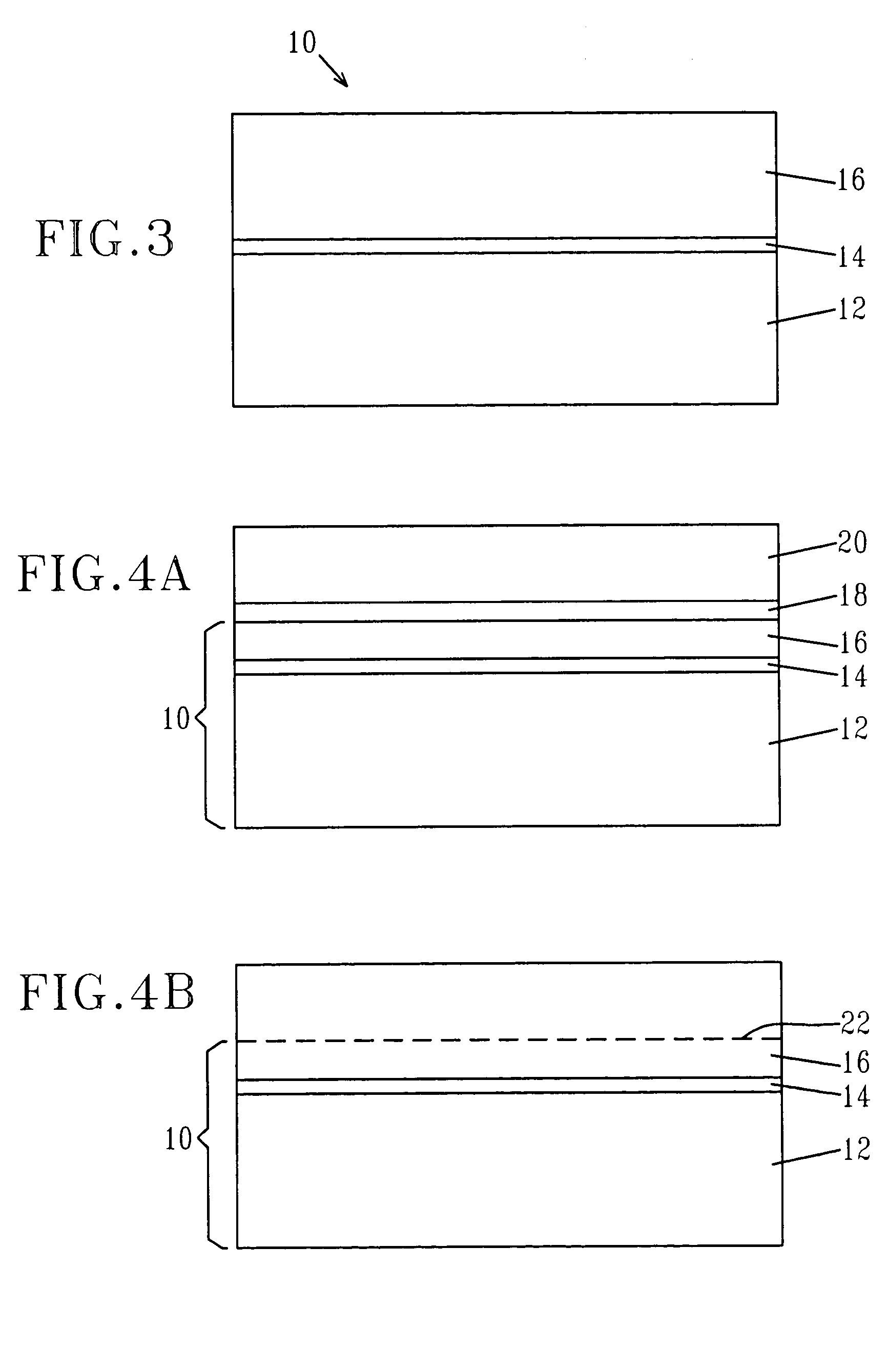

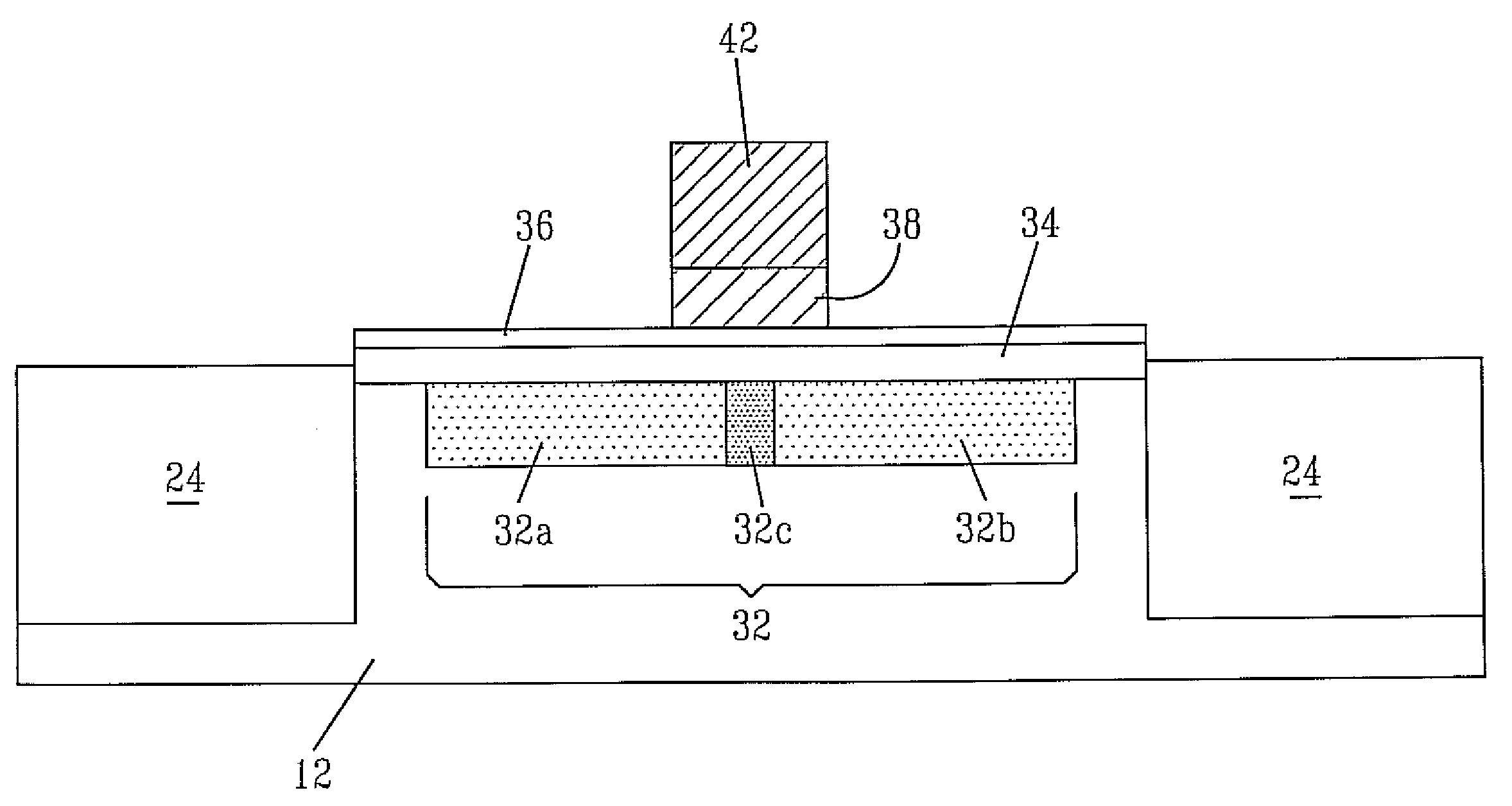

CMOS on hybrid substrate with different crystal orientations using silicon-to-silicon direct wafer bonding

InactiveUS7023055B2Improve performanceImprove device performanceTransistorSolid-state devicesCMOSSemiconductor structure

A method in which semiconductor-to-semiconductor direct wafer bonding is employed to provide a hybrid substrate having semiconductor layers of different crystallographic orientations that are separated by a conductive interface is provided. Also provided are the hybrid substrate produced by the method as well as using the direct bonding method to provide an integrated semiconductor structure in which various CMOS devices are built upon a surface orientation that enhances device performance.

Owner:GLOBALFOUNDRIES INC

Operation scheme for programming charge trapping non-volatile memory

ActiveUS7190614B2Verify operation is reduced and eliminatedShorten the timeRead-only memoriesDigital storageHemt circuitsEngineering

A circuit and method for self-converging programming of a charge storage memory cell, such as NROM or floating gate flash. The method includes determining a data value from one of more than two data values to be stored in the memory cell, and applying a gate voltage to the control gate at one of a predetermined set of gate voltage levels selected in response to the determined data value. Programming parameters are controlled to establish a self-converging threshold state that is determined by the selected gate voltage. In this manner, the threshold voltage converges on a target threshold corresponding with the determined data value for the memory cell. Program verify operations are reduced or eliminated in various embodiments, reducing the overall time required for the program operation, and improving device performance. A second portion of the program operation can include verify operations to improve threshold margins across the array.

Owner:MACRONIX INT CO LTD

Automated robotic measuring system

ActiveUS7152456B2Improve toleranceIncrease temperatureMechanical apparatusTesting/calibration of speed/acceleration/shock measurement devicesData acquisitionEngineering

An automated coordinate measuring system comprising a measuring arm used for acquisition of geometry data that incorporates an exoskeletal structure resilient to physical perturbations including thermal changes and vibrations which may affect coordinate data acquisition. The system may be adapted to a portable platform allowing for convenient positioning and alignment of the measuring arm in a wide variety of environments.

Owner:HEXAGON METROLOGY INC

CMOS on hybrid substrate with different crystal orientations using silicon-to-silicon direct wafer bonding

InactiveUS20050093104A1Improve performanceImprove device performanceTransistorSolid-state devicesCMOSSemiconductor structure

A method in which semiconductor-to-semiconductor direct wafer bonding is employed to provide a hybrid substrate having semiconductor layers of different crystallographic orientations that are separated by a conductive interface is provided. Also provided are the hybrid substrate produced by the method as well as using the direct bonding method to provide an integrated semiconductor structure in which various CMOS devices are built upon a surface orientation that enhances device performance.

Owner:GLOBALFOUNDRIES INC

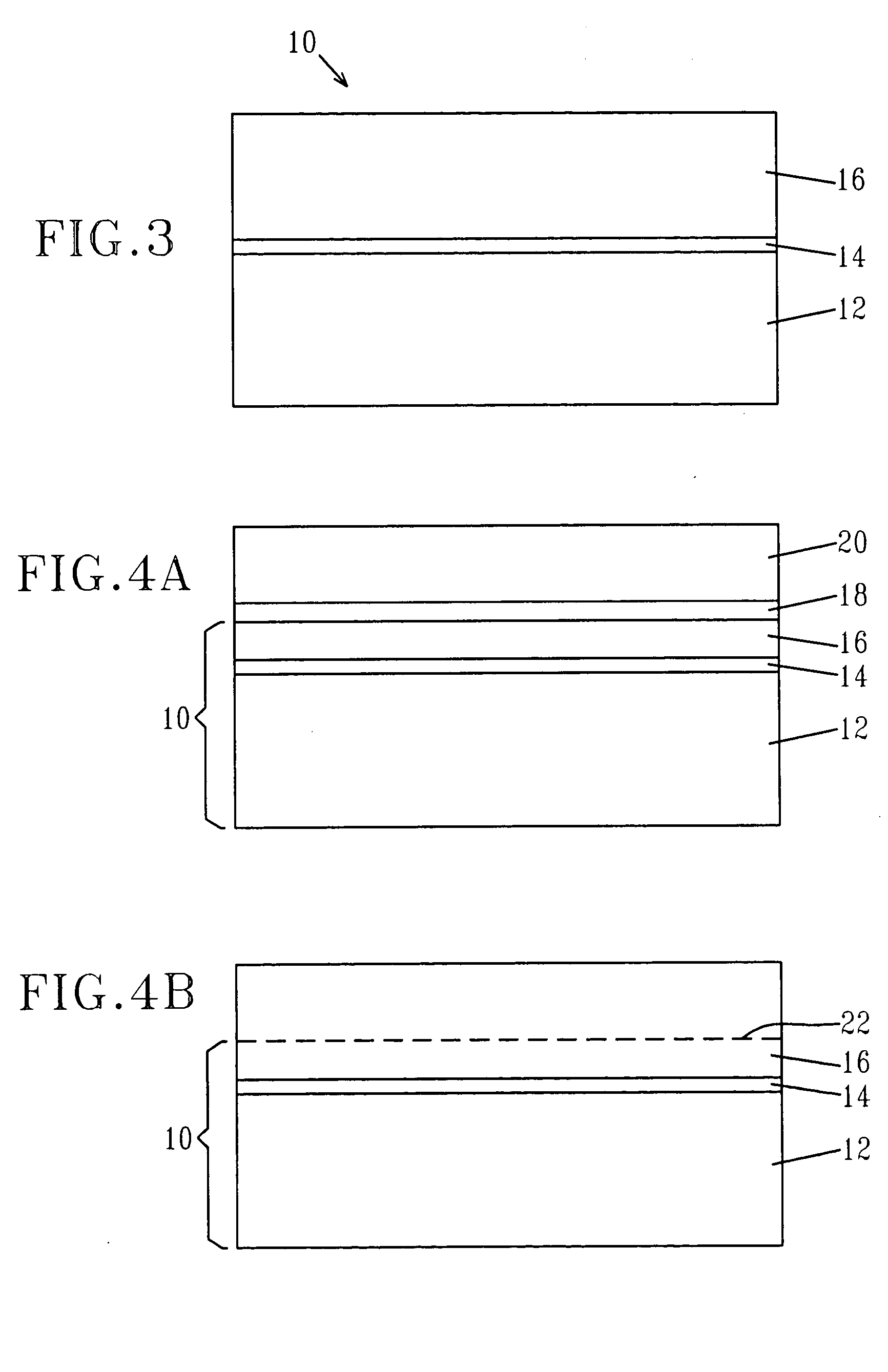

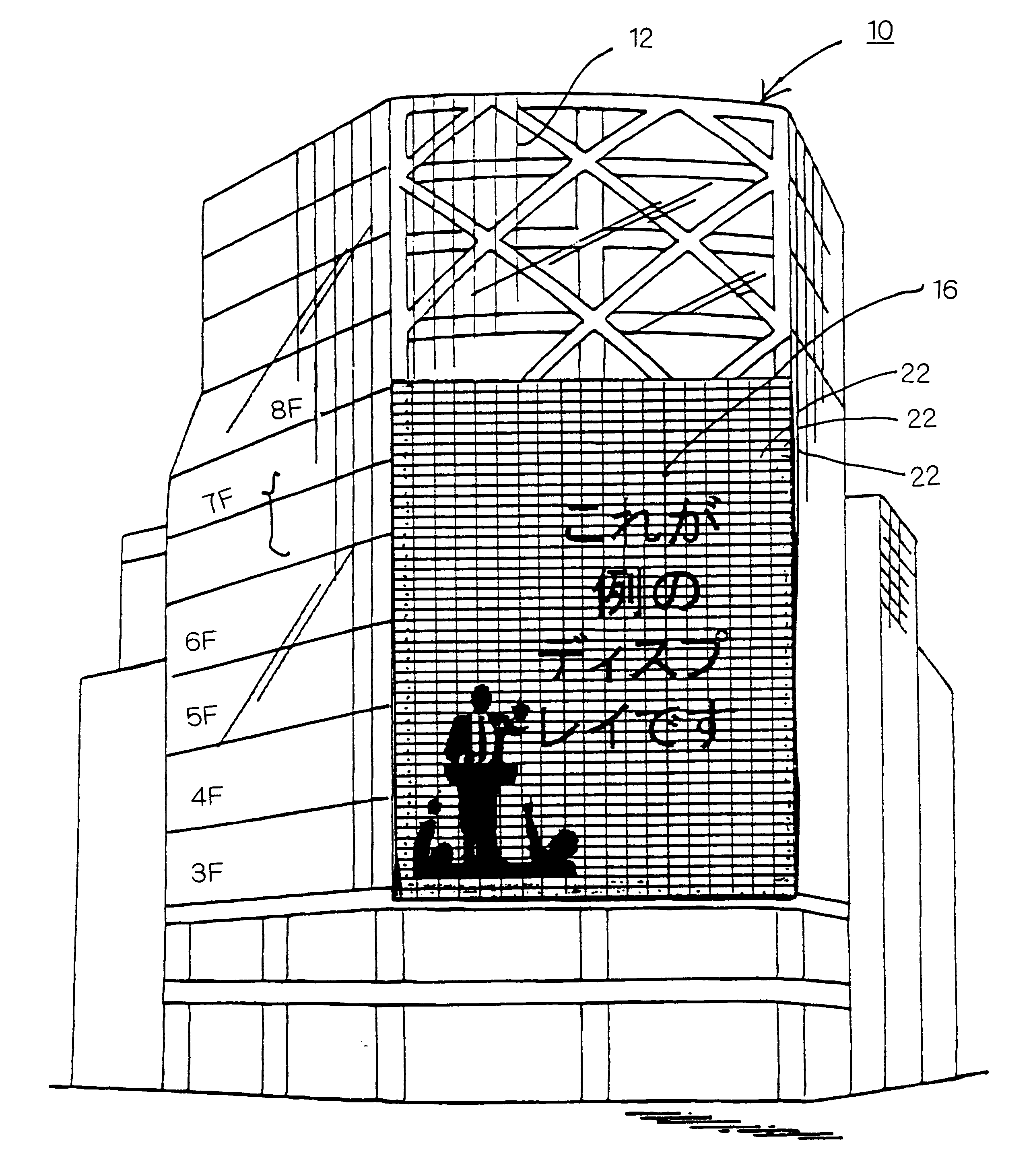

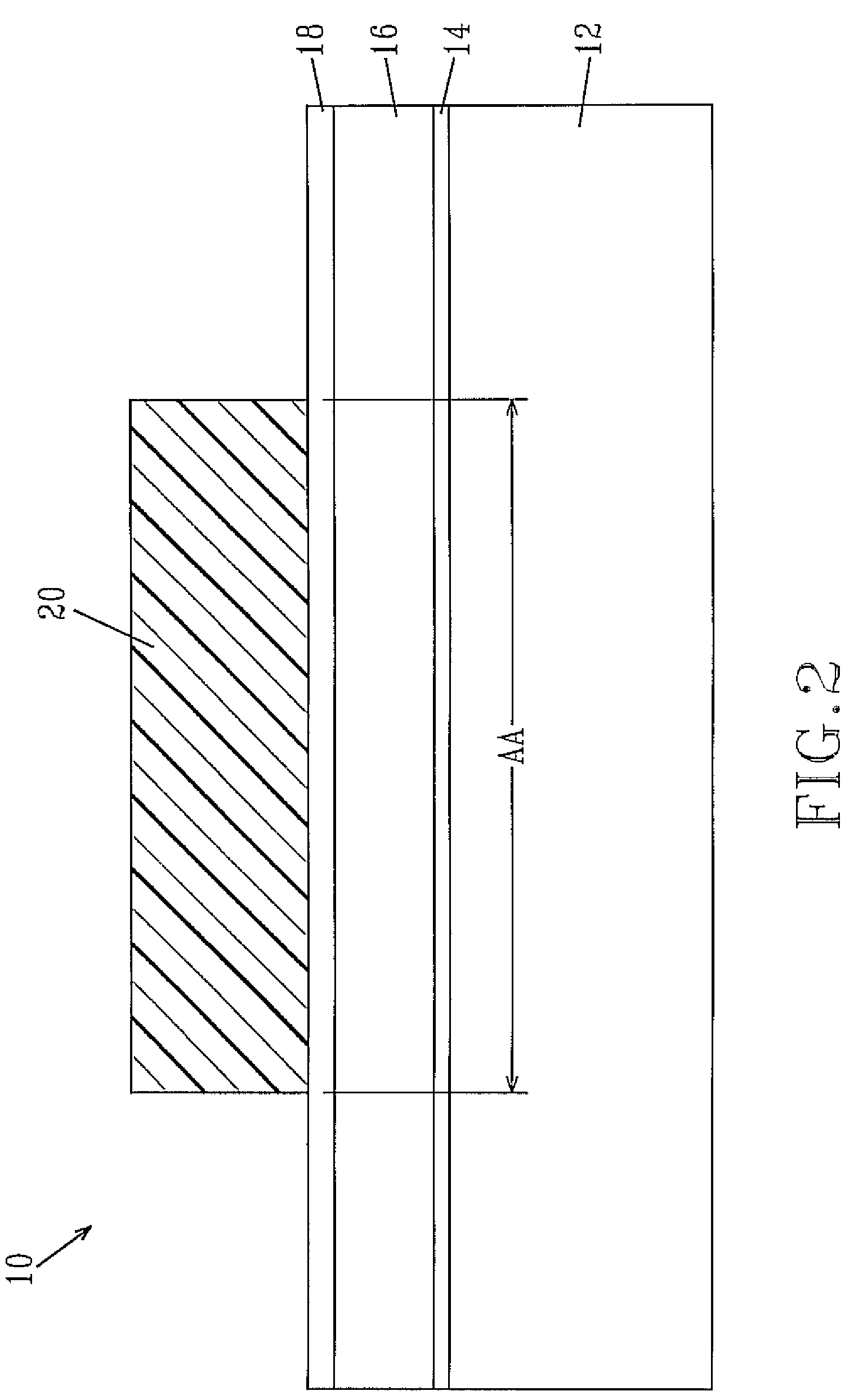

High-rise building with large scale display device inside transparent glass exterior

InactiveUS6237290B1Easy to carryImprove device performanceStampsPublic buildingsFloor slabWindow shutter

A high-rise building with a large scale dot-matrix display device is disclosed. The glass panels arranged in rows and columns form a curtain wall structured transparent outer wall 12 extending over an exterior of a building 10. Each panel is installed apart from end portions of floor slabs to form a void space therebetween. A plurality of louver structured modules 22 are arranged within the void space in rows and columns to form a large scale display area. Each module 22 has a louver-like structure formed of a plurality of posts 24 arranged in substantially parallel relationship and a plurality of parallel, uniformly spaced beams 26 connecting said adjacent posts 24. A plurality of LED combination lamps 28 are mounted on each beam 26 at uniform pitches as those between the adjacent beams 26. The LEDs are driven by drive circuits disposed in each beam 26. The vertical guide members 44 are fixed to the end portions of the floor slabs 20. The guide members 44 are arranged substantially in parallel relationship so that the modules 22 are supported between the adjacent guides 44 at the both lateral sides thereof. A plurality of vertical mullion members 48 fixed to the vertical guide members 44 as spaced apart from each of the vertical guides 44, so that the glass panels 12 are supported therebetween.

Owner:AVIX

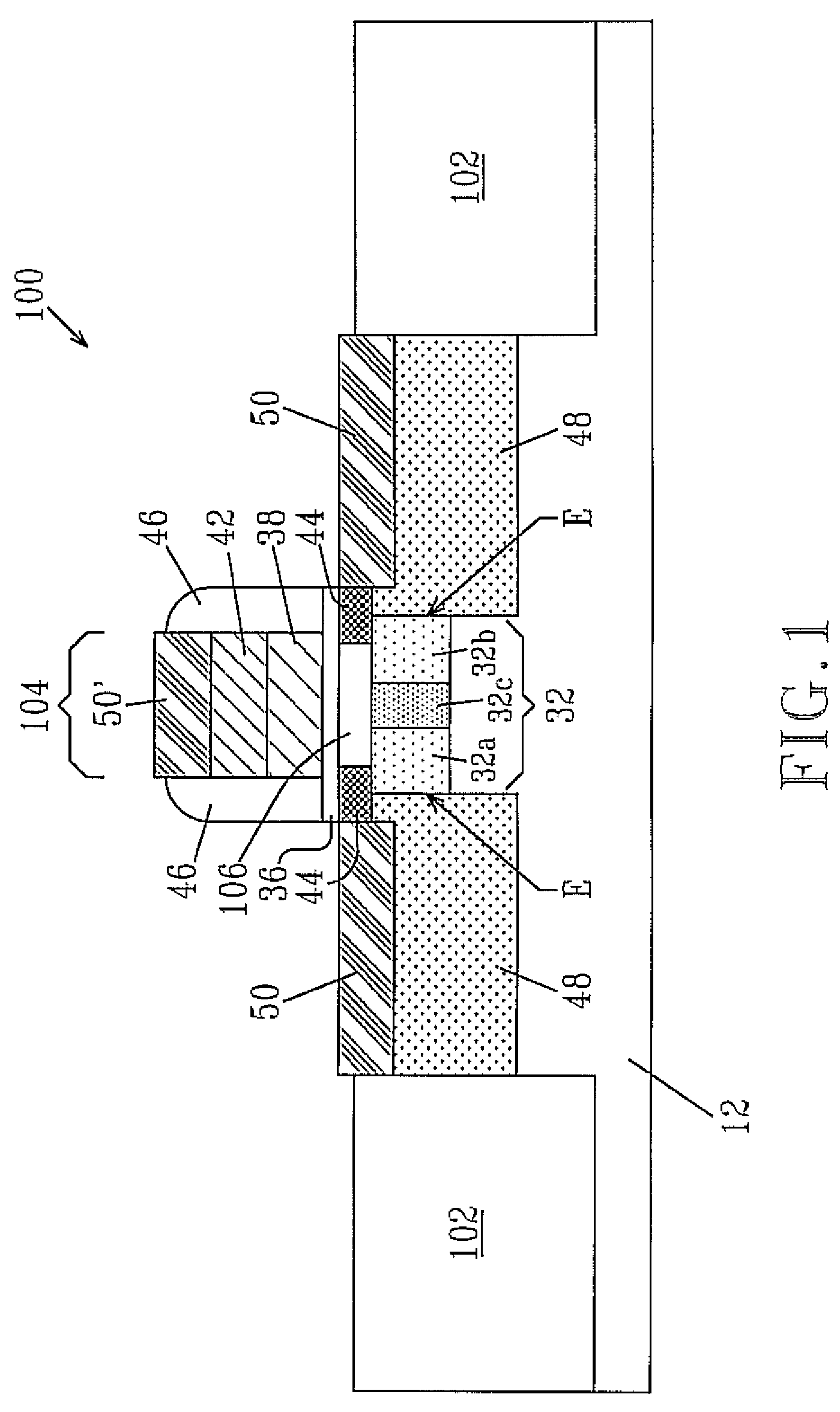

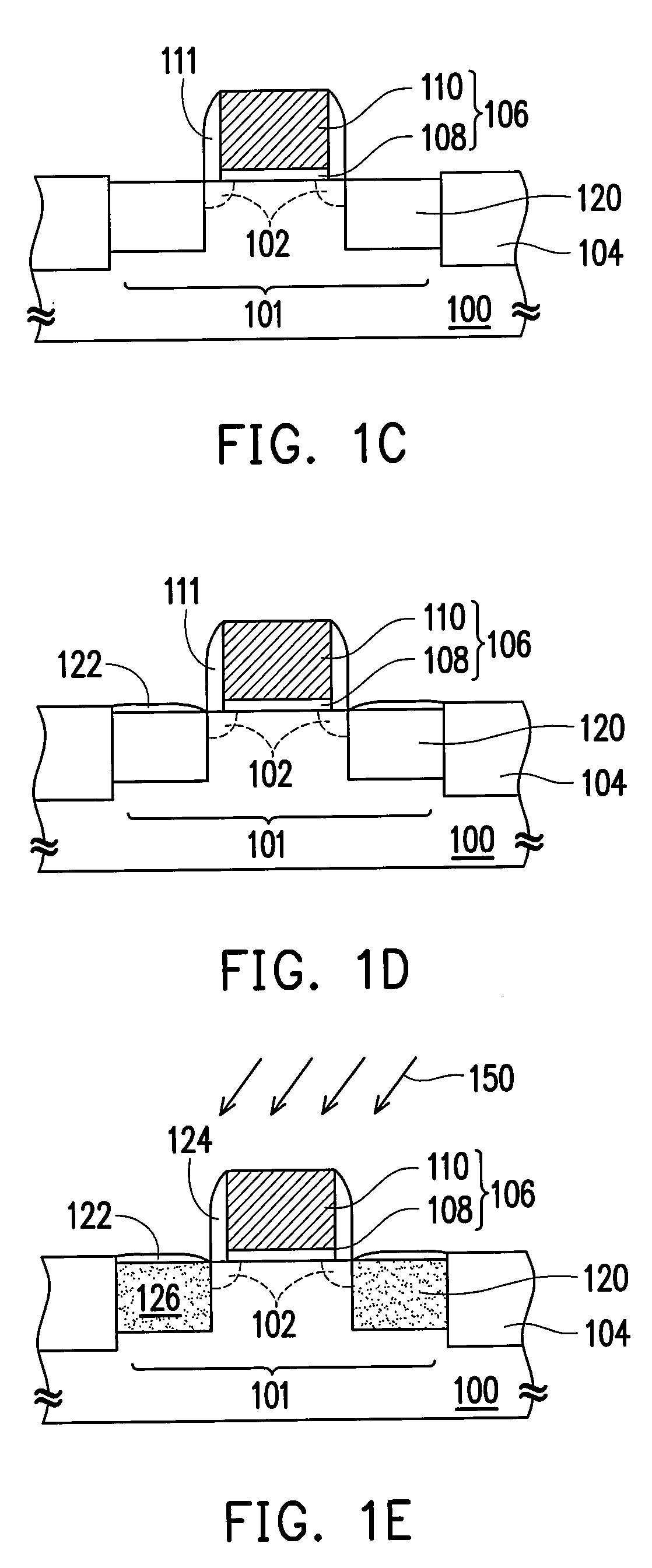

Method of fabricating a MOSFET device with metal containing gate structures

InactiveUS6869868B2Improve device performanceLow working voltageTransistorSemiconductor/solid-state device manufacturingTitanium nitrideTwo step

A method of forming a composite gate structure for a planar MOSFET device, as well as for vertical, double gate, FINFET device, has been developed. The method features a composite gate structure comprised of an overlying silicon gate structure shape, and an underlying titanium nitride gate structure shape. The titanium nitride component allows a lower work function, and thus lower device operating voltages to be realized when compared to counterpart gate structures formed with only polysilicon. A novel, two step gate structure definition procedure, featuring an anisotropic first etch procedure for definition of the polysilicon gate structure shape, followed by a wet or dry isotopic second etch procedure for definition of the titanium nitride gate structure shape, is employed.

Owner:TAIWAN SEMICON MFG CO LTD

High performance MOSFET

InactiveUS7704844B2Improve device performanceImprove short channel effectSemiconductor/solid-state device manufacturingSemiconductor devicesHigh concentrationDopant

A semiconductor structure which exhibits high device performance and improved short channel effects is provided. In particular, the present invention provides a metal oxide semiconductor field effect transistor (MOFET) that includes a low dopant concentration within an inversion layer of the structure; the inversion layer is an epitaxial semiconductor layer that is formed atop a portion of the semiconductor substrate. The inventive structure also includes a well region of a first conductivity type beneath the inversion layer, wherein the well region has a central portion and two horizontally abutting end portions. The central portion has a higher concentration of a first conductivity type dopant than the two horizontally abutting end portions. Such a well region may be referred to as a non-uniform super-steep retrograde well.

Owner:GLOBALFOUNDRIES INC

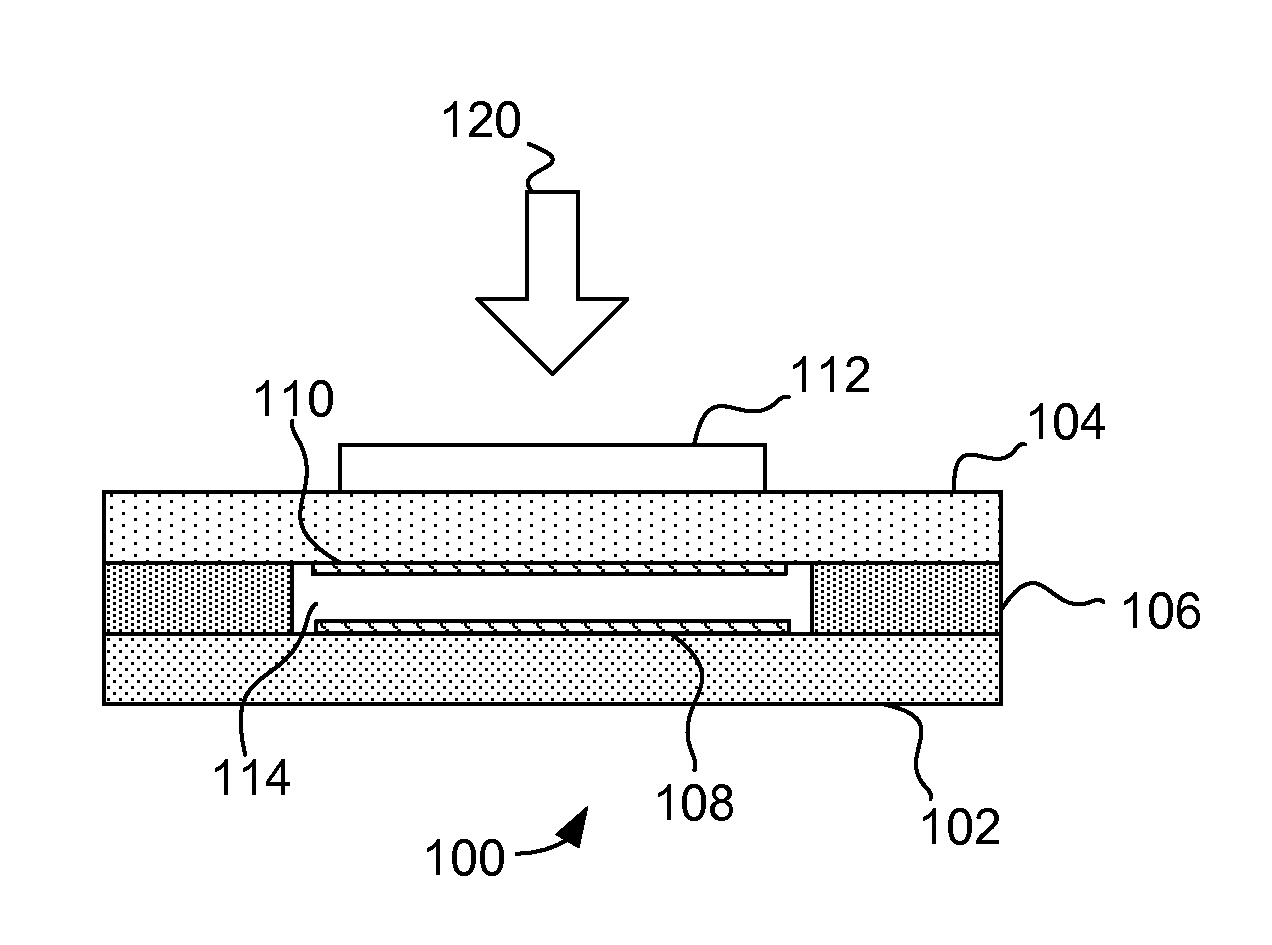

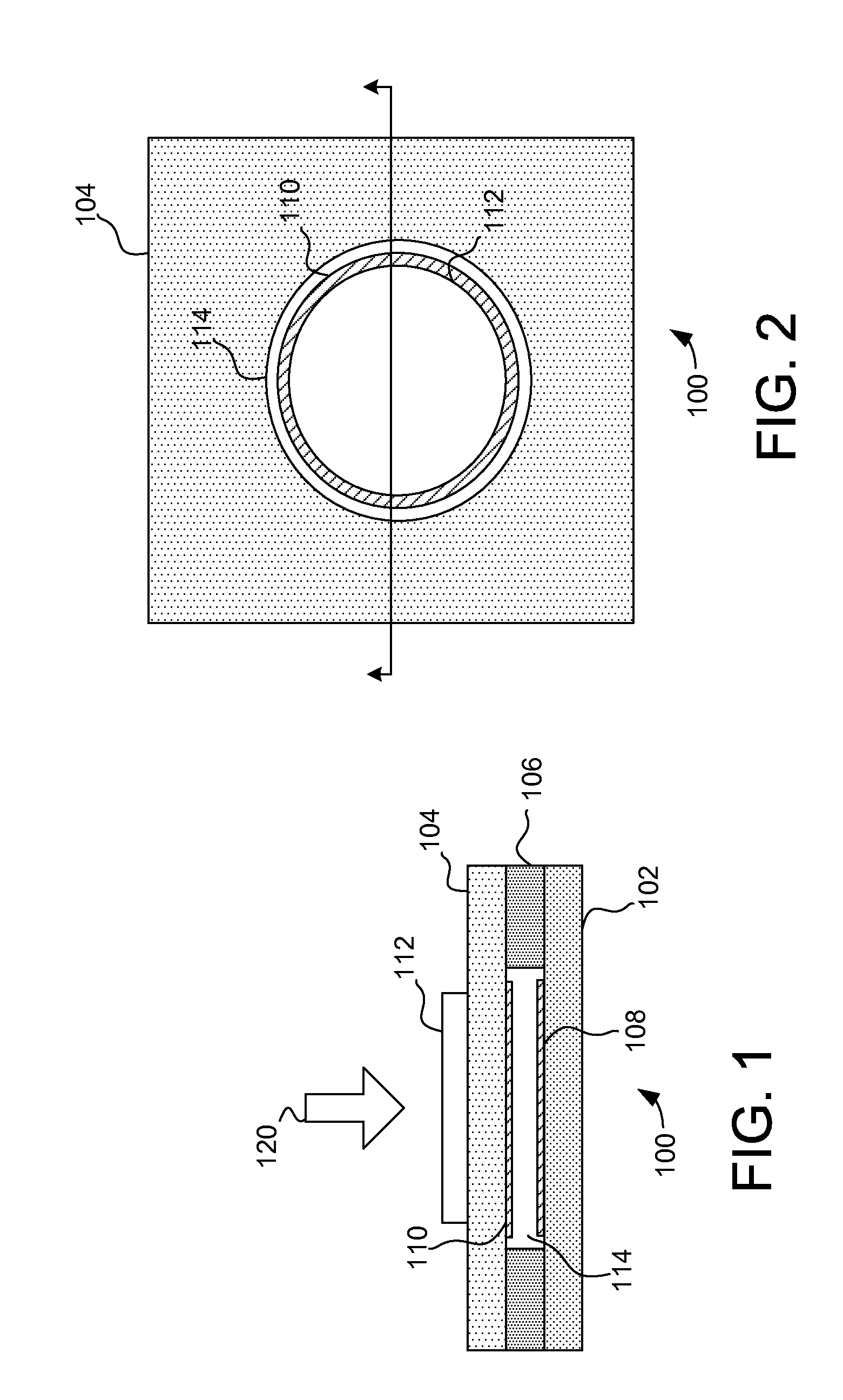

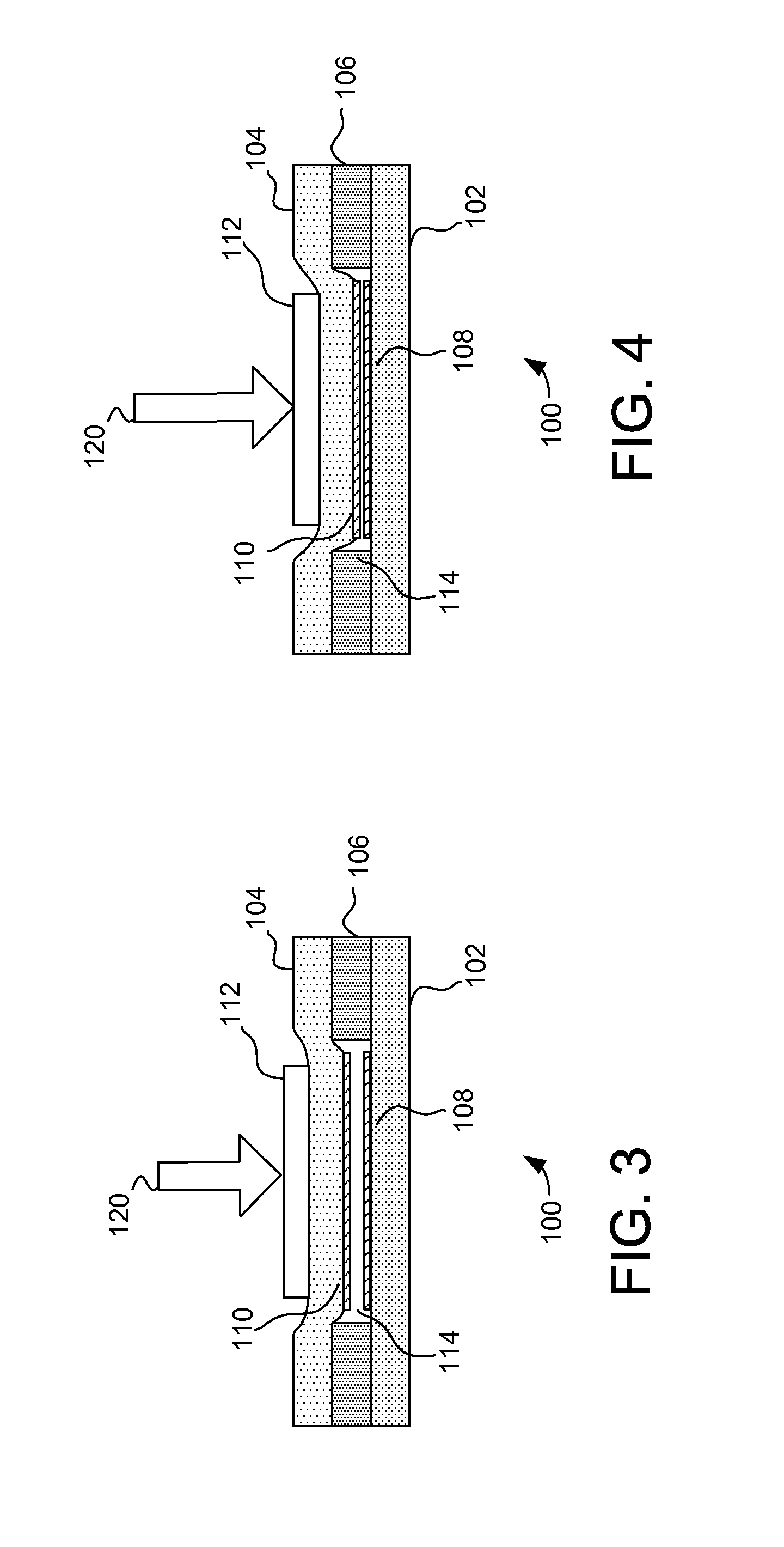

Input device with force sensing

ActiveUS20110278078A1Improve device performanceReduce complexityTransmission systemsResistance/reactance/impedenceCapacitanceEngineering

Devices and methods are provided that utilize a first electrode disposed on a first substrate and a second electrode disposed on a second substrate, where the first electrode and the second electrode define at least part of a variable capacitance. A third substrate is arranged between the first substrate and the second substrate, the third substrate having an opening arranged such that at least a portion of the first electrode and the second electrode overlap the opening. A transmission element is provided that partially overlaps the opening. The transmission element is physically coupled to the second electrode such that a force biasing the transmission element causes the second electrode to deflect relative to the first electrode, thus changing the variable capacitance. A measurement of the variable capacitance may then be used to determine force information.

Owner:SYNAPTICS INC

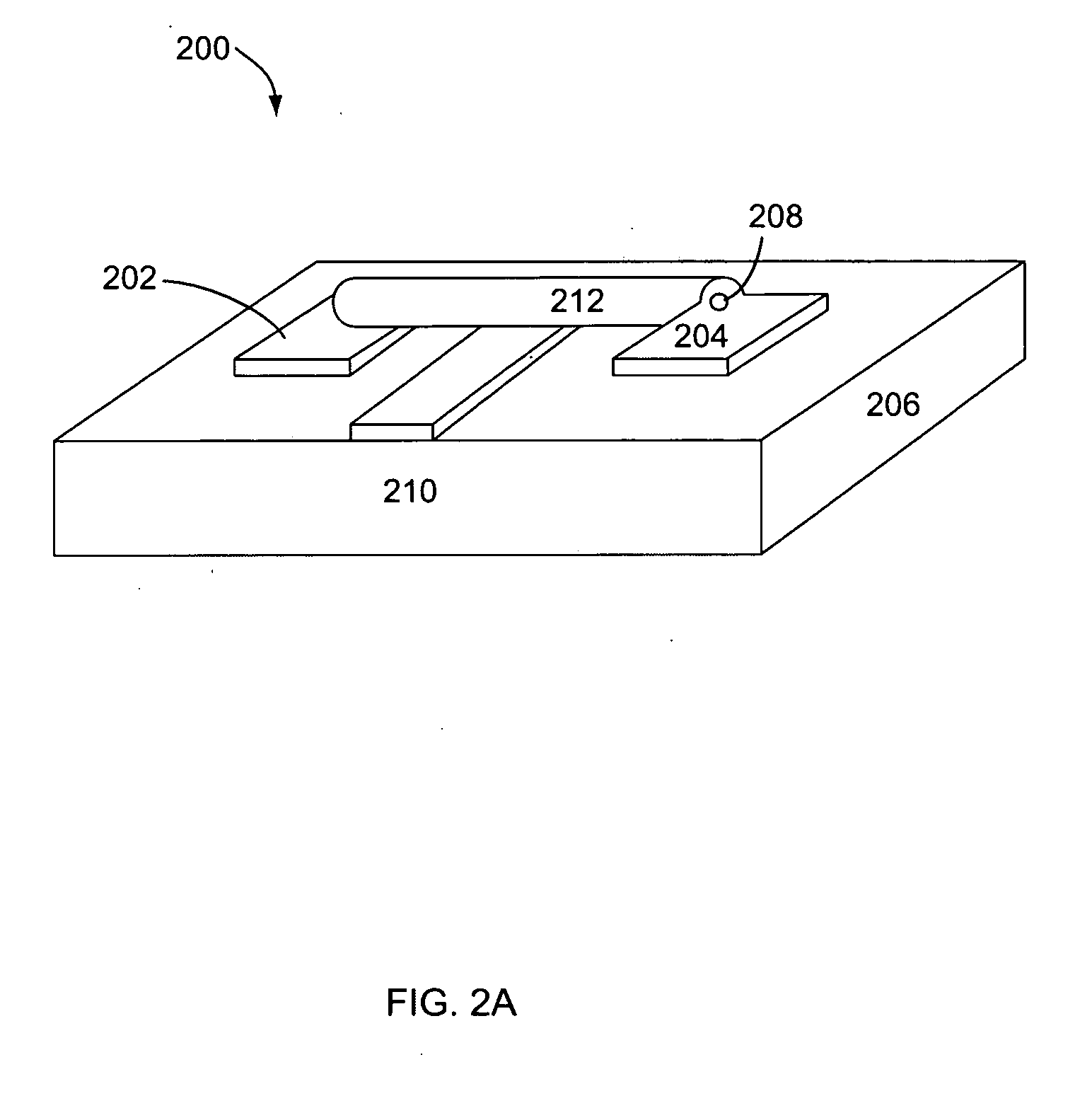

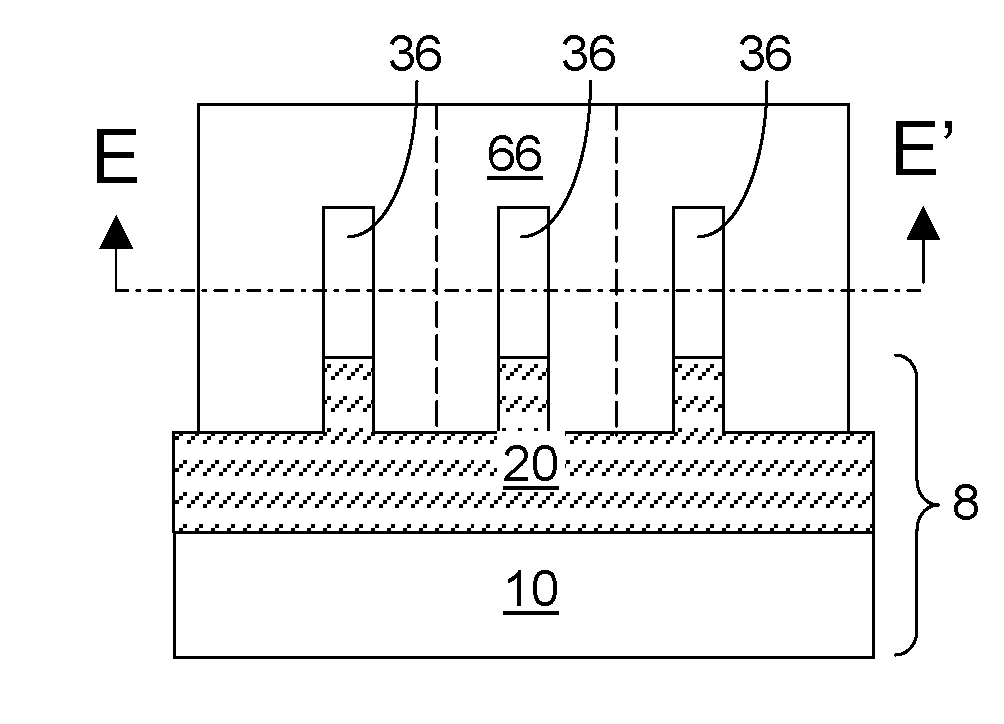

Finfet with longitudinal stress in a channel

ActiveUS20100038679A1Improve device performanceReduce the overall heightSolid-state devicesSemiconductor/solid-state device manufacturingDielectricGate dielectric

At least one gate dielectric, a gate electrode, and a gate cap dielectric are formed over at least one channel region of at least one semiconductor fin. A gate spacer is formed on the sidewalls of the gate electrode, exposing end portions of the fin on both sides of the gate electrode. The exposed portions of the semiconductor fin are vertically and laterally etched, thereby reducing the height and width of the at least one semiconductor fin in the end portions. Exposed portions of the insulator layer may also be recessed. A lattice-mismatched semiconductor material is grown on the remaining end portions of the at least one semiconductor fin by selective epitaxy with epitaxial registry with the at least one semiconductor fin. The lattice-mismatched material applies longitudinal stress along the channel of the finFET formed on the at least one semiconductor fin.

Owner:GLOBALFOUNDRIES US INC

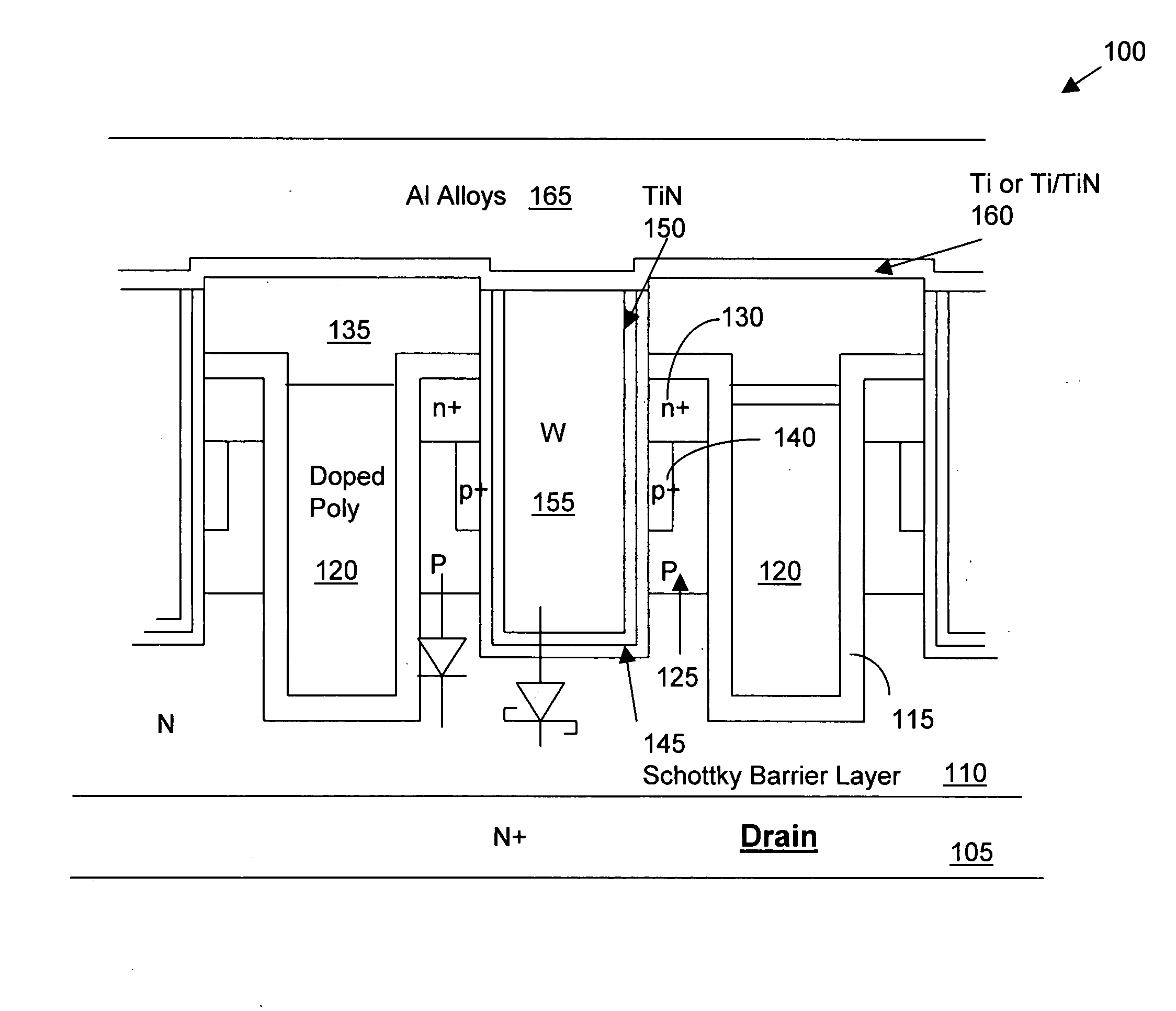

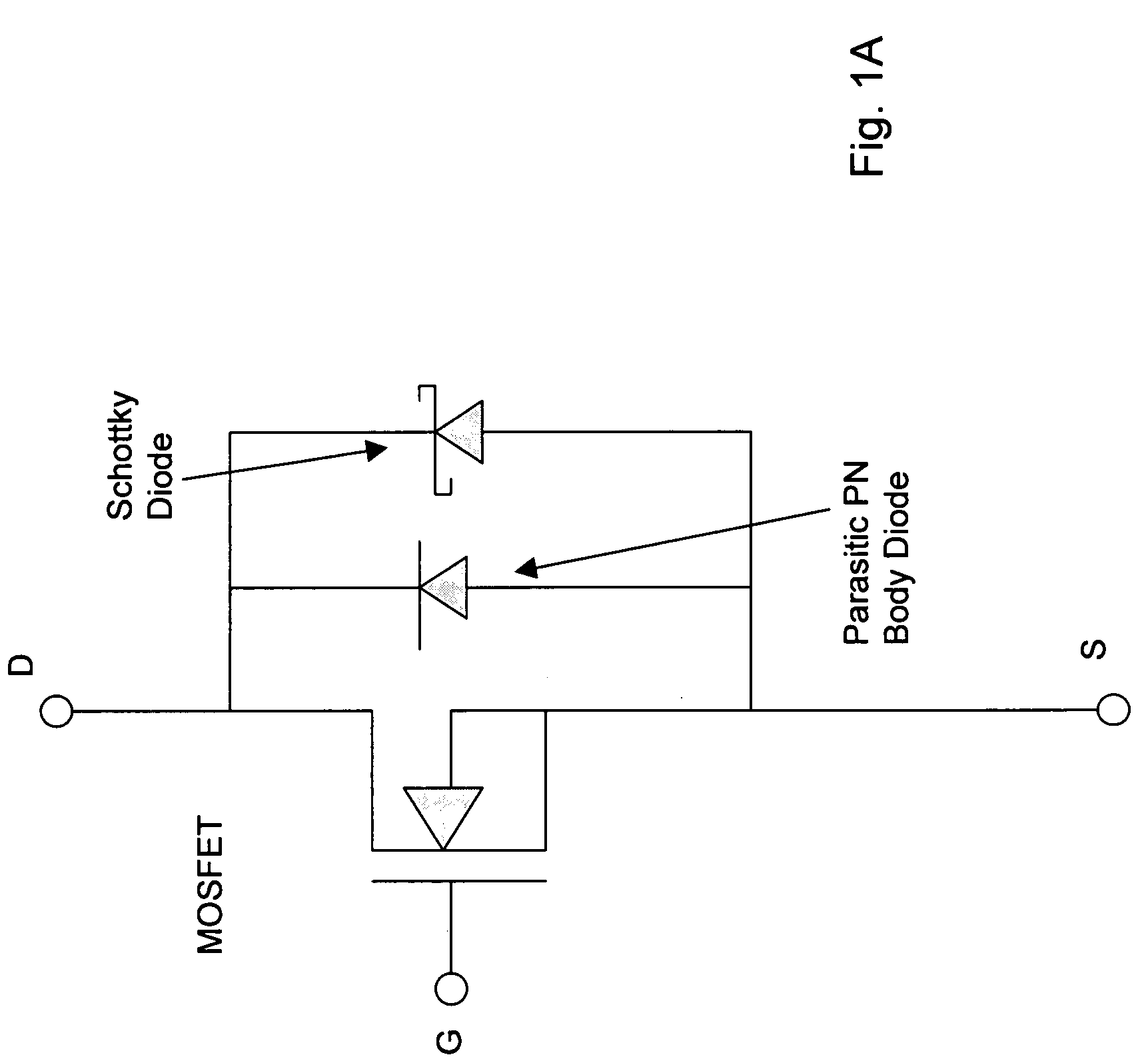

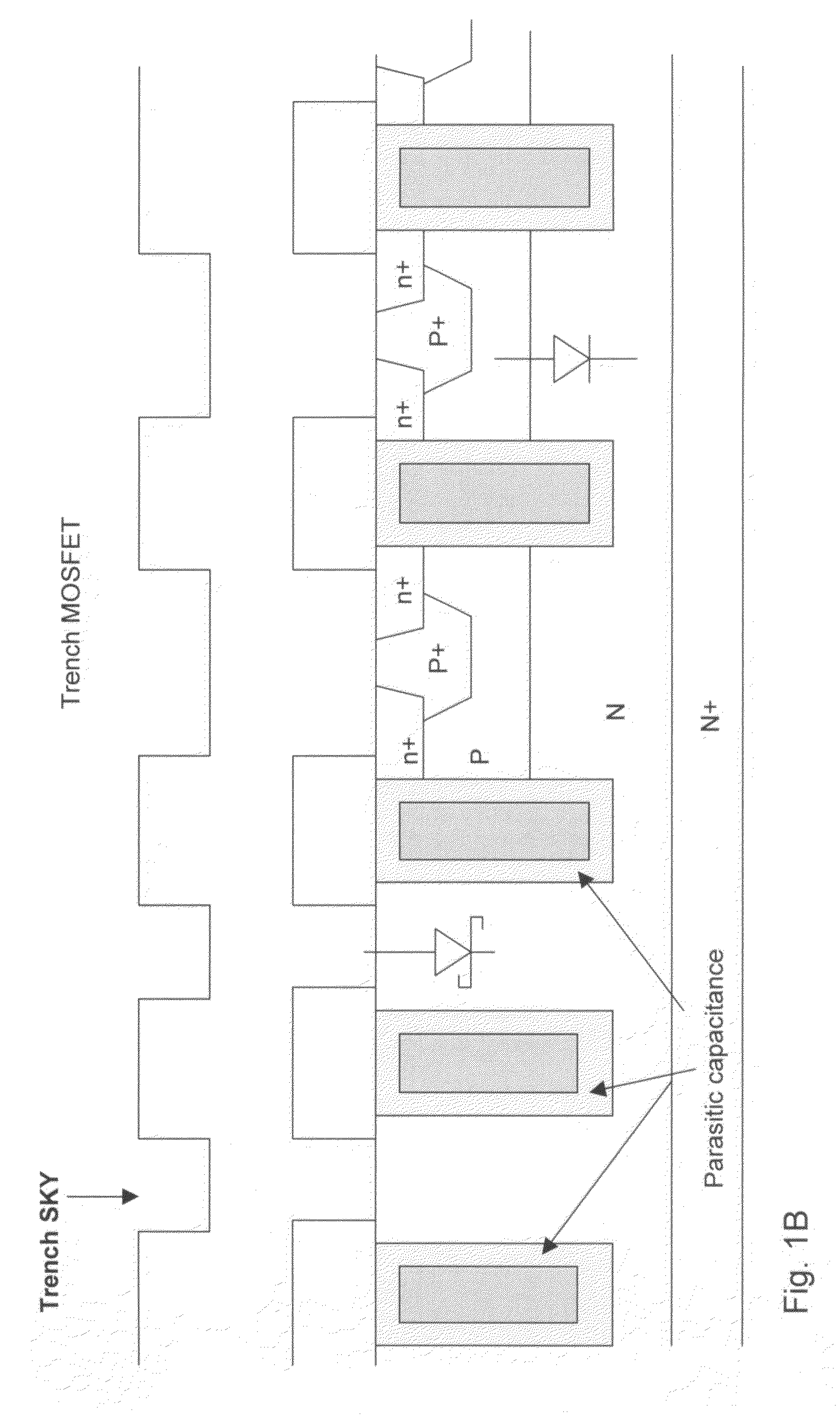

Trenched mosfets with embedded schottky in the same cell

InactiveUS20080246082A1Overcome limitationsReduce parasitic capacitanceSemiconductor/solid-state device manufacturingDiodeMOSFETSchottky barrier

A semiconductor power device includes trenched semiconductor power device comprising a trenched gate surrounded by a source region encompassed in a body region above a drain region disposed on a bottom surface of a substrate. The semiconductor power device further includes an insulation layer covering the trenched semiconductor power device with a source-body contact trench opened therethrough the source and body regions and extending into an epitaxial layer below the body regions and filled with contact metal plug therein. The semiconductor power device further includes an embedded Schottky diode disposed near a bottom of the source-body contact trench below the contact metal plug wherein the Schottky diode further includes a Schottky barrier layer having a barrier height for reducing a leakage current through the embedded Schottky diode during a reverse bias between the drain and the source.

Owner:FORCE MOS TECH CO LTD

Mos device structure

InactiveUS20090166625A1Restrain boron channeling effectReduce harmTransistorSemiconductor/solid-state device manufacturingComputational physicsSemiconductor

The present invention provides a method for forming a metal-oxide-semiconductor (MOS) device and the structure thereof. The method includes at least the steps of forming a silicon germanium layer by the first selective epitaxy growth process and forming a cap layer on the silicon germanium layer by the second selective epitaxy growth process. Hence, the undesirable effects caused by ion implantation can be mitigated.

Owner:UNITED MICROELECTRONICS CORP

Methods for nanowire growth

ActiveUS20060009003A1Ease of mass productionImprove device performancePolycrystalline material growthNanoinformaticsNanowireGas phase

The present invention is directed to methods to produce, process, and exploit nanomaterials, and particularly elongated nanowire materials. The invention provides a method for producing nanowires that includes providing a thin film of a catalyst material with varying thickness on a substrate, heating the substrate and thin film, such that the thin film disassociates at the relatively thinner regions and vapor depositing a semiconductor onto the substrate to produce nanowires. A method is also provided in which two or more thin films of different materials are overlayed over a substrate, selectively etching the first underlying thin film to create a plurality of islands of the second thin film that mask portions of the first thin film and expose other portions and growing nanowires on the first thin film. Additional methods for producing nanowires are provided.

Owner:ONED MATERIAL INC

Operation scheme for programming charge trapping non-volatile memory

ActiveUS20050281085A1Shorten the timeImprove device performanceRead-only memoriesDigital storageHemt circuitsEngineering

A circuit and method for self-converging programming of a charge storage memory cell, such as NROM or floating gate flash. The method includes determining a data value from one of more than two data values to be stored in the memory cell, and applying a gate voltage to the control gate at one of a predetermined set of gate voltage levels selected in response to the determined data value. Programming parameters are controlled to establish a self-converging threshold state that is determined by the selected gate voltage. In this manner, the threshold voltage converges on a target threshold corresponding with the determined data value for the memory cell. Program verify operations are reduced or eliminated in various embodiments, reducing the overall time required for the program operation, and improving device performance. A second portion of the program operation can include verify operations to improve threshold margins across the array.

Owner:MACRONIX INT CO LTD