Patents

Literature

2013 results about "Polysilicon gate" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

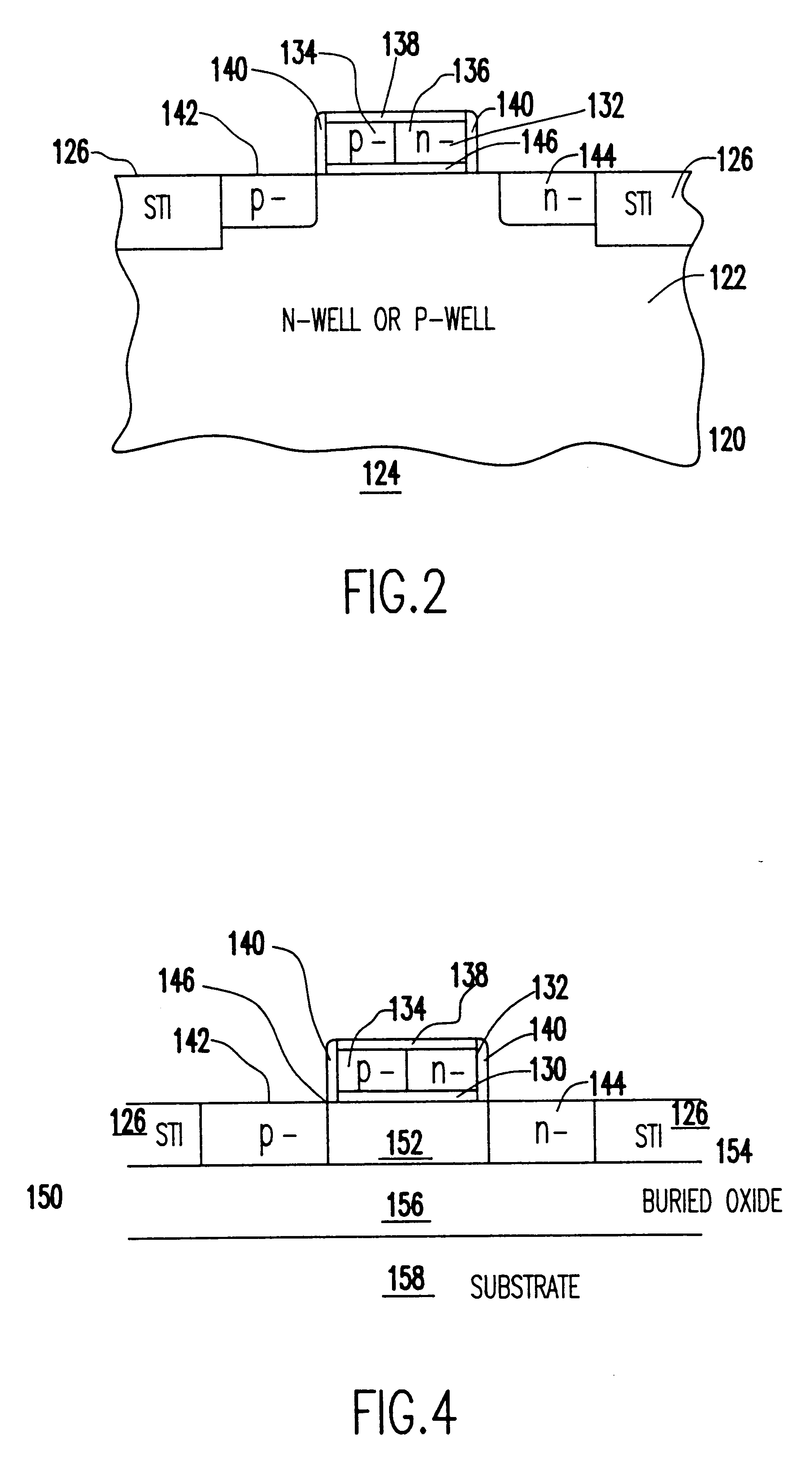

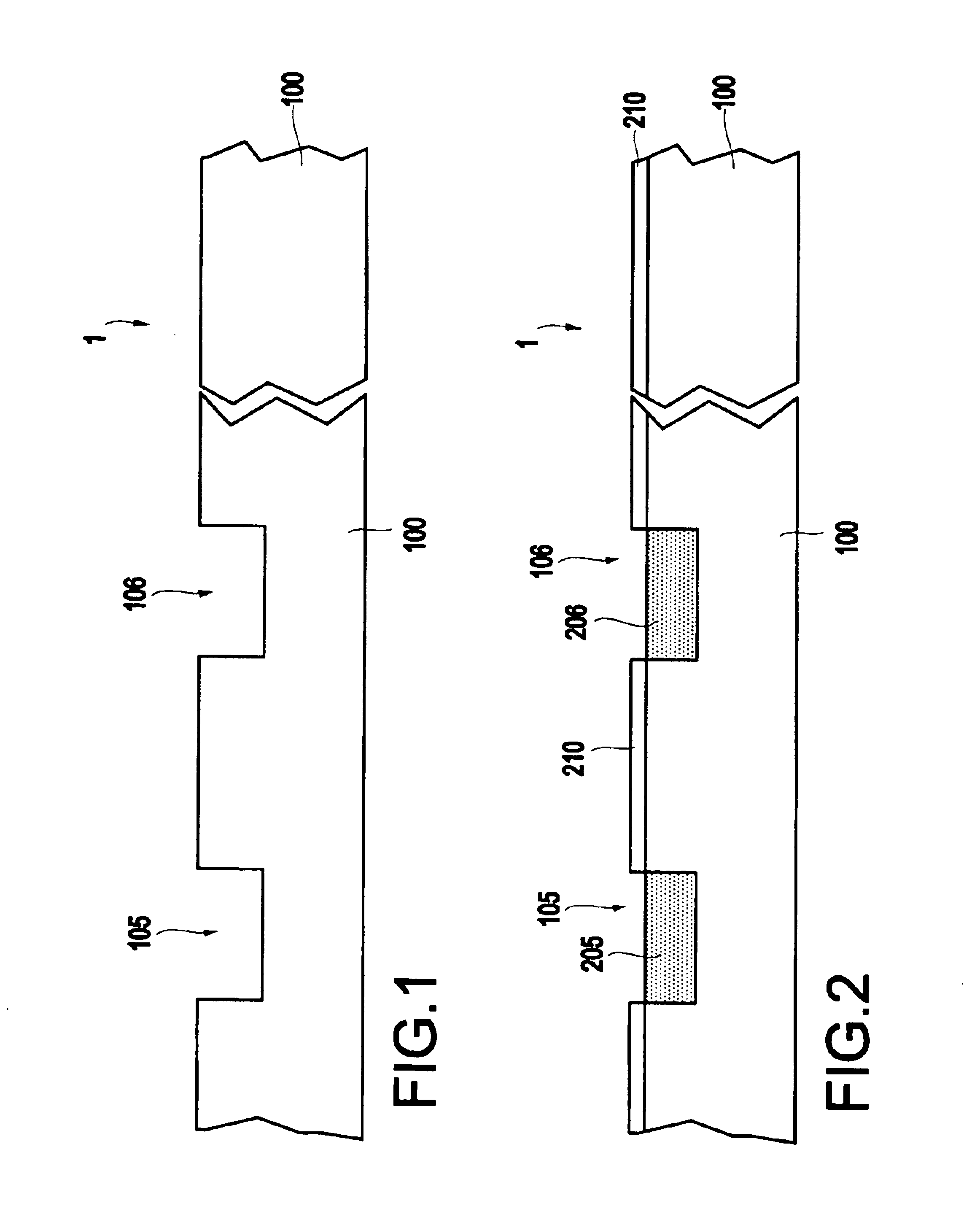

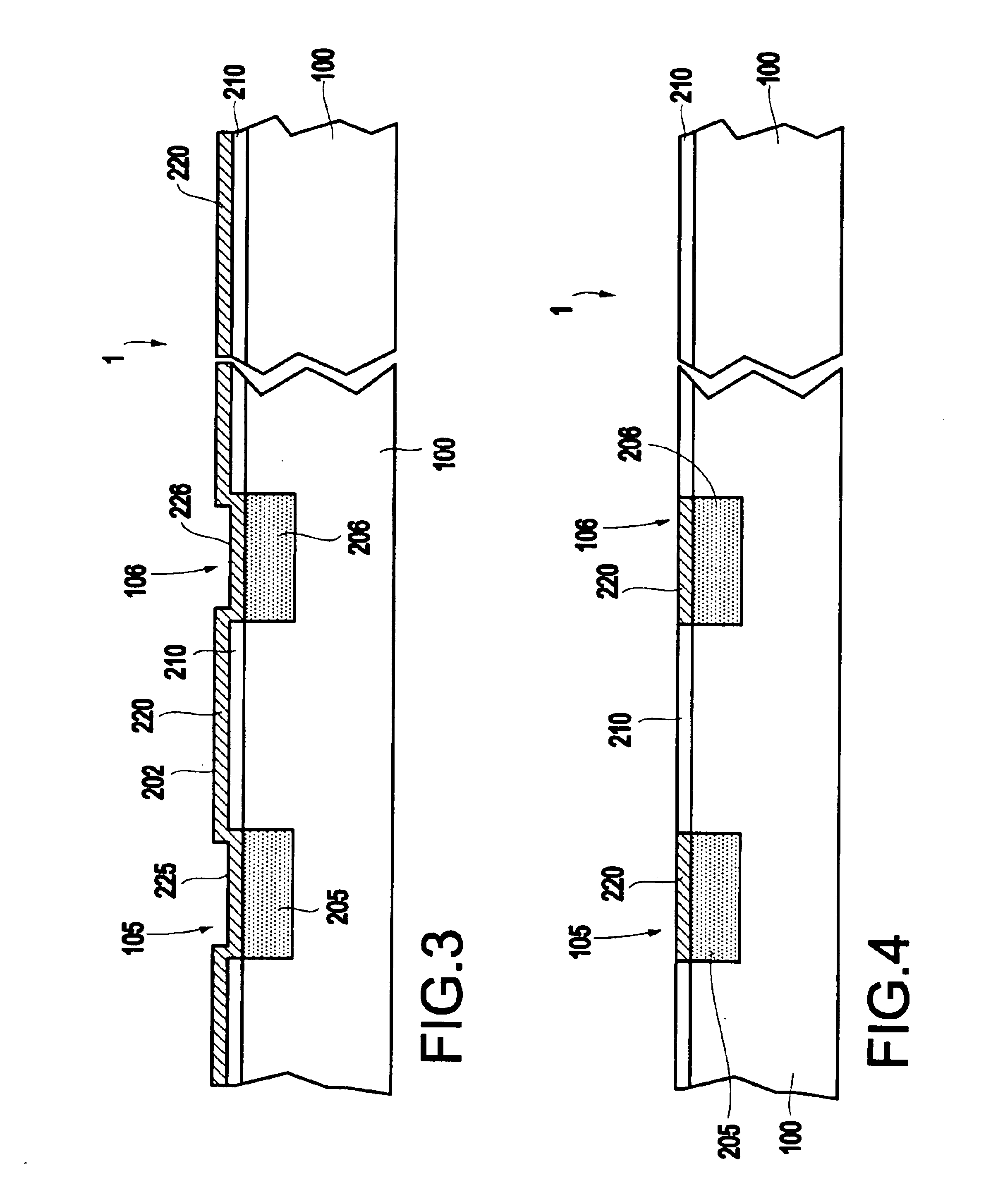

Integrated Circuit (IC) Chip Having Both Metal and Silicon Gate Field Effect Transistors (FETs) and Method of Manufacture

InactiveUS20120292664A1Suppression of short channel effectsWithout impairing performanceTransistorSemiconductor/solid-state device detailsField-effect transistorPolysilicon gate

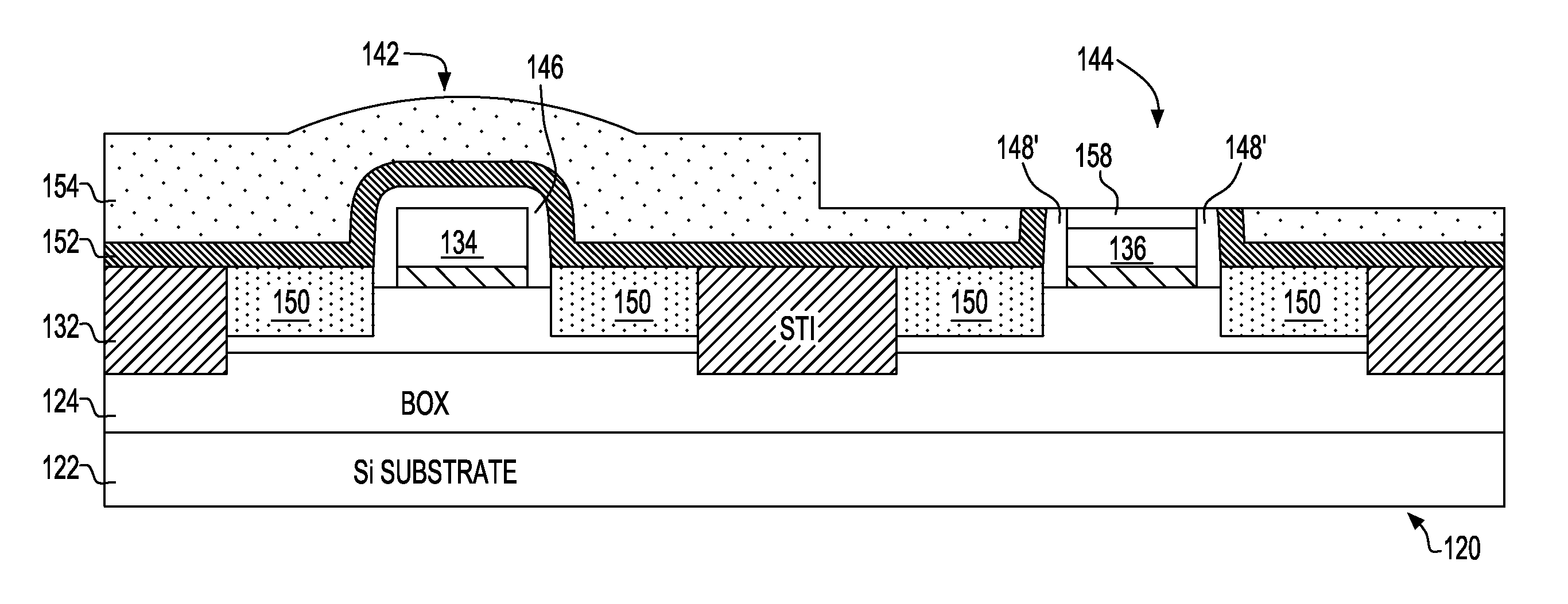

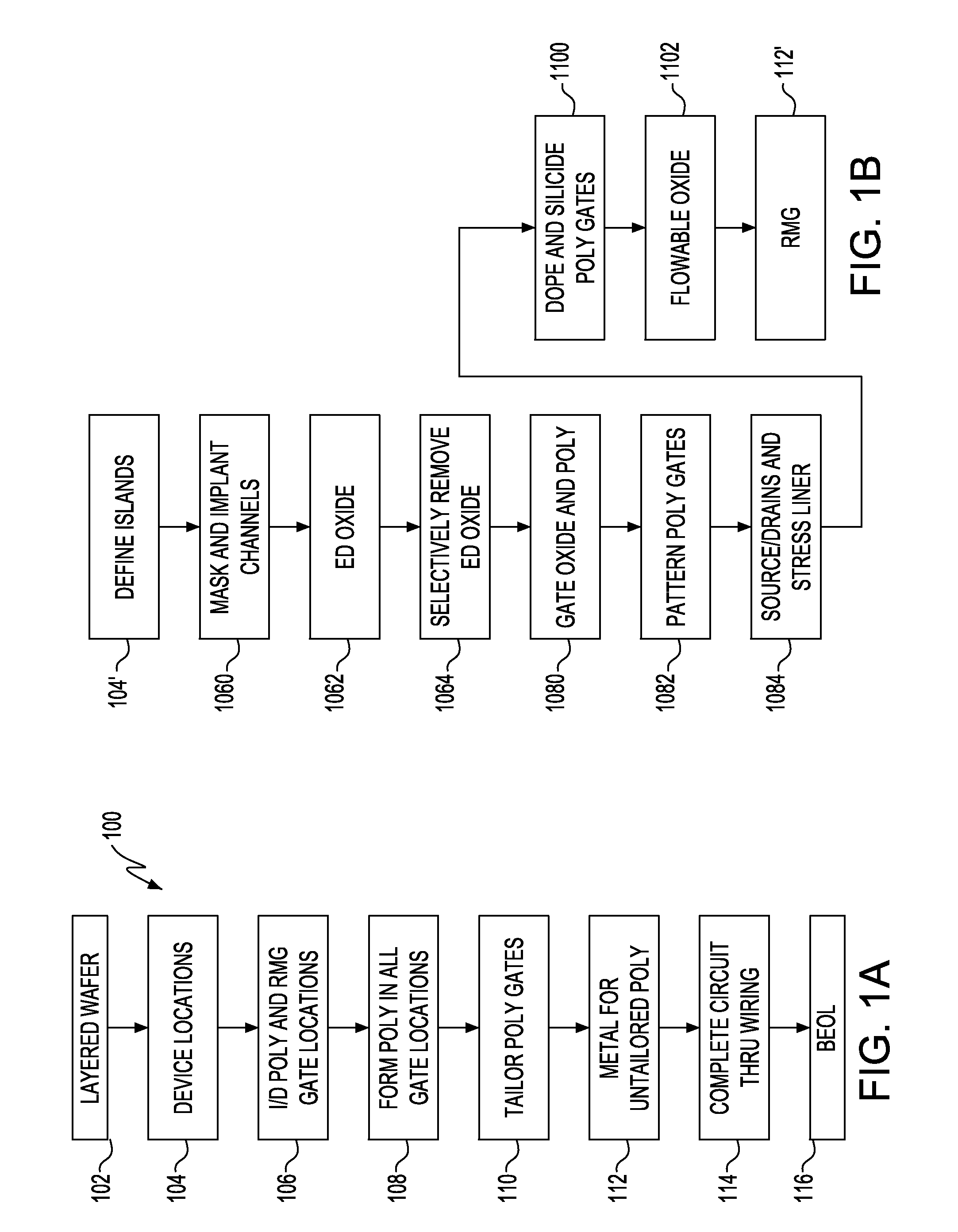

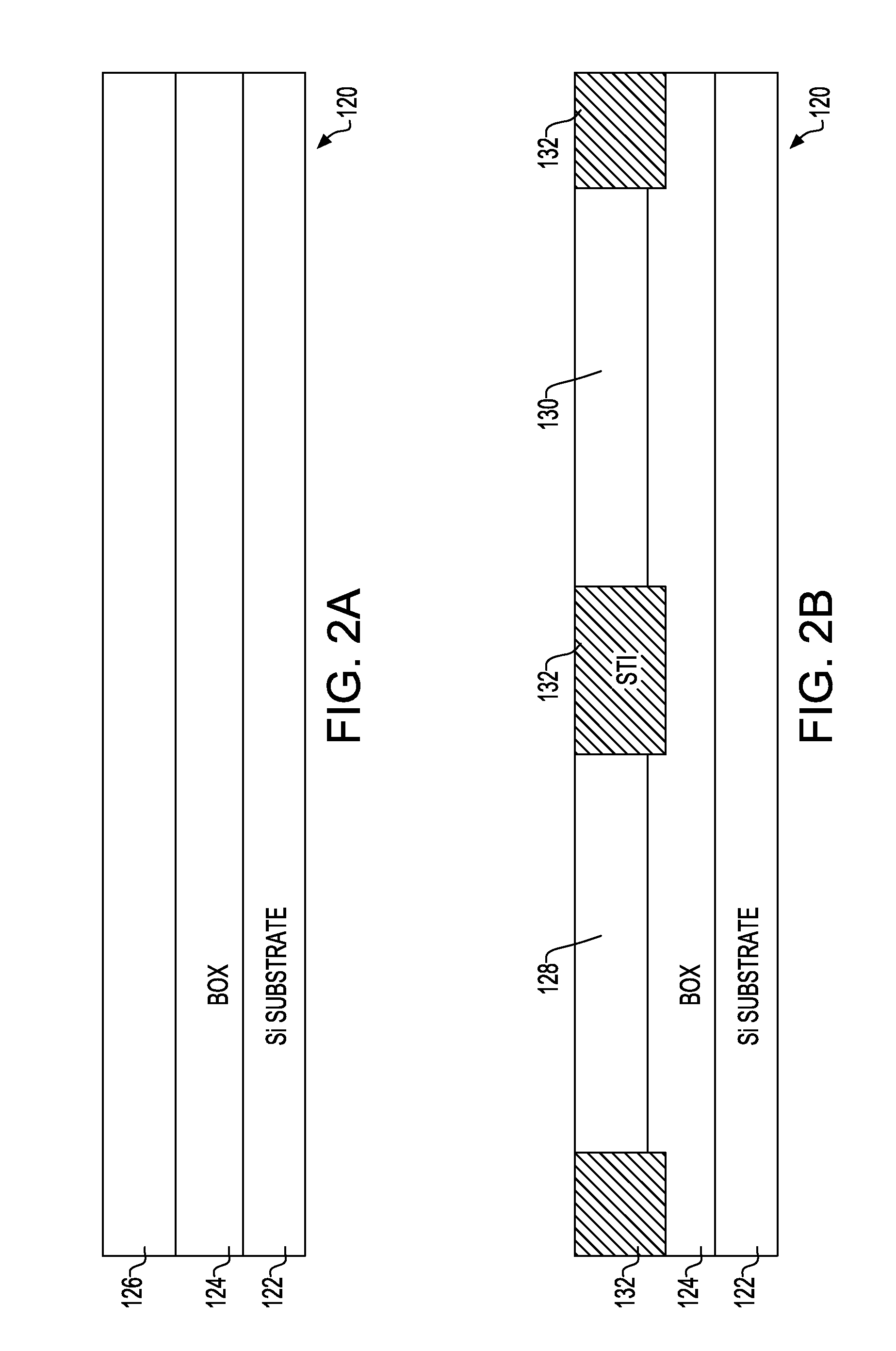

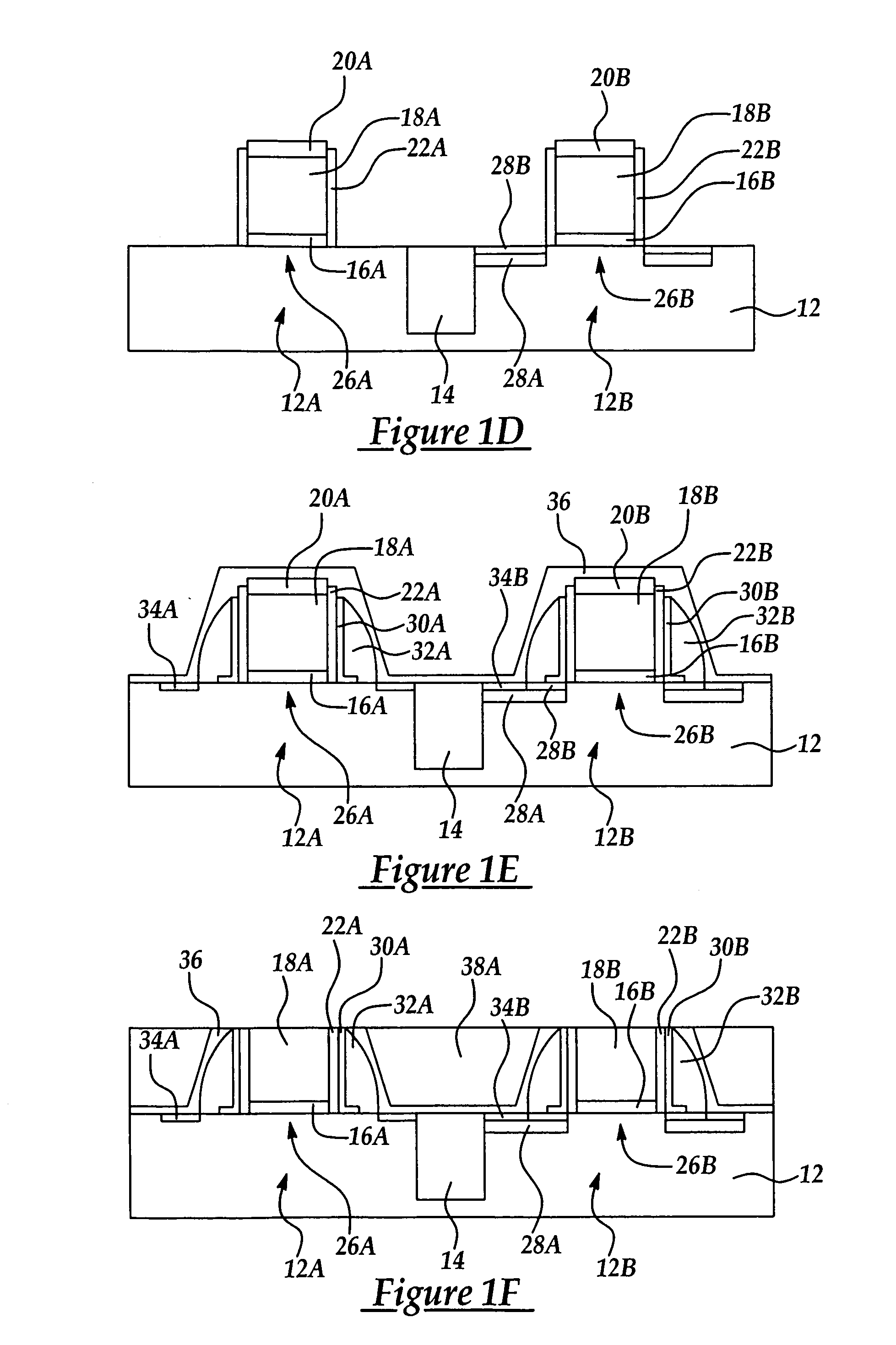

Field Effect Transistors (FETs), Integrated Circuit (IC) chips including the FETs, and a method of forming the FETs on ICs. FET locations are defined on a layered semiconductor wafer, preferably a Silicon On Insulator (SOI) wafer. One or more FET locations are defined as silicon gate locations and remaining as Replacement Metal Gate (RMG) FET locations with at least one of each on the IC. Polysilicon gates are formed in all FET locations. Gates in silicon gate locations are tailored, e.g., doped and silicided. Remaining polysilicon gates are replaced with metal in RMG FET locations. FETs are connected together into circuits with RMG FETs being connected to silicon gate FETs.

Owner:GLOBALFOUNDRIES INC

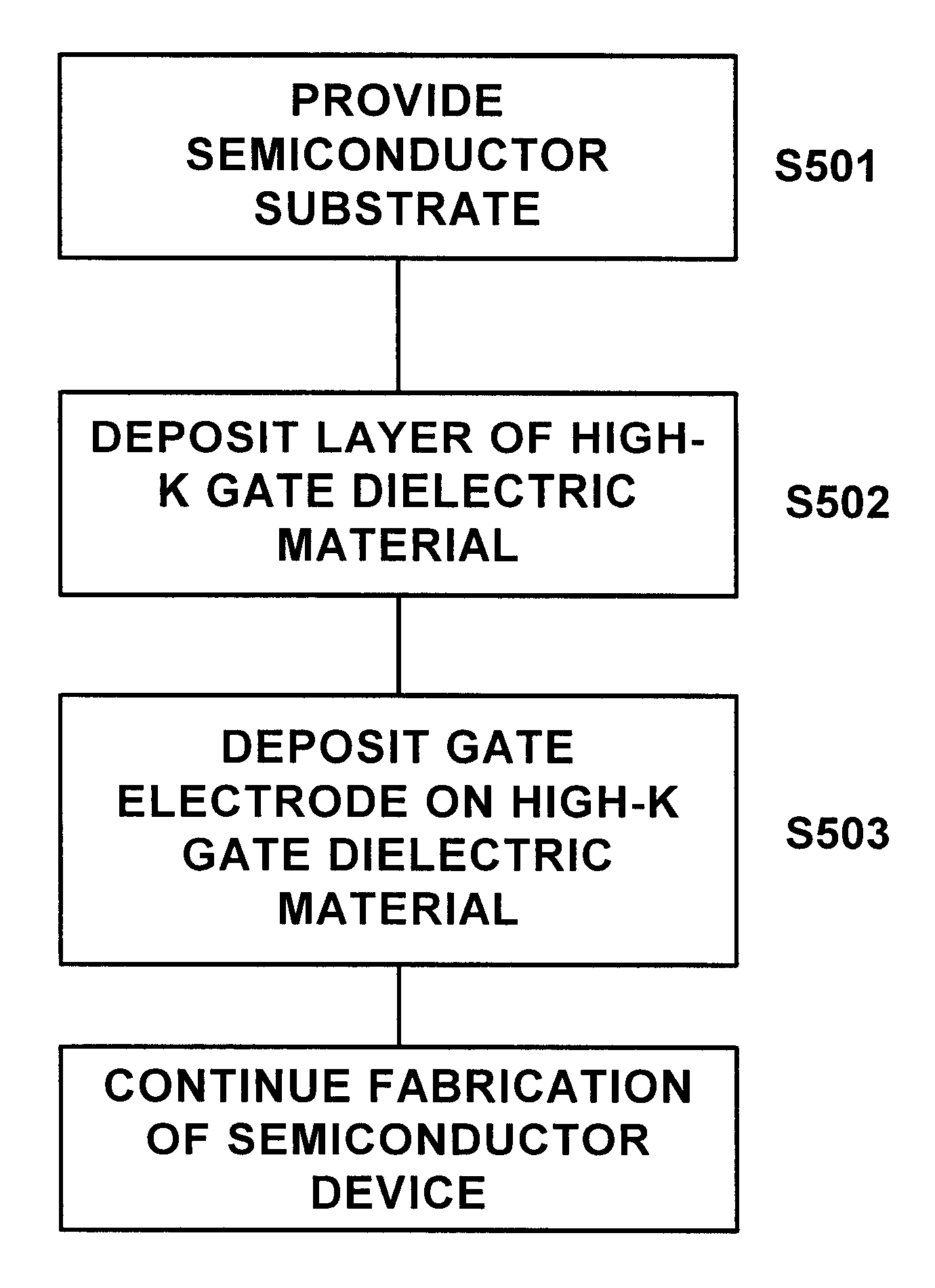

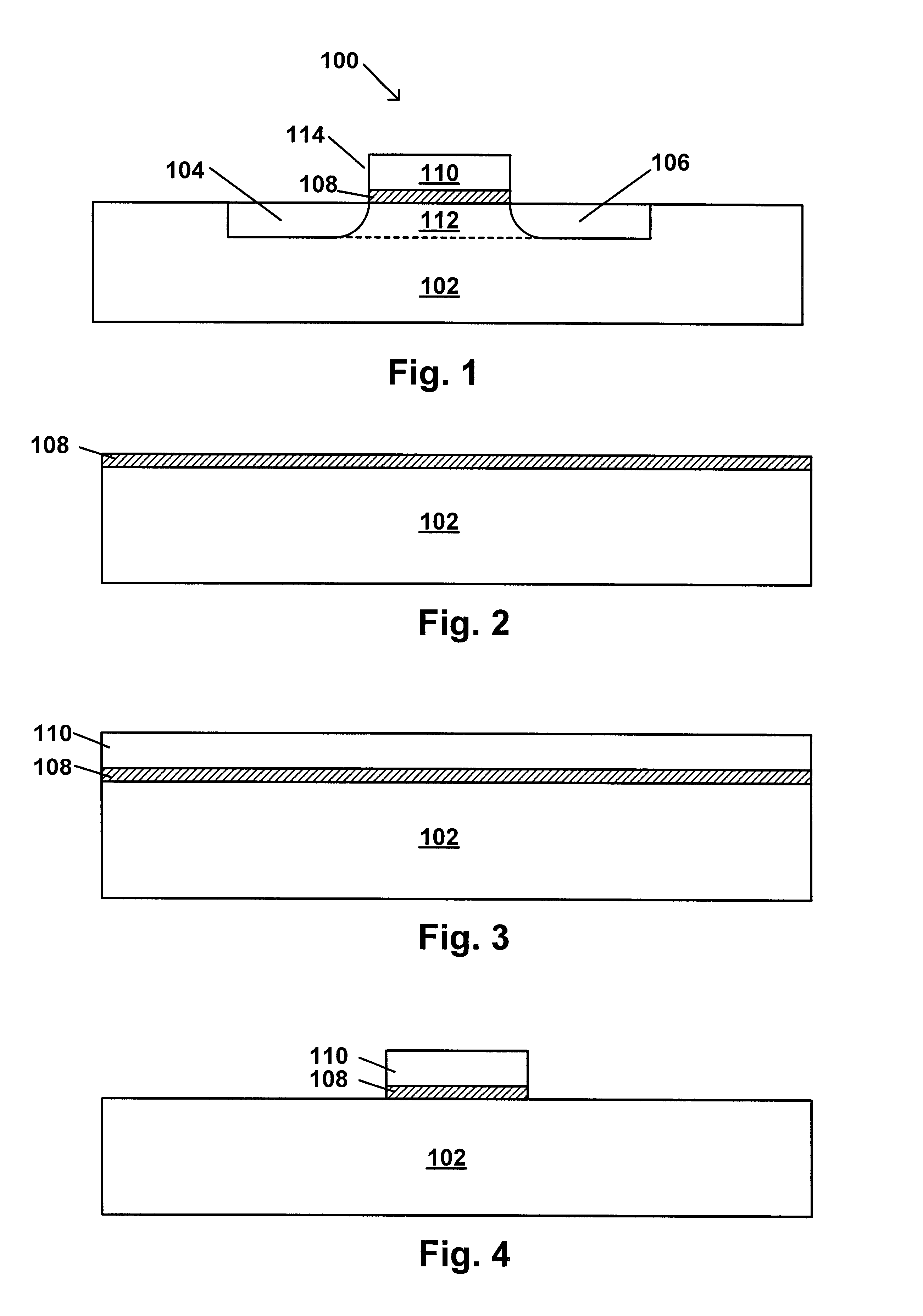

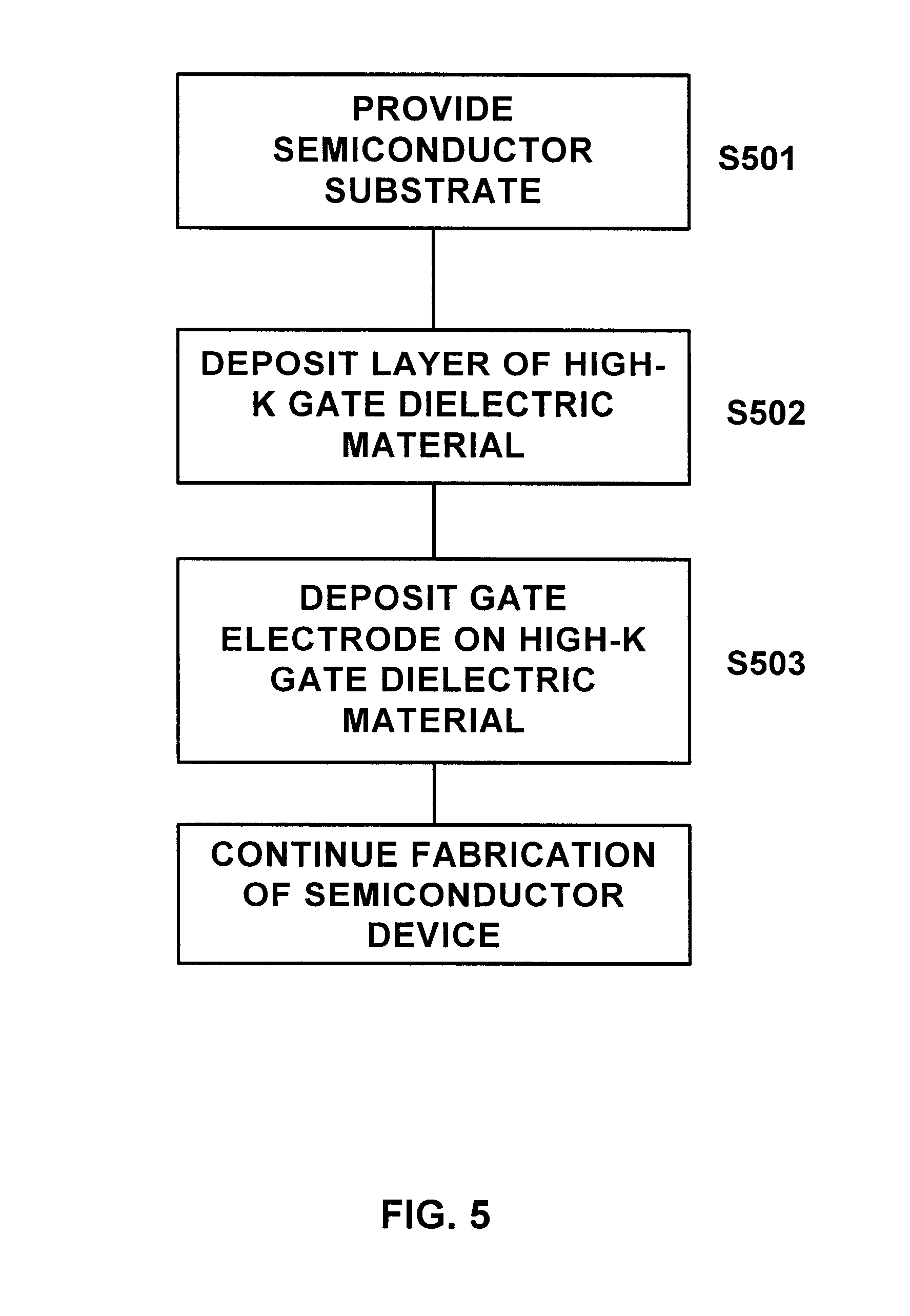

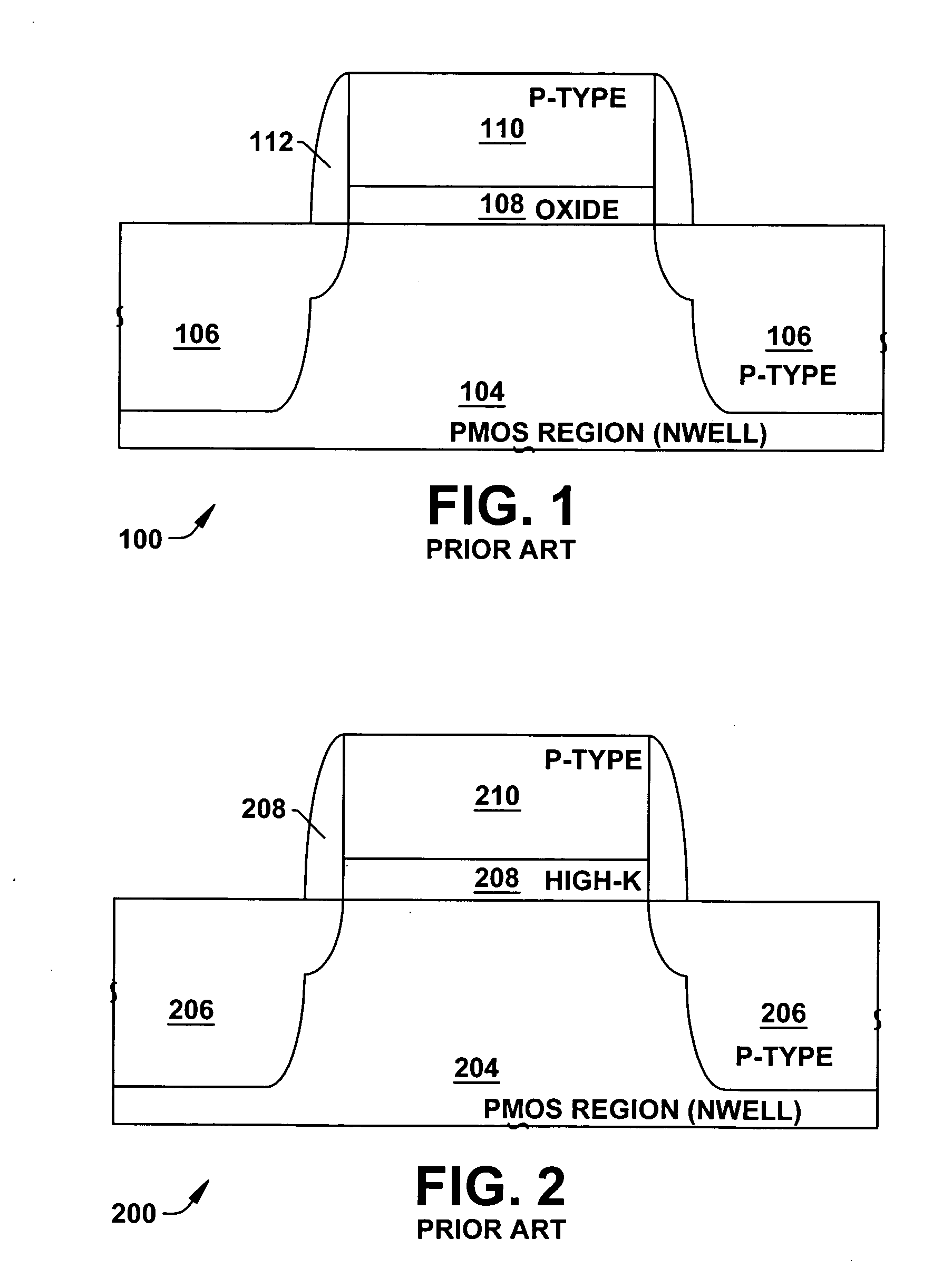

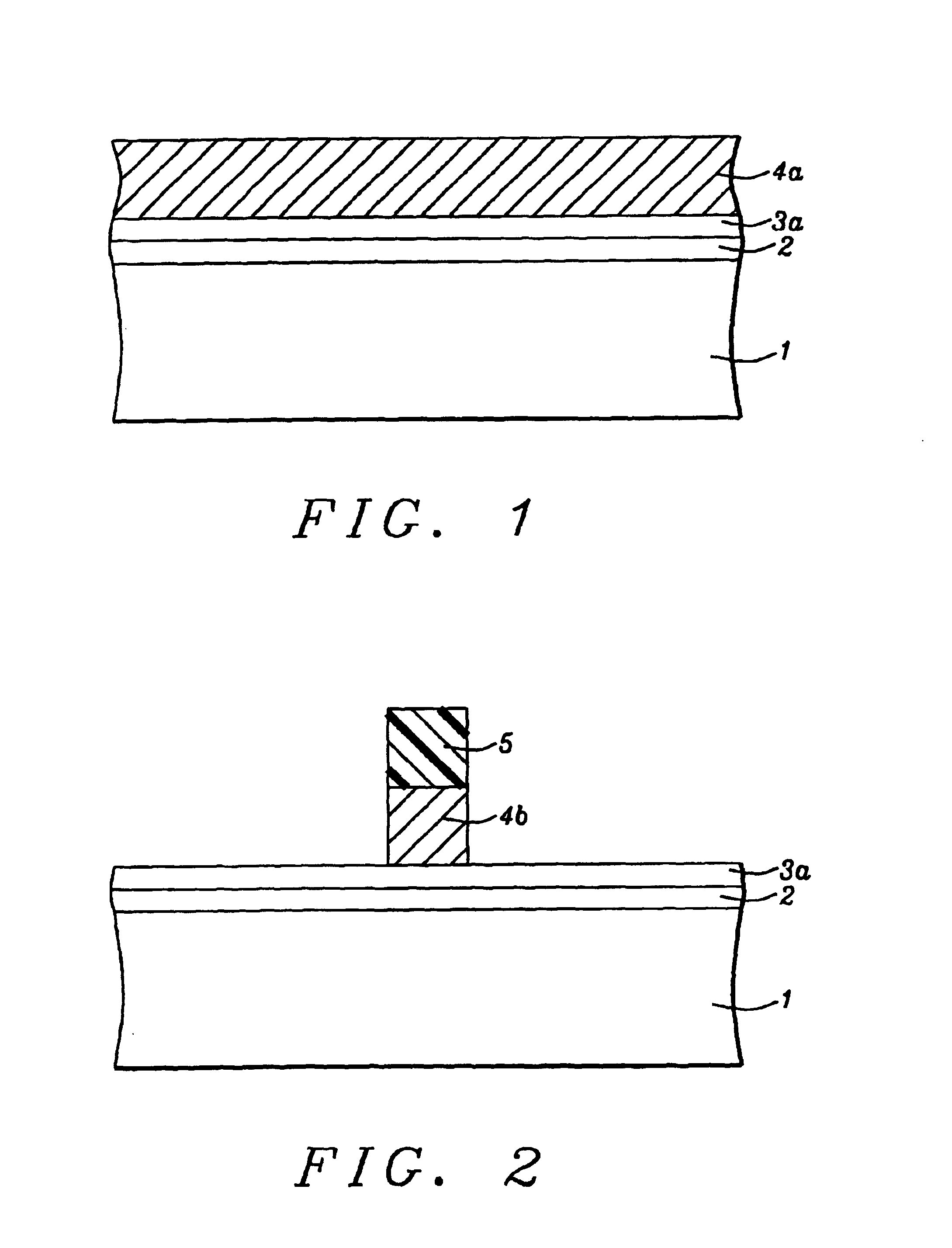

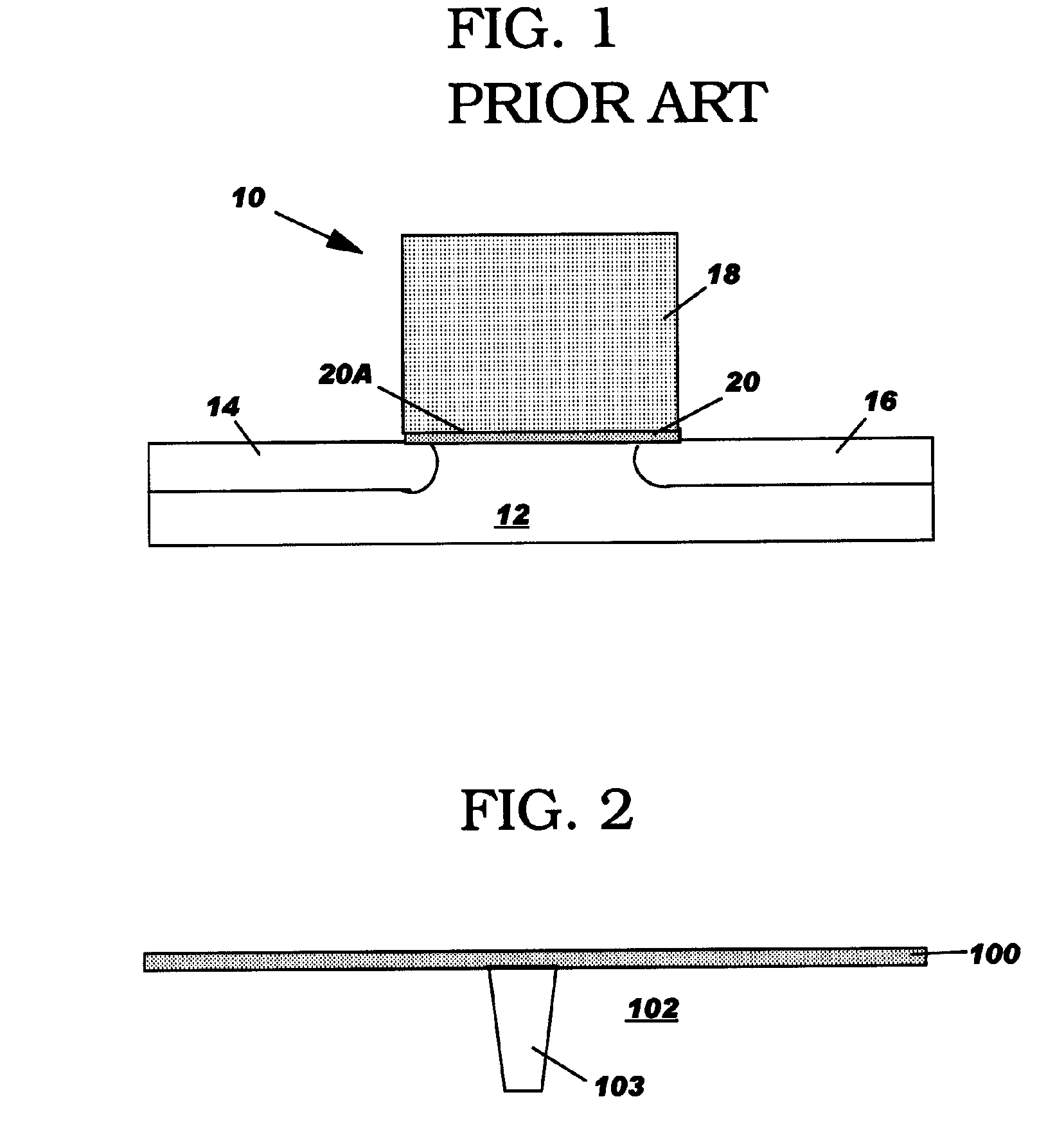

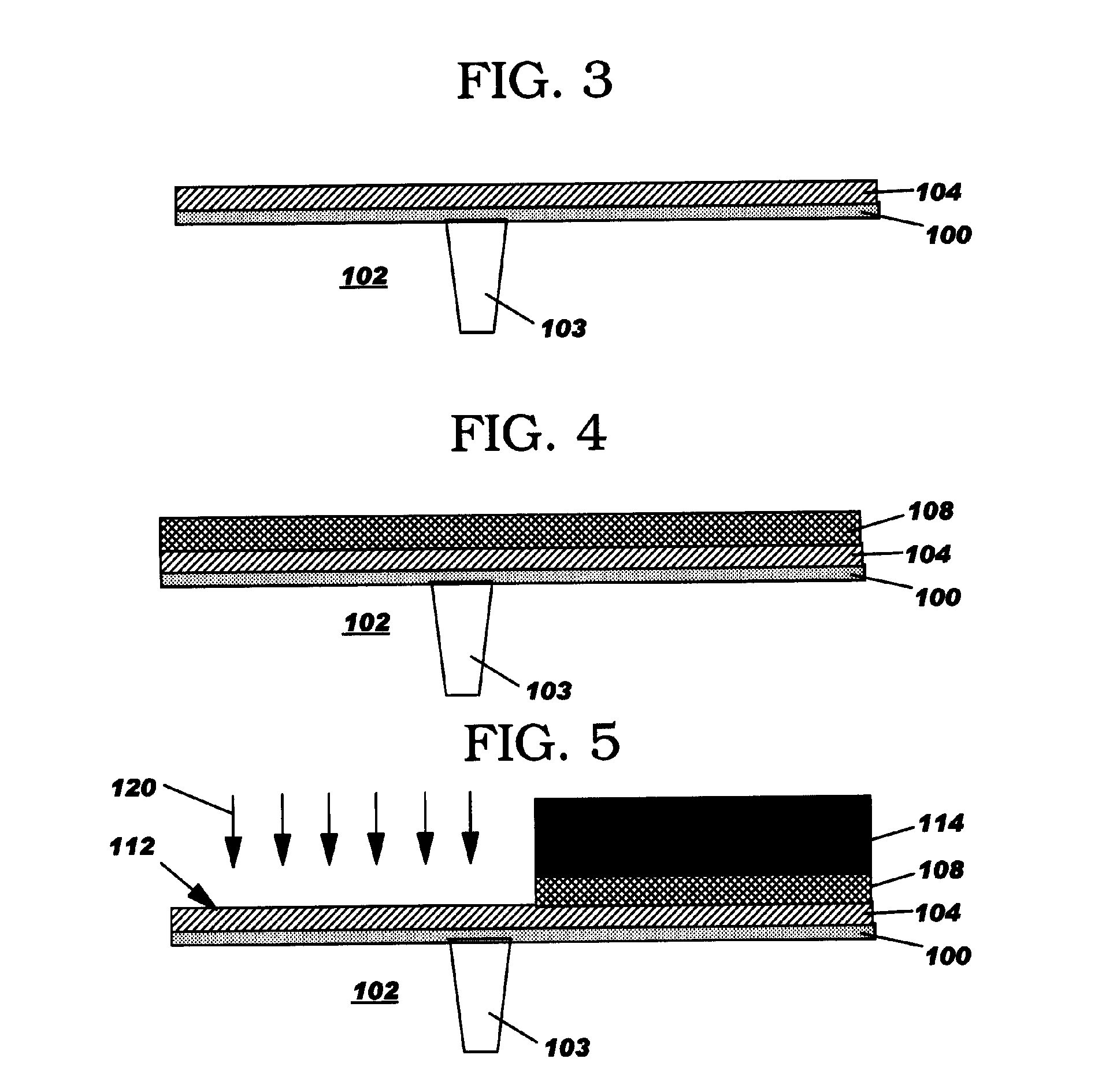

Non-reducing process for deposition of polysilicon gate electrode over high-K gate dielectric material

InactiveUS6451641B1Avoid attenuationSemiconductor/solid-state device manufacturingChemical vapor deposition coatingGate dielectricPolysilicon gate

A process for fabricating a semiconductor device, including providing a semiconductor substrate; depositing on the semiconductor substrate a layer of a high-K gate dielectric material; depositing on the gate dielectric material layer a polysilicon or polysilicon-germanium gate electrode layer, in which the step of depositing the polysilicon or polysilicon-germanium gate electrode layer includes providing non-reducing conditions in a CVD apparatus.

Owner:GLOBALFOUNDRIES US INC

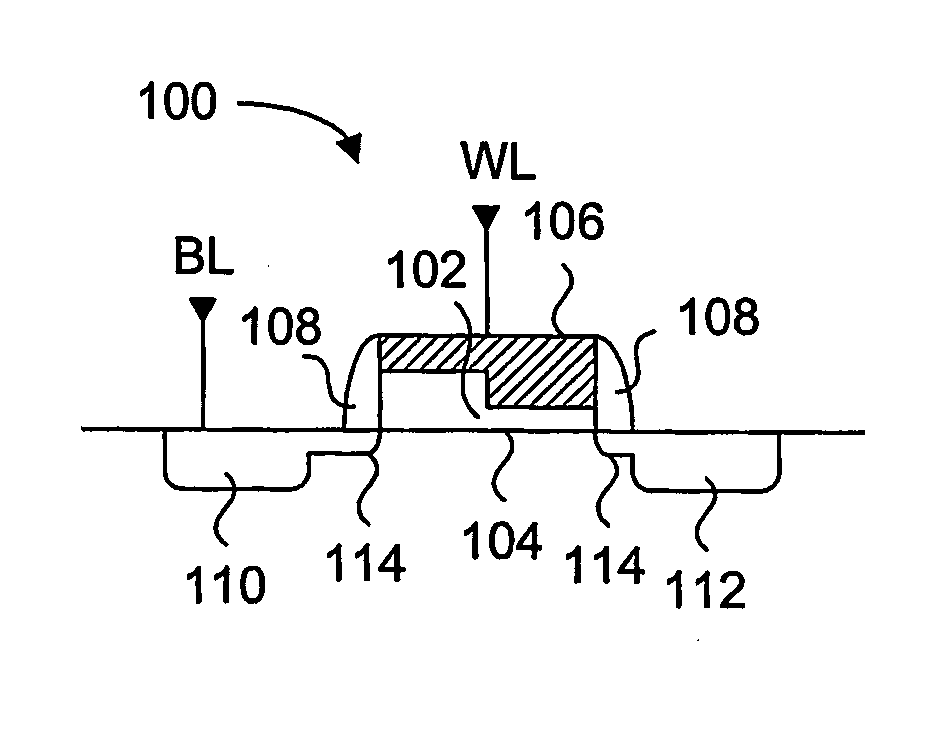

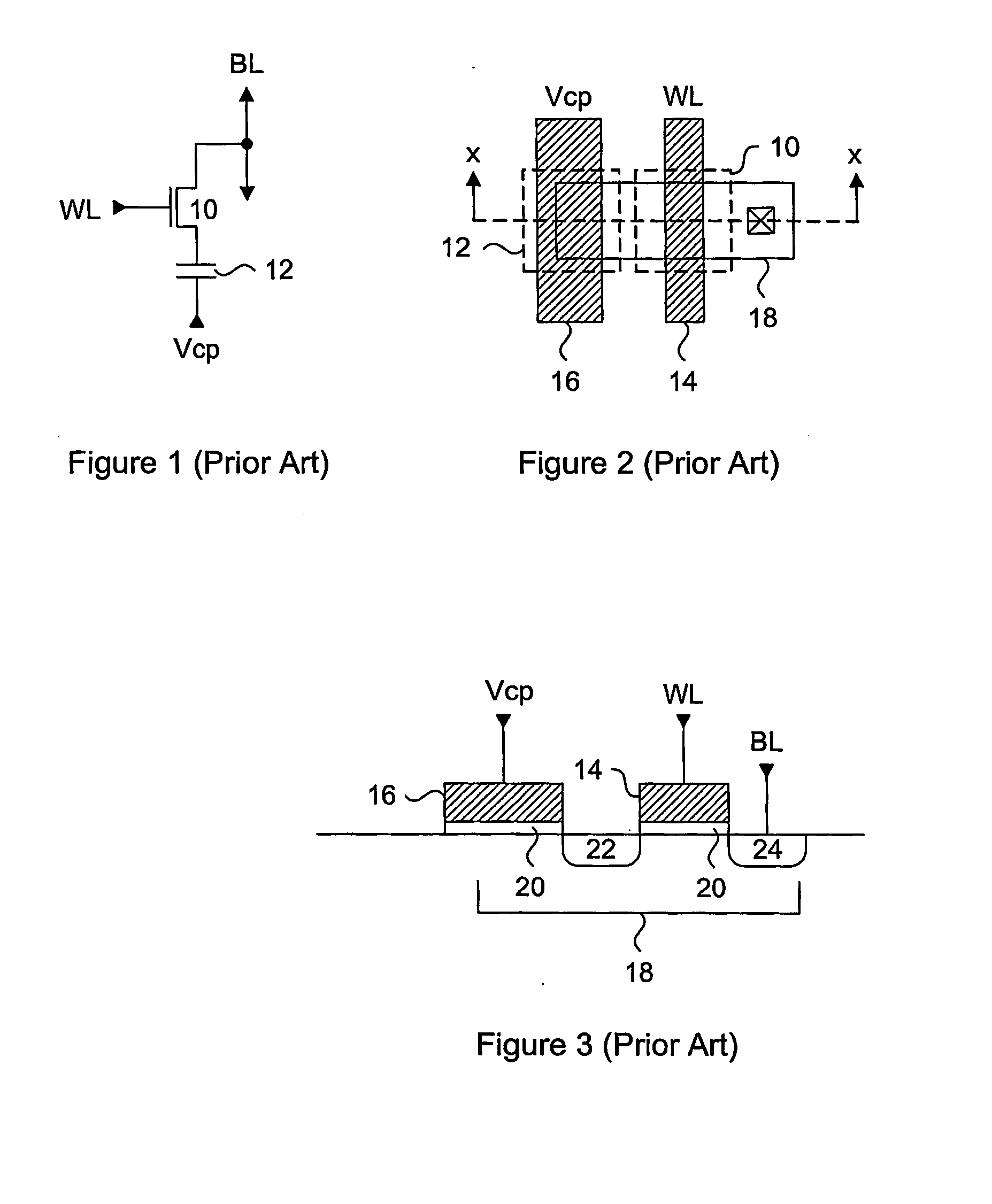

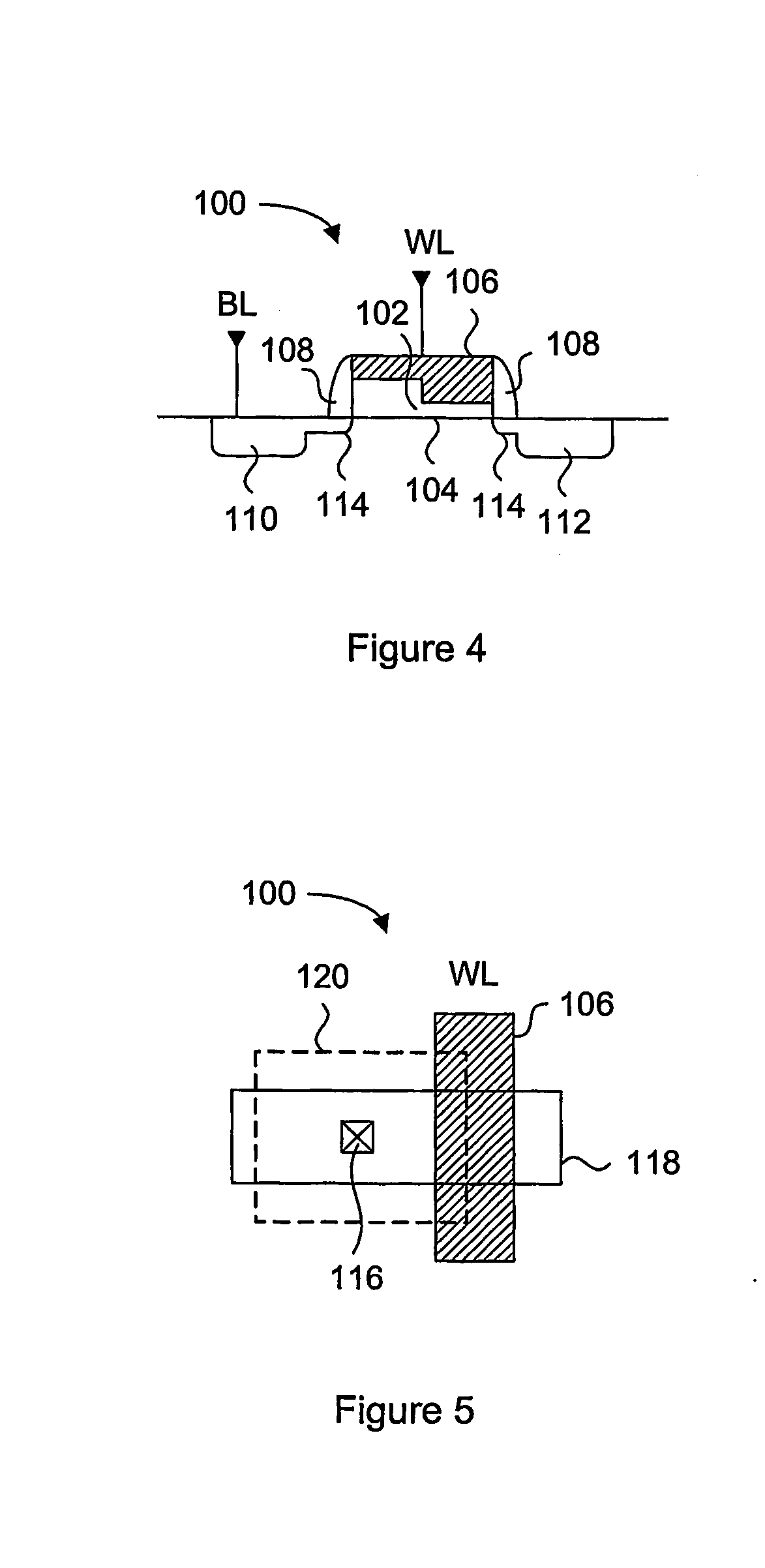

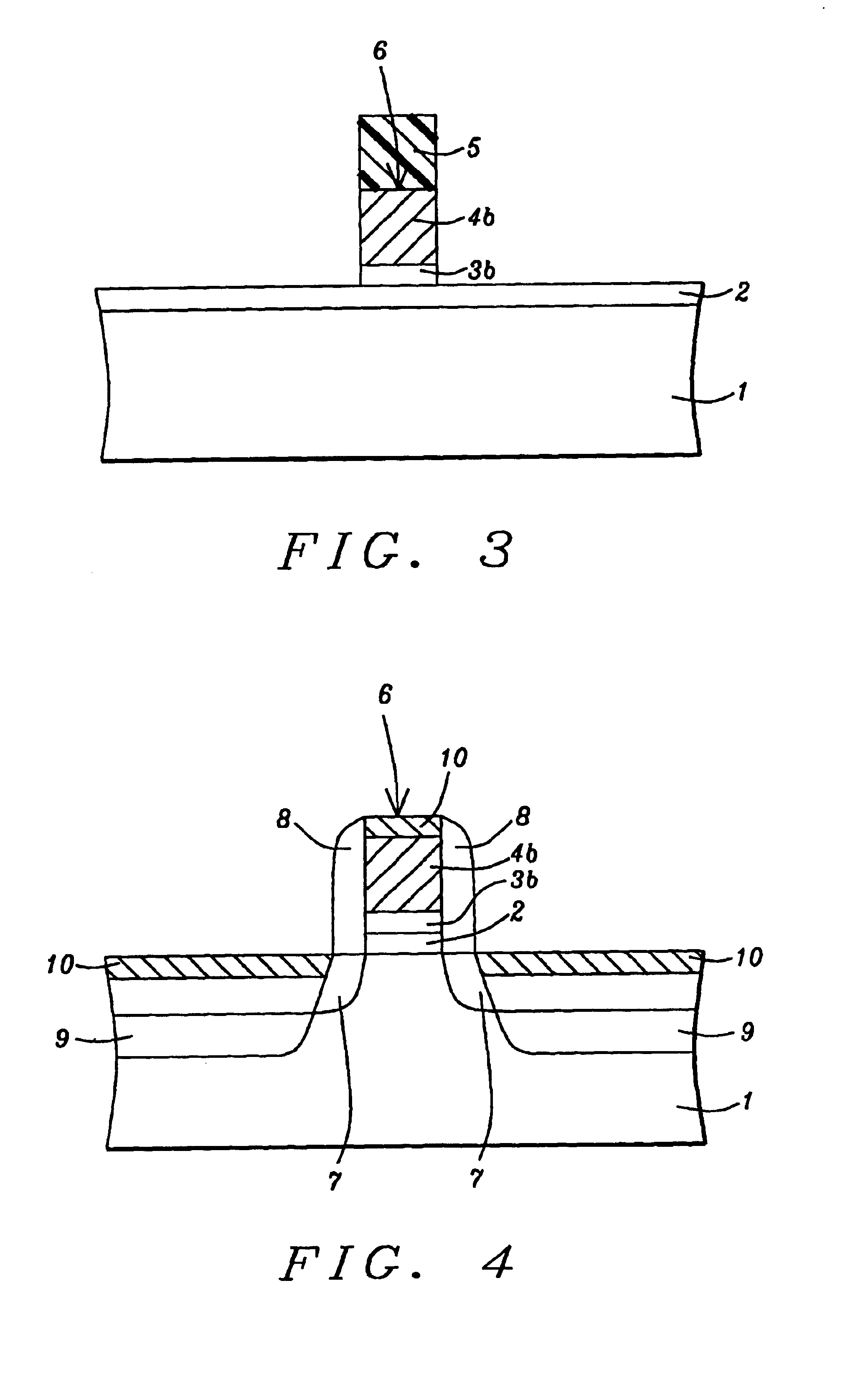

Split-channel antifuse array architecture

InactiveUS20060244099A1Limited over-voltage exposureSimplify and improve and accessTransistorSemiconductor/solid-state device detailsCMOSEngineering

Generally, the present invention provides a variable thickness gate oxide anti-fuse transistor device that can be employed in a non-volatile, one-time-programmable (OTP) memory array application. The anti-fuse transistor can be fabricated with standard CMOS technology, and is configured as a standard transistor element having a source diffusion, gate oxide, polysilicon gate and optional drain diffusion. The variable gate oxide underneath the polysilicon gate consists of a thick gate oxide region and a thin gate oxide region, where the thin gate oxide region acts as a localized breakdown voltage zone. A conductive channel between the polysilicon gate and the channel region can be formed in the localized breakdown voltage zone during a programming operation. In a memory array application, a wordline read current applied to the polysilicon gate can be sensed through a bitline connected to the source diffusion, via the channel of the anti-fuse transistor. More specifically, the present invention provides an effective method for utilizing split channel MOS structures as an anti-fuse cell suitable for OTP memories.

Owner:SYNOPSYS INC

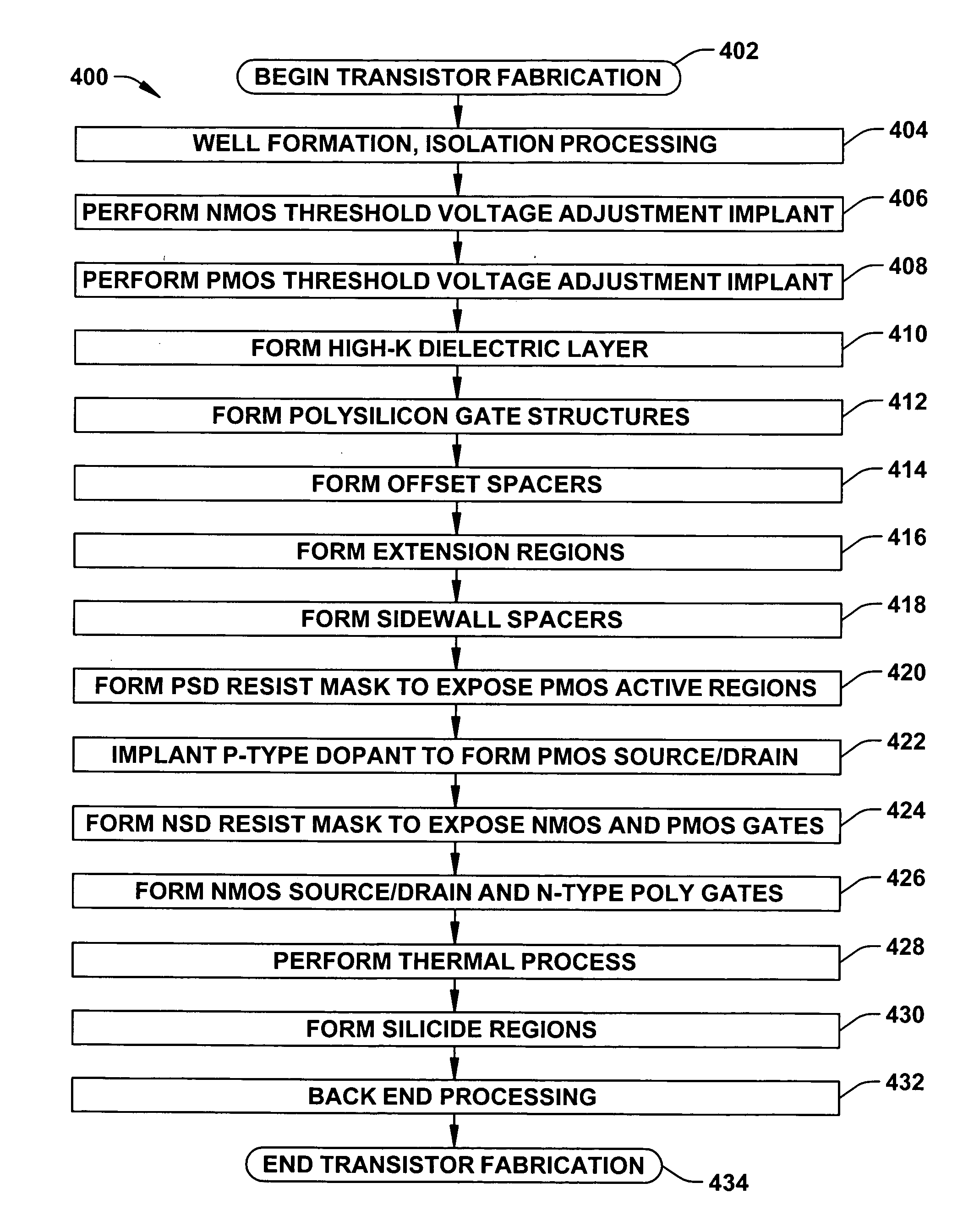

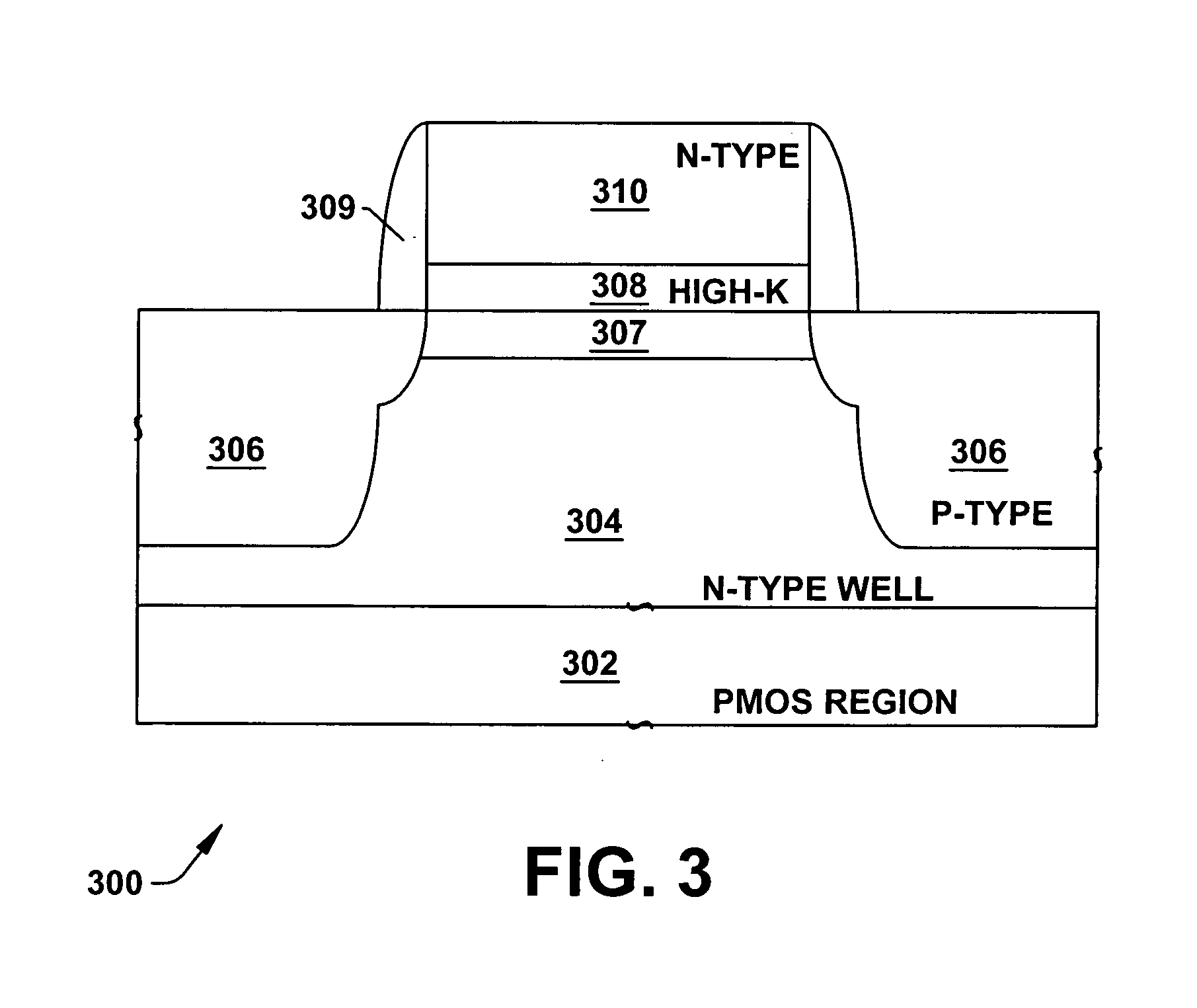

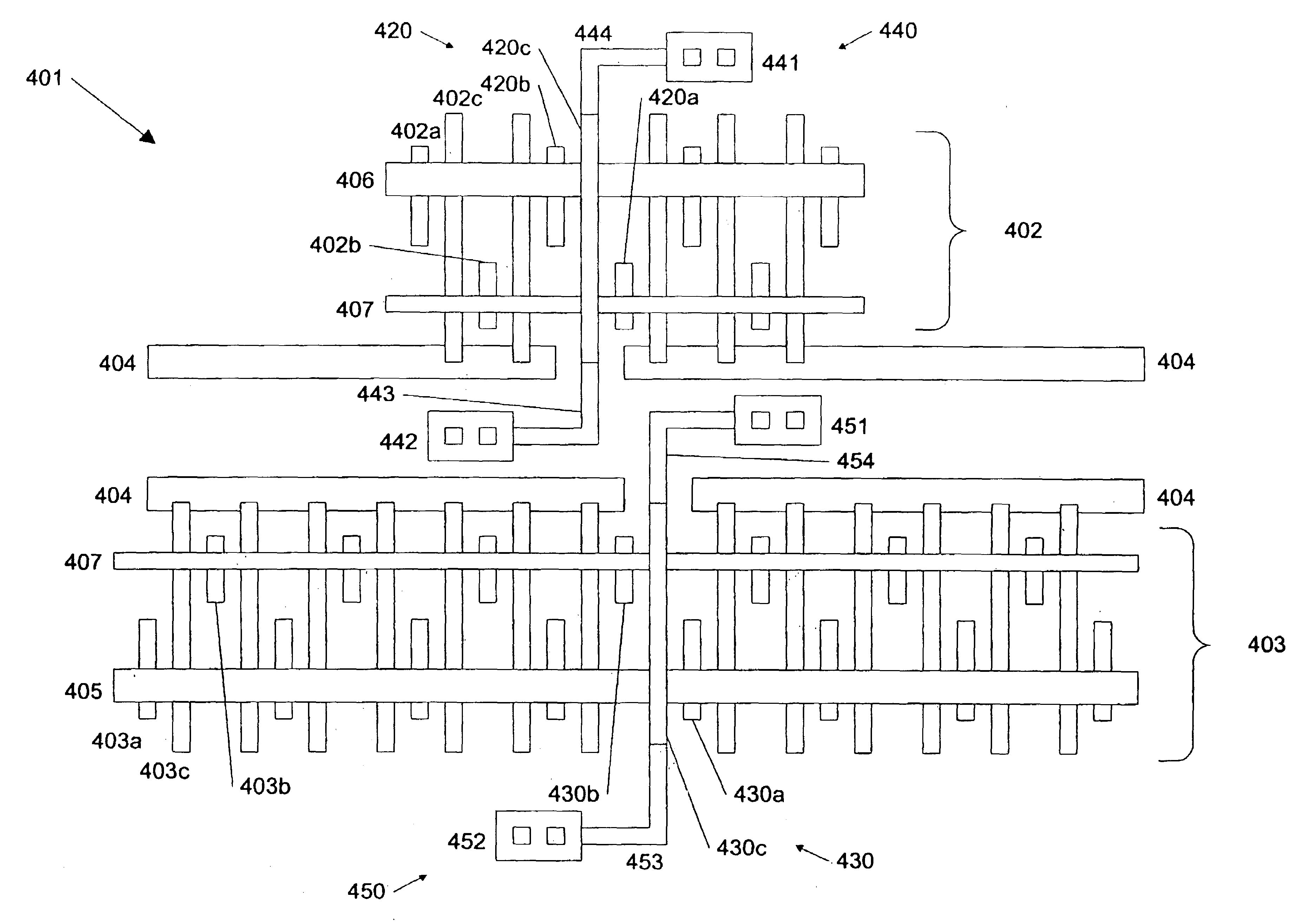

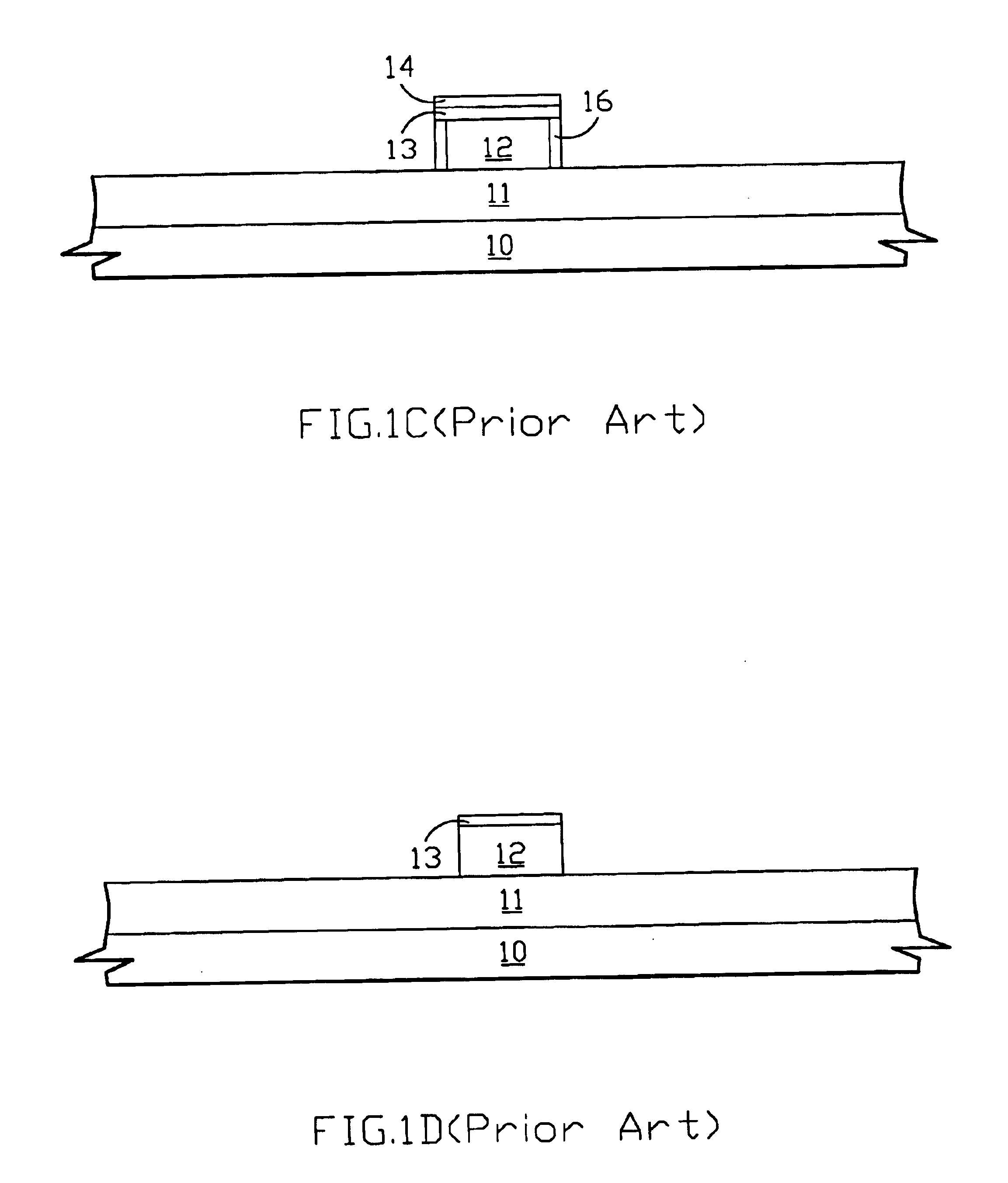

N+ poly on high-k dielectric for semiconductor devices

ActiveUS20060223248A1Mitigates and eliminates poly depletionEasy to manufactureSemiconductor/solid-state device manufacturingSemiconductor devicesDopantDevice material

The present invention facilitates semiconductor fabrication by providing methods of fabrication that employ high-k dielectric layers. An n-type well region (304) is formed within a semiconductor body (302). A threshold voltage adjustment implant is performed by implanting a p-type dopant into the n-type well region to form a counter doped region (307). A high-k dielectric layer (308) is formed over the device (300). A polysilicon layer (310) is formed on the high-k dielectric layer and doped n-type. The high-k dielectric layer (308) and the polysilicon layer (310) are patterned to form polysilicon gate structures. P-type source / drain regions (306) are formed within the n-type well region (304).

Owner:TEXAS INSTR INC

Method of forming a semiconductor diode with depleted polysilicon gate structure

InactiveUS6232163B1Solid-state devicesSemiconductor/solid-state device manufacturingMOSFETPolysilicon gate

A high voltage tolerant diode structure for mixed-voltage, and mixed signal and analog / digital applications. The preferred silicon diode includes a polysilicon gate structure on at least one dielectric film layer on a semiconductor (silicon) layer or body. A well or an implanted area is formed in a bulk semiconductor substrate or in a surface silicon layer on an SOI wafer. Voltage applied to the polysilicon gate film, electrically depletes it, reducing voltage stress across the dielectric film. An intrinsic polysilicon film may be counter-doped, implanted with a low doped implantation, implanted with a low doped source / drain implant, or with a low doped MOSFET LDD or extension implant. Alternatively, a block mask may be formed over the gate structure when defining the depleted-polysilicon gate silicon diode to form low series resistance diode implants, preventing over-doping the film. Optionally, a hybrid photoresist method may be used to form higher doped edge implants in the silicon to reduce diode series resistance without a block mask.

Owner:INT BUSINESS MASCH CORP

Method of fabricating a MOSFET device with metal containing gate structures

InactiveUS6869868B2Improve device performanceLow working voltageTransistorSemiconductor/solid-state device manufacturingTitanium nitrideTwo step

A method of forming a composite gate structure for a planar MOSFET device, as well as for vertical, double gate, FINFET device, has been developed. The method features a composite gate structure comprised of an overlying silicon gate structure shape, and an underlying titanium nitride gate structure shape. The titanium nitride component allows a lower work function, and thus lower device operating voltages to be realized when compared to counterpart gate structures formed with only polysilicon. A novel, two step gate structure definition procedure, featuring an anisotropic first etch procedure for definition of the polysilicon gate structure shape, followed by a wet or dry isotopic second etch procedure for definition of the titanium nitride gate structure shape, is employed.

Owner:TAIWAN SEMICON MFG CO LTD

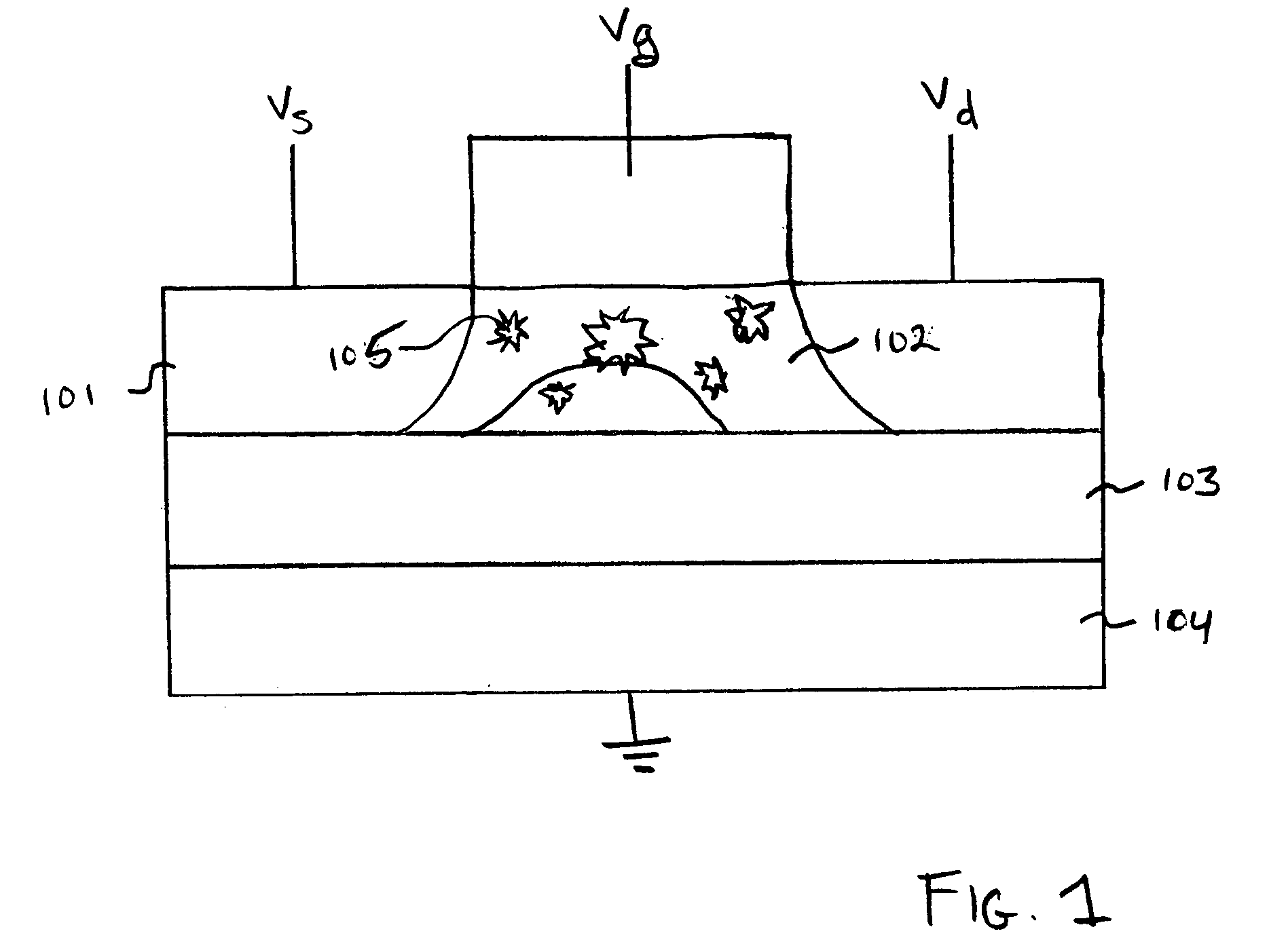

Temperature sensor for high power very large scale integration circuits

ActiveUS7176508B2Improve thermal model-to-hardware correlationSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsElectrical resistance and conductanceEngineering

Disclosed is a temperature sensor for an integrated circuit having at least one field effect transistor (FET) having a polysilicon gate, in which a current and a voltage is supplied to the polysilicon gate, changes in the current and the voltage of the polysilicon gate are monitored, wherein the polysilicon gate of the at least one FET is electrically isolated from other components of the integrated circuit, and the changes in the current or voltage are used to calculate a change in resistance of the polysilicon gate, and the change in resistance of the polysilicon gate is used to calculate a temperature change within the integrated circuit.

Owner:GLOBALFOUNDRIES US INC

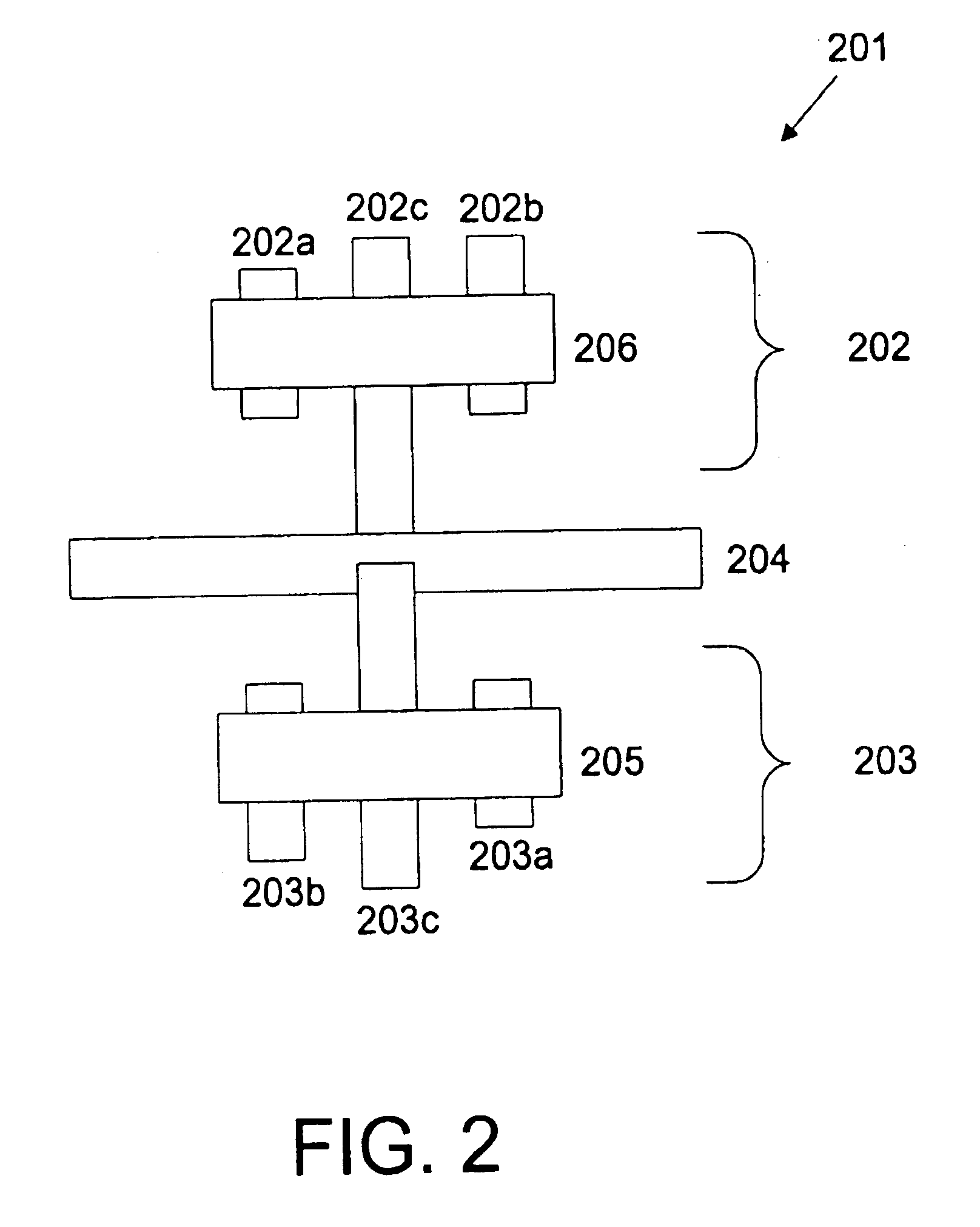

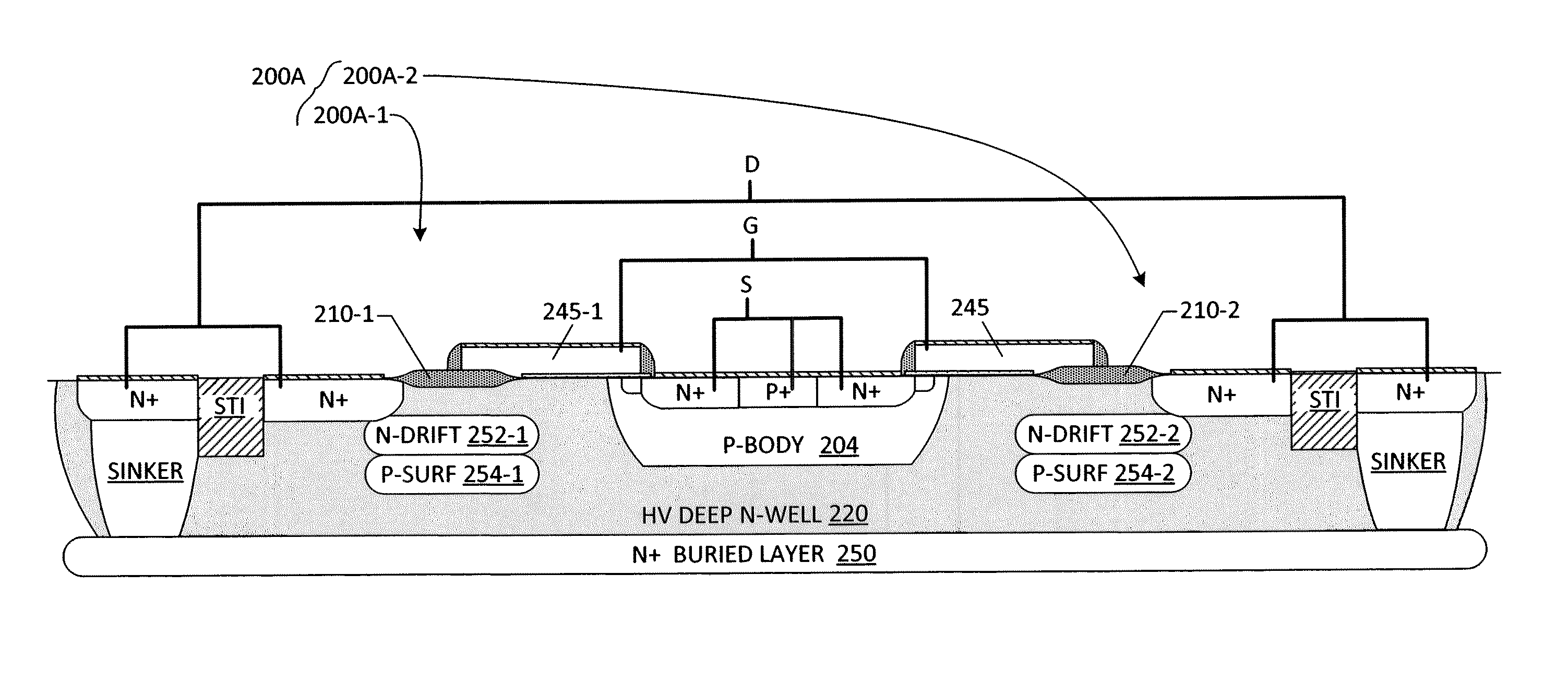

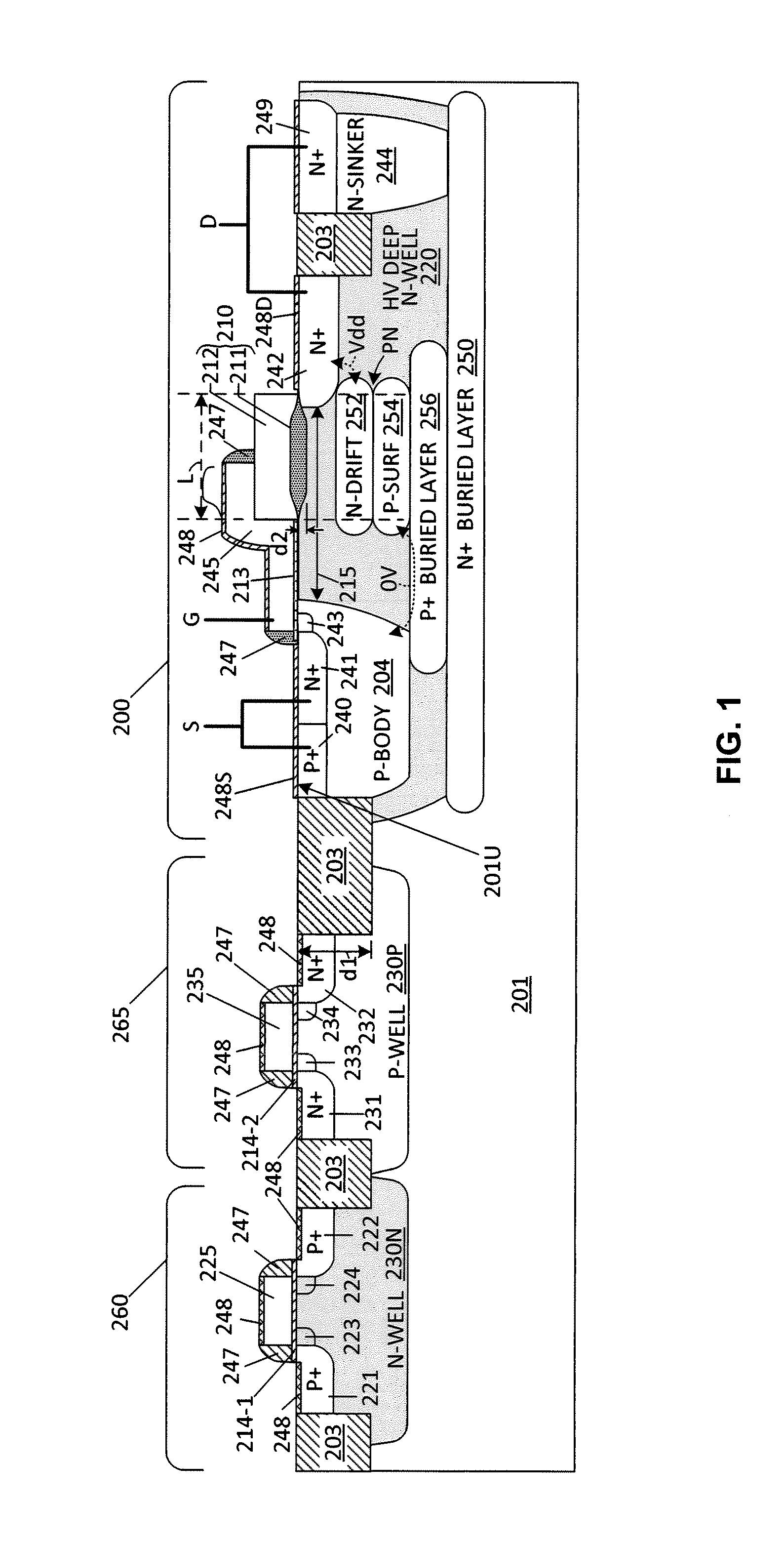

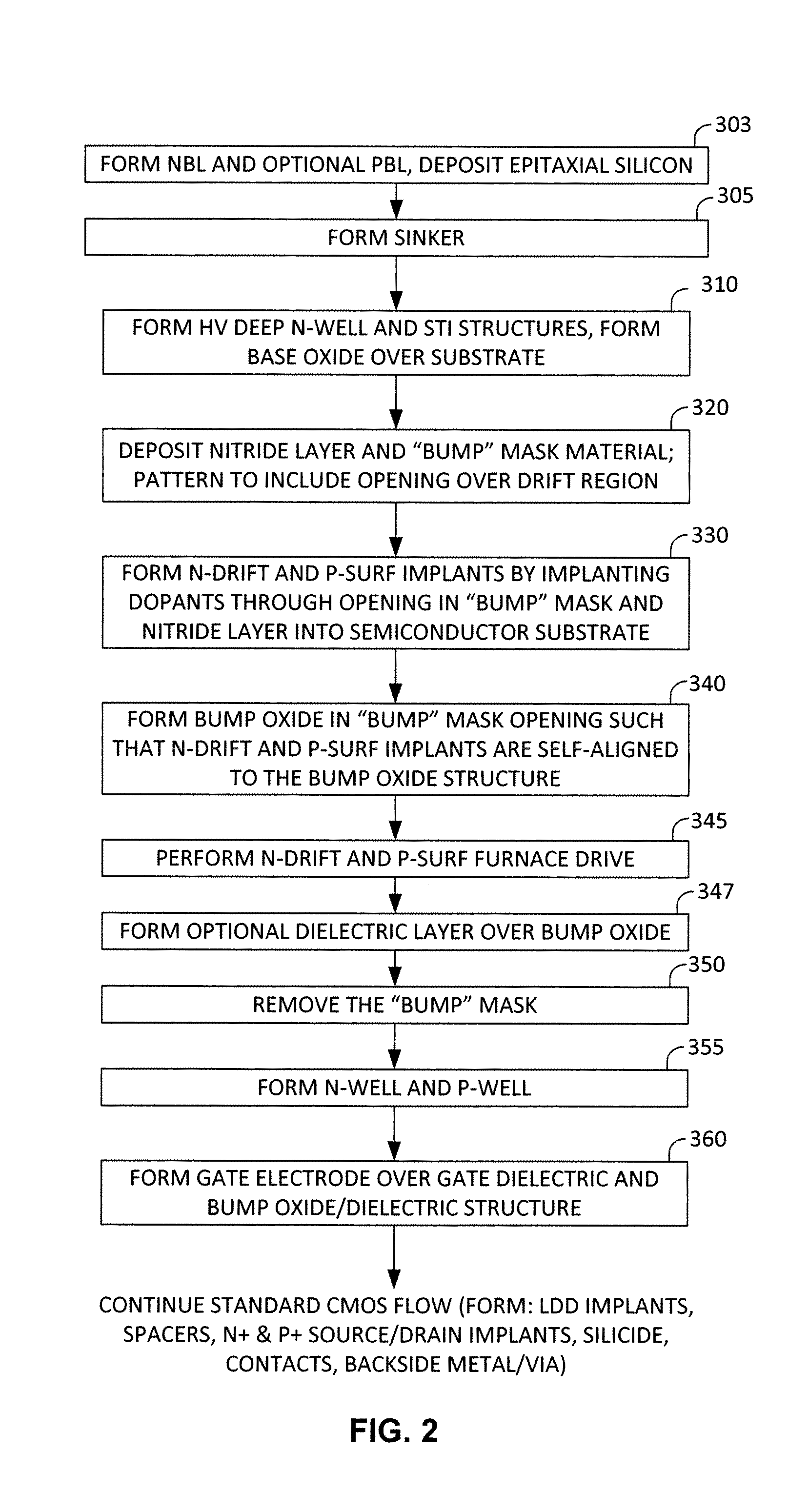

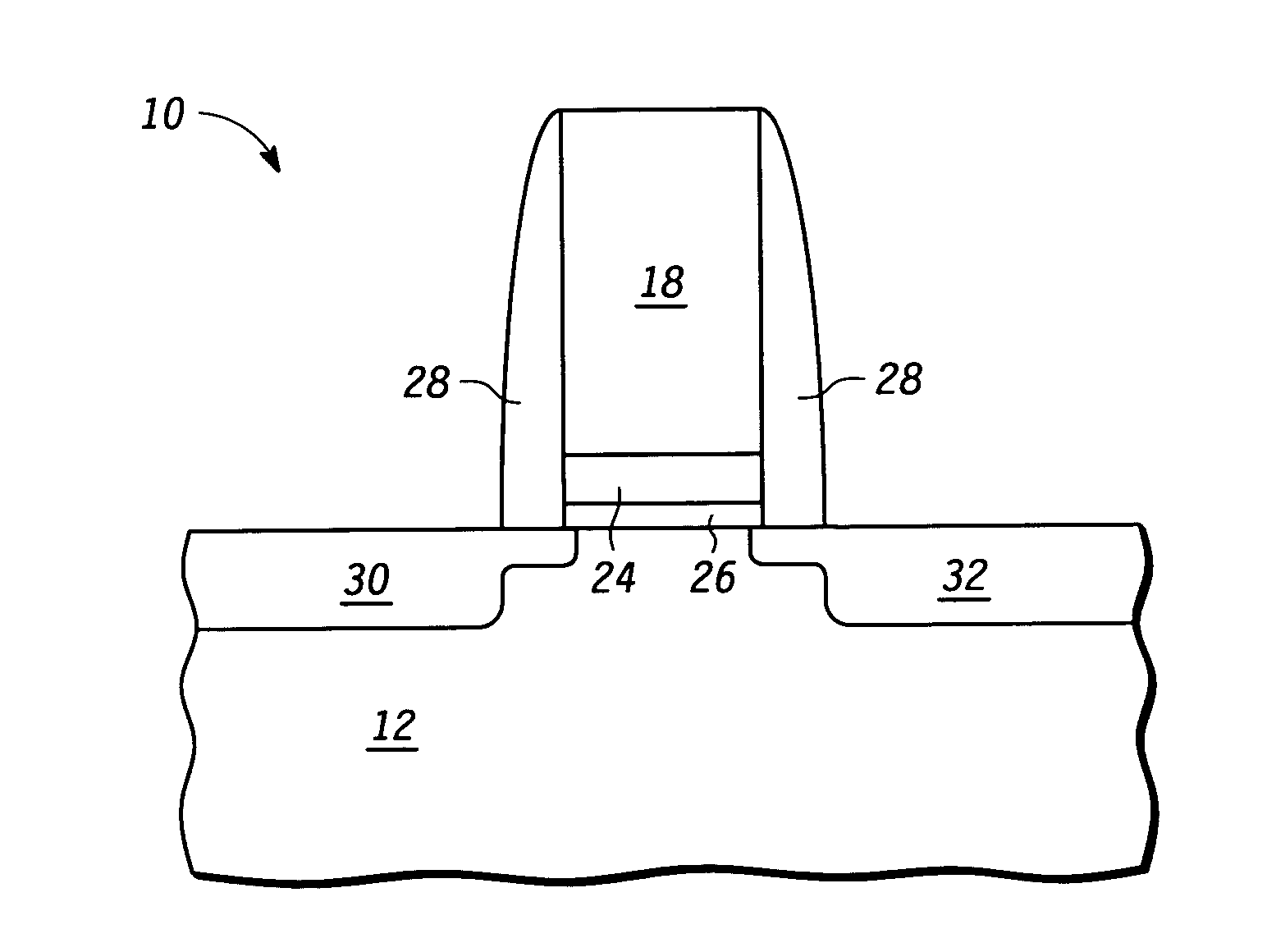

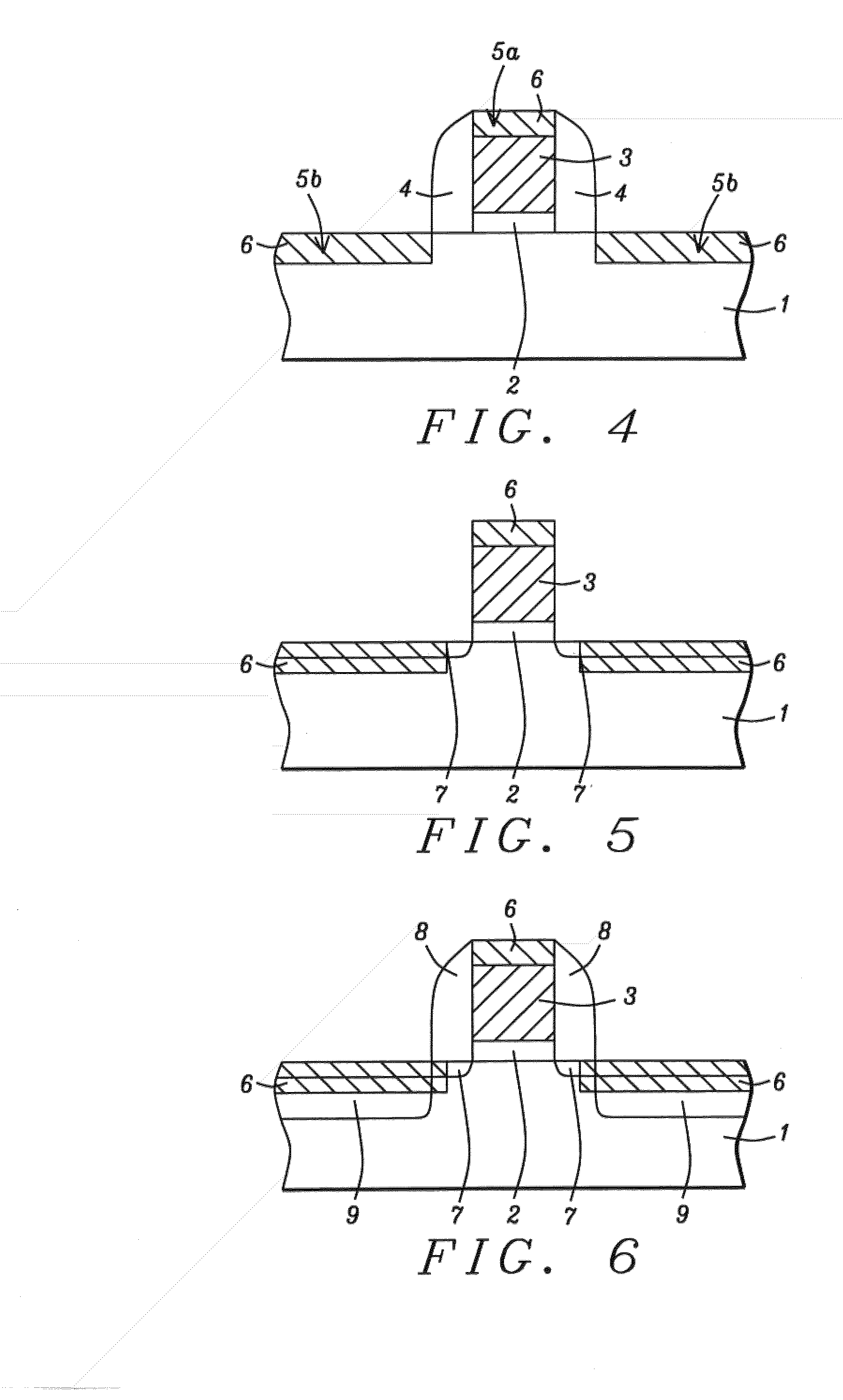

Double-Resurf LDMOS With Drift And PSURF Implants Self-Aligned To A Stacked Gate "BUMP" Structure

ActiveUS20140070315A1Ideal overall performanceHighest possible BVTransistorSolid-state devicesLDMOSGate dielectric

A double-RESURF LDMOS transistor has a gate dielectric structure including a shallow field “bump” oxide region and an optional raised dielectric structure that provides a raised support for the LDMOS transistor's polysilicon gate electrode. Fabrication of the shallow field oxide region is performed through a hard “bump” mask and controlled such that the bump oxide extends a minimal depth into the LDMOS transistor's drift (channel) region. The hard “bump” mask is also utilized to produce an N-type drift (N-drift) implant region and a P-type surface effect (P-surf) implant region, whereby these implants are “self-aligned” to the gate dielectric structure. The N-drift implant is maintained at Vdd by connection to the LDMOS transistor's drain diffusion. An additional Boron implant is utilized to form a P-type buried layer that connects the P-surf implant to the P-body region of the LDMOS transistor, whereby the P-surf implant is maintained at 0V.

Owner:TOWER SEMICONDUCTOR

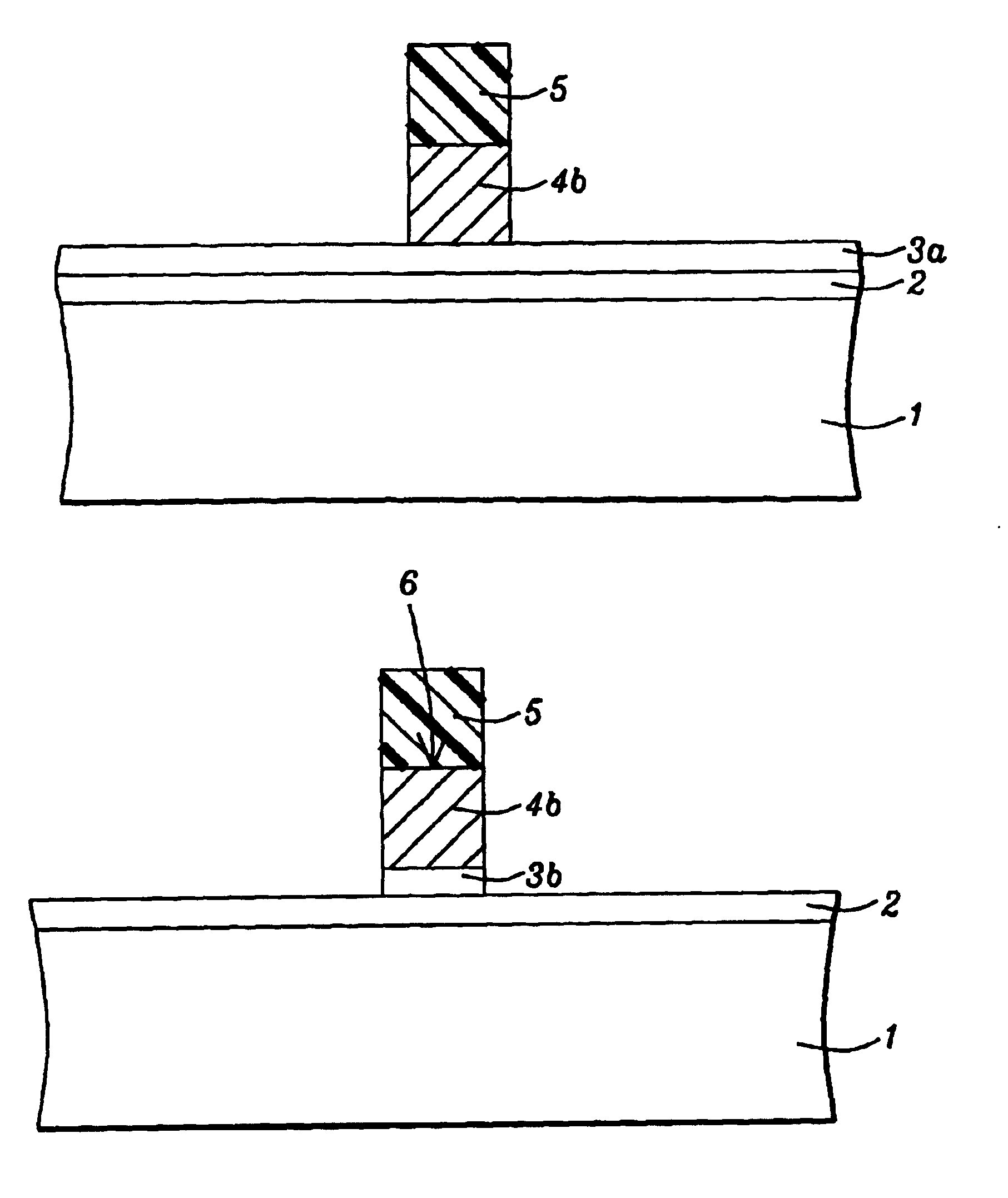

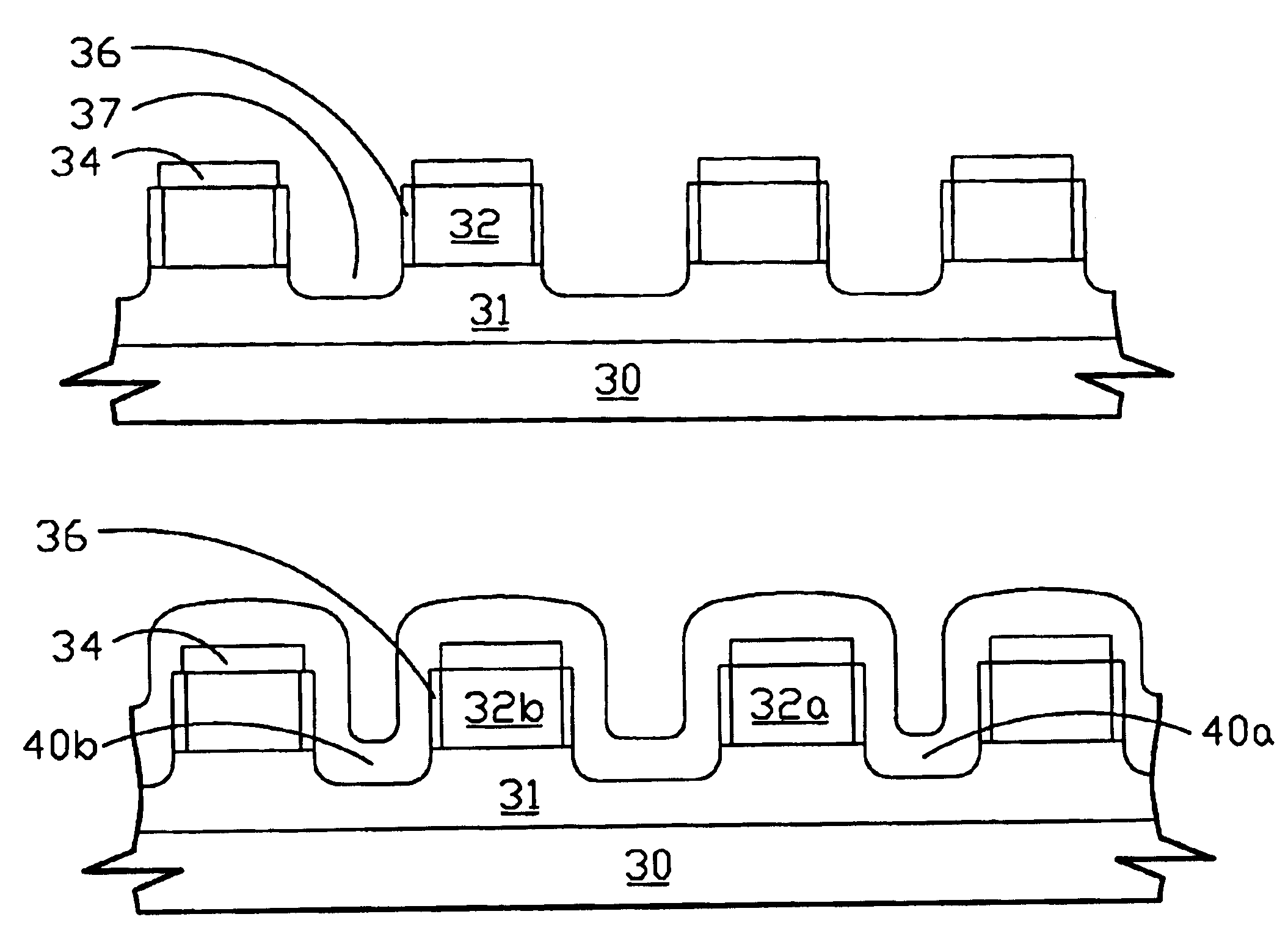

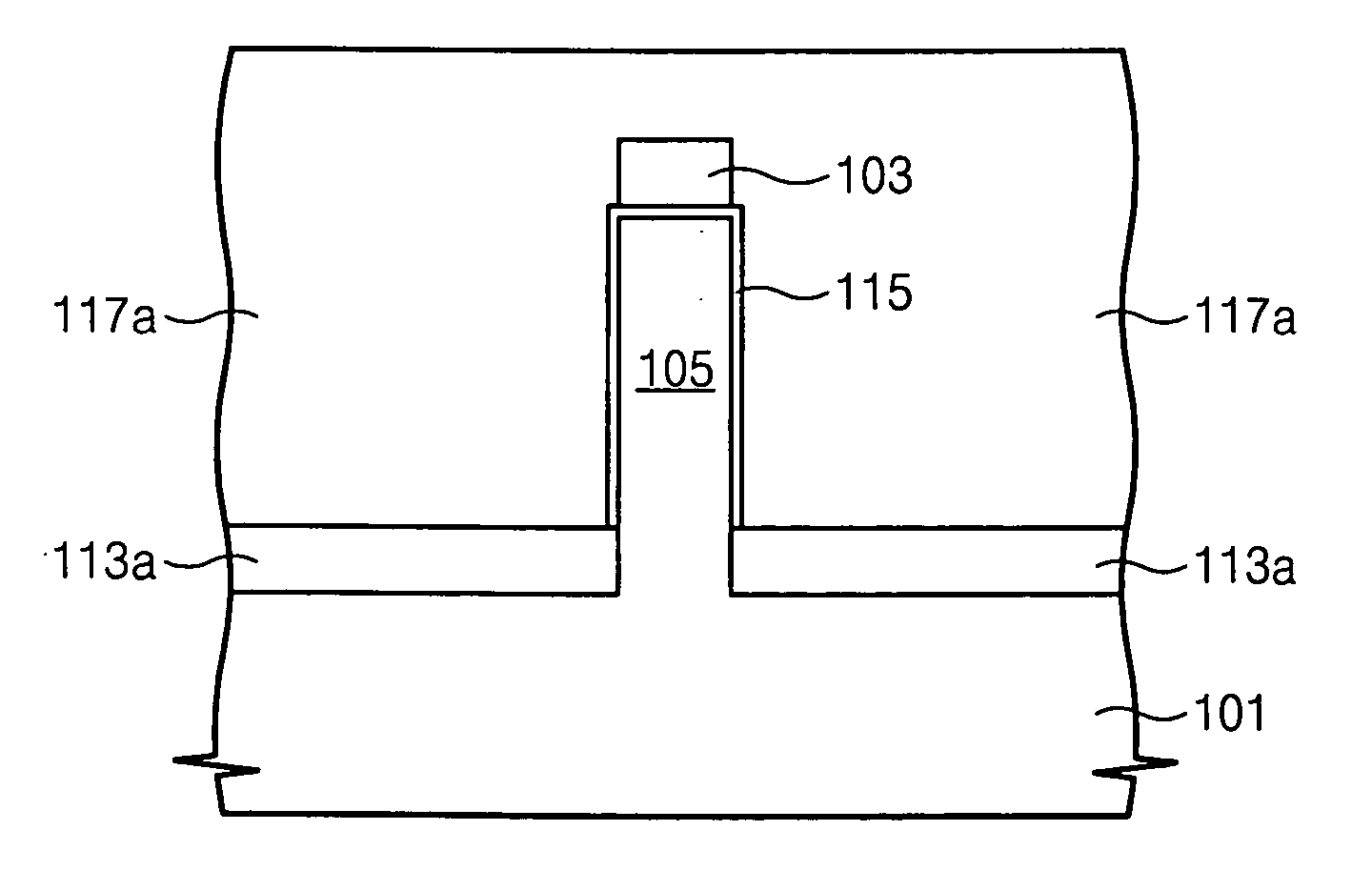

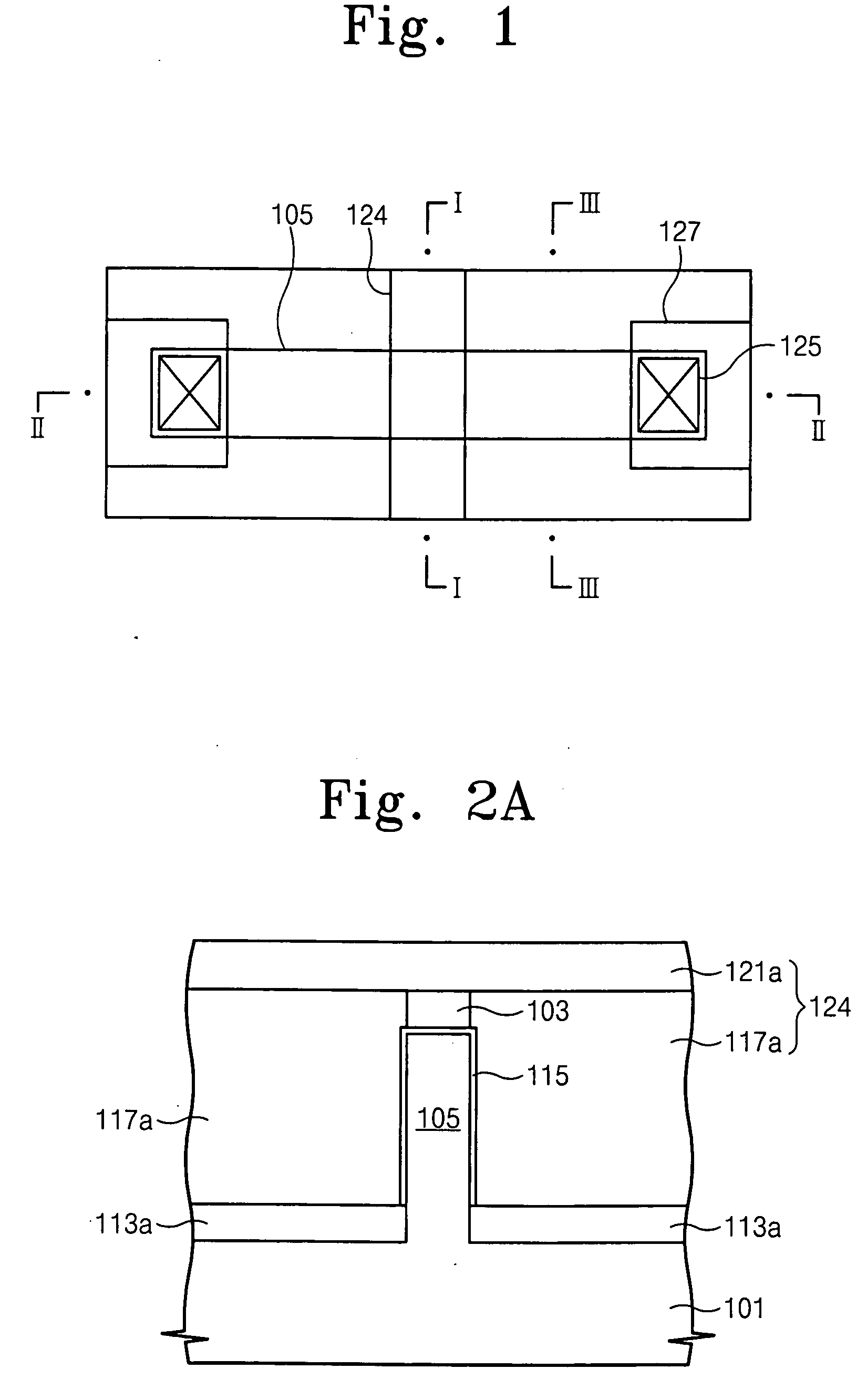

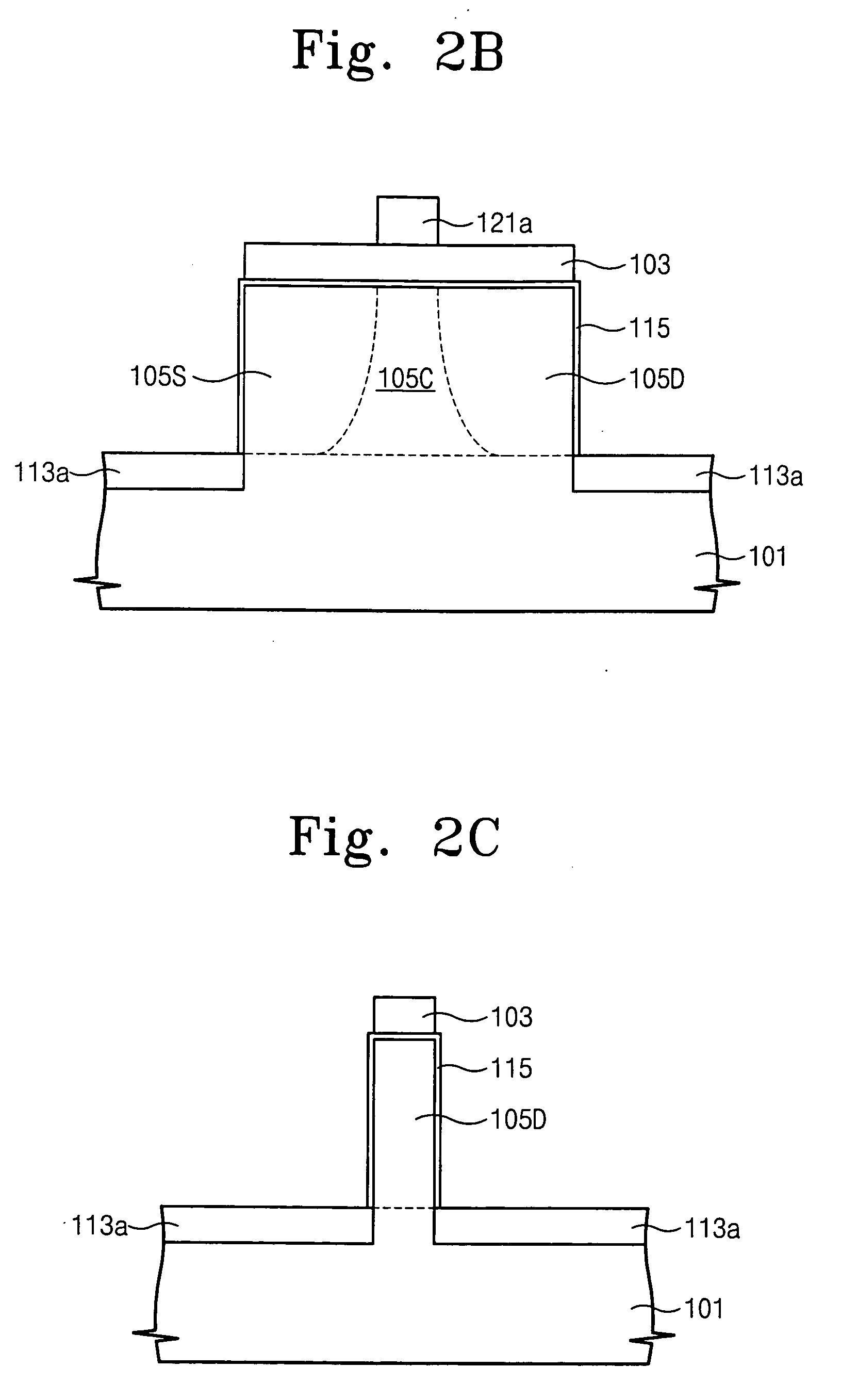

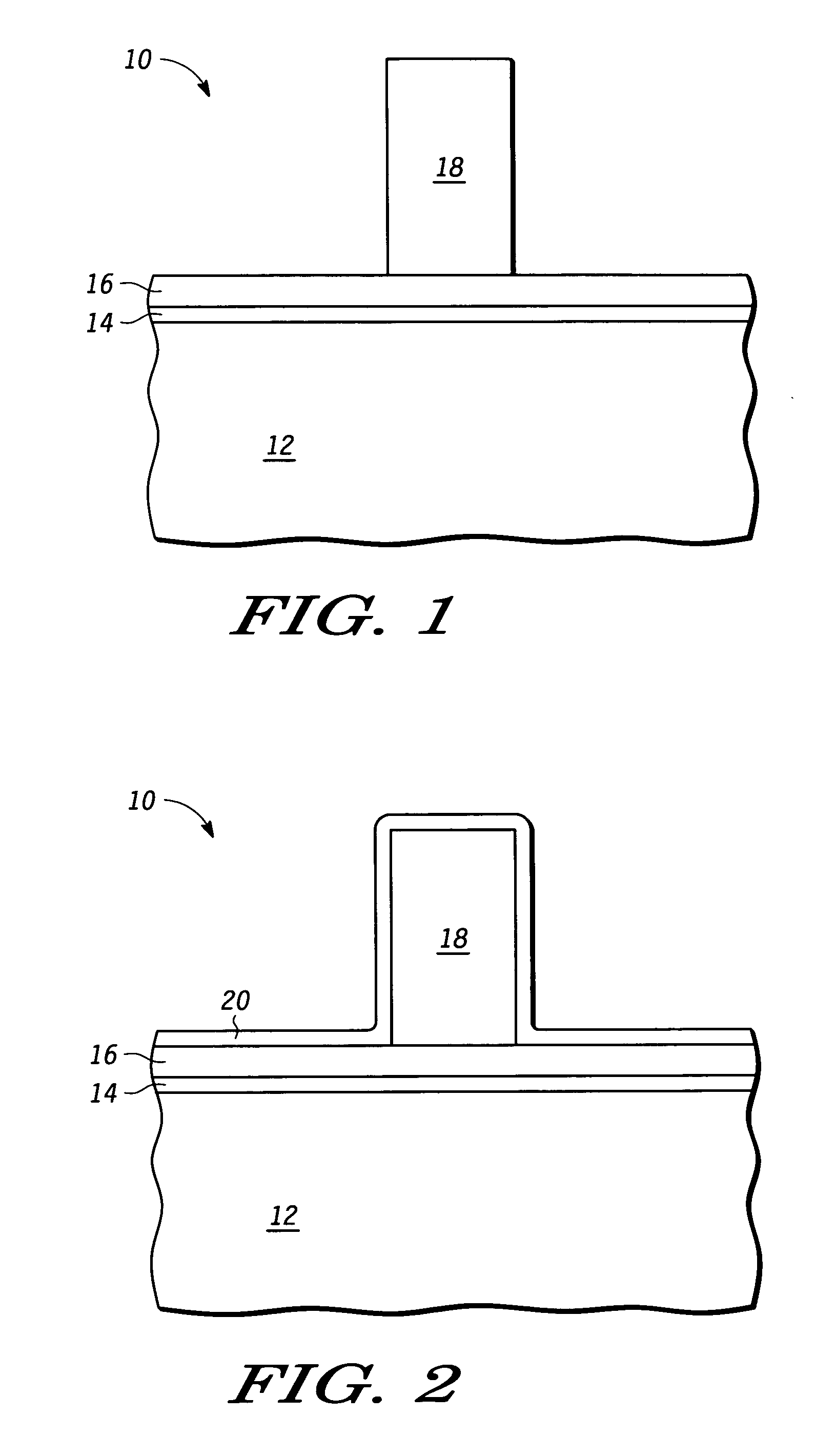

Method of fabricating a double gate MOSFET device

ActiveUS6855588B1Excellent short channel behaviorBetter gate controlTransistorSemiconductor/solid-state device manufacturingDriving currentDouble gate

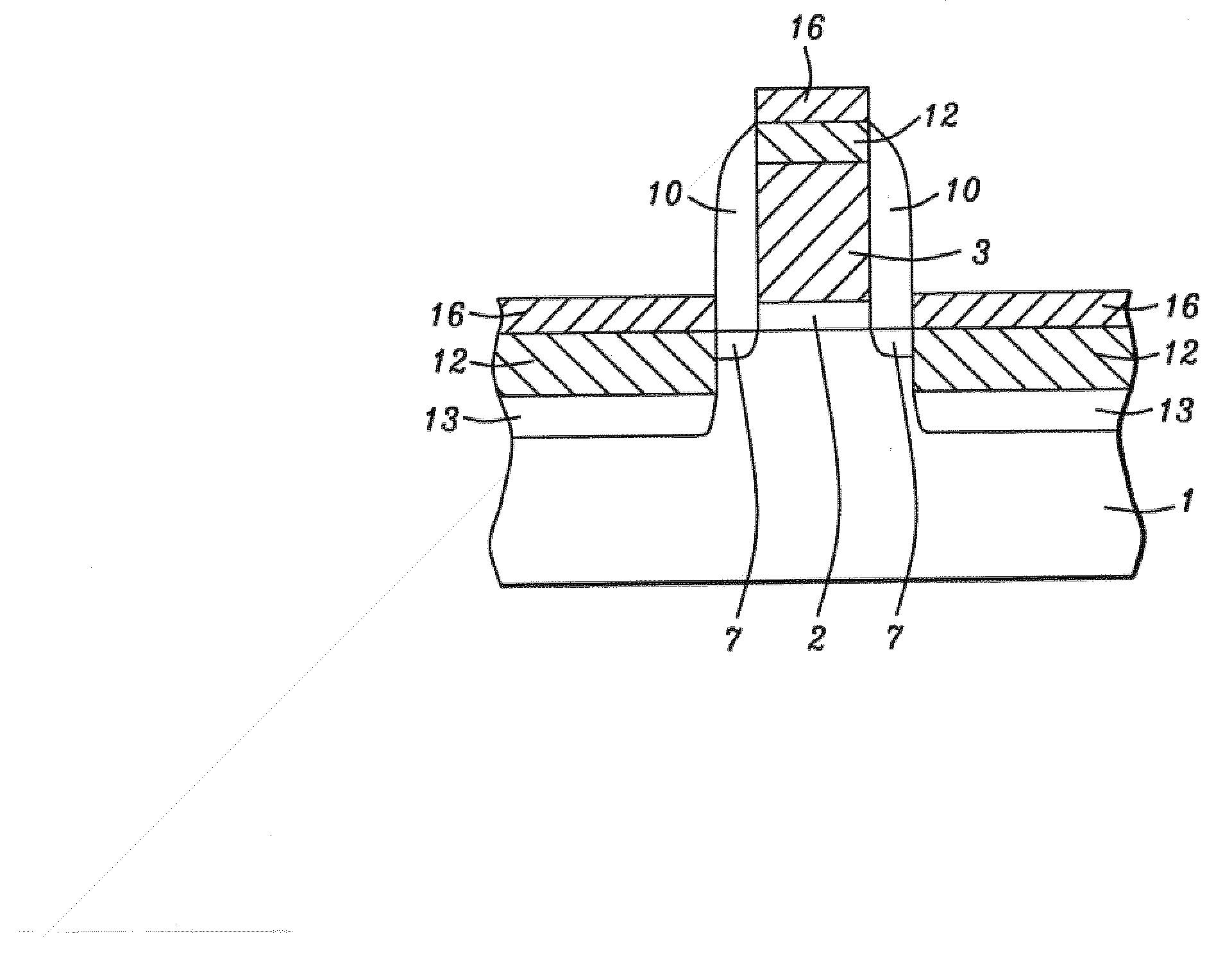

A method of fabricating a double gate MOSFET device is provided. The present invention overetches a silicon layer overlying a buried oxide layer using a hard mask of cap oxide on the silicon layer as an etching mask. As a result, source, drain and channel regions are formed extending from the buried oxide layer, and a pair of recesses are formed under the channel regions in the buried oxide layer. The channel is a fin structure with a top surface and two opposing parallelly sidewalls. The bottom recess is formed under each opposing sidewall of the fin structure. A conductive gate layer is formed straddling the fin structures. The topography of the conductive gate layer significantly deviates from the conventional plainer profile due to the bottom recess structures under the channel regions, and a more uniformly distributed doped conductive gate layer can be obtained. Hence, the depletion effect of the conductive polysilicon gate while operating the device can be suppressed and the device drive-on currents can be further enhanced.

Owner:UNITED MICROELECTRONICS CORP

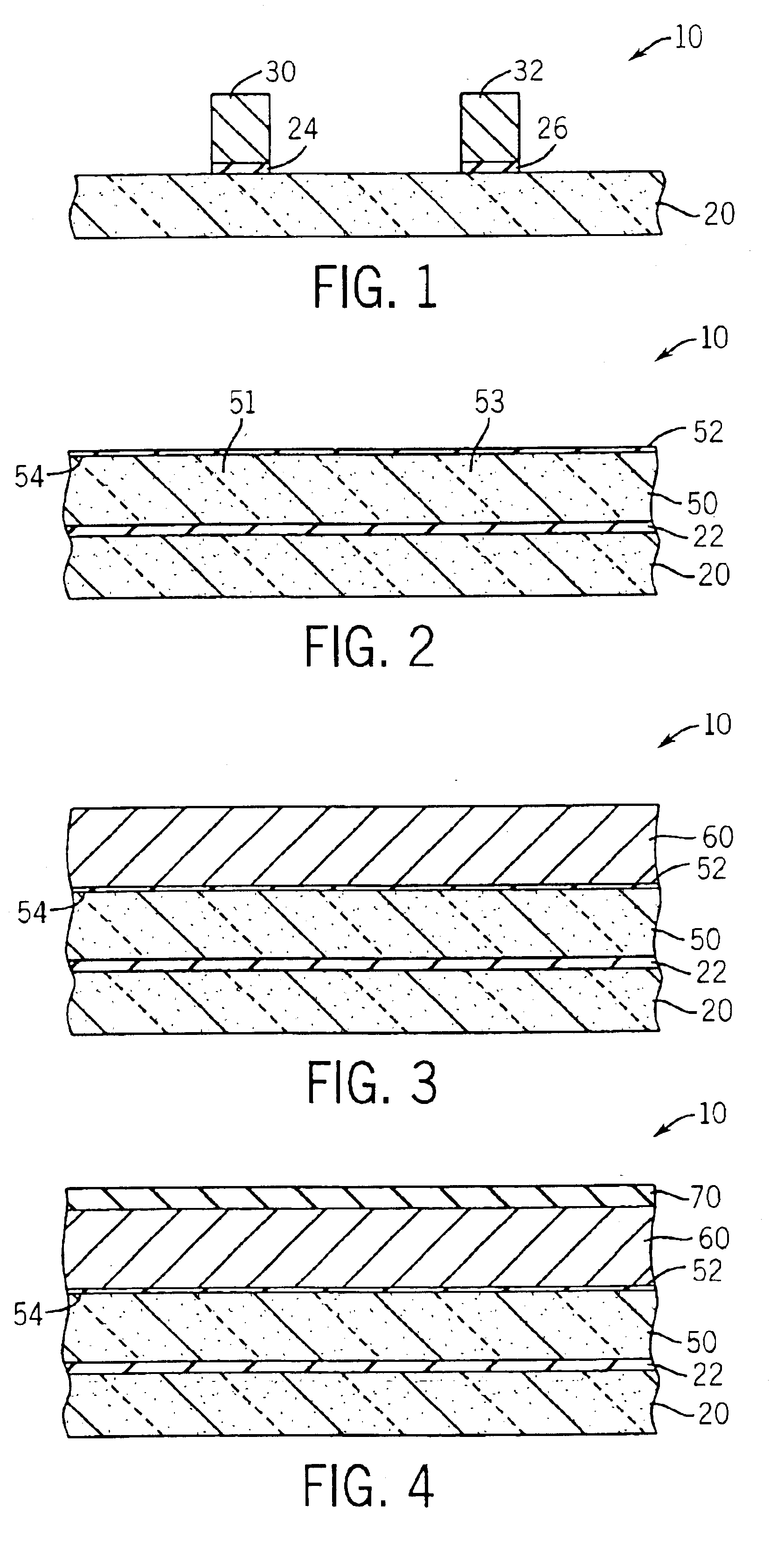

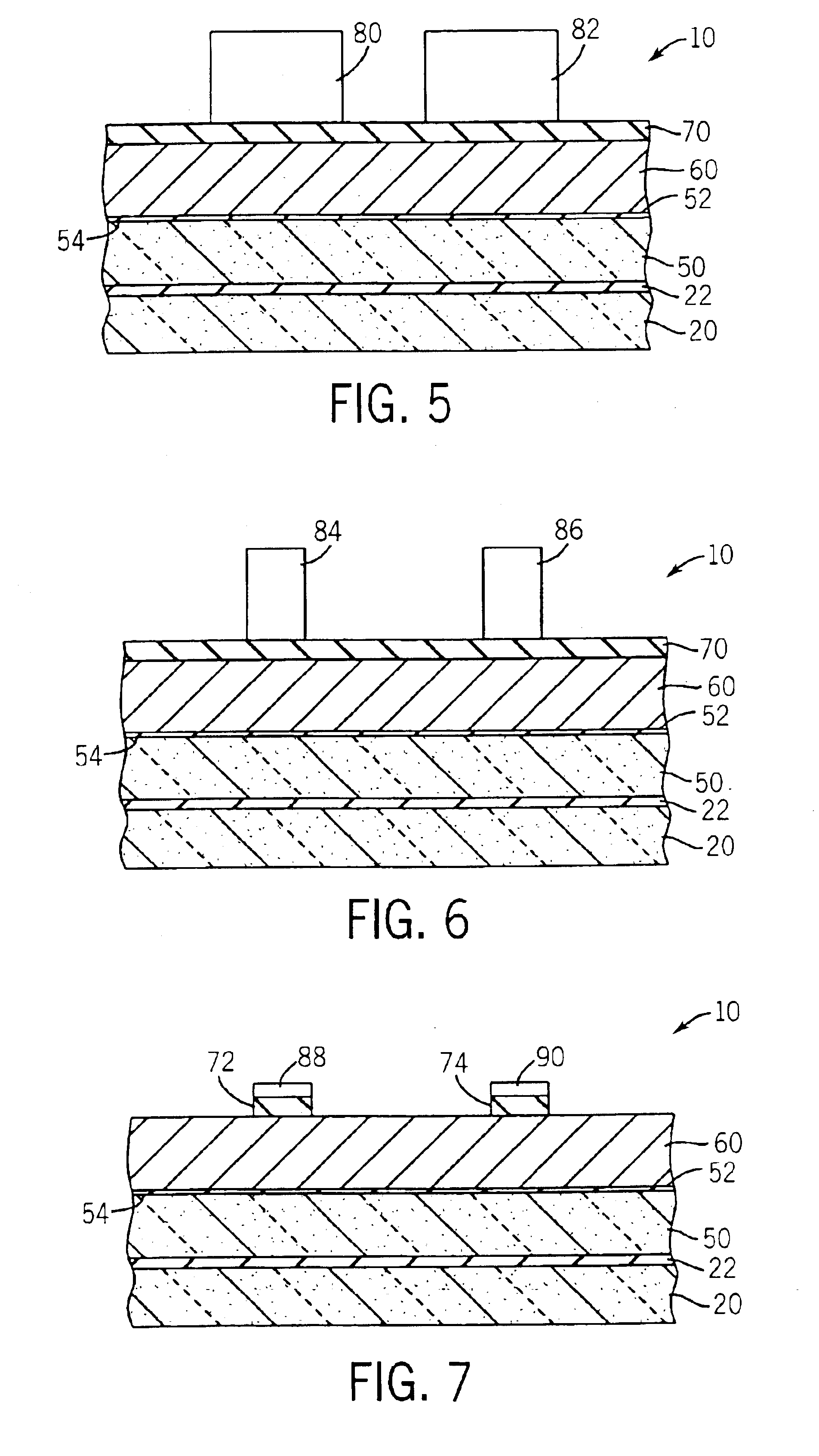

Use of amorphous carbon hard mask for gate patterning to eliminate requirement of poly re-oxidation

InactiveUS6884733B1Semiconductor/solid-state device manufacturingSemiconductor devicesElectrical conductorPolysilicon gate

A method of producing an integrated circuit eliminates the need to re-oxidize polysilicon gate conductors and lines prior to removal of a hard mask used to form the gate conductors. A layer of polysilicon is provided above a semiconductor substrate. The layer of polysilicon is then doped. A mask material comprising amorphous carbon is provided above the layer of polysilicon, and the layer of mask material is patterned to form a mask. A portion of the layer of polysilicon is removed according to the mask, and the mask is removed.

Owner:ADVANCED MICRO DEVICES INC

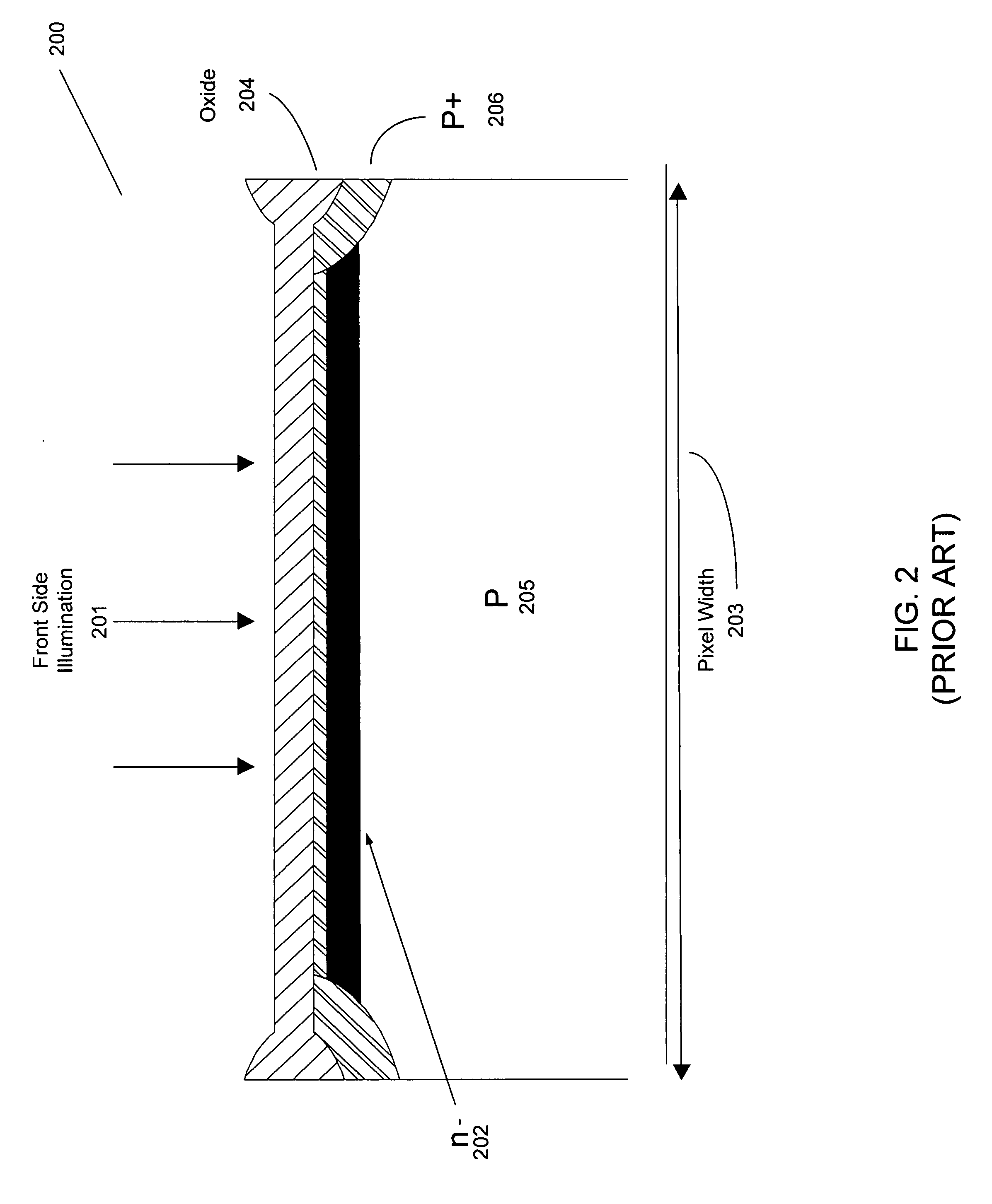

Inspection system using back side illuminated linear sensor

InactiveUS20110073982A1Current requiredKeep powerMaterial analysis by optical meansSemiconductor devicesSensor arrayEngineering

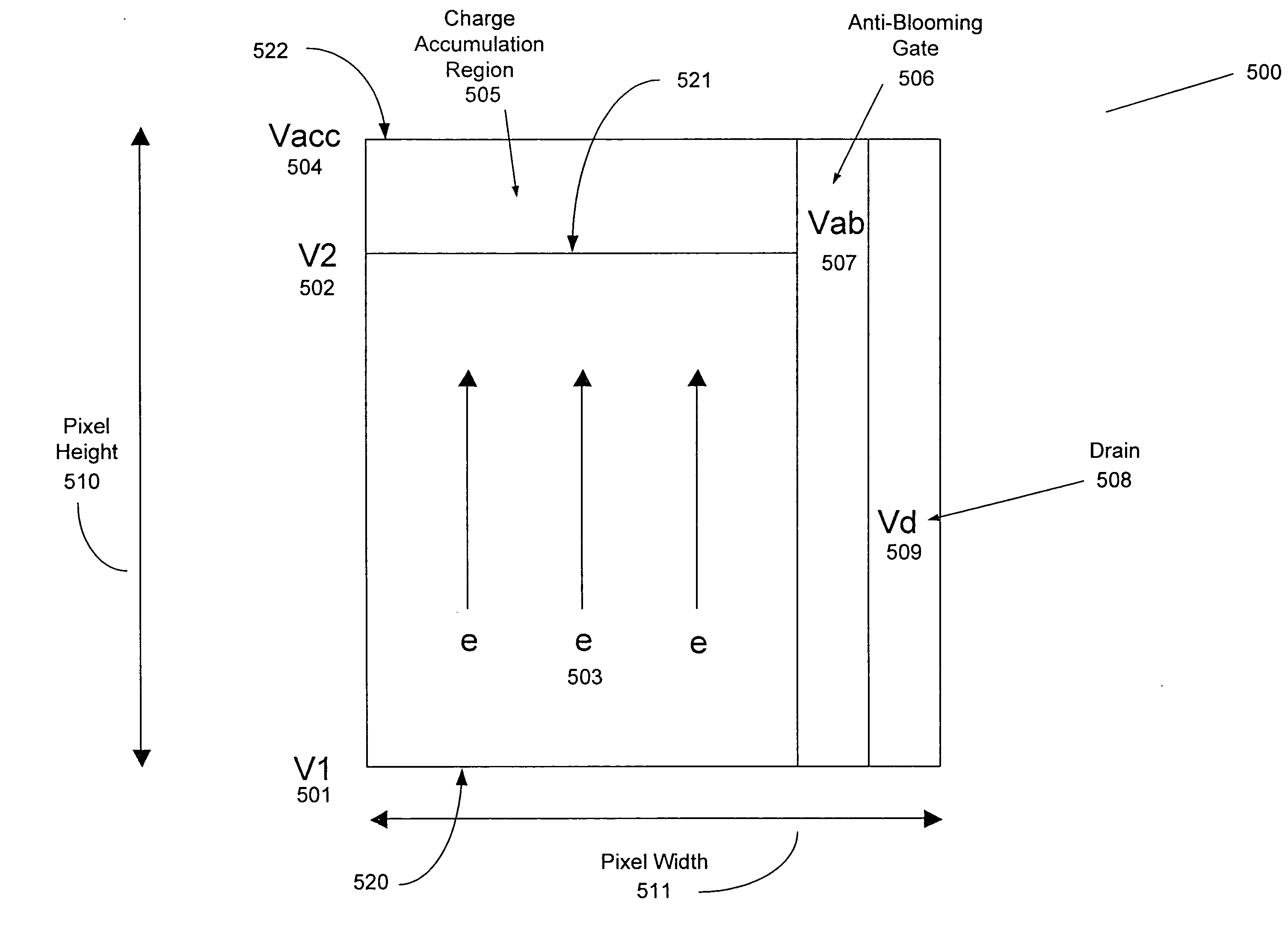

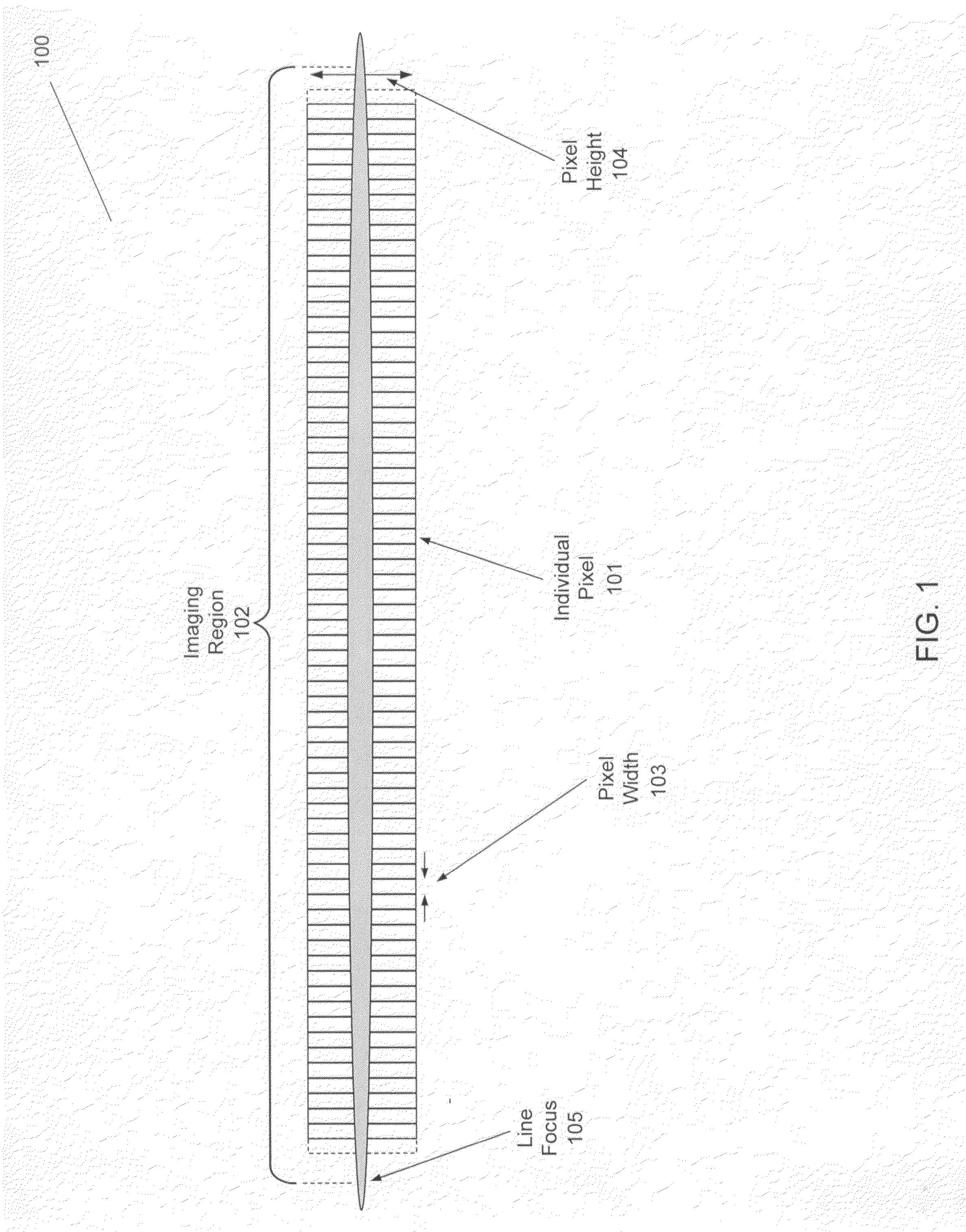

An improved inspection system using back-side illuminated linear sensing for propagating charge through a sensor is provided. Focusing optics may be used with a back side illuminated linear sensor to inspect specimens, the back side illuminated linear sensor operating to advance an accumulated charge from one side of each pixel to the other side. The design comprises controlling voltage profiles across pixel gates from one side to the other side in order to advance charge between to a charge accumulation region. Controlling voltage profiles comprises attaching a continuous polysilicon gate across each pixel within a back side illuminated linear sensor array. Polysilicon gates and voltages applied thereto enable efficient electron advancement using a controlled voltage profile.

Owner:KLA TENCOR TECH CORP

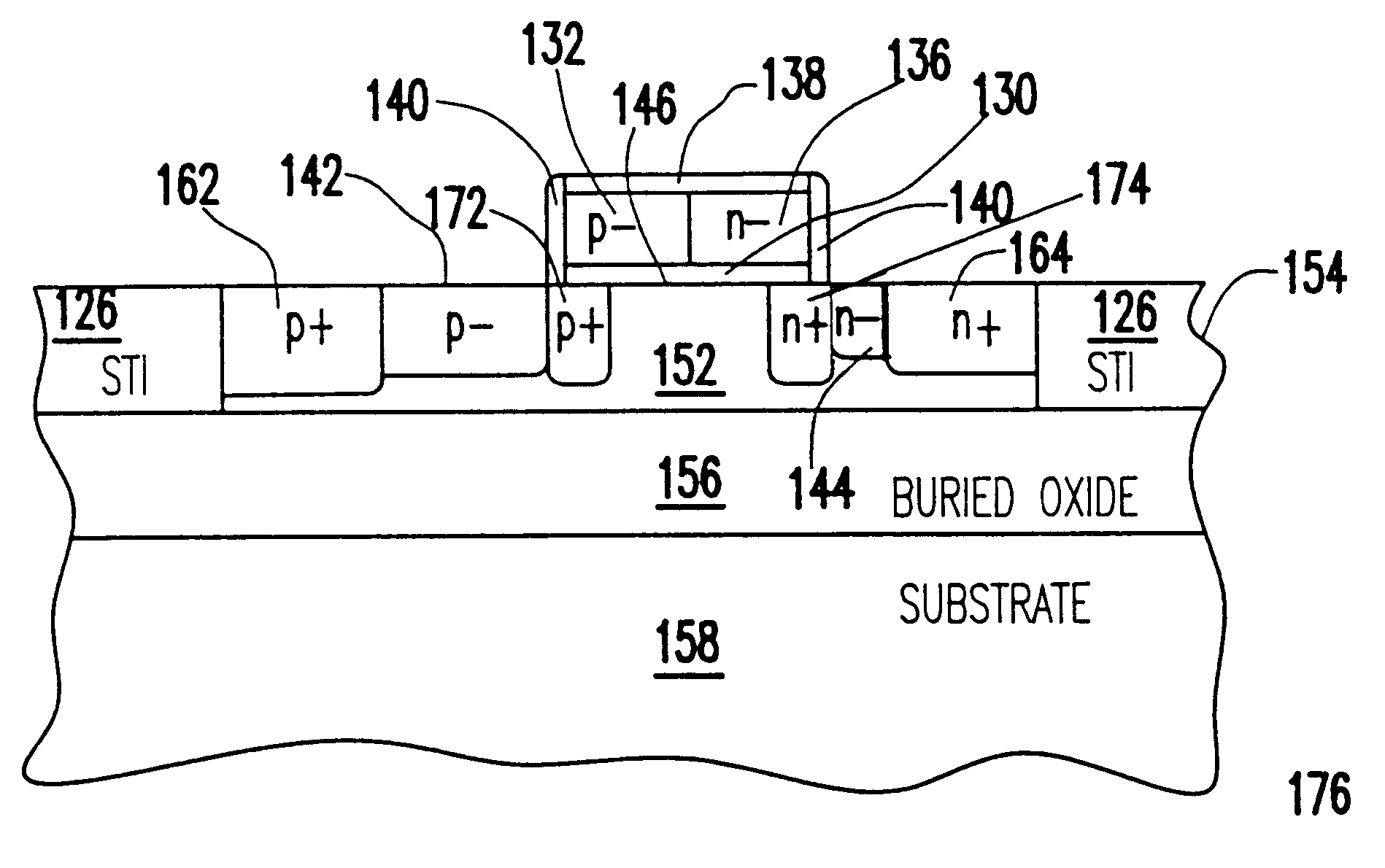

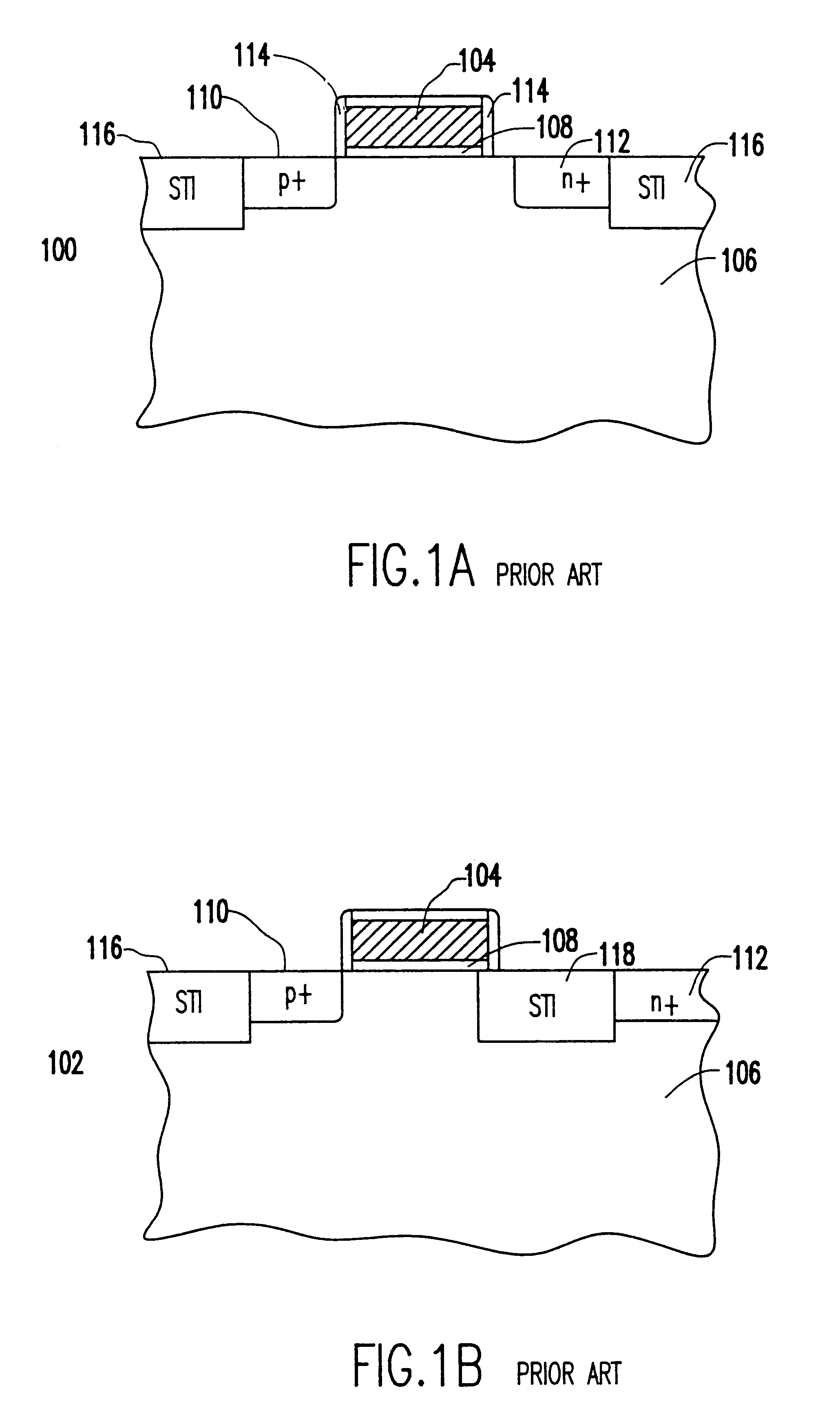

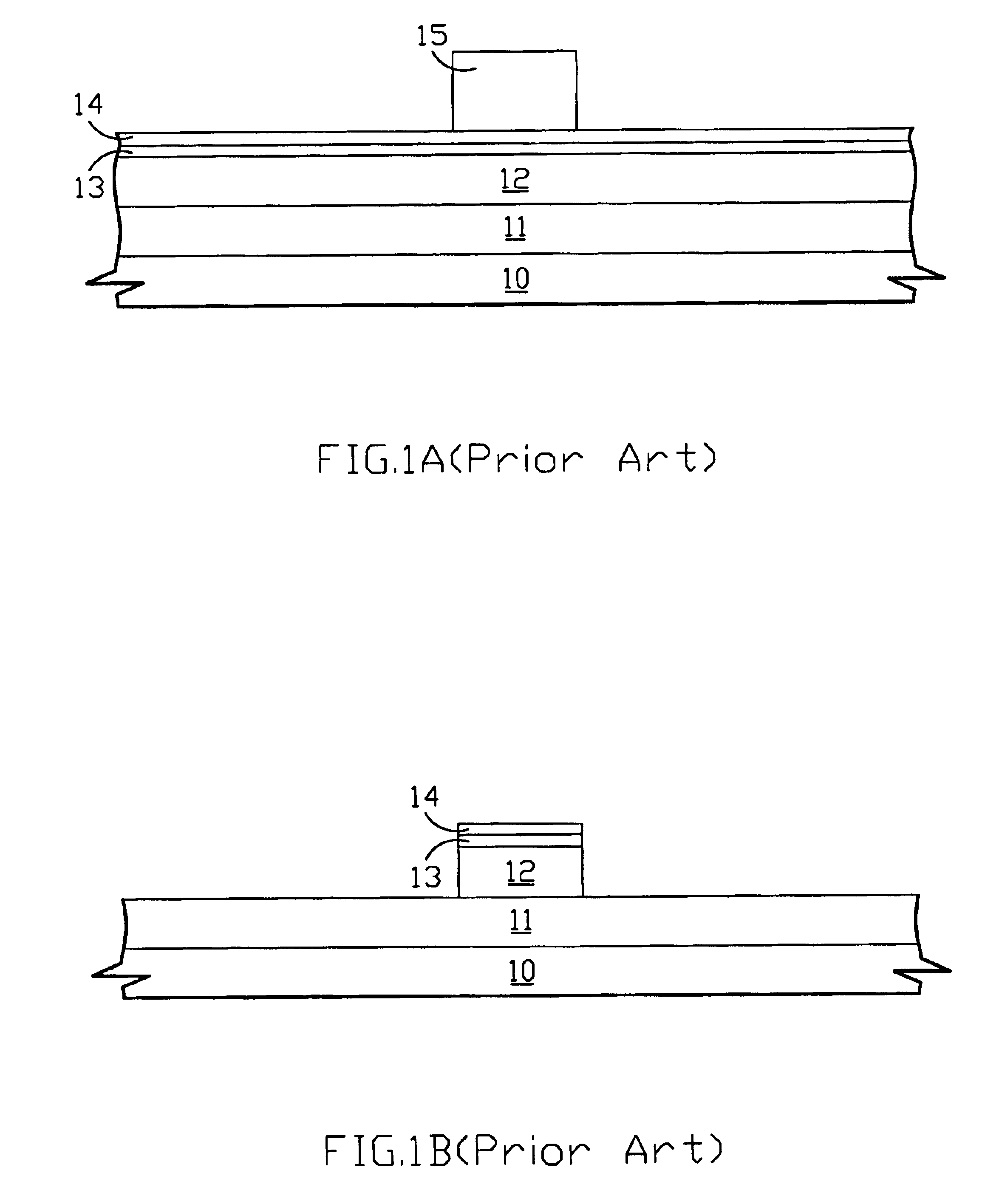

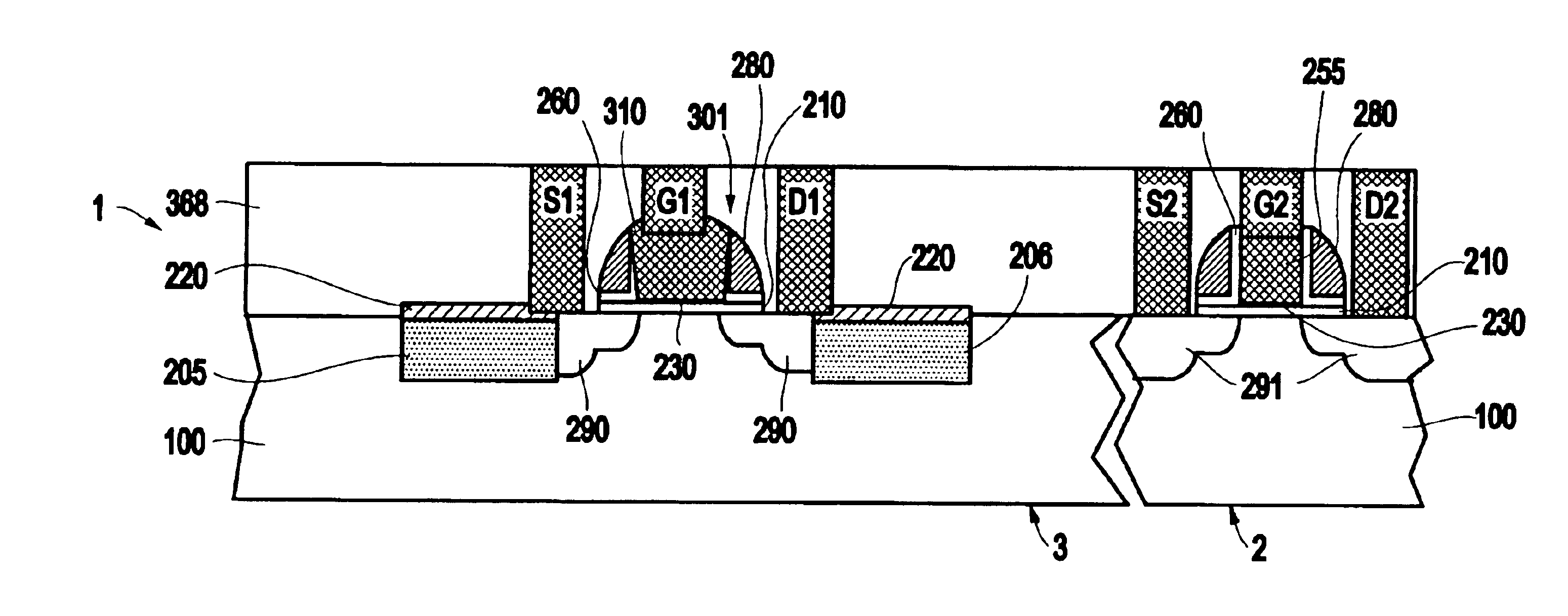

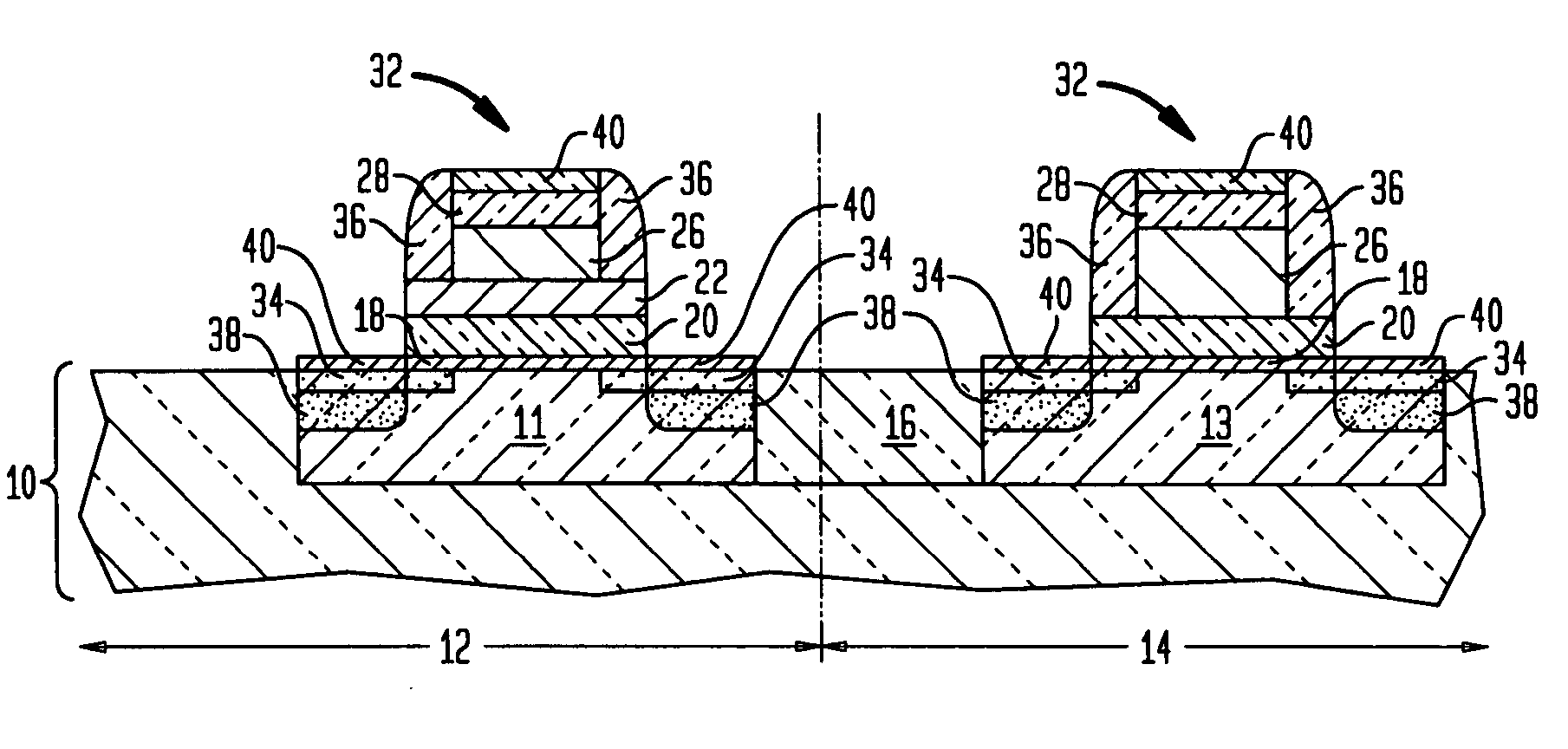

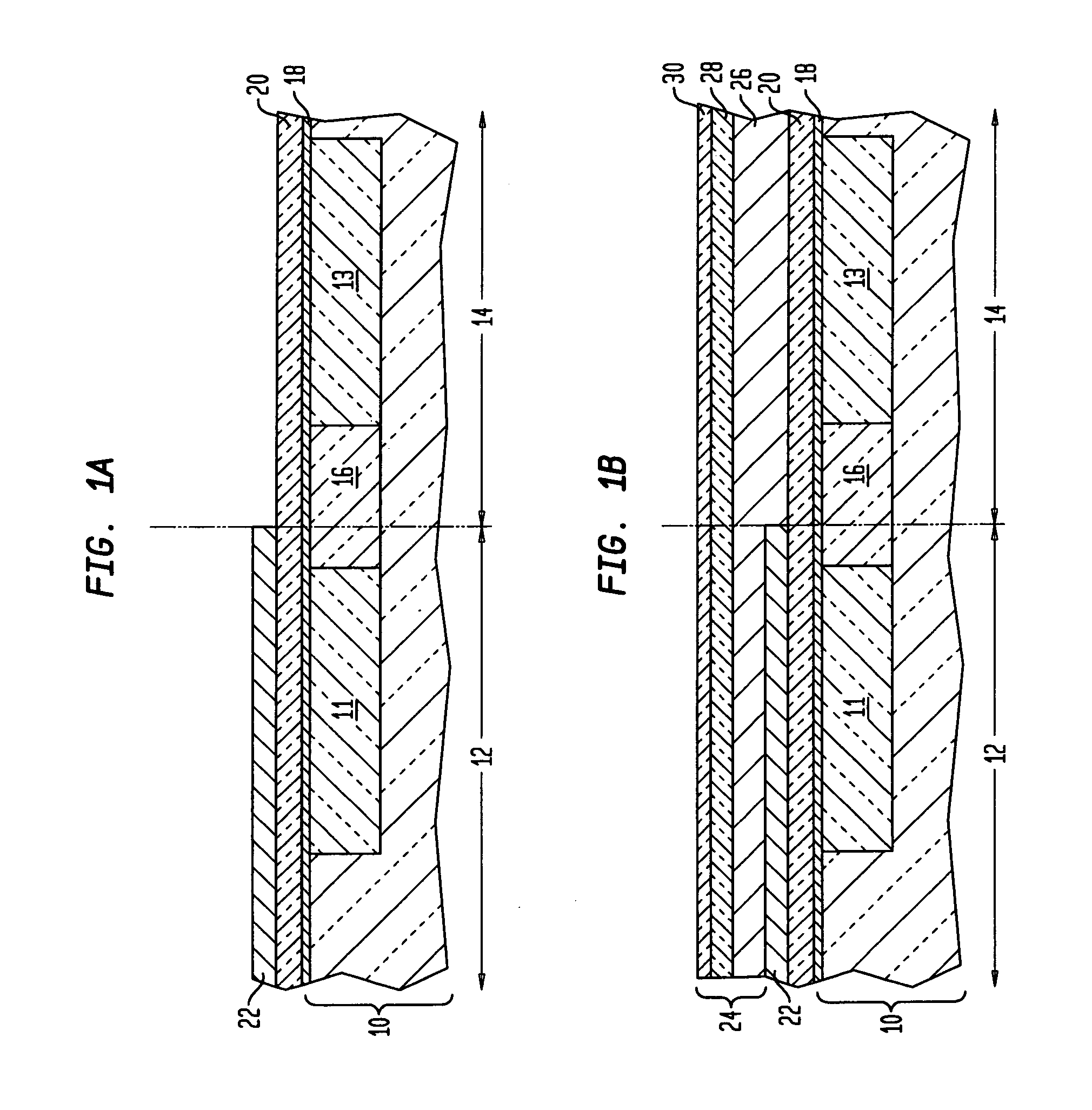

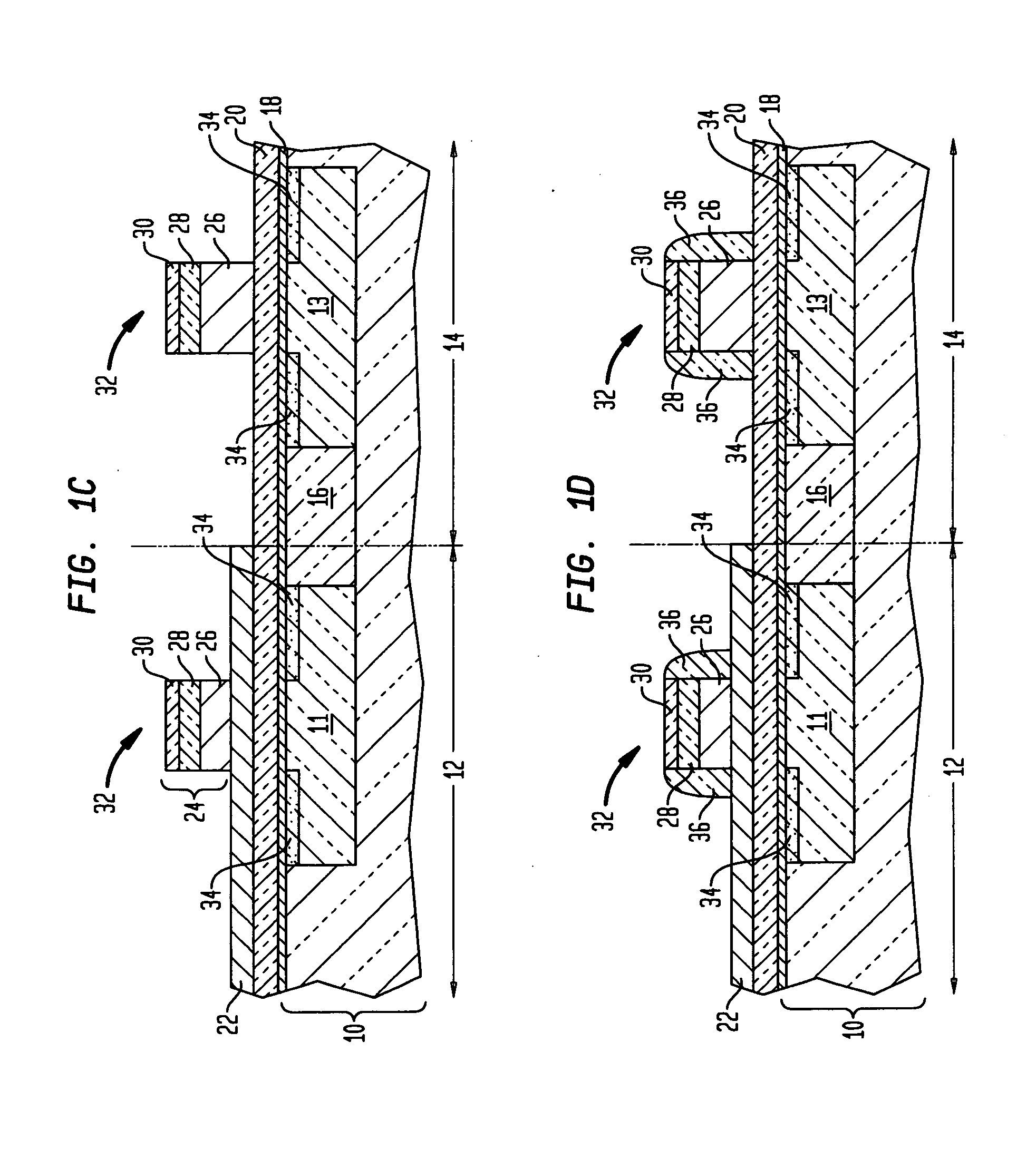

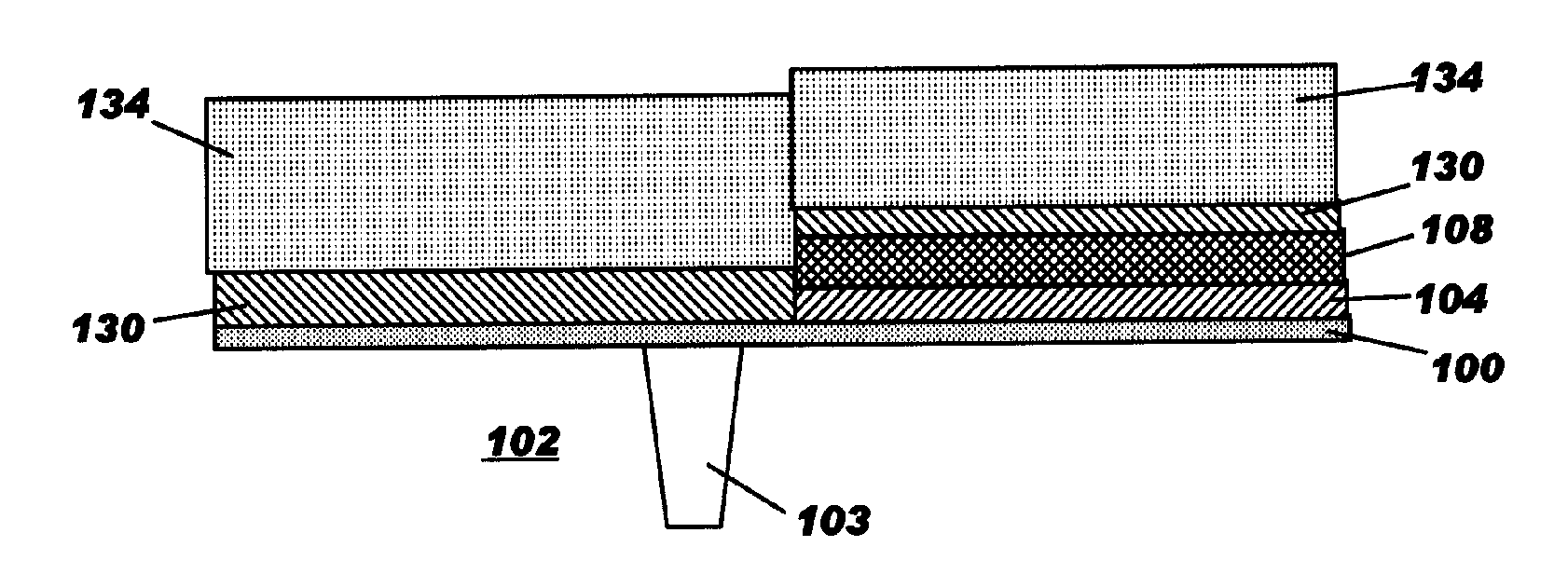

Semiconductor chip using both polysilicon and metal gate devices

InactiveUS6777761B2Improve reliabilityReduce leakage currentTransistorSolid-state devicesSingle processGate dielectric

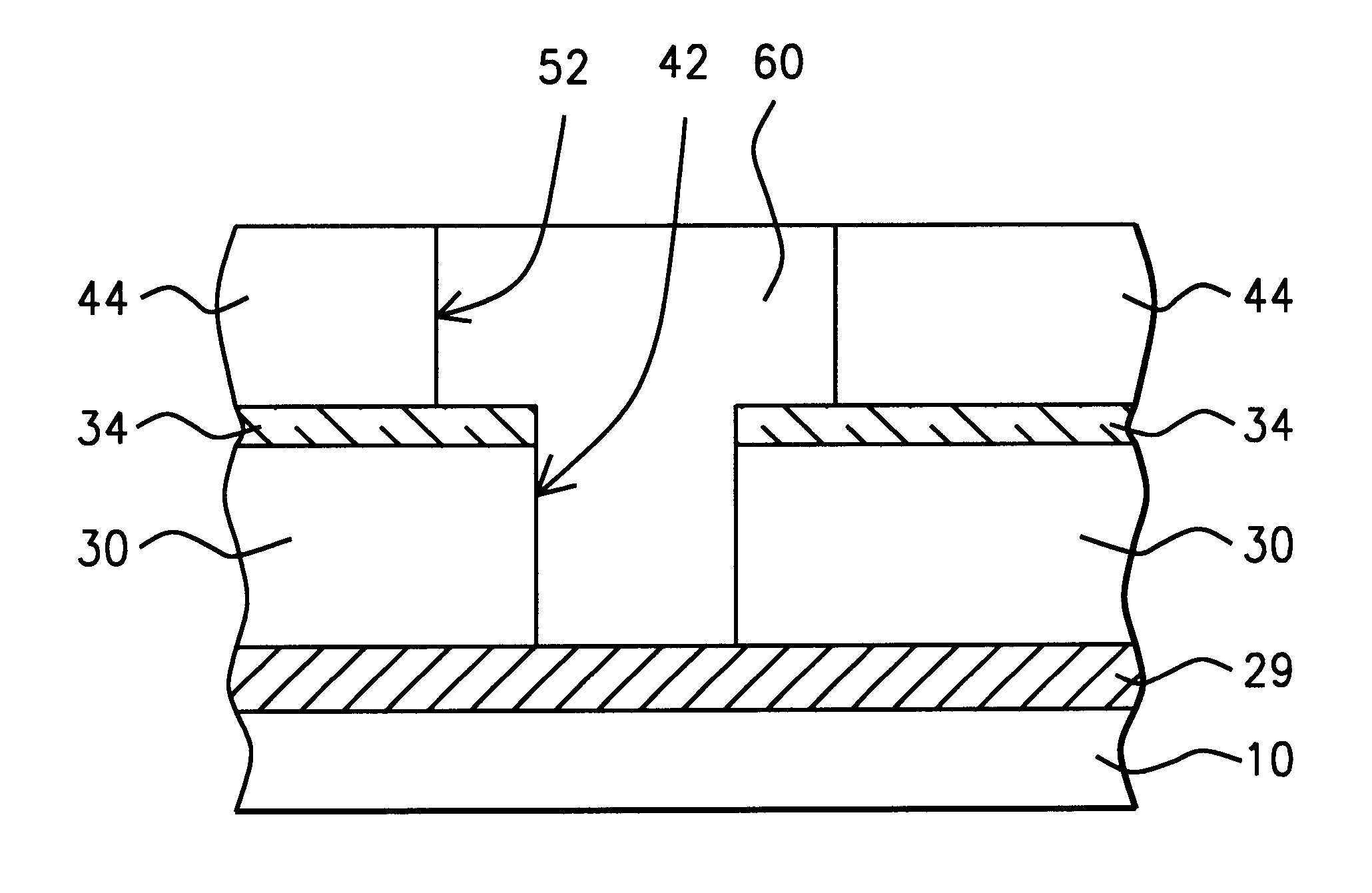

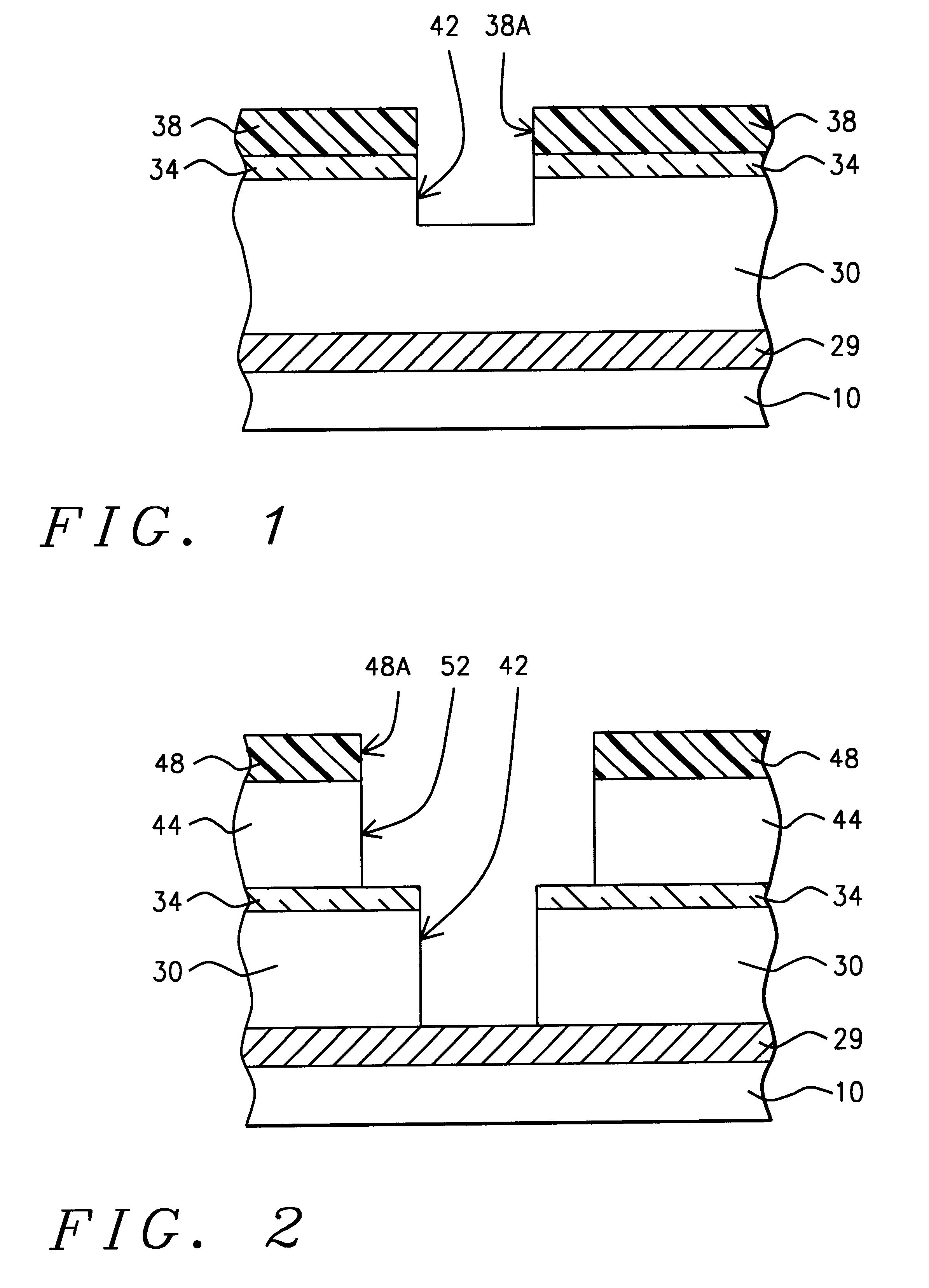

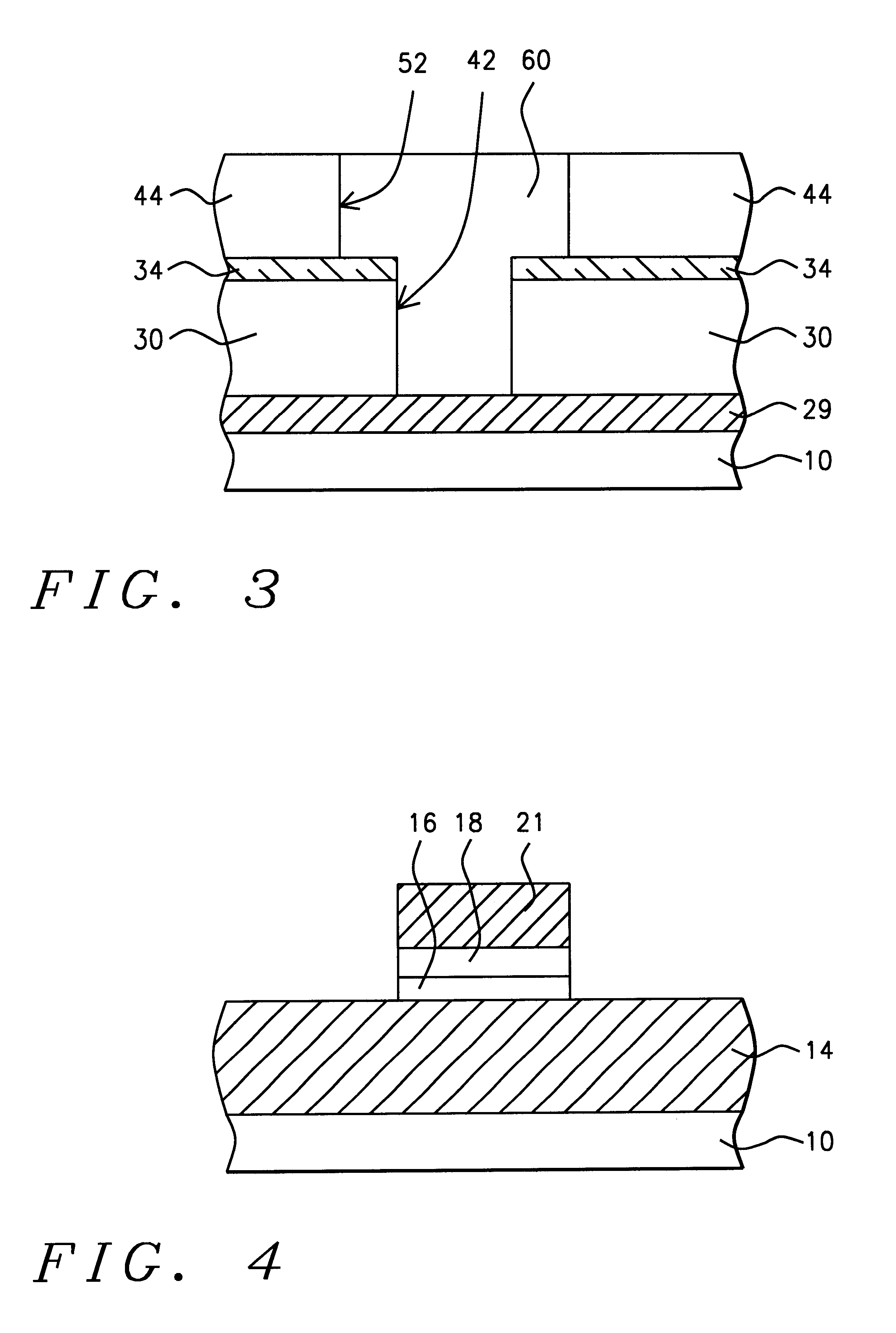

A semiconductor structure (and method for forming) having transistors having both metal gates and polysilicon gates on a single substrate in a single process is disclosed. The method forms a gate dielectric layer on the substrate and forms the metal seed layer on the gate oxide layer. The method patterns the metal seed layer to leave metal seed material in metal gate seed areas above the substrate. Next, the method patterns a polysilicon layer into polysilicon structures above the substrate. Some of the polysilicon structures comprise sacrificial polysilicon structures on the metal gate seed areas and the remaining ones of the polysilicon structures comprise the polysilicon gates. The patterning of the polysilicon gates forms the sacrificial gates above all the metal gate seed areas. Following that, the invention forms sidewall spacers, and source and drain regions adjacent the polysilicon structures. Then, the invention protects the polysilicon gates, removes the sacrificial polysilicon structures, and plates the metal gate seed areas to form the metal gates. The sidewall spacers self-align the metal gates. The plating process forms the metal gates of pure metal. All thermal processing that raises the temperature above a damage threshold for the metal is performed before the plating process.

Owner:ELPIS TECH INC

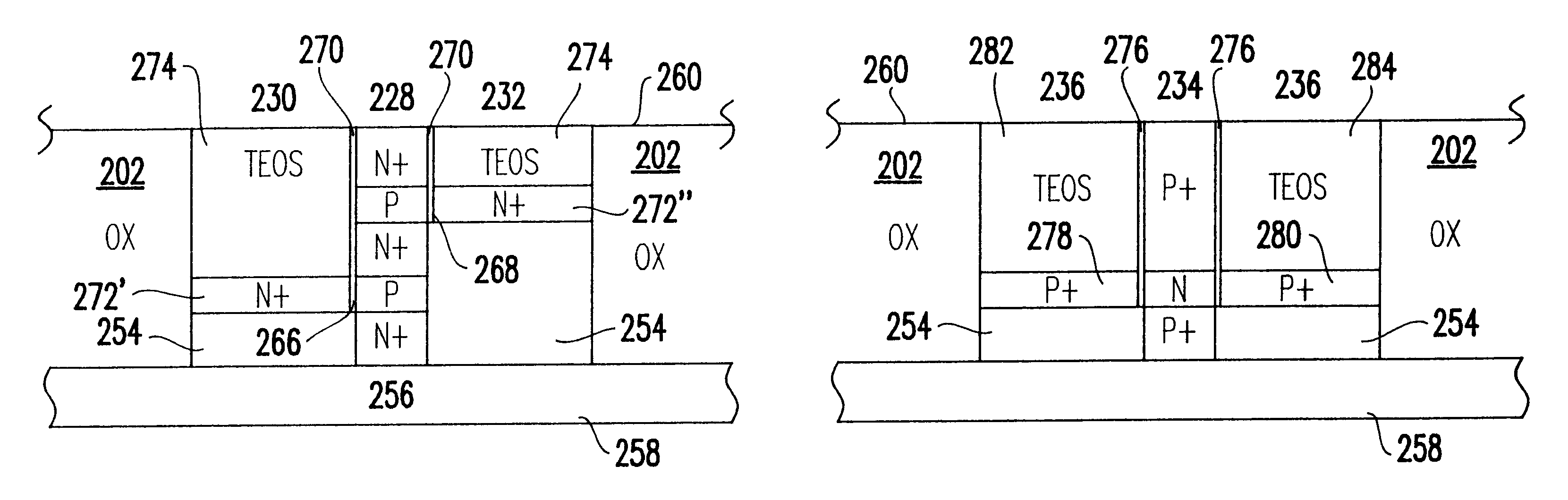

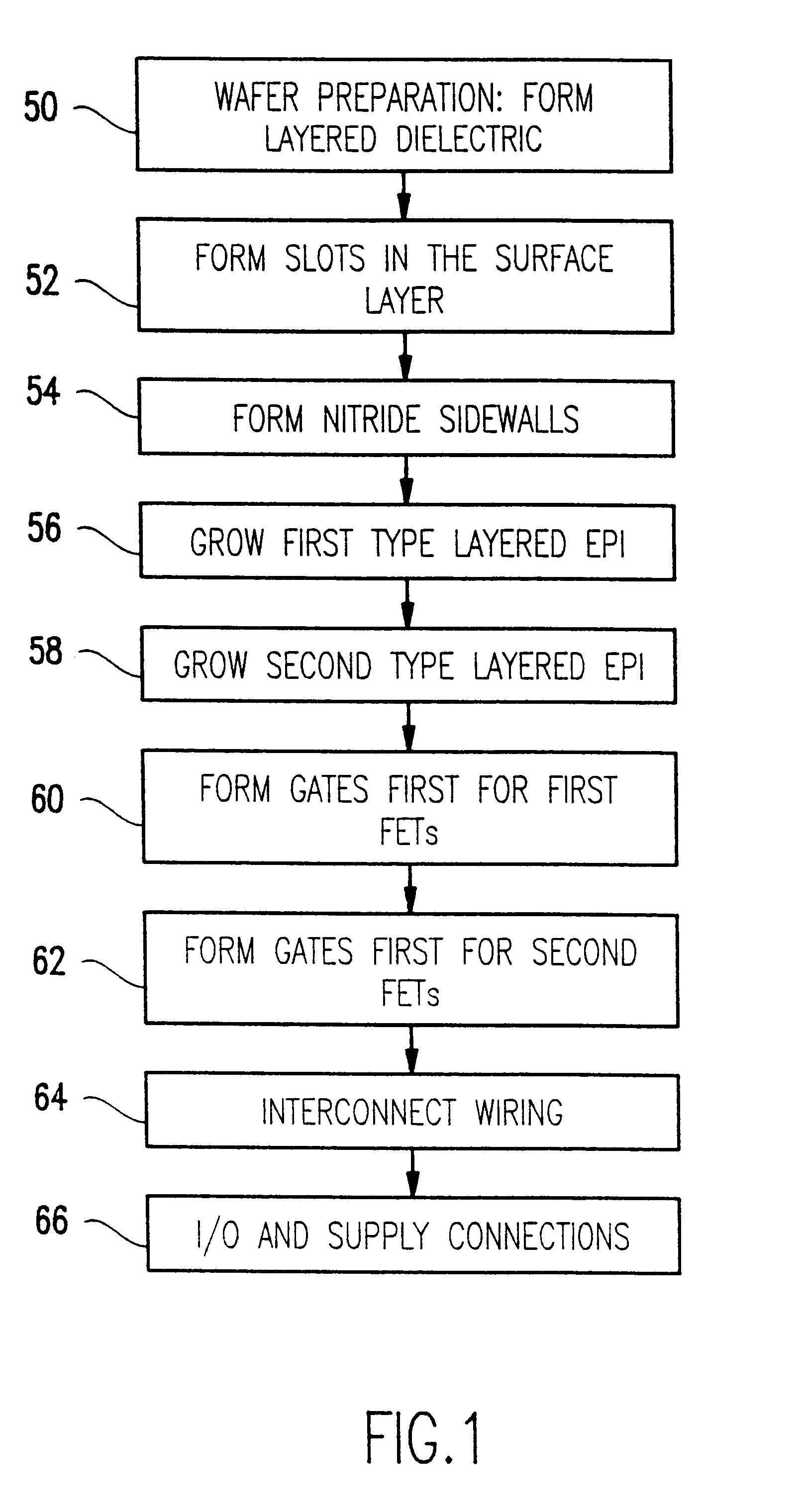

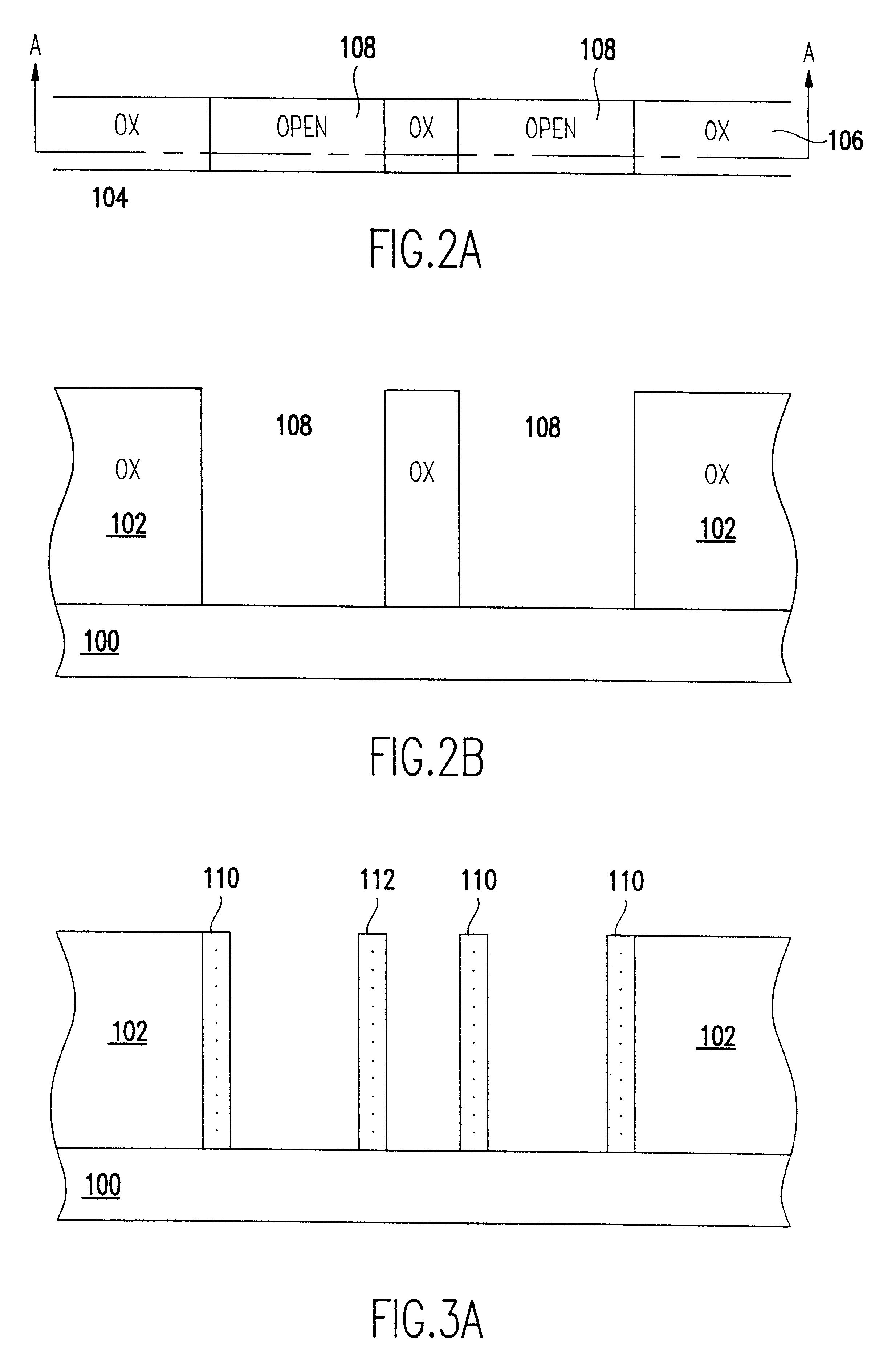

High performance, low power vertical integrated CMOS devices

InactiveUS6297531B2Solid-state devicesSemiconductor/solid-state device manufacturingHigh resistanceCapacitance

Owner:INT BUSINESS MASCH CORP

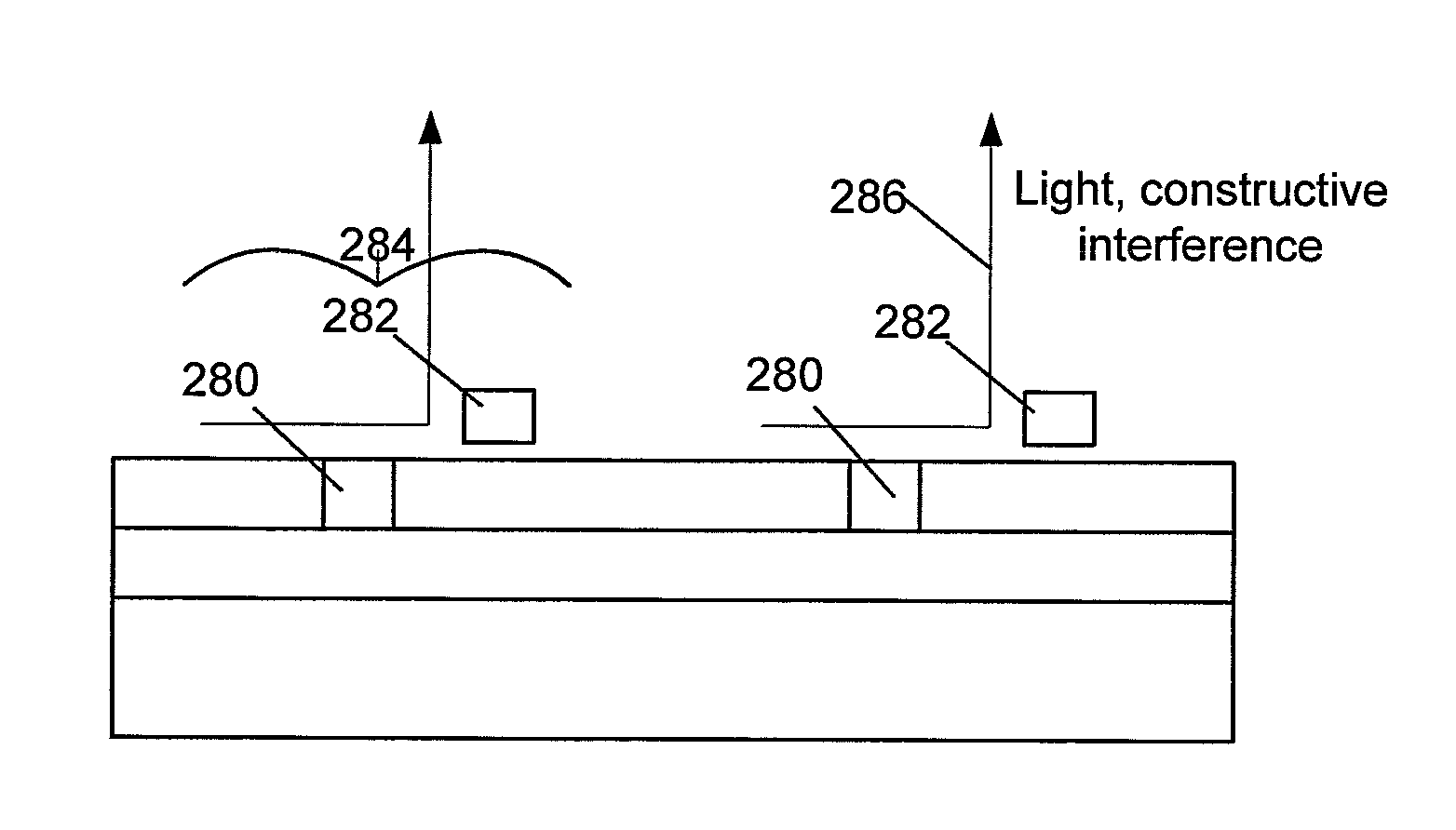

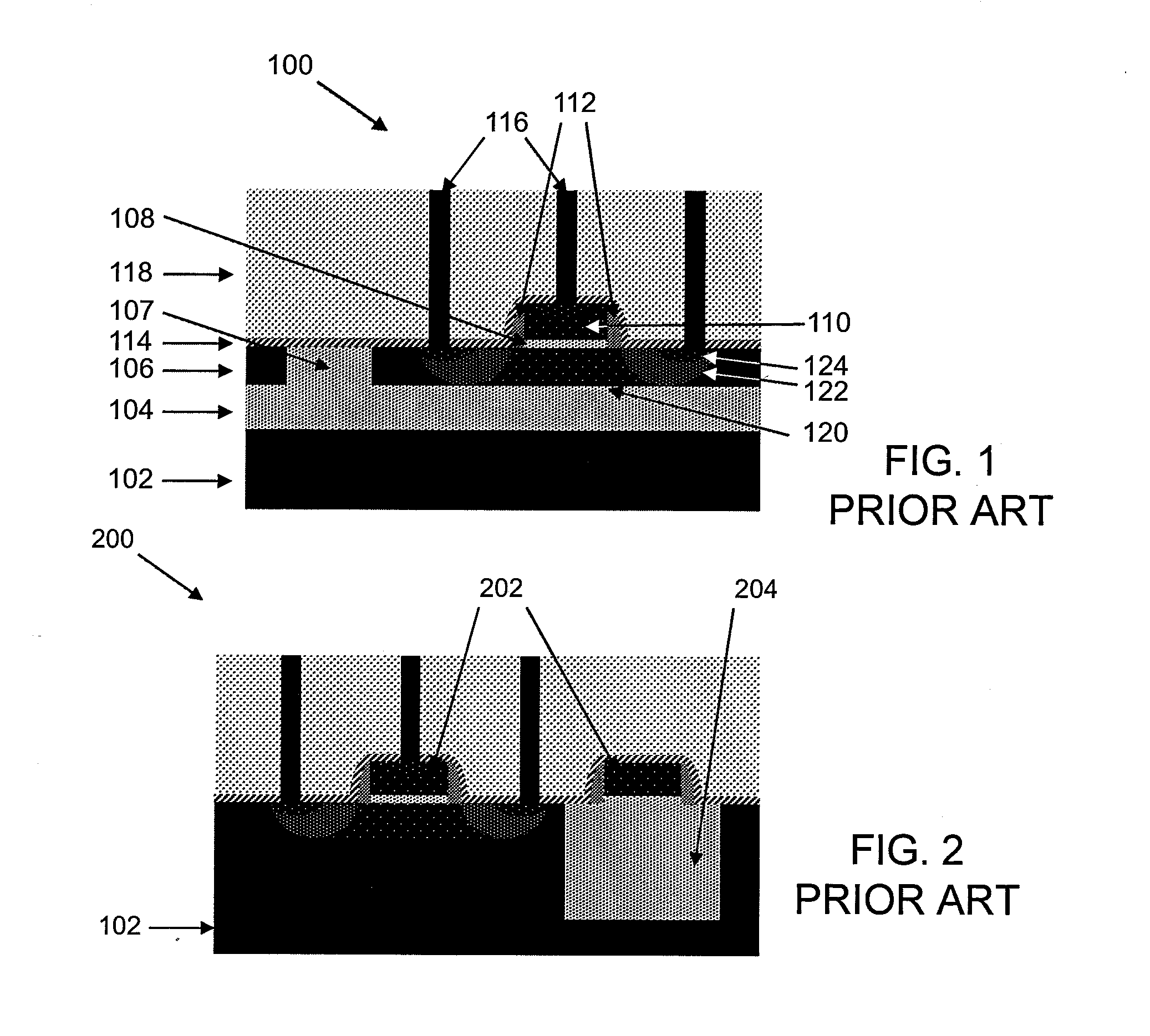

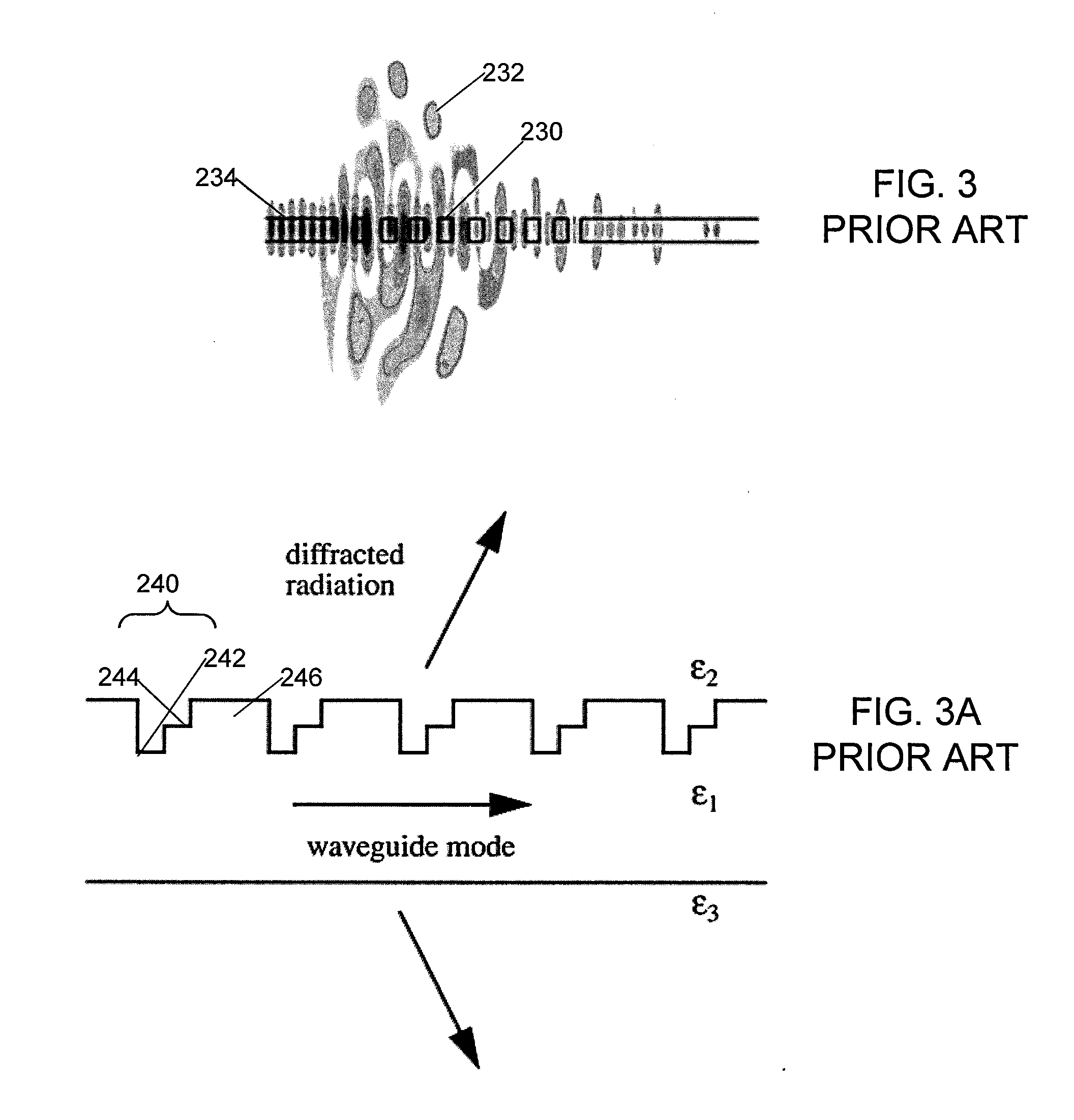

Method and Apparatus for Optical Waveguide-to-Semiconductor Coupling and Optical Vias for Monolithically Integrated Electronic and Photonic Circuits

ActiveUS20140193115A1Coupling light guidesOptical waveguide light guideGratingIntegrated electronics

An optical coupler has a waveguide coupled to a grating of multiple scattering units, each scattering unit having a first scattering element formed of a shape in a polysilicon gate layer and a second scattering element formed of a shape in a body silicon layer of a metal-oxide-semiconductor (MOS) integrated circuit (IC). The couplers may be used in a system having a coupler on each of a first and second IC, infrared light being formed into a beam passing between the couplers. Vias may be interposed in third ICs between the first and second ICs. The couplers may be configured with nonuniform width of scattering elements to produce Gaussian or focused beams.

Owner:MASSACHUSETTS INST OF TECH +1

Dual metal gate self-aligned integration

A semiconductor structure including at least one n-type field effect transistor (nFET) and at least one p-type field effect transistor (pFET) that both include a metal gate having nFET behavior and pFET behavior, respectively, without including an upper polysilicon gate electrode is provided. The present invention also provides a method of fabricating such a semiconductor structure.

Owner:GLOBALFOUNDRIES US INC

Methods of fabricating fin field-effect transistors having silicide gate electrodes and related devices

InactiveUS20050272190A1TransistorSemiconductor/solid-state device manufacturingPolysilicon gateSemiconductor

A method of fabricating a fin field-effect transistor includes forming a fin-shaped active region having first and second source / drain regions therein and a channel region therebetween vertically protruding from a semiconductor substrate, and forming a polysilicon gate electrode on sidewalls of the channel region. Opposing sidewalls of the polysilicon gate electrode are silicided towards a central region thereof to form a silicide gate electrode. Related devices are also discussed.

Owner:SAMSUNG ELECTRONICS CO LTD

Method of making a metal gate semiconductor device

InactiveUS20060292773A1TransistorSemiconductor/solid-state device manufacturingGate dielectricDevice material

A patterned polysilicon gate is over a metal layer that is over a gate dielectric layer, which in turn is over a semiconductor substrate. A thin layer of material is conformally deposited over the polysilicon gate and the exposed metal layer and then etched back to form a sidewall spacer on the polysilicon gate and to re-expose the previously exposed portion of the metal layer. The re-exposed metal layer is etched using an etchant that is selective to the gate dielectric material and the sidewall spacer. Even though this etch is substantially anisotropic, it has an isotropic component that would etch the sidewall of the polysilicon gate but for the protection provided by the sidewall spacer. After the re-exposed metal has been removed, a transistor is formed in which the metal layer sets the work function of the gate of the transistor.

Owner:NXP USA INC

Method for making an ultra thin FDSOI device with improved short-channel performance

InactiveUS6975014B1Excellent Ioff DC characteristicImprove featuresTransistorSemiconductor/solid-state device manufacturingGate dielectricEngineering

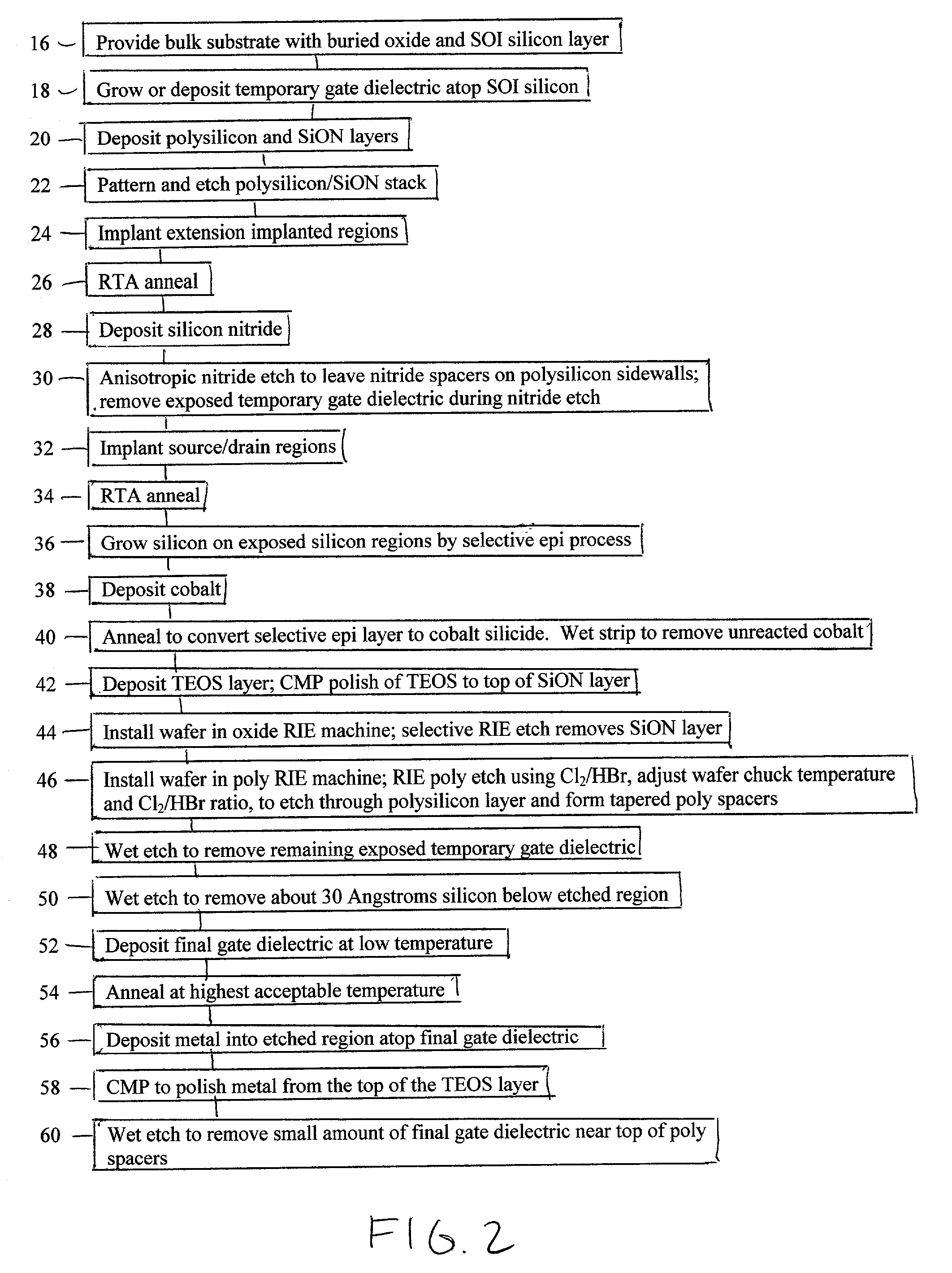

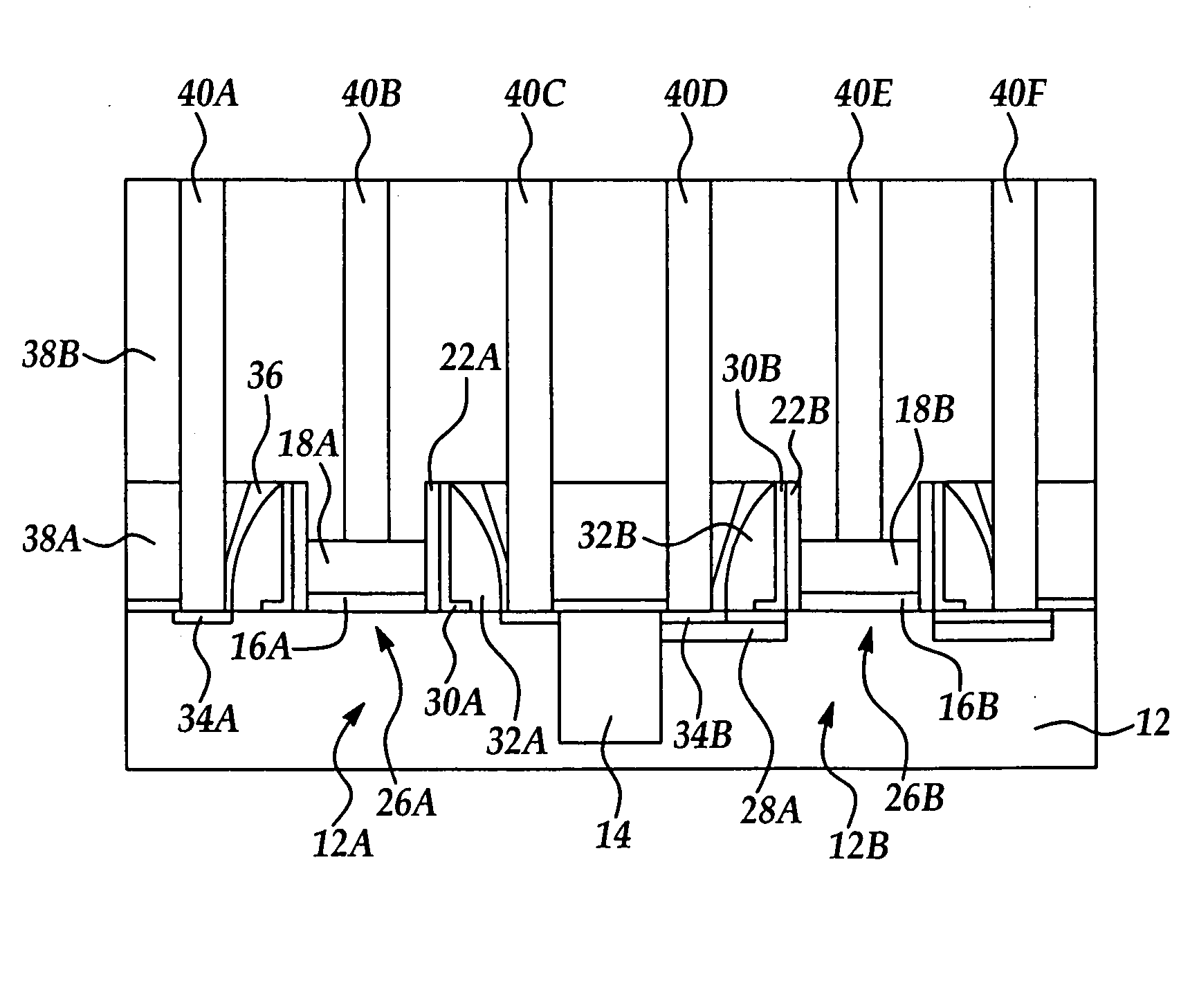

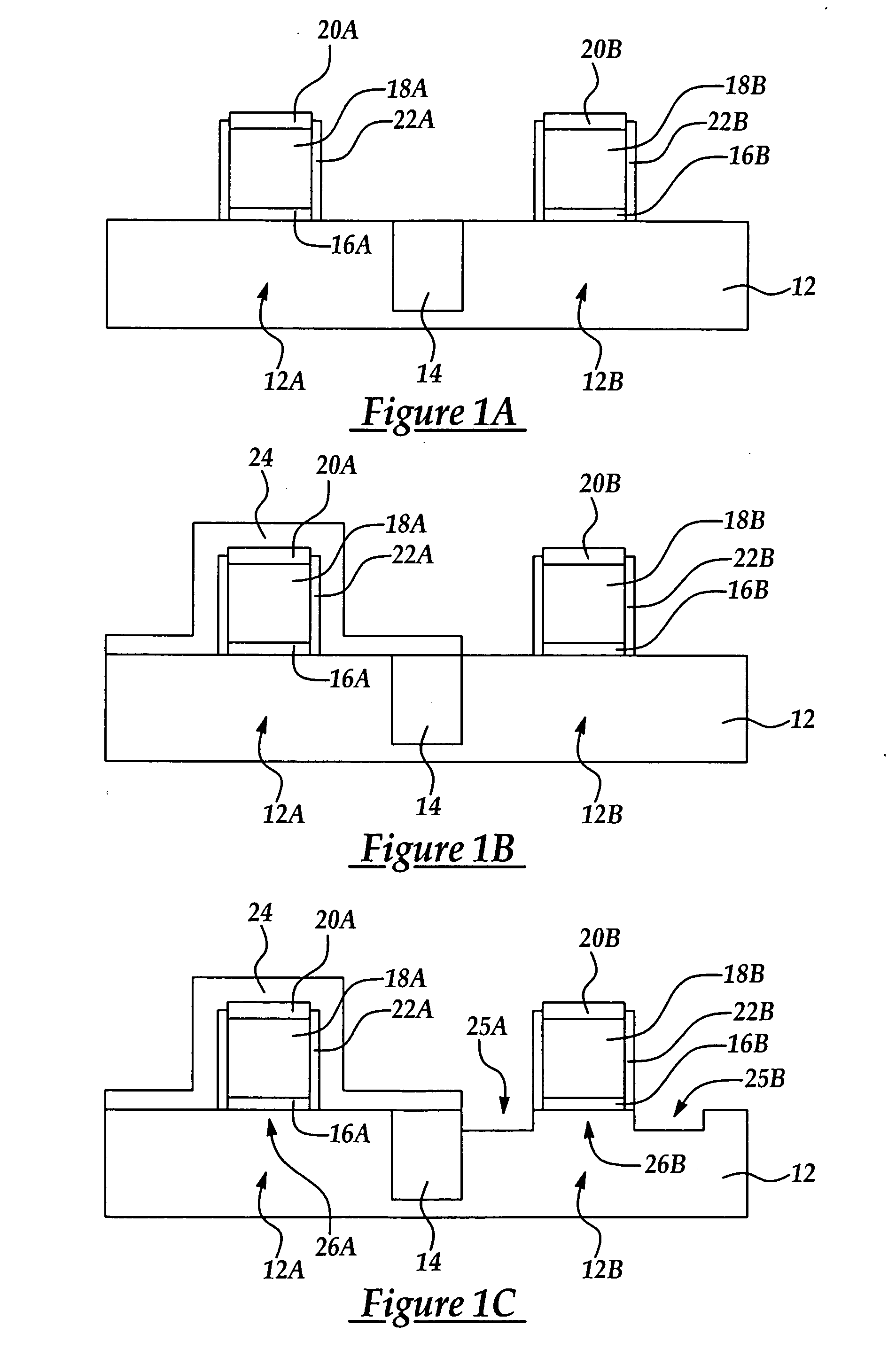

A method for forming a FDSOI device with channel length less than 50 nm with good short channel control. The gate has a tapered polysilicon spacer and a dielectric spacer. A polysilicon gate feature is formed and dielectric sidewall spacers are formed thereon. The polysilicon gate feature is then etched to form tapered poly features separated by a gap. A gate dielectric is deposited at low temperature, then metal is deposited into the gap to form the metal gate.

Owner:ADVANCED MICRO DEVICES INC +1

Strained channel CMOS device with fully silicided gate electrode

InactiveUS20060148181A1Lower electrode resistanceInhibitionSemiconductor/solid-state device manufacturingSemiconductor devicesSilicon alloyMetal silicide

A strained channel NMOS and PMOS device pair including fully silicided gate electrodes and method for forming the same, the method including providing a semiconductor substrate including NMOS and PMOS device regions including respective gate structures including polysilicon gate electrodes; forming recessed regions on either side of a channel region including at least one of the NMOS and PMOS device regions; backfilling portions of the recessed regions with a semiconducting silicon alloy to exert a strain on the channel region; forming offset spacers on either side of the gate structures; thinning the polysilicon gate electrodes to a silicidation thickness to allow full metal silicidation through the silicidation thickness; ion implanting the polysilicon gate electrodes to adjust a work function; and, forming a metal silicide through the silicidation thickness to form metal silicide gate electrodes.

Owner:TAIWAN SEMICON MFG CO LTD

High selectivity Si-rich SiON etch-stop layer

InactiveUS6245669B1Superior light absorption qualityReduce RC delaySemiconductor/solid-state device manufacturingResistSilicon oxide

The present invention provides an anti-reflective Si-Rich Silicon oxynitride (SiON) etch barrier layer and two compatible oxide etch processes. The Si-Rich Silicon oxynitride (SiON) etch barrier layer can be used as a hard mask in a dual damascene structure and as a hard mask for over a polysilicon gate. The invention has the following key elements: 1) Si rich Silicon oxynitride (SiON) ARC layer, 2) Special Silicon oxide Etch process that has a high selectivity of Si-Rich SiON to silicon oxide or SiN; 3) Special Si Rich SiON spacer process for a self aligned contact (SAC).A dual damascene structure is formed by depositing a first dielectric layer. A novel anti-reflective Si-Rich Silicon oxynitride (SiON) etch barrier layer is deposited on top of the first dielectric layer. A first opening is etched in the first insulating layer. A second dielectric layer is deposited on the anti-reflective Si-Rich Silicon oxynitride (SiON) etch barrier layer. A second dual damascene opening is etched into the dielectric layers. The anti-reflective Si-Rich Silicon oxynitride (SiON) etch barrier layer can also serve as an ARC layer during these operations to reduce the amount of reflectance from conductive region to reduce distortion of the photoresist pattern.

Owner:TAIWAN SEMICON MFG CO LTD

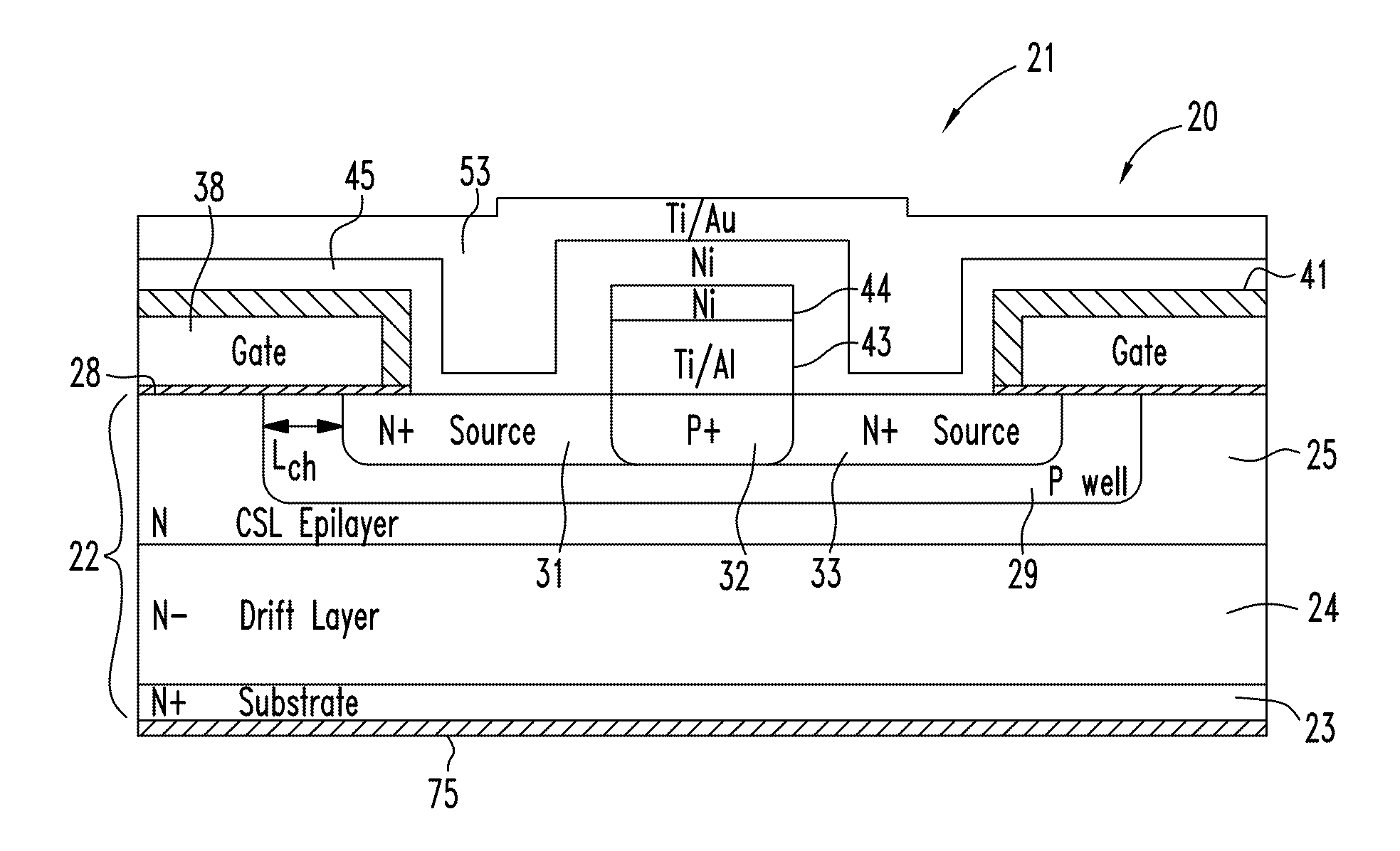

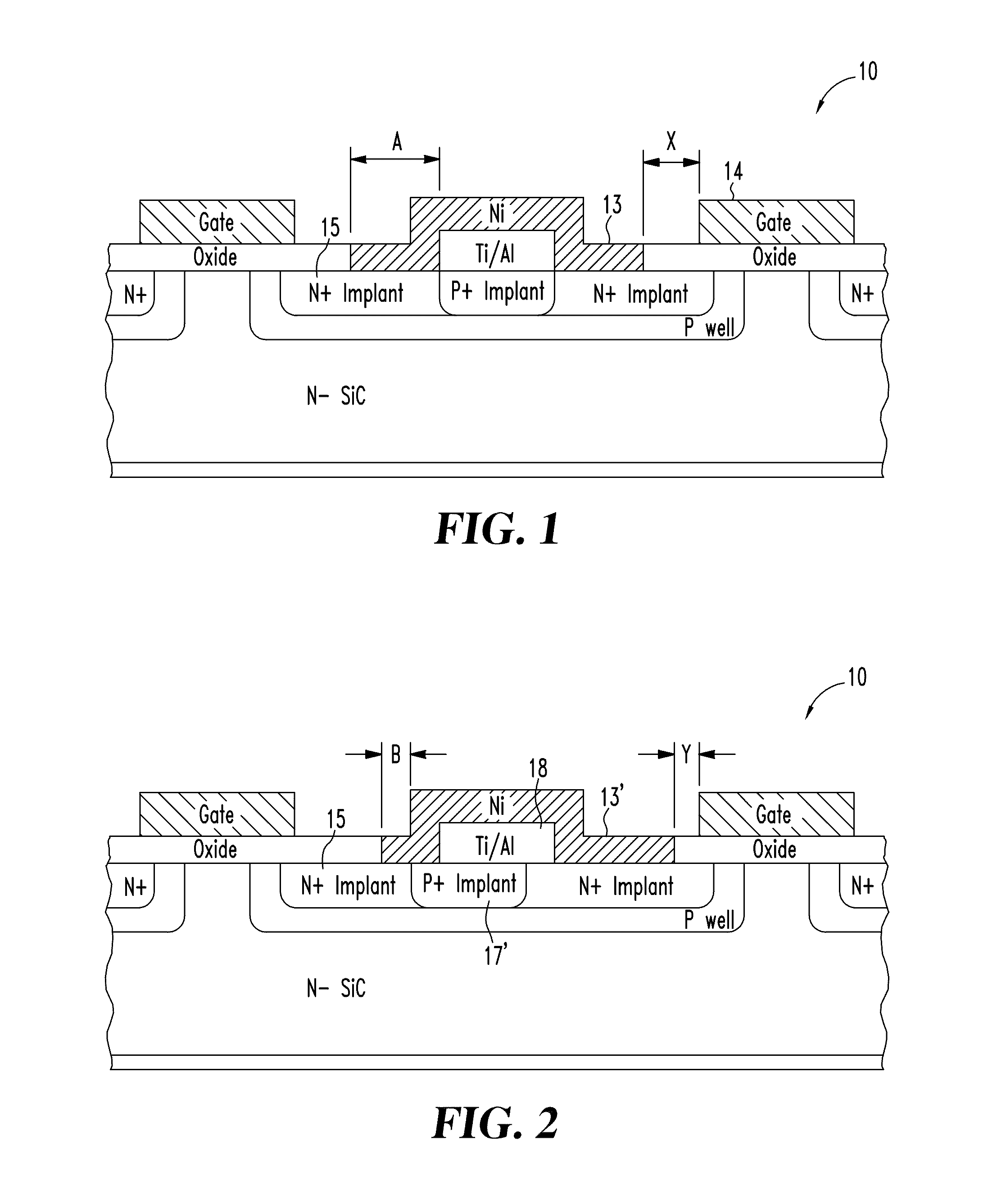

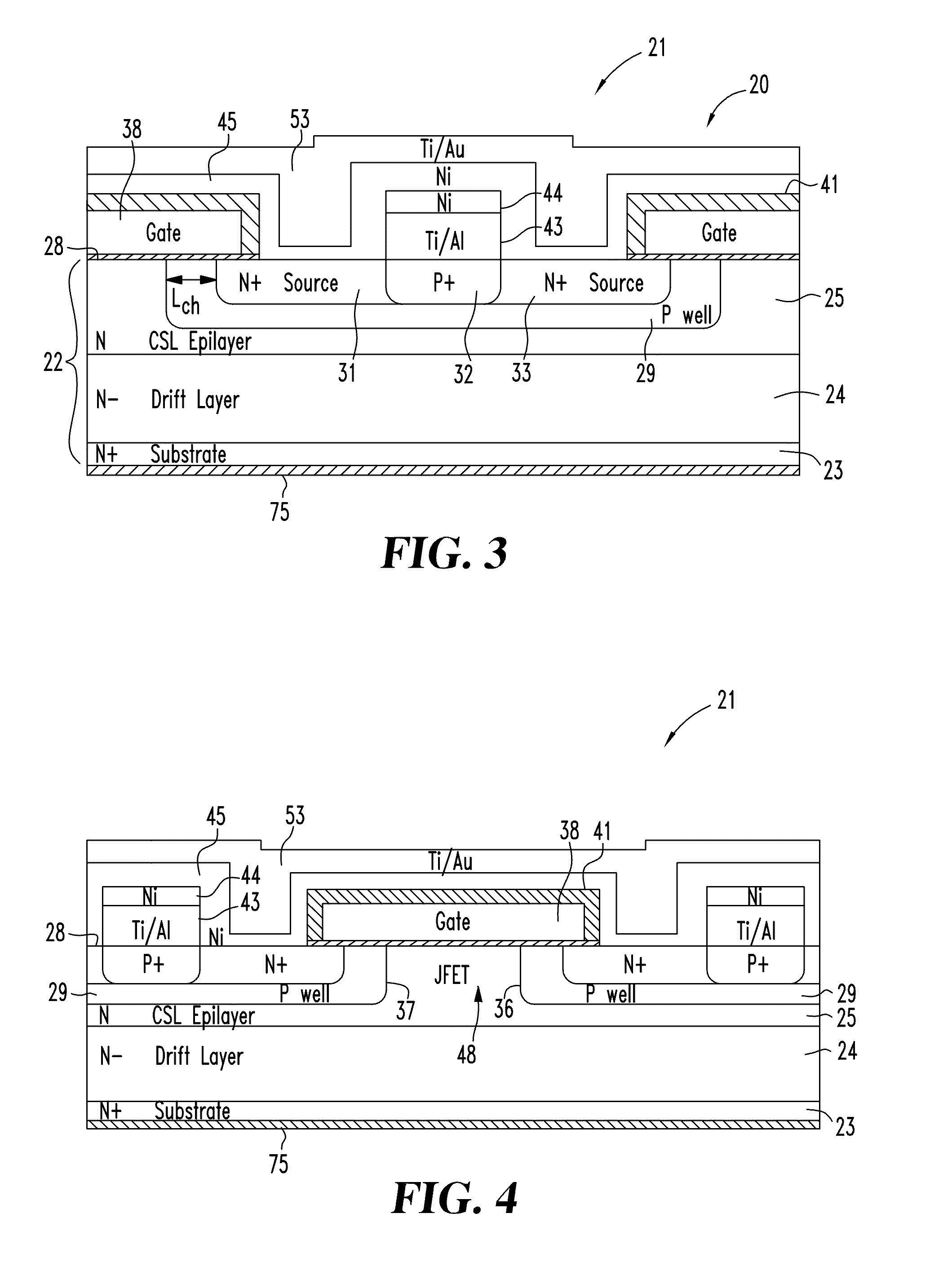

SIC power DMOSFET with self-aligned source contact

An intermediate product in the fabrication of a MOSFET, including a silicon carbide wafer having a substrate and a drift layer on said substrate, said drift layer having a plurality of source regions formed adjacent an upper surface thereof; a first oxide layer on said upper surface of said drift layer; a plurality of polysilicon gates above said first oxide layer, said plurality of polysilicon gates including a first gate adjacent a first of said source regions; an oxide layer over said first source region of greater thickness than said first oxide layer; and, an oxide layer over said first gate of substantially greater thickness than said oxide layer over said first source region.

Owner:THE TRUSTEES OF PURDUE UNIV

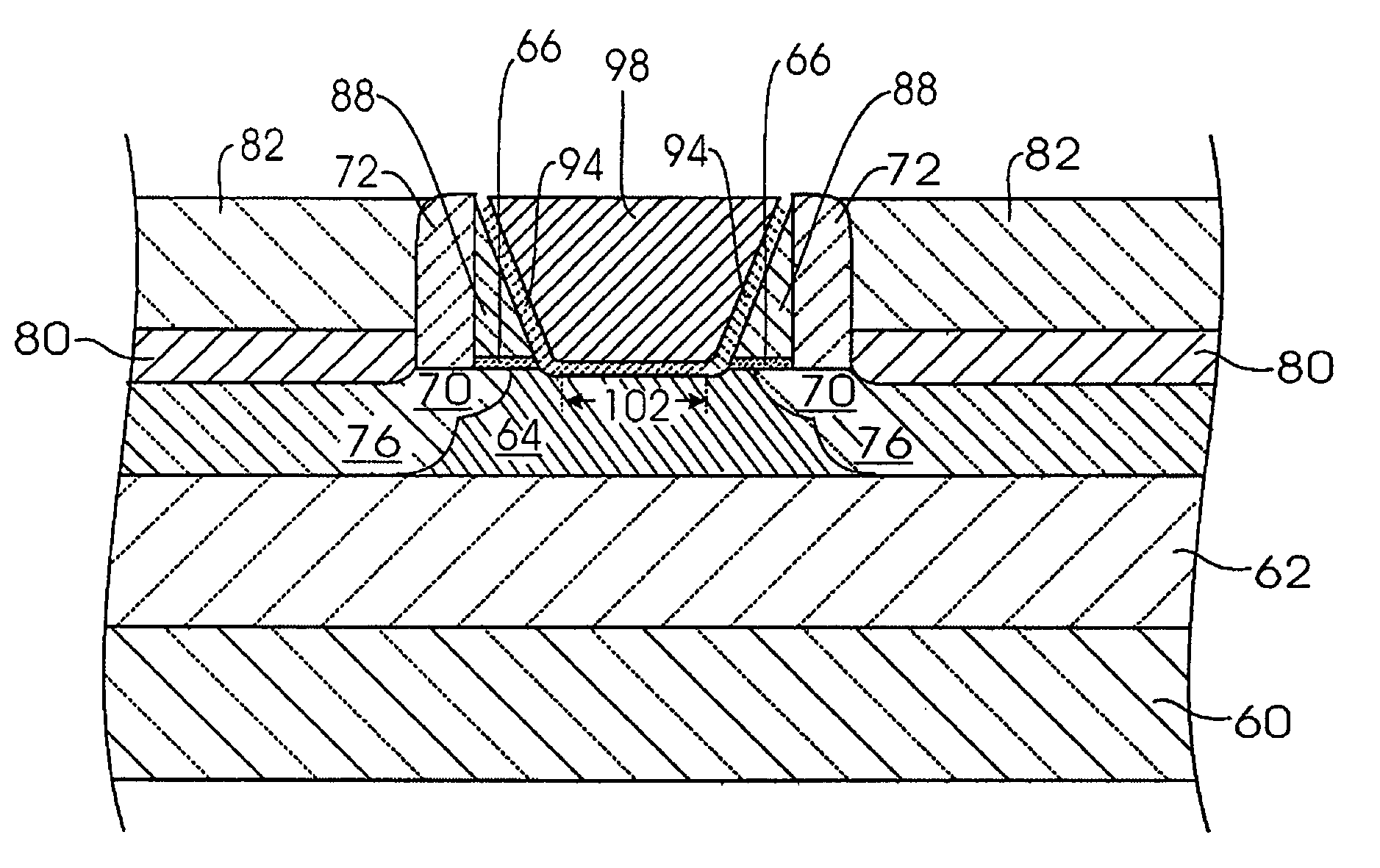

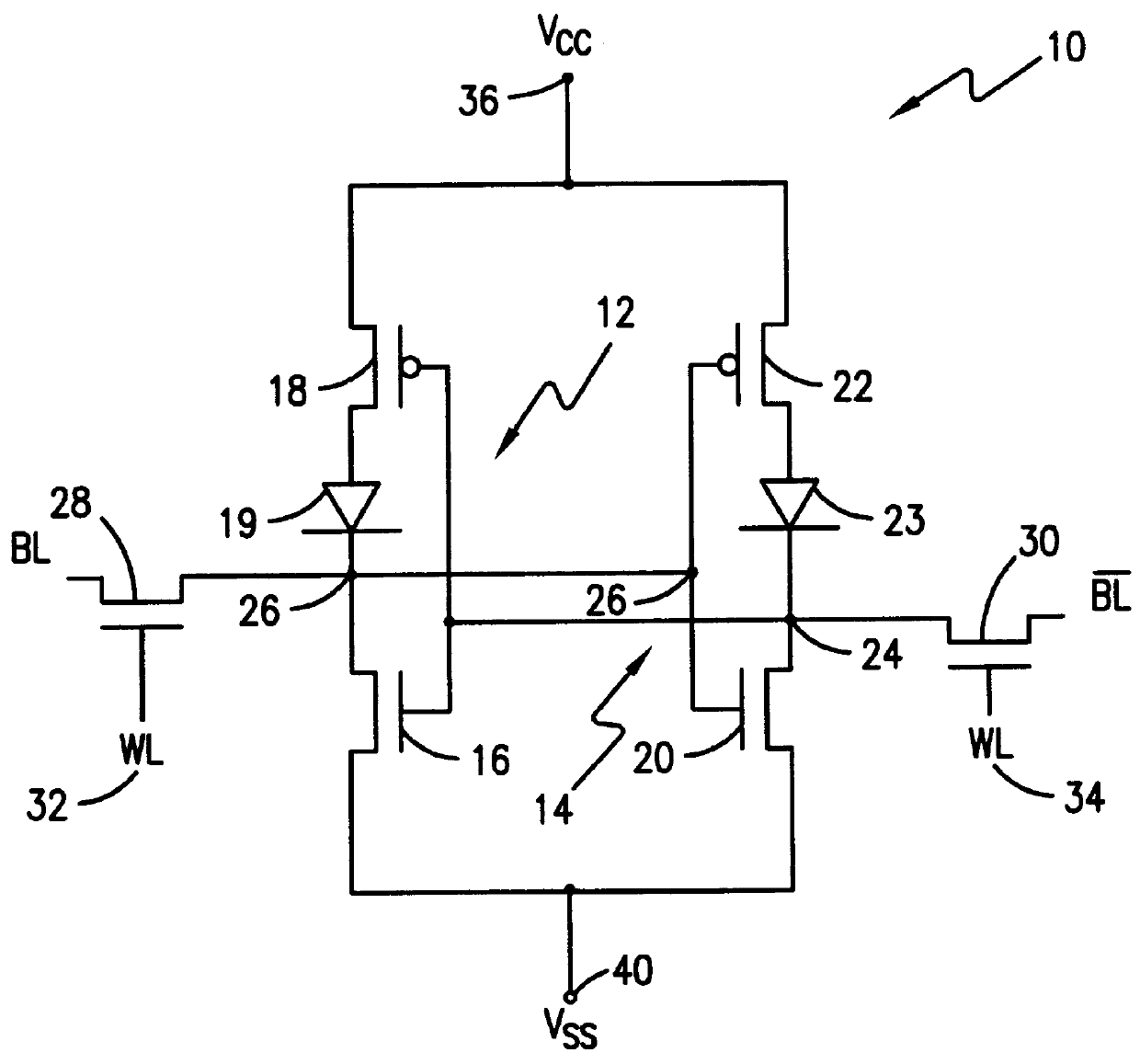

SRAM cell structure with dielectric sidewall spacers and drain and channel regions defined along sidewall spacers

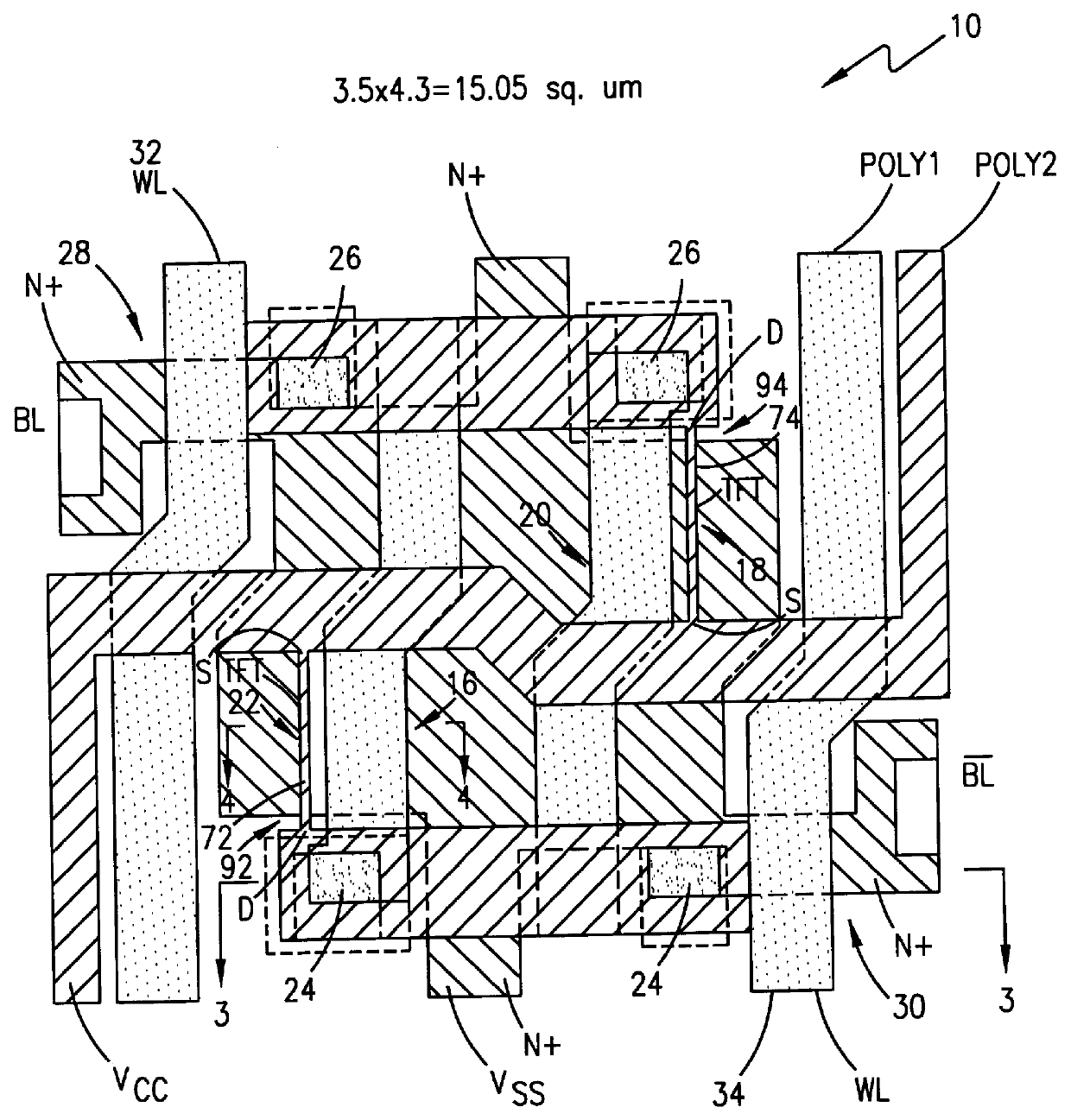

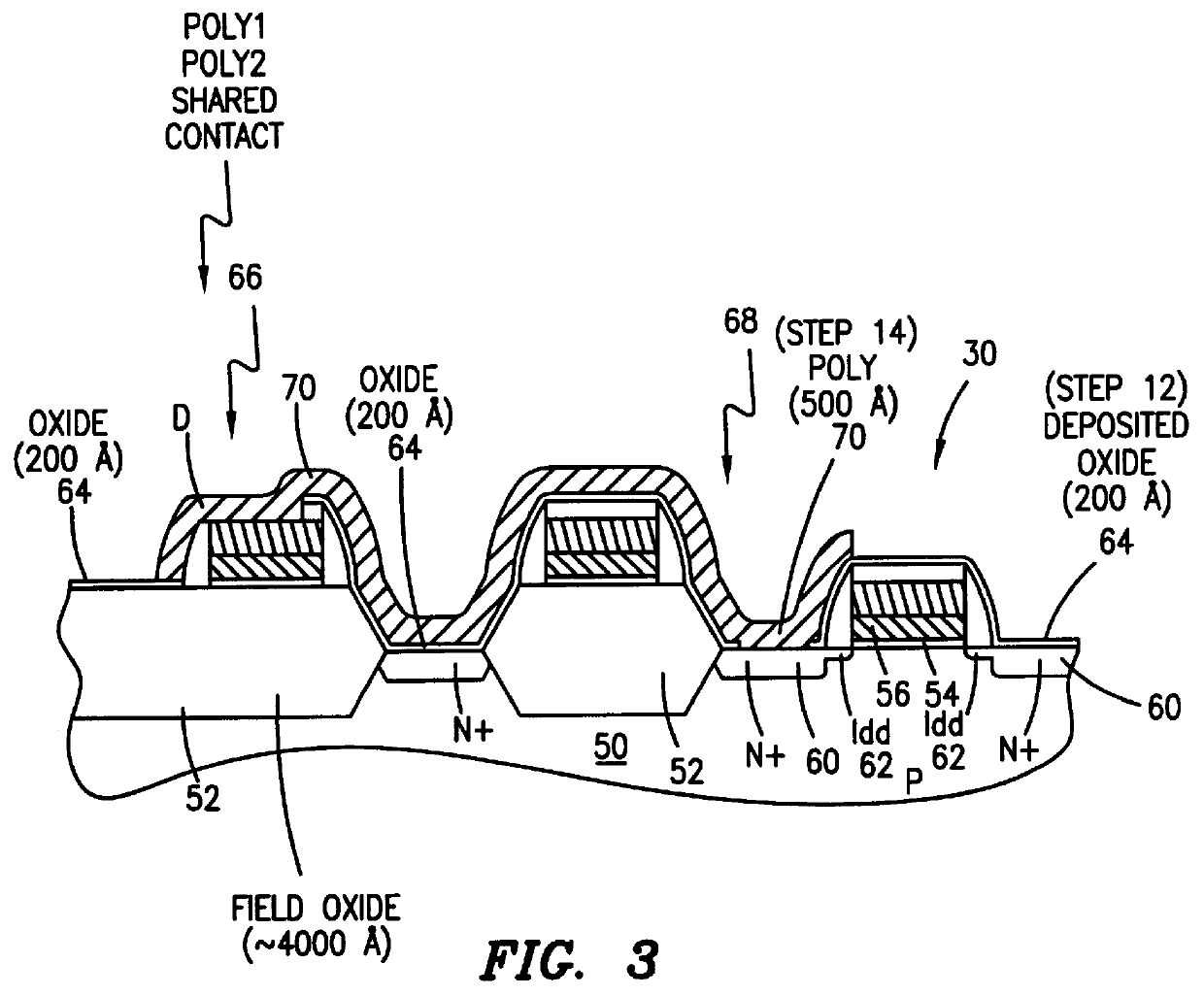

A six transistor static random access memory (SRAM) cell with thin-film pull-up transistors and method of making the same includes providing two bulk silicon pull-down transistors of a first conductivity type, two active gated pull-up thin-film transistors (TFTs) of a second conductivity type, two pass gates, a common word line, and two bit line contacts. The bulk silicon pull-down transistors, two active gated pull-up TFTs, and two pass gates are connected at four shared contacts. In addition, the two bulk silicon pull-down transistors and the two active gated pull-up TFTs are formed with two polysilicon layers, a first of the polysilicon layers (poly1) is salicided and includes poly1 gate electrodes for the two bulk silicon pull-down transistors. A second of the polysilicon layers (poly2) includes desired poly2 stringers disposed along side edges of the poly1 gate electrodes, the desired poly2 stringers forming respective channel regions of the pull-up TFTs.

Owner:STMICROELECTRONICS SRL

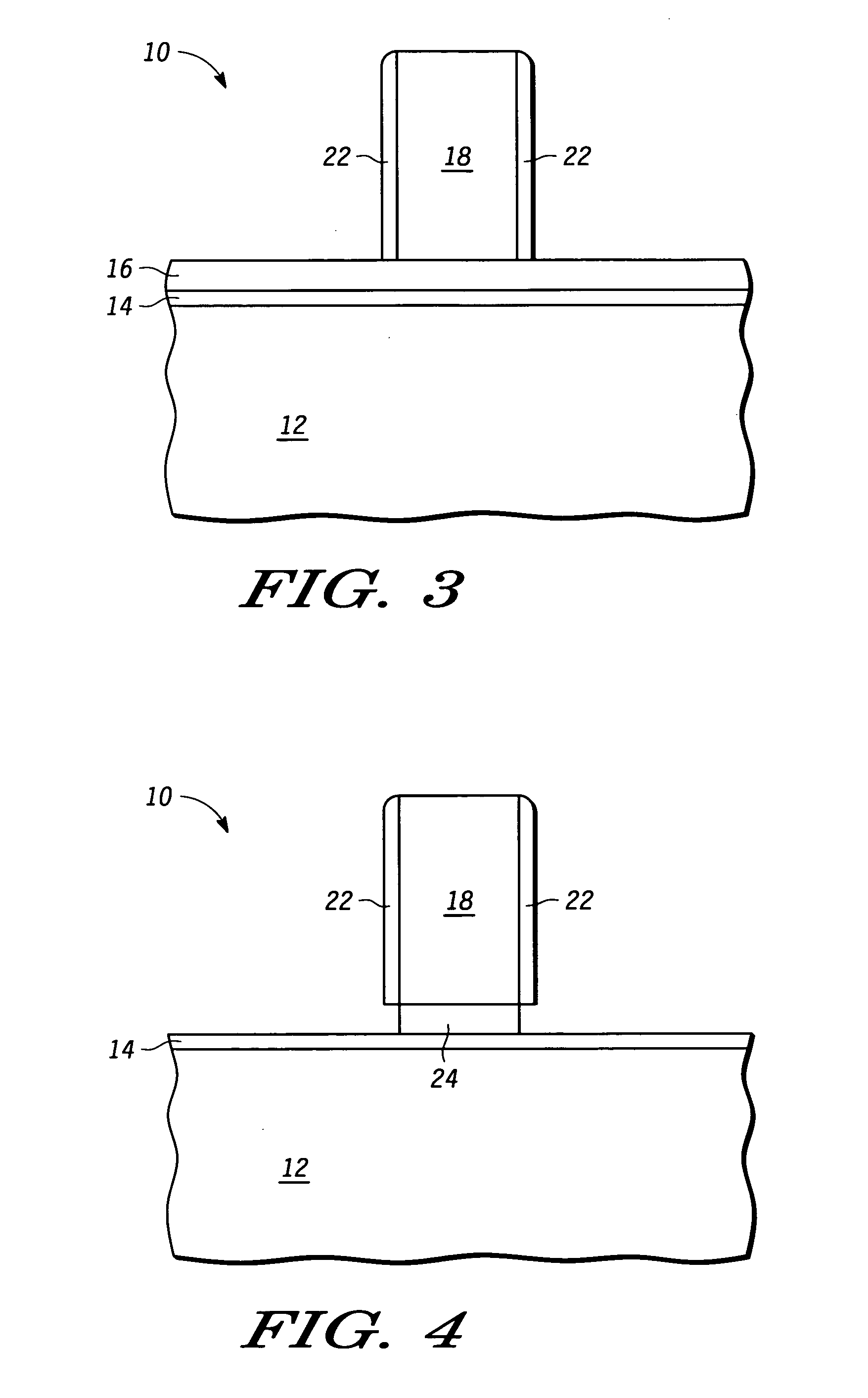

A Recessed Polysilicon Gate Structure for a Strained Silicon MOSFET Device

InactiveUS20060009001A1Semiconductor/solid-state device manufacturingSemiconductor devicesMOSFETEngineering

Abstract of the Disclosure A method of forming a channel region for a MOSFET device in a strained silicon layer via employment of adjacent and surrounding silicon-germanium shapes, has been developed. The method features simultaneous formation of recesses in a top portion of a conductive gate structure and in portions of the semiconductor substrate not occupied by the gate structure or by dummy spacers located on the sides of the conductive gate structure. The selectively defined recesses will be used to subsequently accommodate silicon-germanium shapes, with the silicon-germanium shapes located in the recesses in the semiconductor substrate inducing the desired strained channel region. The recessing of the conductive gate structure and of semiconductor substrate portion reduces the risk of silicon-germanium bridging across the surface of sidewall spacers during epitaxial growth of the alloy layer, thus reducing the risk of gate to substrate leakage or shorts.

Owner:TAIWAN SEMICON MFG CO LTD

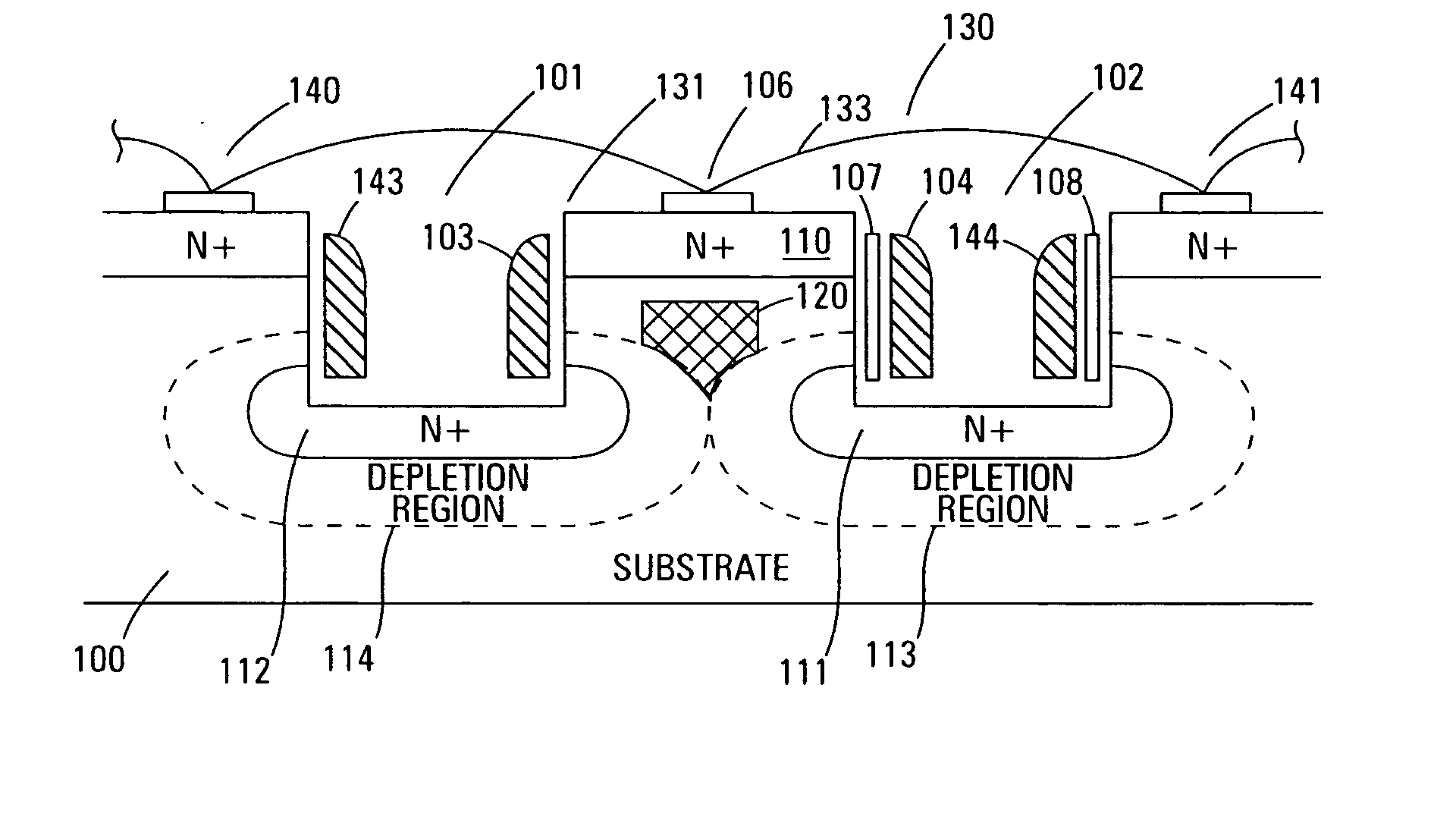

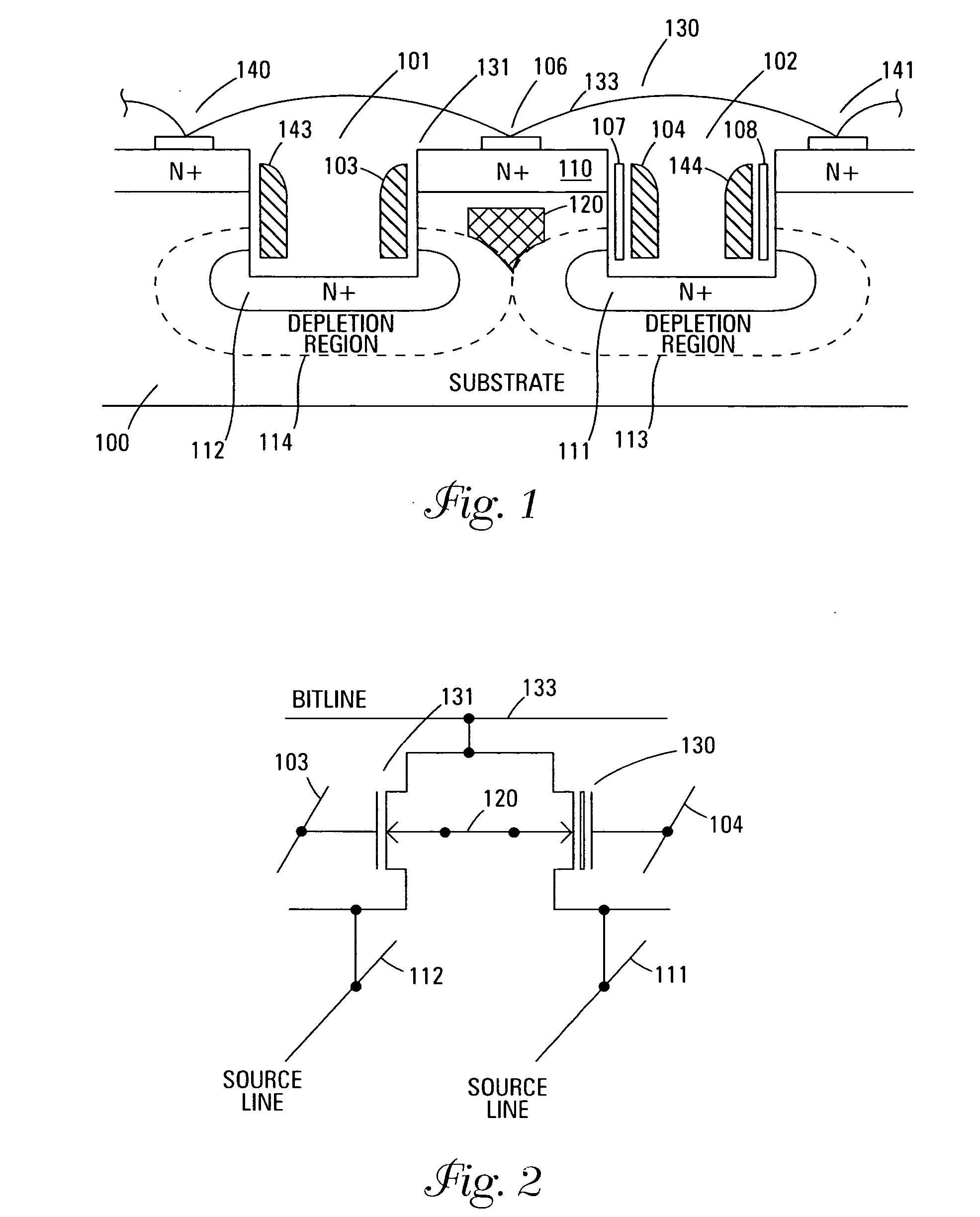

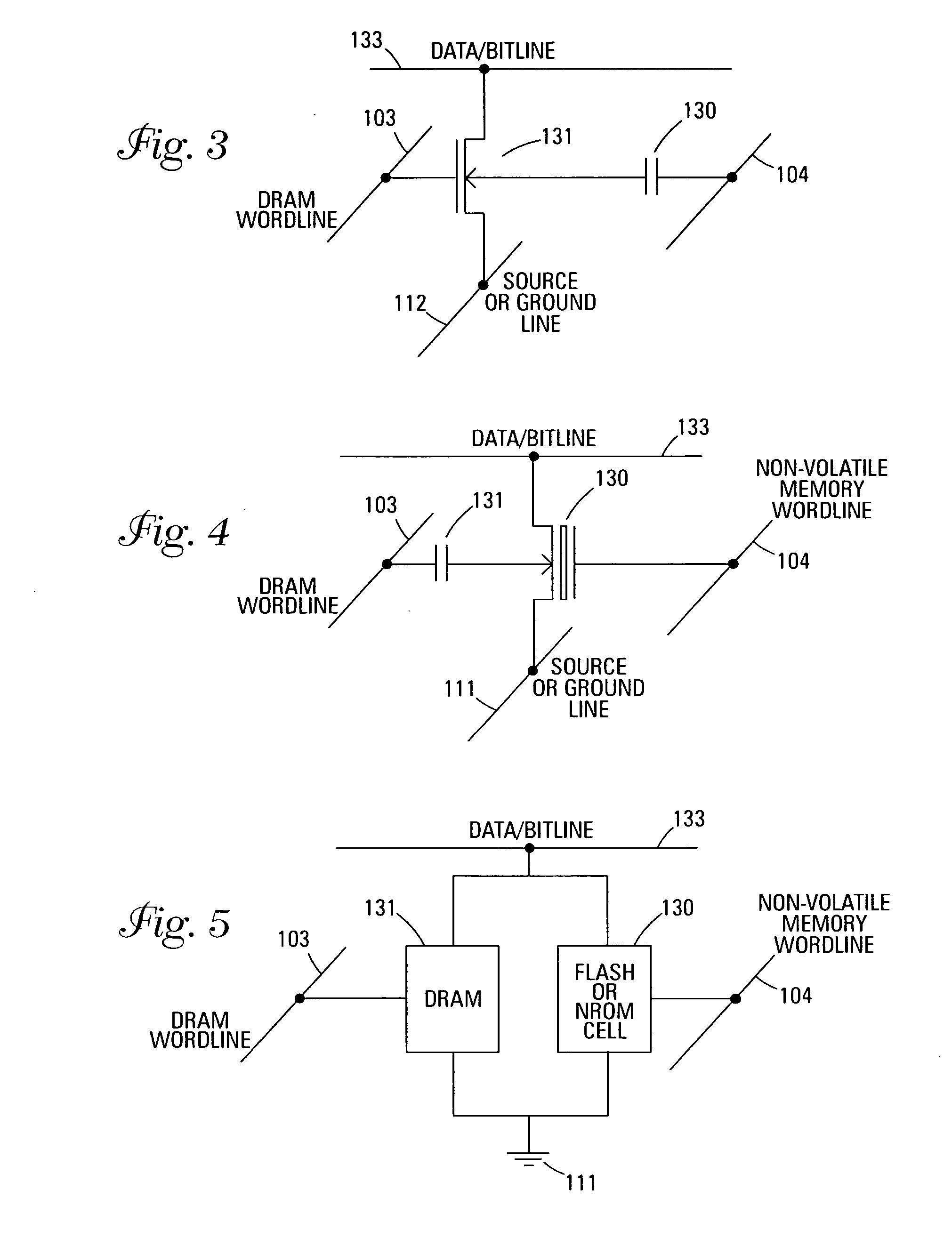

In-service reconfigurable dram and flash memory device

A memory cell that has both a DRAM cell and a non-volatile memory cell. The non-volatile memory cell might include a flash memory or an NROM cell. The memory cell is comprised of a vertical floating body transistor with dual gates, one on either side of a vertical pillar of a substrate. One gate is a polysilicon gate and gate insulator that is adjacent to the floating body of the transistor and acts as a DRAM cell. The non-volatile memory cell is constructed on the other side of the pillar with a floating gate or NROM structure. The DRAM and non-volatile cells are linked by a drain region coupling the two cells to a memory array bitline. The bottom of trenches on either side of the pillar have source regions that are linked to respective source lines of the memory array.

Owner:MICRON TECH INC

Strained silicon carbon alloy MOSFET structure and fabrication method thereof

ActiveUS20050023520A1Minimizing device dimensionImproving device current driving forceTransistorSemiconductor/solid-state device manufacturingMOSFETPolysilicon gate

A MOSFET structure utilizing strained silicon carbon alloy and fabrication method thereof. The MOSFET structure includes a substrate, a graded SiGe layer, a relaxed buffer layer, a strained silicon carbon alloy channel layer, a gate dielectric layer, a polysilicon gate electrode (or metal gate electrode) and a source / drain region.

Owner:TRANSPACIFIC IP LTD

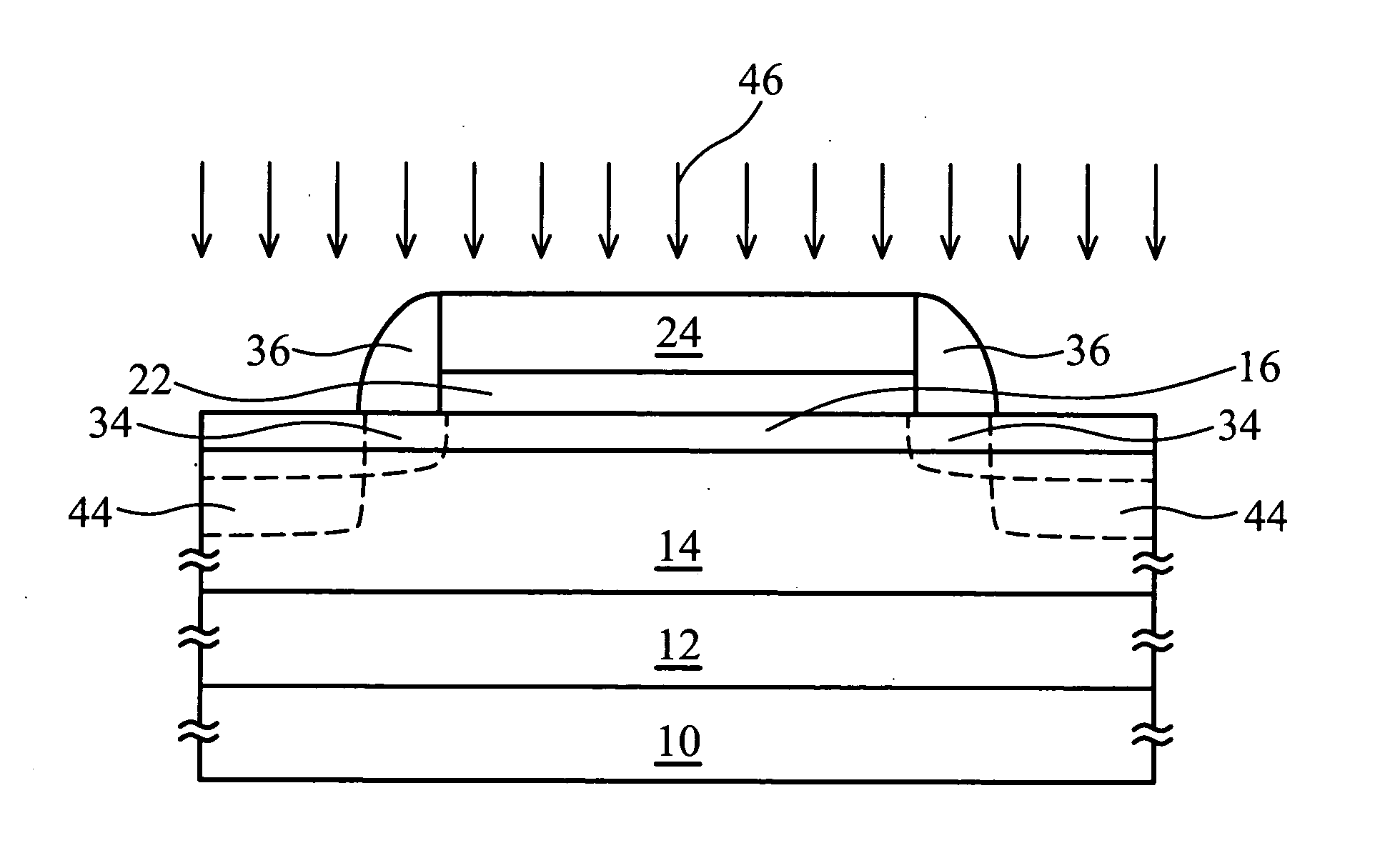

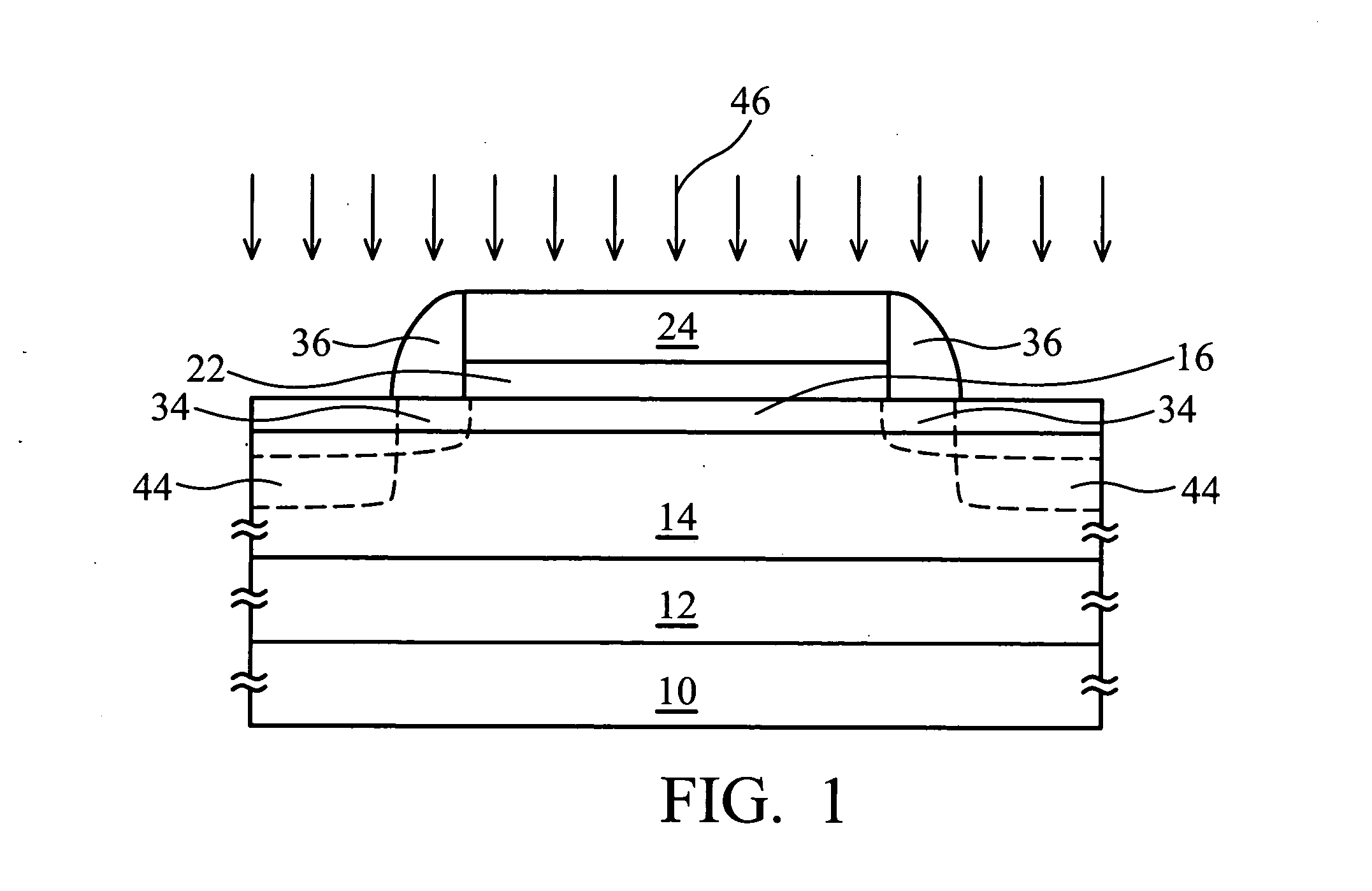

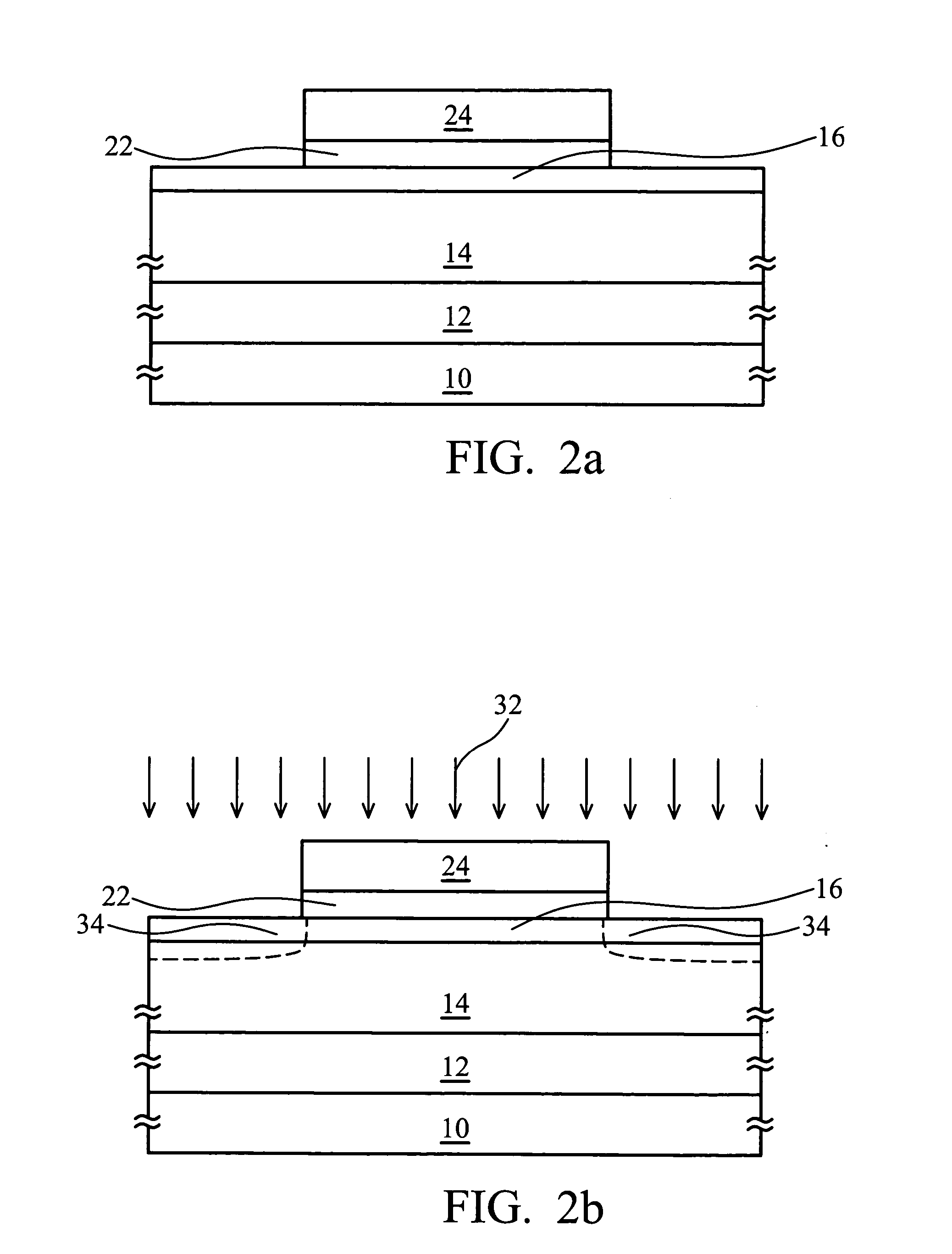

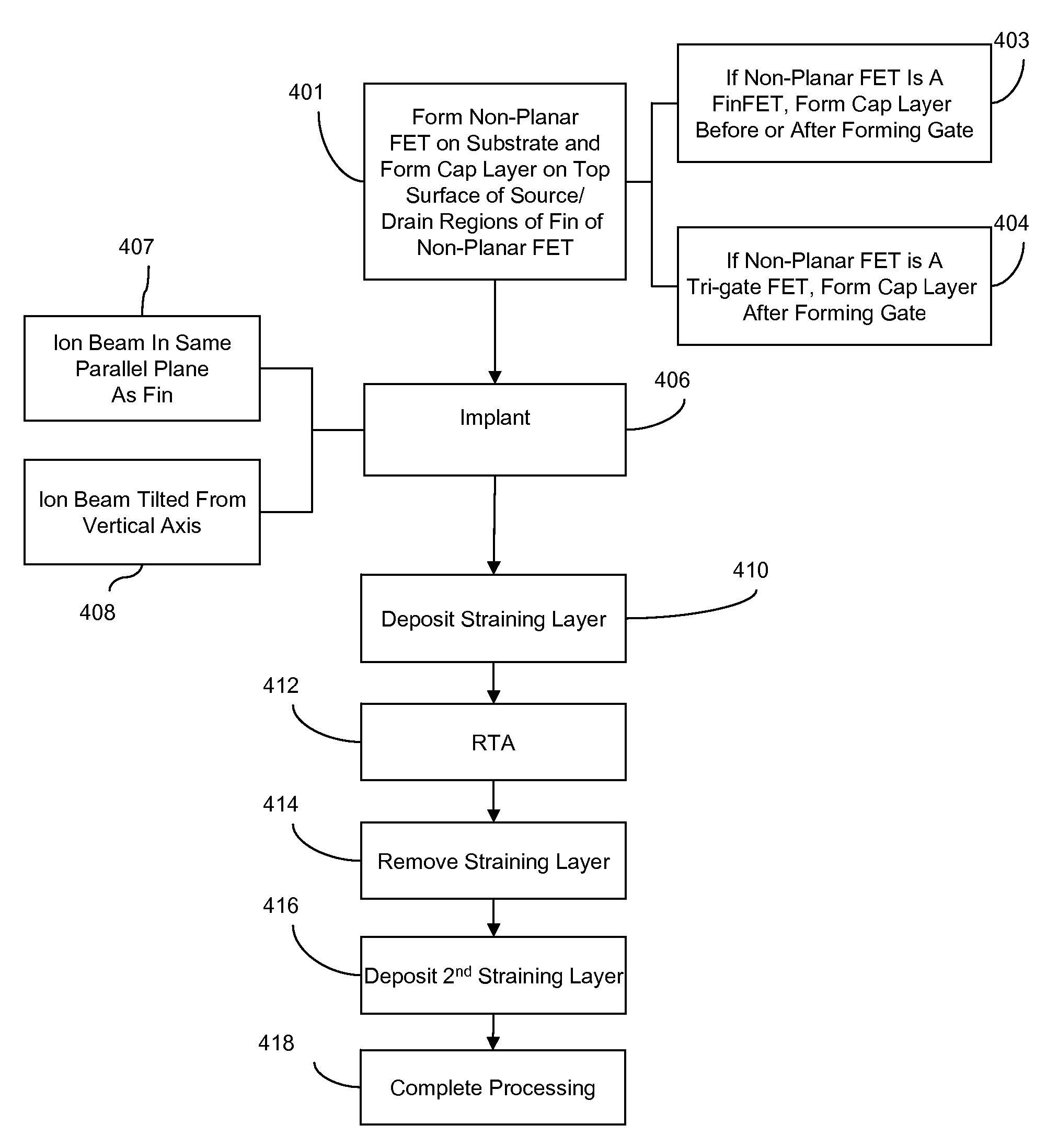

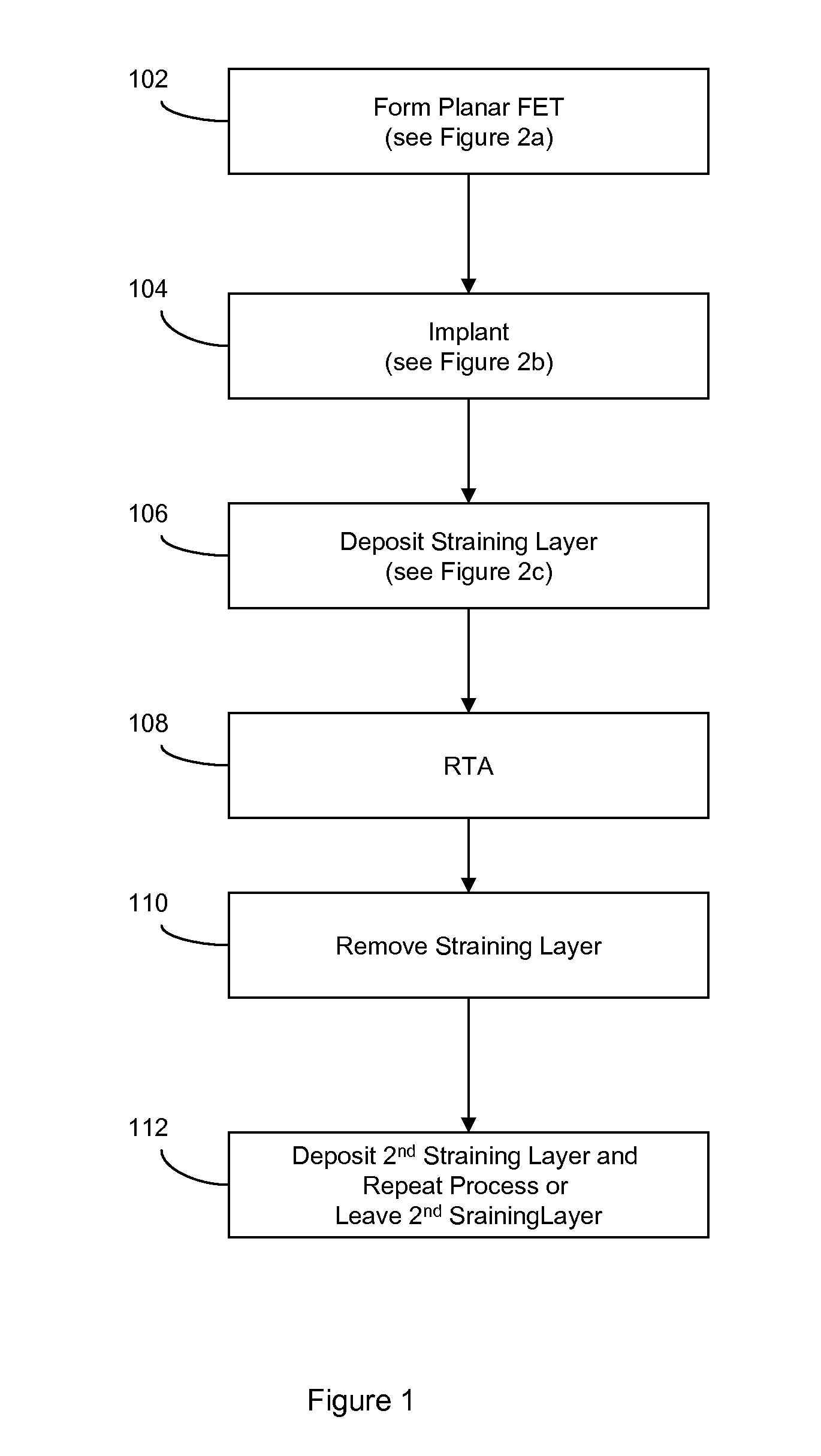

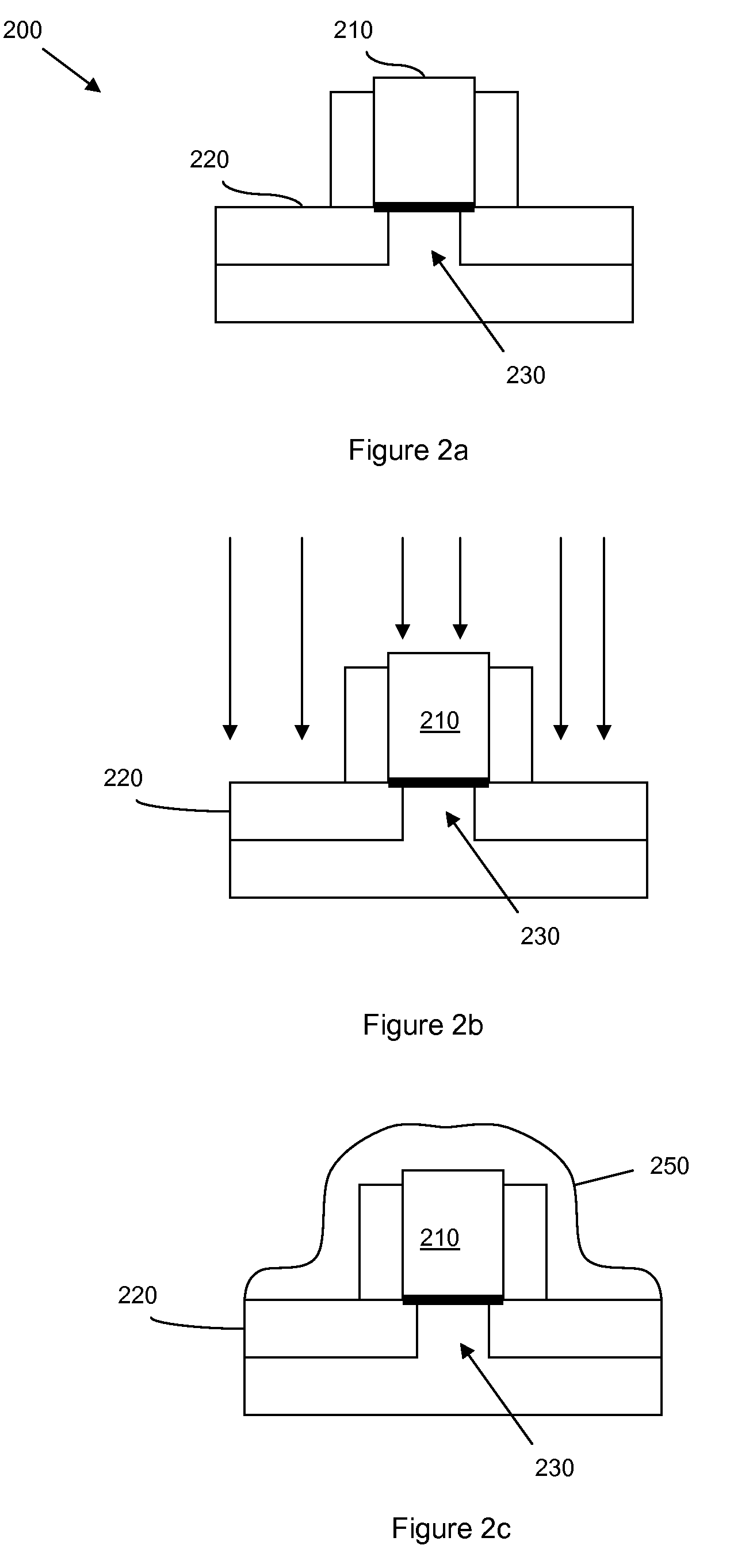

Finfet/trigate stress-memorization method

InactiveUS7341902B2Improve performanceControl damageSemiconductor/solid-state device manufacturingSemiconductor devicesIon beamPolysilicon gate

Disclosed are embodiments a technique for inducing strain into the polysilicon gate of a non-planar FET (e.g., a finFET or trigate FET) in order to impart a similar strain on the FET channel region, while simultaneously protecting the source / drain regions of the semiconductor fin. Specifically, a protective cap layer is formed above the source / drain regions of the fin in order to protect those regions during a subsequent amporphization ion implantation process. The fin is further protected, during this implantation process, because the ion beam is directed towards the gate in a plane that is parallel to the fin and tilted from the vertical axis. Thus, amorphization of the fin and damage to the fin are limited. Following the implantation process and the formation of a straining layer, a recrystallization anneal is performed so that the strain of the straining layer is ‘memorized’ in the polysilicon gate.

Owner:ALSEPHINA INNOVATIONS INC

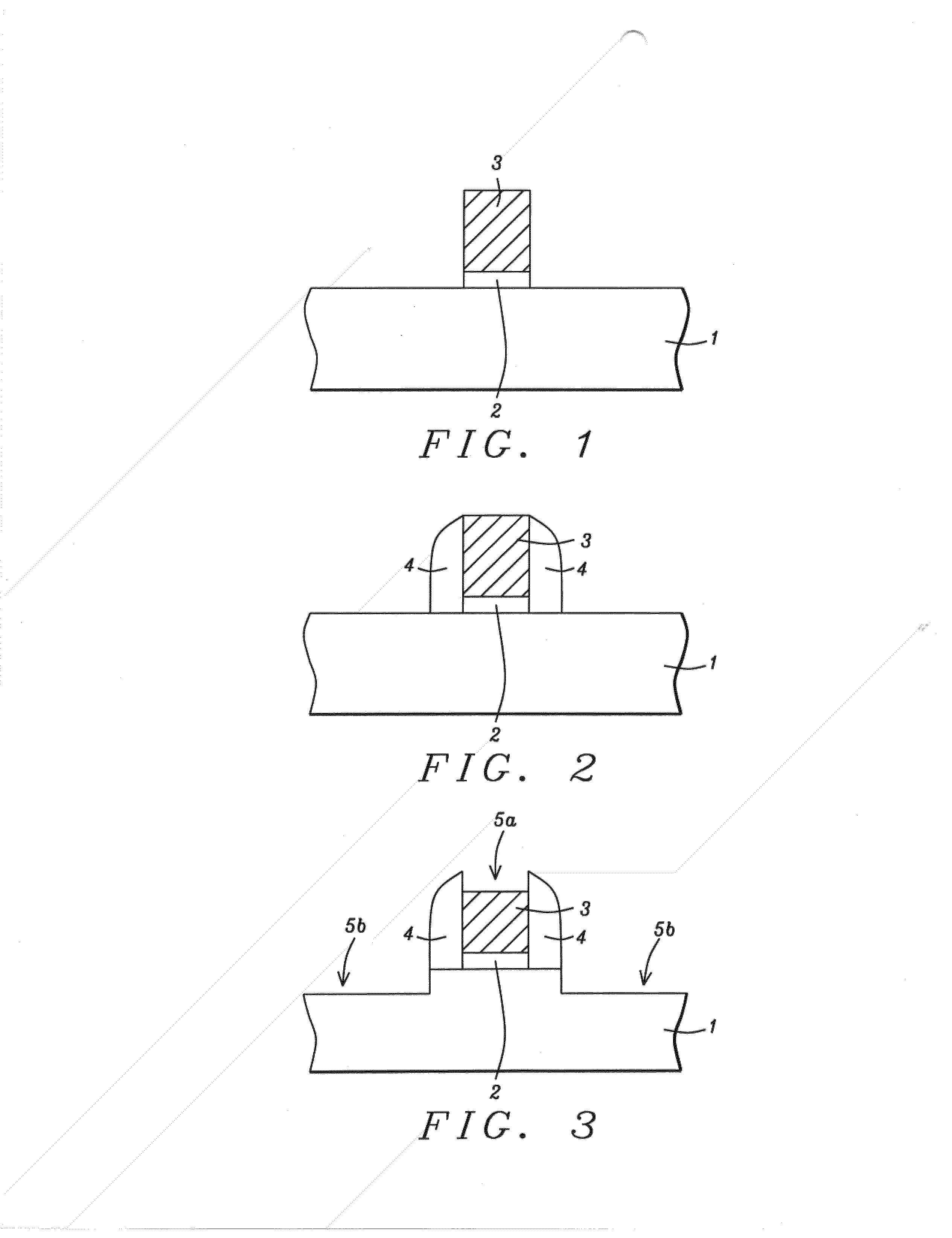

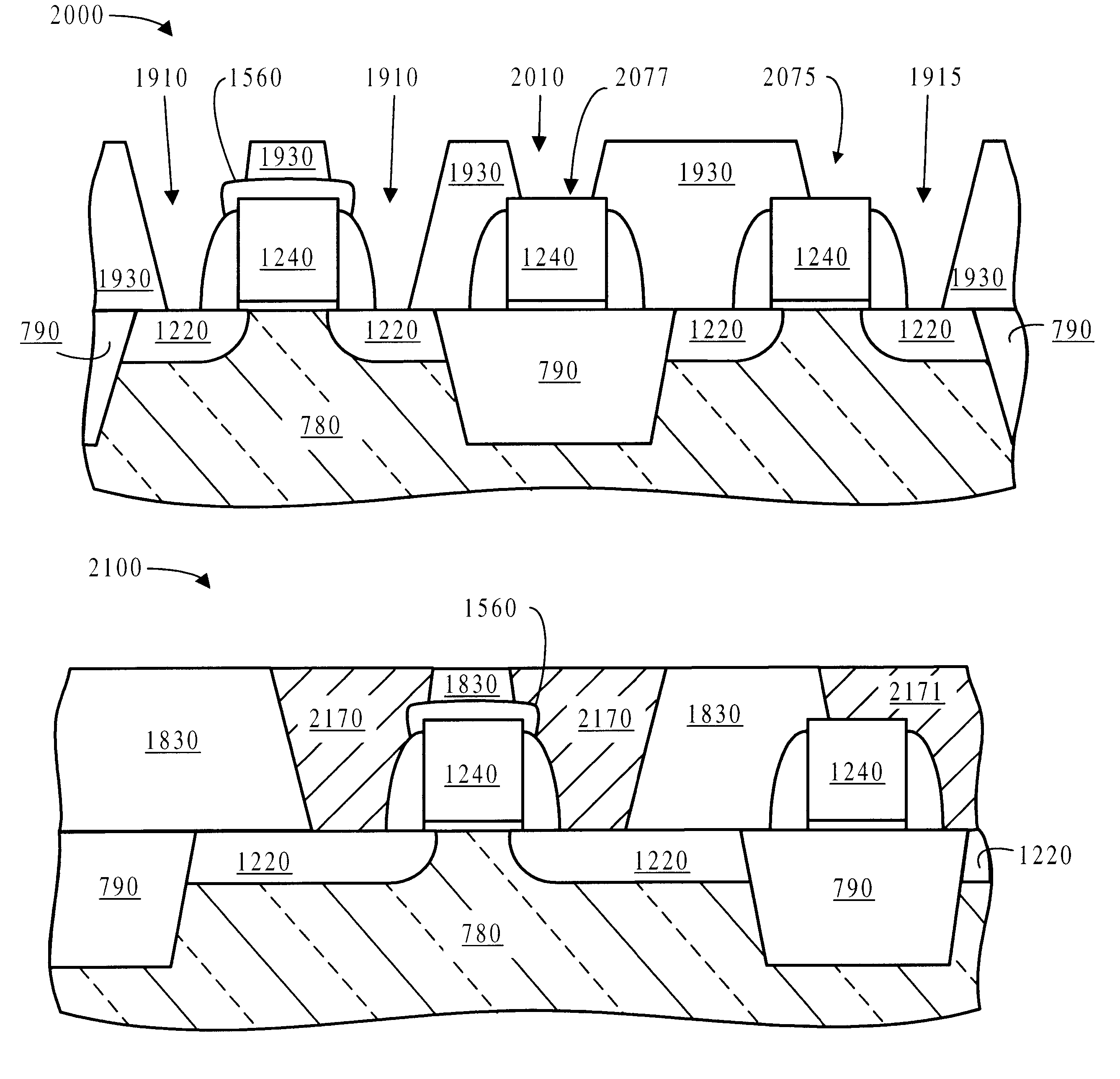

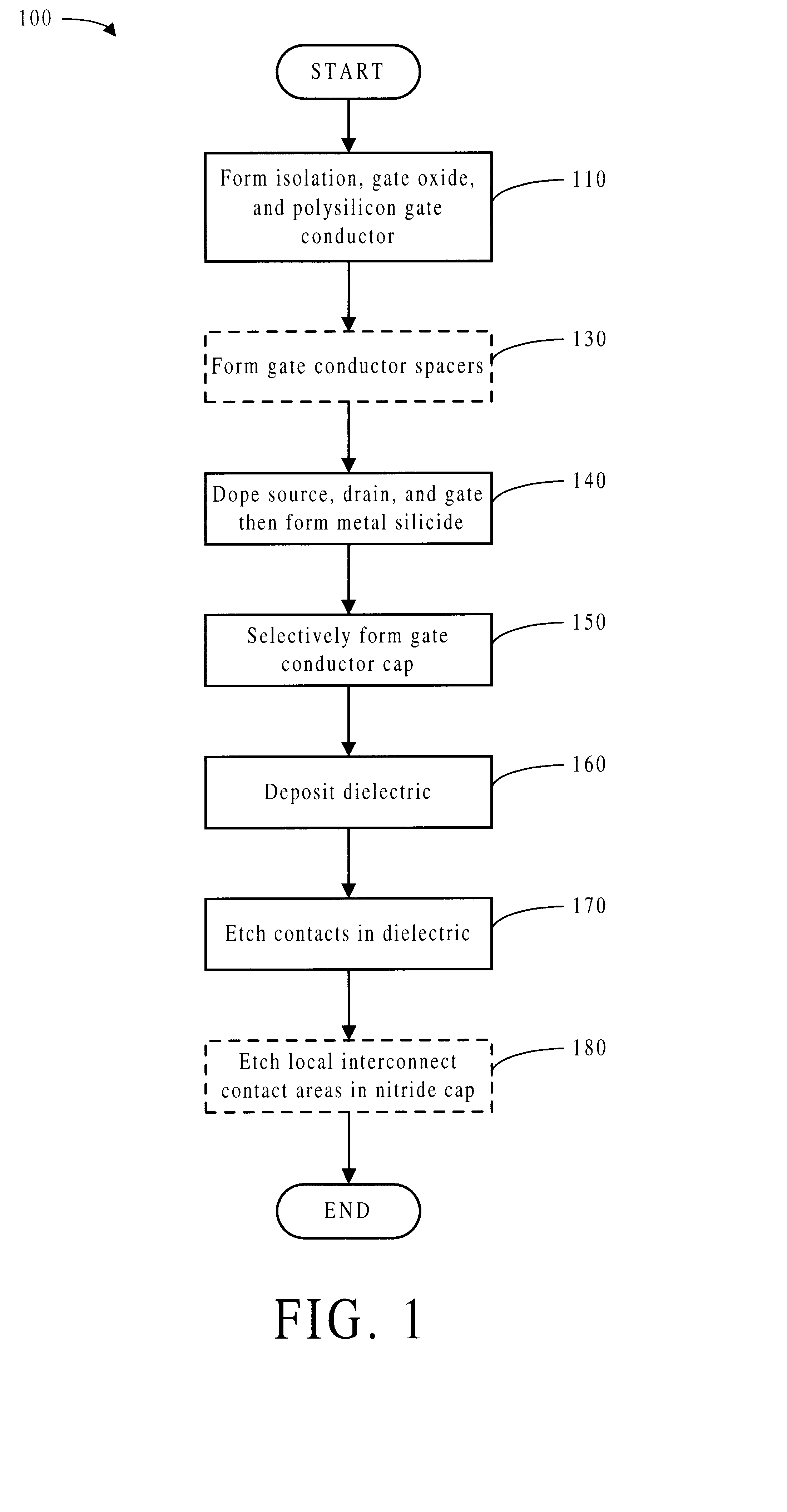

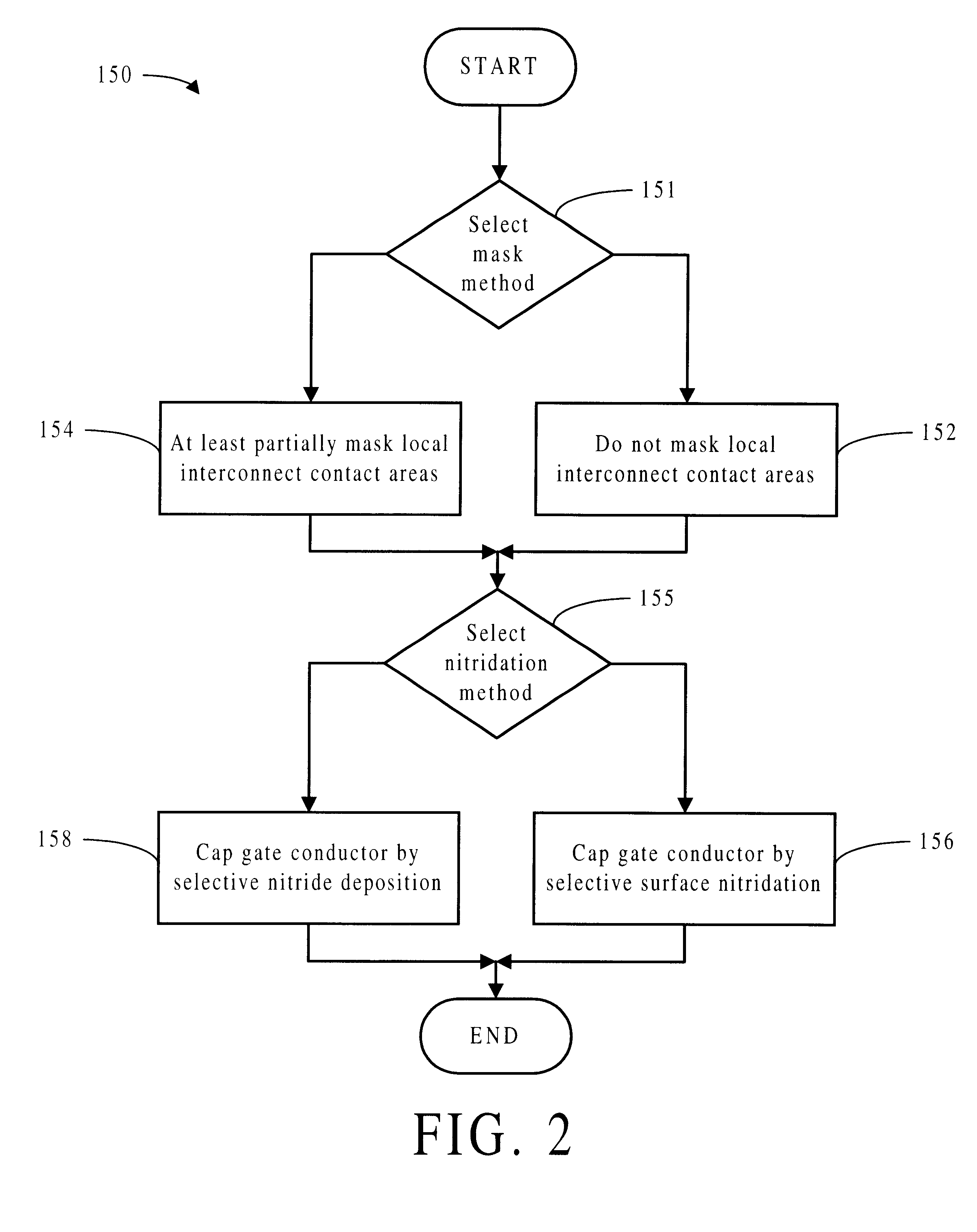

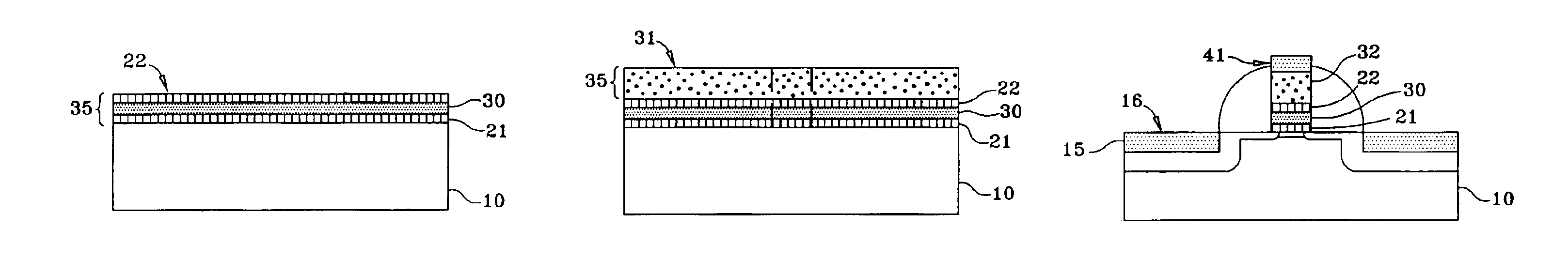

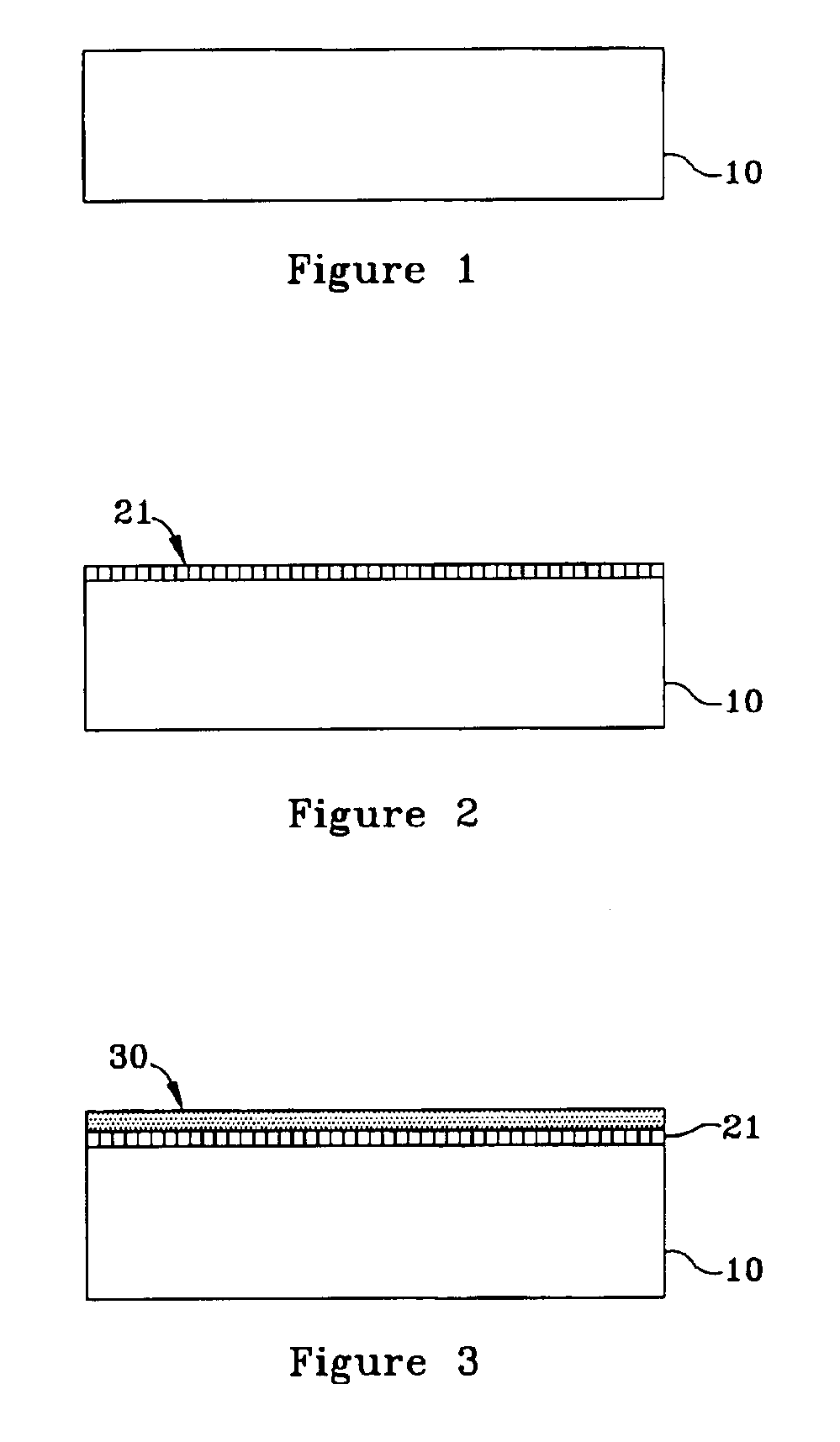

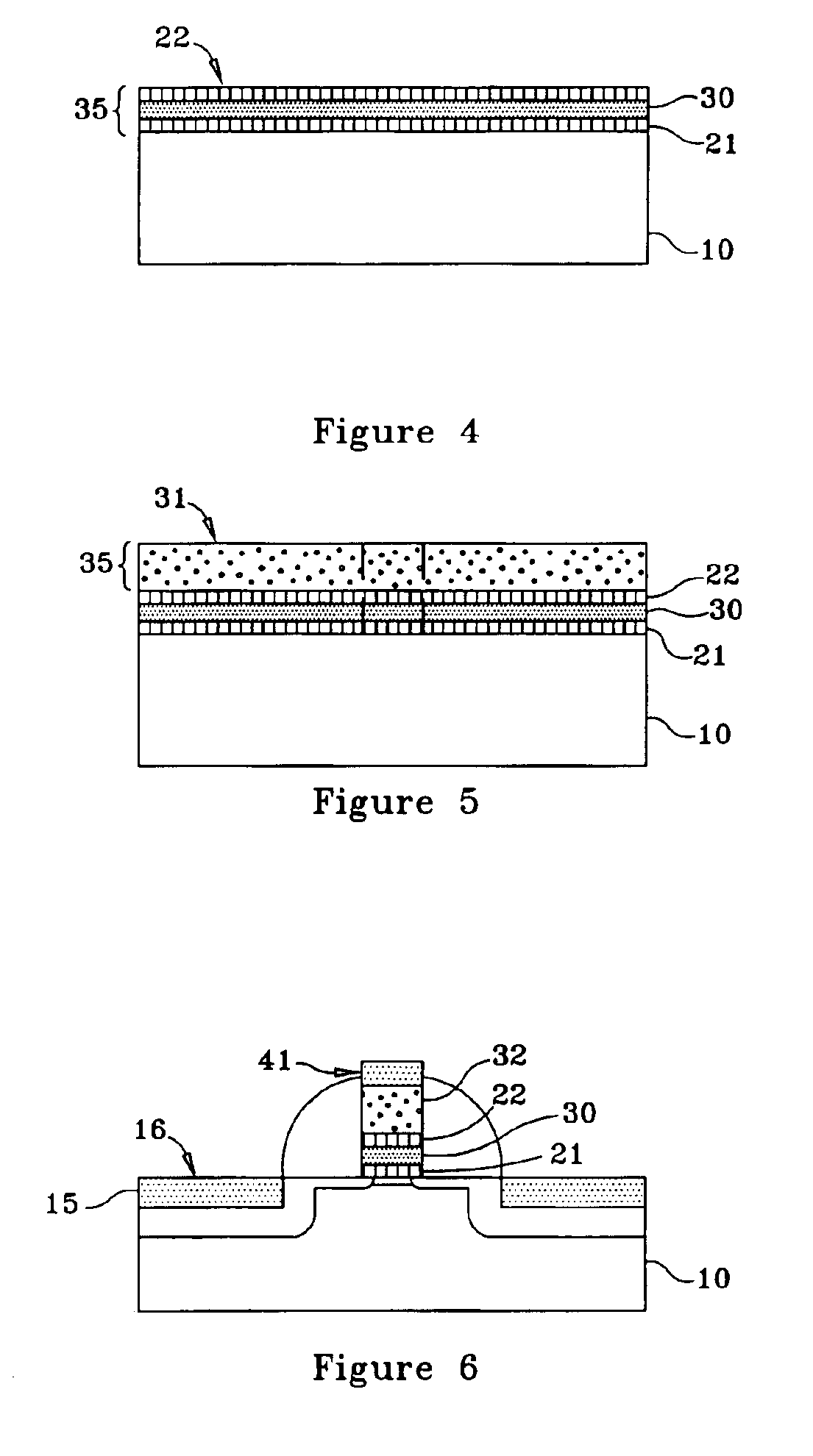

Method for forming borderless gate structures and apparatus formed thereby

InactiveUS6207514B1Low powerAdd dimensionSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical conductorEngineering

A method for forming a gate conductor cap in a transistor comprises the steps of: a) forming a polysilicon gate conductor; b) doping the polysilicon gate; c) doping diffusion areas; and d) capping the gate conductor by a nitridation method chosen from among selective nitride deposition and selective surface nitridation. The resulting transistor may comprise a capped gate conductor and borderless diffusion contacts, wherein the capping occurred by a nitridation method chosen from among selective nitride deposition and selective surface nitridation and wherein a portion of the gate conductor is masked during the nitridation method to leave open a contact area for a local interconnect or a gate contact.

Owner:IBM CORP

Method of fabricating a semiconductor device having a nitride/high-k/nitride gate dielectric stack by atomic layer deposition (ALD) and a device thereby formed

InactiveUS6867101B1Improve thermal stabilitySufficient diffusion resistance and thermal stabilitySemiconductor/solid-state device manufacturingSemiconductor devicesThin metalGate dielectric

A method of fabricating a semiconductor device, having a nitride / high-k material / nitride gate dielectric stack with good thermal stability which does not diffuse into a silicon substrate, a polysilicon gate, or a polysilicon-germanium gate when experiencing subsequent high temperature processes, involving: (a) providing a substrate; (b) initiating formation of the nitride / high-k material / nitride gate dielectric stack by depositing a first ultra-thin nitride film on the substrate; (c) depositing a high-k material, such as a thin metal film, on the first ultra-thin nitride film; (d) depositing a second ultra-thin nitride film on the high-k material, thereby forming a sandwich structure; (e) completing formation of the nitride / high-k material / nitride gate dielectric stack from the sandwich structure; and (f) completing fabrication of the semiconductor device.

Owner:ADVANCED MICRO DEVICES INC

Gate electrode forming methods using conductive hard mask

InactiveUS20060068575A1Prevent processing damageSemiconductor/solid-state device manufacturingSemiconductor devicesResistElectrical conductor

Methods related to formation of a gate electrode are disclosed that employ a conductive hard mask as a protective layer during a photoresist removal process. In preferred embodiments, the conductive hard mask includes a metal containing conductor or a metal silicide. The invention prevents process damage on the gate dielectric during wet and / or dry resist strip, and since the conductive hard mask cannot be etched in typical resist strip chemistries, the invention also protects a metal electrode under the hard mask. The steps disclosed allow creation of a multiple work function metal gate electrode, or a mixed metal and polysilicon gate electrode, which do not suffer from the problems of the related art.

Owner:IBM CORP