Patents

Literature

546 results about "Strained silicon" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

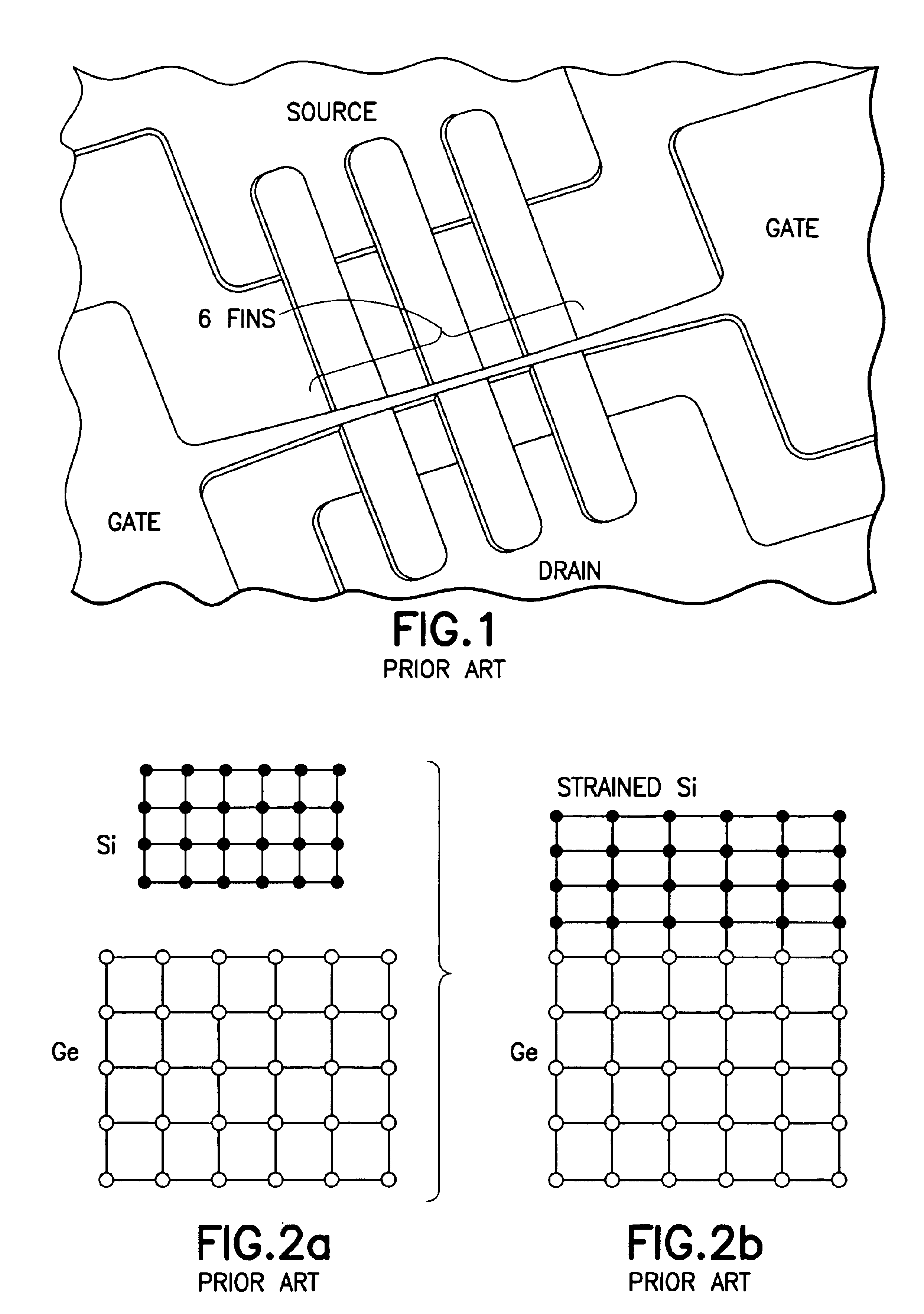

Strained silicon is a layer of silicon in which the silicon atoms are stretched beyond their normal interatomic distance. This can be accomplished by putting the layer of silicon over a substrate of silicon germanium (SiGe). As the atoms in the silicon layer align with the atoms of the underlying silicon germanium layer (which are arranged a little farther apart, with respect to those of a bulk silicon crystal), the links between the silicon atoms become stretched - thereby leading to strained silicon. Moving these silicon atoms farther apart reduces the atomic forces that interfere with the movement of electrons through the transistors and thus better mobility, resulting in better chip performance and lower energy consumption. These electrons can move 70% faster allowing strained silicon transistors to switch 35% faster.

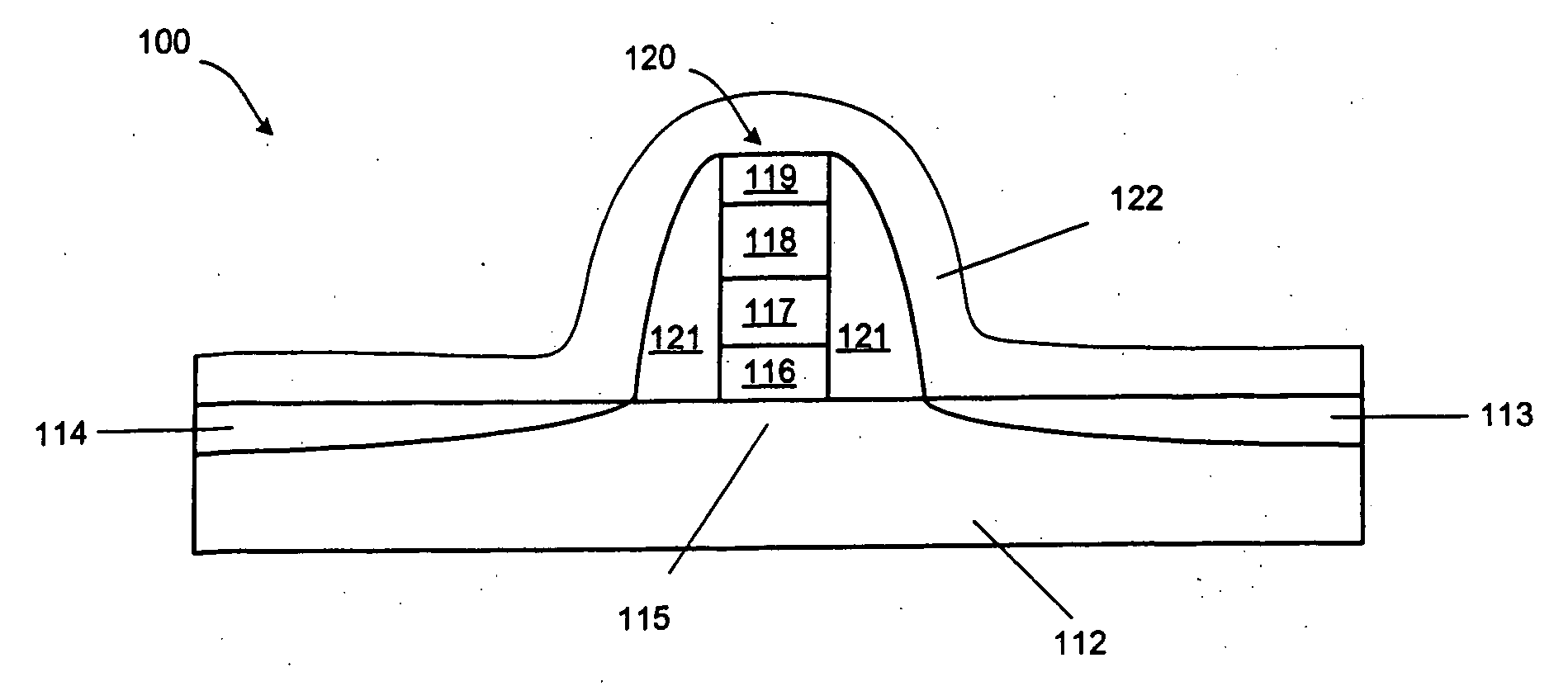

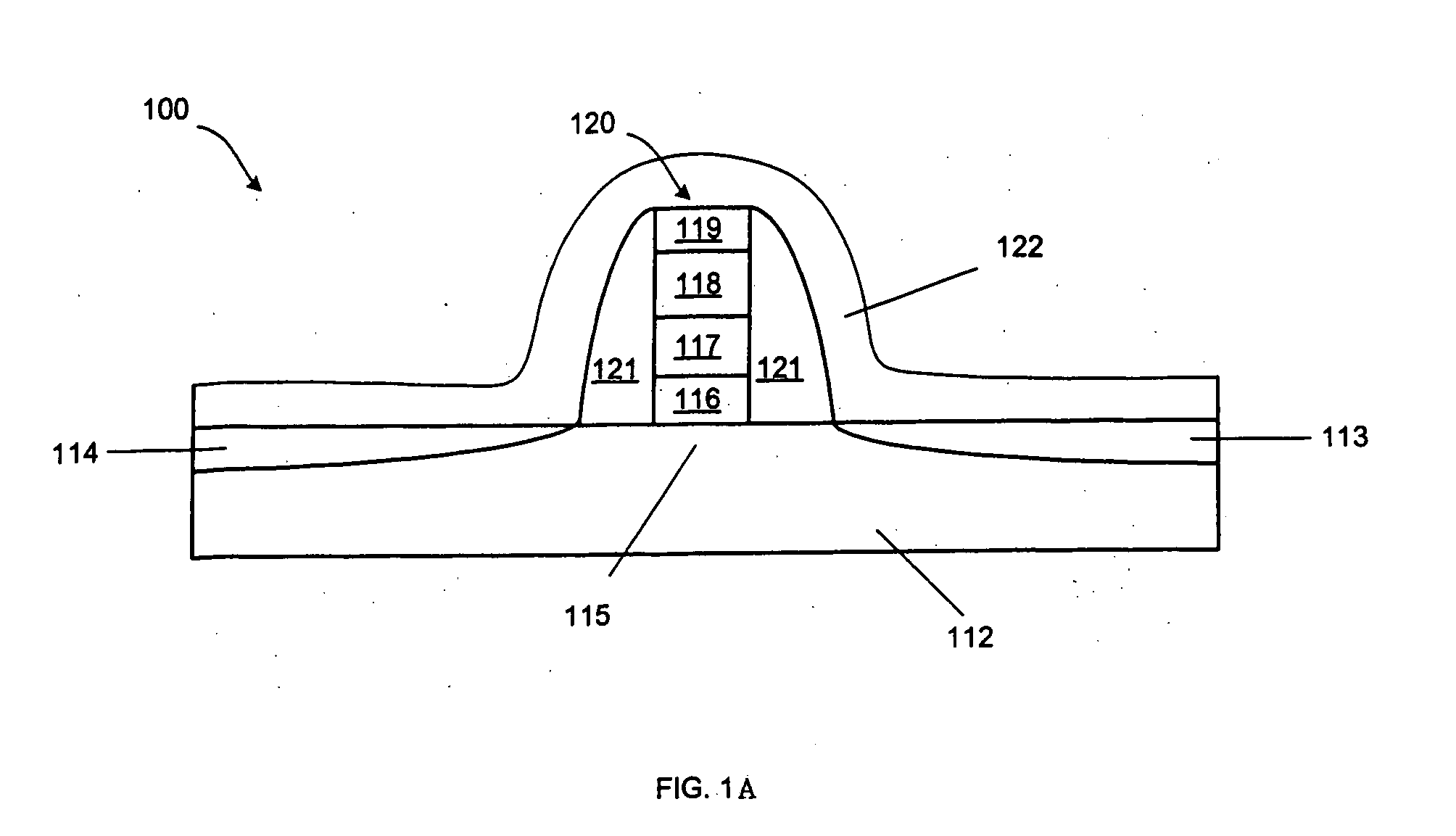

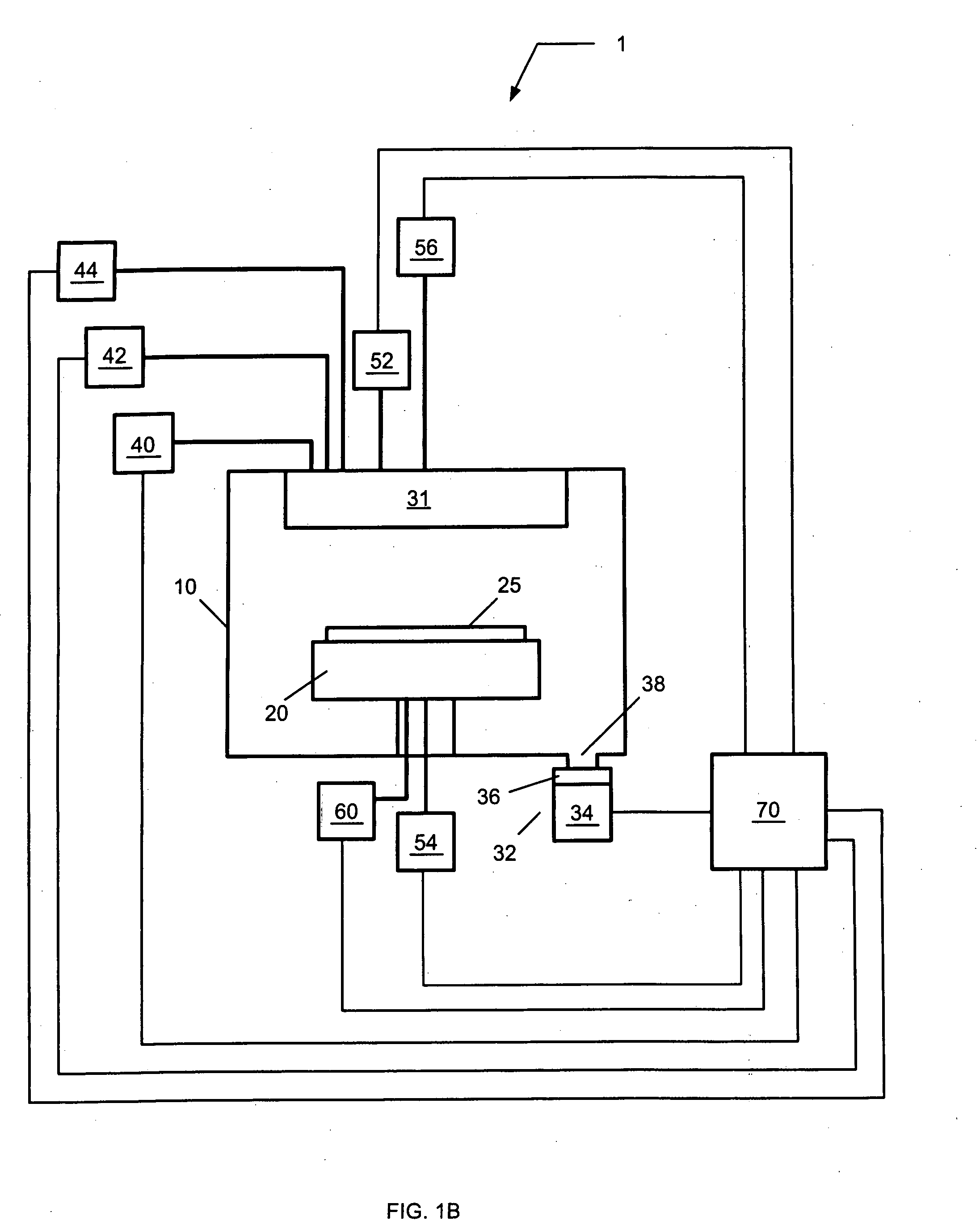

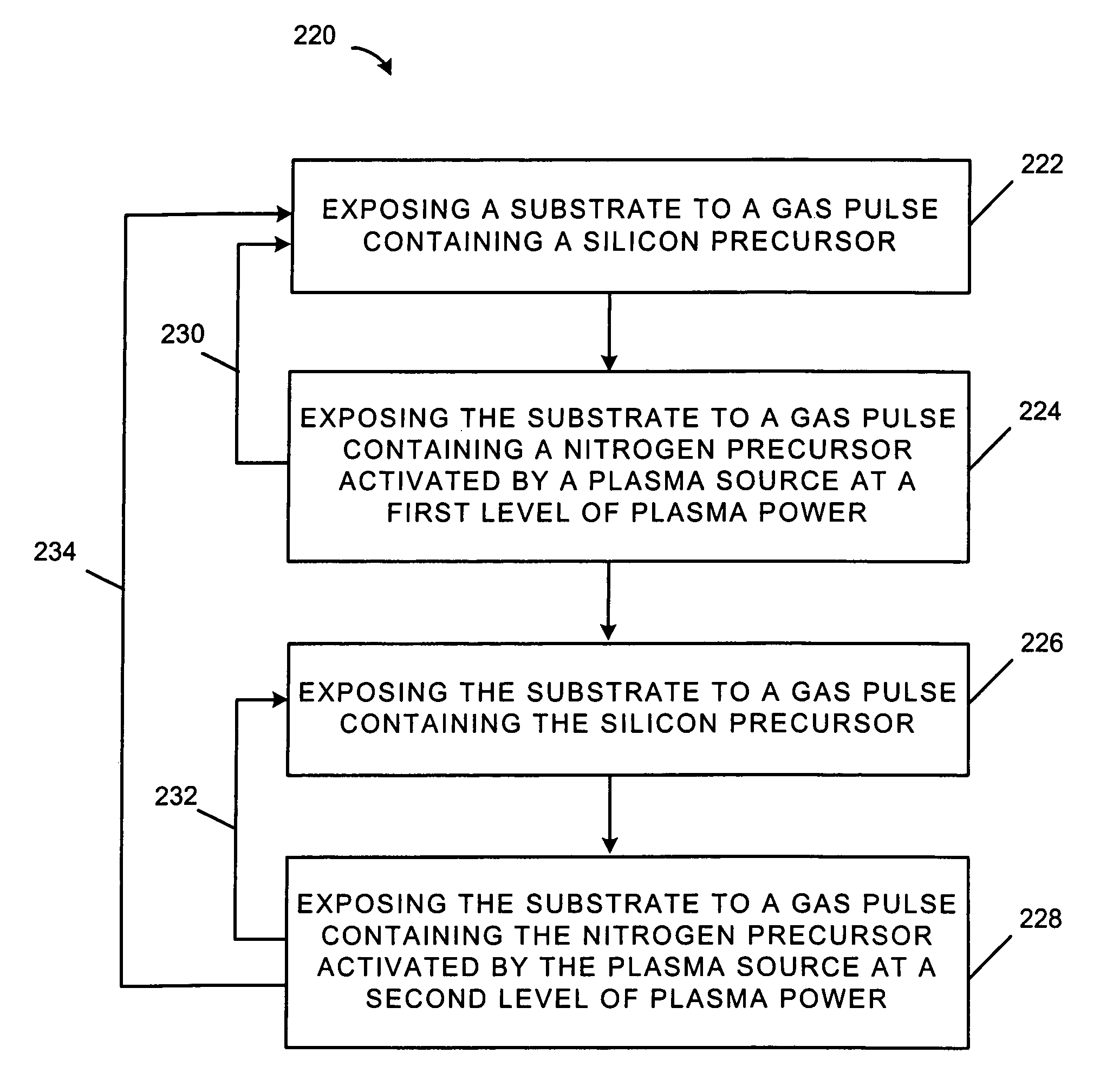

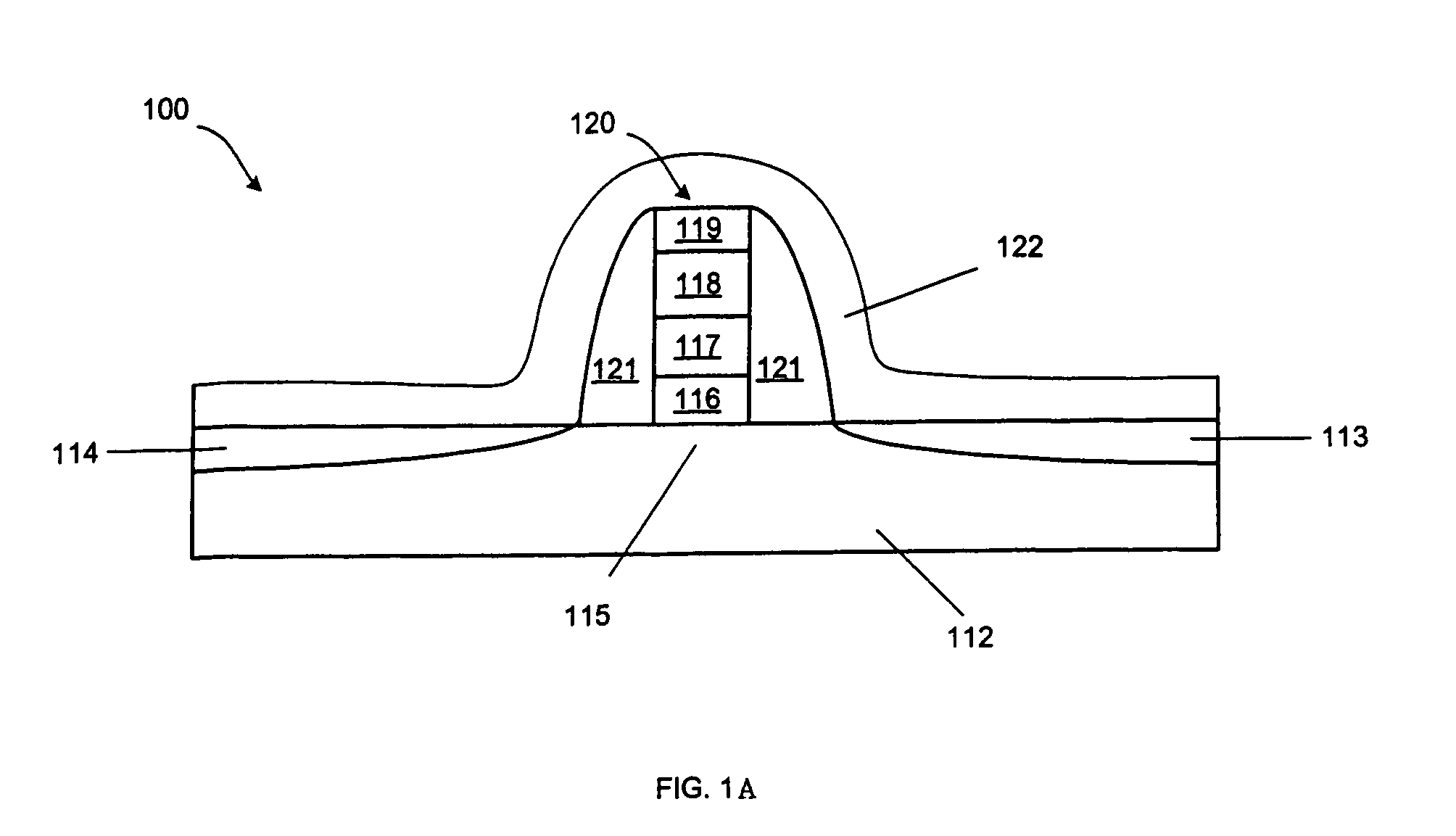

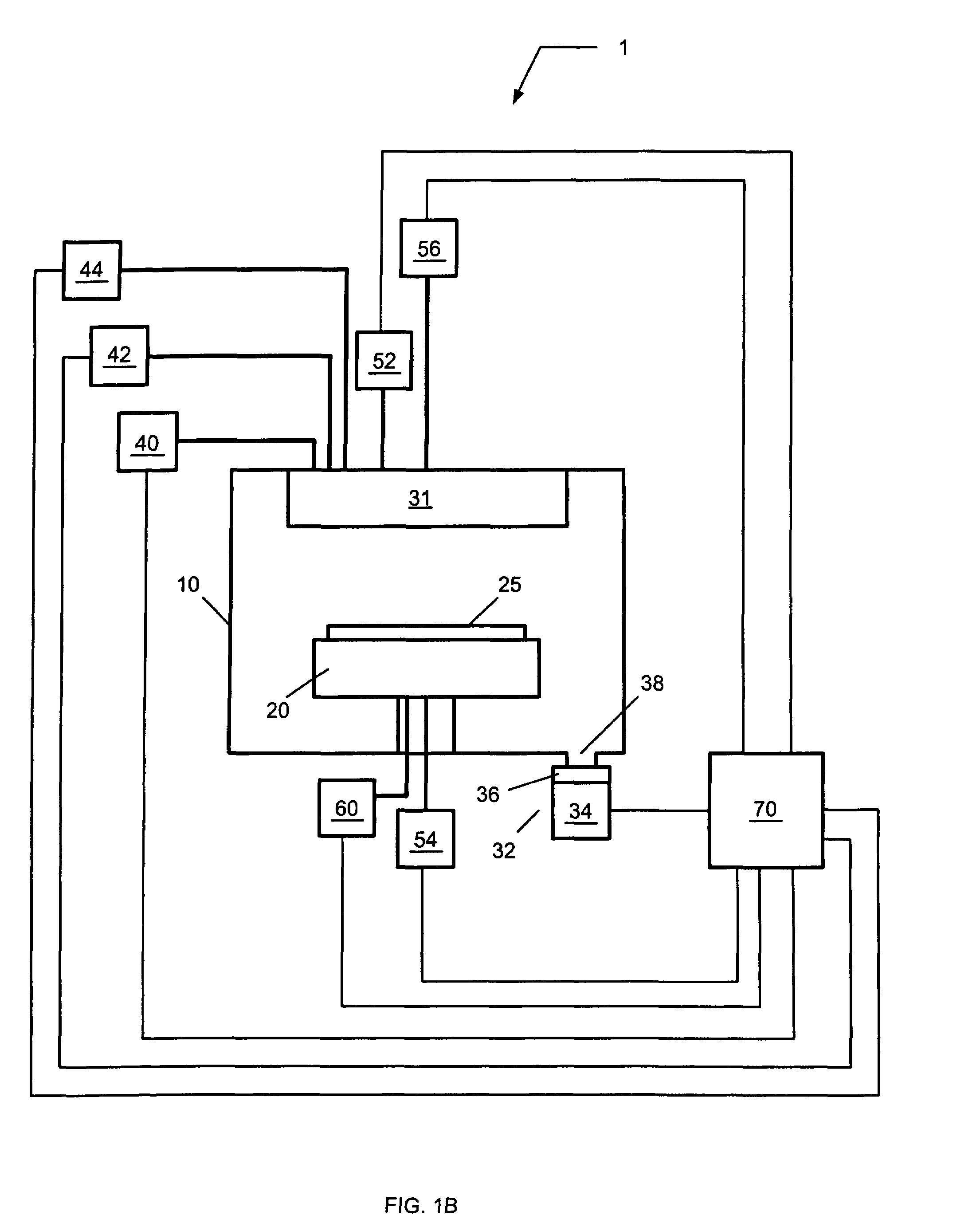

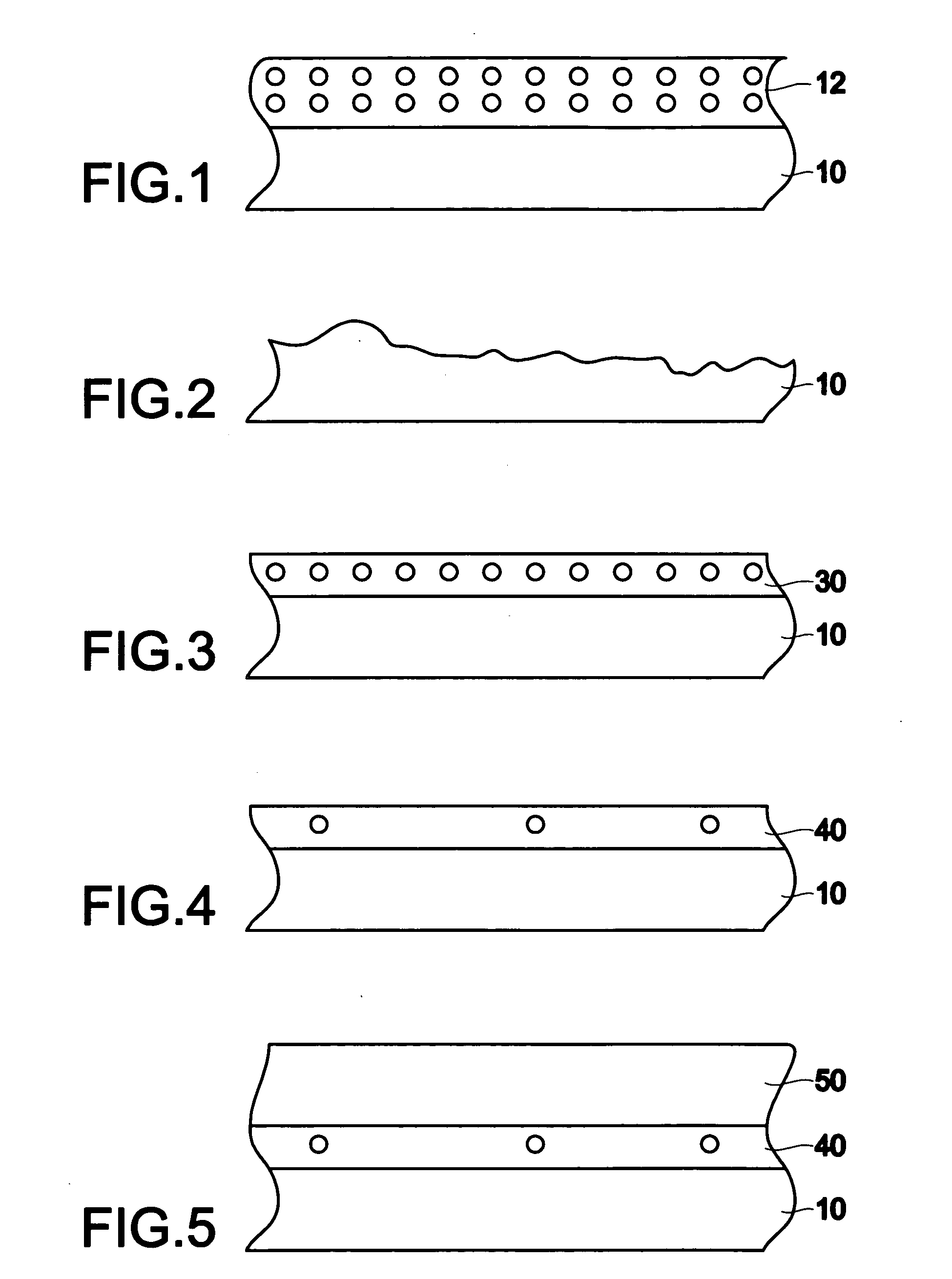

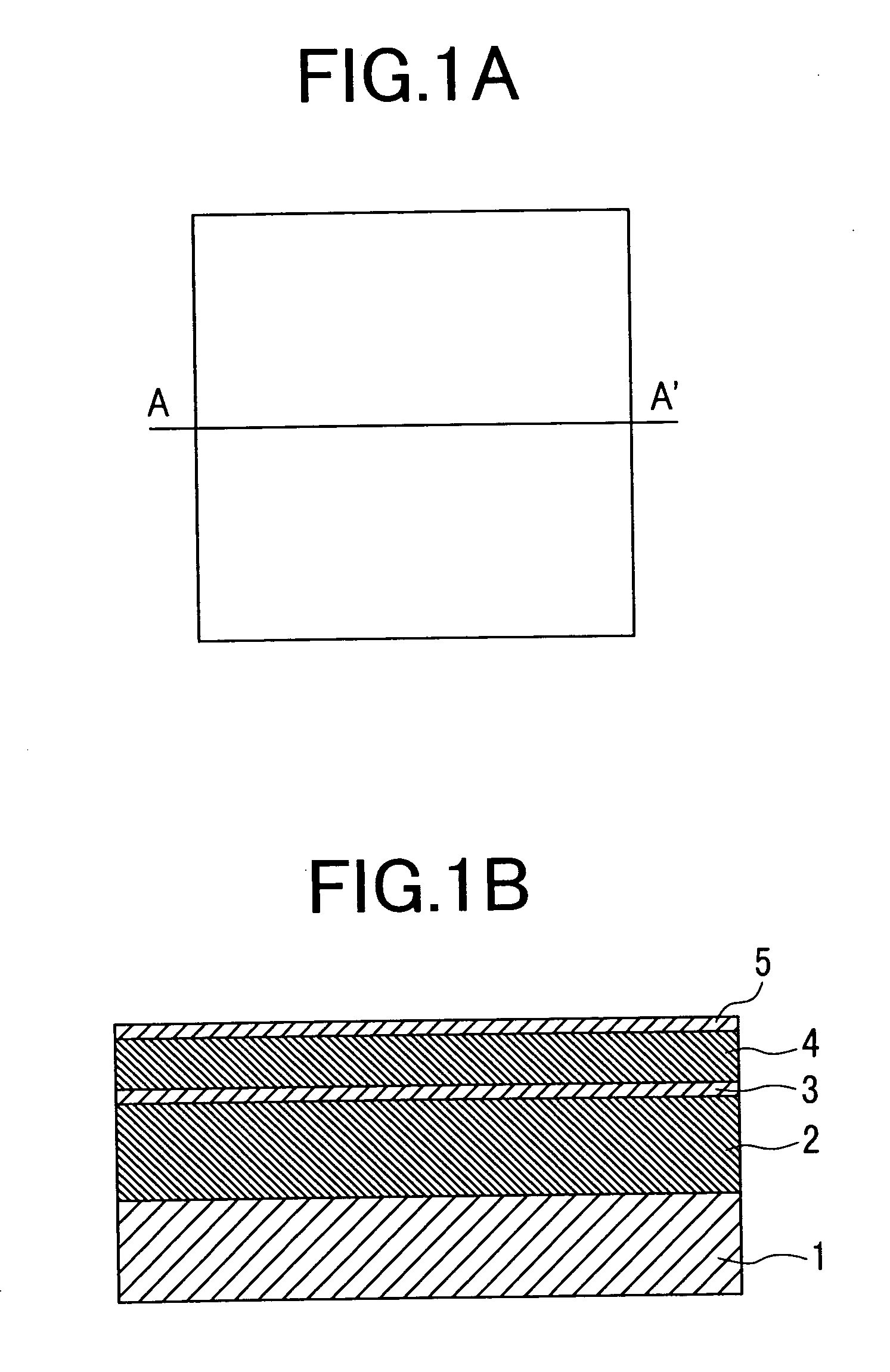

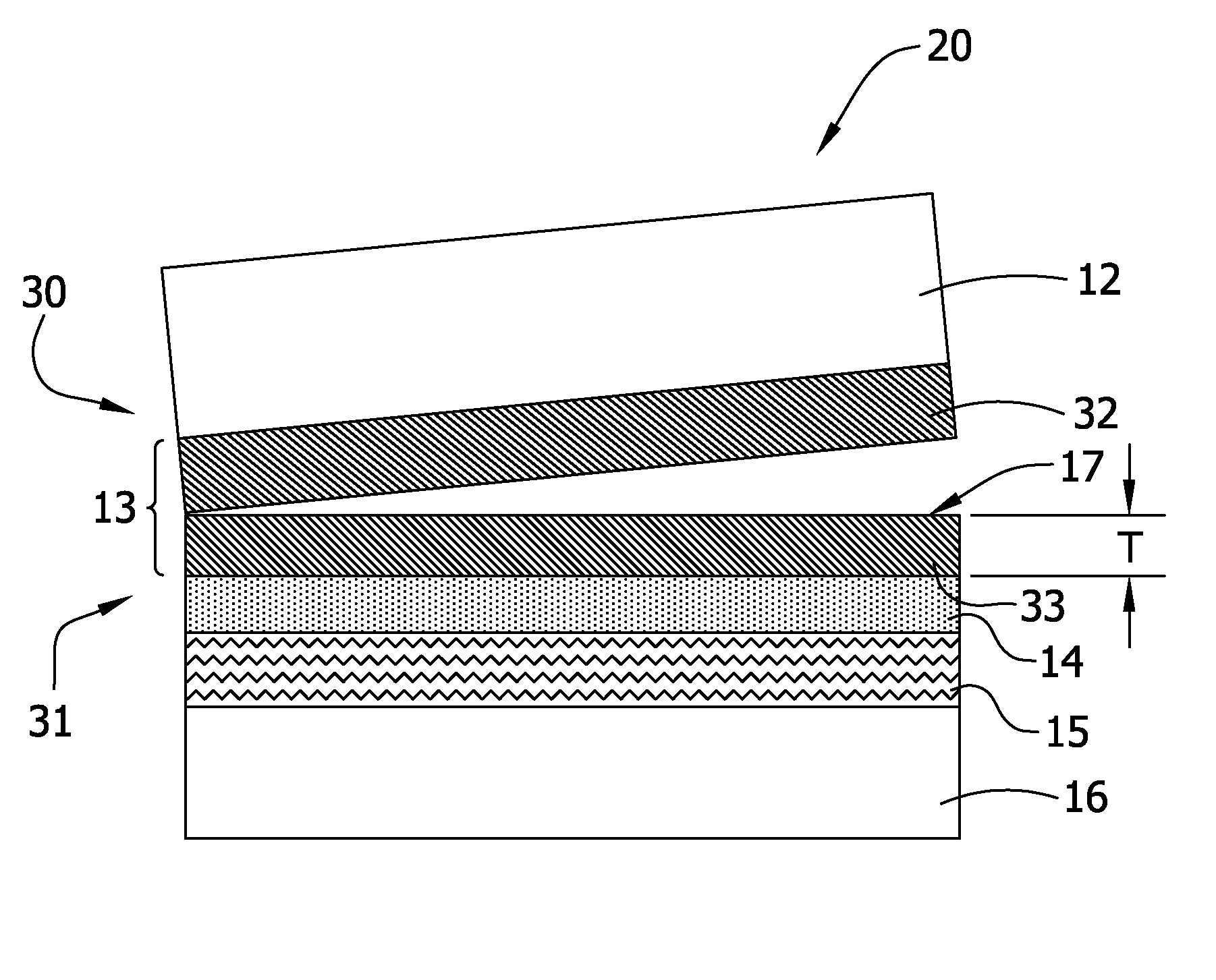

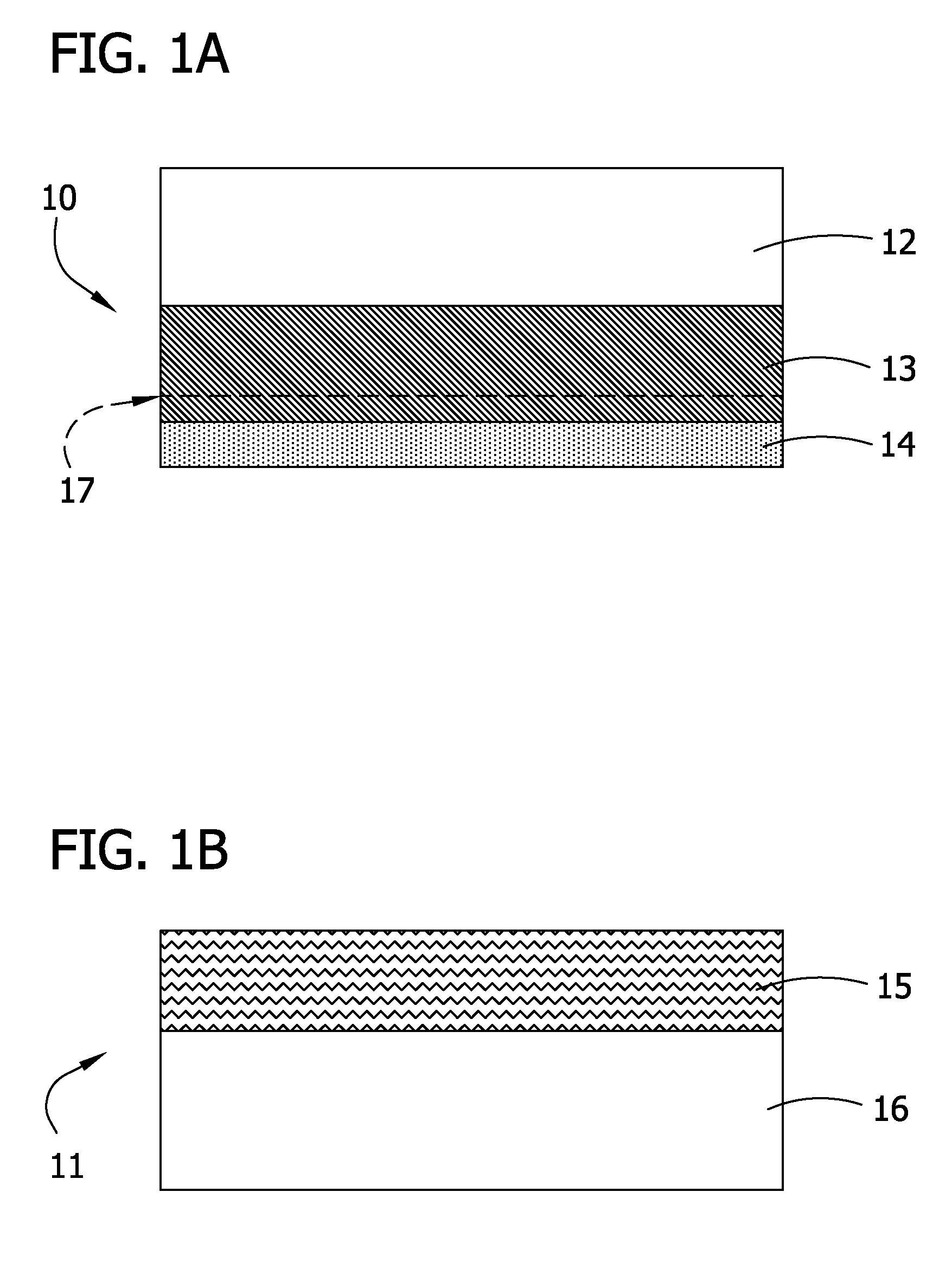

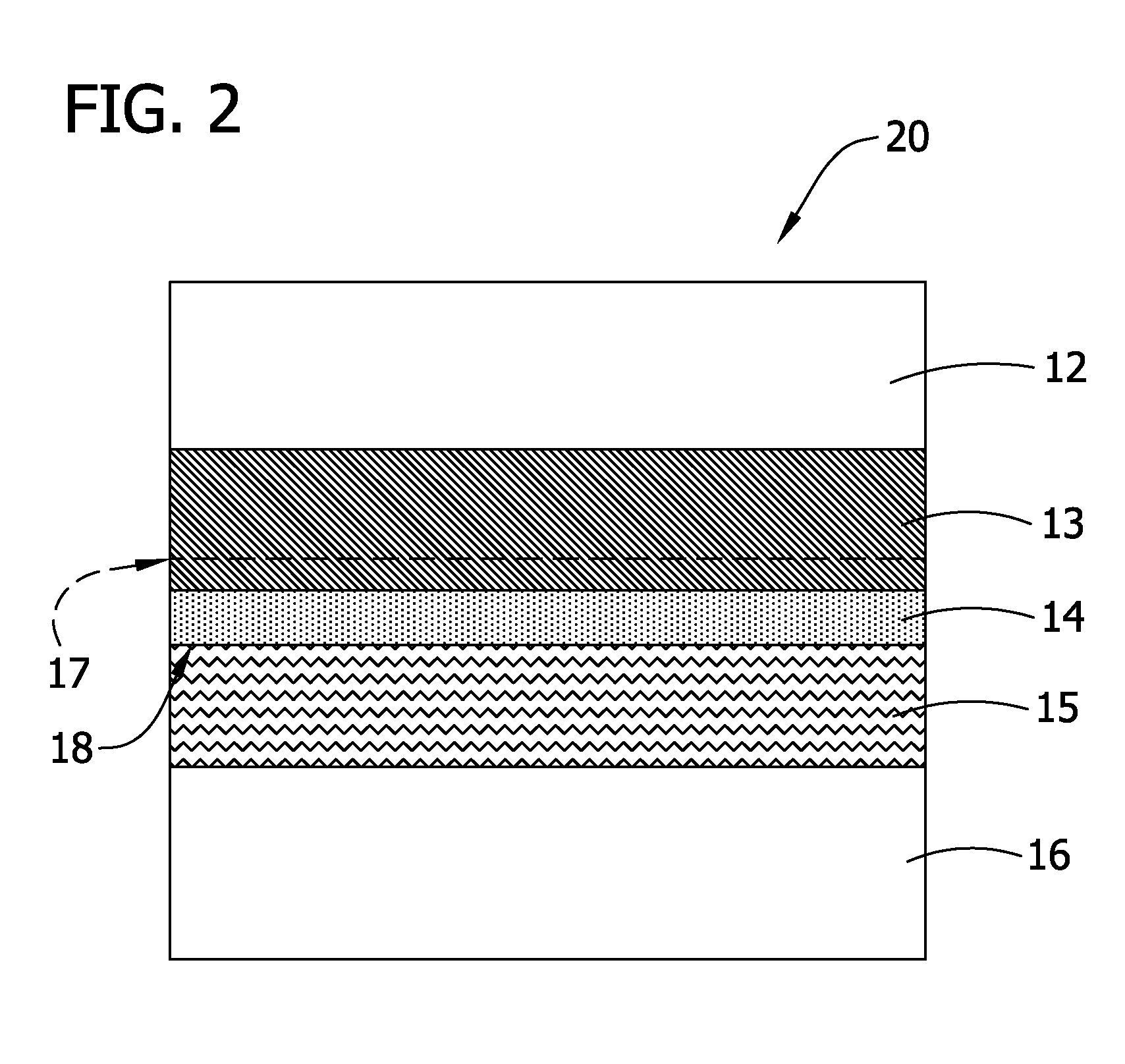

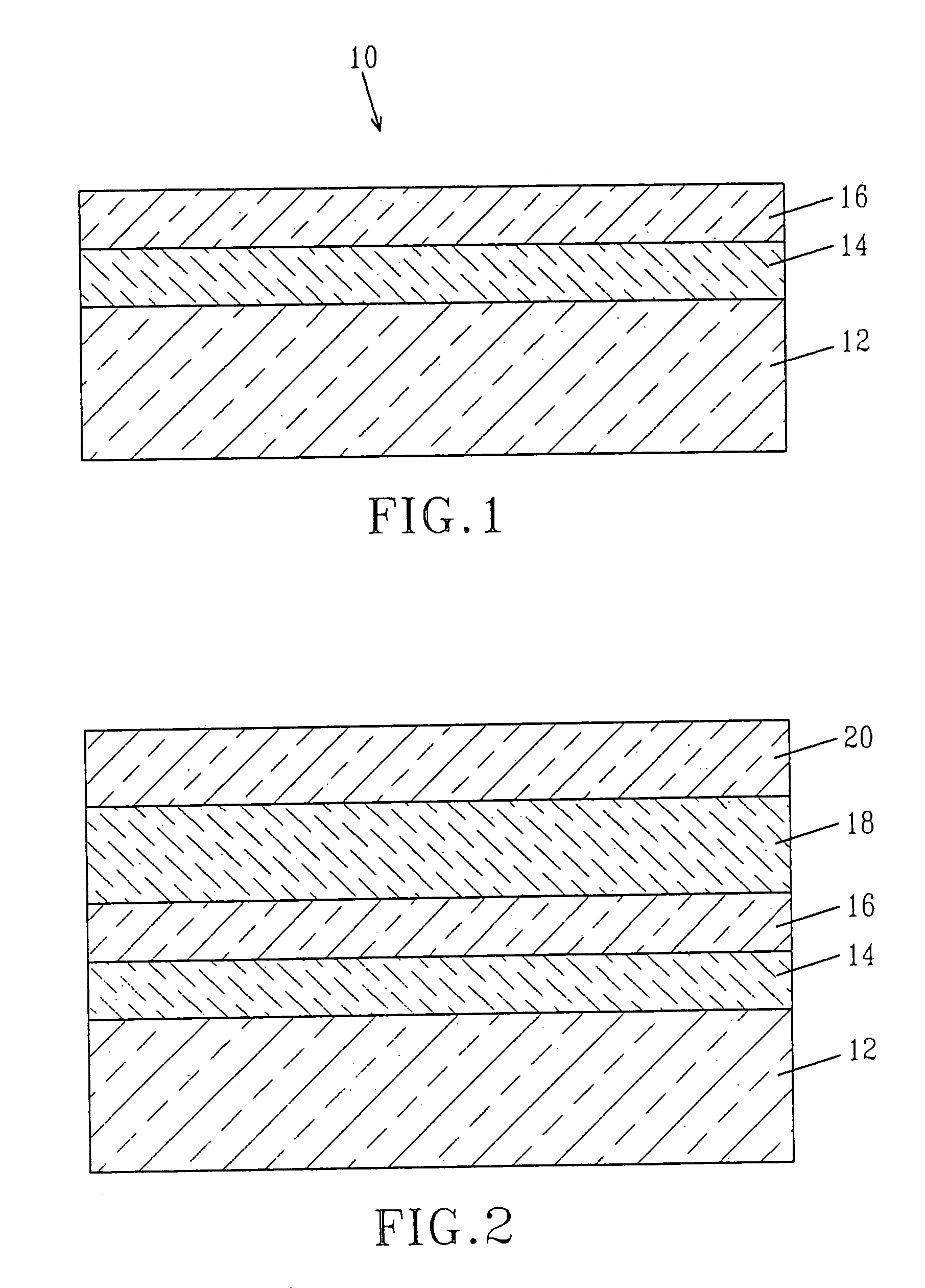

Method for forming strained silicon nitride films and a device containing such films

A method for forming a strained SiN film and a semiconductor device containing the strained SiN film. The method includes exposing the substrate to a gas including a silicon precursor, exposing the substrate to a gas containing a nitrogen precursor activated by a plasma source at a first level of plasma power and configured to react with the silicon precursor with a first reactivity characteristic, and exposing the substrate to a gas containing the nitrogen precursor activated by the plasma source at a second level of plasma power different from the first level and configured to react with the silicon precursor with a second reactivity characteristic such that a property of the silicon nitride film formed on the substrate changes to provide the strained silicon nitride film.

Owner:TOKYO ELECTRON LTD

Method for forming strained silicon nitride films and a device containing such films

ActiveUS7651961B2Vacuum evaporation coatingSemiconductor/solid-state device manufacturingNitrogenNitride

A method for forming a strained SiN film and a semiconductor device containing the strained SiN film. The method includes exposing the substrate to a gas including a silicon precursor, exposing the substrate to a gas containing a nitrogen precursor activated by a plasma source at a first level of plasma power and configured to react with the silicon precursor with a first reactivity characteristic, and exposing the substrate to a gas containing the nitrogen precursor activated by the plasma source at a second level of plasma power different from the first level and configured to react with the silicon precursor with a second reactivity characteristic such that a property of the silicon nitride film formed on the substrate changes to provide the strained silicon nitride film.

Owner:TOKYO ELECTRON LTD

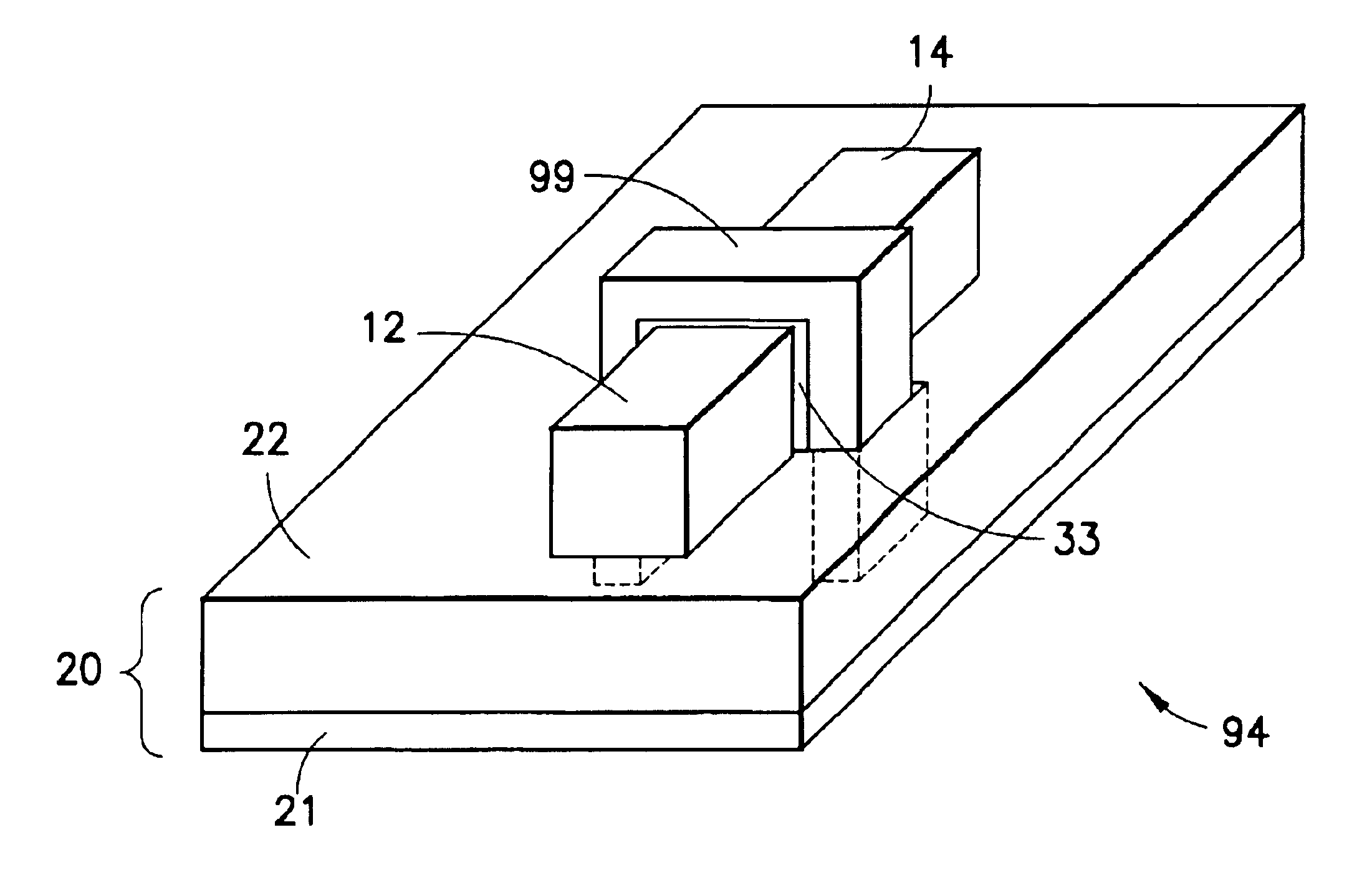

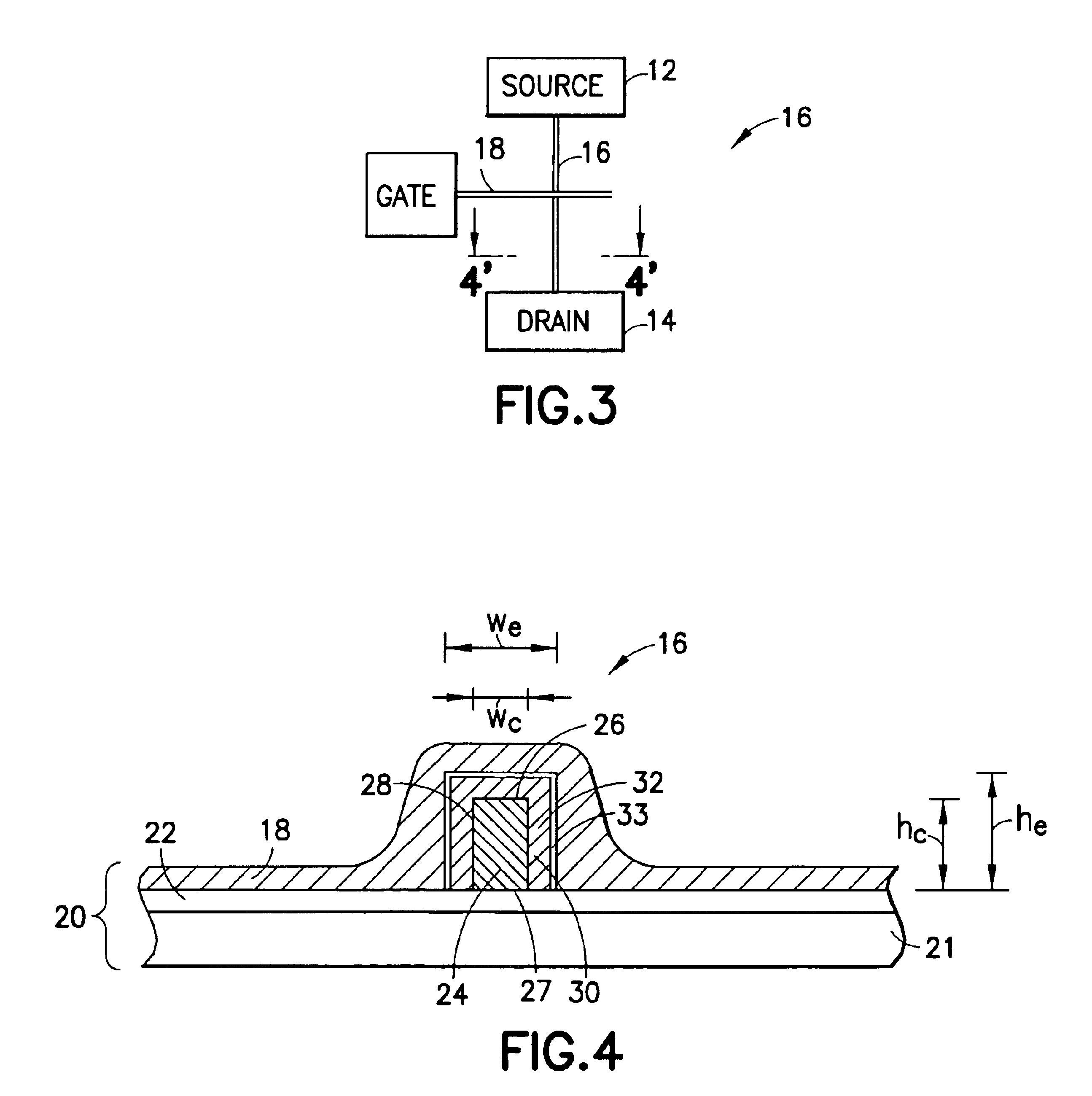

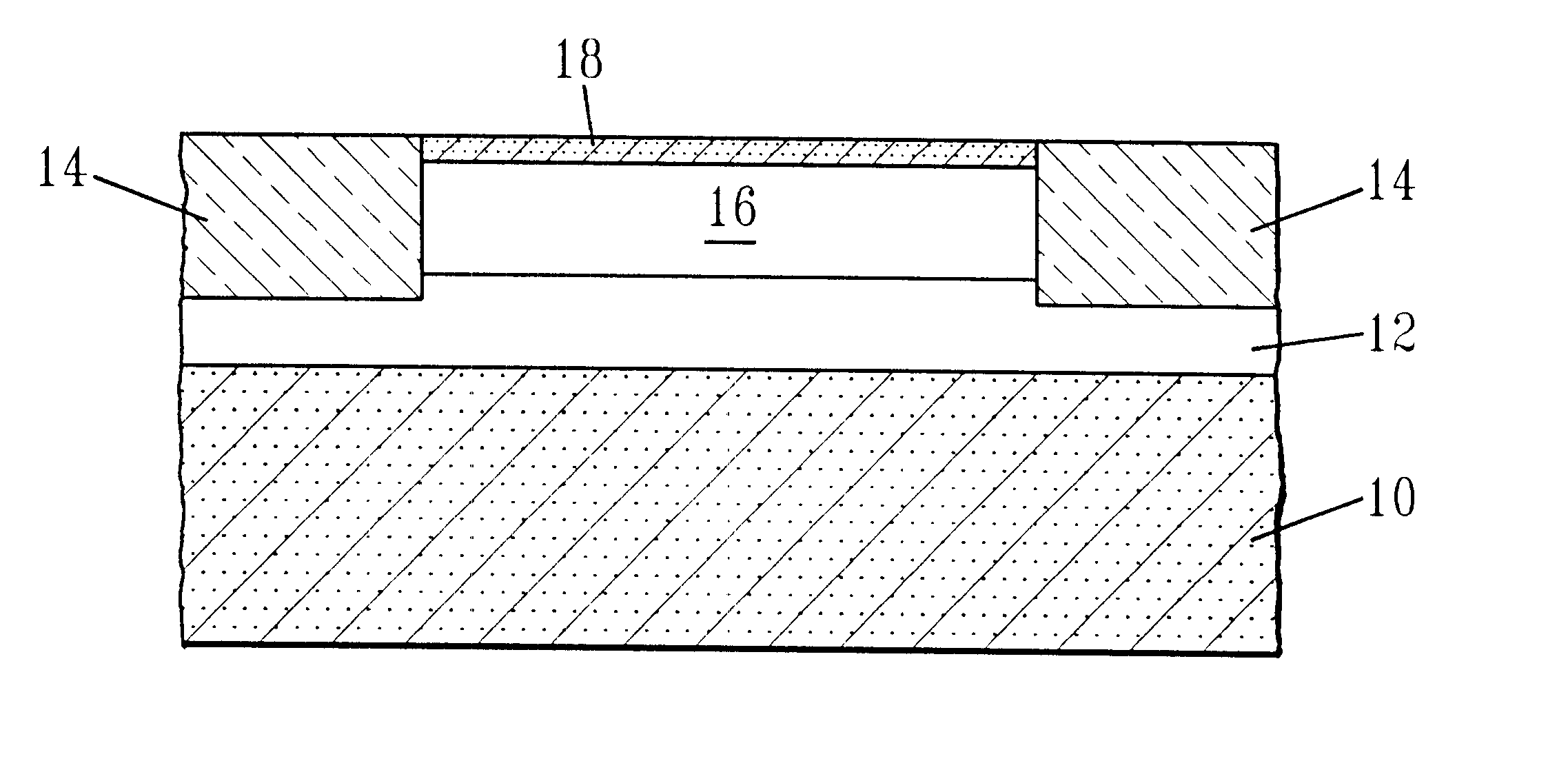

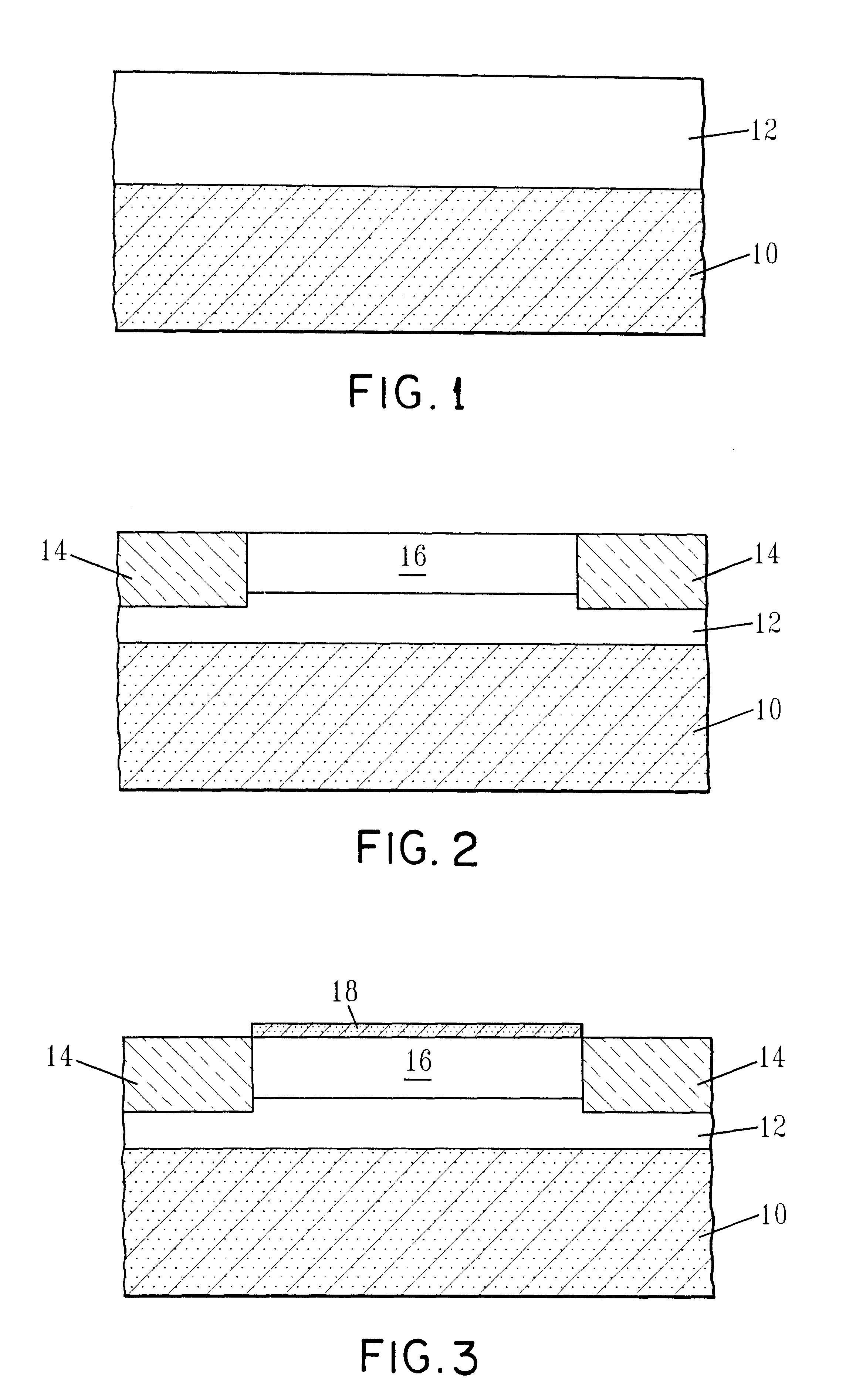

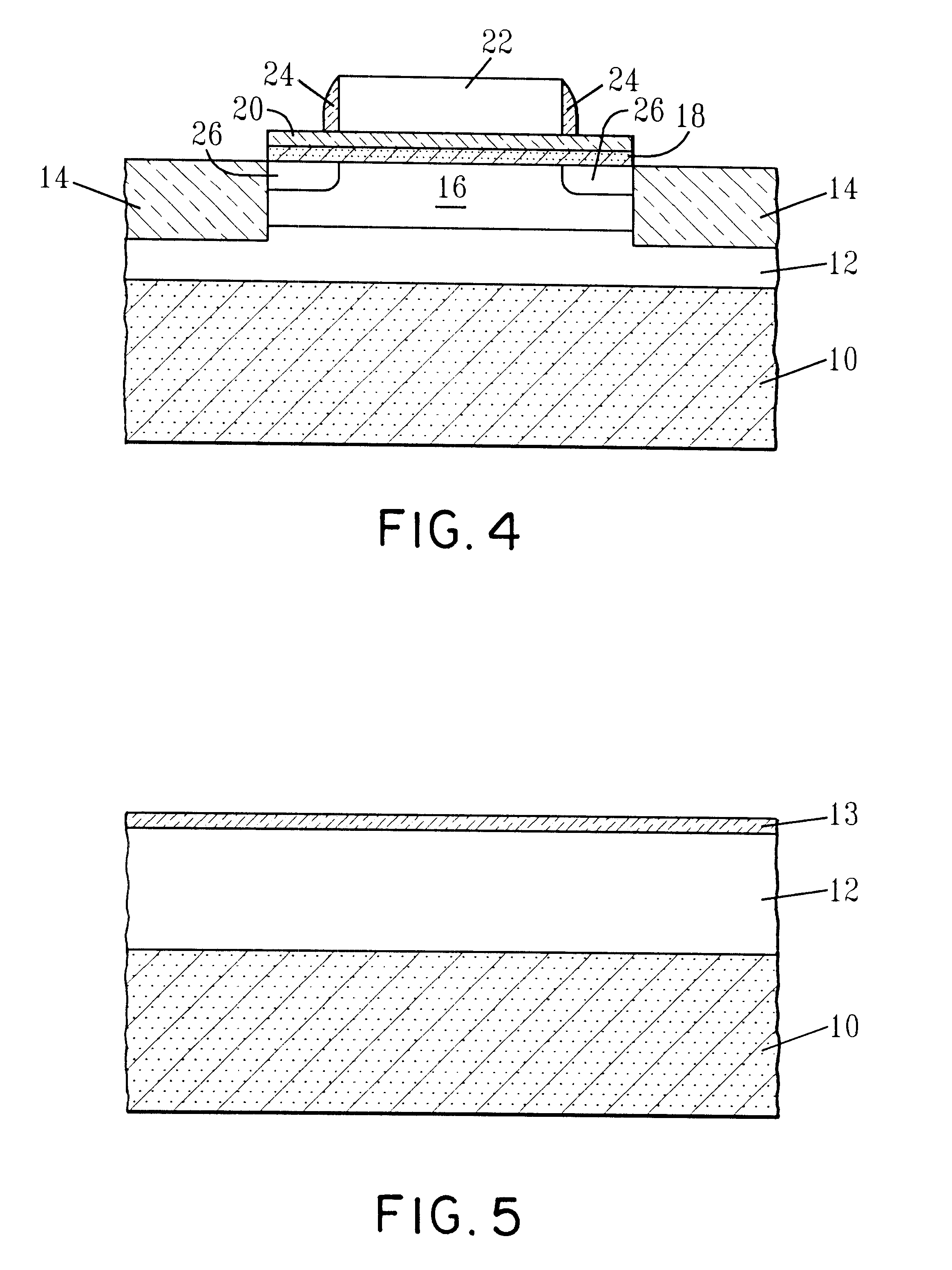

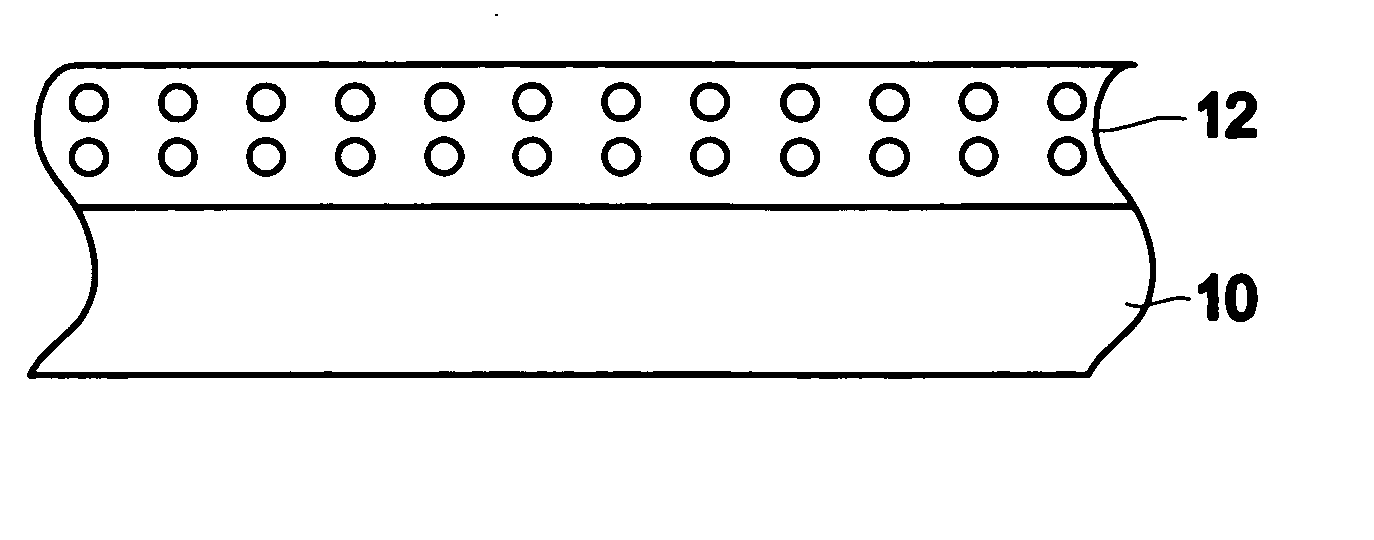

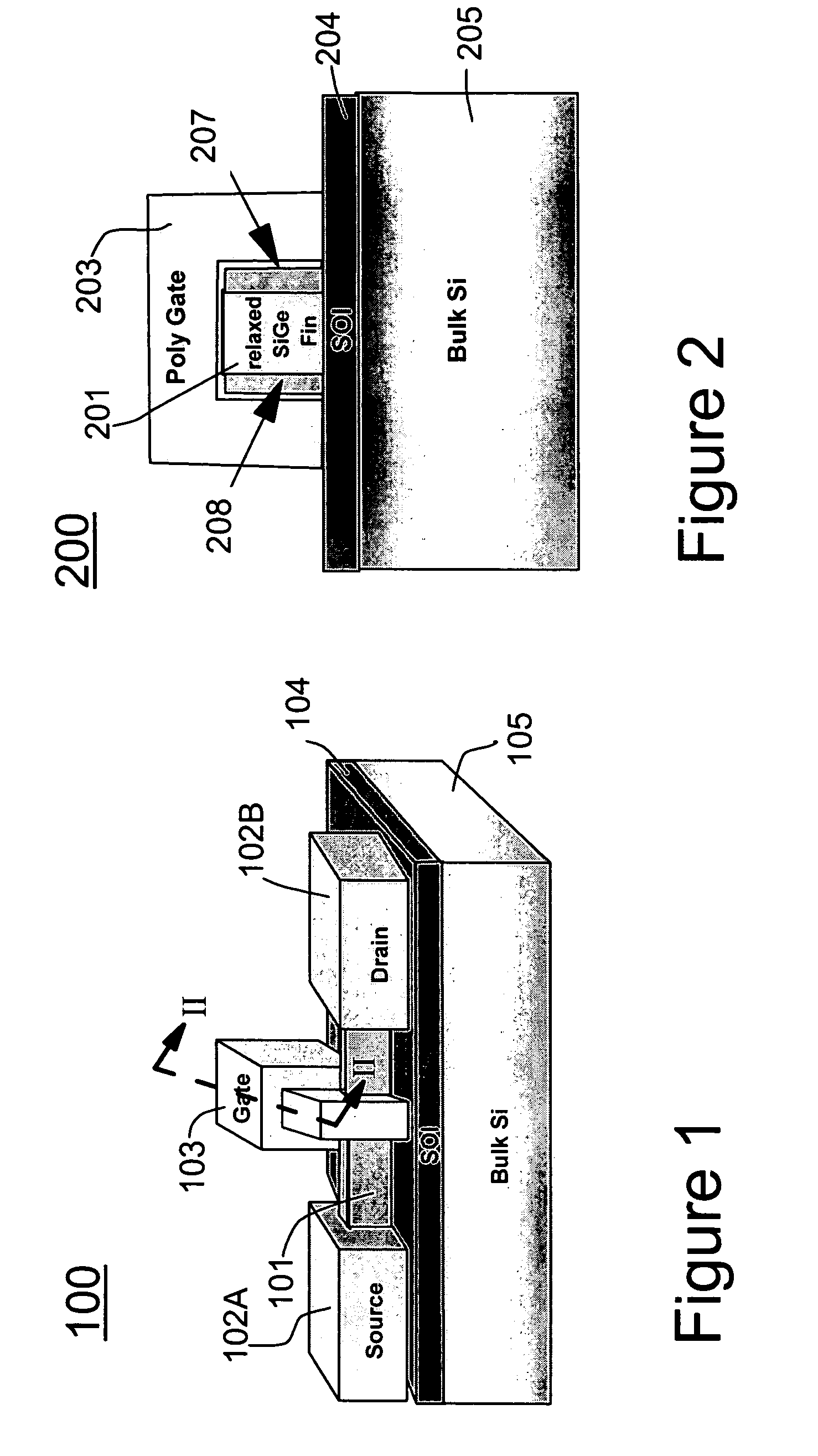

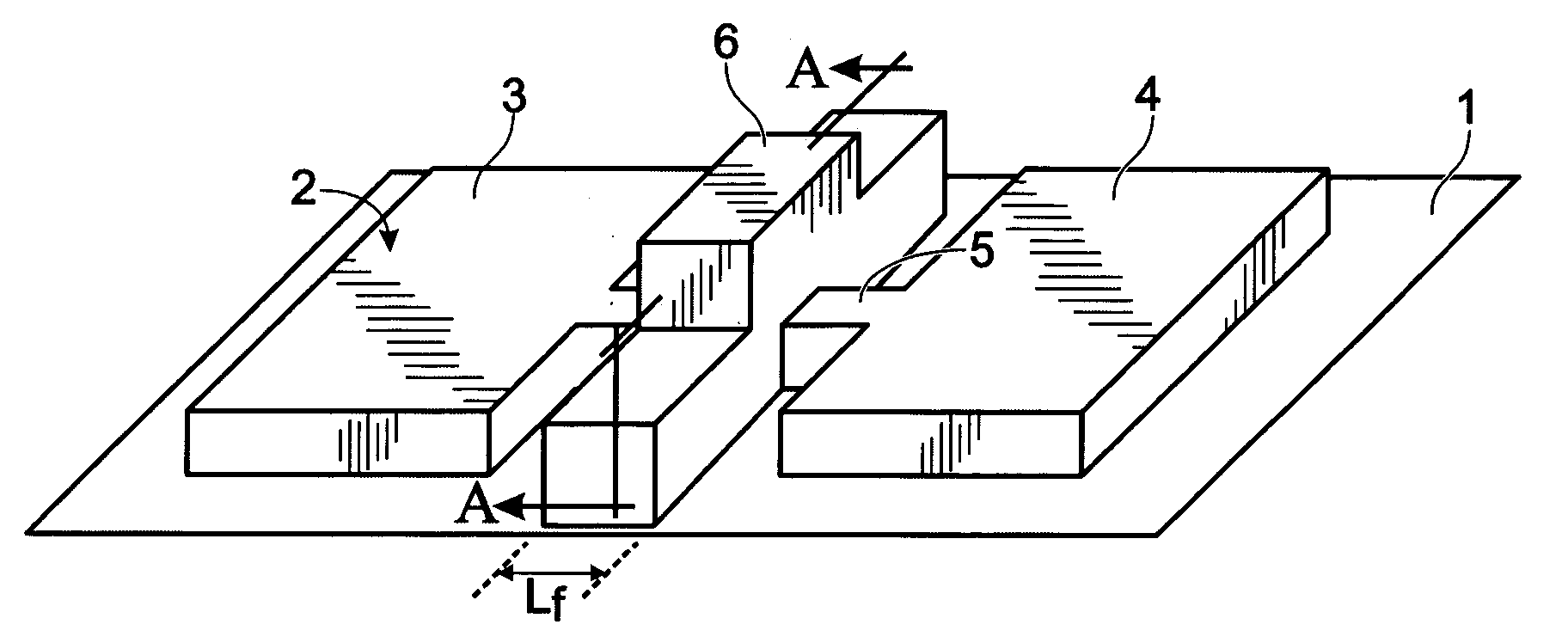

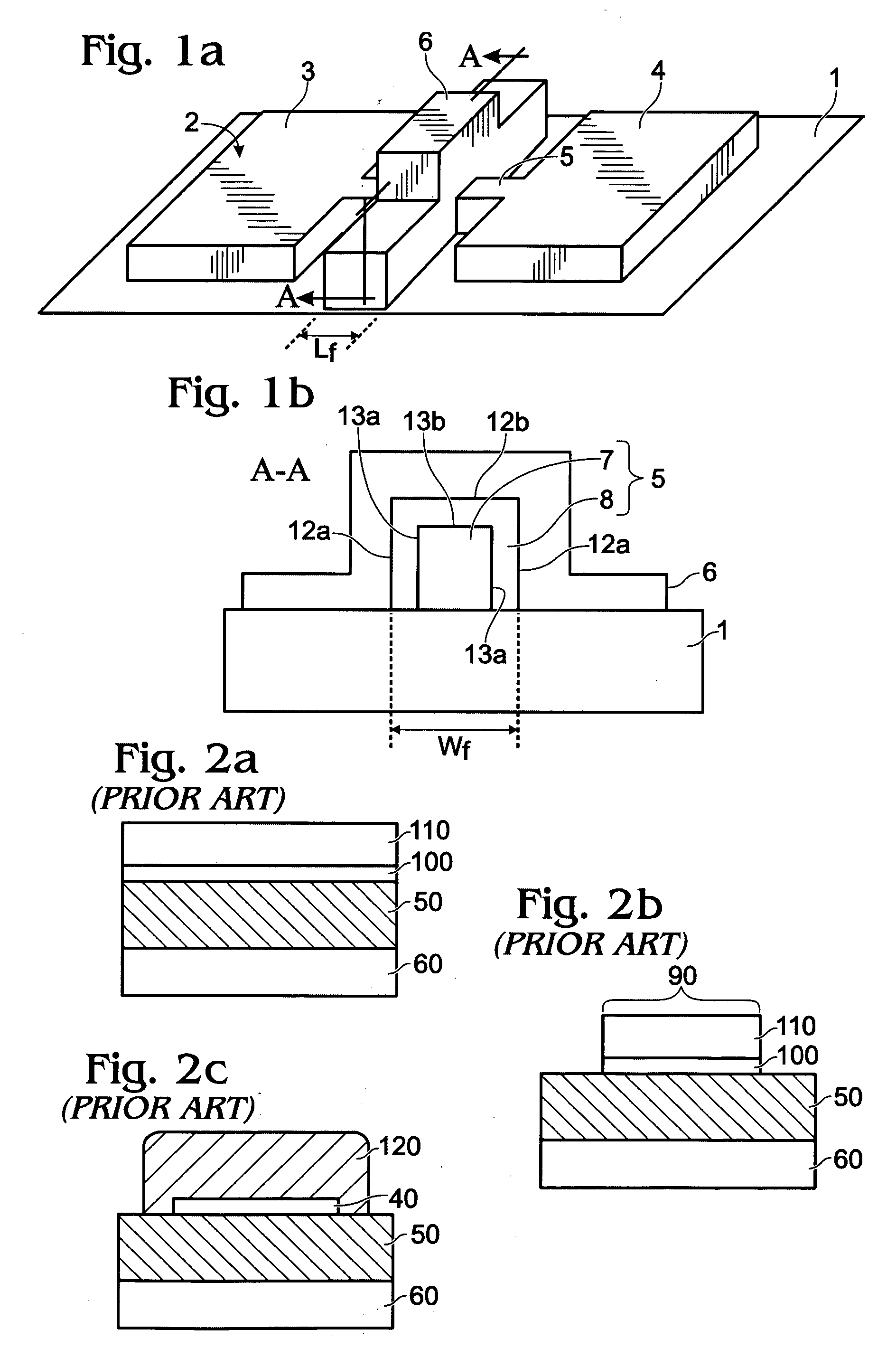

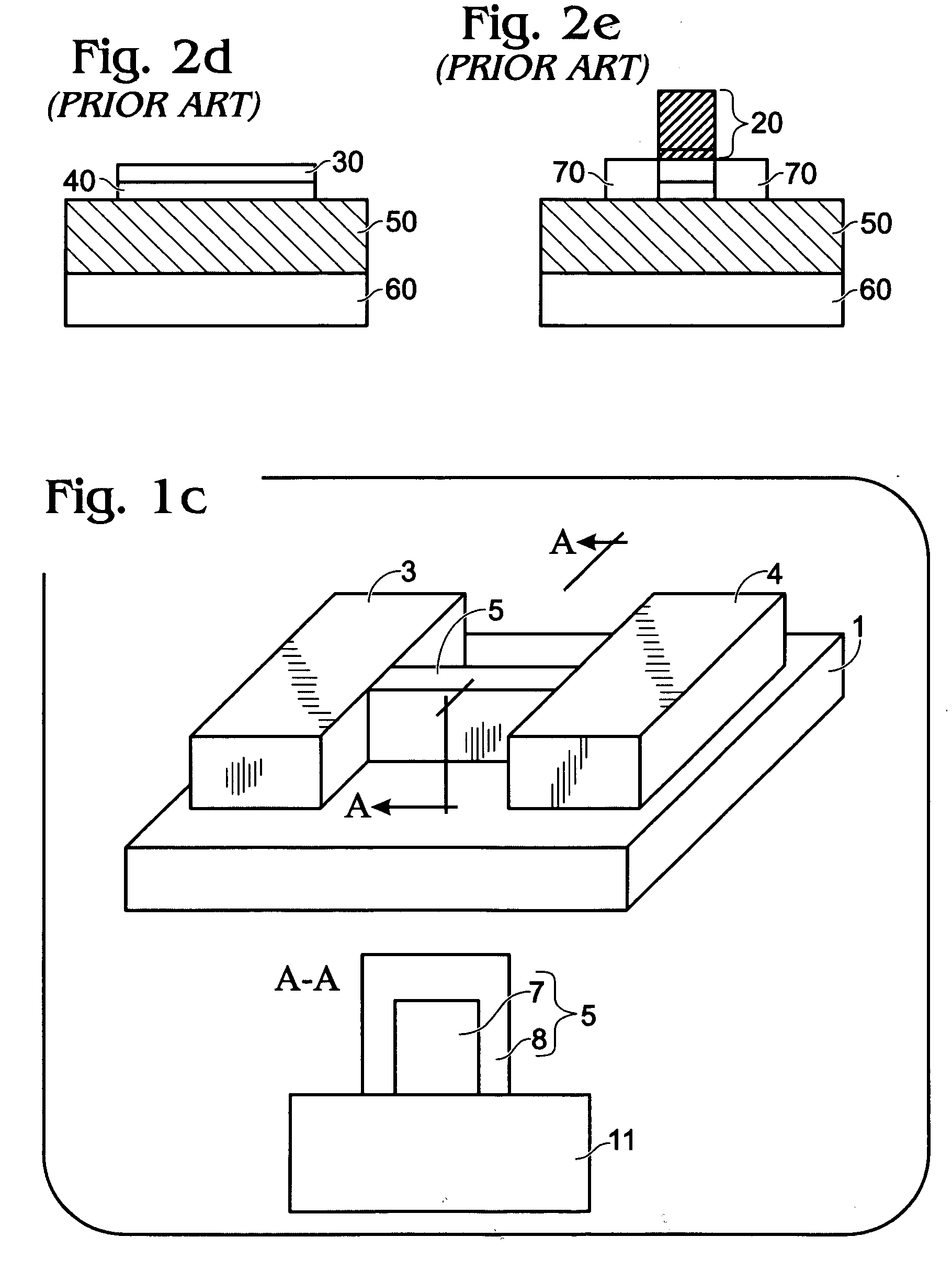

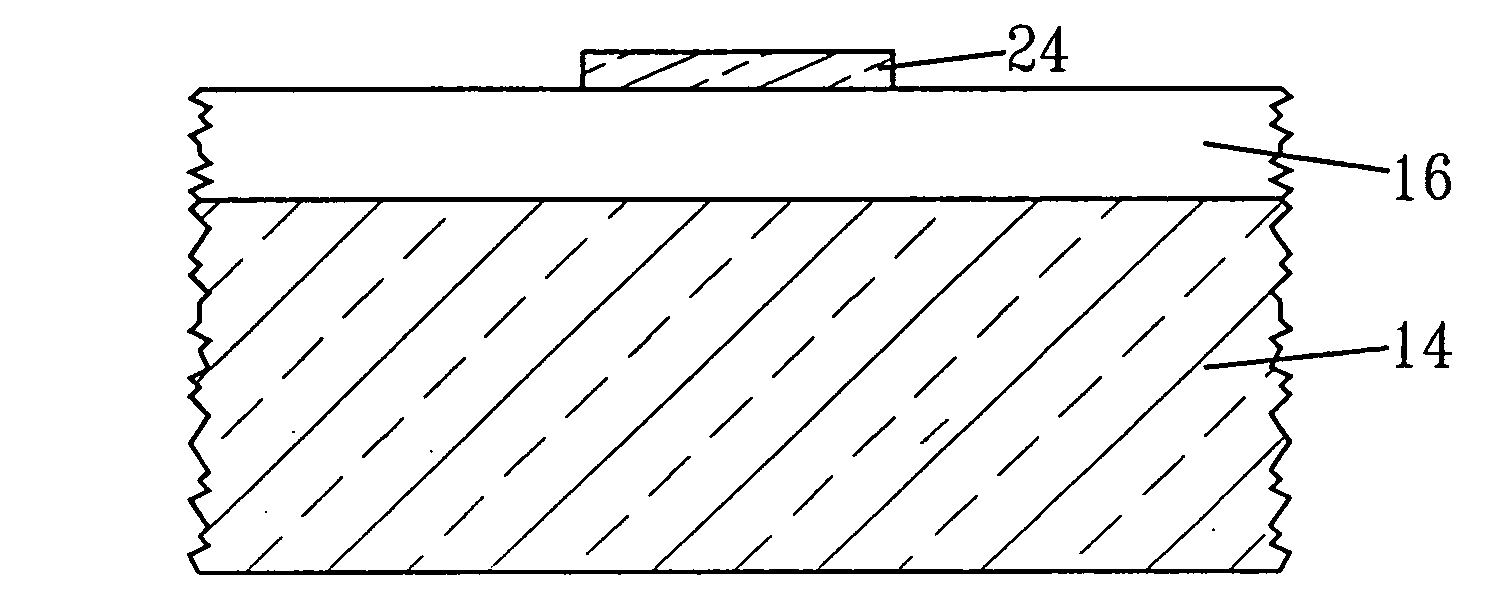

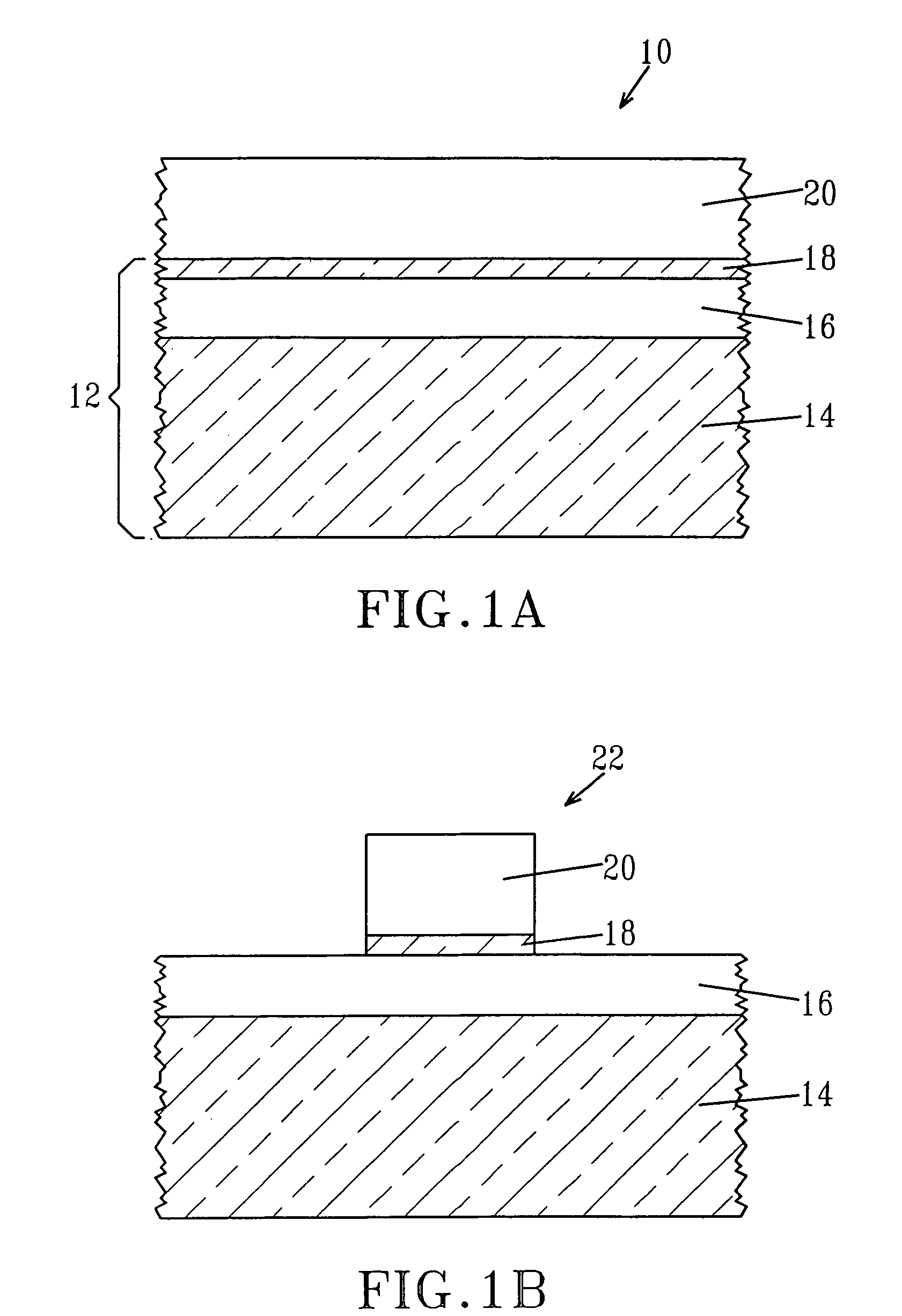

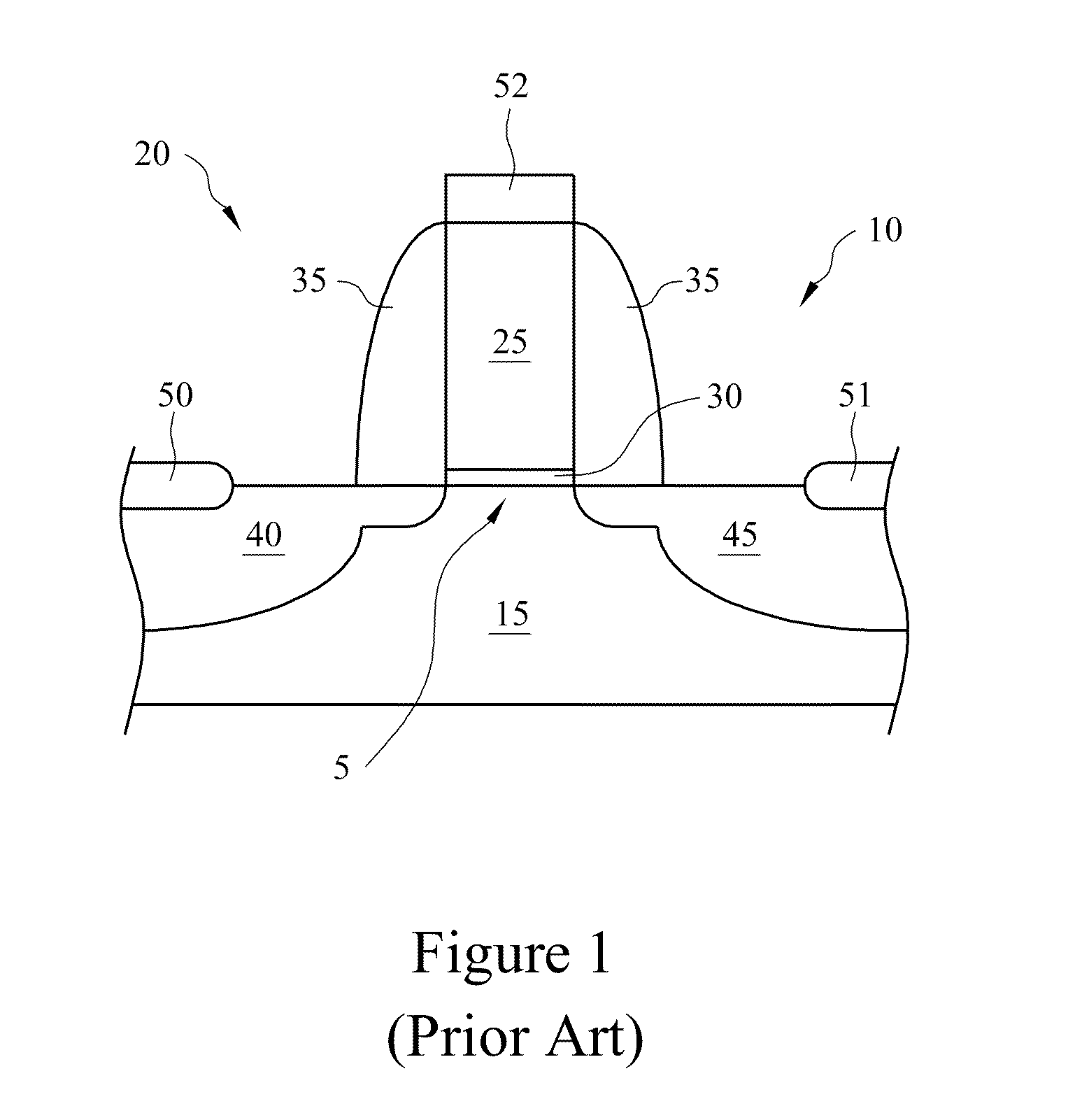

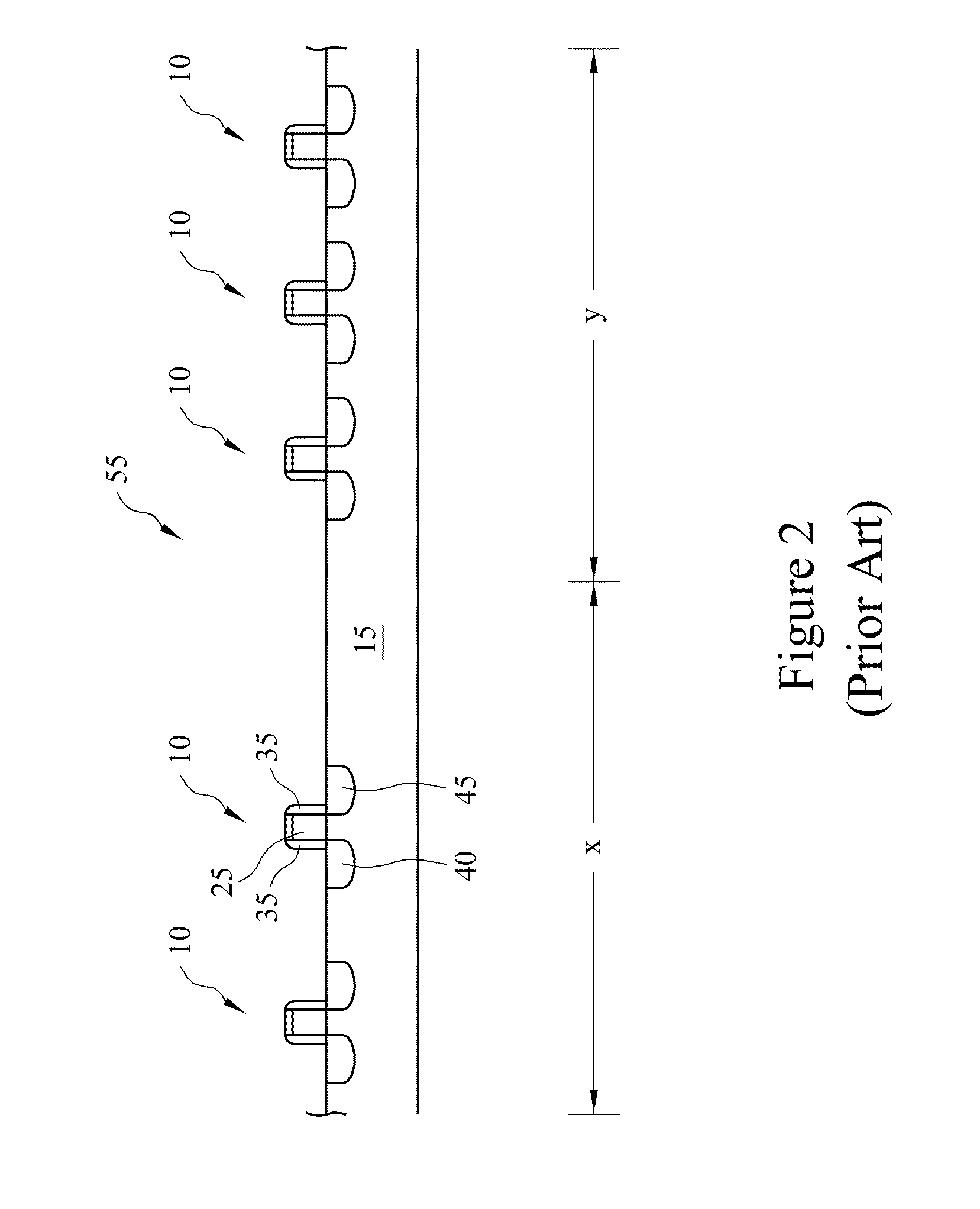

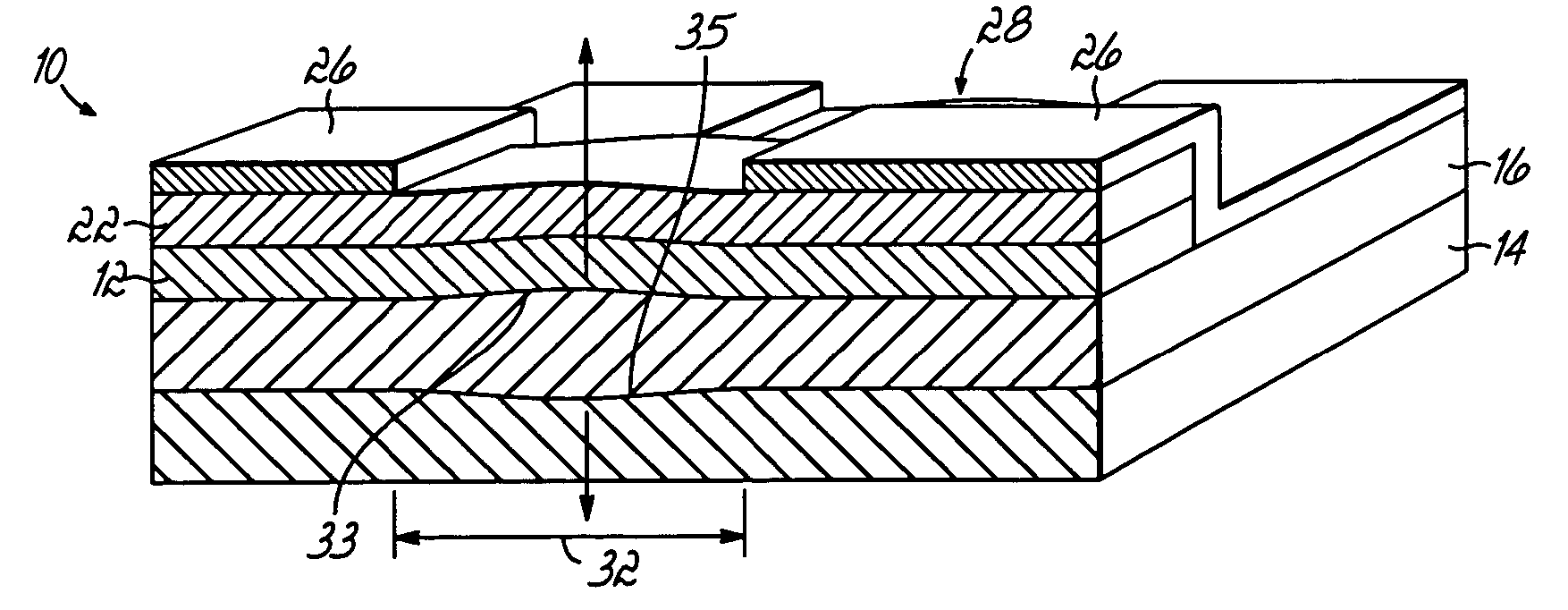

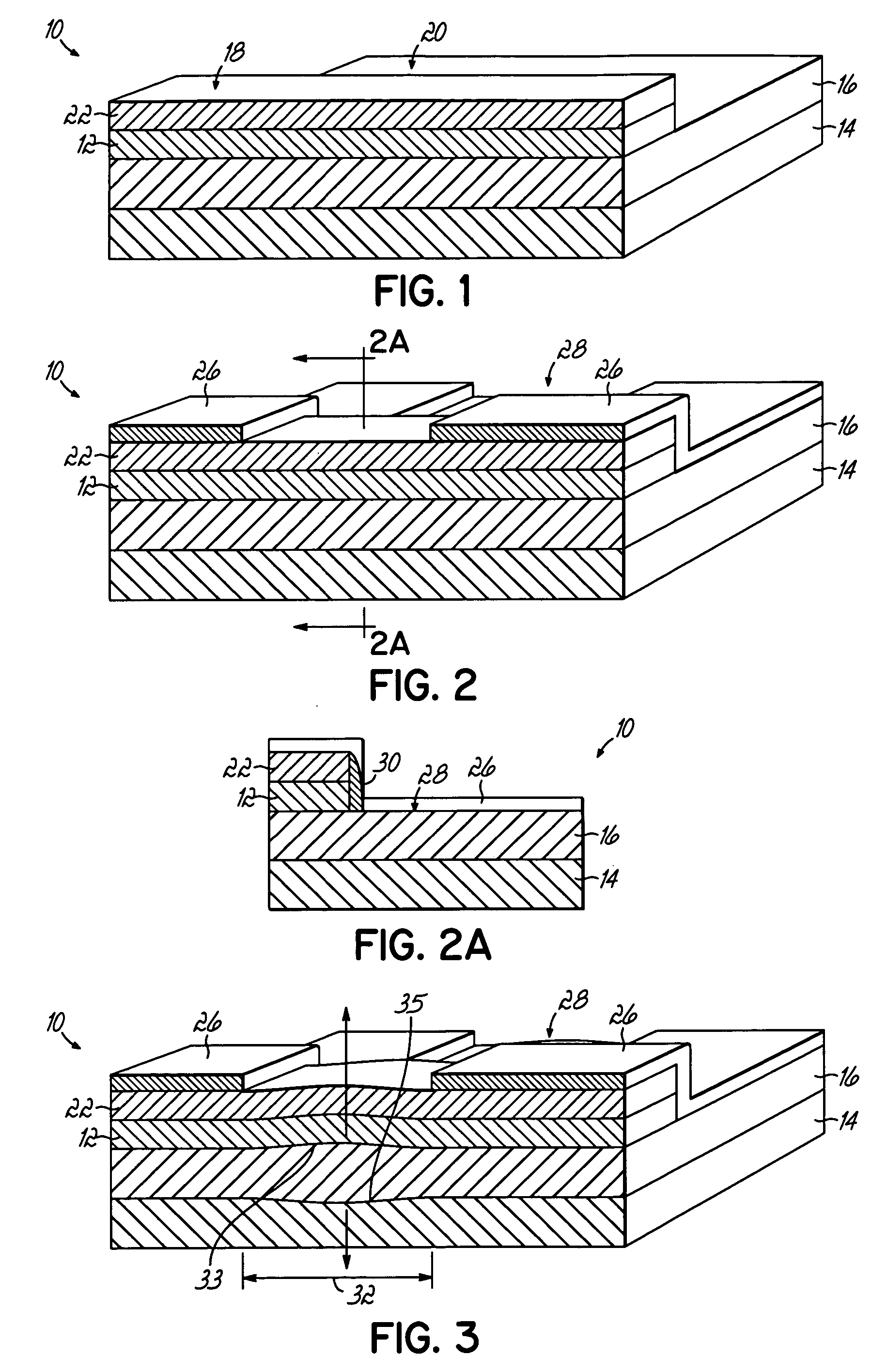

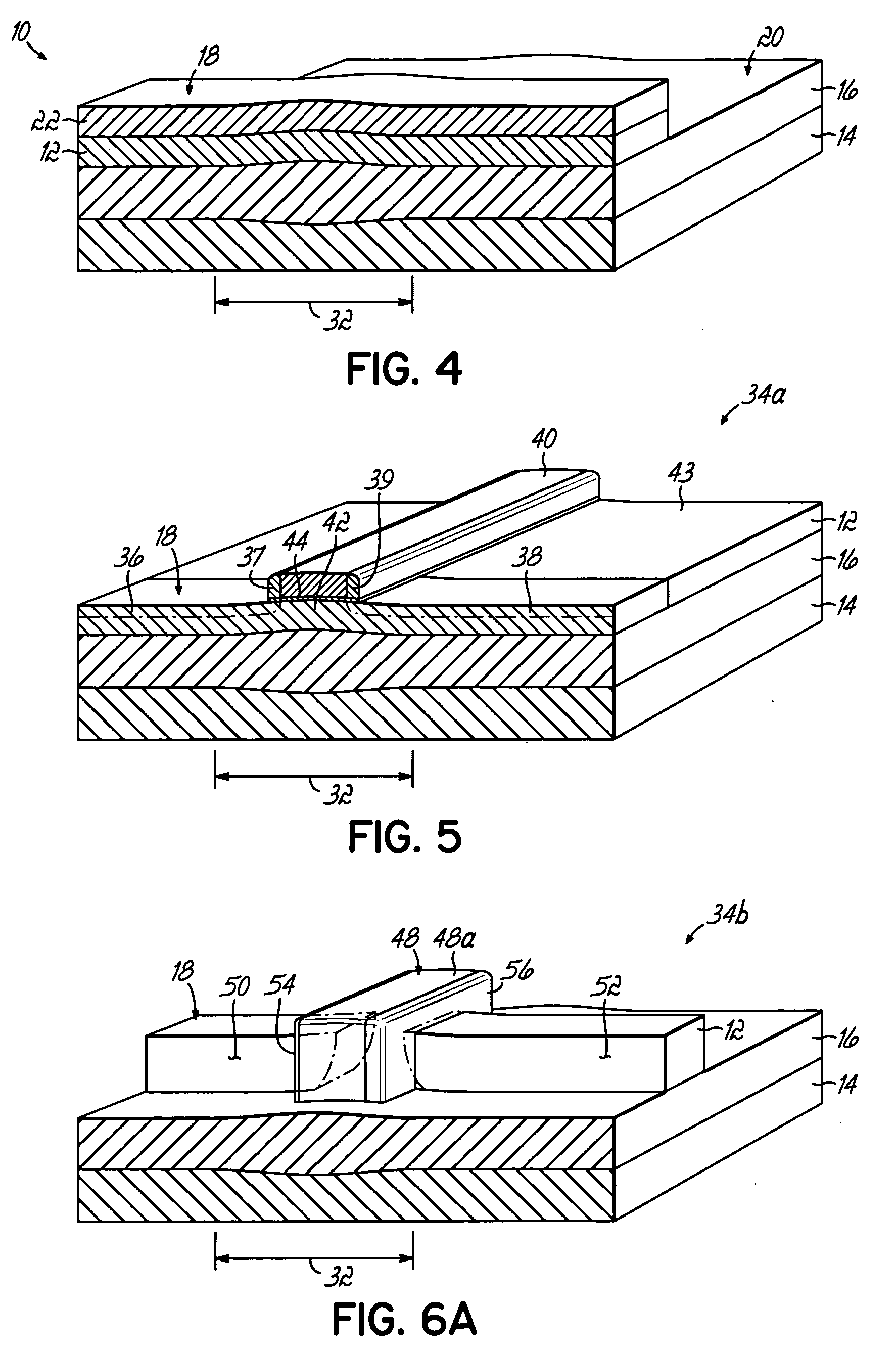

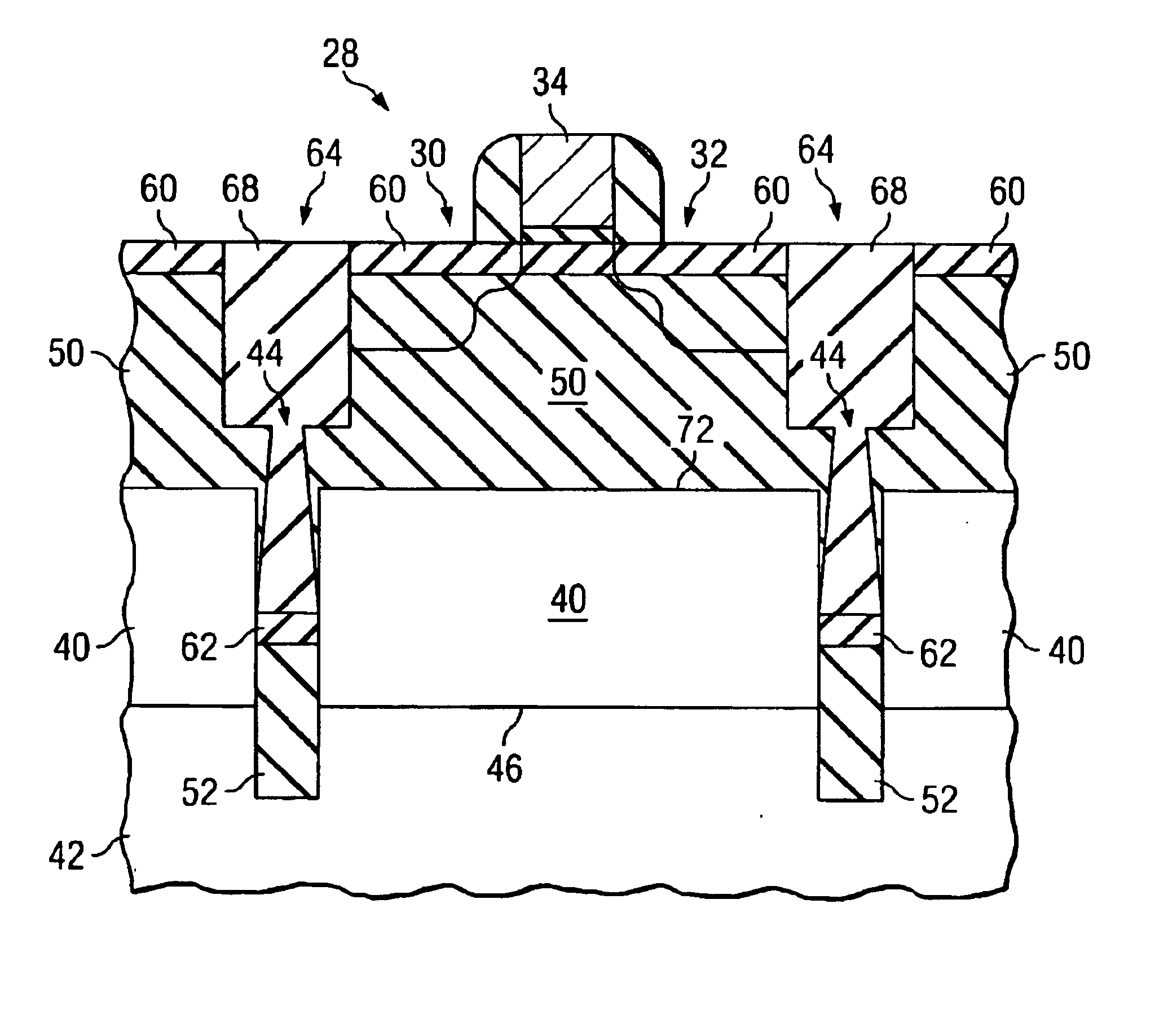

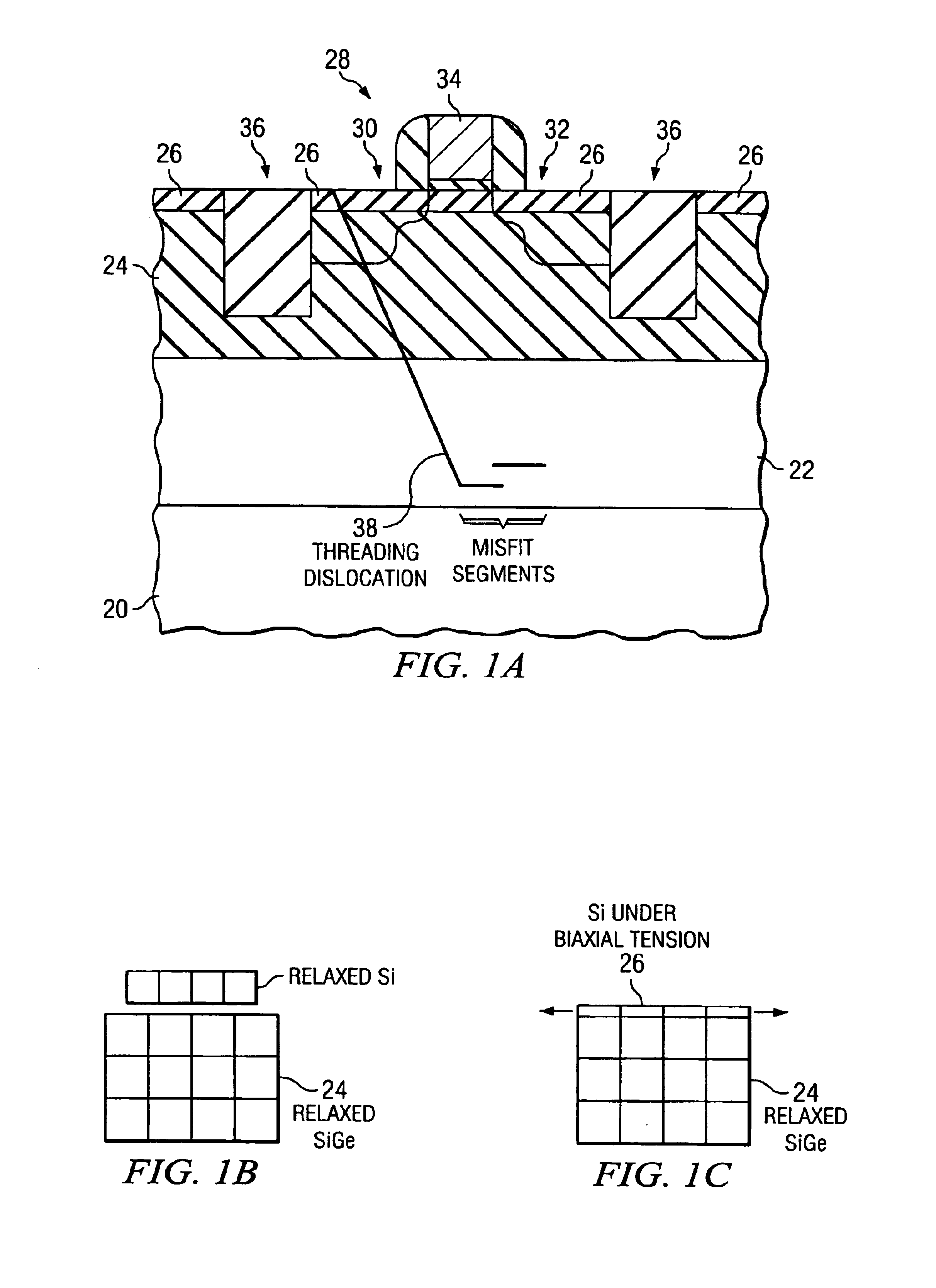

FET channel having a strained lattice structure along multiple surfaces

InactiveUS6921982B2Improve conductivityTransistorSolid-state devicesGate dielectricSemiconductor materials

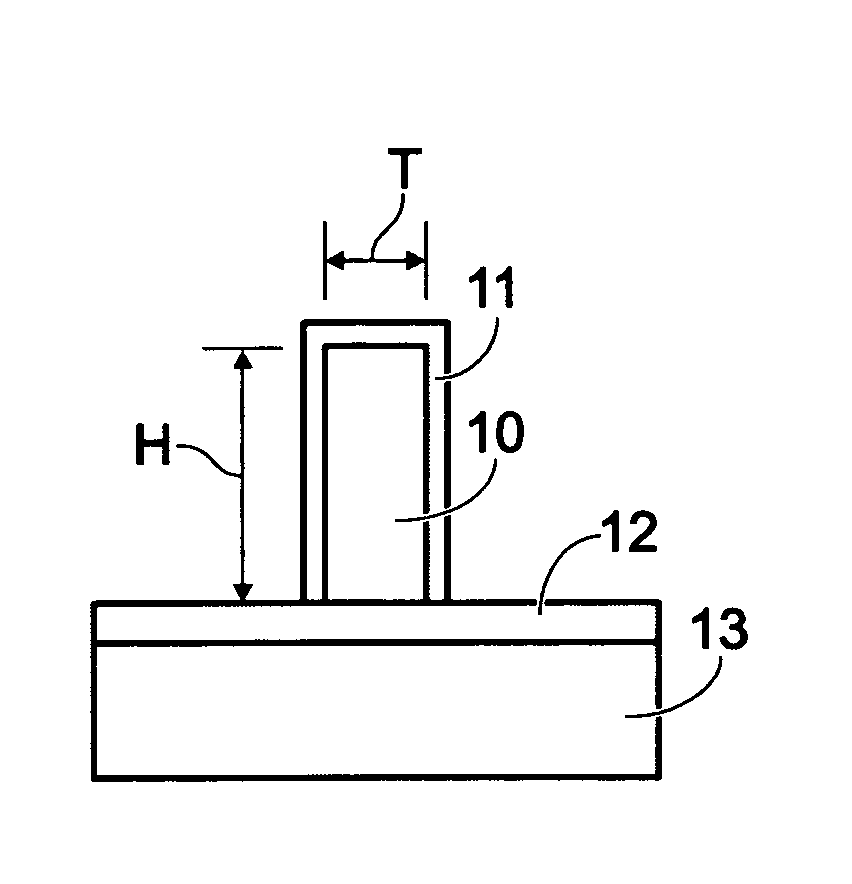

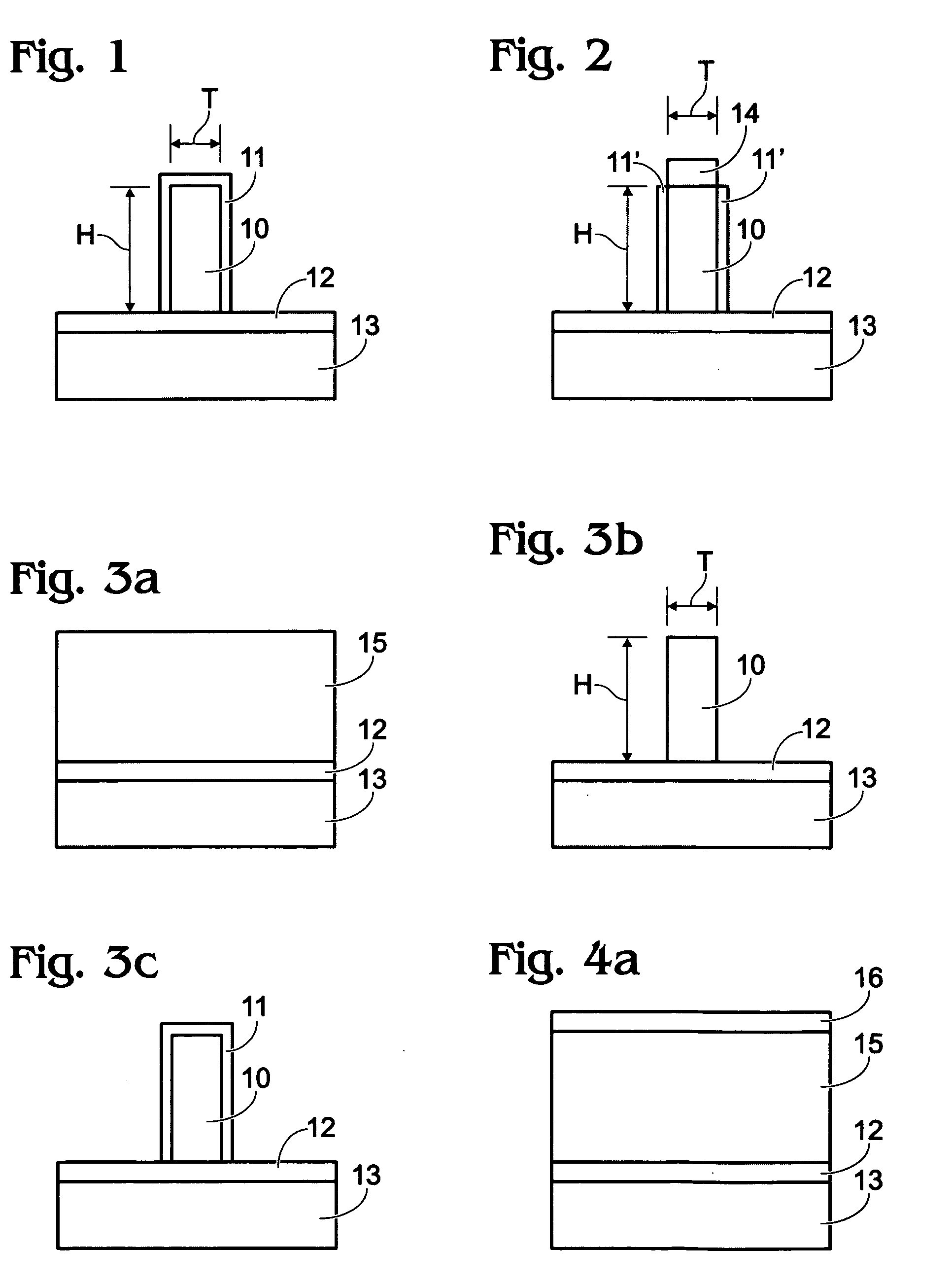

A channel 16 of a FinFET 10 has a channel core 24 and a channel envelope 32, each made from a semiconductor material defining a different lattice structure to exploit strained silicon properties. A gate is coupled to the channel envelope through a gate dielectric. Exemplary materials are Si and SixGe1-x, wherein 78<x<92. The channel core 24 has a top surface 26 of width wc and an upstanding surface 28, 30 of height hc, preferably oriented 90° to one another. The channel envelope 32 is in contact with the top 26 and upstanding surfaces 28, 30 so that the area of interface is increased as compared to contact only along the top surface 26, improving electrical conductivity and gate 18 control over the channel 16. The height hc can be tailored to enable a smaller scale FET 10 within a stabilized SRAM. Various methods of making the channel 16 are disclosed, including a mask and etch method, a handle wafer / carrier wafer method, and a shallow trench method. Embodiments and methods for FinFETs with one to four gates are disclosed.

Owner:MICROSOFT TECH LICENSING LLC

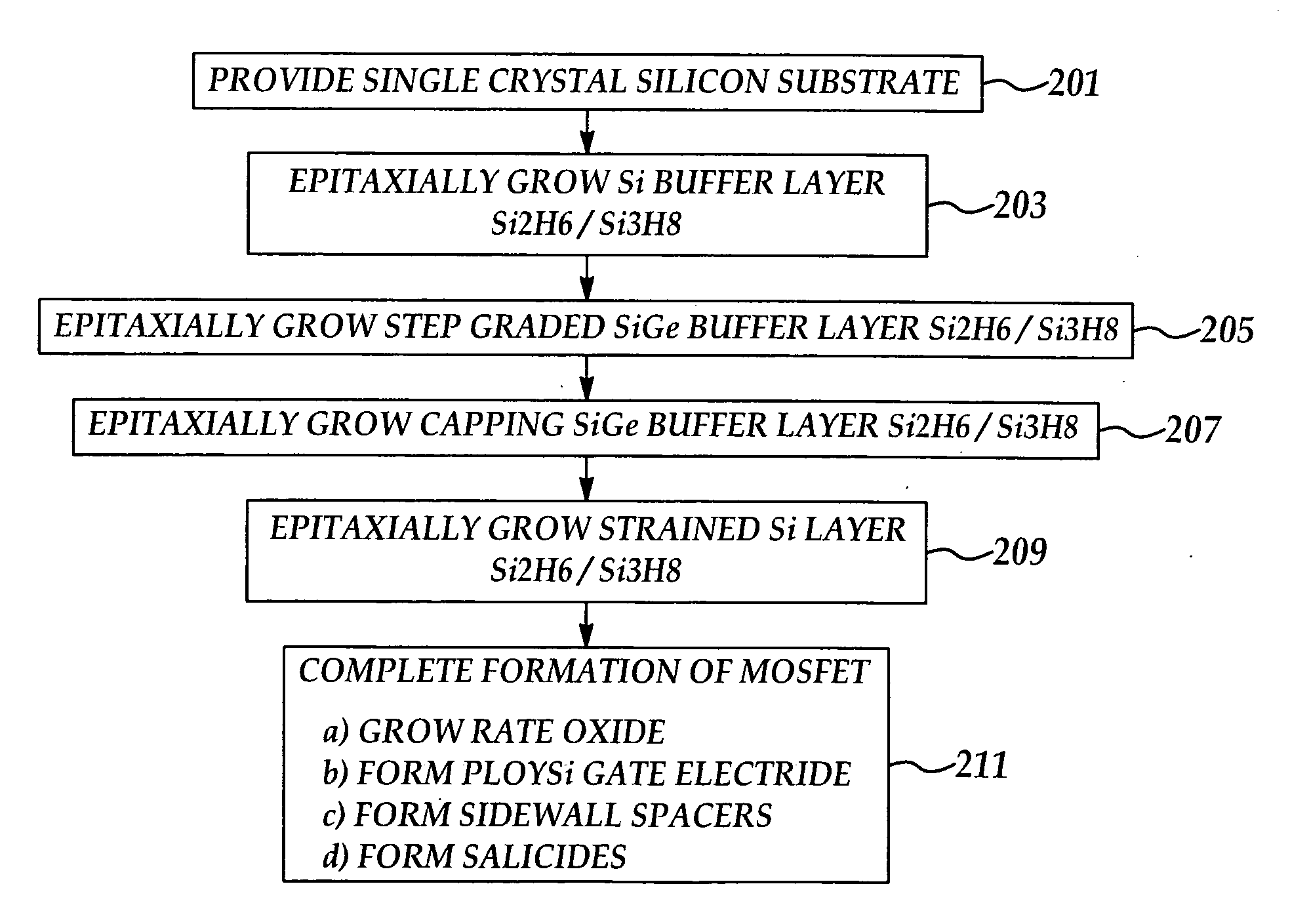

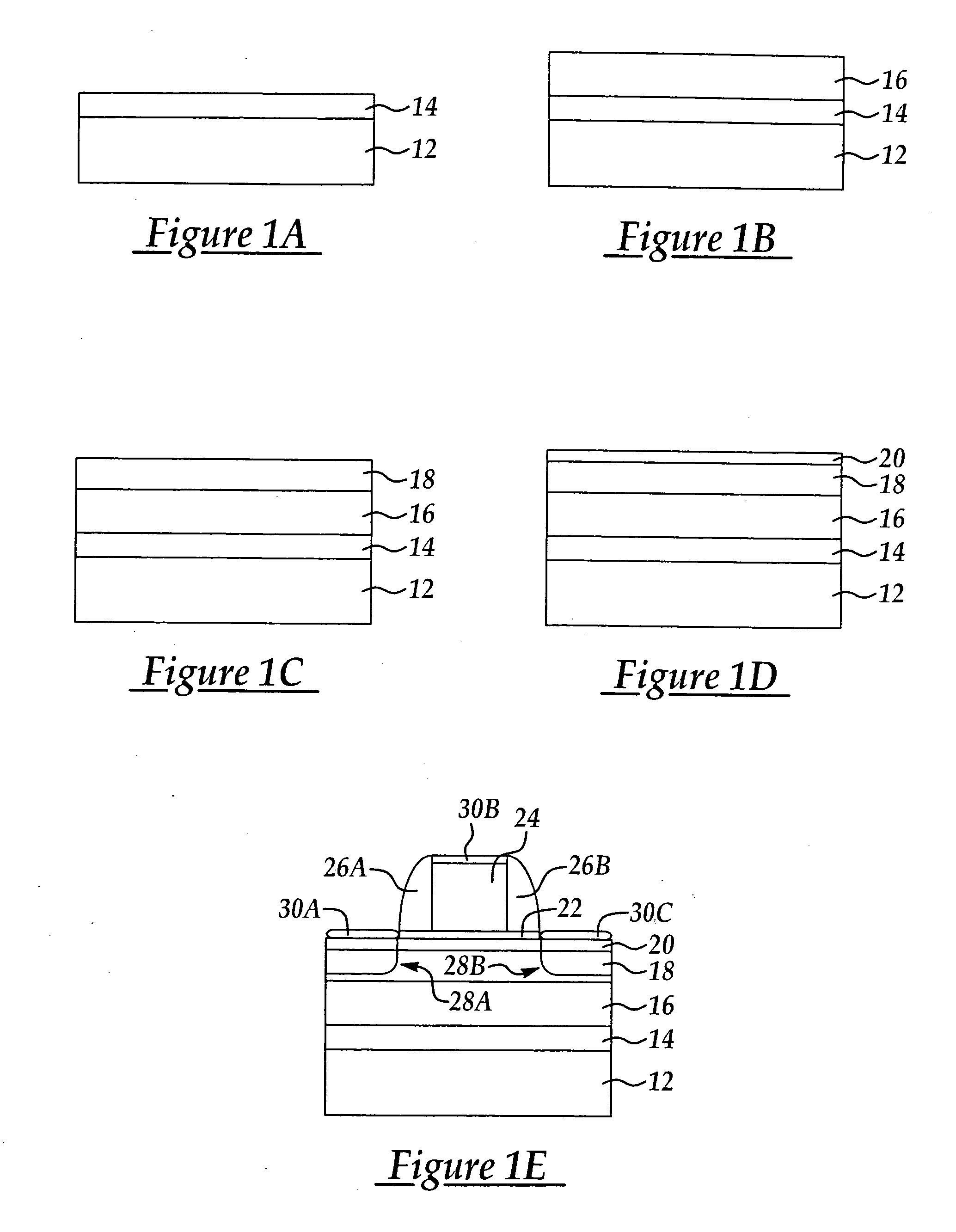

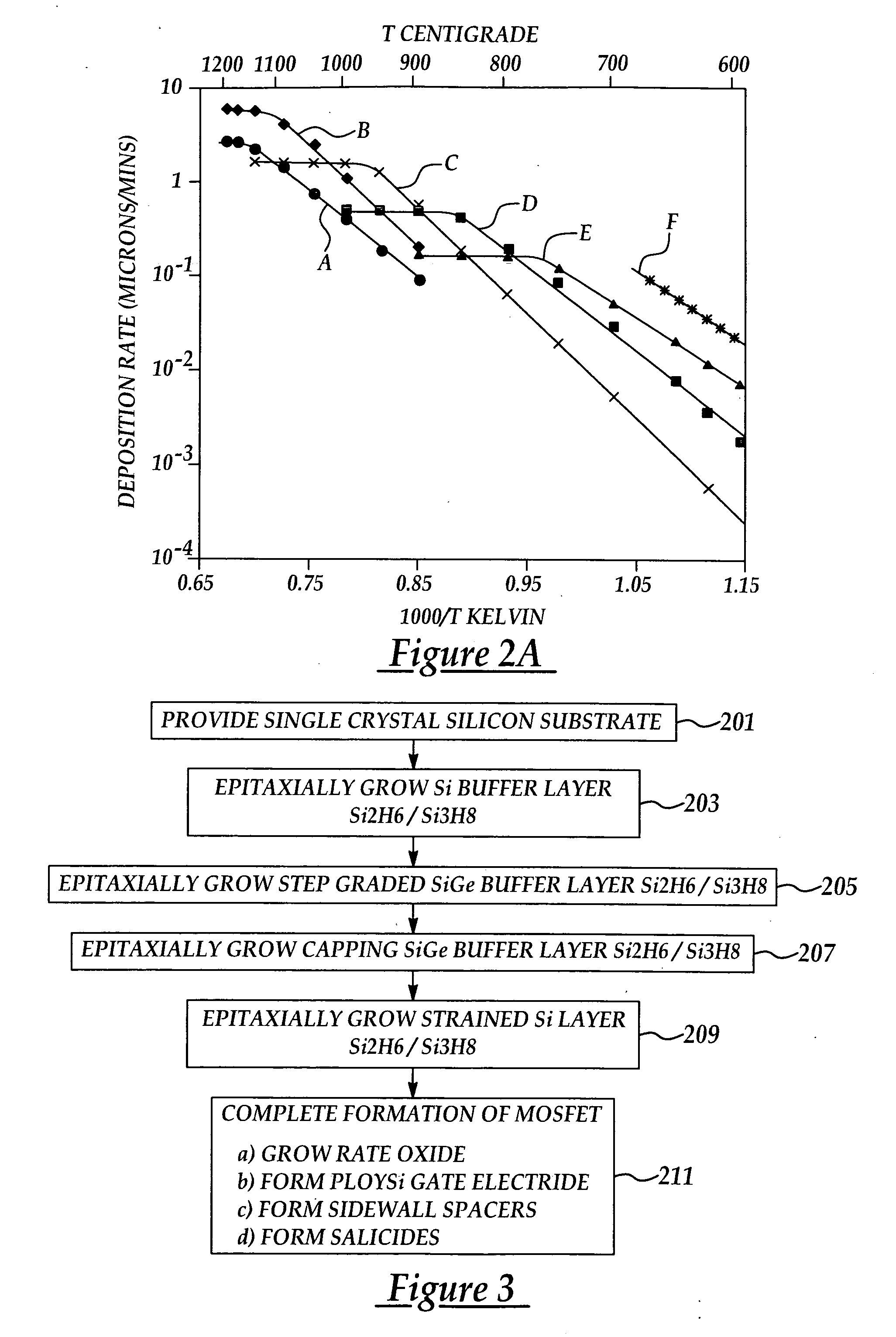

Method for producing high throughput strained-si channel mosfets

InactiveUS20050245058A1Improve throughputReduce defect densityPolycrystalline material growthFrom solid stateSilanesMaterials science

A method for forming a strained silicon layer device with improved wafer throughput and low defect density including providing a silicon substrate; epitaxially growing a first silicon layer using at least one deposition precursor selected from the group consisting of disilane and trisilane; epitaxially growing a step-grade SiGe buffer layer over and contacting the first silicon layer using at least one deposition precursor selected from the group consisting of disilane and trisilane; epitaxially growing a SiGe capping layer over and contacting the step-grade SiGe buffer layer using at least one deposition precursor selected from the group consisting of disilane and trisilane; and, epitaxially growing a second silicon layer using at least one deposition precursor selected from the group consisting of disilane and silane.

Owner:TAIWAN SEMICON MFG CO LTD

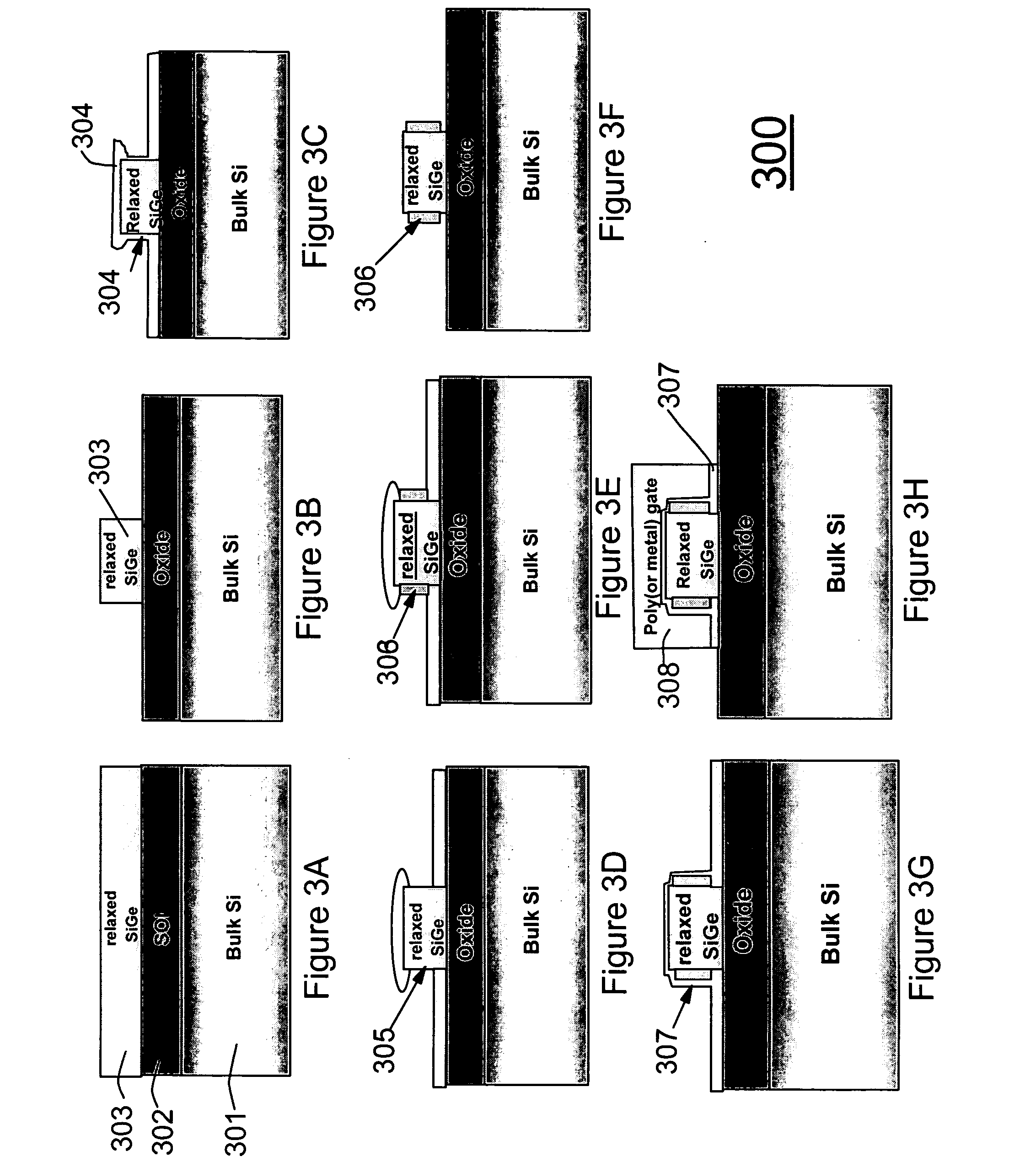

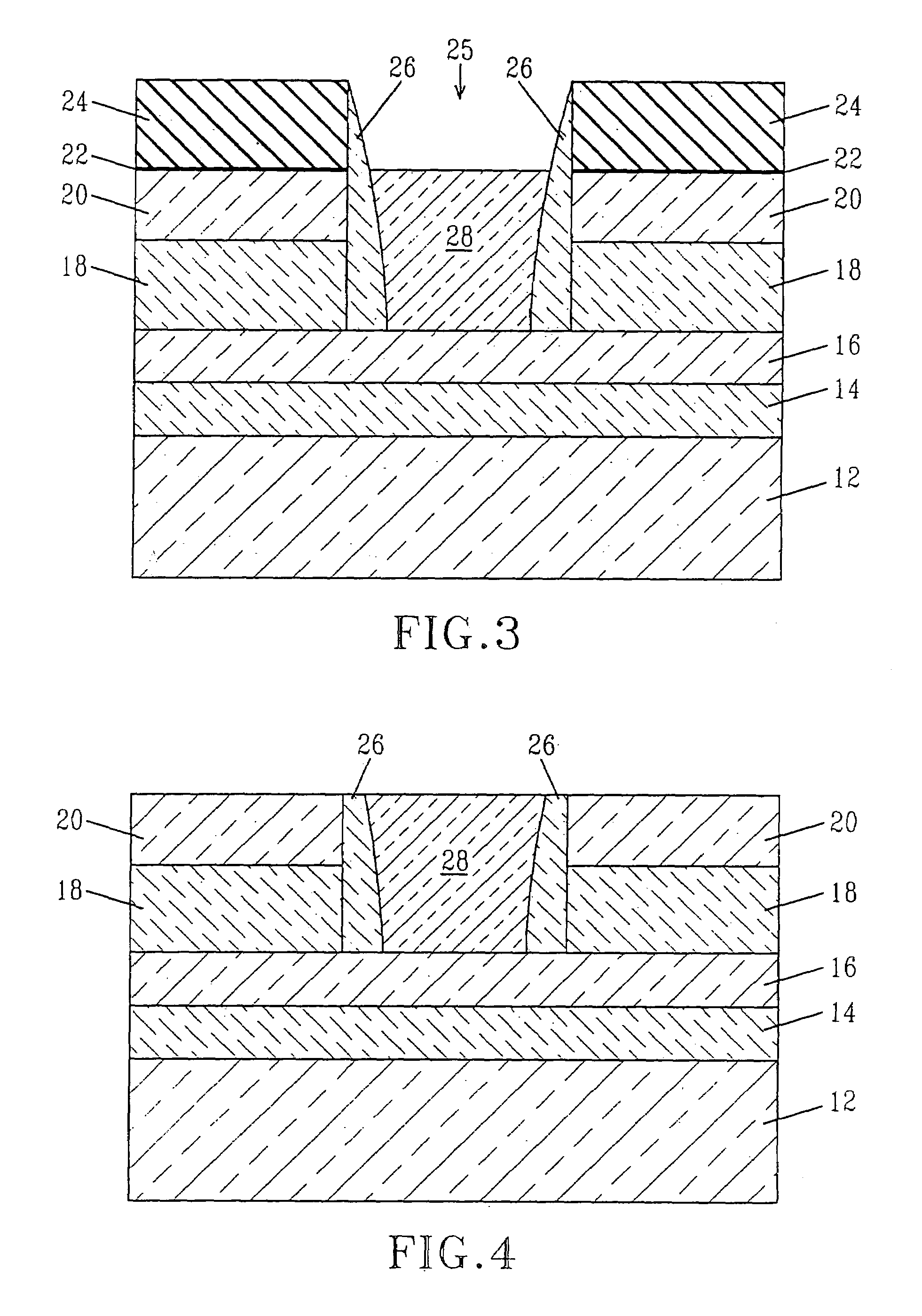

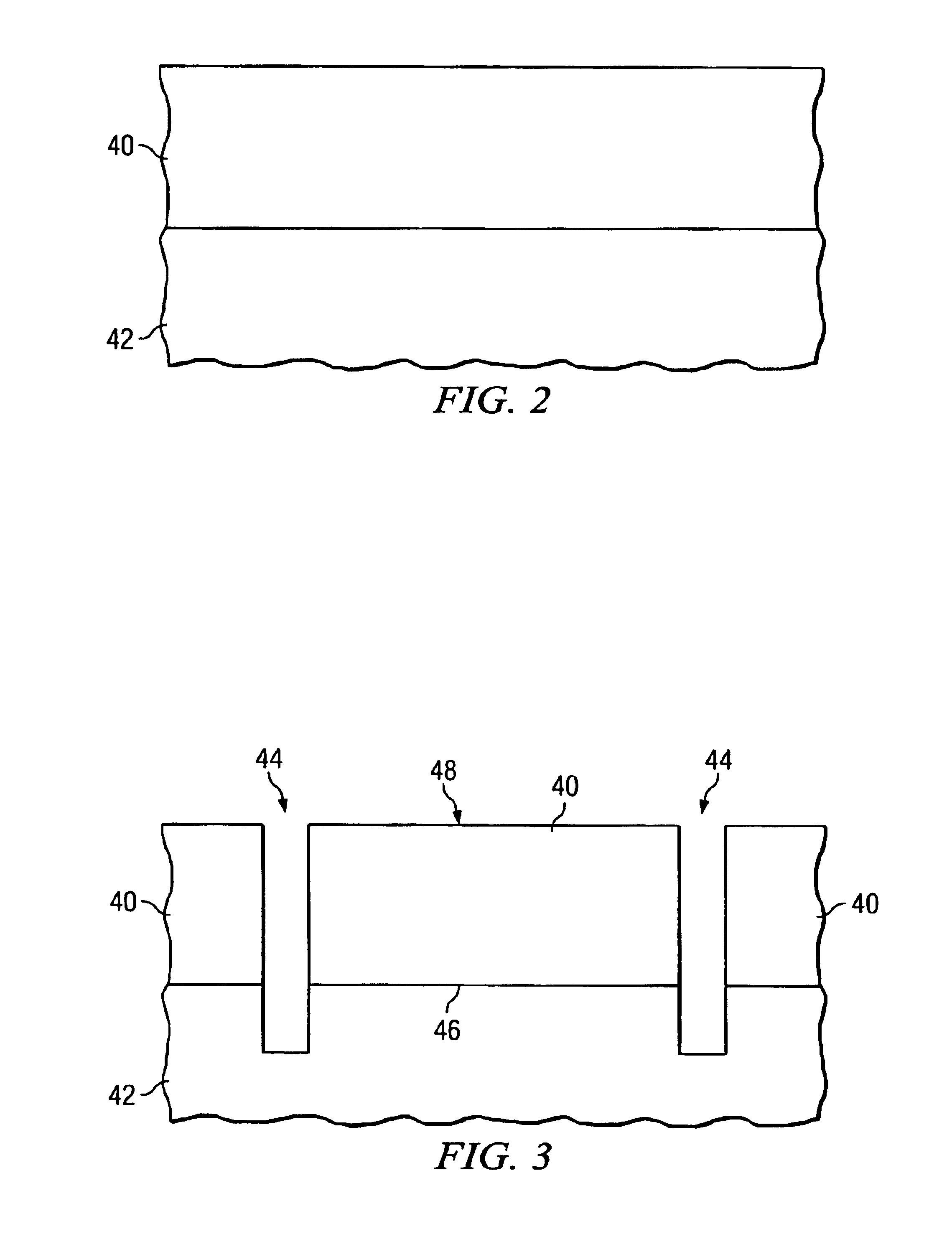

Method to fabricate a strained Si CMOS structure using selective epitaxial deposition of Si after device isolation formation

InactiveUS6429061B1Thickness minimizationTransistorSemiconductor/solid-state device manufacturingCMOSMOSFET

A strained Si CMOS structure is formed by steps which include forming a relaxed SiGe layer on a surface of a substrate; forming isolation regions and well implant regions in said relaxed SiGe layer; and forming a strained Si layer on said relaxed SiGe layer. These processing steps may be used in conjunction with conventional gate processing steps in forming a strained MOSFET structure.

Owner:SAMSUNG ELECTRONICS CO LTD

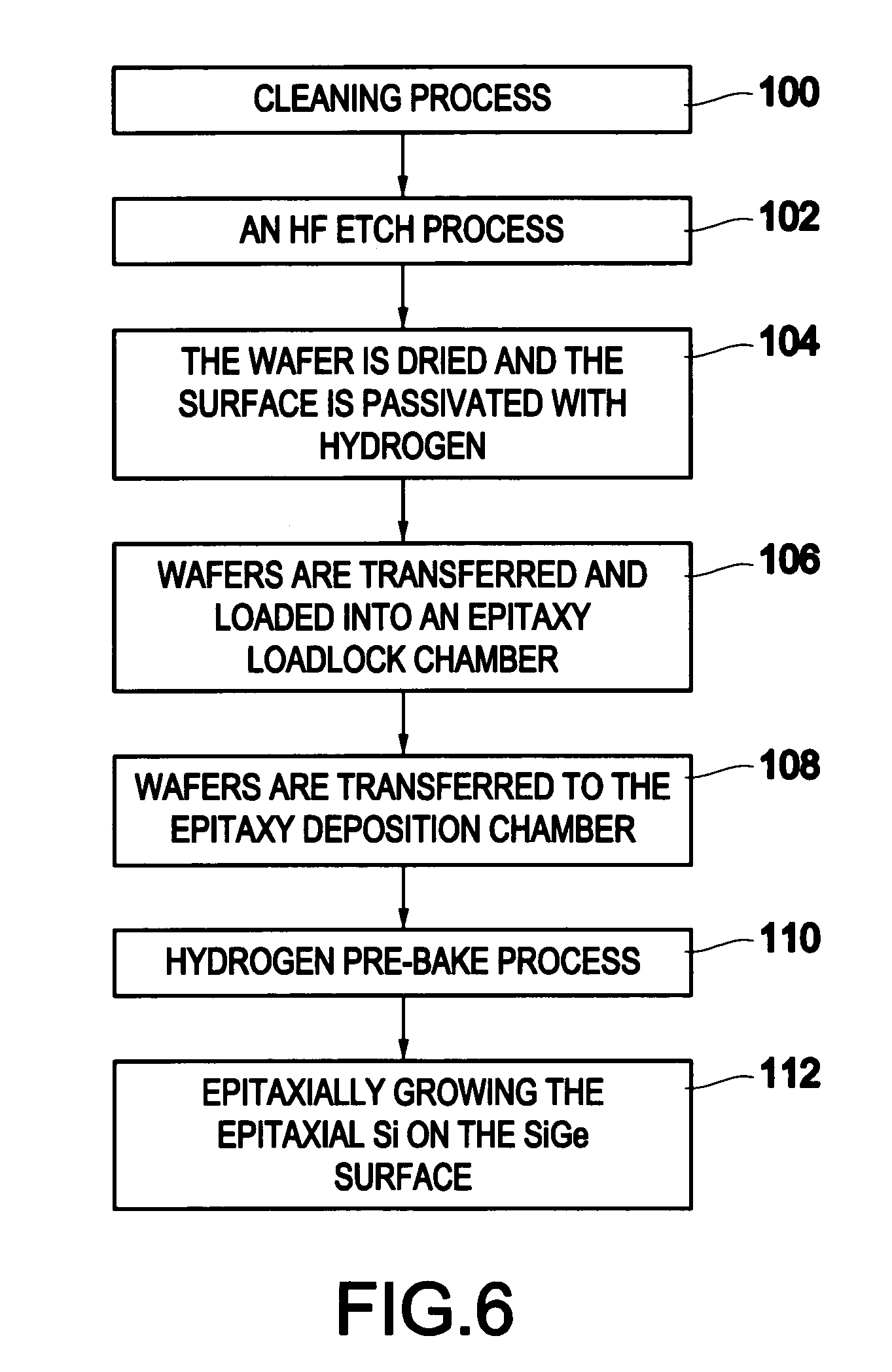

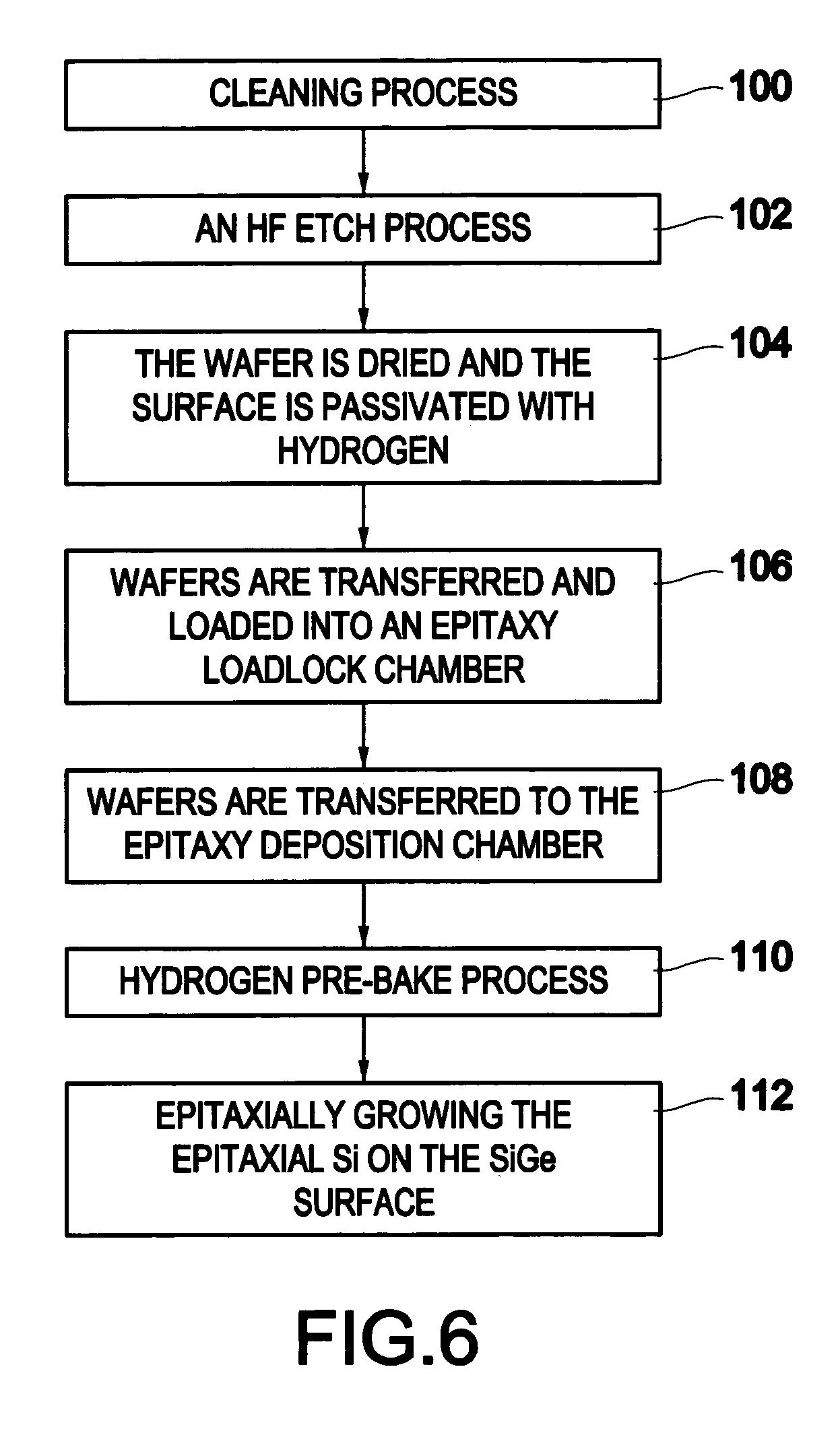

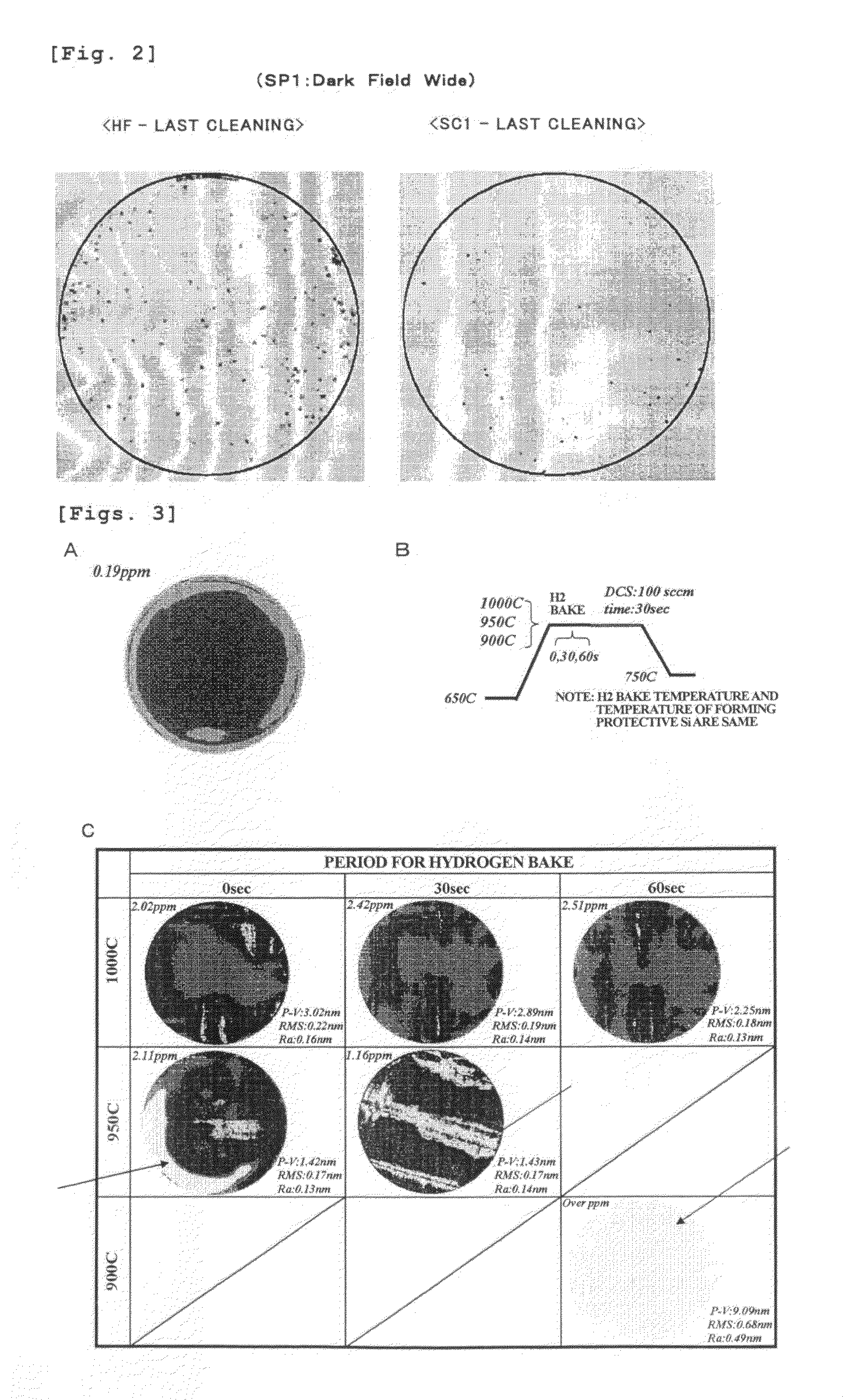

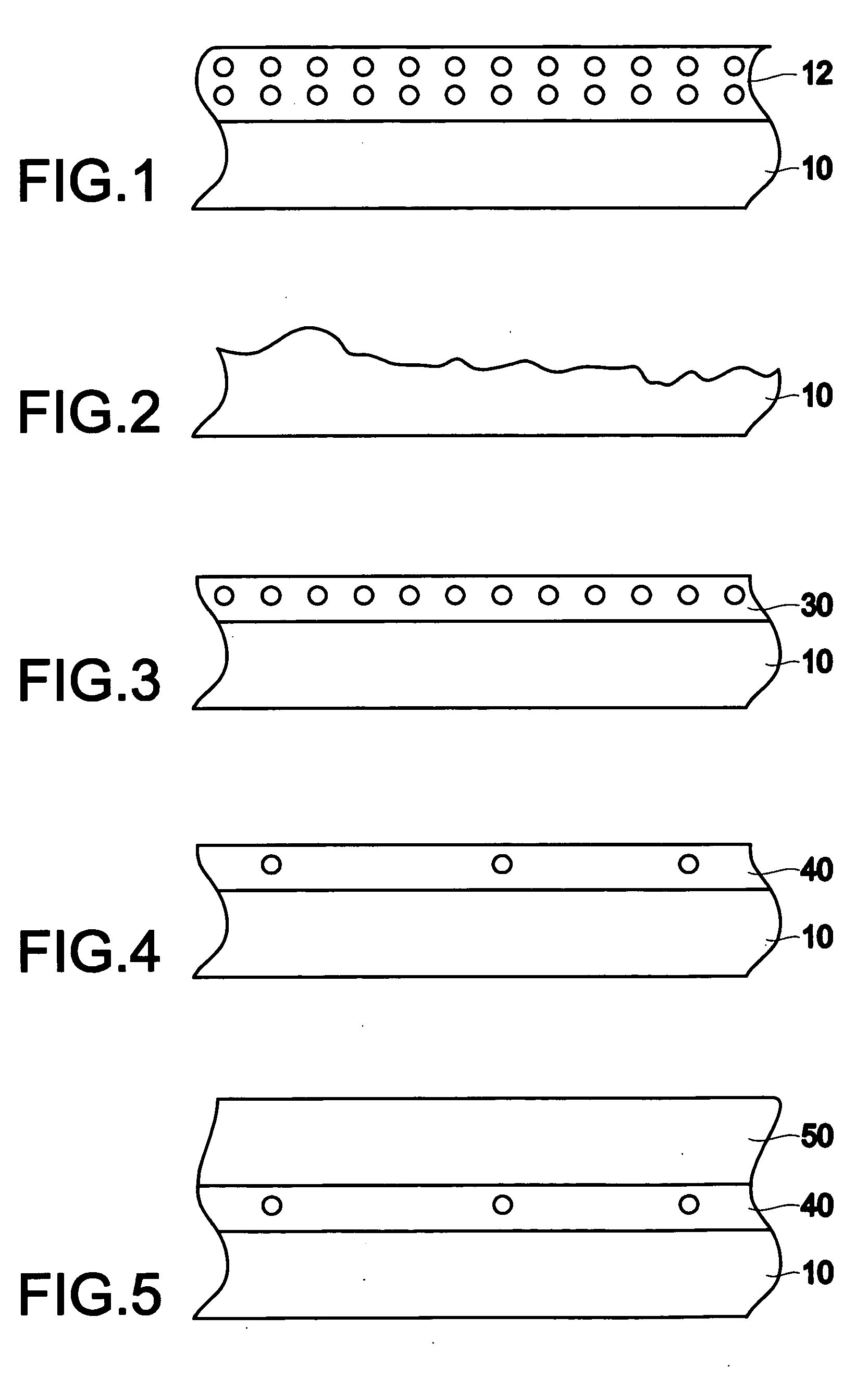

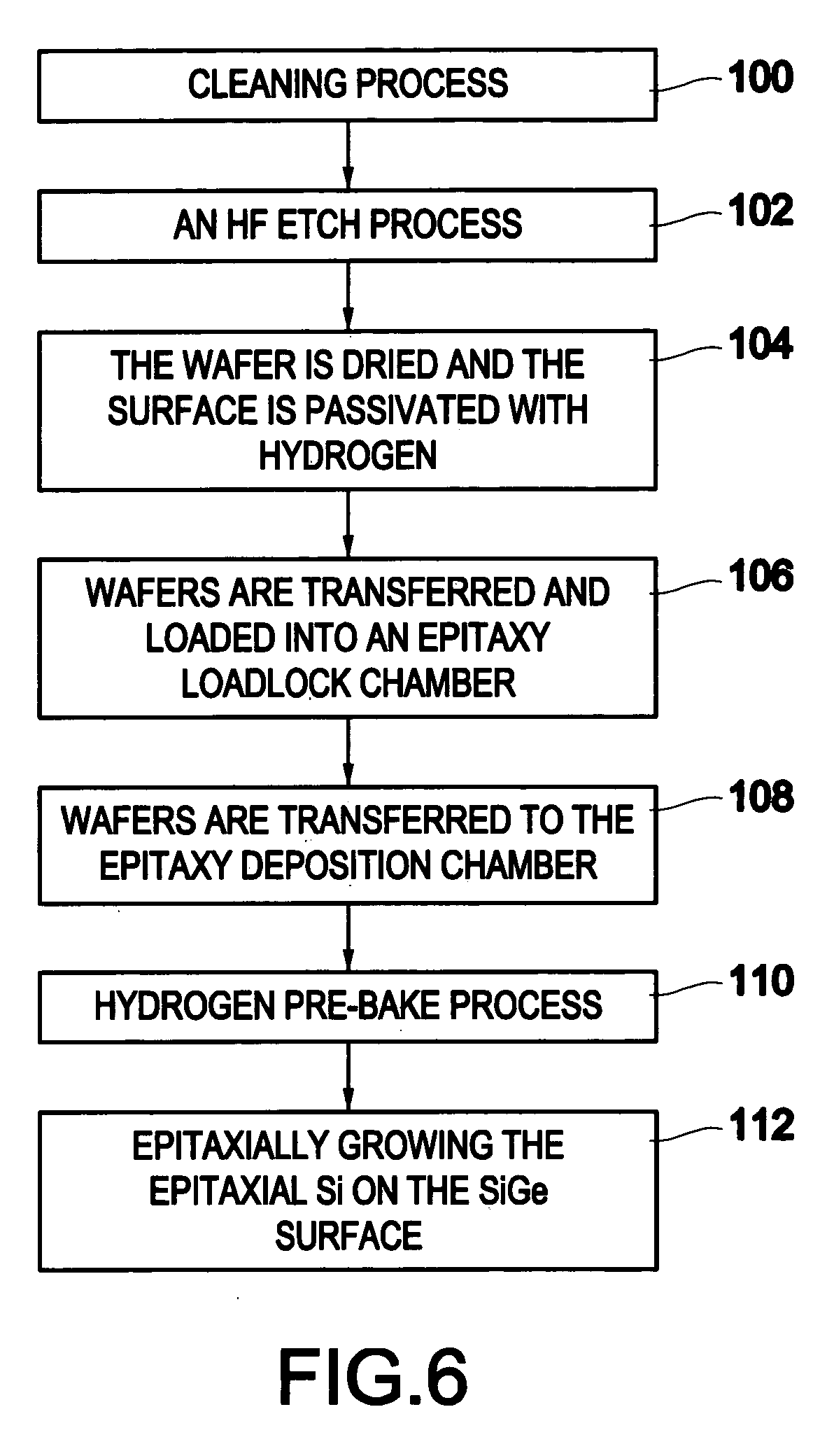

Method of preventing surface roughening during hydrogen pre-bake of SiGe substrates using chlorine containing gases

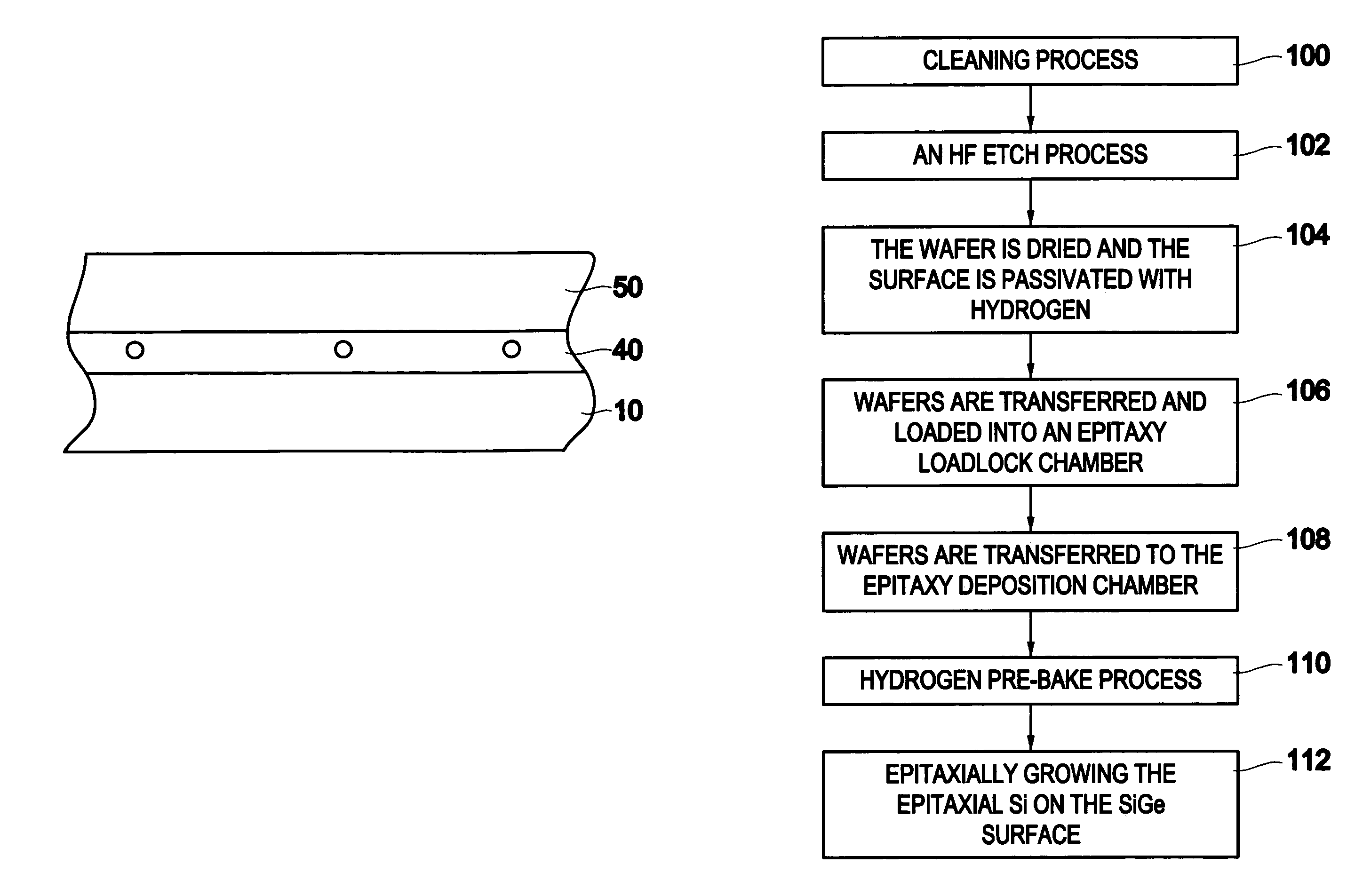

InactiveUS20050148162A1Prevent surfaceAvoid creatingPolycrystalline material growthSemiconductor/solid-state device manufacturingPartial oxidationSilicon on insulator

The invention forms an epitaxial silicon-containing layer on a silicon germanium, patterned strained silicon, or patterned thin silicon-on-insulator surface and avoids creating a rough surface upon which the epitaxial silicon-containing layer is grown. In order to avoid creating the rough surface, the invention first performs a hydrofluoric acid etching process on the silicon germanium, patterned strained silicon, or patterned thin silicon-on-insulator surface. This etching process removes most of oxide from the surface, and leaves only a sub-monolayer of oxygen (typically 1×1013-1×1015 / cm2 of oxygen) at the silicon germanium, patterned strained silicon, or patterned thin silicon-on-insulator surface. The invention then performs a hydrogen pre-bake process in a chlorine containing environment which heats the silicon germanium, strained silicon, or thin silicon-on-insulator surface sufficiently to remove the remaining oxygen from the surface. By introducing a small amount of chlorine containing gases, the heating processes avoid changing the roughness of the silicon germanium, patterned strained silicon, or patterned thin silicon-on-insulator surface. Then the process of epitaxially growing the epitaxial silicon-containing layer on the silicon germanium, patterned strained silicon, or patterned silicon-on-insulator surface is performed.

Owner:IBM CORP

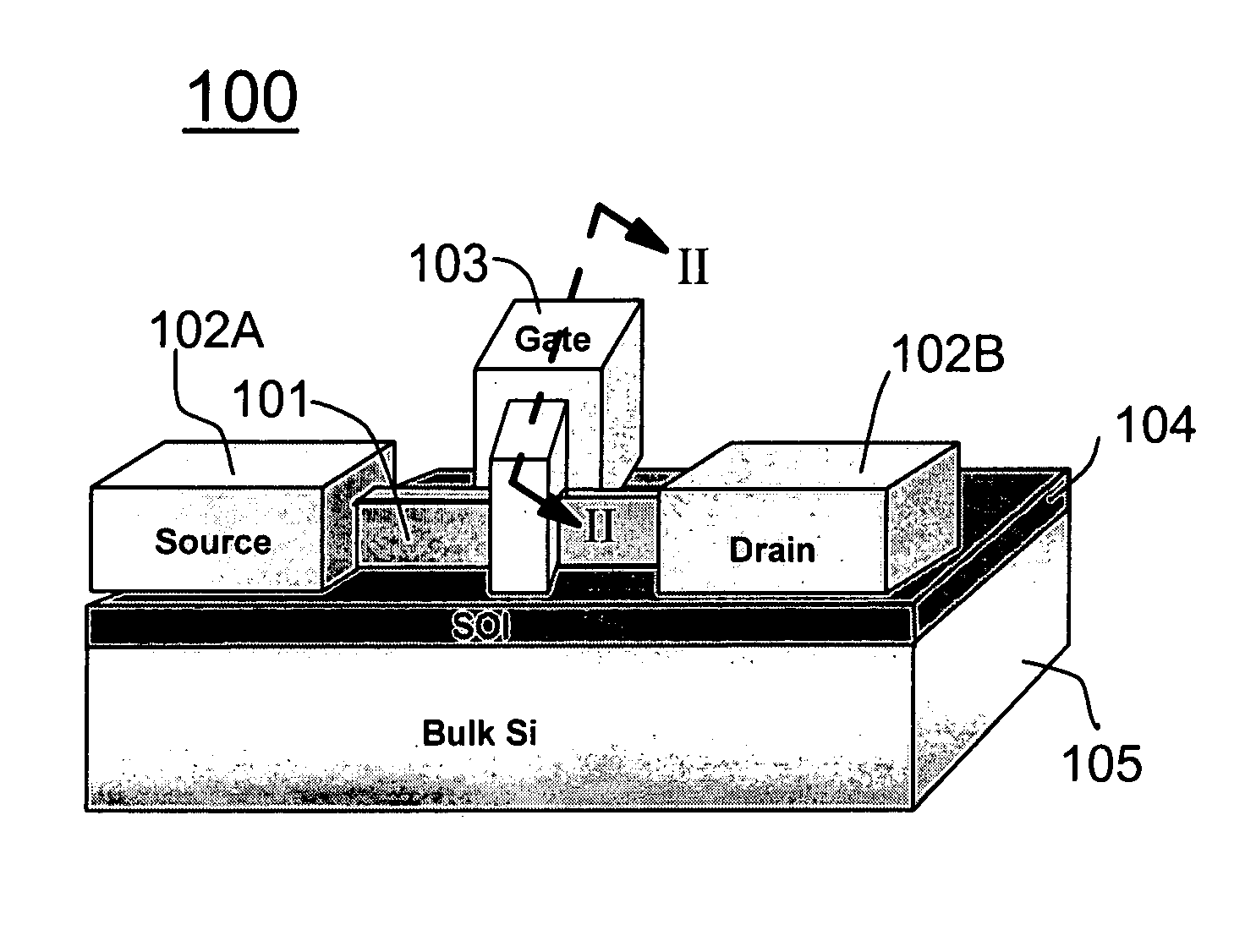

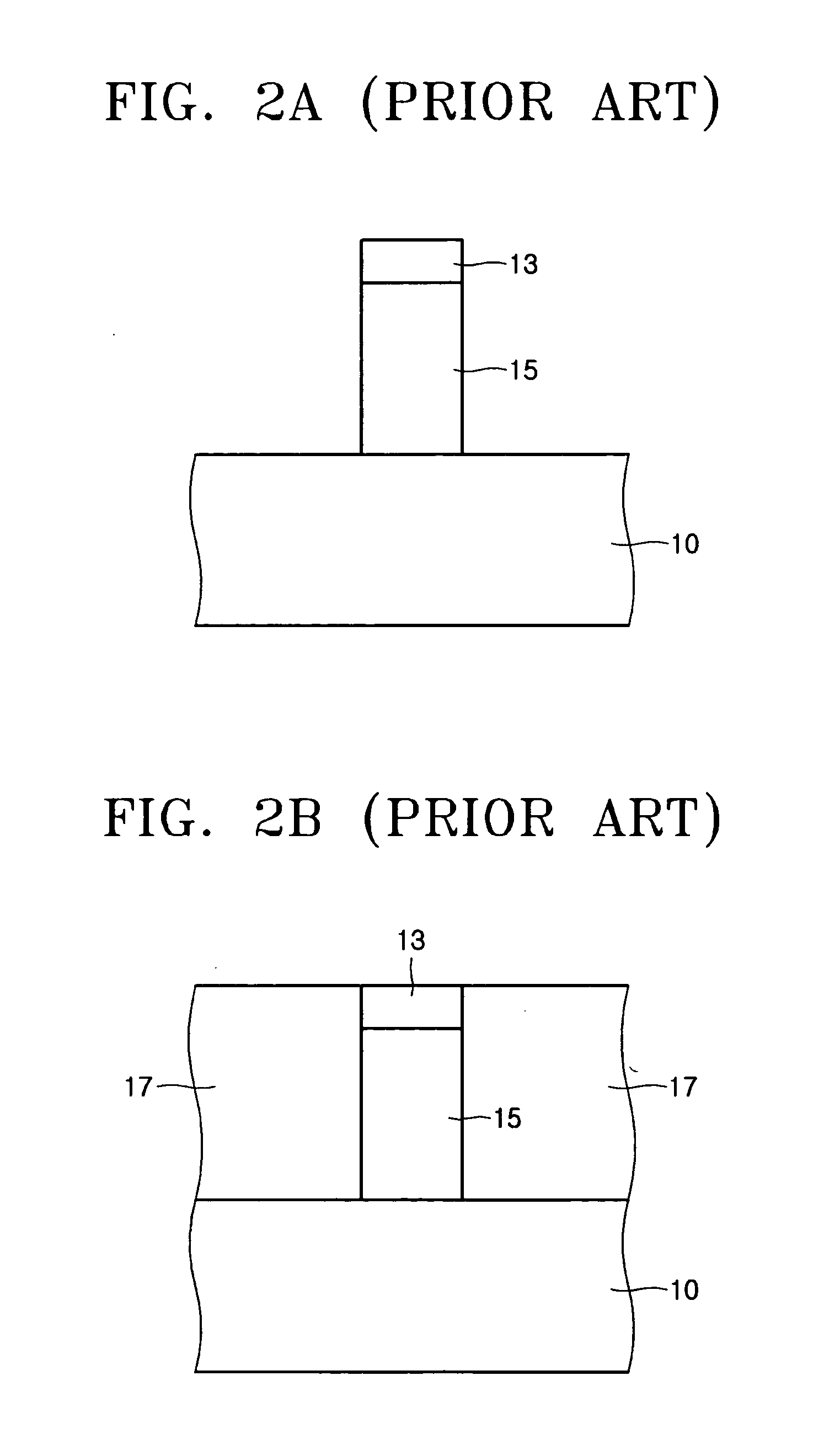

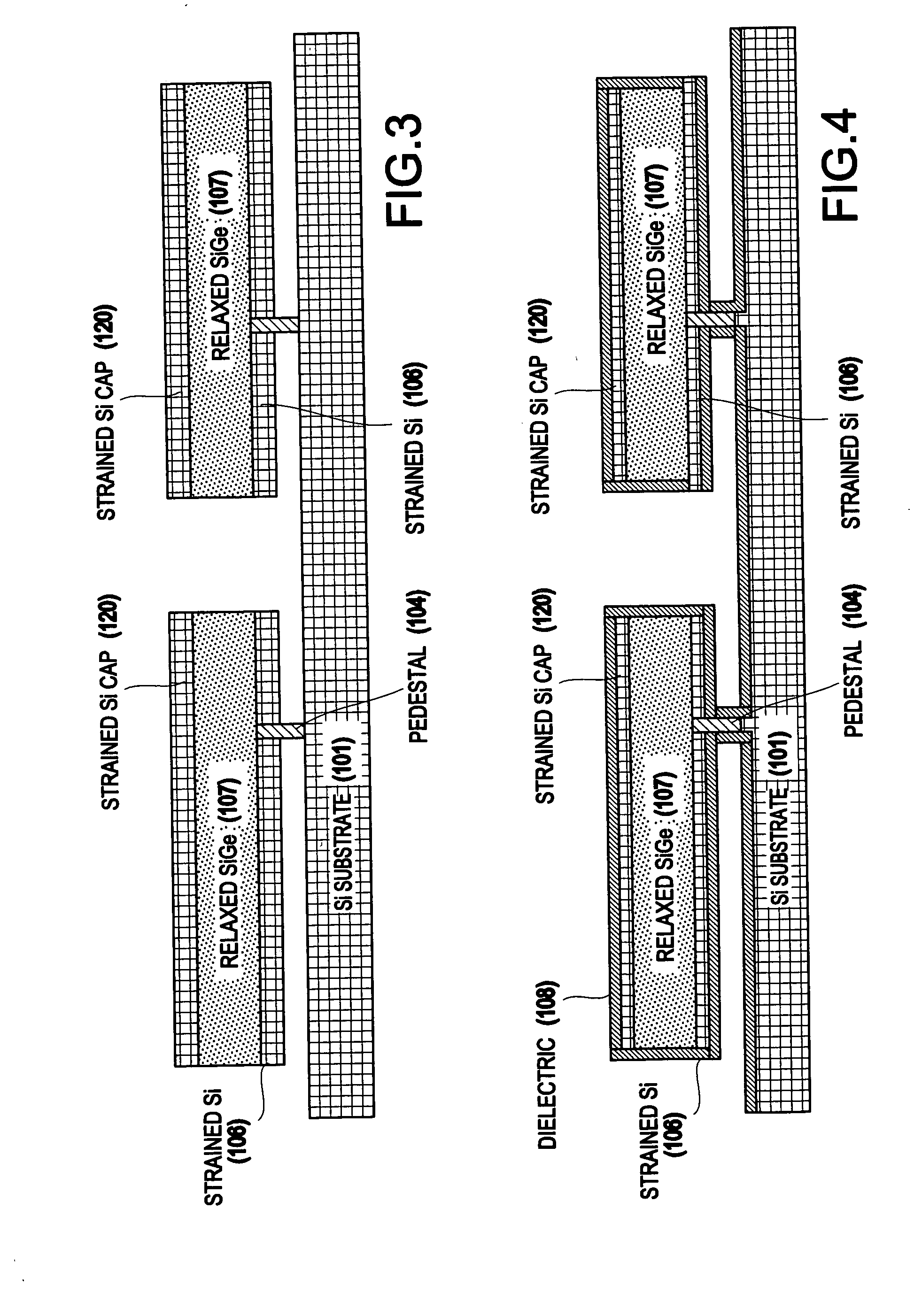

High performance strained silicon FinFETs device and method for forming same

ActiveUS20050145941A1Improve channel mobilityImprove device performanceTransistorSolid-state devicesSiliconMaterials science

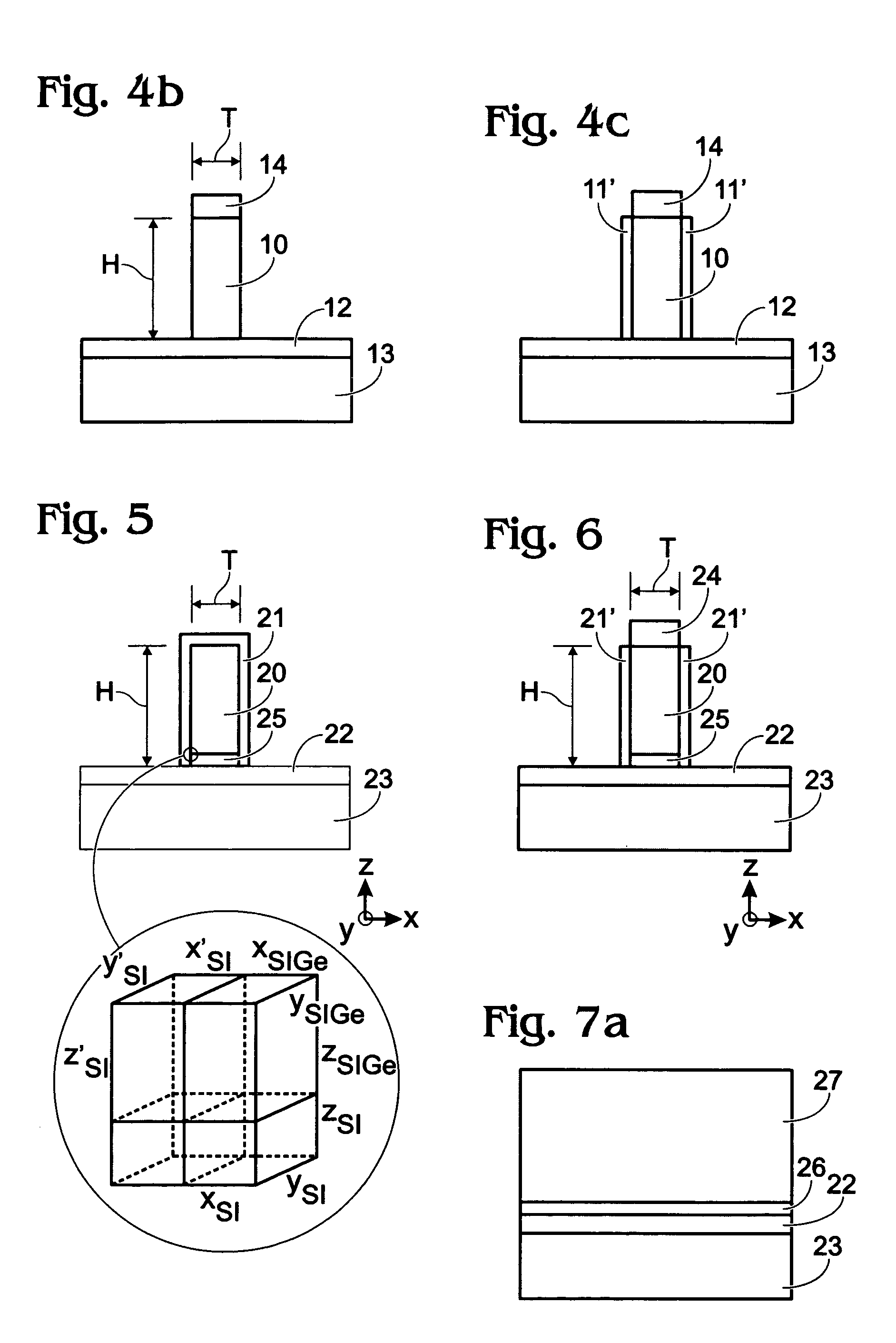

A strained Fin Field Effect Transistor (FinFET) (and method for forming the same) includes a relaxed first material having a sidewall, and a strained second material formed on the sidewall of the first material. The relaxed first material and the strained second material form a fin of the FinFET.

Owner:GLOBALFOUNDRIES US INC

Multiple gate semiconductor device and method for forming same

In accordance with an embodiment of the invention, a FinFET device is disclosed which comprises a strained silicon channel layer formed on, at least, the sidewalls of a strain-relaxed silicon-germanium body.

Owner:INTERUNIVERSITAIR MICRO ELECTRONICS CENT (IMEC VZW)

Strained silicon fin structure

InactiveUS20060113522A1Suppression of short channel effectsIncrease currentTransistorSemiconductor/solid-state device manufacturingDriving currentLattice mismatch

Disclosing is a strained silicon finFET device having a strained silicon fin channel in a double gate finFET structure. The disclosed finFET device is a double gate MOSFET consisting of a silicon fin channel controlled by a self-aligned double gate for suppressing short channel effect and enhancing drive current. The silicon fin channel of the disclosed finFET device is a strained silicon fin channel, comprising a strained silicon layer deposited on a seed fin having different lattice constant, for example, a silicon layer deposited on a silicon germanium seed fin, or a carbon doped silicon layer deposited on a silicon seed fin. The lattice mismatch between the silicon layer and the seed fin generates the strained silicon fin channel in the disclosed finFET device to improve hole and electron mobility enhancement, in addition to short channel effect reduction characteristic inherently in a finFET device.

Owner:MICROSOFT TECH LICENSING LLC +1

Method of preventing surface roughening during hydrogen prebake of SiGe substrates

InactiveUS6958286B2Polycrystalline material growthSemiconductor/solid-state device manufacturingRough surfaceHydrofluoric acid

The invention forms an epitaxial silicon-containing layer on a silicon germanium, patterned strained silicon, or patterned thin silicon-on-insulator surface and avoids creating a rough surface upon which the epitaxial silicon-containing layer is grown. In order to avoid creating the rough surface, the invention first performs a hydrofluoric acid etching process on the silicon germanium, patterned strained silicon, or patterned thin silicon-on-insulator surface. This etching process removes most of oxide from the surface, and leaves a first amount of oxygen (typically 1×1013−1×1015 / cm2 of oxygen) on the silicon germanium, patterned strained silicon, or patterned thin silicon-on-insulator surface. The invention then performs a hydrogen pre-bake process which heats the silicon germanium, patterned strained silicon, or patterned thin silicon-on-insulator surface sufficiently to remove additional oxygen from the surface and leave a second amount of oxygen, less than the first amount, on the silicon germanium, patterned strained silicon, or patterned thin silicon-on-insulator surface. The heating process leaves an amount of at least 5×1012 / cm2 of oxygen (typically, between approximately 1×1013 / cm2 and approximately 5×1013 / cm2 of oxygen) on the silicon germanium, patterned strained silicon, or patterned thin silicon-on-insulator surface. By leaving a small amount of oxygen on the silicon germanium, patterned strained silicon, or patterned silicon-on-insulator surface, the heating processes avoid changing the roughness of the silicon germanium, patterned strained silicon, or patterned thin silicon-on-insulator surface. Then the process of epitaxially growing the epitaxial silicon-containing layer on the silicon germanium, patterned strained silicon, or patterned silicon-on-insulator surface is performed.

Owner:INT BUSINESS MASCH CORP

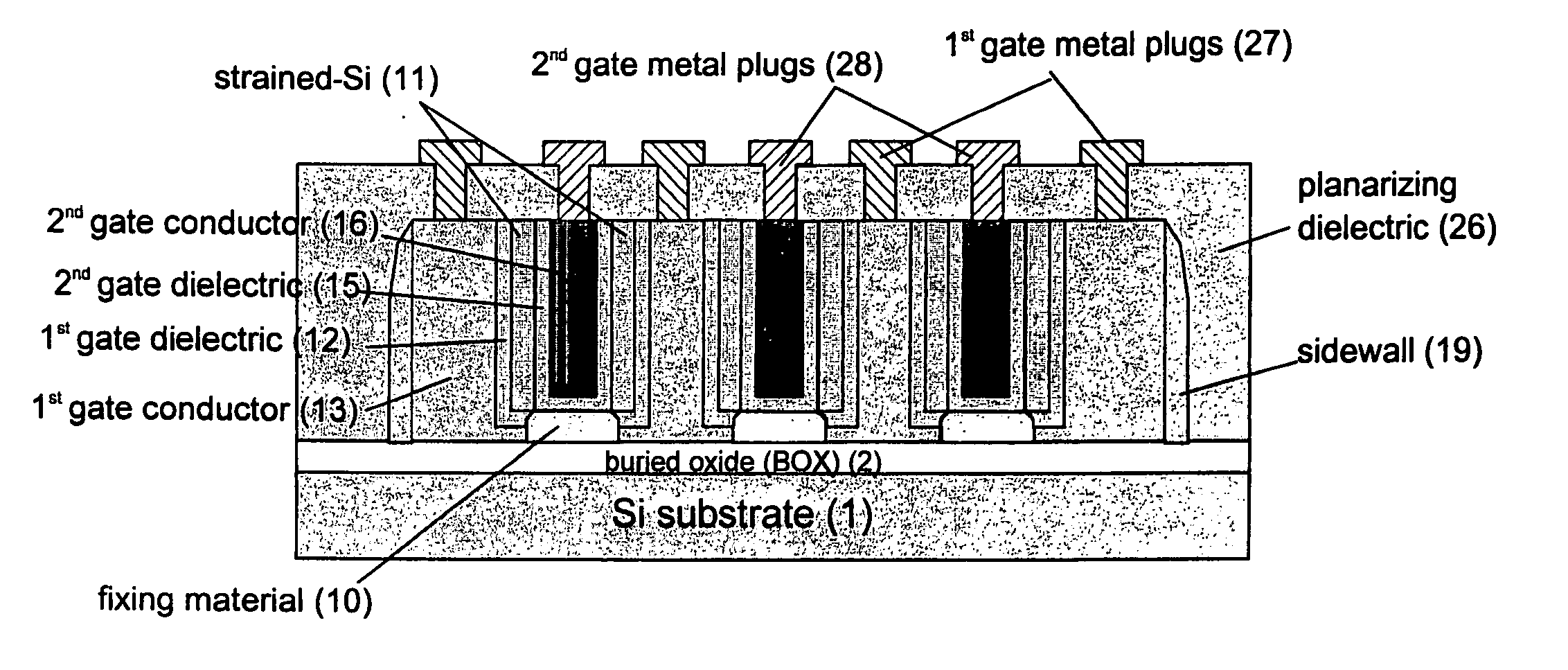

Strained-channel fin field effect transistor (FET) with a uniform channel thickness and separate gates

A semiconductor device (and method for making the same) includes a strained-silicon channel formed adjacent a source and a drain, a first gate formed over a first side of the channel, a second gate formed over a second side of the channel, a first gate dielectric formed between the first gate and the strained-silicon channel, and a second gate dielectric formed between the second gate and the strained-silicon channel. The strained-silicon channel is non-planar.

Owner:IBM CORP

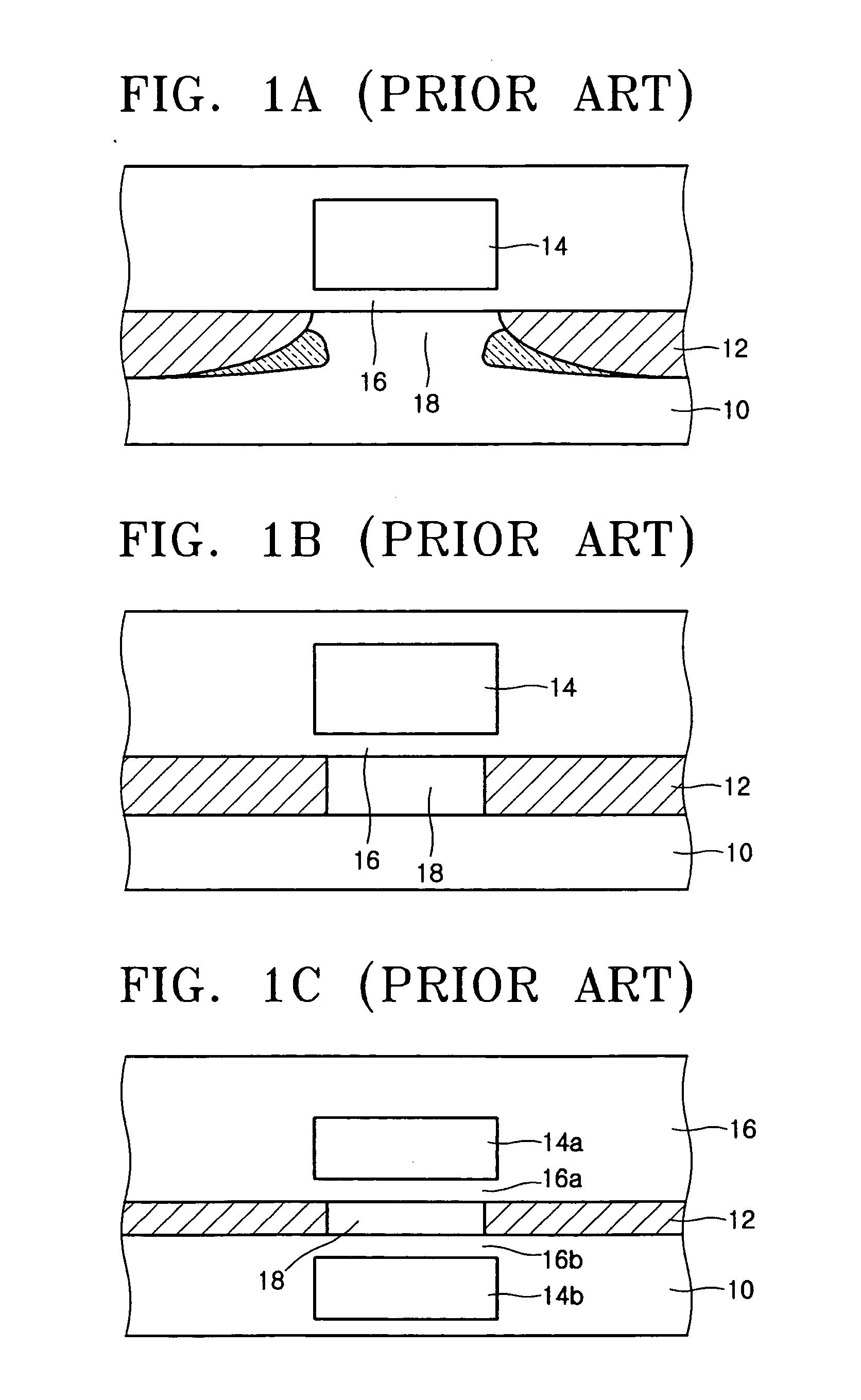

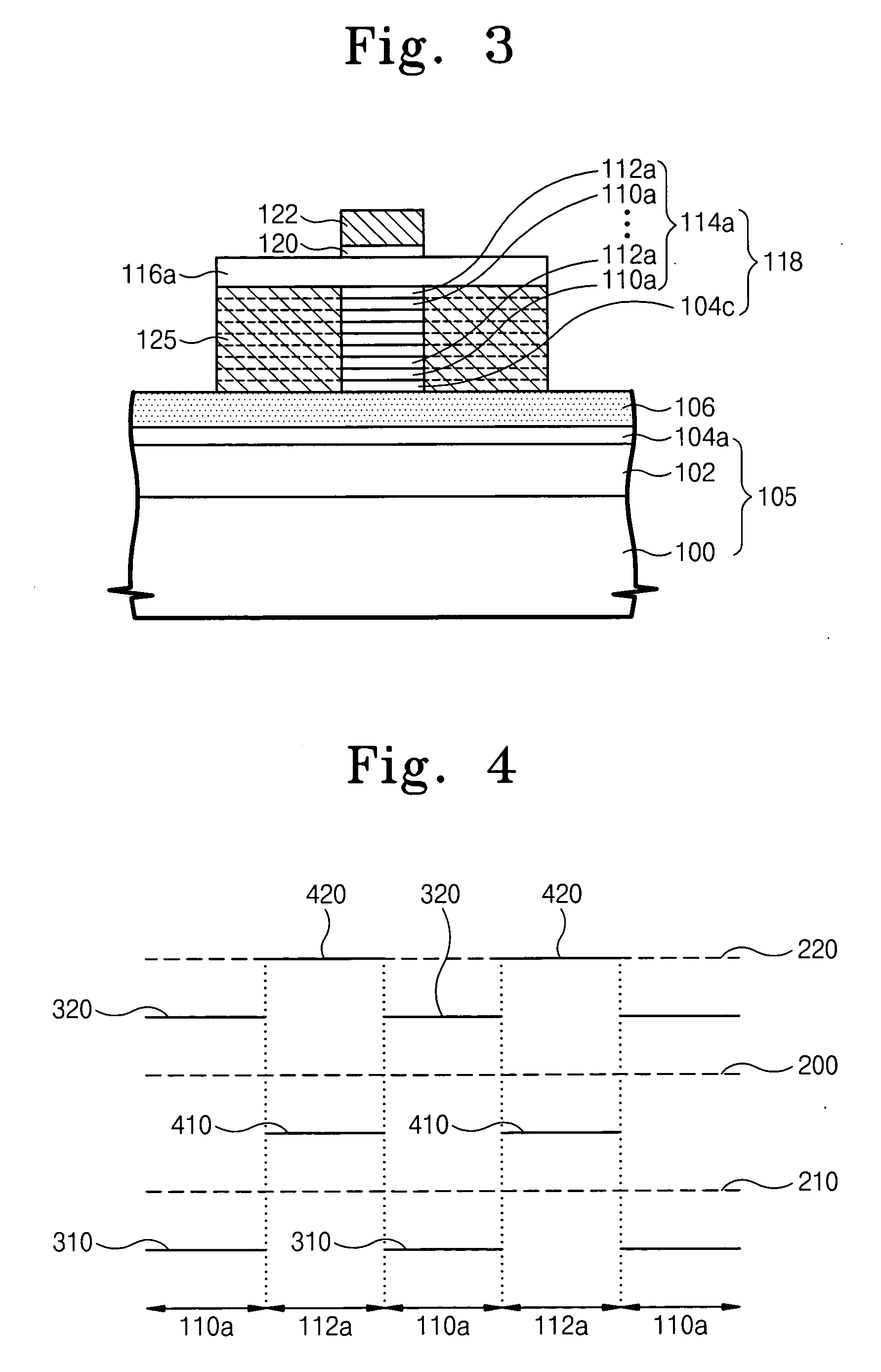

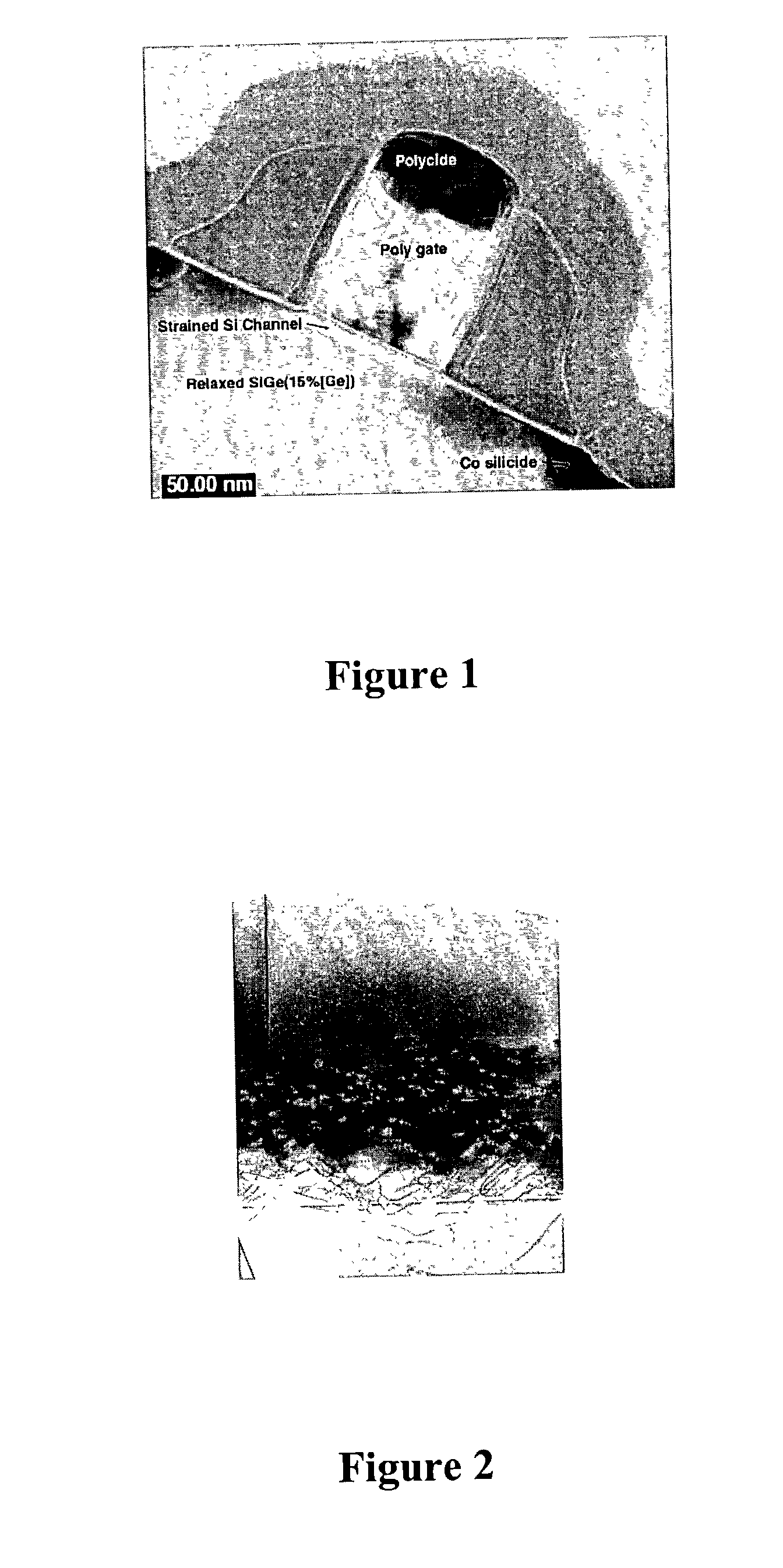

Field effect transistors having a strained silicon channel and methods of fabricating same

InactiveUS20060076625A1Solid-state devicesSemiconductor/solid-state device manufacturingEngineeringField-effect transistor

Field effect transistors (FETs) and methods of fabricating FETs that include a channel layer on sidewalls of a structure on a semiconductor substrate and having at least a portion of the channel layer strained in a direction that the sidewalls of the structure extend from the semiconductor substrate are provided. The transistor may be a FinFET, the structure on the semiconductor substrate that includes a fin structure and the sidewalls may be sidewalls of the fin structure. The channel layer may be a Si epitaxial layer and may be on an inner fin structure that includes alternating layers of SiGe and Si. The channel layer may include strained and unstrained portions. The strained and unstrained portions may be sidewalls of the channel layer.

Owner:SAMSUNG ELECTRONICS CO LTD

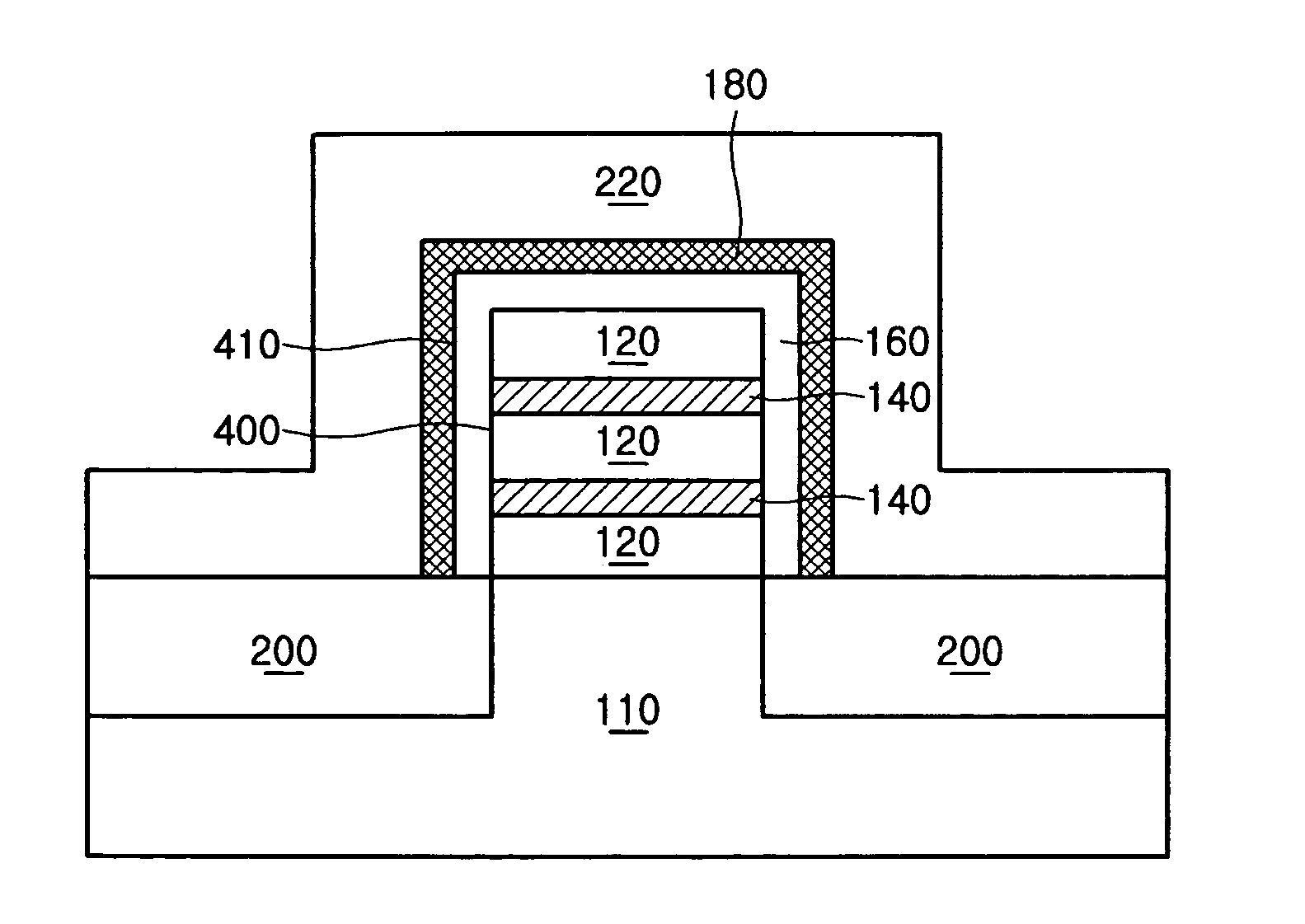

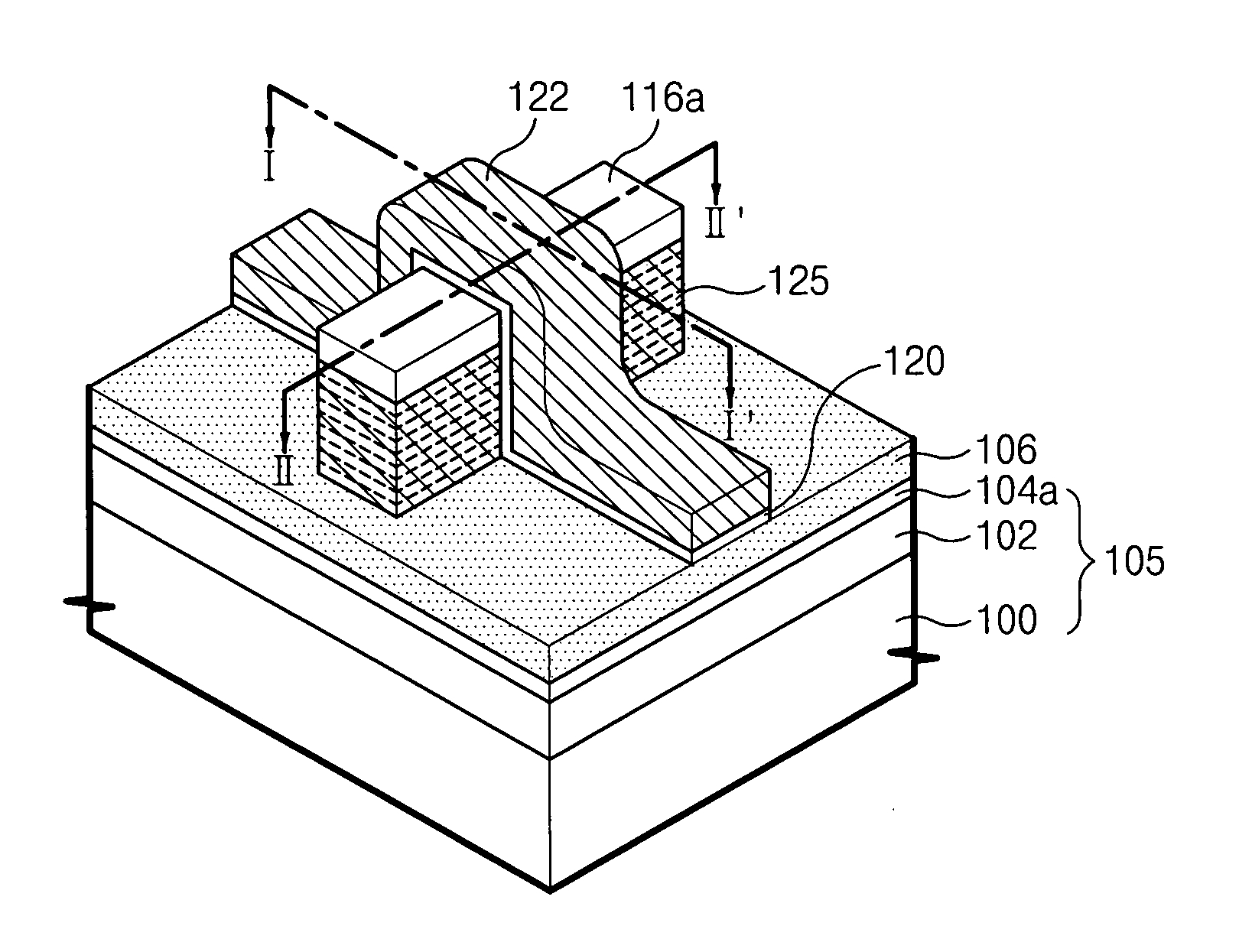

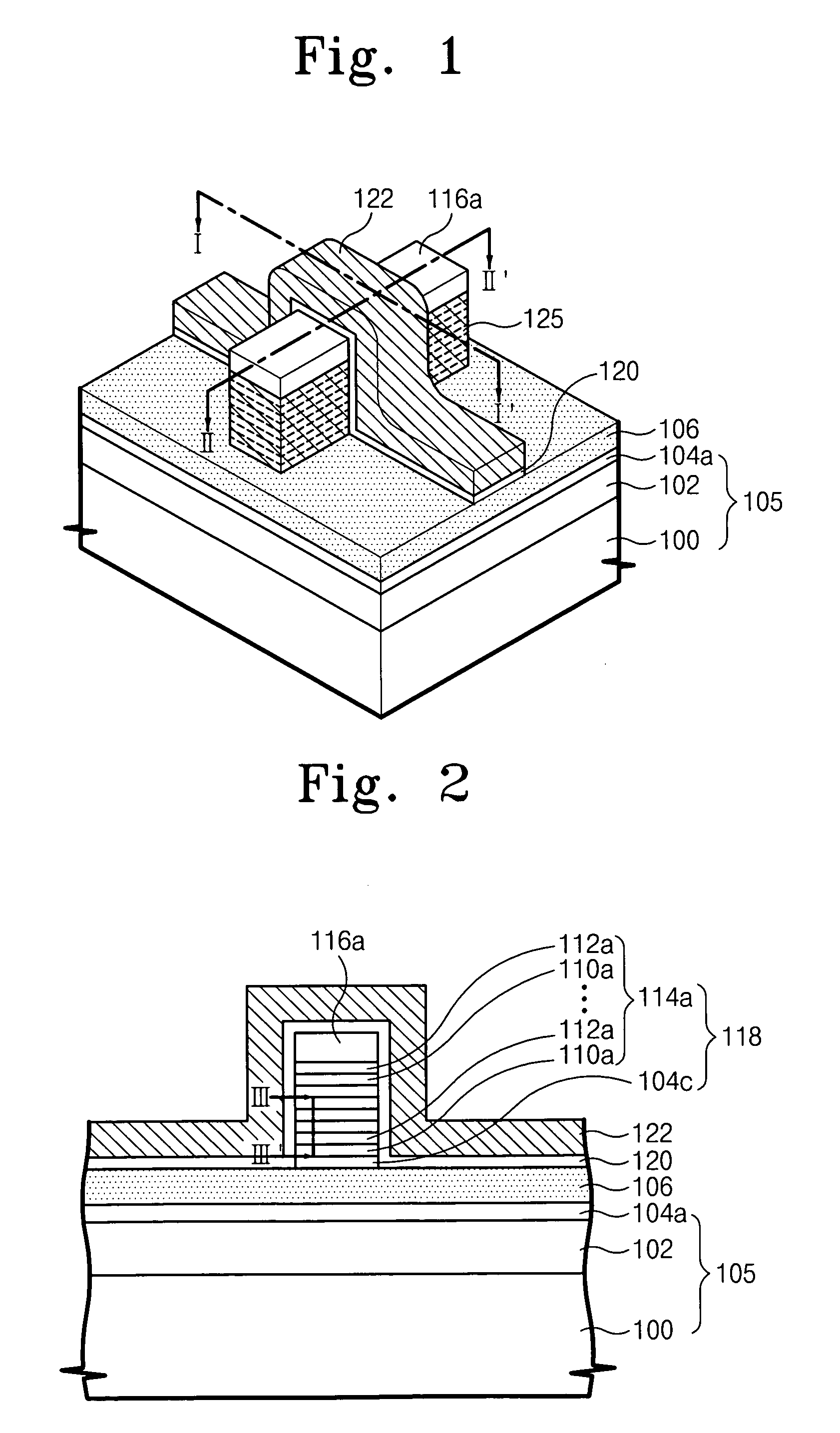

Fin field effect transistors having multi-layer fin patterns and methods of forming the same

ActiveUS20050184316A1Increase heightRelieve pressureTransistorSemiconductor/solid-state device manufacturingCarrier signalEngineering

A fin field effect transistor has a fin pattern protruding from a semiconductor substrate. The fin pattern includes first semiconductor patterns and second semiconductor patterns which are stacked. The first and second semiconductor patterns have lattice widths that are greater than a lattice width of the substrate in at least one direction. In addition, the first and second semiconductor patterns may be alternately stacked to increase the height of the fin pattern, such that one of the first and second patterns can reduce stress from the other of the first and second patterns. The first and second semiconductor patterns may be formed of strained silicon and silicon-germanium, where the silicon-germanium patterns can reduce stress from the strained silicon patterns. Therefore, both the number of carriers and the mobility of carriers in the transistor channel may be increased, improving performance of the fin field effect transistor. Related methods are also discussed.

Owner:SAMSUNG ELECTRONICS CO LTD

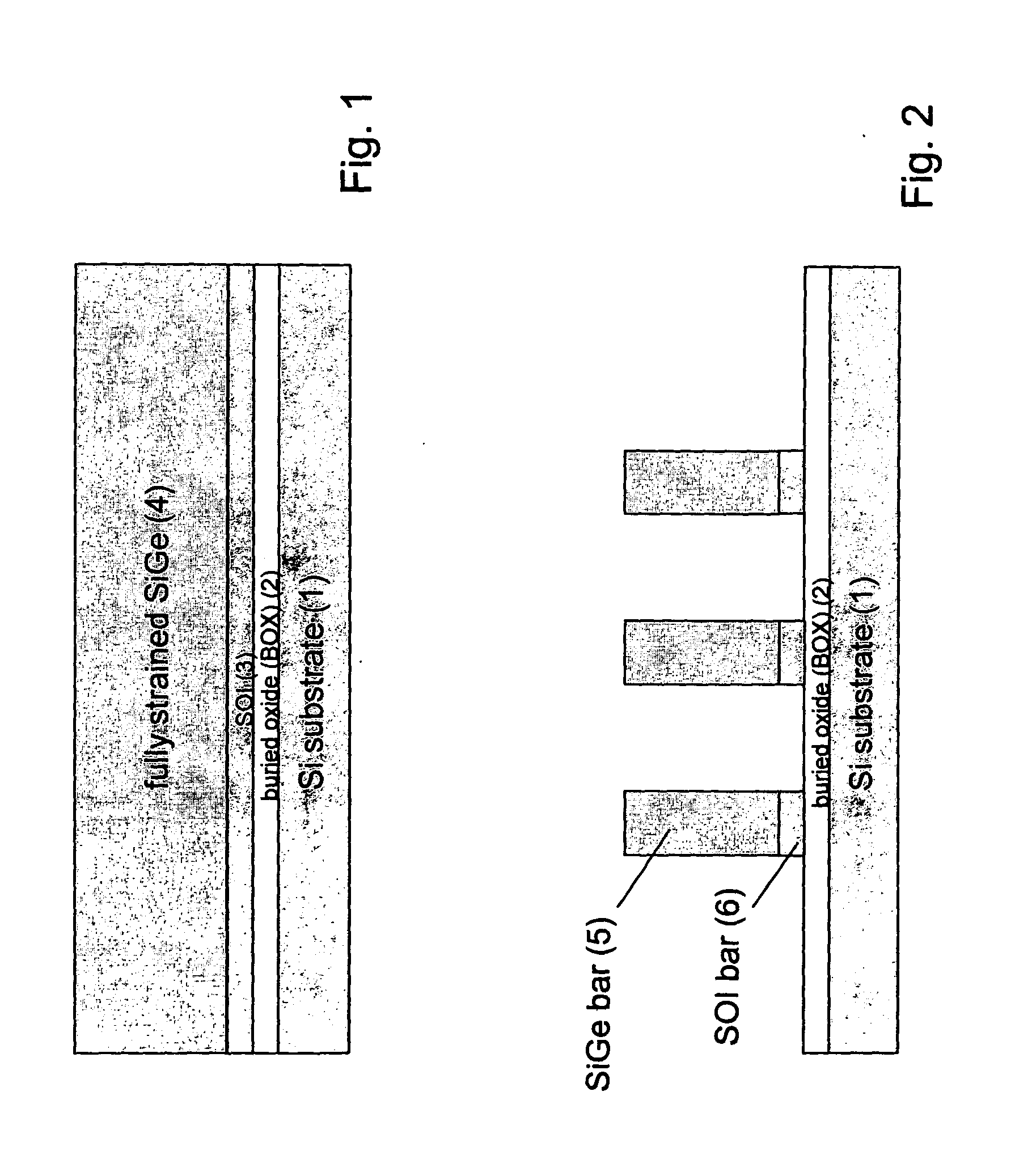

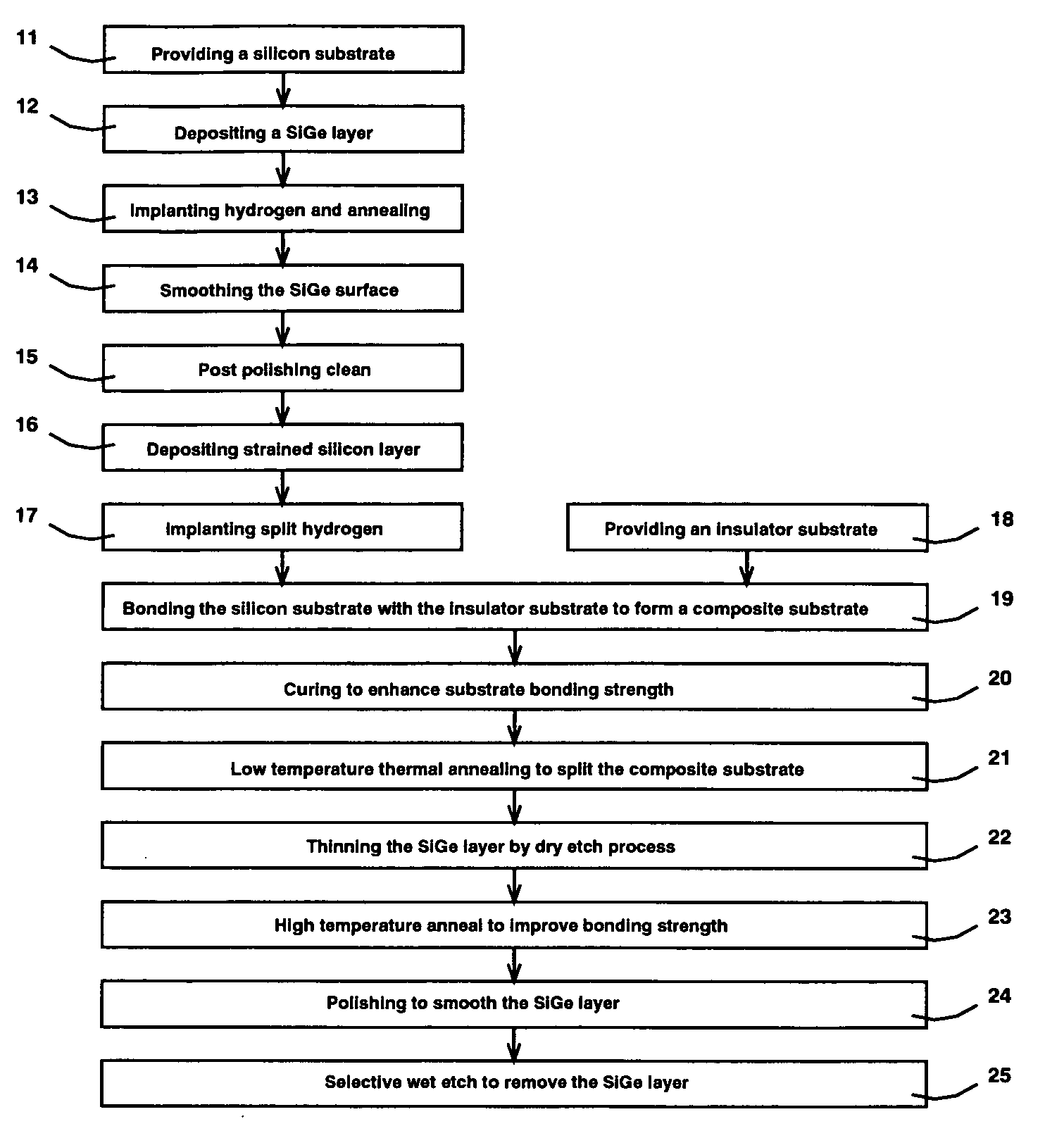

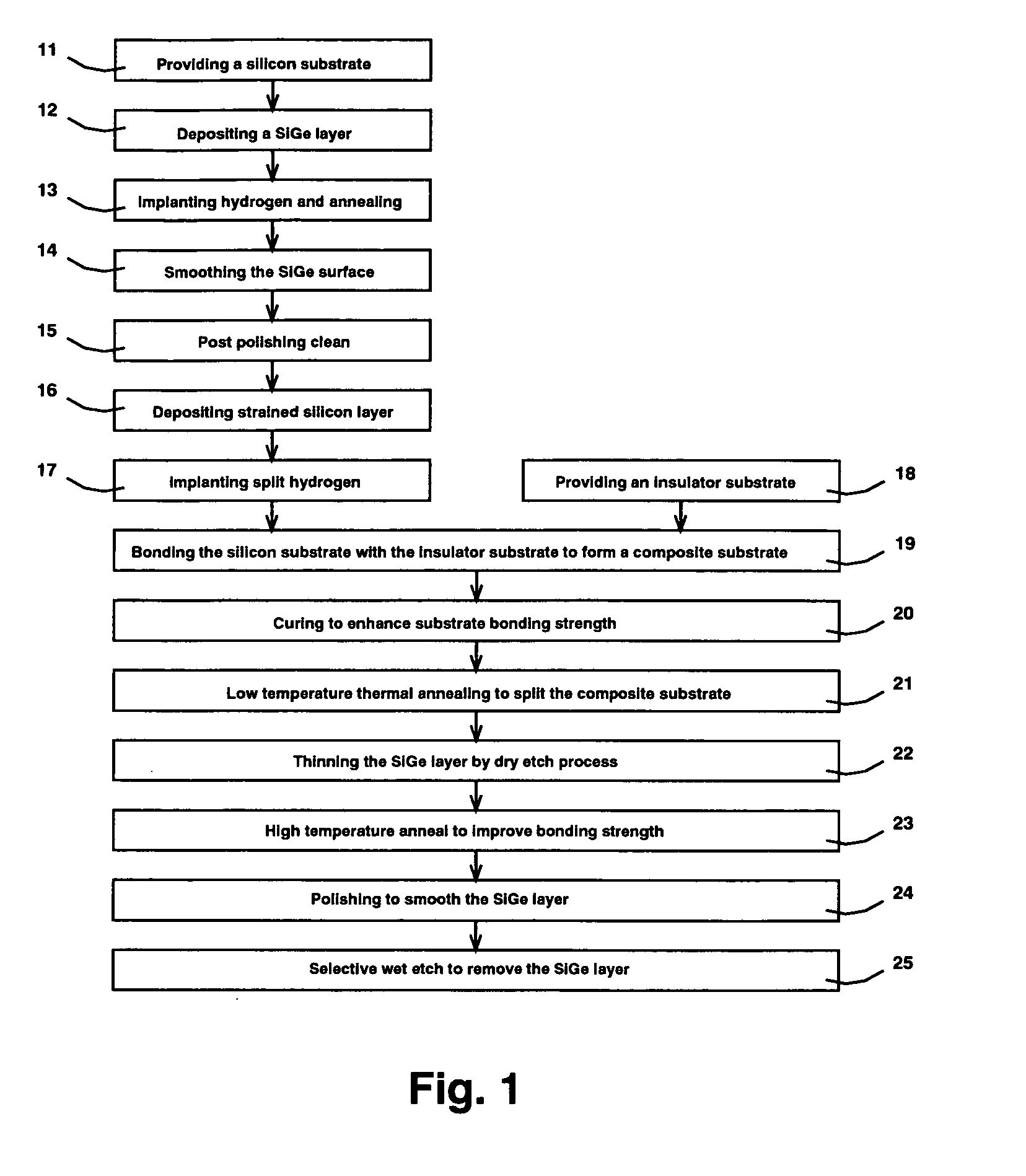

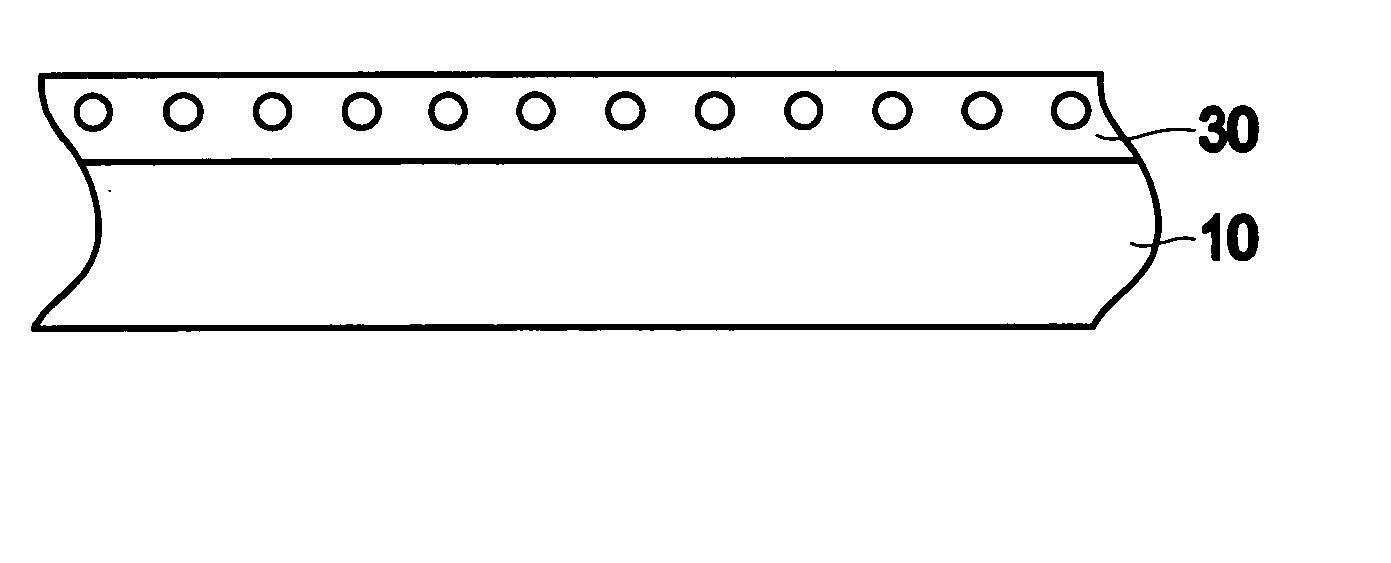

Strained silicon on insulator from film transfer and relaxation by hydrogen implantation

ActiveUS20050153524A1Easy to relaxEasy to integrateSolid-state devicesSemiconductor/solid-state device manufacturingThreading dislocationsHydrogen

Transistors fabricated on SSOI (Strained Silicon On Insulator) substrate, which comprises a strained silicon layer disposed directly on an insulator layer, have enhanced device performance due to the strain-induced band modification of the strained silicon device channel and the limited silicon volume because of the insulator layer. The present invention discloses a SSOI substrate fabrication process comprising various novel approaches. One is the use of a thin relaxed SiGe layer as the strain-induced seed layer to facilitate integration and reduce processing cost. Another is the formation of split implant microcracks deep in the silicon substrate to reduce the number of threading dislocations reaching the strained silicon layer. And lastly is the two step annealing / thinning process for the strained silicon / SiGe multilayer film transfer without blister or flaking formation.

Owner:SHARP KK

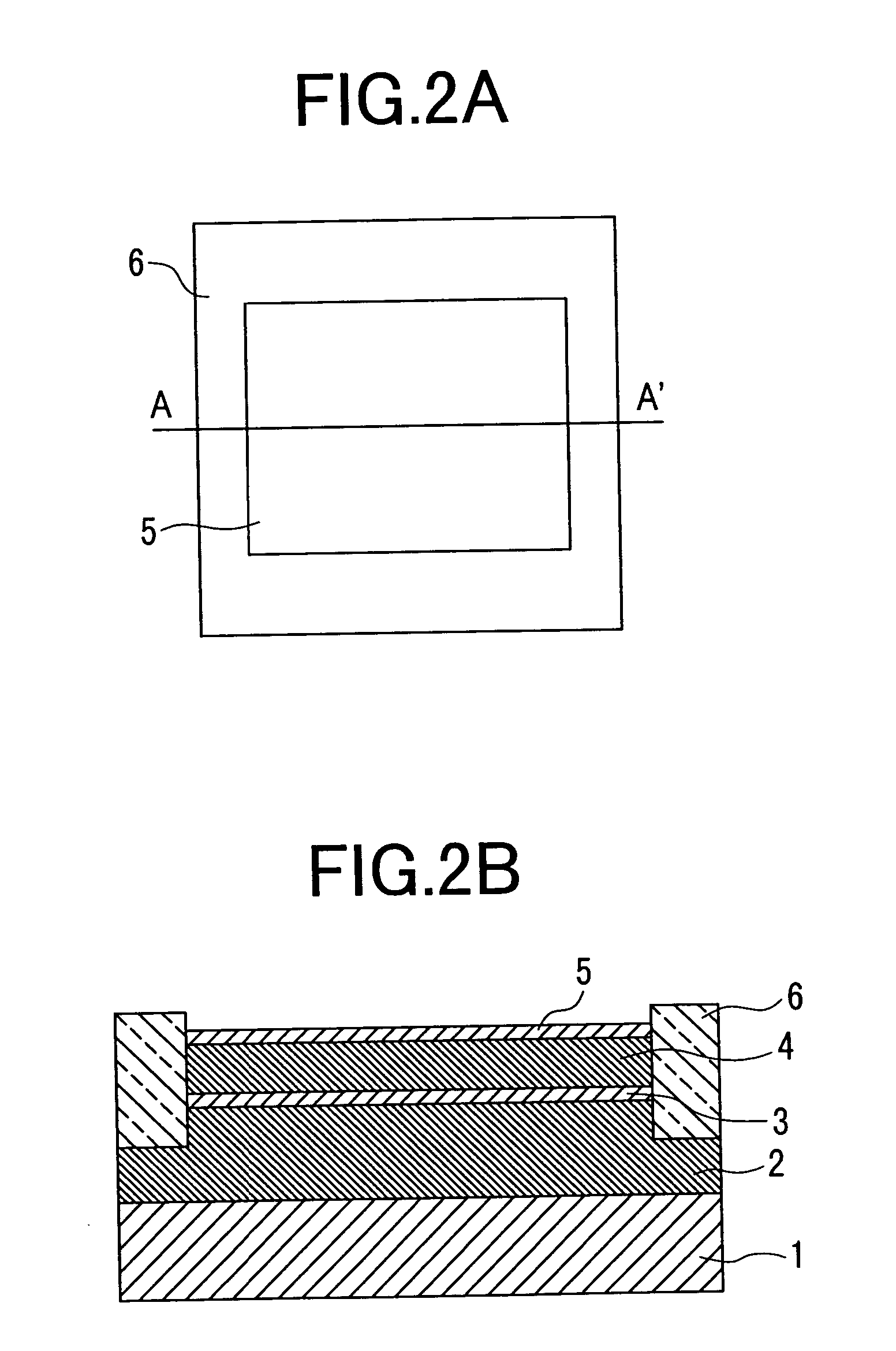

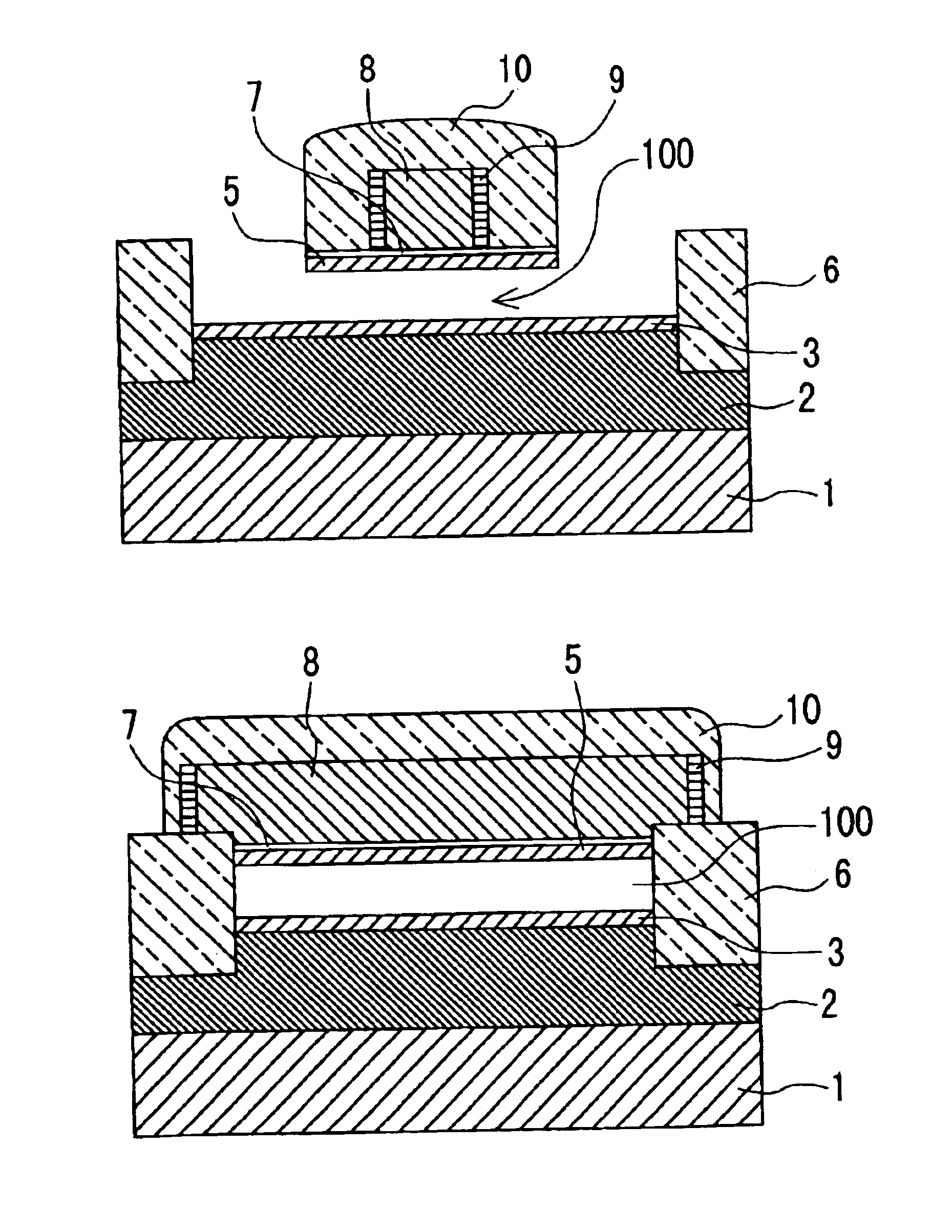

Insulated-gate field-effect transistor, method of fabricating same, and semiconductor device employing same

With the invention, it is possible to avoid deterioration in short-channel characteristics, caused by a silicon germanium layer coming into contact with the channel of a strained SOI transistor. Further, it is possible to fabricate a double-gate type of strained SOI transistor or to implement mixedly mounting the strained SOI transistor and a conventional silicon or SOI transistor on the same wafer. According to the invention, for example, a strained silicon layer is grown on a strain-relaxed silicon germanium layer, and subsequently, portions of the silicon germanium layer are removed, thereby constituting a channel layer in the strained silicon layer.

Owner:RENESAS ELECTRONICS CORP

Method for the manufacture of a strained silicon-on-insulator structure

InactiveUS20070045738A1Solid-state devicesSemiconductor/solid-state device manufacturingSilicon on insulatorContamination

The present invention is directed to a strained silicon on insulator (SSOI) structure having improved surface characteristics, such as reduced roughness, low concentration of LPDs, and lower contamination, and a method for making such a structure.

Owner:MEMC ELECTONIC MATERIALS INC

Strained-silicon CMOS device and method

ActiveUS20050285187A1High carrier mobilitySolid-state devicesSemiconductor/solid-state device manufacturingCMOSDevice material

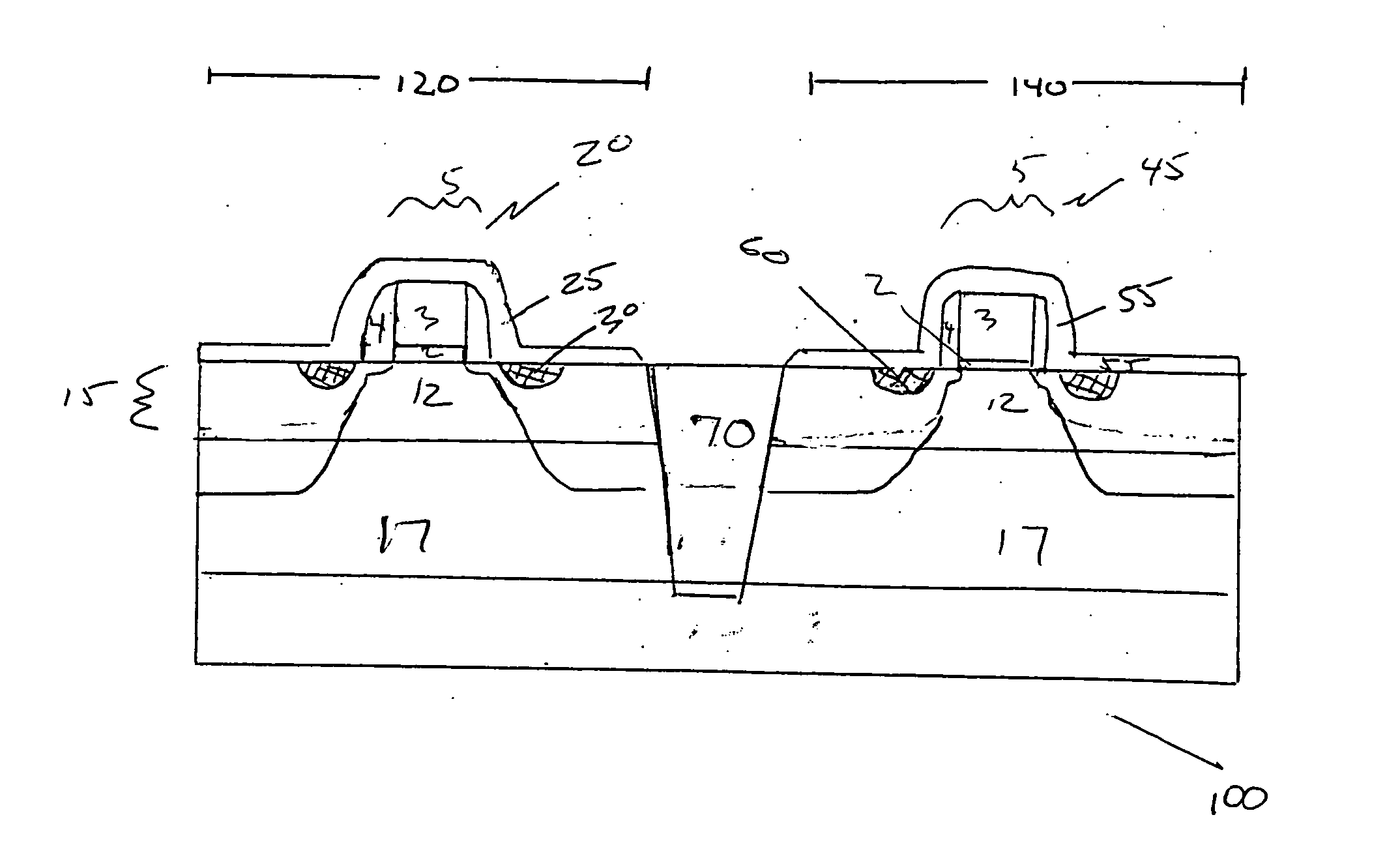

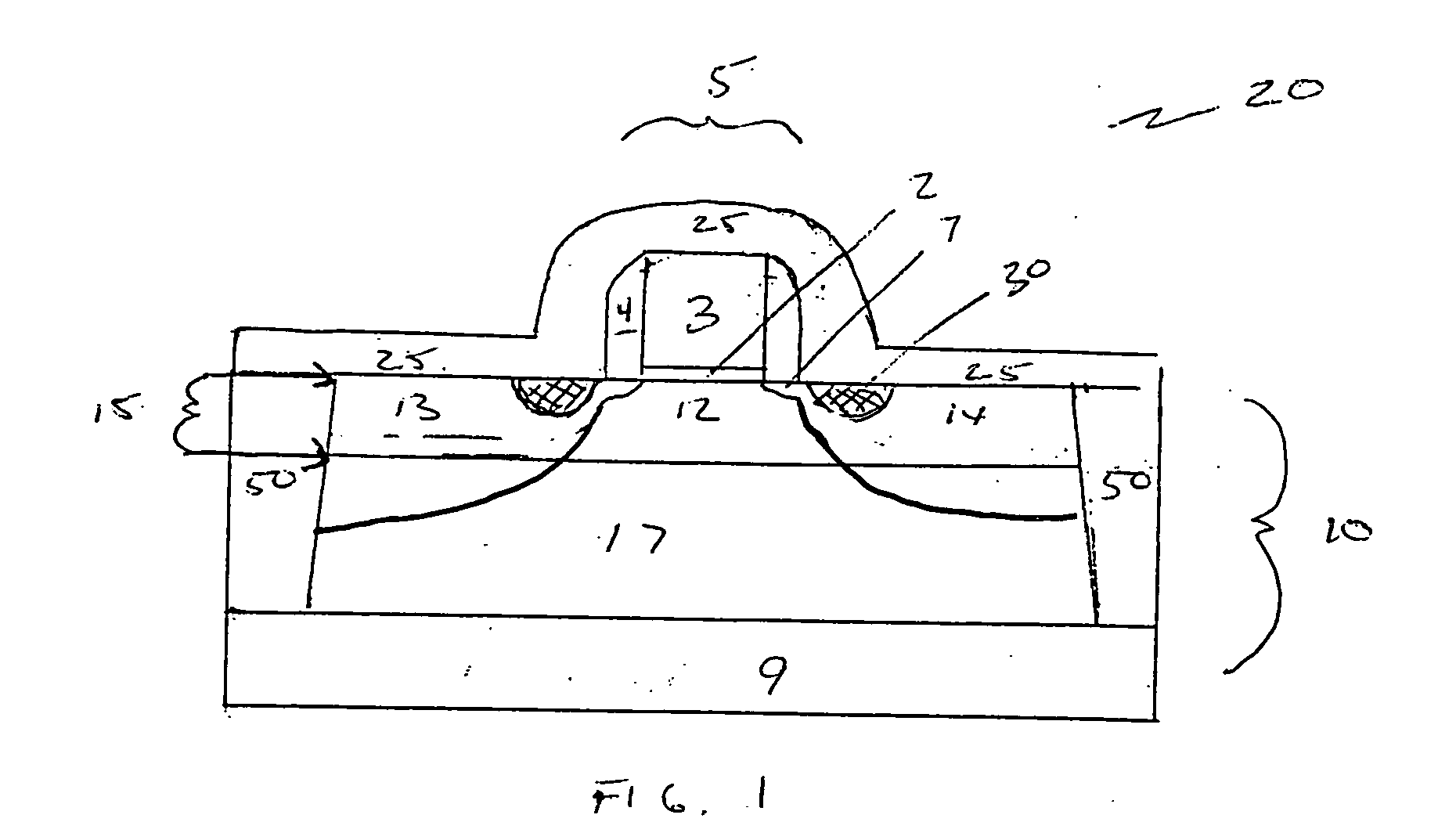

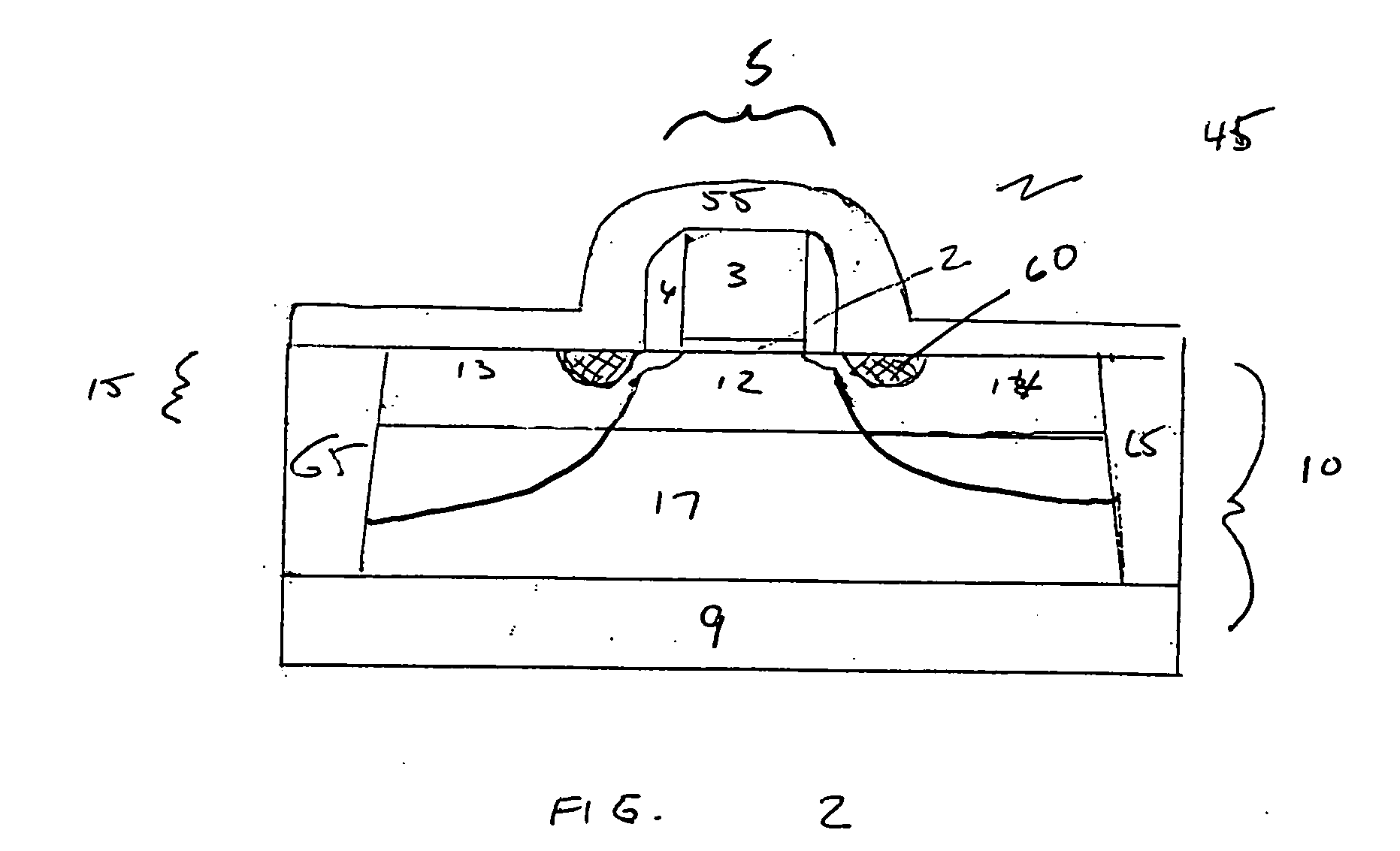

The present invention provides a semiconductor device and a method of forming thereof, in which a uniaxial strain is produced in the device channel of the semiconductor device. The uniaxial strain may be in tension or in compression and is in a direction parallel to the device channel. The uniaxial strain can be produced in a biaxially strained substrate surface by strain inducing liners, strain inducing wells or a combination thereof. The uniaxial strain may be produced in a relaxed substrate by the combination of strain inducing wells and a strain inducing liner. The present invention also provides a means for increasing biaxial strain with strain inducing isolation regions. The present invention further provides CMOS devices in which the device regions of the CMOS substrate may be independently processed to provide uniaxially strained semiconducting surfaces in compression or tension.

Owner:GLOBALFOUNDRIES US INC

Method for producing dislocation-free strained crystalline films

ActiveUS20060292822A1Small thicknessSemiconductor/solid-state device manufacturingHydrogenOptoelectronics

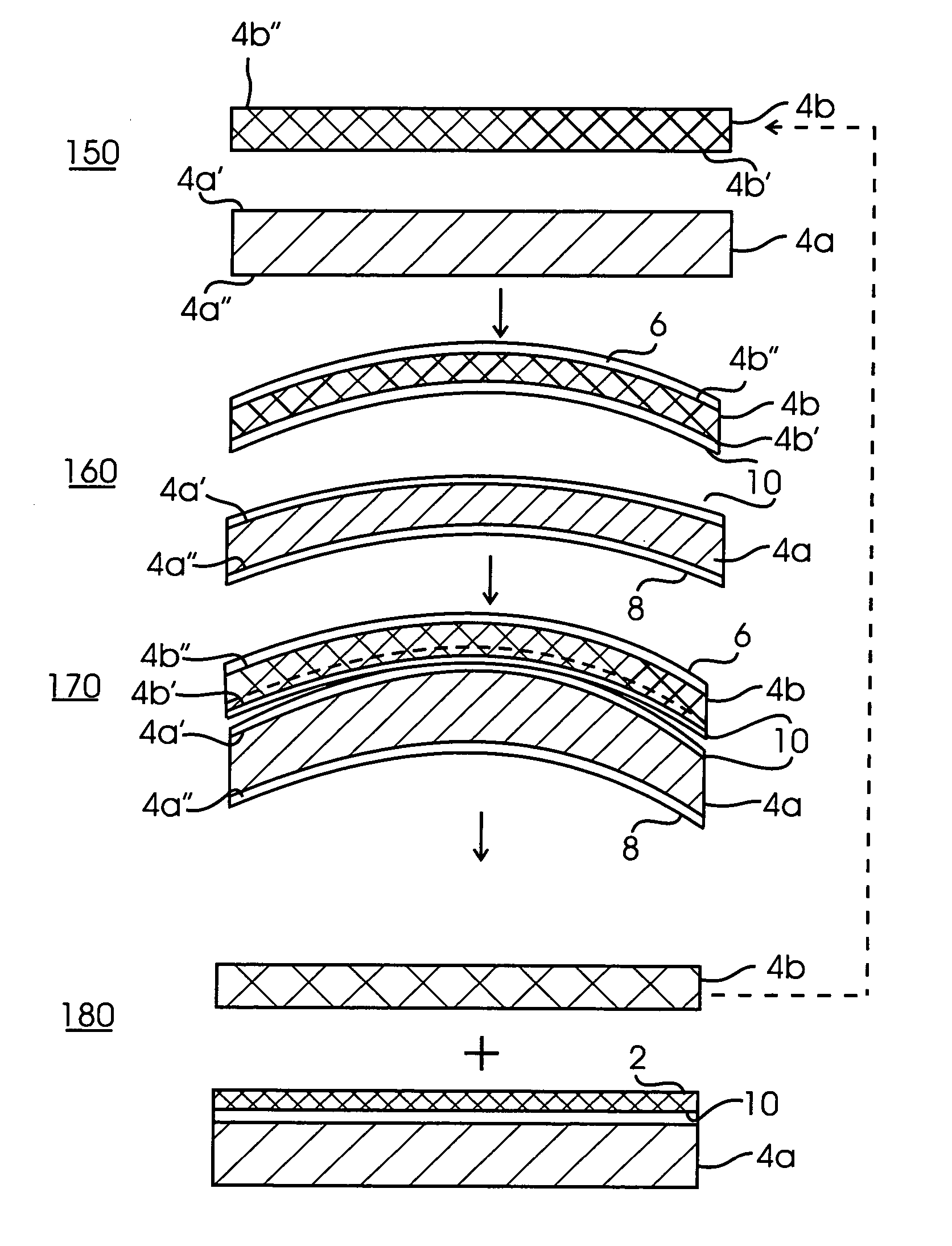

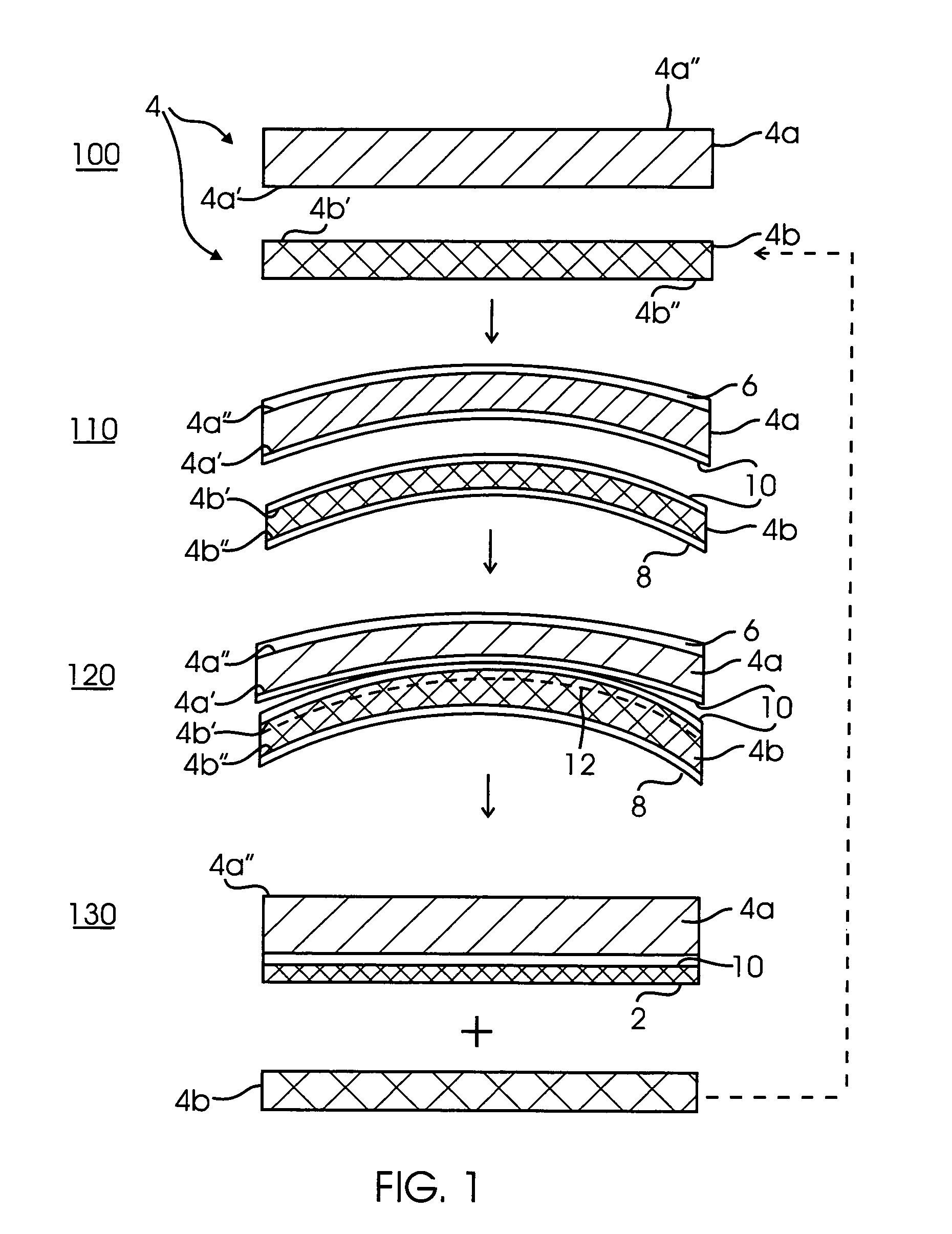

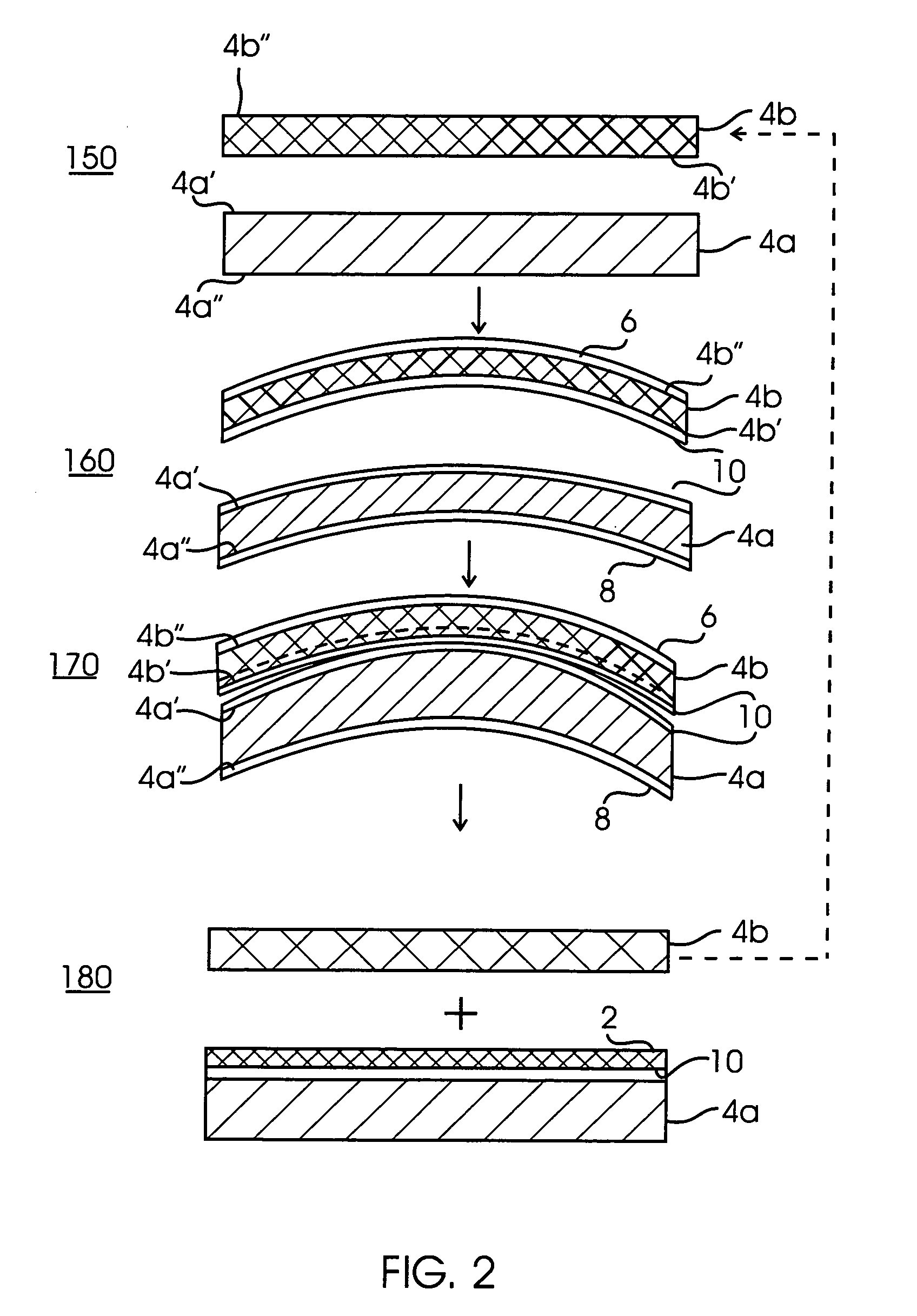

A method for forming dislocation-free strained silicon thin film includes the step of providing two curved silicon substrates. One substrate is curved by the presence of silicon dioxide on a back surface. The other substrate is curved by the presence of a silicon nitride layer. One of the substrates is subject to hydrogen implantation and the two substrates are bonded to one another in an annealing process. The two substrates are separated, thereby leaving a layer of strained silicon on a front side of one of the substrates. A back side layer of silicon dioxide or silicon nitride is then removed to restore the substrate to a substantially planar state. The method may be employed to form dislocation-free strained silicon thin films. The films may be under tensile or compressive strain.

Owner:RGT UNIV OF CALIFORNIA

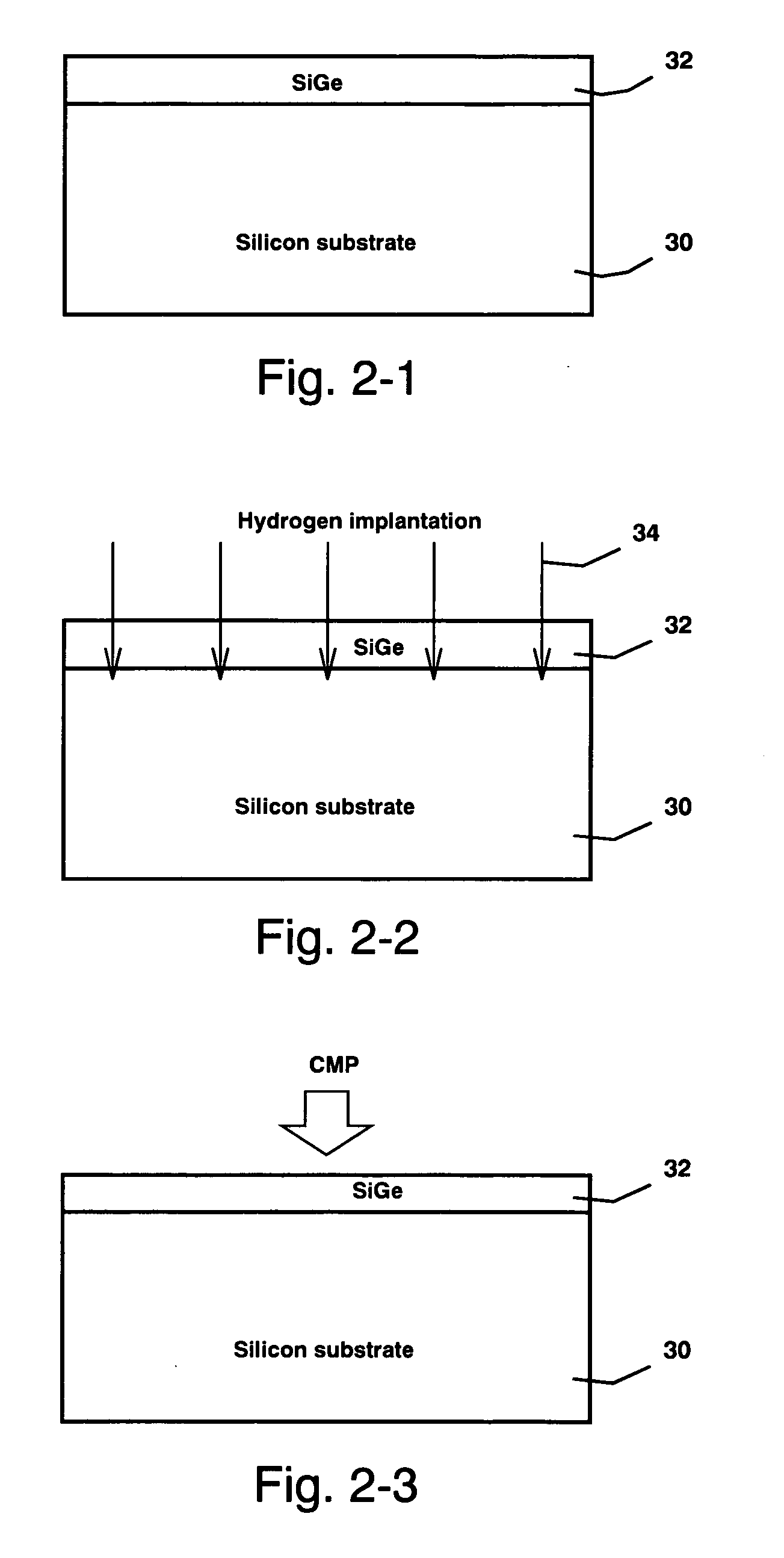

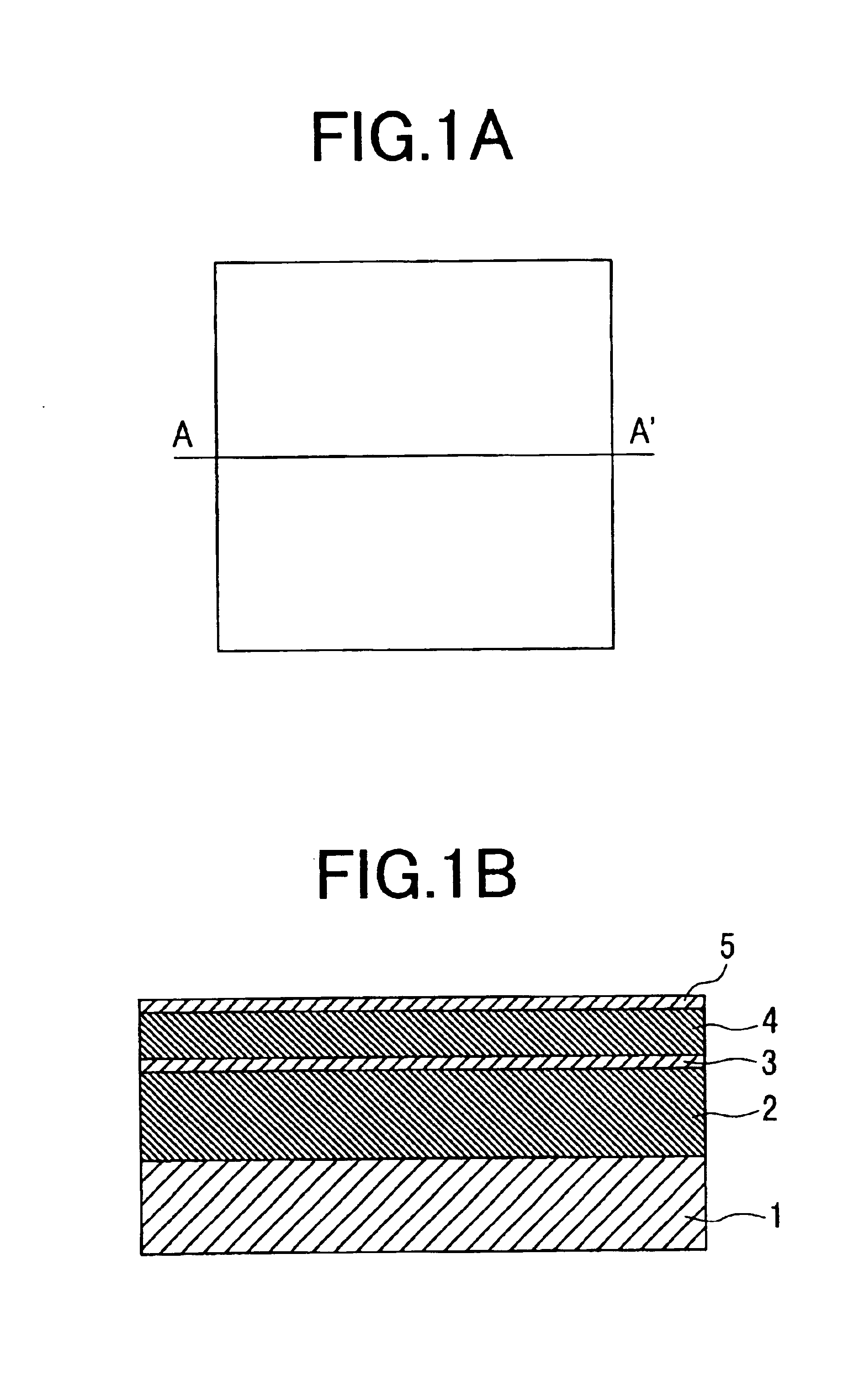

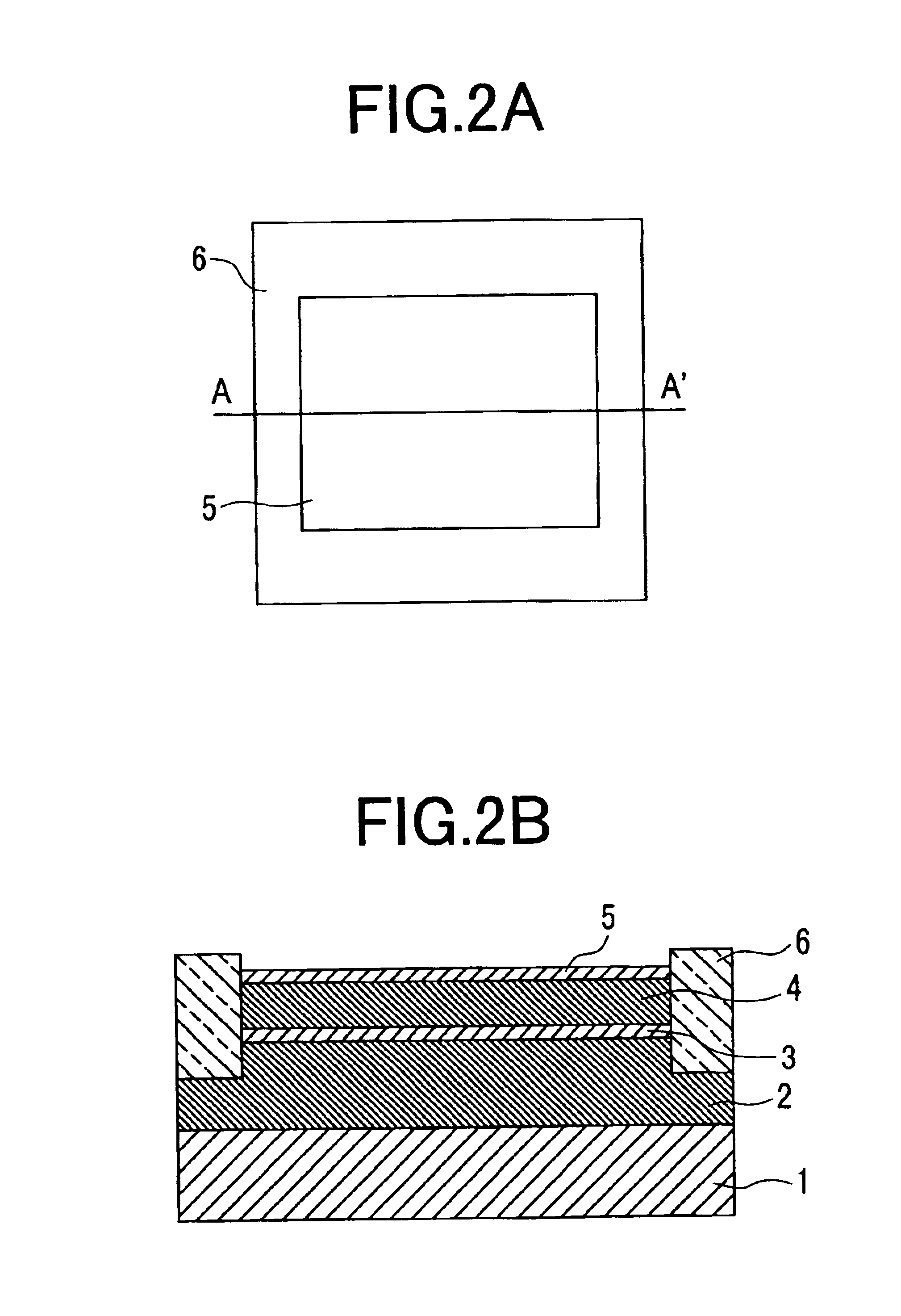

Manufacturing method of strained si substrate

InactiveUS20100003803A1Low densityLow roughness requirementsPolycrystalline material growthSolid-state devicesThreading dislocationsHydrogen

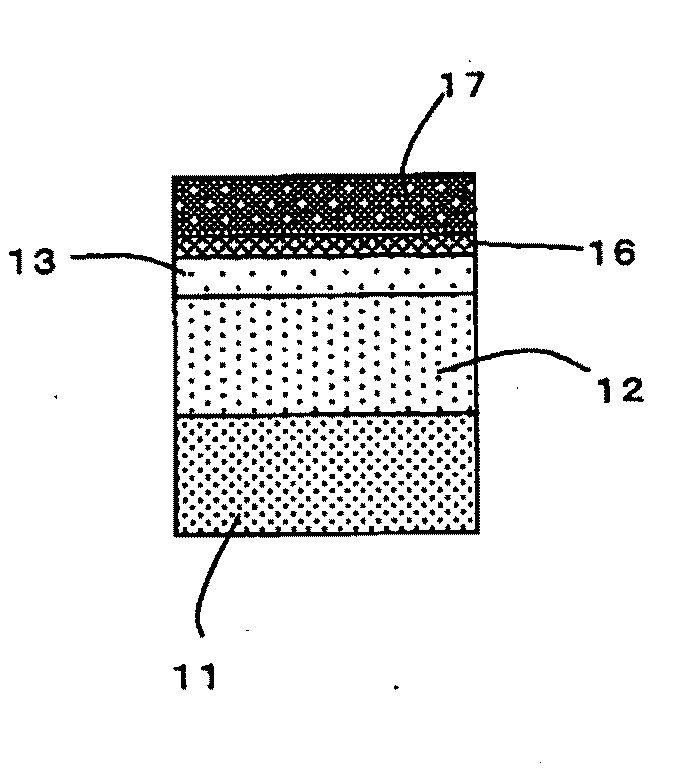

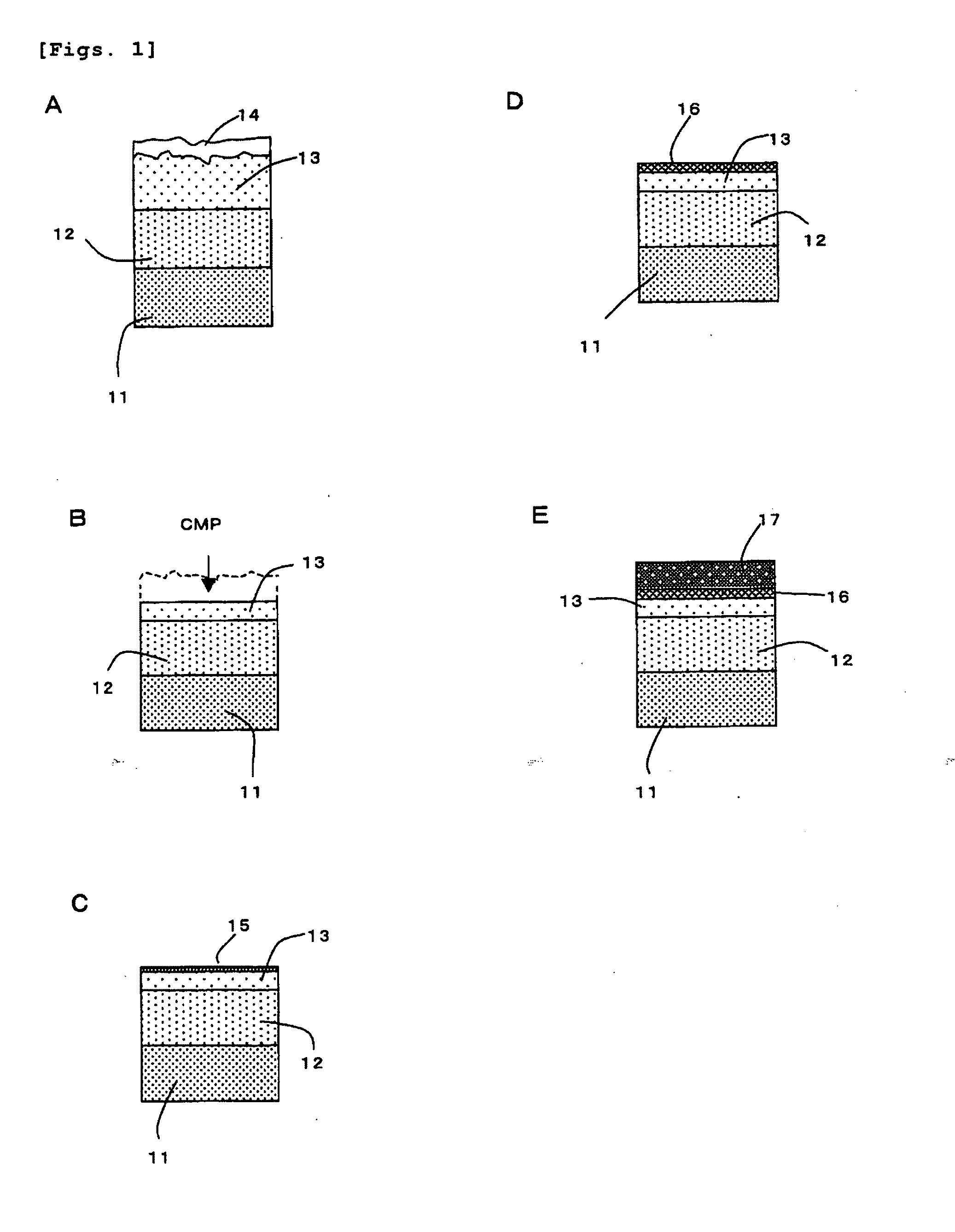

According to the present invention, there is provided a manufacturing method of a strained Si substrate including at least steps of: forming a lattice-relaxed SiGe layer on a silicon single crystal substrate; flattening a surface of the SiGe layer by CMP; and forming a strained Si layer on the surface of the flattened SiGe layer, wherein the method comprises steps of: subjecting the surface of the SiGe layer to SC1 cleaning, before forming the strained Si layer on the lattice-relaxed SiGe layer surface that is flattened; heat-treating the substrate having the SiGe layer after being subjected to SC1 cleaning in a hydrogen-containing atmosphere at 800° C. or higher; immediately forming a protective Si layer on the SiGe layer surface on the heat-treated substrate, without lowering the temperature below 800° C. after the heat treatment; and forming the strained Si layer on the surface of the protective Si layer at a temperature lower than the temperature of forming the protective Si layer. Thereby, a manufacturing method of a strained Si substrate having low surface roughness, threading dislocation density and low particle level can be provided.

Owner:SHIN-ETSU HANDOTAI CO LTD

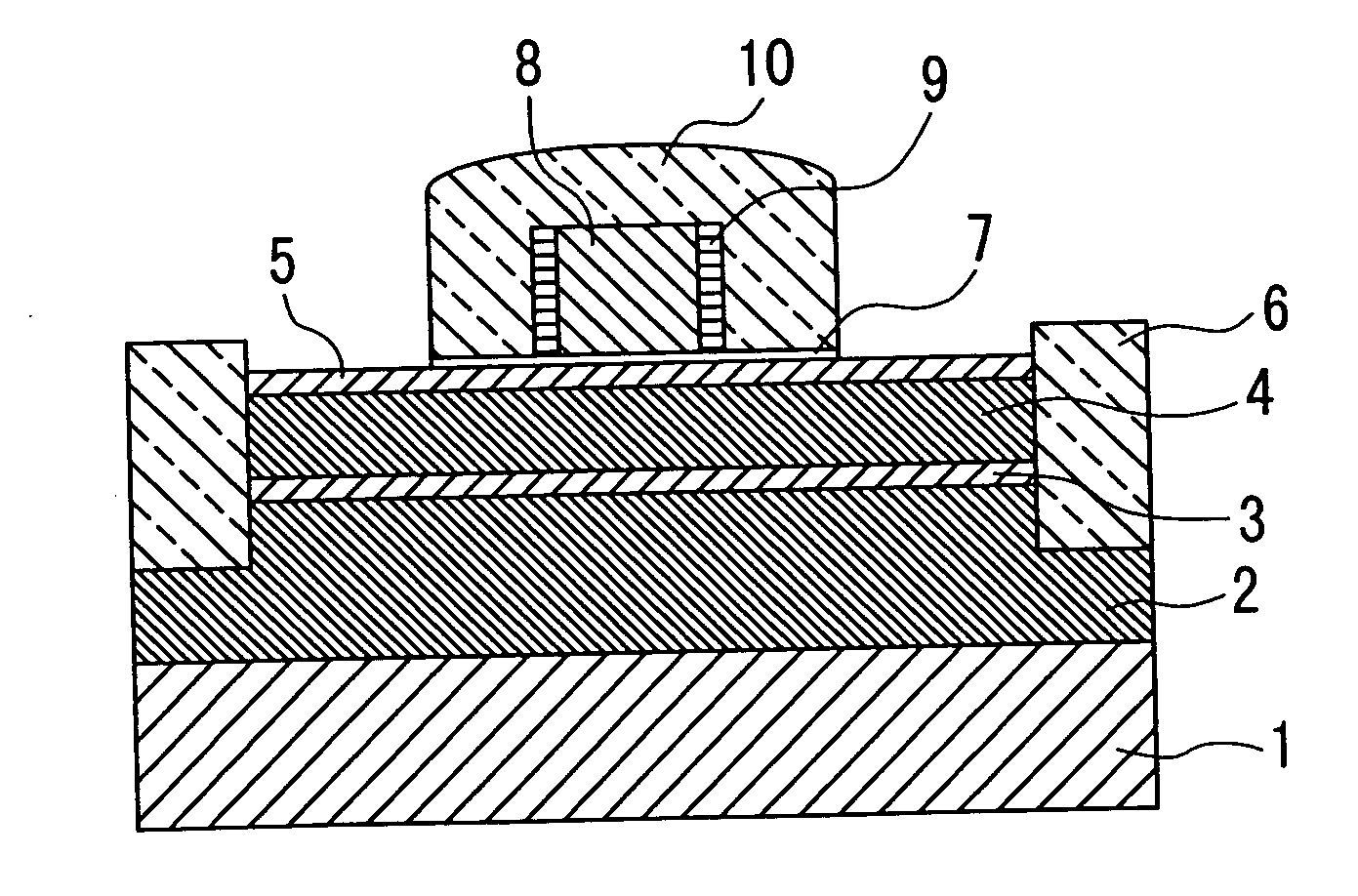

Insulated-gate field-effect transistor, method of fabricating same, and semiconductor device employing same

InactiveUS6936875B2Improve mobilityShorten the lengthTransistorSolid-state devicesDevice materialField-effect transistor

With the invention, it is possible to avoid deterioration in short-channel characteristics, caused by a silicon germanium layer coming into contact with the channel of a strained SOI transistor. Further, it is possible to fabricate a double-gate type of strained SOI transistor or to implement mixedly mounting the strained SOI transistor and a conventional silicon or SOI transistor on the same wafer. According to the invention, for example, a strained silicon layer is grown on a strain-relaxed silicon germanium layer, and subsequently, portions of the silicon germanium layer are removed, thereby constituting a channel layer in the strained silicon layer.

Owner:RENESAS ELECTRONICS CORP

Strained-channel Fin field effect transistor (FET) with a uniform channel thickness and separate gates

A semiconductor device (and method for making the same) includes a strained-silicon channel formed adjacent a source and a drain, a first gate formed over a first side of the channel, a second gate formed over a second side of the channel, a first gate dielectric formed between the first gate and the strained-silicon channel, and a second gate dielectric formed between the second gate and the strained-silicon channel. The strained-silicon channel is non-planar.

Owner:IBM CORP

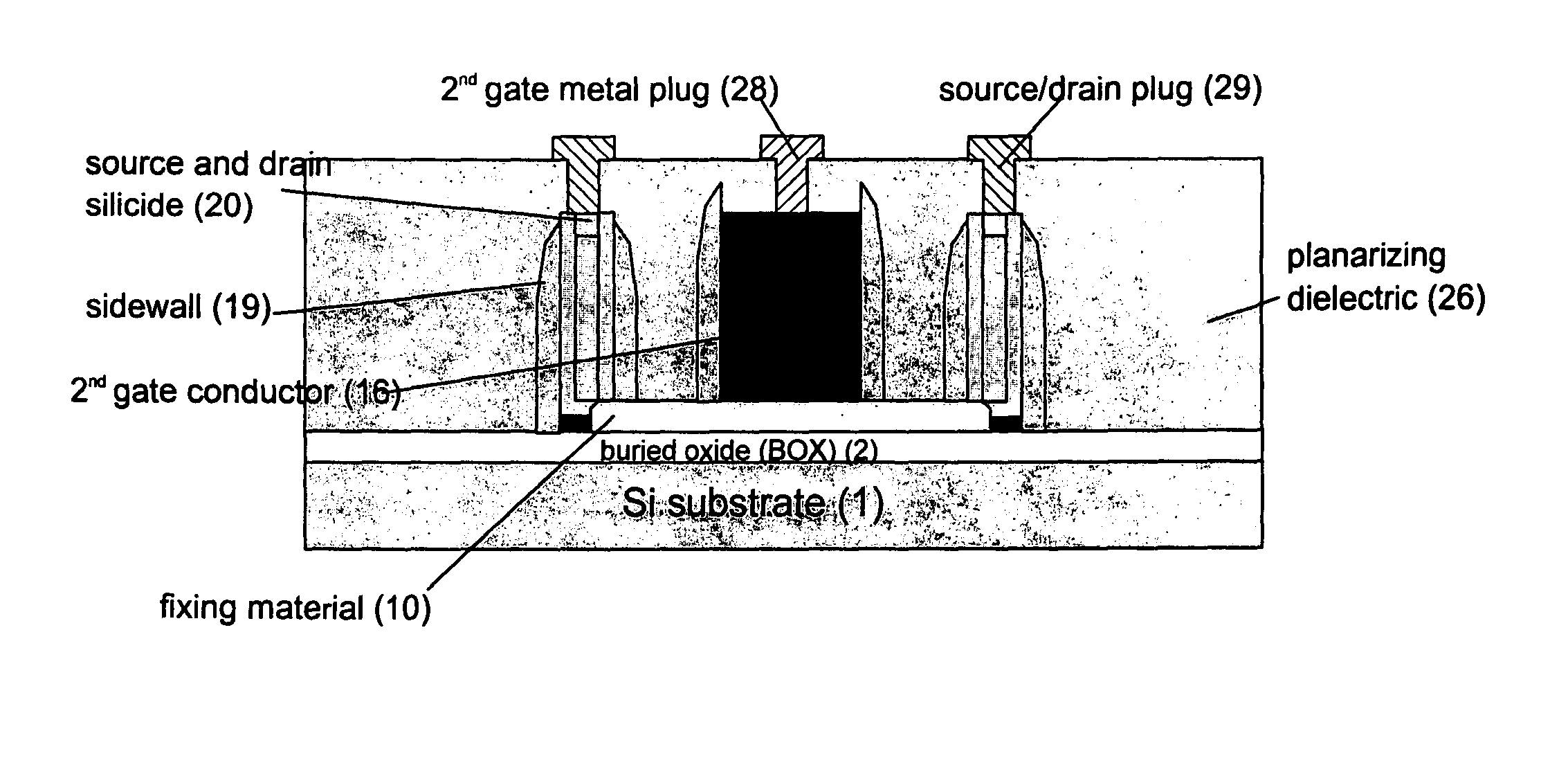

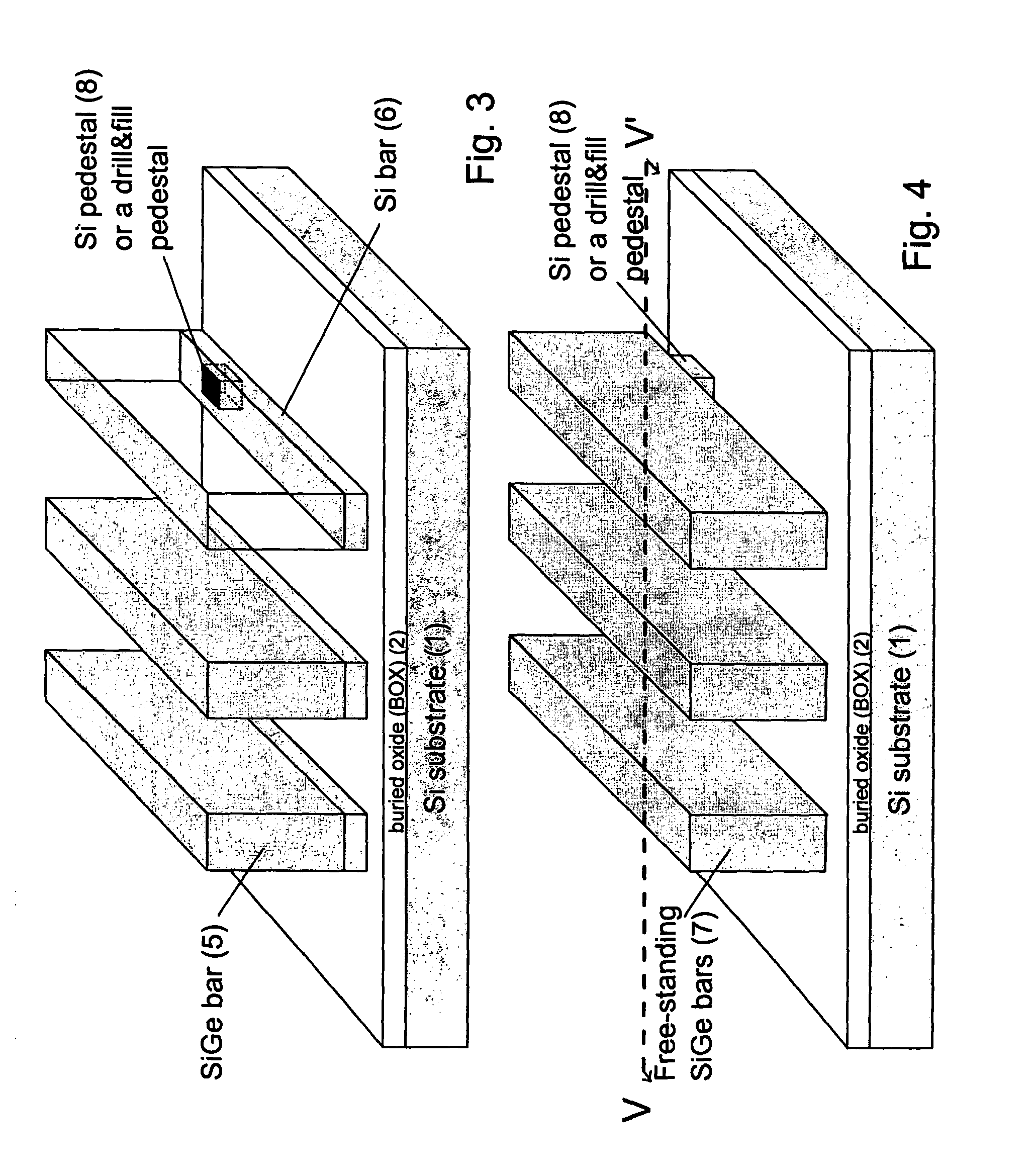

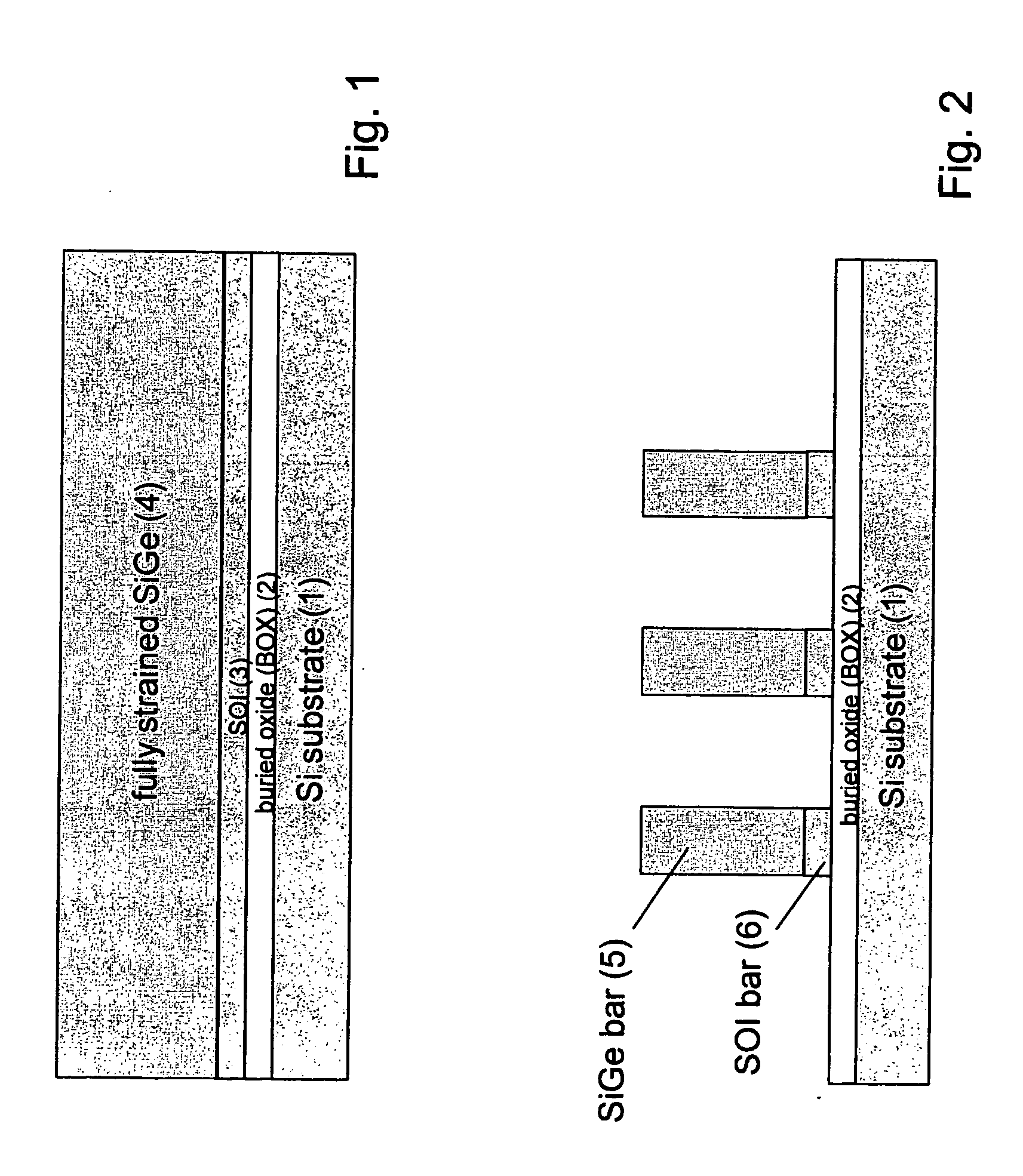

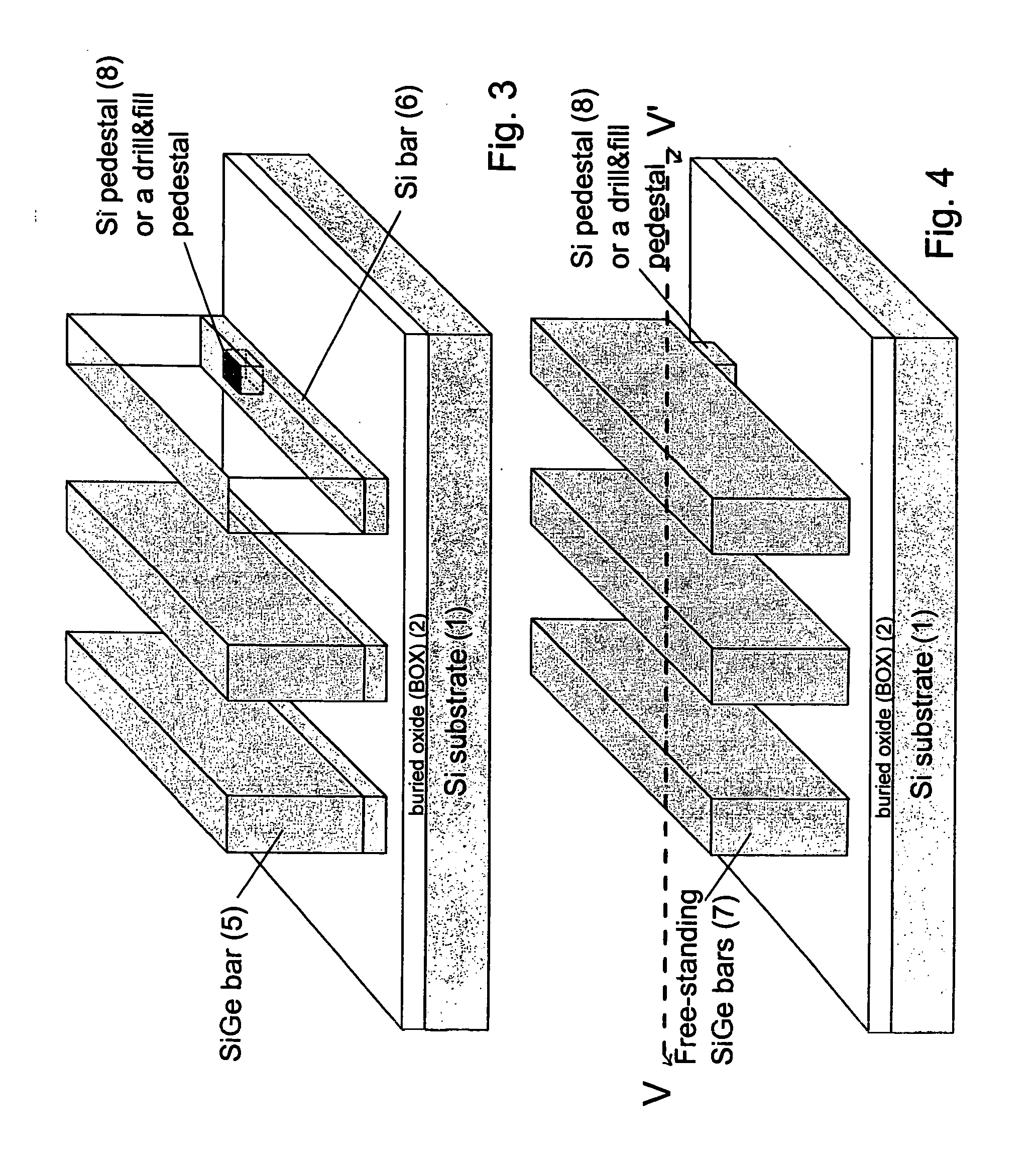

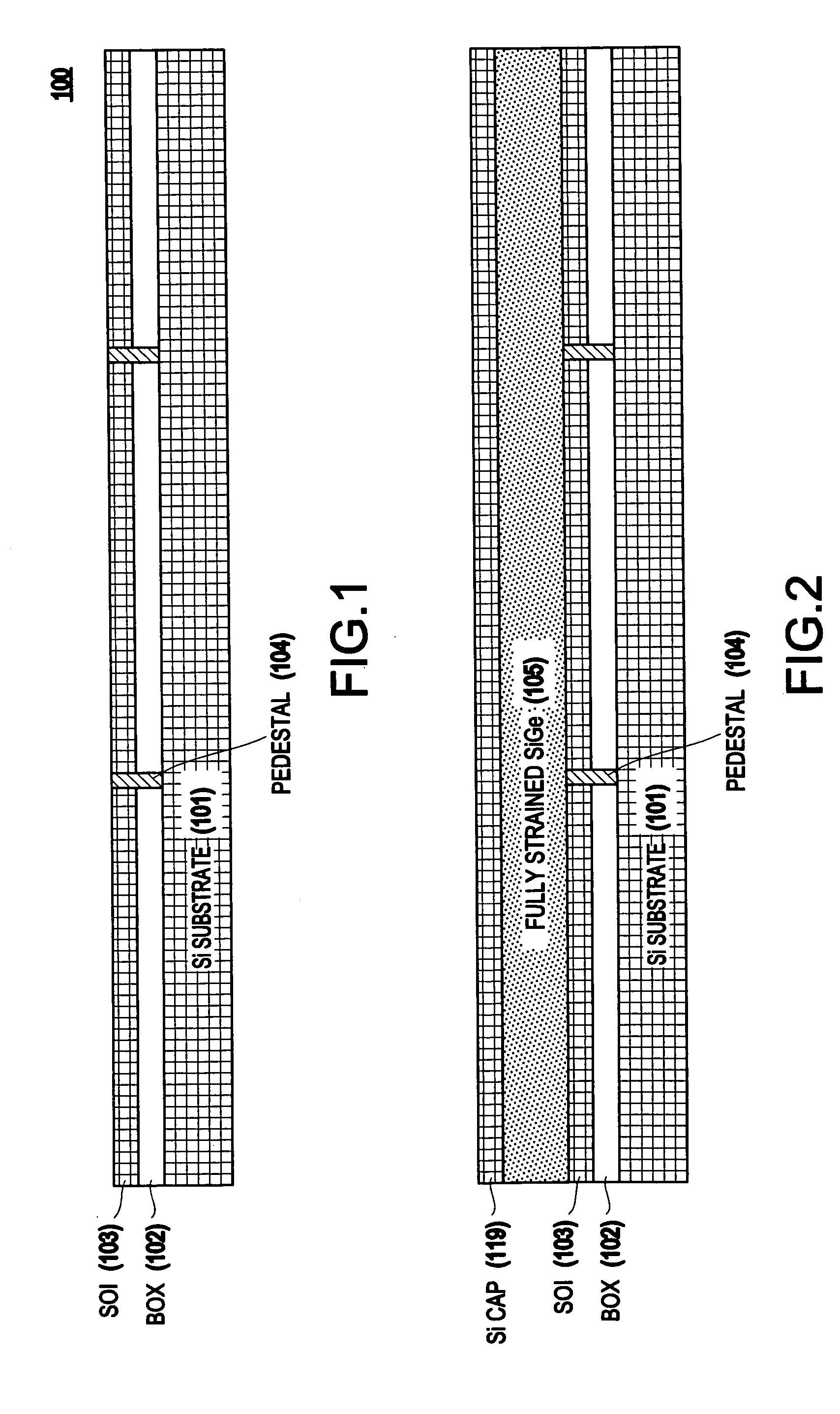

Strained-silicon-on-insulator single-and double-gate MOSFET and method for forming the same

InactiveUS20040253792A1Eliminate difficultiesSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductor structureEngineering

A method of forming a semiconductor structure (and the resulting structure), includes straining a free-standing semiconductor, and fixing the strained, free-standing semiconductor to a substrate.

Owner:IBM CORP

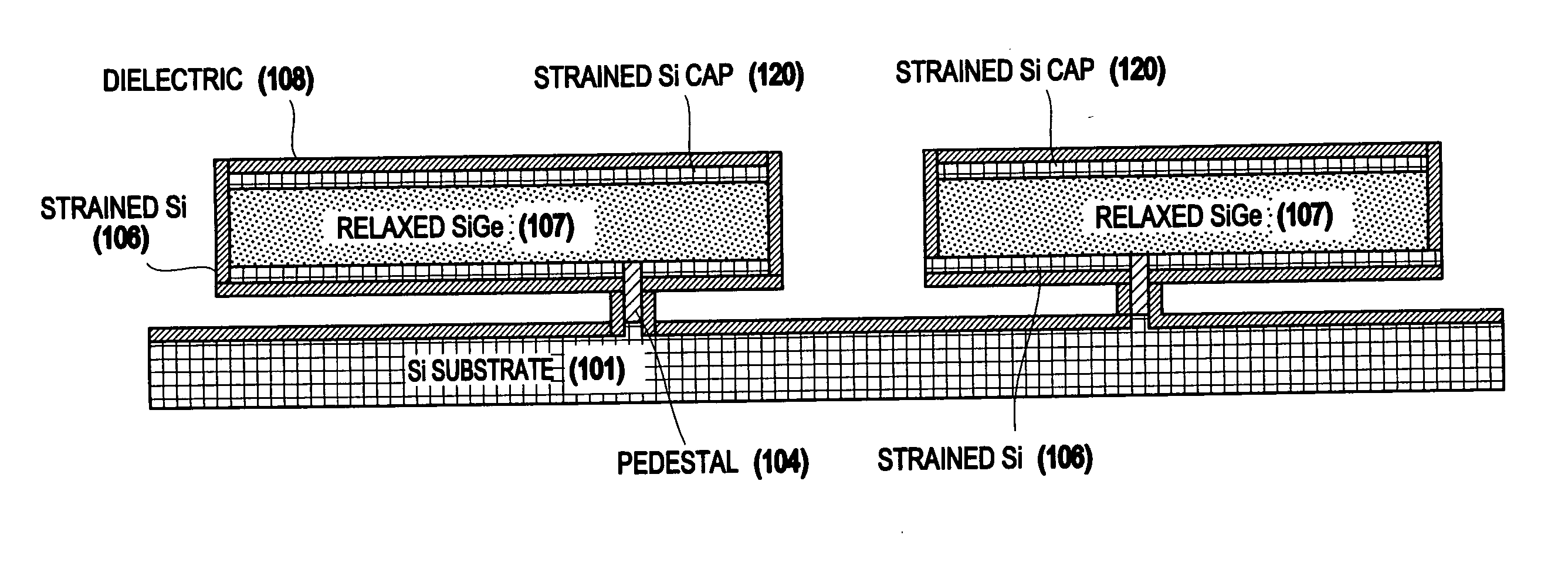

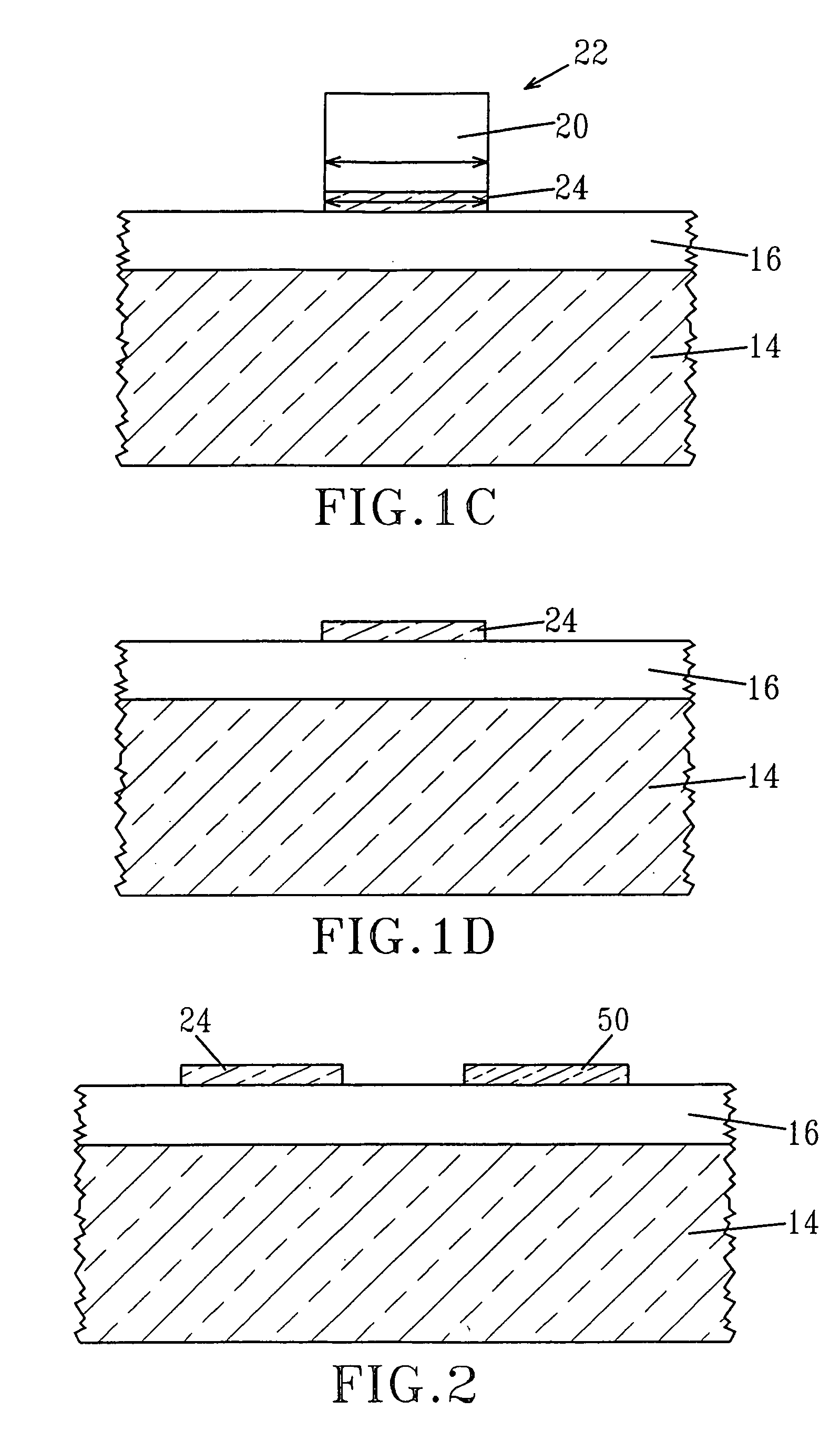

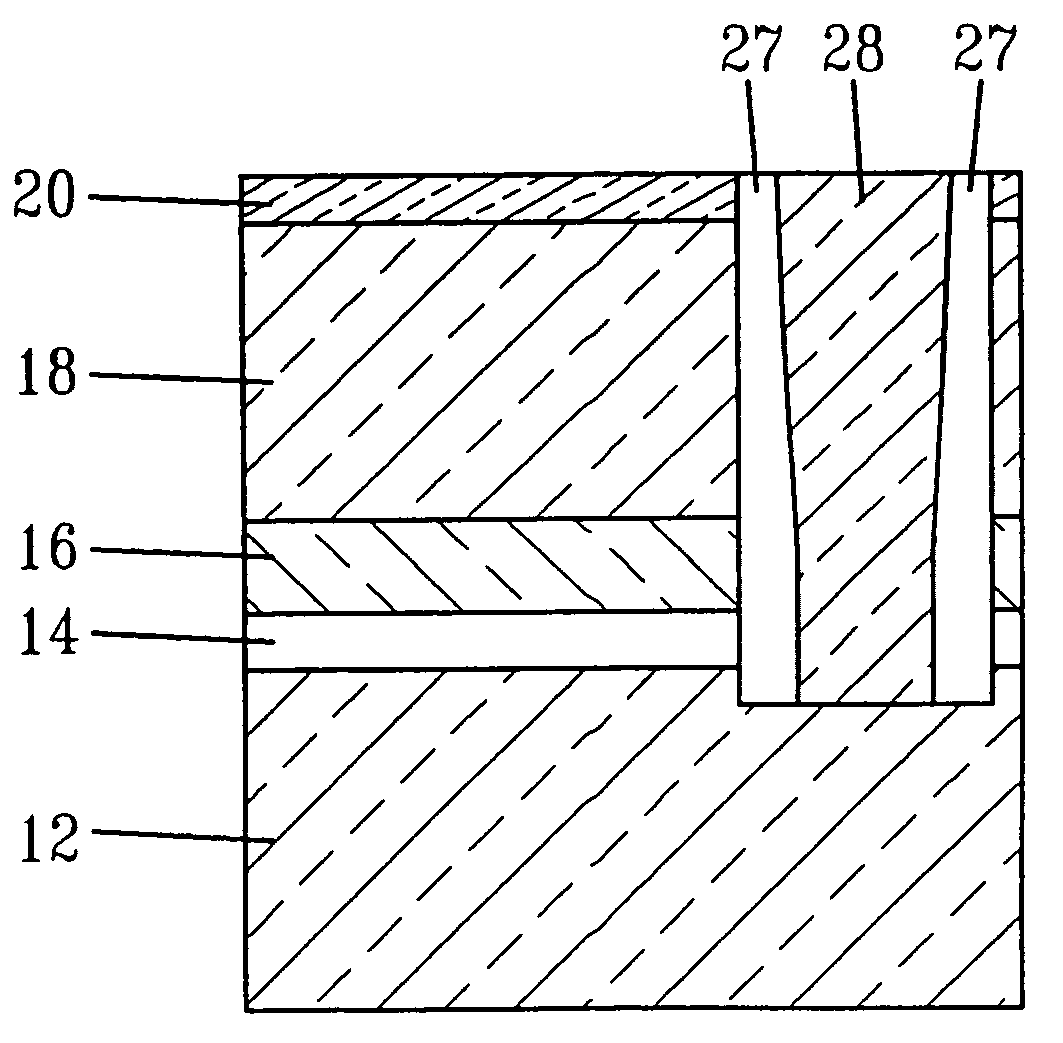

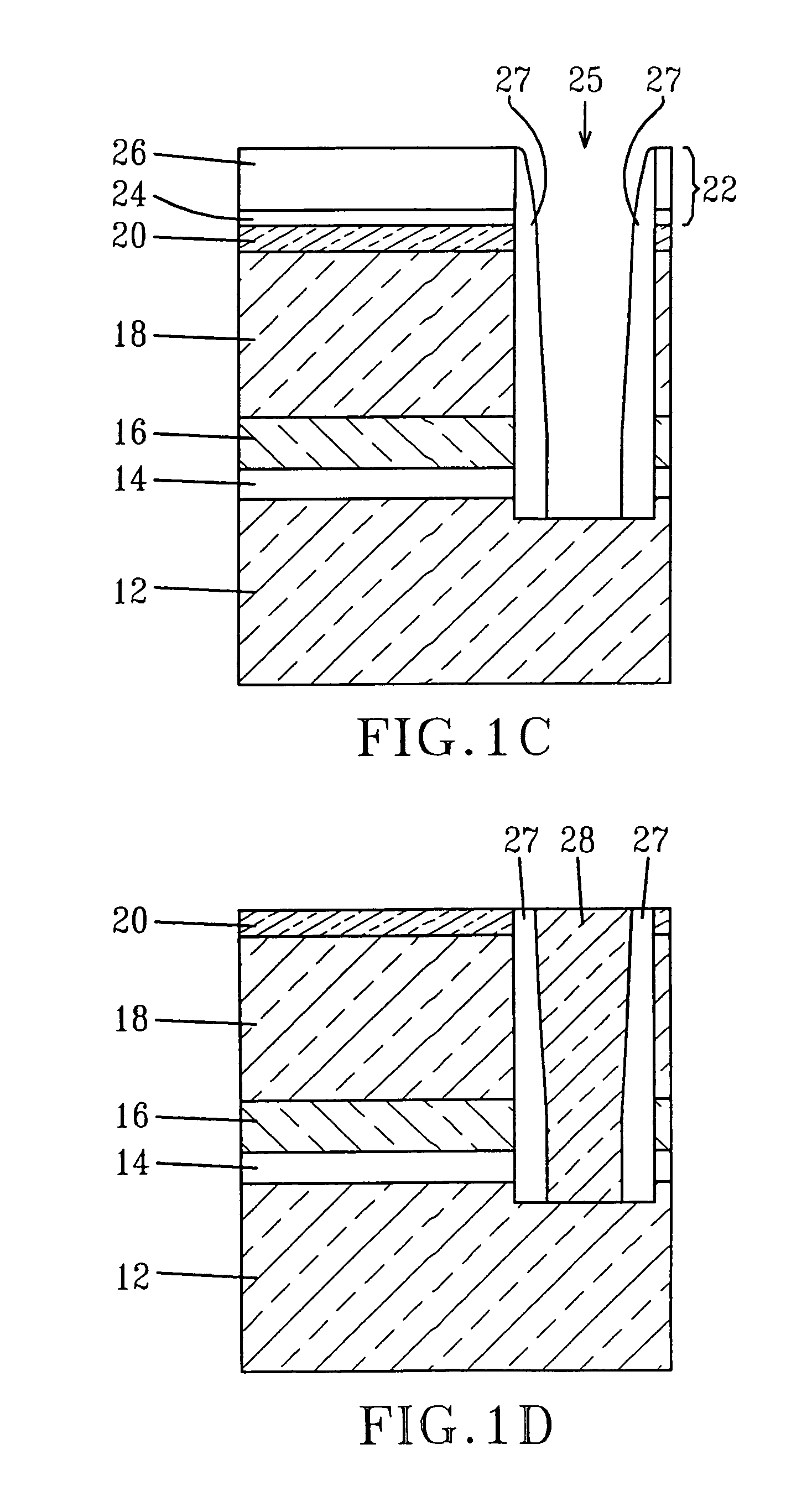

Ultra-thin, high quality strained silicon-on-insulator formed by elastic strain transfer

InactiveUS6991998B2Quantity minimizationReduce the temperatureSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductor structureStacking fault

A method of forming a semiconductor structure comprising a first strained semiconductor layer over an insulating layer is provided in which the first strained semiconductor layer is relatively thin (less than about 500 Å) and has a low defect density (stacking faults and threading defects). The method of the present invention begins with forming a stress-providing layer, such a SiGe alloy layer over a structure comprising a first semiconductor layer that is located atop an insulating layer. The stress-providing layer and the first semiconductor layer are then patterned into at least one island and thereafter the structure containing the at least one island is heated to a temperature that causes strain transfer from the stress-providing layer to the first semiconductor layer. After strain transfer, the stress-providing layer is removed from the structure to form a first strained semiconductor island layer directly atop said insulating layer.

Owner:GLOBALFOUNDRIES INC

Strained silicon CMOS on hybrid crystal orientations

InactiveUS7087965B2Improve performanceImprove device performanceTransistorSolid-state devicesCMOSSemiconductor materials

Methods of forming a strained Si-containing hybrid substrate are provided as well as the strained Si-containing hybrid substrate formed by the methods. In the methods of the present invention, a strained Si layer is formed overlying a regrown semiconductor material, a second semiconducting layer, or both. In accordance with the present invention, the strained Si layer has the same crystallographic orientation as either the regrown semiconductor layer or the second semiconducting layer. The methods provide a hybrid substrate in which at least one of the device layers includes strained Si.

Owner:GLOBALFOUNDRIES INC

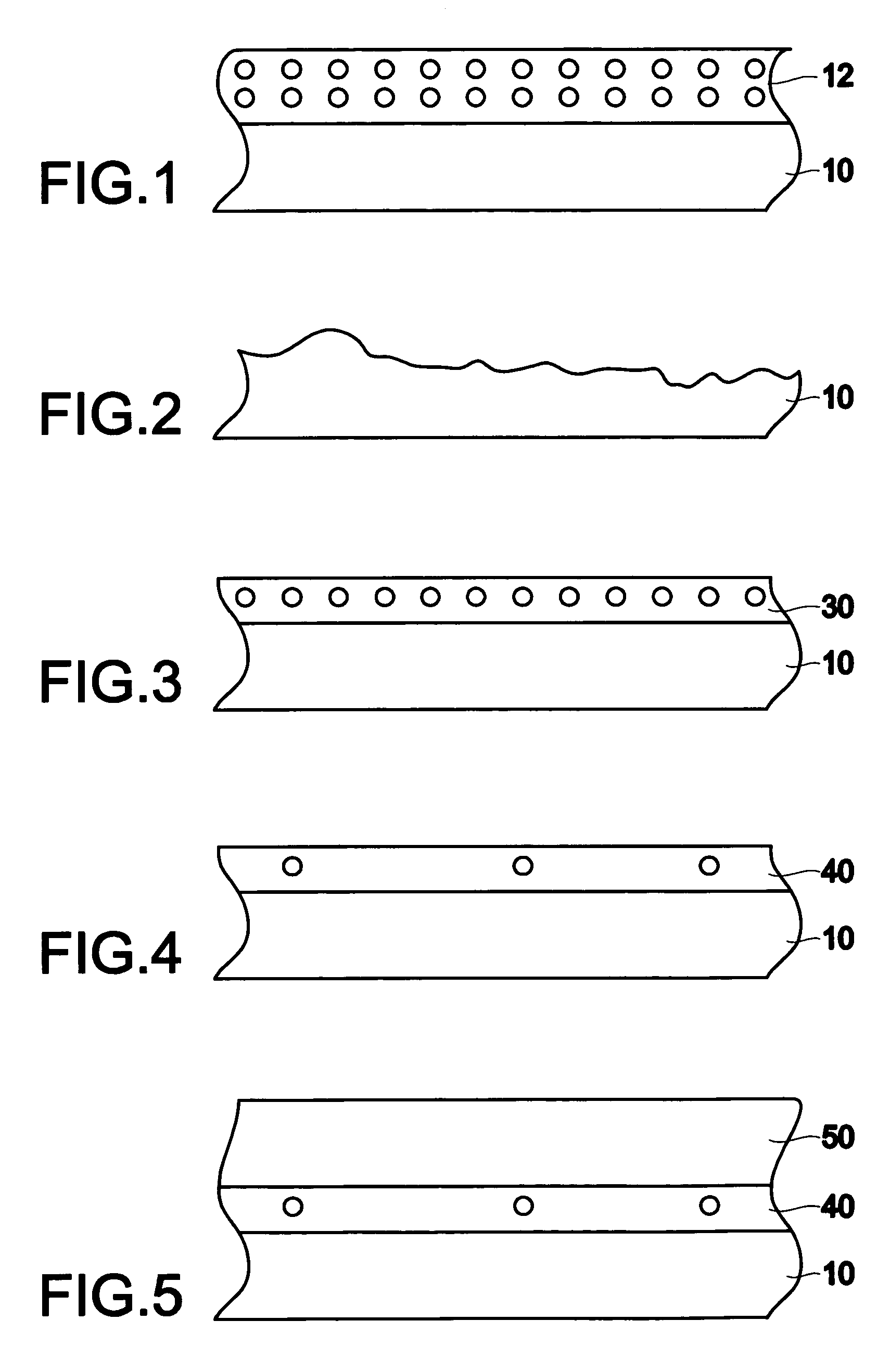

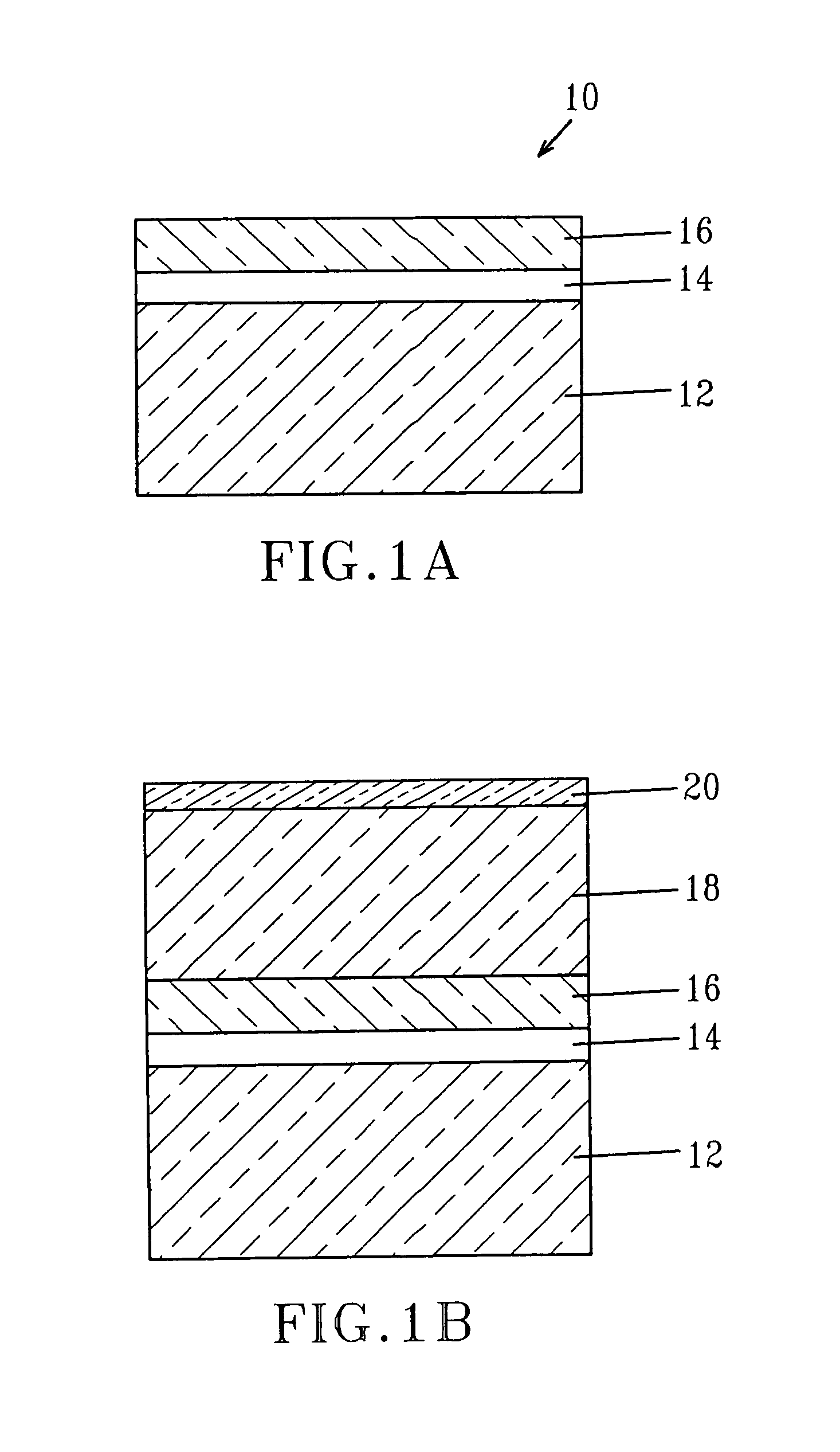

Method of manufacturing strained-silicon semiconductor device

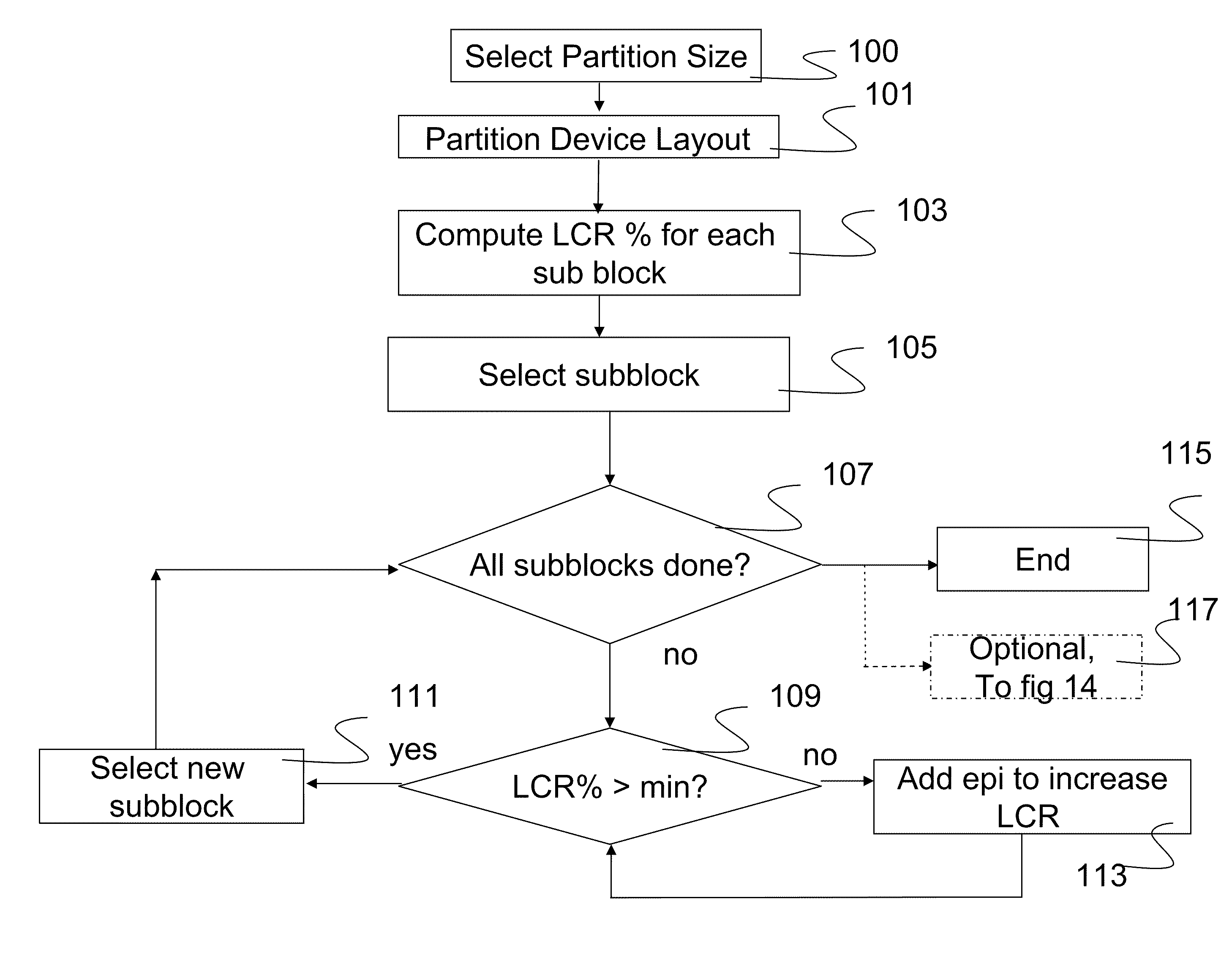

ActiveUS8255843B2Semiconductor/solid-state device testing/measurementSolid-state devicesSemiconductorSilicon

A method for fabricating a strained-silicon semiconductor device to ameliorate undesirable variation in selectively grown epitaxial film thickness. The layout or component configuration for the proposed semiconductor device is evaluated to determine areas of relatively light or dense population in order to determine whether local-loading-effect defects are likely to occur. If a possibility of such defects occurring exists, a dummy pattern of epitaxial structures may be indicated. If so, the dummy pattern appropriate to the proposed layout is created, incorporated into the mask design, and then implemented on the substrate along with the originally-proposed component configuration.

Owner:TAIWAN SEMICON MFG CO LTD

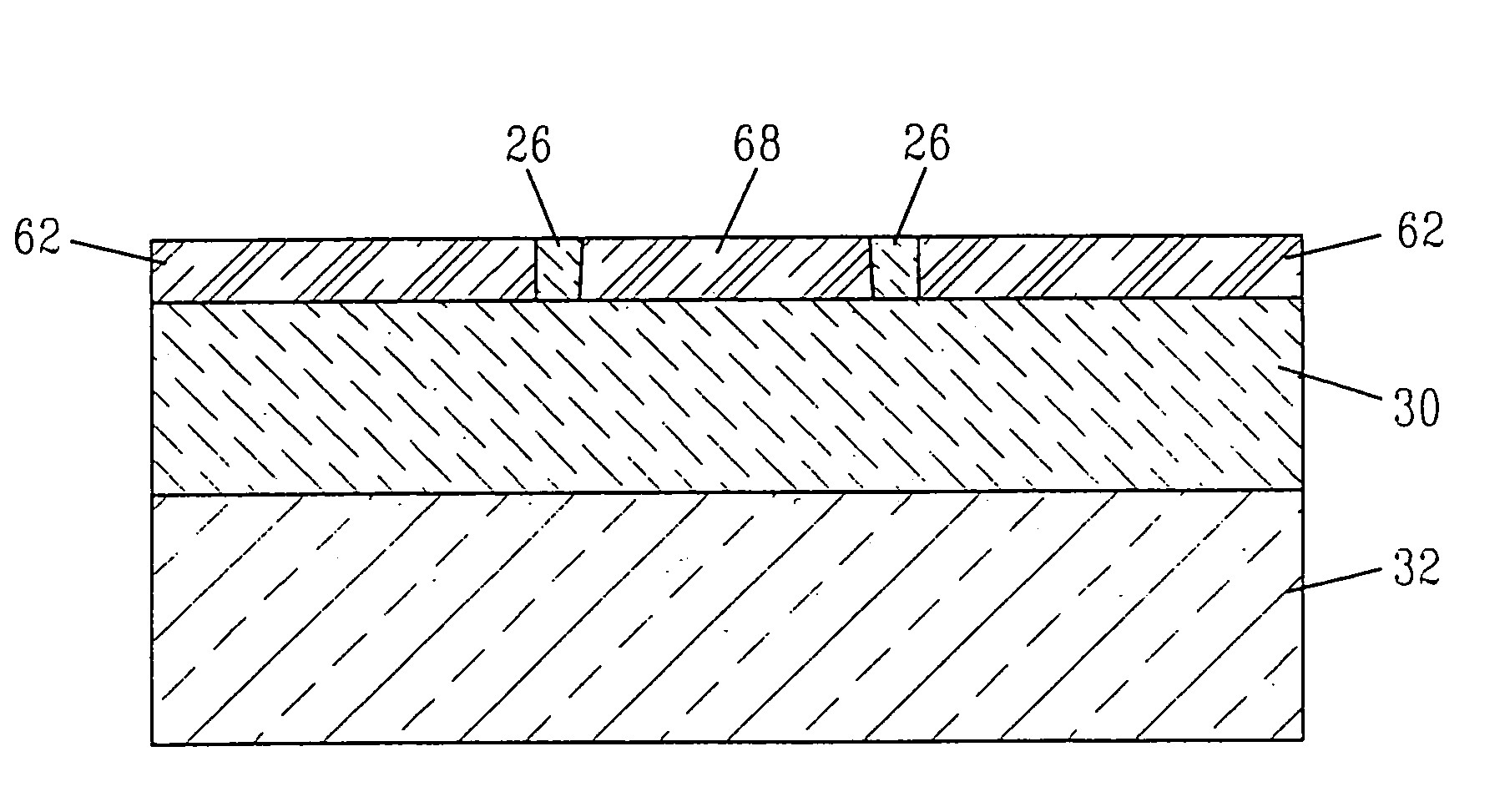

Method for fabricating strained silicon-on-insulator structures and strained silicon-on insulator structures formed thereby

ActiveUS20050227498A1Improve device performanceHigh carrier mobilityTransistorSolid-state devicesDevice formCharge carrier mobility

A silicon-on-insulator (SOI) device and structure having locally strained regions in the silicon active layer formed by increasing the thickness of underlying regions of a buried insulating layer separating the silicon active layer from the substrate. The stress transferred from the underlying thickened regions of the insulating layer to the overlying strained regions increases carrier mobility in these confined regions of the active layer. Devices formed in and on the silicon active layer may benefit from the increased carrier mobility in the spaced-apart strained regions.

Owner:GLOBALFOUNDRIES US INC

Ultra-thin silicon-on-insulator and strained-silicon-direct-on-insulator with hybrid crystal orientations

InactiveUS7098508B2Improve performanceSimple and easy stepTransistorSolid-state devicesEtchingSemiconductor materials

The invention provides integrated semiconductor devices that are formed upon an SOI substrate having different crystal orientations that provide optimal performance for a specific device. Specifically, an integrated semiconductor structure including at least an SOI substrate having a top semiconductor layer of a first crystallographic orientation and a semiconductor material of a second crystallographic orientation, wherein the semiconductor material is substantially coplanar and of substantially the same thickness as that of the top semiconductor layer and the first crystallographic orientation is different from the second crystallographic orientation is provided. The SOI substrate is formed by forming an opening into a structure that includes at least a first semiconductor layer and a second semiconductor layer that have different crystal orientations. The opening extends to the first semiconductor layer. A semiconductor material is epitaxial grown in the opening and then various etching and etch back processing steps are used in forming the SOI substrate.

Owner:GLOBALFOUNDRIES U S INC

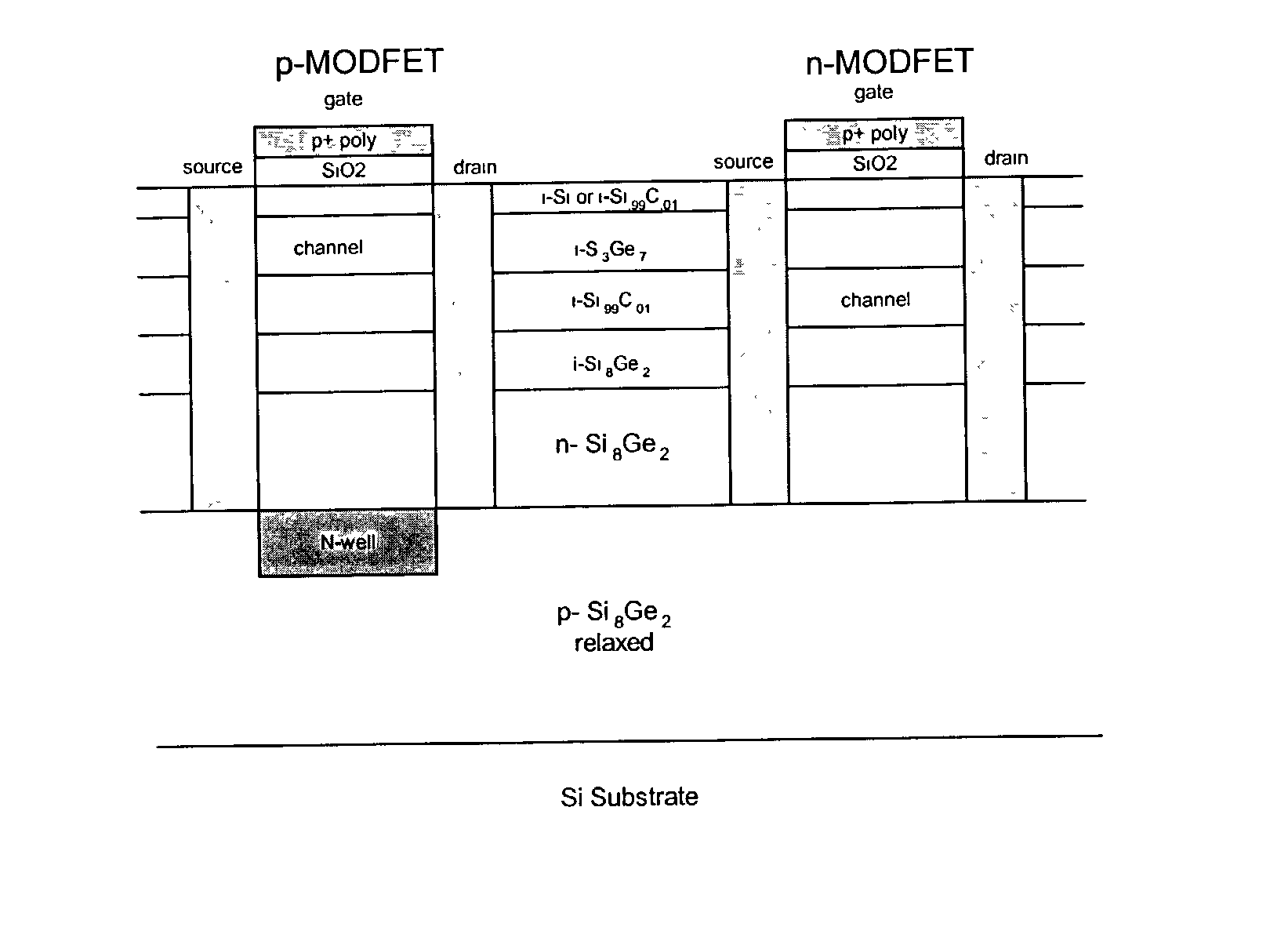

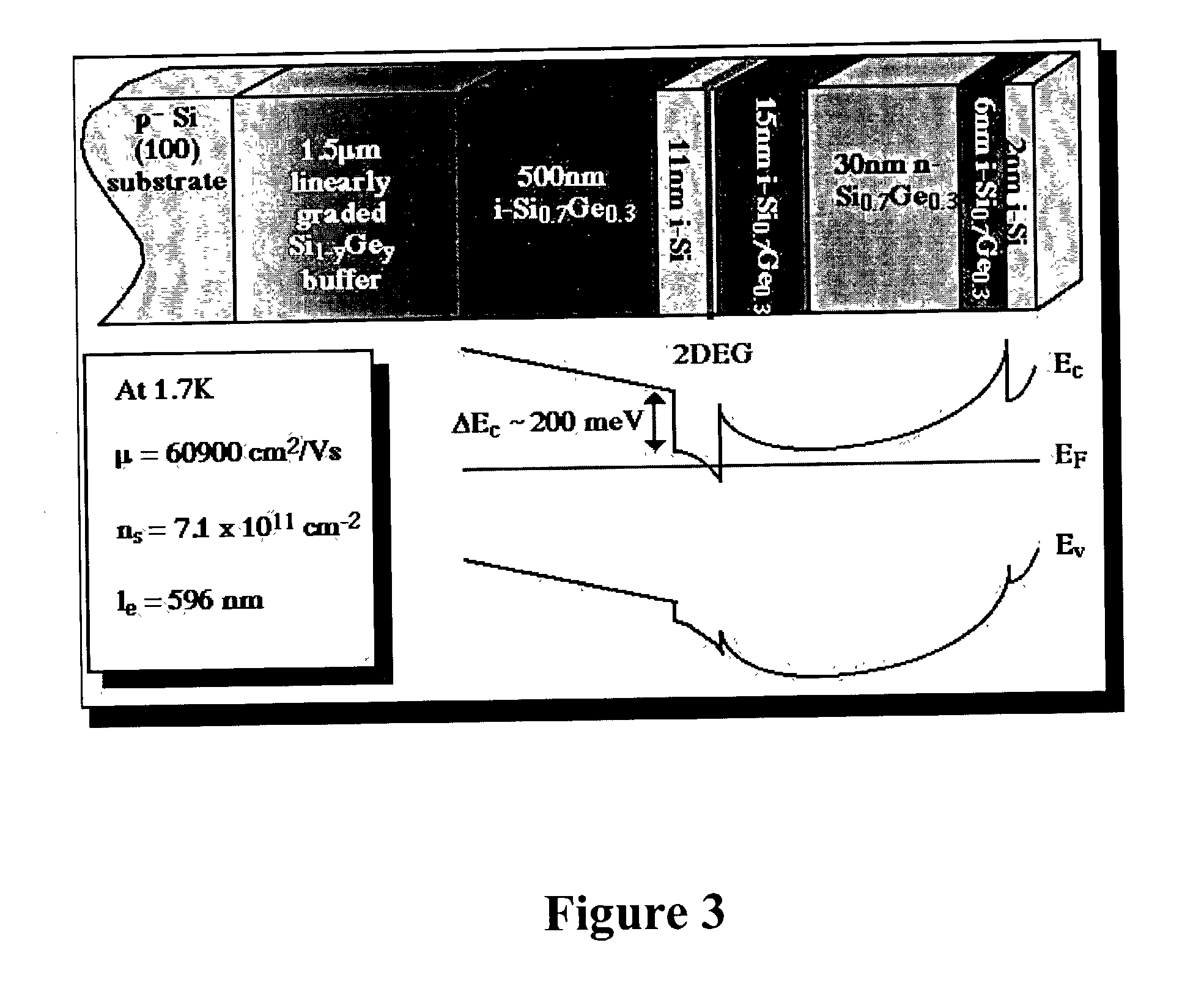

Heterojunction field effect transistors using silicon-germanium and silicon-carbon alloys

InactiveUS20040007715A1Without of performanceWithout strainTransistorSolid-state devicesHeterojunctionSemiconductor

Semiconductor devices, e.g., heterojunction field effect transistors, fabricated with silicon-germnanium buffer layer and silicon-carbon channel layer structures. The invention provides a method of reducing threading defect density via reducing germanium content in a SiGe relaxed buffer layer on which a strained silicon channel layer is formed, by forming the strained silicon channel layer of a silicon-carbon alloy, e.g., containing less than about 1.5 atomic % C substitutionally incorporated in the Si lattice of the alloy.

Owner:INTERNATIONAL RECTIFIER COEP

Strained silicon structure

A semiconductor device includes a substrate, a first epitaxial layer, a second epitaxial layer, a third epitaxial layer, a first trench, and a second trench. The first epitaxial layer is formed on the substrate. The first layer has lattice mismatch relative to the substrate. The second epitaxial layer is formed on the first layer, and the second layer has lattice mismatch relative to the first layer. The third epitaxial layer is formed on the second layer, and the third layer has lattice mismatch relative to the second layer. Hence, the third layer may be strained silicon. The first trench extends through the first layer. The second trench extends through the third layer and at least partially through the second layer. At least part of the second trench is aligned with at lease part of the first trench, and the second trench is at least partially filled with an insulating material.

Owner:TAIWAN SEMICON MFG CO LTD

Method of preventing surface roughening during hydrogen prebake of SiGe substrates

InactiveUS20050148161A1Avoid creatingAvoid roughnessPolycrystalline material growthSemiconductor/solid-state device manufacturingHydrofluoric acidRough surface

The invention forms an epitaxial silicon-containing layer on a silicon germanium, patterned strained silicon, or patterned thin silicon-on-insulator surface and avoids creating a rough surface upon which the epitaxial silicon-containing layer is grown. In order to avoid creating the rough surface, the invention first performs a hydrofluoric acid etching process on the silicon germanium, patterned strained silicon, or patterned thin silicon-on-insulator surface. This etching process removes most of oxide from the surface, and leaves a first amount of oxygen (typically 1×1013-1×1015 / cm2 of oxygen) on the silicon germanium, patterned strained silicon, or patterned thin silicon-on-insulator surface. The invention then performs a hydrogen pre-bake process which heats the silicon germanium, patterned strained silicon, or patterned thin silicon-on-insulator surface sufficiently to remove additional oxygen from the surface and leave a second amount of oxygen, less than the first amount, on the silicon germanium, patterned strained silicon, or patterned thin silicon-on-insulator surface. The heating process leaves an amount of at least 5×1012 / cm2 of oxygen (typically, between approximately 1×1013 / cm2 and approximately 5×1013 / cm2 of oxygen) on the silicon germanium, patterned strained silicon, or patterned thin silicon-on-insulator surface. By leaving a small amount of oxygen on the silicon germanium, patterned strained silicon, or patterned silicon-on-insulator surface, the heating processes avoid changing the roughness of the silicon germanium, patterned strained silicon, or patterned thin silicon-on-insulator surface. Then the process of epitaxially growing the epitaxial silicon-containing layer on the silicon germanium, patterned strained silicon, or patterned silicon-on-insulator surface is performed.

Owner:IBM CORP