Patents

Literature

2083results about "From solid state" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Process for producing oriented inorganic crystalline film, and semiconductor device using the oriented inorganic crystalline film

ActiveUS20090152506A1Orientation can be controlledLow costFrom gel stateFrom solid stateOrganic solventDevice material

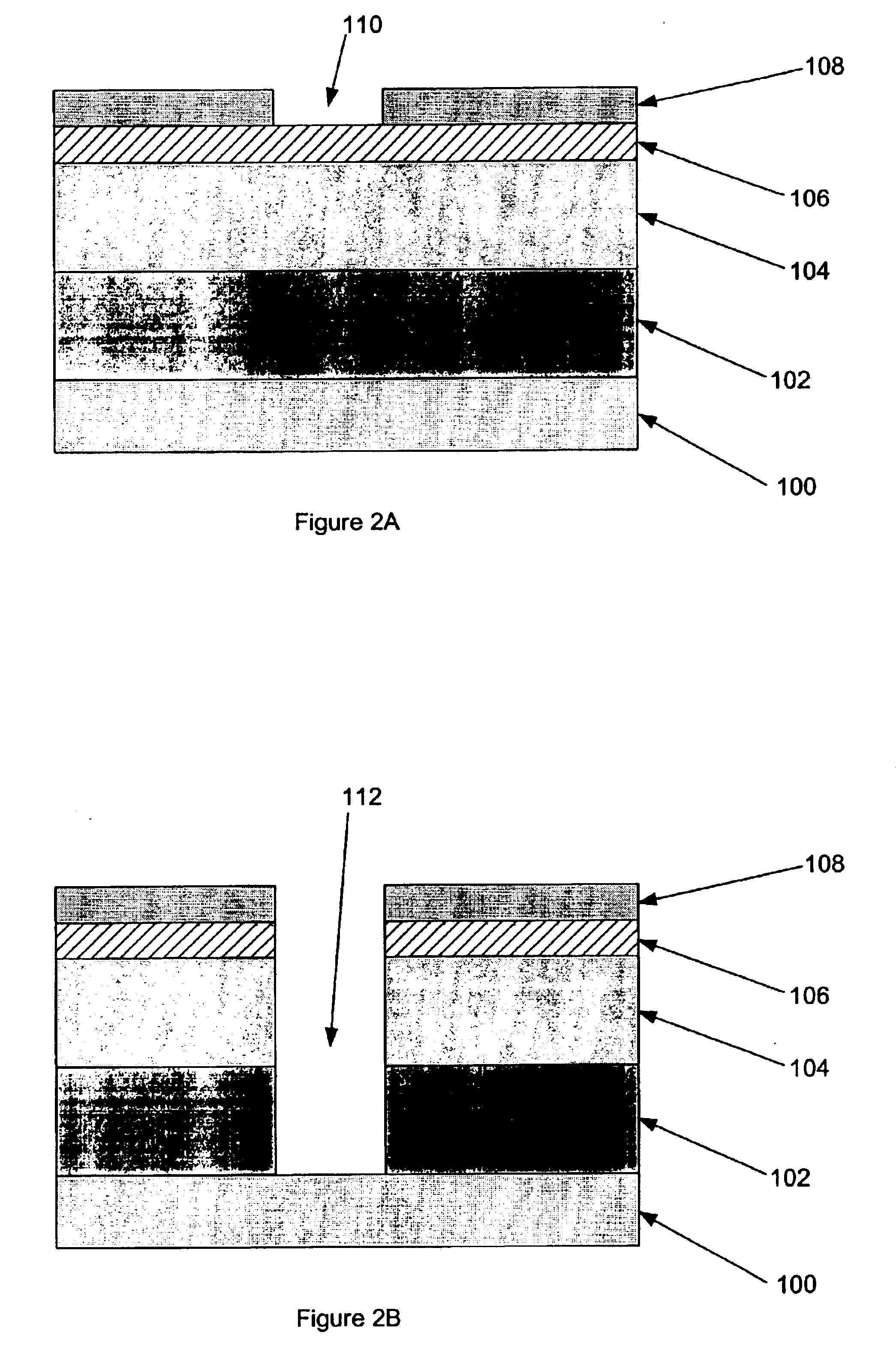

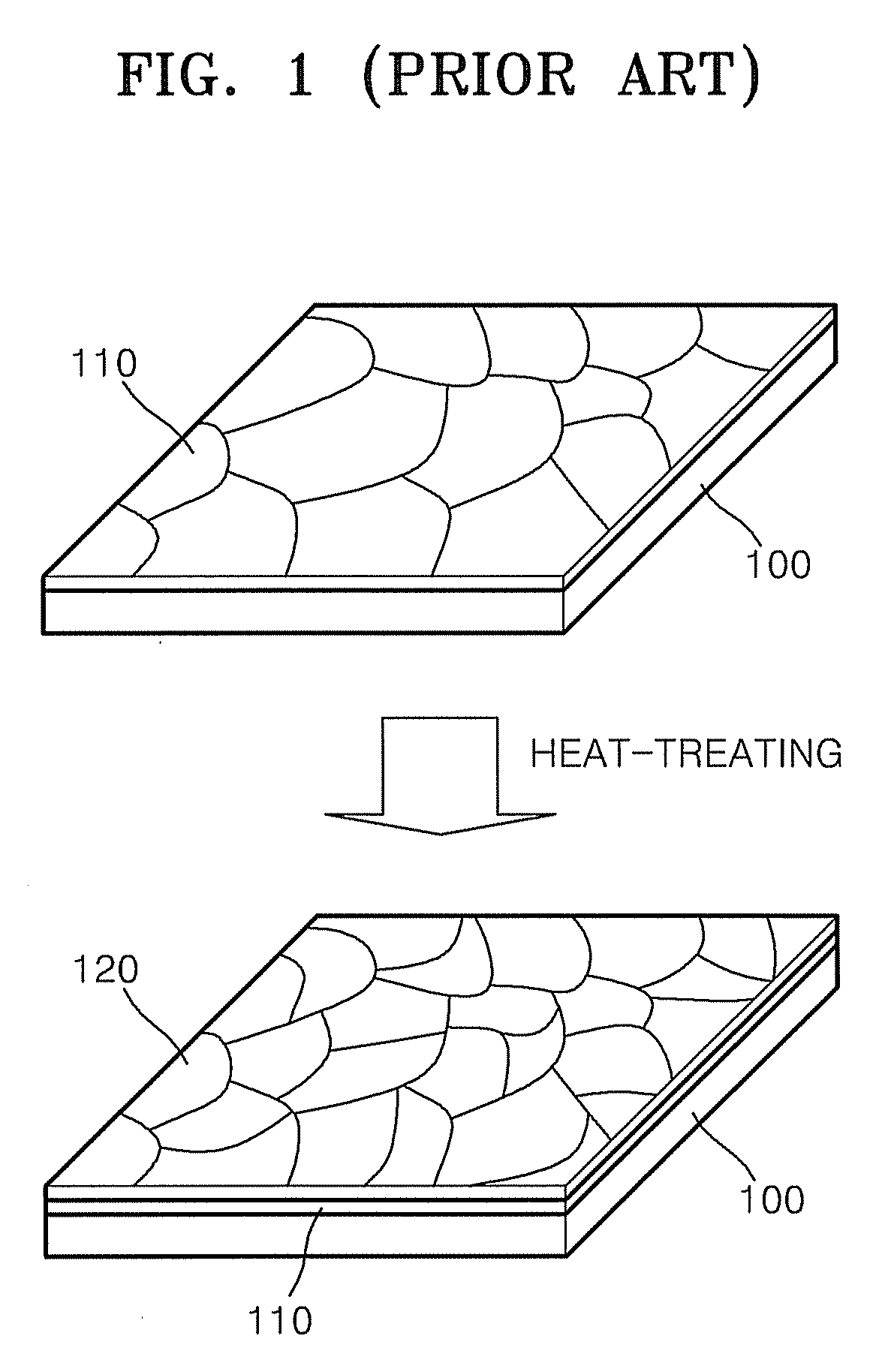

In a process for producing an oriented inorganic crystalline film, a non-monocrystalline film containing inorganic crystalline particles is formed on a substrate by a liquid phase technique using a raw-material solution which contains a raw material and an organic solvent, where the inorganic crystalline particles have a layered crystal structure and are contained in the raw material. Then, the non-monocrystalline film is crystallized by heating the non-monocrystalline film to a temperature equal to or higher than the crystallization temperature of the non-monocrystalline film so that part of the inorganic crystalline particles act as crystal nuclei.

Owner:FUJIFILM CORP

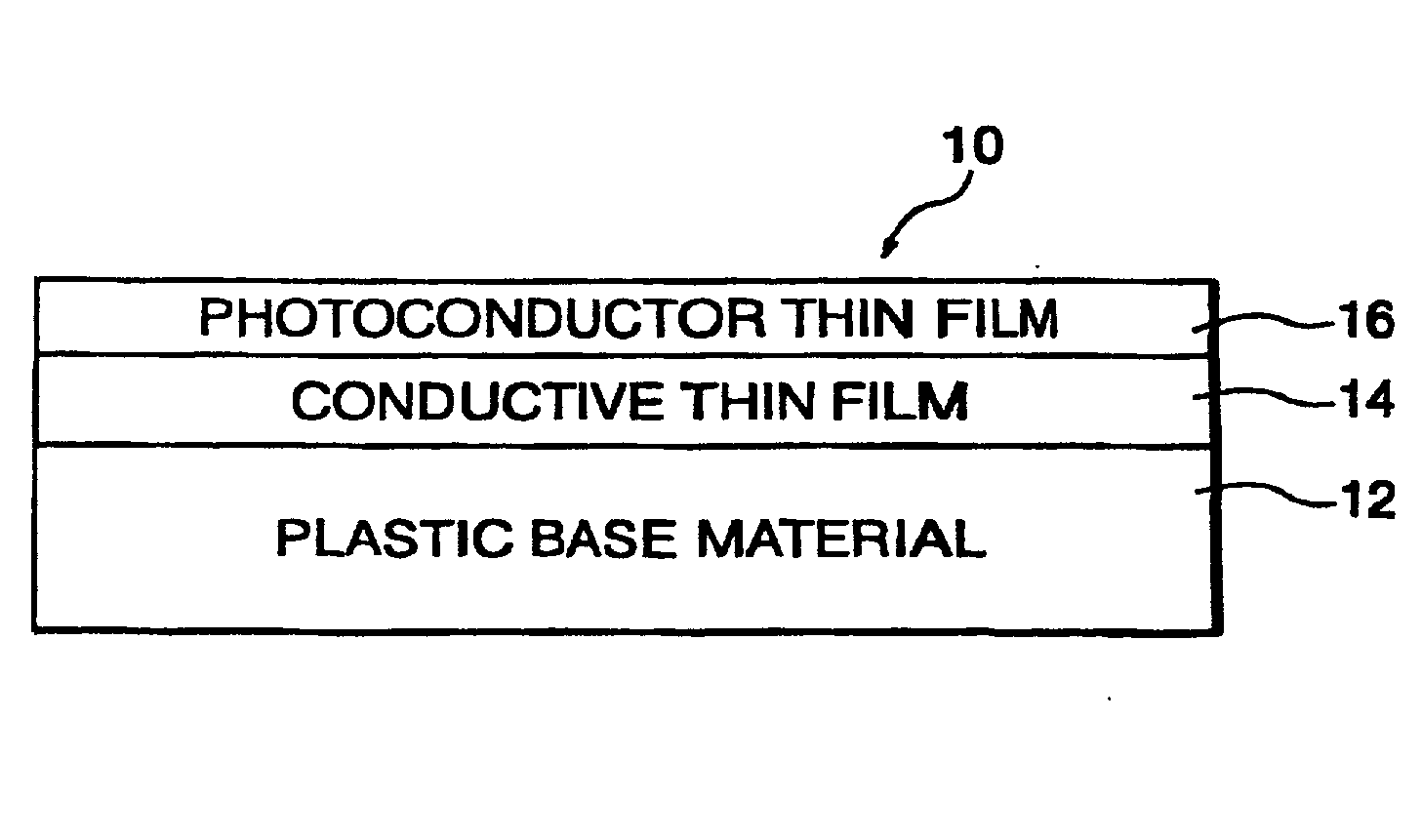

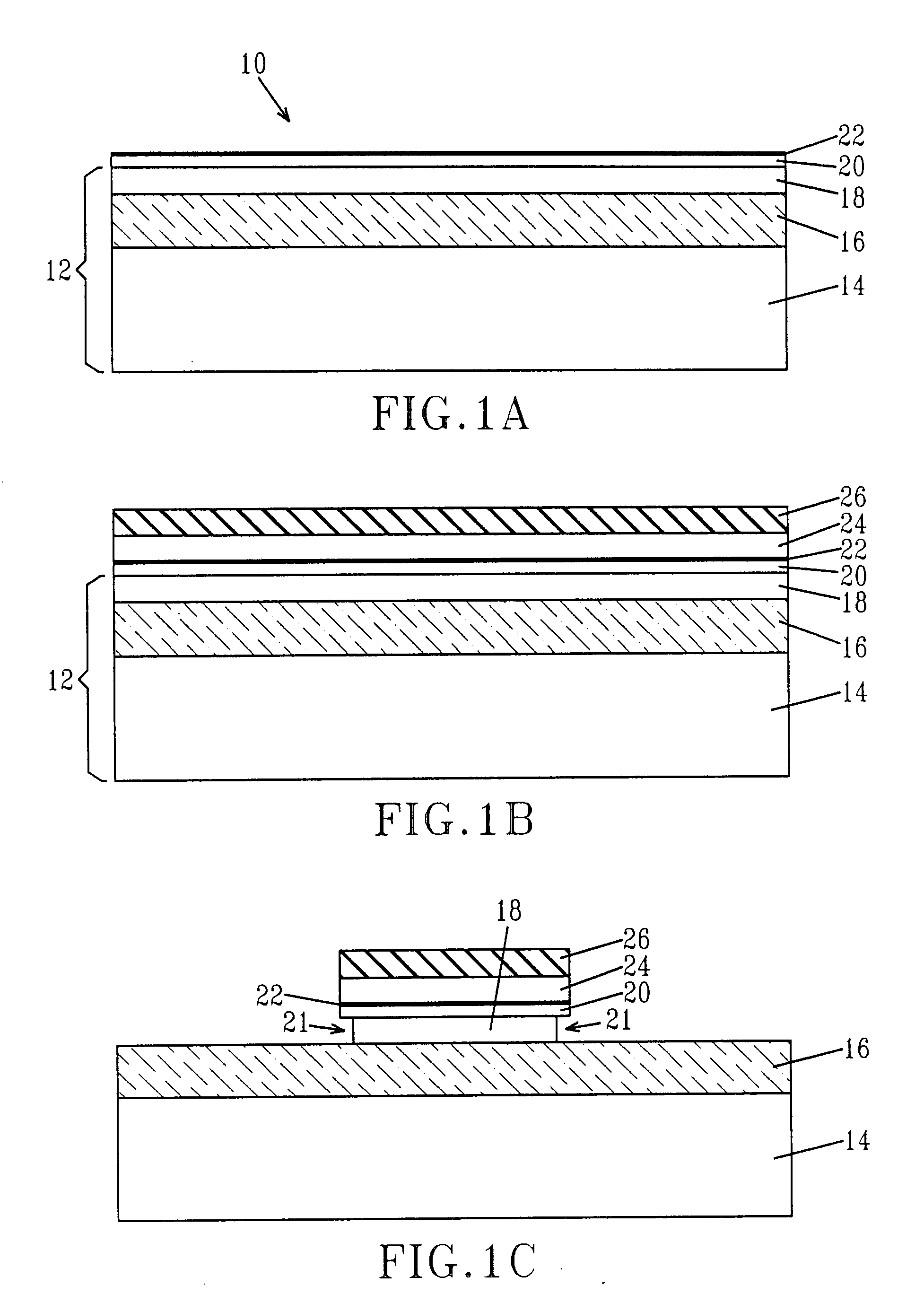

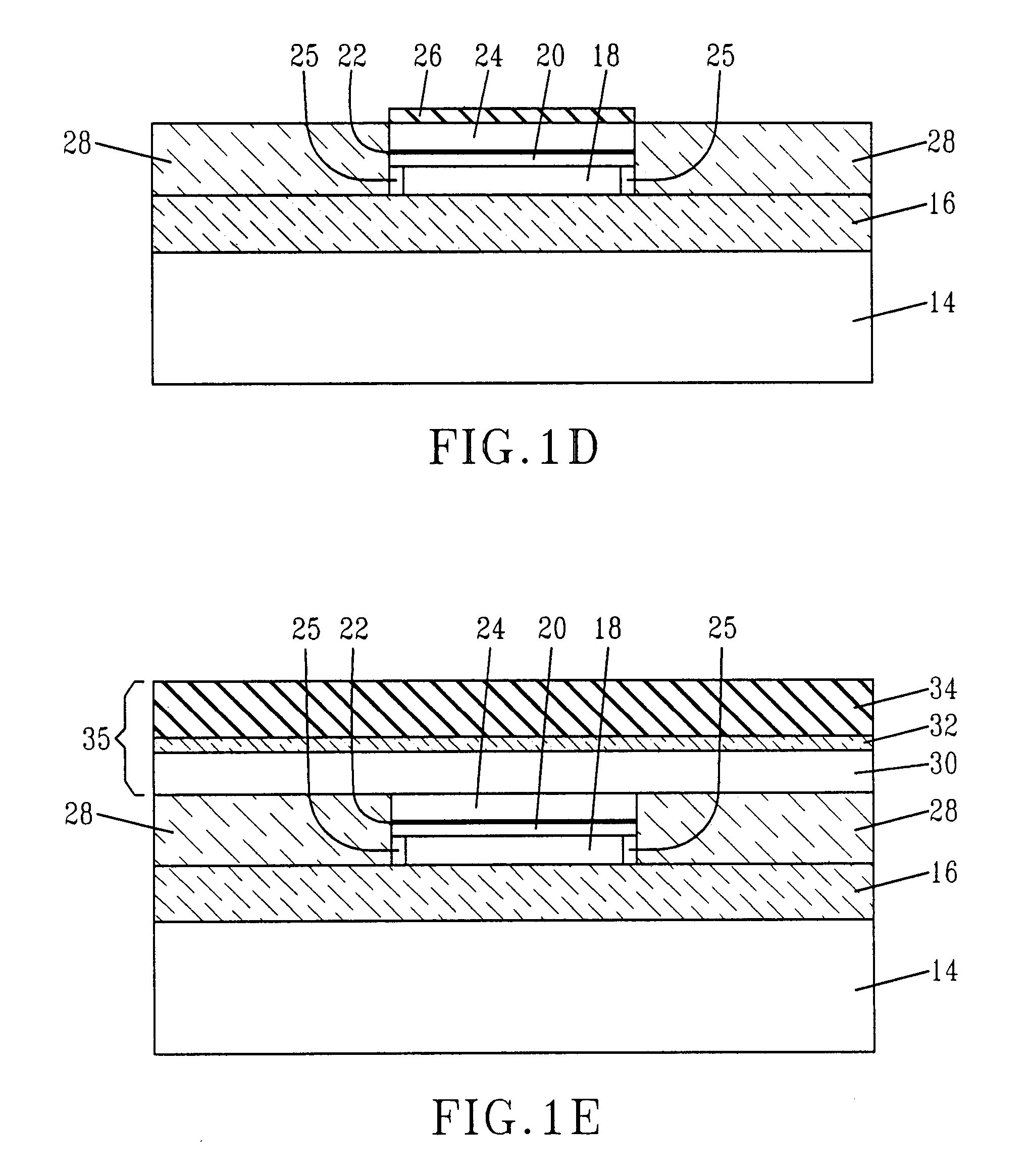

Method of forming crystalline semiconductor thin film on base substrate, lamination formed with crystalline semiconductor thin film and color filter

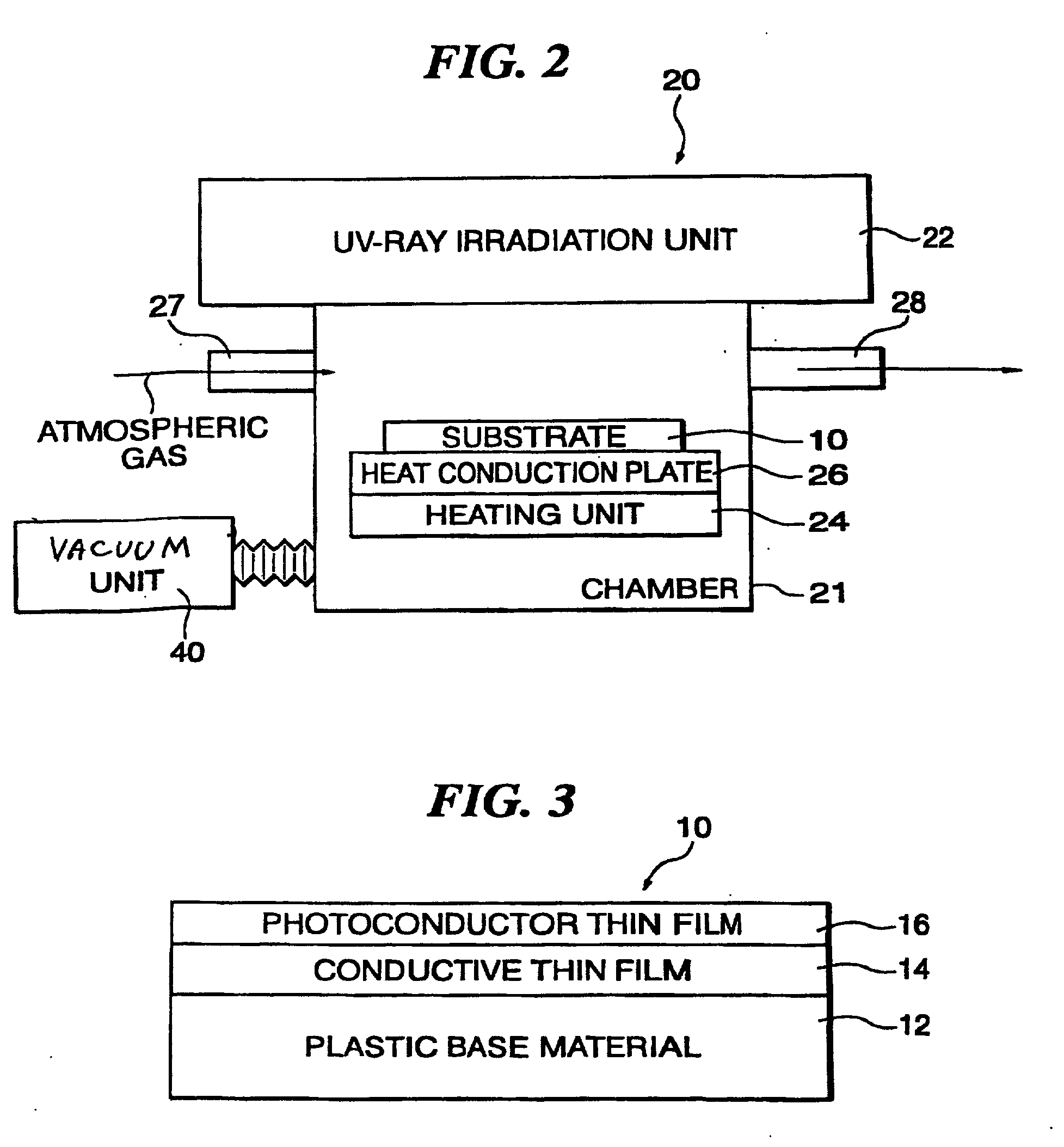

A method of forming a crystalline semiconductor thin film on a base material which can be prepared at a low temperature by simple step and device, the method including a processing step of applying UV-rays to an amorphous semiconductor thin film provided on a base material while keeping a temperature at not less than 25° C. and not more than 300° C. in a vacuum or a reducing gas atmosphere, as well as a substrate having the semiconductor thin film provided on the base material, a substrate for forming a color filter and a color filter using the substrate.

Owner:FUJIFILM BUSINESS INNOVATION CORP

Process for producing oriented inorganic crystalline film, and semiconductor device using the oriented inorganic crystalline film

ActiveUS8202365B2Orientation can be controlledLow costFrom gel stateFrom solid stateOrganic solventCrystal structure

In a process for producing an oriented inorganic crystalline film, a non-monocrystalline film containing inorganic crystalline particles is formed on a substrate by a liquid phase technique using a raw-material solution which contains a raw material and an organic solvent, where the inorganic crystalline particles have a layered crystal structure and are contained in the raw material. Then, the non-monocrystalline film is crystallized by heating the non-monocrystalline film to a temperature equal to or higher than the crystallization temperature of the non-monocrystalline film so that part of the inorganic crystalline particles act as crystal nuclei.

Owner:FUJIFILM CORP

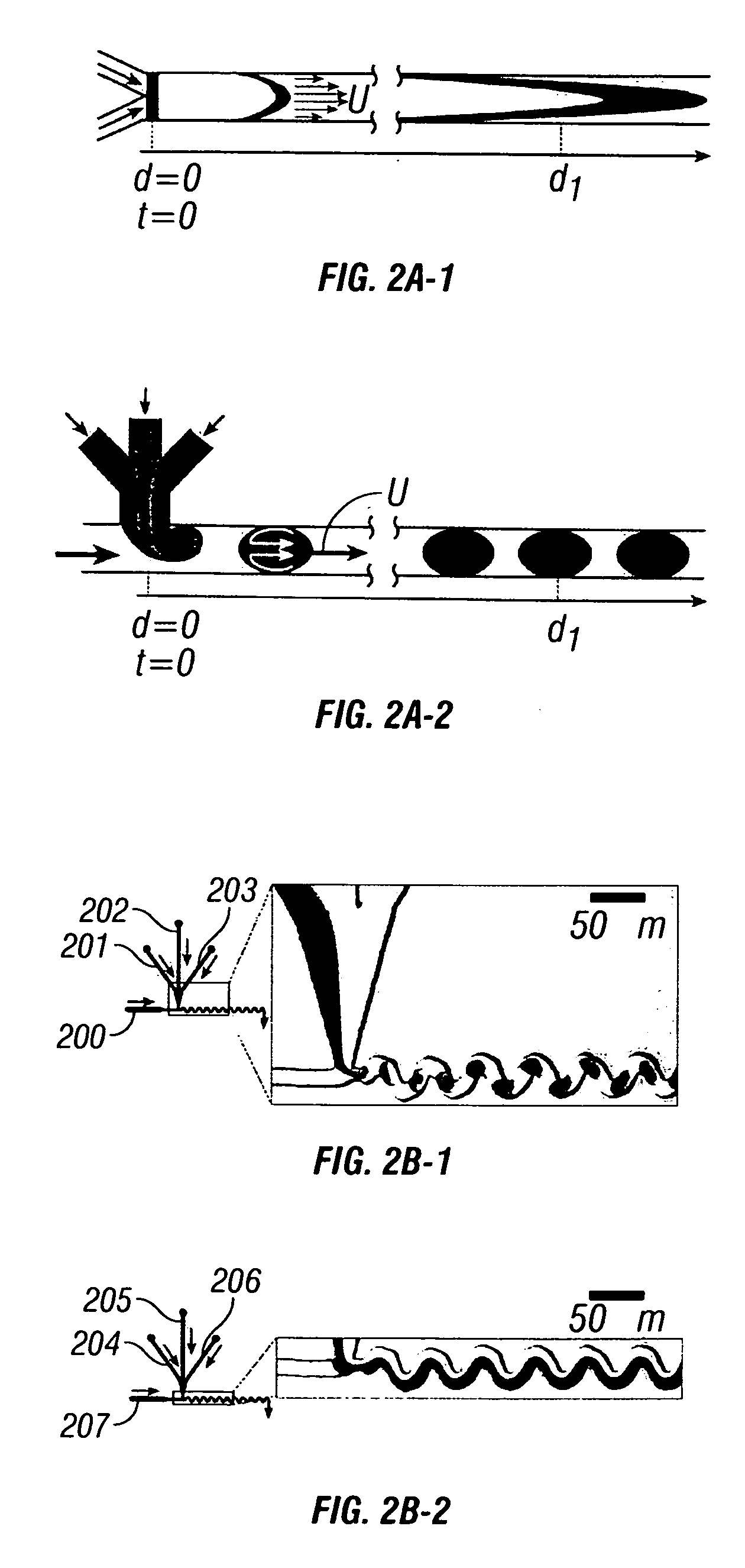

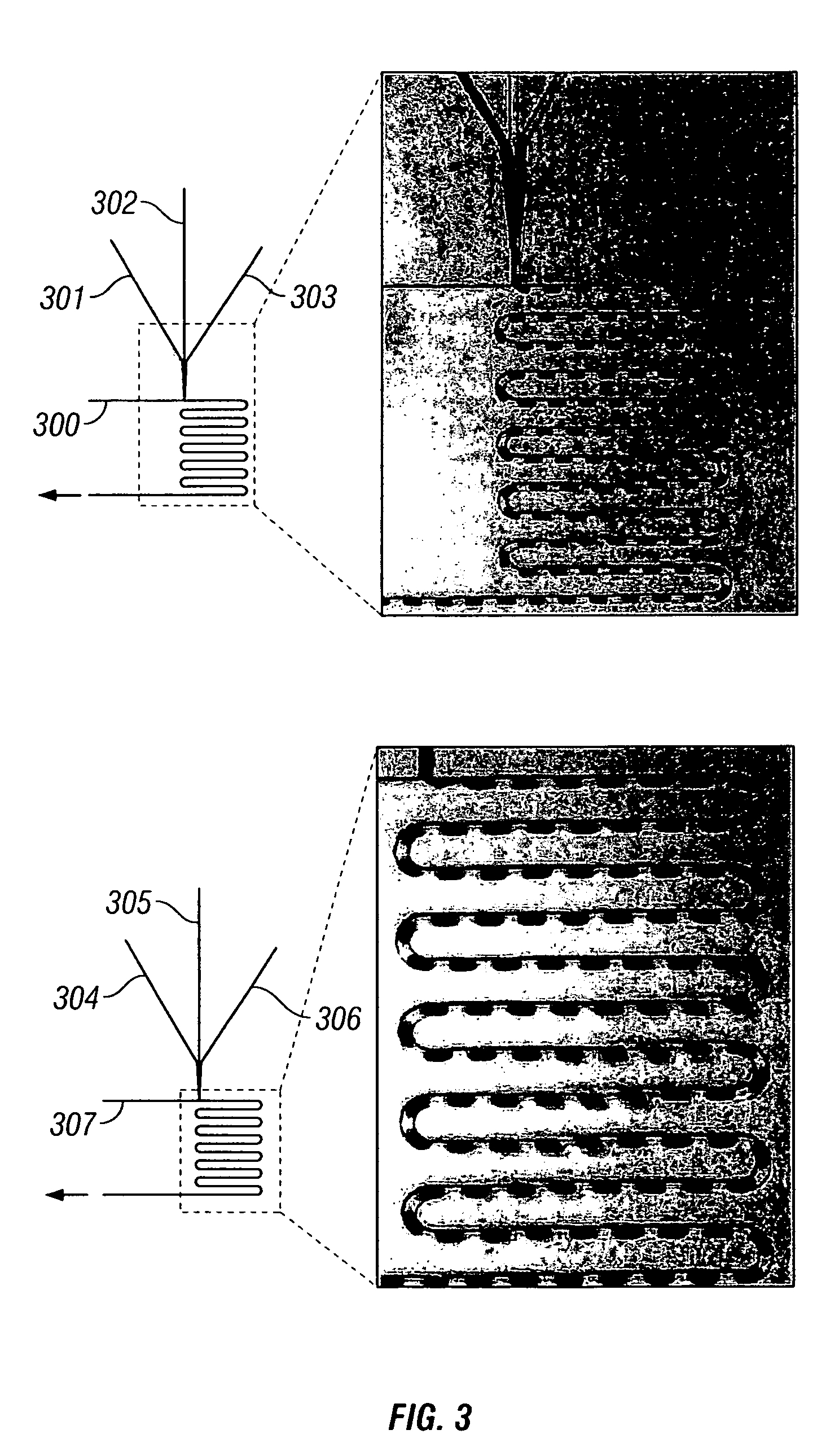

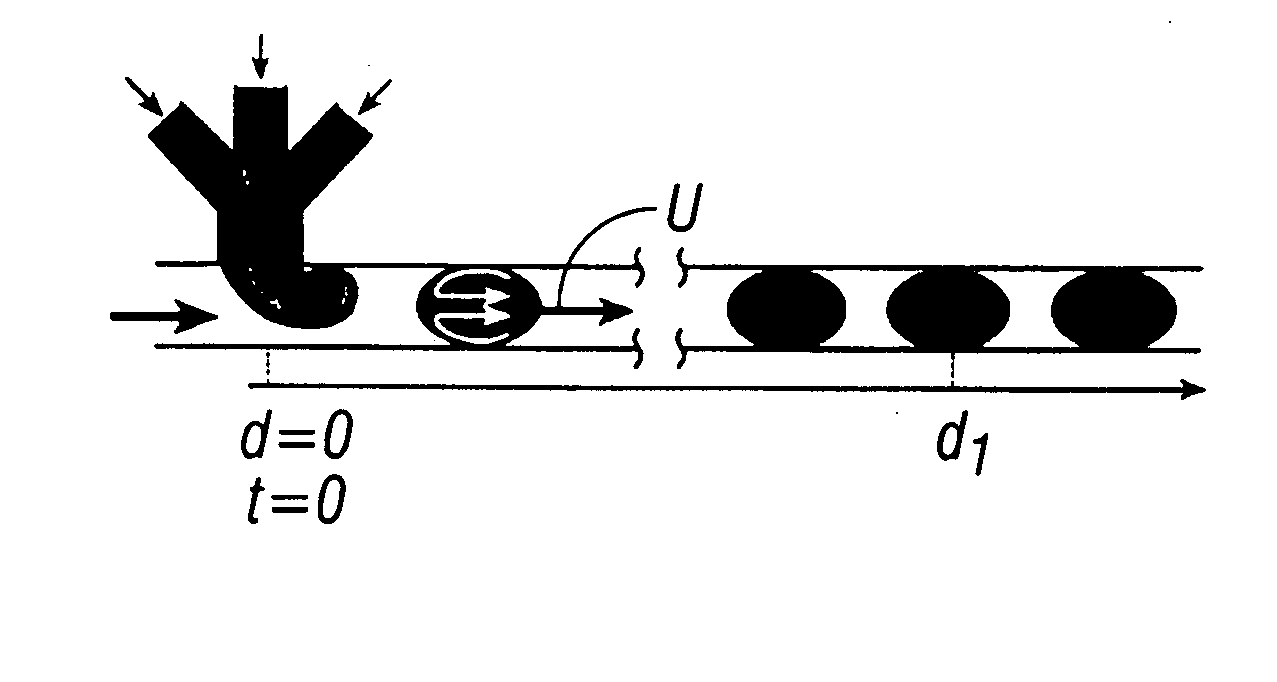

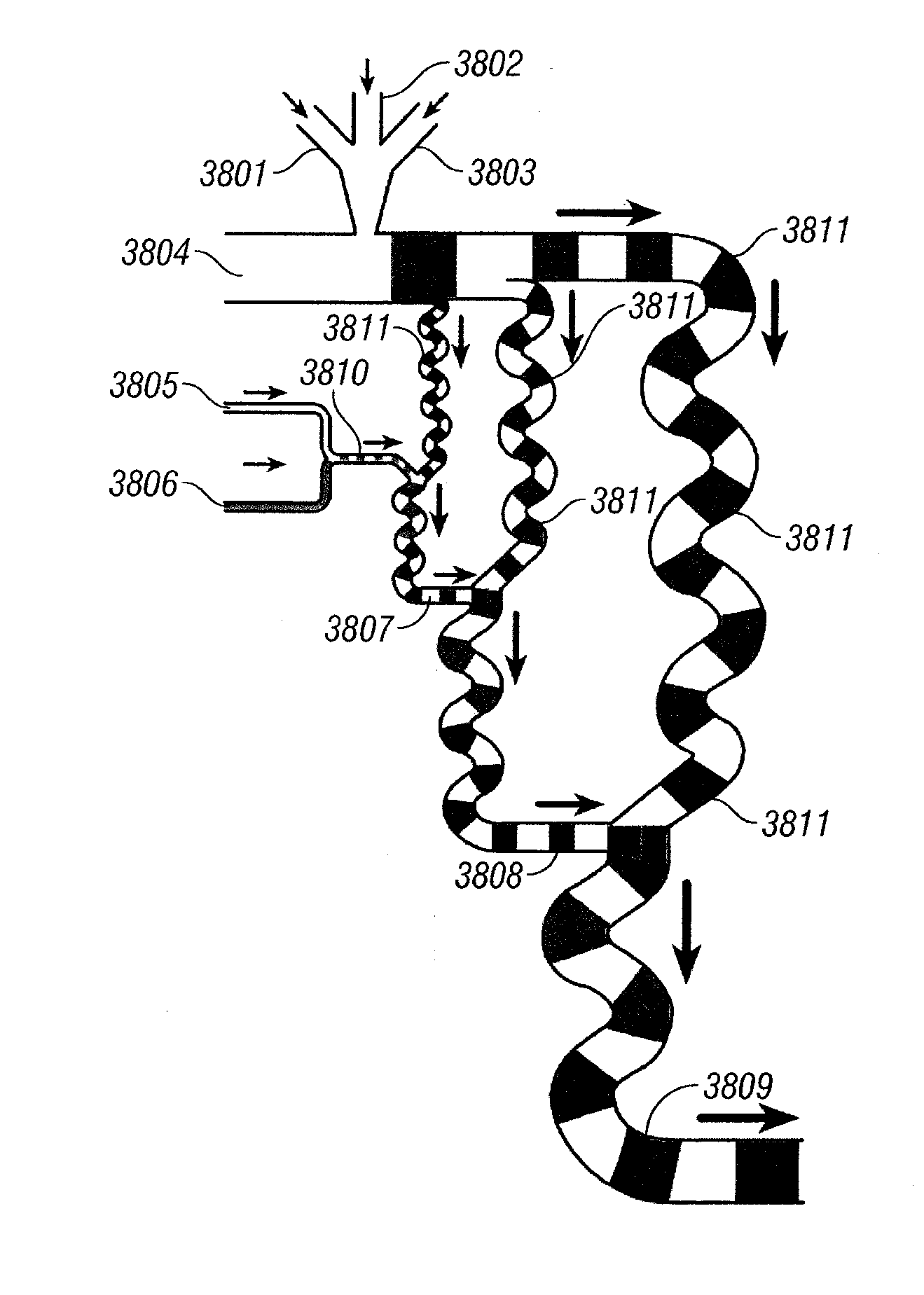

Device and method for pressure-driven plug transport and reaction

InactiveUS7129091B2Well mixedQuick mixMaterial nanotechnologySequential/parallel process reactionsPressure.driveCarrier fluid

Owner:UNIVERSITY OF CHICAGO

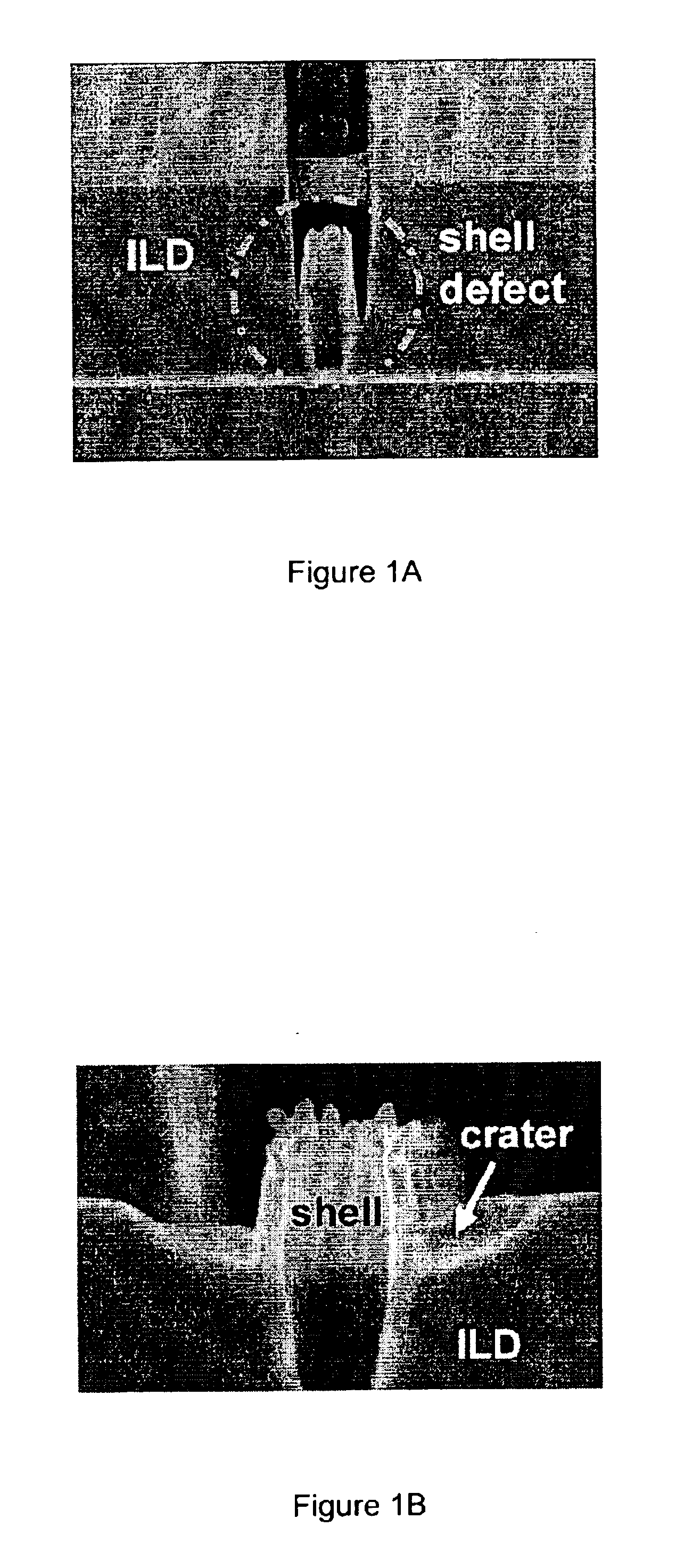

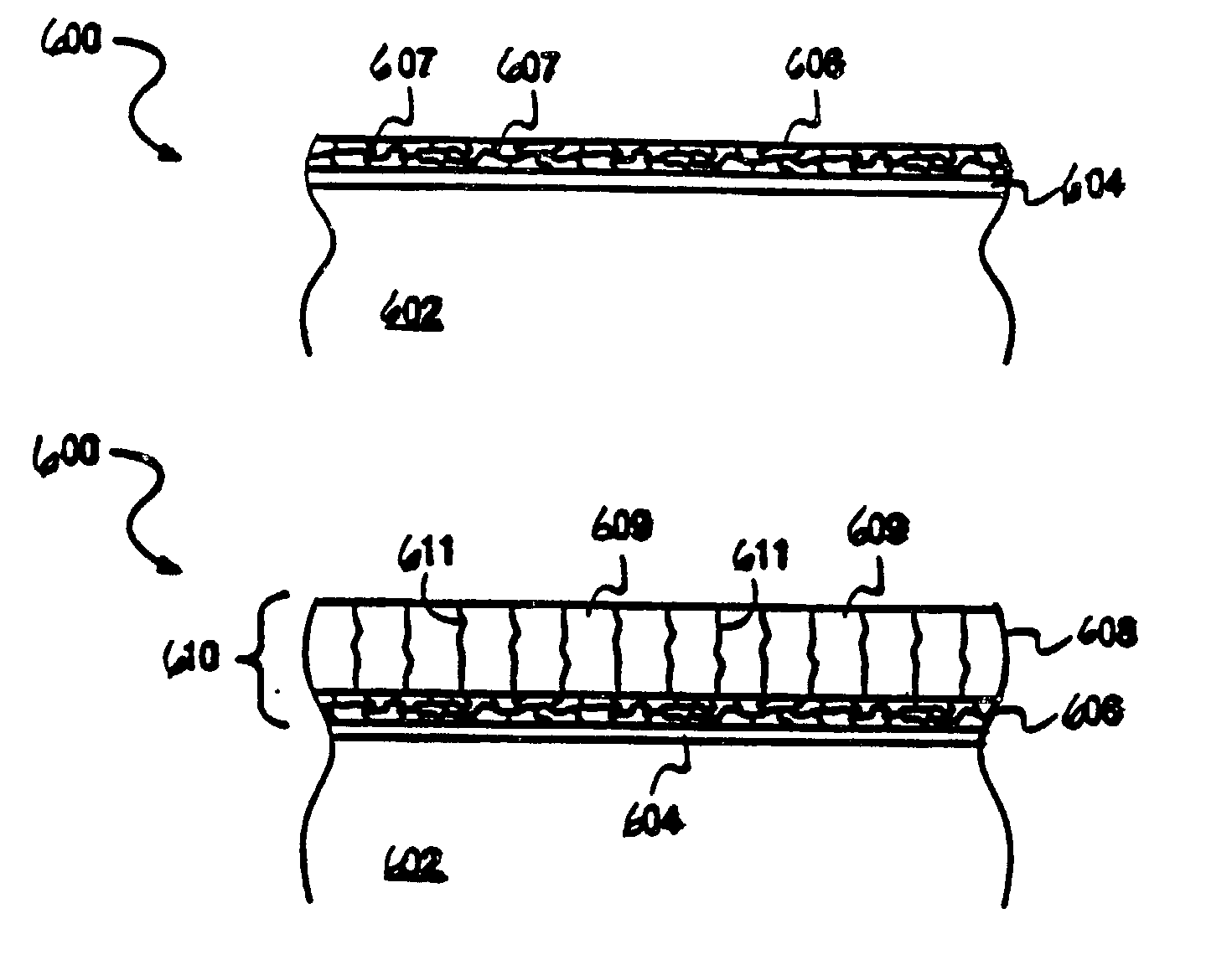

Polymer sacrificial light absorbing structure and method

InactiveUS6876017B2From solid stateSemiconductor/solid-state device detailsSolubilityLithographic artist

Method and structure for optimizing dual damascene patterning with polymeric dielectric materials are disclosed. Certain embodiments of the invention comprise polymeric sacrificial light absorbing materials (“polymer SLAM”) functionalized to have a controllable solubility switch wherein such polymeric materials have substantially the same etch rate as conventionally utilized polymeric dielectric materials, and subsequent to chemical modification of solubility-modifying protecting groups comprising the SLAM materials by thermal treatment or in-situ generation of an acid, such SLAM materials become soluble in weak bases, such as those conventionally utilized to remove materials in lithography treatments.

Owner:INTEL CORP

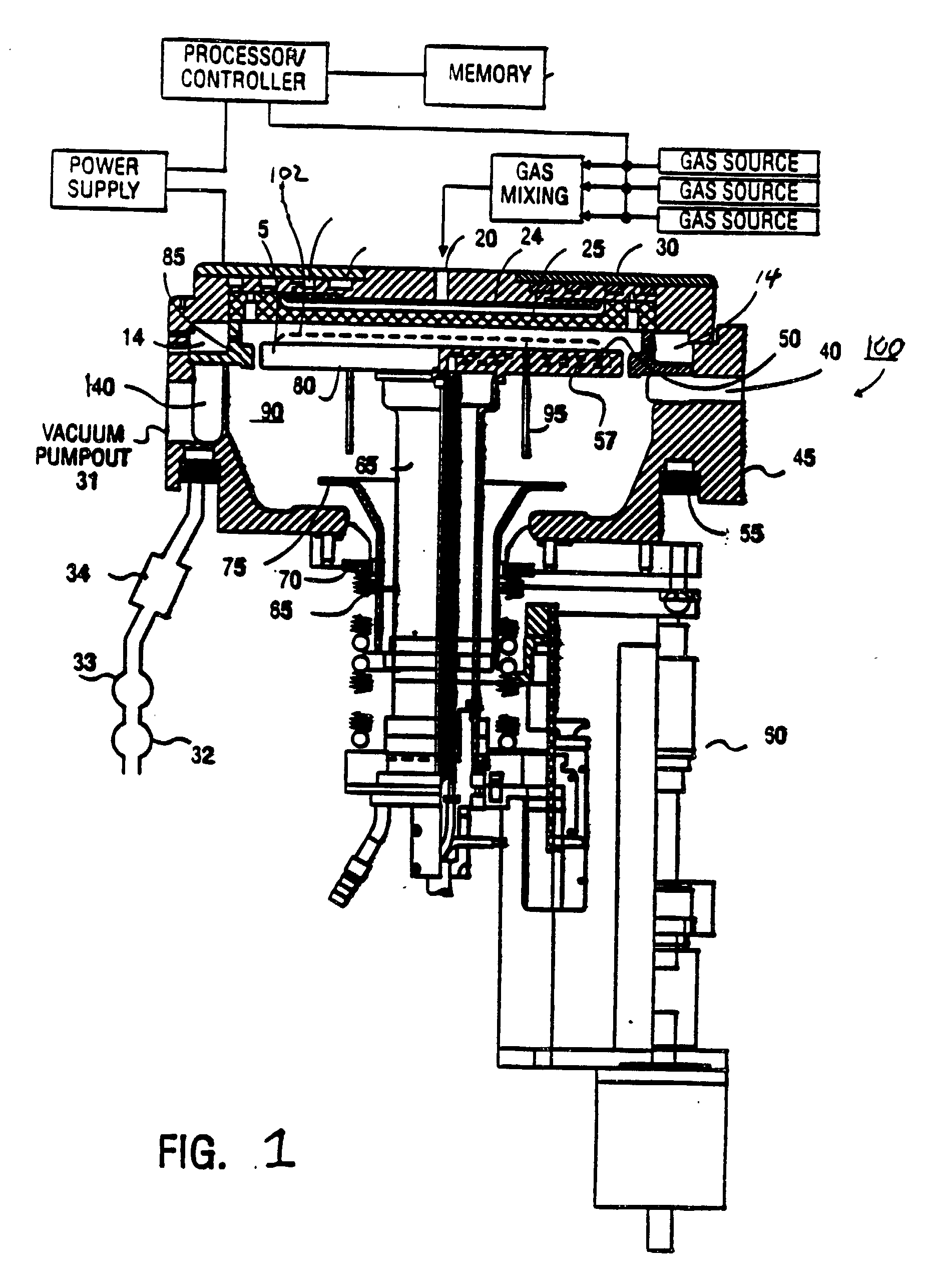

Diamond coatings on reactor wall and method of manufacturing thereof

InactiveUS20020086501A1High purityIncrease resistanceFrom solid stateVacuum evaporation coatingMetallurgySemiconductor

A corrosion resistant component of semiconductor processing equipment such as a plasma chamber includes a diamond containing surface and process for manufacture thereof.

Owner:LAM RES CORP

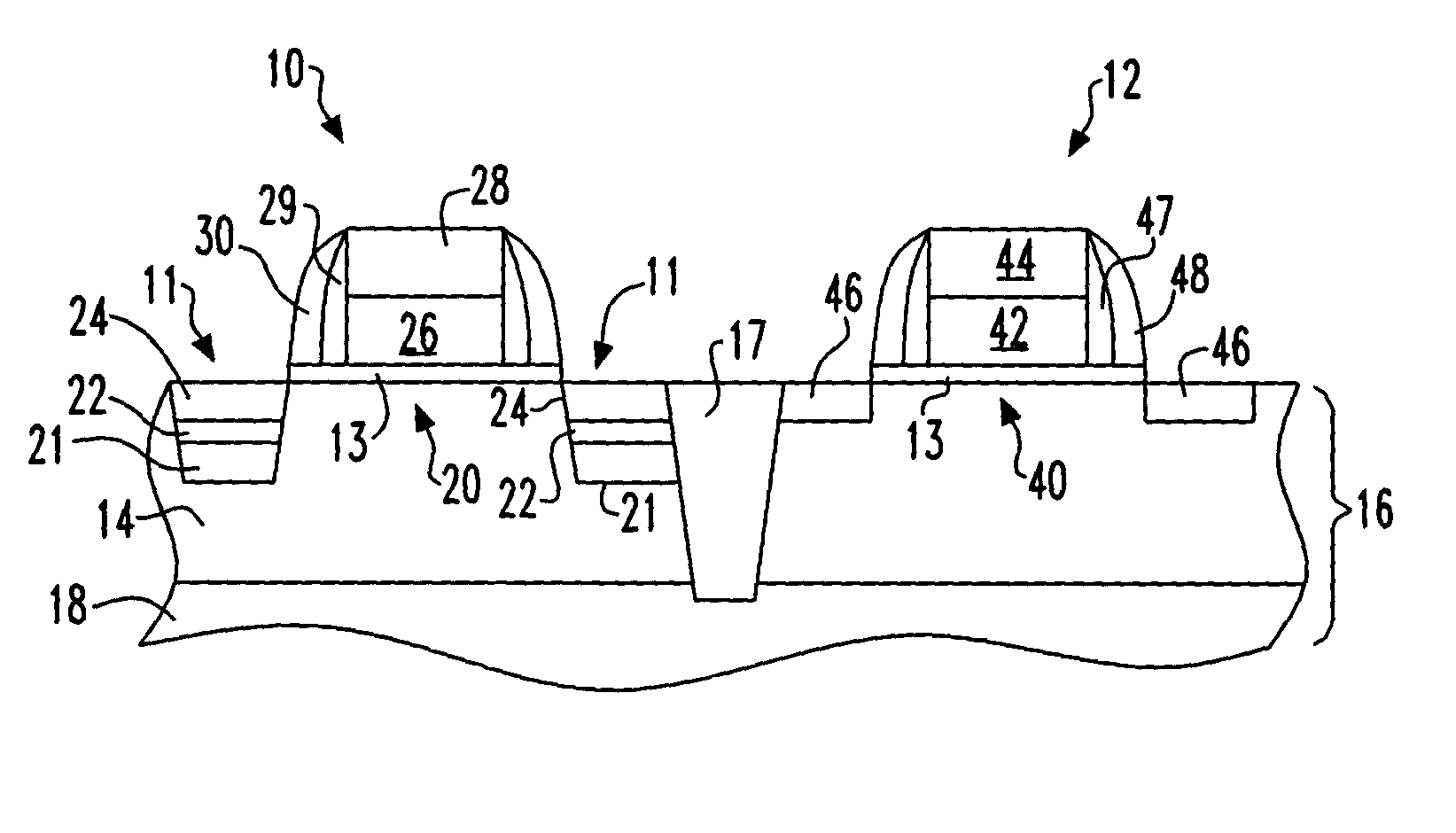

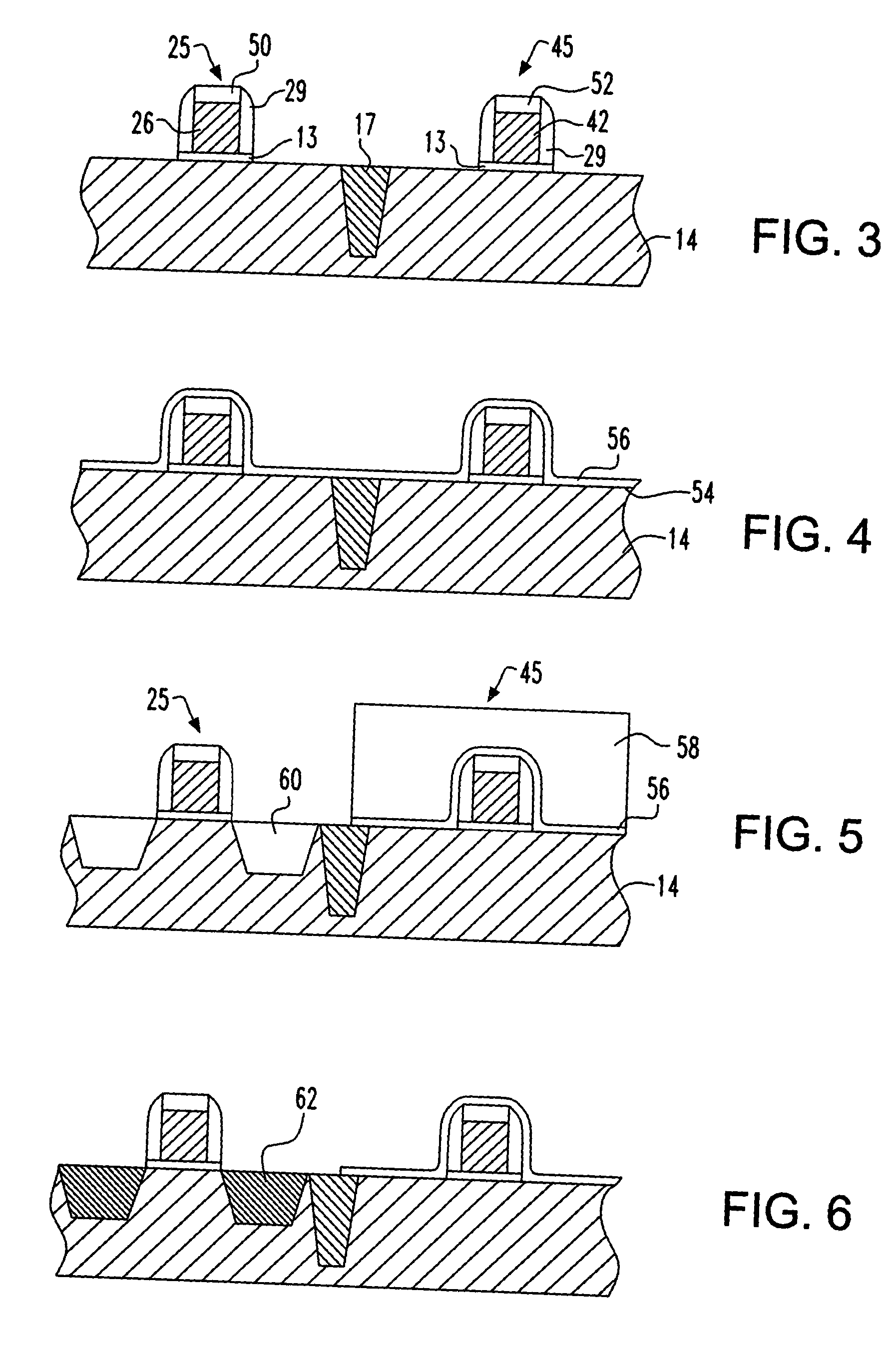

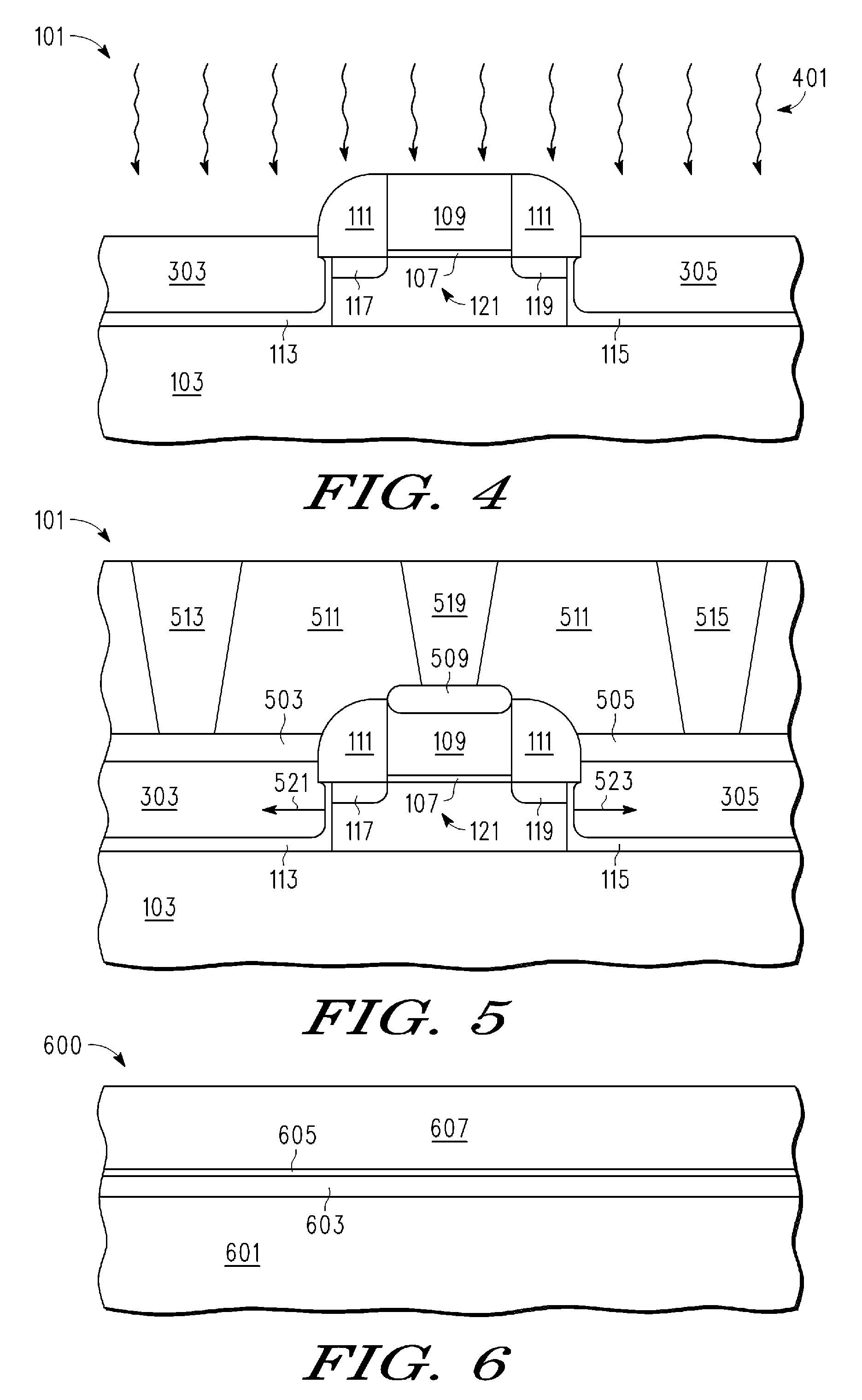

RAISED STI PROCESS FOR MULTIPLE GATE OX AND SIDEWALL PROTECTION ON STRAINED Si/SGOI STRUCTURE WITH ELEVATED SOURCE/DRAIN

InactiveUS20050277271A1Eliminating unnecessary poly over etchingTaller in heightTransistorFrom solid stateGate dielectricActive devices

The present invention provides a strained / SGOI structure that includes an active device region of a relaxed SiGe layer, a strained Si layer located atop the relaxed SiGe layer, a raised source / drain region located atop a portion of the strained Si layer, and a stack comprising at least a gate dielectric and a gate polySi located on another portion of the strained Si layer; and a raised trench oxide region surrounding the active device region. The present invention also provides a method of forming such a structure. In the inventive method, the gate dielectric is formed prior to trench isolation formation thereby avoiding many of the problems associated with prior art processes in which the trench oxide is formed prior to gate dielectric formation.

Owner:GLOBALFOUNDRIES INC

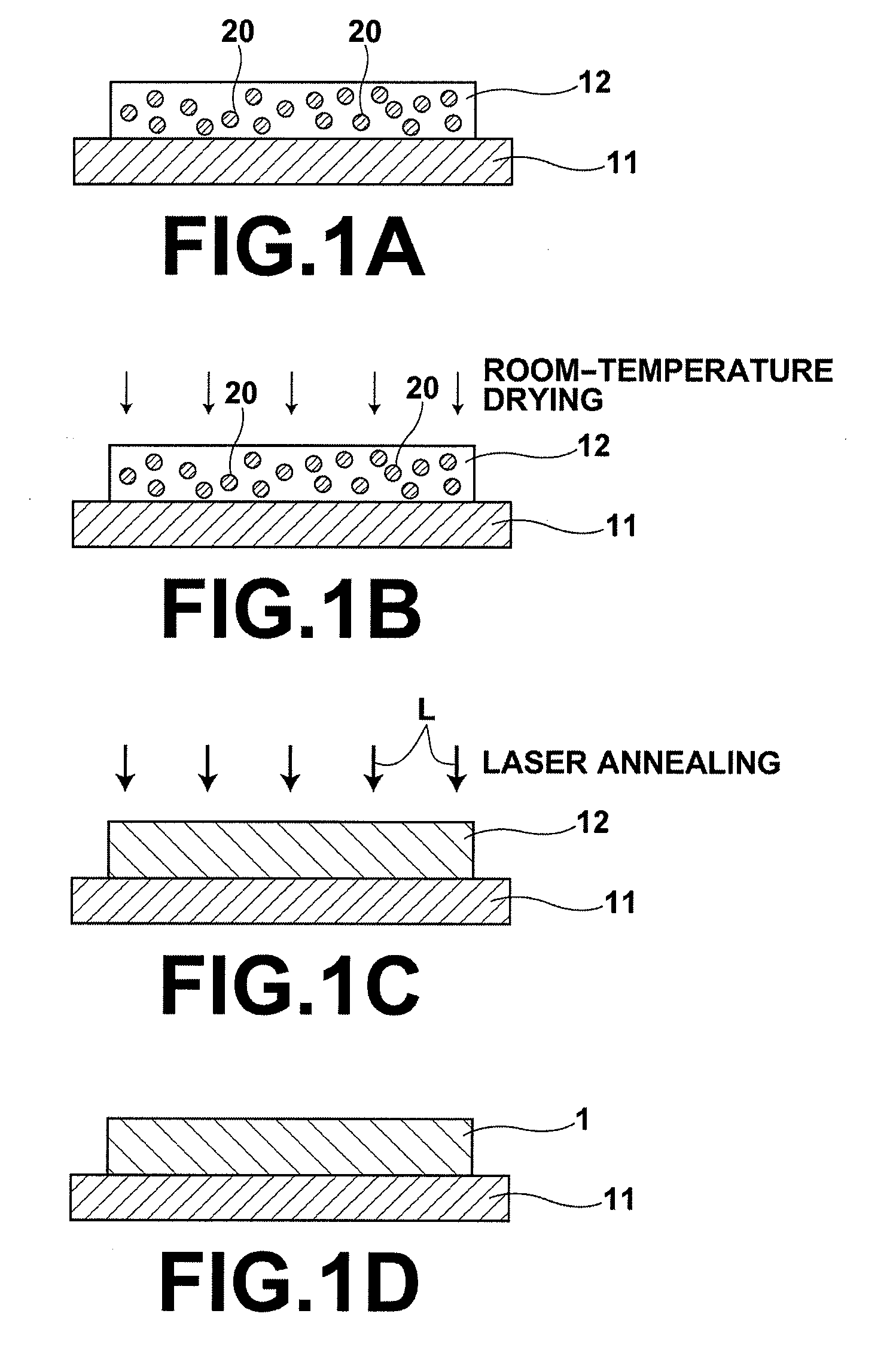

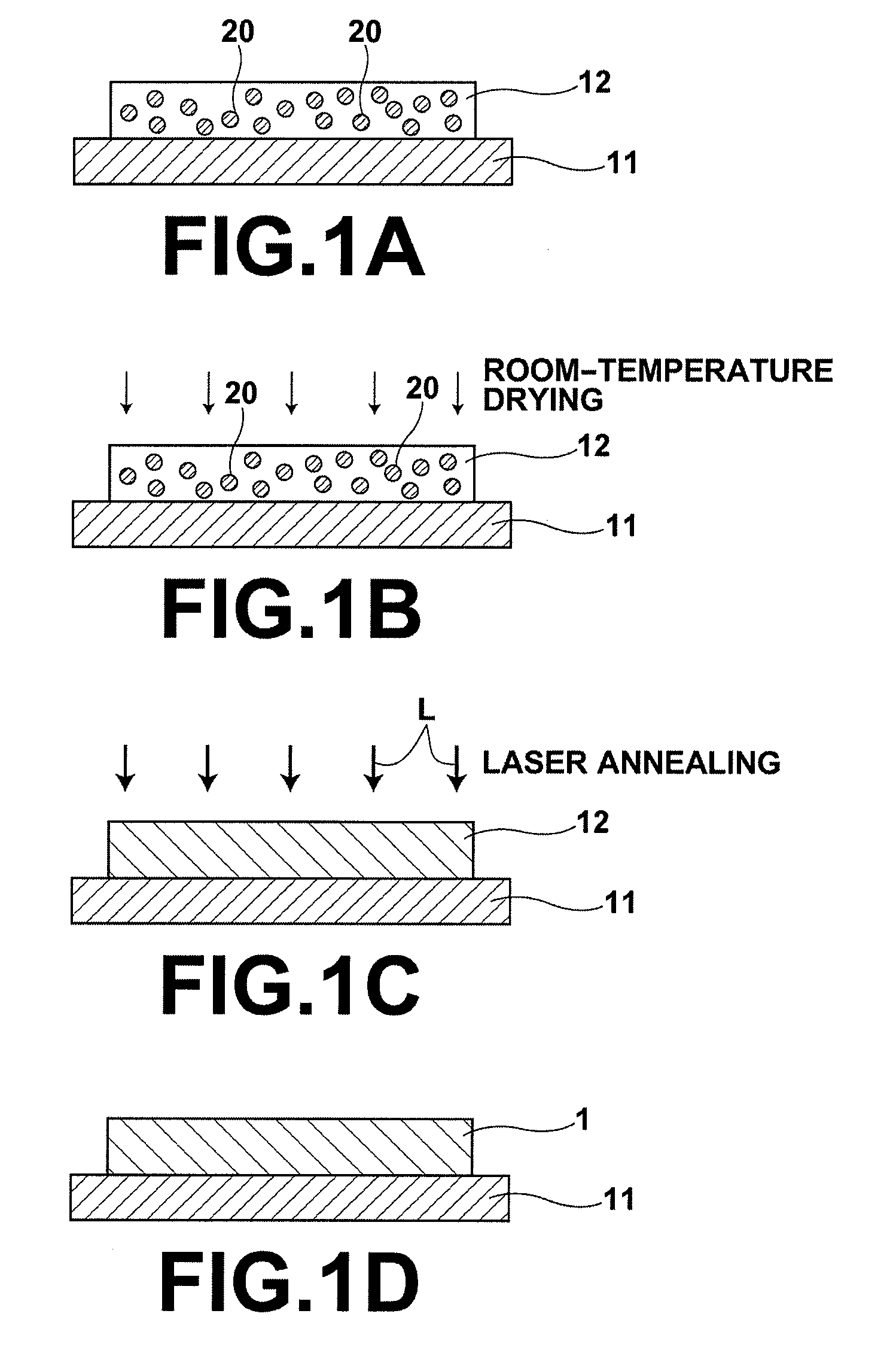

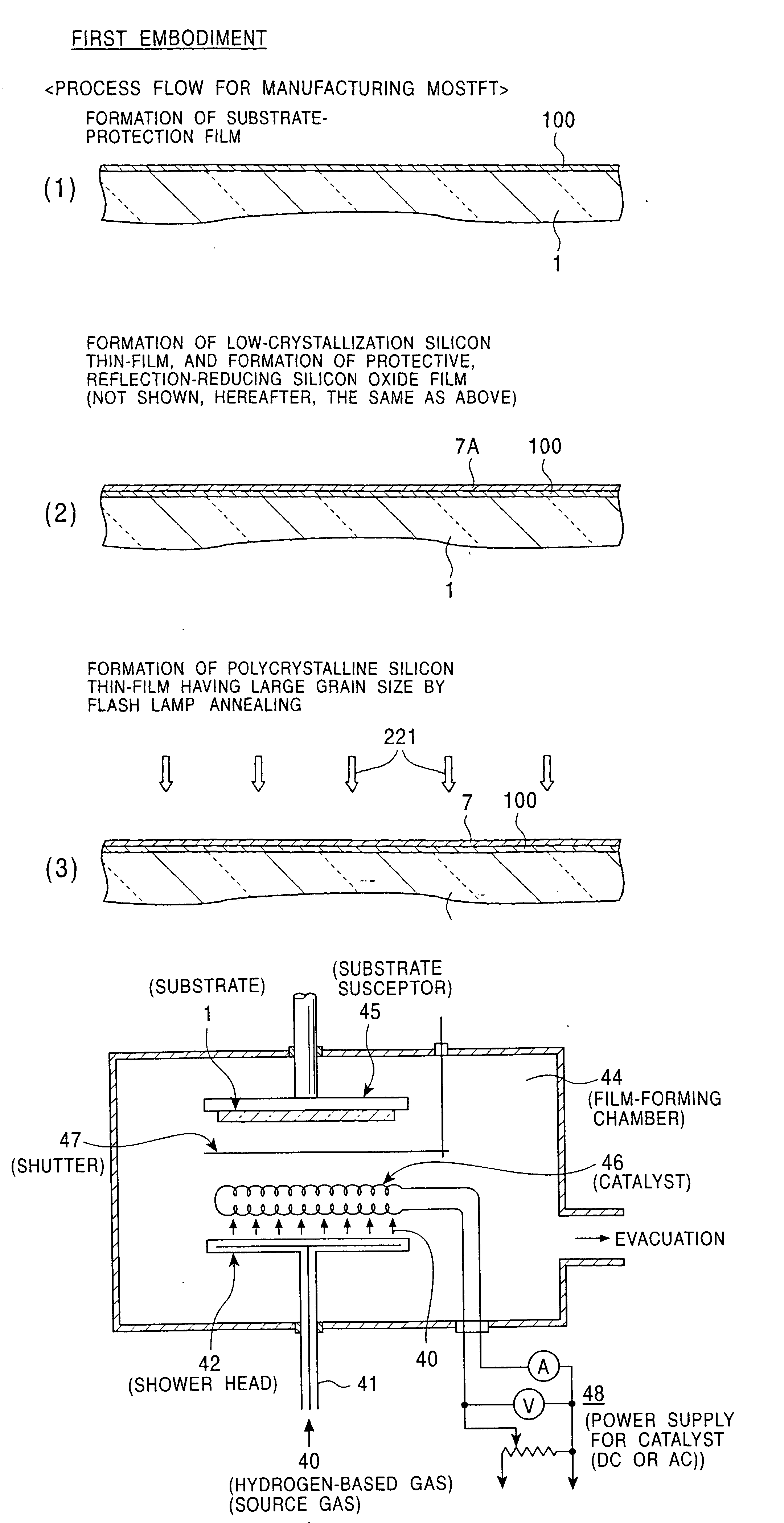

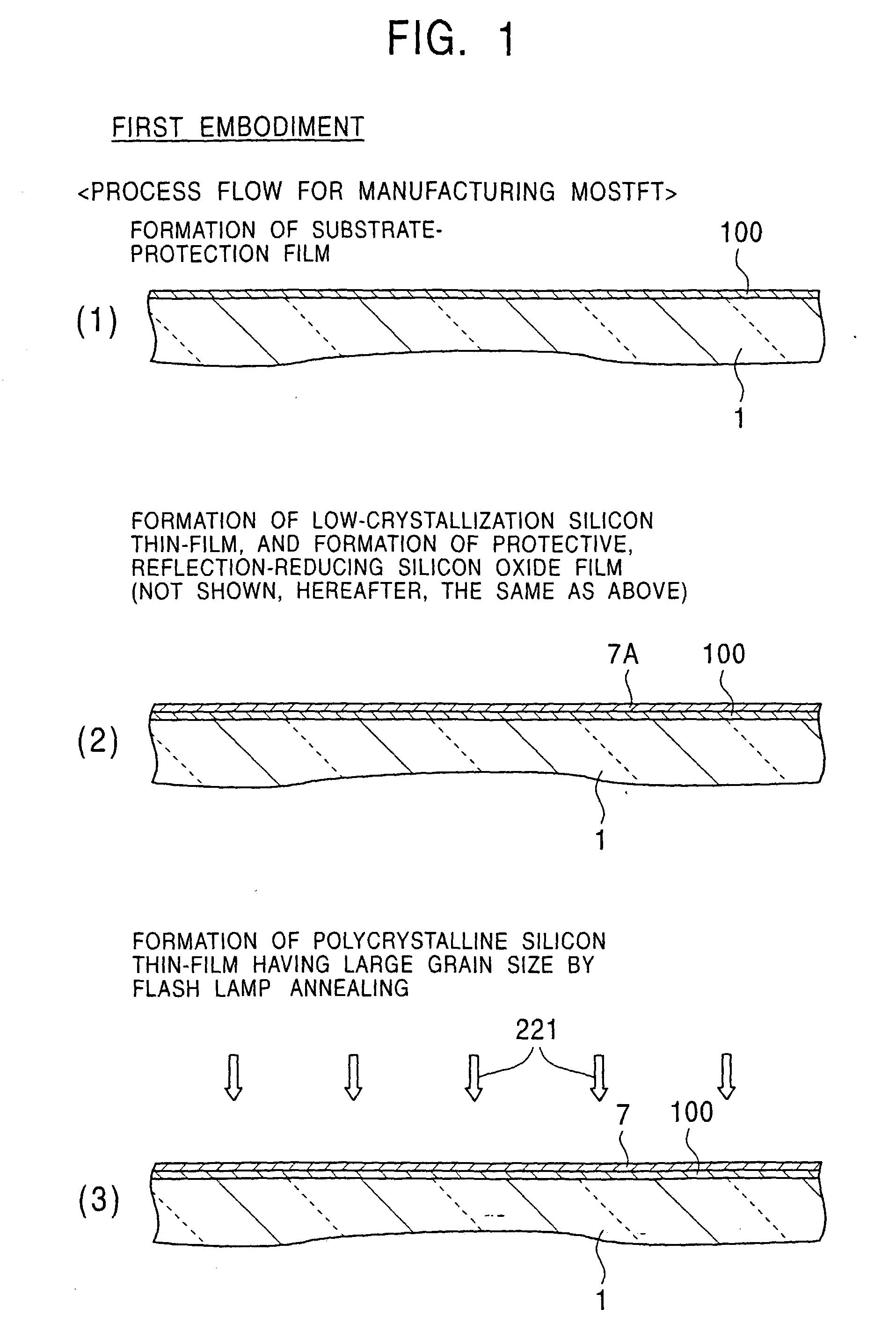

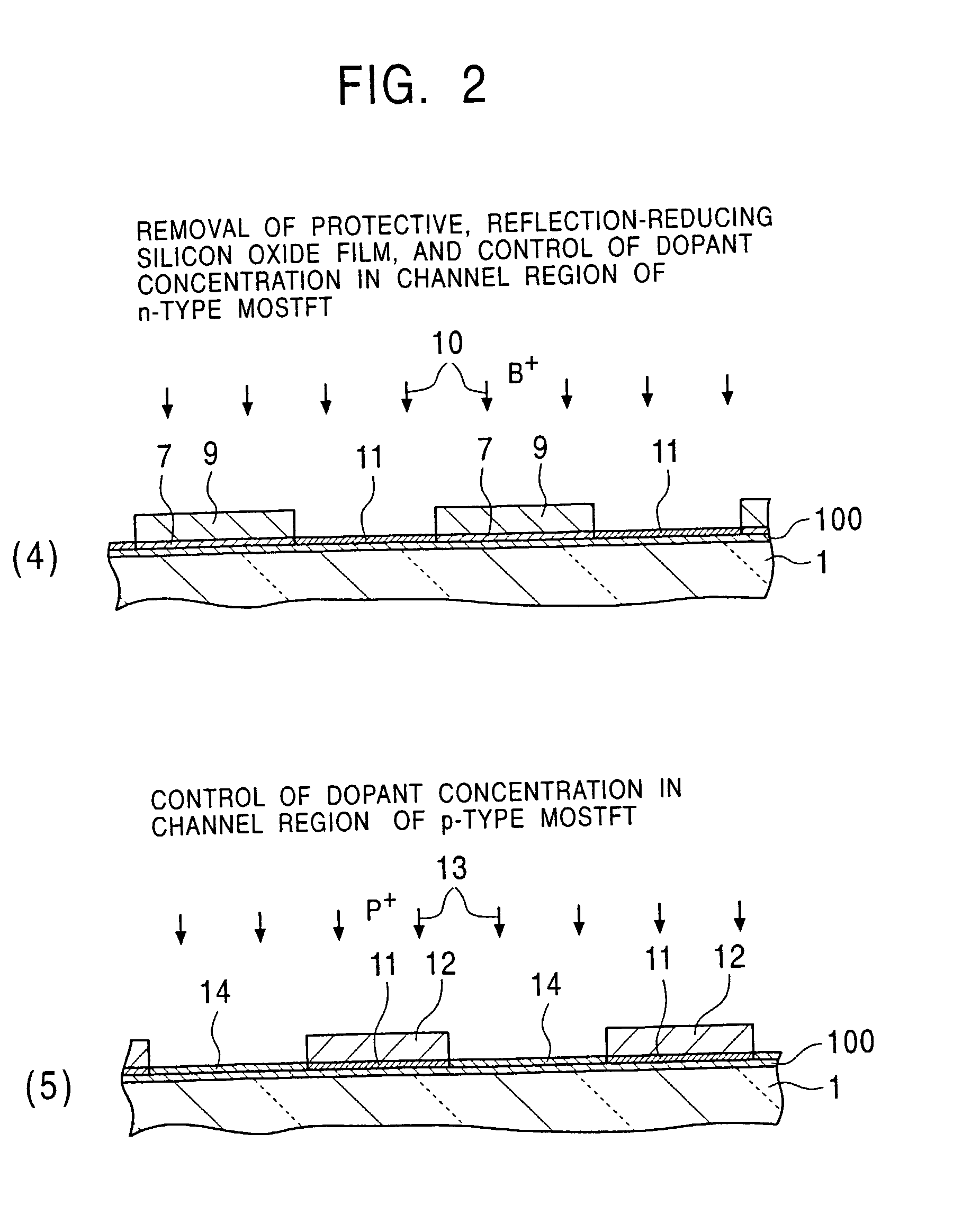

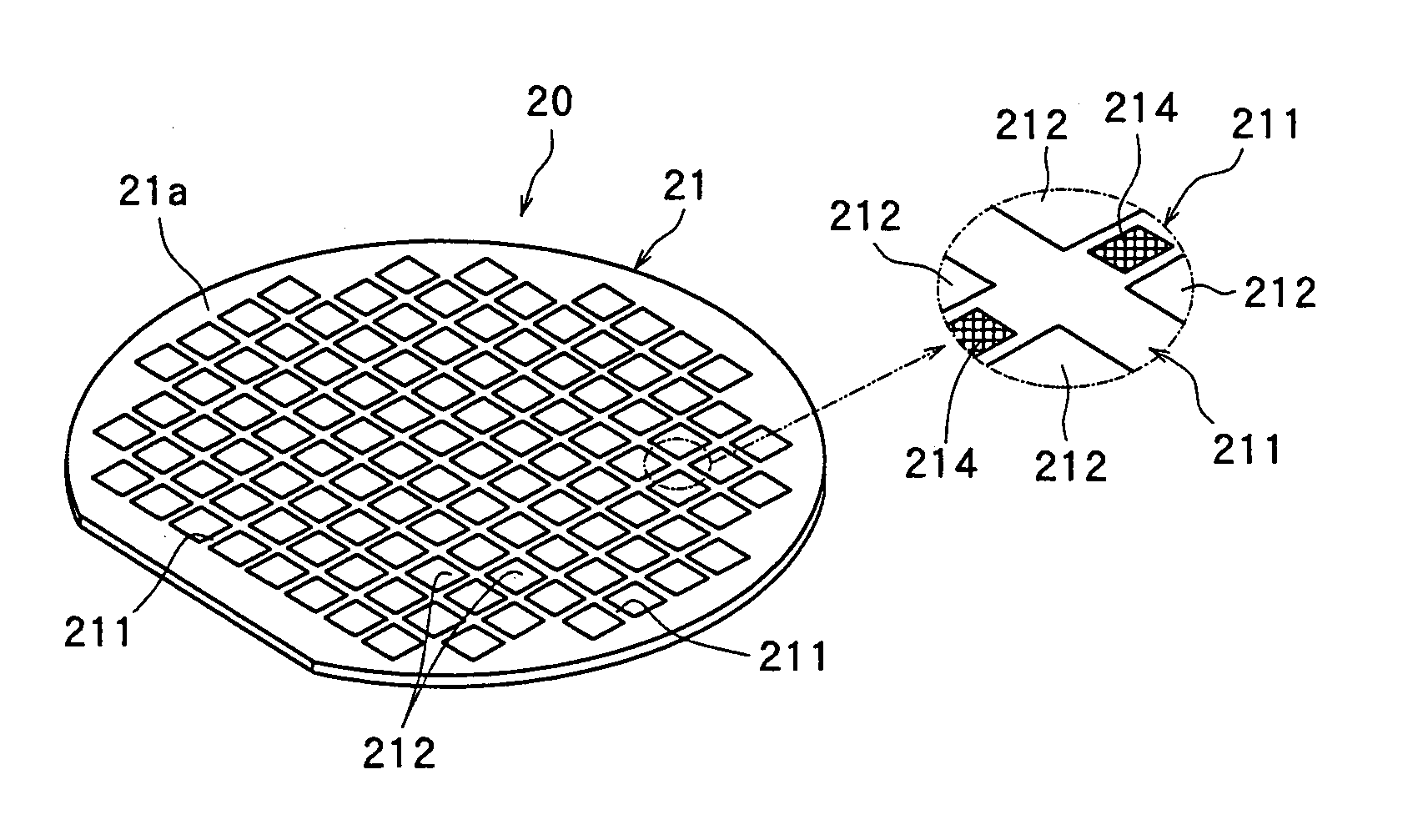

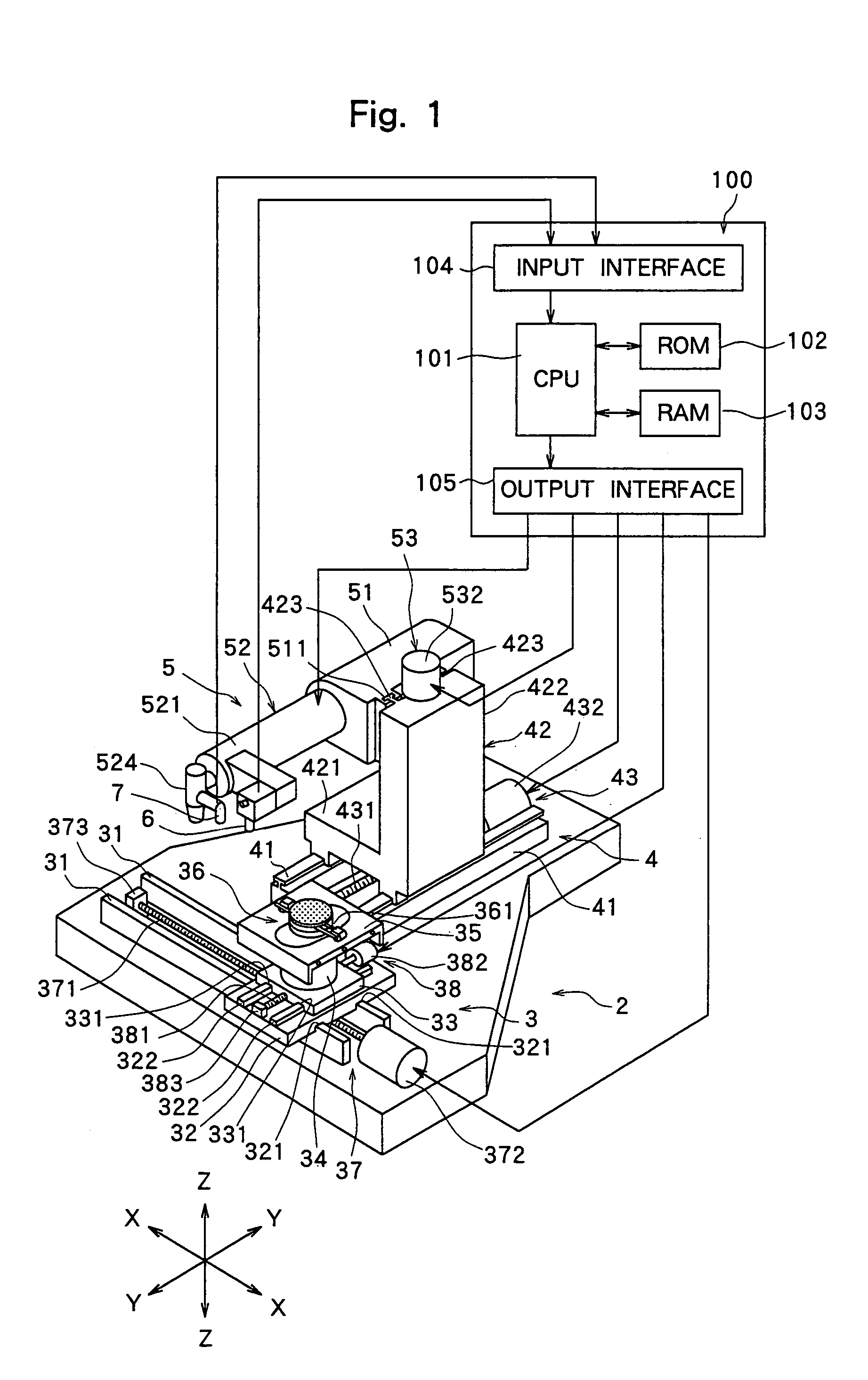

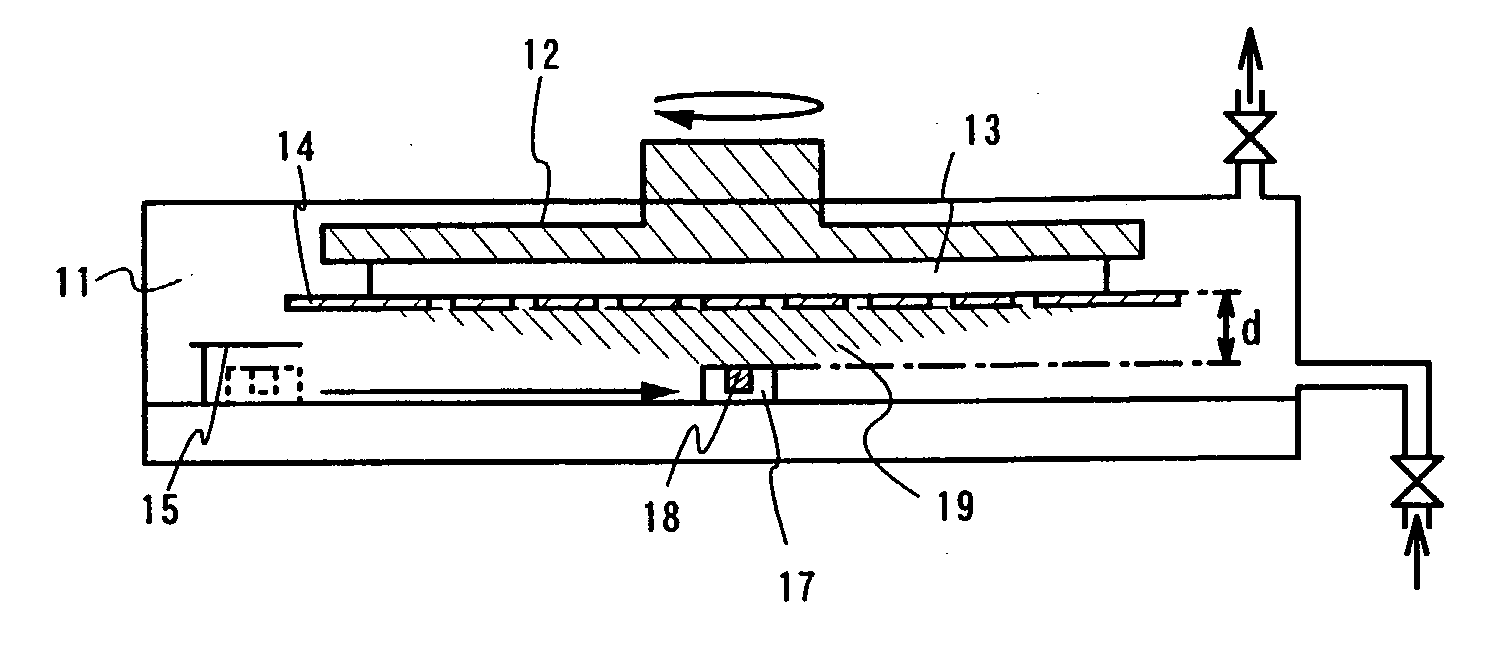

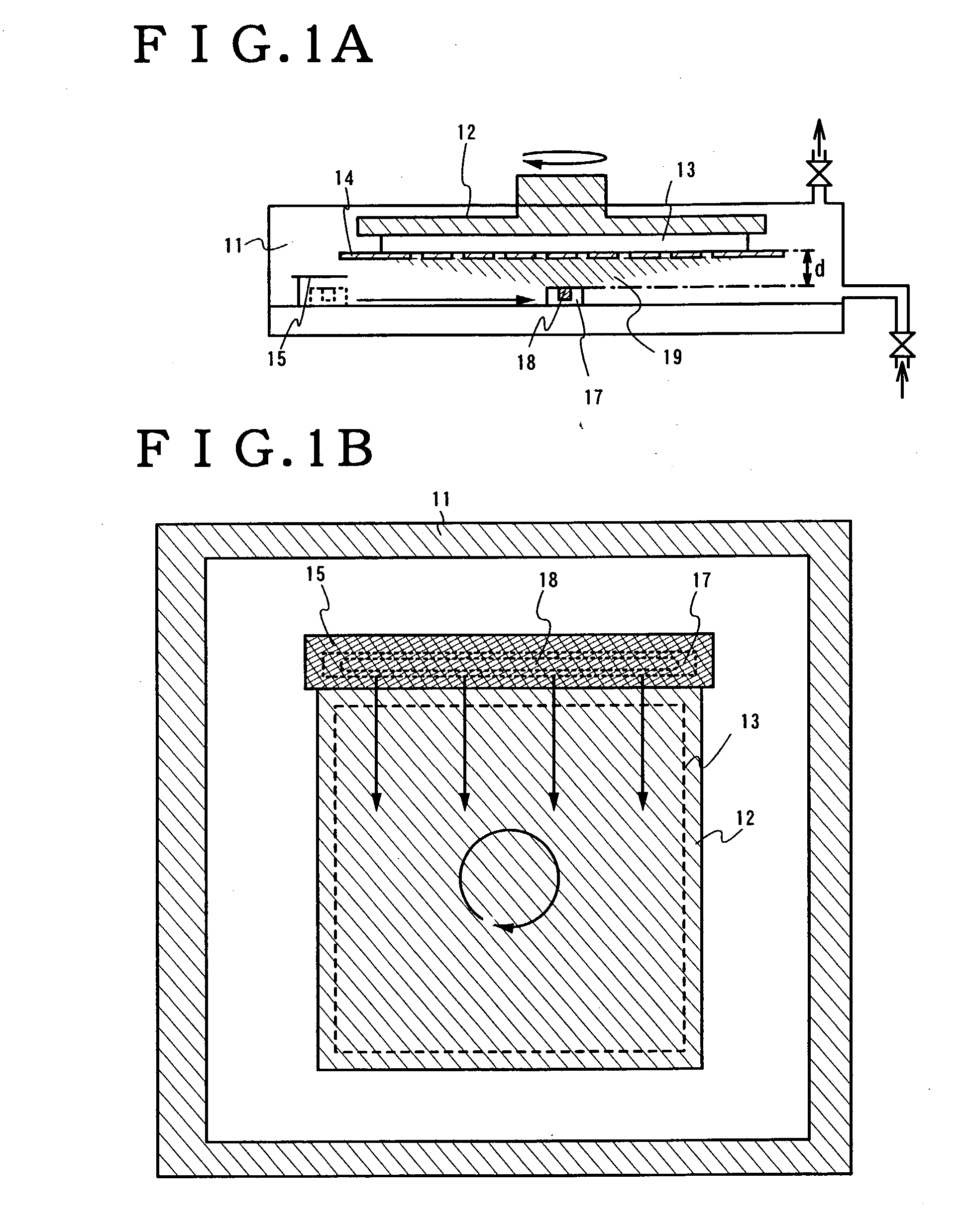

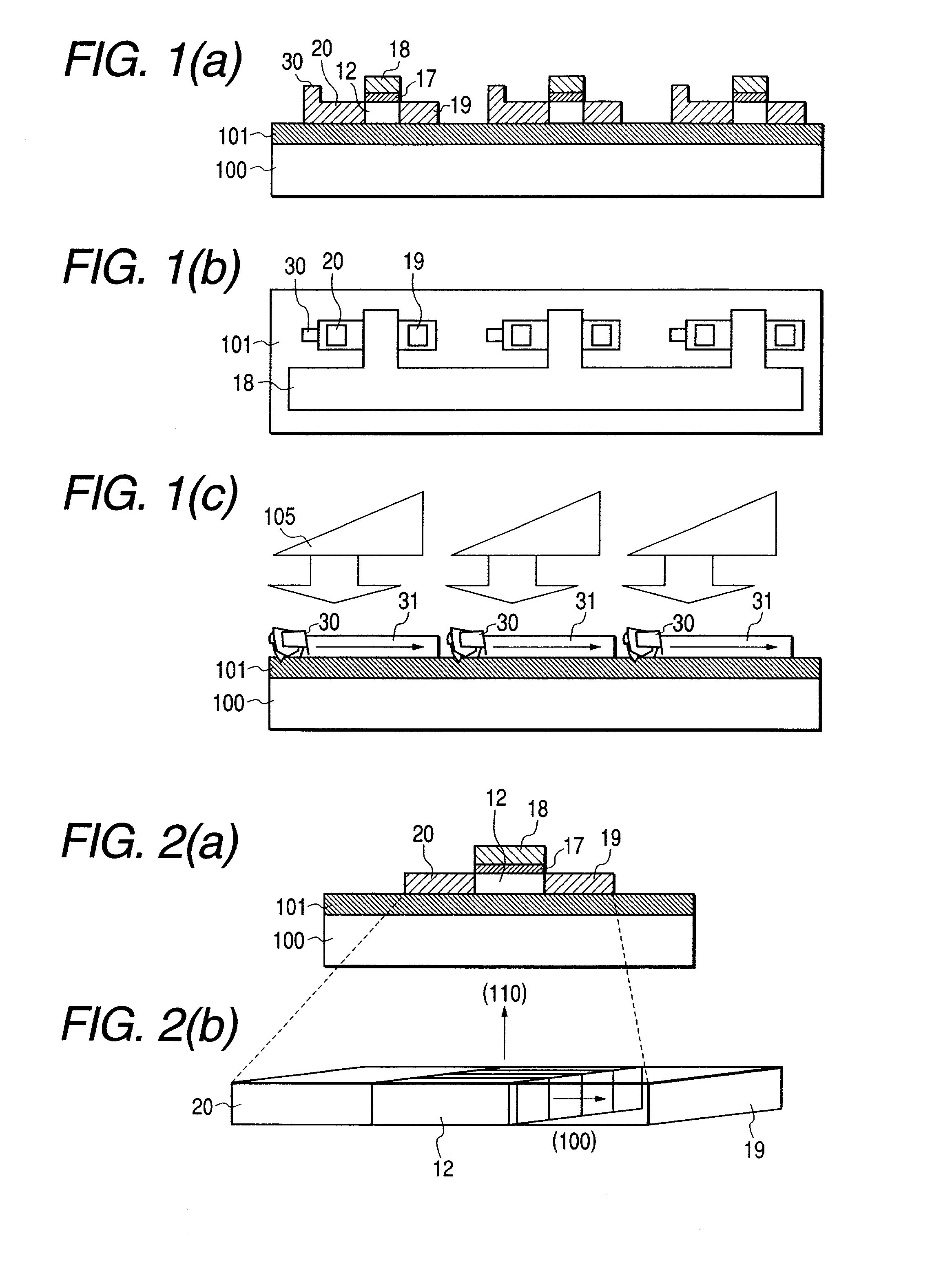

Semiconductor thin film forming method, production methods for semiconductor device and electrooptical device, devices used for these methods, and semiconductor device and electrooptical device

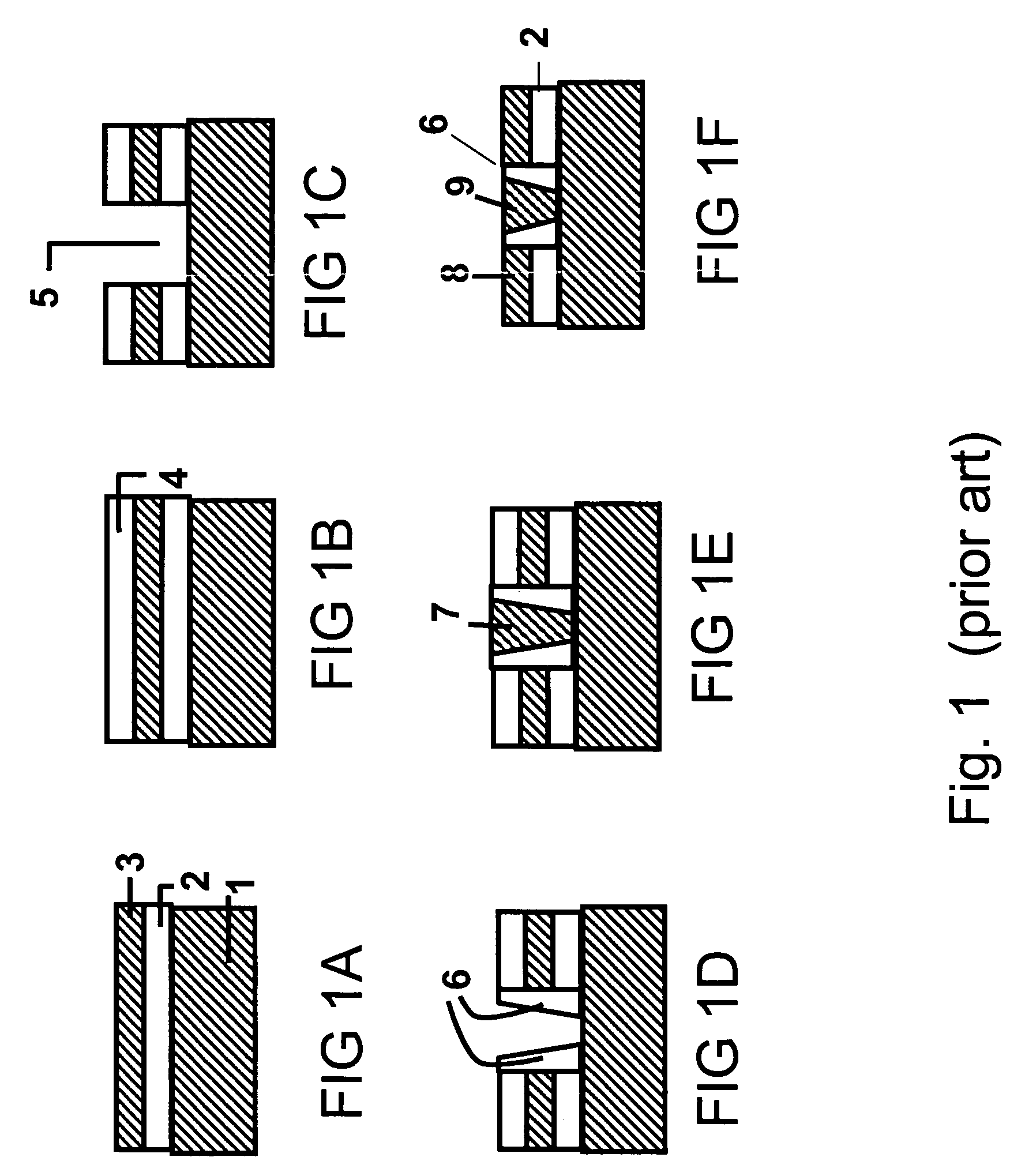

InactiveUS20030013280A1Promote crystallizationTransistorPolycrystalline material growthSingle crystalCrystallinity

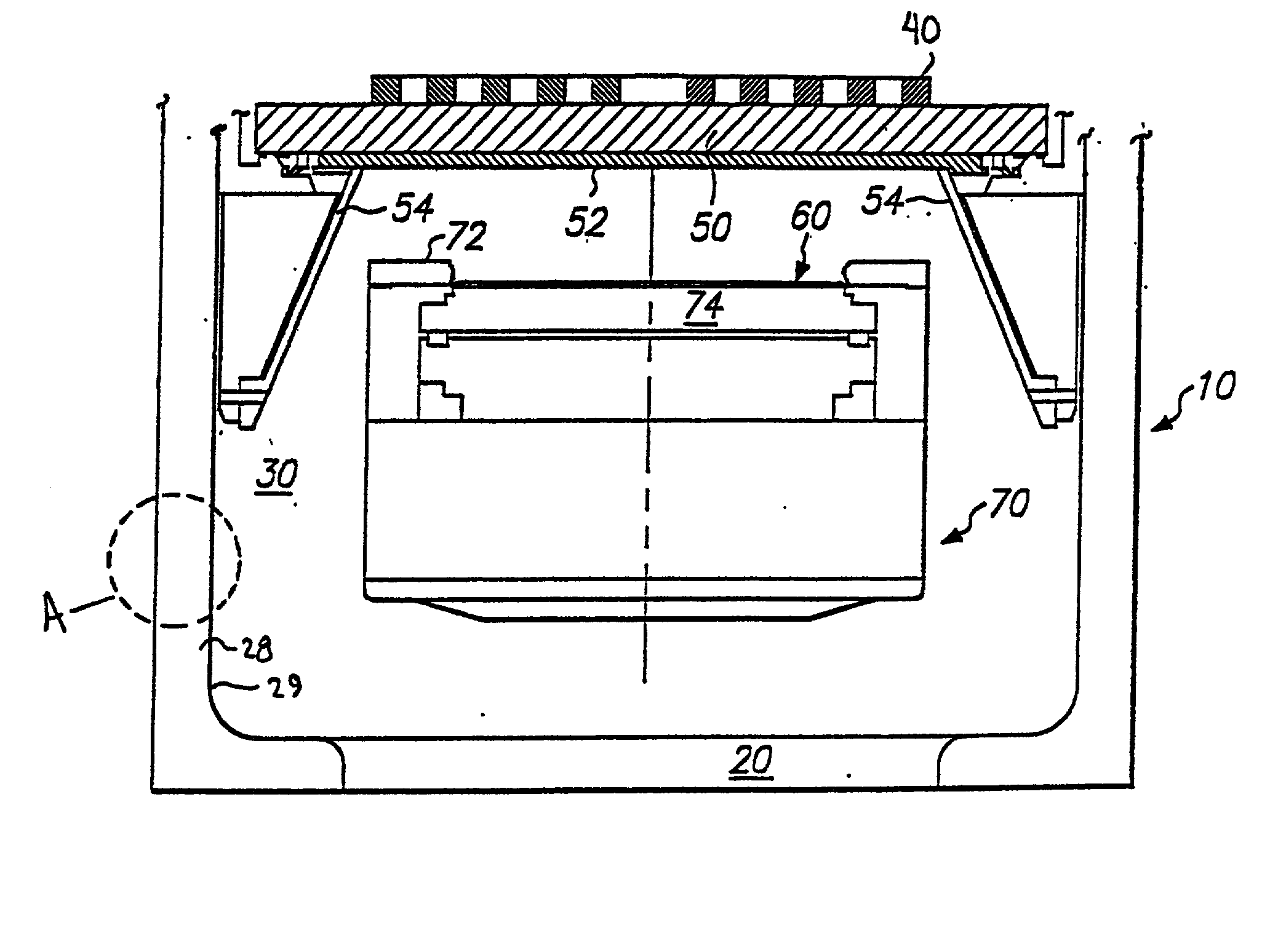

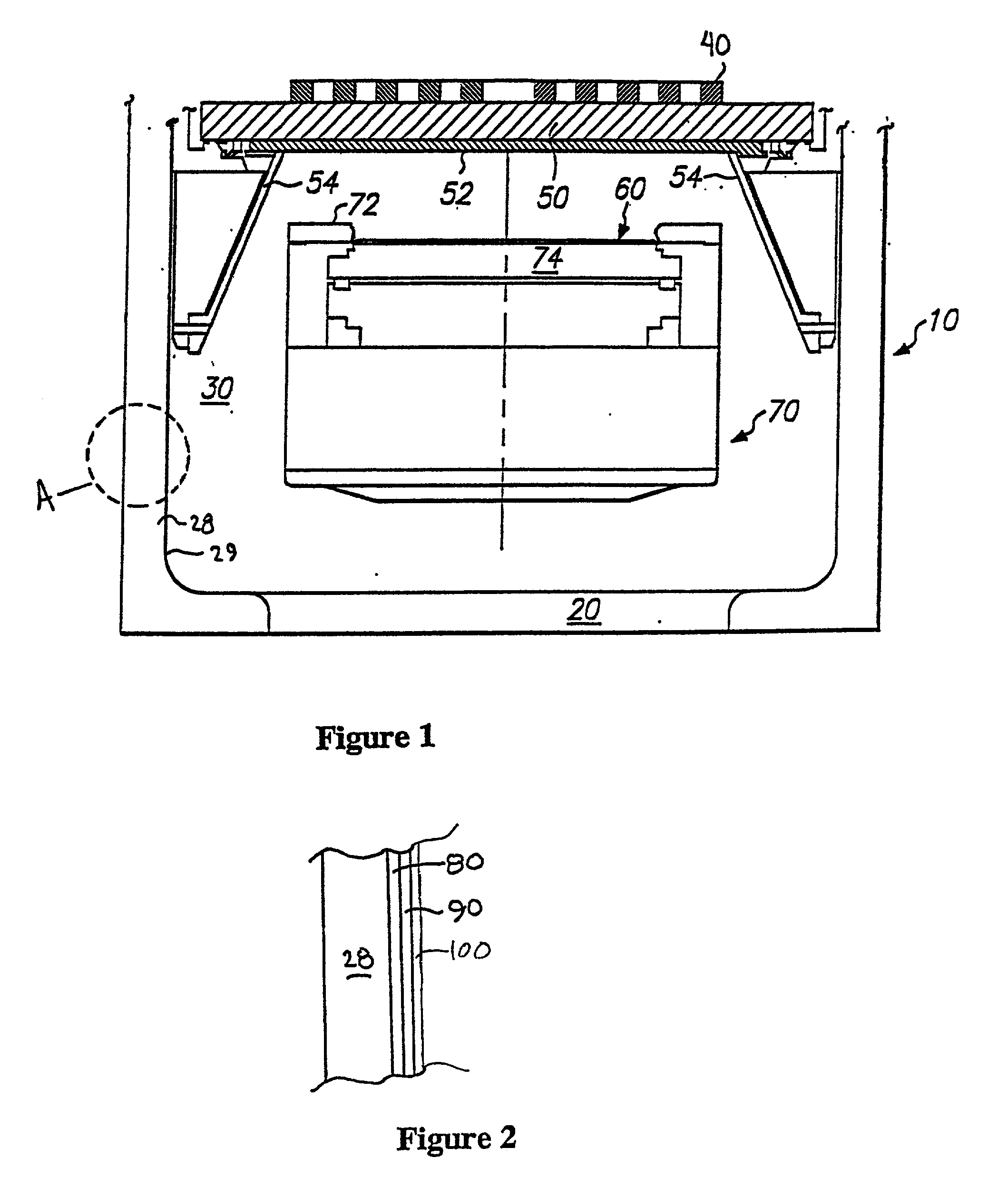

An object of the present invention is to provide a method for easily forming a polycrystalline semiconductor thin-film, such as polycrystalline silicon having high crystallinity and high quality, or a single crystalline semiconductor thin-film at inexpensive cost, the crystalline semiconductor thin-film having a large area, and to provide an apparatus for processing the method described above. In forming a polycrystalline (or single crystalline) semiconductor thin-film (7), such as a polycrystalline silicon thin-film, having high crystallinity and a large grain size on a substrate (1), or in forming a semiconductor device having the polycrystalline (or single crystalline) semiconductor thin-film (7) on the substrate (1), a method comprises forming a low-crystallization semiconductor thin-film (7A) on the substrate (1), and subsequently heating and cooling this low-crystallization semiconductor thin-film (7A) to a fusion, a semi-fusion, or a non-fusion state by flash lamp annealing to facilitate the crystallization of the low-crystallization semiconductor thin-film, whereby a polycrystalline (single crystalline) semiconductor thin-film (7) is obtained. A method for forming the semiconductor device and an apparatus for processing the methods are also disclosed.

Owner:SONY CORP

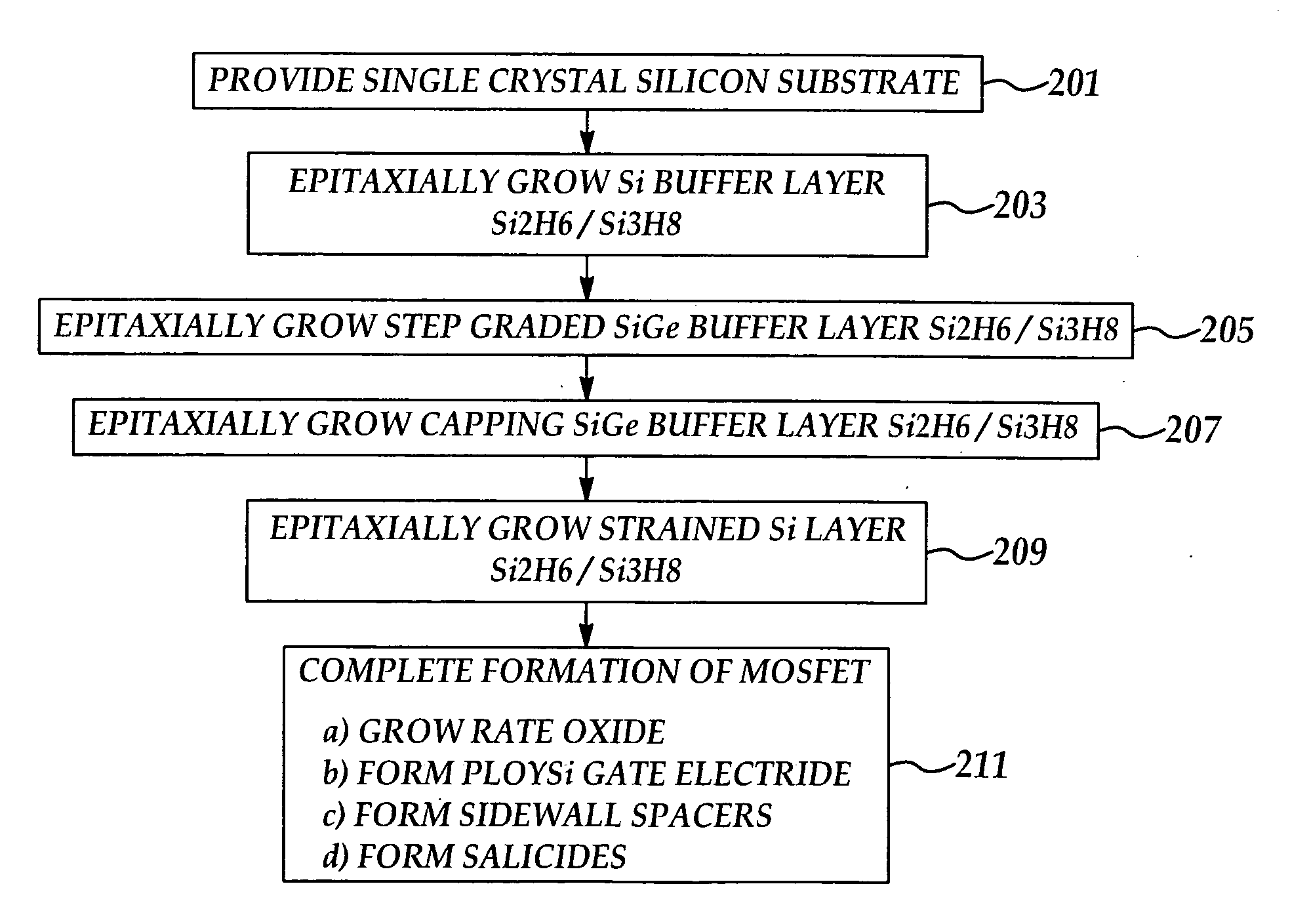

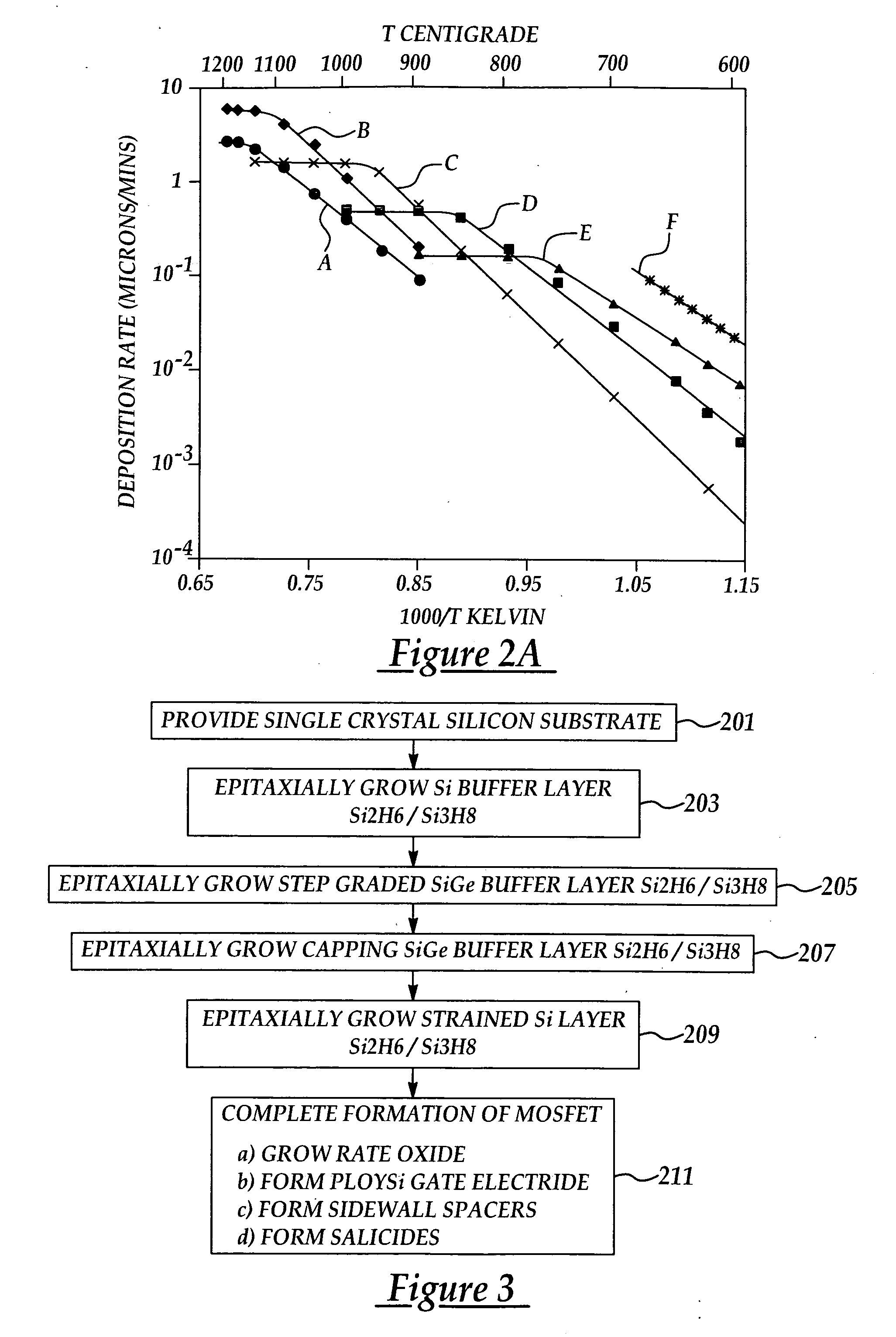

Method for producing high throughput strained-si channel mosfets

InactiveUS20050245058A1Improve throughputReduce defect densityPolycrystalline material growthFrom solid stateSilanesMaterials science

A method for forming a strained silicon layer device with improved wafer throughput and low defect density including providing a silicon substrate; epitaxially growing a first silicon layer using at least one deposition precursor selected from the group consisting of disilane and trisilane; epitaxially growing a step-grade SiGe buffer layer over and contacting the first silicon layer using at least one deposition precursor selected from the group consisting of disilane and trisilane; epitaxially growing a SiGe capping layer over and contacting the step-grade SiGe buffer layer using at least one deposition precursor selected from the group consisting of disilane and trisilane; and, epitaxially growing a second silicon layer using at least one deposition precursor selected from the group consisting of disilane and silane.

Owner:TAIWAN SEMICON MFG CO LTD

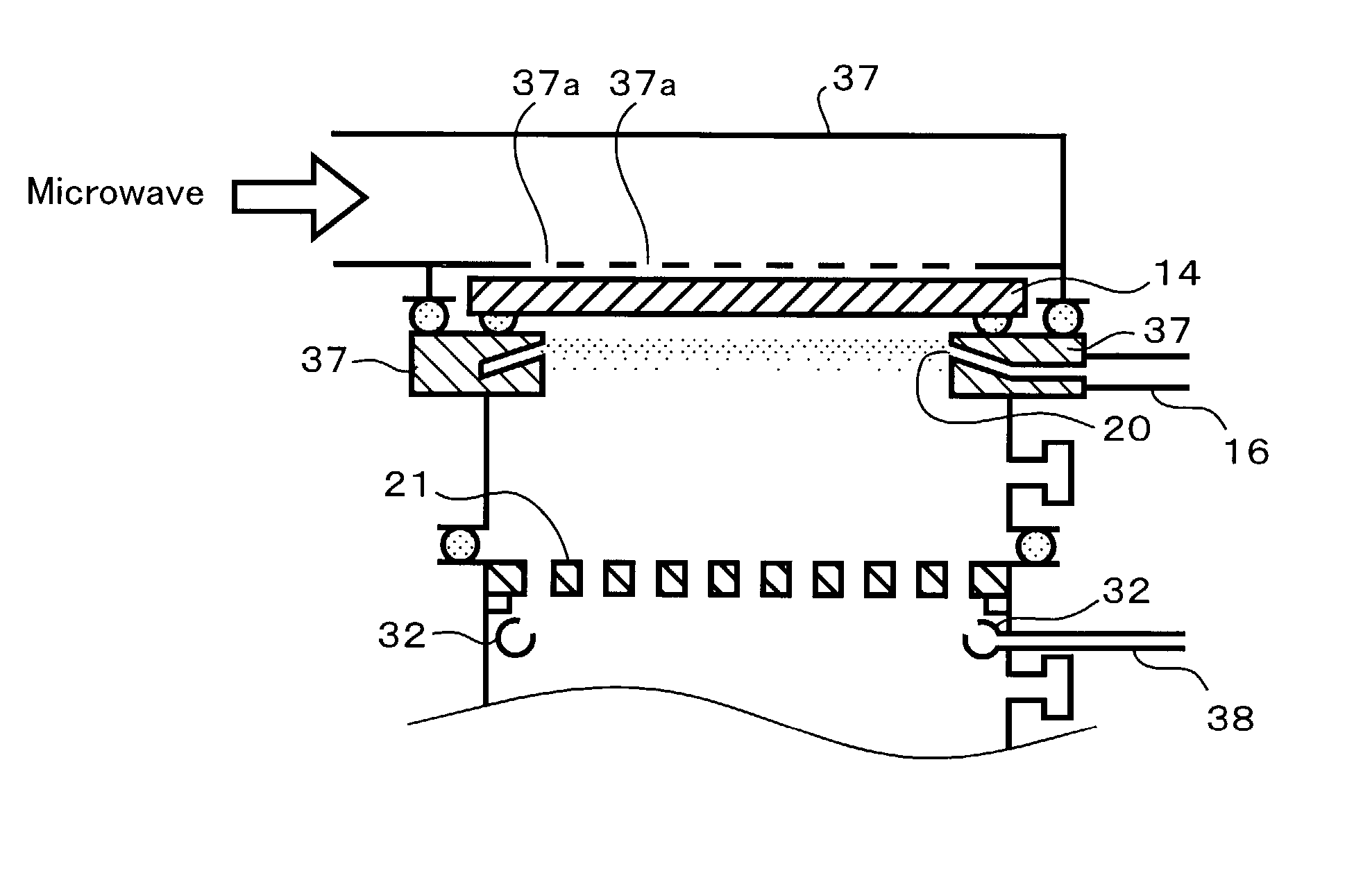

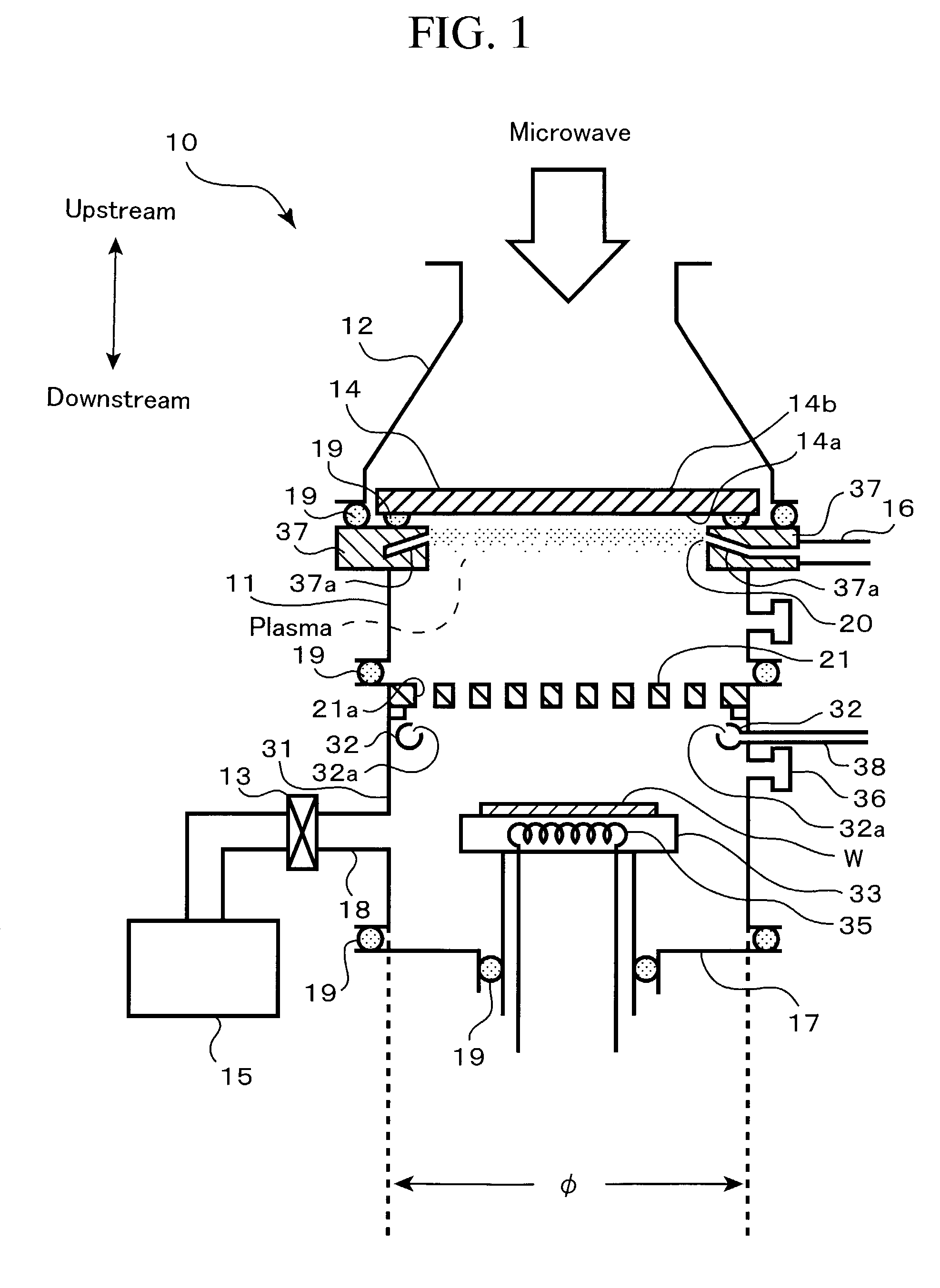

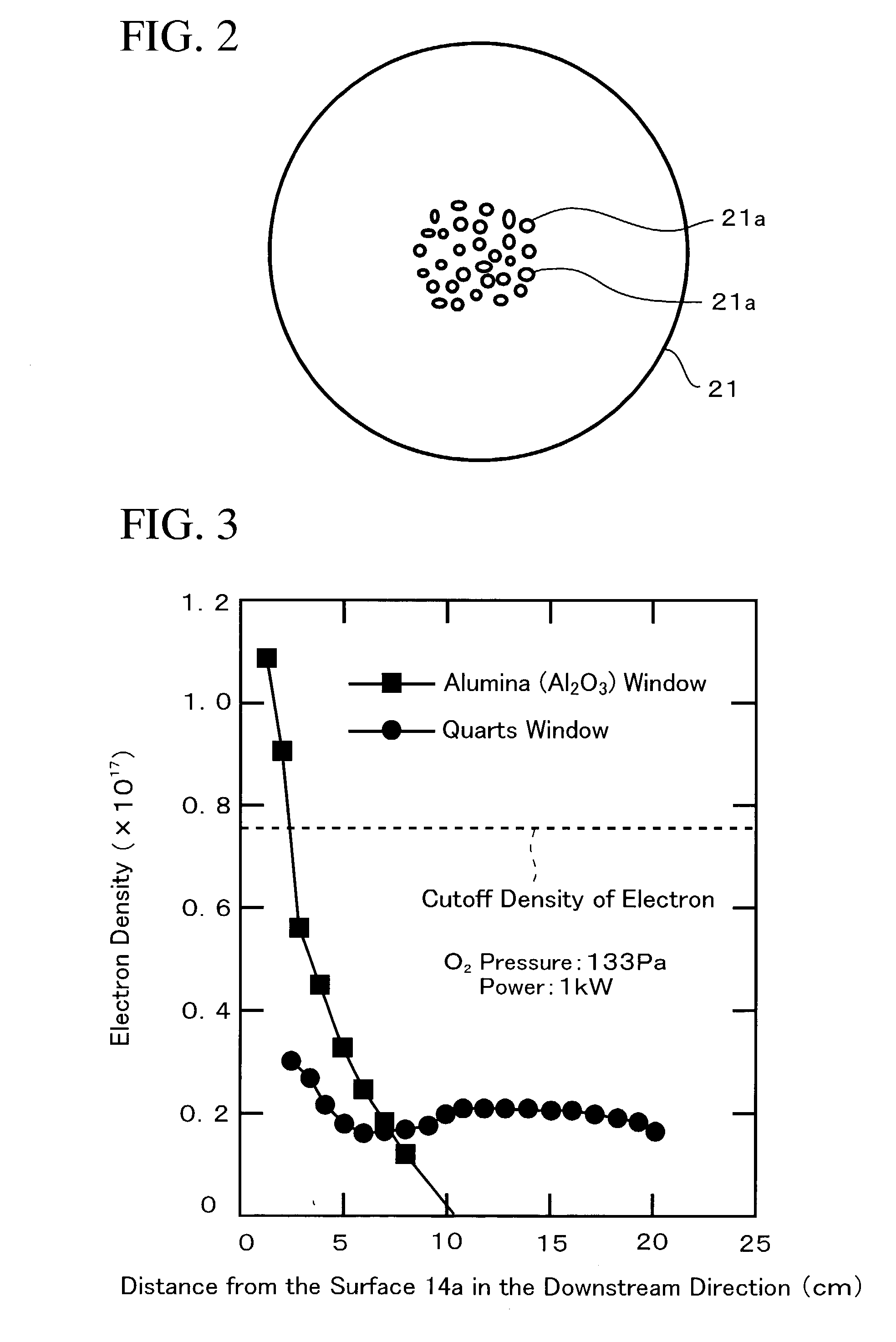

Deposition method, deposition apparatus, and semiconductor device

InactiveUS20030077883A1Avoid it happening againAvoid breakingFrom solid stateSemiconductor/solid-state device detailsMicrowaveReactive gas

To provide a deposition method and a deposition apparatus, in which deposition can be performed under a low temperature and a substrate does not suffer from charge-up damage, and a semiconductor device produced thereby. The deposition method is that reactive gas is made to pass through communication holes and guided toward downstream of the communication holes after the gas is exposed to surface wave of microwave, and it is reacted with silicon compound gas to deposit a silicon-containing film on a substrate arranged in the downstream.

Owner:ARIES RES

Device and method for pressure-driven plug transport and reaction

InactiveUS20050272159A1Well mixedQuick mixMaterial nanotechnologySequential/parallel process reactionsPressure.driveCarrier fluid

Owner:UNIVERSITY OF CHICAGO

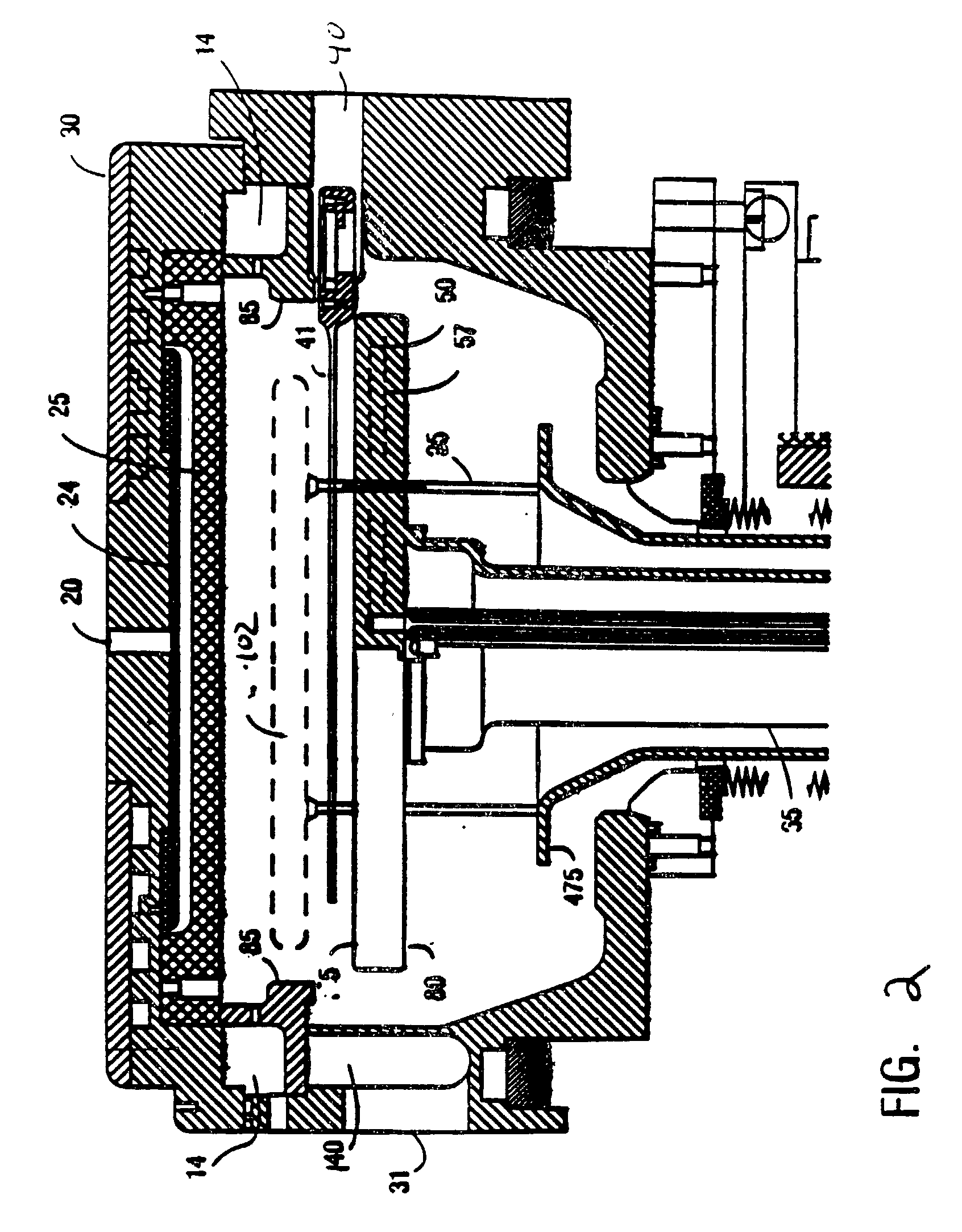

Method and apparatus for forming silicon containing films

InactiveUS20030124818A1Lower activation energyDecomposes faster and more efficientlyFrom solid stateSemiconductor/solid-state device manufacturingElectrical resistance and conductanceActivation energy

The present invention describes a method and apparatus for forming a uniform silicon containing film in a single wafer reactor. According to the present invention, a silicon containing film is deposited in a resistively heated single wafer chamber utilizing a process gas having a silicon source gas and which provides an activation energy less than 0.5 eV at a temperature between 750° C.-550° C.

Owner:APPLIED MATERIALS INC

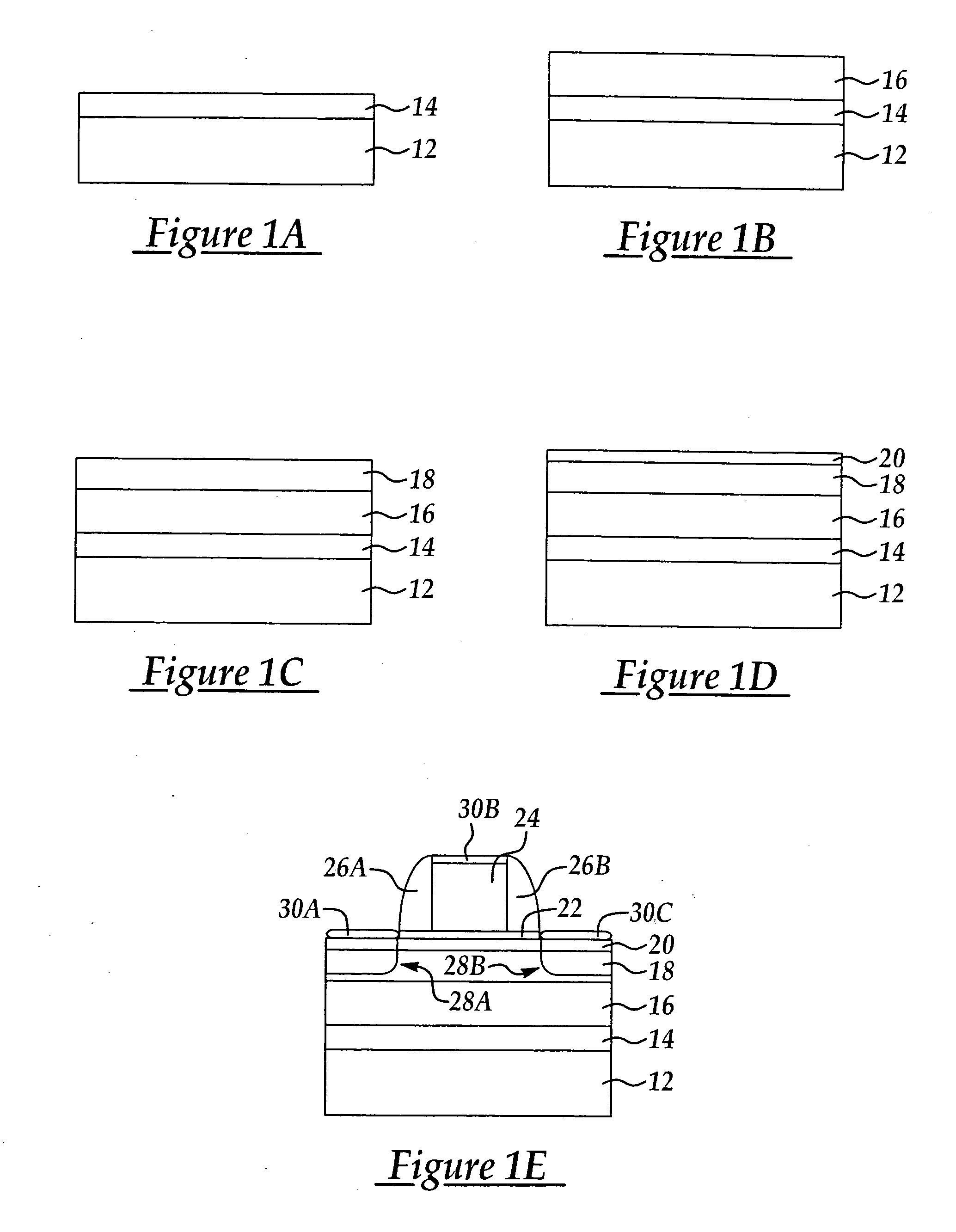

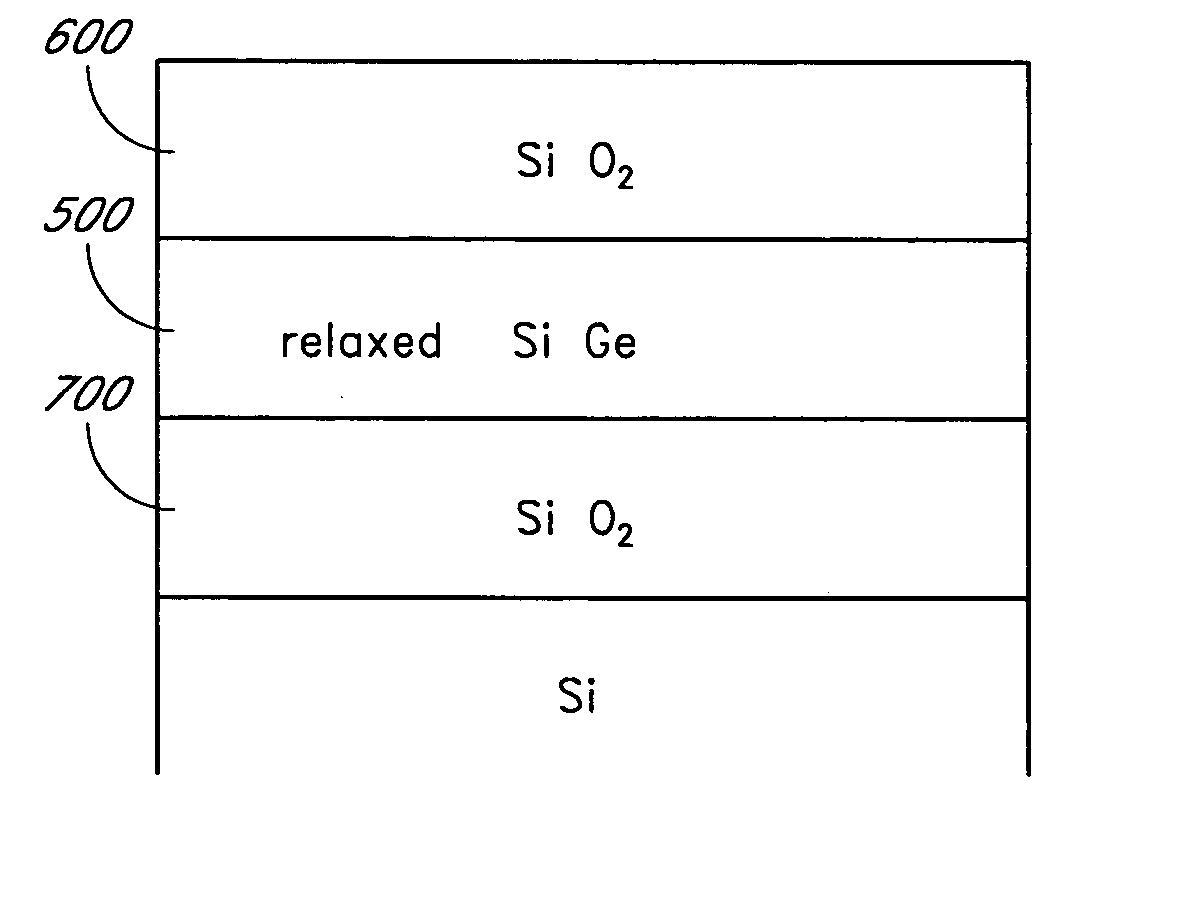

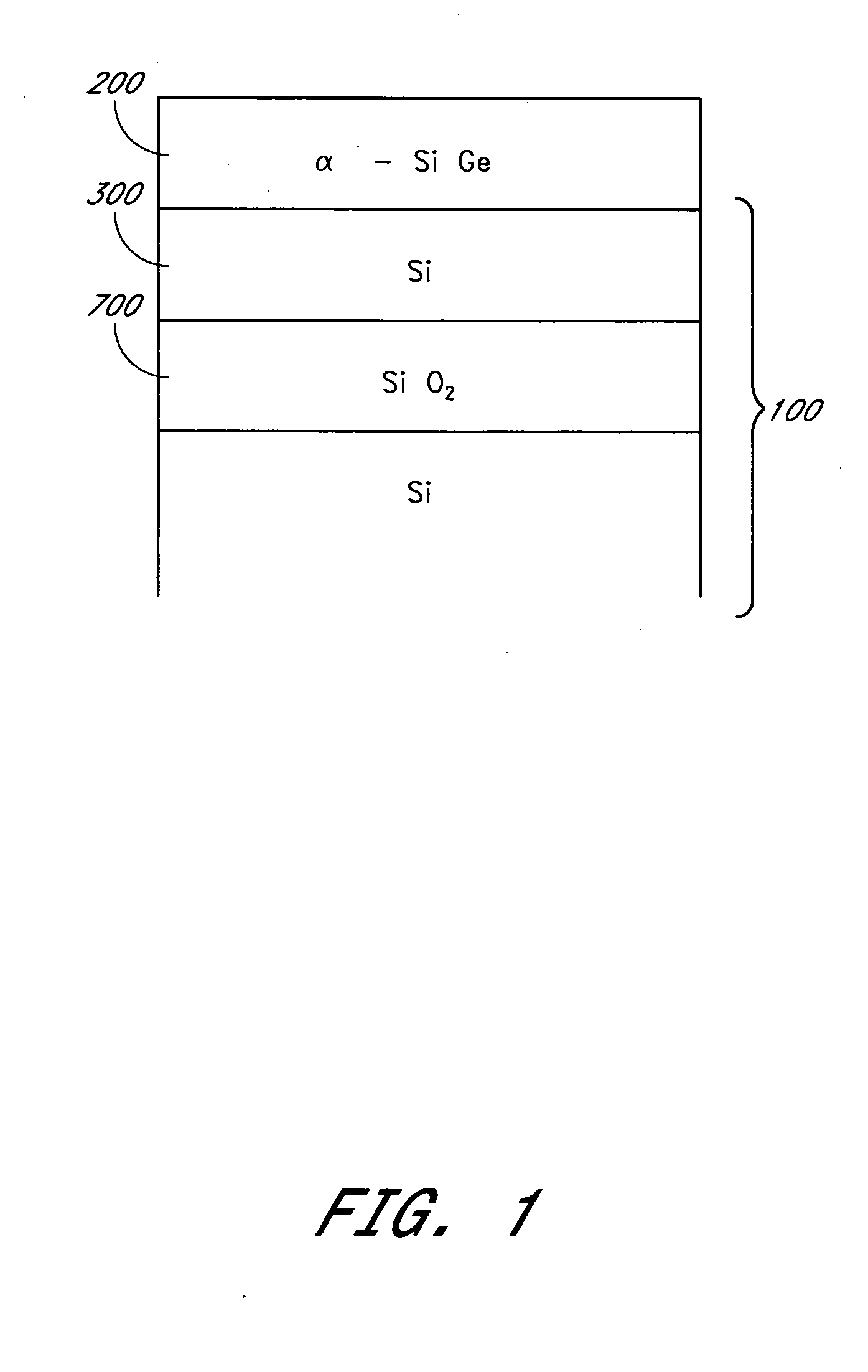

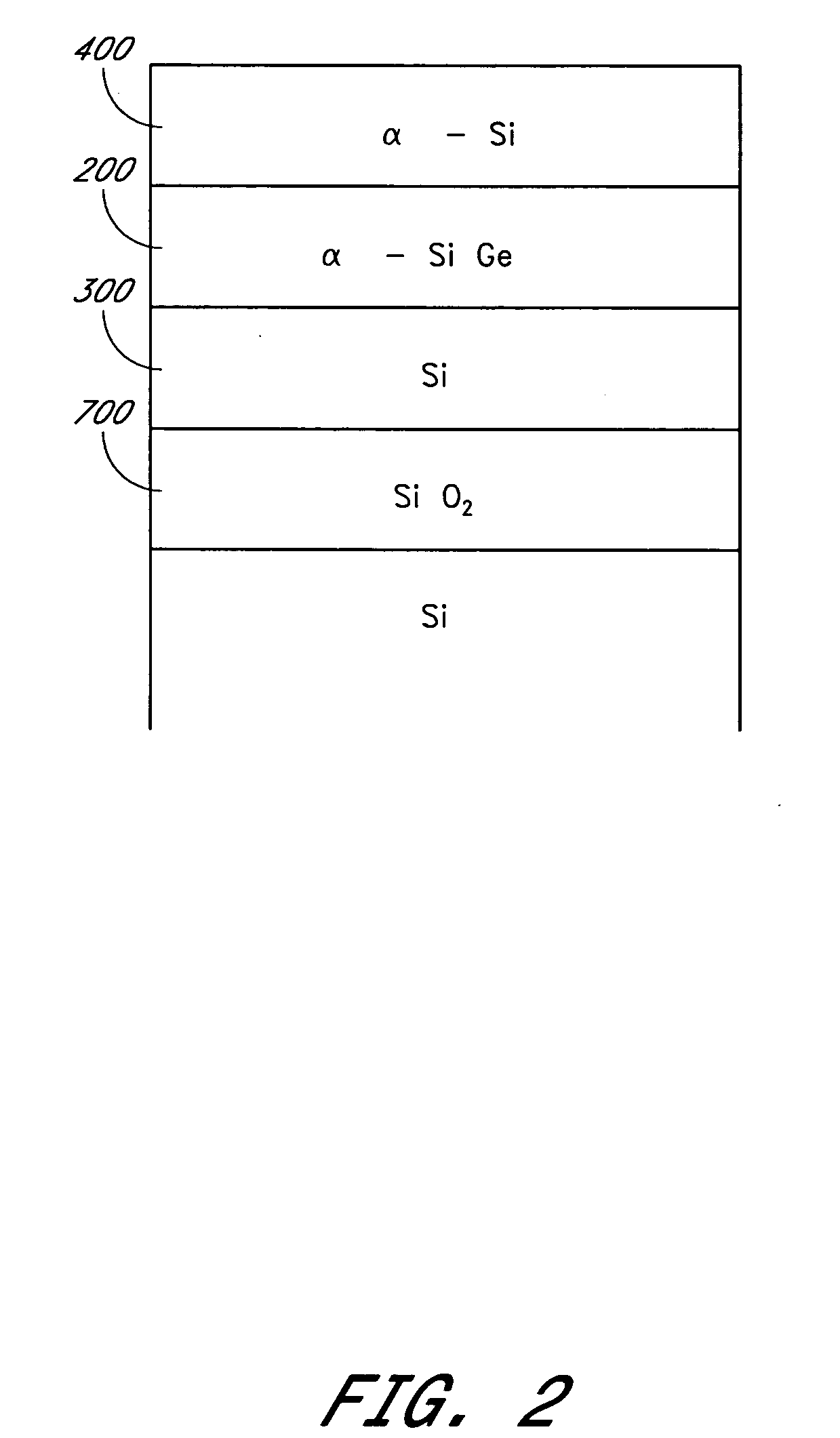

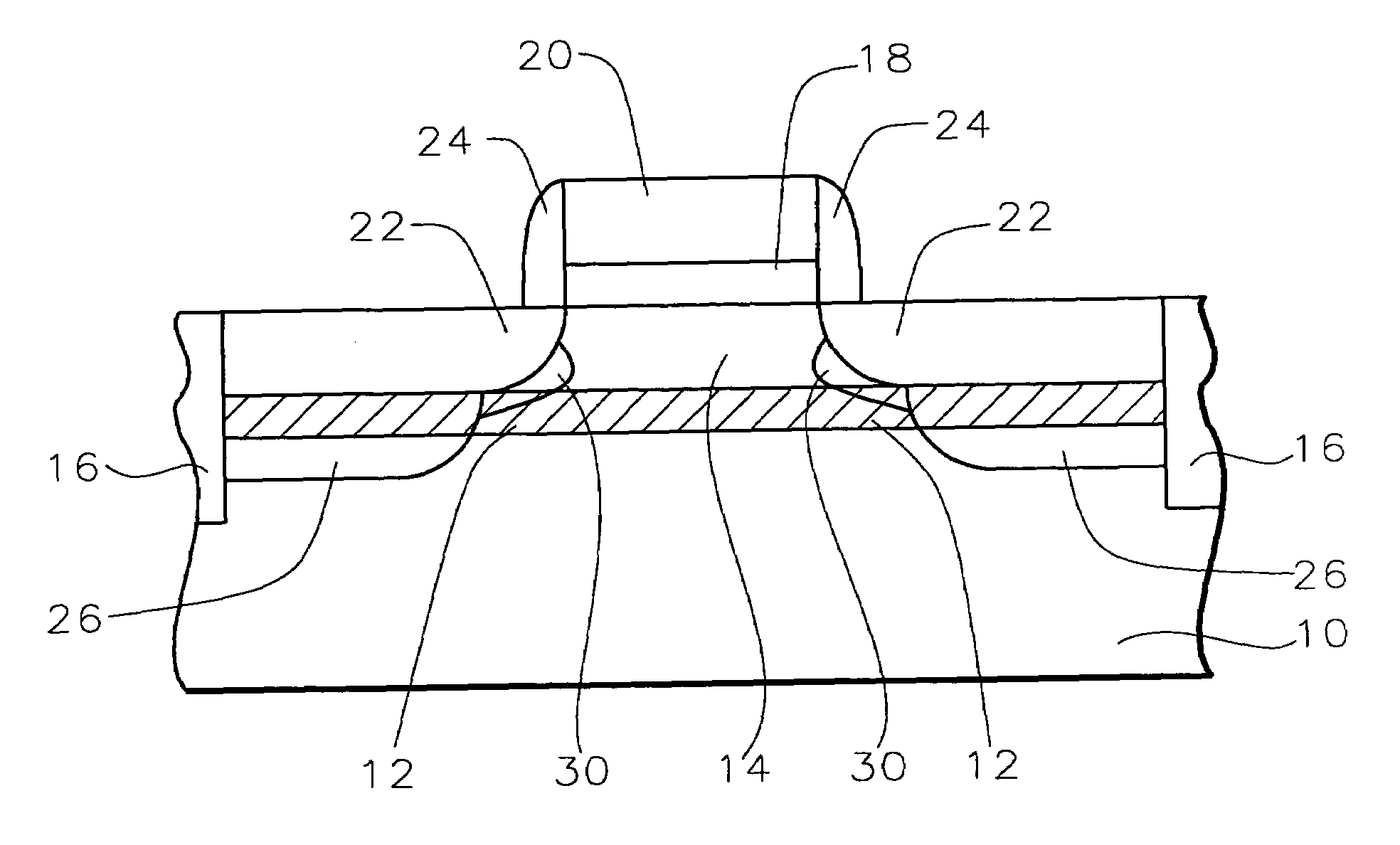

Deposition of silicon germanium on silicon-on-insulator structures and bulk substrates

Methods are provided for producing SiGe-on-insulator structures and for forming strain-relaxed SiGe layers on silicon while minimizing defects. Amorphous SiGe layers are deposited by CVD from trisilane and GeH4. The amorphous SiGe layers are recrystallized over silicon by melt or solid phase epitaxy (SPE) processes. The melt processes preferably also cause diffusion of germanium to dilute the overall germanium content and essentially consume the silicon overlying the insulator. The SPE process can be conducted with or without diffusion of germanium into the underlying silicon, and so is applicable to SOI as well as conventional semiconductor substrates.

Owner:ASM IP HLDG BV

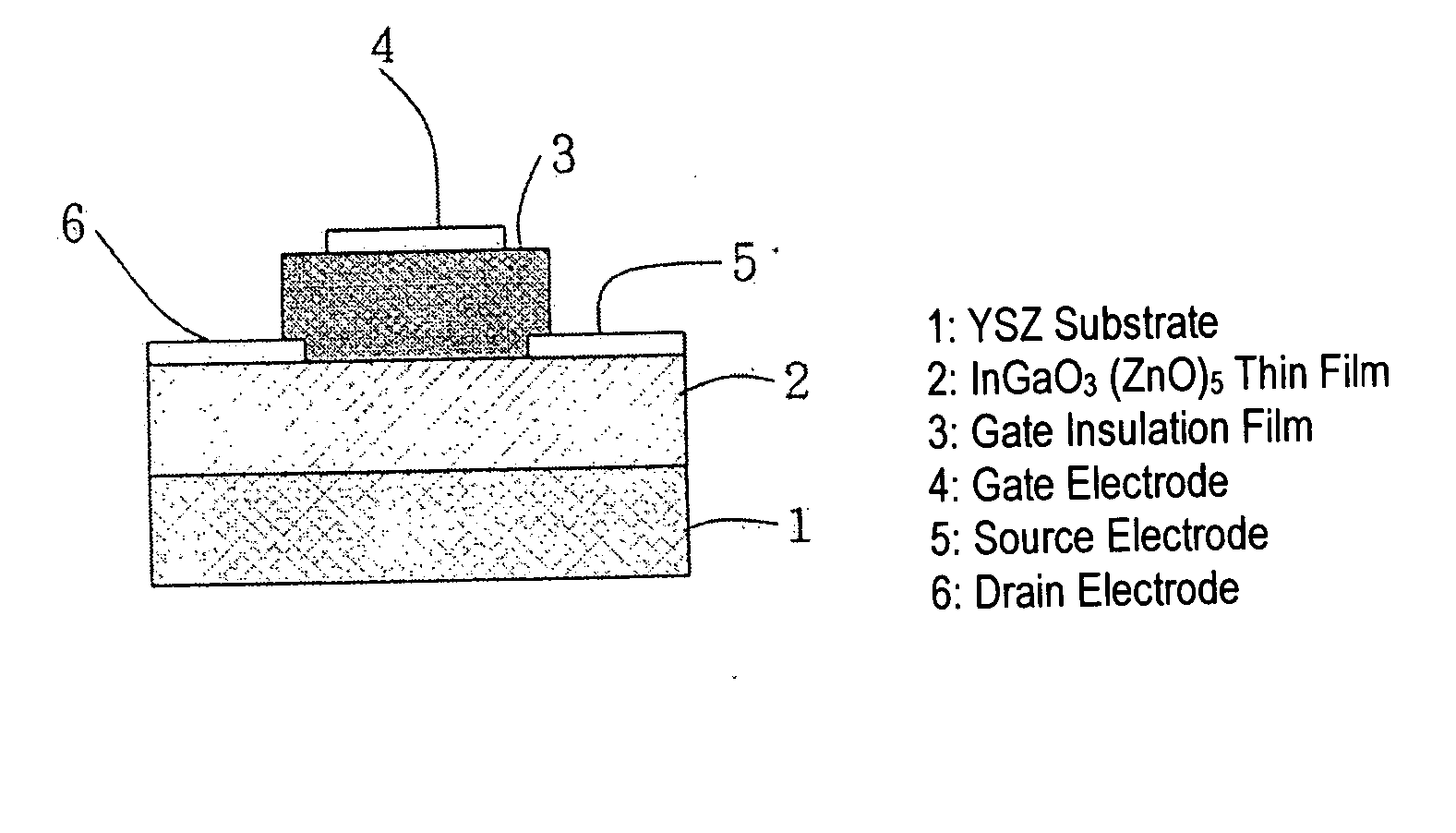

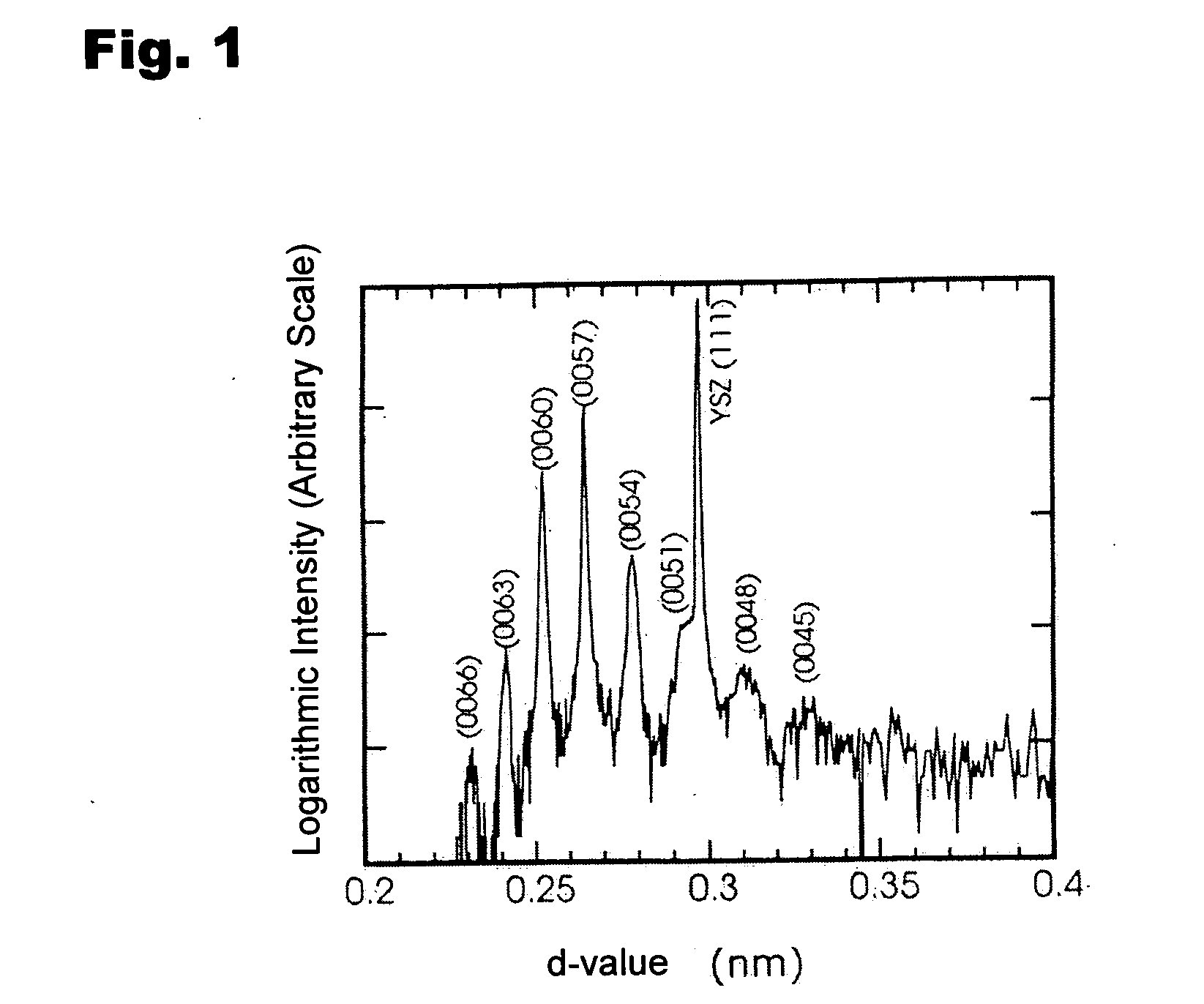

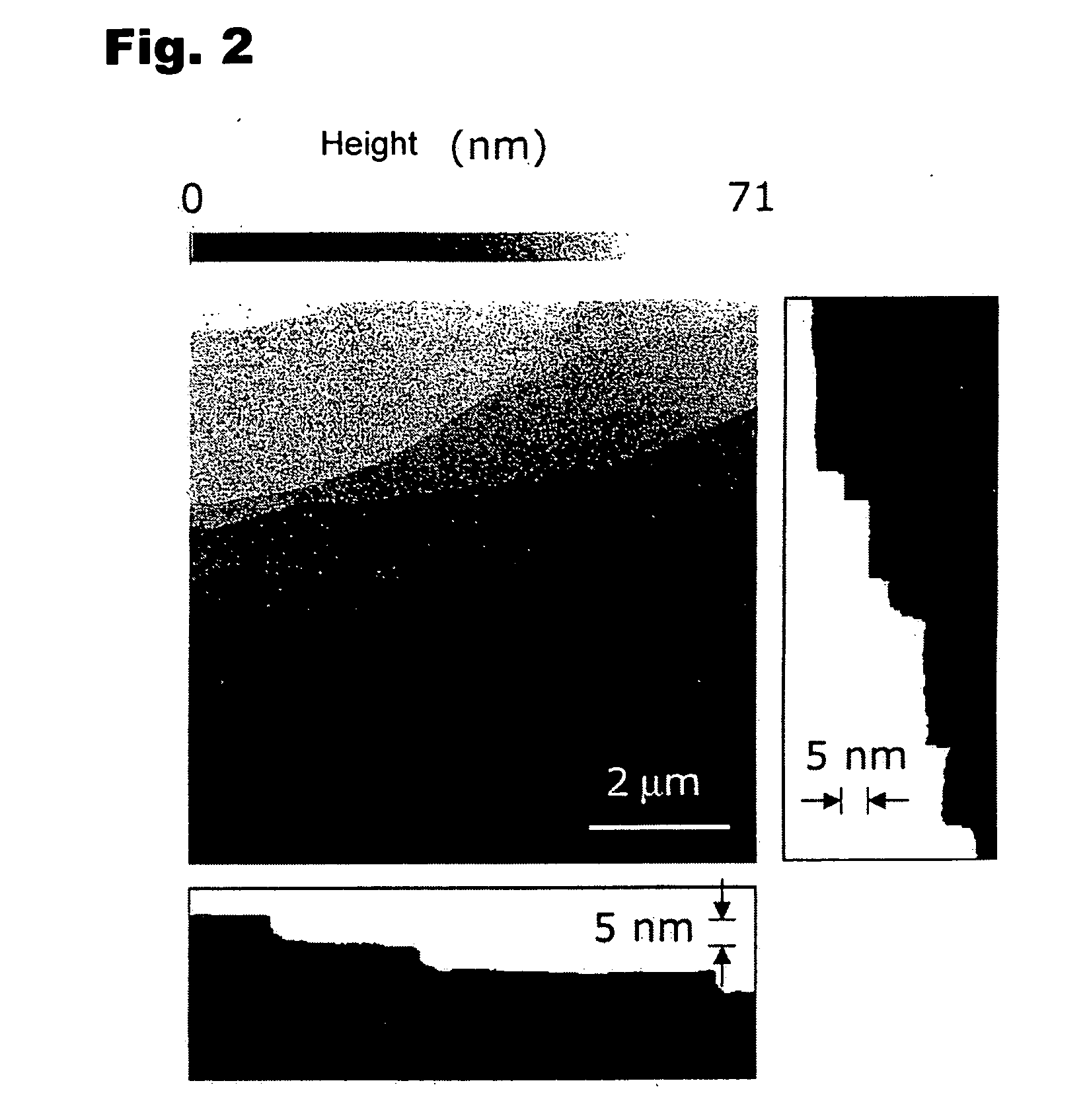

Natural-superlattice homologous single crystal thin film, method for preparation thereof, and device using said single crystal thin film

InactiveUS20050039670A1Avoid large deviationImprove insulation performanceTransistorPolycrystalline material growthX-raySingle crystal substrate

Disclosed is a natural-superlattice homologous single-crystal thin film, which comprises a complex oxide which is epitaxially grown on either one of a ZnO epitaxial thin film formed on a single-crystal substrate, the single-crystal substrate after disappearance of the ZnO epitaxial thin film and a ZnO single crystal. The complex oxide is expressed by the a formula: M1M2O3 (ZnO)m, wherein M1 is at least one selected from the group consisting of Ga, Fe, Sc, In, Lu, Yb, Tm, Er, Ho and Y, M2 is at least one selected from the group consisting of Mn, Fe, Ga, In and Al, and m is a natural number of 1 or more. A natural-superlattice homologous single-crystal thin film formed by depositing the complex oxide and subjecting the obtained layered film to a thermal anneal treatment can be used in optimal devices, electronic devices and X-ray optical devices.

Owner:HOYA CORP +1

Device and method for pressure-driven plug transport and reaction

ActiveUS20050087122A1Eliminate evaporationWell mixedMaterial nanotechnologySequential/parallel process reactionsPressure.driveCarrier fluid

Owner:UNIVERSITY OF CHICAGO

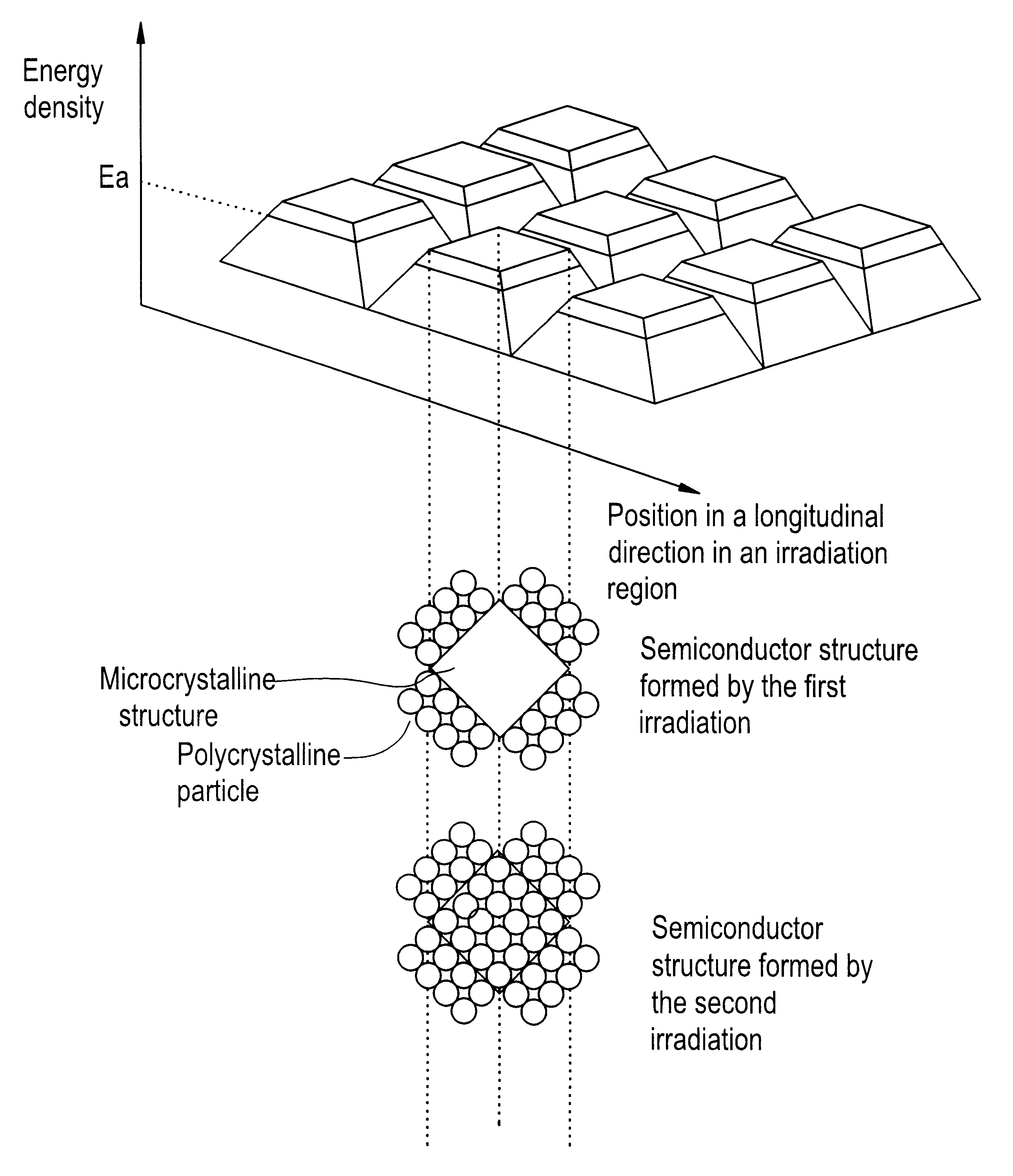

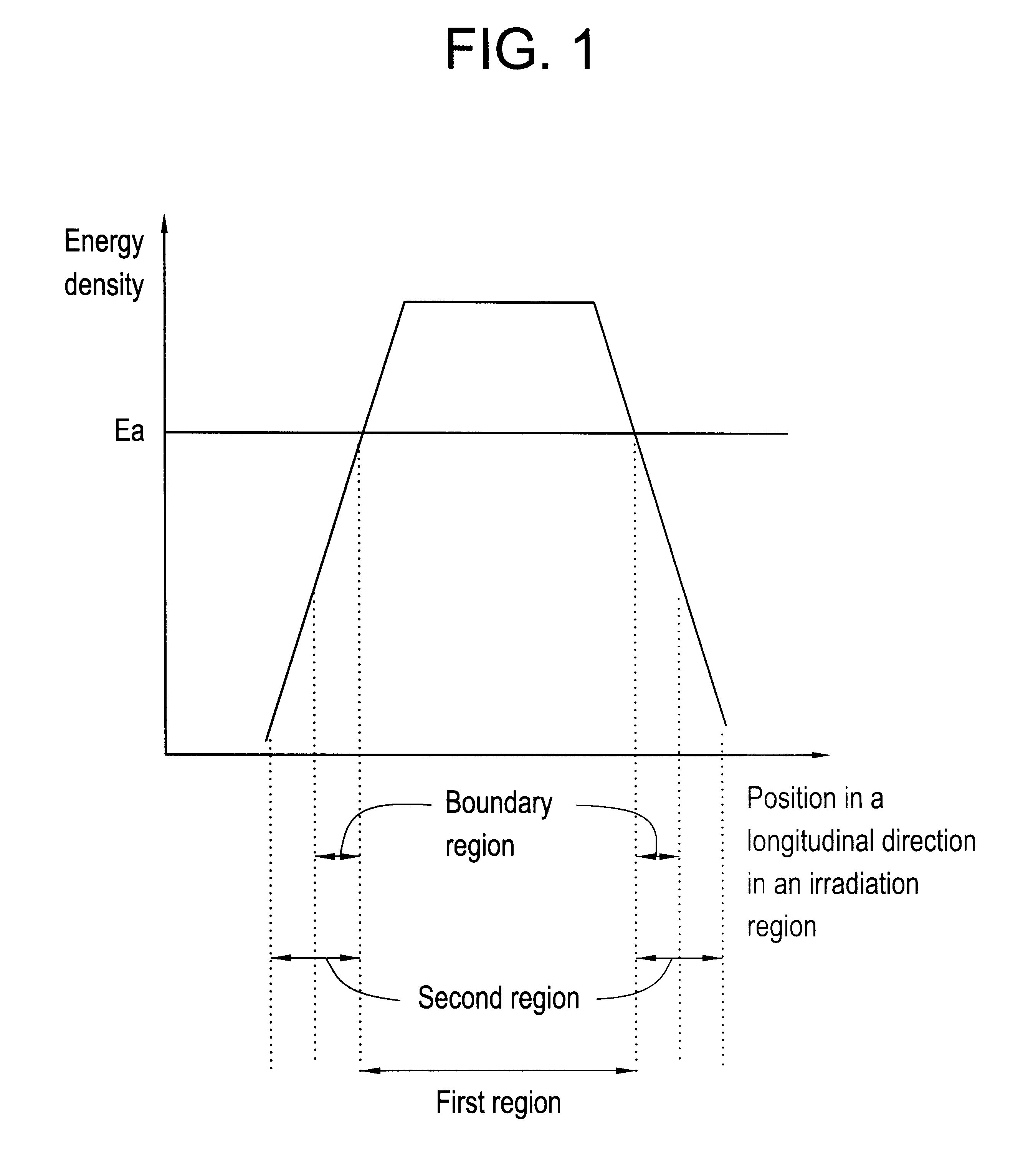

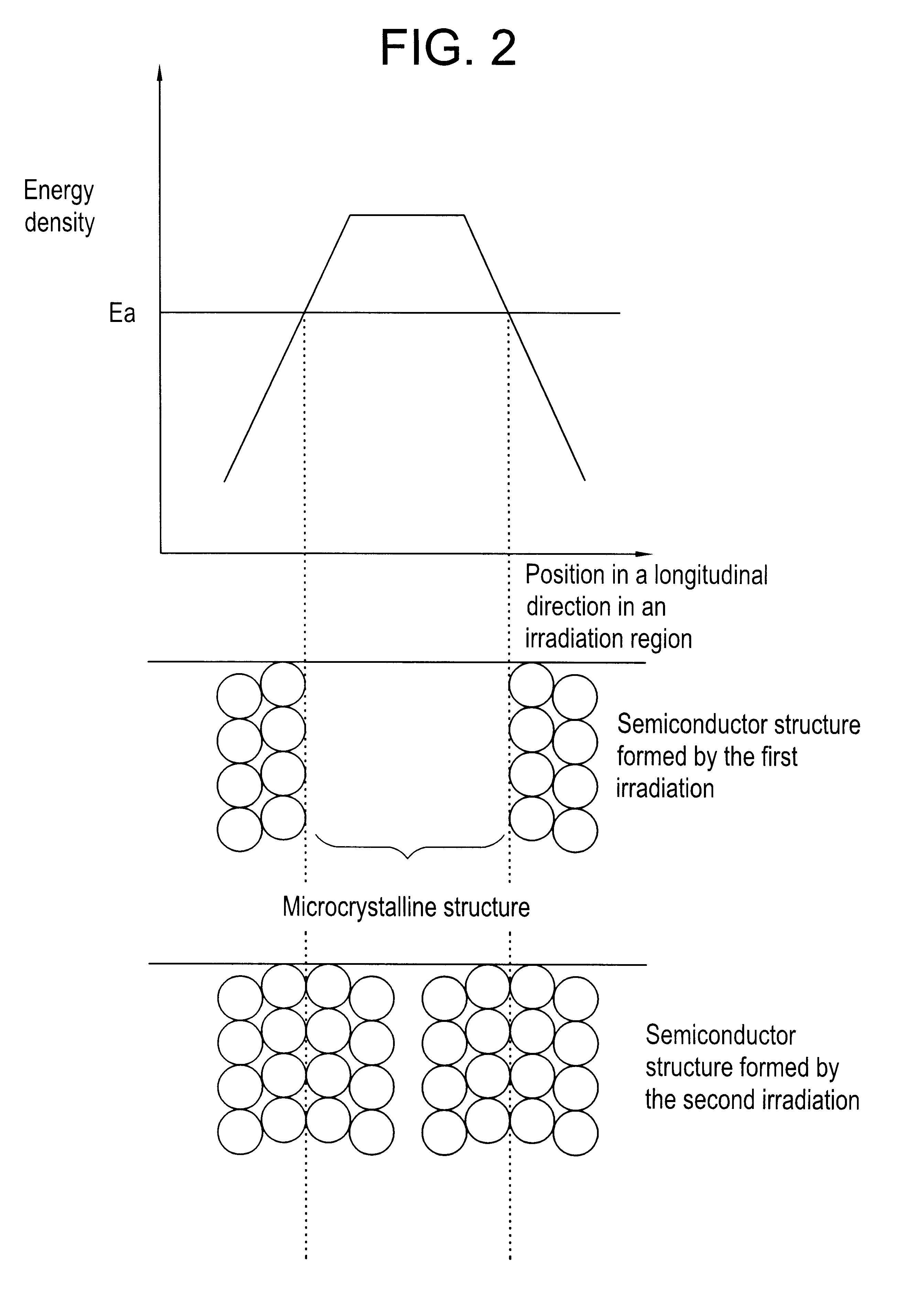

Laser irradiation process

A pulse laser beam having a rectangular irradiation region is irradiated on the same point in a non-single crystal semiconductor film multiple times. The pulse laser beam has an energy profile in a longitudinal direction in the beam irradiation region as follows: (a) there are the first region having an energy density of Ea or higher and the second regions on both sides of the first region having an energy density of less than Ea, and (b) an energy density slope has an absolute value of 20 to 300 J / cm3 in a boundary region extending to 1 mum from the boundary line between the first and the second regions.

Owner:GOLD CHARM LTD

Single crystalline graphene sheet and process of preparing the same

A single-crystal graphene sheet includes a polycyclic aromatic molecule wherein a plurality of carbon atoms are covalently bound to each other, the single-crystal graphene sheet comprising between about 1 layer to about 300 layers; and wherein a peak ratio of a Raman D band intensity to a Raman G band intensity is equal to or less than 0.2. Also described is a method for preparing a single-crystal graphene sheet, the method includes forming a catalyst layer, which includes a single-crystal graphitizing metal catalyst sheet; disposing a carbonaceous material on the catalyst layer; and heat-treating the catalyst layer and the carbonaceous material in at least one of an inert atmosphere and a reducing atmosphere. Also described is a transparent electrode including a single-crystal graphene sheet.

Owner:SAMSUNG ELECTRONICS CO LTD

Device and method for pressure-driven plug transport and reaction

InactiveUS20100233026A1Well mixedQuick mixMaterial nanotechnologySequential/parallel process reactionsPressure.driveCarrier fluid

Owner:ISMAGLIOV RUSTEM F +3

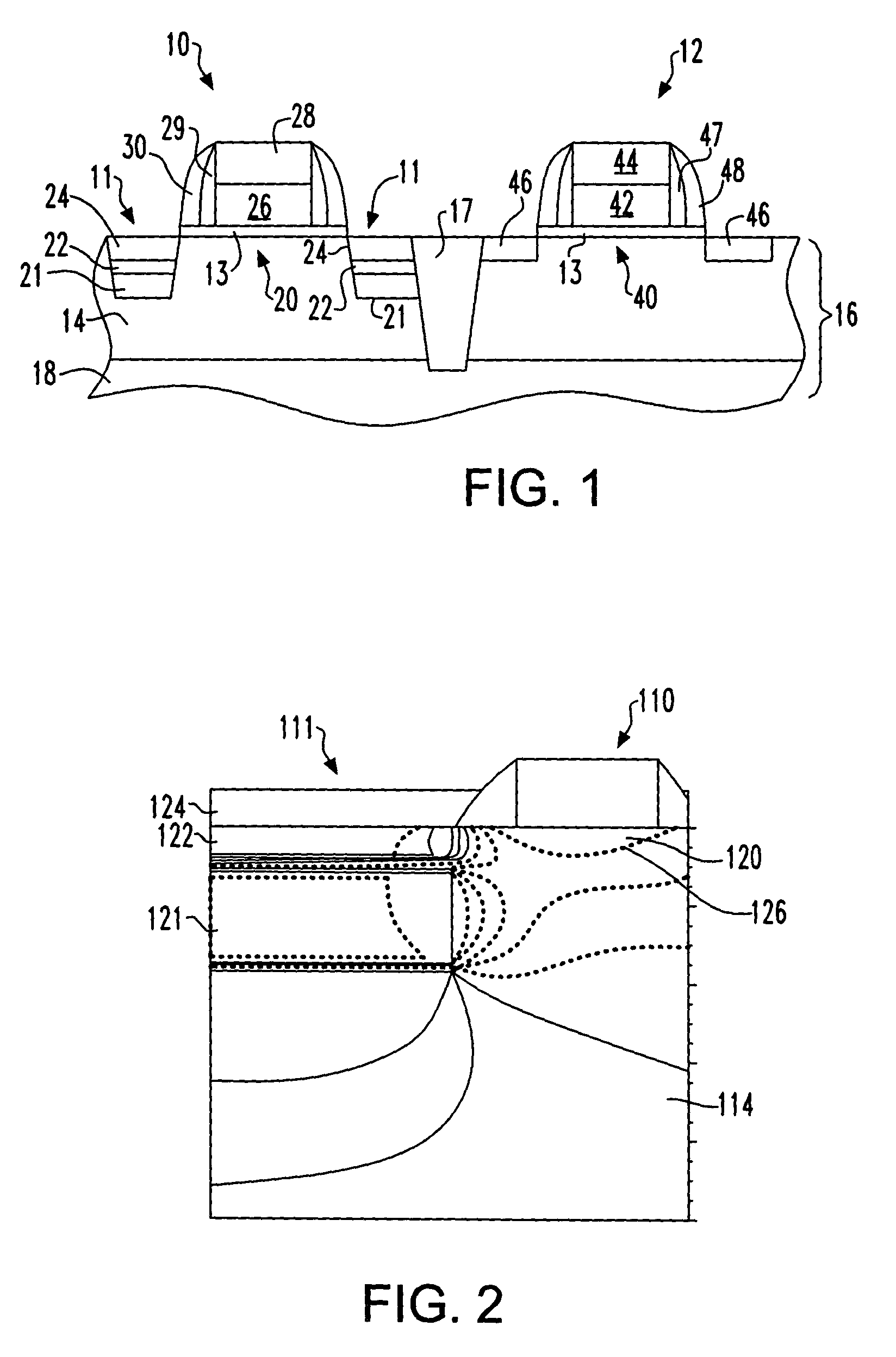

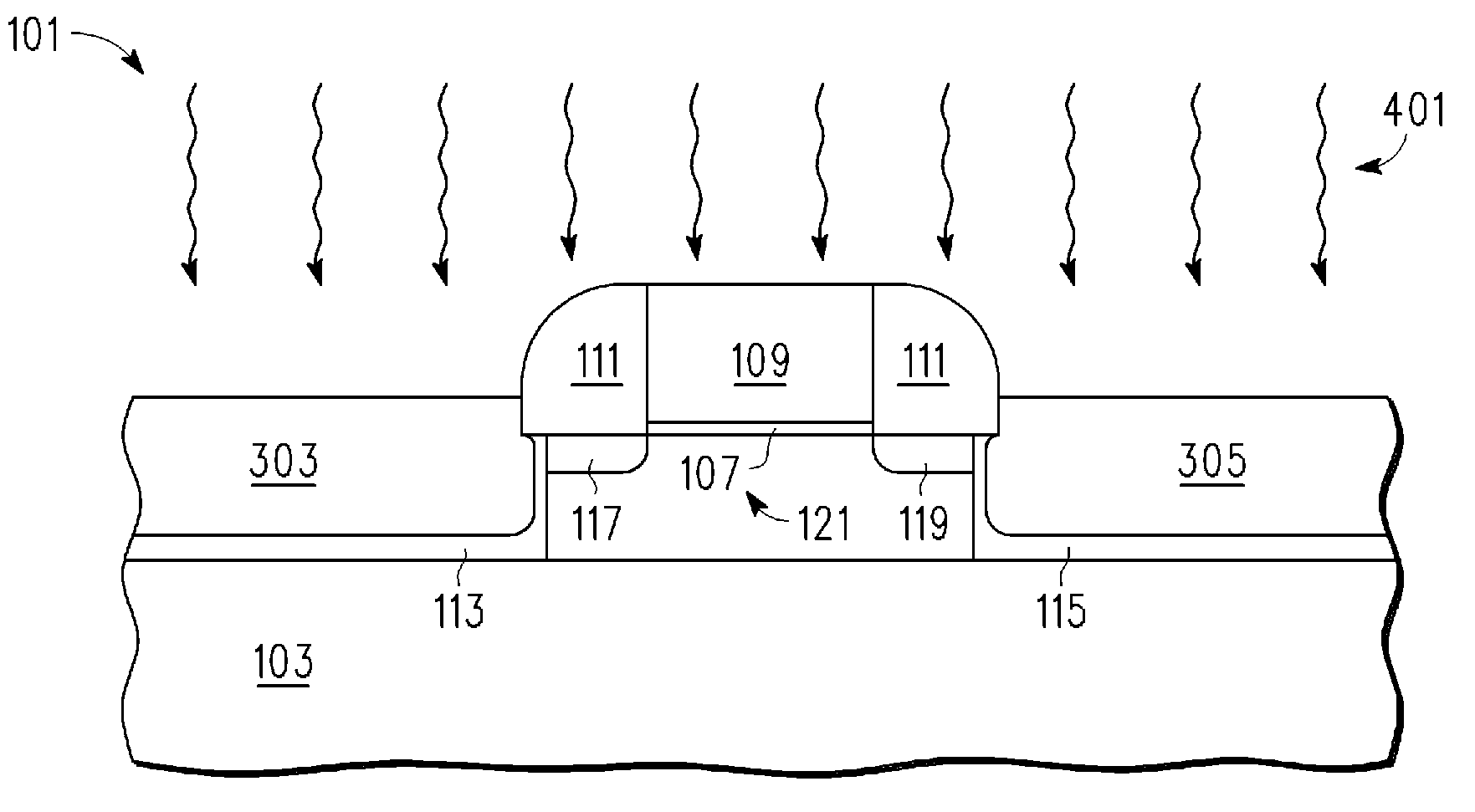

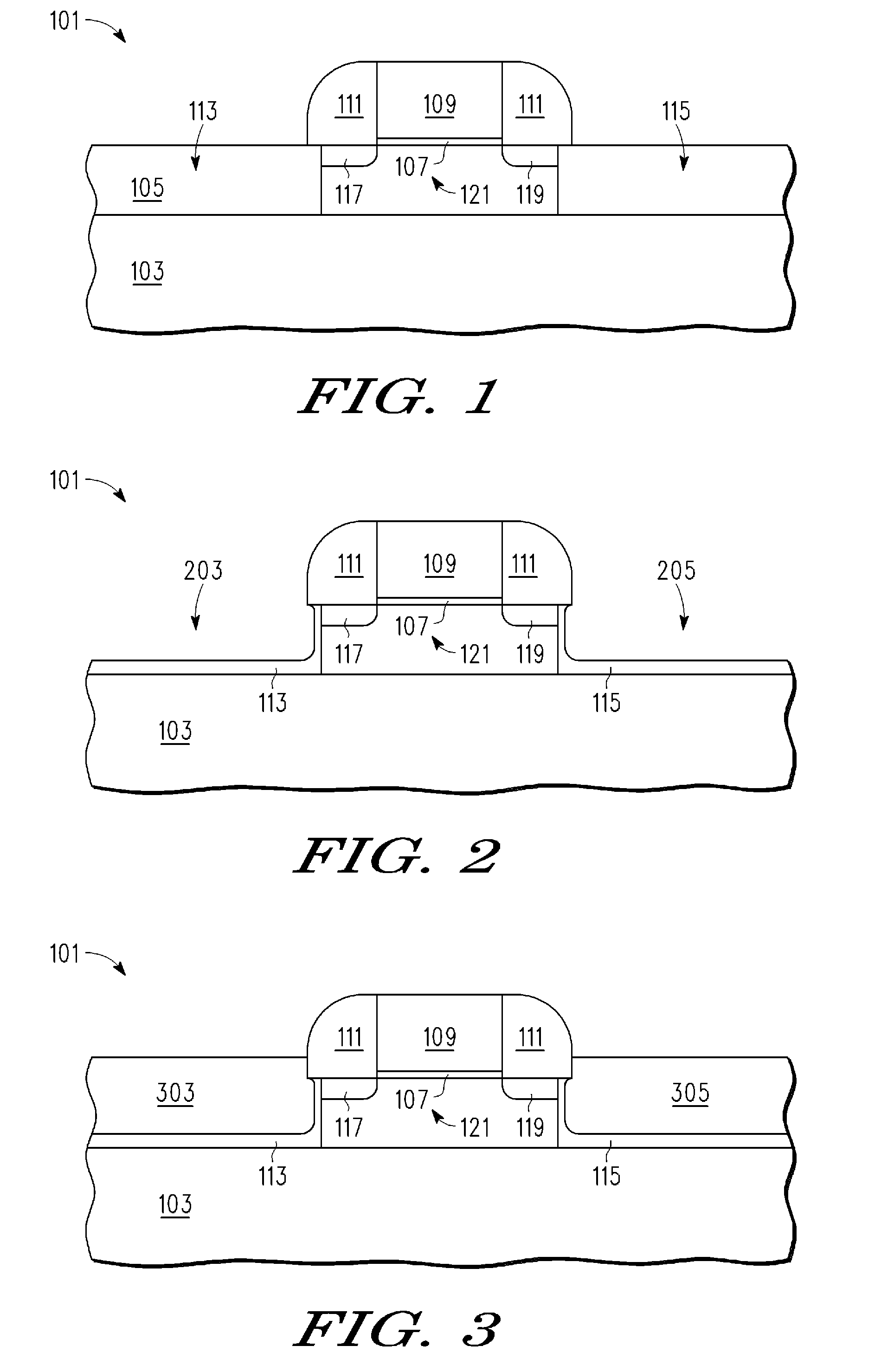

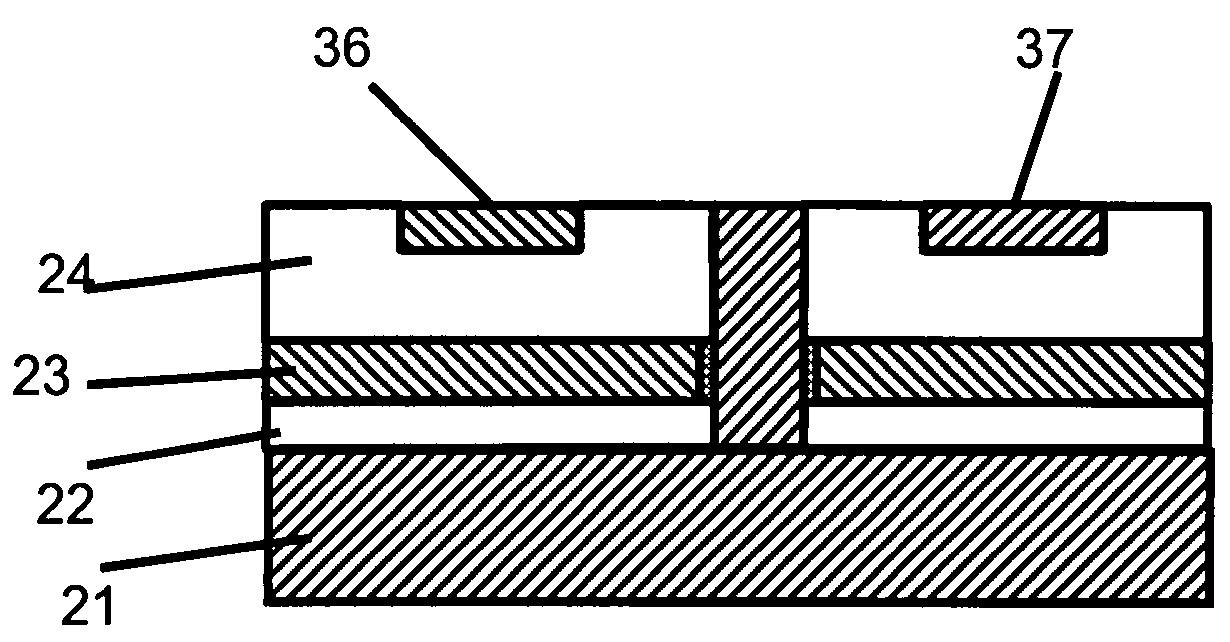

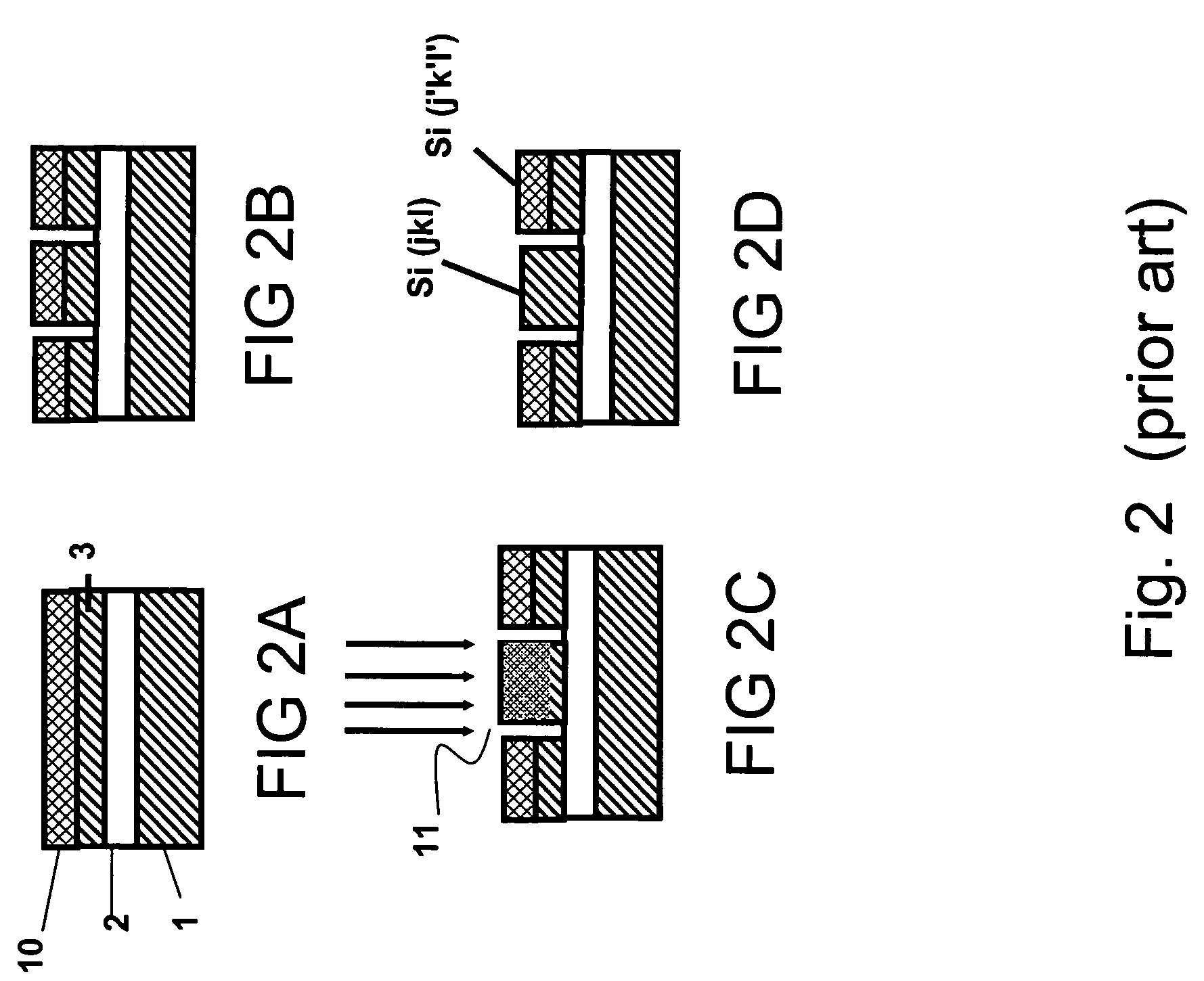

Structure and method of making strained semiconductor CMOS transistors having lattice-mismatched source and drain regions

A p-type field effect transistor (PFET) and an n-type field effect transistor (NFET) of an integrated circuit are provided. A first strain is applied to the channel region of the PFET but not the NFET via a lattice-mismatched semiconductor layer such as silicon germanium disposed in source and drain regions of only the PFET and not of the NFET. A process of making the PFET and NFET is provided. Trenches are etched in the areas to become the source and drain regions of the PFET and a lattice-mismatched silicon germanium layer is grown epitaxially therein to apply a strain to the channel region of the PFET adjacent thereto. A layer of silicon can be grown over the silicon germanium layer and a salicide formed from the layer of silicon to provide low-resistance source and drain regions.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Laser beam processing method for a semiconductor wafer

ActiveUS7265033B2Stable removalFrom solid stateSemiconductor/solid-state device detailsLaser beamsSemiconductor

Owner:DISCO CORP

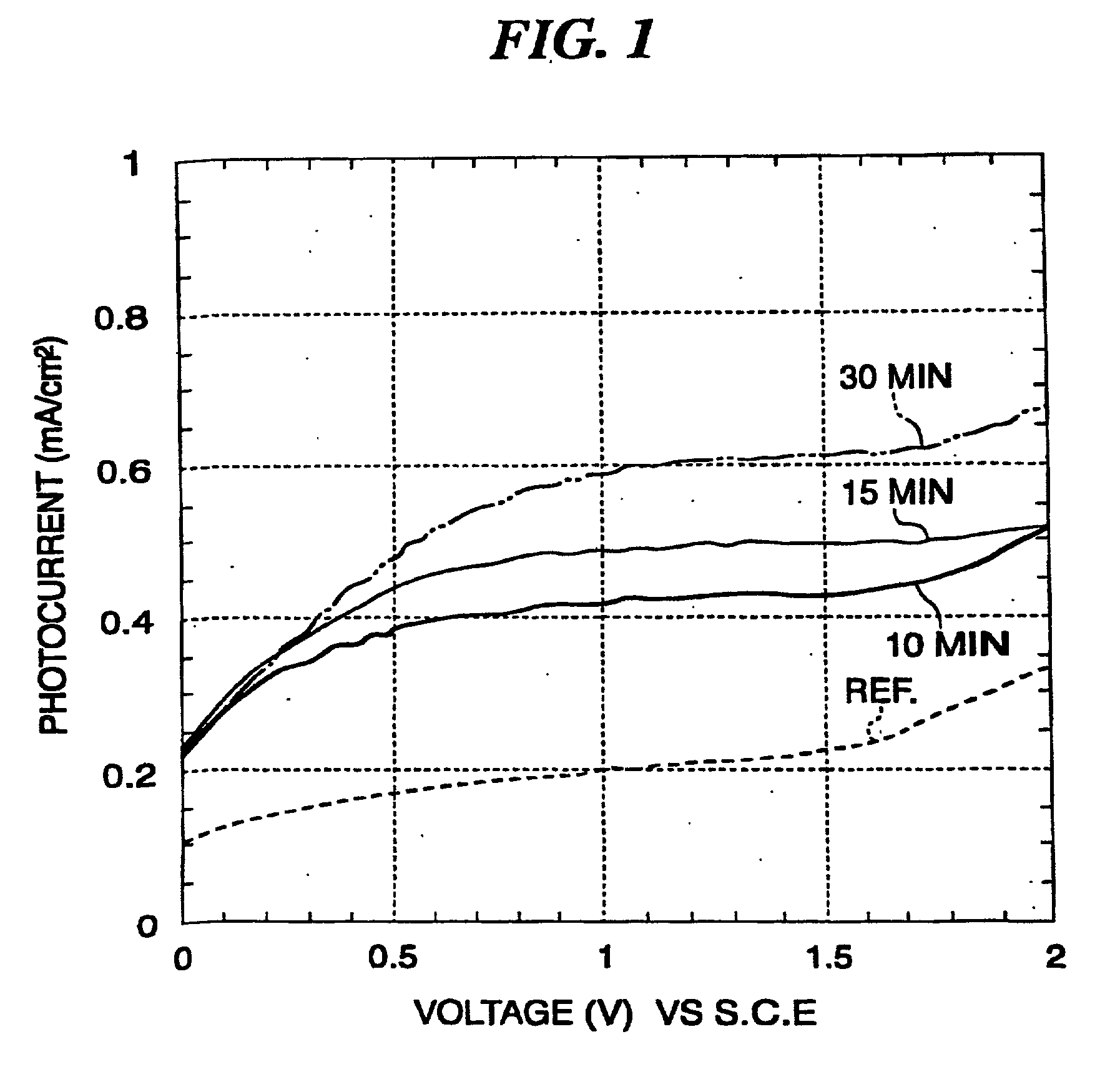

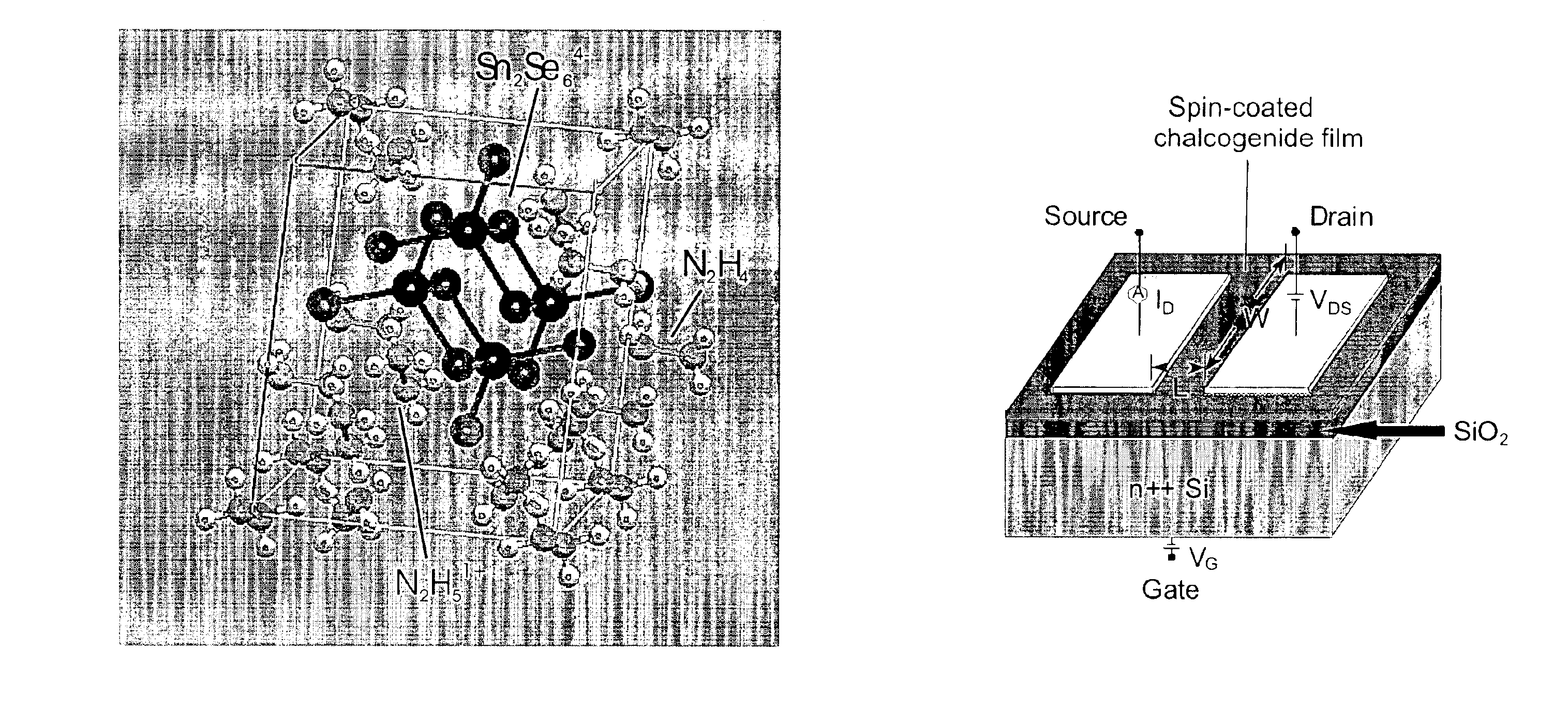

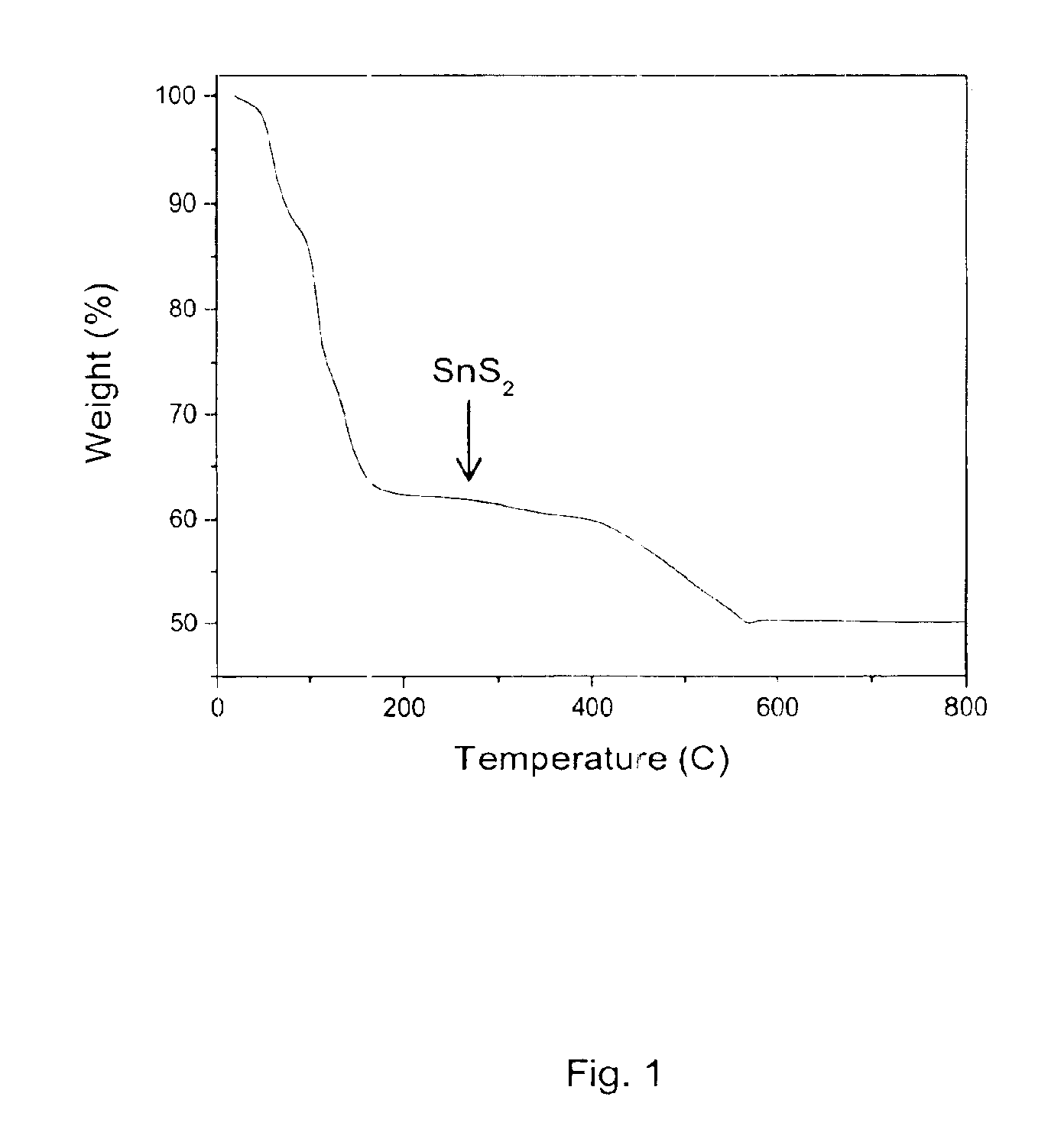

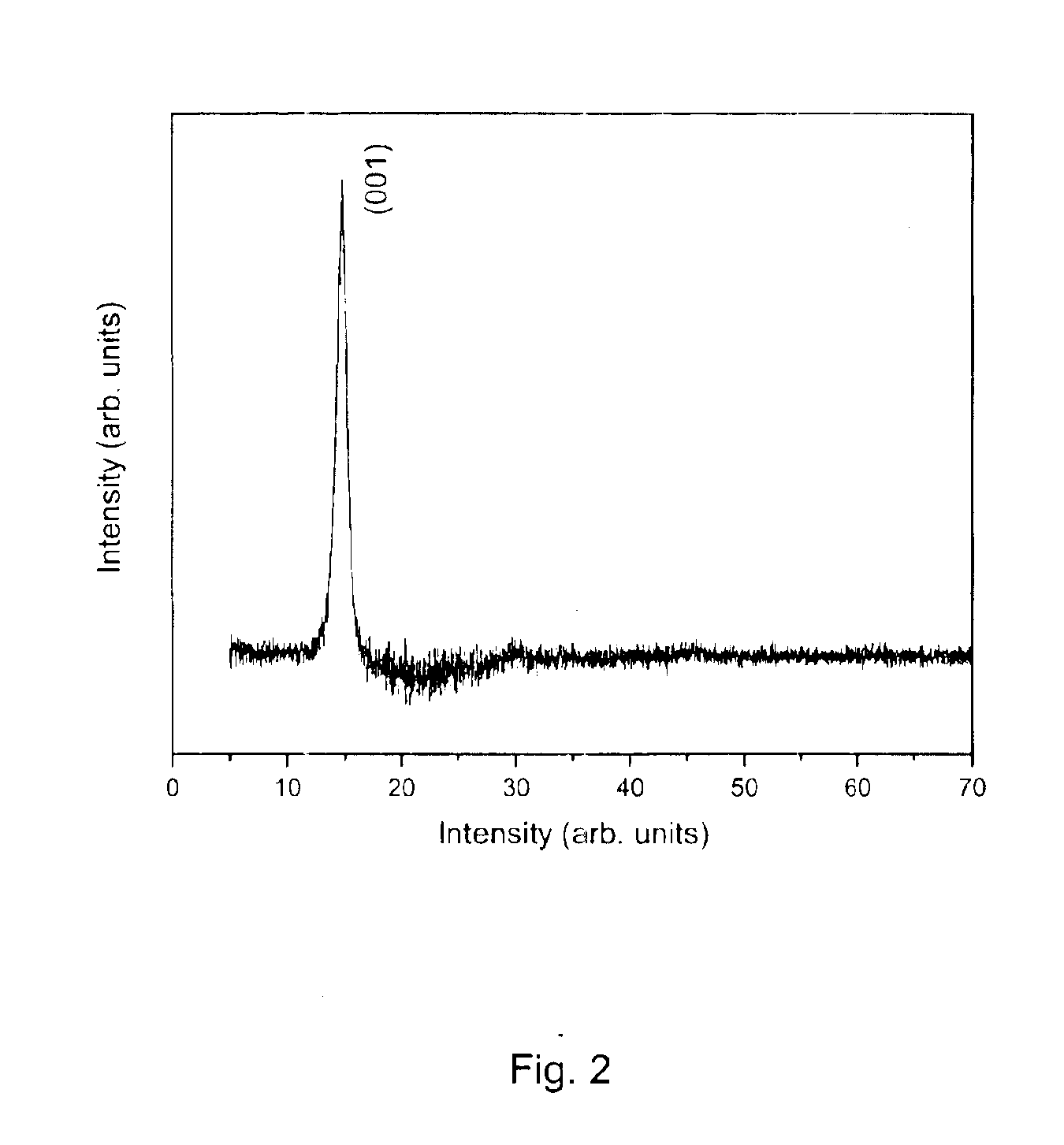

Solution deposition of chalcogenide films

A method of depositing a film of a metal chalcogenide. The first of these methods includes the steps of: contacting at least one metal chalcogenide, a hydrazine compound and optionally, an elemental chalcogen, to produce a solution of a hydrazinium-based precursor of the metal chalcogenide; applying the solution of the hydrazinium-based precursor of the metal chalcogenide onto a substrate to produce a film of the precursor; and thereafter annealing the film of the precursor to remove excess hydrazine and hydrazinium chalcogenide salts to produce a metal chalcogenide film on the substrate. The second of these methods includes the steps of: contacting: at least one metal chalcogenide and a salt of an amine compound to produce an ammonium-based precursor of the metal chalcogenide; contacting the ammonium-based precursor of the metal chalcogenide and a hydrazine compound, and optionally, an elemental chalcogen, to produce a solution of a hydrazinium-based precursor of the metal chalcogenide in the hydrazine compound; applying the solution of the hydrazinium-based precursor onto a substrate to produce a film; and thereafter, annealing to produce a metal chalcogenide film. Also provided is a thin-film field-effect transistor device using the metal chalcogenides as the channel layer.

Owner:GLOBALFOUNDRIES INC

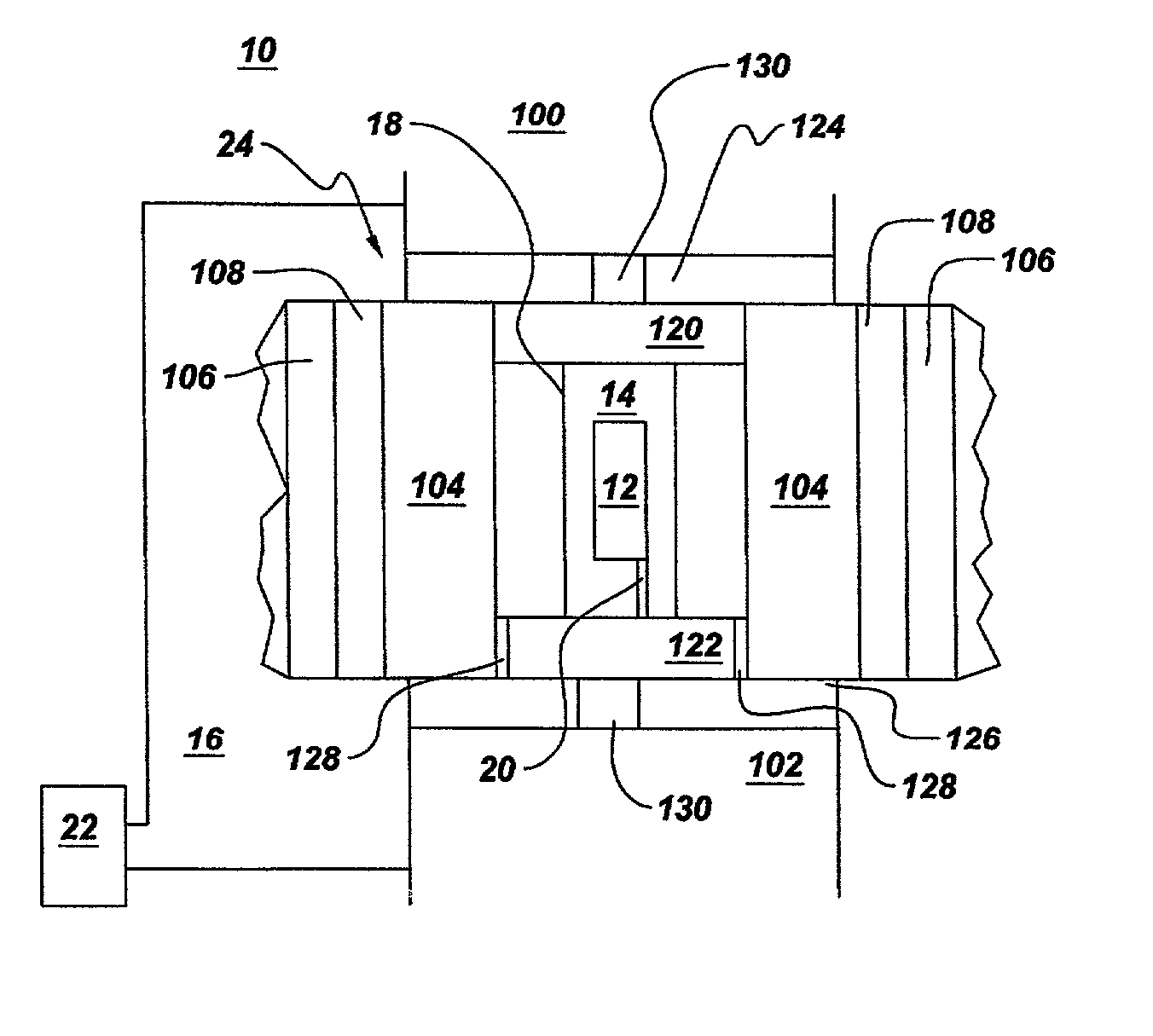

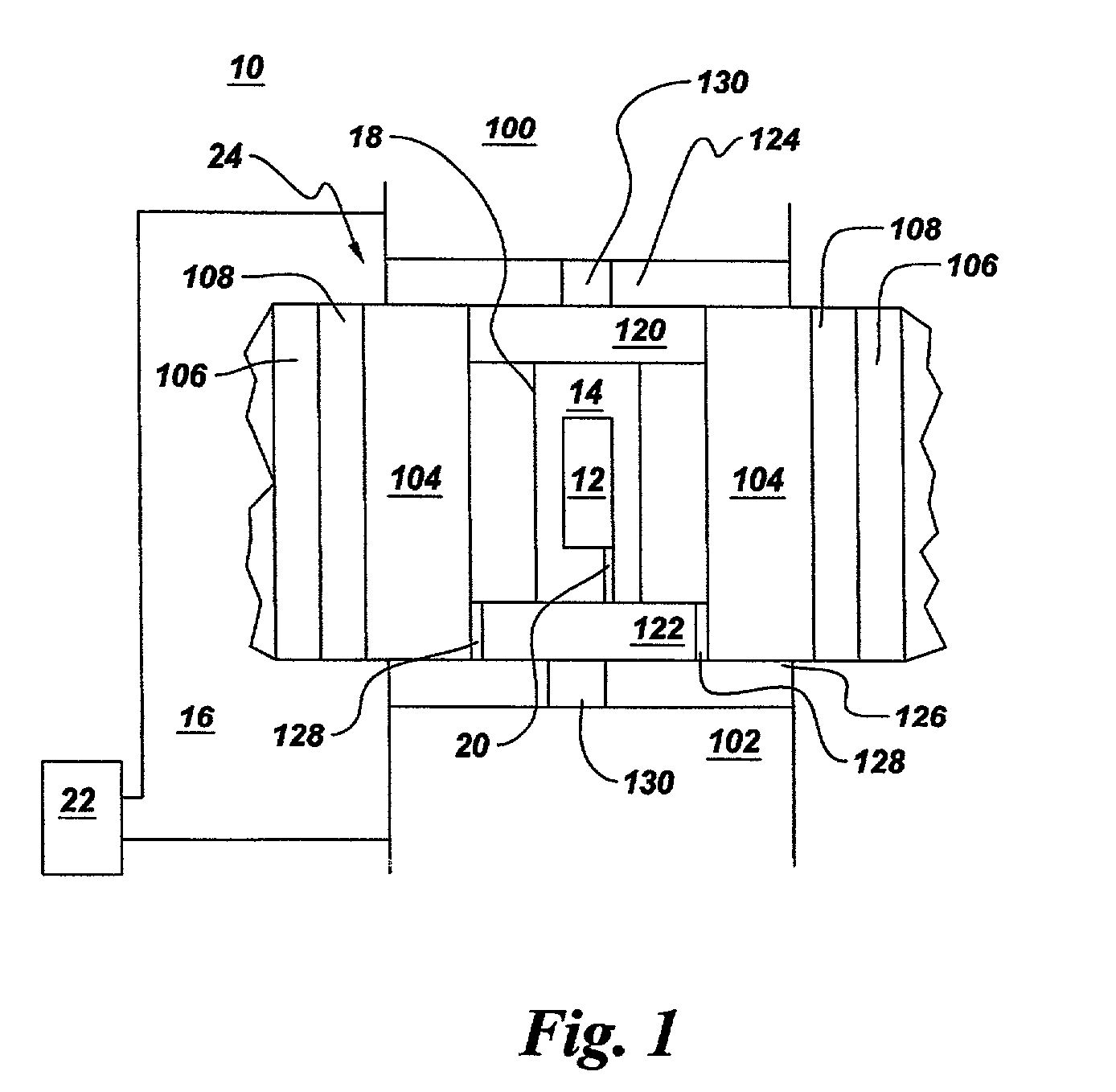

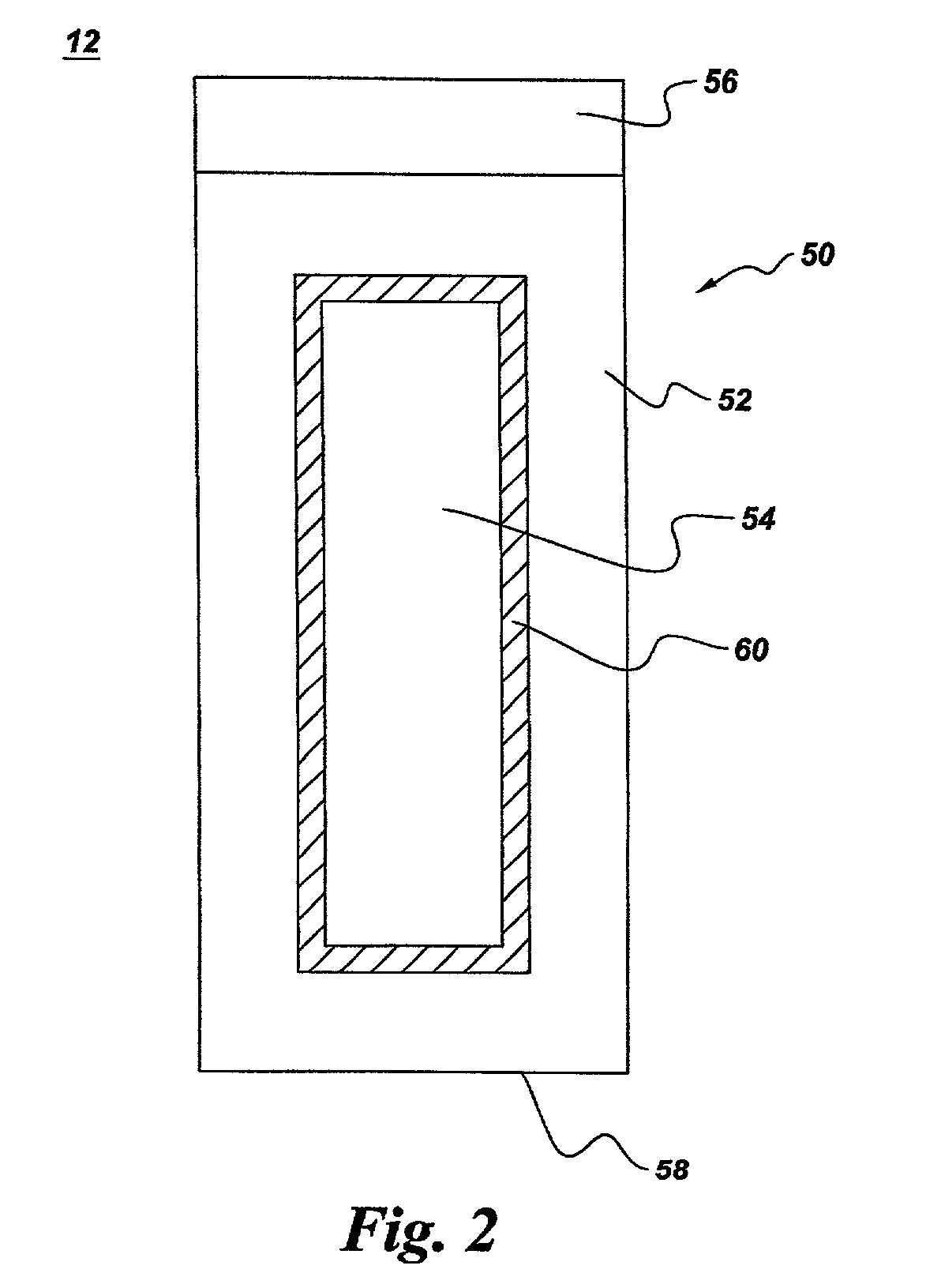

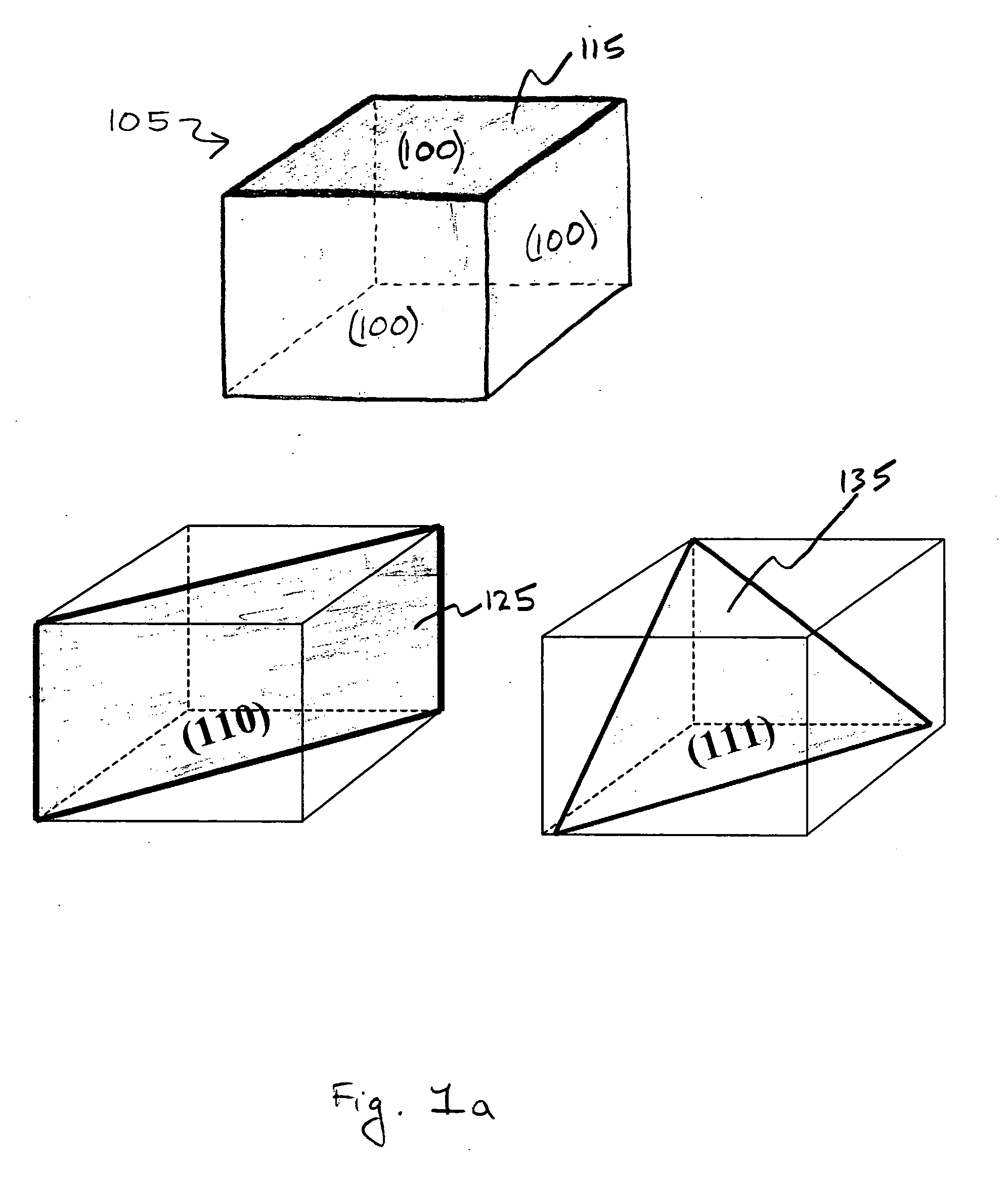

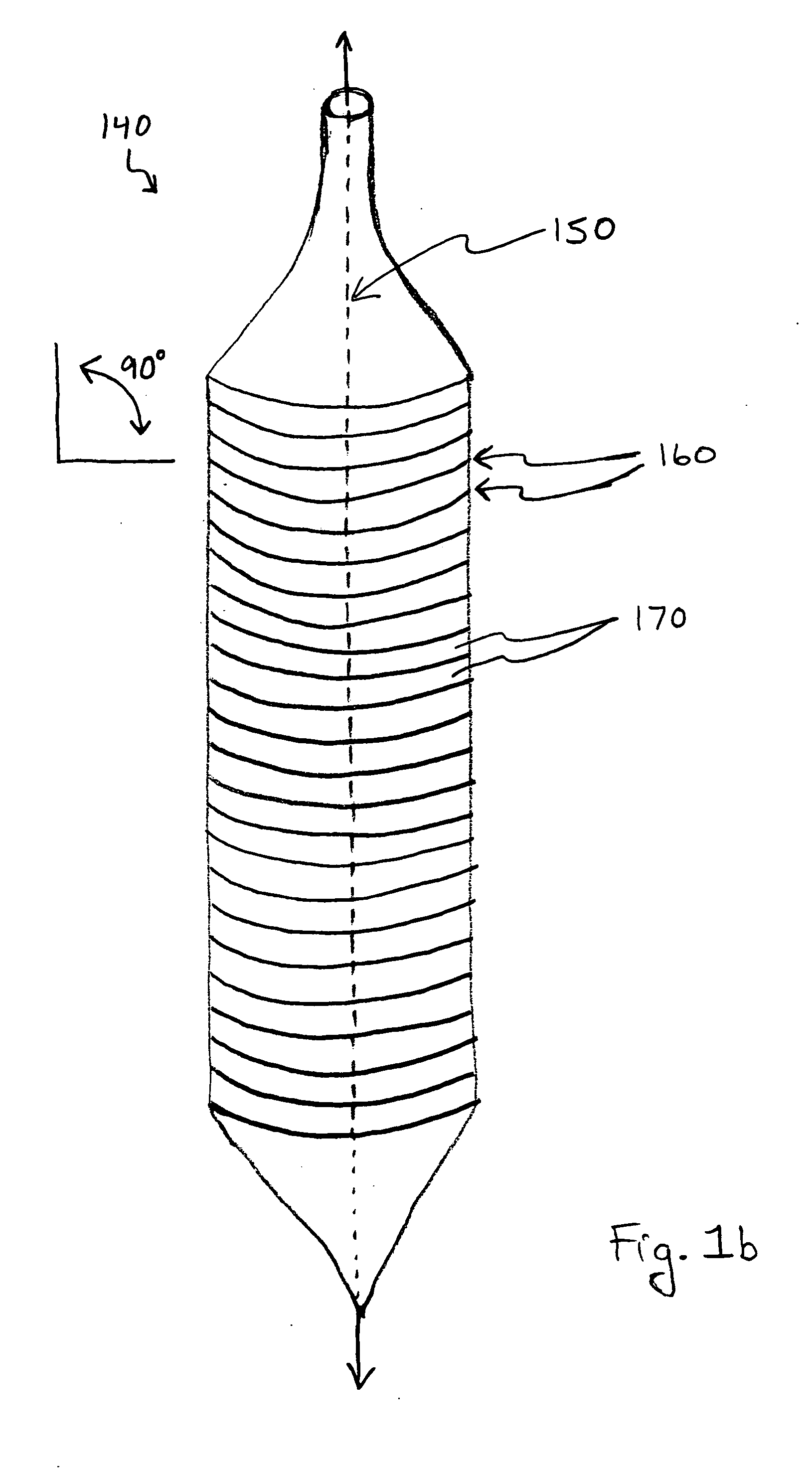

Pressure vessel

InactiveUS20030140845A1Prevent escapeAvoid creatingFrom gel statePolycrystalline material growthTemperature controlPressure transmission

A pressure vessel for processing at least one material in a supercritical fluid. The pressure vessel includes a self-pressurizing capsule for containing at least one material and the supercritical fluid in a substantially air-free environment, a pressure transmission medium surrounding the capsule for maintaining an outer pressure on the capsule, at least one heating element insertable in the pressure transmission medium such that the heating element surrounds the capsule, a temperature measurement means for measuring a temperature of the capsule, a temperature controller for controlling the temperature and providing power to the heating element, a restraint to contain and hold in place the capsule, the pressure transmission medium, and the heating element, and at least one seal between the restraint and the pressure transmission medium for preventing escape of the pressure transmission medium. Methods of using the pressure vessel, processing a material at high temperature and high pressure in the presence of a supercritical fluid within the capsule are also described.

Owner:SORAA

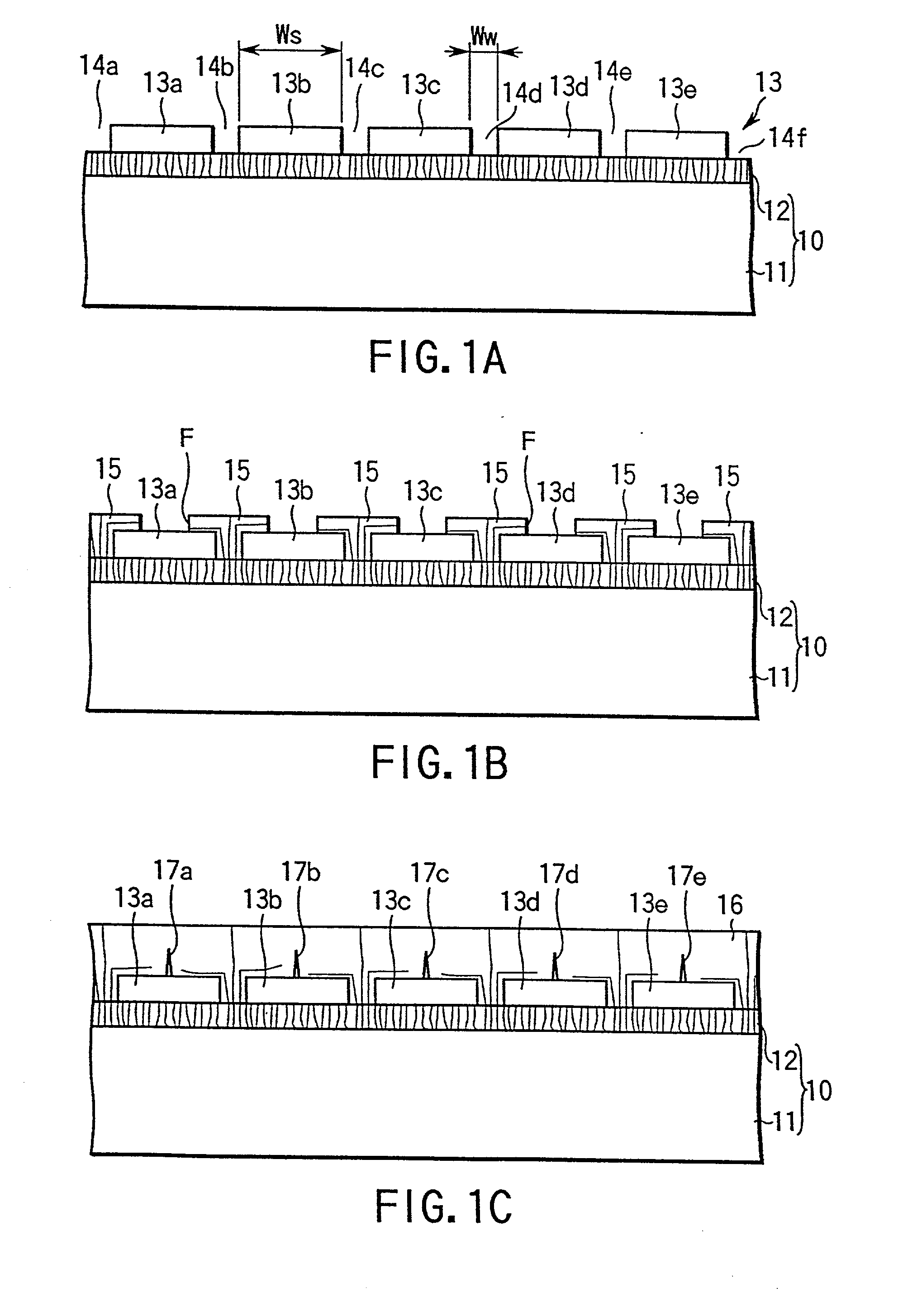

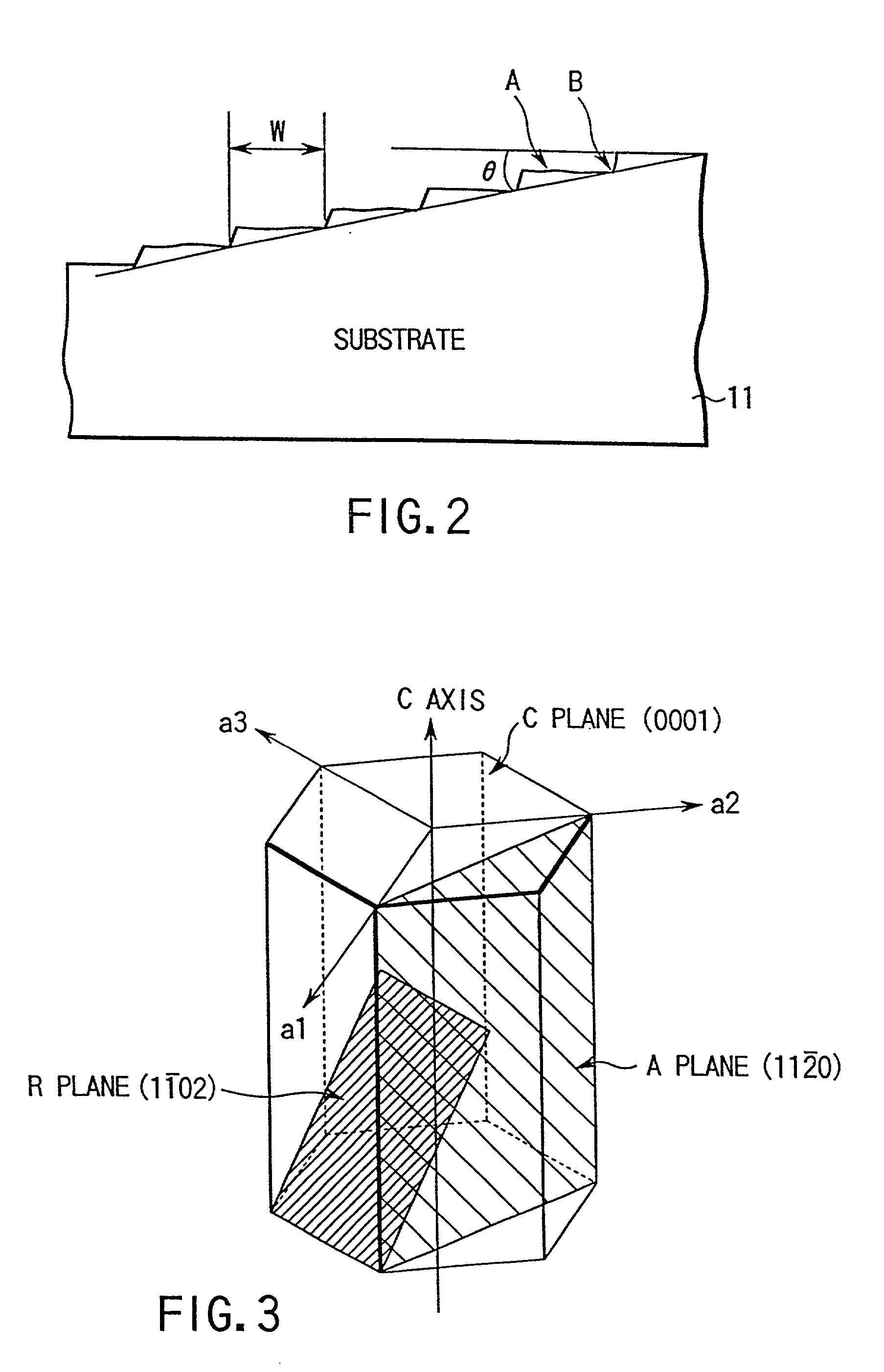

Nitride semiconductor growth method, nitride semiconductor substrate, and nitride semiconductor device

InactiveUS20020046693A1From gel statePolycrystalline material growthCrystallographic defectNitride semiconductors

A method of growing a nitride semiconductor crystal which has very few crystal defects and can be used as a substrate is disclosed. This invention includes the step of forming a first selective growth mask on a support member including a dissimilar substrate having a major surface and made of a material different from a nitride semiconductor, the first selective growth mask having a plurality of first windows for selectively exposing the upper surface of the support member, and the step of growing nitride semiconductor portions from the upper surface, of the support member, which is exposed from the windows, by using a gaseous Group 3 element source and a gaseous nitrogen source, until the nitride semiconductor portions grown in the adjacent windows combine with each other on the upper surface of the selective growth mask.

Owner:NICHIA CORP

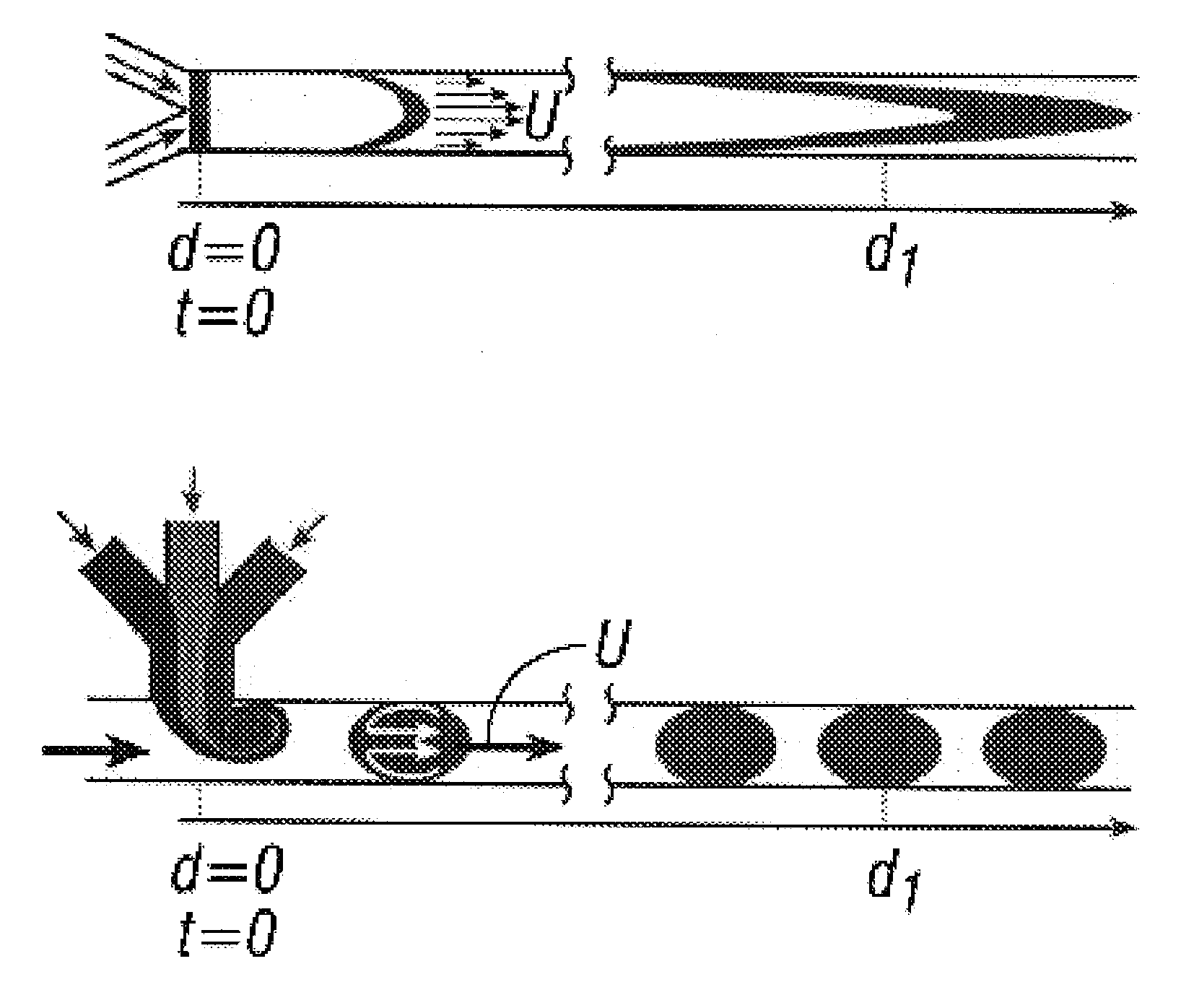

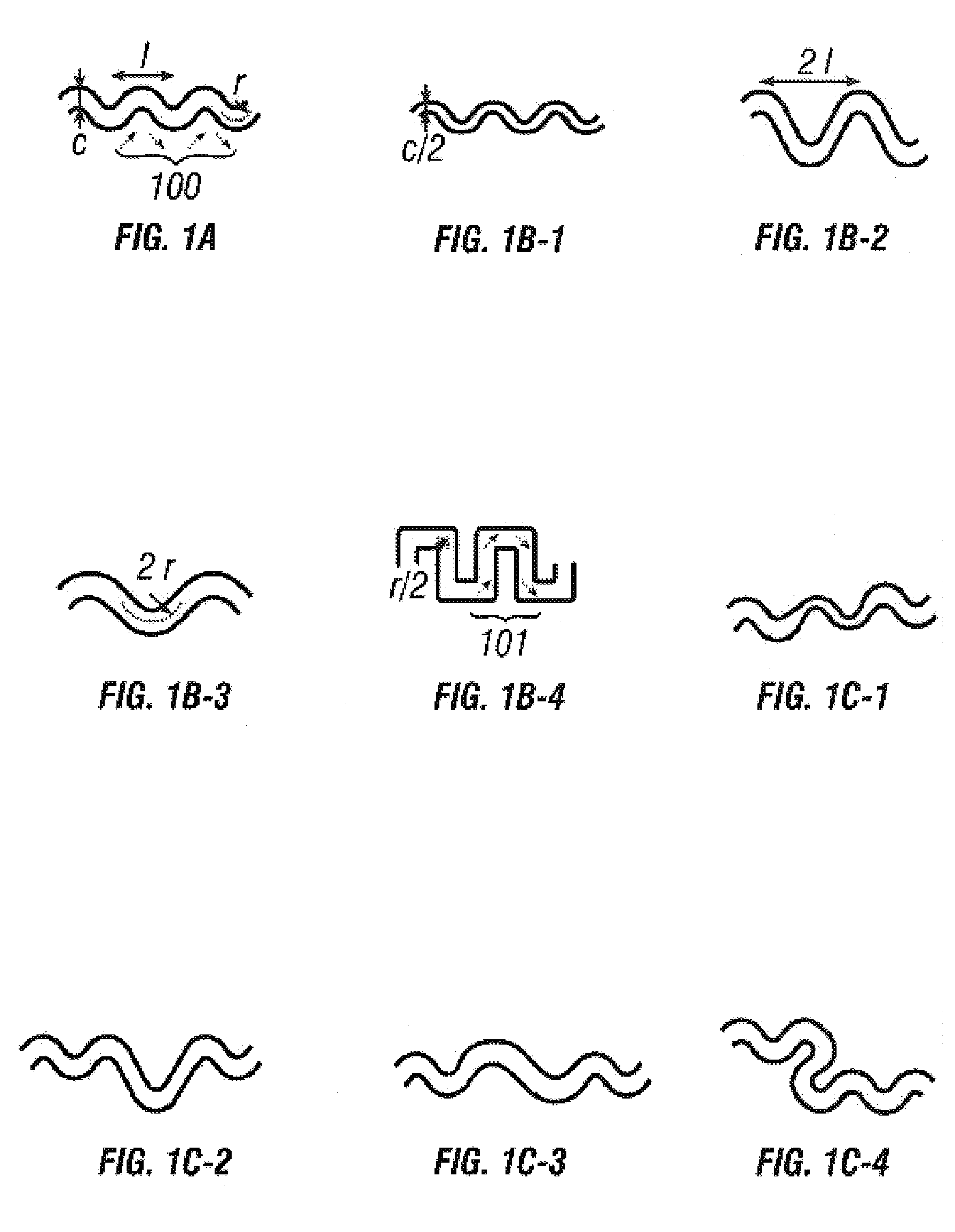

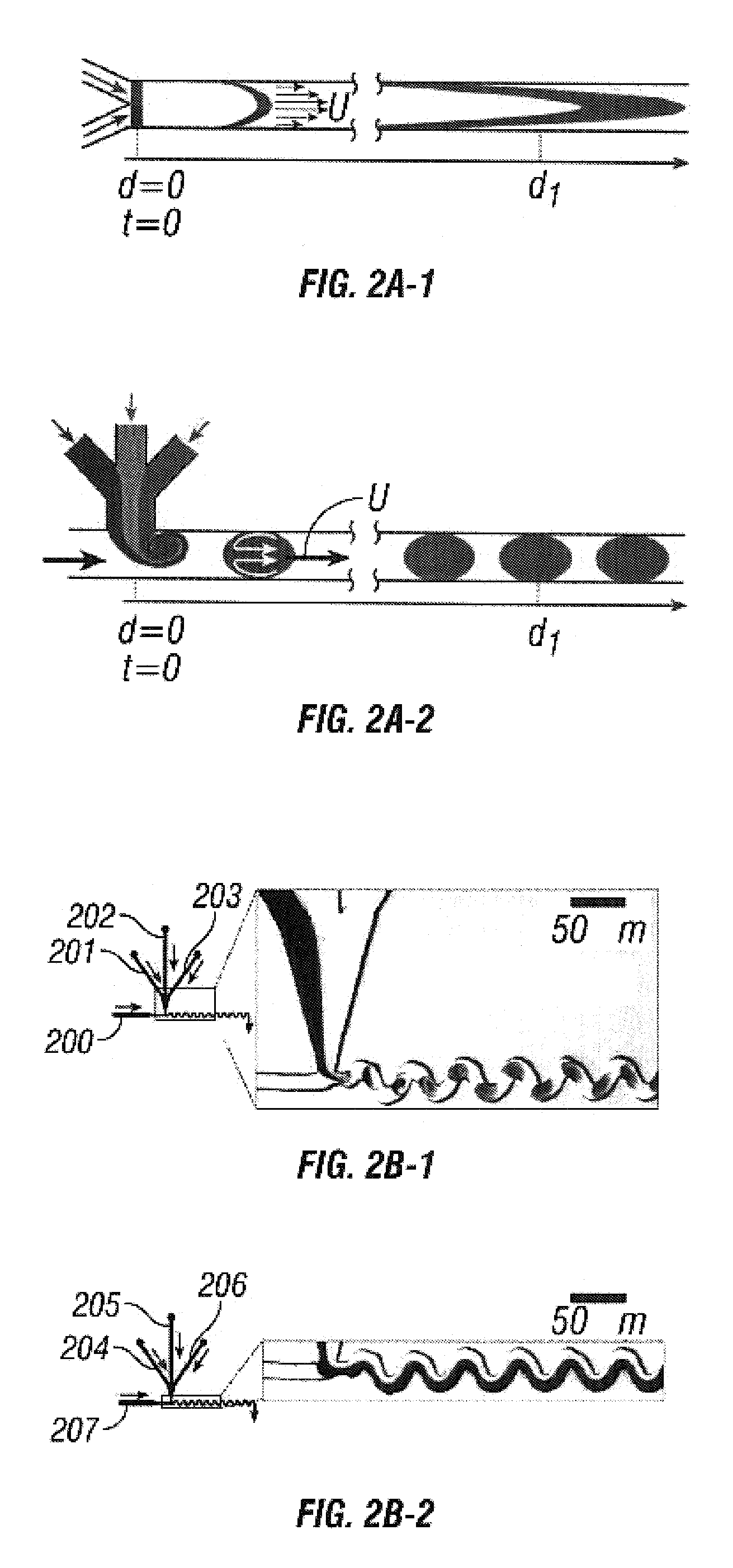

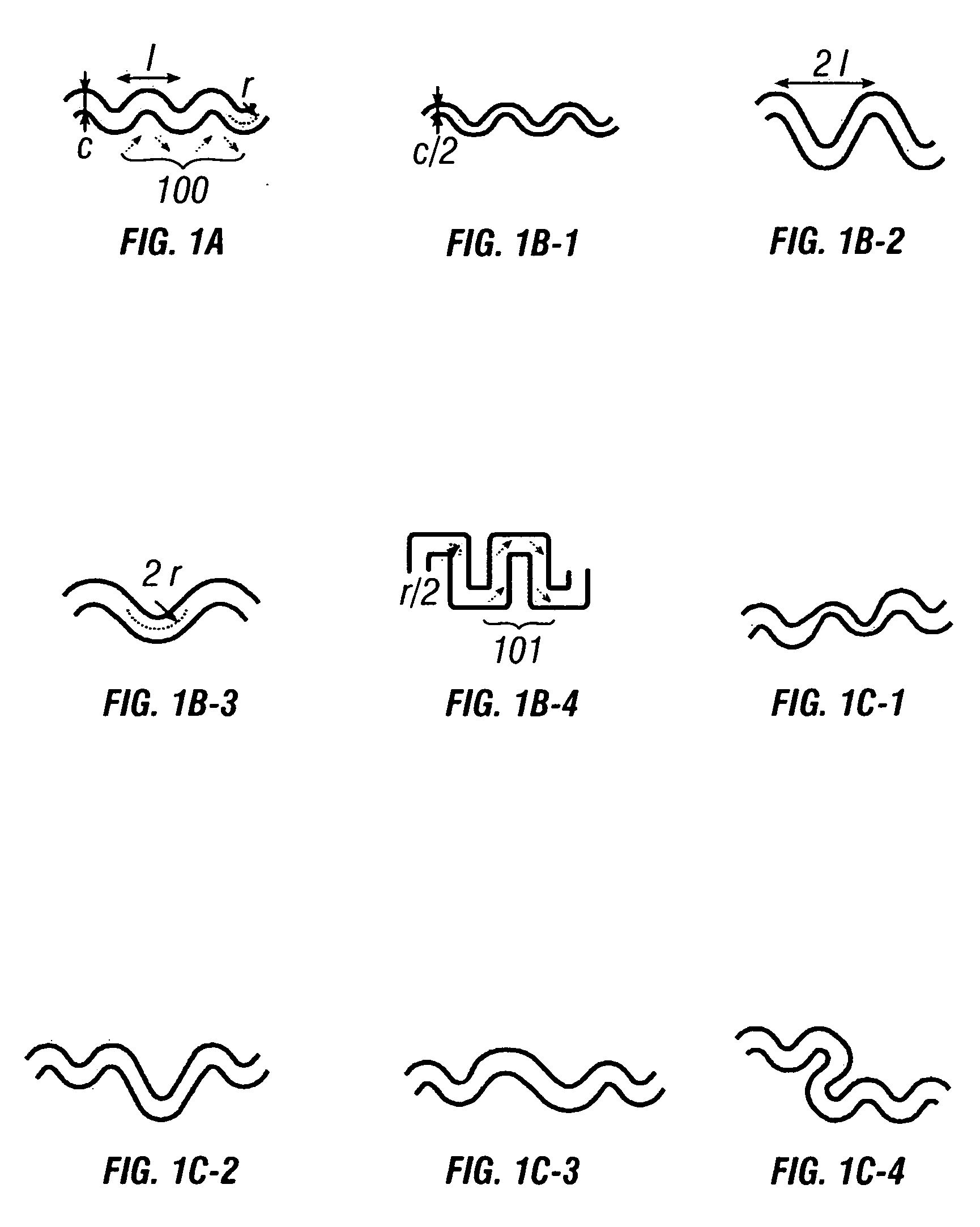

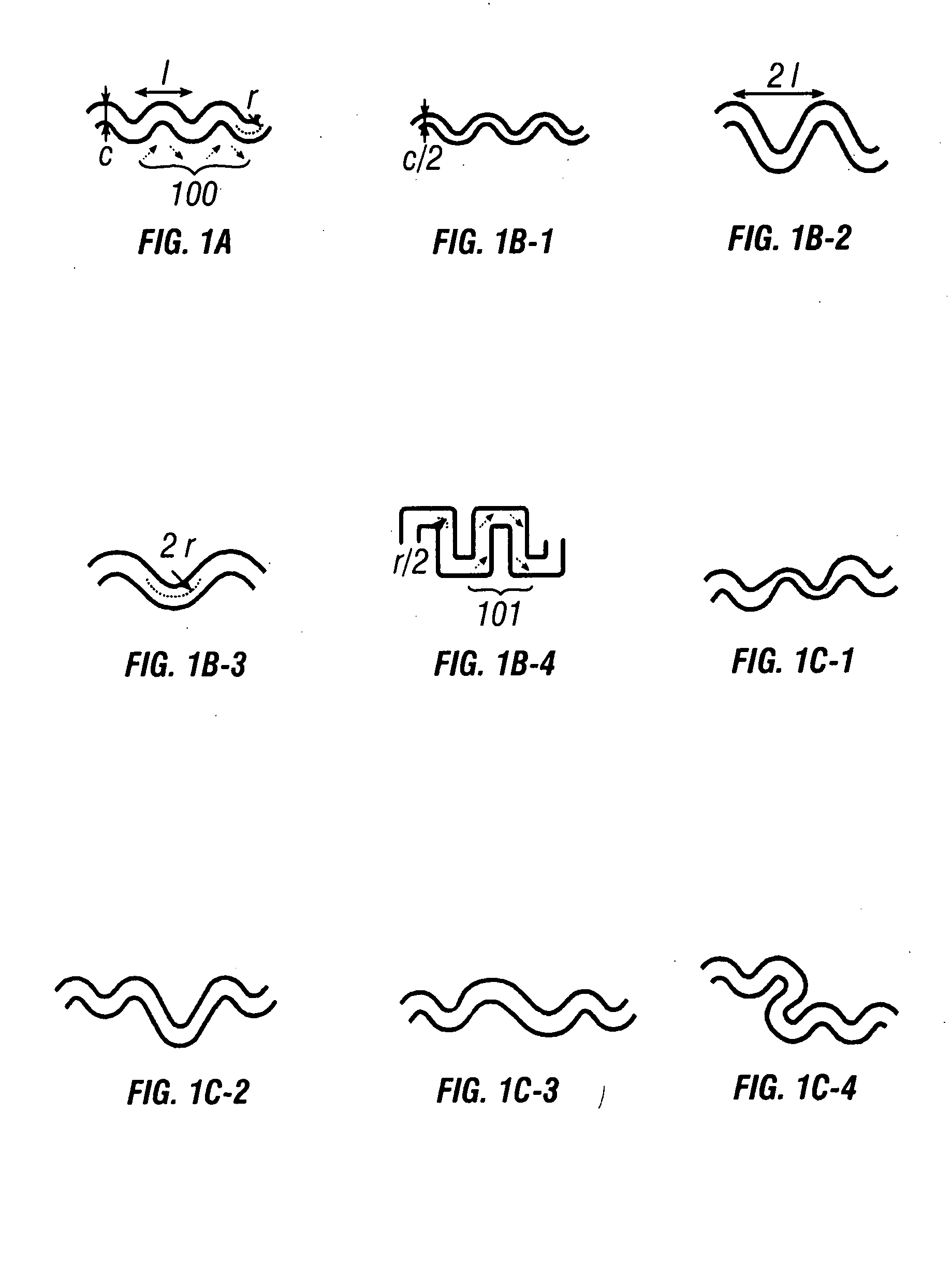

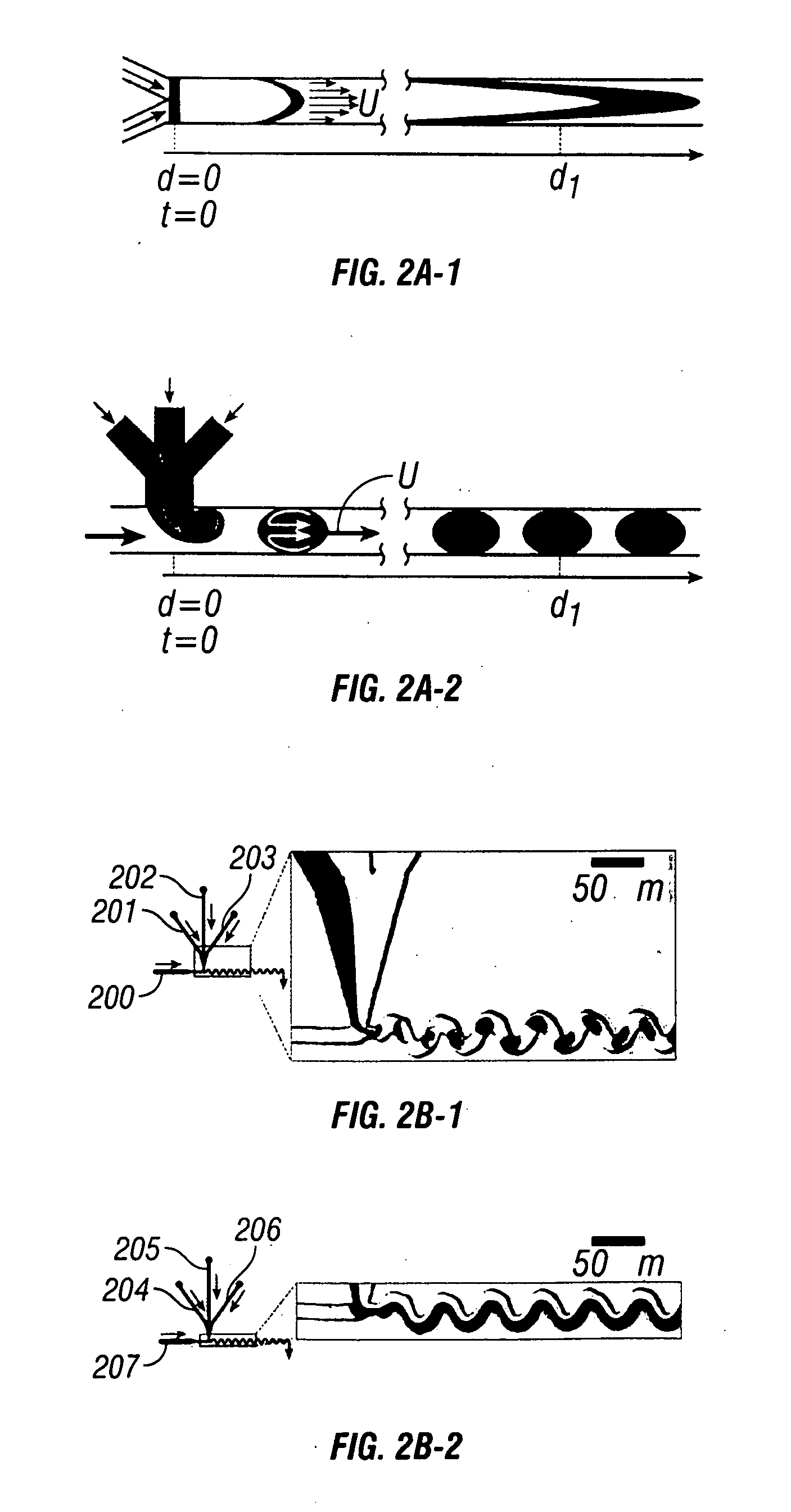

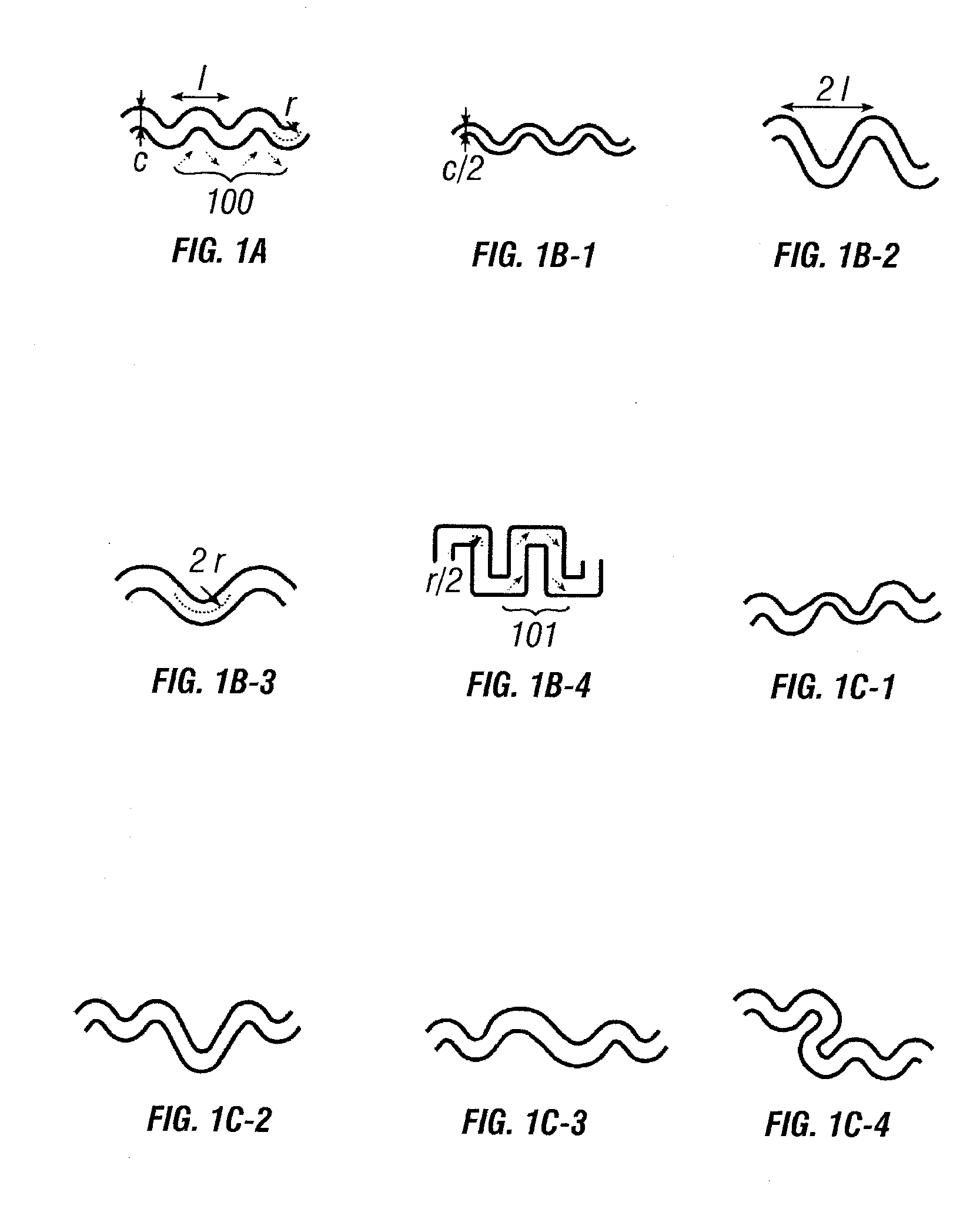

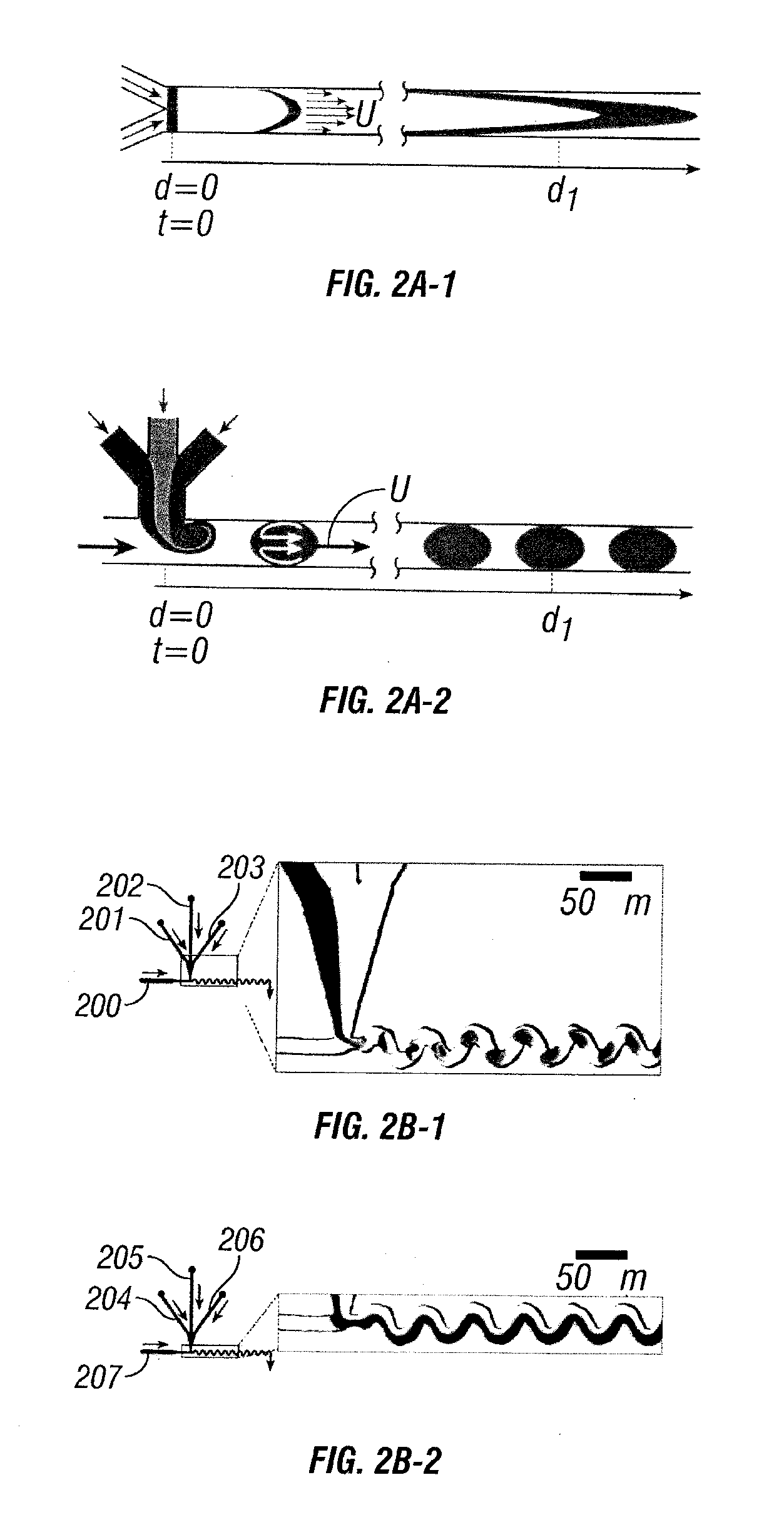

Method for producing uniform large-grained and grain boundary location manipulated polycrystalline thin film semiconductors using sequential lateral solidification

Methods for processing an amorphous silicon thin film sample into a polycrystalline silicon thin film are disclosed. In one preferred arrangement, a method includes the steps of generating a sequence of excimer laser pulses, controllably modulating each excimer laser pulse in the sequence to a predetermined fluence, homoginizing each modulated laser pulse in the sequence in a predetermined plane, masking portions of each homoginized fluence controlled laser pulse in the sequence with a two dimensional pattern of slits to generate a sequence of fluence controlled pulses of line patterned beamlets, each slit in the pattern of slits being sufficiently narrow to prevent inducement of significant nucleation in region of a silicon thin film sample irradiated by a beamlet corresponding to the slit, irradiating an amorphous silicon thin film sample with the sequence of fluence controlled slit patterned beamlets to effect melting of portions thereof corresponding to each fluence controlled patterned beamlet pulse in the sequence of pulses of patterned beamlets, and controllably sequentially translating a relative position of the sample with respect to each of the fluence controlled pulse of slit patterned beamlets to thereby process the amorphous silicon thin film sample into a single or polycrystalline silicon thin film.

Owner:IM JAMES S +2

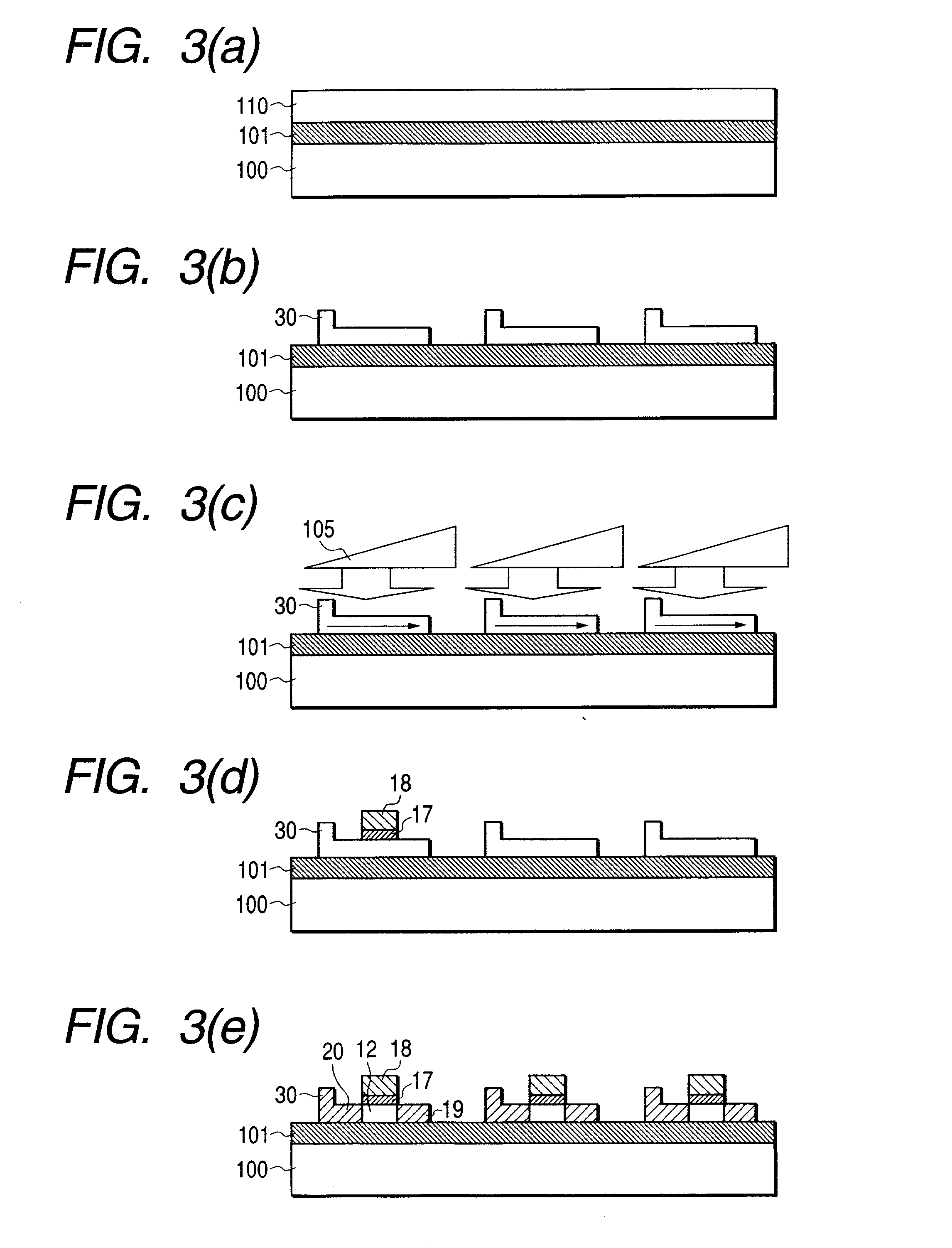

Anneal of epitaxial layer in a semiconductor device

InactiveUS7416605B2From gel statePolycrystalline material growthCharge carrier mobilityDegree Celsius

An anneal of an epitaxially grown crystalline semiconductor layer comprising a combination of group-IV elements. The layer contains at least one of the group of carbon and tin. The layer of epitaxially grown material is annealed at a temperature substantially in a range of 1,000 to 1,400 degrees Celsius for a period not to exceed 100 milliseconds within 10% of the peak temperature. The anneal is performed for example with a laser anneal or a flash lamp anneal. The limited-time anneal may improve carrier mobility of a transistor.

Owner:NORTH STAR INNOVATIONS

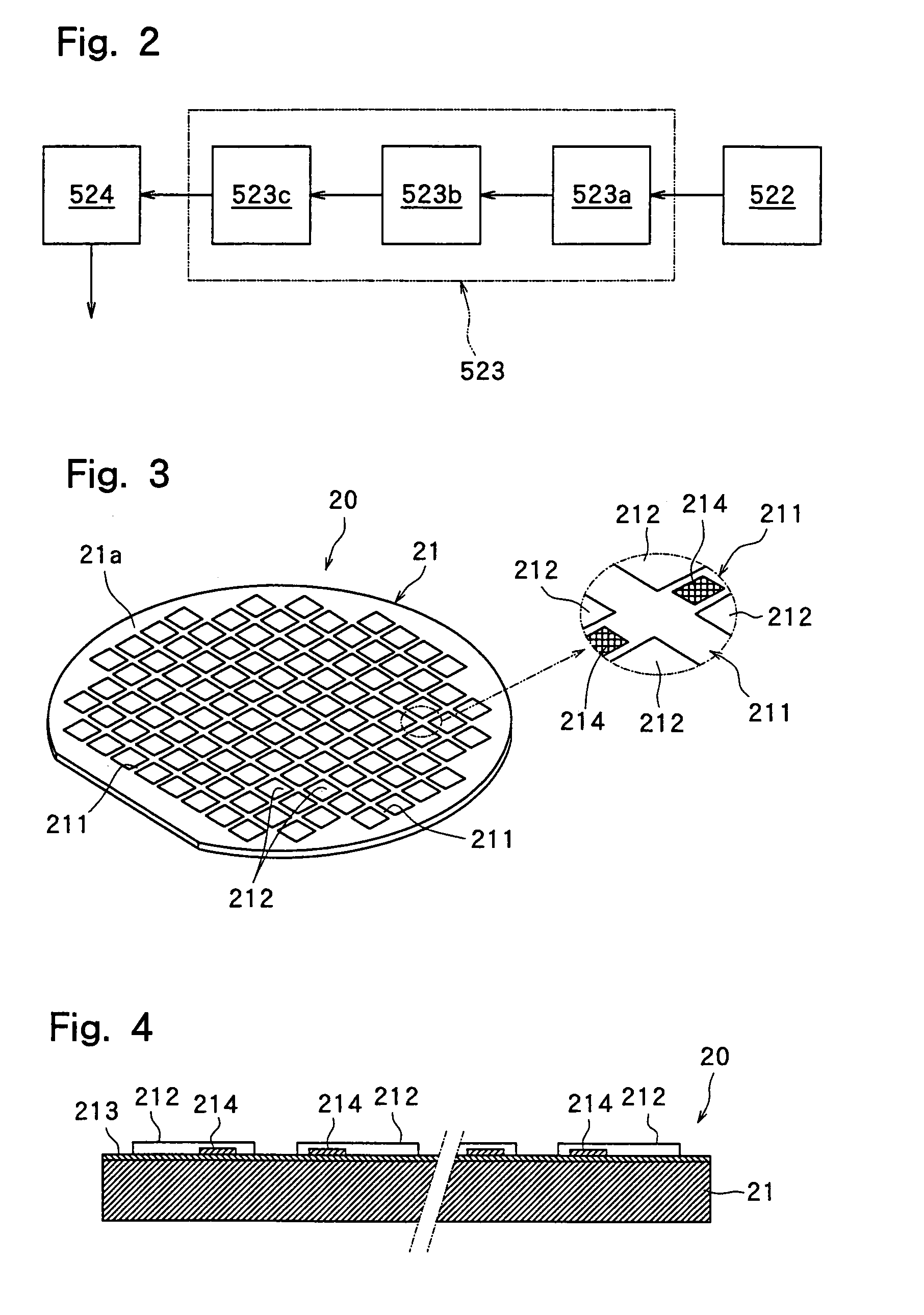

Fabrication system and a fabrication method of light emitting device

InactiveUS20030162314A1Improve utilization efficiencyReduce capacityLiquid surface applicatorsFrom solid stateEvaporationEngineering

An evaporation apparatus with high utilization efficiency for EL materials and excellent film uniformity is provided. The invention is an evaporation apparatus having a movable evaporation source and a substrate rotating unit, in which the space between an evaporation source holder and a workpiece (substrate) is narrowed to 30 cm or below, preferably 20 cm, more preferably 5 to 15 cm, to improve the utilization efficiency for EL materials. In evaporation, the evaporation source holder is moved in the X-direction or the Y-direction, and the workpiece (substrate) is rotated for deposition. Therefore, film uniformity is improved.

Owner:SEMICON ENERGY LAB CO LTD

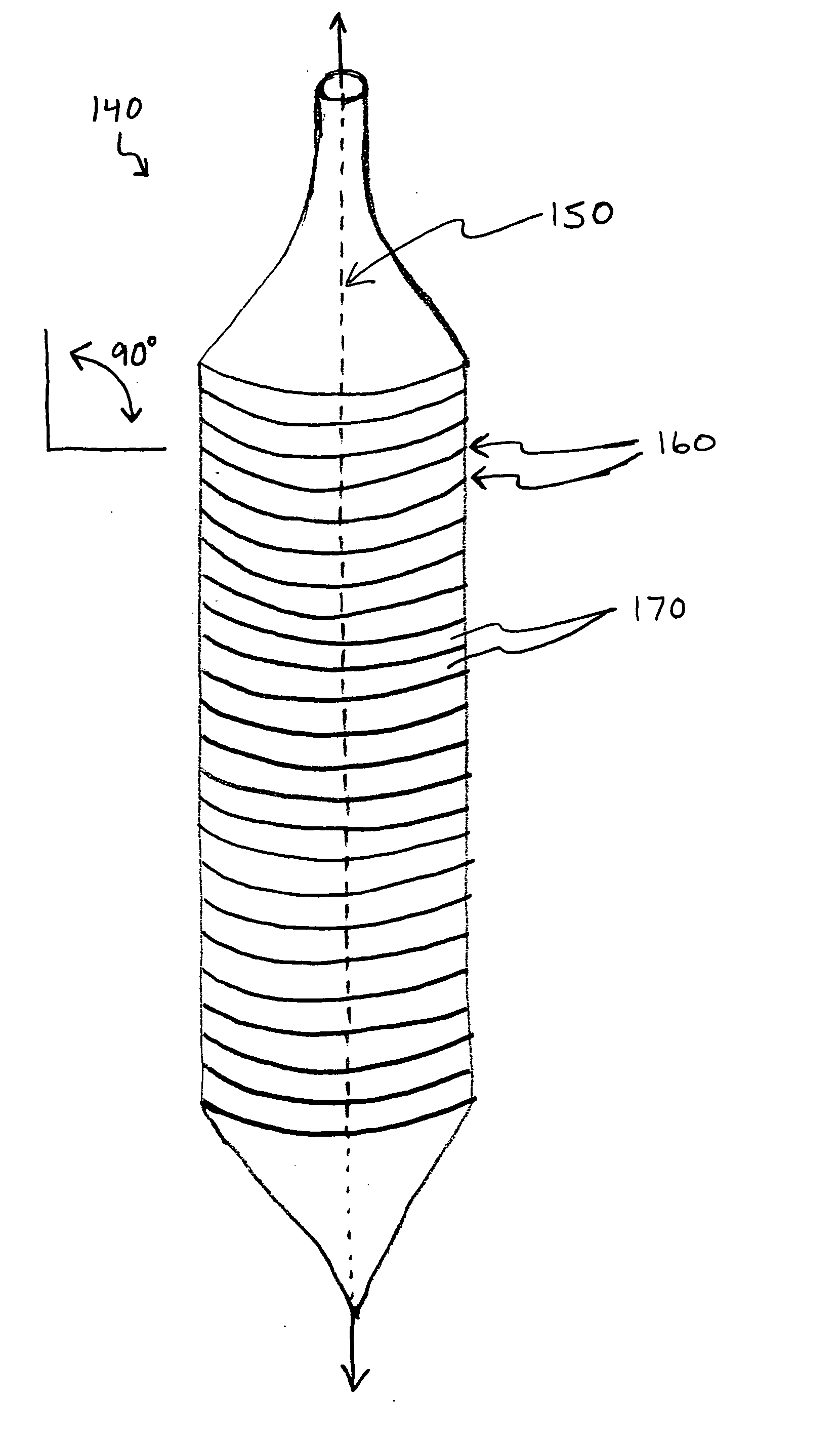

Semiconductor wafers with non-standard crystal orientations and methods of manufacturing the same

The crystal orientations of monocrystalline semiconductor wafers may be varied by four parameters. The first parameter is the type of crystal seed used to grow the monocrystalline semiconductor ingot from which the wafers are cut. The second parameter is the angle at which the wafer is sliced from the ingot. The third parameter is the crystal plane towards which the wafer is cut. And, the fourth parameter is the position of the orientation indication feature that is used to align the wafer during processing. Different combinations of these parameters provide variations of non-standard crystal orientations of monocrystalline semiconductor wafers and semiconductor-on-insulator substrates such as silicon-on-insulator.

Owner:INTEL CORP

Mixed orientation and mixed material semiconductor-on-insulator wafer

The present disclosure relates, generally, to a semiconductor substrate with a planarized surface comprising mixed single-crystal orientation regions and / or mixed single-crystal semiconductor material regions, where each region is electrically isolated. In accordance with one embodiment of the disclosure CMOS devices on SOI regions are manufactured on semiconductors having different orientations. According to another embodiment, an SOI device is contemplated as having a plurality of semiconductor regions having at least one of a different semiconductor material, crystalline lattice constant or lattice strain. Methods and processes for fabricating the different embodiments of the invention is also disclosed.

Owner:GLOBALFOUNDRIES INC

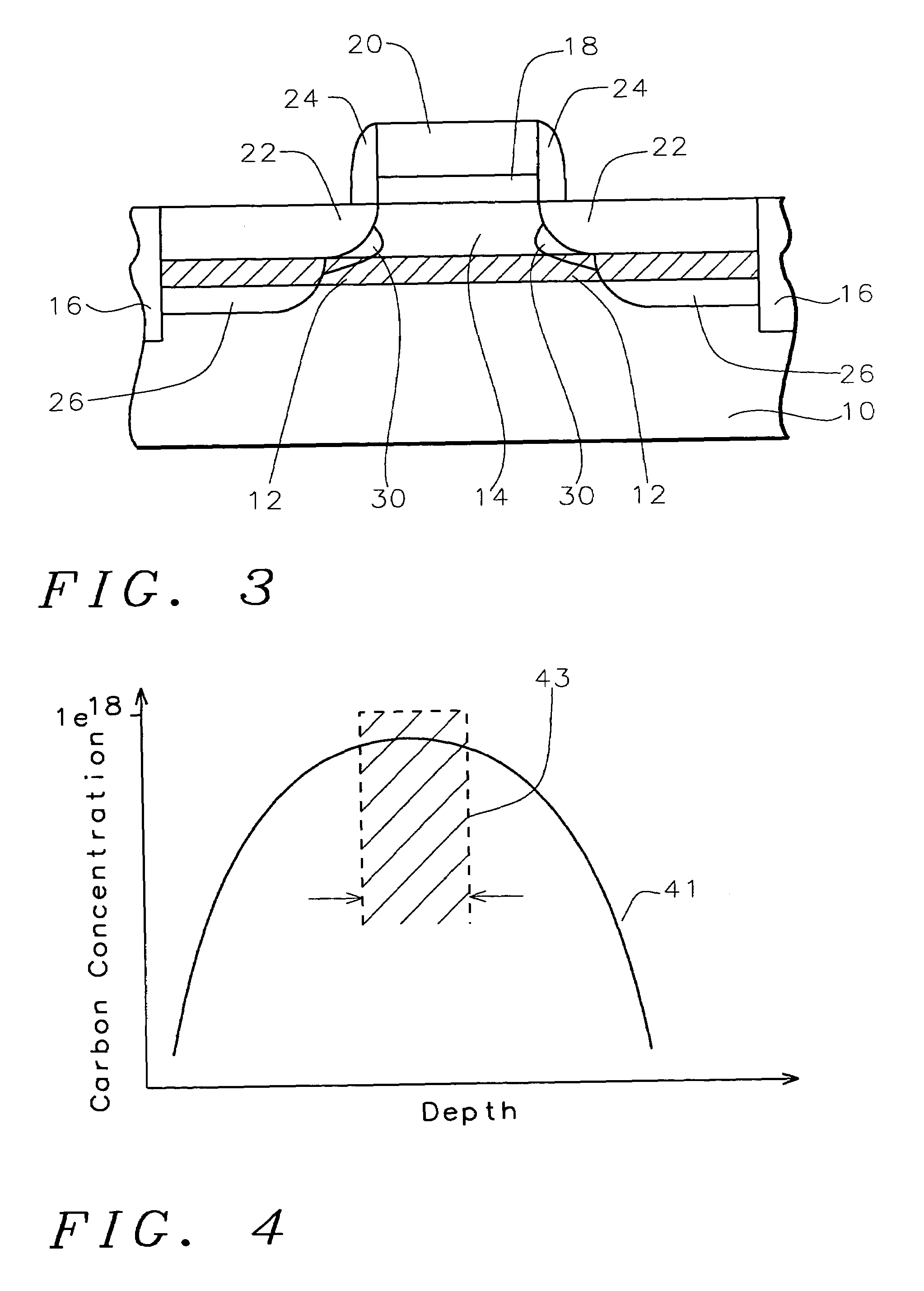

End of range (EOR) secondary defect engineering using substitutional carbon doping

A method for incorporating carbon into a wafer at the interstitial a-c silicon interface of the halo doping profile is achieved. A bulk silicon substrate is provided. A carbon-doped silicon layer is deposited on the bulk silicon substrate. An epitaxial silicon layer is grown overlying the carbon-doped silicon layer to provide a starting wafer for the integrated circuit device fabrication. An integrated circuit device is fabricated on the starting wafer by the following steps. A gate electrode is formed on the starting wafer. LDD and source and drain regions are implanted in the starting wafer adjacent to the gate electrode. Indium is implanted to form halo implants adjacent to the LDD regions and underlying the gate electrode wherein the halo implants extend to an interface between the epitaxial silicon layer and the carbon-doped silicon layer wherein carbon ions in the carbon-doped silicon layer act as a silicon interstitial sink for silicon interstitials formed by the halo implants to prevent end of range secondary defect formation.

Owner:TAIWAN SEMICON MFG CO LTD

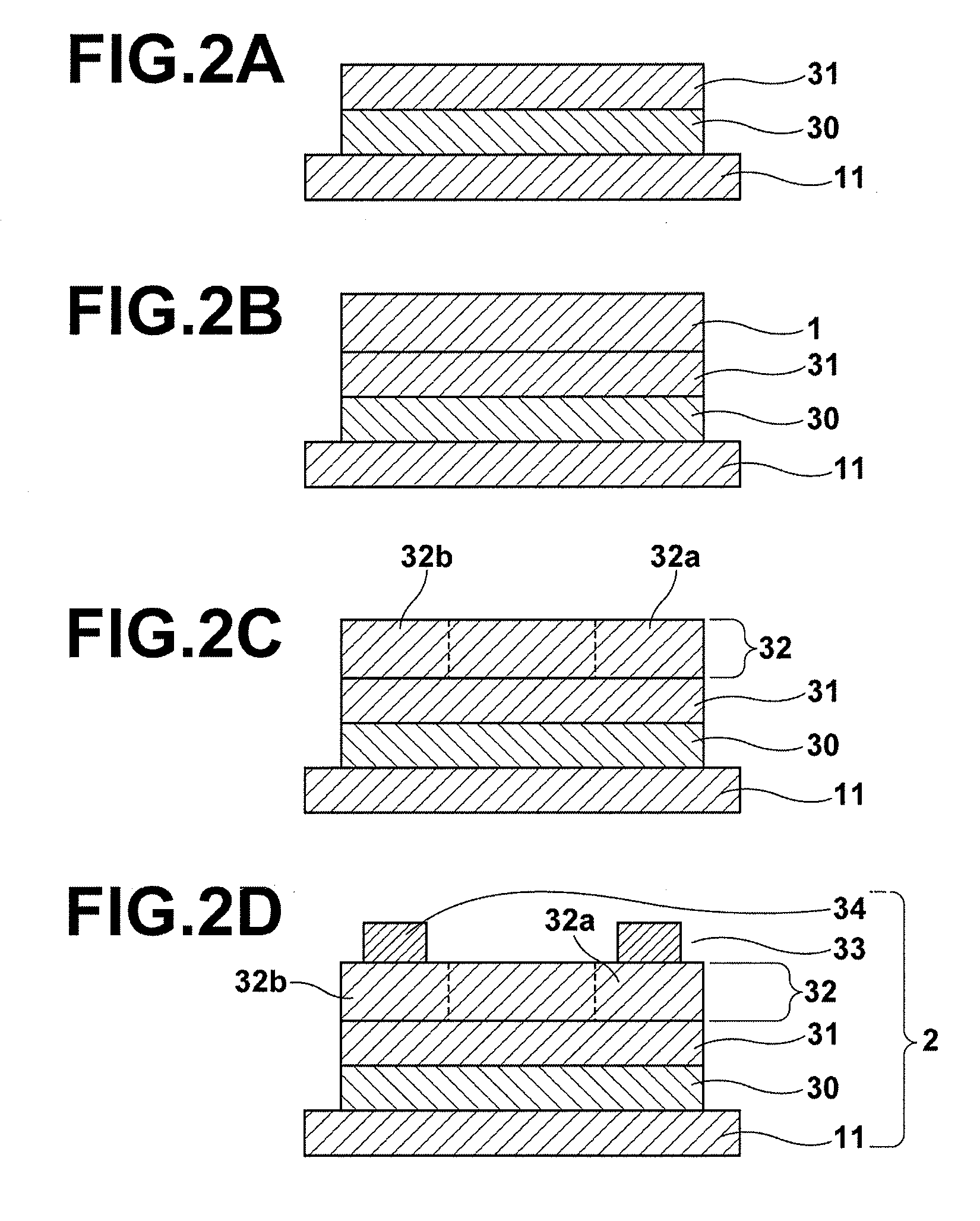

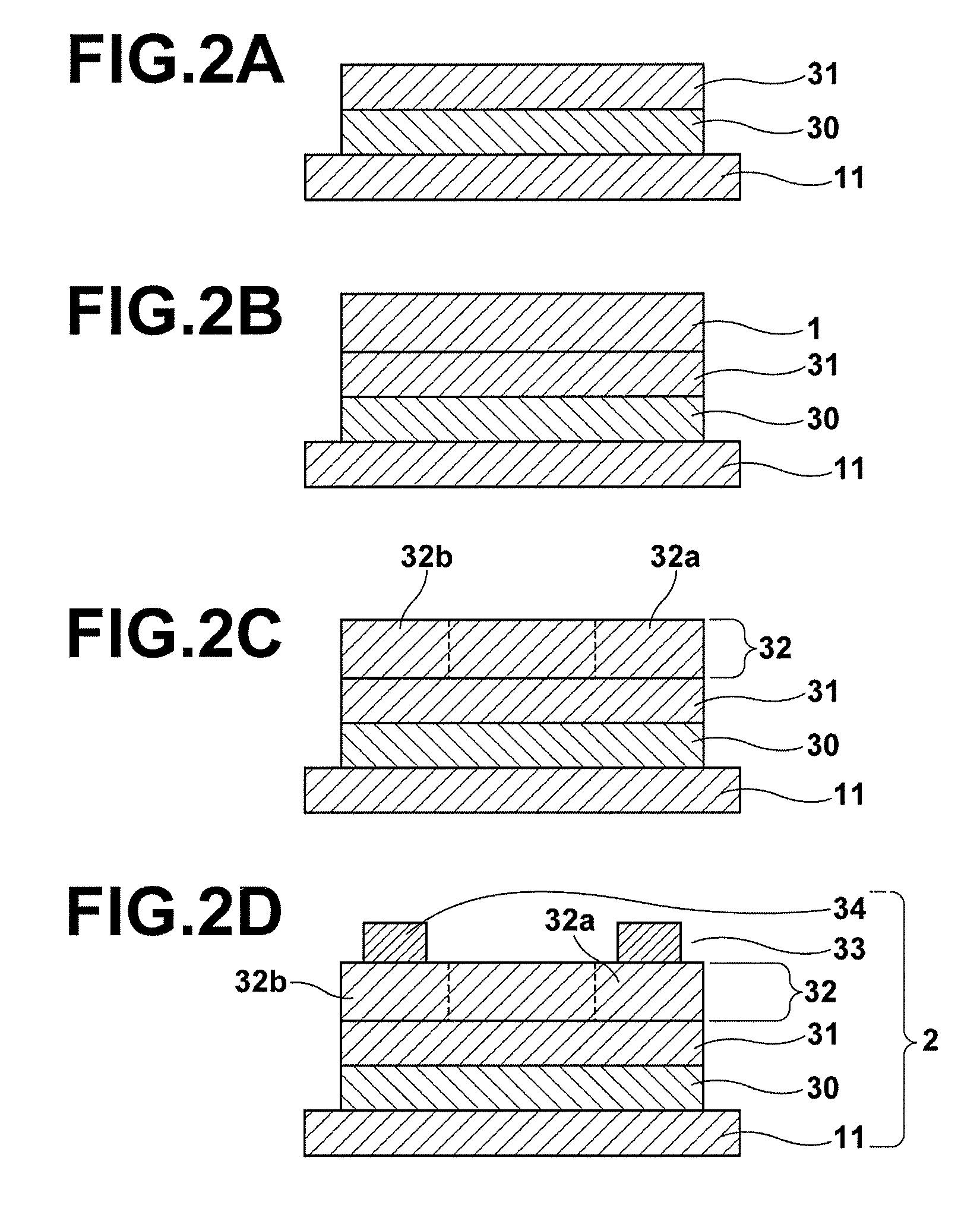

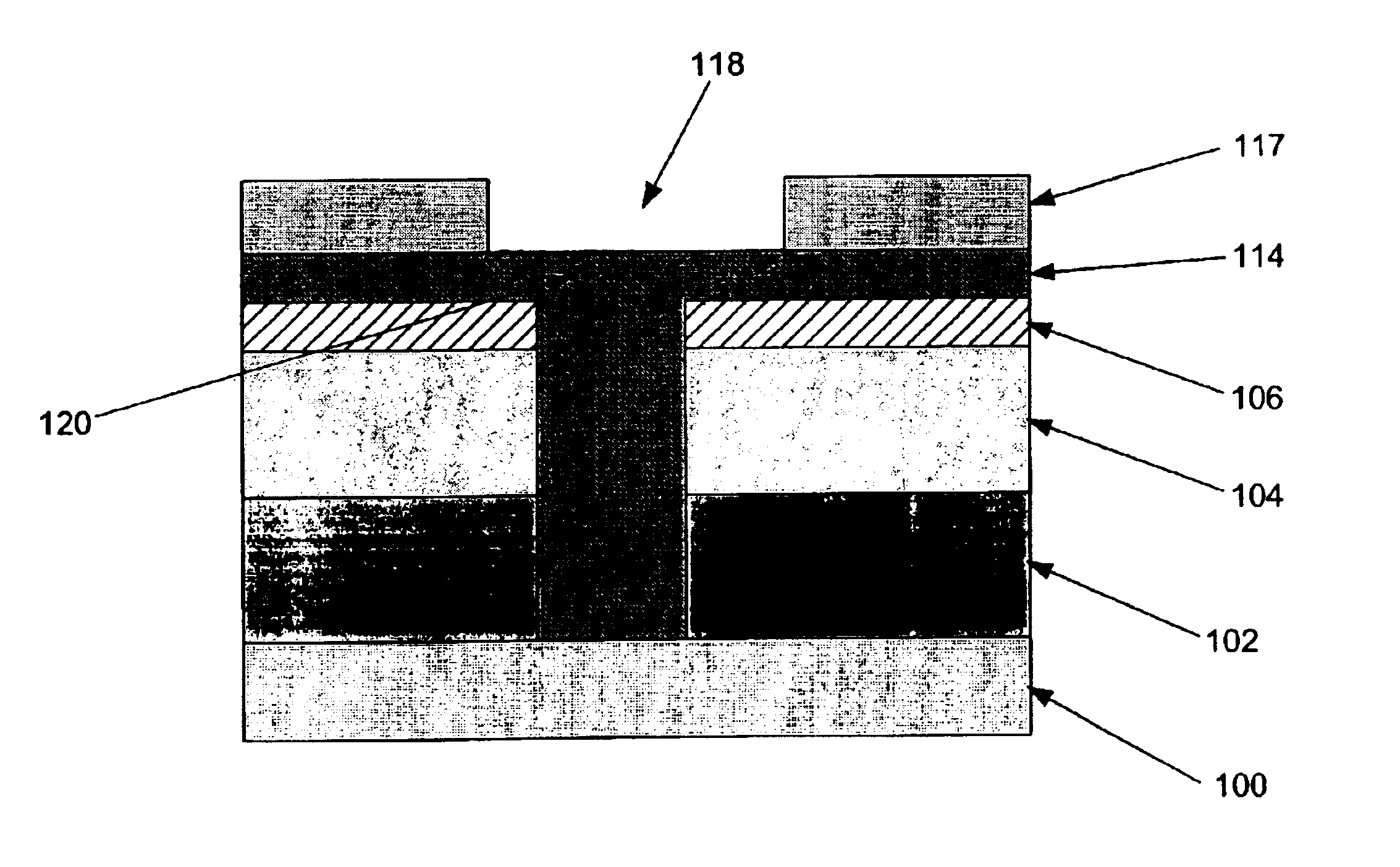

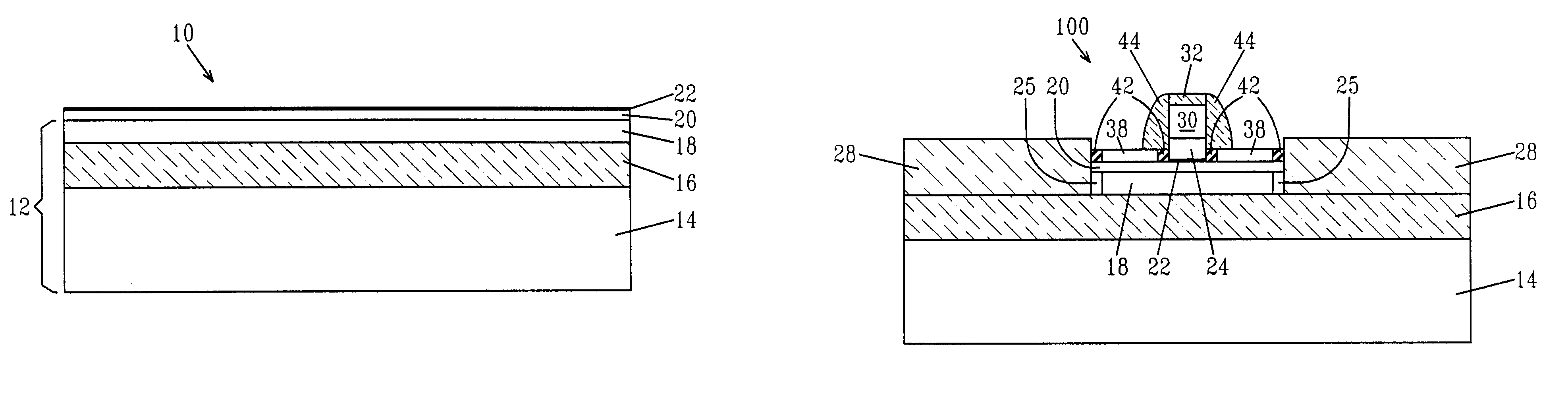

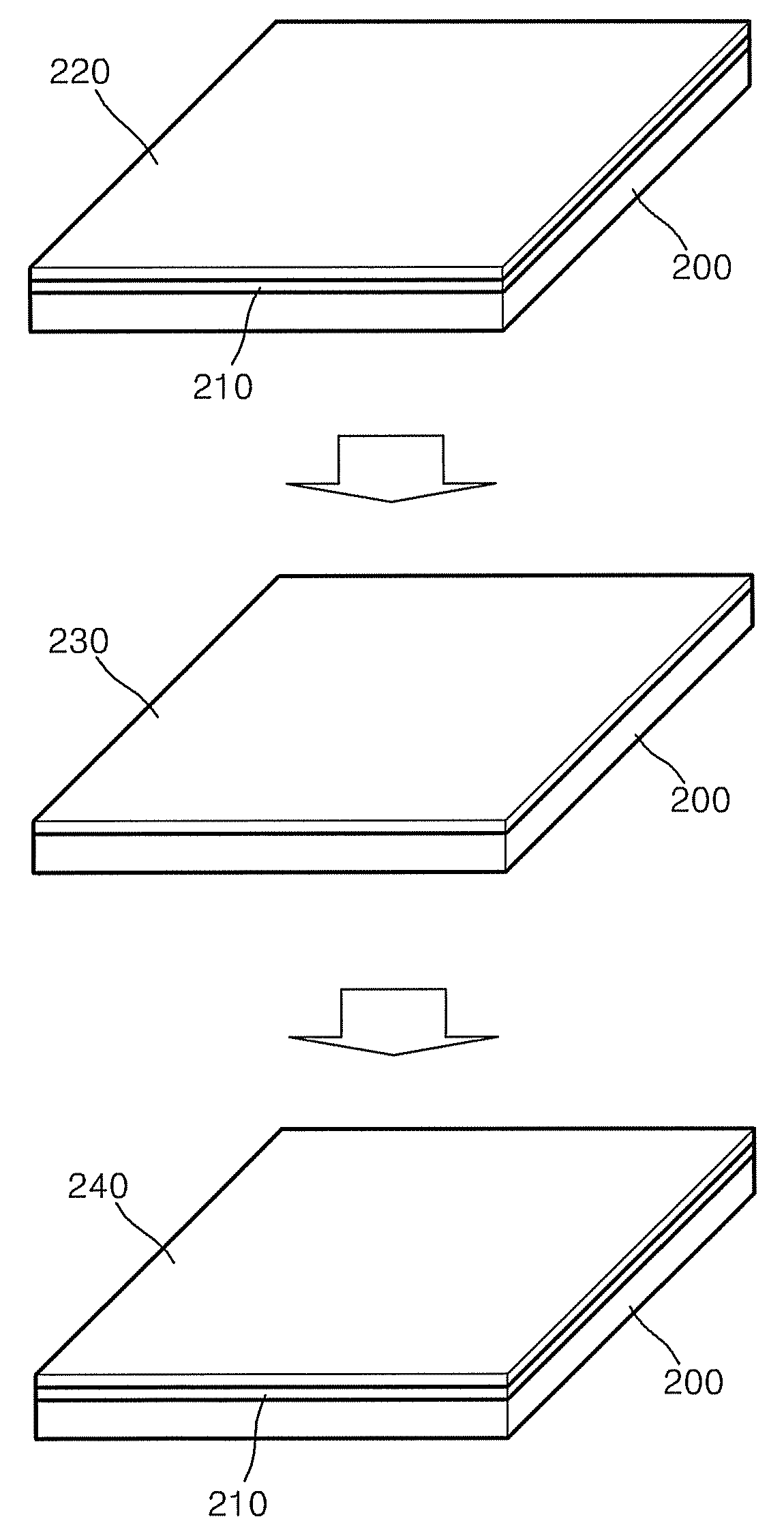

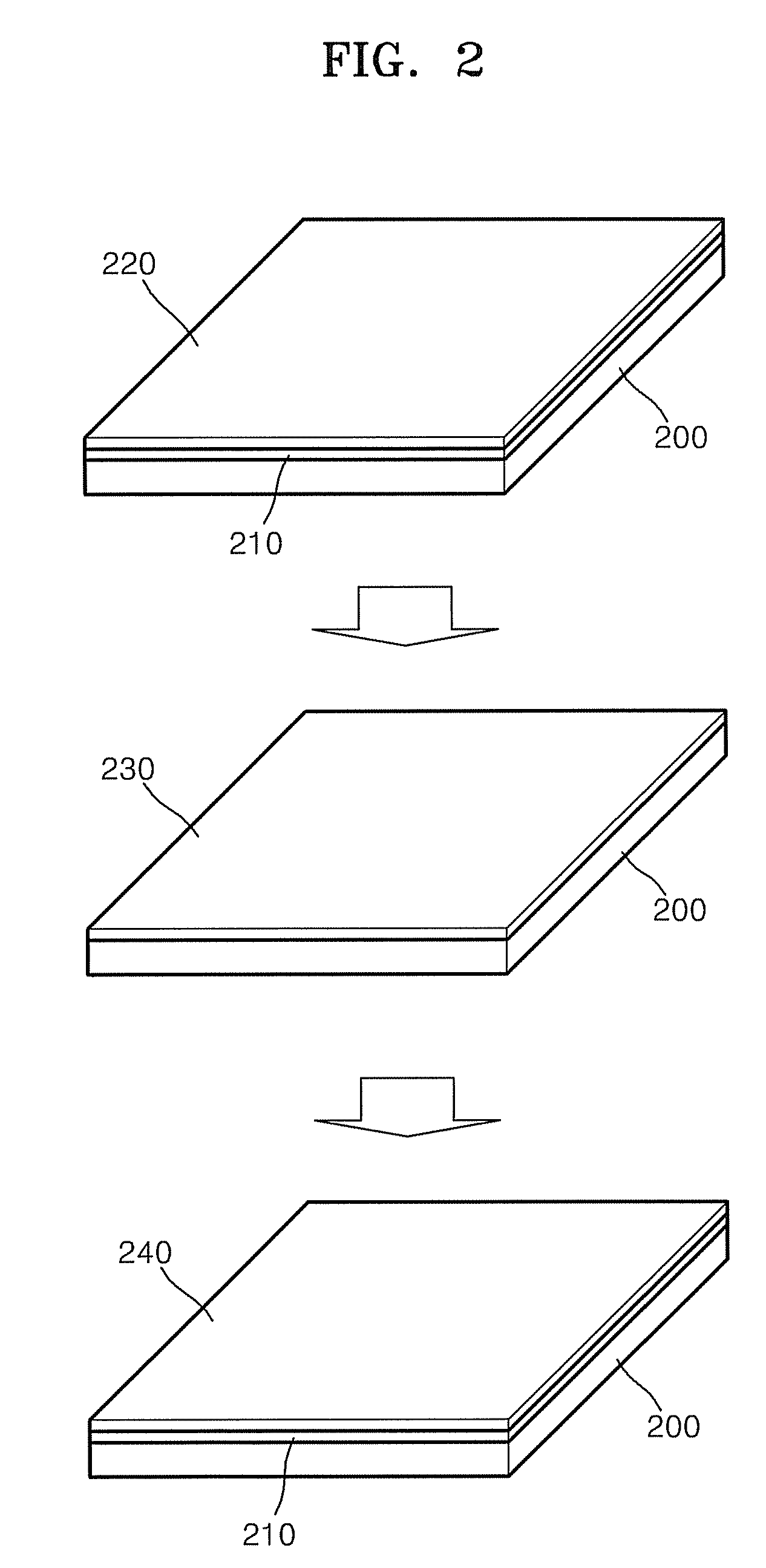

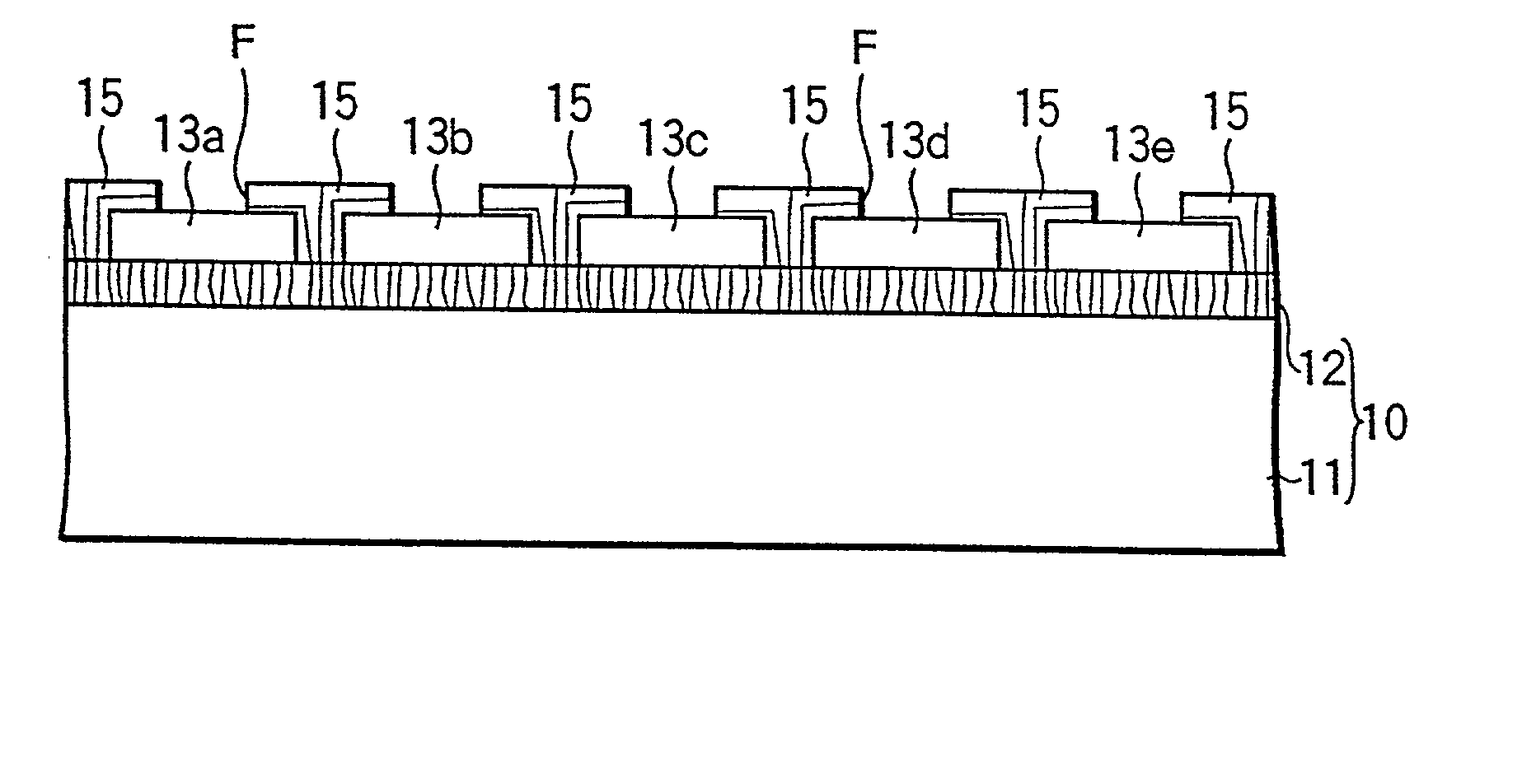

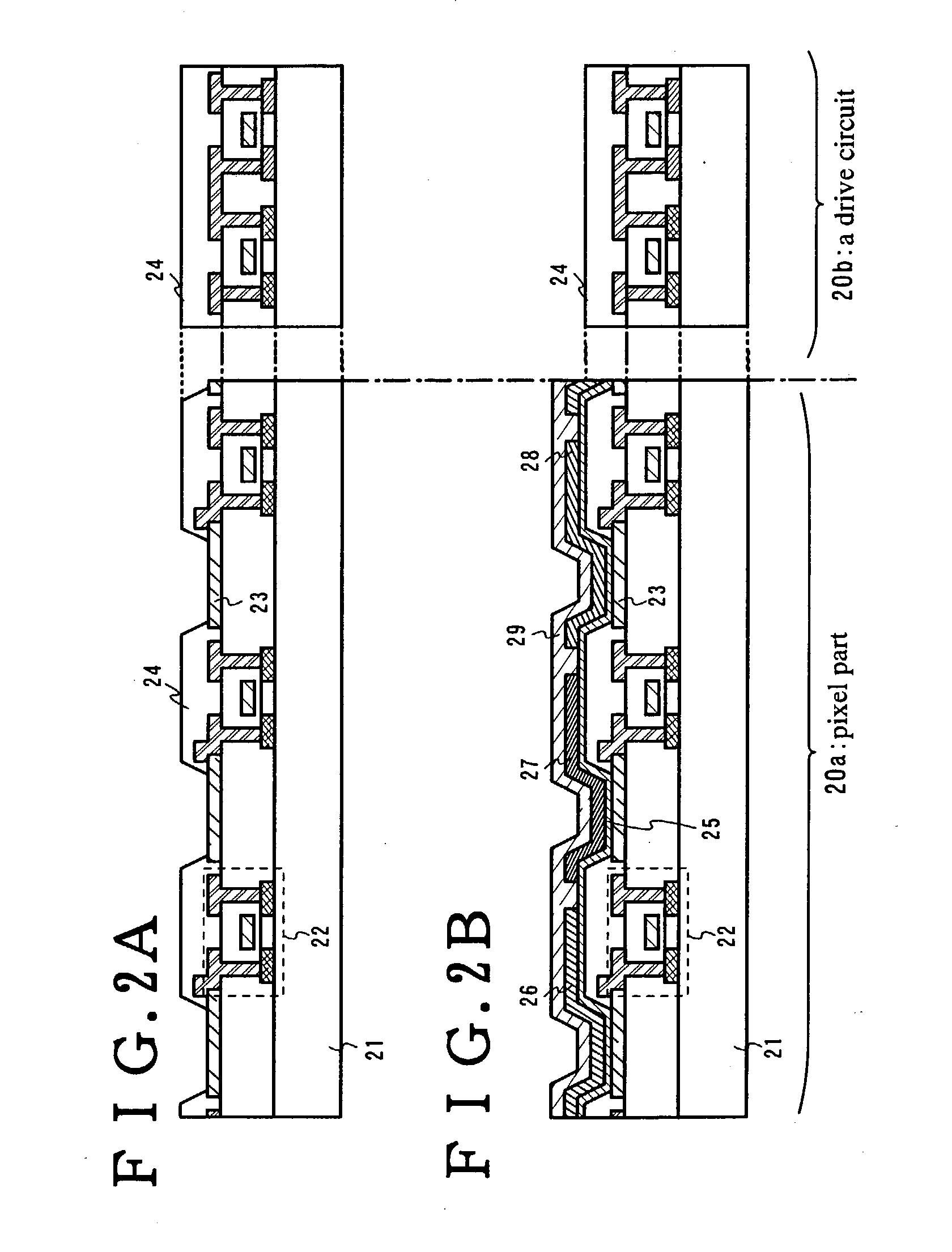

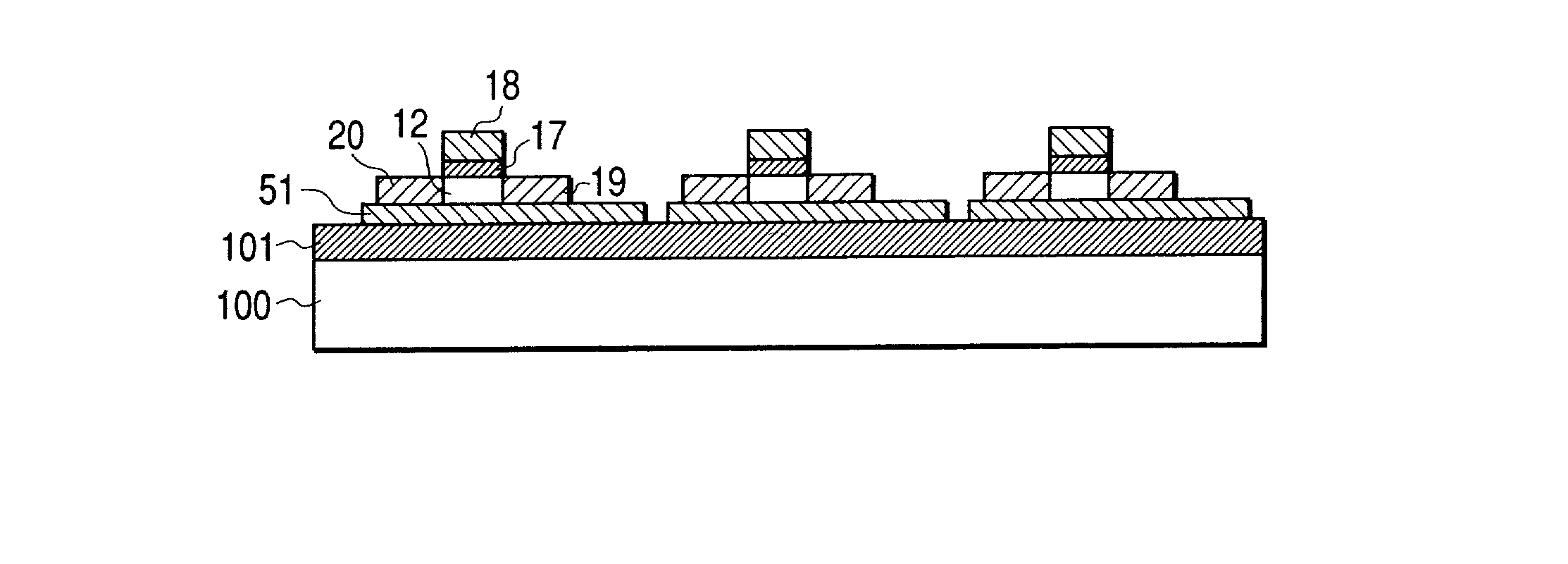

Thin film semiconductor device, polycrystalline semiconductor thin film production process and production apparatus

InactiveUS20020119609A1Reduce in quantityQuality improvementTransistorFrom solid stateElectrical conductorCrystal orientation

In an MIS field effect transistor having a gate electrode formed on a first semiconductor layer which is a polycrystalline silicon film on an insulating substrate through a gate insulating film, a channel region formed in the semiconductor layer and a source region and a drain region arranged on both sides of the channel region, a thin film semiconductor device has a main orientation of at least the channel region of {110} with respect to the surface of the gate insulating film. Further, a polycrystalline semiconductor film having a main orientation of the surface almost perpendicular to a direction for connecting the source and drain regions of {100} is preferably used in the channel of a semiconductor device. According to the present invention, a semiconductor device having a high-quality polycrystalline semiconductor film whose grain boundary, grain size and crystal orientation can be controlled and whose film roughness and crystal defects formed by crystallization have been reduced can be obtained on the insulating substrate.

Owner:PANASONIC LIQUID CRYSTAL DISPLAY CO LTD +1