Patents

Literature

13970 results about "Semiconductor materials" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Methods of making thin film transistors comprising zinc-oxide-based semiconductor materials and transistors made thereby

ActiveUS7402506B2NanoinformaticsSemiconductor/solid-state device manufacturingSemiconductor materialsZinc

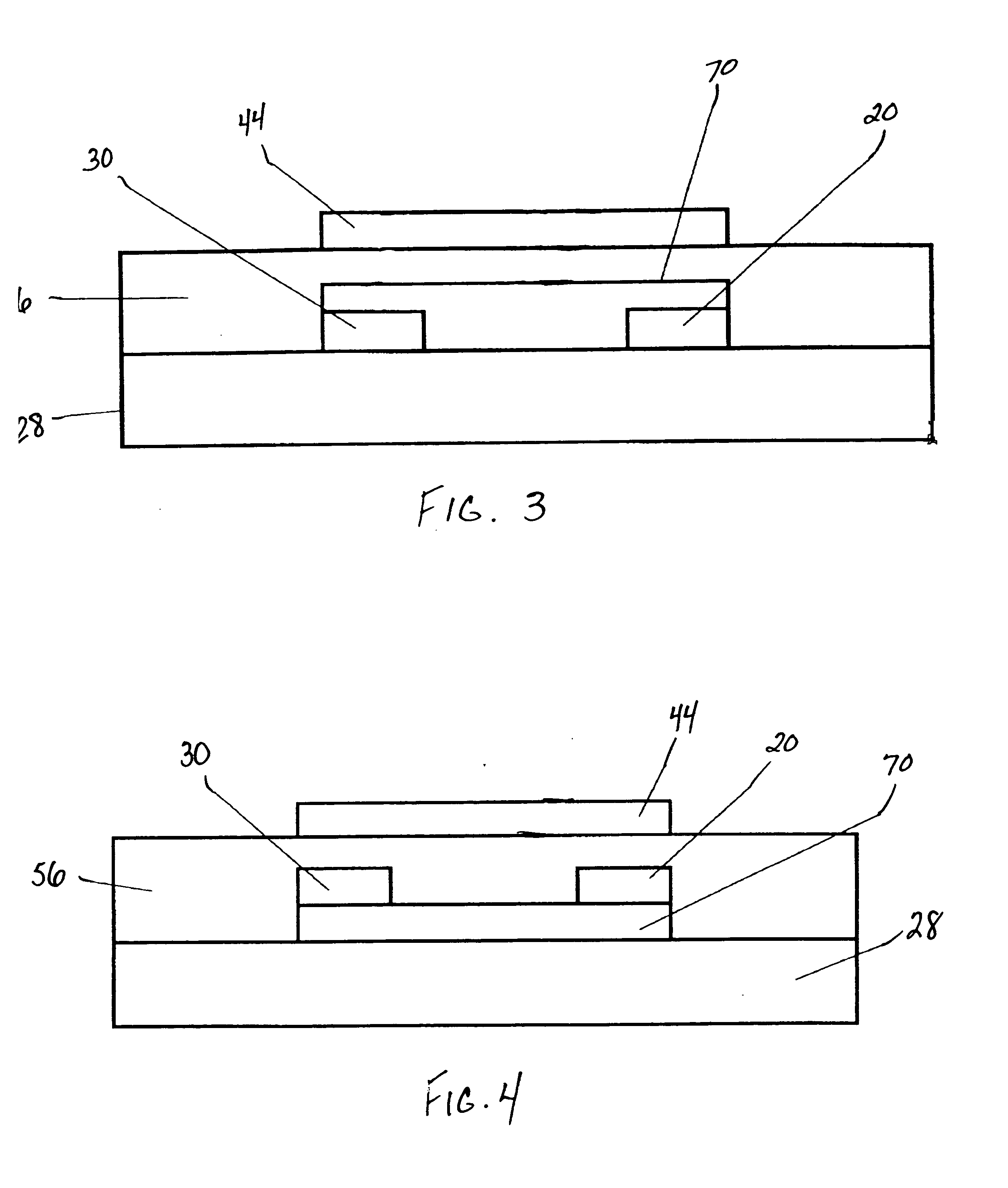

A thin film transistor comprises a zinc-oxide-containing semiconductor material. Such transistors can further comprise spaced apart first and second contact means or electrodes in contact with said material. Further disclosed is a process for fabricating a thin film transistor device, wherein the substrate temperature is no more than 300° C. during fabrication.

Owner:EASTMAN KODAK CO

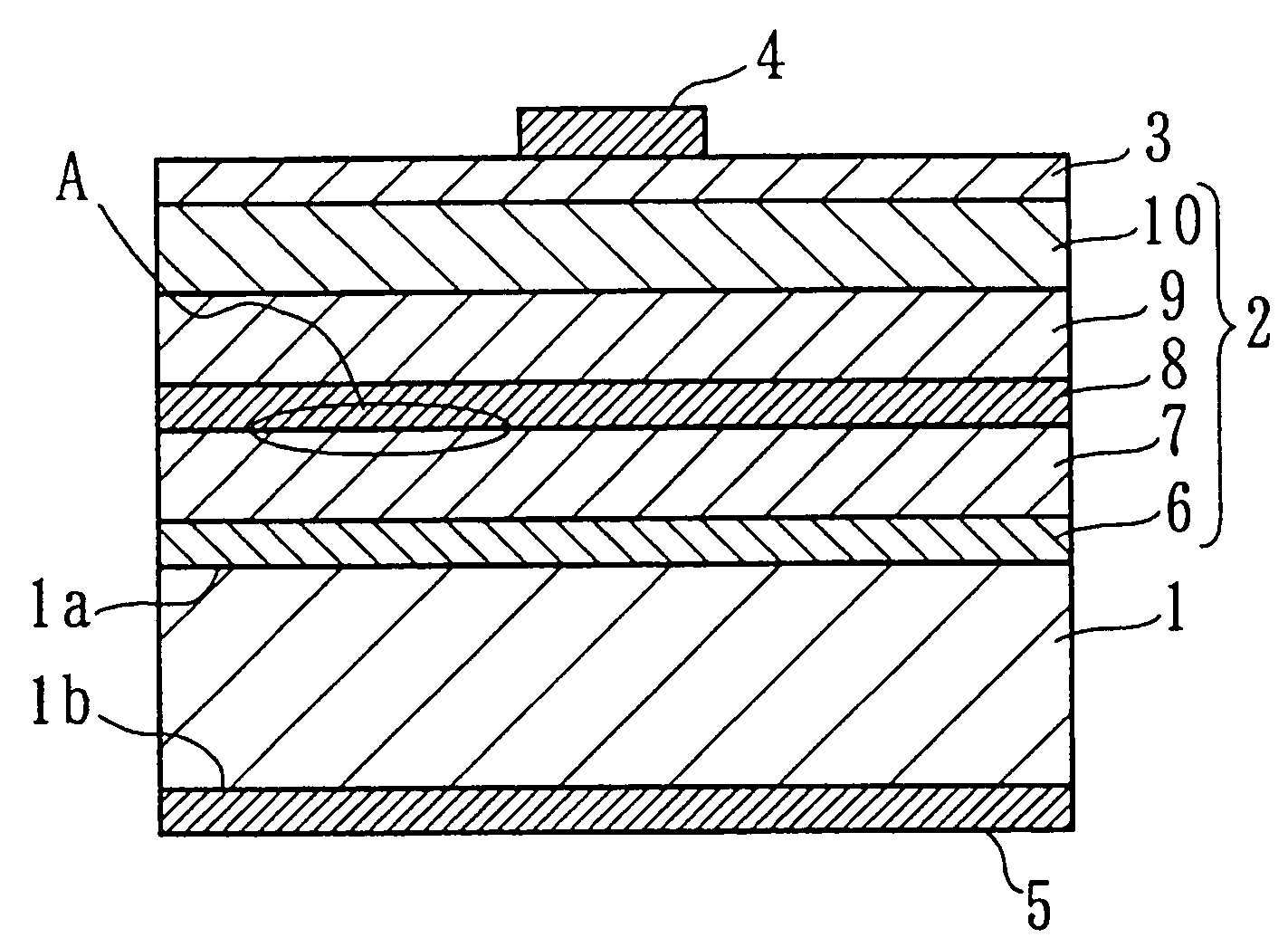

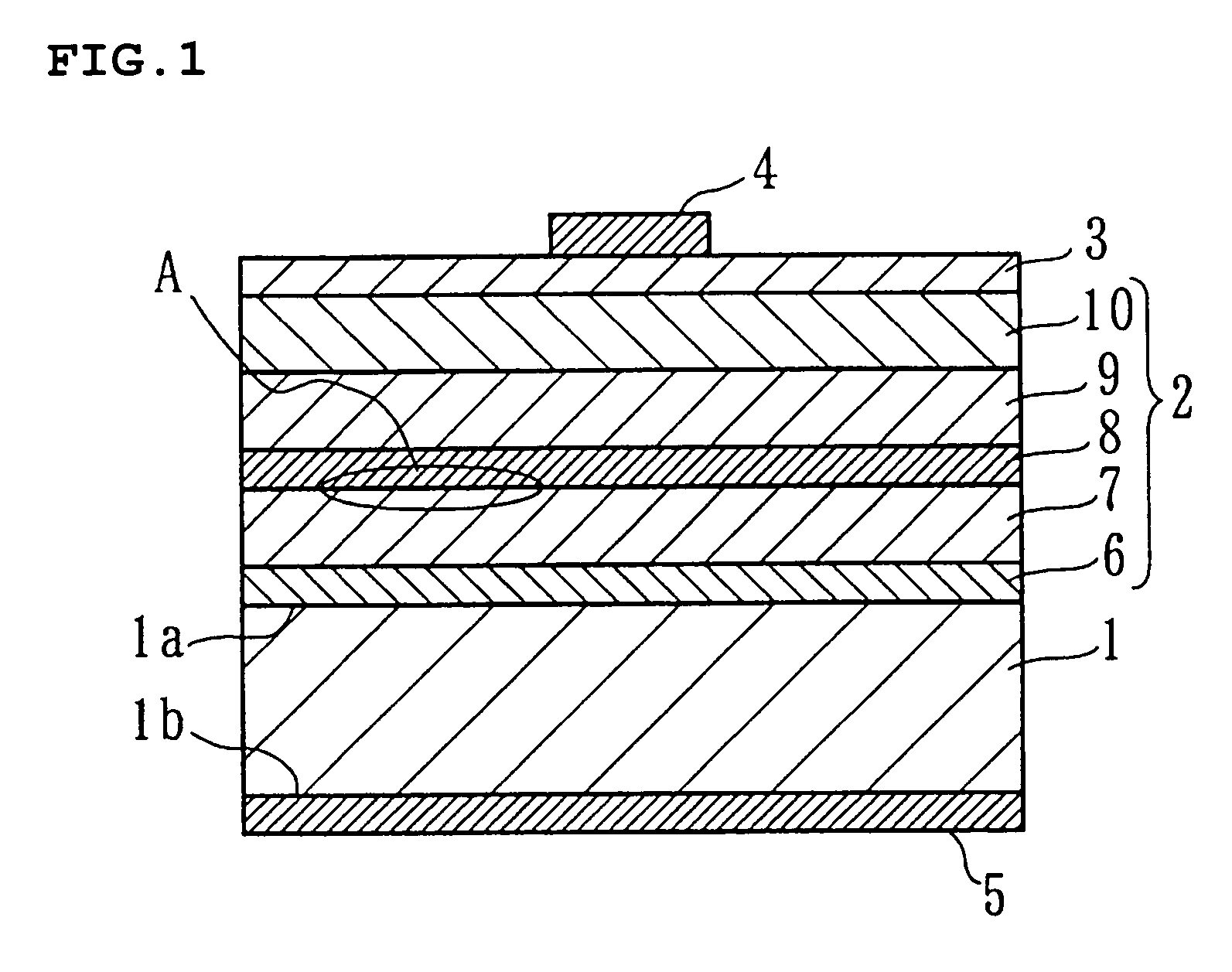

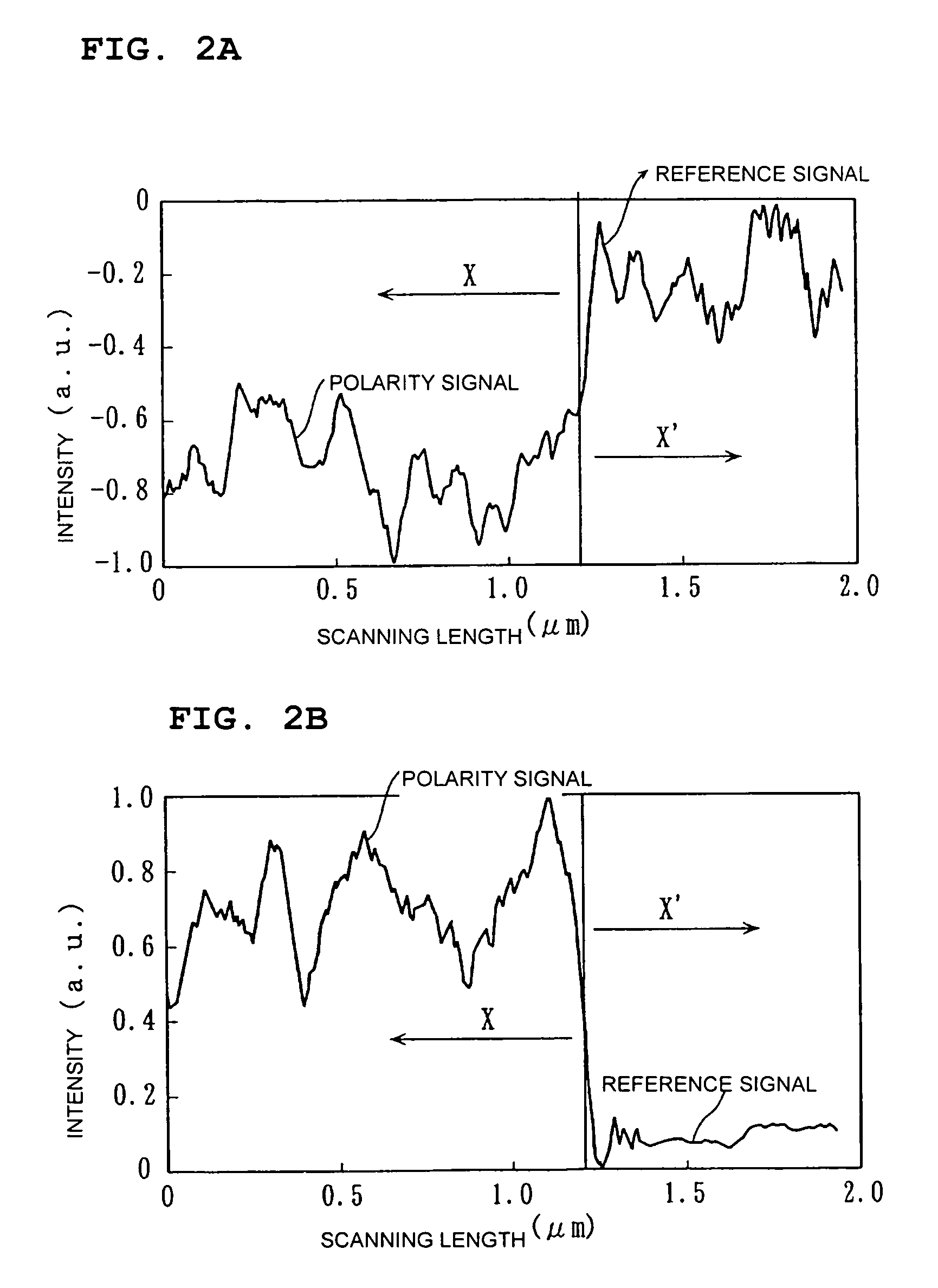

Semiconductor device in which zinc oxide is used as a semiconductor material and method for manufacturing the semiconductor device

ActiveUS7501293B2Improve surface smoothnessHigh crystallinityTransistorLaser detailsSemiconductor materialsDevice material

A semiconductor device having excellent crystallinity and excellent electric characteristics includes a ZnO thin film having excellent surface smoothness. ZnO-based thin films (an n-type contact layer, an n-type clad layer, an active layer, a p-type clad layer, and a p-type contact layer) primarily including ZnO are formed sequentially by an ECR sputtering method or other suitable method on a zinc-polar surface of a ZnO substrate. A transparent electrode and a p-side electrode are formed by an evaporation method or other suitable method on a surface of the p-type contact layer, and an n-side electrode is formed on an oxygen-polar surface of the ZnO substrate.

Owner:MURATA MFG CO LTD

Methods of making thin film transistors comprising zinc-oxide-based semiconductor materials and transistors made thereby

A thin film transistor comprises a zinc-oxide-containing semiconductor material. Such transistors can further comprise spaced apart first and second contact means or electrodes in contact with said material. Further disclosed is a process for fabricating a thin film transistor device, wherein the substrate temperature is no more than 300° C. during fabrication.

Owner:EASTMAN KODAK CO

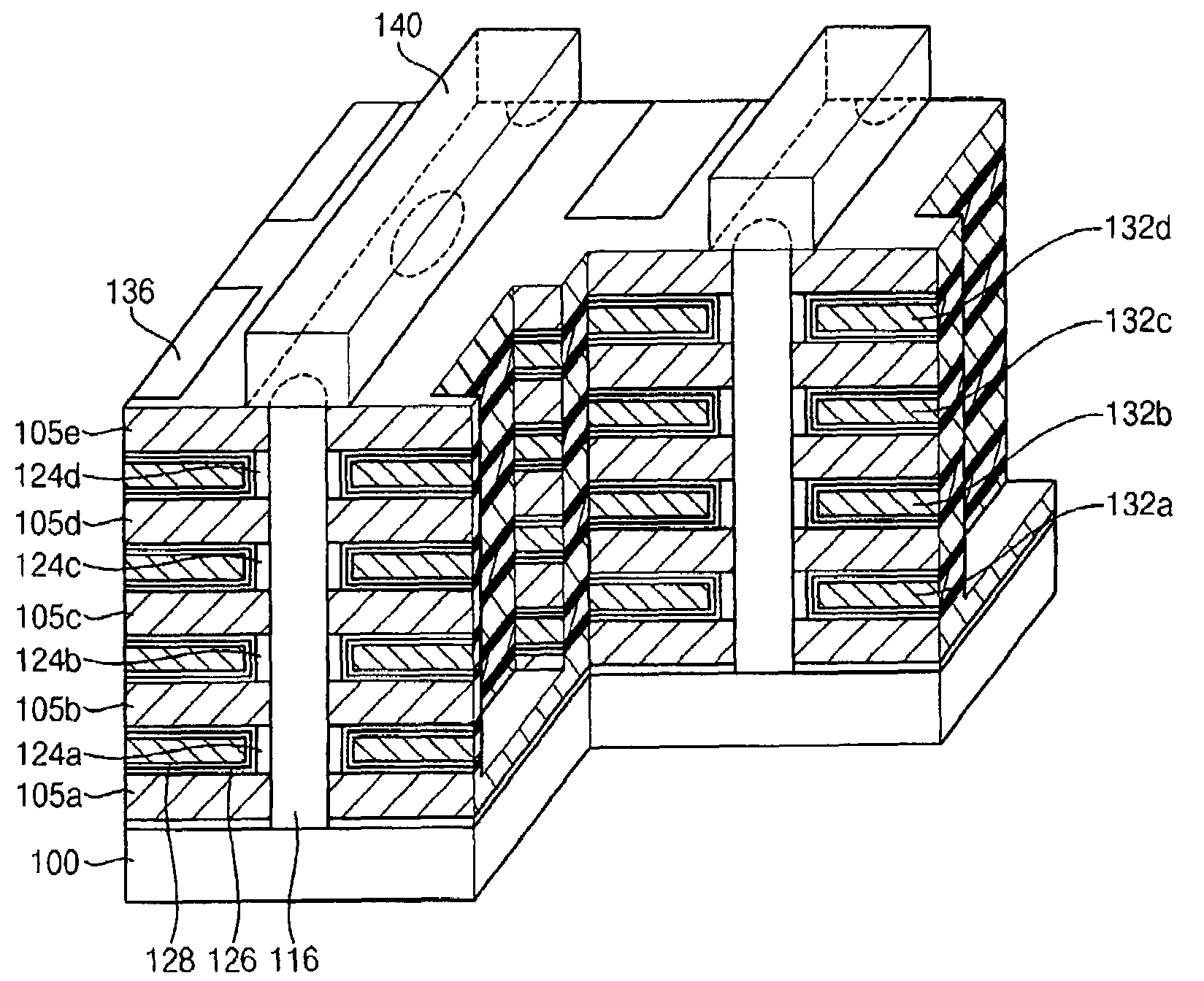

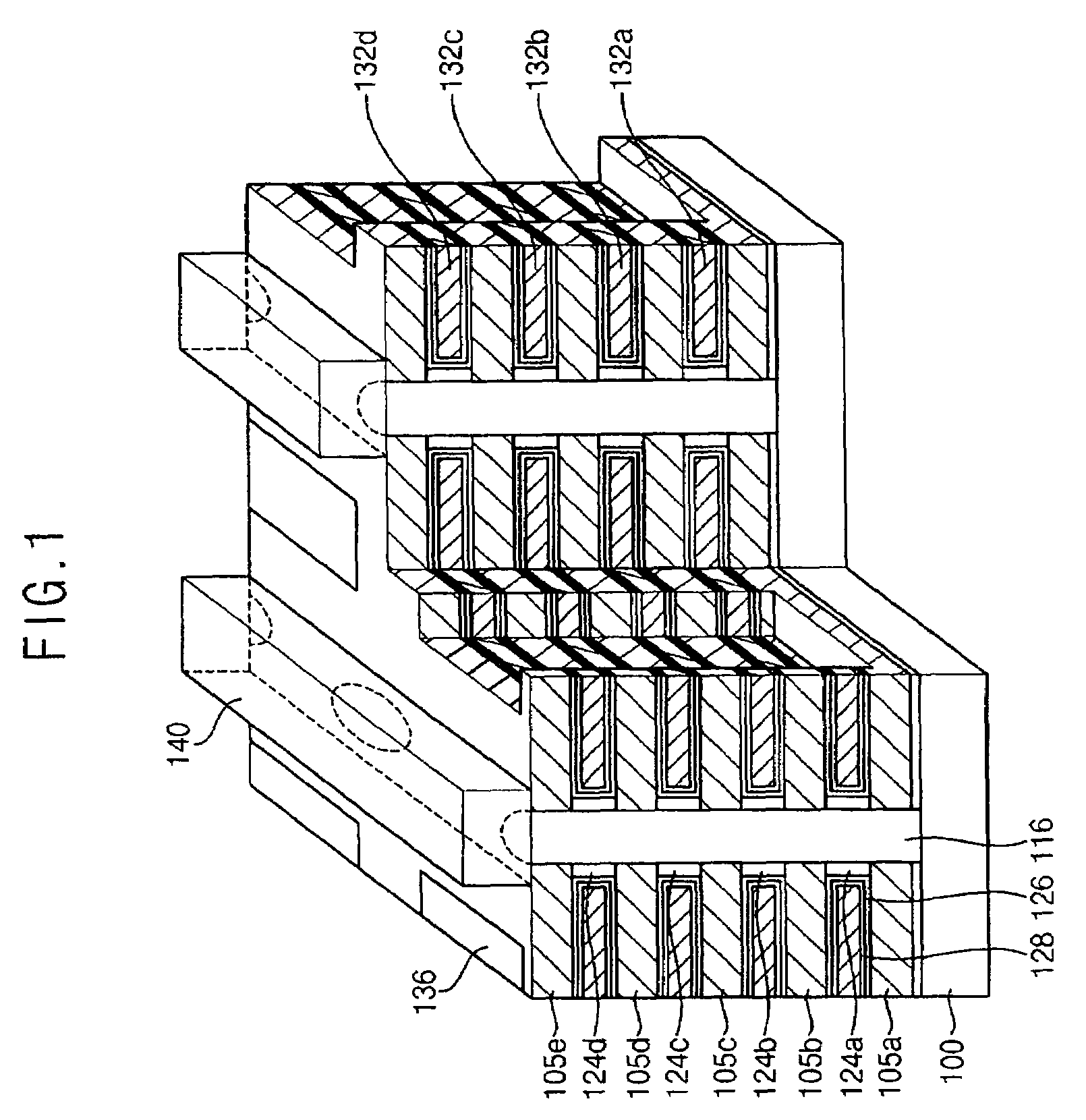

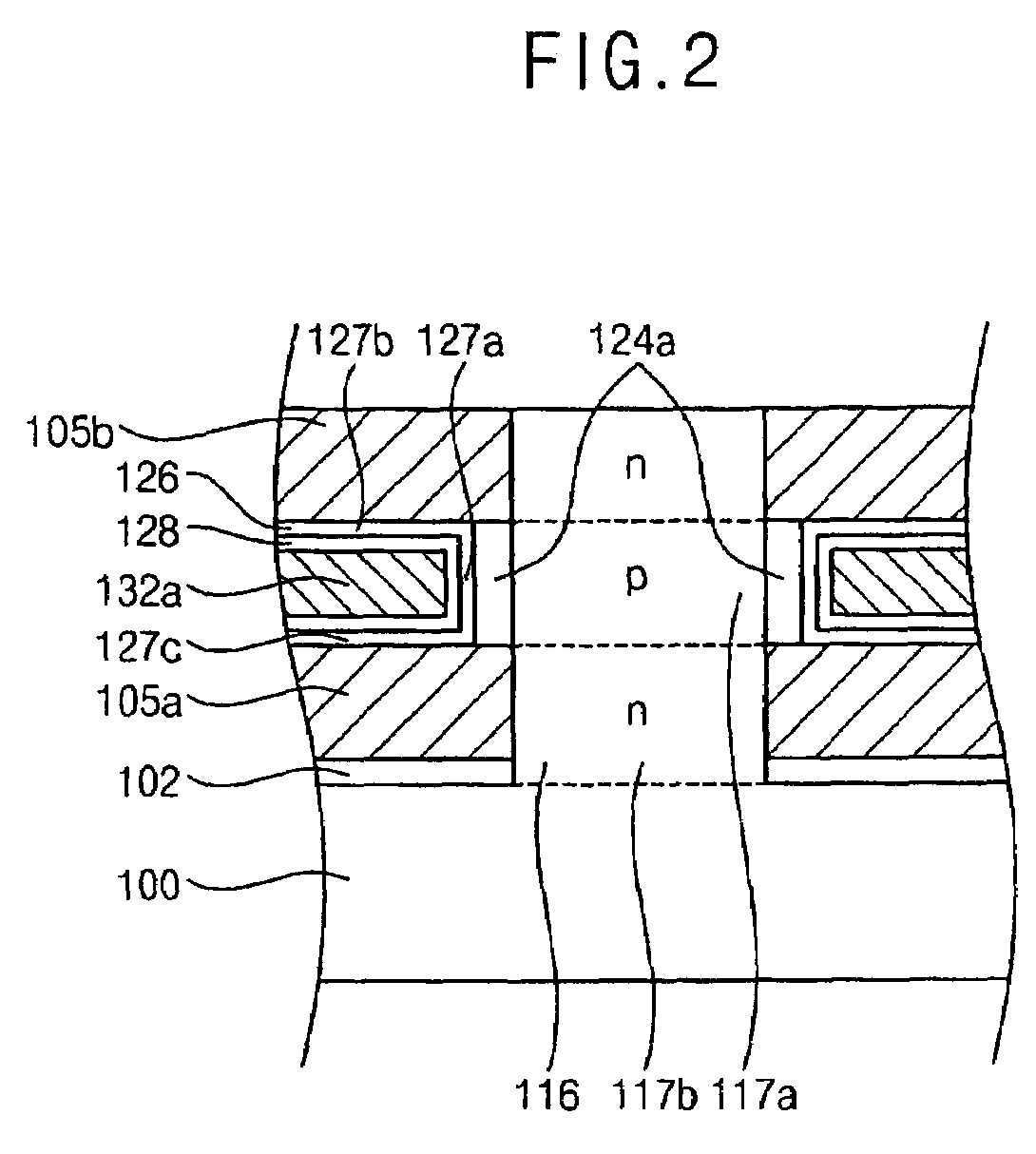

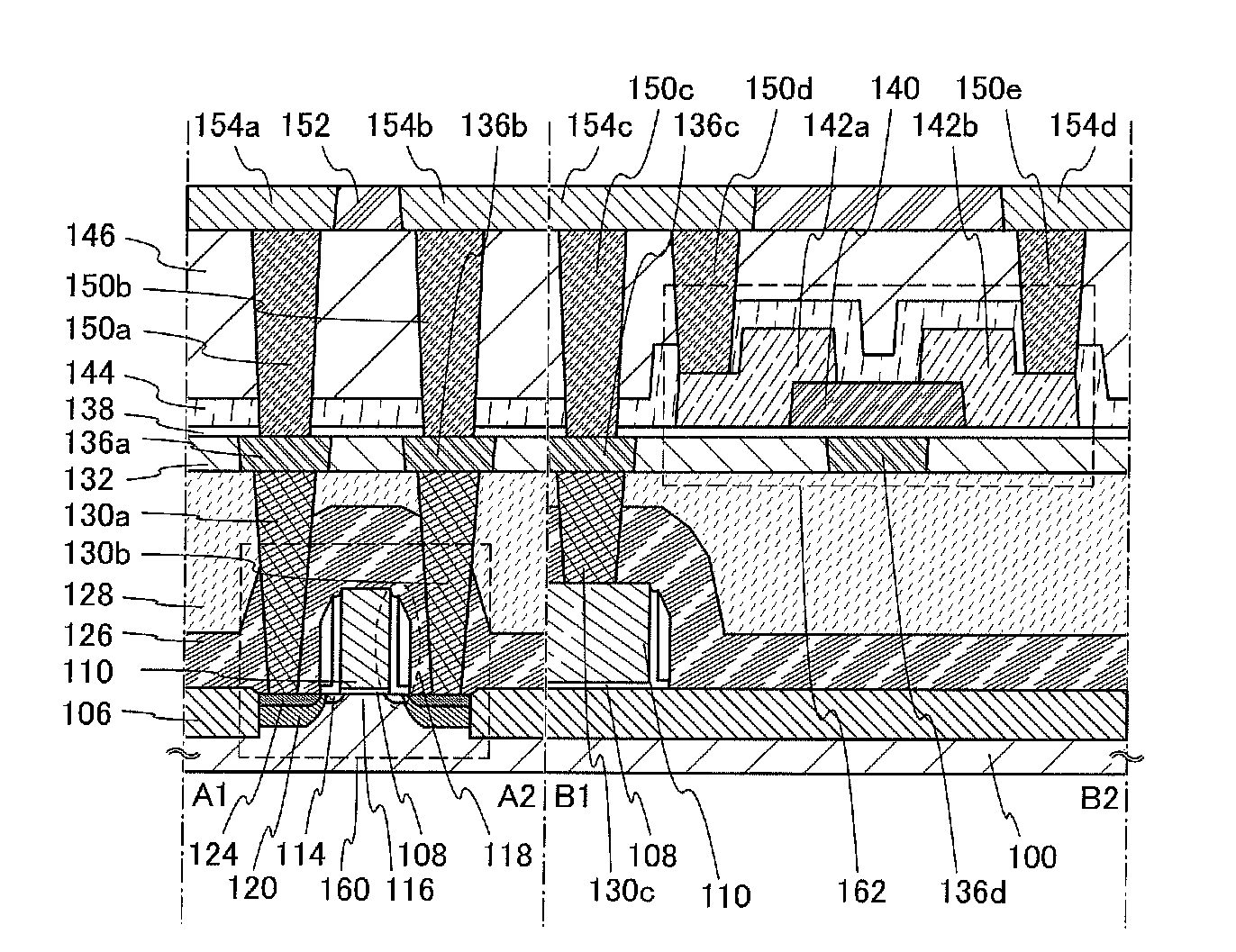

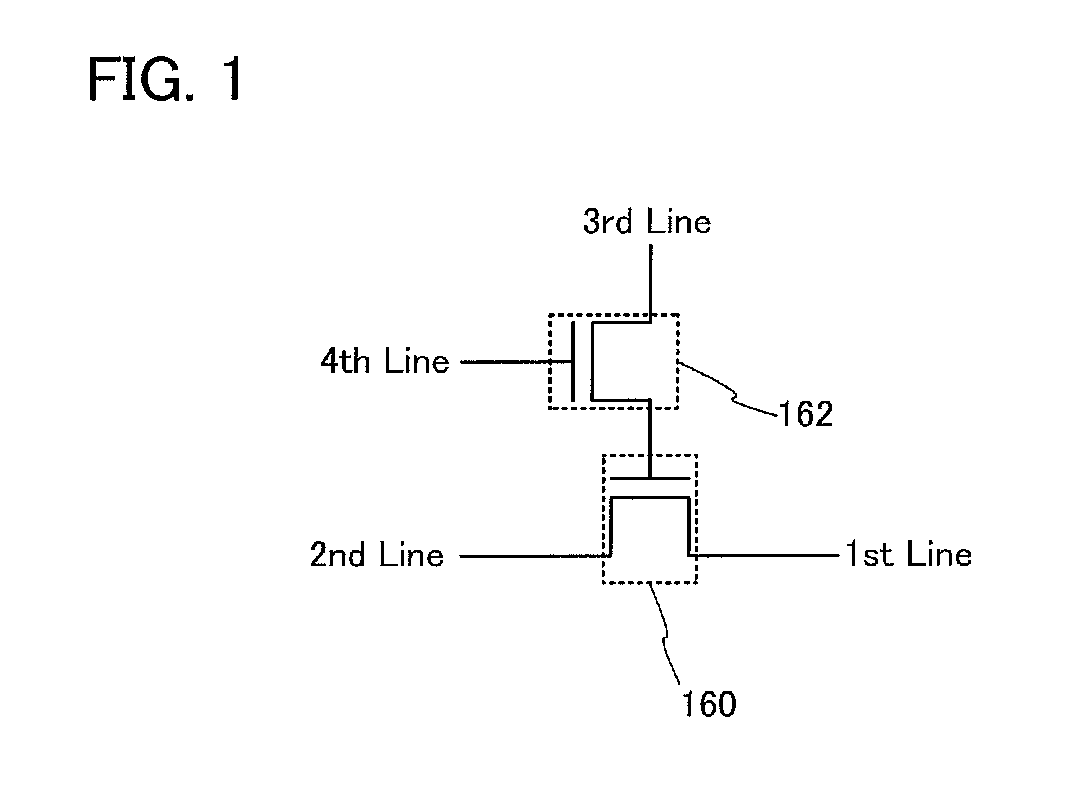

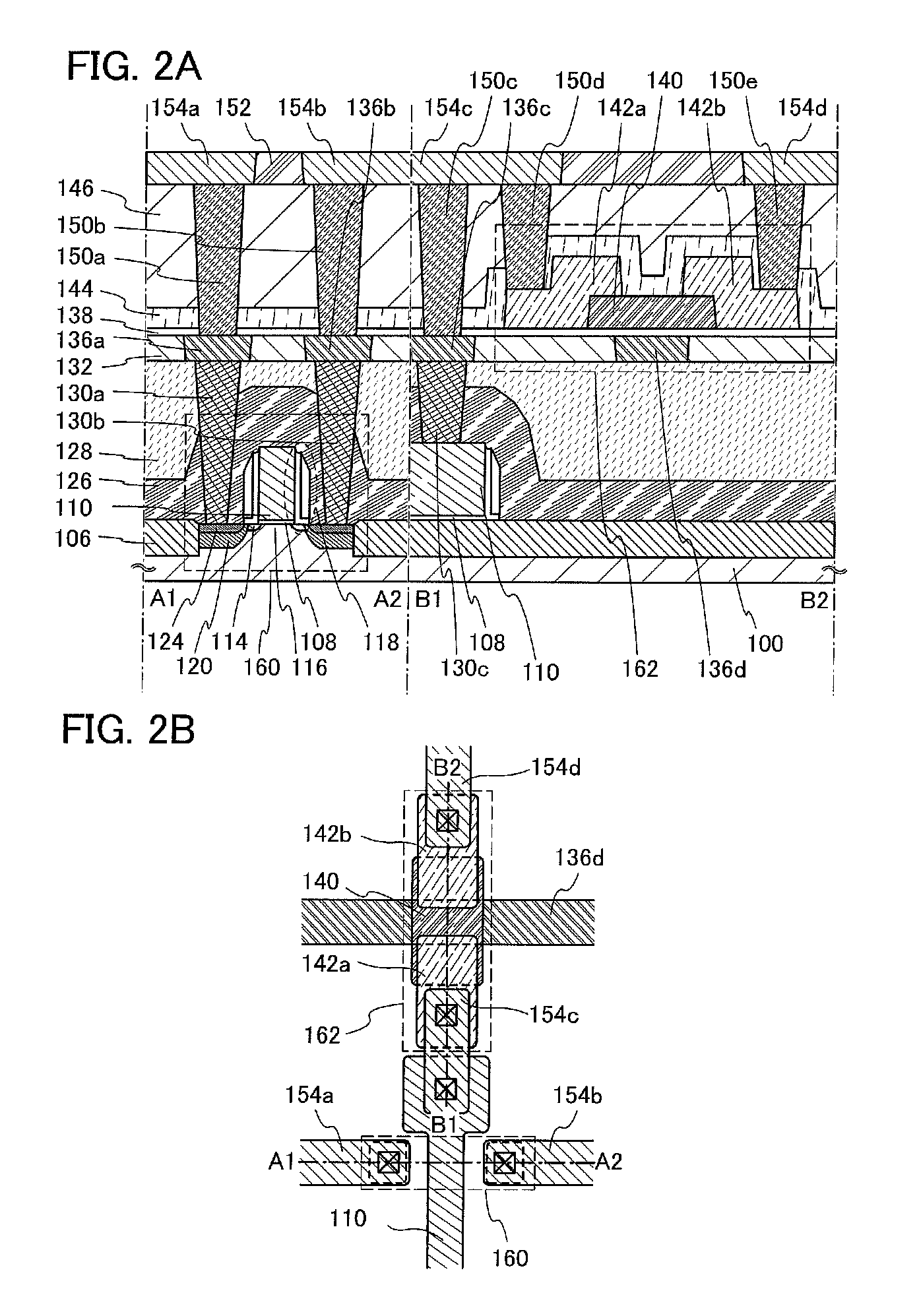

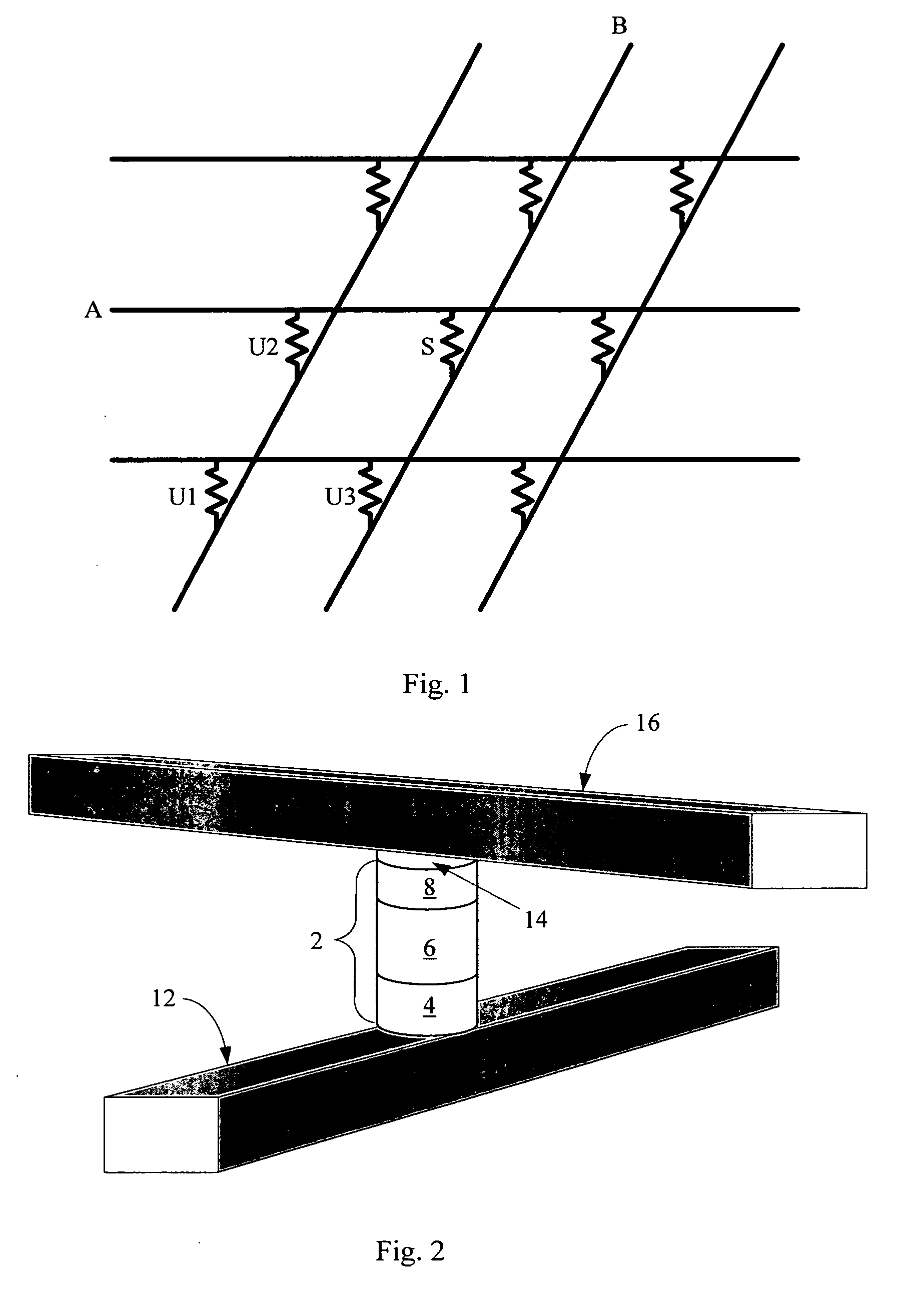

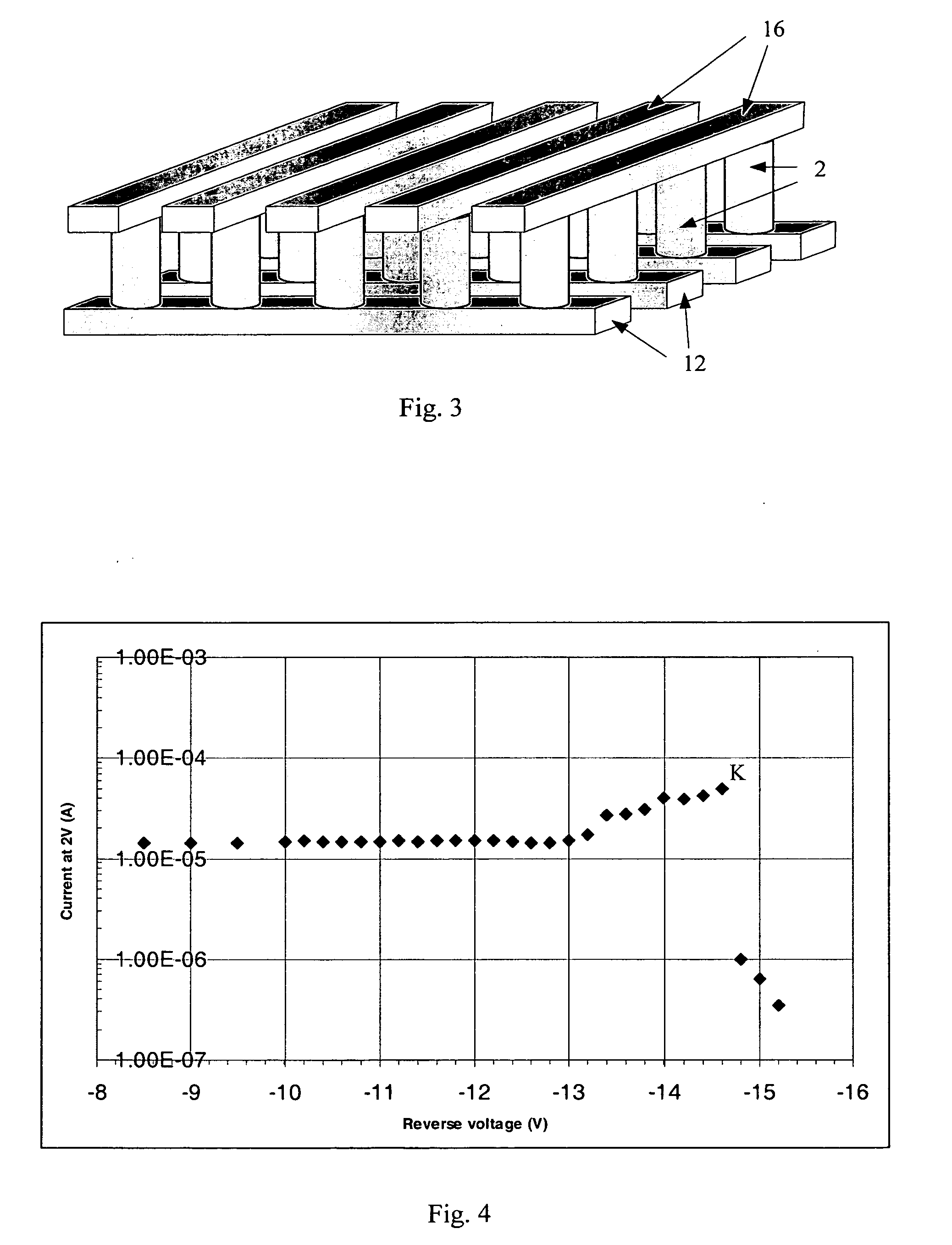

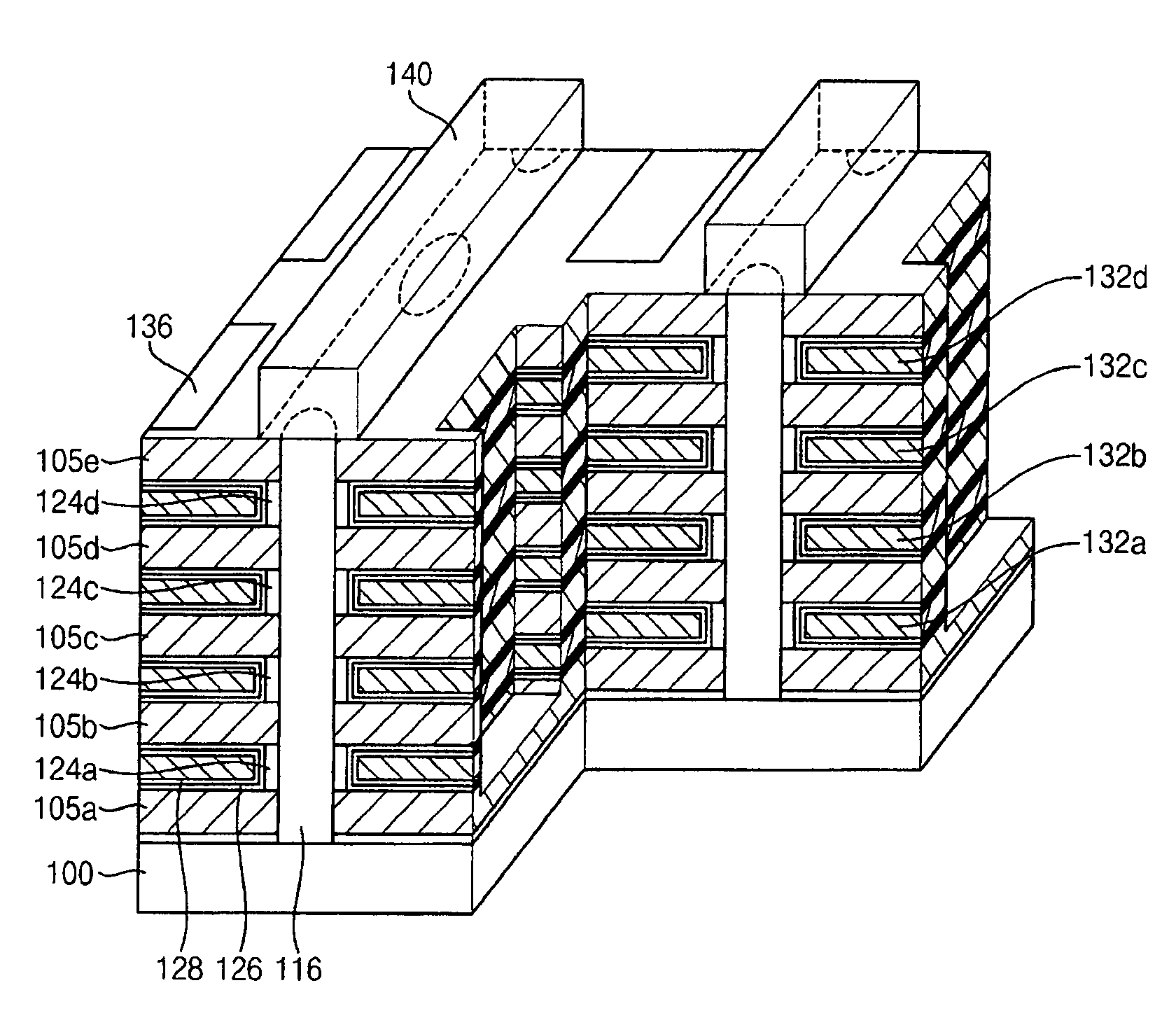

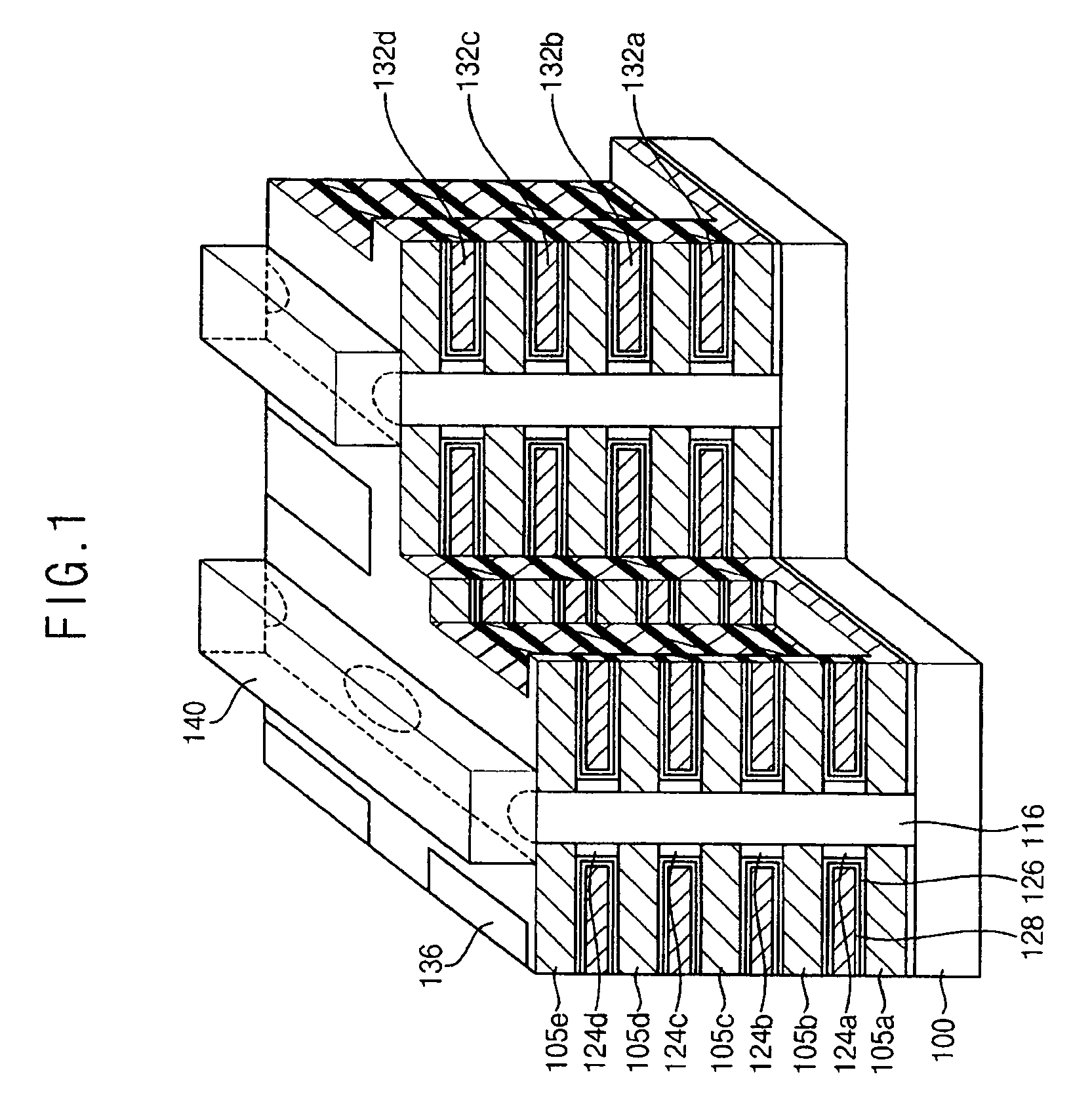

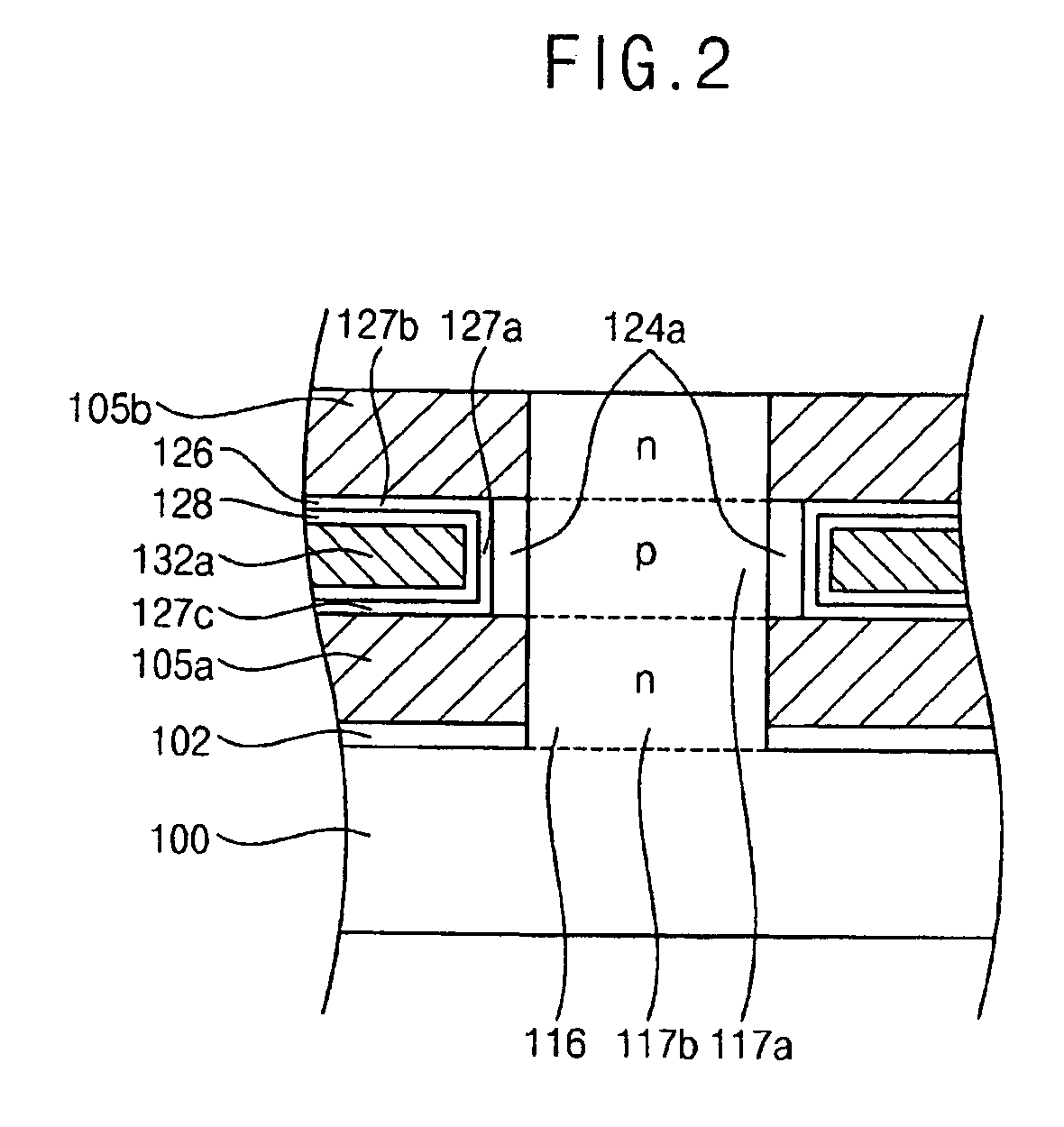

Vertical-type non-volatile memory devices

ActiveUS7679133B2Reduce the possibilityReduce in quantityTransistorSolid-state devicesSemiconductor materialsDevice material

In a semiconductor device, and a method of manufacturing thereof, the device includes a substrate of single-crystal semiconductor material extending in a horizontal direction and a plurality of interlayer dielectric layers on the substrate. A plurality of gate patterns are provided, each gate pattern being between a neighboring lower interlayer dielectric layer and a neighboring upper interlayer dielectric layer. A vertical channel of single-crystal semiconductor material extends in a vertical direction through the plurality of interlayer dielectric layers and the plurality of gate patterns, a gate insulating layer being between each gate pattern and the vertical channel that insulates the gate pattern from the vertical channel.

Owner:SAMSUNG ELECTRONICS CO LTD

Semiconductor device

ActiveUS20110101351A1Reduce power consumptionFrequency of refresh can be lowSolid-state devicesRead-only memoriesSemiconductor materialsData storing

Disclosed is a semiconductor device capable of functioning as a memory device. The memory device comprises a plurality of memory cells, and each of the memory cells contains a first transistor and a second transistor. The first transistor is provided over a substrate containing a semiconductor material and has a channel formation region in the substrate. The second transistor has an oxide semiconductor layer. The gate electrode of the first transistor and one of the source and drain electrodes of the second transistor are electrically connected to each other. The extremely low off current of the second transistor allows the data stored in the memory cell to be retained for a significantly long time even in the absence of supply of electric power.

Owner:SEMICON ENERGY LAB CO LTD

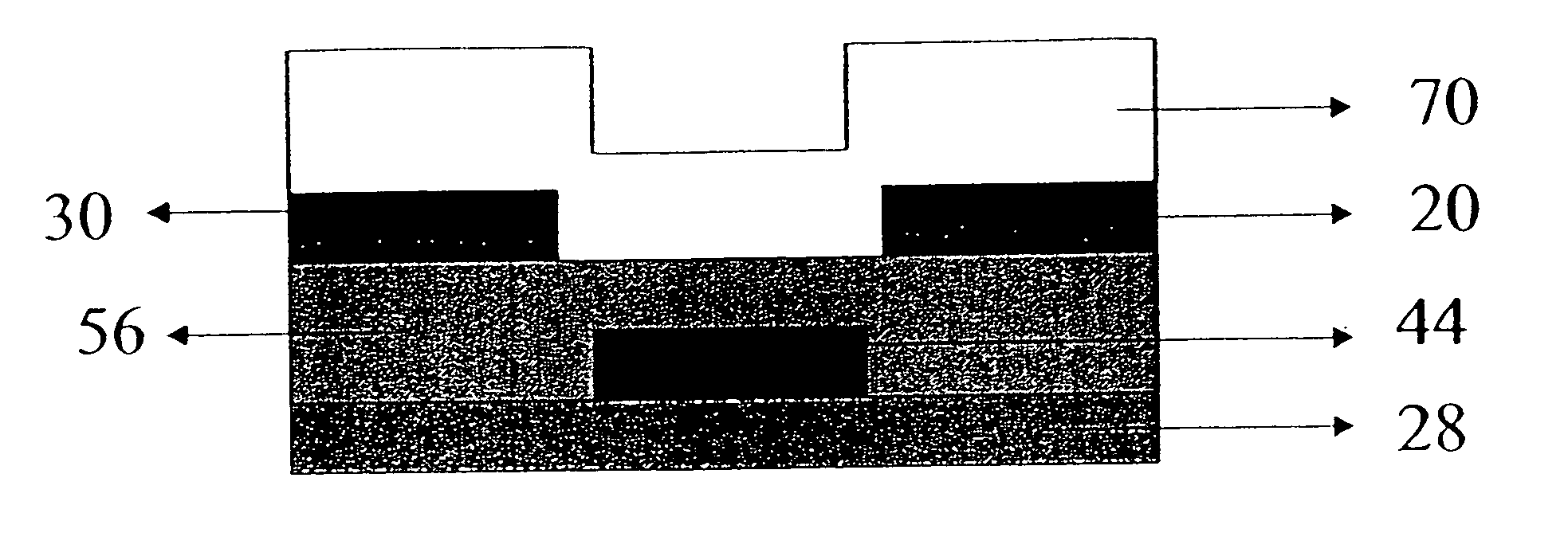

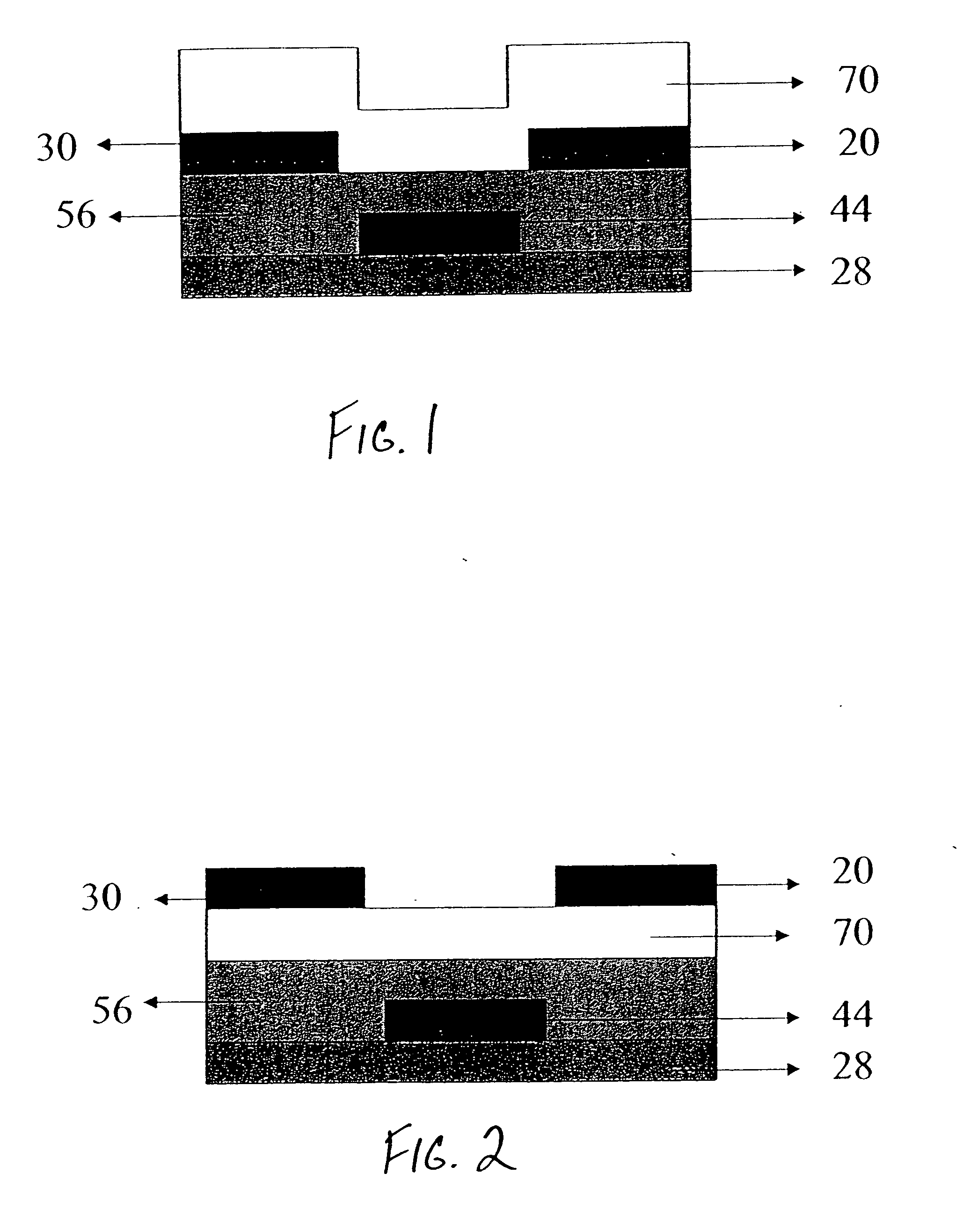

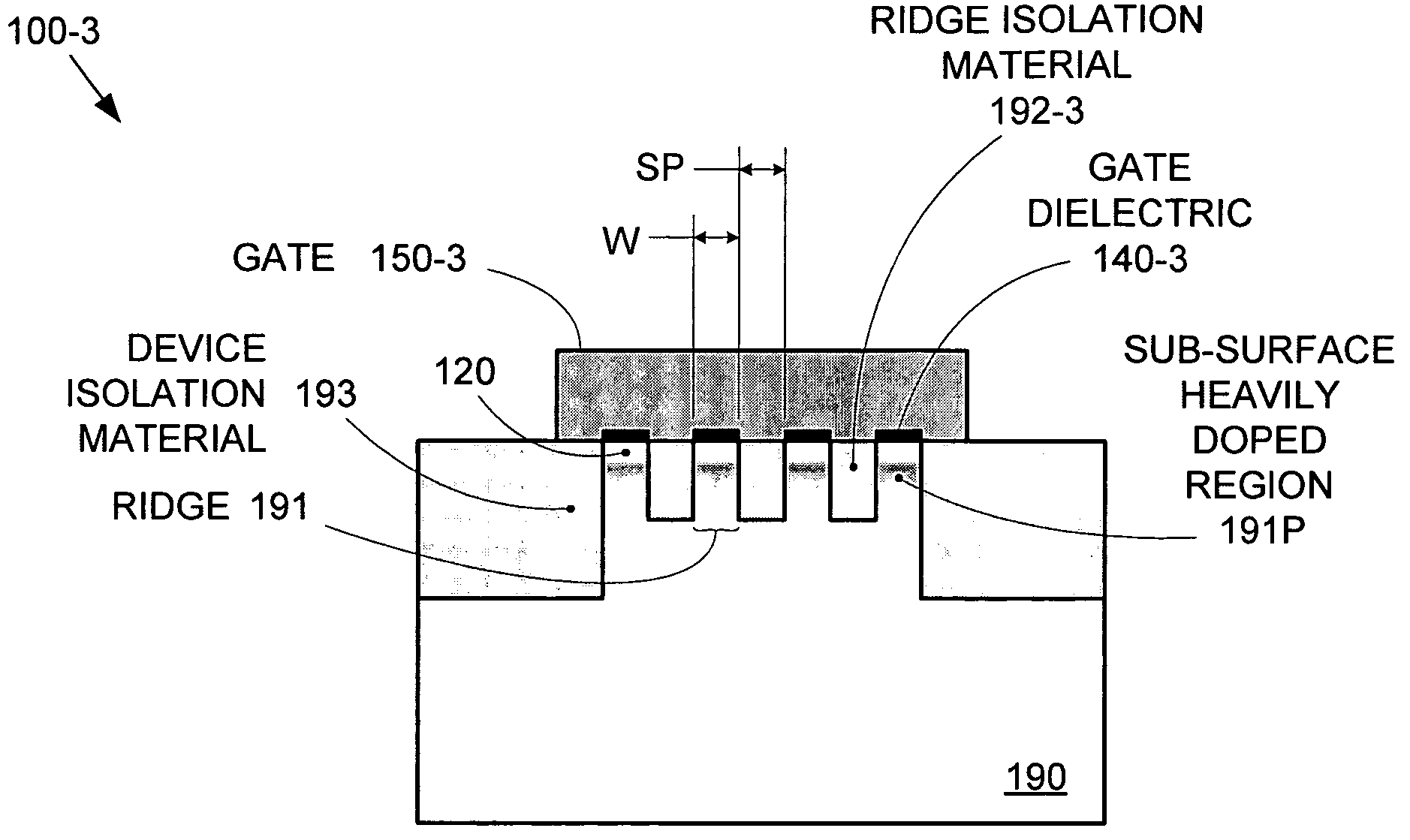

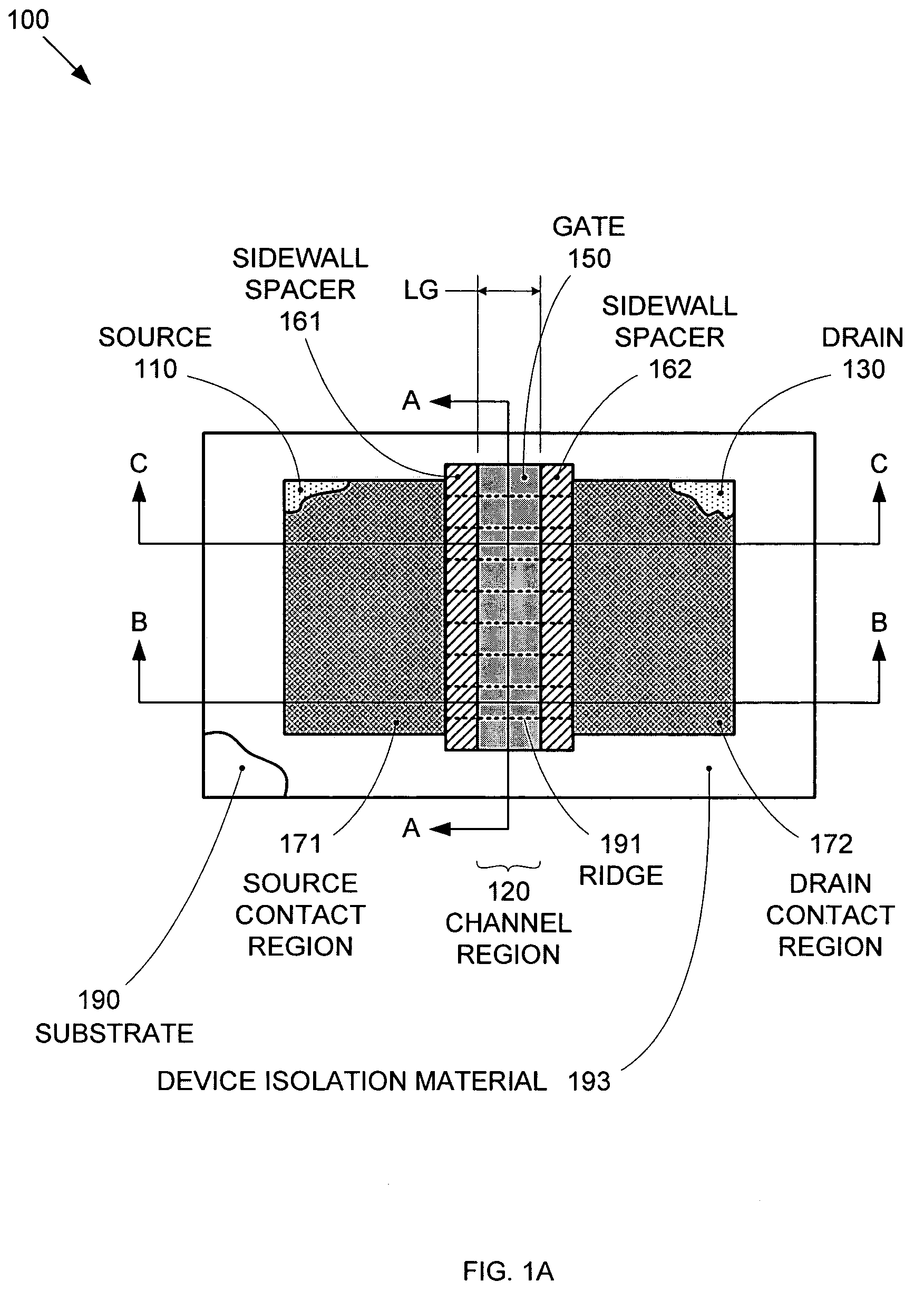

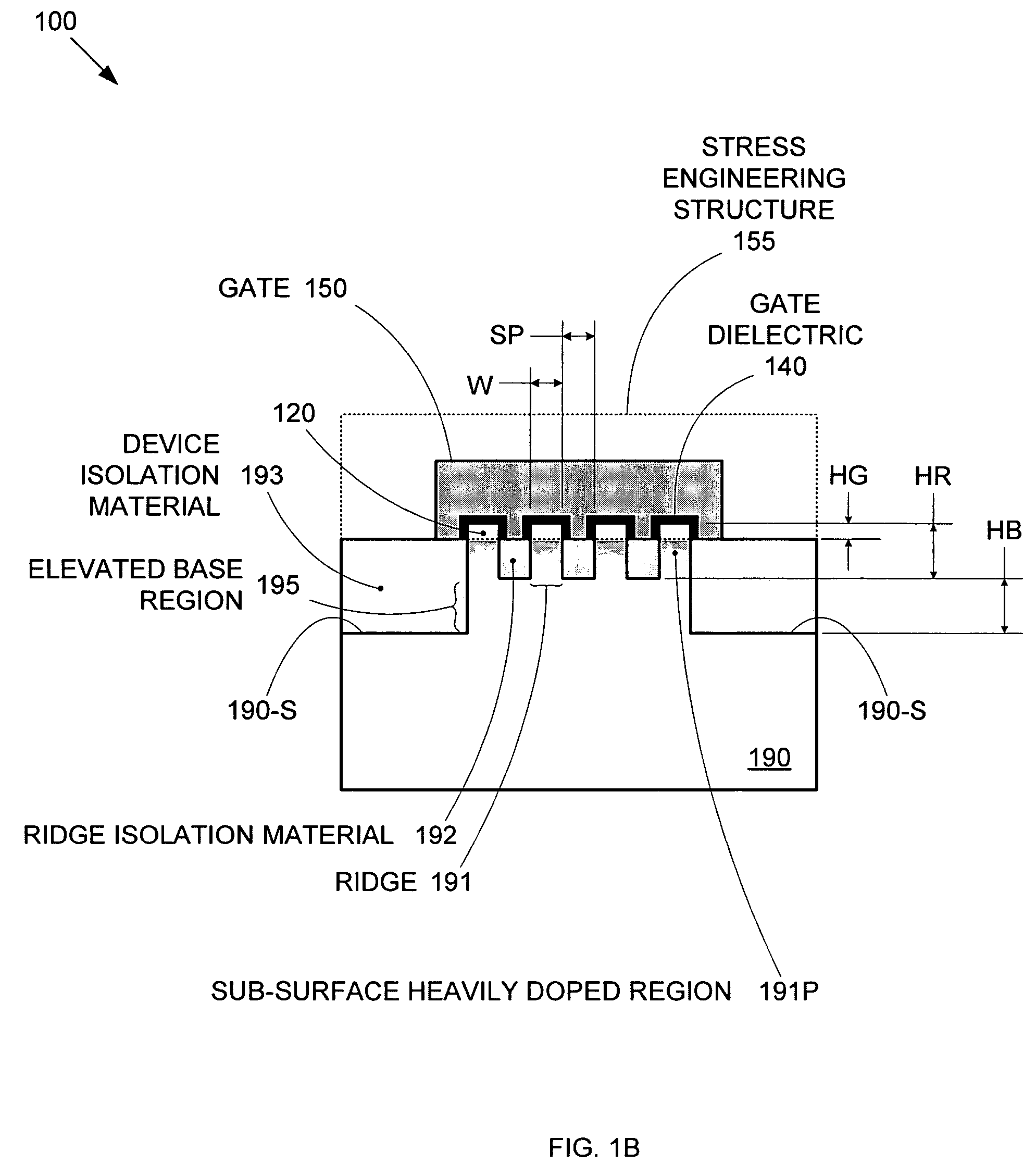

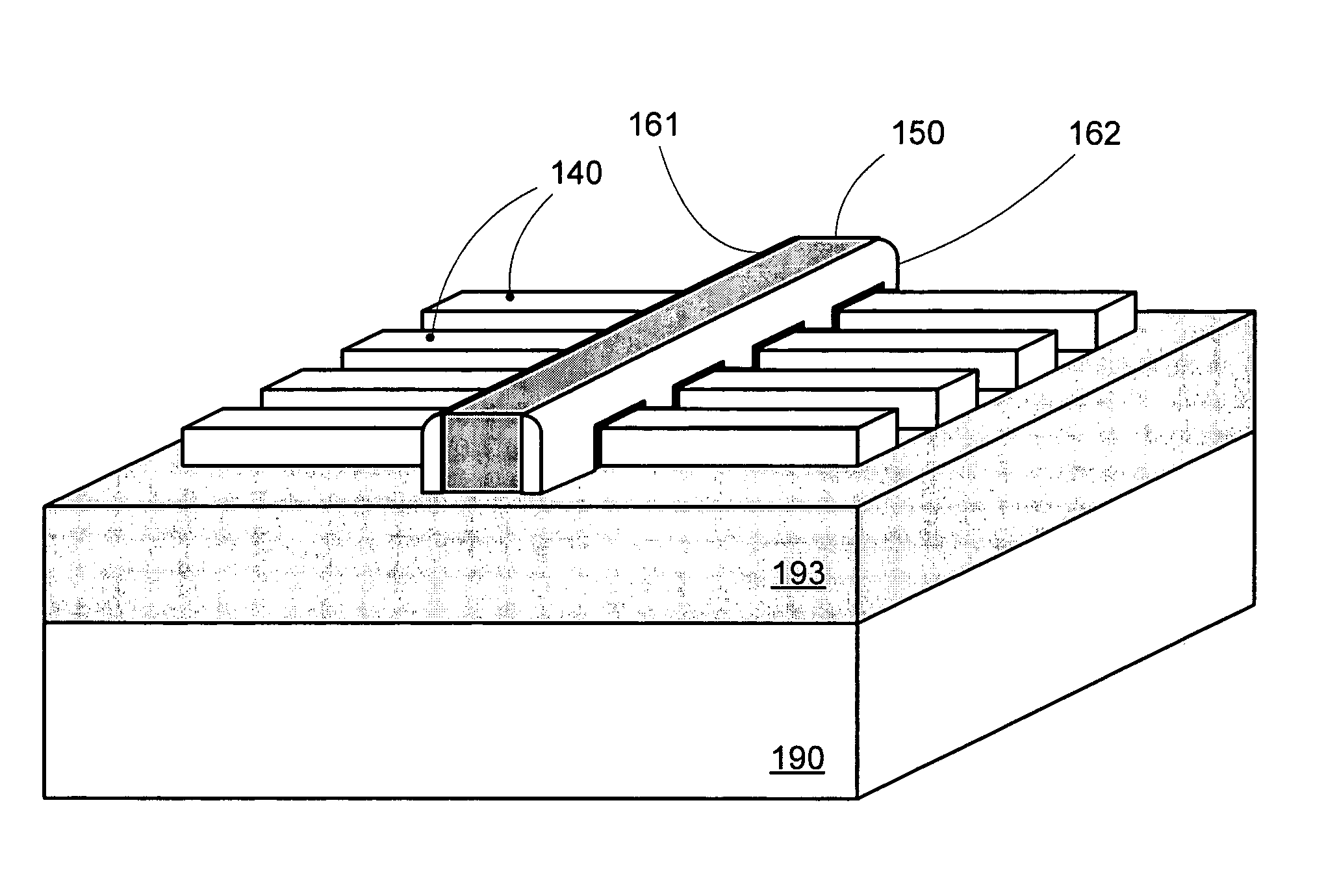

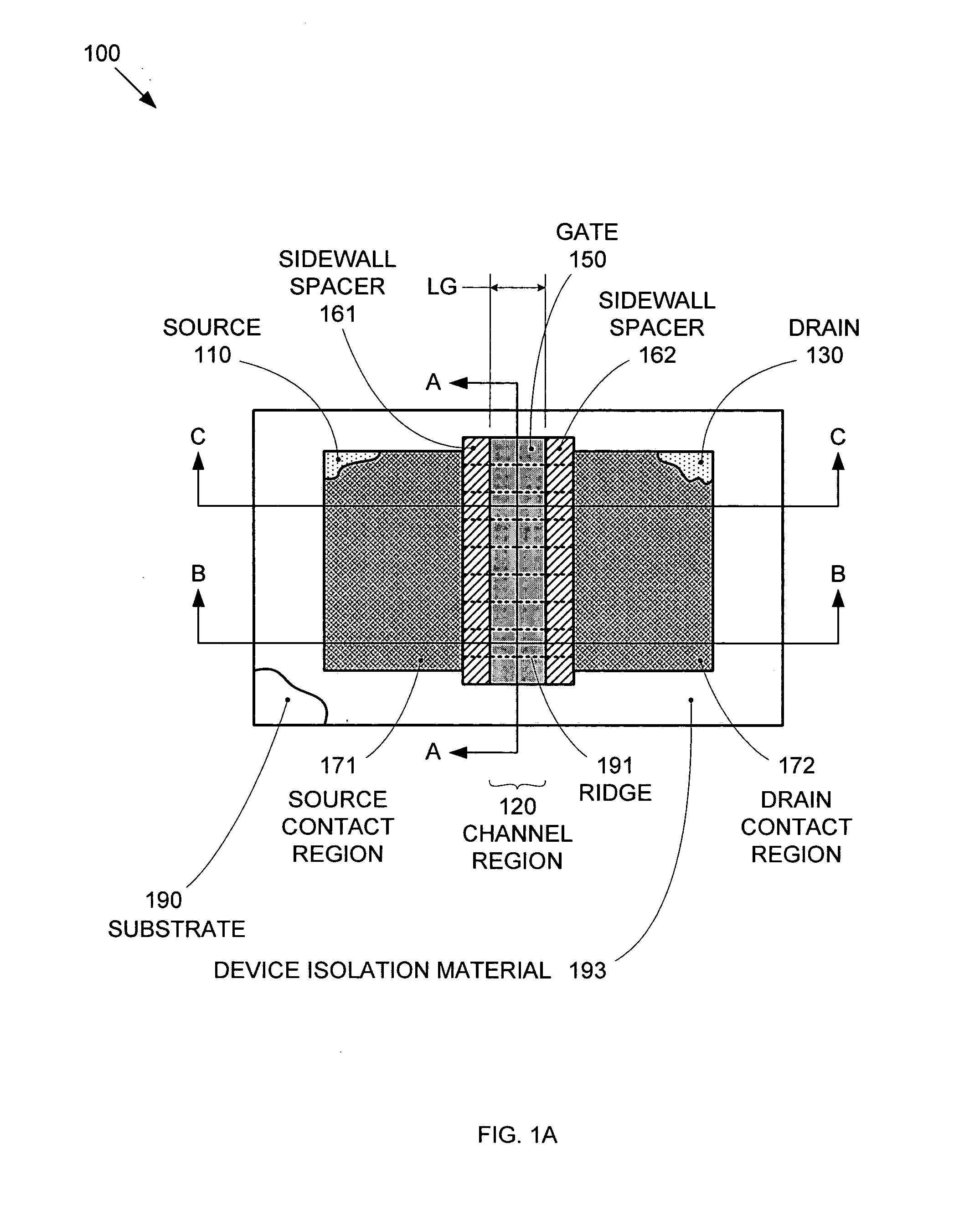

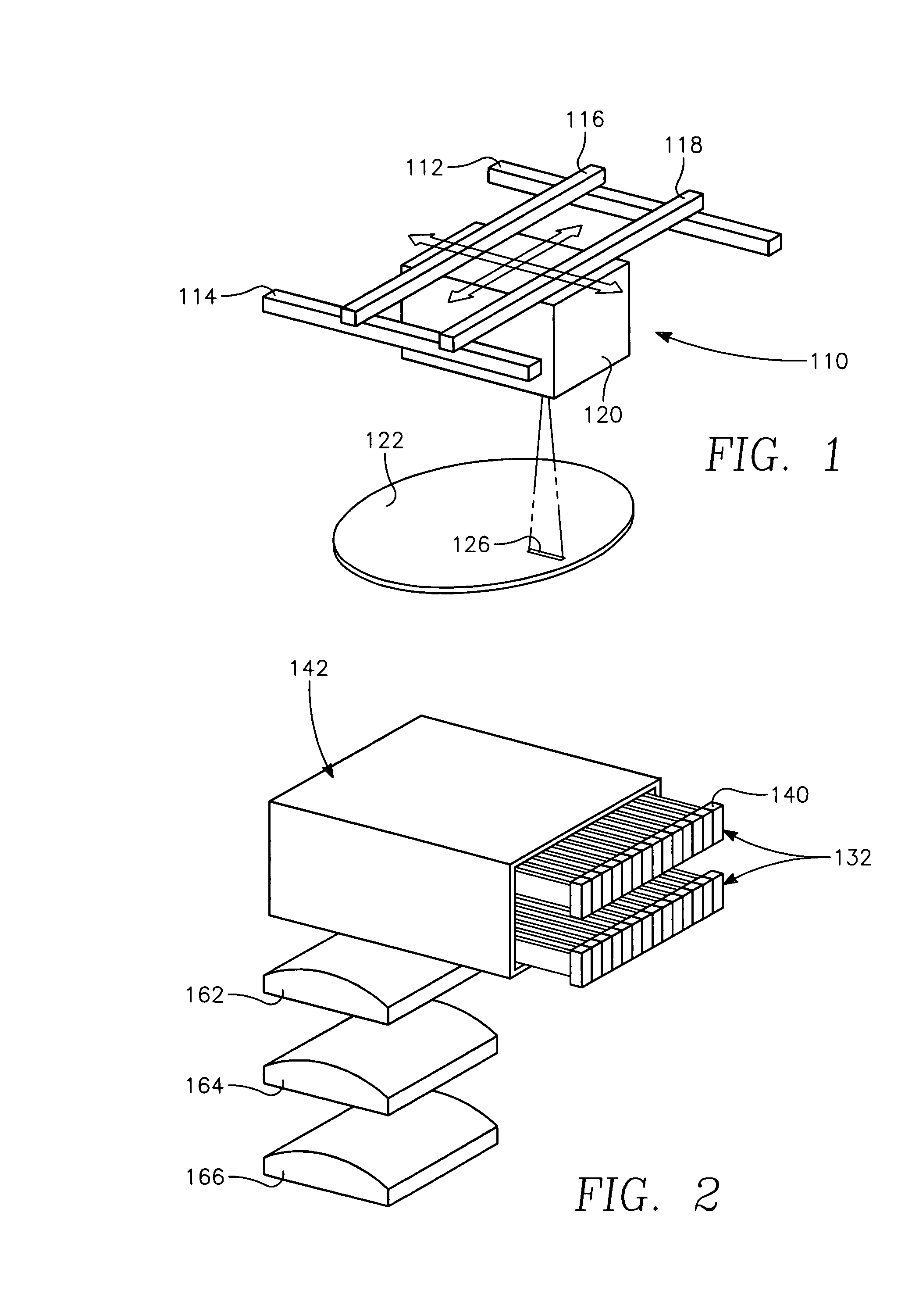

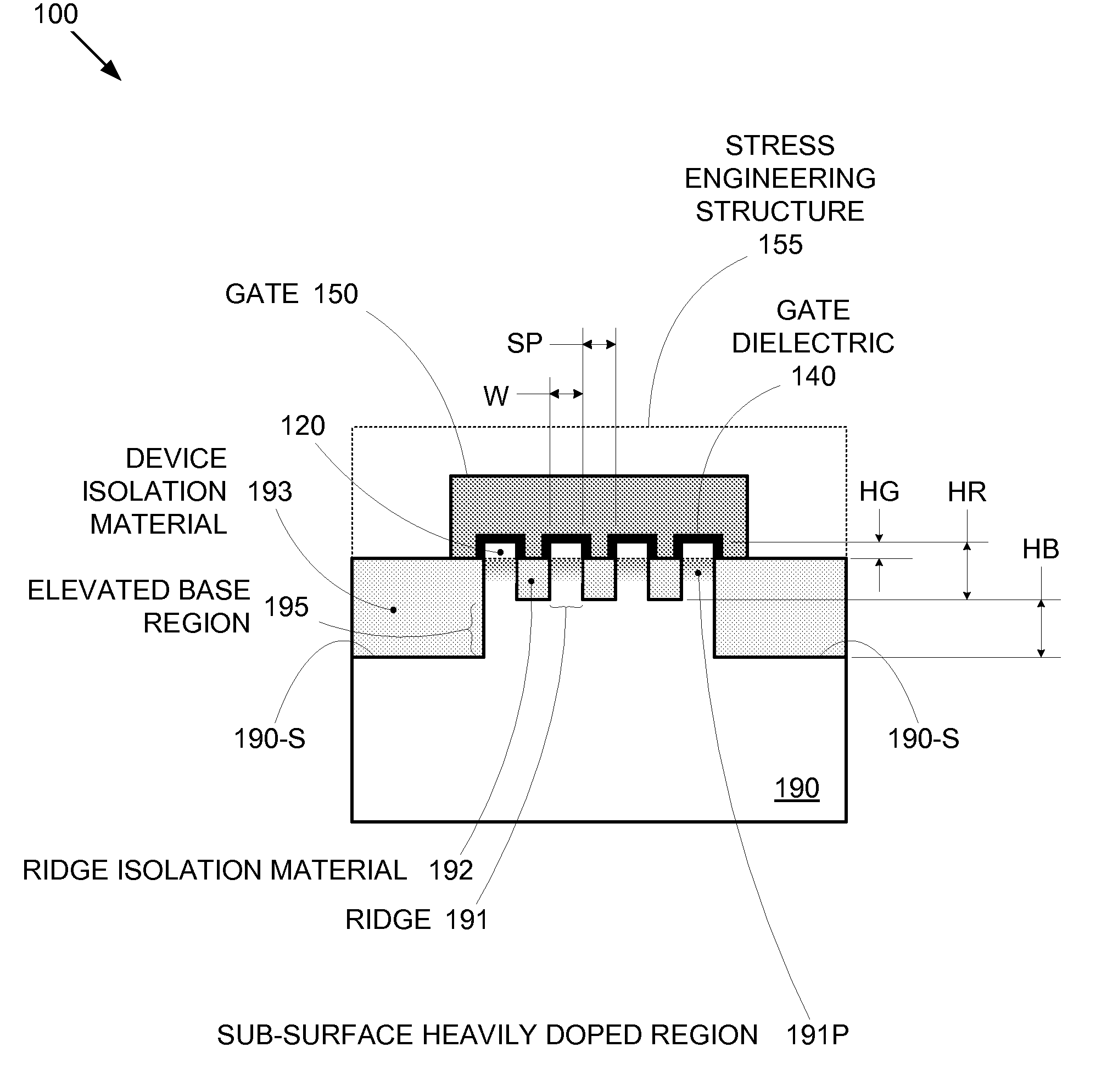

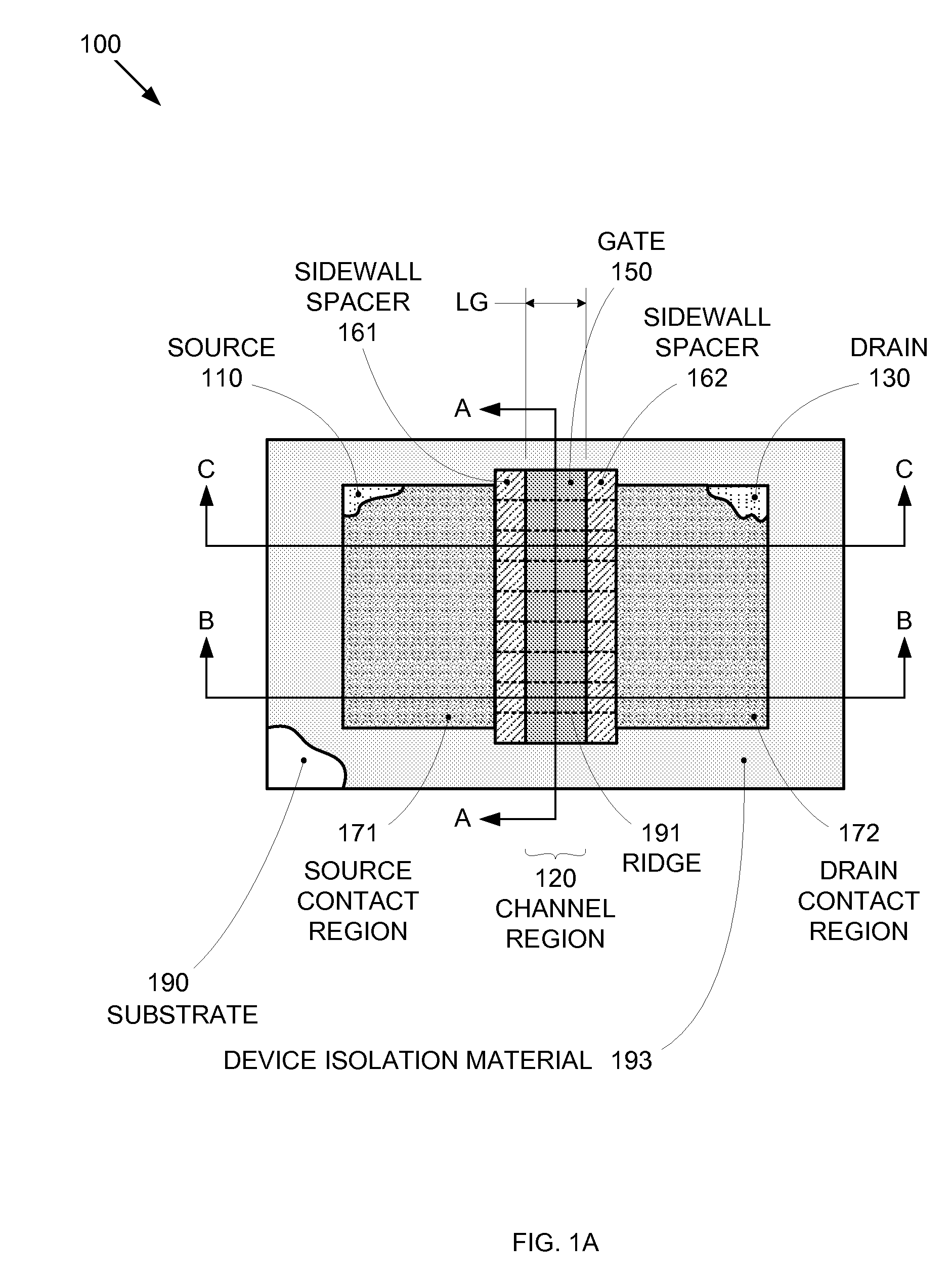

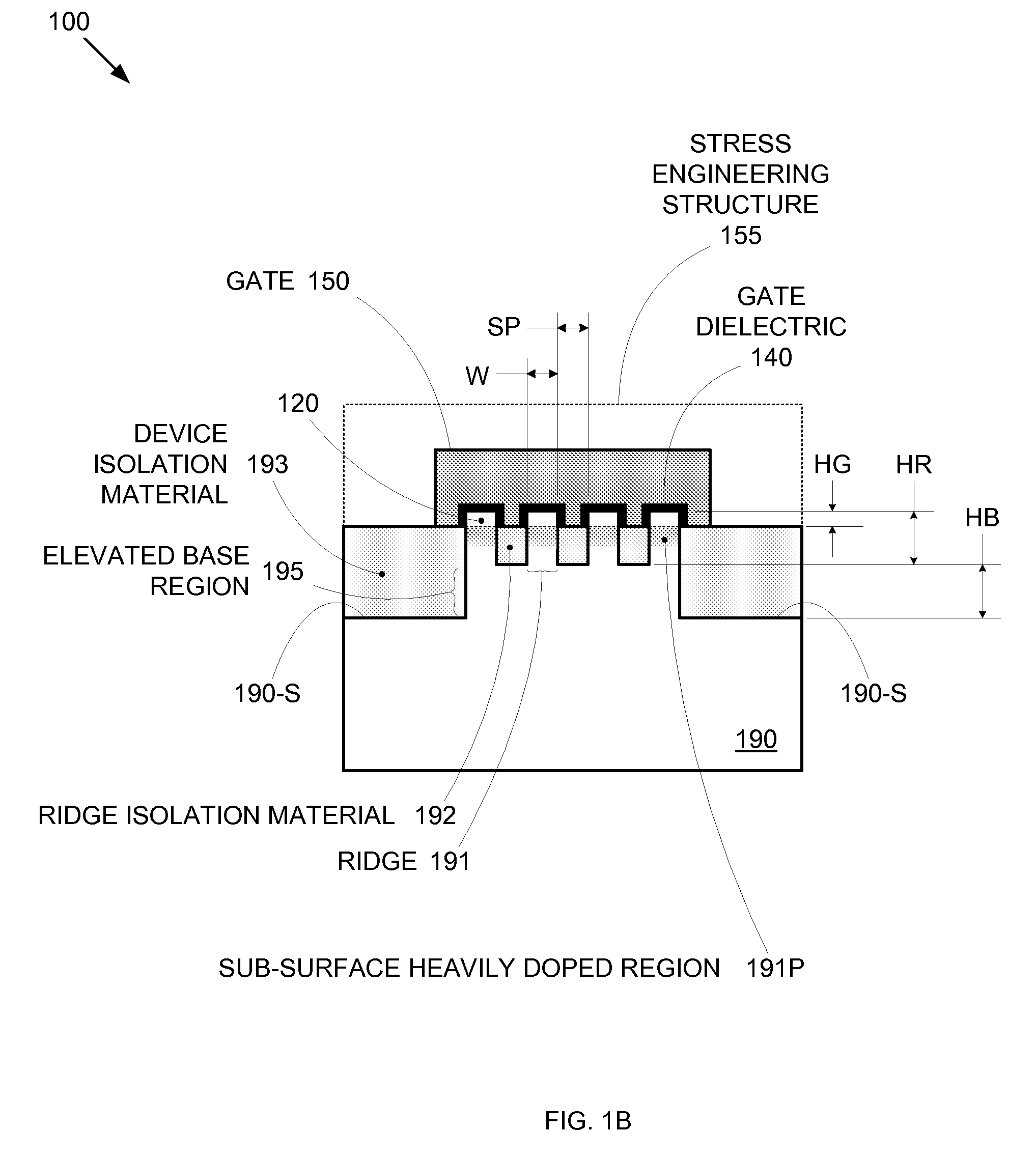

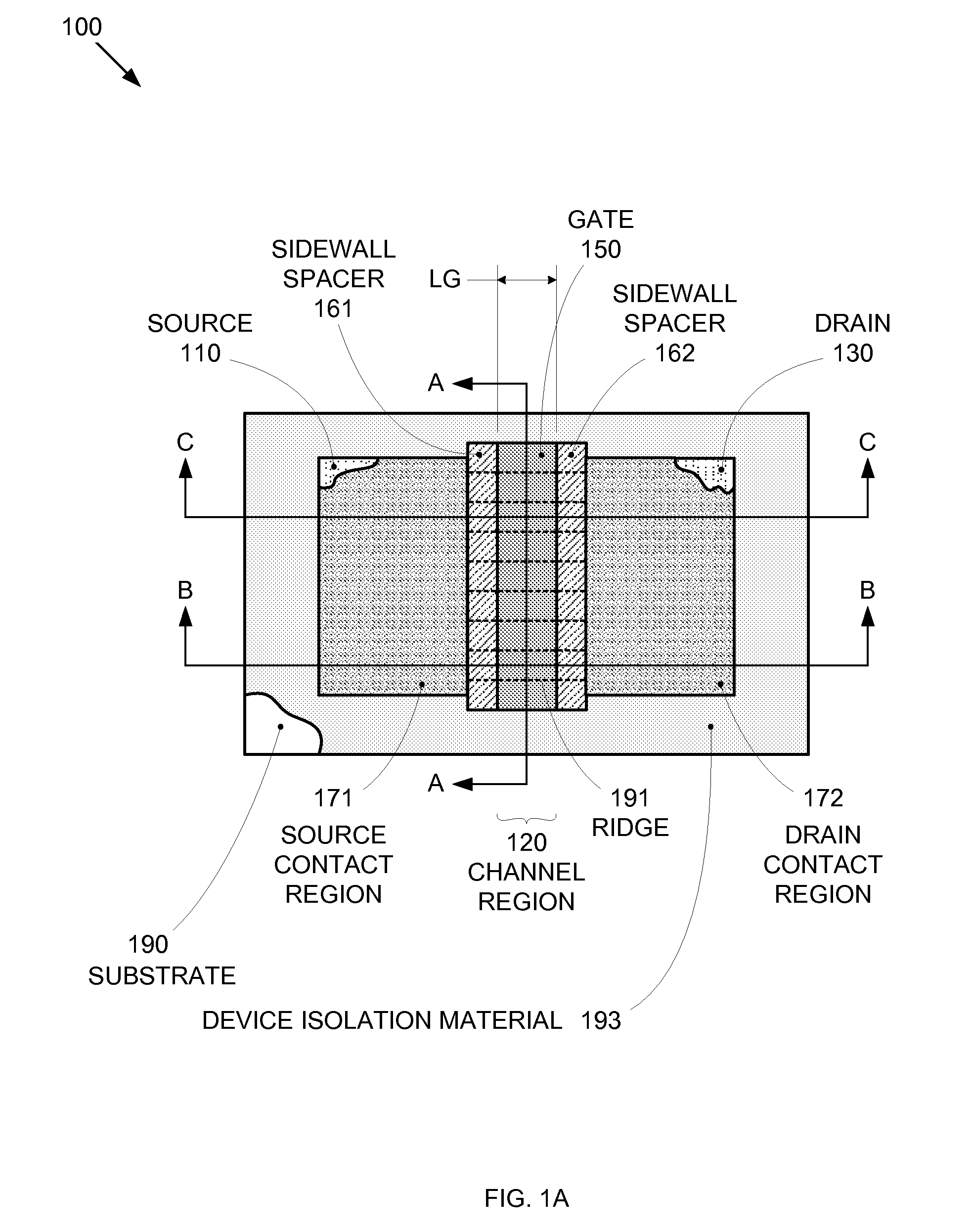

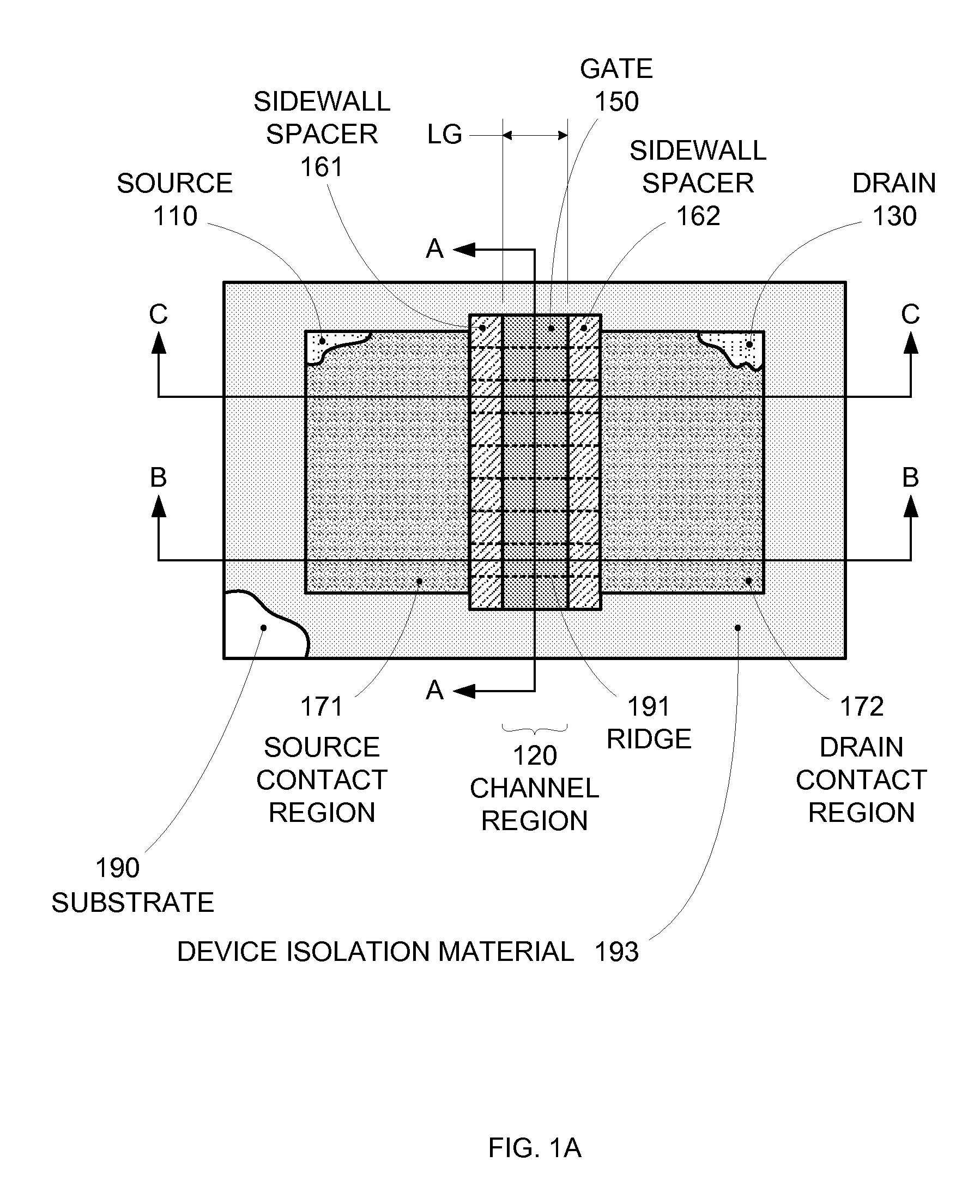

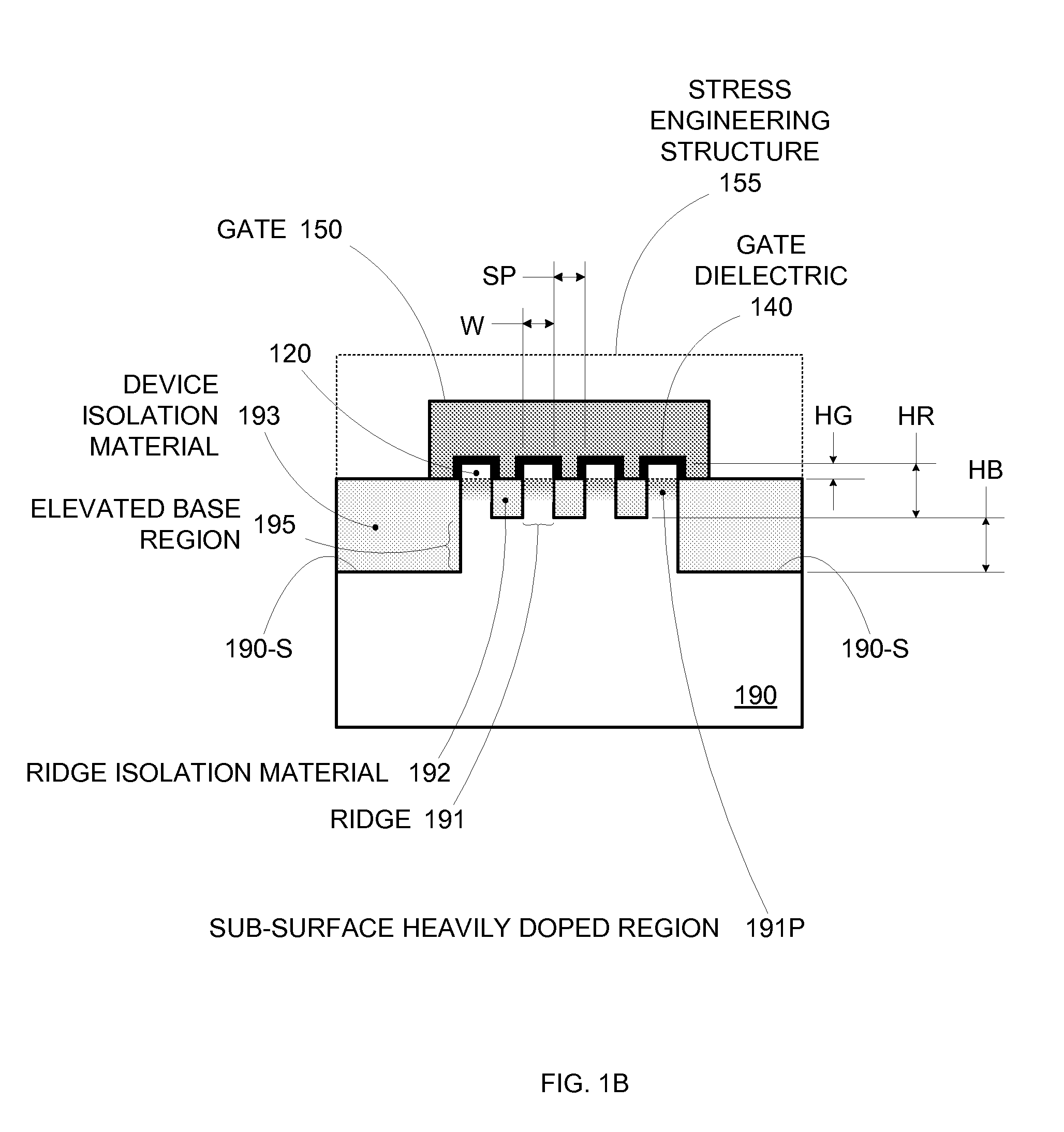

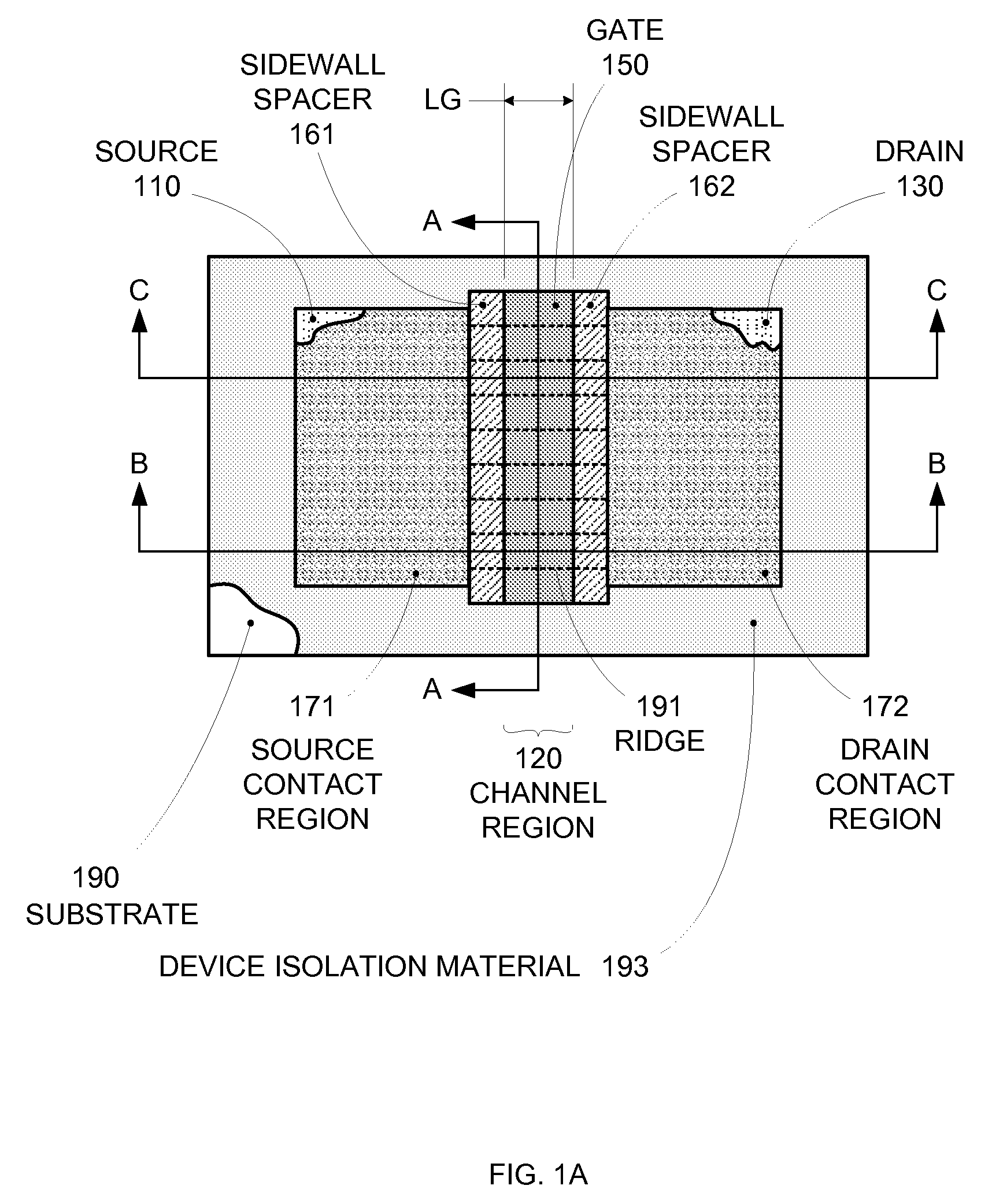

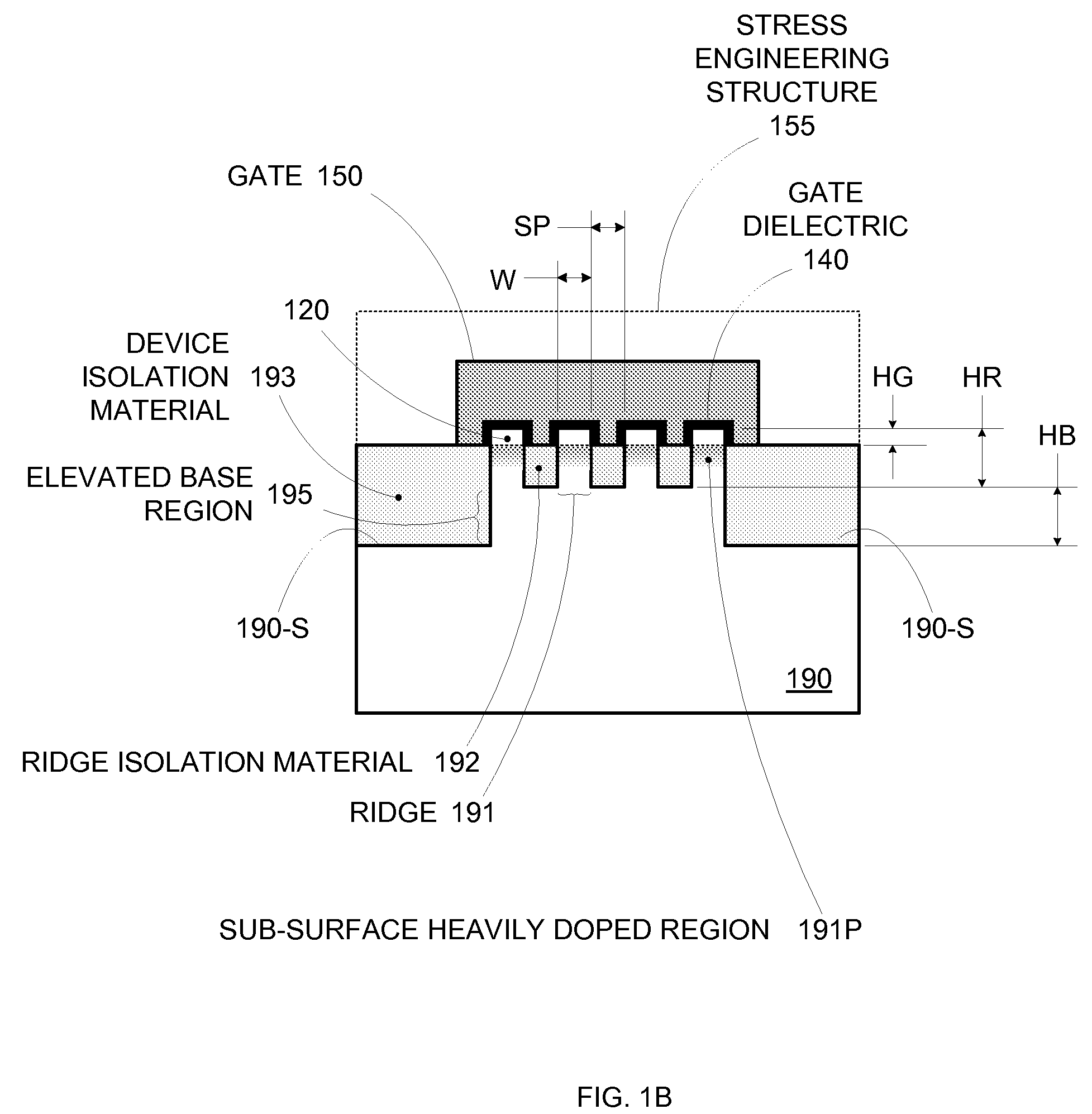

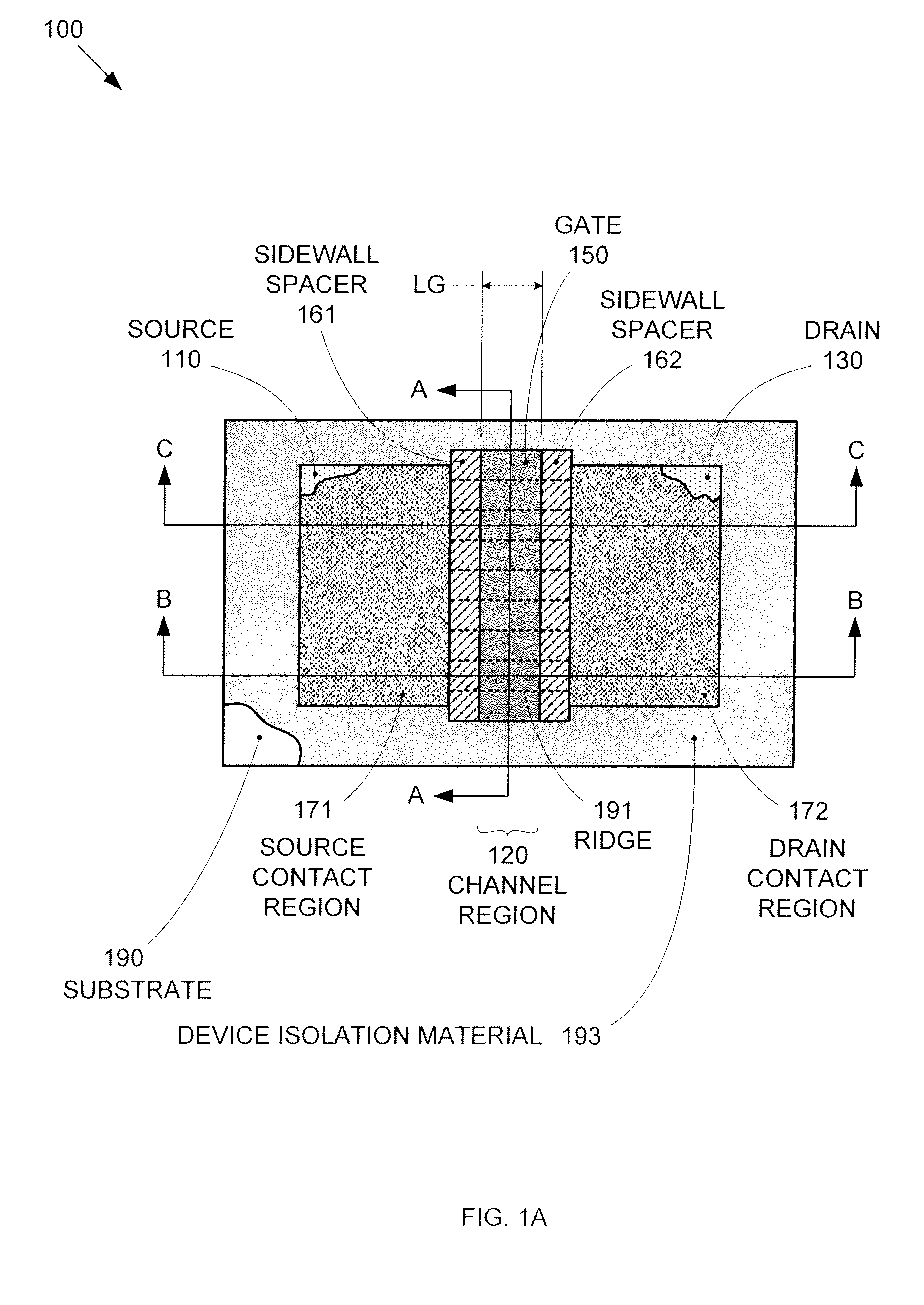

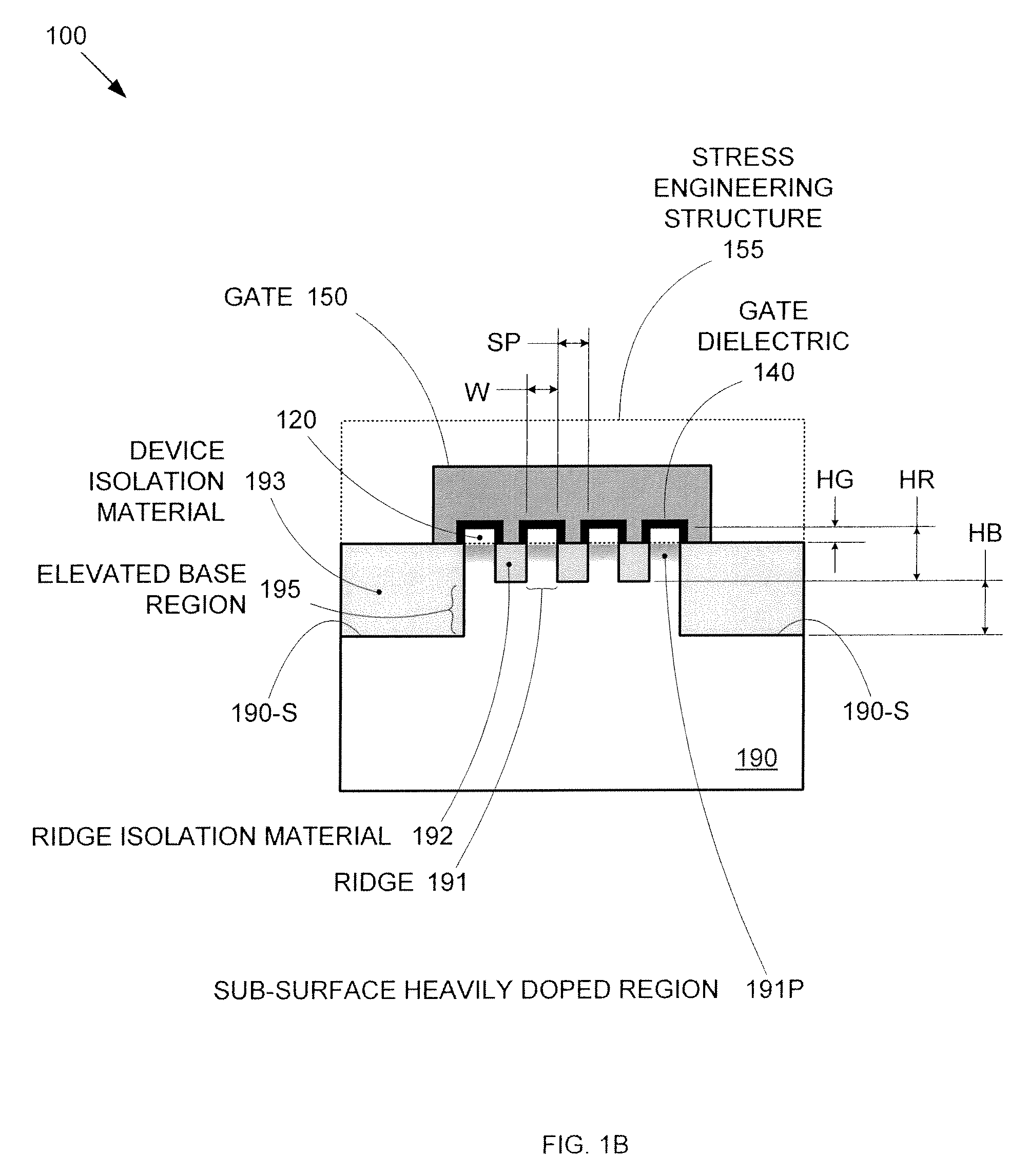

Segmented channel MOS transistor

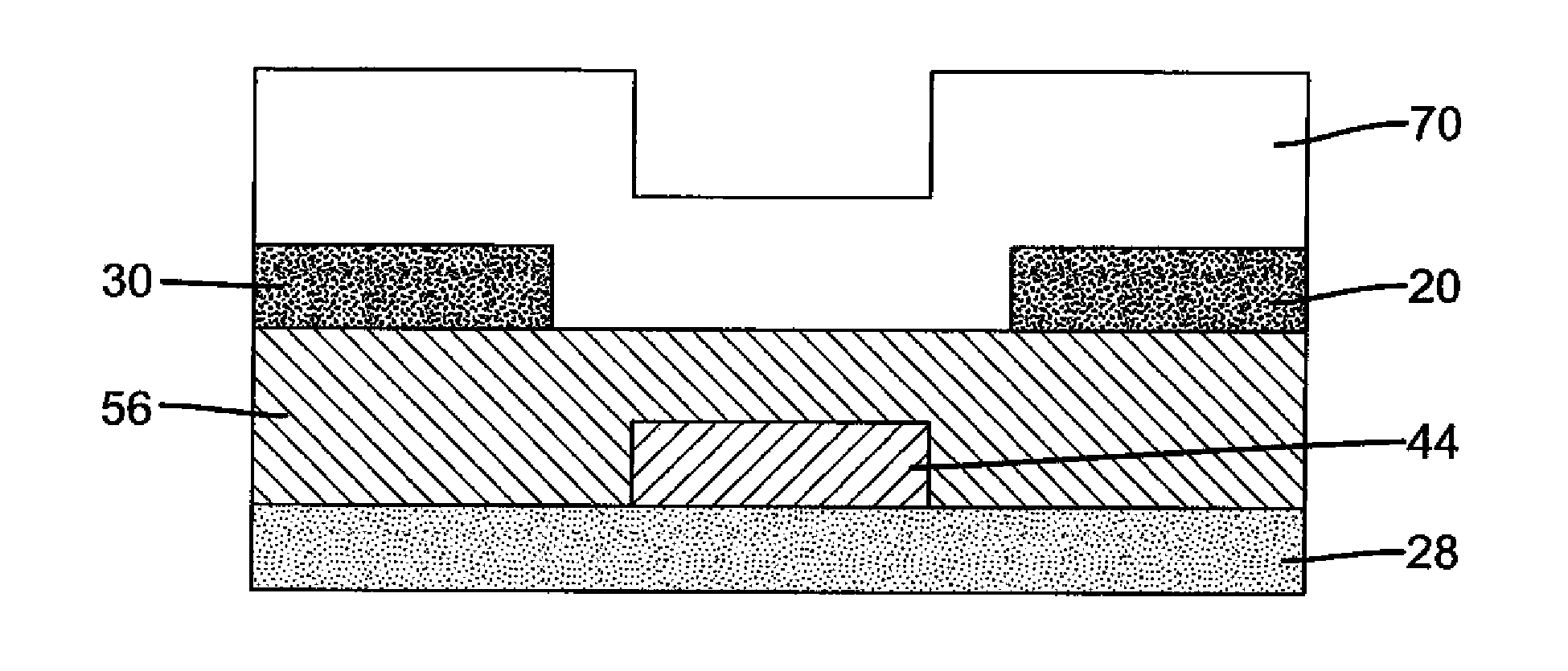

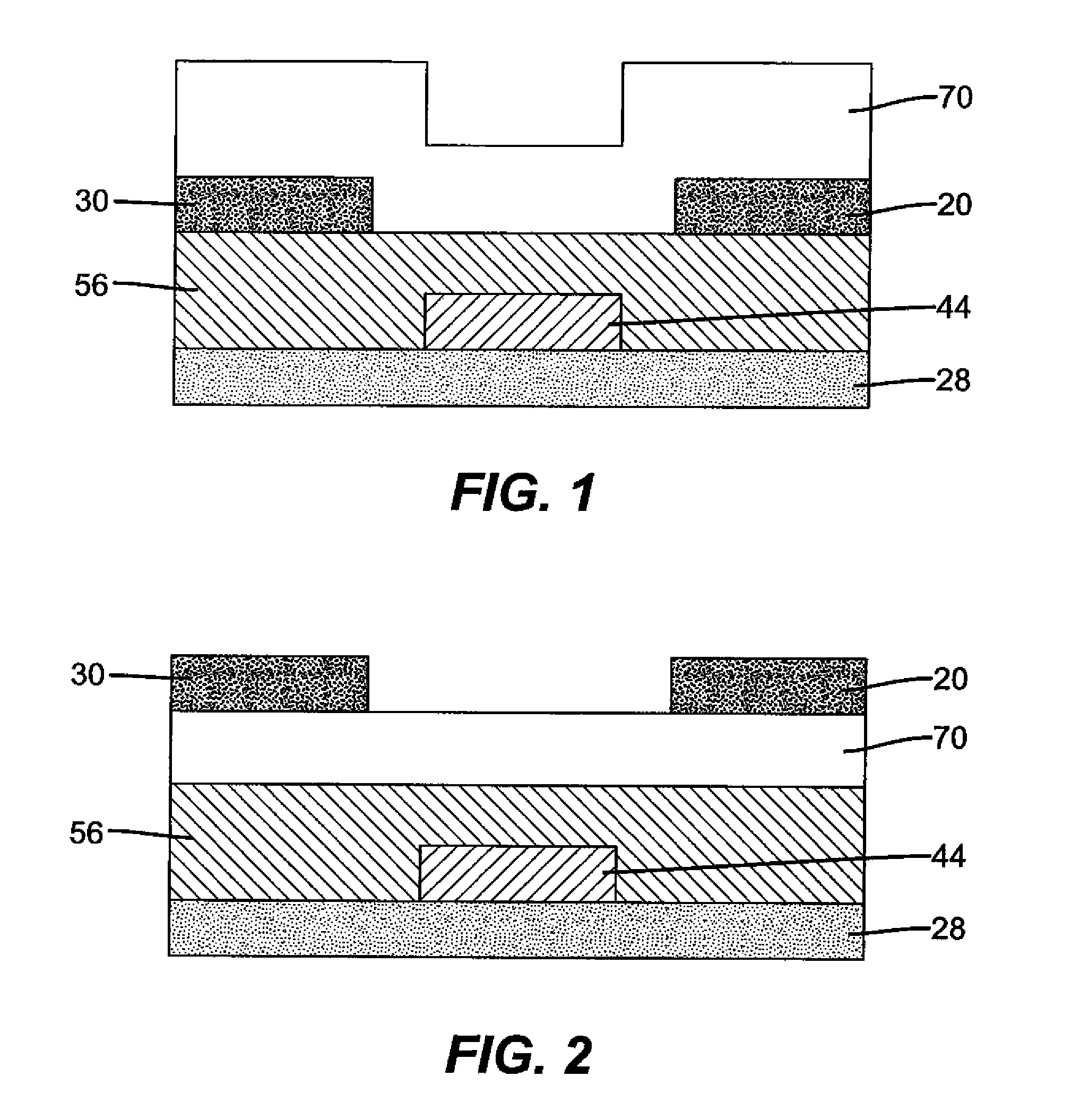

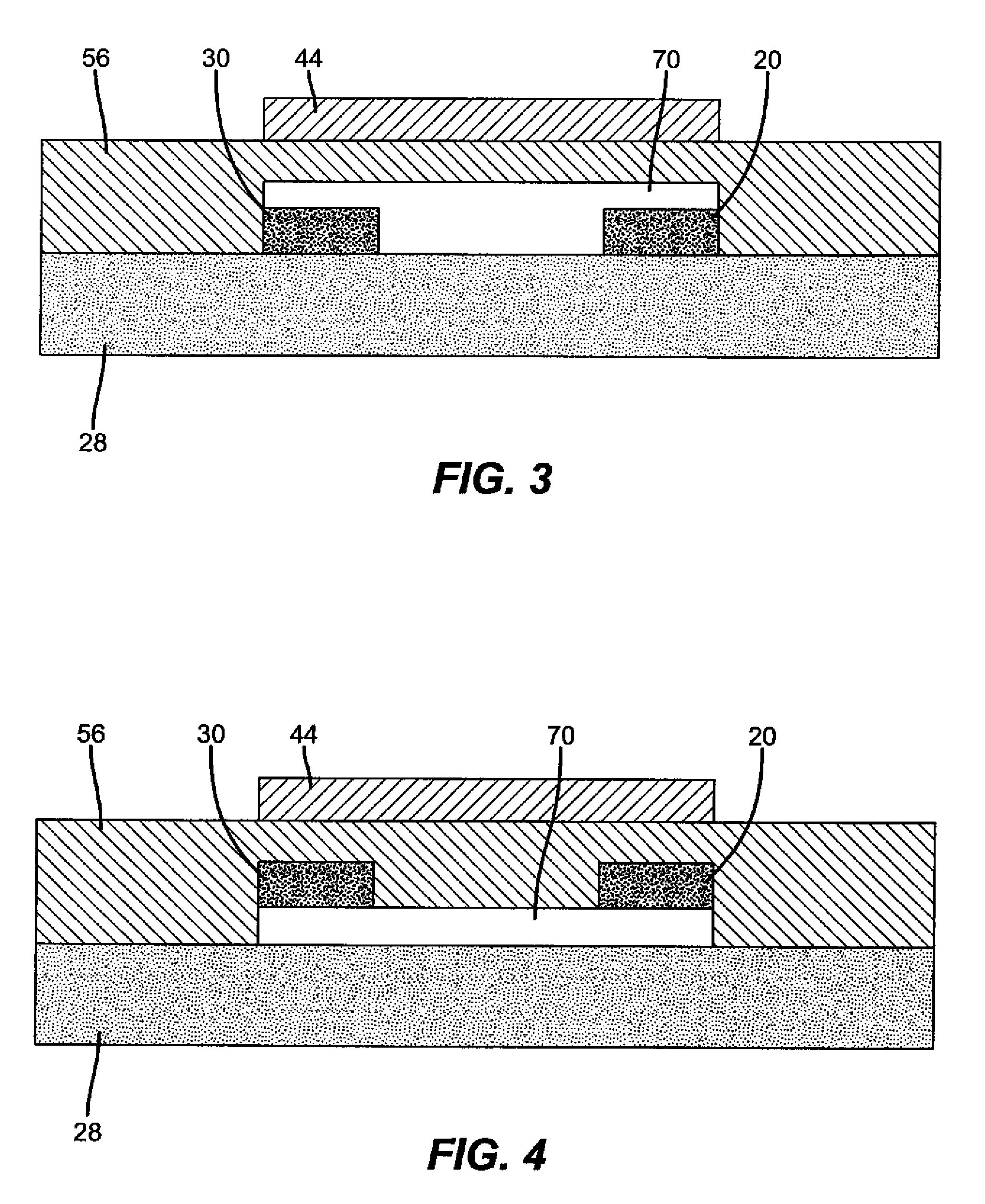

ActiveUS7247887B2Improve performance consistencyImprove performanceTransistorSolid-state devicesMOSFETLithographic artist

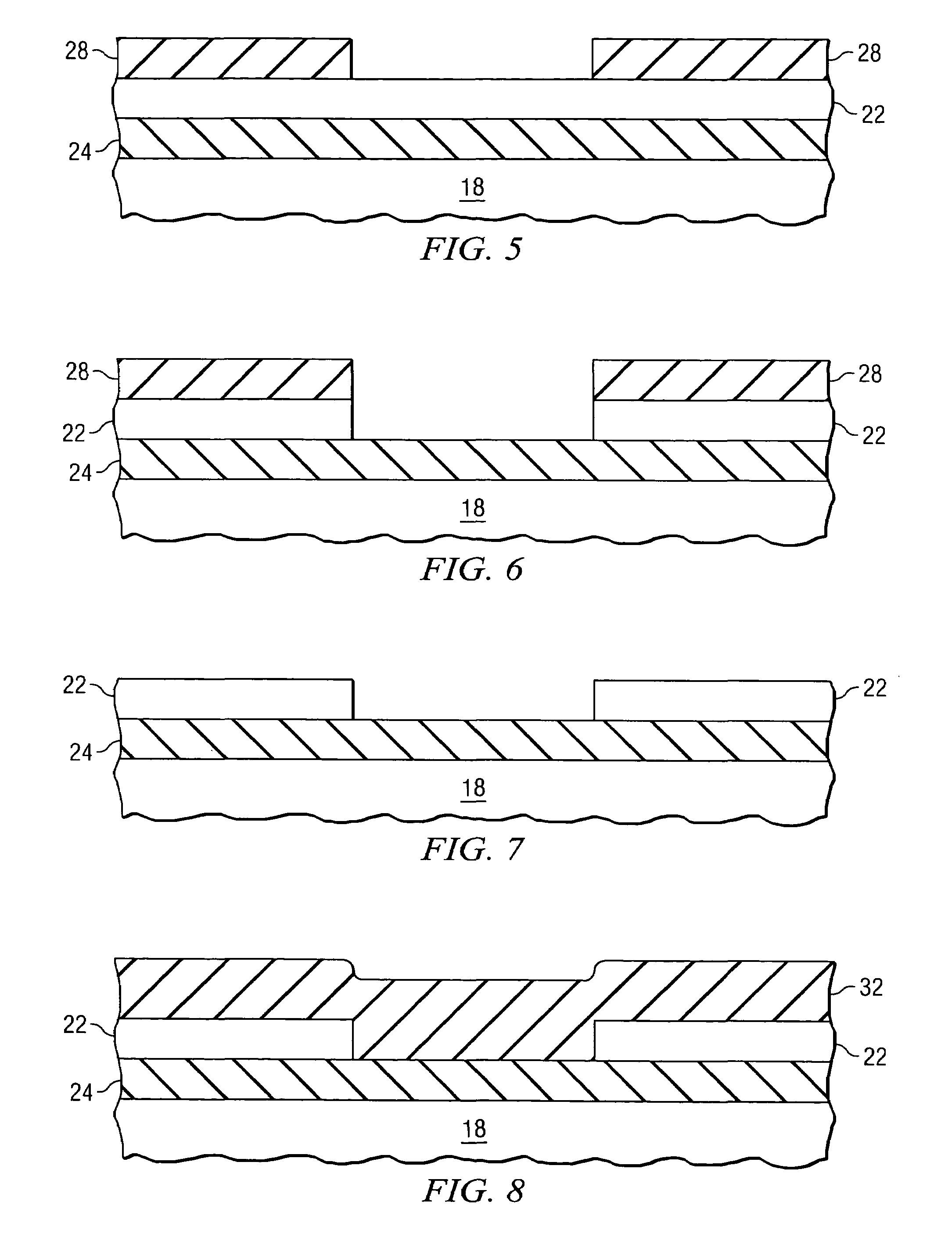

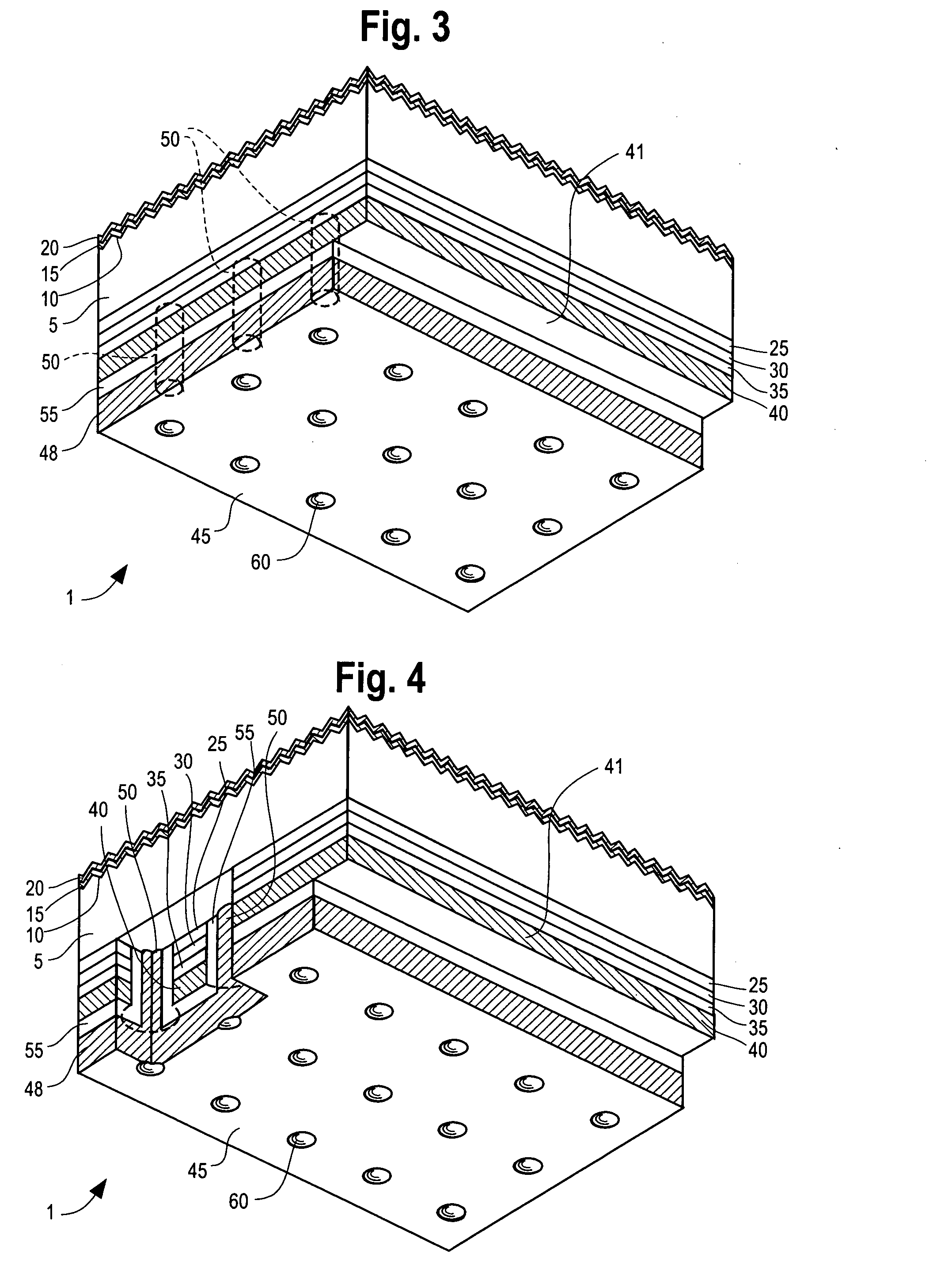

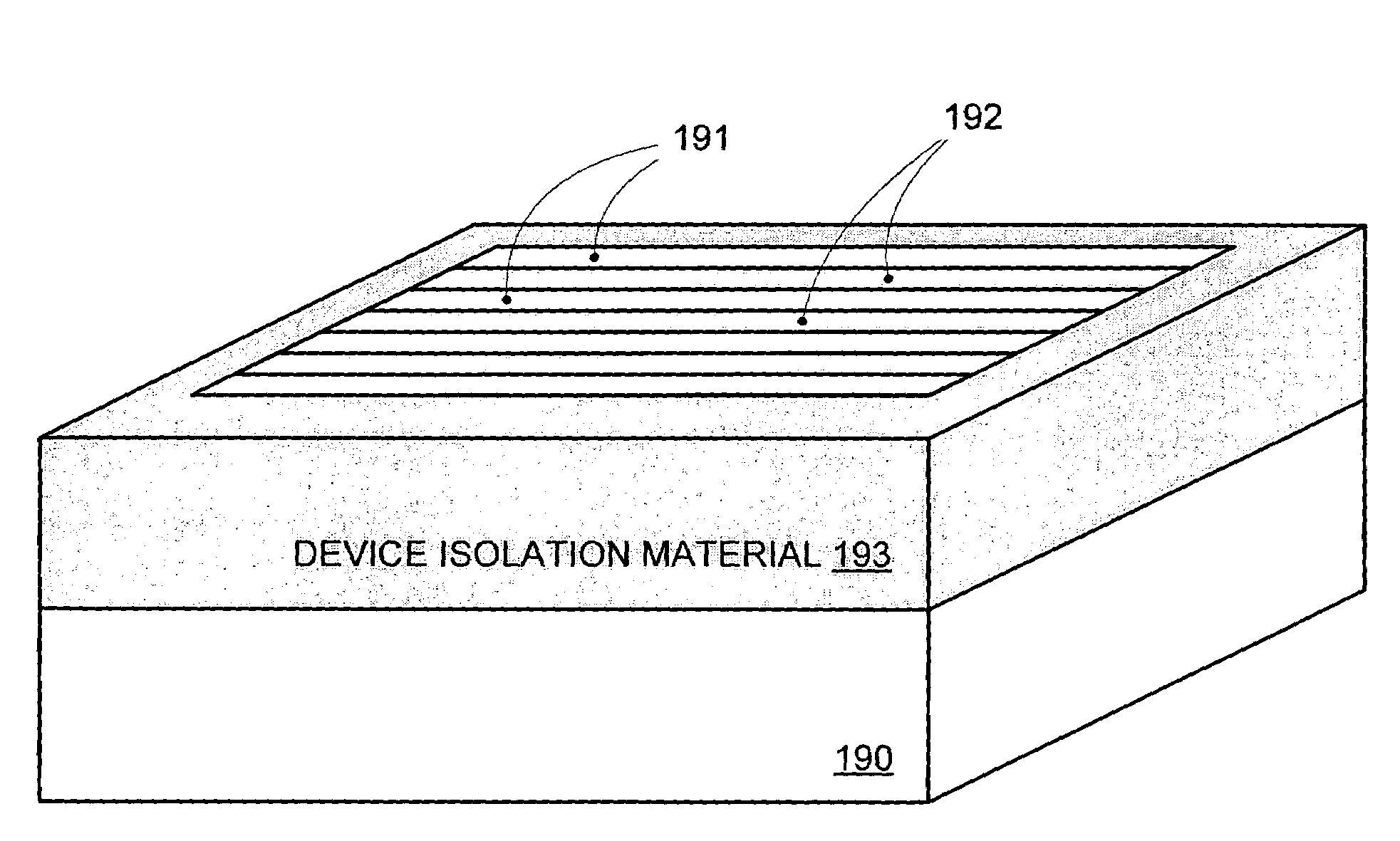

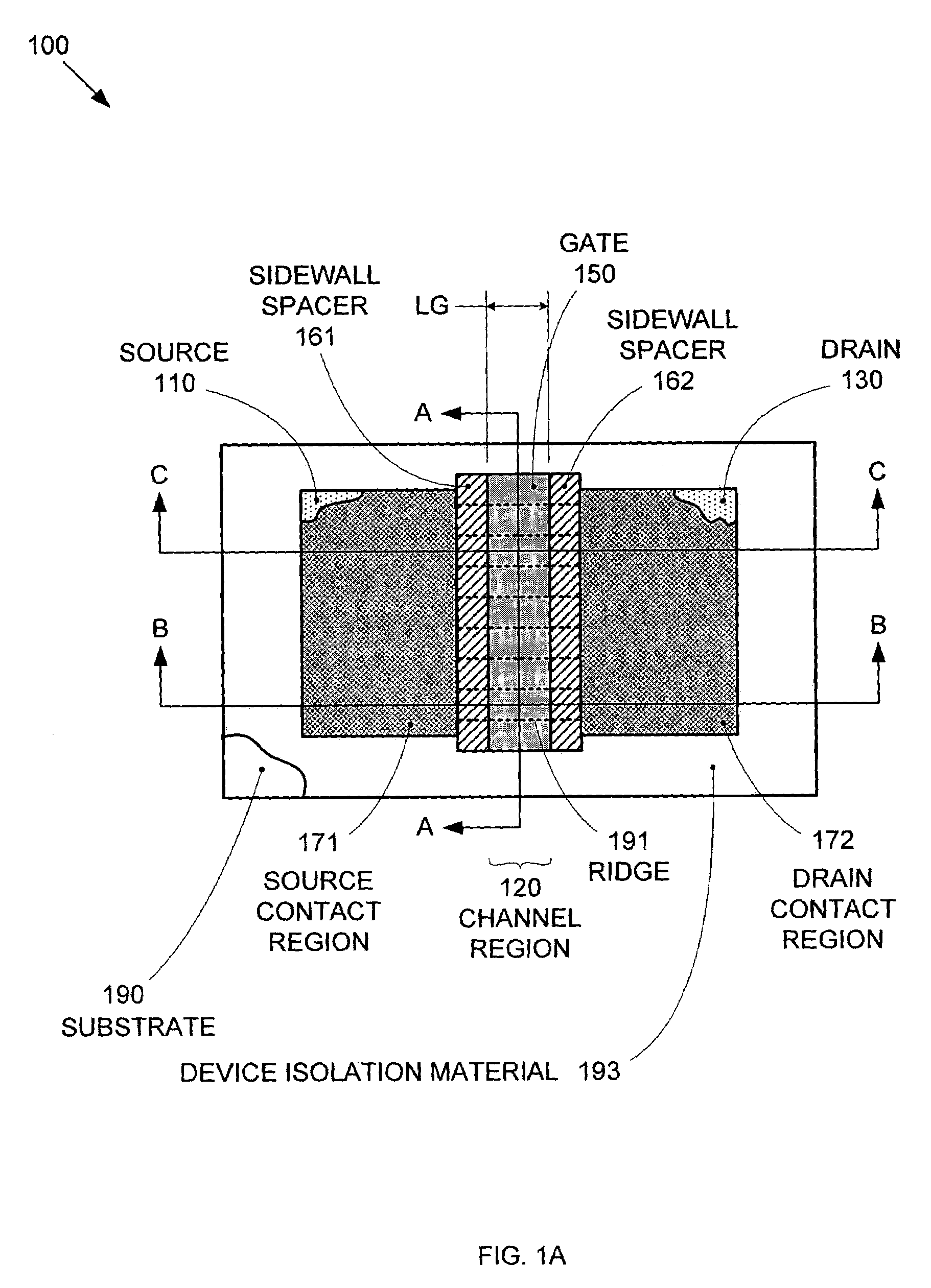

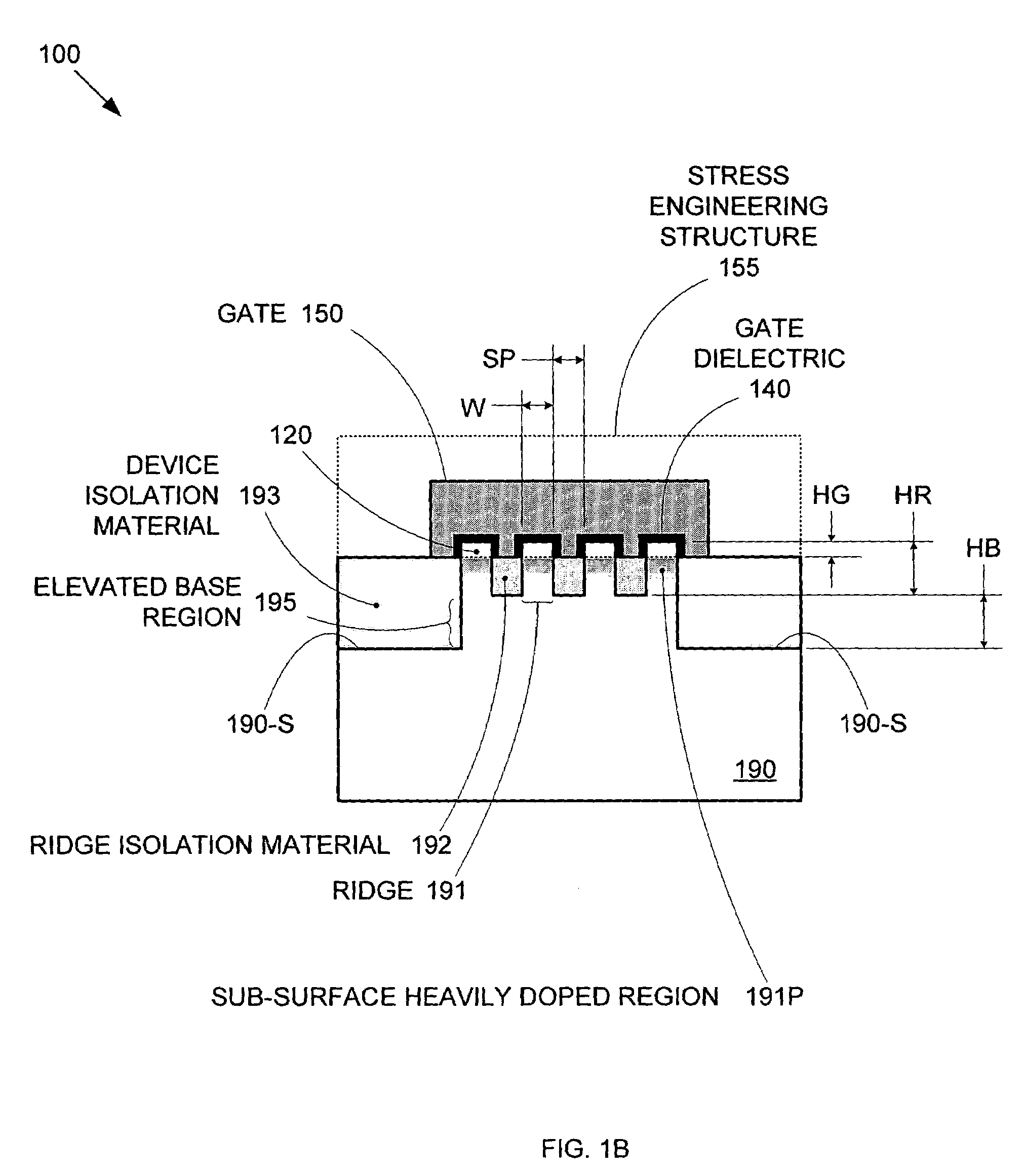

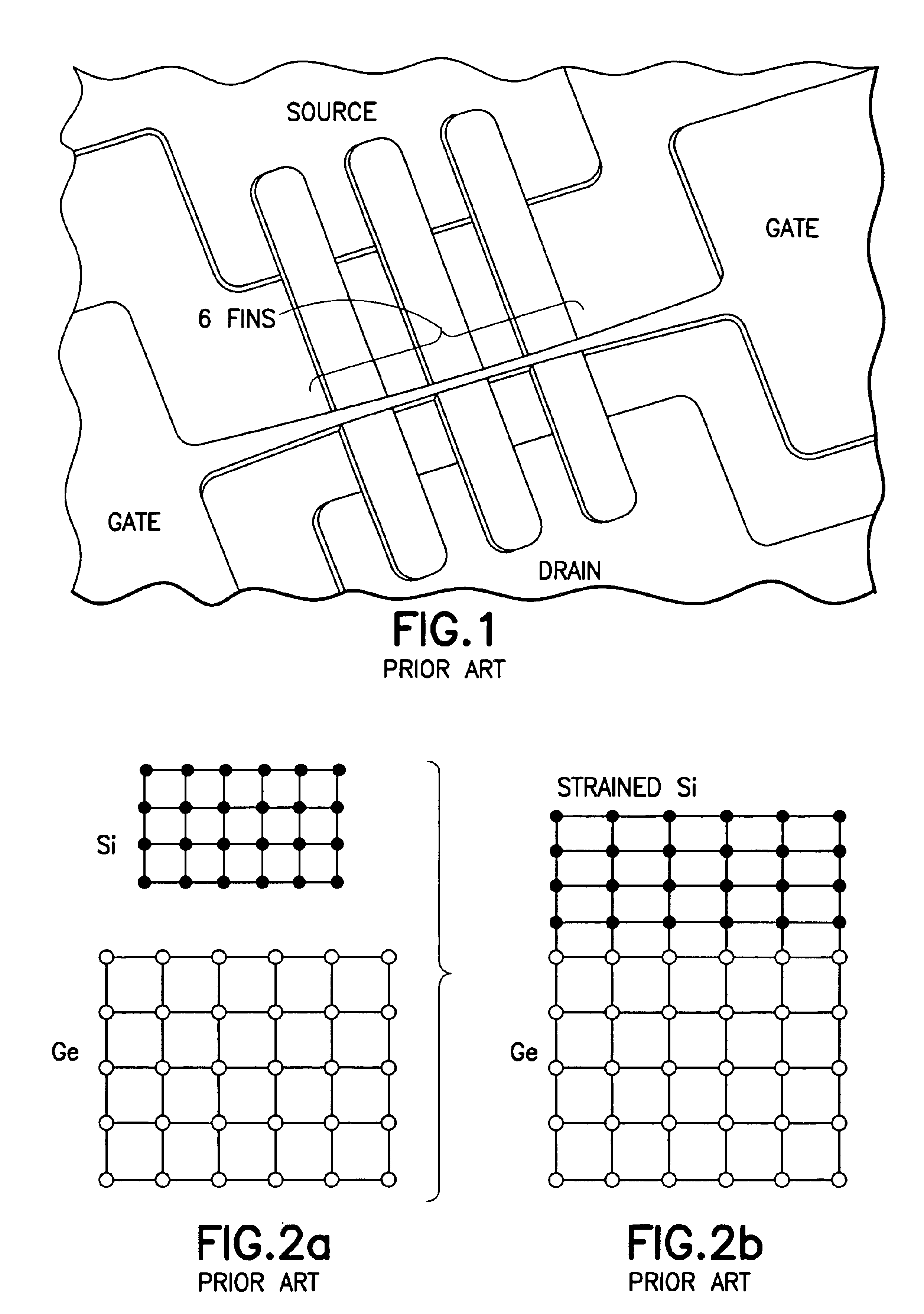

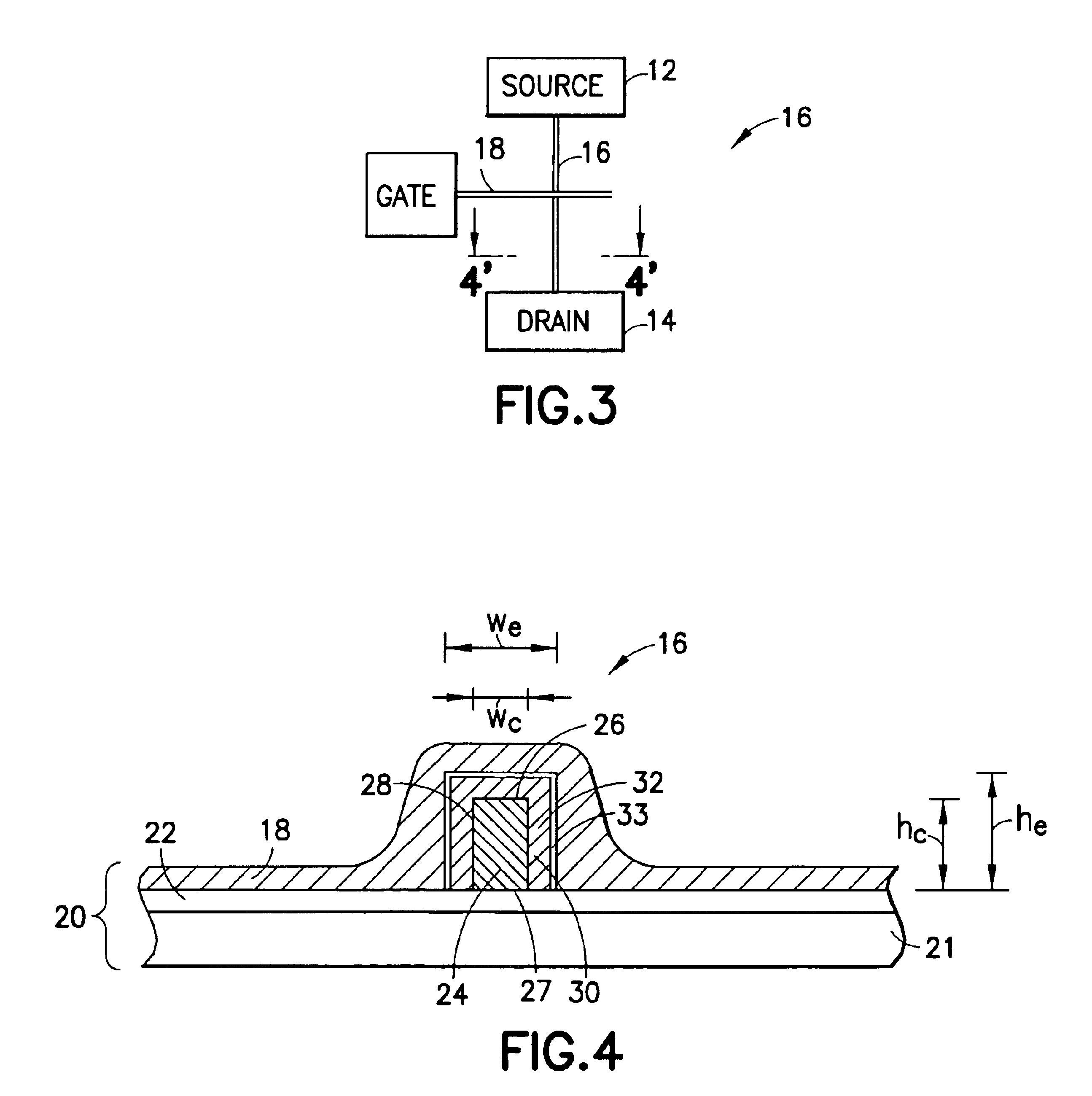

By forming MOSFETs on a substrate having pre-existing ridges of semiconductor material (i.e., a “corrugated substrate”), the resolution limitations associated with conventional semiconductor manufacturing processes can be overcome, and high-performance, low-power transistors can be reliably and repeatably produced. Forming a corrugated substrate prior to actual device formation allows the ridges on the corrugated substrate to be created using high precision techniques that are not ordinarily suitable for device production. MOSFETs that subsequently incorporate the high-precision ridges into their channel regions will typically exhibit much more precise and less variable performance than similar MOSFETs formed using optical lithography-based techniques that cannot provide the same degree of patterning accuracy. Additional performance enhancement techniques such as pulse-shaped doping and “wrapped” gates can be used in conjunction with the segmented channel regions to further enhance device performance.

Owner:SYNOPSYS INC

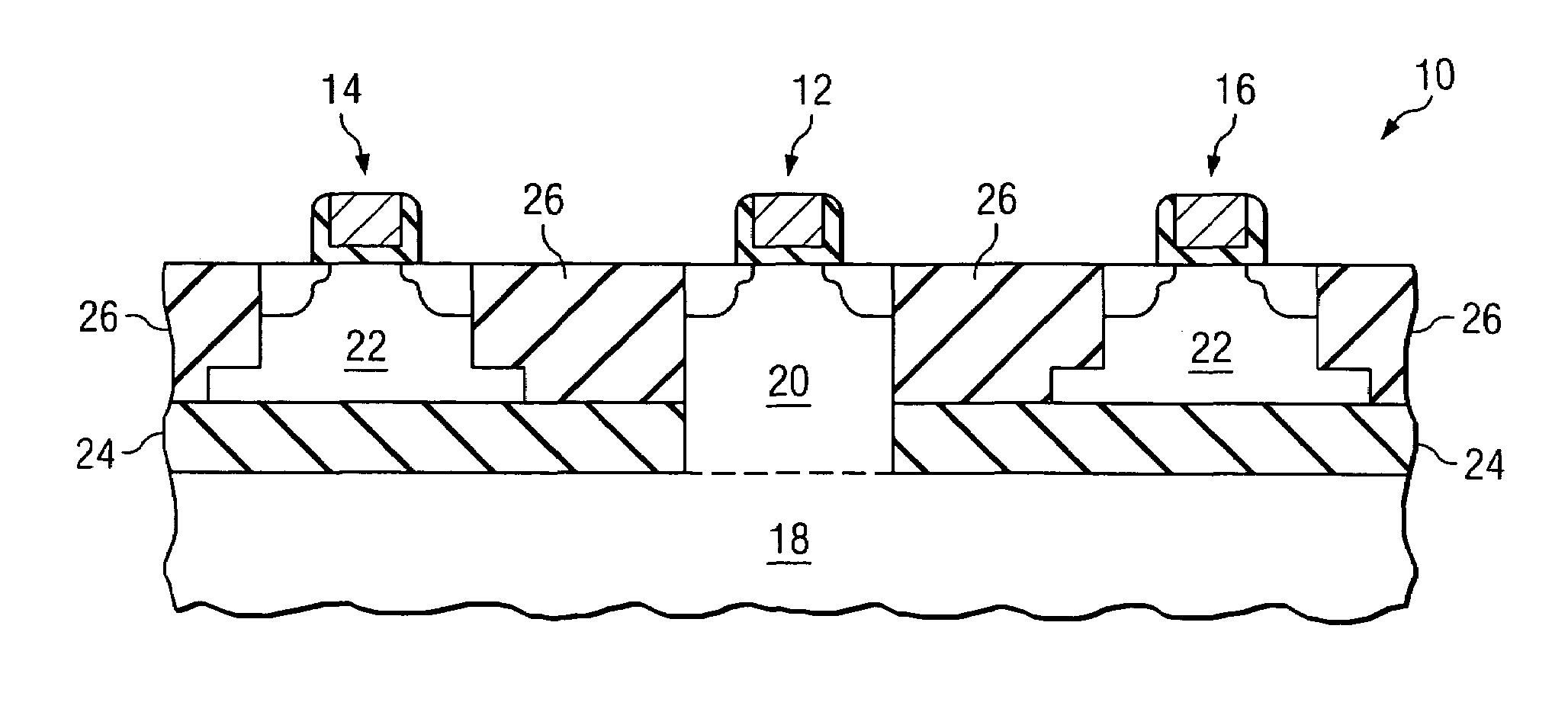

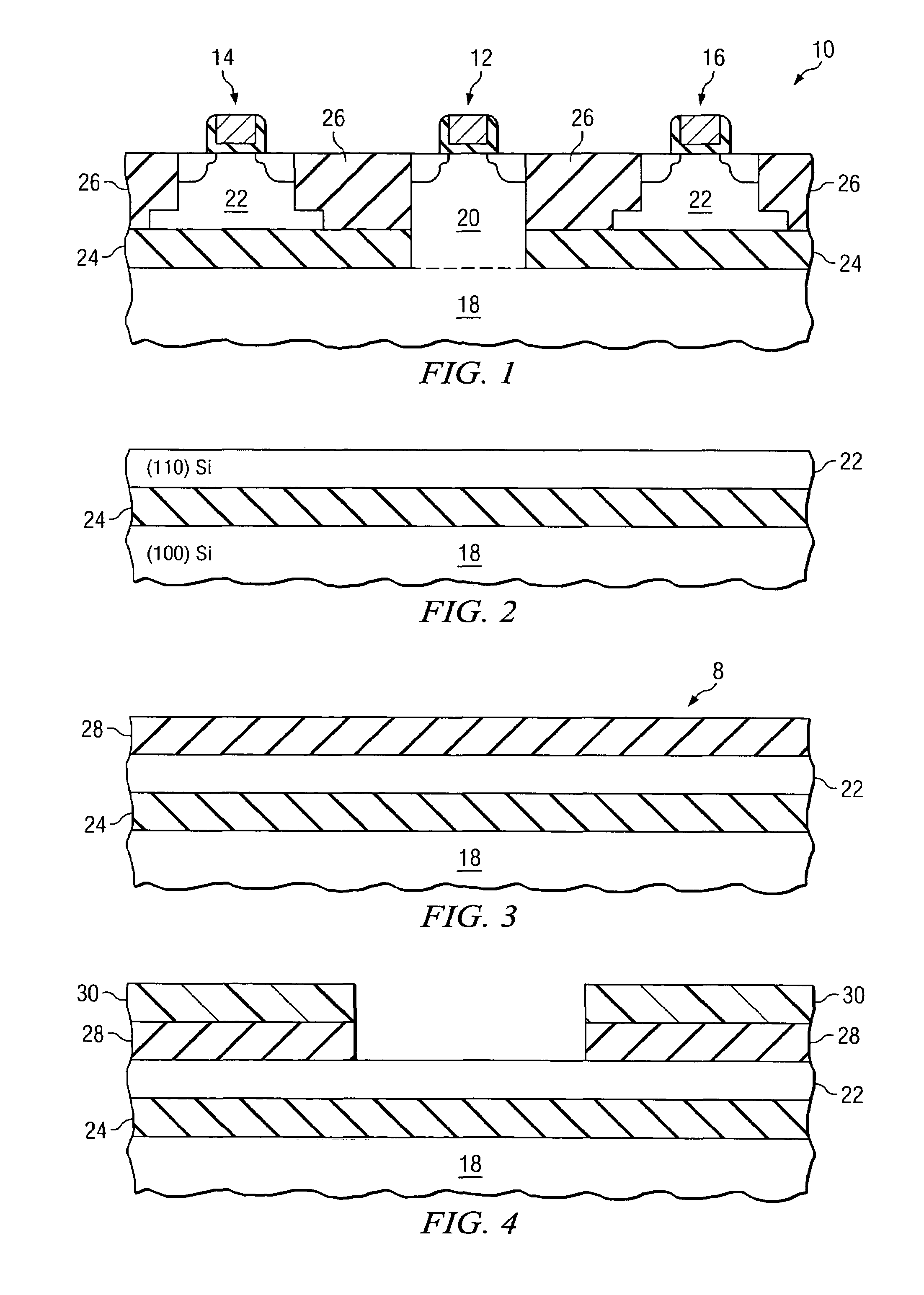

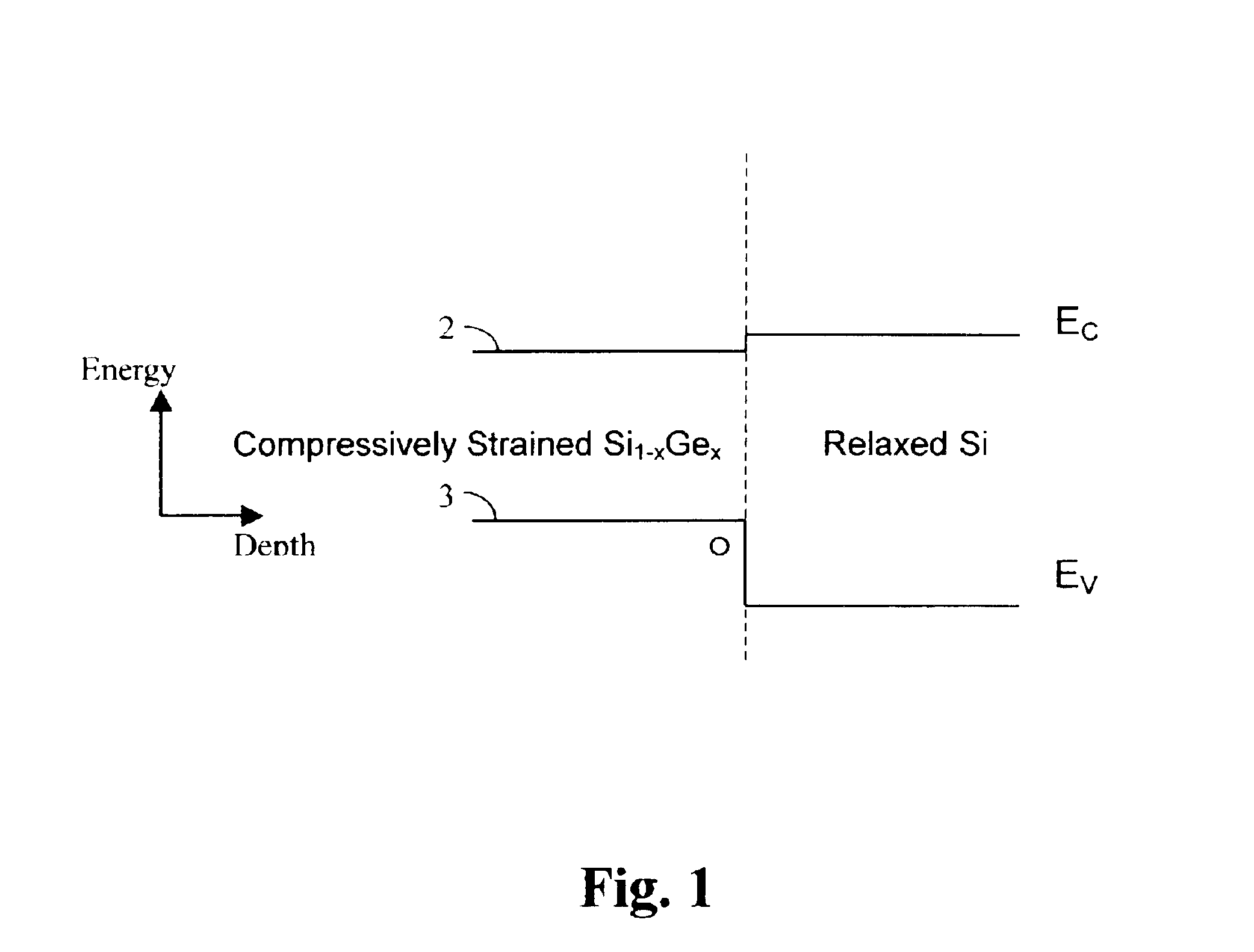

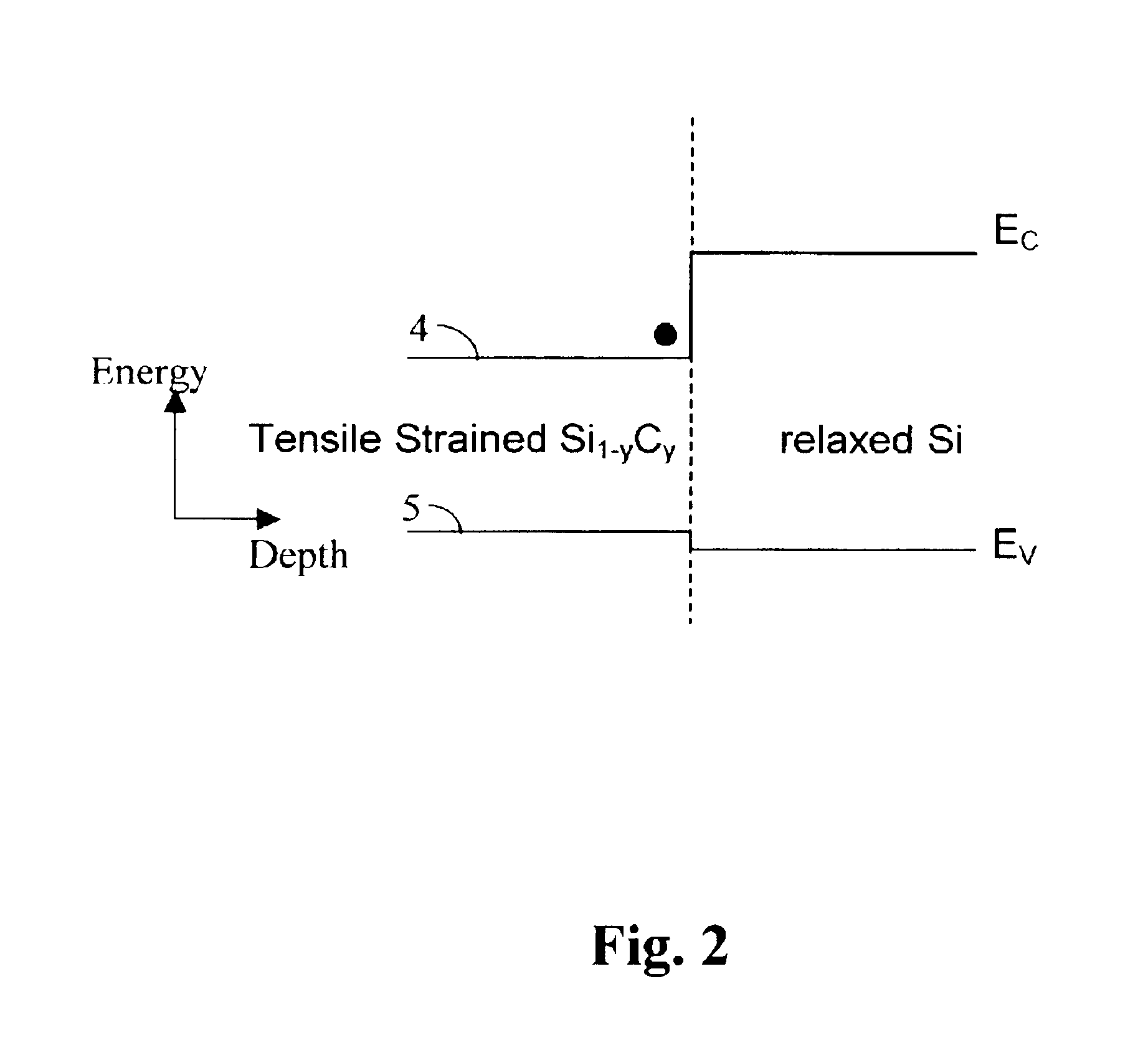

Semiconductor method and device with mixed orientation substrate

InactiveUS7298009B2Critical dimension of this mask is relaxedReduce processing stepsSemiconductor/solid-state device detailsSolid-state devicesSemiconductor materialsCrystal orientation

Owner:INFINEON TECH AG +1

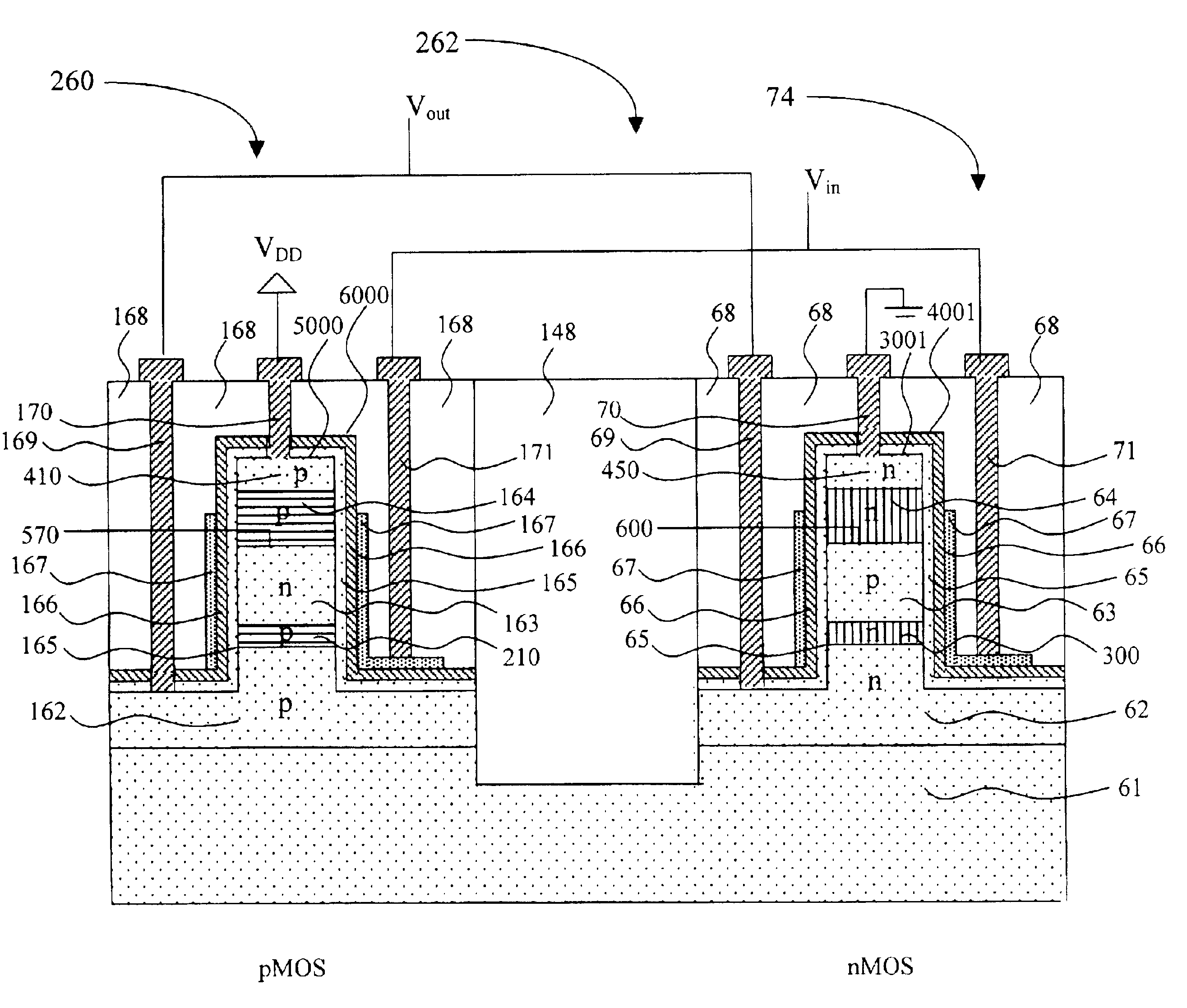

Low leakage heterojunction vertical transistors and high performance devices thereof

InactiveUS6943407B2Superb performanceSuperb scalabilityTransistorSolid-state devicesReverse short-channel effectHeterojunction

A method for forming and the structure of a vertical channel of a field effect transistor, a field effect transistor and CMOS circuitry are described incorporating a drain, body and source region on a sidewall of a vertical single crystal semiconductor structure wherein a hetero-junction is formed between the source and body of the transistor, wherein the source region and channel are independently lattice strained with respect the body region and wherein the drain region contains a carbon doped region to prevent the diffusion of dopants (i.e., B and P) into the body. The invention reduces the problem of short channel effects such as drain induced barrier lowering and the leakage current from the source to drain regions via the hetero-junction and while independently permitting lattice strain in the channel region for increased mobility via choice of the semiconductor materials. The problem of scalability of the gate length below 100 nm is overcome by the heterojunction between the source and body regions.

Owner:GLOBALFOUNDRIES INC

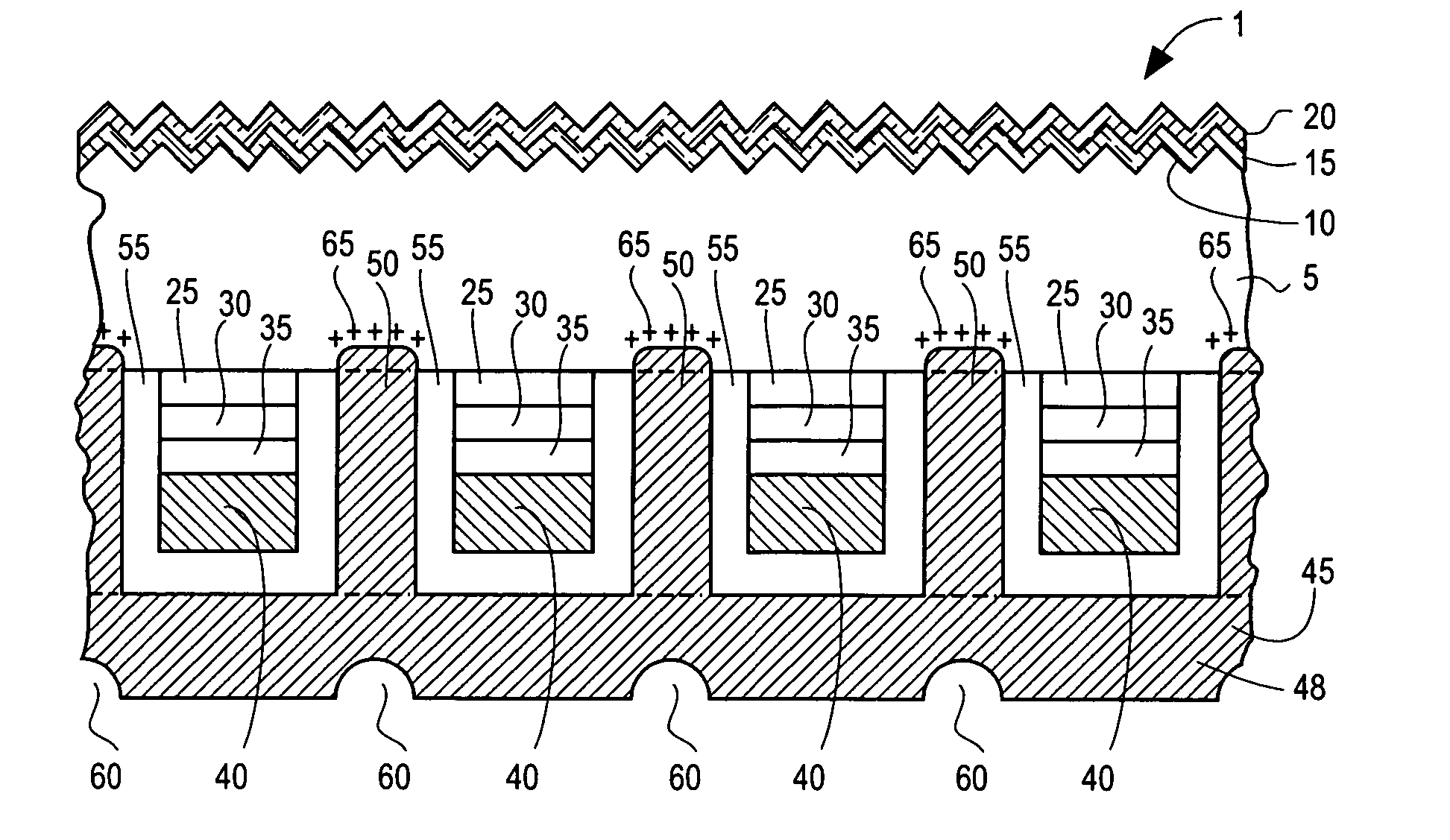

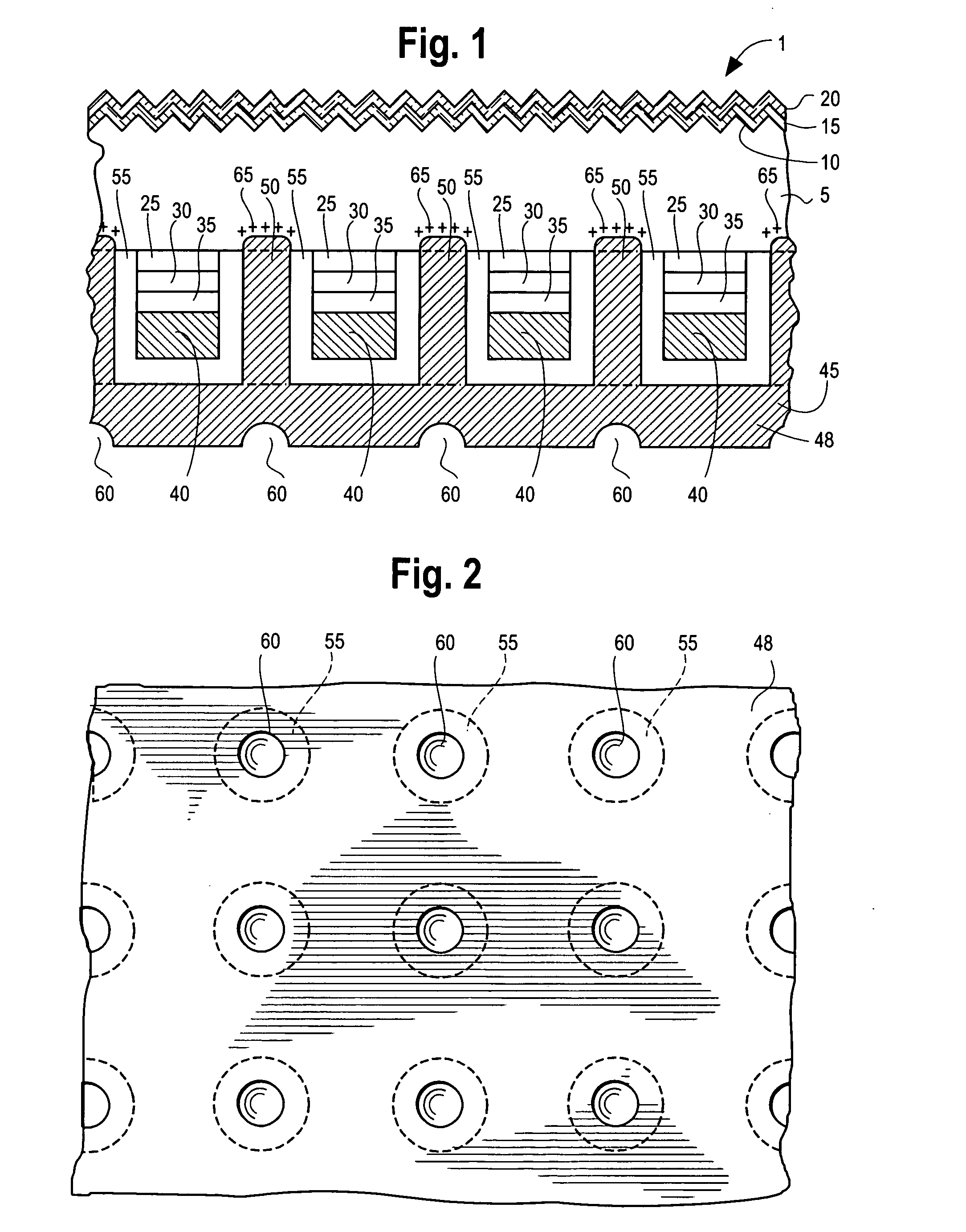

Integrated circuit on corrugated substrate

ActiveUS7190050B2Improve performance consistencyImprove performanceTransistorSemiconductor/solid-state device detailsMOSFETPerformance enhancement

By forming MOSFETs on a substrate having pre-existing ridges of semiconductor material (i.e., a “corrugated substrate”), the resolution limitations associated with conventional semiconductor manufacturing processes can be overcome, and high-performance, low-power transistors can be reliably and repeatably produced. Forming a corrugated substrate prior to actual device formation allows the ridges on the corrugated substrate to be created using high precision techniques that are not ordinarily suitable for device production. MOSFETs that subsequently incorporate the high-precision ridges into their channel regions will typically exhibit much more precise and less variable performance than similar MOSFETs formed using optical lithography-based techniques that cannot provide the same degree of patterning accuracy. Additional performance enhancement techniques such as pulse-shaped doping and “wrapped” gates can be used in conjunction with the segmented channel regions to further enhance device performance.

Owner:SYNOPSYS INC

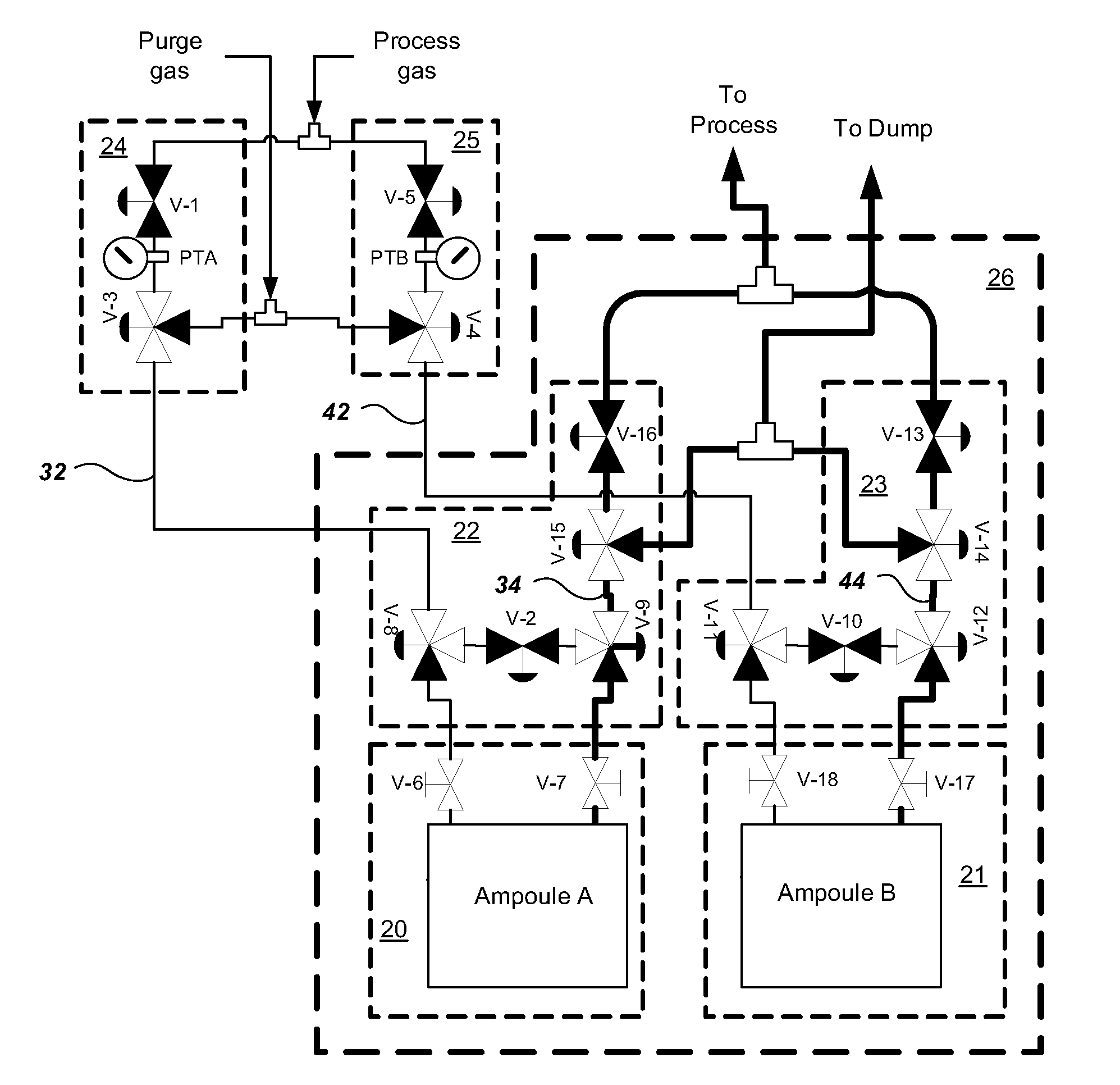

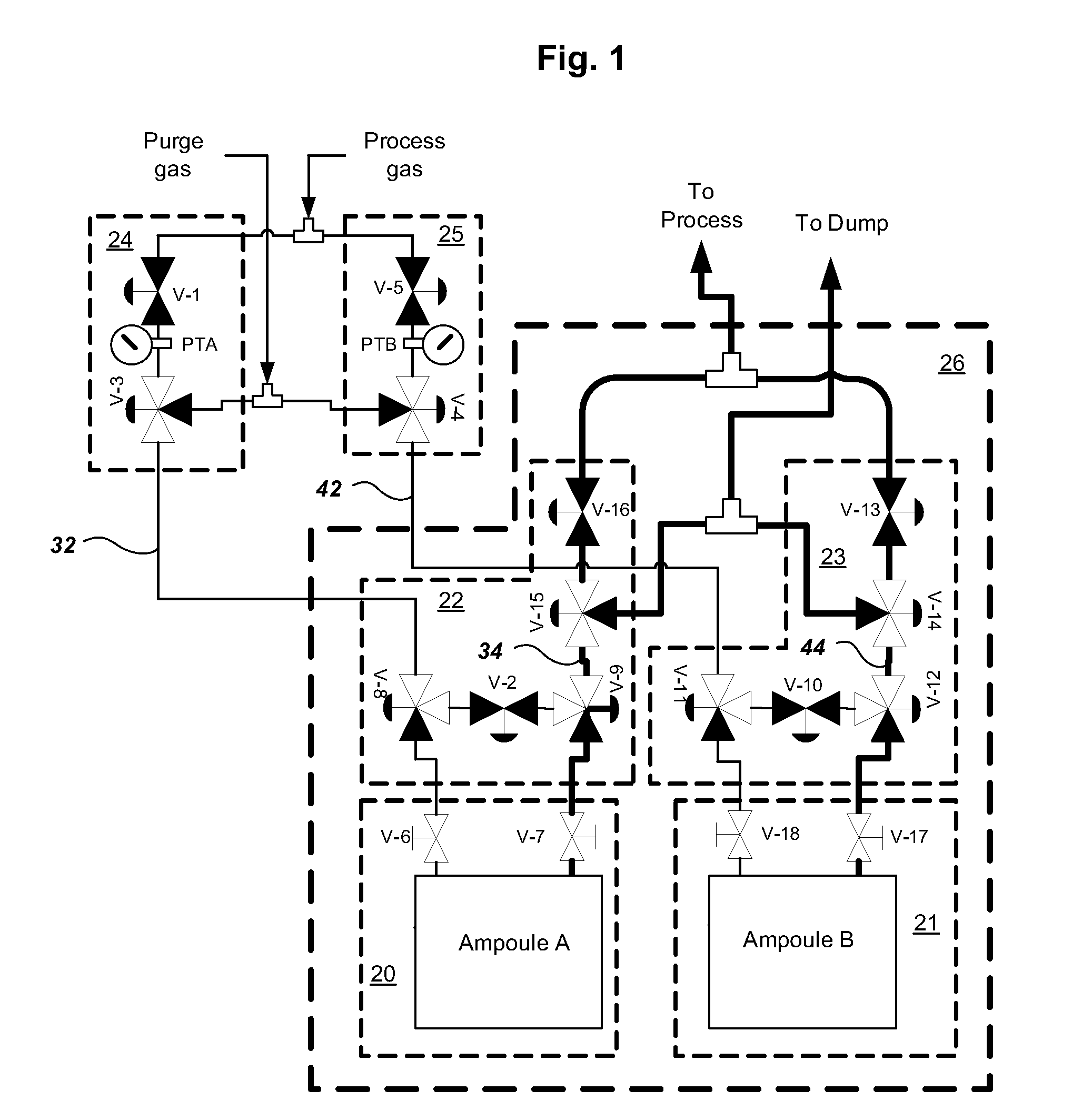

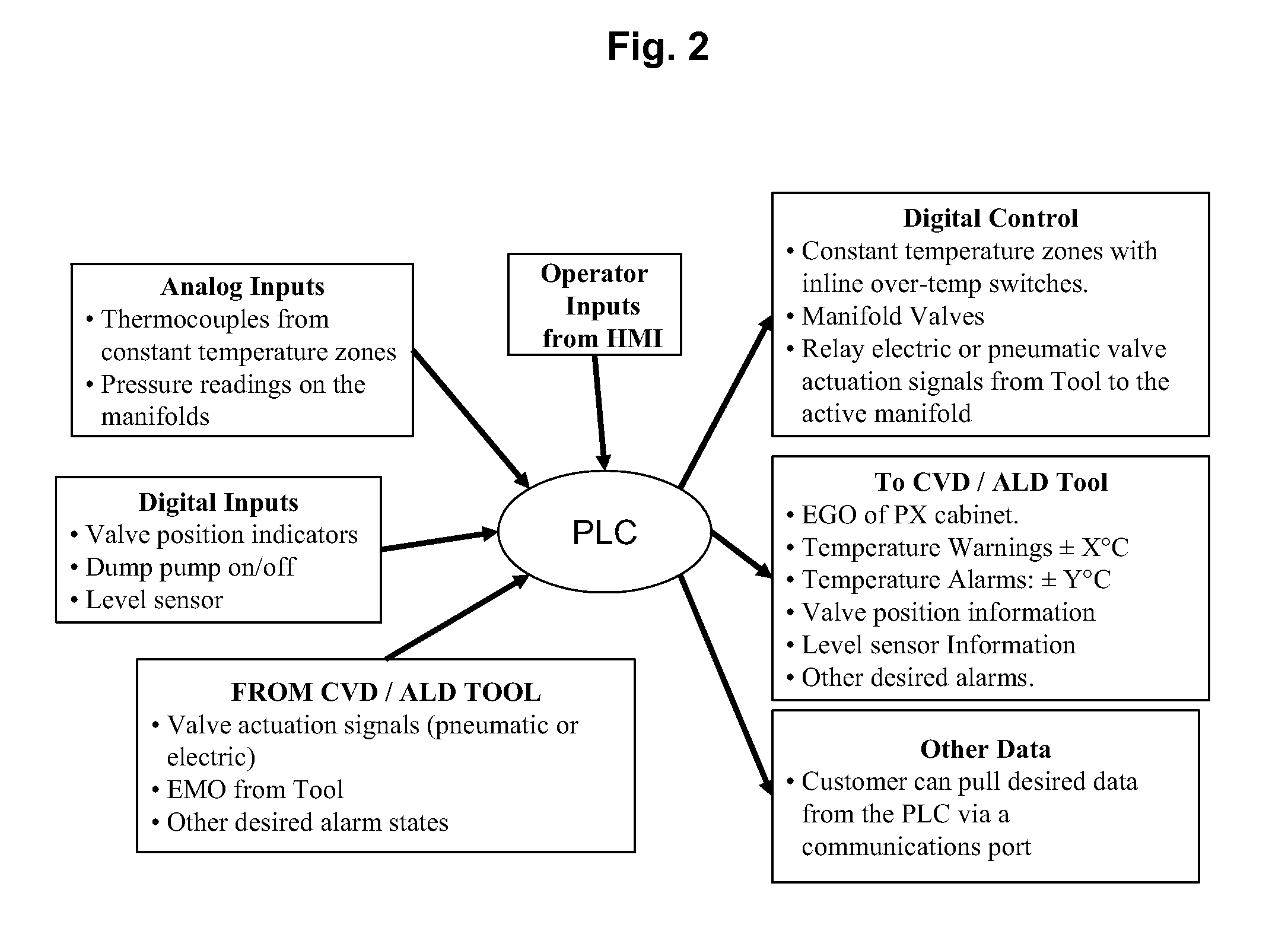

Multiple ampoule delivery systems

InactiveUS20090211525A1Easy to useReduce wasteLiquid surface applicatorsPipeline systemsSemiconductor materialsDelivery system

This invention relates to an integrated vapor or liquid phase reagent dispensing apparatus having a plurality of vessels and a plurality of carrier or inert gas feed / vapor or liquid phase reagent delivery manifolds, that may be used for continuously dispensing vapor or liquid phase reagents such as precursors for deposition of materials in the manufacture of semiconductor materials and devices.

Owner:PRAXAIR TECH INC

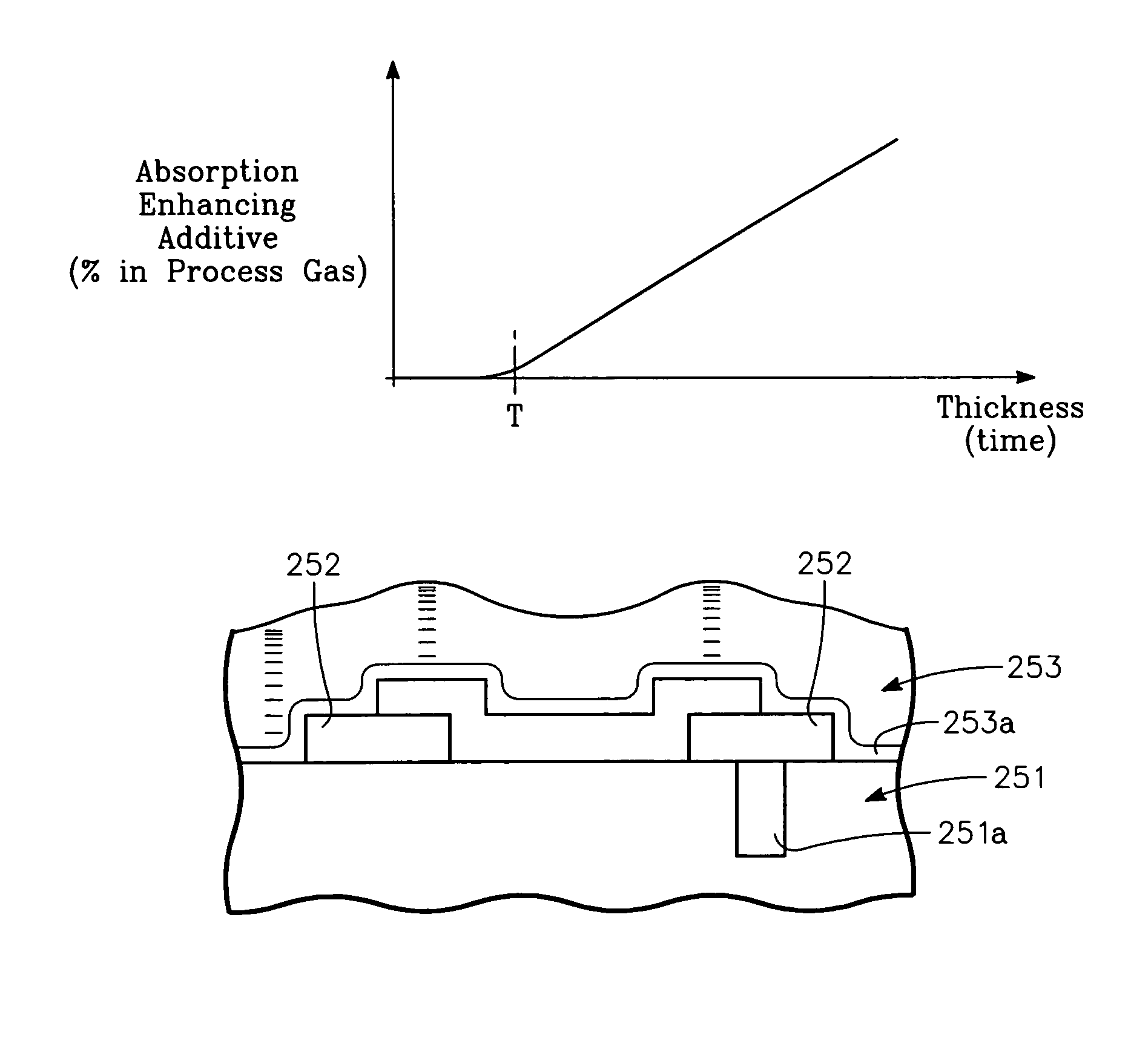

Semiconductor junction formation process including low temperature plasma deposition of an optical absorption layer and high speed optical annealing

A method of forming semiconductor junctions in a semiconductor material of a workpiece includes ion implanting dopant impurities in selected regions of the semiconductor material, introducing an optical absorber material precursor gas into a chamber containing the workpiece, generating an RF oscillating toroidal plasma current in a reentrant path that includes a process zone overlying the workpiece by applying RF source power, so as to deposit a layer of an optical absorber material on the workpiece, and optically annealing the workpiece so as to activate dopant impurities in the semiconductor material.

Owner:APPLIED MATERIALS INC

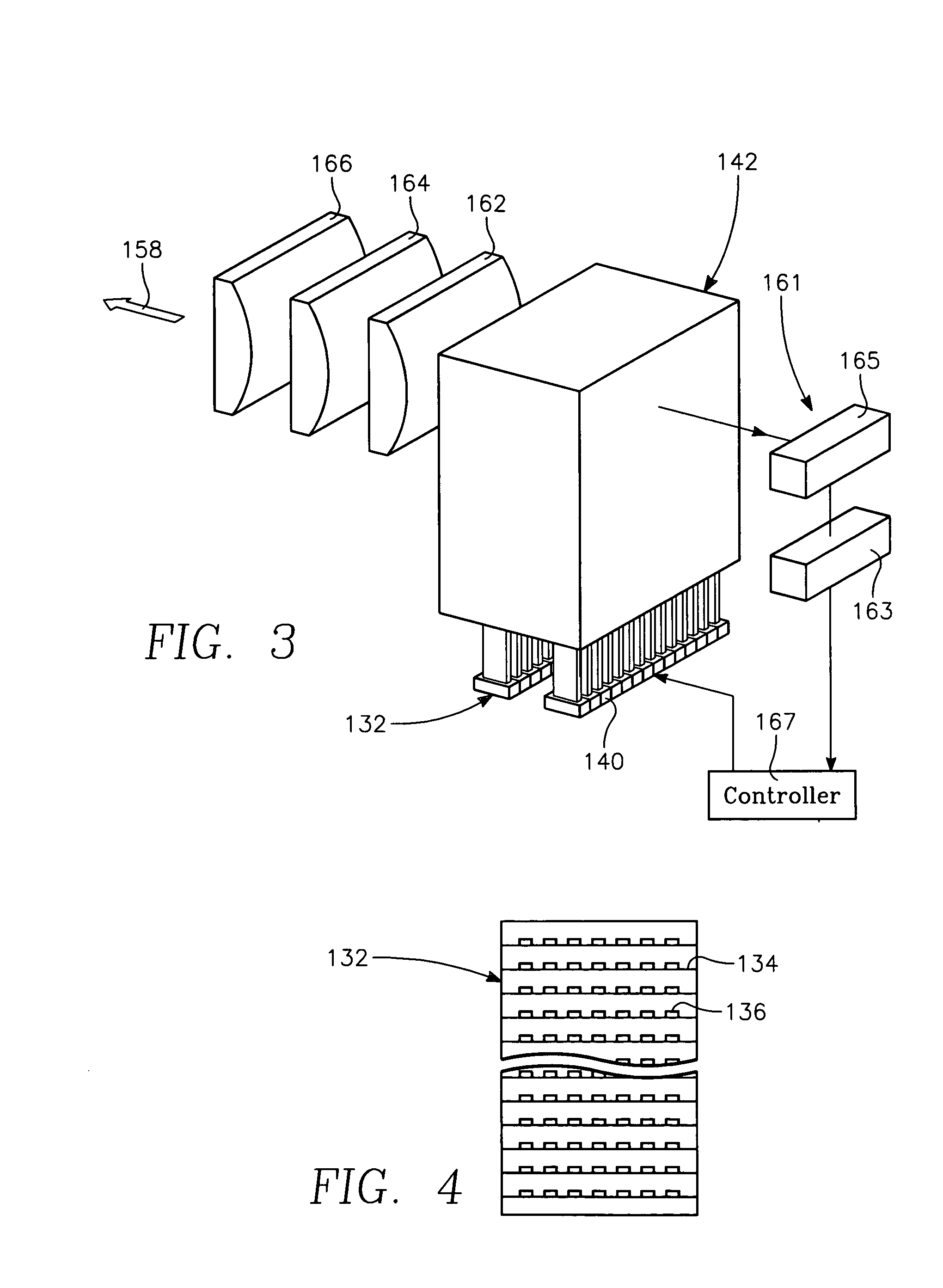

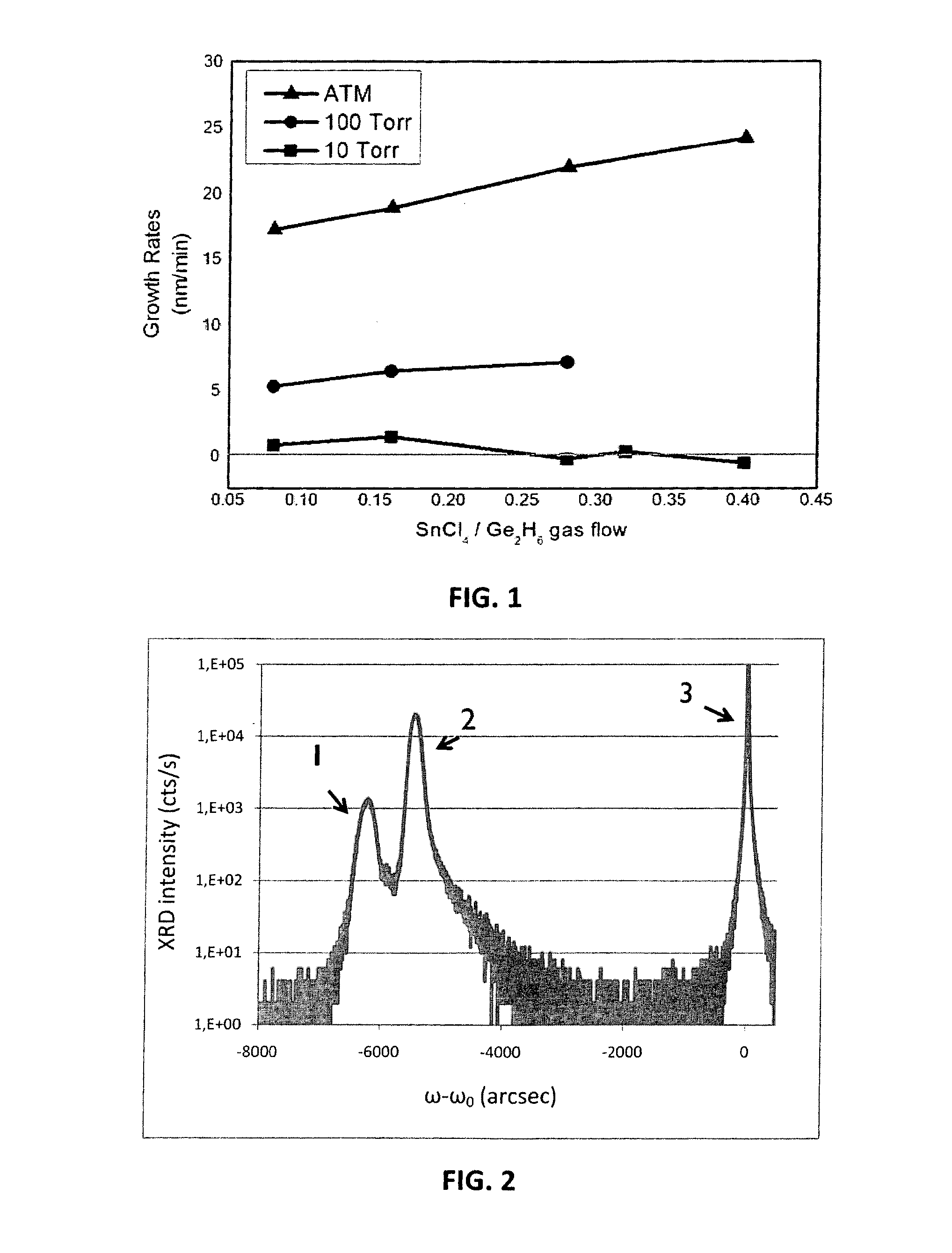

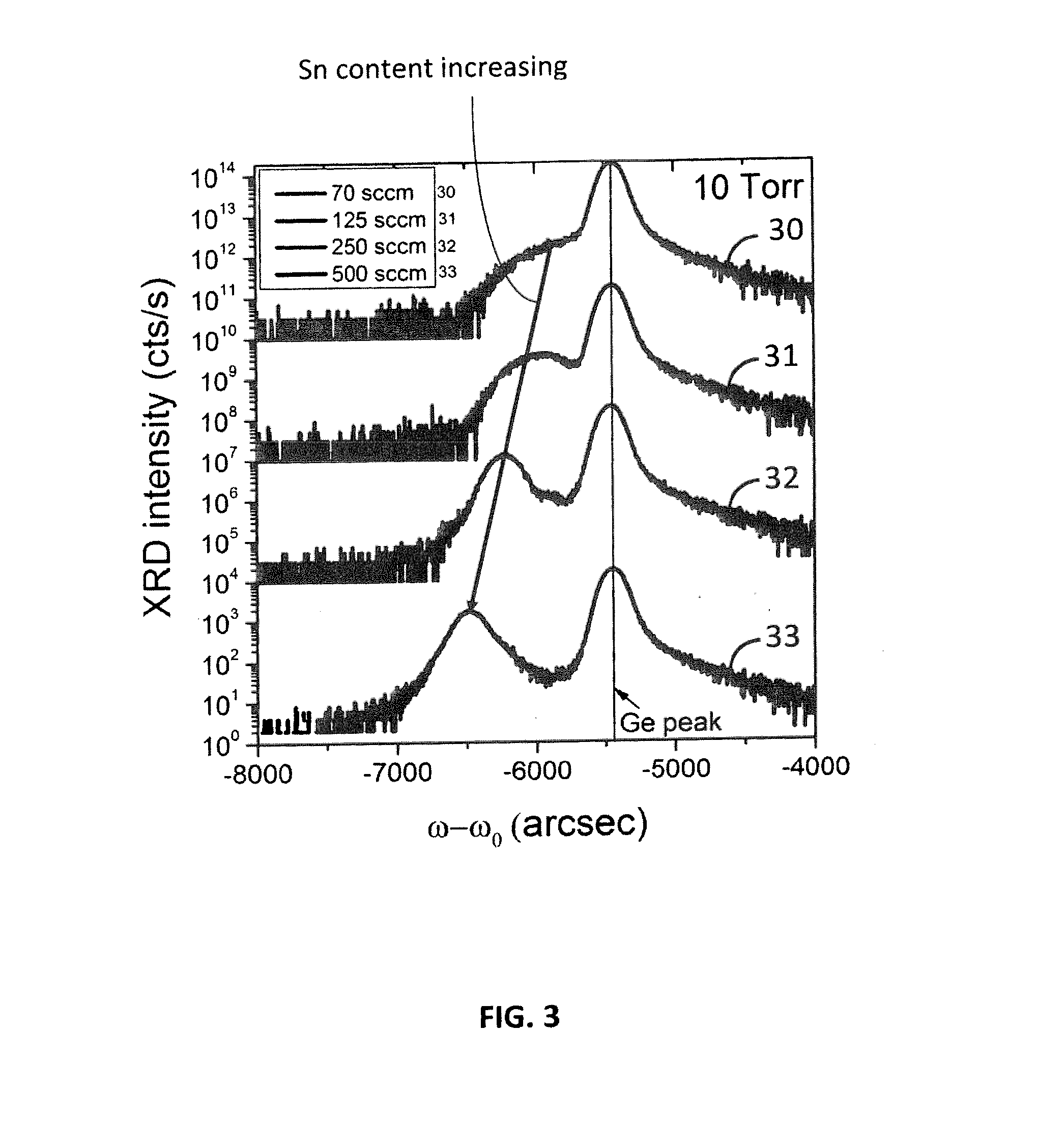

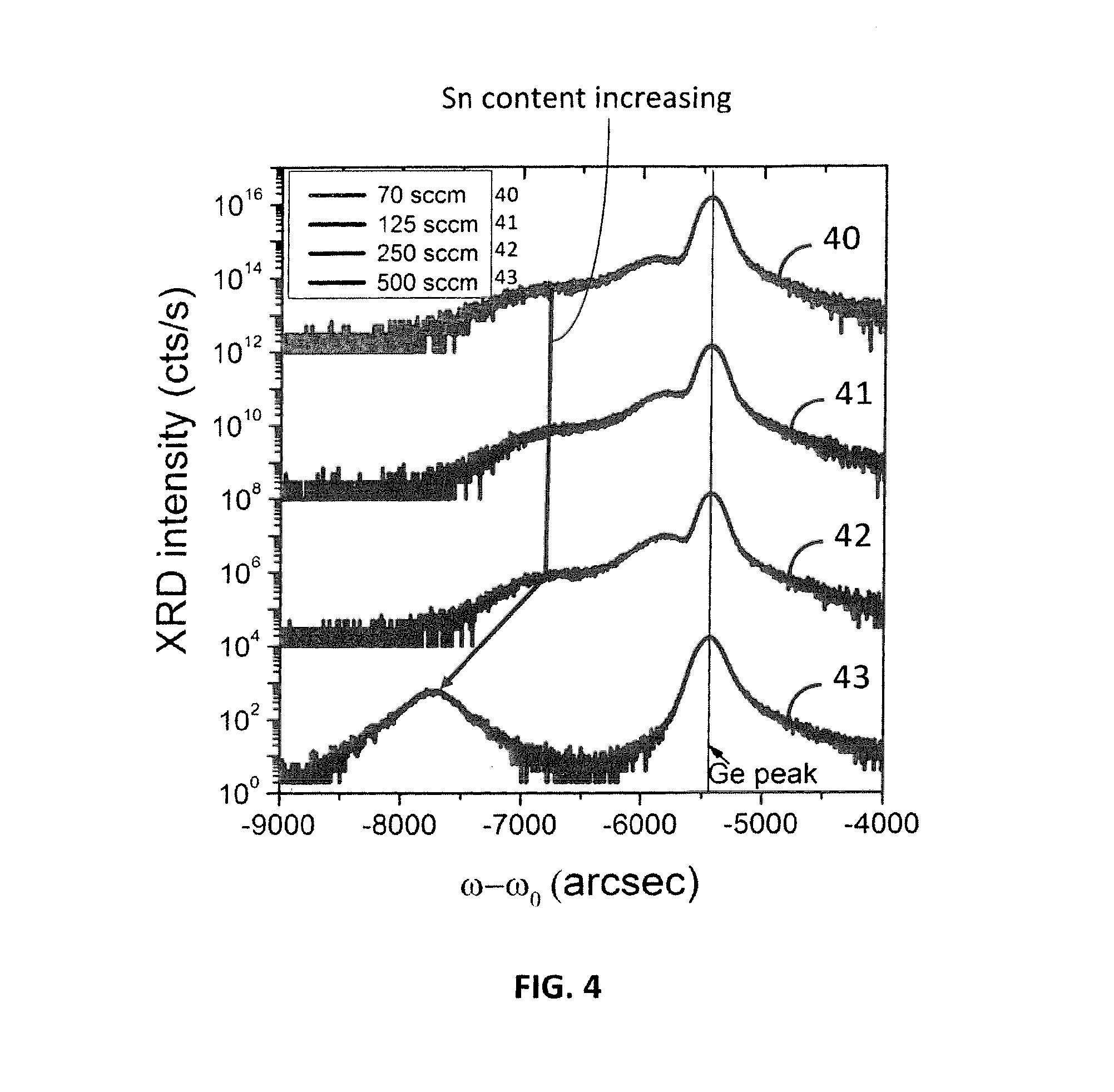

Method for Growing a Monocrystalline Tin-Containing Semiconductor Material

InactiveUS20140020619A1Efficiently provideEfficient methodPolycrystalline material growthAdditive manufacturing apparatusSemiconductor materialsPhysical chemistry

Disclosed are methods for growing Sn-containing semiconductor materials. In some embodiments, an example method includes providing a substrate in a chemical vapor deposition (CVD) reactor, and providing a semiconductor material precursor, a Sn precursor, and a carrier gas in the CVD reactor. The method further includes epitaxially growing a Sn-containing semiconductor material on the substrate, where the Sn precursor comprises tin tetrachloride (SnCl4). The semiconductor material precursor may be, for example, digermane, trigermane, higher-order germanium precursors, or a combination thereof. Alternatively, the semiconductor material precursor may be a silicon precursor.

Owner:INTERUNIVERSITAIR MICRO ELECTRONICS CENT (IMEC VZW) +1

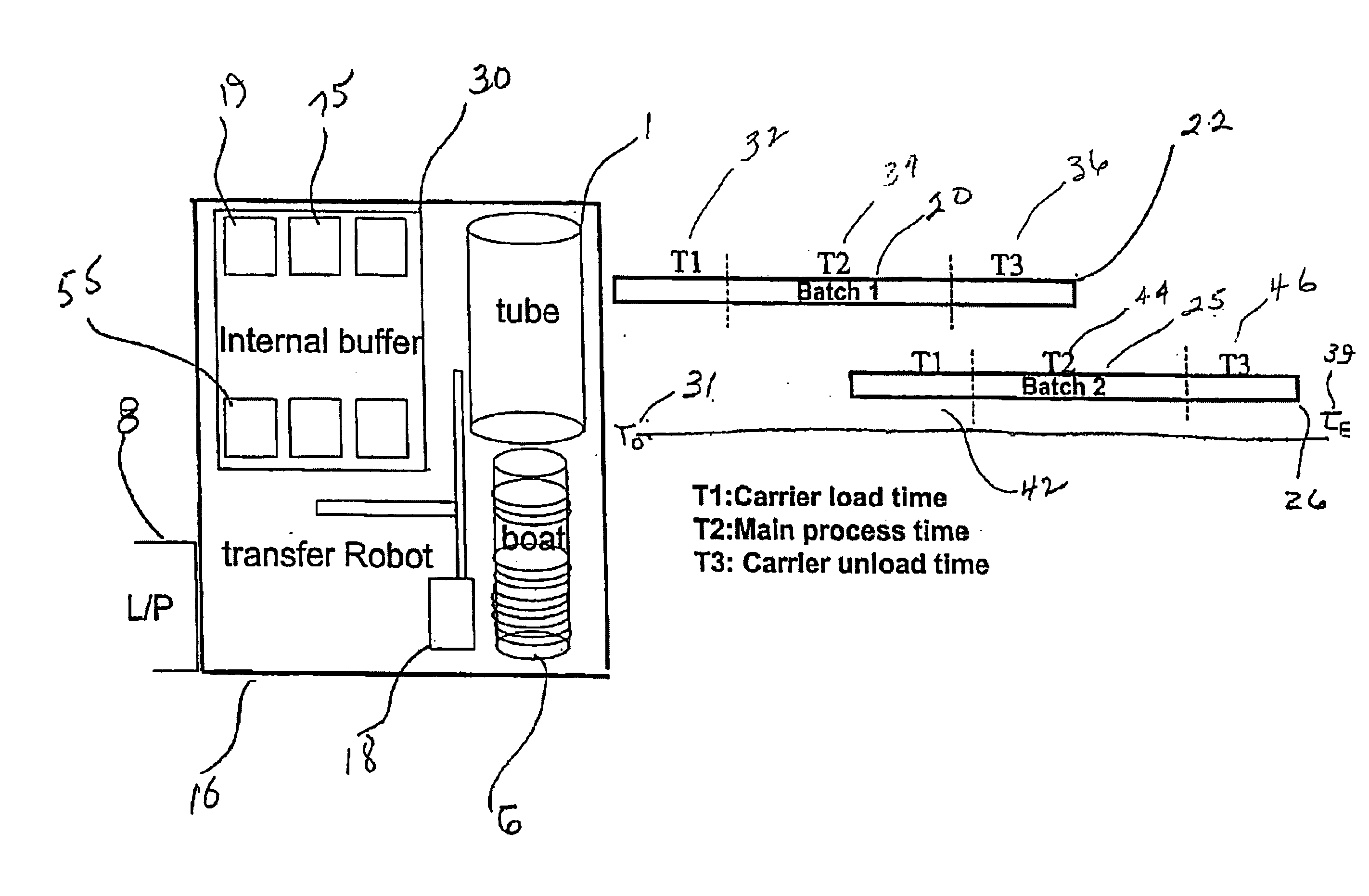

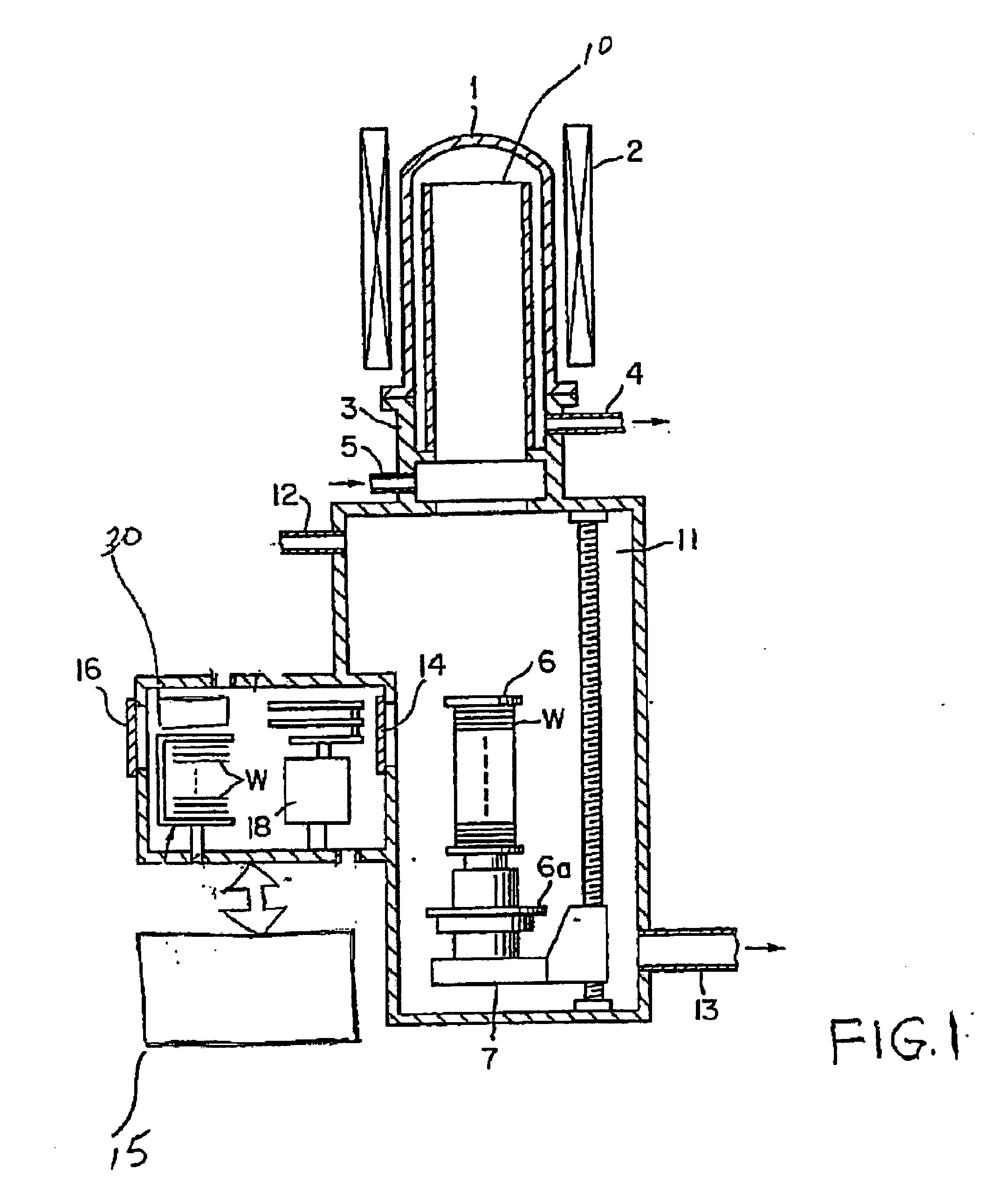

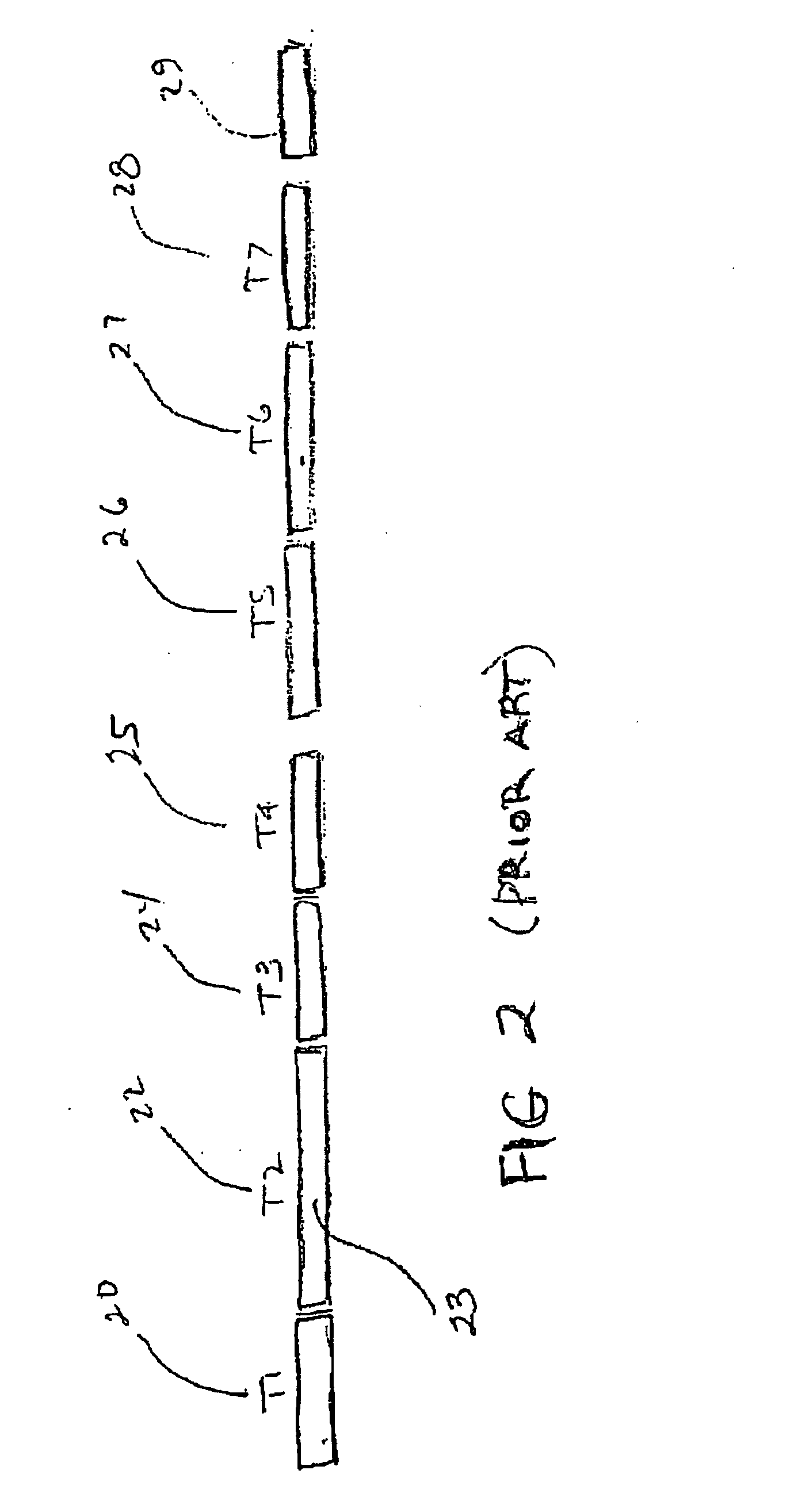

Intelligent full automation controlled flow for a semiconductor furnace tool

InactiveUS20050187647A1Reduce idle timeSemiconductor/solid-state device manufacturingSpecial data processing applicationsControl flowAutomatic control

The present invention relates to an apparatus and method for processing the flow of semiconductor wafers through a furnace tool having a front-opening unified pod (FOUP) material handling system. The invention provides for an automated control flow to realize greater efficiency and assure process quality. In one aspect of the invention the wafer batch completing its operation is discharged simultaneous with the charging of the next batch. Essentially the operation takes place by overlapping processing operations. An embodiment of the invention includes a process comprising the steps of: providing a first batch of semiconductor material, and loading the first batch into a carrier which transports the first batch into a semiconductor manufacturing process, and while the first batch undergoes the process, forming a second batch of semiconductor material, and pausing a second batch process operation until the first batch completes processing, to reduce the idle time of said process.

Owner:TAIWAN SEMICON MFG CO LTD

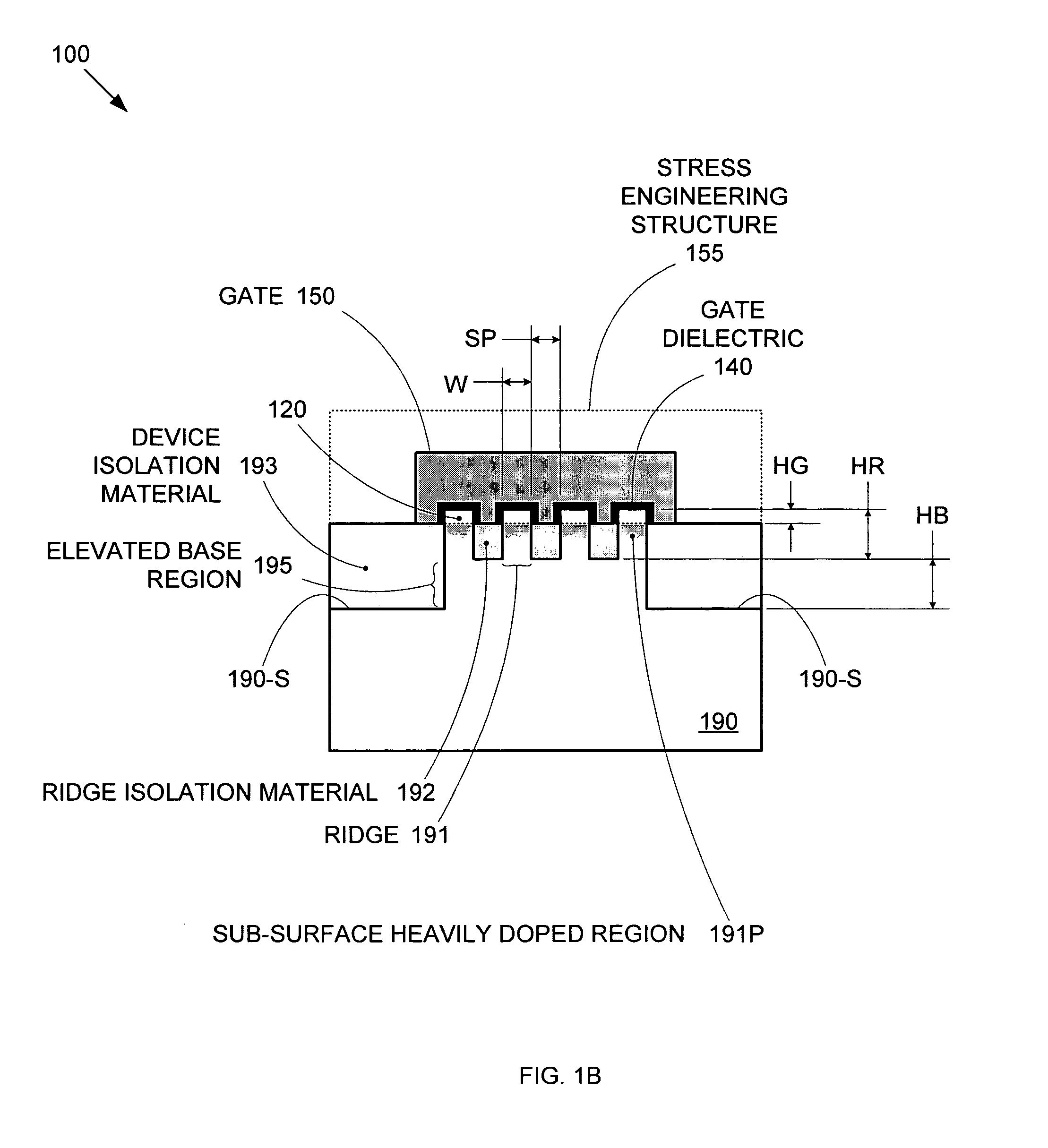

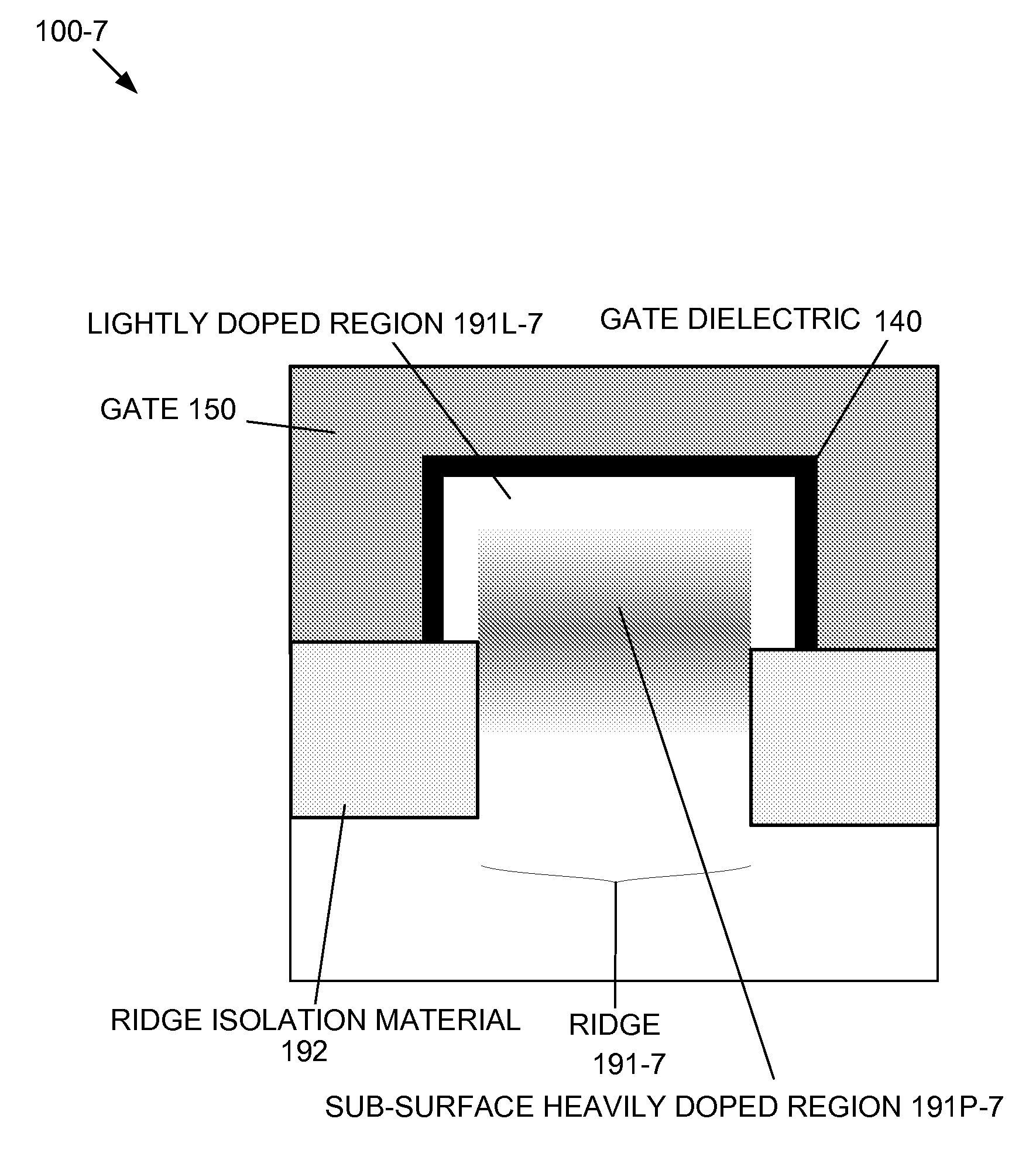

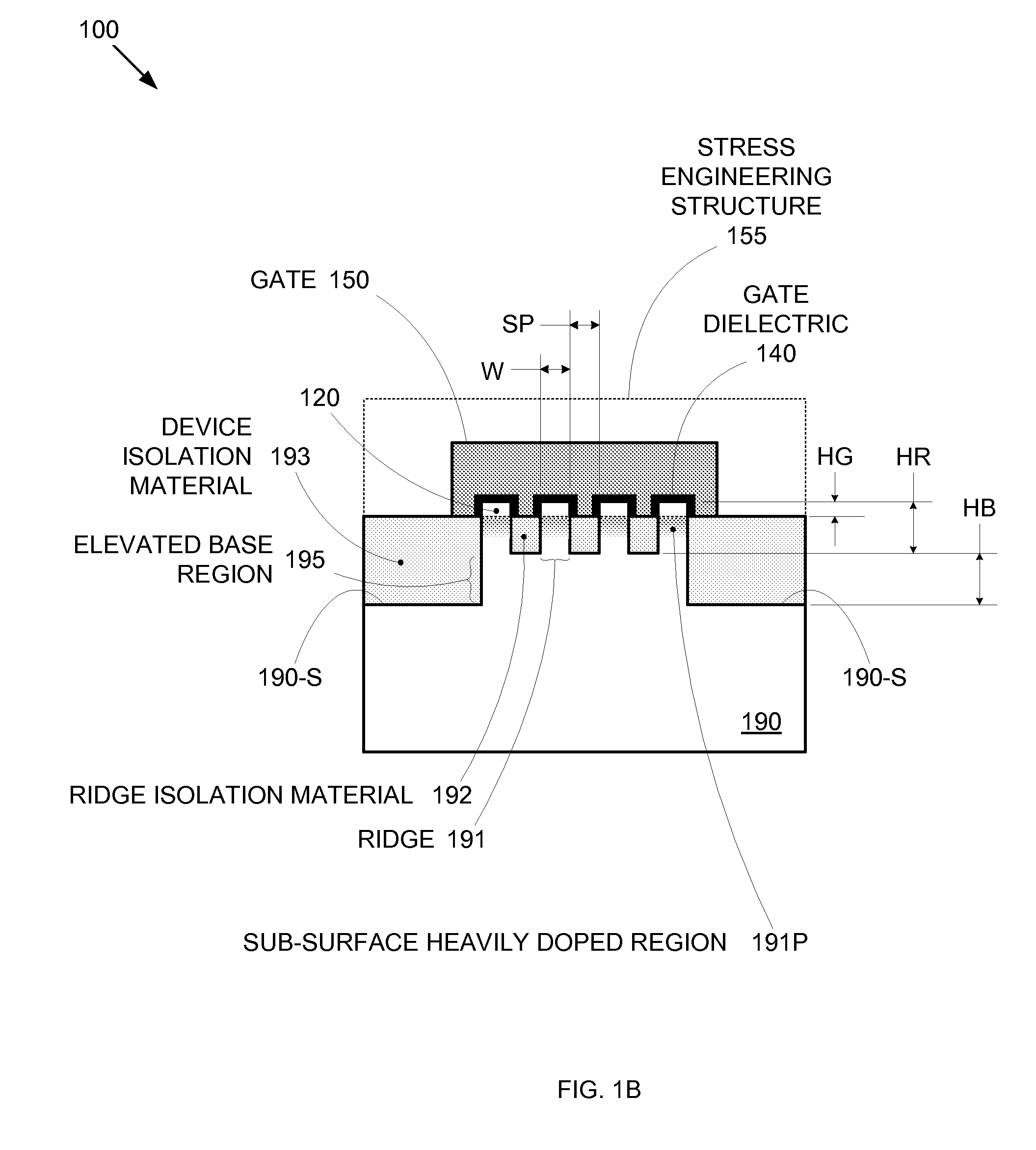

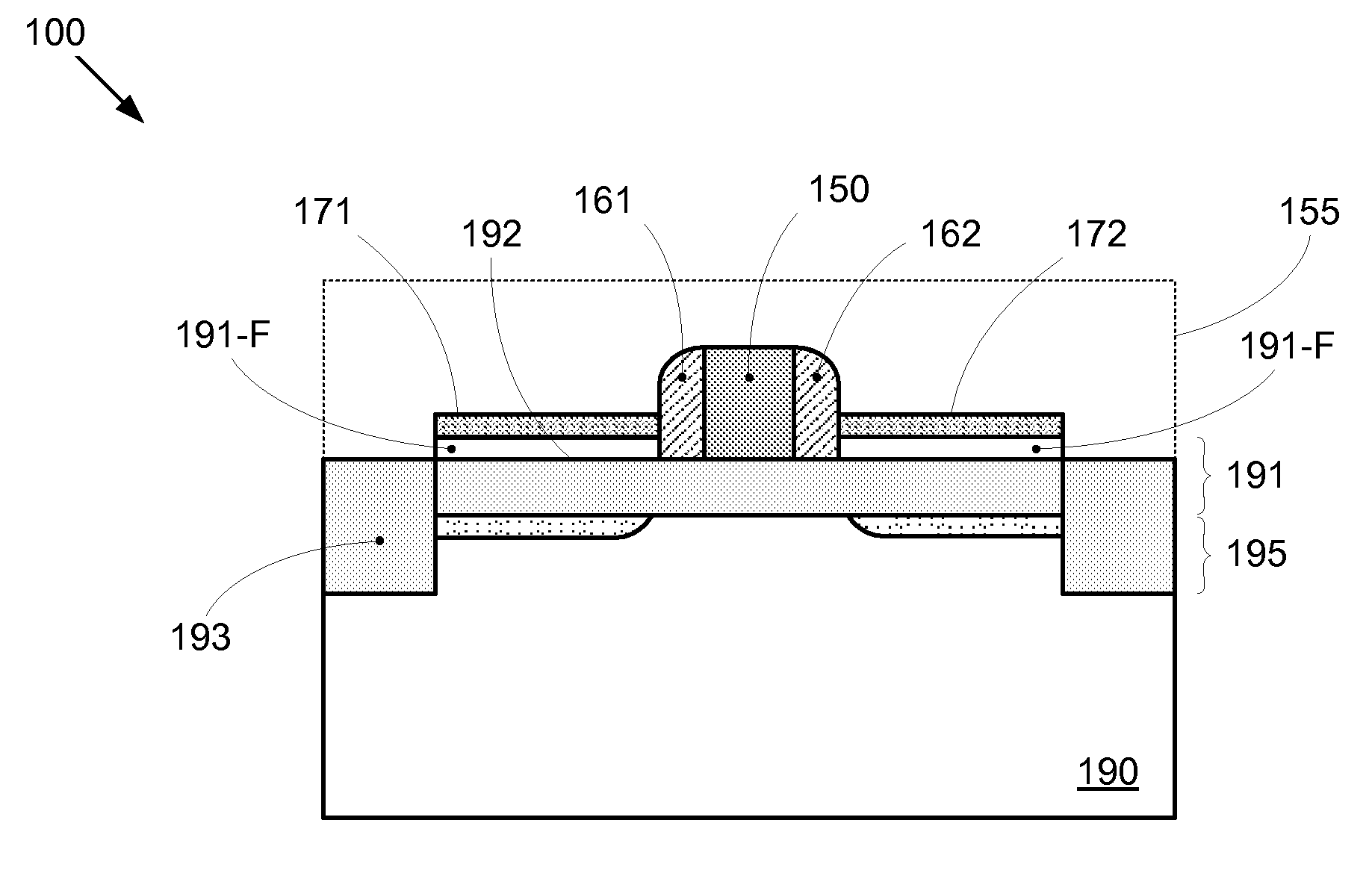

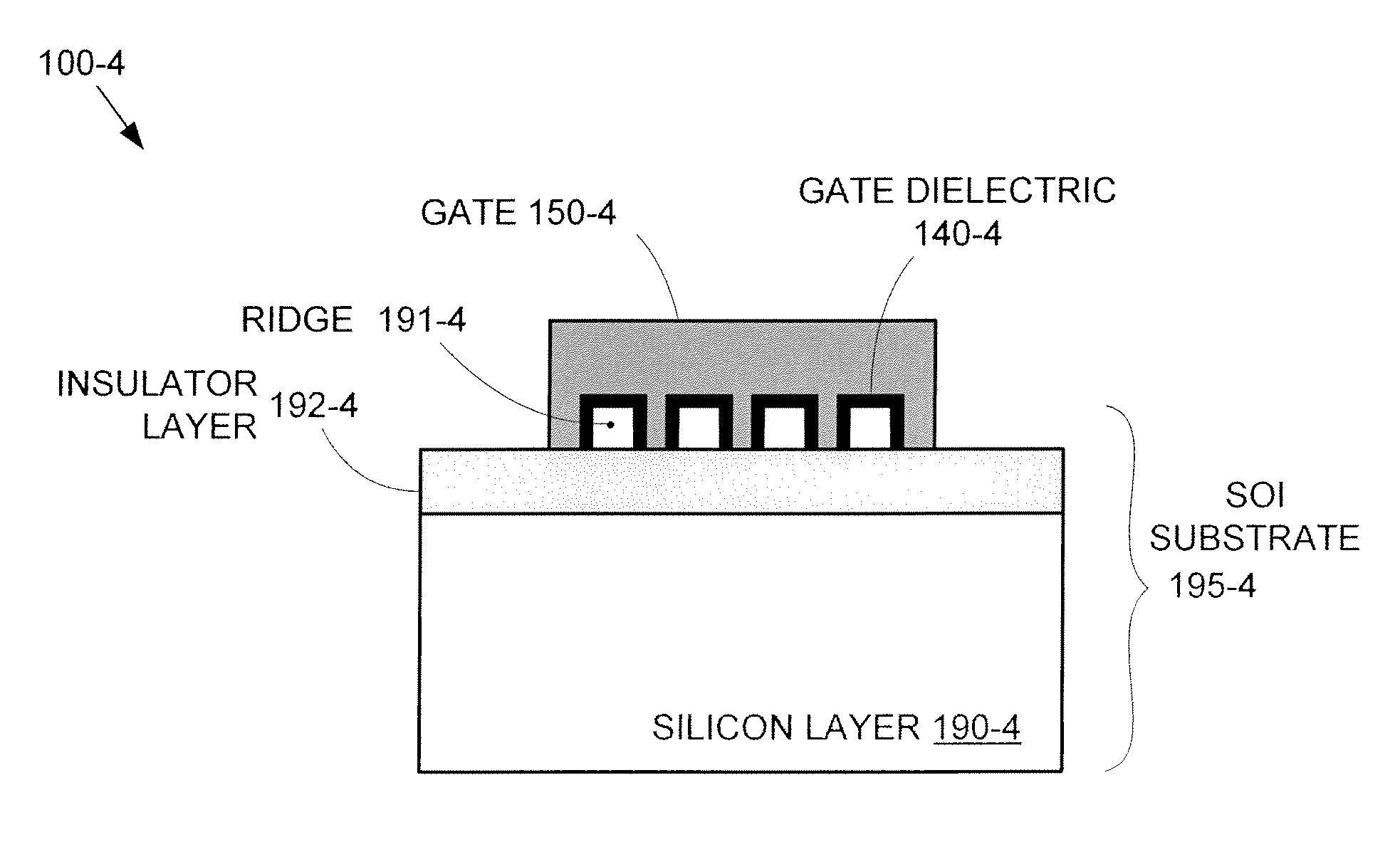

Enhanced Segmented Channel MOS Transistor with Multi Layer Regions

ActiveUS20070120156A1Increase costImprove performanceSolid-state devicesSemiconductor/solid-state device manufacturingMOSFETPerformance enhancement

By forming MOSFETs on a substrate having pre-existing ridges of semiconductor material (i.e., a “corrugated substrate”), the resolution limitations associated with conventional semiconductor manufacturing processes can be overcome, and high-performance, low-power transistors can be reliably and repeatably produced. Forming a corrugated substrate prior to actual device formation allows the ridges on the corrugated substrate to be created using high precision techniques that are not ordinarily suitable for device production. MOSFETs that subsequently incorporate the high-precision ridges into their channel regions will typically exhibit much more precise and less variable performance than similar MOSFETs formed using optical lithography-based techniques that cannot provide the same degree of patterning accuracy. Additional performance enhancement techniques such as pulse-shaped doping, “wrapped” gates, epitaxially grown conductive regions, epitaxially grown high mobility semiconductor materials (e.g. silicon-germanium, germanium, gallium arsenide, etc.), high-permittivity ridge isolation material, and narrowed base regions can be used in conjunction with the segmented channel regions to further enhance device performance.

Owner:SYNOPSYS INC

Back-contact photovoltaic cells

A photovoltaic cell comprising a wafer comprising a semiconductor material of a first conductivity type, the wafer comprising a first light receiving surface and a second surface opposite the first surface; a first passivation layer positioned over the first surface of the wafer; a first electrical contact positioned over the second surface of the wafer; a second electrical contact positioned over the second surface of the wafer and separated electrically from the first electrical contact; a second passivation layer positioned over the second surface of the wafer in the region on the wafer that is at least between the first electrical contact and the second surface of the wafer; and a layer comprising a semiconductor material of a conductivity opposite the conductivity of the wafer and positioned in the region between the second passivation layer and the first contact.

Owner:BP CORP NORTH AMERICA INC

Method of IC production using corrugated substrate

ActiveUS7265008B2Improve performance consistencyImprove performanceLaser detailsSolid-state devicesMOSFETPerformance enhancement

By forming MOSFETs on a substrate having pre-existing ridges of semiconductor material (i.e., a “corrugated substrate”), the resolution limitations associated with conventional semiconductor manufacturing processes can be overcome, and high-performance, low-power transistors can be reliably and repeatably produced. Forming a corrugated substrate prior to actual device formation allows the ridges on the corrugated substrate to be created using high precision techniques that are not ordinarily suitable for device production. MOSFETs that subsequently incorporate the high-precision ridges into their channel regions will typically exhibit much more precise and less variable performance than similar MOSFETs formed using optical lithography-based techniques that cannot provide the same degree of patterning accuracy. Additional performance enhancement techniques such as pulse-shaped doping and “wrapped” gates can be used in conjunction with the segmented channel regions to further enhance device performance.

Owner:SYNOPSYS INC

Enhanced segmented channel MOS transistor with narrowed base regions

ActiveUS7508031B2Improve performance consistencyImprove performanceSolid-state devicesSemiconductor/solid-state device manufacturingMOSFETPerformance enhancement

By forming MOSFETs on a substrate having pre-existing ridges of semiconductor material (i.e., a “corrugated substrate”), the resolution limitations associated with conventional semiconductor manufacturing processes can be overcome, and high-performance, low-power transistors can be reliably produced. Ridges on the corrugated substrate can be created using high precision techniques that are not ordinarily suitable for device production. MOSFETs that subsequently incorporate the high-precision ridges into their channel regions will typically exhibit much more precise and less variable performance than similar MOSFETs formed using optical lithography-based techniques that cannot provide the same degree of patterning accuracy. Additional performance enhancement techniques such as pulse-shaped doping, “wrapped” gates, epitaxially grown conductive regions, epitaxially grown high mobility semiconductor materials, high-permittivity ridge isolation material, and narrowed base regions can be used in conjunction with the segmented channel regions to further enhance device performance.

Owner:SYNOPSYS INC

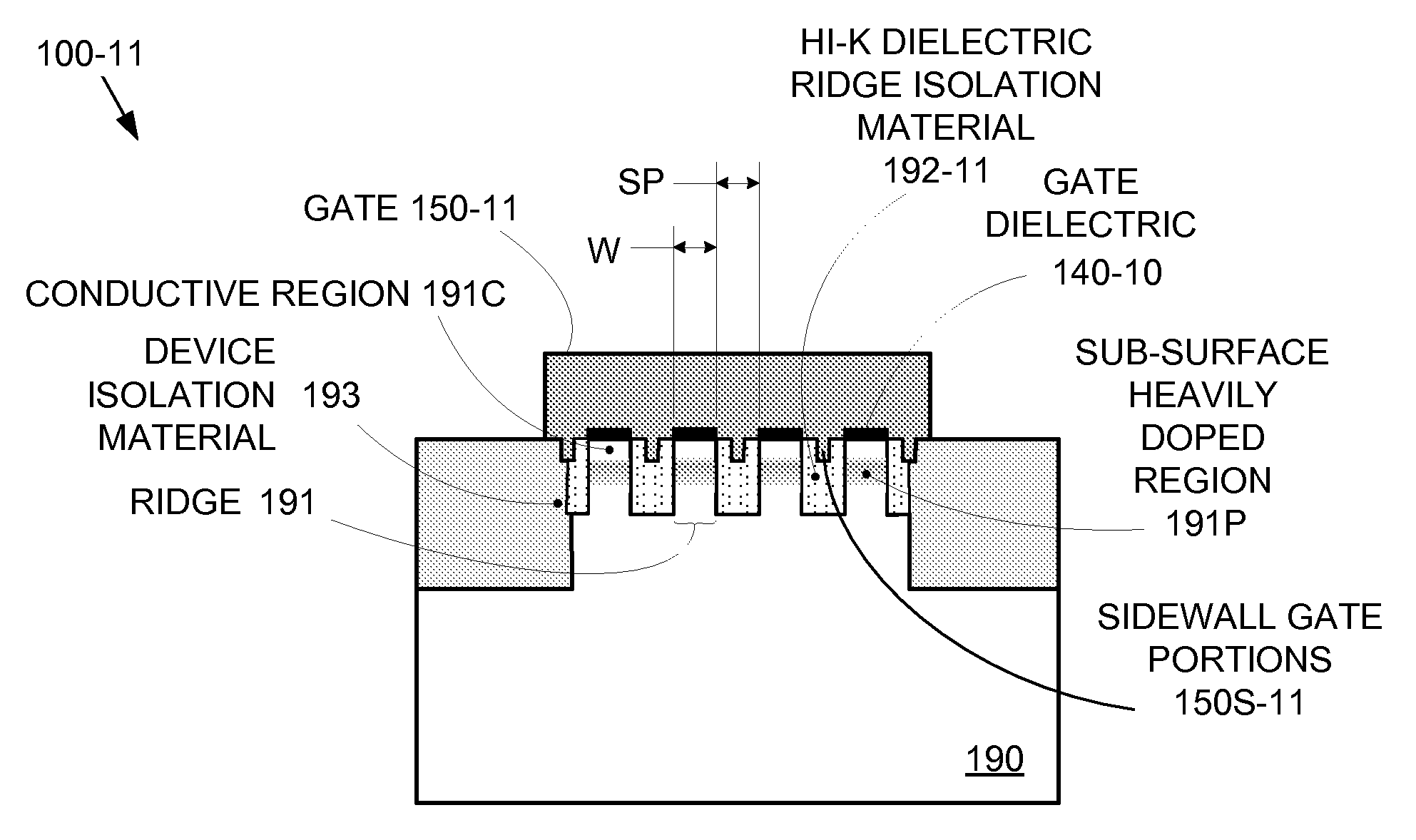

Enhanced Segmented Channel MOS Transistor with High-Permittivity Dielectric Isolation Material

ActiveUS20070122953A1Increase costImprove performanceTransistorSolid-state devicesMOSFETPerformance enhancement

By forming MOSFETs on a substrate having pre-existing ridges of semiconductor material (i.e., a “corrugated substrate”), the resolution limitations associated with conventional semiconductor manufacturing processes can be overcome, and high-performance, low-power transistors can be reliably and repeatably produced. Forming a corrugated substrate prior to actual device formation allows the ridges on the corrugated substrate to be created using high precision techniques that are not ordinarily suitable for device production. MOSFETs that subsequently incorporate the high-precision ridges into their channel regions will typically exhibit much more precise and less variable performance than similar MOSFETs formed using optical lithography-based techniques that cannot provide the same degree of patterning accuracy. Additional performance enhancement techniques such as pulse-shaped doping, “wrapped” gates, epitaxially grown conductive regions, epitaxially grown high mobility semiconductor materials (e.g. silicon-germanium, germanium, gallium arsenide, etc.), high-permittivity ridge isolation material, and narrowed base regions can be used in conjunction with the segmented channel regions to further enhance device performance.

Owner:SYNOPSYS INC

Enhanced segmented channel MOS transistor with high-permittivity dielectric isolation material

ActiveUS7605449B2Improve performance consistencyImprove performanceTransistorSolid-state devicesMOSFETPerformance enhancement

By forming MOSFETs on a substrate having pre-existing ridges of semiconductor material (i.e., a “corrugated substrate”), the resolution limitations associated with conventional semiconductor manufacturing processes can be overcome, and high-performance, low-power transistors can be reliably and repeatably produced. Forming a corrugated substrate prior to actual device formation allows the ridges on the corrugated substrate to be created using high precision techniques that are not ordinarily suitable for device production. MOSFETs that subsequently incorporate the high-precision ridges into their channel regions will typically exhibit much more precise and less variable performance than similar MOSFETs formed using optical lithography-based techniques that cannot provide the same degree of patterning accuracy. Additional performance enhancement techniques such as pulse-shaped doping, “wrapped” gates, epitaxially grown conductive regions, epitaxially grown high mobility semiconductor materials (e.g. silicon-germanium, germanium, gallium arsenide, etc.), high-permittivity ridge isolation material, and narrowed base regions can be used in conjunction with the segmented channel regions to further enhance device performance.

Owner:SYNOPSYS INC

Semiconductor fin isolation by a well trapping fin portion

ActiveUS20140252479A1Solid-state devicesSemiconductor/solid-state device manufacturingDopantSemiconductor materials

A bulk semiconductor substrate including a first semiconductor material is provided. A well trapping layer including a second semiconductor material and a dopant is formed on a top surface of the bulk semiconductor substrate. The combination of the second semiconductor material and the dopant within the well trapping layer is selected such that diffusion of the dopant is limited within the well trapping layer. A device semiconductor material layer including a third semiconductor material can be epitaxially grown on the top surface of the well trapping layer. The device semiconductor material layer, the well trapping layer, and an upper portion of the bulk semiconductor substrate are patterned to form at least one semiconductor fin. Semiconductor devices formed in each semiconductor fin can be electrically isolated from the bulk semiconductor substrate by the remaining portions of the well trapping layer.

Owner:IBM CORP

Integrated Circuit On Corrugated Substrate

ActiveUS20070132053A1Improve performance consistencyImprove performanceTransistorSemiconductor/solid-state device detailsMOSFETSemiconductor materials

By forming MOSFETs on a substrate having pre-existing ridges of semiconductor material (i.e., a “corrugated substrate”), the resolution limitations associated with conventional semiconductor manufacturing processes can be overcome, and high-performance, low-power transistors can be reliably and repeatably produced. Forming a corrugated substrate prior to actual device formation allows the ridges on the corrugated substrate to be created using high precision techniques that are not ordinarily suitable for device production. MOSFETs that subsequently incorporate the high-precision ridges into their channel regions will typically exhibit much more precise and less variable performance than similar MOSFETs formed using optical lithography-based techniques that cannot provide the same degree of patterning accuracy. Additional performance enhancement techniques such as pulse-shaped doping and “wrapped” gates can be used in conjunction with the segmented channel regions to further enhance device performance.

Owner:SYNOPSYS INC

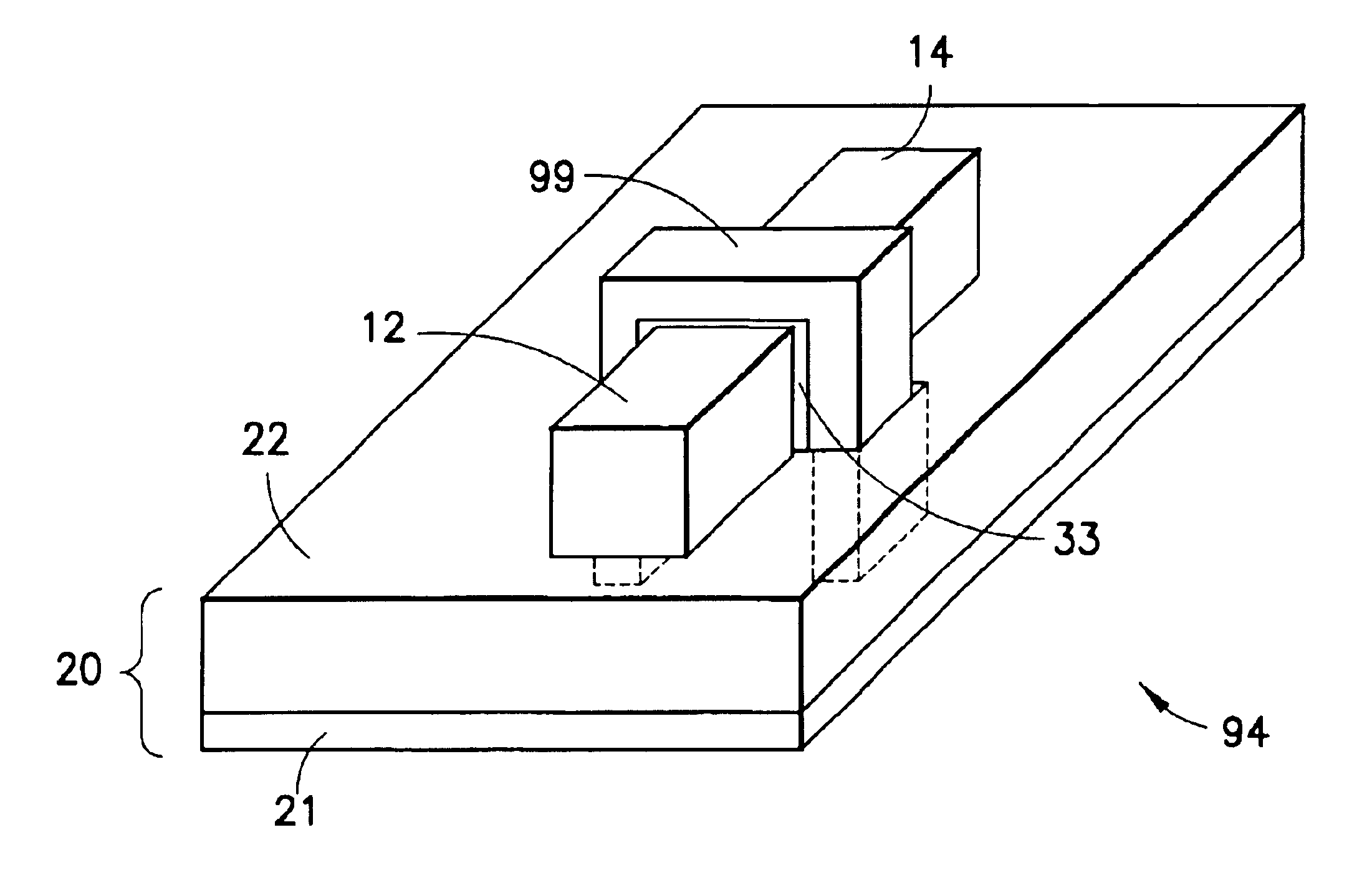

FET channel having a strained lattice structure along multiple surfaces

InactiveUS6921982B2Improve conductivityTransistorSolid-state devicesGate dielectricSemiconductor materials

A channel 16 of a FinFET 10 has a channel core 24 and a channel envelope 32, each made from a semiconductor material defining a different lattice structure to exploit strained silicon properties. A gate is coupled to the channel envelope through a gate dielectric. Exemplary materials are Si and SixGe1-x, wherein 78<x<92. The channel core 24 has a top surface 26 of width wc and an upstanding surface 28, 30 of height hc, preferably oriented 90° to one another. The channel envelope 32 is in contact with the top 26 and upstanding surfaces 28, 30 so that the area of interface is increased as compared to contact only along the top surface 26, improving electrical conductivity and gate 18 control over the channel 16. The height hc can be tailored to enable a smaller scale FET 10 within a stabilized SRAM. Various methods of making the channel 16 are disclosed, including a mask and etch method, a handle wafer / carrier wafer method, and a shallow trench method. Embodiments and methods for FinFETs with one to four gates are disclosed.

Owner:MICROSOFT TECH LICENSING LLC

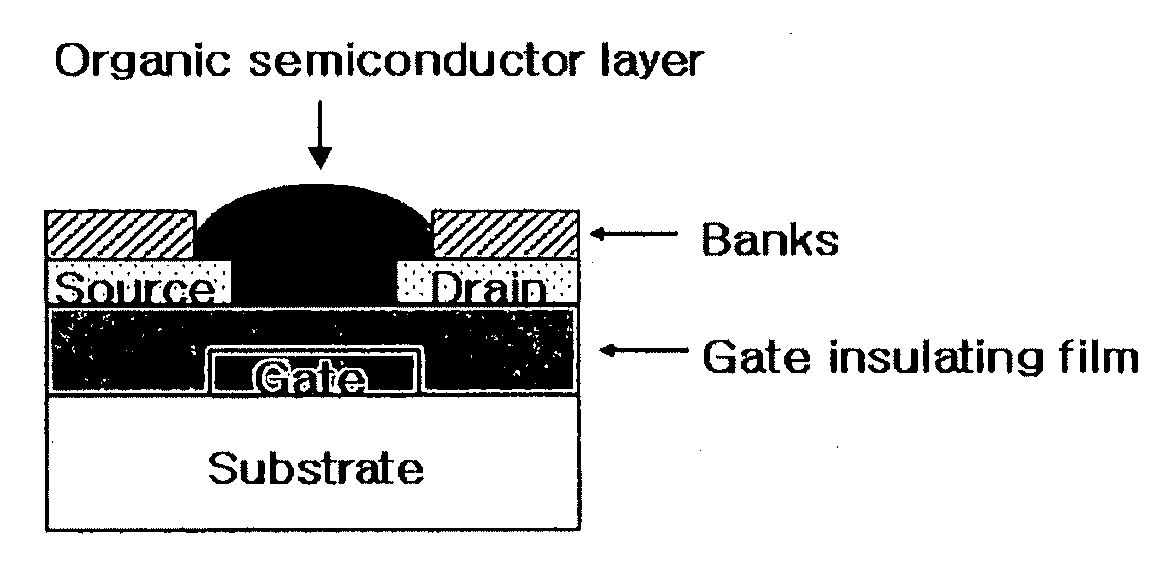

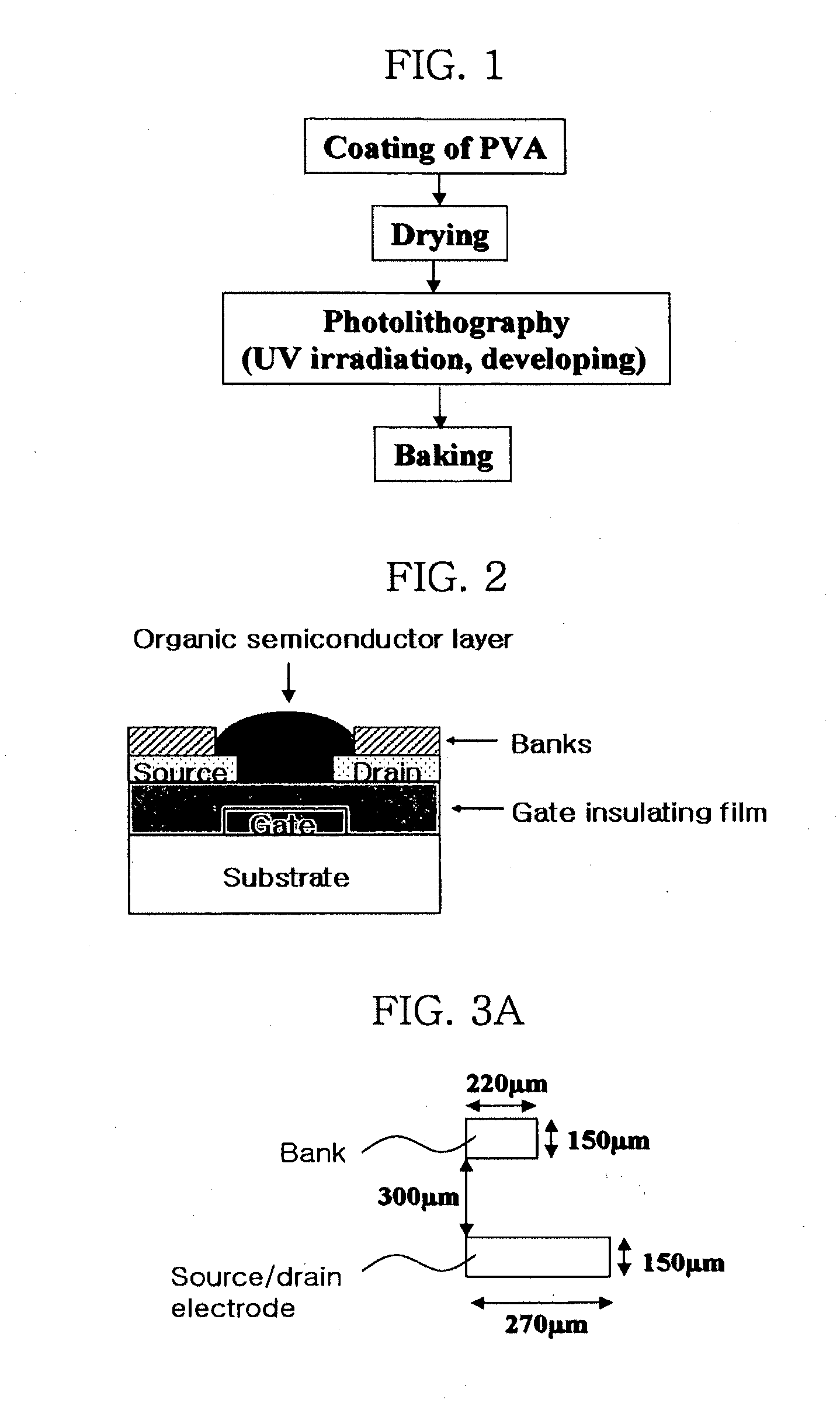

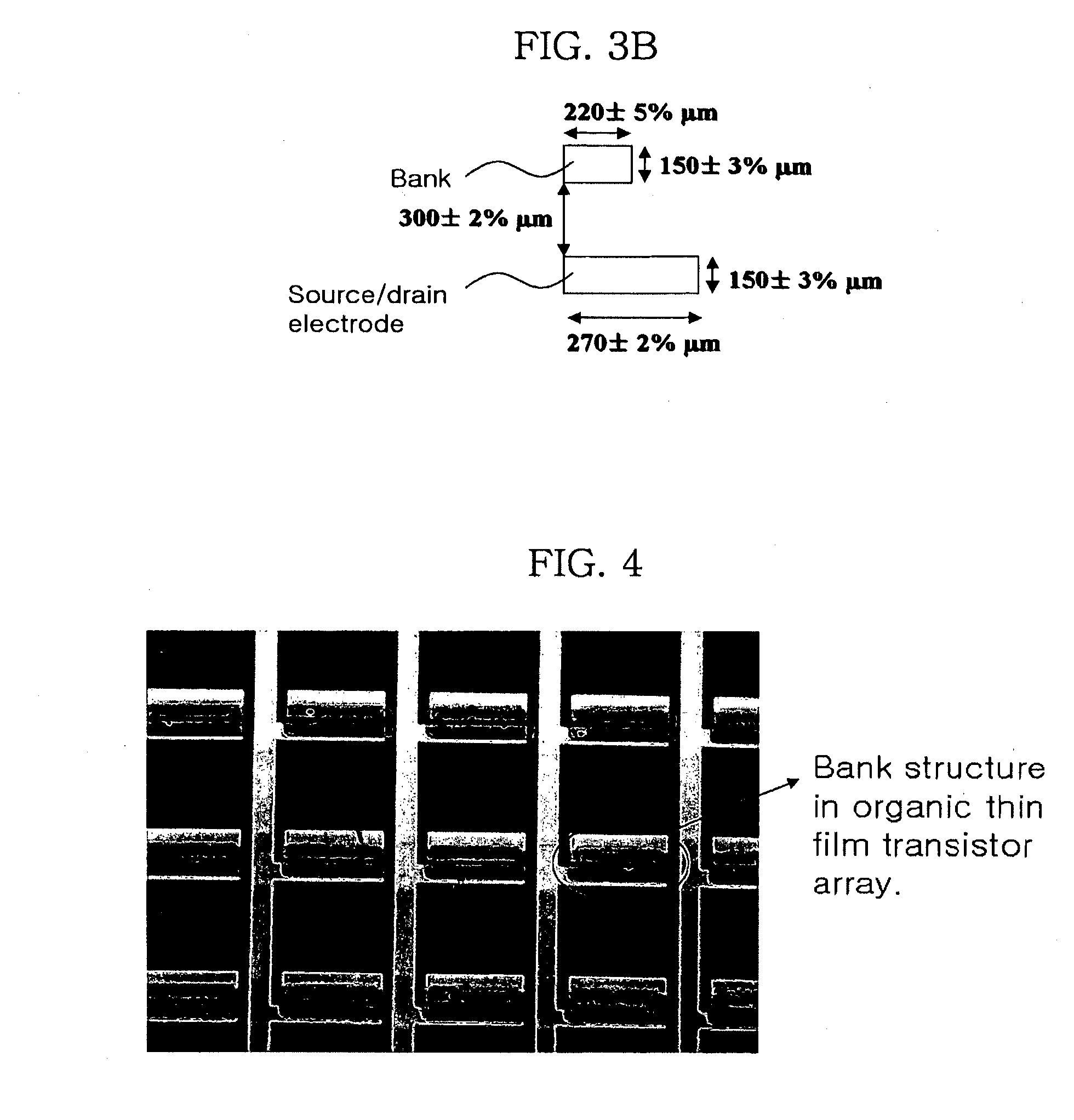

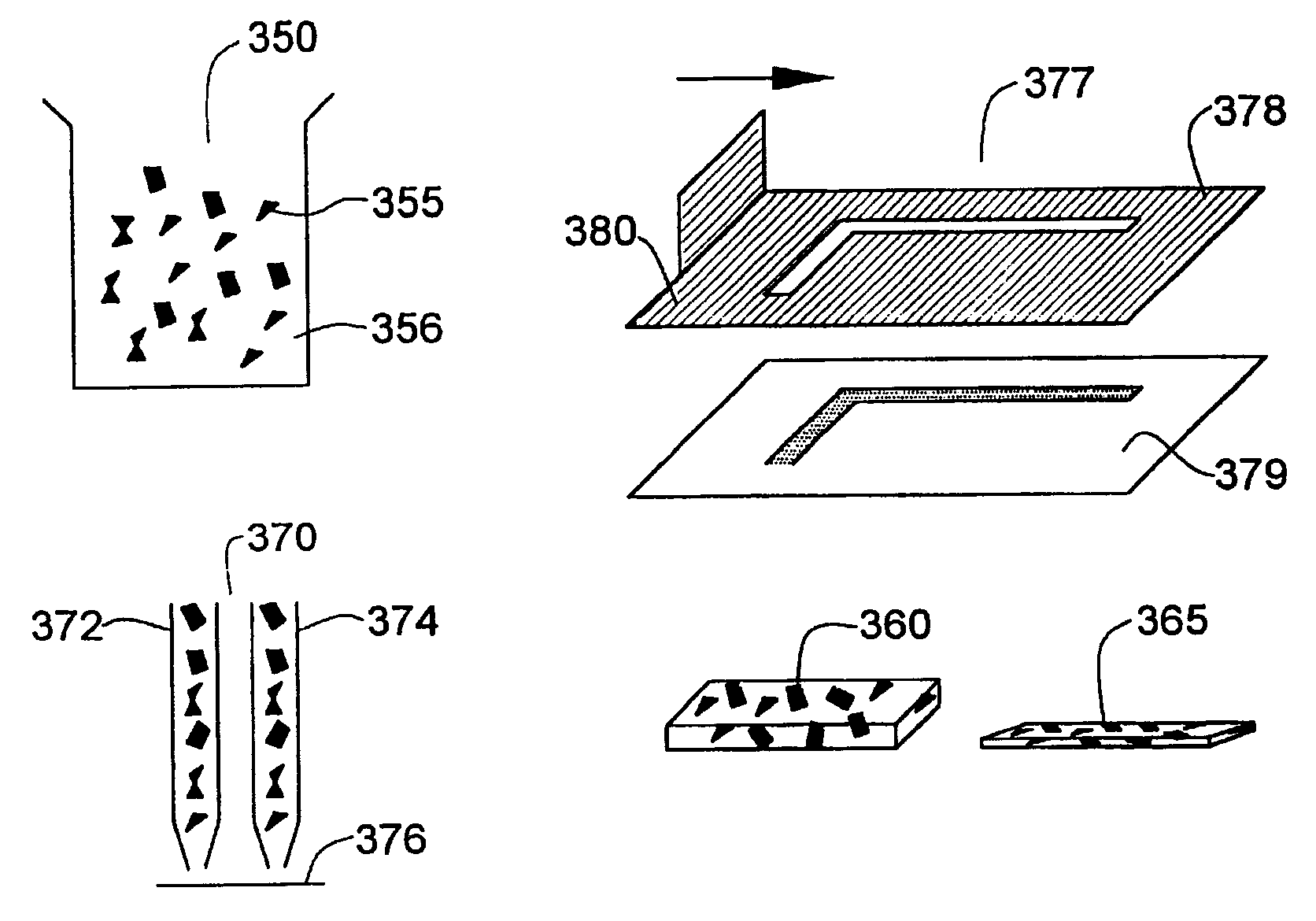

Methods of fabricating organic thin film transistors

InactiveUS20120122275A1Suppresses and eliminates adverse effectSuppress and eliminate degradationSolid-state devicesSemiconductor/solid-state device manufacturingOrganic structureSemiconductor materials

Disclosed is a method for forming banks during the fabrication of electronic devices incorporating an organic semiconductor material that includes preparing an aqueous coating composition having at least a water-soluble polymer, a UV curing agent and a water-soluble fluorine compound. This coating composition is applied to a substrate, exposed using UV radiation and then developed using an aqueous developing composition to form the bank pattern. Because the coating composition can be developed using an aqueous composition rather than an organic solvent or solvent system, the method tends to preserve the integrity of other organic structures present on the substrate. Further, the incorporation of the fluorine compound in the aqueous solution provides a degree of control over the contact angles exhibited on the surface of the bank pattern and thereby can avoid or reduce subsequent surface treatments.

Owner:SAMSUNG ELECTRONICS CO LTD

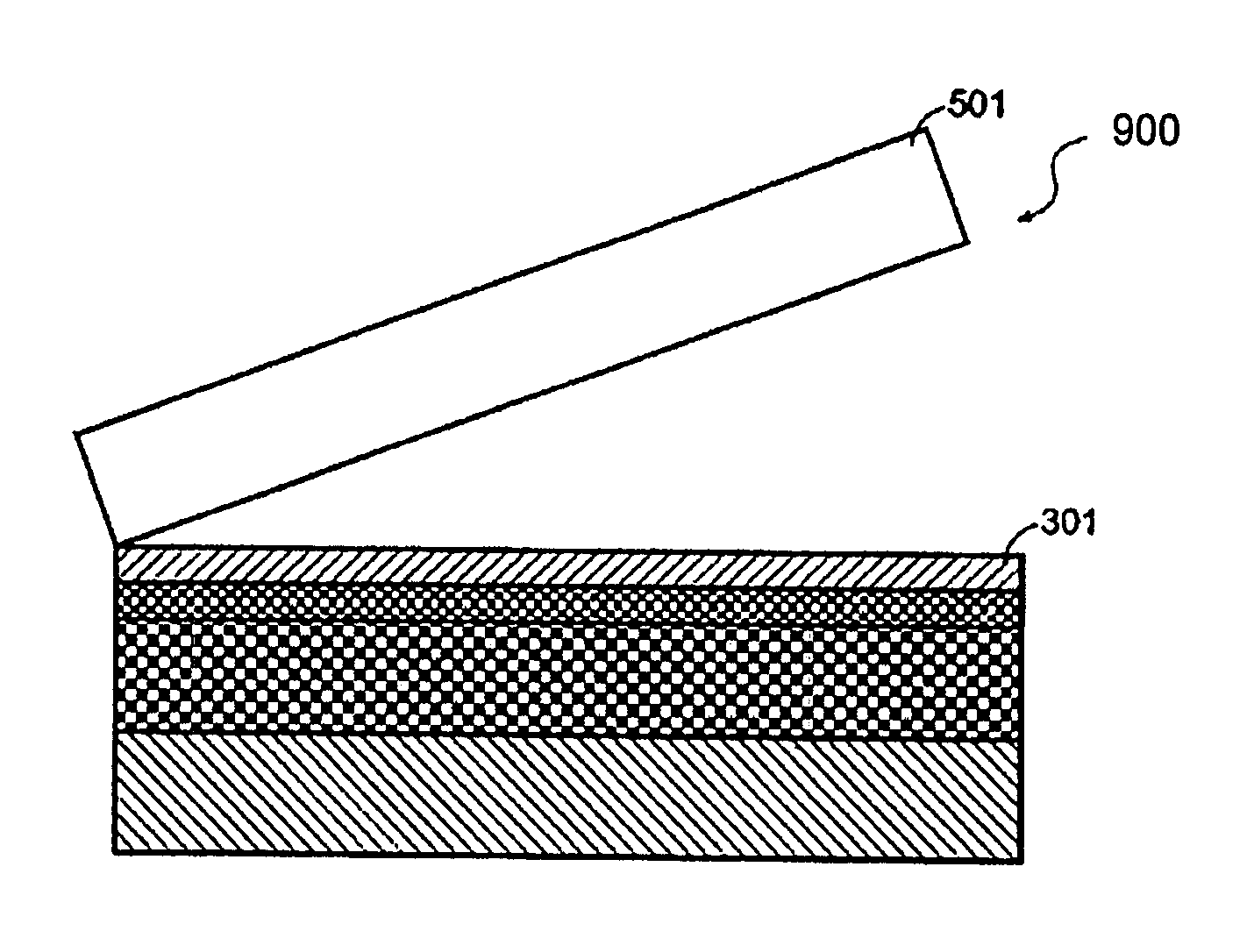

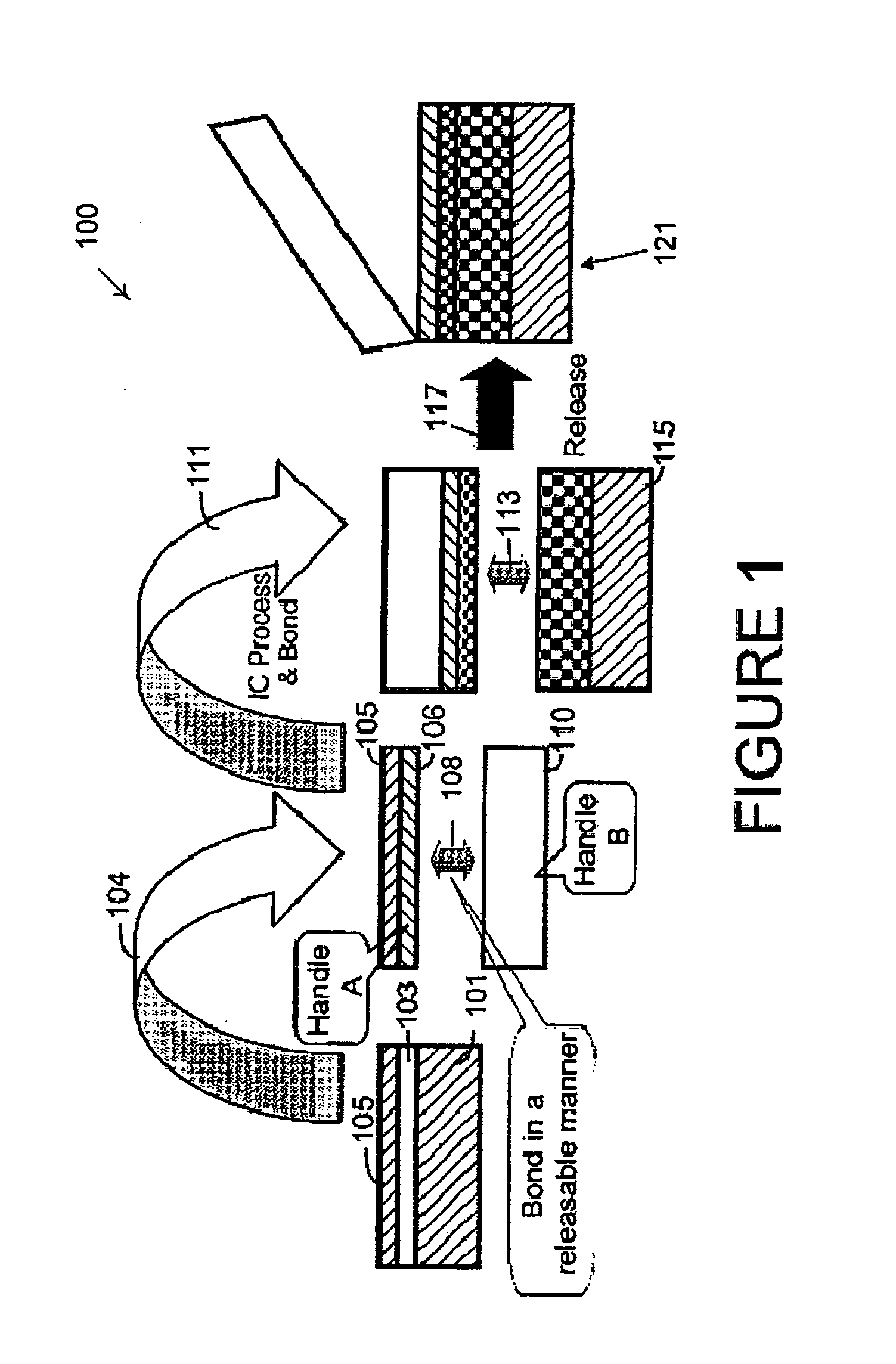

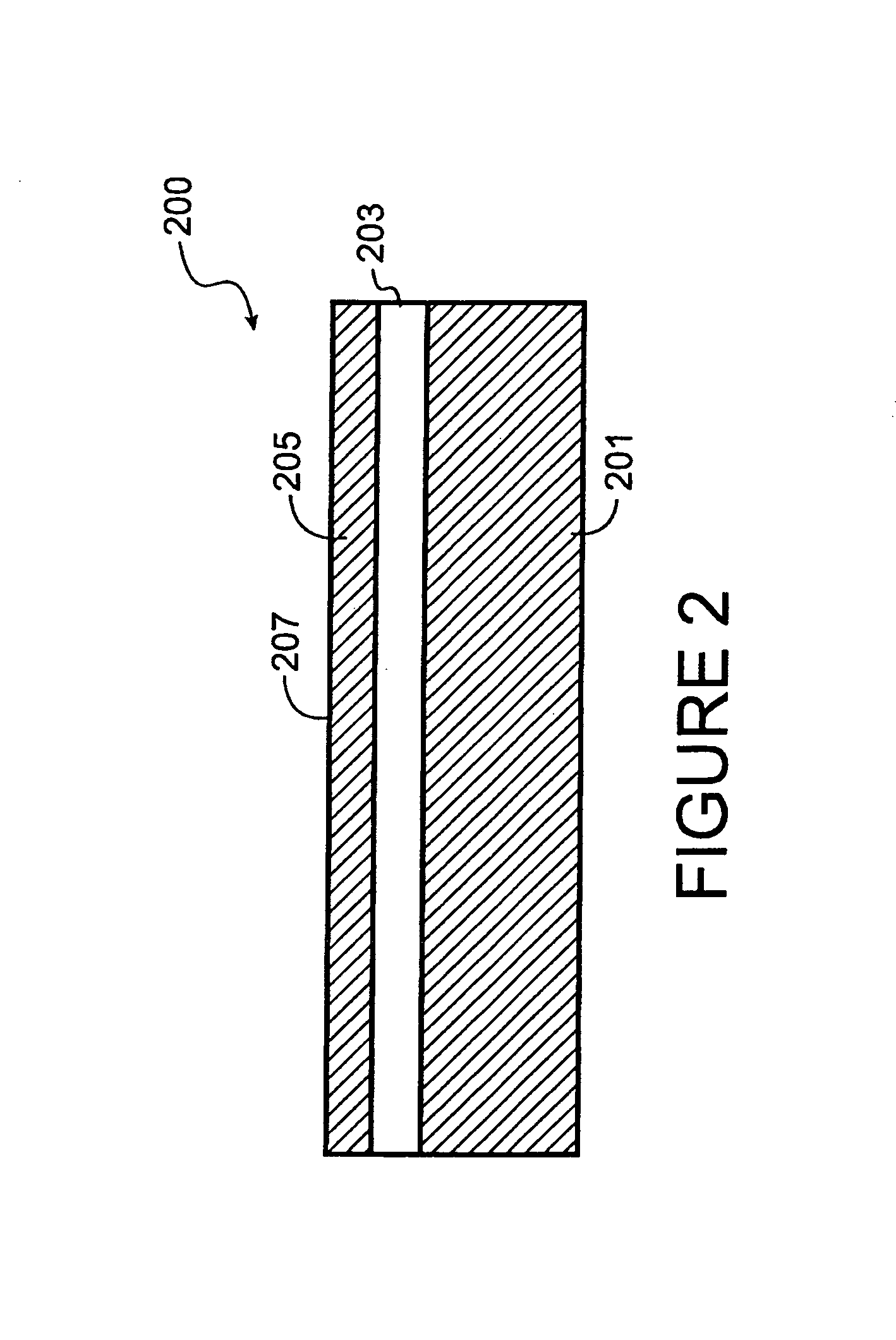

Thin handle substrate method and structure for fabricating devices using one or more films provided by a layer transfer process

ActiveUS7166520B1Avoid the possibility of damageEfficient processingSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductor materialsEngineering

A method for fabricating one or more devices, e.g., integrated circuits. The method includes providing a substrate (e.g., silicon), which has a thickness of semiconductor material and a surface region. The substrate also has a cleave plane provided within the substrate to define the thickness of semiconductor material. The method includes joining the surface region of the substrate to a first handle substrate. In a preferred embodiment, the first handle substrate is termed a “thin” substrate, which provides suitable bonding characteristics, can withstand high temperature processing often desired during the manufacture of semiconductor devices, and has desirable de-bonding characteristics between it and a second handle substrate, which will be described in more detail below. In a preferred embodiment, the first handle substrate is also thick enough and rigid enough to allow for cleaving according to a specific embodiment.

Owner:SILICON GENERAL CORPORATION

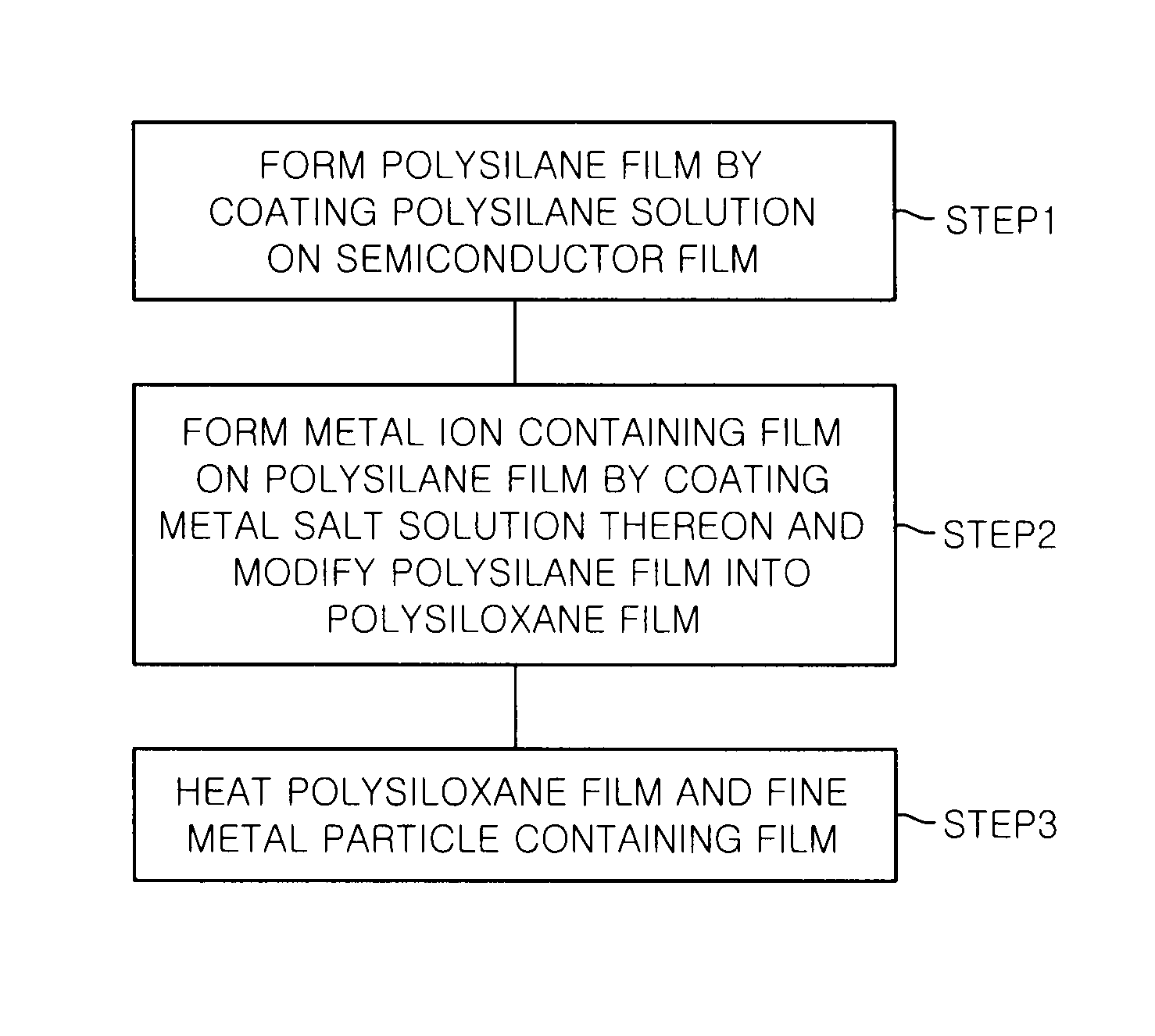

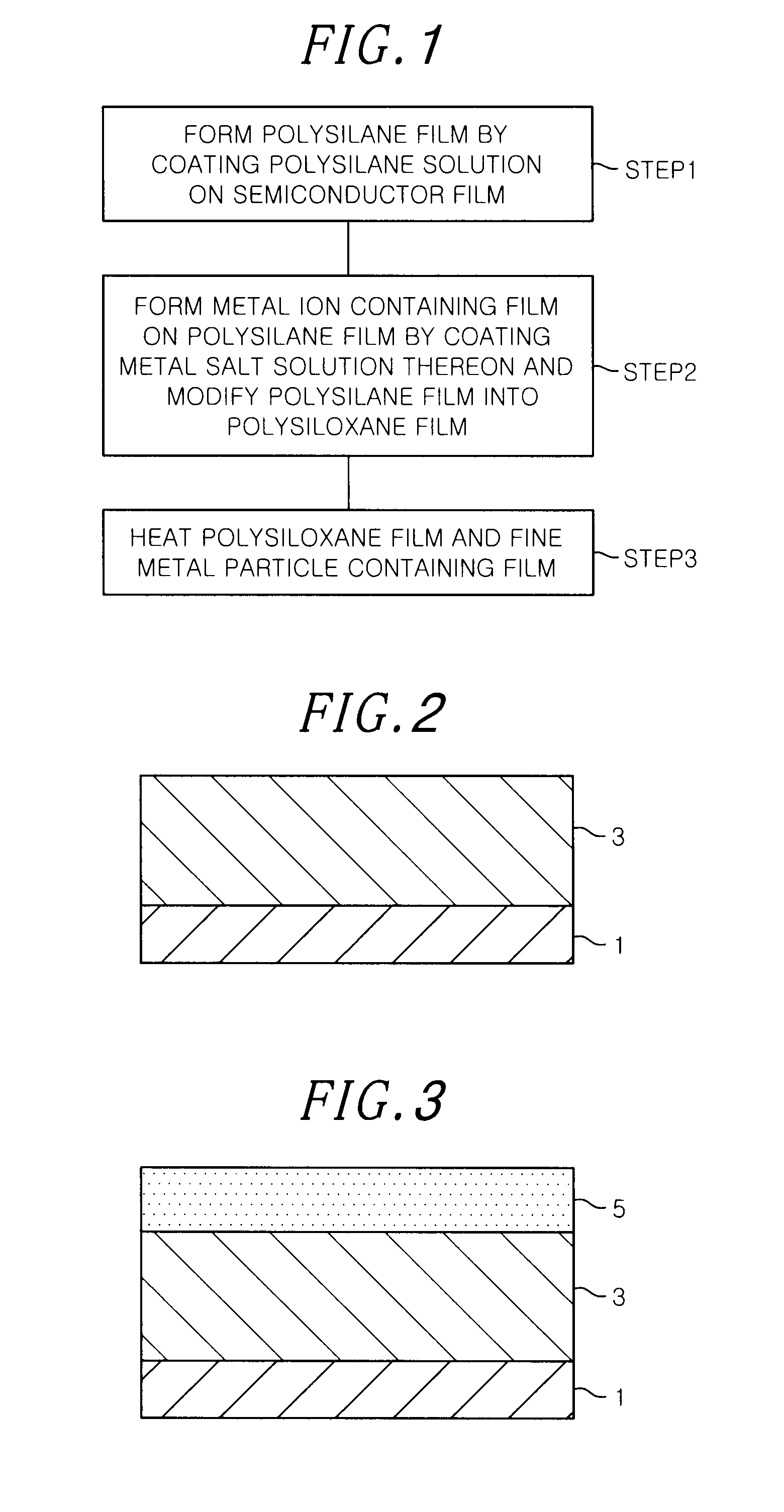

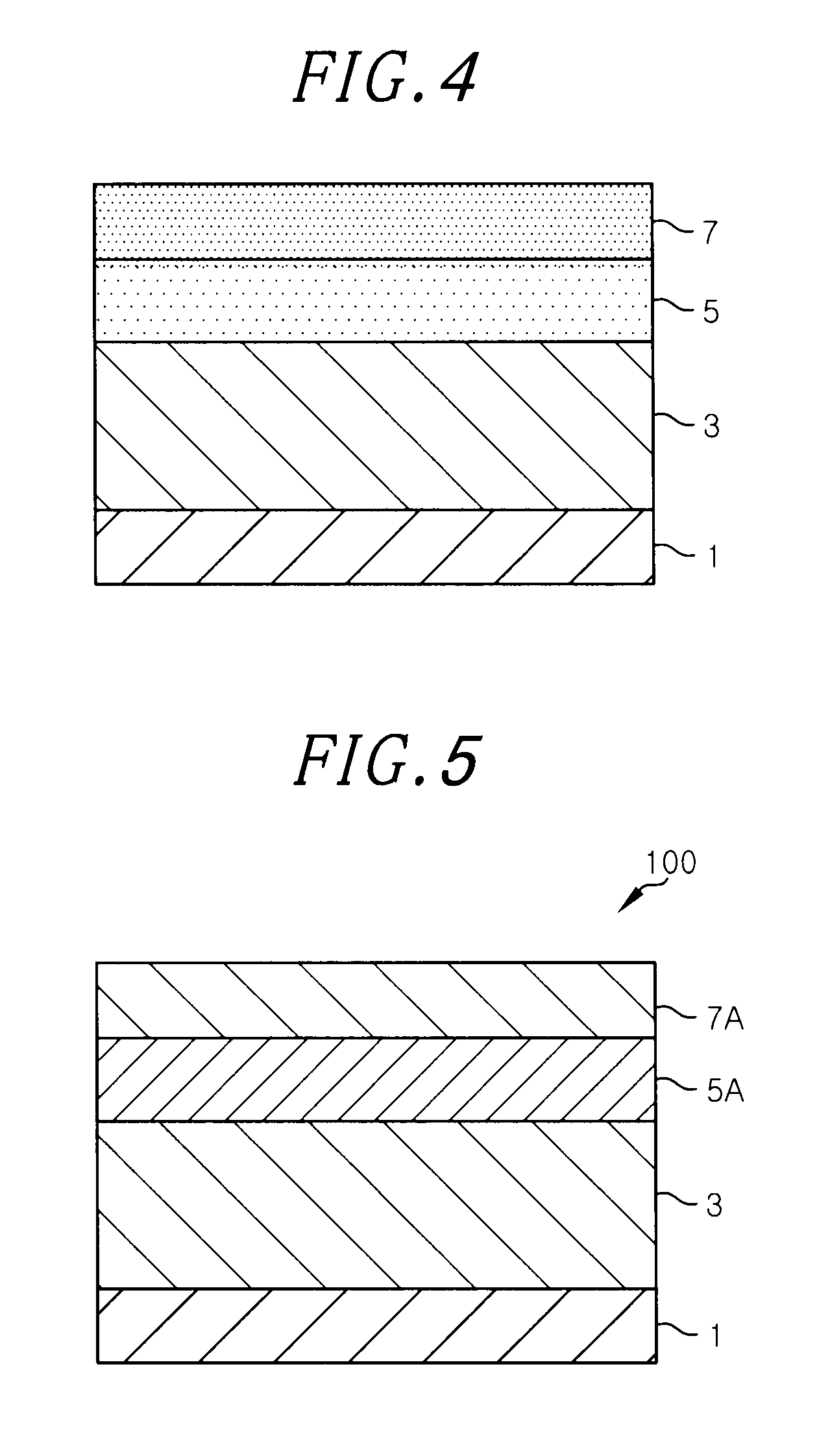

Film forming method, semiconductor device, manufacturing method thereof and substrate processing apparatus therefor

InactiveUS8785311B2Solid-state devicesSemiconductor/solid-state device manufacturingSemiconductor materialsSilanes

In a method for forming a stacked substrate of a MOS (Metal Oxide Semiconductor) structure including an oxide film serving as a gate insulating film formed on a semiconductor material layer having a film or substrate shape; and a conductive film serving as a gate electrode formed on the oxide film, a polysilane film on the semiconductor material layer is formed by coating a polysilane solution on a surface of a substrate to which the semiconductor material layer is exposed. A film containing metal ions is formed on the polysilane film by coating a metal salt solution thereon, and the polysilane film and the film containing metal ions are respectively modified into a polysiloxane film and a film containing fine metal particles to form the stacked substrate.

Owner:TOKYO ELECTRON LTD

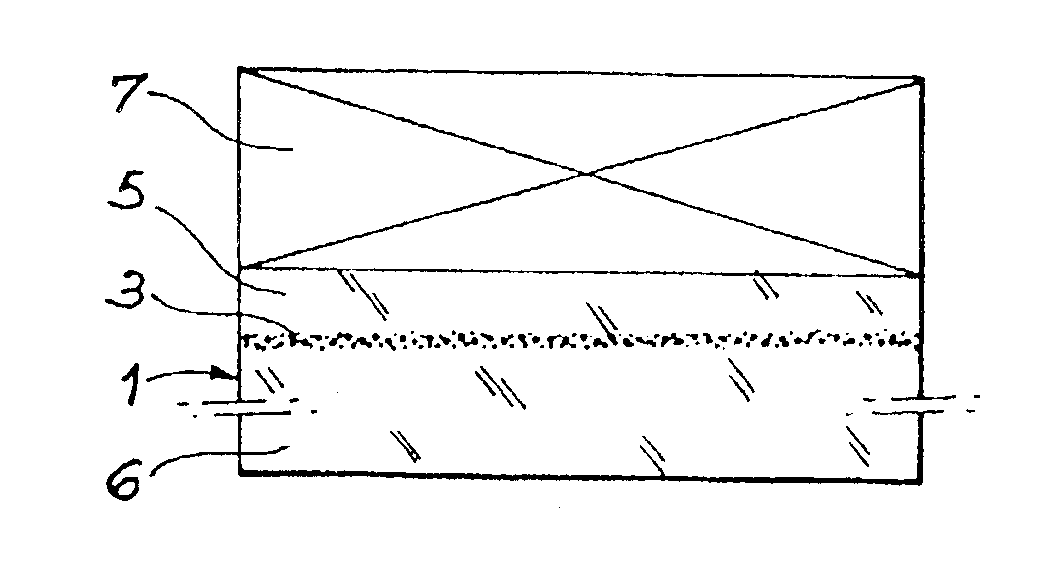

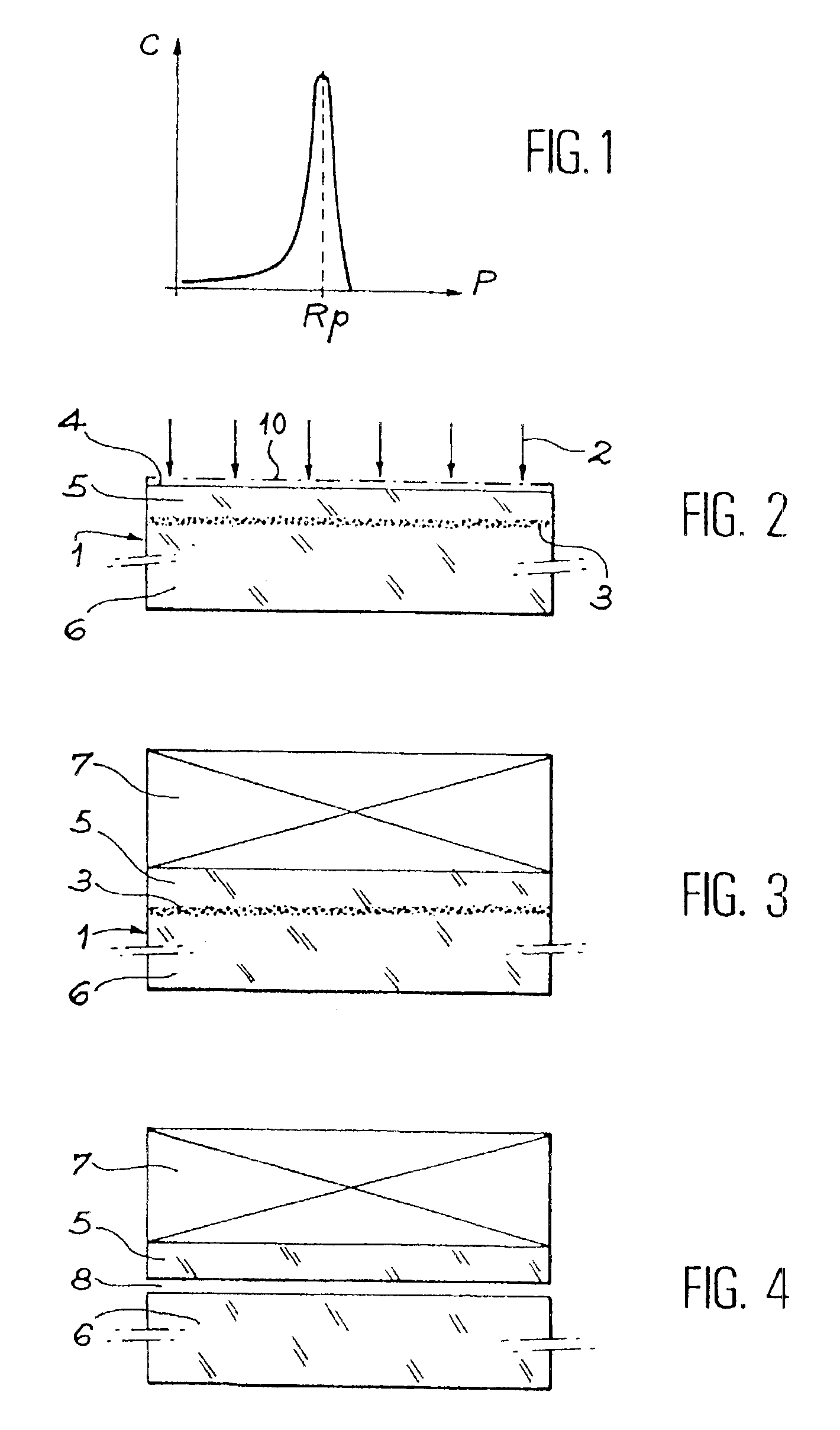

Process for the production of thin semiconductor material films

InactiveUSRE39484E1Uniform and controlled thicknessHigh implantationFluid pressure measurement by electric/magnetic elementsSolid-state devicesIon bombardmentMicrobubbles

Process for the preparation of thin monocrystalline or polycrystalline semiconductor material films, characterized in that it comprises subjecting a semiconductor material wafer having a planar face to the three following stages: a first stage of implantation by bombardment (2) of the face (4) of the said wafer (1) by means of ions creating in the volume of said wafer a layer (3) of gaseous microbubbles defining in the volume of said wafer a lower region (6) constituting the mass of the substrate and an upper region (5) constituting the thin film, a second stage of intimately contacting the planar face (4) of said wafer with a stiffener (7) constituted by at least one rigid material layer, a third stage of heat treating the assembly of said wafer (1) and said stiffener (7) at a temperature above that at which the ion bombardment (2) was carried out and sufficient to create by a crystalline rearrangement effect in said wafer (1) and a pressure effect in the said microbubbles, a separation between the thin film (5) and the mass of the substrate (6).

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES

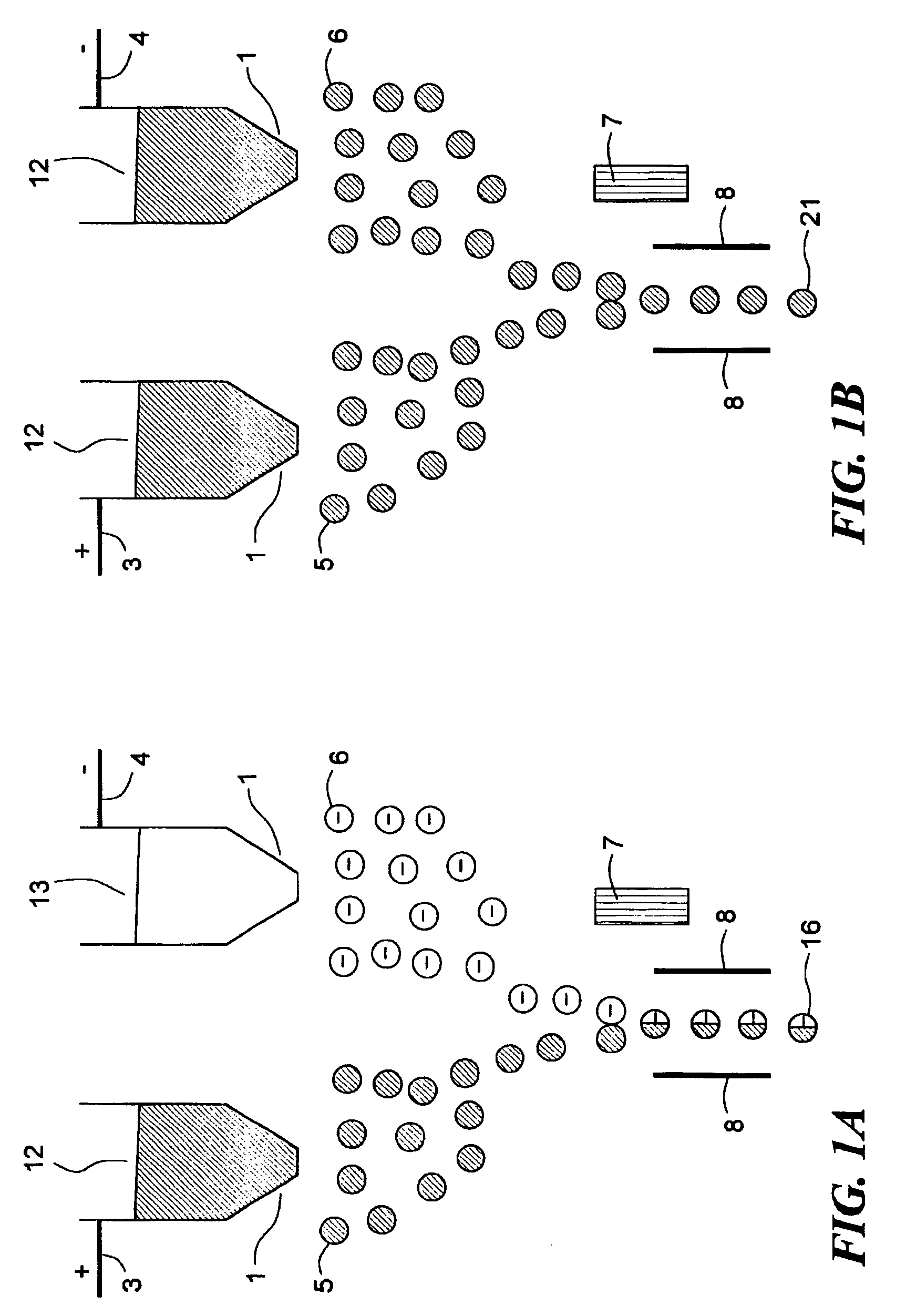

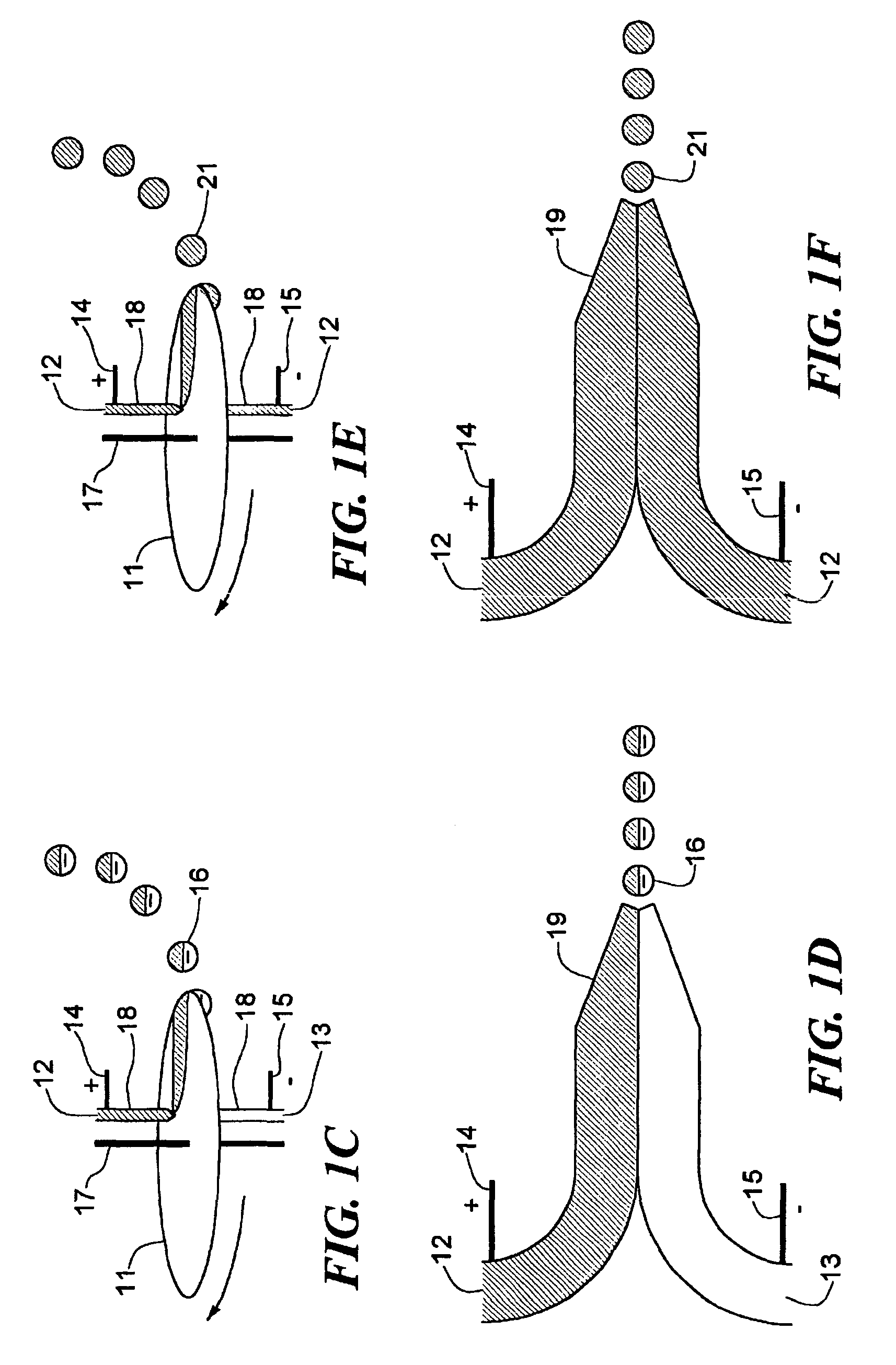

Electronically addressable microencapsulated ink and display thereof

InactiveUS7148128B2Inexpensive displayInking apparatusMechanical clocksSemiconductor materialsDisplay device

We describe a system of electronically active inks which may include electronically addressable contrast media, conductors, insulators, resistors, semiconductive materials, magnetic materials, spin materials, piezoelectric materials, optoelectronic, thermoelectric or radio frequency materials. We further describe a printing system capable of laying down said materials in a definite pattern. Such a system may be used for instance to: print a flat panel display complete with onboard drive logic; print a working logic circuit onto any of a large class of substrates; print an electrostatic or piezoelectric motor with onboard logic and feedback or print a working radio transmitter or receiver.

Owner:E INK CORPORATION

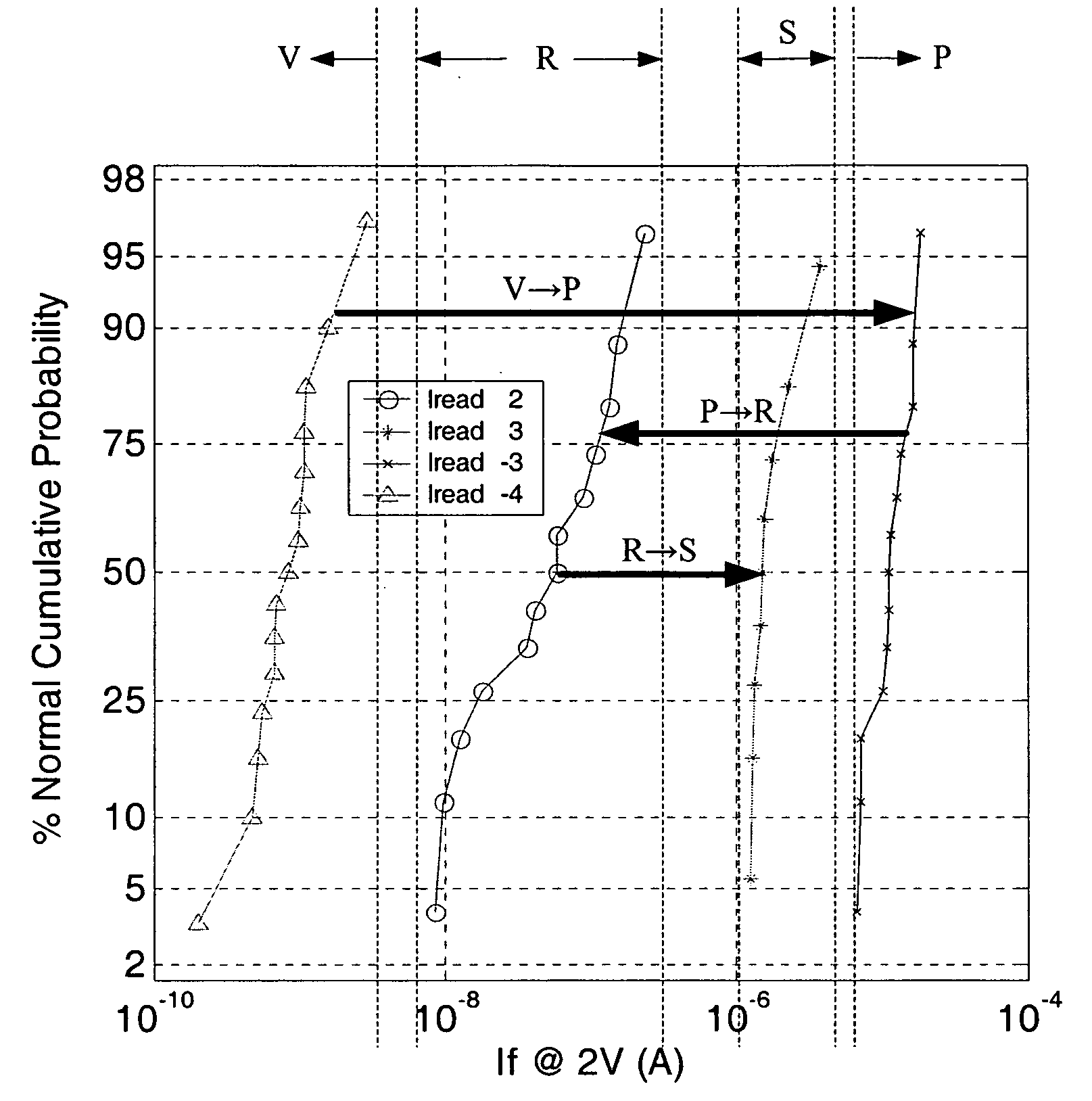

Method for using a memory cell comprising switchable semiconductor memory element with trimmable resistance

ActiveUS20070072360A1Solid-state devicesRead-only memoriesElectrical resistance and conductanceSemiconductor materials

A nonvolatile memory cell comprising a diode formed of semiconductor material can store memory states by changing the resistance of the semiconductor material by application of a set pulse (decreasing resistance) or a reset pulse (increasing resistance.) In preferred embodiments, set pulses are applied with the diode under forward bias, while reset pulses are applied with the diode in reverse bias. By switching resistivity of the semiconductor material of the diode, a memory cell can be either one-time programmable or rewriteable, and can achieve two, three, four, or more distinct data states.

Owner:WODEN TECH INC

Vertical-type non-volatile memory devices

ActiveUS20090121271A1Reduce the possibilityReduce in quantityTransistorSolid-state devicesSemiconductor materialsDevice material

In a semiconductor device, and a method of manufacturing thereof, the device comprises a substrate of single-crystal semiconductor material extending in a horizontal direction and a plurality of interlayer dielectric layers on the substrate. A plurality of gate patterns are provided, each gate pattern being between a neighboring lower interlayer dielectric layer and a neighboring upper interlayer dielectric layer. A vertical channel of single-crystal semiconductor material extends in a vertical direction through the plurality of interlayer dielectric layers and the plurality of gate patterns, a gate insulating layer being between each gate pattern and the vertical channel that insulates the gate pattern from the vertical channel.

Owner:SAMSUNG ELECTRONICS CO LTD

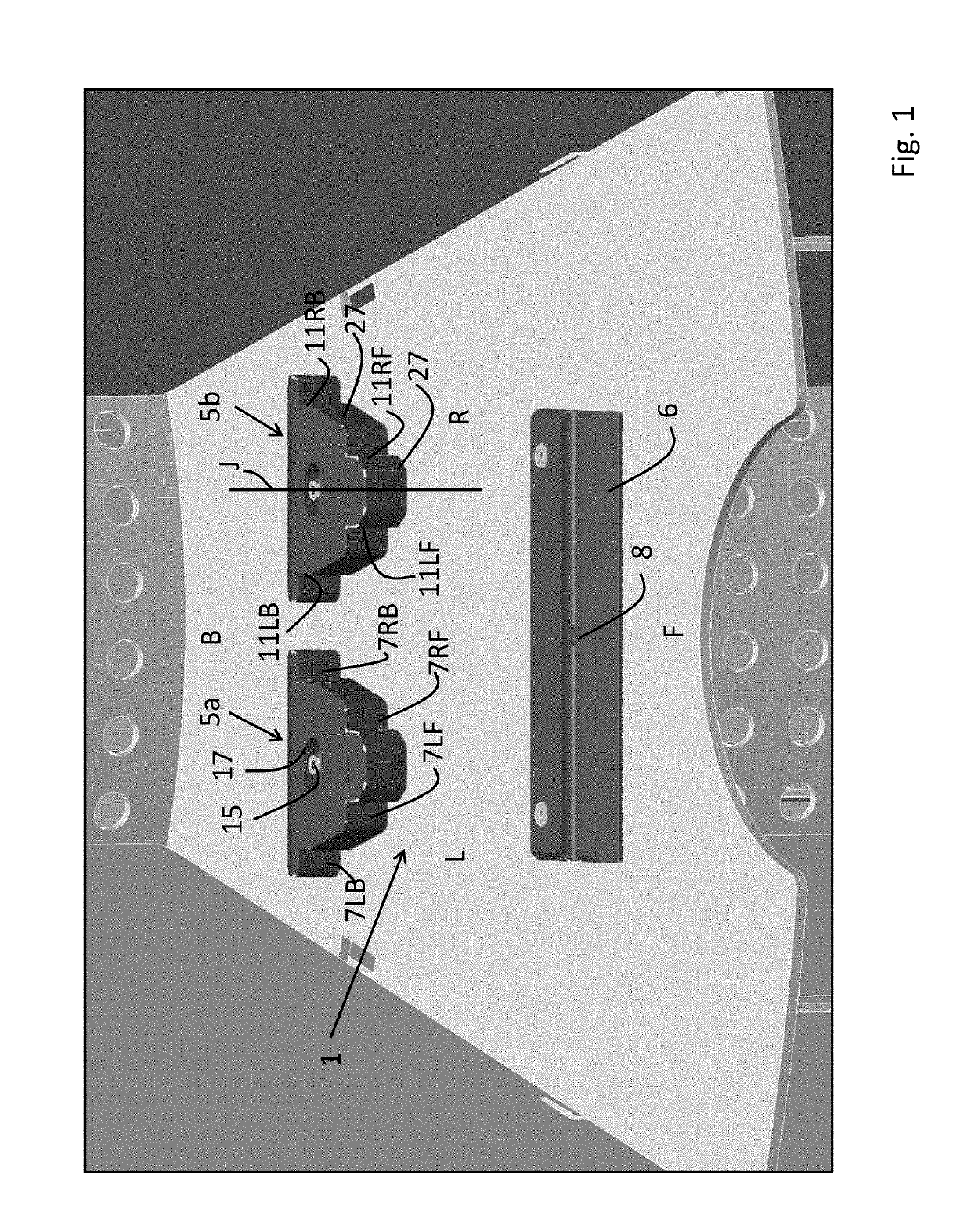

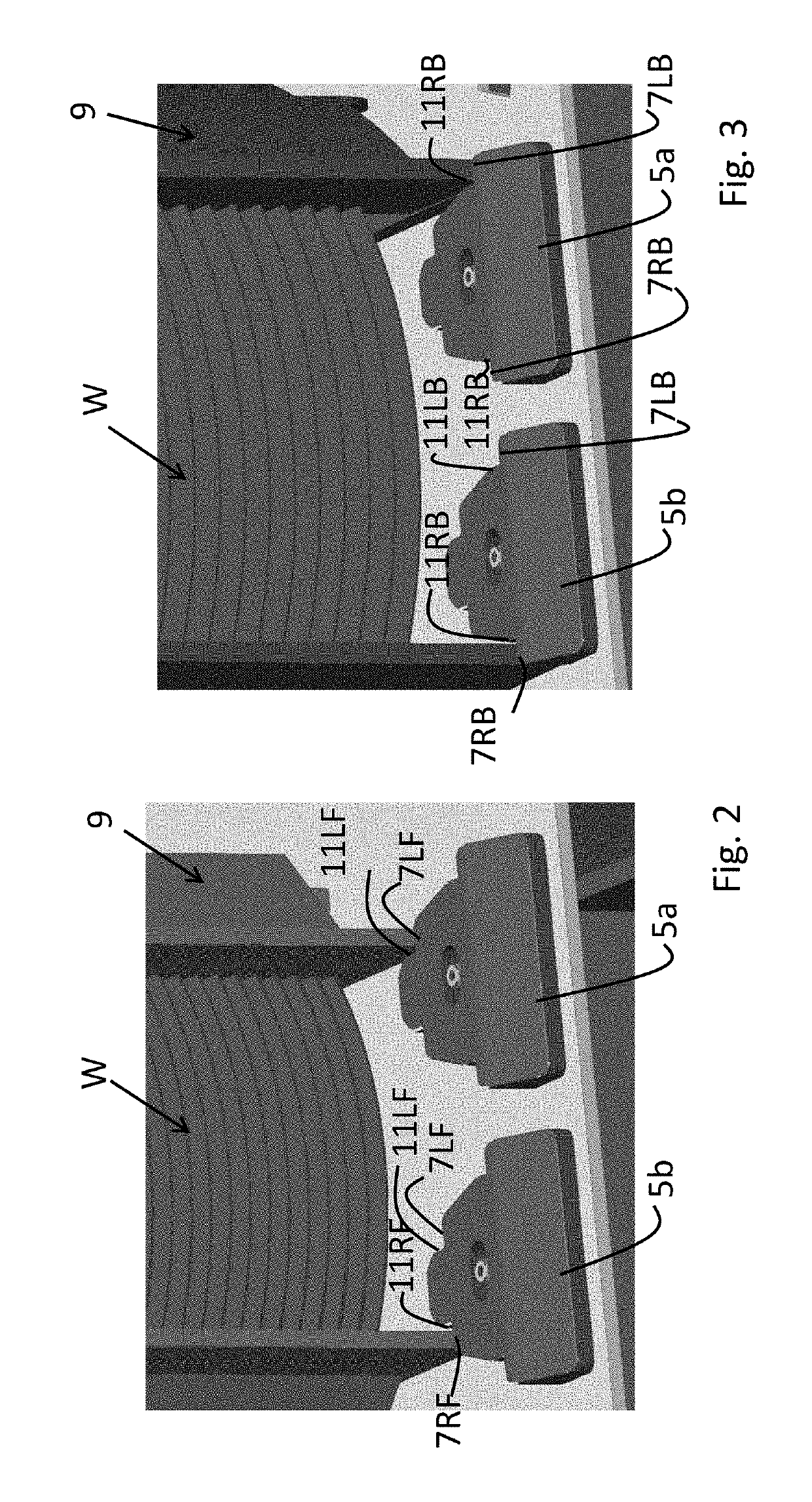

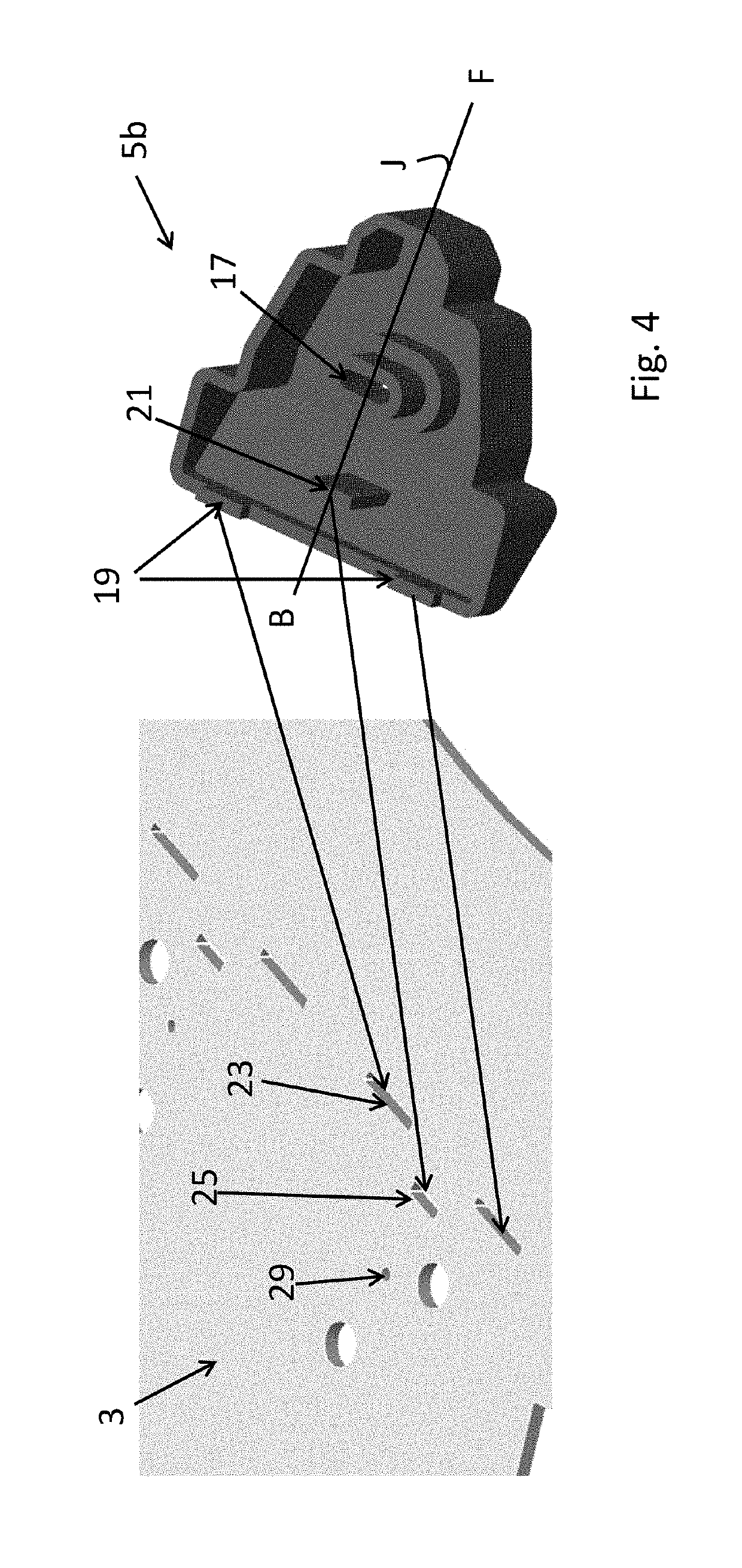

Cassette holder assembly for a substrate cassette and holding member for use in such assembly

ActiveUS10249524B2Increase the number ofEasy maintenanceSemiconductor/solid-state device detailsSolid-state devicesInterior spaceSemiconductor materials

The invention relates to a cassette holder assembly for holding a cassette for storing at least one semiconductor material substrate in an interior space accessible from a front end of the cassette. The cassette holder assembly may have a base plate for receiving the cassette. Two holding members supported by the base plate may be positioning the cassette on the plate in the assembly. The holding members may be substantially identical to each other.

Owner:ASM IP HLDG BV