Patents

Literature

2441 results about "Crystal orientation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Semiconductor method and device with mixed orientation substrate

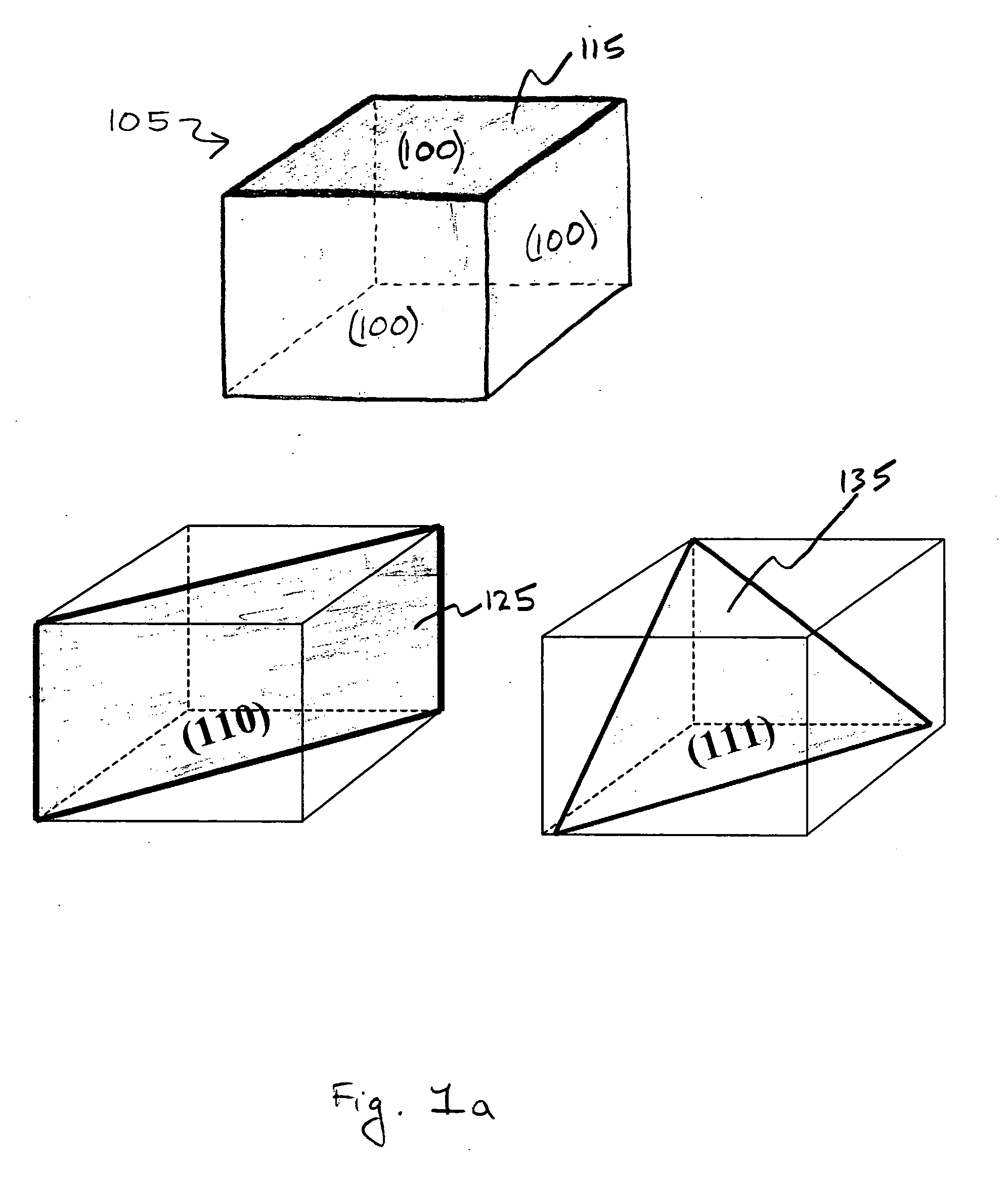

InactiveUS7298009B2Critical dimension of this mask is relaxedReduce processing stepsSemiconductor/solid-state device detailsSolid-state devicesSemiconductor materialsCrystal orientation

Owner:INFINEON TECH AG +1

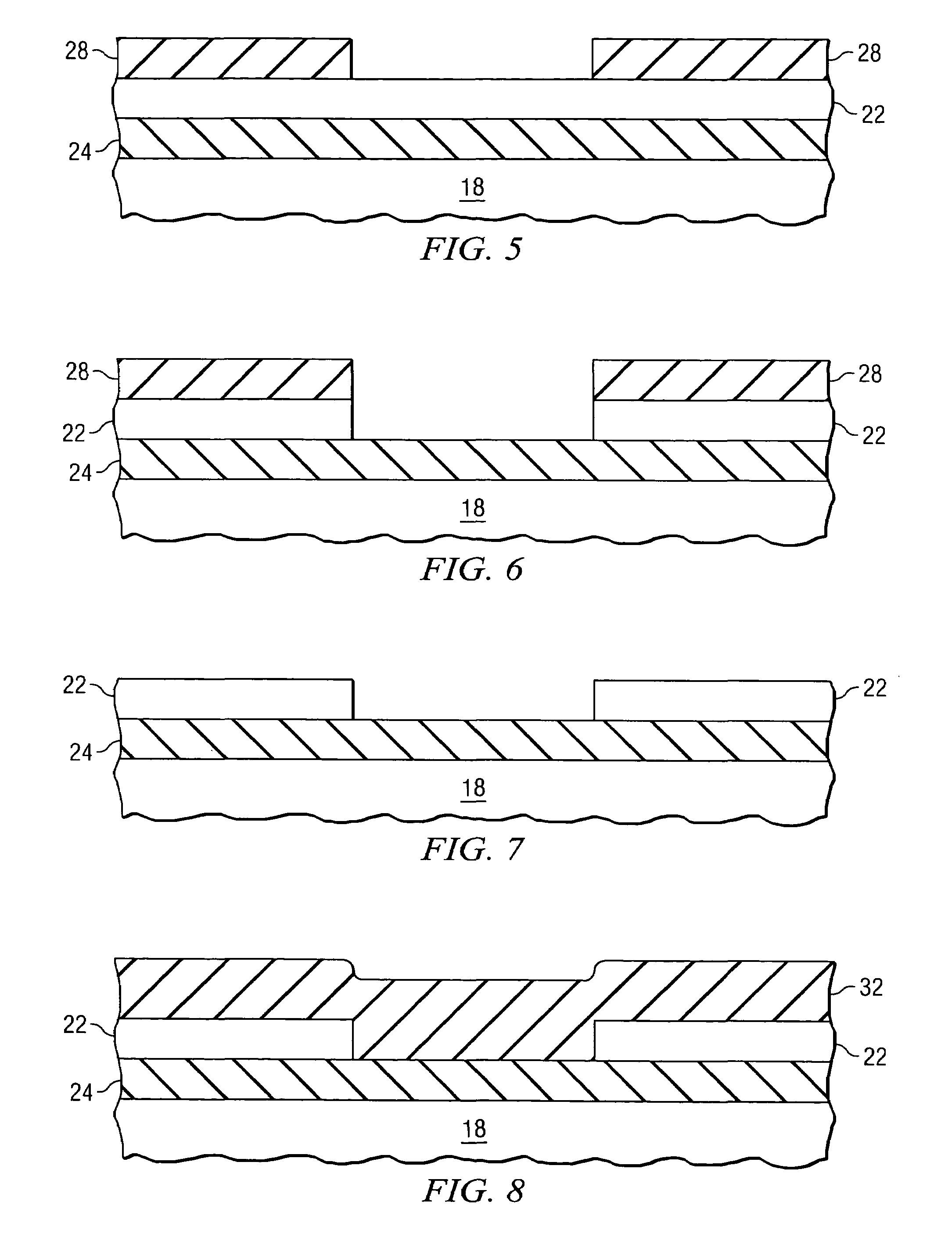

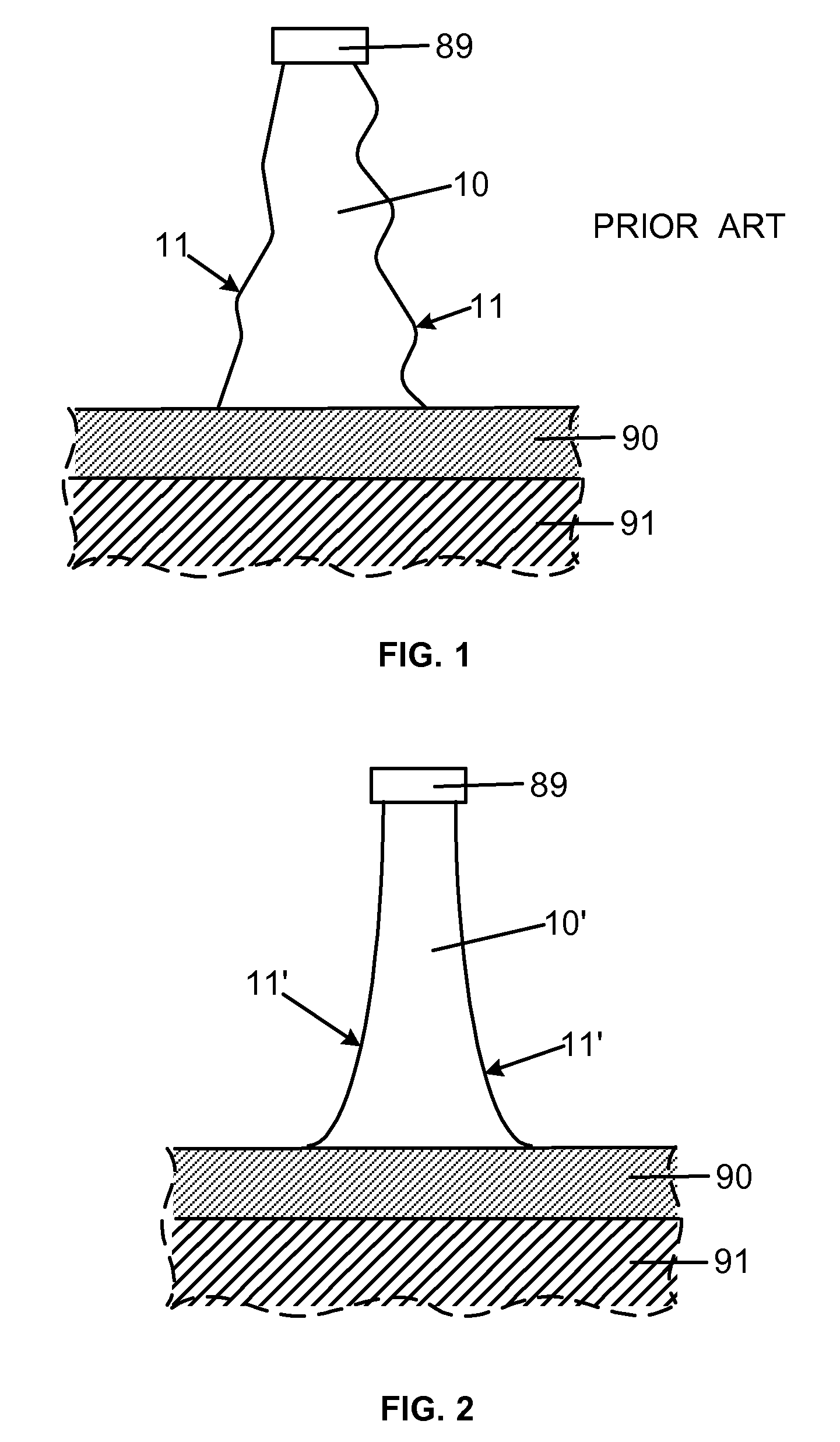

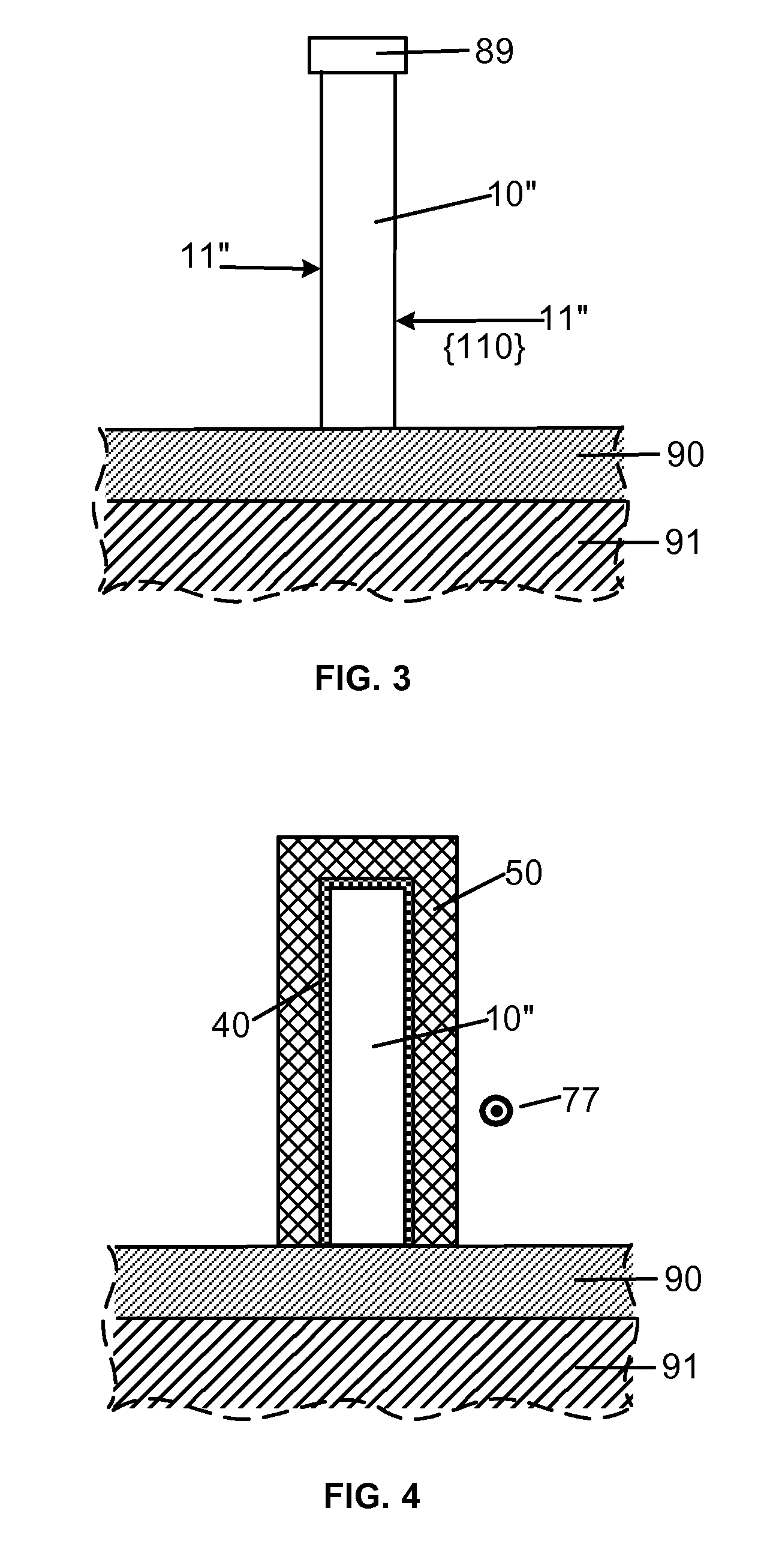

Smooth and vertical semiconductor fin structure

InactiveUS20100048027A1Semiconductor/solid-state device manufacturingSemiconductor devicesSelf limitingCrystal orientation

A method for processing a semiconductor fin structure is disclosed. The method includes thermal annealing a fin structure in an ambient containing an isotope of hydrogen. Following the thermal annealing step, the fin structure is etched in a crystal-orientation dependent, self-limiting, manner. The crystal-orientation dependent etch may be selected to be an aqueous solution containing ammonium hydroxide (NH4OH). The completed fin structure has smooth sidewalls and a uniform thickness profile. The fin structure sidewalls are {110} planes.

Owner:GLOBALFOUNDRIES INC

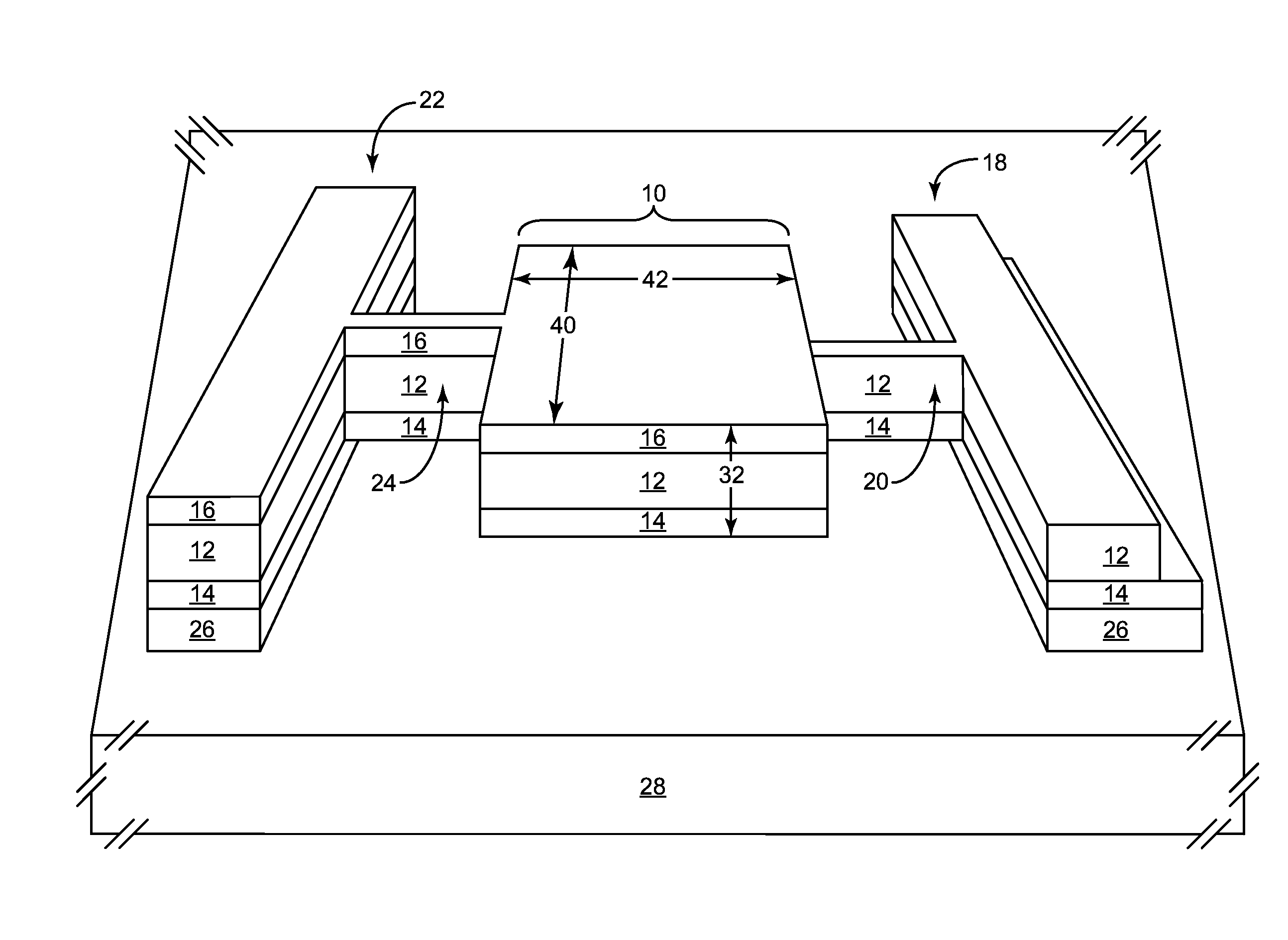

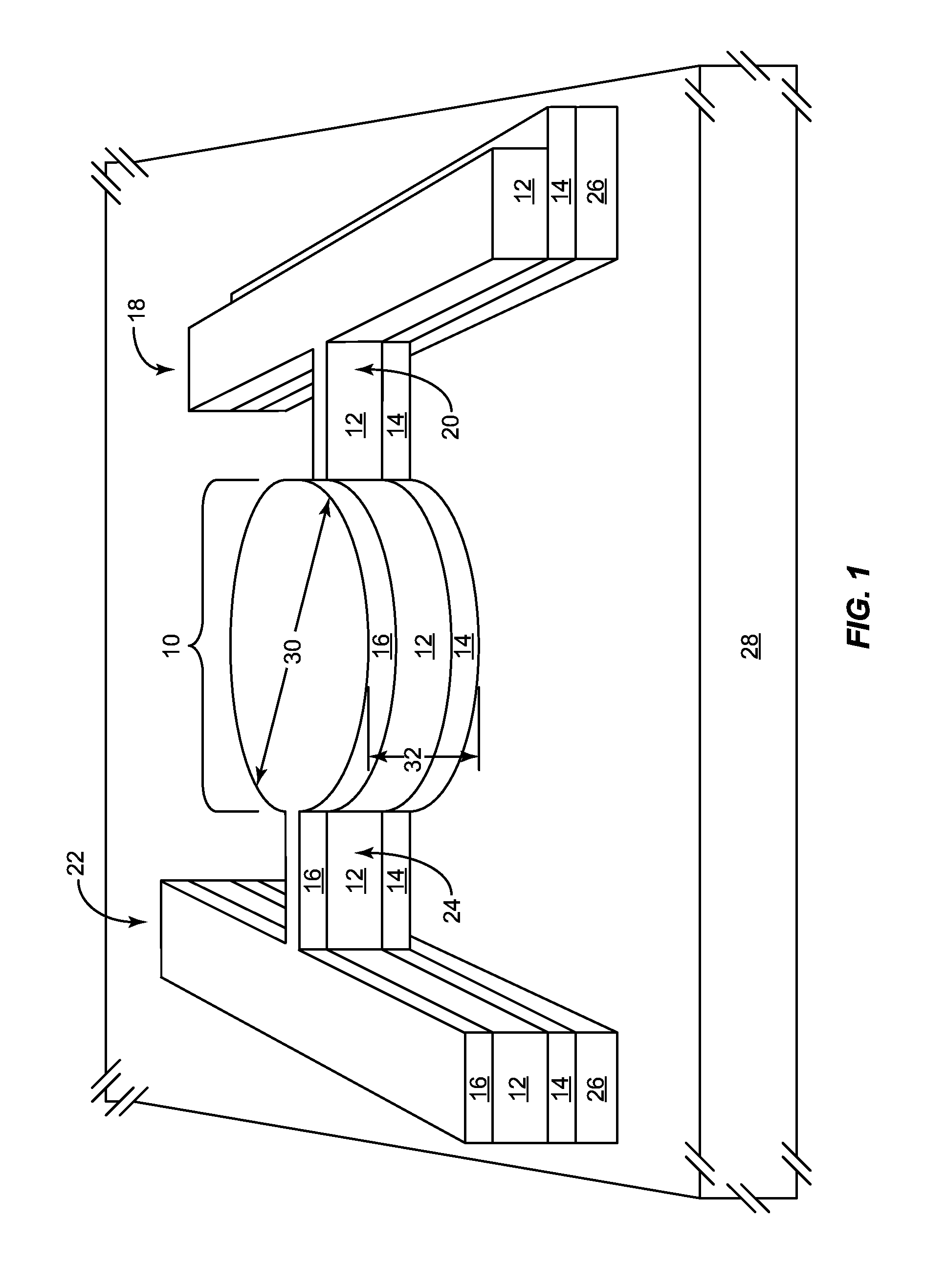

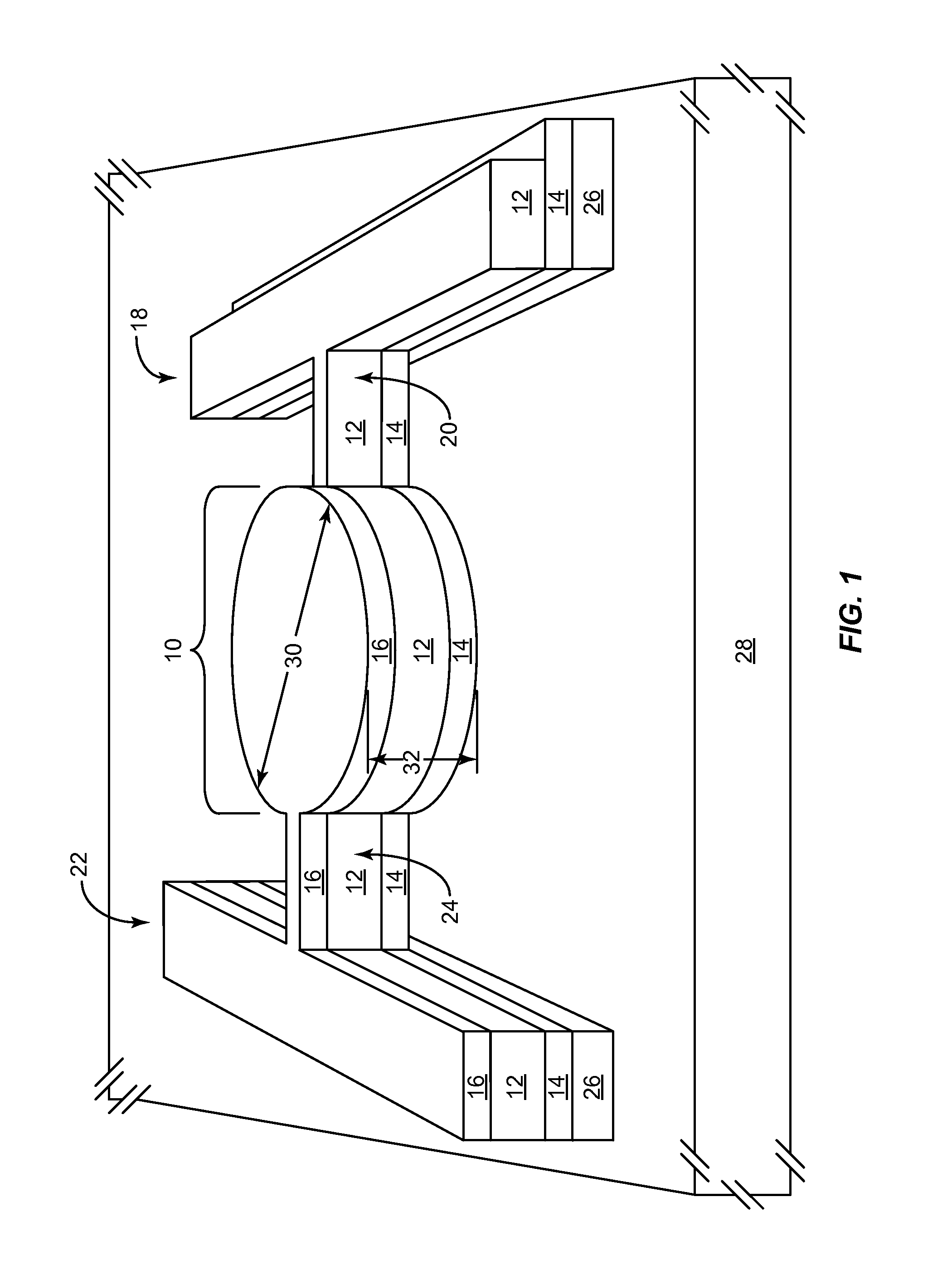

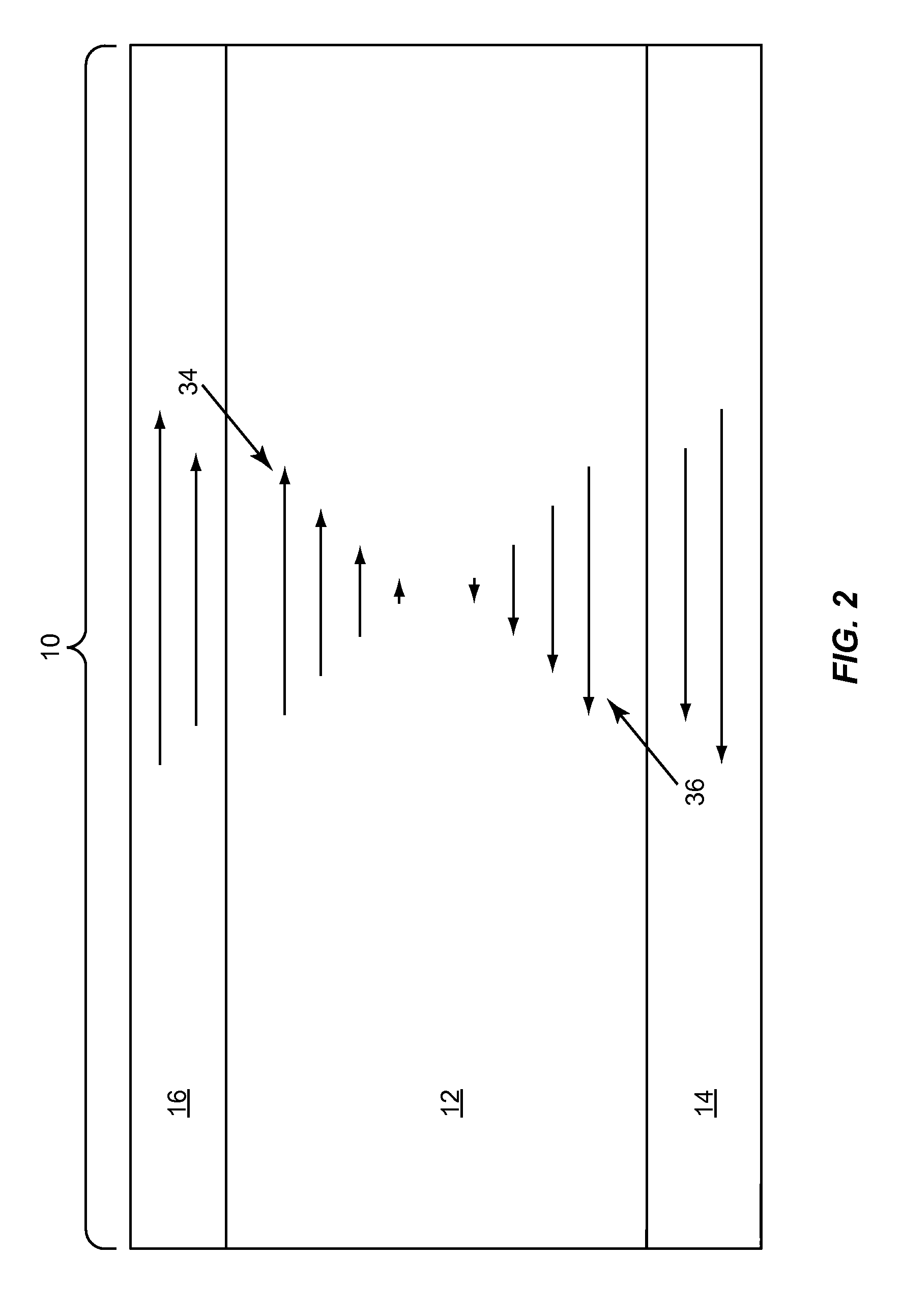

MEMS vibrating structure using an orientation dependent single-crystal piezoelectric thin film layer

ActiveUS20140210314A1Impedence networksPiezoelectric/electrostriction/magnetostriction machinesSingle crystalPiezoelectric thin films

A micro-electrical-mechanical system (MEMS) vibrating structure includes a carrier substrate, a first anchor, a second anchor, a single crystal piezoelectric body, and a conducting layer. The first anchor and the second anchor are provided on the surface of the carrier substrate. The single-crystal piezoelectric body is suspended between the first anchor and the second anchor, and includes a uniform crystalline orientation defined by a set of Euler angles. The single-crystal piezoelectric body includes a first surface parallel to and facing the surface of the carrier substrate on which the first anchor and the second anchor are formed and a second surface opposite the first surface. The conducting layer is inter-digitally dispersed, and is formed on the second surface of the single-crystal piezoelectric body. The first surface of the single-crystal piezoelectric body is left exposed.

Owner:QORVO US INC

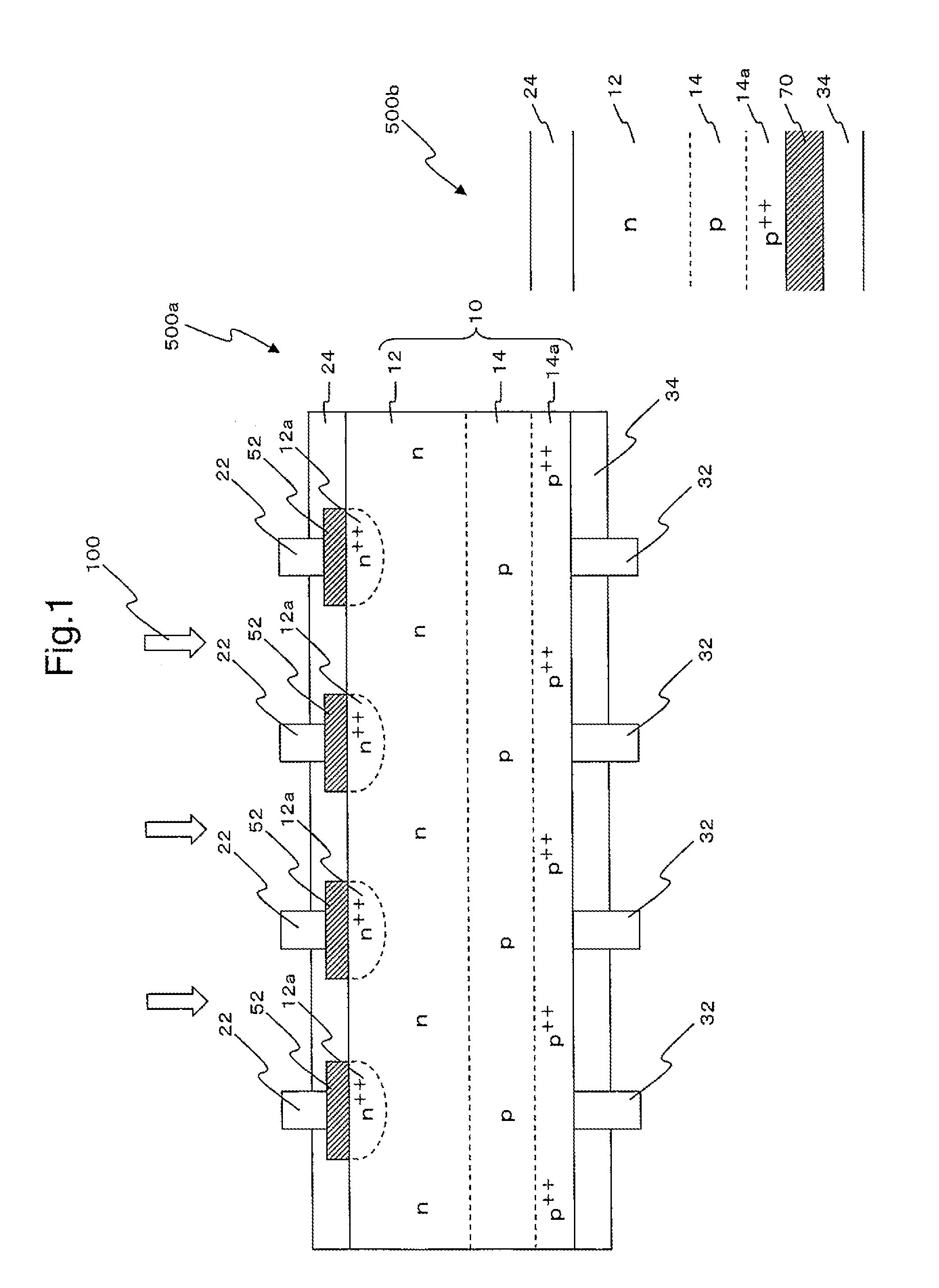

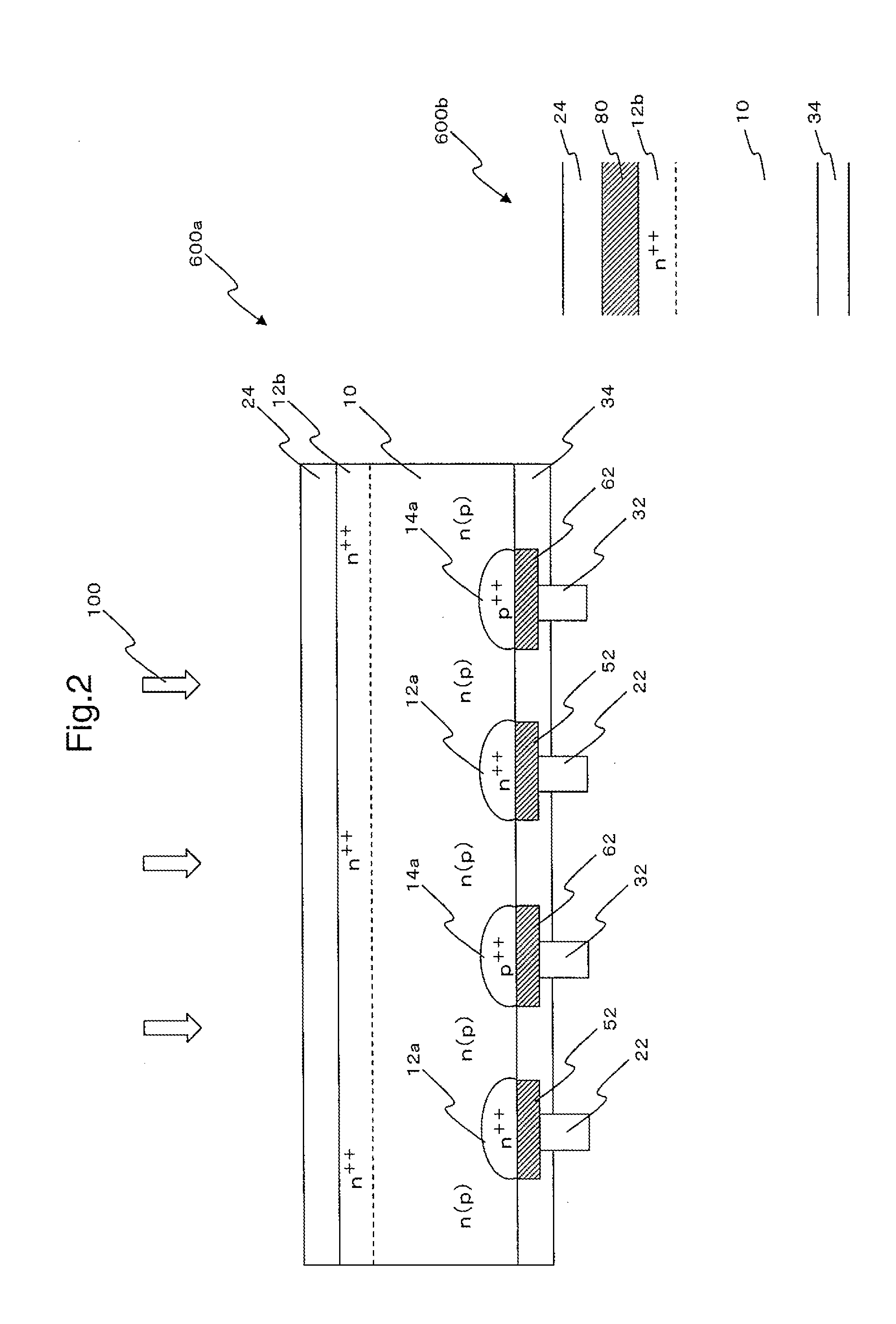

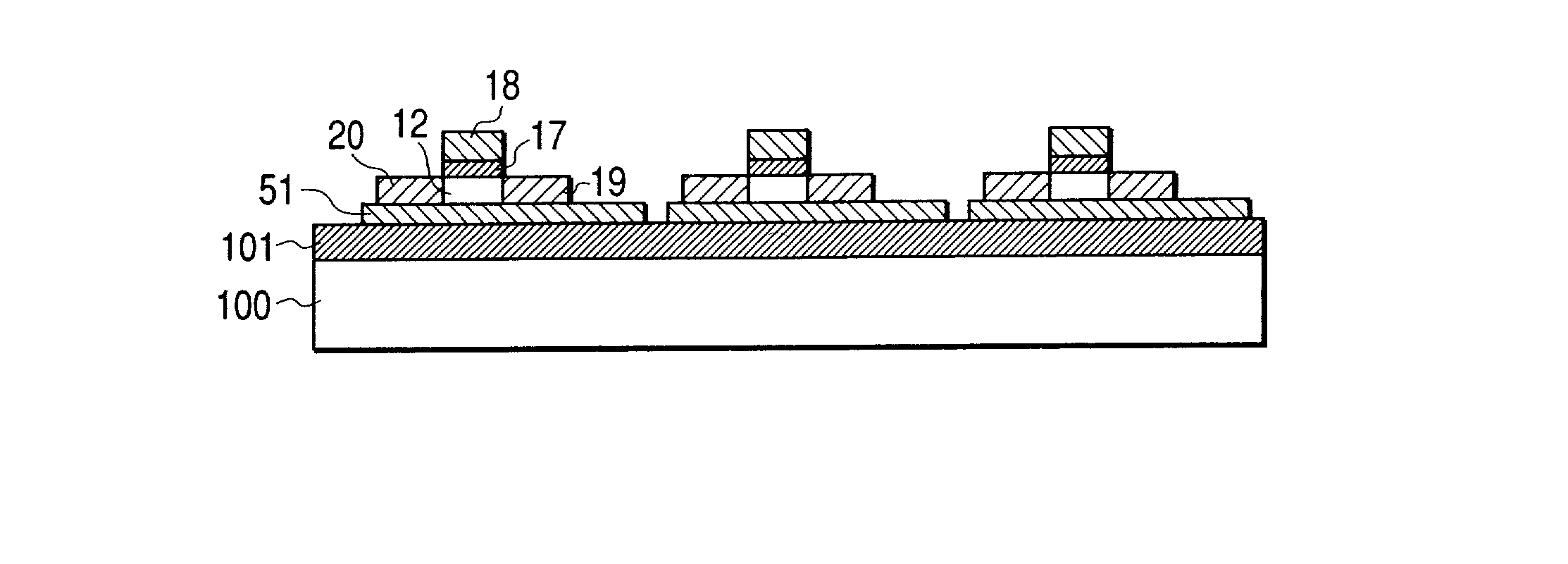

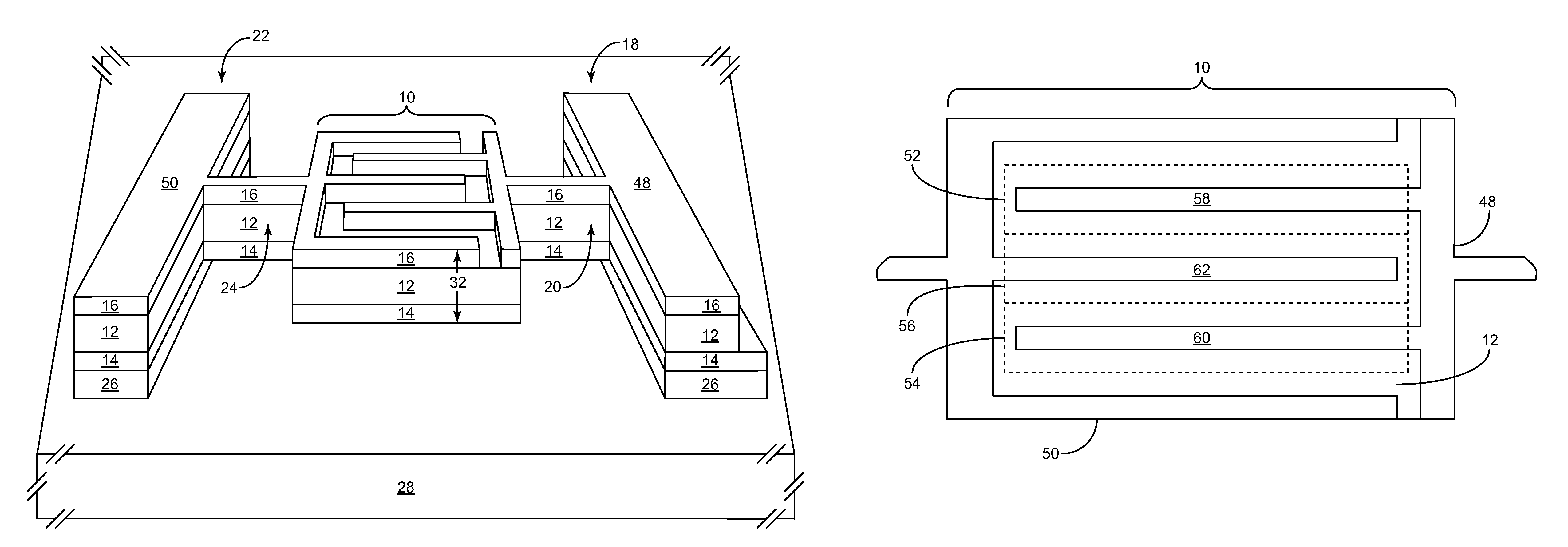

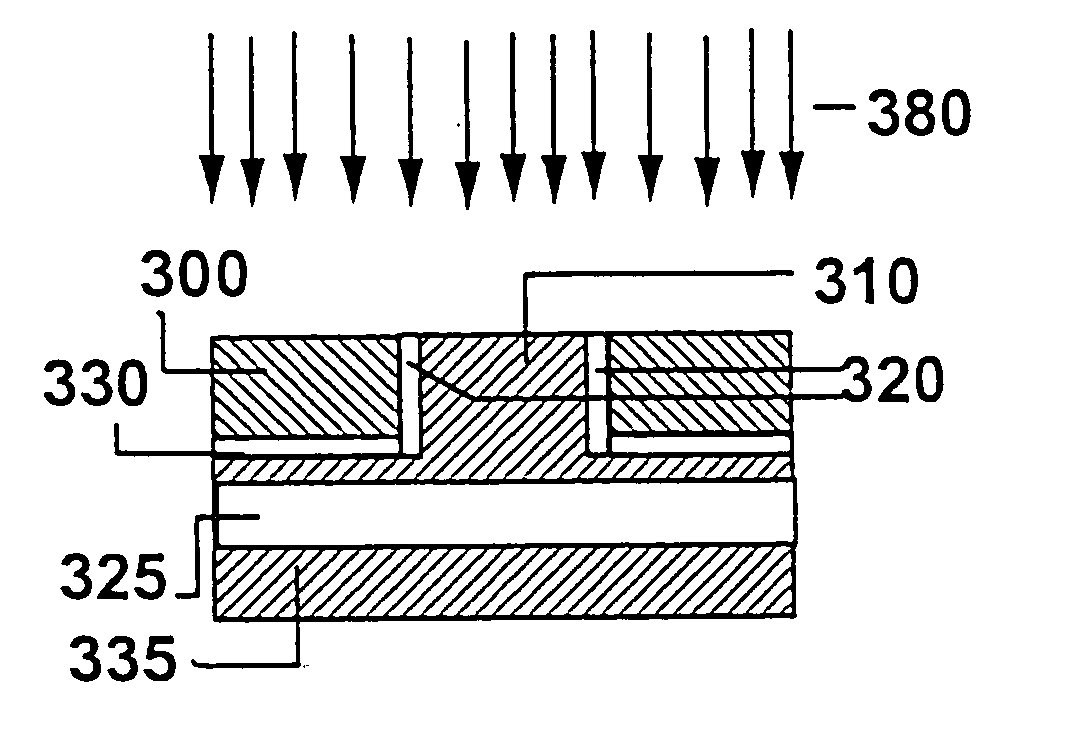

Semiconductor laminate, semiconductor device, and production method thereof

InactiveUS20130228902A1Avoid entrapmentLight absorptionSiliconFinal product manufactureDopantCrystal orientation

Provided is a method for manufacturing a semiconductor device. Also provided are: a semiconductor device which can be obtained by the method; and a dispersion that can be used in the method. A method for manufacturing a semiconductor device (500a) of the present invention comprises the steps (a)-(c) described below and is characterized in that the crystal orientation of a first dopant implanted layer (52) is the same as the crystal orientation of a semiconductor layer or a base (10) that is formed of a semiconductor element. (a) A dispersion which contains doped particles is applied to a specific part of a layer or a base. (b) An unsintered dopant implanted layer is obtained by drying the applied dispersion. (c) The specific part of the layer or the base is doped with a p-type or n-type dopant by irradiating the unsintered dopant implanted layer with light, and the unsintered dopant implanted layer is sintered, thereby obtaining a dopant implanted layer that is integrated with the layer or the base.

Owner:TEIJIN LTD

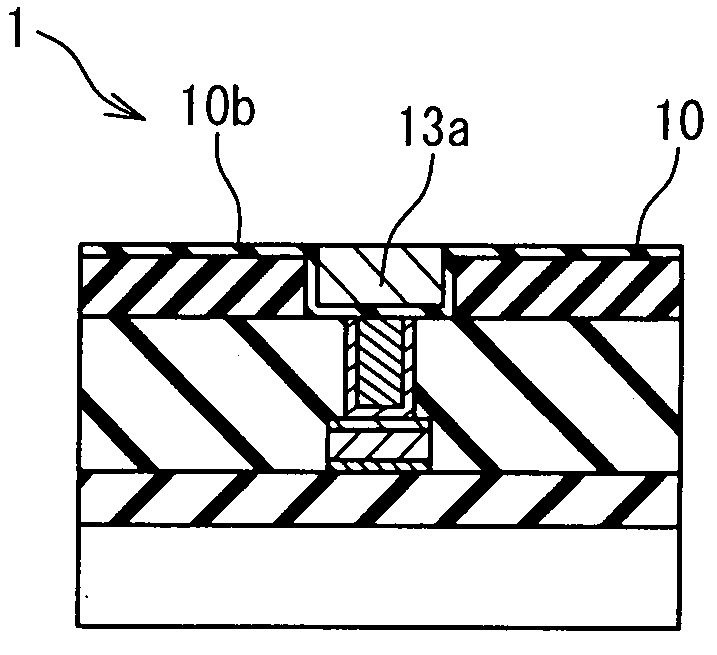

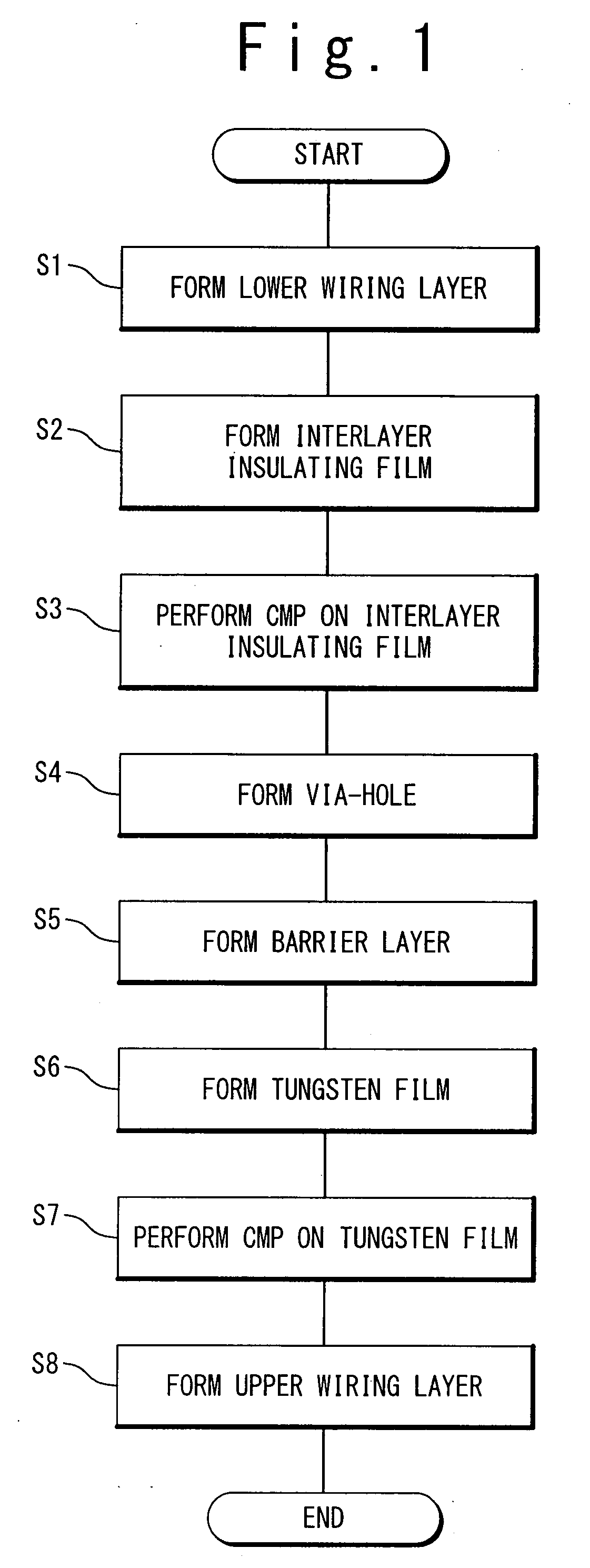

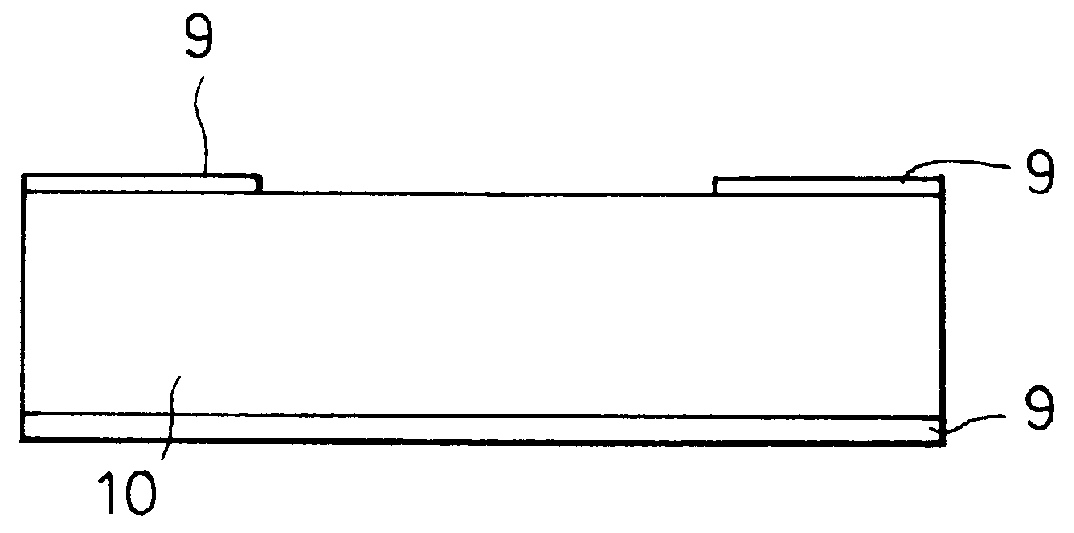

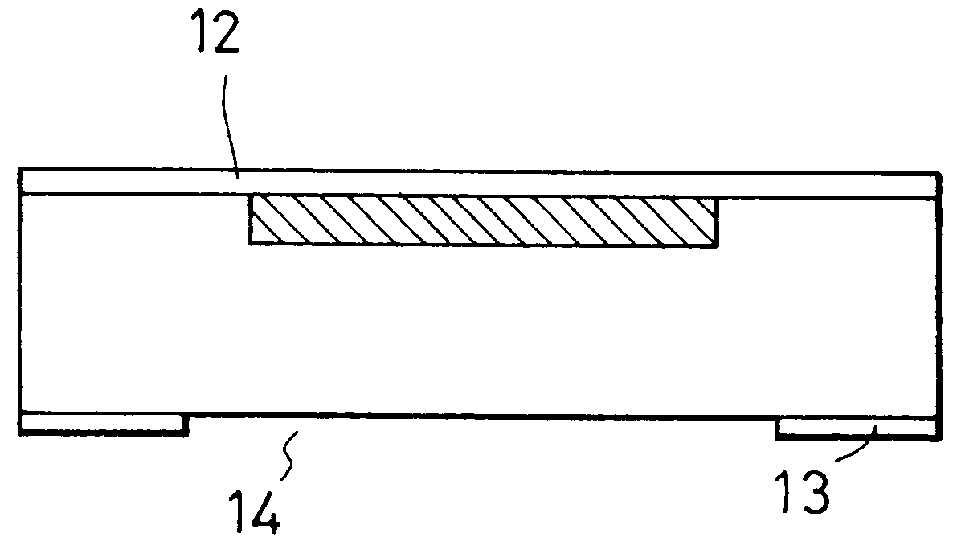

Method of manufacturing semiconductor device

InactiveUS20080102630A1Raise the ratioSolid-state devicesSemiconductor/solid-state device manufacturingCompound (substance)Crystal orientation

In a method of manufacturing a semiconductor device, an insulating film with a concave portion is formed on a semiconductor wafer. A barrier layer is formed on the insulating film to cover a surface of the insulating film such that the barrier layer has a uniform crystal orientation over a whole wafer surface of the semiconductor wafer. A metal film is formed on the barrier layer such that a portion of the metal film fills the concave portion, and a CMP (Chemical Mechanical Polishing) method is performed on the metal film to leave the filling portion of the metal film.

Owner:ELPIDA MEMORY INC

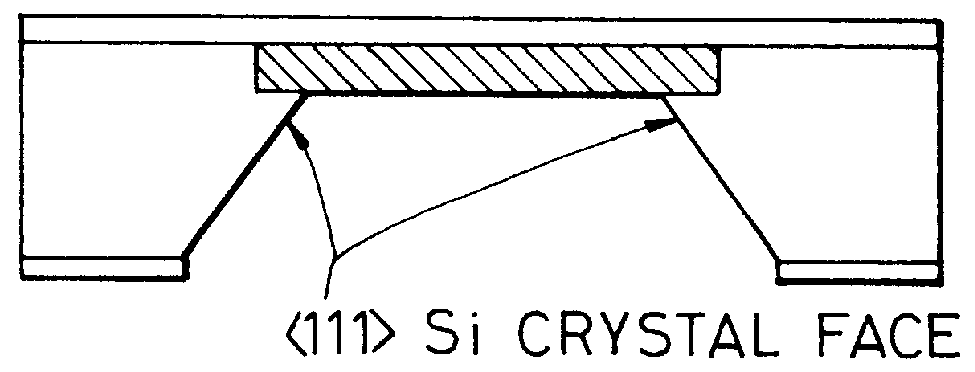

Method of producing a through-hole, silicon substrate having a through-hole, device using such a substrate, method of producing an ink-jet print head, and ink-jet print head

The invention provides a method of producing a through-hole, a substrate used to produce a through-hole, a substrate having a through-hole, and a device using such a through-hole or a substrate having such a through-hole, which are characterized in that: a through-hole can be produced only by etching a silicon substrate from its back side; the opening length d can be precisely controlled to a desired value regardless of the variations in the silicon wafer thickness, and the orientation flat angle, and also regardless of the type of a silicon crystal orientation-dependent anisotropic etchant employed; high productivity, high production reproducibility, and ease of production can be achieved; a high-liberality can be achieved in the shape of the opening end even if temperature treatment is performed at a high temperature for a long time; and a high-precision through-hole can be produced regardless of the shape of a device formed on the surface of a substrate.

Owner:CANON KK

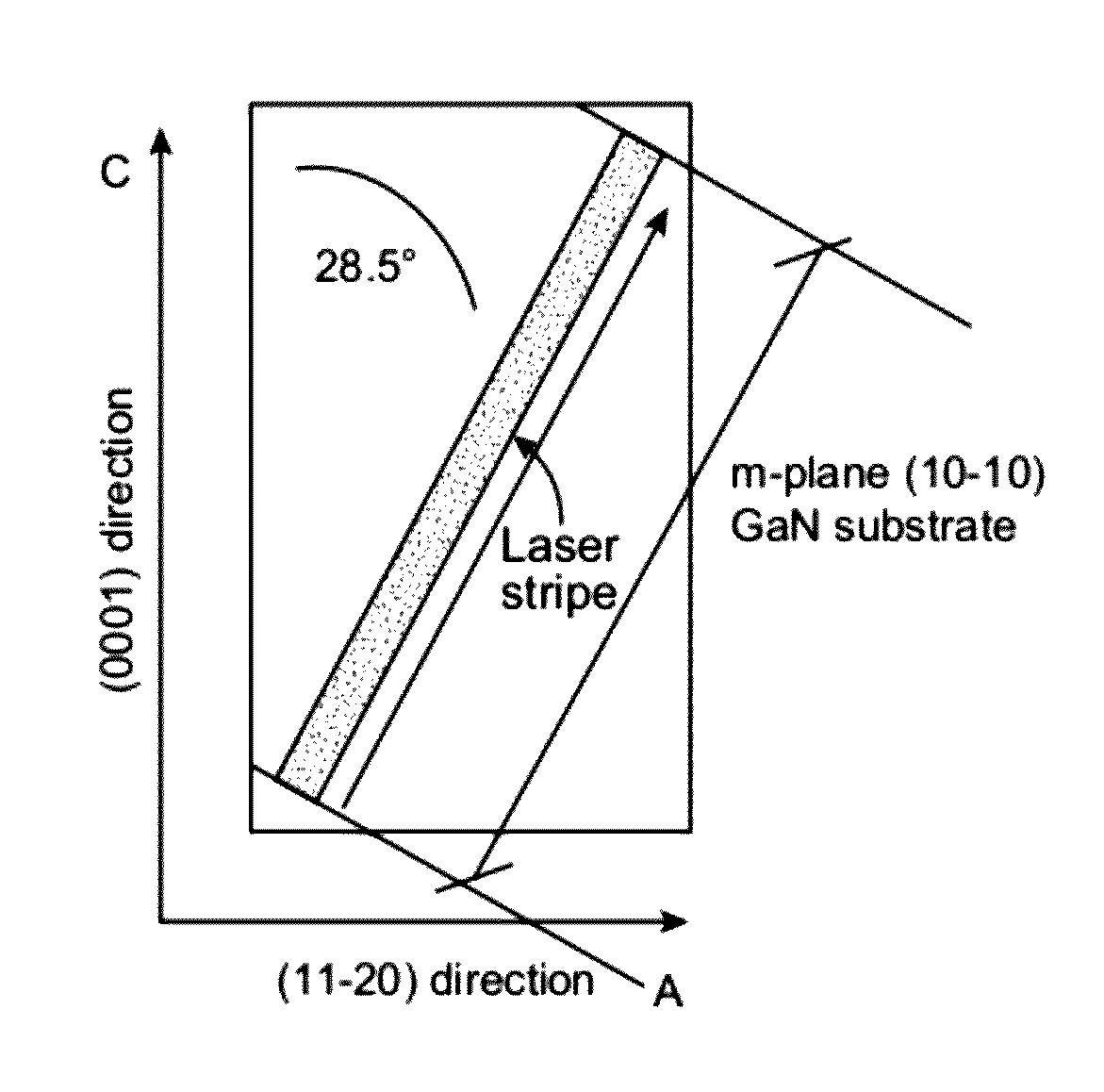

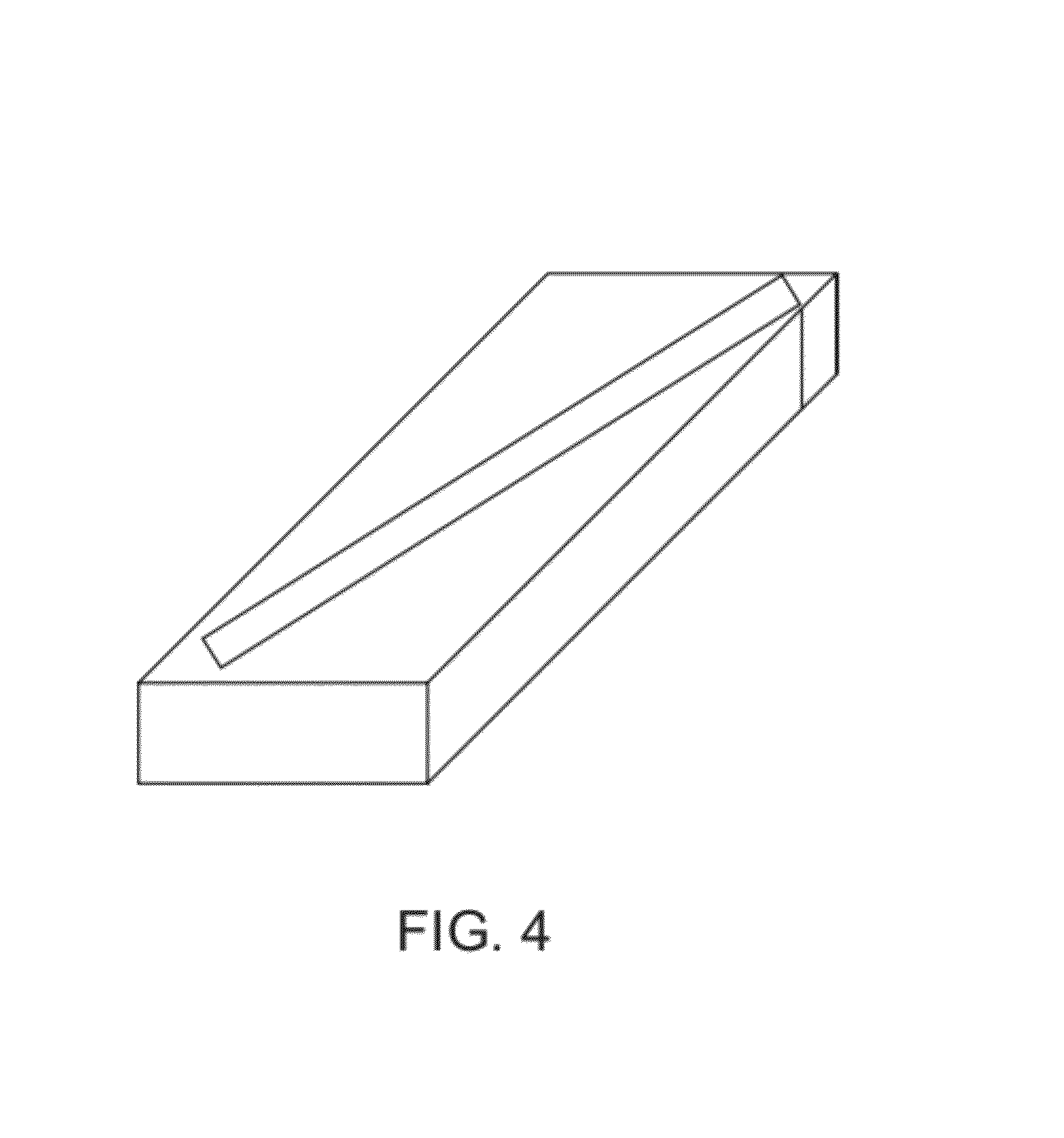

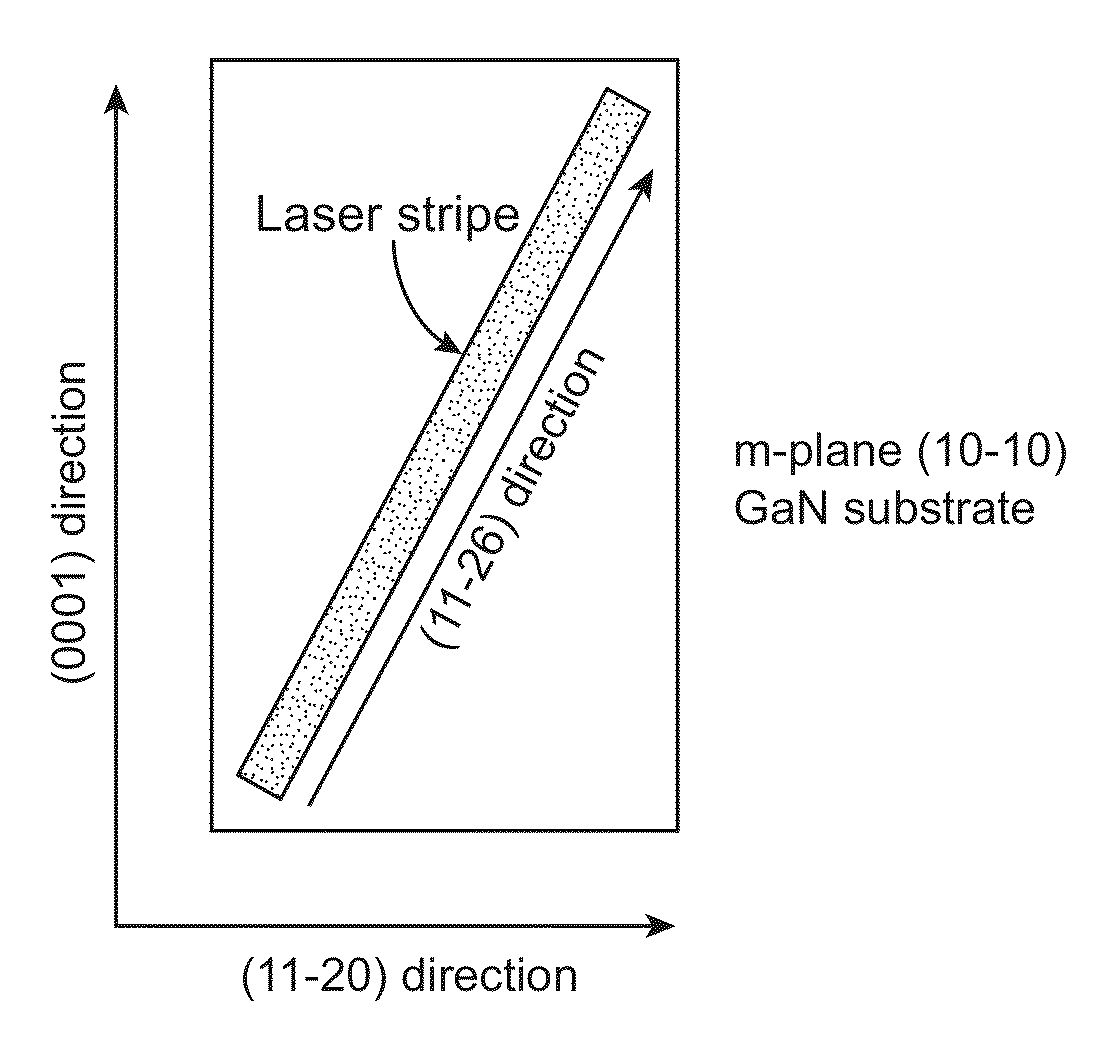

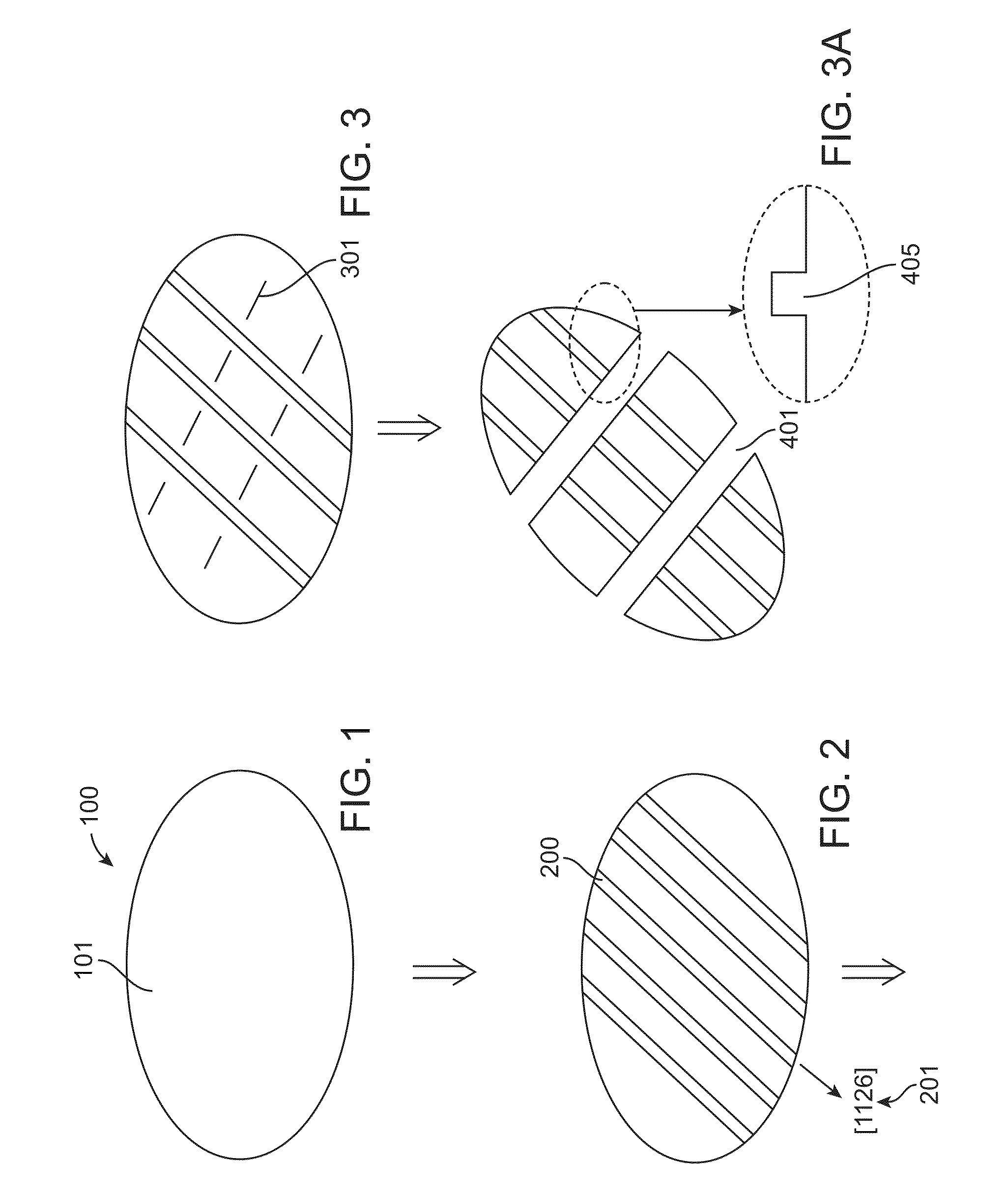

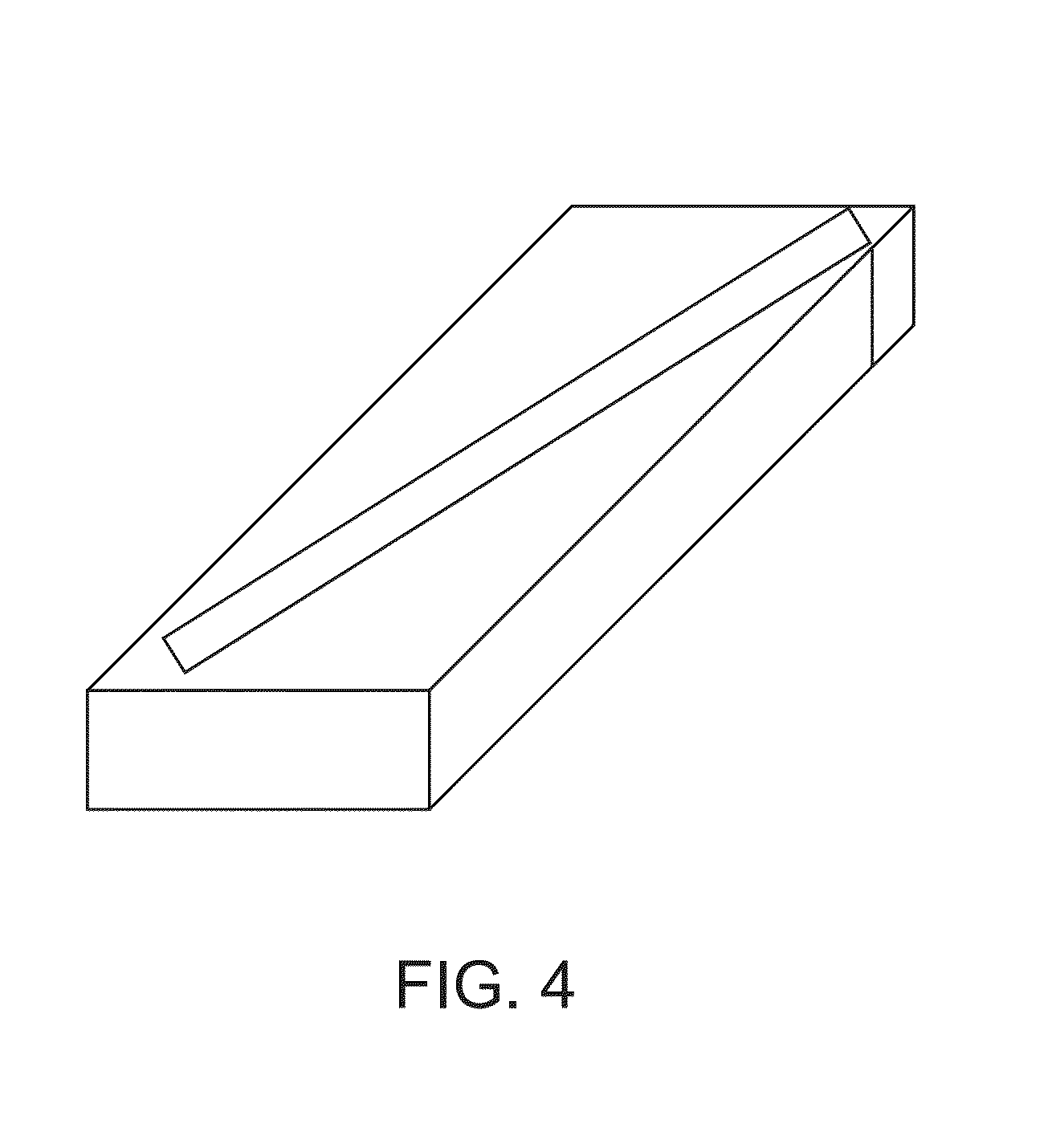

Solid state laser device using a selected crystal orientation in non-polar or semi-polar GaN containing materials and methods

ActiveUS8284810B1Facilitates parallel facetReduce surface roughnessNanoopticsSemiconductor lasersHigh current densitySolid-state laser device

An edge emitting solid state laser and method. The laser comprises at least one AlInGaN active layer on a bulk GaN substrate with a non-polar or semi-polar orientation. The edges of the laser comprise {1 1 −2 ±6} facets. The laser has high gain, low threshold currents, capability for extended operation at high current densities, and can be manufactured with improved yield. The laser is useful for optical data storage, projection displays, and as a source for general illumination.

Owner:KYOCERA SLD LASER INC

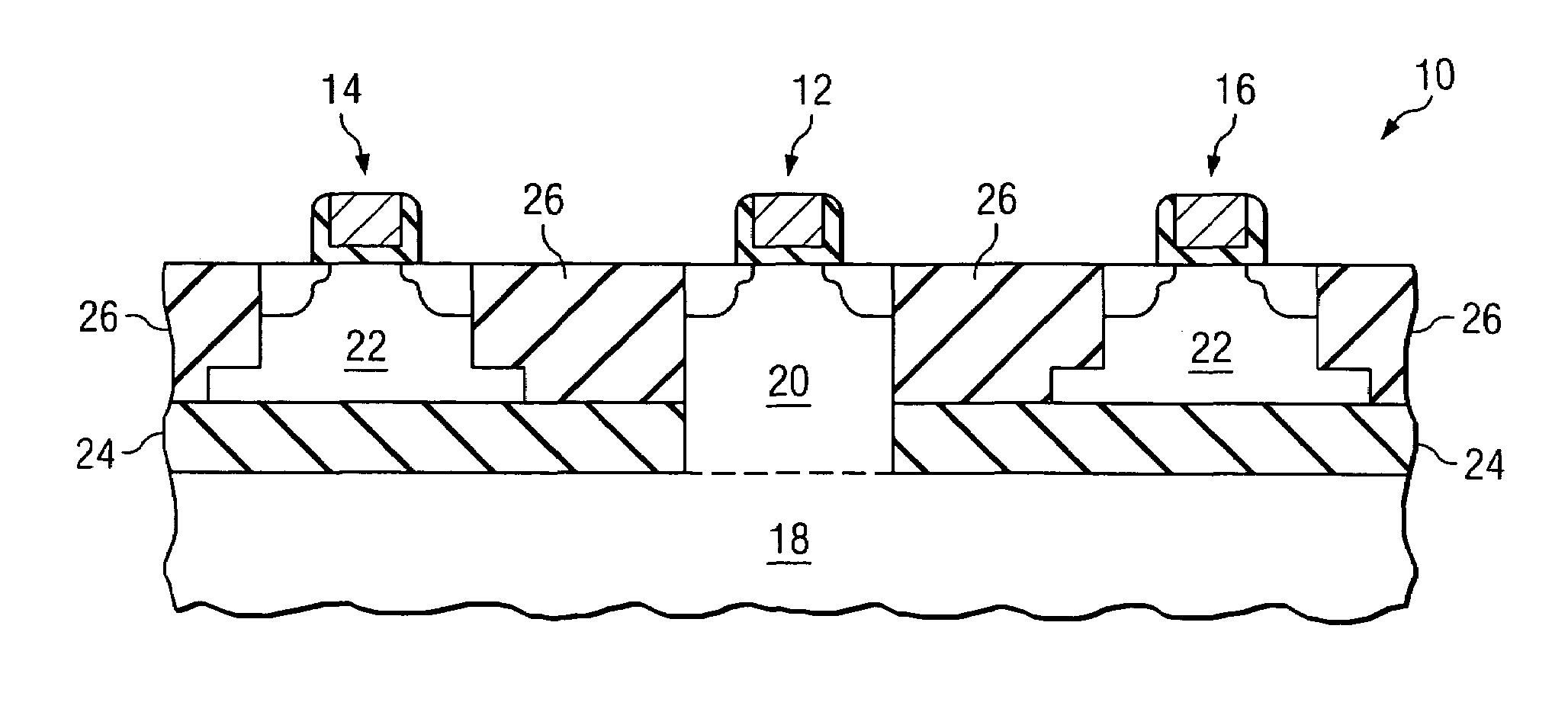

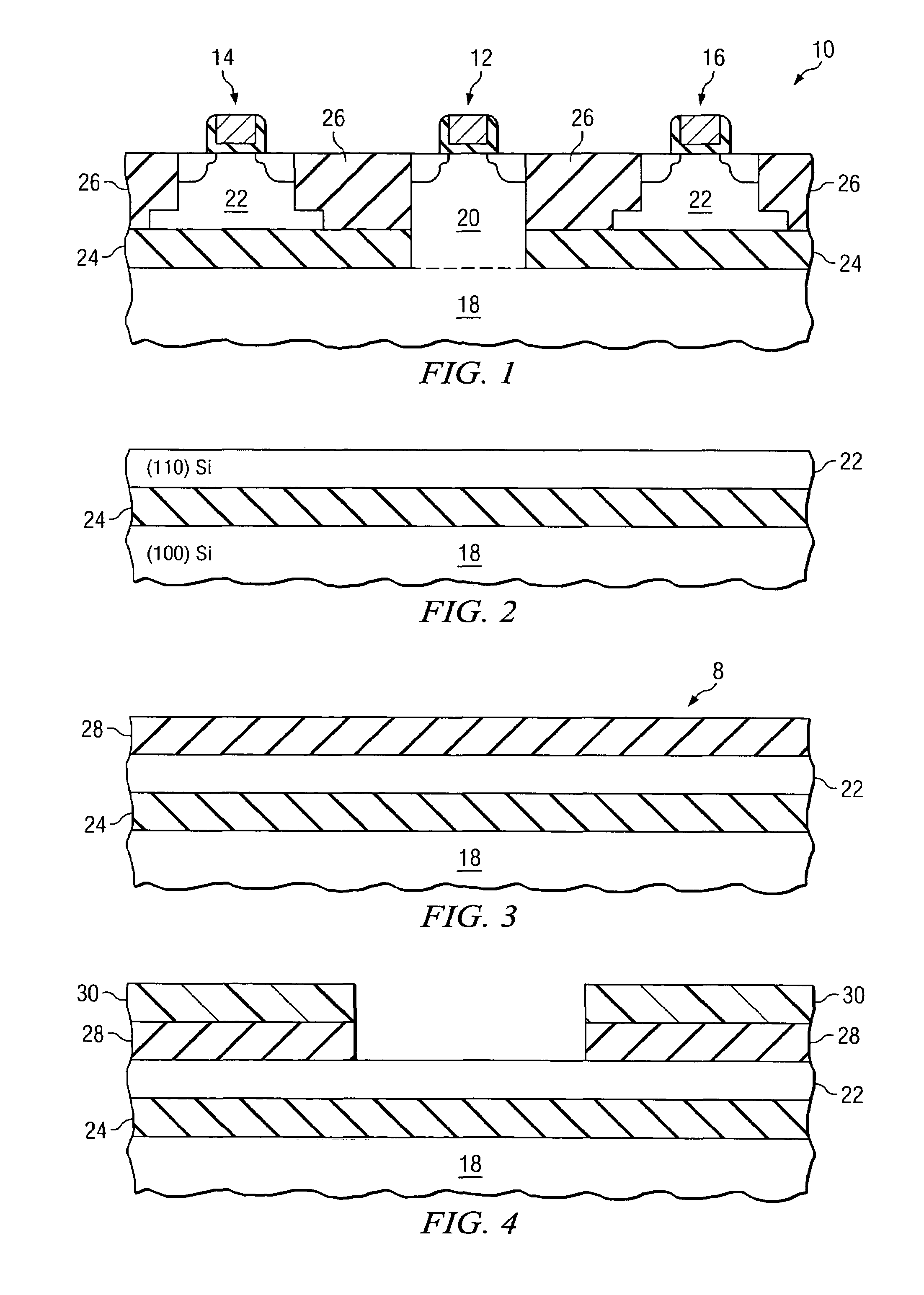

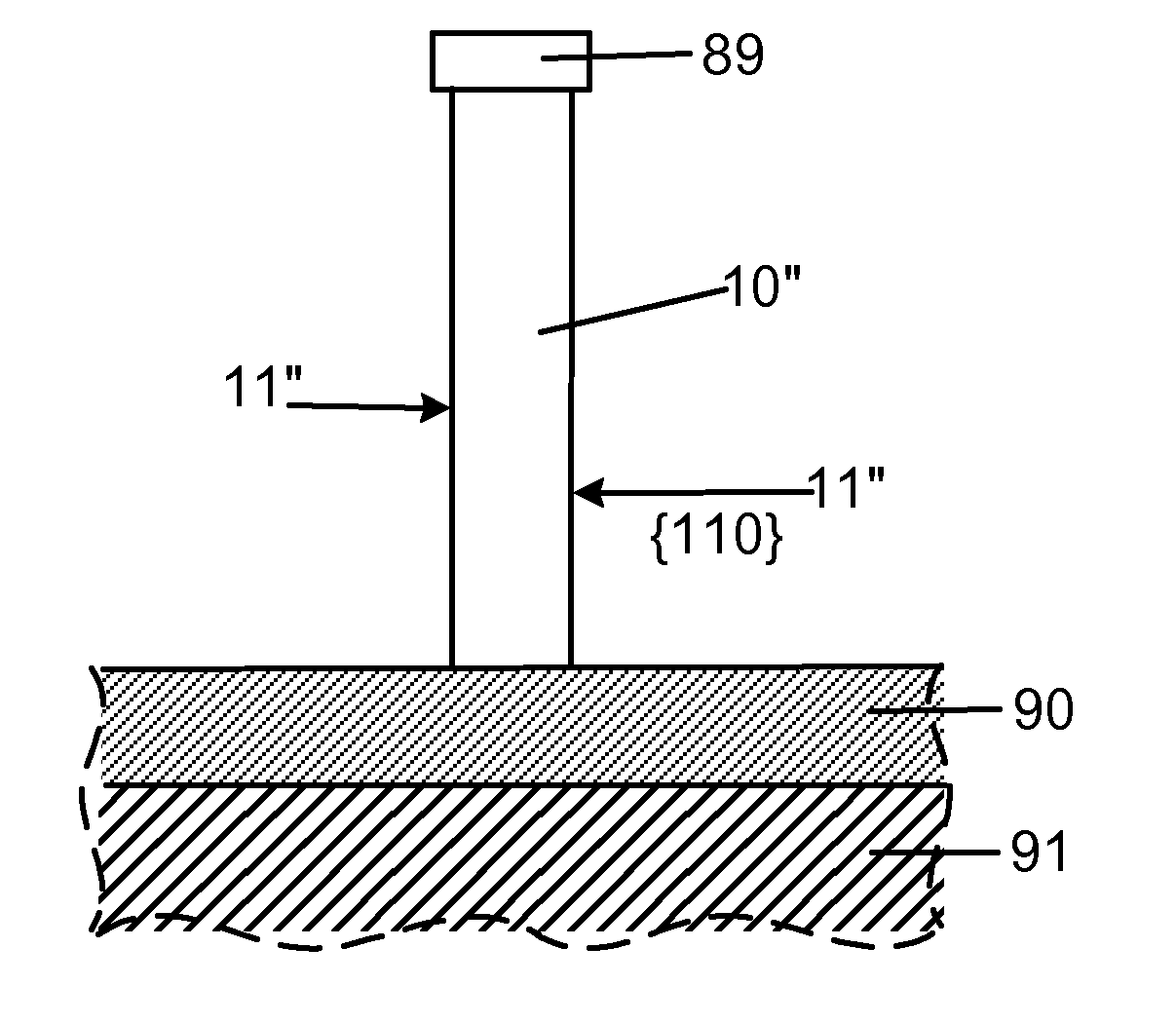

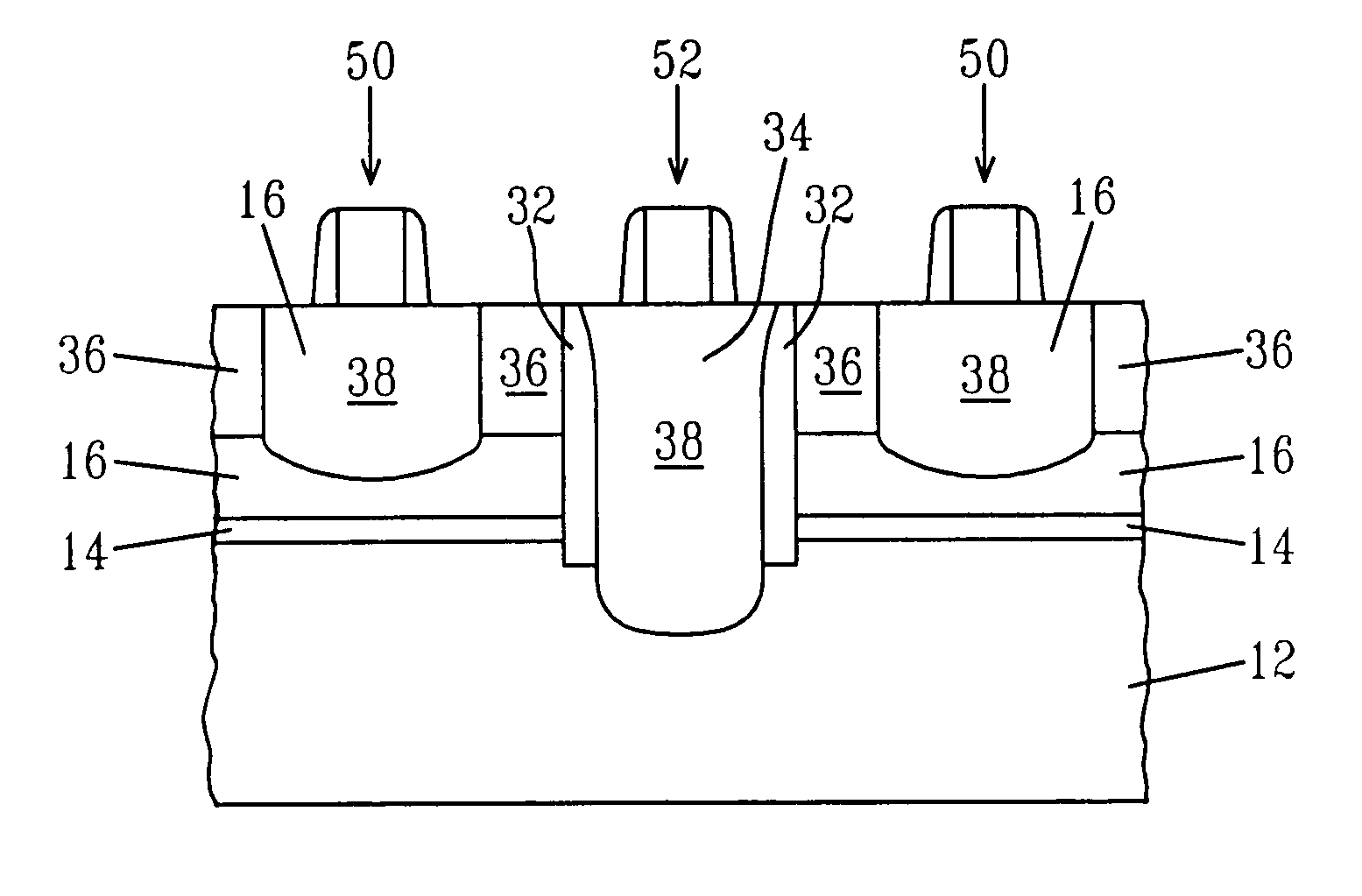

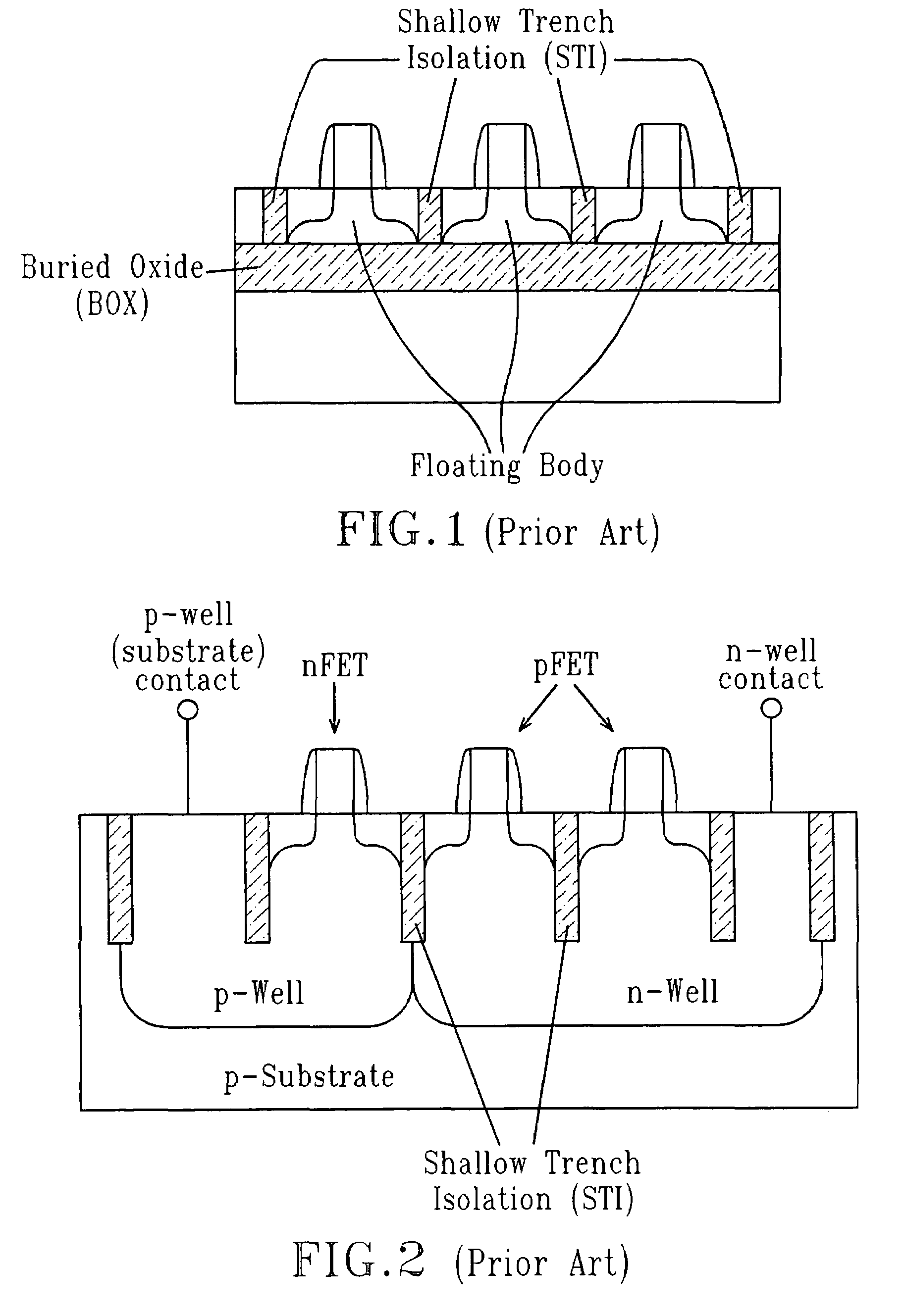

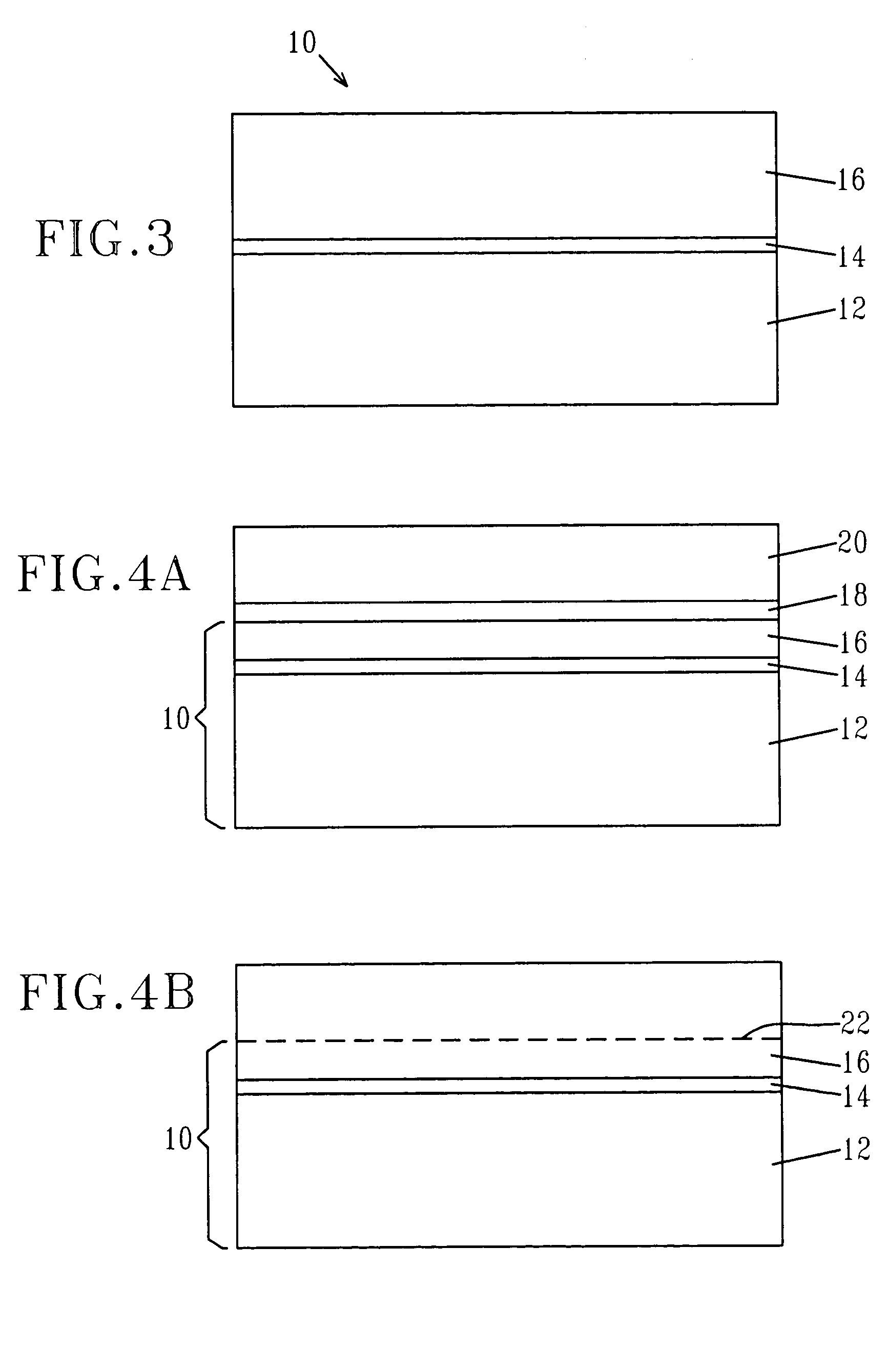

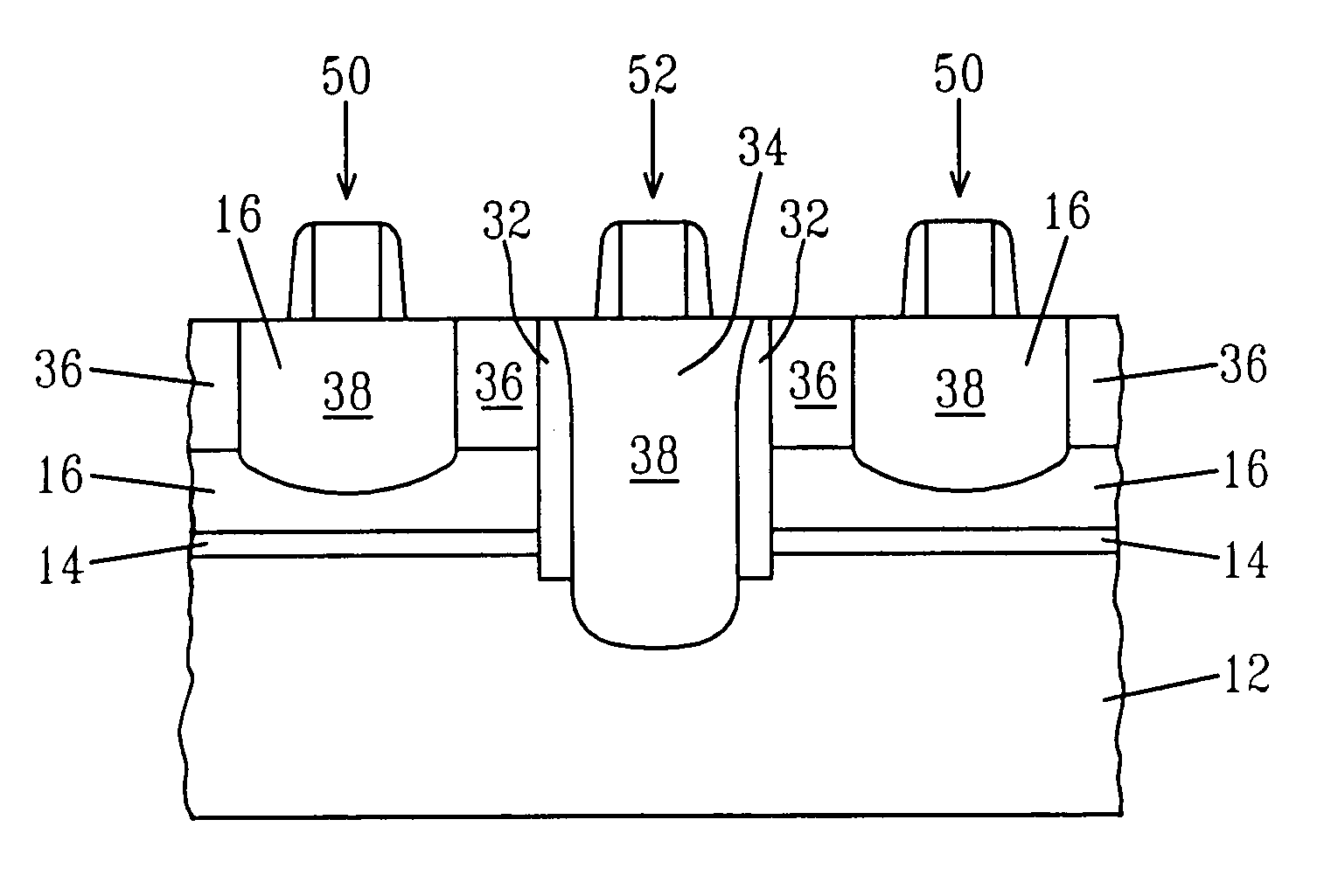

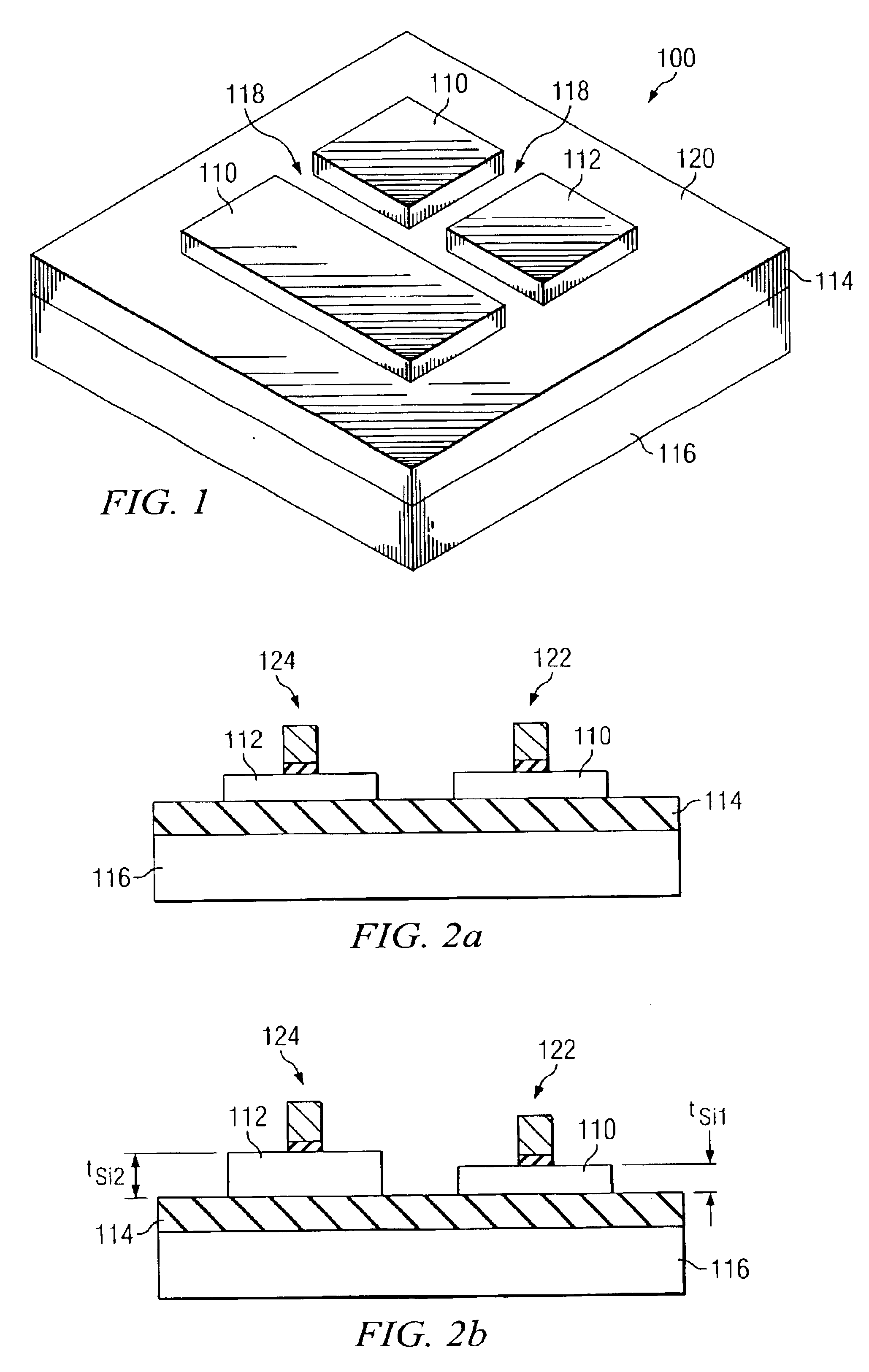

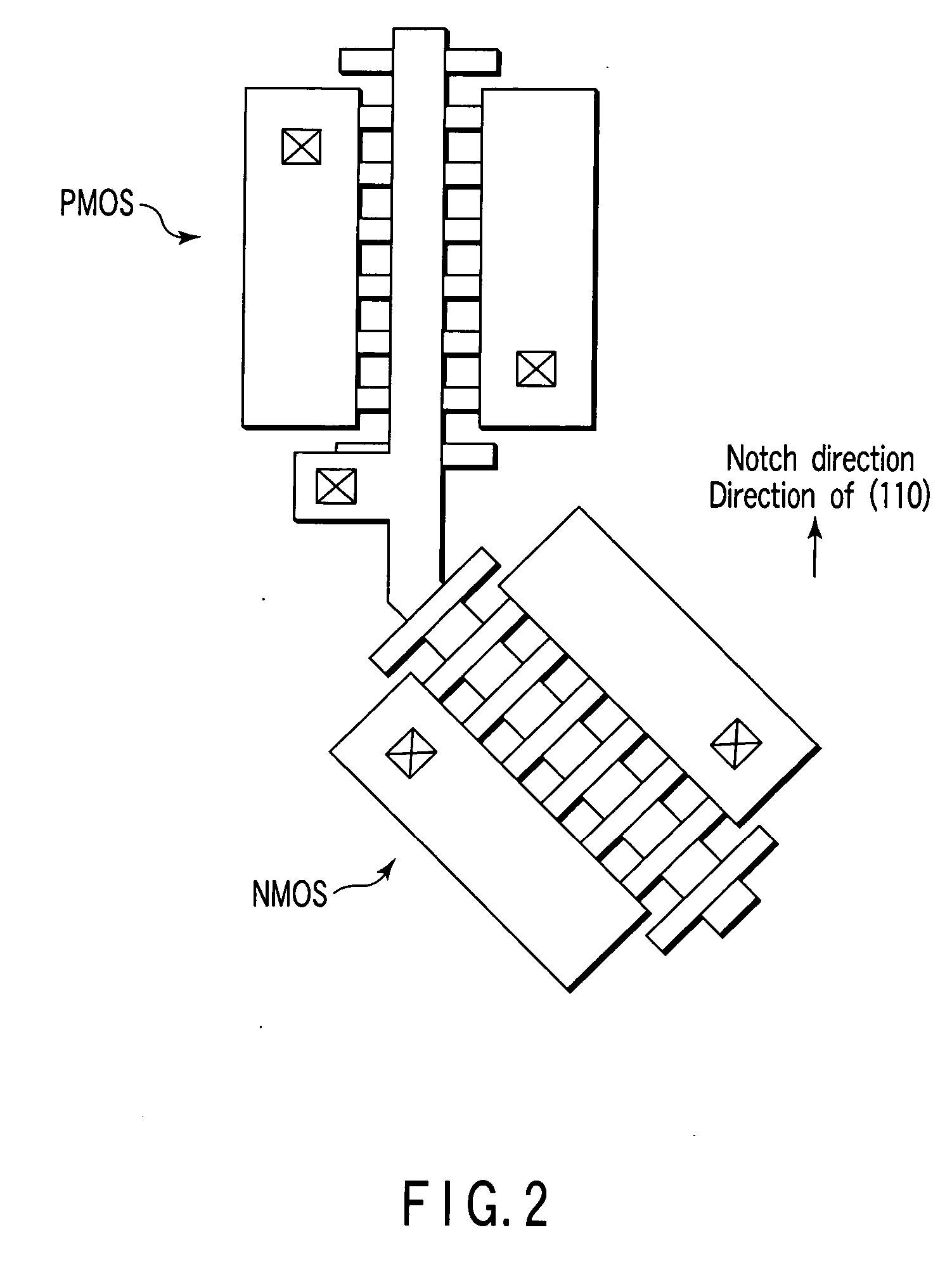

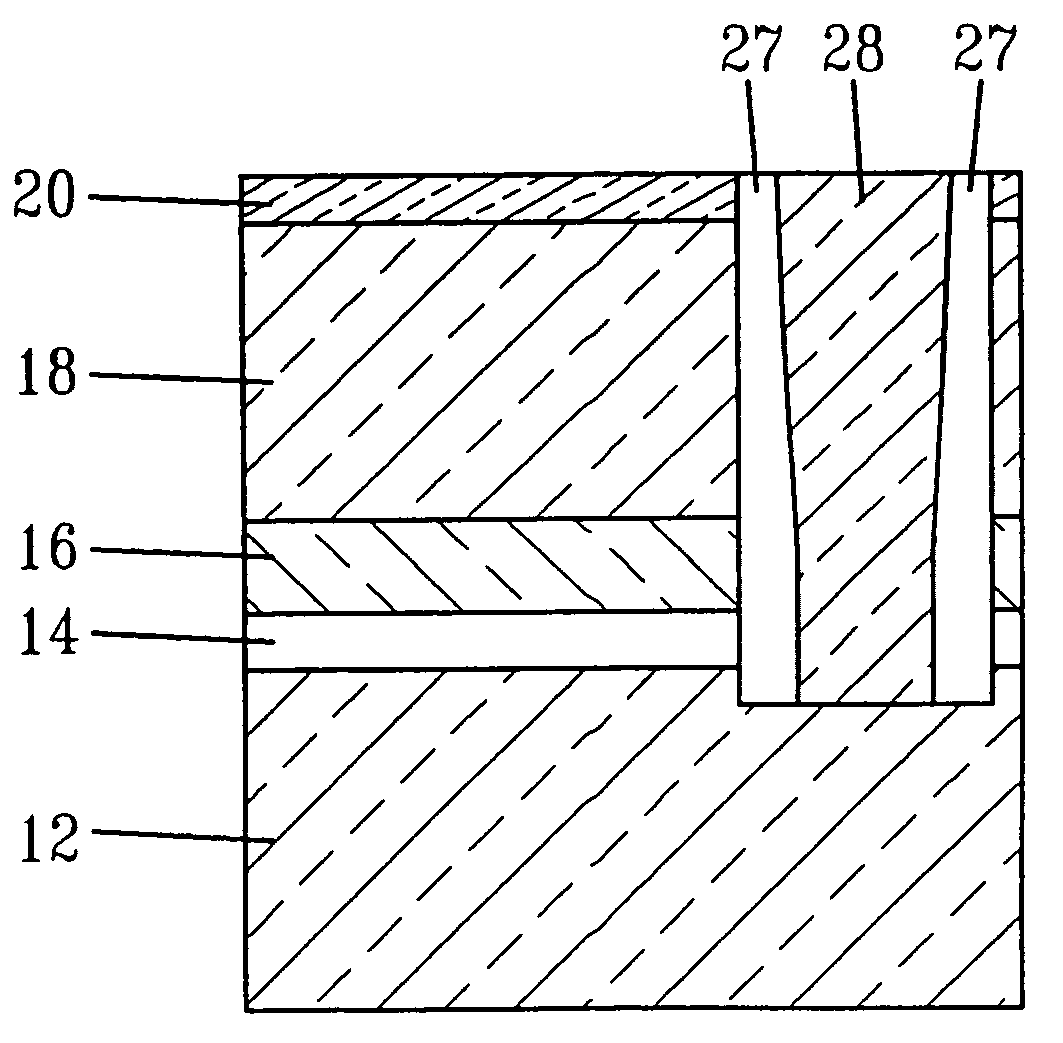

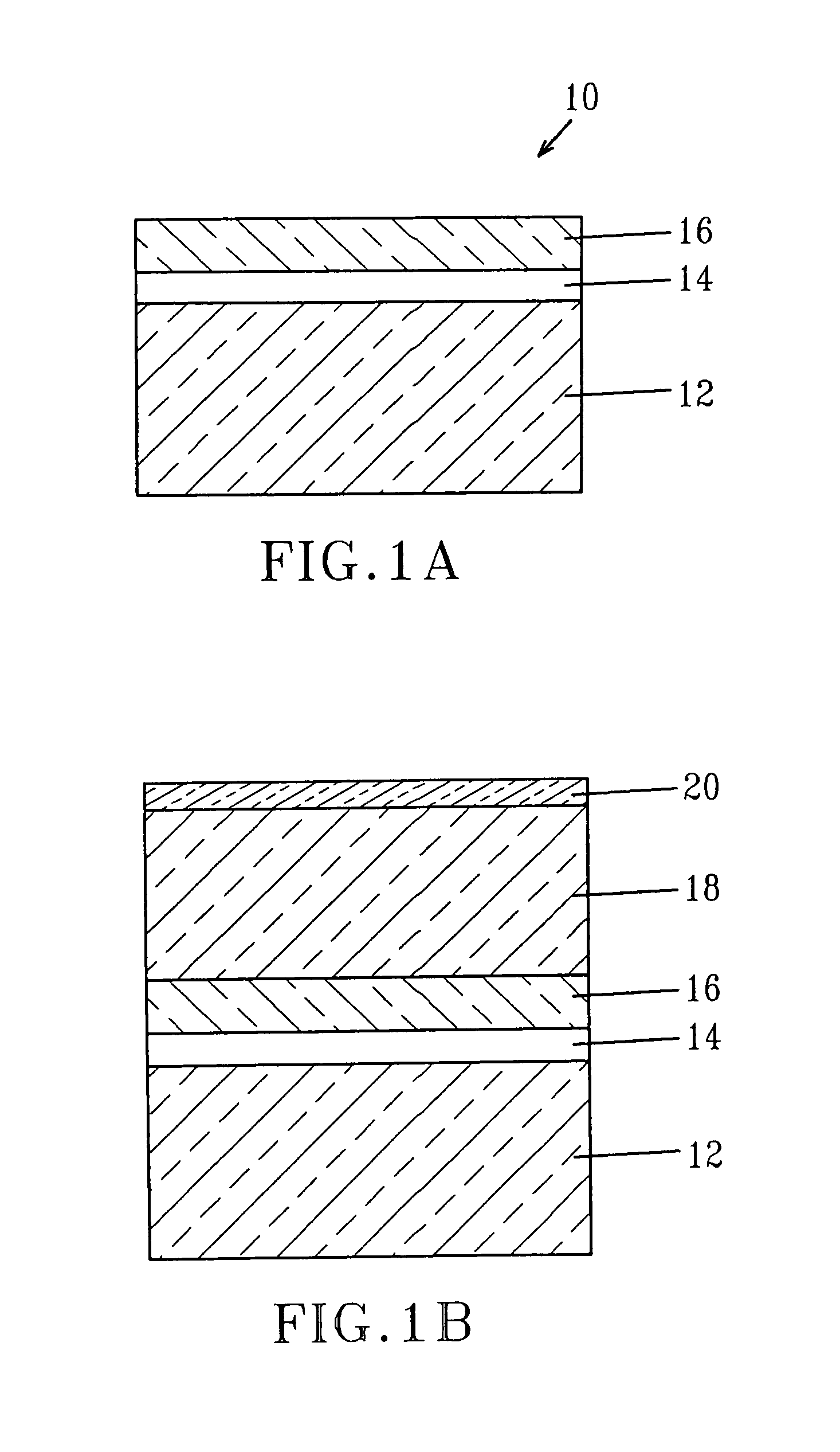

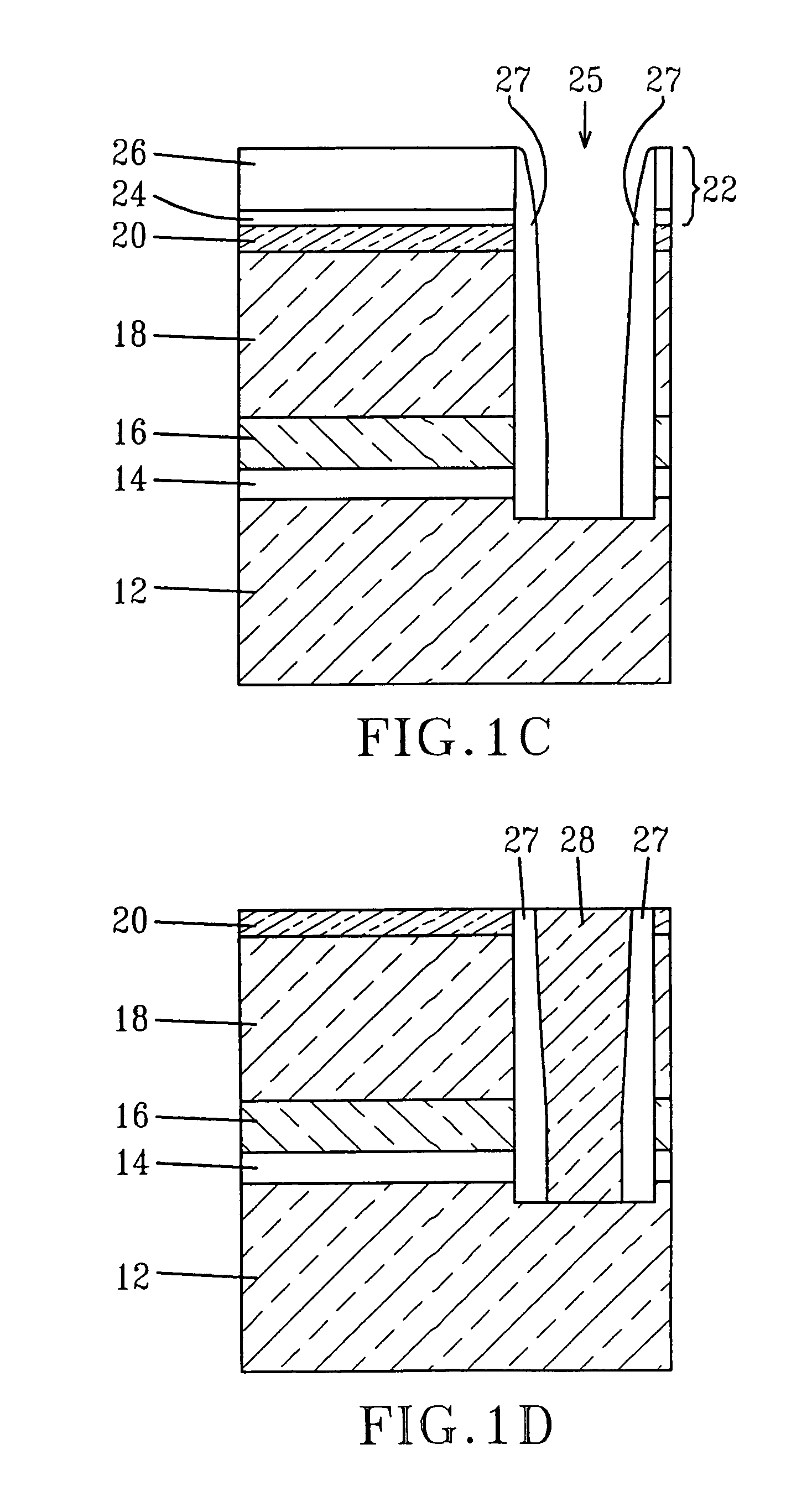

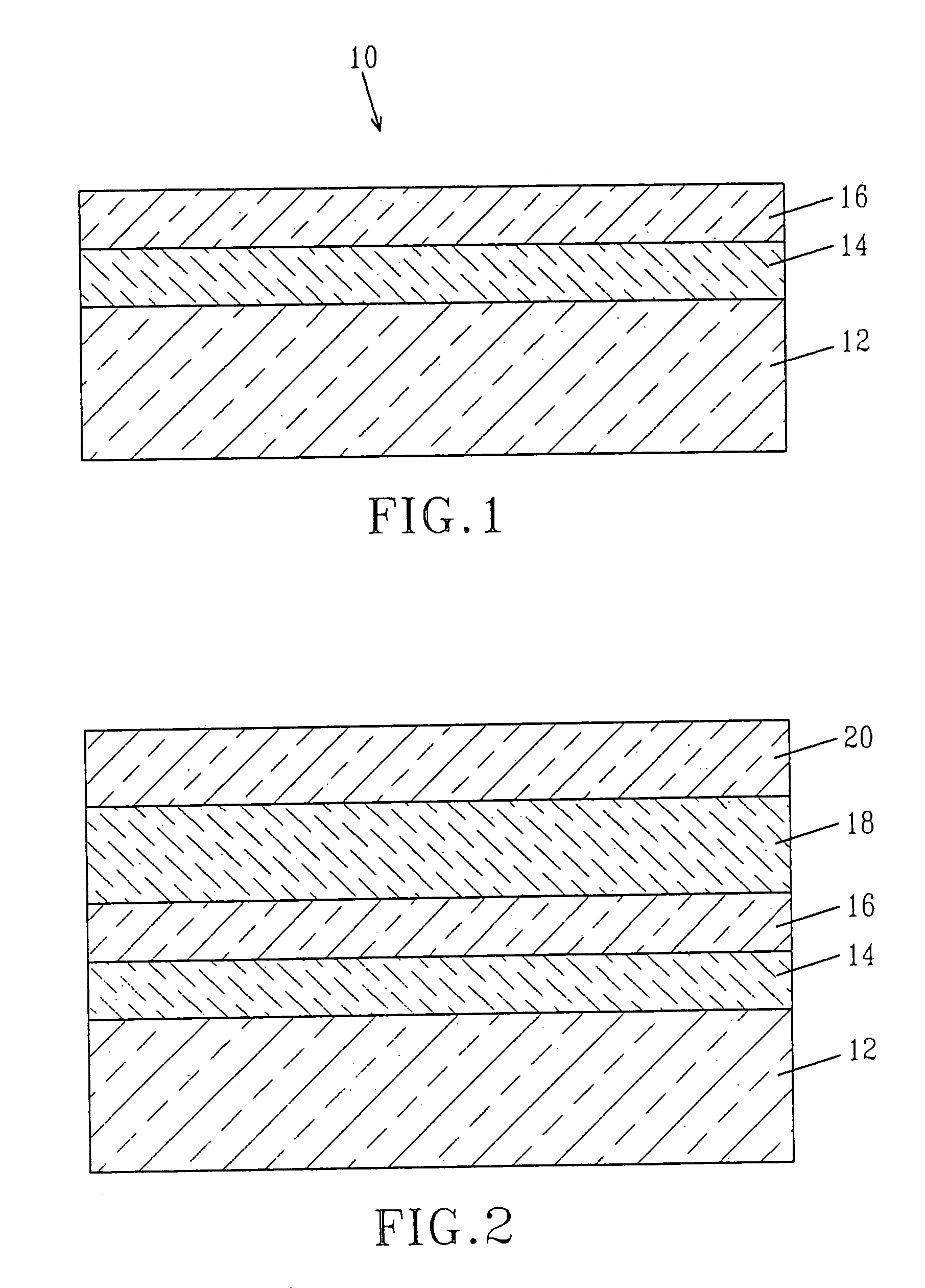

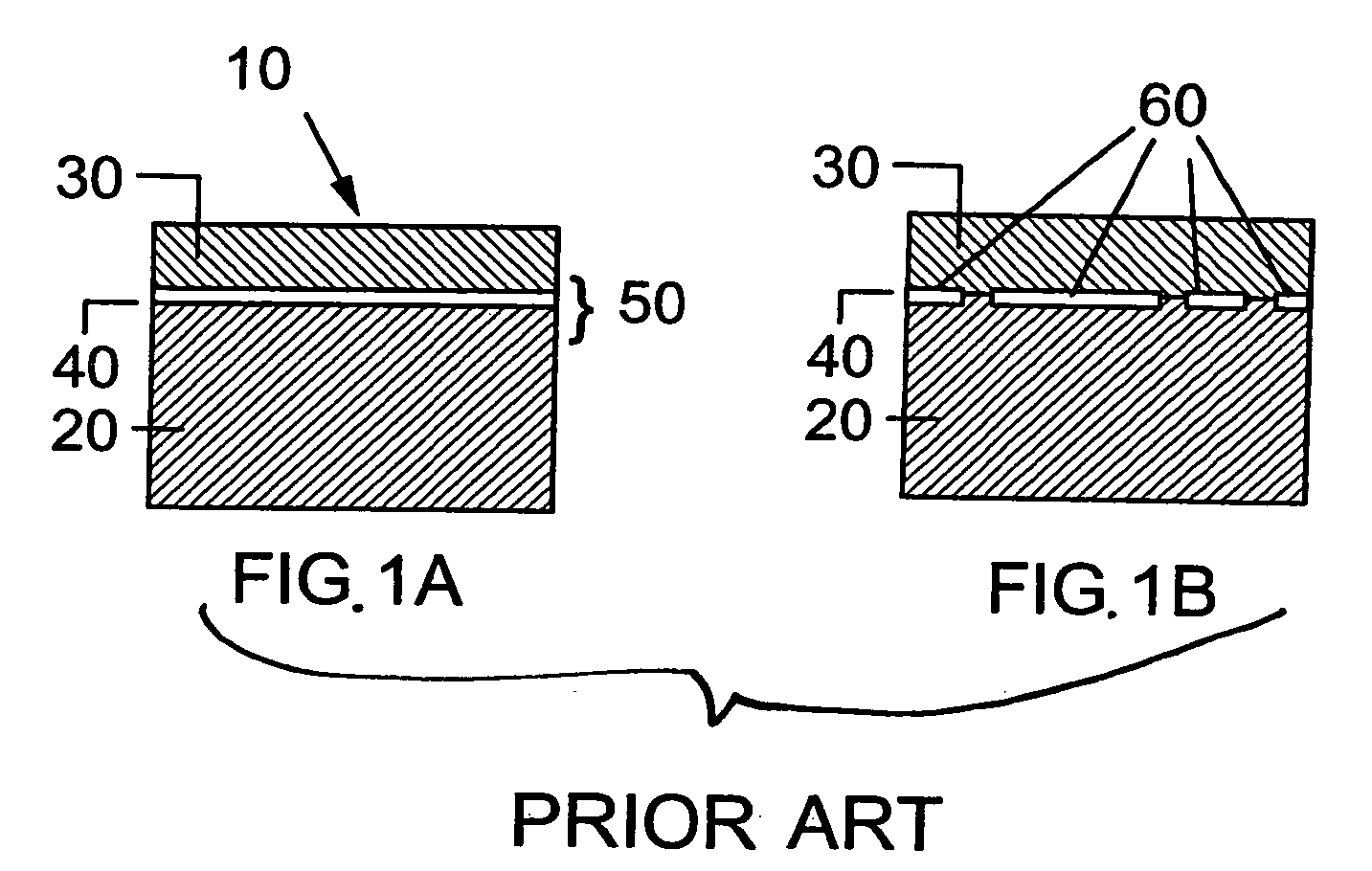

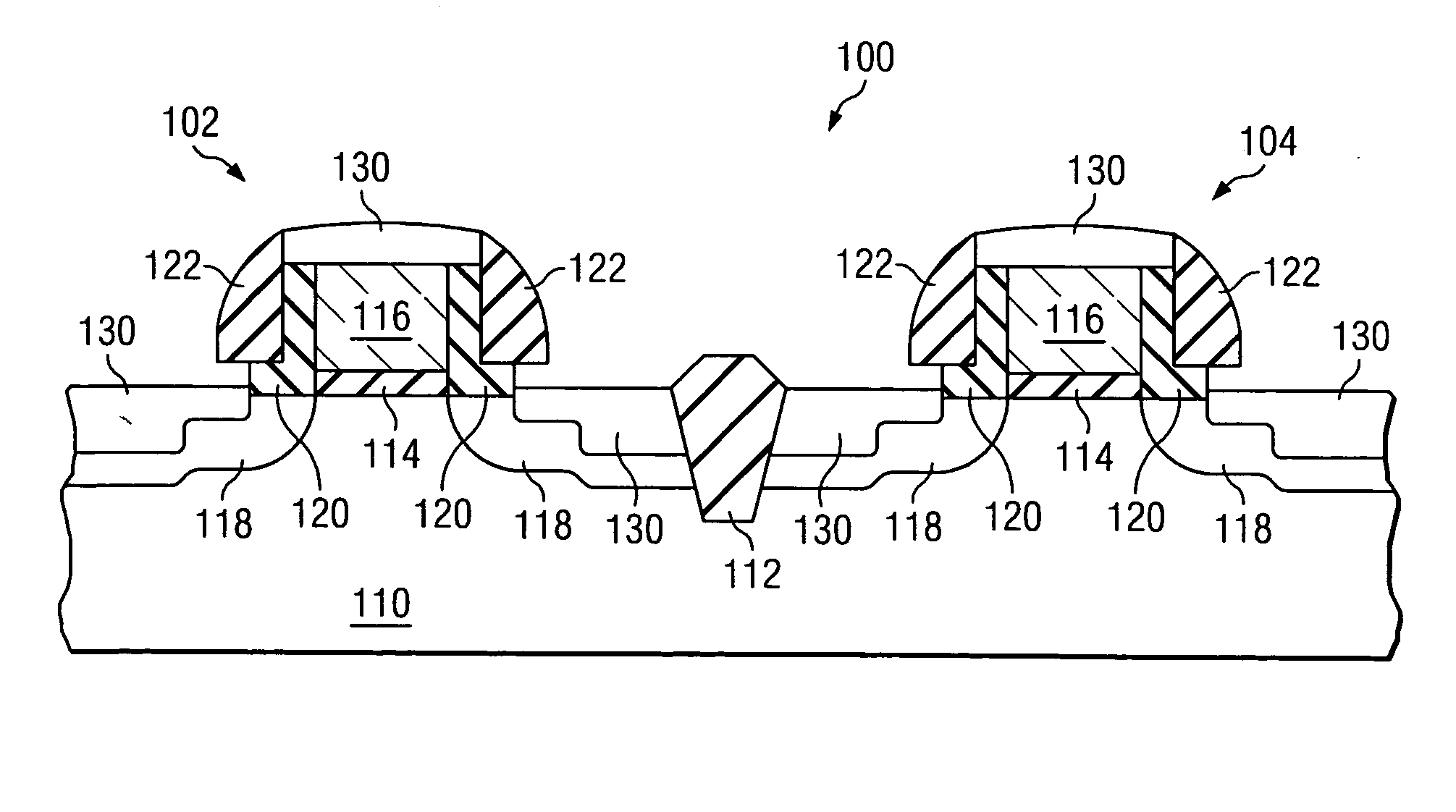

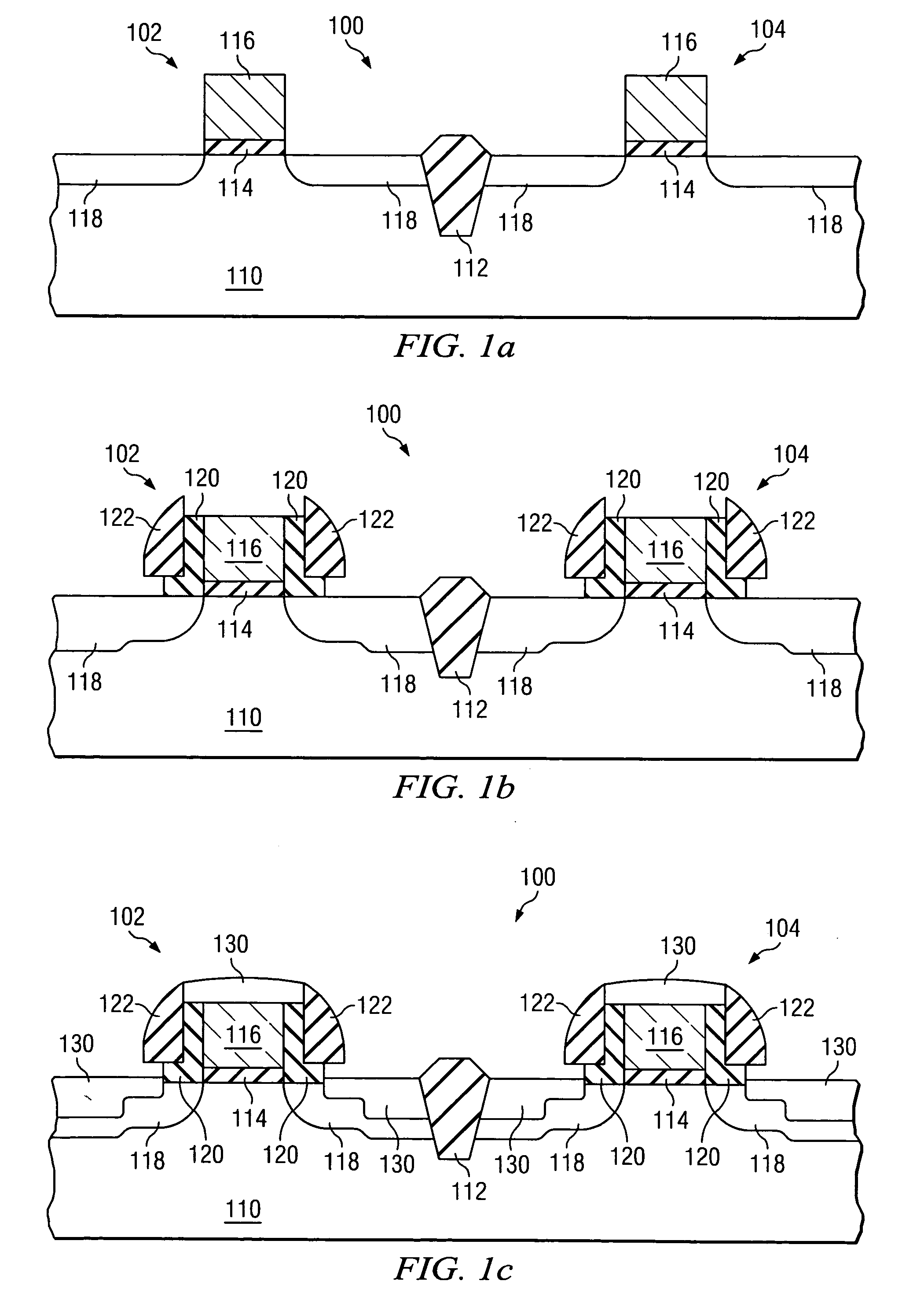

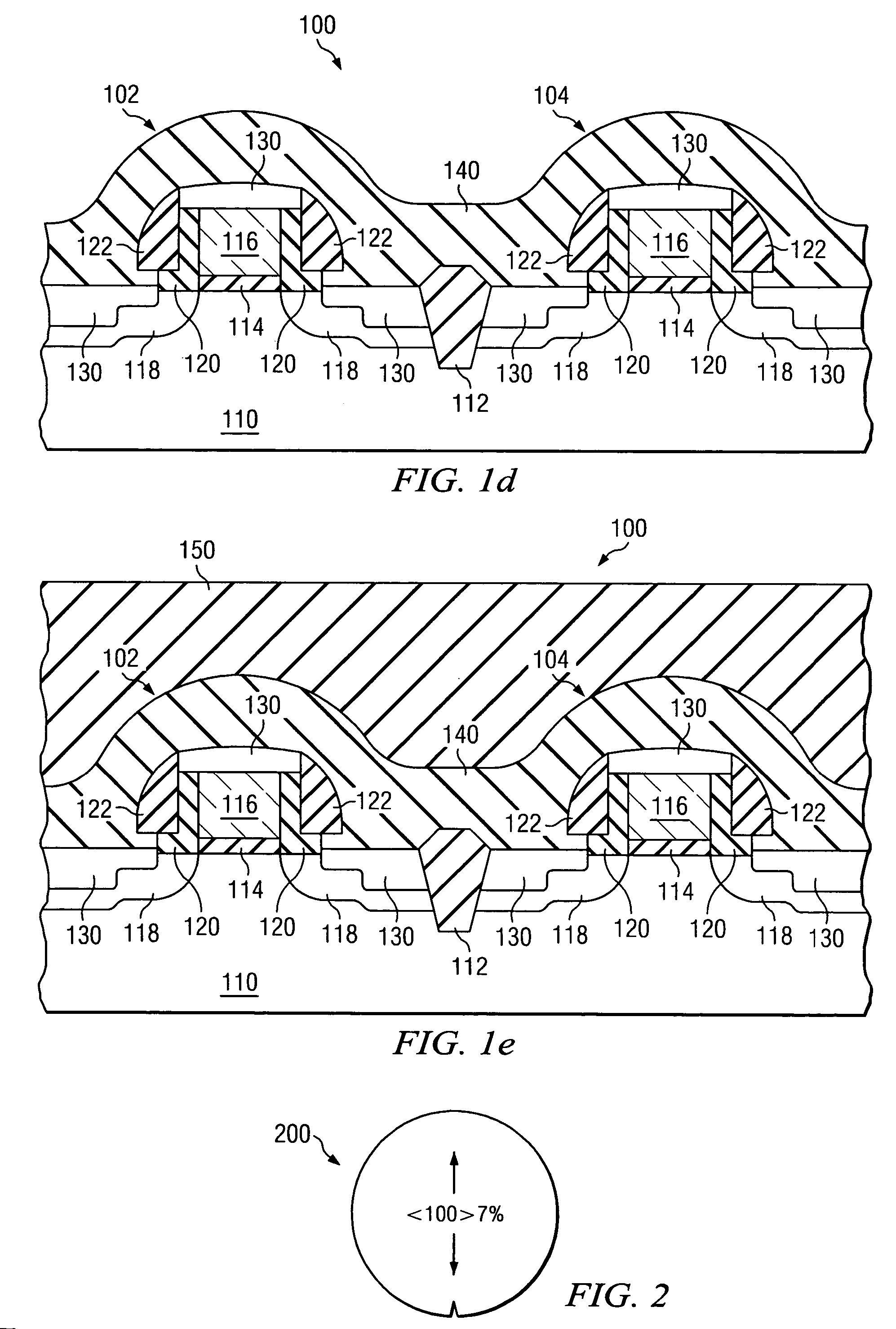

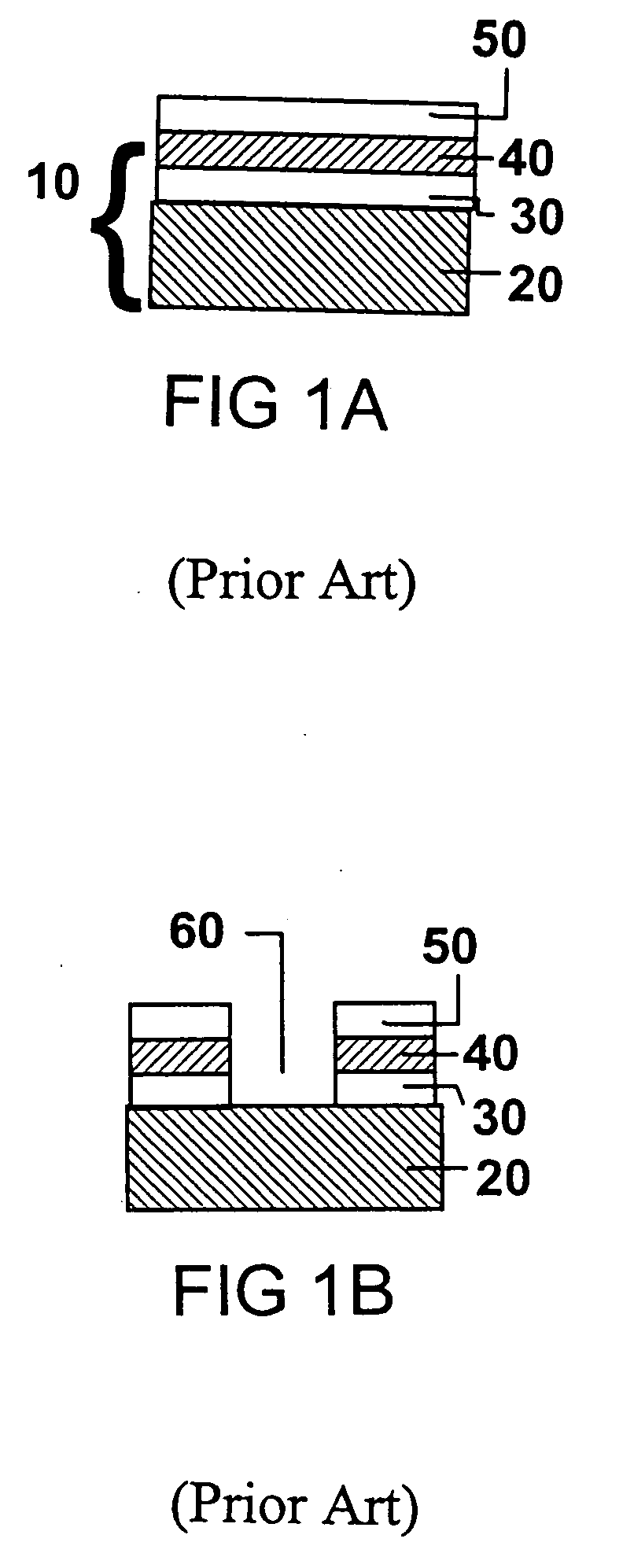

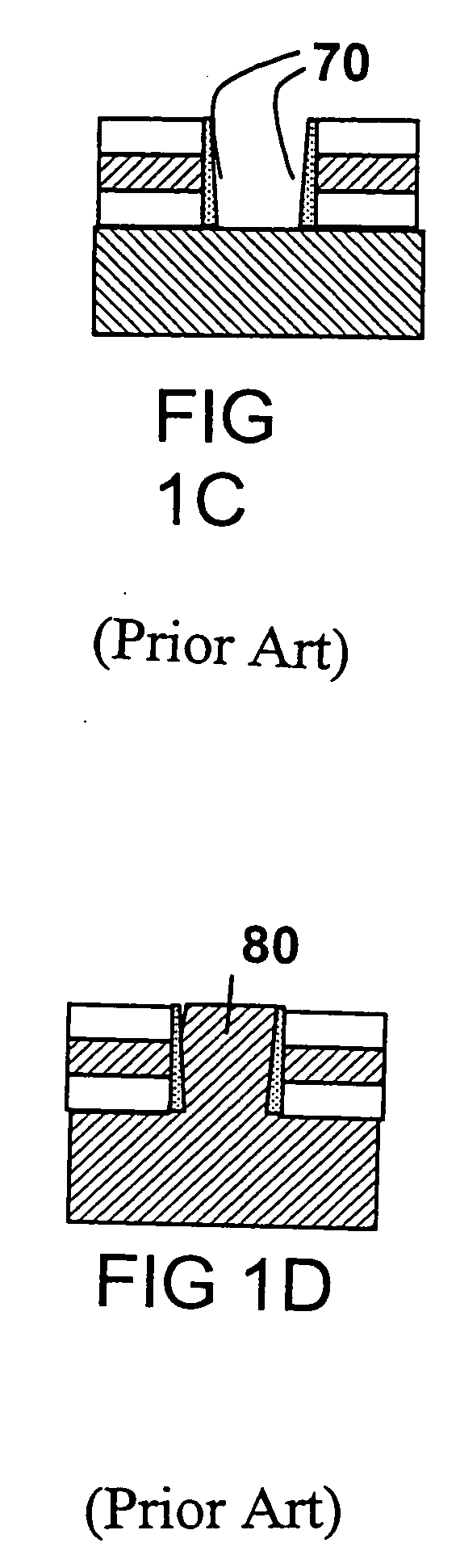

CMOS on hybrid substrate with different crystal orientations using silicon-to-silicon direct wafer bonding

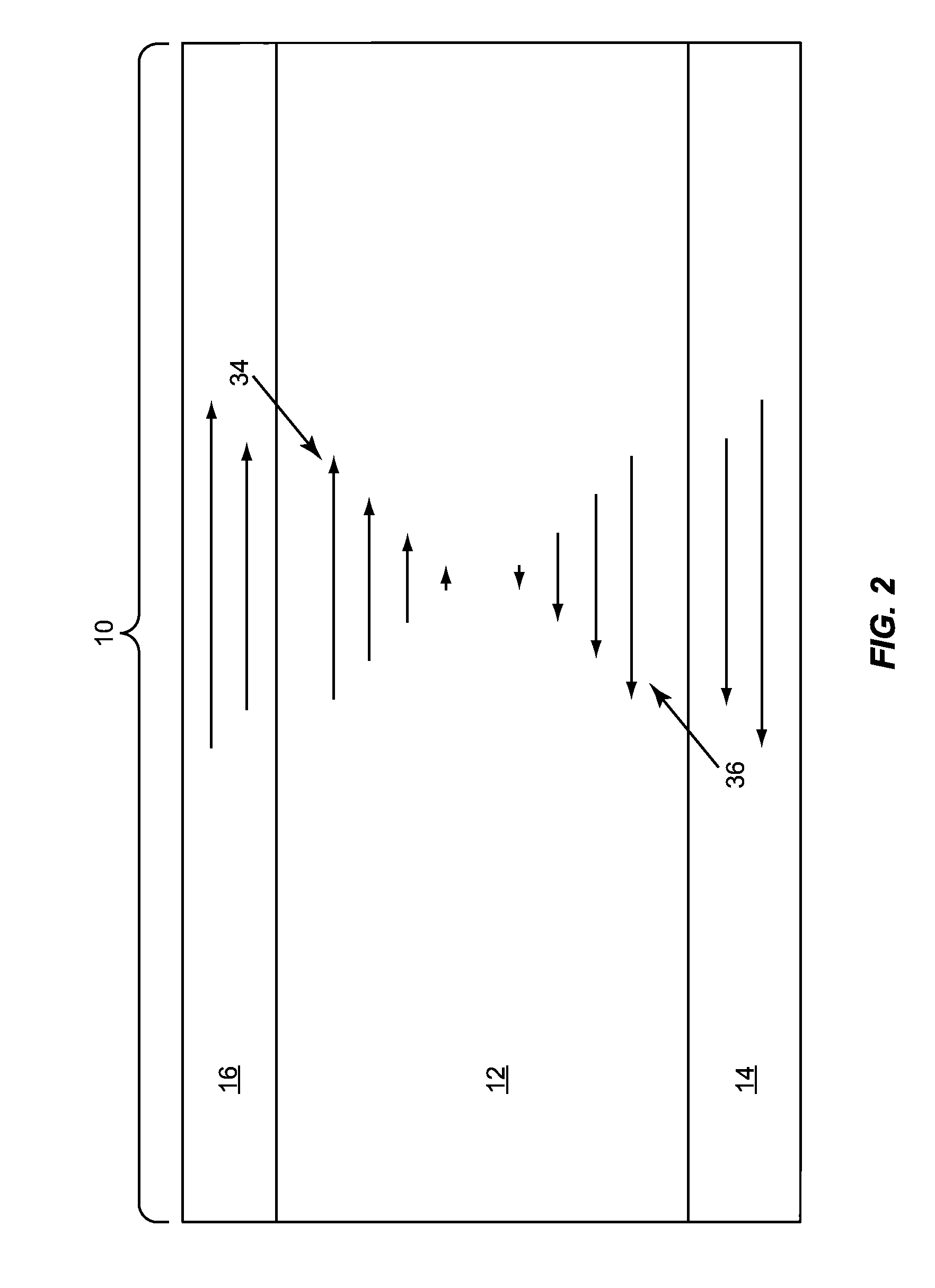

InactiveUS7023055B2Improve performanceImprove device performanceTransistorSolid-state devicesCMOSSemiconductor structure

A method in which semiconductor-to-semiconductor direct wafer bonding is employed to provide a hybrid substrate having semiconductor layers of different crystallographic orientations that are separated by a conductive interface is provided. Also provided are the hybrid substrate produced by the method as well as using the direct bonding method to provide an integrated semiconductor structure in which various CMOS devices are built upon a surface orientation that enhances device performance.

Owner:GLOBALFOUNDRIES INC

CMOS on hybrid substrate with different crystal orientations using silicon-to-silicon direct wafer bonding

InactiveUS20050093104A1Improve performanceImprove device performanceTransistorSolid-state devicesCMOSSemiconductor structure

A method in which semiconductor-to-semiconductor direct wafer bonding is employed to provide a hybrid substrate having semiconductor layers of different crystallographic orientations that are separated by a conductive interface is provided. Also provided are the hybrid substrate produced by the method as well as using the direct bonding method to provide an integrated semiconductor structure in which various CMOS devices are built upon a surface orientation that enhances device performance.

Owner:GLOBALFOUNDRIES INC

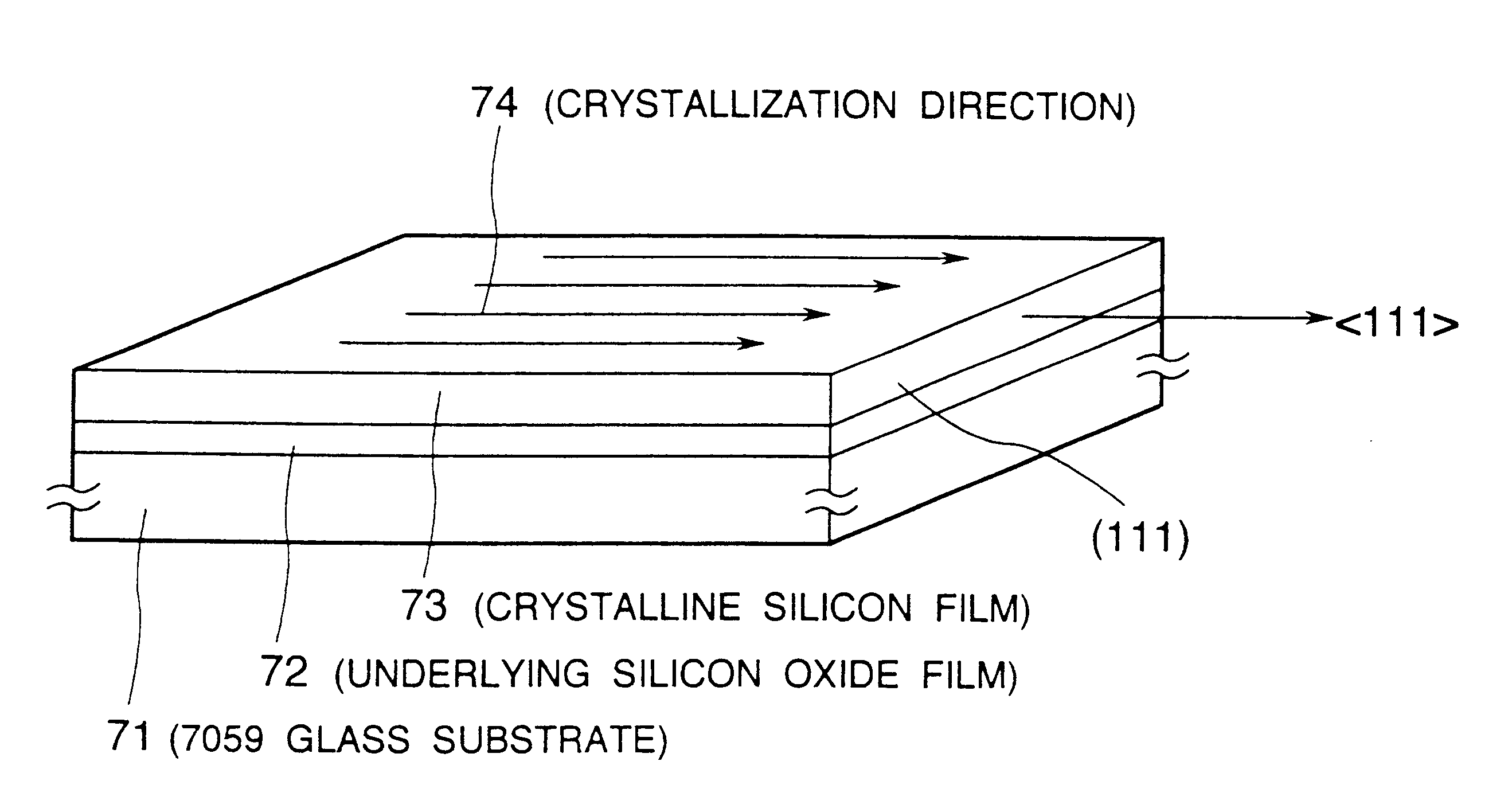

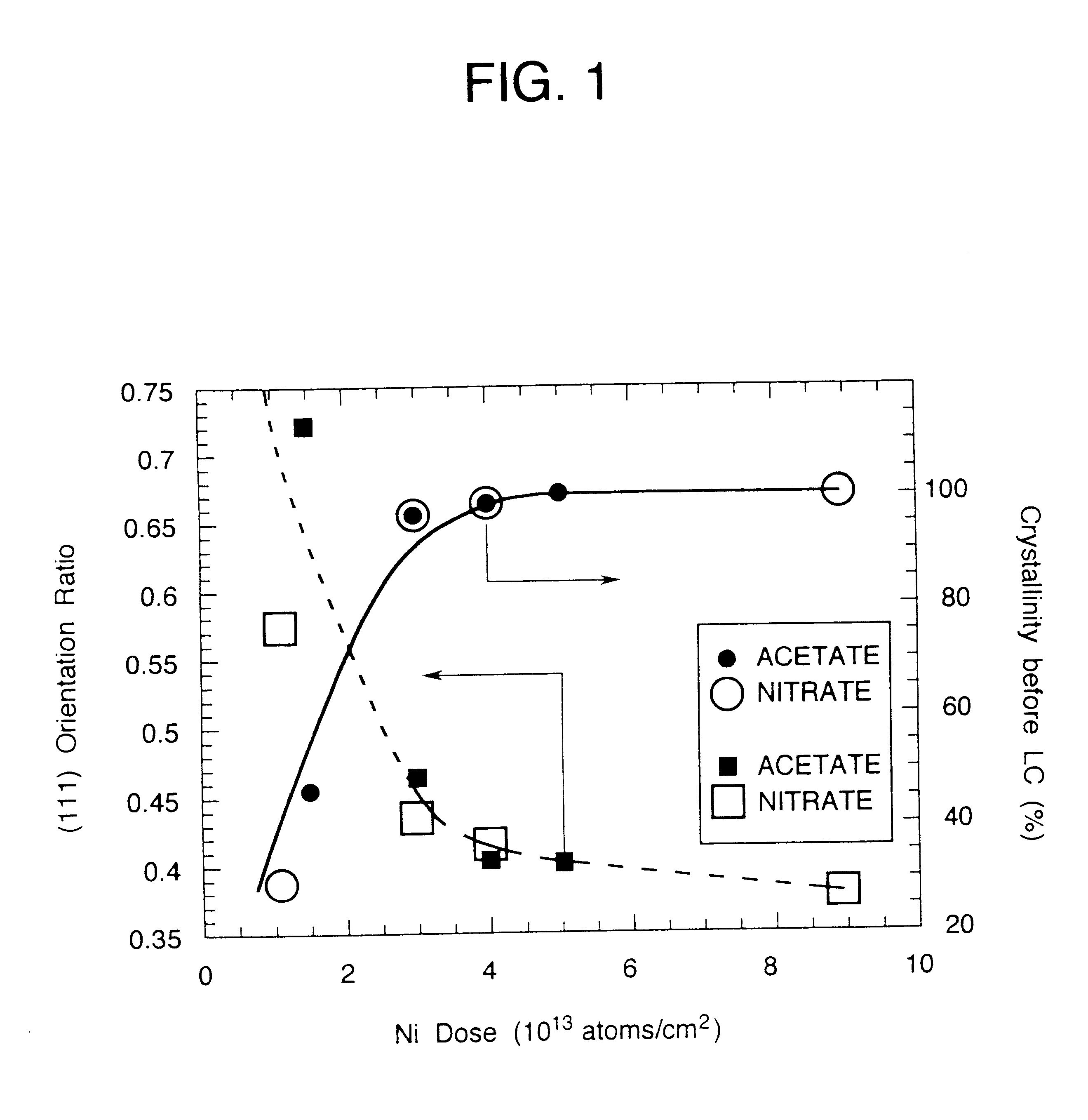

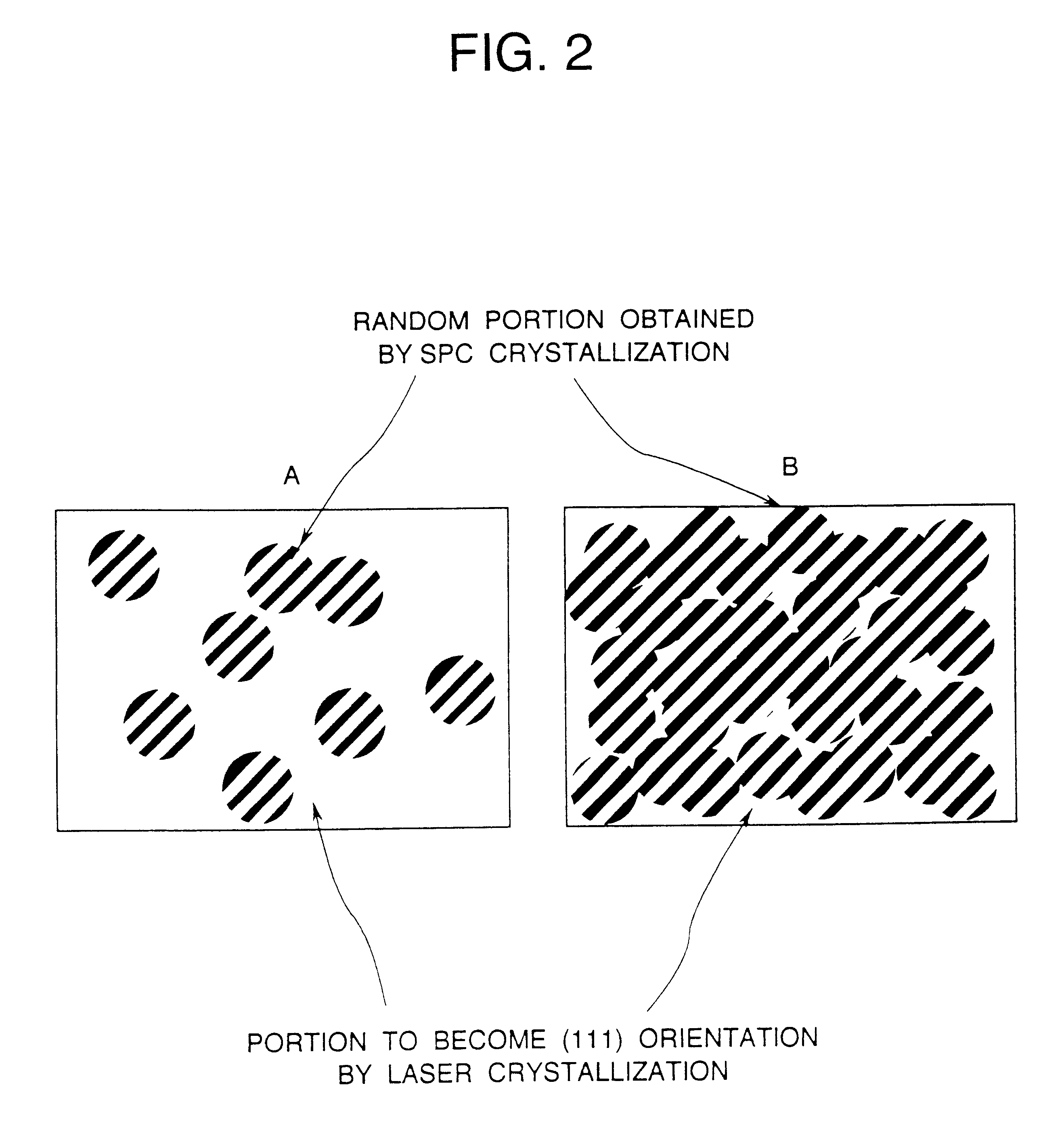

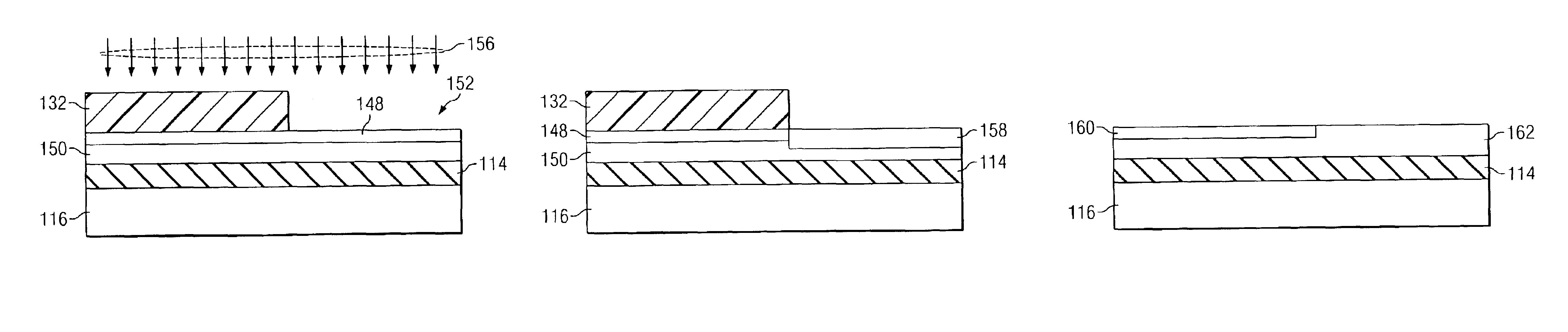

Method of preparing a semiconductor having controlled crystal orientation

InactiveUS6756657B1TransistorSemiconductor/solid-state device manufacturingAmorphous siliconCrystal orientation

A semiconductor device is disclosed. The semiconductor device has a crystalline silicon film as an active layer region. The crystalline silicon film has needle-like or columnar crystals oriented parallel to the substrate and having a crystal growth direction of (111) axis. A method for preparing the semiconductor device comprises steps of adding a catalytic element to an amorphous silicon film; and heating the amorphous silicon film containing the catalytic element at a low temperature to crystallize the silicon film.

Owner:SEMICON ENERGY LAB CO LTD

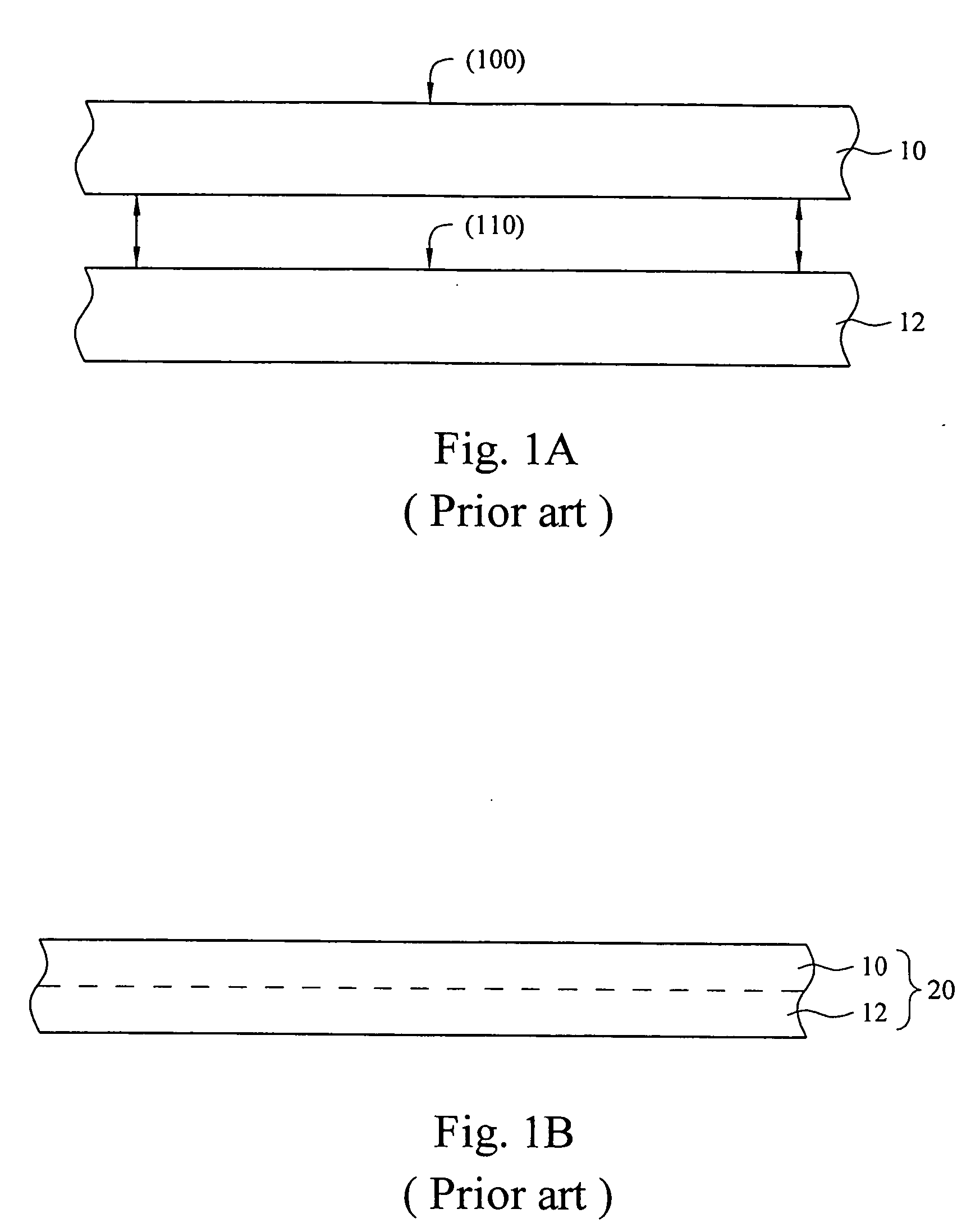

Silicon-on-insulator chip with multiple crystal orientations

A silicon-on-insulator chip includes an insulator layer, typically formed over a substrate. A first silicon island with a surface of a first crystal orientation overlies the insulator layer and a second silicon island with a surface of a second crystal orientation also overlies the insulator layer. In one embodiment, the silicon-on-insulator chip also includes a first transistor of a first conduction type formed on the first silicon island, and a second transistor of a second conduction type formed on the second silicon island. For example, the first crystal orientation can be (110) while the first transistor is a p-channel transistor, and the second crystal orientation can be (100) while the second transistor is an n-channel transistor.

Owner:TAIWAN SEMICON MFG CO LTD

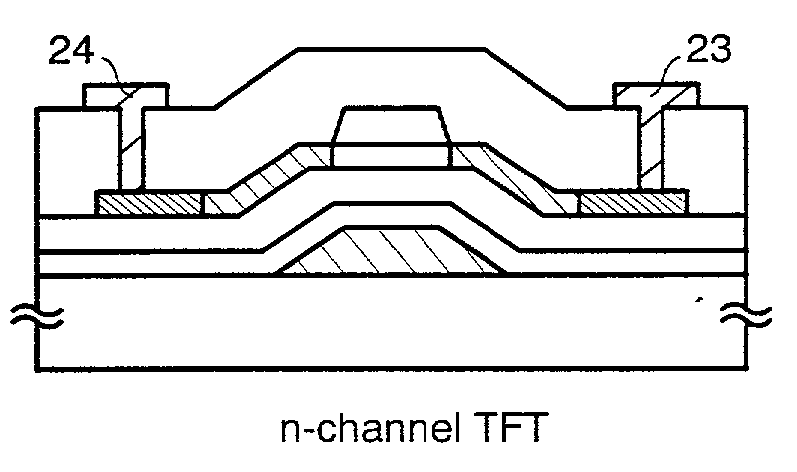

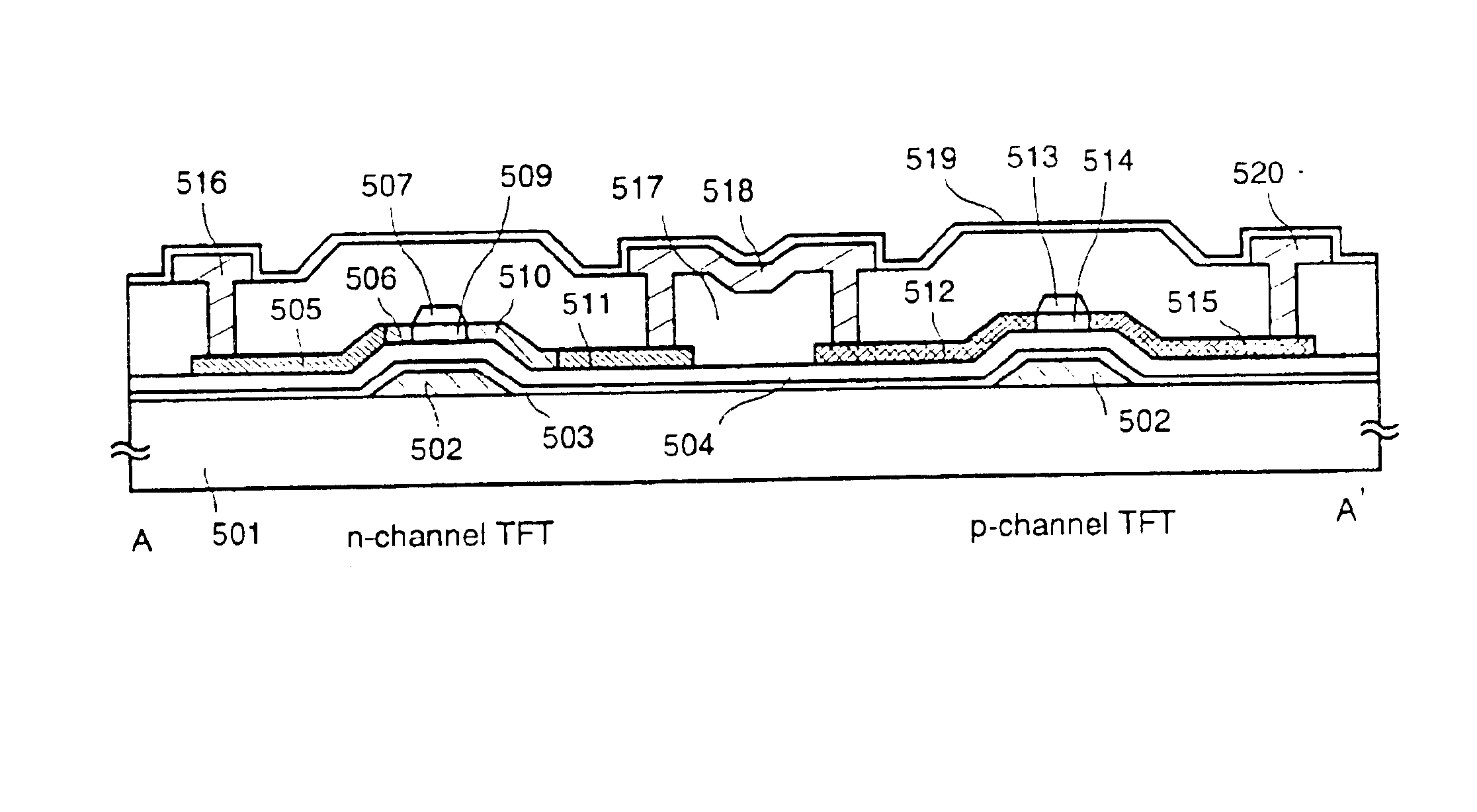

Semiconductor device

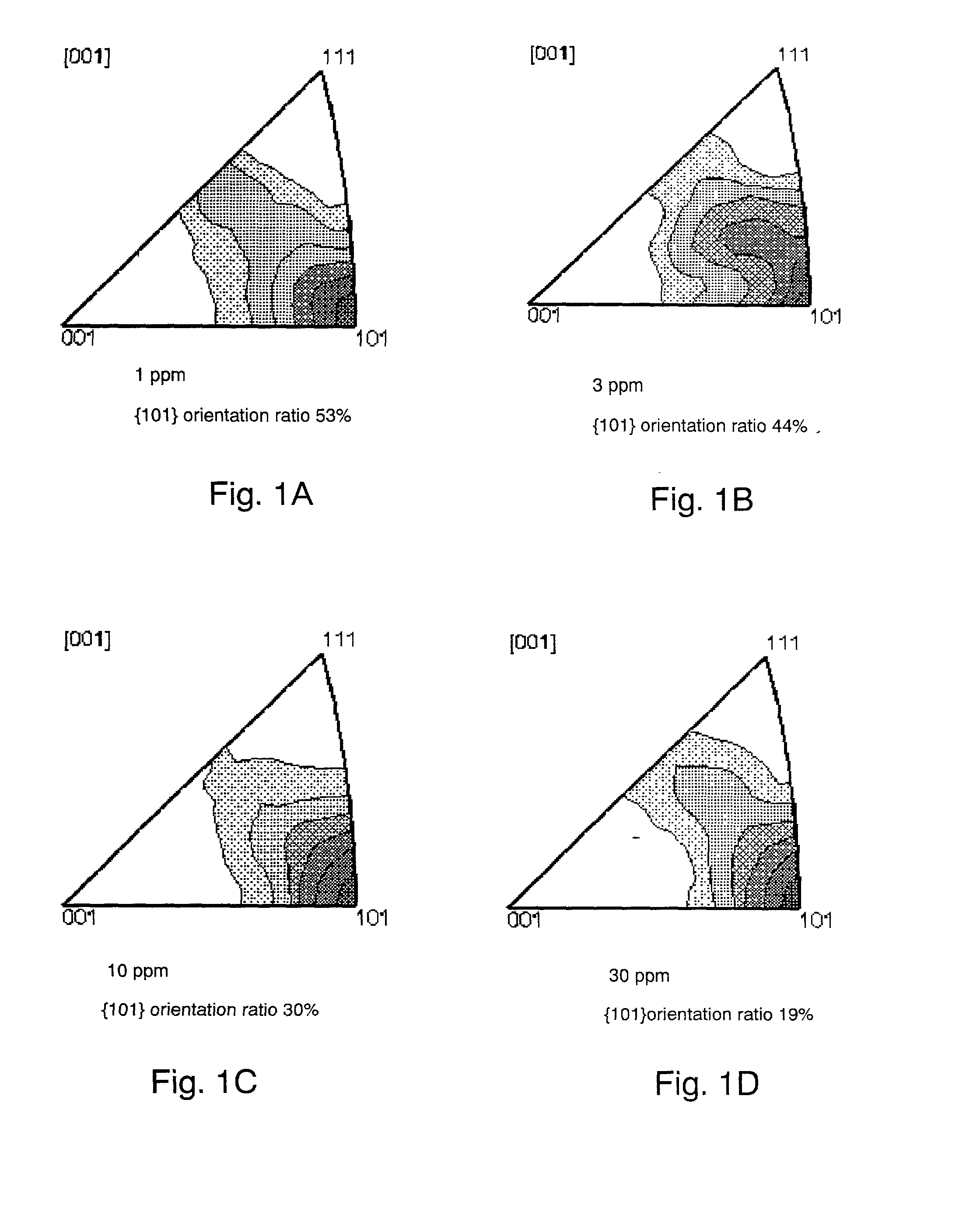

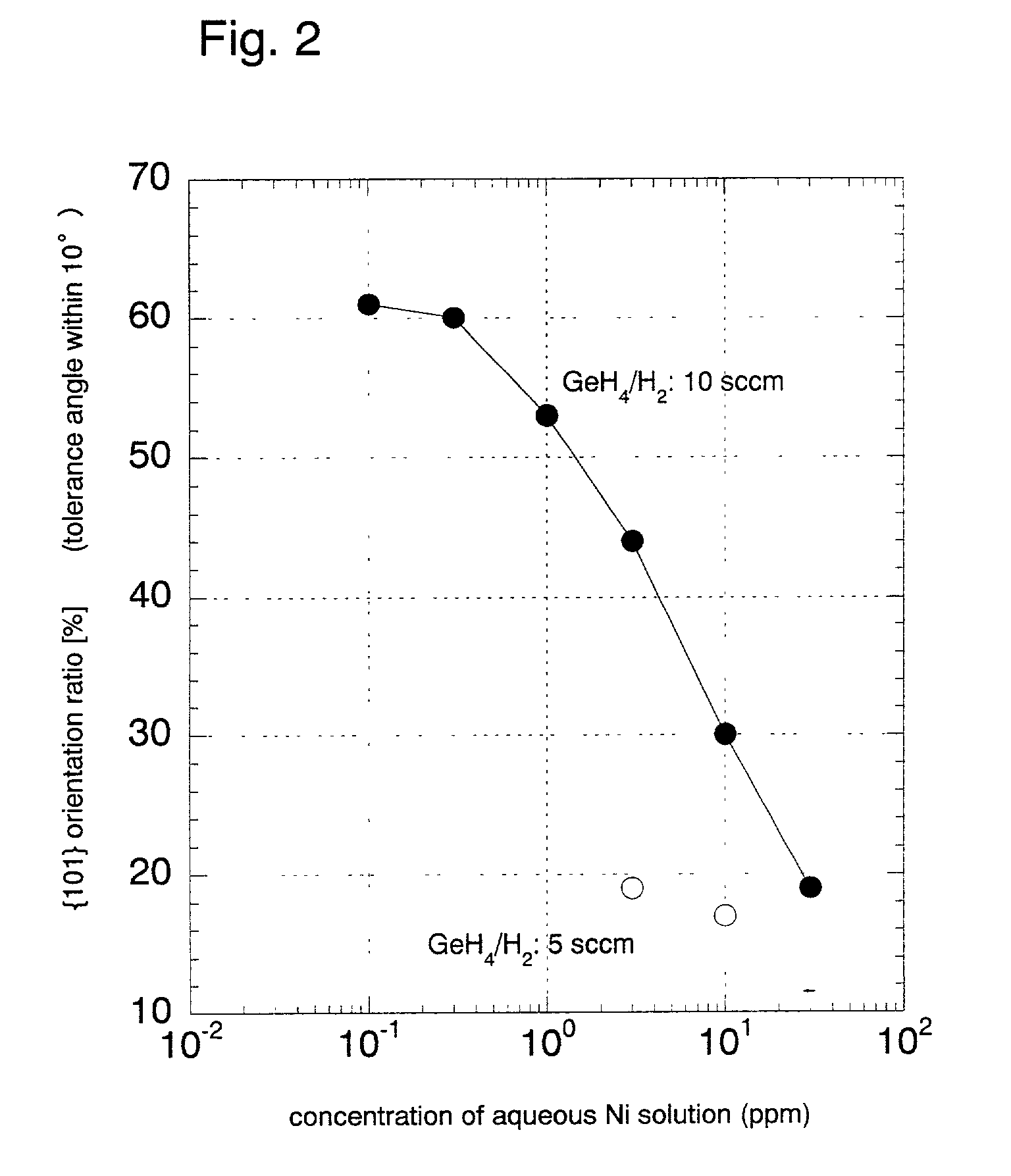

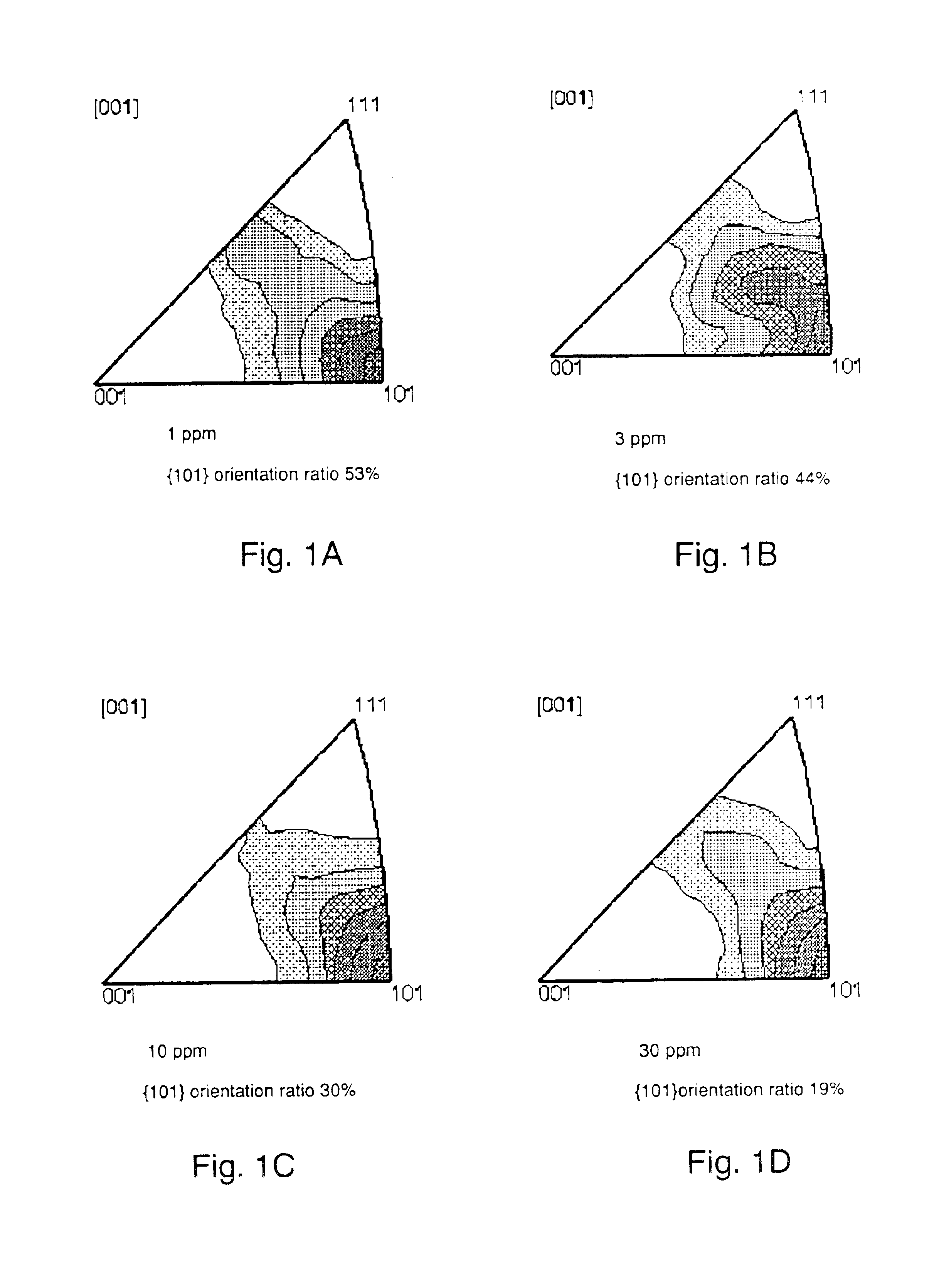

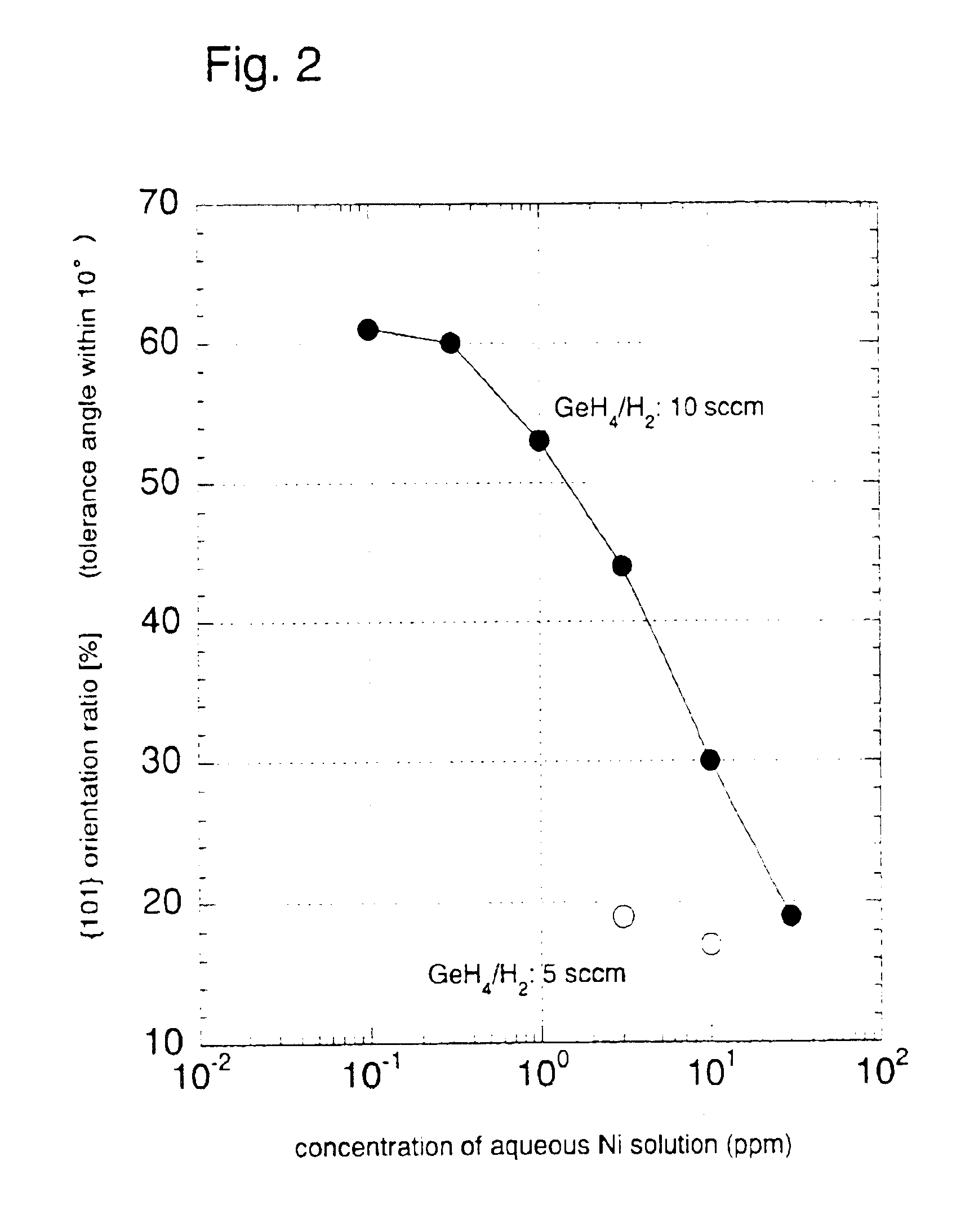

Crystal orientation planes exist randomly in a crystalline silicon film manufactured by a conventional method, and the orientation ratio is low with respect to a specific crystal orientation. A semiconductor film having a high orientation ratio for the {101} lattice plane is obtained if crystallization of an amorphous semiconductor film, which has silicon as its main constituent and contains from 0.1 to 10 atom % germanium, is performed after introduction of a metal element. A TFT is manufactured utilizing the semiconductor film.

Owner:SEMICON ENERGY LAB CO LTD

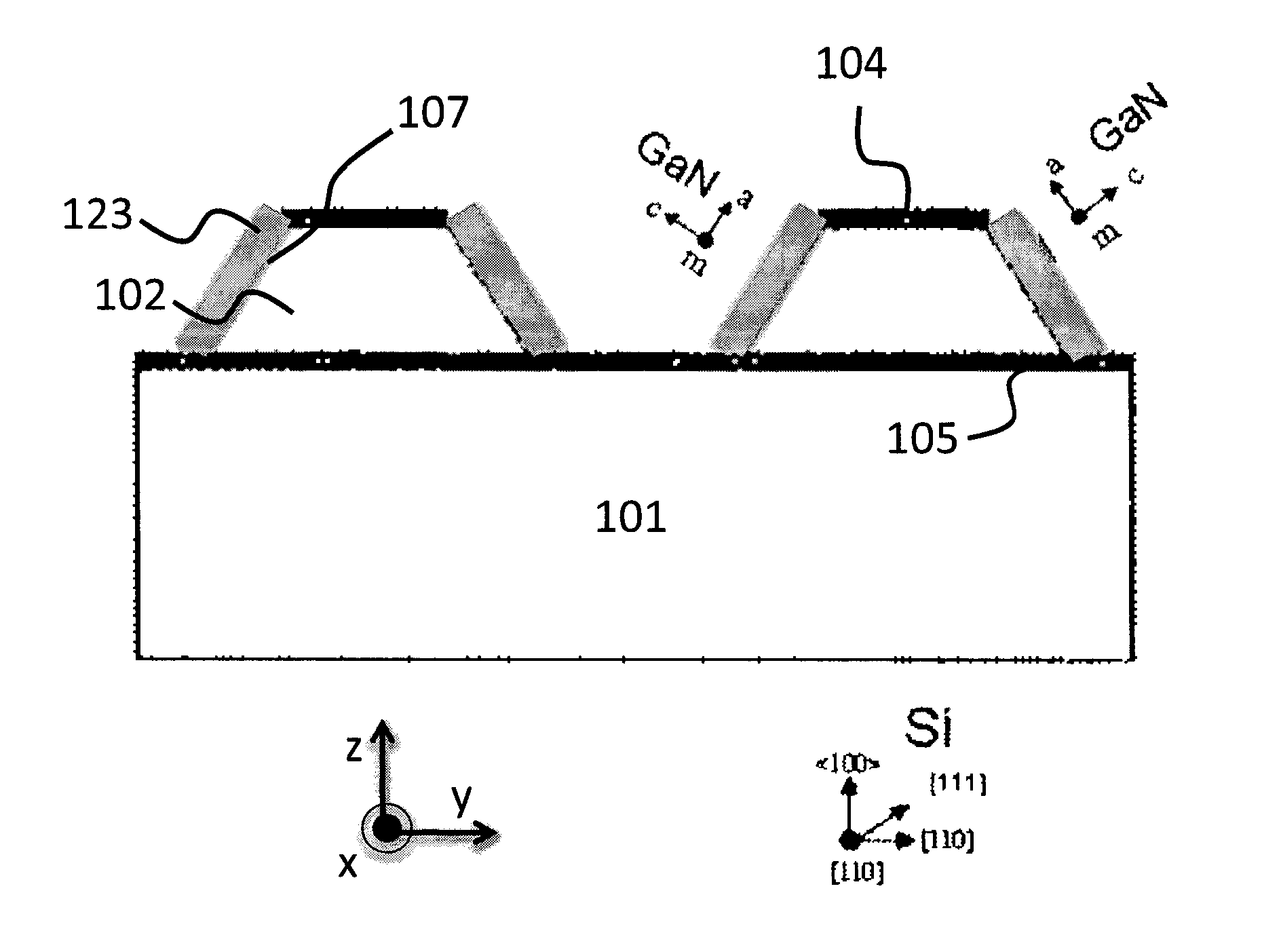

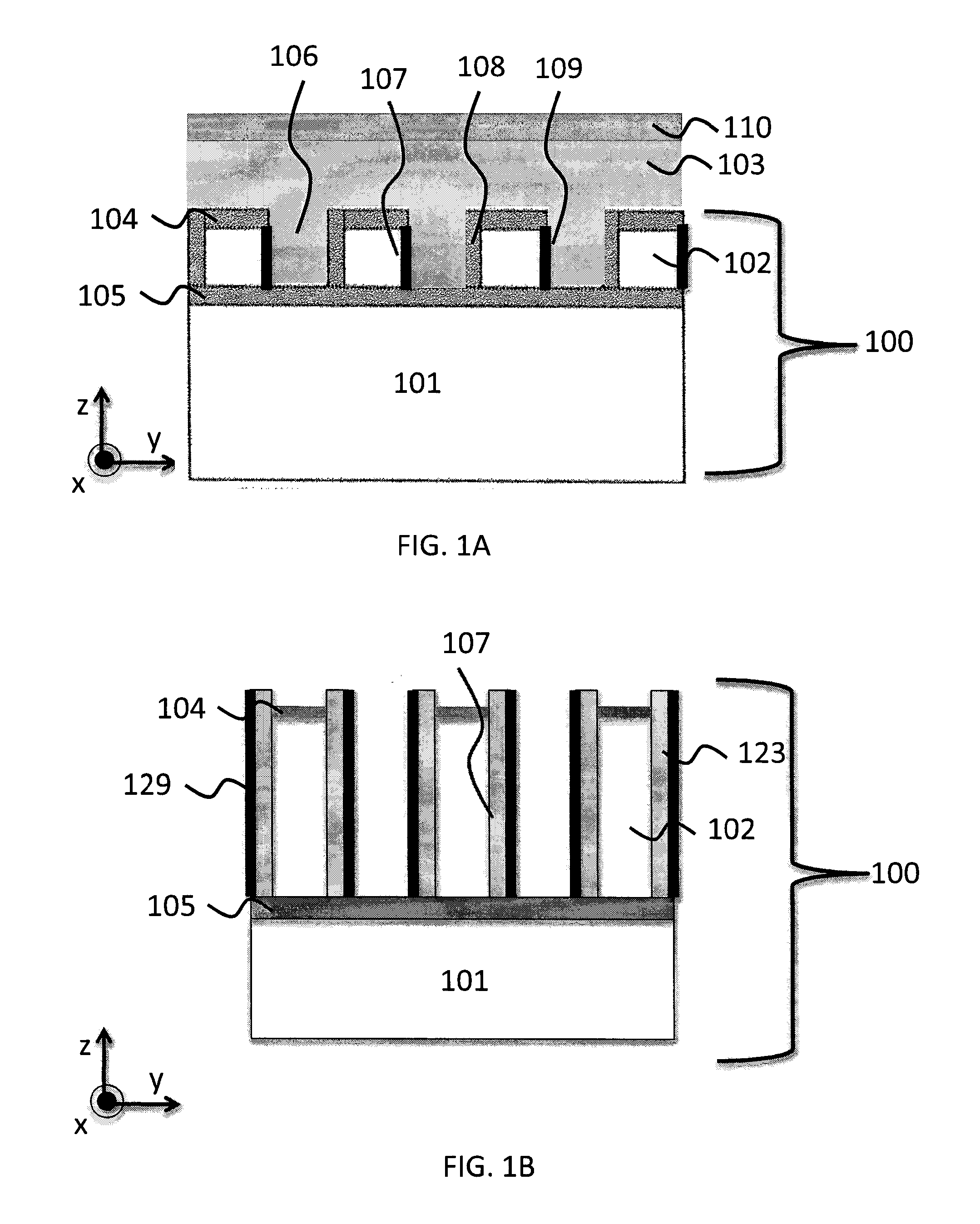

Method for forming a semiconductor device using selective epitaxy of group iii-nitride

InactiveUS20120119218A1Polycrystalline material growthSemiconductor/solid-state device manufacturingCrystal orientationDeposition process

A method for forming a single crystalline Group-III Nitride film. A substrate is provided, having a first passivation layer, a monocrystalline layer, and a second passivation layer. The substrate is patterned to form a plurality of features with elongated sidewalls having a second crystal orientation. Group-III Nitride films are formed on the elongated sidewalls, but not on the first or second passivation layers. In one embodiment, the dimensions of the patterned features and the film deposition process result in a single crystalline Group-III Nitride film having a third crystal orientation normal to the substrate surface. In another embodiment, the dimensions and orientation of the patterned features and the film deposition process result in a plurality of single crystalline Group-III Nitride films. In other embodiments, additional layers are formed on the Group-III Nitride film or films to form semiconductor devices, for example, a light-emitting diode.

Owner:APPLIED MATERIALS INC

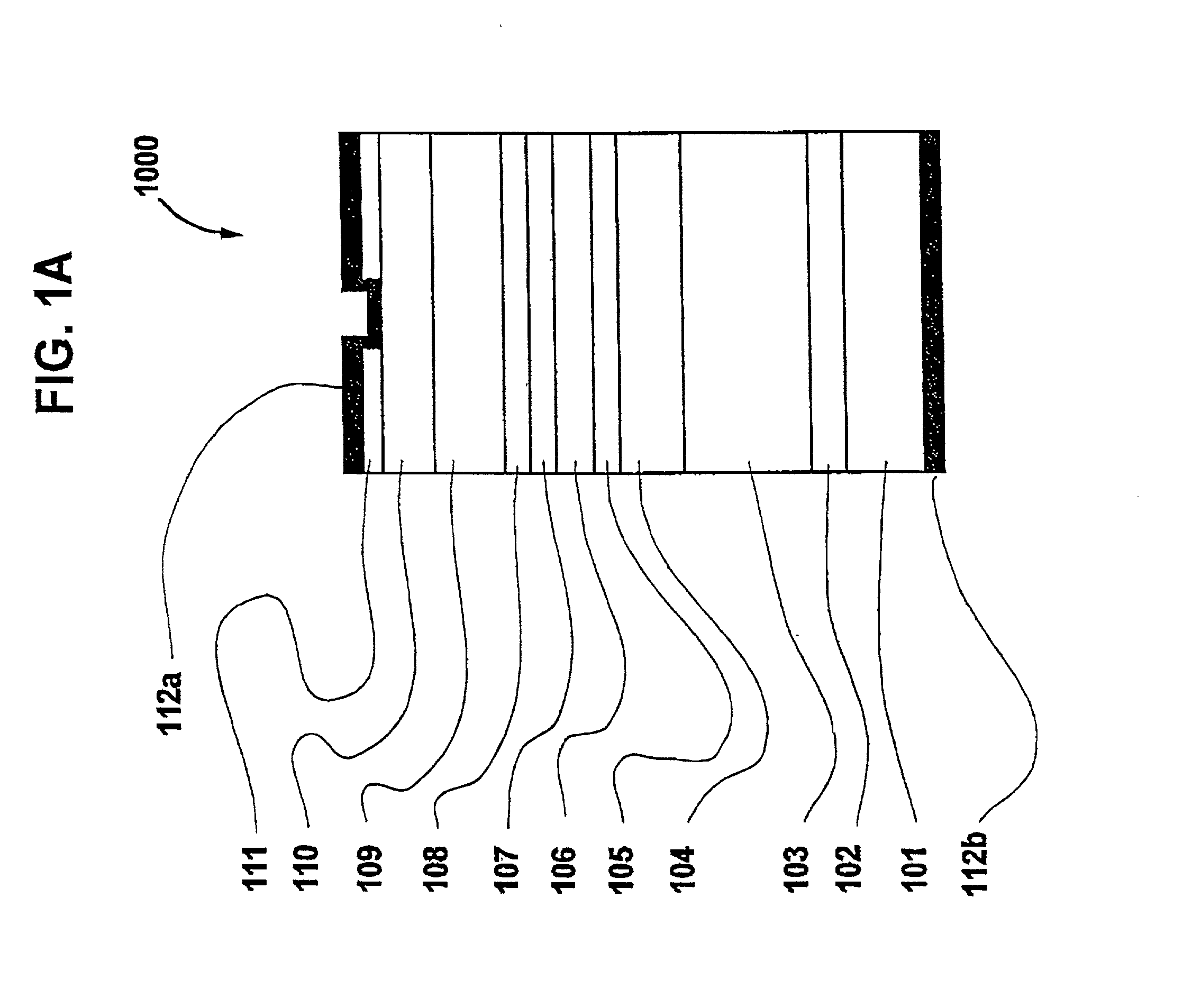

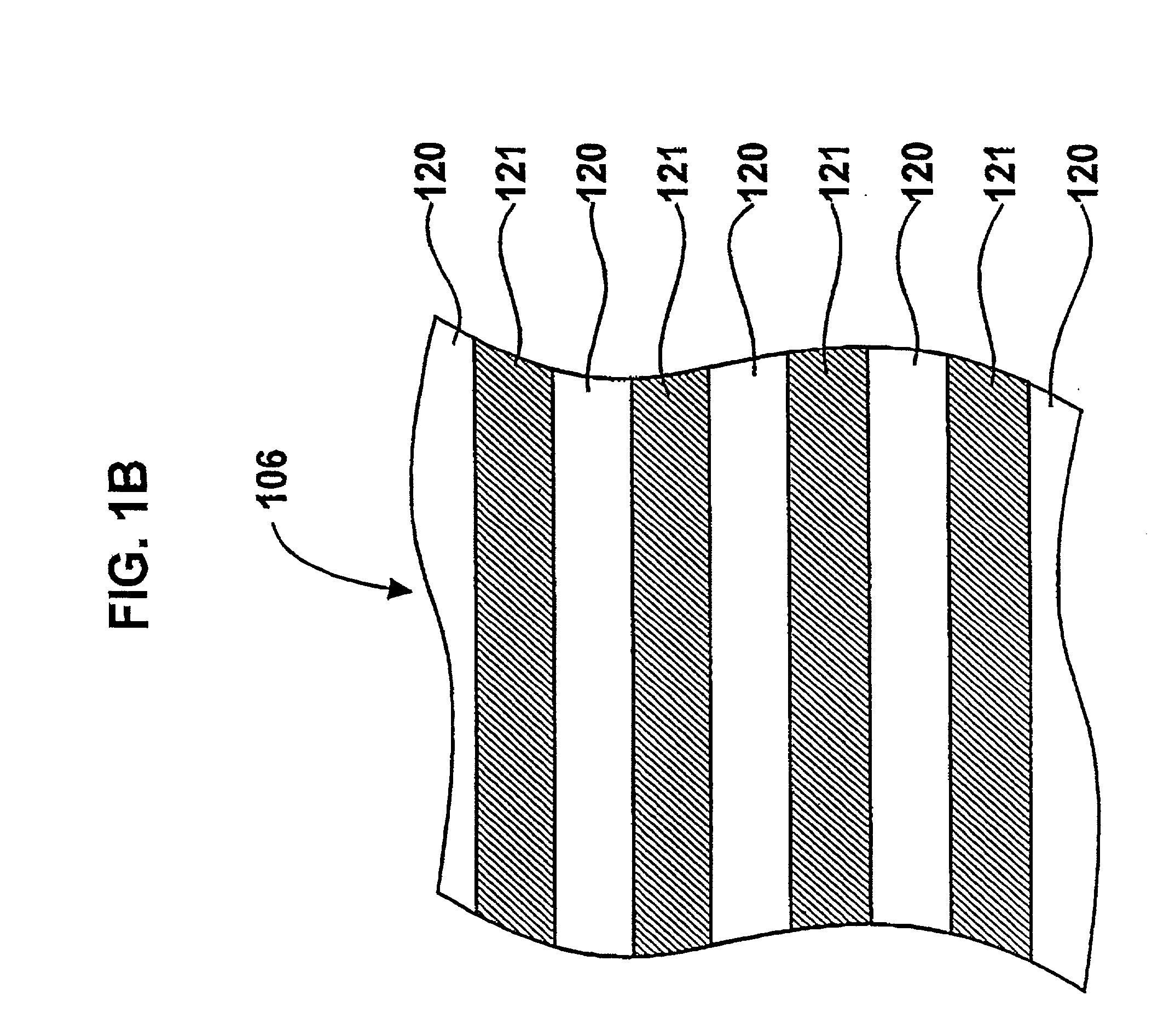

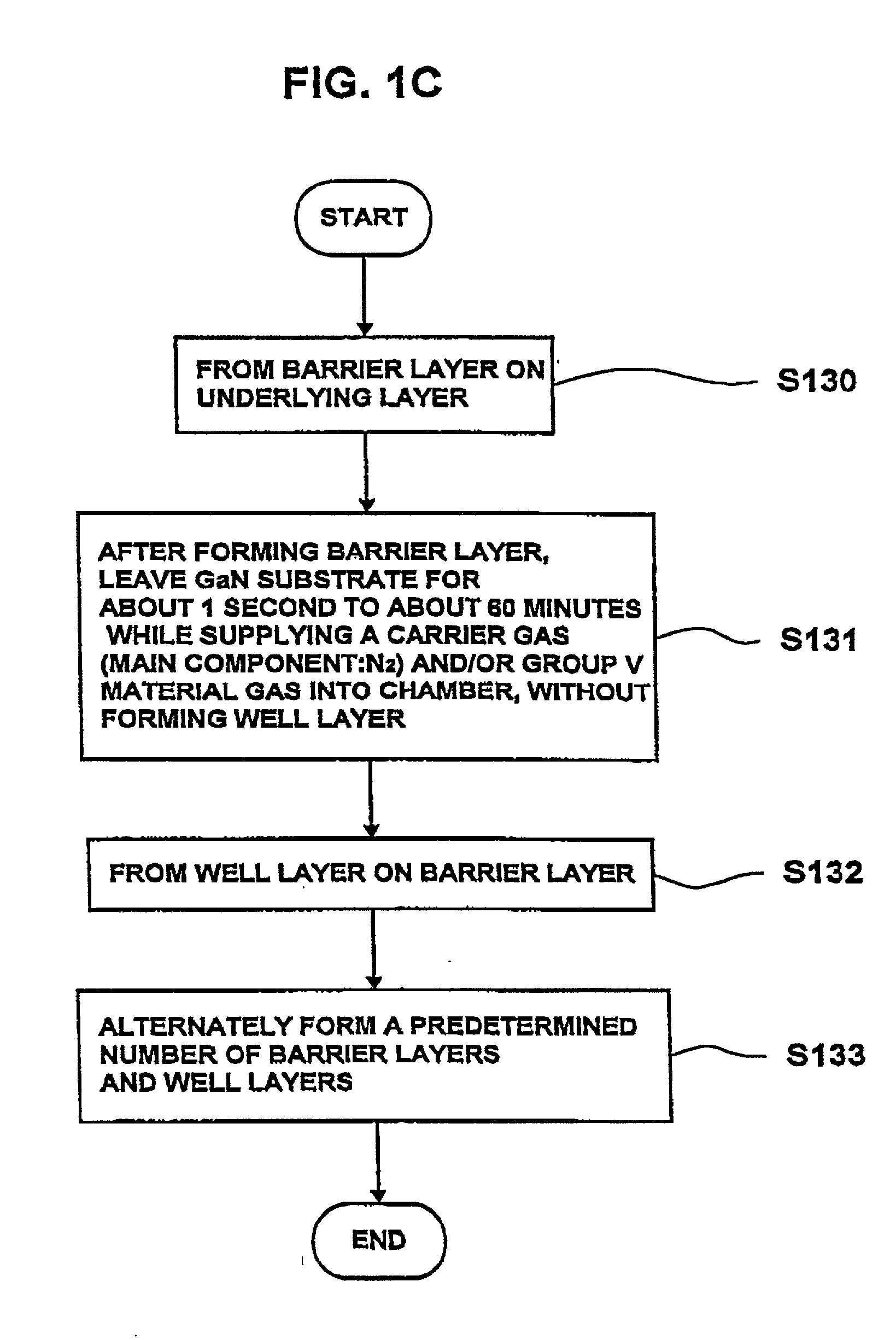

Nitride compound semiconductor light emitting device and method for producing the same

InactiveUS20010030329A1Low working voltageLaser detailsLaser active region structureCrystal orientationActive layer

A nitride compound semiconductor light emitting device includes: a GaN substrate having a crystal orientation which is tilted away from a <0001> direction by an angle which is equal to or greater than about 0.05° and which is equal to or less than about 2°, and a semiconductor multilayer structure formed on the GaN substrate, wherein the semiconductor multilayer structure includes: an acceptor doping layer containing a nitride compound semiconductor; and an active layer including a light emitting region.

Owner:SHARP KK

Solid State Laser Device Using a Selected Crystal Orientation in Non-Polar or Semi-Polar GaN Containing Materials and Methods

ActiveUS20130064261A1Facilitates parallel facetsReduce surface roughnessLaser detailsLaser active region structureHigh current densitySolid-state laser device

An edge emitting solid state laser and method. The laser comprises at least one AlInGaN active layer on a bulk GaN substrate with a non-polar or semi-polar orientation. The edges of the laser comprise {1 1−2±6} facets. The laser has high gain, low threshold currents, capability for extended operation at high current densities, and can be manufactured with improved yield. The laser is useful for optical data storage, projection displays, and as a source for general illumination.

Owner:KYOCERA SLD LASER INC +1

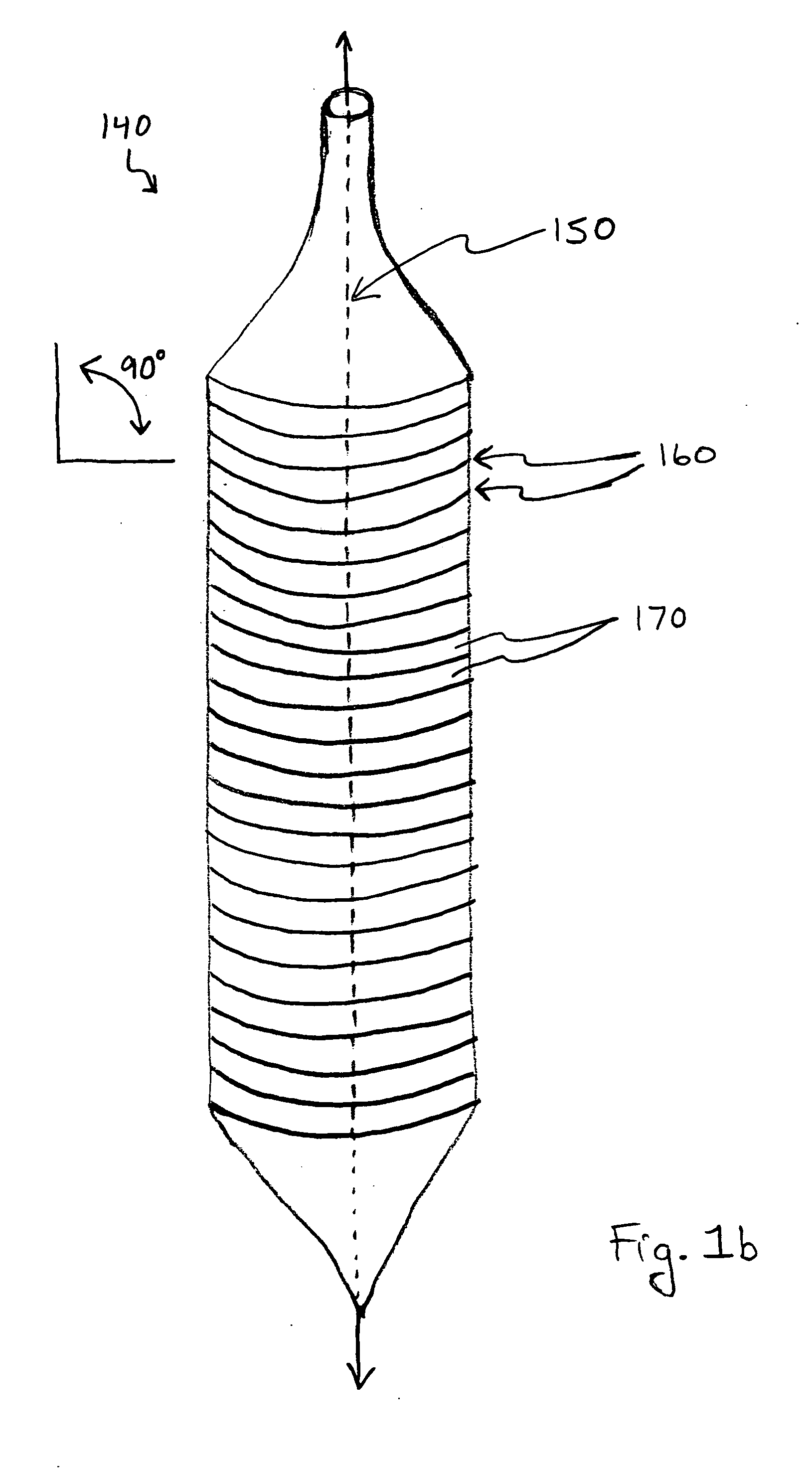

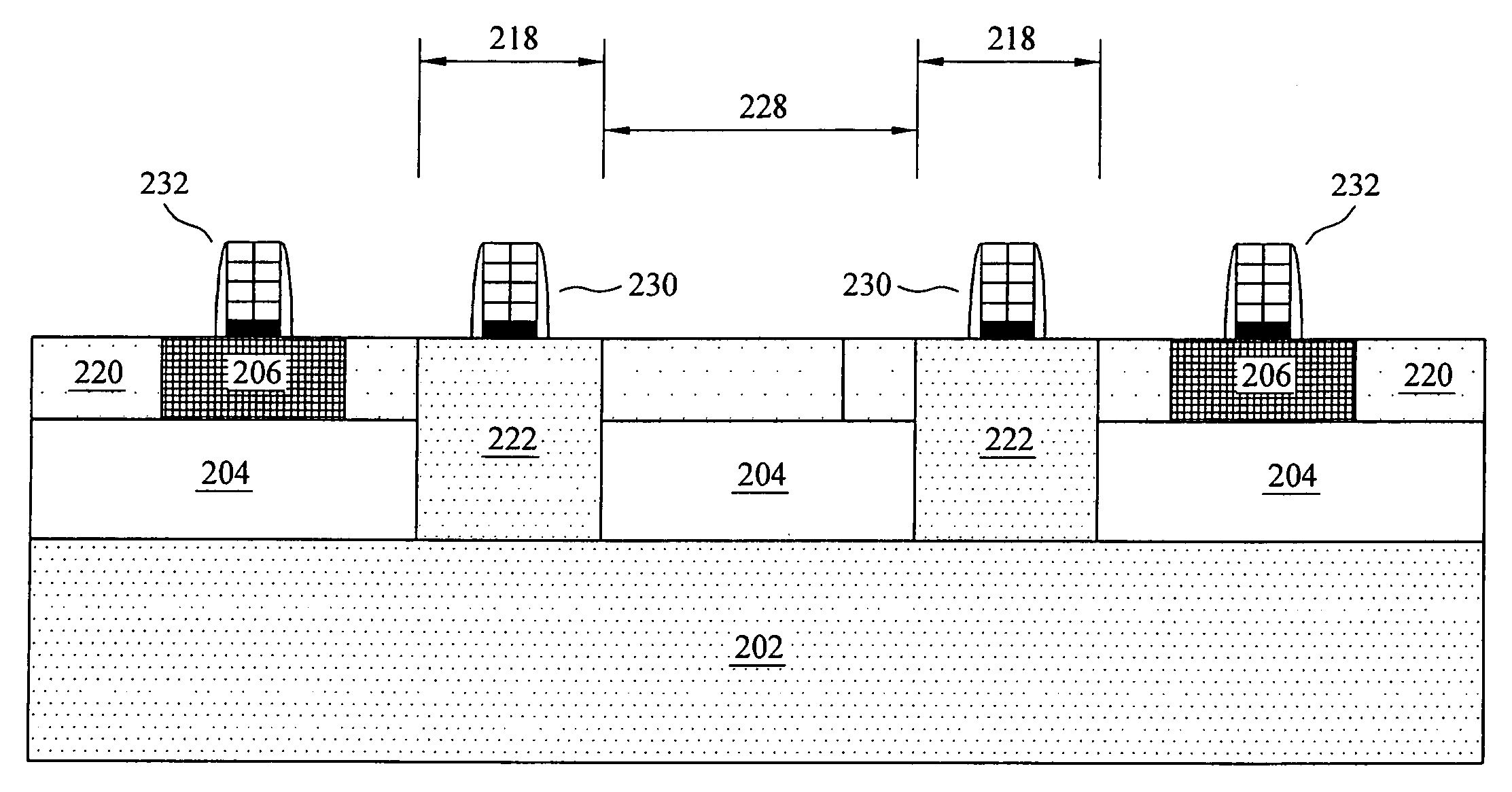

Semiconductor wafers with non-standard crystal orientations and methods of manufacturing the same

The crystal orientations of monocrystalline semiconductor wafers may be varied by four parameters. The first parameter is the type of crystal seed used to grow the monocrystalline semiconductor ingot from which the wafers are cut. The second parameter is the angle at which the wafer is sliced from the ingot. The third parameter is the crystal plane towards which the wafer is cut. And, the fourth parameter is the position of the orientation indication feature that is used to align the wafer during processing. Different combinations of these parameters provide variations of non-standard crystal orientations of monocrystalline semiconductor wafers and semiconductor-on-insulator substrates such as silicon-on-insulator.

Owner:INTEL CORP

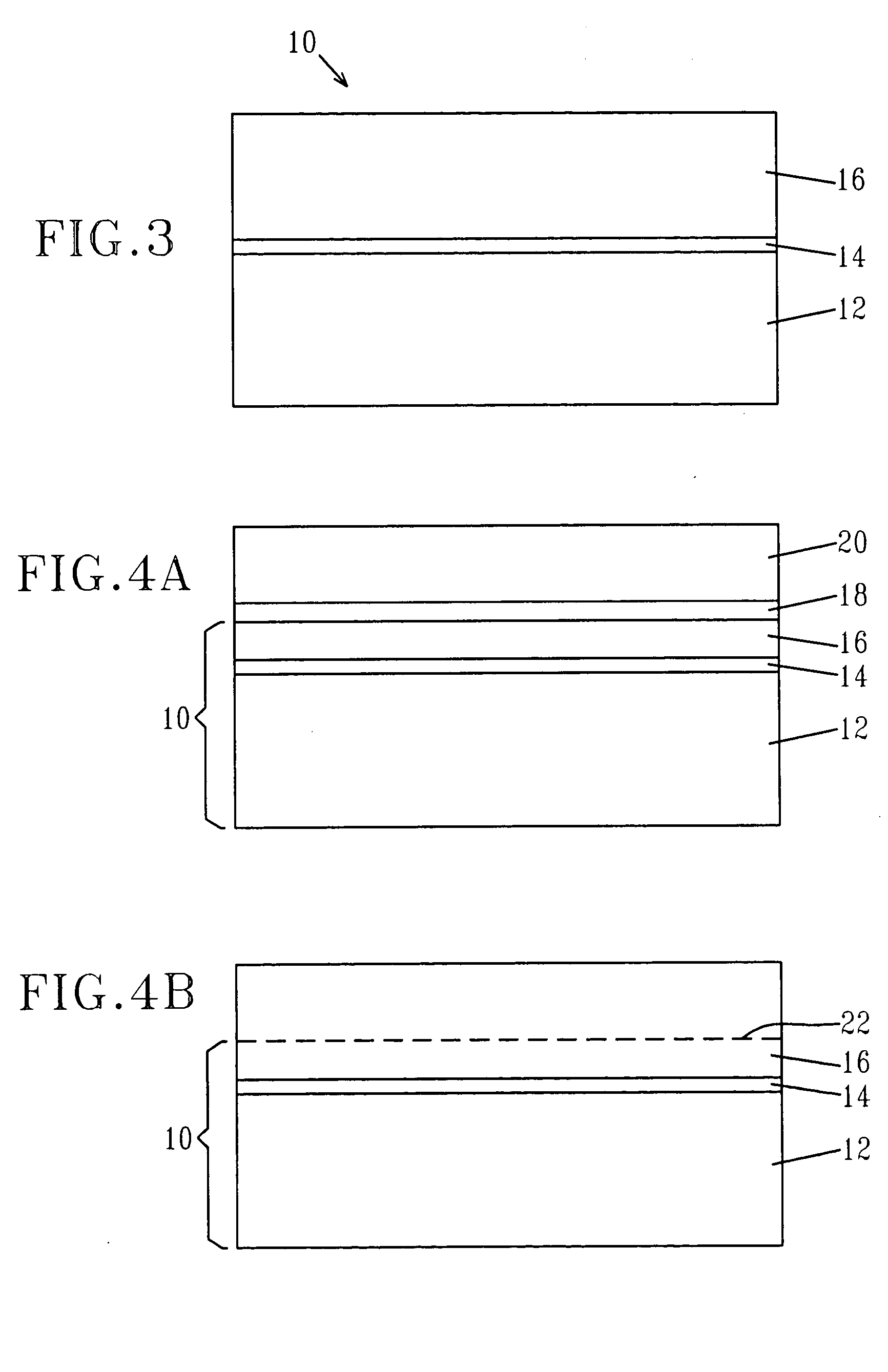

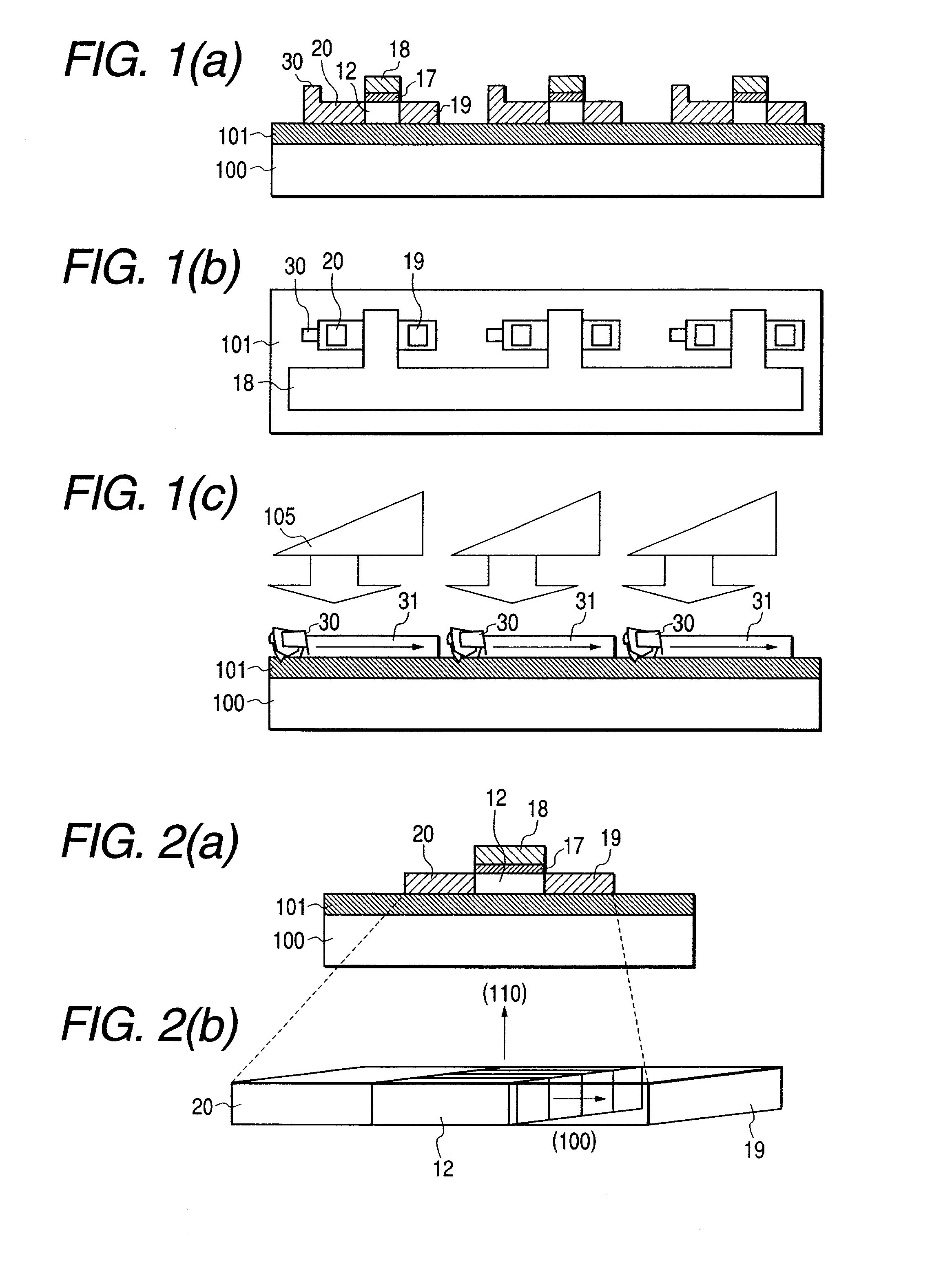

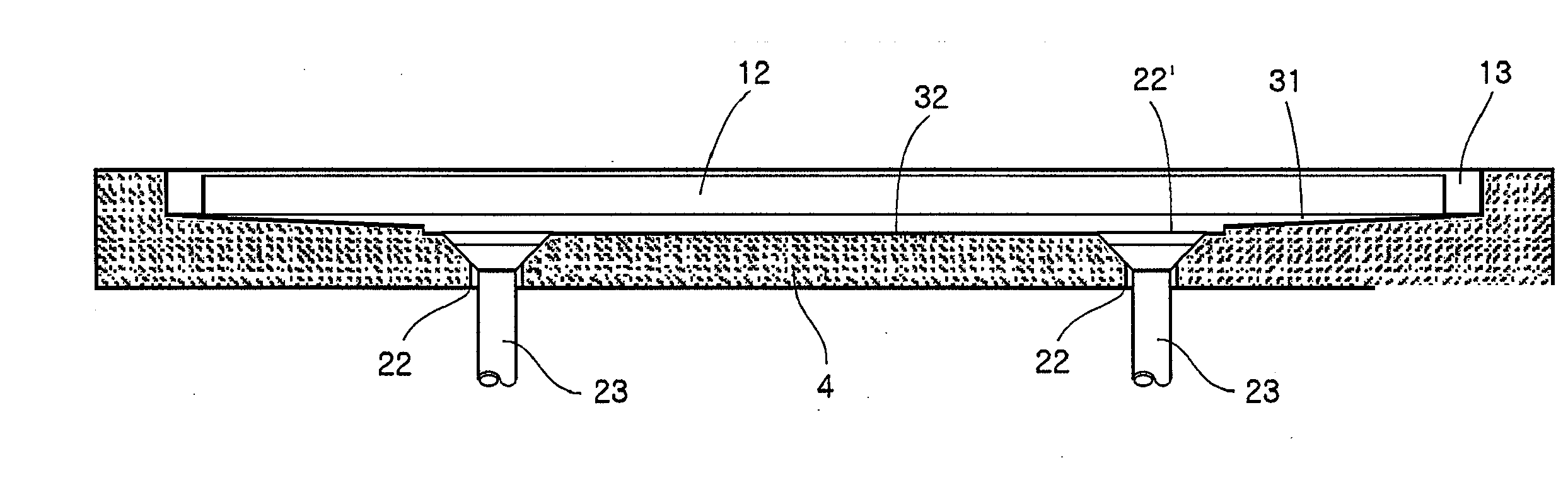

Thin film semiconductor device, polycrystalline semiconductor thin film production process and production apparatus

InactiveUS20020119609A1Reduce in quantityQuality improvementTransistorFrom solid stateElectrical conductorCrystal orientation

In an MIS field effect transistor having a gate electrode formed on a first semiconductor layer which is a polycrystalline silicon film on an insulating substrate through a gate insulating film, a channel region formed in the semiconductor layer and a source region and a drain region arranged on both sides of the channel region, a thin film semiconductor device has a main orientation of at least the channel region of {110} with respect to the surface of the gate insulating film. Further, a polycrystalline semiconductor film having a main orientation of the surface almost perpendicular to a direction for connecting the source and drain regions of {100} is preferably used in the channel of a semiconductor device. According to the present invention, a semiconductor device having a high-quality polycrystalline semiconductor film whose grain boundary, grain size and crystal orientation can be controlled and whose film roughness and crystal defects formed by crystallization have been reduced can be obtained on the insulating substrate.

Owner:PANASONIC LIQUID CRYSTAL DISPLAY CO LTD +1

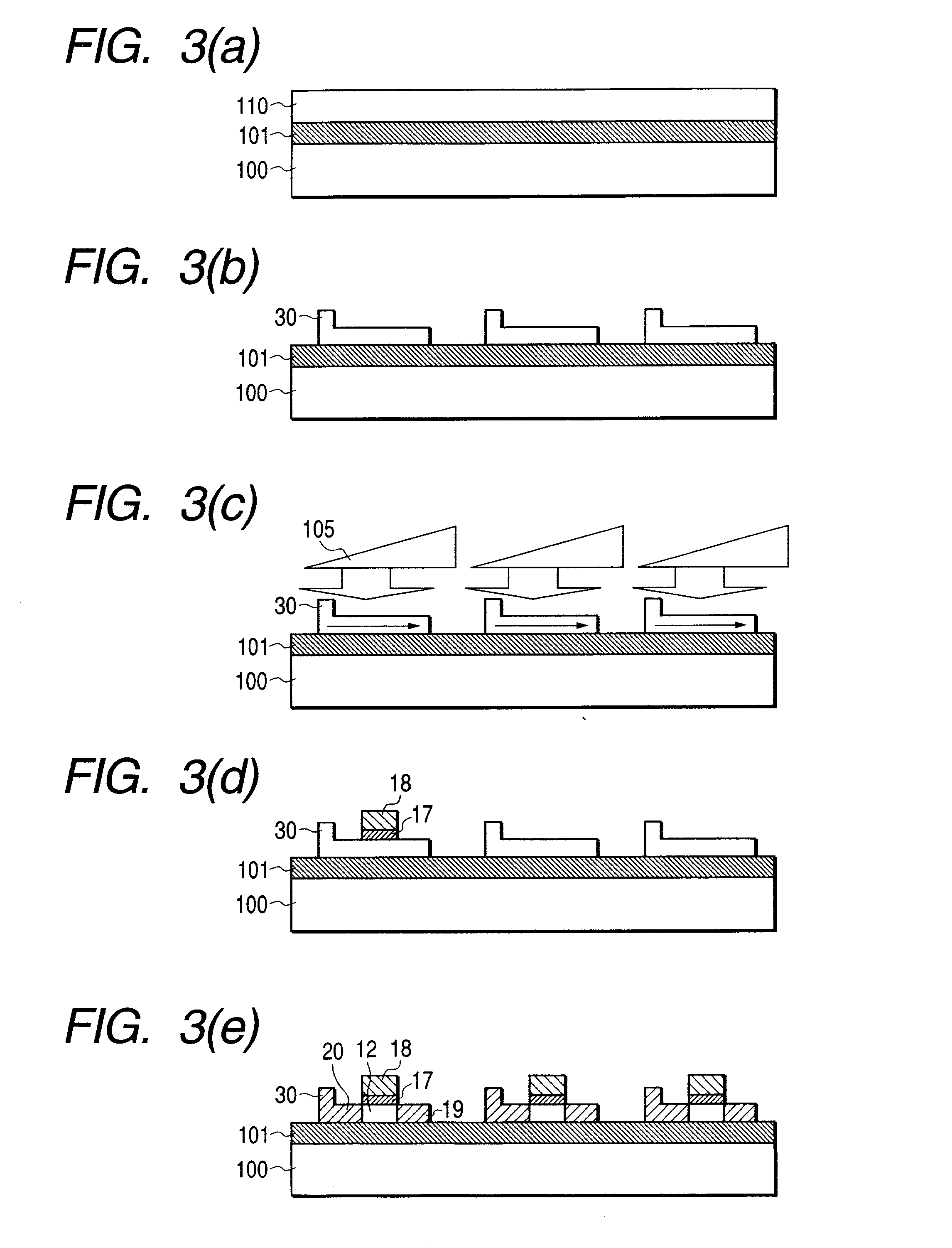

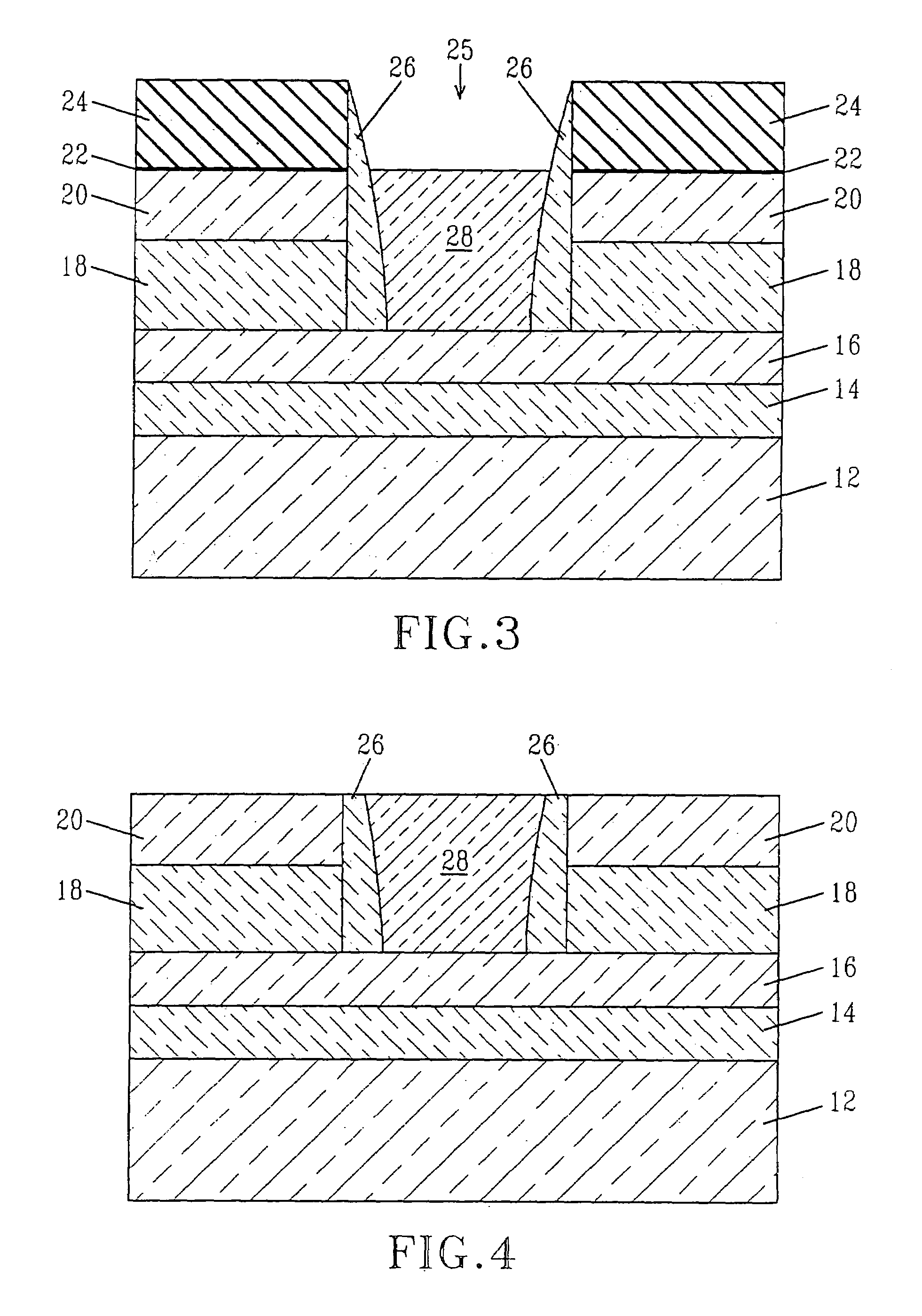

FinFET and method for manufacturing the same

InactiveUS20070045736A1Solid-state devicesSemiconductor devicesCrystal orientationCondensed matter physics

A gate electrode is arranged in a direction parallel or perpendicular to a specified crystal orientation of a substrate. A first transistor of a first conductivity type has a first active region, which is arranged in a direction perpendicular to the gate electrode. A second transistor of a second conductivity type has a second active region, which is inclined relative to the gate electrode.

Owner:KK TOSHIBA

Strained silicon CMOS on hybrid crystal orientations

InactiveUS7087965B2Improve performanceImprove device performanceTransistorSolid-state devicesCMOSSemiconductor materials

Methods of forming a strained Si-containing hybrid substrate are provided as well as the strained Si-containing hybrid substrate formed by the methods. In the methods of the present invention, a strained Si layer is formed overlying a regrown semiconductor material, a second semiconducting layer, or both. In accordance with the present invention, the strained Si layer has the same crystallographic orientation as either the regrown semiconductor layer or the second semiconducting layer. The methods provide a hybrid substrate in which at least one of the device layers includes strained Si.

Owner:GLOBALFOUNDRIES INC

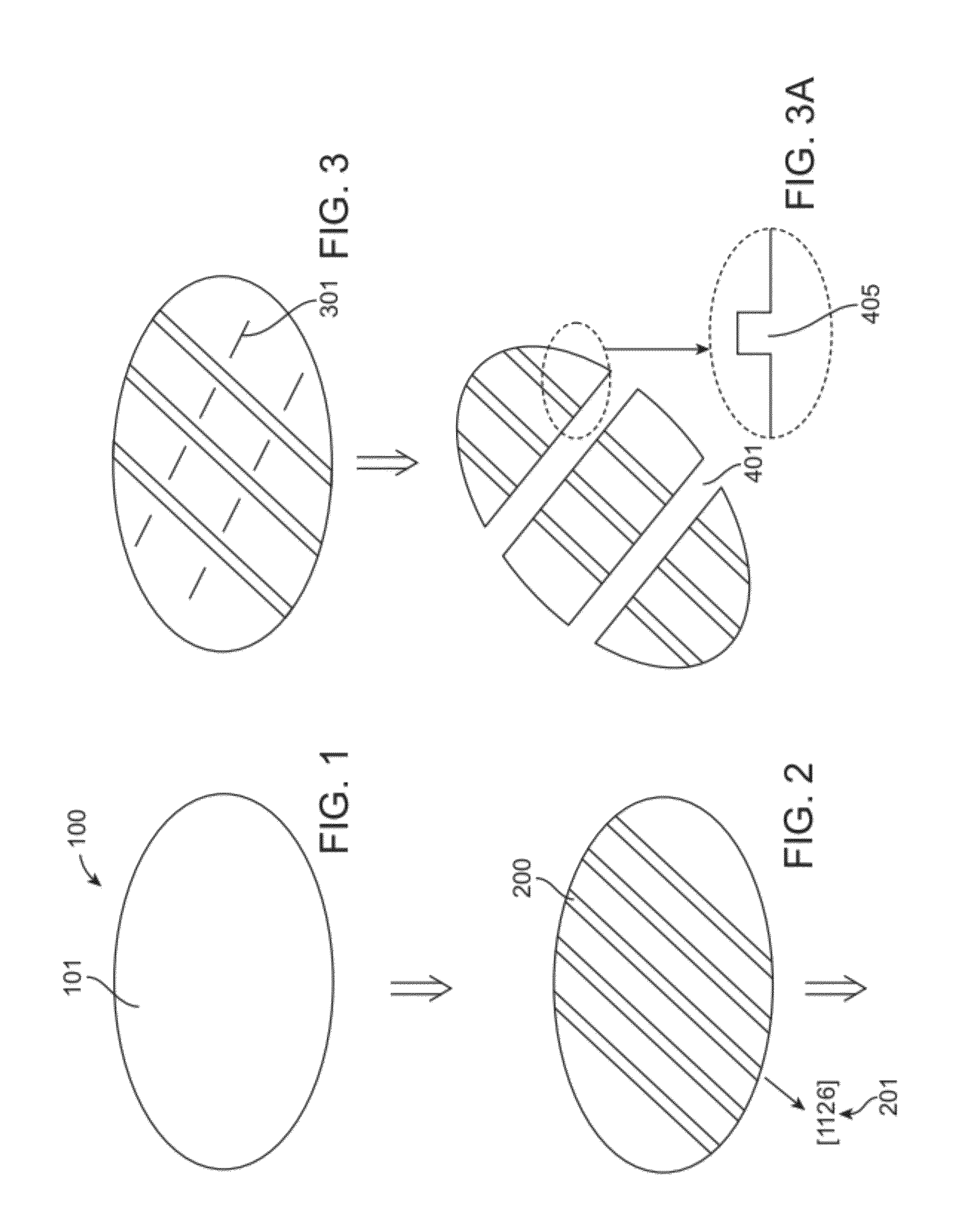

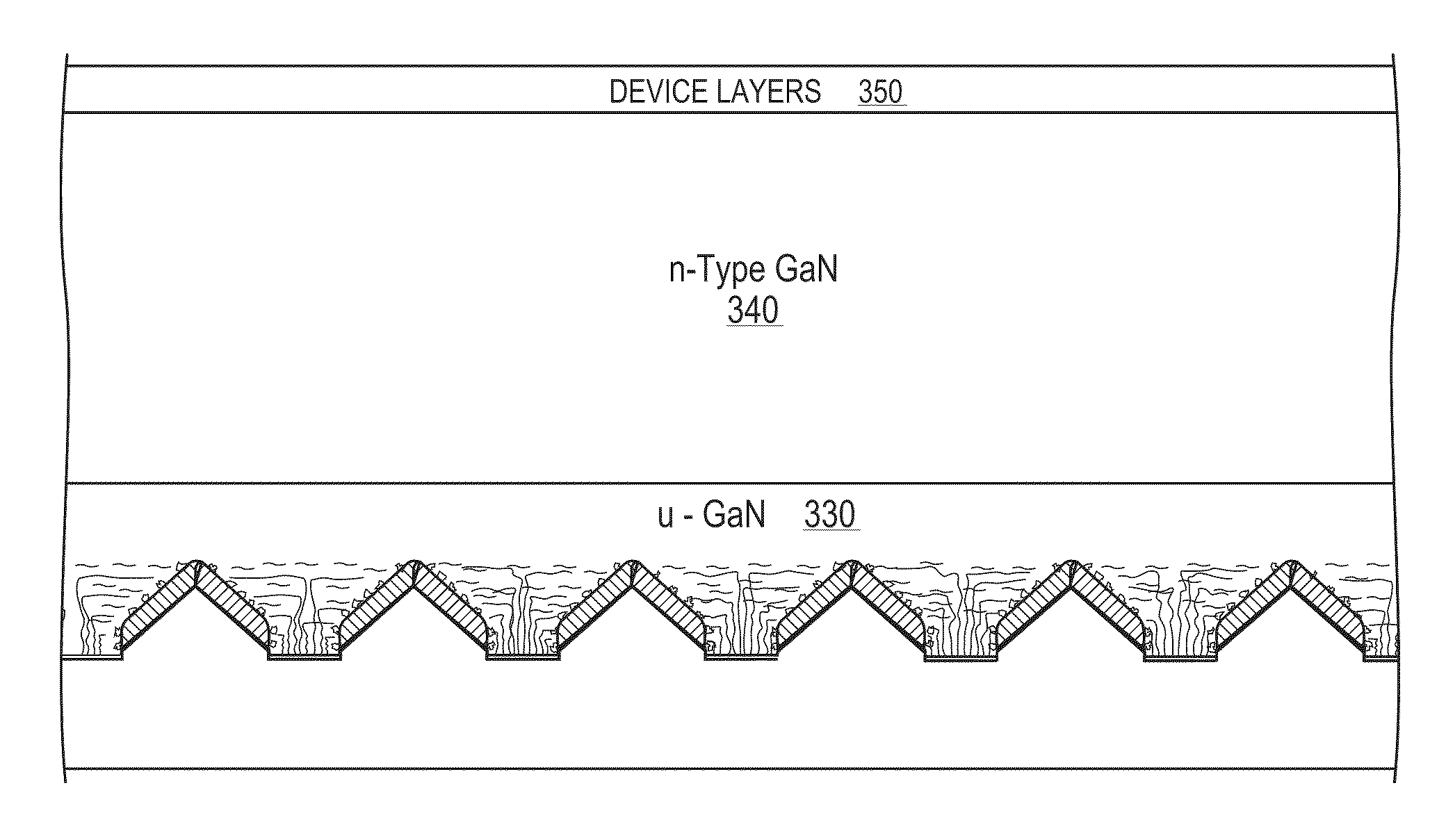

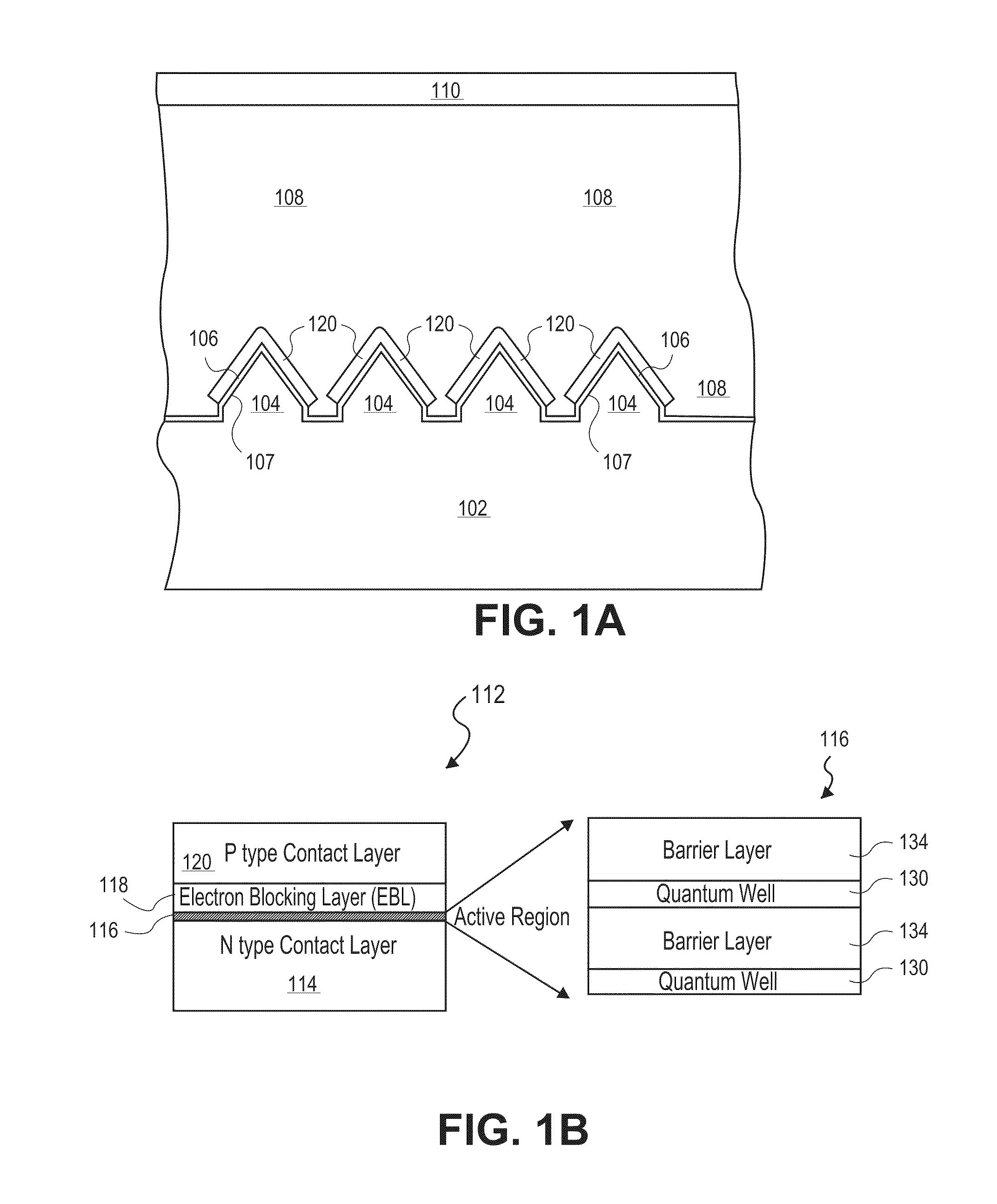

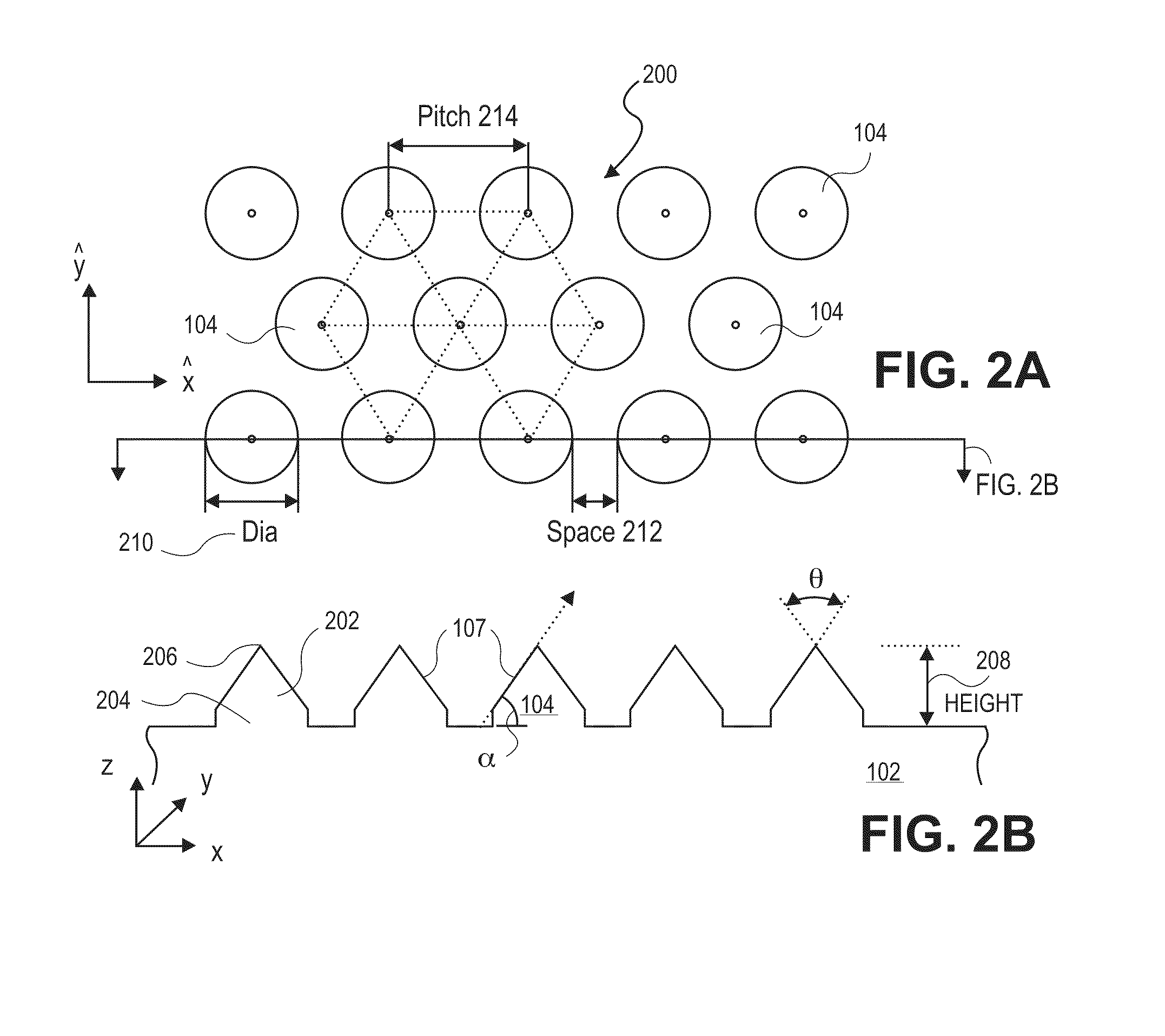

Method of forming a group iii-nitride crystalline film on a patterned substrate by hydride vapor phase epitaxy (HVPE)

ActiveUS20110012109A1Quality improvementSemiconductor/solid-state device manufacturingChemical vapor deposition coatingCrystal orientationPatterned substrate

A method of depositing a high quality low defect single crystalline Group III-Nitride film. A patterned substrate having a plurality of features with inclined sidewalls separated by spaces is provided. A Group III-Nitride film is deposited by a hydride vapor phase epitaxy (HVPE) process over the patterned substrate. The HVPE deposition process forms a Group III-Nitride film having a first crystal orientation in the spaces between features and a second different crystal orientation on the inclined sidewalls. The first crystal orientation in the spaces subsequently overgrows the second crystal orientation on the sidewalls and in the process turns over and terminates treading dislocations formed in the first crystal orientation.

Owner:APPLIED MATERIALS INC

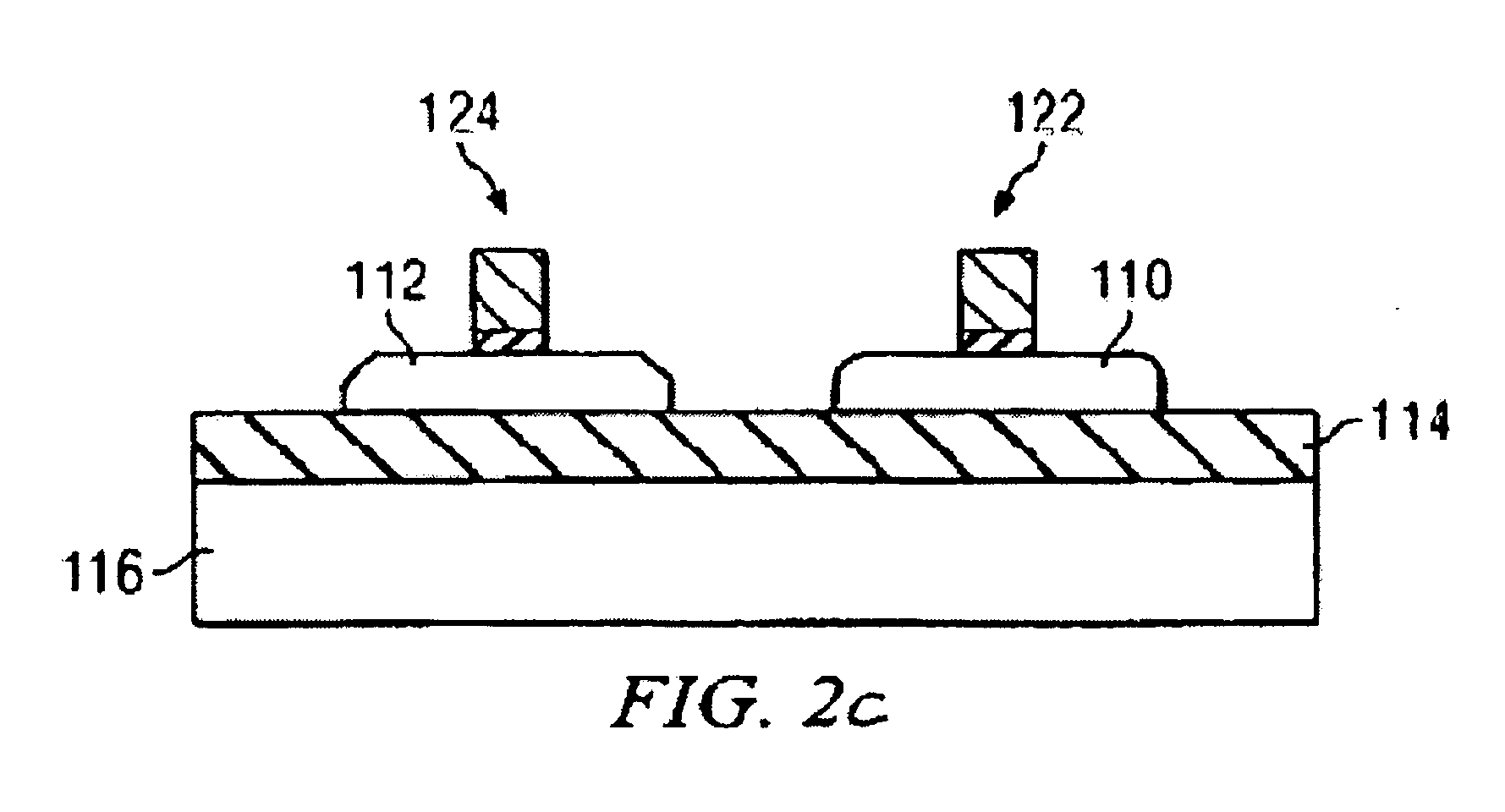

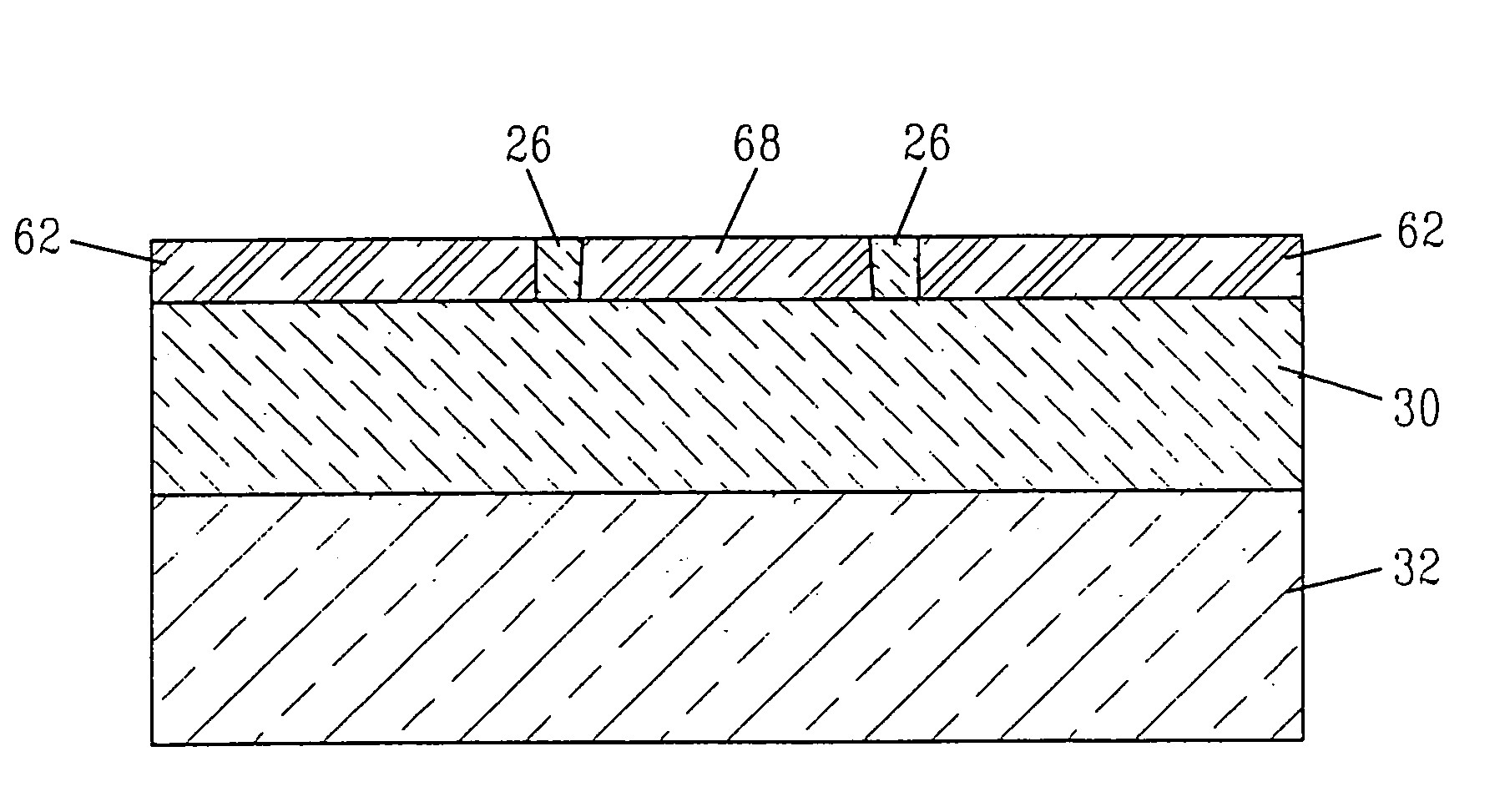

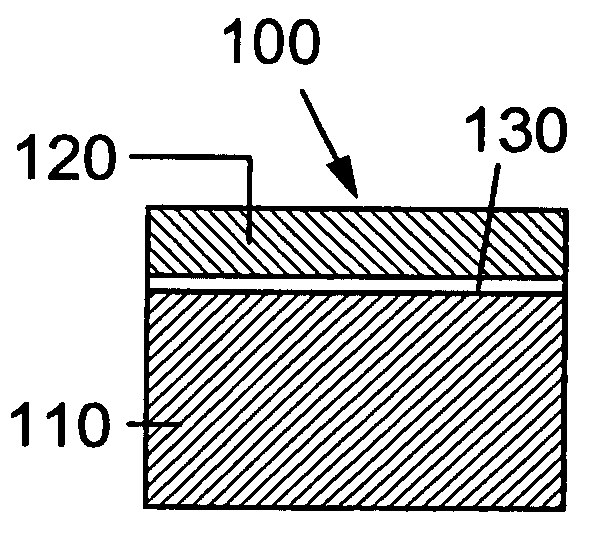

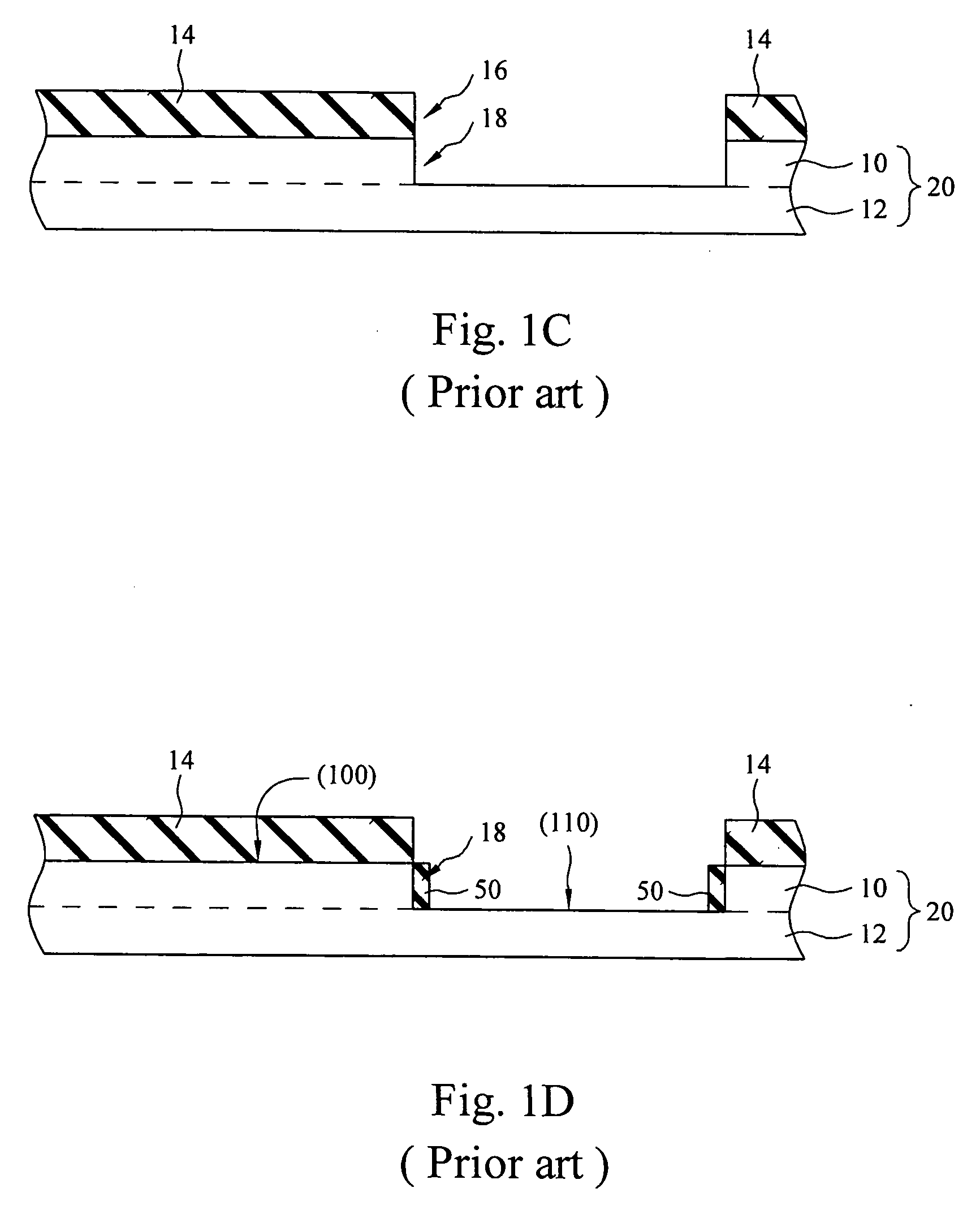

Ultra-thin silicon-on-insulator and strained-silicon-direct-on-insulator with hybrid crystal orientations

InactiveUS7098508B2Improve performanceSimple and easy stepTransistorSolid-state devicesEtchingSemiconductor materials

The invention provides integrated semiconductor devices that are formed upon an SOI substrate having different crystal orientations that provide optimal performance for a specific device. Specifically, an integrated semiconductor structure including at least an SOI substrate having a top semiconductor layer of a first crystallographic orientation and a semiconductor material of a second crystallographic orientation, wherein the semiconductor material is substantially coplanar and of substantially the same thickness as that of the top semiconductor layer and the first crystallographic orientation is different from the second crystallographic orientation is provided. The SOI substrate is formed by forming an opening into a structure that includes at least a first semiconductor layer and a second semiconductor layer that have different crystal orientations. The opening extends to the first semiconductor layer. A semiconductor material is epitaxial grown in the opening and then various etching and etch back processing steps are used in forming the SOI substrate.

Owner:GLOBALFOUNDRIES U S INC

Quasi-hydrophobic Si-Si wafer bonding using hydrophilic Si surfaces and dissolution of interfacial bonding oxide

InactiveUS20060154442A1Thinning and removing materialSemiconductor/solid-state device manufacturingInterfacial oxideSemiconductor materials

The present invention provides a method for removing or reducing the thickness of ultrathin interfacial oxides remaining at Si—Si interfaces after silicon wafer bonding. In particular, the invention provides a method for removing ultrathin interfacial oxides remaining after hydrophilic Si—Si wafer bonding to create bonded Si—Si interfaces having properties comparable to those achieved with hydrophobic bonding. Interfacial oxide layers of order of about 2 to about 3 nm are dissolved away by high temperature annealing, for example, an anneal at 1300°-1330° C. for 1-5 hours. The inventive method is used to best advantage when the Si surfaces at the bonded interface have different surface orientations, for example, when a Si surface having a (100) orientation is bonded to a Si surface having a (110) orientation. In a more general aspect of the invention, the similar annealing processes may be used to remove undesired material disposed at a bonded interface of two silicon-containing semiconductor materials. The two silicon-containing semiconductor materials may be the same or different in surface crystal orientation, microstructure (single-crystal, polycrystalline, or amorphous), and composition.

Owner:GLOBALFOUNDRIES INC

Members with multi-layer coatings

InactiveUS6254984B1Improve adhesionGuaranteed uptimeVacuum evaporation coatingSputtering coatingCarbideCrystal orientation

In the multi-layer-coated member composed of an ultra-hard alloy substrate and a multi-layer coating formed thereon, the multi-layer coating comprises two or more first layers each composed of at least one of carbides, nitrides and carbonitrides of elements of Groups 4a, 5a and 6a of the Periodic Table and Al, and two or more second layers each composed of at least one of oxides, carboxides, oxinitrides and carboxinitrides of elements of Groups 4a, 5a and 6a of the Periodic Table and Al laminated alternately. The first layers adjacent via the second layer are continuous in crystal orientation.

Owner:HITACHI TOOL ENG LTD

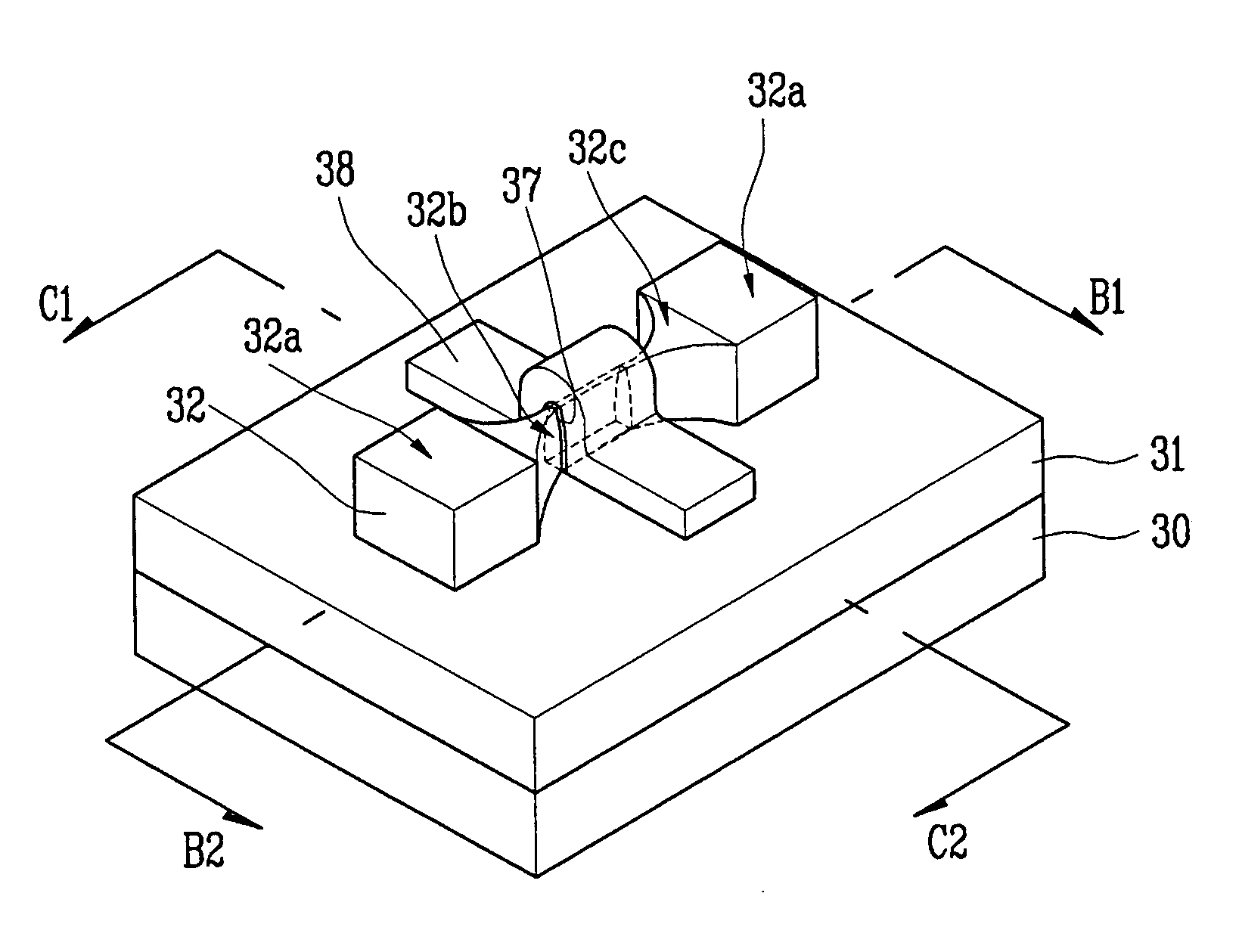

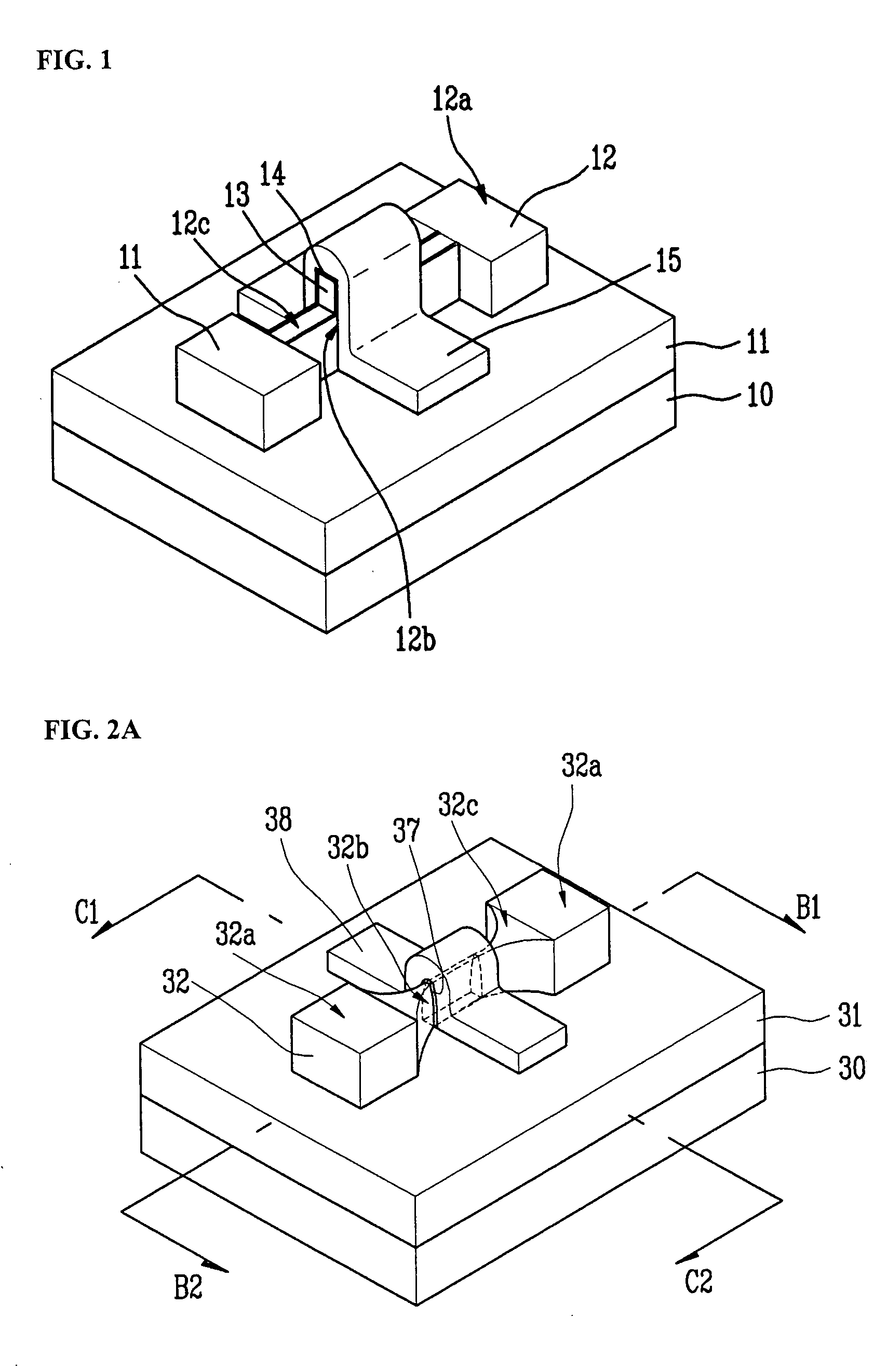

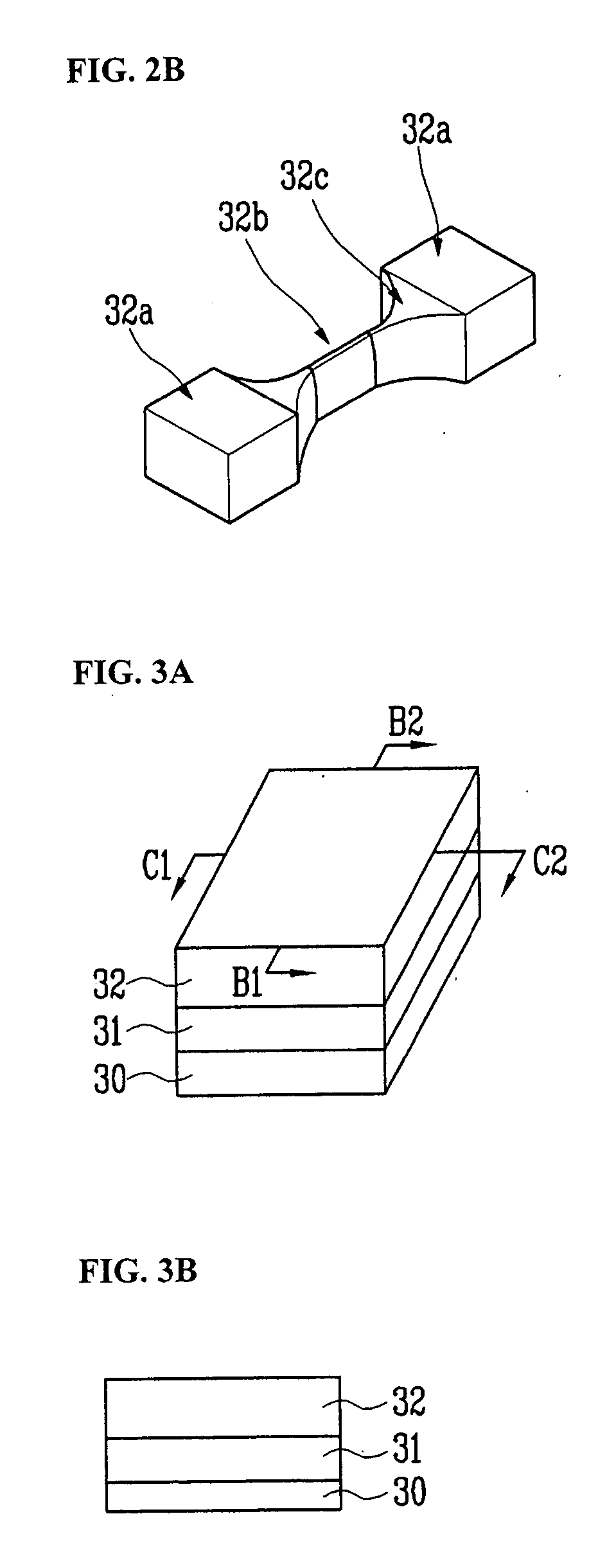

Multiple-gate MOS transistor and a method of manufacturing the same

InactiveUS20050263821A1Improve reliabilityImprove rendering capabilitiesTransistorGrinding drivesCrystal orientationGate voltage

Provided is a multiple-gate metal oxide semiconductor (MOS) transistor and a method for manufacturing the same, in which a channel is implemented in a streamline shape, an expansion region is implemented in a gradually increased form, and source and drain regions is implemented in an elevated structure by using a difference of a thermal oxidation rate depending on a crystal orientation of silicon and a geographical shape of the single-crystal silicon pattern. As the channel is formed in a streamline shape, it is possible to prevent the degradation of reliability due to concentration of an electric field and current driving capability by the gate voltage is improved because the upper portion and both sides of the channel are surrounded by the gate electrodes. In addition, a current crowding effect is prevented due to the expansion region increased in size and source and drain series resistance is reduced by elevated source and drain structures, thereby increasing the current driving capability.

Owner:III HLDG 2

Semiconductor device

Crystal orientation planes exist randomly in a crystalline silicon film manufactured by a conventional method, and the orientation ratio is low with respect to a specific crystal orientation. A semiconductor film having a high orientation ratio for the {101} lattice plane is obtained if crystallization of an amorphous semiconductor film, which has silicon as its main constituent and contains from 0.1 to 10 atom % germanium, is performed after introduction of a metal element. A TFT is manufactured utilizing the semiconductor film.

Owner:SEMICON ENERGY LAB CO LTD

Complementary field-effect transistors and methods of manufacture

InactiveUS20050116360A1Easy to operateTransistorSemiconductor/solid-state device manufacturingDielectricSurface layer

A complementary FET and a method of manufacture is provided. The complementary FET utilizes a substrate having a surface layer with a <100> crystal orientation. Tensile stress, which increases performance of the NMOS FETs, is added by silicided source / drain regions, tensile-stress film, shallow trench isolations, inter-layer dielectric, or the like.

Owner:TAIWAN SEMICON MFG CO LTD

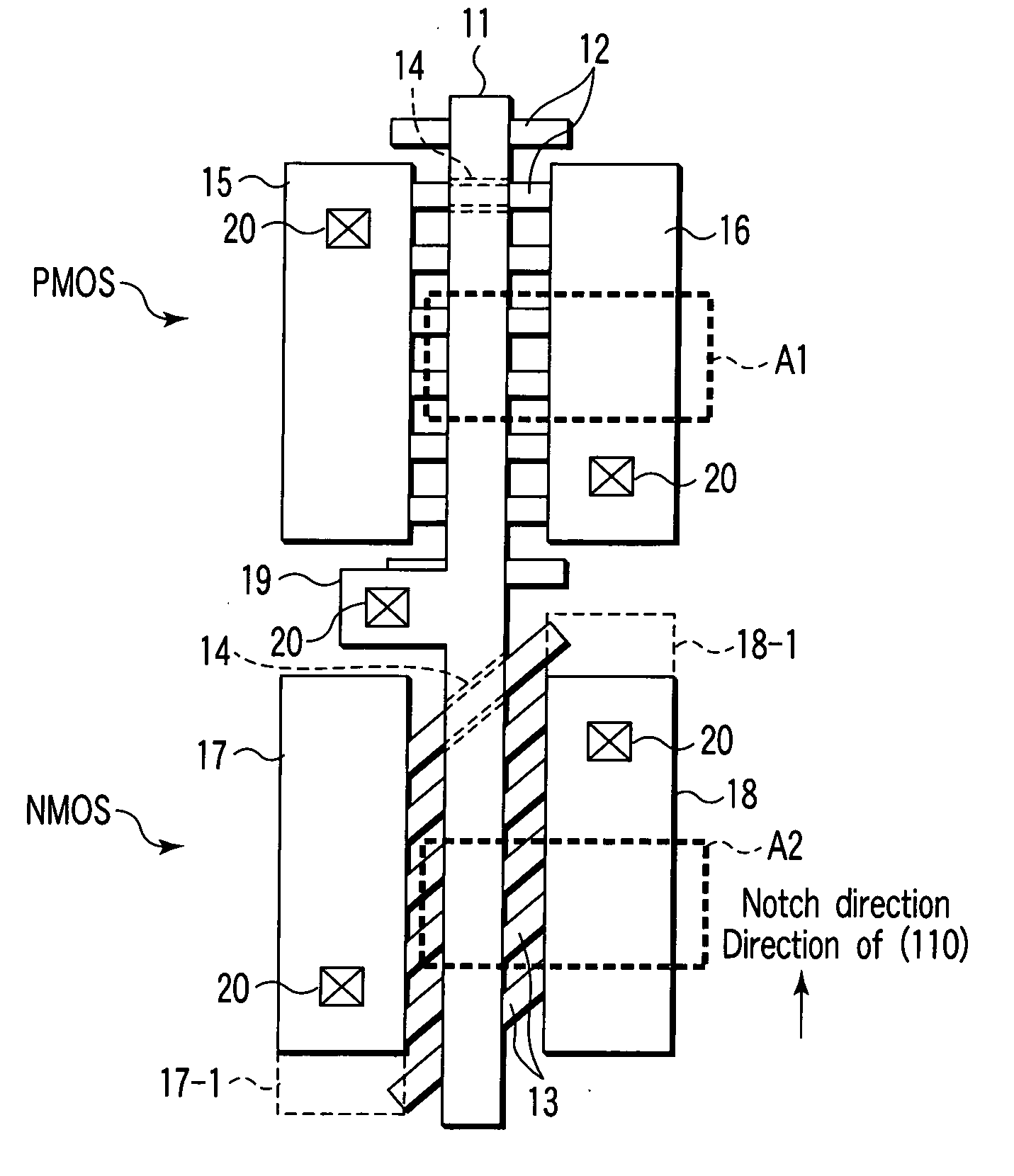

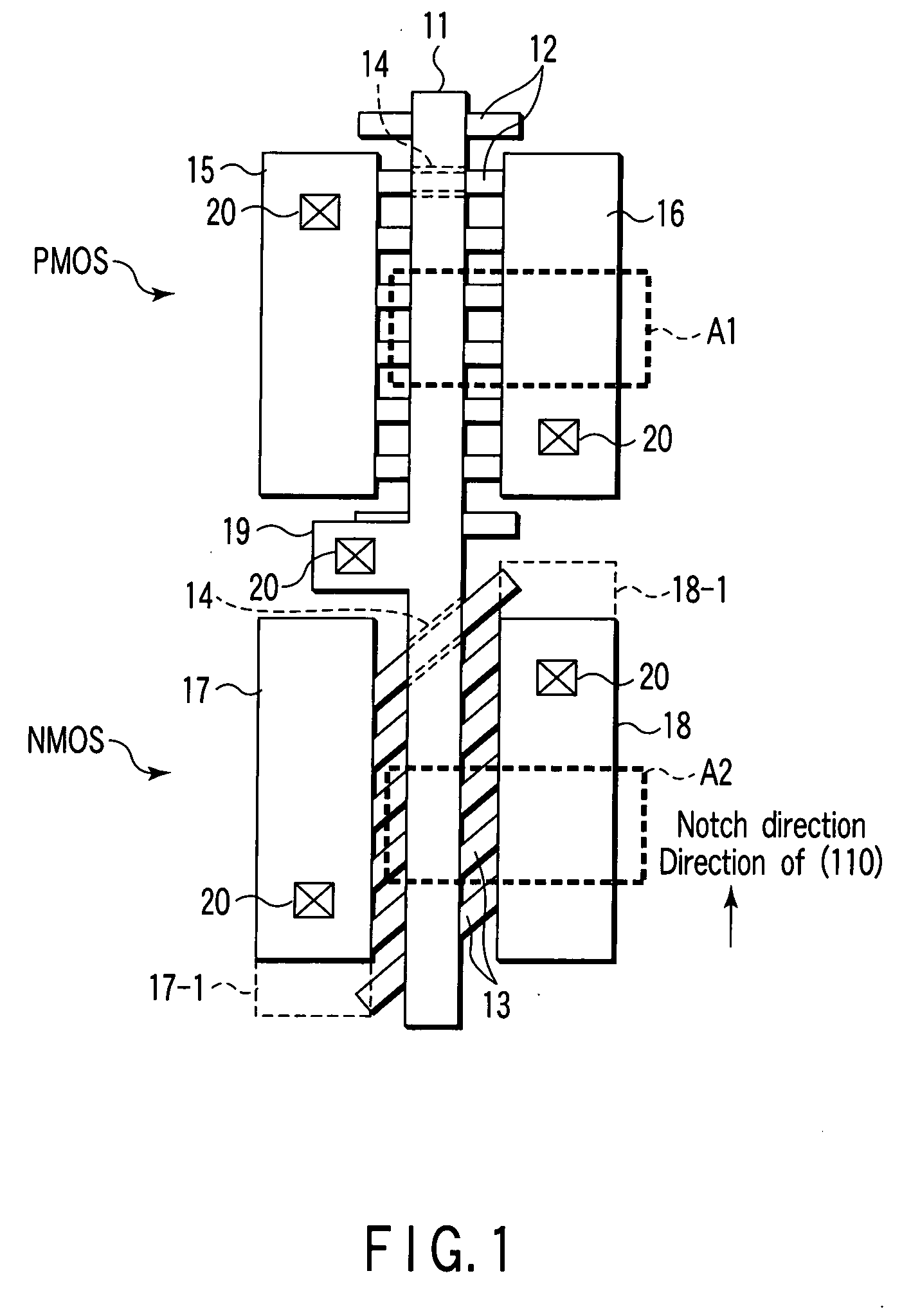

CMOS logic gate fabricated on hybrid crystal orientations and method of forming thereof

ActiveUS20060049460A1Harmful effectHarmful microloading effects are avoidedTransistorSolid-state devicesCMOSCrystal orientation

In preferred embodiments of the present invention, a method of forming CMOS devices using SOI and hybrid substrate orientations is described. In accordance with a preferred embodiment, a substrate may have multiple crystal orientations. One logic gate in the substrate may comprise at least one N-FET on one crystal orientation and at least one P-FET on another crystal orientation. Another logic gate in the substrate may comprise at least one N-FET and at least one P-FET on the same orientation. Alternative embodiments further include determining the preferred cleavage planes of the substrates and orienting the substrates relative to each other in view of their respective preferred cleavage planes. In a preferred embodiment, the cleavage planes are not parallel.

Owner:TAIWAN SEMICON MFG CO LTD

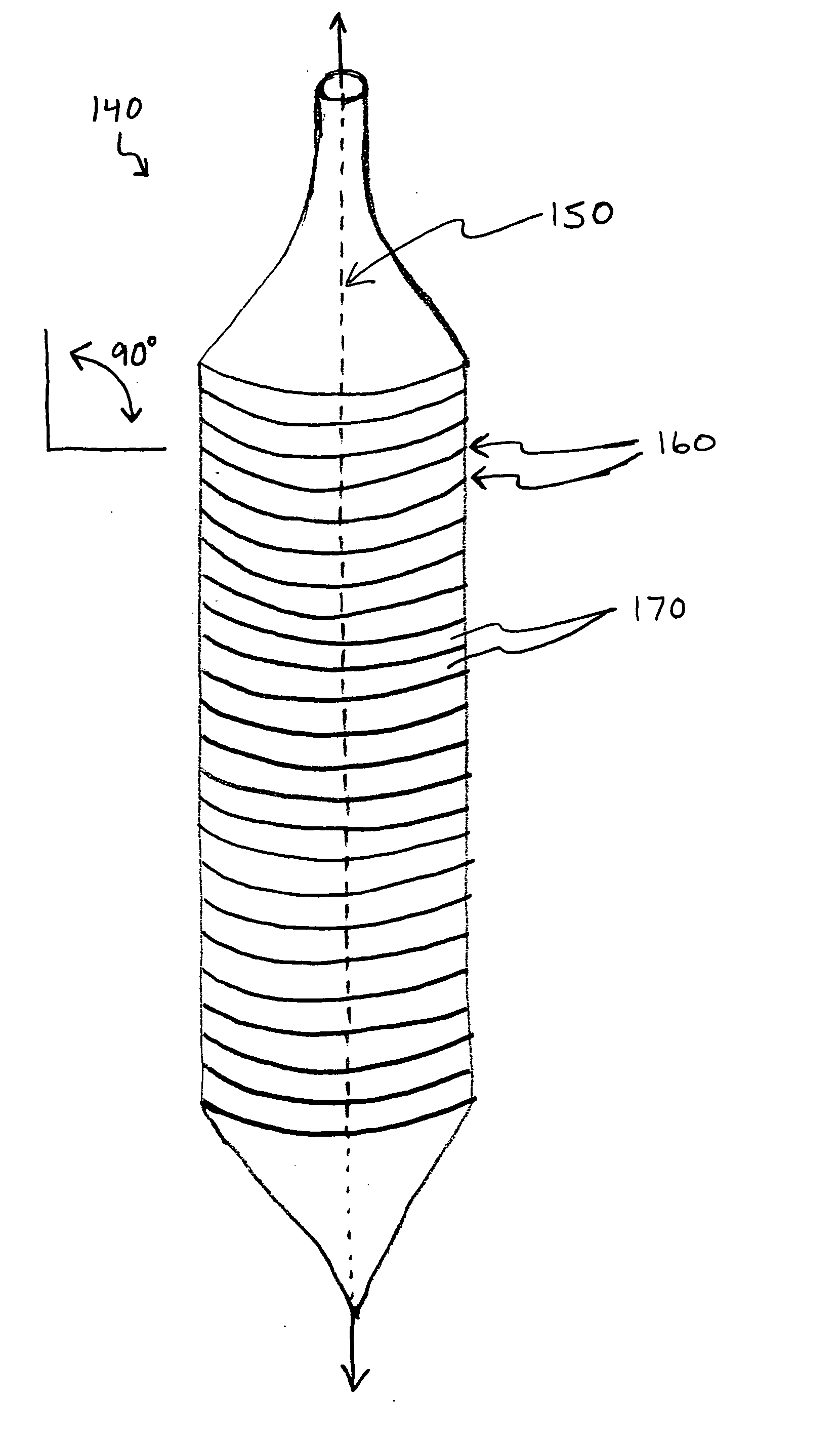

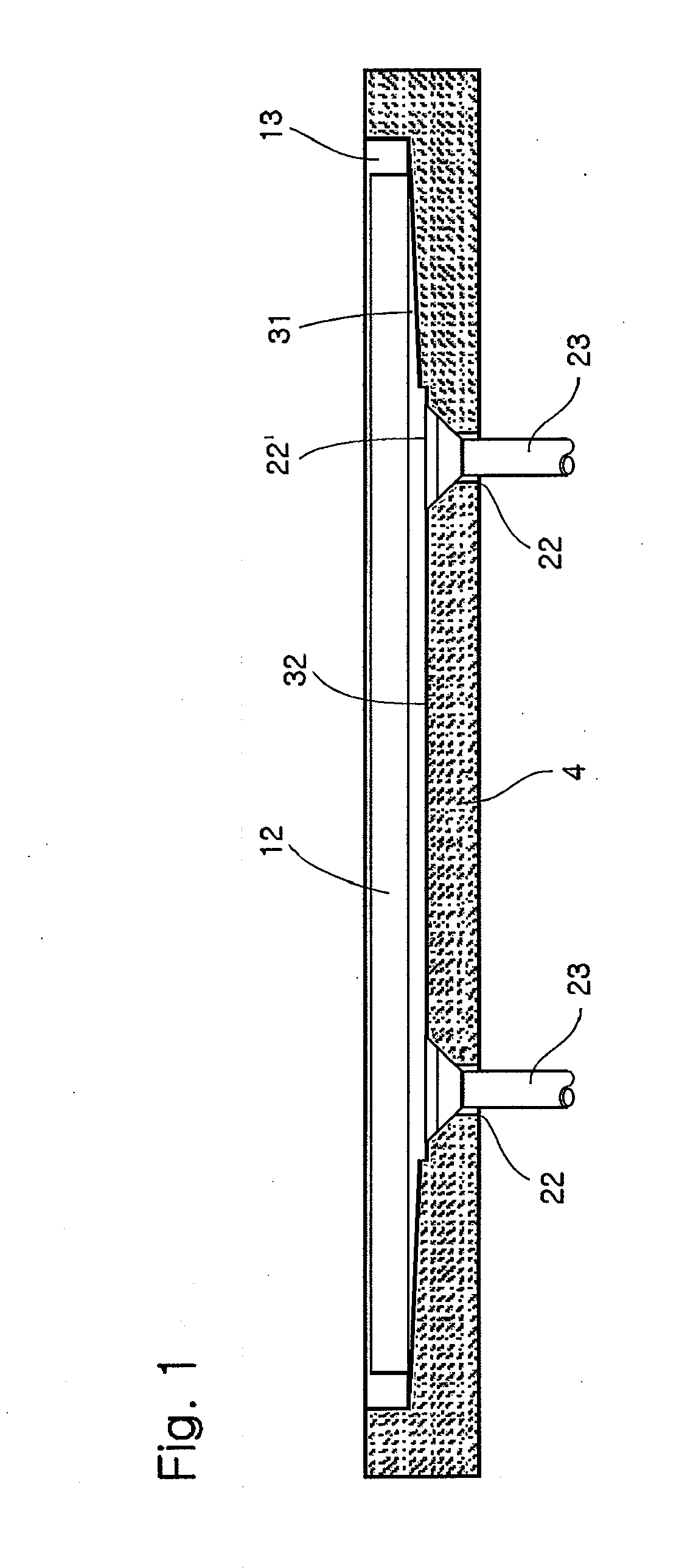

Method of manufacturing epitaxial silicon wafer and apparatus thereof

ActiveUS20070227441A1Improve uniformityPolycrystalline material growthSemiconductor/solid-state device manufacturingSusceptorWafering

A method of forming an epitaxial layer to increase flatness of an epitaxial silicon wafer is provided. In particular, a method of controlling the epitaxial layer thickness in a peripheral part of the wafer is provided. An apparatus for manufacturing an epitaxial wafer by growing an epitaxial layer with reaction of a semiconductor wafer and a source gas in a reaction furnace comprising: a pocket in which the semiconductor wafer is placed; a susceptor fixing the semiconductor; orientation-dependent control means dependent on a crystal orientation of the semiconductor wafer and / or orientation-independent control means independent from the crystal orientation of the semiconductor wafer, wherein the apparatus may improve flatness in a peripheral part of the epitaxial layer.

Owner:SUMCO TECHXIV

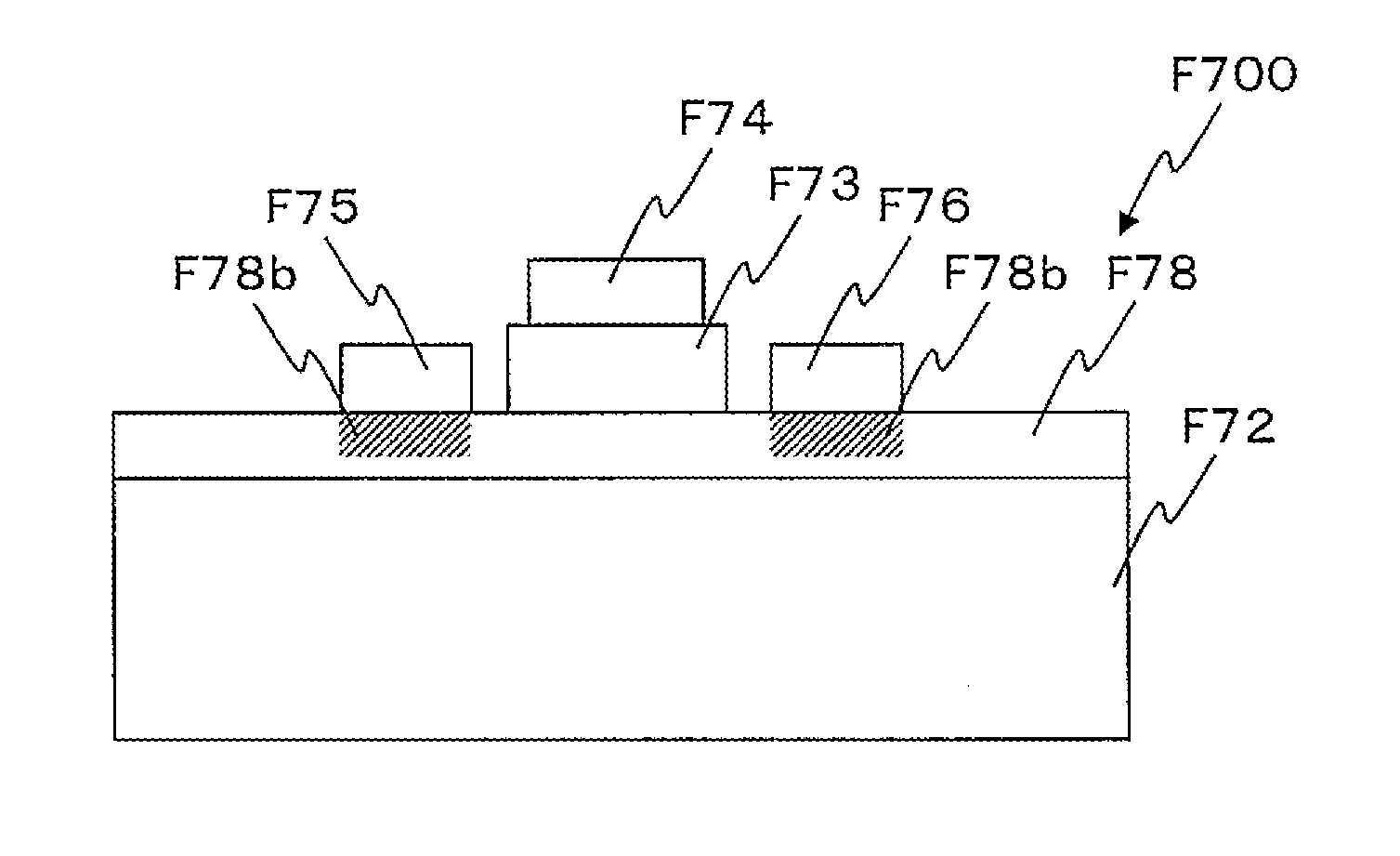

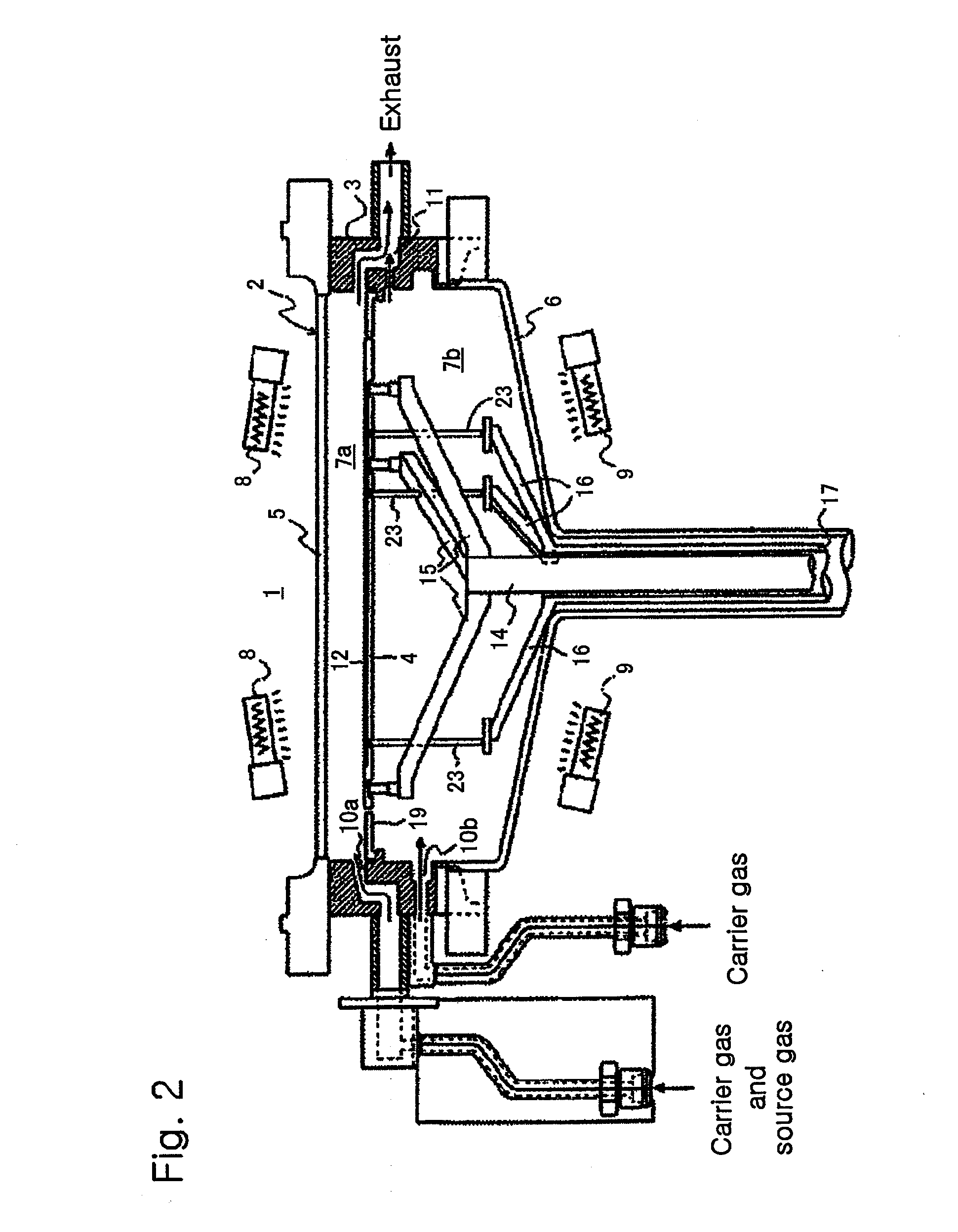

Method for manufacturing a vibrating MEMS circuit

ActiveUS9369105B1Low temperature coefficientAccurate shapePiezoelectric/electrostrictive device manufacture/assemblyImpedence networksElectromechanical coupling coefficientCrystal orientation

A method for making a micro-electro-mechanical systems (MEMS) vibrating structure is disclosed. The MEMS is supported by a MEMS anchor system and includes a single-crystal piezoelectric thin-film layer that has a specific non-standard crystal orientation, which may be selected to increase an electromechanical coupling coefficient, decrease a temperature coefficient of frequency, or both. The MEMS vibrating structure may have dominant lateral vibrations or dominant thickness vibrations. The single-crystal piezoelectric thin-film layer may include Lithium Tantalate or Lithium Niobate, and may provide MEMS vibrating structures with precise sizes and shapes, which may provide high accuracy and enable fabrication of multiple resonators having different resonant frequencies on a single substrate.

Owner:QORVO US INC

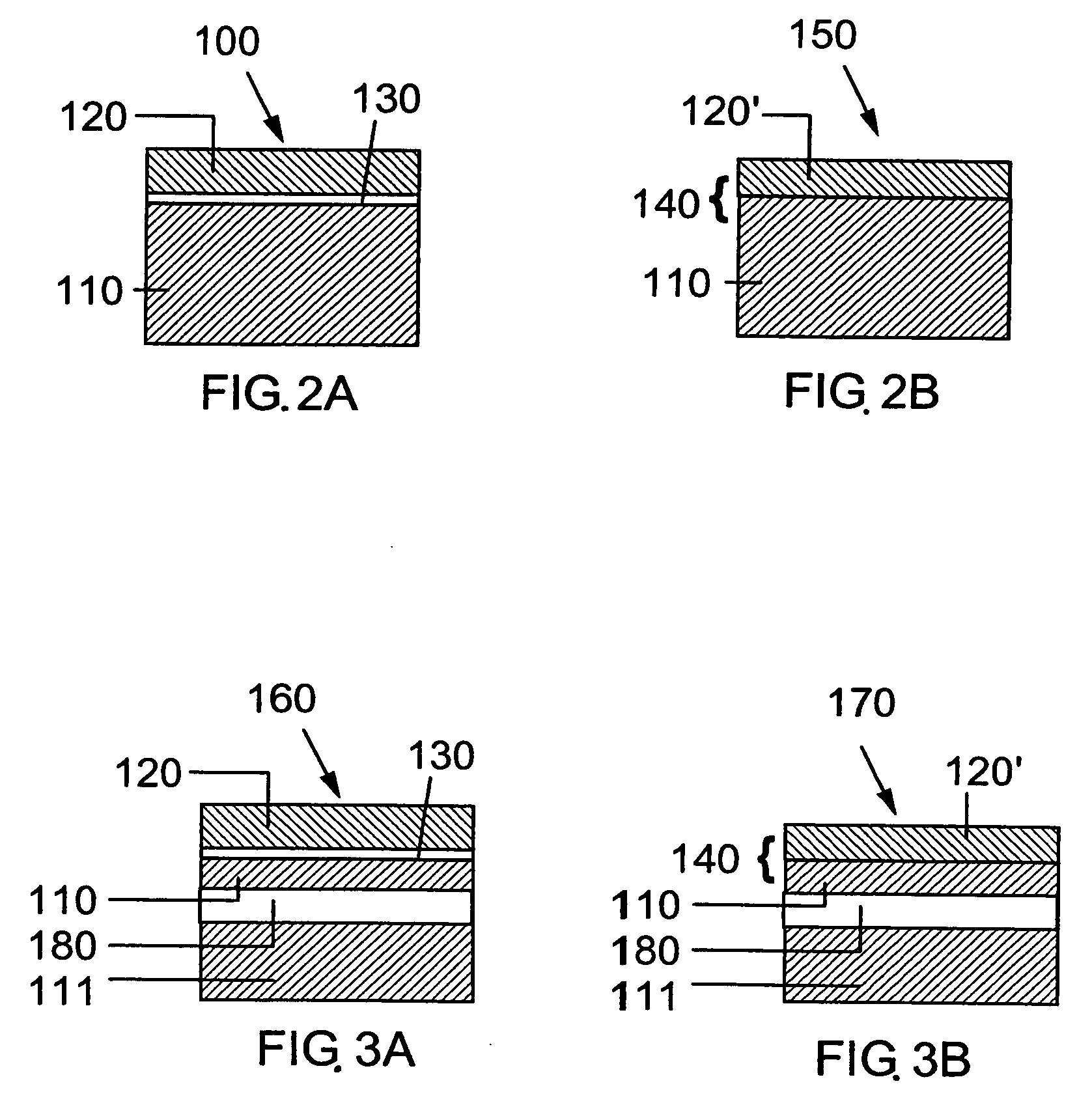

Dual SIMOX hybrid orientation technology (HOT) substrates

InactiveUS20060024931A1Improve performanceSimple and easy stepSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductor materialsCrystal orientation

This invention provides a separation by implanted oxygen (SIMOX) method for forming planar hybrid orientation semiconductor-on-insulator (SOI) substrates having different crystal orientations, thereby making it possible for devices to be fabricated on crystal orientations providing optimal performance. The method includes the steps of selecting a substrate having a base semiconductor layer having a first crystallographic orientation separated by a thin insulating layer from a top semiconductor layer having a second crystallographic orientation; replacing the top semiconductor layer in selected regions with an epitaxially grown semiconductor having the first crystallographic orientation; then using an ion implantation and annealing method to (i) form a buried insulating region within the epitaxially grown semiconductor material, and (ii) thicken the insulating layer underlying the top semiconductor layer, thereby forming a hybrid orientation substrate in which the two semiconductor materials with different crystallographic orientations have substantially the same thickness and are both disposed on a common buried insulator layer. In a variation of this method, an ion implantation and annealing method is instead used to extend an auxiliary buried insulator layer (initially underlying the base semiconductor layer) upwards (i) into the epitaxially grown semiconductor, and (ii) up to the insulating layer underlying the top semiconductor layer.

Owner:IBM CORP