Patents

Literature

2505 results about "Logic gate" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In electronics, a logic gate is an idealized or physical device implementing a Boolean function; that is, it performs a logical operation on one or more binary inputs and produces a single binary output. Depending on the context, the term may refer to an ideal logic gate, one that has for instance zero rise time and unlimited fan-out, or it may refer to a non-ideal physical device (see Ideal and real op-amps for comparison).

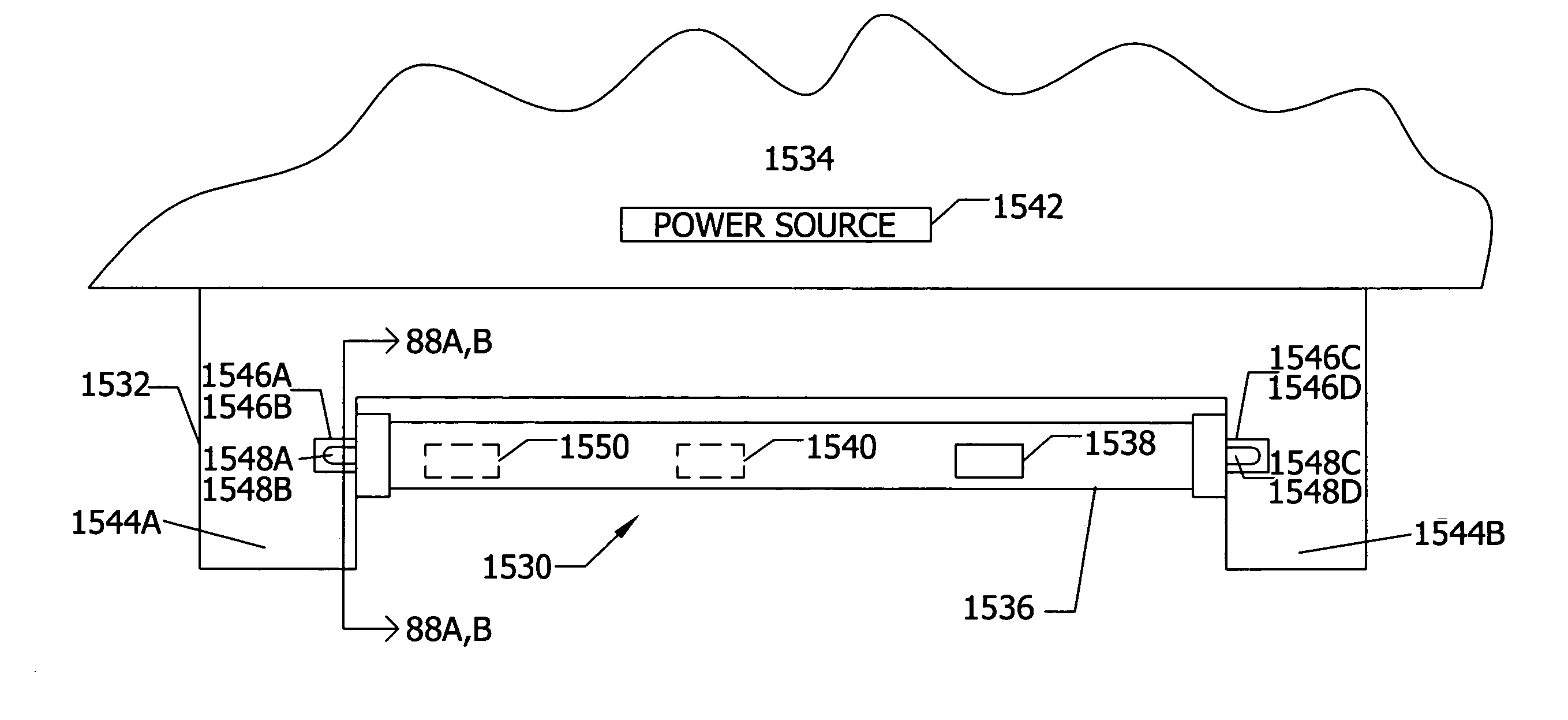

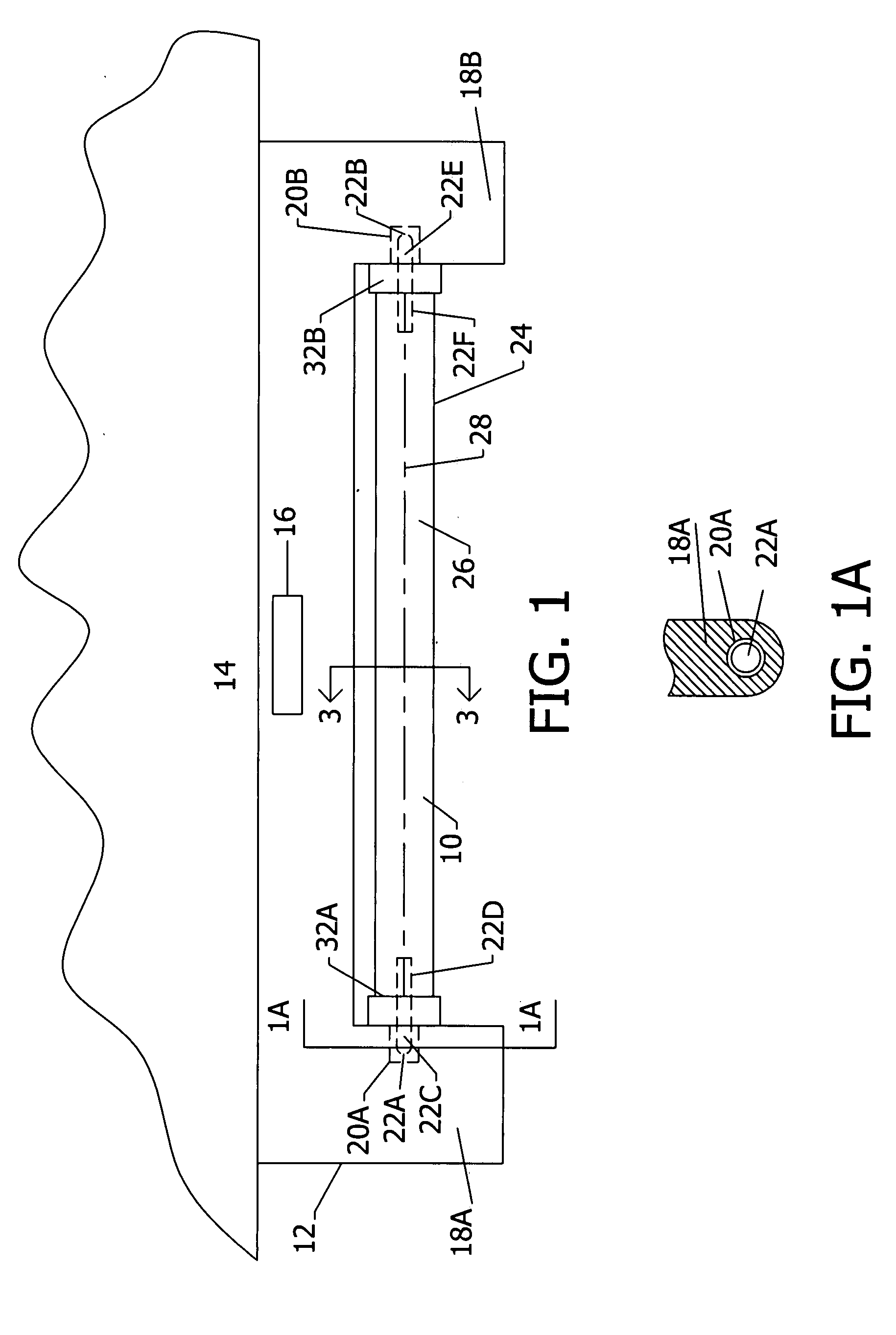

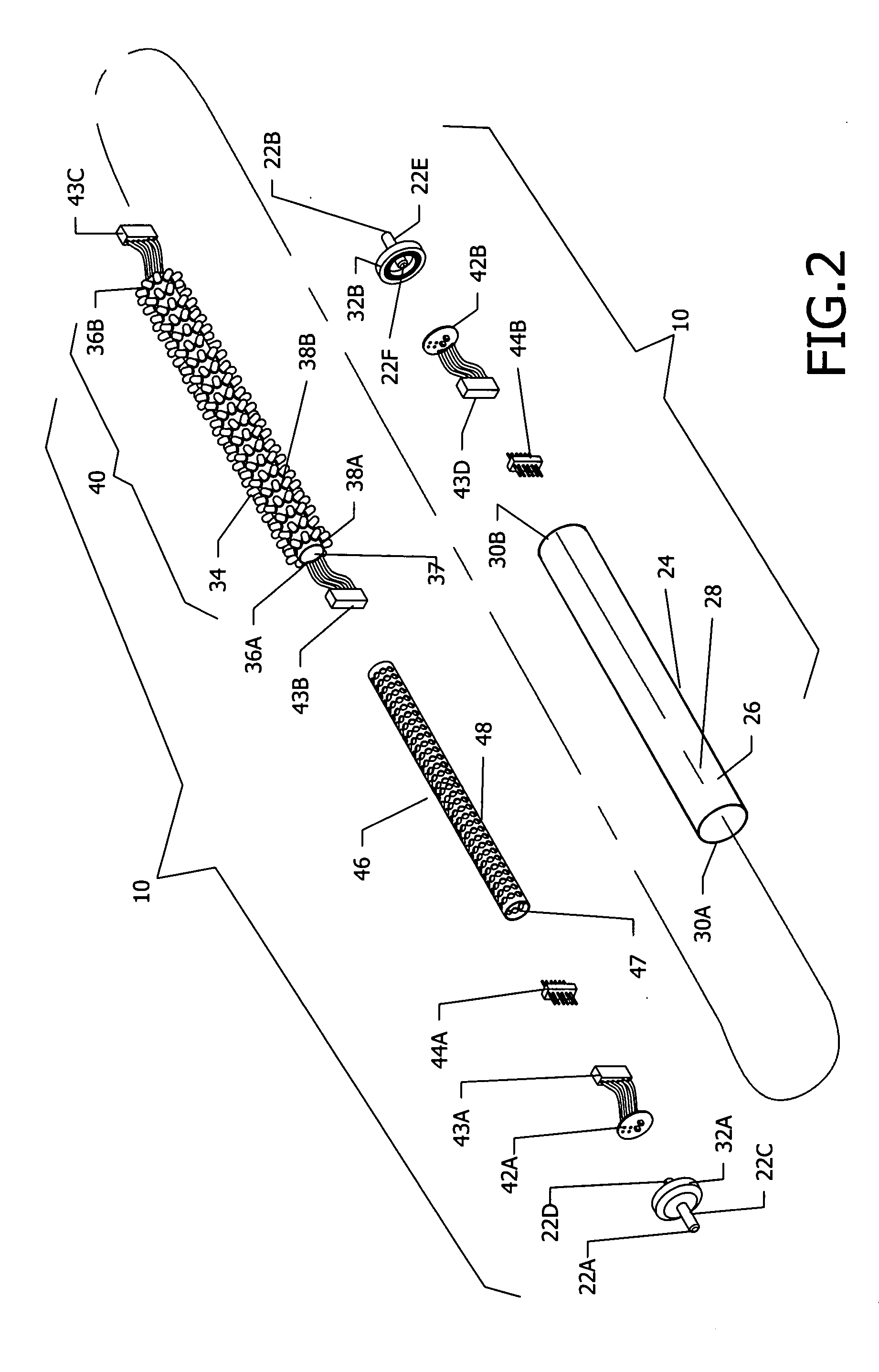

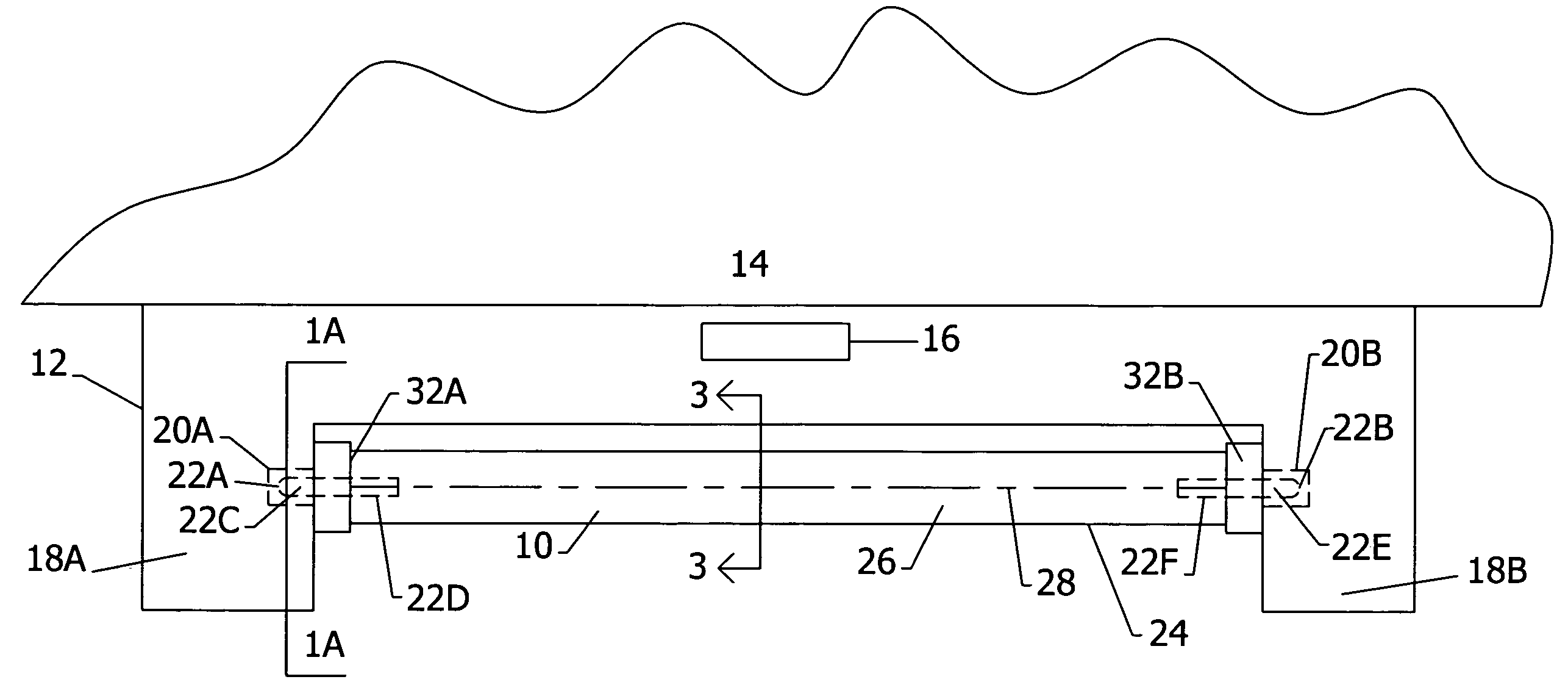

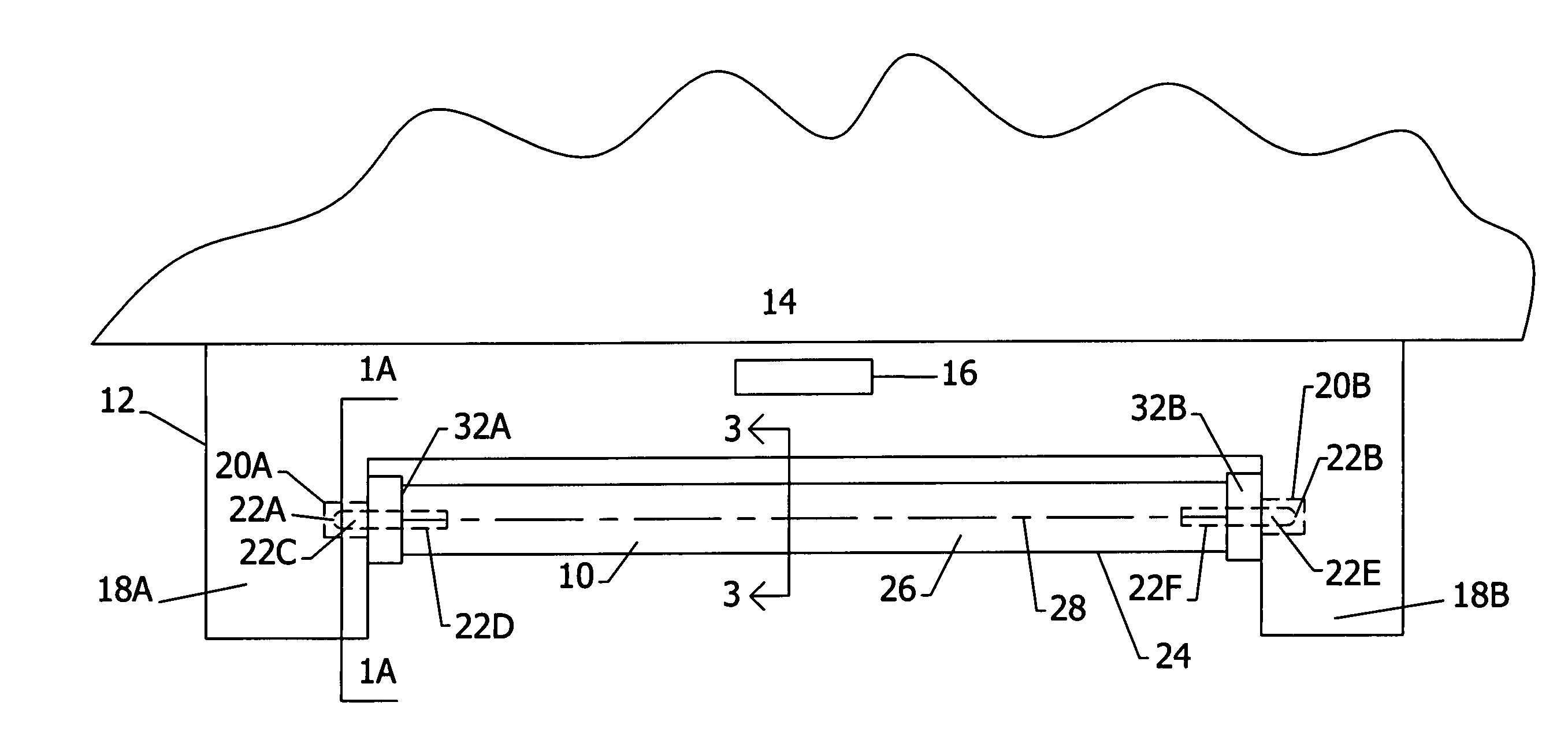

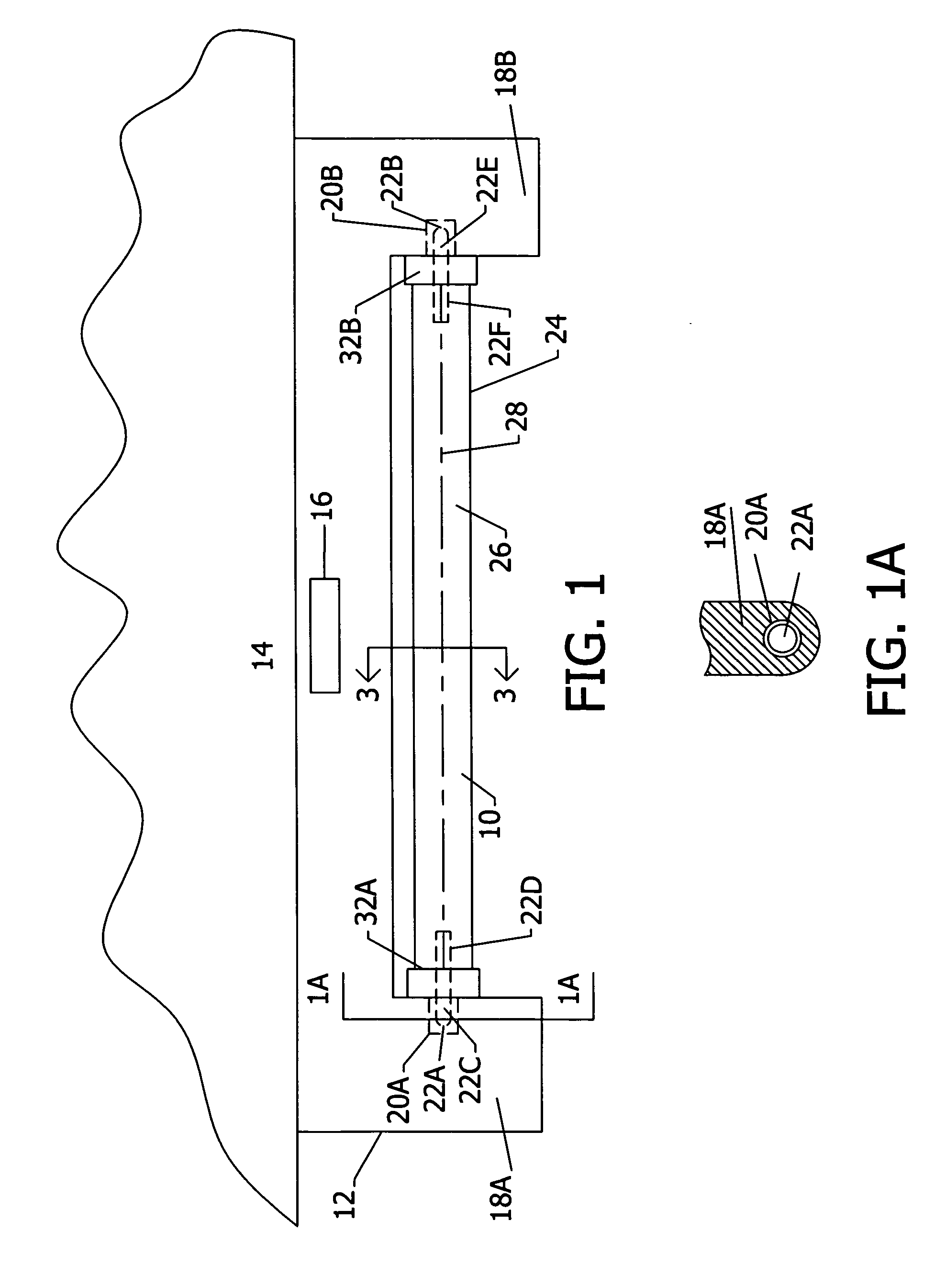

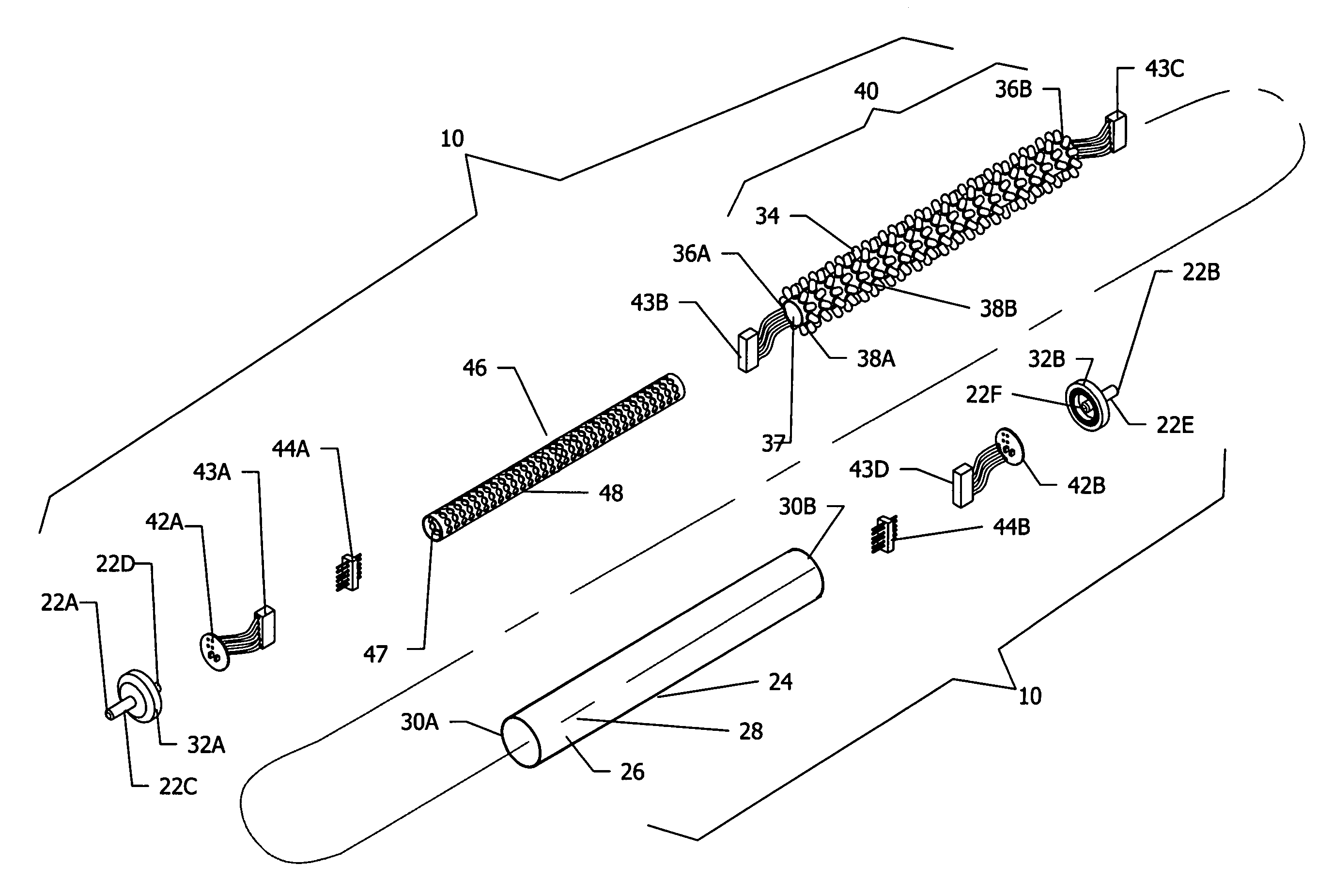

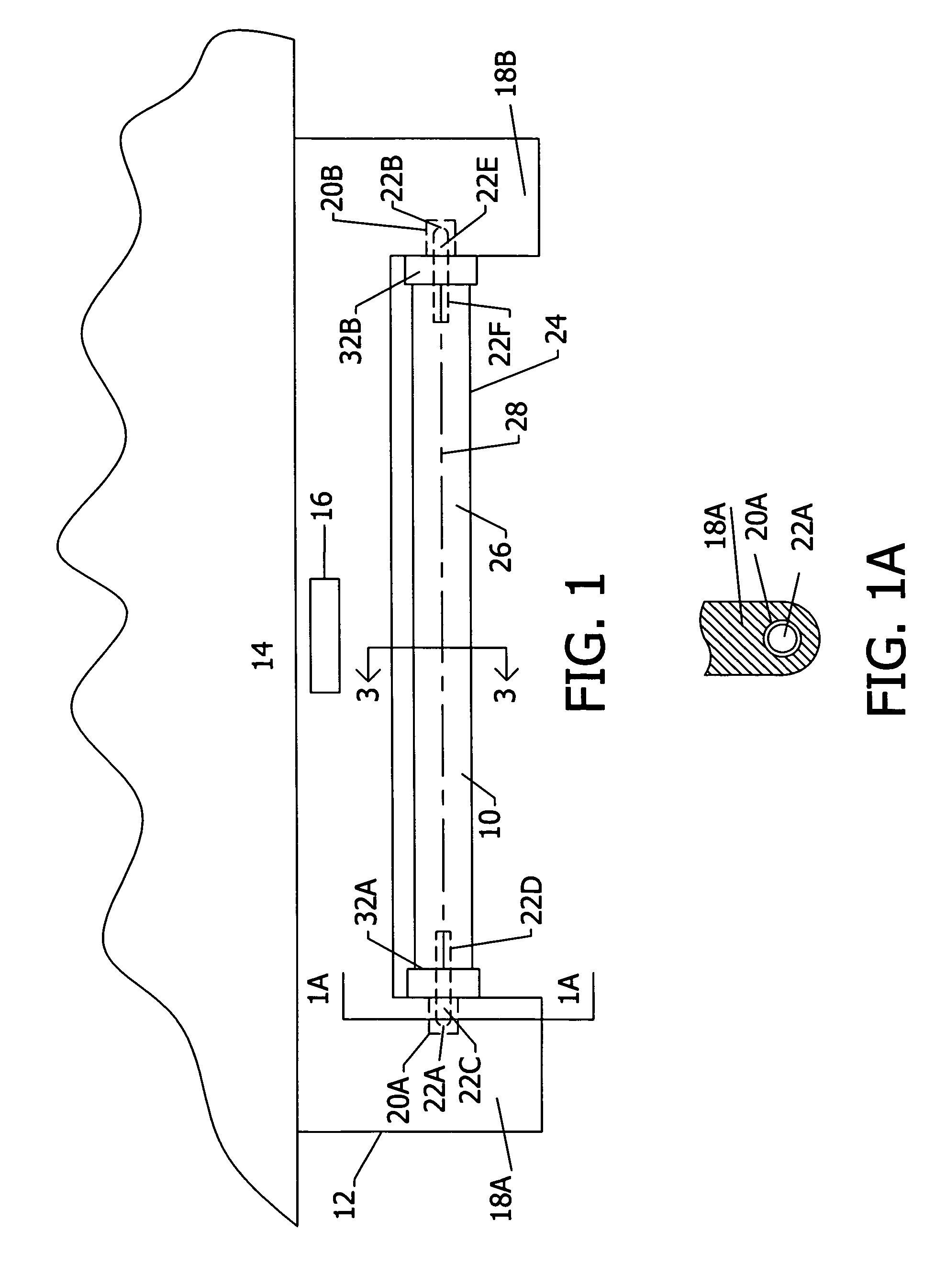

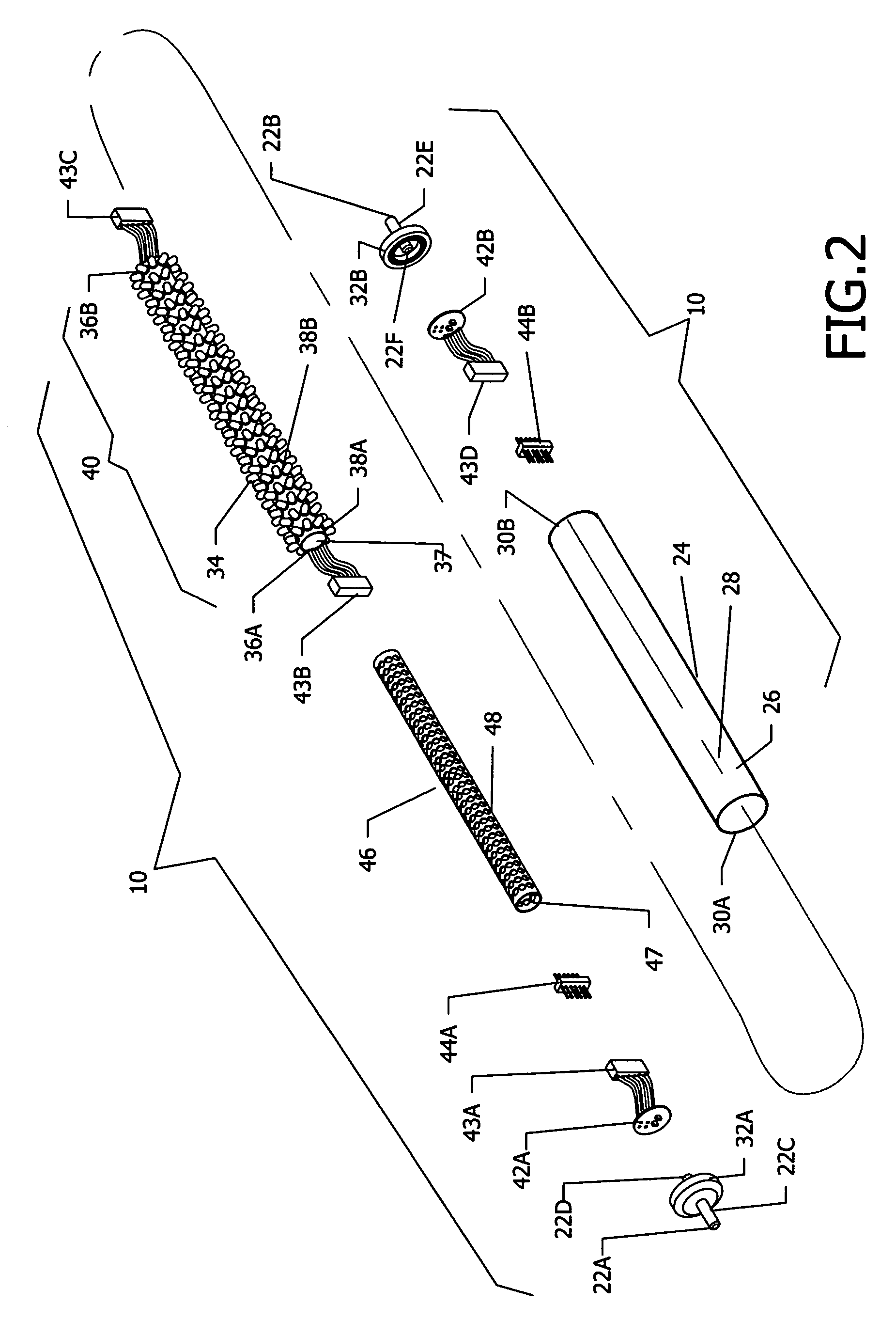

Retrofit LED lamp for fluorescent fixtures without ballast

ActiveUS20070228999A1Increase costLow costLighting support devicesPoint-like light sourceFluorescenceNetwork communication

An energy saving device for an LED lamp mounted to an existing fixture for a fluorescent lamp where the ballast is removed or bypassed. The LEDs are positioned within a tube and electrical power is delivered from a power source to the LEDs. The LED lamp includes means for controlling the delivery of the electrical power from the power source to the LEDs, wherein the use of electrical power can be reduced or eliminated automatically during periods of non-use. Such means for controlling includes means for detecting the level of daylight in the illumination area of said least one LED, in particular a light level photosensor, and means for transmitting to the means for controlling relating to the detected level of daylight from the photosensor. The photosensor can be used in operative association with an on-off switch in power connection to the LEDs, a timer, or with a computer or logic gate array in operative association with a switch, timer, or dimmer that regulates the power to the LEDs. An occupancy sensor that detects motion or a person in the illumination area of the LEDs can be also be used in association with the photosensor and the computer, switch, timer, or dimmer, or in solo operation by itself. Two or more such LED lamps with a computer or logic gate array used with at least one of the lamps can be in network communication with at least one photosensor and / or at least one occupancy sensor to control the power to all the LEDs.

Owner:SIGNIFY HLDG BV

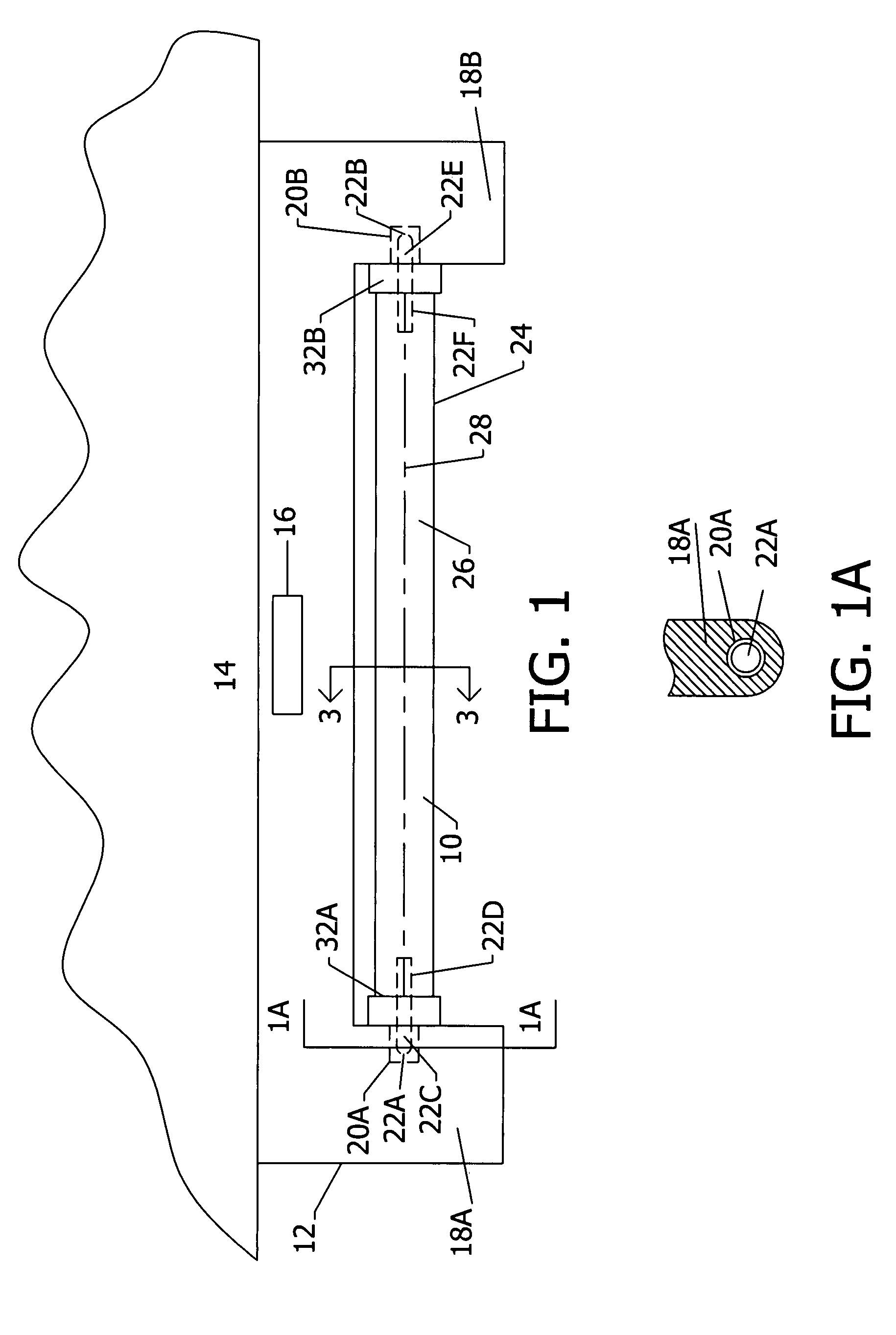

Retrofit LED lamp for fluorescent fixtures without ballast

ActiveUS7507001B2Reduce flickerReduce usageLighting support devicesPoint-like light sourceFluorescenceNetwork communication

An energy saving device for an LED lamp mounted to an existing fixture for a fluorescent lamp where the ballast is removed or bypassed. The LEDs are positioned within a tube and electrical power is delivered from a power source to the LEDs. The LED lamp includes means for controlling the delivery of the electrical power from the power source to the LEDs, wherein the use of electrical power can be reduced or eliminated automatically during periods of non-use. Such means for controlling includes means for detecting the level of daylight in the illumination area of said least one LED, in particular a light level photosensor, and means for transmitting to the means for controlling relating to the detected level of daylight from the photosensor. The photosensor can be used in operative association with an on-off switch in power connection to the LEDs, a timer, or with a computer or logic gate array in operative association with a switch, timer, or dimmer that regulates the power to the LEDs. An occupancy sensor that detects motion or a person in the illumination area of the LEDs can be also be used in association with the photosensor and the computer, switch, timer, or dimmer, or in solo operation by itself. Two or more such LED lamps with a computer or logic gate array used with at least one of the lamps can be in network communication with at least one photosensor and / or at least one occupancy sensor to control the power to all the LEDs.

Owner:SIGNIFY HLDG BV

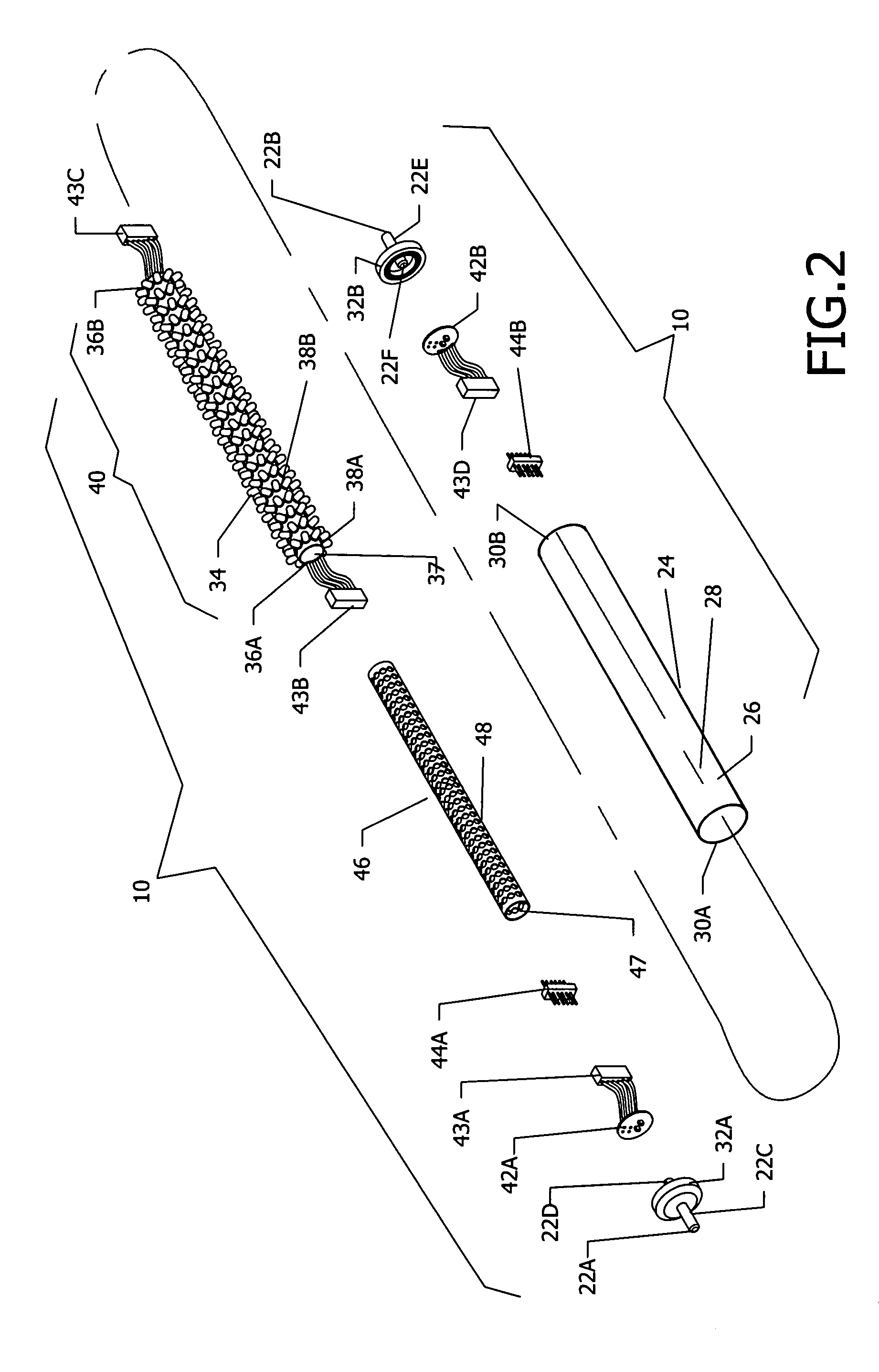

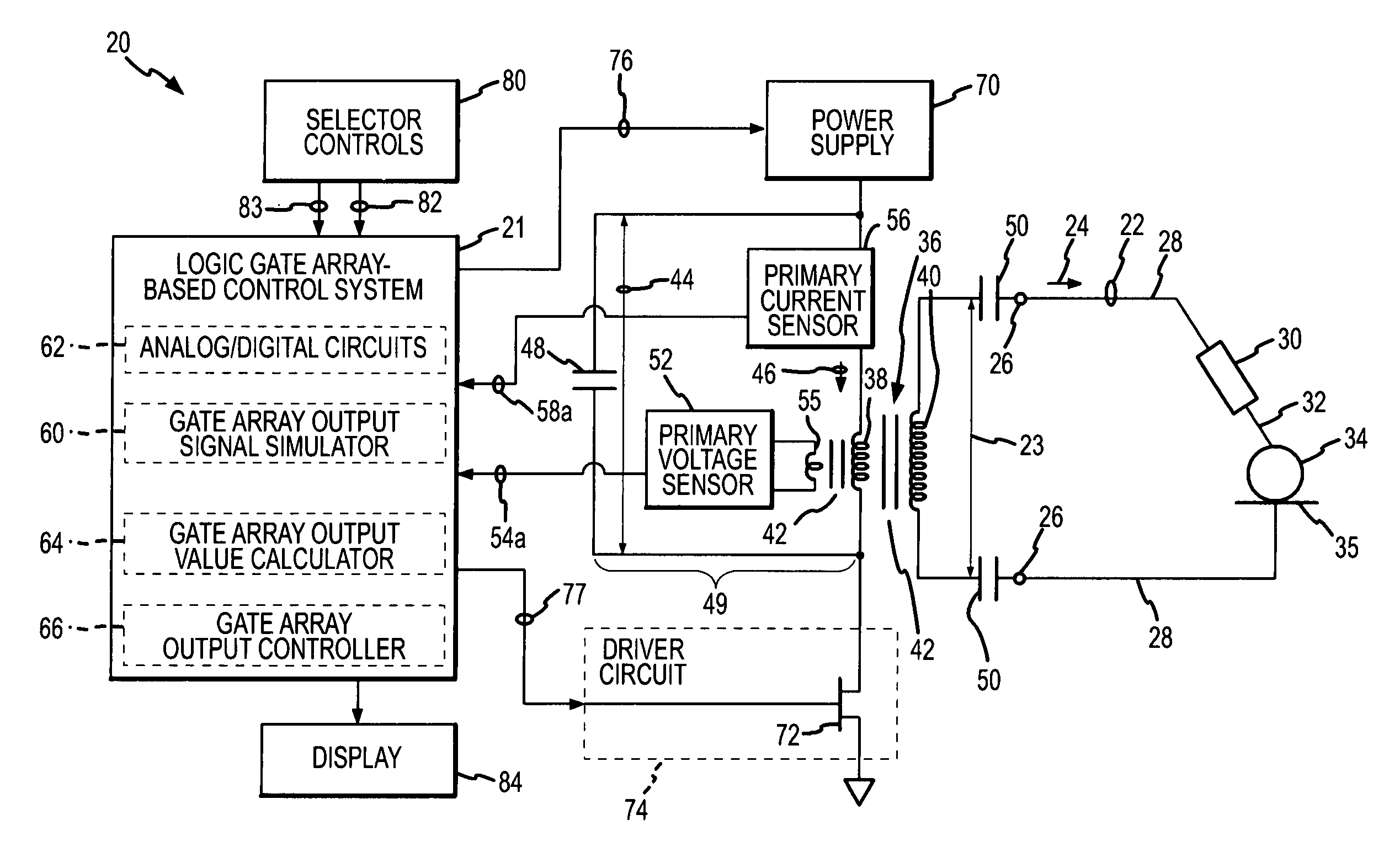

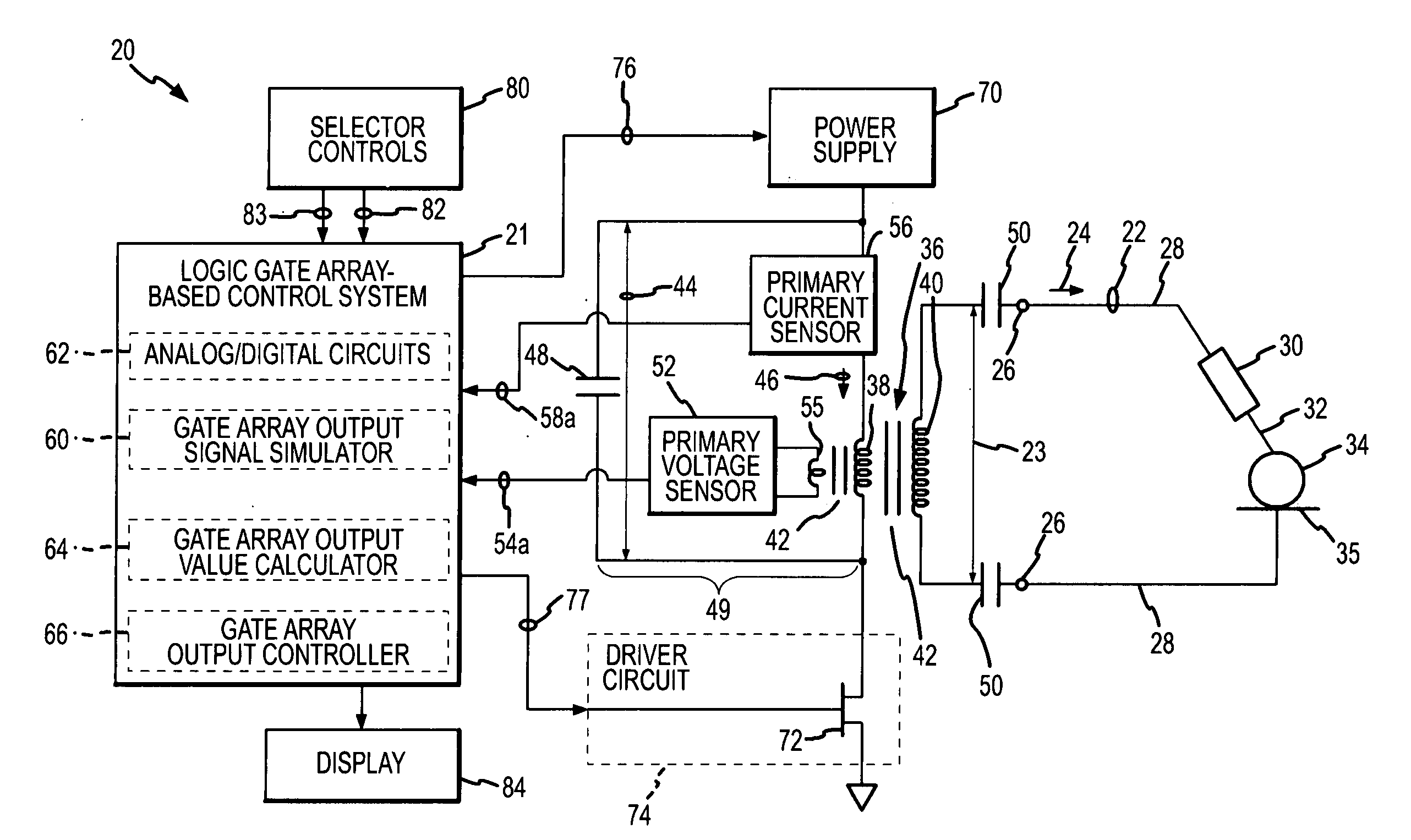

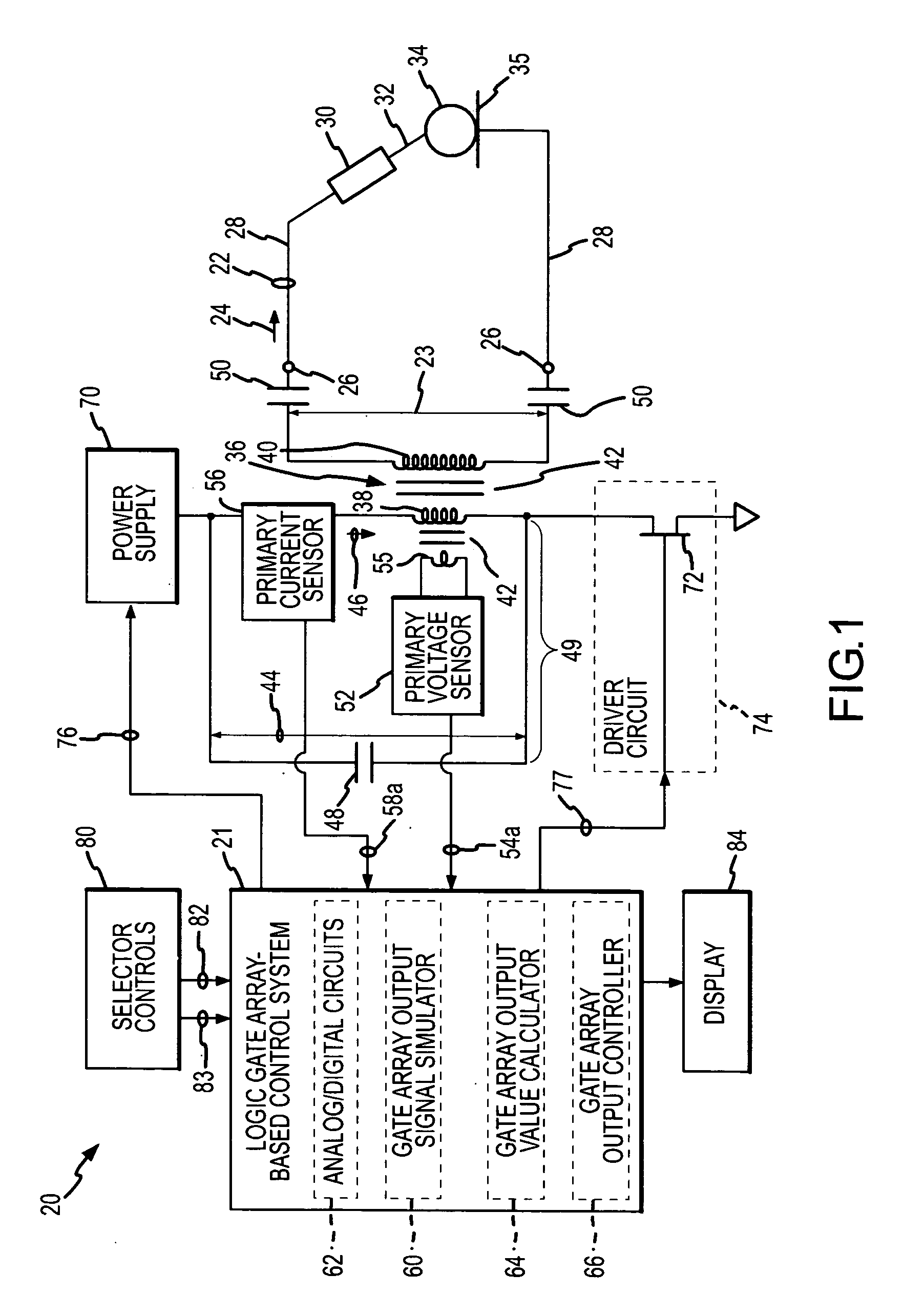

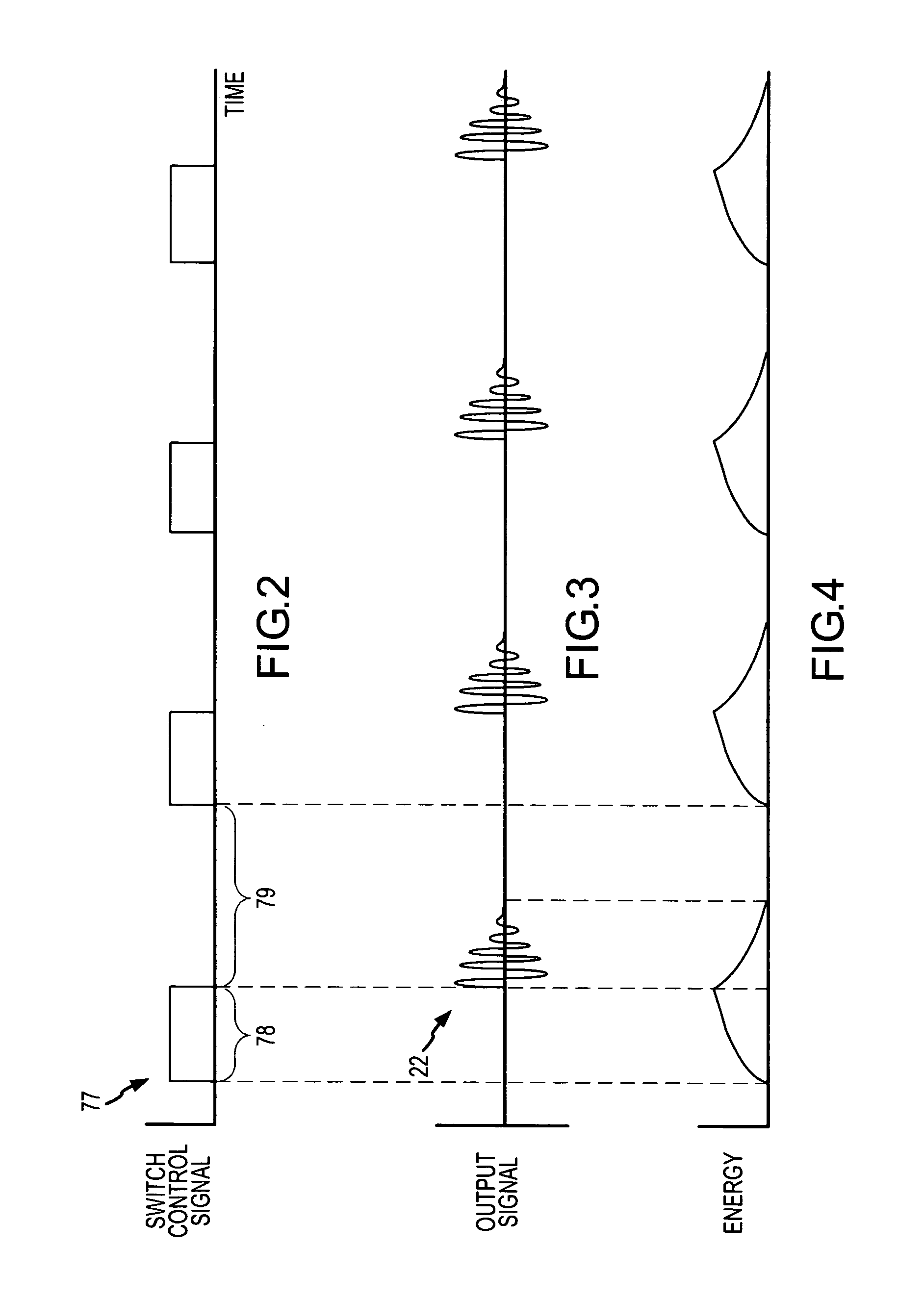

Near-instantaneous responsive closed loop control electrosurgical generator and method

ActiveUS7799020B2Quick and accurate adjustmentFast response timeSurgical instruments for heatingPower flowControl system

Owner:CONMED CORP +1

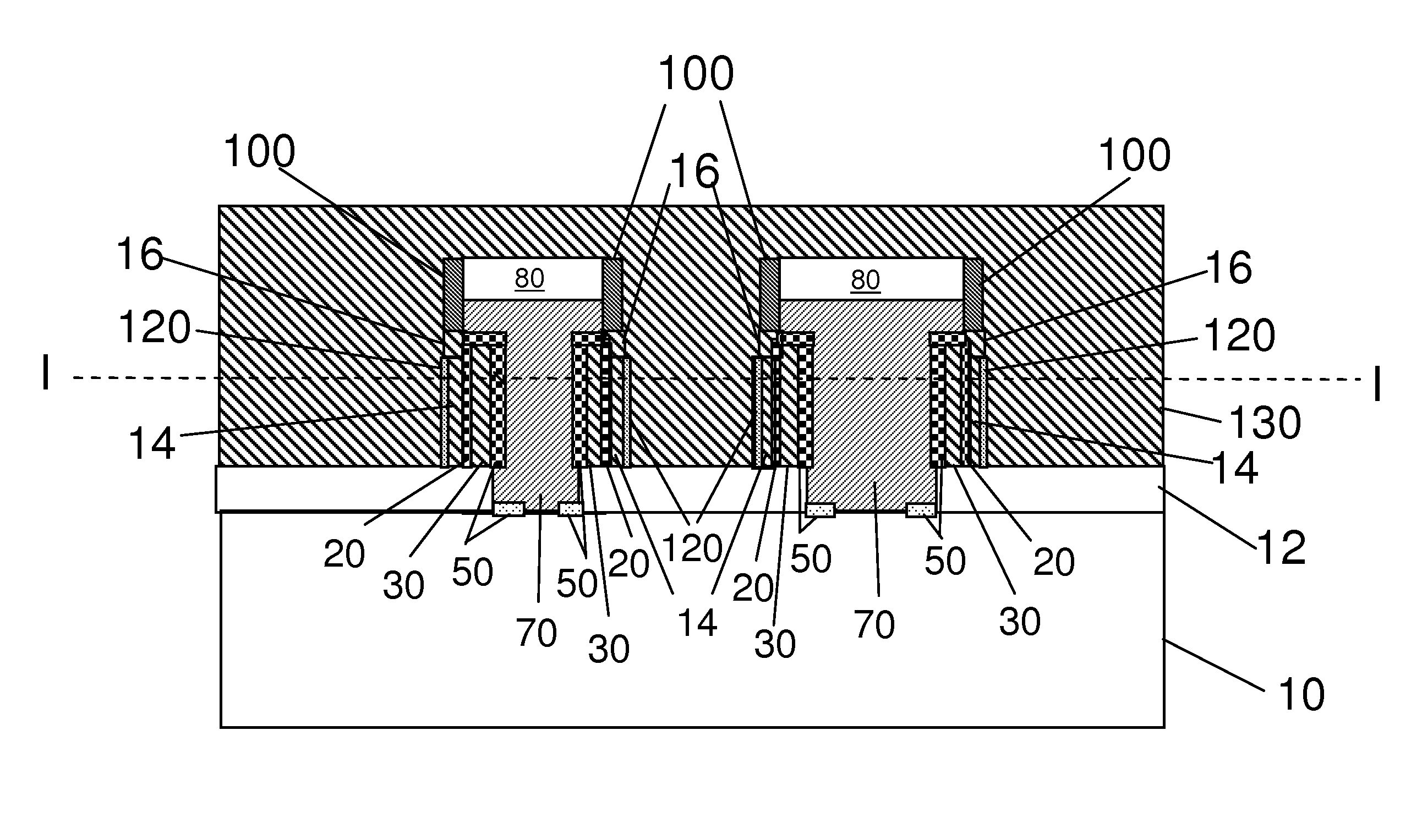

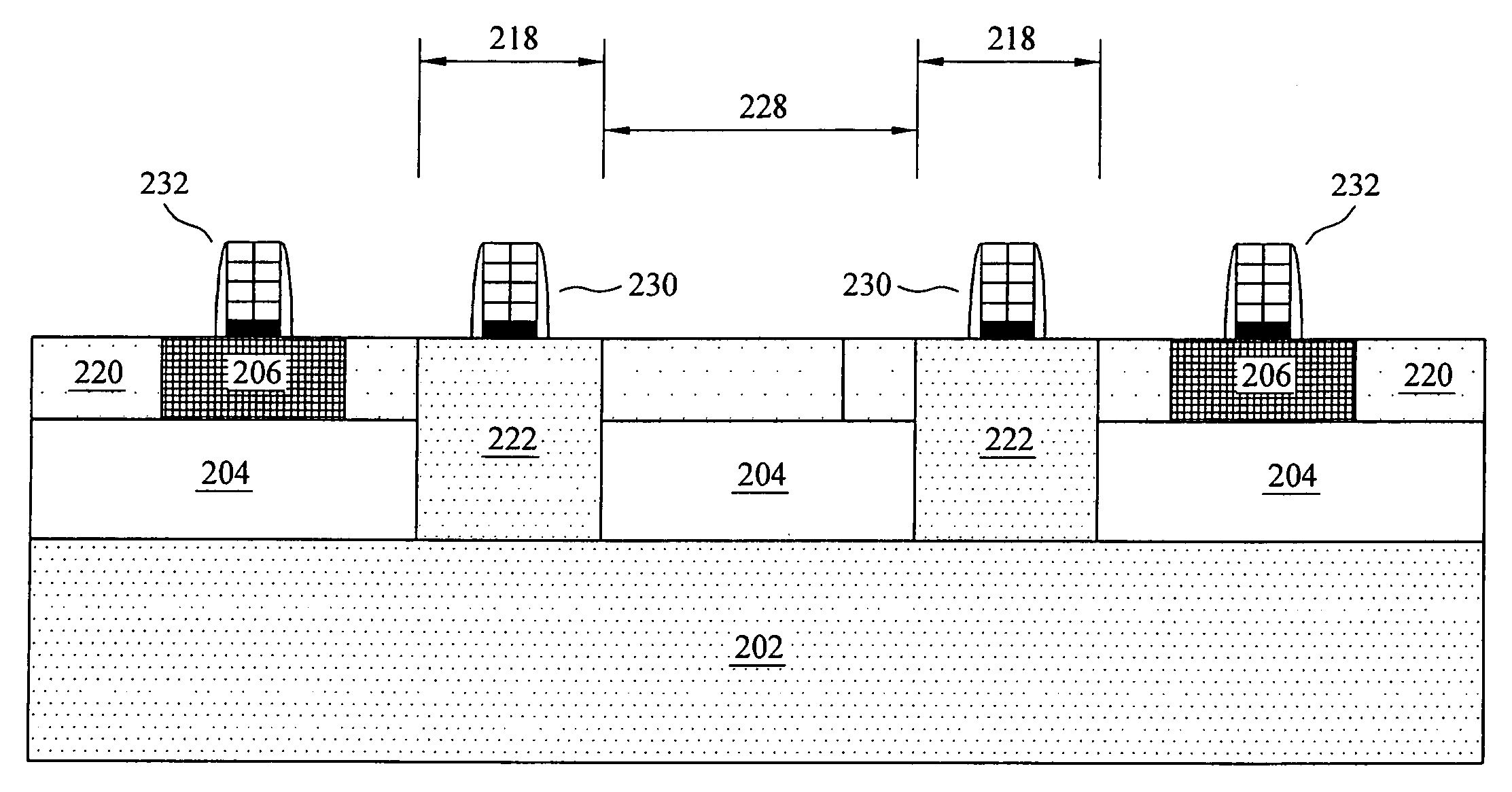

Multiple-gate device with floating back gate

Disclosed is a multiple-gate transistor that includes a channel region and source and drain regions at ends of the channel region. A gate oxide is positioned between a logic gate and the channel region and a first insulator is formed between a floating gate and the channel region. The first insulator is thicker than the gate oxide. The floating gate is electrically insulated from other structures. Also, a second insulator is positioned between a programming gate and the floating gate. Voltage in the logic gate causes the transistor to switch on and off, while stored charge in the floating gate adjusts the threshold voltage of the transistor. The transistor can comprise a fin-type field effect transistor (FinFET), where the channel region comprises the middle portion of a fin structure and the source and drain regions comprise end portions of the fin structure.

Owner:GLOBALFOUNDRIES U S INC

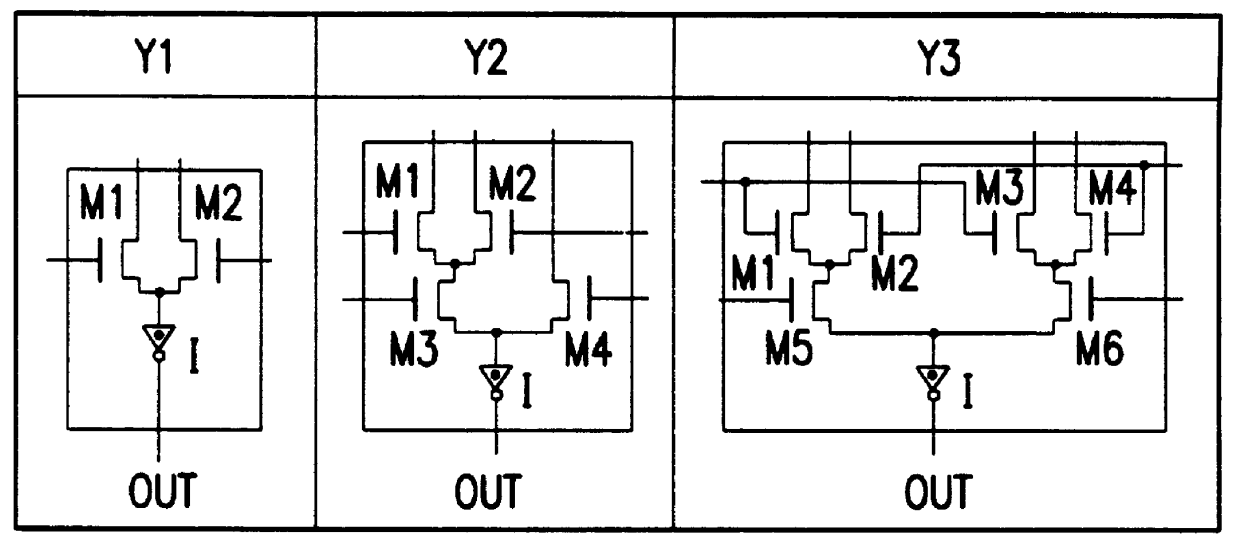

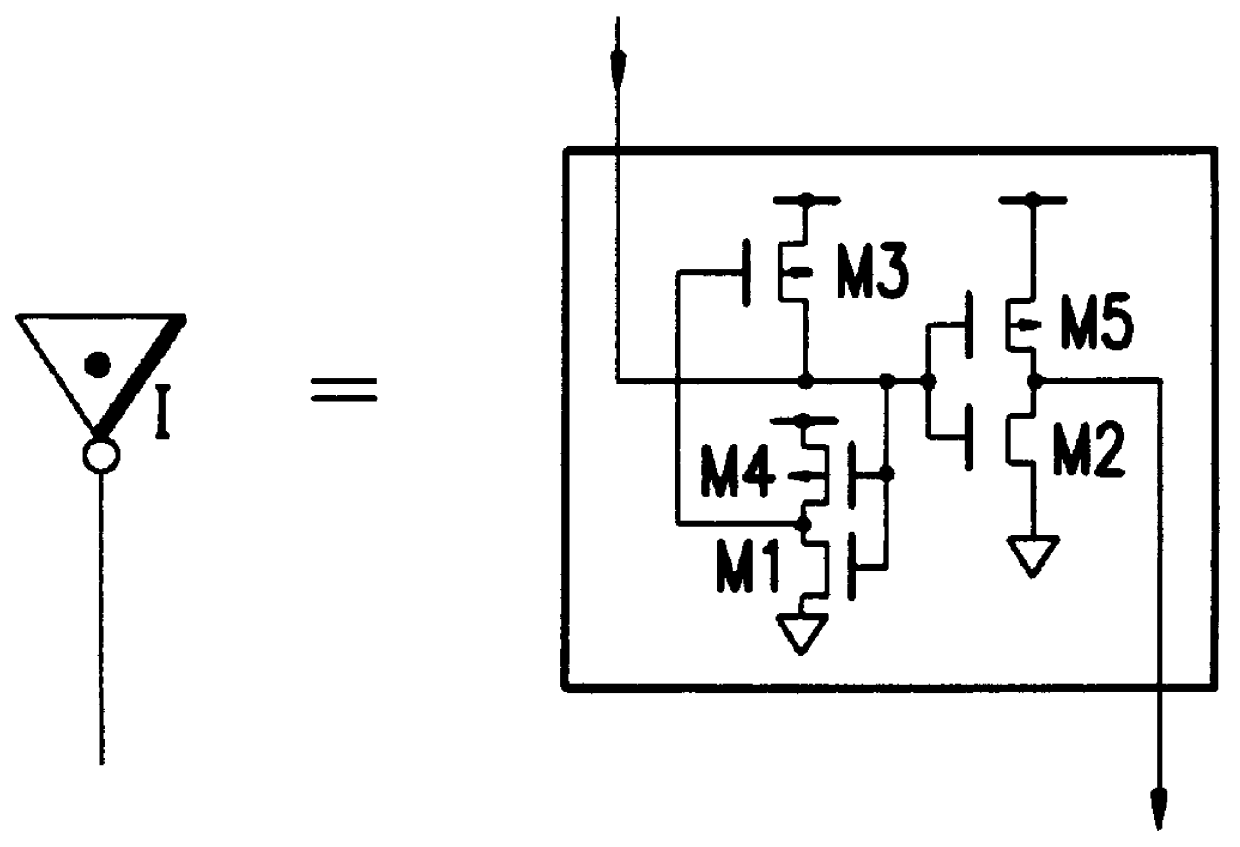

Logic circuit utilizing pass transistors and logic gate

InactiveUS6084437ATransistorReliability increasing modificationsCmos logic circuitsLogical operations

A logic circuit combines a plurality of pass-transistor logic trees and a multiple-input logic gate for receiving intermediate logic signals from the respective pass-transistor logic trees, and can express a complex logical operation while decreasing the number of stages in pass-transistor logic trees and improving operation speed. Even a logical operation that cannot be expressed efficiently by a known or conventional pass-transistor logic circuit can be expressed efficiently with performance higher than that of a known CMOS logic circuit. Furthermore, when a static feedthrough current of the multiple-input logic gate is suppressed, power consumption can be reduced. In some embodiments, since circuitry for suppressing a static feedthrough current of the multiple-input logic gate is arranged so that a probability of occurrence of logical collision with a preceding stage will decrease or will be nil, power consumption can further be reduced.

Owner:KAWASAKI MICROELECTRONICS

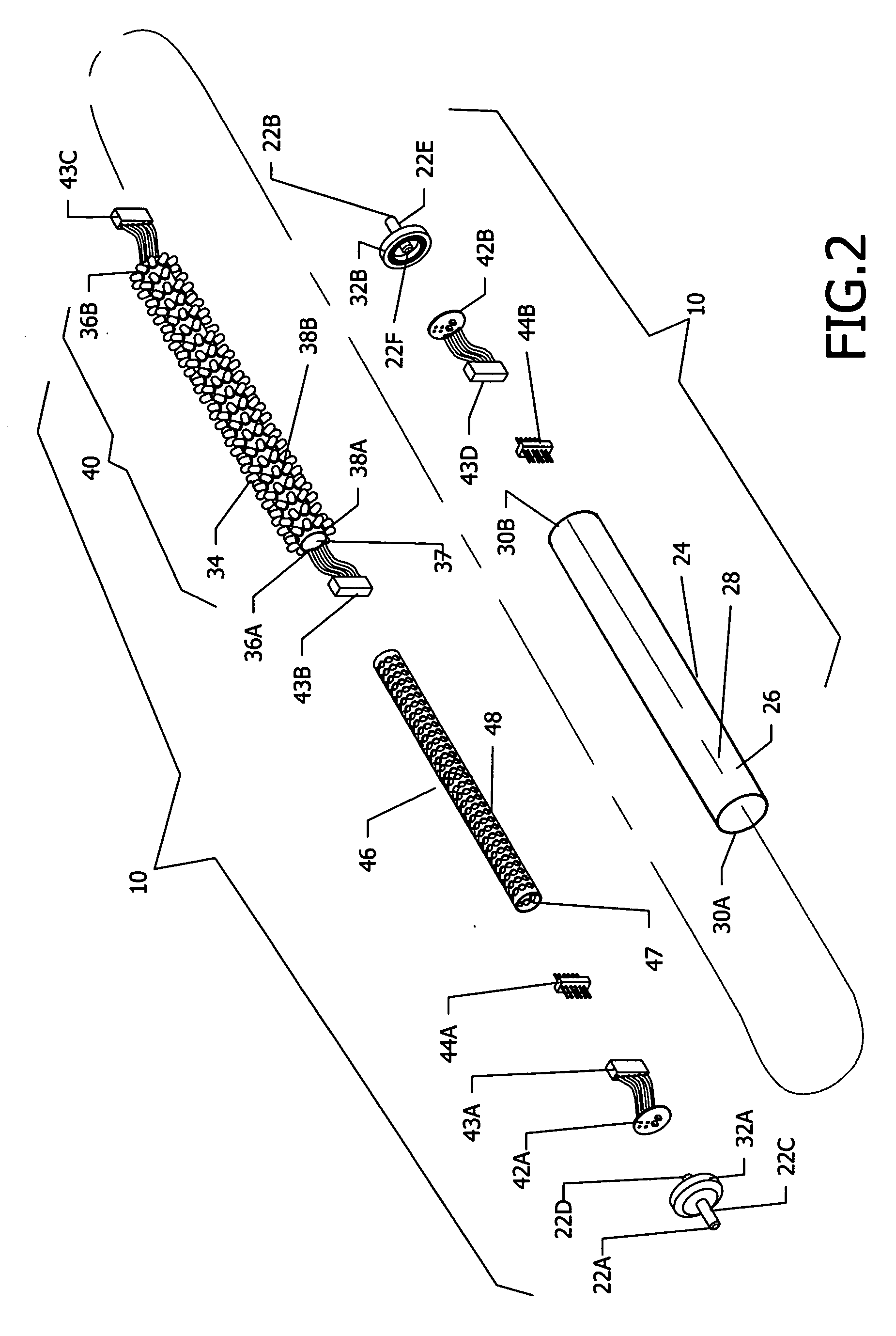

Power controls with photosensor for tube mounted LEDs with ballast

InactiveUS20050281030A1Easy to controlReduce flickerPoint-like light sourceElongate light sourcesControl signalNetwork communication

A power saving device for a light emitting diode (LED) lamp mounted to an existing fixture for a fluorescent lamp having a ballast assembly and LEDs positioned within a tube and electrical power delivered from the ballast assembly to the LEDs. The LED lamp includes means for controlling the delivery of the electrical power from the ballast assembly to the LEDs wherein the use of electrical power can be reduced or eliminated automatically during periods of non-use. Such means for controlling include means for detecting the level of daylight in the illumination area of said least one LED in particular a light level photosensor and means for transmitting to the means for controlling a control signal relating to the detected level of daylight from the photosensor. The photosensor can be used in operative association with an on-off switch in power connection to the LEDs, or with a computer or logic gate array in operative association with a dimmer that controls the power to the LEDs. An occupancy sensor that detects motion or a person in the illumination area of the LEDs can be optionally used in association with the photosensor and the computer and dimmer. Two or more such LED lamps with one or more computers or logic gate arrays can be in network communication with the photosensors and the occupancy sensors to control the power to the LEDs.

Owner:SIGNIFY HLDG BV

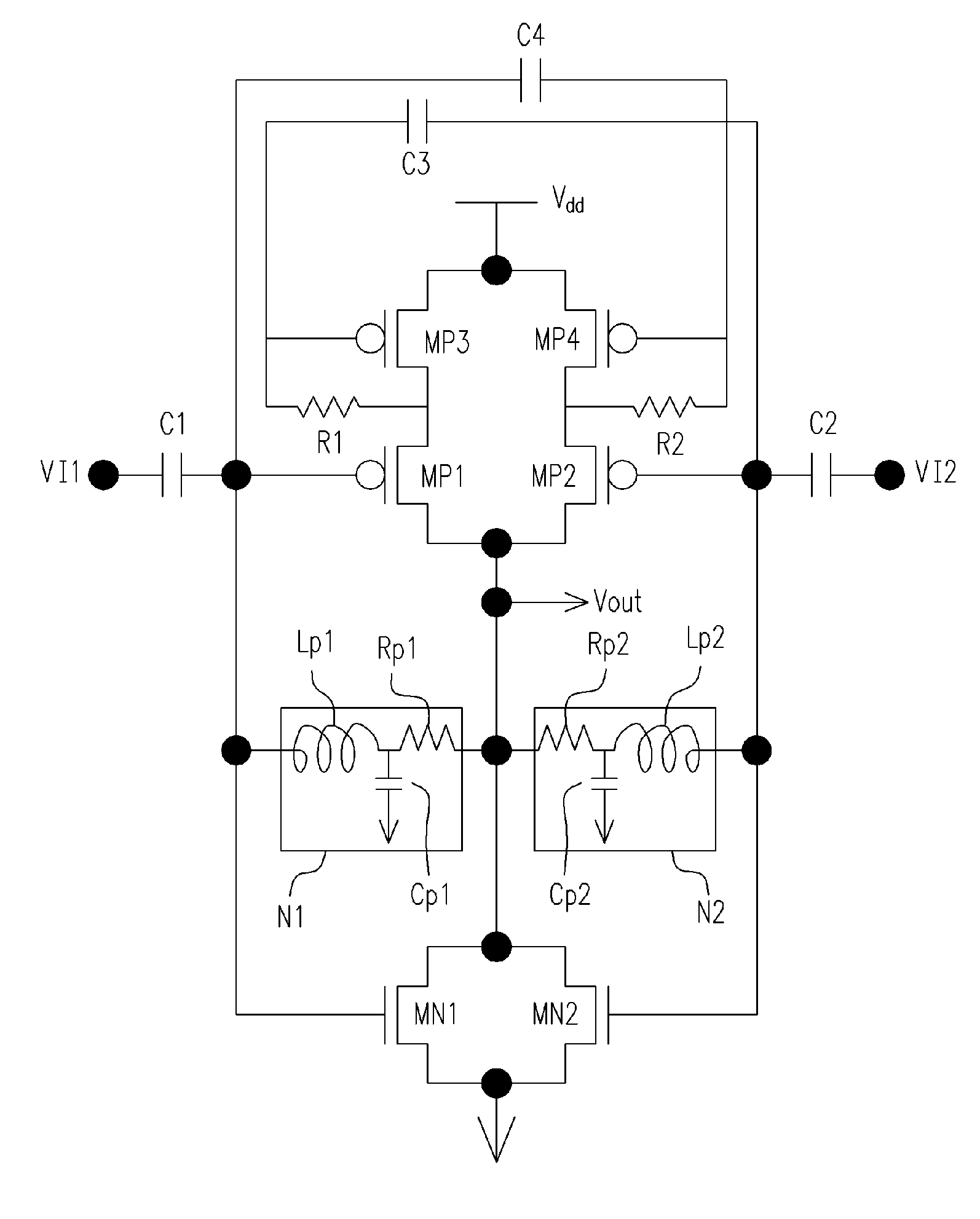

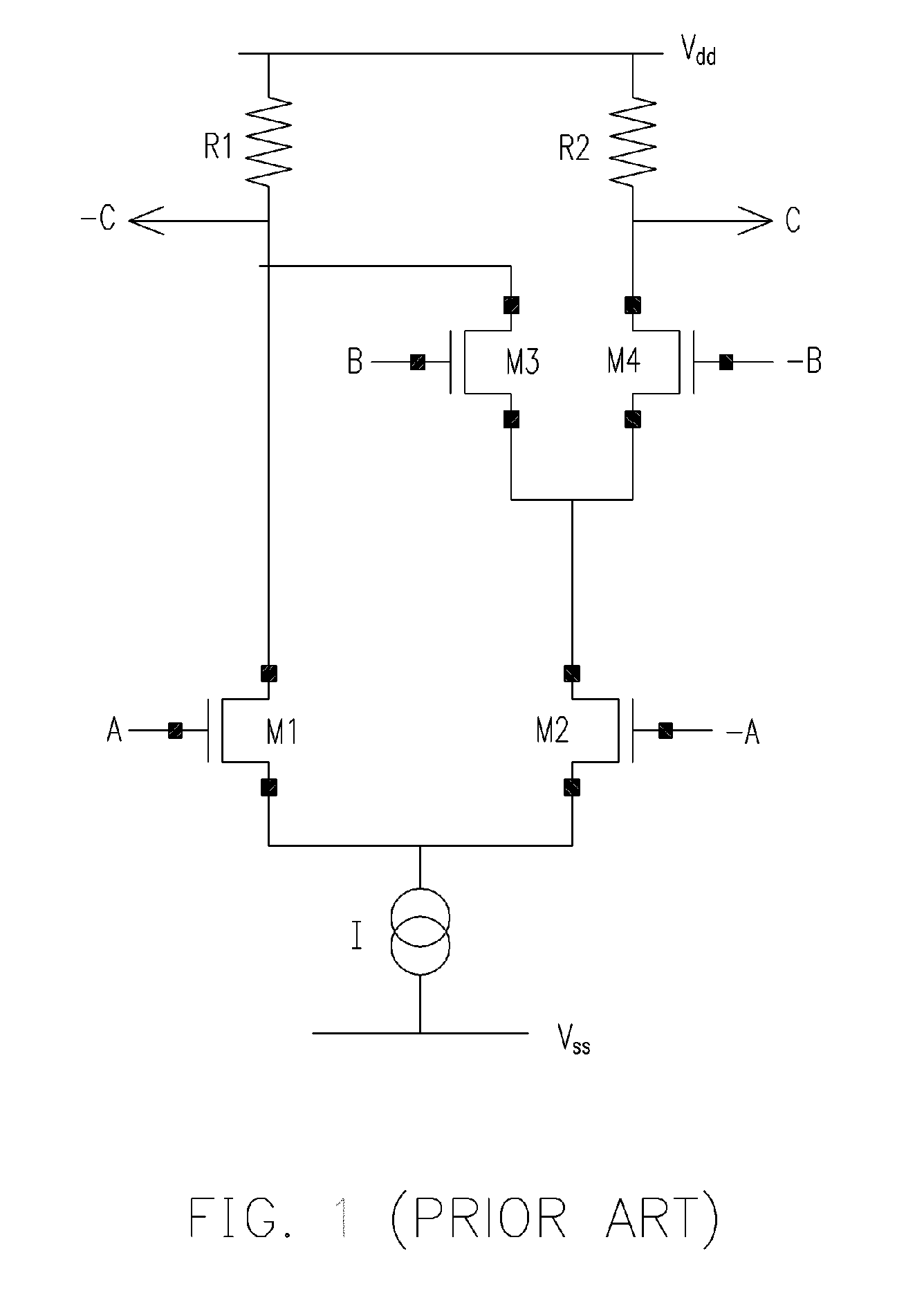

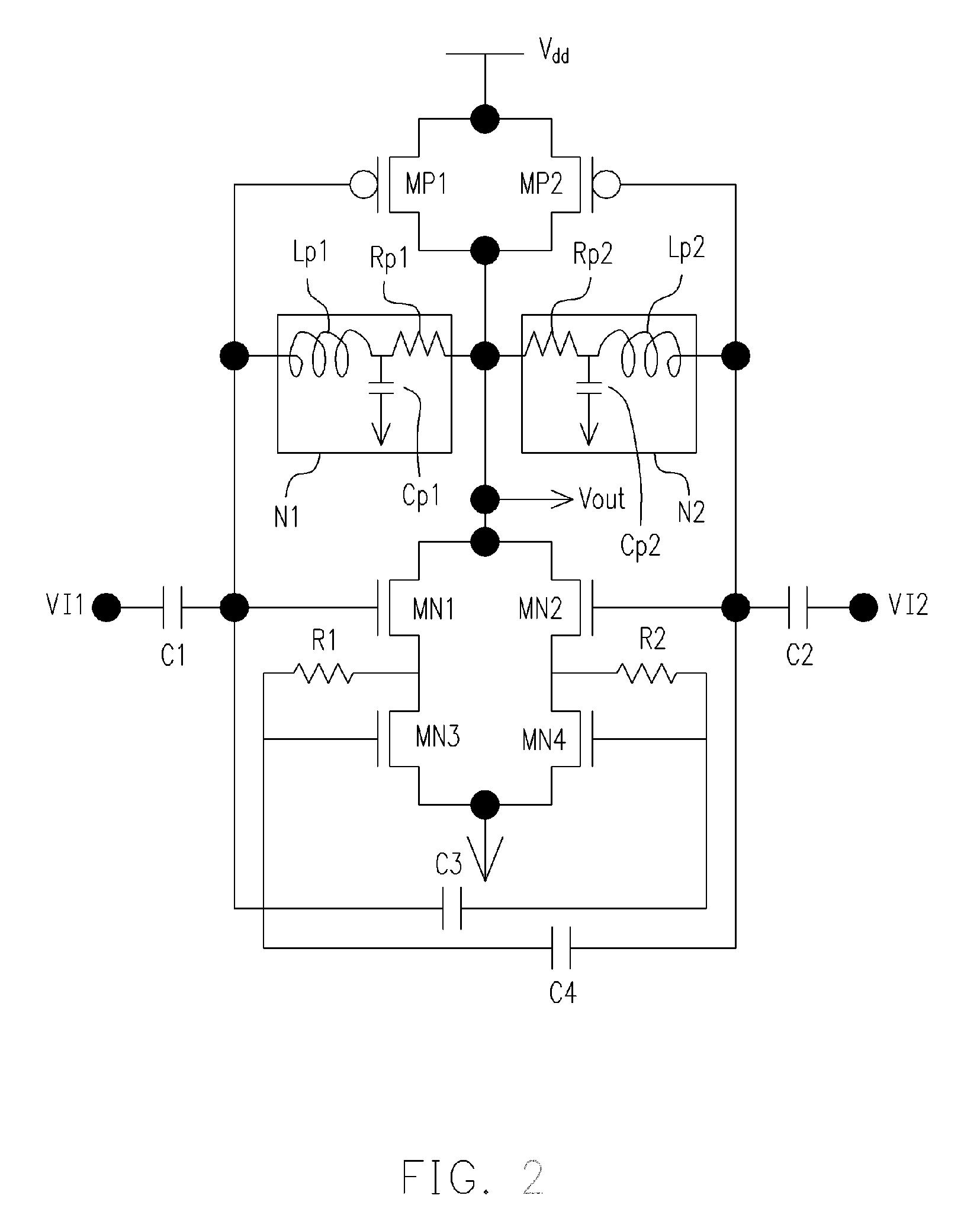

Self dc-bias high frequency logic gate, high frequency NAND gate and high frequency nor gate

InactiveUS20060197557A1Electric power will not be wastedNot to wasteReliability increasing modificationsMultiple input and output pulse circuitsNOR gateNAND gate

A self DC-bias high frequency logic gate is disclosed. The logic gate comprises at least one input terminal and one output terminal for performing Boolean operation on the high frequency input signals. The logic gate is characterized in that each transistor is coupled to an impedance matching network. The impedance matching network comprises a first terminal and a second terminal. Wherein, the first terminal is coupled to a gate of the transistor, and the second terminal is coupled to a drain of the transistor for providing an operation voltage to the transistor. When a gate of an N-type transistor and a gate of a P-type transistor are coupled with each other, and a drain of the N-type transistor and a drain of the P-type transistor are also coupled with each other, a common impedance matching network is shared with both the N-type transistor and the P-type transistor.

Owner:SUNPLUS TECH CO LTD

Power controls with photosensor for tube mounted LEDs with ballast

InactiveUS7490957B2Reduce flickerReduce usageLighting support devicesPoint-like light sourceControl signalNetwork communication

Owner:SIGNIFY HLDG BV

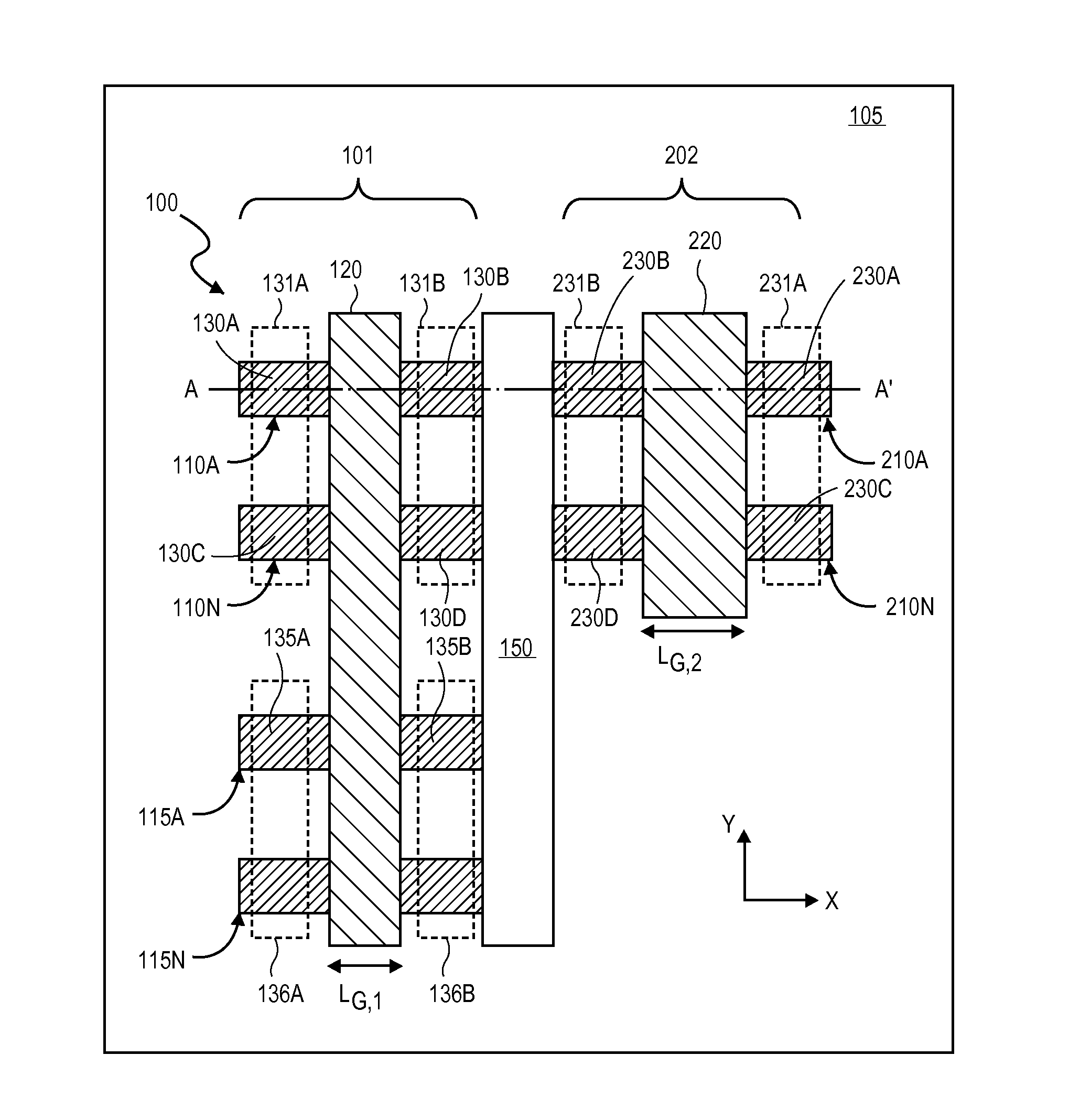

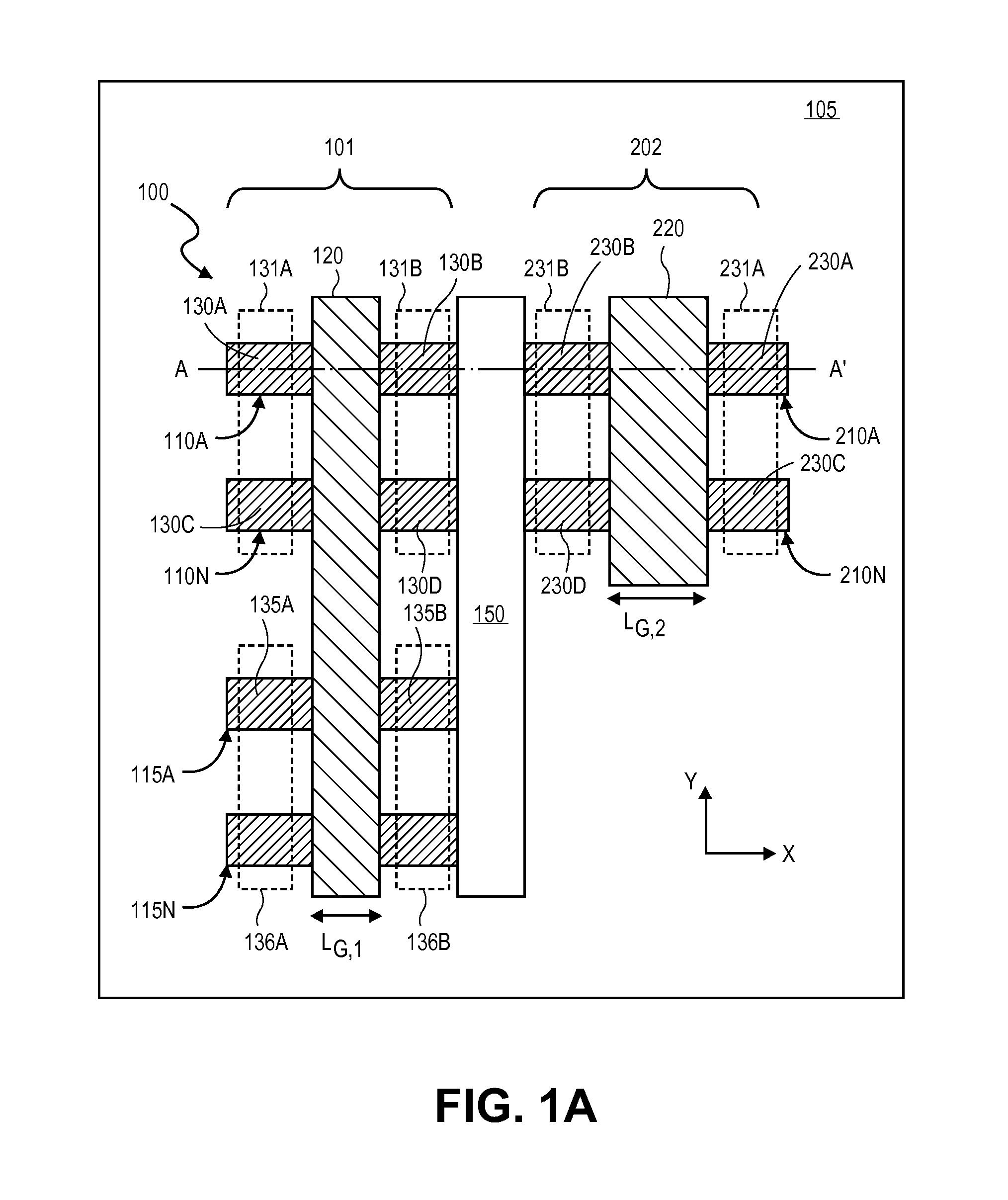

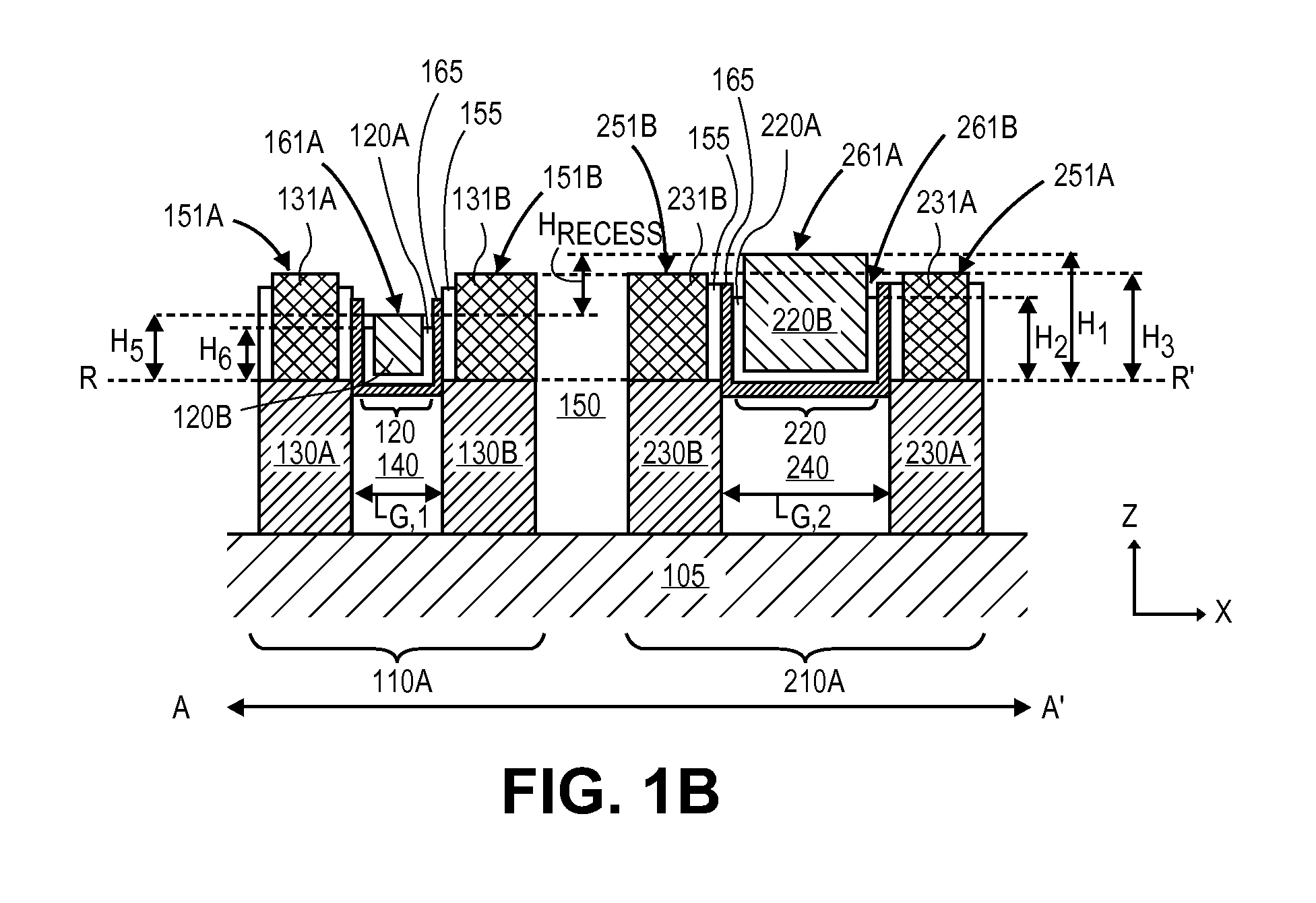

Integrated circuits with selective gate electrode recess

Integrated circuits including MOSFETs with selectively recessed gate electrodes. Transistors having recessed gate electrodes with reduced capacitive coupling area to adjacent source and drain contact metallization are provided alongside transistors with gate electrodes that are non-recessed and have greater z-height. In embodiments, analog circuits employ transistors with gate electrodes of a given z-height while logic gates employ transistors with recessed gate electrodes of lesser z-height. In embodiments, subsets of substantially planar gate electrodes are selectively etched back to differentiate a height of the gate electrode based on a given transistor's application within a circuit.

Owner:INTEL CORP

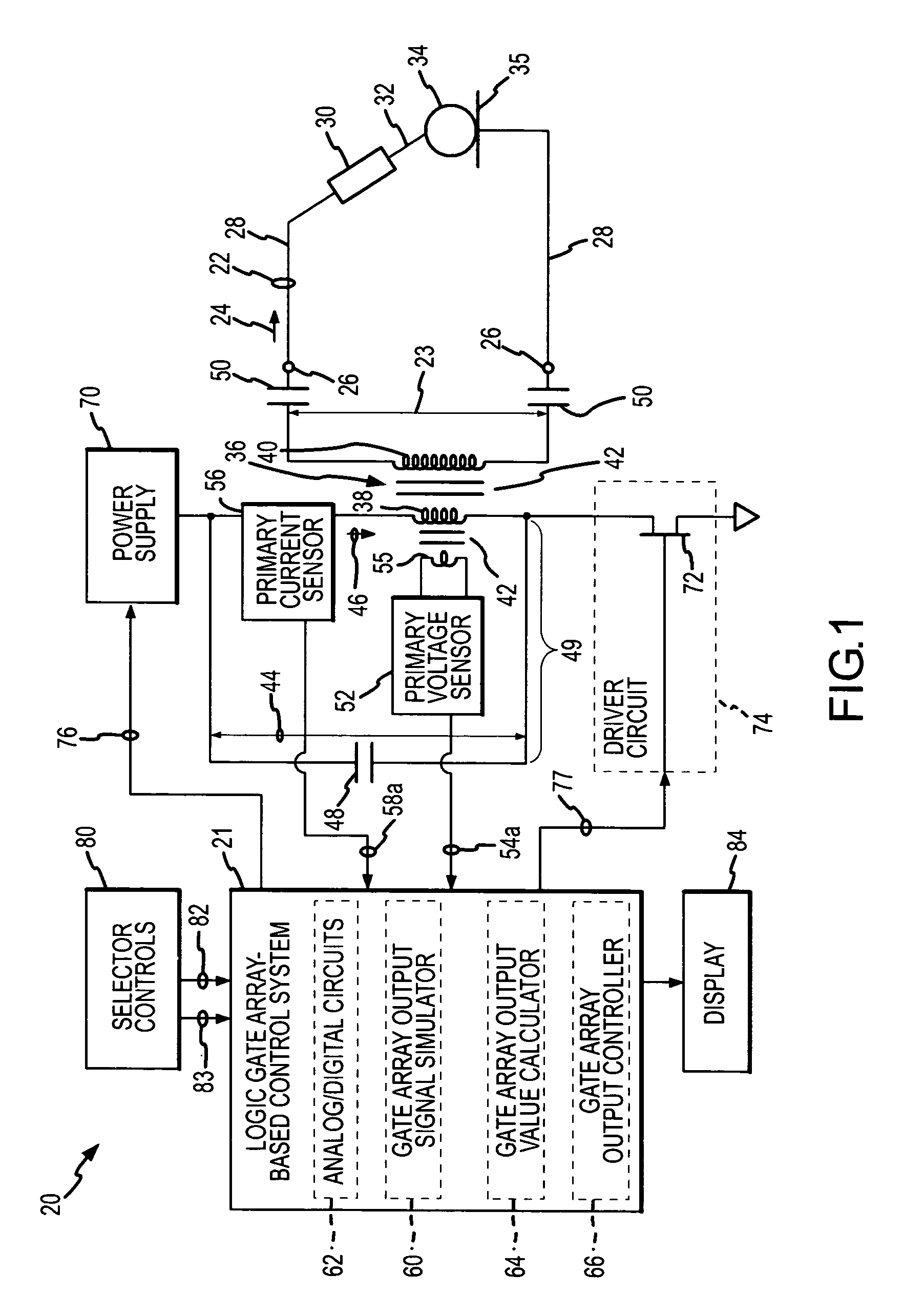

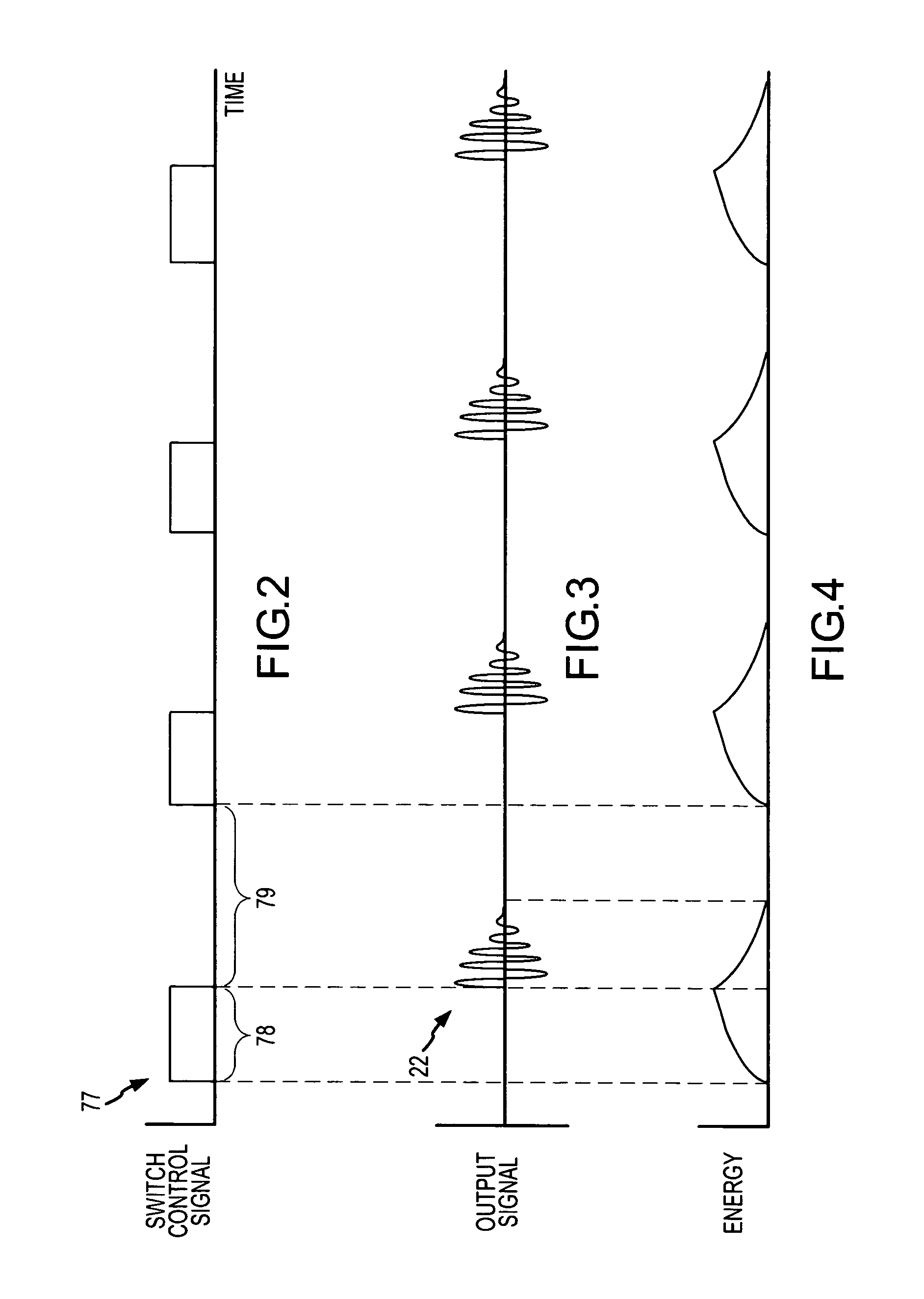

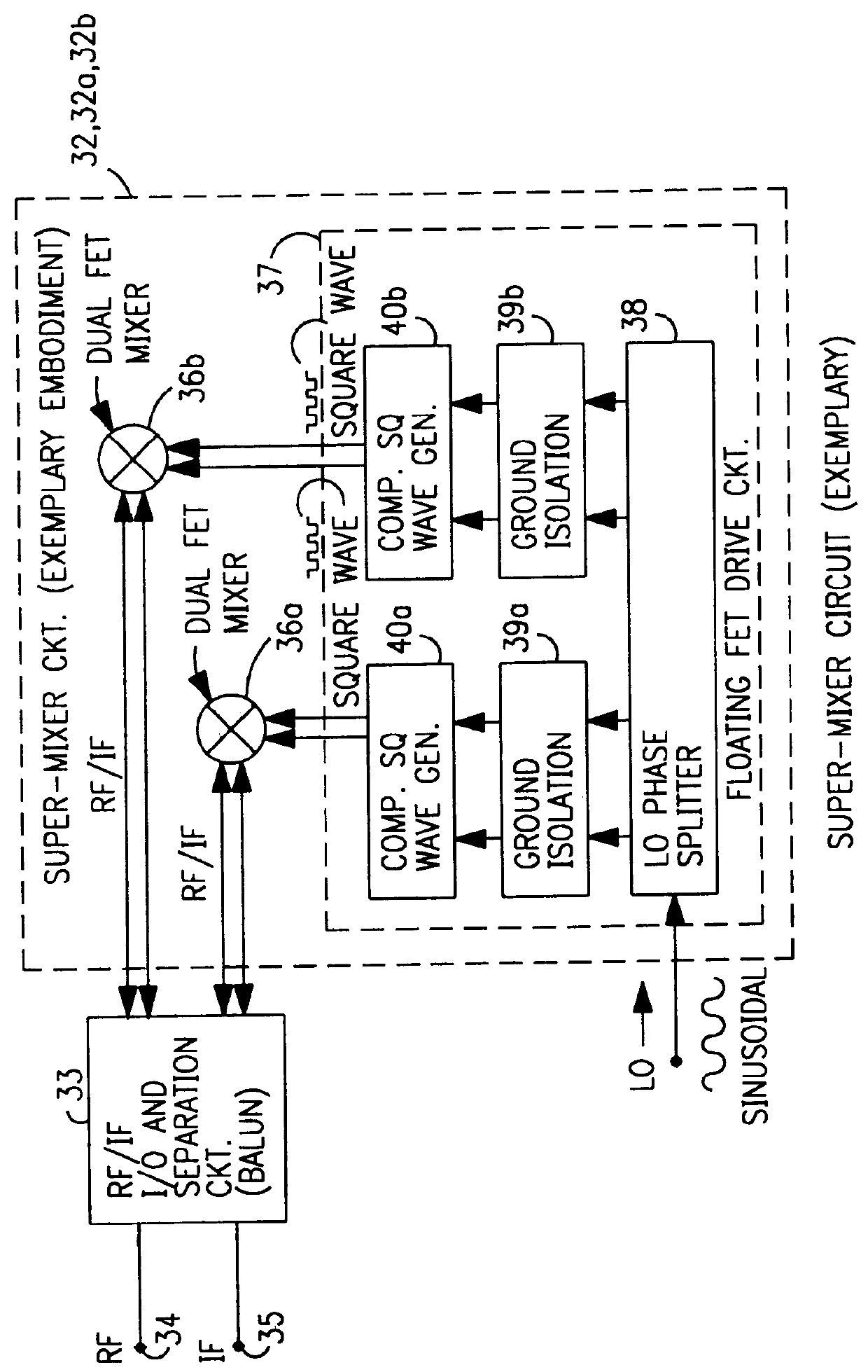

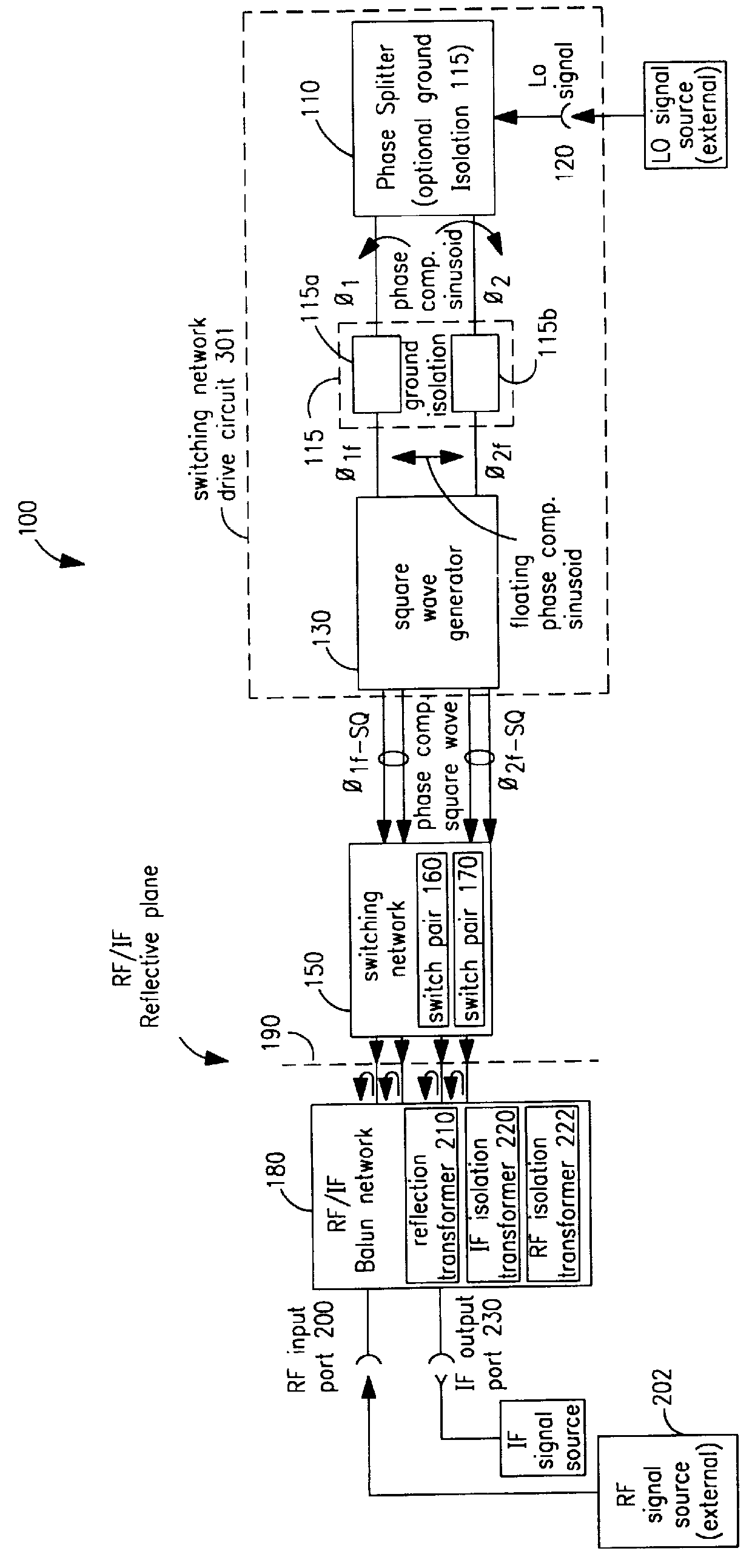

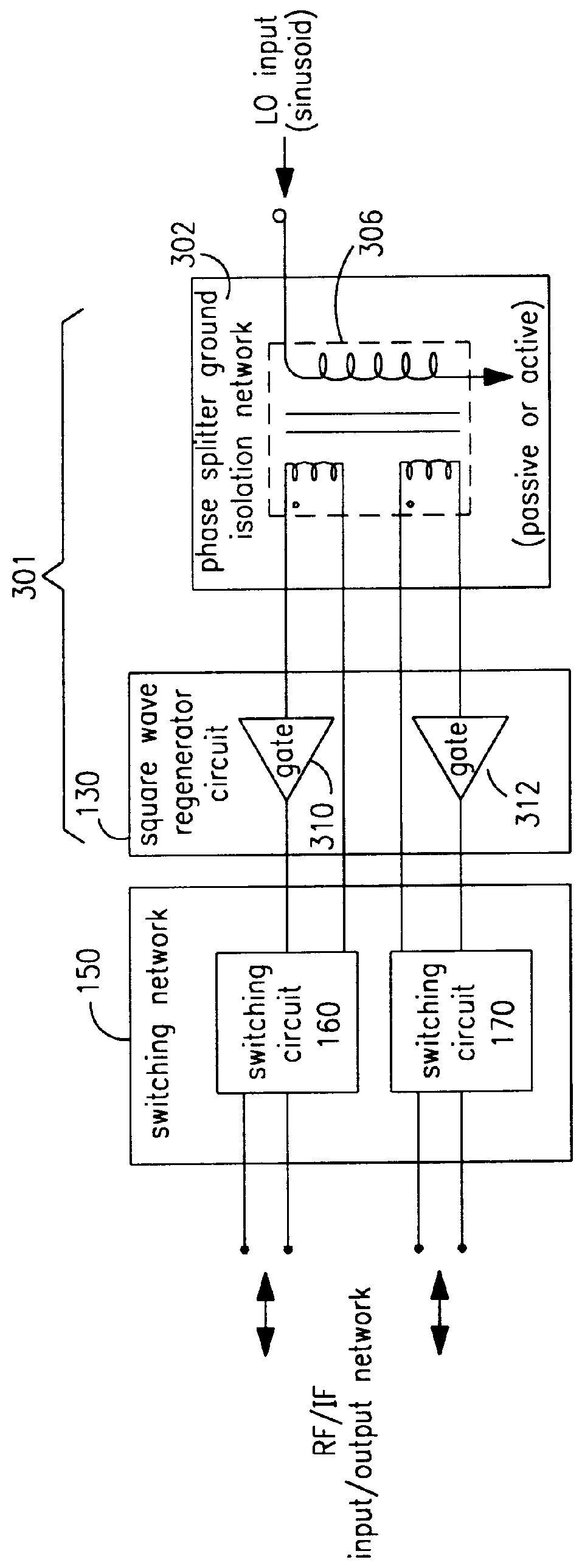

Structure and method for super FET mixer having logic-gate generated FET square-wave switching signal

InactiveUS6144236AModulation transference by semiconductor devices with minimum 2 electrodesModulation transference balanced arrangementsRadio receiverTransformer

A mixing method and mixer structure provide a circuit topology suitable for use in radio receivers, transmitters, tuners, instrumentation systems, telemetry systems, and other systems and devices performing frequency conversion in either homodyne or heterodyne implementations. The inventive mixer may be used for wireless communication devices including radios, cellular telephones, and telemetry systems whether land, sea, airborne, or space based, and whether fixed or mobile. The mixer provides superior intermodulation and harmonic distortion suppression and features excellent conversion loss, noise figure, port match, and port isolation as a result of its circuit topology. The mixer device circuit combines the advantages of series mixing FETs, a triple balanced design using a balanced passive reflection transformer, a precise local oscillator phase splitter, and square wave gate drive having high slew rate signal characteristics to achieve high levels of performance. It is power conservative and offers the advantage of long battery life in portable devices such as portable radios and cellular telephones as it requires only a modest amount of DC and local oscillator drive power, and is useful for operation over at least a multi-decade bandwidth.

Owner:DRS SIGNAL SOLUTIONS

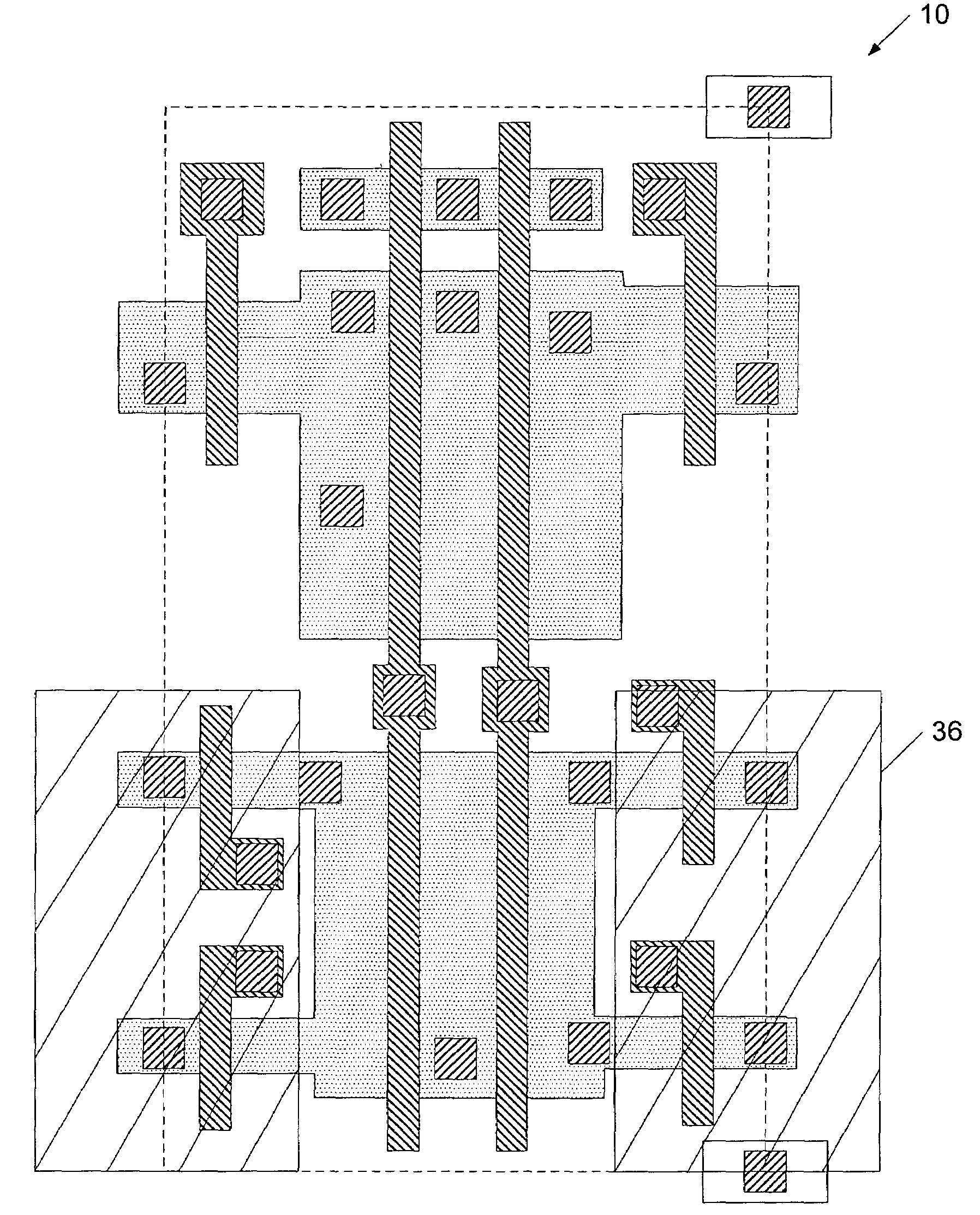

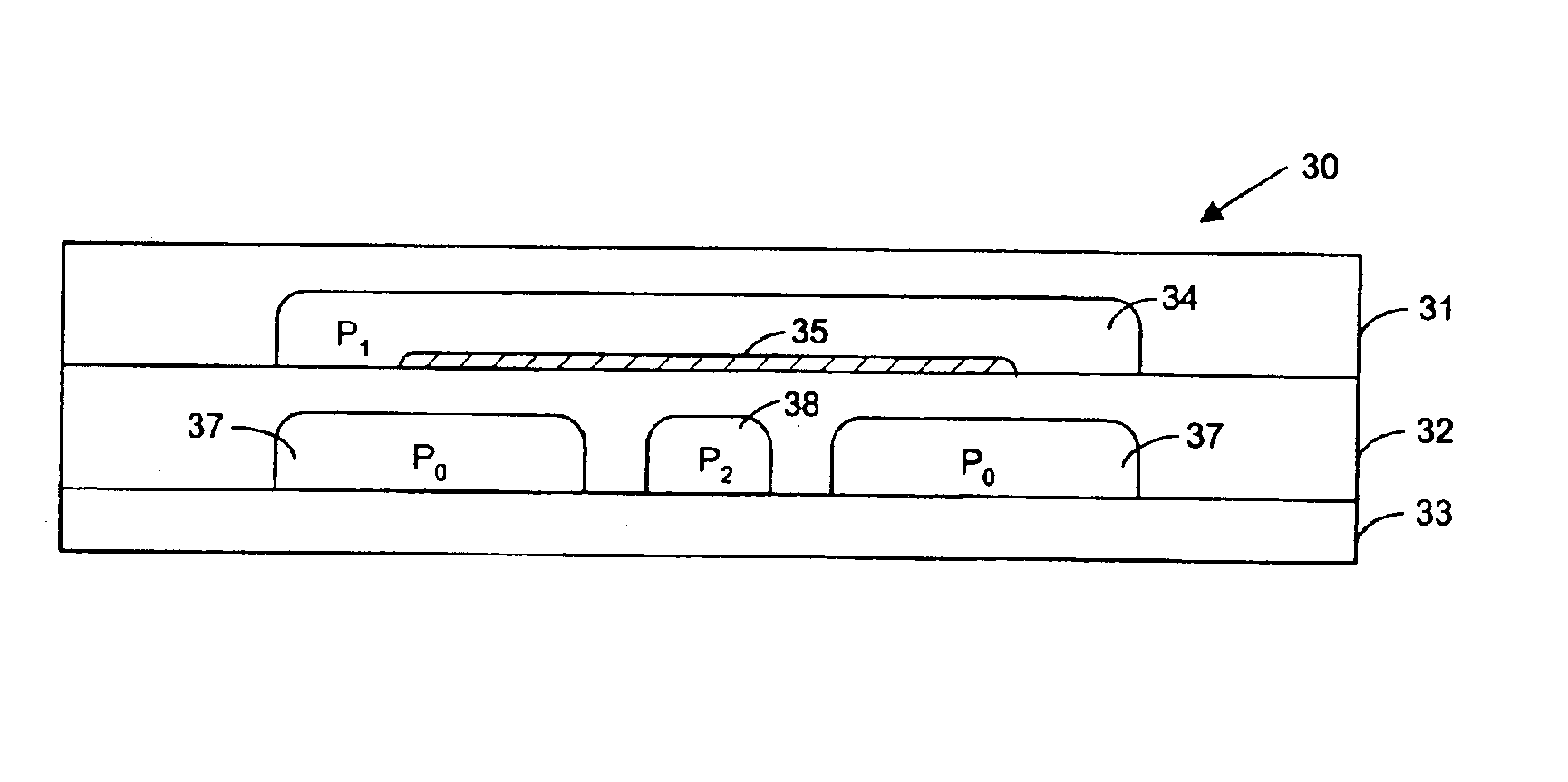

Basic cell architecture for structured application-specific integrated circuits

A basic cell circuit architecture having plurality of cells with fixed transistors configurable for the formation of logic devices and / or single / dual port memory devices within a structured ASIC is provided. Different configurations of ensuing integrated circuits are achieved by forming variable interconnect layers above the fixed structures. The circuit architecture can achieve interconnection of transistors within a single cell and / or across multiple cells. The interconnection can be configured to form basic logic gates as well as more complex digital and analog subsystems. In addition, each cell contains a layout of transistors that can be variably coupled to achieve a memory device, such as a SRAM device. By having the capability of forming either a logic circuit element, a memory device, or both, the circuit architecture is both memory-centric and logic-centric, and more fully adaptable to modern-day SoCs.

Owner:AVAGO TECH INT SALES PTE LTD

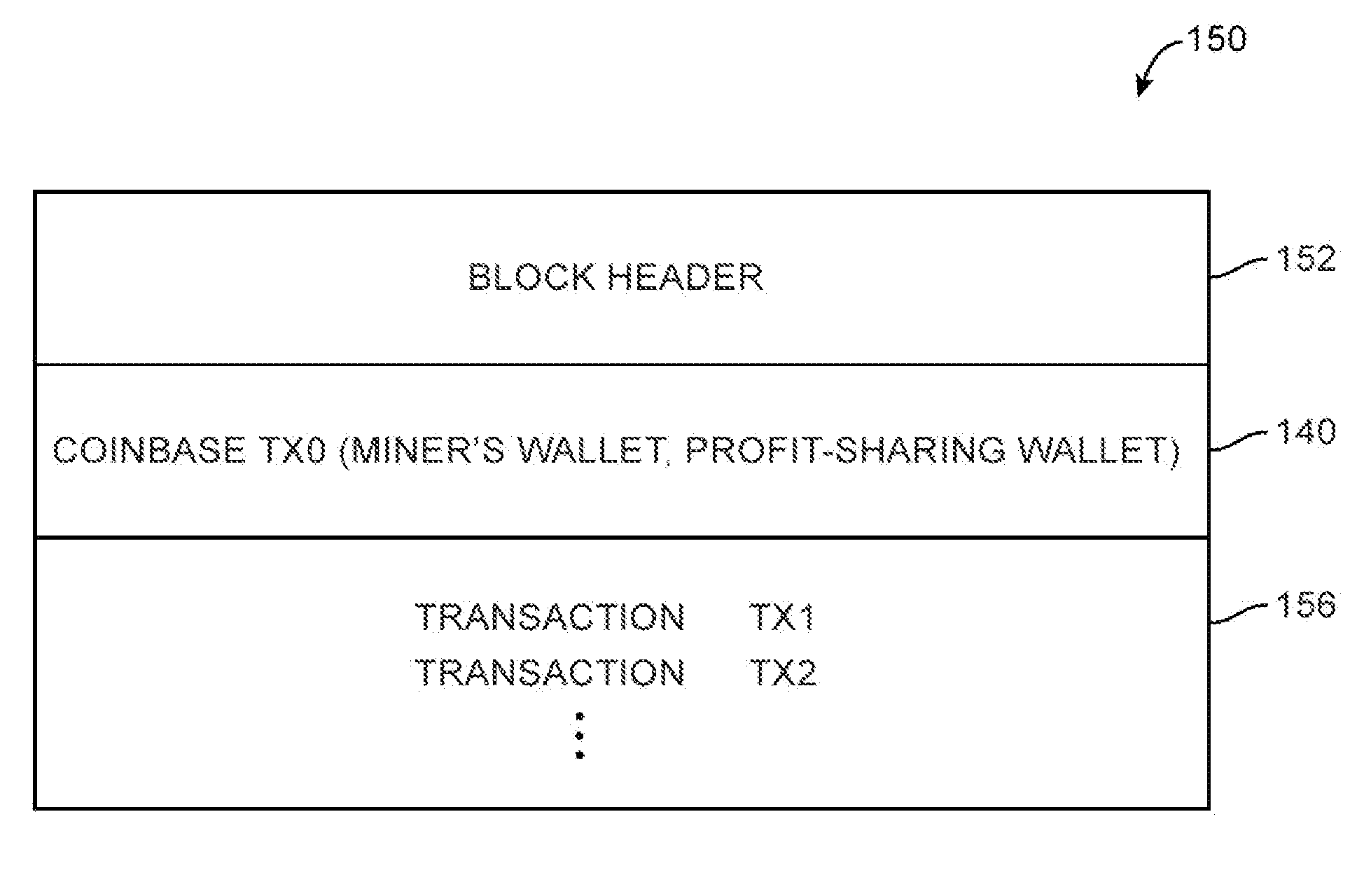

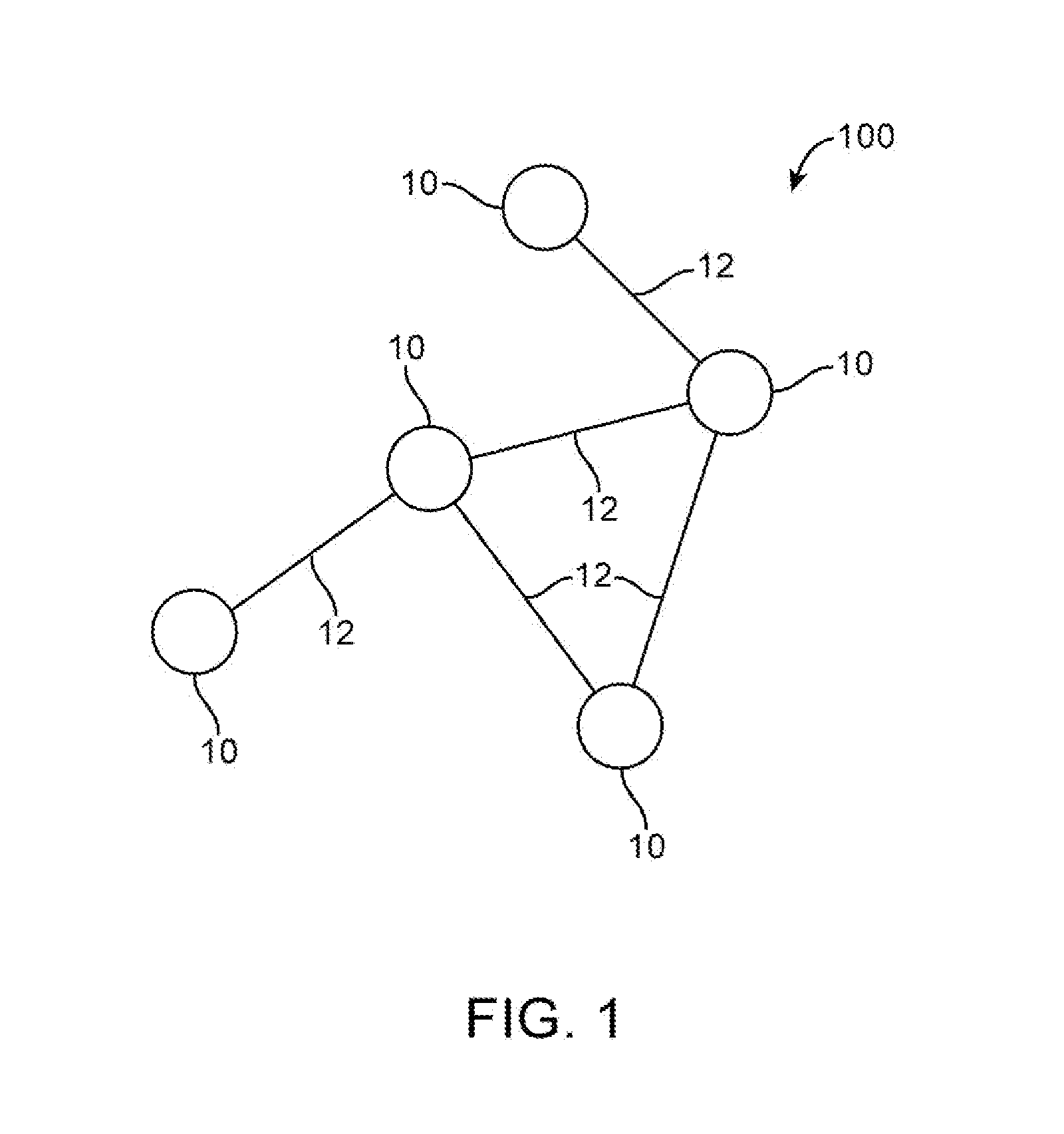

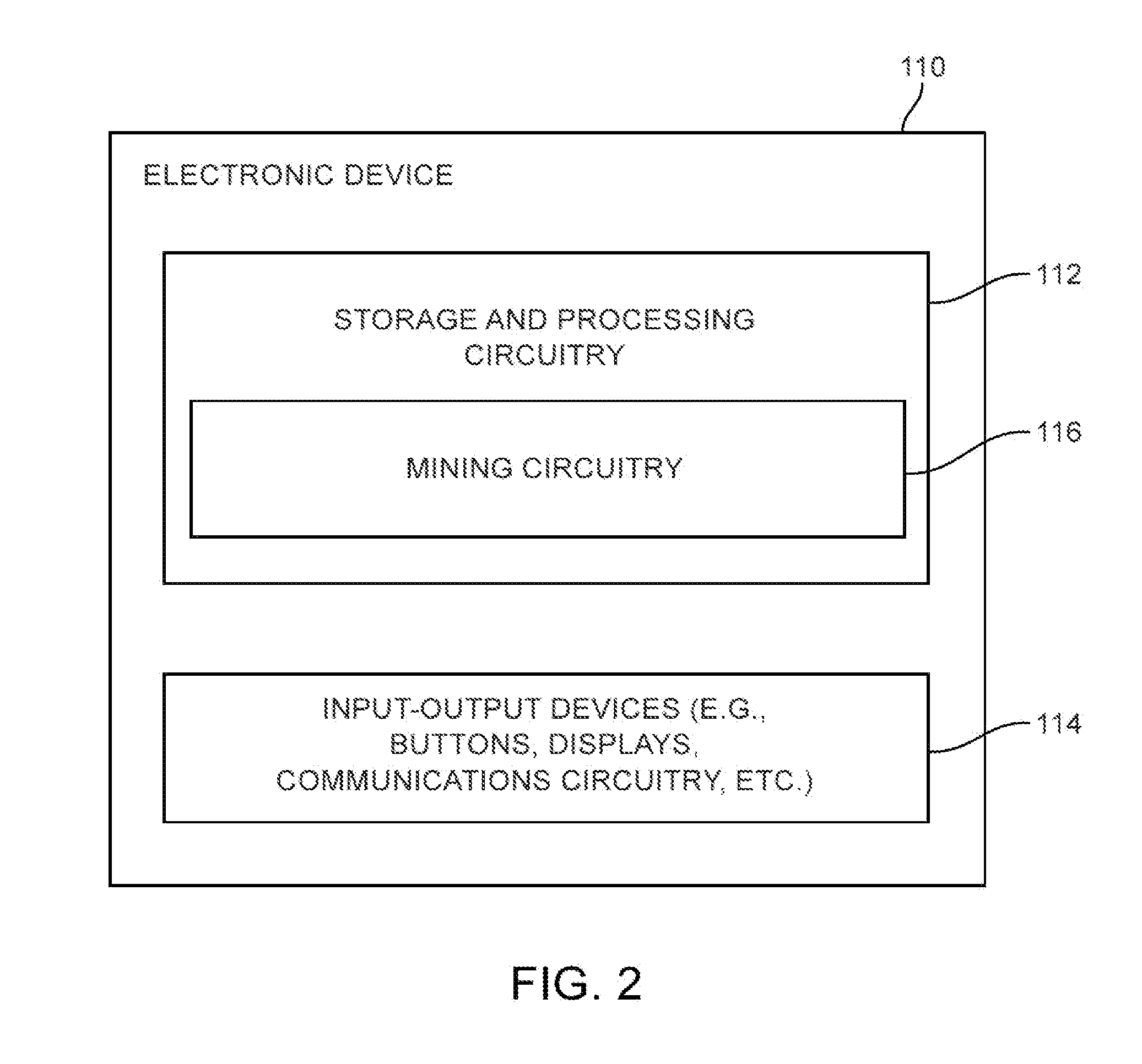

Digital currency mining circuitry with adaptable difficulty compare capabilities

Cryptographic hashing circuitry such as mining circuitry used to mine digital currency may be formed on an integrated circuit. The hashing circuitry may include sequential rounds of register and logic circuitry that perform operations of a cryptographic protocol. A final hash output from the hashing circuitry may be checked using a difficulty comparison circuit to determine whether the hash output satisfies predetermined difficulty criteria. The difficulty comparison circuit may be configured as a hardwired comparison circuit having logic gates for checking only a subset of bits in the hash output. The comparison circuit may be adapted to change the number of bits that is checked based on a target number of bits for comparison set by the Bitcoin protocol. Candidate solutions found using the hardwired comparison circuit may then be fed to a host controller that checks the entire hash output to determine whether the candidate solution is valid.

Owner:COINBASE

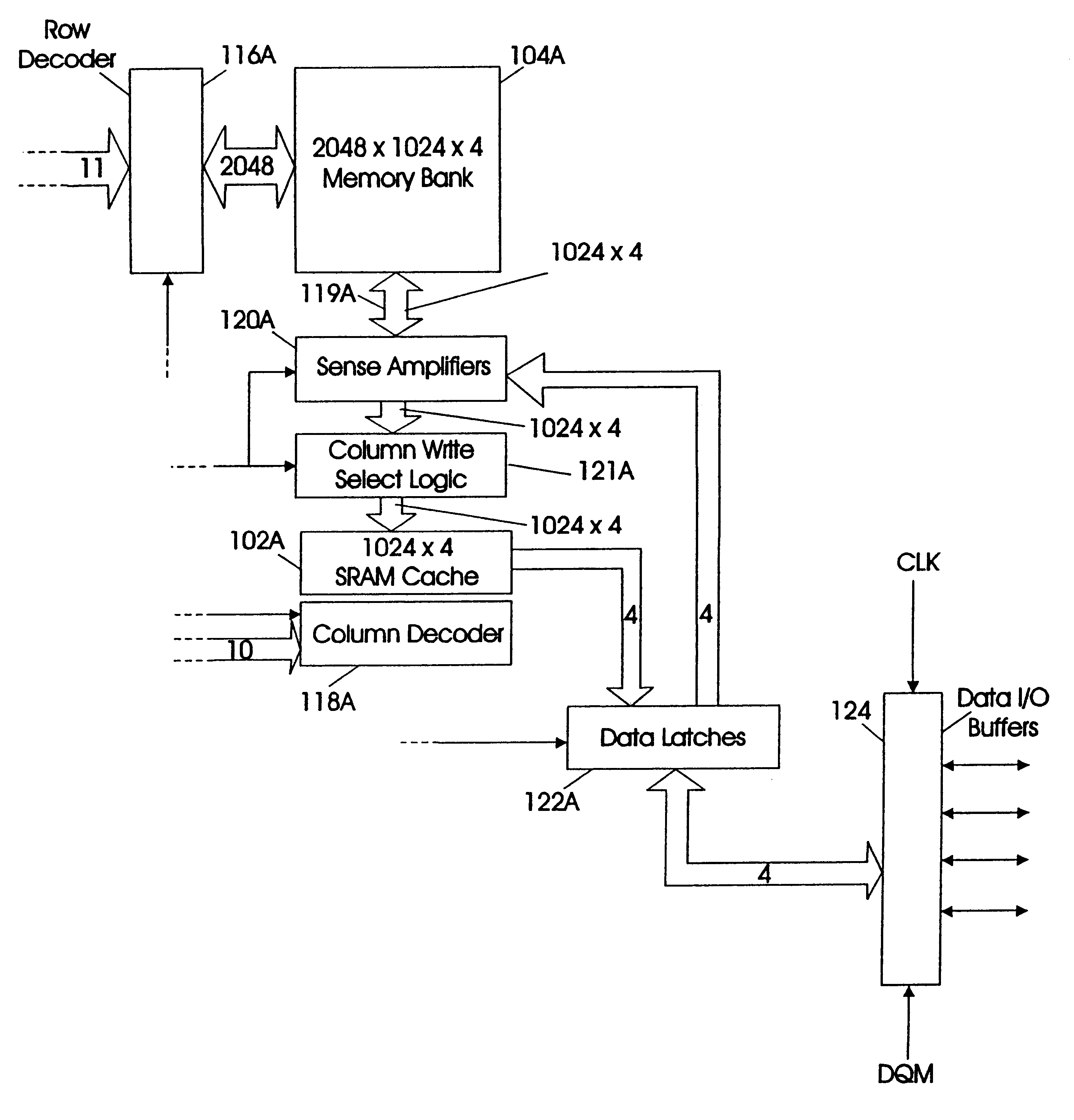

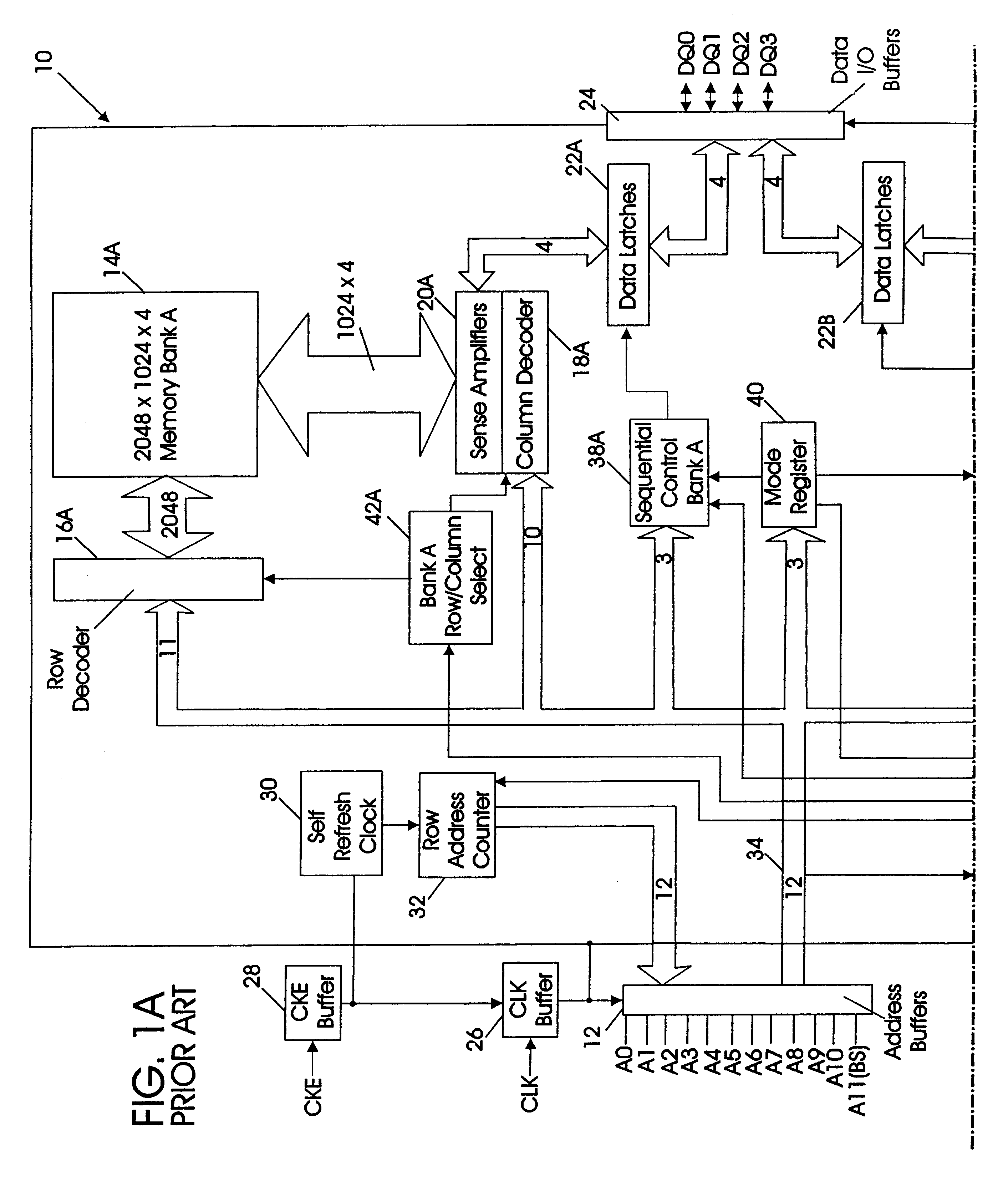

Cached synchronous DRAM architecture having a mode register programmable cache policy

InactiveUS6289413B1Memory adressing/allocation/relocationDigital storageBit lineAudio power amplifier

A cached synchronous dynamic random access memory (cached SDRAM) device having a multi-bank architecture and a programmable caching policy includes a synchronous dynamic random access memory (SDRAM) bank, a synchronous static randomly addressable row register, a select logic gating circuit, and mode register for programming of the cached SDRAM to operate in a Write Transfer mode corresponding to a Normal Operation mode of a standard SDRAM during a Write cycle, and to operate in a No Write Transfer mode according to an alternate operation mode during a Write cycle, thereby operating under a first and a second caching policy, respectively. The SDRAM includes a row decoder for selecting a row of data in a memory bank array, sense amplifiers for latching the row of data selected by the row decoder, and a synchronous column selector for selecting a desired column of the row of data. The row register stores a row of data latched by the sense amplifiers and the select logic gating circuit, disposed between the sense amplifiers and the row register, selectively gates the row of data present on the bit lines to the row register in accordance to particular synchronous memory operations being performed.

Owner:IBM CORP +2

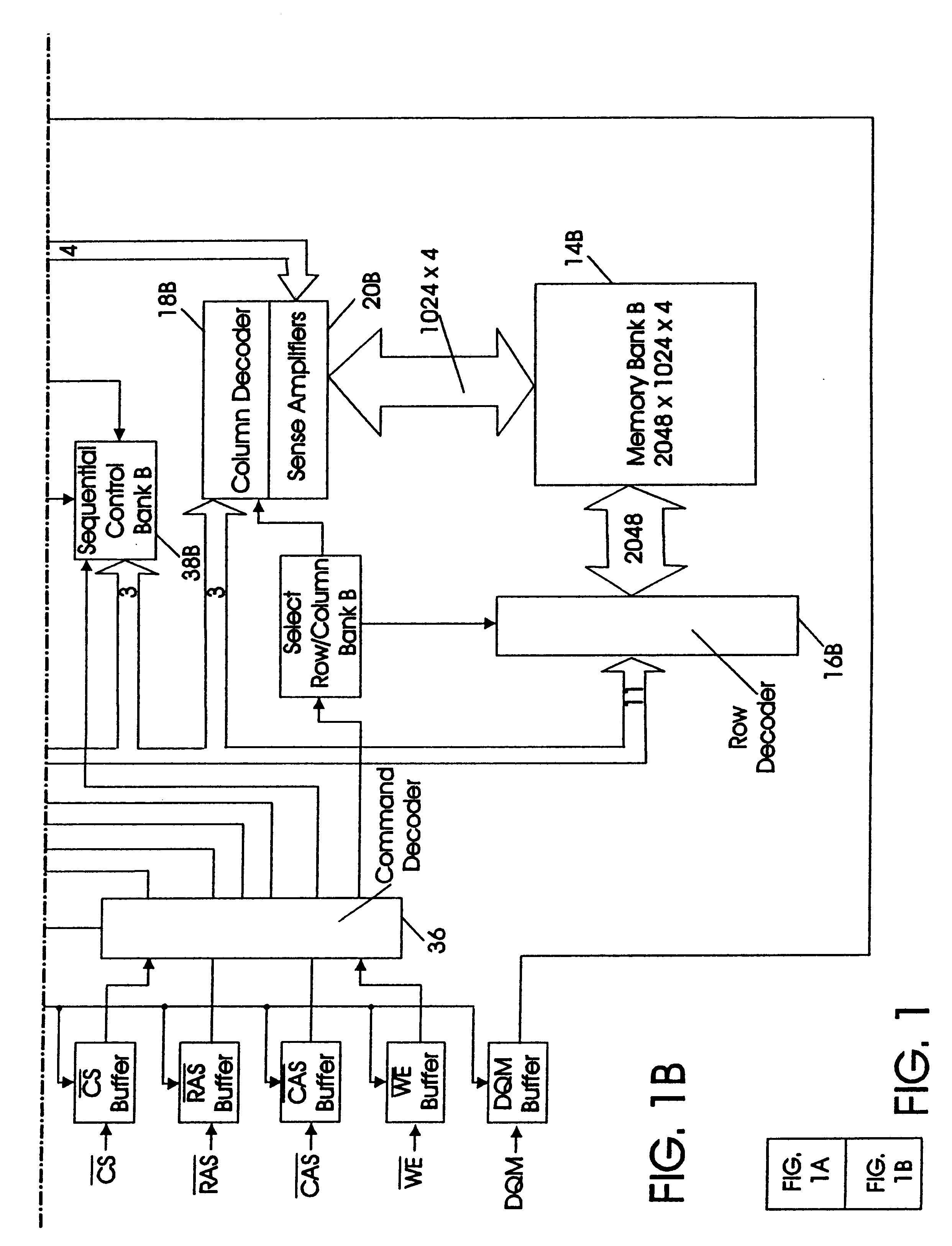

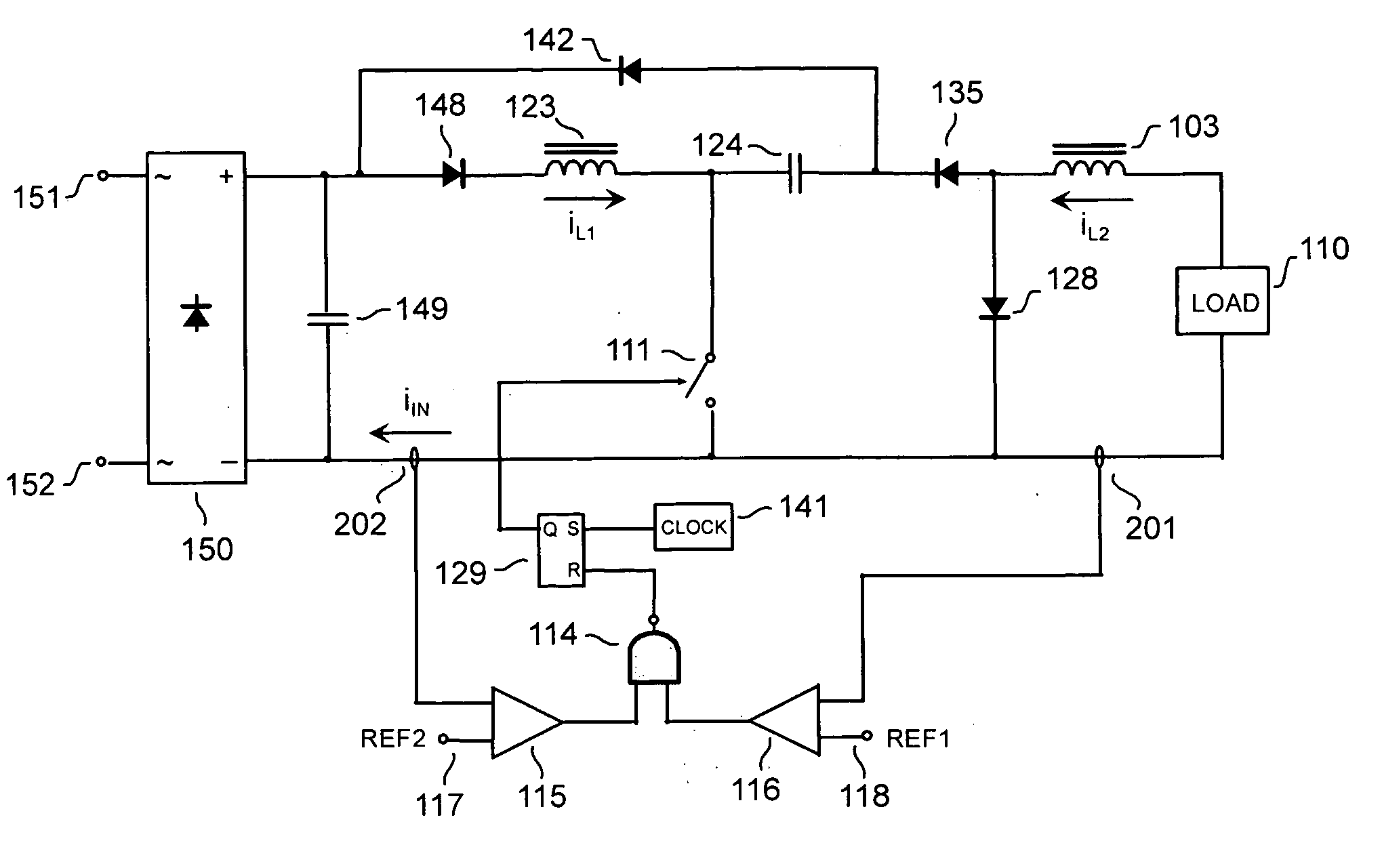

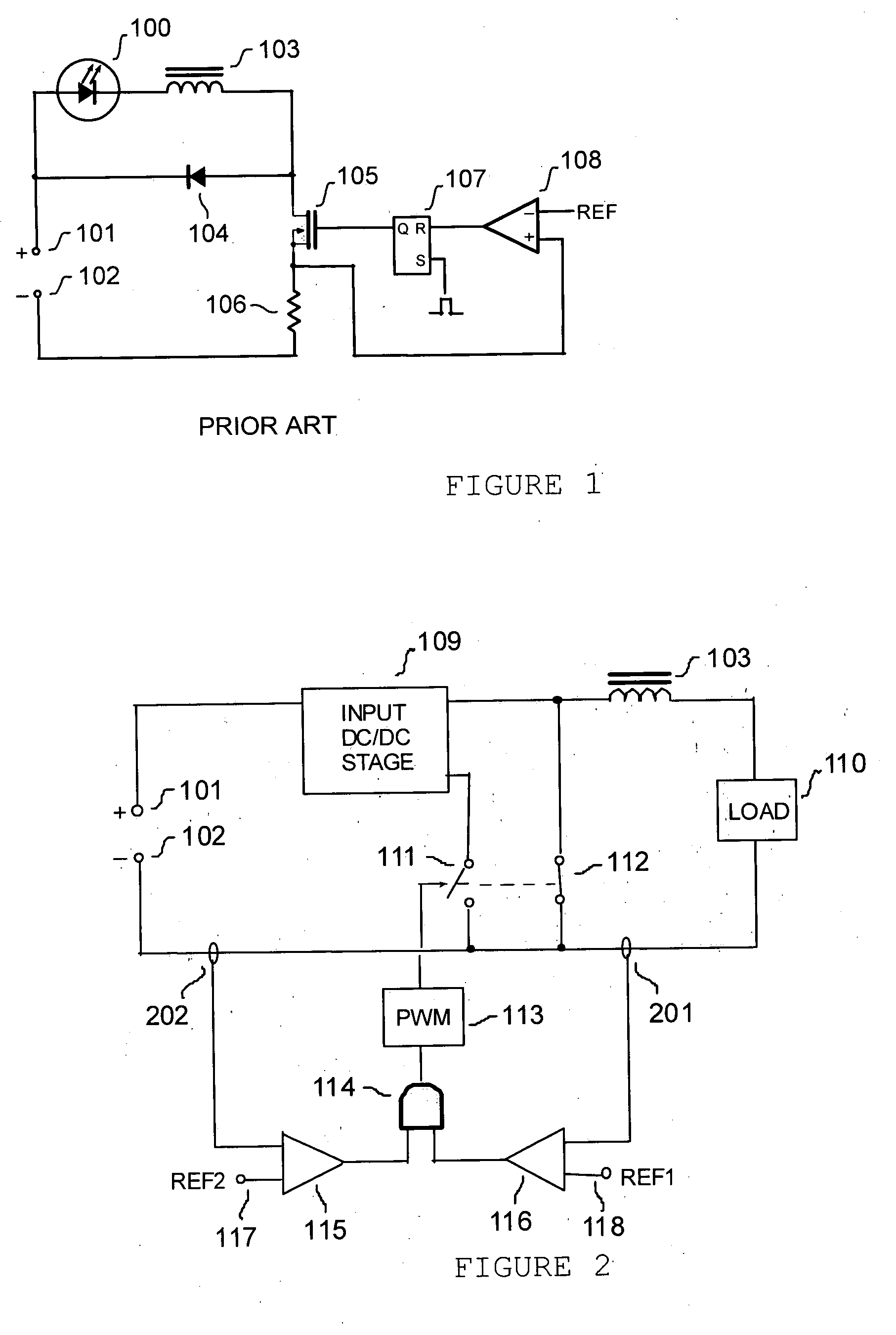

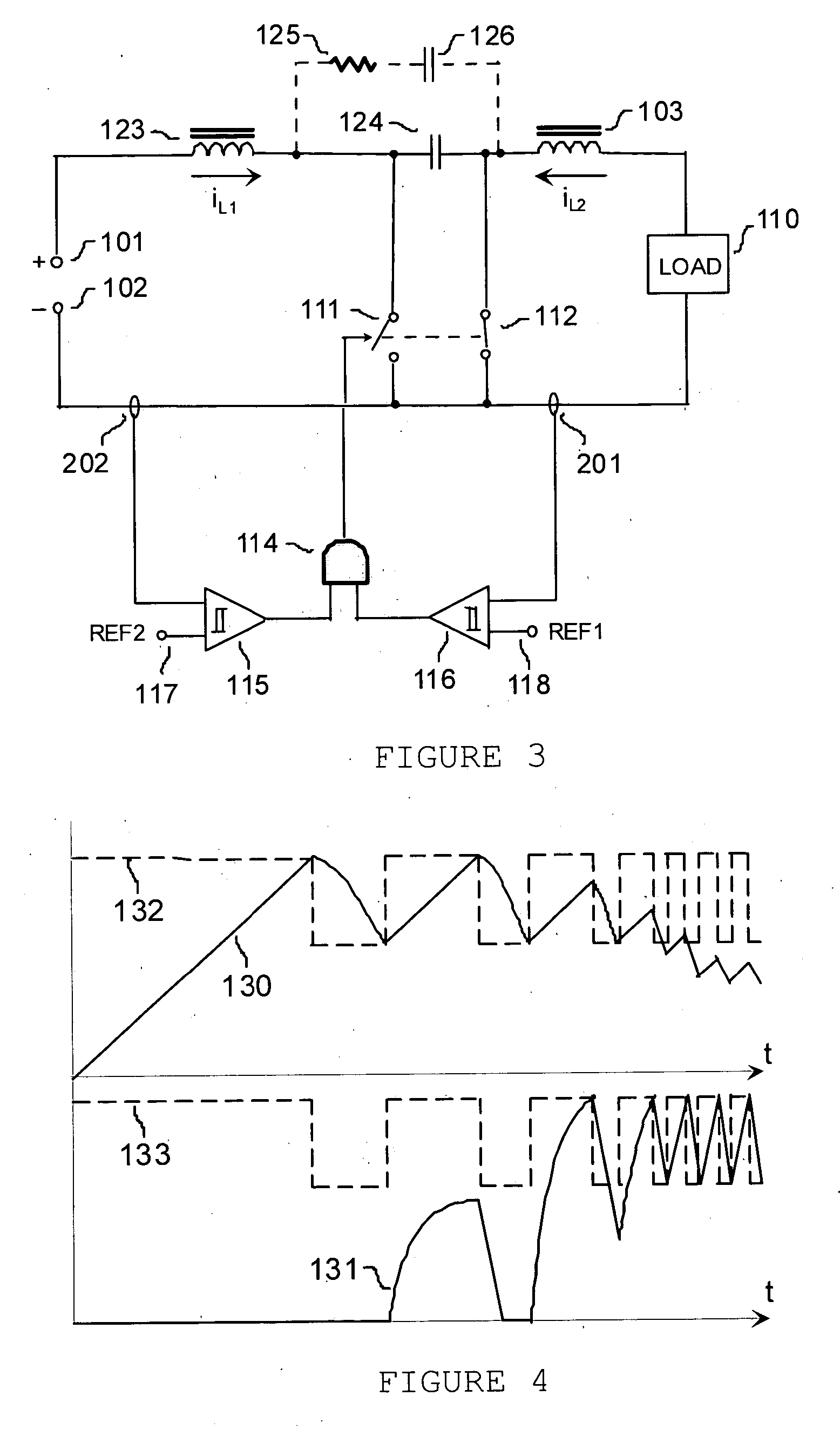

Method and apparatus for controlling output current of a cascaded DC/DC converter

ActiveUS20060113975A1Efficient power electronics conversionDc-dc conversionCascade converterEngineering

A circuit and a method for controlling output current of cascaded switching power converters having a buck type output stage are disclosed. The circuit comprises two comparators for sensing input and output current, a logic gate for processing the output states of the comparators, and a pulse width modulator circuit for receiving the output of the logic gate and for controlling a switching power converter in accordance with this output. The method comprises simultaneous monitoring current in the stages of the converter, comparing the currents to the corresponding reference levels, generating the corresponding error signals, and controlling a pulse-width modulator circuit of a switching converter in accordance with these error signals.

Owner:MICROCHIP TECH INC

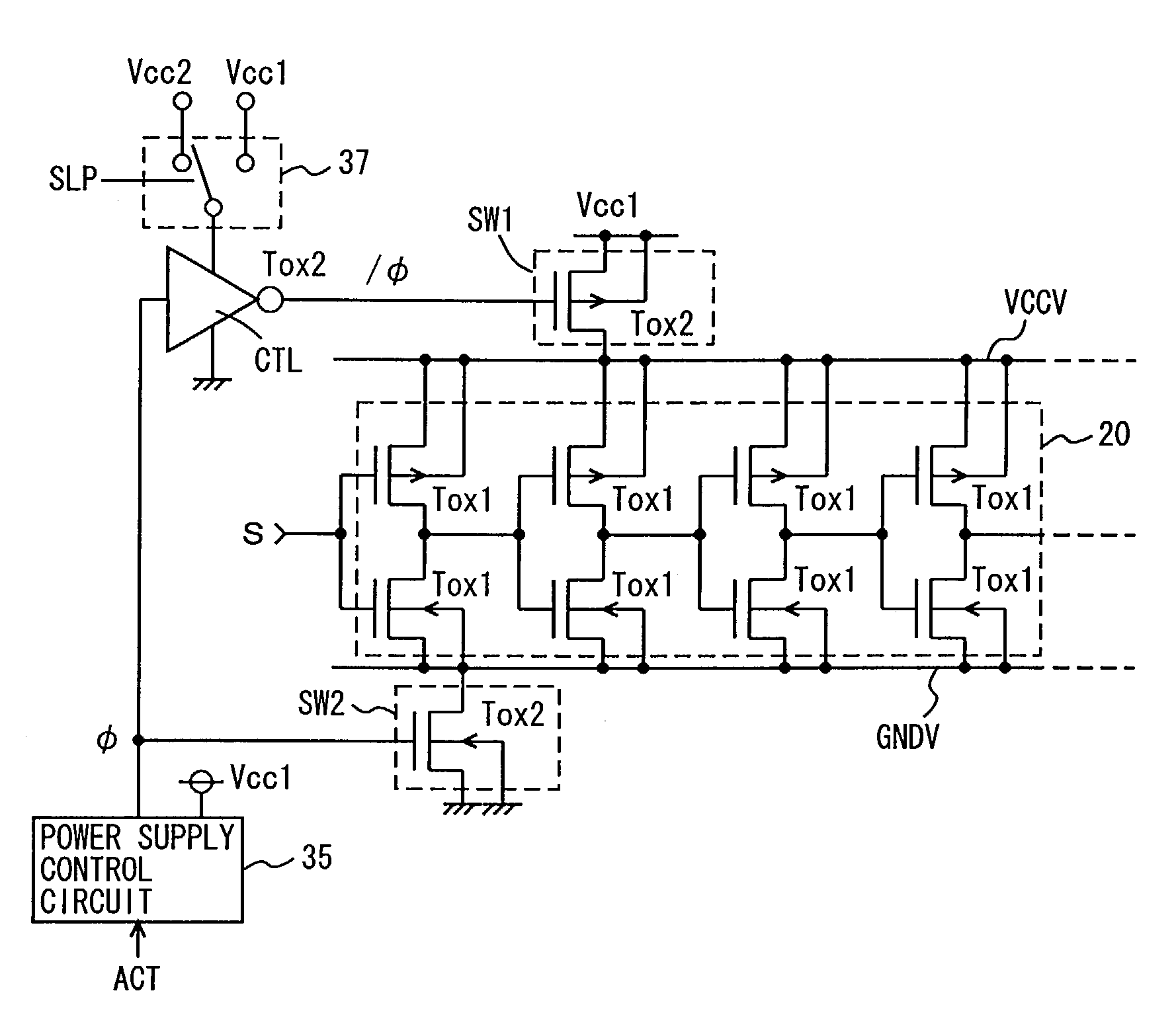

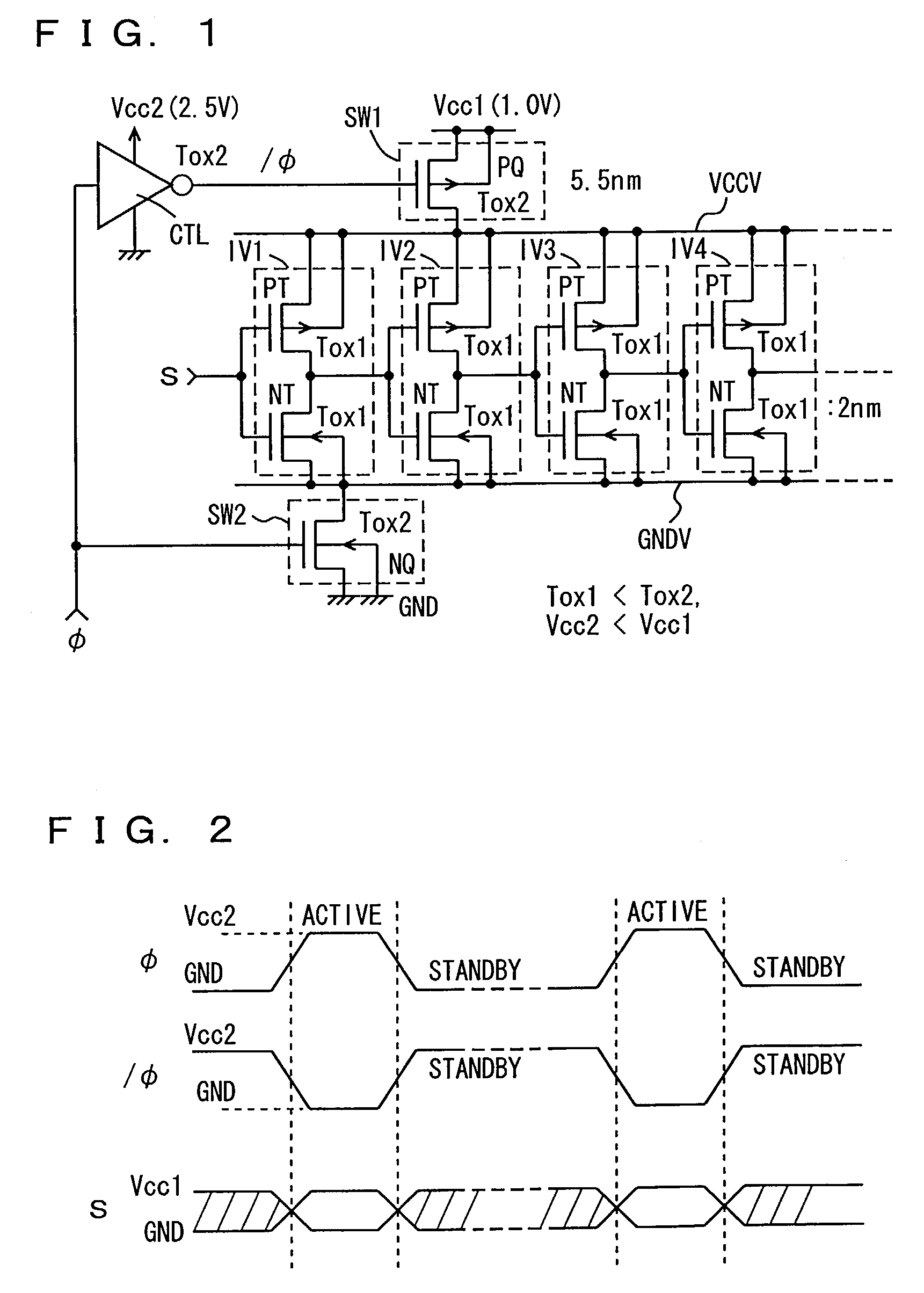

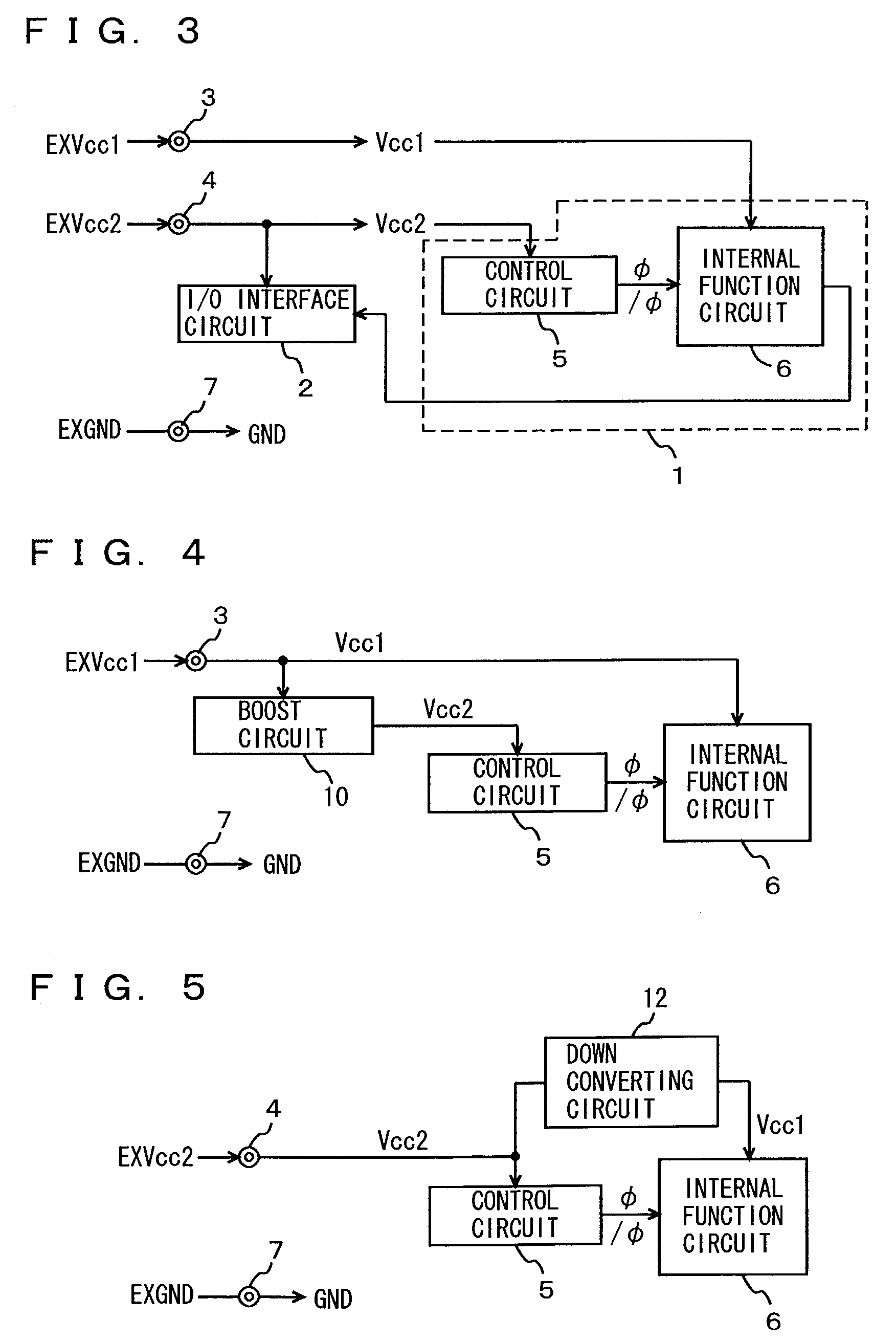

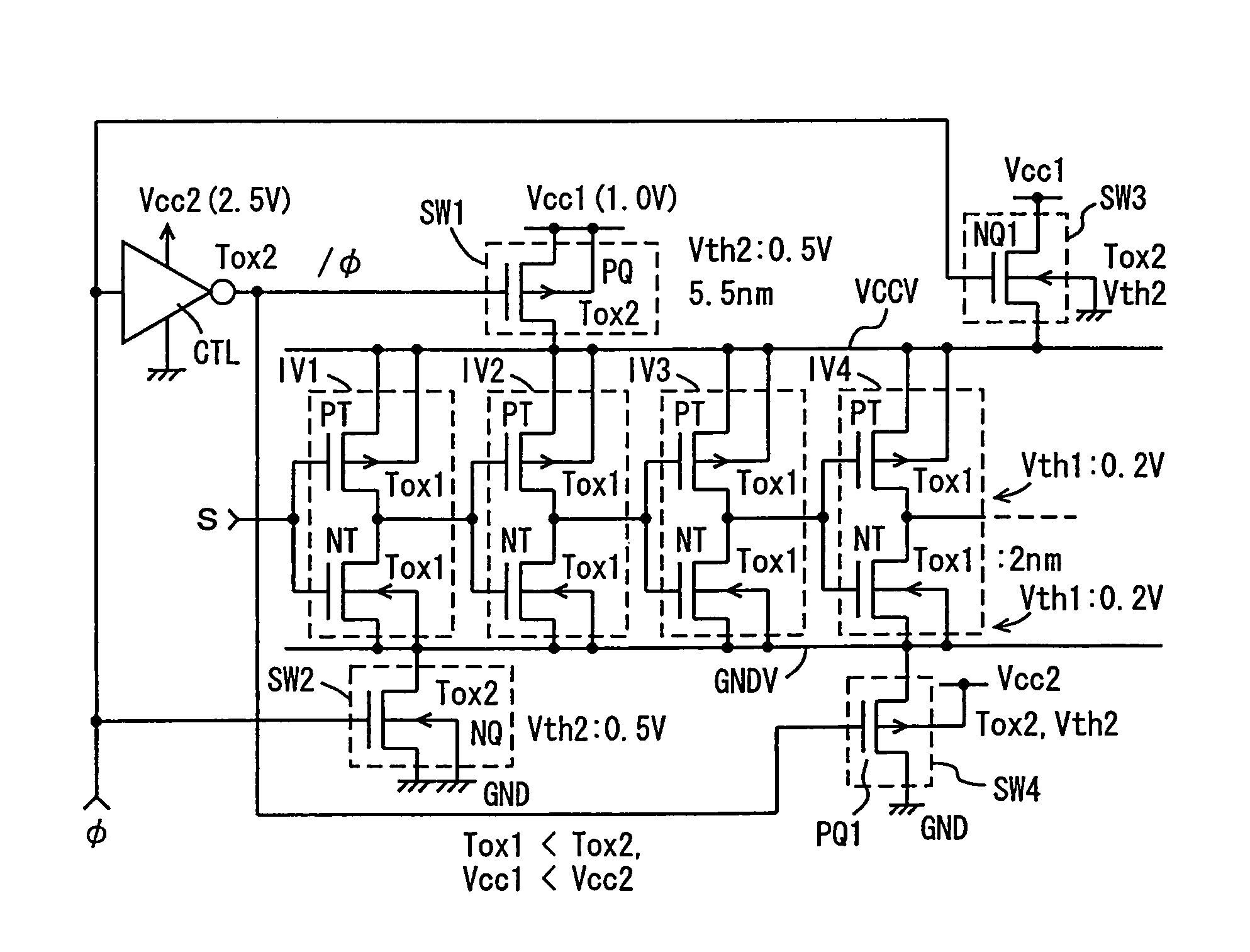

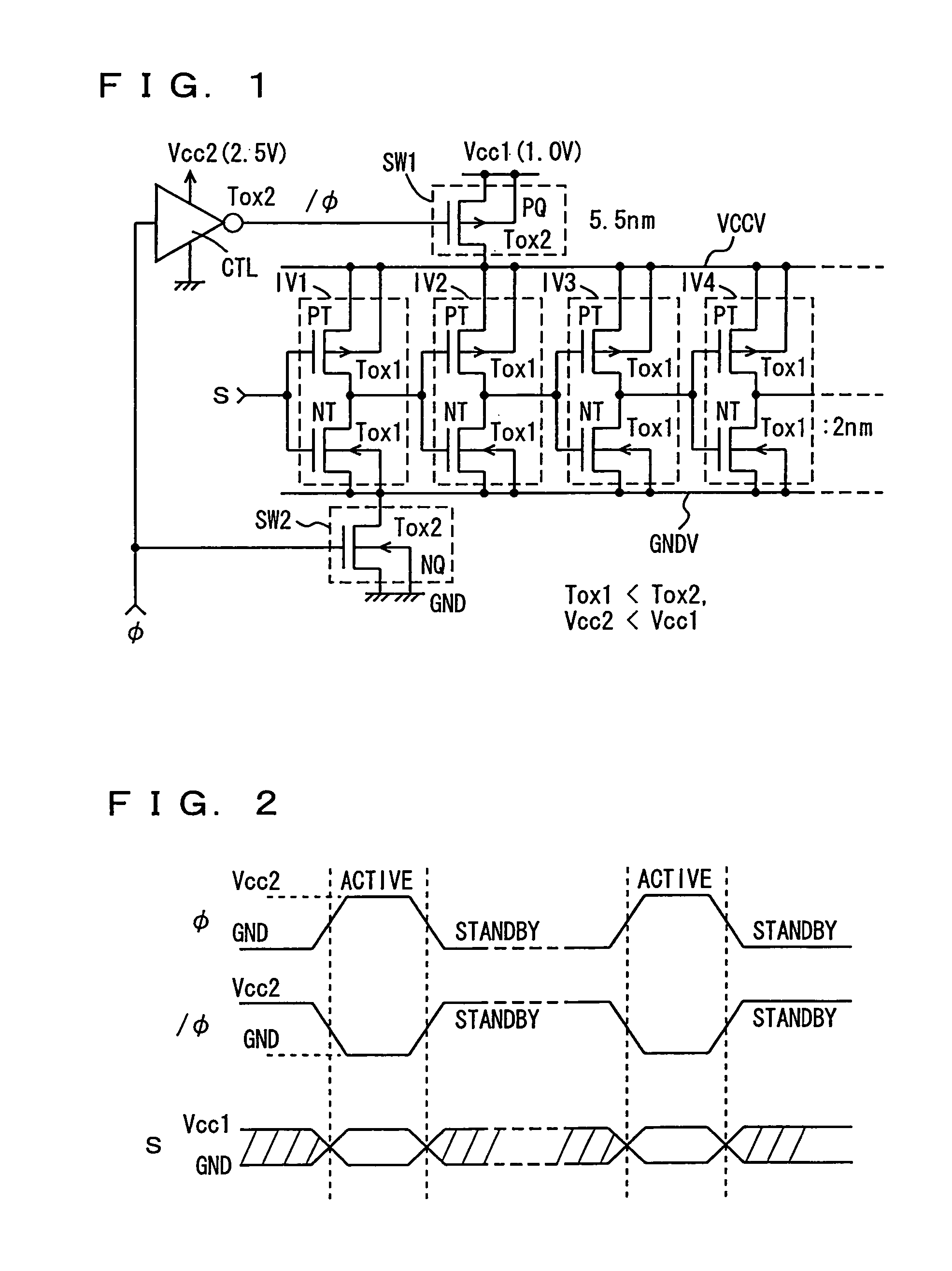

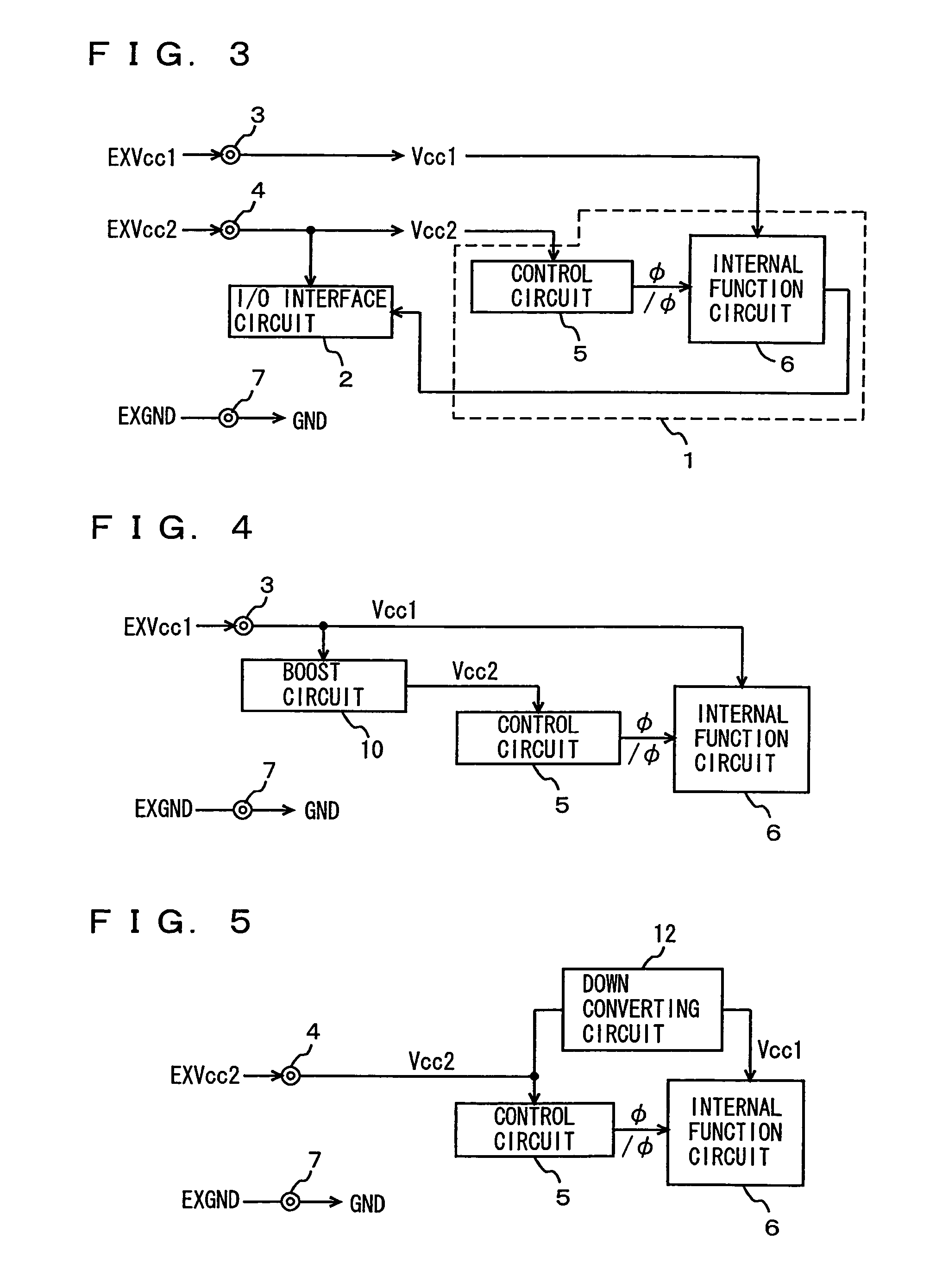

Low power consumption MIS semiconductor device

InactiveUS7042245B2Total current dropSimple circuit configurationTransistorReliability increasing modificationsCurrent consumptionLogic gate

A logic gate is constructed of an insulated gate field effect transistor (MIS transistor) having a thin gate insulation film. An operation power supply line to the logic gate is provided with an MIS transistor having a thick gate insulation film for switching the supply and stop of an operation power source voltage. A voltage of the gate of the power source switching transistor is made changing in an amplitude greater than an amplitude of an input and an output signal to the logic gate. Current consumption in a semiconductor device configured of MIS transistor of a thin gate insulation film can be reduced and an power source voltage thereof can be stabilized.

Owner:RENESAS ELECTRONICS CORP

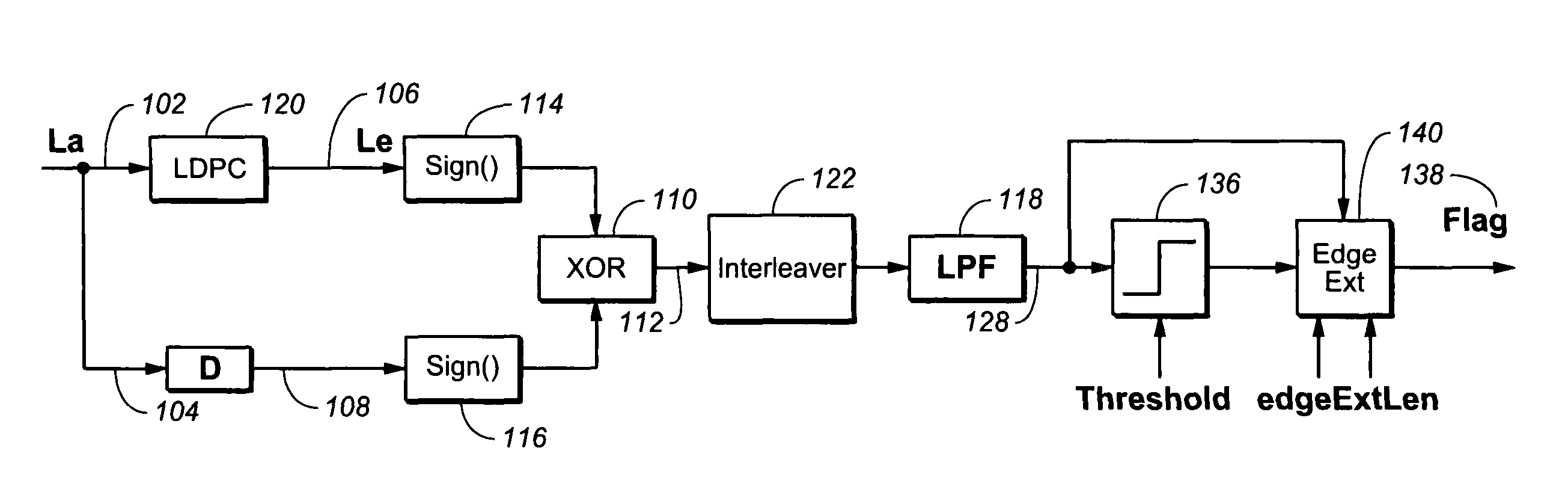

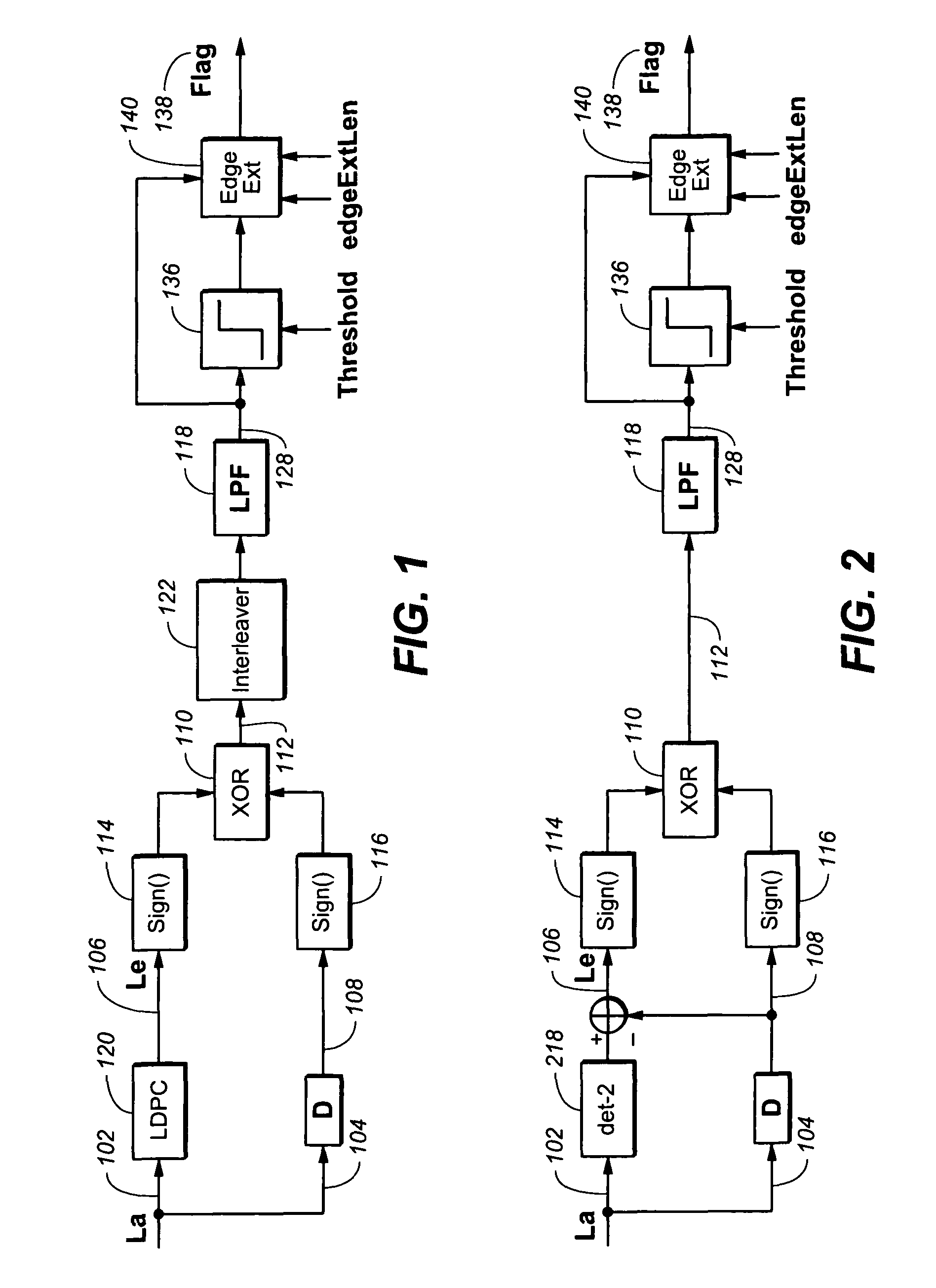

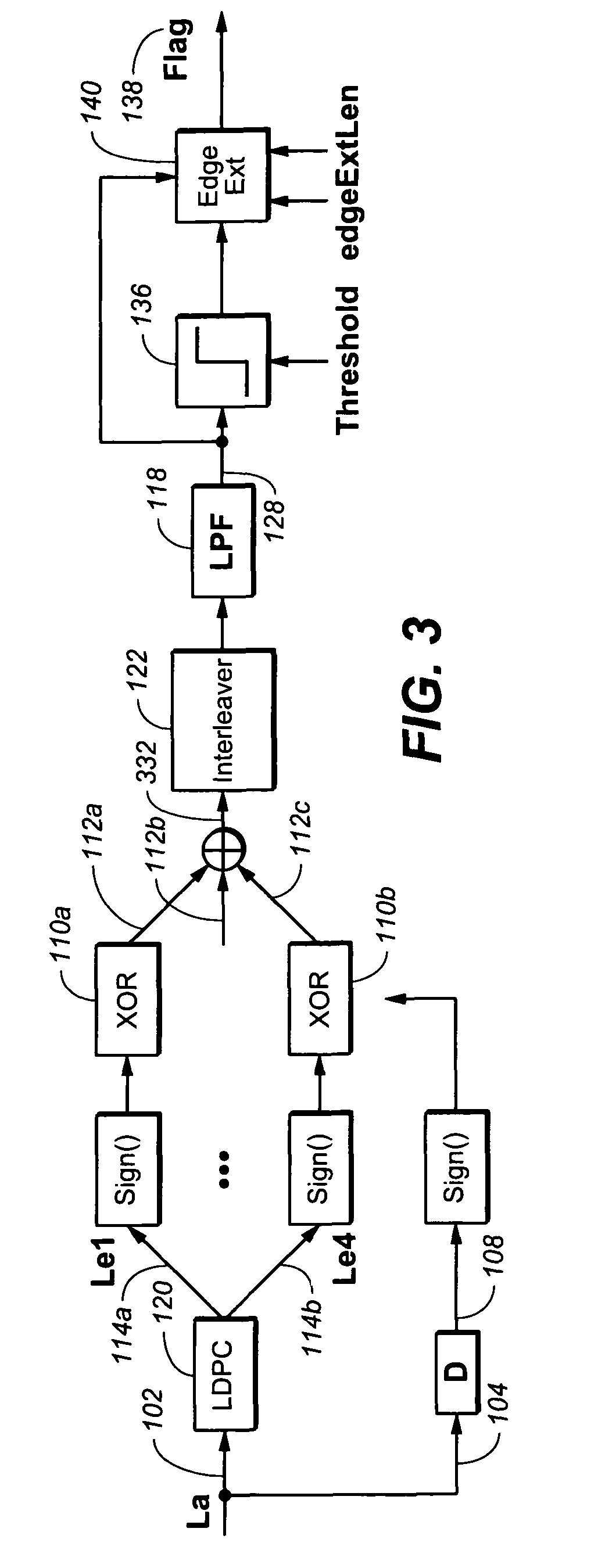

Method for detecting short burst errors in LDPC system

The present invention is a device for detecting short burst errors. The device includes a first signal input, wherein the first signal input is configured to receive a first signal. The device includes a second signal input, wherein the second signal input is configured to receive a second signal. The device includes a logic gate, wherein the logic gate is operable for receiving the first signal vial the first signal input, receiving the second signal via the second signal input, and generating a logic output gate signal based on the received first signal and the second signal. Furthermore, the device includes a filter, wherein the filter is configured for receiving the logic output gate signal from the logic gate and generates a filter output signal based upon the received logic output gate signal, wherein the filter output signal is operable for flagging errors.

Owner:AVAGO TECH INT SALES PTE LTD

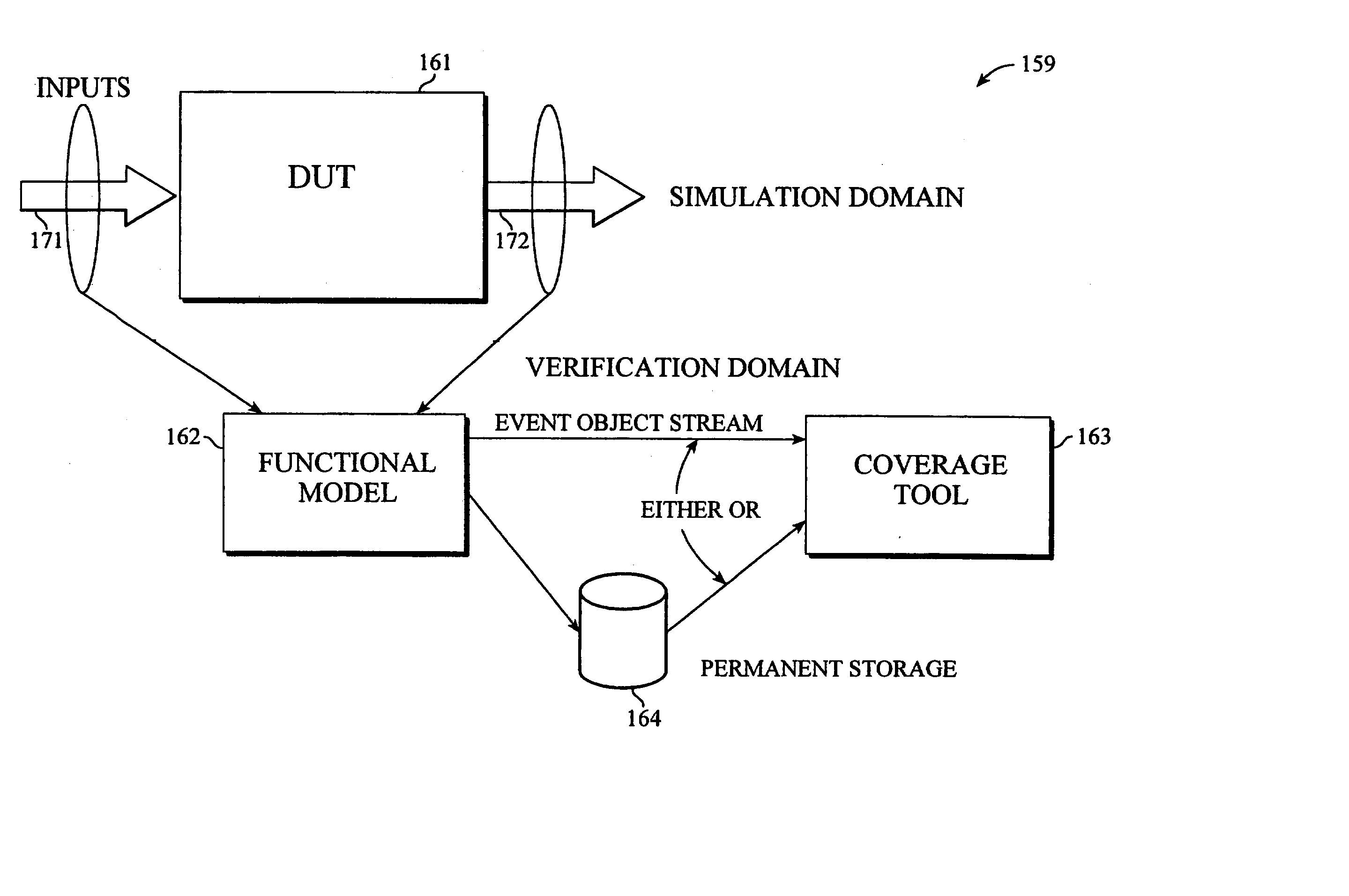

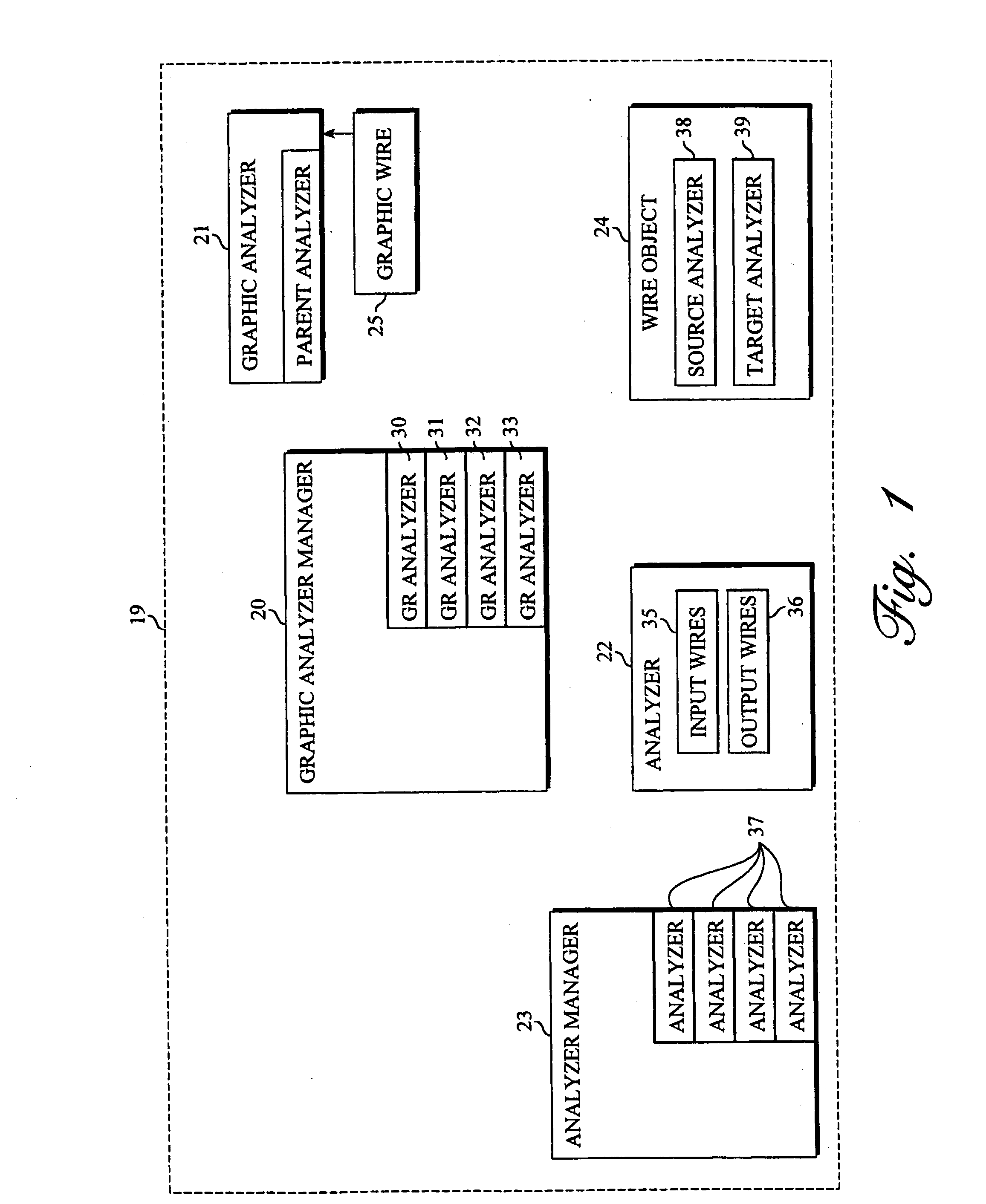

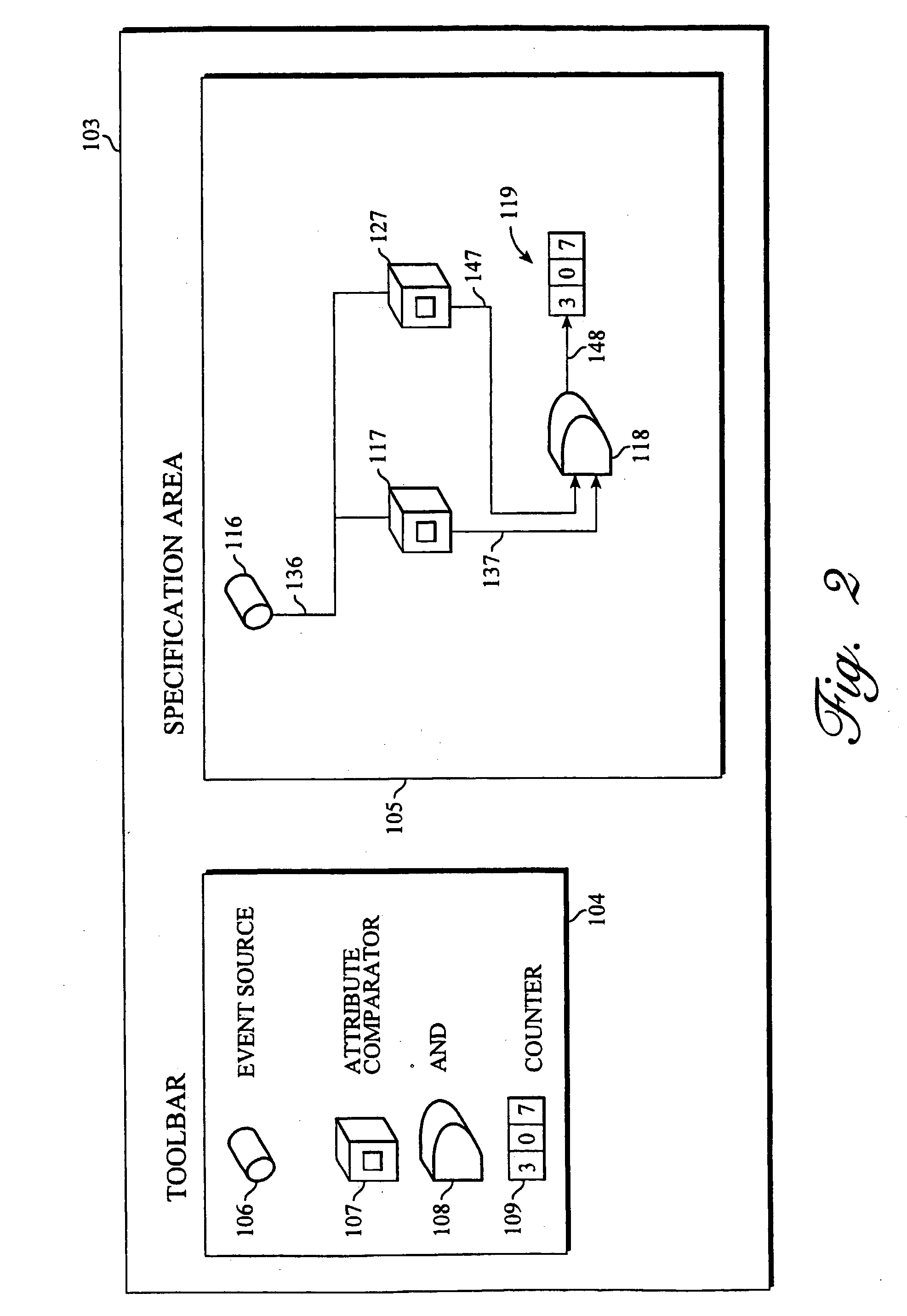

Functional coverage analysis systems and methods for verification test suites

Coverage metrics are expressed with an intuitive graphical interface based upon data flow. Coverage analysis and presentation objects are integrated to produce coverage results which enable device functionality in a device under test to be modeled as objects, subject to event occurrence. Event objects are introspected at run-time, allowing the user to determine the event object's attributes with specification of coverage metrics subject to a selected combination of the event object's attributes. The event objects are serialized into permanent storage, allowing the user to specify and execute new coverage metrics at any time after simulation. Operations used to describe coverage metrics are modeled as analysis objects. Such analysis objects accept event objects as inputs, using a predetermined, well-defined interface. The combination of event objects and analysis objects allows coverage metrics to be specified in a simple data flow manner. With such a coverage metric, the user attaches or wires (metaphorically) the analysis objects together in a visual builder environment. Using the analysis objects, the user specifies desired coverage metrics, such as coverage of sequences of events and / or coverage of events that occur during the same time window of a simulation. The display functionality of the coverage tool is expandable because the presentation objects use the same event object interface as the analysis operator objects. Coverage metrics are subject to specification either before or after event occurrence. The user specifies coverage metrics using an intuitive graphical interface based upon data flow, without any specific programming language skills being necessary. Functional events in the device under test are treated as event objects. Each event object may be passed to selected analysis tools chosen by the user, such as analyzers, logic gates, and coincidence counters.

Owner:CIRRUS LOGIC INC

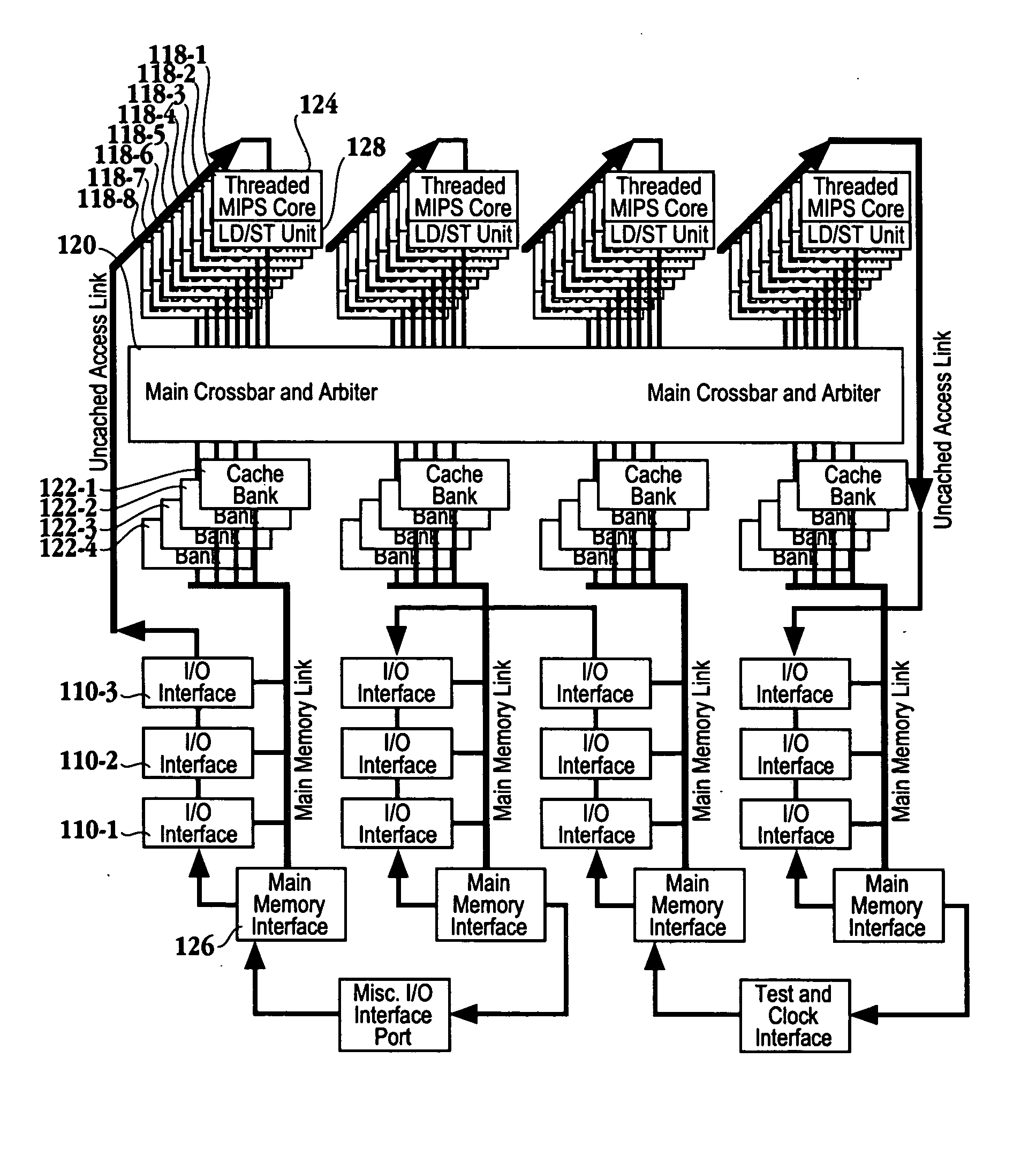

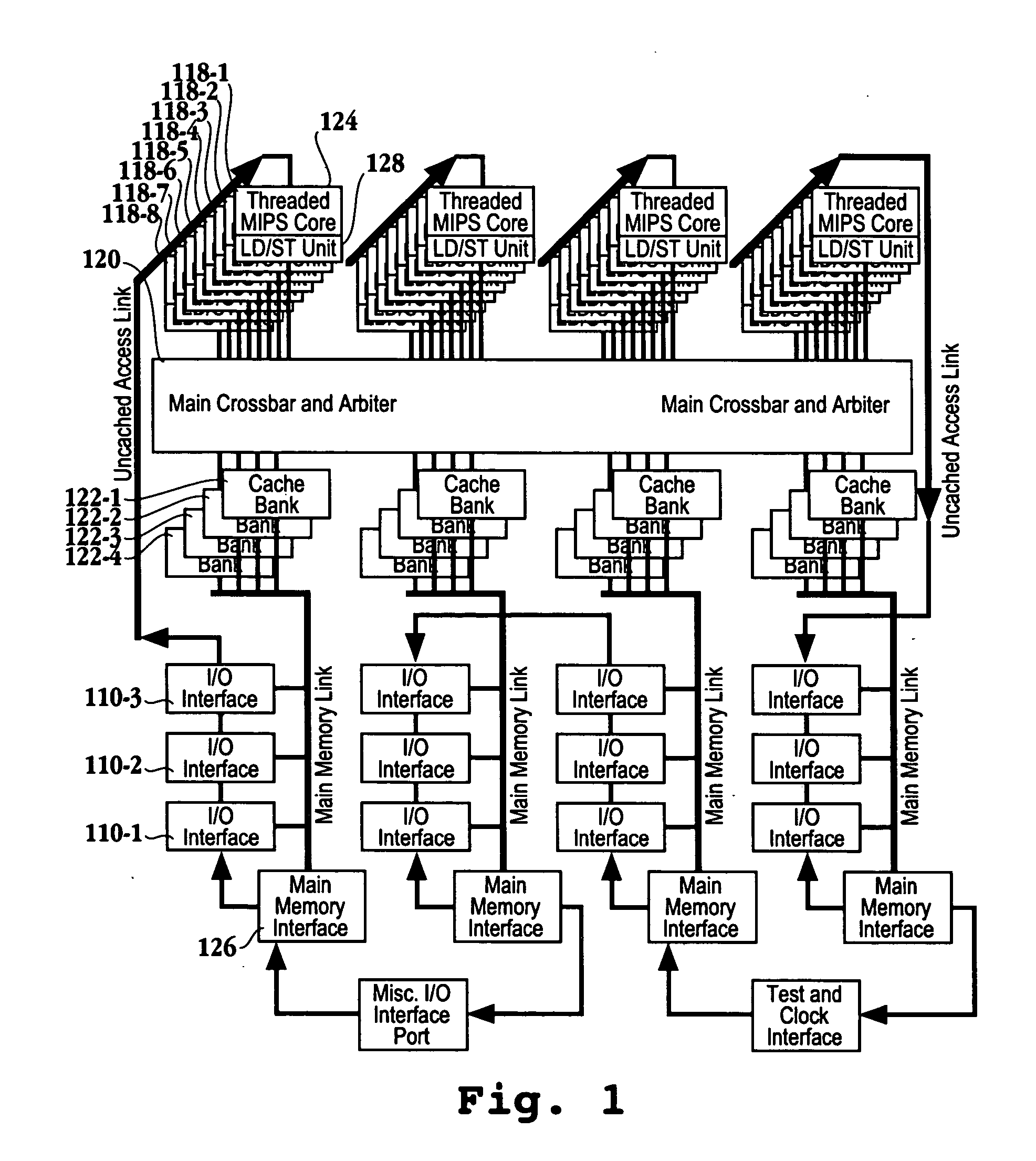

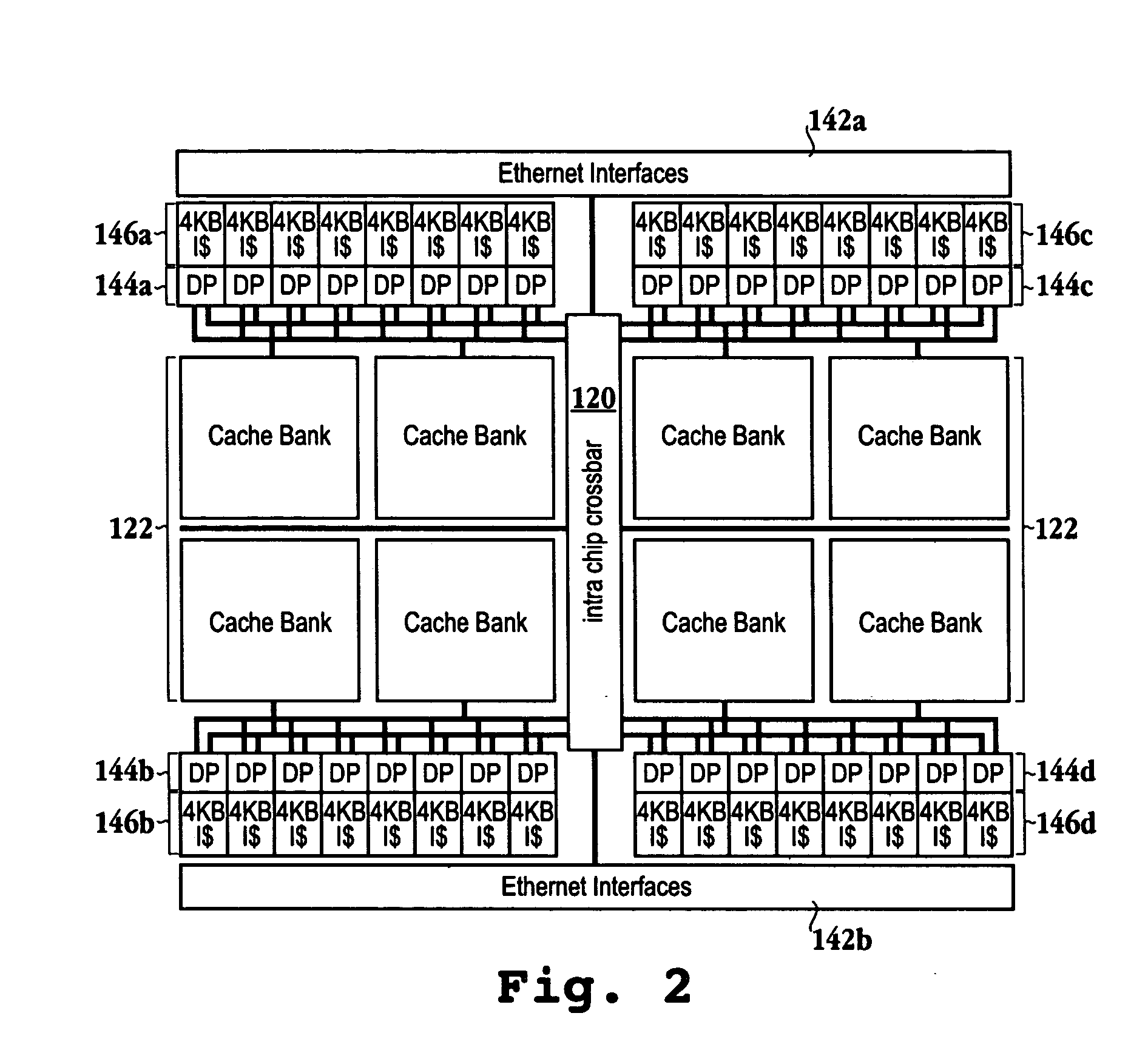

Cache crossbar arbitration

ActiveUS20050060457A1Efficient processingMemory adressing/allocation/relocationConcurrent instruction executionProcessing coreParallel computing

A processor chip is provided. The processor chip includes a plurality of processing cores, where each of the processing cores are multi-threaded. The plurality of processing cores are located in a center region of the processor chip. A plurality of cache bank memories are included. A crossbar enabling communication between the plurality of processing cores and the plurality of cache bank memories is provided. The crossbar includes an arbiter configured to arbitrate multiple requests received from the plurality of processing cores with available outputs. The arbiter includes a barrel shifter configured to rotate the multiple requests for dynamic prioritization, and priority encoders associated with each of the available outputs. Each of the priority encoders have logic gates configured to disable priority encoder outputs. A method for arbitrating requests within a multi-core multi-thread processor is included.

Owner:ORACLE INT CORP

Low power consumption MIS semiconductor device

InactiveUS7355455B2Total current dropSimple circuit configurationTransistorReliability increasing modificationsCurrent consumptionLogic gate

A logic gate is constructed of an insulated gate field effect transistor (MIS transistor) having a thin gate insulation film. An operation power supply line to the logic gate is provided with an MIS transistor having a thick gate insulation film for switching the supply and stop of an operation power source voltage. A voltage of the gate of the power source switching transistor is made changing in an amplitude greater than an amplitude of an input and an output signal to the logic gate. Current consumption in a semiconductor device configured of MIS transistor of a thin gate insulation film can be reduced and an power source voltage thereof can be stabilized.

Owner:RENESAS ELECTRONICS CORP

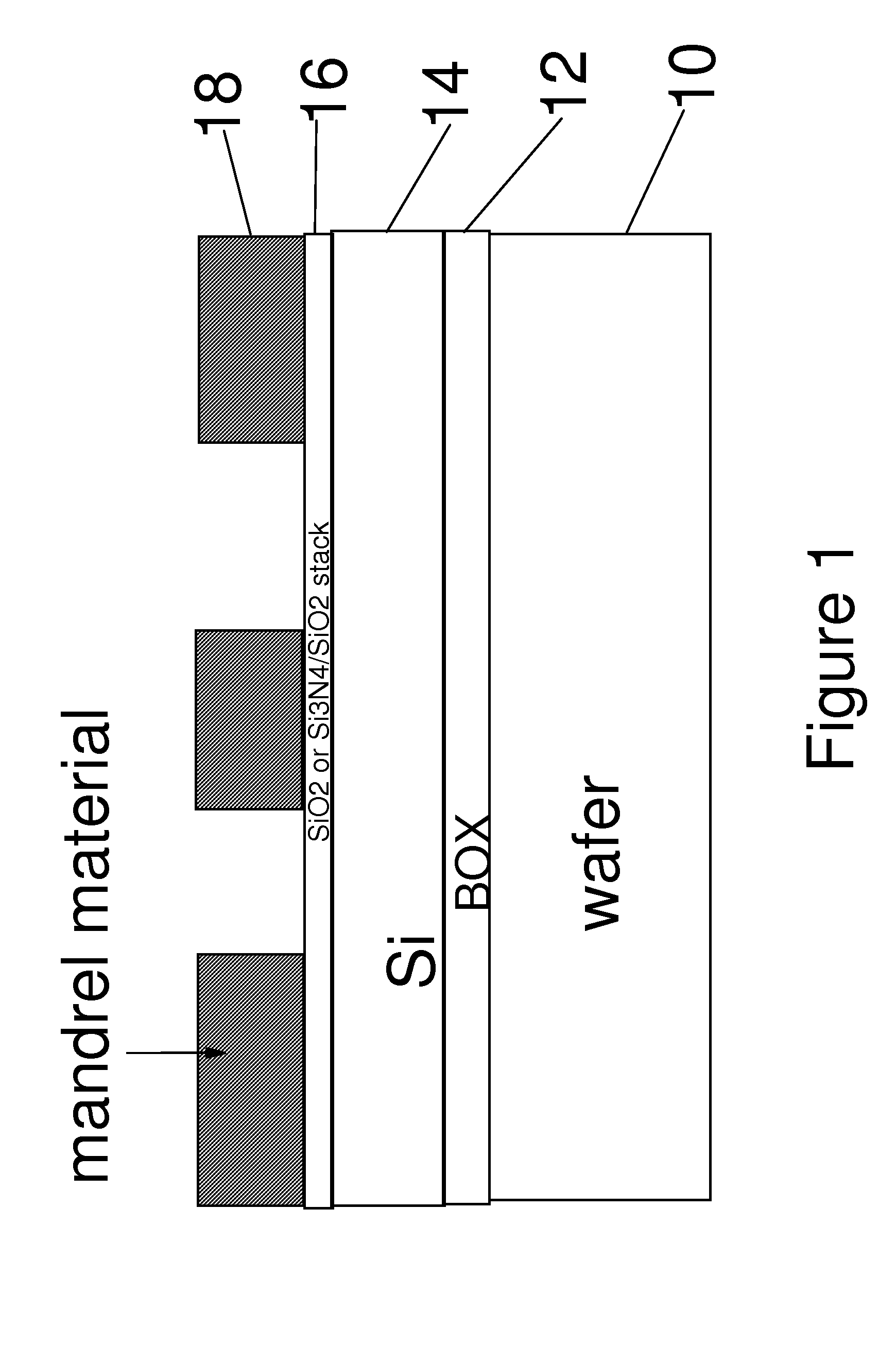

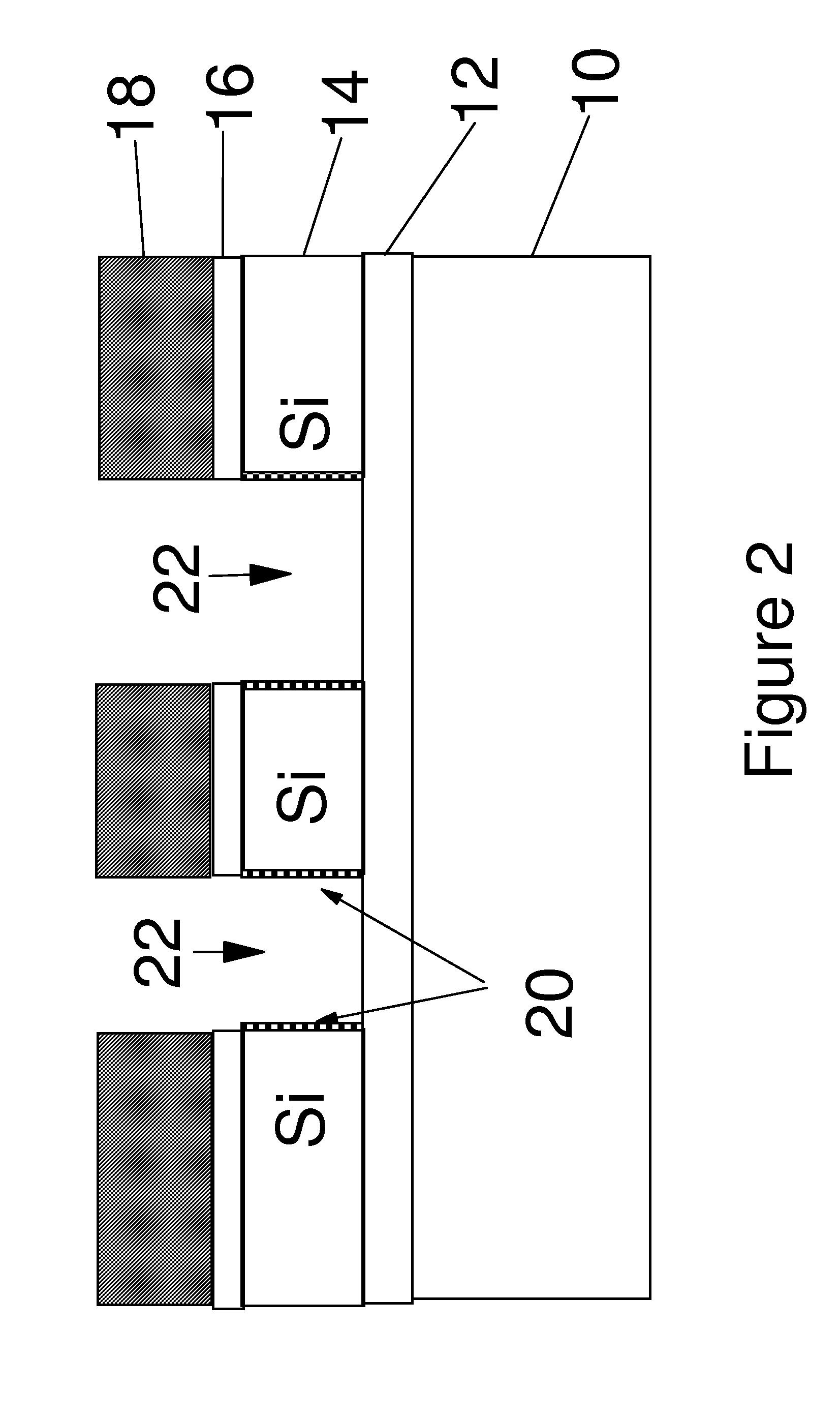

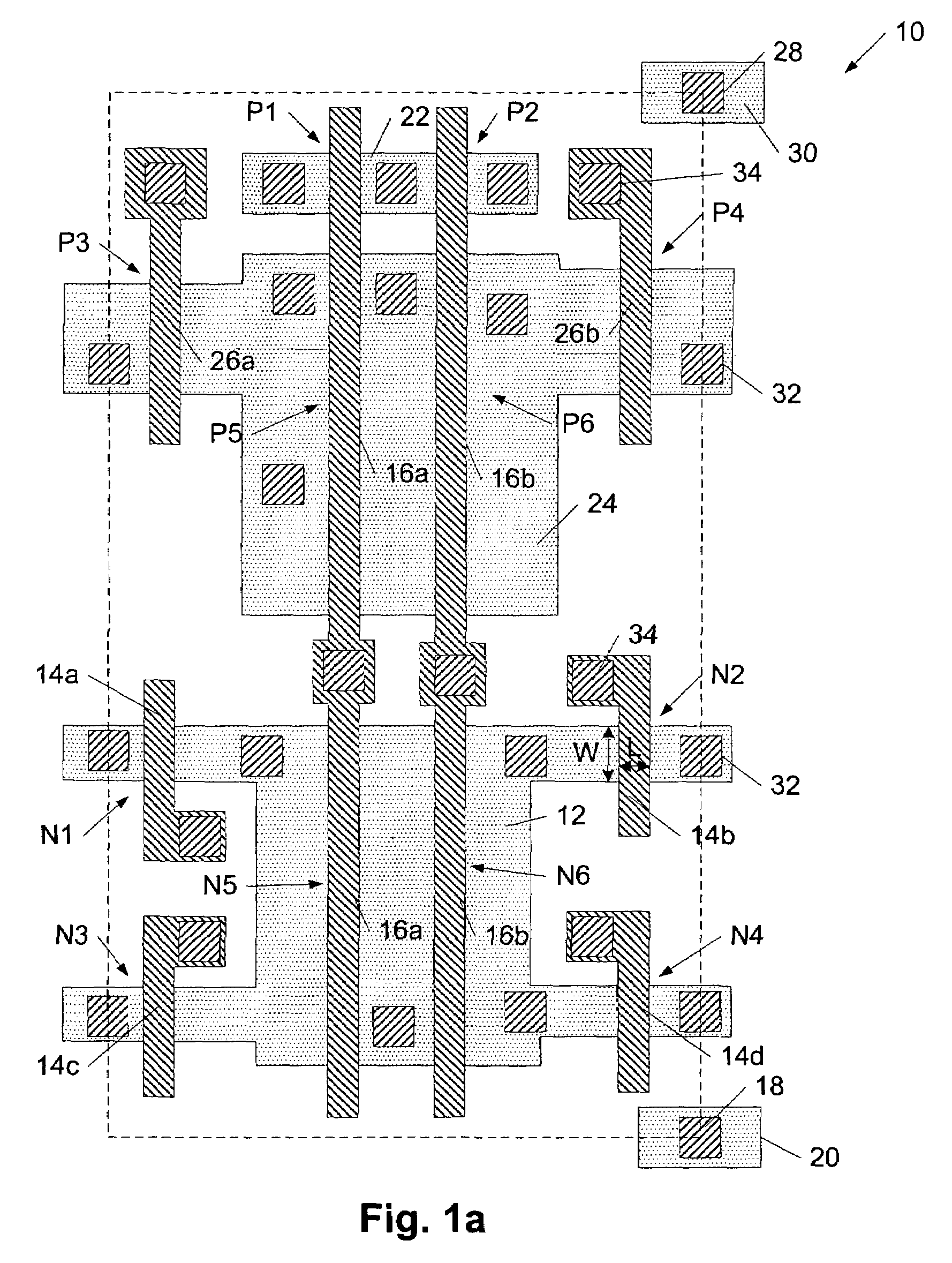

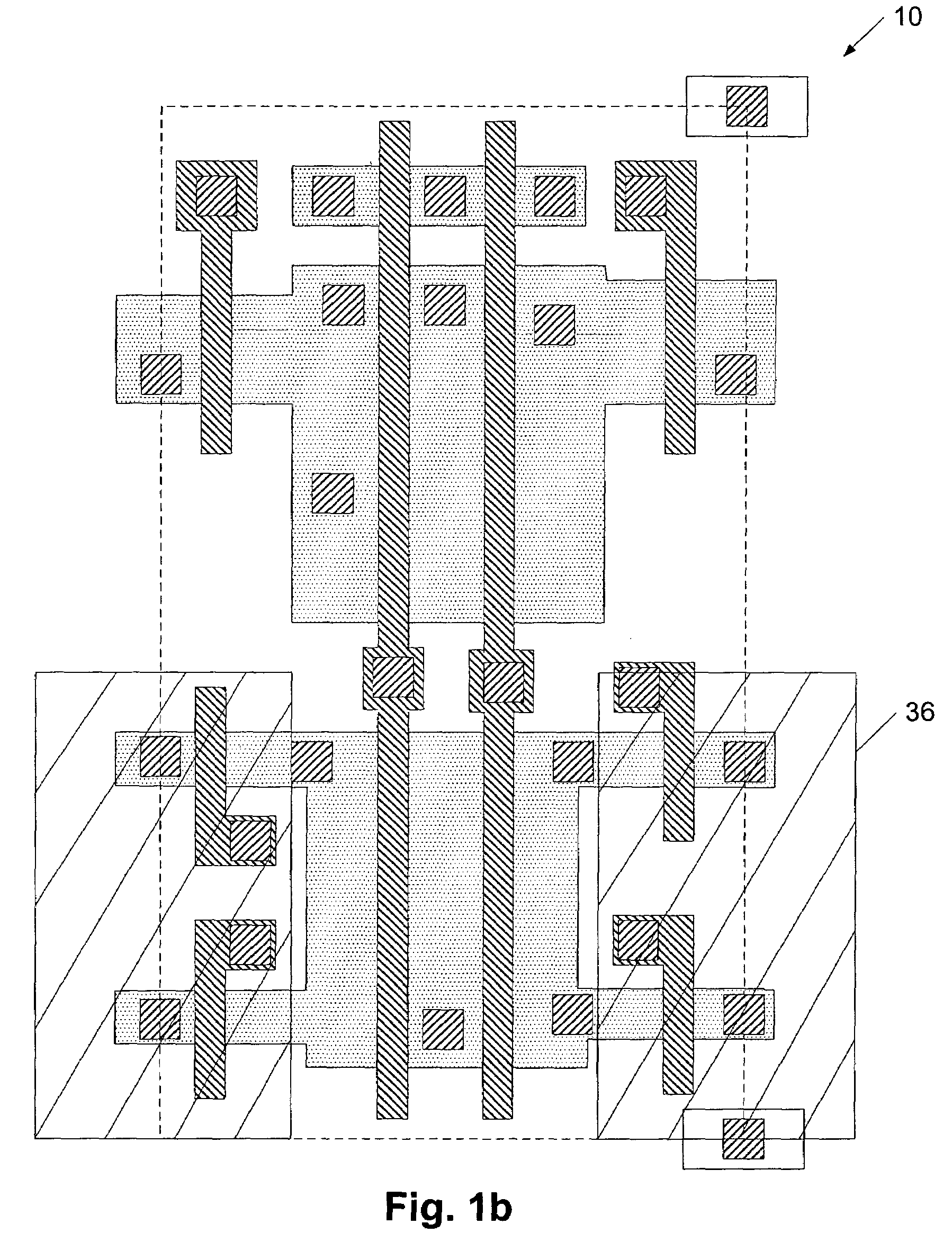

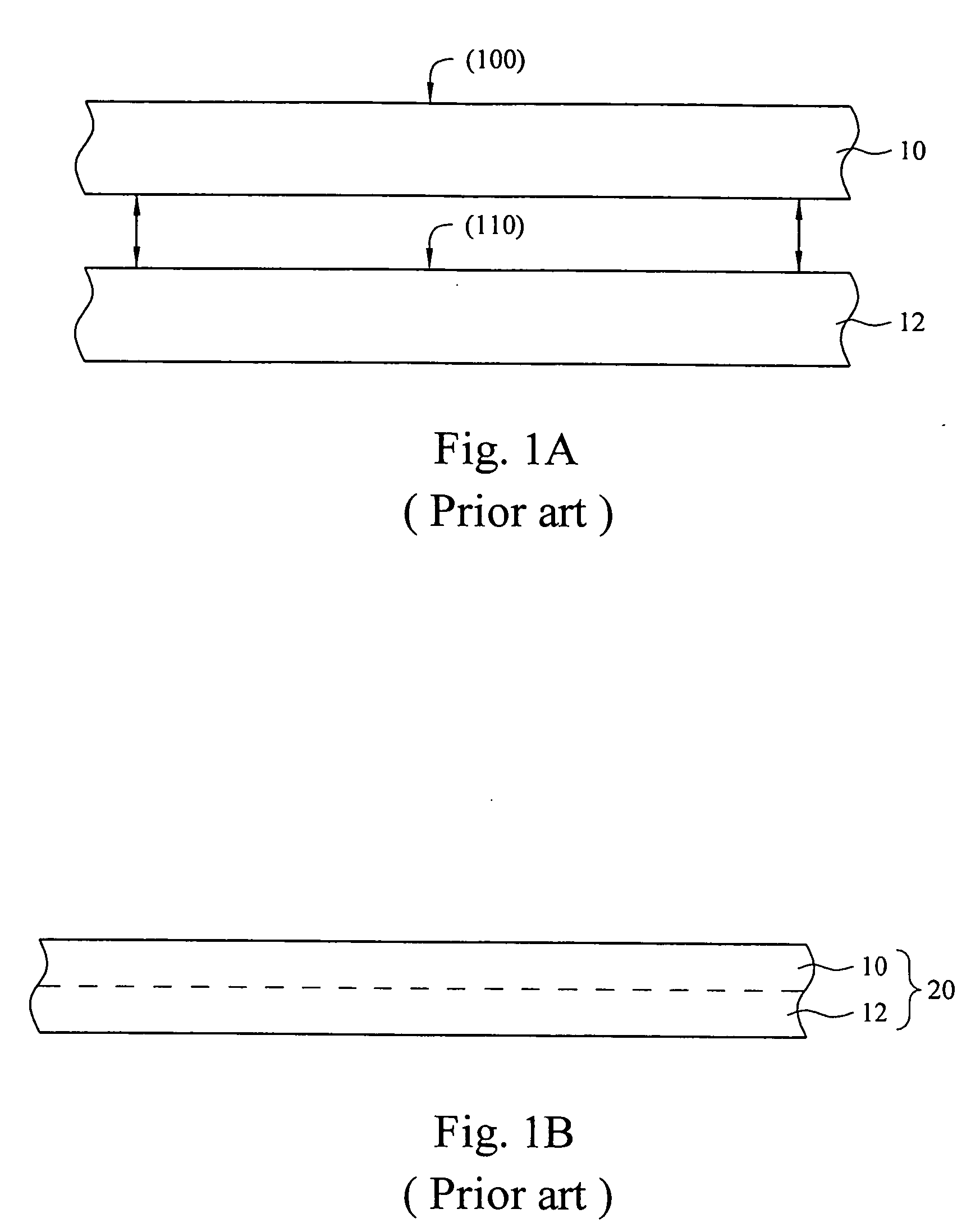

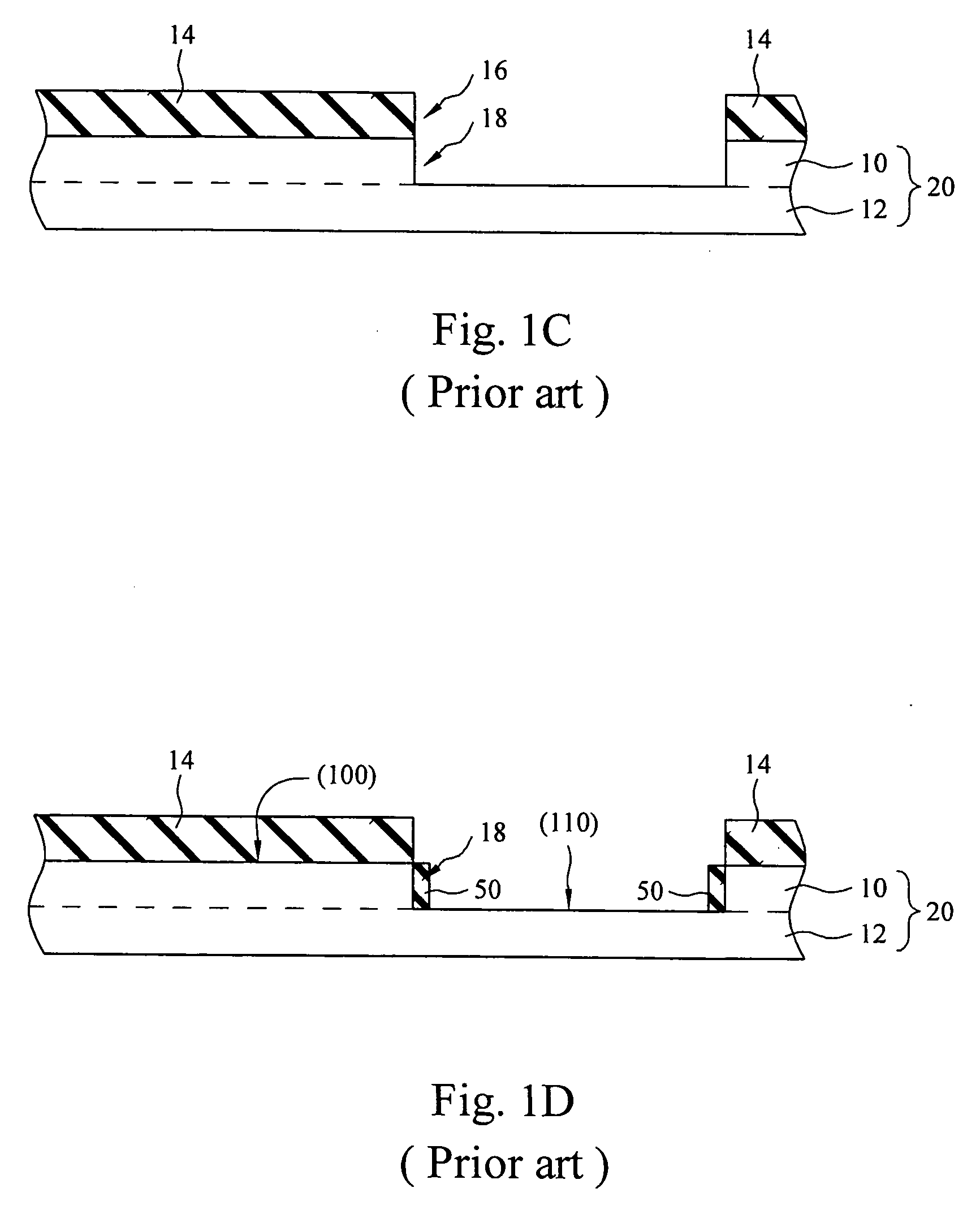

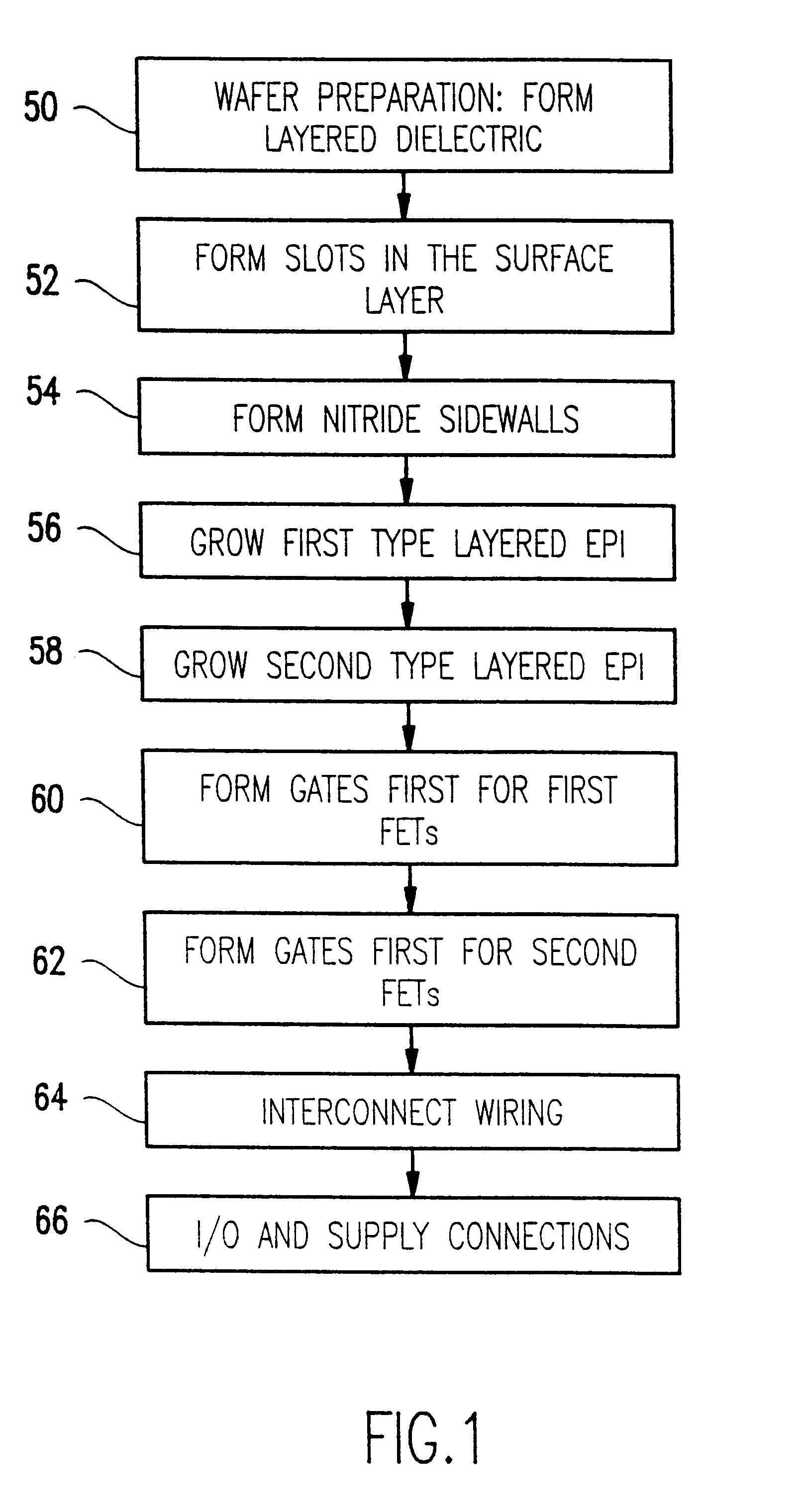

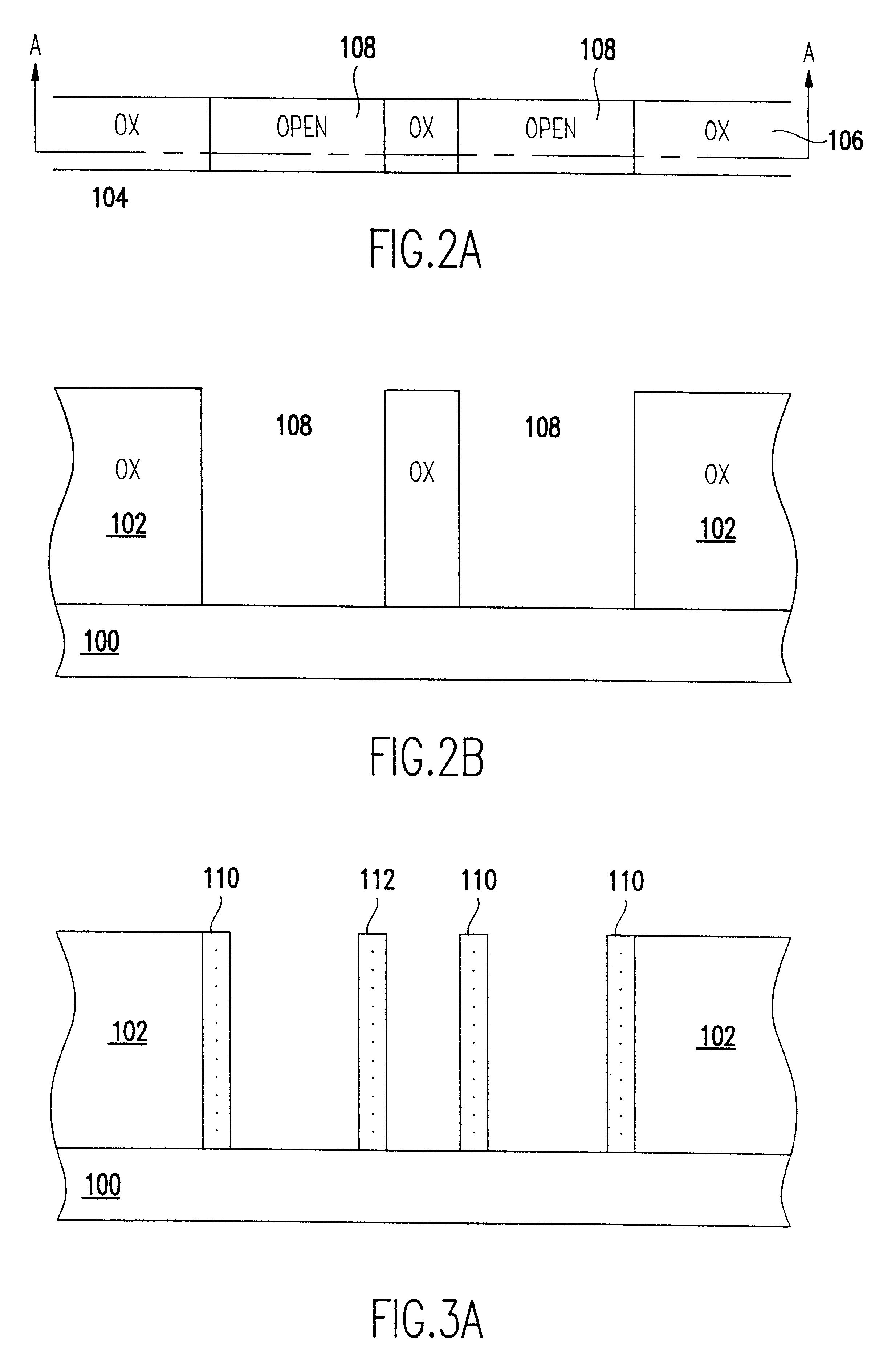

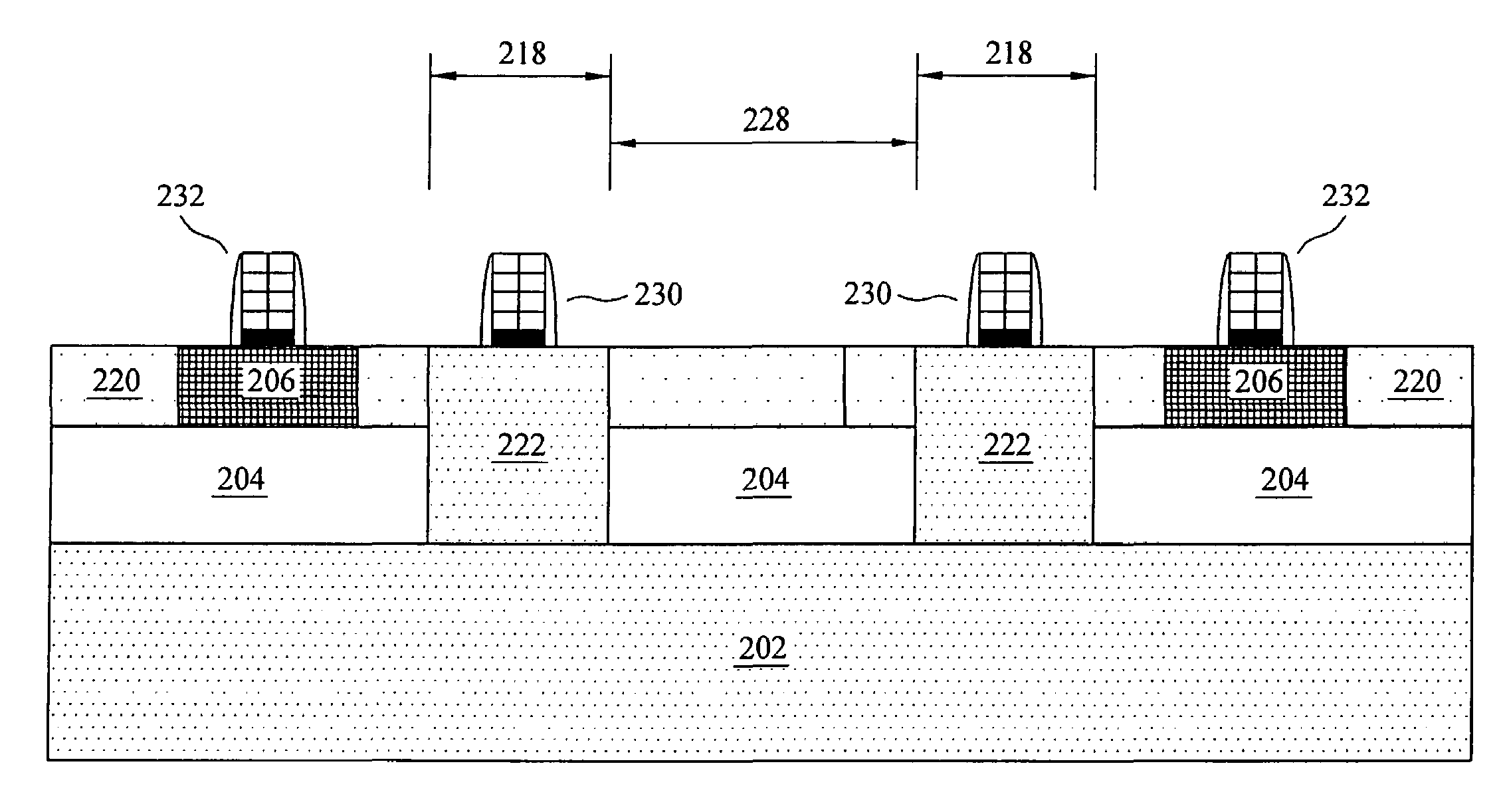

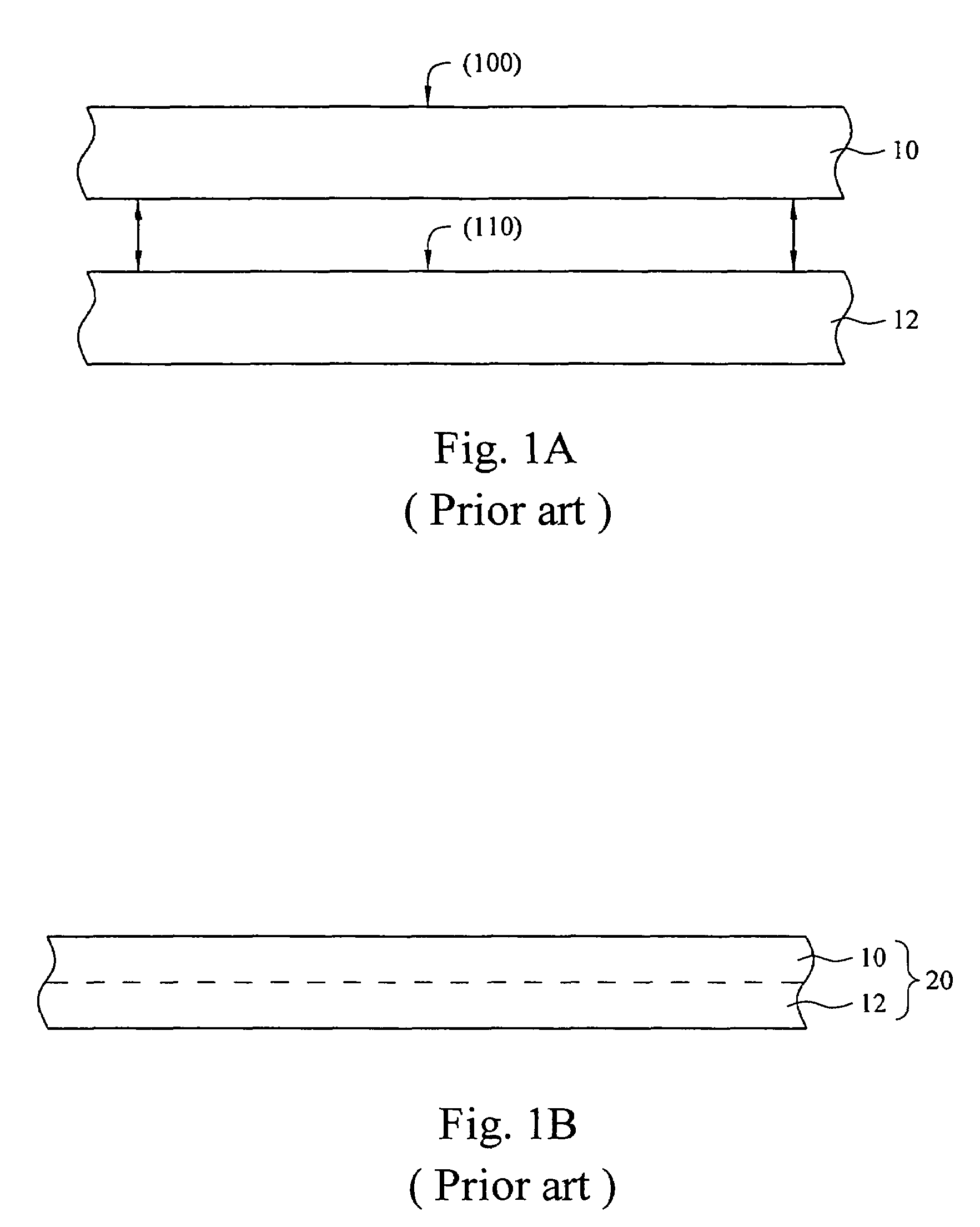

CMOS logic gate fabricated on hybrid crystal orientations and method of forming thereof

ActiveUS20060049460A1Harmful effectHarmful microloading effects are avoidedTransistorSolid-state devicesCMOSCrystal orientation

In preferred embodiments of the present invention, a method of forming CMOS devices using SOI and hybrid substrate orientations is described. In accordance with a preferred embodiment, a substrate may have multiple crystal orientations. One logic gate in the substrate may comprise at least one N-FET on one crystal orientation and at least one P-FET on another crystal orientation. Another logic gate in the substrate may comprise at least one N-FET and at least one P-FET on the same orientation. Alternative embodiments further include determining the preferred cleavage planes of the substrates and orienting the substrates relative to each other in view of their respective preferred cleavage planes. In a preferred embodiment, the cleavage planes are not parallel.

Owner:TAIWAN SEMICON MFG CO LTD

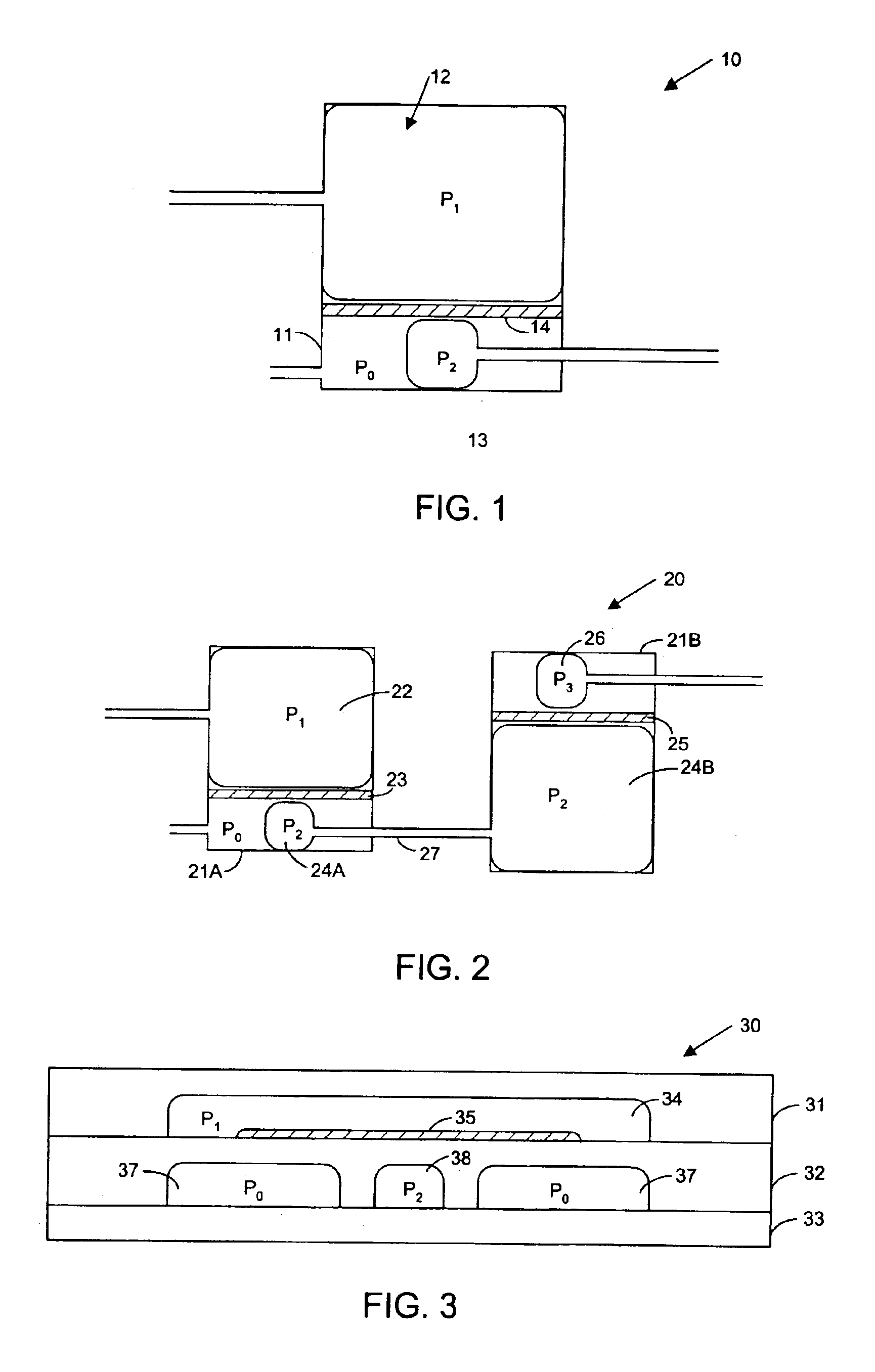

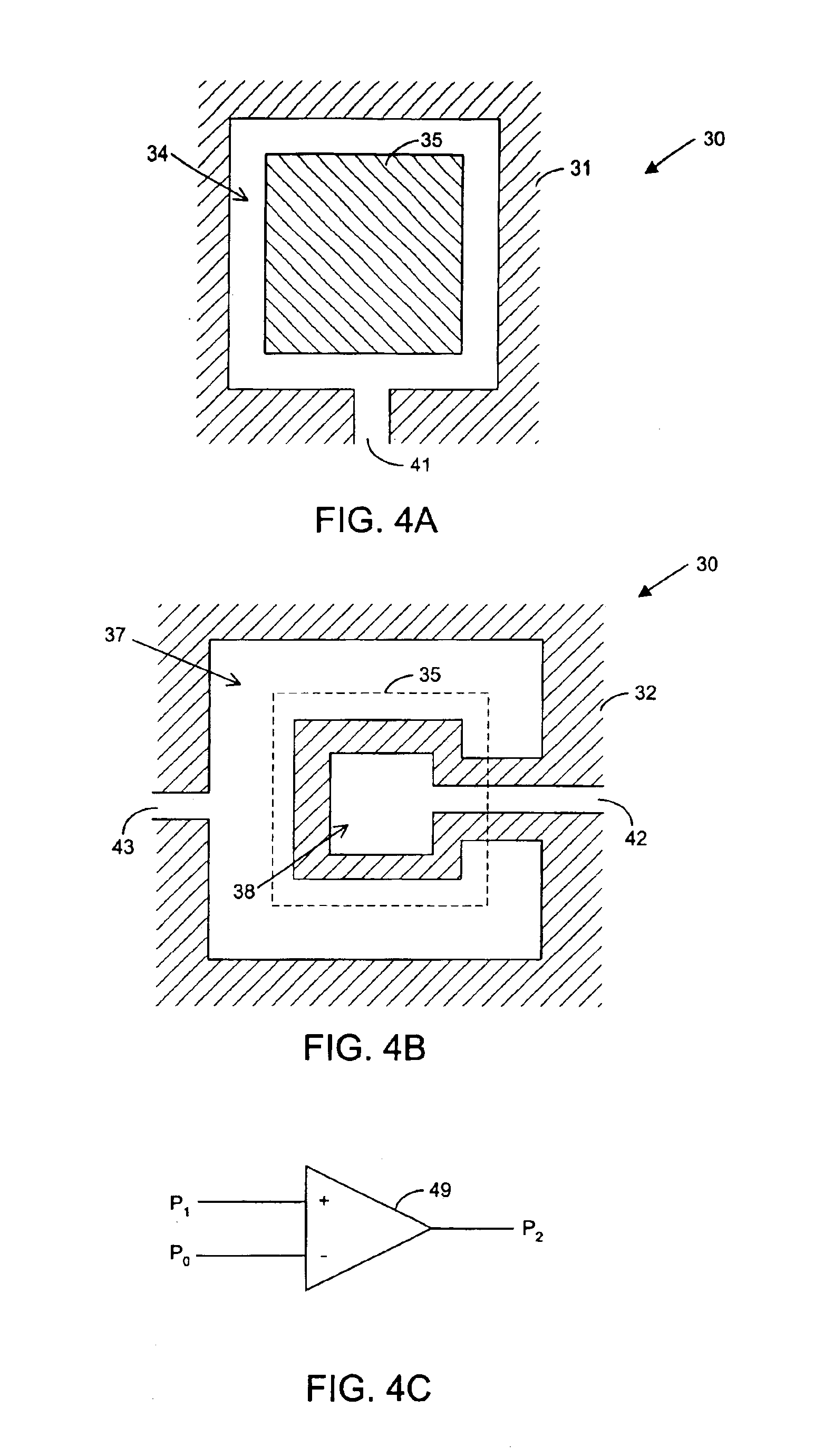

Microfabricated fluidic circuit elements and applications

InactiveUS6953058B2Macroscopic control lines exiting the chip are minimized or eliminatedGeometric CADOperating means/releasing devices for valvesFluidicsNOR gate

The present invention provides microfabricated fluidic systems and methods. Microfabricated fluidic devices of the present invention include switches that can be opened and closed to allow or block the flow of fluid through a channel in response to the pressure level in a gate of the switch. The microfabricated fluidic switches may be coupled together to perform logic functions and Boolean algebra, such as inverters, AND gates, NAND, gates, NOR gates, and OR gates. The logic gates may be coupled together to form flip-flops that latch signals. The present invention also includes microfabricated fluidic pressure multipliers that increase the pressure in a second chamber relative to a first chamber. Microfabricated fluidic devices of the present invention also include pressure sources. A pressure source of the present includes a pump coupled to a reservoir through unidirectional valves. The pressure source may be high pressure source or a low pressure source. Microfabricated fluidic devices of the present invention may also include devices that perform analog functions such as switching regulator.

Owner:FLUIDIGM CORP

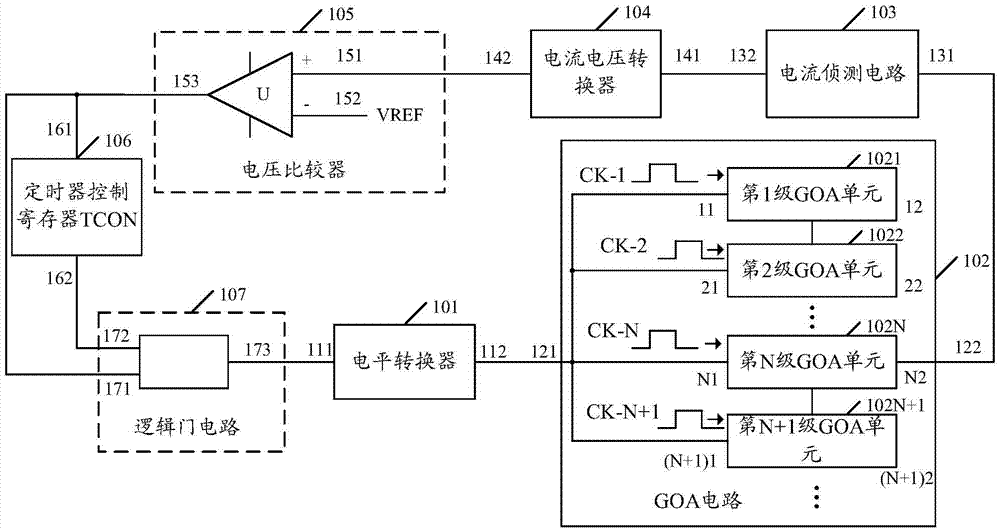

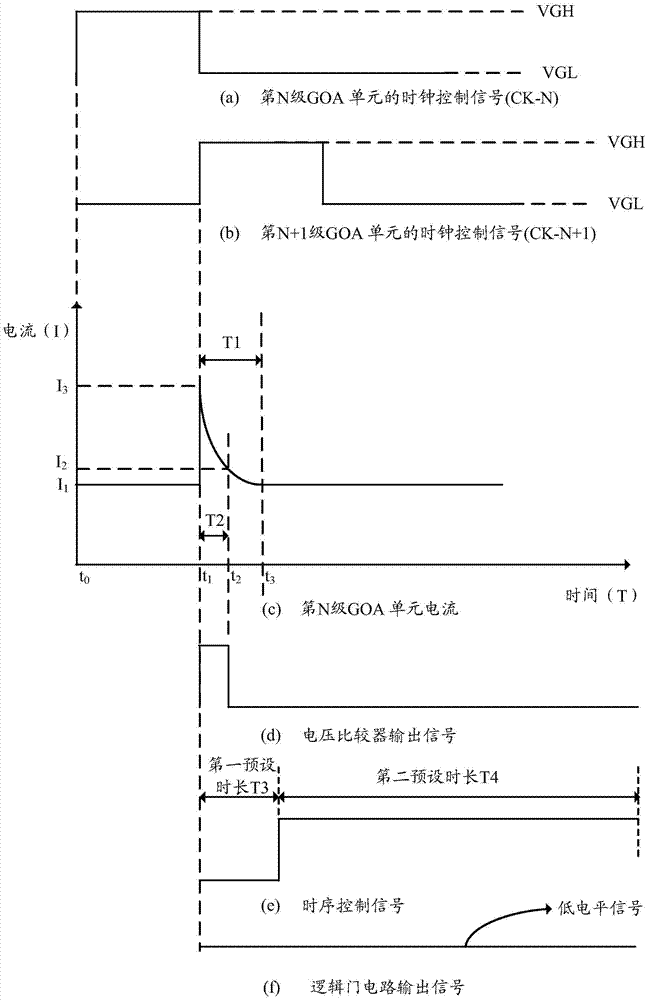

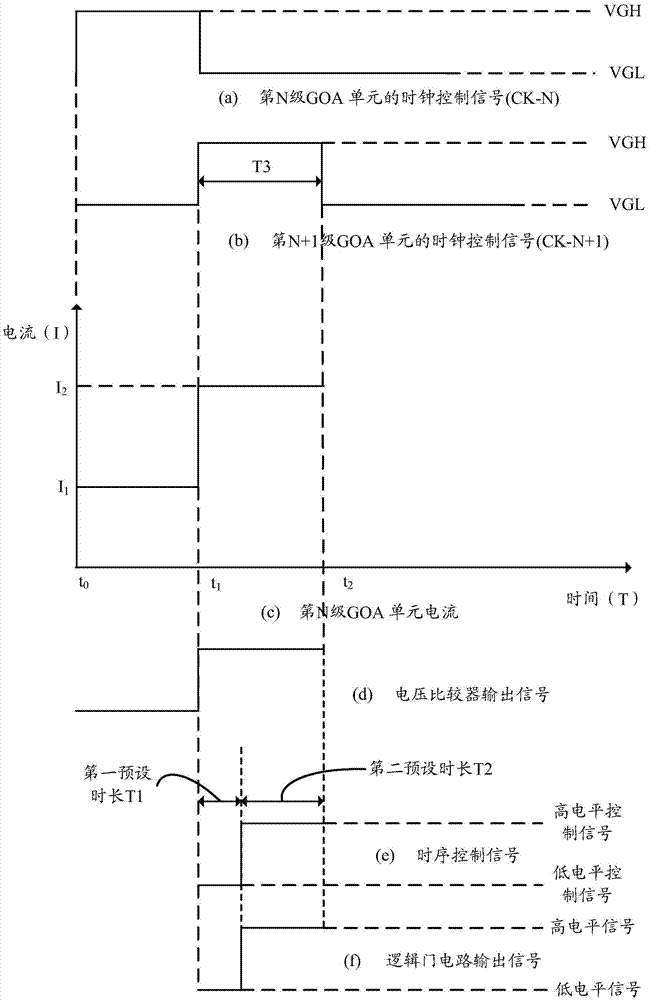

Overcurrent protection circuit and liquid crystal display

The embodiment of the invention discloses an overcurrent protection circuit, and the circuit comprises a level converter and a substrate array line drive (GOA) circuit in electrical connection with the level converter. The circuit also comprises a current detection circuit, a current-voltage converter, a voltage comparator, a timer control register, and a logic gate circuit. The GOA circuit is connected with the current detection circuit, and the current detection circuit is connected with the current-voltage converter. The current-voltage converter is connected with the in-phase input end of the voltage comparator, and the inverted-phase input end of the voltage comparator is connected with a reference voltage. The output end of the voltage comparator is connected with the input end of the timer control register and the first input end of the logic gate circuit. The output end of the timer control register is connected with the second input end of the logic gate circuit. The output end of the logic gate circuit is connected with the level converter. According to the embodiment of the invention, the circuit can prevent the wrong triggering of an overcurrent protection operation. The invention also provides a liquid crystal display comprising the circuit.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

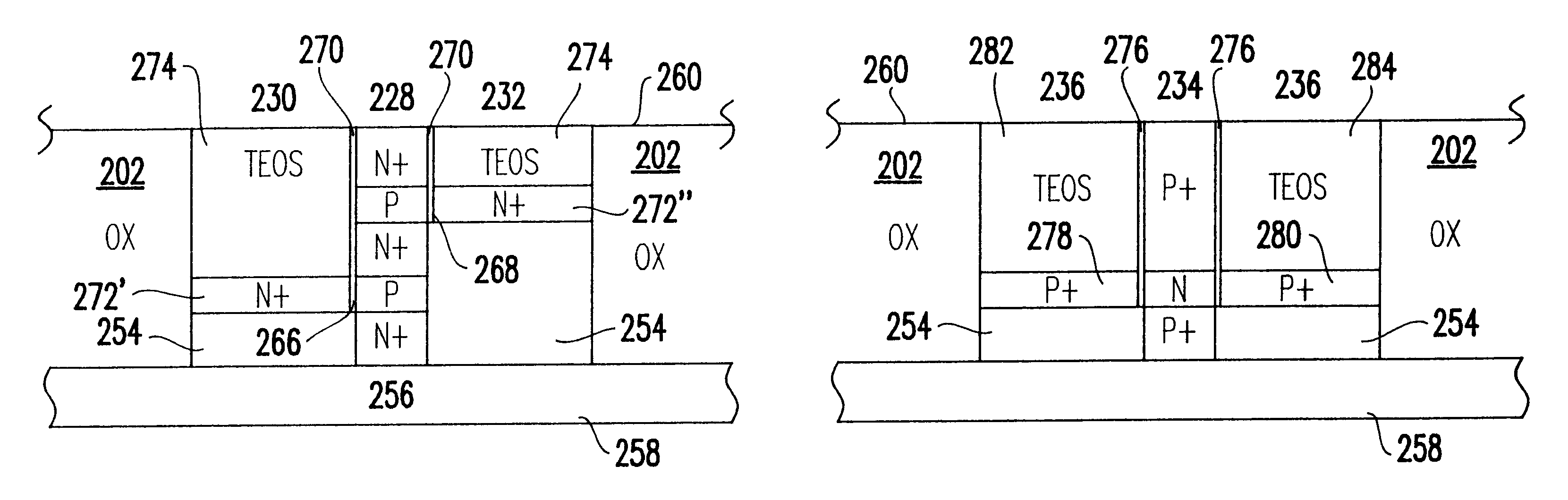

High performance, low power vertical integrated CMOS devices

InactiveUS6297531B2Solid-state devicesSemiconductor/solid-state device manufacturingHigh resistanceCapacitance

Owner:INT BUSINESS MASCH CORP

Near-instantaneous responsive closed loop control electrosurgical generator and method

ActiveUS20080082095A1Quick and accurate adjustmentFast response timeSurgical instruments for heatingPower flowControl system

An electrosurgical generator has a control system formed by an array of logic gates programmed to execute mathematical algorithms for regulating at least one parameter of output power, output voltage or output current of an output electrosurgical signal in a closed loop response to sensed values of the output voltage and the output current.

Owner:CONMED CORP +1

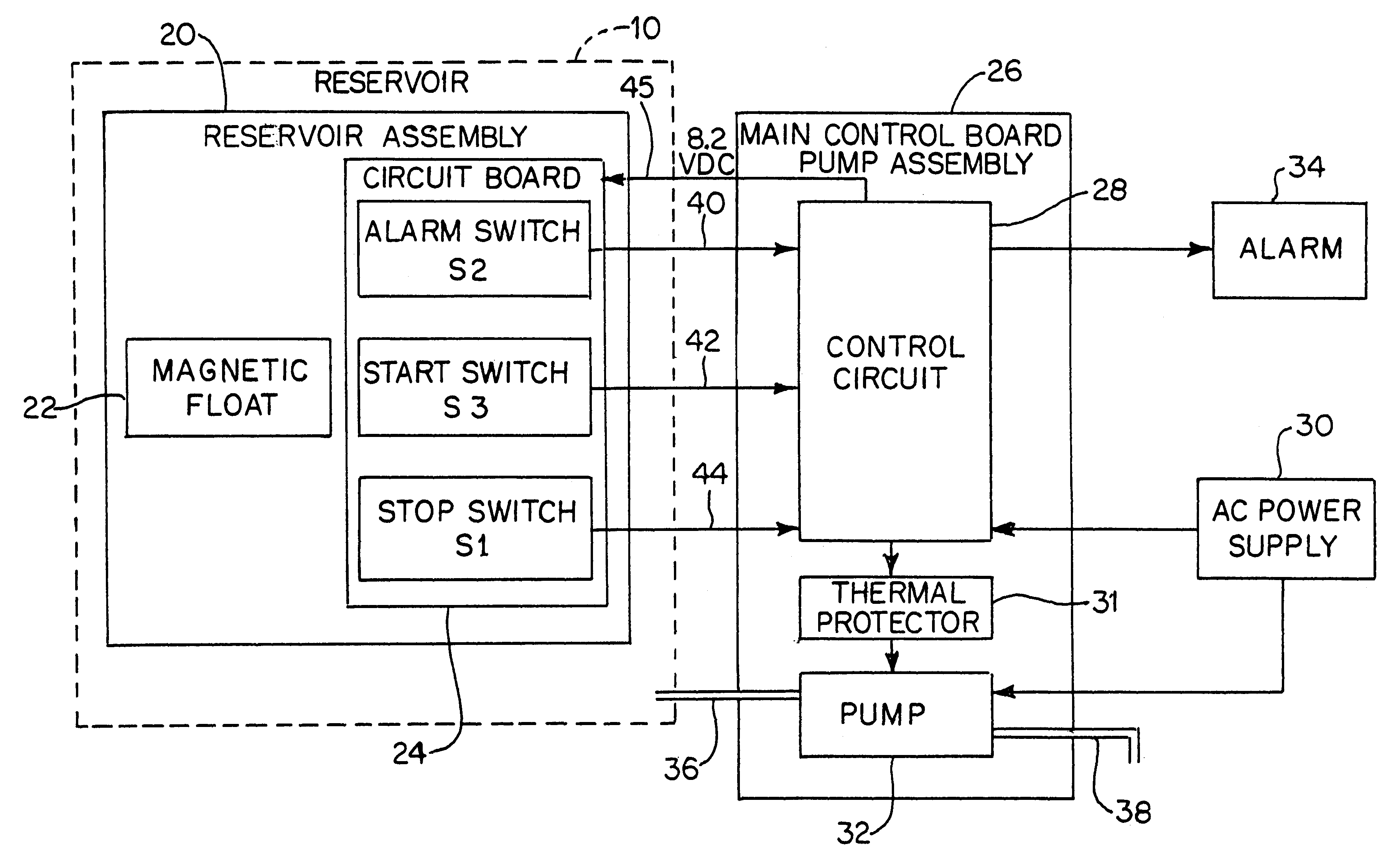

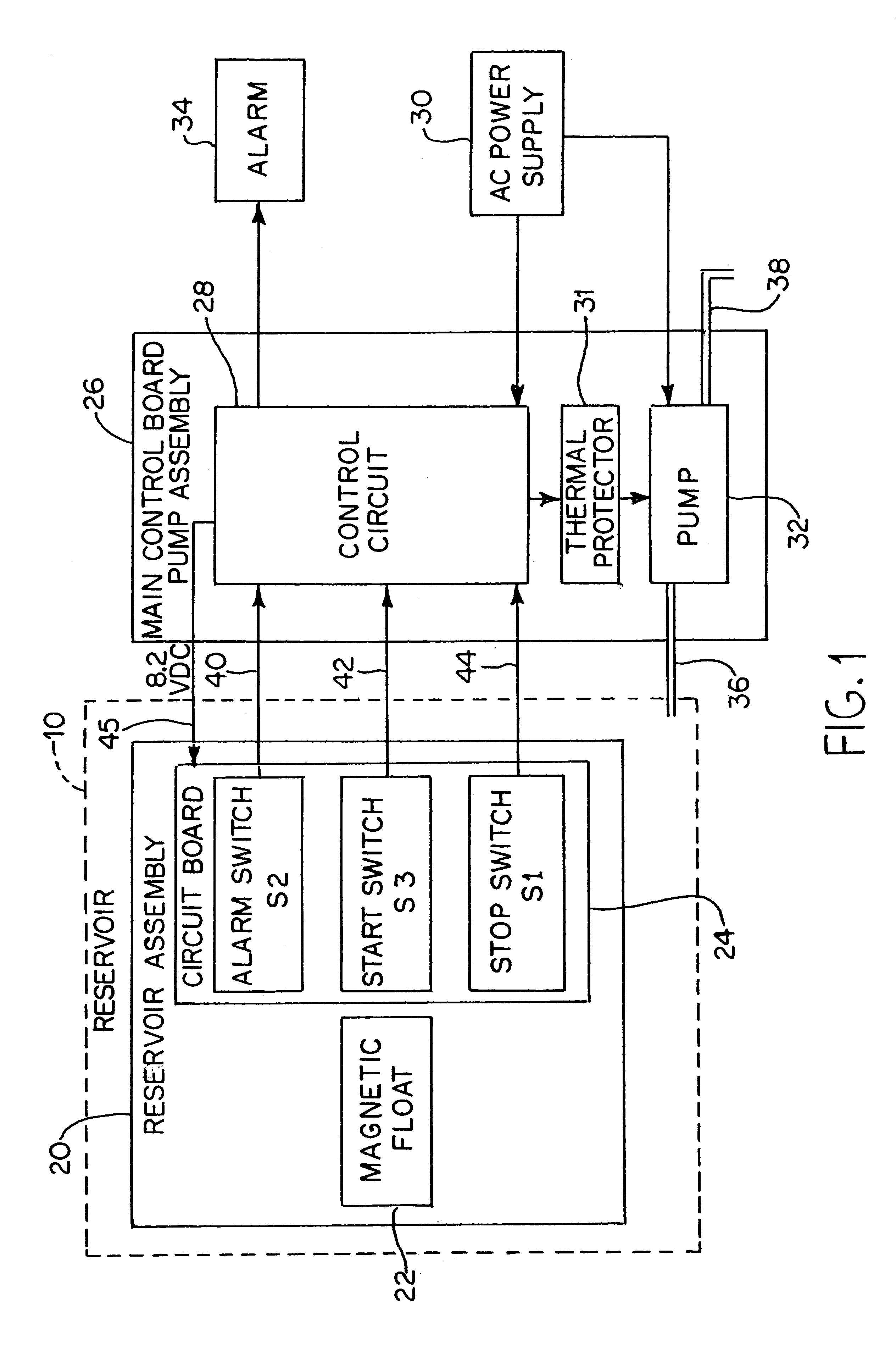

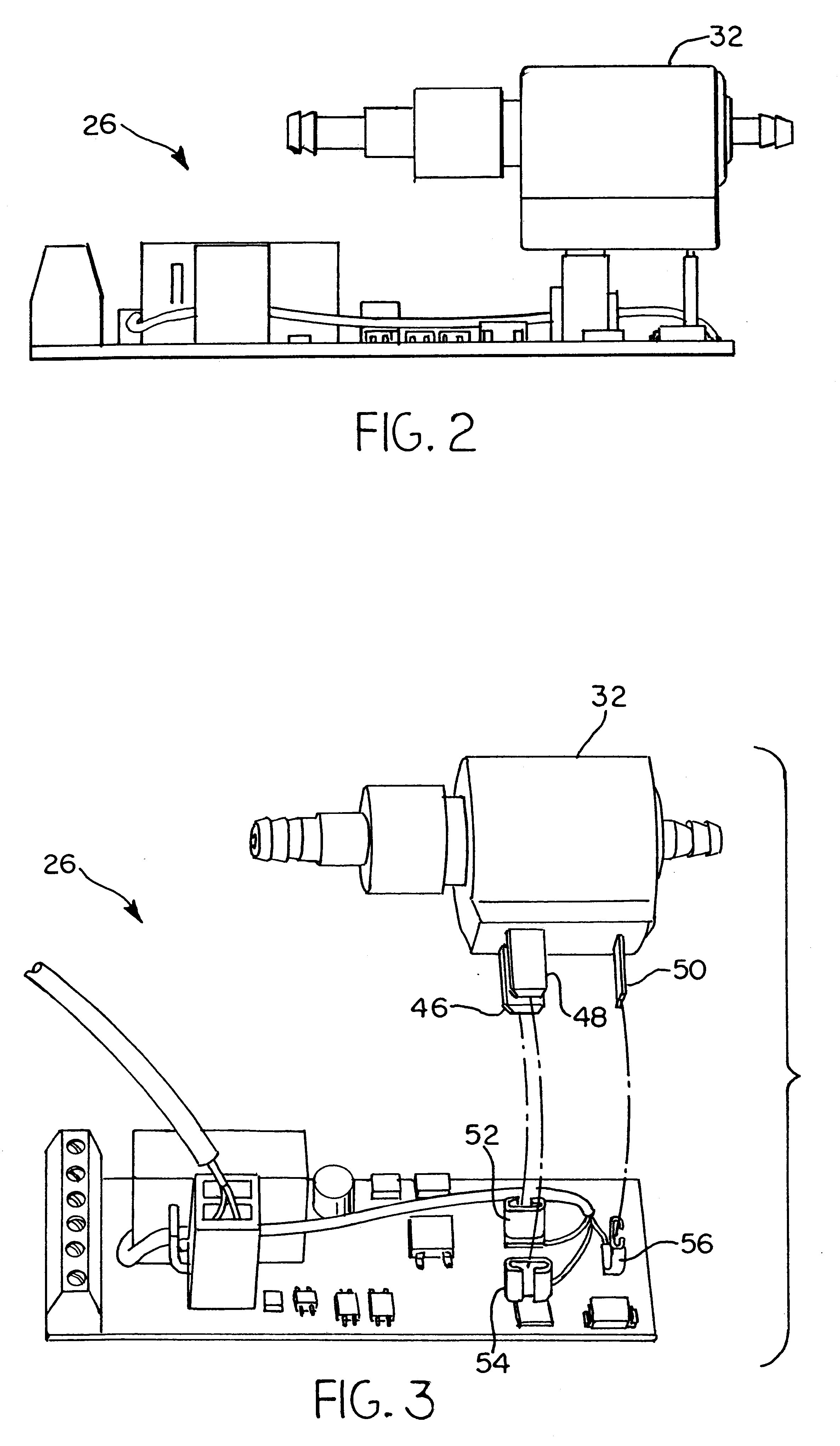

Solid state liquid level sensor and pump controller

A liquid level controller for a device having a liquid reservoir includes a control board and a reservoir assembly. The reservoir assembly is disposed within the reservoir and includes a liquid level sensor, which is electrically connected to the control circuit. The control board includes a control circuit and a pump. The control circuit has a control circuit and a resistive power supply to power the control circuit. The control circuit controls the pump in response to signals from the level sensor and includes a CMOS logic gate and a MOSFET transistor to switch the pump. The control circuit further includes a second resistive power supply connected to a relay which controls an alarm. The second power supply is activated by a transistor responsive to an alarm signal from the level sensor, and powers the relay only when the alarm signal is present.

Owner:TECUMSEH PROD CO

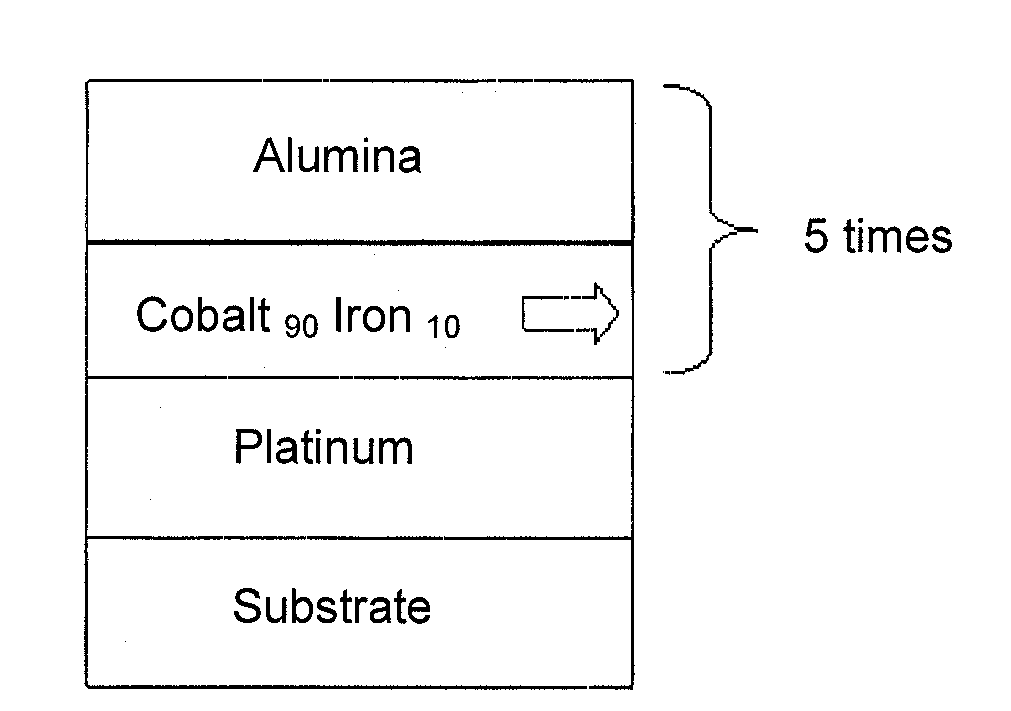

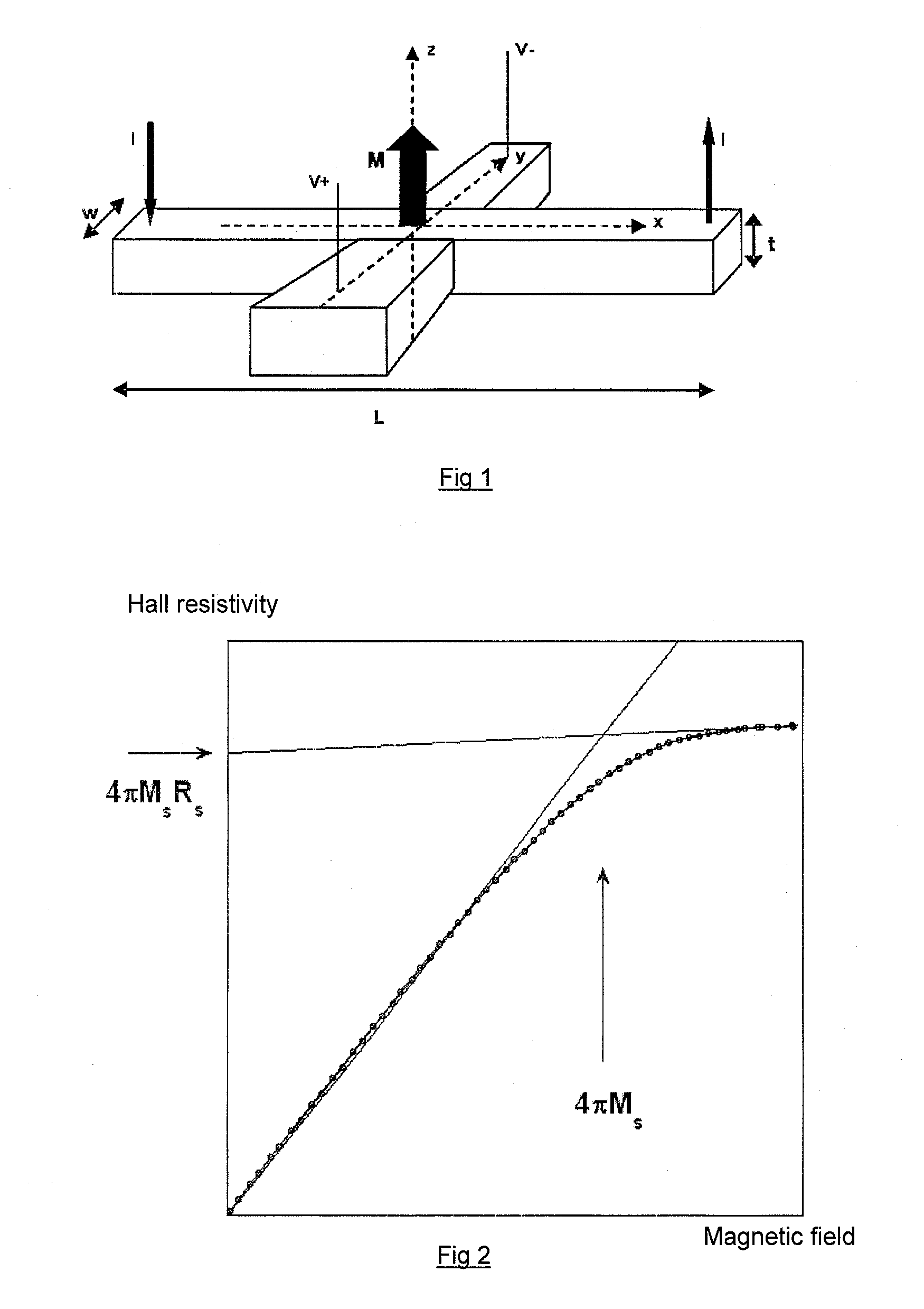

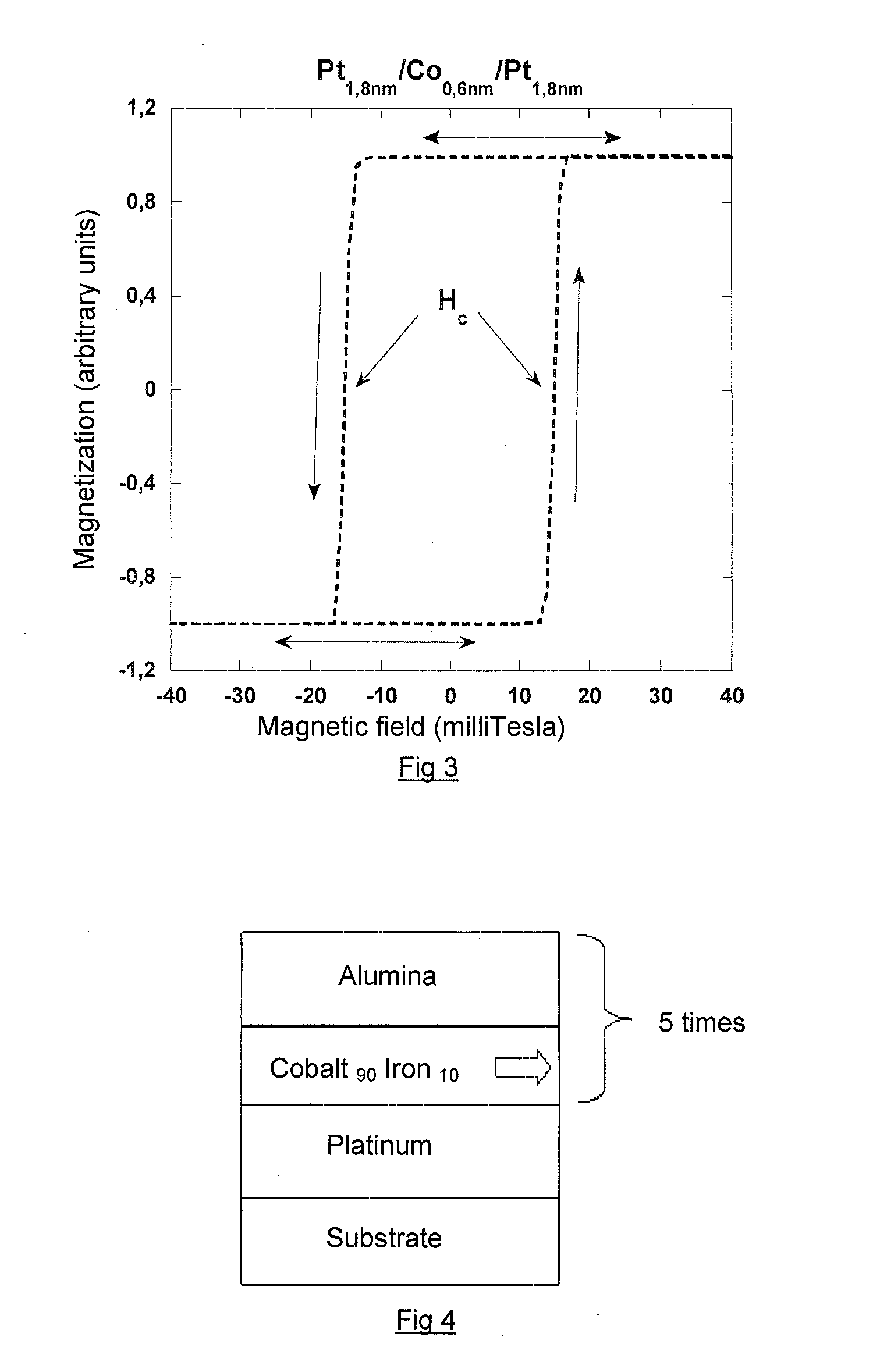

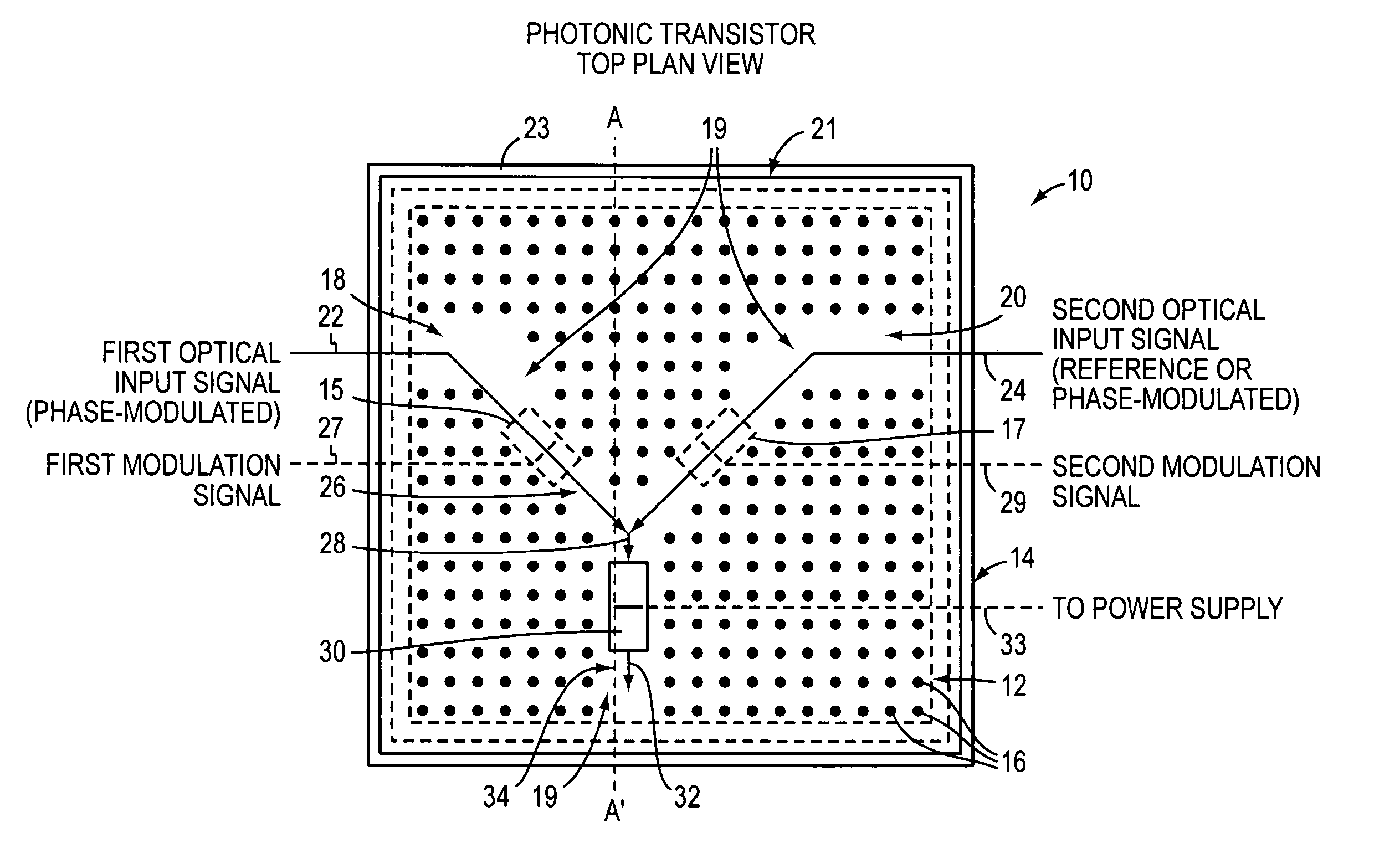

Magnetic multilayer device, method for producing such a device, magnetic field sensor, magnetic memory and logic gate using such a device

ActiveUS20080151615A1High perpendicular anisotropyHigh resistivityNanostructure applicationNanomagnetismMagnetic anisotropyMagnetic memory

This magnetic multilayer device comprises, on a substrate, an alternating sequence of magnetic metallic layers M and oxide, hydride or nitride layers O. The number of layers M equals at least two. The layers M are continuous. There is interfacial magnetic anisotropy perpendicular to the plane of the layers at the level of the M / O interfaces.

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES +1

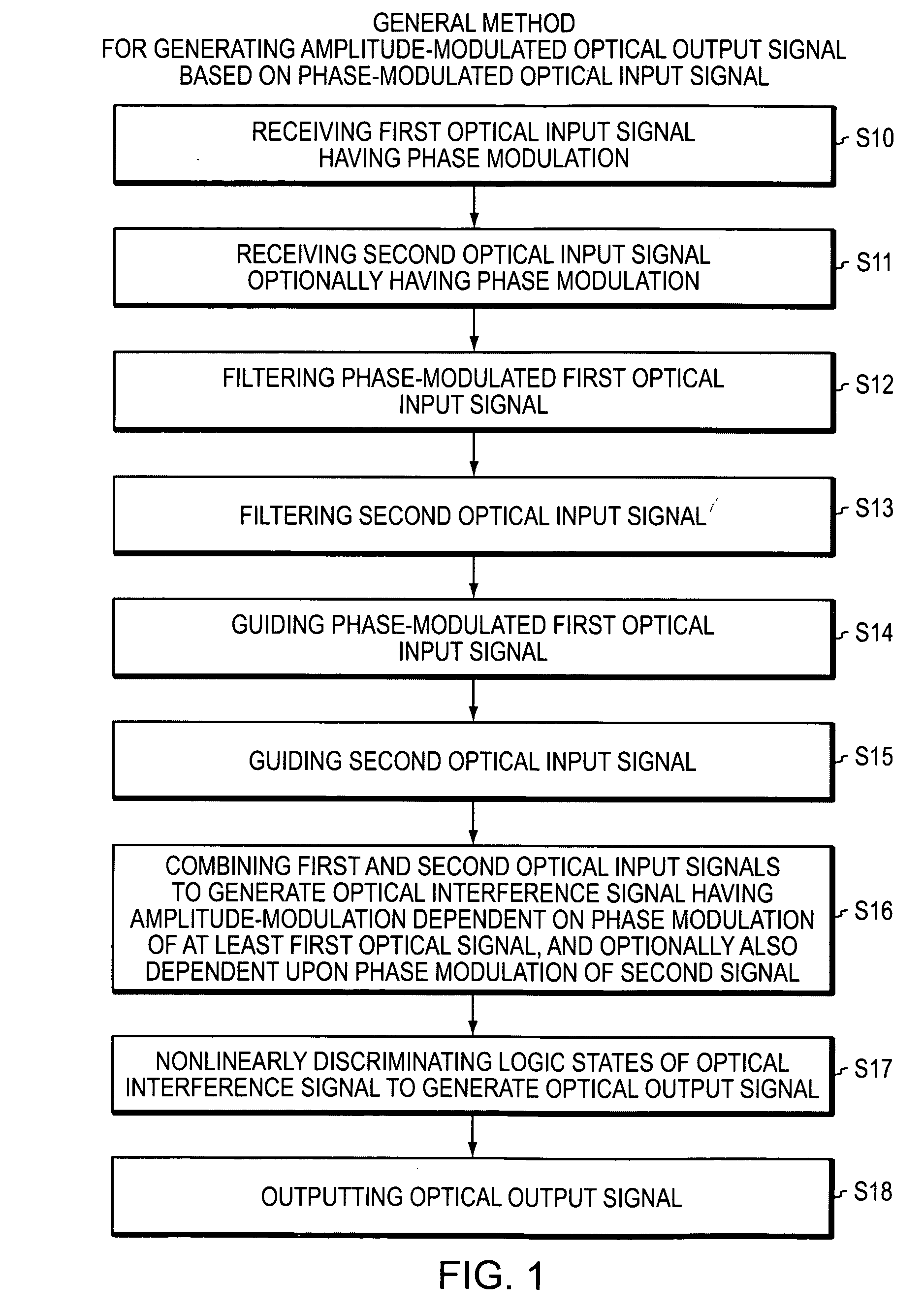

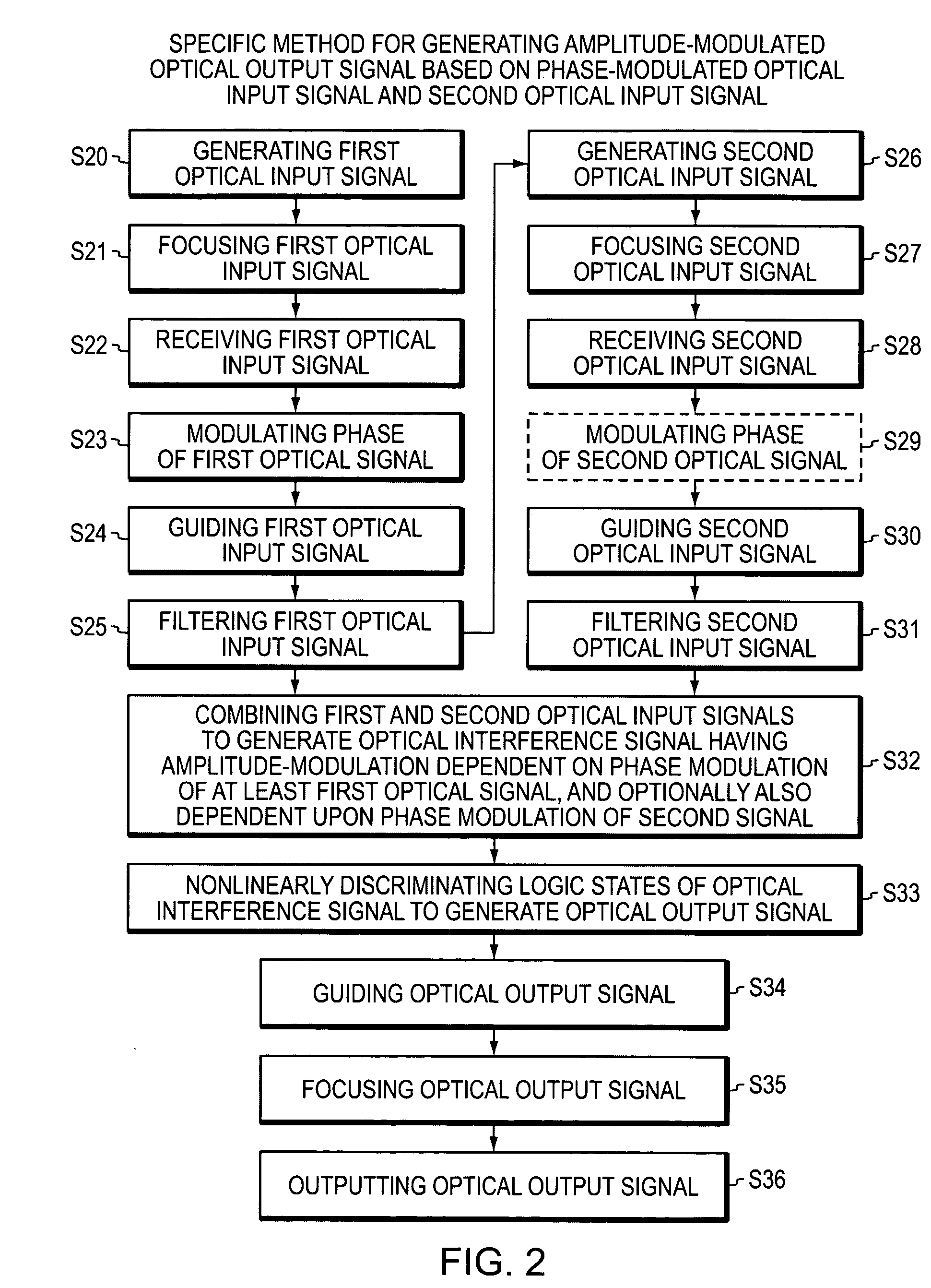

Optical device and circuit using phase modulation and related methods

InactiveUS20050259999A1Logic circuits using opto-electronic devicesElectromagnetic transmittersNonlinear elementLogic gate

A disclosed apparatus comprises a guiding element and a nonlinear element. The guiding element guides optical input signals, at least one of which is phase-modulated, to an interference area where such signals meet and interfere. The resulting interference signal is nonlinearly discriminated by the nonlinear element to produce an optical output signal that can be amplitude- or phase-modulated according to the phase modulation of the input signals. The invention also includes related methods and photonic logic gates.

Owner:COVEY JOHN

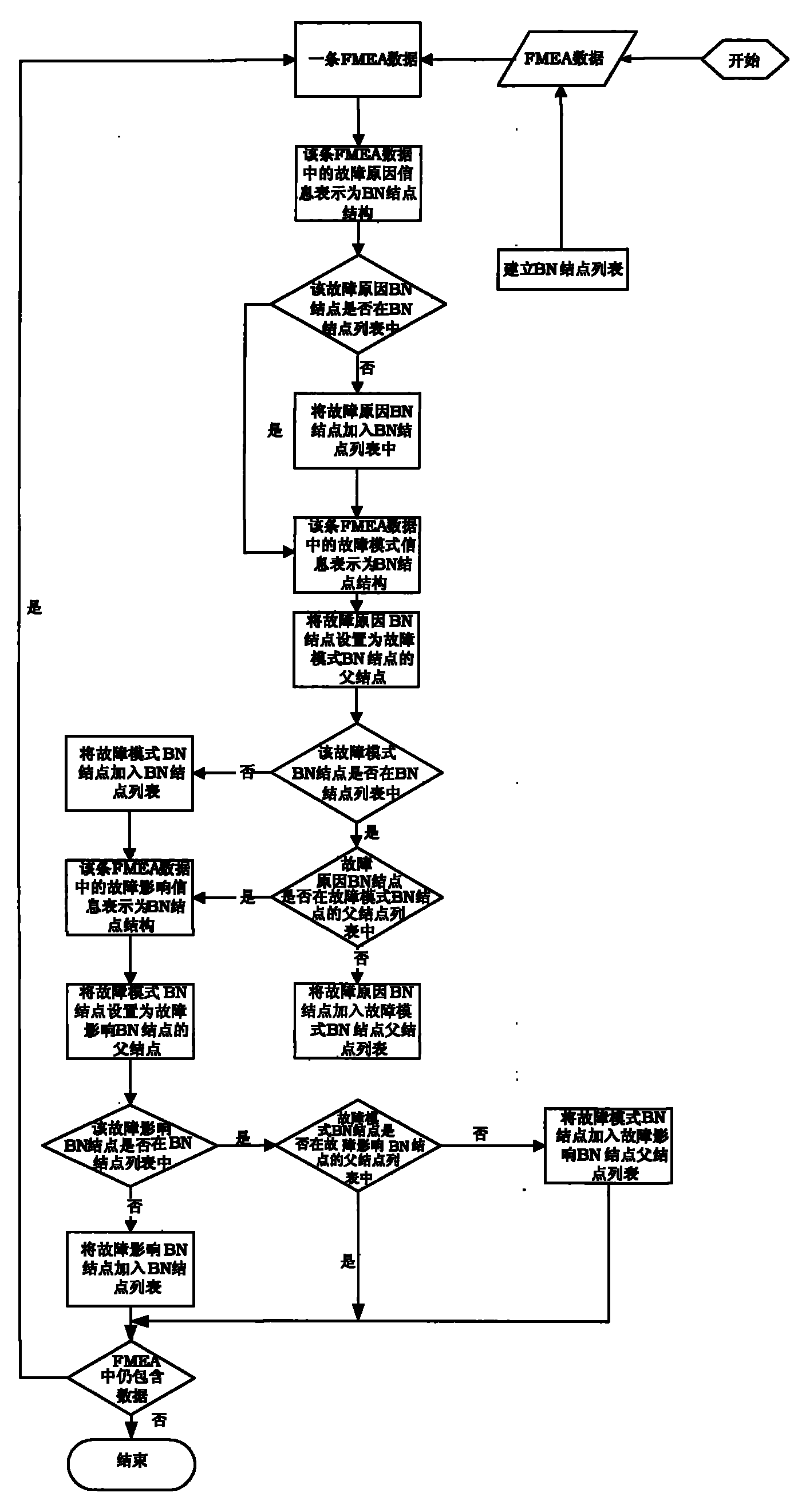

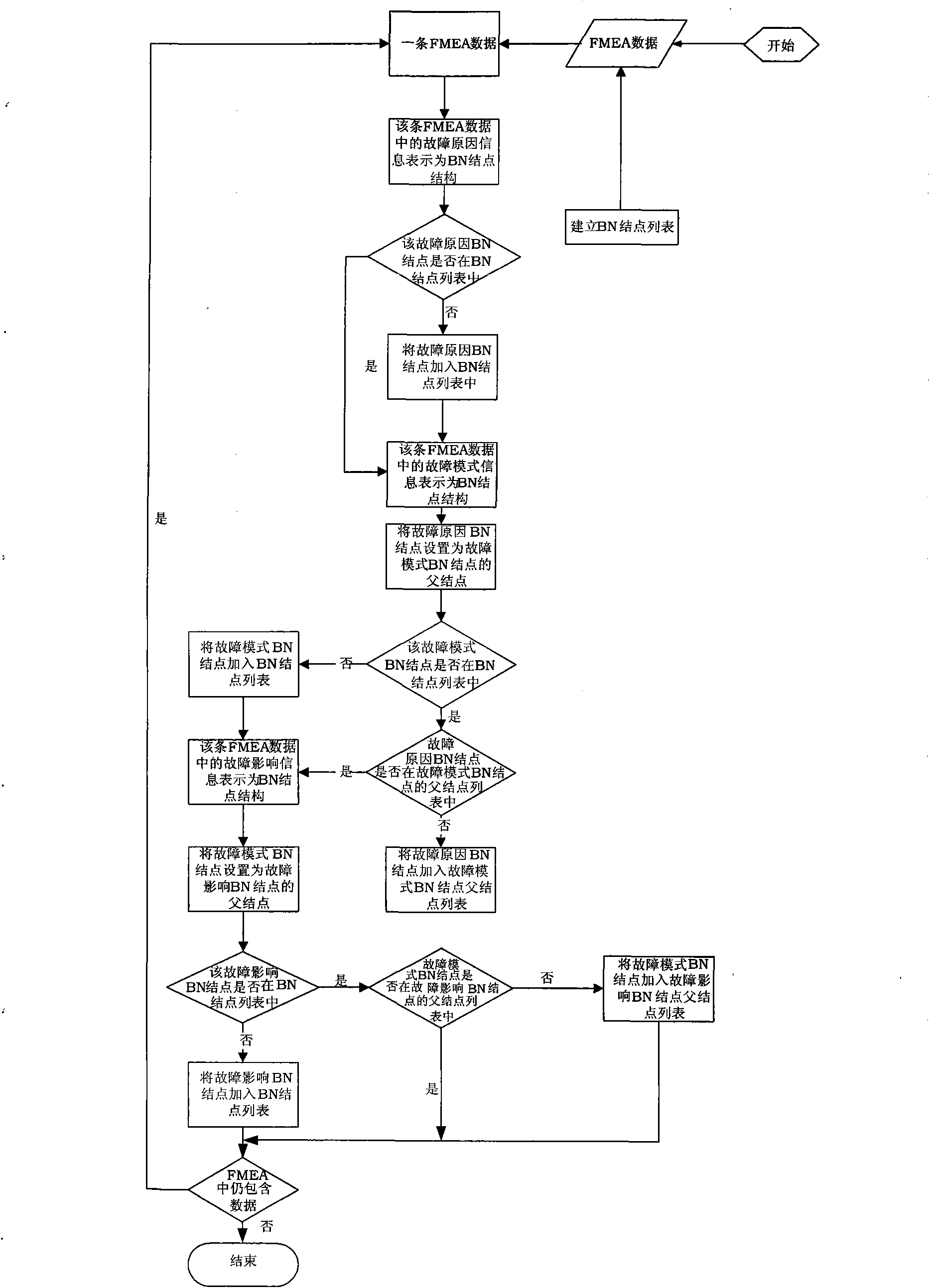

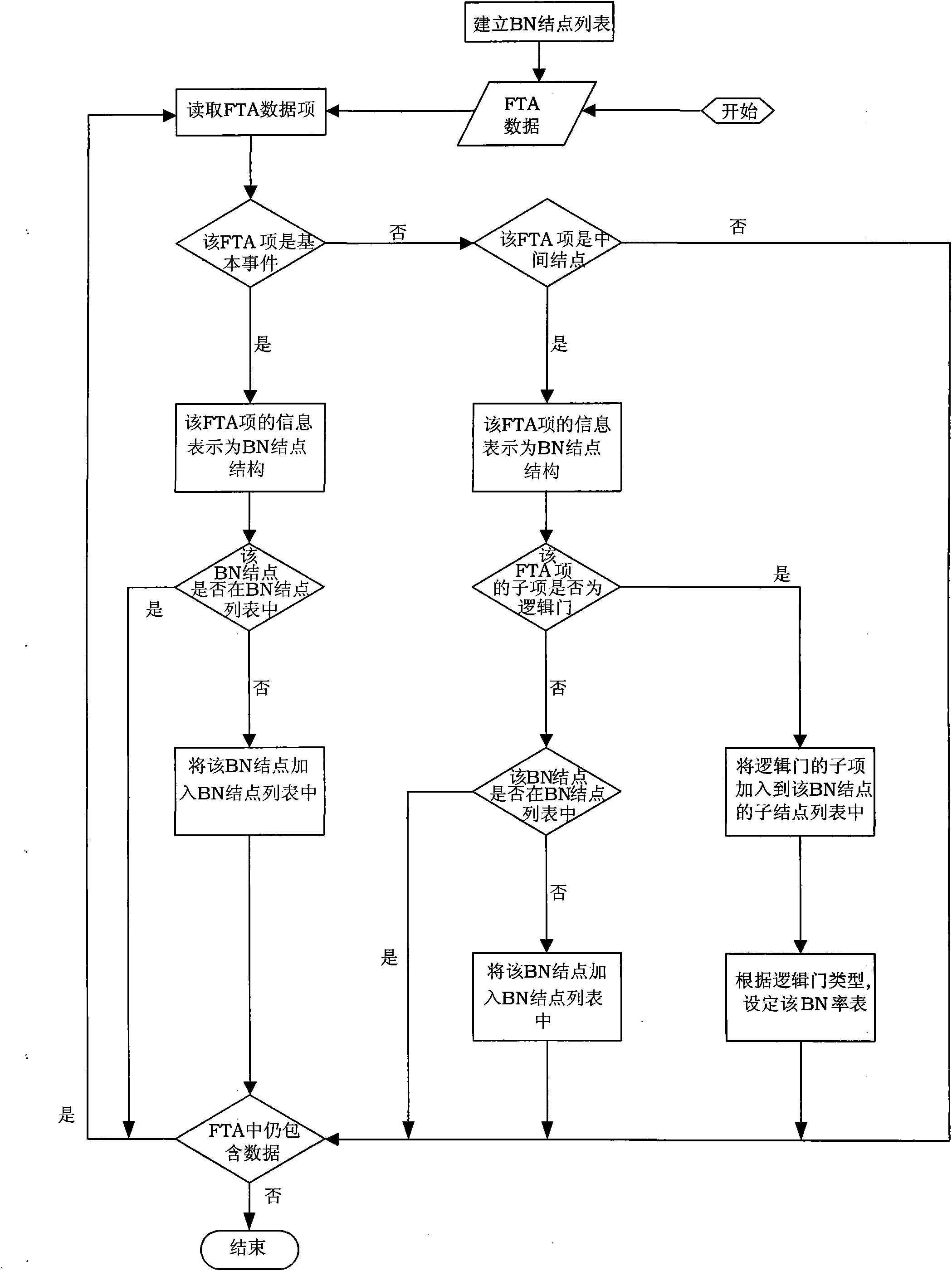

Method for performing fault diagnosis by using model conversion

ActiveCN101814114AEasy to useImprove diagnostic accuracyMathematical modelsSpecial data processing applicationsCorresponding conditionalLogic gate

The invention discloses a method for performing fault diagnosis by using model conversion. According to the method, processed related information of a fault mode effect analysis model is converted into a corresponding Bayesian network model by using a self-defined data structure while ensuring complete data, an elementary event, a logic gate and an intermediate event of a fault tree in a fault tree analysis model are converted into nodes in a Bayesian network respectively, and a corresponding conditional probability table in the Bayesian network is set. The fault diagnosis is performed through the converted Bayesian network model. The method of the invention expands the use of the Bayesian network model in the fault diagnosis, improves the diagnosis accuracy of a fault diagnosis model in practical application, ensures the universality of model conversion, and can realize cross-tool conversion among different fault mode effect analysis, fault tree analysis result and the generated Bayesian network.

Owner:BEIHANG UNIV

CMOS logic gate fabricated on hybrid crystal orientations and method of forming thereof

ActiveUS7208815B2Harmful microloading effects are avoidedTransistorSolid-state devicesCMOSCrystal orientation

In preferred embodiments of the present invention, a method of forming CMOS devices using SOI and hybrid substrate orientations is described. In accordance with a preferred embodiment, a substrate may have multiple crystal orientations. One logic gate in the substrate may comprise at least one N-FET on one crystal orientation and at least one P-FET on another crystal orientation. Another logic gate in the substrate may comprise at least one N-FET and at least one P-FET on the same orientation. Alternative embodiments further include determining the preferred cleavage planes of the substrates and orienting the substrates relative to each other in view of their respective preferred cleavage planes. In a preferred embodiment, the cleavage planes are not parallel.

Owner:TAIWAN SEMICON MFG CO LTD