Patents

Literature

4281 results about "Device under test" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A device under test (DUT), also known as equipment under test (EUT) and unit under test (UUT), is a manufactured product undergoing testing, either at first manufacture or later during its life cycle as part of ongoing functional testing and calibration checks. This can include a test after repair to establish that the product is performing in accordance with the original product specification.

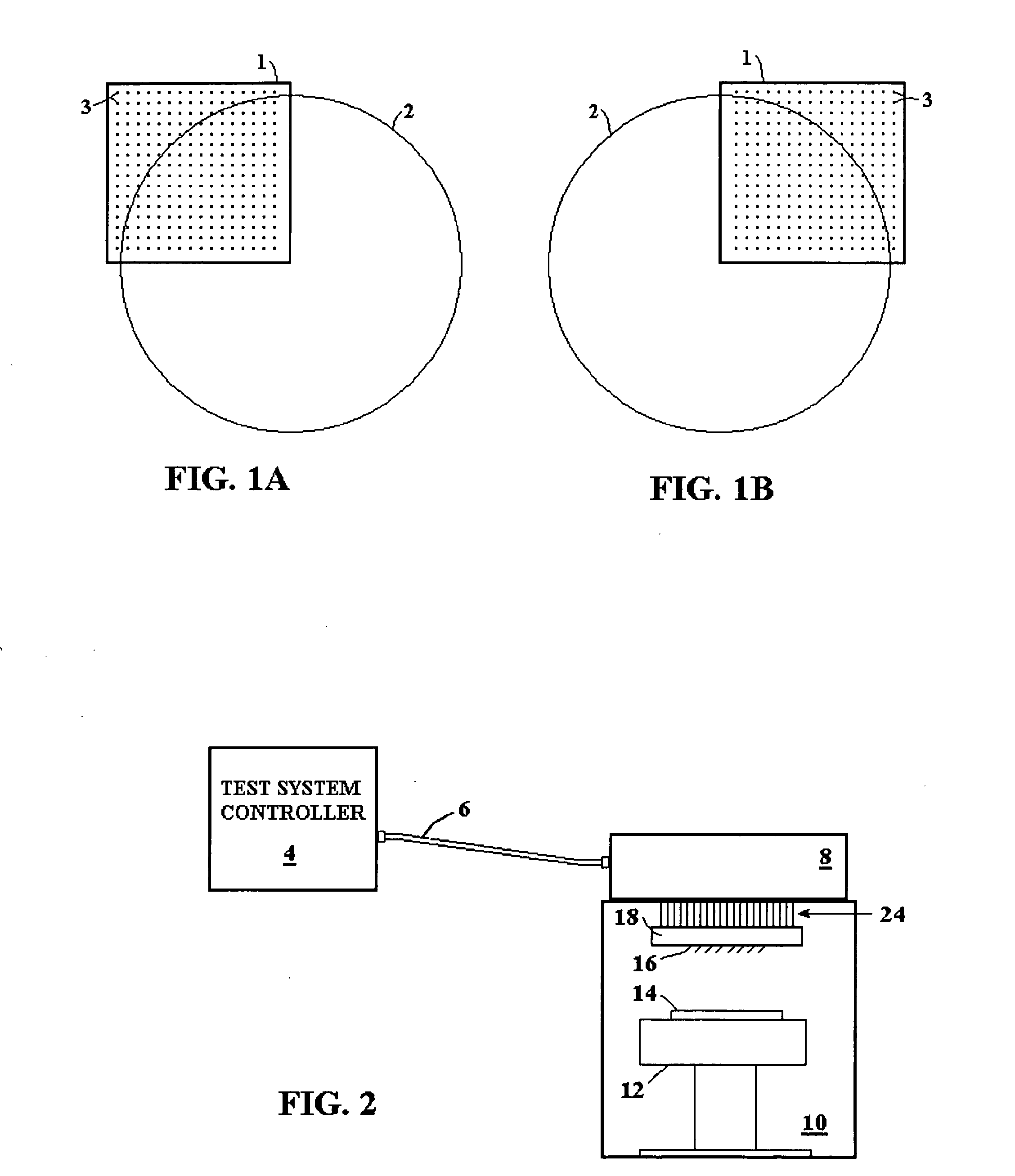

Location-based testing for wireless data communication networks

ActiveUS7539489B1Easy to optimizeFacilitate data communicationError preventionFrequency-division multiplex detailsTest stimulusSystem under test

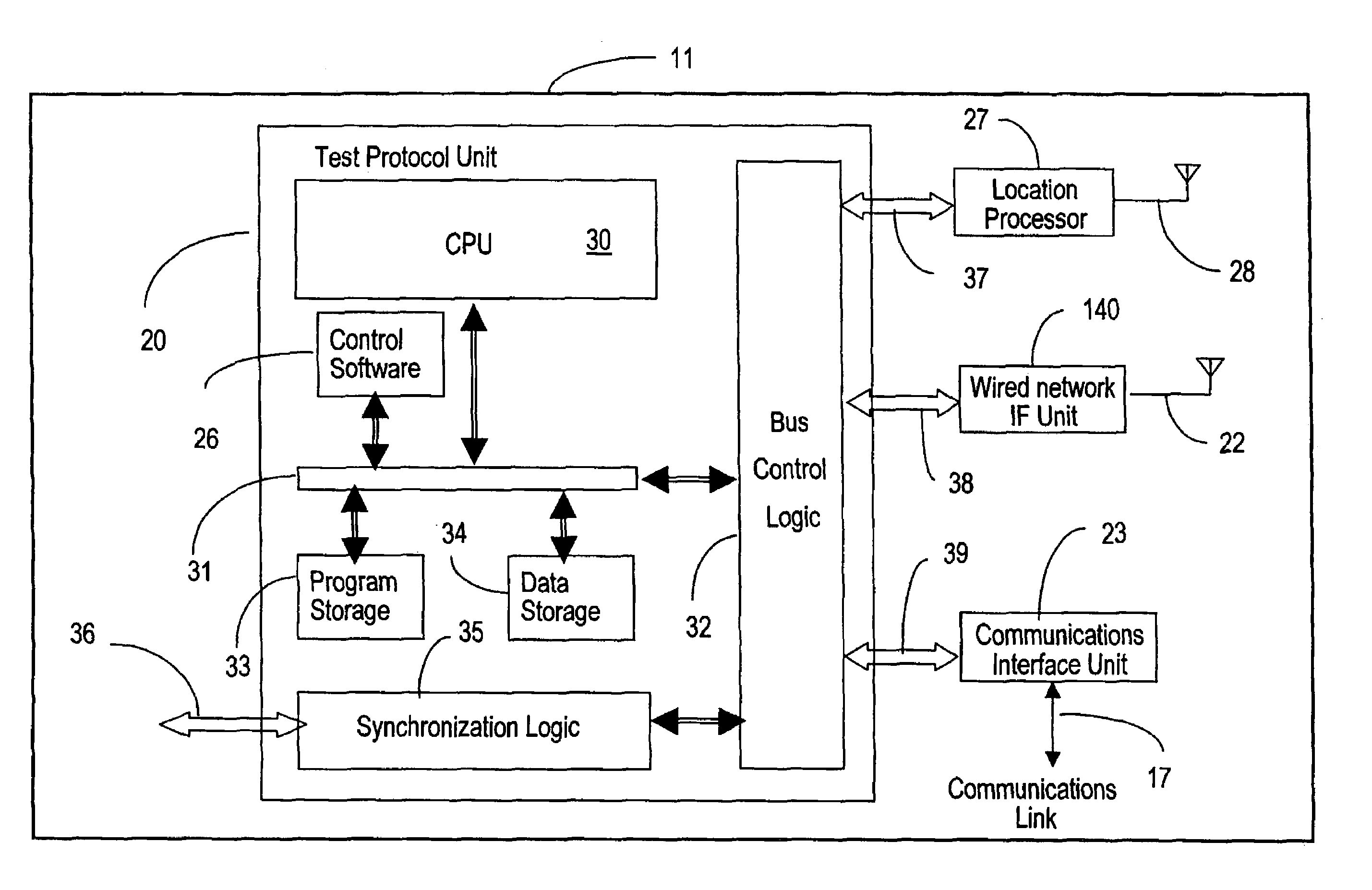

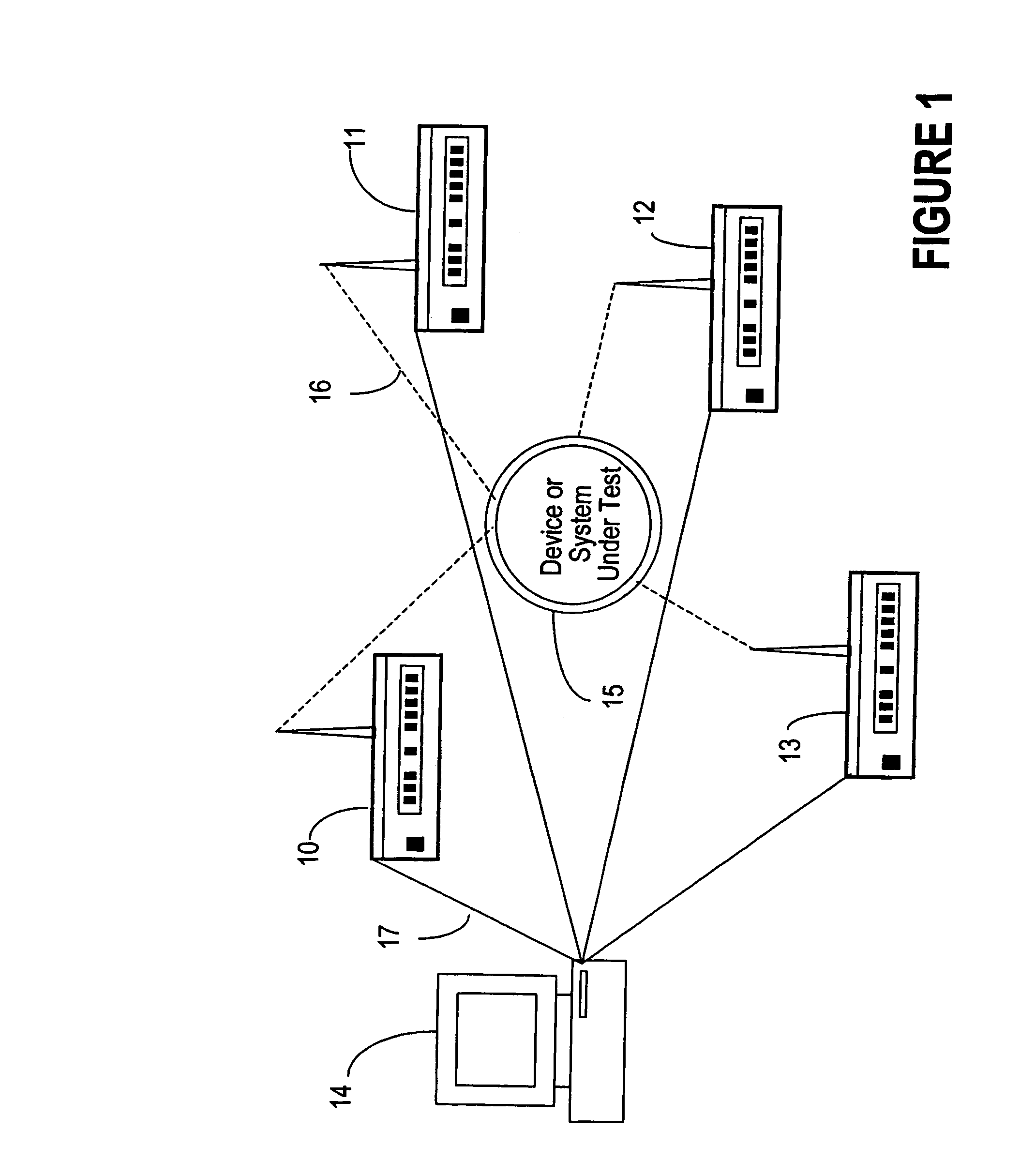

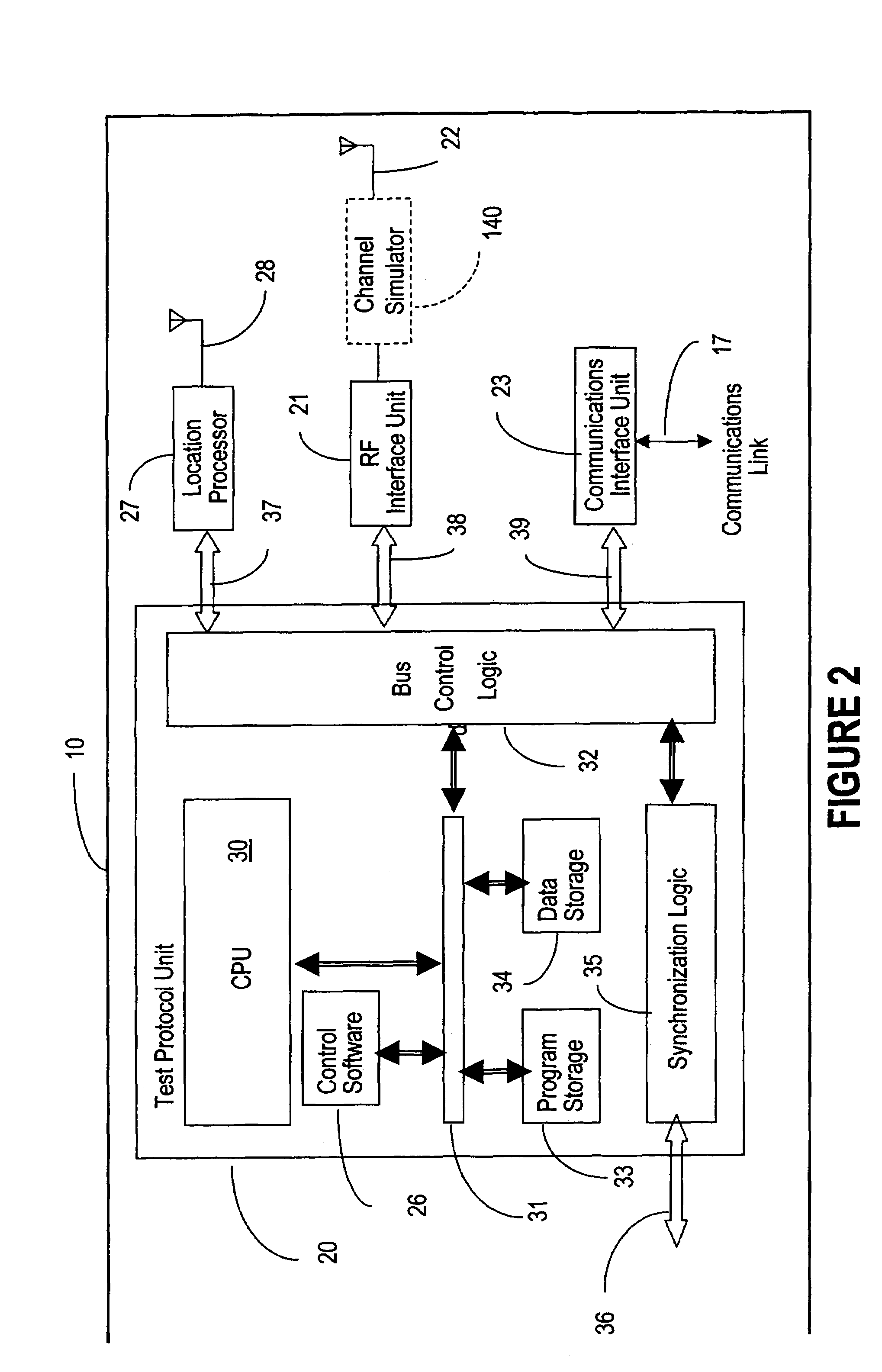

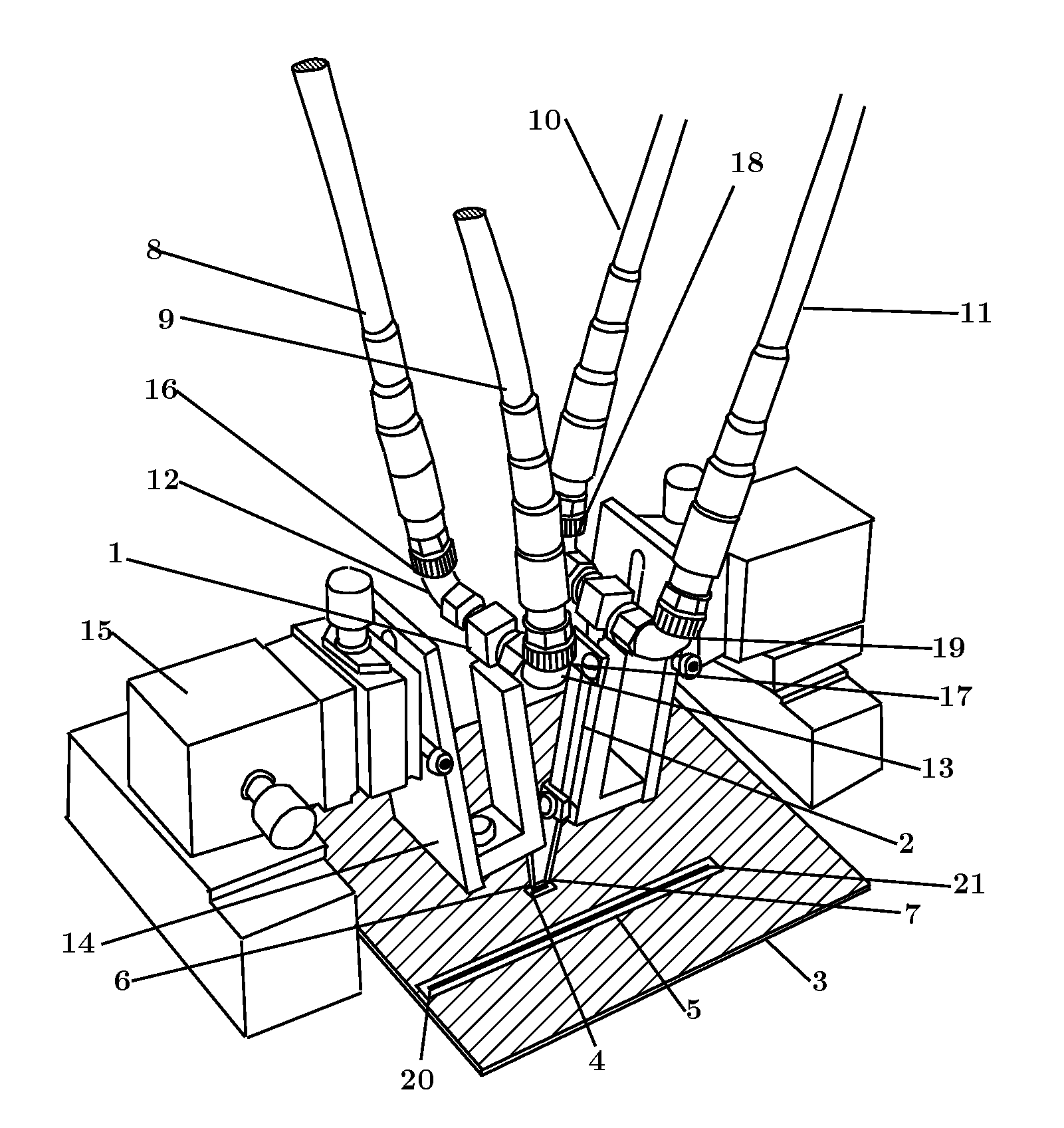

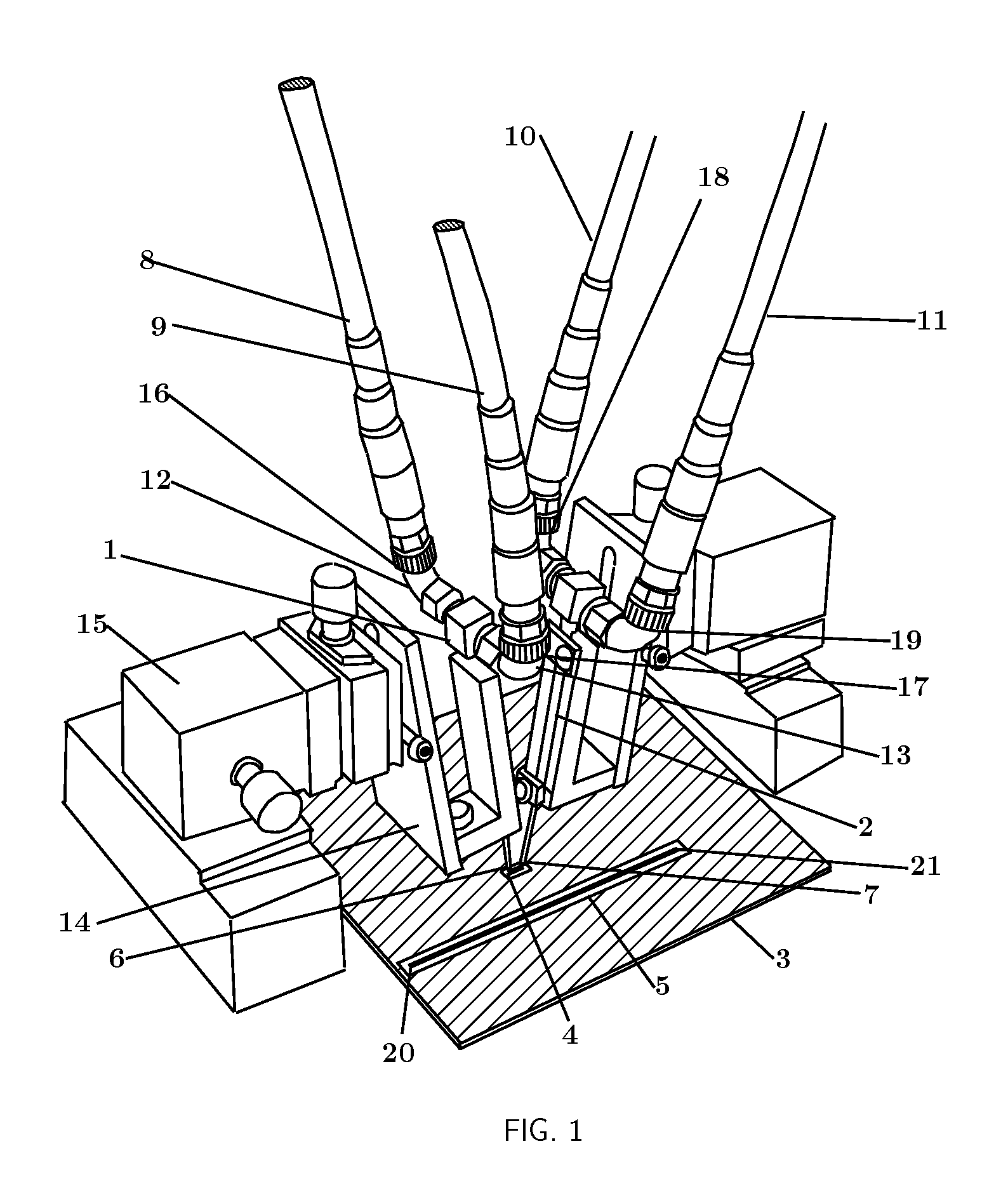

Apparatus and methods facilitating a distributed approach to performance and functionality testing of location-sensitive wireless data communication systems and equipment are described. A plurality of test units, geographically distributed at arbitrary points in a three-dimensional volume surround the system or equipment under test. Each test unit generates test stimuli and records responses from the device under test, and emulates the effects of changes in spatial location within an actual wireless network environment. A central controller co-ordinates the set of test units to ensure that they act as a logical whole, and enables testing to be performed in a repeatable manner in spite of the variations introduced by the location sensitive characteristics of wireless data communication networks. The central controller also maintains a user interface that provides a unified view of the complete test system, and a unified view of the behavior of the system or equipment under test. For diagnostic purposes, the recorded responses may be regenerated to view any defects as many times as necessary to correct them. Alternatively, each test unit may have either wired network interface units, instead of a wireless interface unit to test systems or equipment forming part of a wired network portion in the wireless data communication system.

Owner:KEYSIGHT TECH SINGAPORE (SALES) PTE LTD

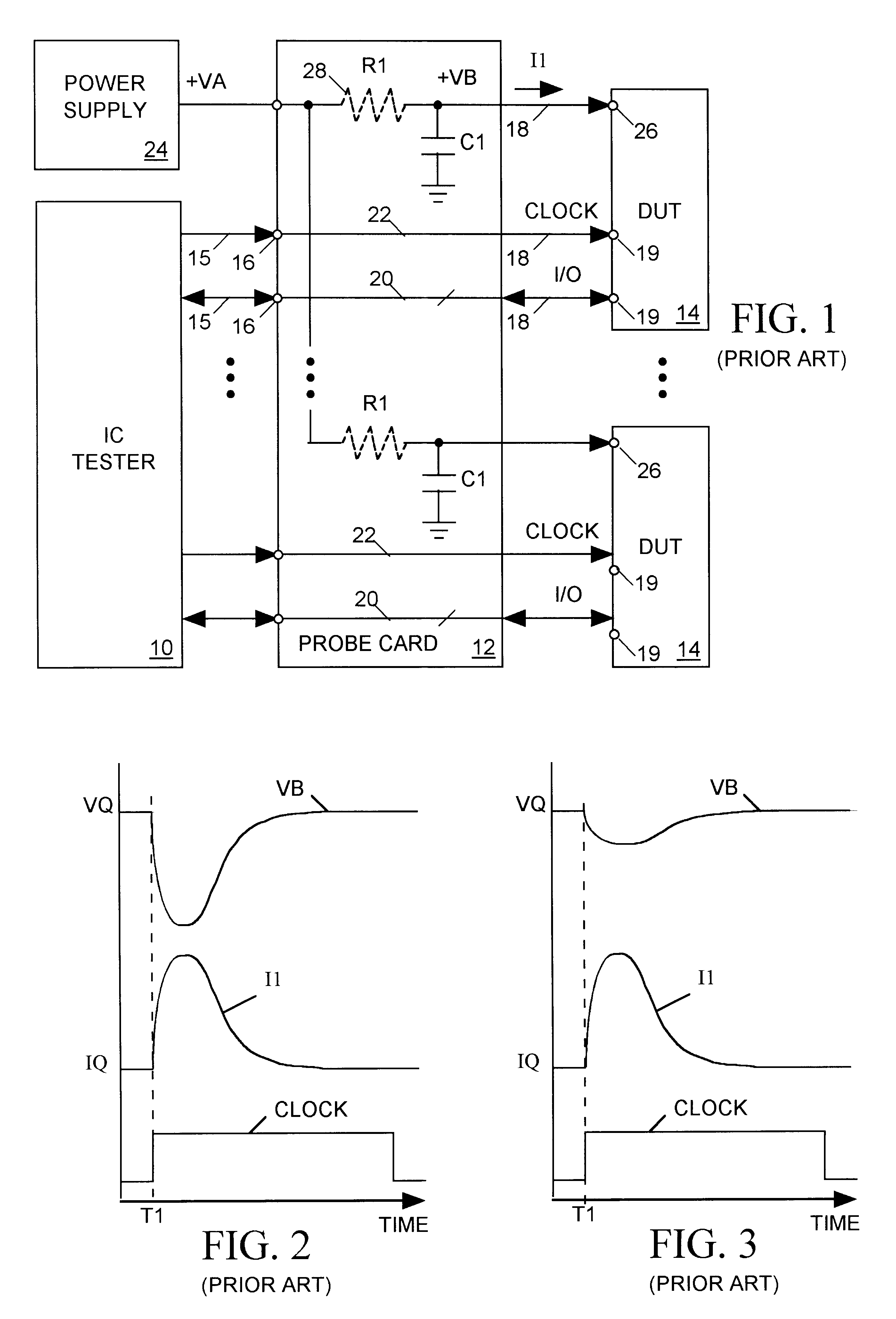

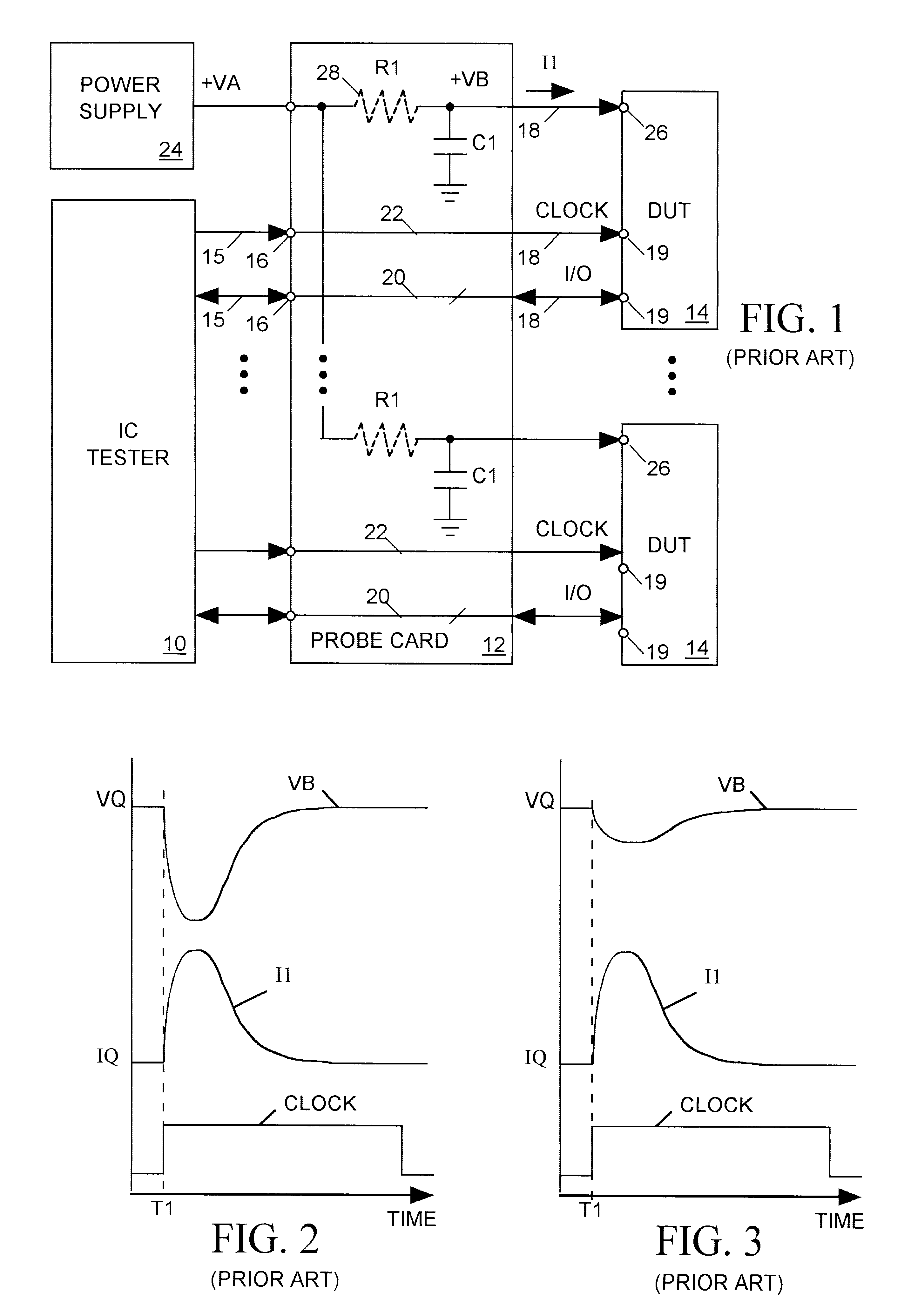

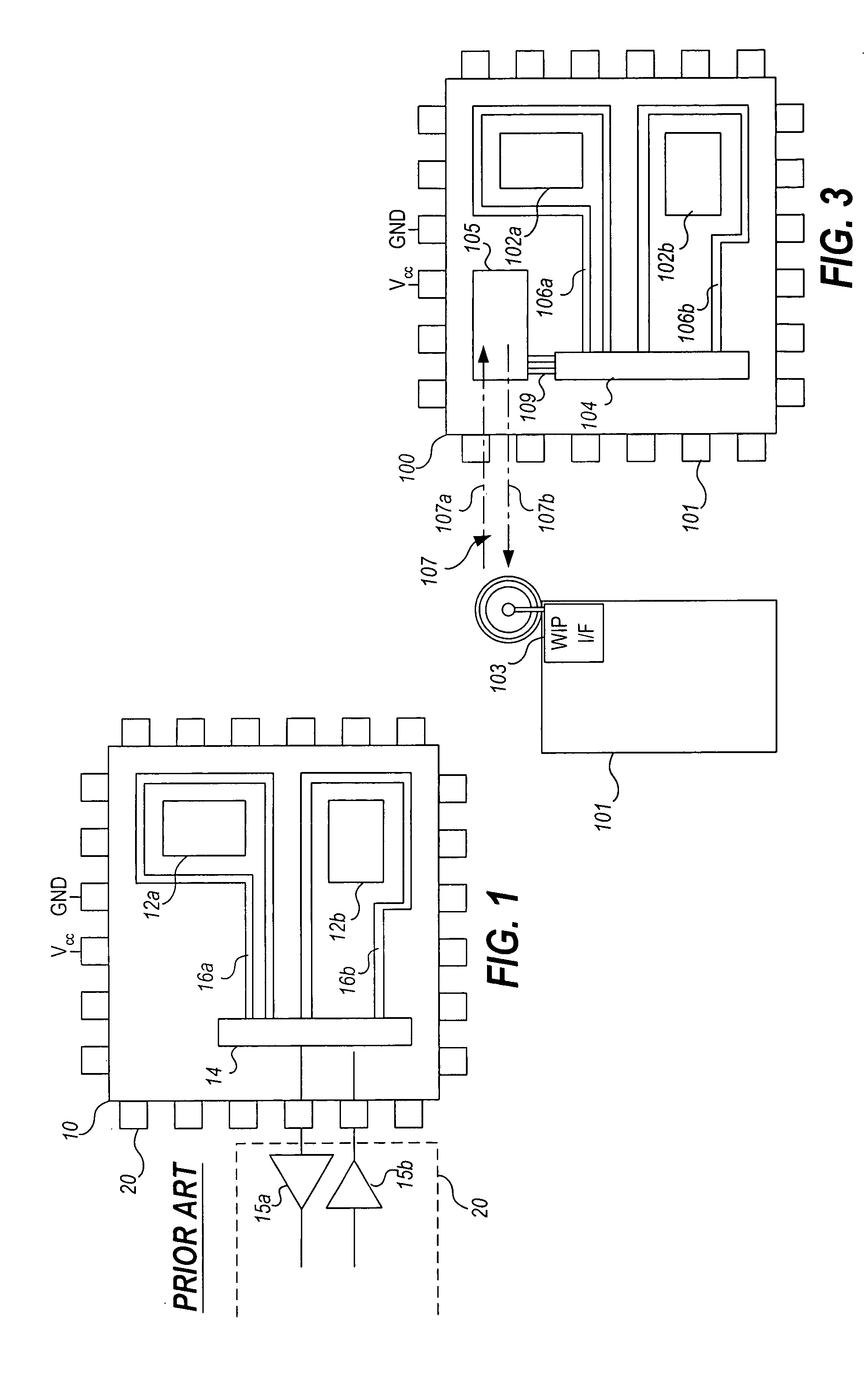

Apparatus for reducing power supply noise in an integrated circuit

InactiveUS6339338B1Reduce power supply noiseSuppress mutationDigital circuit testingVolume/mass flow measurementCapacitanceState variation

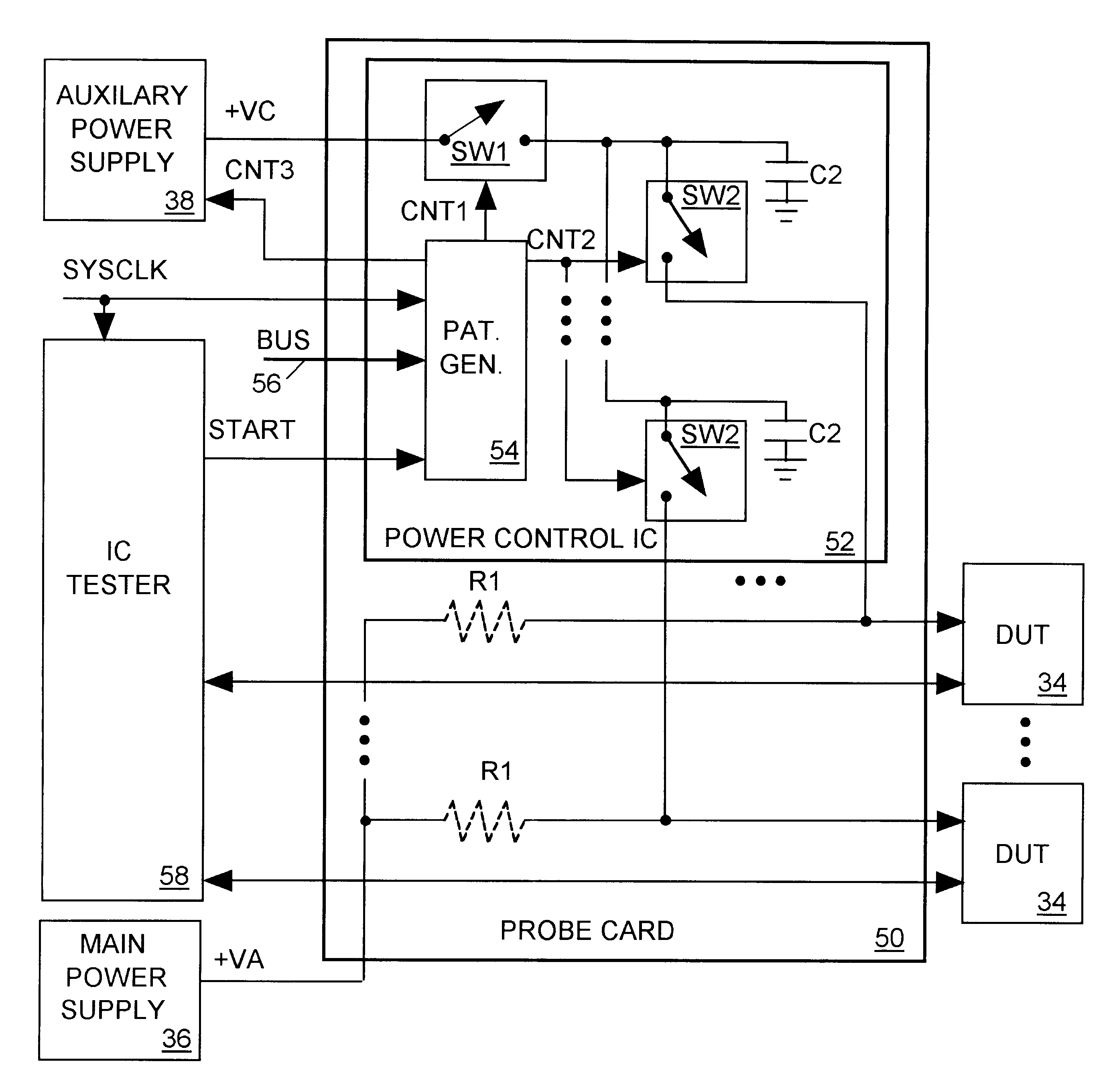

A main power supply continuously provides a current to a power input terminal of an integrated circuit device under test (DUT). The DUT's demand for current at the power input terminal temporarily increases during state changes in synchronous logic circuits implemented within the DUT. To limit variation (noise) in voltage at the power input terminal arising from these temporary increases in current demand, a charged capacitor is connected to the power input terminal during each DUT state change. The capacitor discharges into the power input terminal to supply additional current to meet the DUT's increased demand. Following each DUT state change the capacitor is disconnected from the power input terminal and charged to a level sufficient to meet a predicted increase in current demand during a next DUT state change.

Owner:FORMFACTOR INC

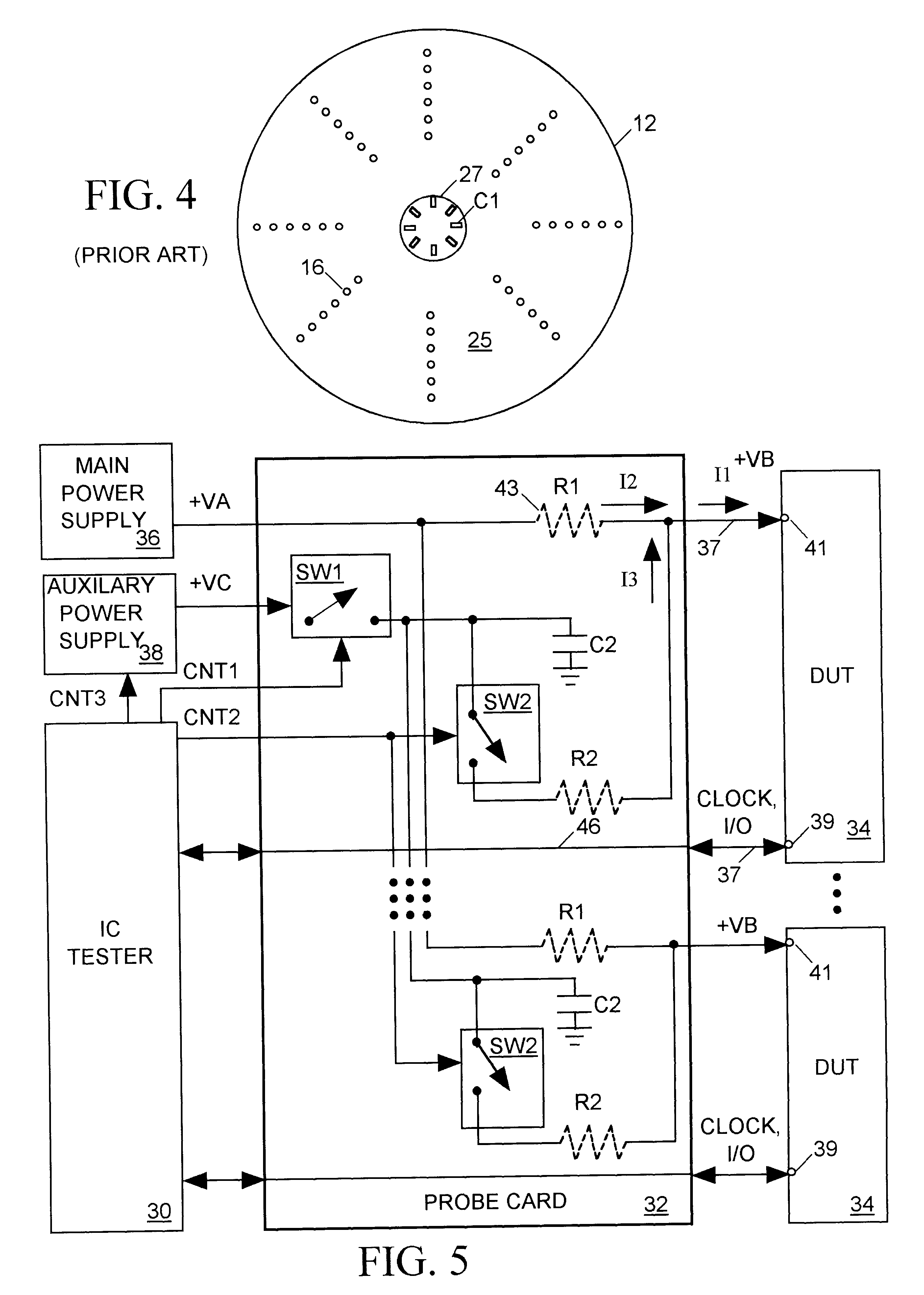

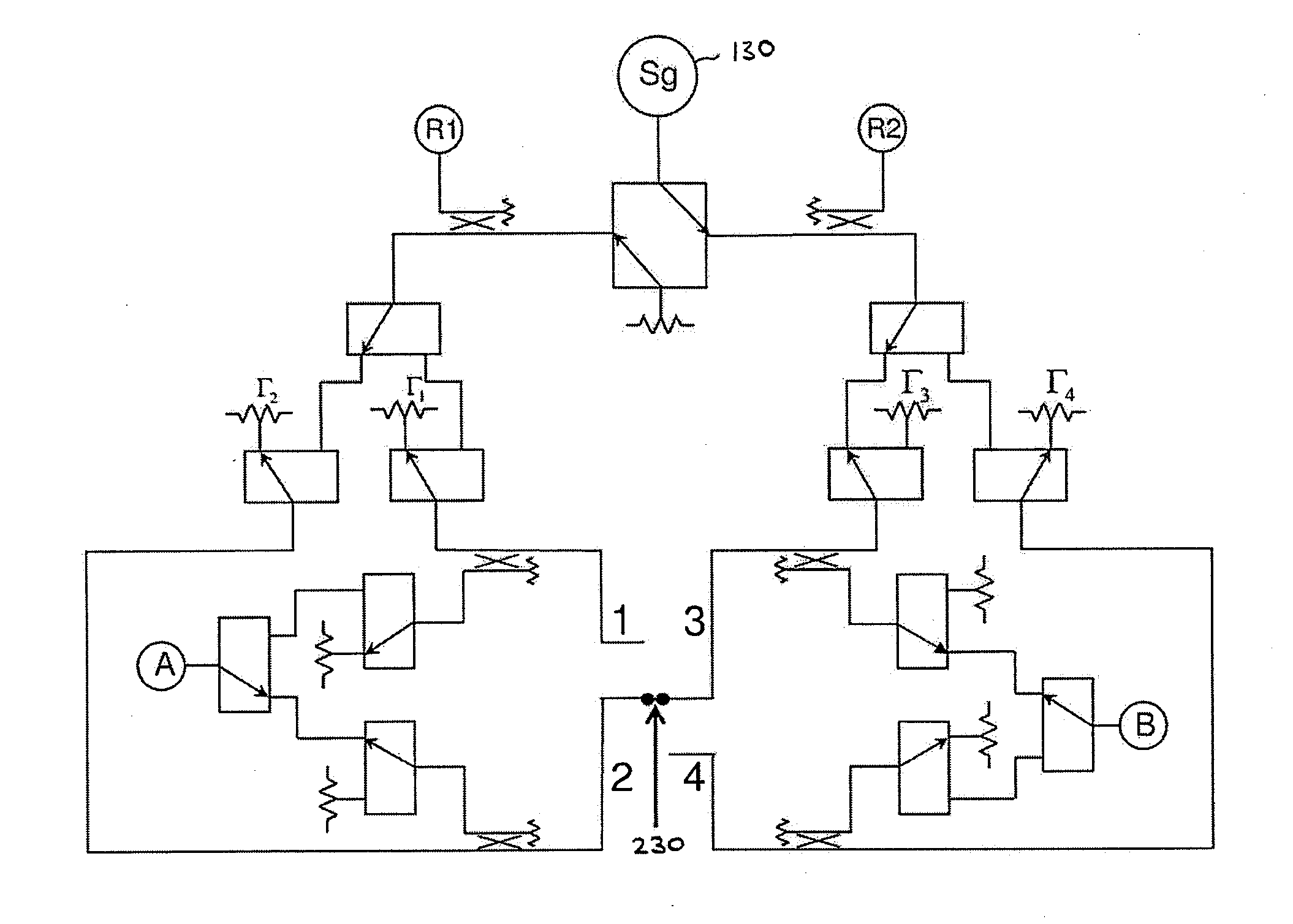

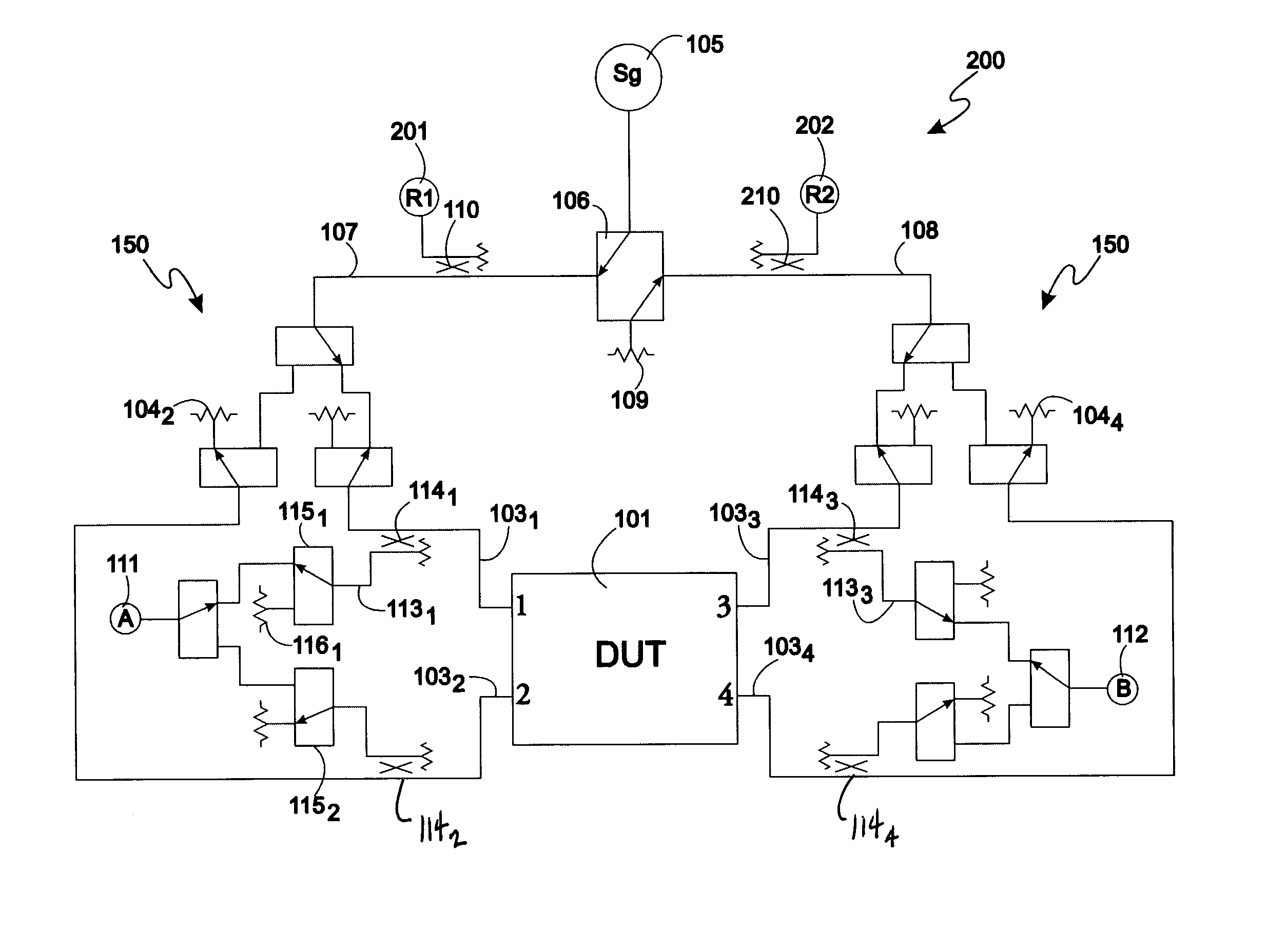

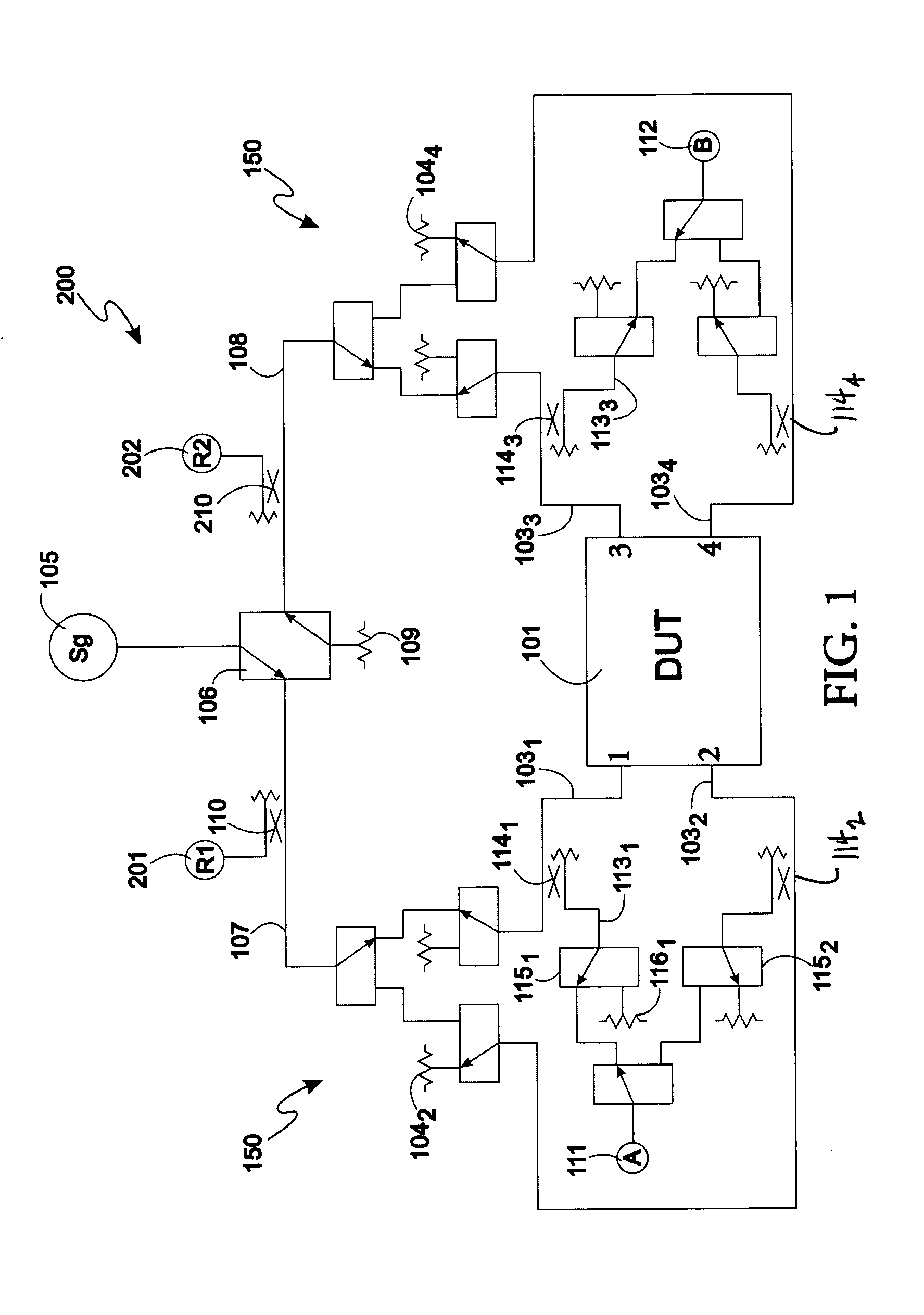

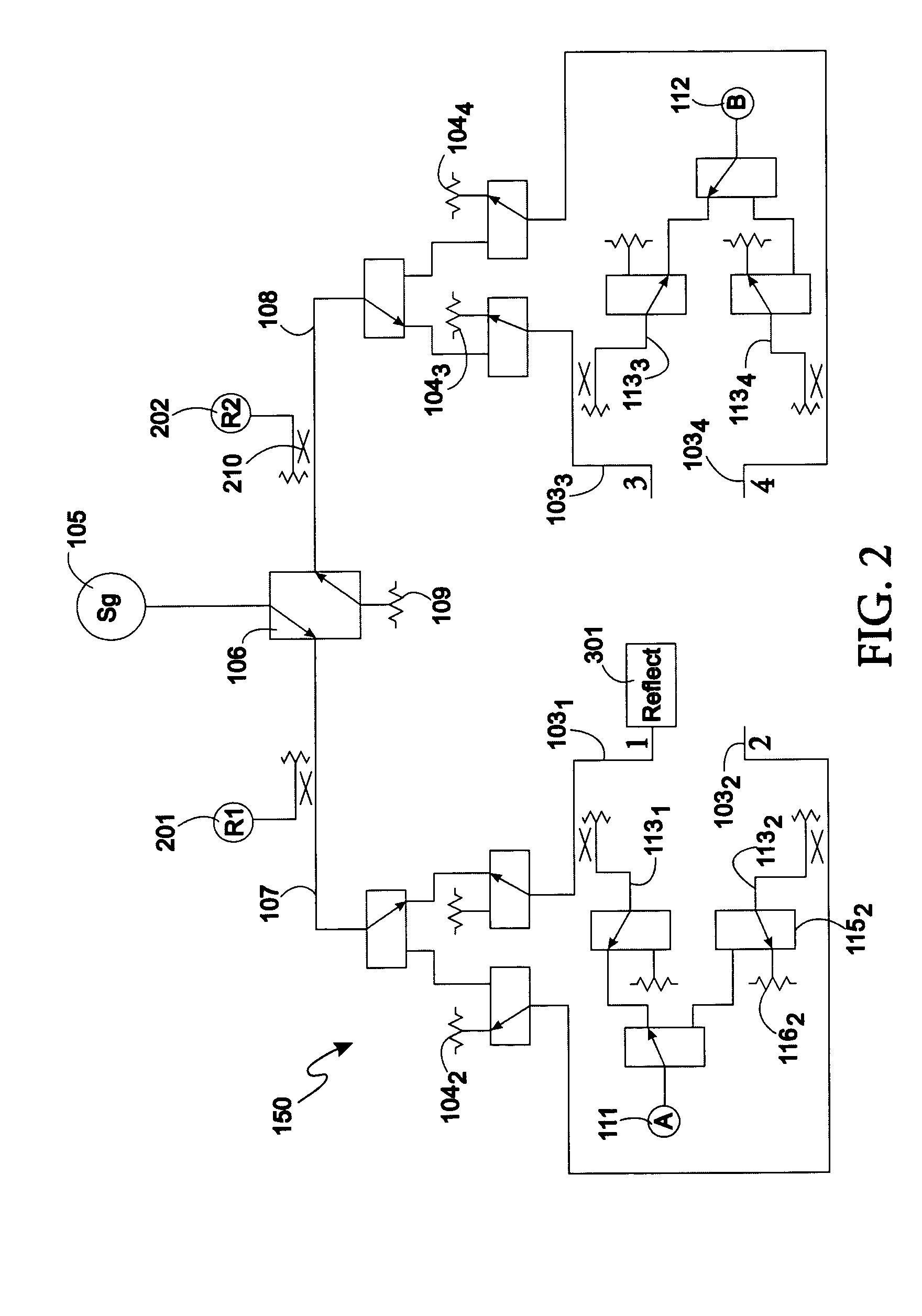

Method and apparatus for calibrating a test system for measuring a device under test

InactiveUS20120109566A1High precisionResistance/reactance/impedenceSpecial data processing applicationsTime domainImpulse response

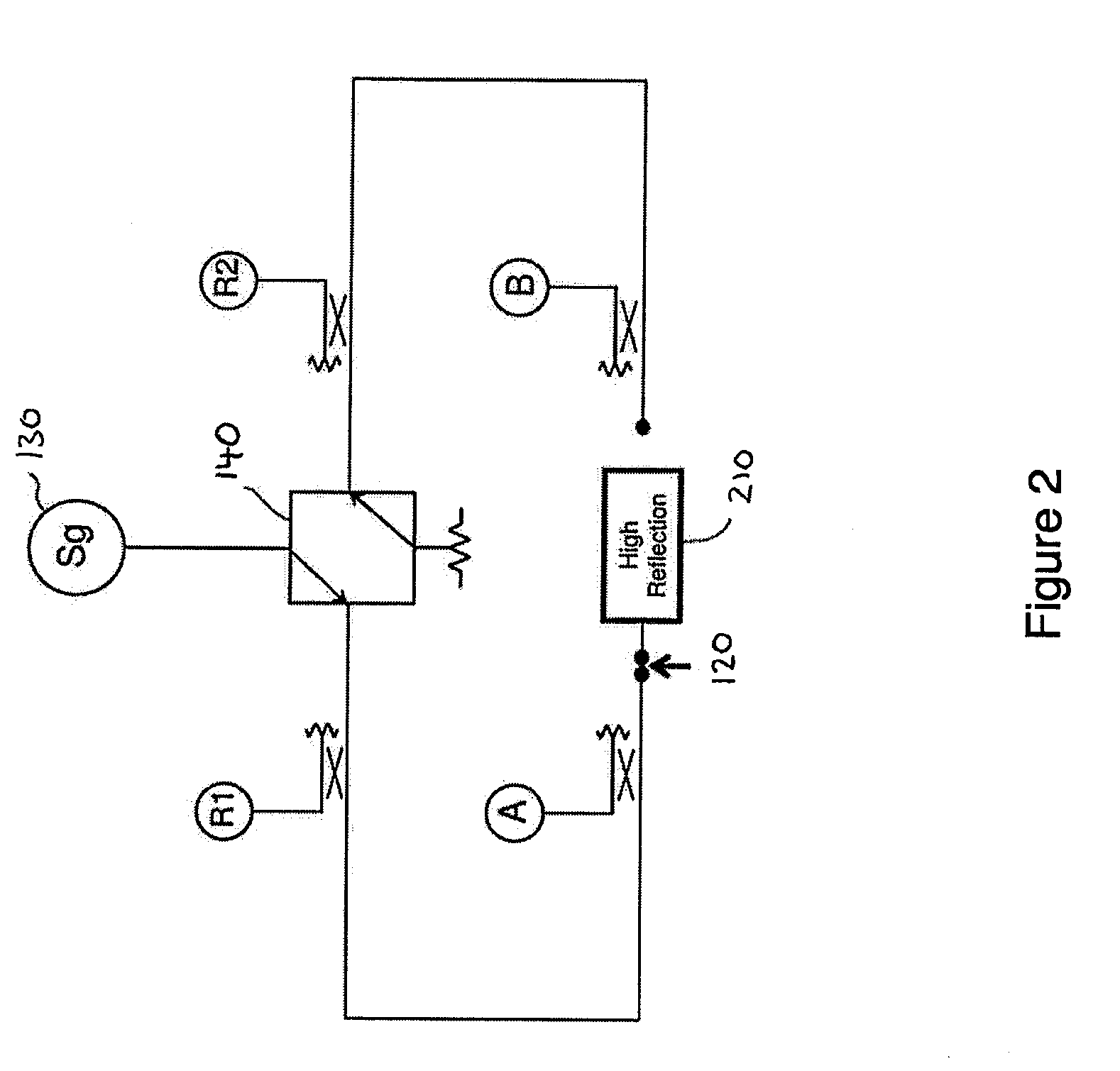

A calibration method for a two-port VNA includes presenting a high reflection calibration standard and measuring reflection data for each of the two ports, calculating a location of the high reflection calibration standard at each of the two ports, presenting a load calibration standard and measuring the reflection characteristic for each of the two ports to provide load data, converting the load data to the time domain to provide time domain impulse response load data, and gating the time domain impulse response load data based on the locations of the high reflection calibration standard at each of two ports. The method further includes reconstructing frequency domain load data from the gated time domain data, connecting the two ports together and determining forward and reverse transmission characteristics, and calculating systematic error coefficients for the VNA based on the reconstructed frequency domain data and the forward and reverse transmission characteristics.

Owner:ATE SYST

User Interface for Signal Integrity Network Analyzer

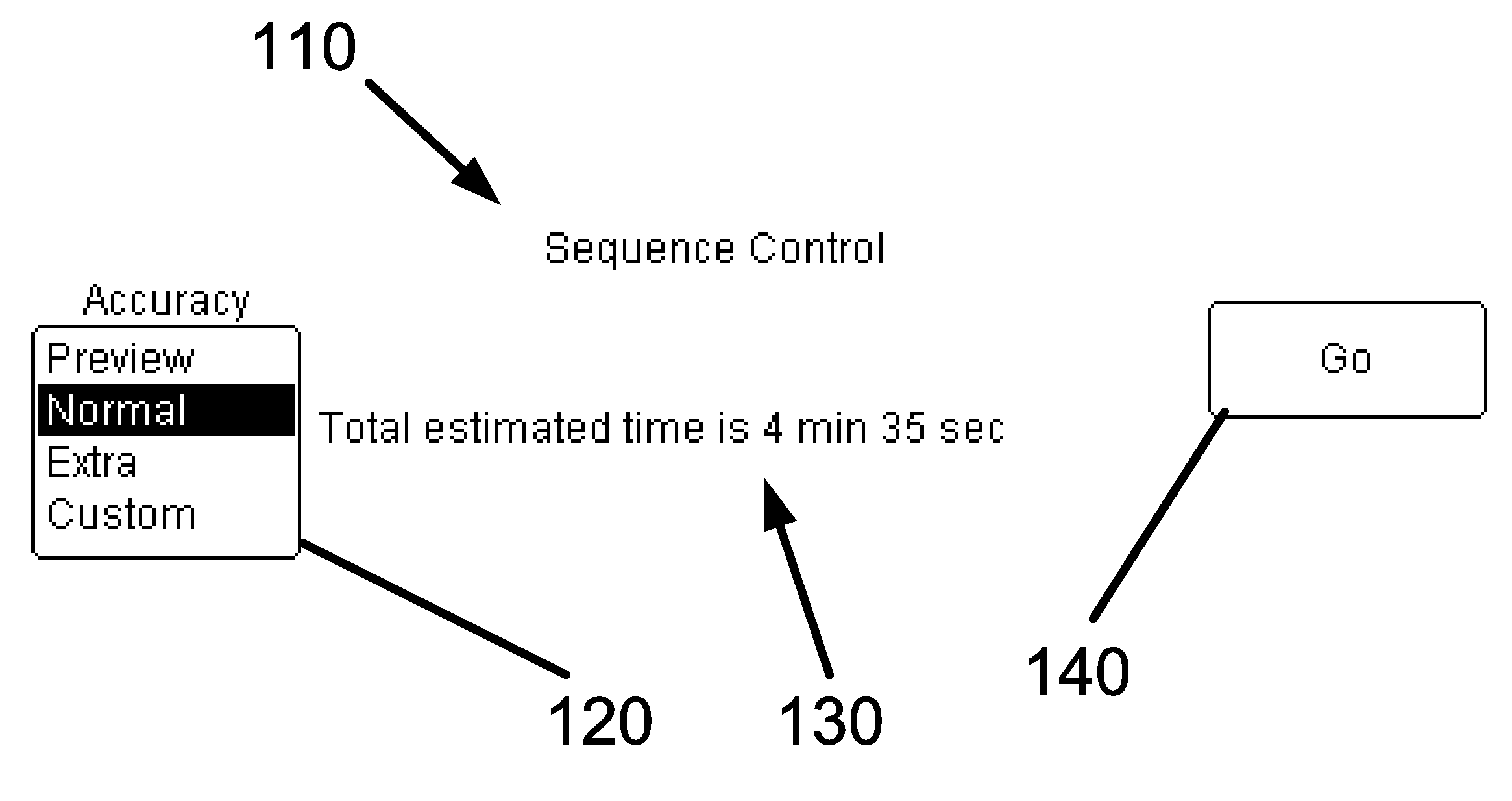

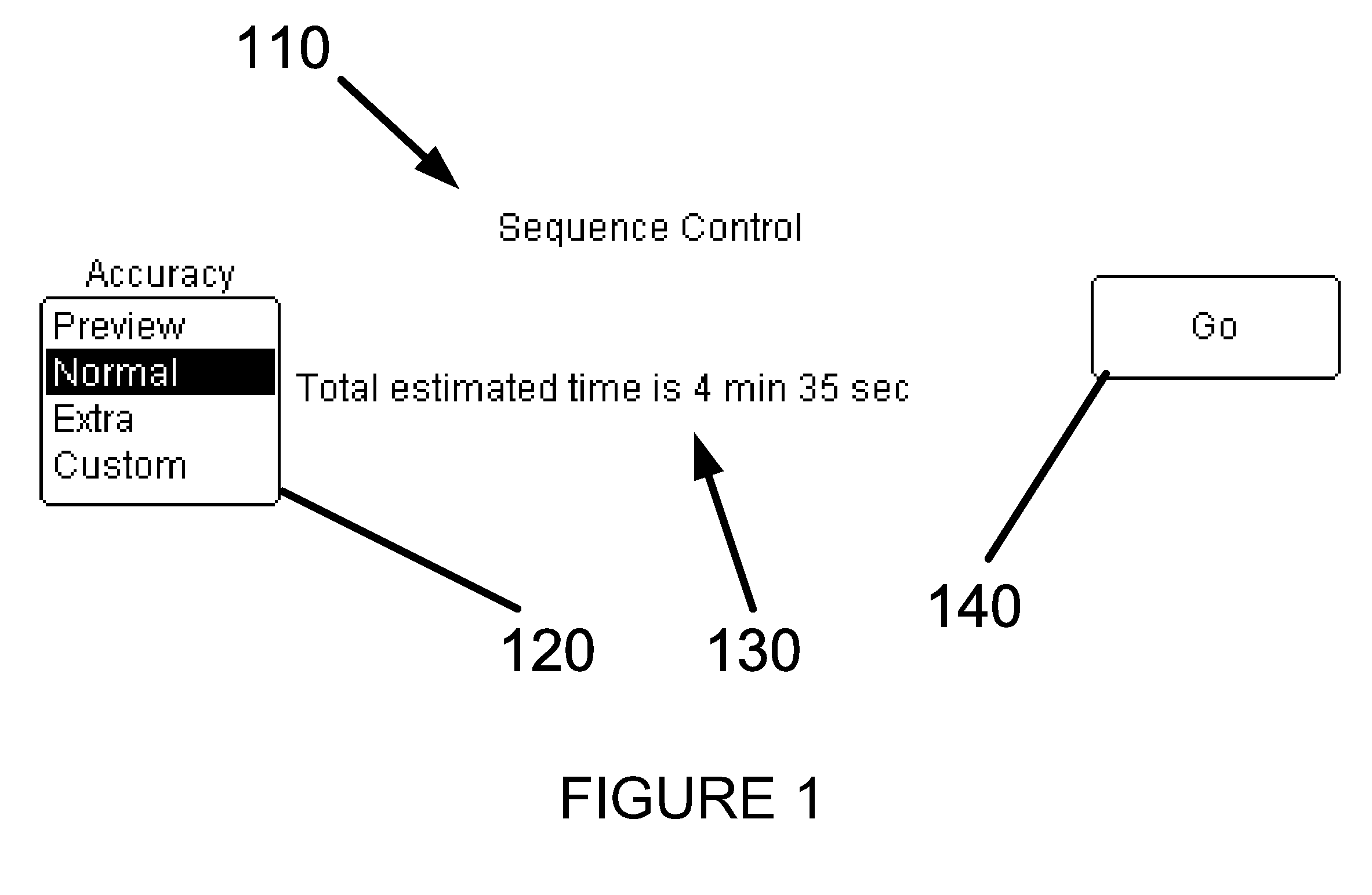

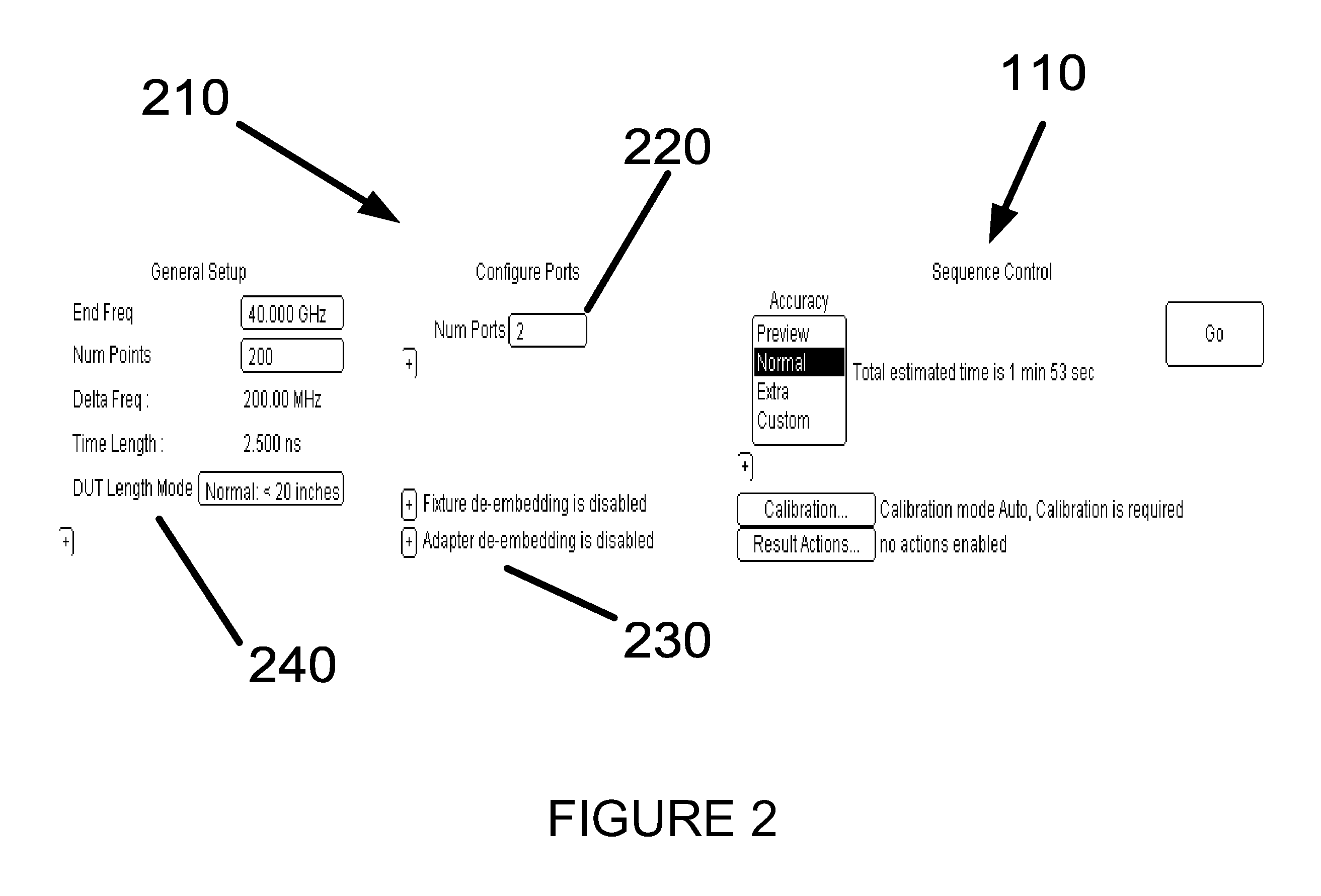

InactiveUS20110286506A1Easy to implementImprove user experienceResistance/reactance/impedenceElectrical measurement instrument detailsComputer scienceUser interface

A signal integrity network analyzer is provided. The analyzer preferably includes a characterization module for characterizing a device under test, an acquisition module for acquiring a waveform, a de-embedding module for selectively embedding and de-embedding on or more system fixtures, and an analysis module for performing analysis on the acquired waveform, with one or more system features selectively embedded or de-embedded. A single user interface is provided and is adapted to control the characterization module, the acquisition module, the de-embedding module and the analysis module.

Owner:TELEDYNE LECROY

Method for de-embedding in network analysis

ActiveUS9194930B2Easier, less complicated and less error-proneMultiplex system selection arrangementsResistance/reactance/impedenceEngineeringInstrumentation

Owner:TELEDYNE LECROY

Successive approximate capacitance measurement circuit

Owner:MONTEREY RES LLC

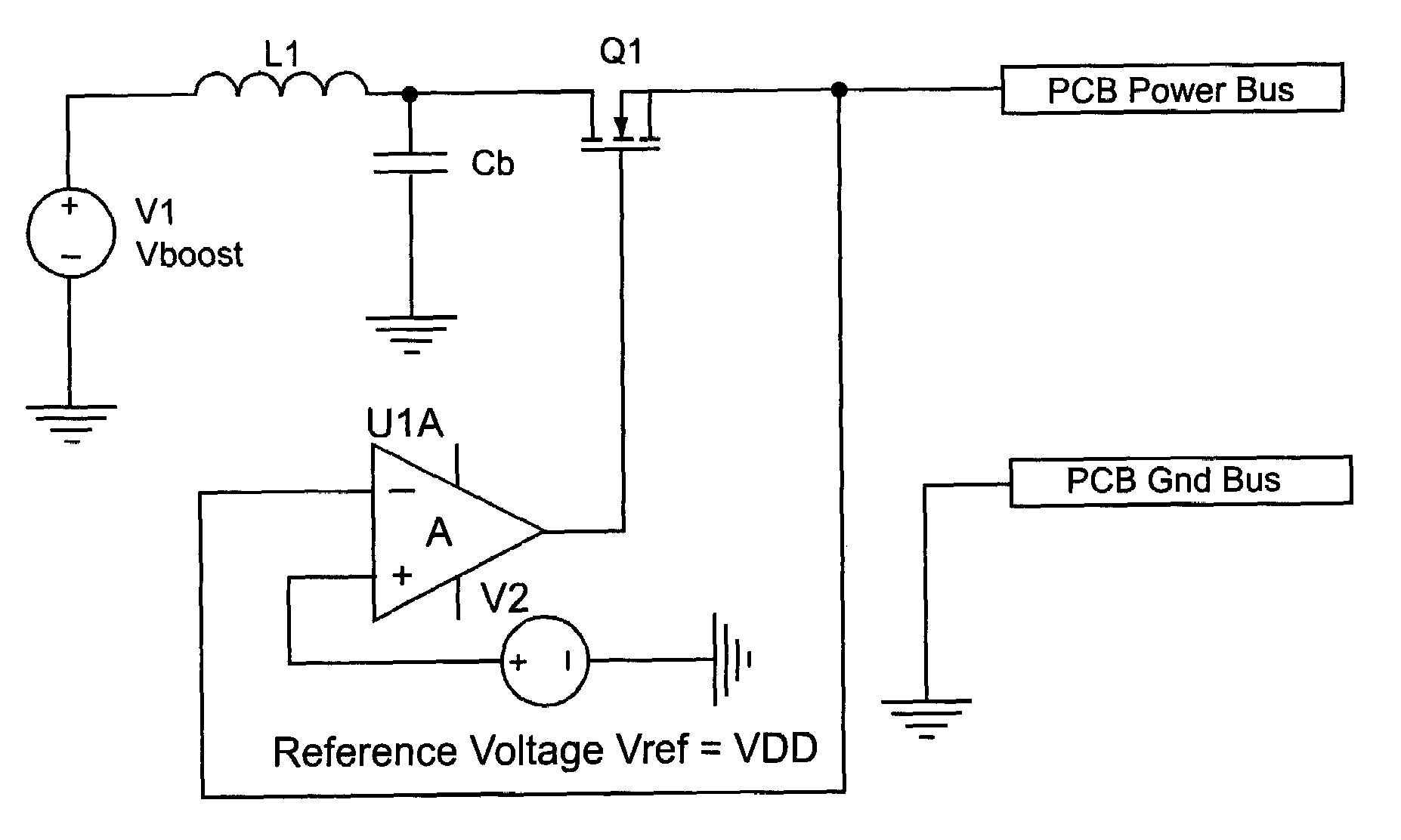

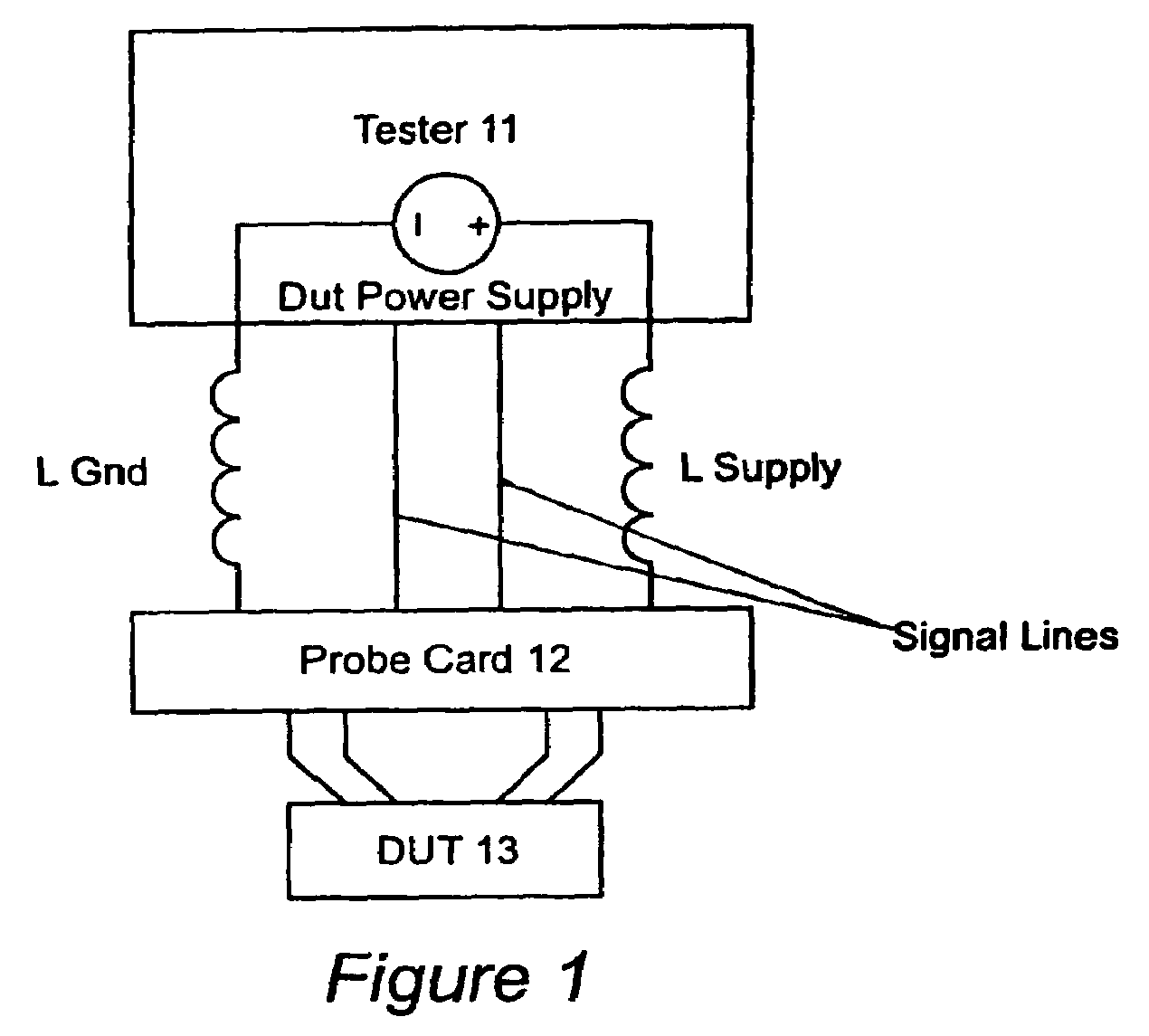

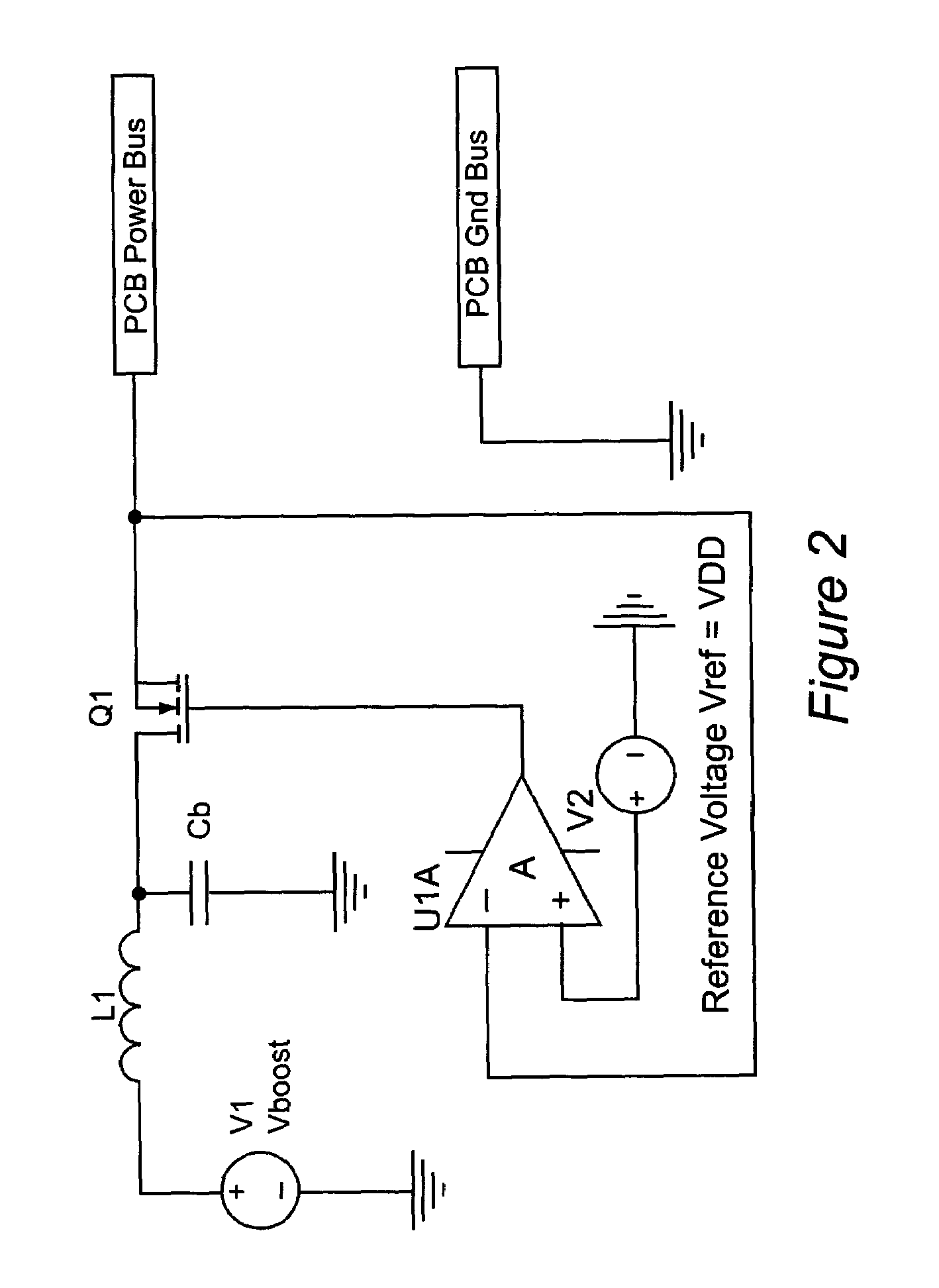

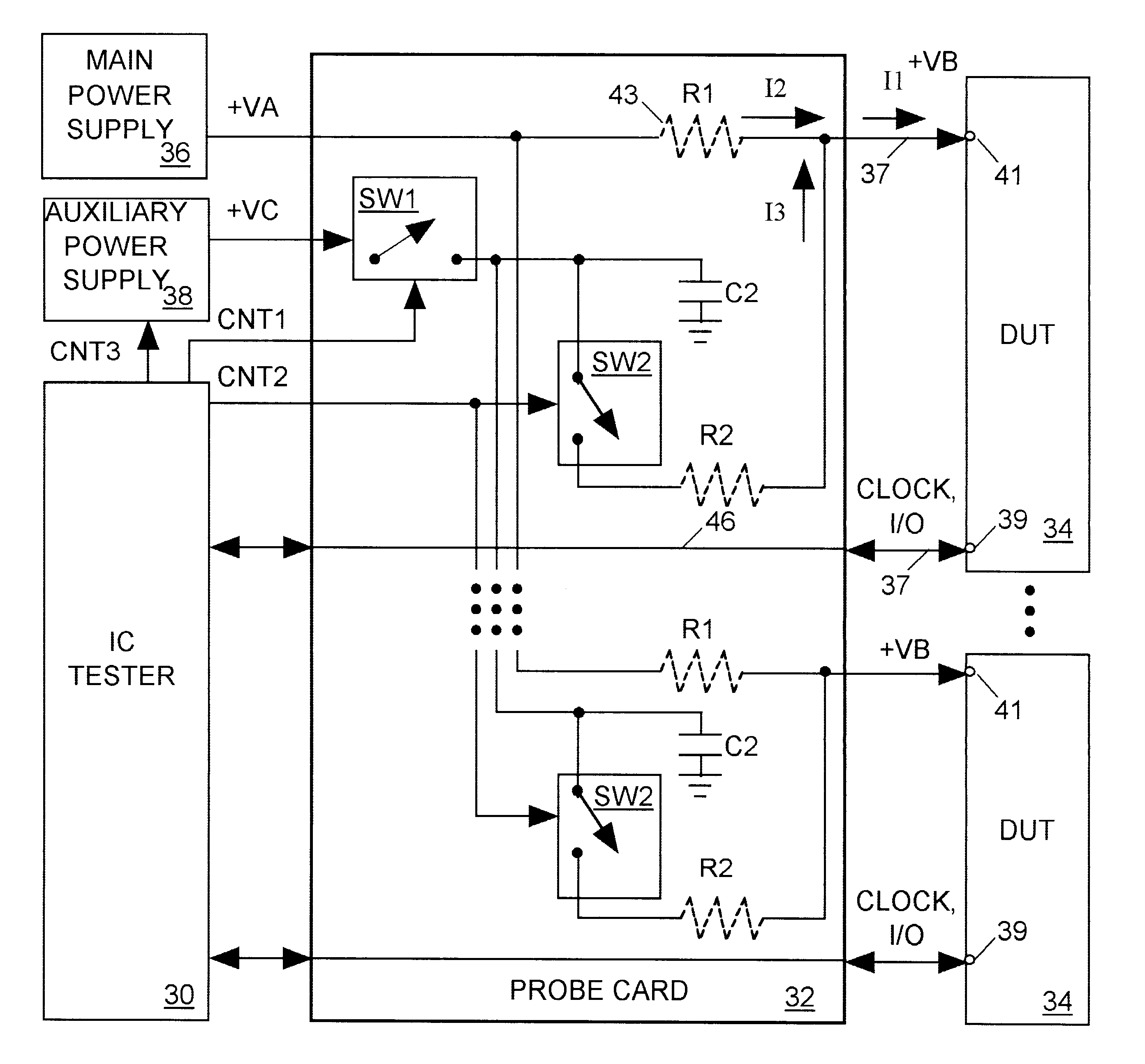

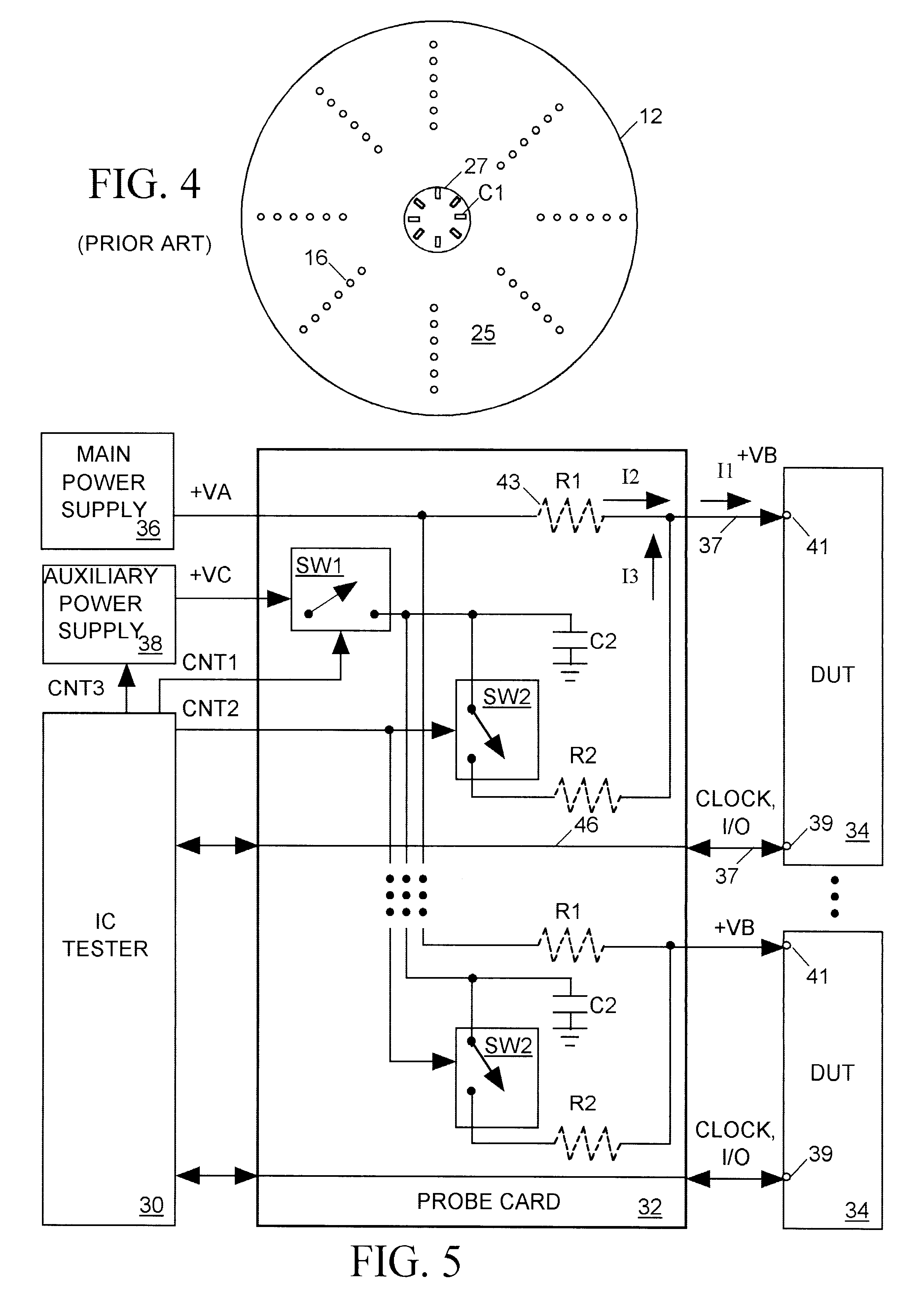

Device for probe card power bus noise reduction

InactiveUS7005879B1Reducing probe card power supply spikeEasy to superviseElectronic circuit testingIndividual semiconductor device testingCapacitancePhysical space

Noise reduction for application of structural test patterns to a Device Under Test (DUT) is accomplished with a capacitor “booster” bypass network on the probe card in which the capacitors are charged to a much higher voltage Vboost than the DUT power supply voltage VDD. Charging the capacitors to a voltage N×VDD allows the buster network to store N times the charge of a conventionally configured capacitance network, and effectively provides N times the capacitance of the original network in the same physical space.

Owner:GLOBALFOUNDRIES INC

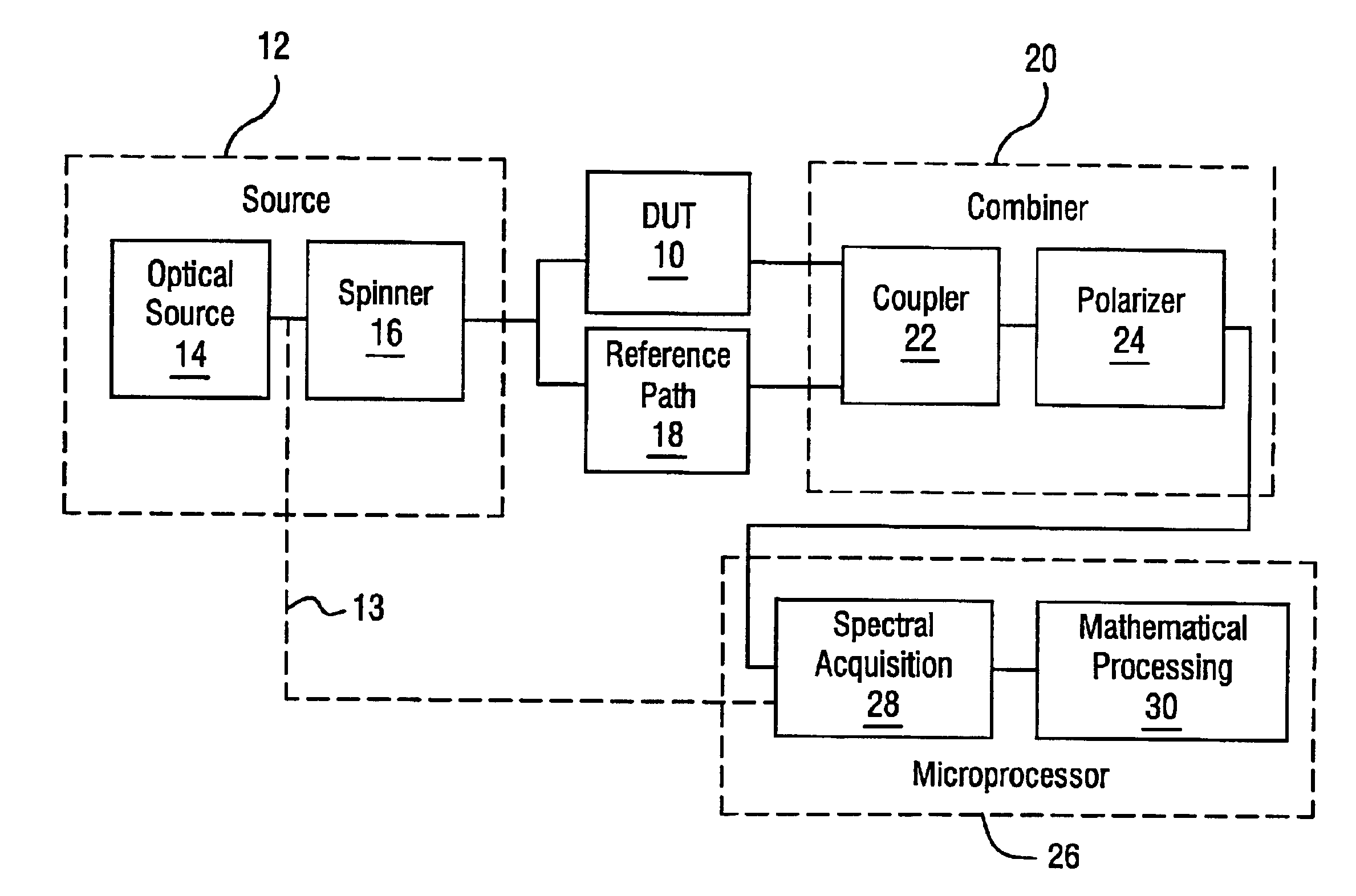

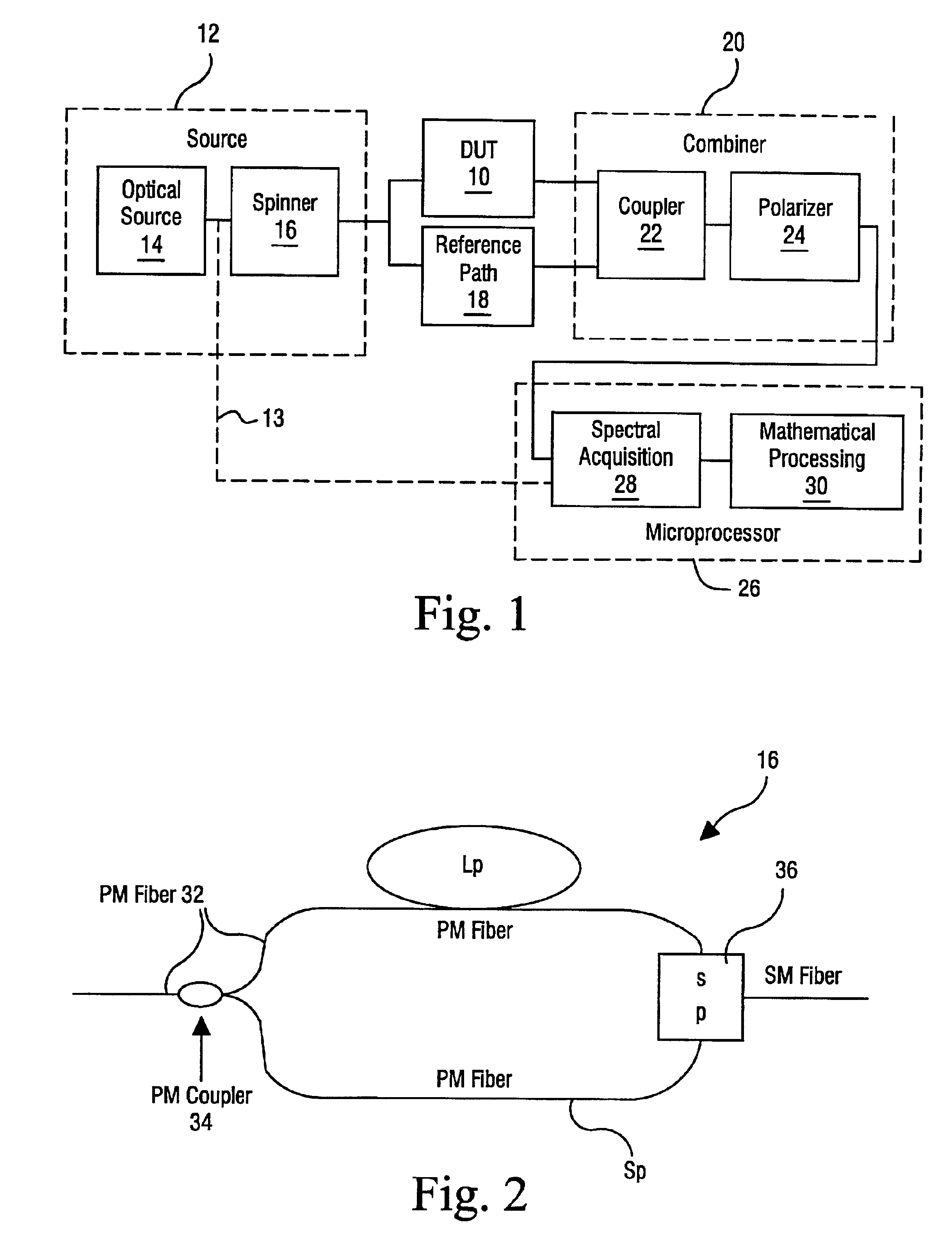

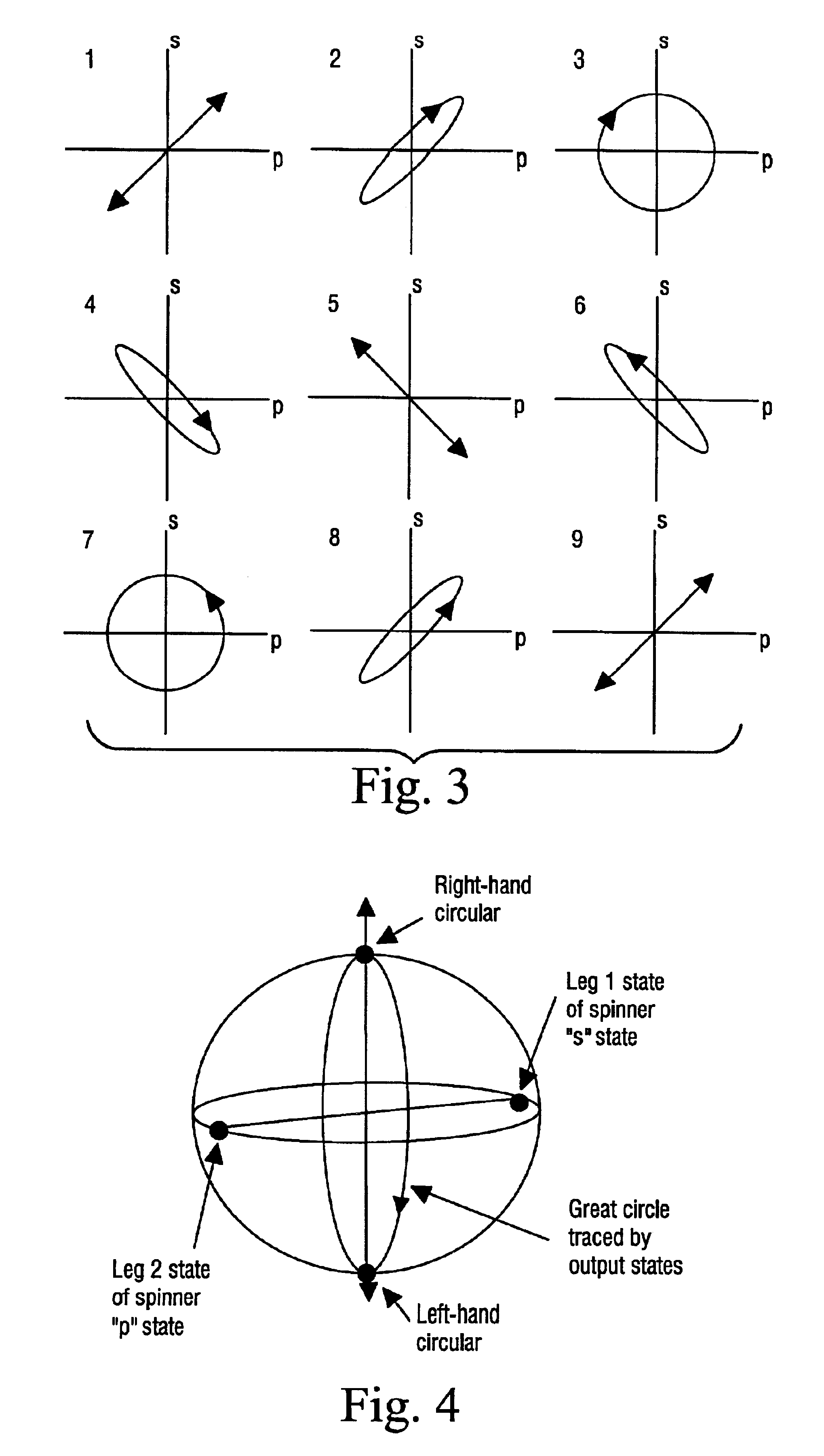

Apparatus and method for the complete characterization of optical devices including loss, birefringence and dispersion effects

InactiveUS6856400B1Reflectometers dealing with polarizationMaterial analysis by optical meansOptical frequenciesCurve fitting

In order to characterize the optical characteristics of a device, a source of light having a variable frequency with a polarization state which varies linearly with frequency is provided as an input to the device under test. The input light is also passed through a known reference path and is added to the light output from the device under test in a beam combiner. The combined light for the frequencies of interest is split into two orthogonal polarizations which are then detected in a spectral acquisition apparatus and supplied to a microprocessor. The spectral measurements are digitized and curve-fitted to provide optical power versus optical frequency curves. Fourier transforms of each of the curves are calculated by the microprocessor. From the Fourier transforms, the four arrays of constants are calculated for the Jones matrix characterizing the device under test.

Owner:INTUITIVE SURGICAL OPERATIONS INC

Method and apparatus for measuring a device under test using an improved through-reflect-line measurement calibration

Owner:AGILENT TECH INC

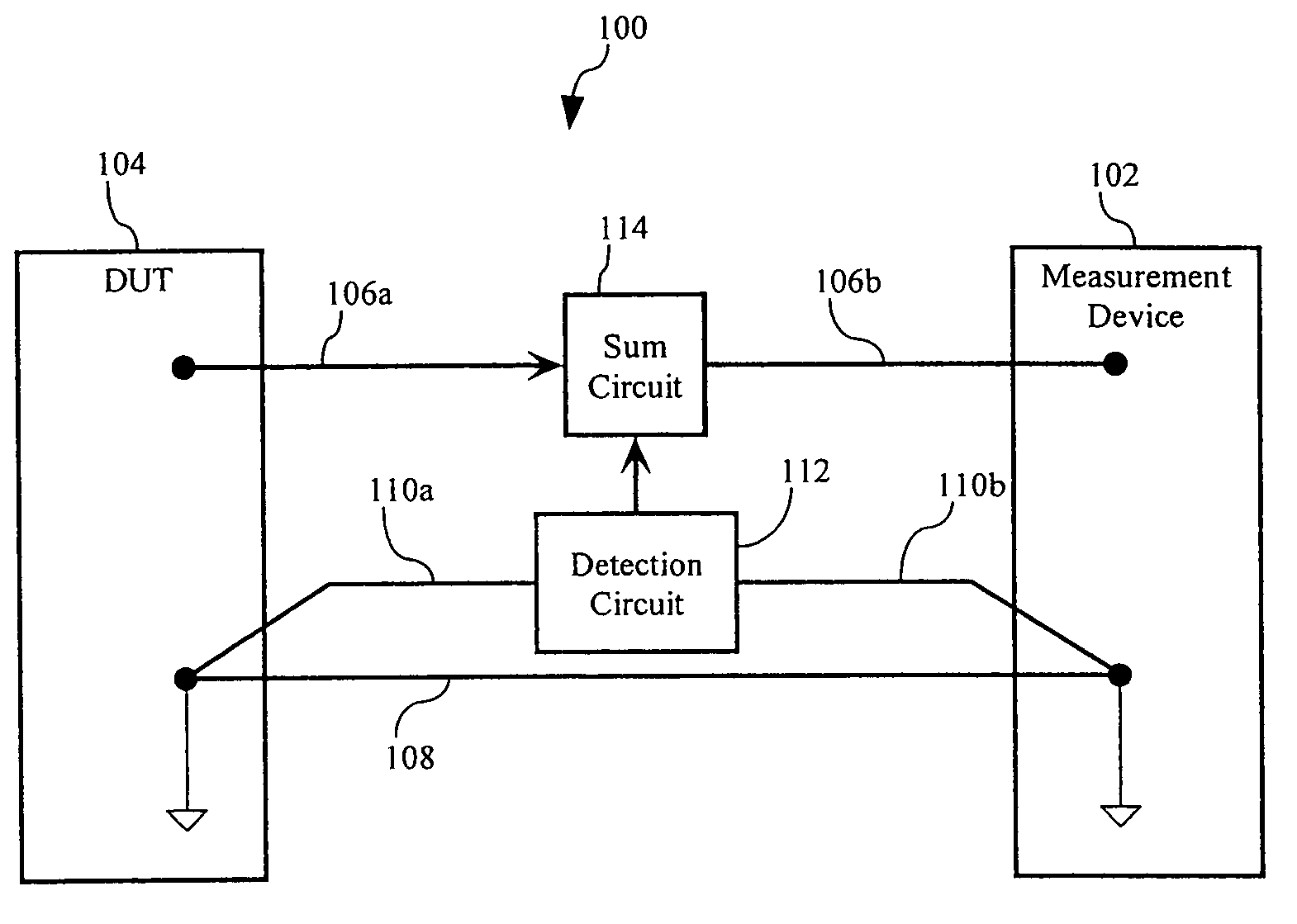

Apparatus and method for canceling DC errors and noise generated by ground shield current in a probe

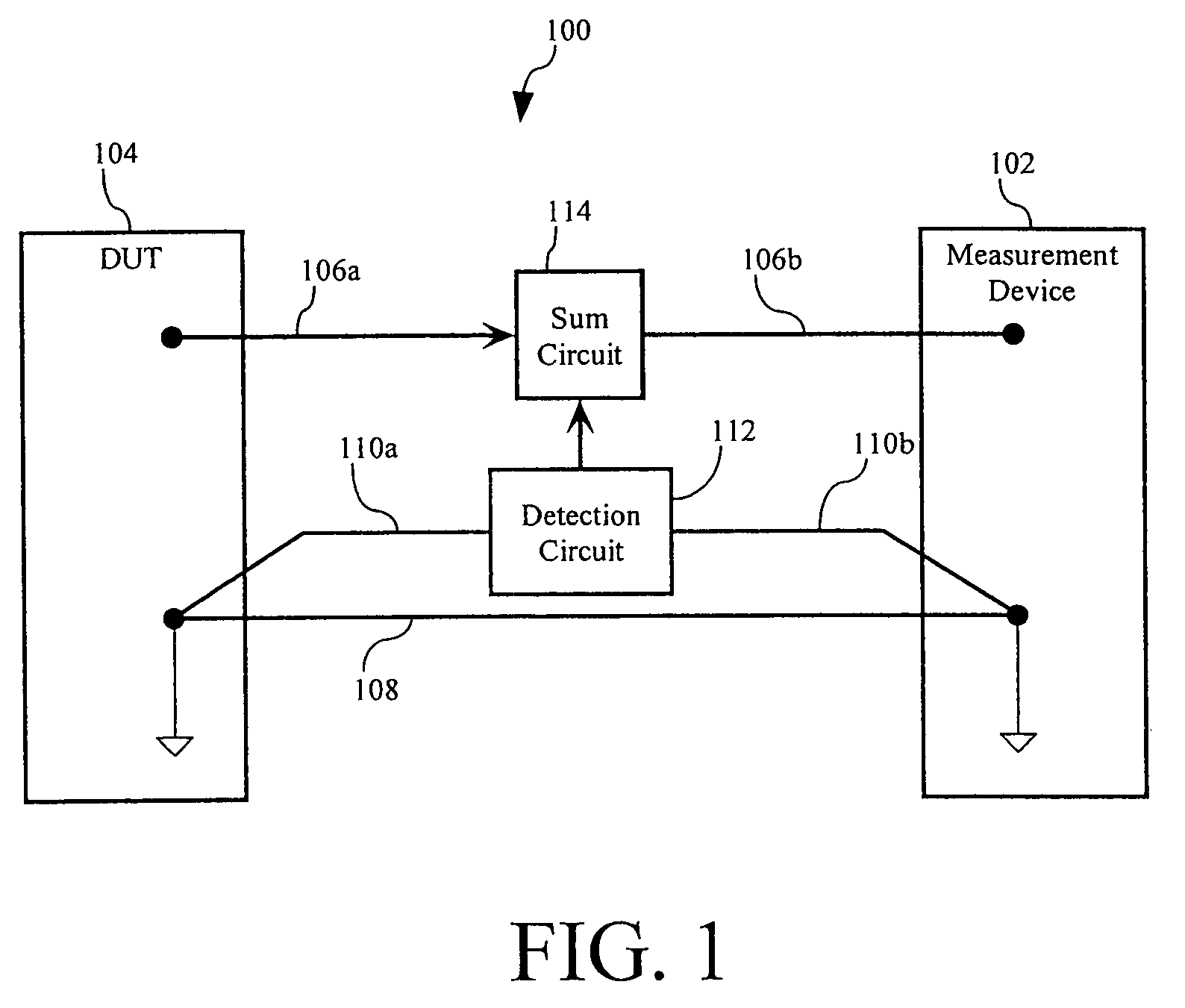

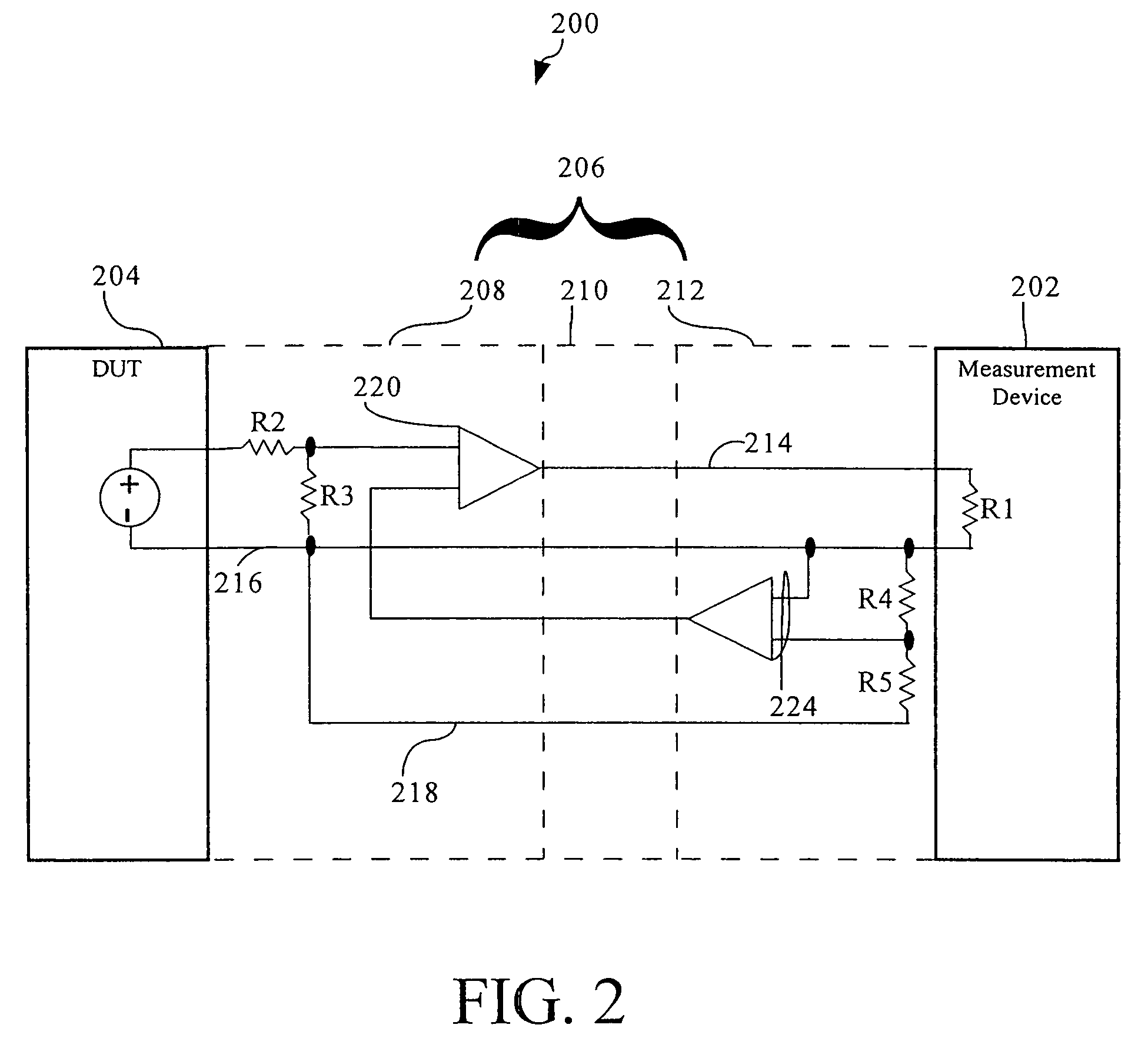

A probe for connecting a device under test to a measurement device that corrects for dc errors and noise generated by the current flowing through the ground shield of a transmission line used by the probe. The probe identifies a voltage drop in the ground preferably using an additional line between the device under test and the measurement device. The signal provided to the measurement device is corrected based on the identified voltage drop.

Owner:AGILENT TECH INC

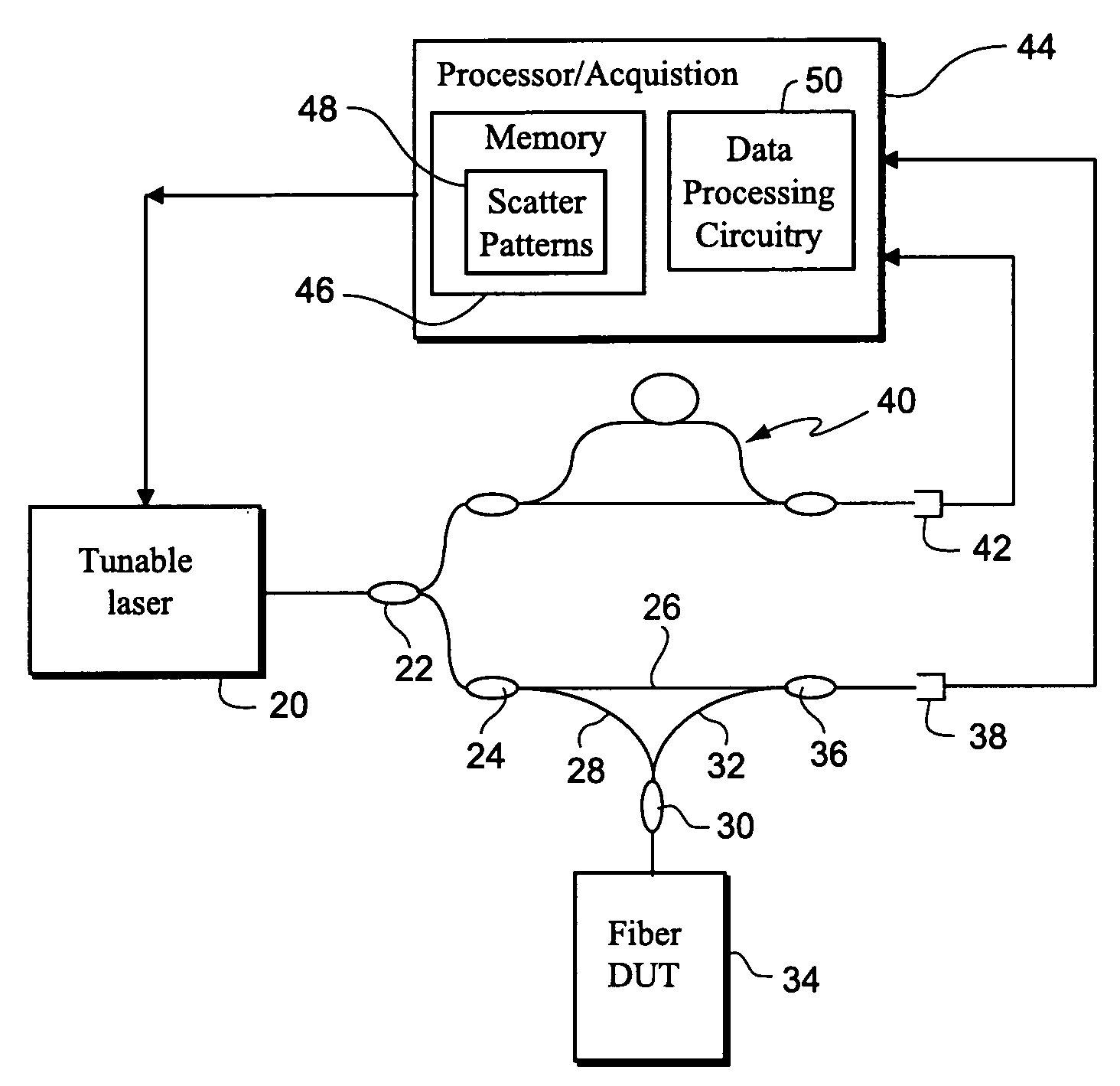

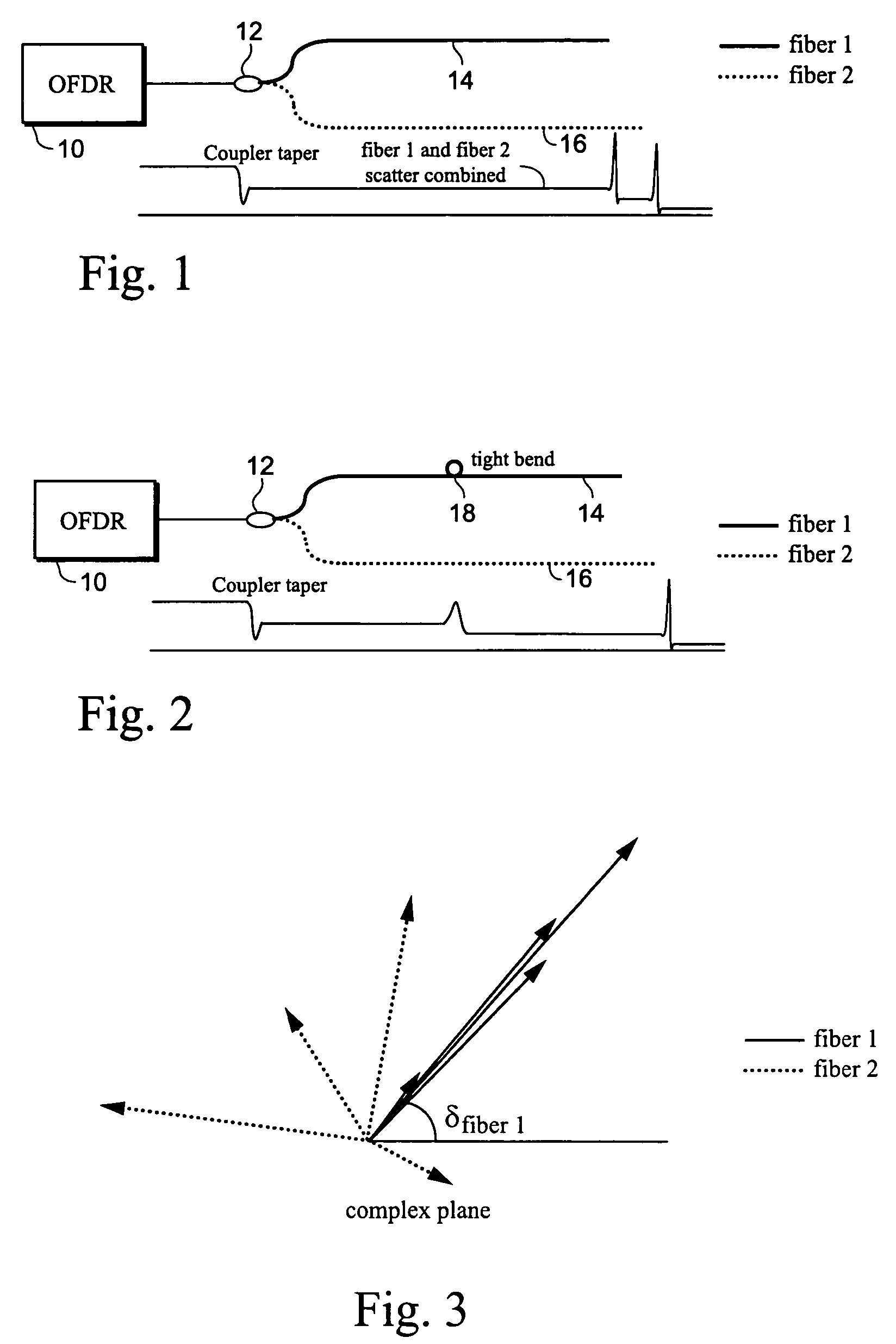

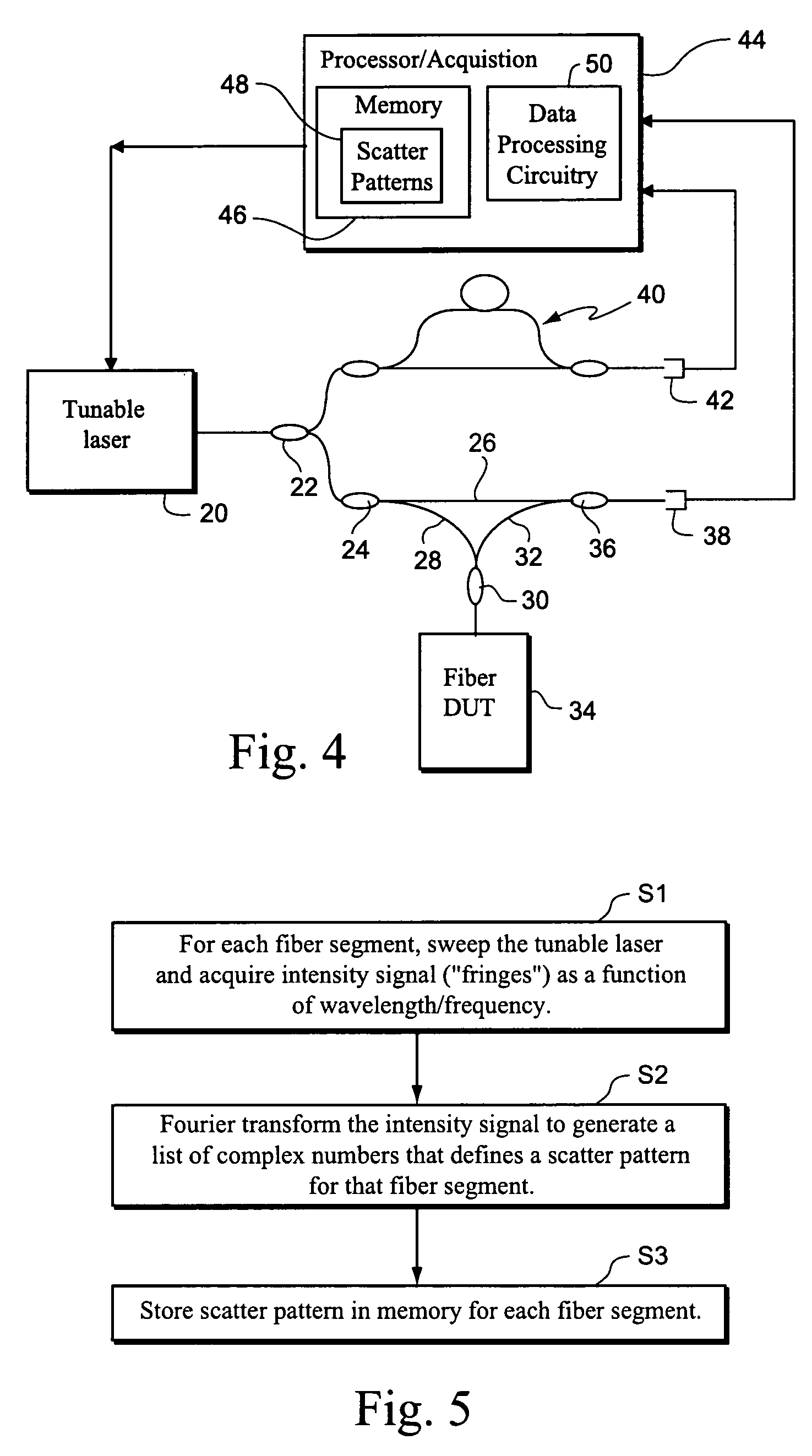

Identifying optical fiber segments and determining characteristics of an optical device under test based on fiber segment scatter pattern data

ActiveUS7440087B2Quick and efficient repairMaterial analysis by optical meansOptical light guidesComputer scienceDevice under test

Complex data is obtained from OFDR backscatter measurements for an optical device under test (DUT). That complex scatter pattern data may be used along with a previously-determined fiber segment pattern to identify the fiber segment within the DUT, even when the DUT is an optical network DUT that includes multiple fibers coupled to perform one or more functions. In other non-limiting example applications, the OFDR scatter pattern data can be used to identify where in the DUT a loss occurred and where in the DUT a temperature change occurred.

Owner:INTUITIVE SURGICAL OPERATIONS INC

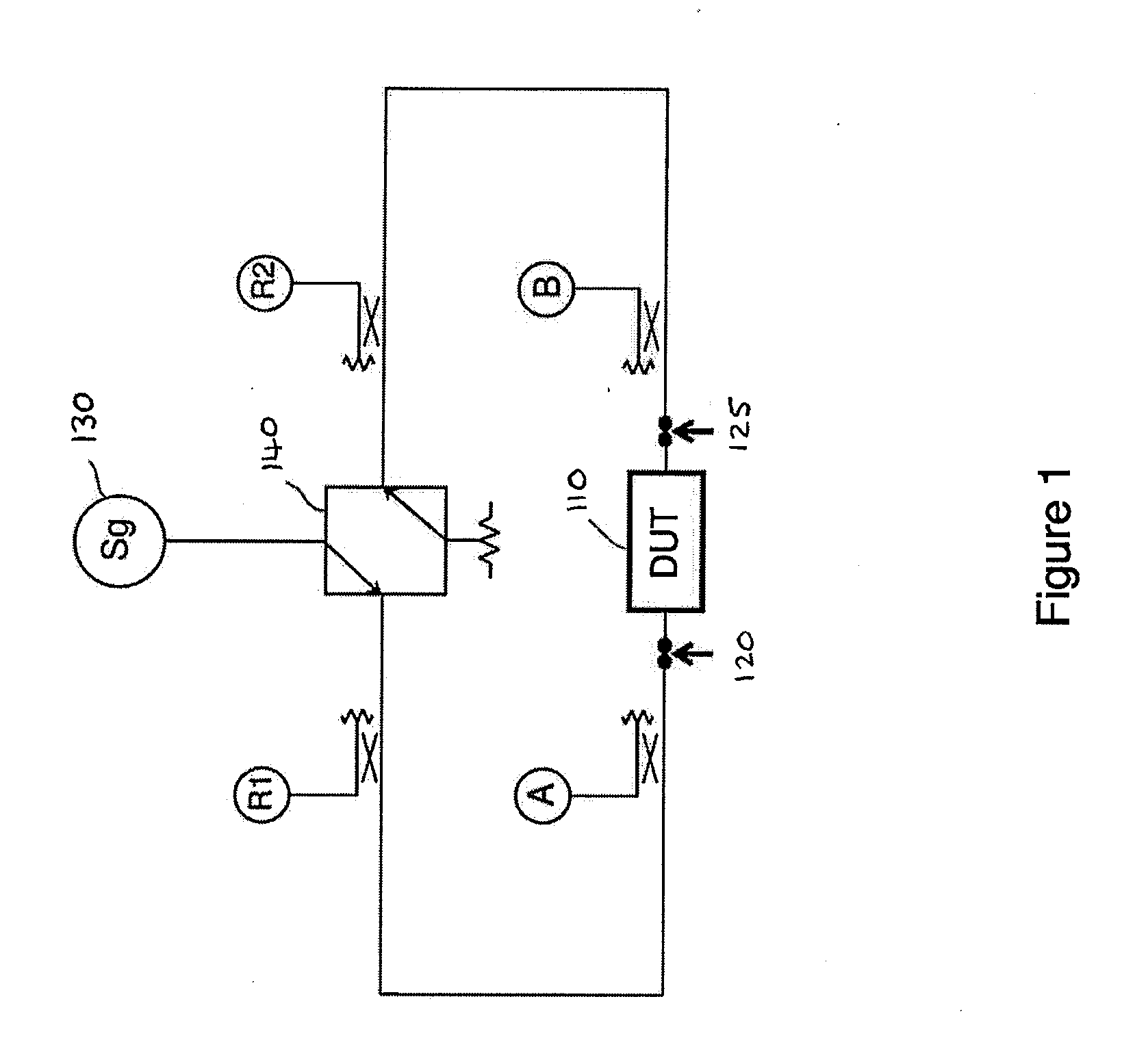

Predictive, adaptive power supply for an integrated circuit under test

InactiveUS6657455B2Suppress mutationReduce noiseDigital circuit testingSemiconductor/solid-state device testing/measurementPower flowFeedback circuits

Owner:FORMFACTOR INC

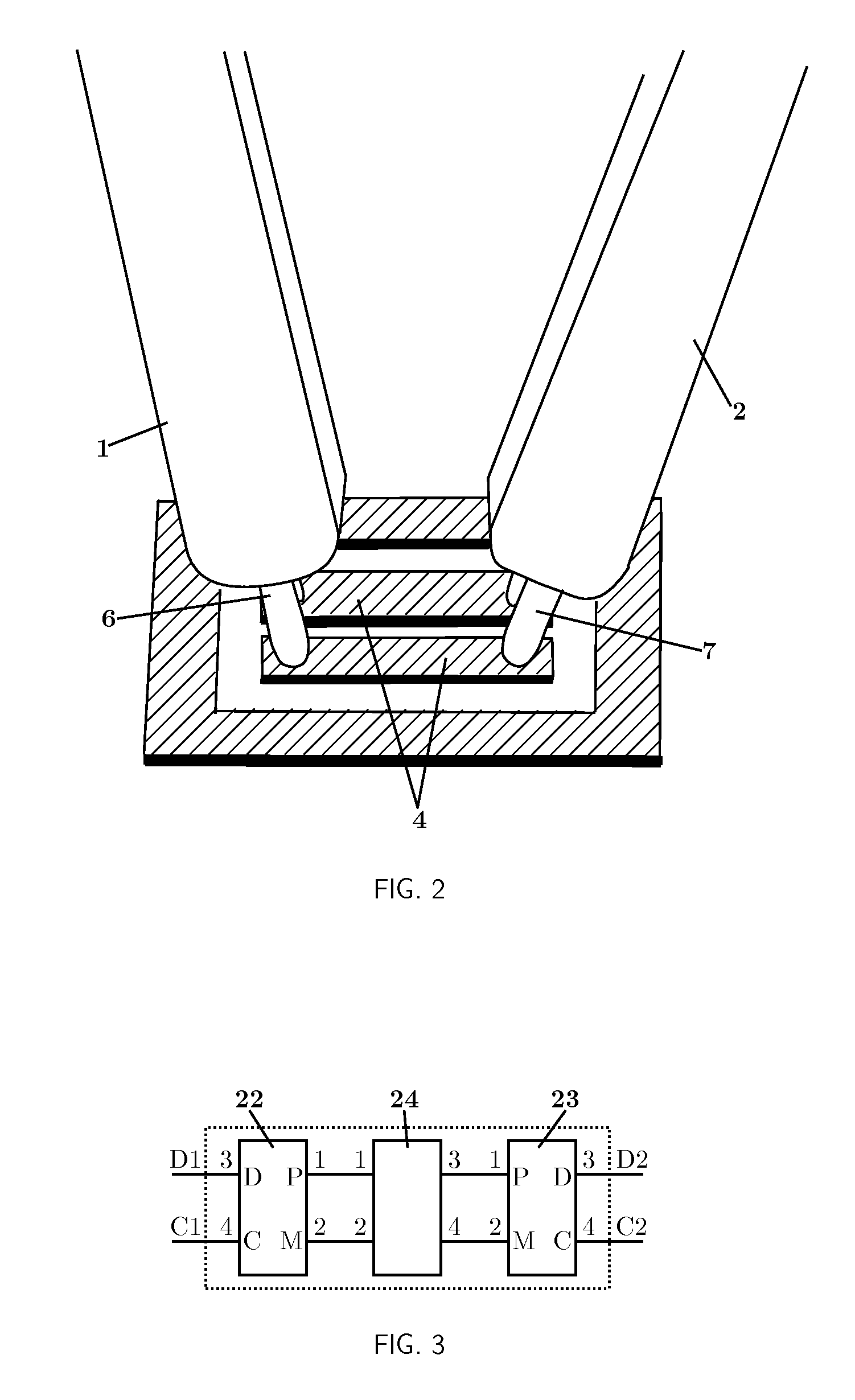

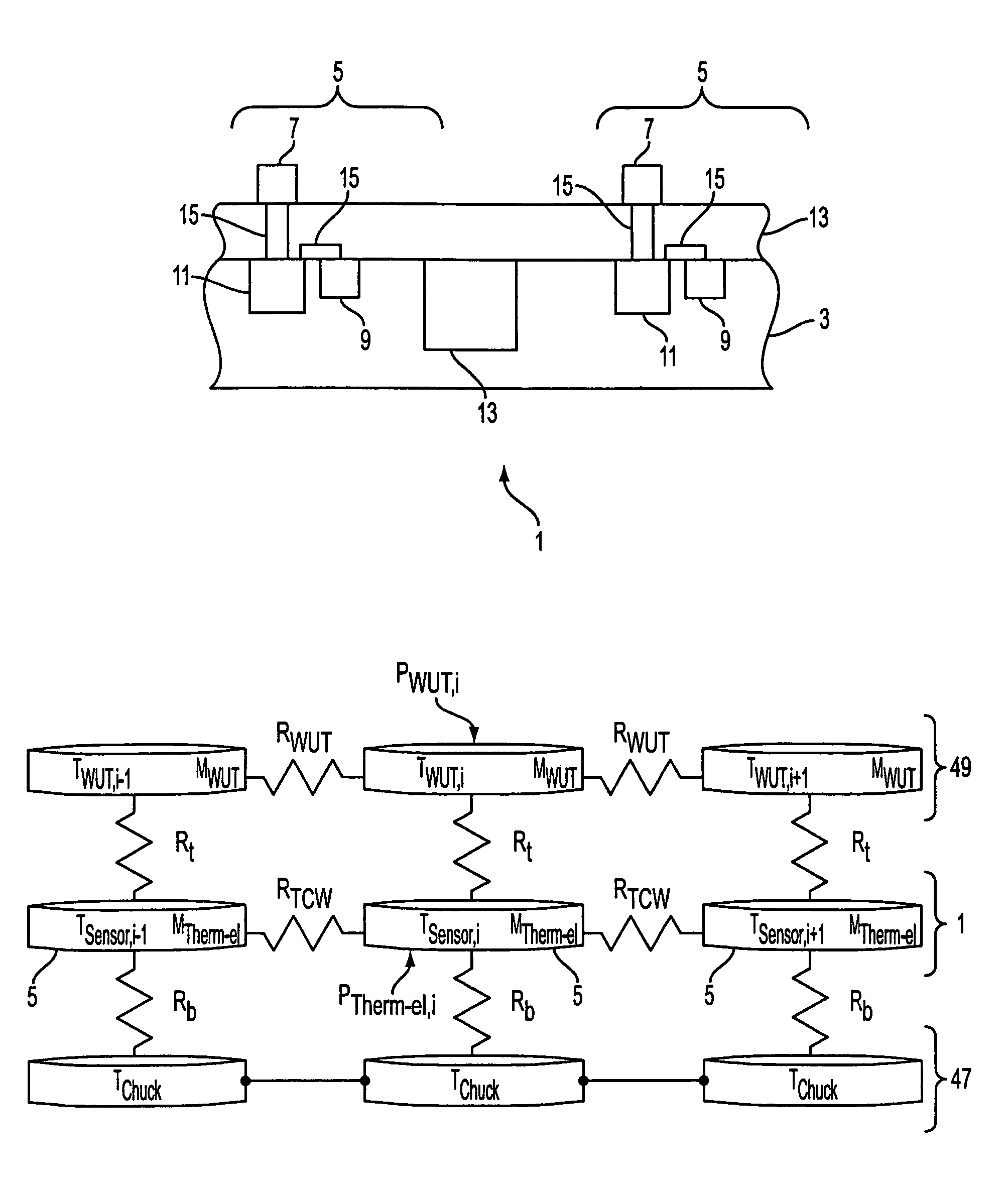

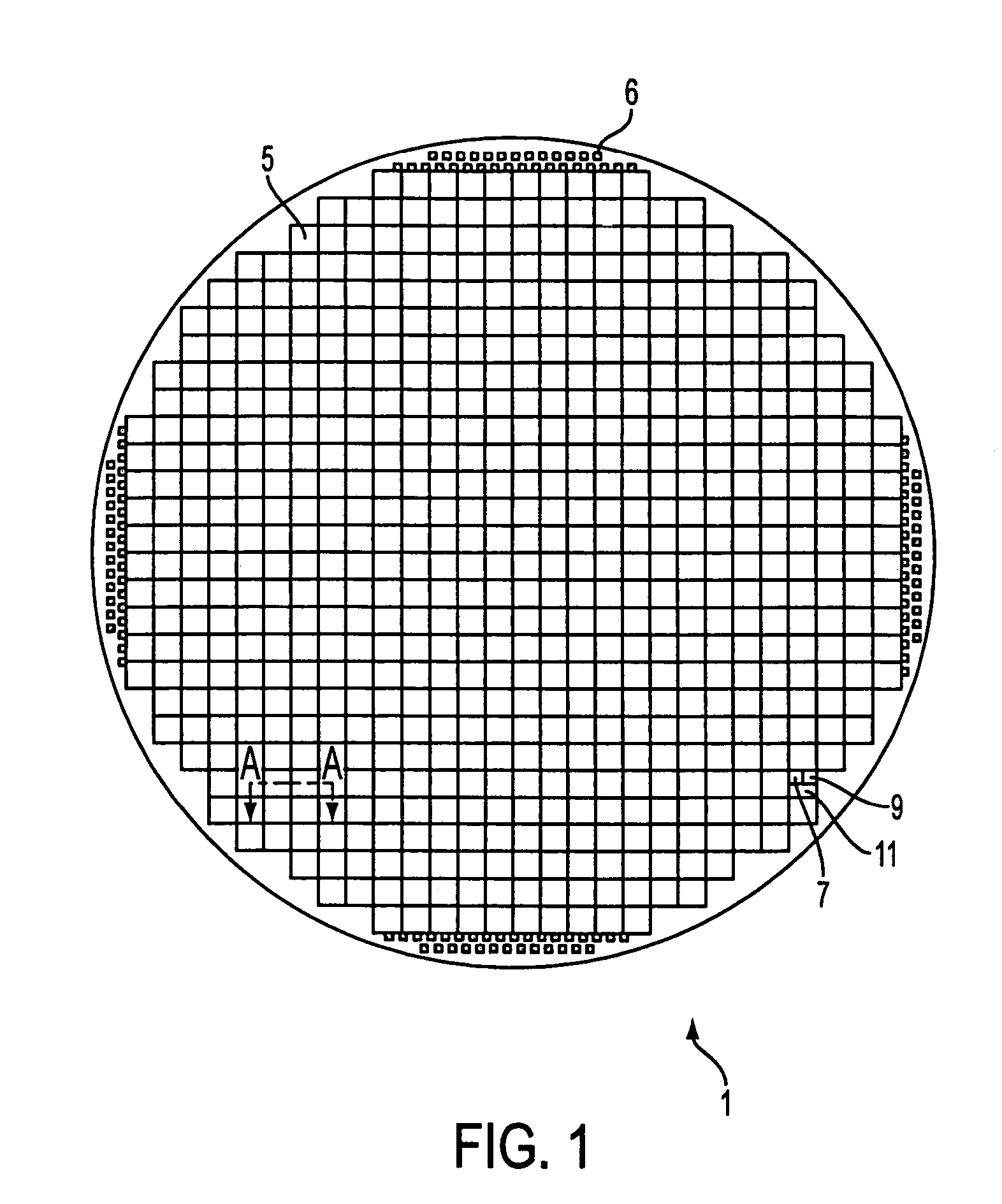

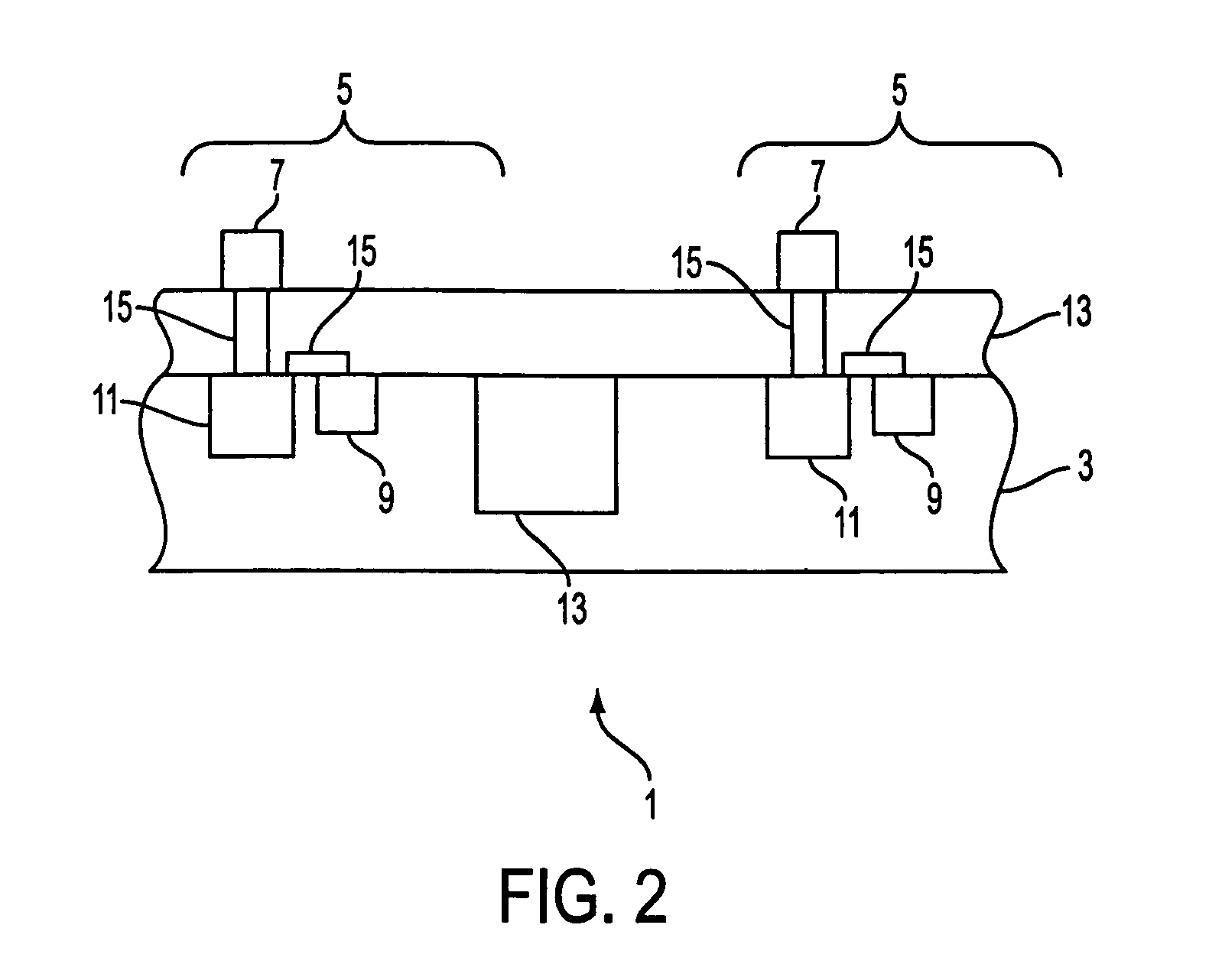

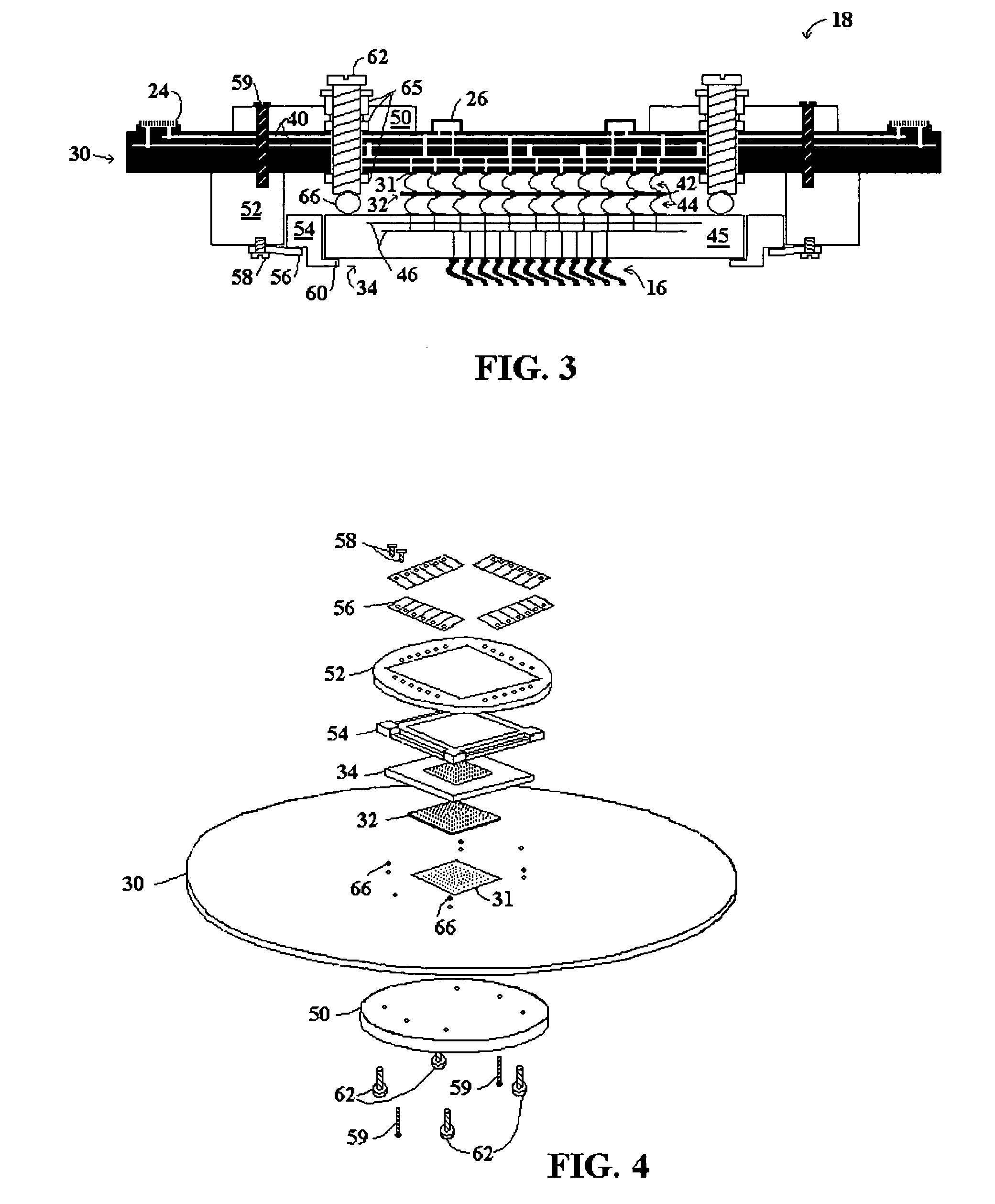

Thermal control of a DUT using a thermal control substrate

A solid state thermal control device contains a substrate and a plurality of solid state thermal elements on the substrate. The thermal elements are adapted to provide thermal control to a device under test (DUT). Each solid state thermal element contains at least one solid state heater and an active control circuit adapted to control a thermal output of the heater. Optionally, the each thermal element may also include a solid state temperature sensor.

Owner:DELTA DESIGN

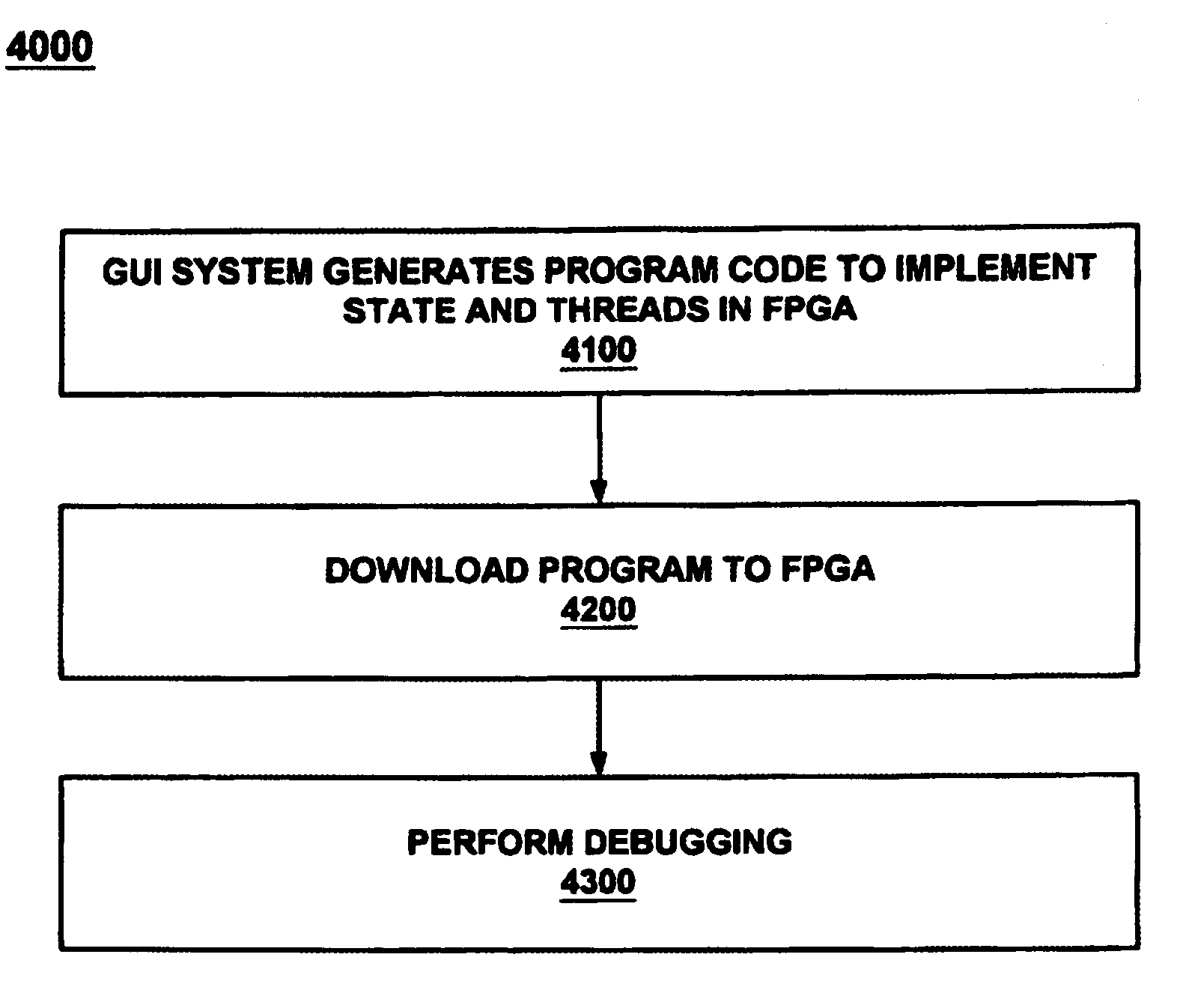

Graphical user interface with logic unifying functions

ActiveUS7150002B1Easy programmingError detection/correctionSpecific program execution arrangementsGraphical user interfaceSoftware engineering

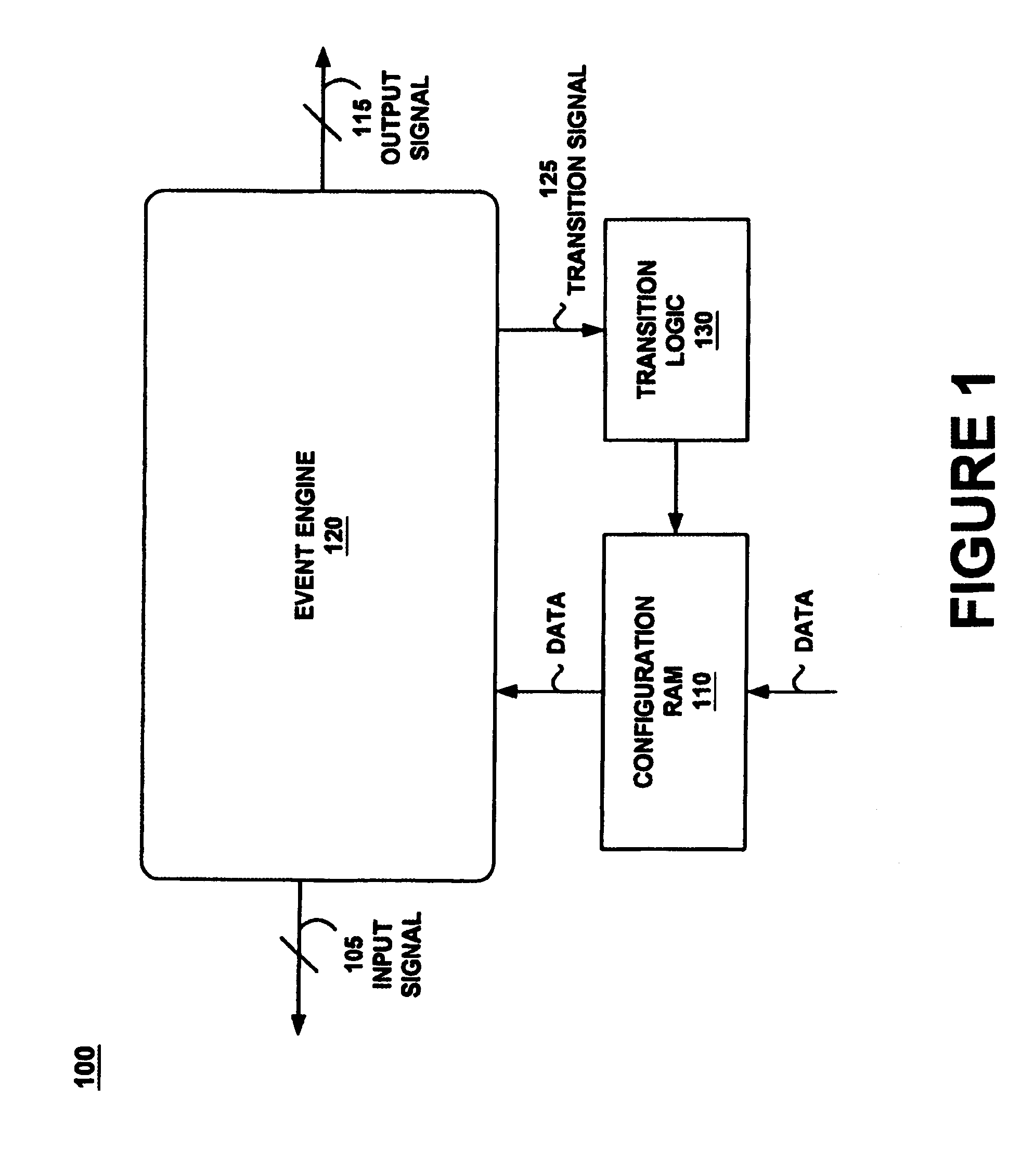

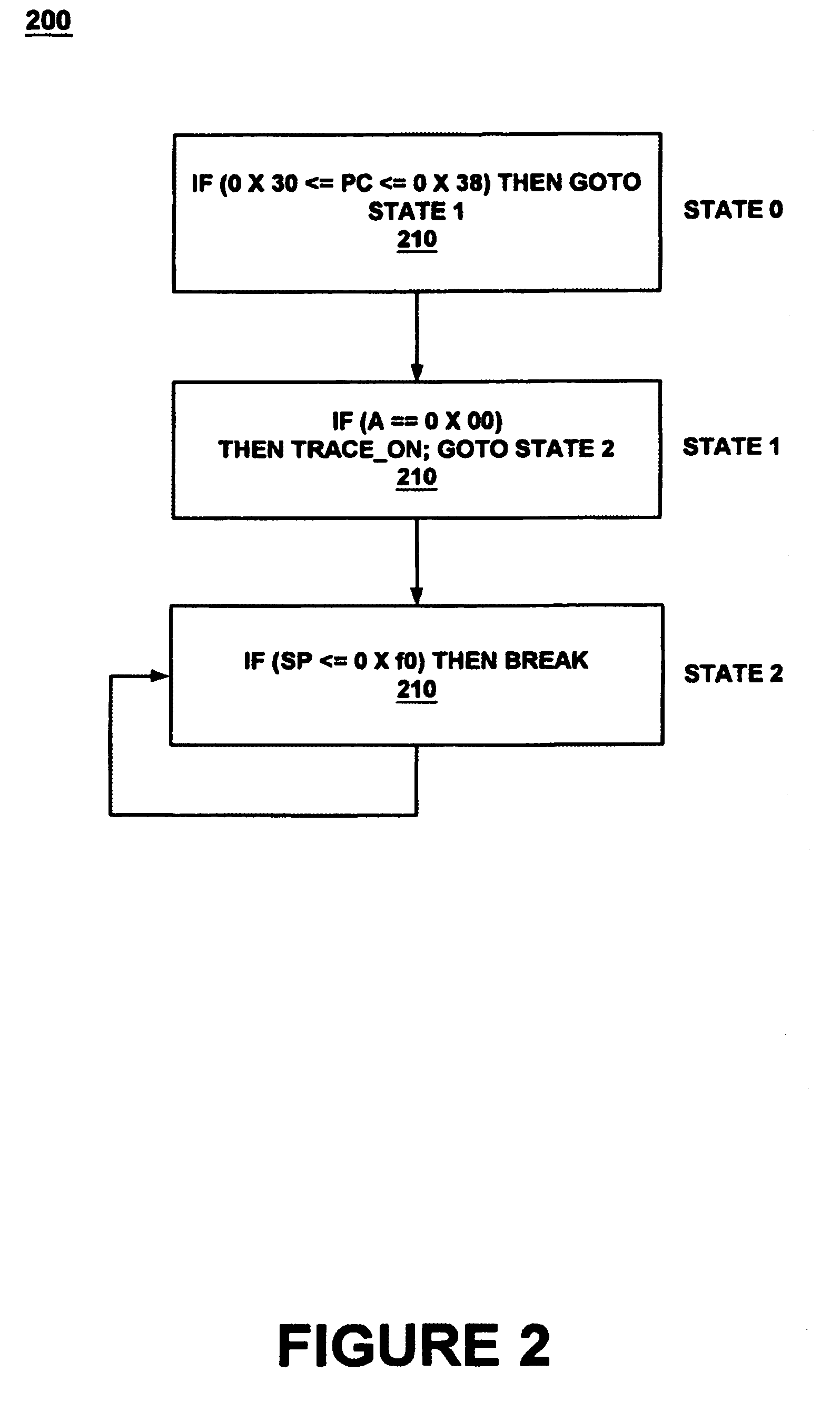

Programming a plurality of states having respective threads is achieved by an event engine and a computer controlled GUI causing the event engine to monitor a signal and execute an action based thereon. The GUI programs an event and several states and causes the event engine to traverse between the states upon reaching the event. The GUI further programs a logic chain which unifies the threads. A method unifies several threads by selecting and executing a logic operation. The method further configures several states and causes traversing between them. The GUI may be deployed co-functionally with debuggers, logic analyzers, scopes, utilities, and software development tools. The results of the GUI are automatically transformed into program code which programs the event engine to operate during debug of a device under test by monitoring for events and taking action based thereon.

Owner:MONTEREY RES LLC

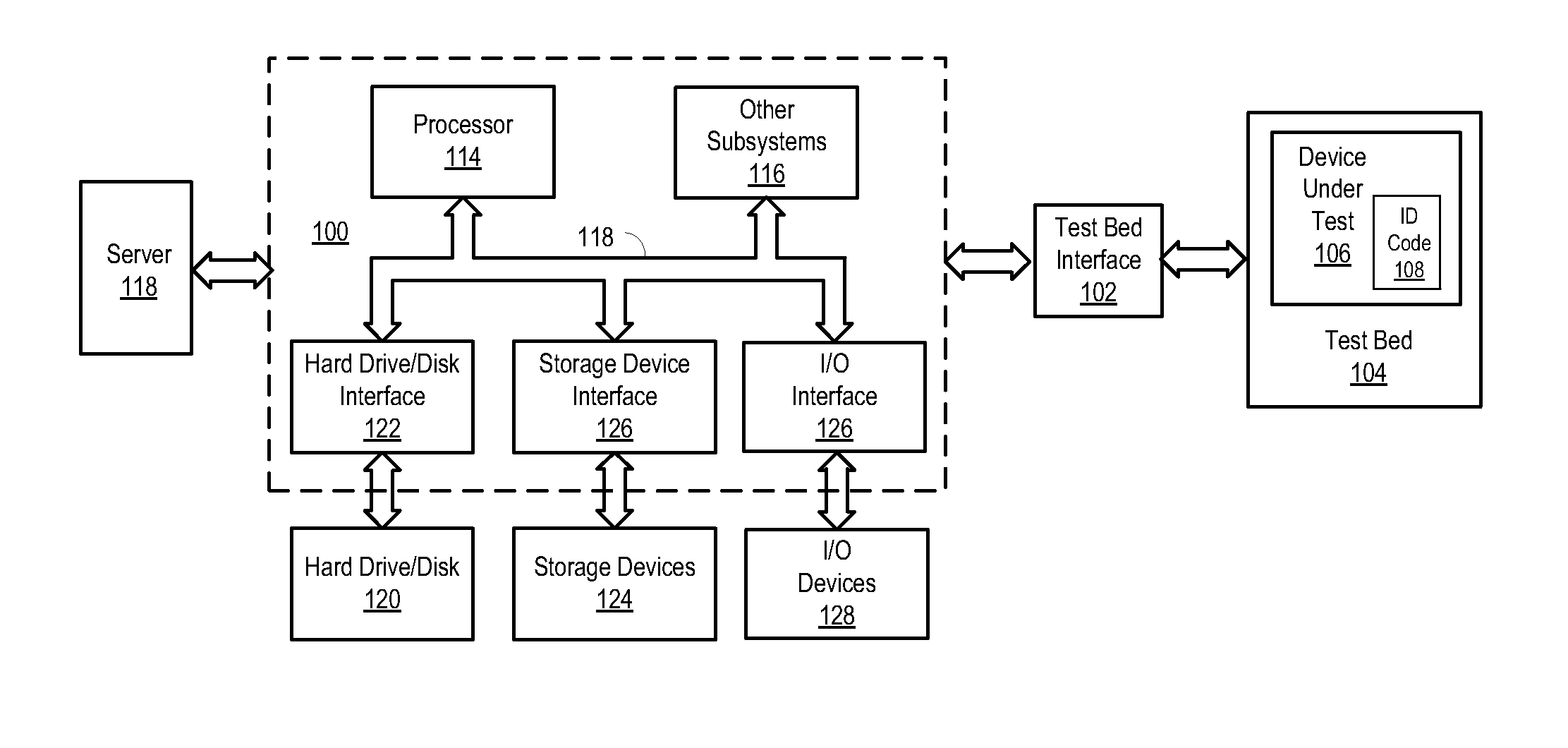

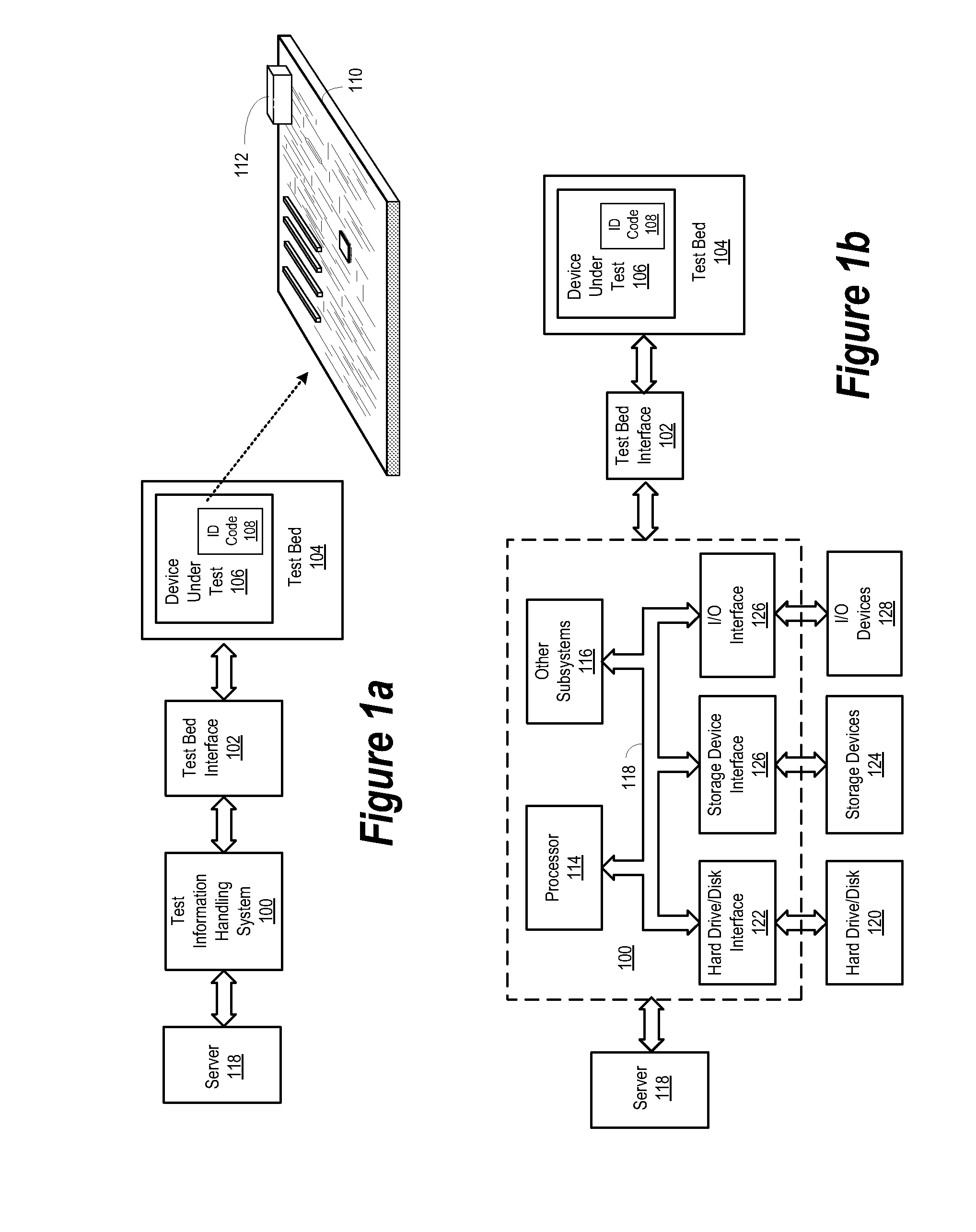

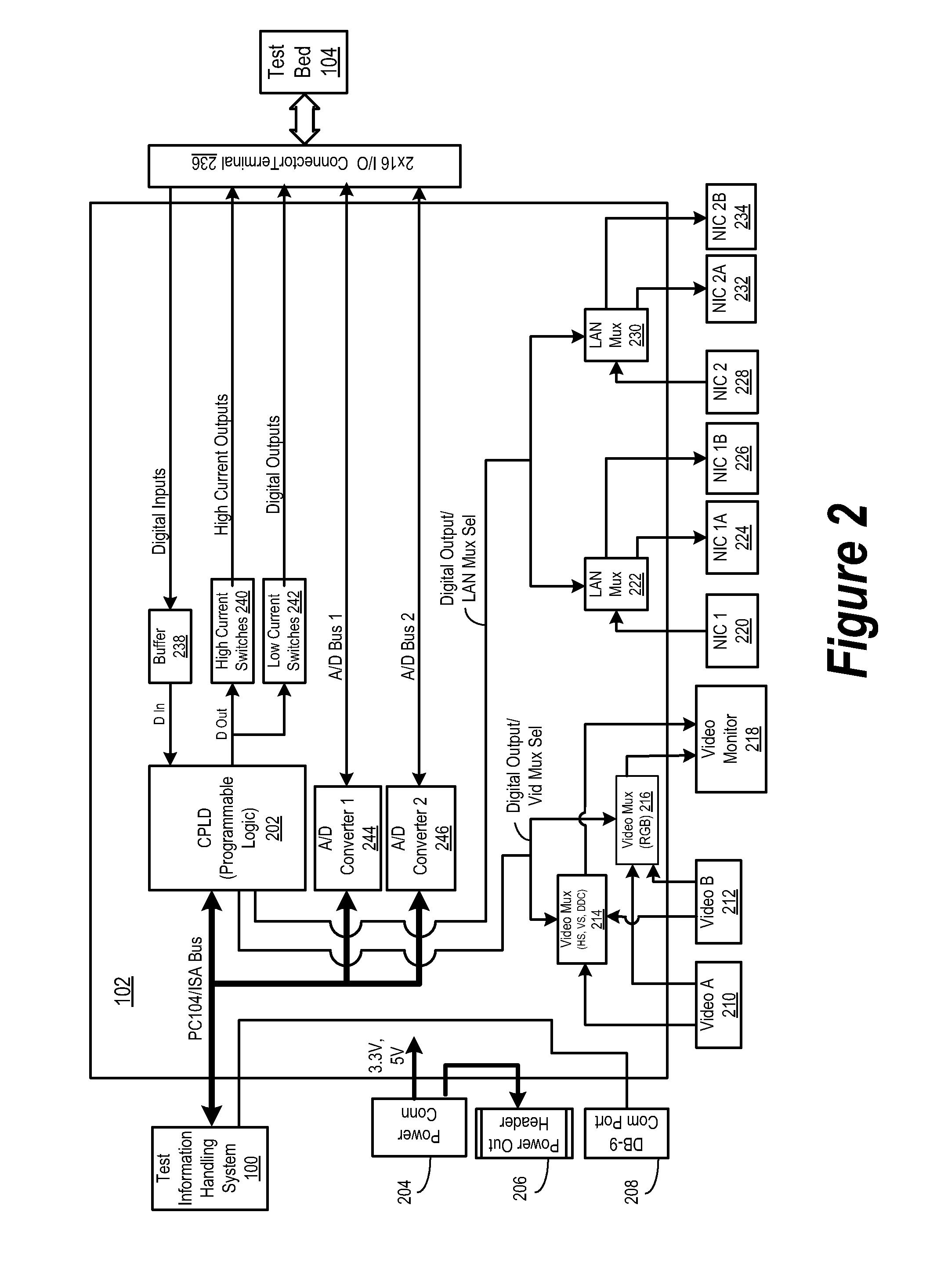

System and method for testing information handling system components

InactiveUS20080262759A1Quickly and easily swappedElectrical testingSpecial data processing applicationsControl signalHandling system

A system and method is disclosed for testing components used in the manufacture of information handling systems. In embodiments of the invention, a device-under-test (DUT) comprises a DUT identifier code. The DUT is operably coupled to a test bed. An information handling system is operable to use the identifier code to select and execute a predetermined test program to generate a plurality of test commands. A test bed interface is operable to receive the test commands and to generate a plurality of test control signals therefrom to perform a predetermined set of tests of said DUT.

Owner:DELL PROD LP

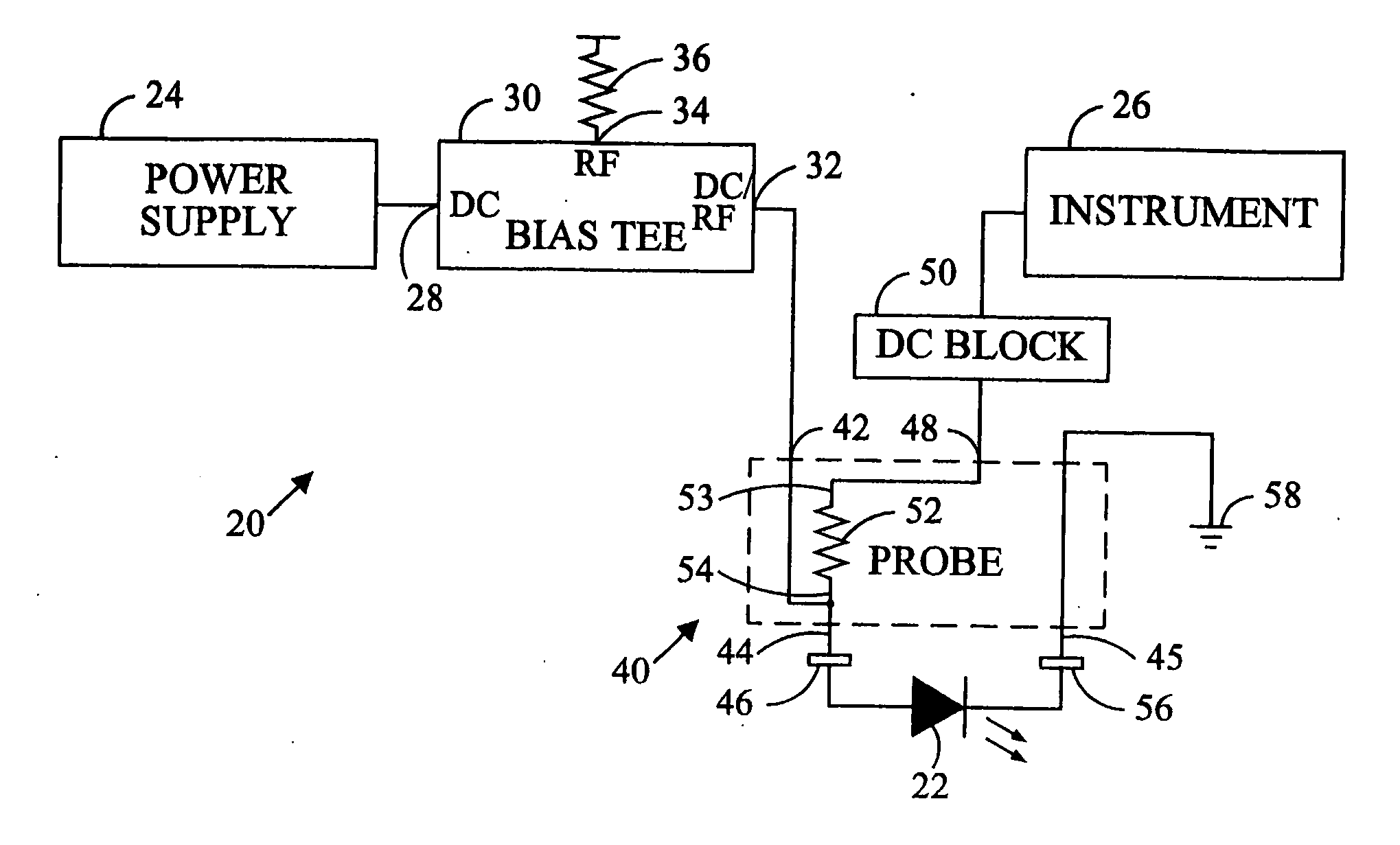

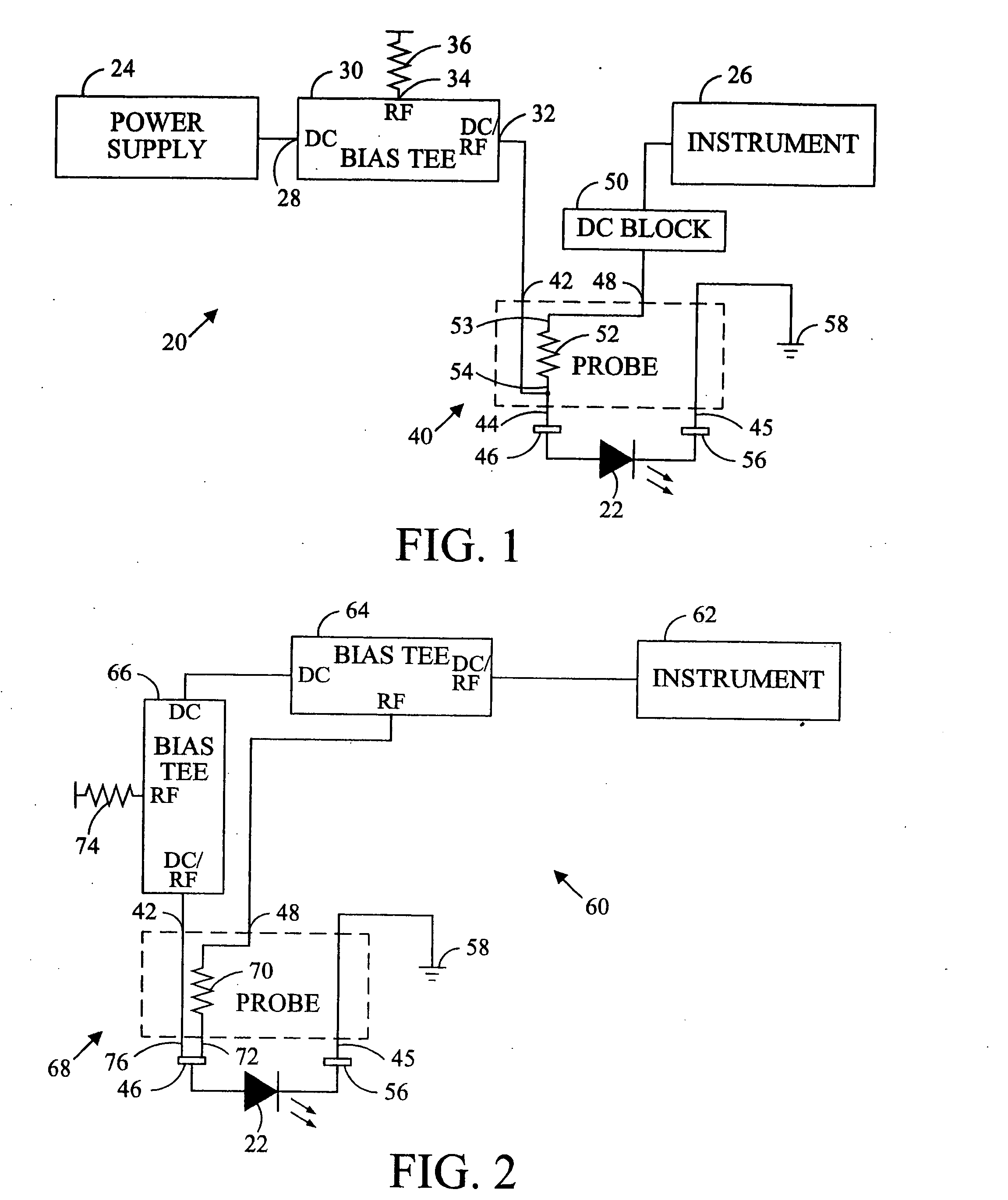

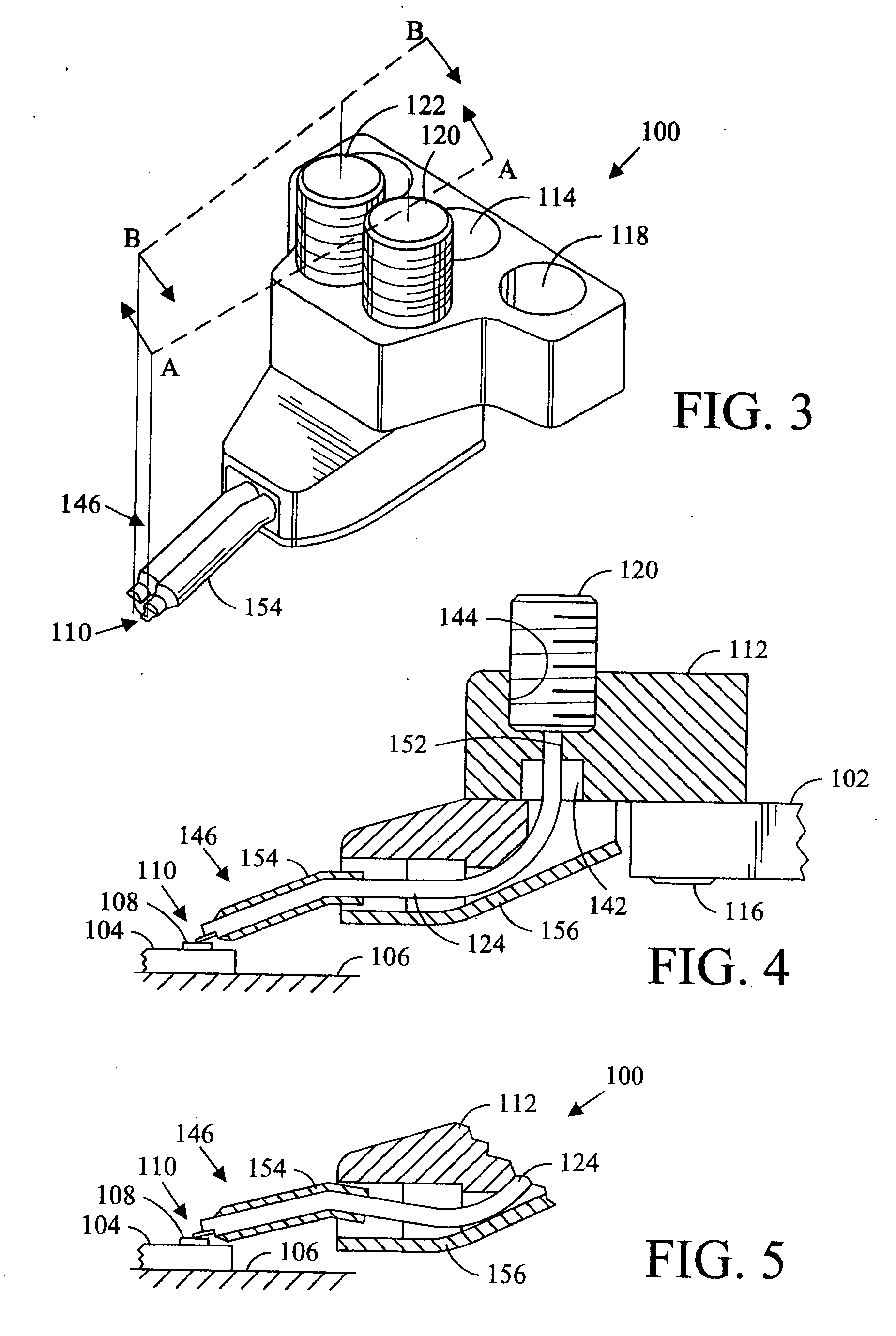

Probe for combined signals

InactiveUS20050024069A1Semiconductor/solid-state device testing/measurementElectronic circuit testingContact padImpedance matching

A direct current and a modulation signal are simultaneously applied to contact pads on a device under test, such as a laser diode. A probe and method of probing reduces signal distortion and power dissipation by transmitting a modulated signal to the device-under-test through an impedance matching resistor and transmitting of a direct current to the device-under-test over a second signal path that avoids the impedance matching resistor.

Owner:CASCADE MICROTECH

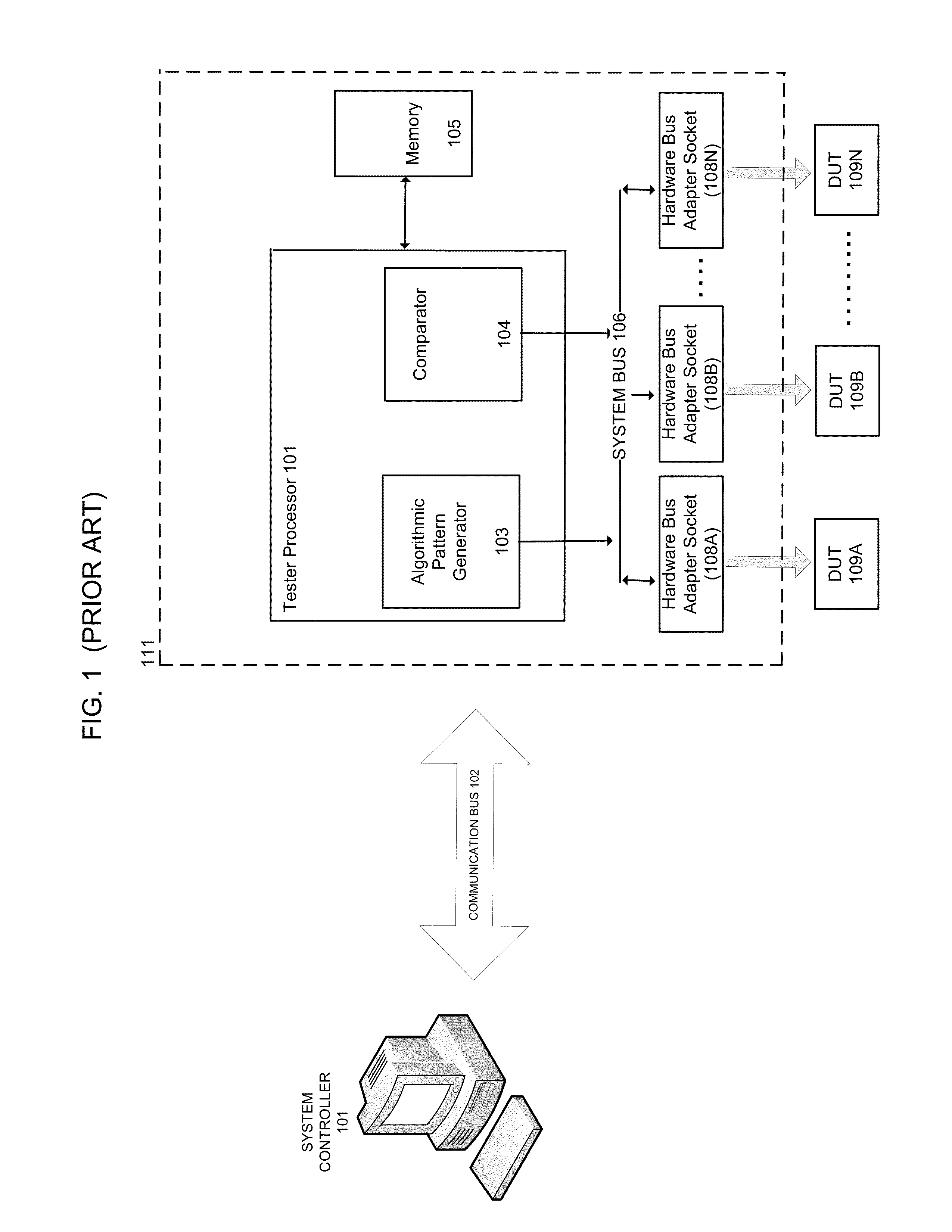

Method and apparatus for testing integrated circuits

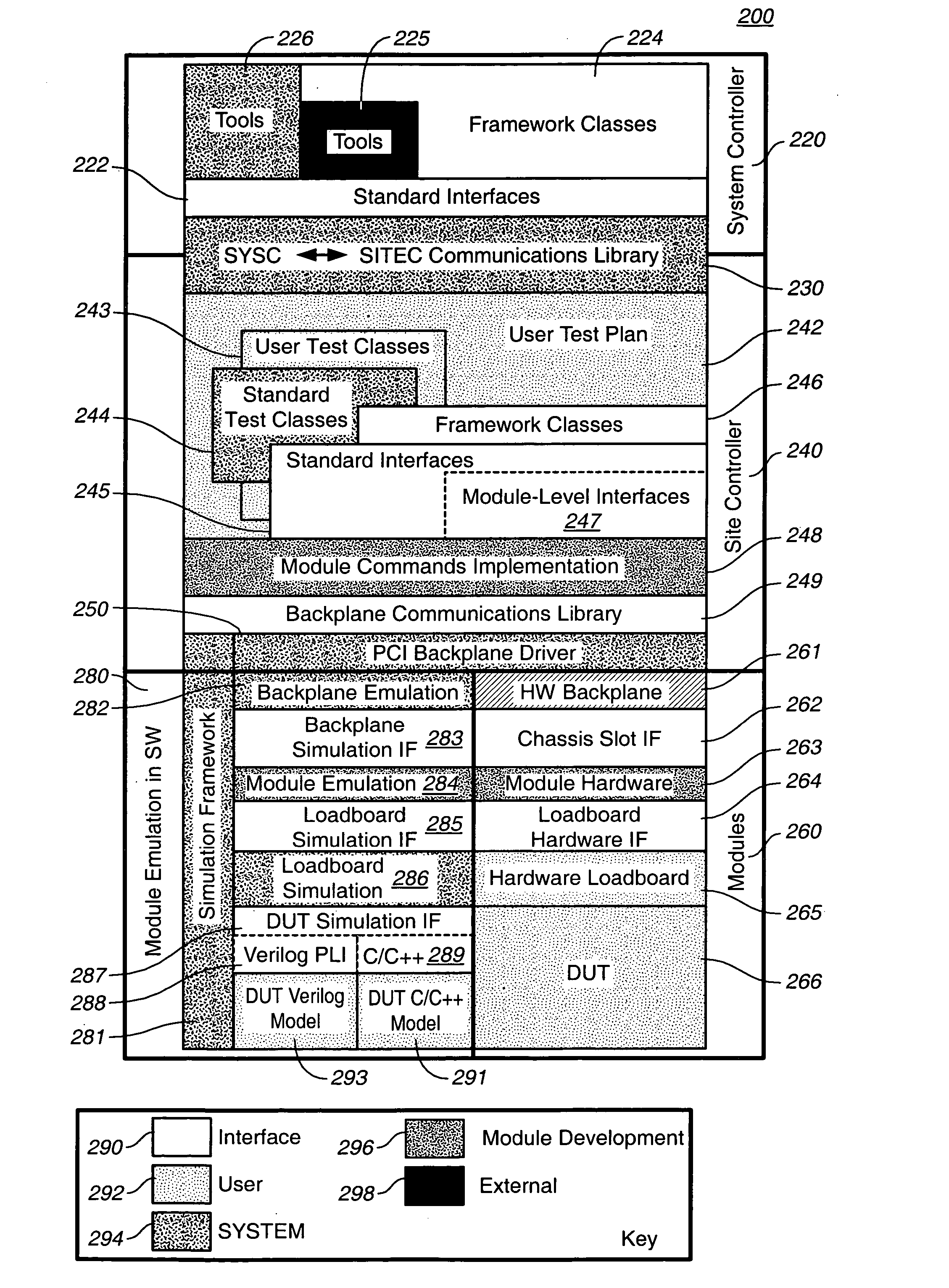

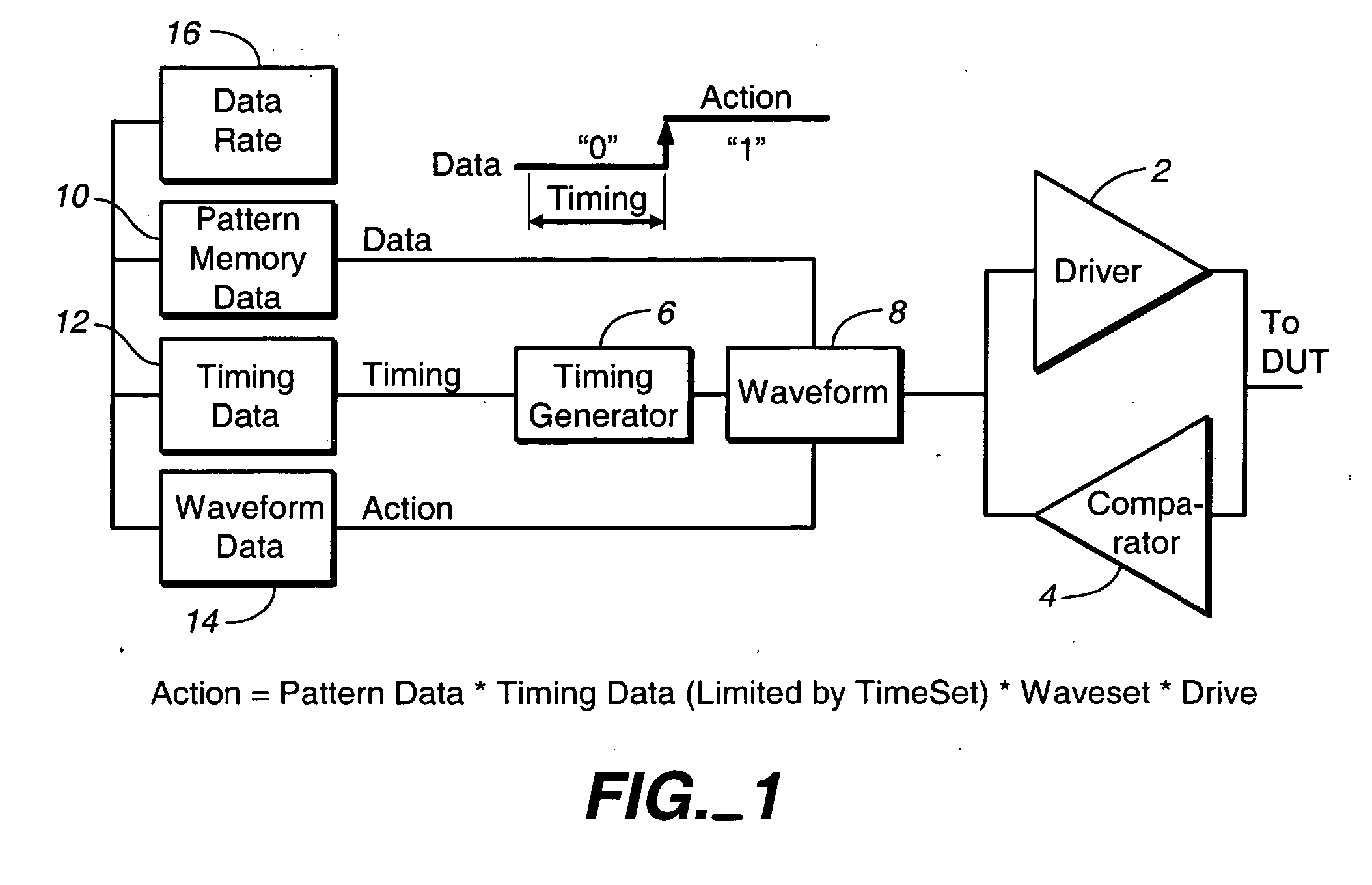

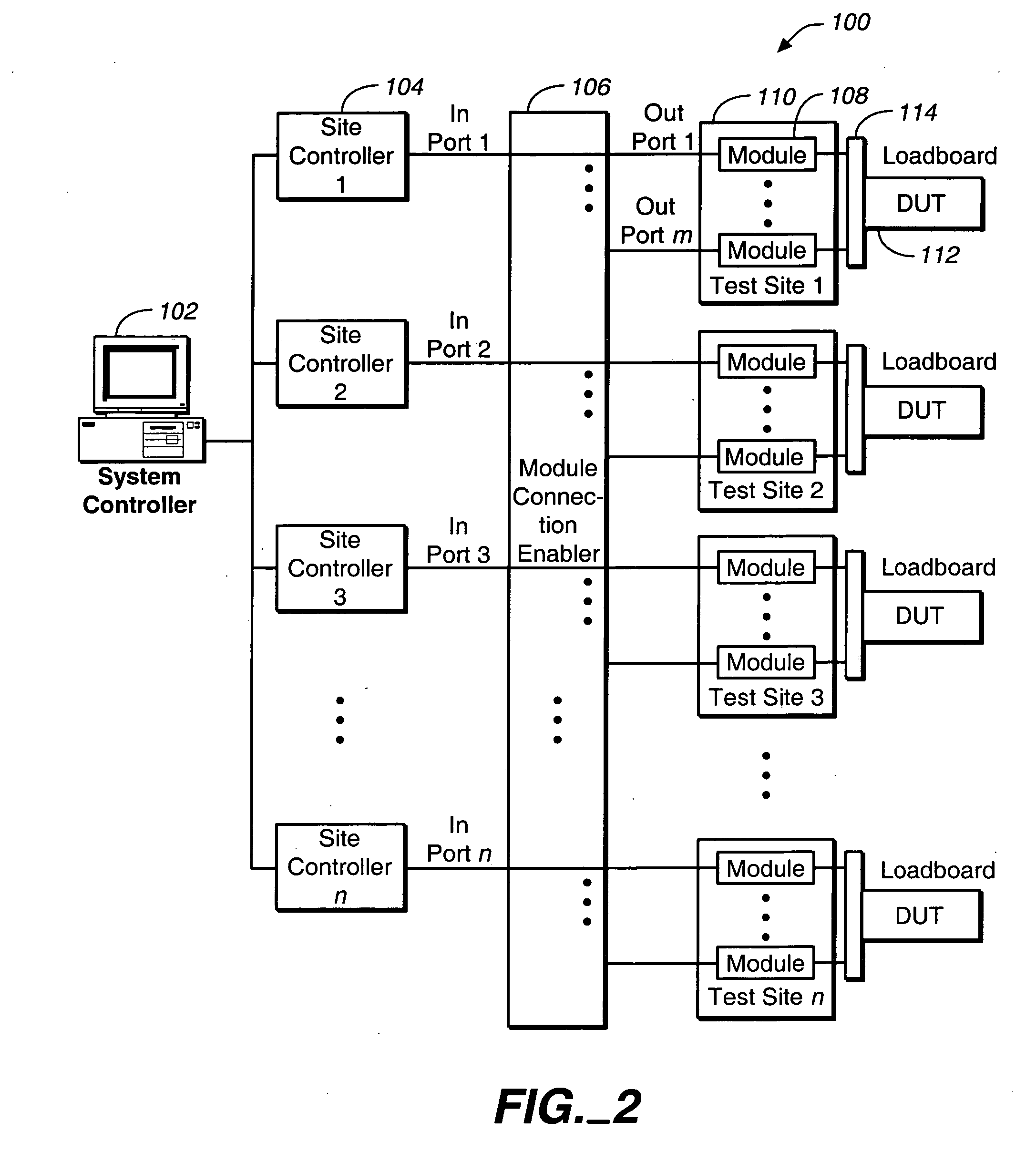

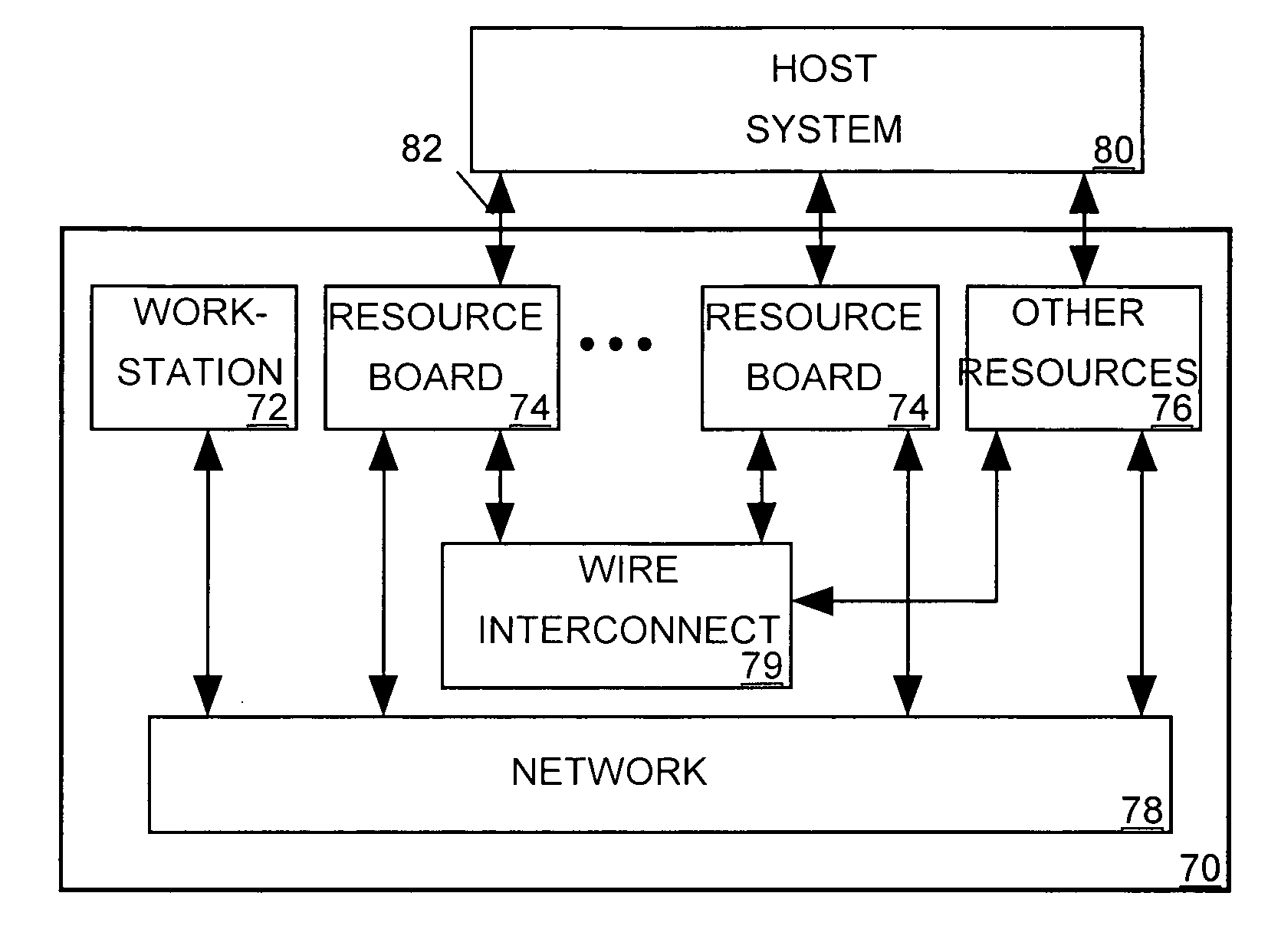

ActiveUS20040225465A1Digital circuit testingResistance/reactance/impedenceOperational systemEngineering

A distributed operating system for a semiconductor test system, such as automated test equipment (ATE), is described. The operating system includes a host operating system for enabling control of one or more site controllers by a system controller. One or more local operating systems, each associated with a site controller, enable control of one or more test modules by an associated site controller. Each test module performs testing on a corresponding device-under-test at a test site.

Owner:ADVANTEST CORP

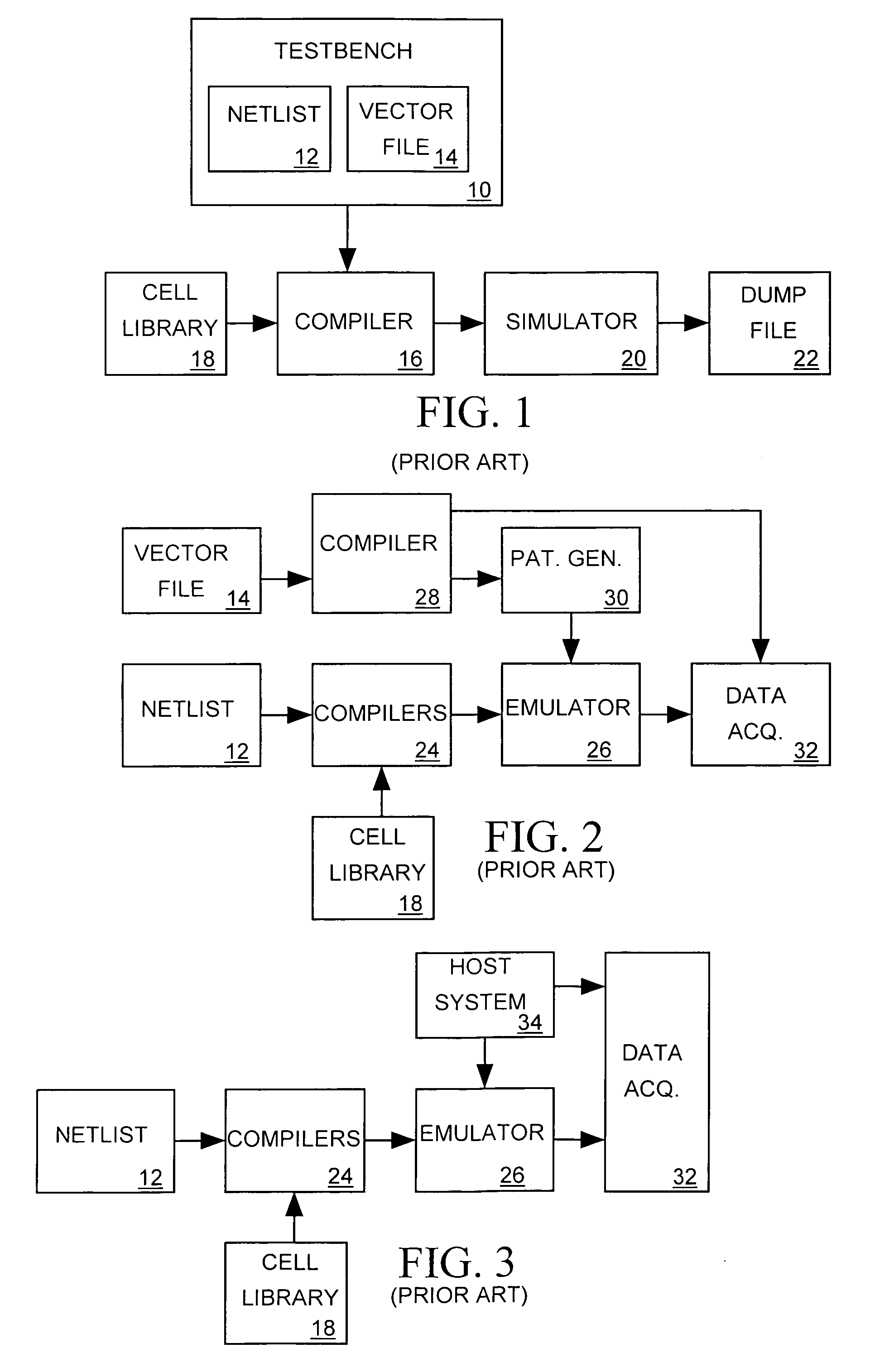

Method of programming a co-verification system

ActiveUS20060015313A1Detecting faulty computer hardwareComputer aided designAnalog signalTerm memory

A co-verification system includes a computer programmed to act as a simulator for simulating behavior of a first portion of an electronic device under test (DUT) by acquiring, processing and generating data representing DUT signals. The co-verification system also includes emulation resources programmed to emulate a second portion of the DUT by receiving, processing and generating emulation signals representing DUT signals. The signals of the DUT are mapped to separate addresses within a memory space, and the simulator controls and reads states of emulation signals by writing data to and reading data from addresses of the memory space states mapped to the DUT signals the emulation signals represent. The computer and the emulation resources are also programmed to implement transactors communicating with one another through a packet routing network. The transactors set states of the emulation signals when the simulator writes to memory space addresses and for reading states of the emulation signals. The transactors monitor states of emulation signals and return data indicating those states to the simulator when the simulator reads memory space addresses mapped to DUT signals represented by the emulation signals.

Owner:SYNOPSYS INC

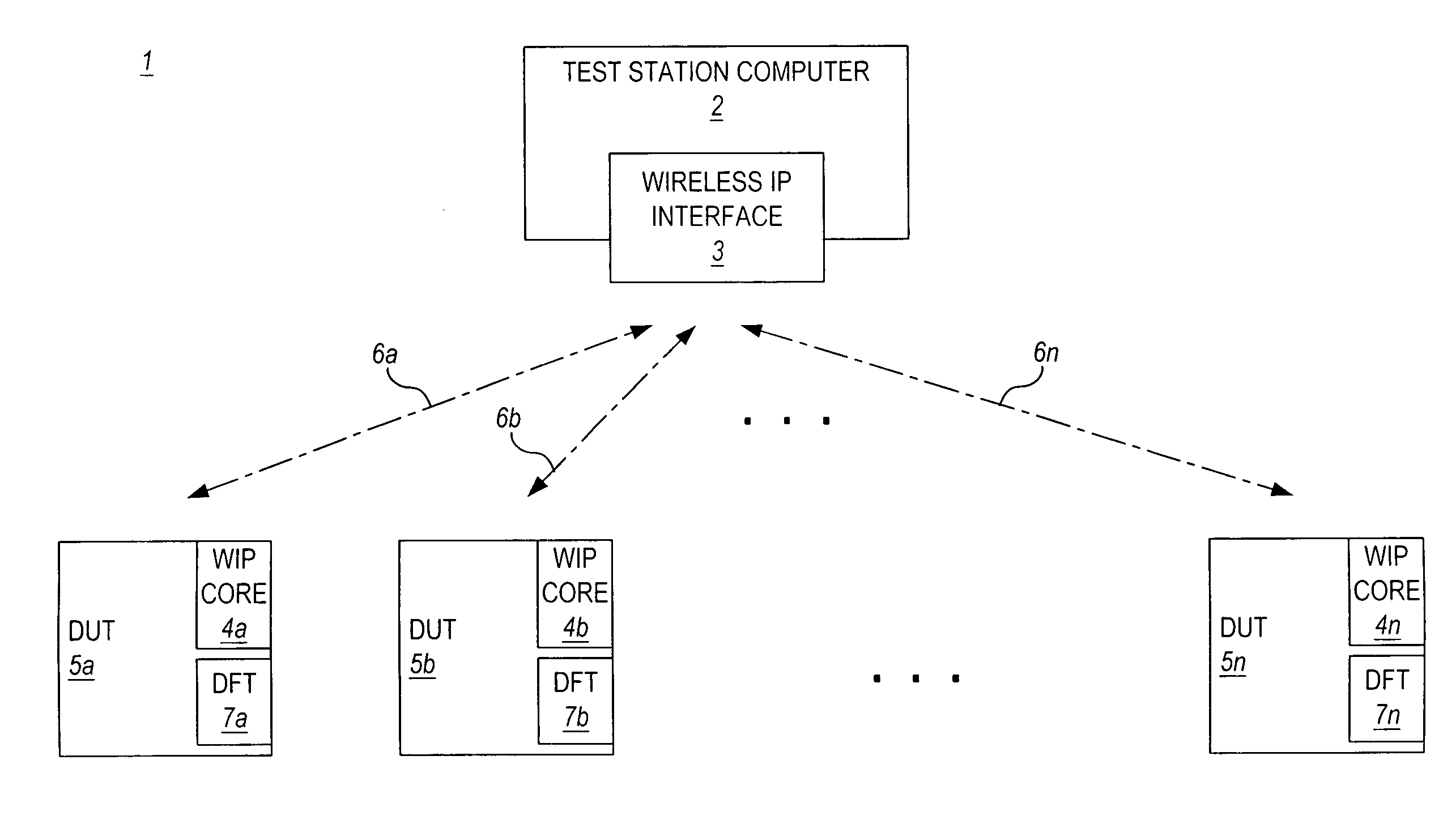

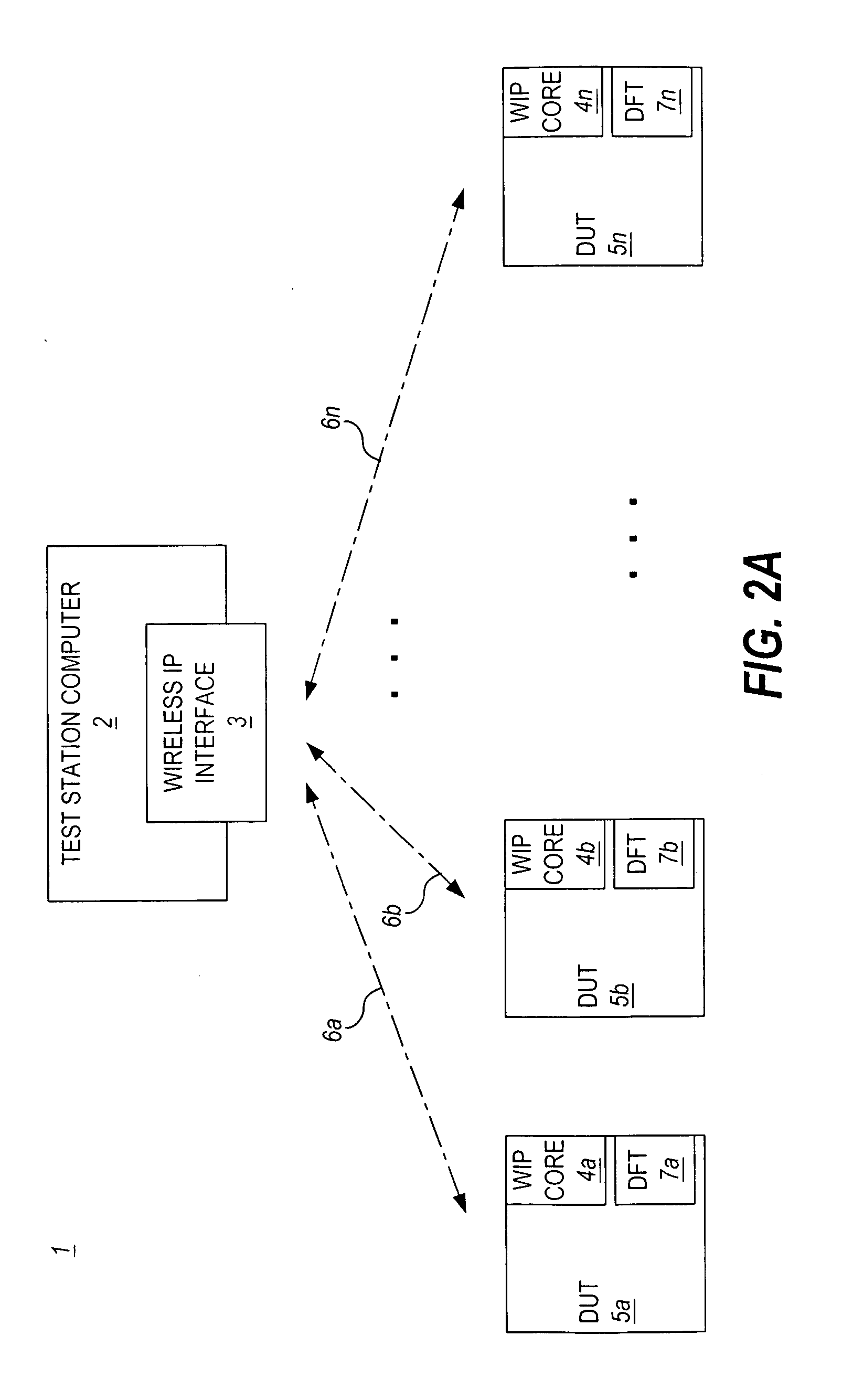

Wireless no-touch testing of integrated circuits

ActiveUS20050193294A1Immediate cost-reduction impactIncrease speedDigital circuit testingSemiconductor/solid-state device testing/measurementCircuit under testEngineering

A wireless integrated circuit test method and system is presented. The invention allows testing of one or more integrated circuits configured with a wireless interface and a test access mechanism which controls input of test data received over a wireless connection from a test station to test structures which test functional blocks on the integrated circuit. Via the wireless connection, multiple integrated circuits or similarly equipped devices under test can be tested simultaneously. The invention also enables concurrent testing of independently testable functional blocks on any given integrated circuit under test.

Owner:ADVANTEST CORP

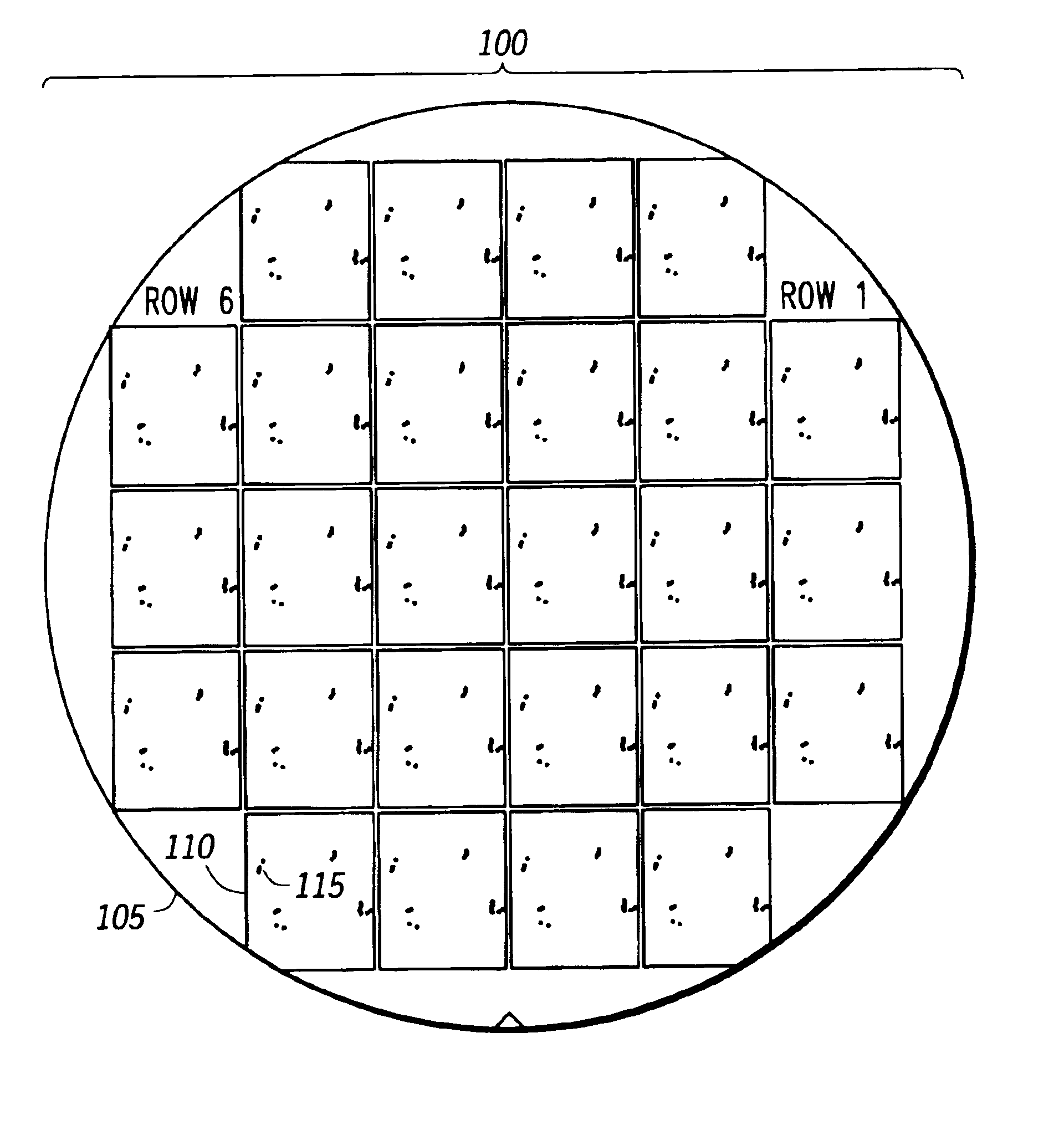

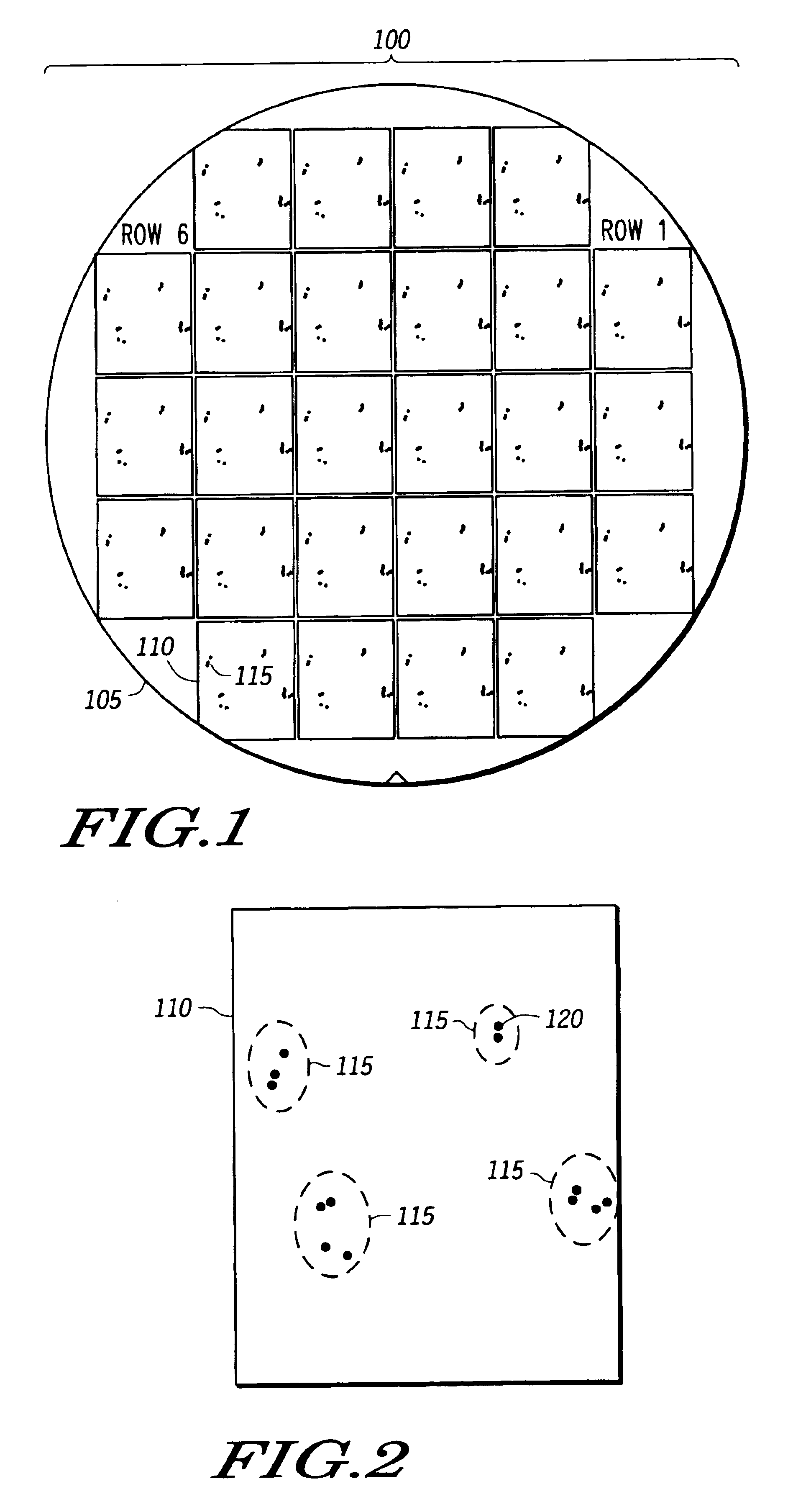

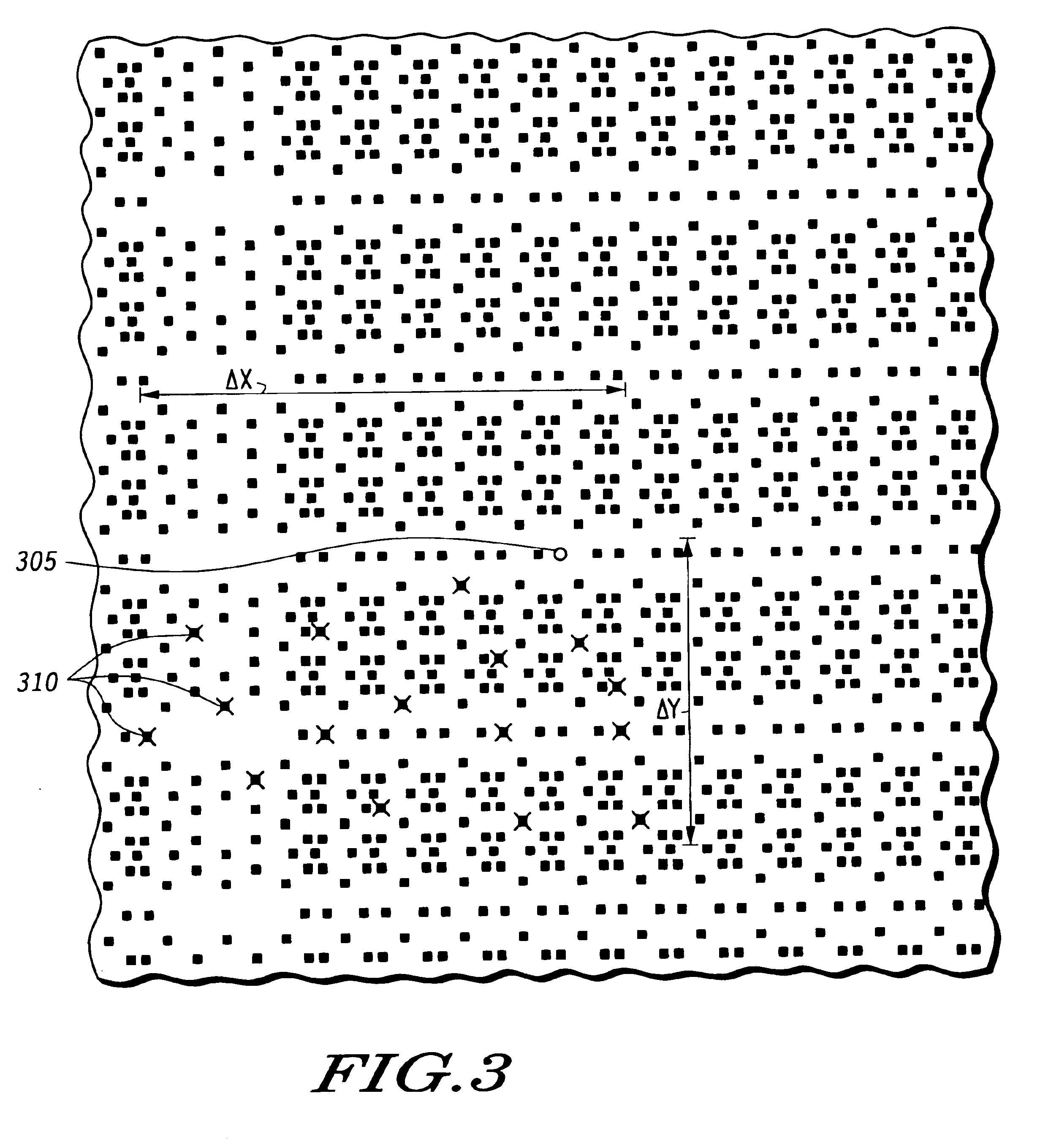

Method and apparatus for translating detected wafer defect coordinates to reticle coordinates using CAD data

Systems and methods are described for translating detected wafer defect coordinates to reticle coordinates using CAD data. A wafer inspection image is provided and coordinates of potential defects in the wafer are determined. Then the wafer inspection image is converted into a predetermined image format. CAD data for the device under test is then used to produce a second image, also in the predetermined image format. The CAD-derived image and the wafer-derived image are then aligned, and the coordinates of potential defects in the wafer are converted into CAD coordinates. The CAD coordinates are then used to navigate through the reticle for the wafer in order to locate reticle defects corresponding to the detected wafer defects.

Owner:NXP USA INC

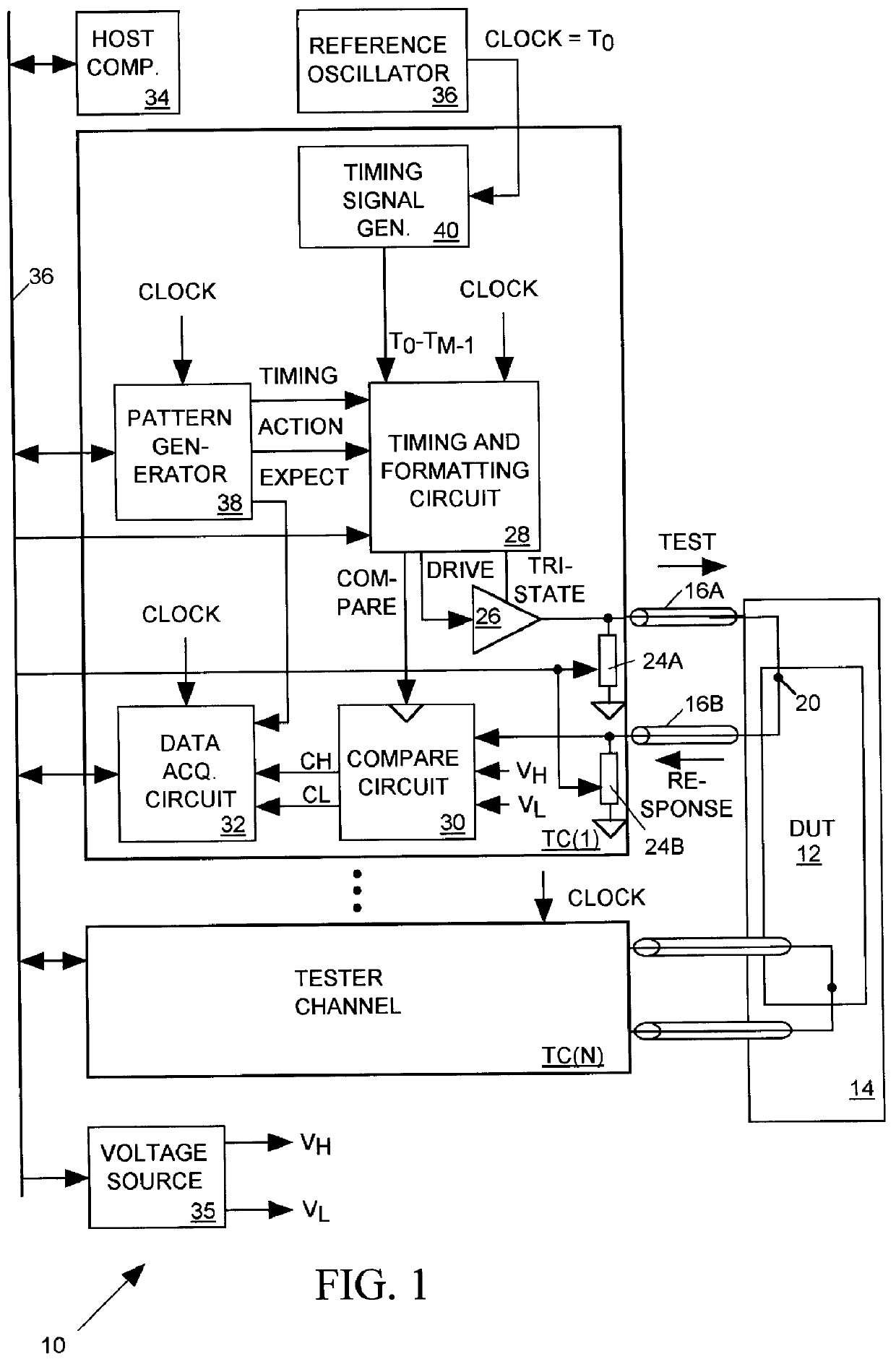

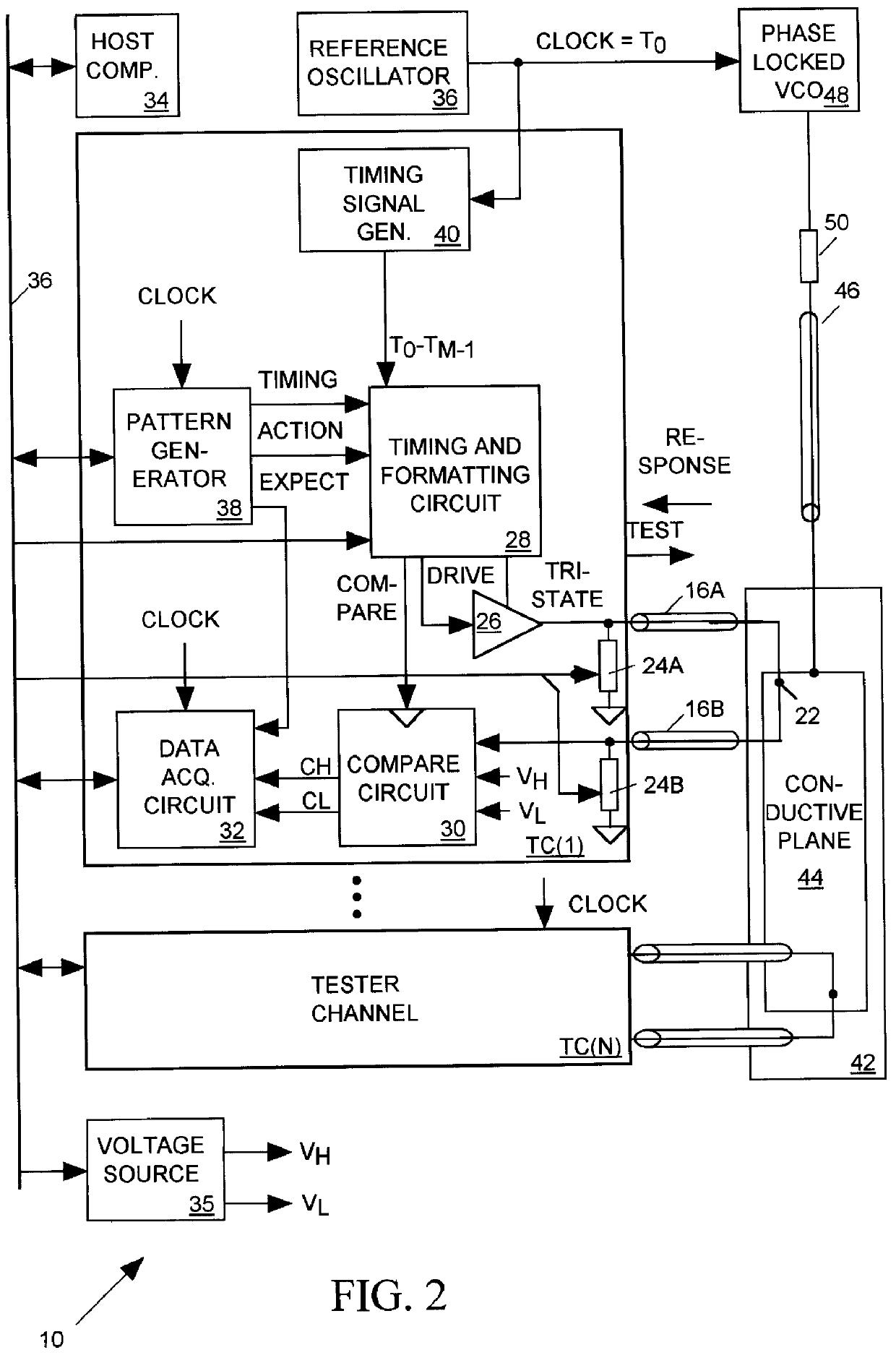

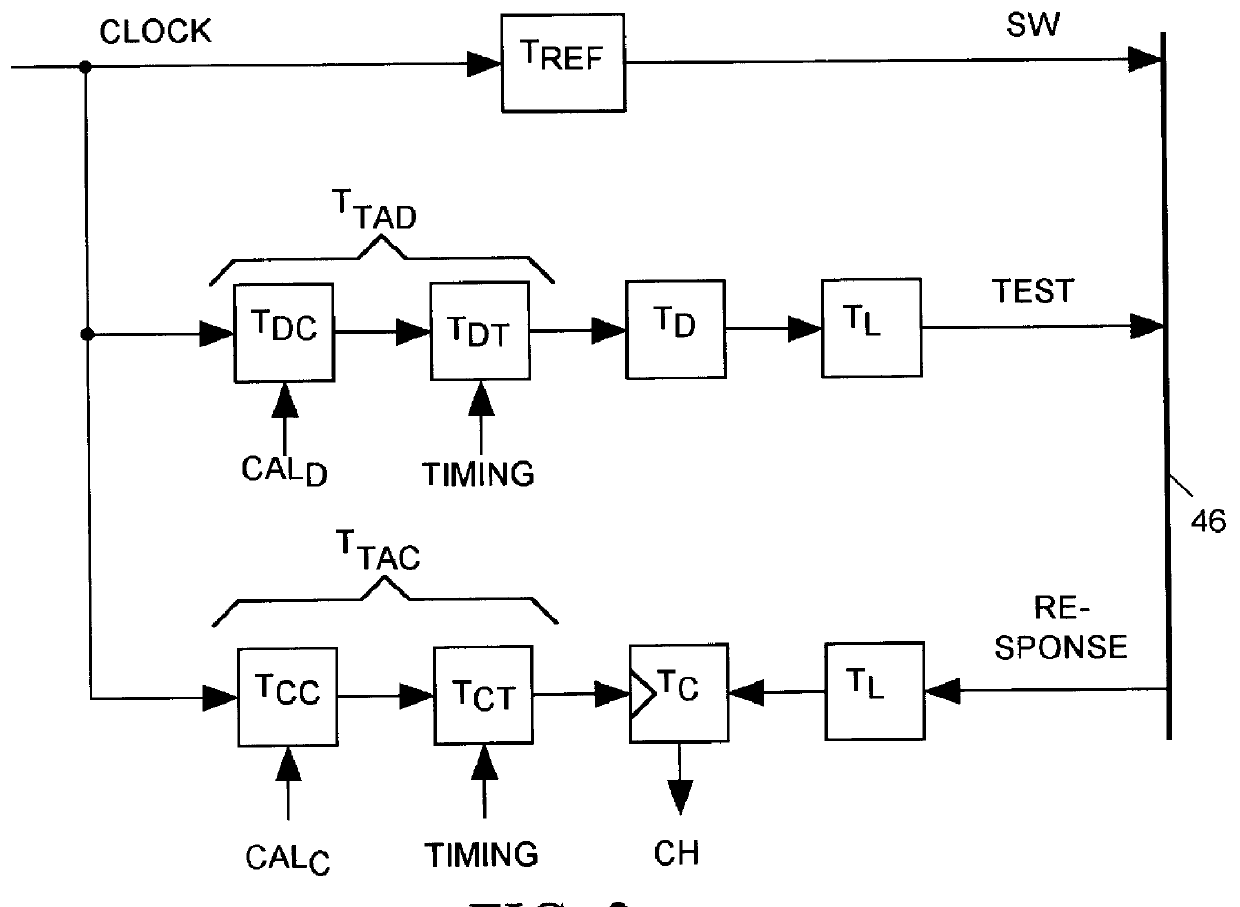

Salphasic timing calibration system for an integrated circuit tester

InactiveUS6105157AQuickly and easily calibratingDigital circuit testingError detection/correctionTester deviceEngineering

An integrated circuit tester produces an output TEST signal following a pulse of a reference CLOCK signal with a delay that is a sum of an inherent drive delay and an adjustable drive delay. The tester also samples an input RESPONSE signal following a pulse of the reference CLOCK signal with a delay that is a sum of an inherent compare delay and an adjustable compare delay. The inherent drive and compare signal path delays within an integrated circuit tester are measured by first connecting a salphasic plane to transmission lines that normally convey signals between the tester and terminals of an integrated circuit device under test. A standing wave signal appearing on that salphasic plane is phase locked to the CLOCK signal so that a zero crossing of the standing wave occurs at a fixed interval after each pulse of the CLOCK signal. Each transmission line concurrently conveys the standing wave to the tester to provide timing references for measuring the inherent drive and compare signal path delays within the tester. Transmission line signal paths are also measured. Delays are added to the drive and compare signal paths to compensate for the measured inherent drive, compare and transmission line delays.

Owner:CREDENCE SYSTEMS

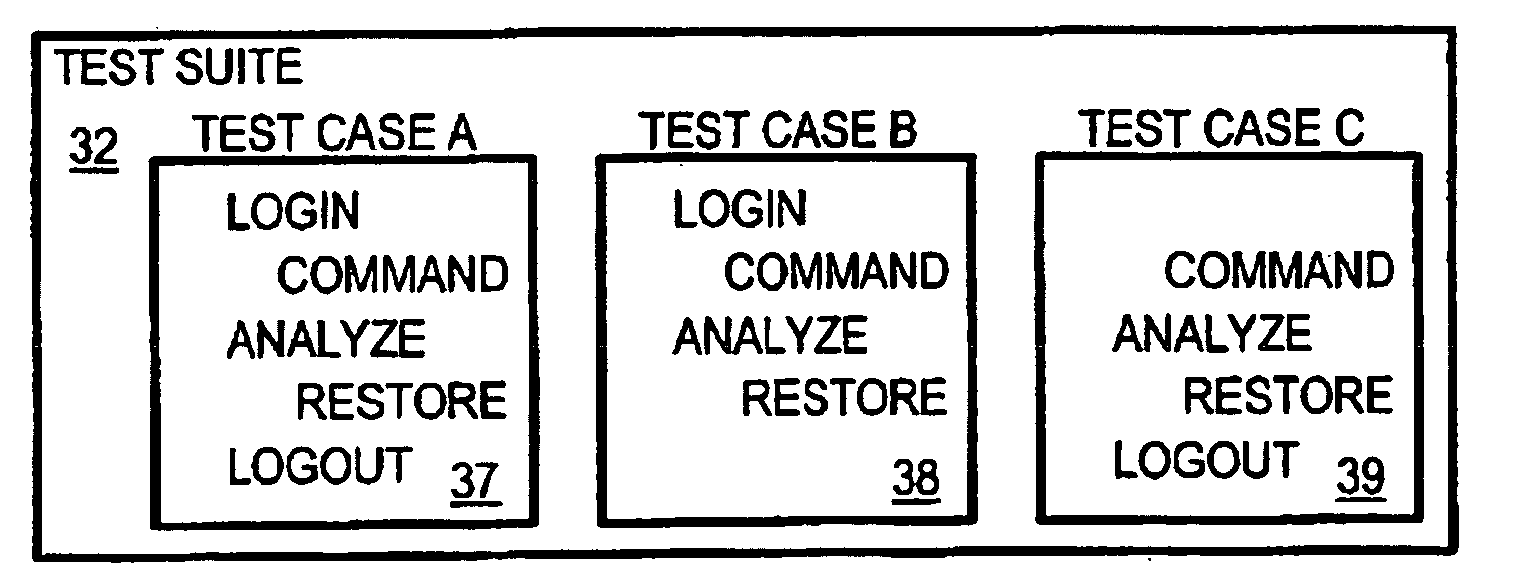

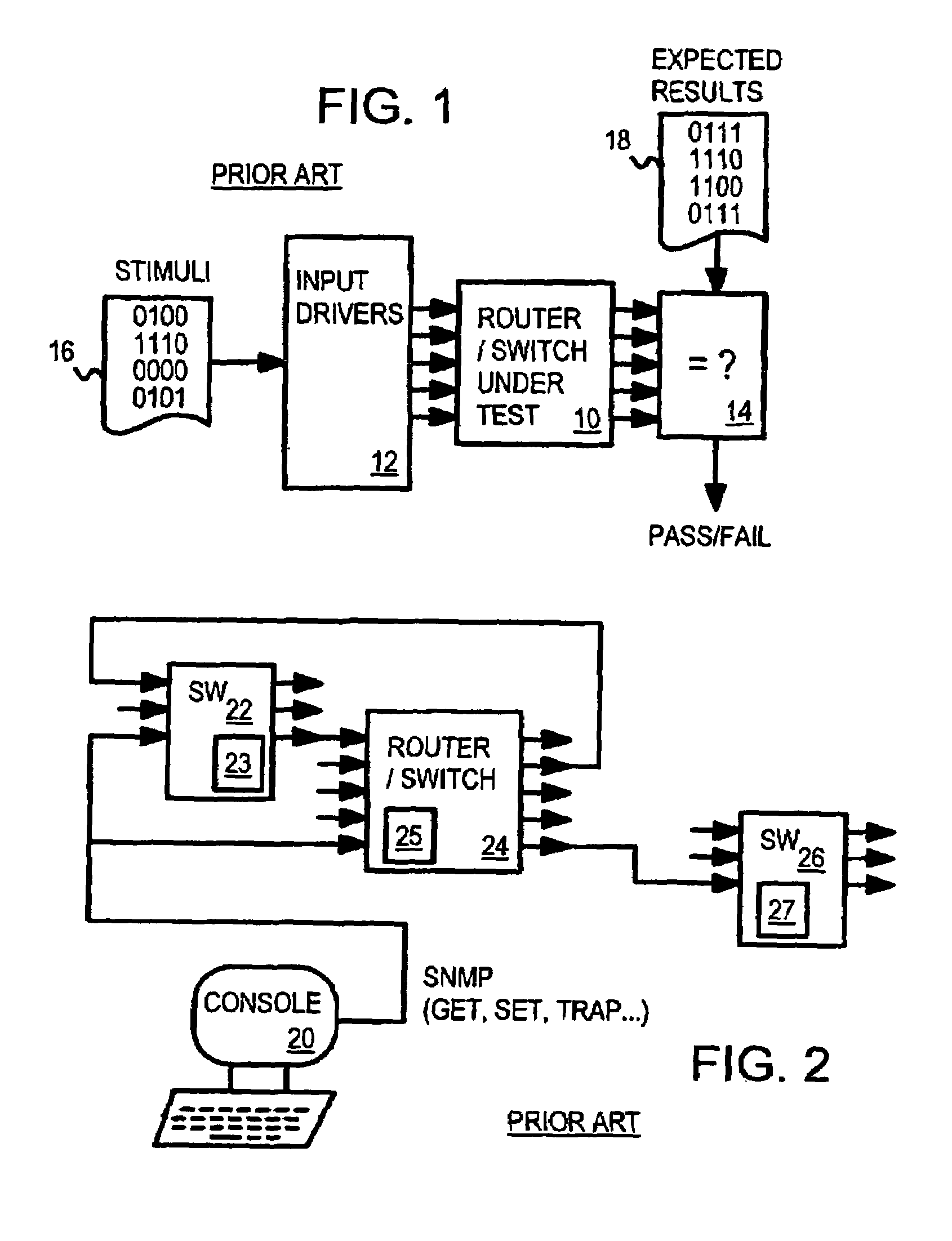

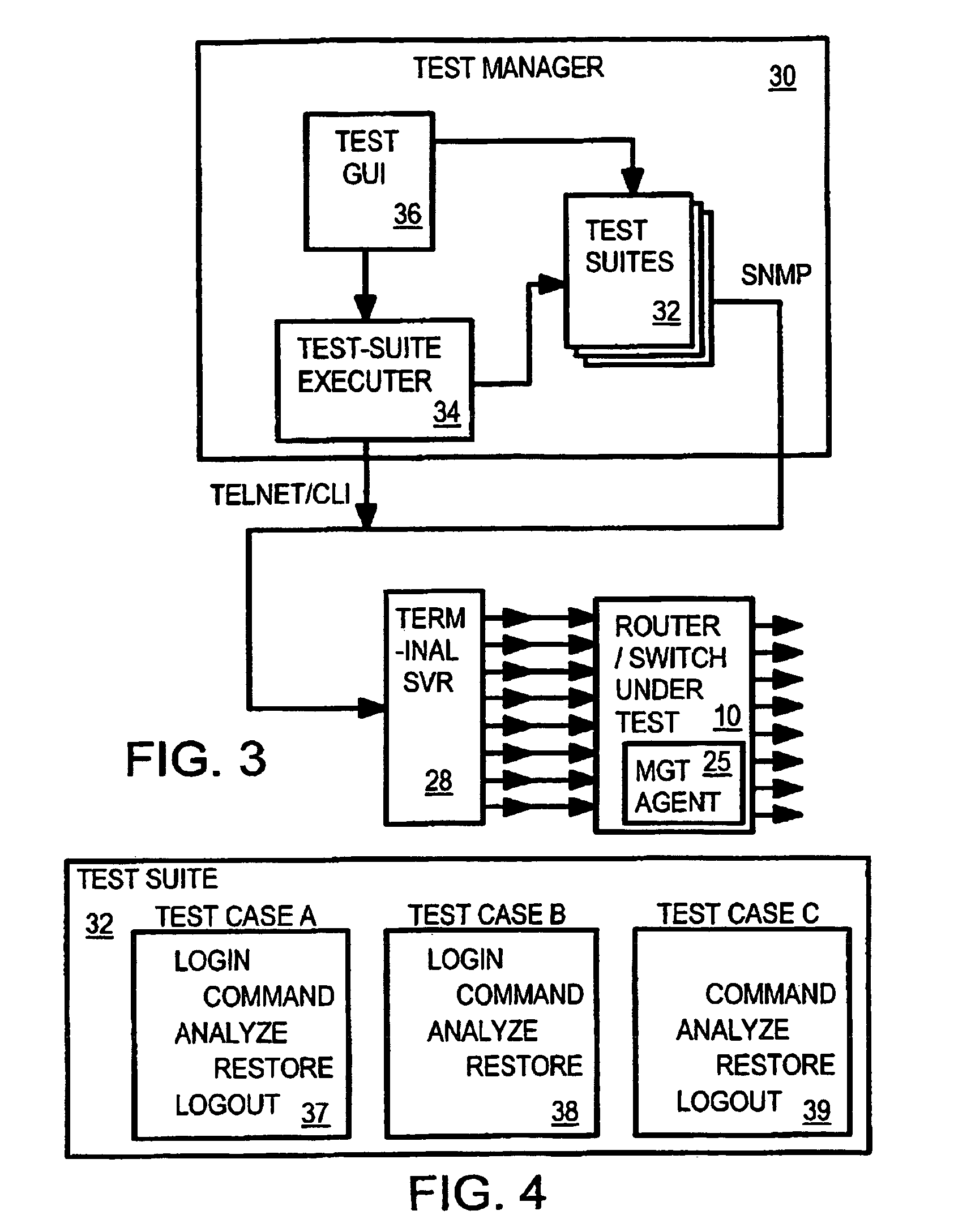

Interactive automatic-test GUI for testing devices and equipment using shell-level, CLI, and SNMP commands

ActiveUS7010782B2Digital variable displayResistance/reactance/impedenceComputer hardwareCommand-line interface

A test manager software program includes an interactive test graphical-user-interface (GUI) for testing network devices using high-level networking commands. The test GUI allows the test engineer user to enter high-level commands such as Simple Networking Management Protocol (SNMP) commands that read values in a management information database in a network device under test. The high-level commands can be sent from the test manager using a command-line interface (CLI) in a telnet session opened to the network device during testing. The user specifies high-level test, analyze, and restore commands in test cases that are collected into test suites. Rules for logging on to the network device under test are stored that include expected prompts from the network device and user responses such as passwords. Addresses of the network device under test can be re-mapped for testing other devices so the test suites can be reused.

Owner:SAPPHIRE INFOTECH

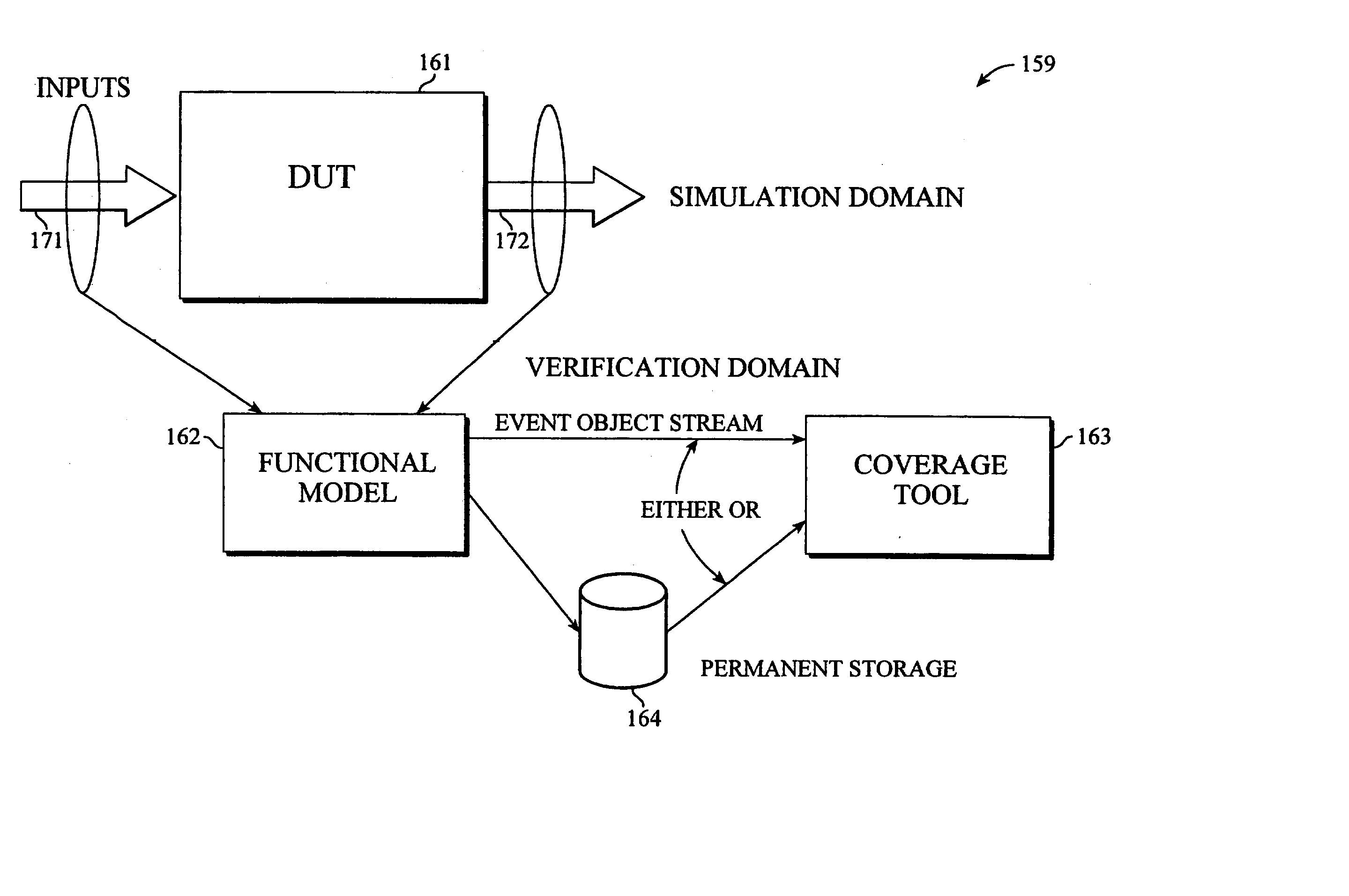

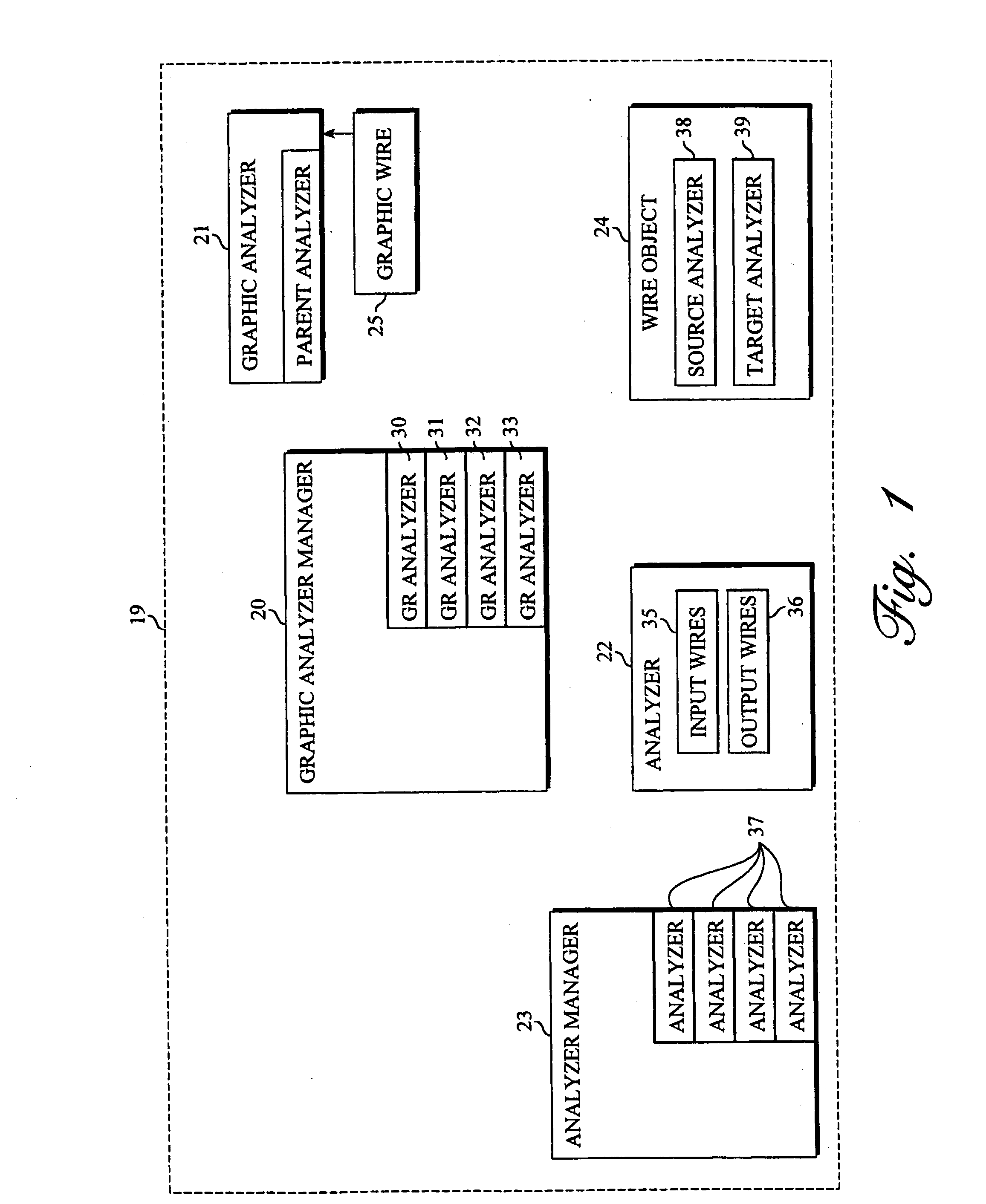

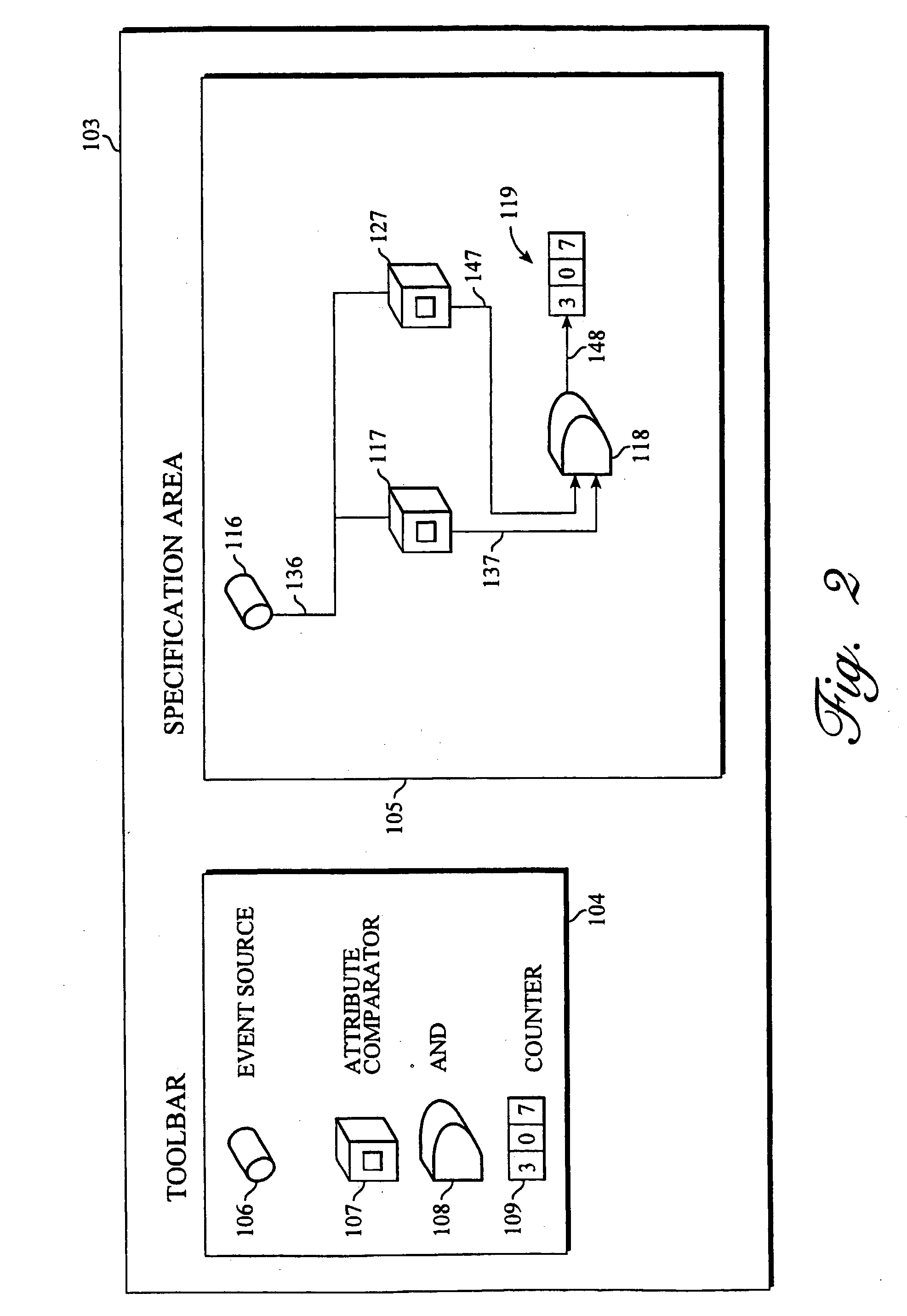

Functional coverage analysis systems and methods for verification test suites

Coverage metrics are expressed with an intuitive graphical interface based upon data flow. Coverage analysis and presentation objects are integrated to produce coverage results which enable device functionality in a device under test to be modeled as objects, subject to event occurrence. Event objects are introspected at run-time, allowing the user to determine the event object's attributes with specification of coverage metrics subject to a selected combination of the event object's attributes. The event objects are serialized into permanent storage, allowing the user to specify and execute new coverage metrics at any time after simulation. Operations used to describe coverage metrics are modeled as analysis objects. Such analysis objects accept event objects as inputs, using a predetermined, well-defined interface. The combination of event objects and analysis objects allows coverage metrics to be specified in a simple data flow manner. With such a coverage metric, the user attaches or wires (metaphorically) the analysis objects together in a visual builder environment. Using the analysis objects, the user specifies desired coverage metrics, such as coverage of sequences of events and / or coverage of events that occur during the same time window of a simulation. The display functionality of the coverage tool is expandable because the presentation objects use the same event object interface as the analysis operator objects. Coverage metrics are subject to specification either before or after event occurrence. The user specifies coverage metrics using an intuitive graphical interface based upon data flow, without any specific programming language skills being necessary. Functional events in the device under test are treated as event objects. Each event object may be passed to selected analysis tools chosen by the user, such as analyzers, logic gates, and coincidence counters.

Owner:CIRRUS LOGIC INC

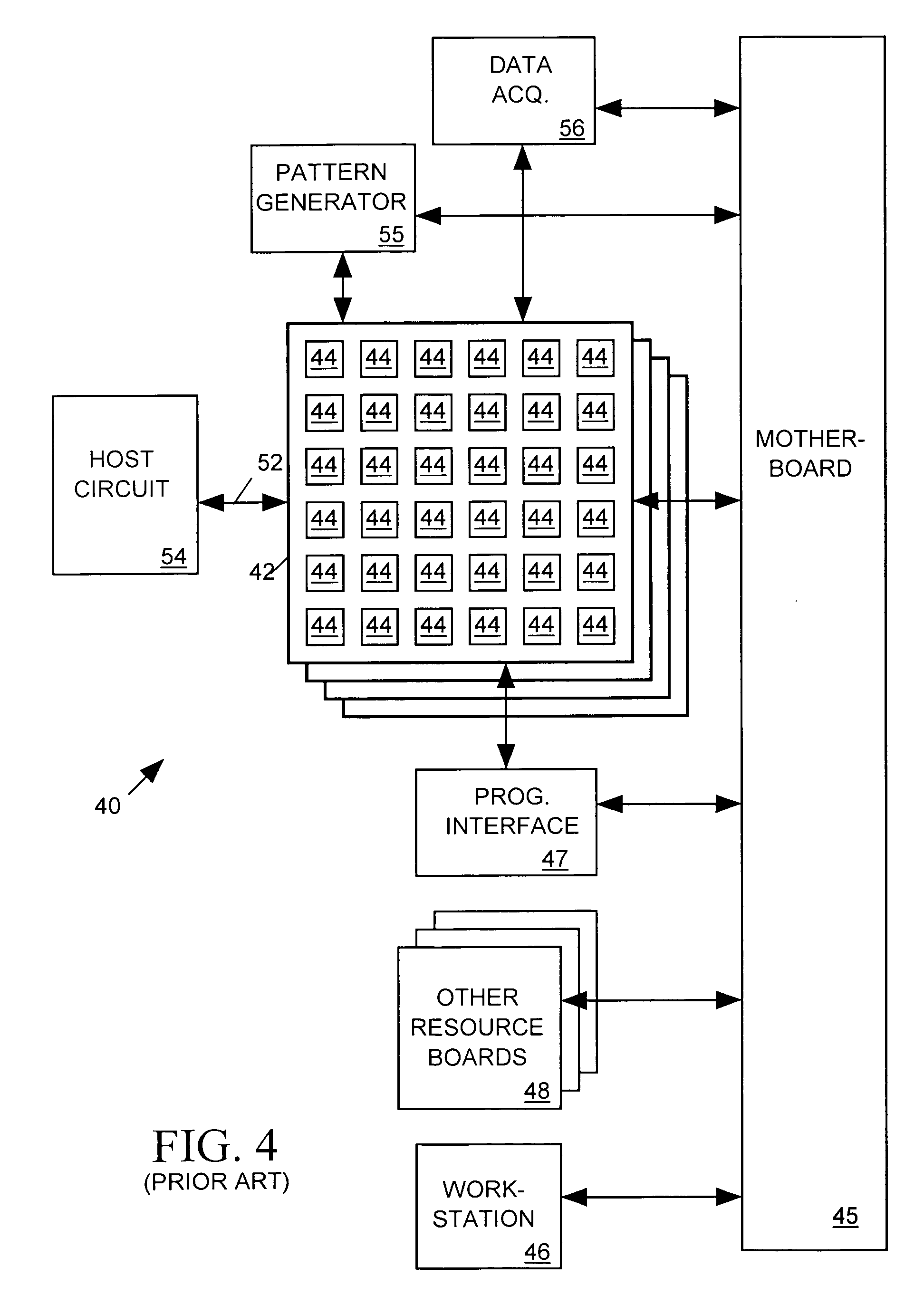

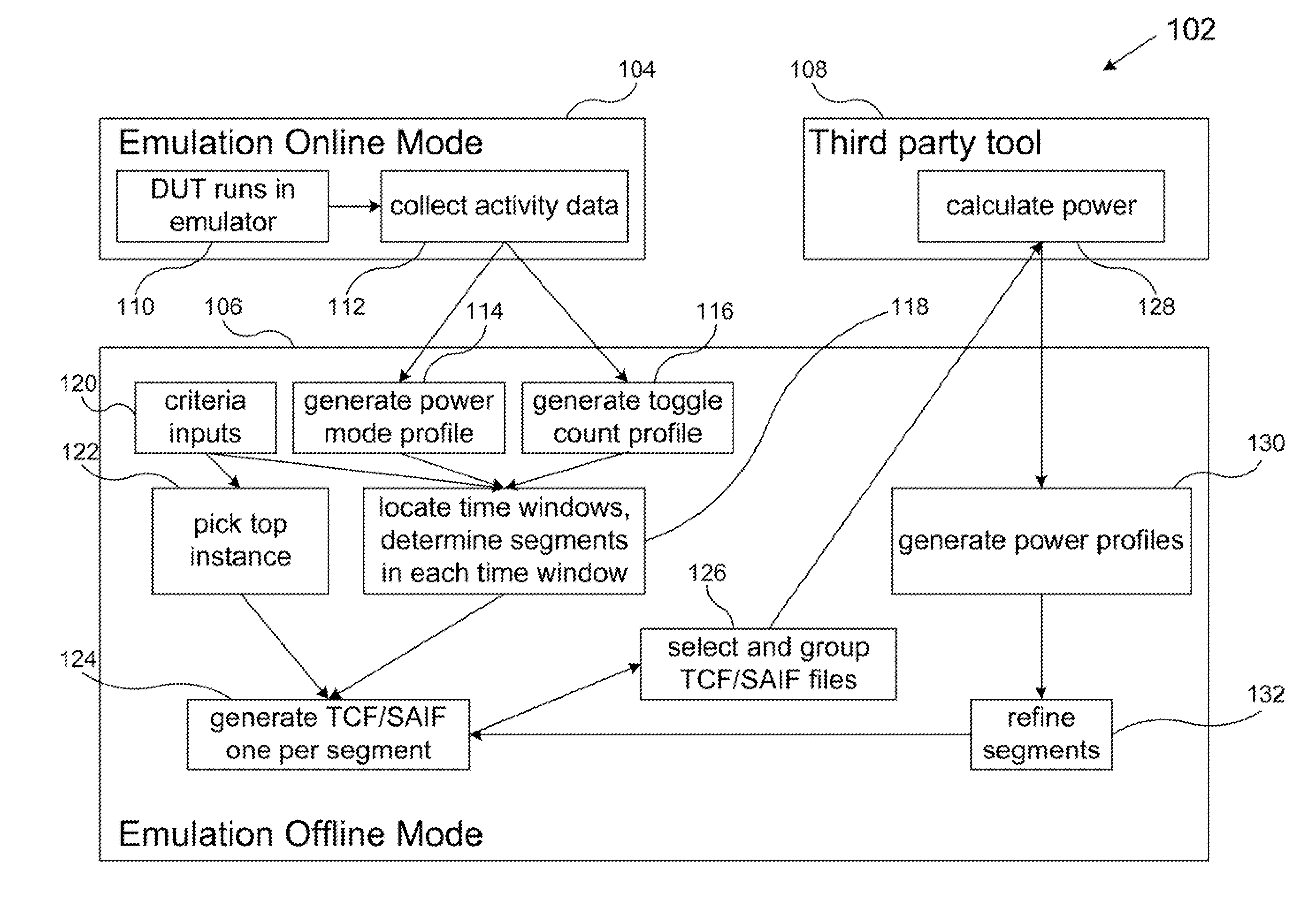

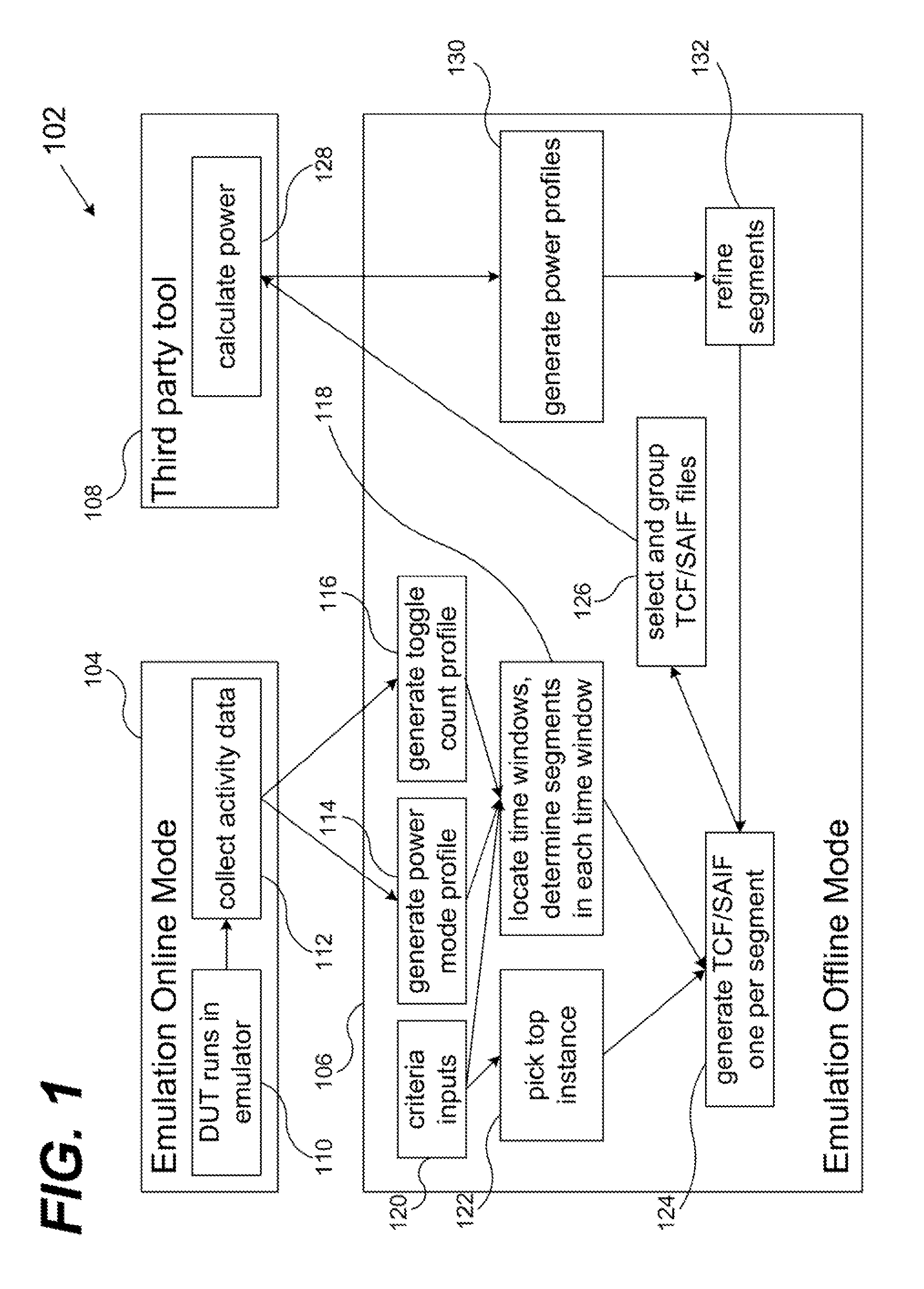

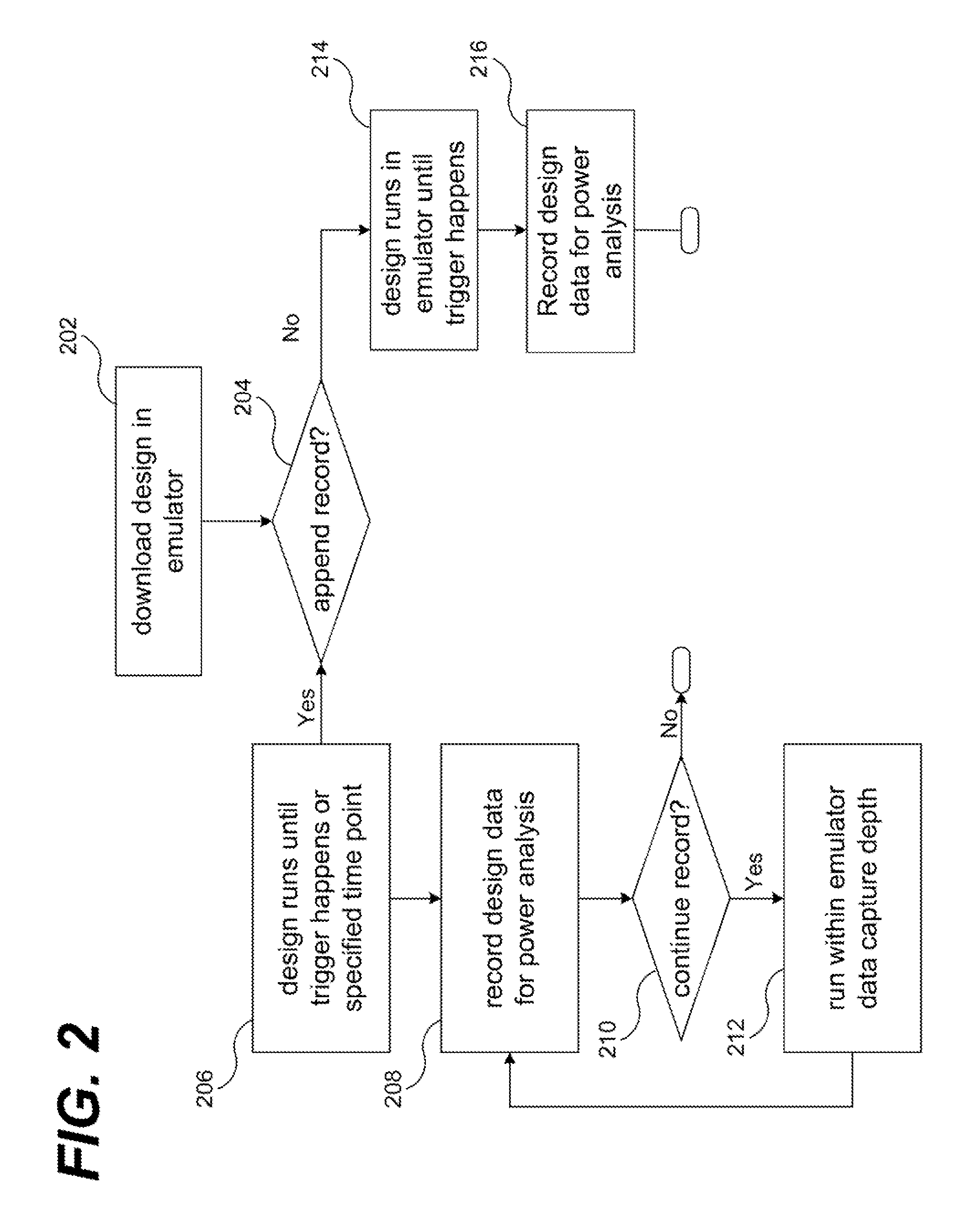

Peak power detection in digital designs using emulation systems

ActiveUS20090271167A1High activityIncrease valueAnalogue computers for nuclear physicsComputer aided designElectronic systemsPeak value

A method of analyzing power consumption for a DUT (device under test) that includes an integrated circuit or an electronic system includes: providing emulation data for states of the DUT in one or more time windows; determining operational mode values from the emulation data and a selection of operational modes that characterize circuit behavior in the one or more time windows; dividing each time window into one or more segments based on at least one power criterion; determining power-activity values for the one or more segments; determining power-consumption values for the one or more segments from the power-activity values; using the power-activity values and the power-consumption values to determine relative power activity across the one or more segments and adjusting the one or more segments to target high power activity over operational modes in the one or more time windows; and saving one or more values for power activity of the DUT in a computer-readable medium.

Owner:CADENCE DESIGN SYST INC

GUI implementations on central controller computer system for supporting protocol independent device testing

InactiveUS20140237292A1Quick configurationError detection/correctionComputer hardwareGraphical user interface

Owner:ADVANTEST CORP

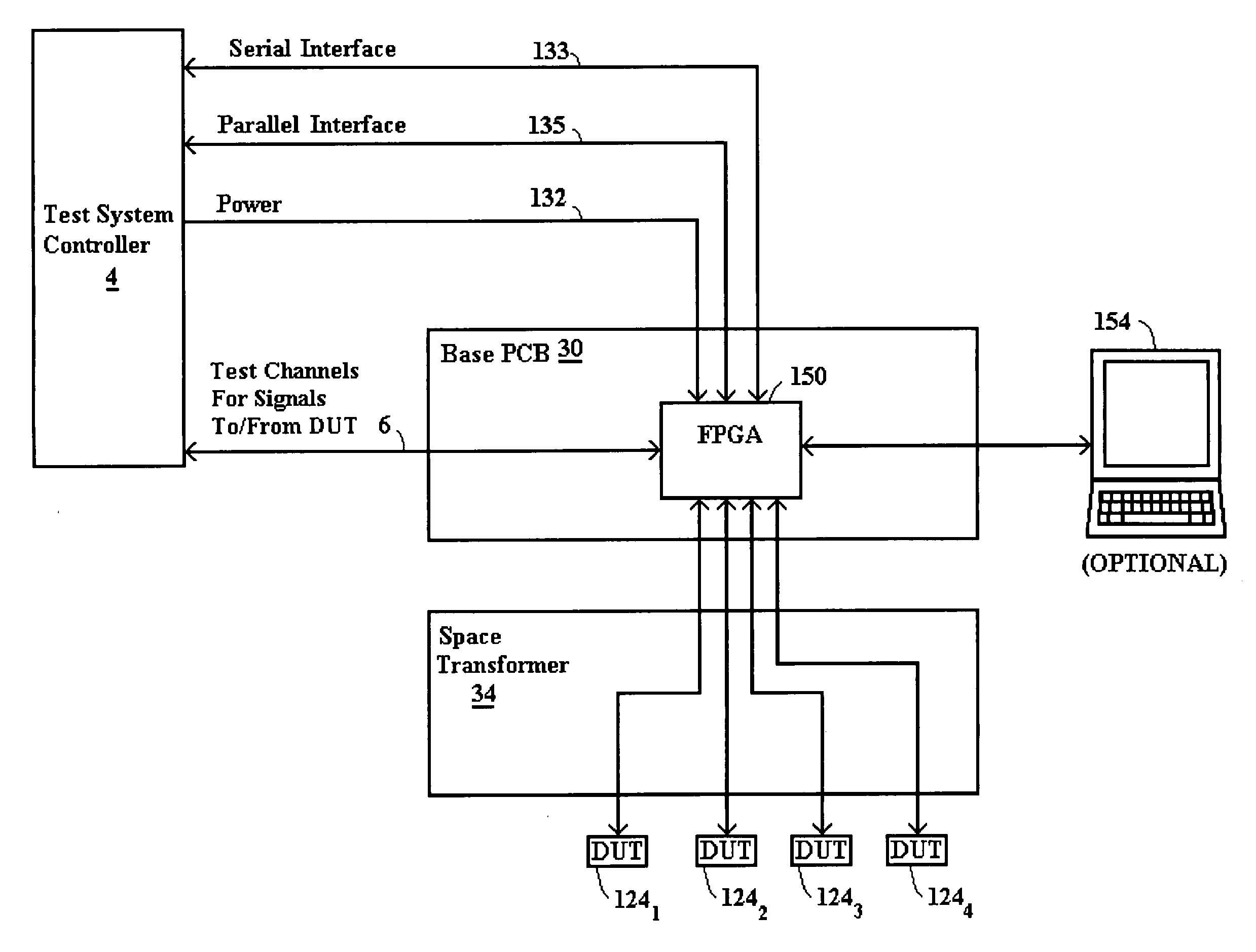

Programmable devices to route signals on probe cards

InactiveUS20060170435A1Great switching densityLong life cycleSemiconductor/solid-state device testing/measurementElectrical measurement instrument detailsProbe cardTest engineer

A probe card of a wafer test system includes one or more programmable ICs, such as FPGAs, to provide routing from individual test signal channels to one of multiple probes. The programmable ICs can be placed on a base PCB of the probe card, or on a daughtercard attached to the probe card. With programmability, the PCB can be used to switch limited test system channels away from unused probes. Programmability further enables a single probe card to more effectively test devices having the same pad array, but having different pin-outs for different device options. Reprogrammability also allows test engineers to re-program as they are debugging a test program. Because the programmable IC typically includes buffers that introduce an unknown delay, in one embodiment measurement of the delay is accomplished by first programming the programmable IC to provide a loop back path to the test system so that buffer delay can be measured, and then reprogramming the programmable IC now with a known delay to connect to a device being tested.

Owner:FORMFACTOR INC

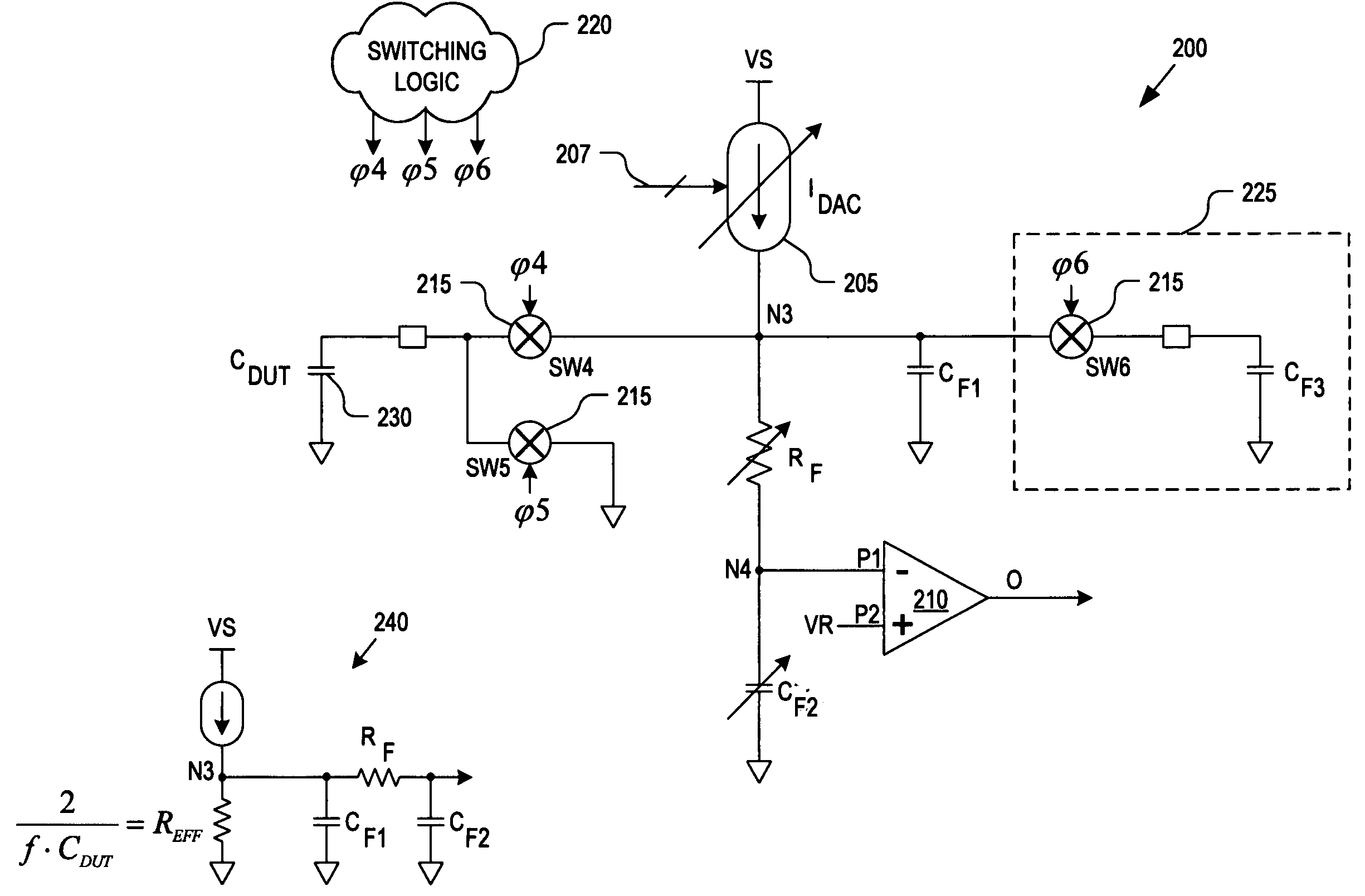

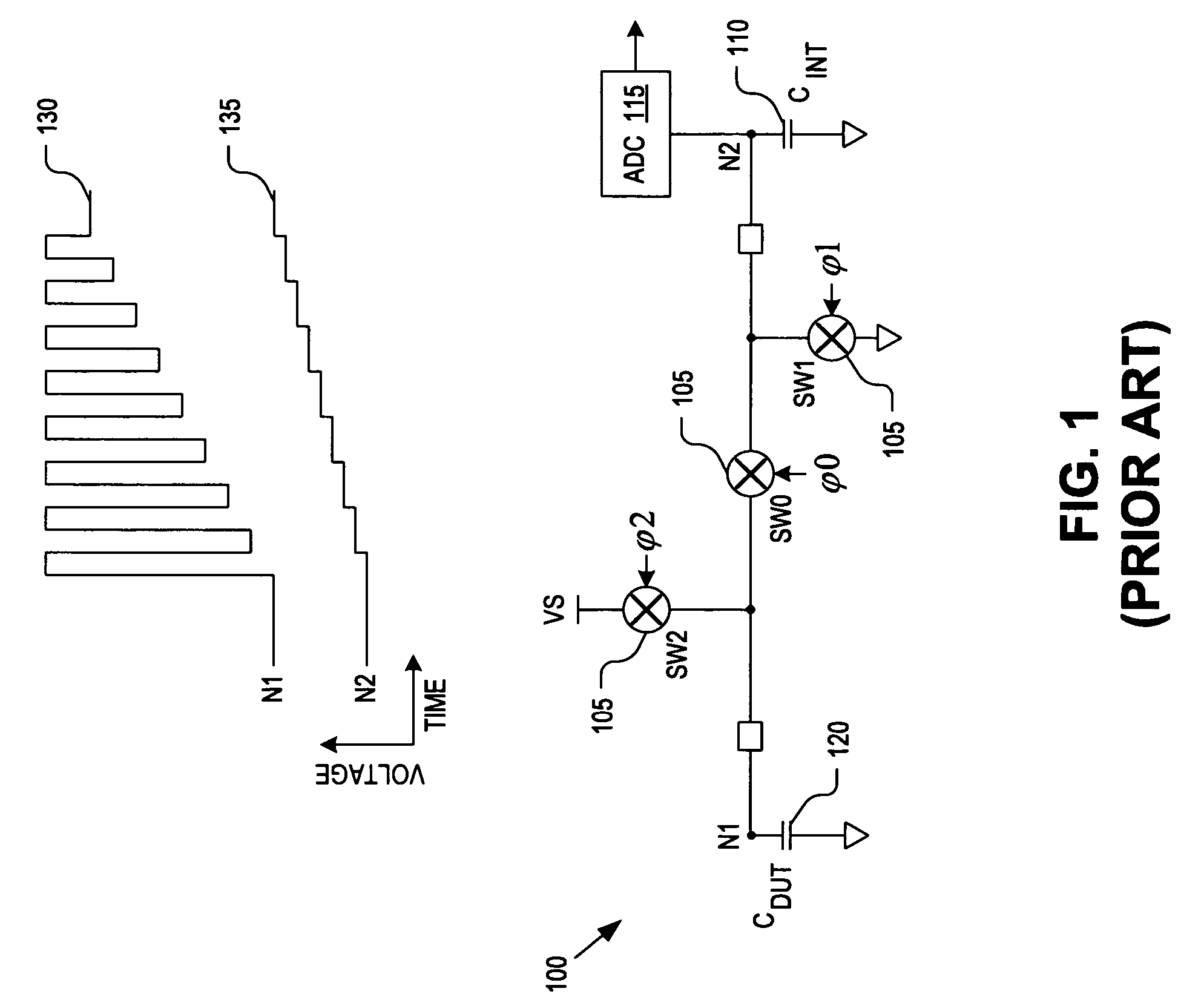

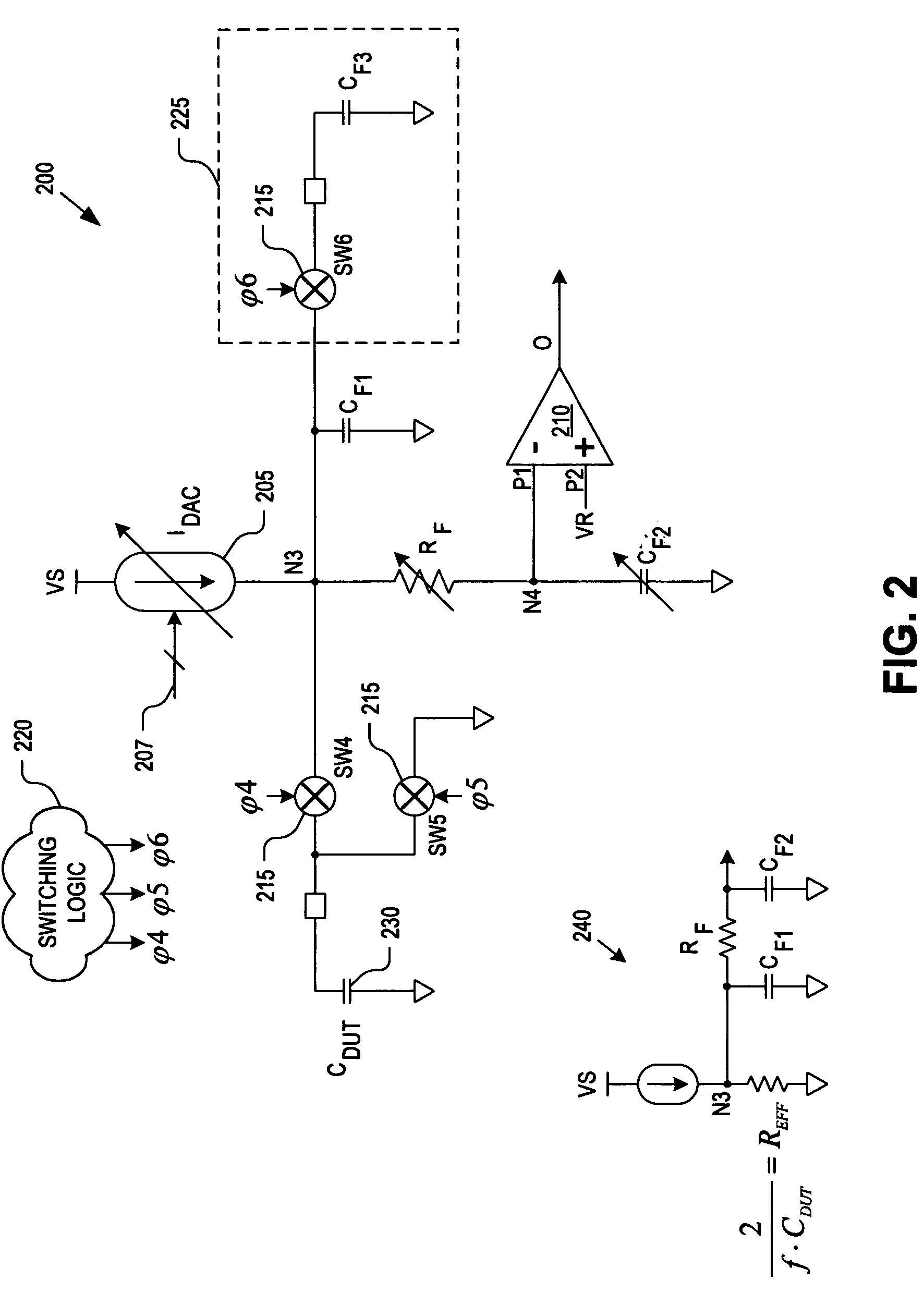

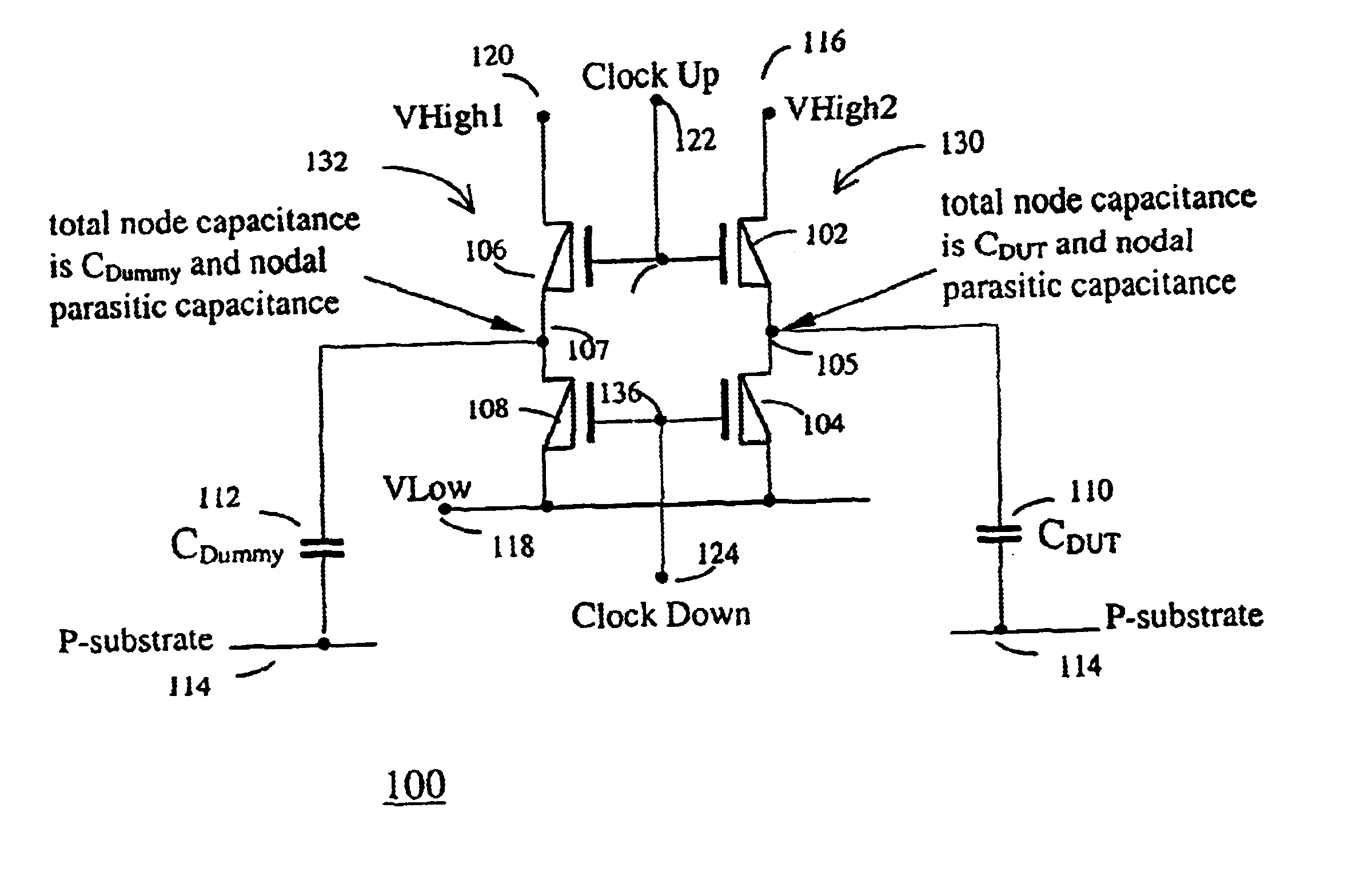

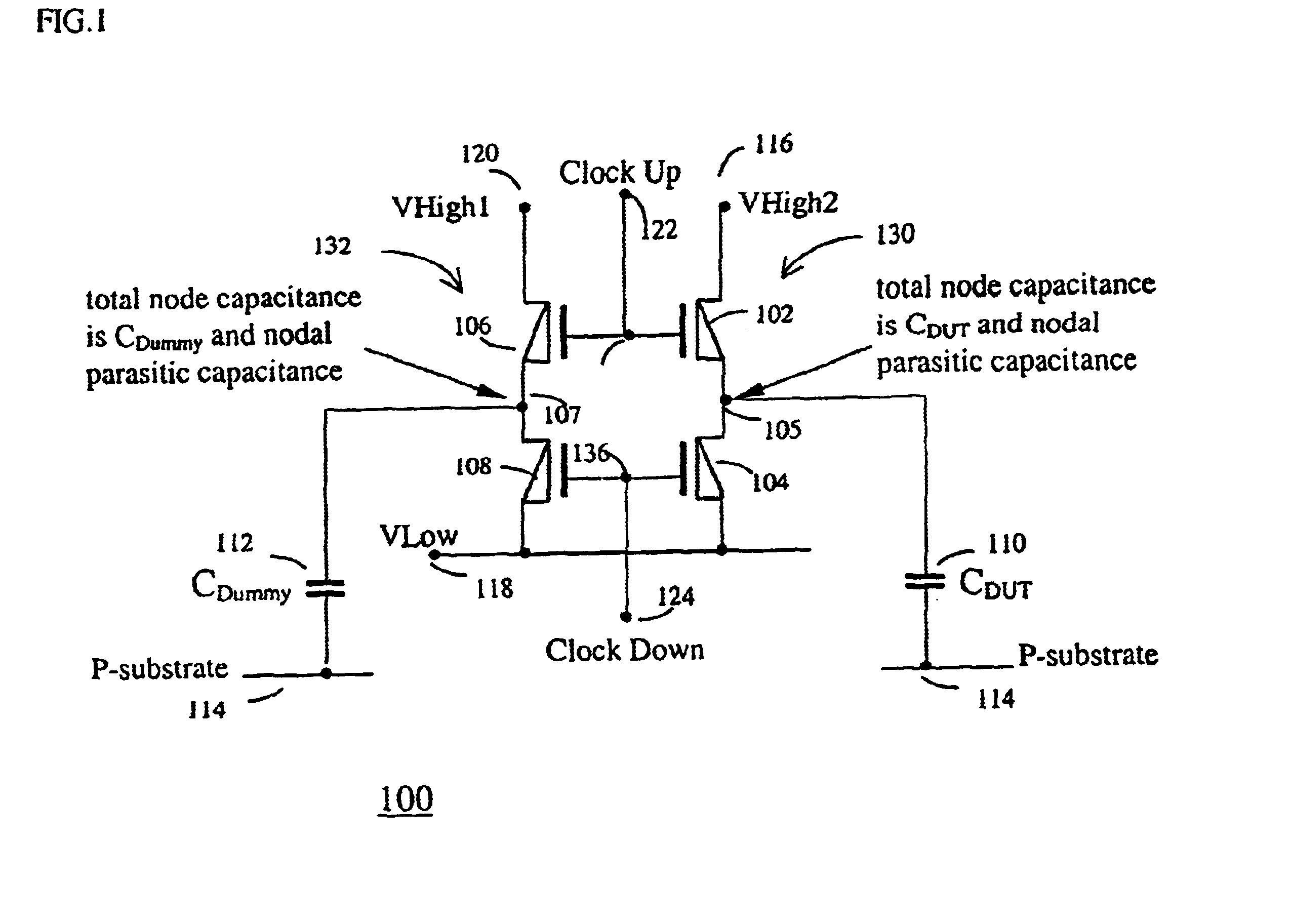

Clocked based method and devices for measuring voltage-variable capacitances and other on-chip parameters

InactiveUS6838869B1Capacitance measurementsSemiconductor/solid-state device testing/measurementCapacitanceEngineering

A characterization method for a device under test includes applying a bias voltage to a test circuit. The test circuit includes a first transistor coupled to the device under test, a second transistor coupled to the device under test and to the first transistor. A third transistor is coupled to a dummy device, a fourth transistor is coupled to the dummy device and to the third transistor. The transistors are of a common type. The characterization method further includes applying non-overlapping clocking signals to transistors of the test circuit to produce test signals for application to the device under test and detecting a current in one or more transistors from the device under test. The bias voltage is further varied to characterize the device under test.

Owner:MONTEREY RES LLC

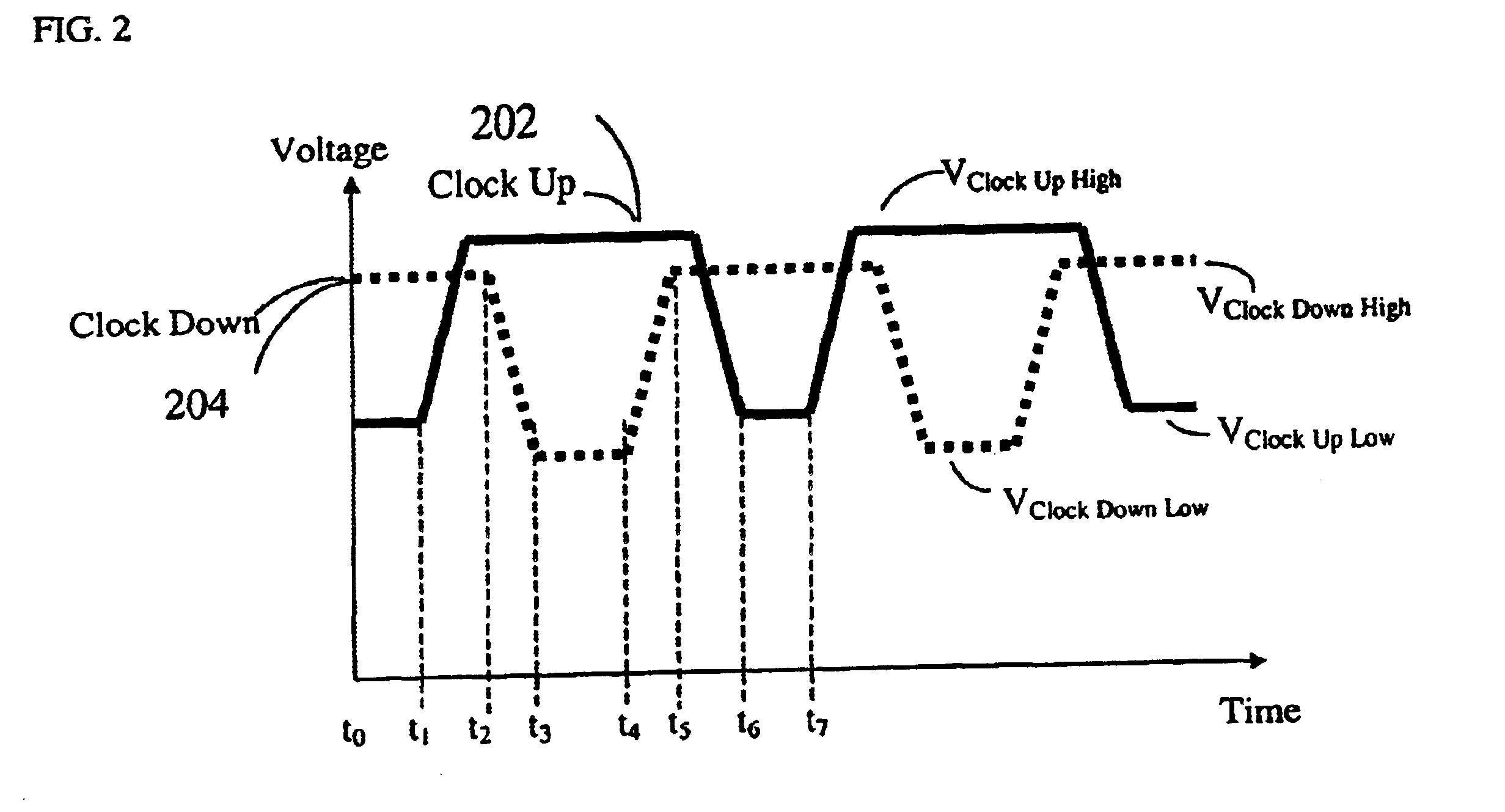

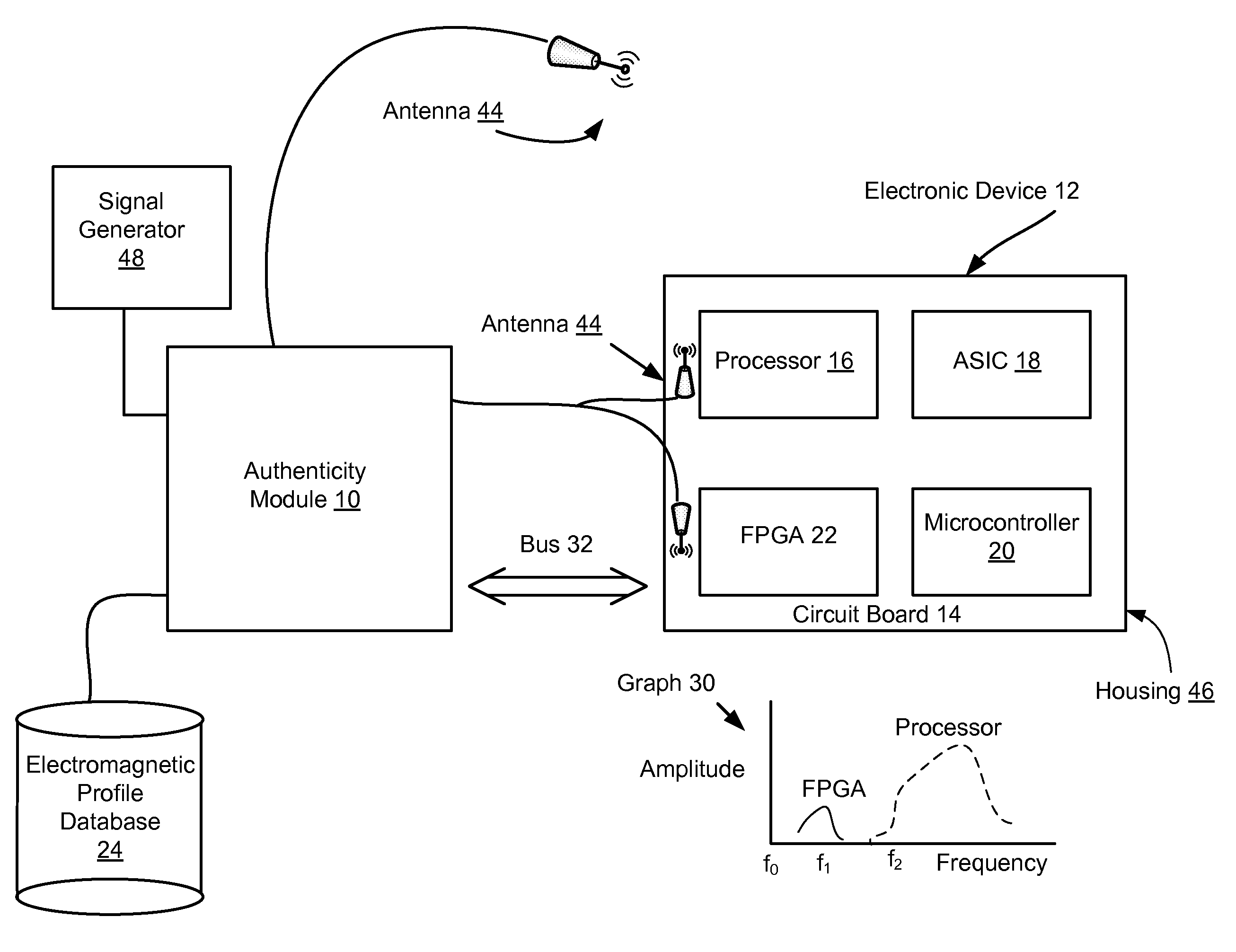

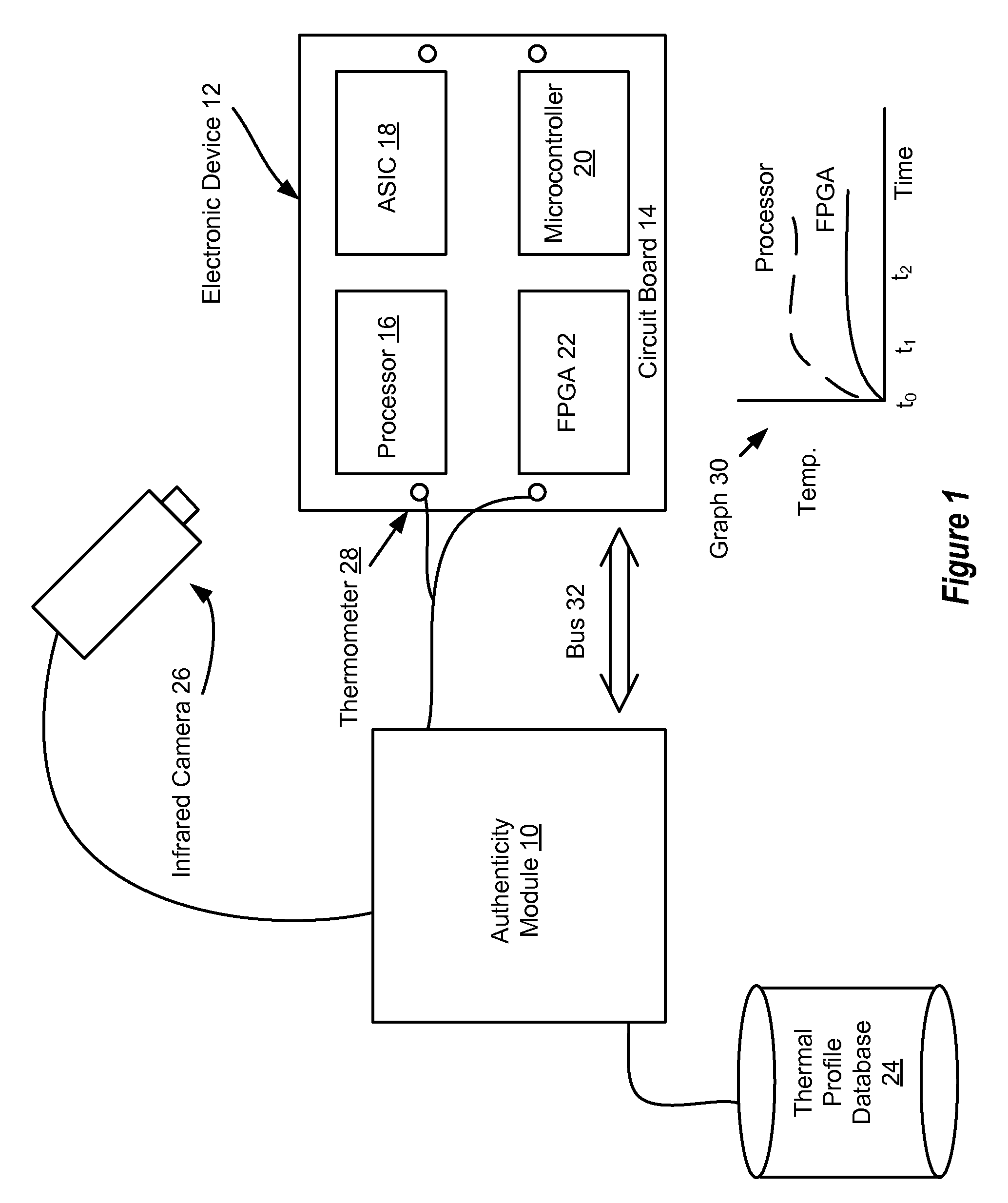

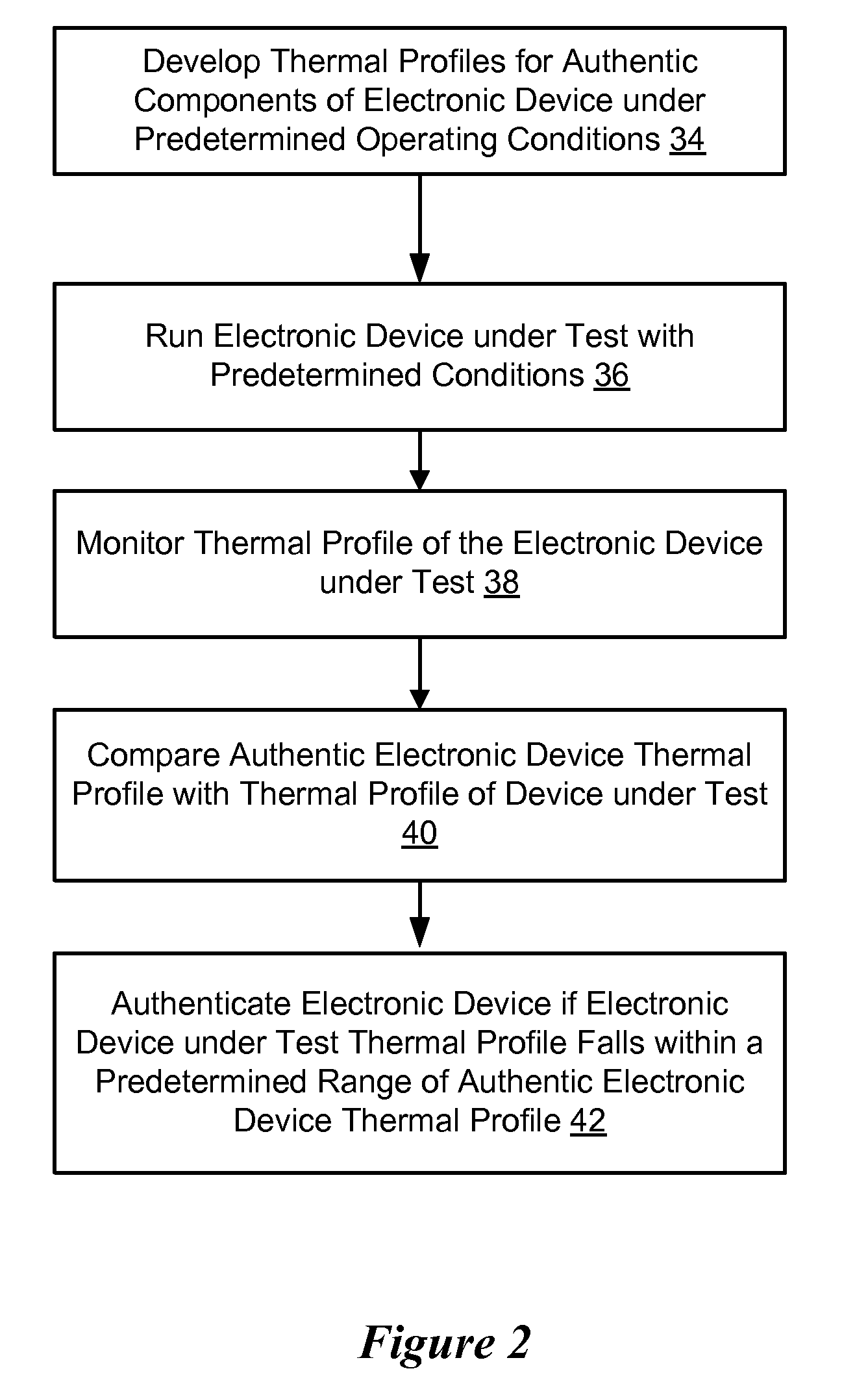

Electromagnetic Profiling To Validate Electronic Device Authenticity

InactiveUS20100237854A1Magnetic measurementsElectrical testingOperant conditioningField-programmable gate array

Counterfeit electronic devices are detected by comparing a thermal profile of the counterfeit device and an authentic device under predetermined operating conditions. A thermal profile for an authentic electronic device is recorded executing an instruction set over time, such as with static infrared images at predetermined times, video infrared images over a predetermined time period or temperature measurements made at predetermined locations of the electronic device. In one embodiment, a thermal profile indicates that a processor device has been used in the place of a field programmable grid array device. In an alternative embodiment, an electromagnetic profile is detected instead of or in addition to the thermal profile. The electromagnetic profile of an authentic device is used to create an expected profile for comparison with an electromagnetic profile of electronic devices under test.

Owner:IBM CORP

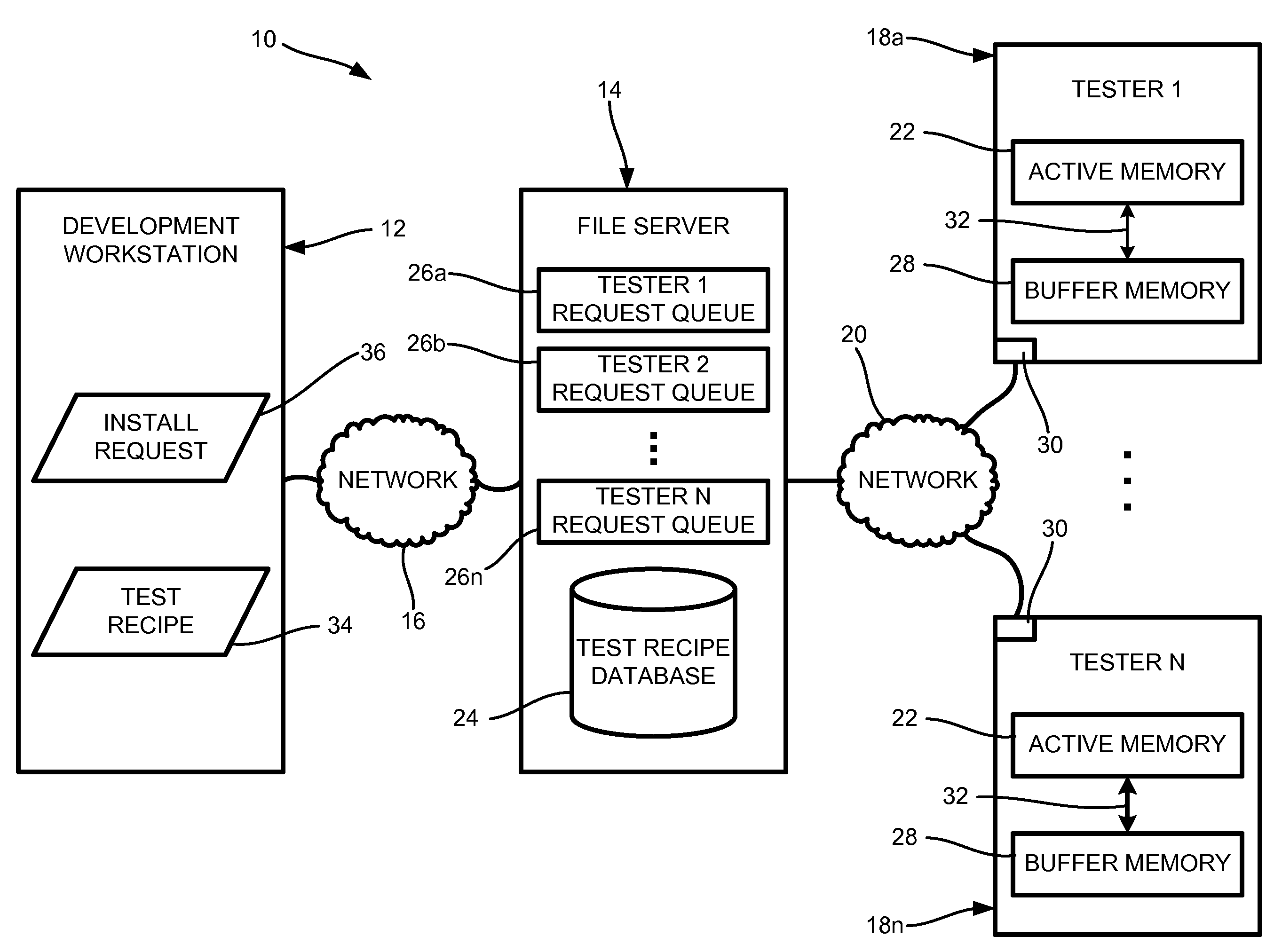

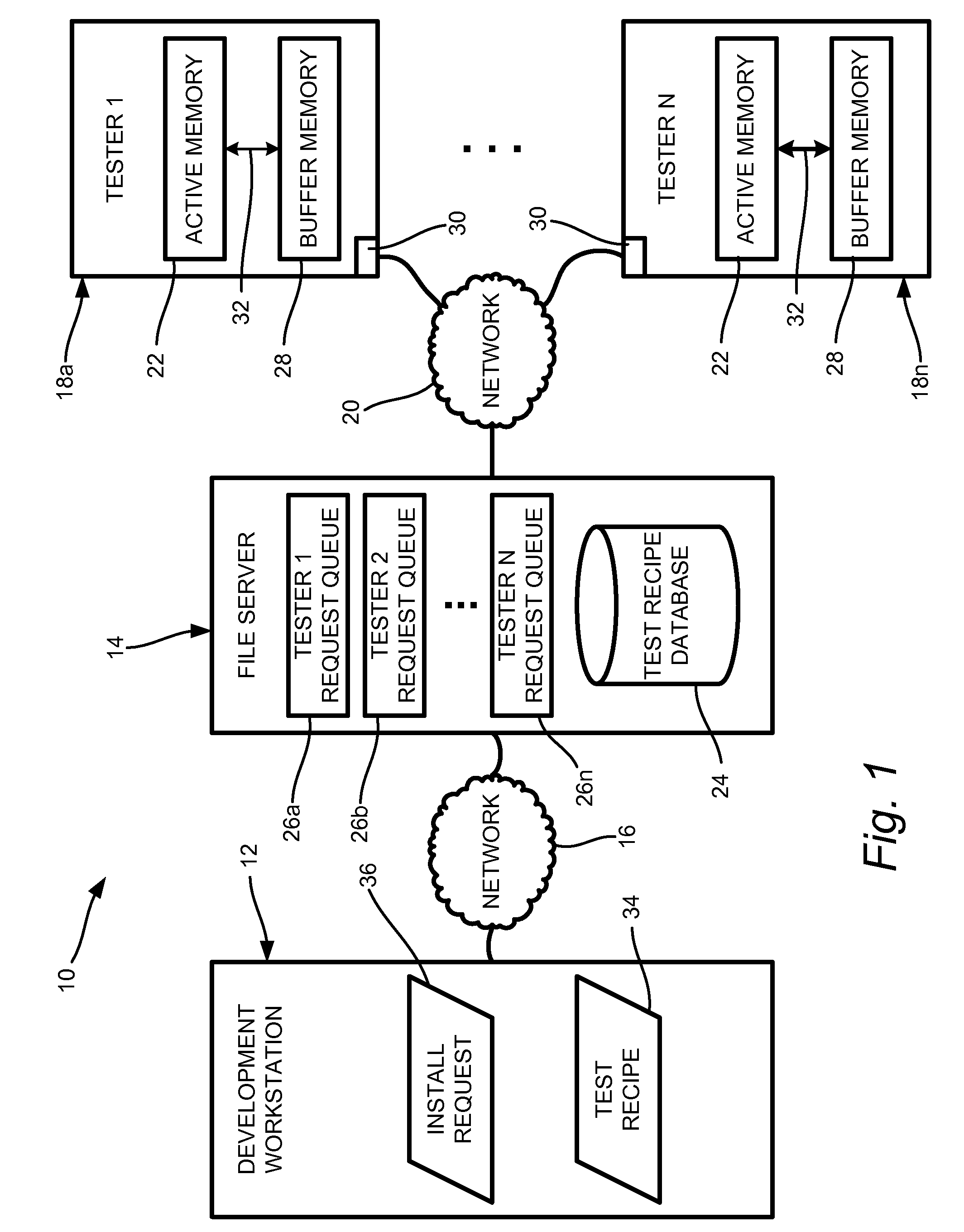

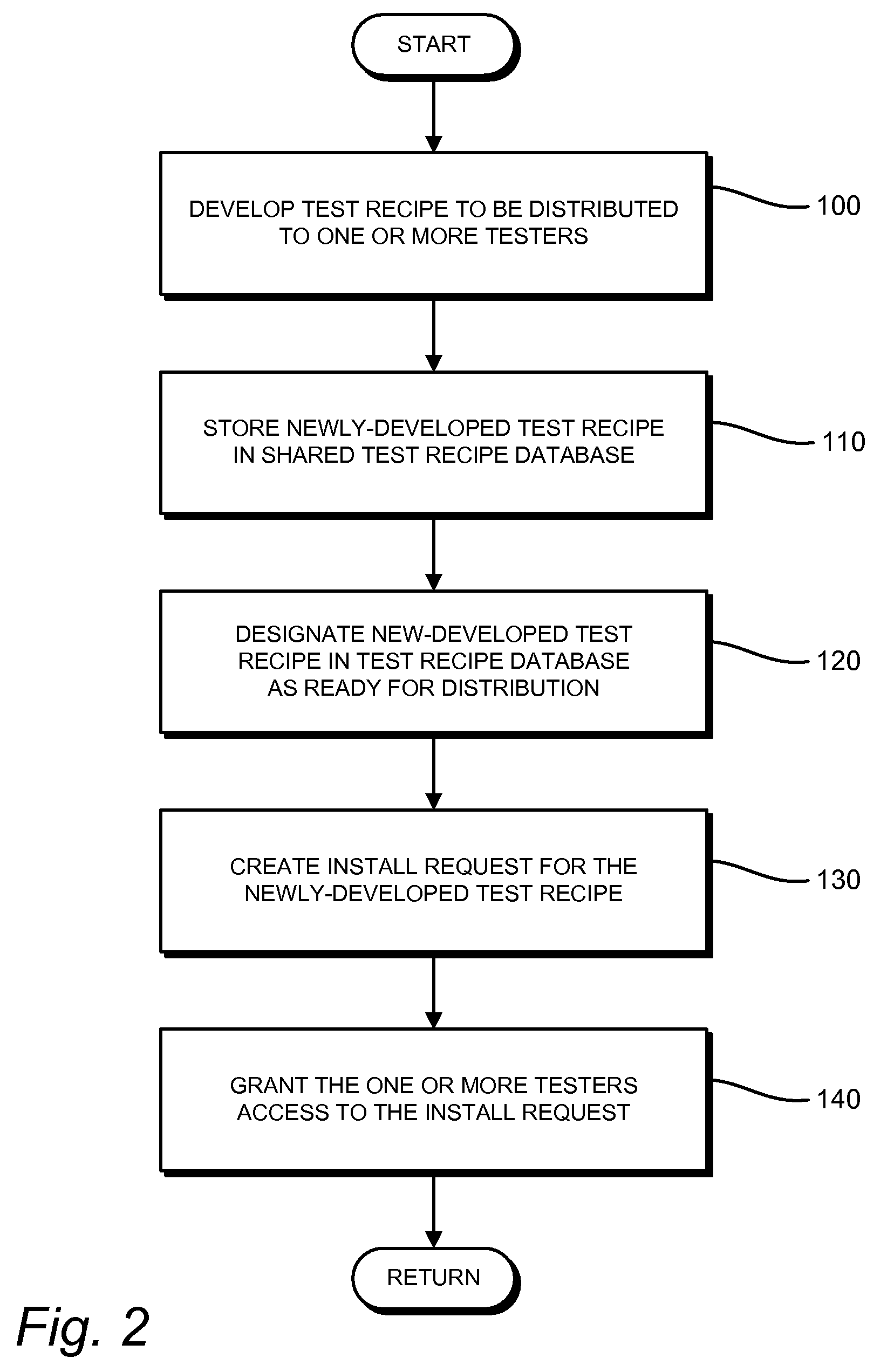

Test recipe distribution method and system

InactiveUS8452567B1Error detection/correctionSpecial data processing applicationsDistribution methodActive memory

Provided is a method and system for distributing a test recipe to a tester for conducting a test to determine if a device under test operates as designed. The method includes storing an active test recipe in an active memory in local communication with the tester, and initiating the test of the device under test to be performed by the tester according to a parameter included in the active test recipe stored in the active memory. A second parameter included in a second test recipe is received by the tester while conducting the test of the device under test according to the parameter included in the active test recipe. The method further includes storing the second parameter in a buffer memory in local communication with the active memory, and initiating a transfer of the second parameter from the buffer memory to the active memory. After initiation of the transfer of the second parameter to the active memory, a subsequent test to be performed by the tester according to the second parameter included in the second test recipe is initiated.

Owner:KEITHLEY INSTRUMENTS INC

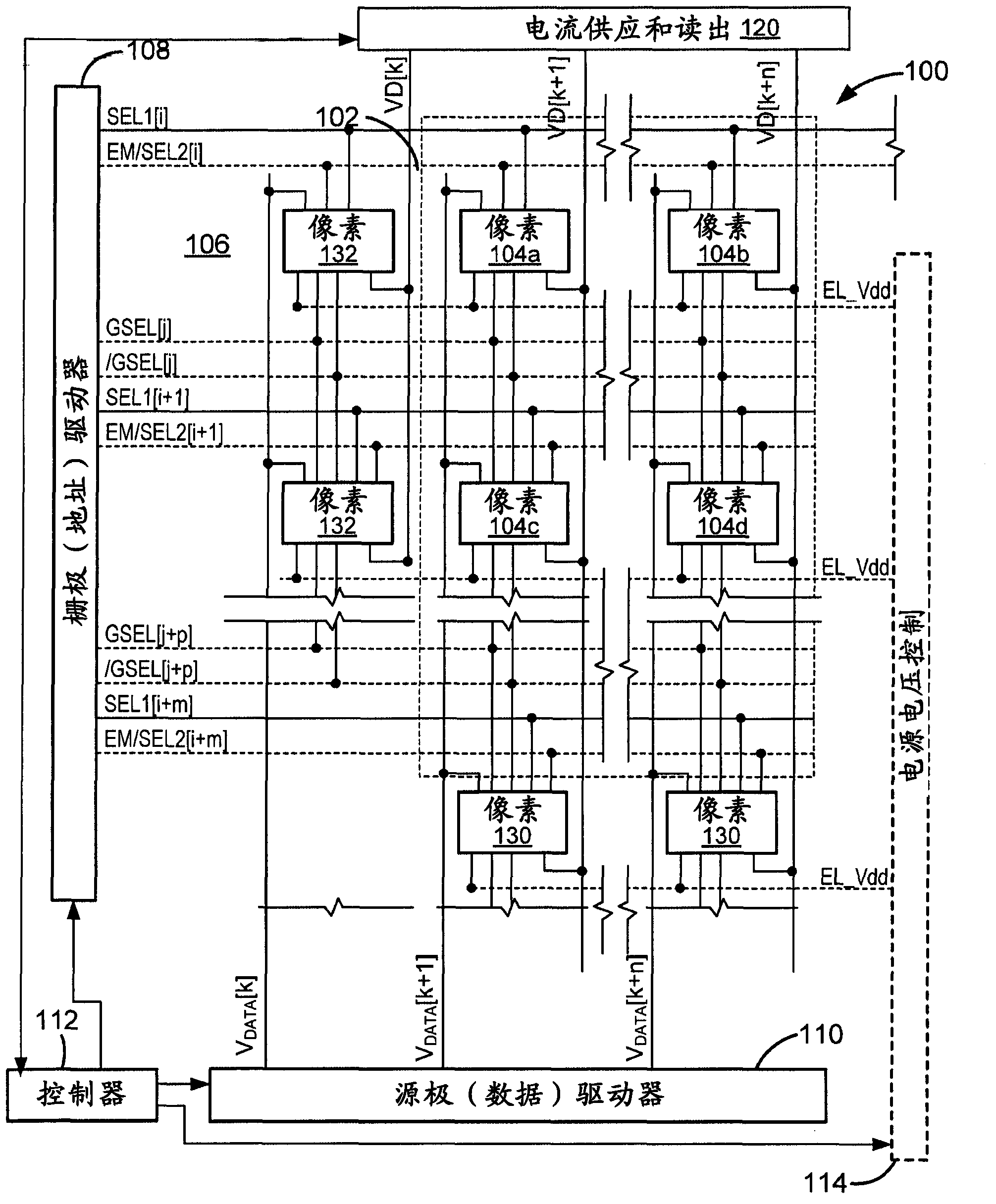

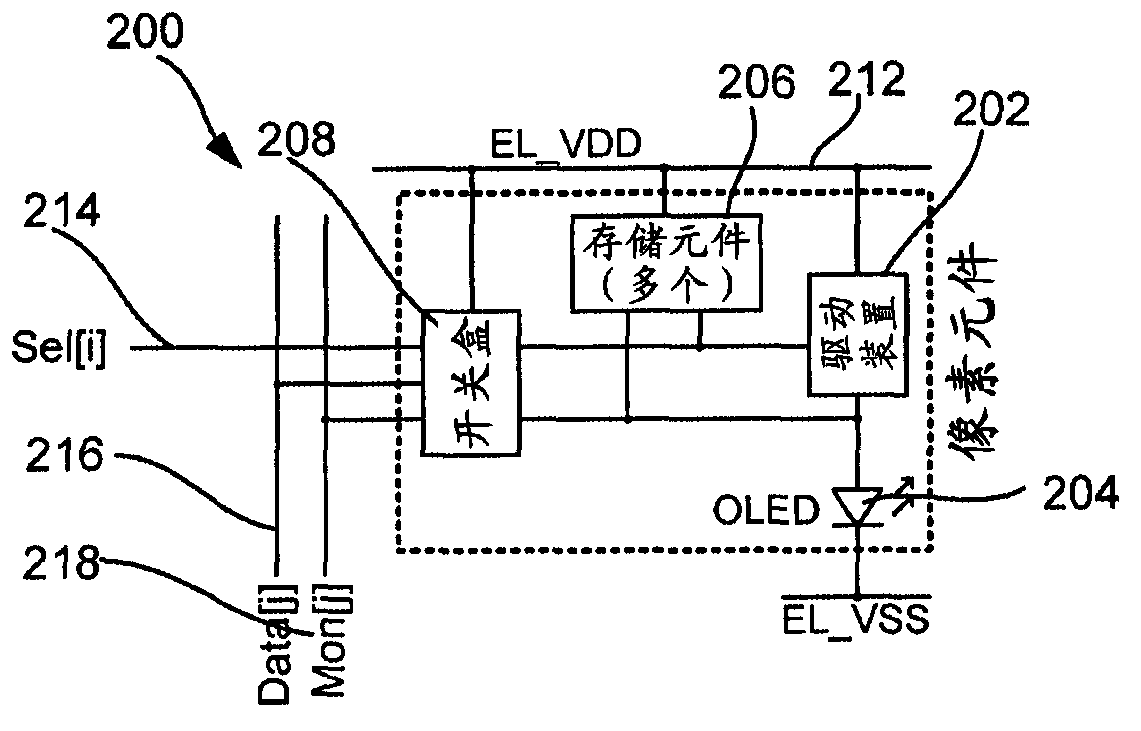

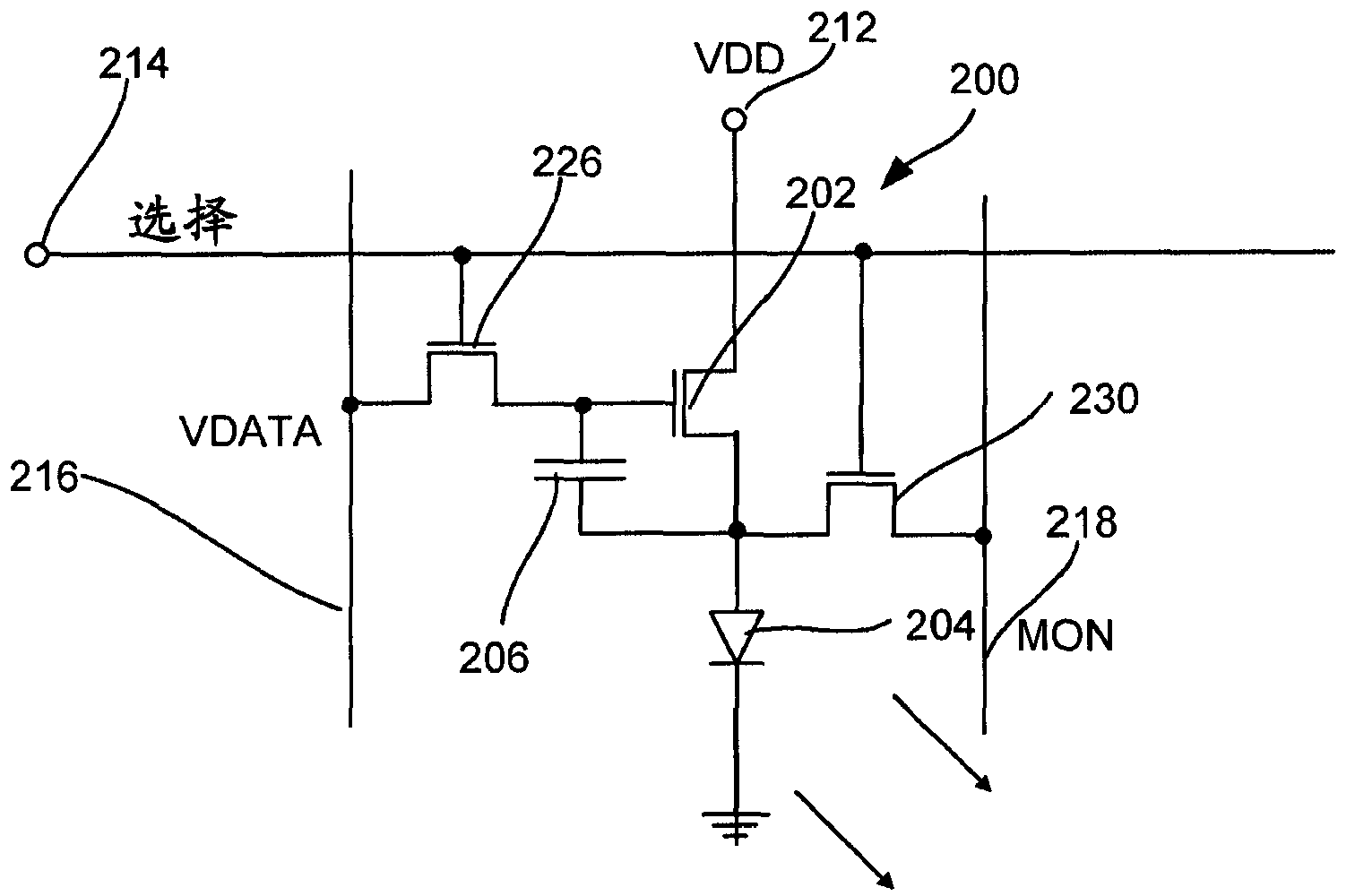

System and methods for aging compensation in AMOLED displays

Methods and systems to provide baseline measurements for aging compensation for a display device are disclosed. An example display system has a plurality of active pixels and a reference pixel. Common input signals are provided to the reference pixel and the plurality of active pixels. The outputs of the reference pixel is measured and compared to the output of the active pixels to determine aging effects. The display system may also be tested applying a first known reference current to a current comparator with a second variable reference current and the output of a device under test such as one of the pixels. The variable reference current is adjusted until the second current and the output of the device under test is equivalent of the first current. The resulting current of the device under test is stored in a look up table for a baseline for aging measurements during the display system operation. The display system may also be tested to determine production flaws by determining anomalies such as short circuits in pixel components such as OLEDs and drive transistors.

Owner:IGNIS INNOVATION