Patents

Literature

3516results about "Digital circuit testing" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

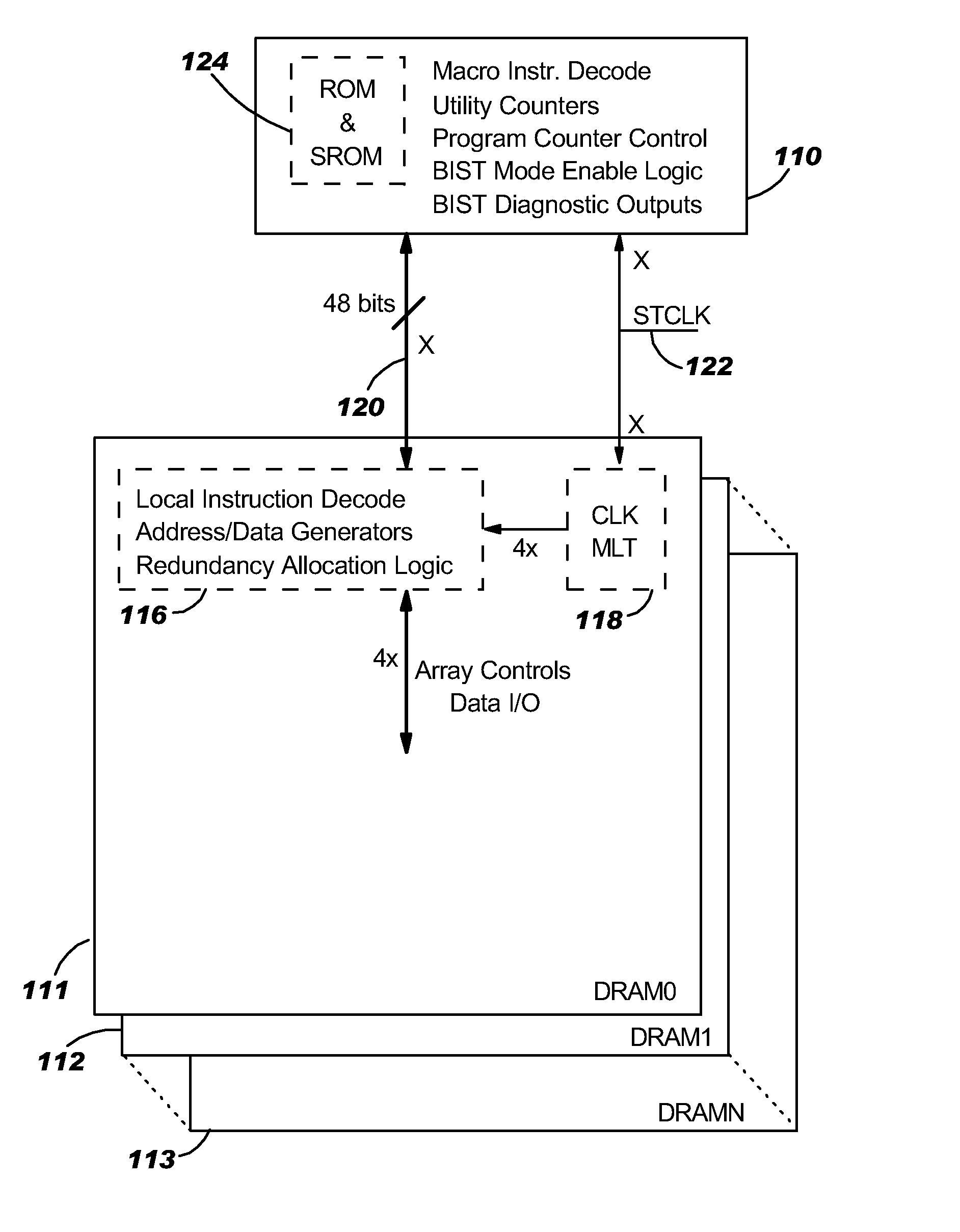

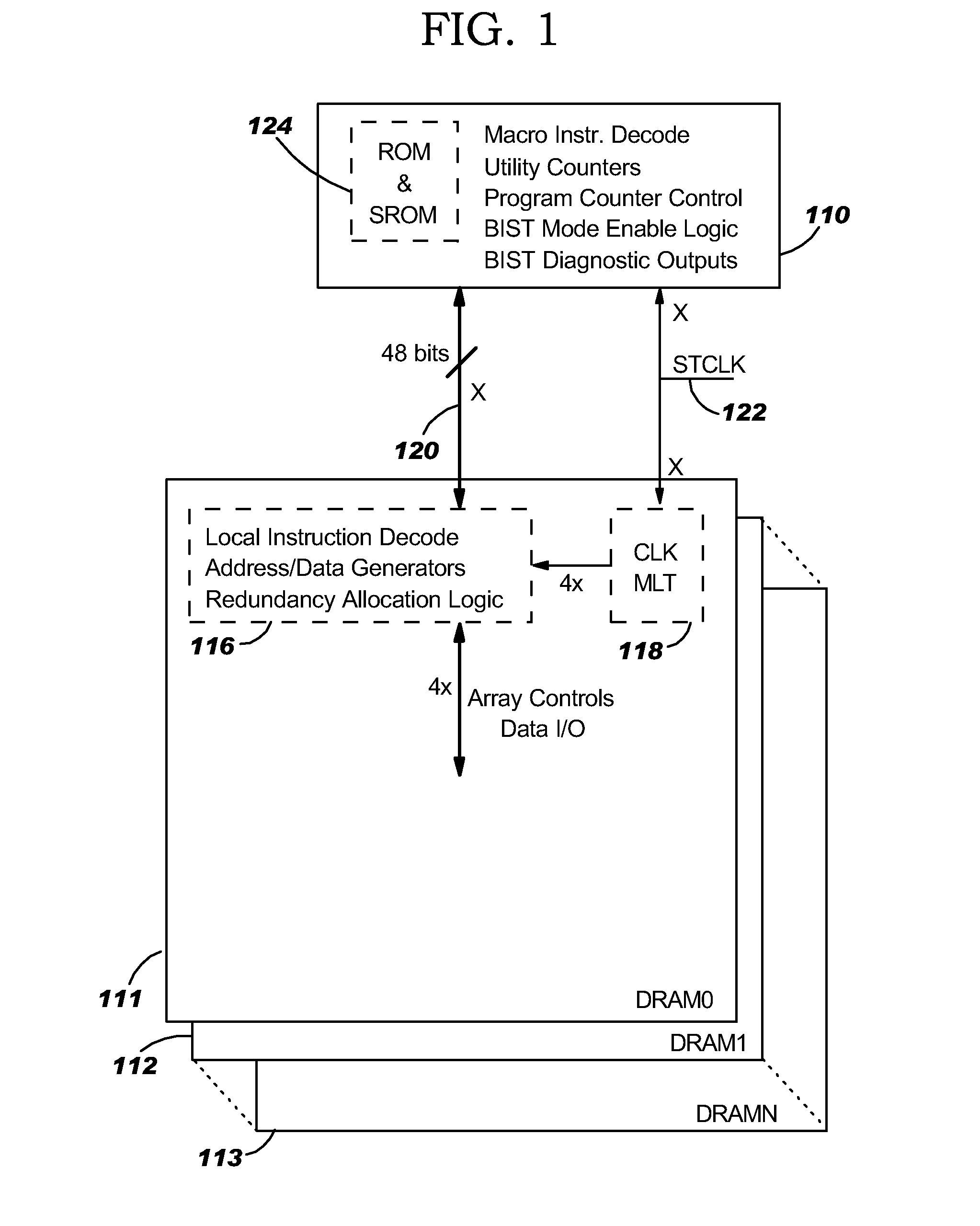

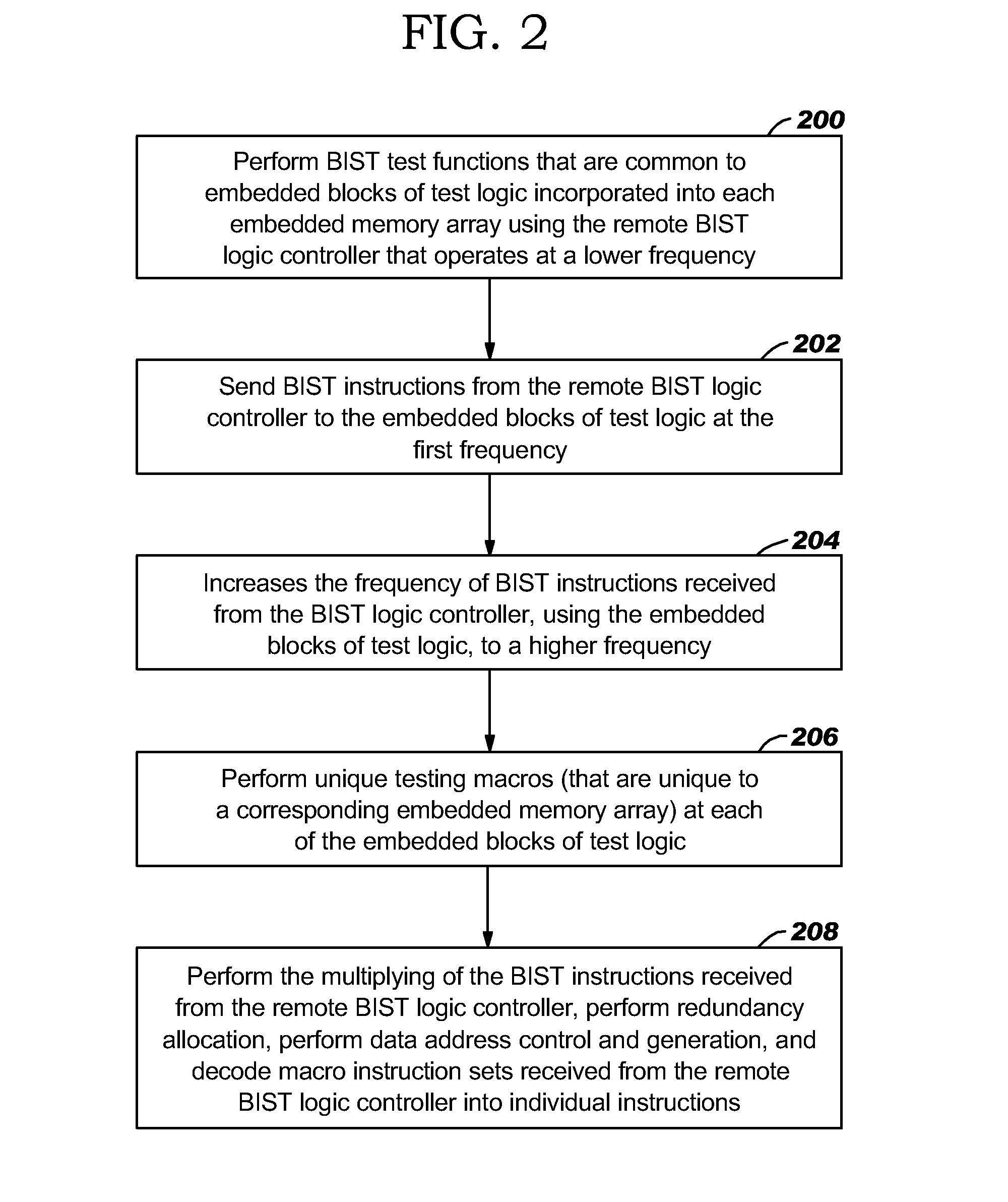

Remote bist for high speed test and redundancy calculation

InactiveUS20080215937A1Reduce frequencyIncrease processing frequencyDigital circuit testingFunctional testingLow speedSpeed test

Disclosed in a hybrid built-in self test (BIST) architecture for embedded memory arrays that segments BIST functionality into remote lower-speed executable instructions and local higher-speed executable instructions. A standalone BIST logic controller operates at a lower frequency and communicates with a plurality of embedded memory arrays using a BIST instruction set. A block of higher-speed test logic is incorporated into each embedded memory array under test and locally processes BIST instructions received from the standalone BIST logic controller at a higher frequency. The higher-speed test logic includes a multiplier for increasing the frequency of the BIST instructions from the lower frequency to the higher frequency. The standalone BIST logic controller enables a plurality of higher-speed test logic structures in a plurality of embedded memory arrays.

Owner:META PLATFORMS INC

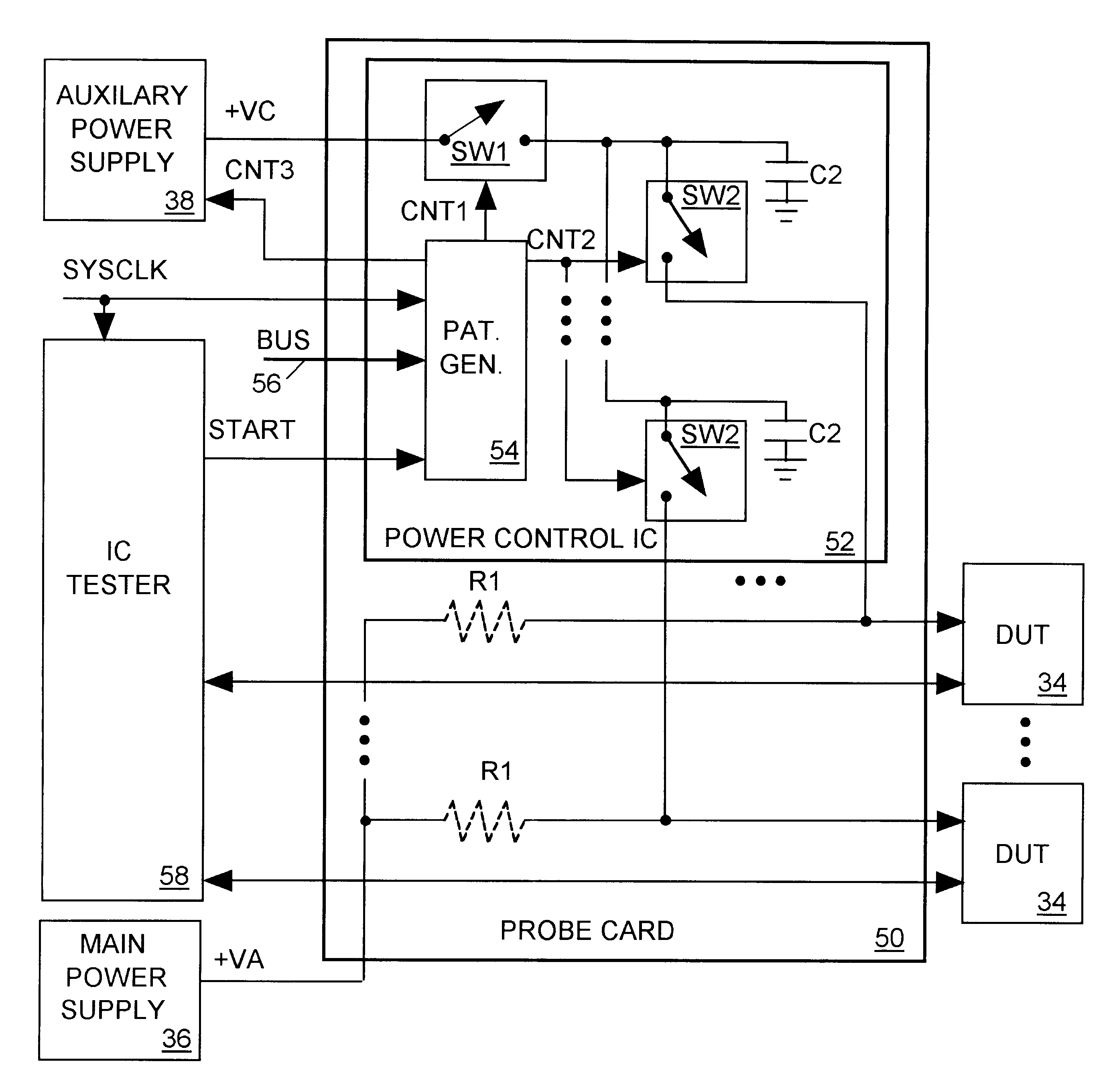

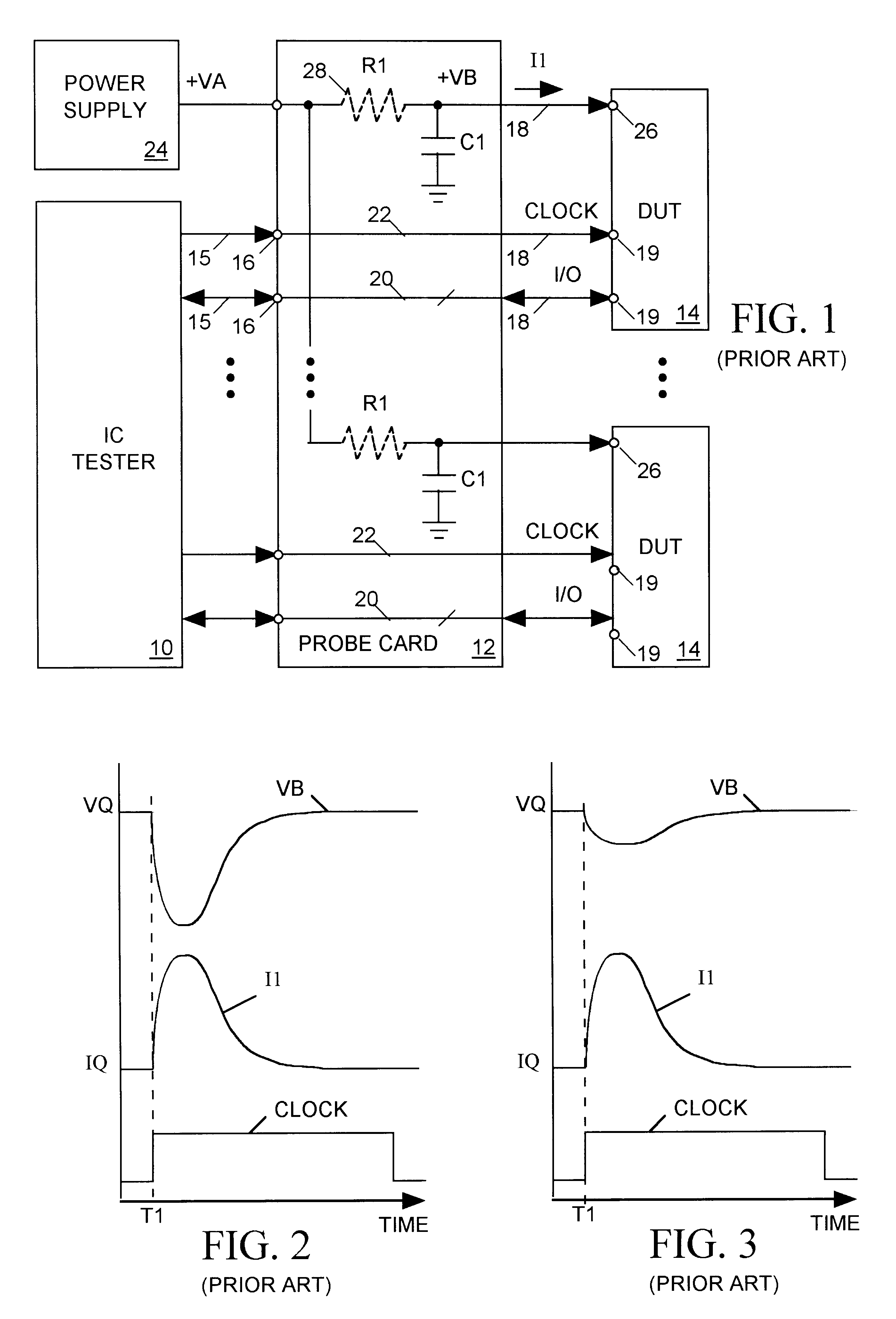

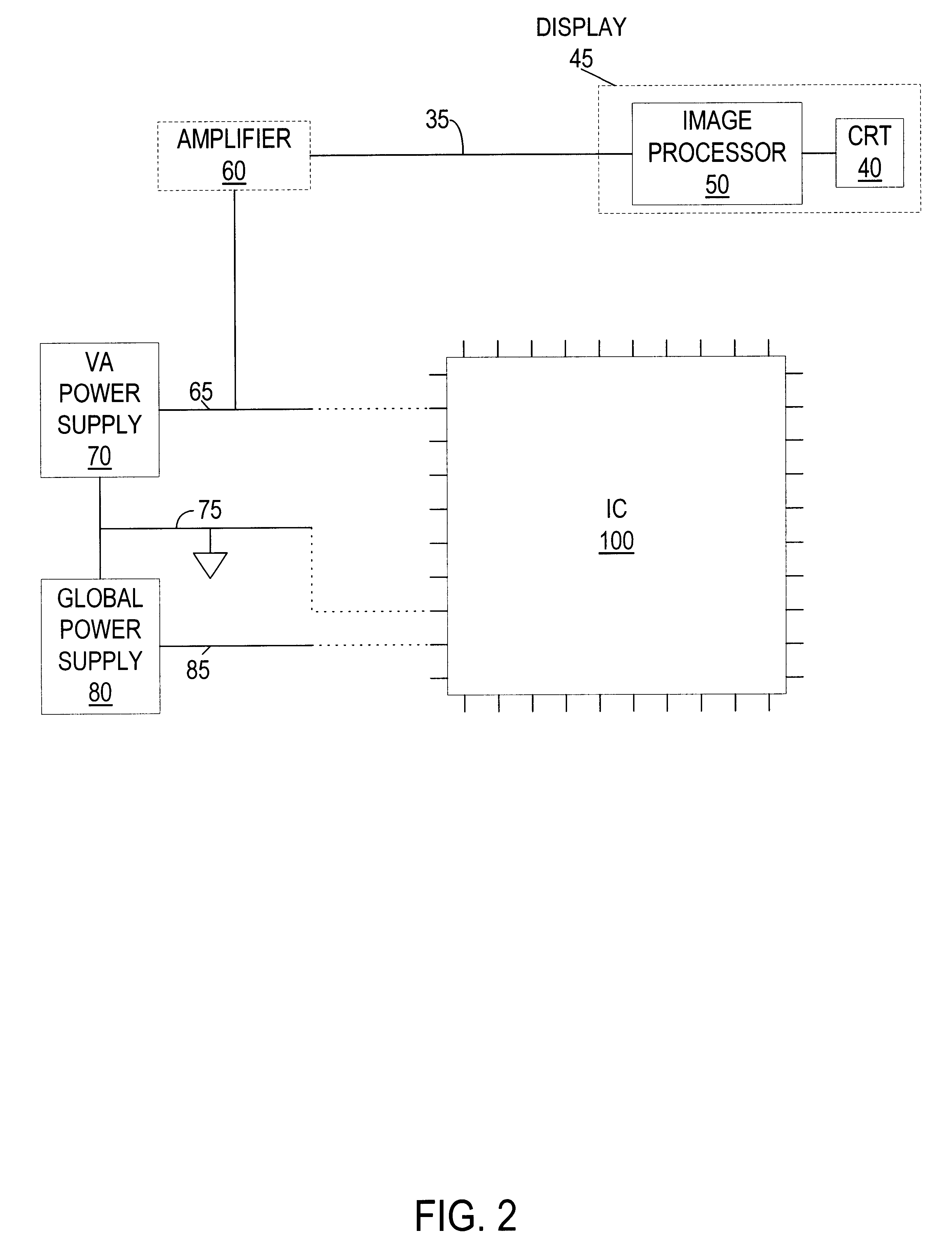

Apparatus for reducing power supply noise in an integrated circuit

InactiveUS6339338B1Reduce power supply noiseSuppress mutationDigital circuit testingVolume/mass flow measurementCapacitanceState variation

A main power supply continuously provides a current to a power input terminal of an integrated circuit device under test (DUT). The DUT's demand for current at the power input terminal temporarily increases during state changes in synchronous logic circuits implemented within the DUT. To limit variation (noise) in voltage at the power input terminal arising from these temporary increases in current demand, a charged capacitor is connected to the power input terminal during each DUT state change. The capacitor discharges into the power input terminal to supply additional current to meet the DUT's increased demand. Following each DUT state change the capacitor is disconnected from the power input terminal and charged to a level sufficient to meet a predicted increase in current demand during a next DUT state change.

Owner:FORMFACTOR INC

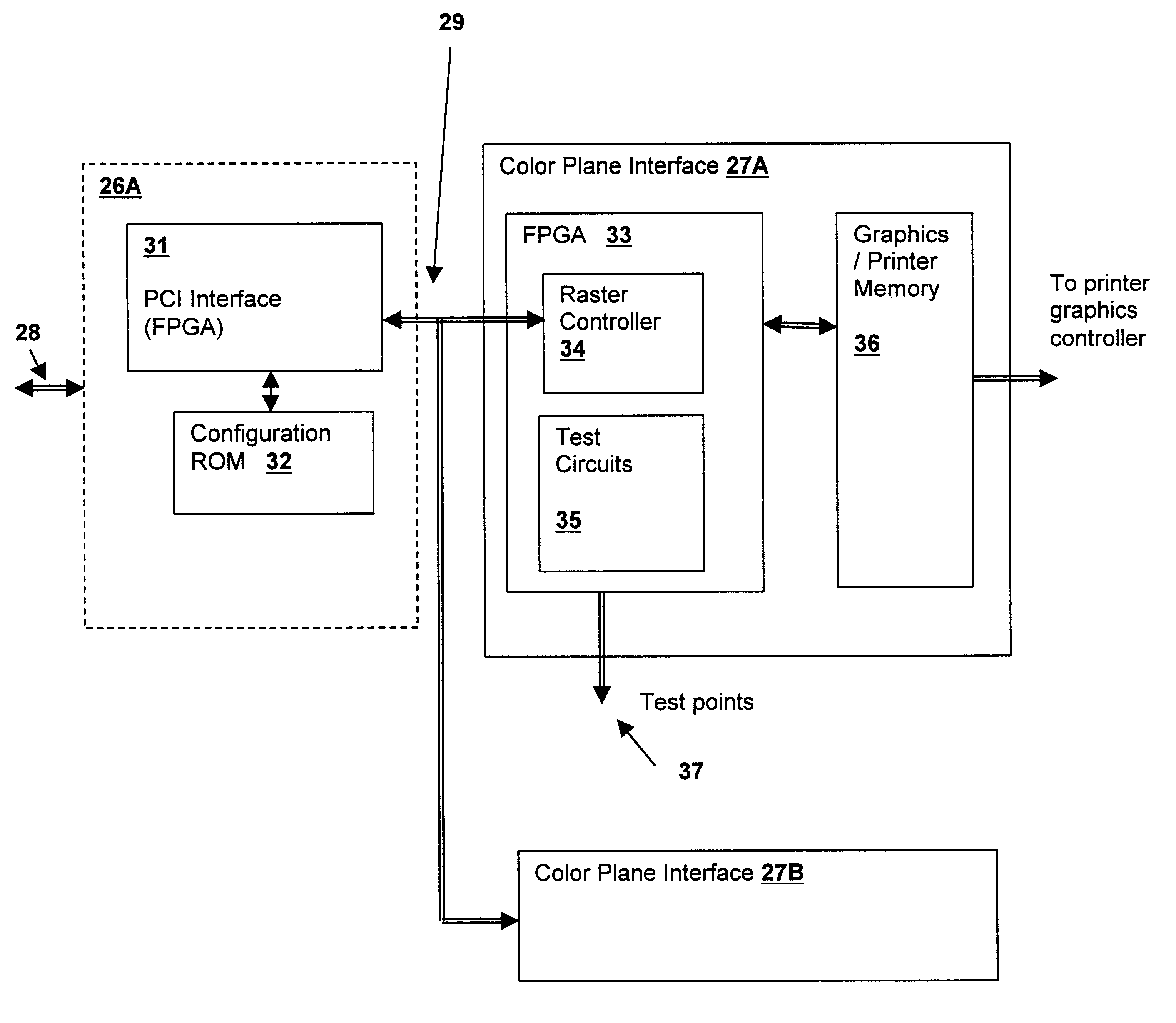

Method and apparatus for tracing hardware states using dynamically reconfigurable test circuits

A method and apparatus for tracing hardware states using dynamically reconfigurable test circuits provides improved debug and troubleshooting capability for functional logic implemented within field programmable logic arrays (FPGAs). Special test logic configurations may be loaded to enhance the debugging of a system using FPGAs. Registers are used to capture snapshots of internal signals for access by a trace program and a test multiplexer is used to provide real-time output to test pins for use with external test equipment. By retrieving the hardware snapshot information with a trace program running on a system in which the FPGA is used, software and hardware debugging are coordinated, providing a sophisticated model of overall system behavior. Special test circuits are implemented within the test logic configurations to enable detection of various events and errors. Counters are used to capture count values when system processor execution reaches a hardware trace point or when events occur. Comparators are used to detect specific data or address values and event detectors are used to detect particular logic value combinations that occur within the functional logic.

Owner:IBM CORP

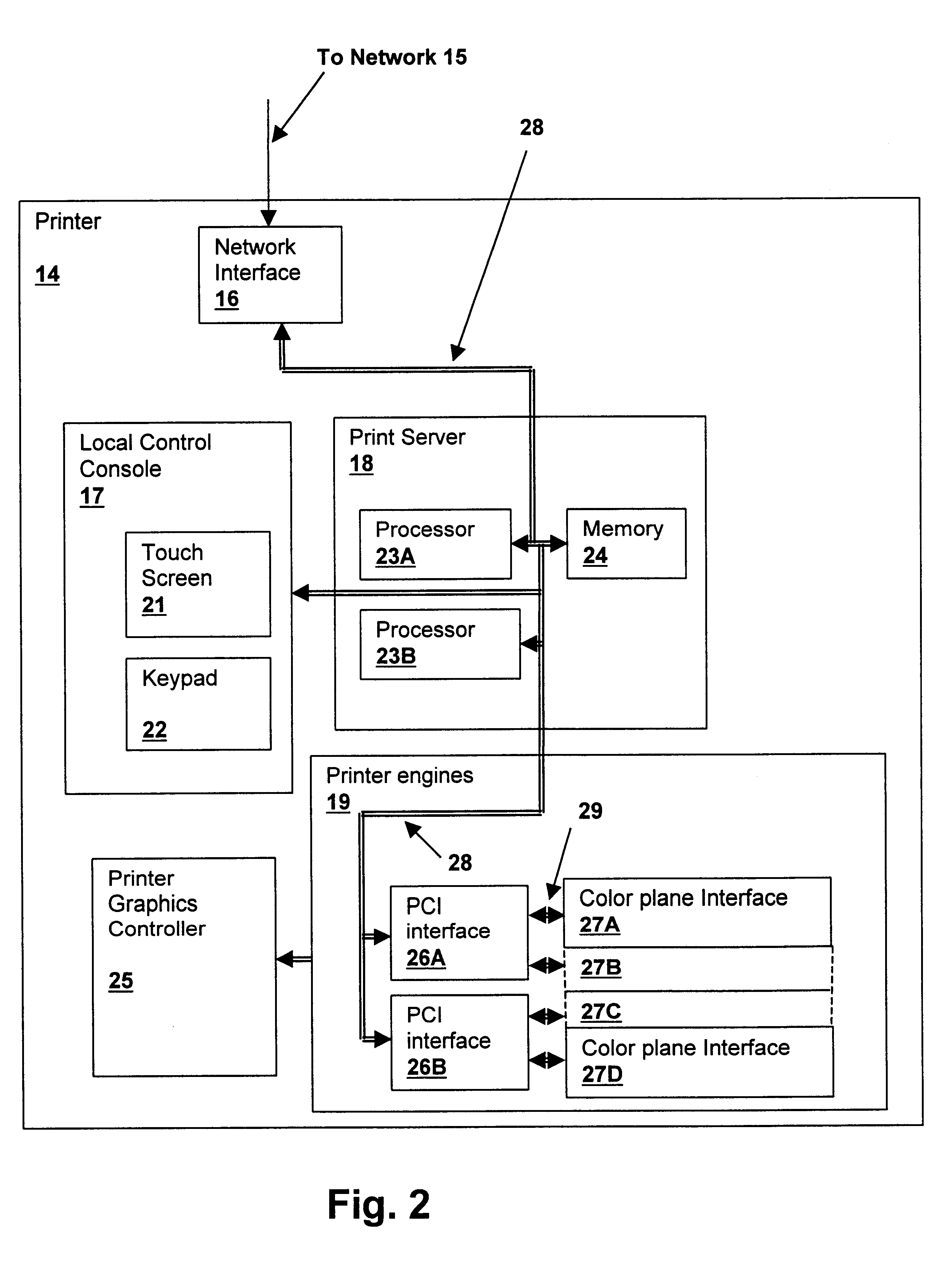

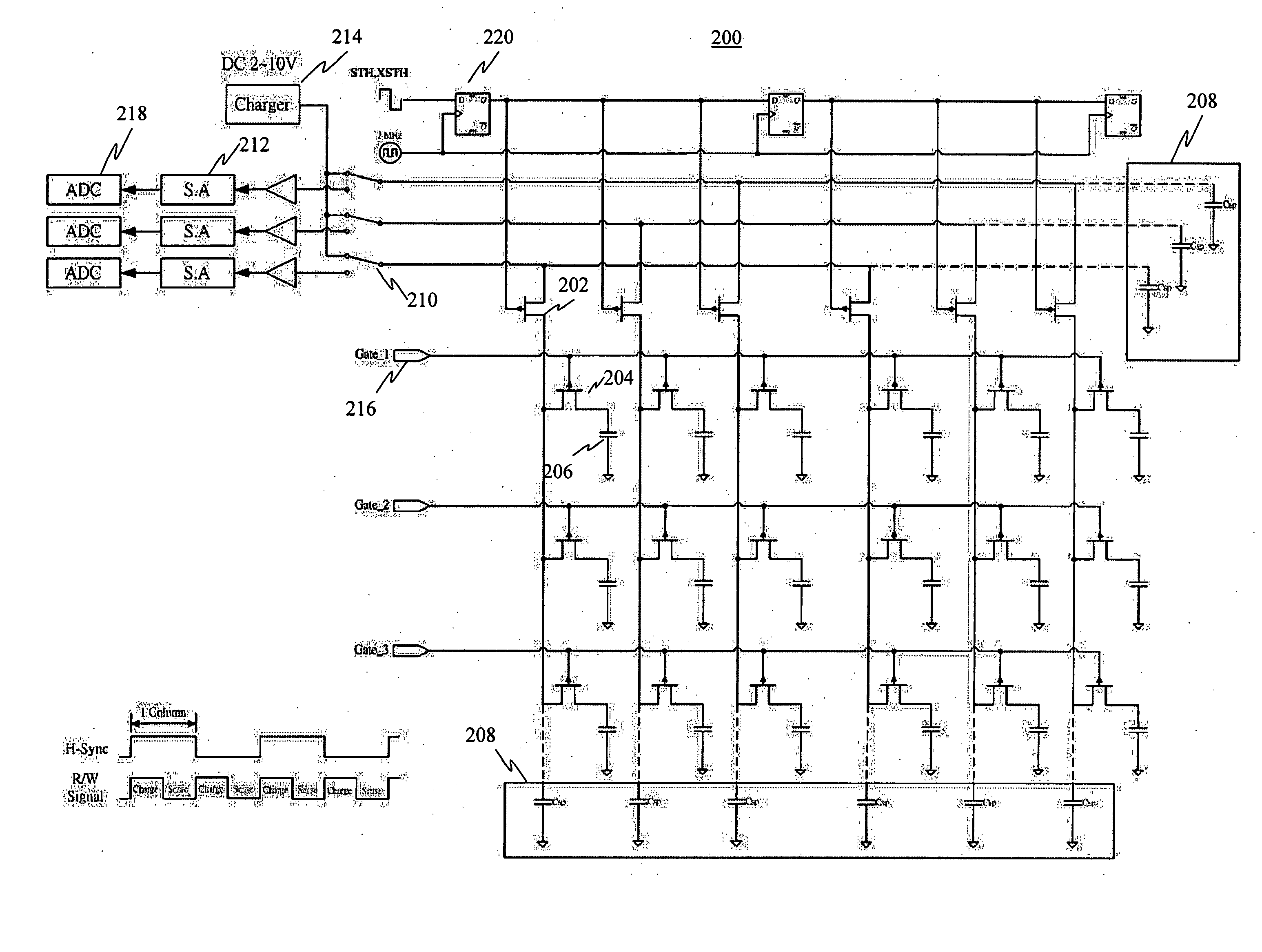

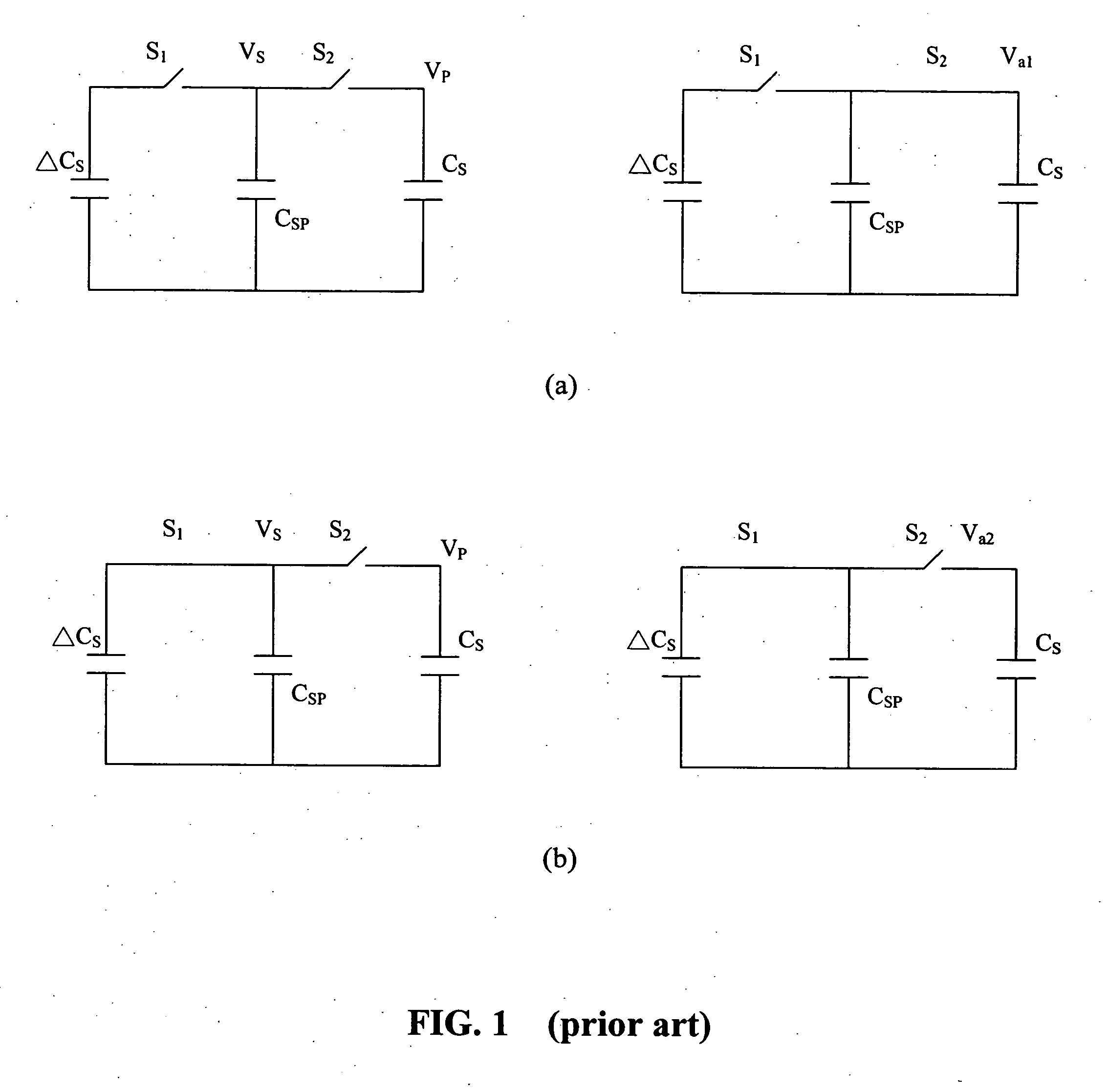

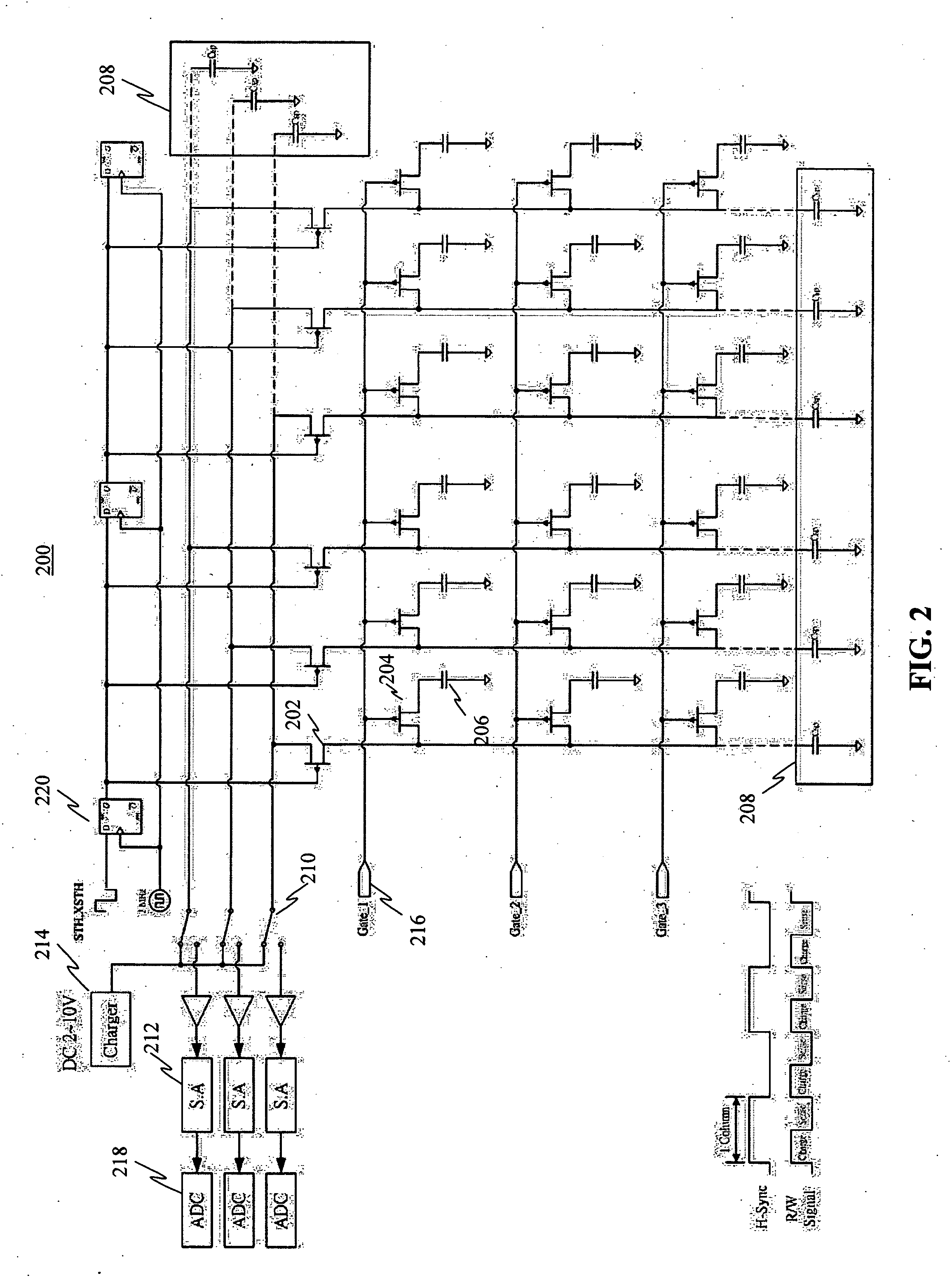

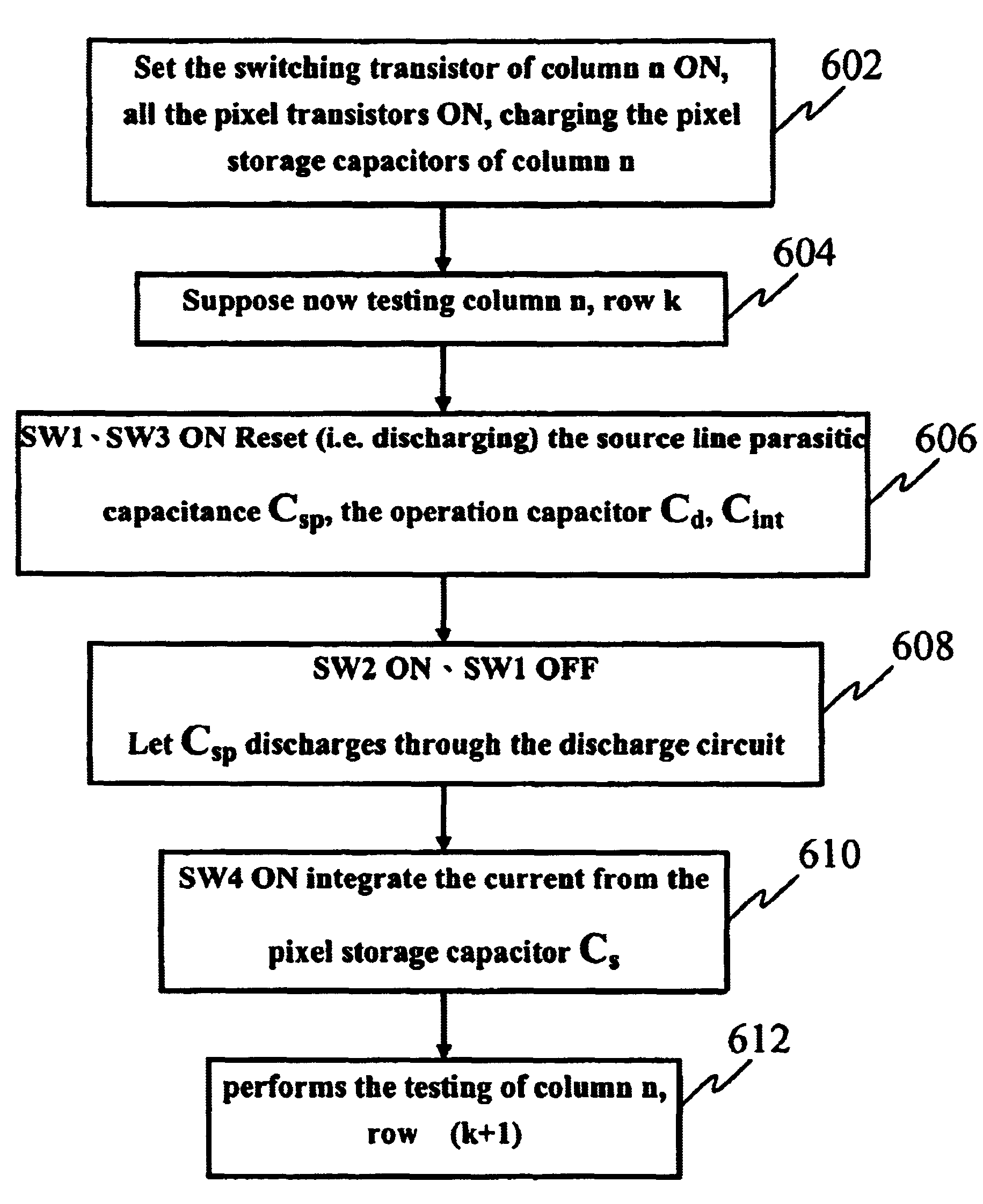

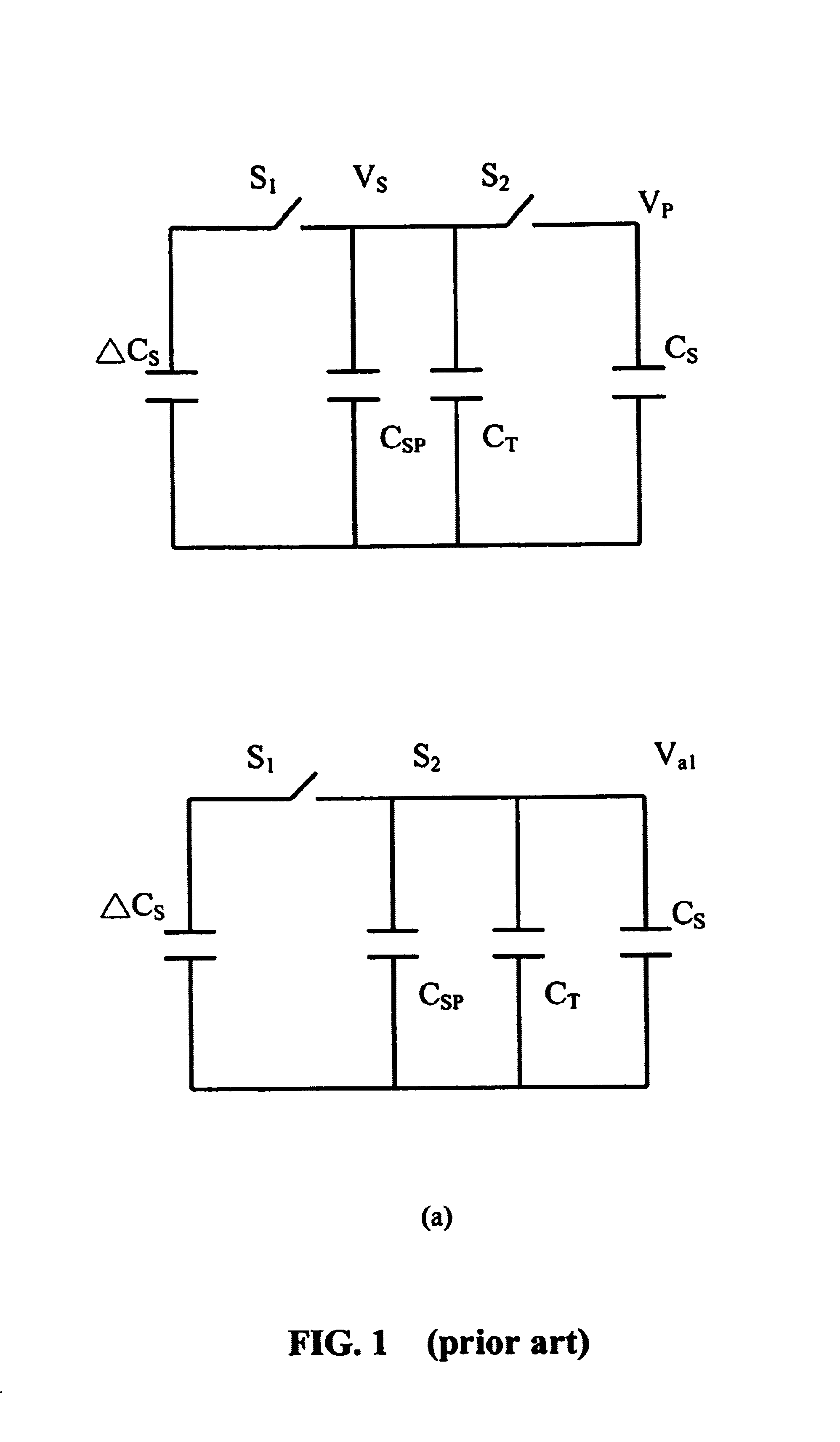

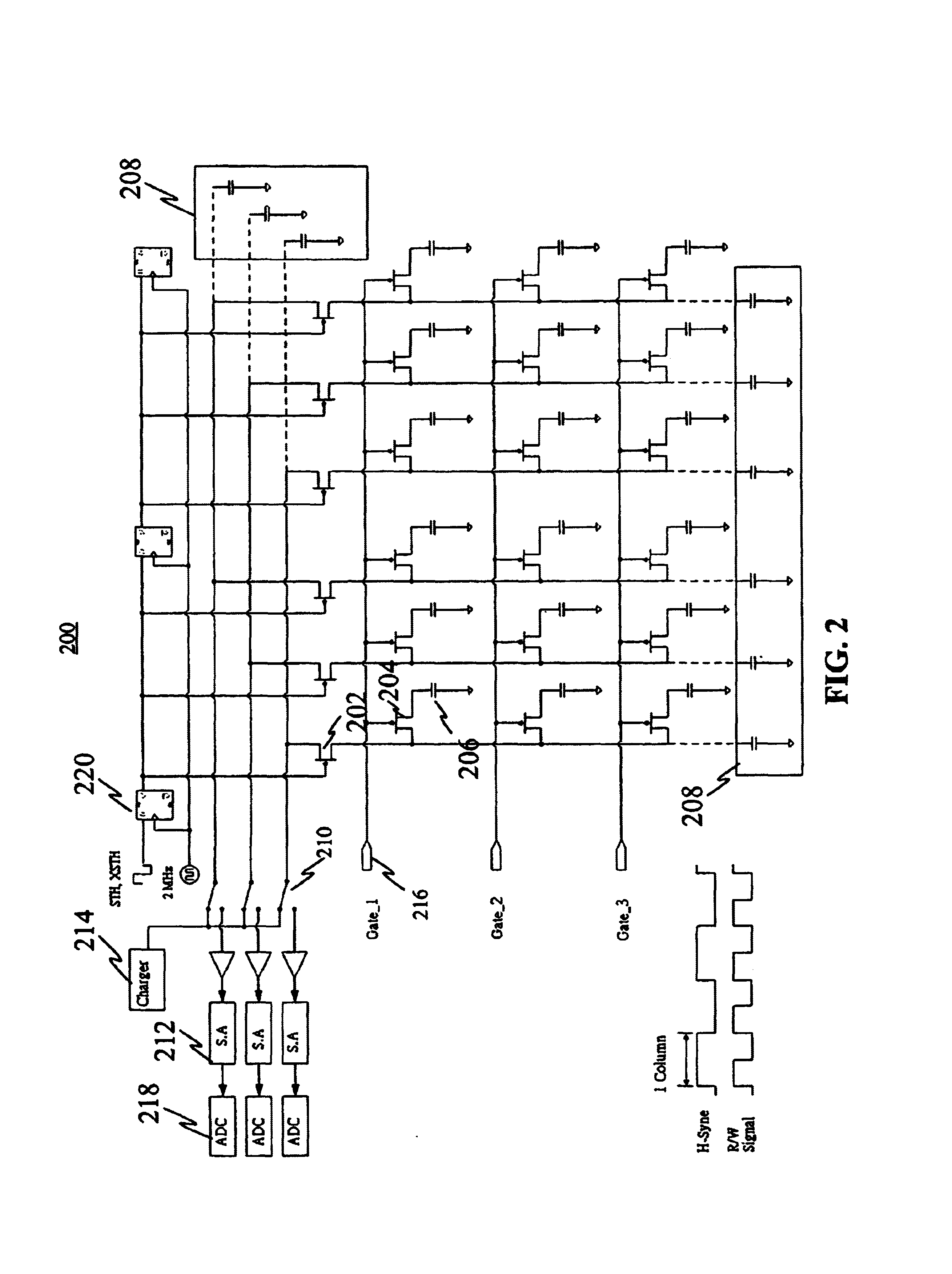

Testing apparatus and method for thin film transistor display array

InactiveUS20050024081A1Improve accuracyImprove reliabilityDigital circuit testingResistance/reactance/impedenceTransistor arrayHemt circuits

The present invention discloses a testing circuit and method for thin film transistor display array, for testing the yield of thin film transistor array. The testing circuit comprising: An array tester, a test panel (DUT), a sense amplifier array. The sense amplifier is composed by a plurality of trans- impedance amplifier unit and a plurality of parasitic capacitance discharge circuit unit. Every sense amplifier includes: a trans-impedance amplifier, which is implemented by an operational amplifier, two switches and an operation capacitance, the trans-impedance amplifier is used to form an integrated circuit, the output is transmitted to a sampling / hold circuit via a switch; a parasitic capacitance discharge circuit is used to form a discharge rout for the charge of the parasitic capacitance.

Owner:PRIMETECH INT CORP

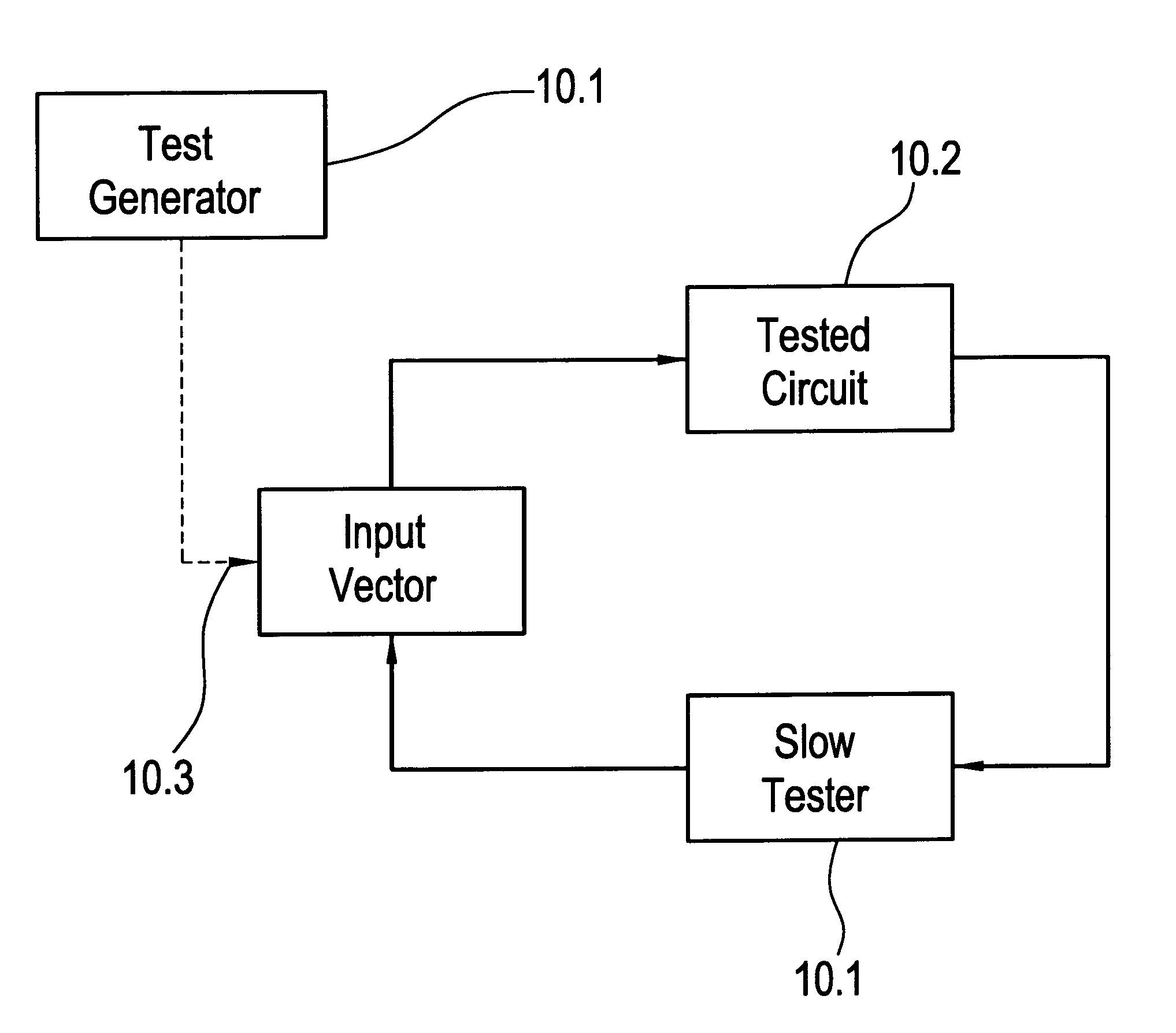

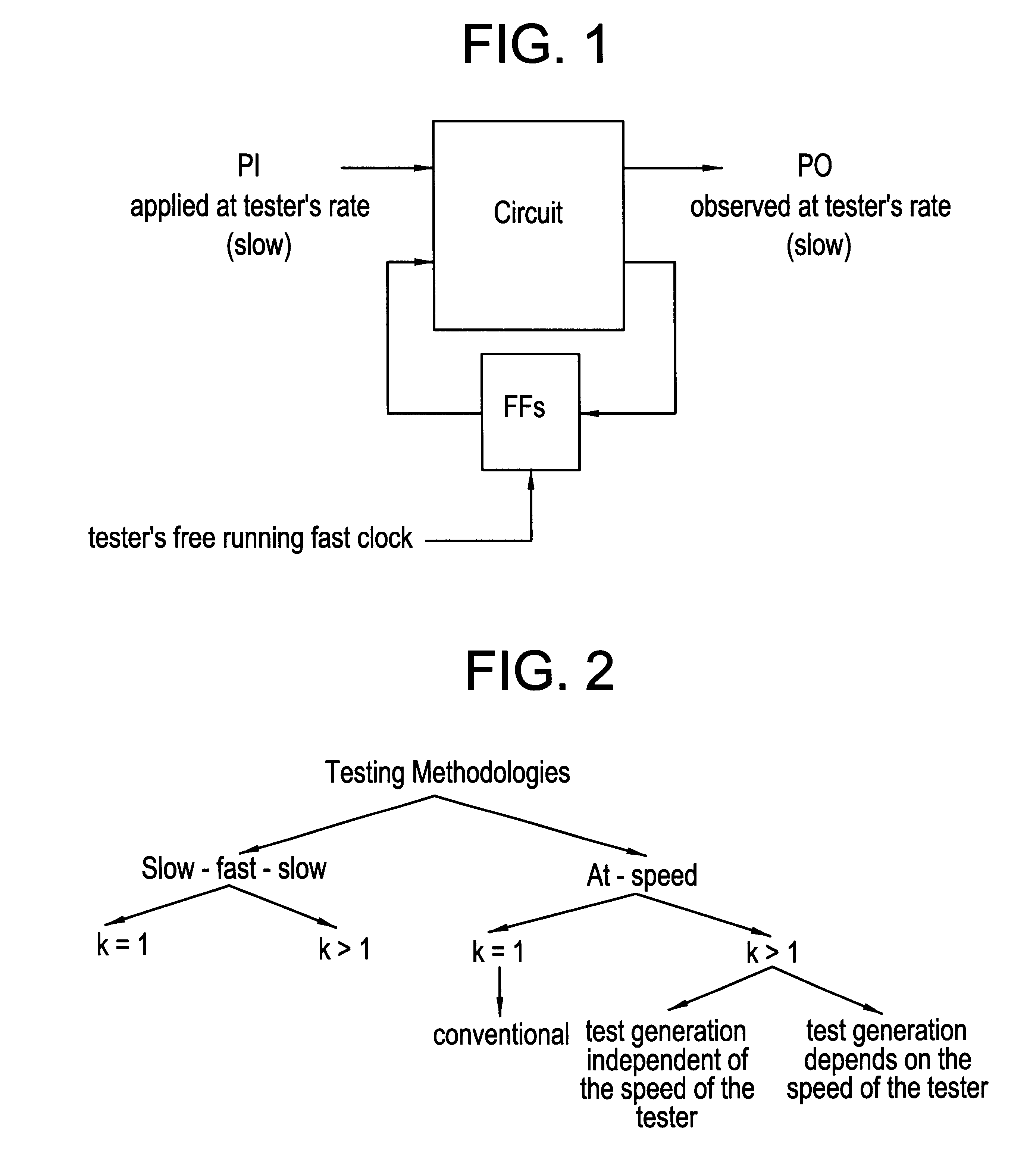

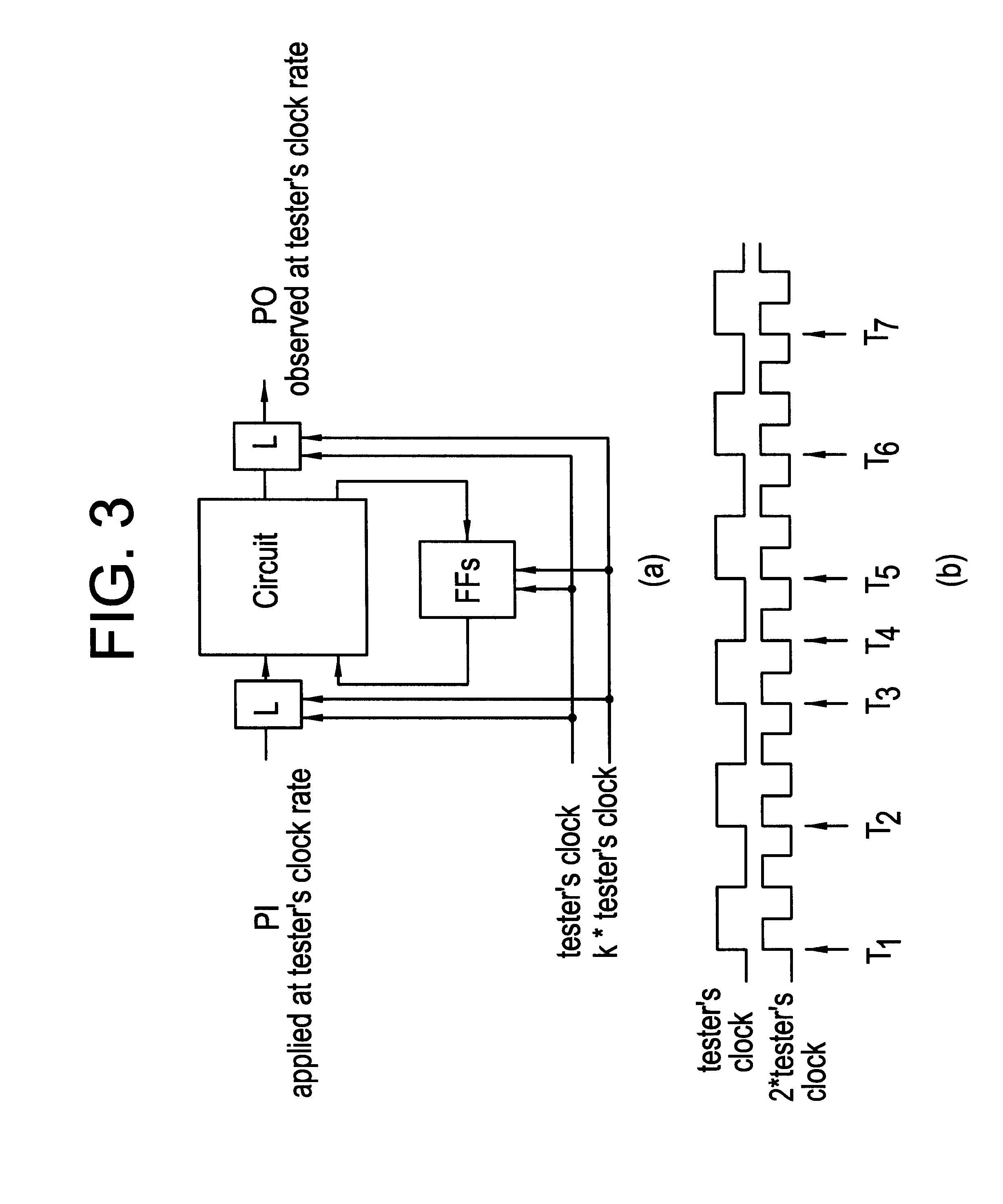

System and method for testing high speed VLSI devices using slower testers

InactiveUS6345373B1Shorten application timeLow fault coverageDigital circuit testingError detection/correctionGeneration processFault coverage

At-speed strategies for testing high speed designs on slower testers. At-speed testing schemes is provided that integrates the tester's speed limitations with the test generation process. Due to constraints placed at the test generation process, these schemes might result in a reduced fault coverage. To increase the fault coverage and reduce the test application time, the slow-fast-slow and at-speed strategies can be combined for testing high speed designs on slower testers. A slow tester that uses test vectors that are generated while taking into account the speed of the tester.

Owner:NEC CORP +1

Testing apparatus and method for thin film transistor display array

InactiveUS7102378B2Improve accuracyImprove reliabilityDigital circuit testingResistance/reactance/impedenceTransistor arrayAudio power amplifier

A testing circuit and method for thin film transistor display array, for testing the yield of a thin film transistor array is provided. The testing circuit includes an array tester, a test panel (DUT) and a sense amplifier array. The sense amplifier is composed of a plurality of trans-impedance amplifier units and a plurality of parasitic capacitance discharge circuit units. Every sense amplifier includes a trans-impedance amplifier, which is implemented by an operational amplifier, two switches and an operation capacitance. The trans-impedance amplifier is used to form an integrated circuit and the output is transmitted to a sampling / hold circuit via a switch. Also included is a parasitic capacitance discharge circuit that is used to form a discharge route for the charge of the parasitic capacitance.

Owner:PRIMETECH INT CORP

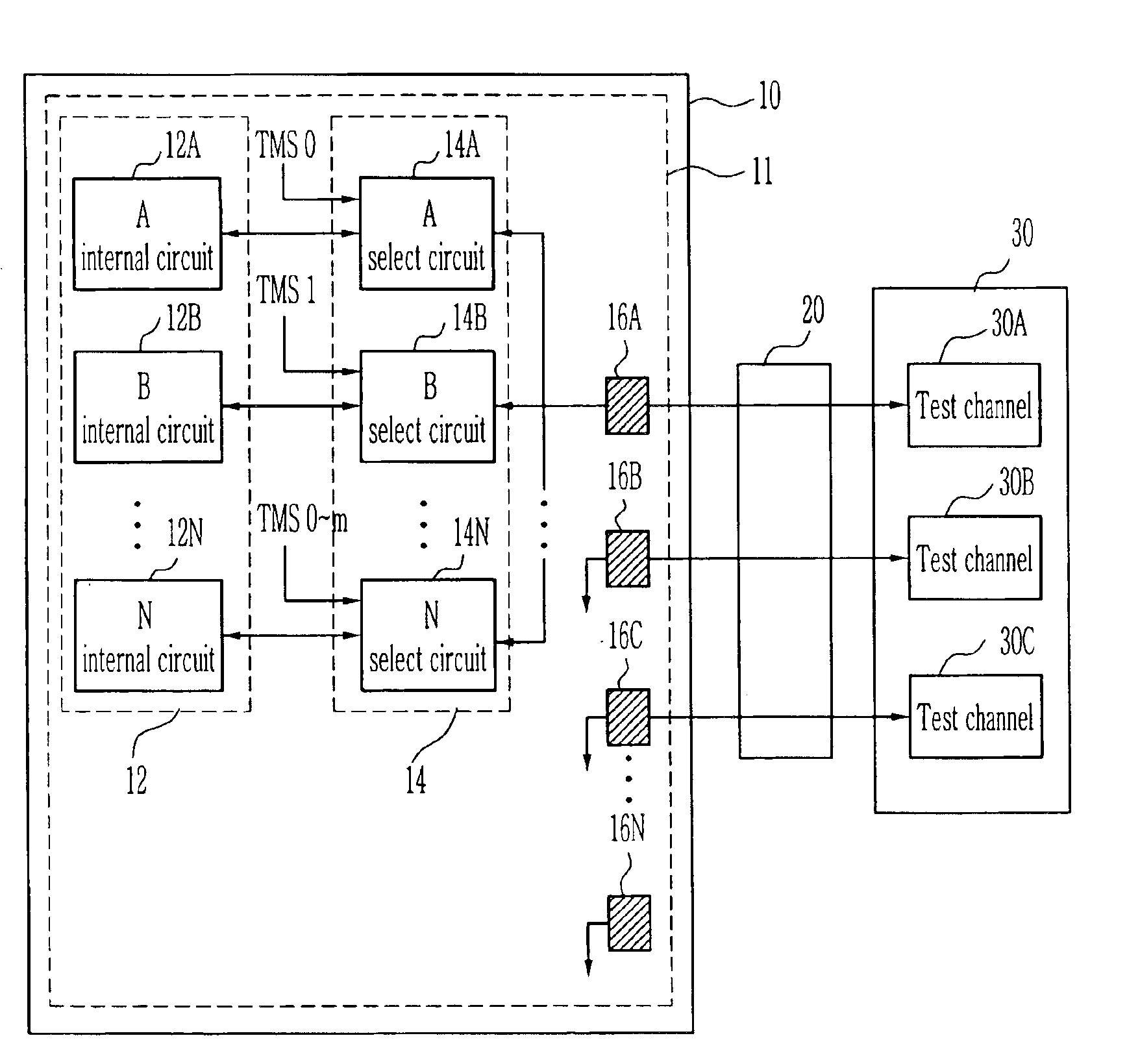

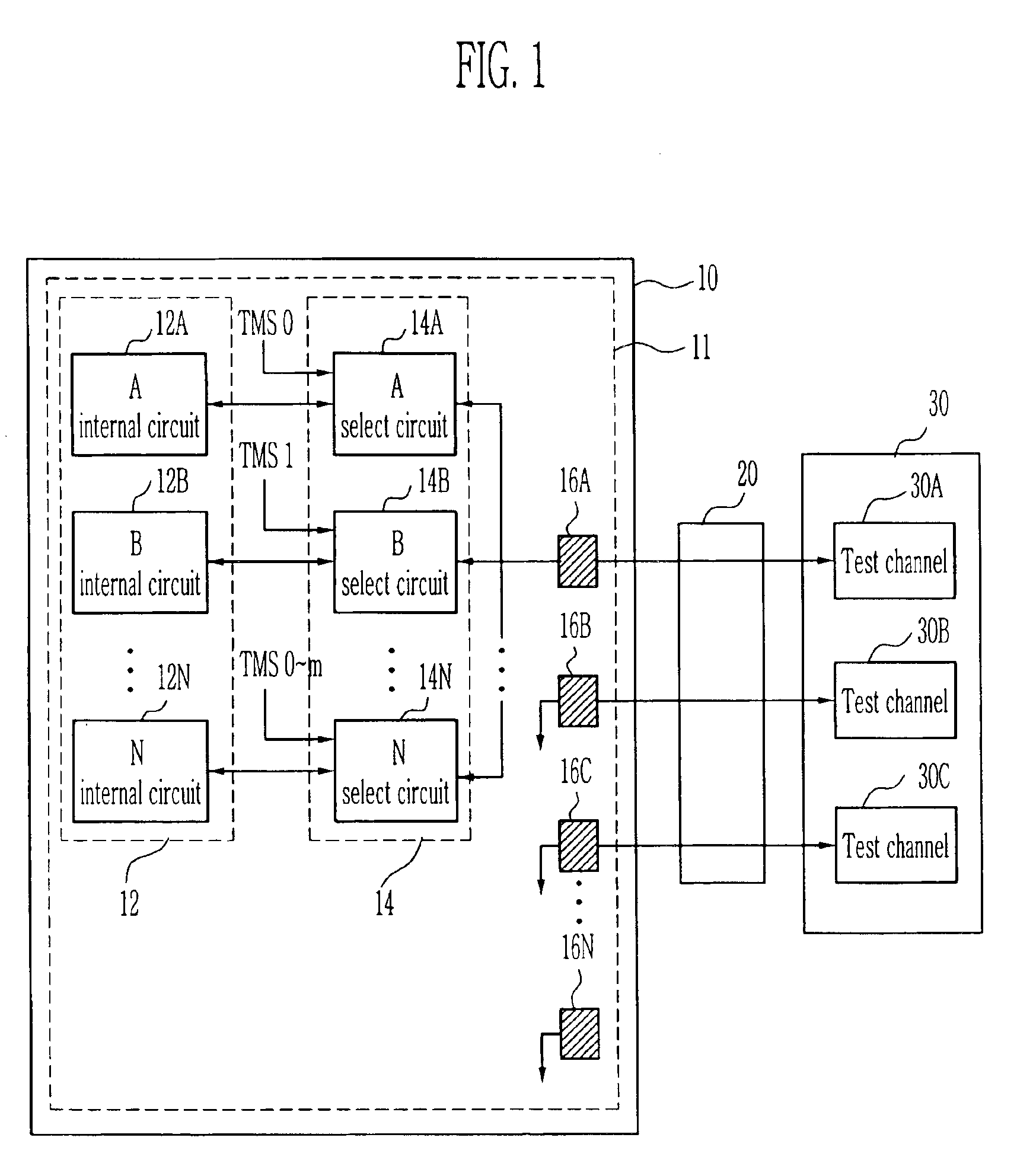

Semiconductor device for reducing the number of probing pad used during wafer test and method for testing the same

The present invention relates to a semiconductor device and a method for testing the same capable of reducing the number of probing pads used during wafer test. The semiconductor device includes a select circuit connected between a plurality of internal circuits to be tested and a single probing pad, for transmitting test signals inputted from the probing pads to any one of the plurality of the internal circuits according to a test mode signal generated in a wafer test mode. It is possible to reduce the number of the probing pads in the integrated circuit used for connection to a probe for contact of a probe card during wafer test. It is therefore possible to reduce test time.

Owner:SK HYNIX INC

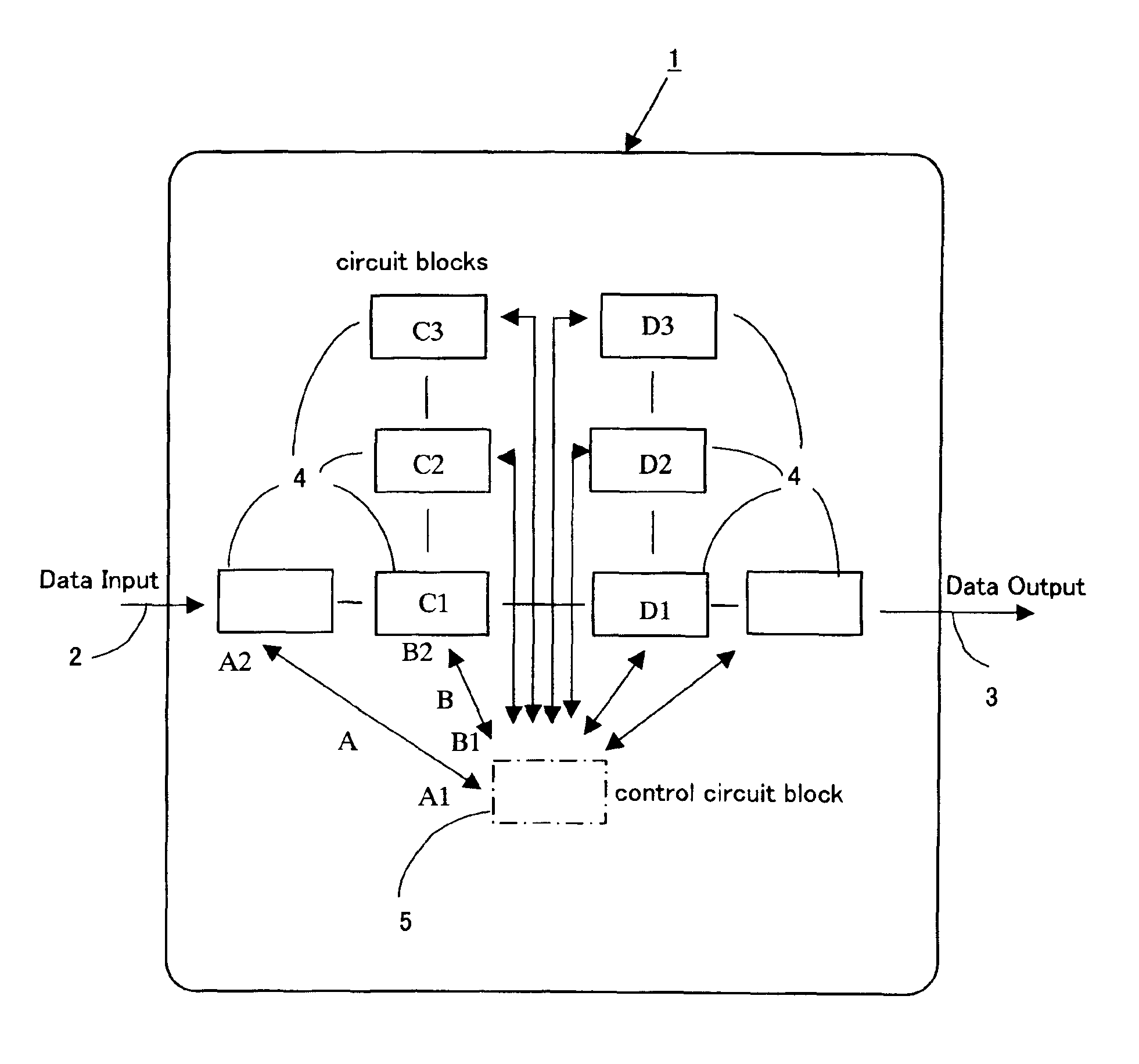

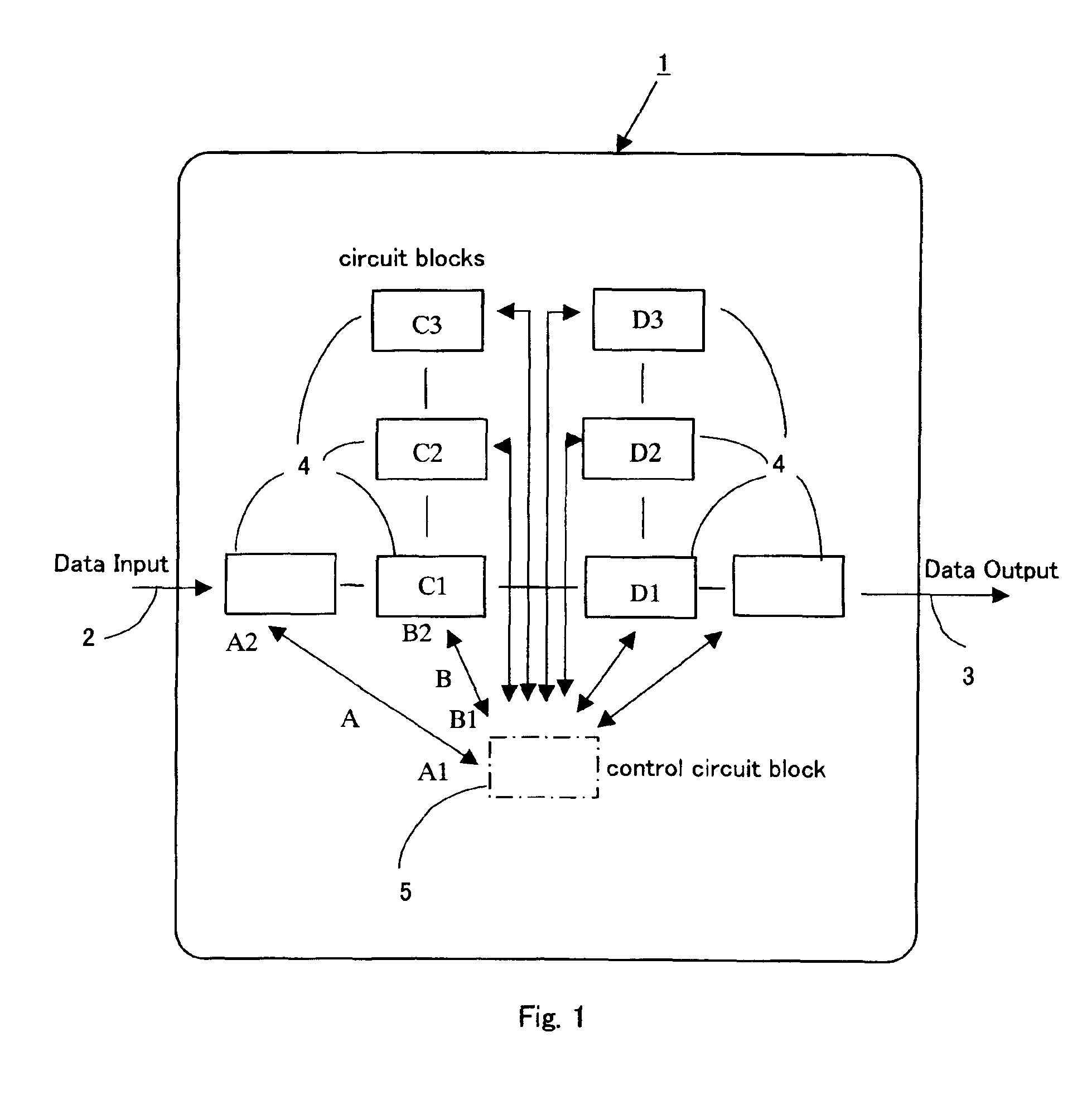

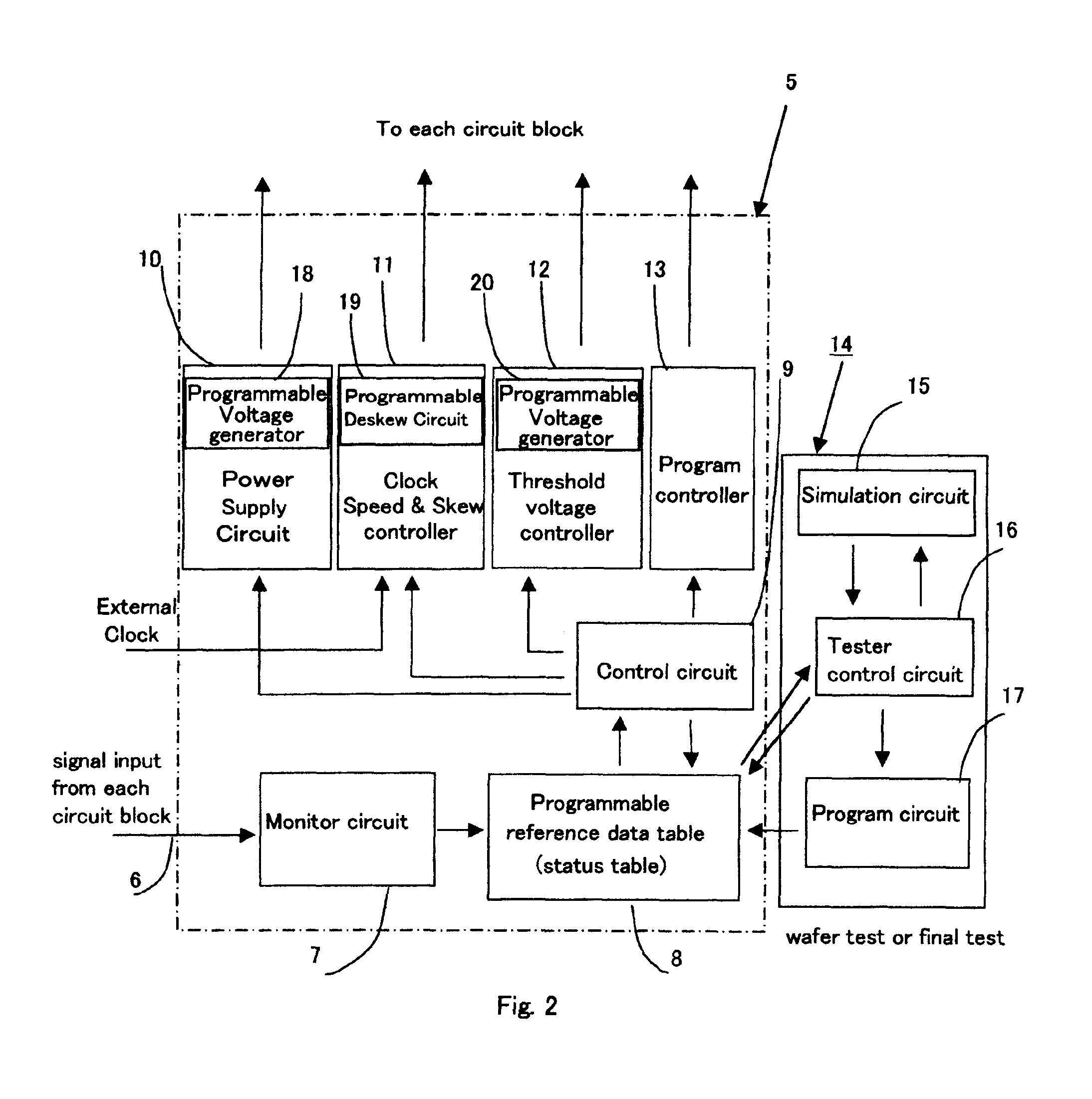

Integrated circuits having post-silicon adjustment control

InactiveUS6957163B2Double program execution timeReduce power consumptionThermometer detailsDigital circuit testingControl systemIntegrated circuit layout

An integrated circuit system has a reference data table for holding information that is used to control at least one circuit block in the system and also has a power supply circuit, a body bias control circuit, a clock delivery circuit, a temperature monitor circuit, and / or a configuration control circuit. The performance of the system is improved by obtaining system performance data by testing the system at different supply voltages, different body-bias voltages, different clock speeds, and / or different temperatures. Values based on the data are entered into the reference data table. The power supply circuit, the body bias control circuit, the clock delivery circuit, and / or the temperature monitor circuit data is adjusted using the entered values.

Owner:RPX CORP

Lockstep mechanism to ensure security in hardware at power-up

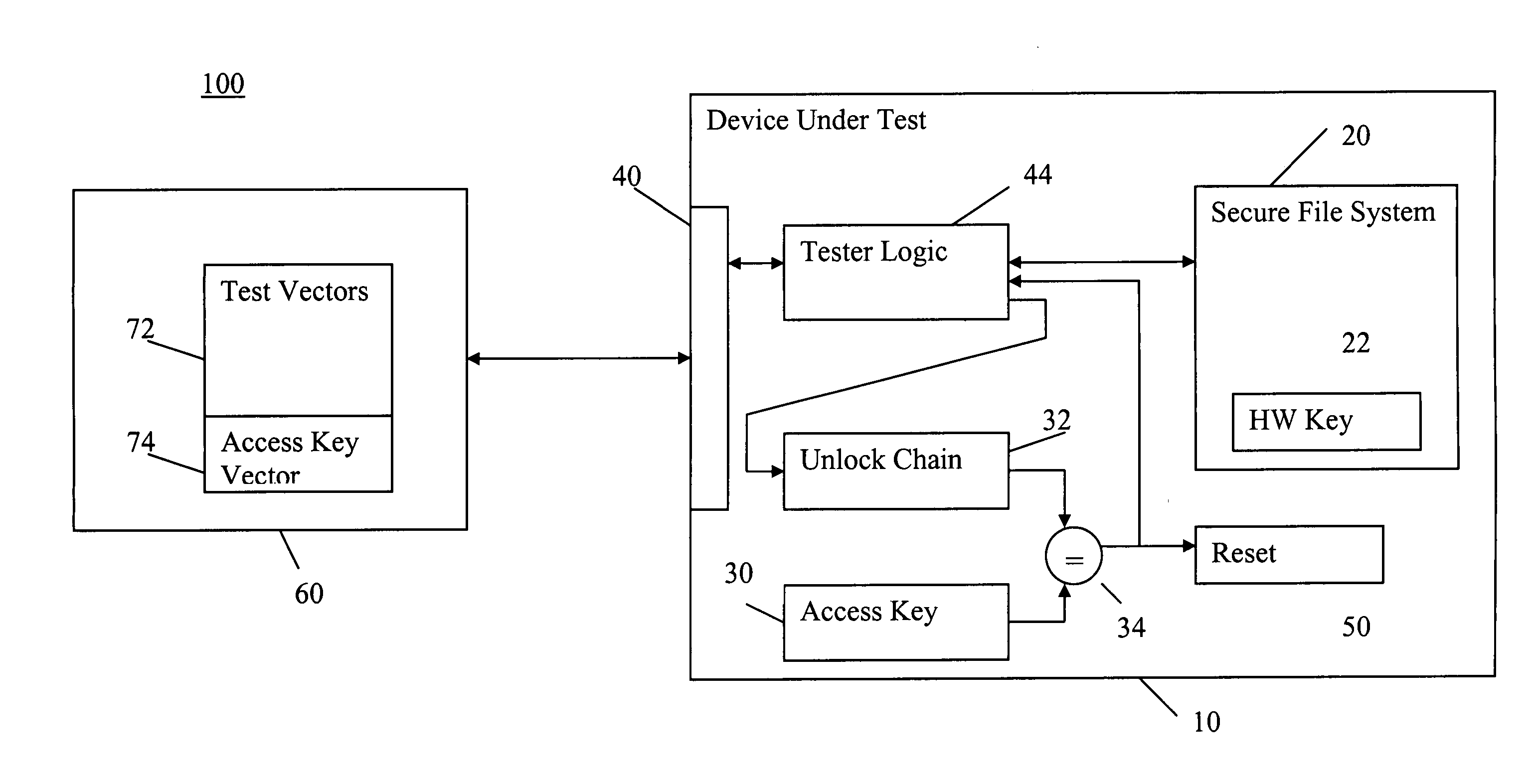

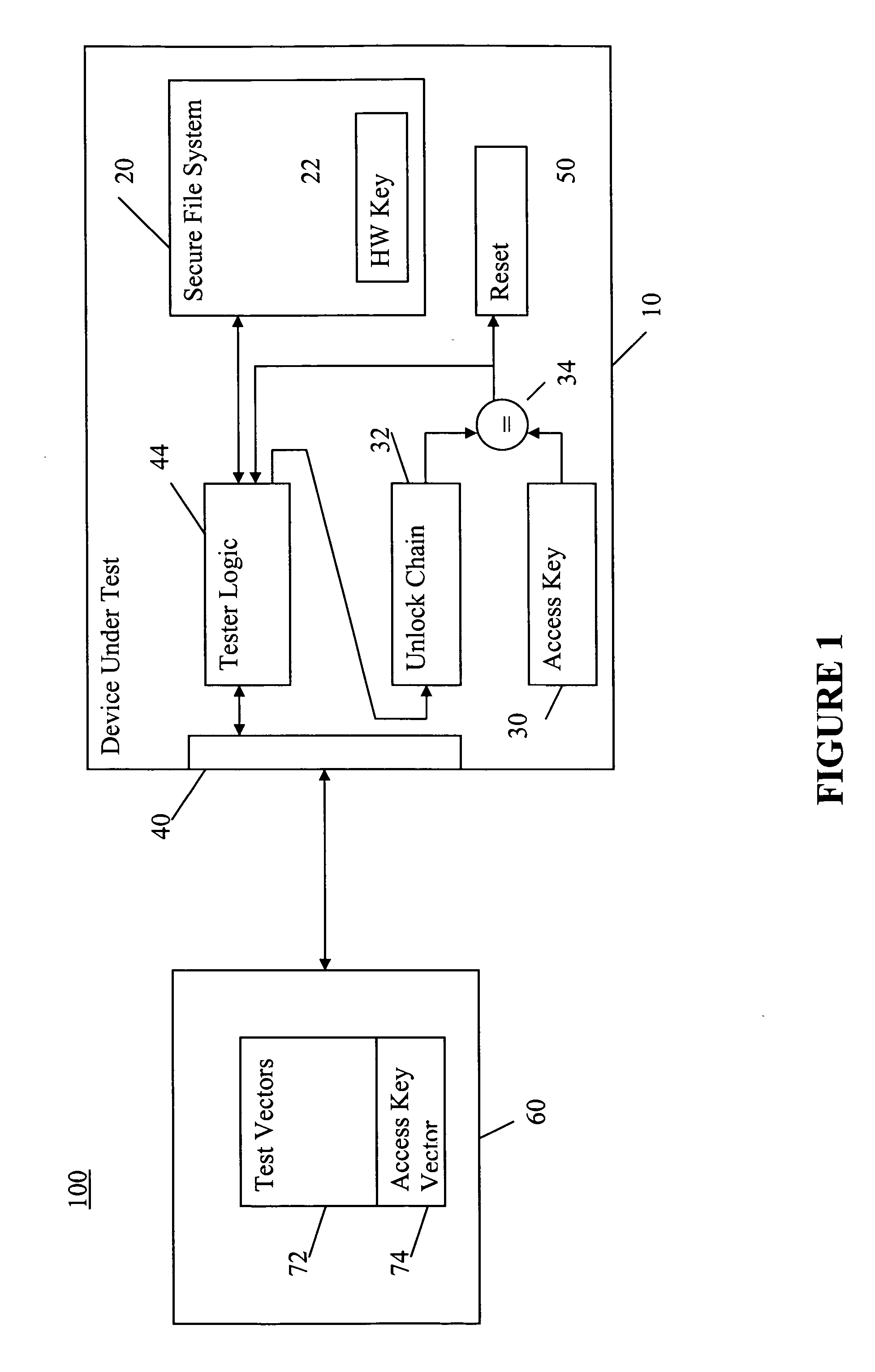

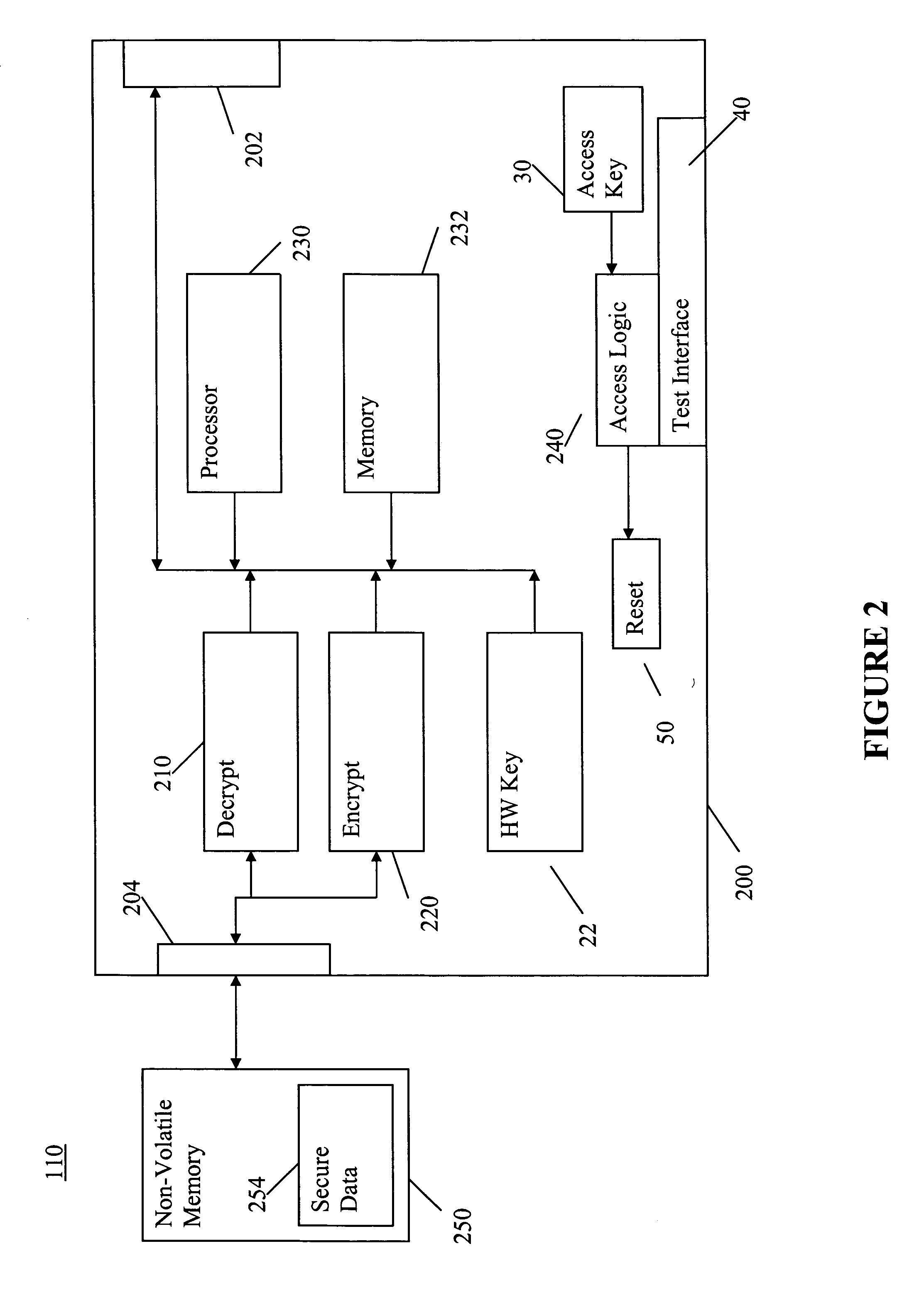

InactiveUS20050289355A1Digital circuit testingDigital data processing detailsElectricityData storing

A system and method of ensuring hardware security of a device, such as an integrated circuit having secure data stored thereon. The integrated circuit or other hardware device can implement one or more configurable fuses that limit access to one or more secure locations within the device. The secure locations may contain secure data. The state of the configurable fuses can be ensured, thereby limiting access to secure locations, by forcing the occurrence of a logical state prior to allowing access to hardware locations configured by the fuses. A configurable non-secure access code can be used to force the occurrence of the logical state. Receipt of the non-secure access code by the hardware device forces the occurrence of the hardware state, thereby ensuring access only to those secure locations configured by the fuses.

Owner:QUALCOMM INC

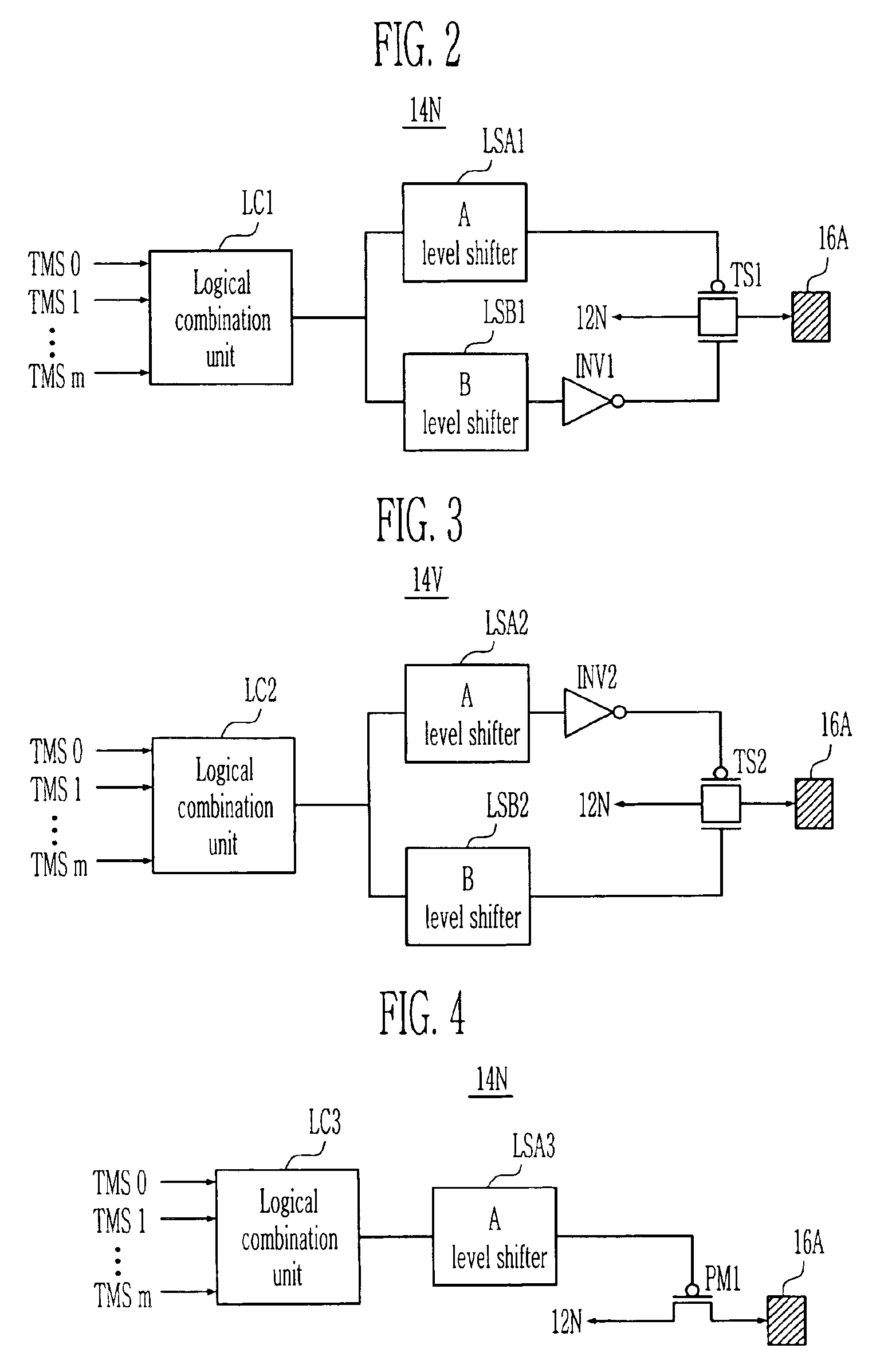

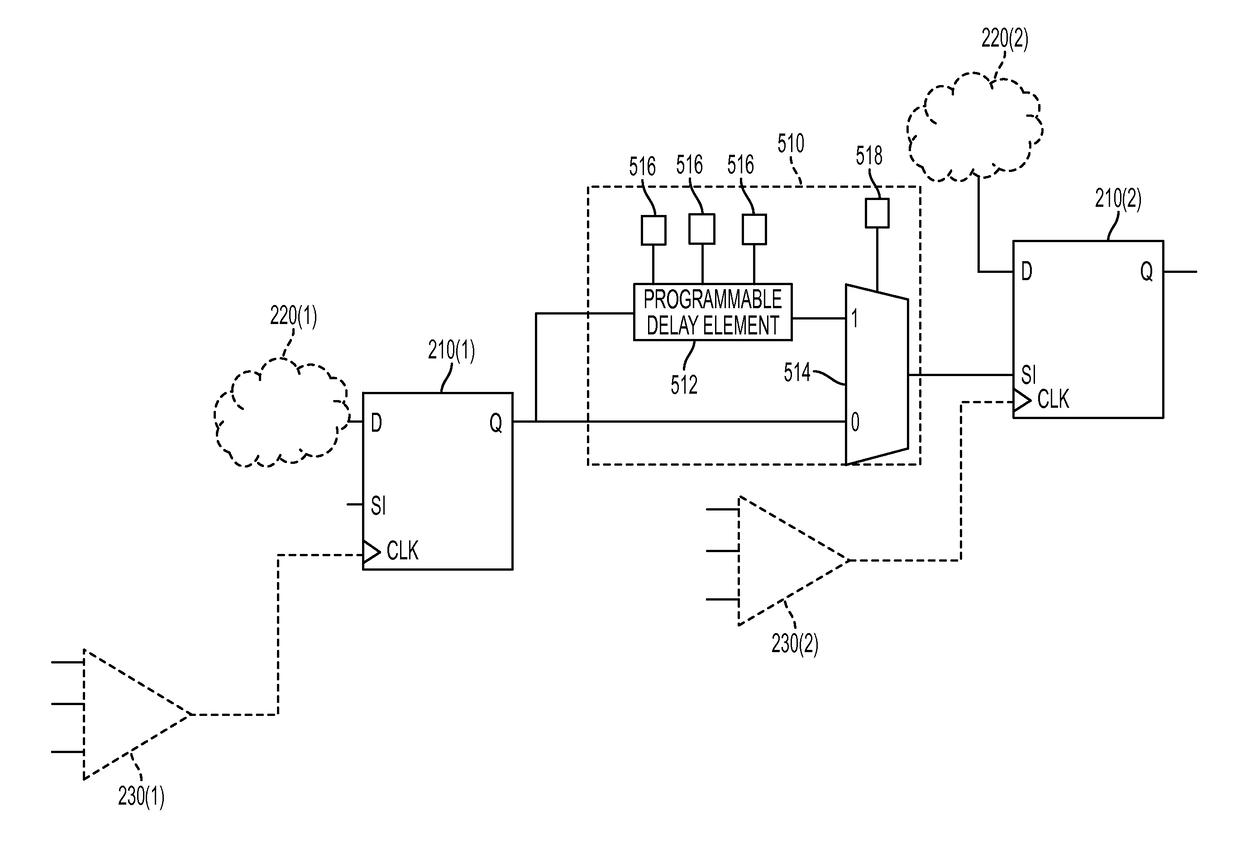

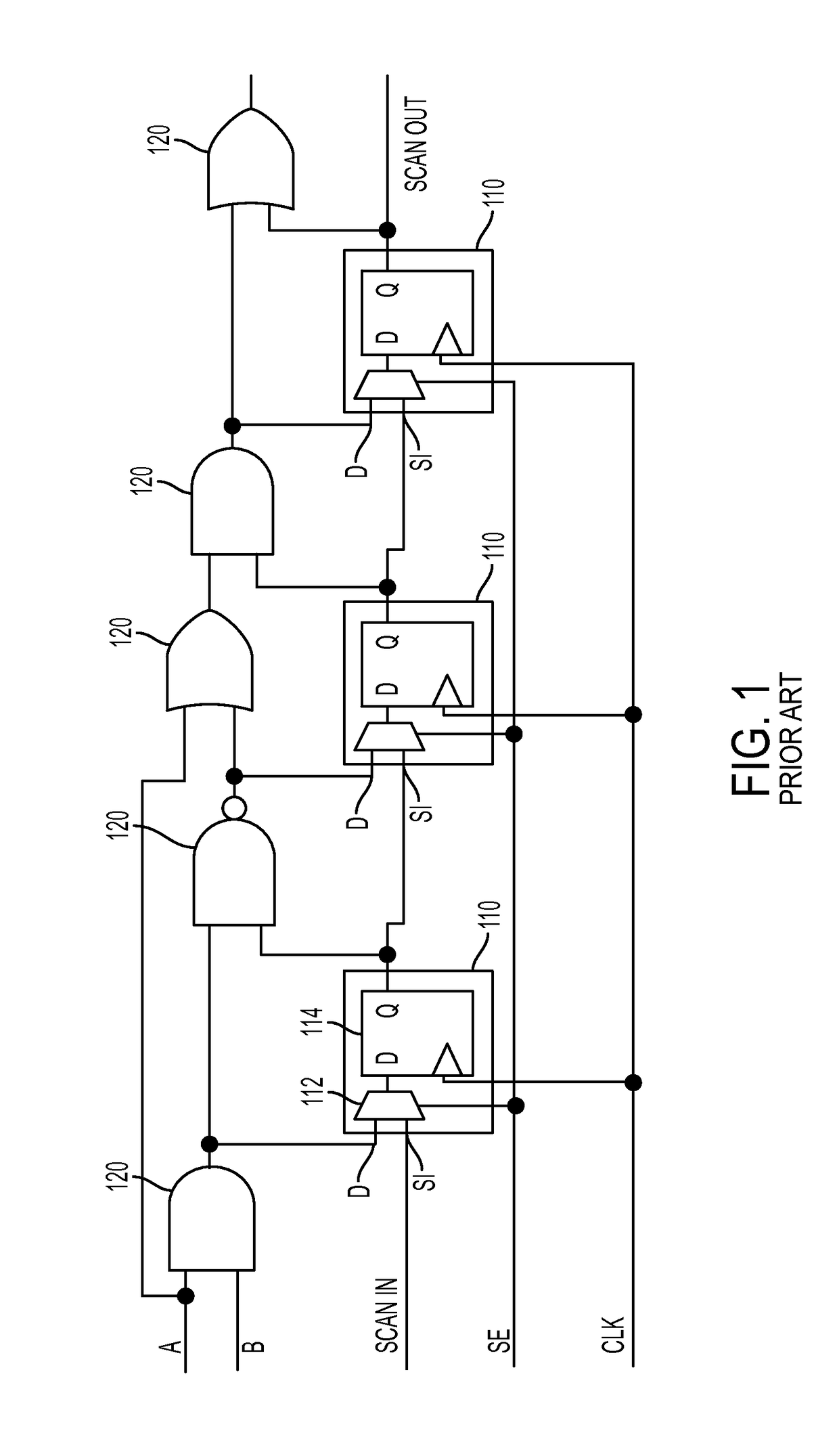

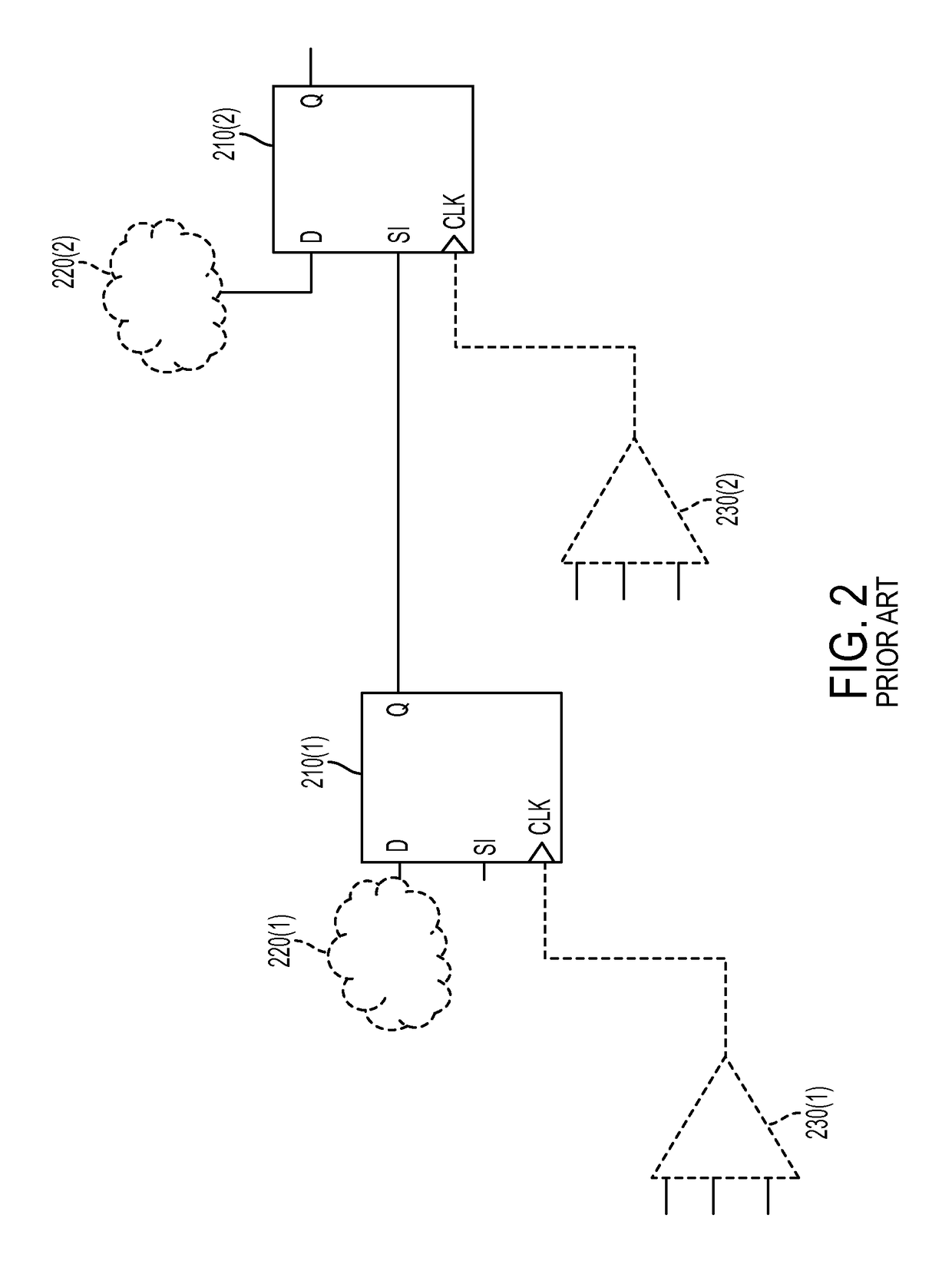

Programmable circuits for correcting scan-test circuitry defects in integrated circuit designs

ActiveUS9618579B2Digital circuit testingDetecting faulty computer hardwareComputer hardwareComputer architecture

In certain embodiments, an integrated circuit has scan-test circuitry that performs scan testing on circuitry under scan test (CUST) within the IC, where the scan-test circuitry is susceptible to a defect. In order to enable the defect to be corrected after it occurs, the scan-test circuitry includes a set of programmable circuitry connected to provide a signal to other circuitry (e.g., a scan chain) within the scan-test circuitry, where the set of programmable circuitry includes one or more configurable memory cells connected to control the programming of the set of programmable circuitry. The memory cell(s) can be configured to program the set of programmable circuitry to enable the scan testing to be performed without modification. The memory cell(s) can also be configured to program the set of programmable circuitry to modify the scan testing to correct the defect in the scan-test circuitry.

Owner:LATTICE SEMICON CORP

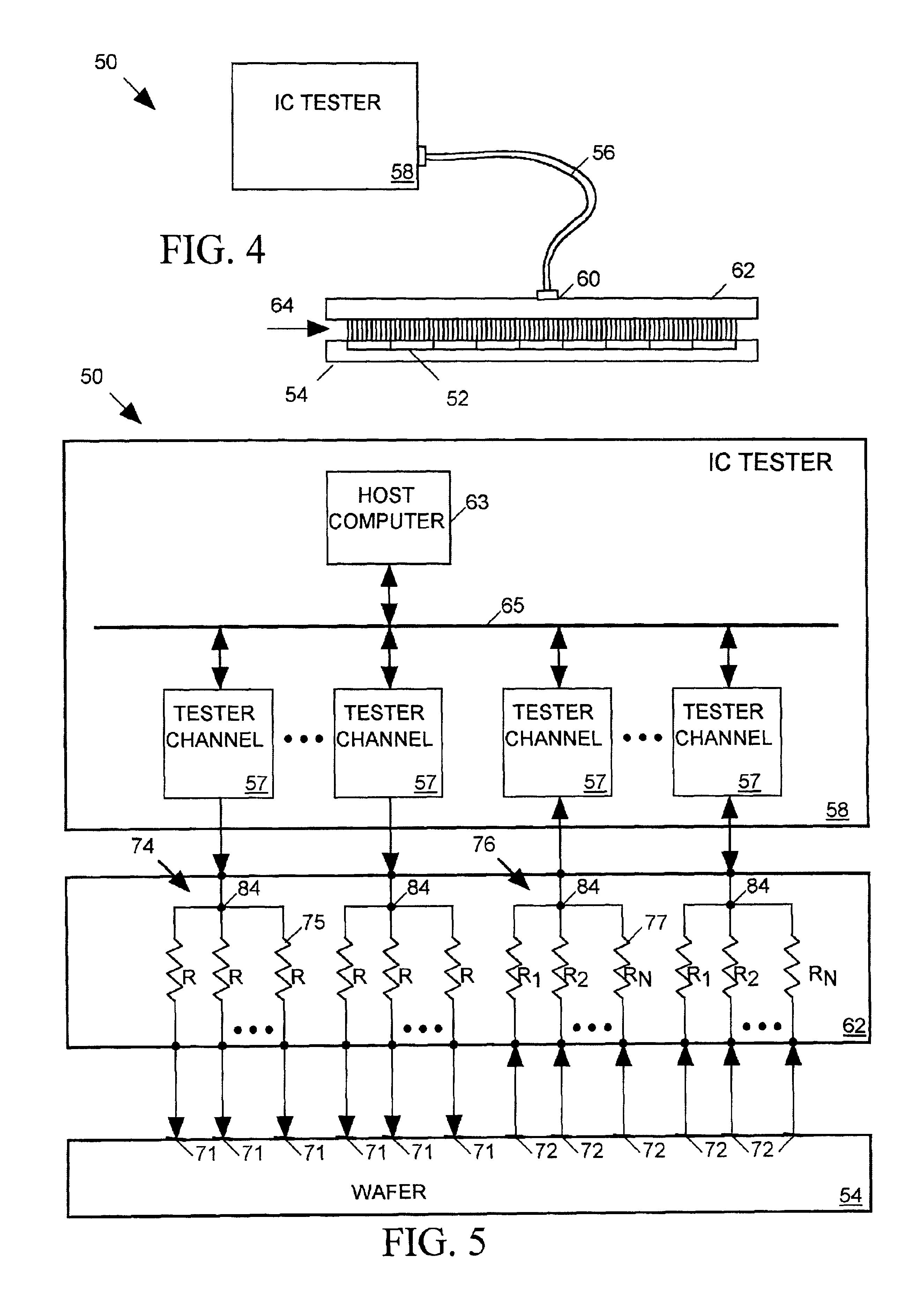

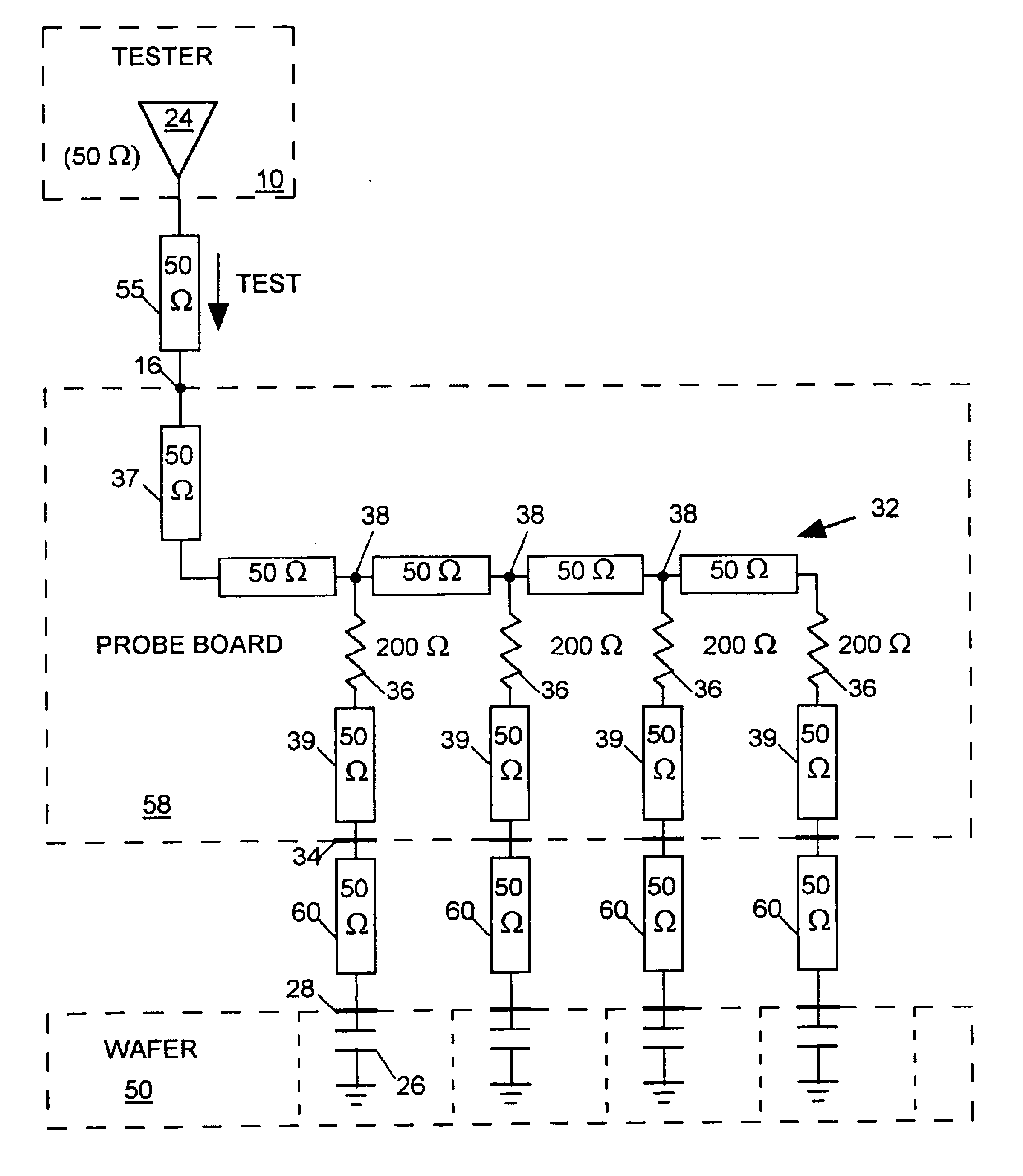

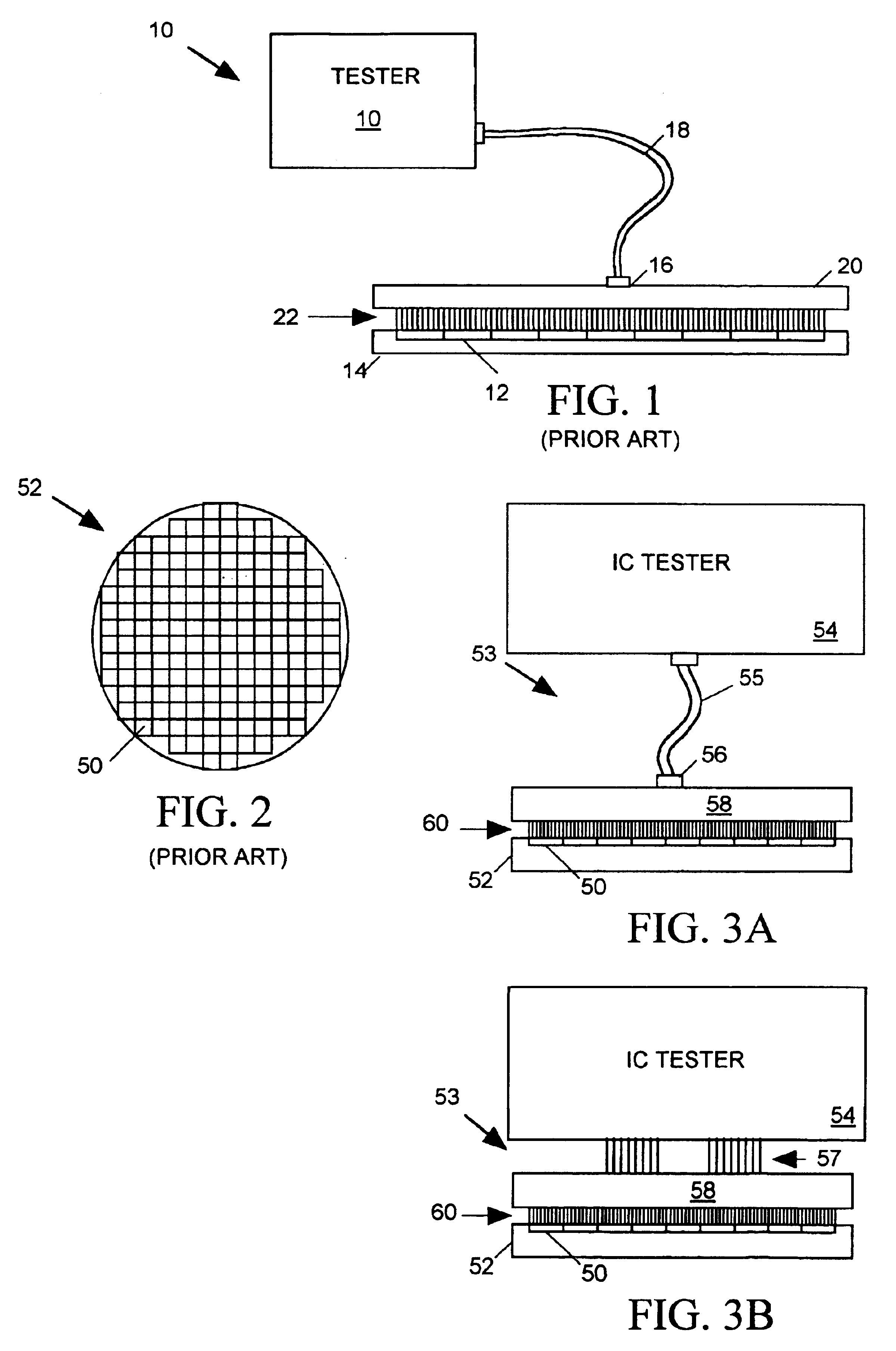

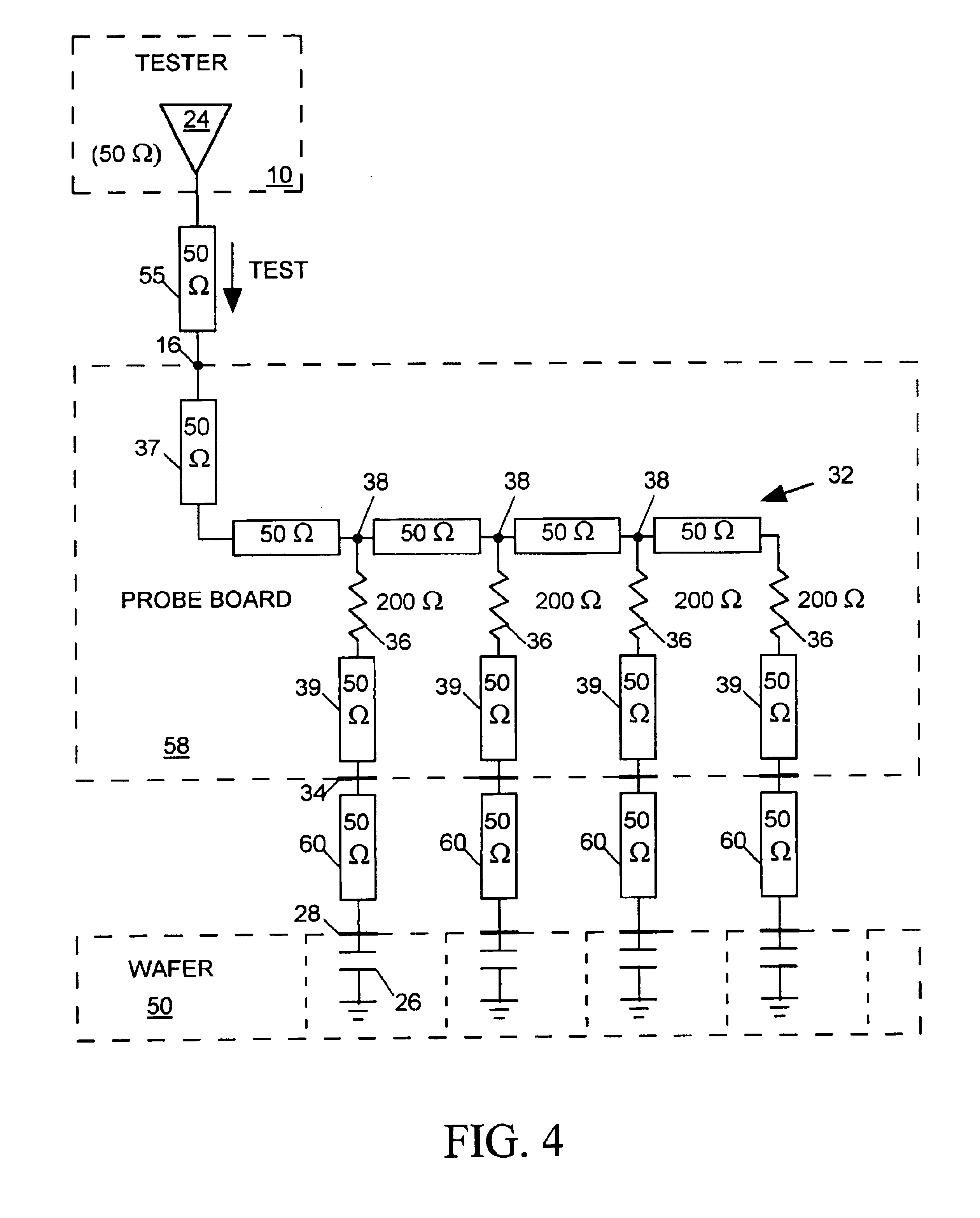

Tester channel to multiple IC terminals

InactiveUS6798225B2Digital circuit testingElectrical measurement instrument detailsElectrical resistance and conductanceProbe card

A probe card provides signal paths between integrated circuit (IC) tester channels and probes accessing input and output pads of ICs to be tested. When a single tester channel is to access multiple (N) IC pads, the probe card provides a branching path linking the channel to each of the N IC input pads. Each branch of the test signal distribution path includes a resistor for isolating the IC input pad accessed via that branch from all other branches of the path so that a fault on that IC pad does not substantially affect the voltage of signals appearing on any other IC pad. When a single tester channel is to monitor output signals produced at N IC pads, the resistance in each branch of the signal path linking the pads of the tester channel is uniquely sized to that the voltage of the input signal supplied to the tester channel is a function of the combination of logic states of the signals produced at the N IC pads. The tester channel measures the voltage of its input signal so that the logic state of the signals produced at each of the N IC output pads can be determined from the measured voltage.

Owner:FORMFACTOR INC

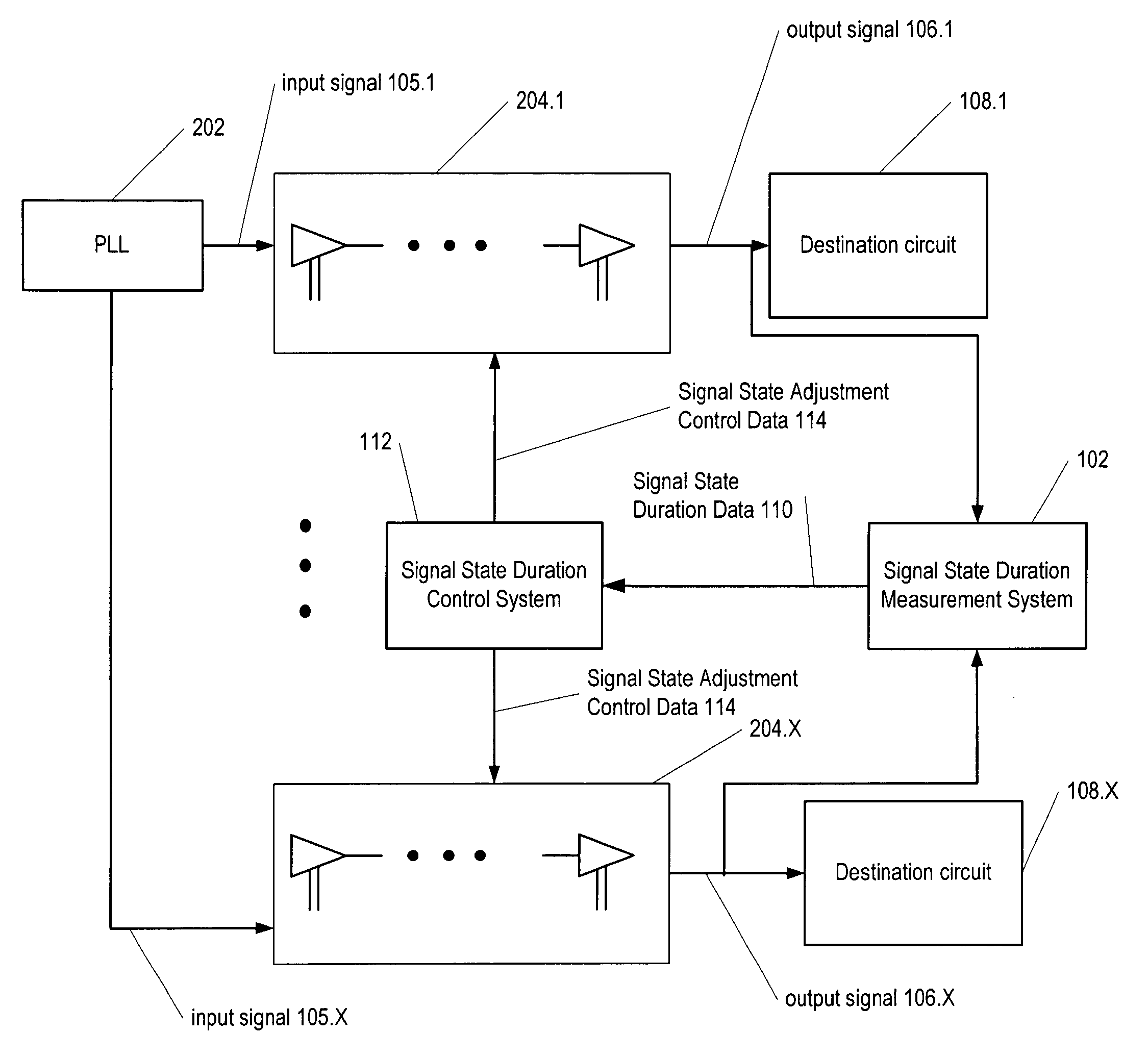

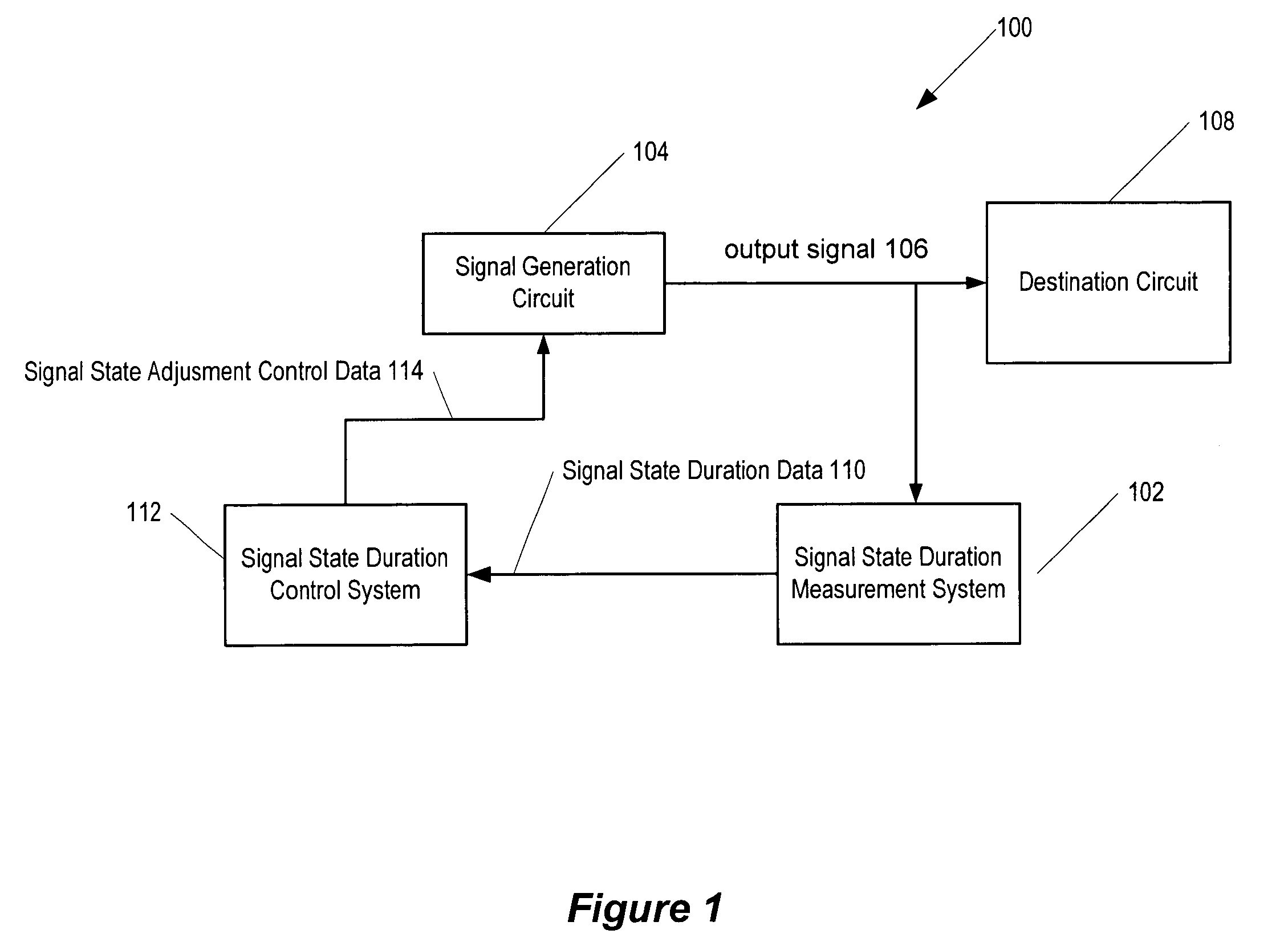

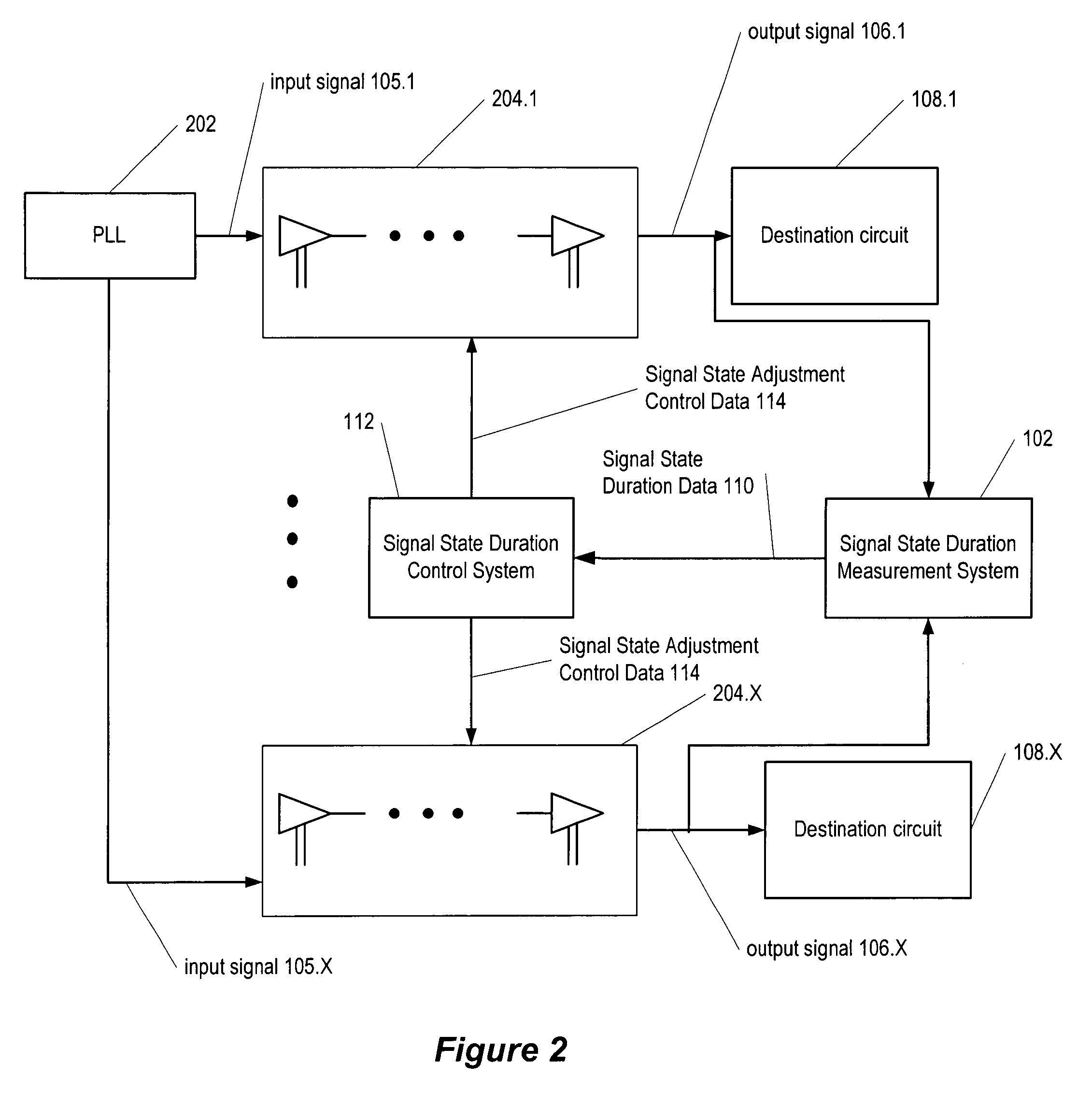

On-chip signal state duration measurement and adjustment

Signal state durations, such as the pulse-width, of on-chip signals are often critical to the successful operation of an integrated circuit. The signal state durations measured by on-chip technology provide signal state duration information to an on-chip signal state duration control system. The signal state duration control system uses the information to adjust the signal state duration of an on-chip signal. In one embodiment, the signal state duration of the on-chip signal is the pulse width of the on-chip signal. The signal duration measurement and adjustment system is, for example, useful for measuring the state duration of signals such as self-resetting signals, which are difficult to externally measure and adjust signal state durations using on-chip technology.

Owner:ORACLE INT CORP

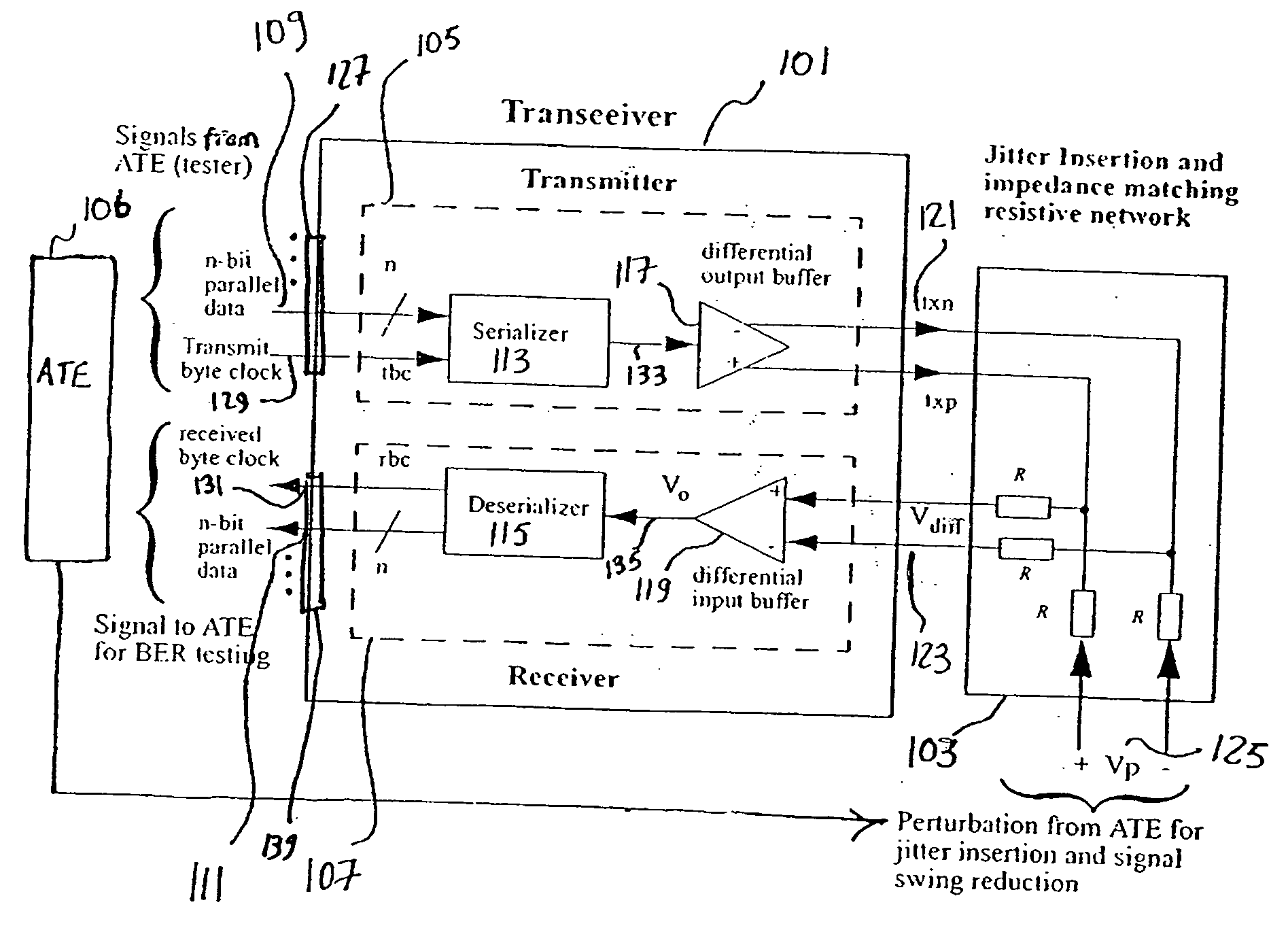

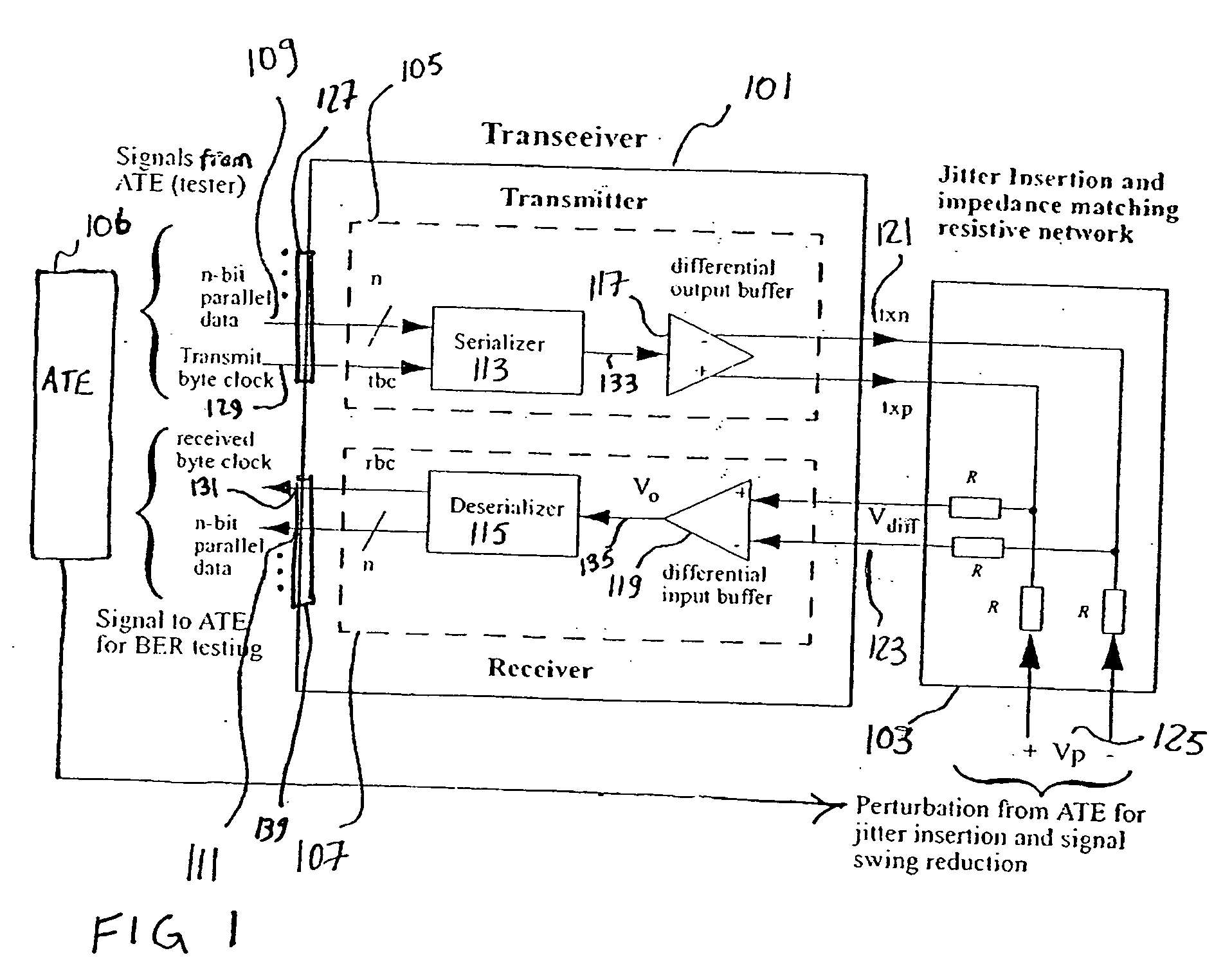

System and method for production testing of high speed communications receivers

InactiveUS20050172181A1Digital circuit testingElectrical measurement instrument detailsTransceiverLow voltage

A method for testing a semiconductor device with a multi-gigabit communications receiver includes combining a data output from a high-speed communications transmitter with a perturbation signal generated by automatic test equipment. The combined signal data signal including jitter and low voltage swings is input to the communications receiver port under test. The automatic test equipment determines the bit error rate of the parallel data output from the receiver port under test. This test method is appropriate for semiconductor devices with multiple transceiver ports.

Owner:MELLANOX TECHNOLOGIES LTD

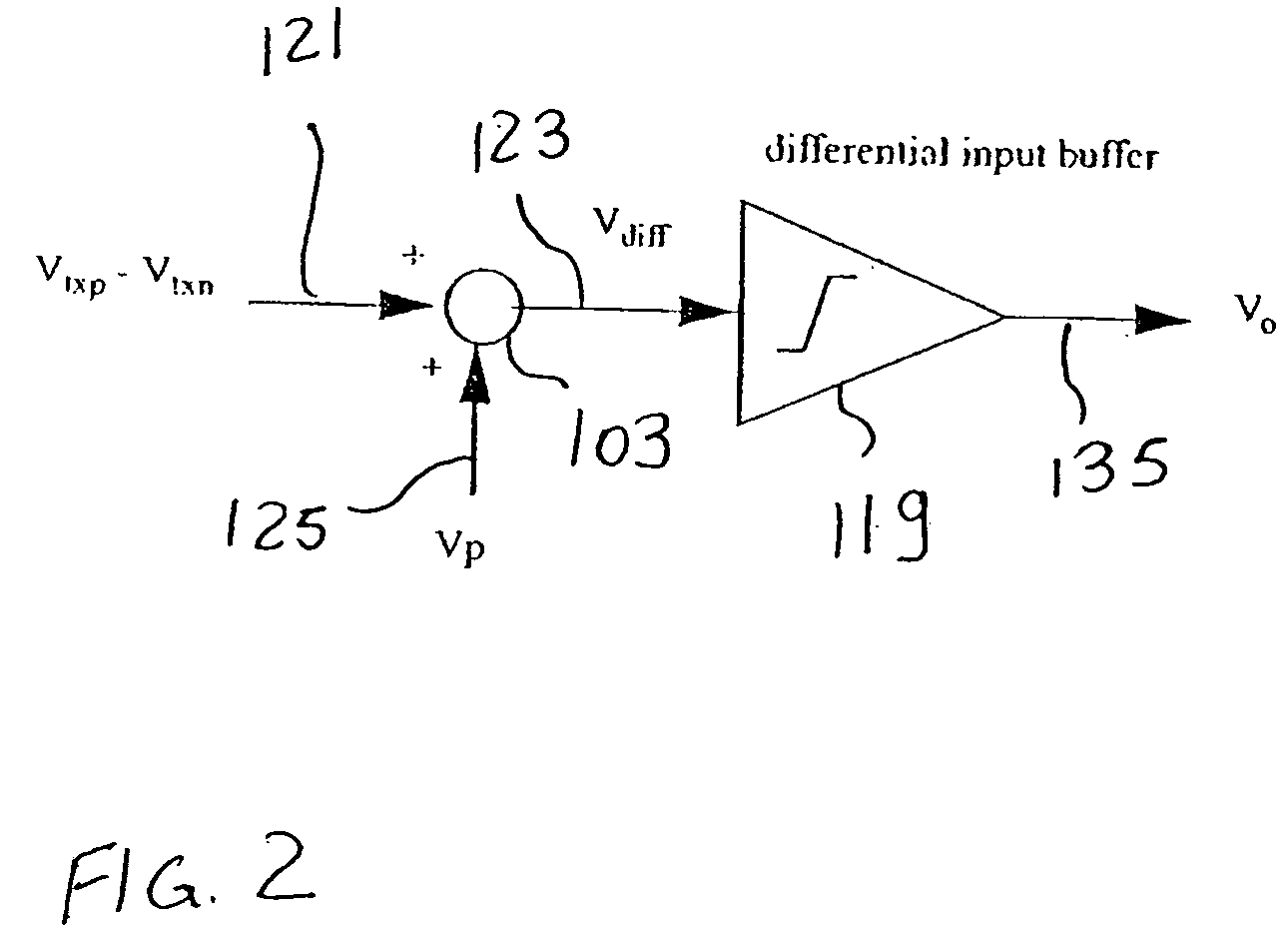

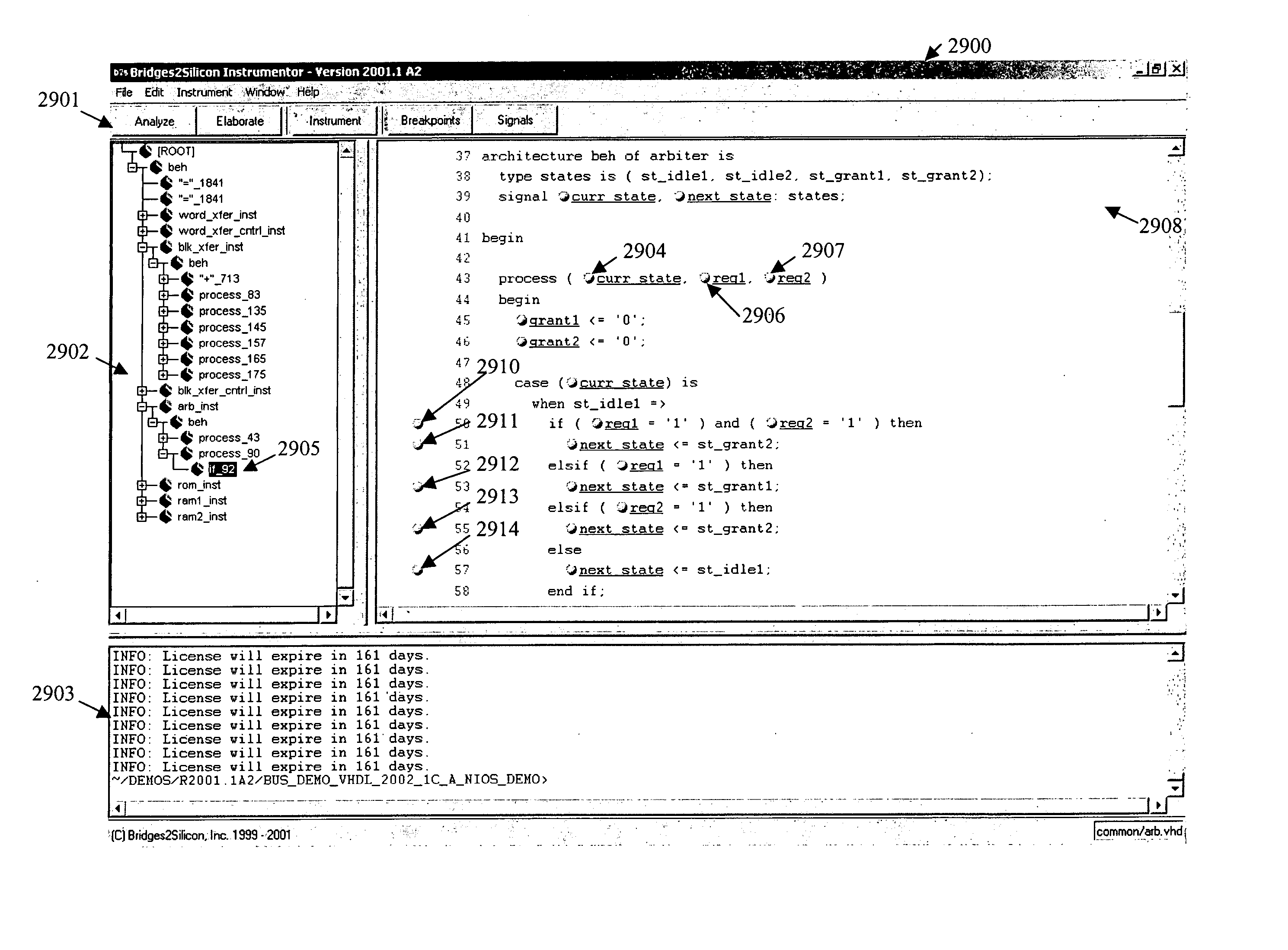

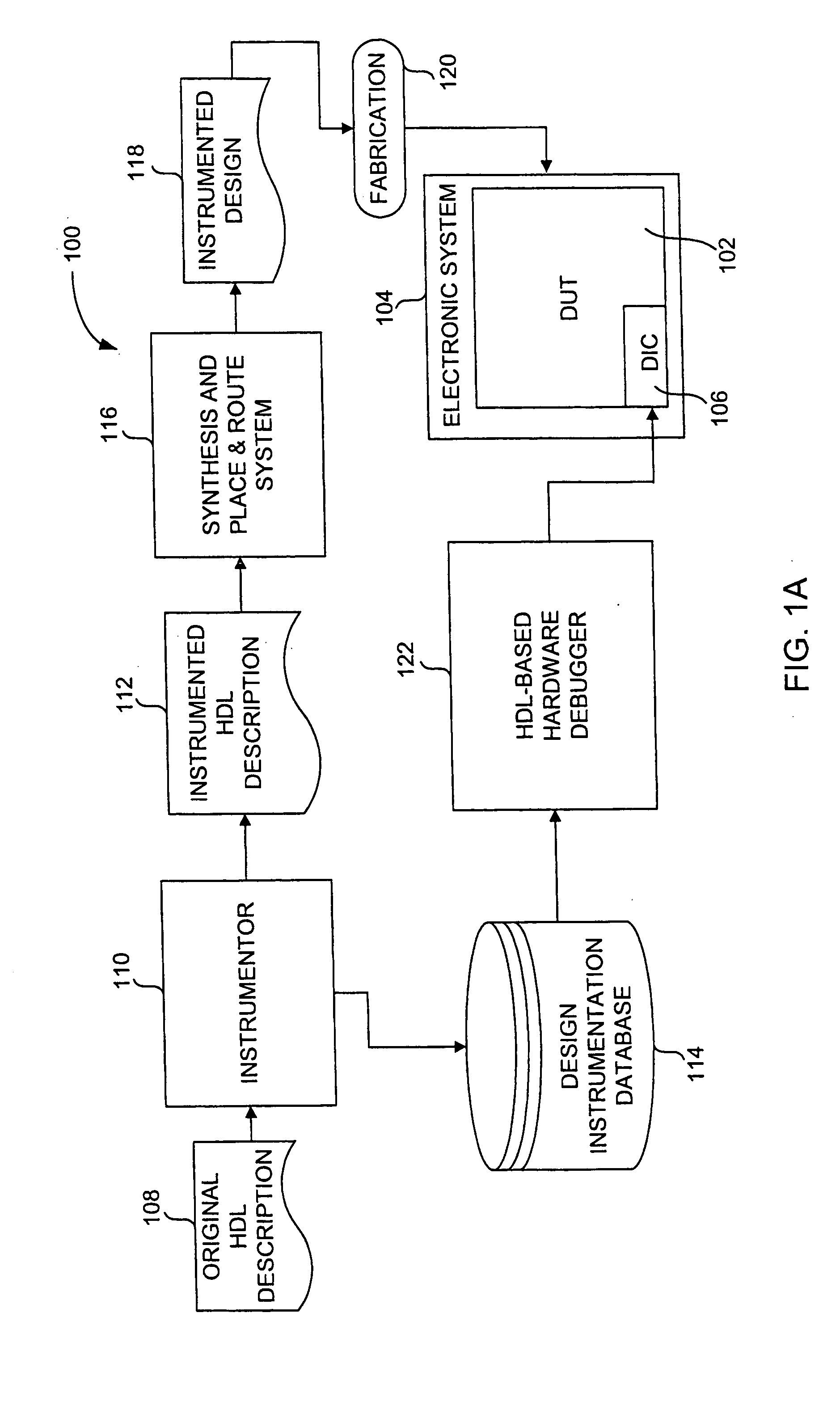

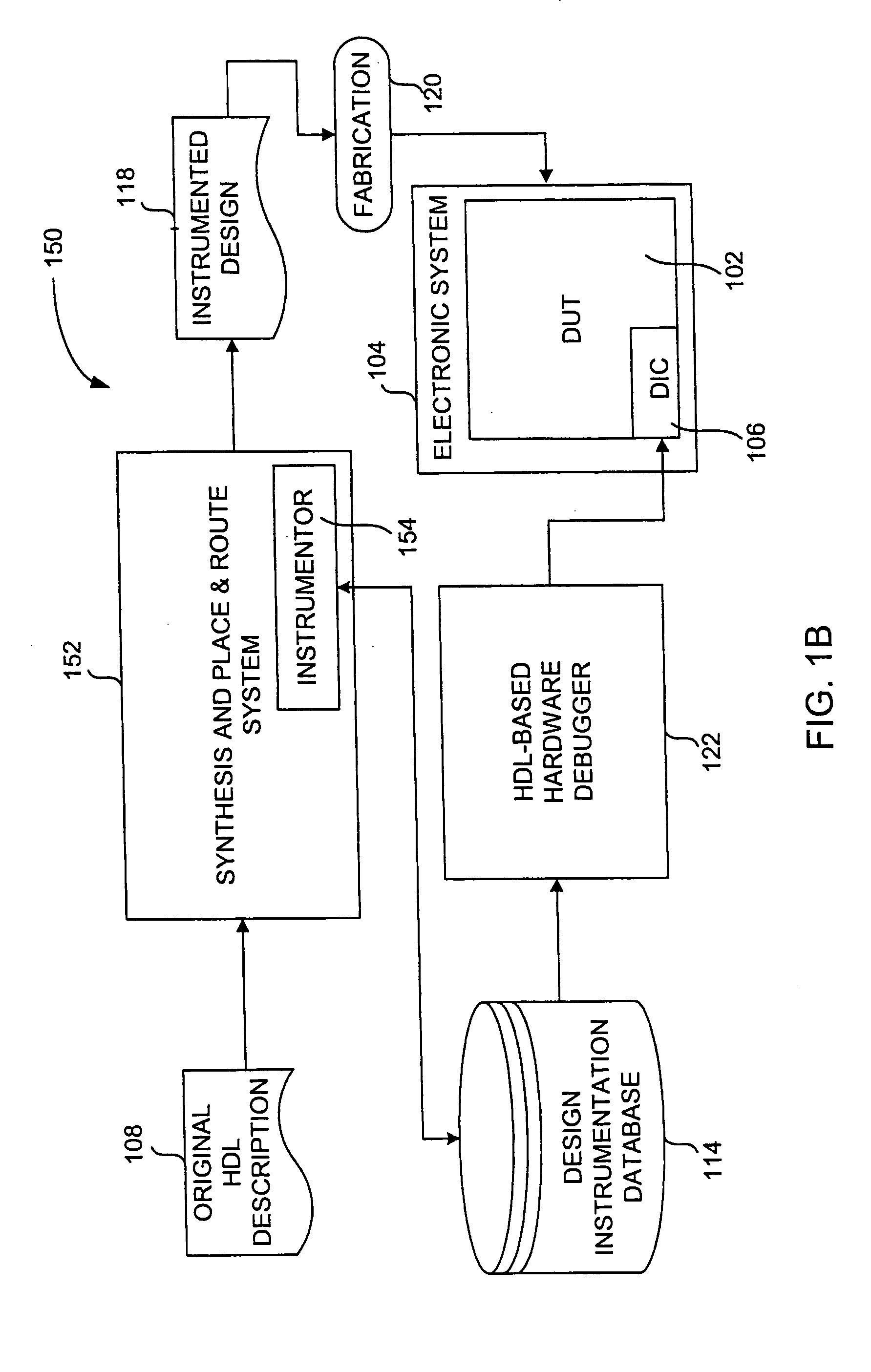

Method and user interface for debugging an electronic system

InactiveUS20050010880A1Easy to correctEasy to adjustDigital circuit testingCAD circuit designElectronic systemsEmbedded system

Techniques and systems for analysis, diagnosis and debugging fabricated hardware designs at a Hardware Description Language (HDL) level are described. Although the hardware designs (which were designed in HDL) have been fabricated in integrated circuit products with limited input / output pins, the techniques and systems enable the hardware designs within the integrated circuit products to be comprehensively analyzed, diagnosed, and debugged at the HDL level at speed. The ability to debug hardware designs at the HDL level facilitates correction or adjustment of the HDL description of the hardware designs.

Owner:SYNOPSYS INC

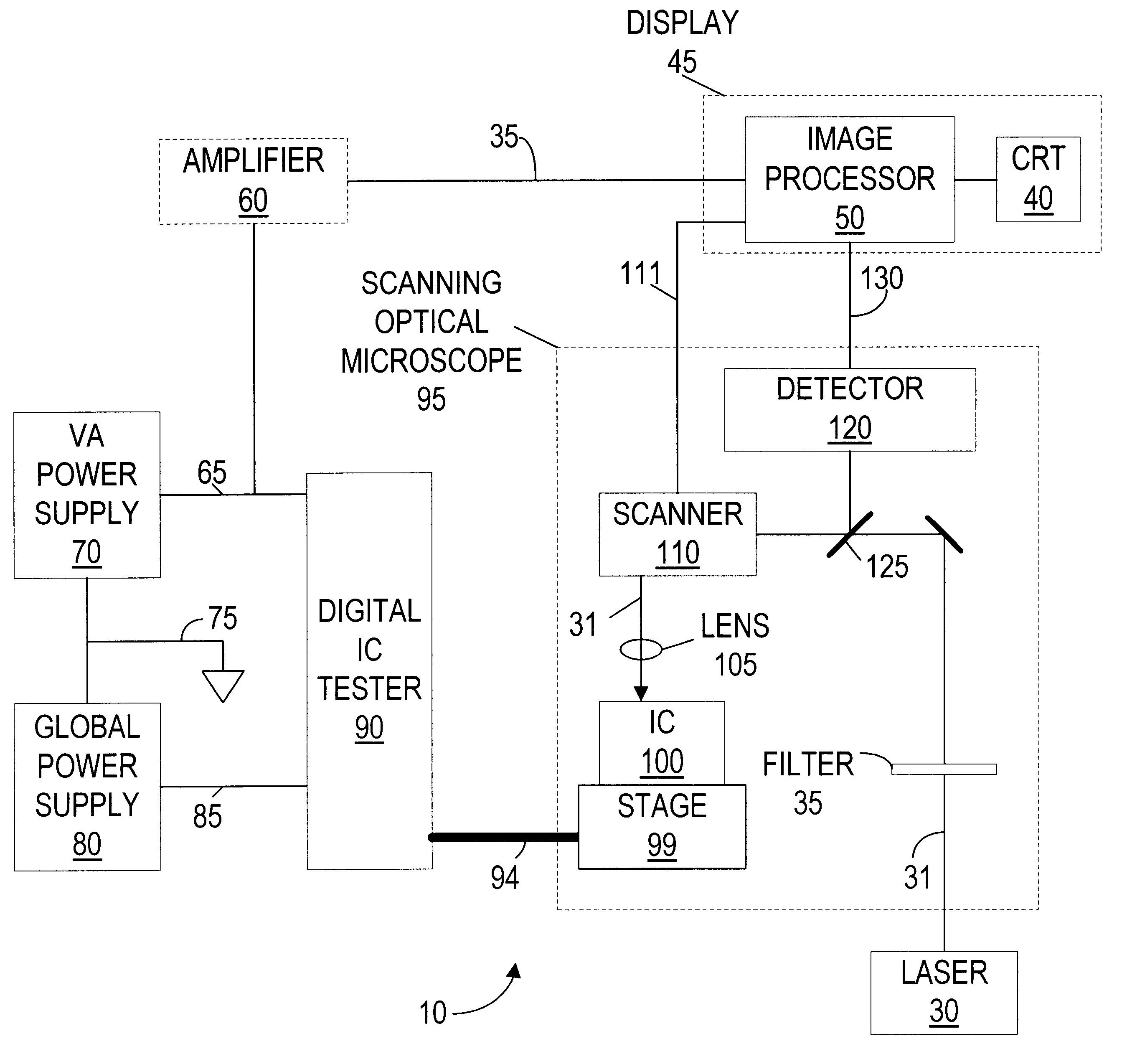

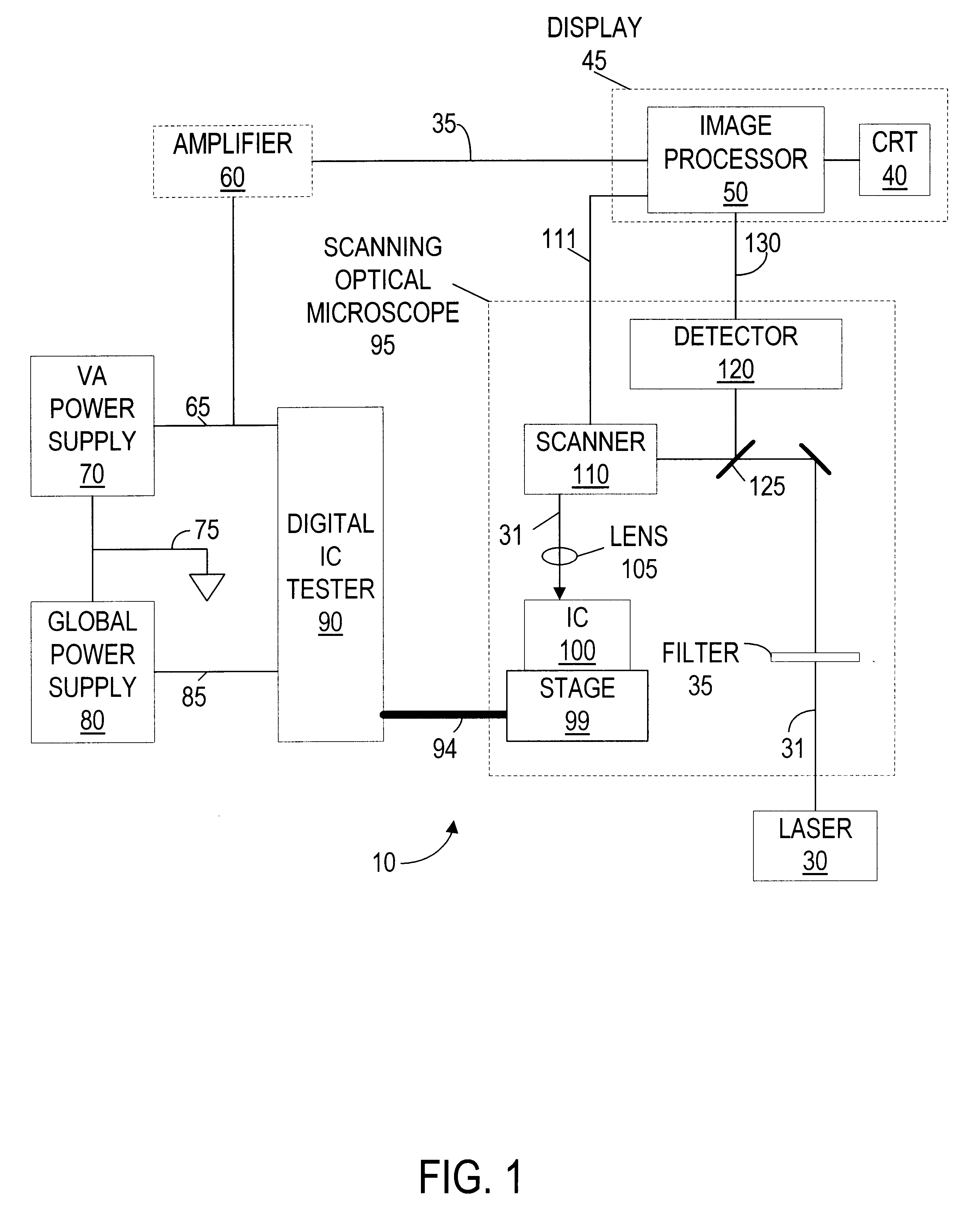

Laser intrusive technique for locating specific integrated circuit current paths

InactiveUS6617862B1Reduce the noise floorHigh sensitivityDigital circuit testingIndividual semiconductor device testingVoltage variationLaser beams

A method and apparatus for locating integrated circuit defects associated with different aspects of the integrated circuit industry. The integrated circuit is configured in a known failing mode, with a first power supply providing a constant voltage and variable current. Next, one or more additional dedicated power supplies are connected to various points of interest throughout the integrated circuit, wherein these dedicated power supplies have a preset current and the voltage is allowed to vary. The integrated circuit is then scanned with a laser beam, which induces current changes on in the integrated circuit especially in defective areas. These current changes then cause voltage changes on the dedicated power supplies. When such a voltage change occurs on the dedicated power supplies, its position is noted.

Owner:GLOBALFOUNDRIES INC

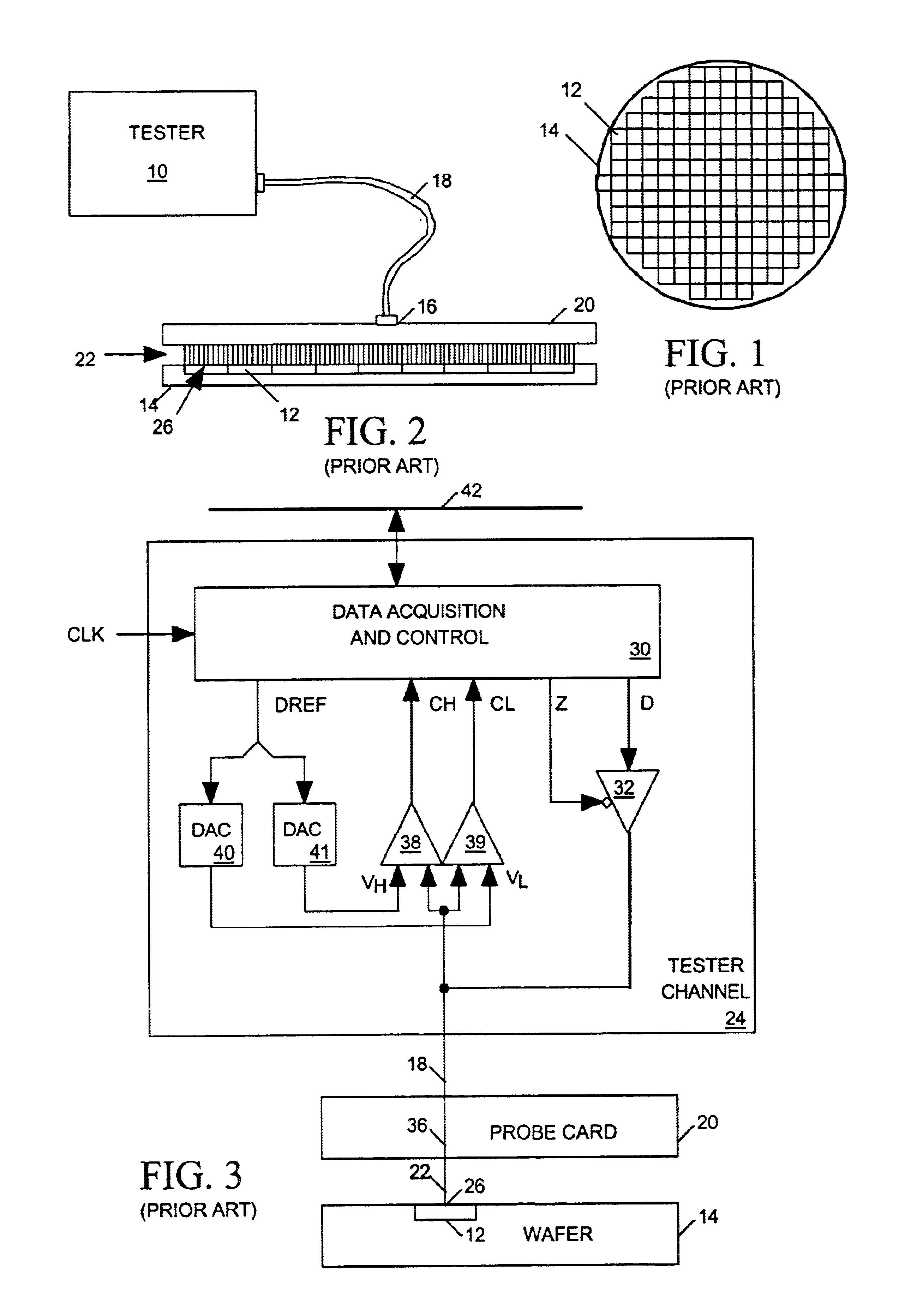

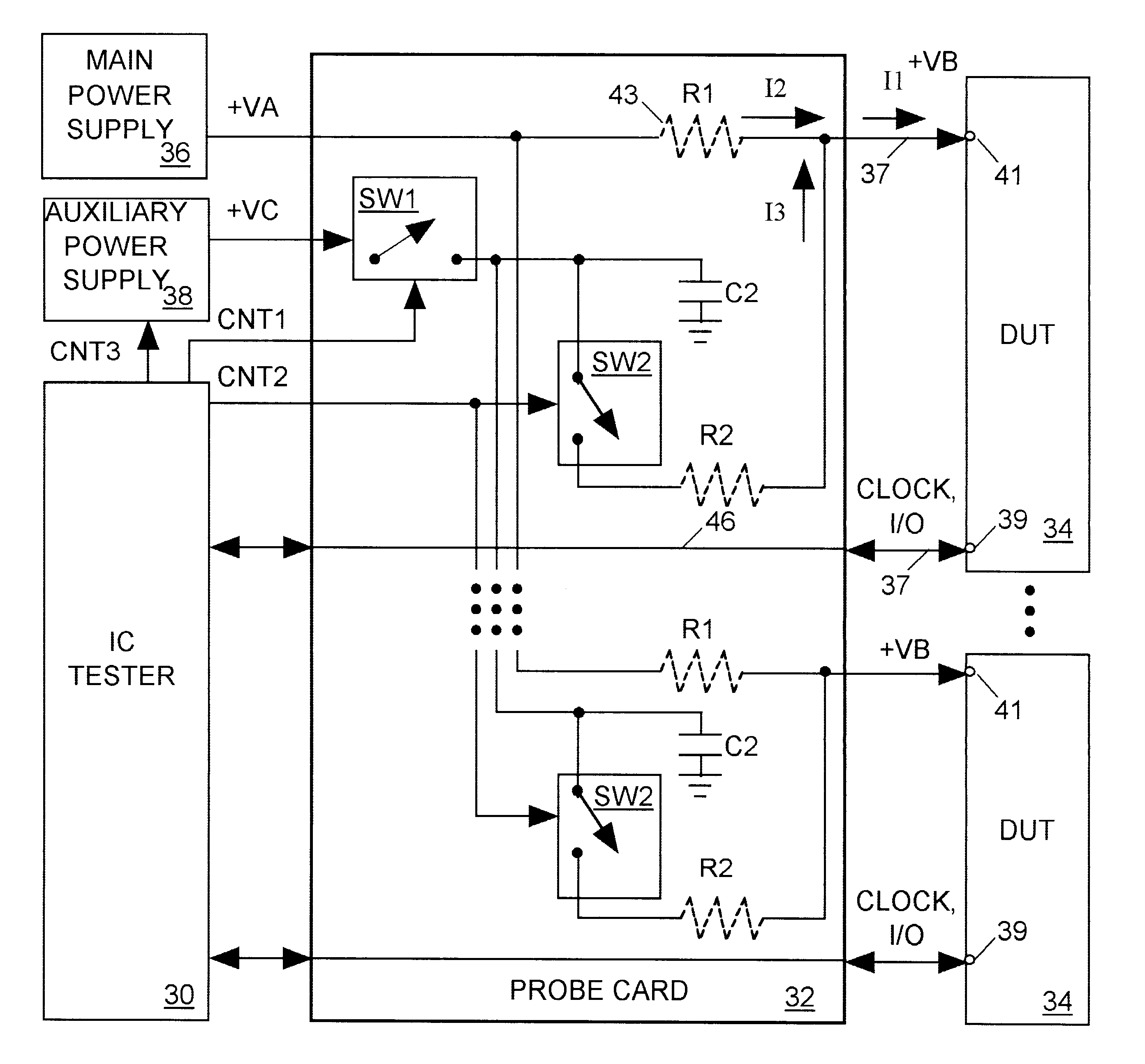

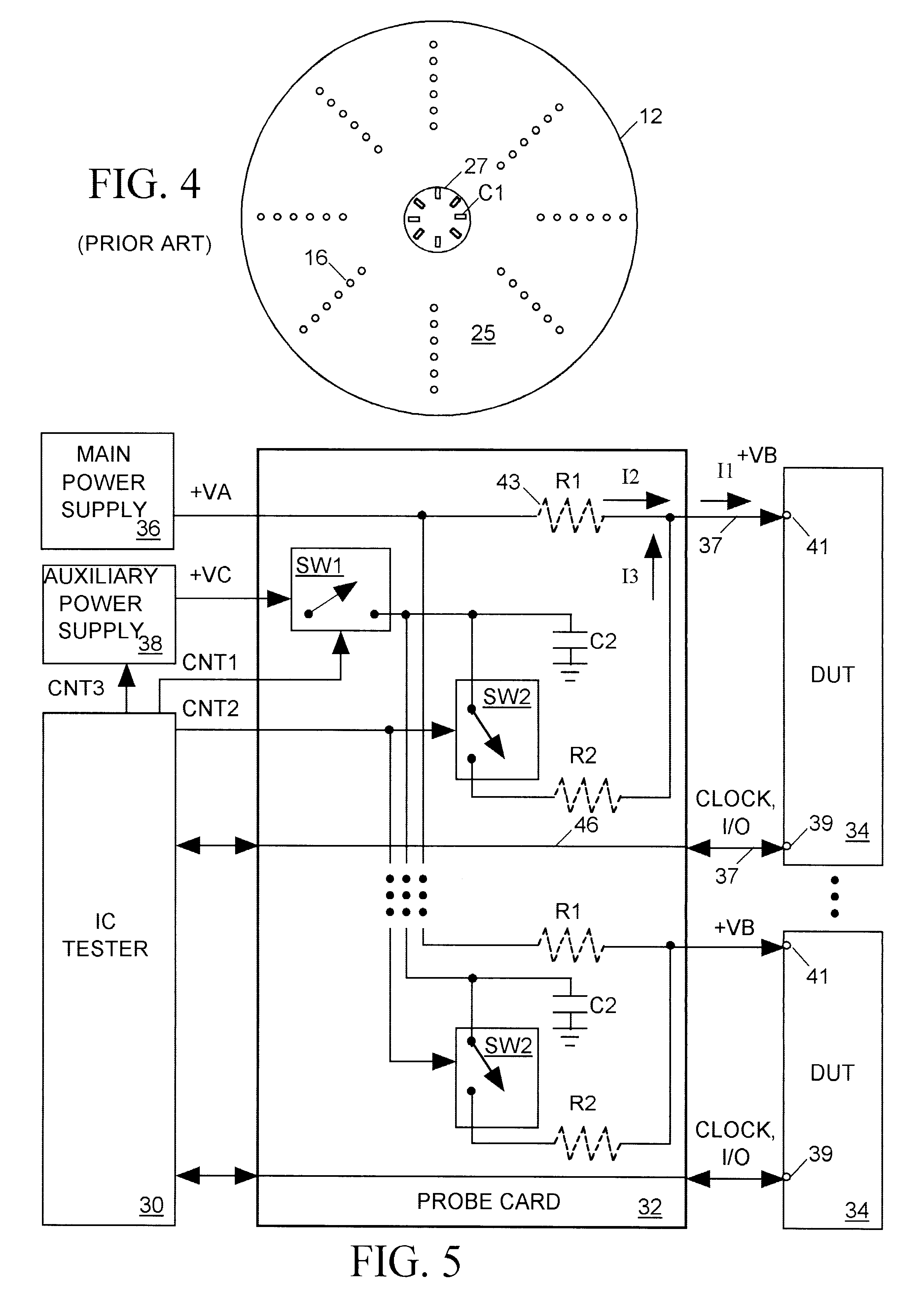

Predictive, adaptive power supply for an integrated circuit under test

InactiveUS6657455B2Suppress mutationReduce noiseDigital circuit testingSemiconductor/solid-state device testing/measurementPower flowFeedback circuits

Owner:FORMFACTOR INC

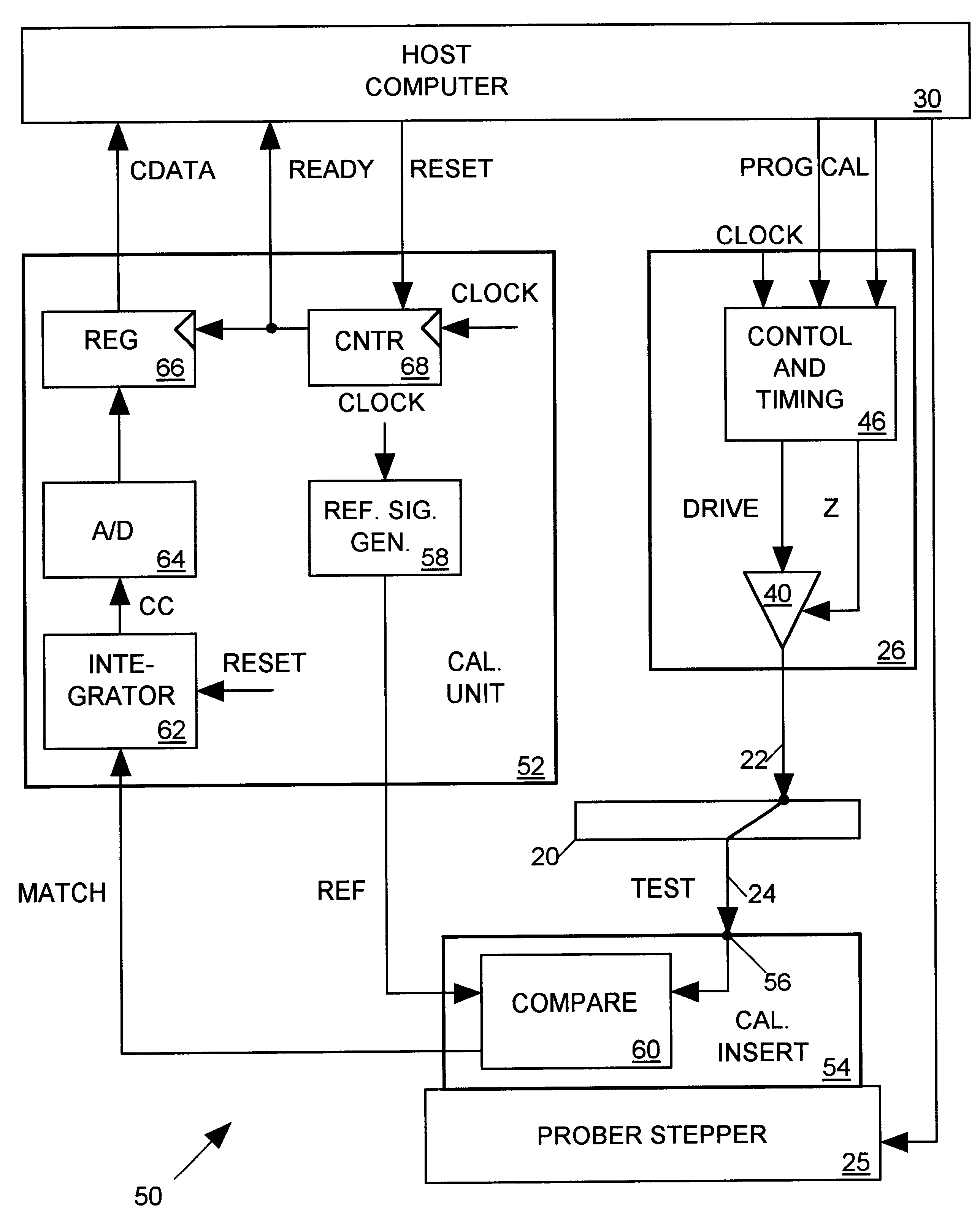

Cross-correlation timing calibration for wafer-level IC tester interconnect systems

InactiveUS6606575B2Easy accessDigital circuit testingTesting/calibration apparatusEngineeringSignal edge

To calibrate timing of test signals generated by all channels of an integrated circuit, each channel is programmed to generate a test signal having a repetitive pseudo-random test signal edge pattern. The test signal pattern of each channel is compared to a reference signal having the same edge pattern and the delay of each channel is adjusted to maximize cross-correlation between the test signal and the reference signal.

Owner:FORMFACTOR INC

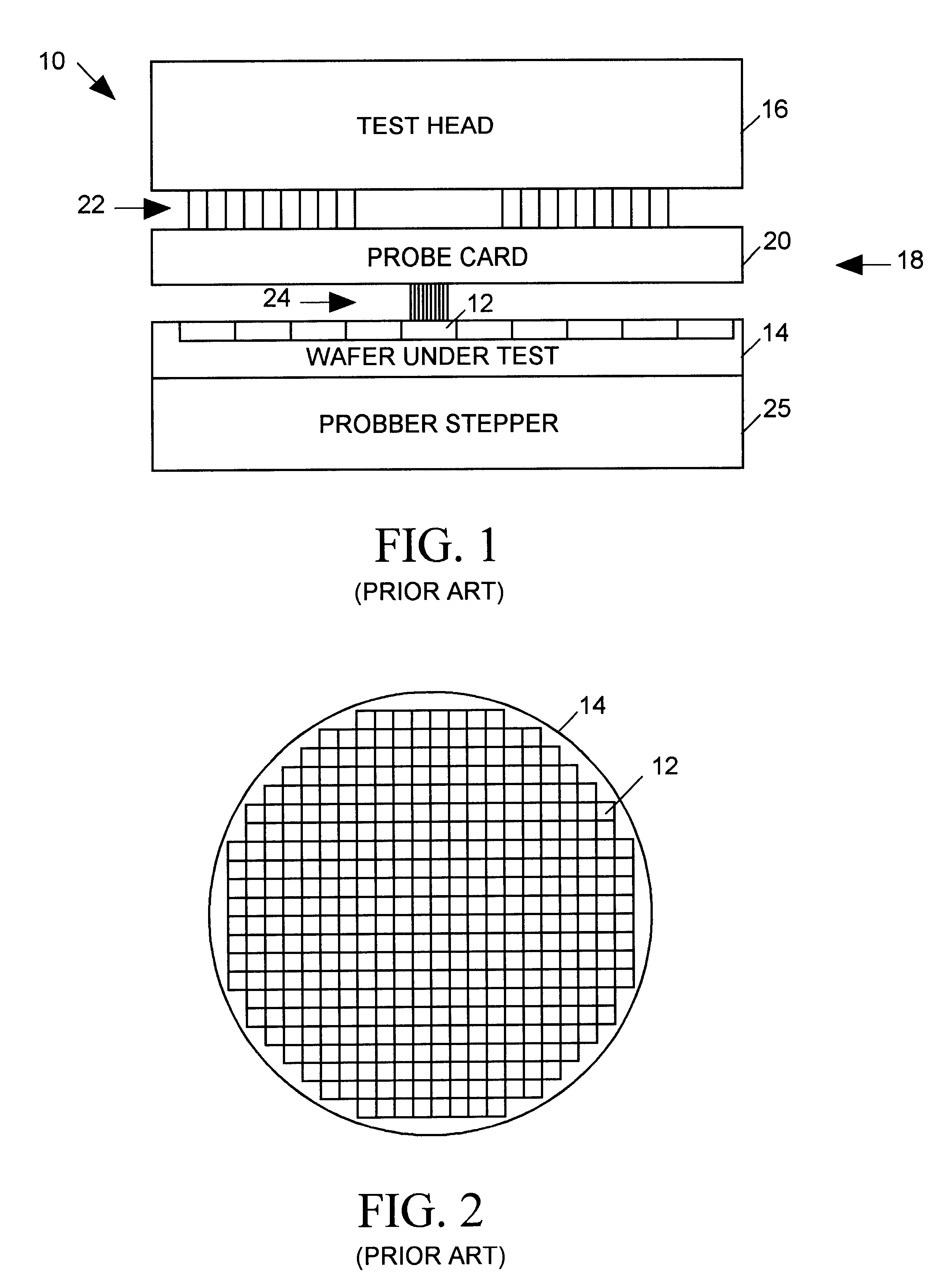

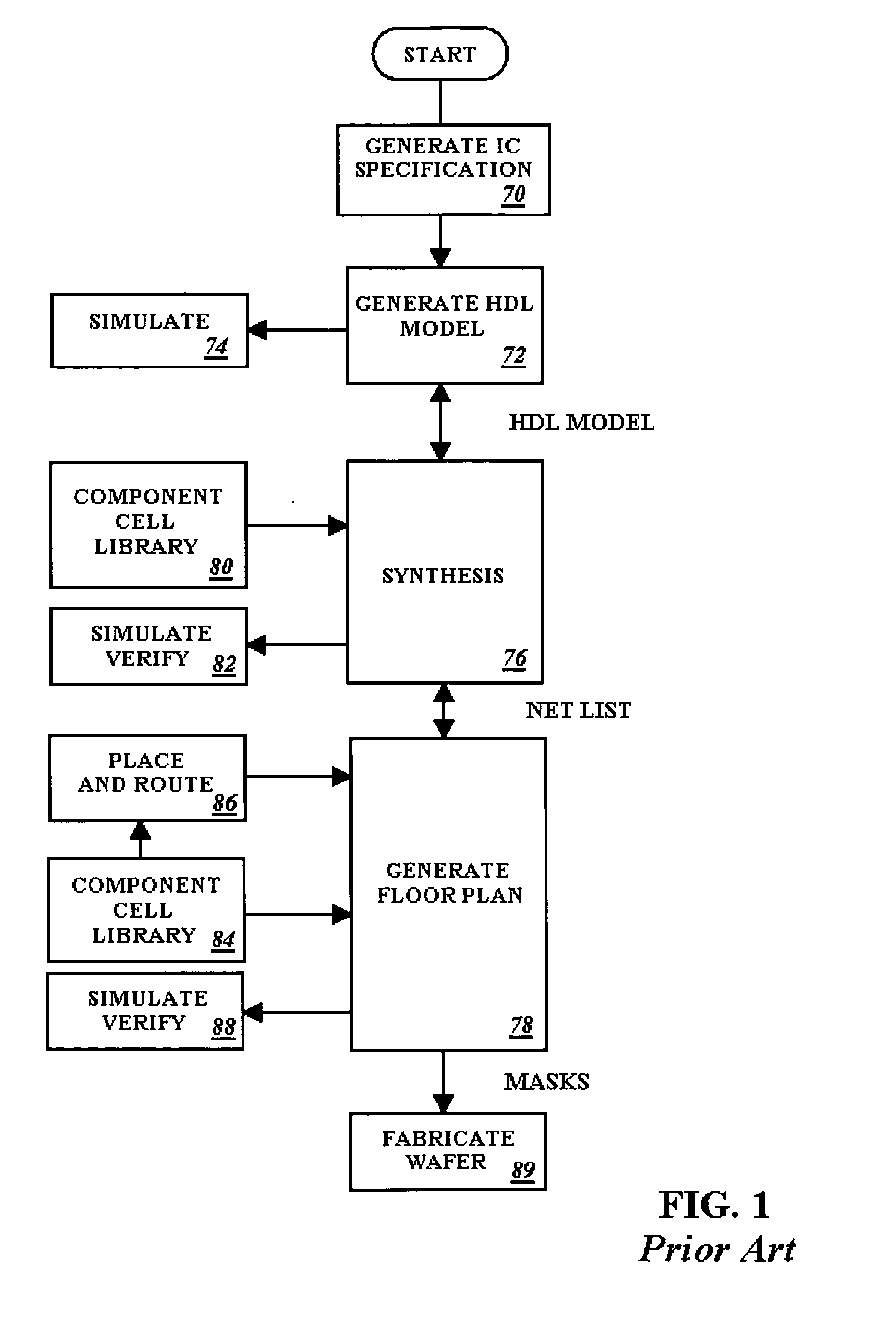

Method of designing an application specific probe card test system

InactiveUS20060273809A1Eliminate needDigital circuit testingOverload protection arrangementsProbe cardOn board

A method is provided for design and programming of a probe card with an on-board programmable controller in a wafer test system. Consideration of introduction of the programmable controller is included in a CAD wafer layout and probe card design process. The CAD design is further loaded into the programmable controller, such as an FPGA to program it: (1) to control direction of signals to particular ICs, even during the test process (2) to generate test vector signals to provide to the ICs, and (3) to receive test signals and process test results from the received signals. In some embodiments, burn-in only testing is provided to limit test system circuitry needed so that with a programmable controller on the probe card, text equipment external to the probe card can be eliminated or significantly reduced from conventional test equipment.

Owner:FORMFACTOR INC

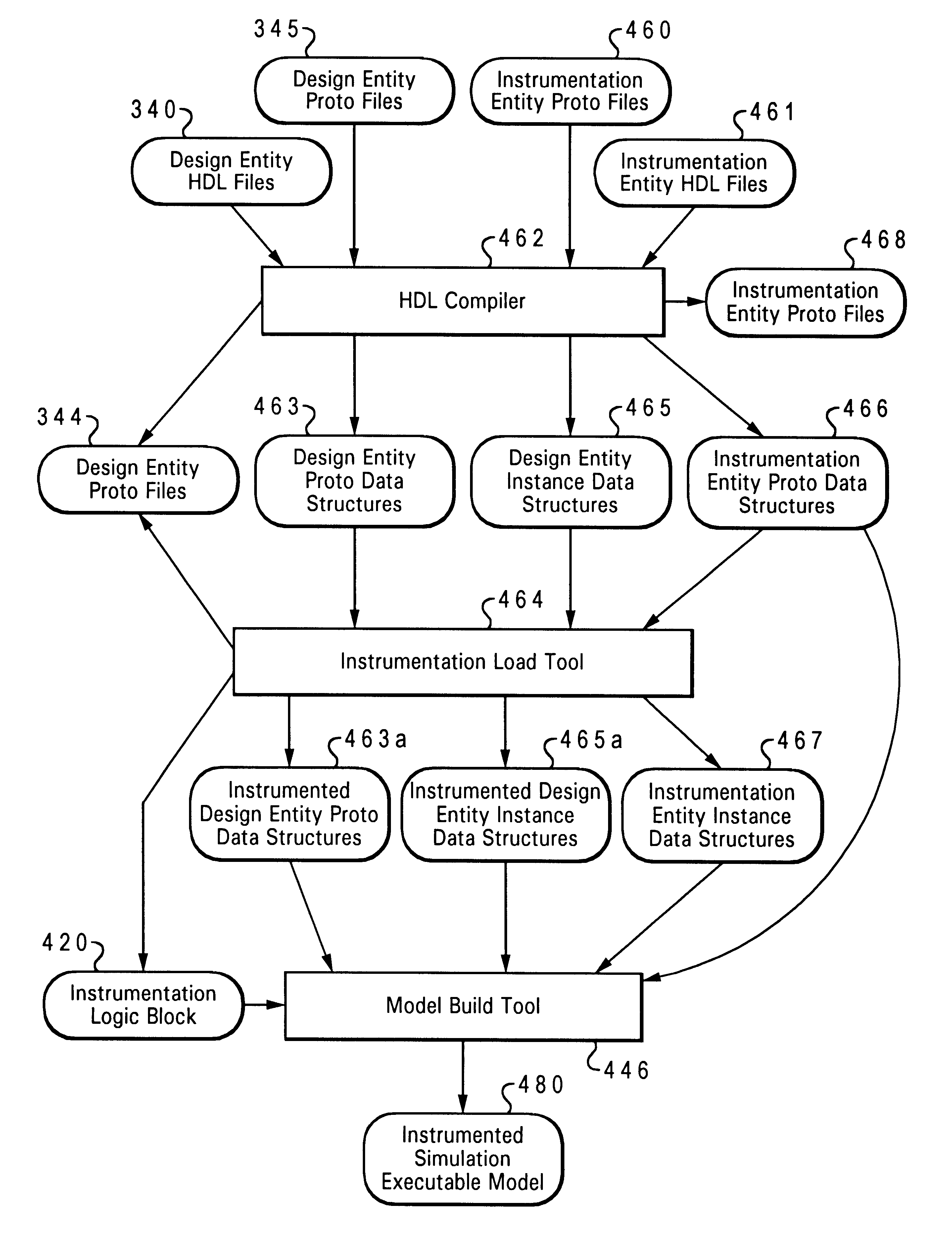

Method and system for counting events within a simulation model

InactiveUS6470478B1Monitor performanceDigital circuit testingDetecting faulty computer hardwareTheoretical computer scienceLinear feedback shift register

A method and system that utilize the expressiveness of hardware description languages for efficiently and comprehensively monitoring performance characteristics of a digital circuit design during simulation. According to the present invention, a design entity that is part of a digital circuit design is first described utilizing a hardware description language. Next, a counting instrument is described utilizing the same hardware description language. The counting instrument is designed to detect occurrences of a count event within the design entity during simulation of the digital circuit design. The counting instrument is associated with the design entity utilizing a non-conventional call, such that the counting instrument may be utilized to monitor each instantiation of the design entity within the simulation model without the instrumentation entity becoming incorporated into the digital circuit design. In association with the counting instrument, a linear feedback shift register is automatically generated for recording the number of occurrences of the count event within the design entity.

Owner:GLOBALFOUNDRIES INC

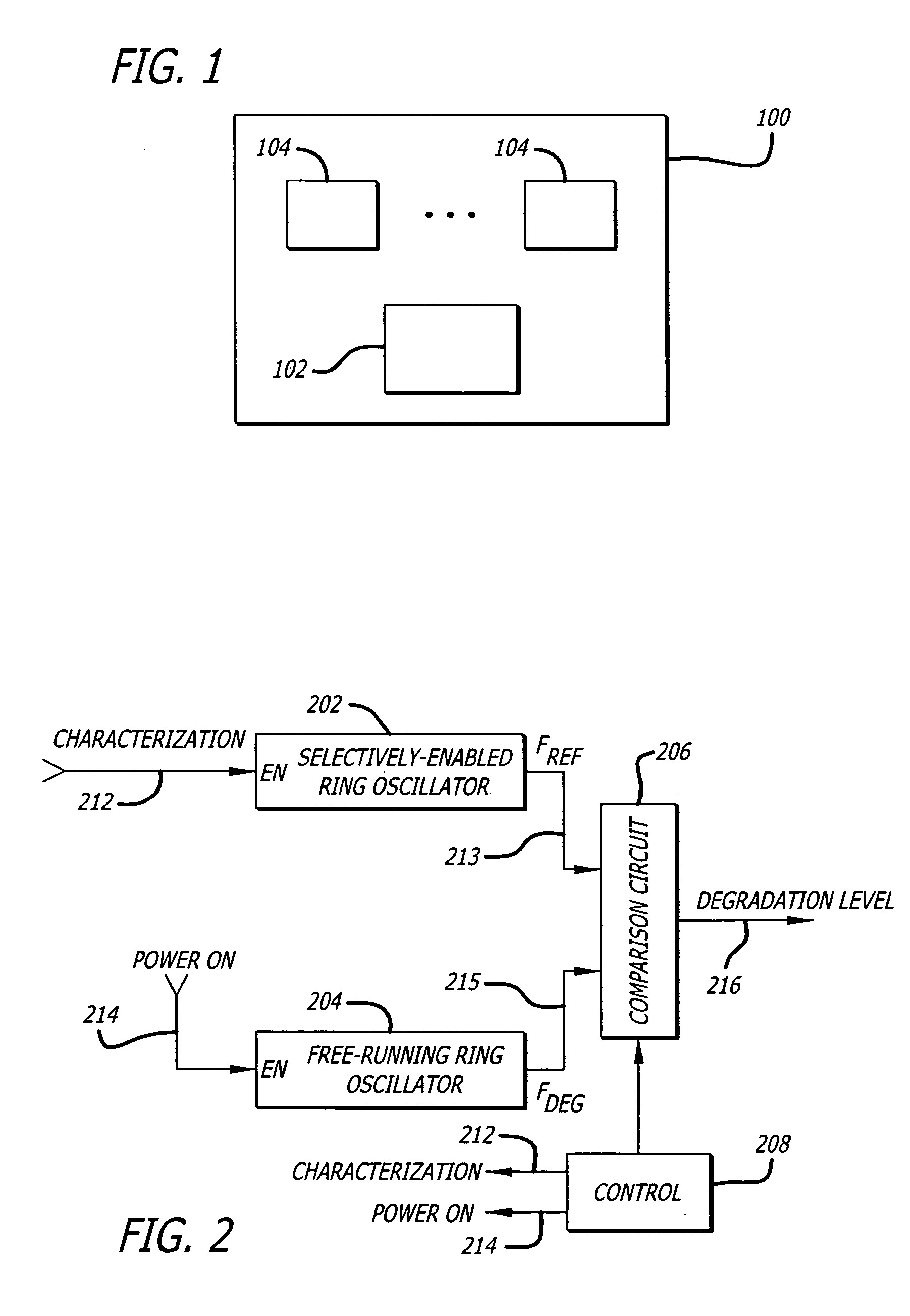

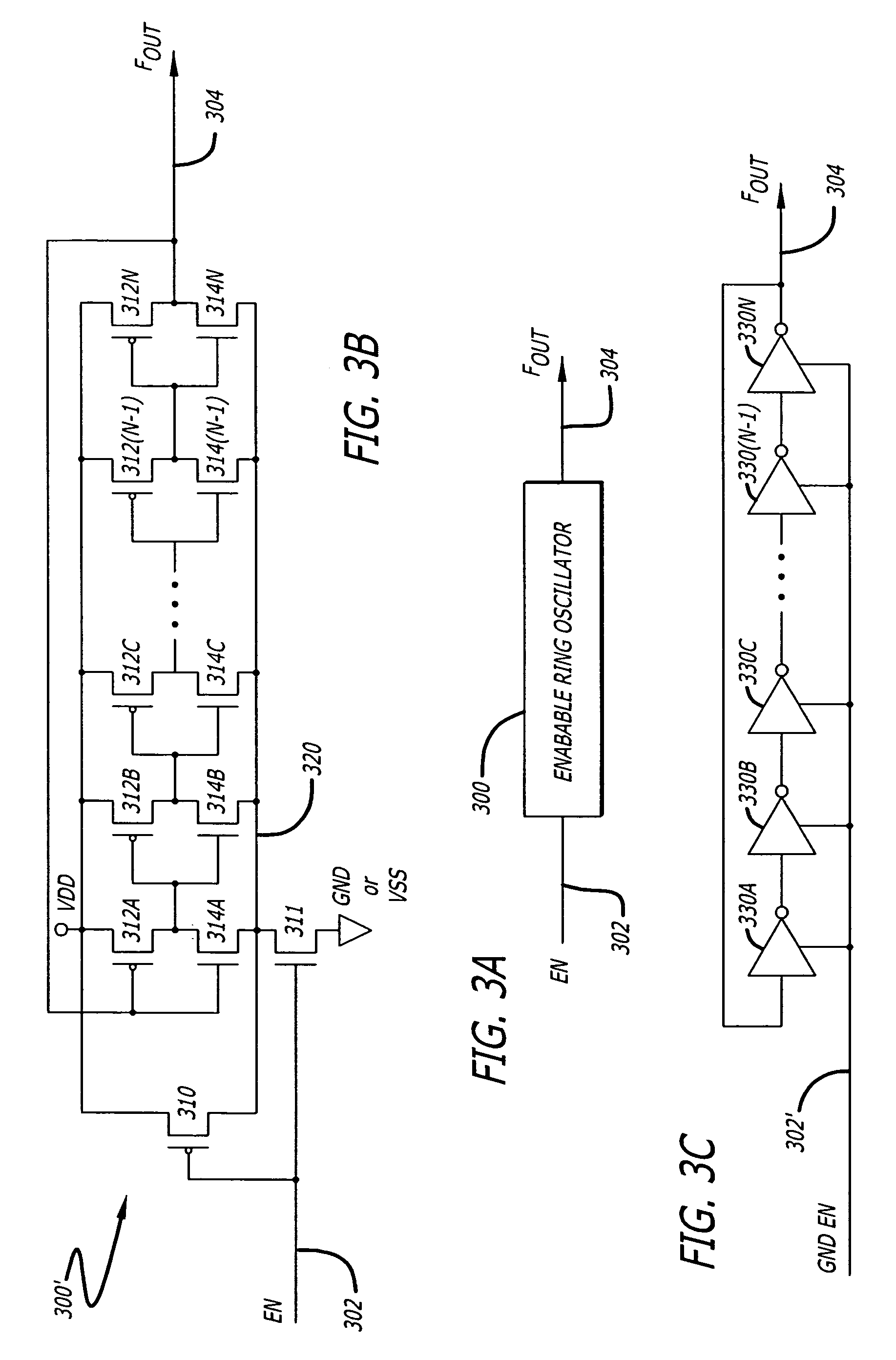

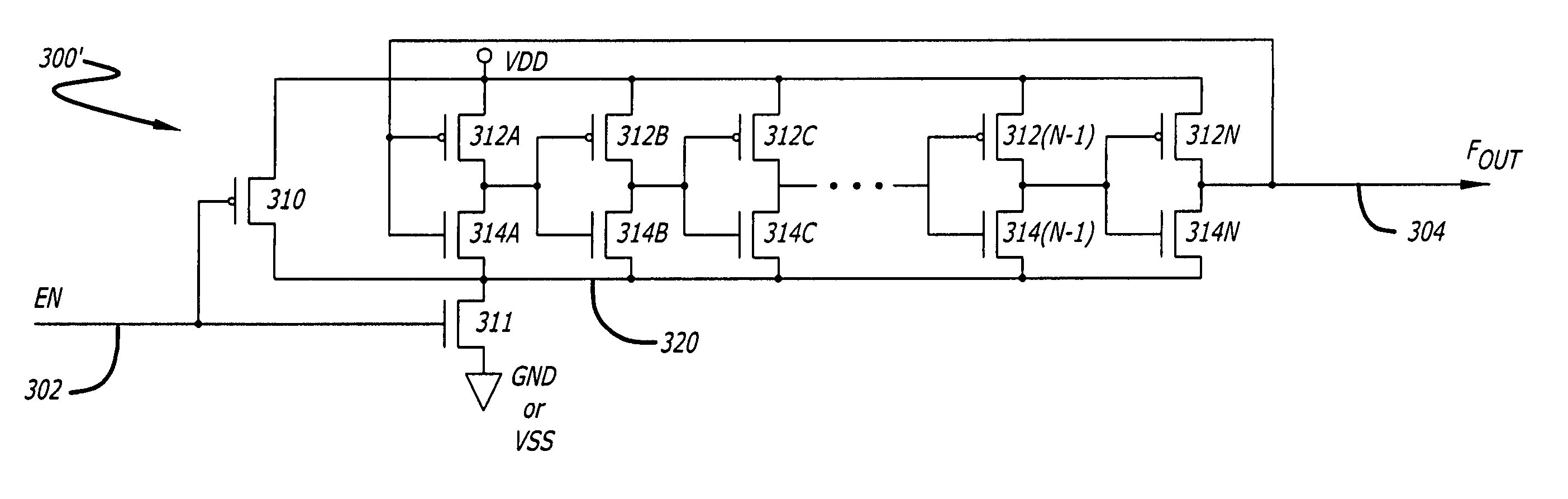

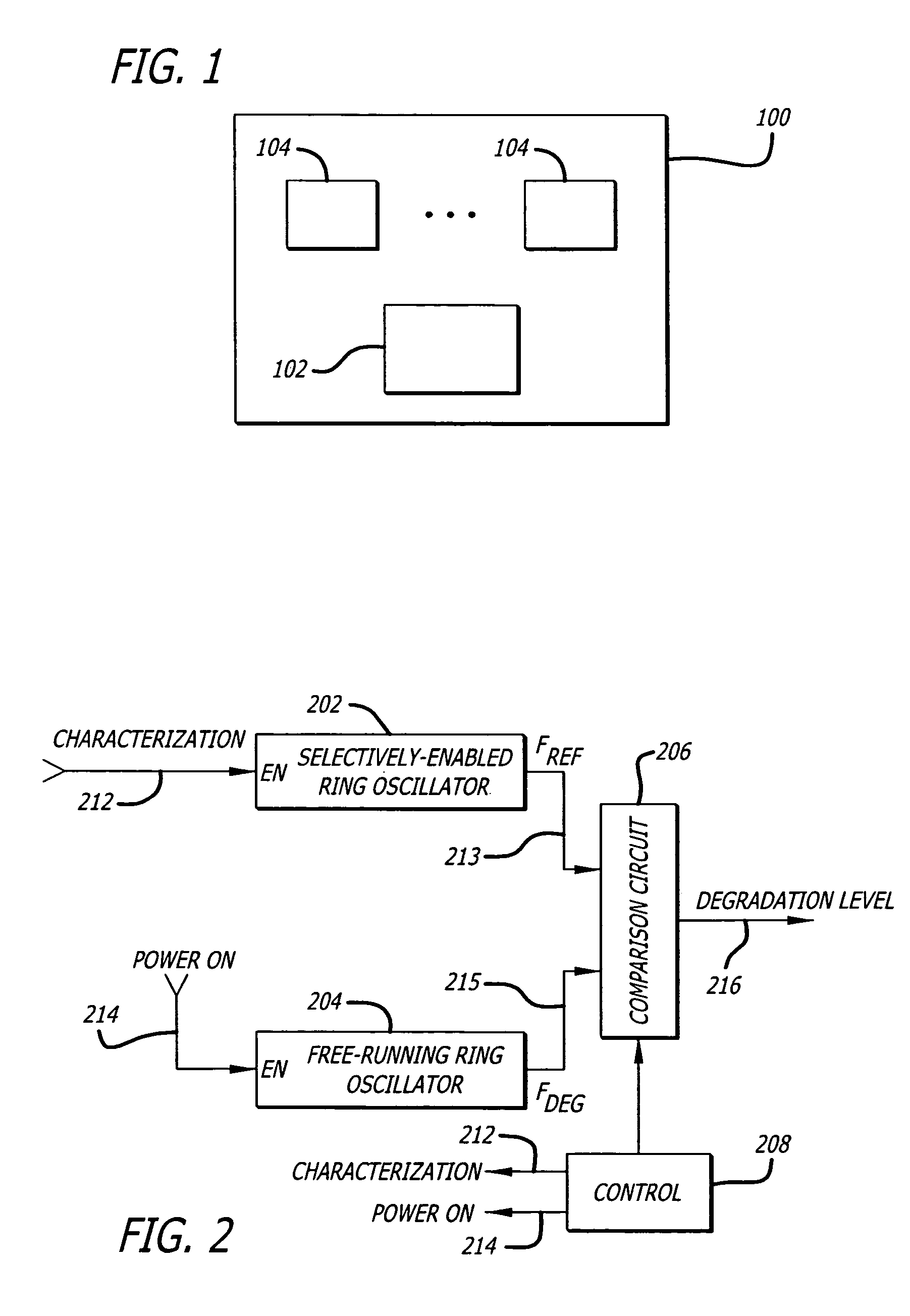

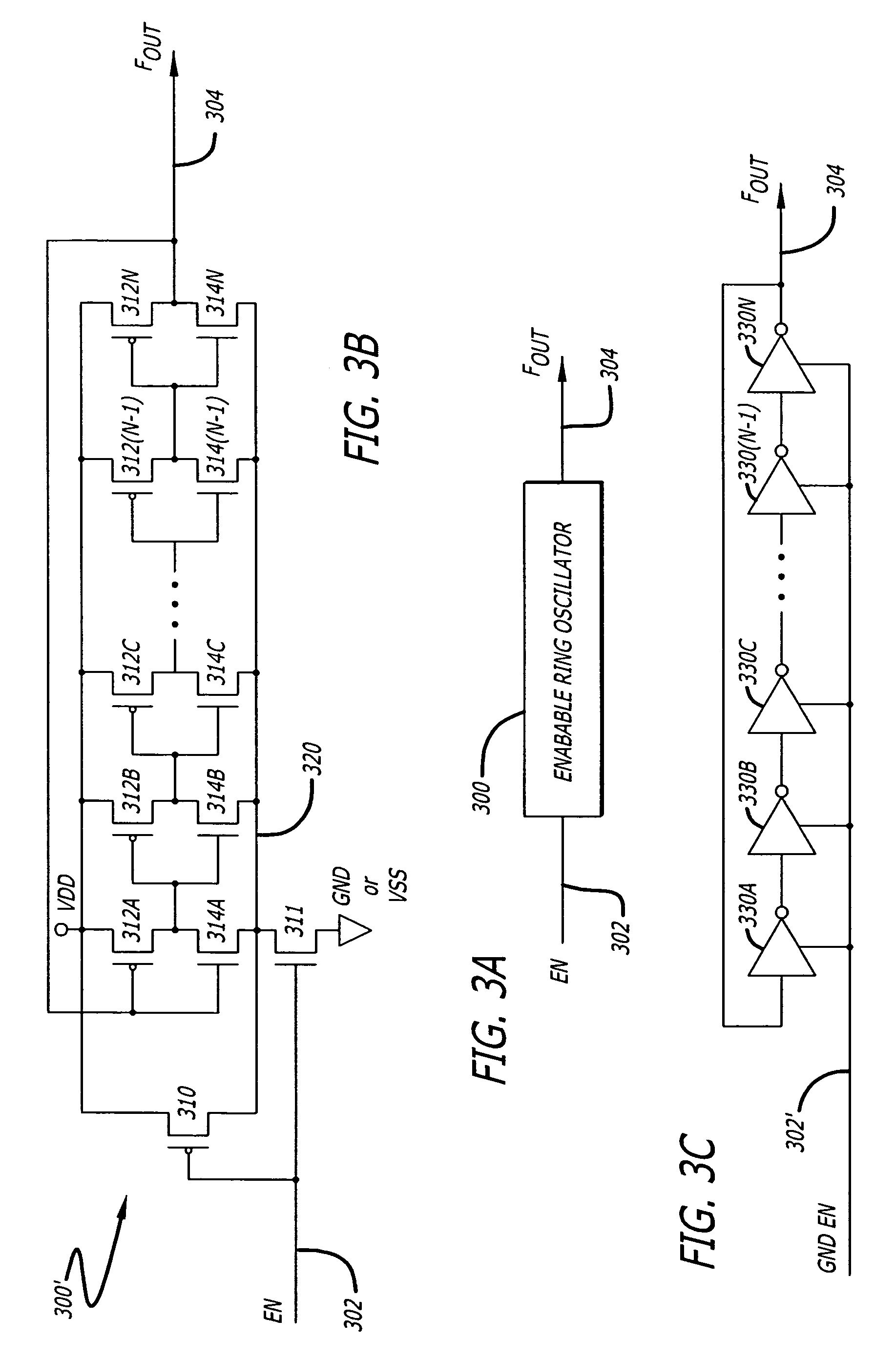

On-chip transistor degradation monitoring

InactiveUS20050134394A1Digital circuit testingPulse generation by logic circuitsEngineeringRing oscillator

Embodiments of the invention include on-chip characterization of transistor degradation. In one embodiment, includes one or more functional blocks to perform one or more functions and an integrated on-chip characterization circuit to perform on-chip characterization of transistor degradation. The integrated on-chip characterization circuit includes a selectively enabled ring oscillator to generate a reference oscillating signal, a free-running ring oscillator to generate a free-running oscillating signal, and a comparison circuit coupled to the selectively enabled ring oscillator and the free-running ring oscillator. From the reference oscillating signal and the free-running oscillating signal, the comparison circuit determine a measure of transistor degradation.

Owner:INTEL CORP

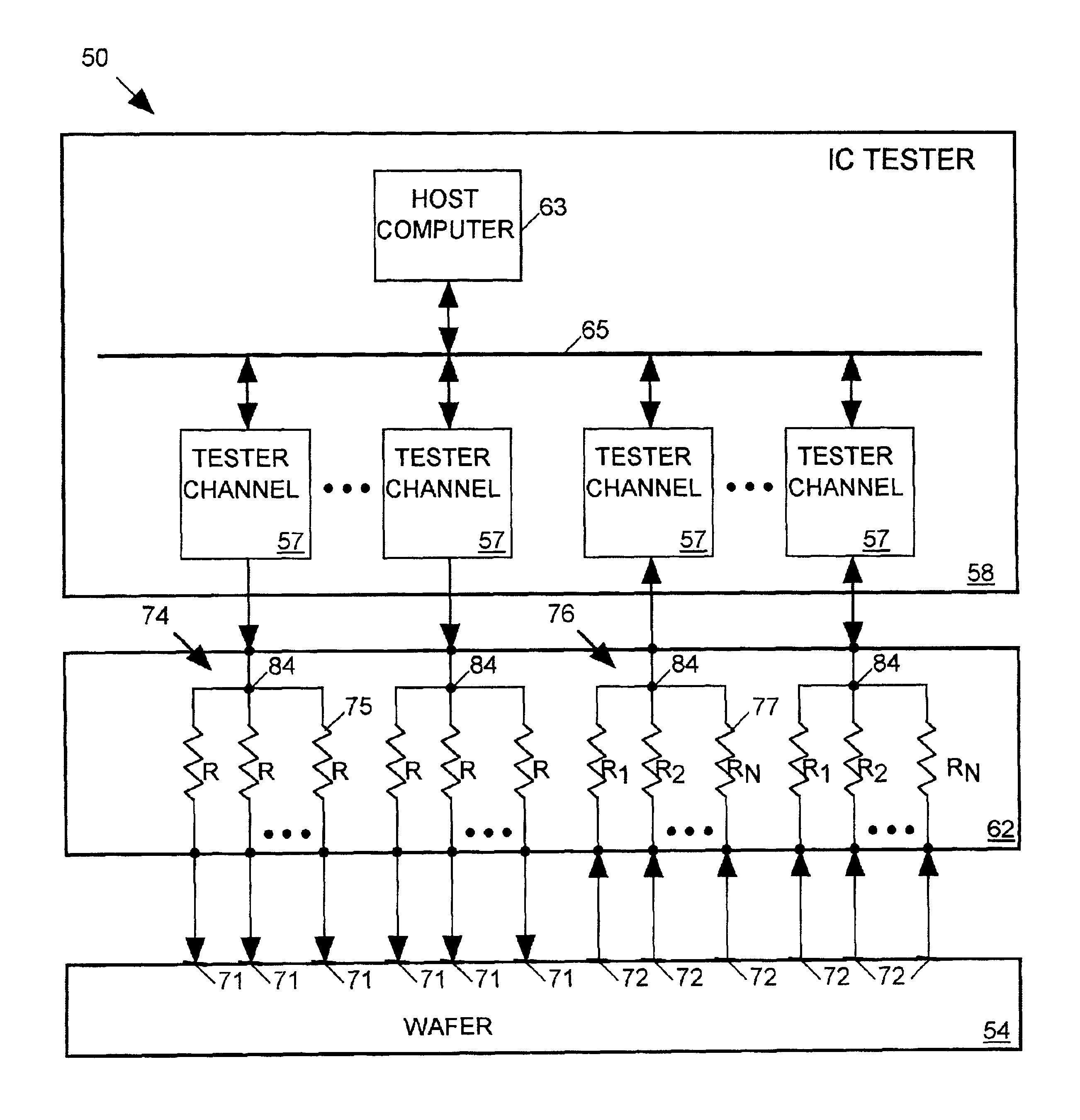

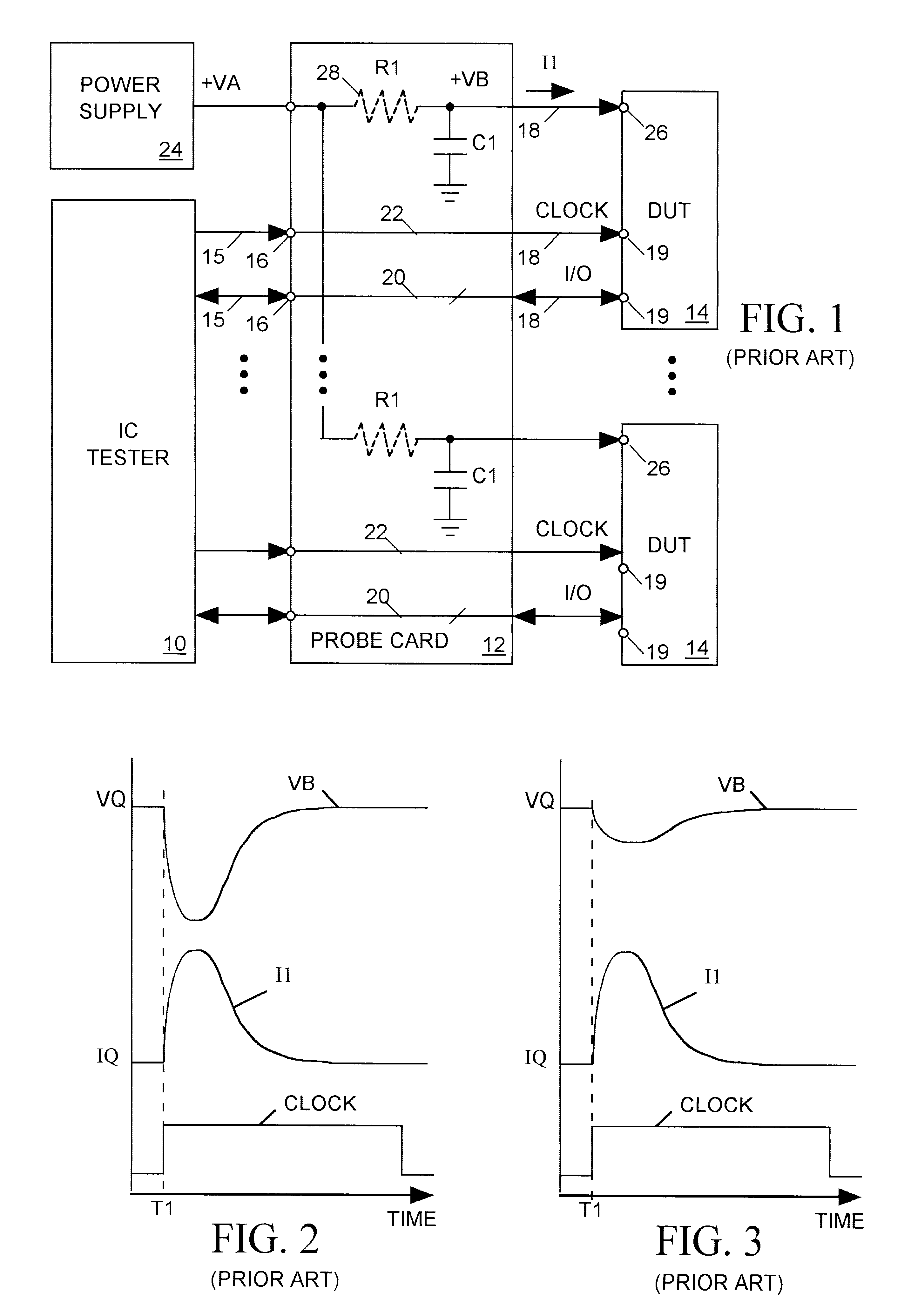

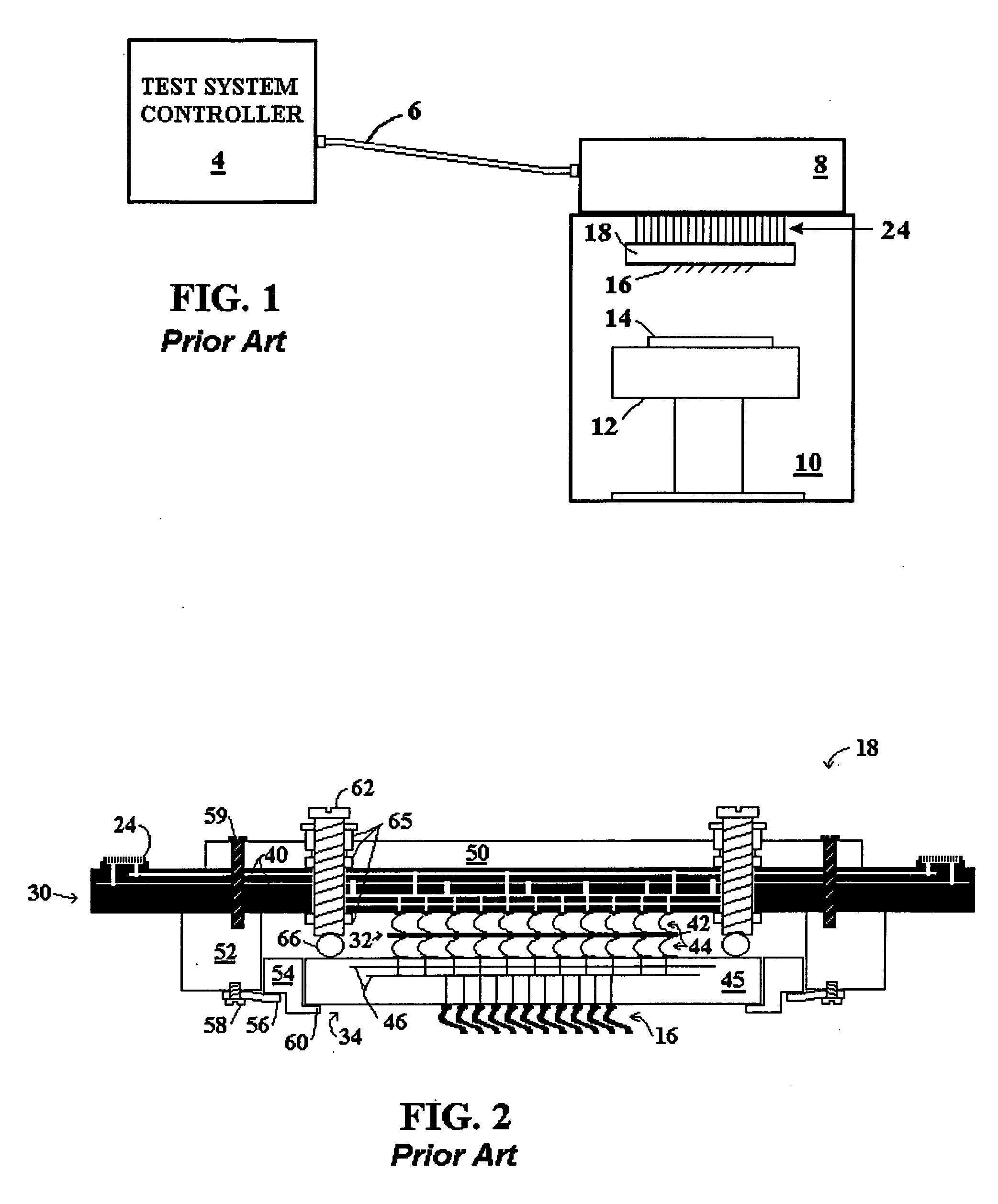

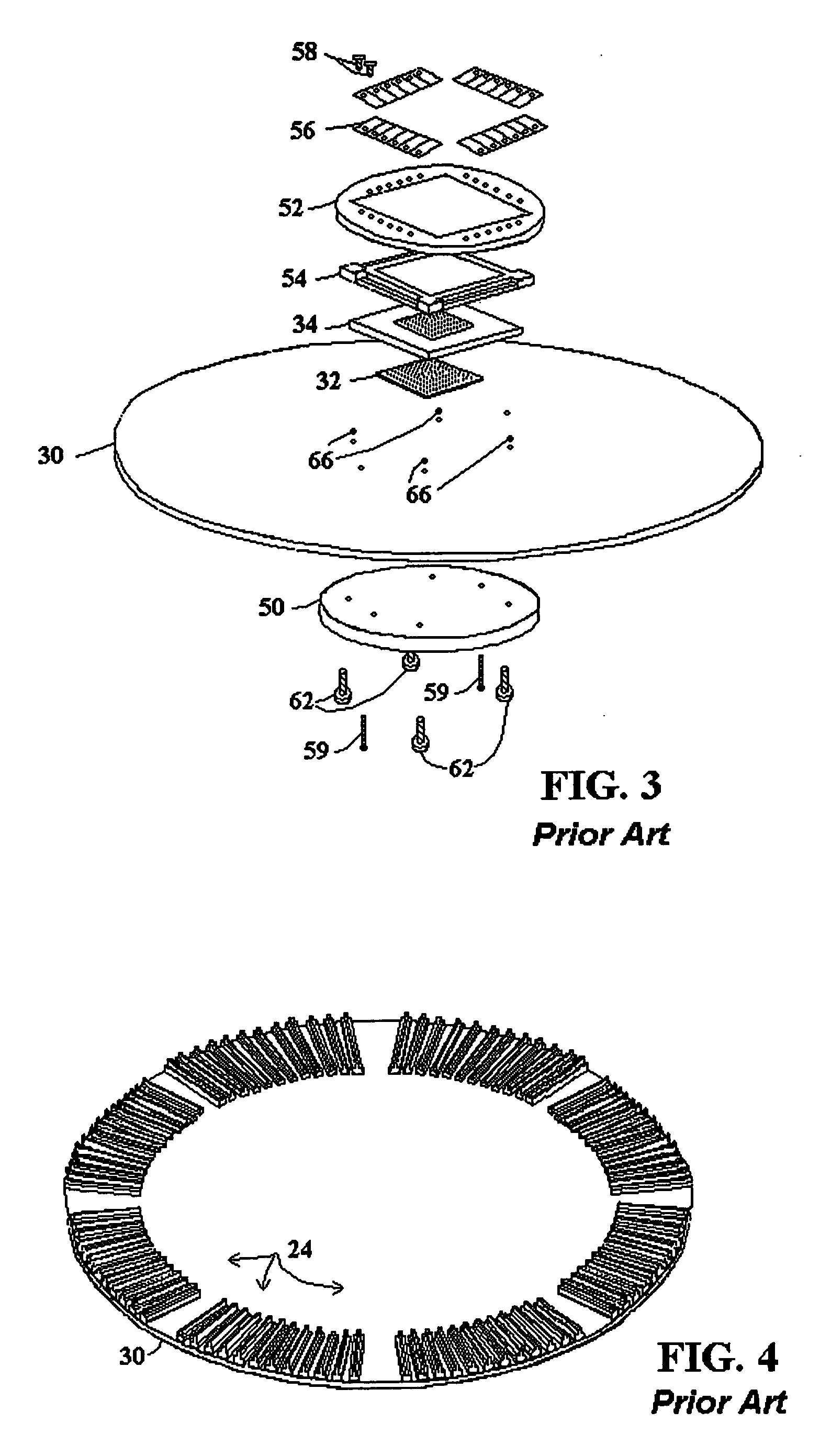

Test signal distribution system for IC tester

InactiveUS6784674B2Digital circuit testingElectrical measurement instrument detailsDistribution systemEngineering

A probe board provides signal paths between an integrated circuit (IC) tester and probes accessing terminals on the surfaces of ICs formed on a semiconductor wafer for receiving test signals form the IC tester. A branching signal path within the probe board distributes a test signal produced by one channel of the IC tester to several probes. Resistors within the branching signal path resistively isolate the probes from one another so that a fault occurring at any one IC terminal will not affect the logic state of the test signal arriving at any other IC terminal. The isolation resistors are sized relative to signal path characteristic impedances so as to substantially minimize test signal reflections at the branch points.

Owner:FORMFACTOR INC

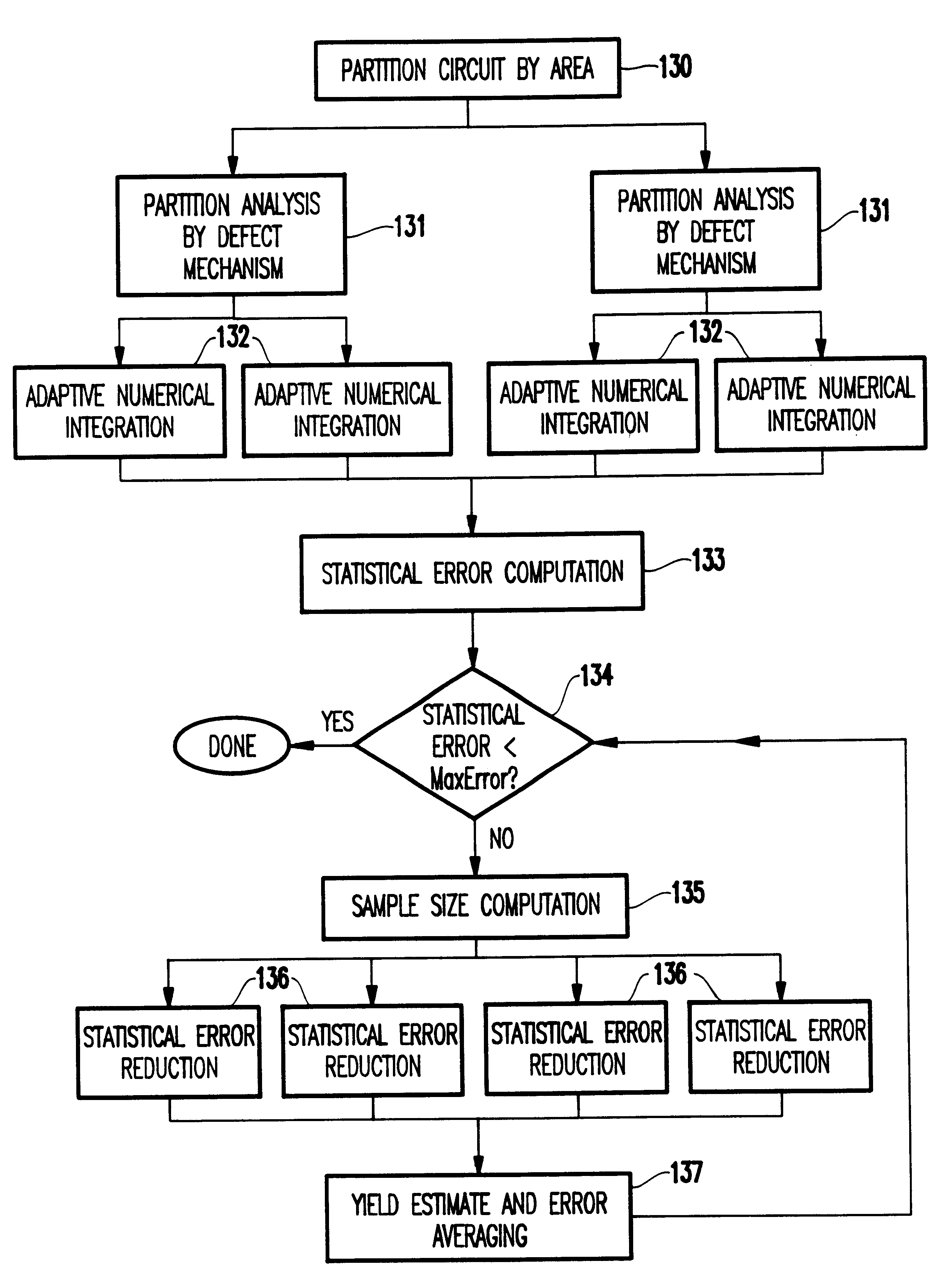

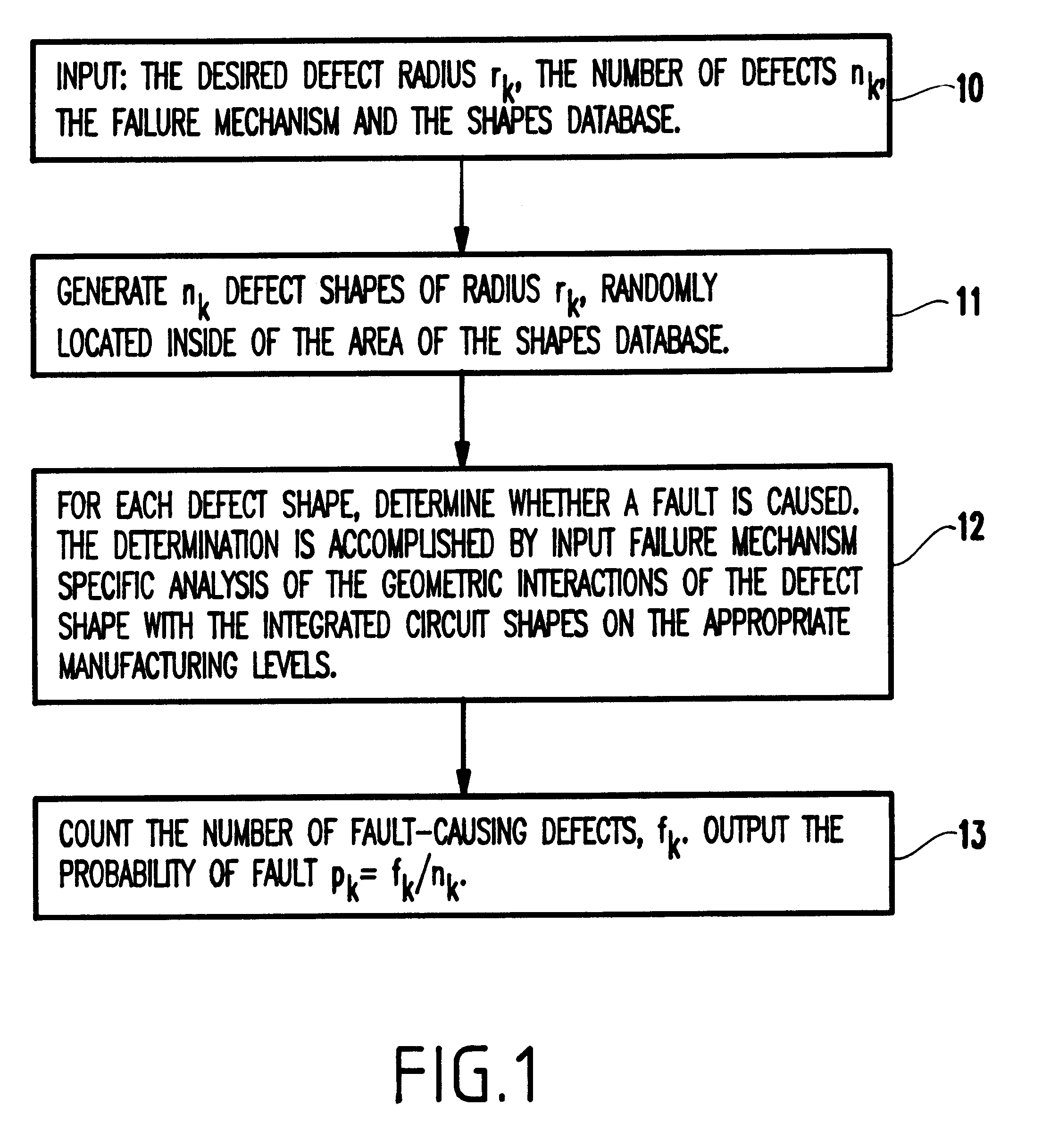

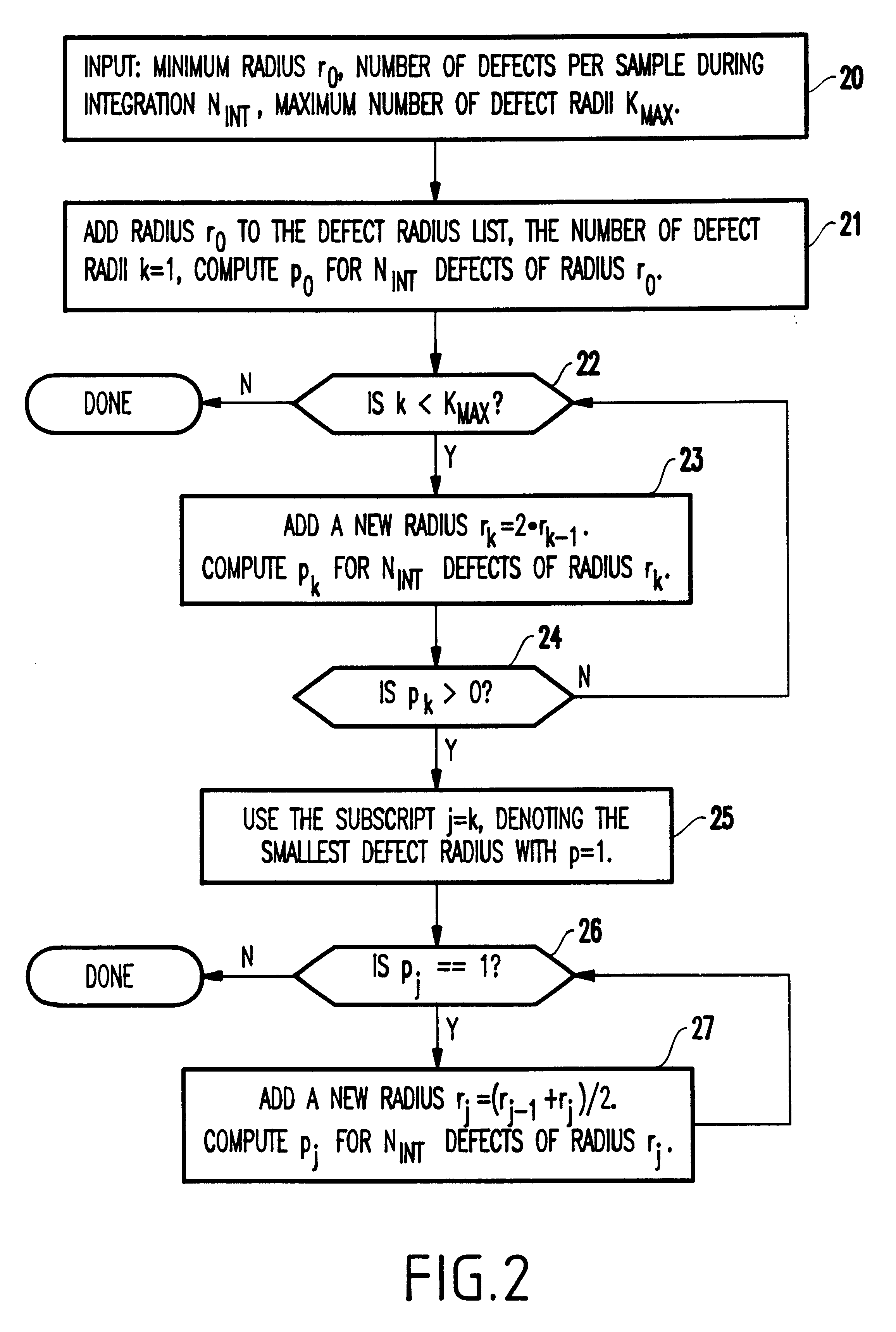

Method for prediction random defect yields of integrated circuits with accuracy and computation time controls

InactiveUS6738954B1Reduce the amount of calculationReduce errorsDigital circuit testingSemiconductor/solid-state device testing/measurementDefect sizeIntegrated circuit layout

A method of computing a manufacturing yield of an integrated circuit having device shapes includes sub-dividing the integrated circuit into failure mechanism subdivisions (each of the failure mechanism subdivisions includes one or more failure mechanism and each of the failure mechanisms includes one or more defect mechanisms), partitioning the failure mechanism subdivisions by area into partitions, pre-processing the device shapes in each partition, computing an initial average number of faults for each of the failure mechanisms and for each partition by numerical integration of an average probability of failure of each failure mechanism, (the numerical integration produces a list of defect sizes for each defect mechanism, and the computing of the initial average includes setting a maximum integration error limit, a maximum sample size for a population of each defect size, and a maximum number of allowable faults for each failure mechansim), and computing a final average number of faults for the integrated circuit by iterativelly reducing a statistical error of the initial average number of faults for each of the failure mechanisms until the statistical error is below an error limit.

Owner:GOOGLE LLC

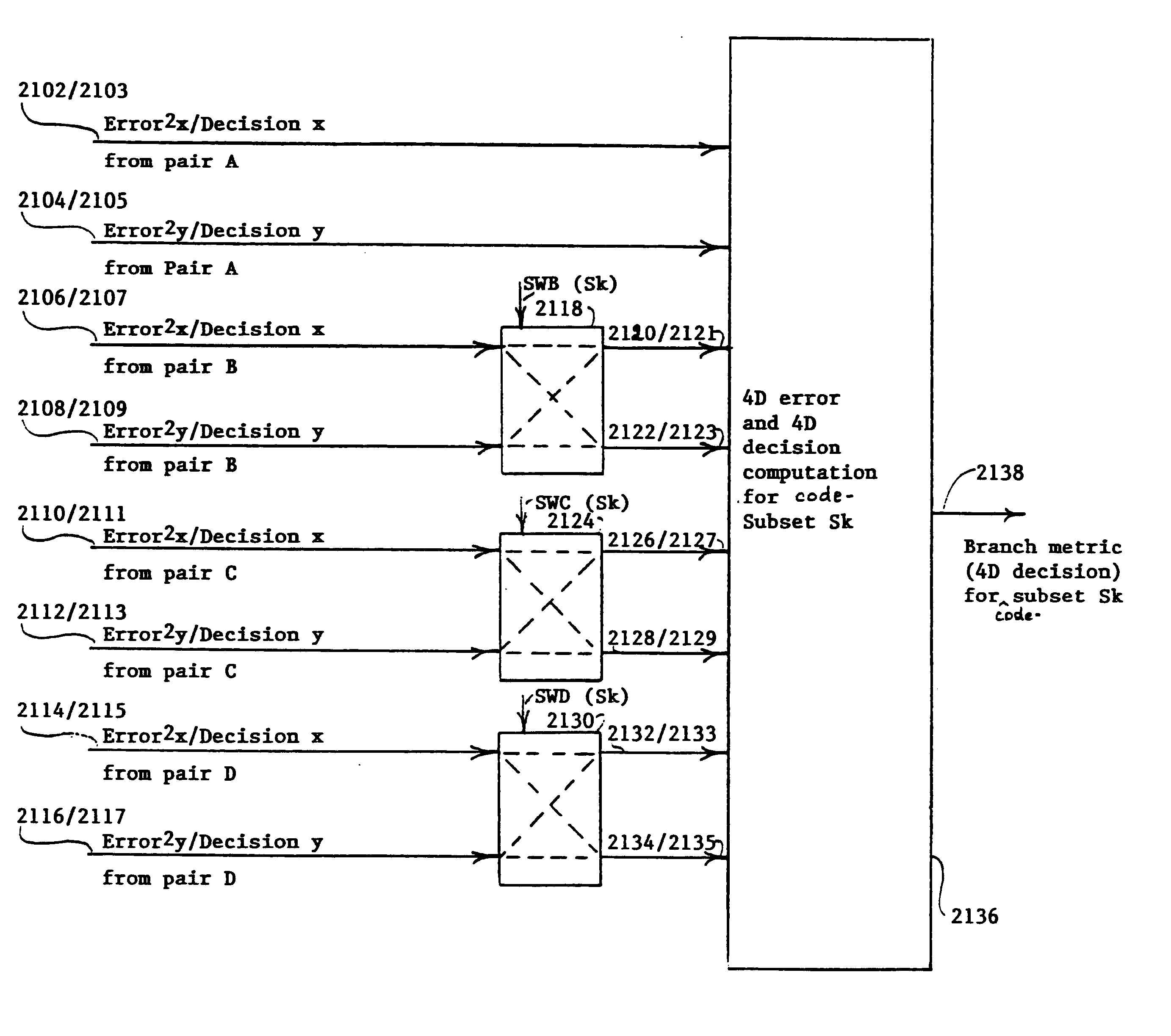

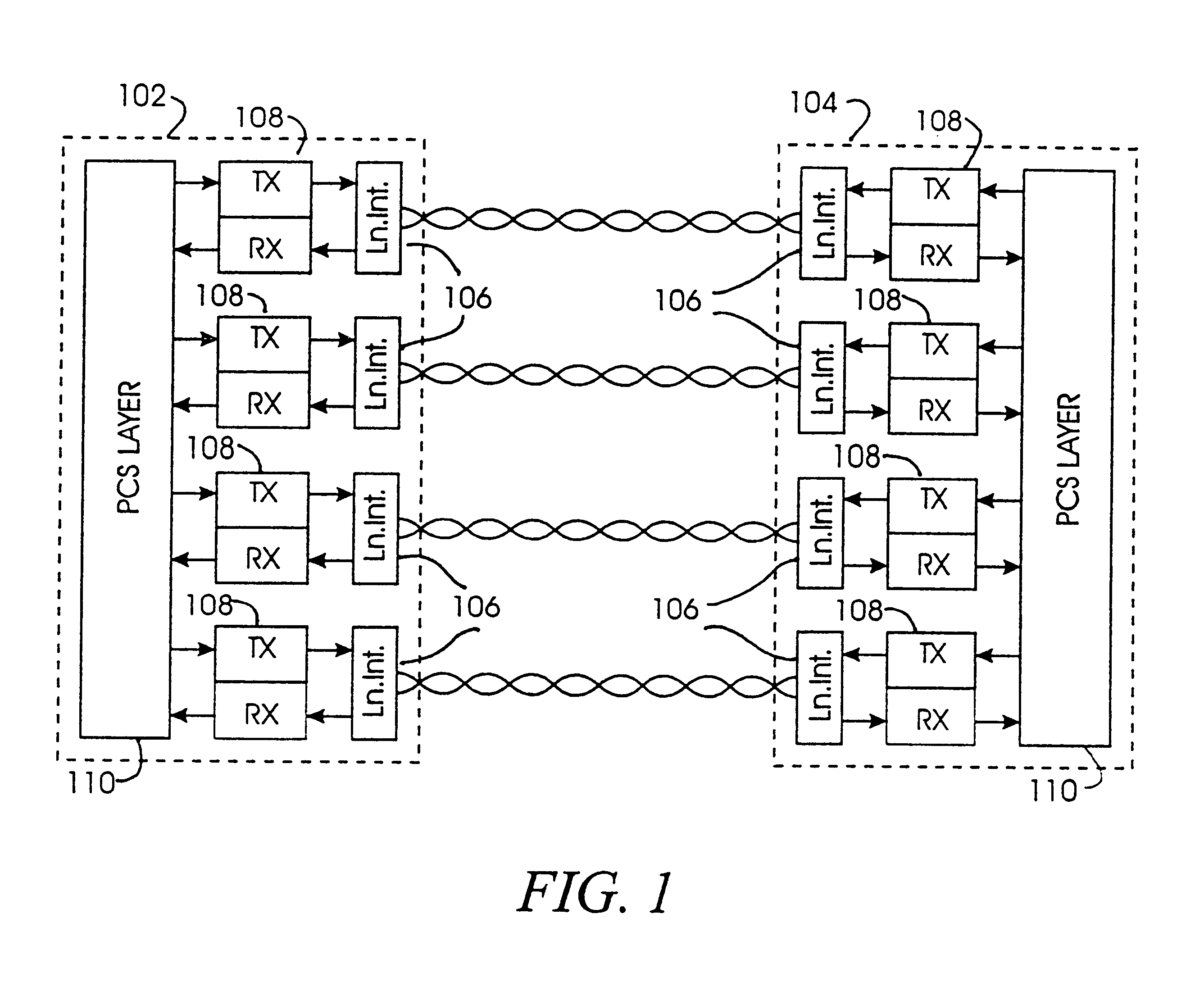

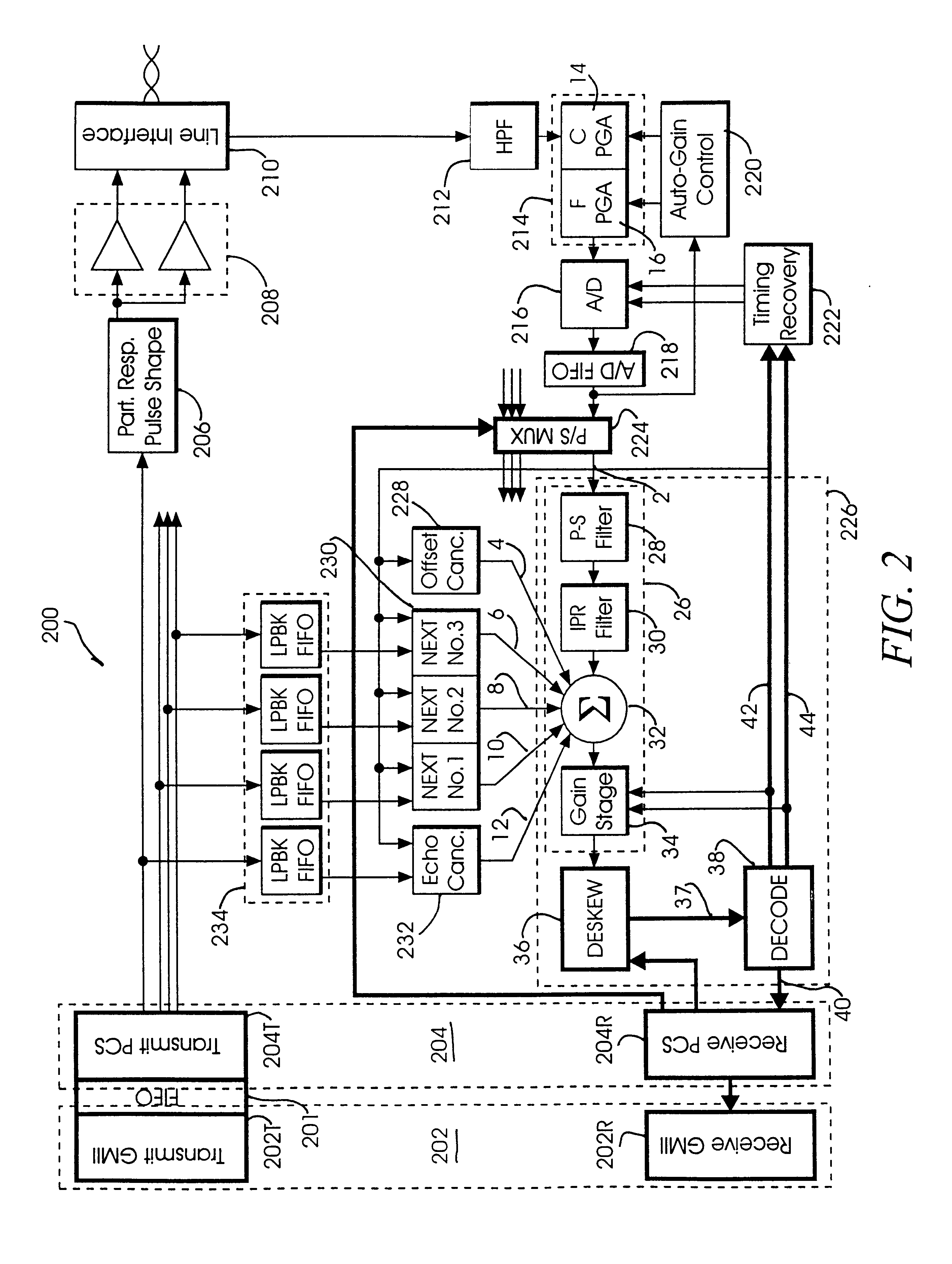

Pair-swap independent trellis decoder for a multi-pair gigabit transceiver

InactiveUS6865234B1Channel dividing arrangementsDigital circuit testingGigabitMulti-gigabit transceiver

A method and a system for compensating for a permutation of L pairs of cable such that the compensation is localized in a trellis decoder of a receiver. The L pairs of cable correspond to L dimensions of a trellis code associated with the trellis decoder. The trellis code includes a plurality of code-subsets. The permutation of the L pairs of cable is determined. A plurality of sets of swap indicators based on the permutation of the L pairs of cable is generated. Each of the sets of swap indicators corresponds to one of the code-subsets. The code-subsets are remapped based on the corresponding sets of swap indicators.

Owner:AVAGO TECH INT SALES PTE LTD

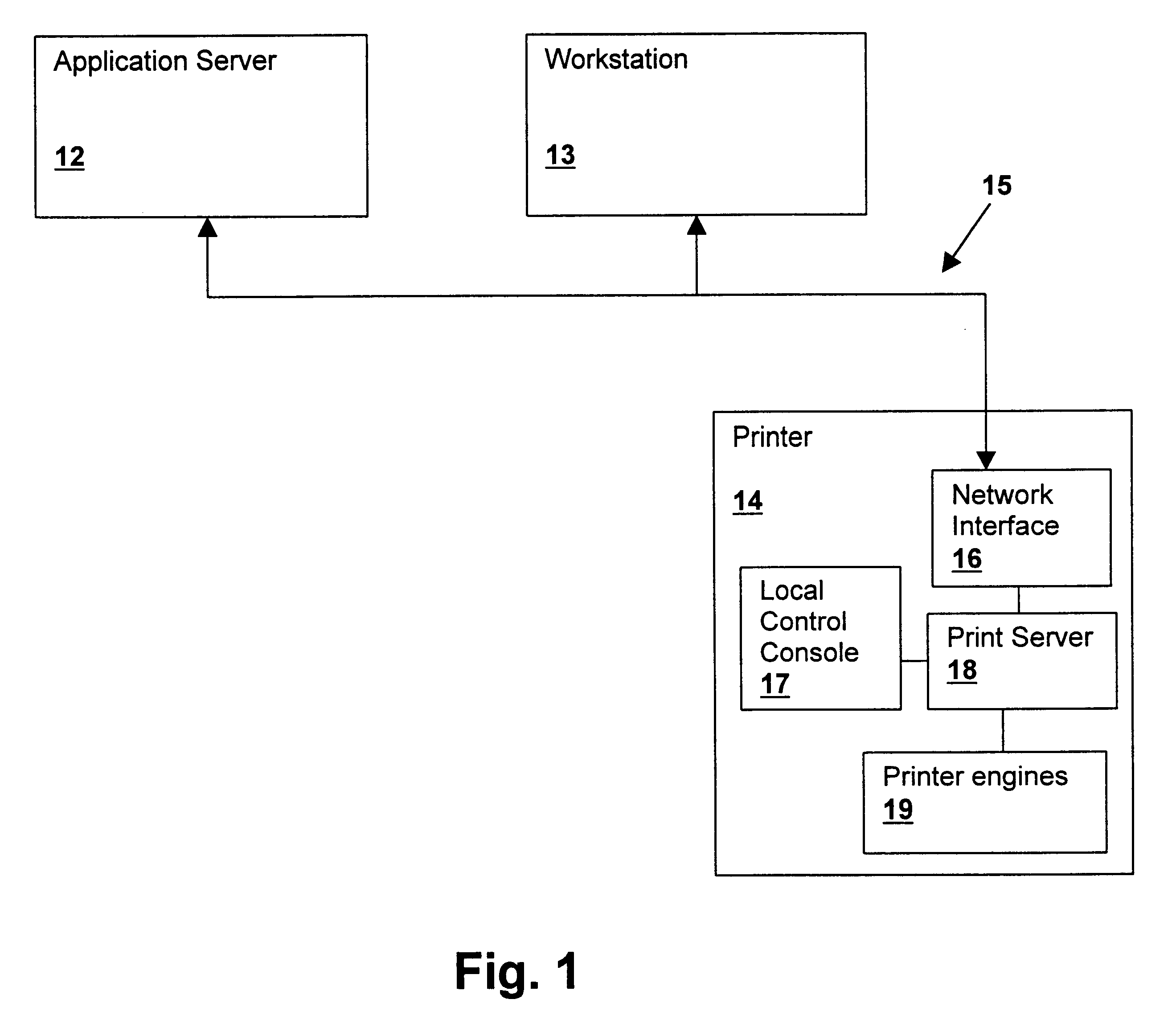

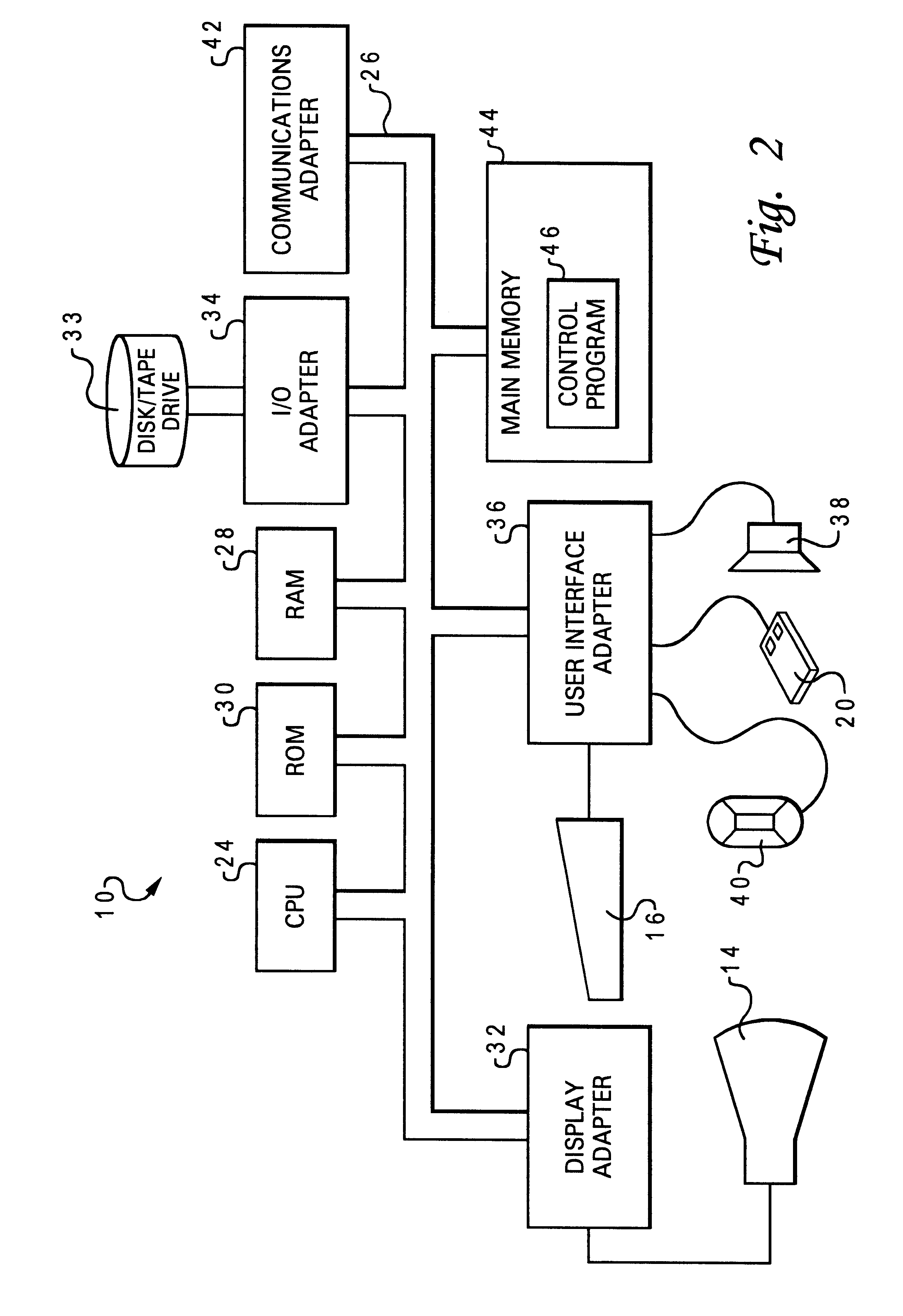

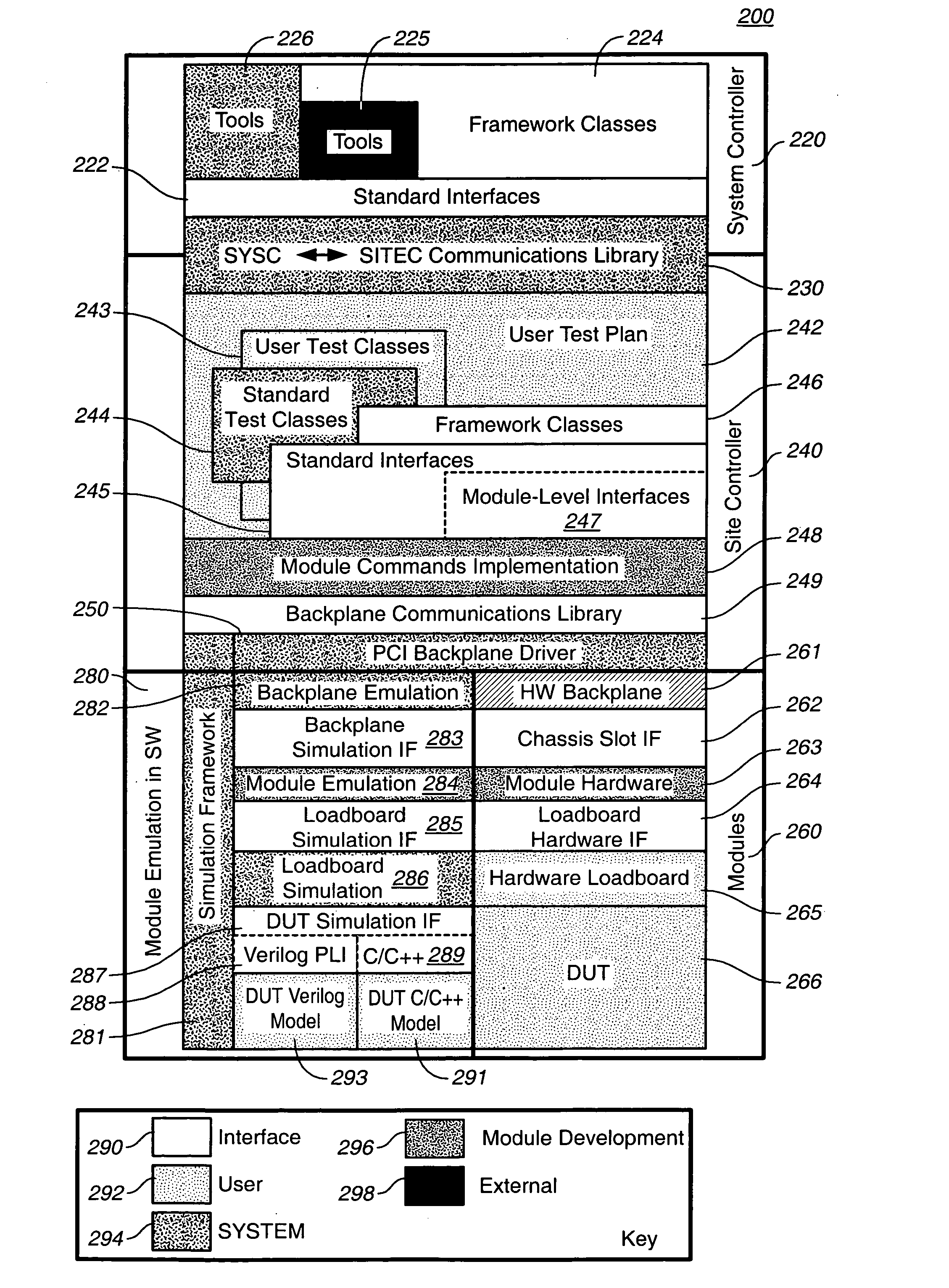

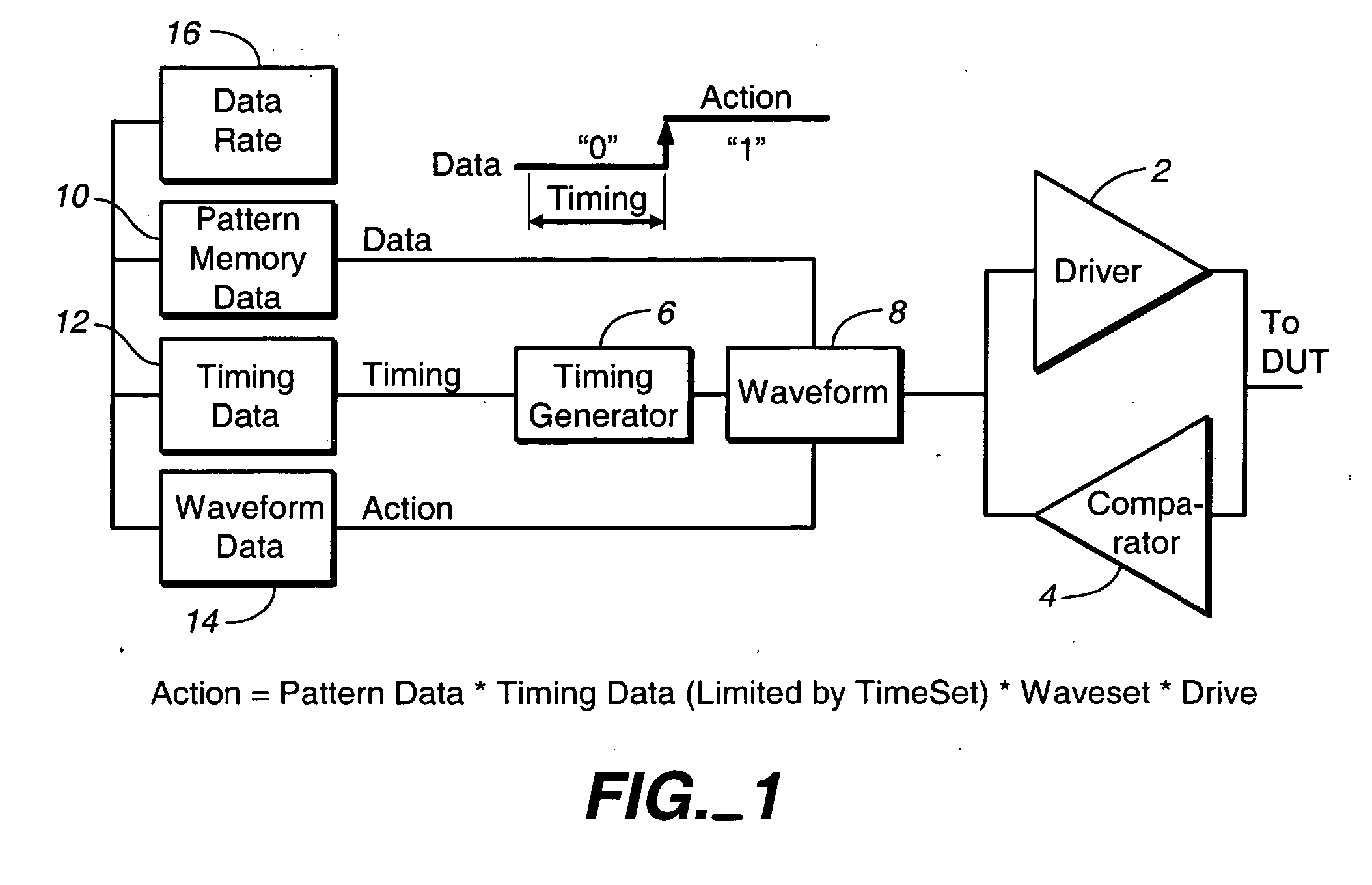

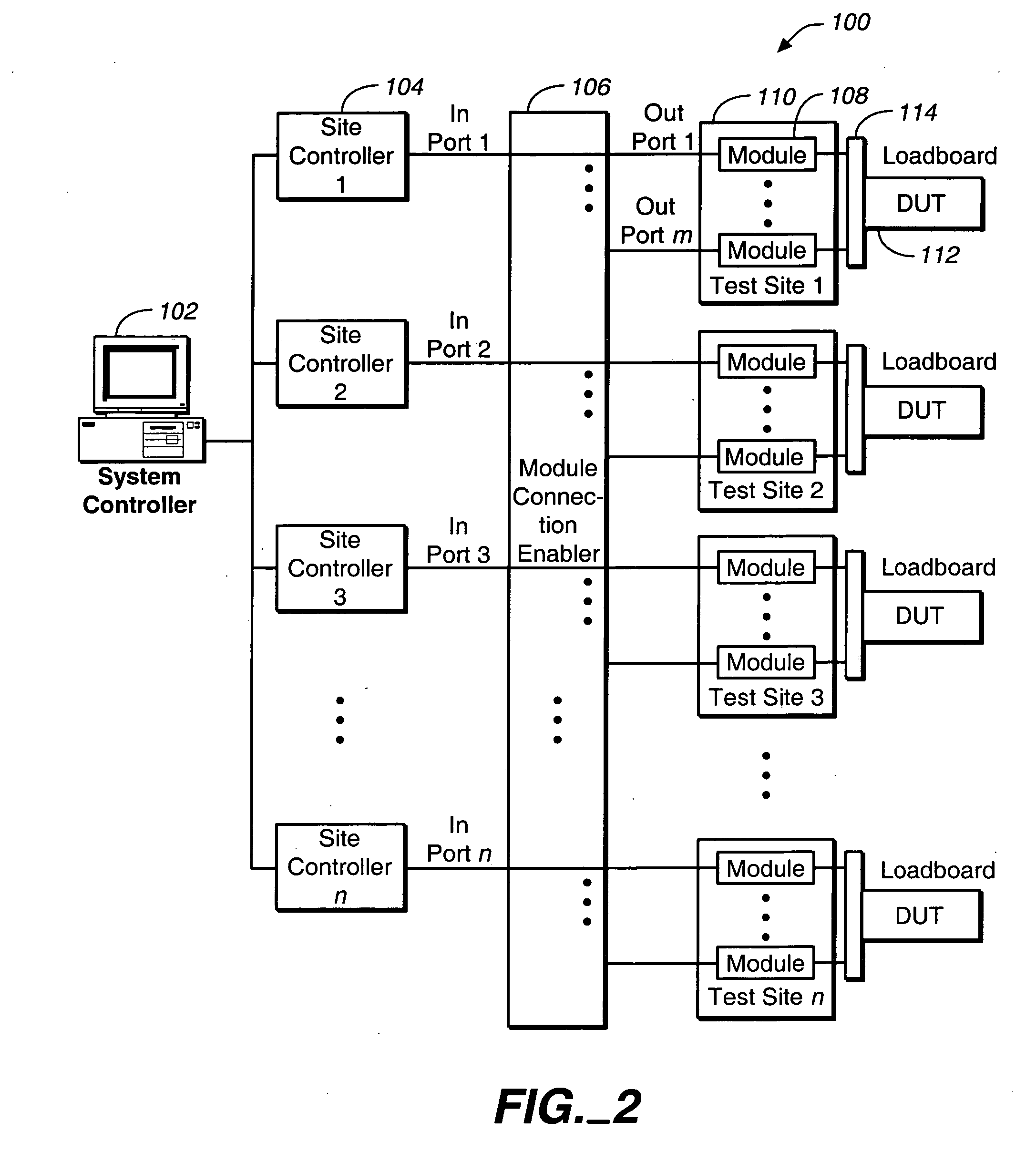

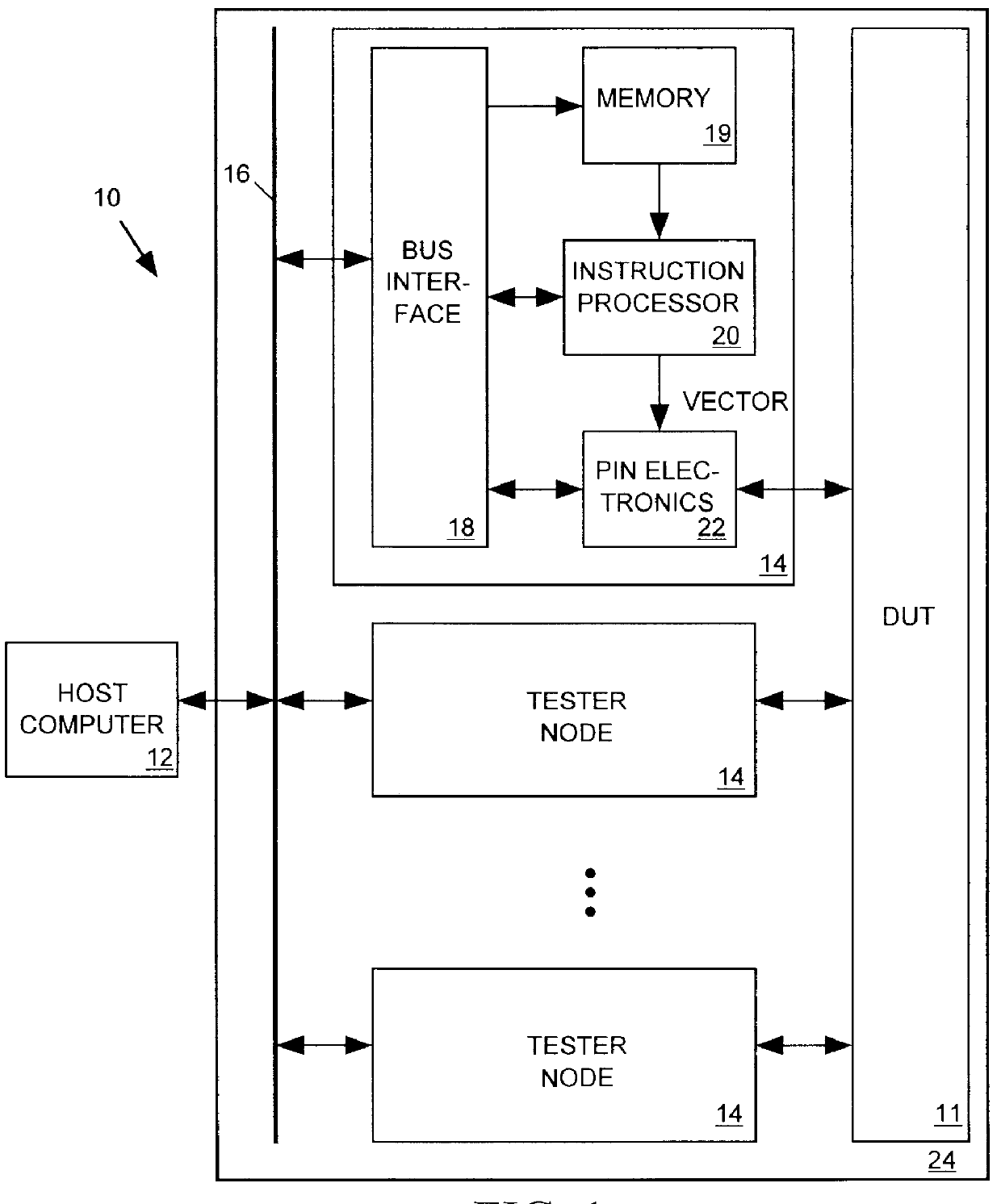

Method and apparatus for testing integrated circuits

ActiveUS20040225465A1Digital circuit testingResistance/reactance/impedenceOperational systemEngineering

A distributed operating system for a semiconductor test system, such as automated test equipment (ATE), is described. The operating system includes a host operating system for enabling control of one or more site controllers by a system controller. One or more local operating systems, each associated with a site controller, enable control of one or more test modules by an associated site controller. Each test module performs testing on a corresponding device-under-test at a test site.

Owner:ADVANTEST CORP

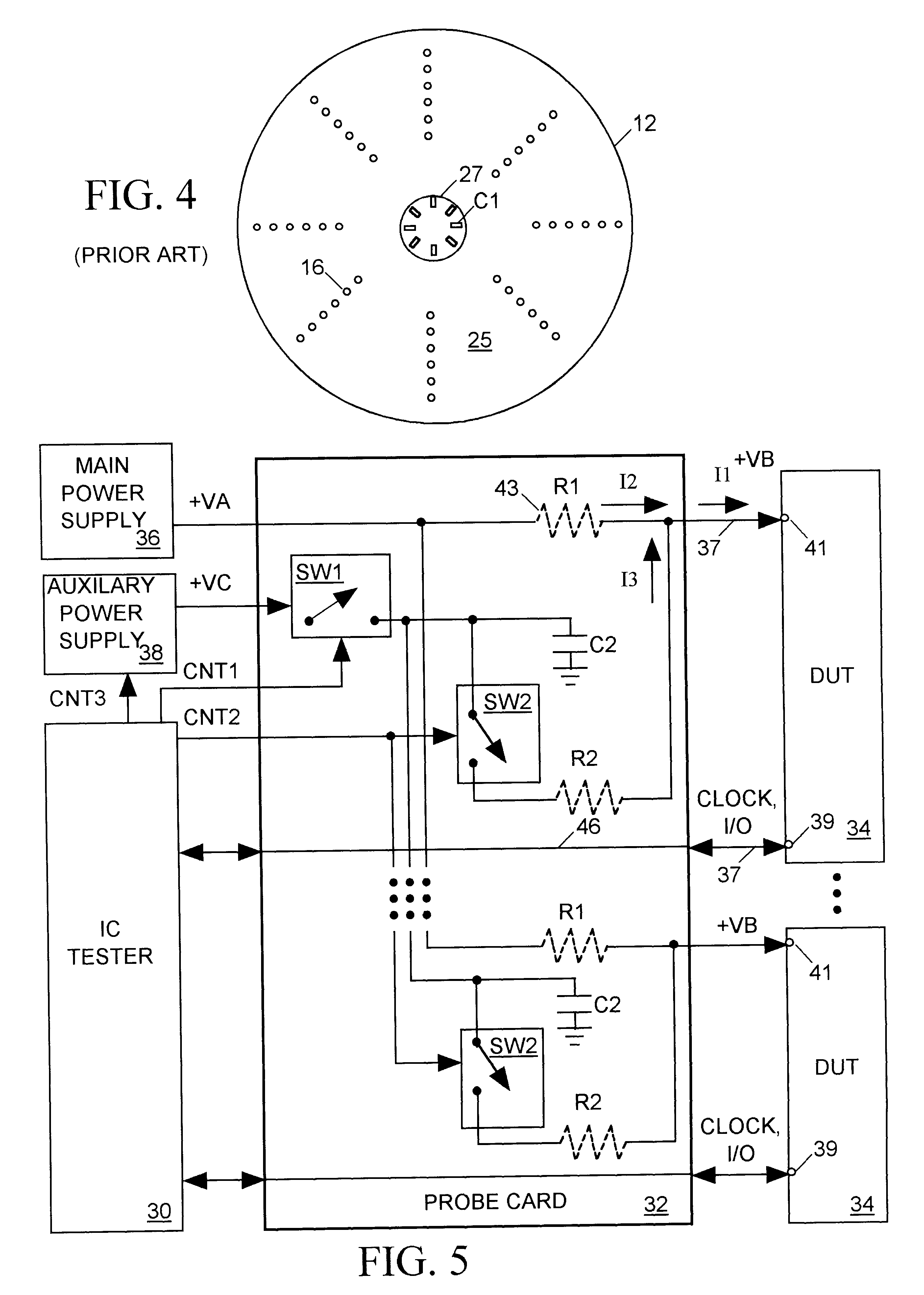

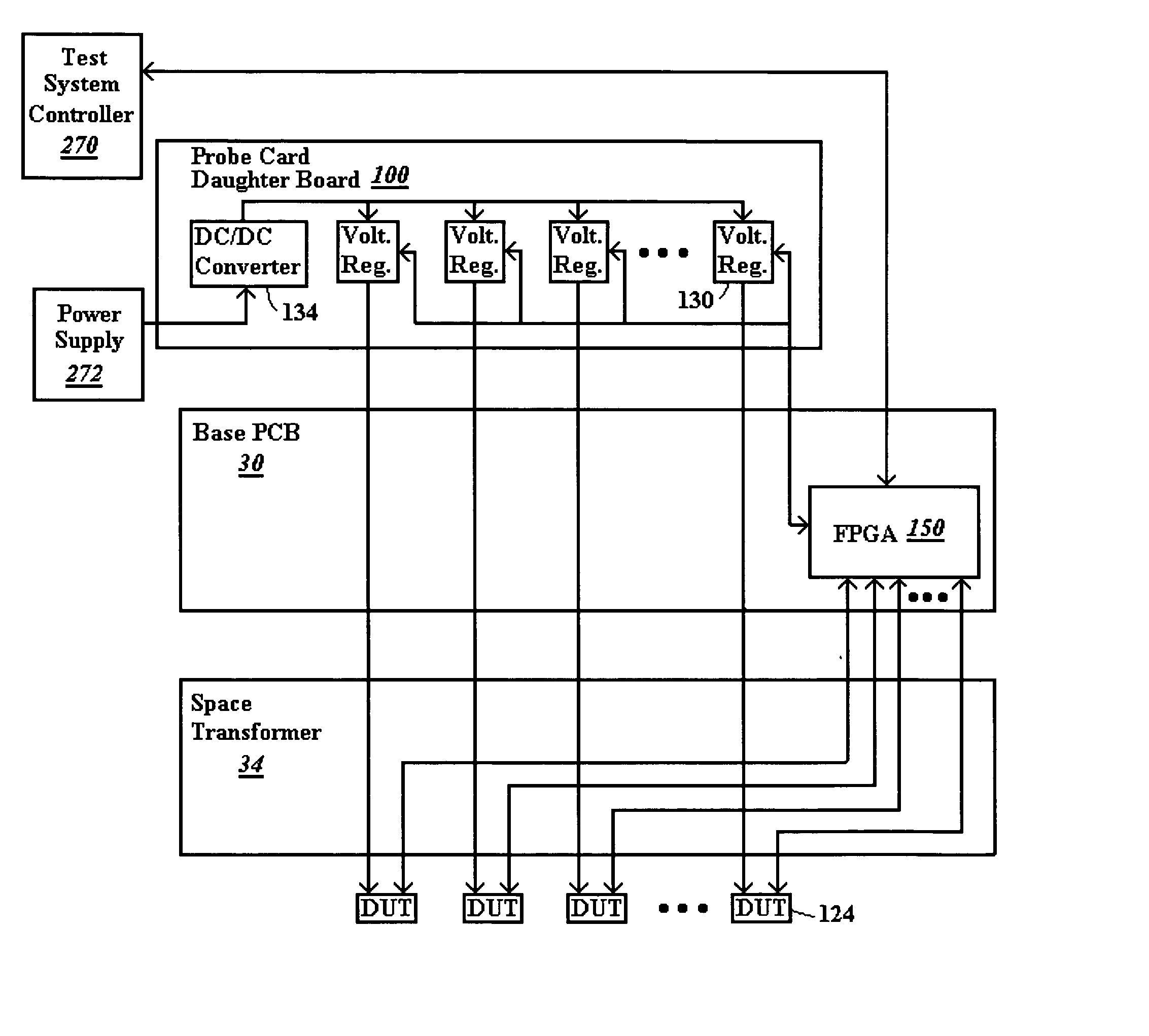

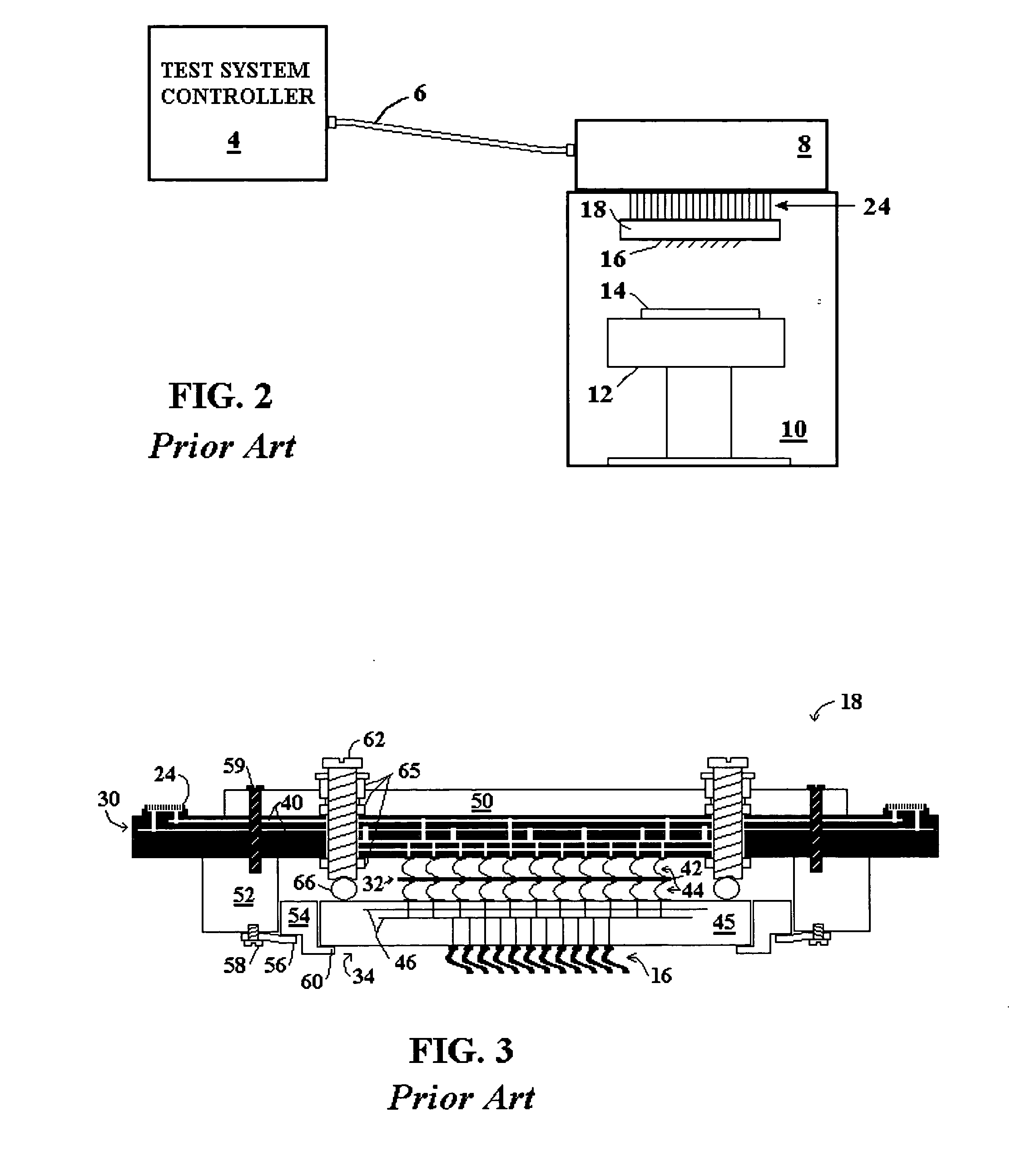

Intelligent probe card architecture

ActiveUS20050237073A1Digital circuit testingOverload protection arrangementsElectrical resistance and conductanceProbe card

A probe card for a wafer test system is provided with a number of on board features enabling fan out of a test system controller channel to test multiple DUTs on a wafer, while limiting undesirable effects of fan out on test results. On board features of the probe card include one or more of the following: (a) DUT signal isolation provided by placing resistors in series with each DUT input to isolate failed DUTs; (b) DUT power isolation provided by switches, current limiters, or regulators in series with each DUT power pin to isolate the power supply from failed DUTs; (c) self test provided using an on board micro-controller or FPGA; (d) stacked daughter cards provided as part of the probe card to accommodate the additional on board test circuitry; and (e) use of a interface bus between a base PCB and daughter cards of the probe card, or the test system controller to minimize the number of interface wires between the base PCB and daughter cards or between the base PCB and the test system controller.

Owner:FORMFACTOR INC

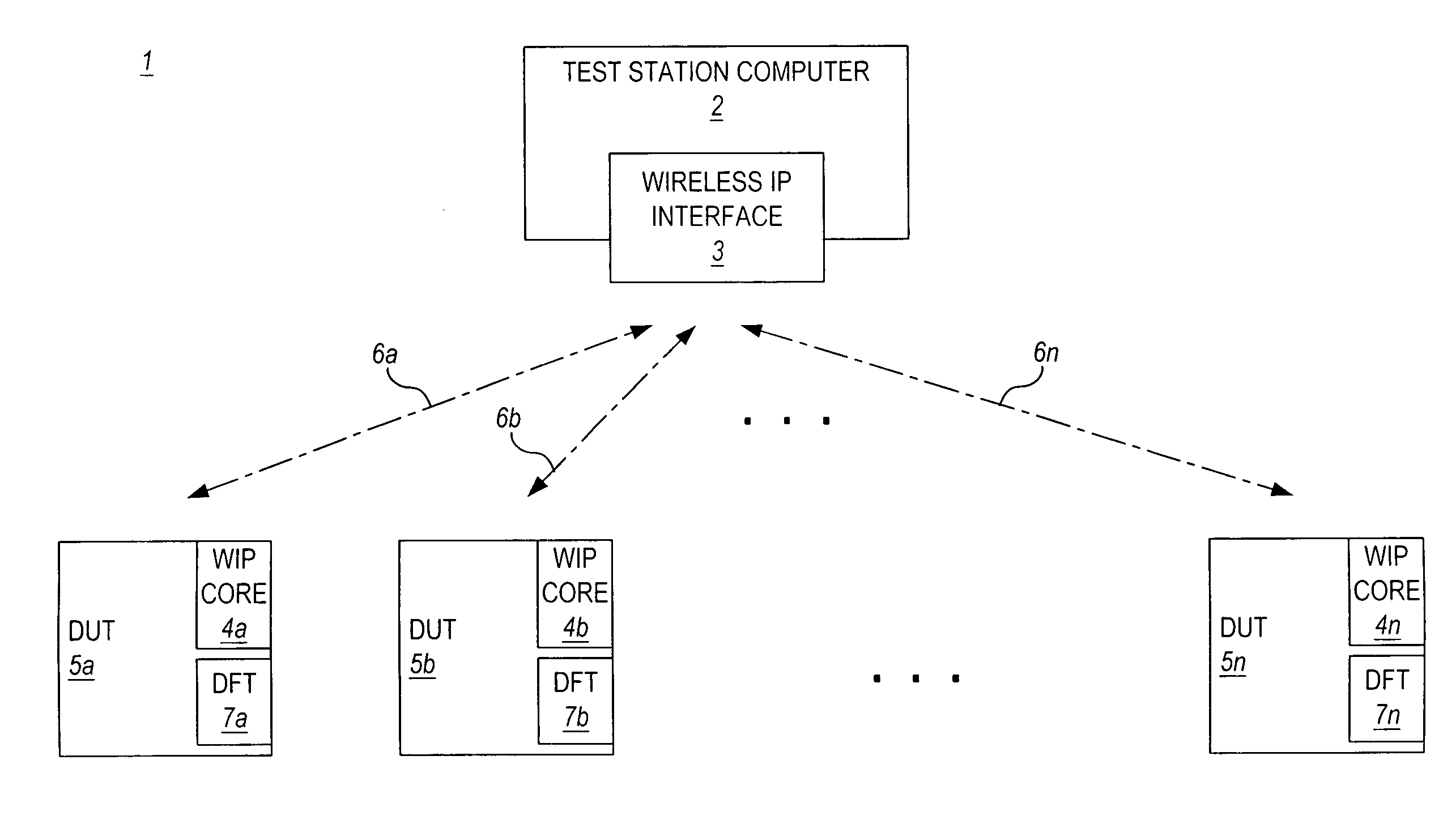

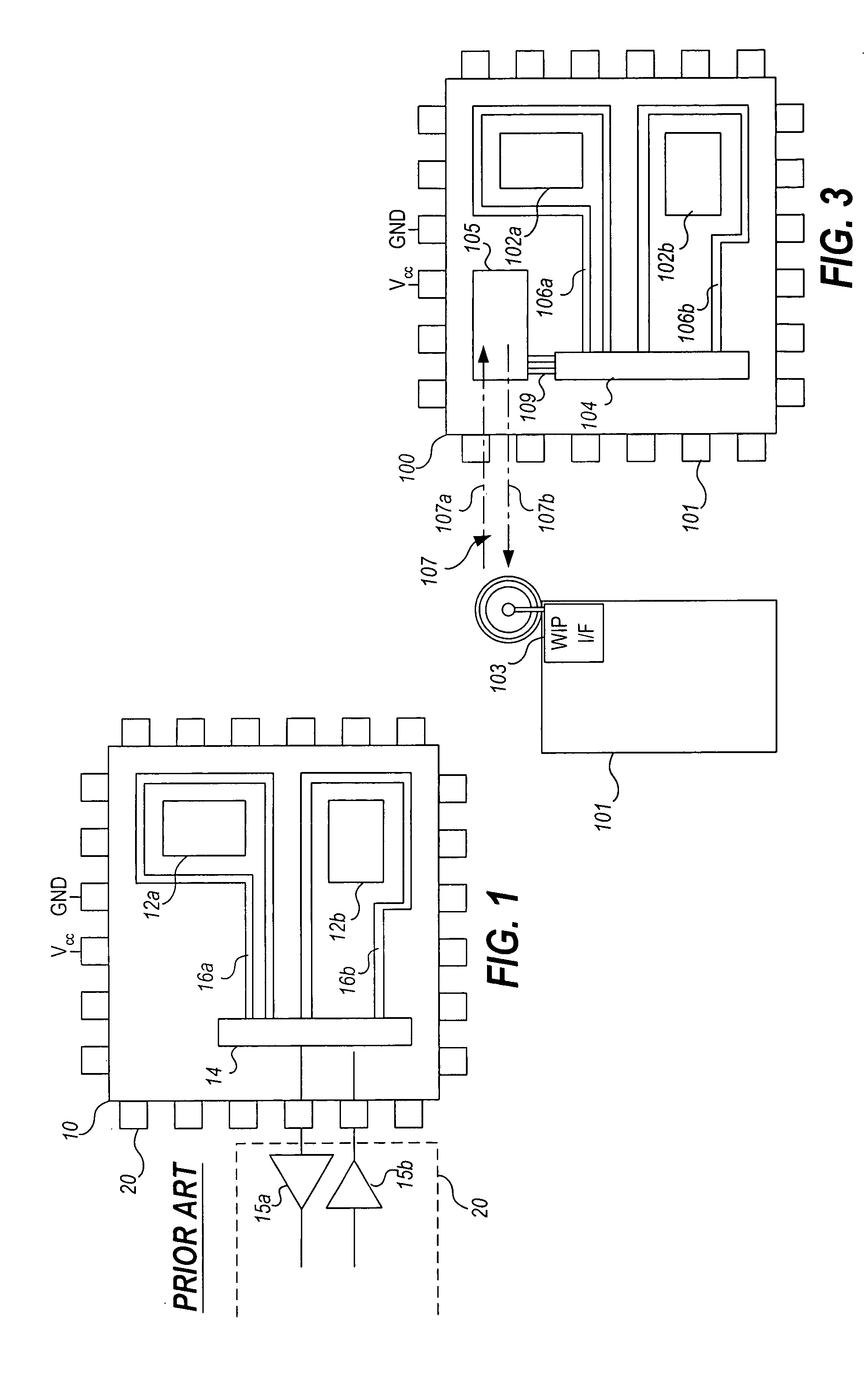

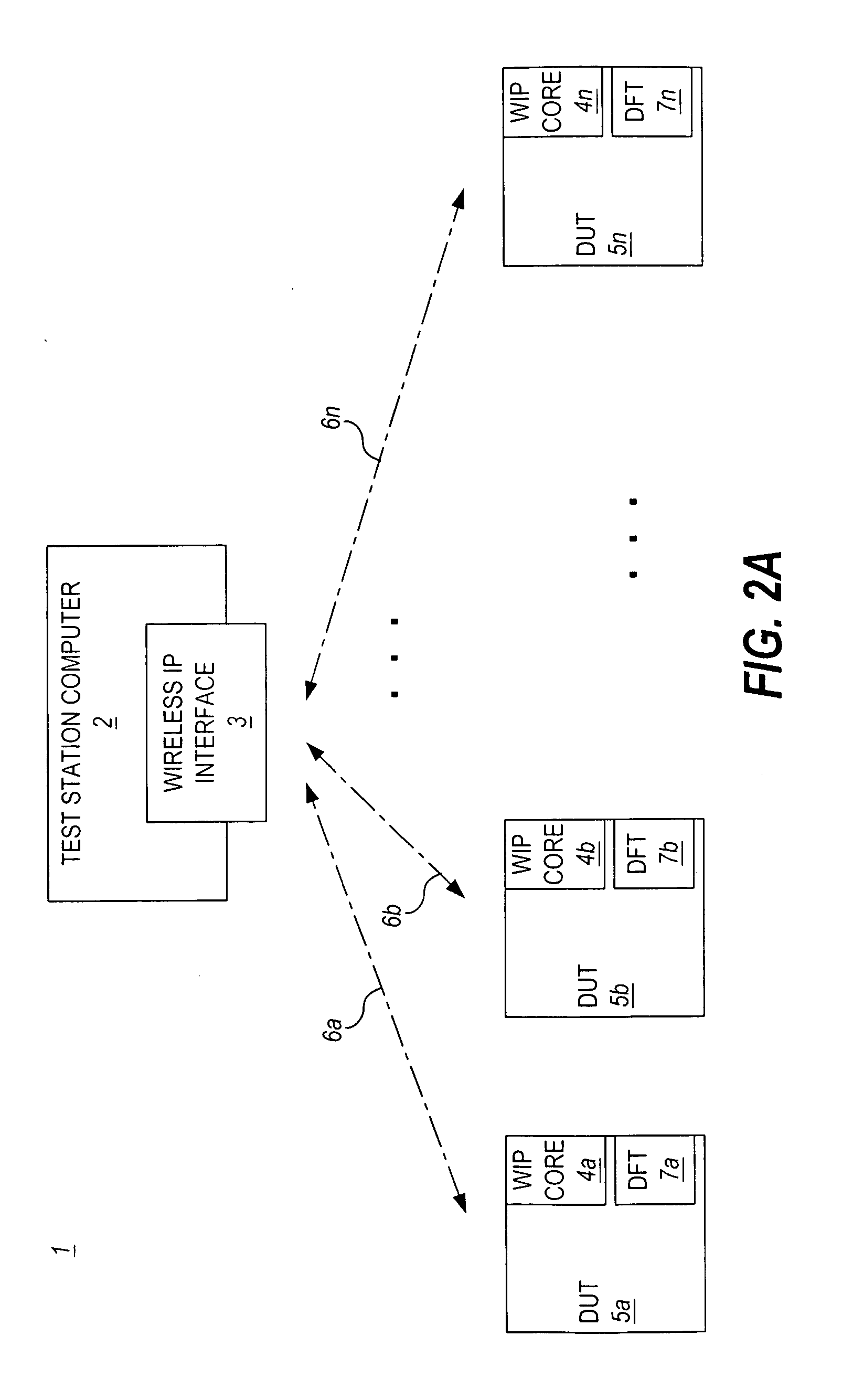

Wireless no-touch testing of integrated circuits

ActiveUS20050193294A1Immediate cost-reduction impactIncrease speedDigital circuit testingSemiconductor/solid-state device testing/measurementCircuit under testEngineering

A wireless integrated circuit test method and system is presented. The invention allows testing of one or more integrated circuits configured with a wireless interface and a test access mechanism which controls input of test data received over a wireless connection from a test station to test structures which test functional blocks on the integrated circuit. Via the wireless connection, multiple integrated circuits or similarly equipped devices under test can be tested simultaneously. The invention also enables concurrent testing of independently testable functional blocks on any given integrated circuit under test.

Owner:ADVANTEST CORP

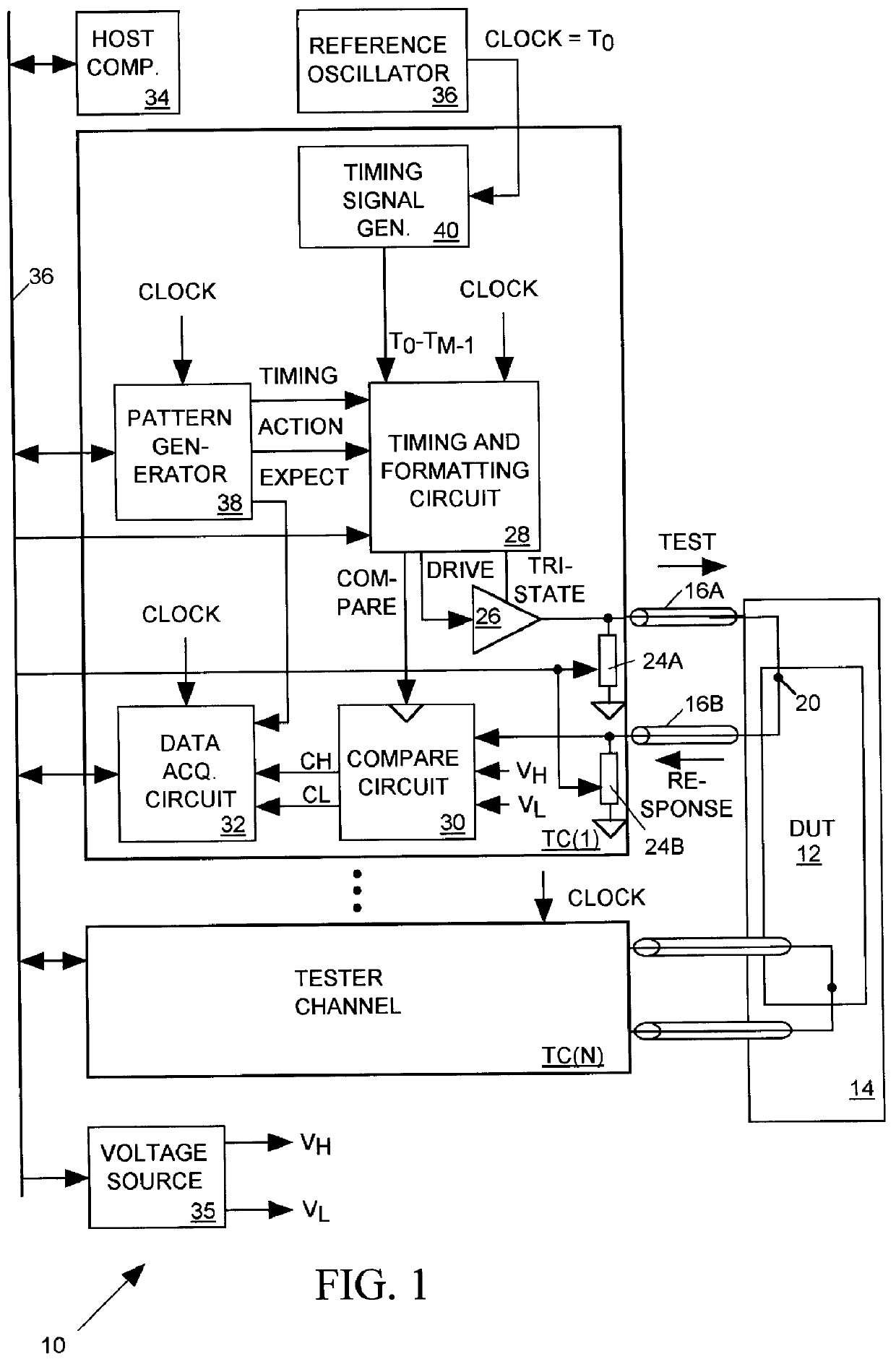

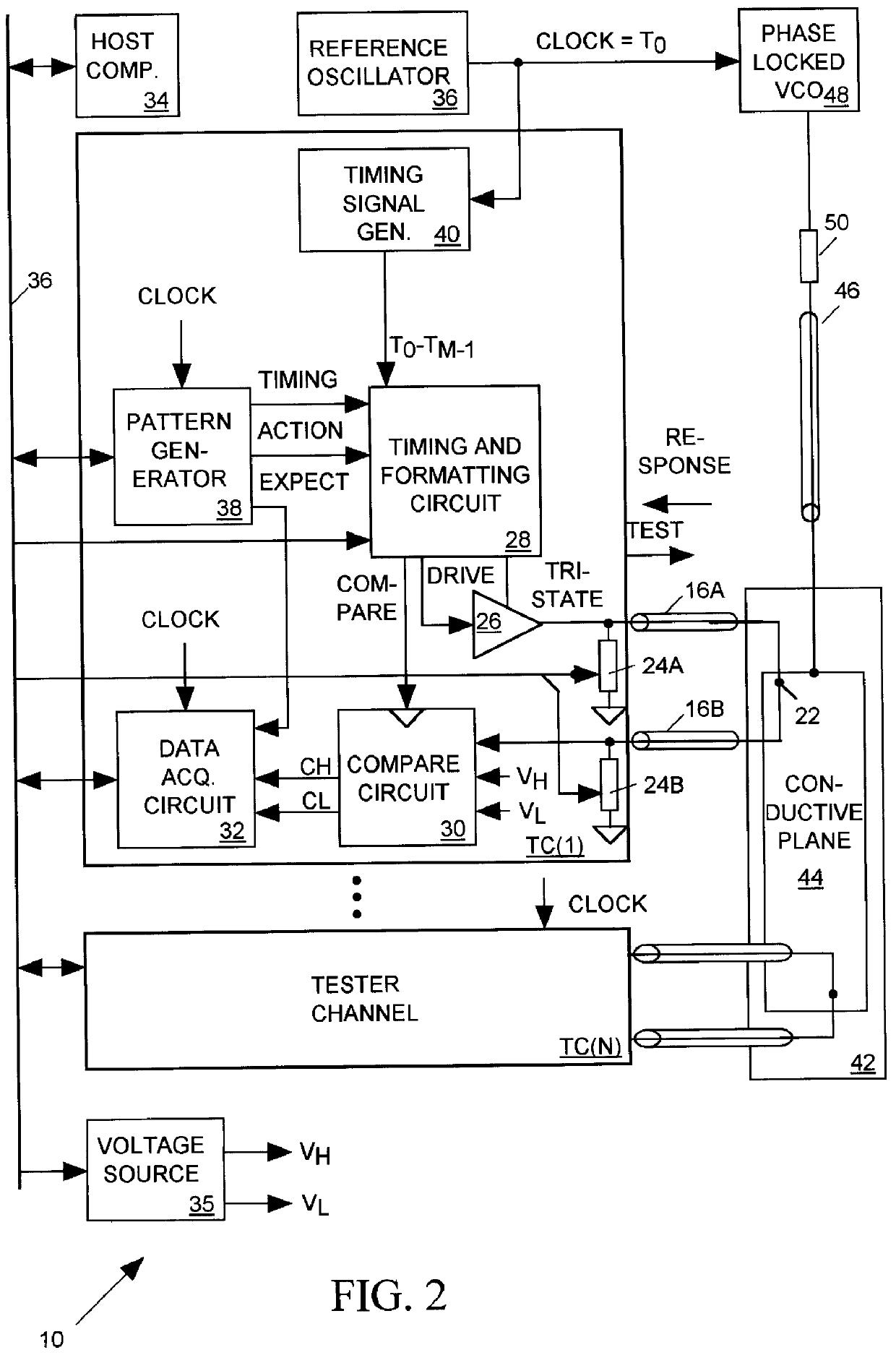

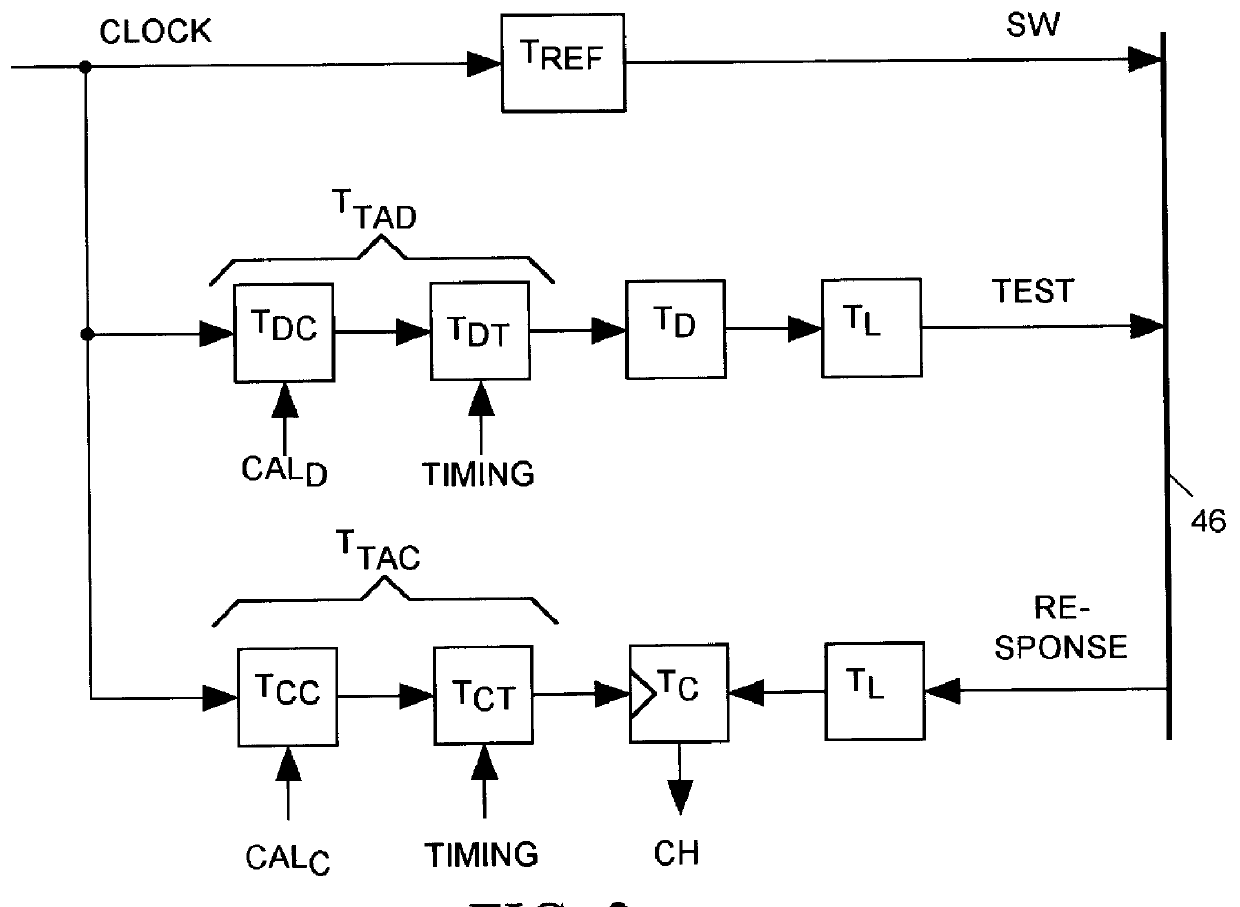

Salphasic timing calibration system for an integrated circuit tester

InactiveUS6105157AQuickly and easily calibratingDigital circuit testingError detection/correctionTester deviceEngineering

An integrated circuit tester produces an output TEST signal following a pulse of a reference CLOCK signal with a delay that is a sum of an inherent drive delay and an adjustable drive delay. The tester also samples an input RESPONSE signal following a pulse of the reference CLOCK signal with a delay that is a sum of an inherent compare delay and an adjustable compare delay. The inherent drive and compare signal path delays within an integrated circuit tester are measured by first connecting a salphasic plane to transmission lines that normally convey signals between the tester and terminals of an integrated circuit device under test. A standing wave signal appearing on that salphasic plane is phase locked to the CLOCK signal so that a zero crossing of the standing wave occurs at a fixed interval after each pulse of the CLOCK signal. Each transmission line concurrently conveys the standing wave to the tester to provide timing references for measuring the inherent drive and compare signal path delays within the tester. Transmission line signal paths are also measured. Delays are added to the drive and compare signal paths to compensate for the measured inherent drive, compare and transmission line delays.

Owner:CREDENCE SYSTEMS

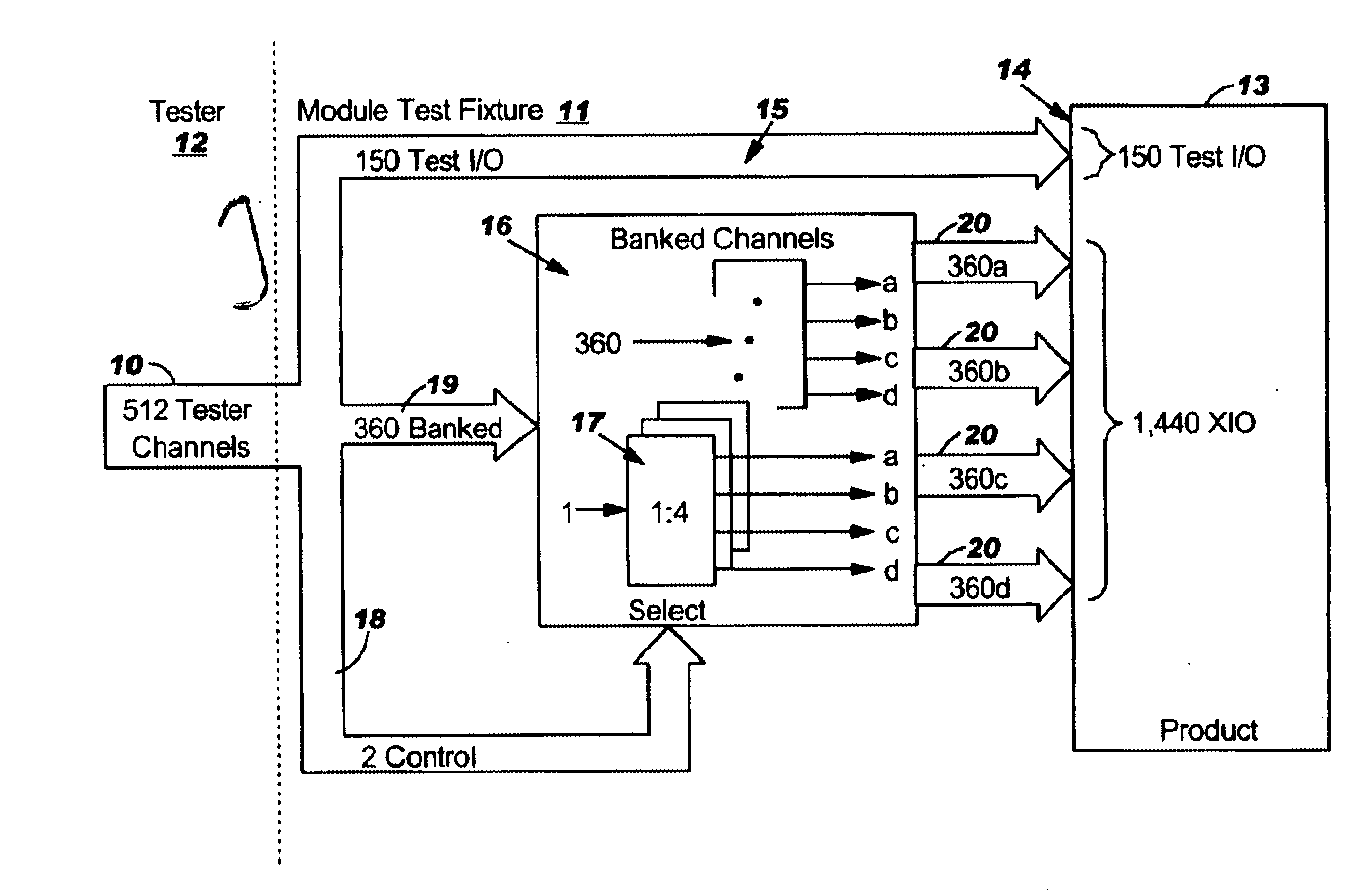

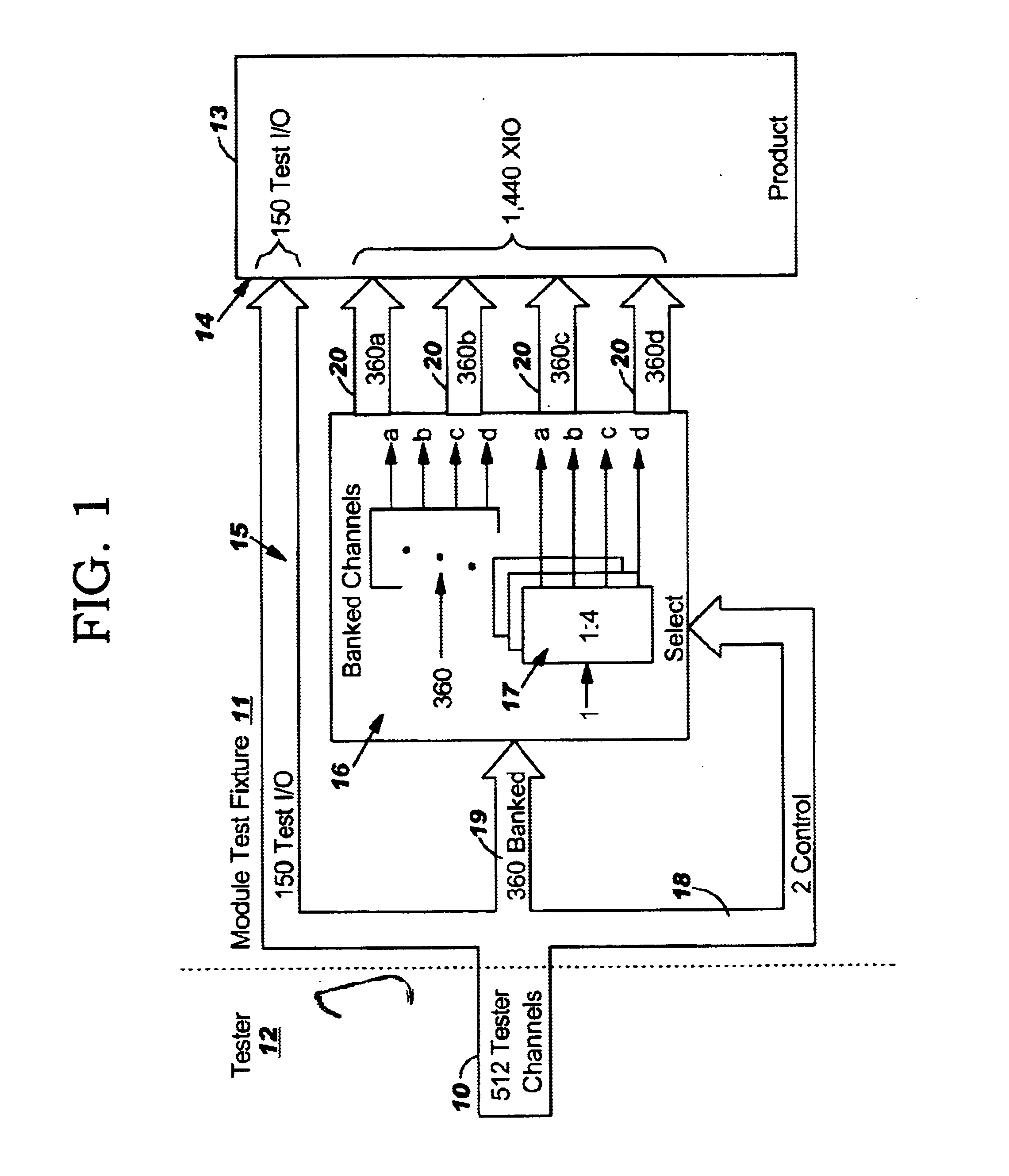

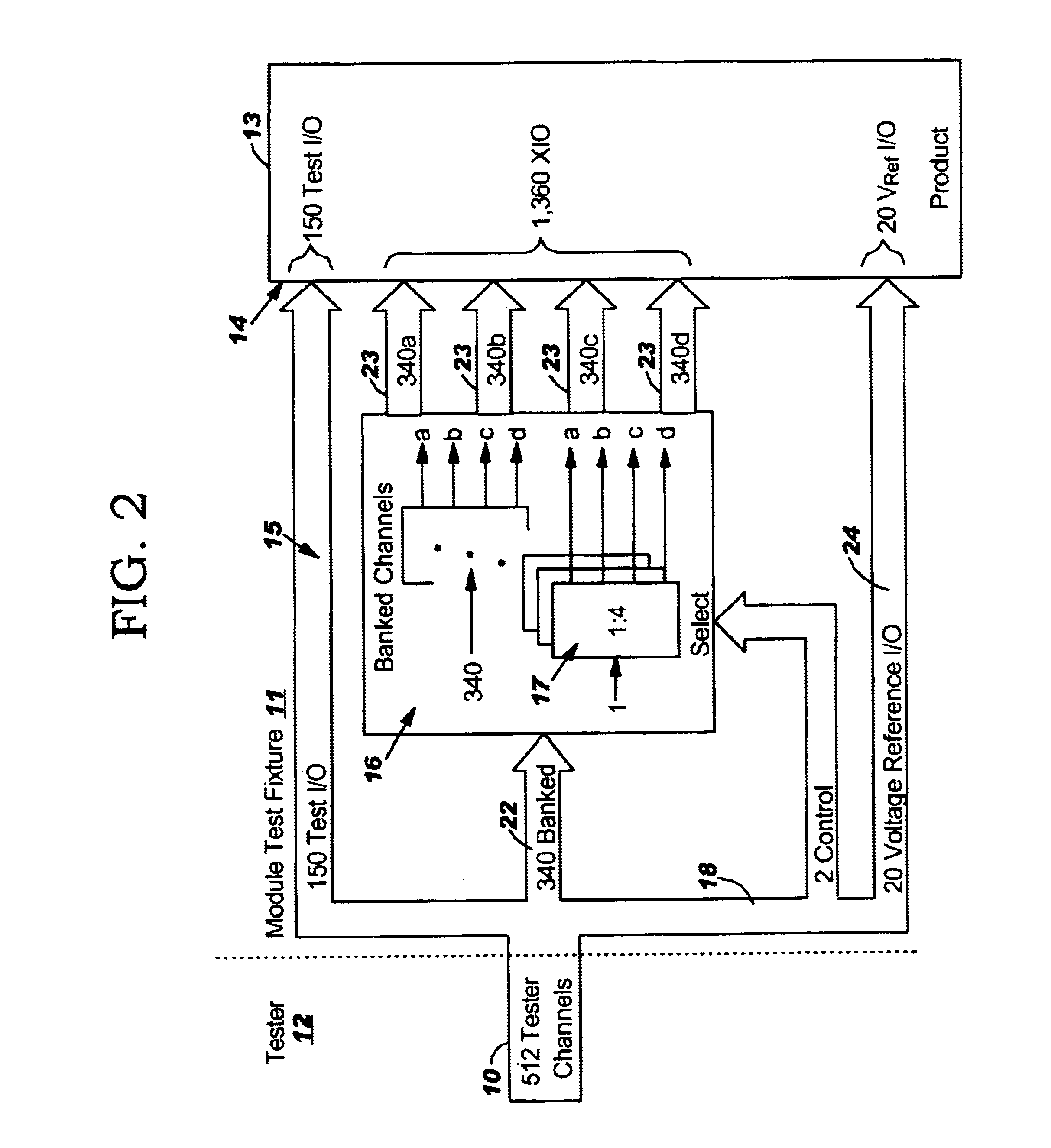

Applying parametric test patterns for high pin count ASICs on low pin count testers

InactiveUS6847203B1Digital circuit testingElectrical measurement instrument detailsContact padComputer module

Disclosed is an integrated circuit chip test apparatus that has a module test fixture having contact pads that are adapted to make contact with signal input / output pins on an integrated circuit chip being tested. An intermediate banking box is connected to the module text fixture and a tester is connected to the intermediate banking box. The tester includes at least one bank of channels there are more pins on the integrated circuit chip than there are channels in the tester. The intermediate banking box includes switches that are connected between the contact pads and the channels. The switches are adapted to selectively connect a subset of the contact pads to the channels to connect the tester to a subset of pins, thereby allowing the tester to test a portion of the integrated circuit that corresponds to the subset of pins.

Owner:IBM CORP

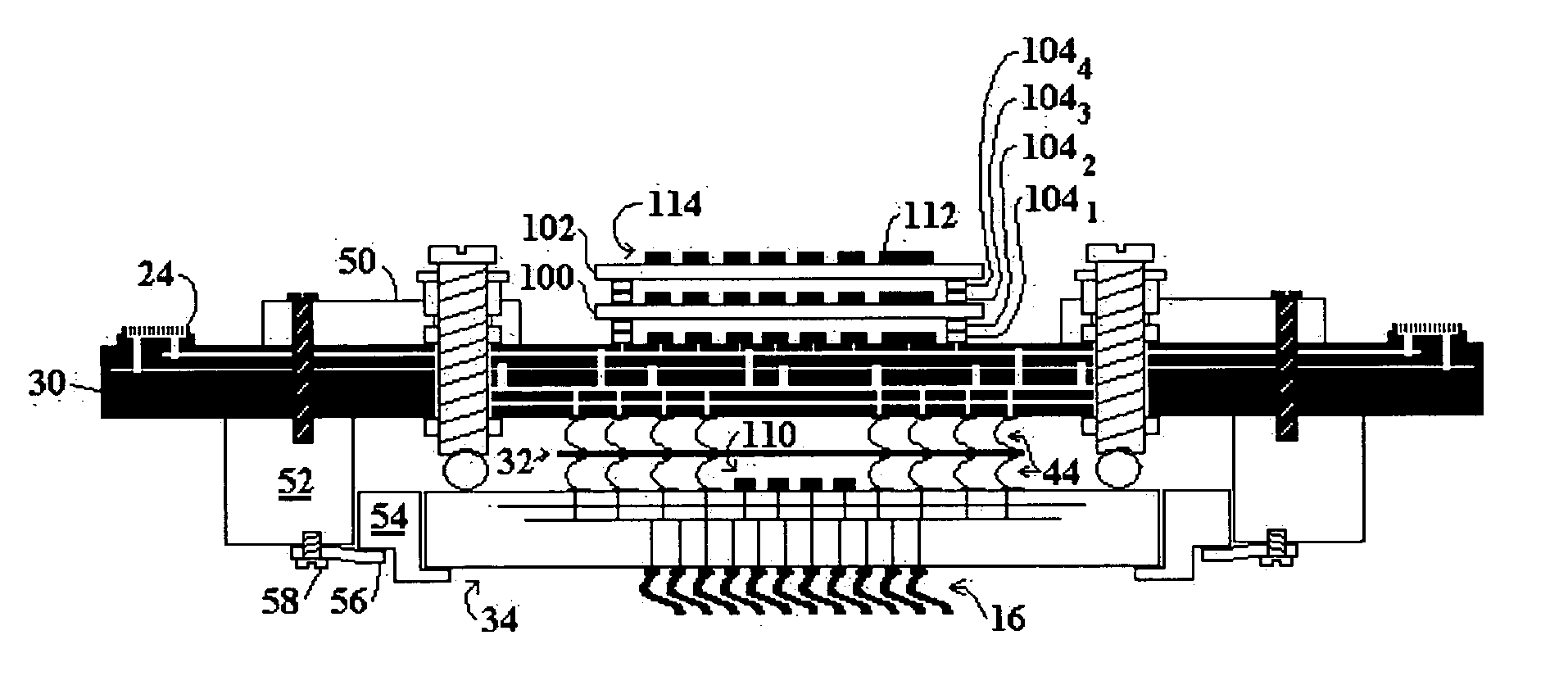

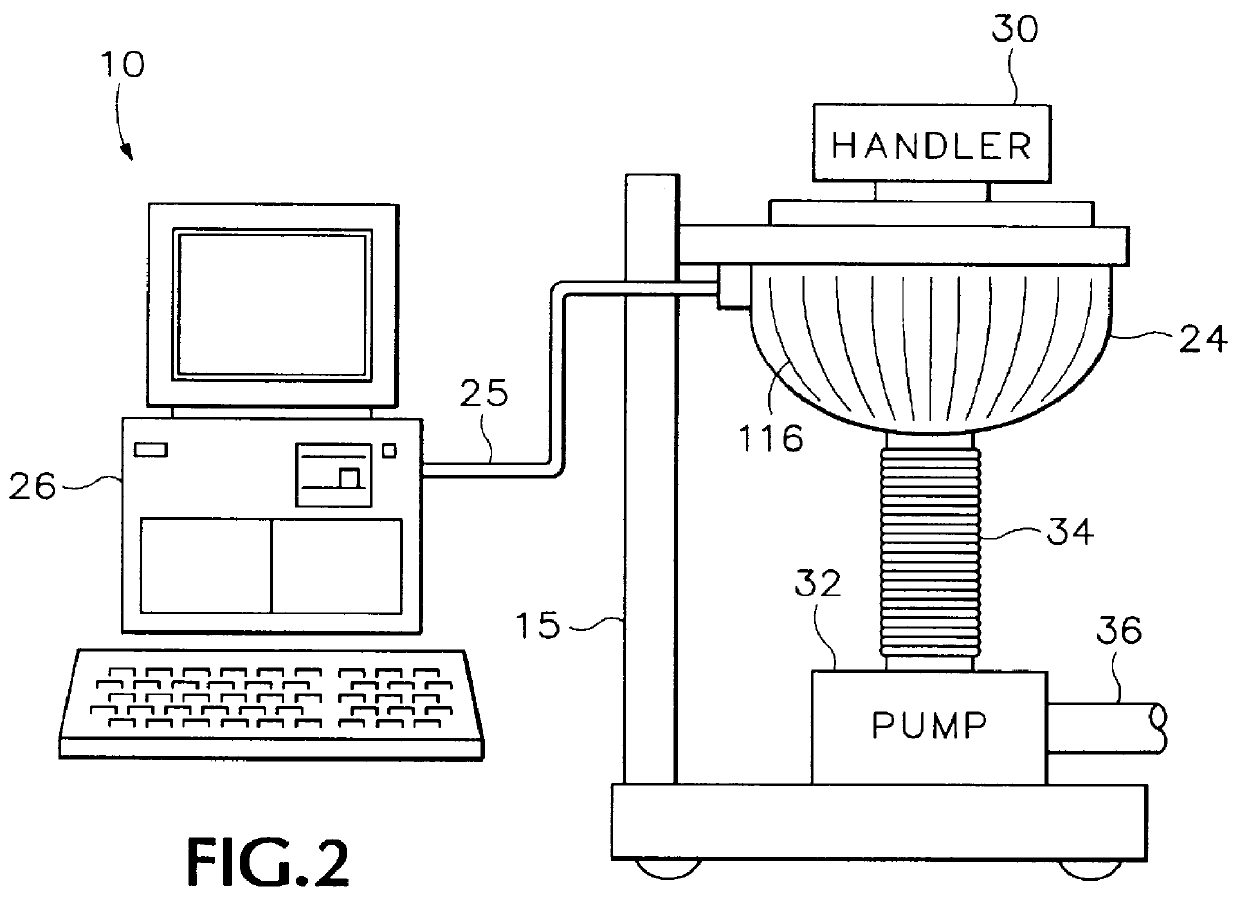

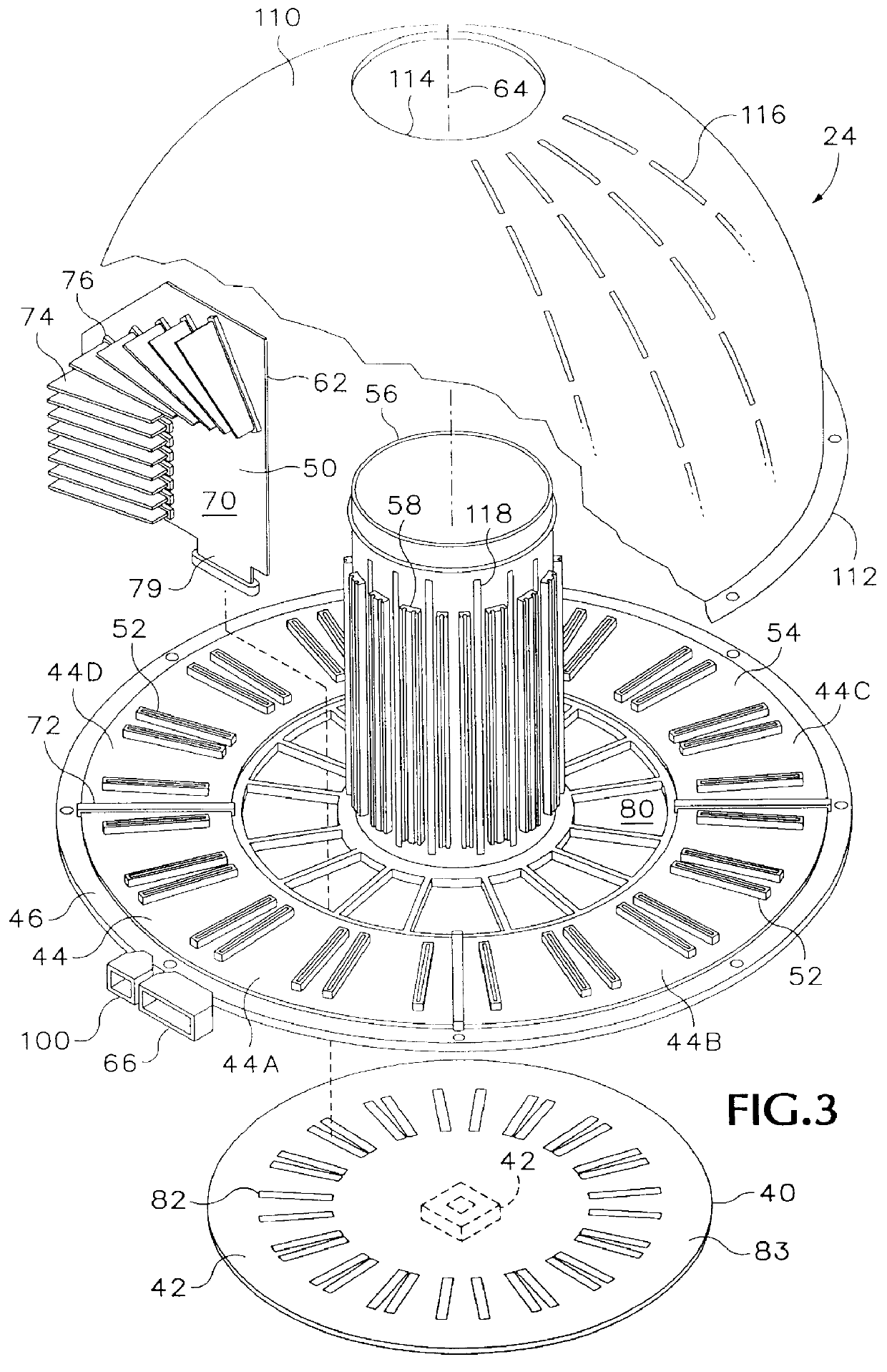

Test head for integrated circuit tester arranging tester component circuit boards on three dimensions

A test head for an integrated circuit tester includes a horizontal base holding a motherboard. The motherboard distributes test instructions to an array of daughterboards mounted thereon, the daughterboards being radially distributed about a central vertical axis of the motherboard. Each daughterboard holds a set of node cards and includes data paths for forwarding the test instructions from the motherboard to the node cards. Each node card contains circuits for transmitting test signals to and receiving response signals from a separate terminal of a device under test (DUT) in response to the test instructions forwarded thereto. Edges of the daughterboards extend downward through apertures in the base to contact pads on an interface board holding the DUT. The daughterboards provide conductive paths for the test and response signals extending between the node cards and pads on the DUT interface board. The interface board extends those conductive paths from the pads to terminals of the DUT.

Owner:CREDENCE SYSTEMS

On-chip transistor degradation monitoring

InactiveUS7205854B2Digital circuit testingPulse generation by logic circuitsEngineeringSelf excited oscillation

Embodiments of the invention include on-chip characterization of transistor degradation. In one embodiment, includes one or more functional blocks to perform one or more functions and an integrated on-chip characterization circuit to perform on-chip characterization of transistor degradation. The integrated on-chip characterization circuit includes a selectively enabled ring oscillator to generate a reference oscillating signal, a free-running ring oscillator to generate a free-running oscillating signal, and a comparison circuit coupled to the selectively enabled ring oscillator and the free-running ring oscillator. From the reference oscillating signal and the free-running oscillating signal, the comparison circuit determine a measure of transistor degradation.

Owner:INTEL CORP