Patents

Literature

1526 results about "Transistor array" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Transistor arrays are used for general purpose applications, function generation and low-level, low-noise amplifiers. They include two or more transistors on a common substrate to ensure close parameter matching and thermal tracking, characteristics that are especially important for 'long tailed pair' differential amplifiers, current mirrors, log amplifiers.

Indium oxide-based thin film transistors and circuits

In electronic displays or imaging units, the control of pixels is achieved by an array of transistors. These transistors are in a thin film form and arranged in a two-dimensional configuration to form switching circuits, driving circuits or even read-out circuits. In this invention, thin film transistors and circuits with indium oxide-based channel layers are provided. These thin film transistors and circuits may be fabricated at low temperatures on various substrates and with high charge carrier mobilities. In addition to conventional rigid substrates, the present thin film transistors and circuits are particularly suited for the fabrication on flexible and transparent substrates for electronic display and imaging applications. Methods for the fabrication of the thin film transistors with indium oxide-based channels are provided.

Owner:SHIH YI CHI +3

Indium oxide-based thin film transistors and circuits

In electronic displays or imaging units, the control of pixels is achieved by an array of transistors. These transistors are in a thin film form and arranged in a two-dimensional configuration to form switching circuits, driving circuits or even read-out circuits. In this invention, thin film transistors and circuits with indium oxide-based channel layers are provided. These thin film transistors and circuits may be fabricated at low temperatures on various substrates and with high charge carrier mobilities. In addition to conventional rigid substrates, the present thin film transistors and circuits are particularly suited for the fabrication on flexible and transparent substrates for electronic display and imaging applications. Methods for the fabrication of the thin film transistors with indium oxide-based channels are provided.

Owner:SHIH YI CHI +3

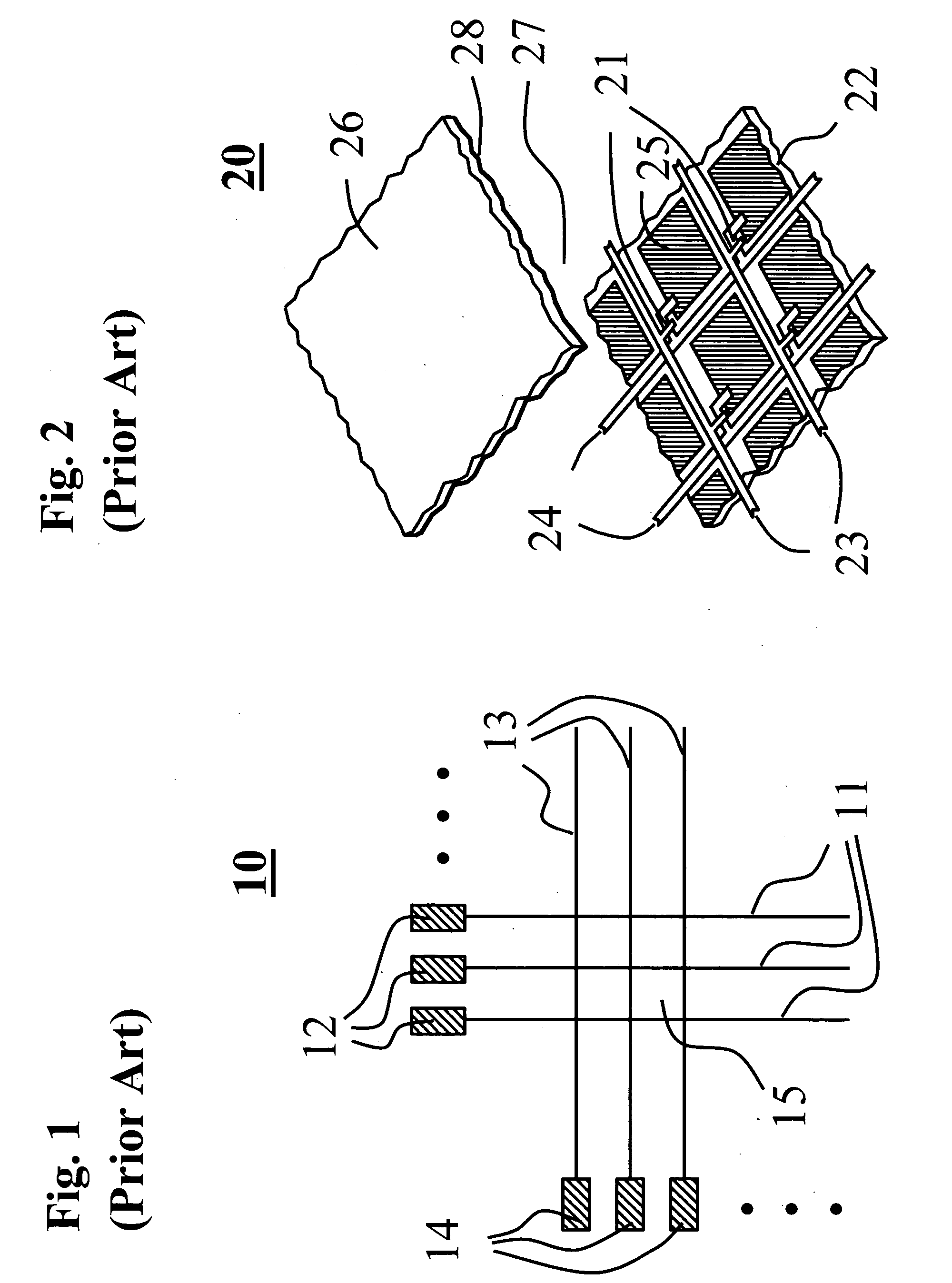

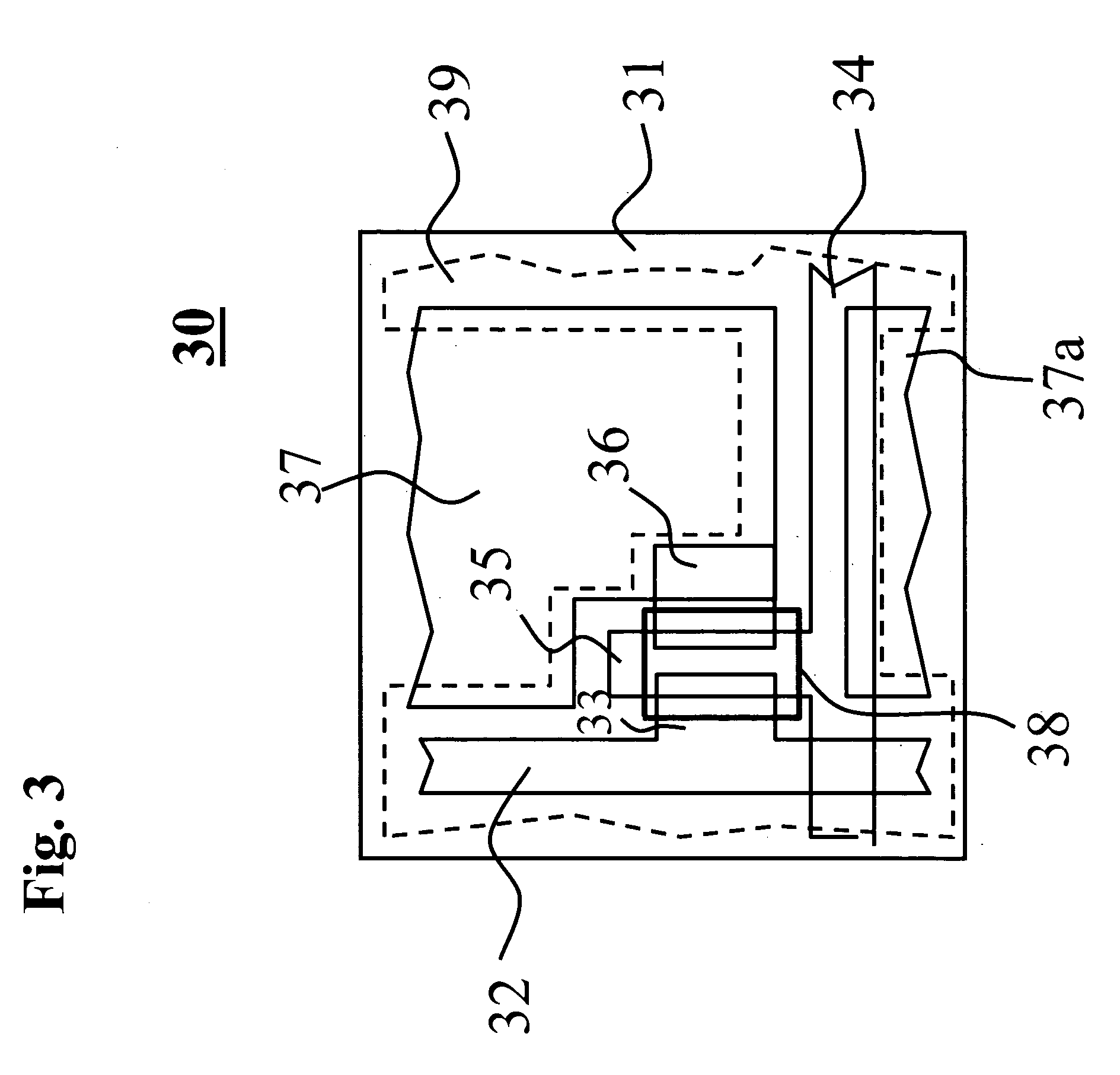

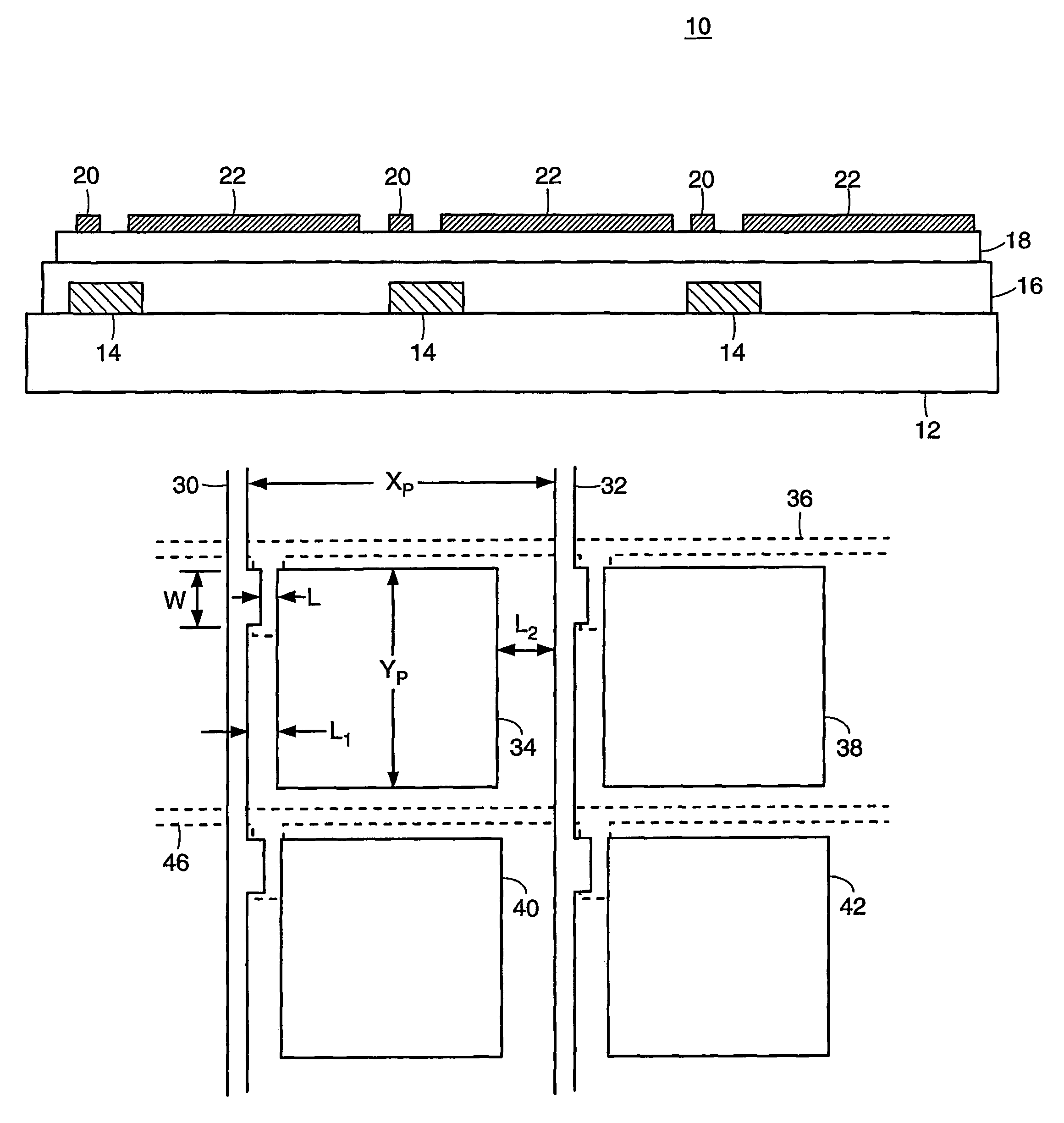

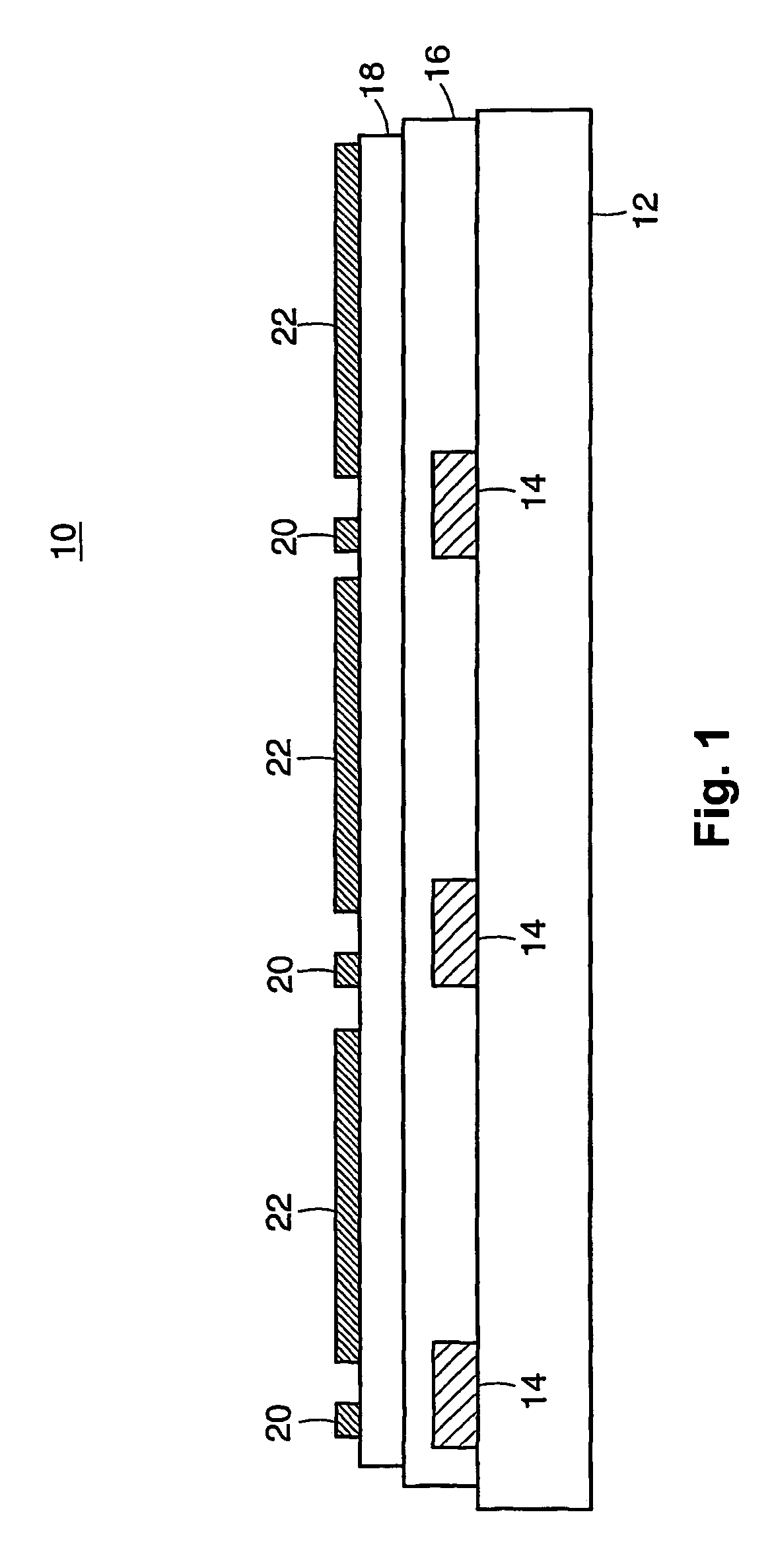

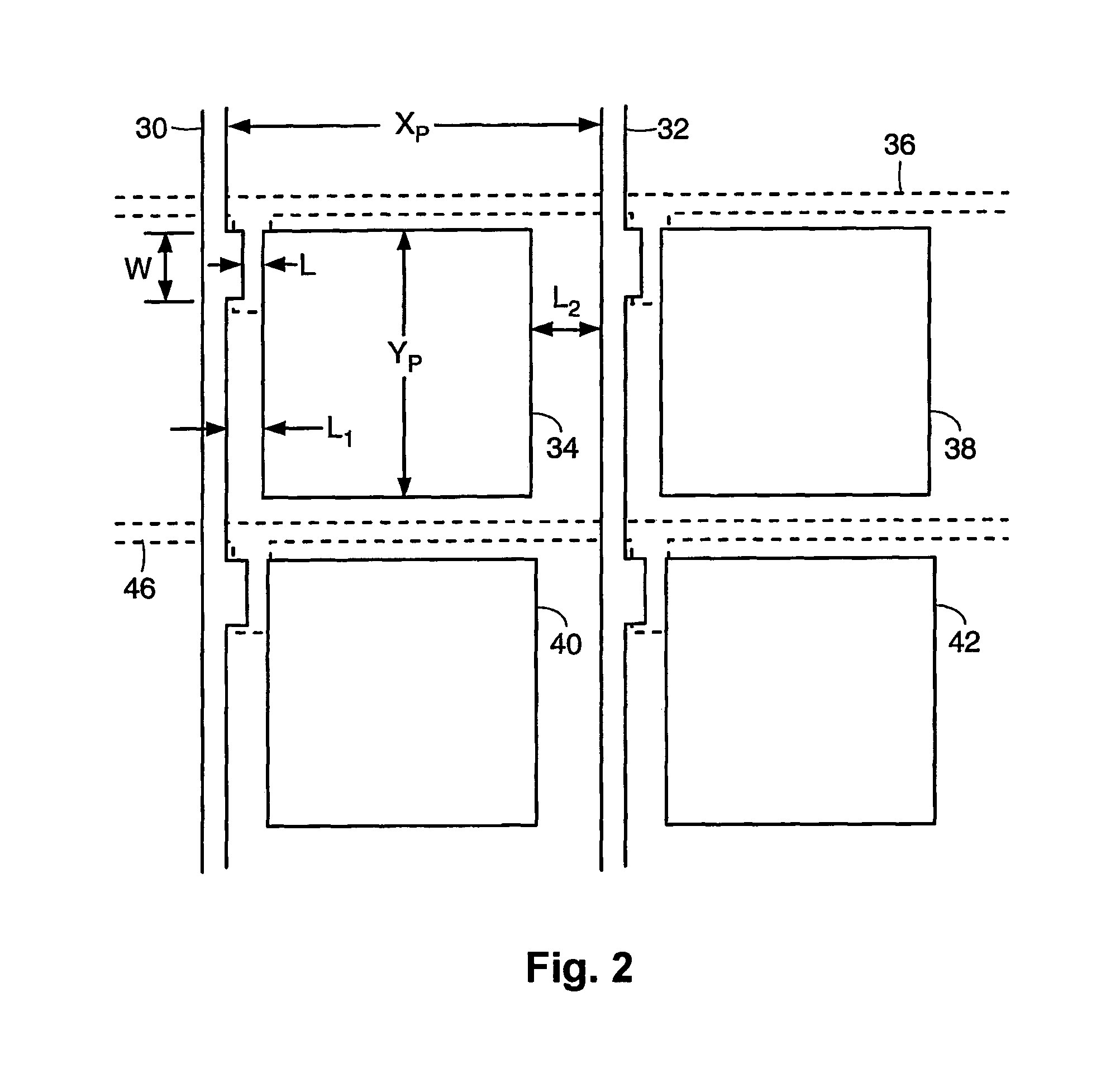

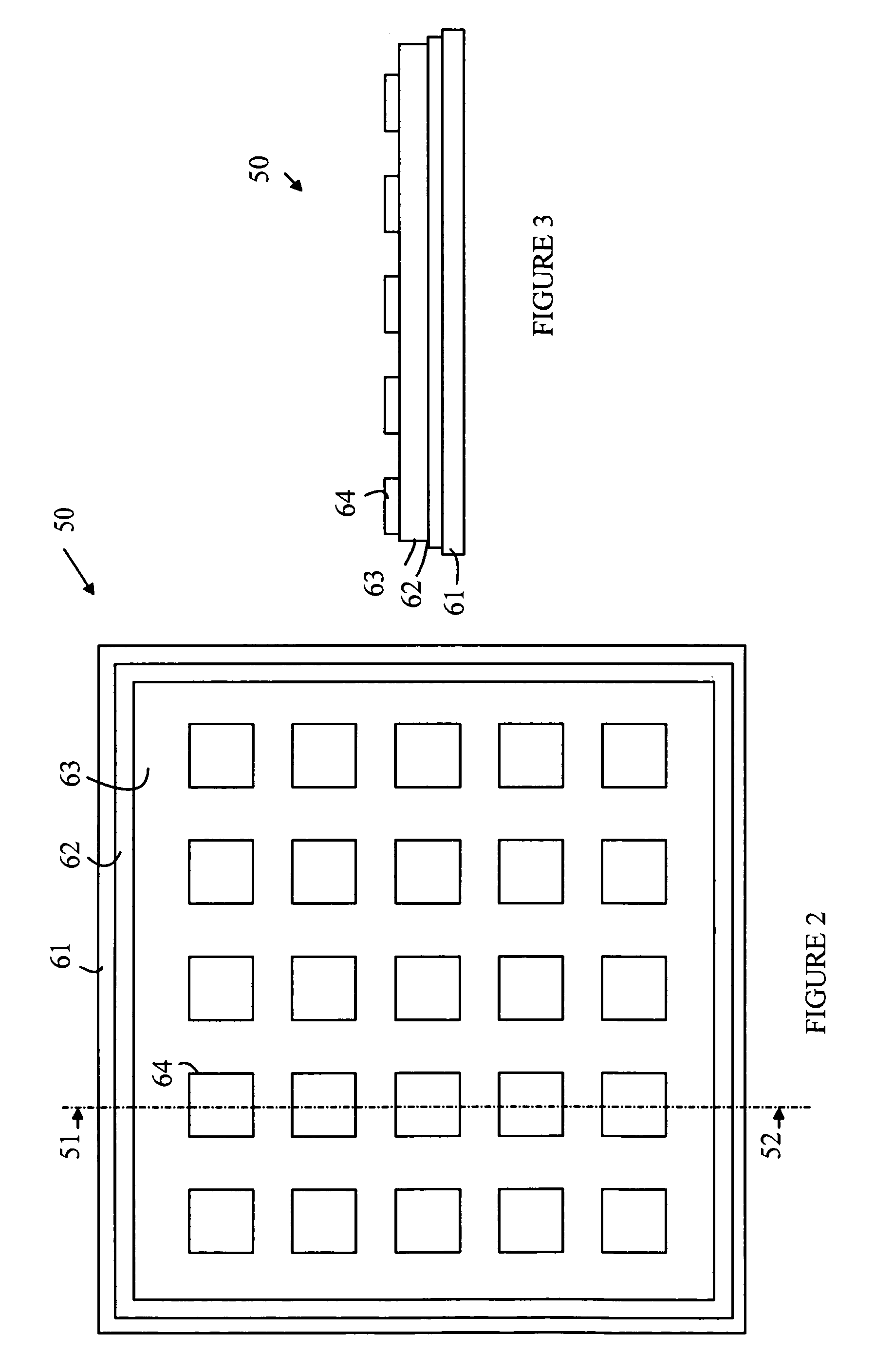

Minimally-patterned semiconductor devices for display applications

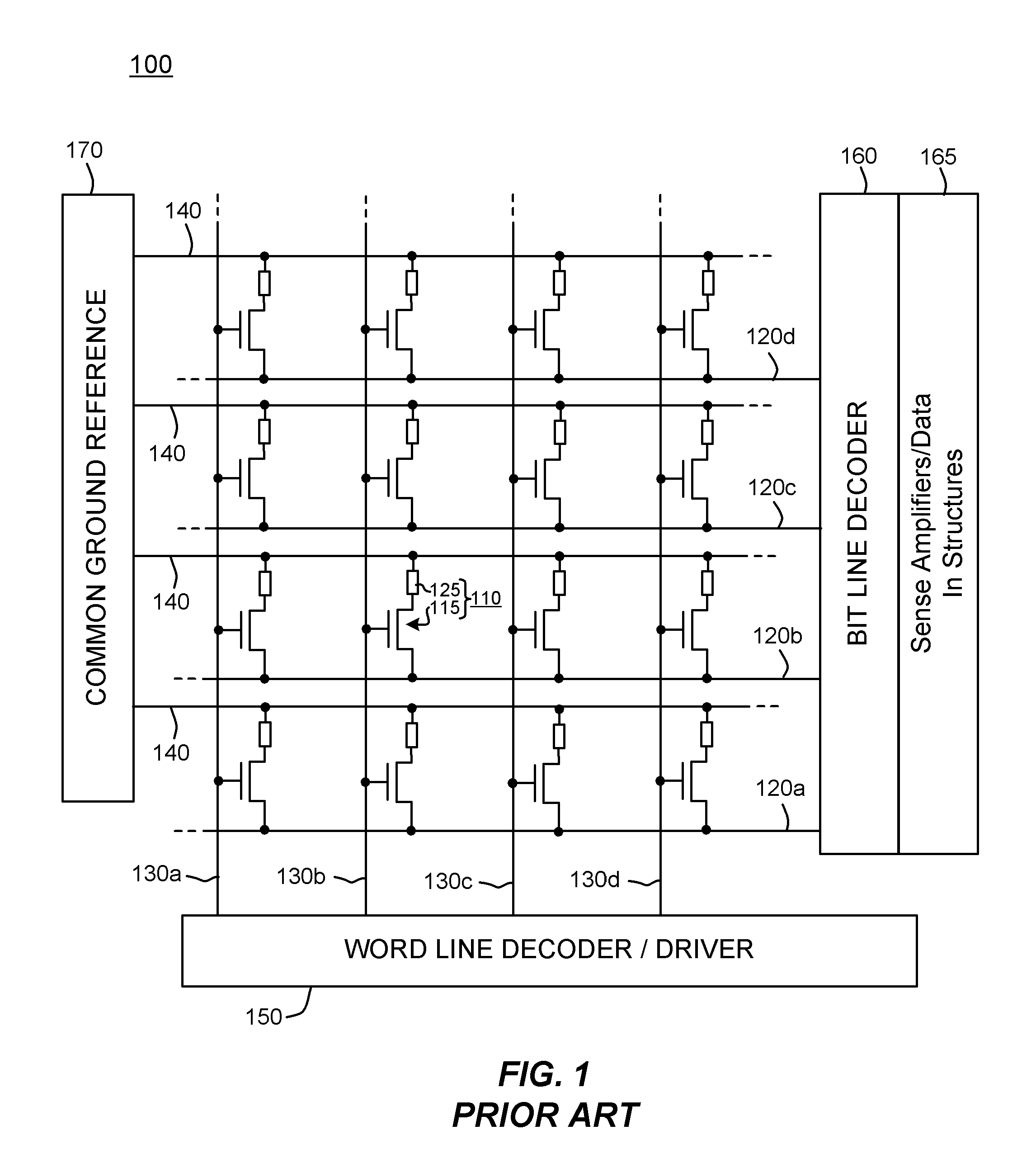

InactiveUS7030412B1Potential greatly variesSolid-state devicesSemiconductor devicesSemiconductor electrodeTransistor array

A thin-film transistor array comprises at least first and second transistors. Each transistor comprises a source electrode, a drain electrode a semiconductor electrode, a gate electrode, and a semiconductor layer. The semiconductor layer is continuous between the first and second transistors. The semiconductor layer is preferably unpatterned. In various display applications, the geometry of the transistors is selected to provide acceptable leakage currents. In a preferred embodiment, the transistor array is employed in an encapsulated electrophoretic display.

Owner:E INK CORPORATION

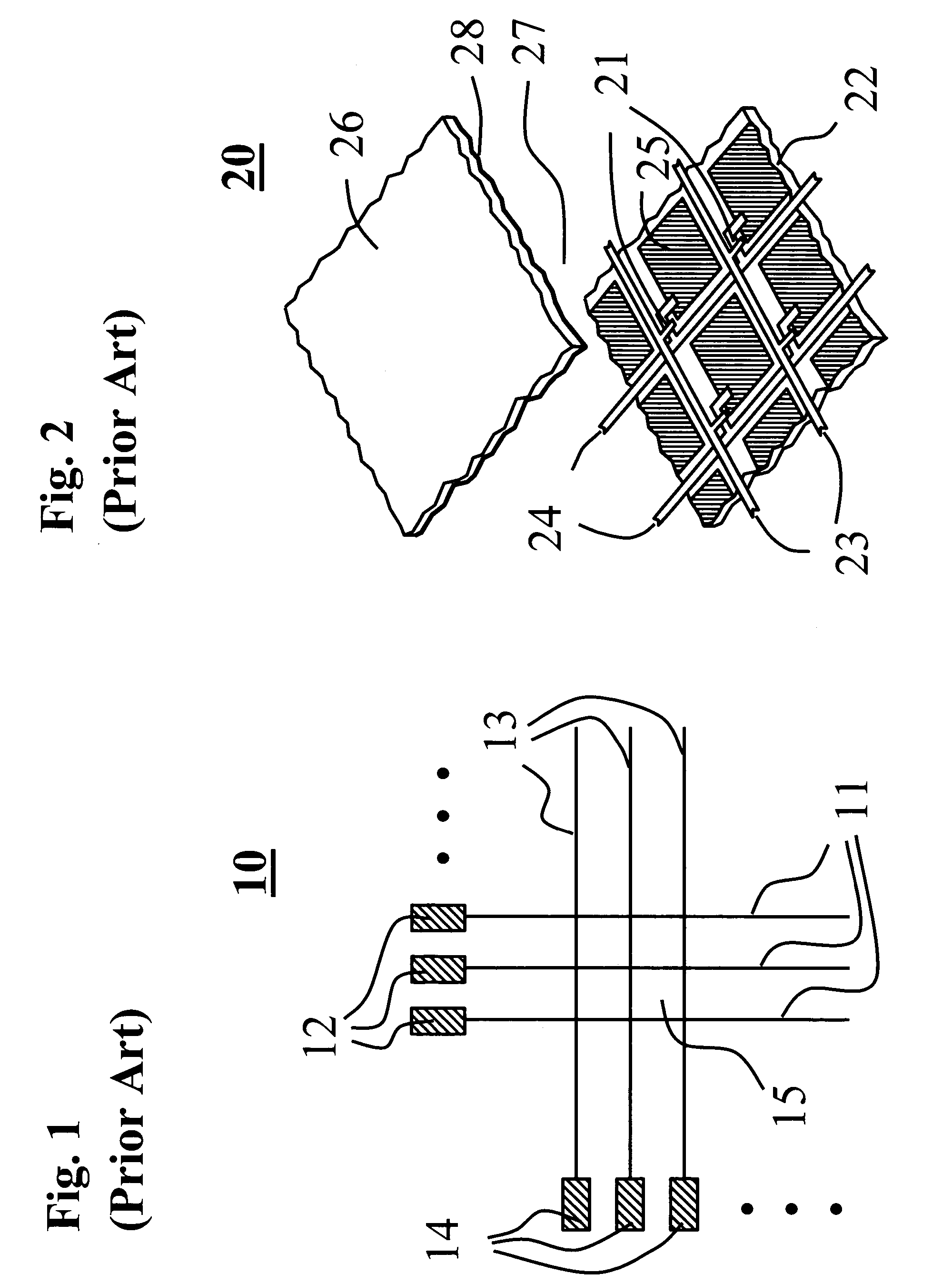

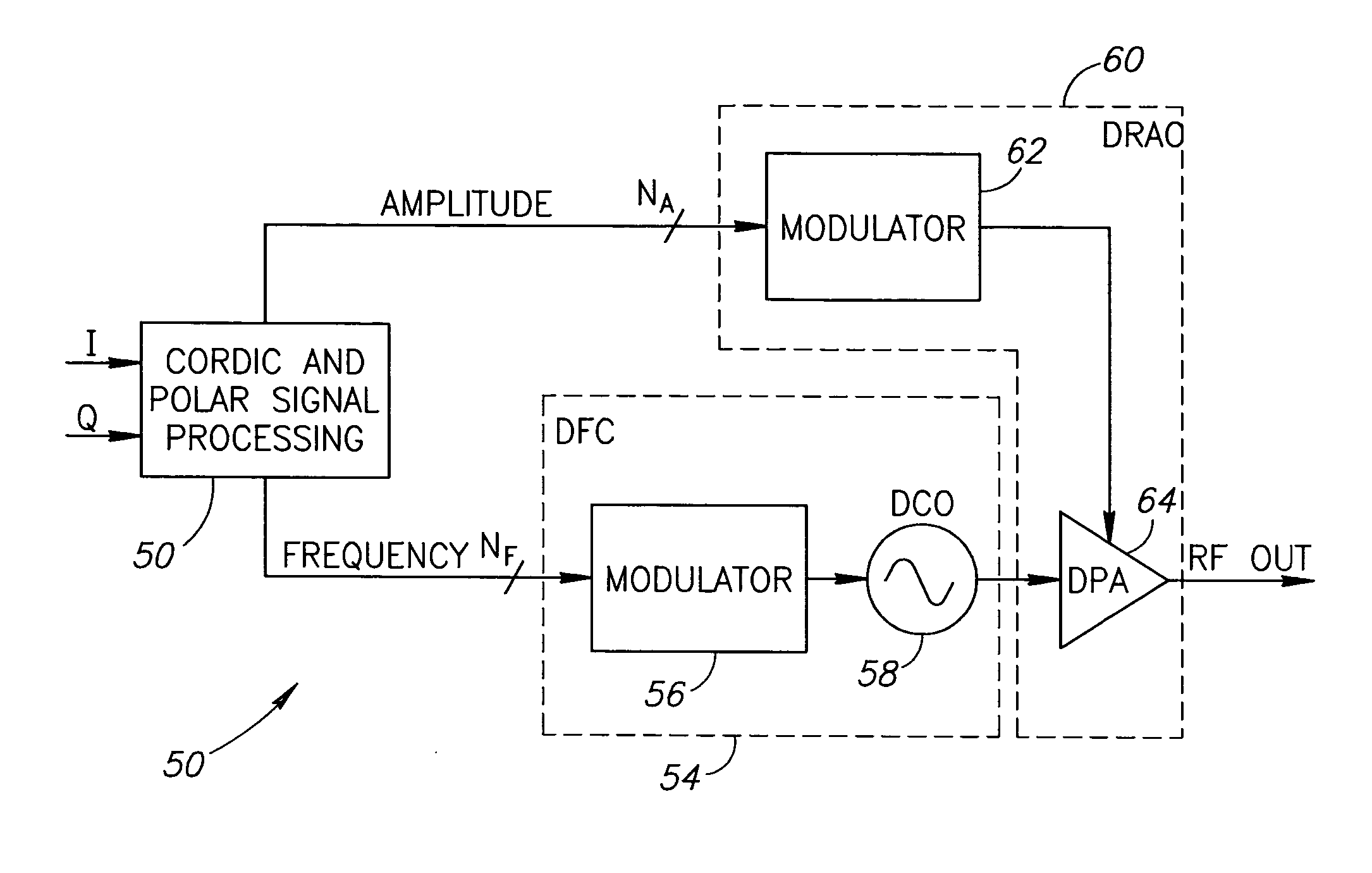

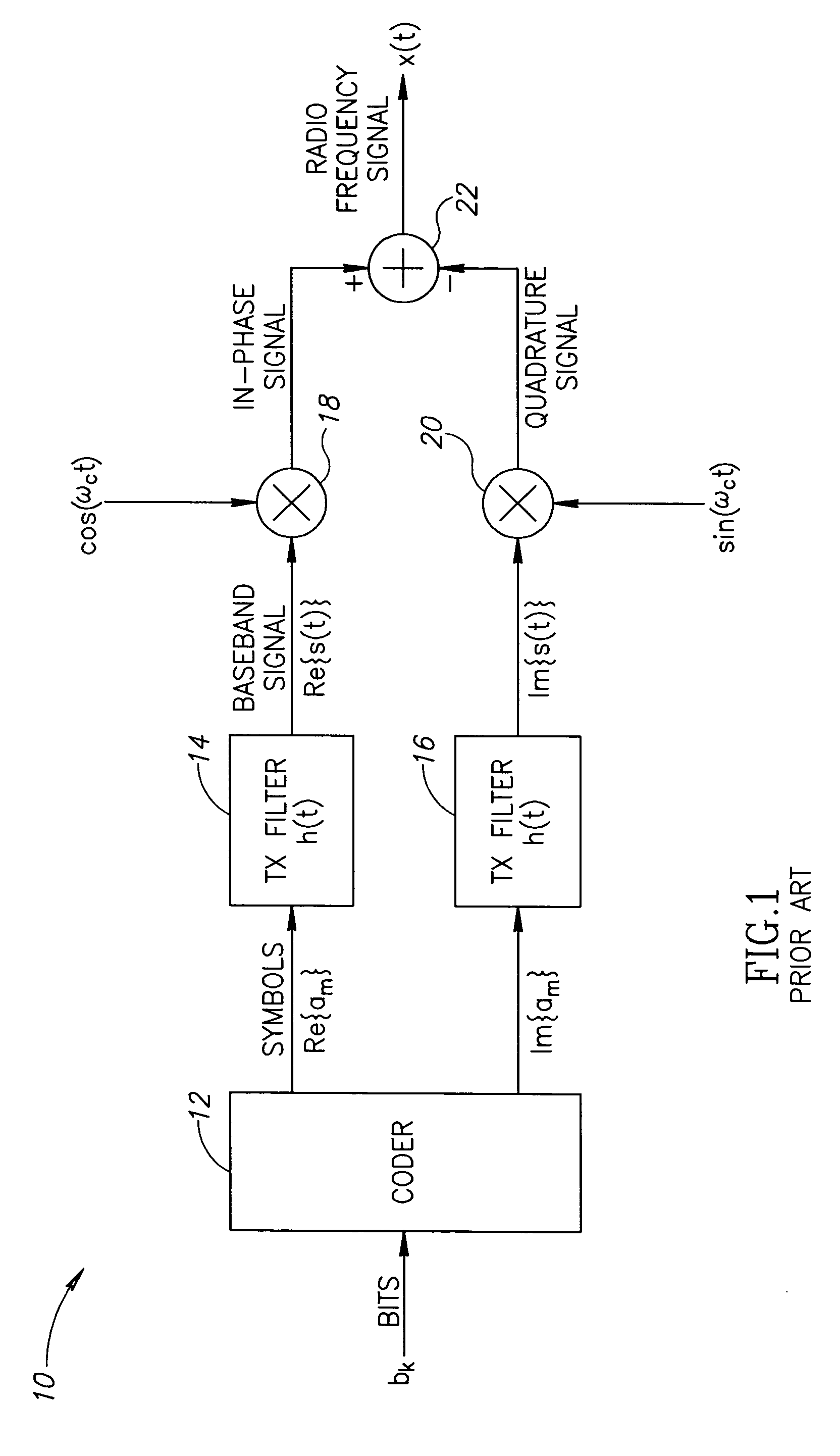

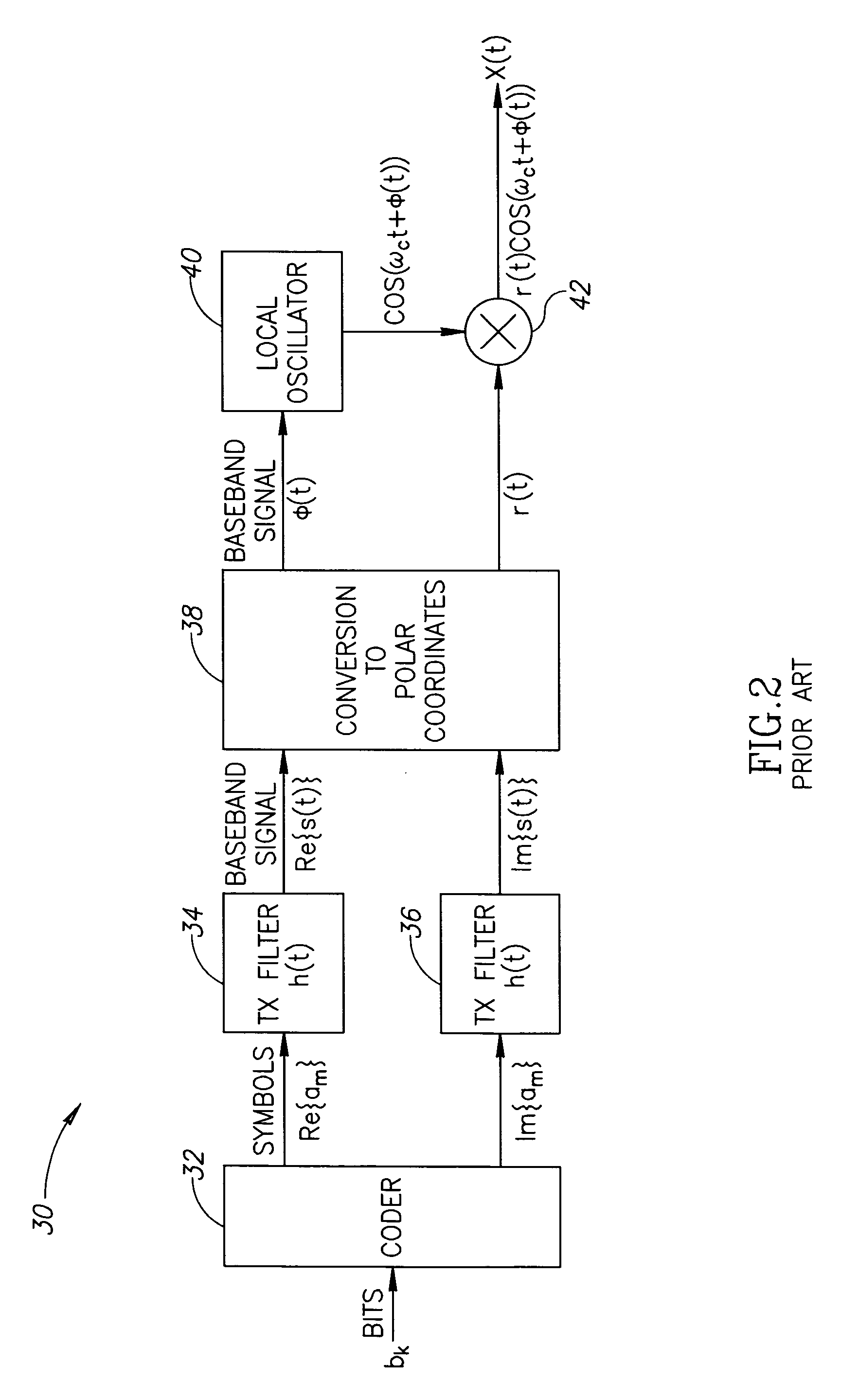

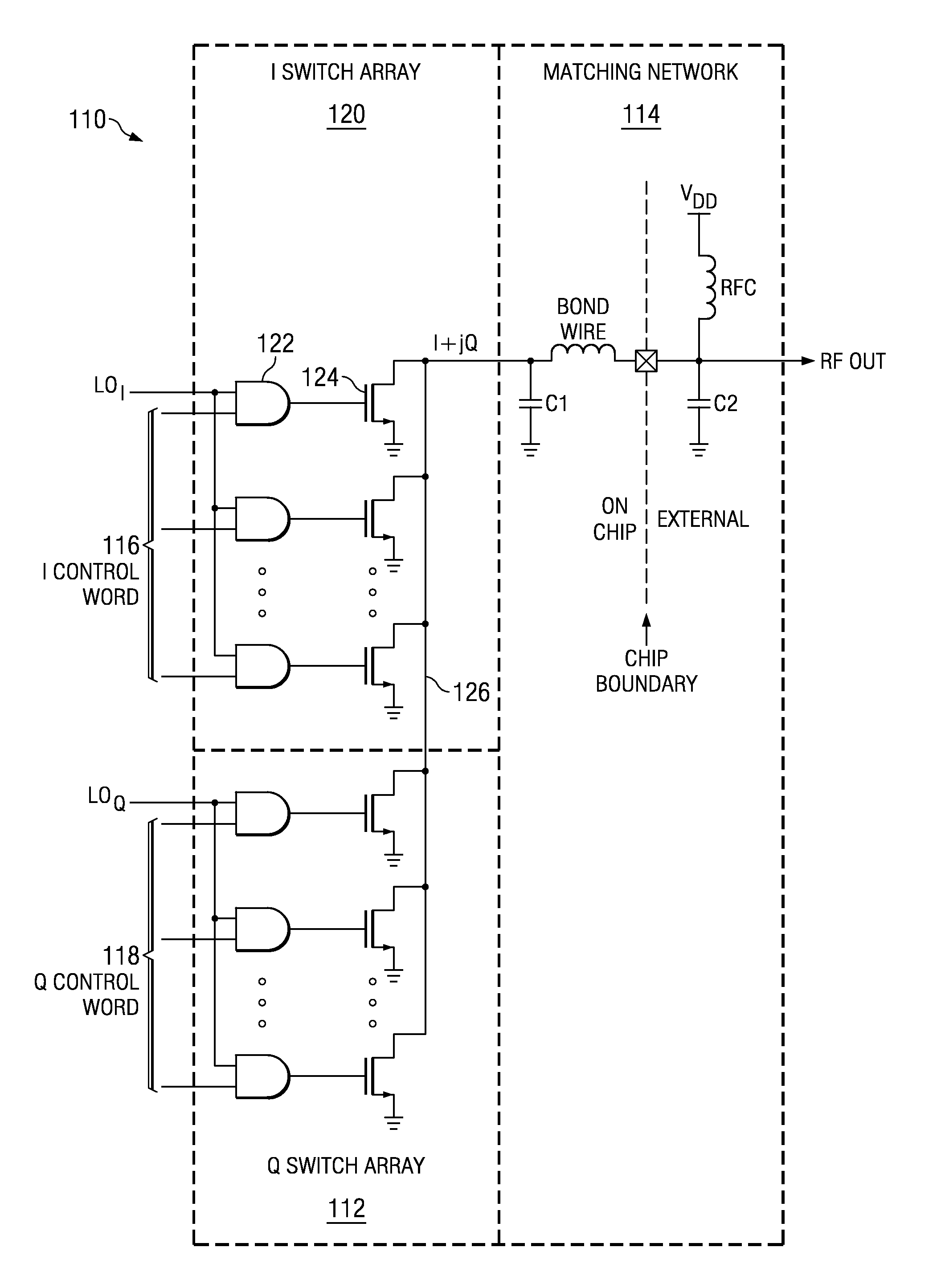

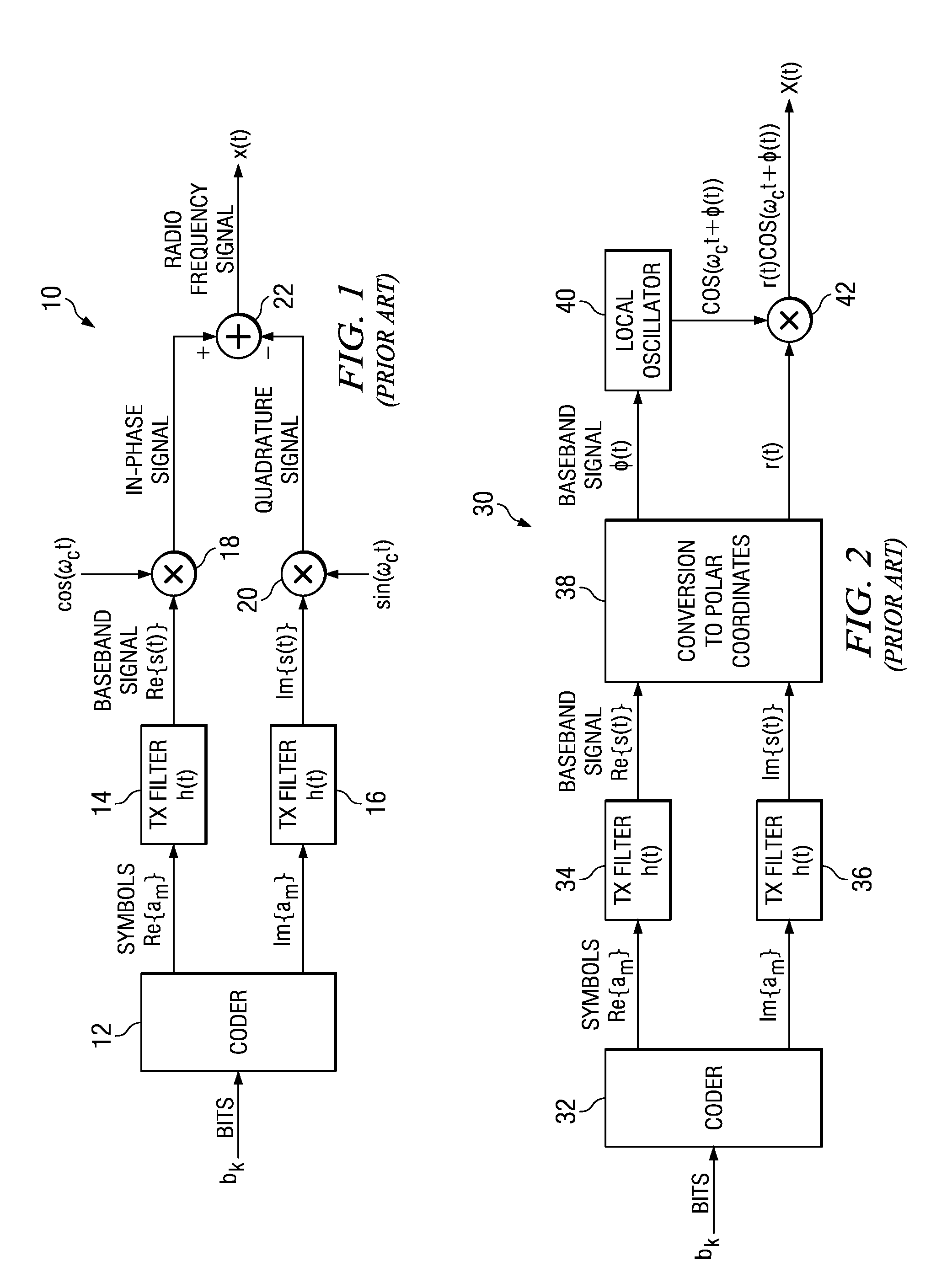

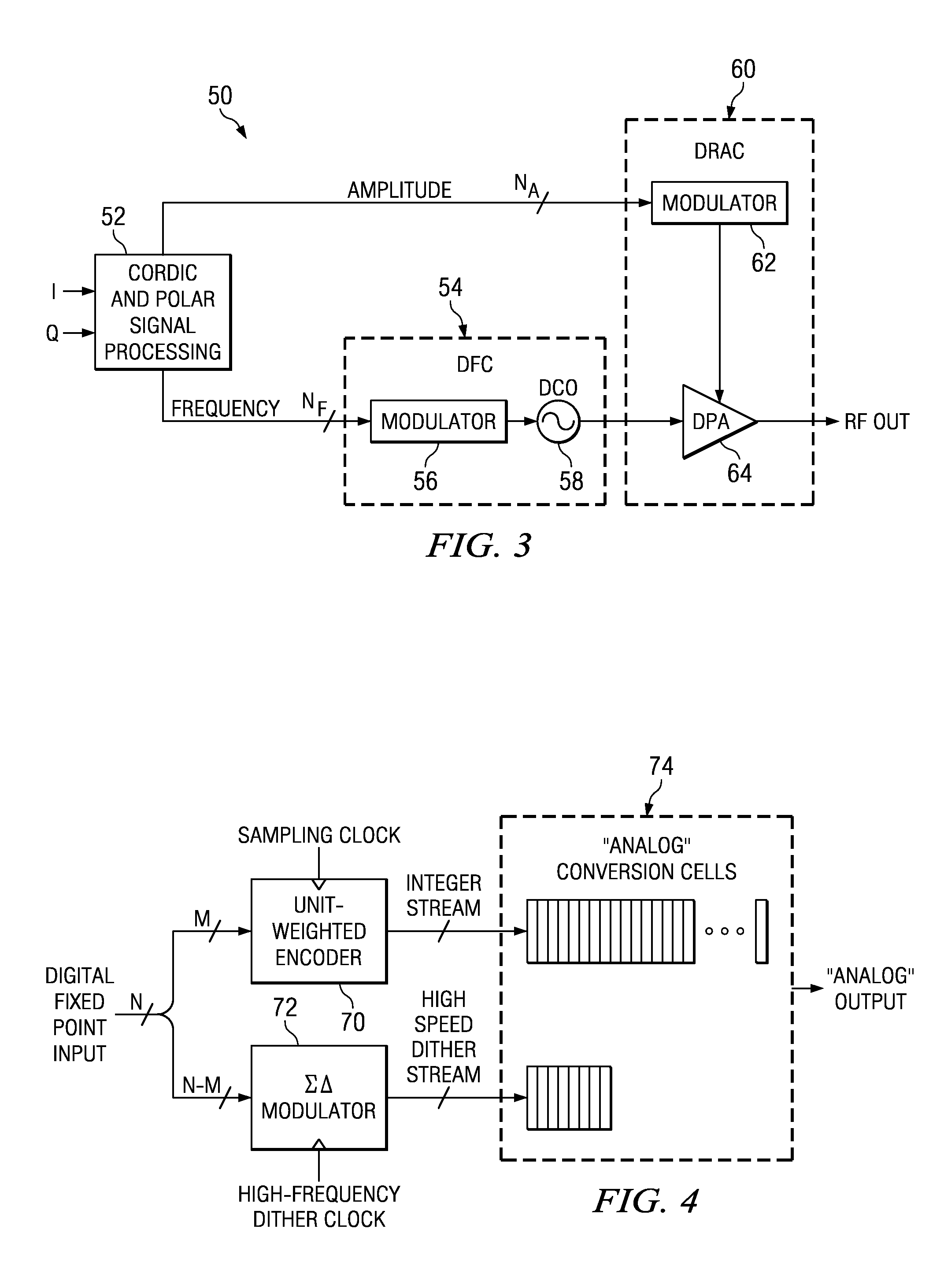

Method and apparatus for a fully digital quadrature modulator

ActiveUS20060291589A1Little or no reuseMinimize impactSimultaneous amplitude and angle modulationPower amplifiersTransistor arrayQuadrature modulator

A novel apparatus and method for a fully digital quadrature architecture for a complex modulator. The complex modulator can substitute for existing prior art analog quadrature modulator structures and those based on a digital polar architecture (r, θ). The modulator effectively operates as a complex digital-to-analog converter where the digital inputs are given in Cartesian form, namely I and Q representing the complex number I+jQ, while the output is a modulated RF signal having a corresponding amplitude and phase shift. The phase shift being with respect to a reference phase dictated by the local oscillator, which is also input to the converter / modulator. Several embodiments are provided including modulators incorporating dual I and Q transistor arrays, a single shared I / Q transistor array, modulators with single ended and differential outputs and modulators with single and dual polarity clock and I / Q data signals.

Owner:TEXAS INSTR INC

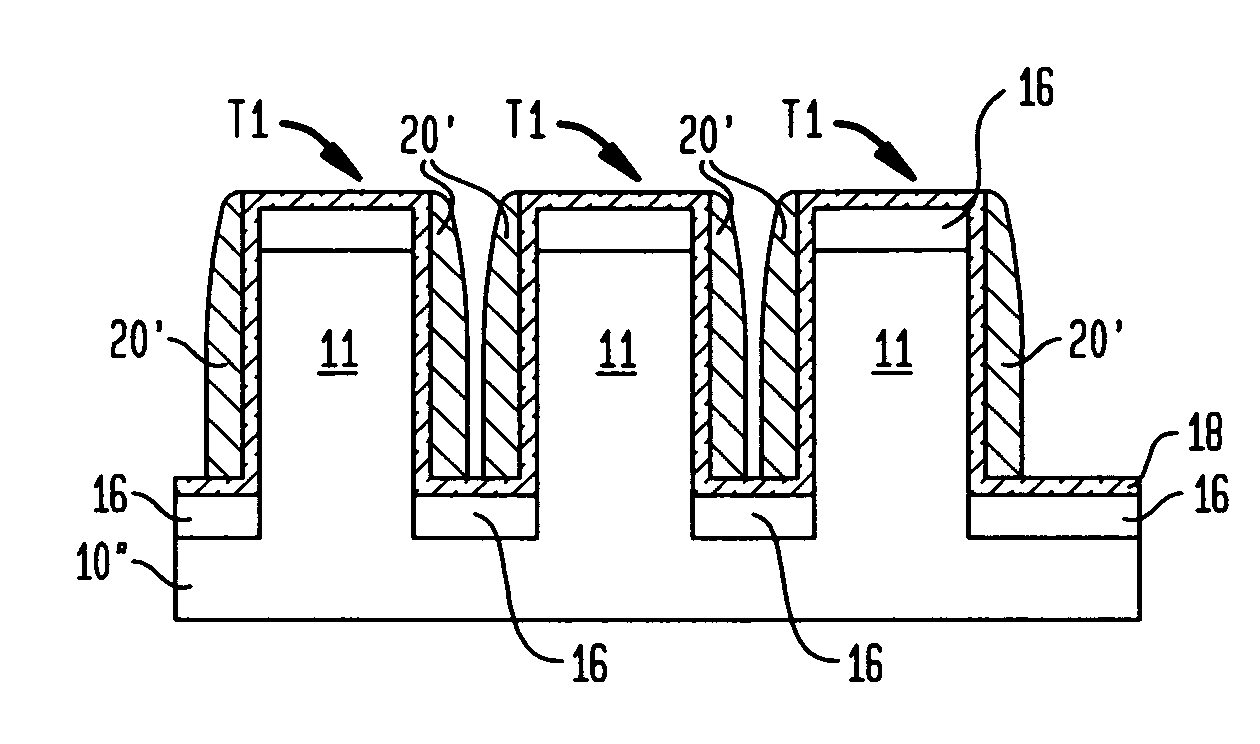

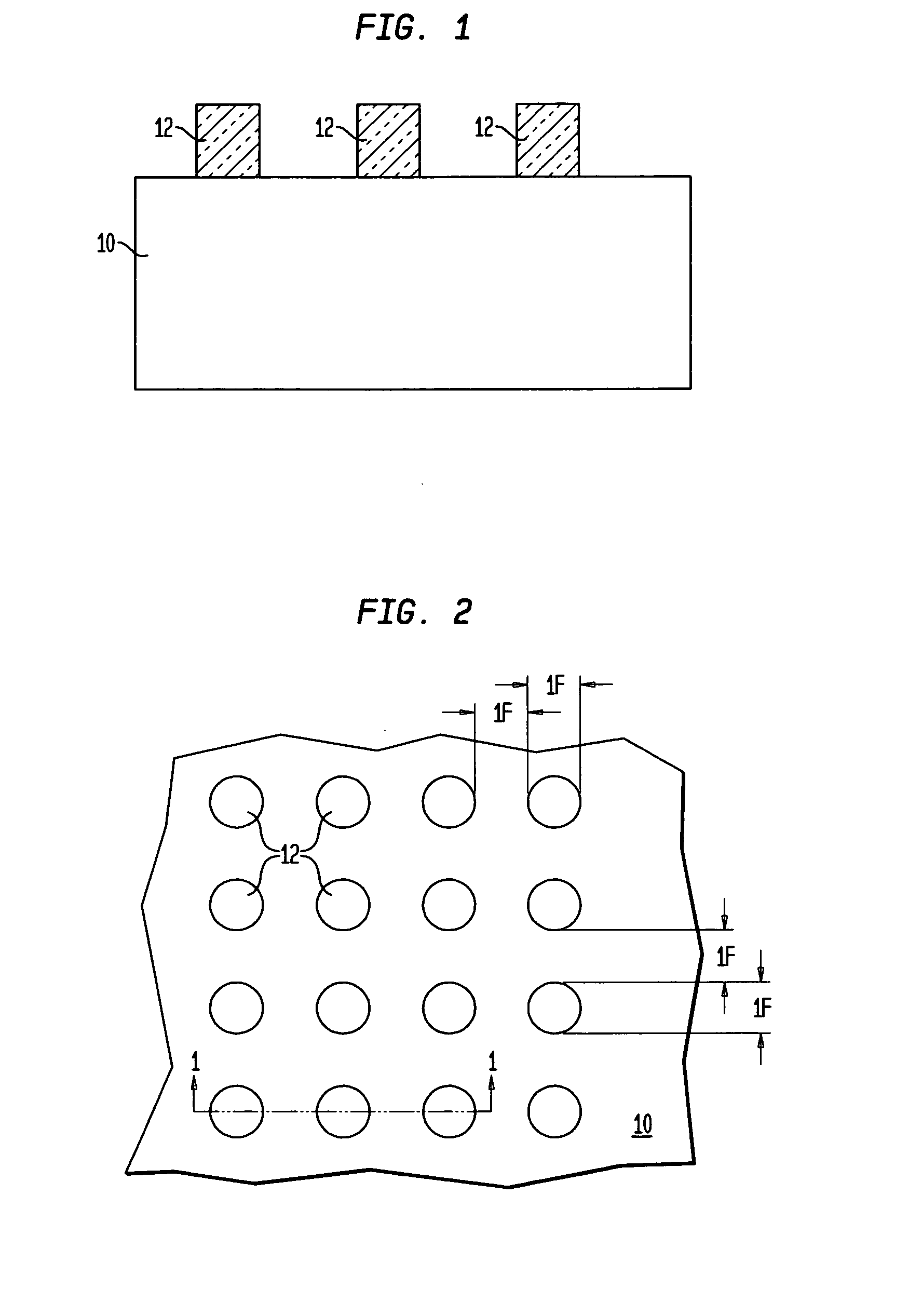

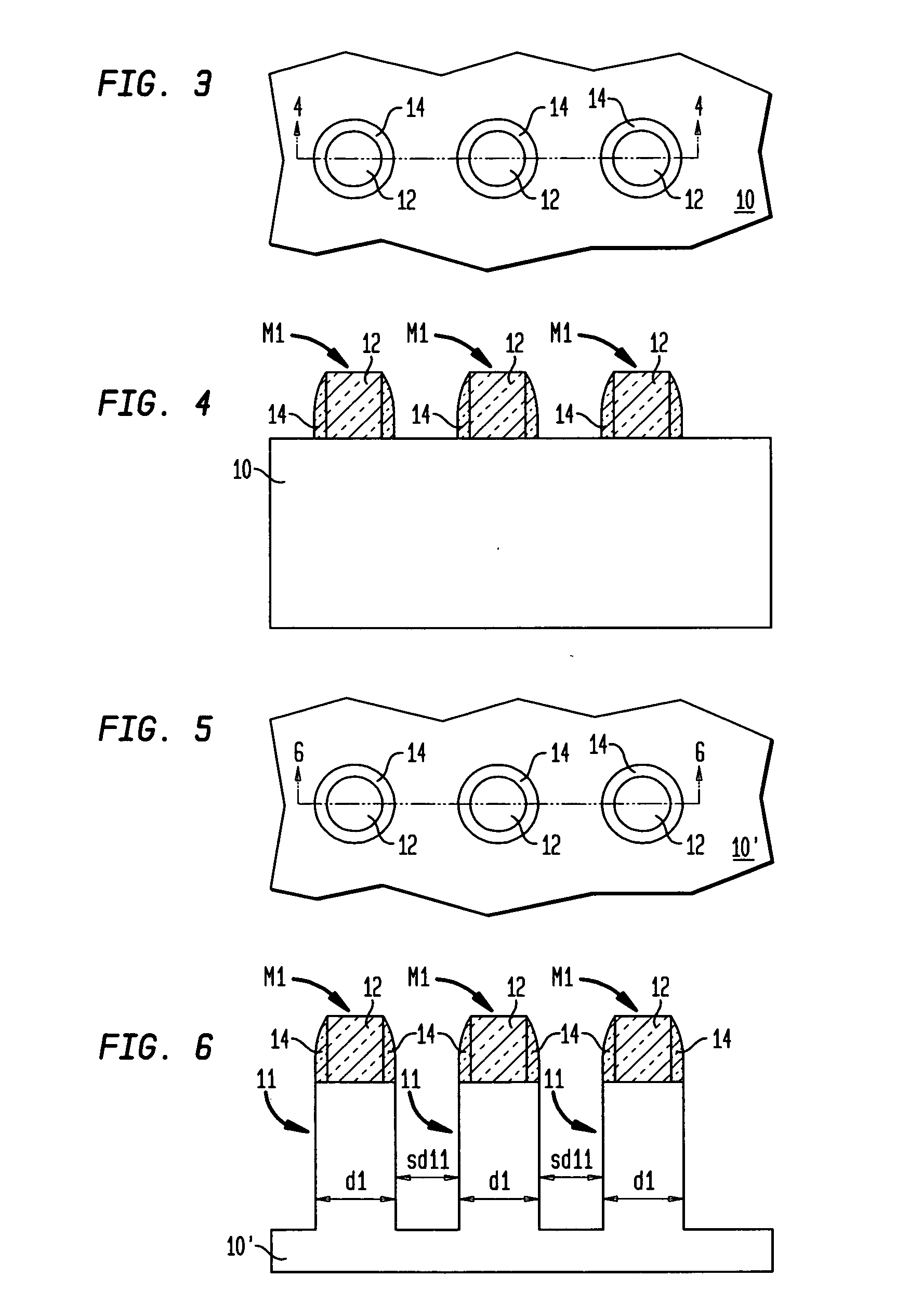

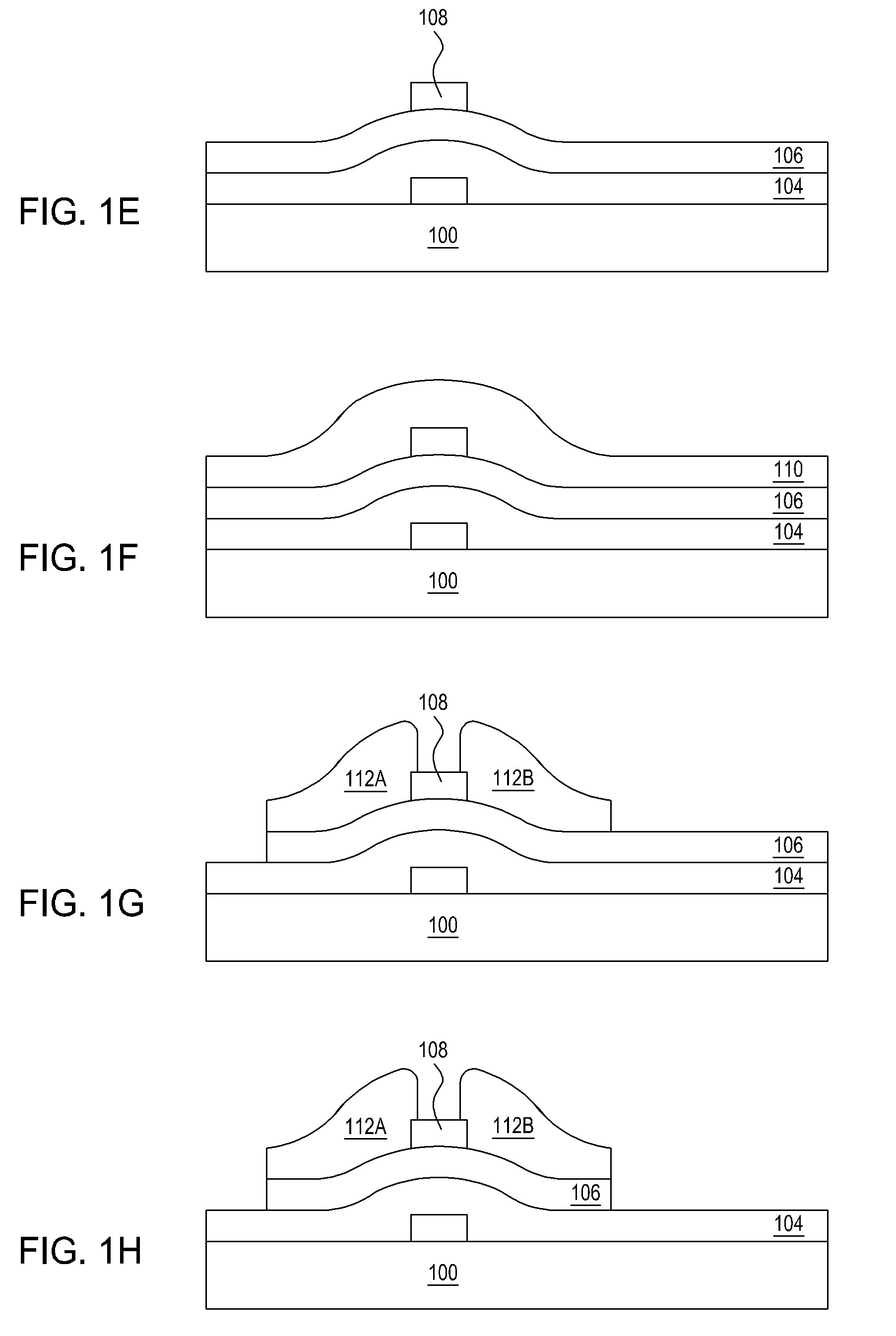

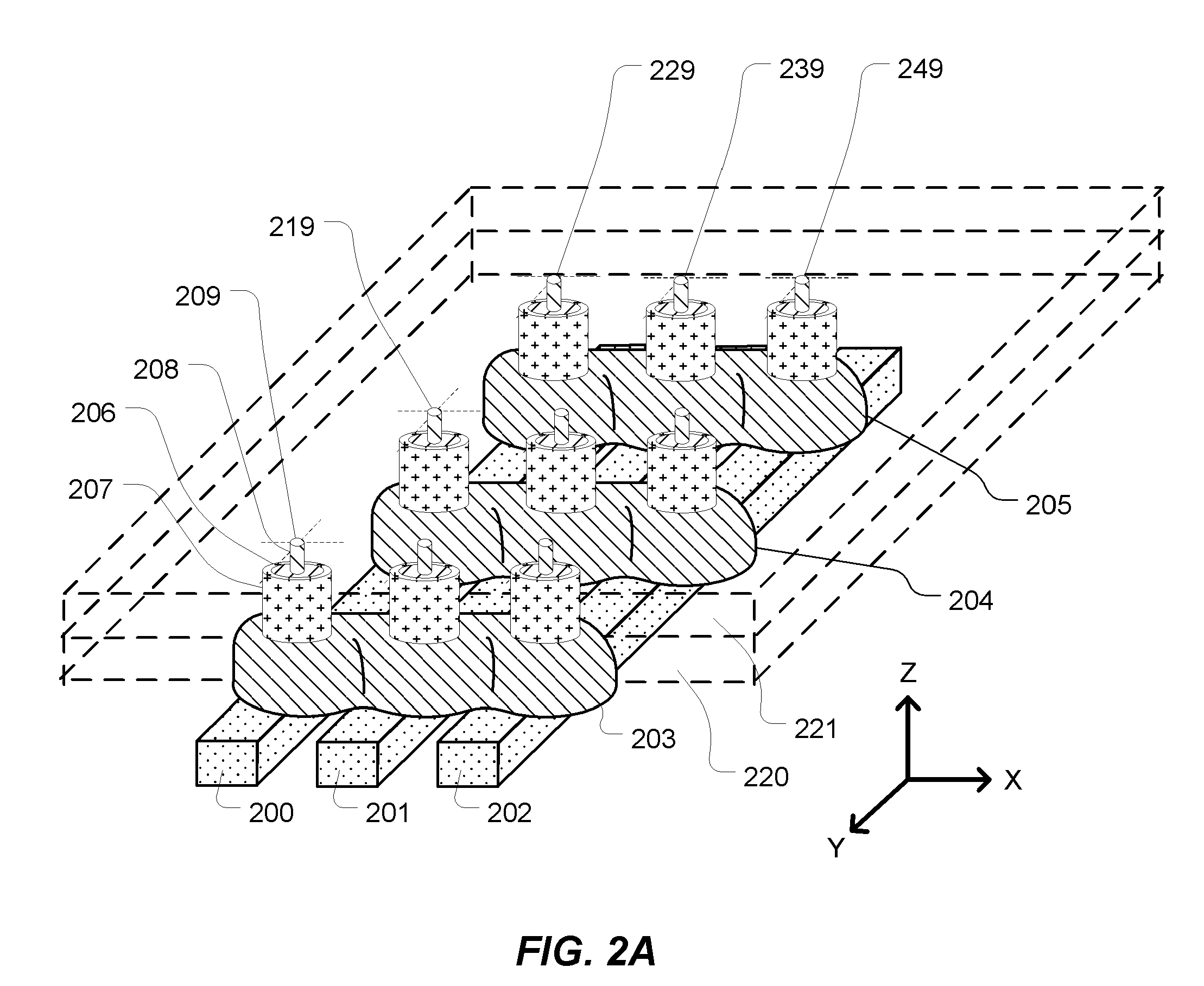

Vertical field effect transistor arrays and methods for fabrication thereof

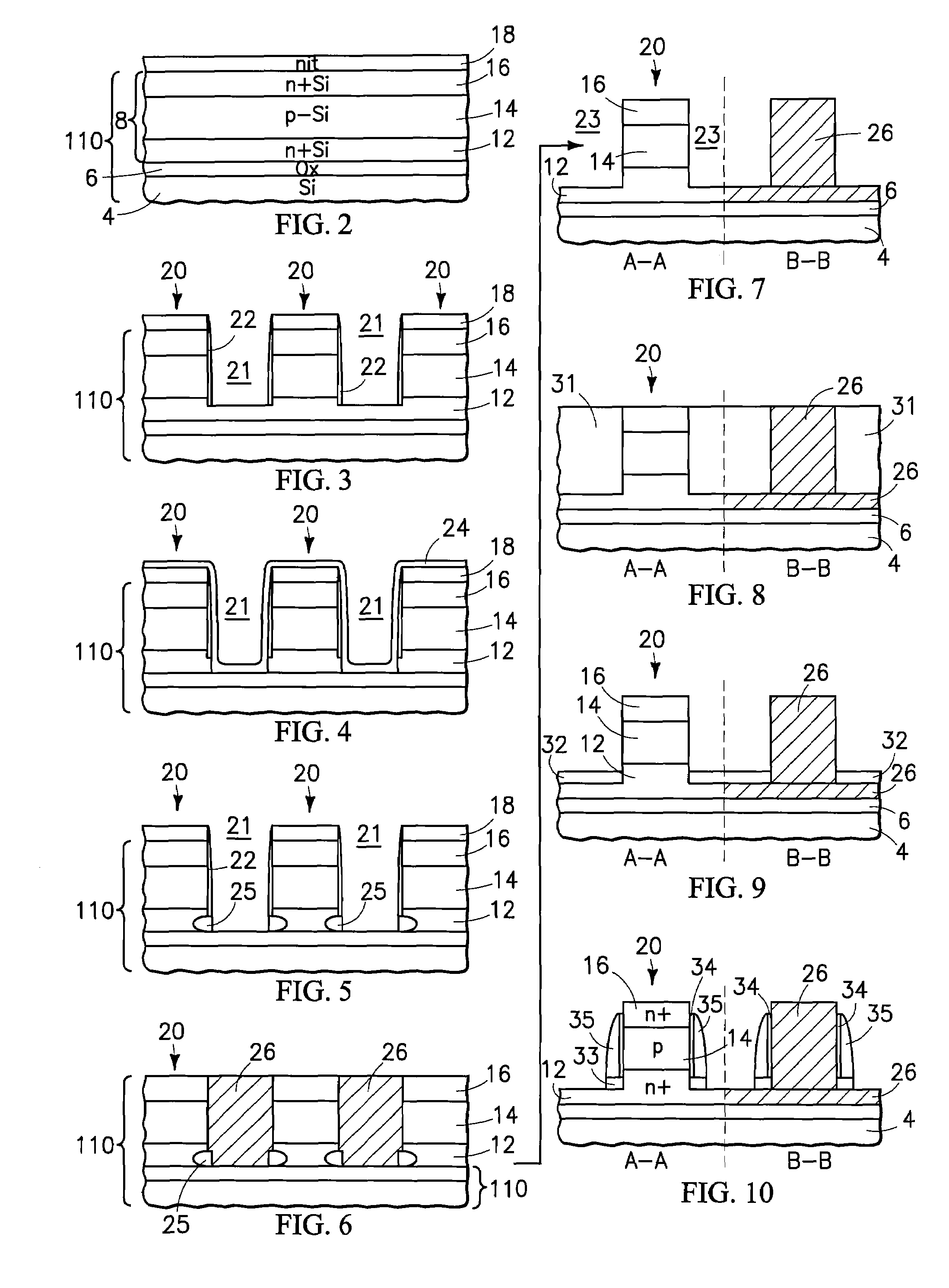

Vertical field effect transistor semiconductor structures and methods for fabrication of the vertical field effect transistor semiconductor structures provide an array of semiconductor pillars. Each vertical portion of each semiconductor pillar in the array of semiconductor pillars has a linewidth greater than a separation distance to an adjacent semiconductor pillar. Alternatively, the array may comprise semiconductor pillars with different linewidths, optionally within the context of the foregoing linewidth and separation distance limitations. A method for fabricating the array of semiconductor pillars uses a minimally photolithographically dimensioned pillar mask layer that is annularly augmented with at least one spacer layer prior to being used as an etch mask.

Owner:TAIWAN SEMICON MFG CO LTD

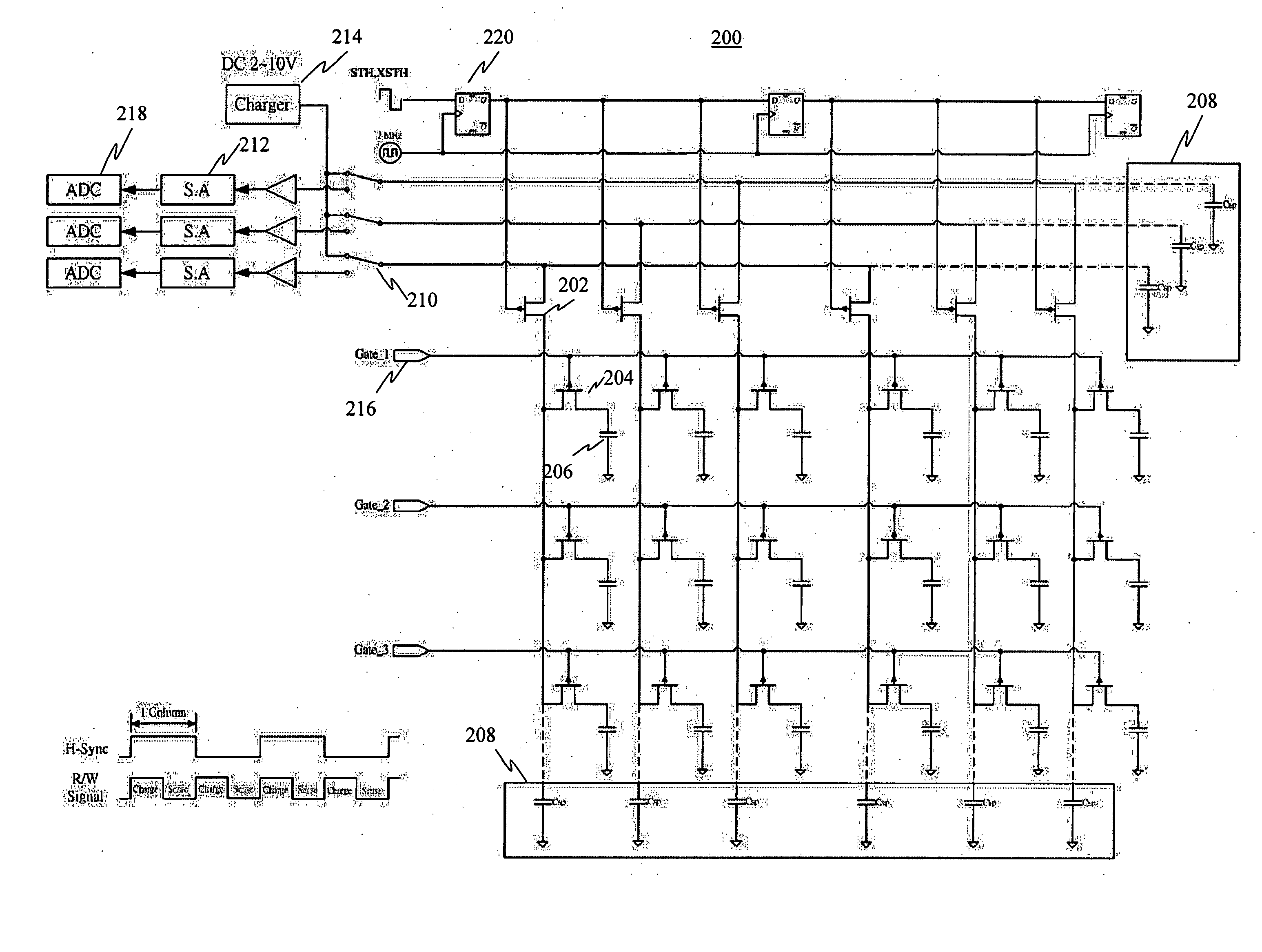

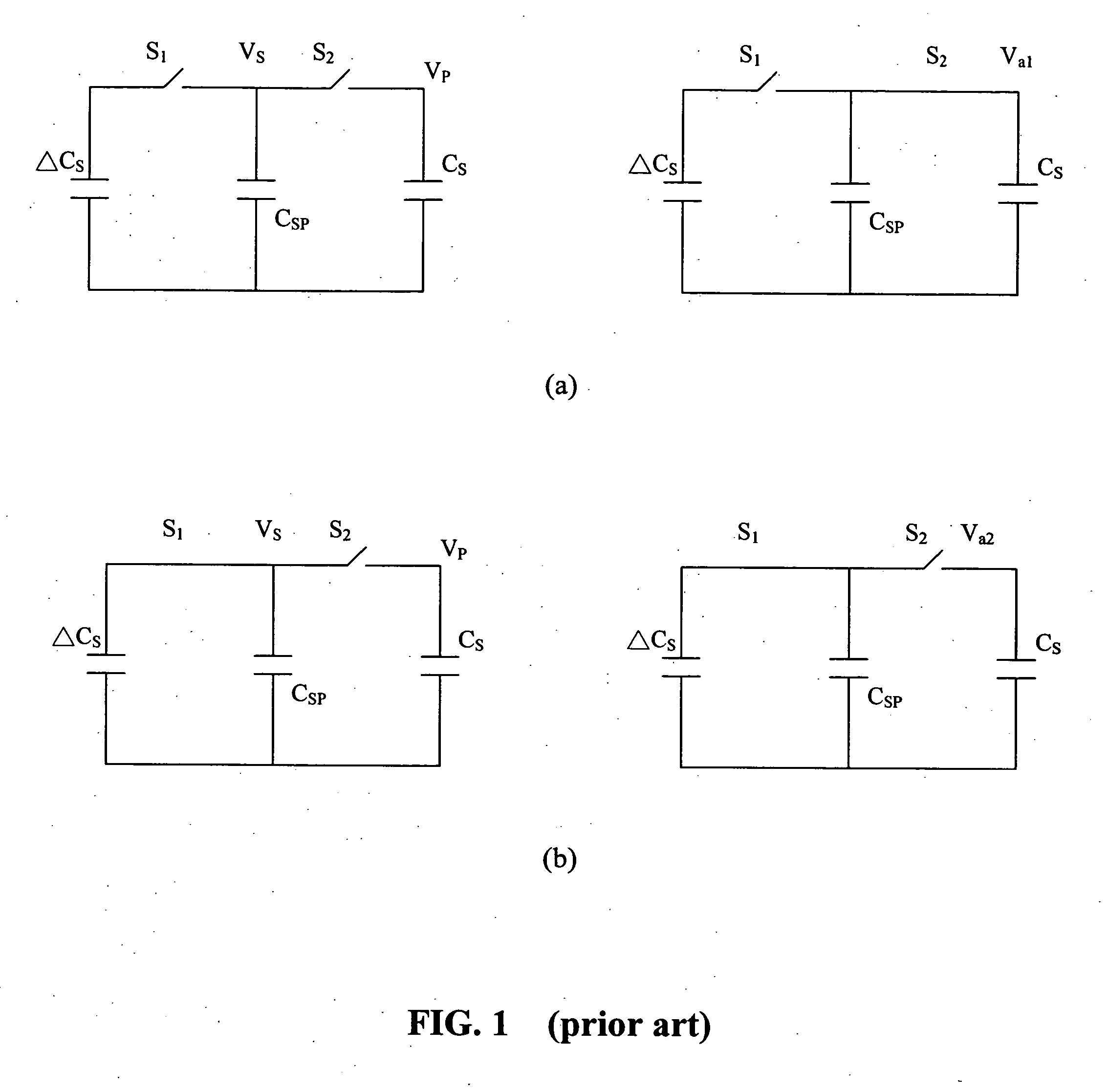

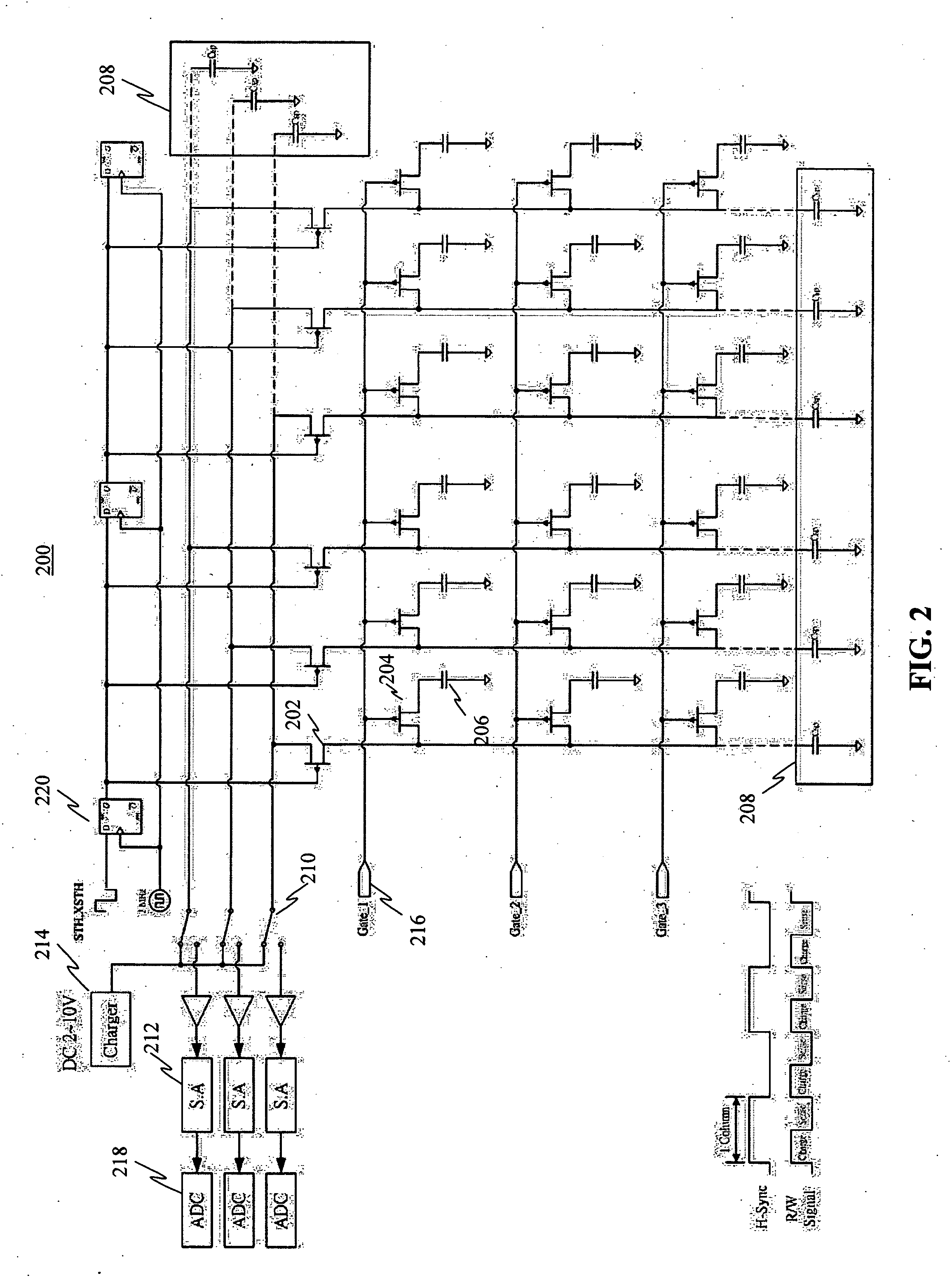

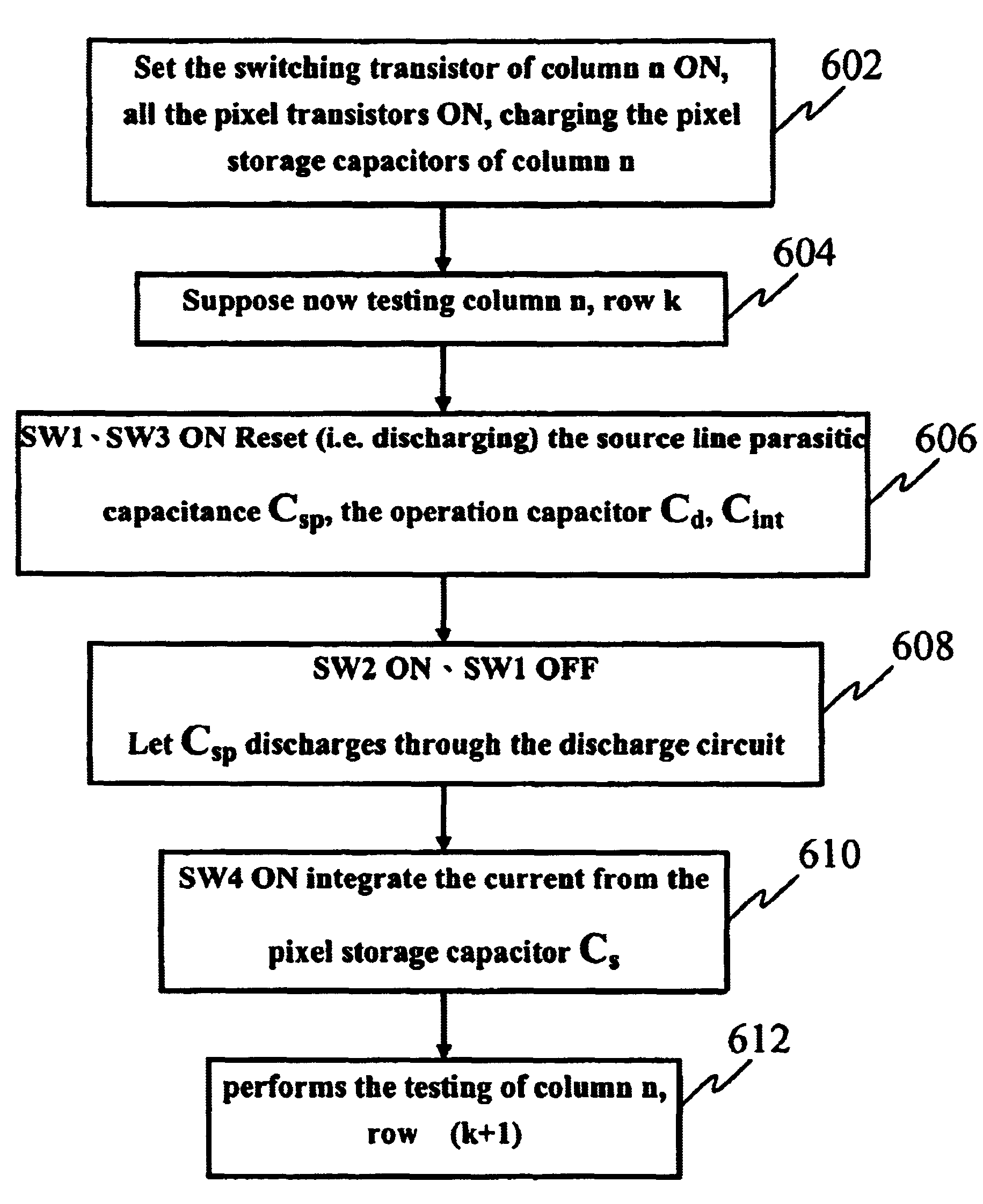

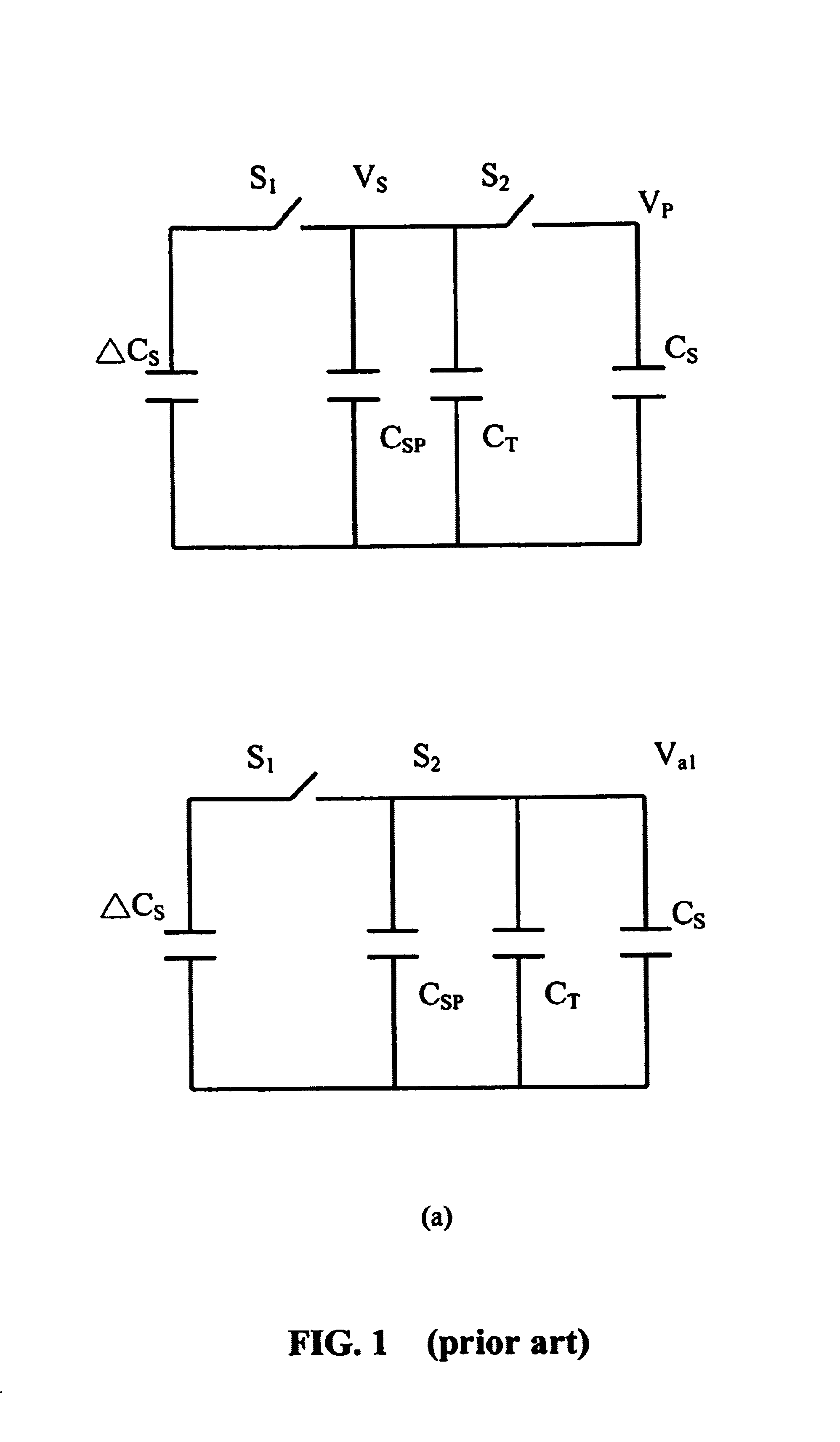

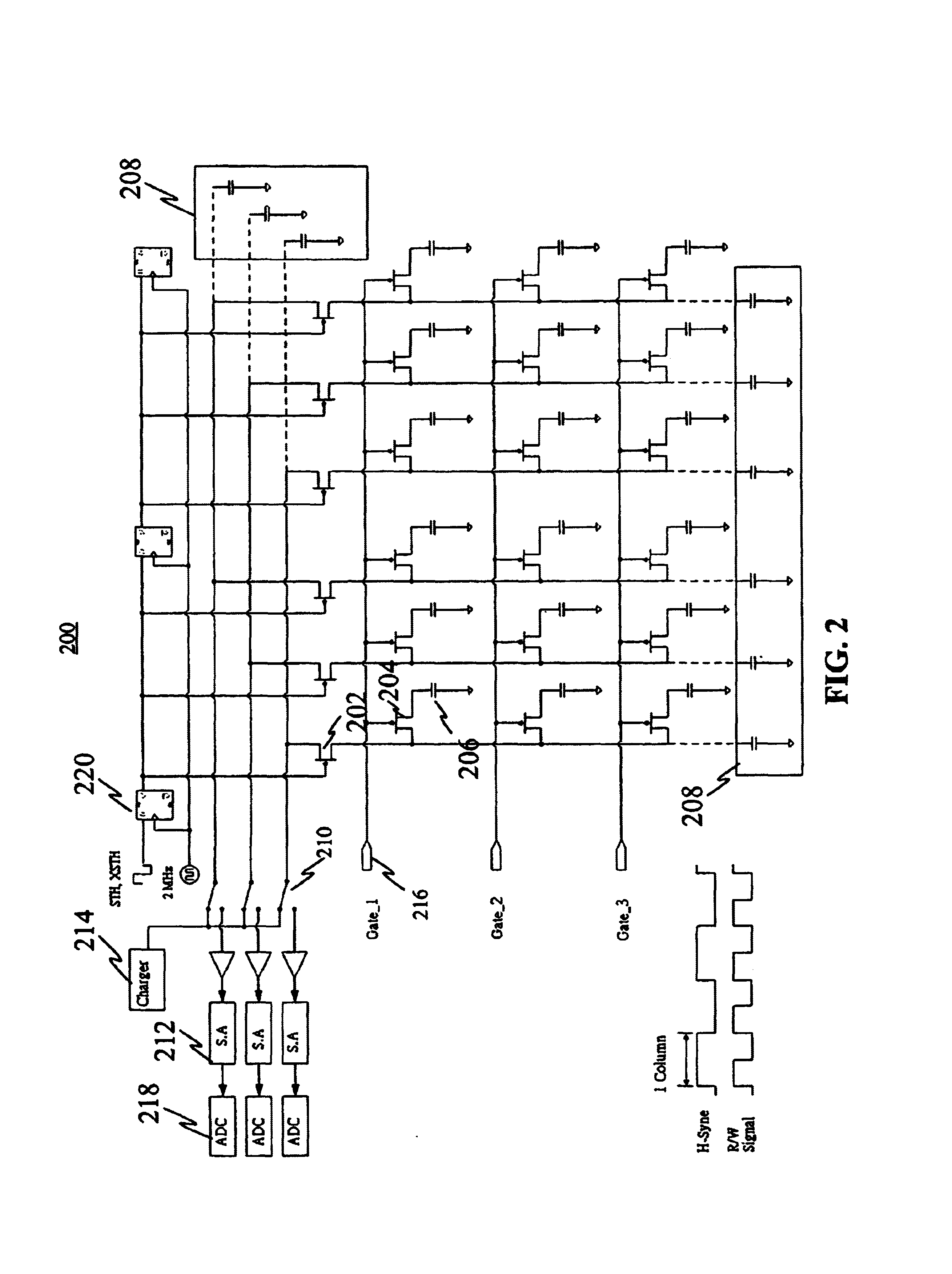

Testing apparatus and method for thin film transistor display array

InactiveUS20050024081A1Improve accuracyImprove reliabilityDigital circuit testingResistance/reactance/impedenceTransistor arrayHemt circuits

The present invention discloses a testing circuit and method for thin film transistor display array, for testing the yield of thin film transistor array. The testing circuit comprising: An array tester, a test panel (DUT), a sense amplifier array. The sense amplifier is composed by a plurality of trans- impedance amplifier unit and a plurality of parasitic capacitance discharge circuit unit. Every sense amplifier includes: a trans-impedance amplifier, which is implemented by an operational amplifier, two switches and an operation capacitance, the trans-impedance amplifier is used to form an integrated circuit, the output is transmitted to a sampling / hold circuit via a switch; a parasitic capacitance discharge circuit is used to form a discharge rout for the charge of the parasitic capacitance.

Owner:PRIMETECH INT CORP

Testing apparatus and method for thin film transistor display array

InactiveUS7102378B2Improve accuracyImprove reliabilityDigital circuit testingResistance/reactance/impedenceTransistor arrayAudio power amplifier

A testing circuit and method for thin film transistor display array, for testing the yield of a thin film transistor array is provided. The testing circuit includes an array tester, a test panel (DUT) and a sense amplifier array. The sense amplifier is composed of a plurality of trans-impedance amplifier units and a plurality of parasitic capacitance discharge circuit units. Every sense amplifier includes a trans-impedance amplifier, which is implemented by an operational amplifier, two switches and an operation capacitance. The trans-impedance amplifier is used to form an integrated circuit and the output is transmitted to a sampling / hold circuit via a switch. Also included is a parasitic capacitance discharge circuit that is used to form a discharge route for the charge of the parasitic capacitance.

Owner:PRIMETECH INT CORP

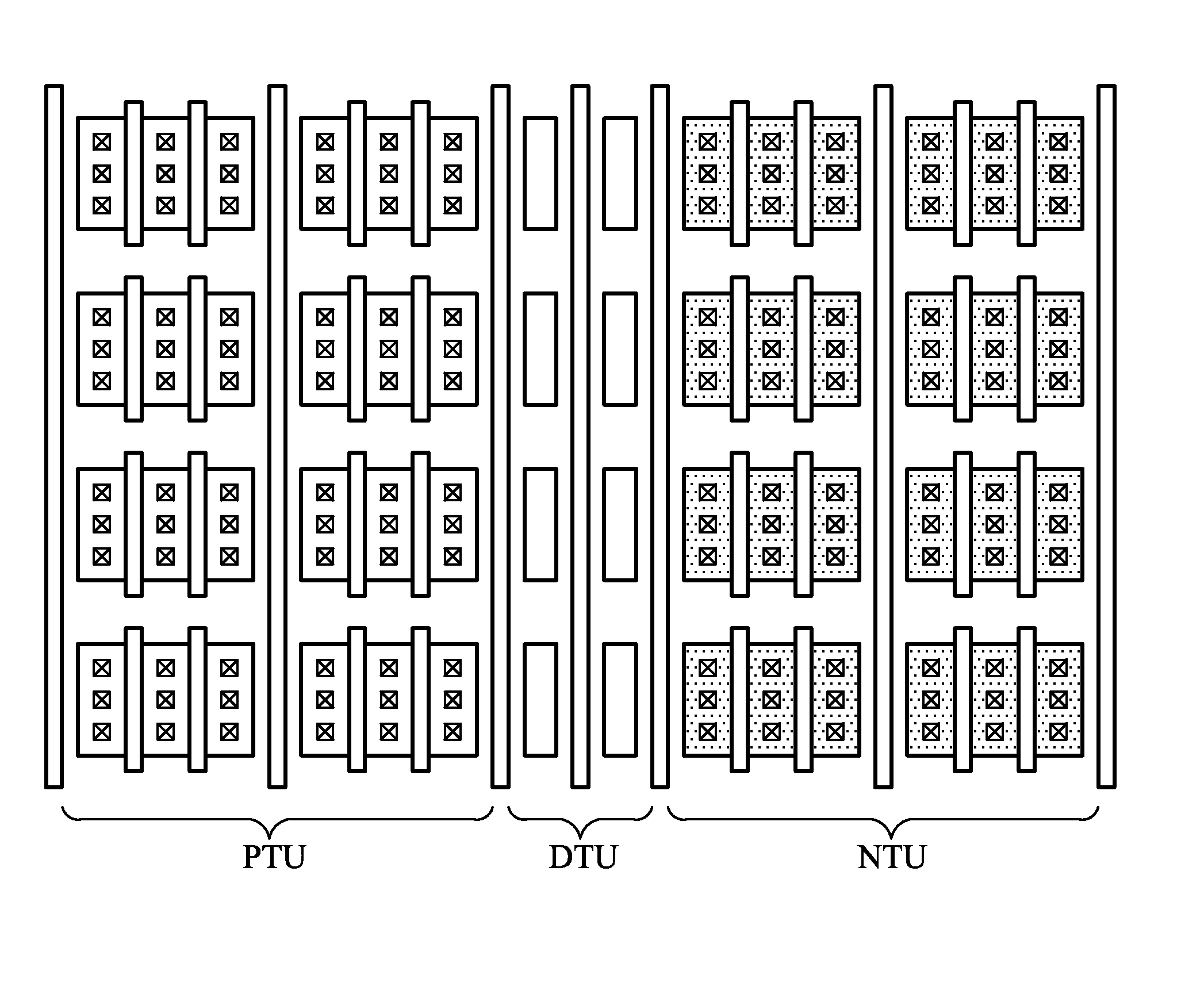

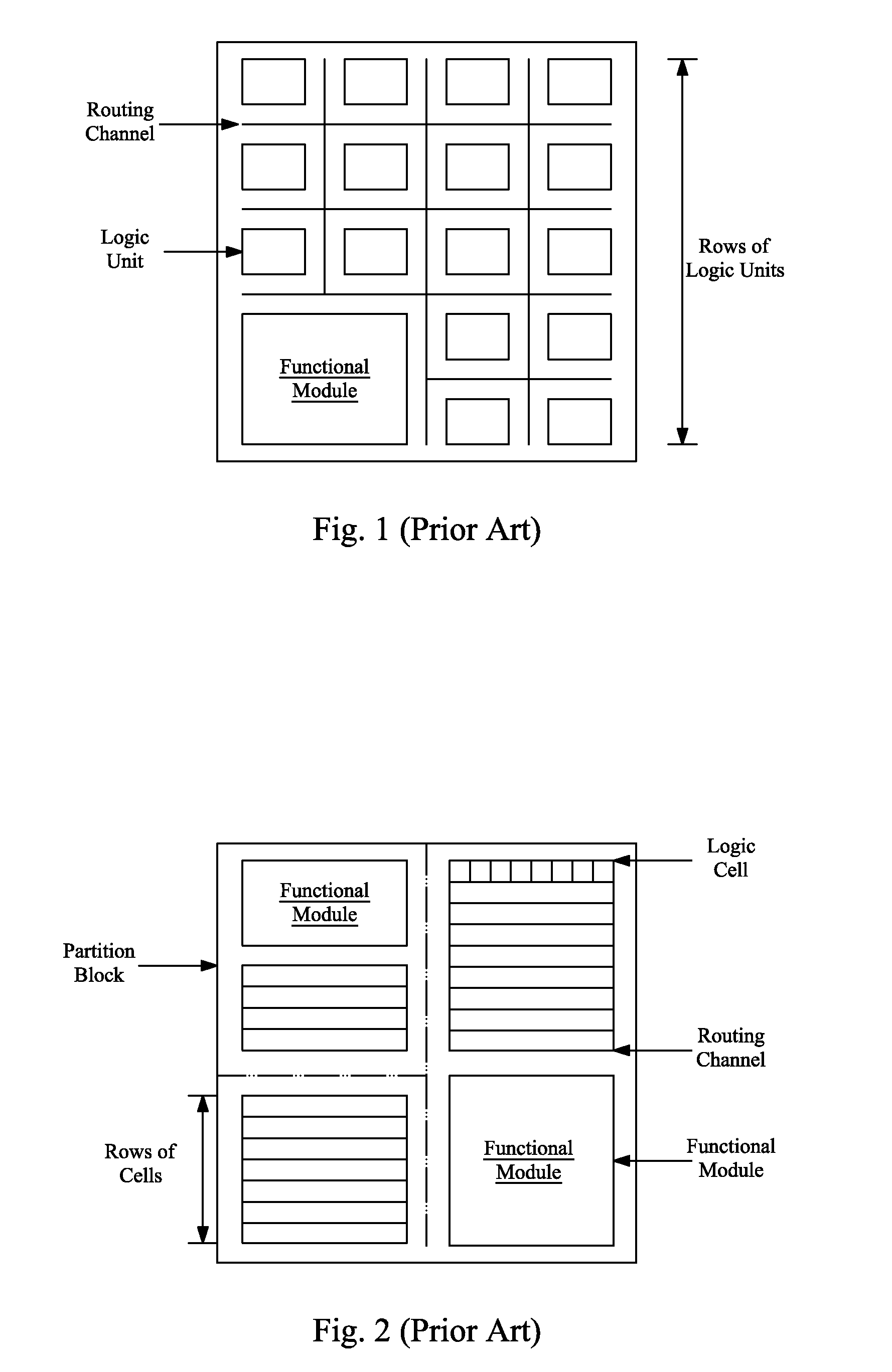

Programmable Transistor Array Design Methodology

ActiveUS20100181600A1Low costShorten cycle timeTransistorSolid-state devicesTransistor arrayIntegrated circuit

A method of designing integrated circuits includes providing a first chip and a second chip identical to each other. Each of the first chip and the second chip includes a base layer including a Logic Transistor Unit (LTU) array. The LTU array includes LTUs identical to each other and arranged in rows and columns. The method further includes connecting the base layer of the first chip to form a first application chip; and connecting the base layer of the second chip to form a second application chip different from the first application chip.

Owner:TAIWAN SEMICON MFG CO LTD

Thin film transistor array panel and method for manufacturing the same

ActiveUS20060102907A1Low resistivityImprove reliabilitySolid-state devicesNon-linear opticsTransistor arrayEngineering

The present invention provides a thin film transistor array panel comprising an insulating substrate; a gate line formed on the insulating substrate; a gate insulating layer formed on the gate line; a drain electrode and a data line having a source electrode formed on the gate insulating layer, the drain electrode being adjacent to the source electrode with a gap therebetween; and a pixel electrode coupled to the drain electrode, wherein at least one of the gate line, the data line, and the drain electrode comprises a first conductive layer comprising a conductive oxide and a second conductive layer comprising copper (Cu).

Owner:SAMSUNG DISPLAY CO LTD

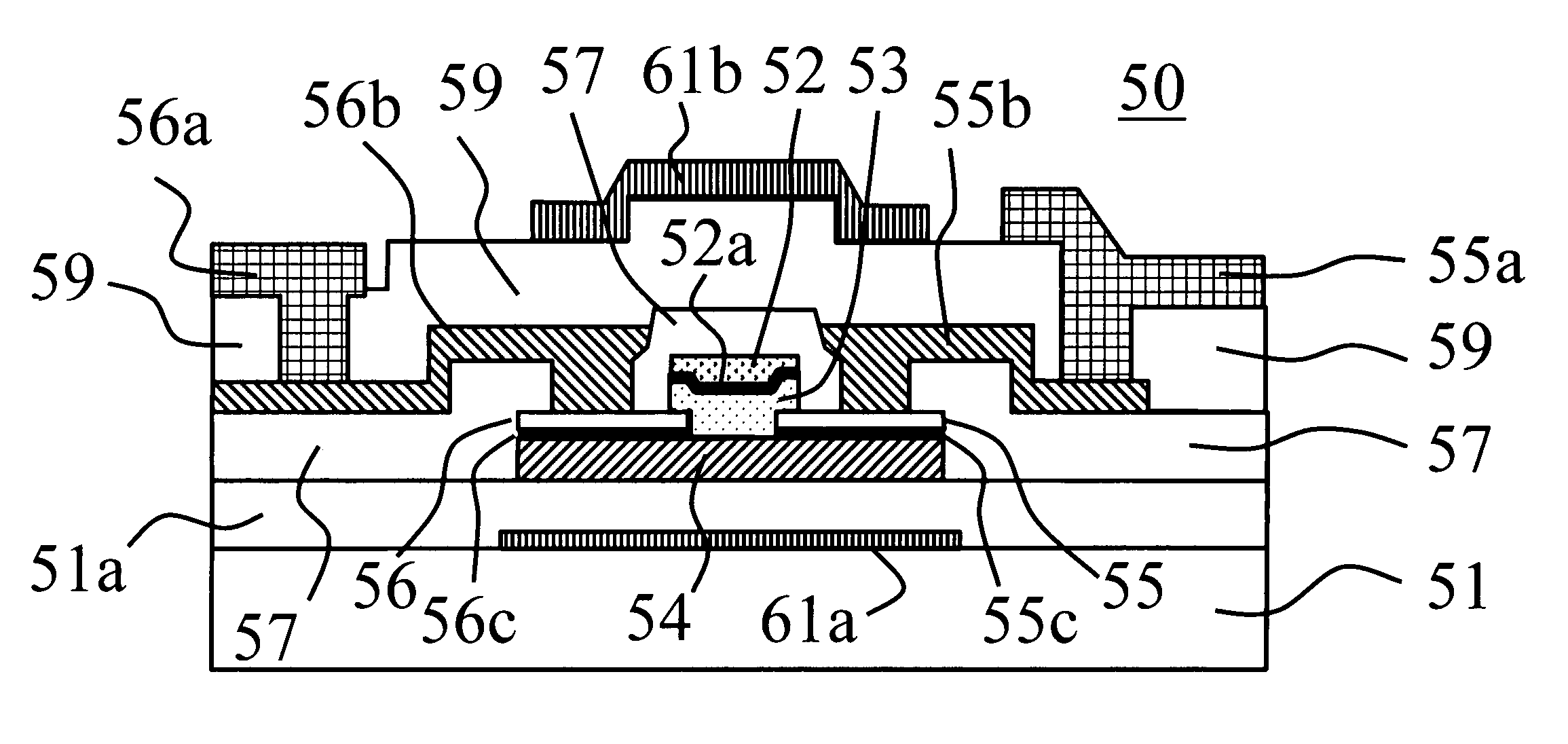

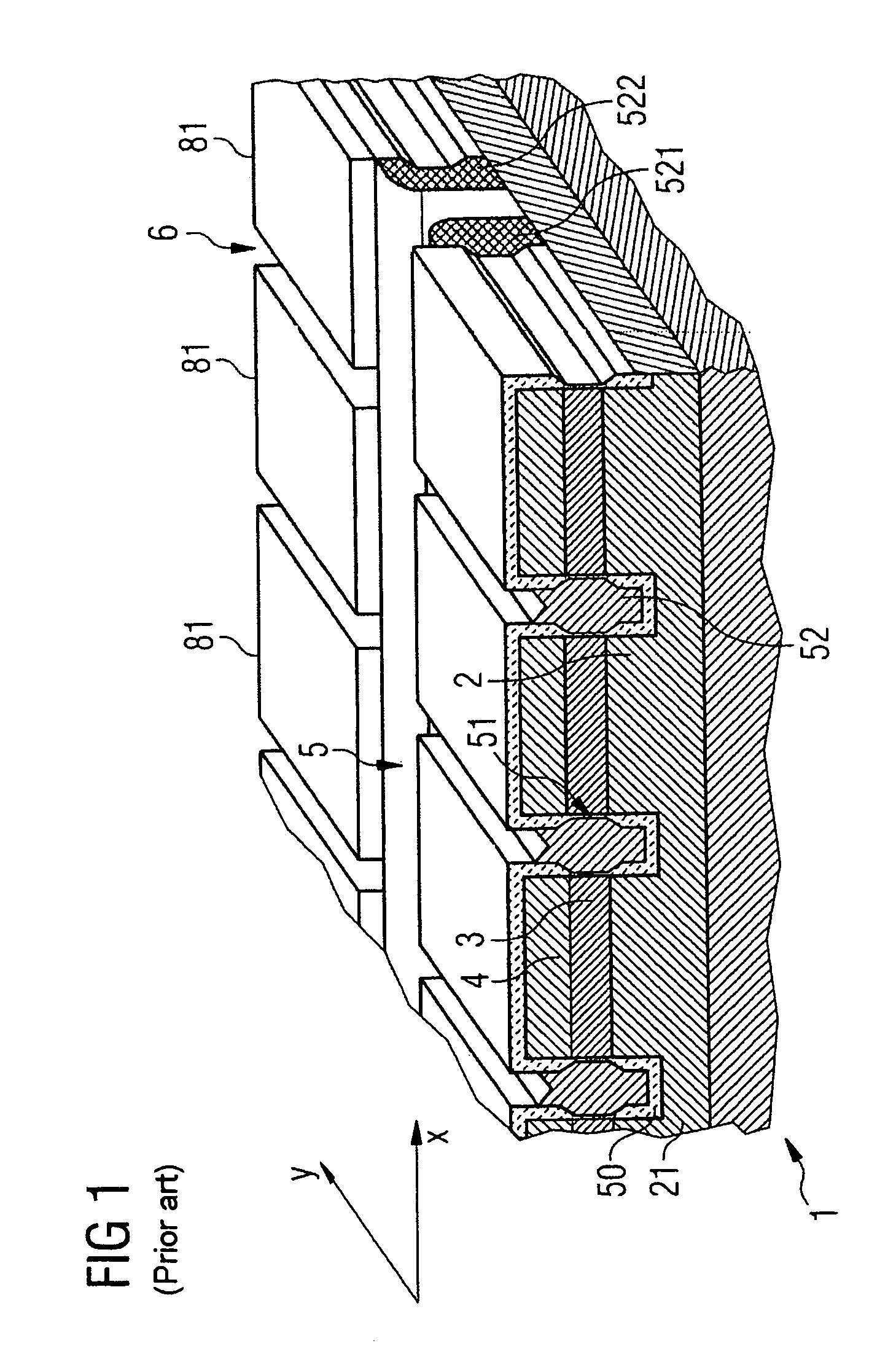

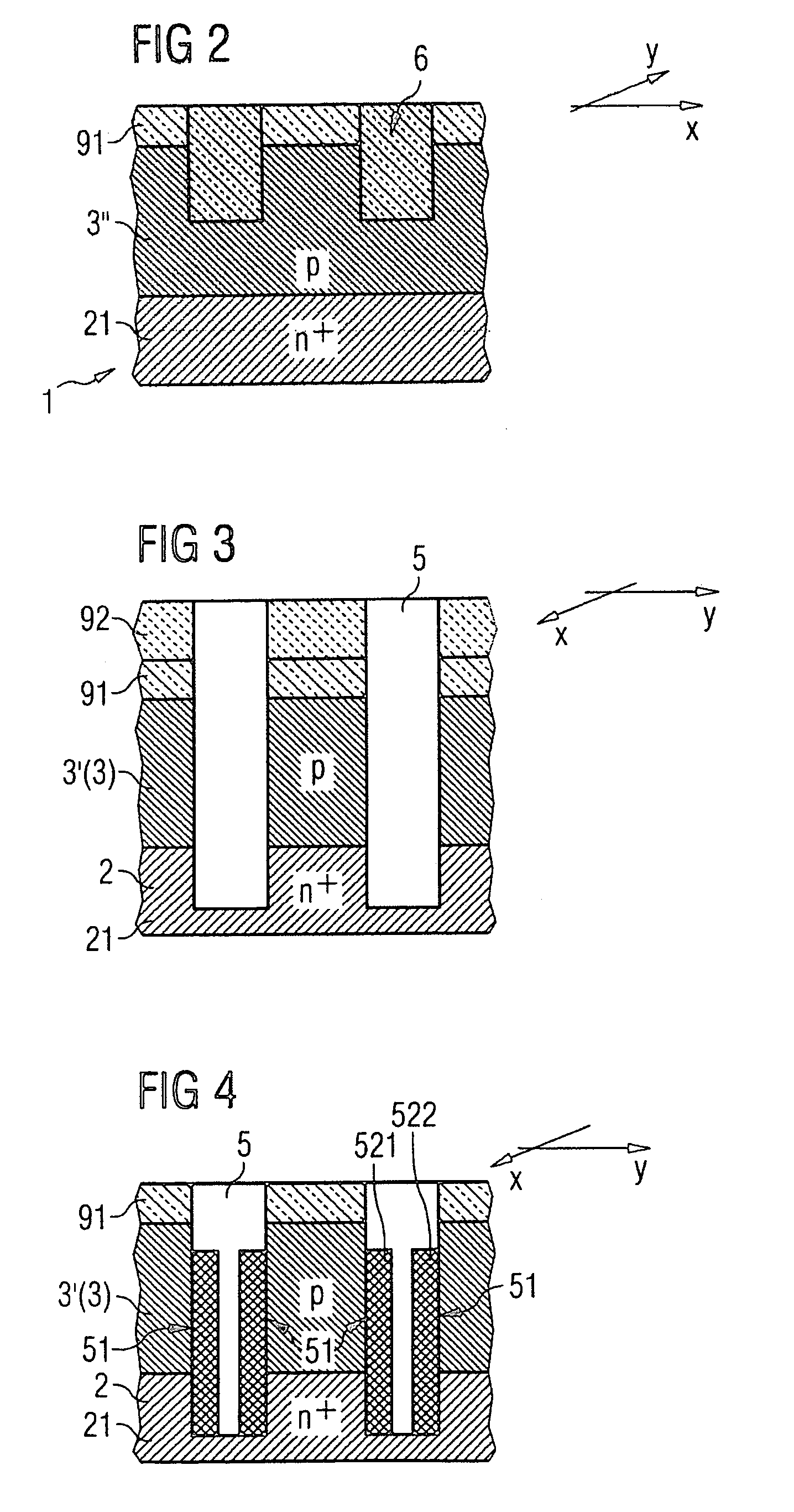

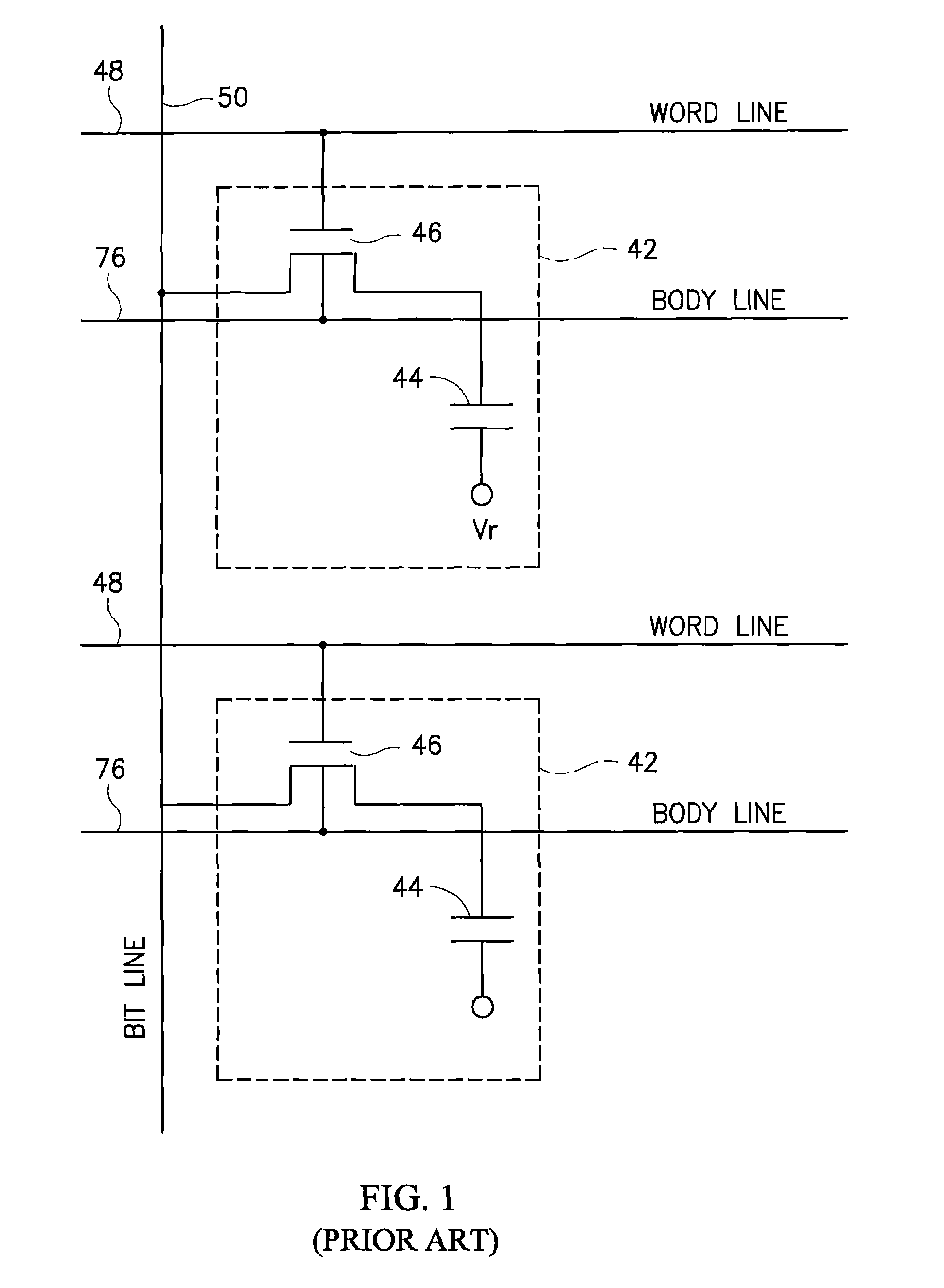

Architecture for vertical transistor cells and transistor-controlled memory cells

InactiveUS7109544B2Meet growth requirementsFunctional restriction of the transistor cells by a floating body effect is reducedTransistorSolid-state devicesTransistor arrayFloating body effect

Owner:POLARIS INNOVATIONS LTD

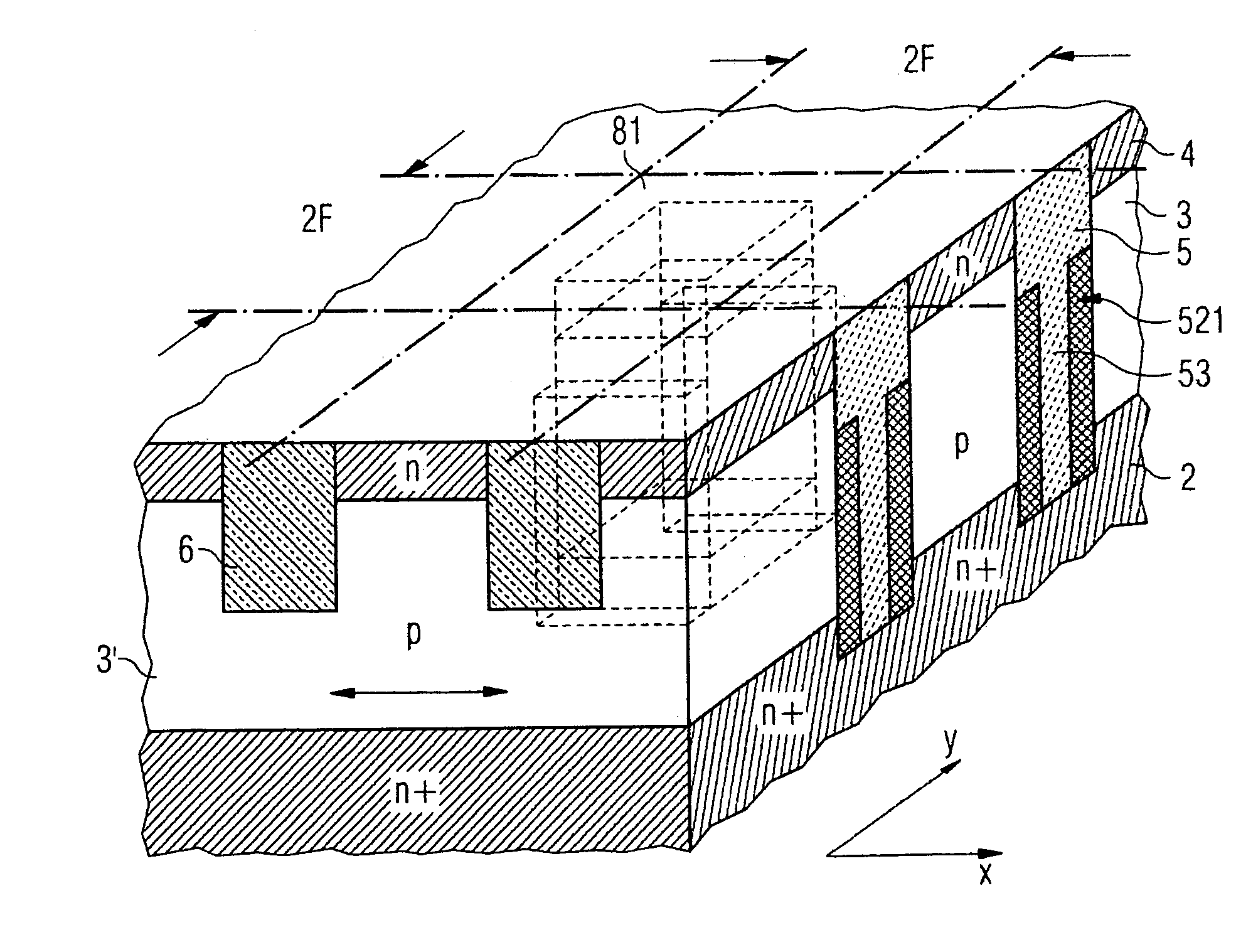

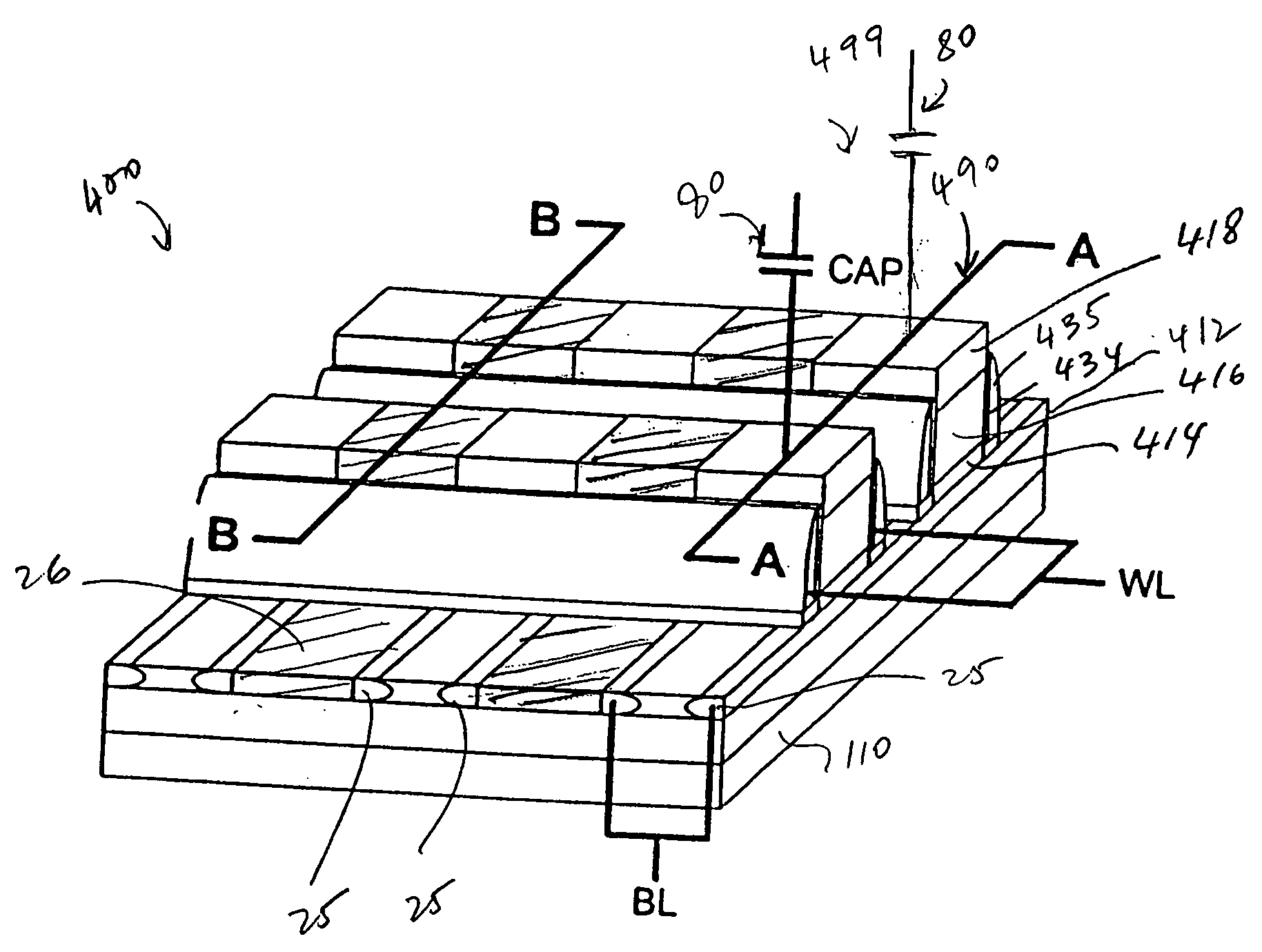

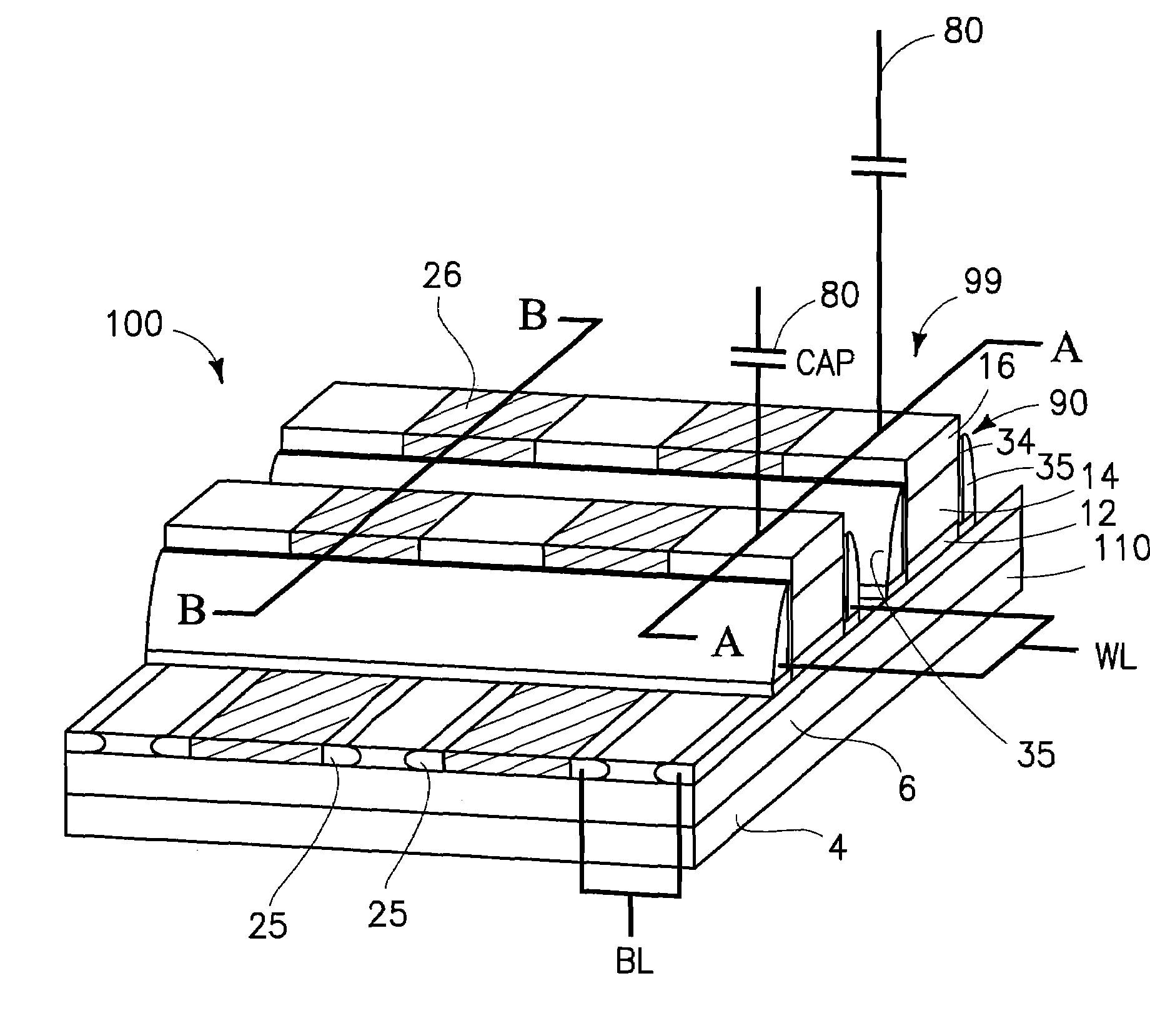

DRAM layout with vertical FETS and method of formation

DRAM cell arrays having a cell area of about 4F2 comprise an array of vertical transistors with buried bit lines and vertical double gate electrodes. The buried bit lines comprise a silicide material and are provided below a surface of the substrate. The word lines are optionally formed of a silicide material and form the gate electrode of the vertical transistors. The vertical transistor may comprise sequentially formed doped polysilicon layers or doped epitaxial layers. At least one of the buried bit lines is orthogonal to at least one of the vertical gate electrodes of the vertical transistors.

Owner:MICRON TECH INC

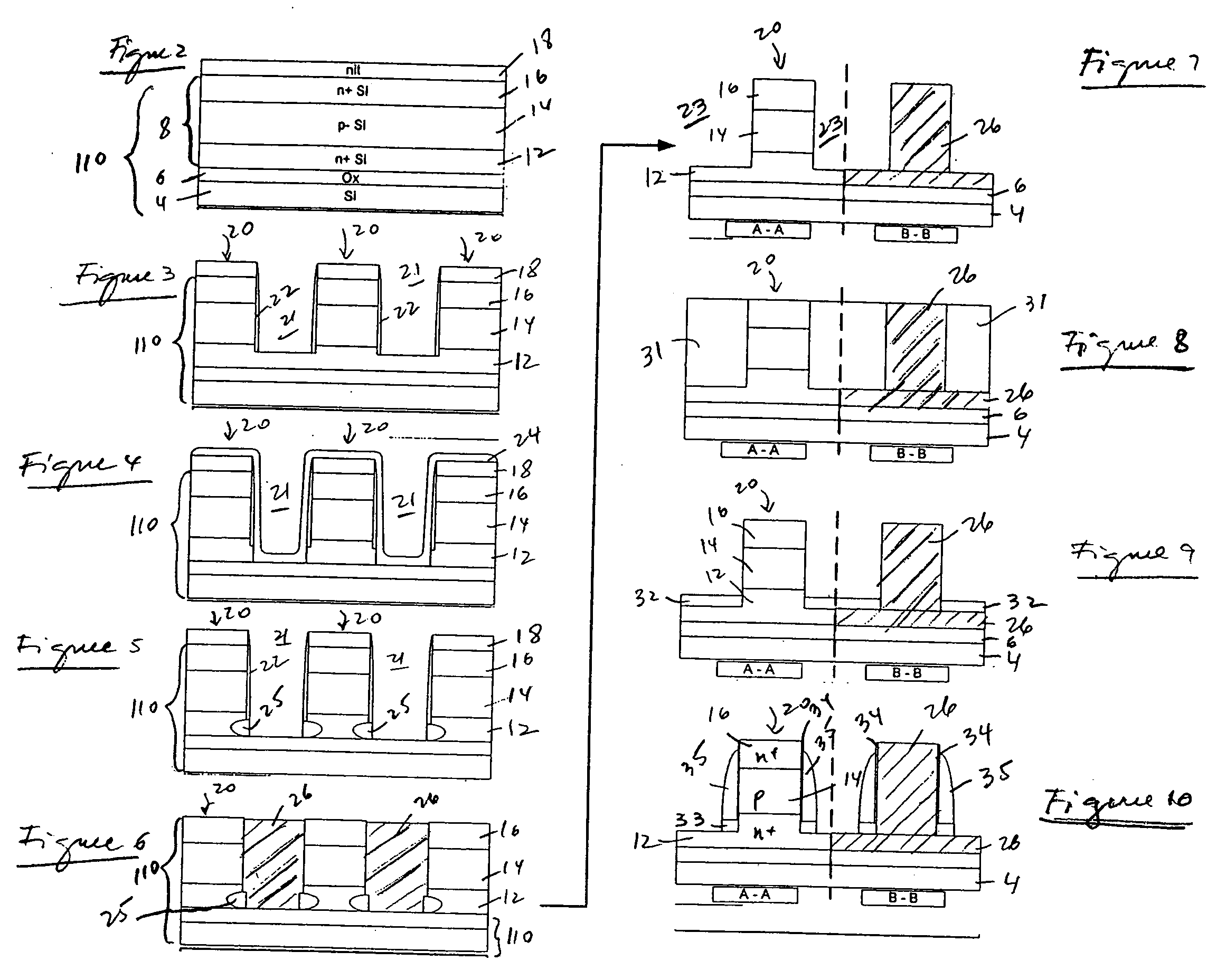

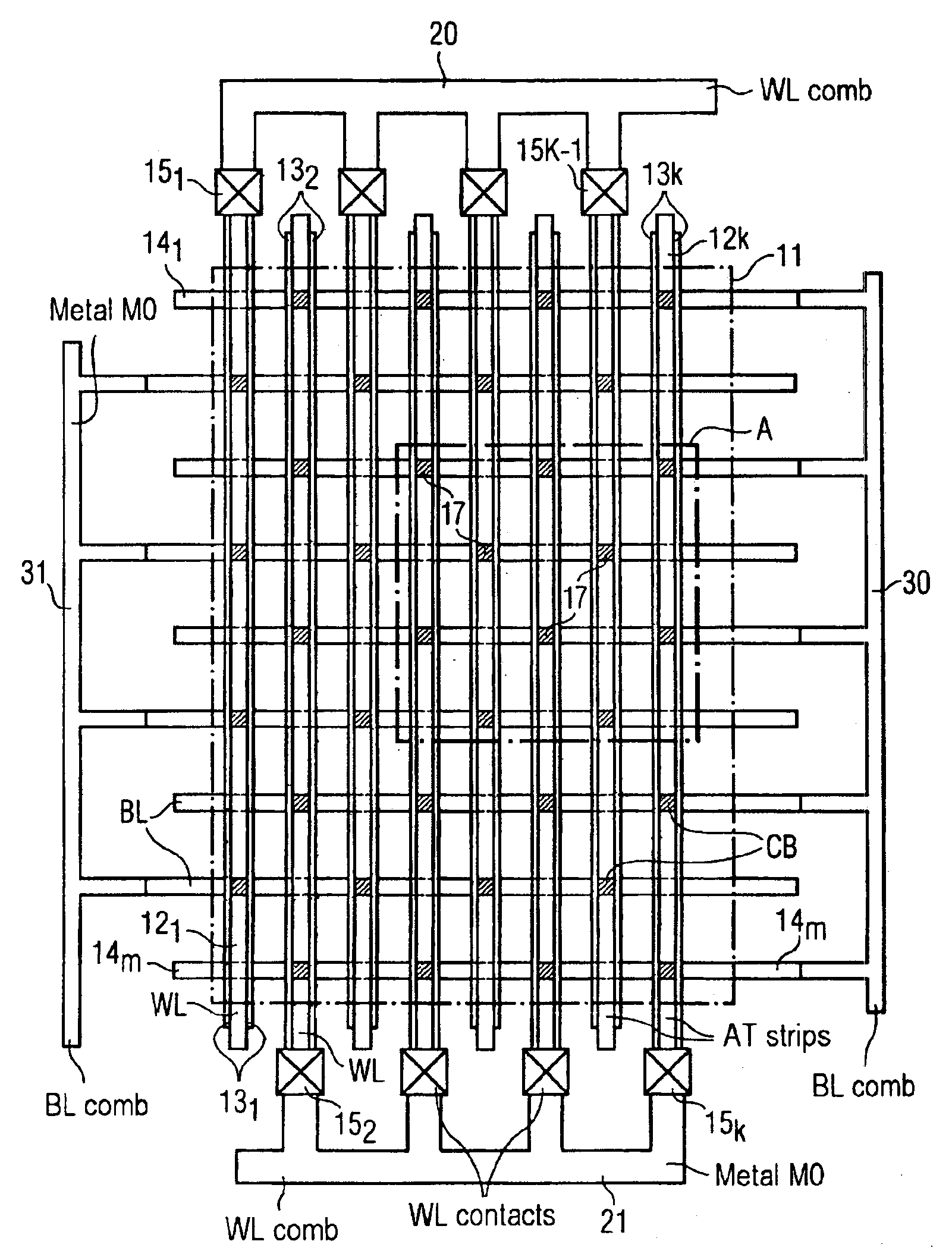

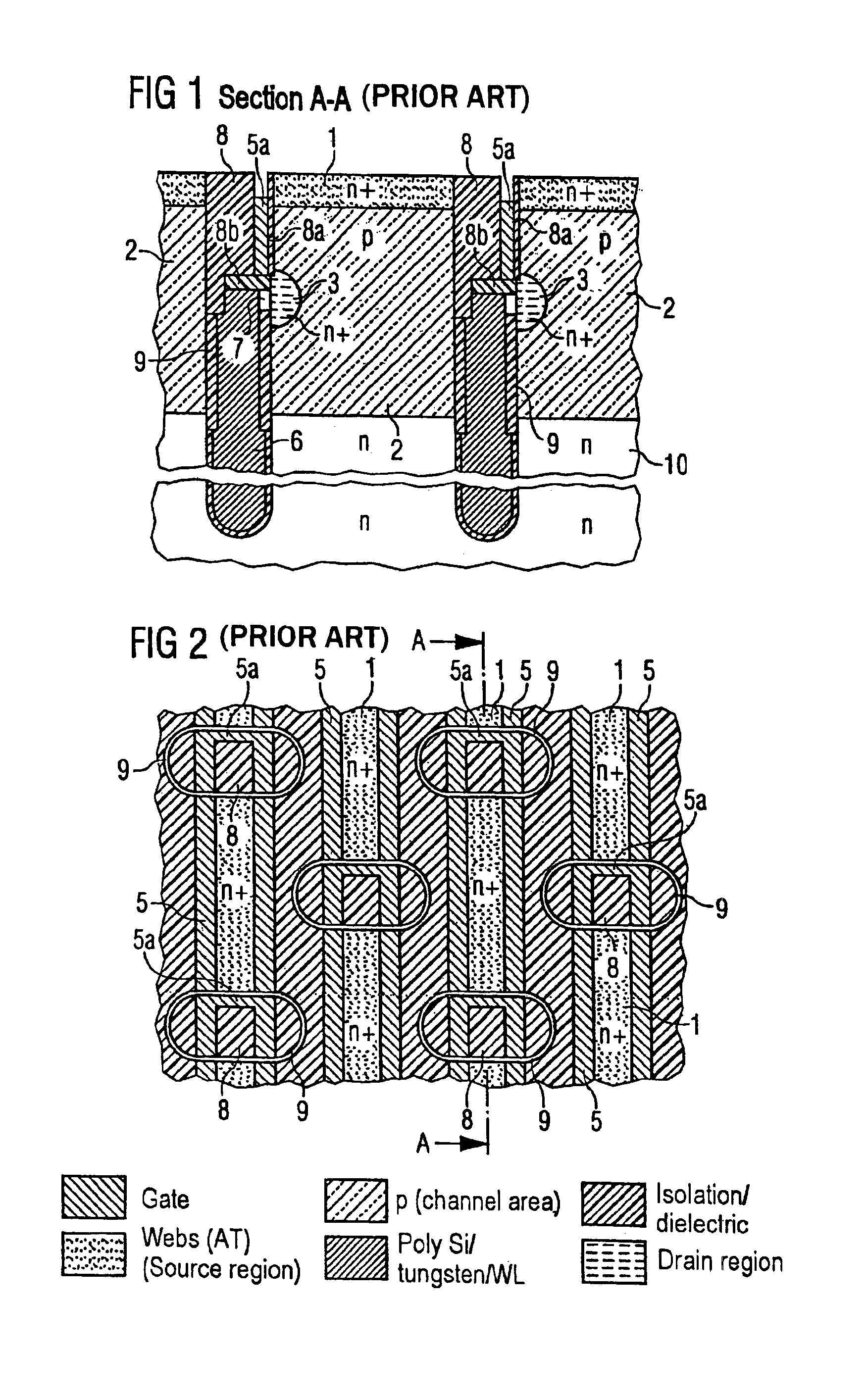

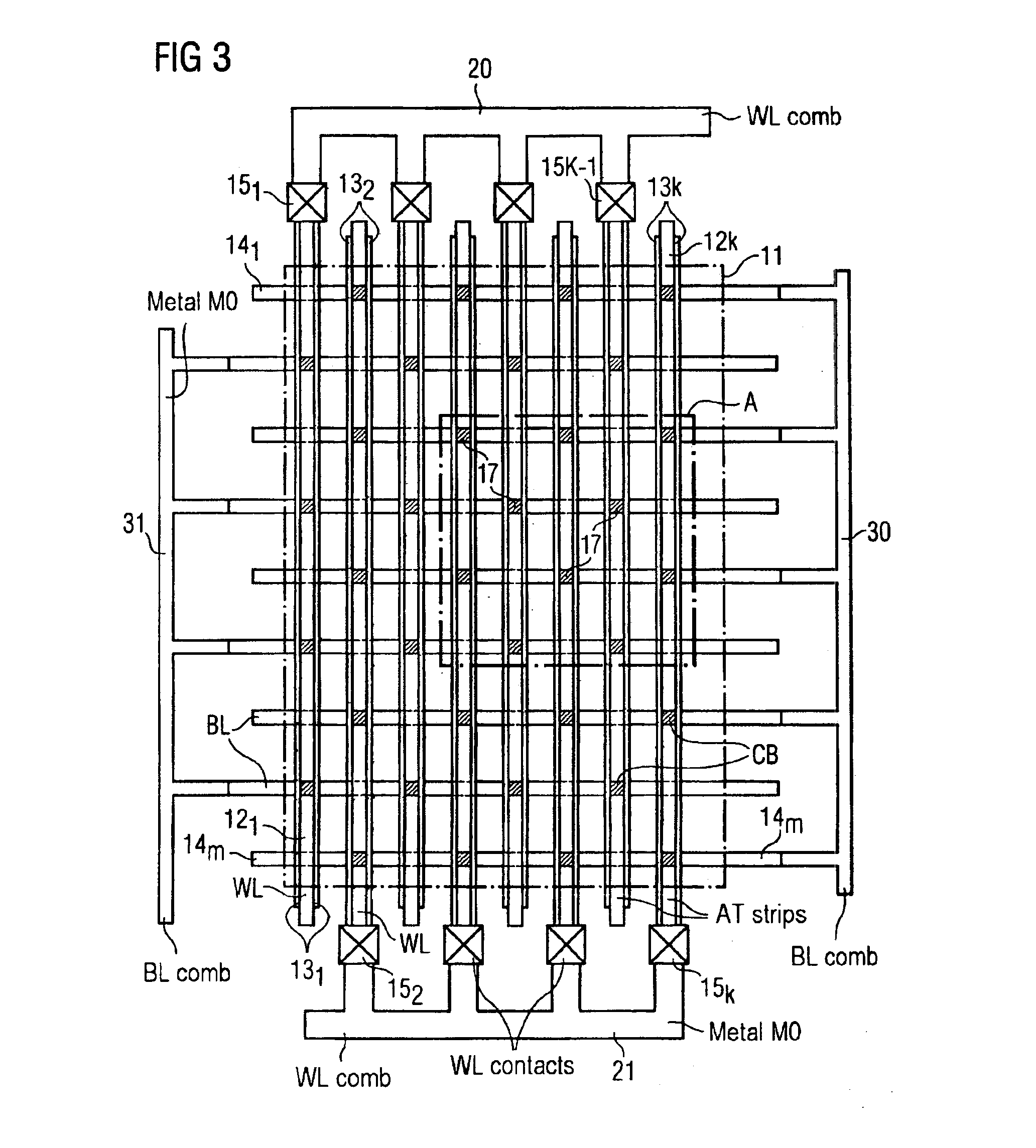

Device architecture and process for improved vertical memory arrays

InactiveUS6930324B2TransistorSemiconductor/solid-state device testing/measurementTransistor arrayDielectric

An array process diagnosis test structure for an integrated circuit including a transistor array composed of vertical FET memory cell access transistors, which are formed into the depth of a substrate in the form of active webs which run parallel in the lateral direction of the circuit is disclosed. Memory cell storage capacitors in the array test structure are formed in deep trenches on the end faces of those sections of the active webs which form the vertical FET transistors. Word lines are arranged along the webs and along parallel intersecting bit lines of the array, outside of which, and on two mutually opposite edges, are located a first and second word line comb. The wordline combs are offset and connected alternately to different word lines. In addition, a first and a second bit line comb are formed on the two other opposing edges of the transistor array mutually offset and each connected to different bit lines. The test structure provides a convenient means to carry out reliability investigations on the gate oxide of the vertical FET transistors and on the capacitor dielectric in the deep trenches, capacitance measurements between the word lines, and between the word lines and other circuit layers, as well as capacitance measurements between the bit lines and between the bit lines and other circuit layers, and thus facilitates diagnosis of possible fault sources arising during the production process.

Owner:POLARIS INNOVATIONS

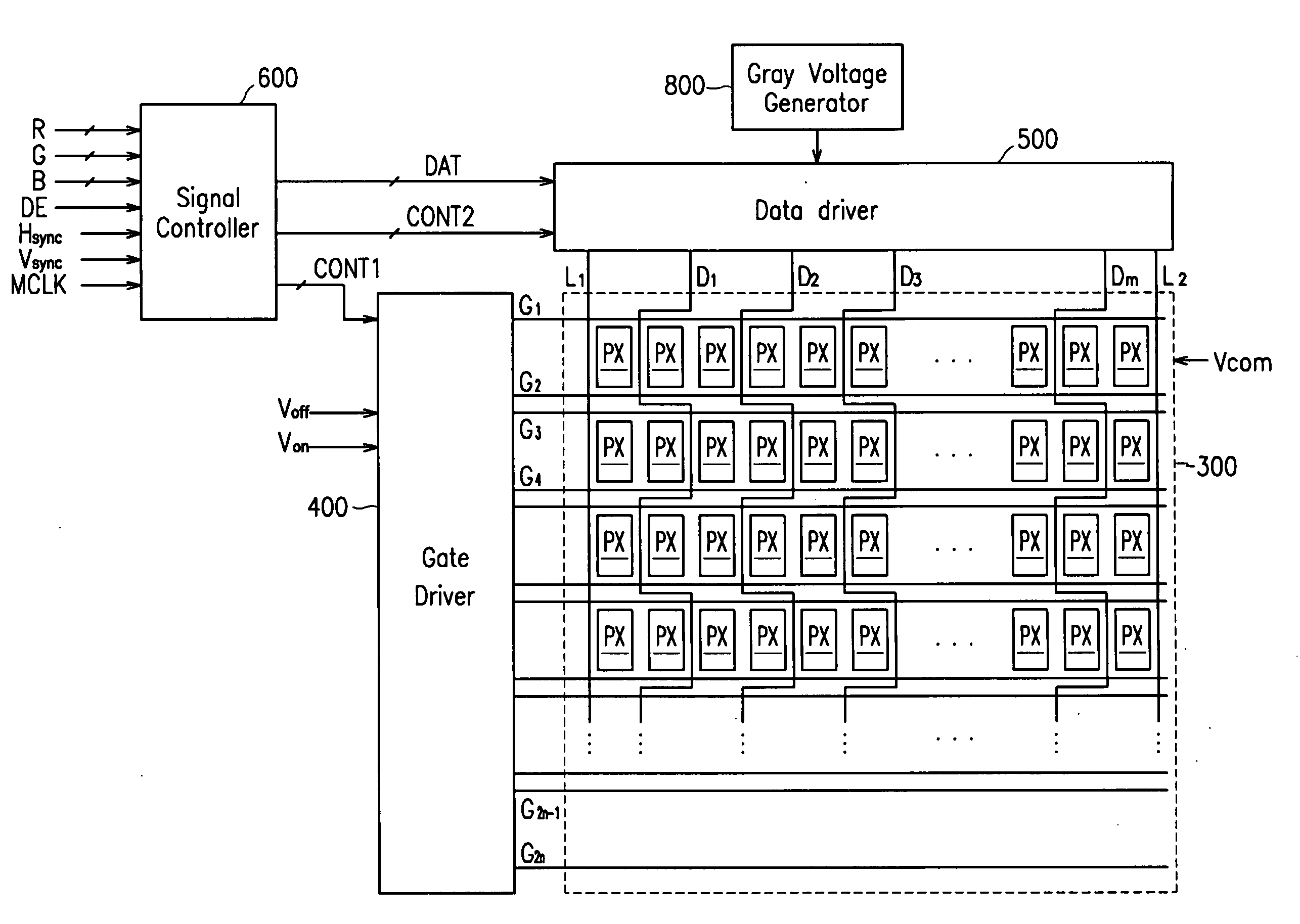

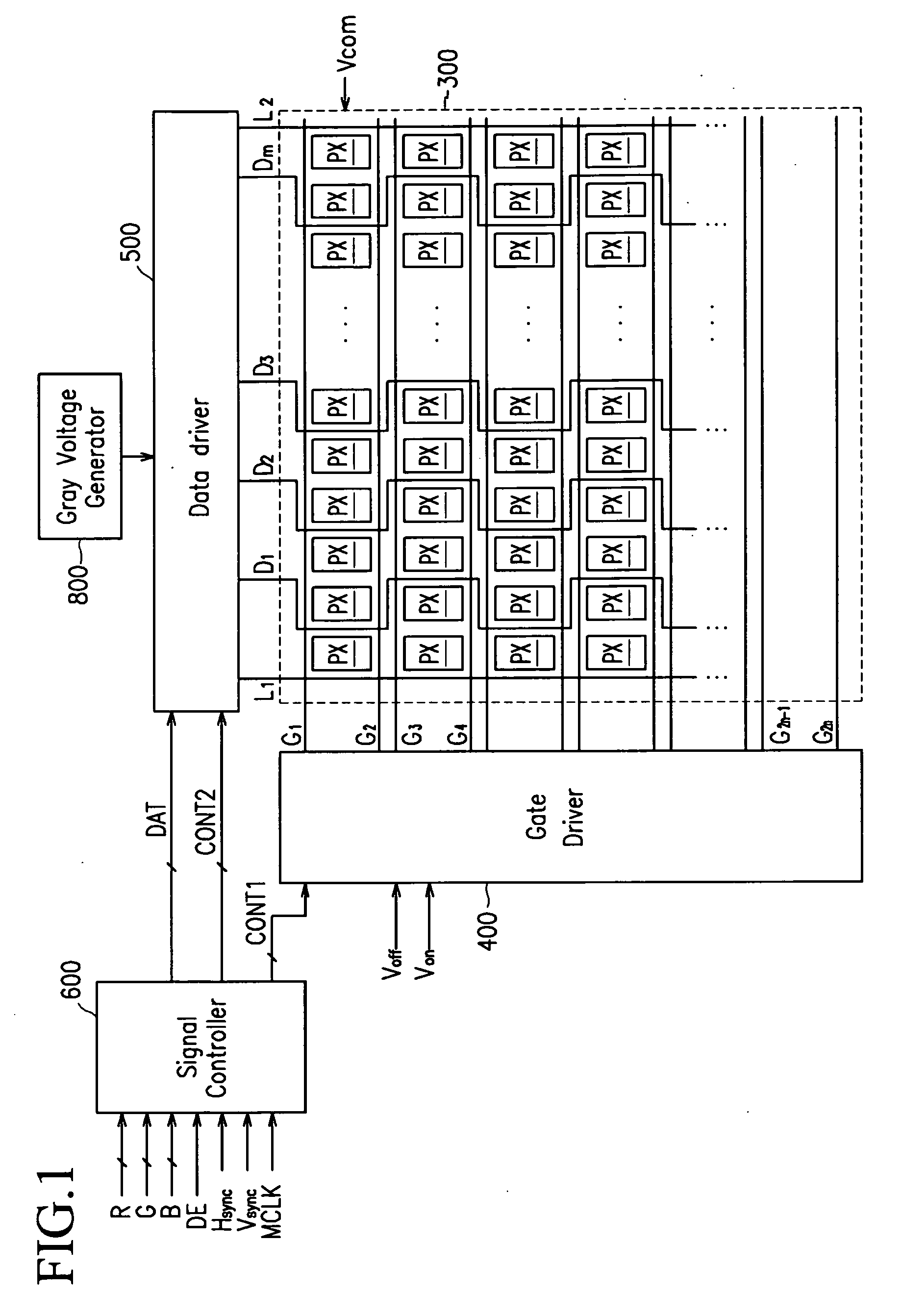

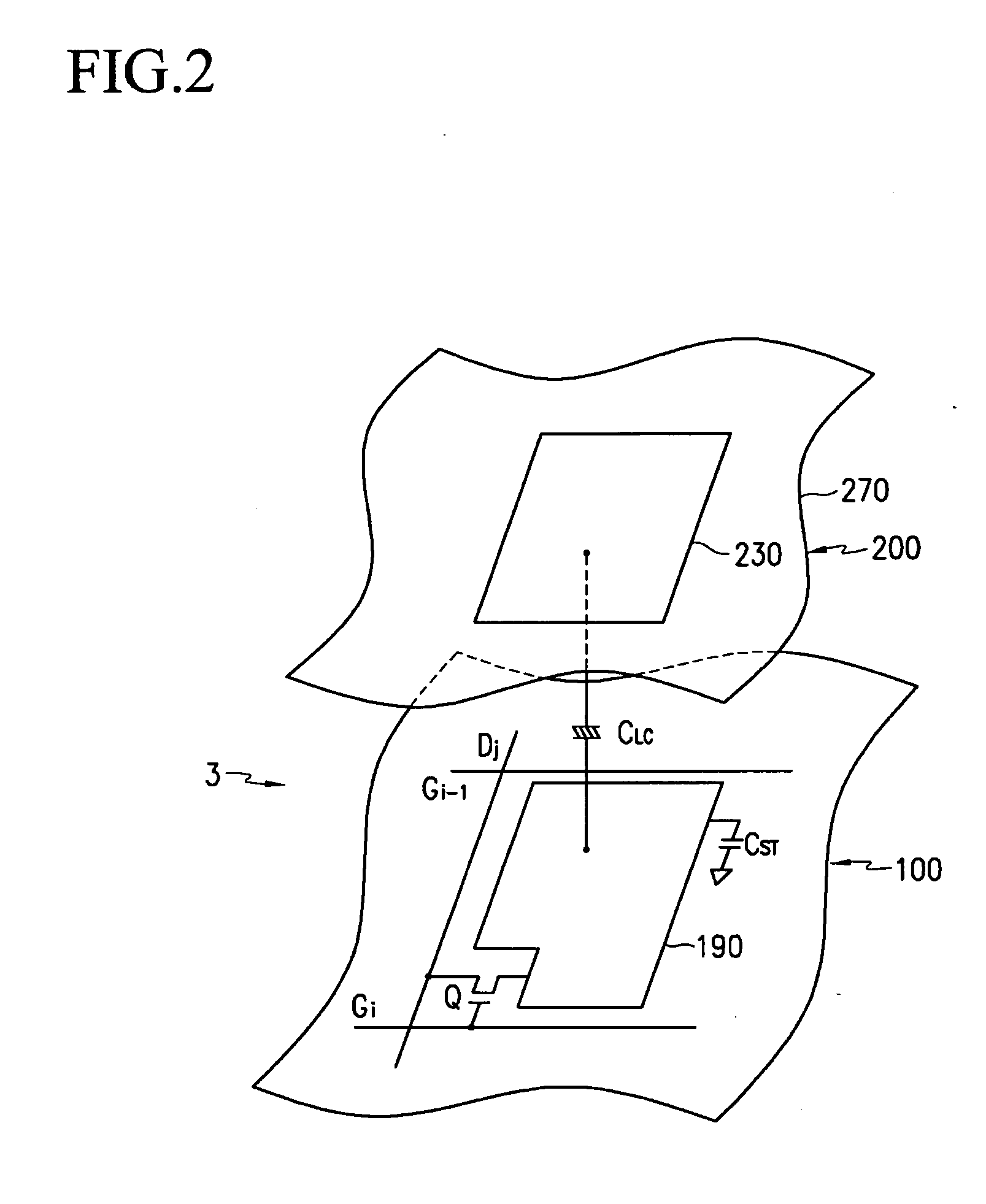

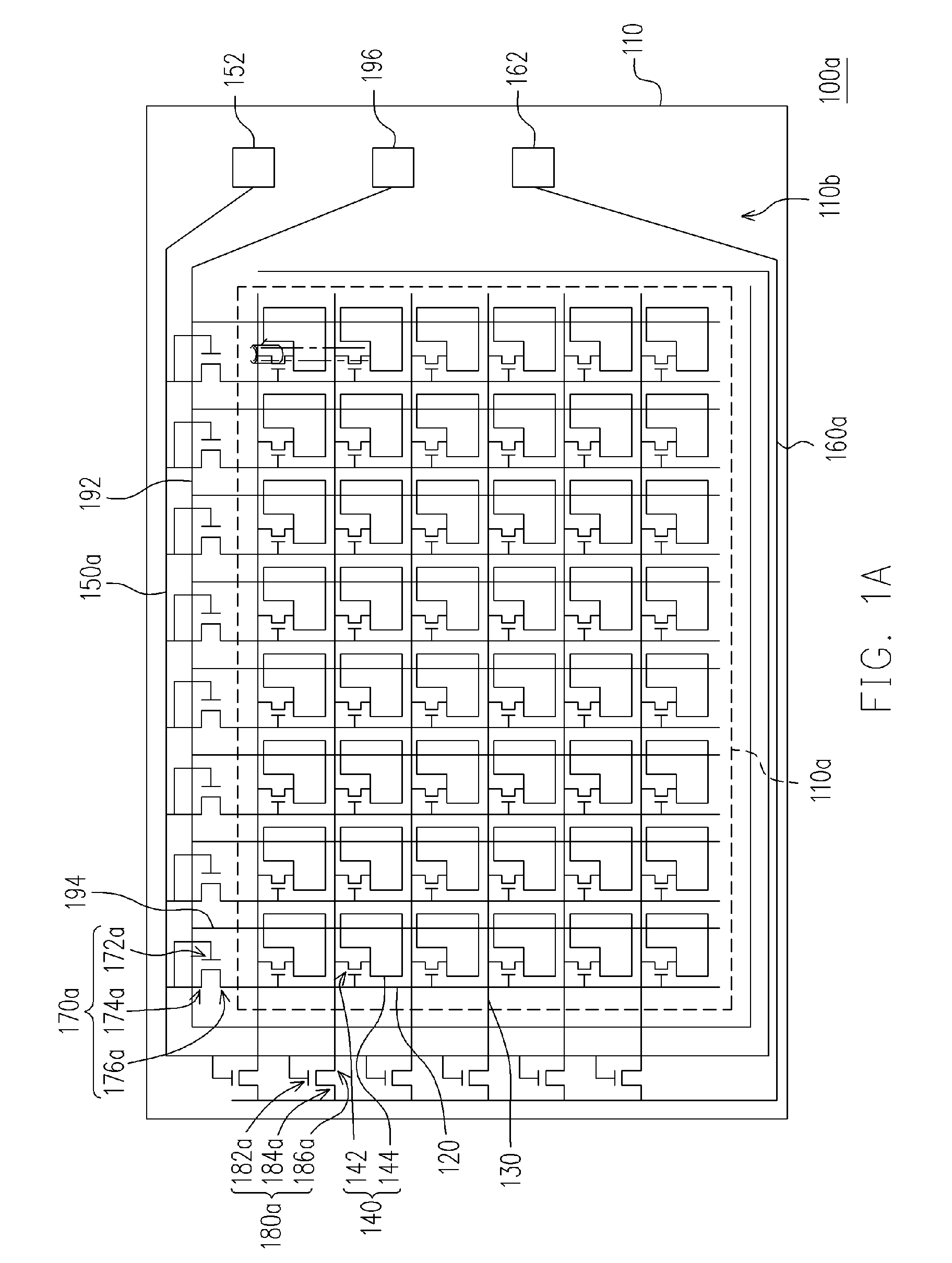

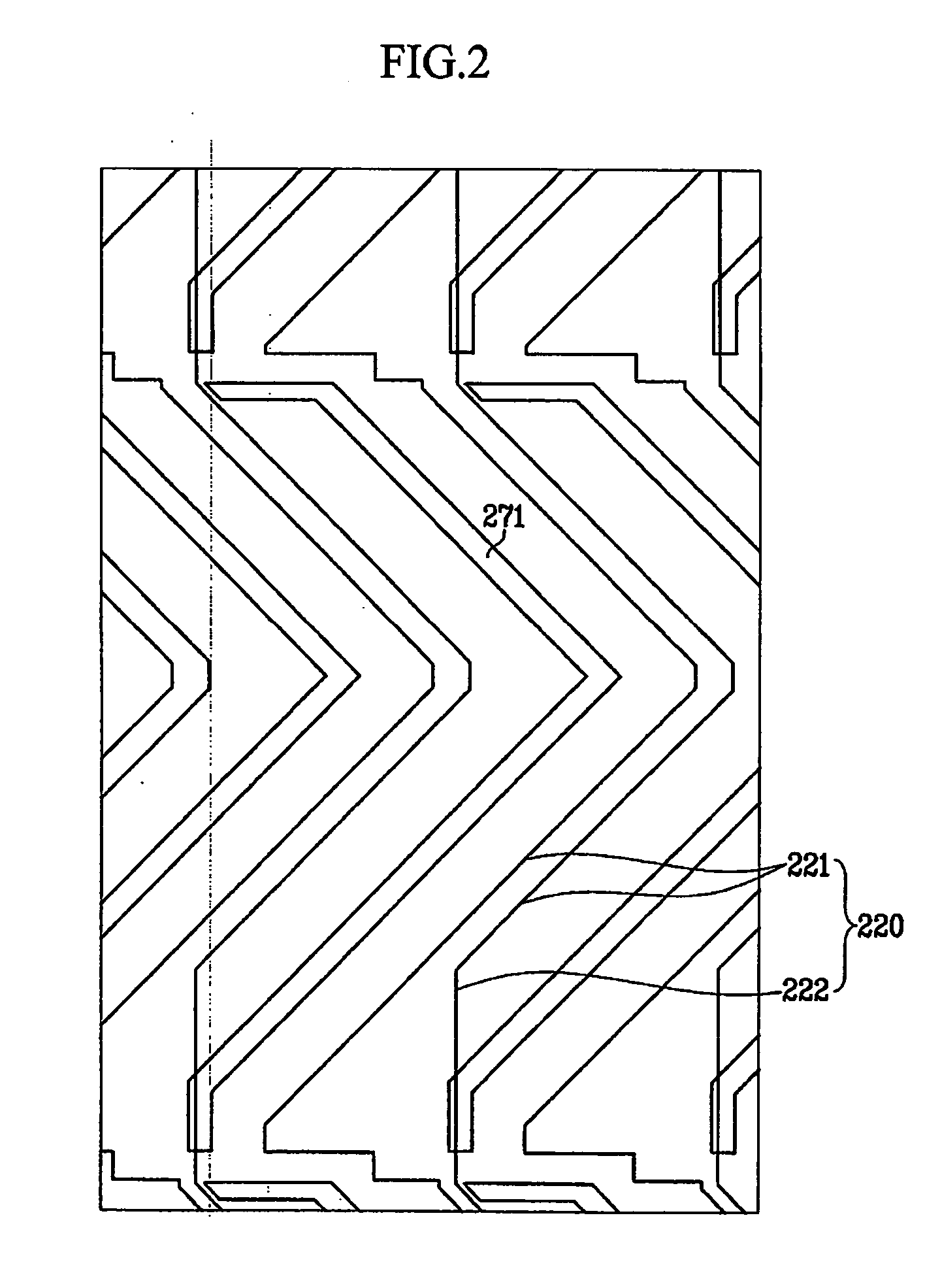

Thin film transistor array panel and display device

ActiveUS20060164350A1Low production costReduce the number of drivesStatic indicating devicesNon-linear opticsTransistor arrayDisplay device

Disclosed is a thin film transistor array panel. The panel includes a plurality of pixels arranged in the form of a matrix each with a pixel electrode and a switching element connected to the pixel electrode, and a plurality of gate lines connected to the switching elements and extending in the row direction. A pair of the gate lines are connected to pixels in each pixel row. A plurality of data lines are connected to the switching elements, and elongated in the column direction. Each data line is provided between two columns of the pixels. The respective data lines are horizontally bent between the two adjacent gate lines, and vertically extend between the two pixel rows.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

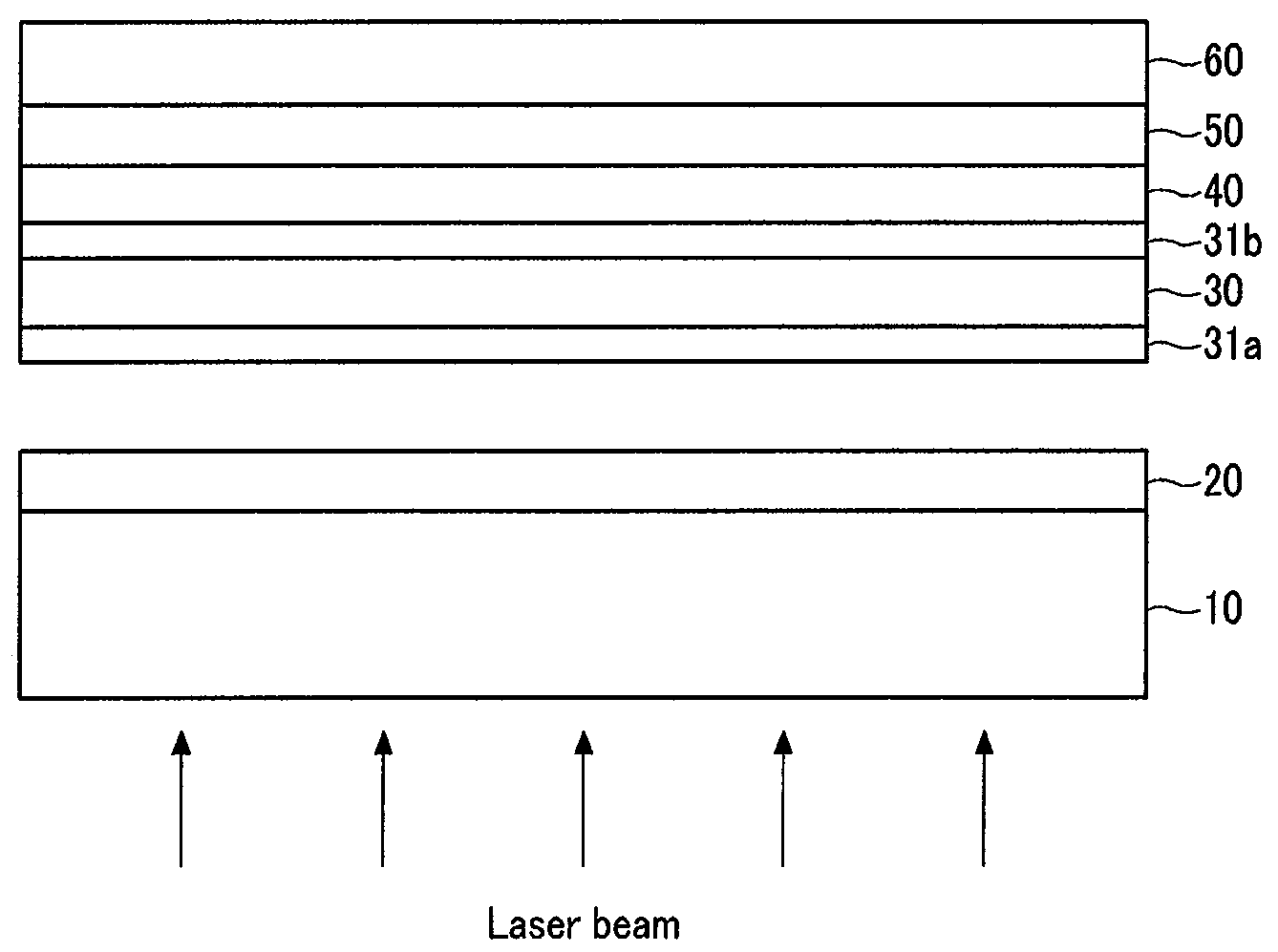

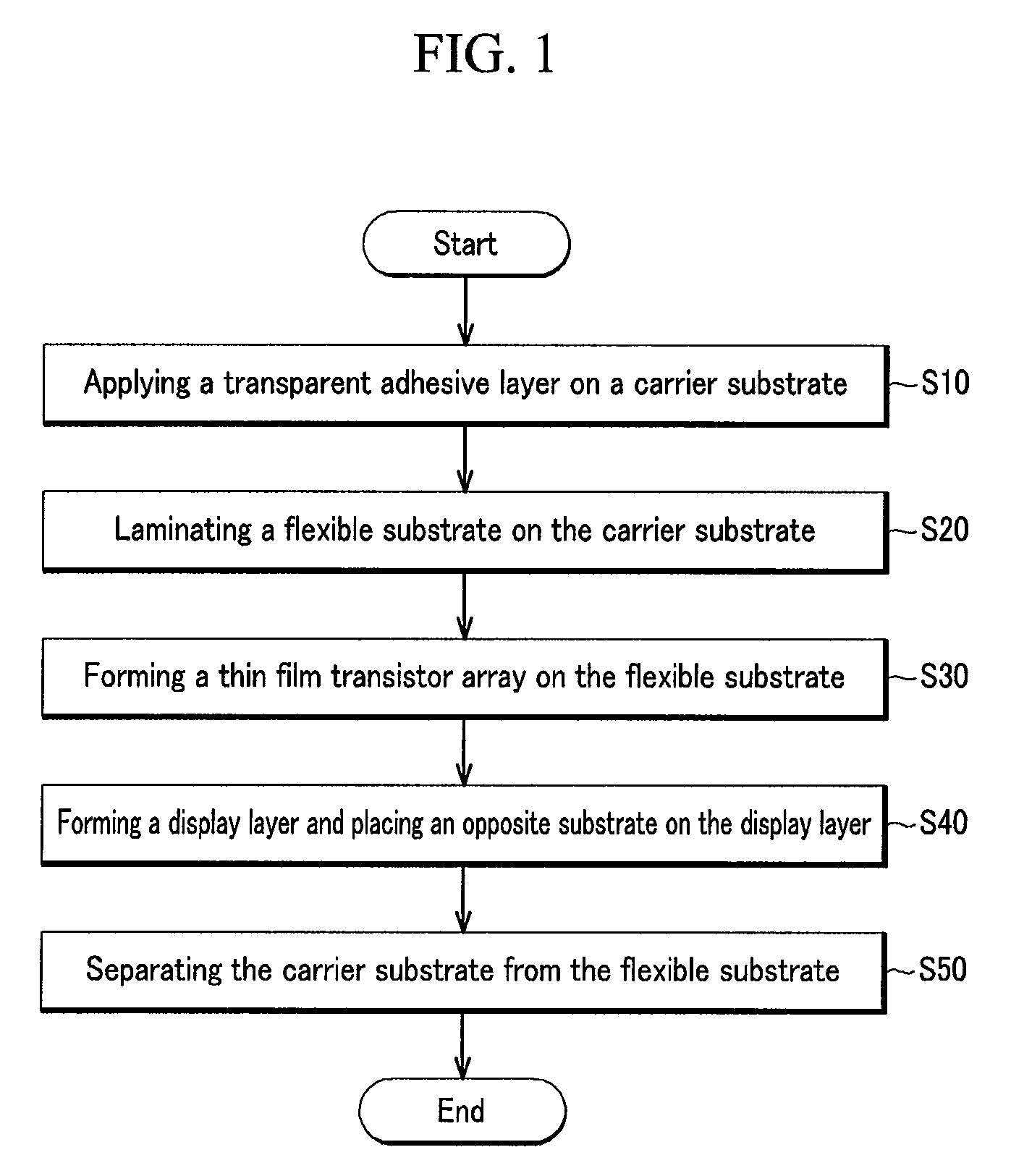

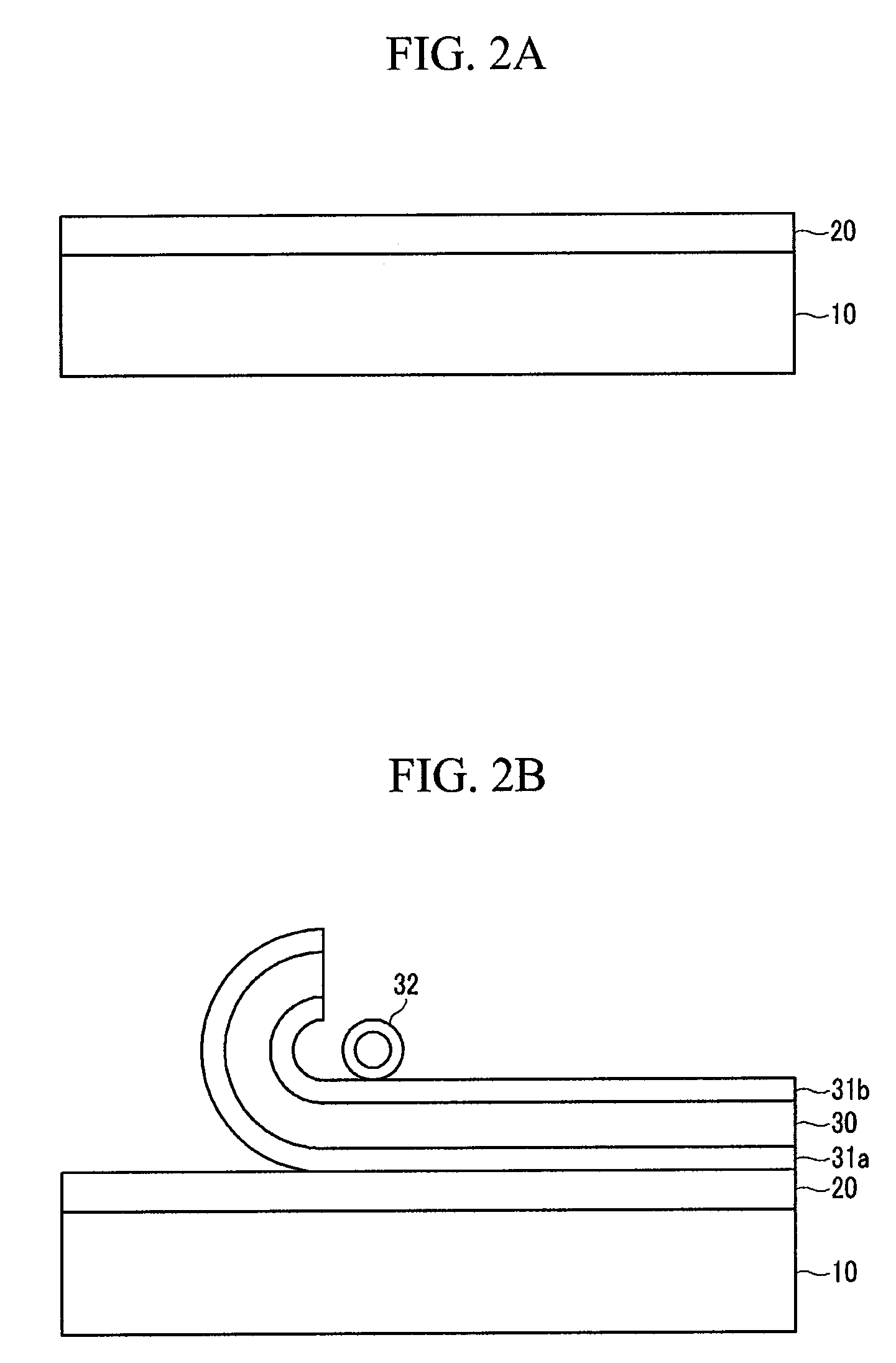

Method of fabricating flexible display device

ActiveUS20090266471A1Photography auxillary processesPhotosensitive materialsTransistor arrayEngineering

A method of fabricating a flexible display device, the method including applying a transparent adhesive layer on a carrier substrate, laminating a flexible substrate comprising a barrier layer on the transparent adhesive layer, forming a thin film transistor array on the flexible substrate, and separating the carrier substrate from the flexible substrate by irradiating a laser beam onto the barrier layer.

Owner:SAMSUNG DISPLAY CO LTD

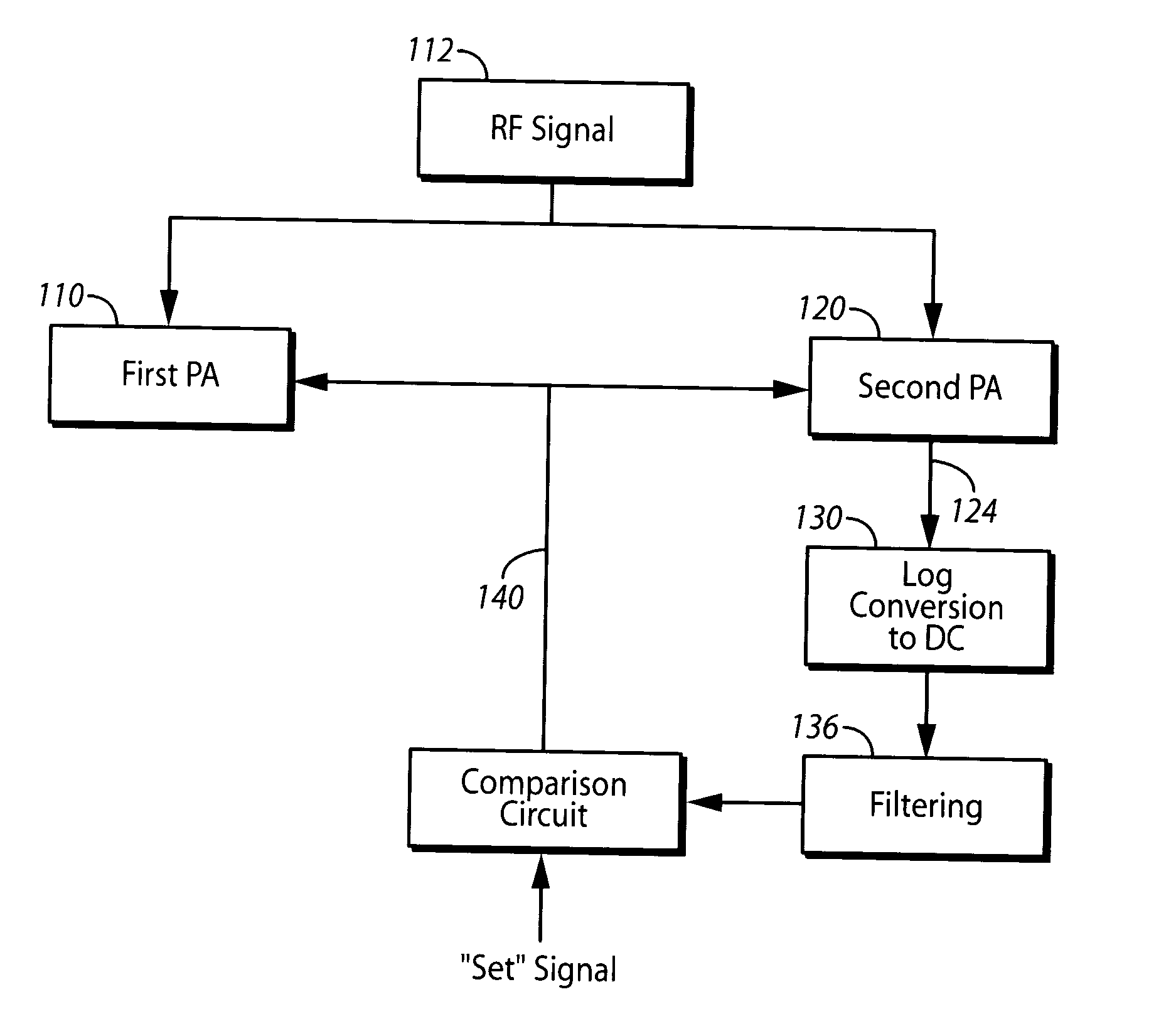

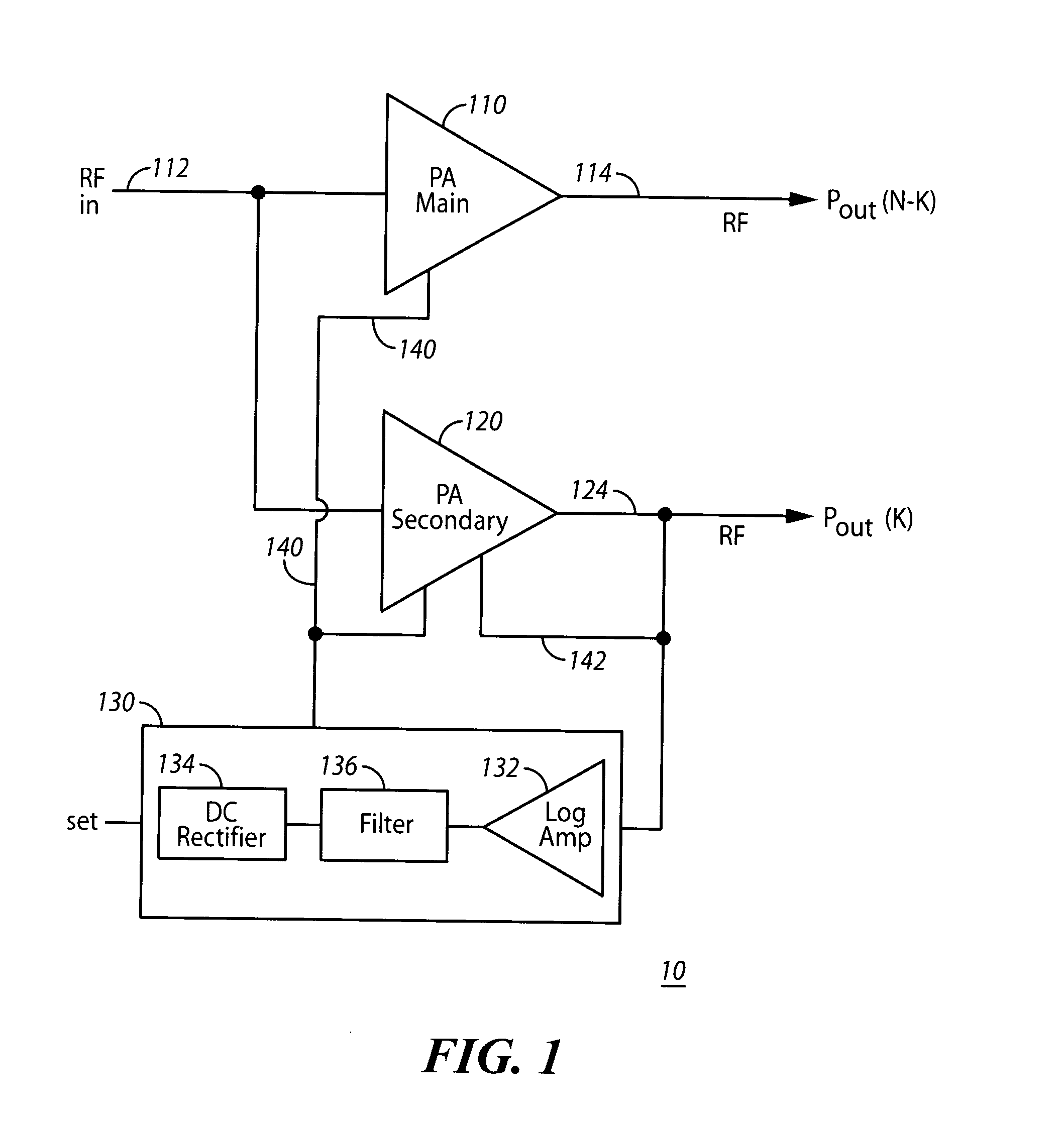

Radio frequency power detecting circuit and method therefor

A circuit for detecting the amount of radio frequency power provided by an amplifier. The circuit contains an array of coupled transistors in two power amplifiers, and a log-detector circuit, all resident on a single semiconductor die. The main power amplifier contains the larger array of transistors to amplify the radio frequency signal for feeding to an antenna, and a secondary power amplifier contains a smaller array of transistors to provide a scaled output that is proportional to the amplified radio frequency signal and is used to control the main power amplifier. The log-detector circuit converts the signal from the secondary power amplifier to a full-wave rectified log-linear DC signal that is logarithmically proportional to the controlling signal. The DC signal output from the log-detector circuit is fed to the main power amp to control it.

Owner:YUANTONIX

DRAM layout with vertical FETs and method of formation

DRAM cell arrays having a cell area of about 4F2 comprise an array of vertical transistors with buried bit lines and vertical double gate electrodes. The buried bit lines comprise a silicide material and are provided below a surface of the substrate. The word lines are optionally formed of a silicide material and form the gate electrode of the vertical transistors. The vertical transistor may comprise sequentially formed doped polysilicon layers or doped epitaxial layers. At least one of the buried bit lines is orthogonal to at least one of the vertical gate electrodes of the vertical transistors.

Owner:MICRON TECH INC

Method and apparatus for a fully digital quadrature modulator

ActiveUS7460612B2Little or no reuseMinimize impactSimultaneous amplitude and angle modulationPower amplifiersTransistor arrayQuadrature modulator

A novel apparatus and method for a fully digital quadrature architecture for a complex modulator. The complex modulator can substitute for existing prior art analog quadrature modulator structures and those based on a digital polar architecture (r, θ). The modulator effectively operates as a complex digital-to-analog converter where the digital inputs are given in Cartesian form, namely I and Q representing the complex number I+jQ, while the output is a modulated RF signal having a corresponding amplitude and phase shift. The phase shift being with respect to a reference phase dictated by the local oscillator, which is also input to the converter / modulator. Several embodiments are provided including modulators incorporating dual I and Q transistor arrays, a single shared I / Q transistor array, modulators with single ended and differential outputs and modulators with single and dual polarity clock and I / Q data signals.

Owner:TEXAS INSTR INC

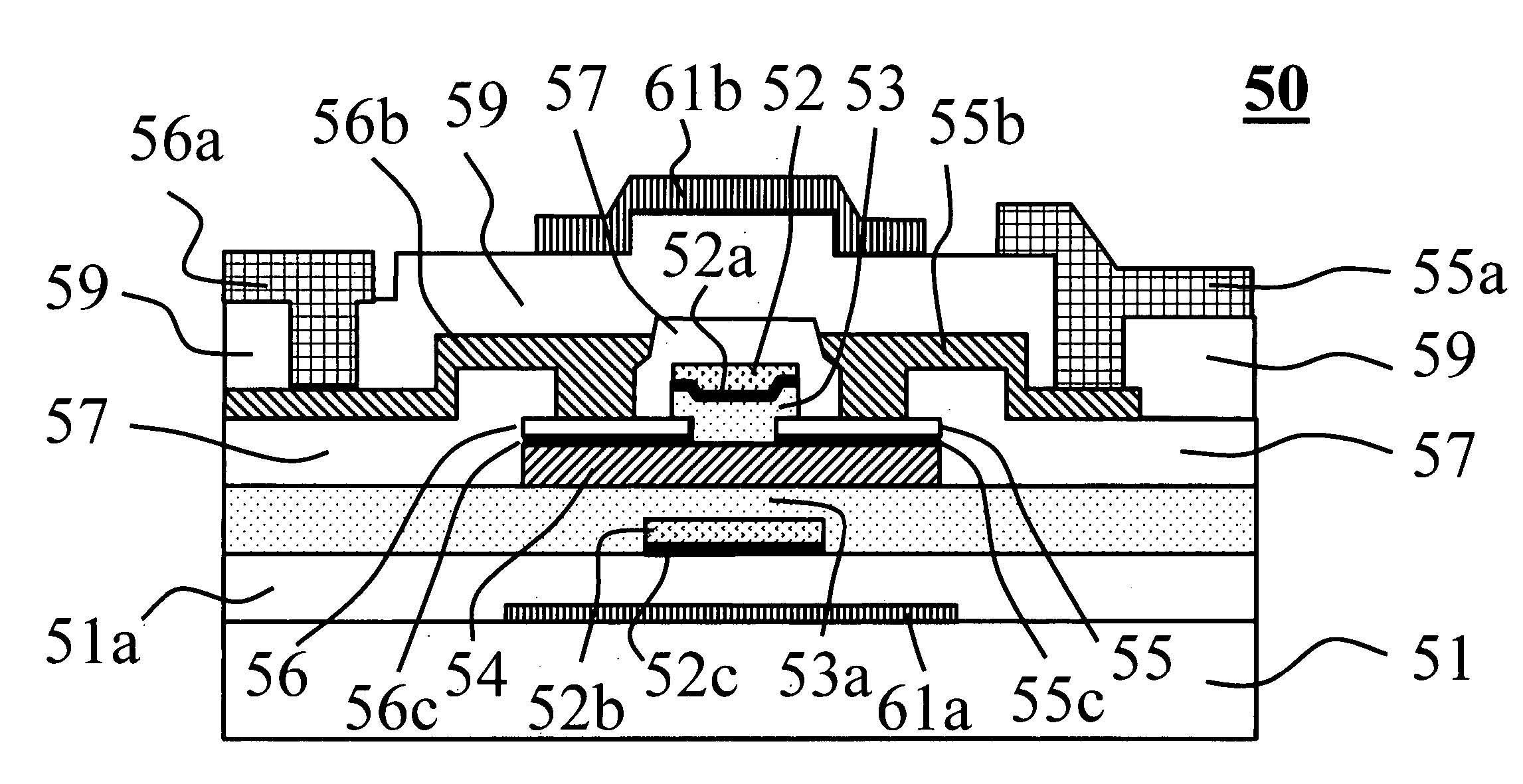

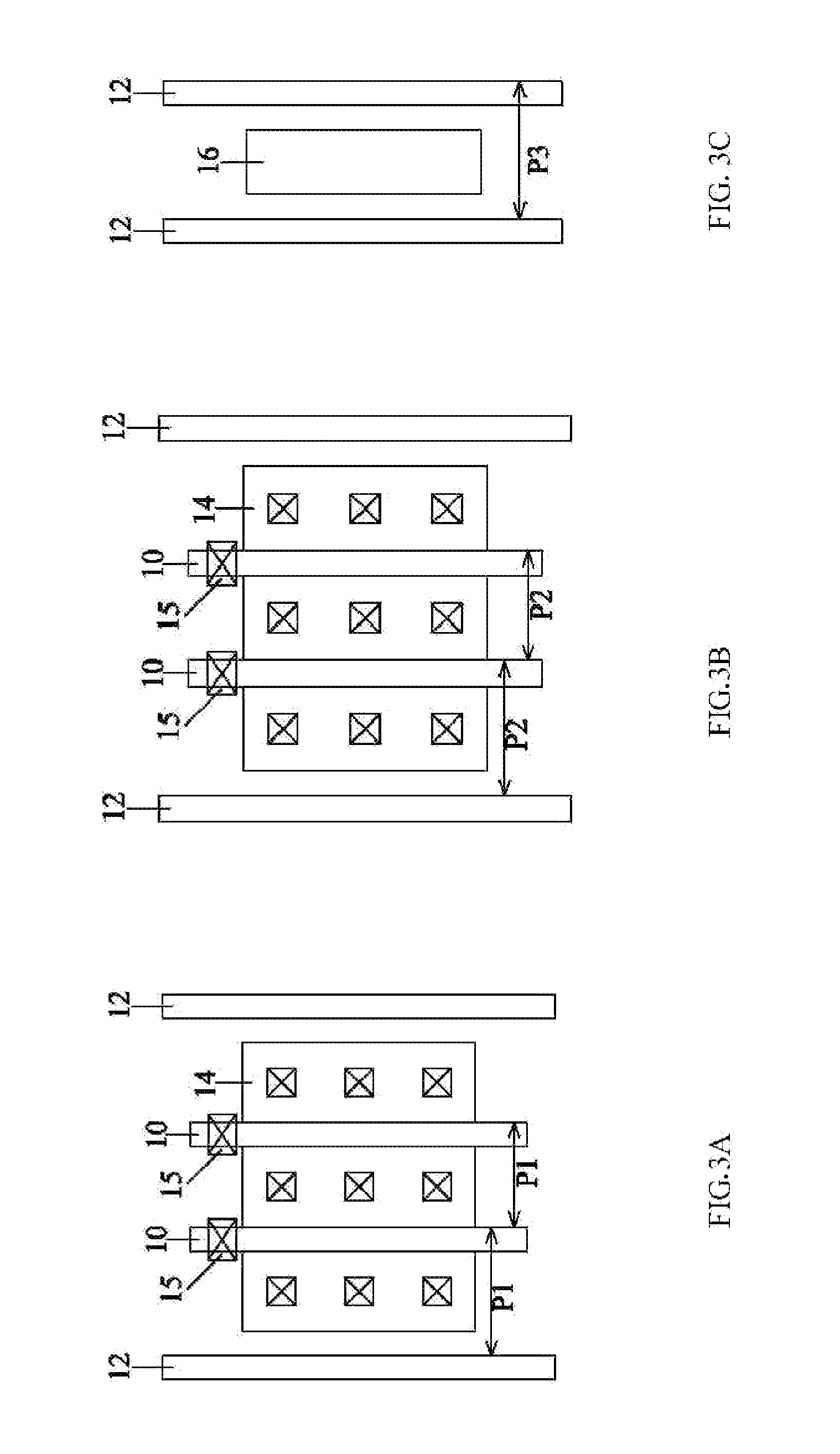

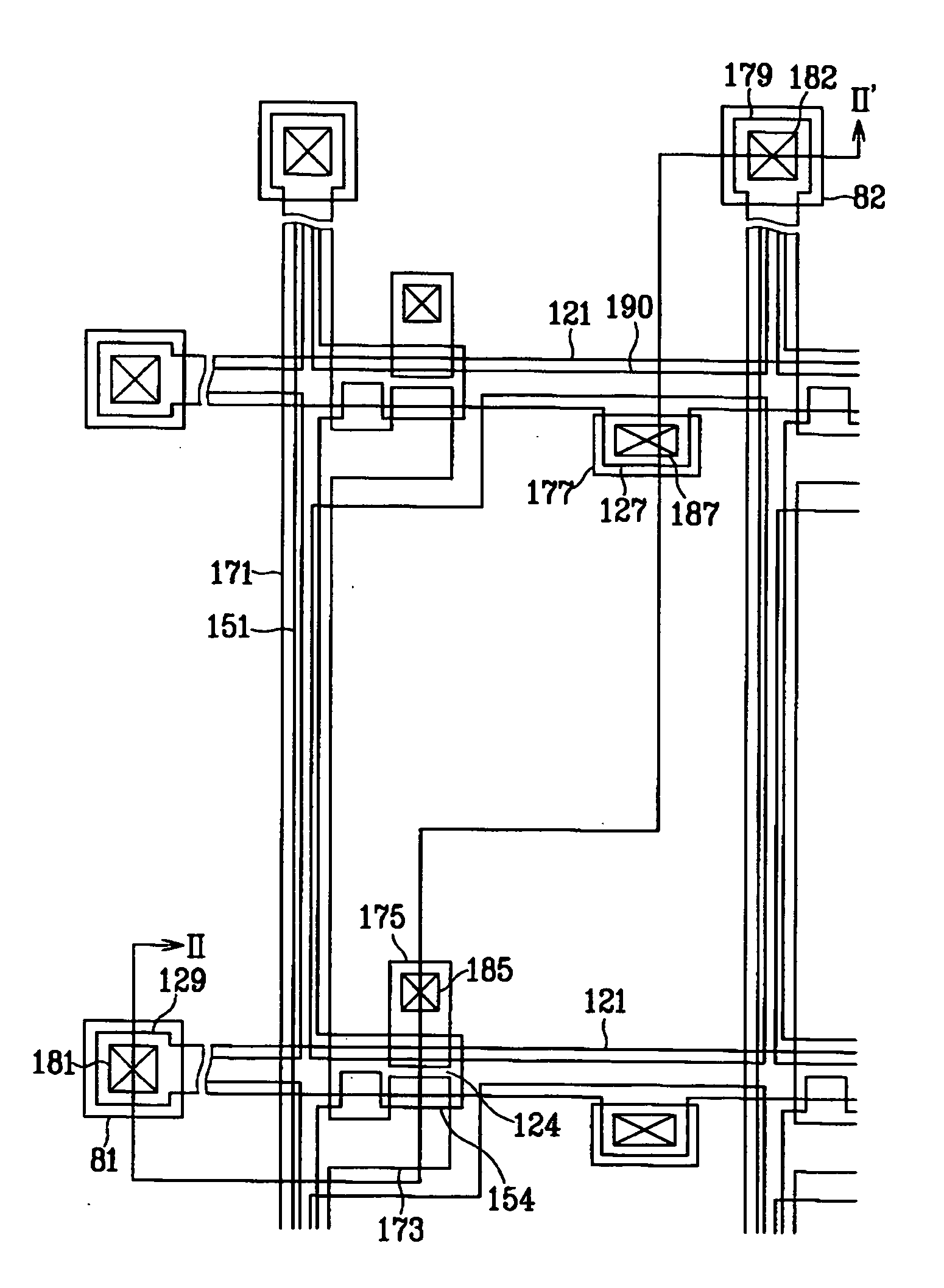

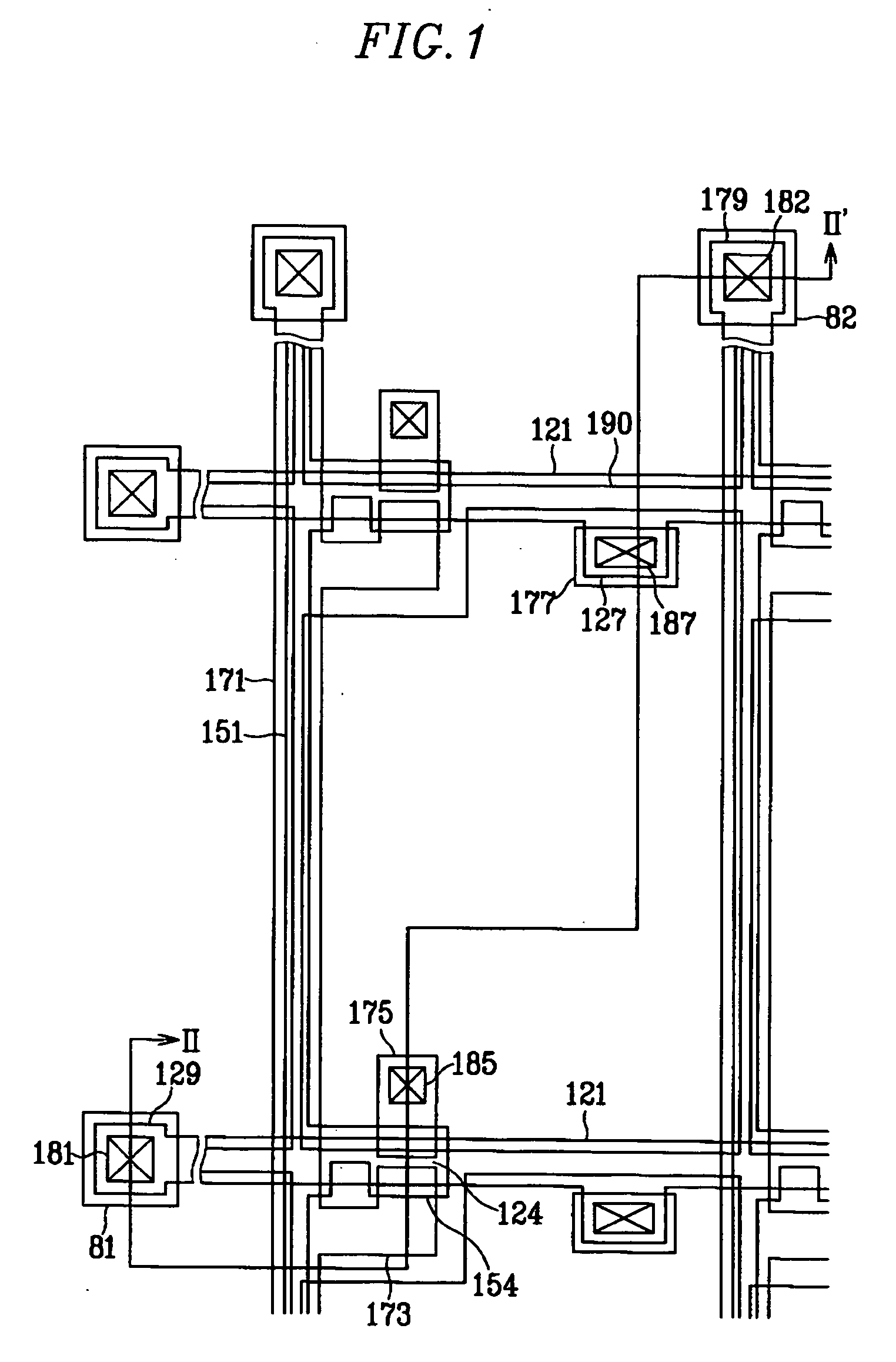

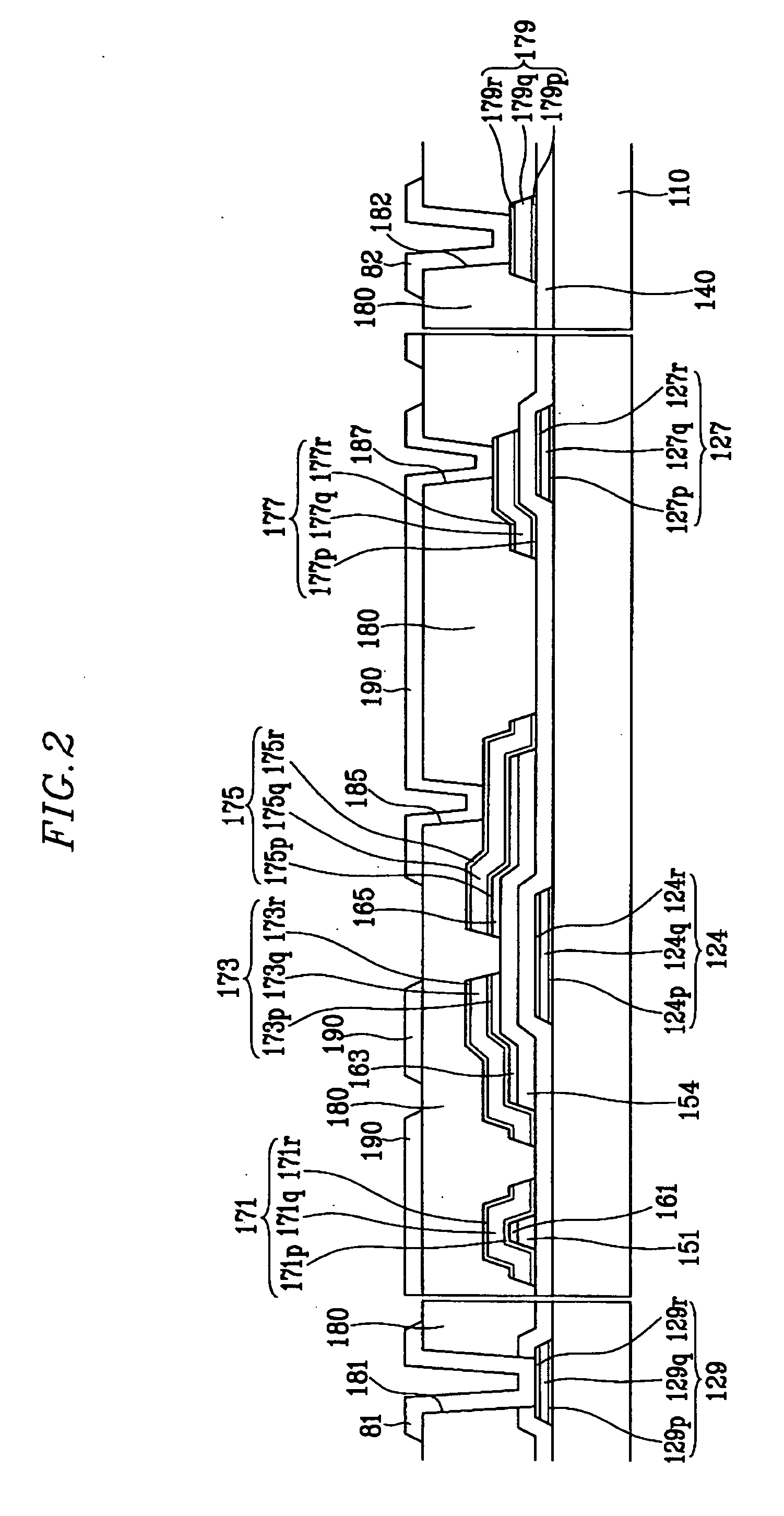

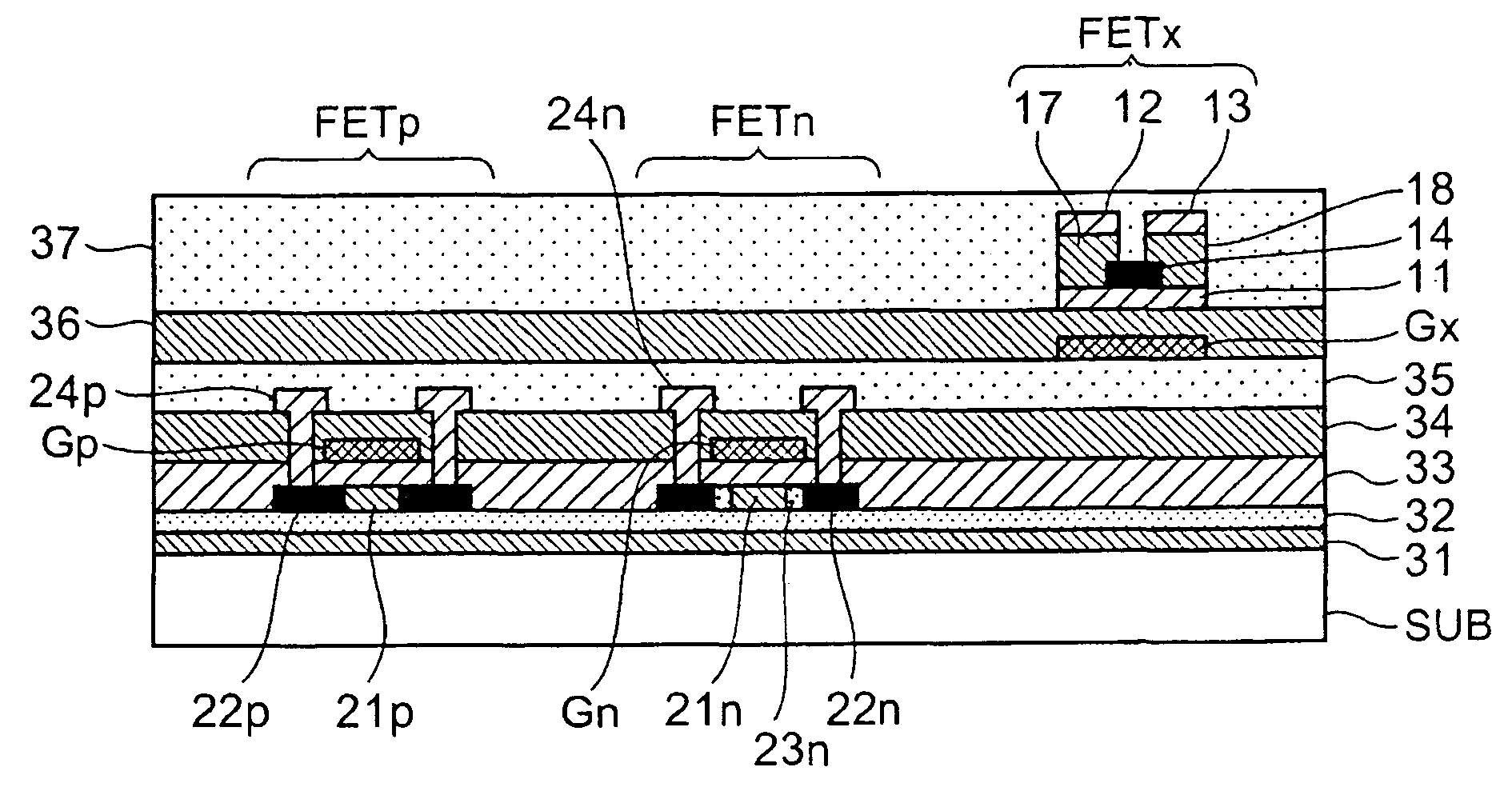

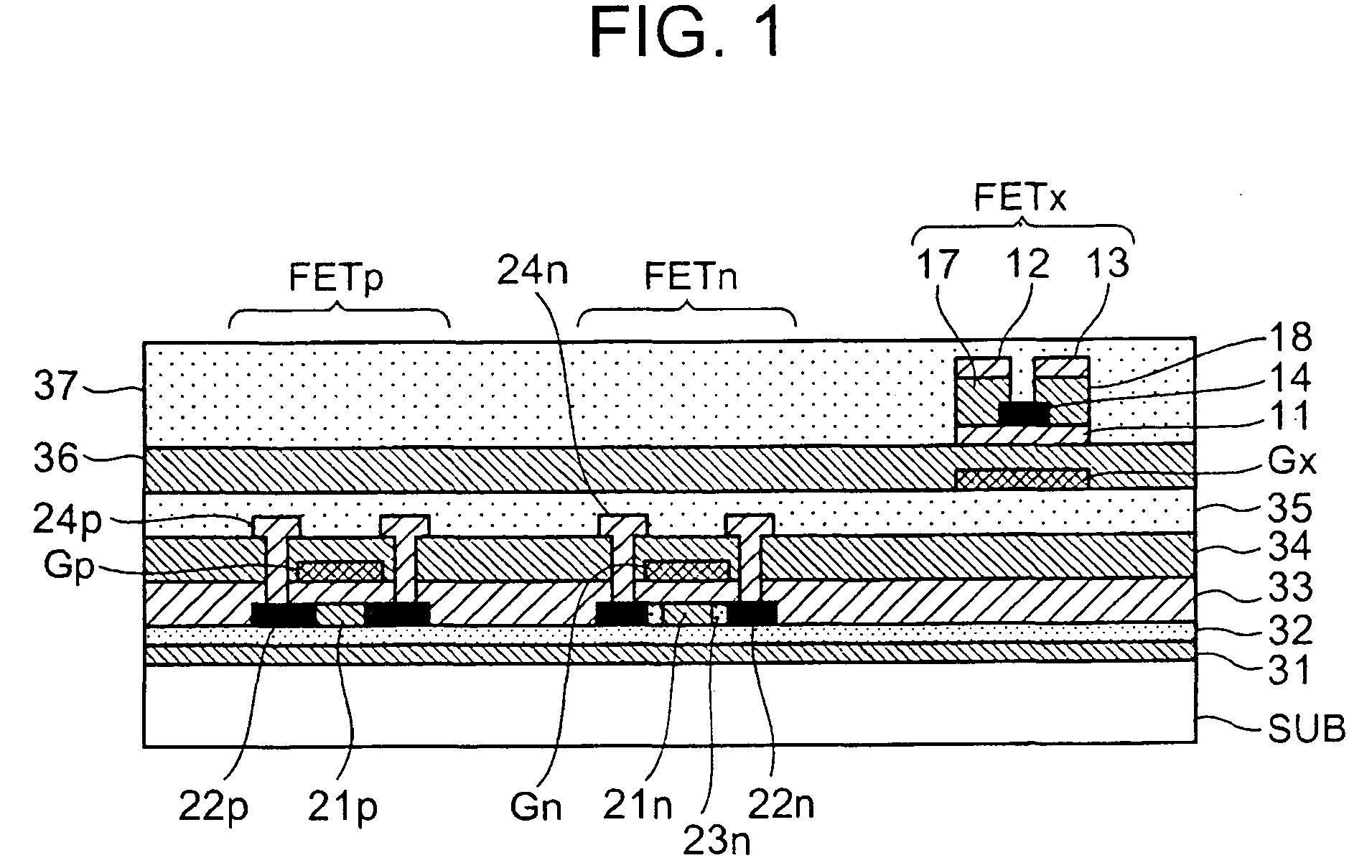

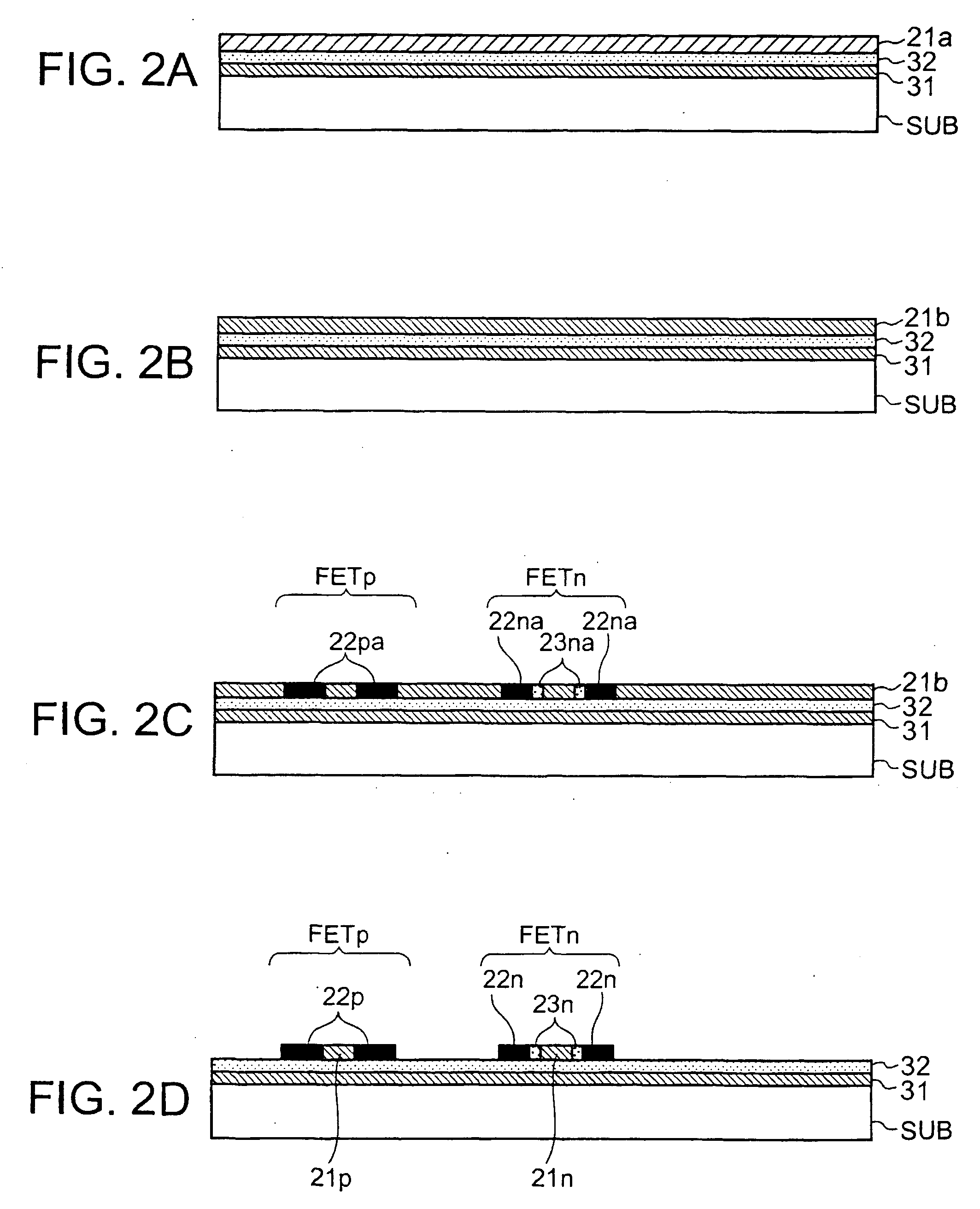

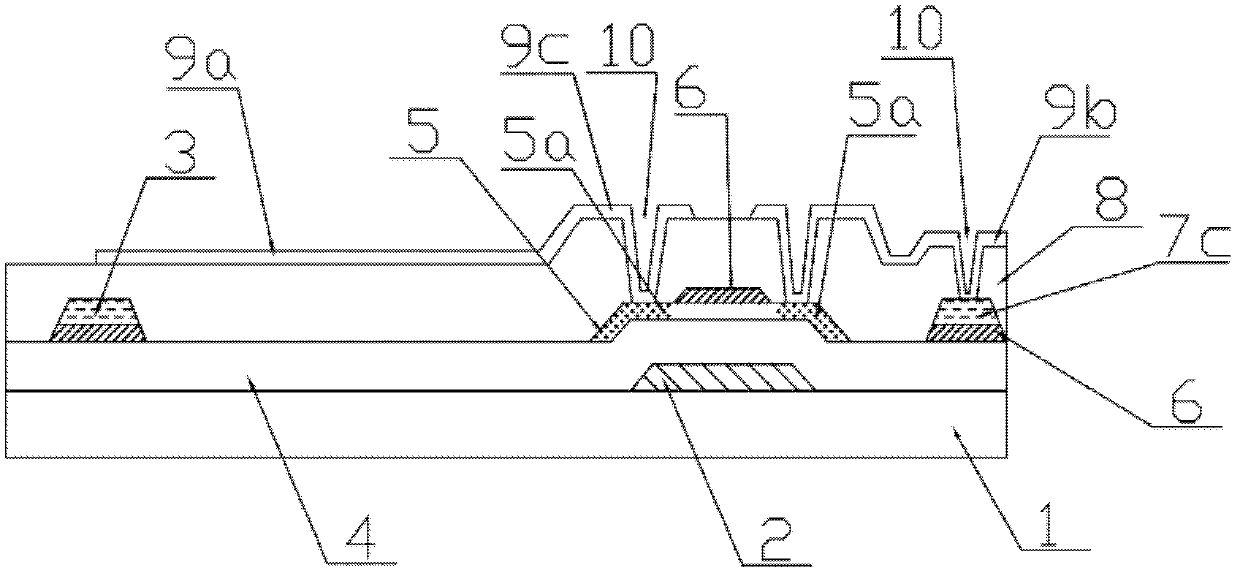

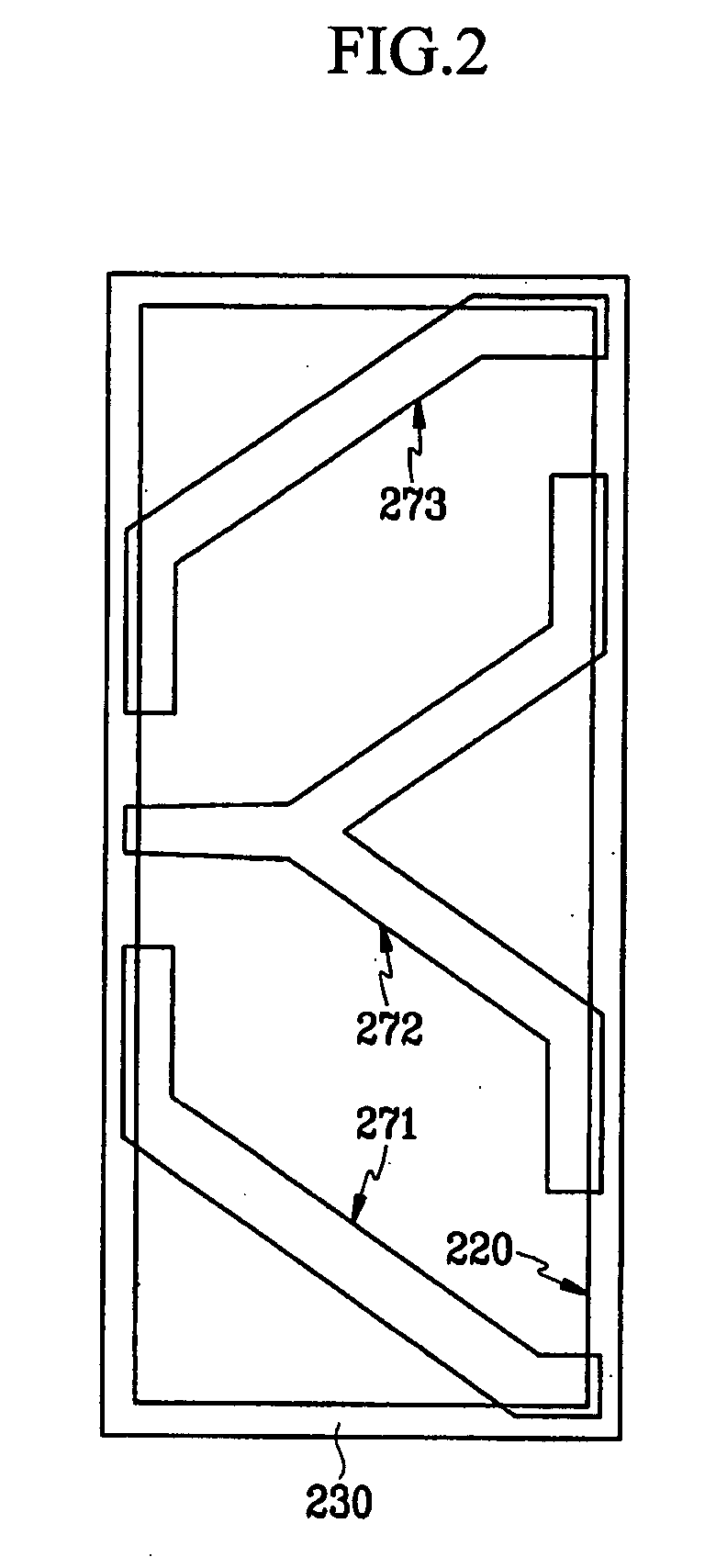

Transistor arrray, manufacturing method thereof and image processor

ActiveUS20050176194A1Highly reliable operating characteristicReduce component countSemiconductor/solid-state device detailsSolid-state devicesTransistor arrayElectrical conductor

An image processor by way of a transistor array in which a plurality of transistors are formed on a substrate comprising a plurality of polysilicon thin-film transistors using a first semiconductor layer composed of polysilicon formed on the substrate and functional devices having a plurality of amorphous silicon thin-film transistors using a second semiconductor layer composed of amorphous silicon which are formed in an upper layer more superior than the first semiconductor layer. The polysilicon thin-film transistors and functional devices include a plurality of electrode layers composed of a conductor layer, for instance, the functional devices at least of any one of the electrode layers are formed in the same layer as any one the electrode layers of the polysilicon thin-film transistors.

Owner:BOE TECH GRP CO LTD

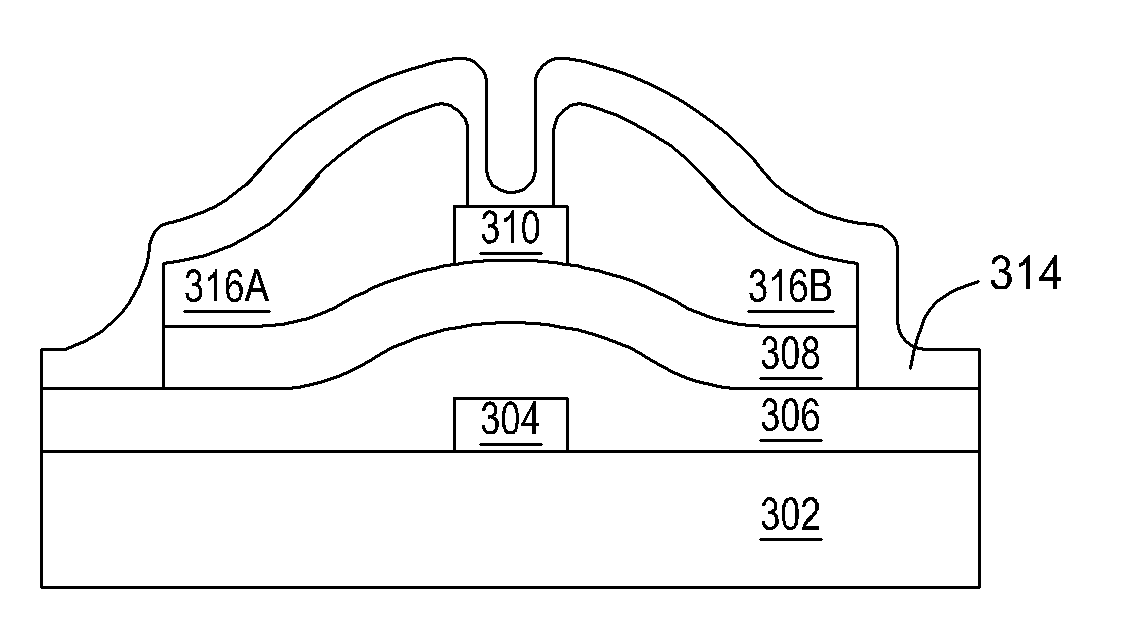

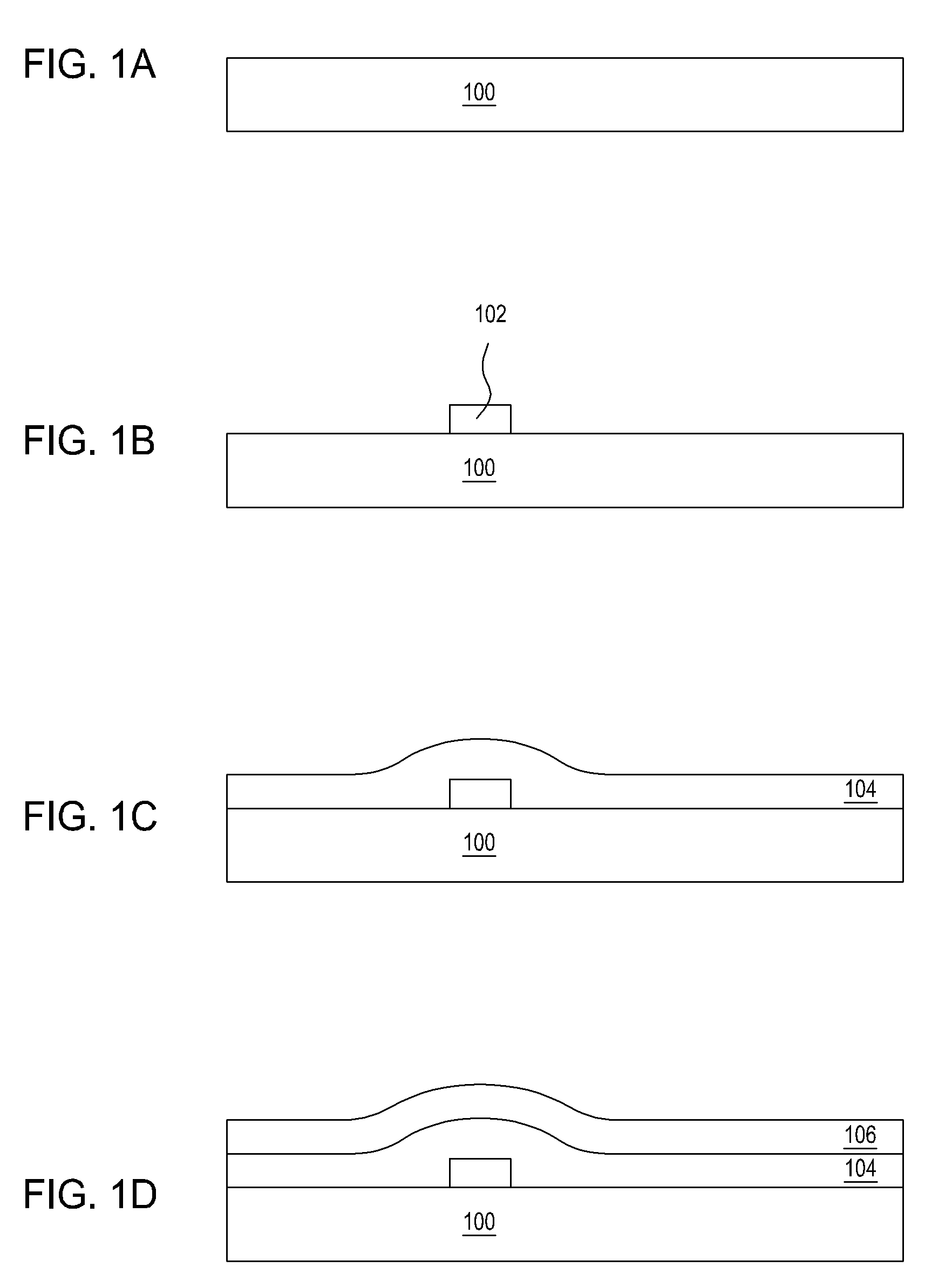

Process to make metal oxide thin film transistor array with etch stopping layer

The present invention generally relates to thin film transistors (TFTs) and methods of making TFTs. The active channel of the TFT may comprise one or more metals selected from the group consisting of zinc, gallium, tin, indium, and cadmium. The active channel may also comprise nitrogen and oxygen. To protect the active channel during source-drain electrode patterning, an etch stop layer may be deposited over the active layer. The etch stop layer prevents the active channel from being exposed to the plasma used to define the source and drain electrodes. The etch stop layer and the source and drain electrodes may be used as a mask when wet etching the active material layer that is used for the active channel.

Owner:APPLIED MATERIALS INC

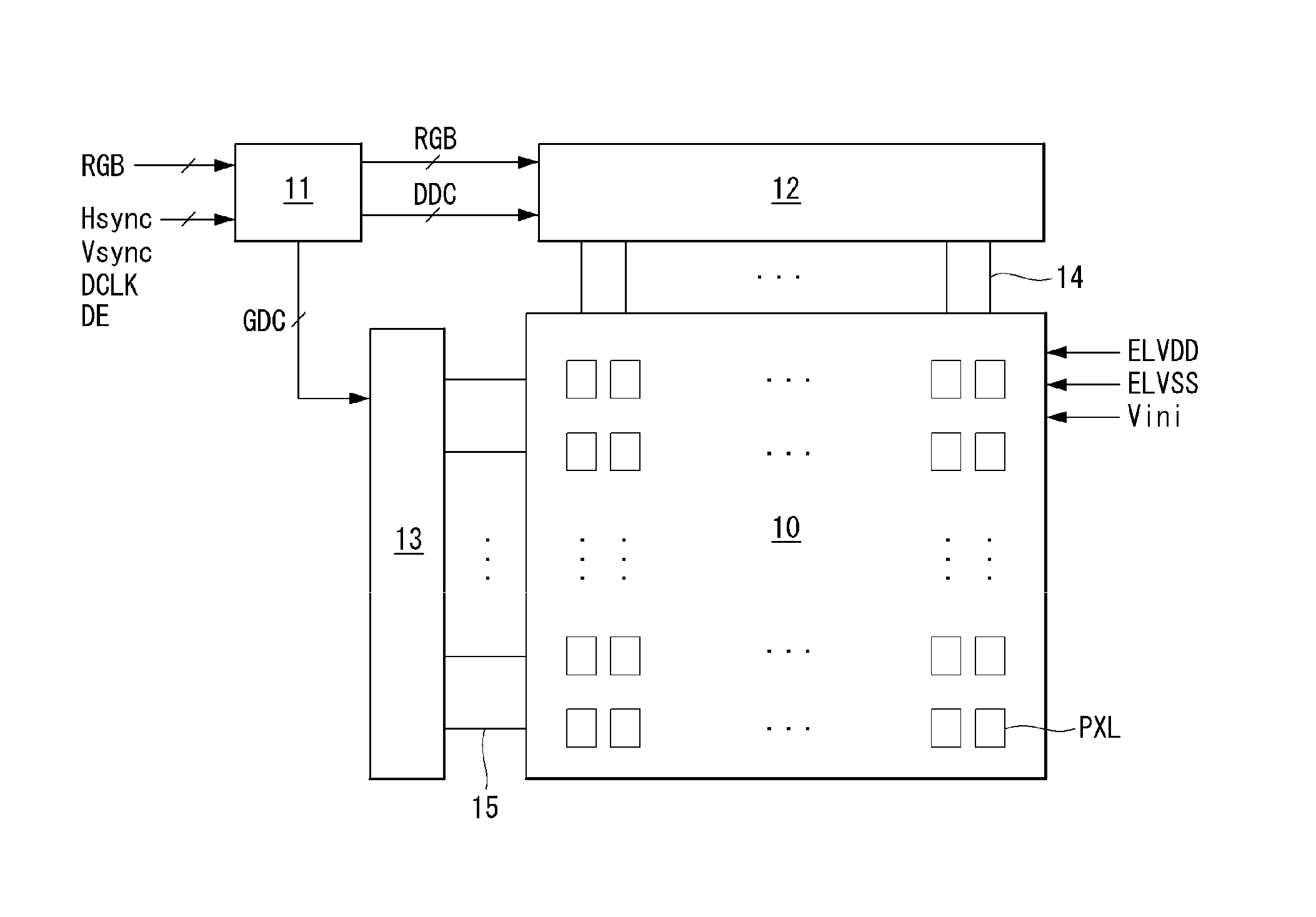

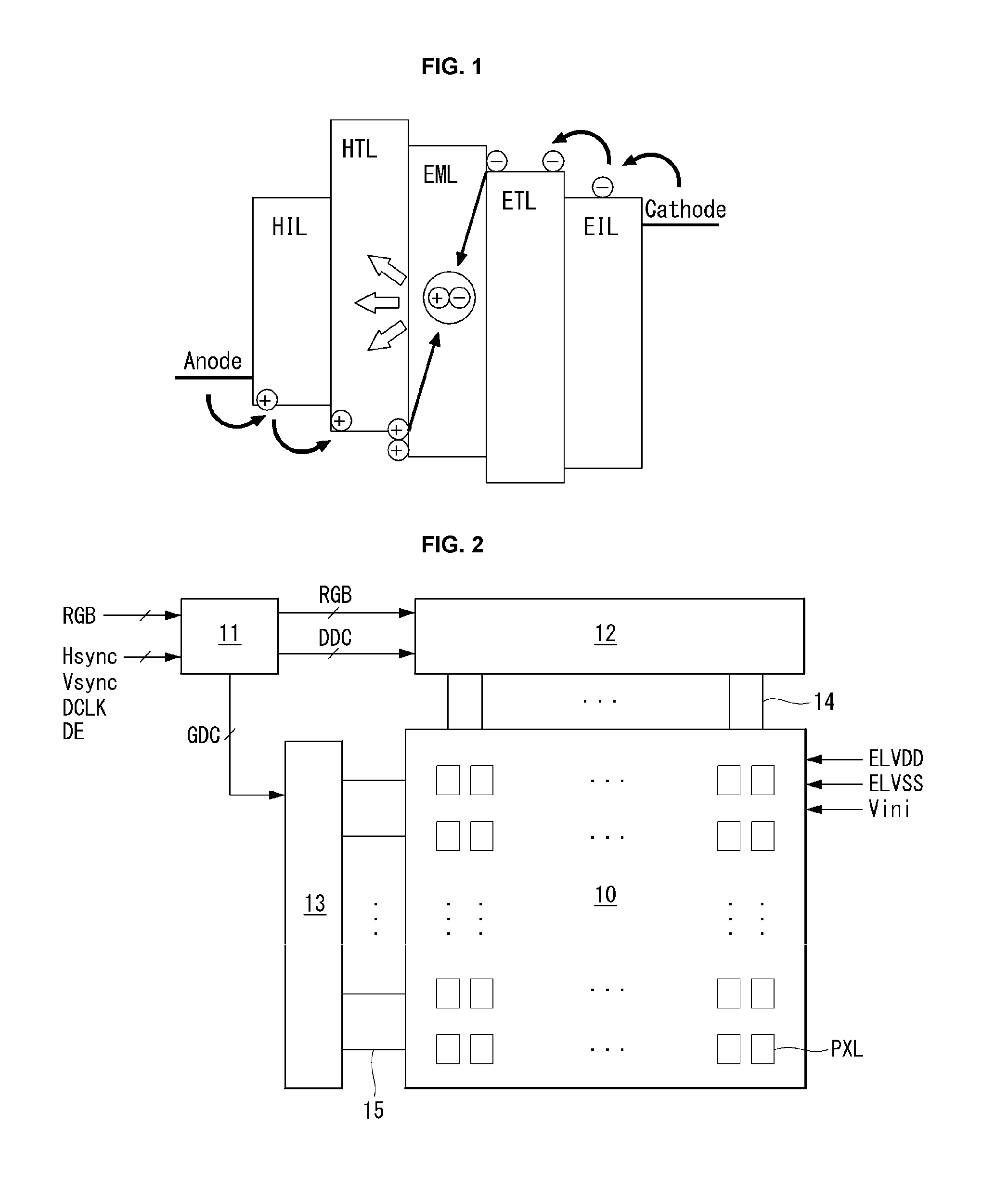

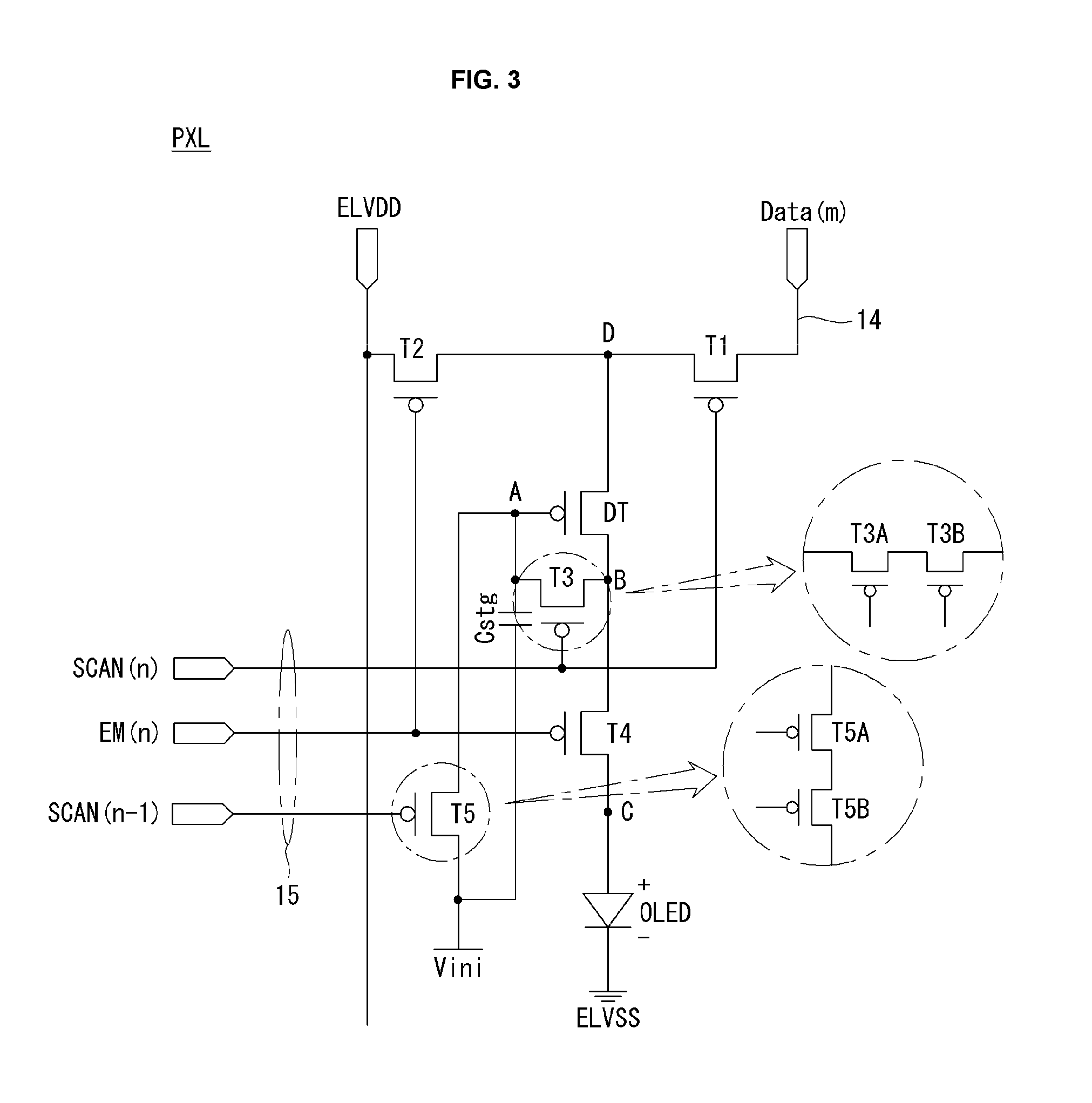

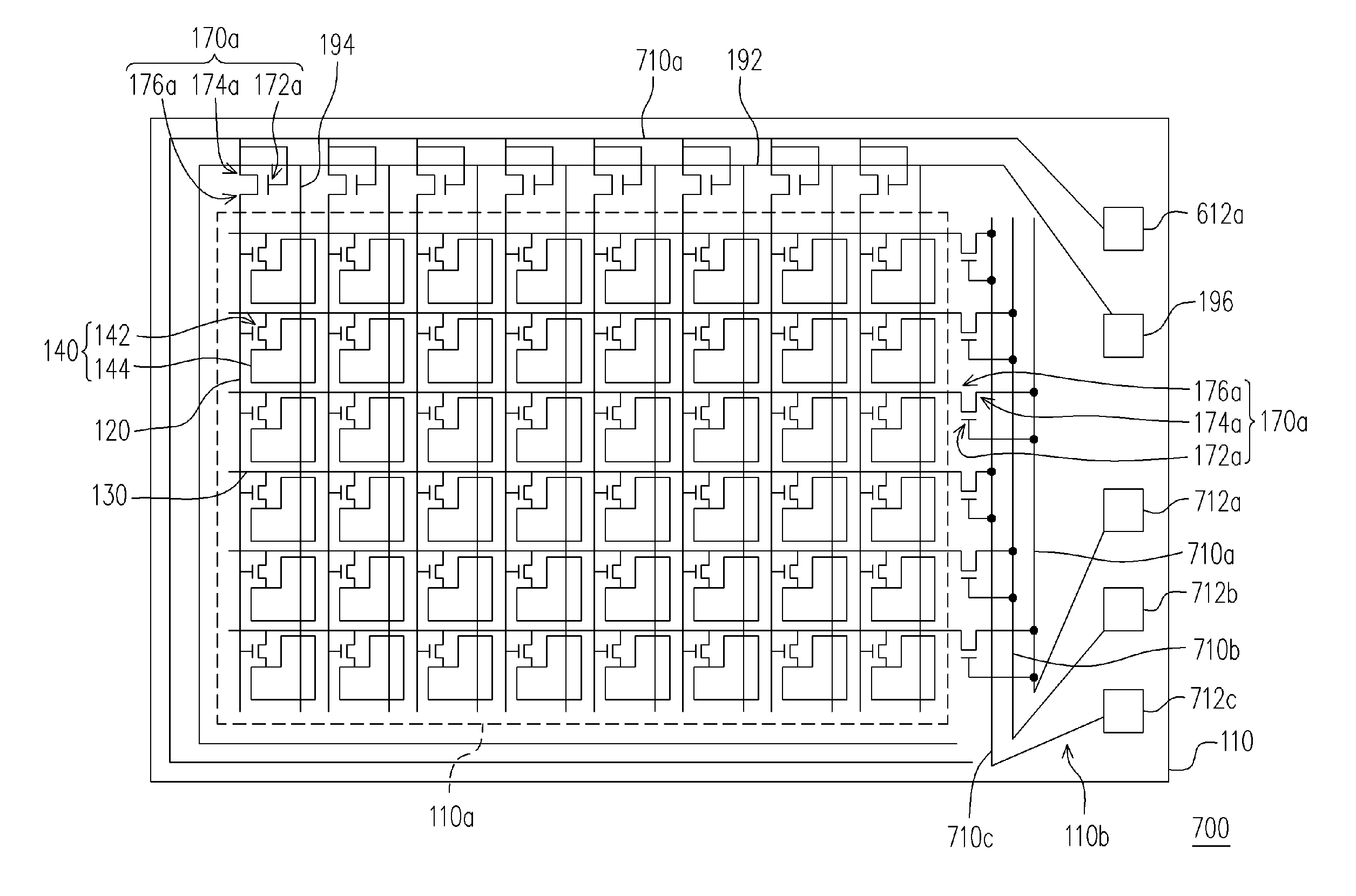

Organic Light Emitting Display

ActiveUS20160351124A1Guaranteed accuracyEnsure designStatic indicating devicesSolid-state devicesTransistor arrayScan line

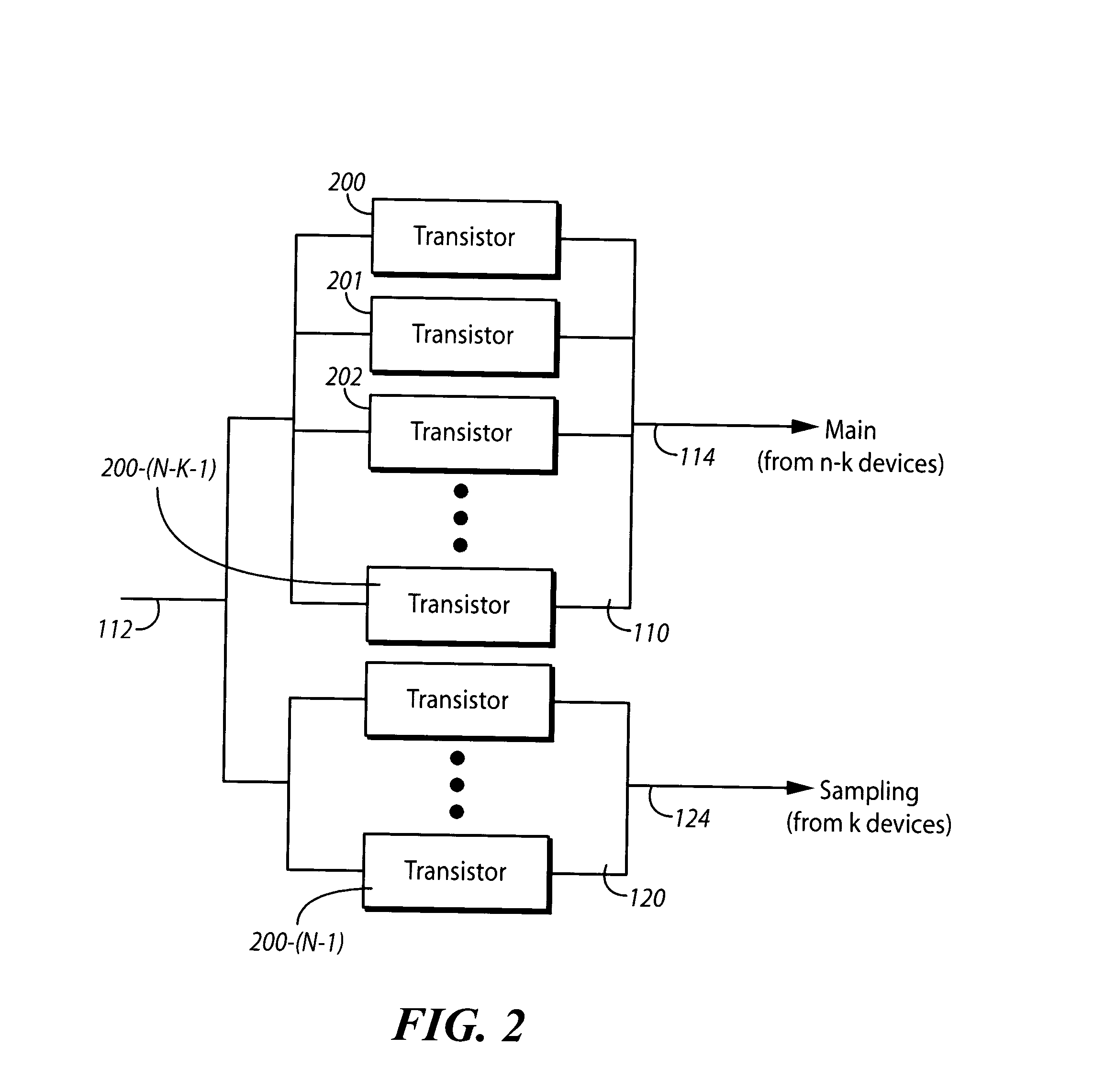

An organic light emitting display comprises a display panel having a plurality of pixels, a gate drive circuit that drives scan lines and emission lines on the display panel, and a data drive circuit that drives data lines on the display panel, (n−1)th and nth pixels arranged in a row, a transistor array having a driving transistor, a sampling transistor, and a first initial transistor, and a capacitor connected between an initial voltage input terminal and the sampling transistor. A gate electrode of the first initial transistor for initializing the driving transistor of the nth pixel is connected to a scan line in the (n−1)th pixel.

Owner:LG DISPLAY CO LTD

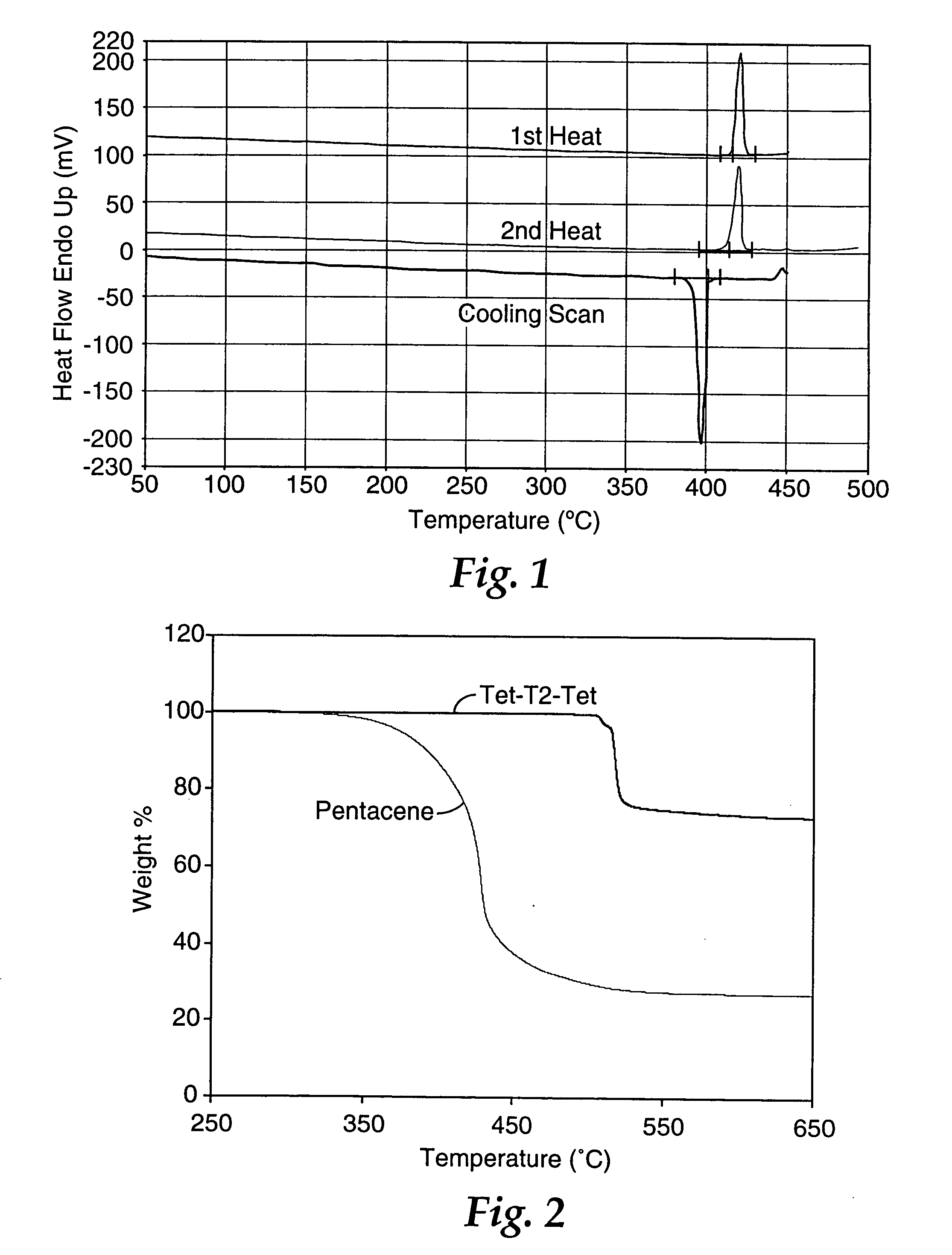

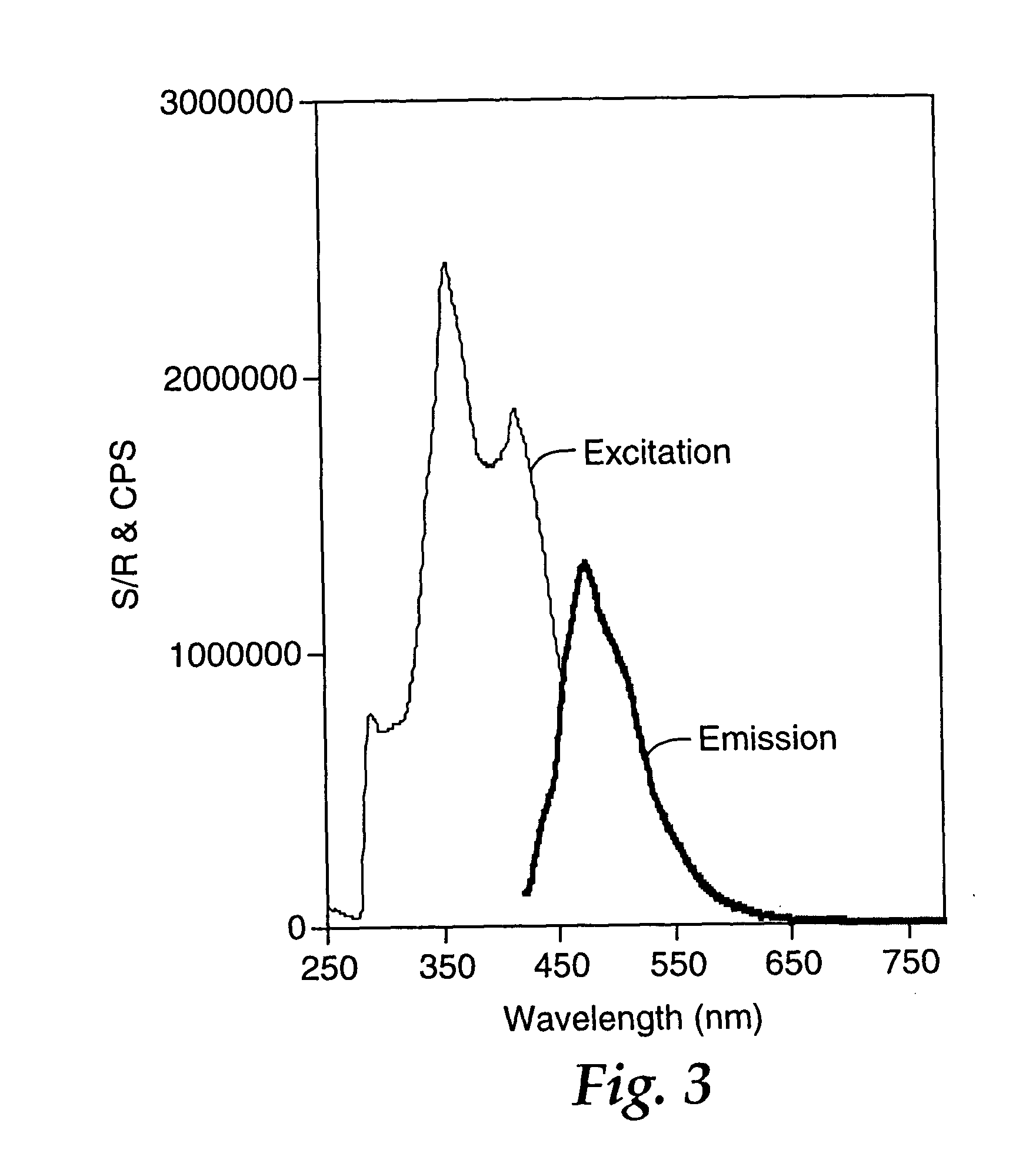

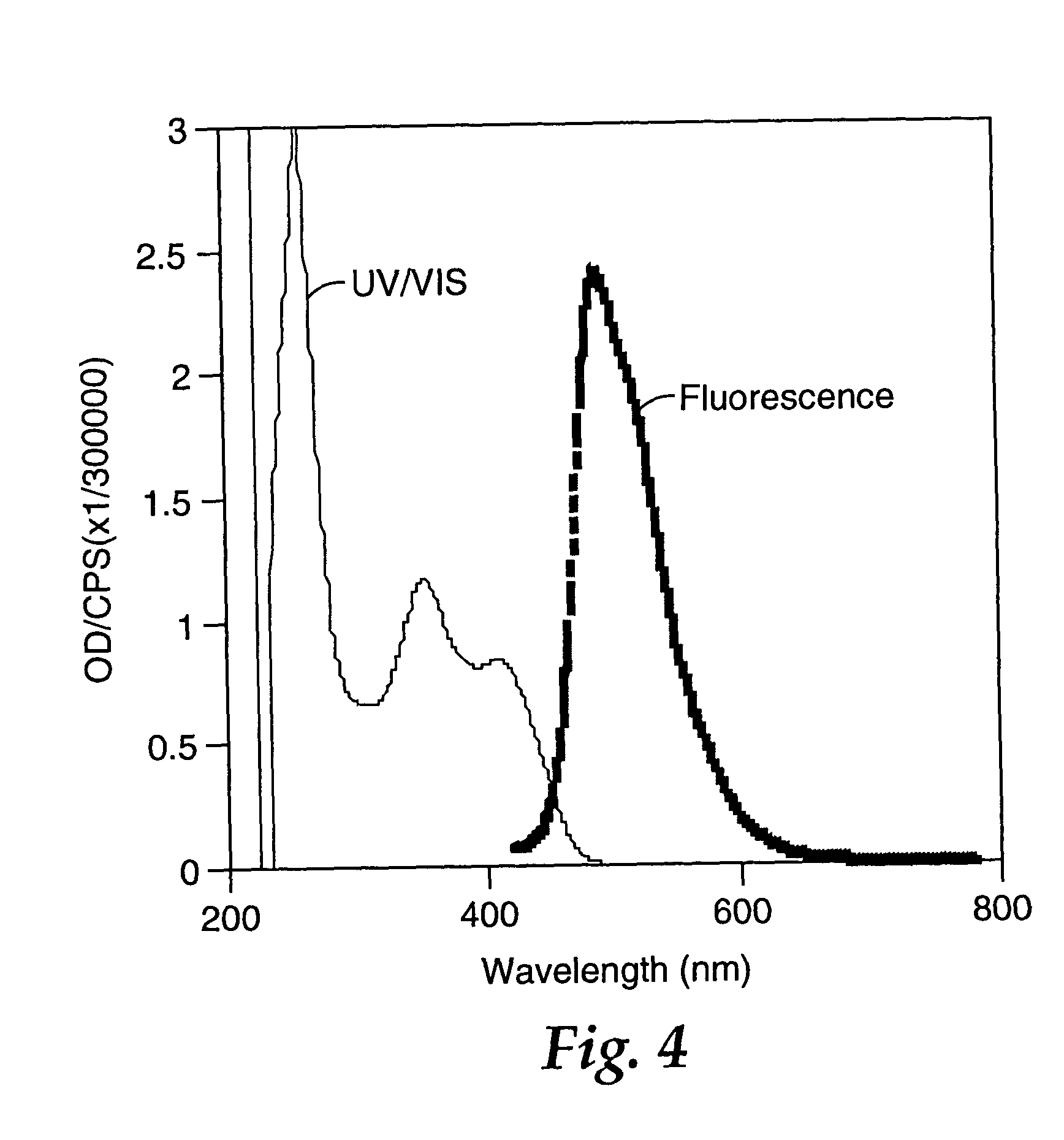

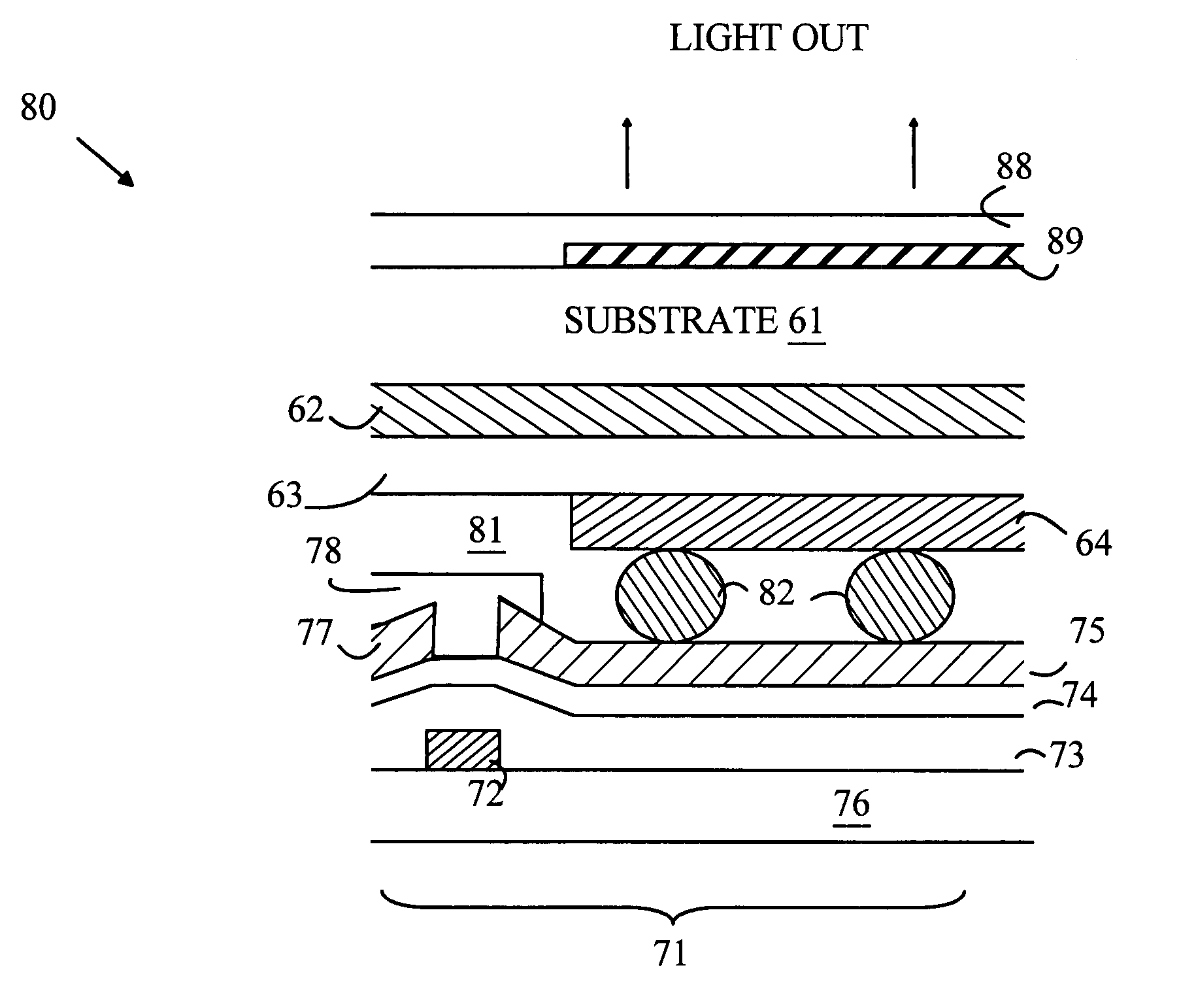

Acene-thiophene semiconductors

InactiveUS20050035333A1Improve performanceUse performanceMaterial nanotechnologyOrganic chemistryTransistor arrayDevice material

Acene-thiophene compounds are disclosed that are useful as organic semiconductors. The compounds, when used as the semiconductor layer in organic thin-film transistors exhibit device characteristics, like charge-carrier mobilities and current on / off ratios, that are comparable to those of pentacene. Also described are semiconductor devices comprising at least one compound of the invention; and articles comprising the semiconductor devices such as thin film transistors or transistor arrays, and electroluminescent lamps.

Owner:3M INNOVATIVE PROPERTIES CO

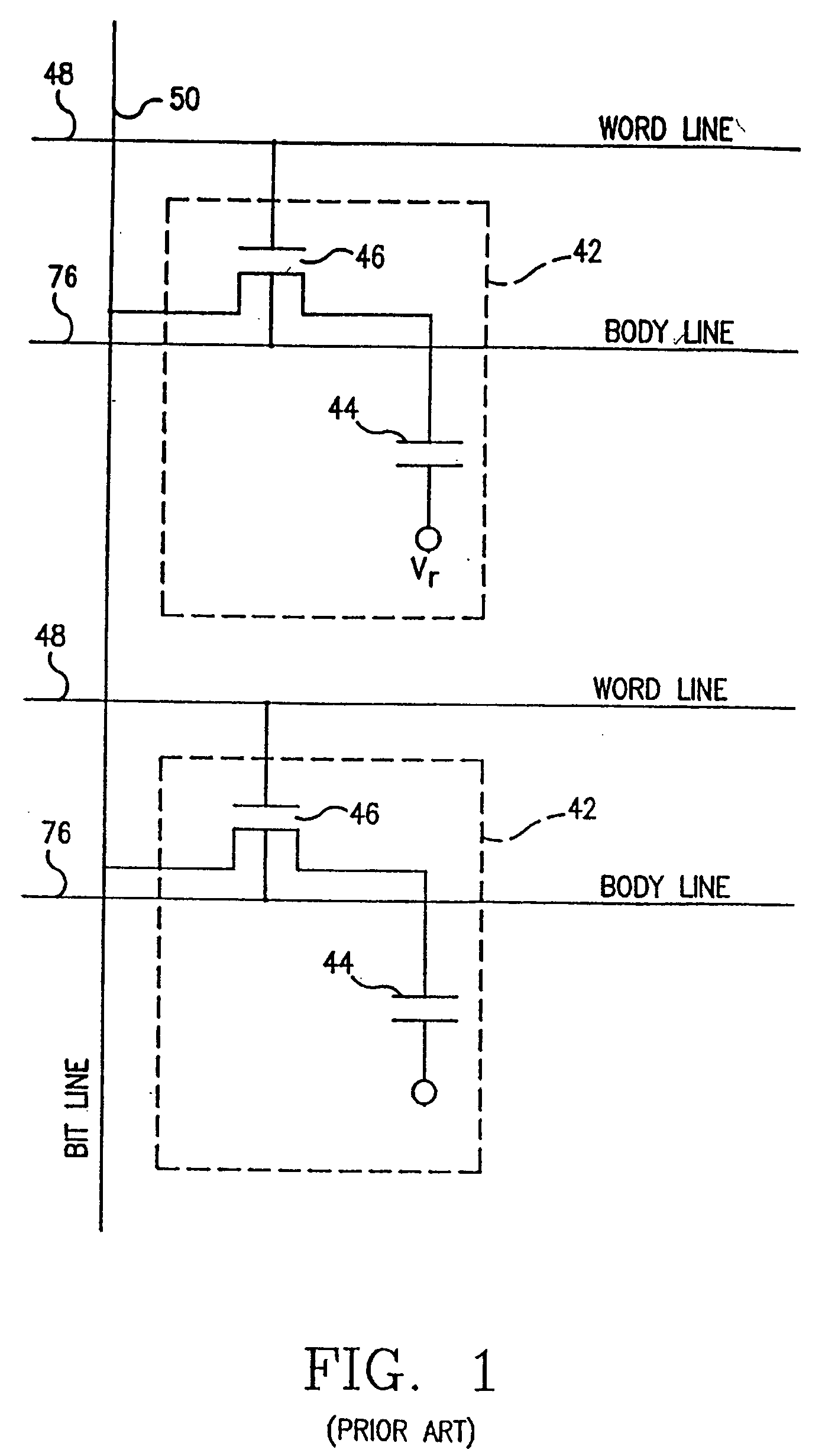

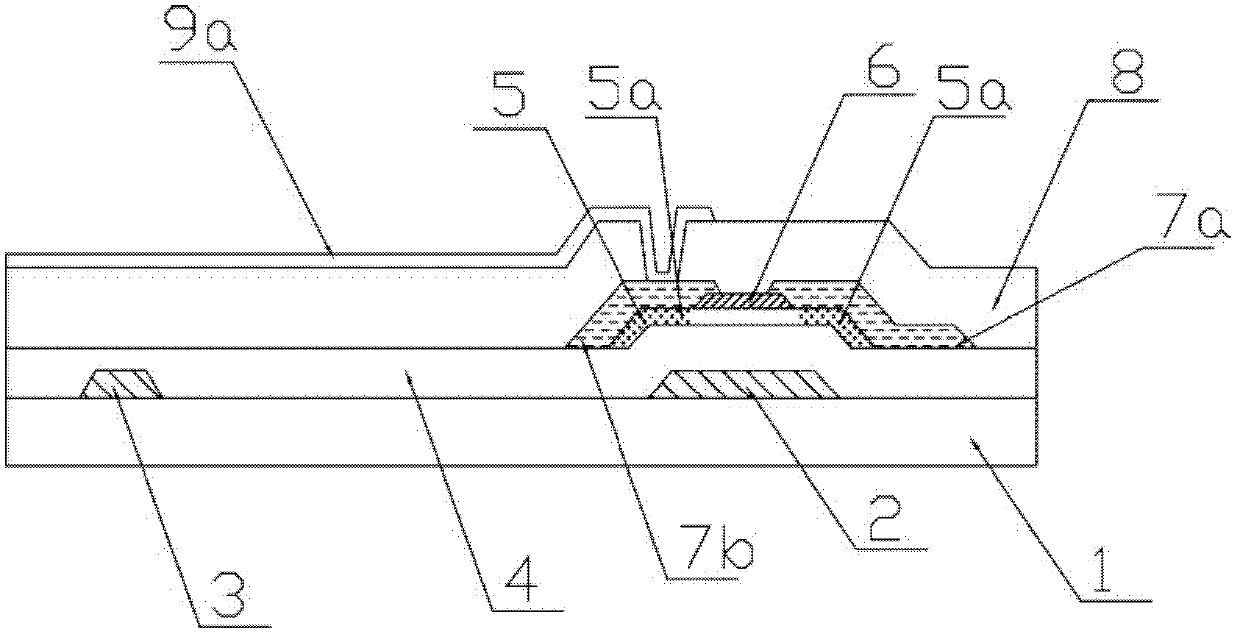

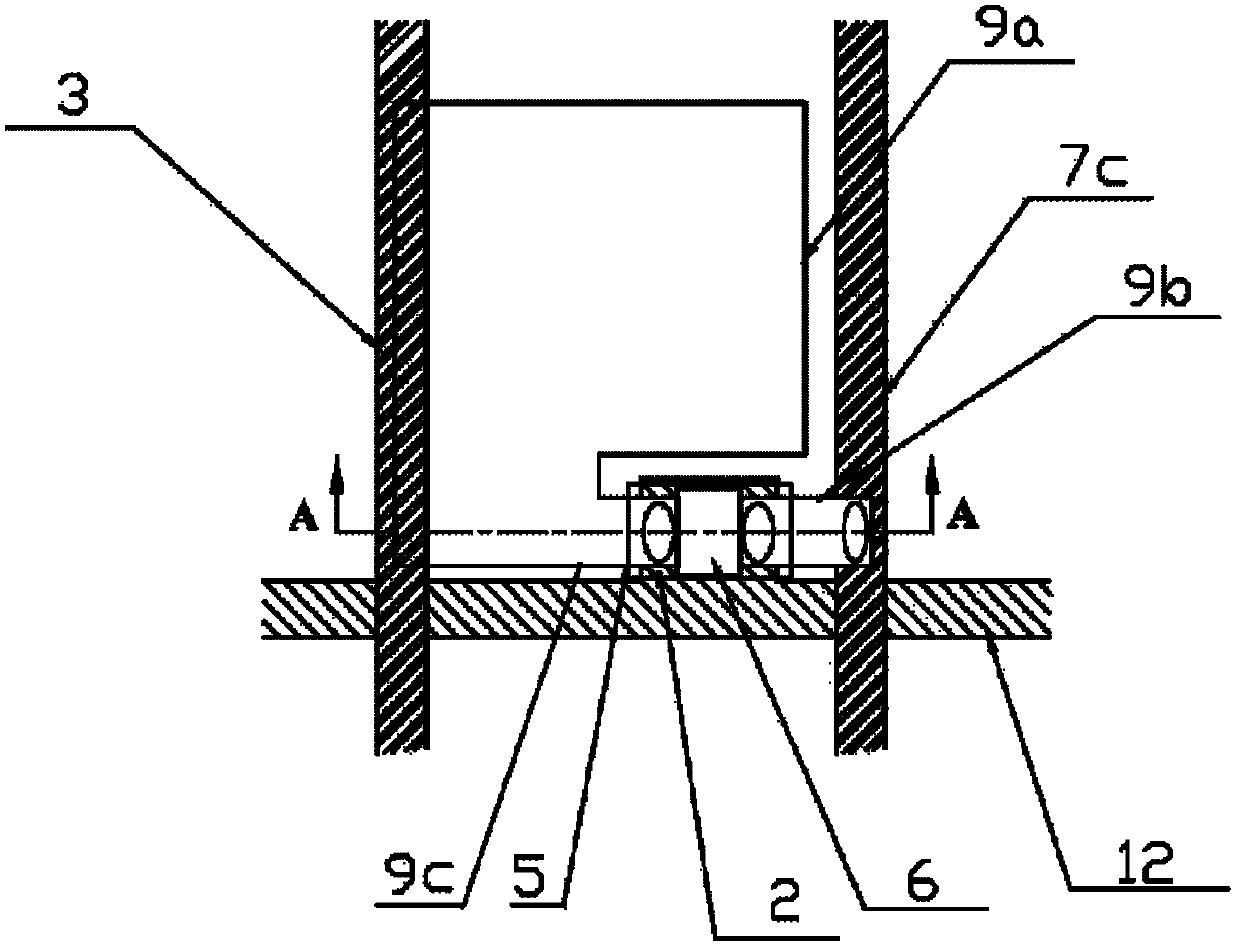

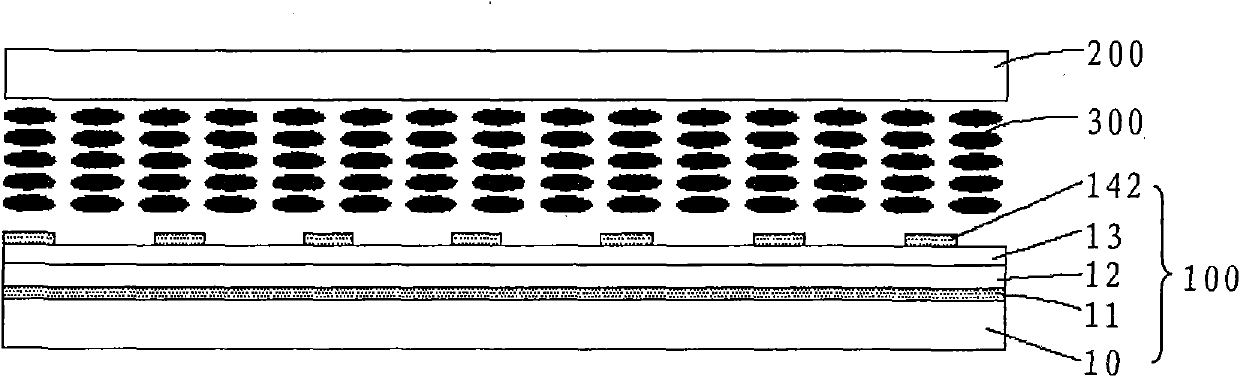

Method of manufacture of active matrix addressed polymer LED display

A display having a plurality of light emitting pixels. Each pixels includes an isolation transistor, a driving circuit, and an organic light emitting diode (OLED). The driving circuit storing a value that determines the magnitude of the light emitted by that pixels, the driving circuit placing the OLED in a conducting path between the first and second power terminals. The driving circuit is programmed through the isolation transistor. In one embodiment of the present invention, the driving circuit includes a storage capacitor and a driving transistor. The OLEDs are part of an array of OLEDs. The array of OLEDs is constructed on a flexible sheet having first and second surfaces, the flexible sheet being transparent to light of a first wavelength. A transparent first electrode layer is in contact with the first surface. A light emitting layer including an organic polymer is in contact with the first electrode layer. A plurality of second electrodes, one such second electrode corresponding to each of the OLEDs, is in contact with the light emitting layer. Each second electrode has an isolated conducting area. The driving transistor are part of a transistor array having a plurality of connection points disposed on a surface, each connection point corresponding to one of the second electrodes in the array of OLEDs. The connection points are arranged such that each second electrode overlies the corresponding connection point when the array of OLEDs is properly aligned with the transistor array. The connection points are bonded to the corresponding second electrodes by a bonding layer.

Owner:INNOLUX CORP

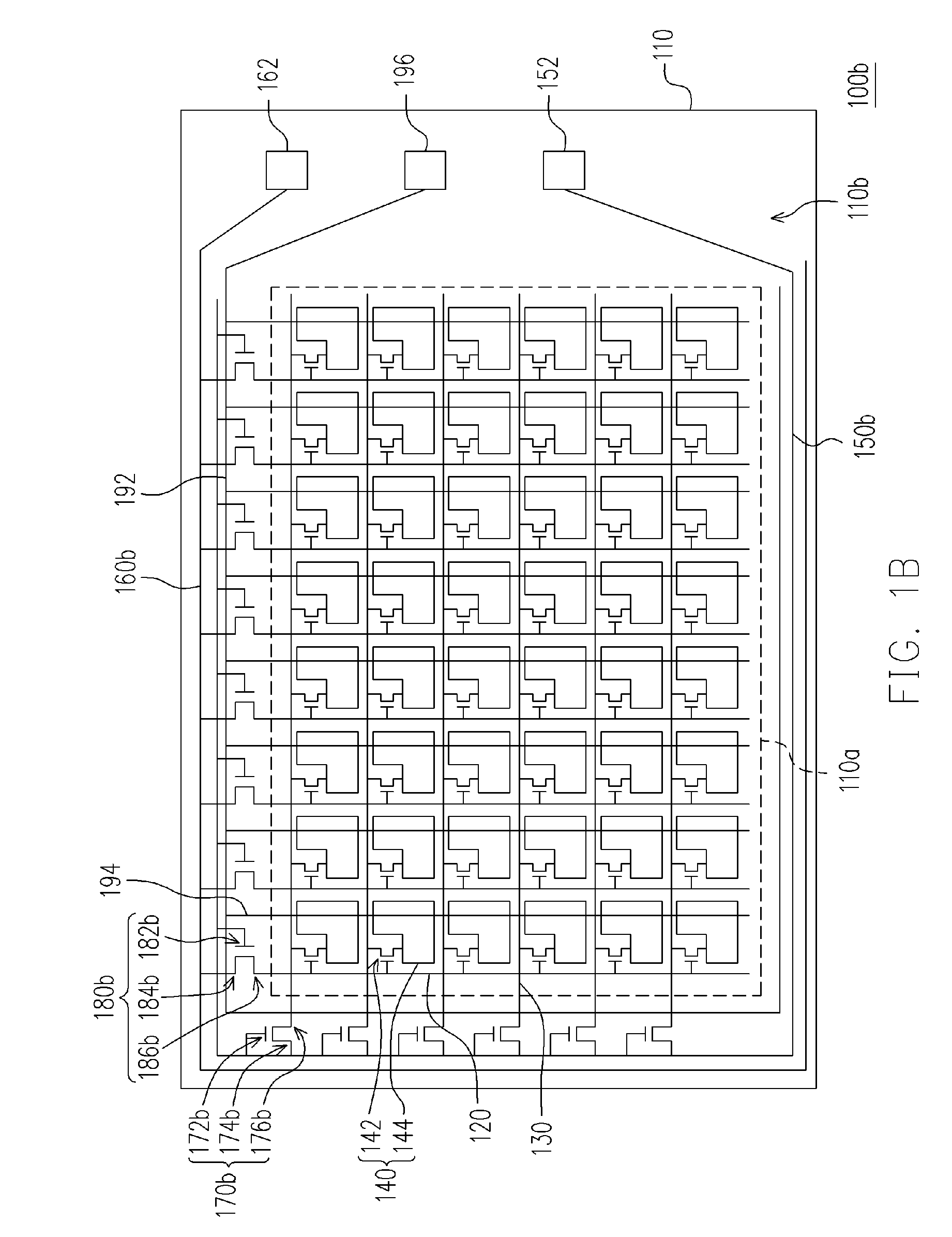

Liquid crystal display panel, thin film transistor array substrate and detection methods therefor

A thin film transistor (TFT) array substrate including a substrate, pixel units, scan and data lines, inner anti-static rings, first and second thin film transistors is provided. The pixel units are arranged on a display region of the substrate, and the scan and data lines are arranged on the substrate. Each pixel unit is controlled by the corresponding scan and data line. The inner anti-static rings, the first and second TFTs are arranged on a peripheral circuit region of the substrate around the display region. The gate and source of each first TFT are connected to one part of the inner anti-static ring, and the drain of each first TFT is connected to the scan line respectively. The gate and source of each second TFT are connected to the other part of the inner anti-static ring, and the drain of each second TFT is connected to the data line respectively.

Owner:CHUNGHWA PICTURE TUBES LTD

Thin film transistor array panel and liquid crystal display including the same

A thin film transistor array panel is provided, which includes: a gate line; a data line intersecting the gate line; a thin film transistor connected to the gate line and the data line; a pixel electrode connected to the thin film transistor; a passivation layer formed on the data line; and a shielding electrode overlapping the data line at least in part and electrically disconnected from the data line.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

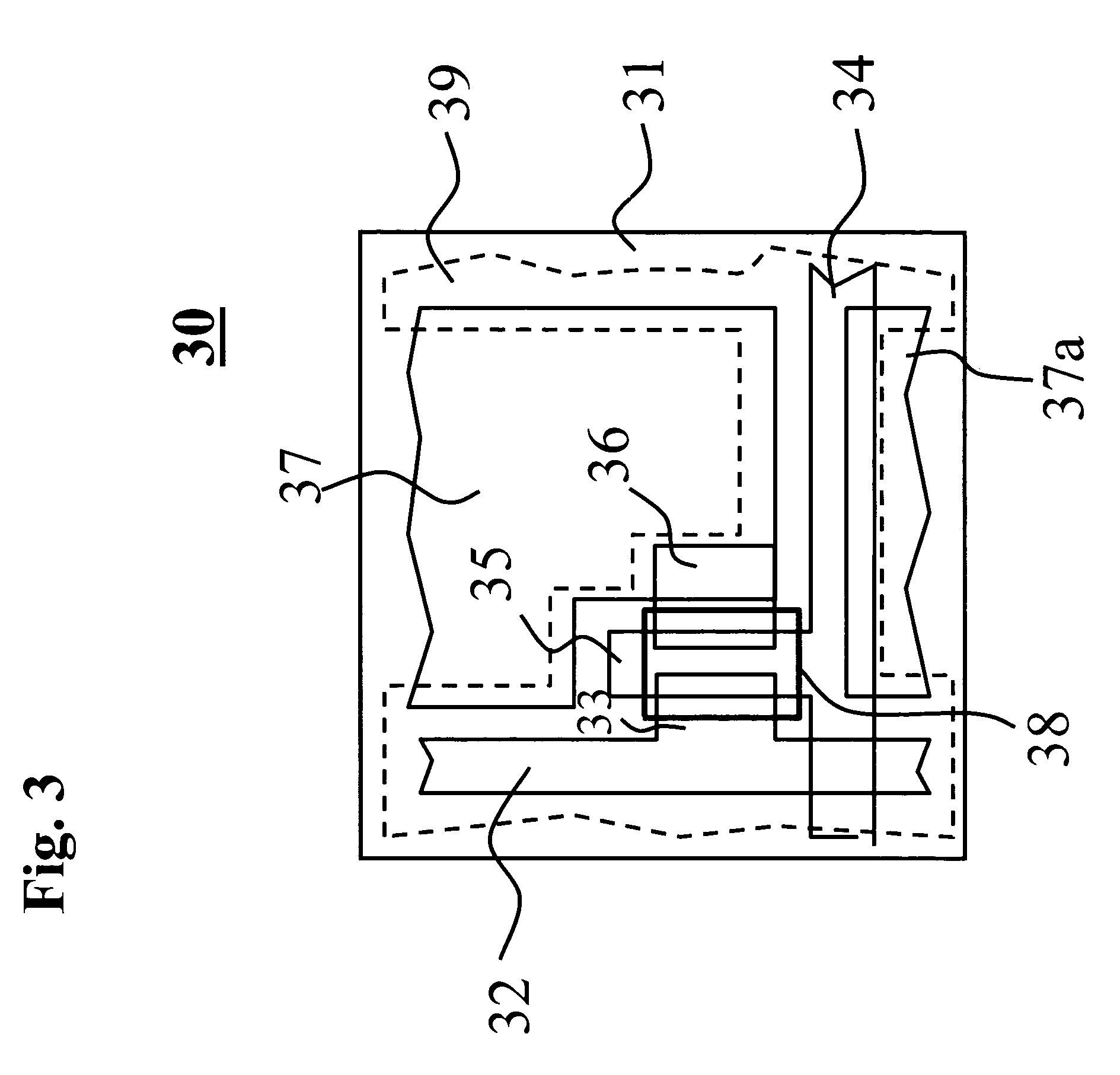

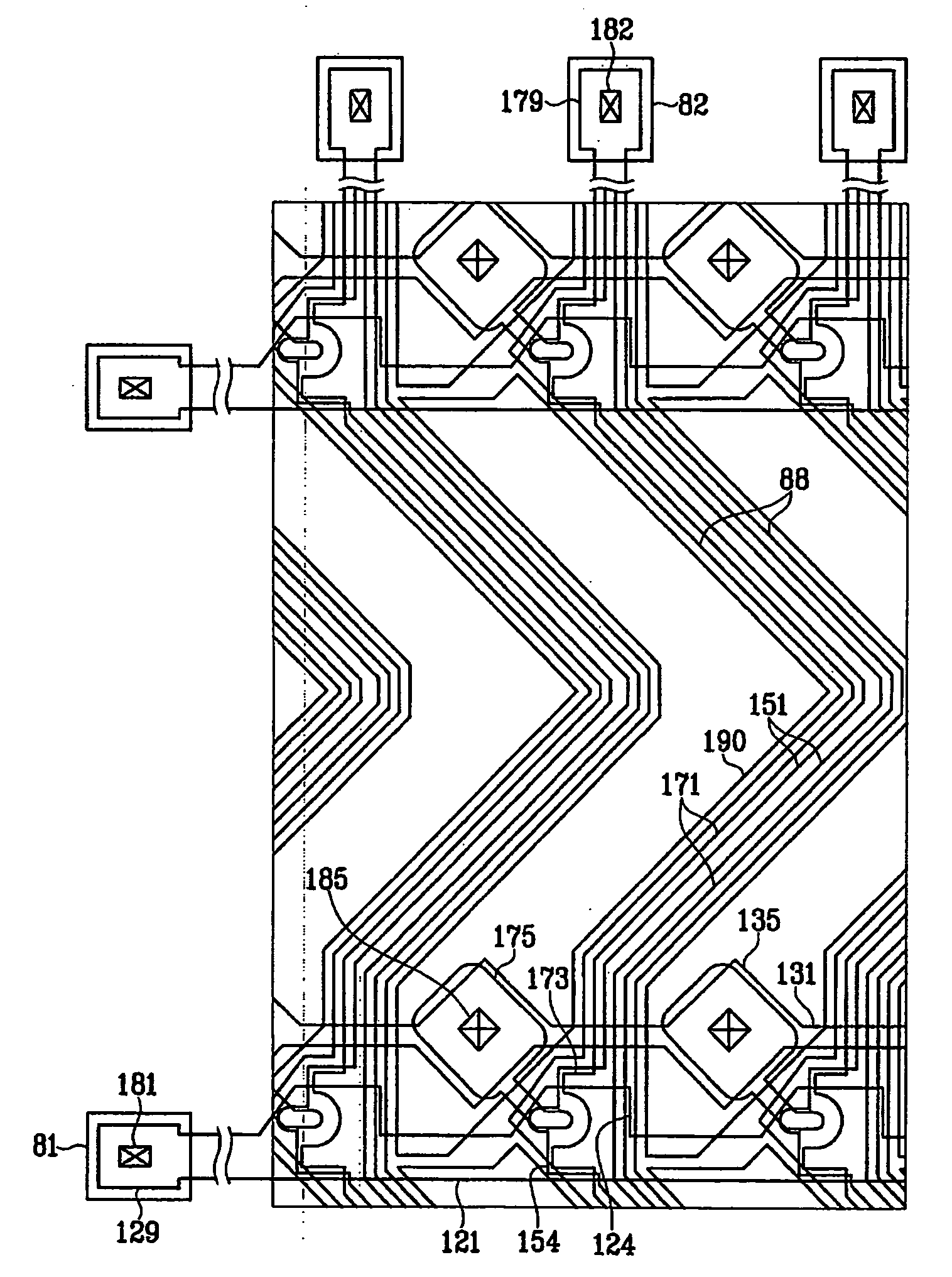

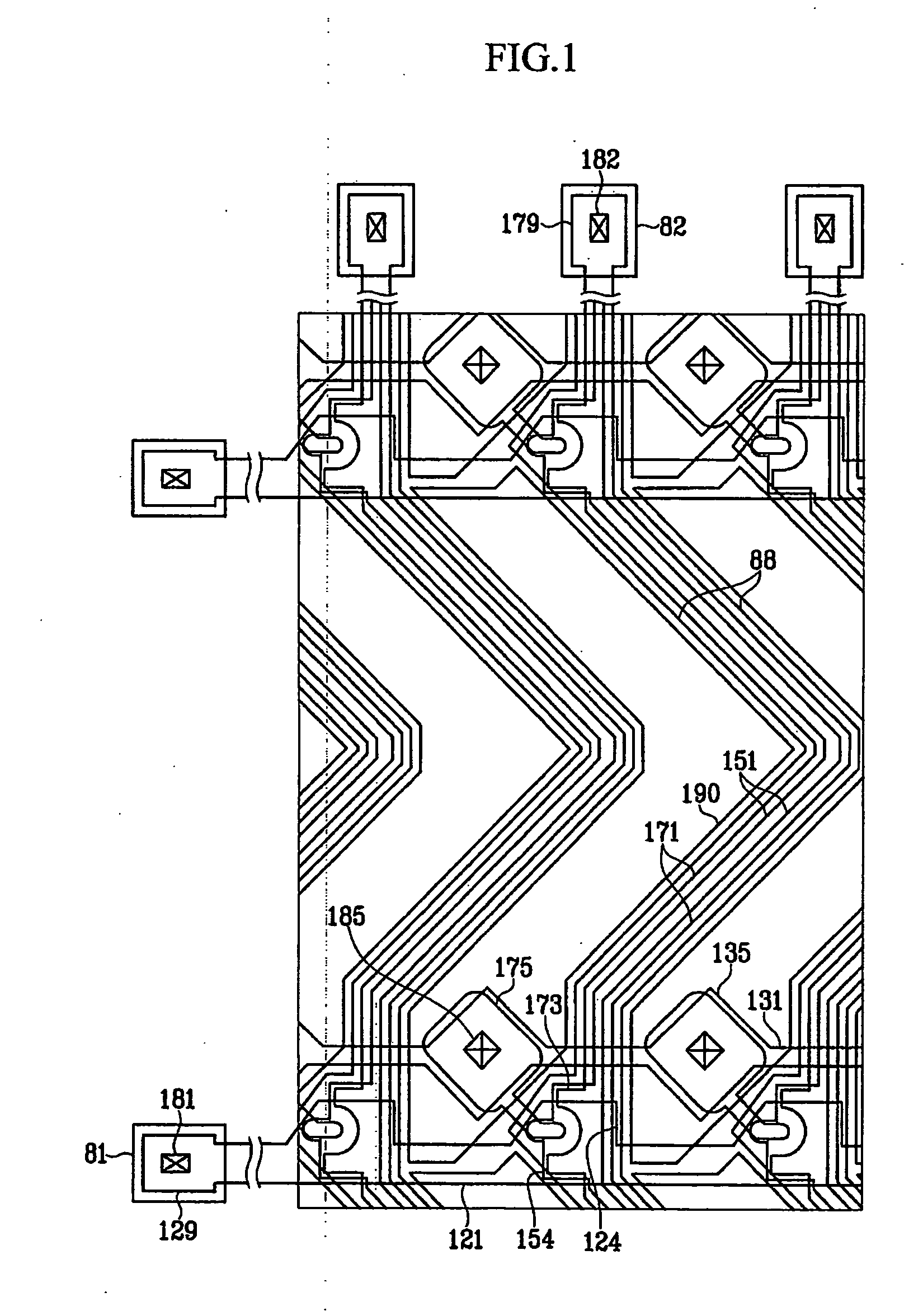

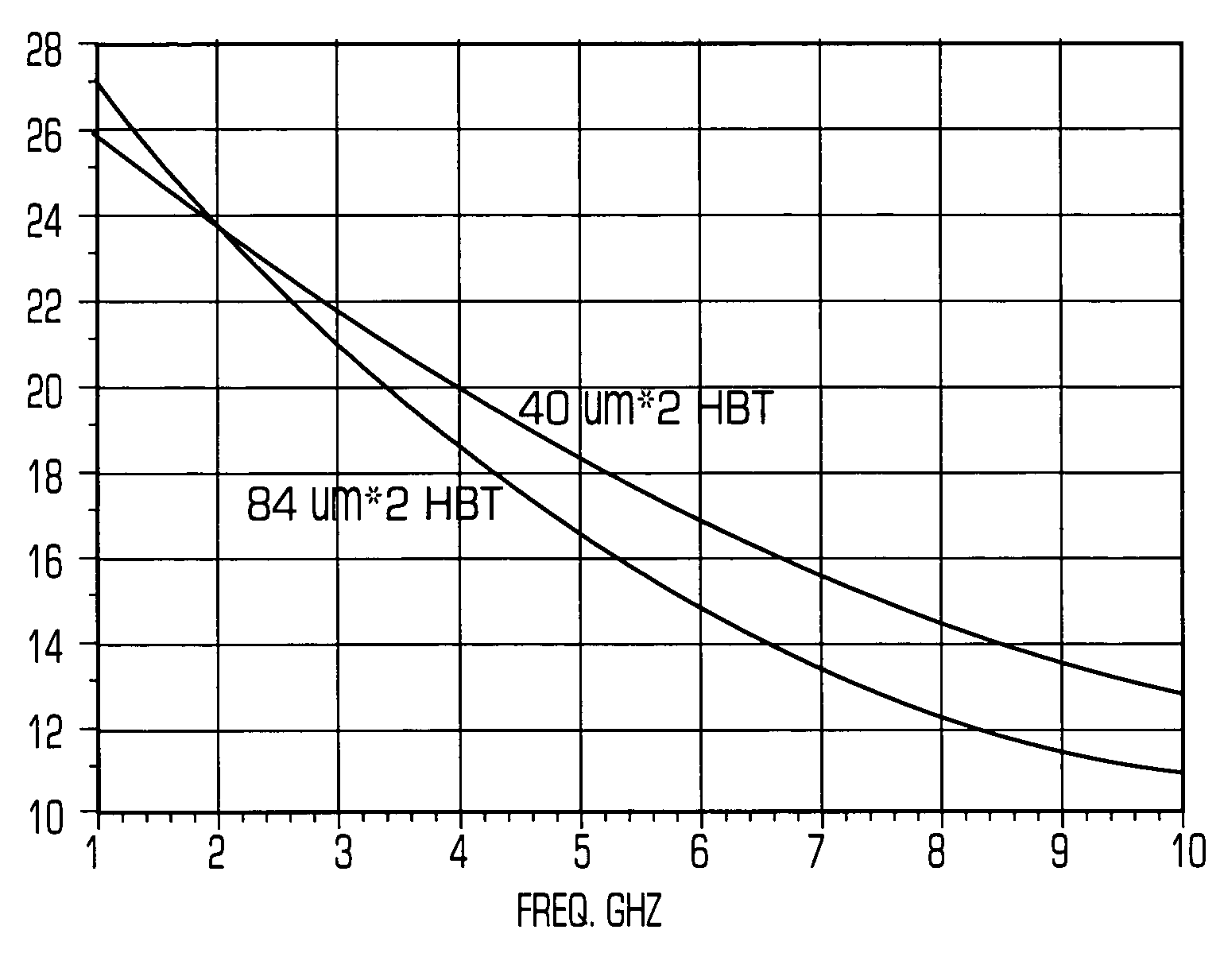

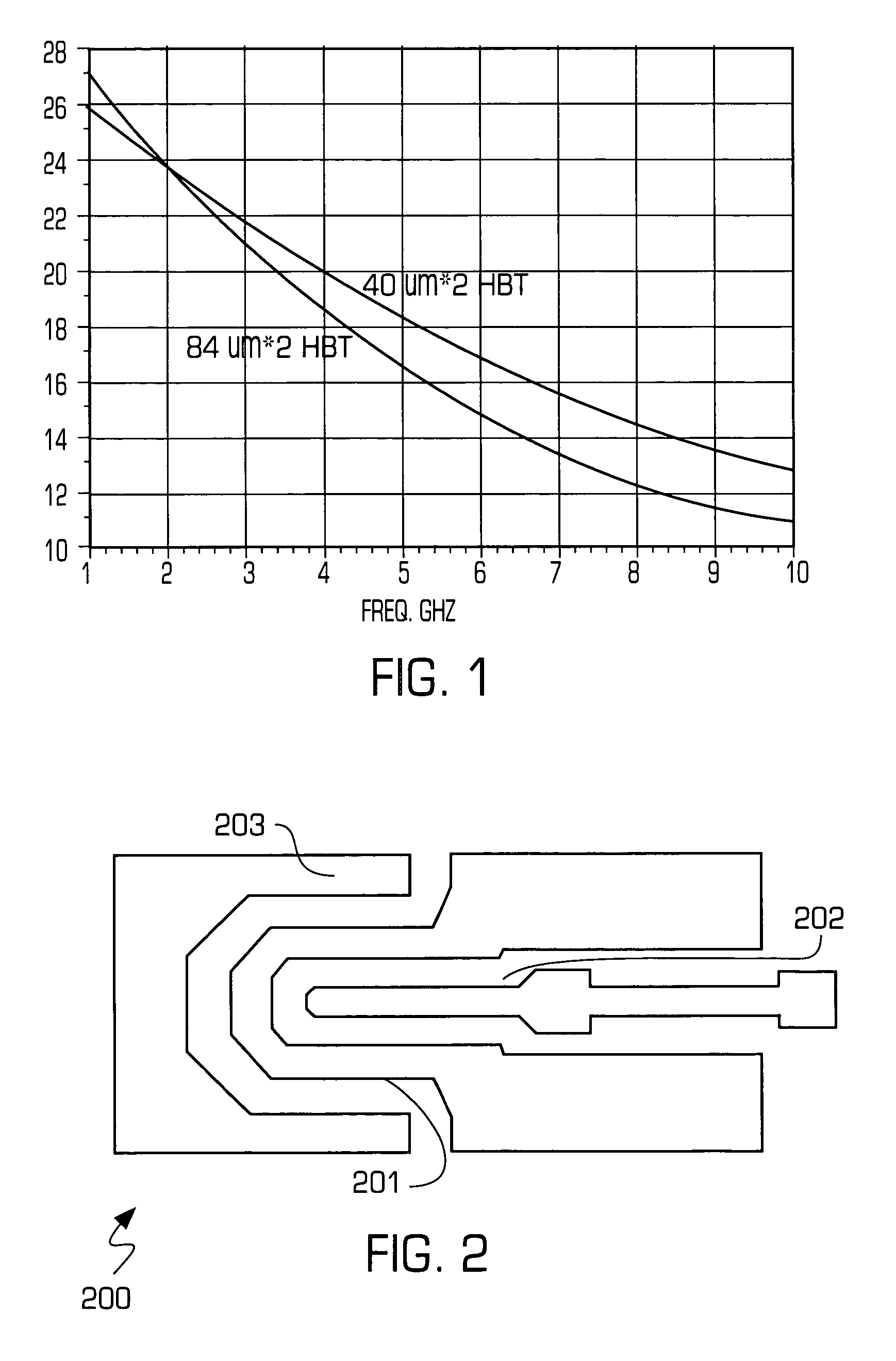

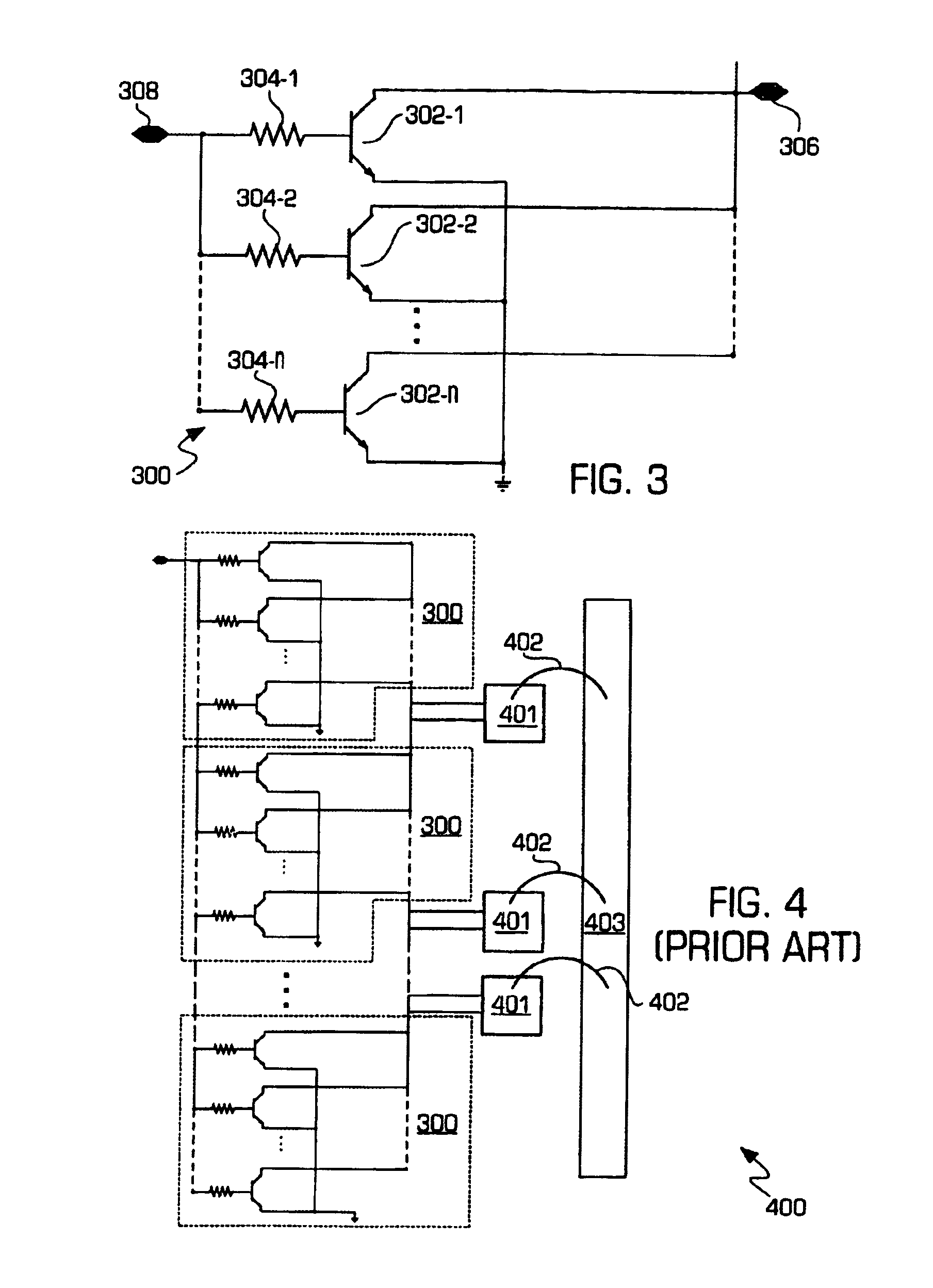

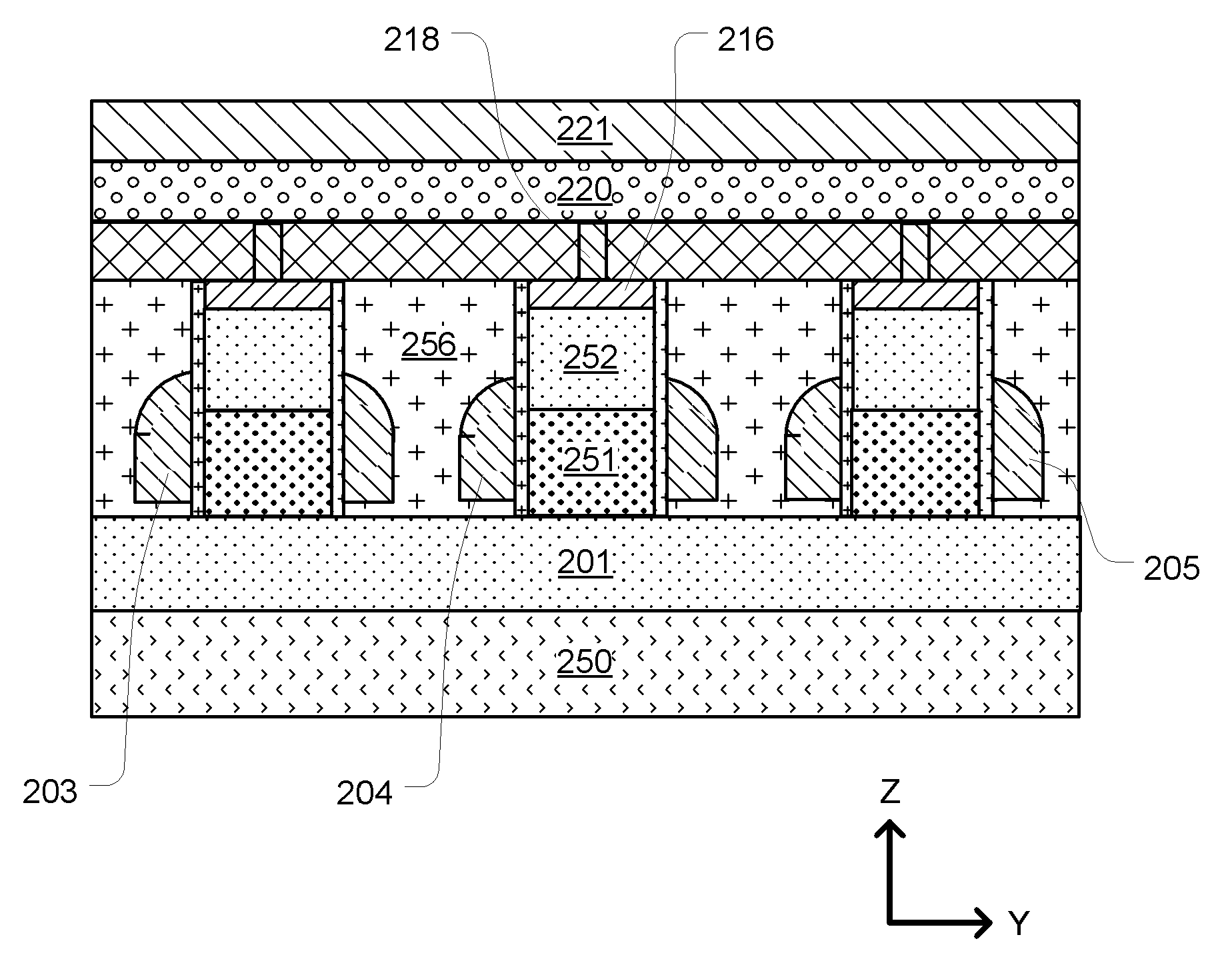

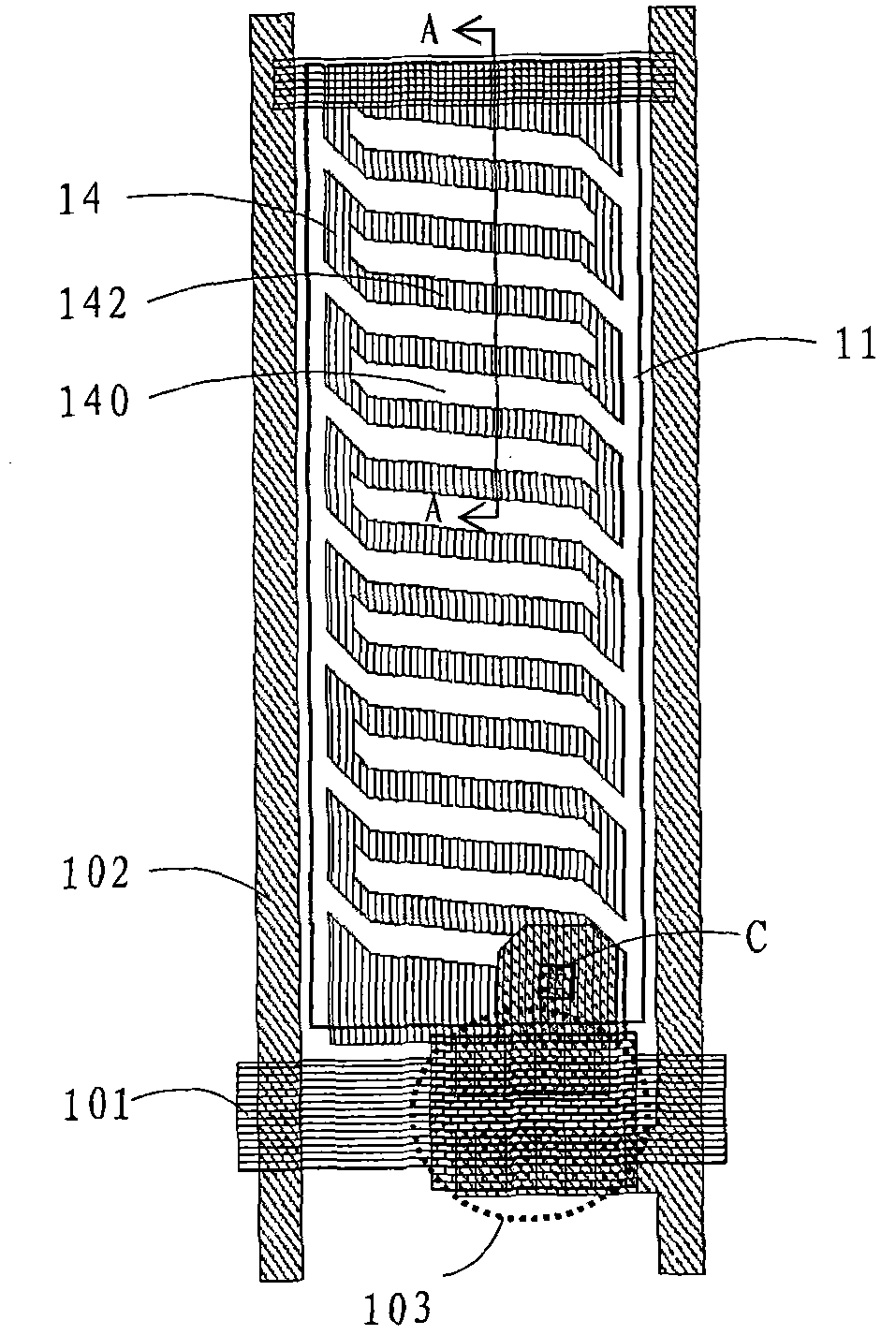

High linearity smart HBT power amplifiers for CDMA/WCDMA application

ActiveUS7026876B1Increase power gainImprove RF efficiencyHigh frequency amplifiersAmplifier combinationsTransistor arrayHbt power amplifier

A power amplifier includes larger size transistors to provide higher power gain at lower frequencies. Transistors of transistor unit cells include a horseshoe-shaped emitter and a strip-shaped base to increase gain. Transistors are combined at a first level to form transistor arrays, which are combined with bonding wires at a second level to an output micro strip transmission line. A Vbe referenced bias circuit may include a smart function to lower quiescent current.

Owner:CALLAHAN CELLULAR L L C

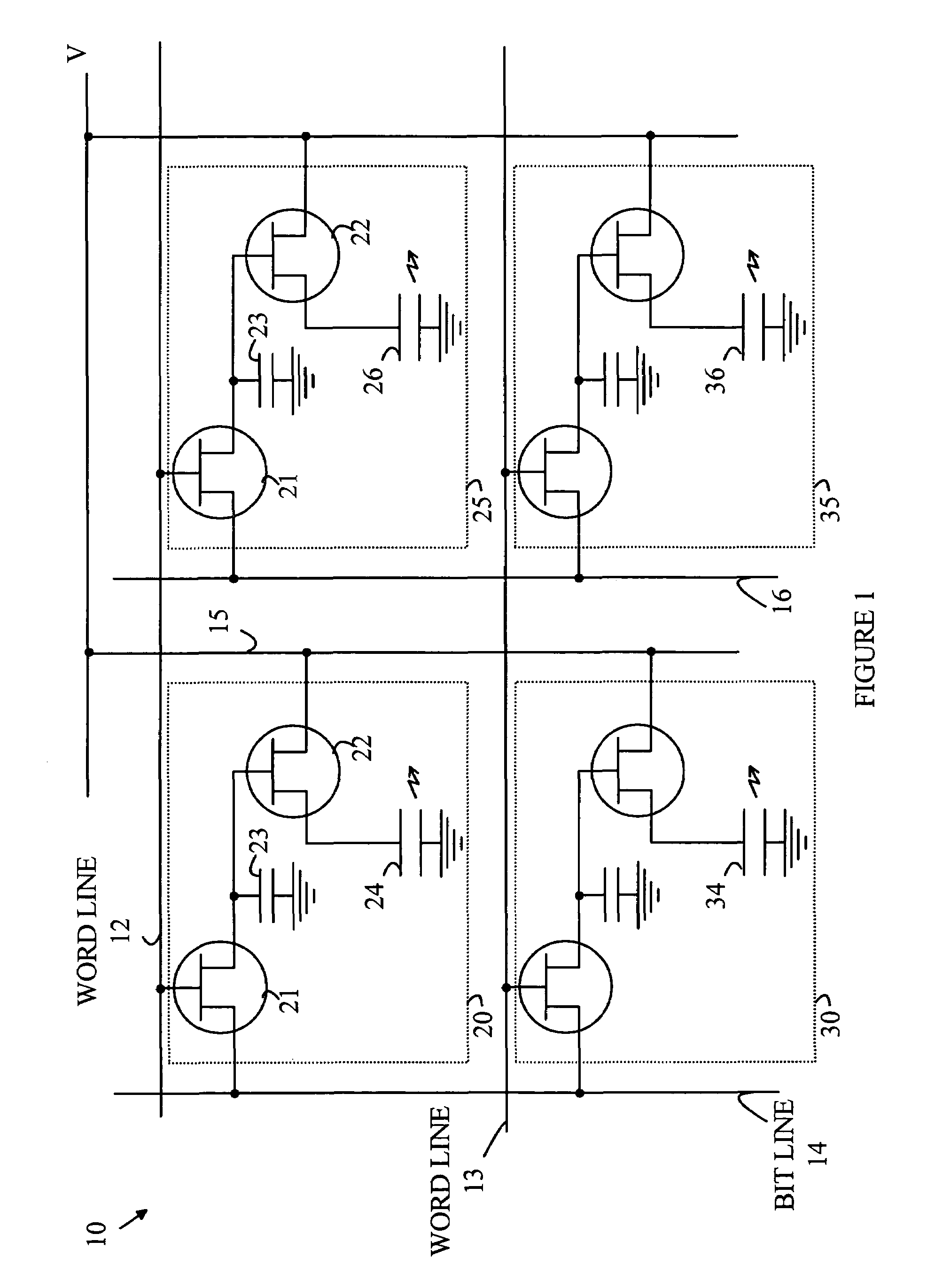

Self-aligned bit line under word line memory array

ActiveUS20110305074A1Free from damageSuitable for useSolid-state devicesSemiconductor/solid-state device manufacturingTransistor arrayBit line

A memory device is described that comprises a plurality of bit lines and an array of vertical transistors arranged on the plurality of bit lines. A plurality of word lines is formed along rows of vertical transistors in the array which comprise thin film sidewalls of word line material and arranged so that the thin film sidewalls merge in the row direction, and do not merge in the column direction, to form word lines. The word lines provide “surrounding gate” structures for embodiments in which the vertical transistors are field effect transistors. Memory elements are formed in electrical communication with the vertical transistors. A fully self-aligned process is provided in which the word lines and memory elements are aligned with the vertical transistors without additional patterning steps.

Owner:IBM CORP +1

Array substrate and method for manufacturing same

ActiveCN102636927ASimple structureIncrease opening ratioSemiconductor/solid-state device manufacturingNon-linear opticsCapacitanceTransistor array

The invention belongs to the technical field of liquid crystal display, and particularly relates to an array substrate and a method for manufacturing the same. The oxide film transistor array substrate is provided with a source electrode and / or a drain electrode made of transparent conductive materials, a thin film transistor structure is simplified, and the aperture opening of a liquid crystal display device using the array substrate is increased. A common electrode wire and a data line are arranged on the same layer, the distance between the common electrode wire and a pixel electrode is shortened, storage capacitance is increased, and the performance of the array substrate is improved. When the array substrate is manufactured, by the aid of a half gray-level mask multi-step etching method, an etching protective film and the data line are obtained by means of mask exposure once, only five times of mask exposure are needed during manufacture of the array substrate, the process is simplified, and the manufacturing cost is reduced.

Owner:BOE TECH GRP CO LTD

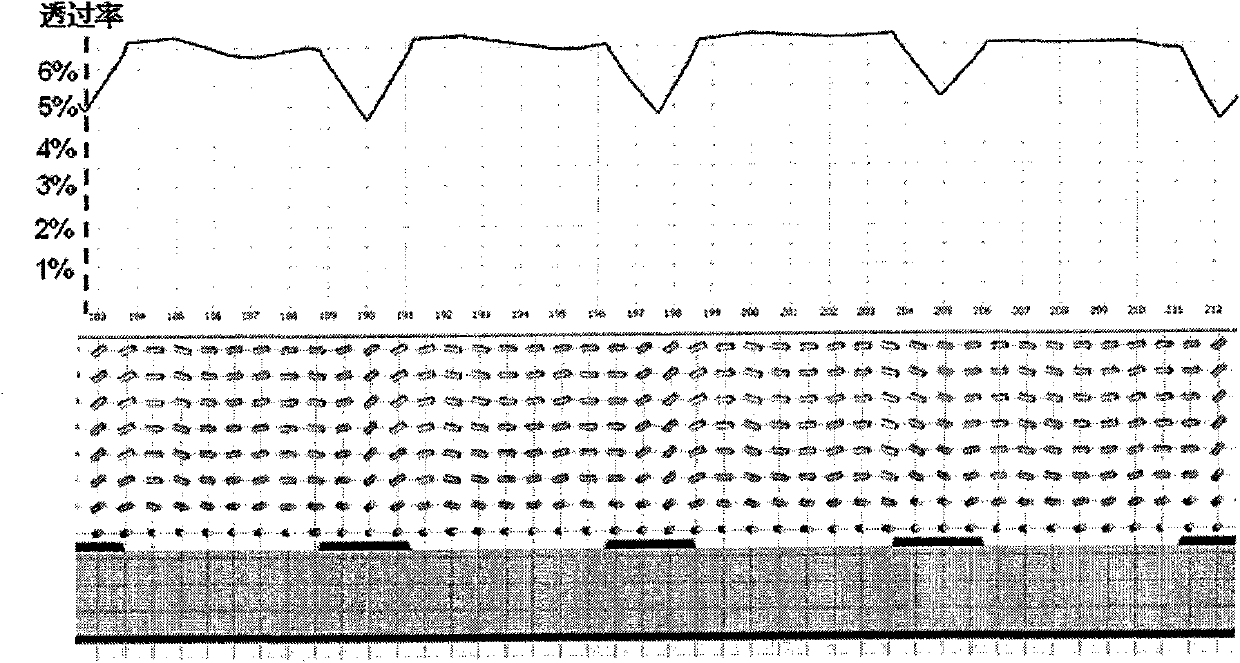

Fringe field switching (FFS) liquid crystal display (LCD) panel, manufacturing method thereof and LCD

ActiveCN101995707AReduce differential pressureReduce the driving voltageSolid-state devicesSemiconductor/solid-state device manufacturingTransistor arrayLiquid-crystal display

The invention discloses a fringe field switching (FFS) liquid crystal display (LCD) panel, a manufacturing method thereof and an LCD. The LCD panel comprises a thin film transistor (TFT) array substrate, and the TFT array substrate comprises a transparent substrate as well as a plurality of scanning lines and a plurality of data lines which are formed on the transparent substrate, wherein, the plurality of scanning lines are crossed with the plurality of data lines to limit a plurality of pixel regions; each pixel region comprises a first transparent electrode, a second transparent electrode and a TFT; the first transparent electrode is equipped with a plurality of strip slots so that a plurality of first strip transparent electrode parts which are respectively spaced by the plurality of strip slots and electrically connected with each other are formed on the first transparent electrode; and each pixel region further comprises a plurality of strip projections which are positioned below the second transparent electrode and are corresponding to the positions of the plurality of slots of the first transparent electrode. The invention has the advantages that the driving voltage of theLCD panel can be lowered and the transmissivity can be improved.

Owner:KUSN INFOVISION OPTOELECTRONICS

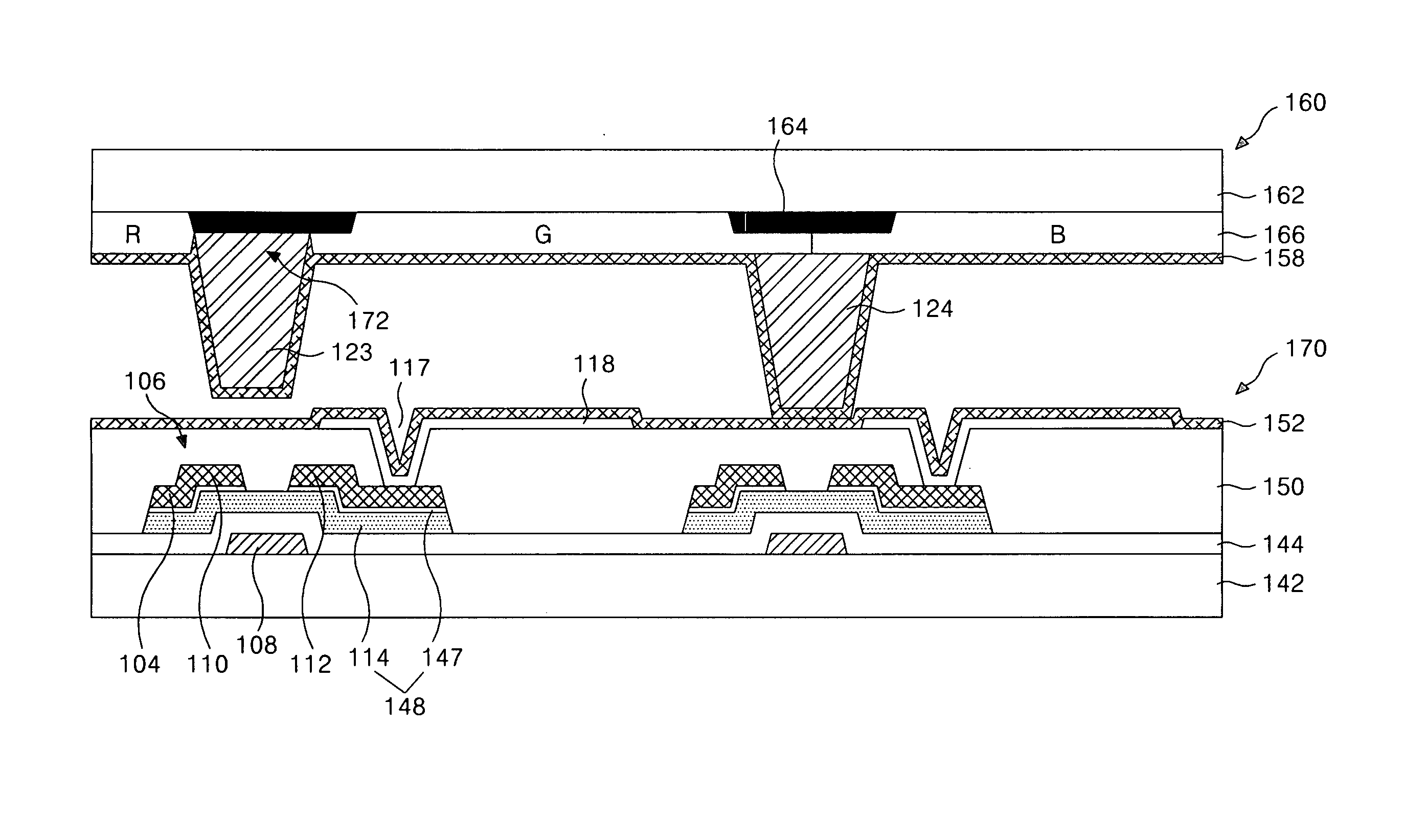

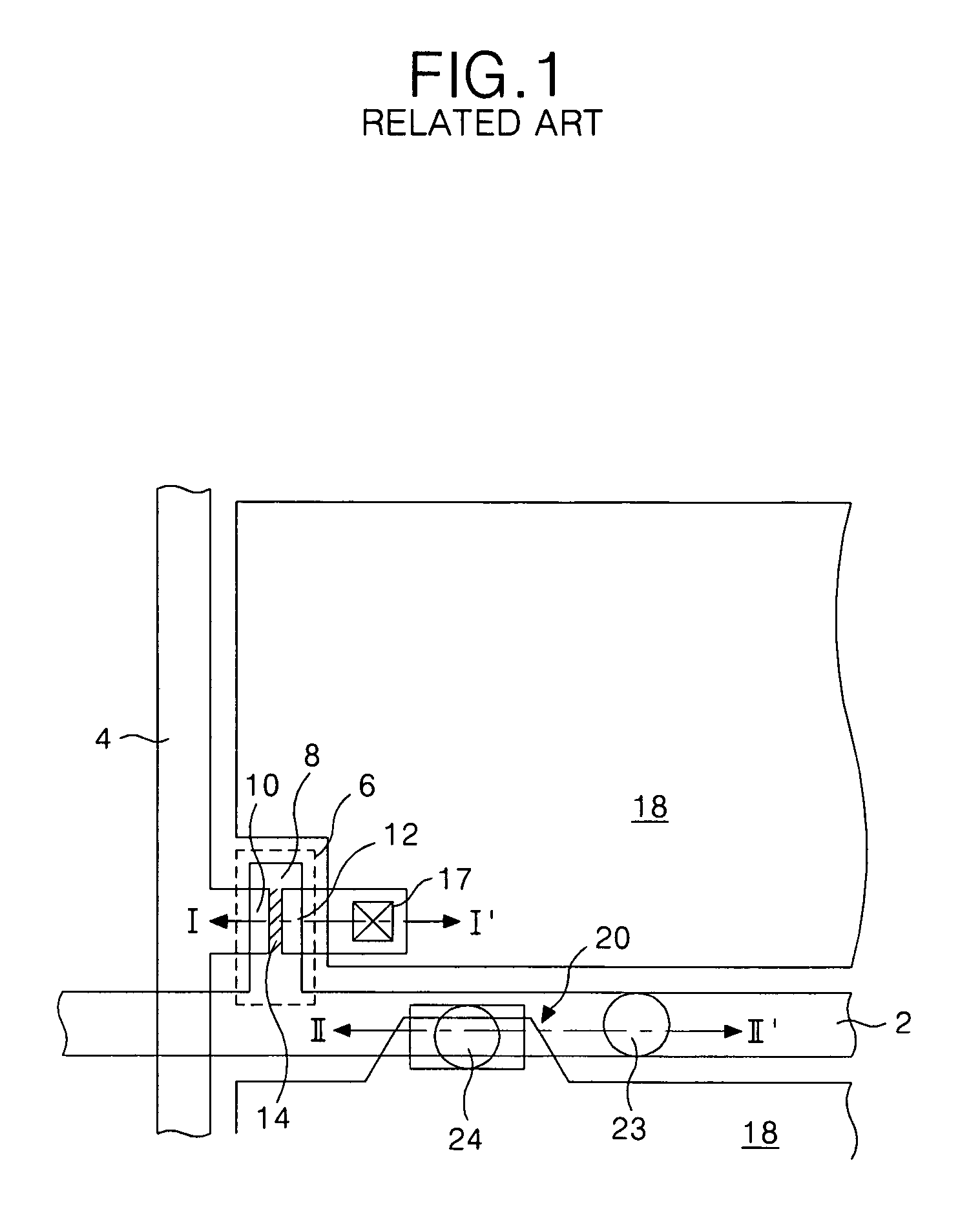

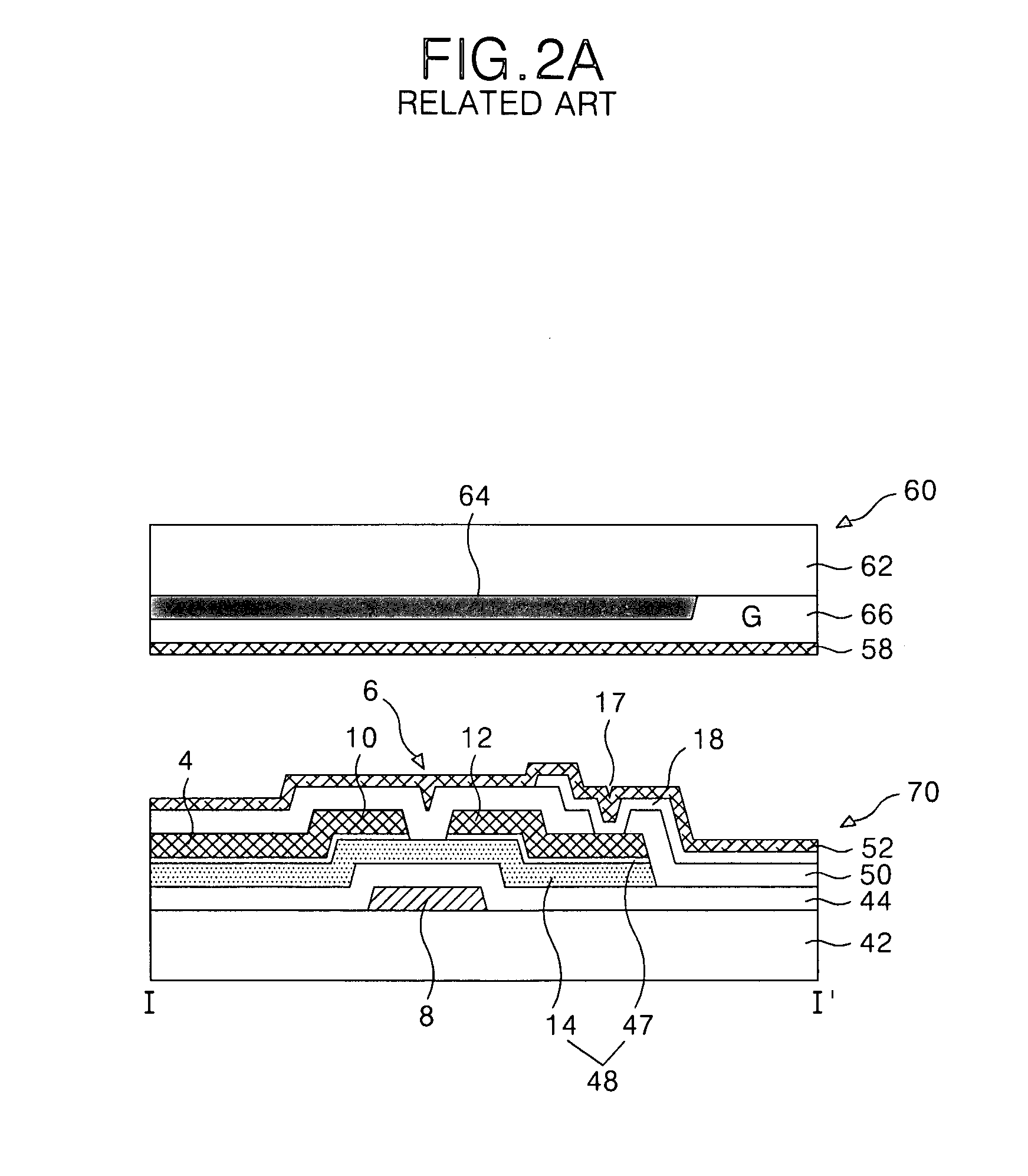

Liquid crystal display panel and method of fabricating the same

ActiveUS20070002263A1Improve reliabilityAvoid defectsNon-linear opticsTransistor arrayLiquid-crystal display

A liquid crystal display panel includes a color filter array substrate having a first column spacer and a second column spacer, the first column spacer being partially inserted in a first hole, and a thin film transistor (TFT) array substrate facing the color filter array substrate having a protective passivation film.

Owner:LG DISPLAY CO LTD

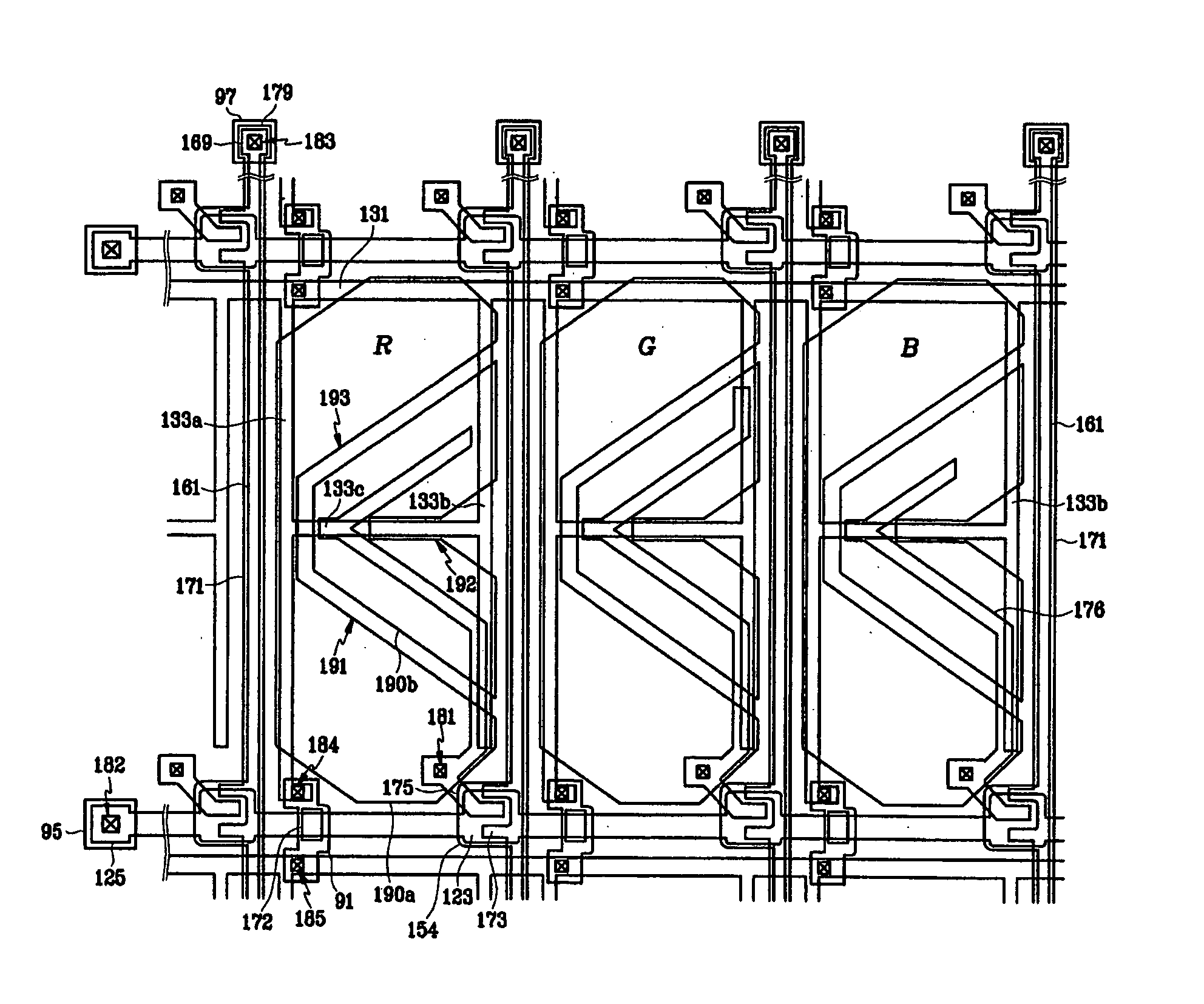

Thin film transistor array panel

InactiveUS20050030439A1Increase awarenessTransistorSemiconductor/solid-state device manufacturingCapacitanceVisibility

A thin film transistor array panel comprising an insulating substrate; a plurality of first signal lines formed on the insulating substrate; a plurality of second signal lines intersecting the first signal lines in an insulated manner to define pixel areas; a plurality of first pixel electrodes formed in each of the pixel areas; a plurality of thin film transistors having three electrodes respectively connected to the first signal line, the second signal line, and the first pixel electrode; and a plurality of second pixel electrodes formed in each of the pixel areas and electrically coupled with the first pixel electrodes, wherein the pixels include red, green, and blue pixels, and coupling capacitances between the first pixel electrodes and the second pixel electrodes are different among the red, green, and blue pixels. An LCD using such a thin film transistor array panel shows improved side visibility and has a wide viewing angle.

Owner:SAMSUNG DISPLAY CO LTD