Patents

Literature

2233 results about "Charge carrier mobility" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Charge carrier mobility. The performance of any organic device depends on the mobility of the charge carriers. For example, if the charge applied to an OLED remains stuck next to the electrodes for a long time this will not lead a internal current that is transformed into the emission of photons.

Indium oxide-based thin film transistors and circuits

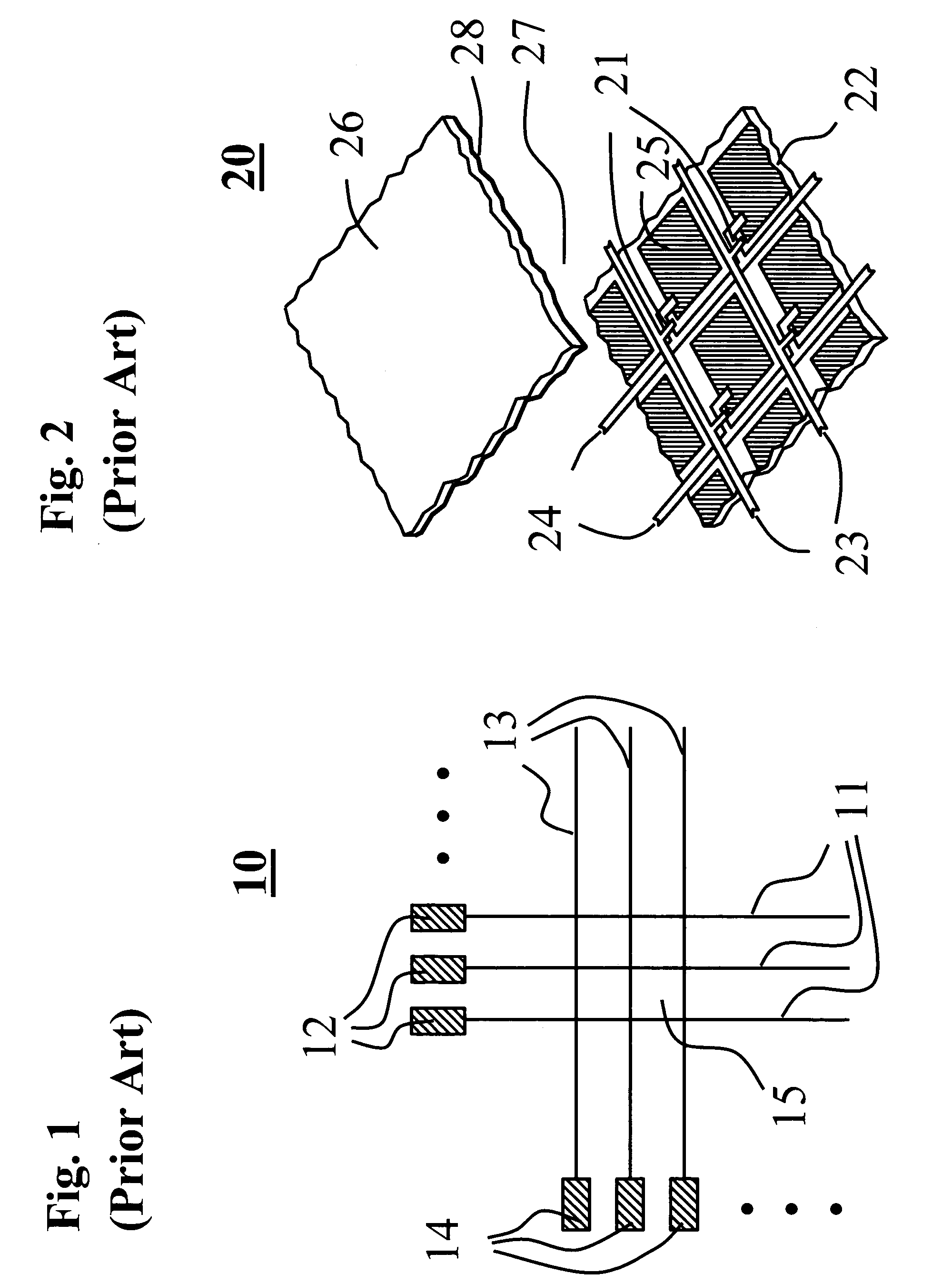

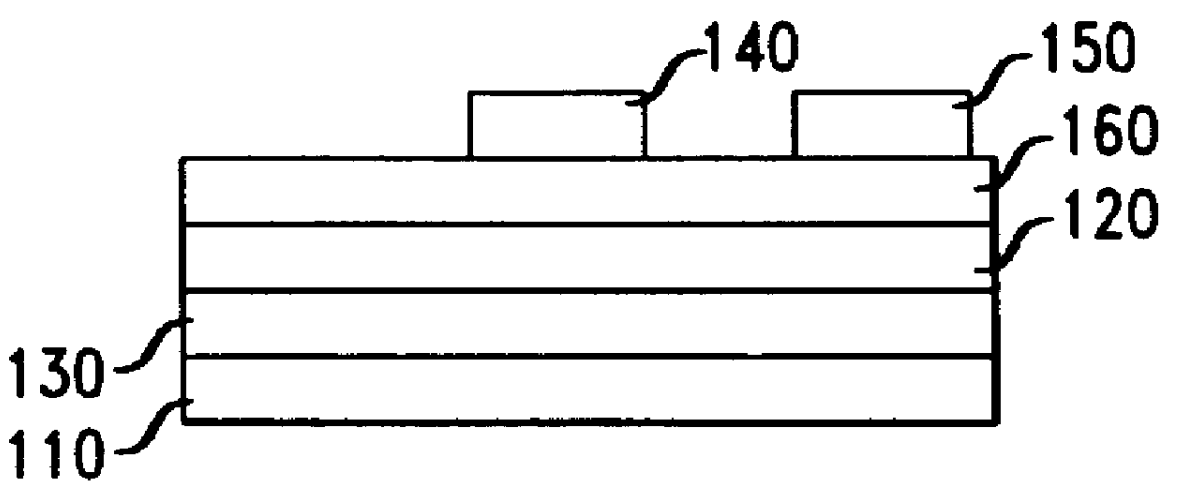

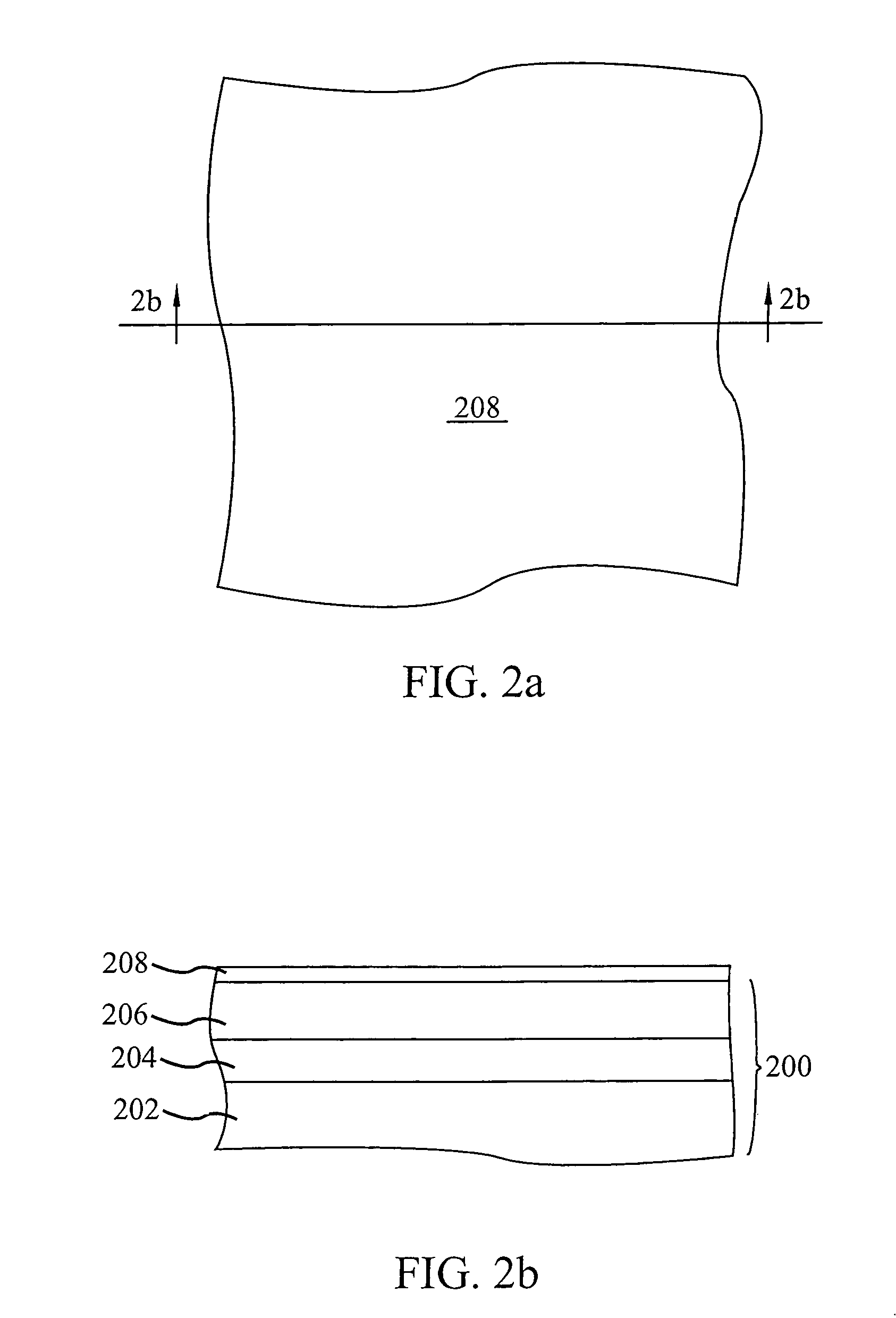

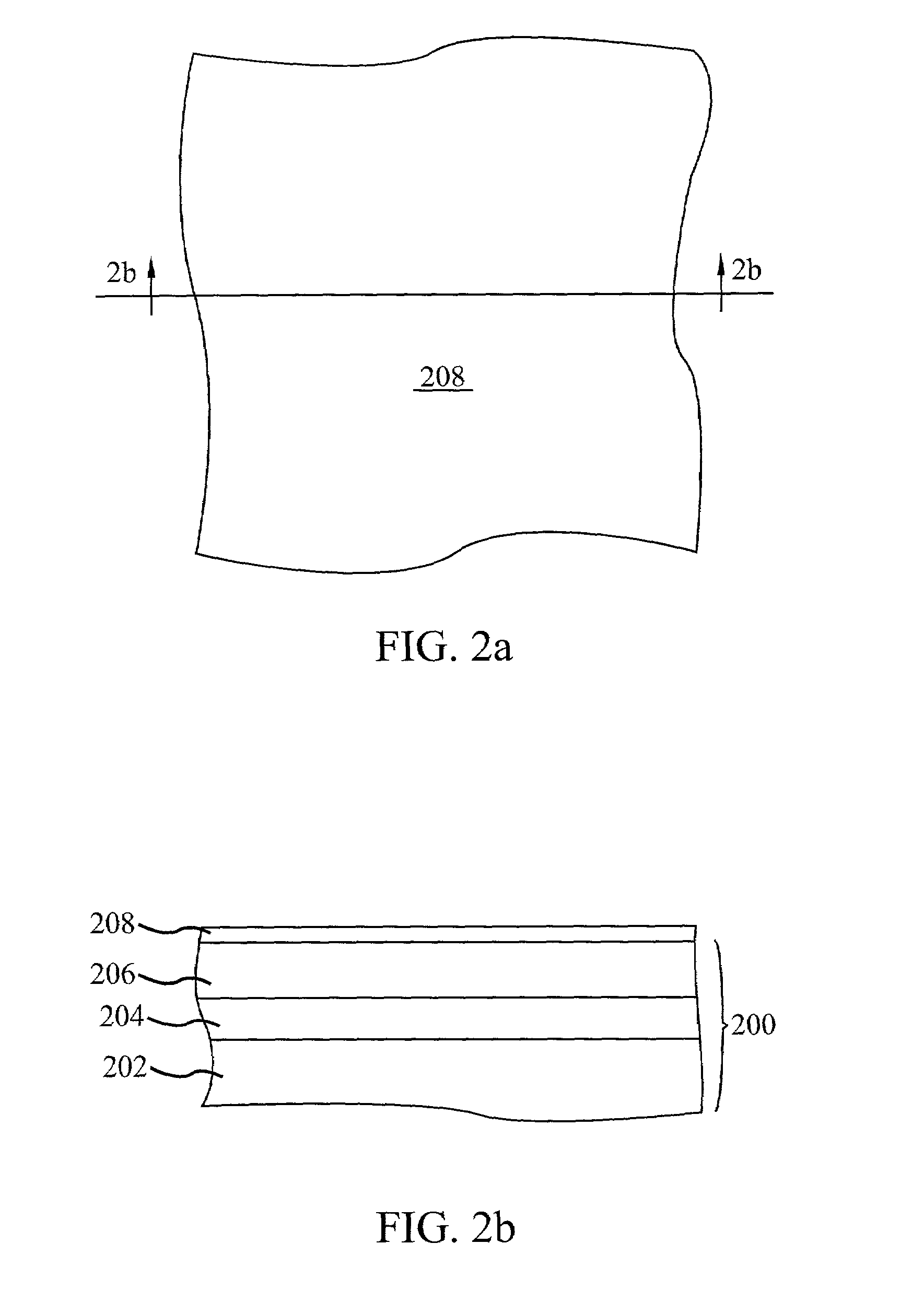

In electronic displays or imaging units, the control of pixels is achieved by an array of transistors. These transistors are in a thin film form and arranged in a two-dimensional configuration to form switching circuits, driving circuits or even read-out circuits. In this invention, thin film transistors and circuits with indium oxide-based channel layers are provided. These thin film transistors and circuits may be fabricated at low temperatures on various substrates and with high charge carrier mobilities. In addition to conventional rigid substrates, the present thin film transistors and circuits are particularly suited for the fabrication on flexible and transparent substrates for electronic display and imaging applications. Methods for the fabrication of the thin film transistors with indium oxide-based channels are provided.

Owner:SHIH YI CHI +3

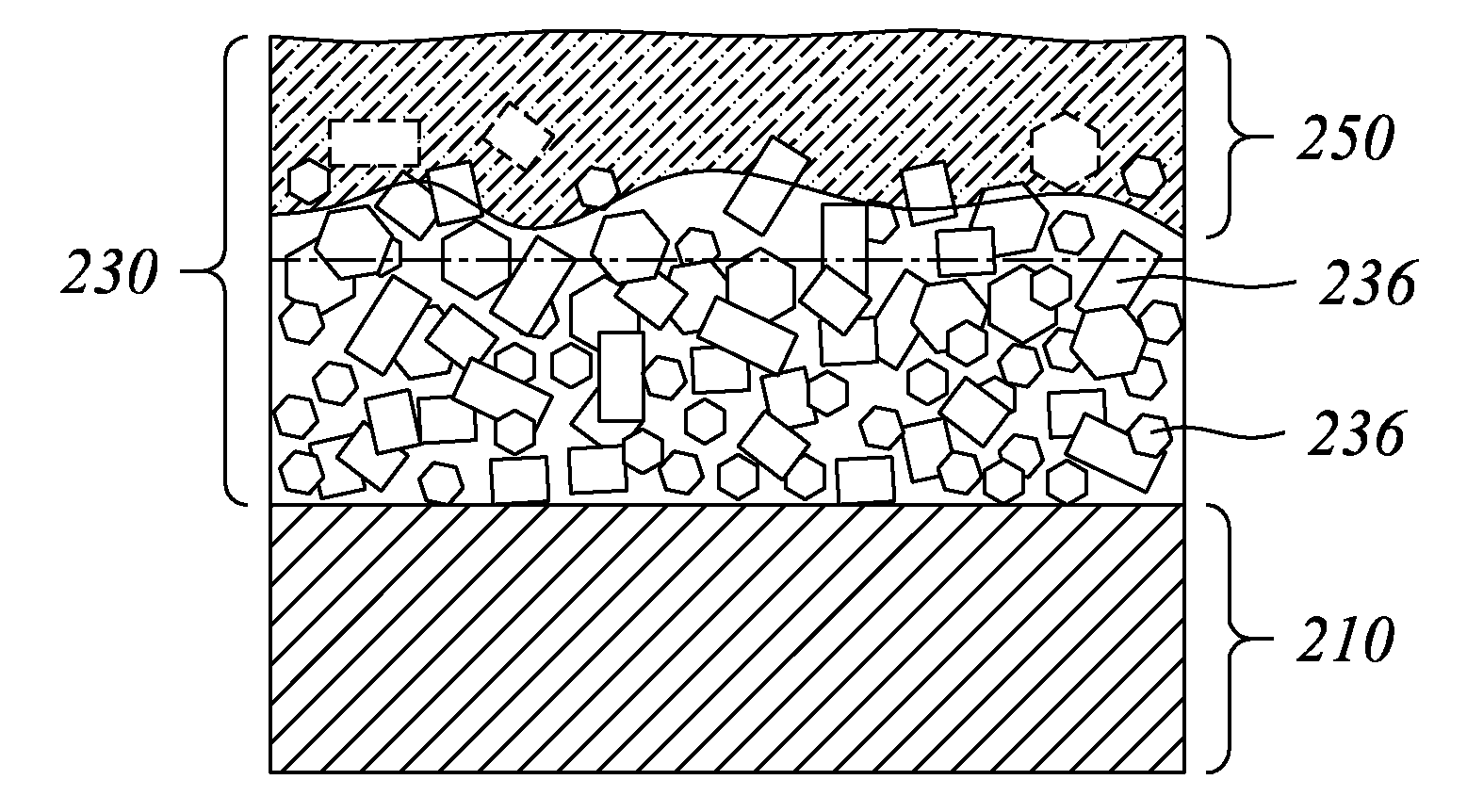

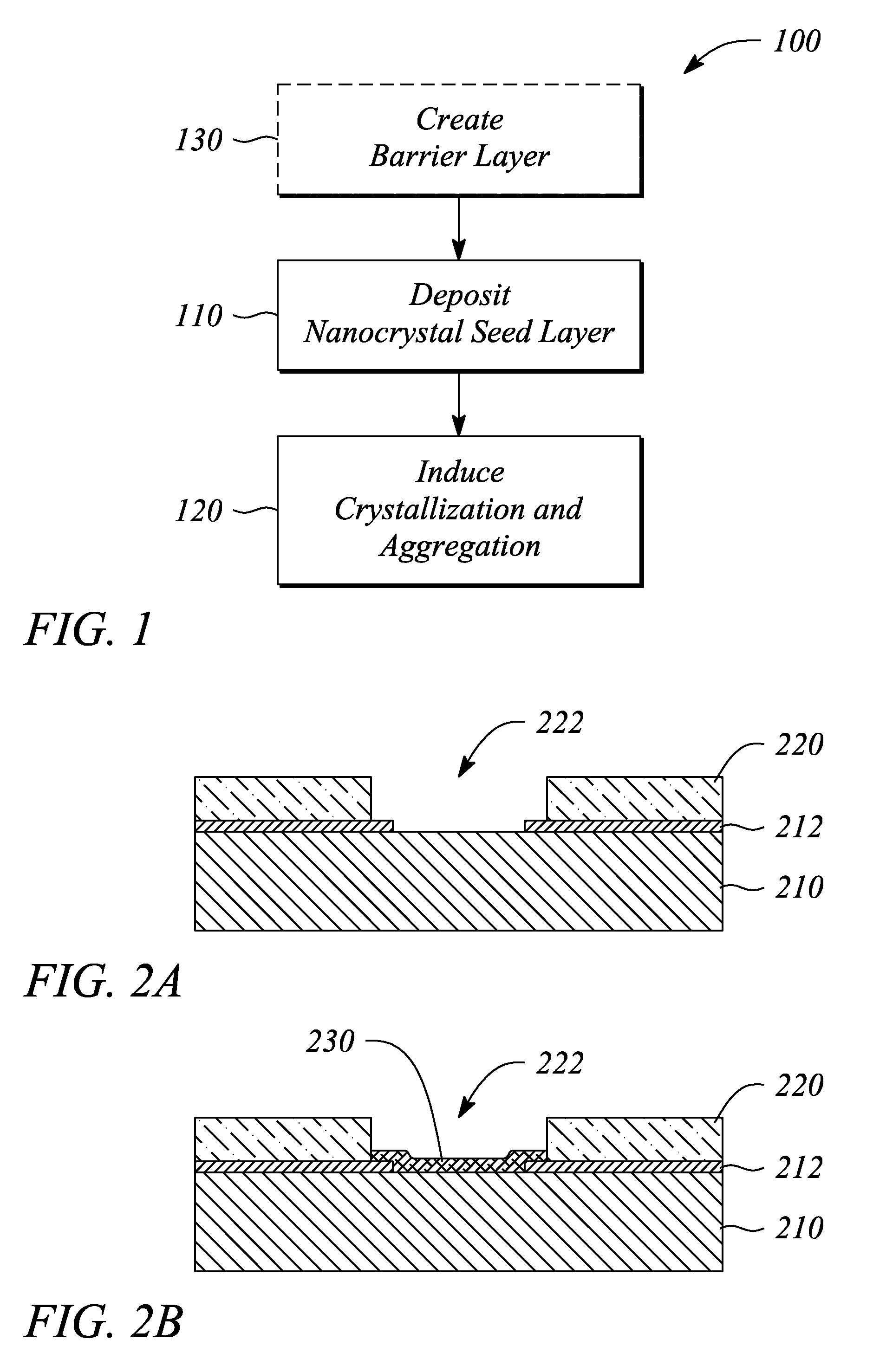

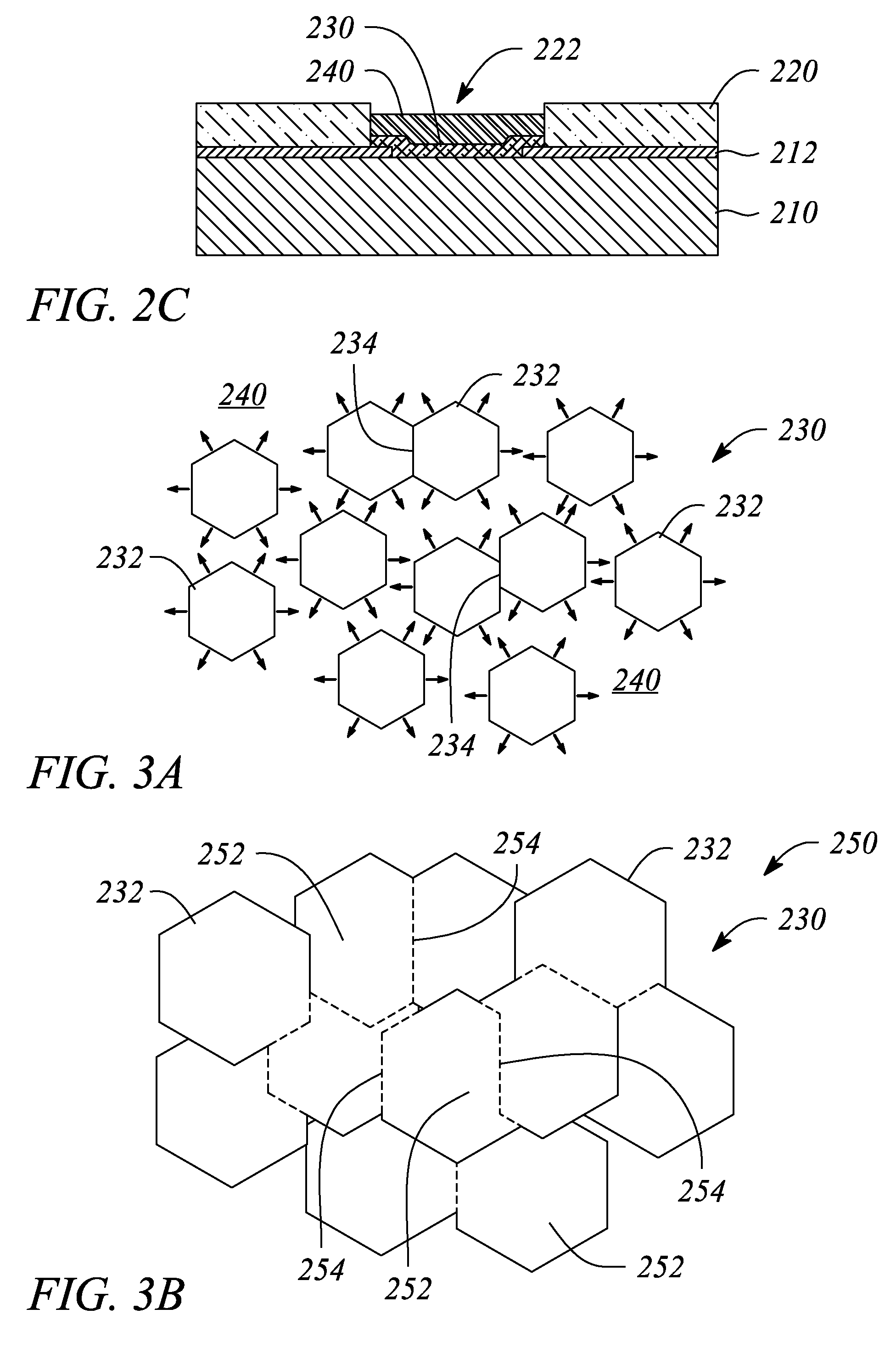

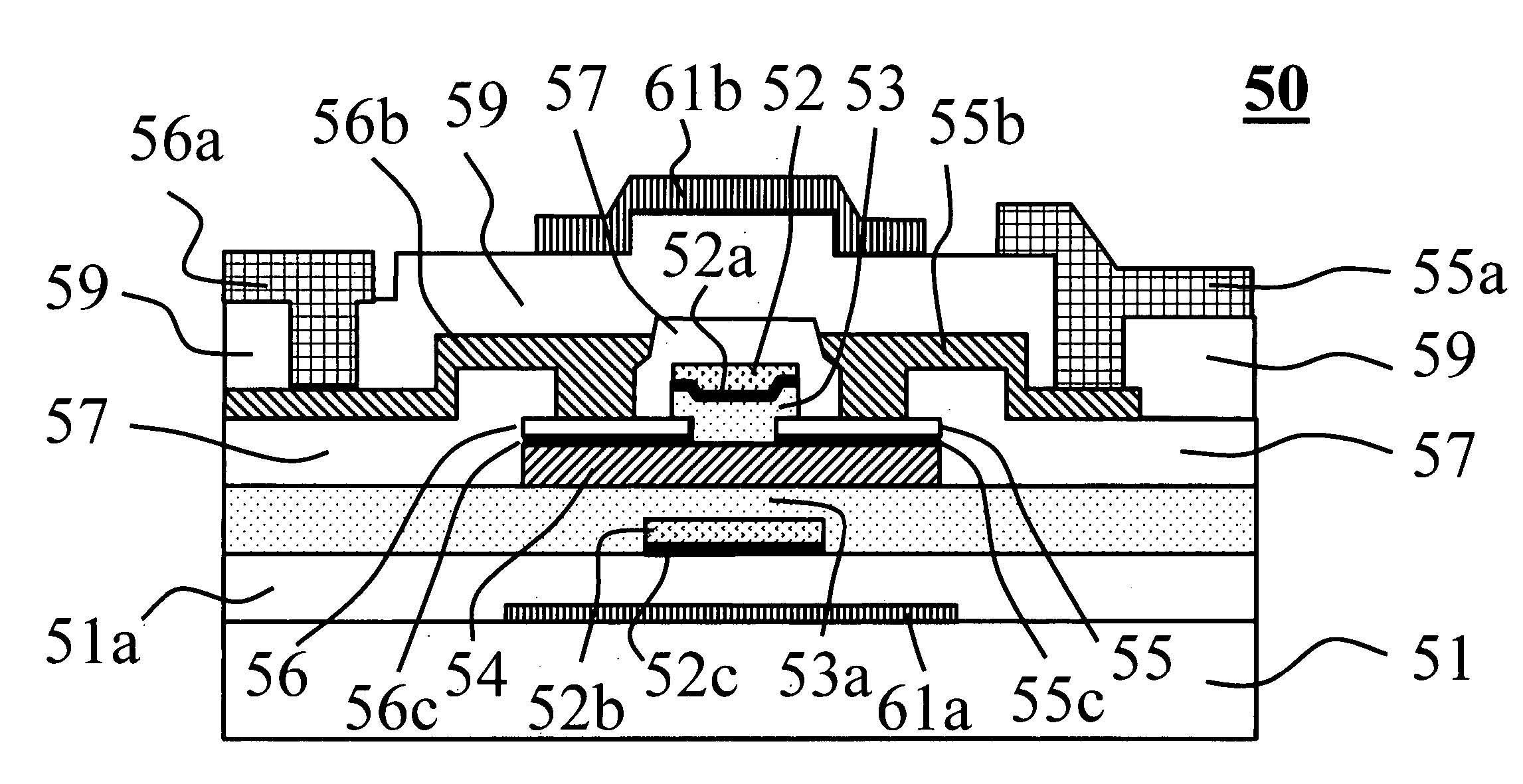

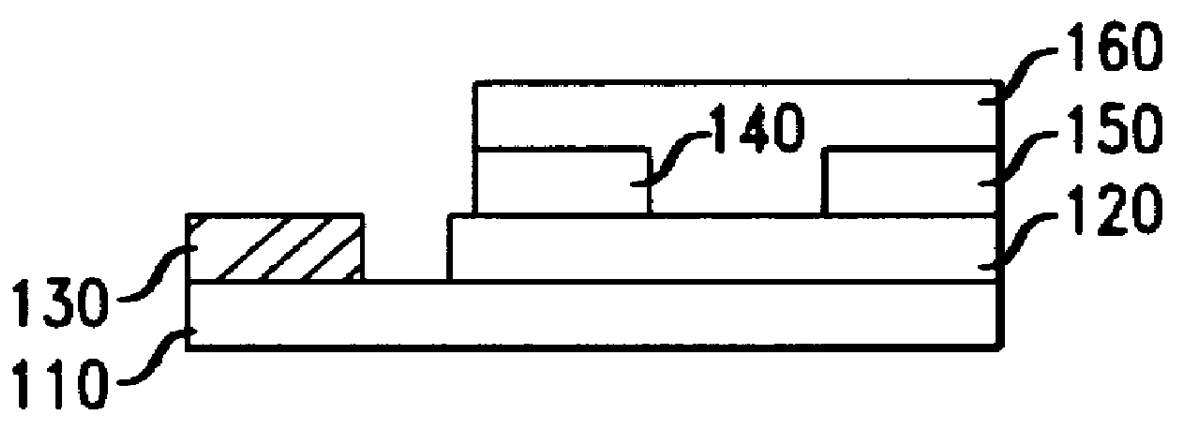

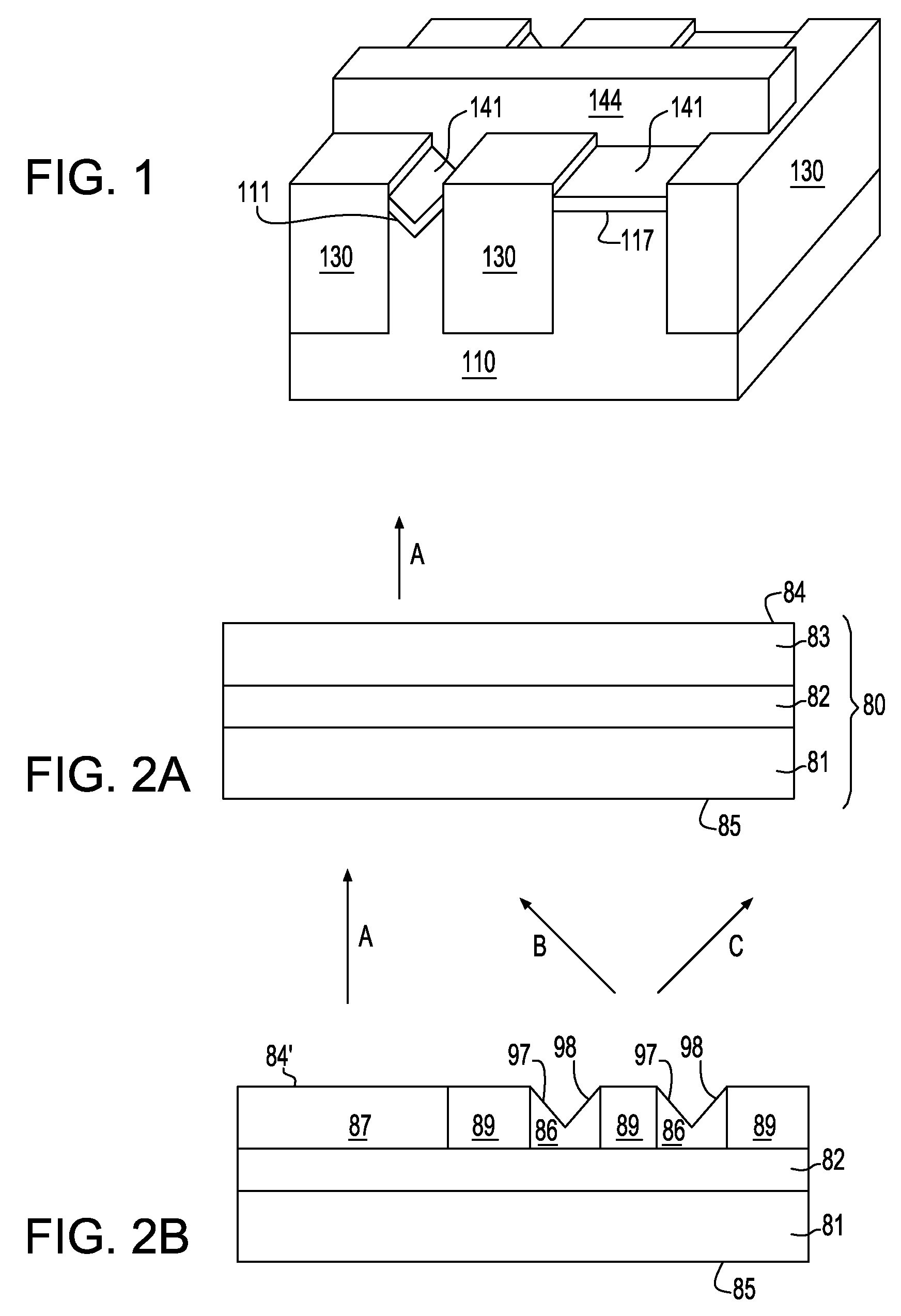

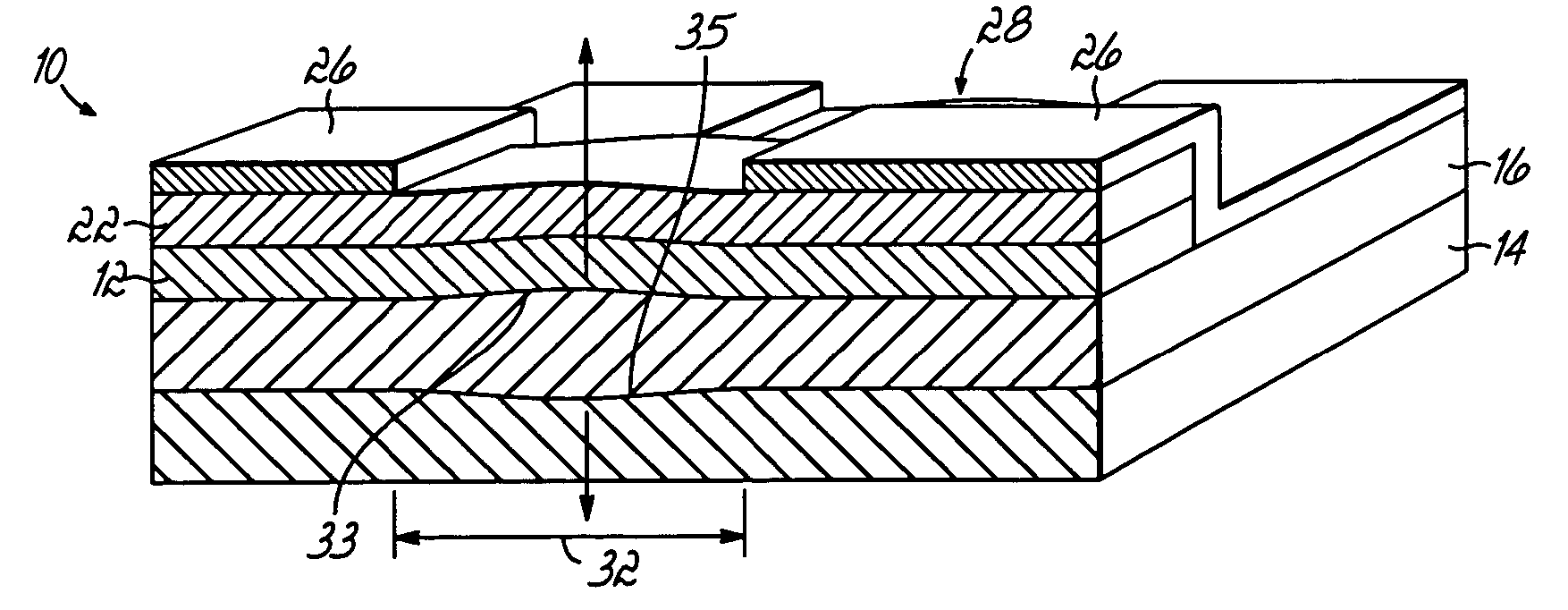

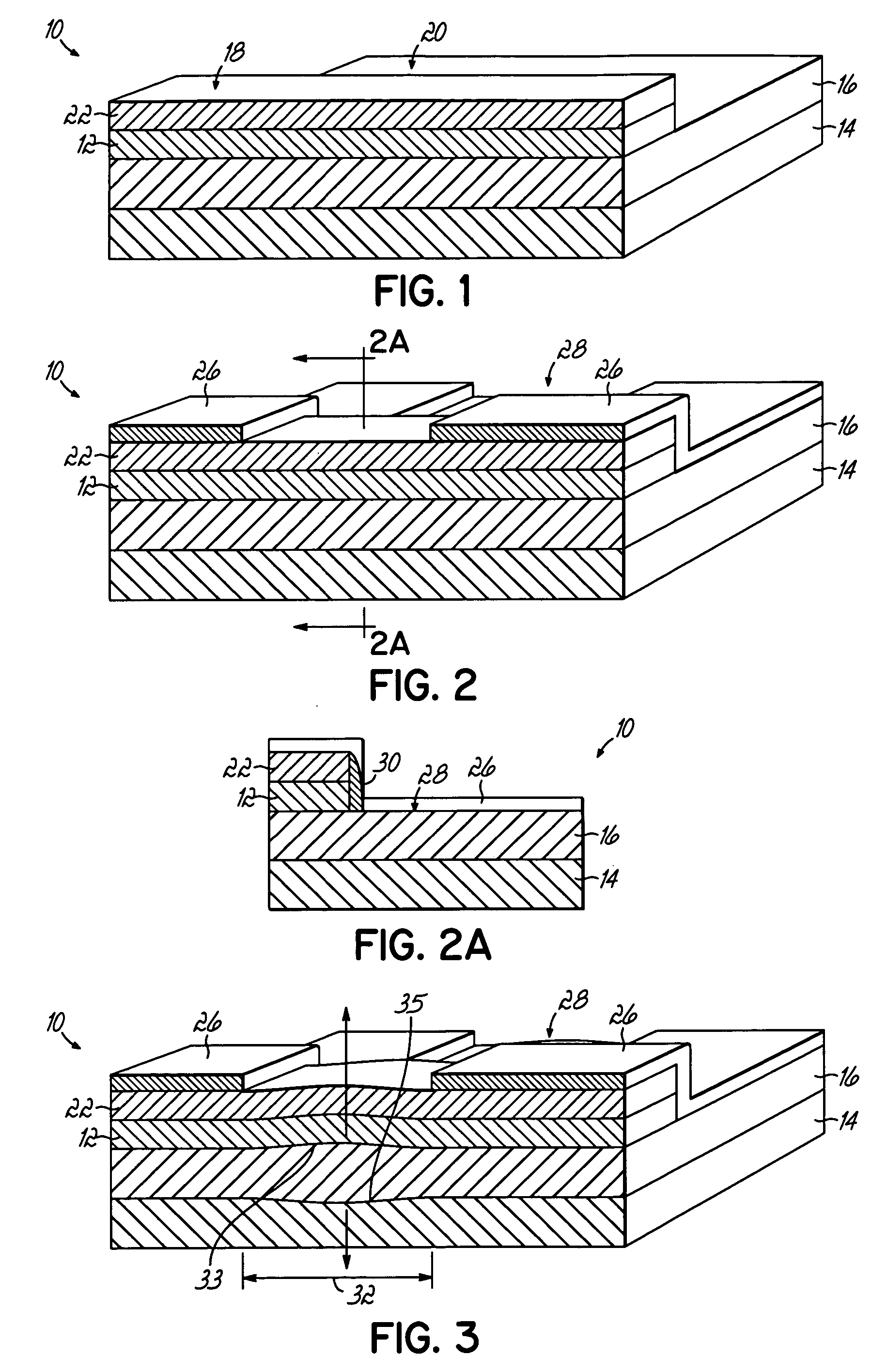

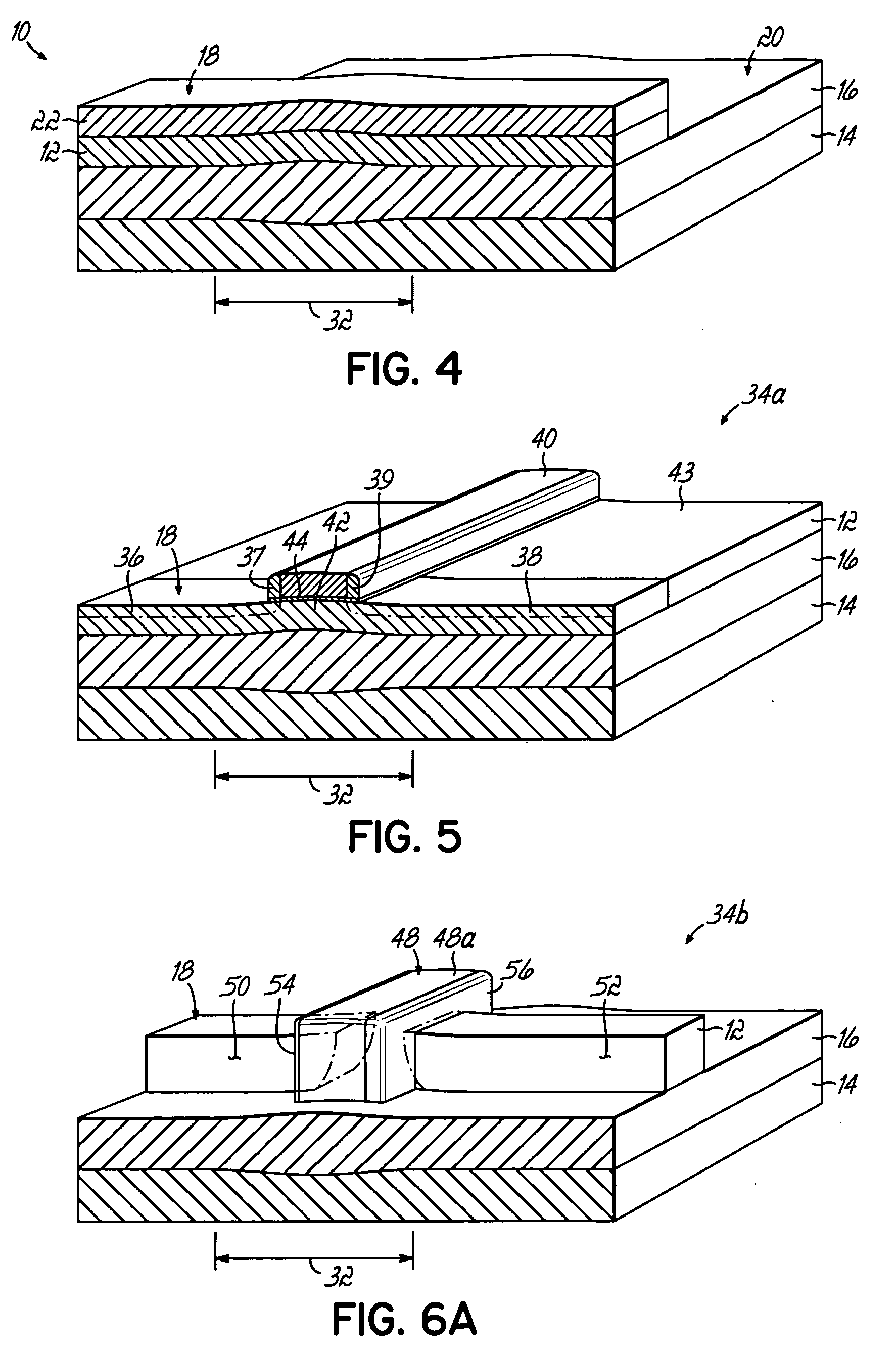

Fused nanocrystal thin film semiconductor and method

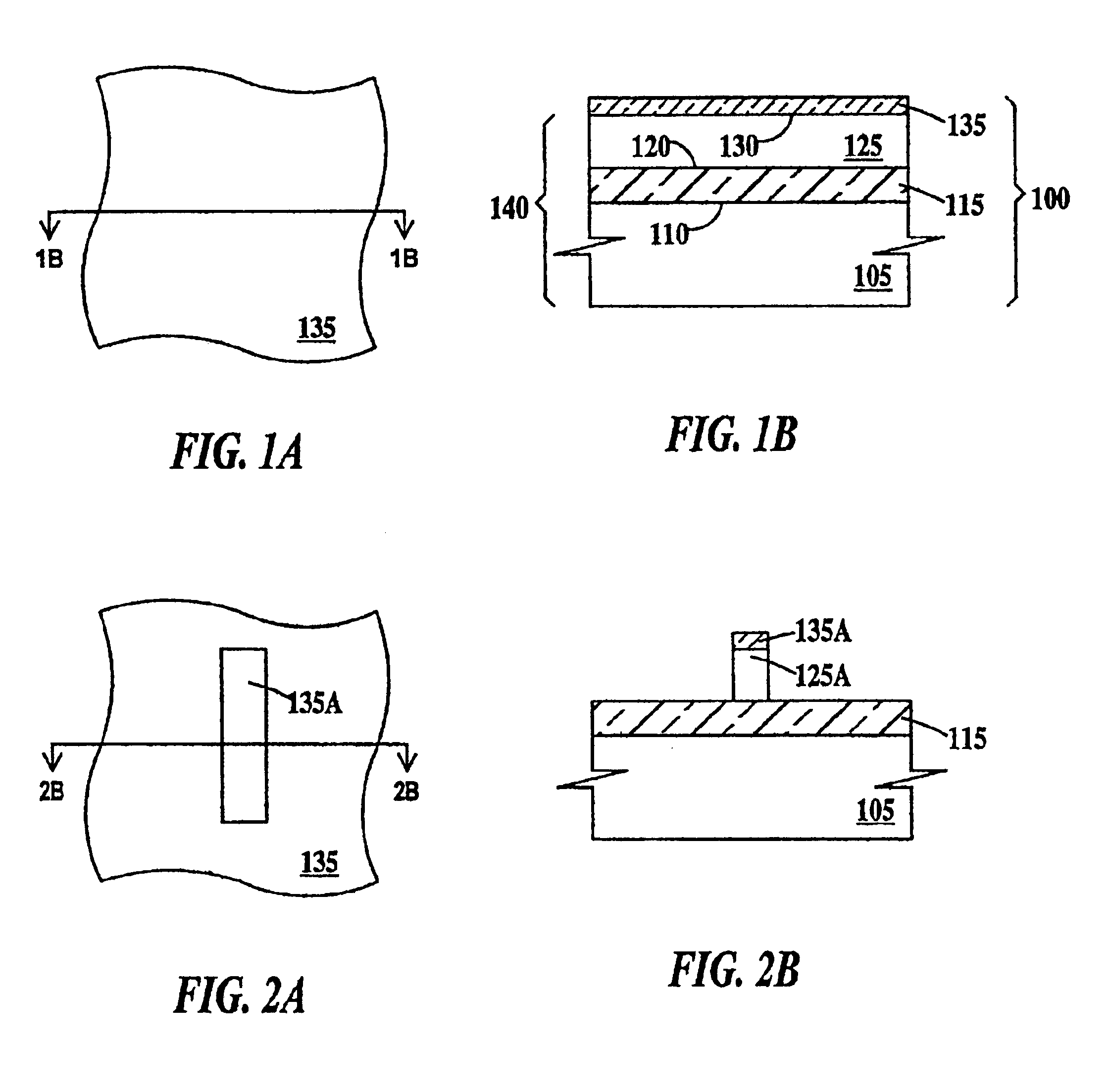

A thin film semiconductor and a method of its fabrication use induced crystallization and aggregation of a nanocrystal seed layer to form a merged-domain layer. The nanocrystal seed layer is deposited onto a substrate surface within a defined boundary. A reaction temperature below a boiling point of a reaction solution is employed. A thin film metal-oxide transistor and a method of its production employ the thin film semiconductor as a channel of the transistor. The merged-domain layer exhibits high carrier mobility.

Owner:HEWLETT PACKARD DEV CO LP

Indium oxide-based thin film transistors and circuits

In electronic displays or imaging units, the control of pixels is achieved by an array of transistors. These transistors are in a thin film form and arranged in a two-dimensional configuration to form switching circuits, driving circuits or even read-out circuits. In this invention, thin film transistors and circuits with indium oxide-based channel layers are provided. These thin film transistors and circuits may be fabricated at low temperatures on various substrates and with high charge carrier mobilities. In addition to conventional rigid substrates, the present thin film transistors and circuits are particularly suited for the fabrication on flexible and transparent substrates for electronic display and imaging applications. Methods for the fabrication of the thin film transistors with indium oxide-based channels are provided.

Owner:SHIH YI CHI +3

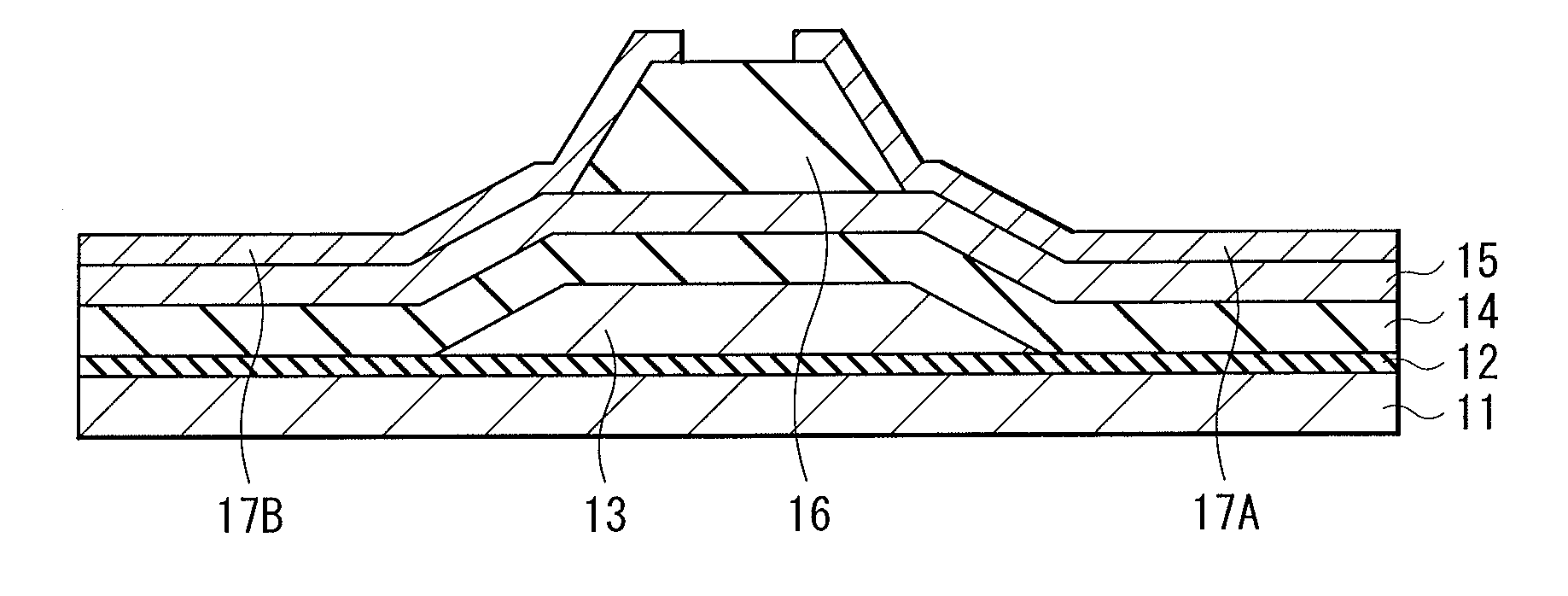

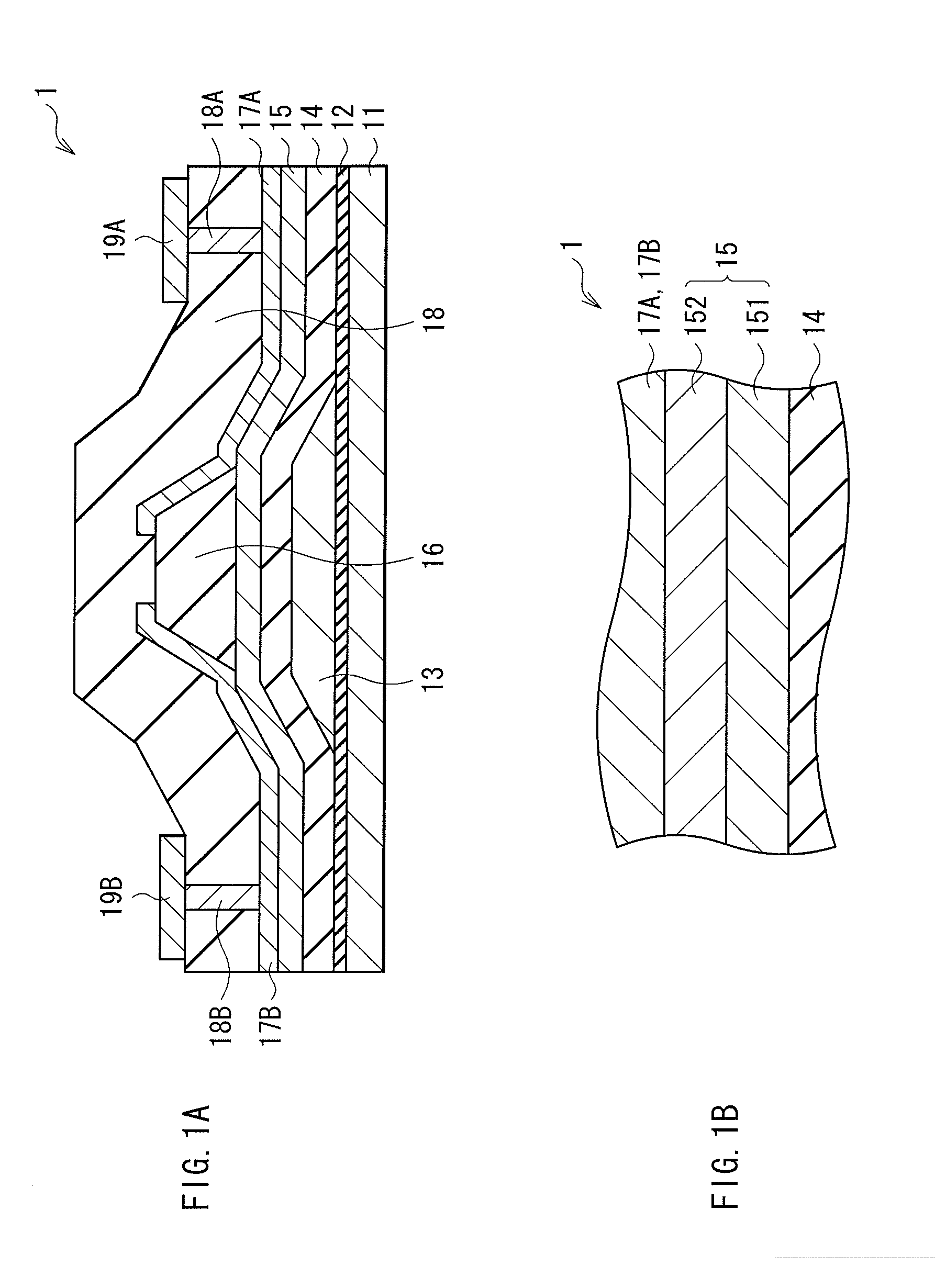

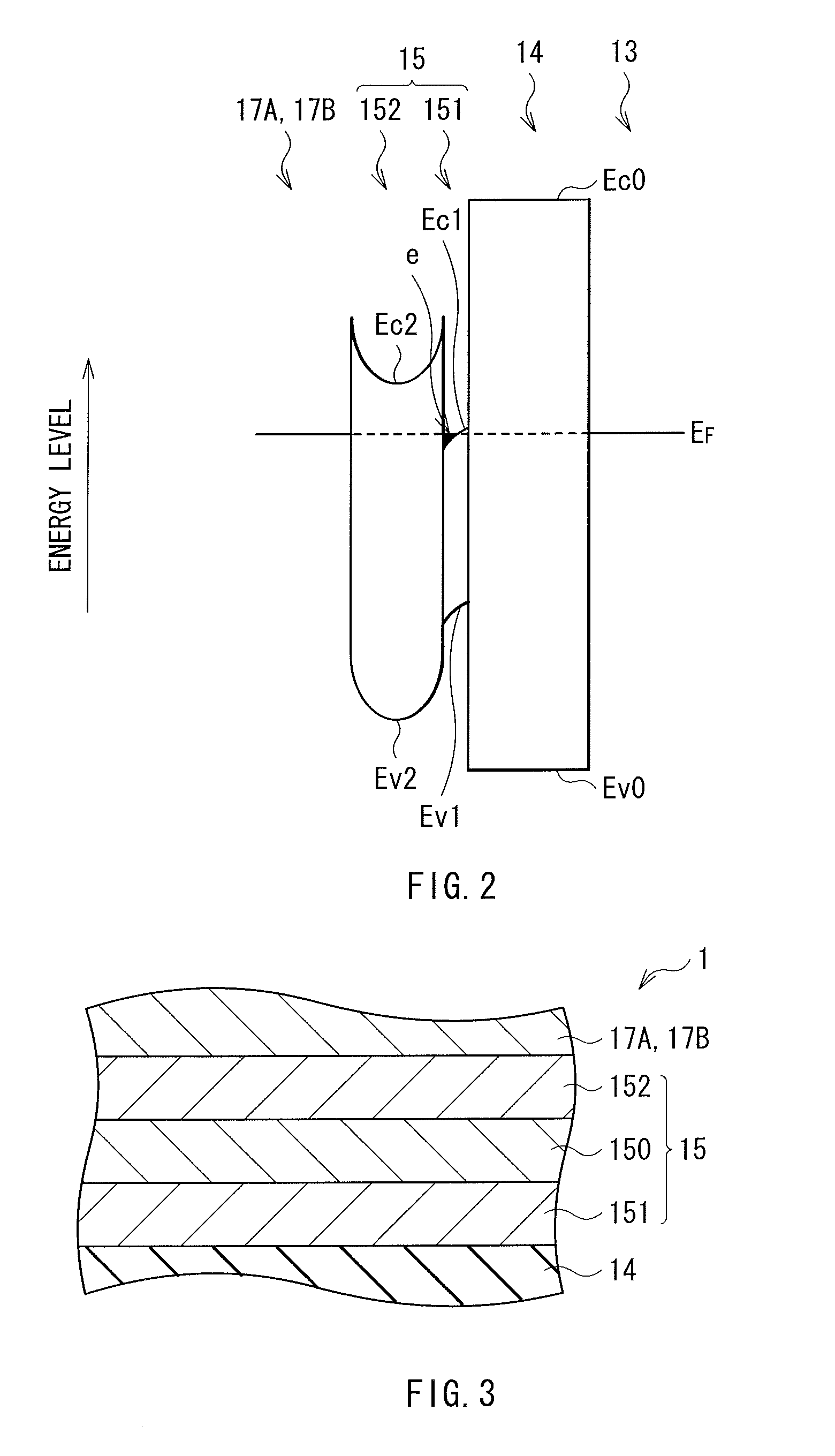

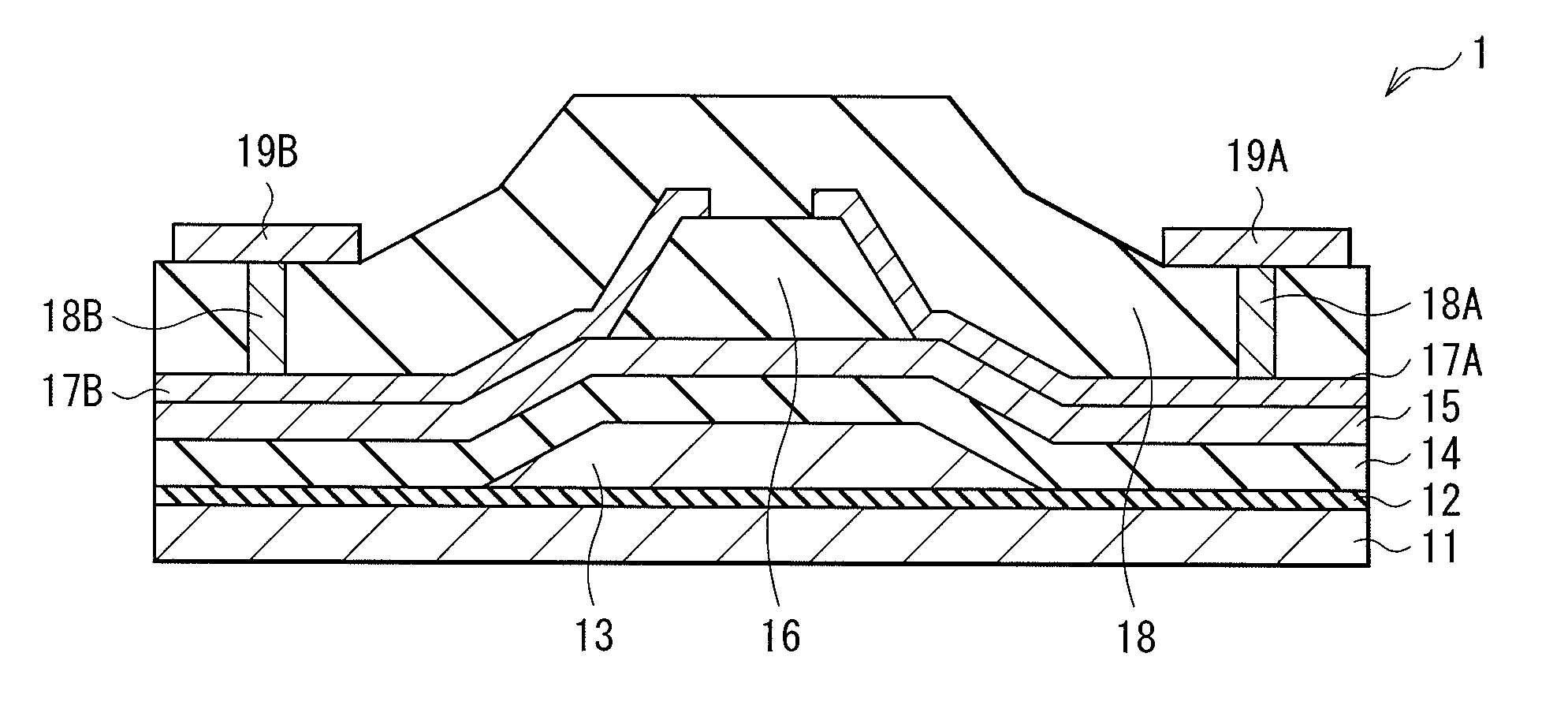

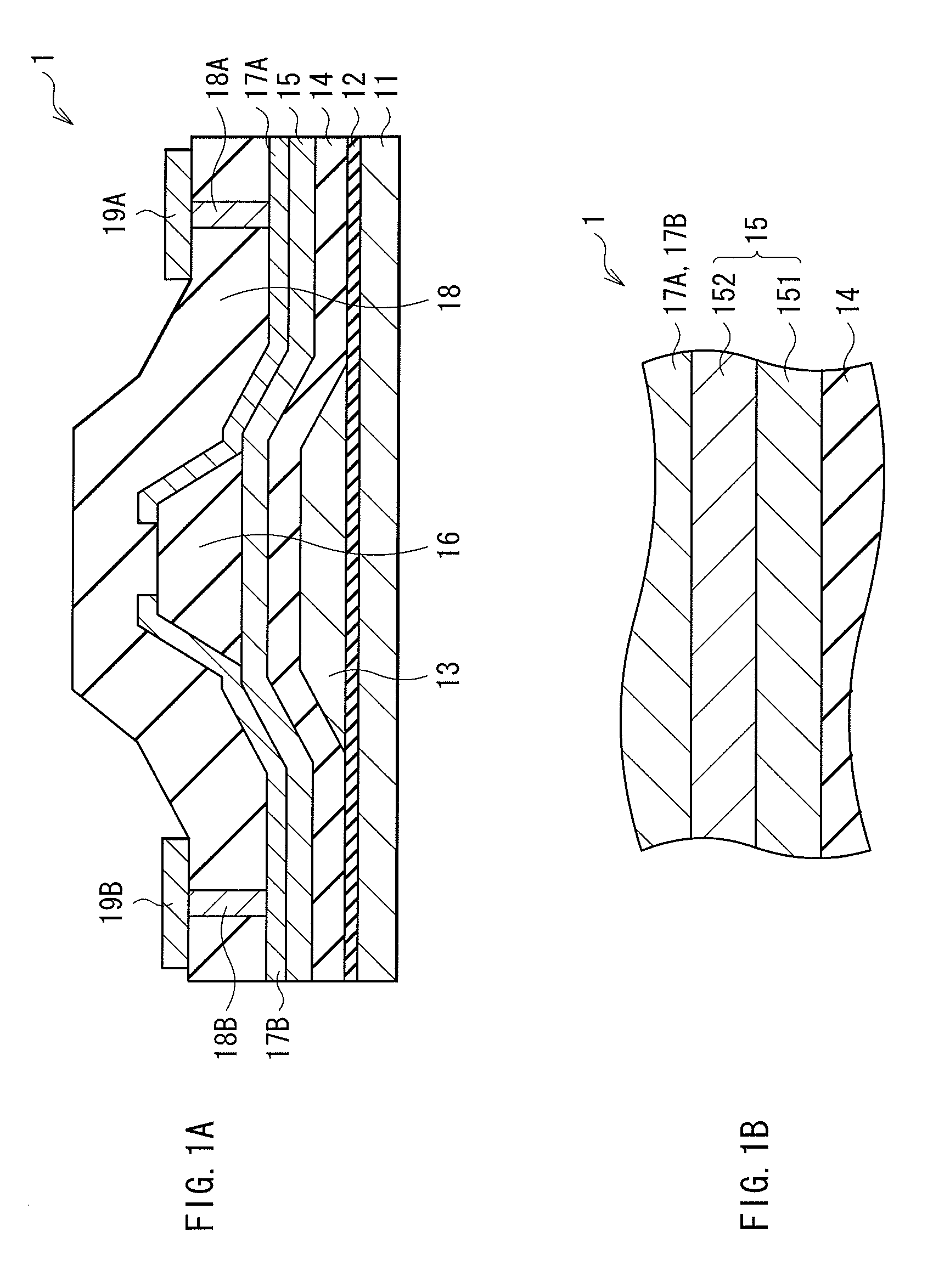

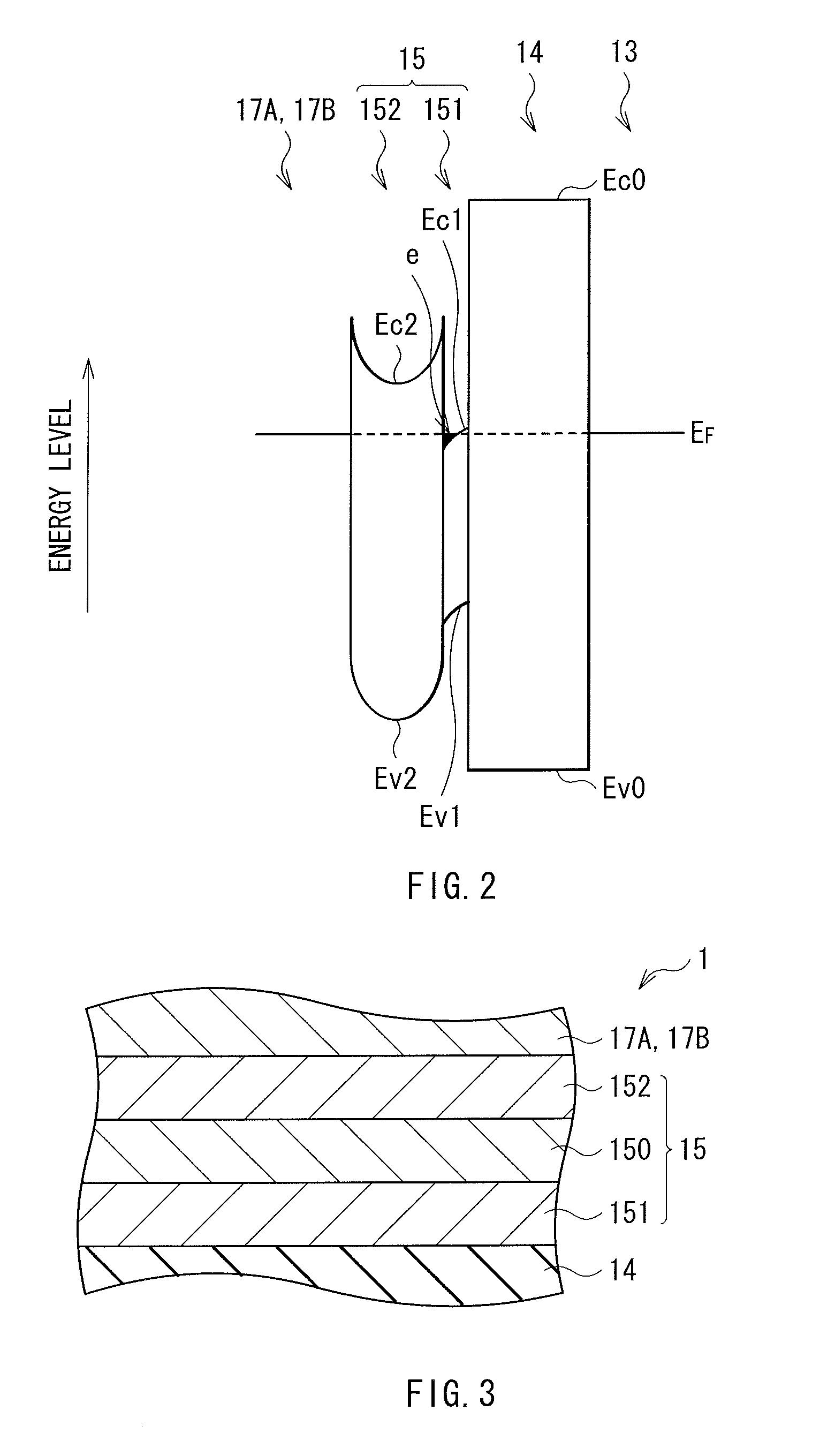

Thin film transistor, display device, and electronic device

ActiveUS20120119205A1Maintain good propertiesLarge carrier mobilityTransistorSemiconductor/solid-state device manufacturingValence bandMaximum level

A thin film transistor, which is capable of improving carrier mobility, and a display device and an electronic device, each of which uses the thin film transistor, are provided. The thin film transistor includes: a gate electrode; an oxide semiconductor layer including a multilayer film including a carrier travel layer configuring a channel and a carrier supply layer for supplying carriers to the carrier travel layer; a gate insulating film provided between the gate electrode and the oxide semiconductor layer; and a pair of electrodes as a source and a drain. A conduction band minimum level or a valence band maximum level corresponding to a carrier supply source of the carrier supply layer is higher in energy than a conduction band minimum level or a valence band maximum level corresponding to a carrier supply destination of the carrier travel layer.

Owner:JOLED INC

Method of making an organic thin film transistor

A process for fabricating thin film transistors in which the active layer is an organic semiconducting material with a carrier mobility greater than 10-3 cm2 / Vs and a conductivity less than about 10-6 S / cm at 20 DEG C. is disclosed. The organic semiconducting material is a regioregular (3-alkylthiophene) polymer. The organic semiconducting films are formed by applying a solution of the regioregular polymer and a solvent over the substrate. The poly (3-alkylthiophene) films have a preferred orientation in which the thiophene chains has a planar stacking so the polymer backbone is generally parallel to the substrate surface.

Owner:BELL SEMICON LLC +2

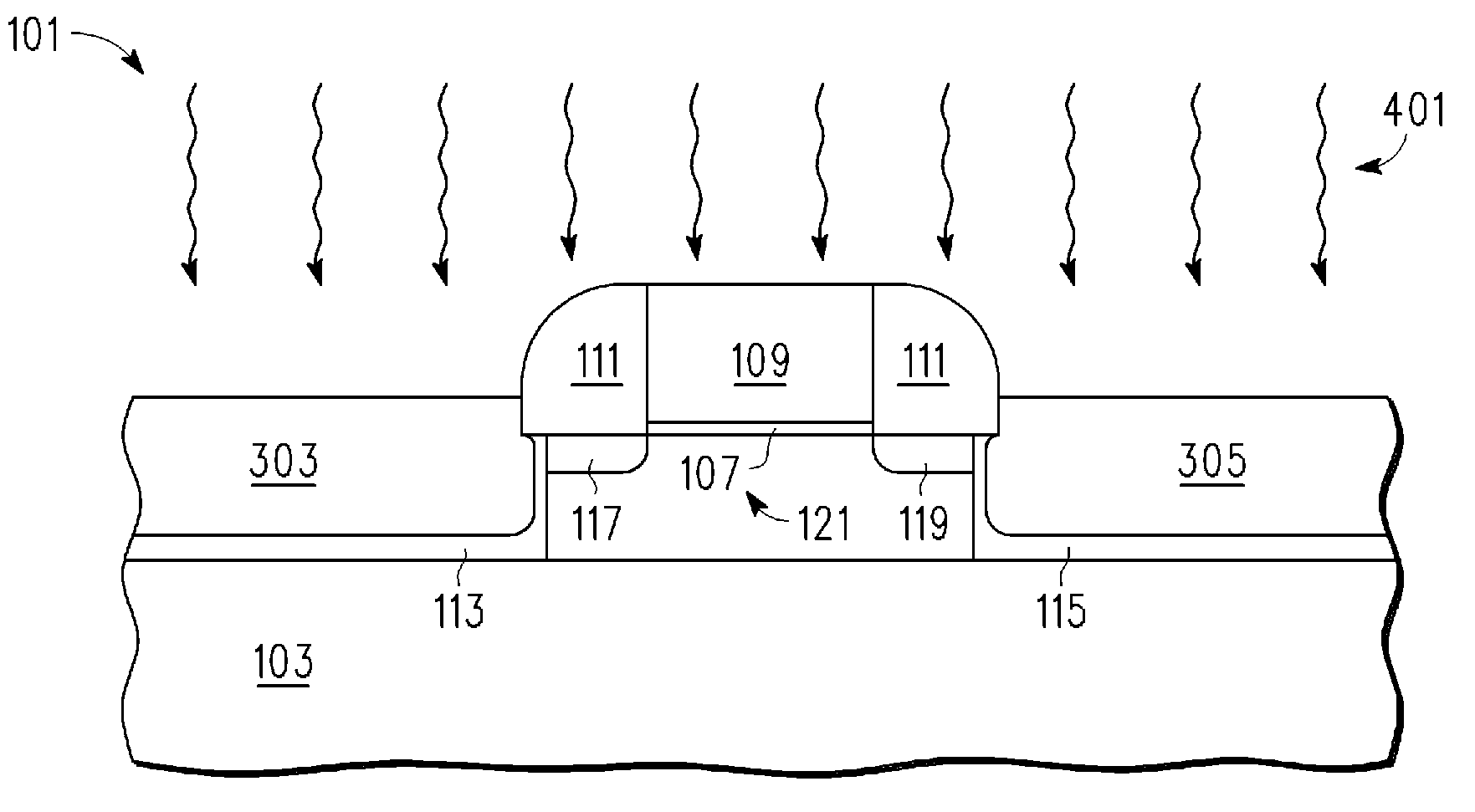

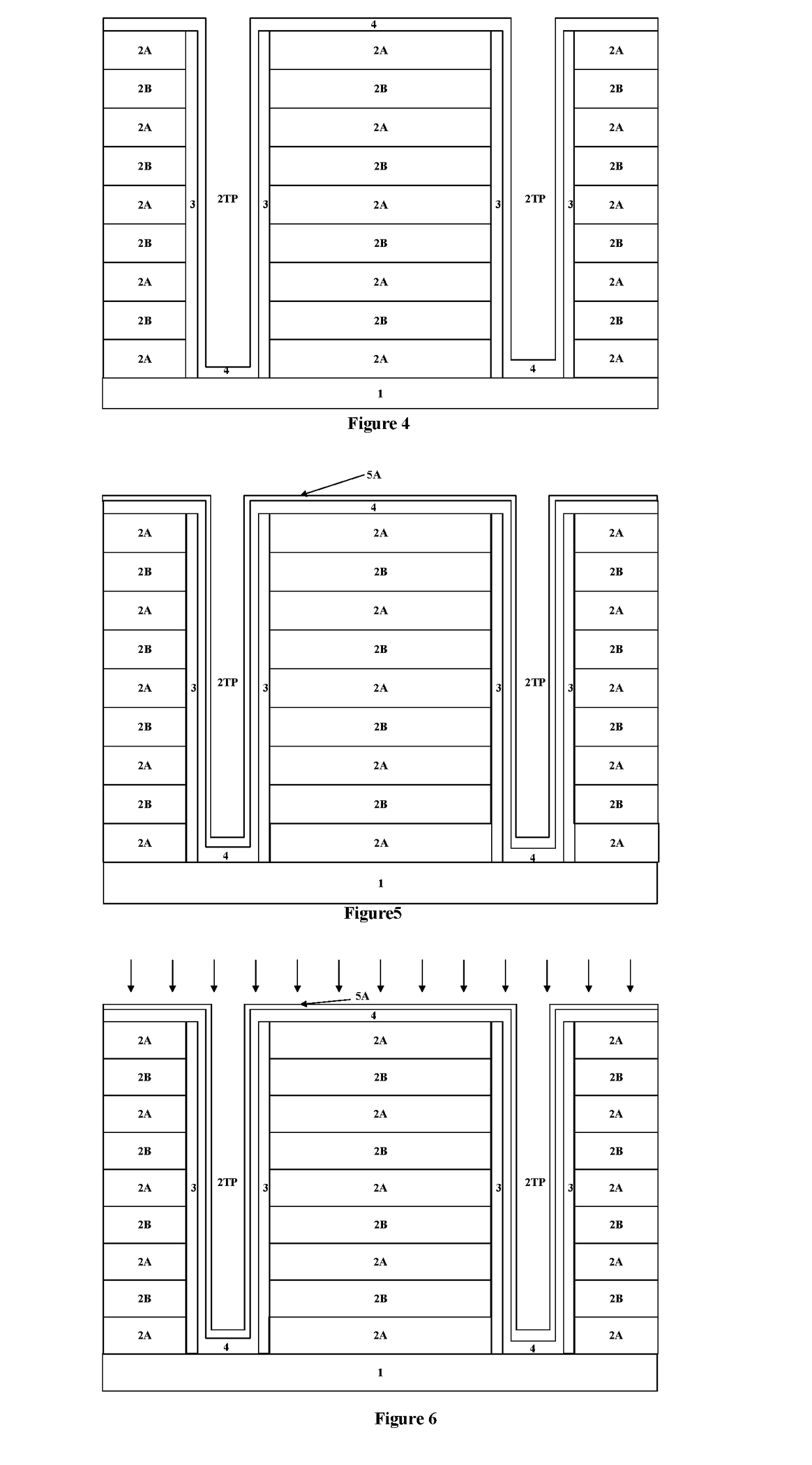

Graphene-based transistor

ActiveUS20090020764A1Semiconductor/solid-state device manufacturingSemiconductor devicesDopantGate dielectric

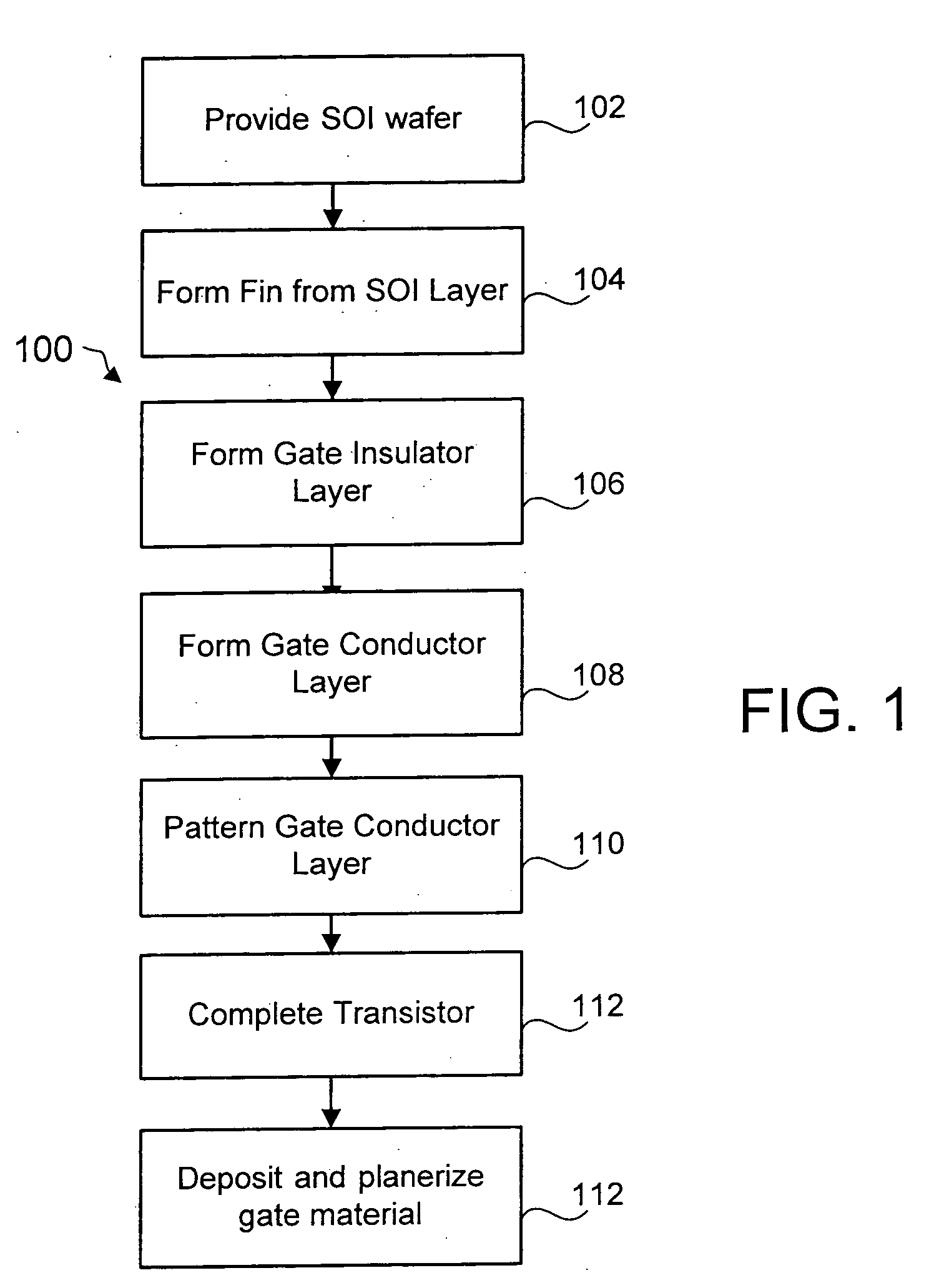

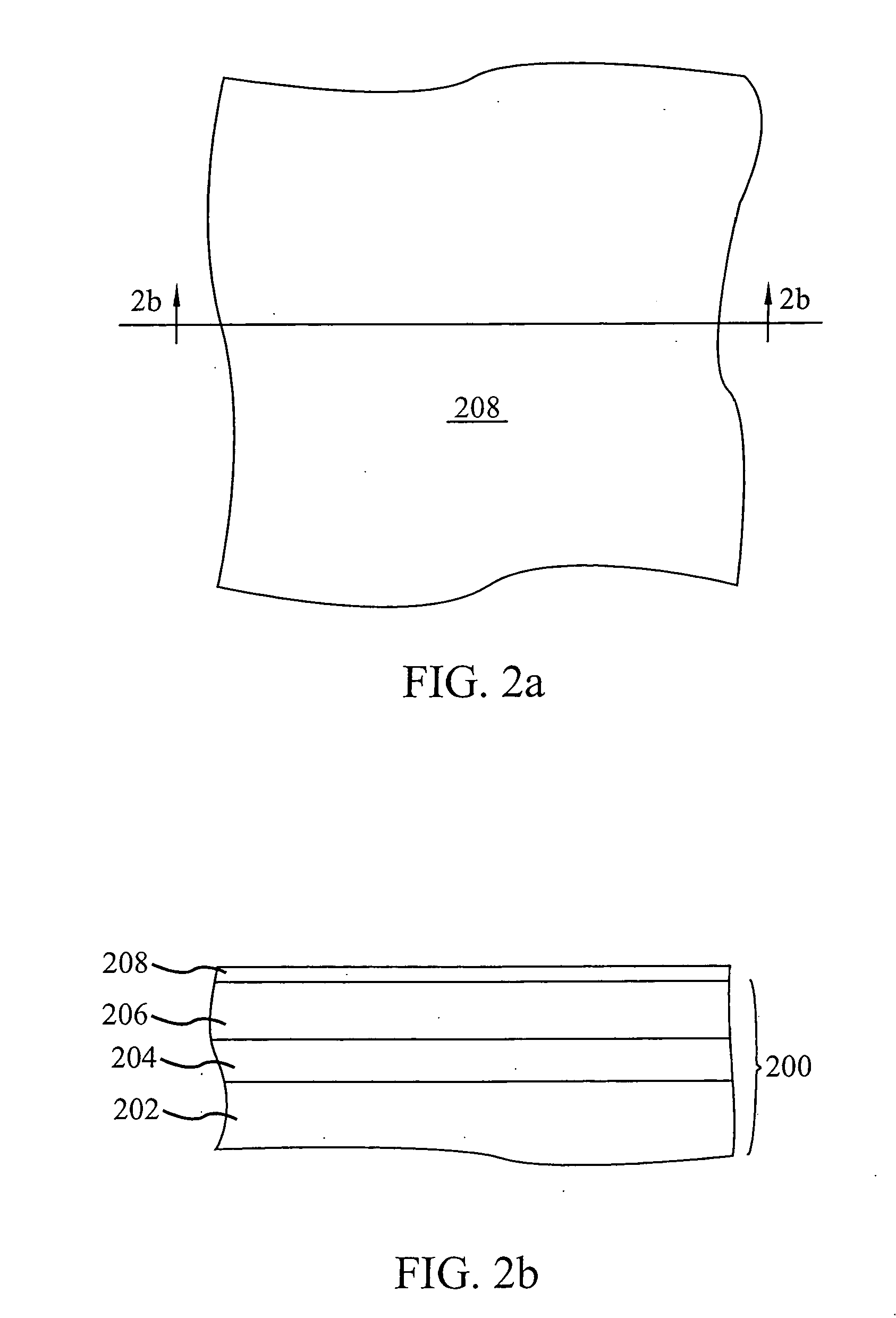

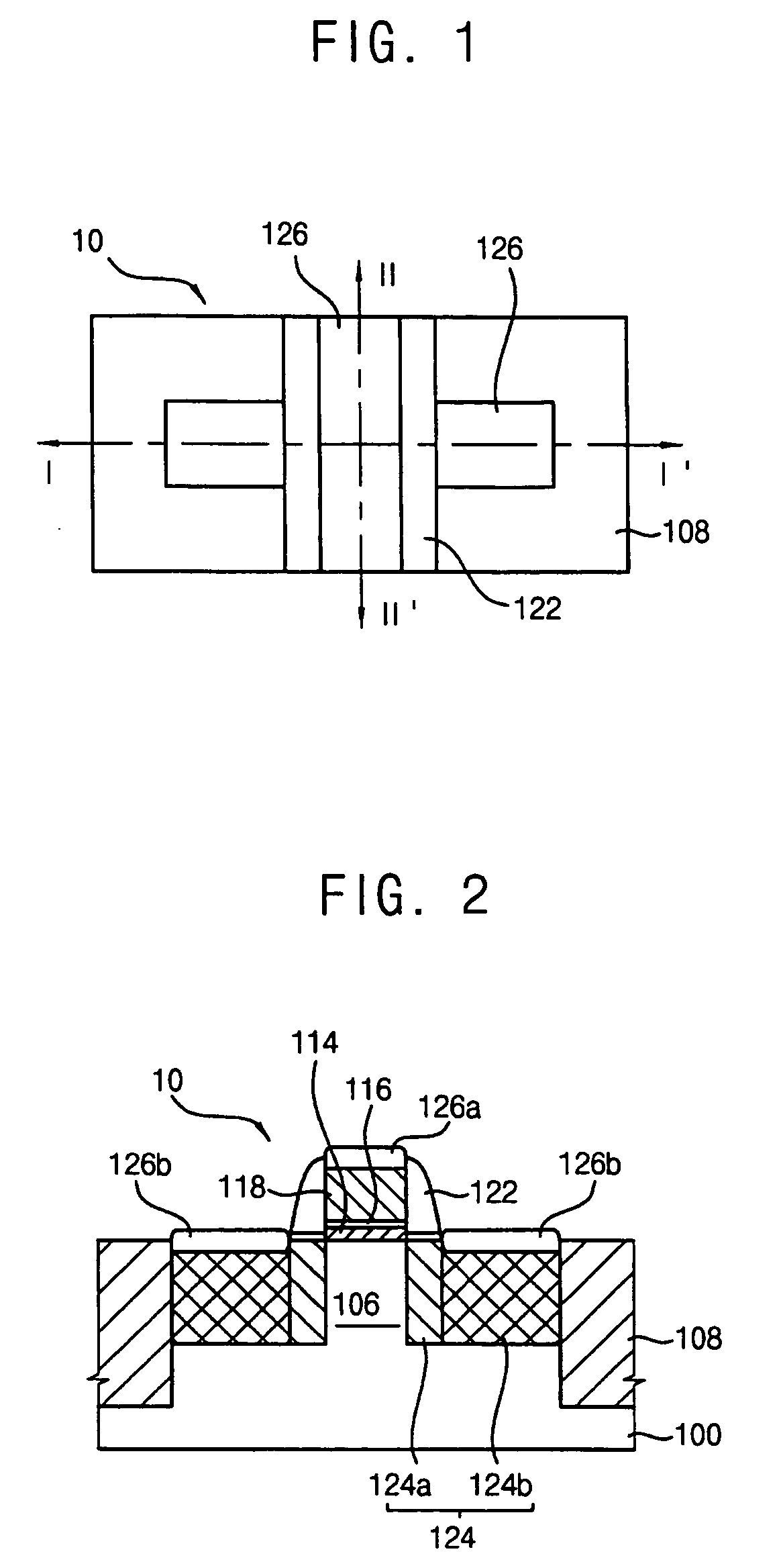

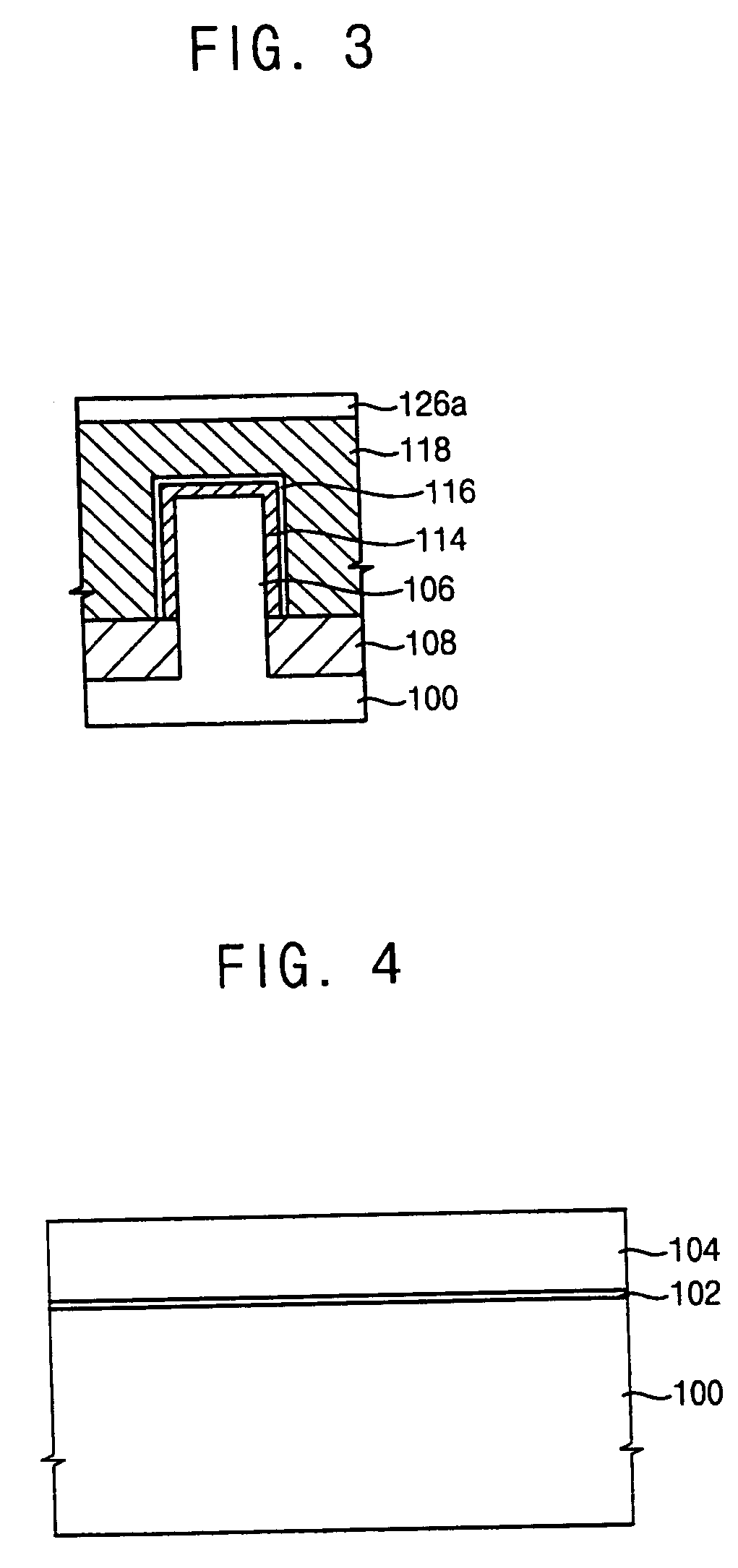

A graphene layer is formed on a surface of a silicon carbide substrate. A dummy gate structure is formed over the fin, in the trench, or on a portion of the planar graphene layer to implant dopants into source and drain regions. The dummy gate structure is thereafter removed to provide an opening over the channel of the transistor. Threshold voltage adjustment implantation may be performed to form a threshold voltage implant region directly beneath the channel, which comprises the graphene layer. A gate dielectric is deposited over a channel portion of the graphene layer. After an optional spacer formation, a gate conductor is formed by deposition and planarization. The resulting graphene-based field effect transistor has a high carrier mobility due to the graphene layer in the channel, low contact resistance to the source and drain region, and optimized threshold voltage and leakage due to the threshold voltage implant region.

Owner:GLOBALFOUNDRIES US INC

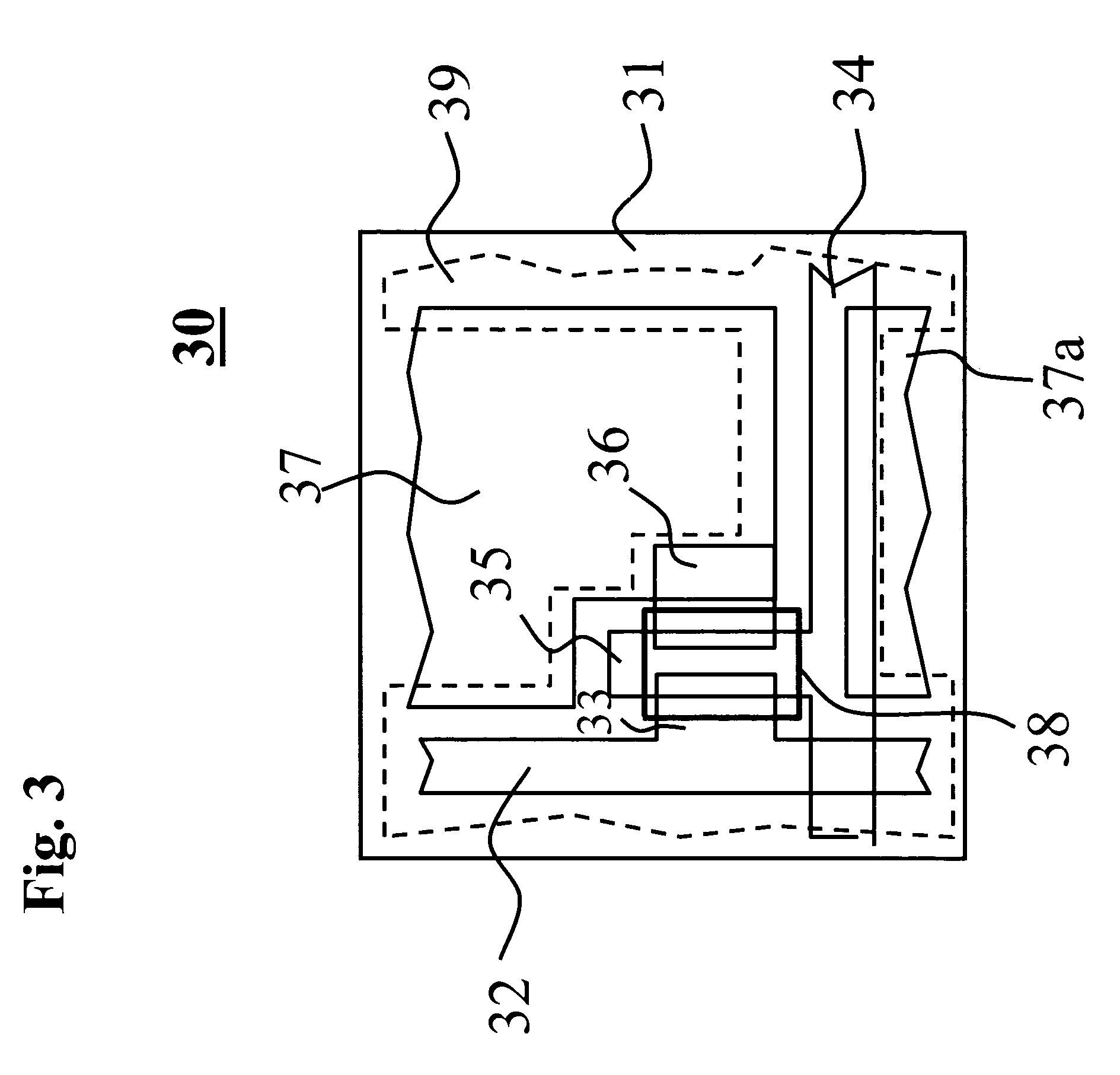

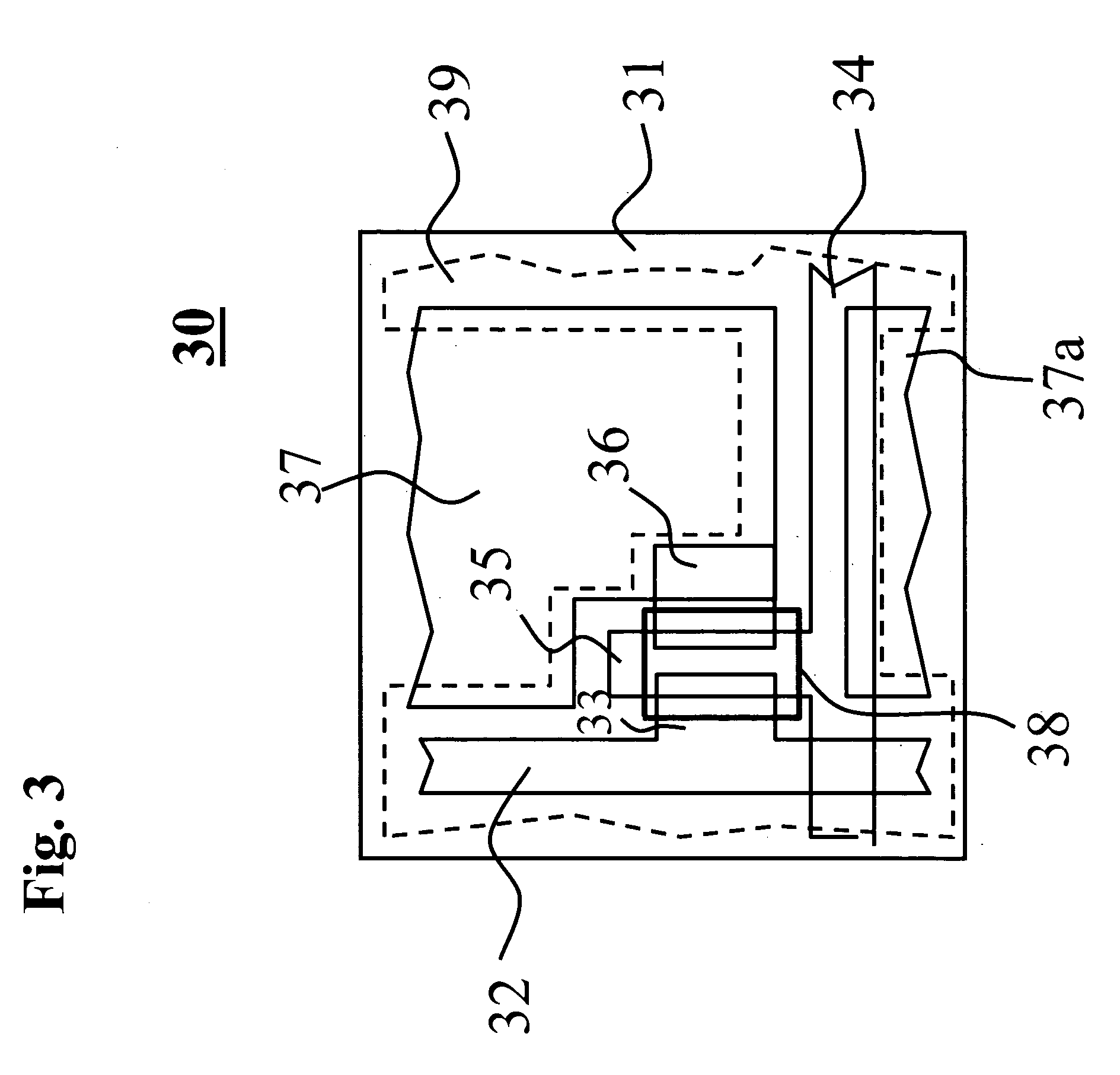

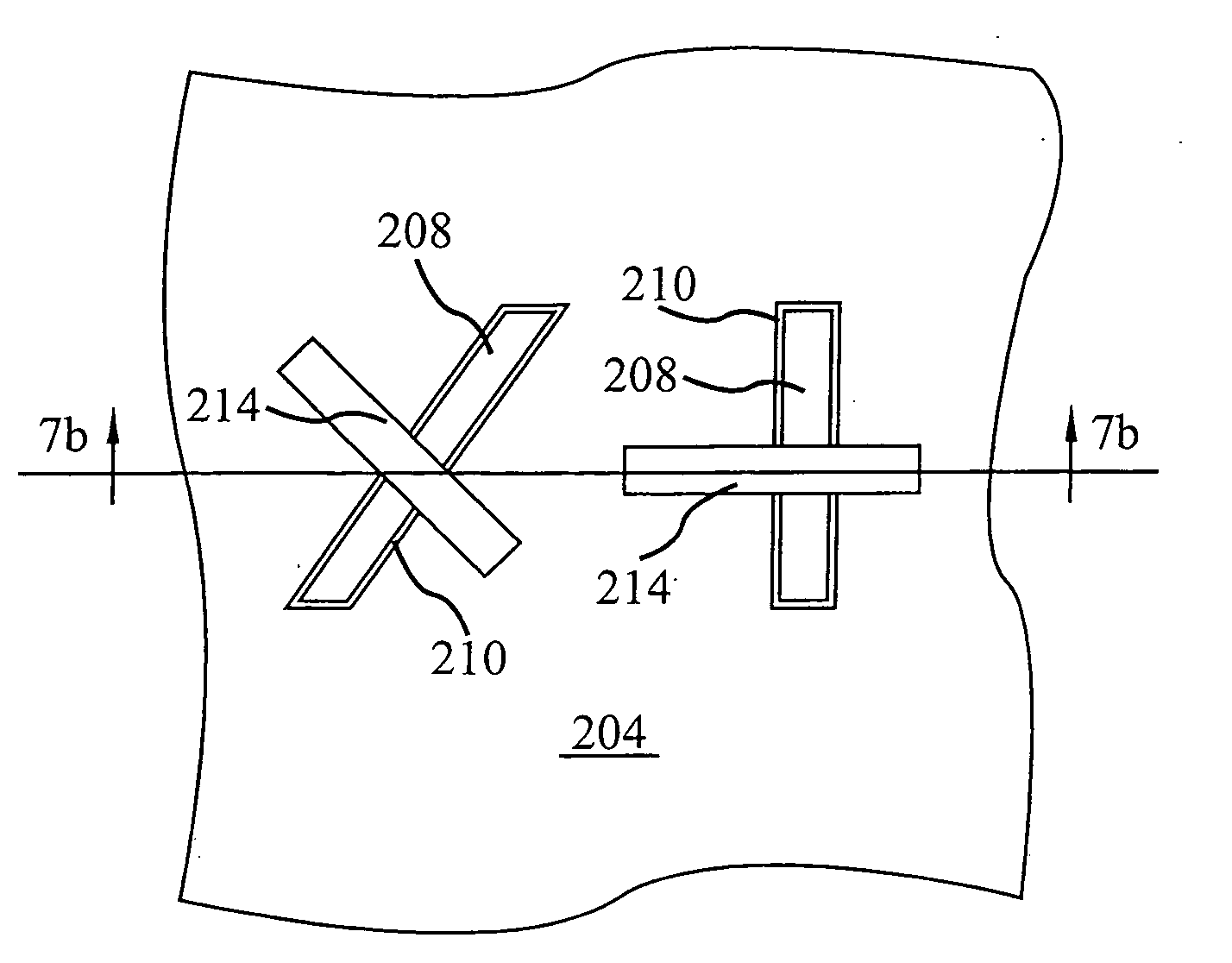

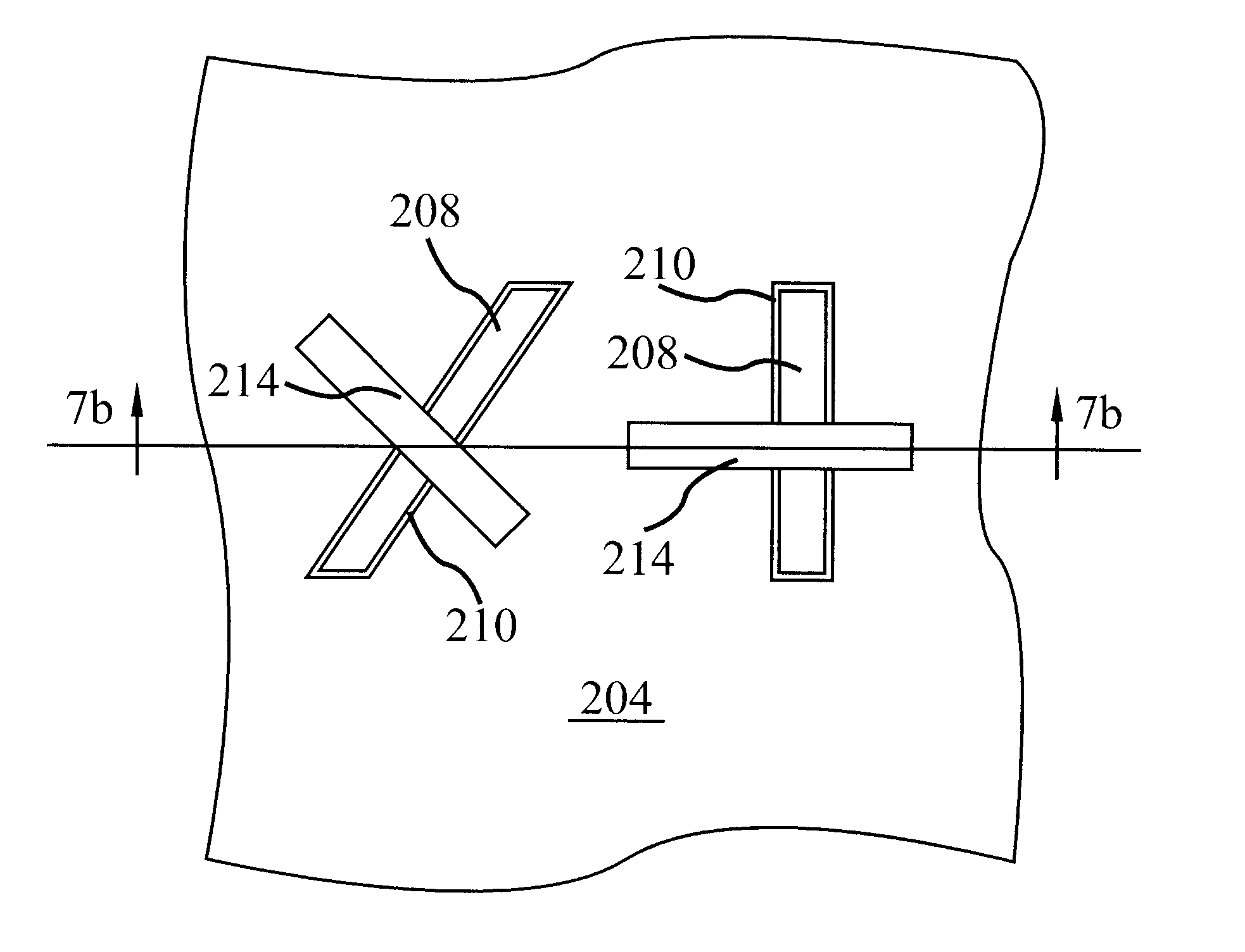

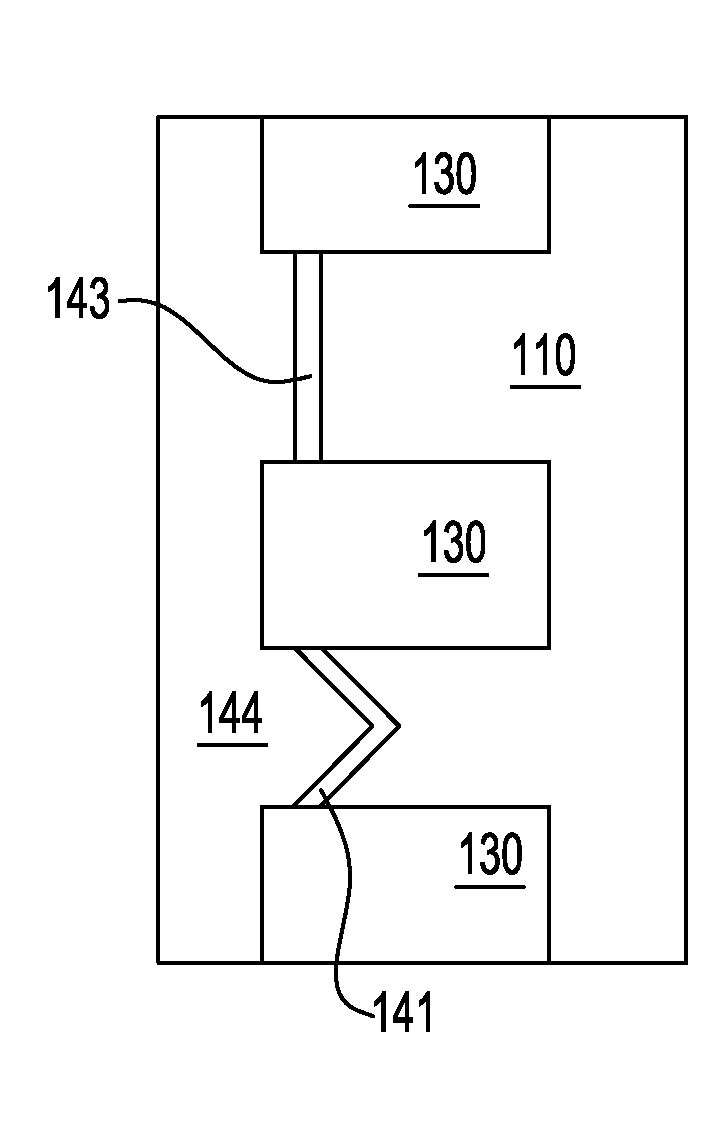

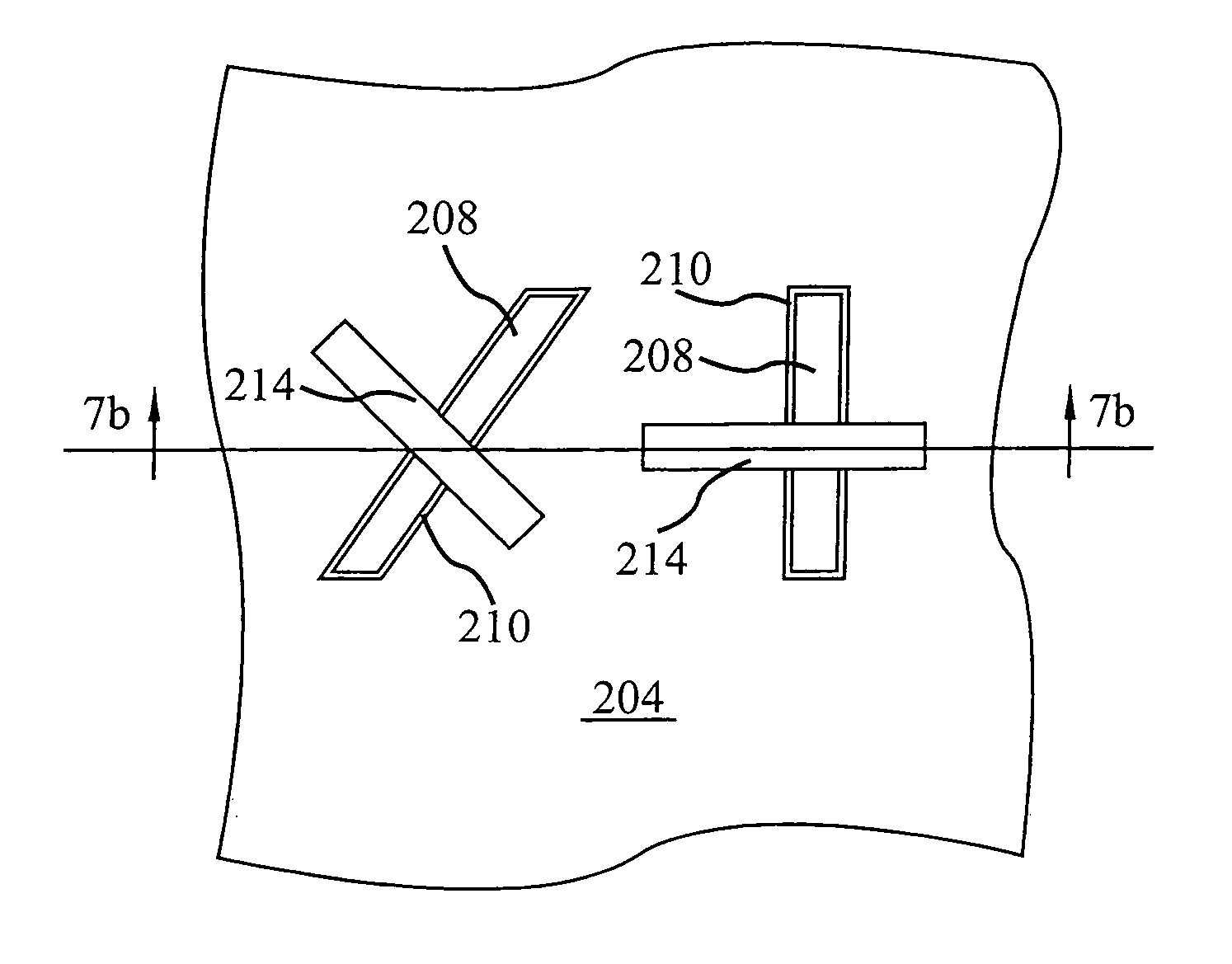

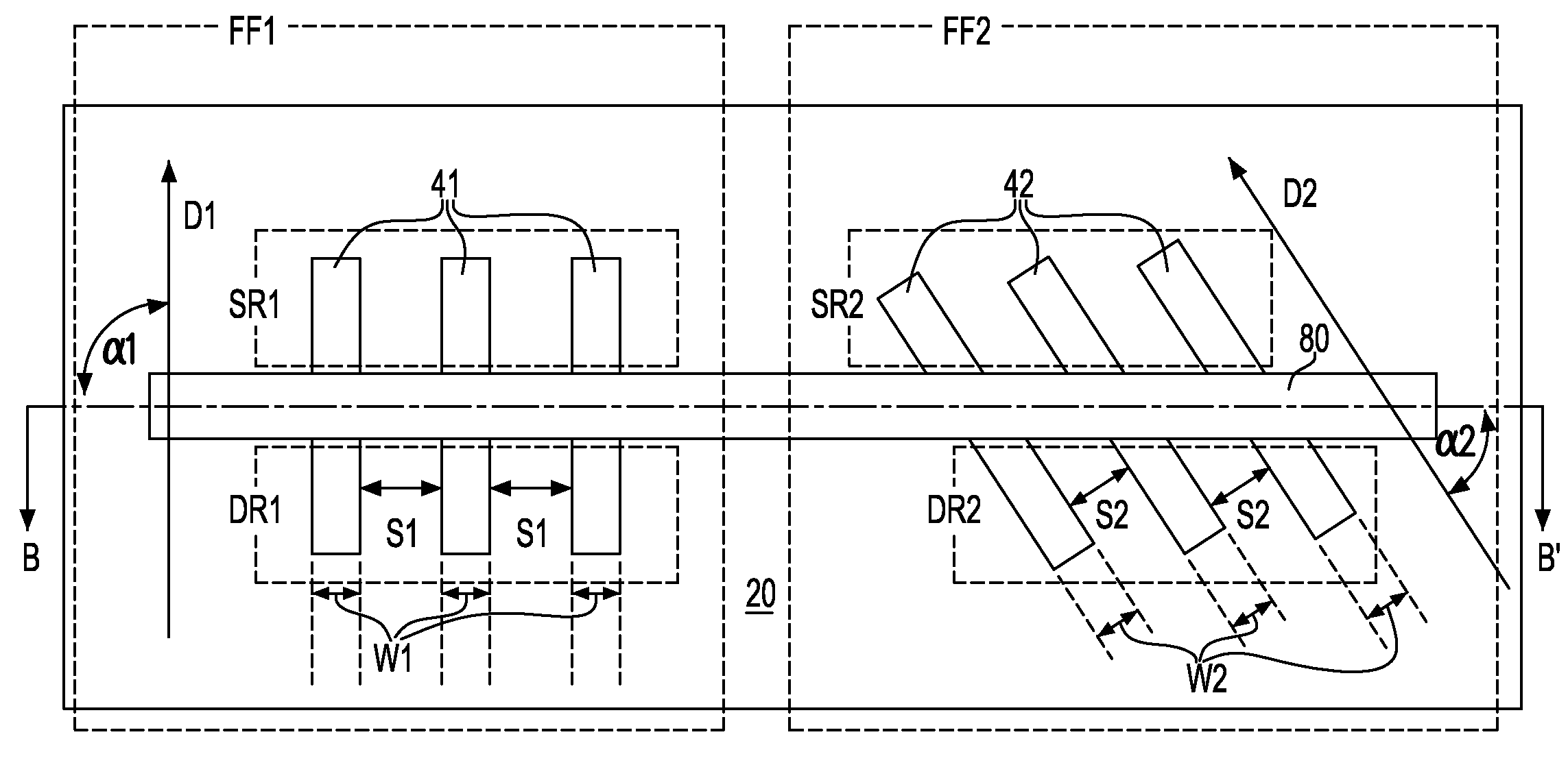

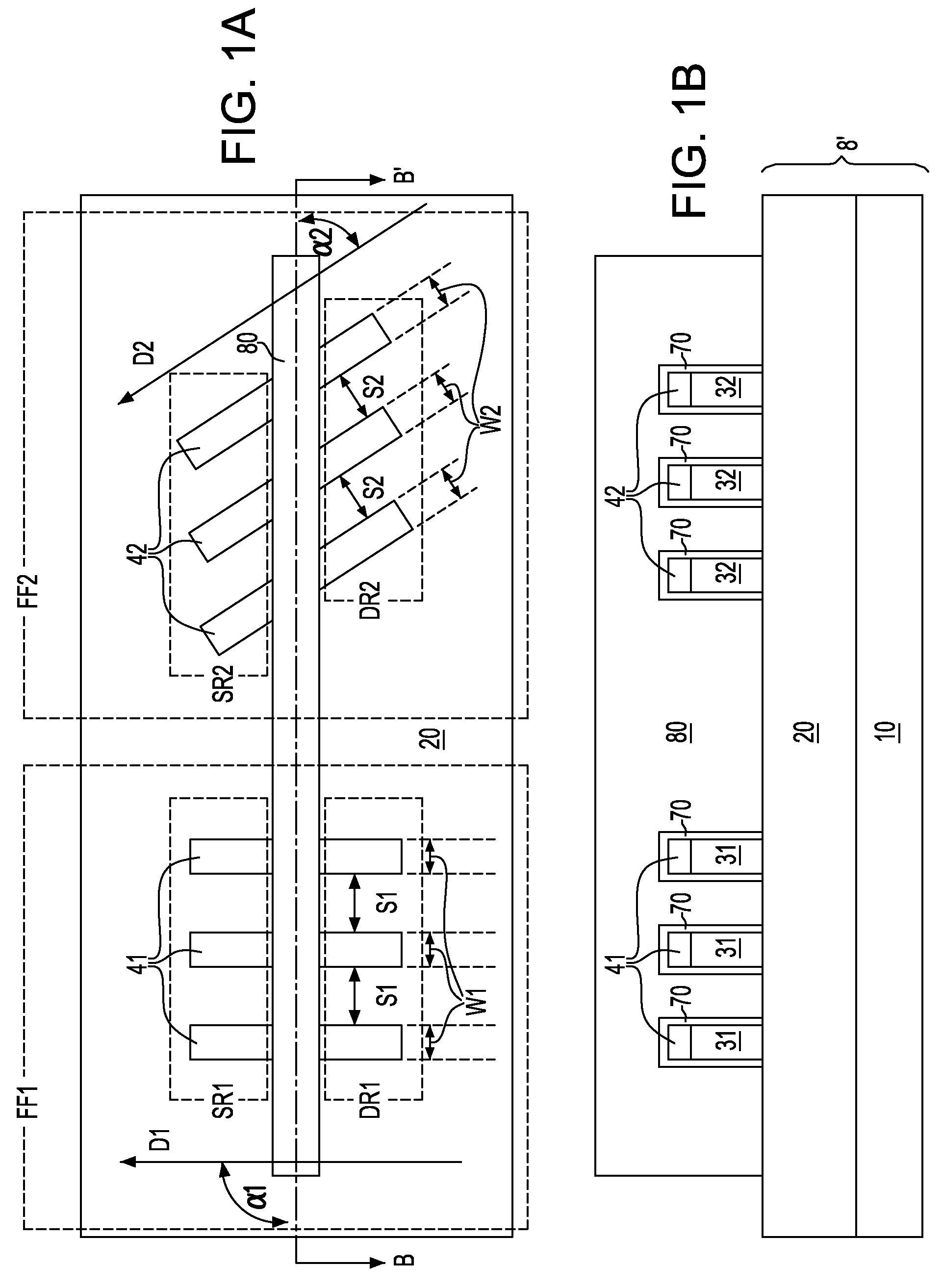

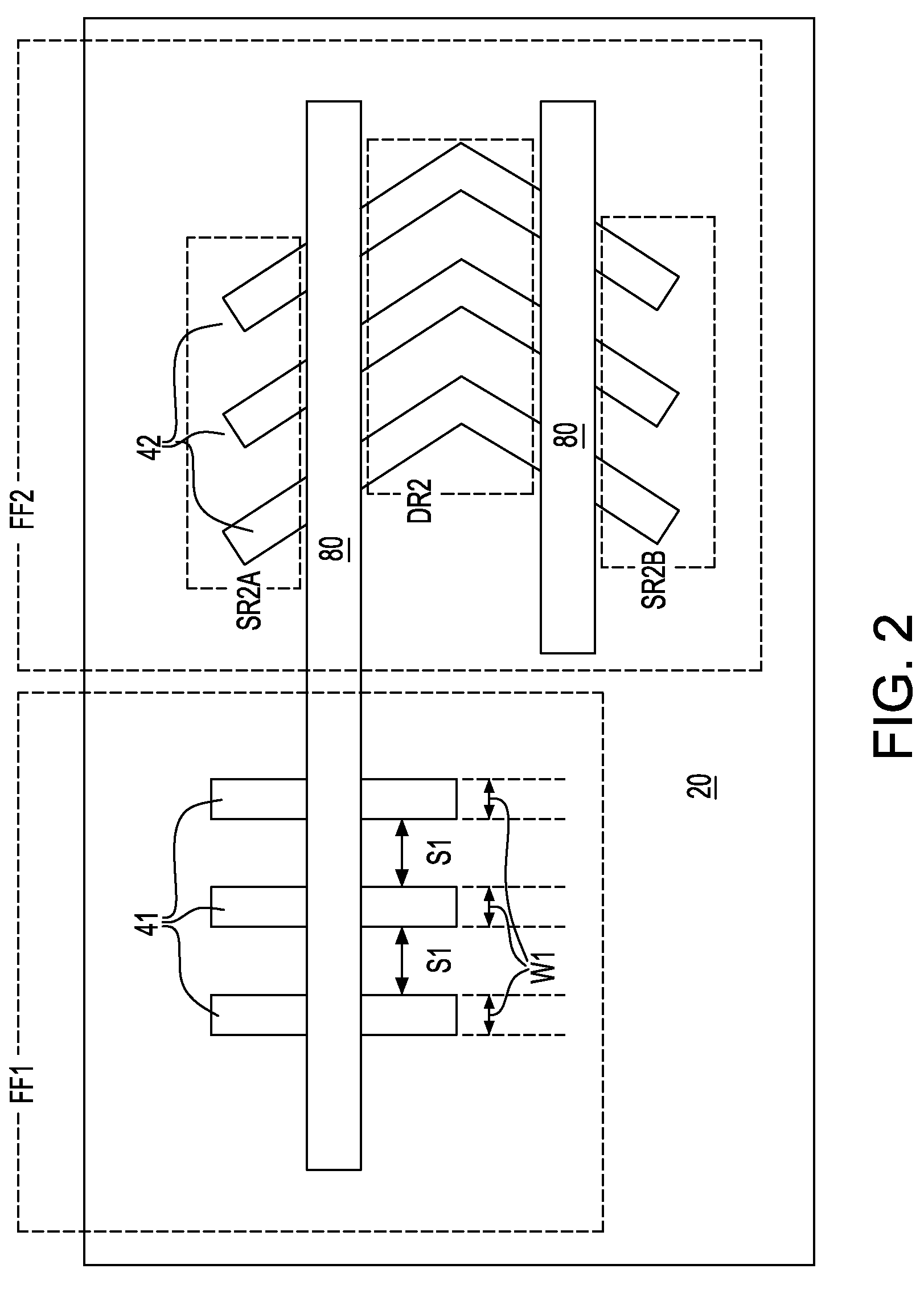

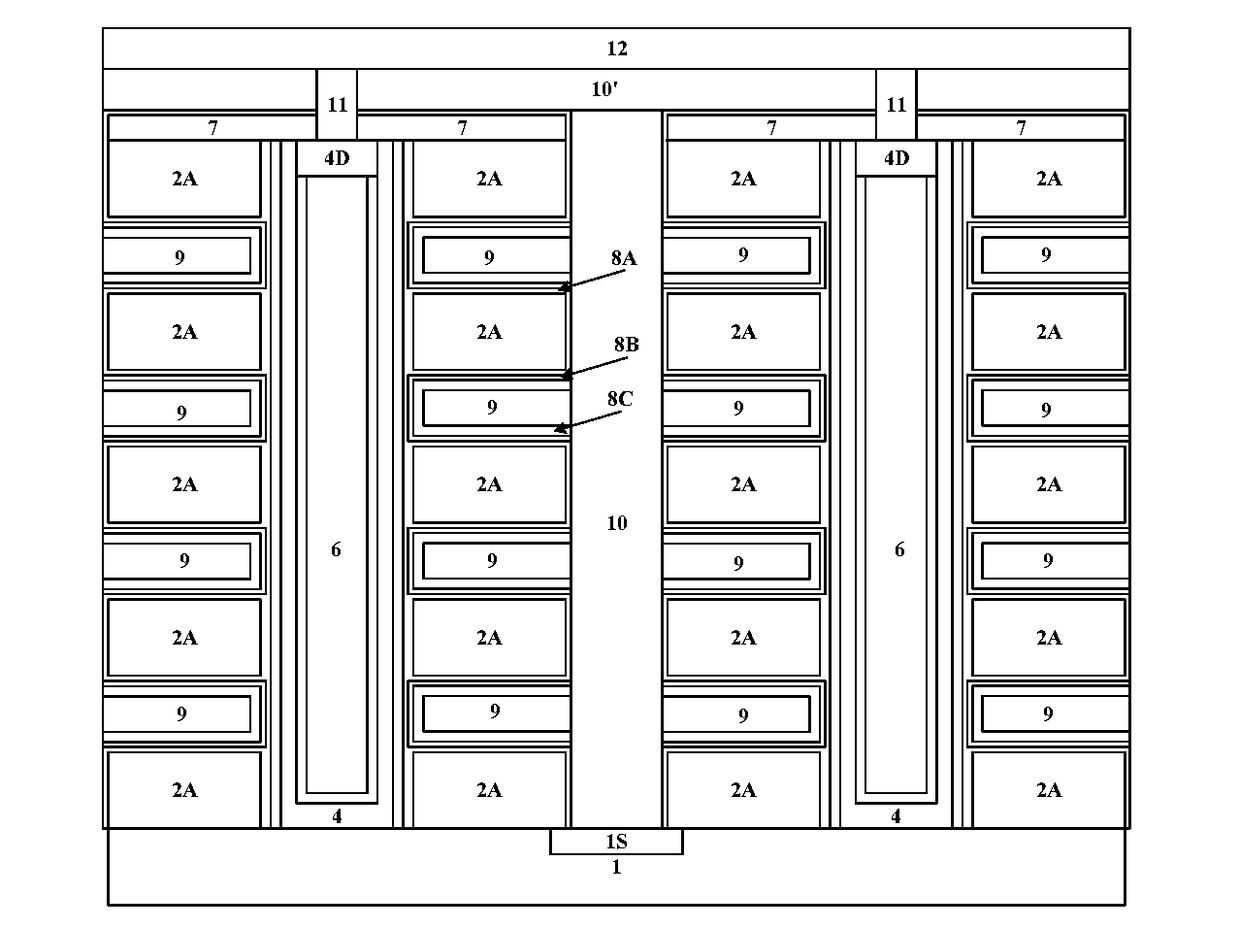

FinFET SRAM cell with chevron FinFET logic

An electronic device, and SRAM and a method of forming the electronic device and SRAM. The semiconductor device including: a pass gate transistor having a fin body having opposing sidewalls aligned in a first direction and having a first majority carrier mobility and a gate adjacent to both sidewalls of the fin body; a pull down latch transistor having a fin body having opposing sidewalls aligned in a second direction and having a second majority carrier mobility and a gate adjacent to both sidewalls of thc fin body; a pull up latch transistor having a fin body having opposing sidewalls aligned in a third direction and having a third majority carrier mobility and a gate adjacent to both sidewalls of the fin body; and CMOS chevron logic circuits, wherein crystal planes of each fin body and of CMOS transistor of the chevron logic are co-aligned.

Owner:IBM CORP

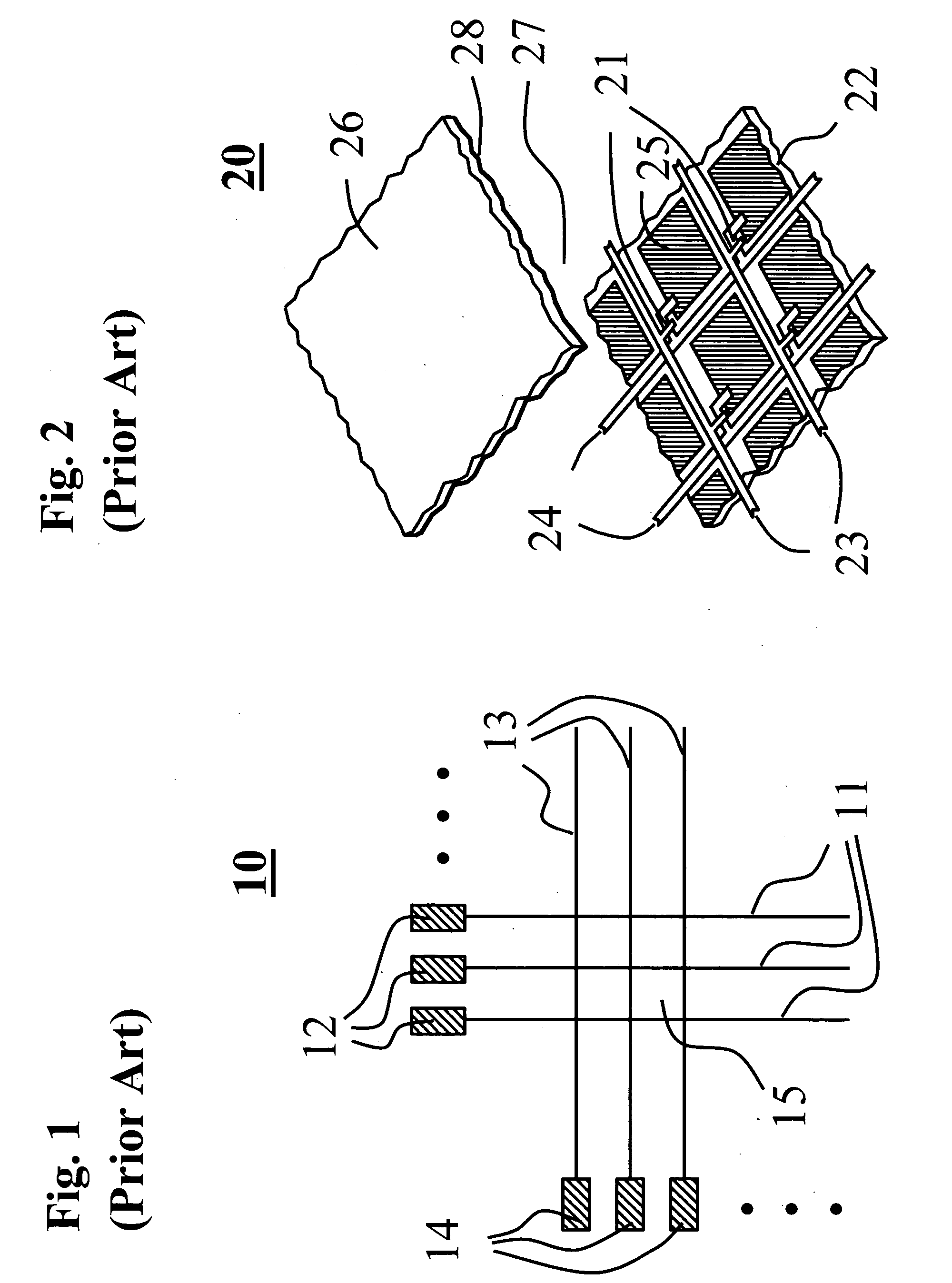

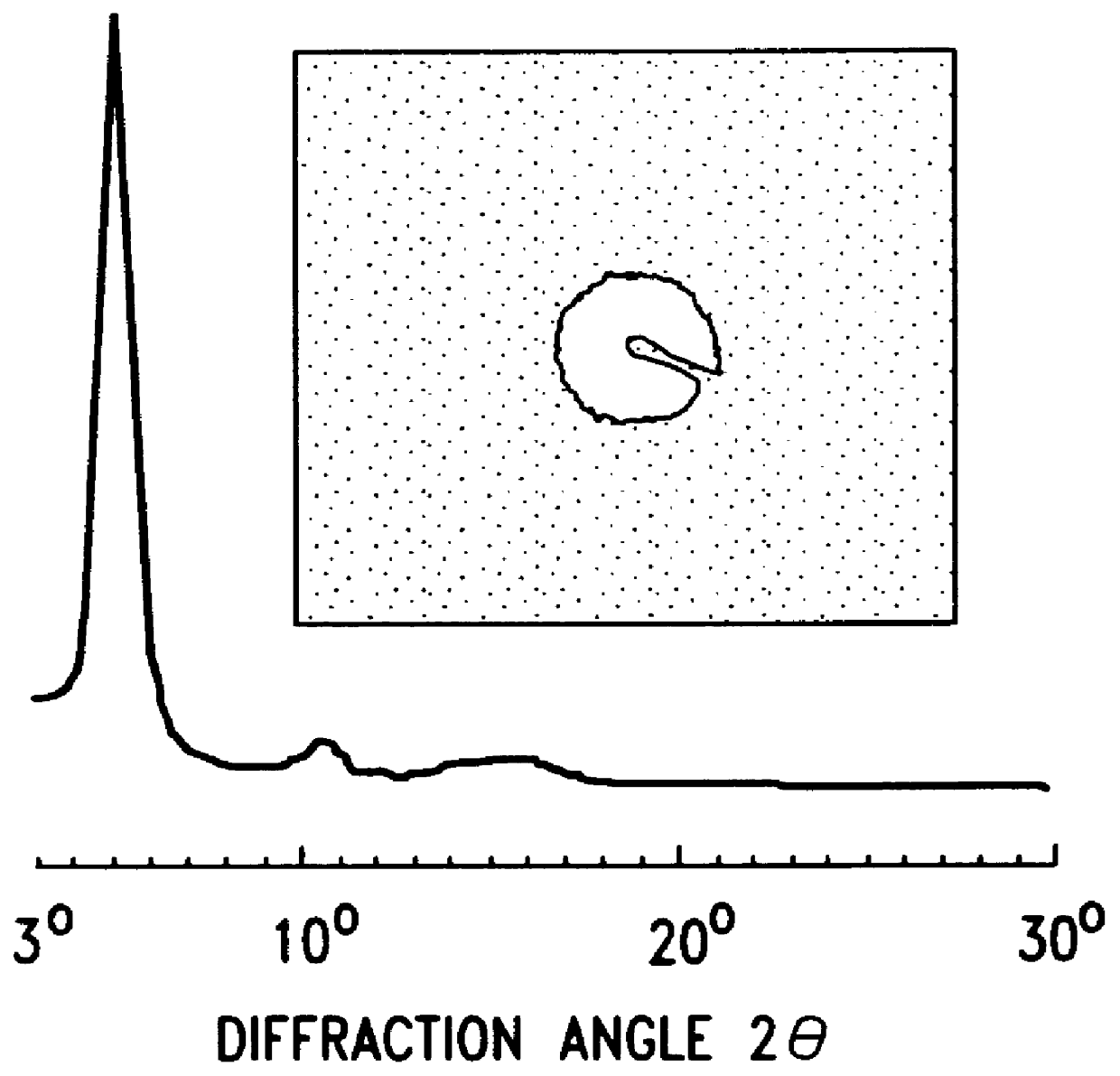

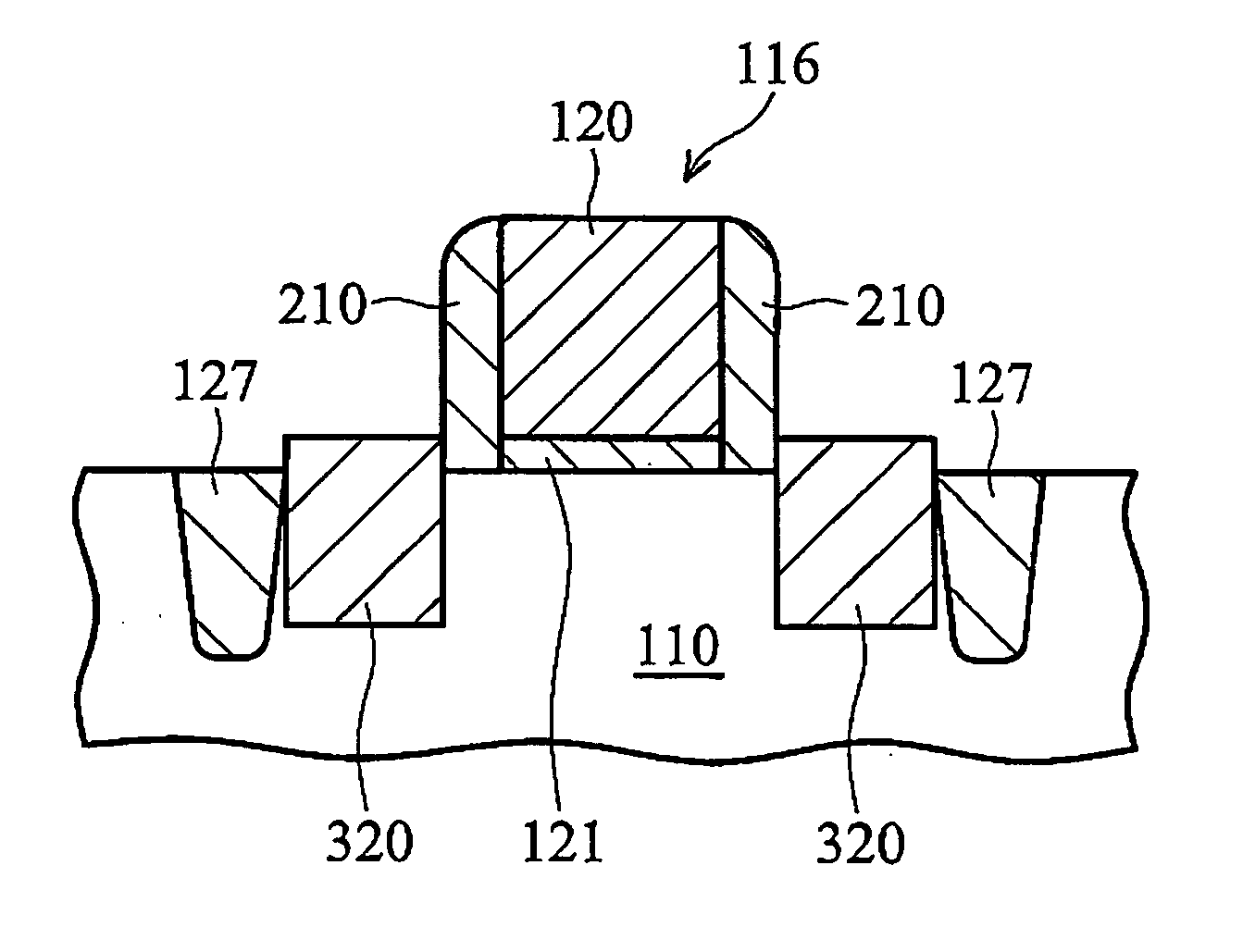

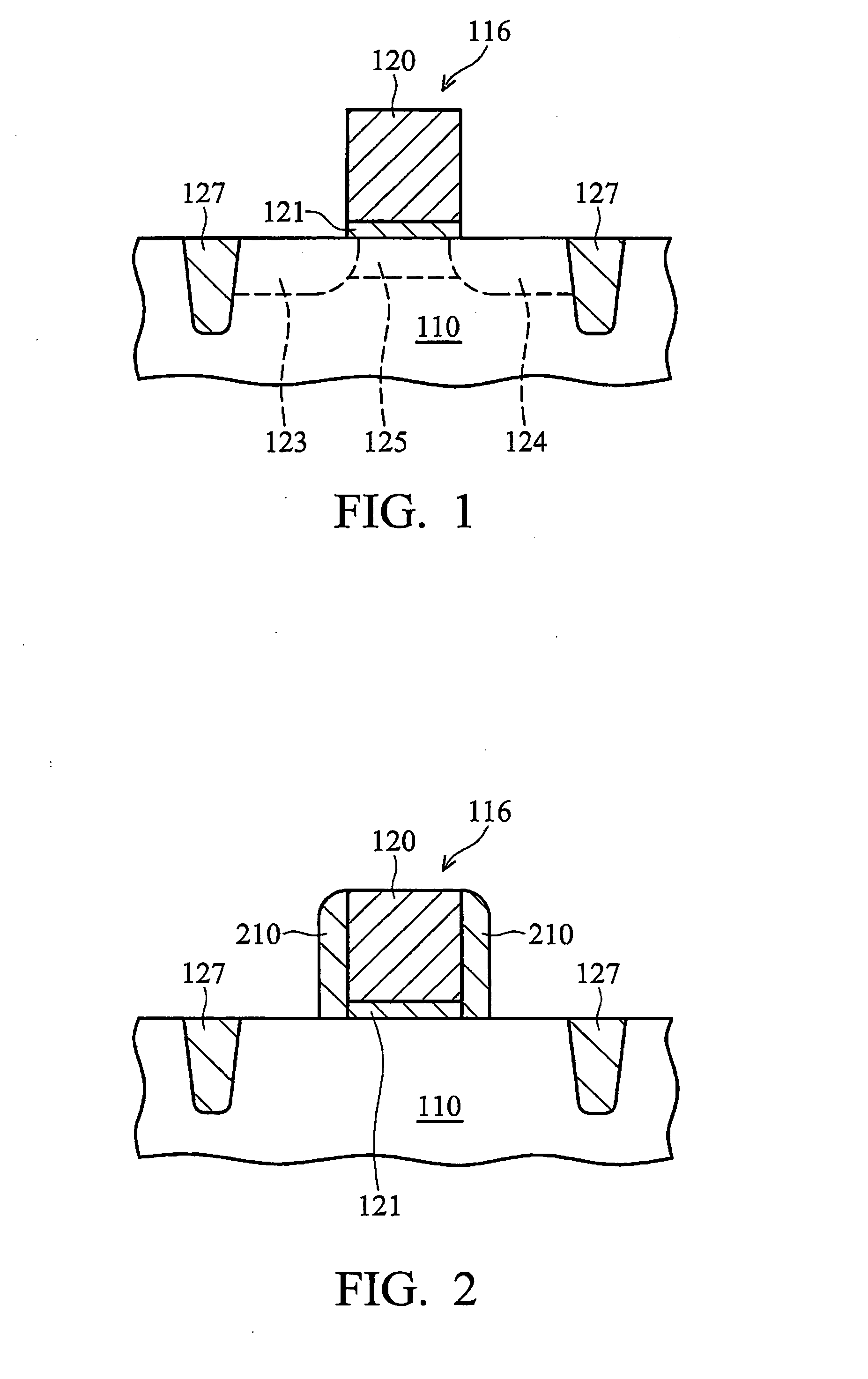

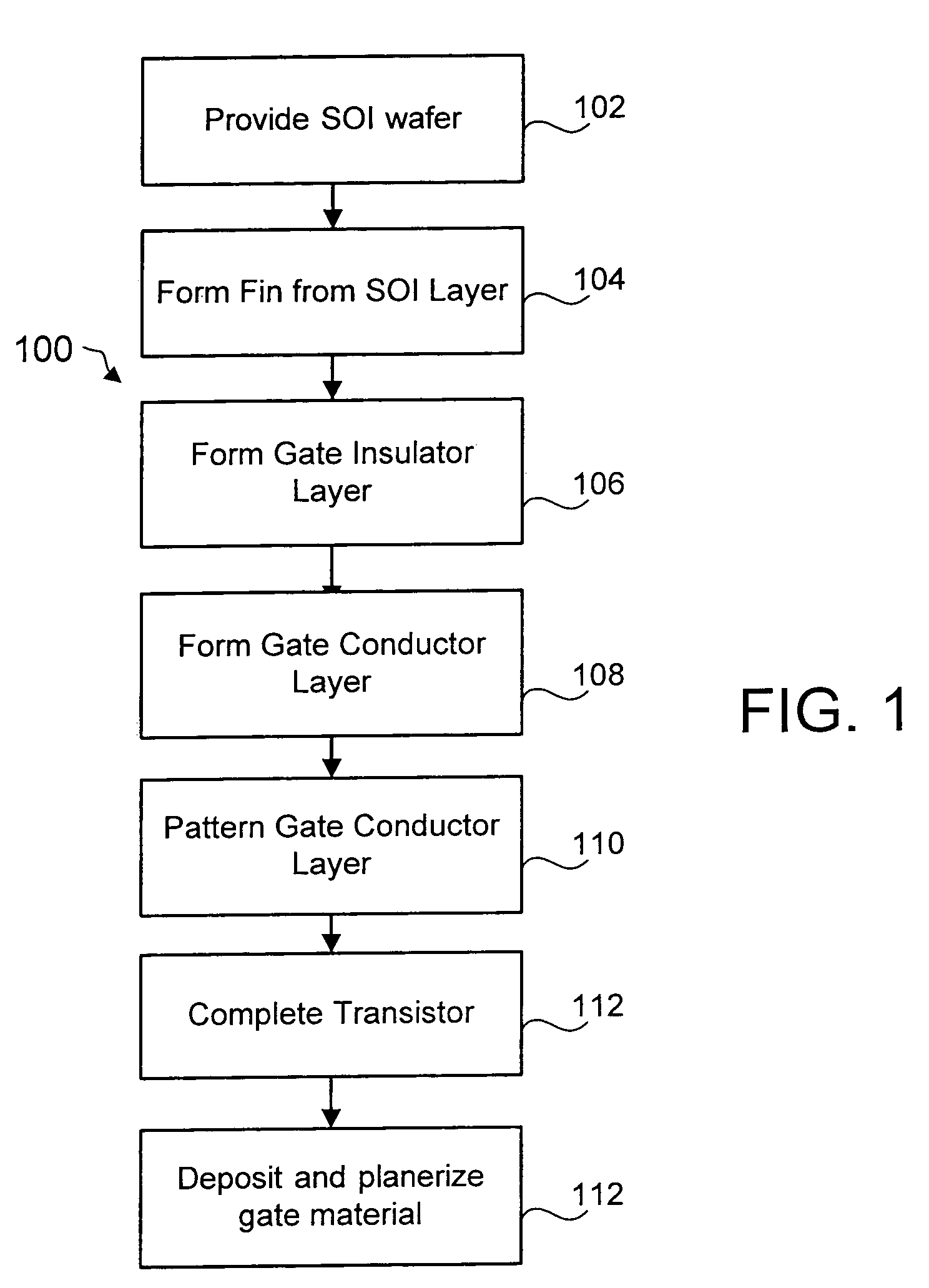

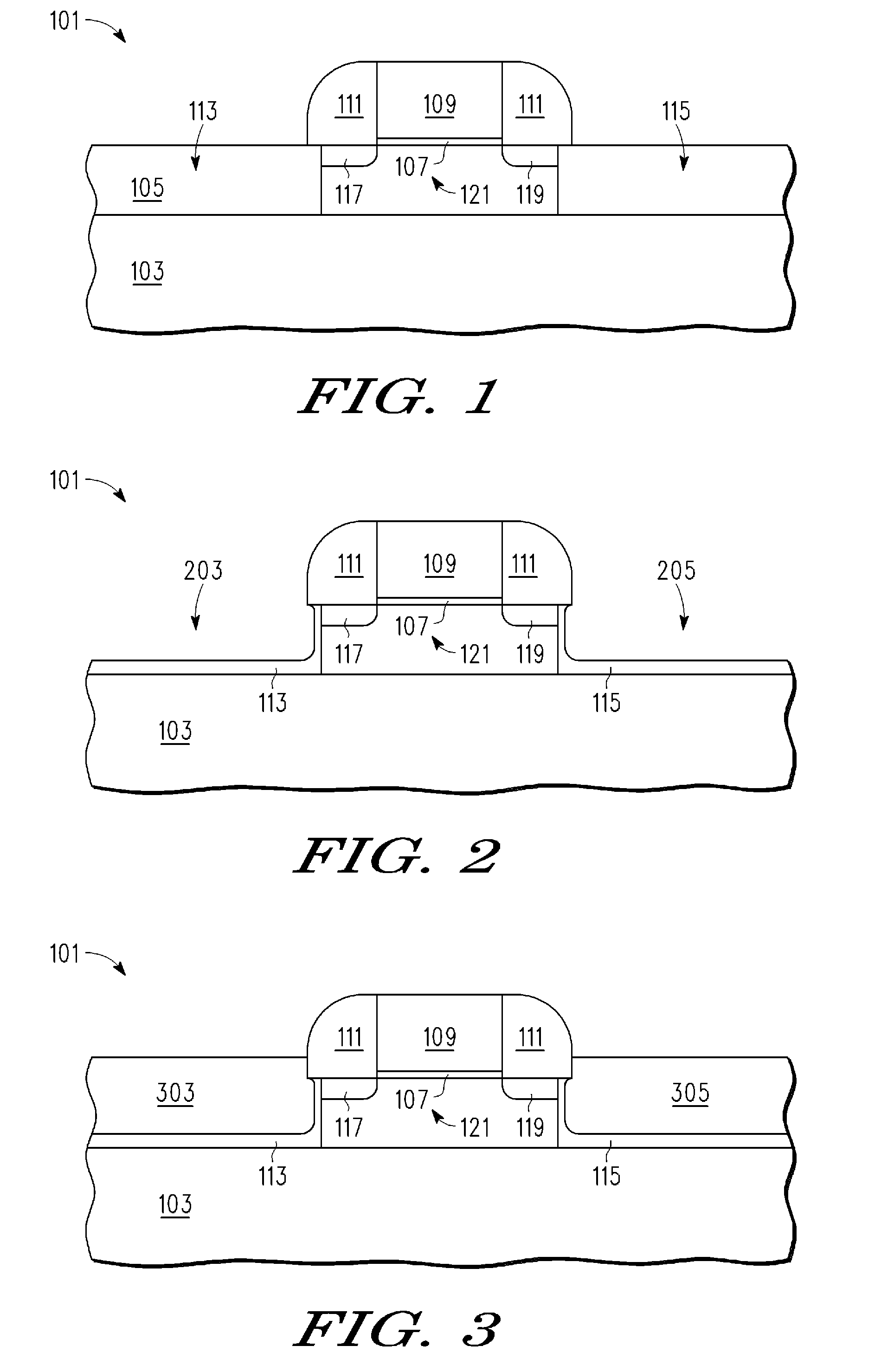

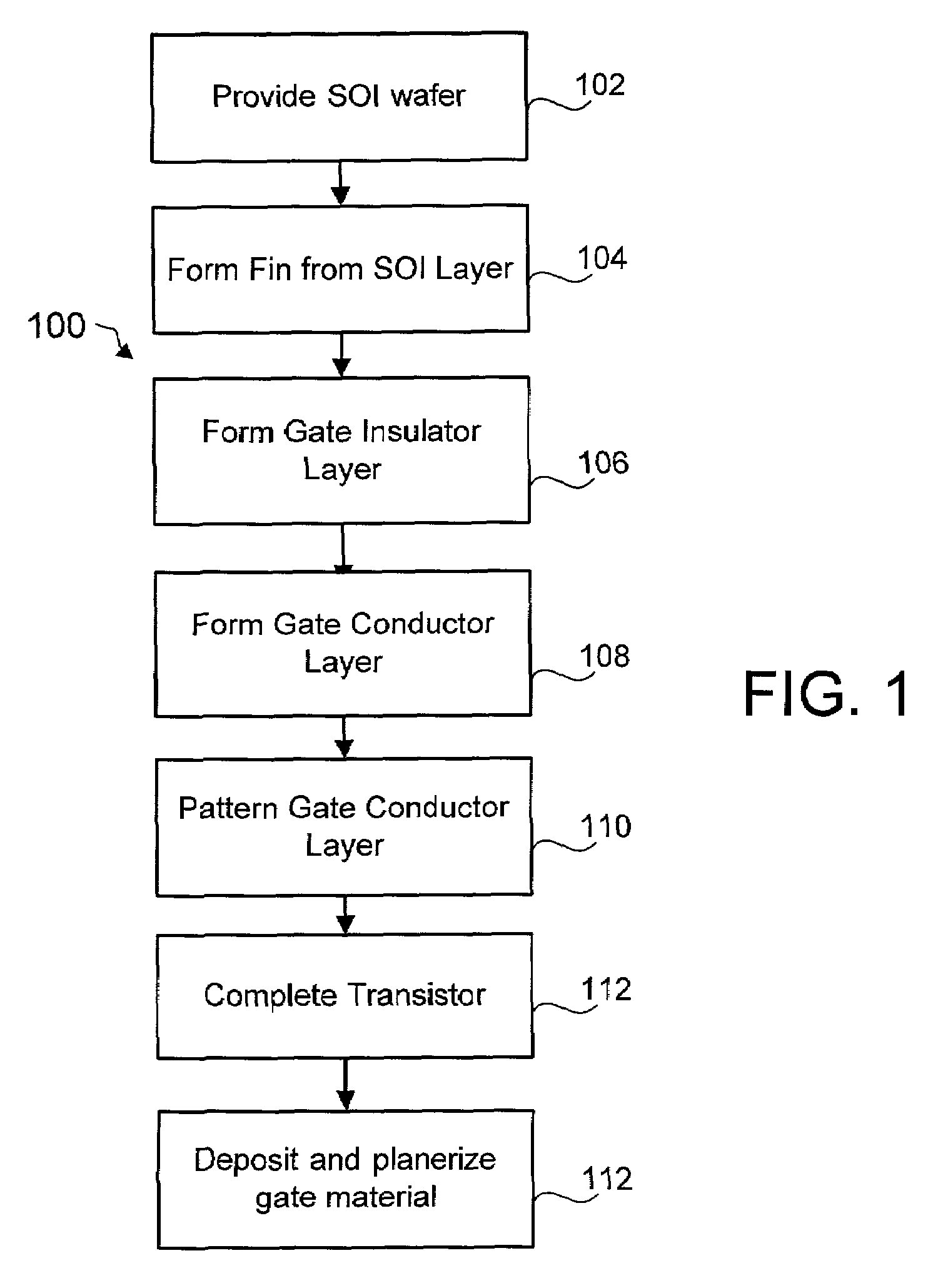

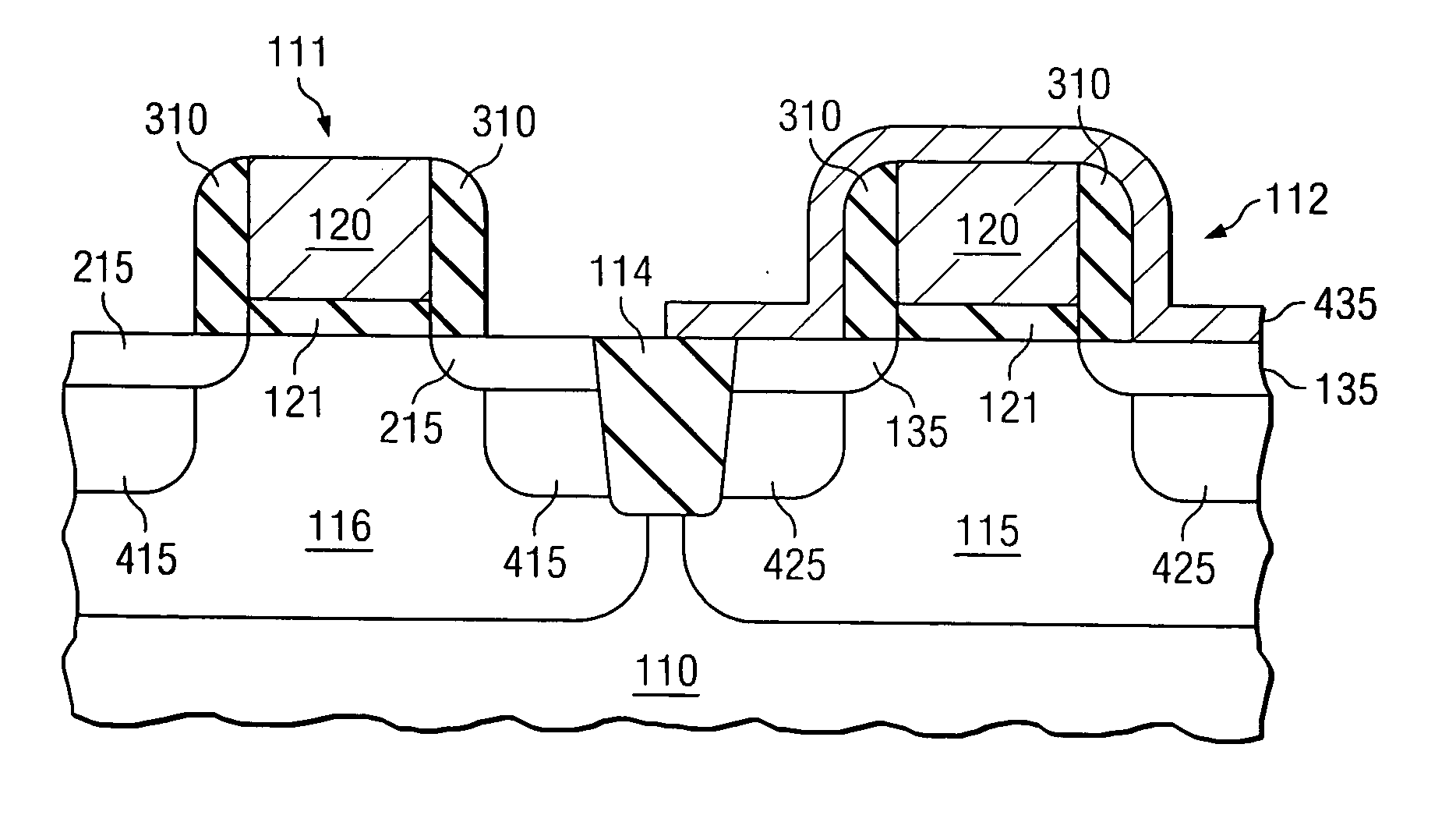

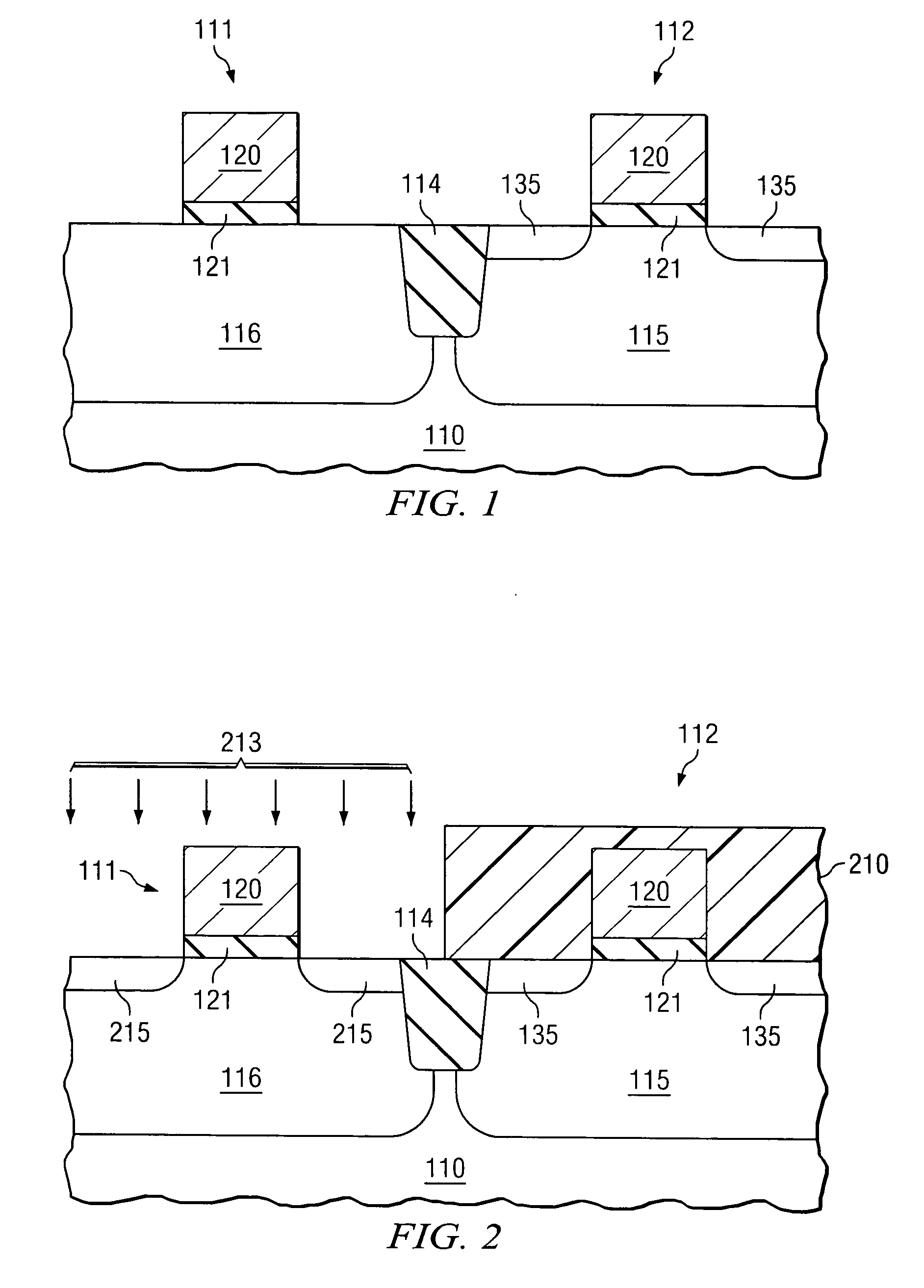

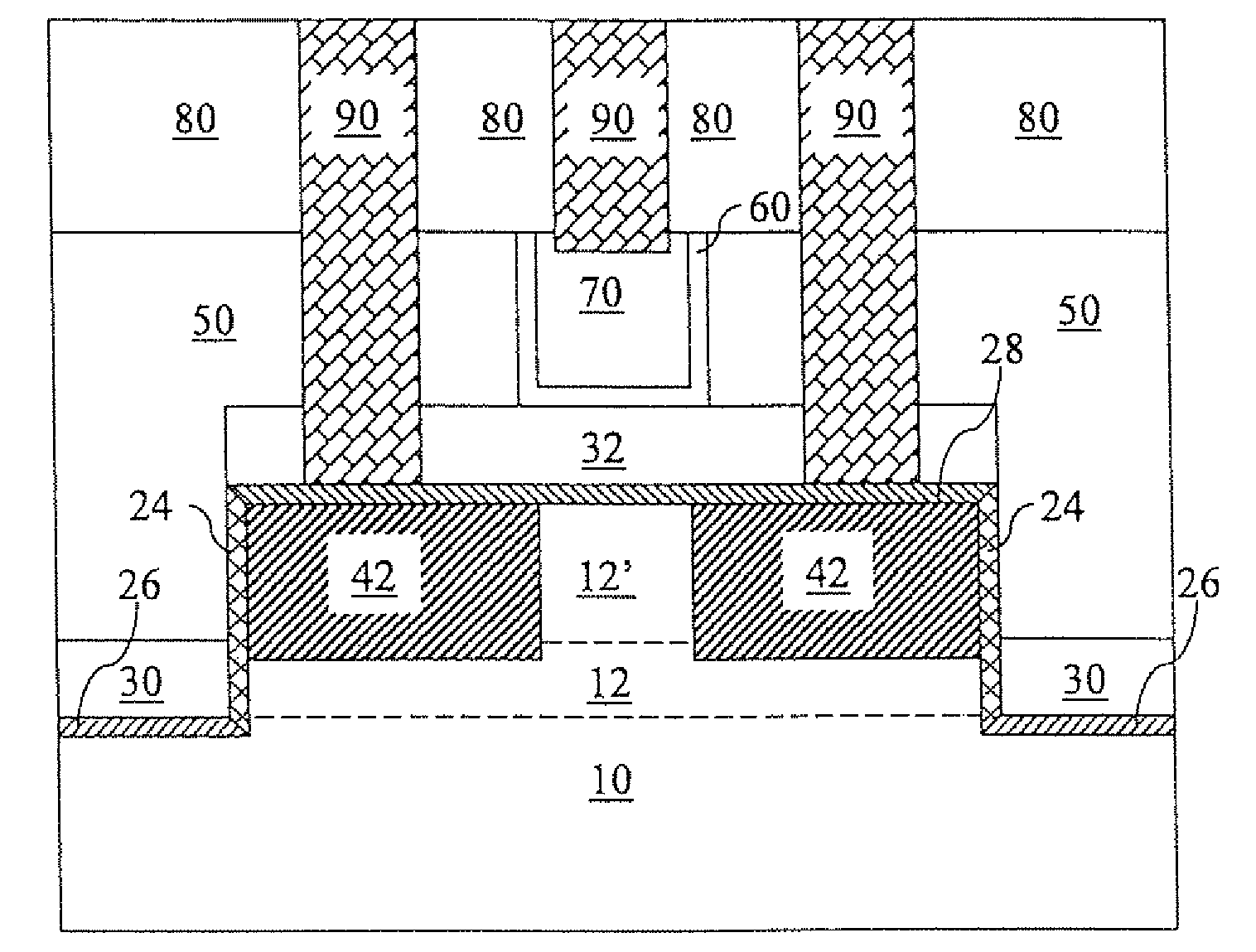

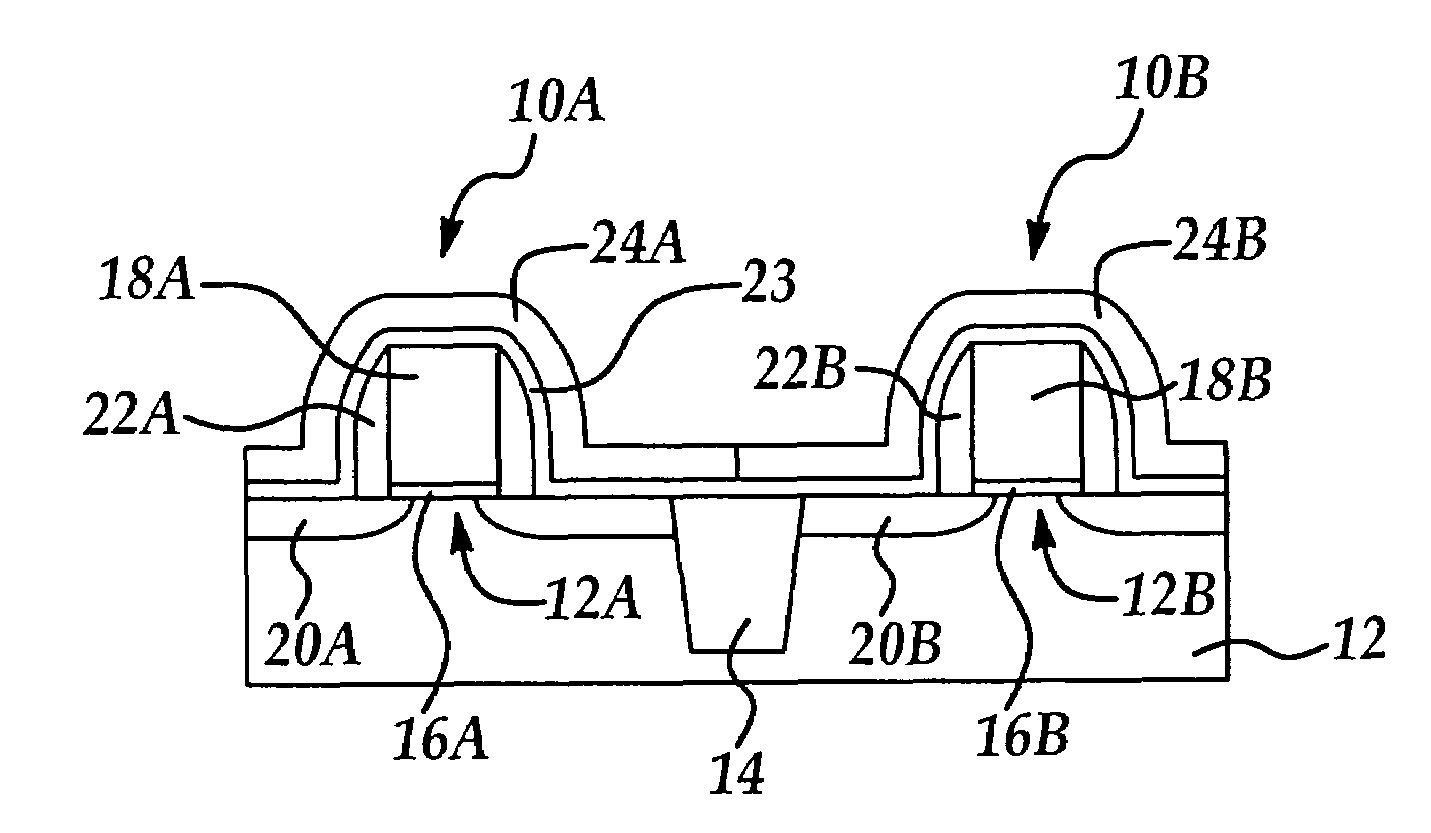

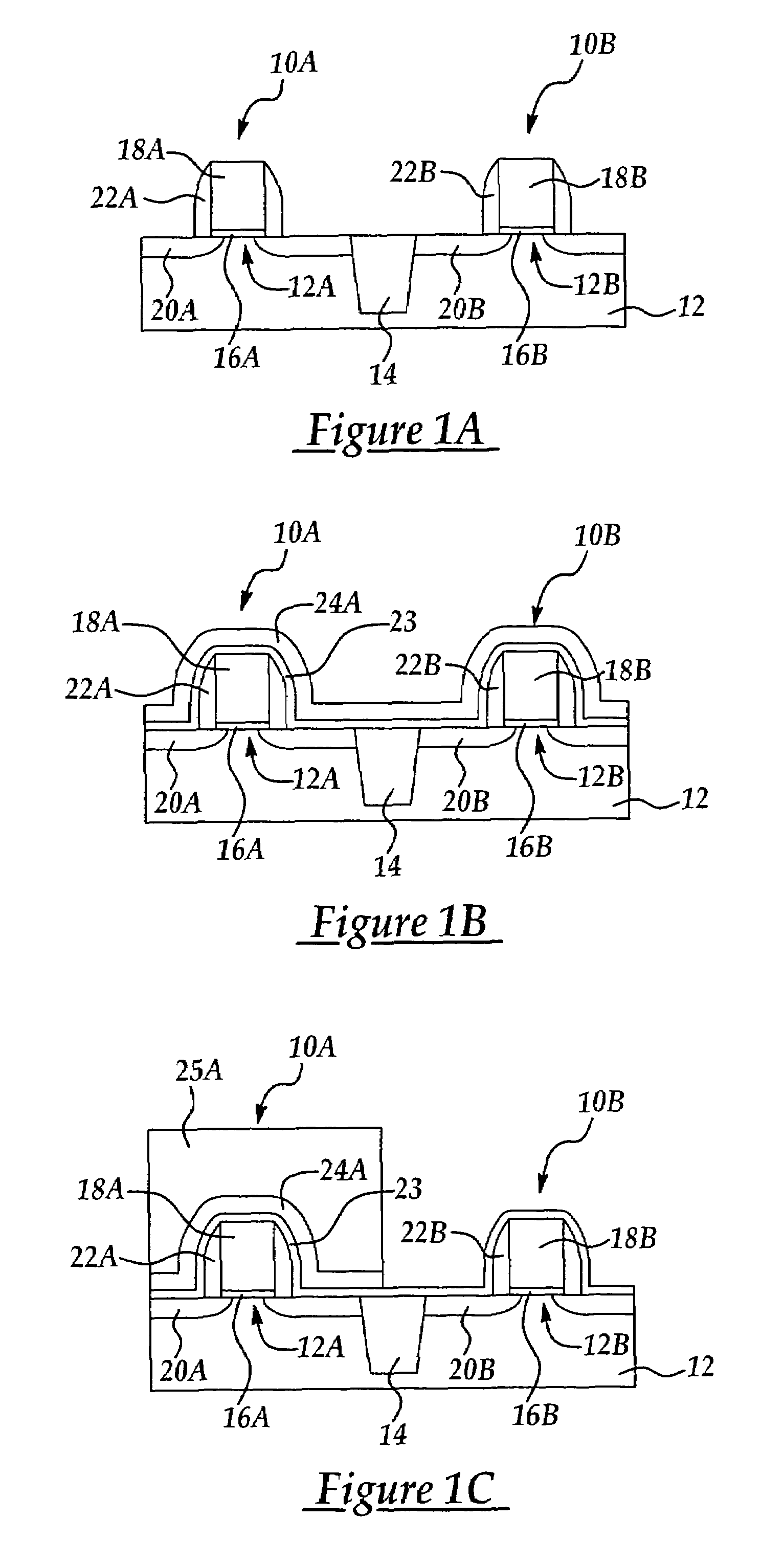

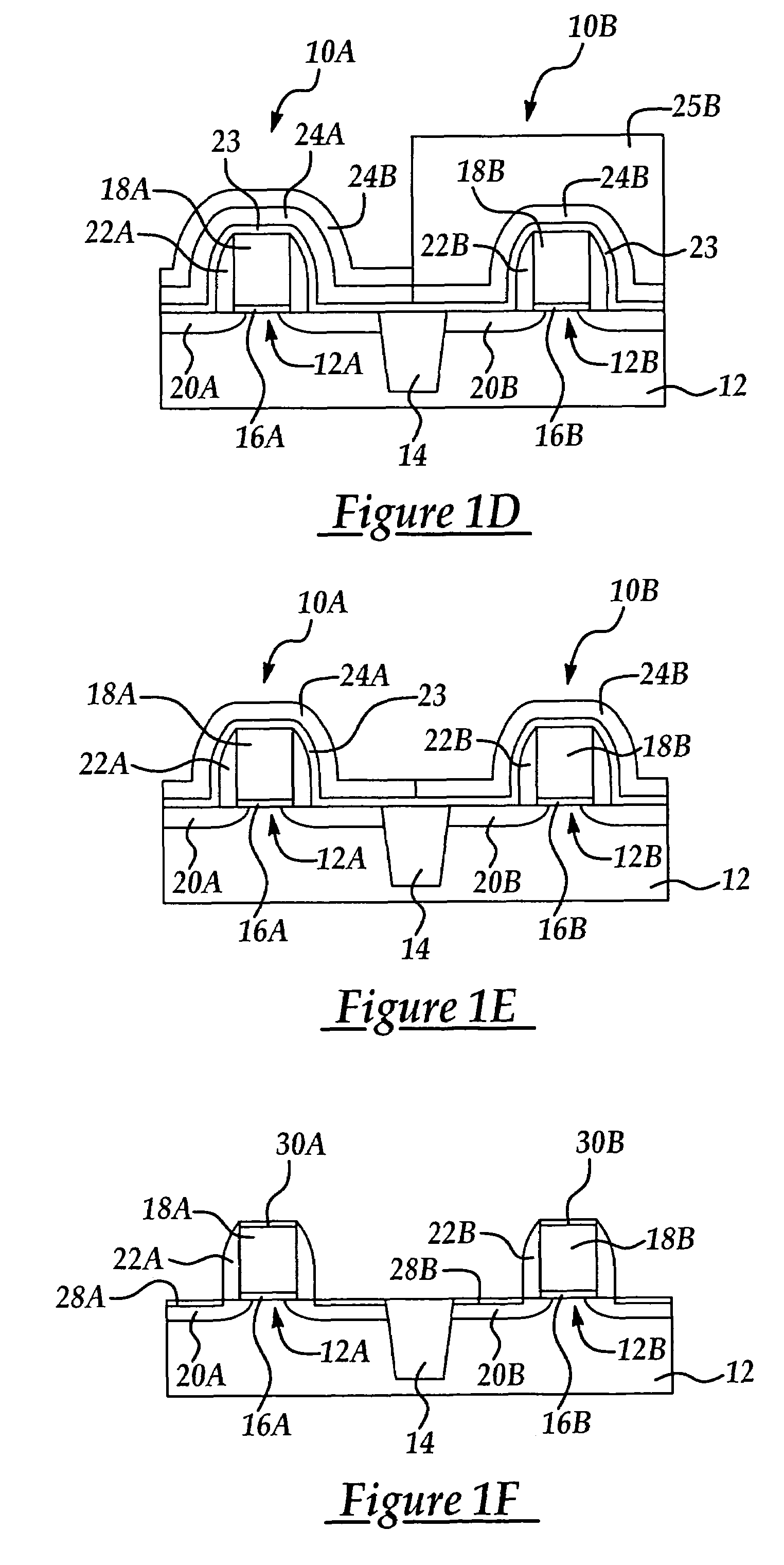

FinFET SRAM cell using low mobility plane for cell stability and method for forming

InactiveUS20050121676A1High gainAccurate operationSolid-state devicesSemiconductor/solid-state device manufacturingStatic random-access memoryLow mobility

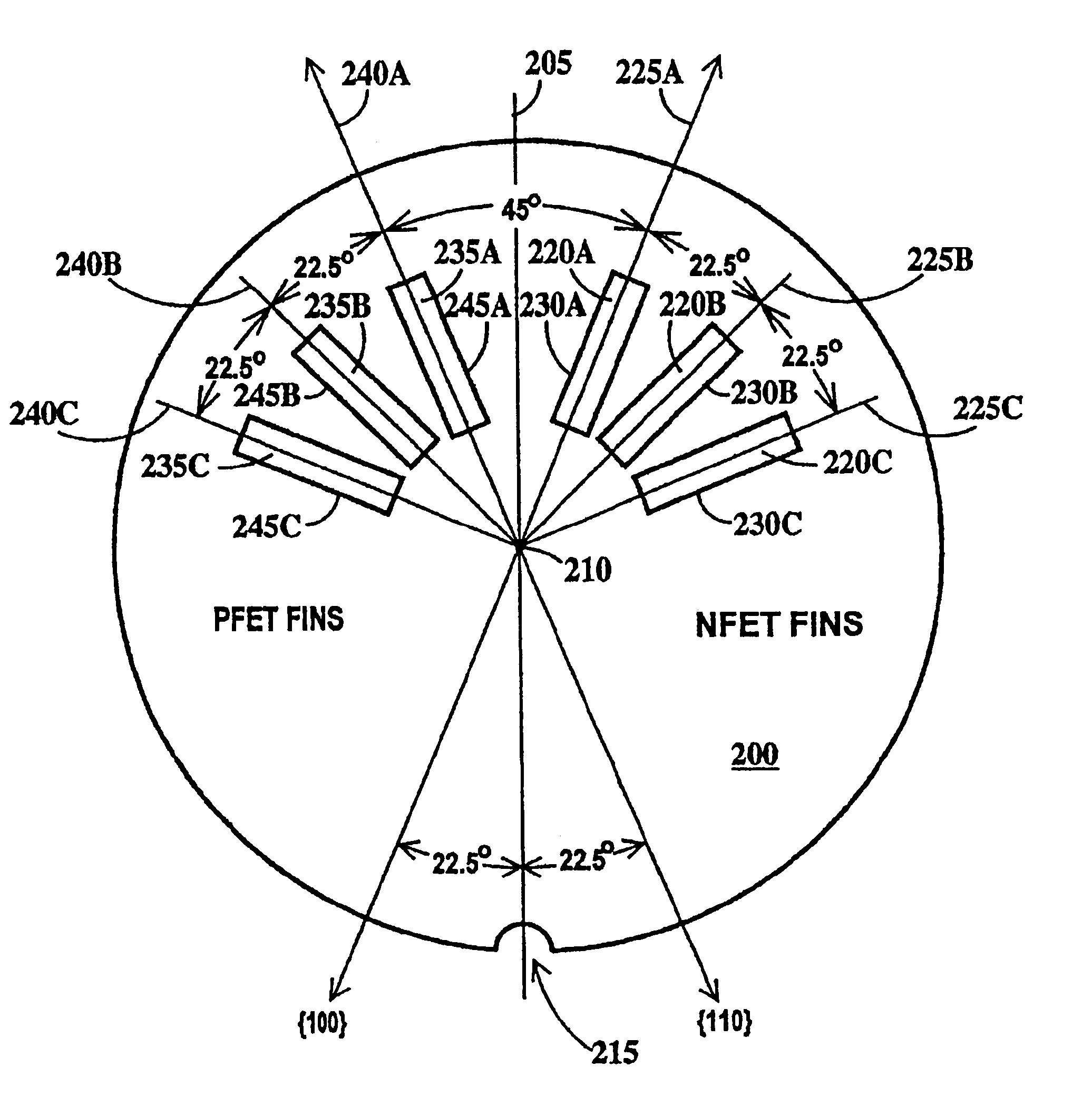

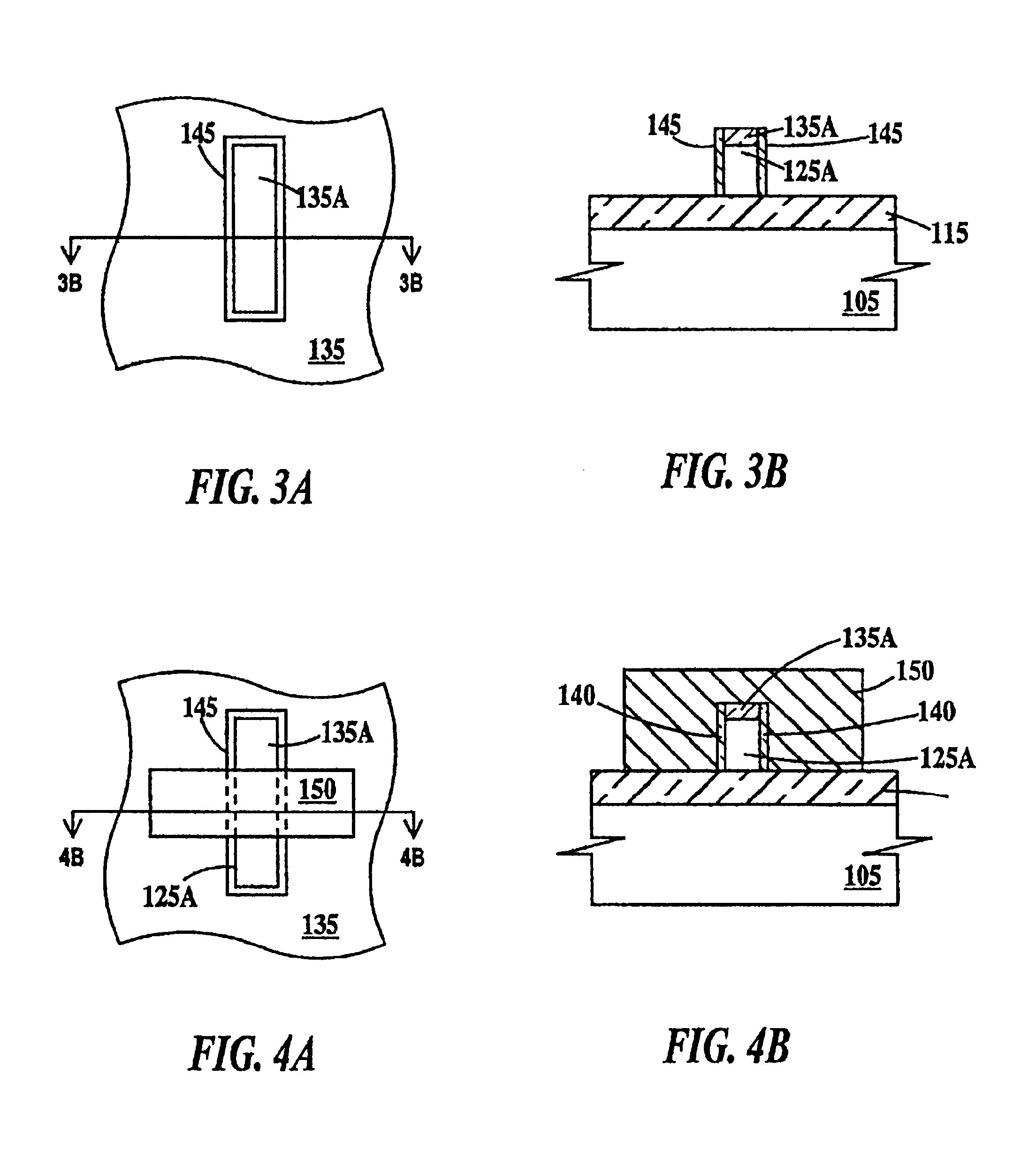

The present invention provides a device design and method for forming the same that results in Fin Field Effect Transistors having different gains without negatively impacting device density. The present invention forms relatively low gain FinFET transistors in a low carrier mobility plane and relatively high gain FinFET transistors in a high carrier mobility plane. Thus formed, the FinFETs formed in the high mobility plane have a relatively higher gain than the FinFETs formed in the low mobility plane. The embodiments are of particular application to the design and fabrication of a Static Random Access Memory (SRAM) cell. In this application, the bodies of the n-type FinFETs used as transfer devices are formed along the {110} plane. The bodies of the n-type FinFETs and p-type FinFETs used as the storage latch are formed along the {100}. Thus formed, the transfer devices will have a gain approximately half that of the n-type storage latch devices, facilitating proper SRAM operation

Owner:GLOBALFOUNDRIES INC

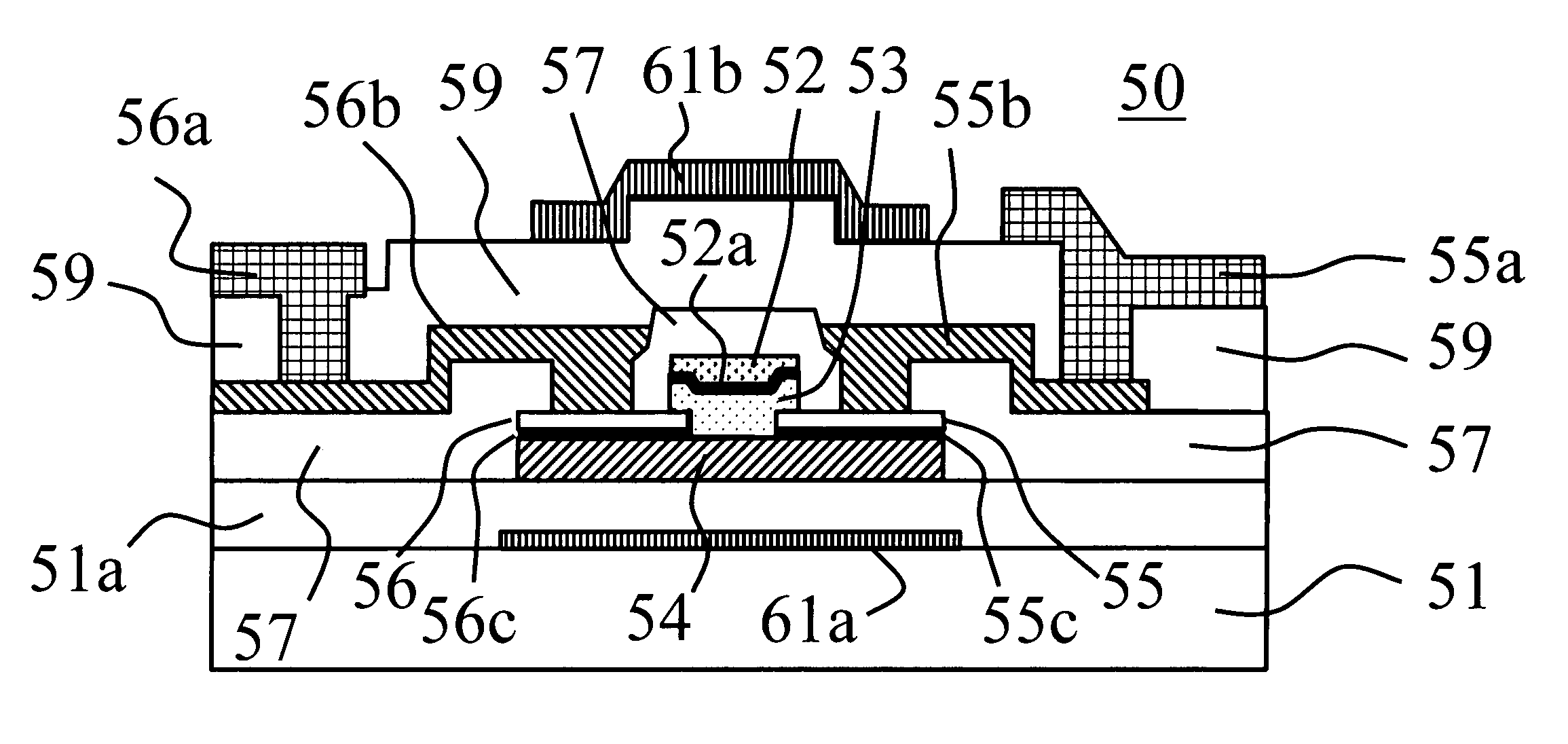

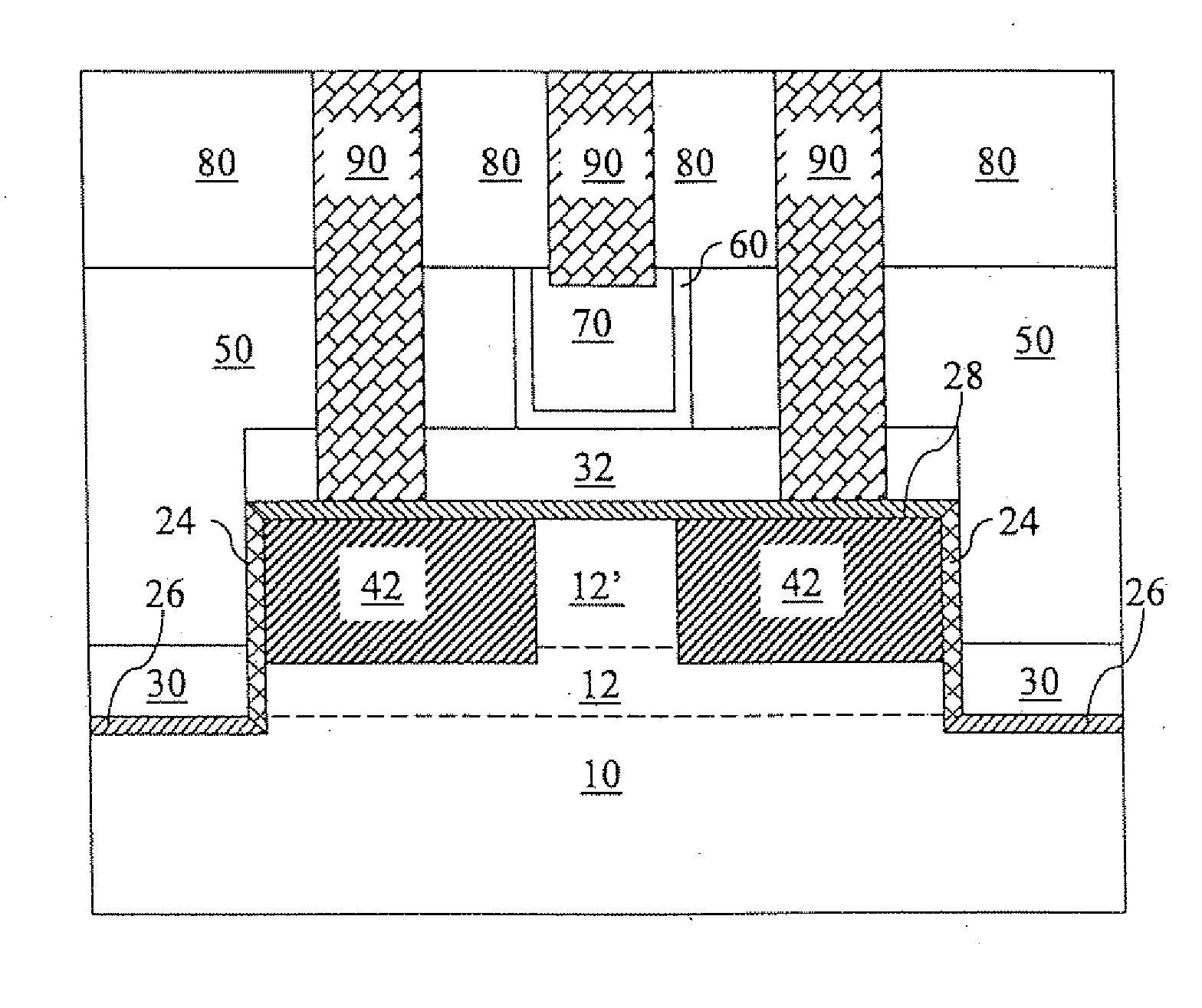

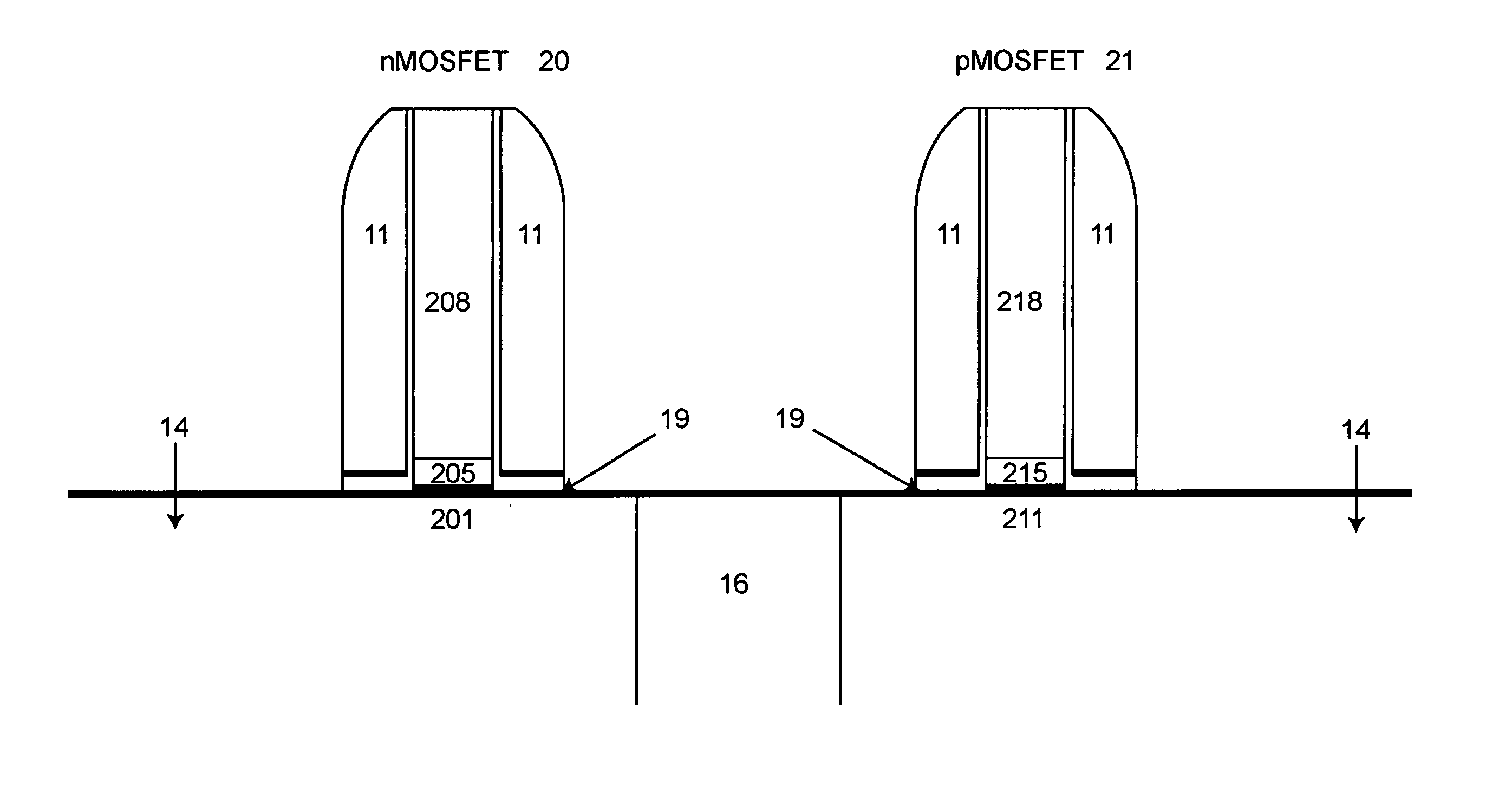

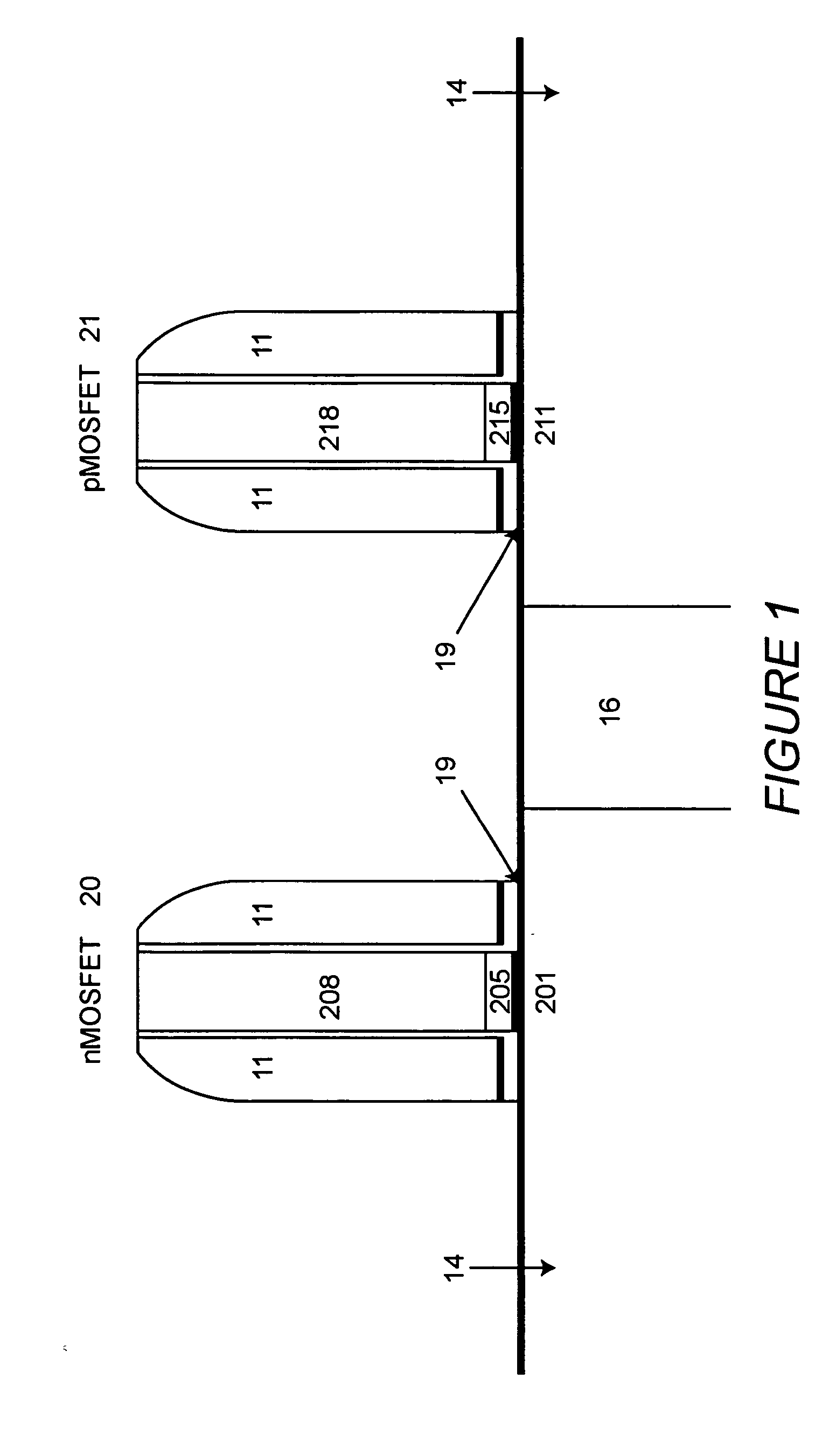

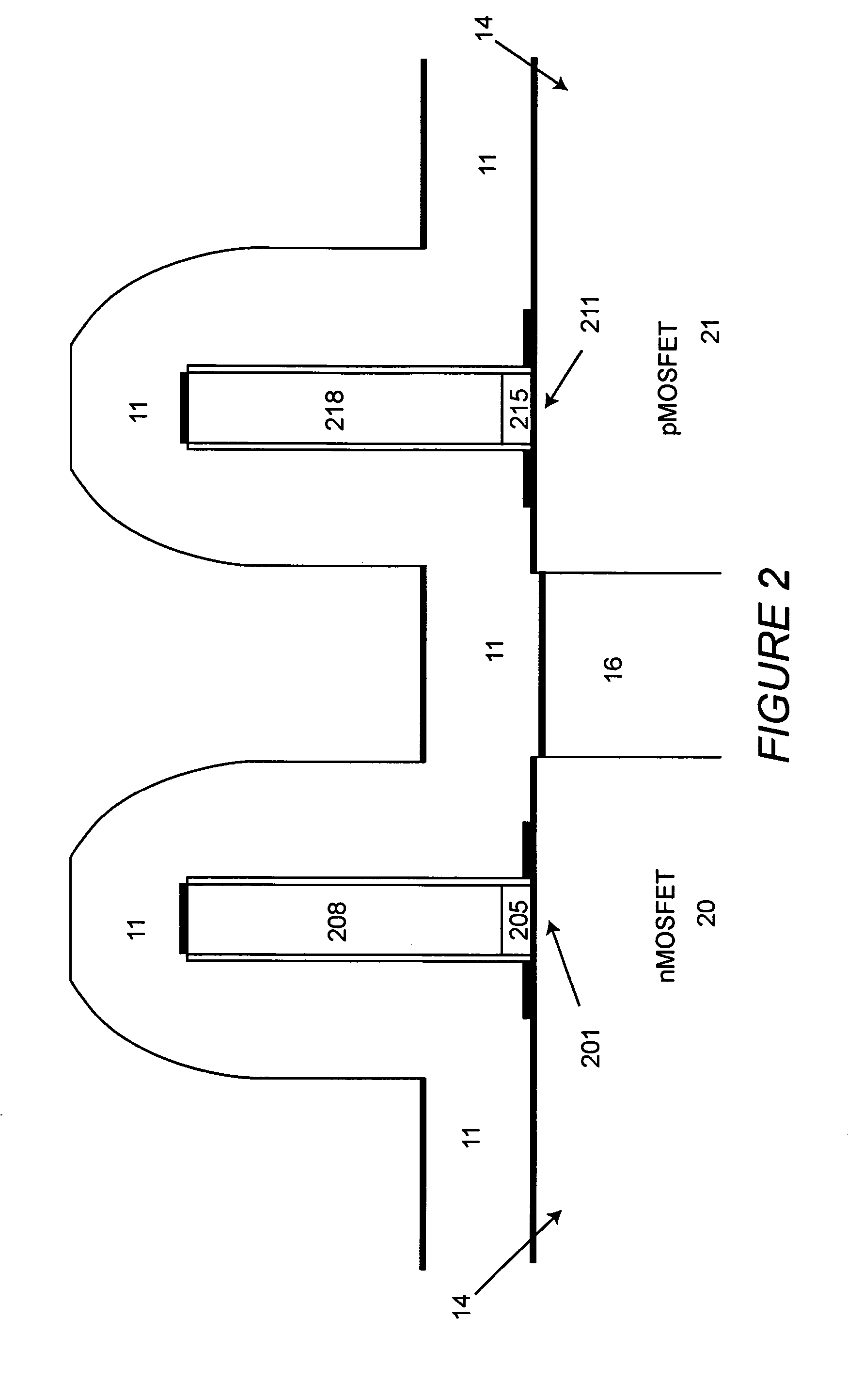

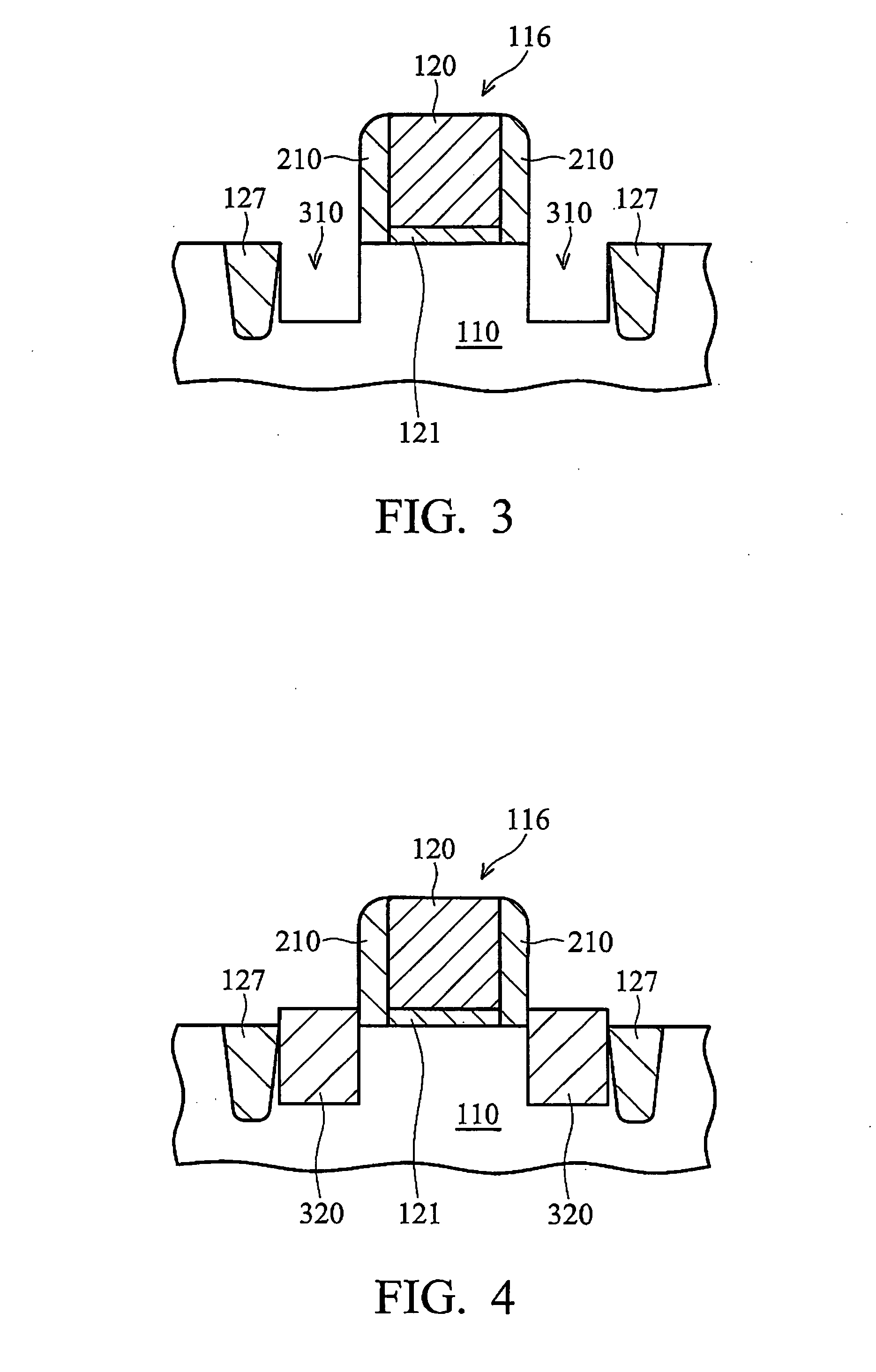

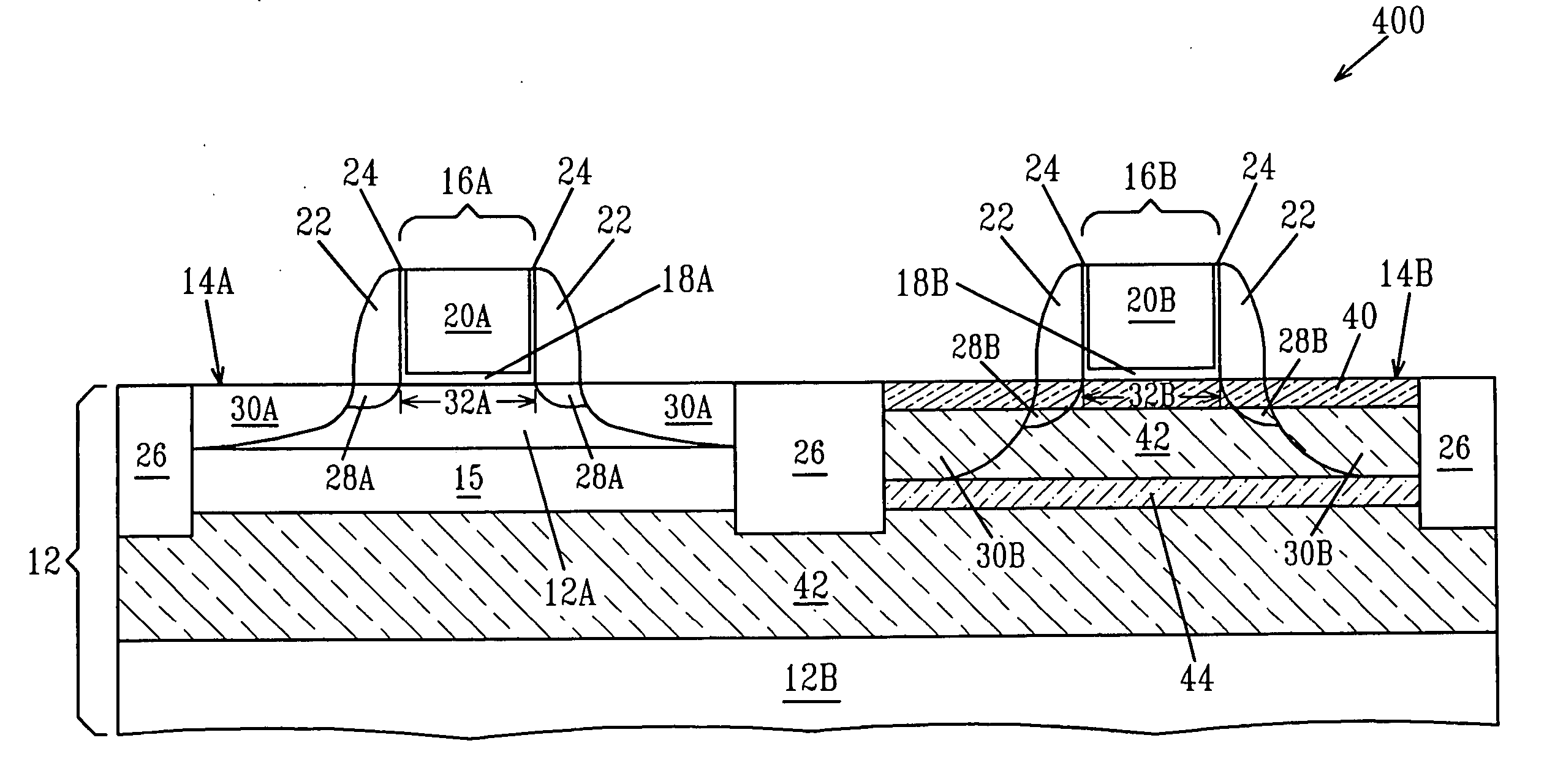

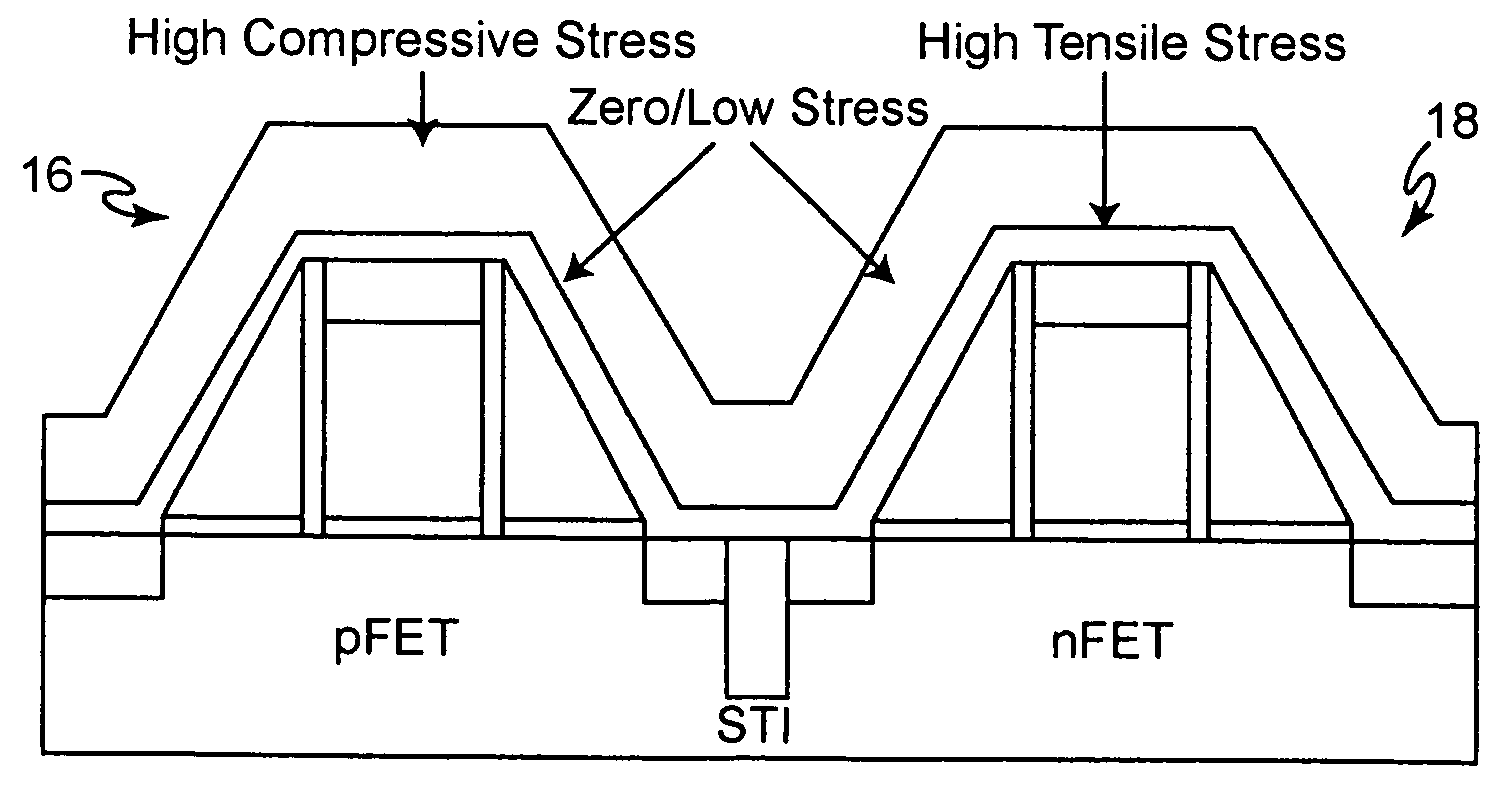

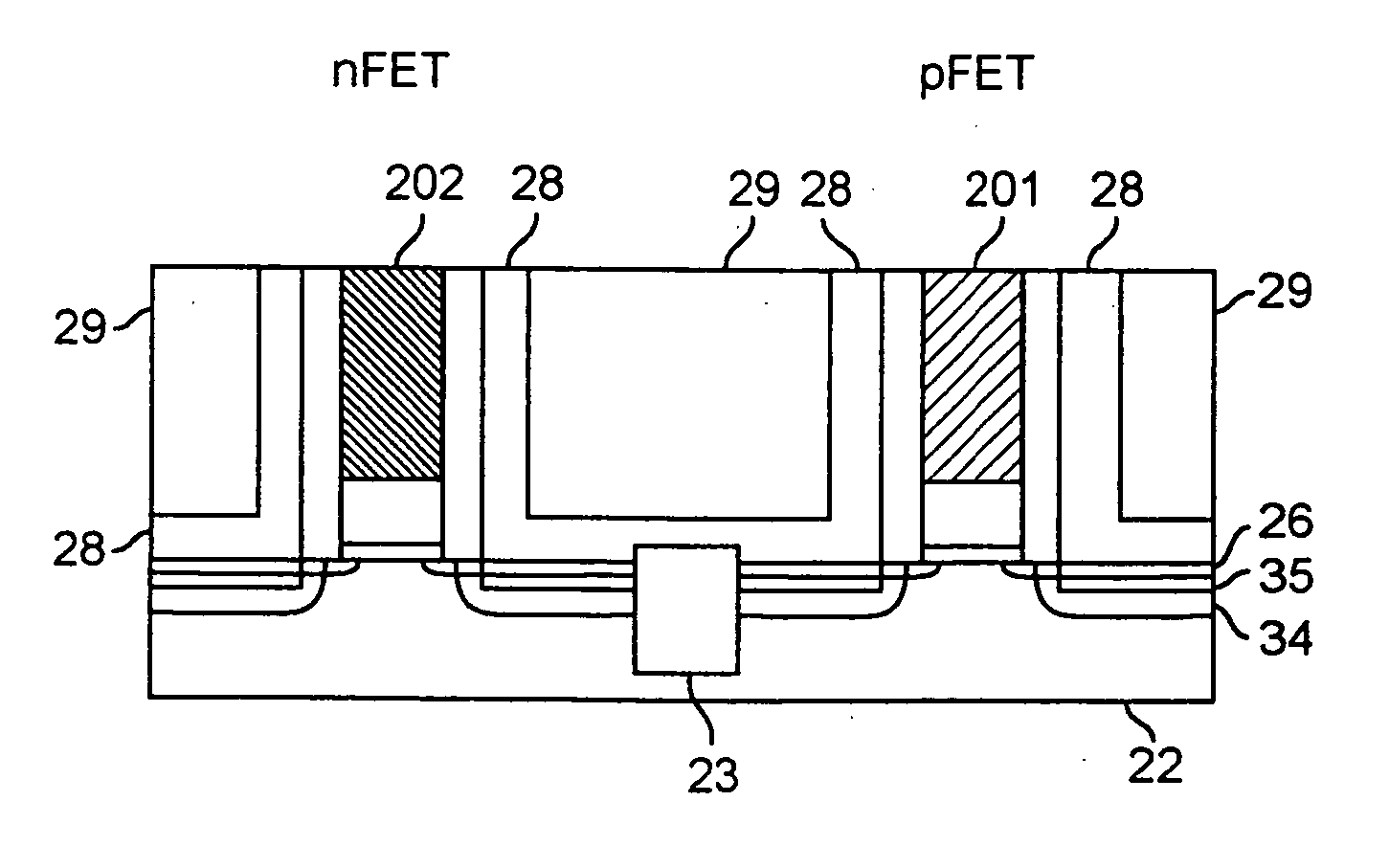

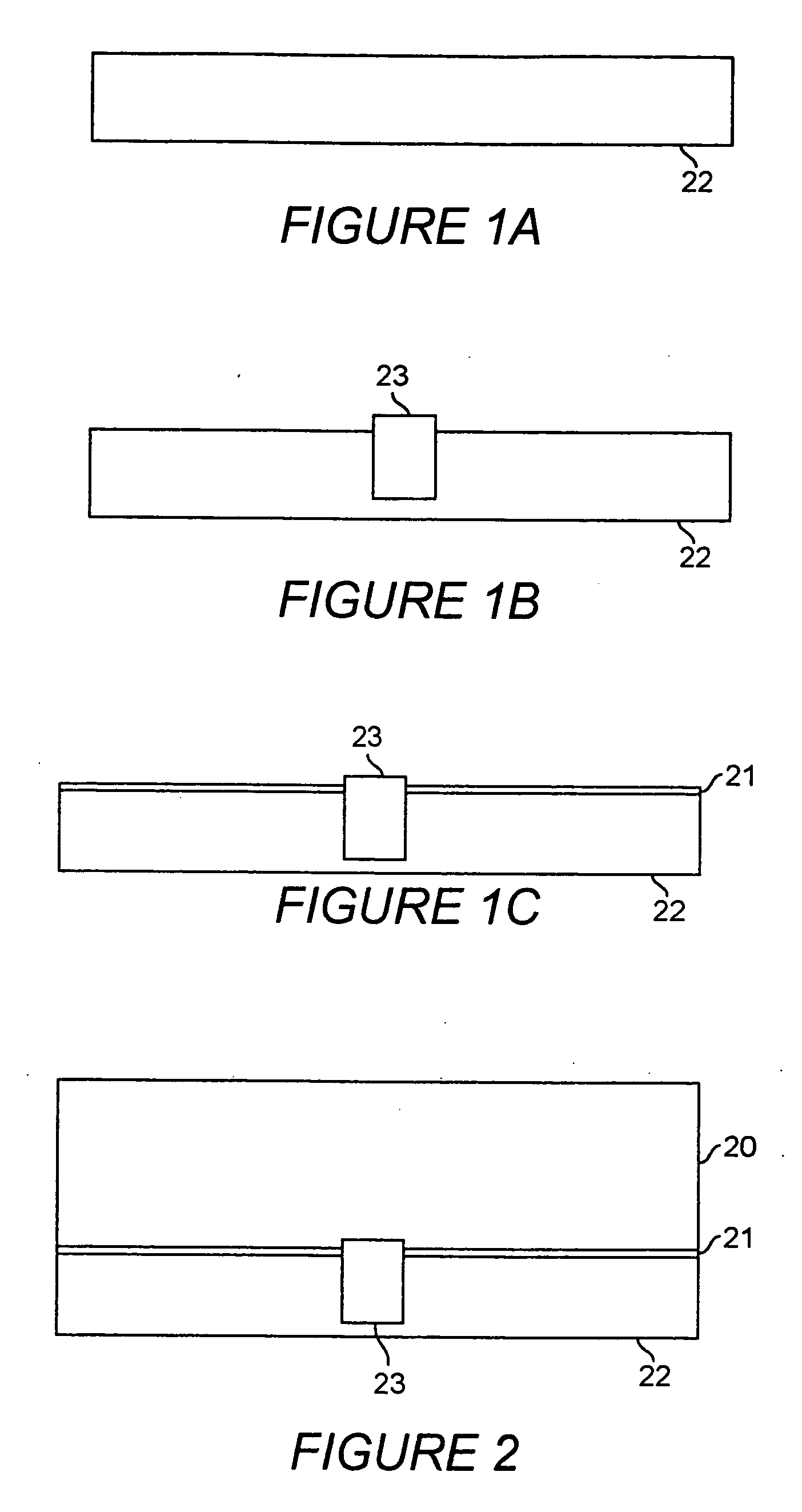

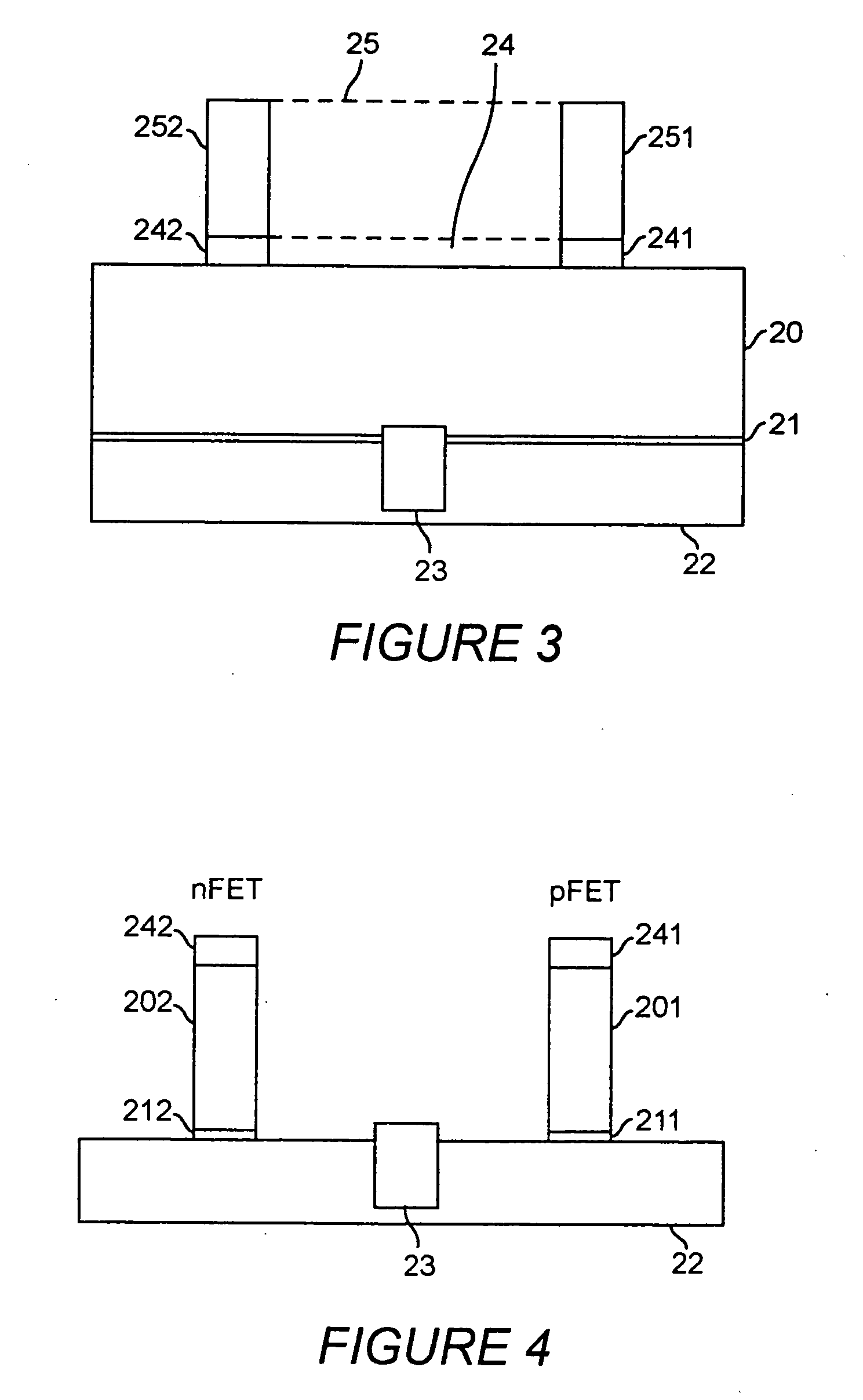

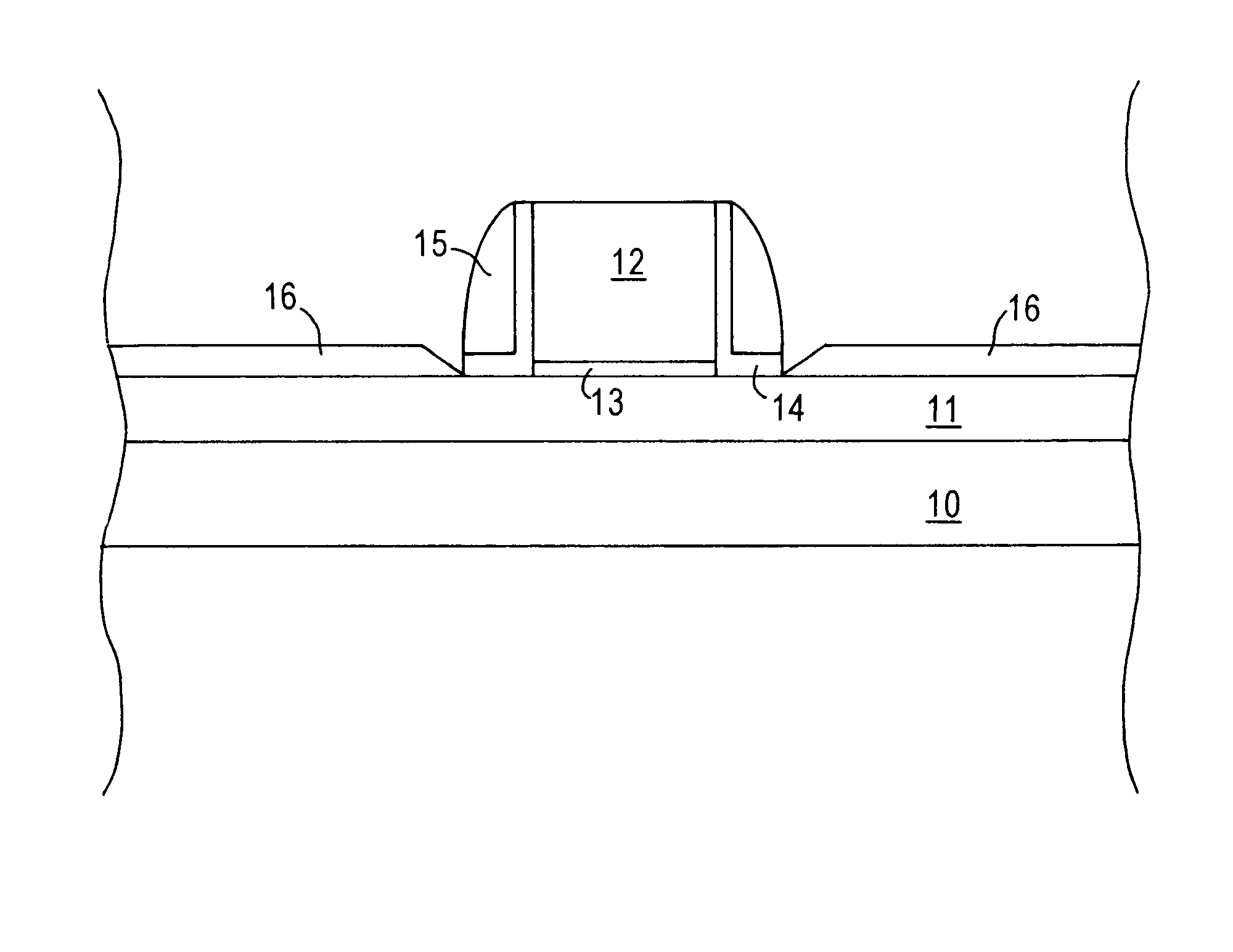

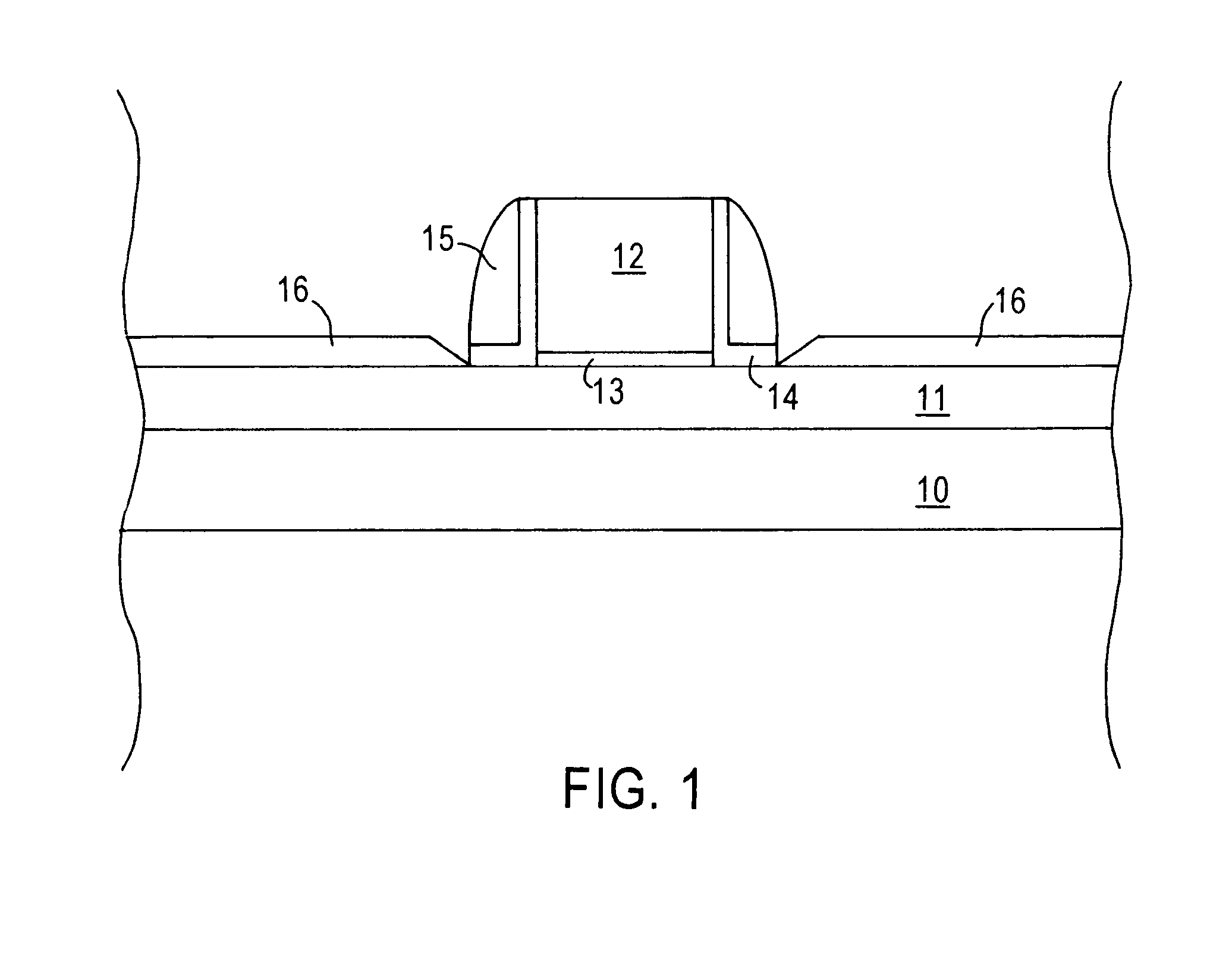

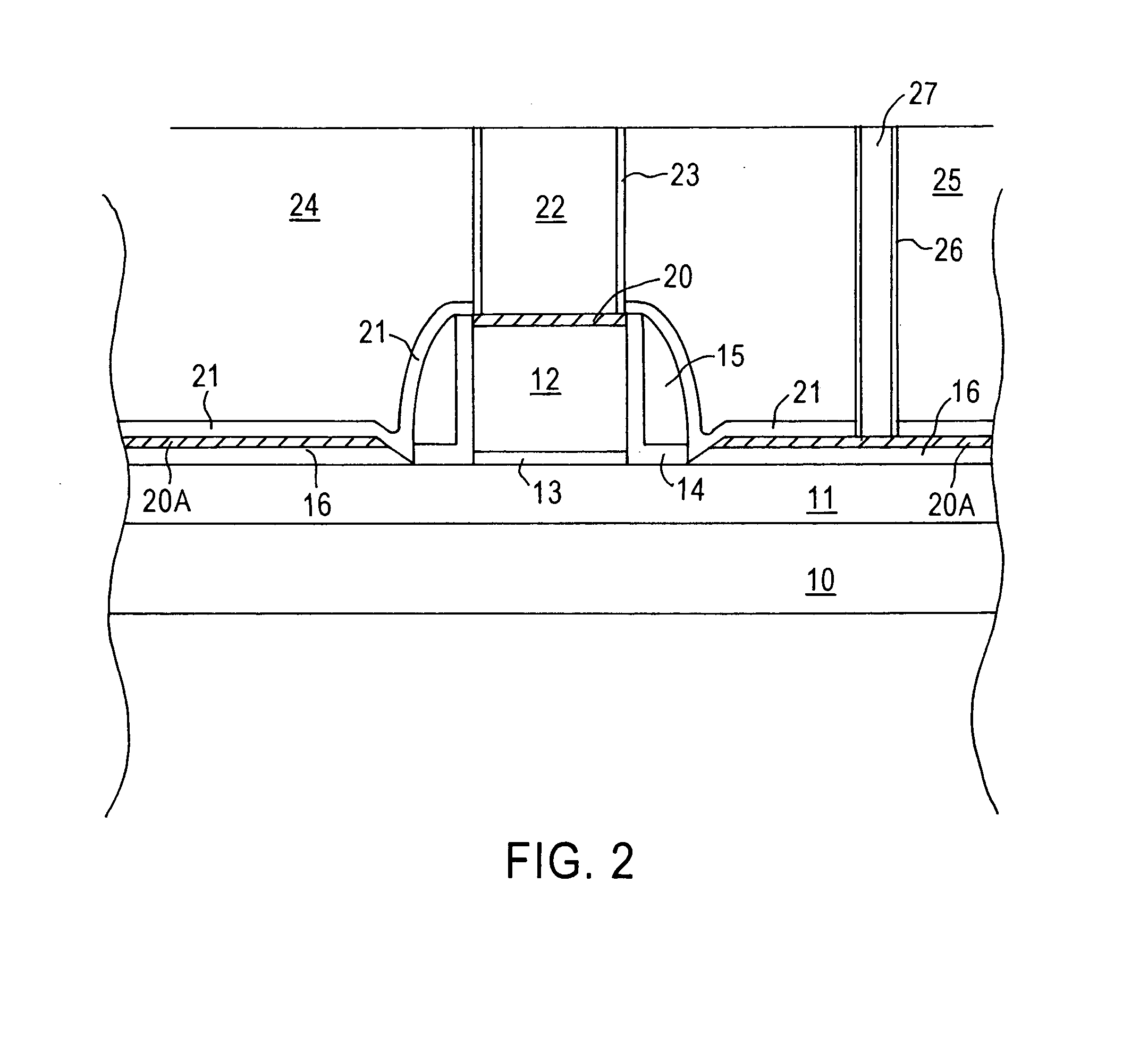

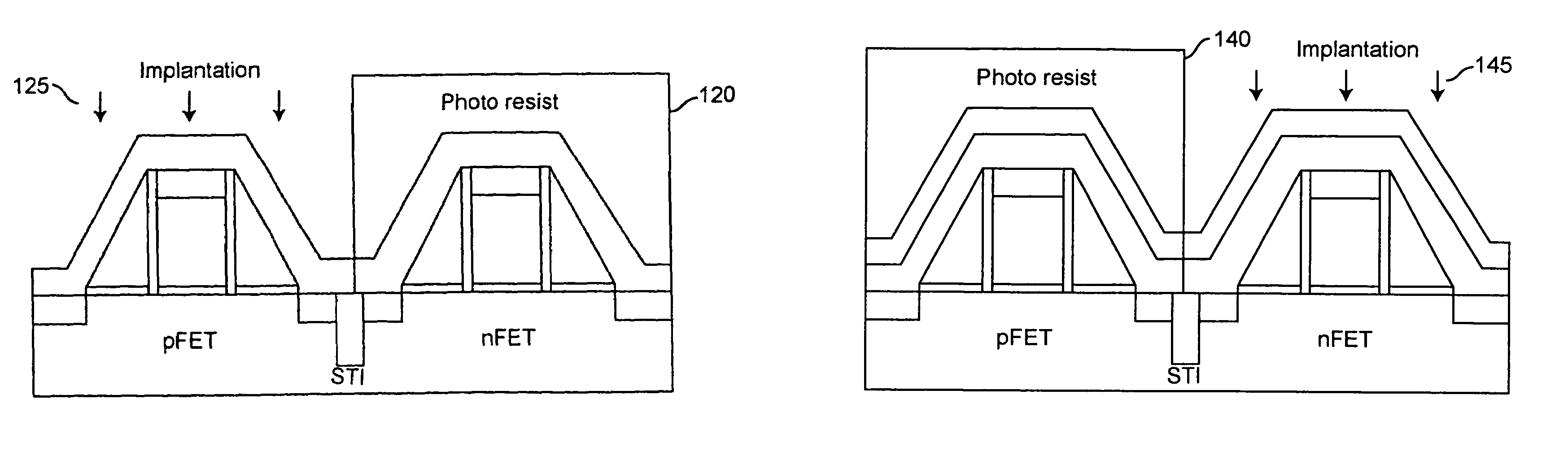

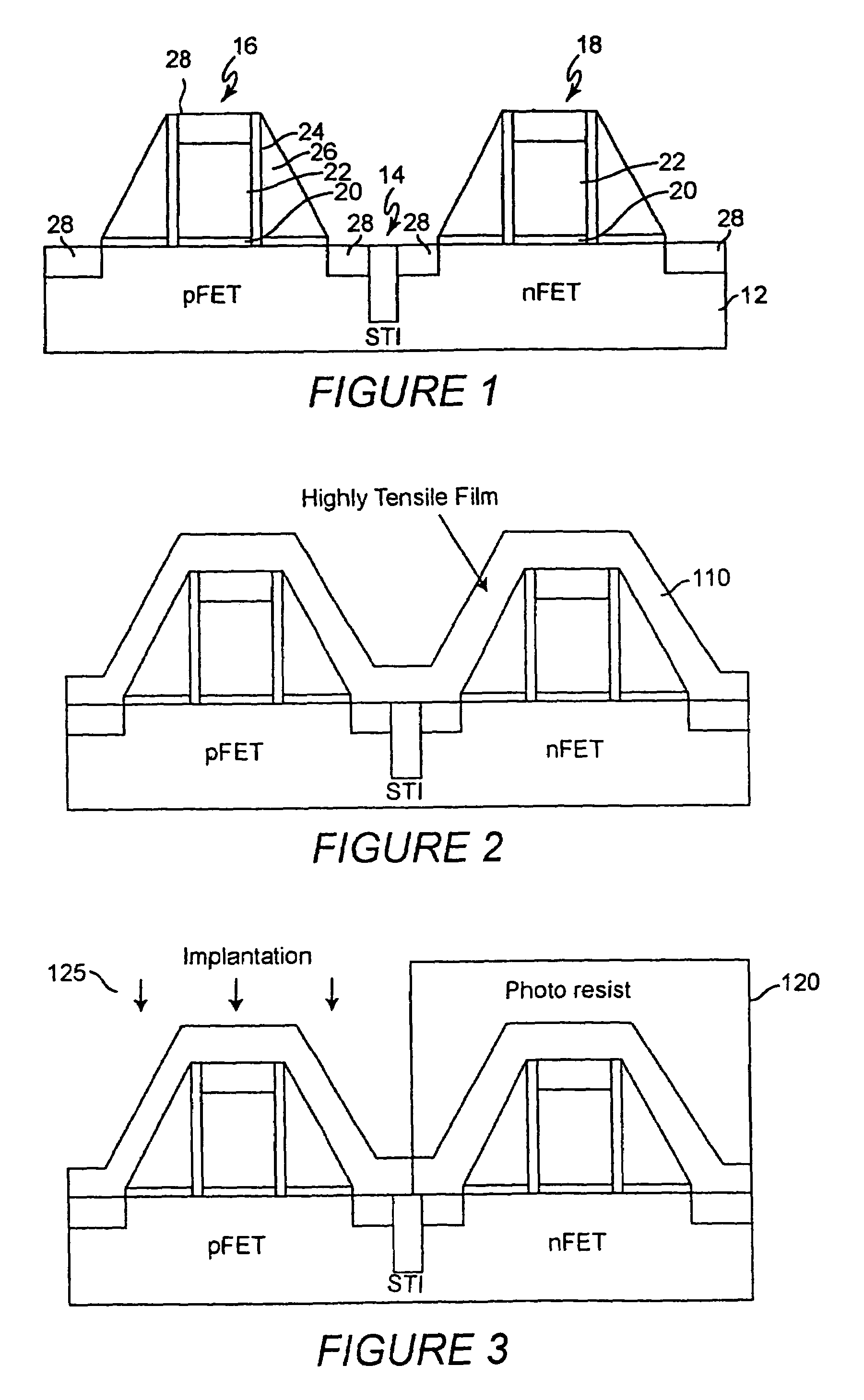

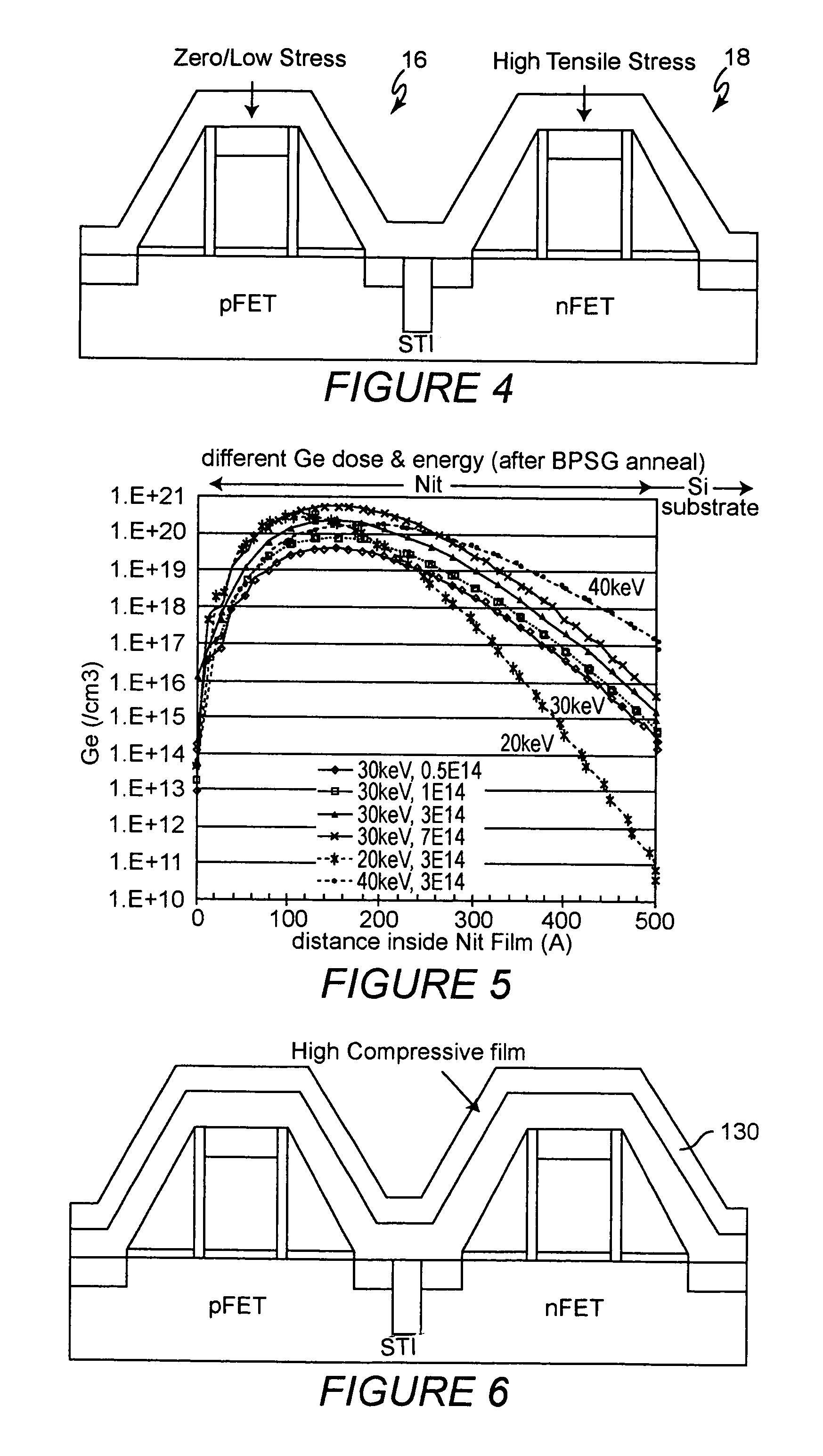

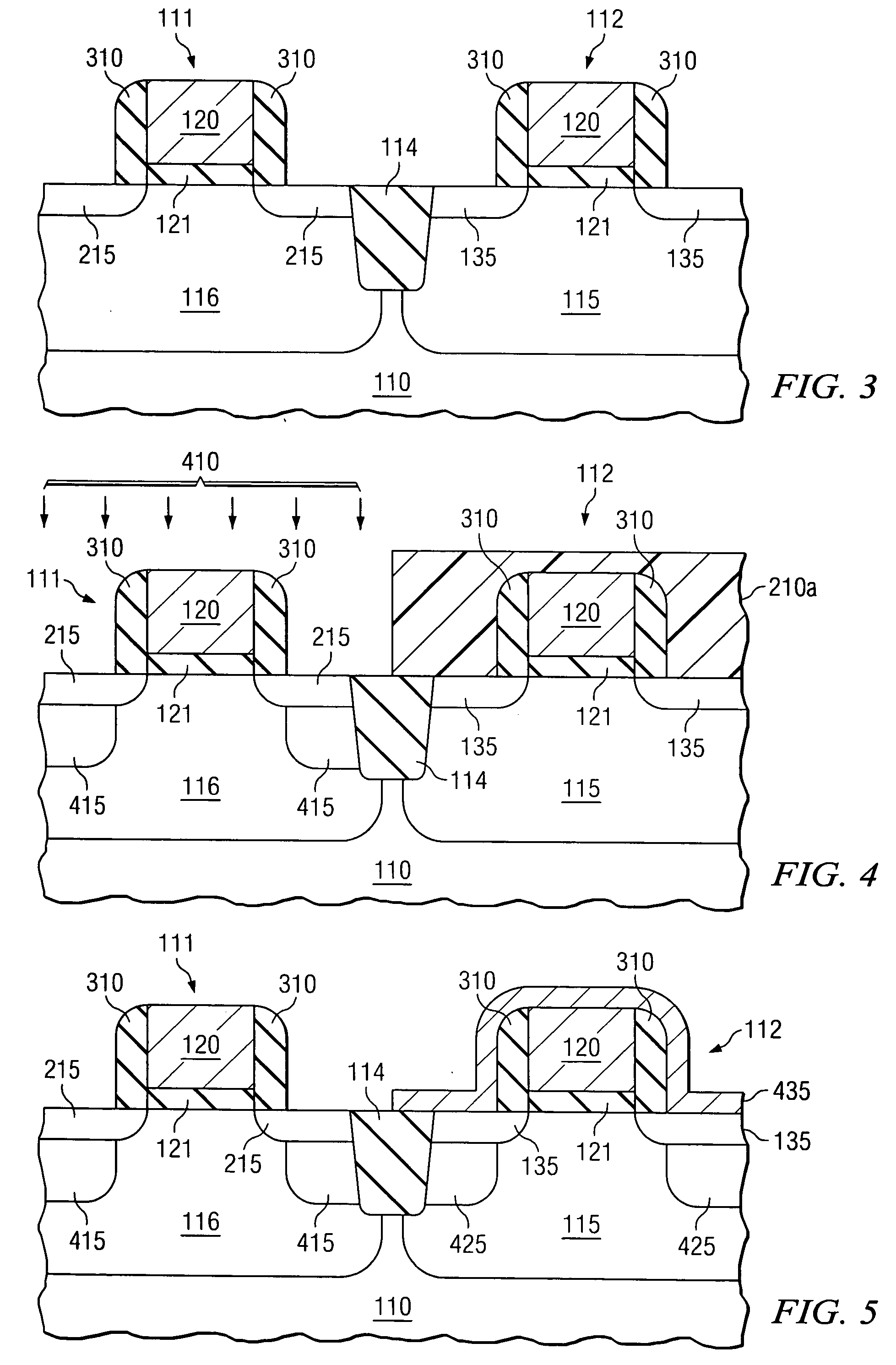

Structure and method to enhance both nFET and pFET performance using different kinds of stressed layers

InactiveUS20050093030A1Improve performanceTransistorSemiconductor/solid-state device detailsCMOSCharge carrier mobility

In producing complementary sets of metal-oxide-semiconductor (CMOS) field effect transistors, including nMOS and pMOS transistors), carrier mobility is enhanced or otherwise regulated through the use of layering various stressed films over either the nMOS or pMOS transistor (or both), depending on the properties of the layer and isolating stressed layers from each other and other structures with an additional layer in a selected location. Thus both types of transistors on a single chip or substrate can achieve an enhanced carrier mobility, thereby improving the performance of CMOS devices and integrated circuits.

Owner:GLOBALFOUNDRIES INC

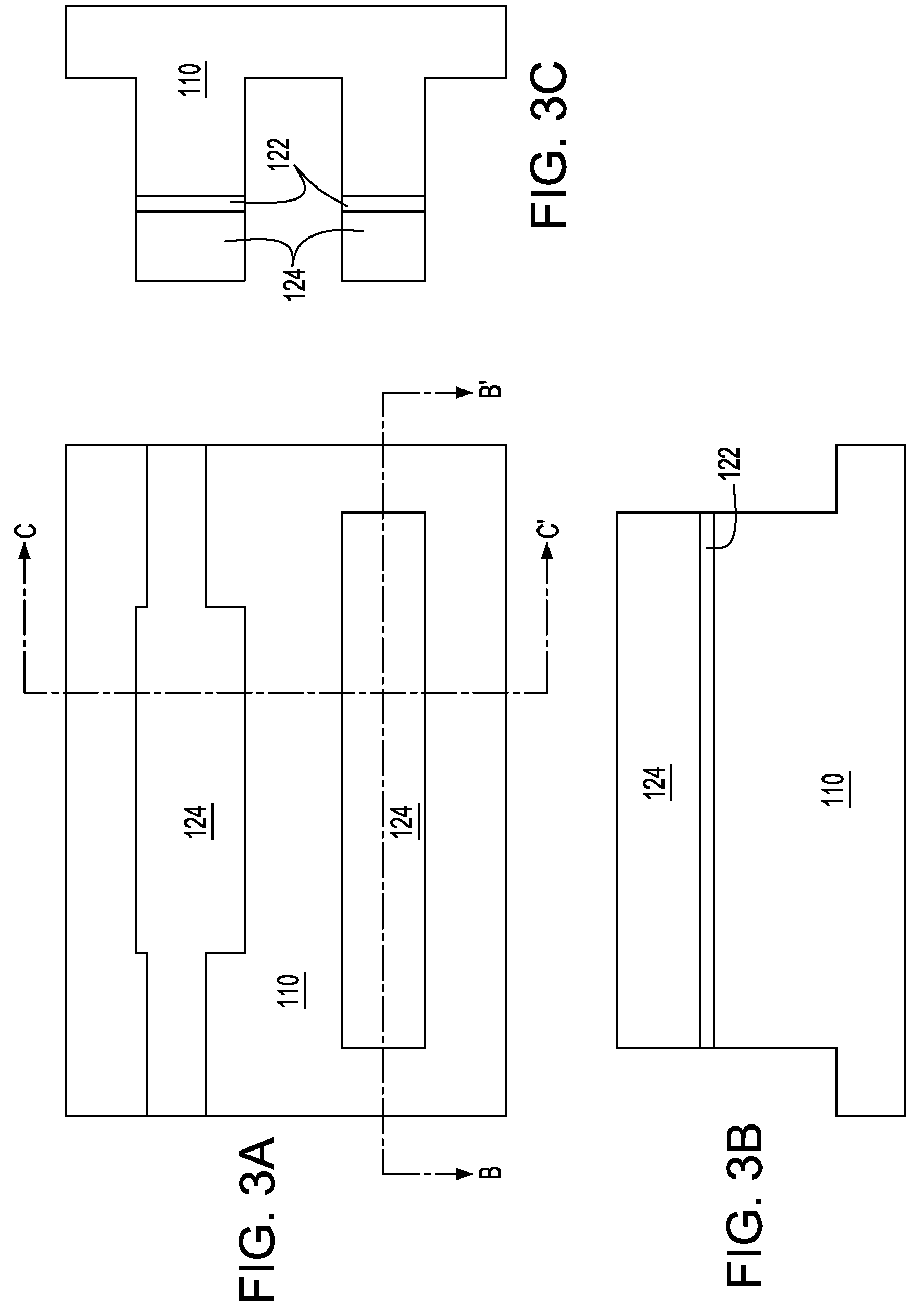

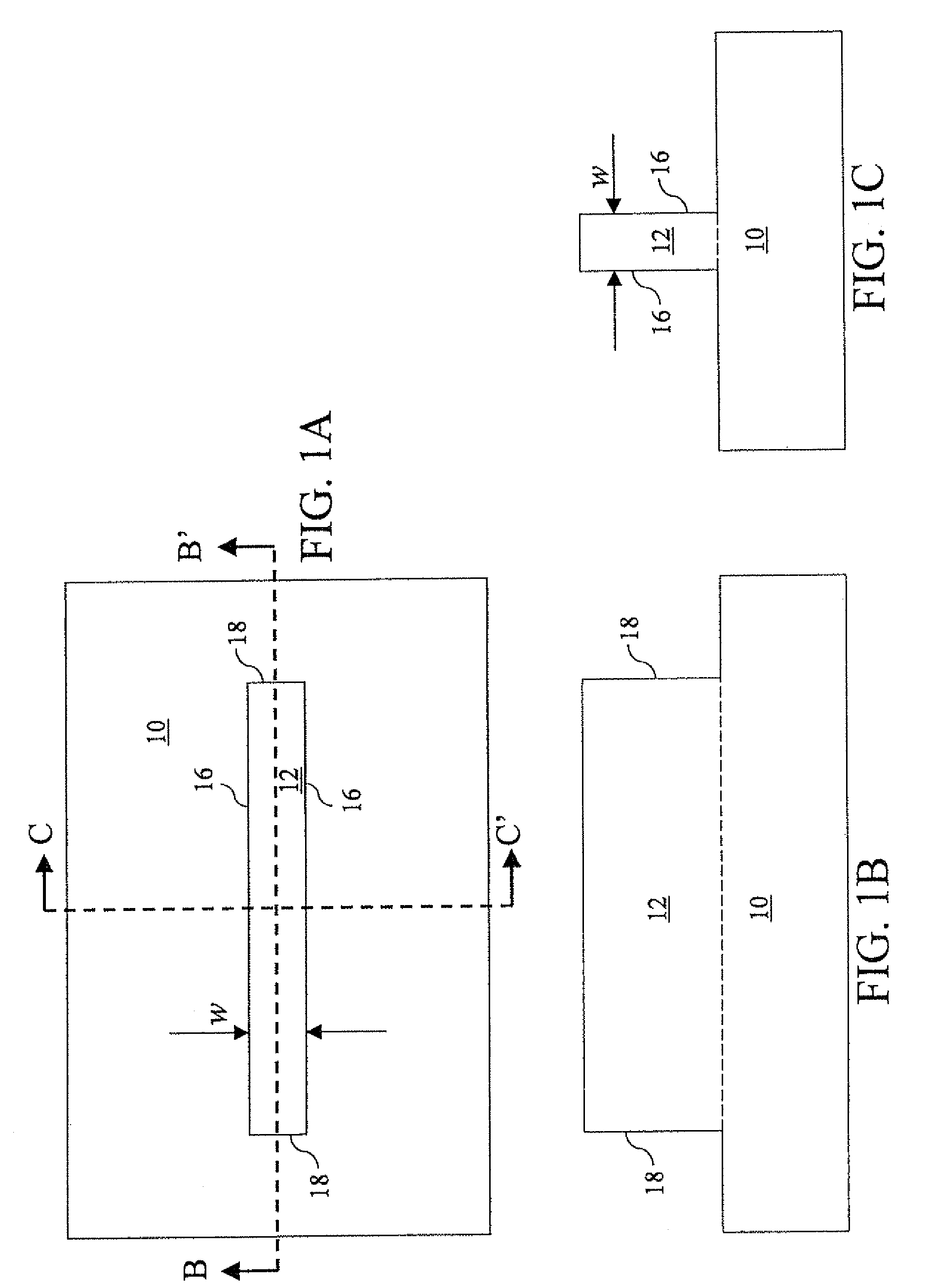

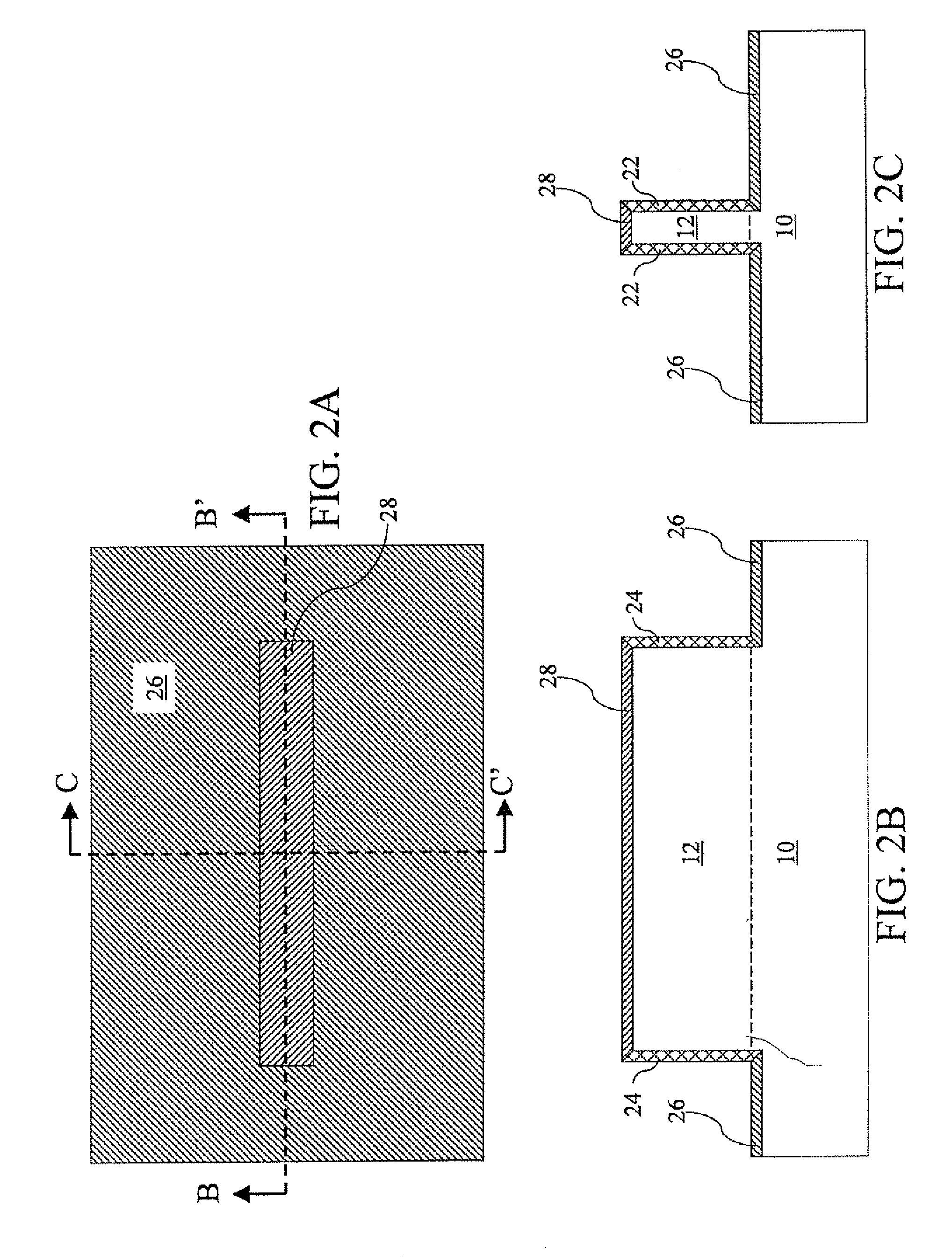

Multiple-plane FinFET CMOS

InactiveUS6657259B2Improve mobilityReduced carrier mobilityTransistorSolid-state devicesCMOSCurrent channel

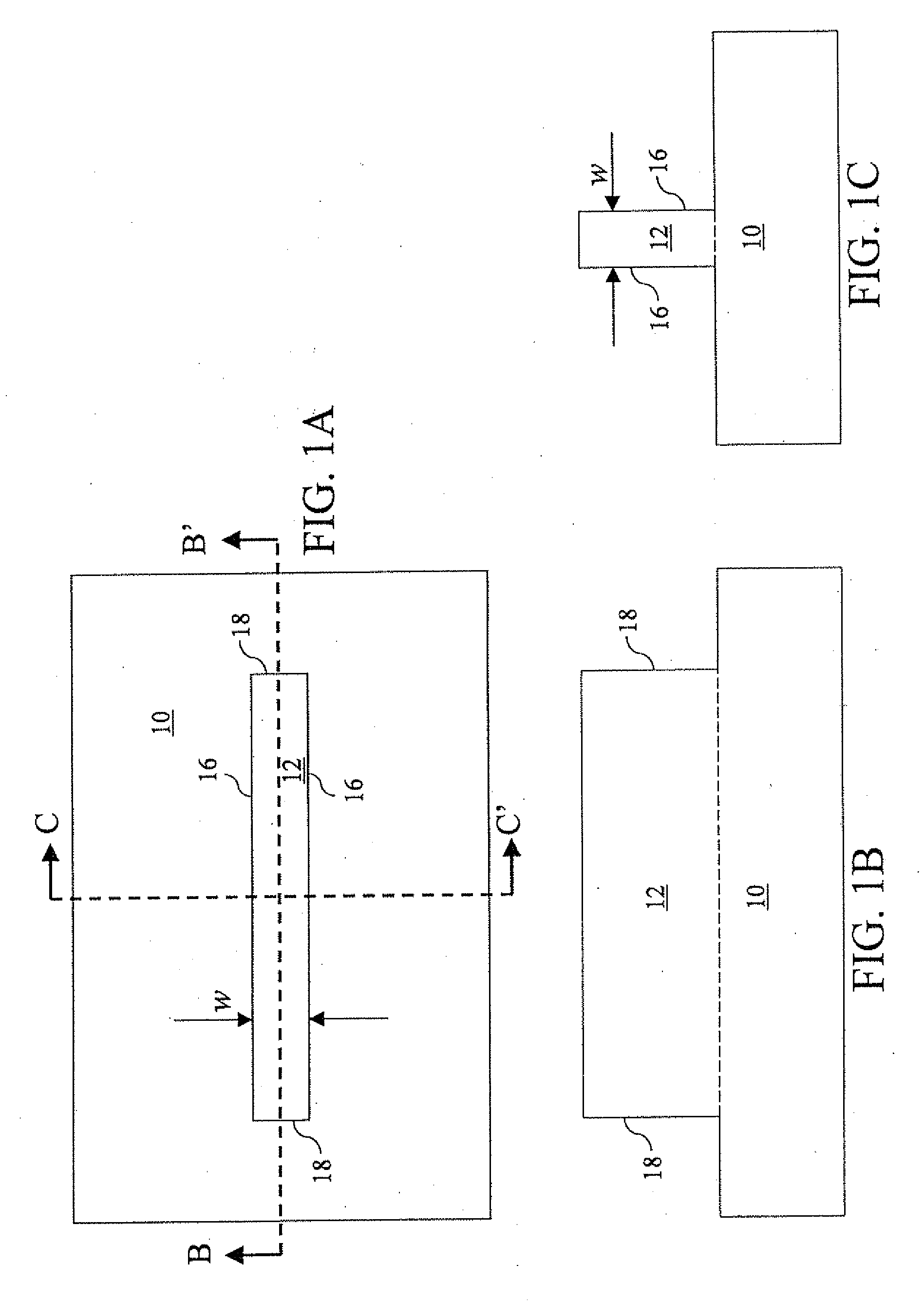

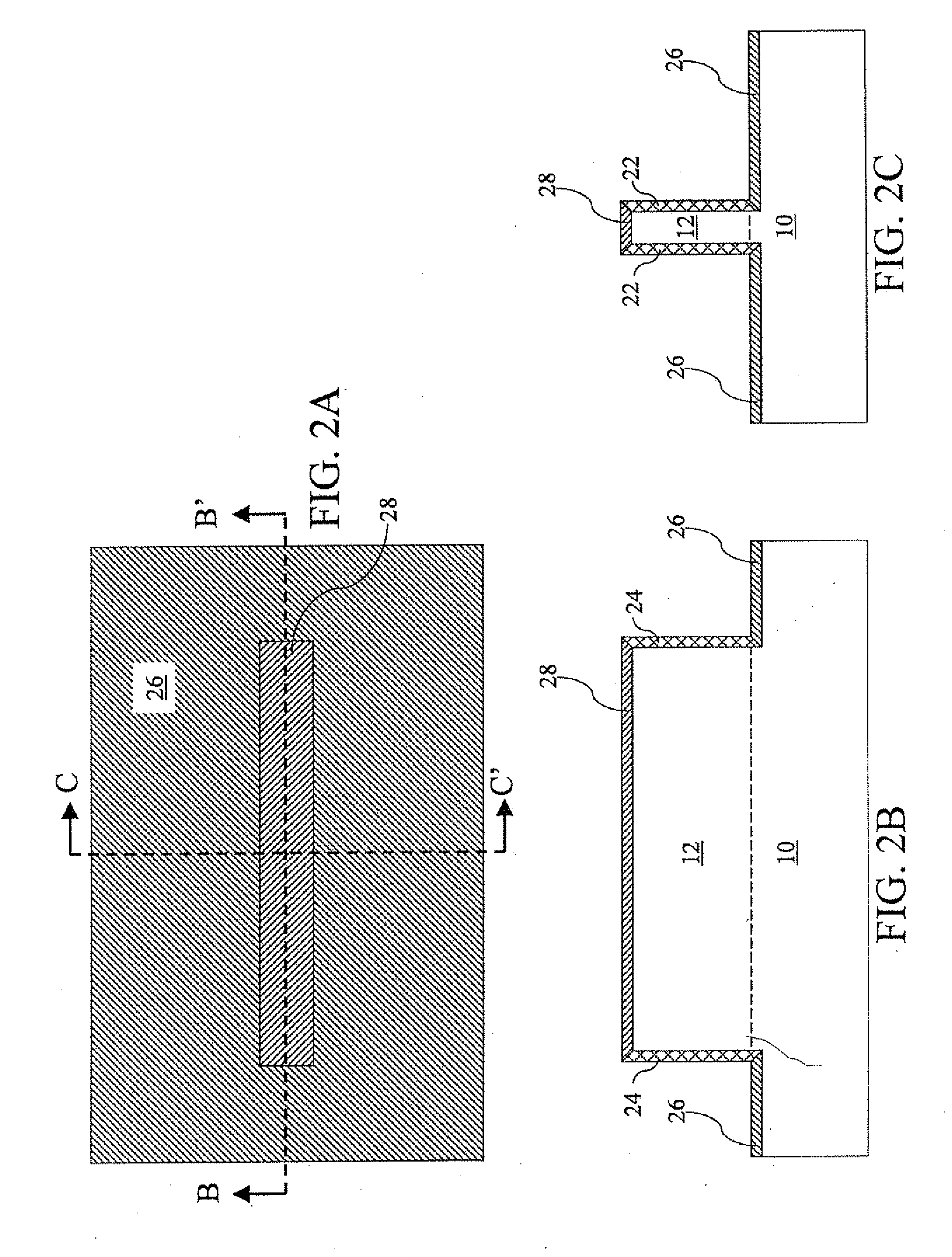

The present invention provides FinFETs on the same substrate utilizing various crystal planes for FET current channels in order to optimize mobility and / or to reduce mobility. An embodiment of the present invention provides a substrate having a surface oriented on a first crystal plane that enables subsequent crystal planes for channels to be utilized. A first transistor is also provided having a first fin body. The first fin body has a sidewall forming a first channel, the sidewall oriented on a second crystal plane to provide a first carrier mobility. A second transistor is also provided having a second fin body. The second fin body has a sidewall forming a second channel, the sidewall oriented on a third crystal plane to provide a second carrier mobility that is different from the first carrier mobility.

Owner:GLOBALFOUNDRIES U S INC

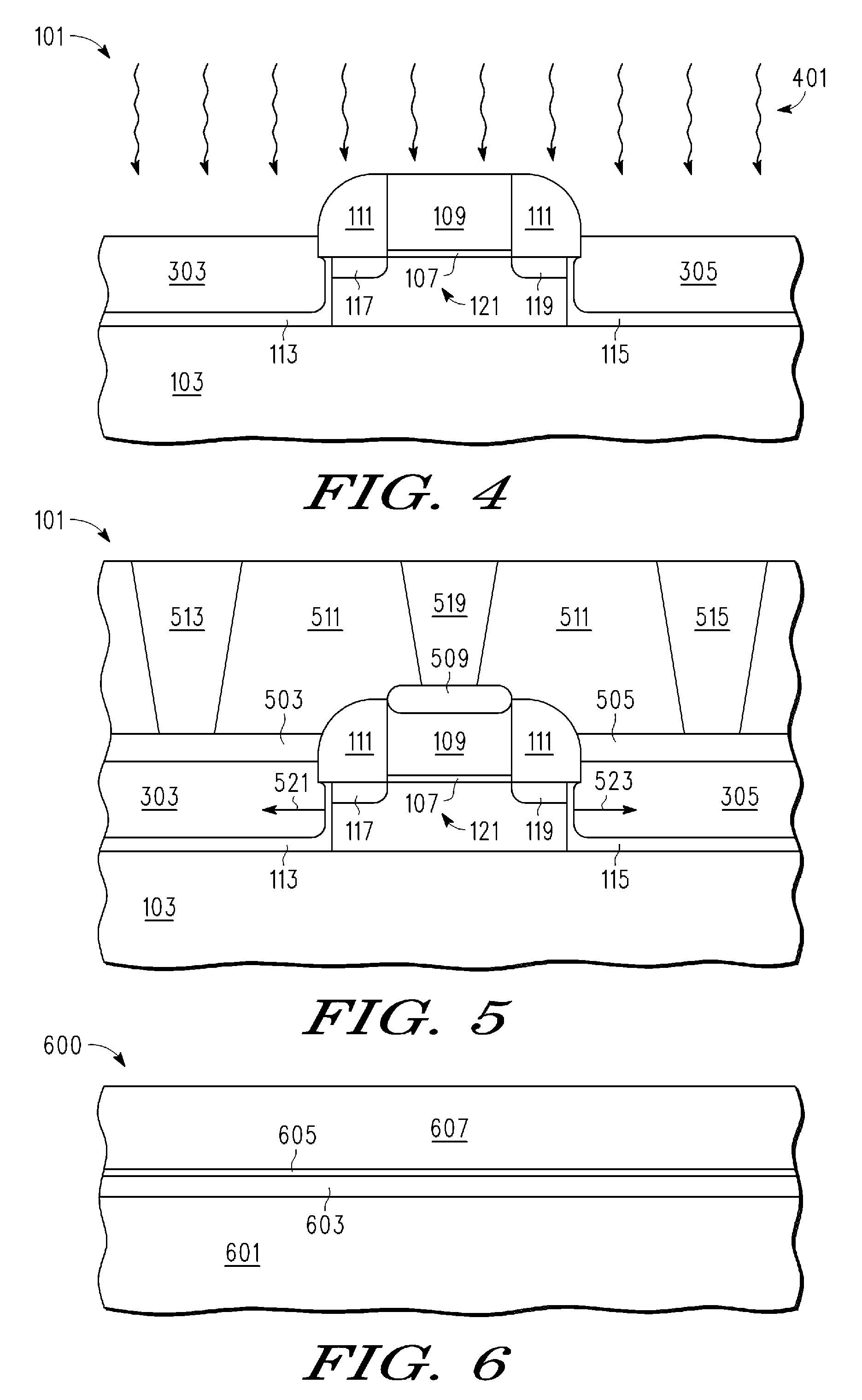

SiGe selective growth without a hard mask

InactiveUS20080083948A1Semiconductor/solid-state device manufacturingSemiconductor devicesTensile strainCharge carrier mobility

MOS transistors having localized stressors for improving carrier mobility are provided. Embodiments of the invention comprise a gate electrode formed over a substrate, a carrier channel region in the substrate under the gate electrode, and source / drain regions on either side of the carrier channel region. The source / drain regions include an embedded stressor having a lattice spacing different from the substrate. In a preferred embodiment, the substrate is silicon and the embedded stressor is SiGe or SiC. An epitaxy process that includes using HCl gas selectively forms a stressor layer within the crystalline source / drain regions and not on polycrystalline regions of the structure. A preferred epitaxy process dispenses with the source / drain hard mask required of conventional methods. The embedded SiGe stressor applies a compressive strain to a transistor channel region. In another embodiment, the embedded stressor comprises SiC, and it applies a tensile strain to the transistor channel region.

Owner:TAIWAN SEMICON MFG CO LTD

Enhanced mobility CMOS transistors with a v-shaped channel with self-alignment to shallow trench isolation

InactiveUS20080173906A1Improve performanceIncrease the on-currentTransistorSolid-state devicesCMOSCharge carrier mobility

The present invention provides structures and methods for a transistor formed on a V-shaped groove. The V-shaped groove contains two crystallographic facets joined by a ridge. The facets have different crystallographic orientations than what a semiconductor substrate normally provides such as the substrate orientation or orientations orthogonal to the substrate orientation. Unlike the prior art, the V-shaped groove is formed self-aligned to the shallow trench isolation, eliminating the need to precisely align the V-shaped grooves with lithographic means. The electrical properties of the new facets, specifically, the enhanced carrier mobility, are utilized to enhance the performance of transistors. In a transistor with a channel on the facets that are joined to form a V-shaped profile, the current flows in the direction of the ridge joining the facets avoiding any inflection in the direction of the current.

Owner:GLOBALFOUNDRIES INC

Stressed field effect transistors on hybrid orientation substrate

InactiveUS20060145264A1High carrier mobilitySolid-state devicesSemiconductor/solid-state device manufacturingCMOSSemiconductor structure

Owner:GLOBALFOUNDRIES INC

Semiconductor device having a channel layer and method of manufacturing the same

InactiveUS20050263795A1High carrier mobilityImprove channel mobilityTransistorPaper-money handling devicesDriving currentInsulation layer

In a method of forming a semiconductor device having an improved channel layer, the channel layer is formed on a surface of a semiconductor substrate and comprises a material of high carrier mobility such as silicon germanium (SiGe), germanium (Ge) and silicon carbide (SiC) using a selective epitaxial growth process. A gate insulation layer and a gate electrode are formed on the channel layer. Accordingly, a driving current of the semiconductor device increases to thereby improve operation characteristics.

Owner:SAMSUNG ELECTRONICS CO LTD

FinFET SRAM cell using low mobility plane for cell stability and method for forming

InactiveUS7087477B2Accurate operationSolid-state devicesSemiconductor/solid-state device manufacturingStatic random-access memoryLow mobility

The present invention provides a device design and method for forming the same that results in Fin Field Effect Transistors having different gains without negatively impacting device density. The present invention forms relatively low gain FinFET transistors in a low carrier mobility plane and relatively high gain FinFET transistors in a high carrier mobility plane. Thus formed, the FinFETs formed in the high mobility plane have a relatively higher gain than the FinFETs formed in the low mobility plane. The embodiments are of particular application to the design and fabrication of a Static Random Access Memory (SRAM) cell. In this application, the bodies of the n-type FinFETs used as transfer devices are formed along the {110} plane. The bodies of the n-type FinFETs and p-type FinFETs used as the storage latch are formed along the {100}. Thus formed, the transfer devices will have a gain approximately half that of the n-type storage latch devices, facilitating proper SRAM operation.

Owner:GLOBALFOUNDRIES INC

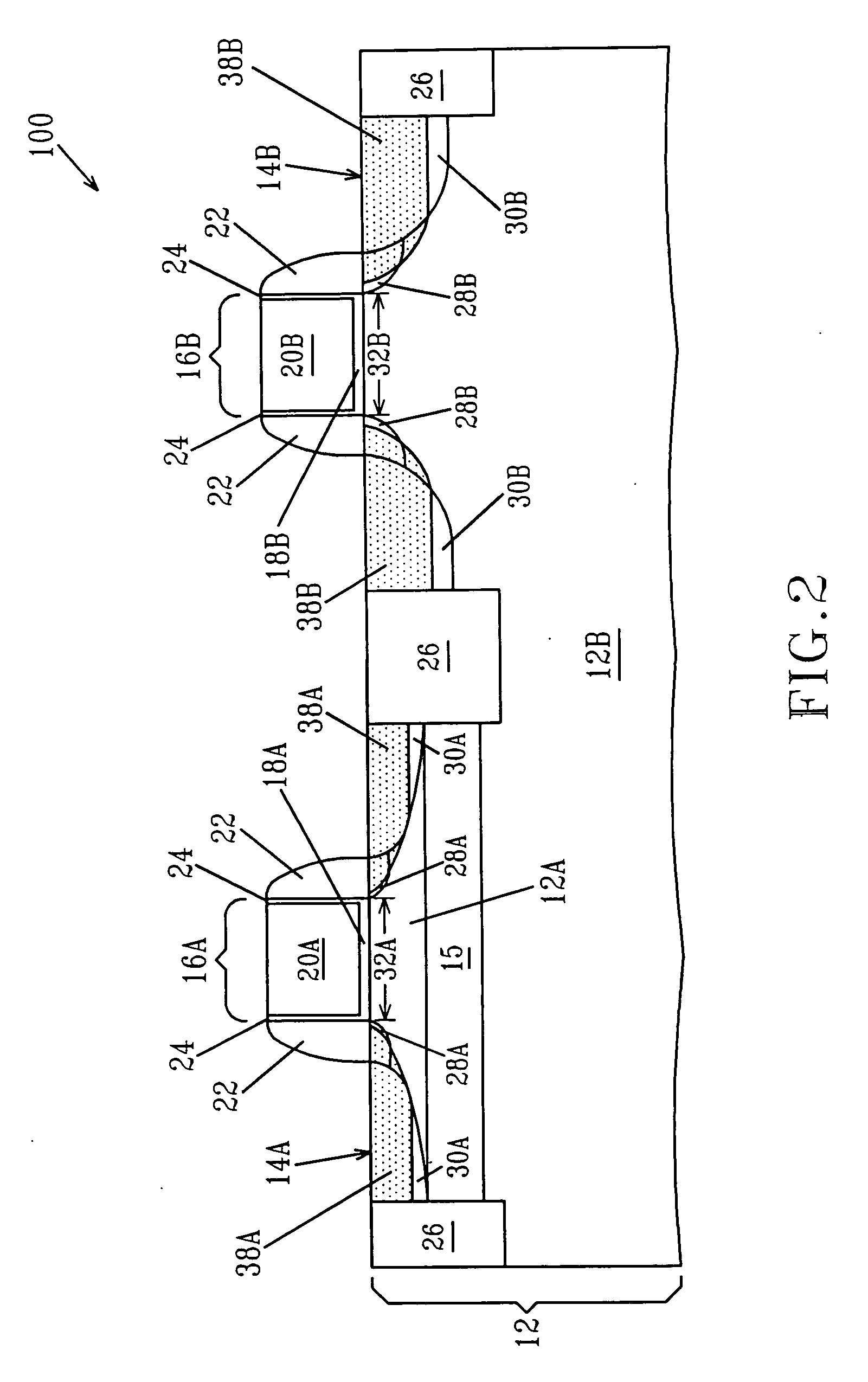

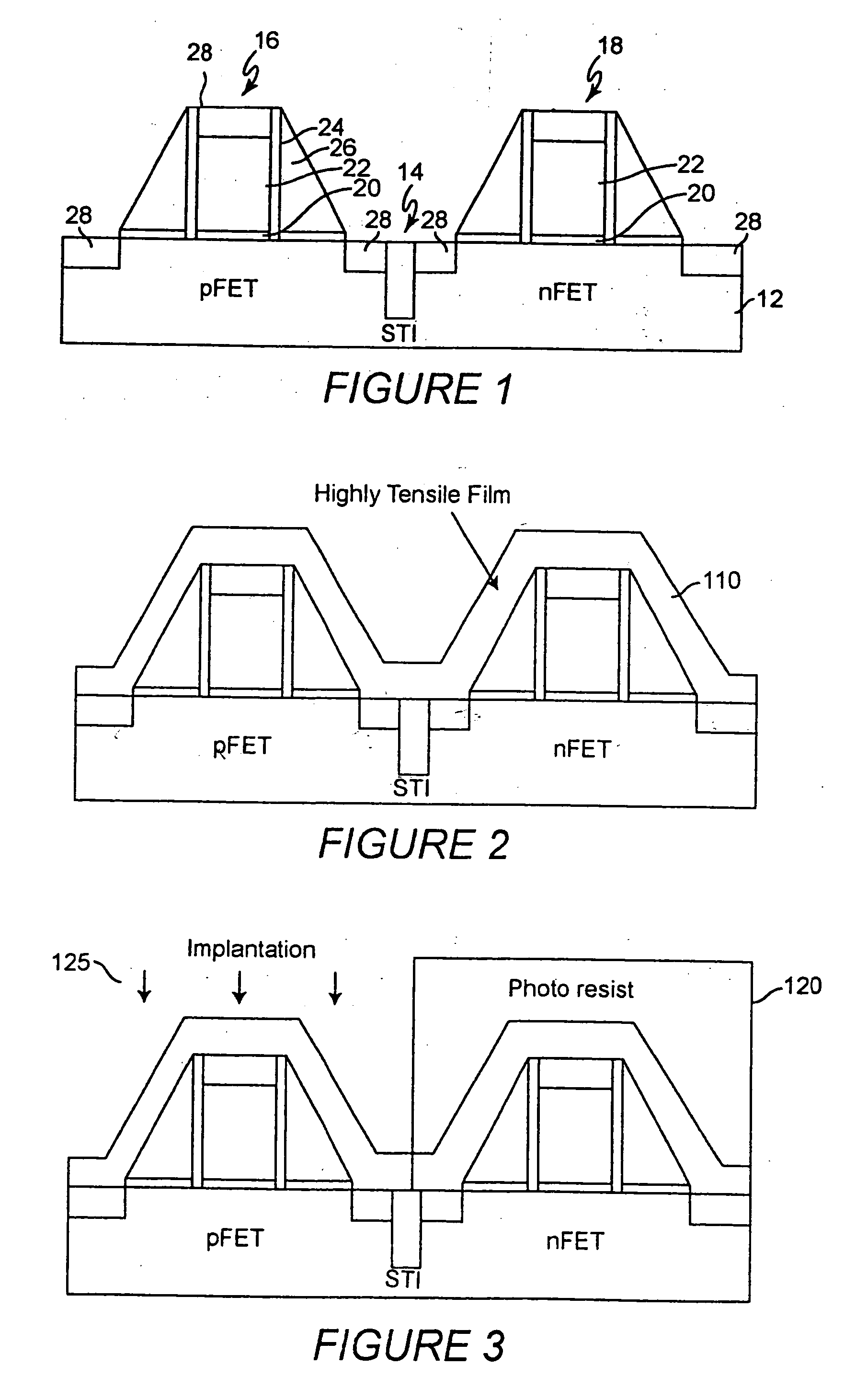

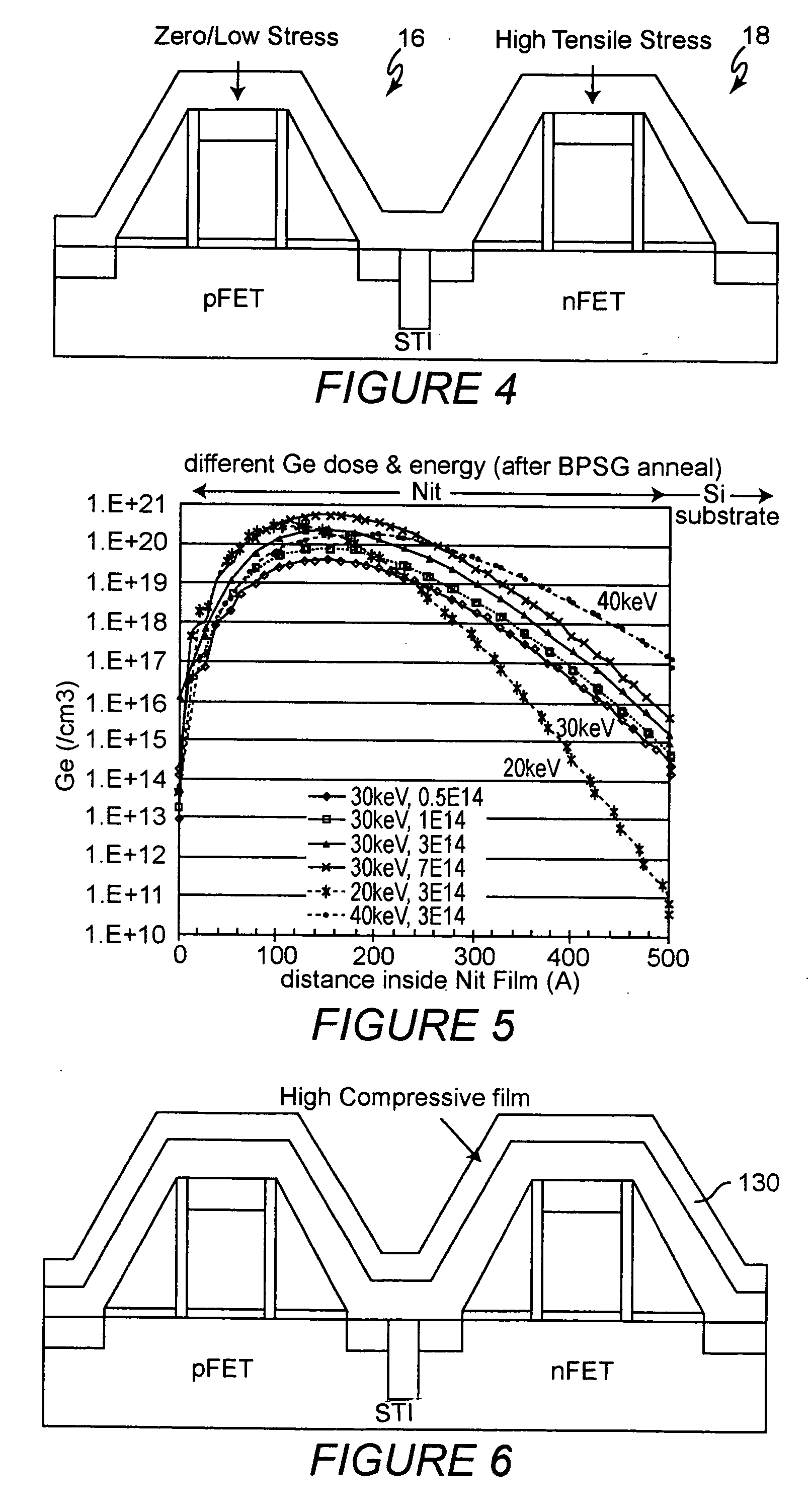

Increasing carrier mobility in NFET and PFET transistors on a common wafer

ActiveUS20050093078A1Easily and repeatably formedImprove production yieldTransistorSemiconductor/solid-state device manufacturingIndiumCharge carrier mobility

Enhanced carrier mobility in transistors of differing (e.g. complementary) conductivity types is achieved on a common chip by provision of two or more respective stressed layers, such as etch stop layers, overlying the transistors with stress being wholly or partially relieved in portions of the respective layers, preferably by implantations with heavy ions such as germanium, arsenic, xenon, indium, antimony, silicon, nitrogen oxygen or carbon in accordance with a block-out mask. The distribution and small size of individual areas of such stressed structures also prevents warping or curling of even very thin substrates.

Owner:IBM CORP

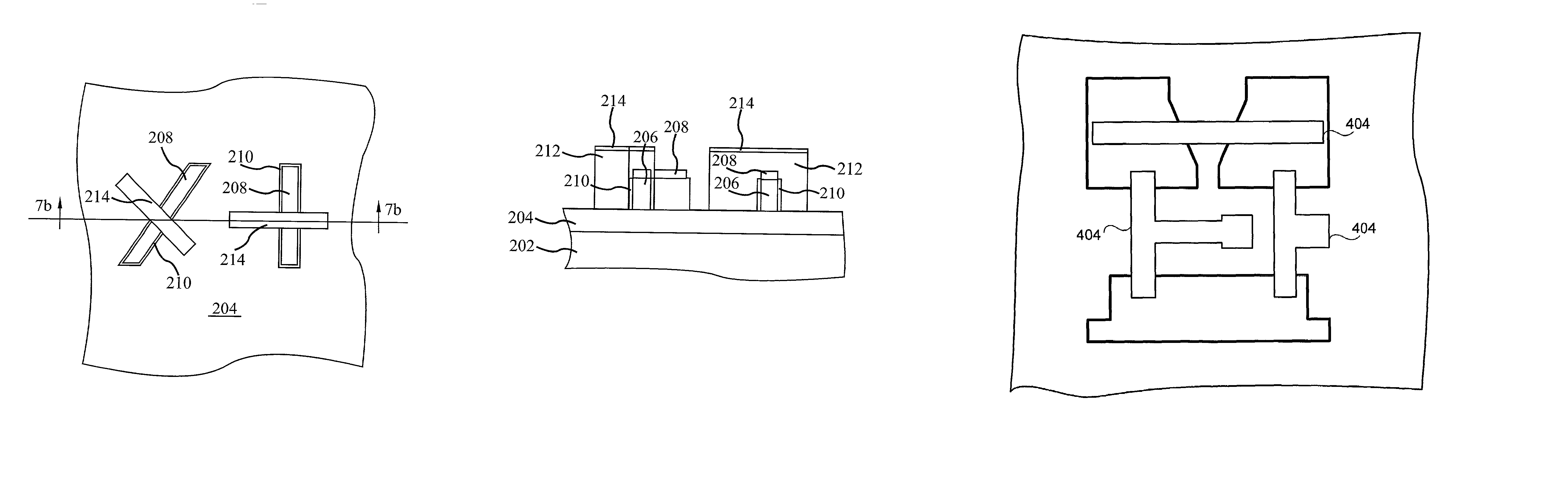

FinFET with sublithographic fin width

ActiveUS7625790B2Solid-state devicesSemiconductor/solid-state device manufacturingSemiconductor materialsCharge carrier mobility

At least one recessed region having two parallel edges is formed in an insulator layer over a semiconductor layer such that the lengthwise direction of the recessed region coincides with optimal carrier mobility surfaces of the semiconductor material in the semiconductor layer for finFETs to be formed. Self-assembling block copolymers are applied within the at least one recessed region and annealed to form a set of parallel polymer block lines having a sublithographic width and containing a first polymeric block component. The pattern of sublithographic width lines is transferred into the semiconductor layer employing the set of parallel polymer block lines as an etch mask. Sublithographic width semiconductor fins thus formed may have sidewalls for optimal carrier mobility for p-type finFETs and n-type finFETs.

Owner:INT BUSINESS MASCH CORP

Structure and method to improve channel mobility by gate electrode stress modification

InactiveUS20050245017A1Easily and repeatably formedImprove production yieldTransistorSolid-state devicesCMOSCharge carrier mobility

Owner:GLOBALFOUNDRIES INC

Thin film transistor, display device, and electronic device

ActiveUS8384080B2Maintain good propertiesLarge carrier mobilityTransistorSemiconductor/solid-state device manufacturingValence bandMaximum level

A thin film transistor, which is capable of improving carrier mobility, and a display device and an electronic device, each of which uses the thin film transistor, are provided. The thin film transistor includes: a gate electrode; an oxide semiconductor layer including a multilayer film including a carrier travel layer configuring a channel and a carrier supply layer for supplying carriers to the carrier travel layer; a gate insulating film provided between the gate electrode and the oxide semiconductor layer; and a pair of electrodes as a source and a drain. A conduction band minimum level or a valence band maximum level corresponding to a carrier supply source of the carrier supply layer is higher in energy than a conduction band minimum level or a valence band maximum level corresponding to a carrier supply destination of the carrier travel layer.

Owner:JOLED INC

Anneal of epitaxial layer in a semiconductor device

InactiveUS7416605B2From gel statePolycrystalline material growthCharge carrier mobilityDegree Celsius

An anneal of an epitaxially grown crystalline semiconductor layer comprising a combination of group-IV elements. The layer contains at least one of the group of carbon and tin. The layer of epitaxially grown material is annealed at a temperature substantially in a range of 1,000 to 1,400 degrees Celsius for a period not to exceed 100 milliseconds within 10% of the peak temperature. The anneal is performed for example with a laser anneal or a flash lamp anneal. The limited-time anneal may improve carrier mobility of a transistor.

Owner:NORTH STAR INNOVATIONS

Semiconductor device based on Si-Ge with high stress liner for enhanced channel carrier mobility

ActiveUS20050247926A1Increase drive currentIncrease currentSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialCharge carrier mobility

The carrier mobility in transistor channel regions of Si—Ge devices is increased by employing a stressed liner. Embodiments include applying a high compressive or tensile stressed film overlying relaxed source / drain regions. Other embodiments include applying a high compressively or high tensilely stressed film, after post silicide spacer removal, over gate electrodes and strained Si source / drain regions of P-channel or N-channel transistors, respectively.

Owner:ADVANCED MICRO DEVICES INC

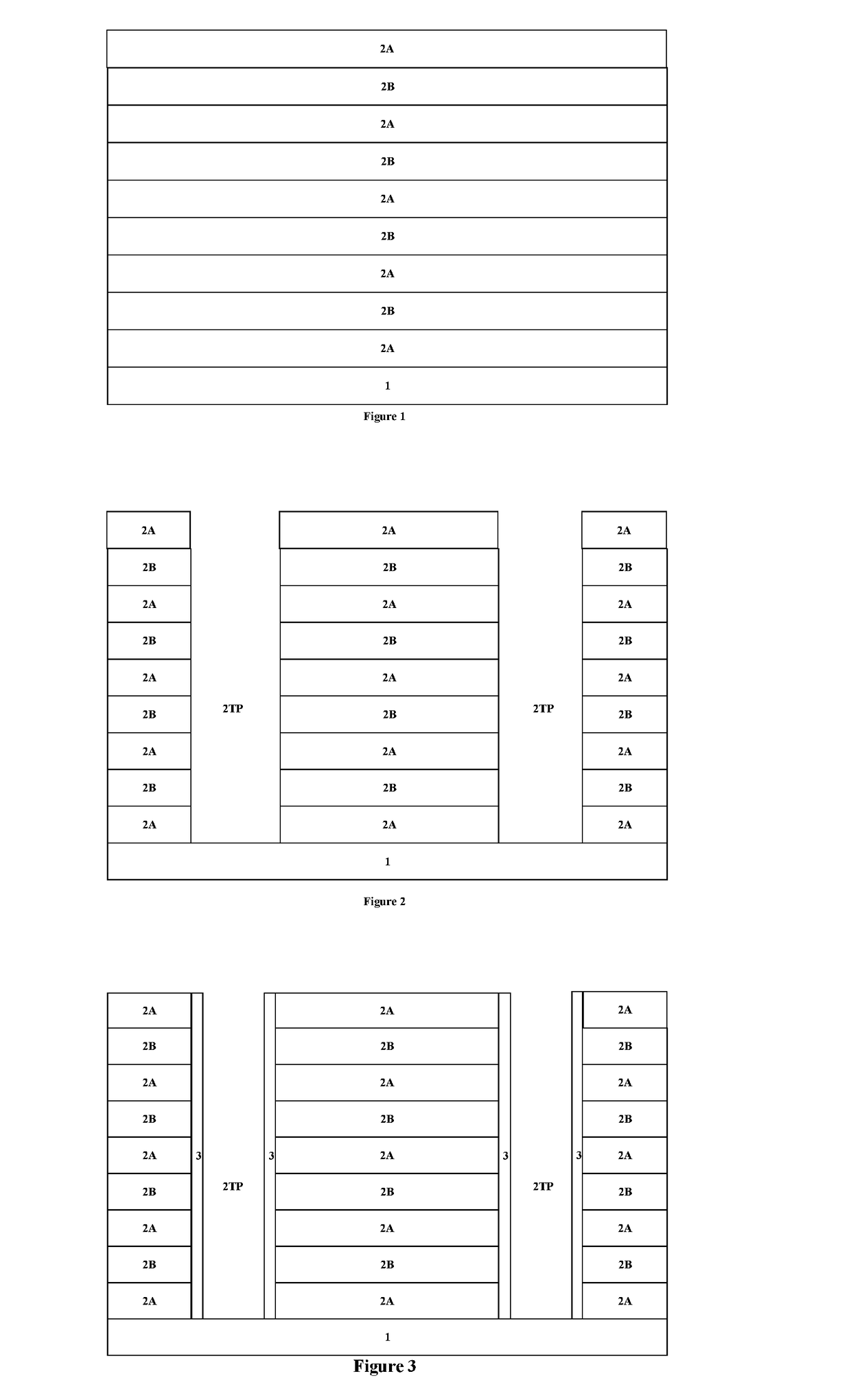

Method of manufacturing three-dimensional semiconductor device

ActiveUS20170250193A1Reduce channel surface roughnessEnhance channel carrier mobilitySolid-state devicesSemiconductor/solid-state device manufacturingCharge carrier mobilitySurface roughness

A method of manufacturing three-dimensional semiconductor device, comprising the steps of: forming a stack structure of a plurality of a first material layers and a second material layers on a substrate in the memory cell region; etching said stack structure to form a plurality of trenches; forming channel layers in said plurality of trenches; performing annealing treatment to at least one surface of the channel layers to reduce the surface roughness and the interface state. In accordance with the three-dimensional semiconductor device manufacturing method of the present invention, the formation of interface states is depressed by introducing a dummy channel sacrificial layer for the interface treatment on the channel surface and back surface, and / or the channel surface roughness is reduced by introducing a buffer layer on the channel surface and back surface during the treatment, which can improve the channel carrier mobility, improve the channel current as well as the reliability of the memory cell.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

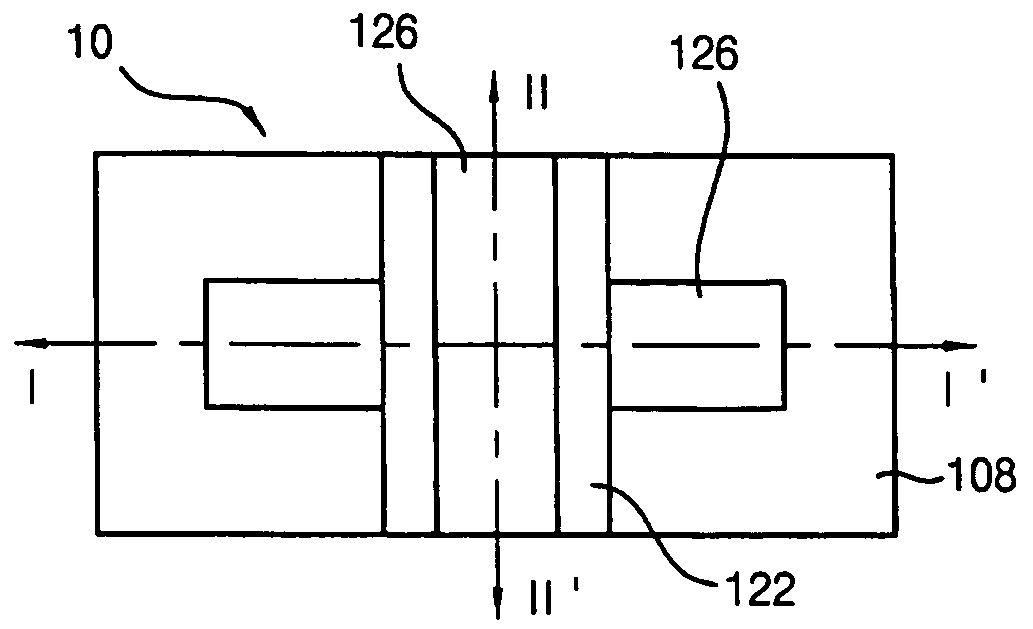

Finfet SRAM cell using low mobility plane for cell stability and method for forming

InactiveUS6967351B2Accurate operationSolid-state devicesSemiconductor/solid-state device manufacturingStatic random-access memoryLow mobility

The present invention provides a device design and method for forming the same that results in Fin Field Effect Transistors having different gains without negatively impacting device density. The present invention forms relatively low gain FinFET transistors in a low carrier mobility plane and relatively high gain FinFET transistors in a high carrier mobility plane. Thus formed, the FinFETs formed in the high mobility plane have a relatively higher gain than the FinFETs formed in the low mobility plane. The embodiments are of particular application to the design and fabrication of a Static Random Access Memory (SRAM) cell. In this application, the bodies of the n-type FinFETs used as transfer devices are formed along the {110} plane. The bodies of the n-type FinFETs and p-type FinFETs used as the storage latch are formed along the {100}. Thus formed, the transfer devices will have a gain approximately half that of the n-type storage latch devices, facilitating proper SRAM operation.

Owner:GLOBALFOUNDRIES U S INC

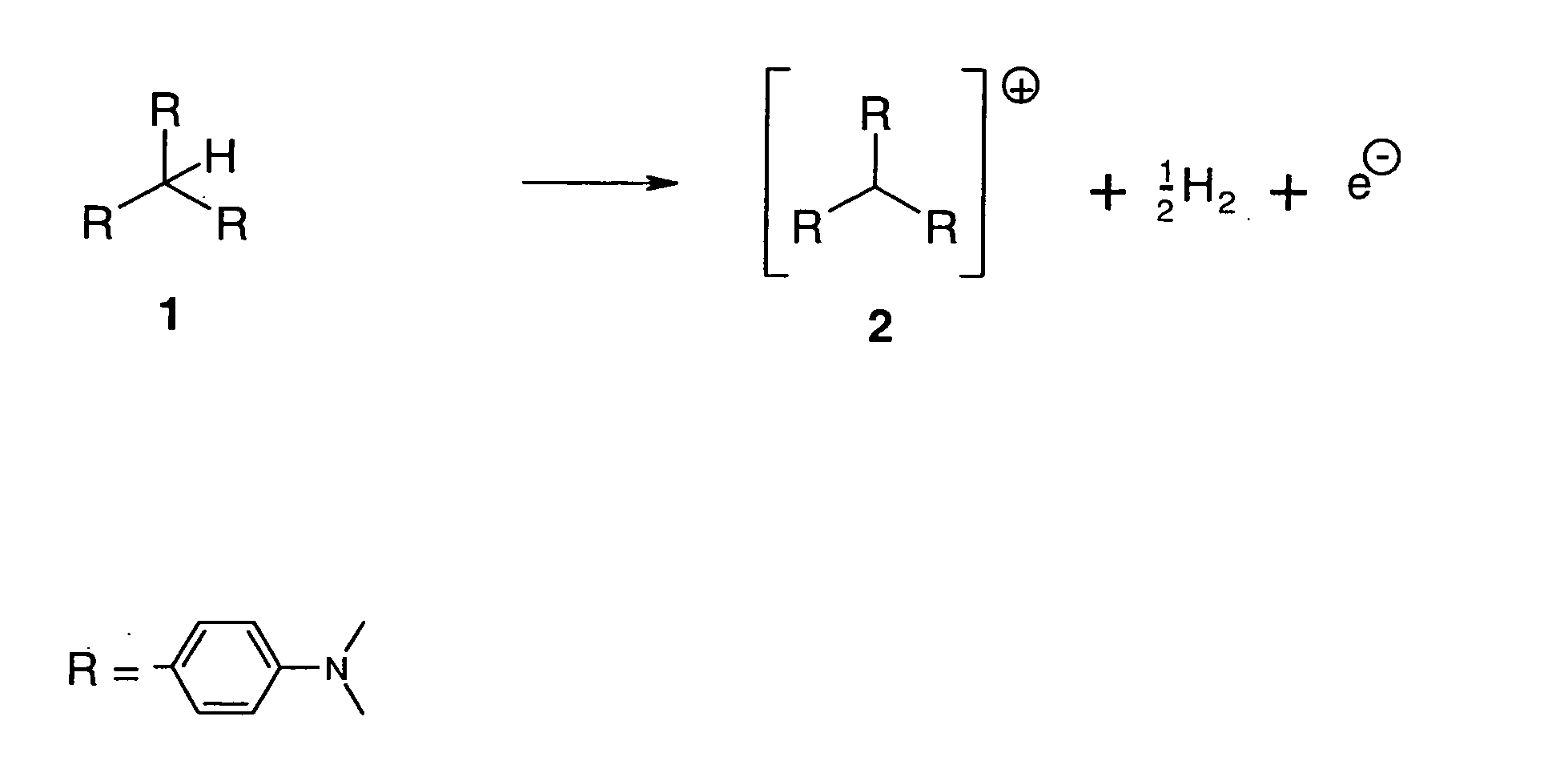

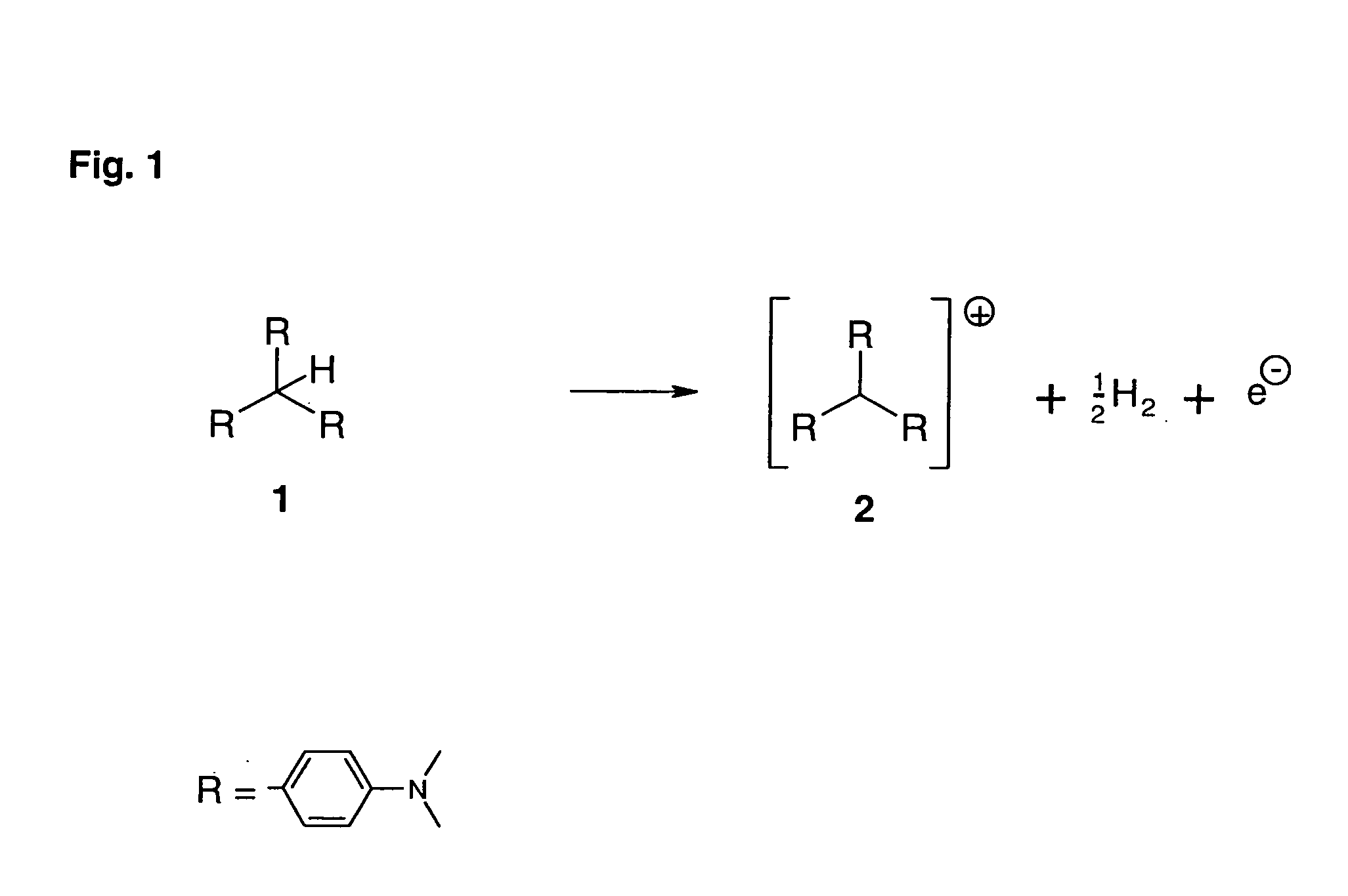

Doped organic semiconductor materials and process for their preparation

ActiveUS20050061232A1Simple materialHigh light efficiencyOrganic chemistryFinal product manufactureSemiconductor materialsCharge carrier mobility

The present invention relates to a process for the preparation of doped organic semiconductor materials having an increased charge carrier density and effective charge carrier mobility, by doping with a dopant, a process in which after mixing the dopant into the organic semiconductor material, hydrogen, carbon monoxide, nitrogen or hydroxyl radicals are split off and at least one electron is transferred to the semiconductor material or from the semiconductor material. The process is distinguished by the fact that an uncharged organic compound is used as dopant. Doped organic semiconductor materials are obtainable by one of the processes. The semiconductor materials are distinguished by the fact that the doped layer contains cations of at least one organic compound, the uncharged form of the organic compound being unstable in air.

Owner:NOVALED GMBH

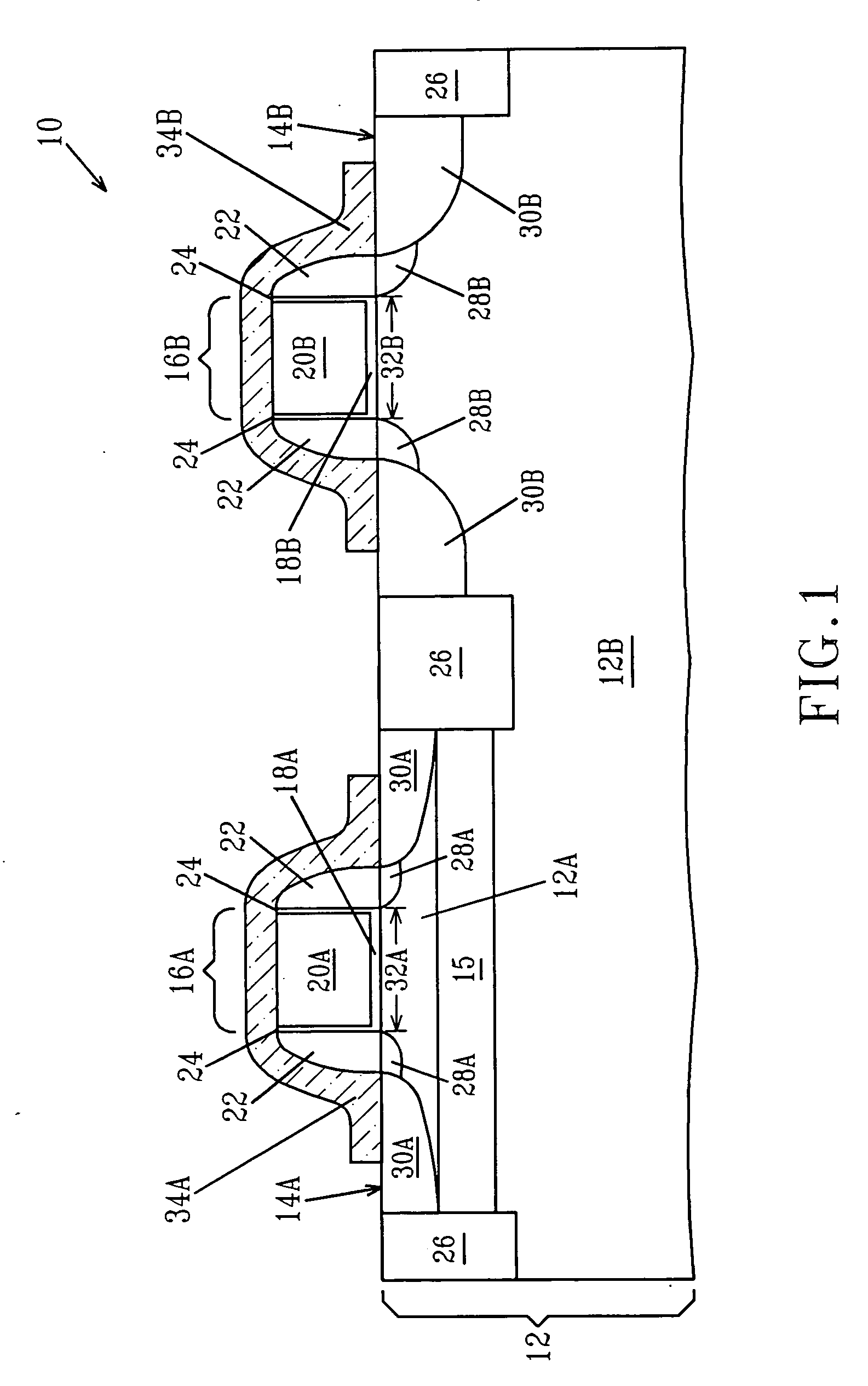

Increasing carrier mobility in NFET and PFET transistors on a common wafer

InactiveUS6939814B2Easily and repeatably formedImprove production yieldTransistorSolid-state devicesIndiumCharge carrier mobility

Enhanced carrier mobility in transistors of differing (e.g. complementary) conductivity types is achieved on a common chip by provision of two or more respective stressed layers, such as etch stop layers, overlying the transistors with stress being wholly or partially relieved in portions of the respective layers, preferably by implantations with heavy ions such as germanium, arsenic, xenon, indium, antimony, silicon, nitrogen oxygen or carbon in accordance with a block-out mask. The distribution and small size of individual areas of such stressed structures also prevents warping or curling of even very thin substrates.

Owner:IBM CORP

Structures and methods for forming a locally strained transistor

InactiveUS20060234455A1TransistorSemiconductor/solid-state device manufacturingDevice materialCharge carrier mobility

Embodiments of the invention provide structures and methods for forming a strained MOS transistor. A preferred embodiment includes creating a compressive strain in a PMOS transistor for improving carrier mobility without the need for source / drain recess formation and SiGe epitaxy. Embodiments comprise forming a gate electrode on a silicon substrate, and forming a lightly doped source / drain (LDS / LDD) region in the substrate by simultaneously implanting germanium and boron in the substrate using the gate electrode as a mask. Embodiments further comprise forming spacers on opposite sidewalls of the gate electrode and forming a heavily doped source / drain region in the substrate by simultaneously implanting germanium and boron using the gate electrode and the spacers as a mask. Embodiments may further include annealing the semiconductor device to recrystallize SiGe.

Owner:TAIWAN SEMICON MFG CO LTD

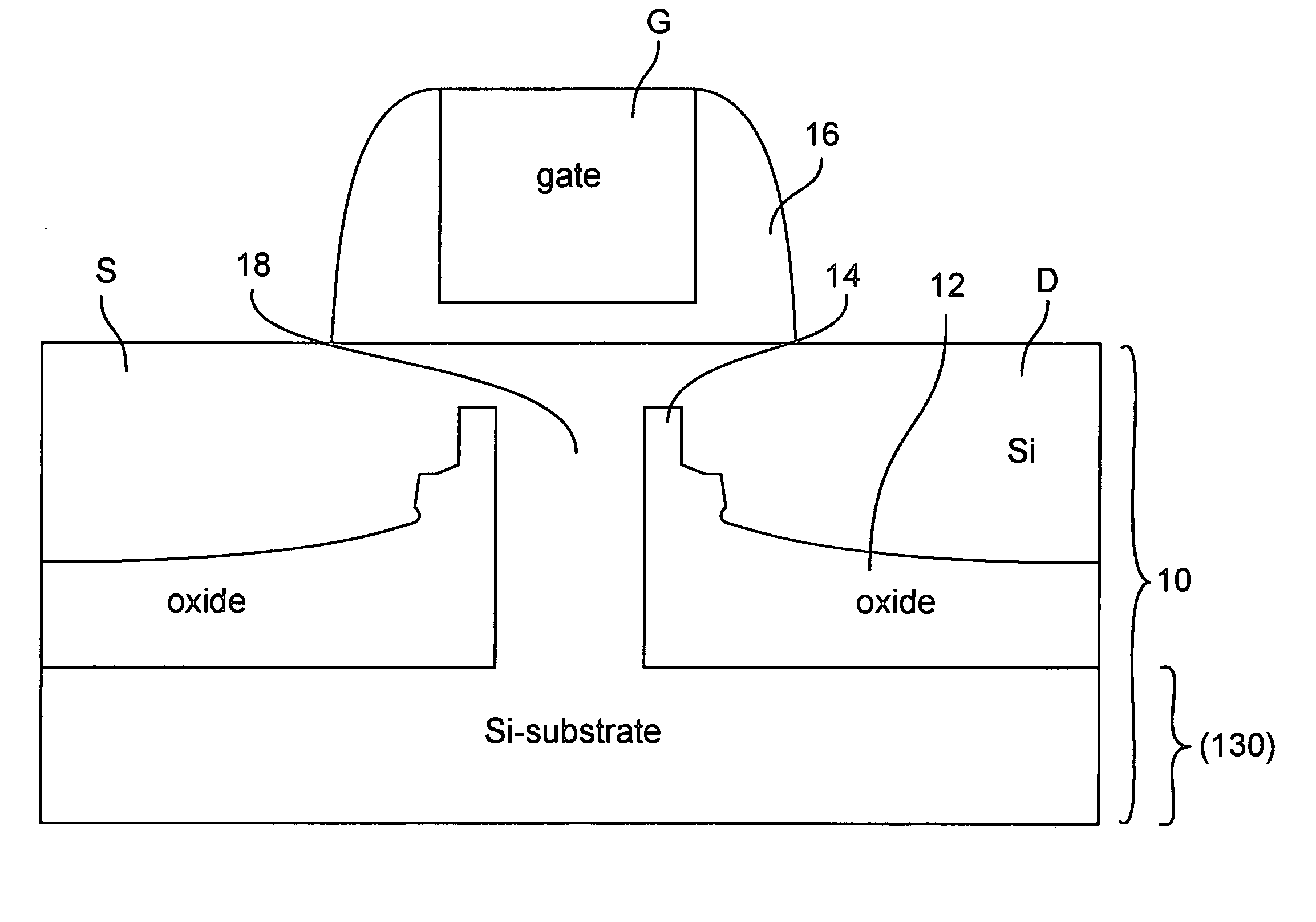

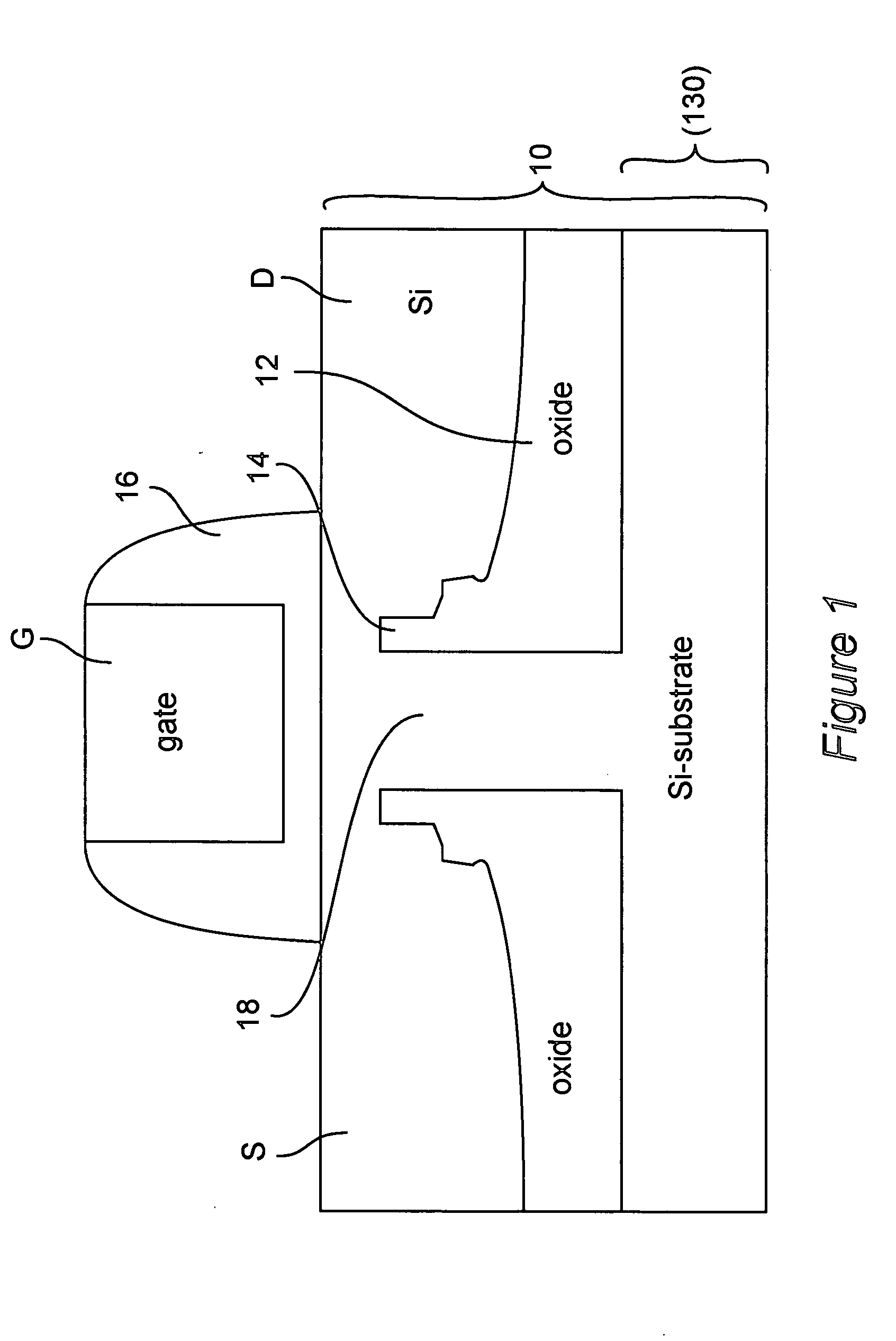

Hybrid SOI/bulk semiconductor transistors

ActiveUS20050189589A1Increase resistanceDesirable propertyTransistorSolid-state devicesCapacitanceElectrical resistance and conductance

Channel depth in a field effect transistor is limited by an intra-layer structure including a discontinuous film or layer formed within a layer or substrate of semiconductor material. Channel depth can thus be controlled much in the manner of SOI or UT-SOI technology but with less expensive substrates and greater flexibility of channel depth control while avoiding floating body effects characteristic of SOI technology. The profile or cross-sectional shape of the discontinuous film may be controlled to an ogee or staircase shape to improve short channel effects and reduce source / drain and extension resistance without increase of capacitance. Materials for the discontinuous film may also be chosen to impose stress on the transistor channel from within the substrate or layer and provide increased levels of such stress to increase carrier mobility. Carrier mobility may be increased in combination with other meritorious effects.

Owner:GLOBALFOUNDRIES US INC

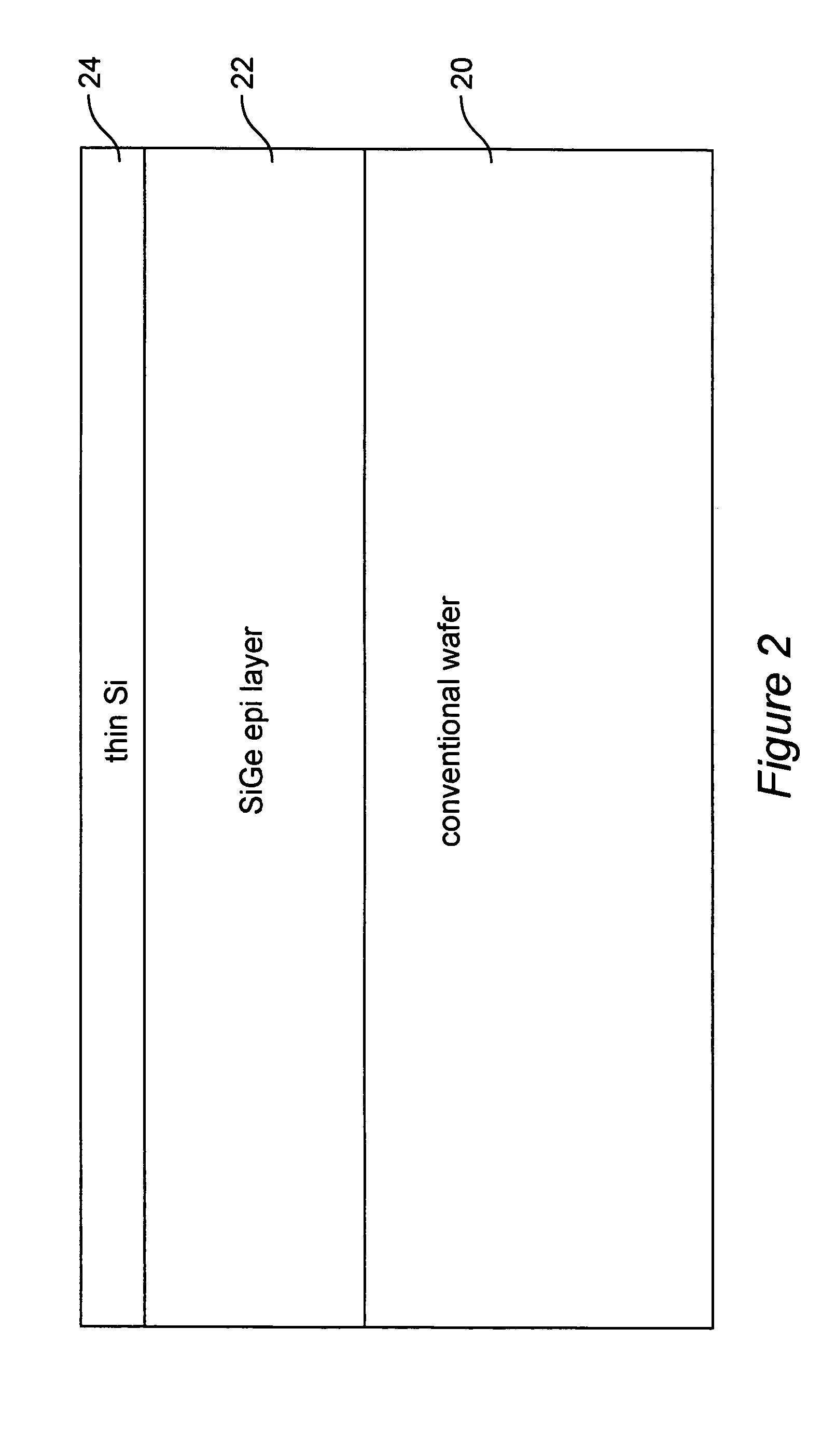

Method for fabricating strained silicon-on-insulator structures and strained silicon-on insulator structures formed thereby

ActiveUS20050227498A1Improve device performanceHigh carrier mobilityTransistorSolid-state devicesDevice formCharge carrier mobility

A silicon-on-insulator (SOI) device and structure having locally strained regions in the silicon active layer formed by increasing the thickness of underlying regions of a buried insulating layer separating the silicon active layer from the substrate. The stress transferred from the underlying thickened regions of the insulating layer to the overlying strained regions increases carrier mobility in these confined regions of the active layer. Devices formed in and on the silicon active layer may benefit from the increased carrier mobility in the spaced-apart strained regions.

Owner:GLOBALFOUNDRIES US INC

Graphene-based transistor

ActiveUS7732859B2Semiconductor/solid-state device manufacturingSemiconductor devicesDopantGate dielectric

A graphene layer is formed on a surface of a silicon carbide substrate. A dummy gate structure is formed over the fin, in the trench, or on a portion of the planar graphene layer to implant dopants into source and drain regions. The dummy gate structure is thereafter removed to provide an opening over the channel of the transistor. Threshold voltage adjustment implantation may be performed to form a threshold voltage implant region directly beneath the channel, which comprises the graphene layer. A gate dielectric is deposited over a channel portion of the graphene layer. After an optional spacer formation, a gate conductor is formed by deposition and planarization. The resulting graphene-based field effect transistor has a high carrier mobility due to the graphene layer in the channel, low contact resistance to the source and drain region, and optimized threshold voltage and leakage due to the threshold voltage implant region.

Owner:GLOBALFOUNDRIES U S INC

Method for selectively stressing MOSFETs to improve charge carrier mobility

InactiveUS7052946B2Improve methodImprove mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETCharge carrier mobility

A strained channel MOSFET device with improved charge mobility and method for forming the same, the method including providing a first gate with a first semiconductor conductive type and second gate with a semiconductor conductive type on a substrate; forming a first strained layer with a first type of stress on said first gate; and, forming a second strained layer with a second type of stress on said second gate.

Owner:TAIWAN SEMICON MFG CO LTD