Patents

Literature

20562 results about "Single chip" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The RISC Single Chip, or RSC, is a single-chip microprocessor developed and fabricated by International Business Machines (IBM). The RSC was a feature-reduced single-chip implementation of the POWER1, a multi-chip central processing unit (CPU) which implemented the POWER instruction set architecture (ISA).

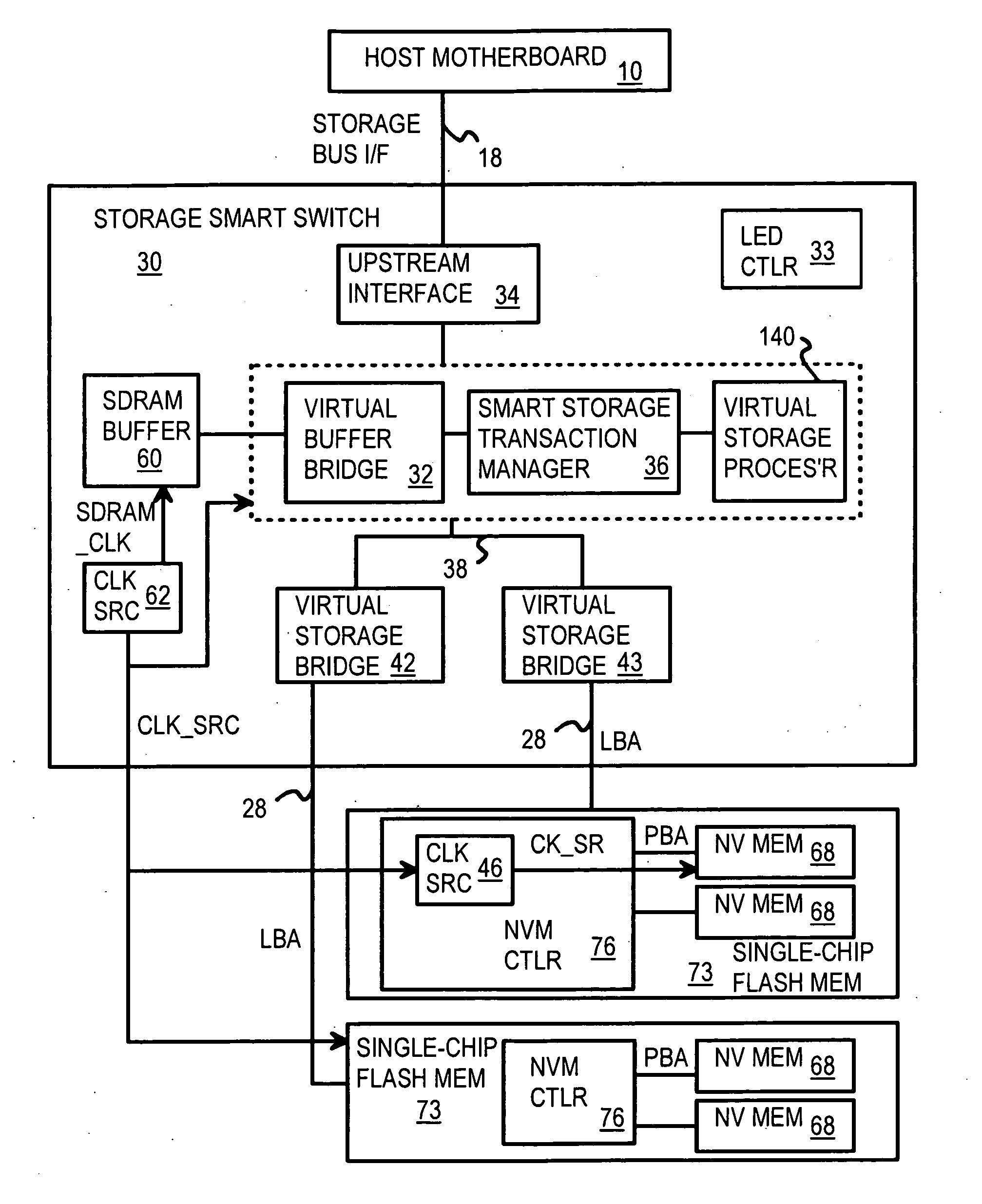

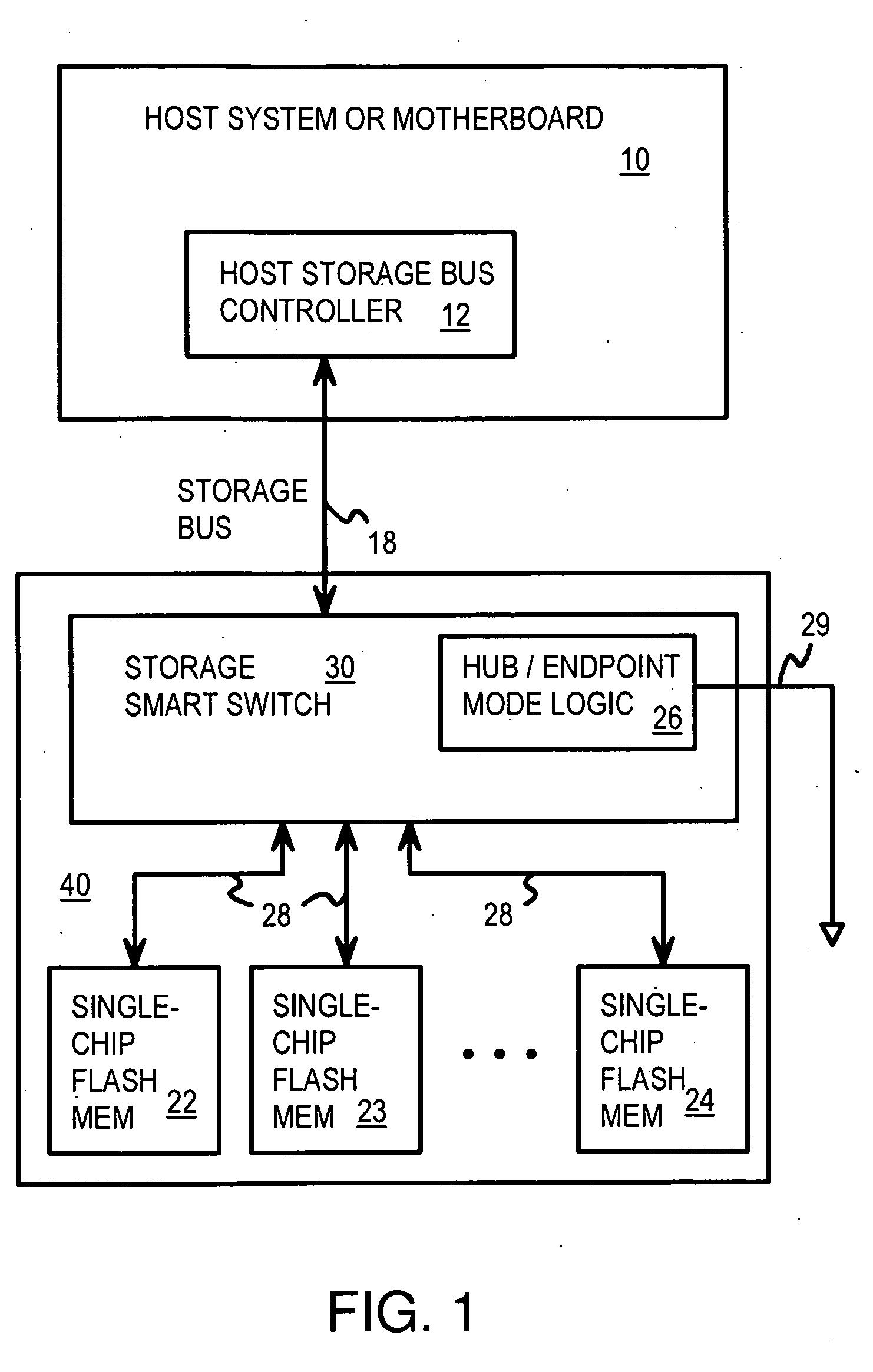

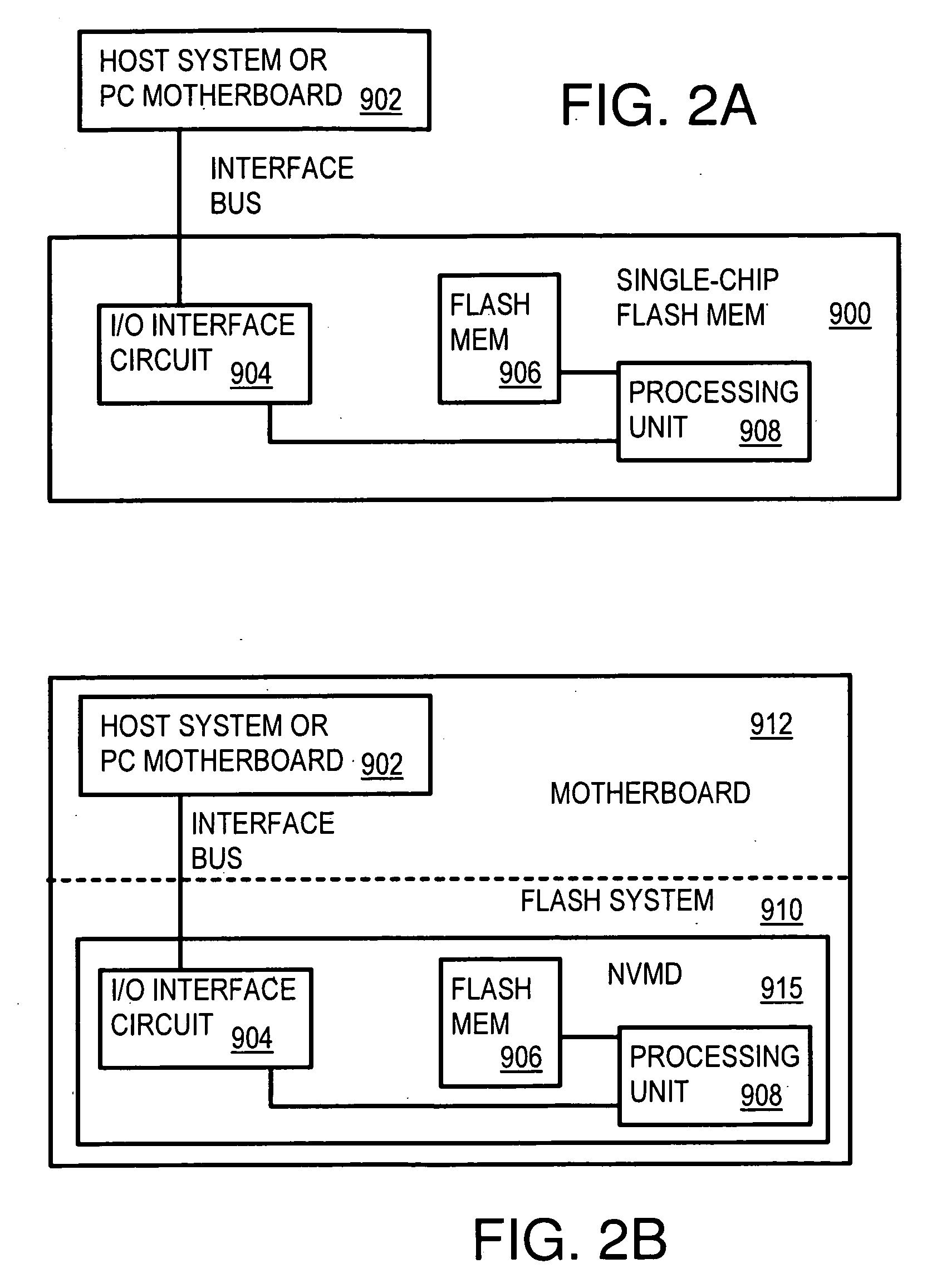

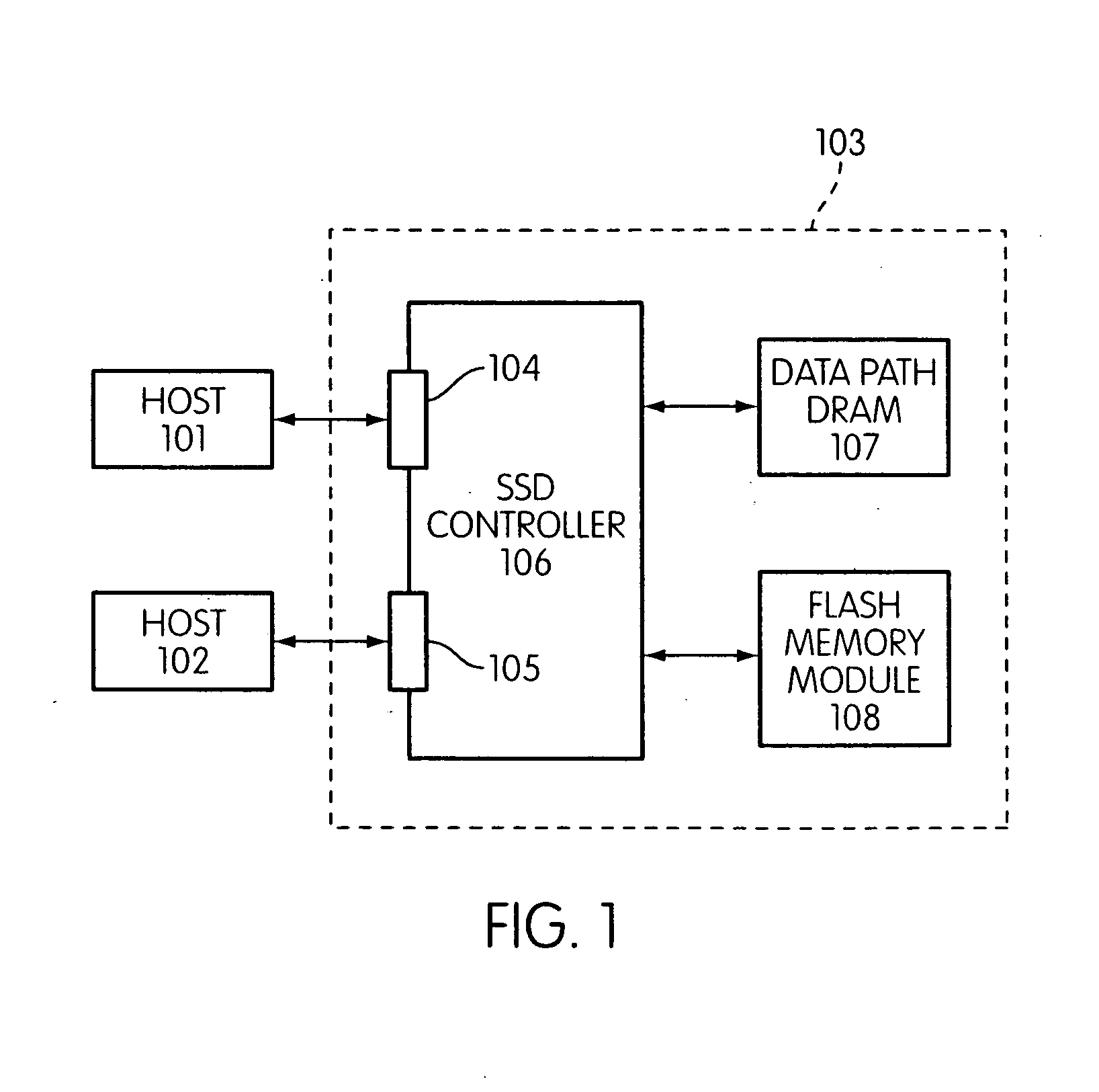

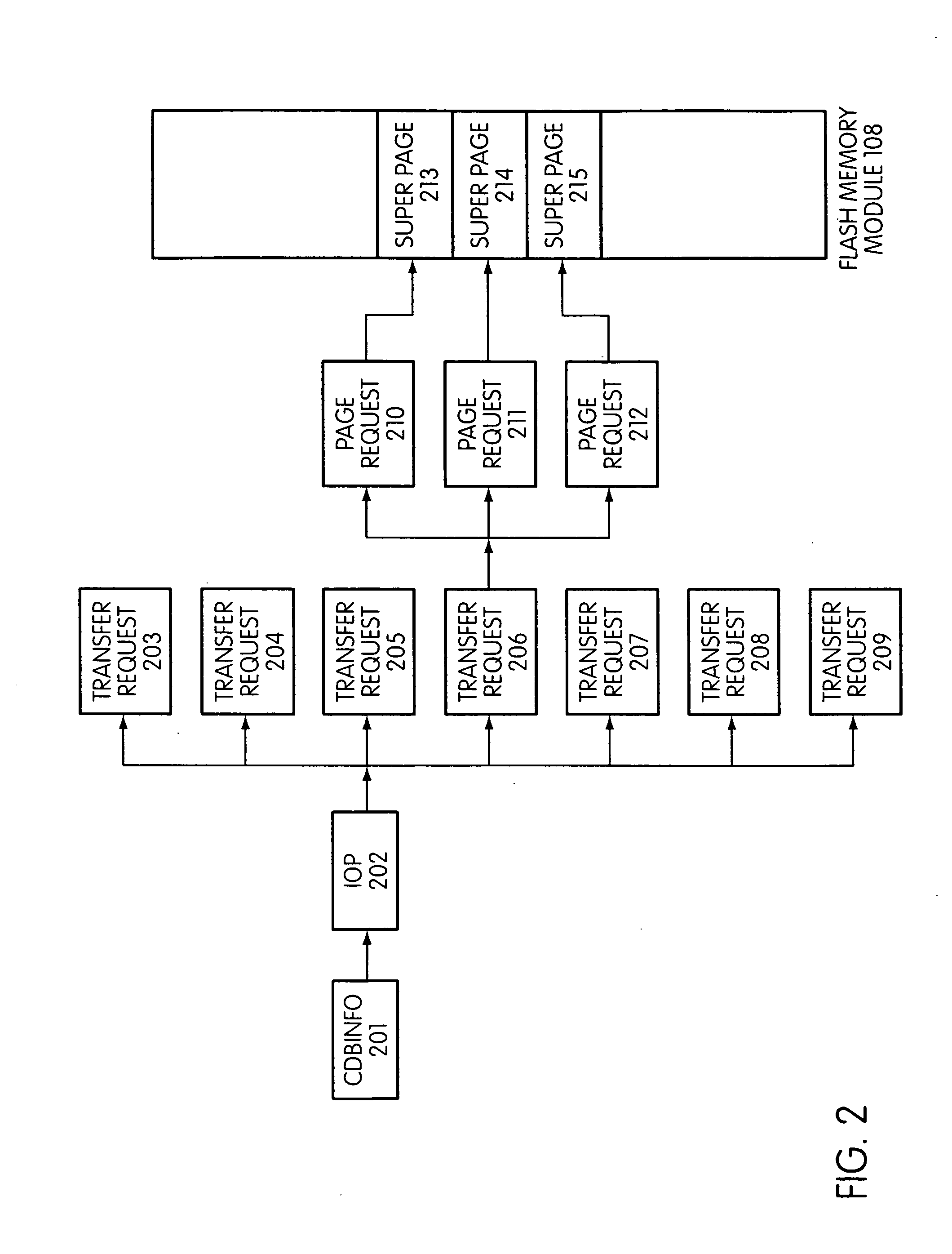

Multi-Level Controller with Smart Storage Transfer Manager for Interleaving Multiple Single-Chip Flash Memory Devices

InactiveUS20080320214A1Memory architecture accessing/allocationMemory adressing/allocation/relocationLogical block addressingSolid-state drive

A solid-state disk (SSD) has a smart storage switch with a smart storage transaction manager that re-orders host commands for accessing downstream single-chip flash-memory devices. Each single-chip flash-memory device has a lower-level controller that converts logical block addresses (LBA) to physical block addresses (PBA) that access flash memory blocks in the single-chip flash-memory device. Wear-leveling and bad block remapping are preformed by each single-chip flash-memory device, and at a higher level by a virtual storage processor in the smart storage switch. Virtual storage bridges between the smart storage transaction manager and the single-chip flash-memory devices bridge LBA transactions over LBA buses to the single-chip flash-memory devices. Data striping and interleaving among multiple channels of the single-chip flash-memory device is controlled at a high level by the smart storage transaction manager, while further interleaving and remapping may be performed within each single-chip flash-memory device.

Owner:SUPER TALENT TECH CORP

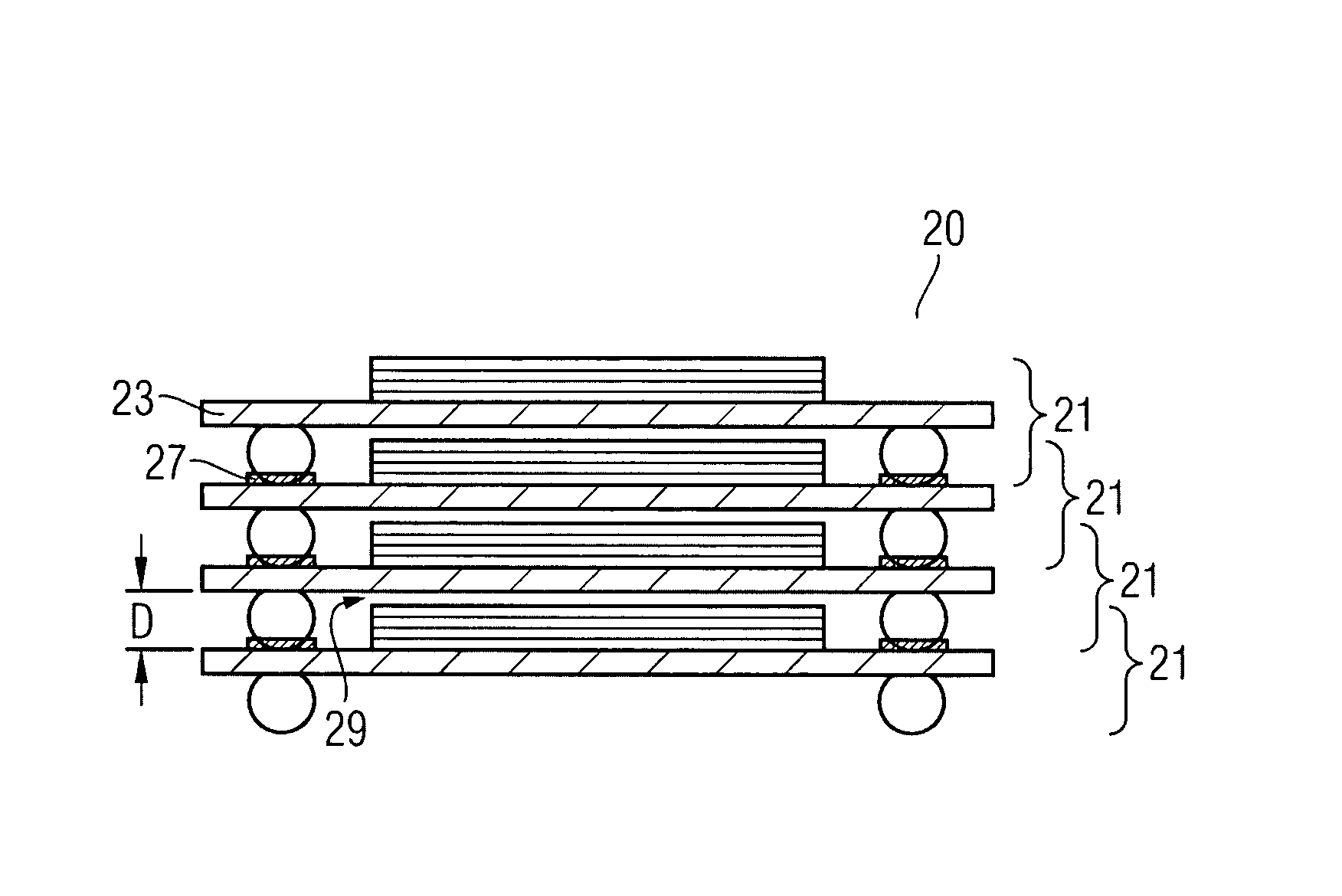

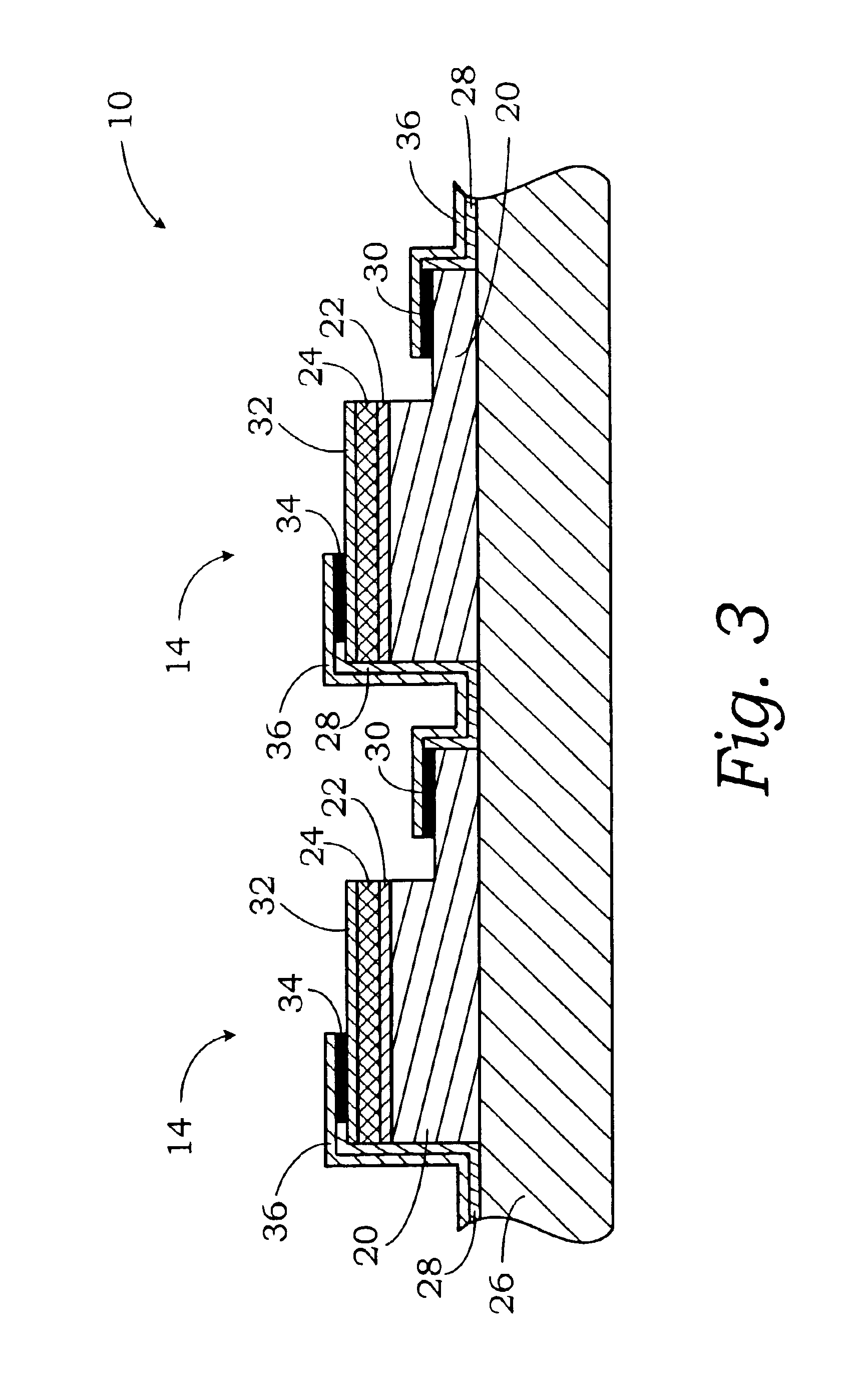

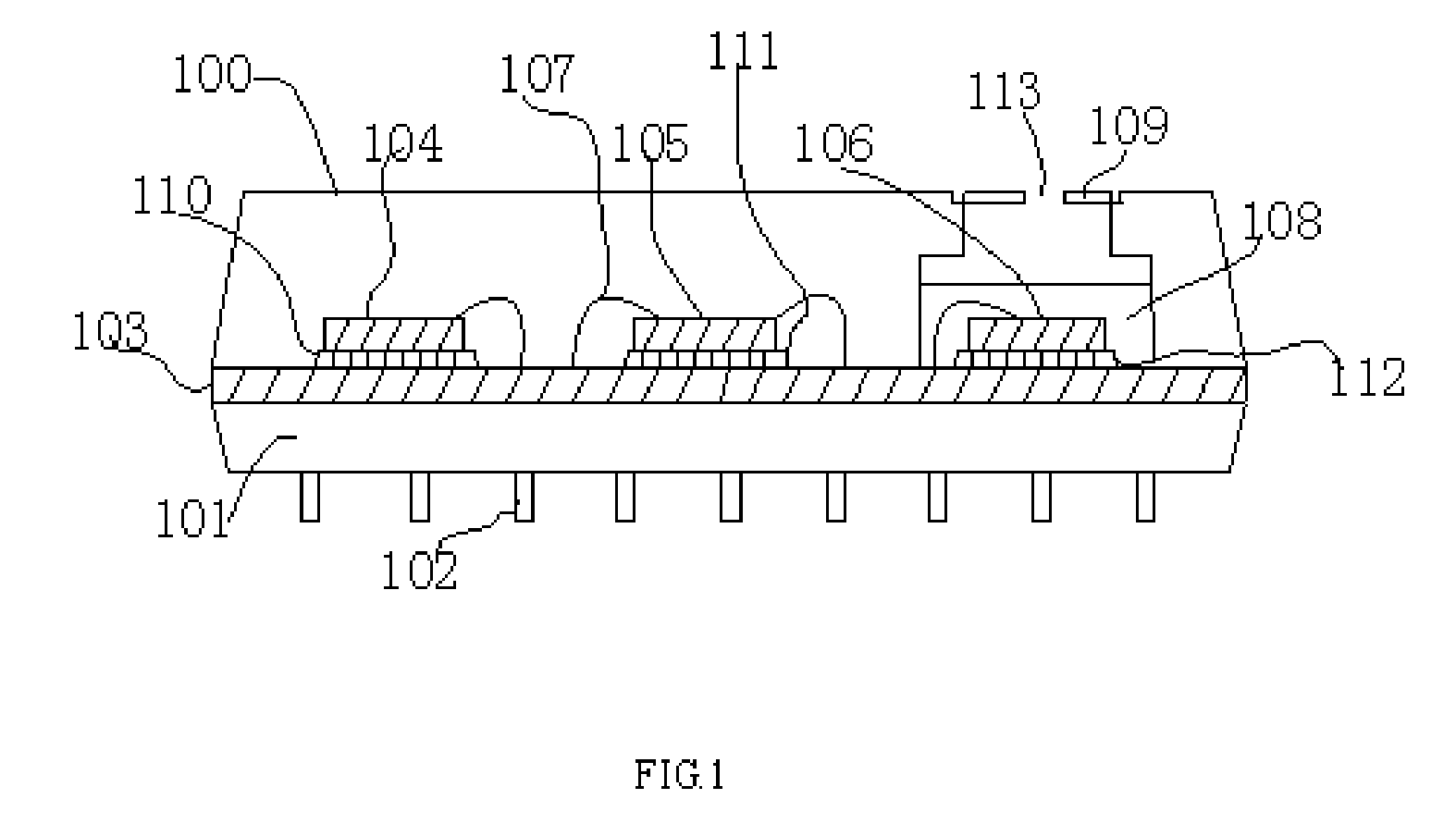

Multi-chip device and method for producing a multi-chip device

InactiveUS7297574B2Increase productionIncrease memory capacitySemiconductor/solid-state device detailsSolid-state devicesEngineeringContact element

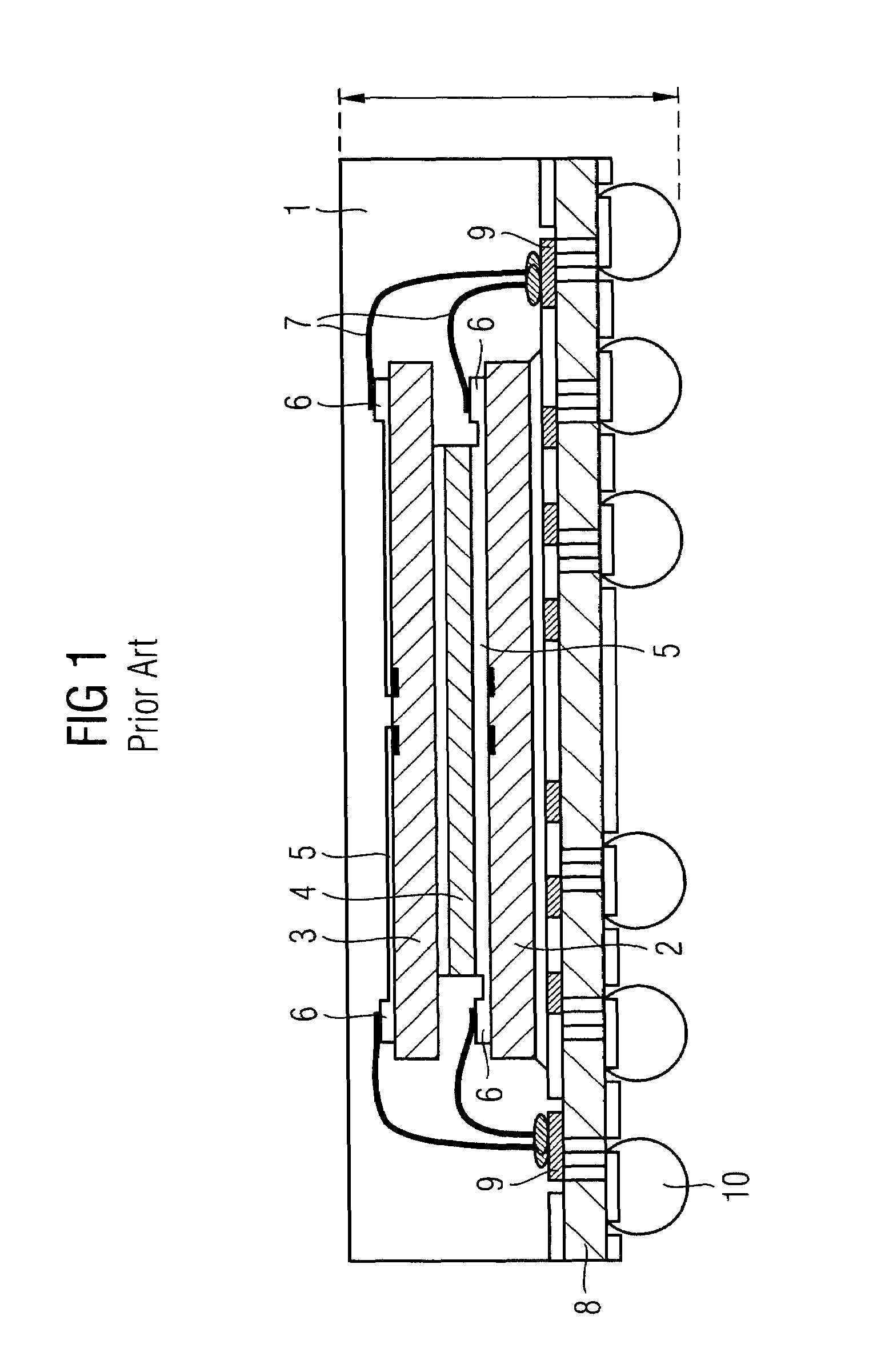

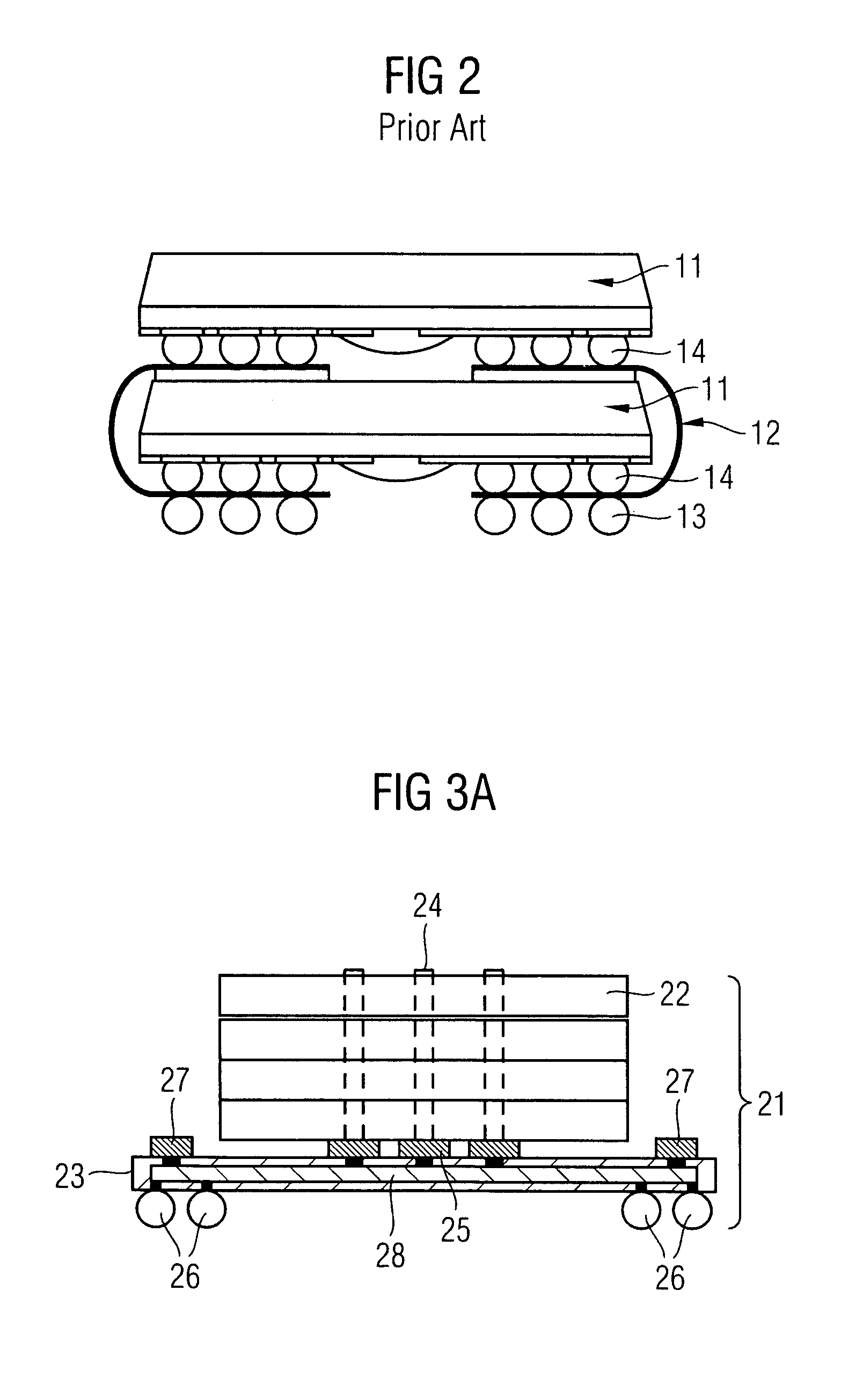

The present invention relates to a multi-chip device comprising a plurality of chip stacks each including a plurality of single chips stacked on each other, wherein the stacked single chips are electrically interconnected by one or more through-chip-connection extending through at least one of the single chips and a substrate providing one or more first contact elements each of which is in contact with one of the through-chip-connections and providing one or more second contact elements being in electrical contact with the first contact elements, wherein the plurality of chip stacks are stacked onto each other and wherein the second contact elements of one of the chip stacks each being arranged to be in contact to one or more third contact elements of an adjacent one of the chip stacks.

Owner:POLARIS INNOVATIONS LTD

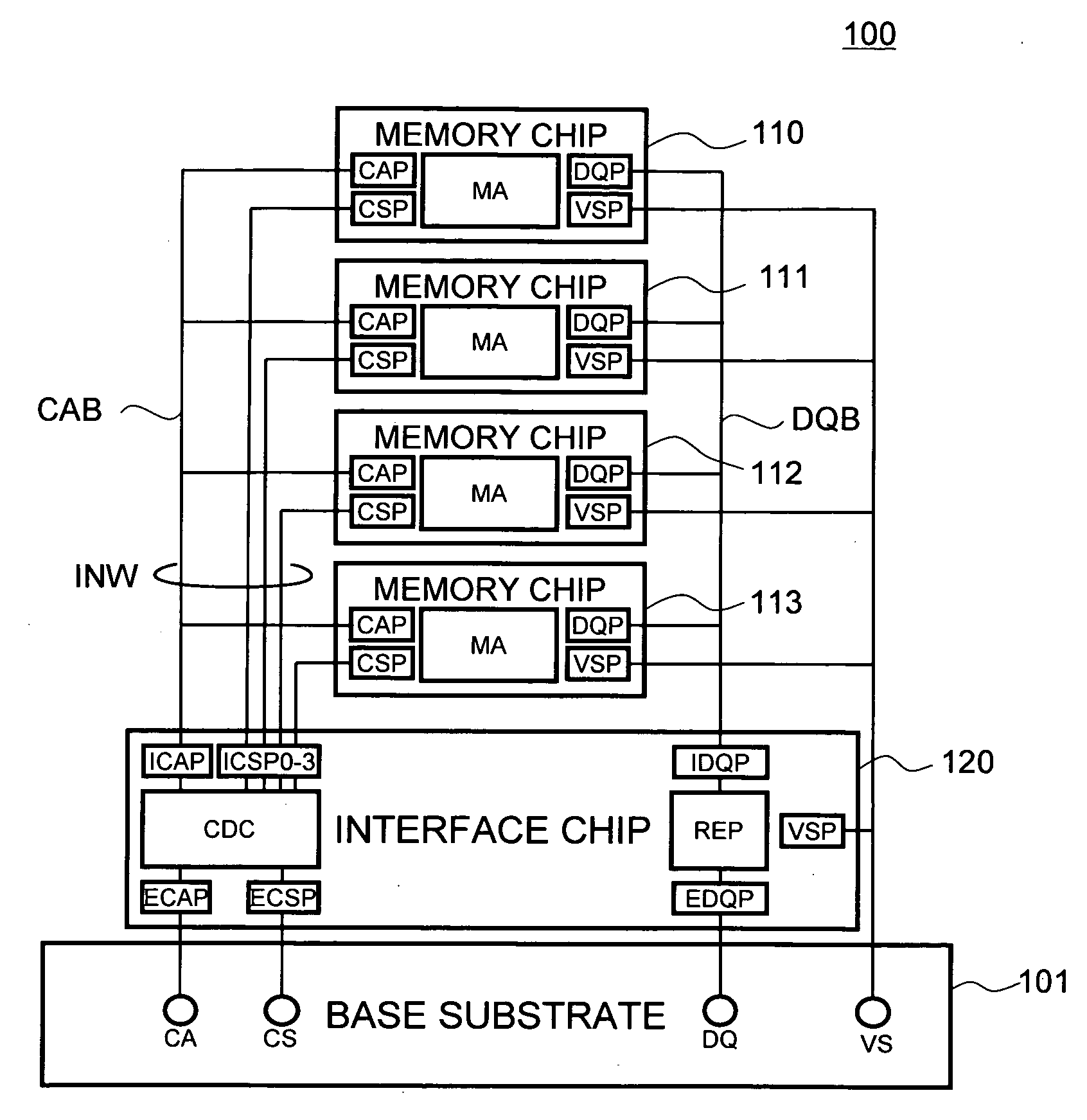

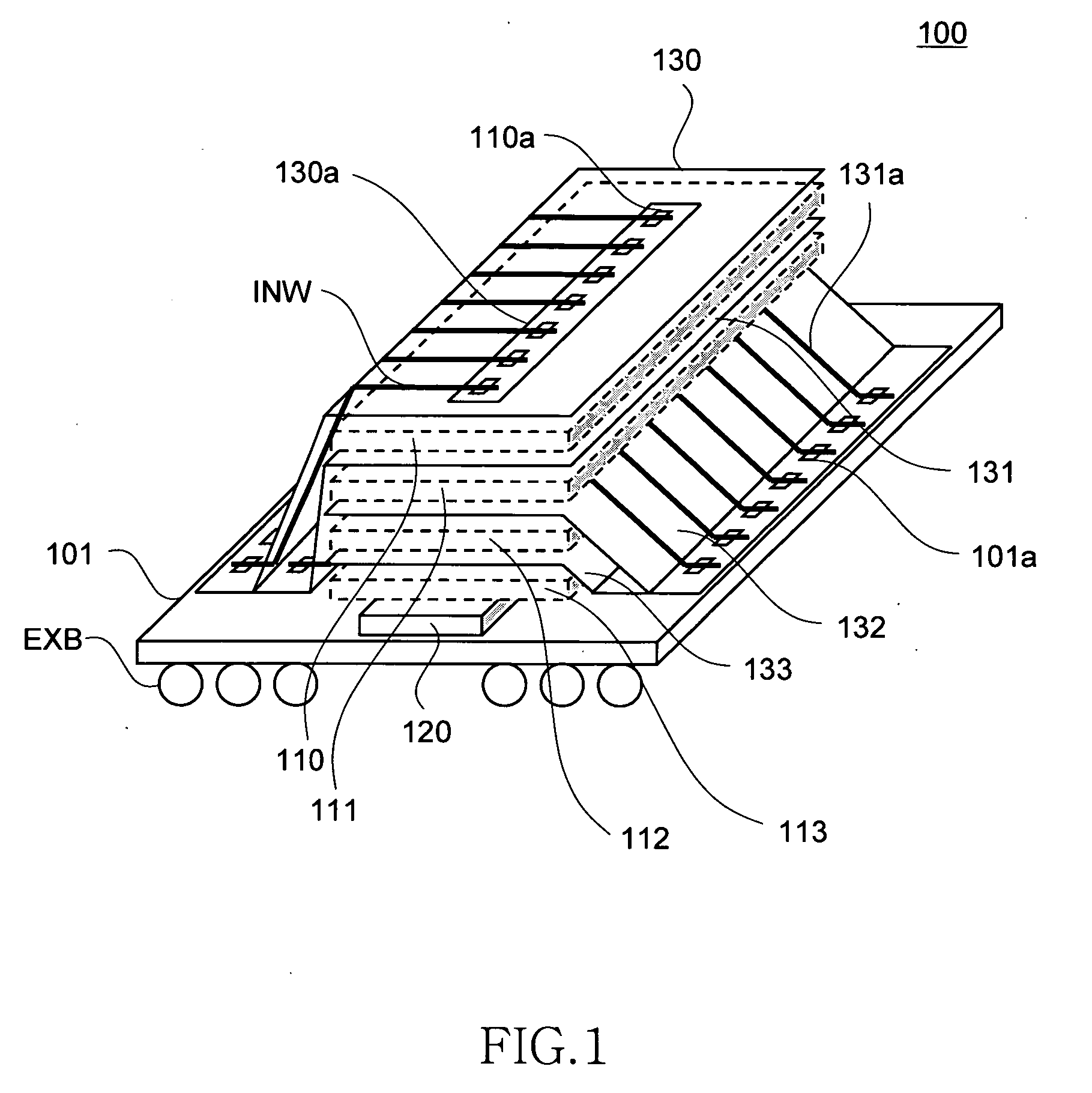

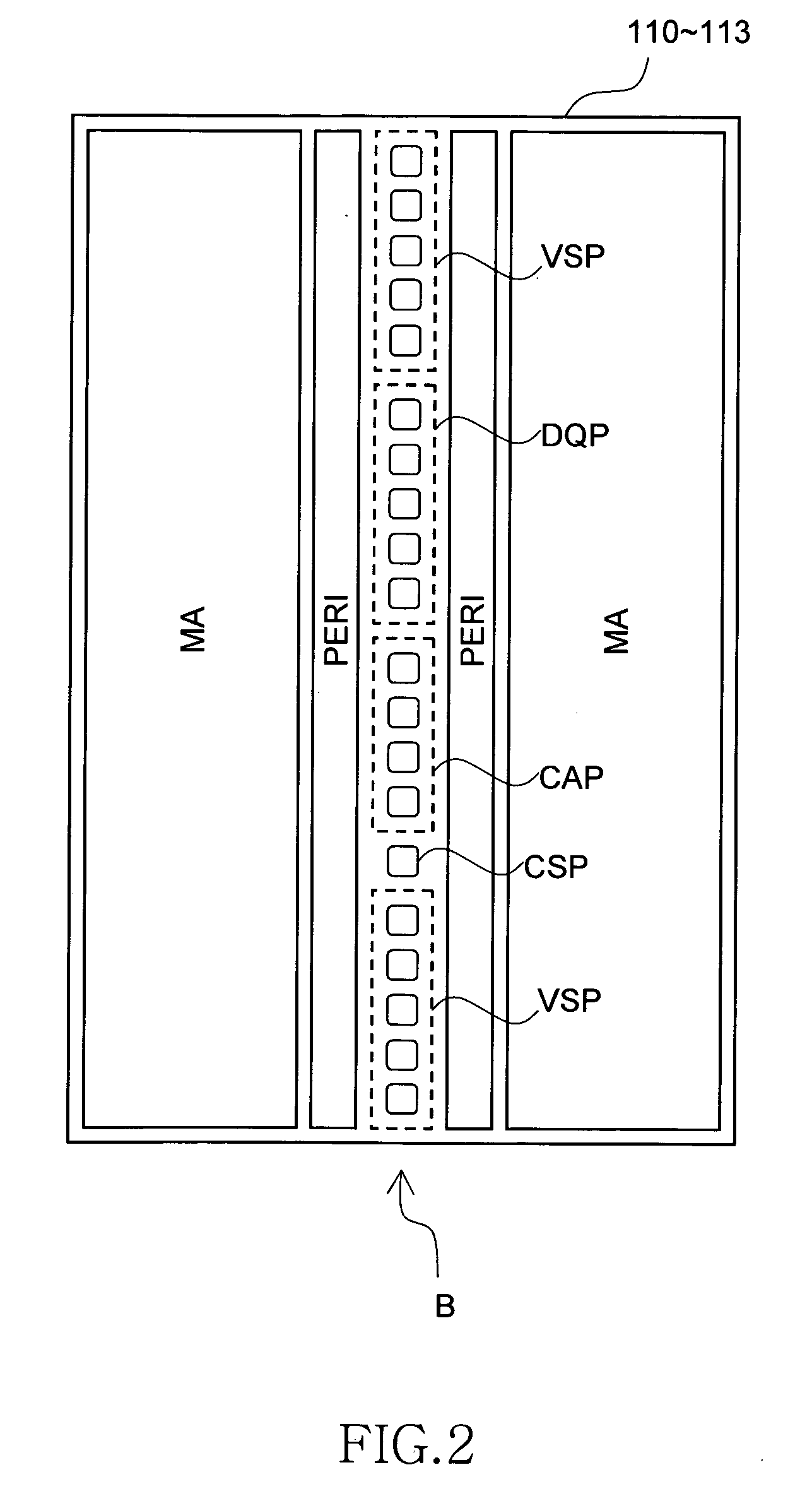

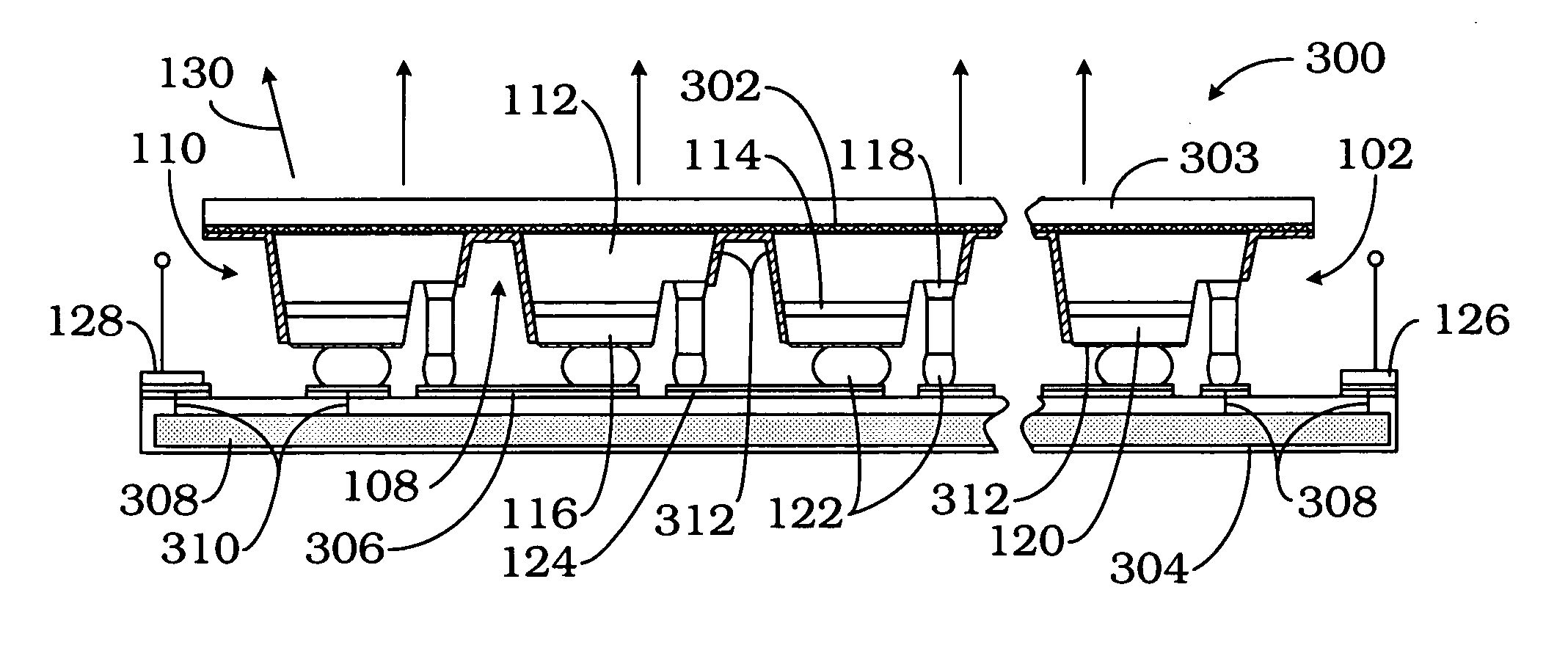

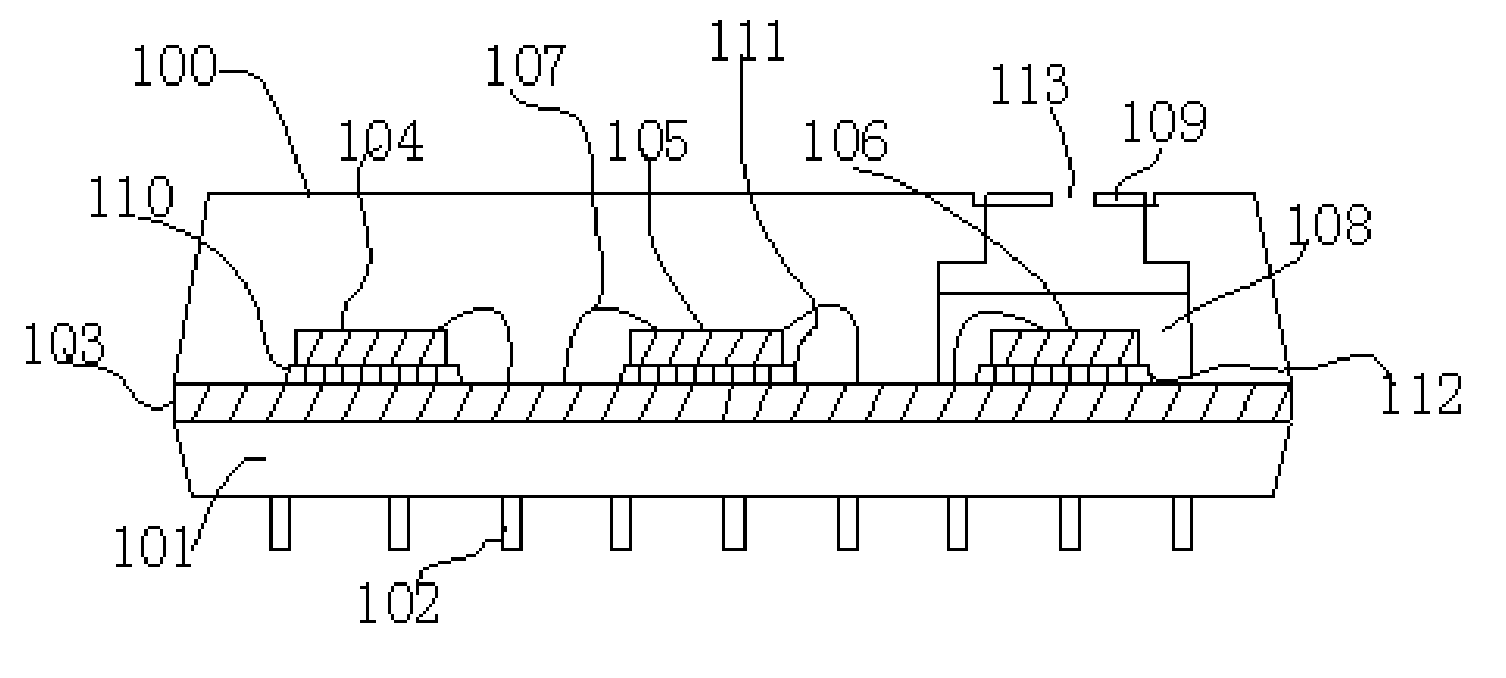

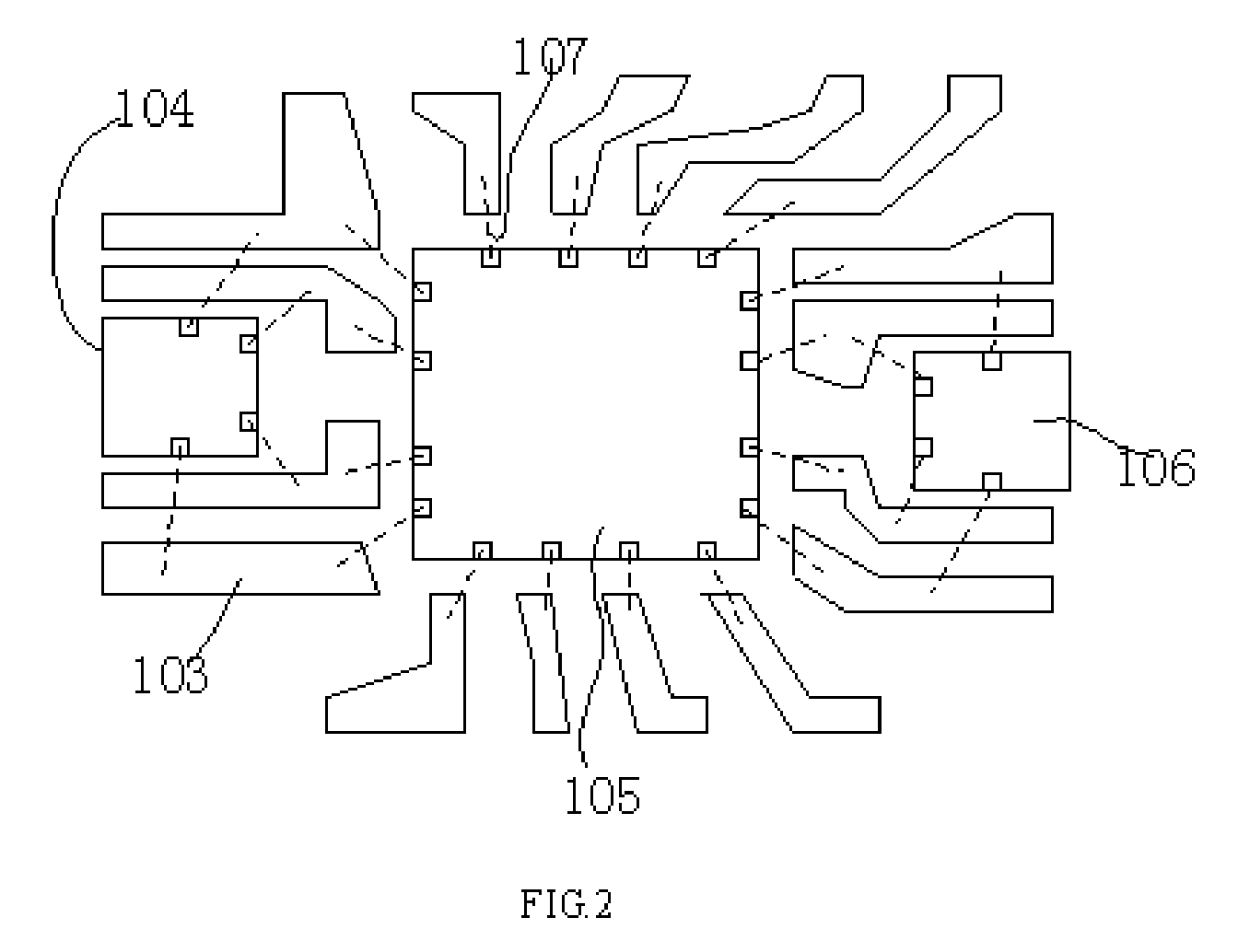

Semiconductor storage device having a plurality of stacked memory chips

ActiveUS20060233012A1Reduce in quantityReduction in wiring capacitanceSemiconductor/solid-state device detailsSolid-state devicesMemory chipChip select

A semiconductor storage employs a base substrate (101) having a command / address external terminal group (CA), a data input / output external terminal group (DQ), and a single chip select external terminal (CS), and also comprises a plurality of memory chips (110) to (113) mounted on a base substrate (101), each of which can individually carry out read and write operations. The terminals (CA), (DQ), and (CS) are connected to an interface chip (120). The interface chip (120) has a chip select signal generation circuit that can individually activate a plurality of memory chips (110) to (113) on the basis of an address signal fed by way of the terminal (CA) and on the basis of a chip select signal fed by way of the terminal (CS).

Owner:LONGITUDE LICENSING LTD

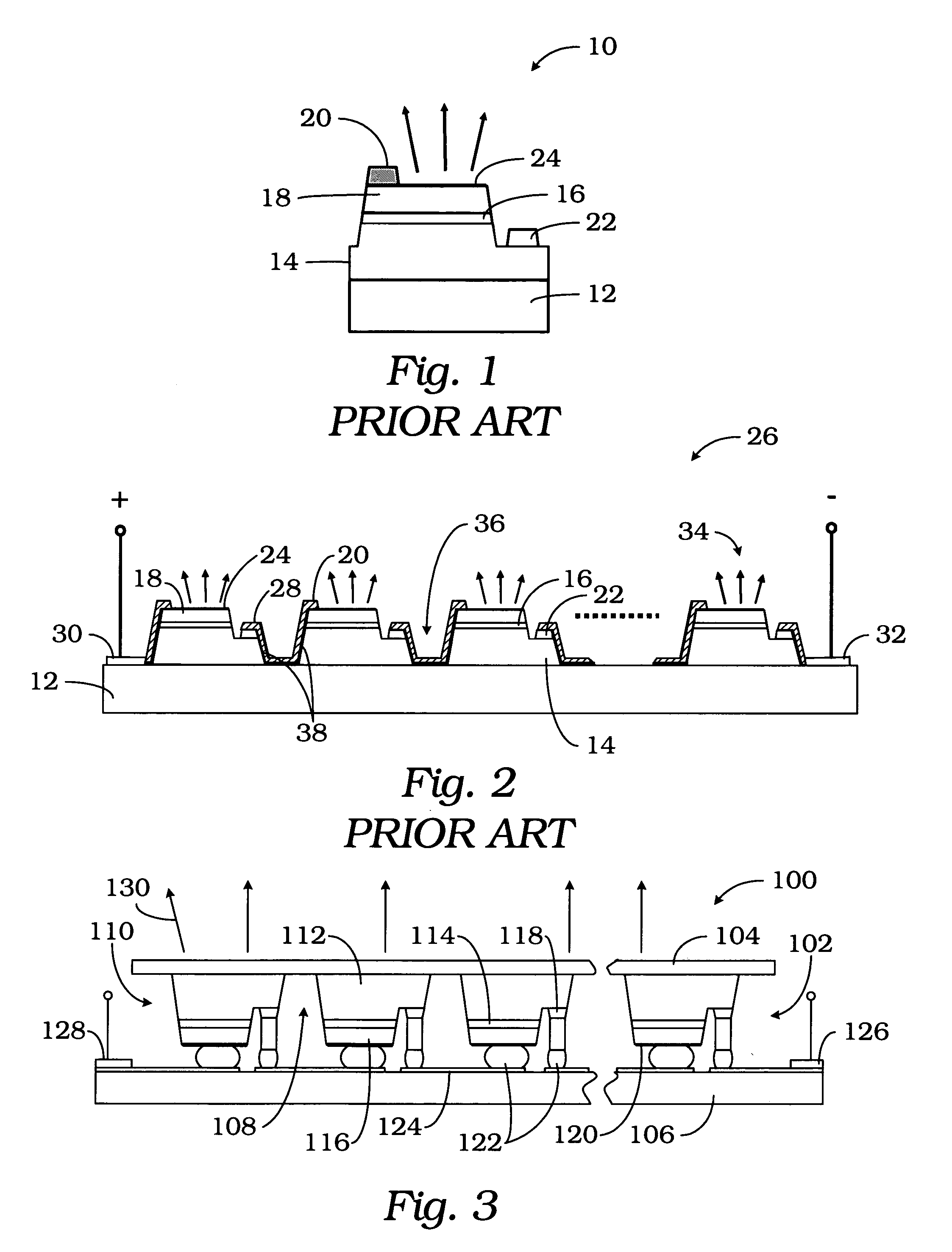

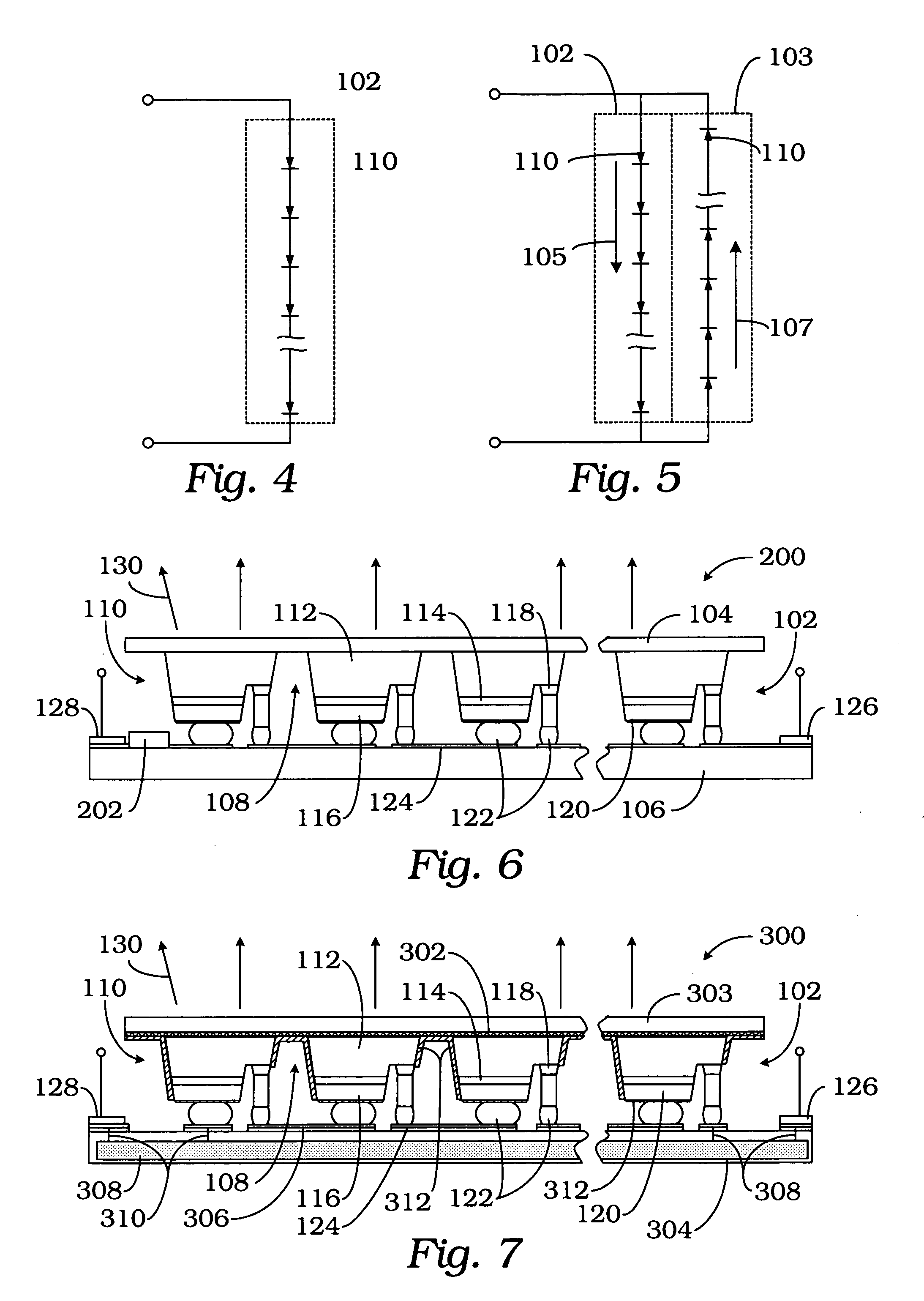

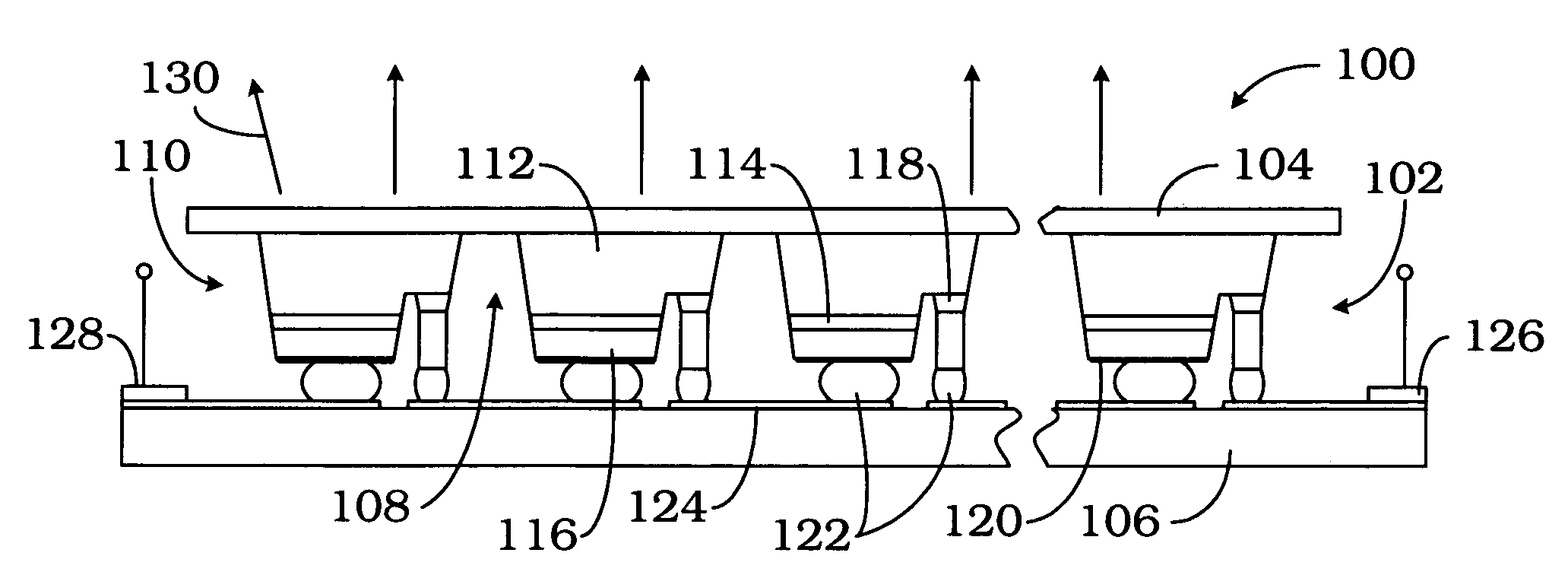

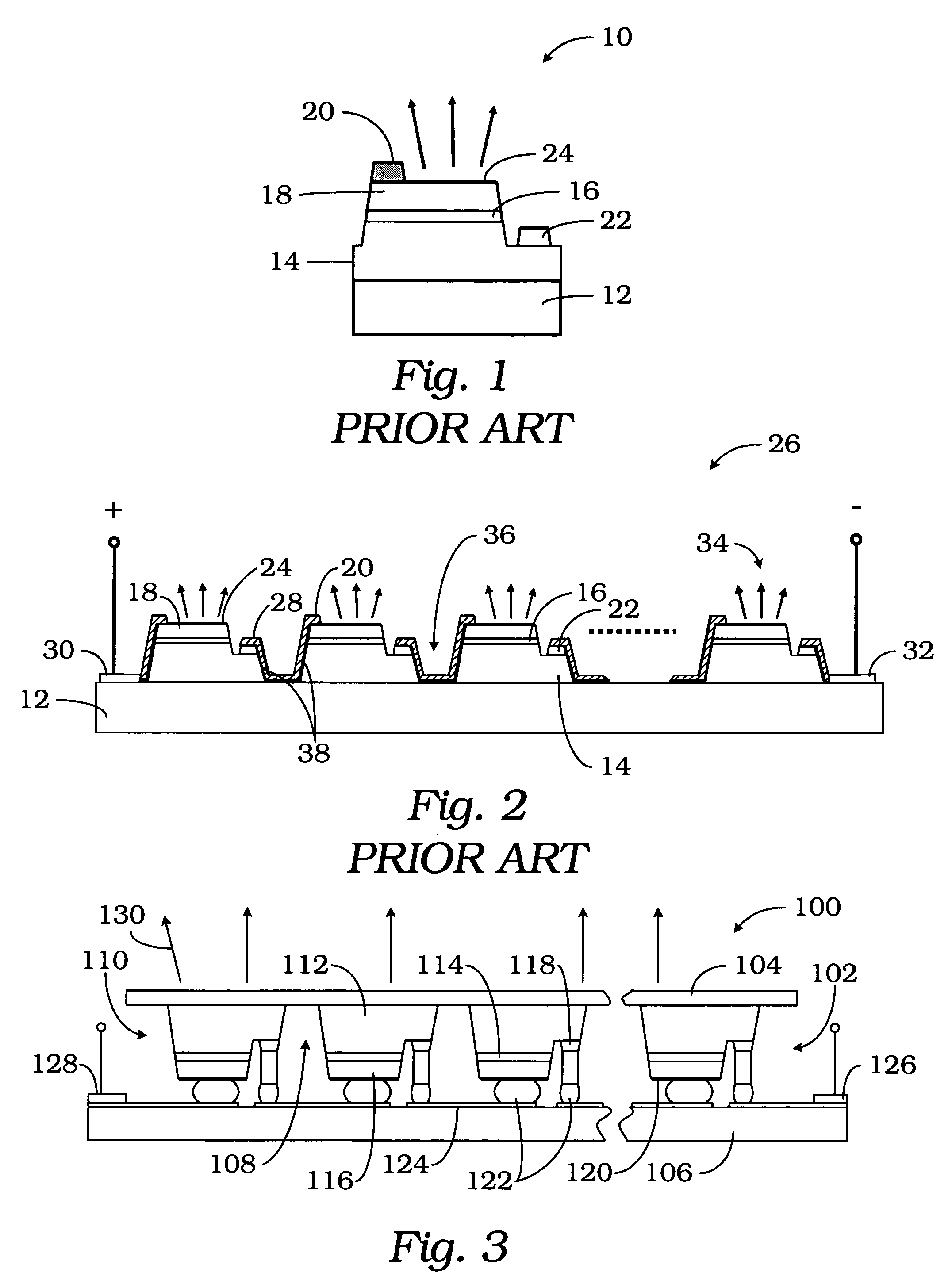

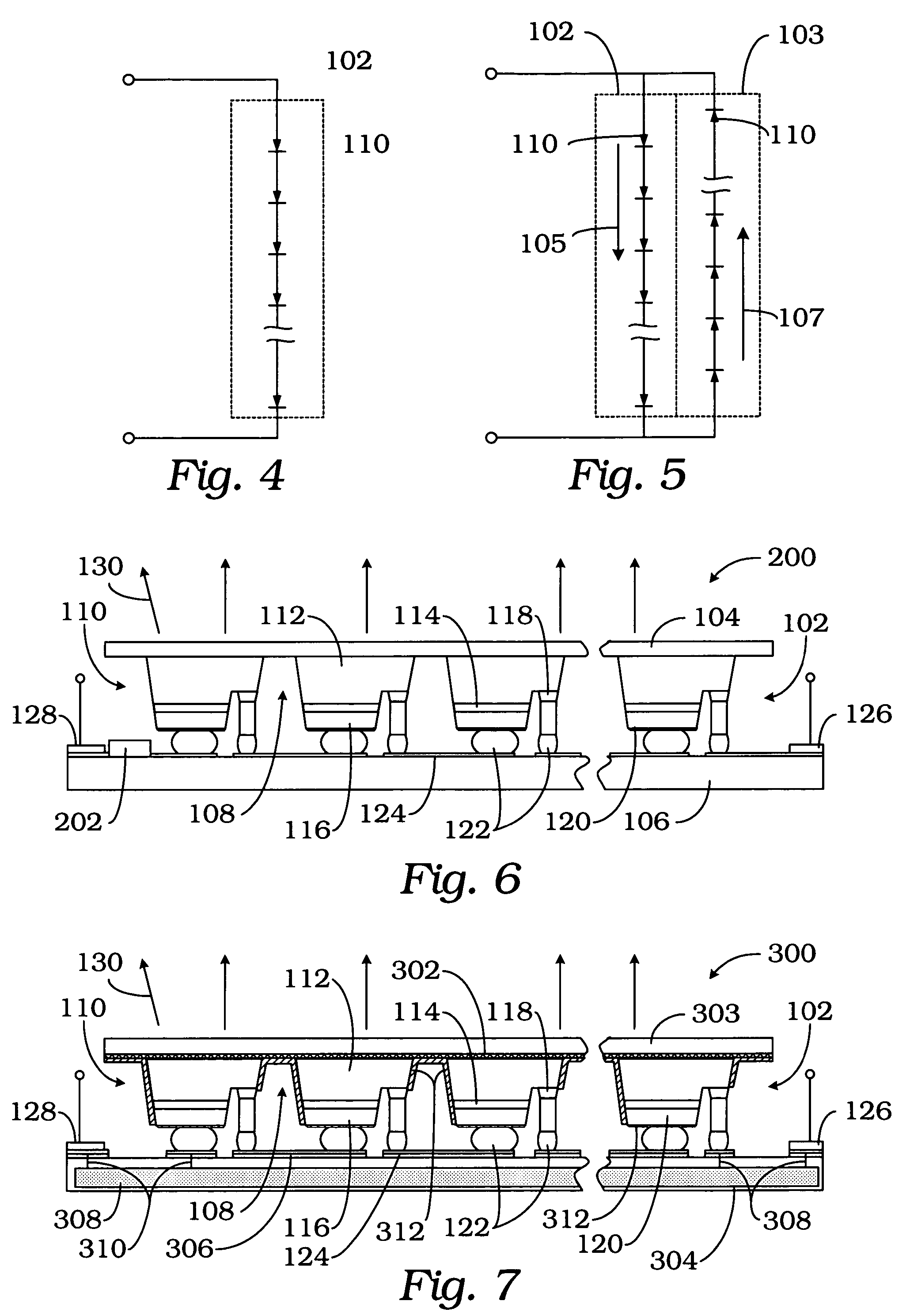

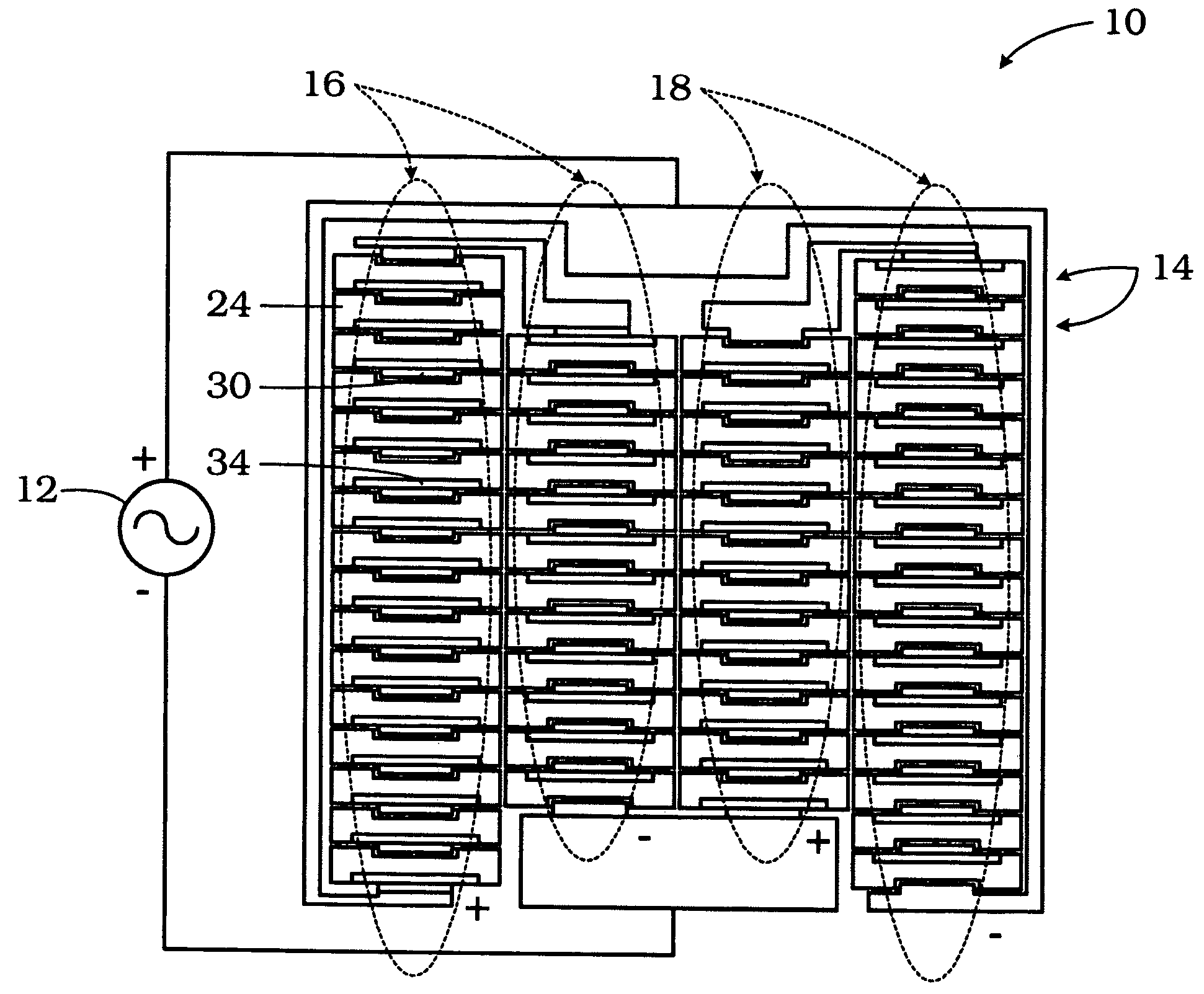

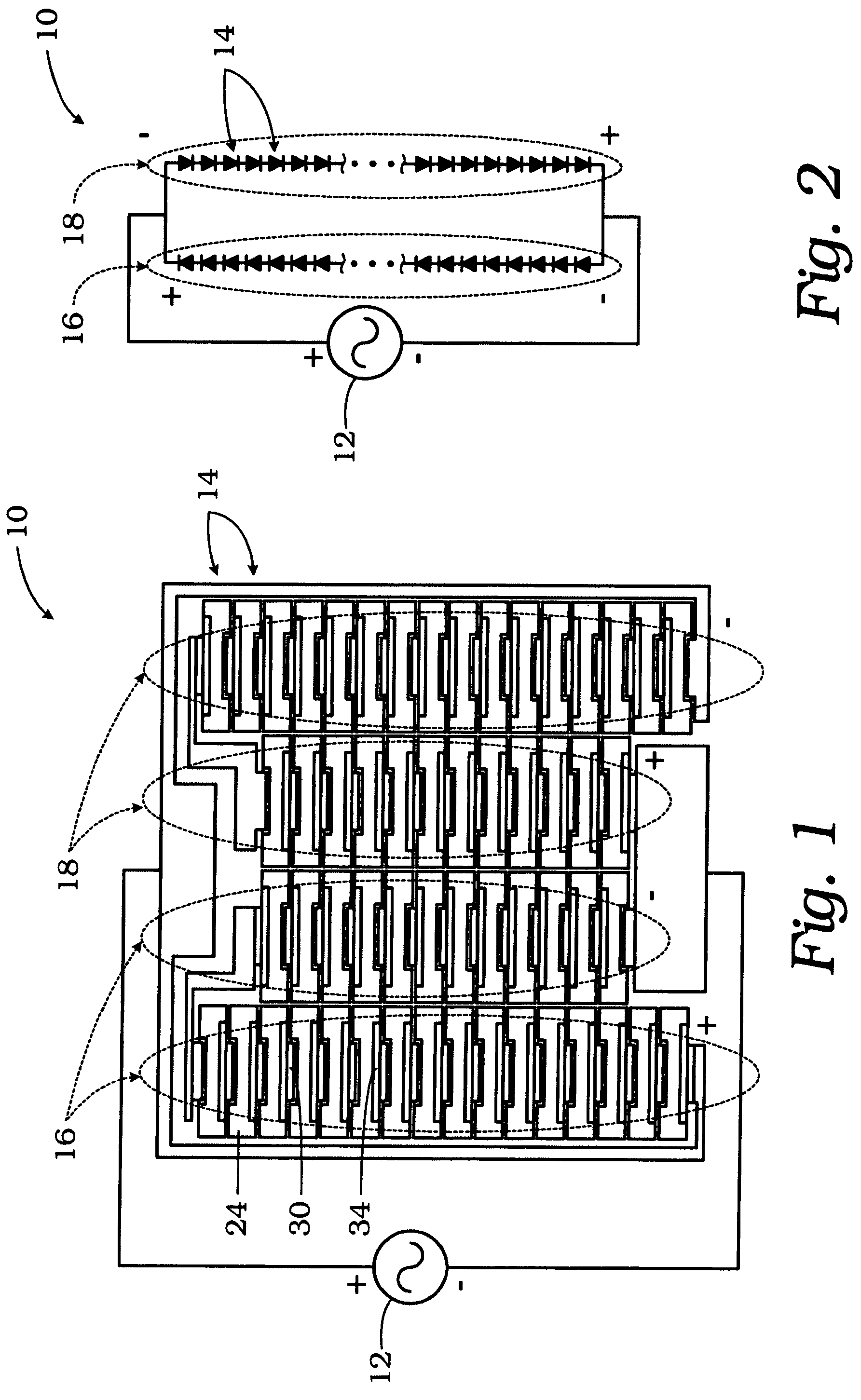

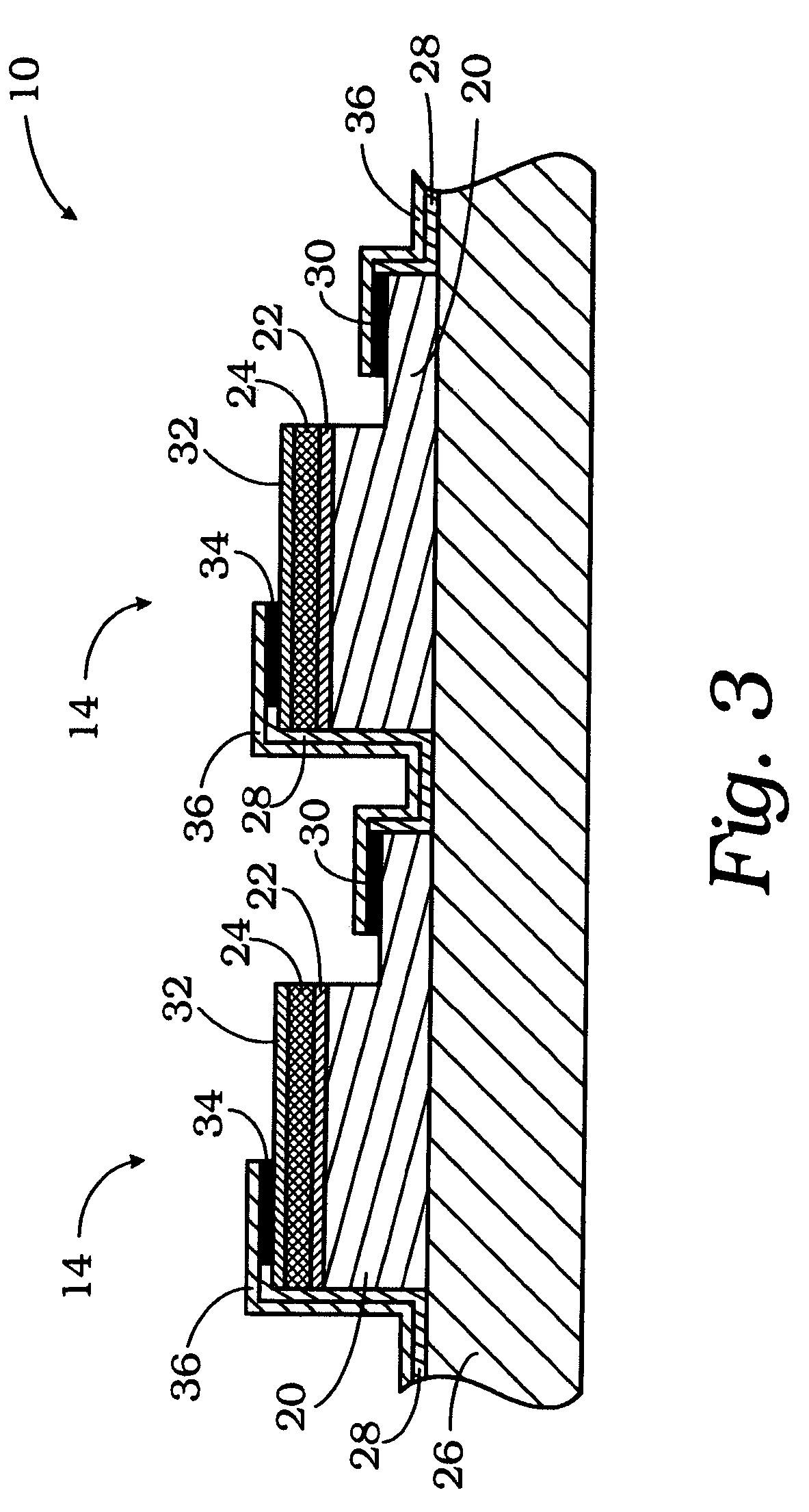

Heterogeneous integrated high voltage DC/AC light emitter

ActiveUS20060163589A1Accelerated dissipationConvenient lightingElectric indicationSemiconductor/solid-state device detailsElectricityHigh pressure

A single-chip integrated LED particularly adapted for direct use with a high voltage DC or AC power sources comprises a plurality of electrically isolated LEDs on a generally transparent substrate and bonded to electrically conductive elements on a thermally conductive mount. A reflective coating may be applied to the area between LEDs.

Owner:LED LIGHTING

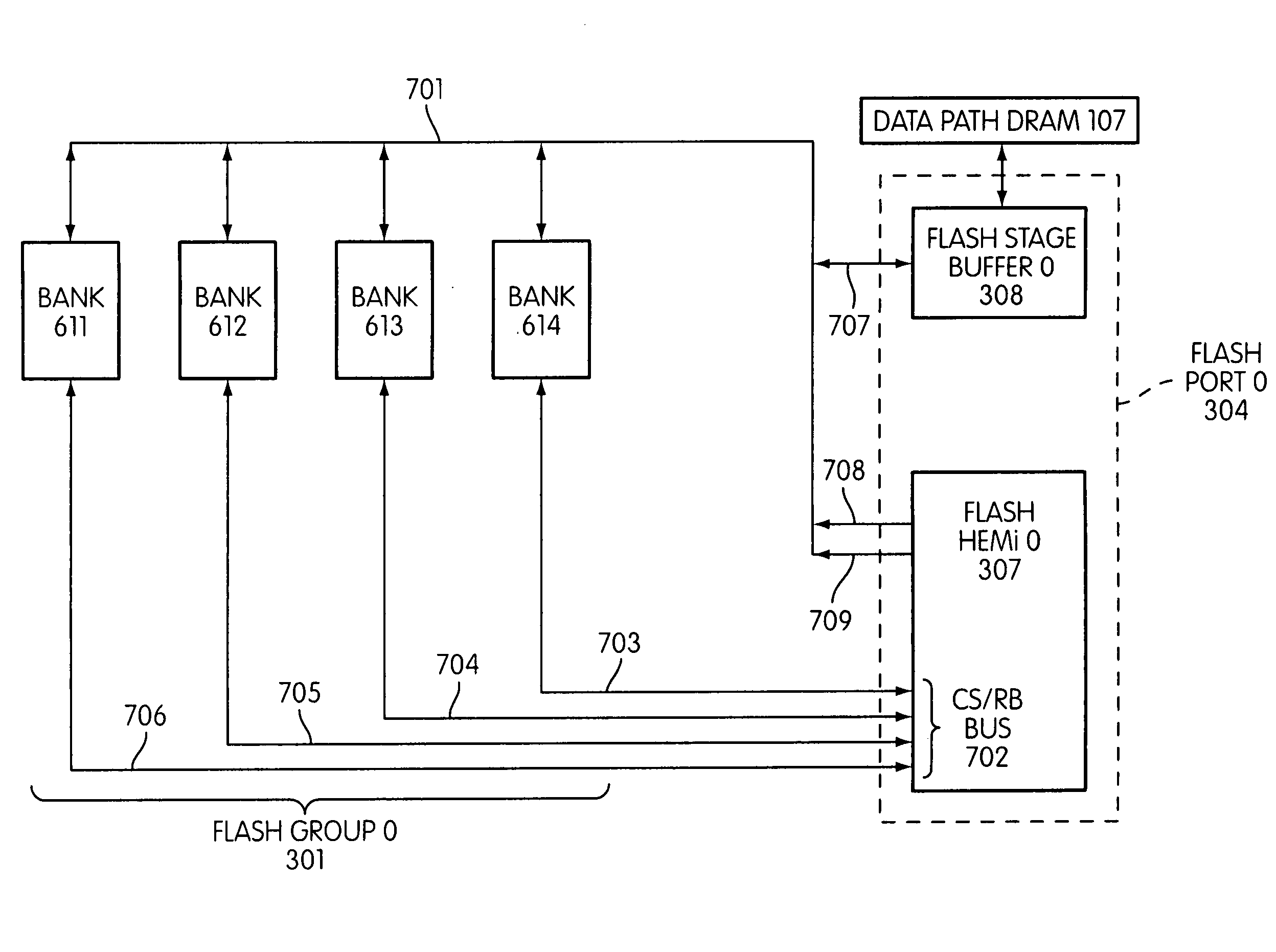

Flash memory controller having reduced pinout

InactiveUS20090168525A1Affect performanceMaximize useMemory architecture accessing/allocationMemory adressing/allocation/relocationChip selectFlash memory controller

Disclosed is a flash memory controller connected to a flash memory module. The pin-out of the flash memory controller combines ready-busy and chip-select signals. In one embodiment, the flash memory module is made up of a set of banks, each consisting of a plurality of devices, with each bank sharing a single chip-select / ready-busy connection to the controller.

Owner:SANDISK TECH LLC

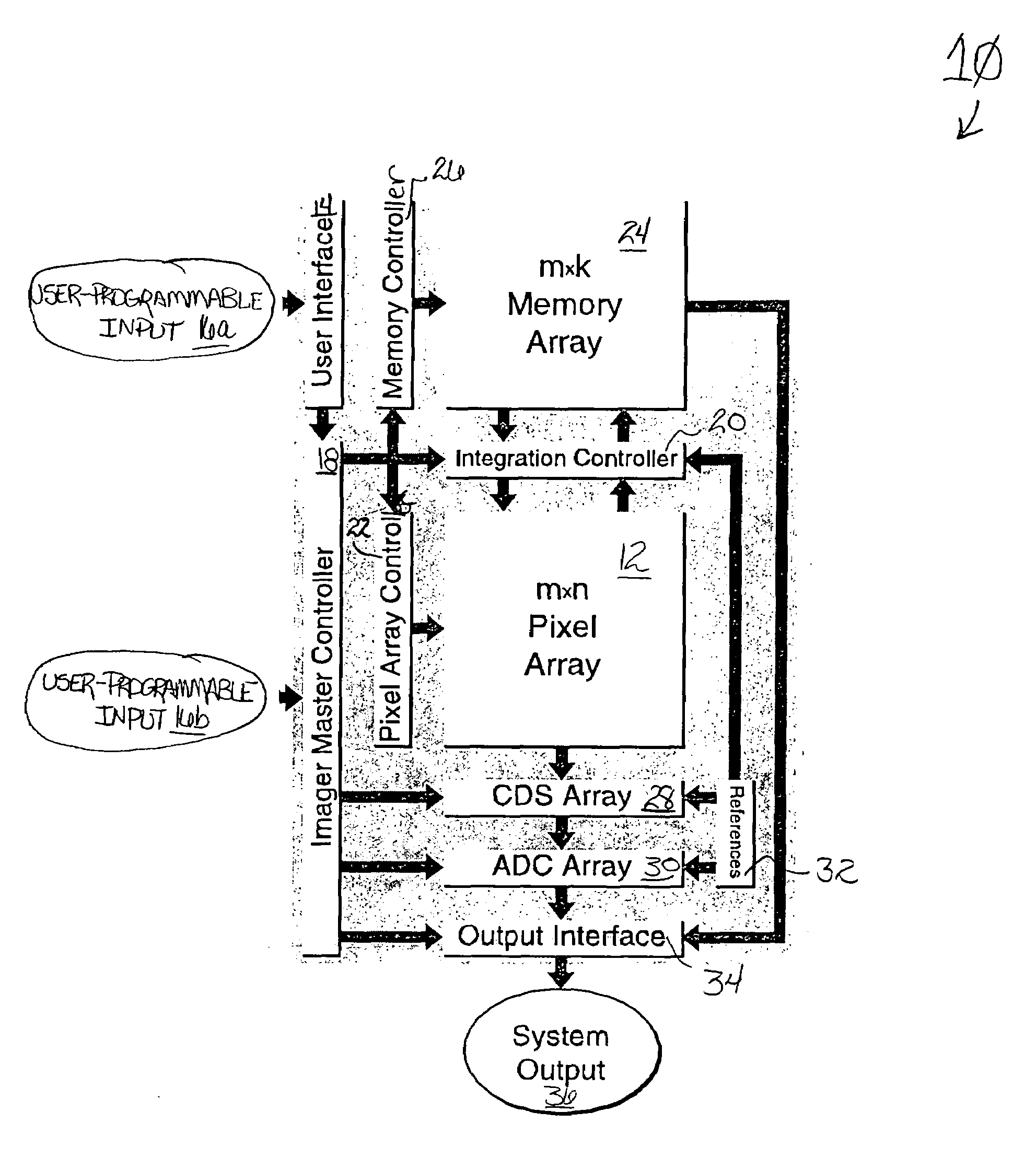

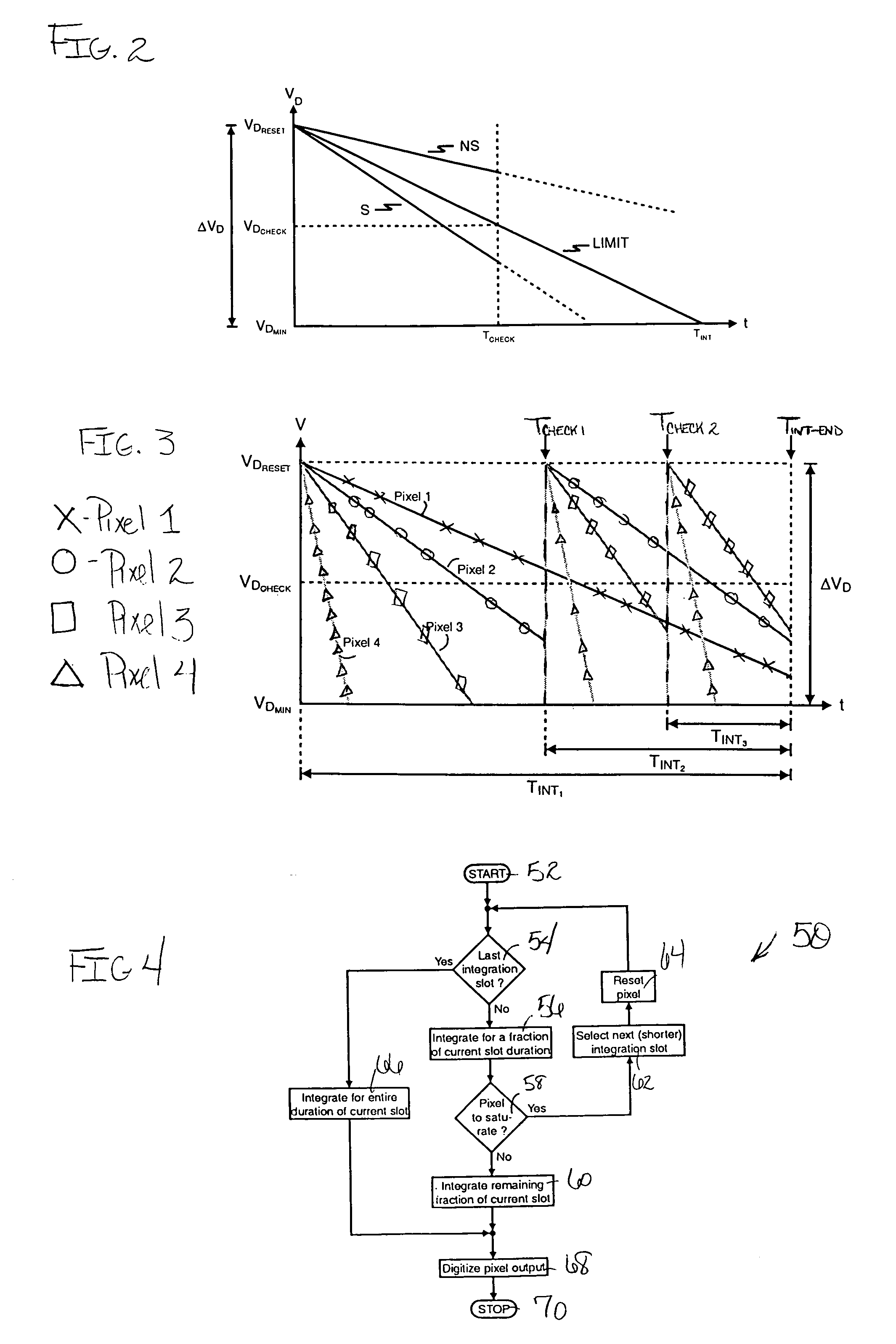

Single-chip imager system with programmable dynamic range

InactiveUS6977685B1Elegantly simple input/output connectionProduced cost-effectivelyTelevision system detailsTelevision system scanning detailsControl signalEngineering

The imager system of the invention, provided in a semiconductor substrate, includes a plurality of photosensitive, charge integrating pixels that are arranged in rows and columns of a pixel array for capturing illumination of a scene to be imaged. Each pixel includes a photogenerated charge accumulation region of the semiconductor substrate and a sense node at which an electrical signal, indicative of pixel charge accumulation, can be measured without discharging the accumulation region. Pixel access control circuitry is connected to pixel array rows and columns to deliver pixel access signals generated by the access control circuitry for independently accessing a selected pixel in the array. An input interface circuit is connected to accept a dynamic range specification input for the array pixels. Integration control circuitry is connected to access a selected pixel of the array to read the sense node electrical signal of the selected pixel, and configured to generate pixel-specific integration control signals delivered to the selected pixel, independent of other pixels, based on dynamic range specification input provided by the input interface circuit. An output interface circuit is connected to the pixel array to produce output image data based on sense node electrical signals from the pixel array.

Owner:MASSACHUSETTS INST OF TECH

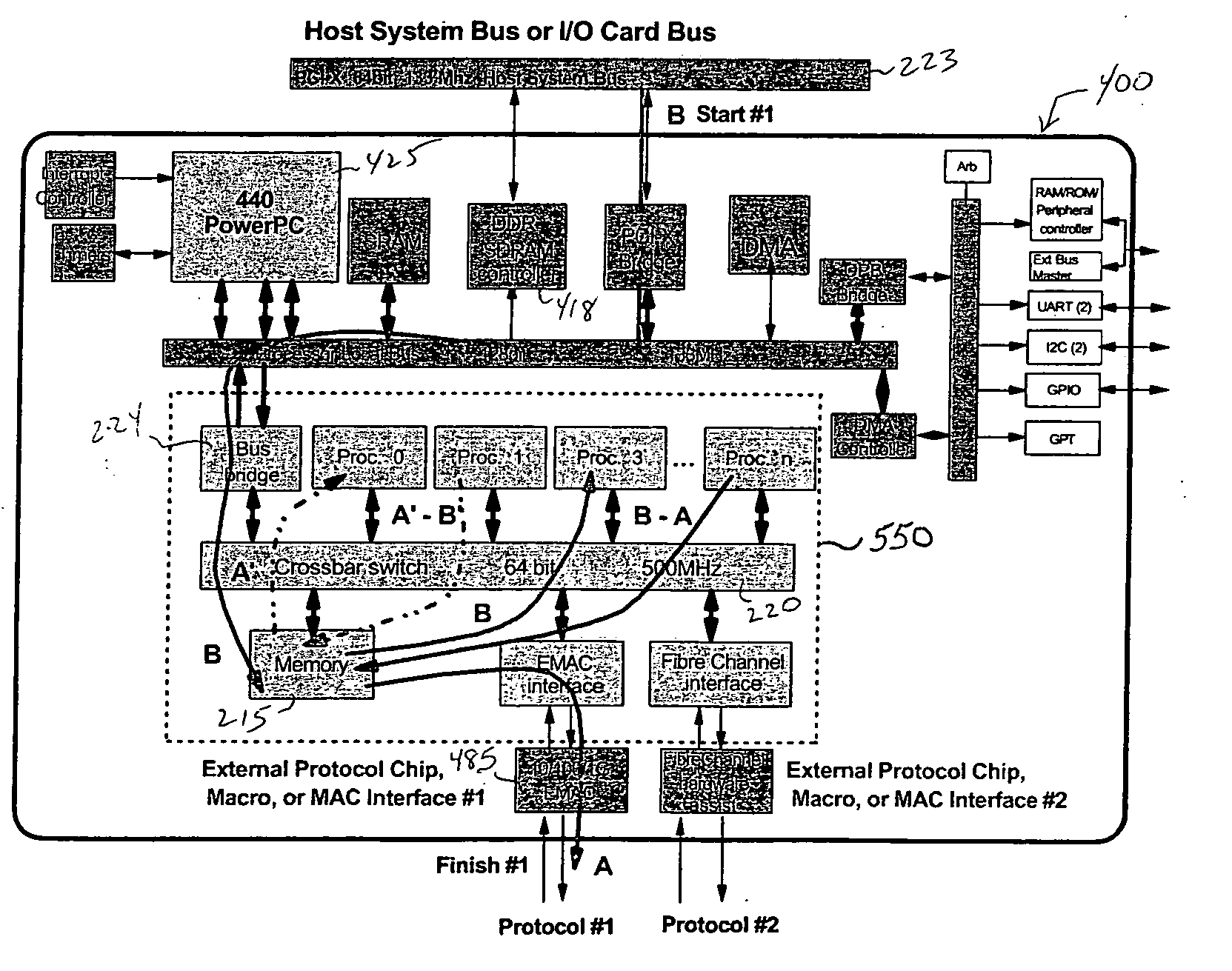

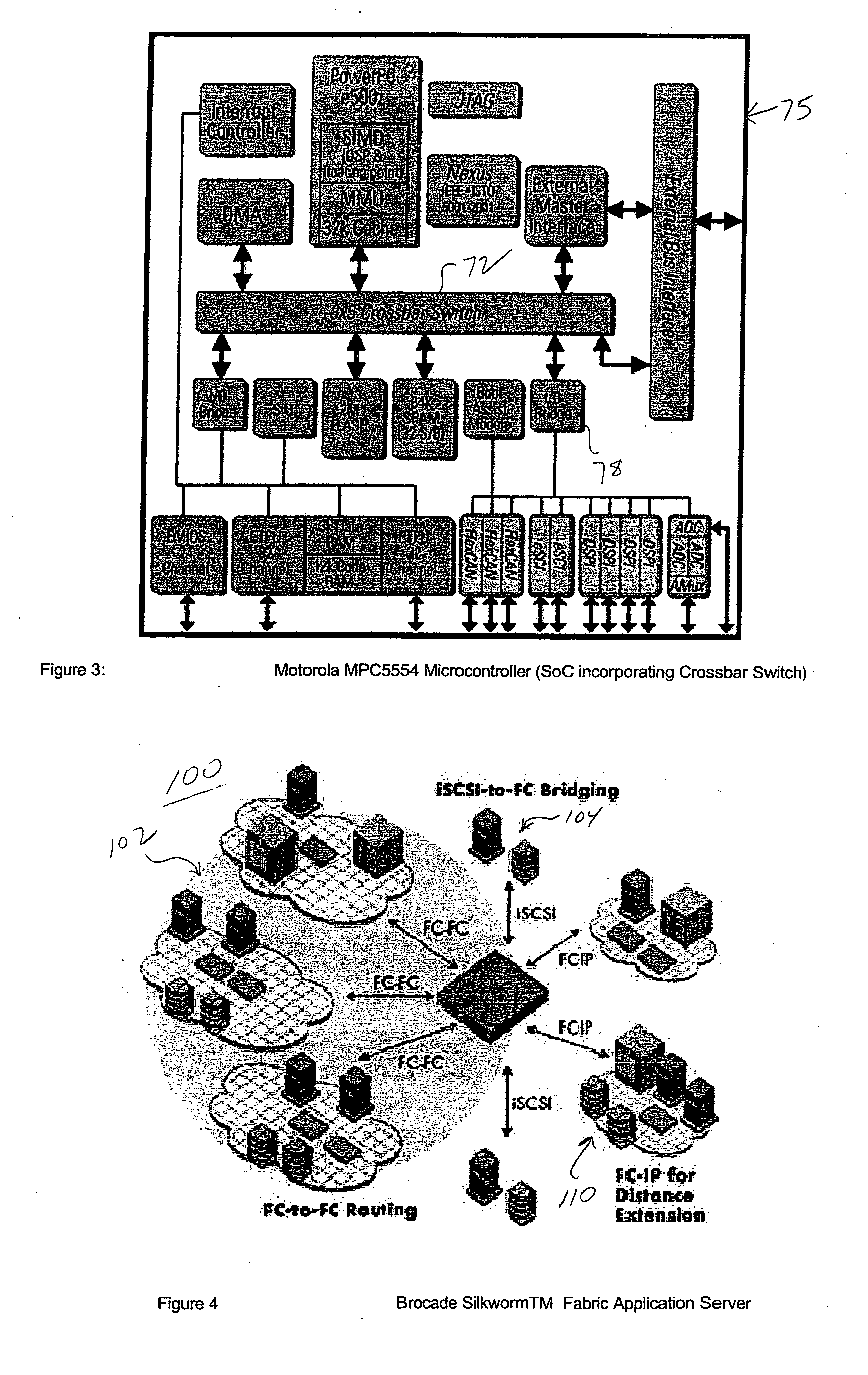

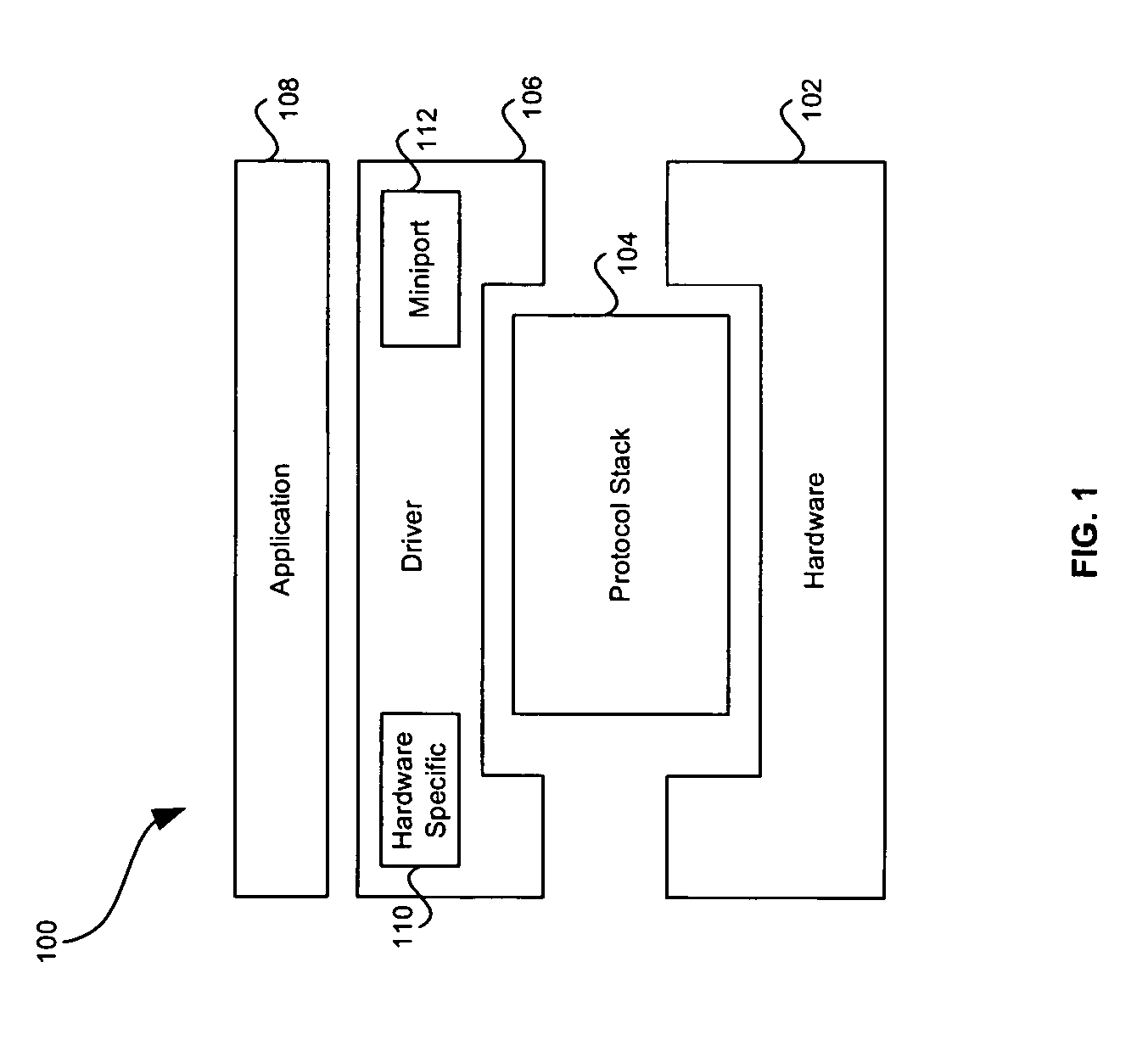

Single chip protocol converter

ActiveUS20050021874A1Increase the number ofHigh bandwidthConcurrent instruction executionMultiple digital computer combinationsSingle chipMultiprocessing

A single chip protocol converter integrated circuit (IC) capable of receiving packets generating according to a first protocol type and processing said packets to implement protocol conversion and generating converted packets of a second protocol type for output thereof, the process of protocol conversion being performed entirely within the single integrated circuit chip. The single chip protocol converter can be further implemented as a macro core in a system-on-chip (SoC) implementation, wherein the process of protocol conversion is contained within a SoC protocol conversion macro core without requiring the processing resources of a host system. Packet conversion may additionally entail converting packets generated according to a first protocol version level and processing the said packets to implement protocol conversion for generating converted packets according to a second protocol version level, but within the same protocol family type. The single chip protocol converter integrated circuit and SoC protocol conversion macro implementation include multiprocessing capability including processor devices that are configurable to adapt and modify the operating functionality of the chip.

Owner:MICROSOFT TECH LICENSING LLC

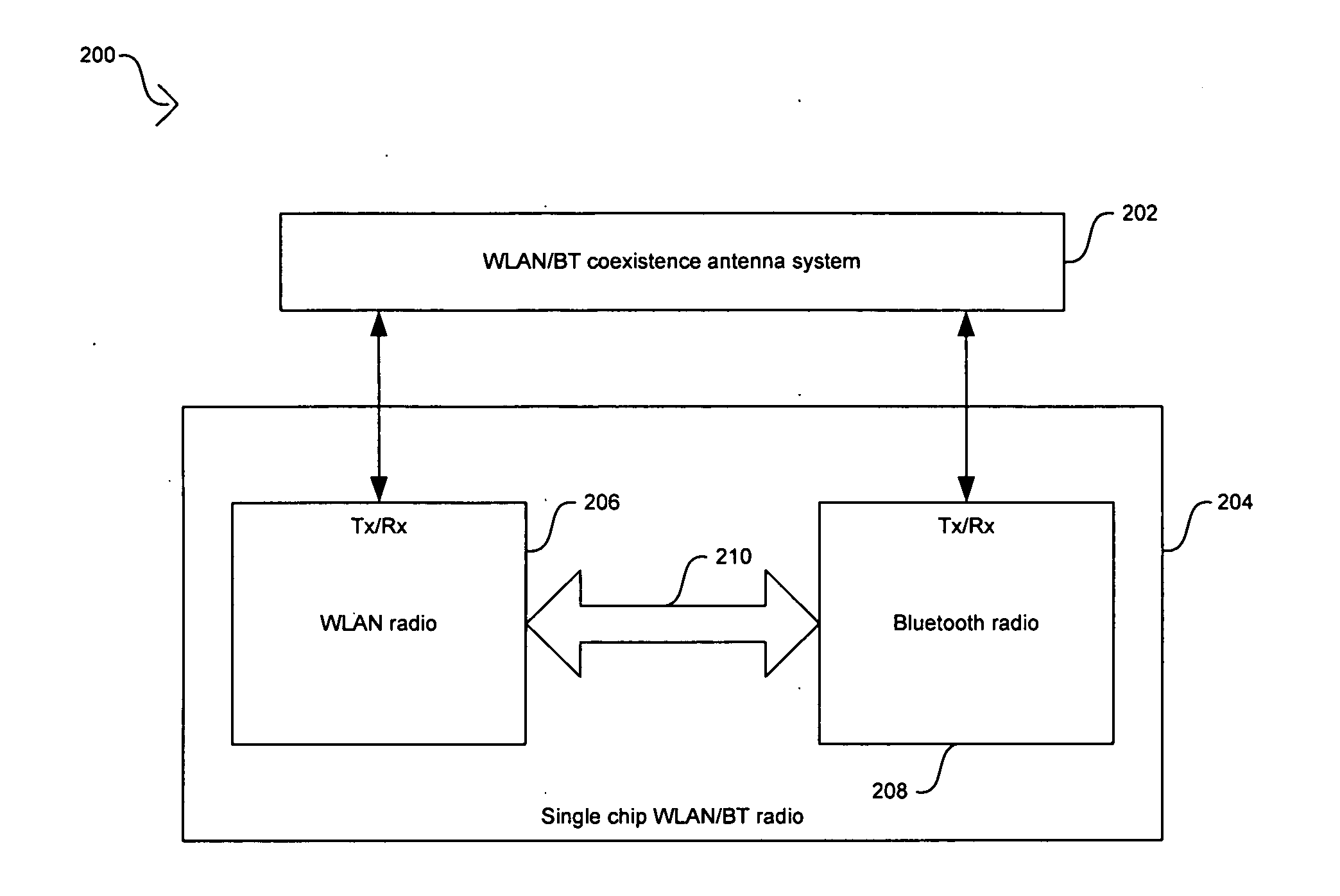

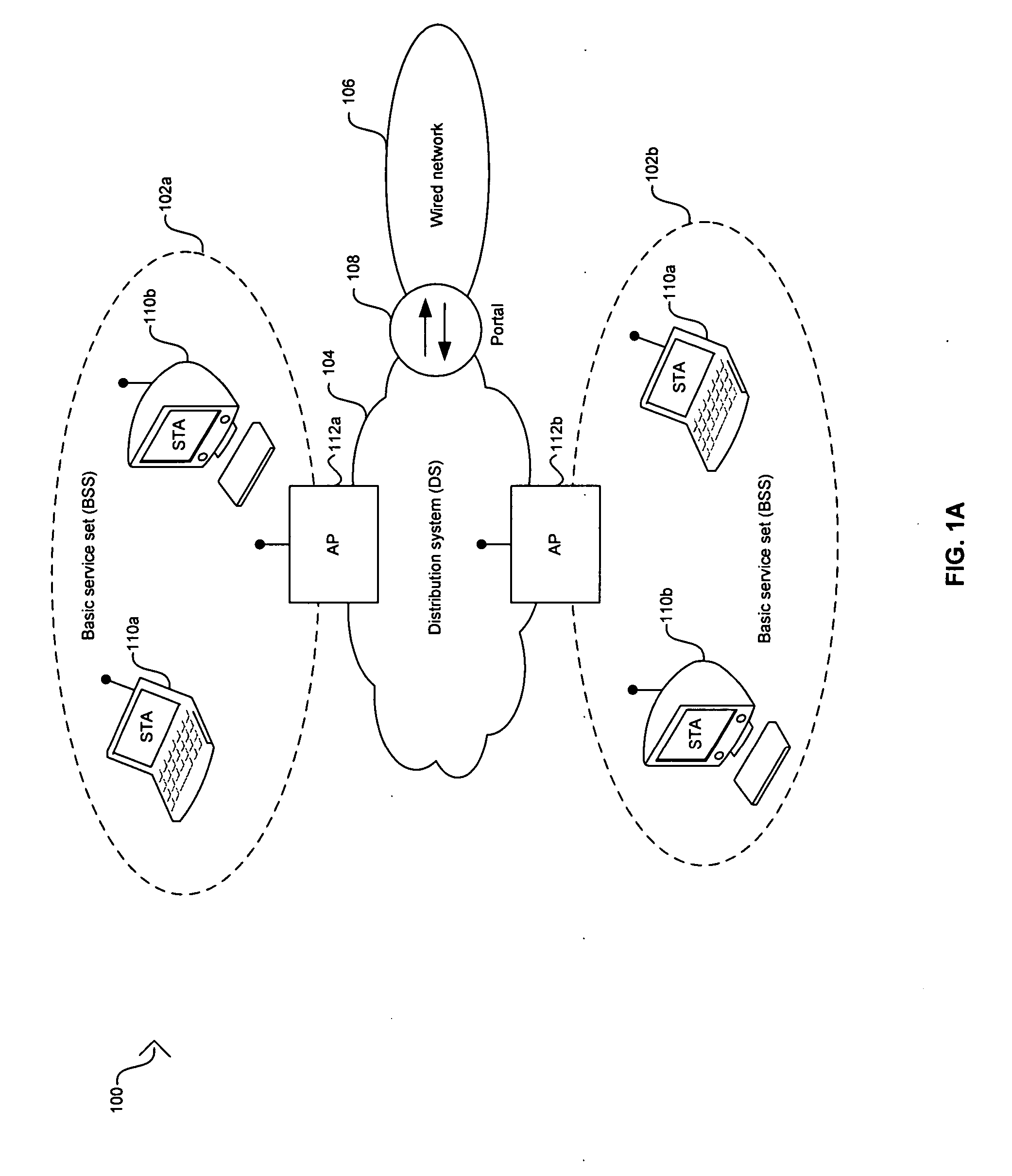

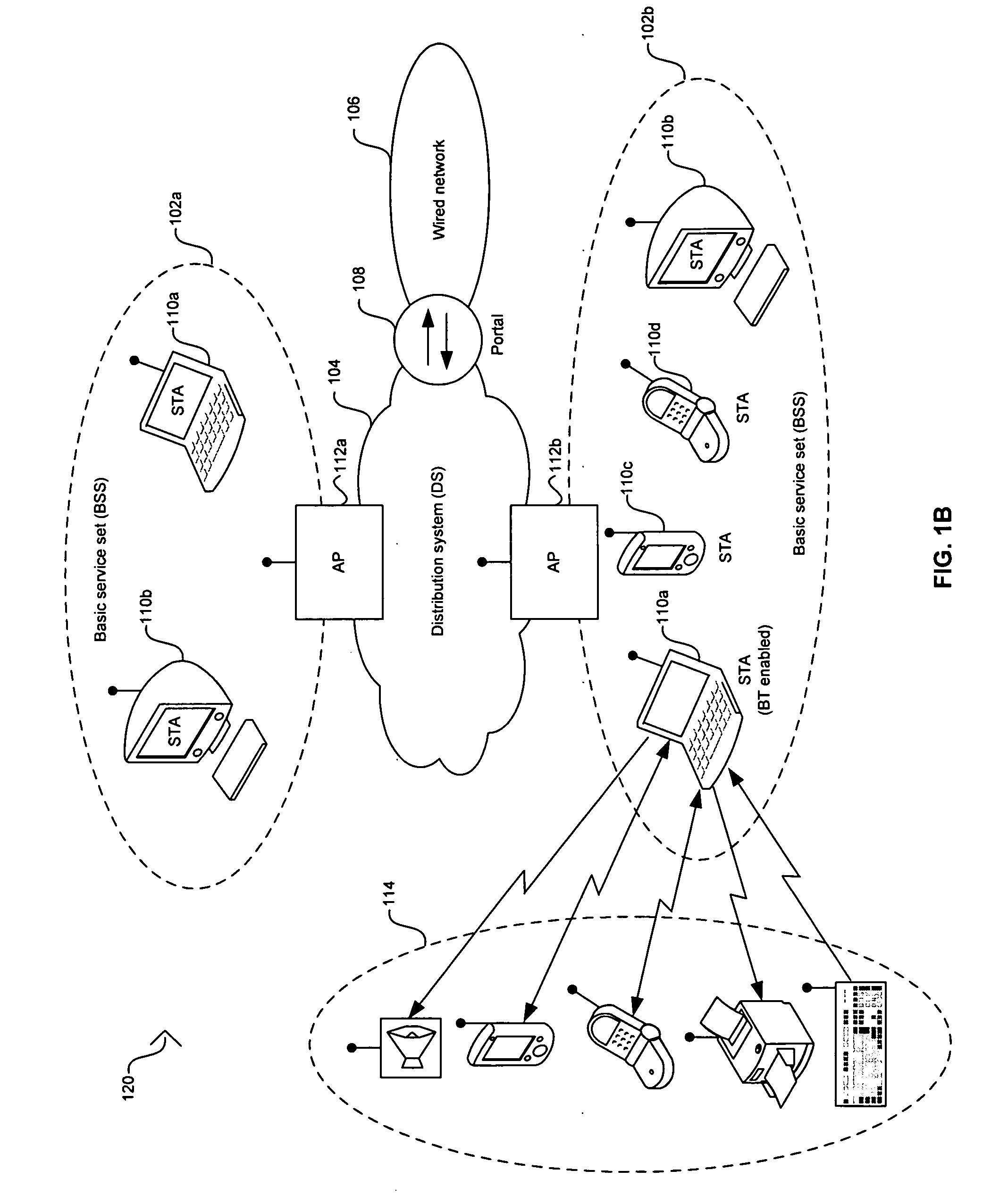

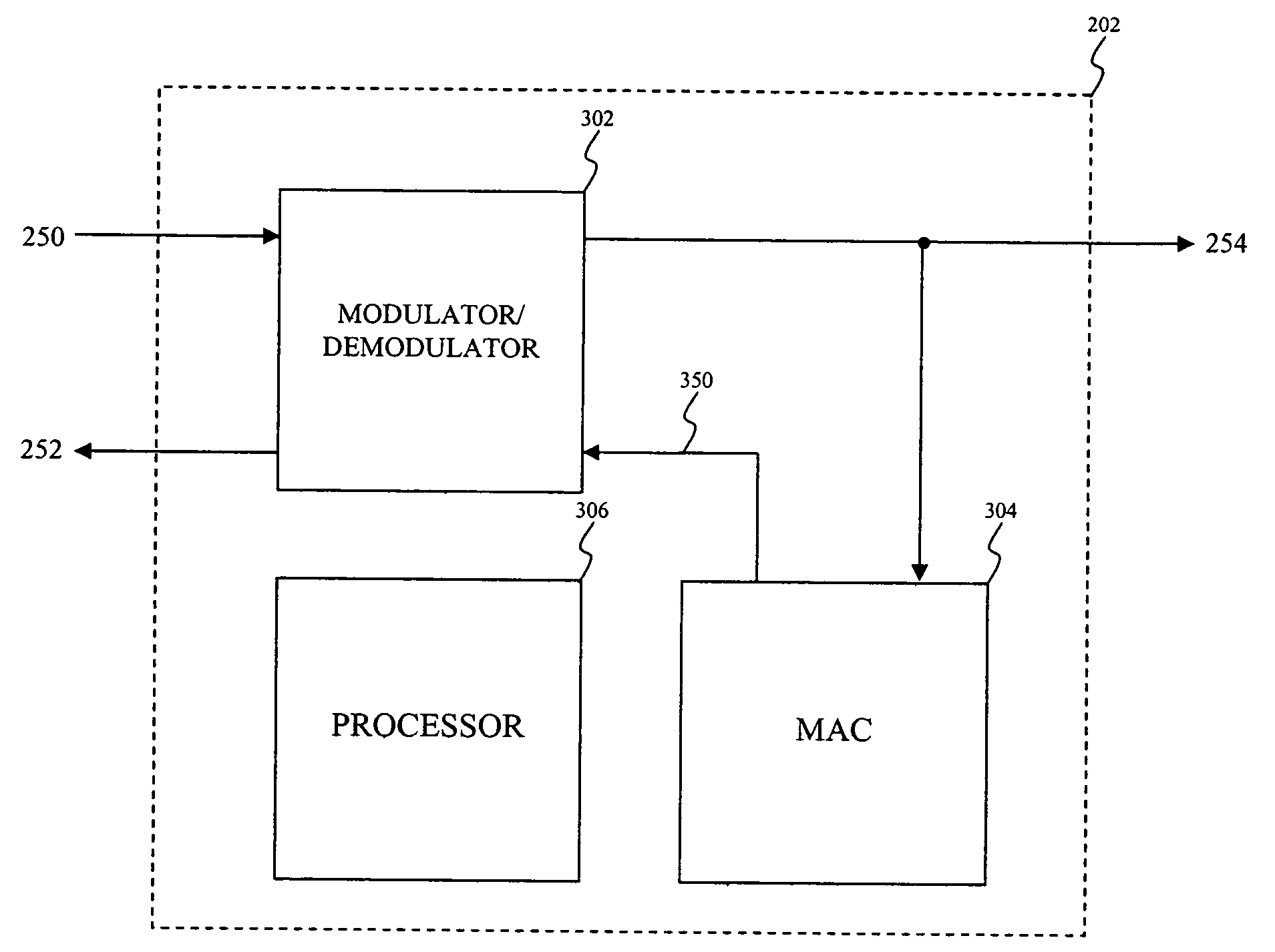

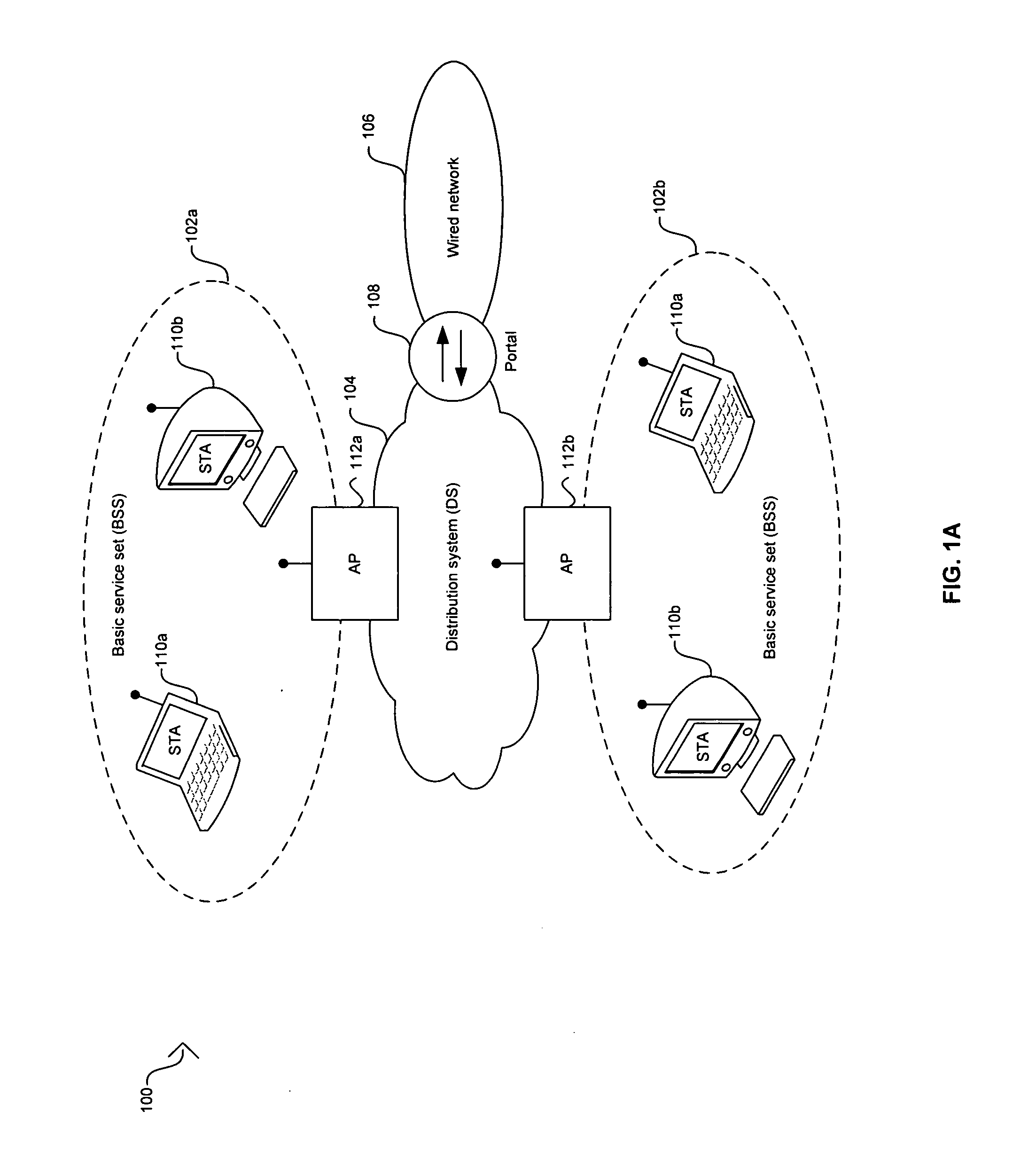

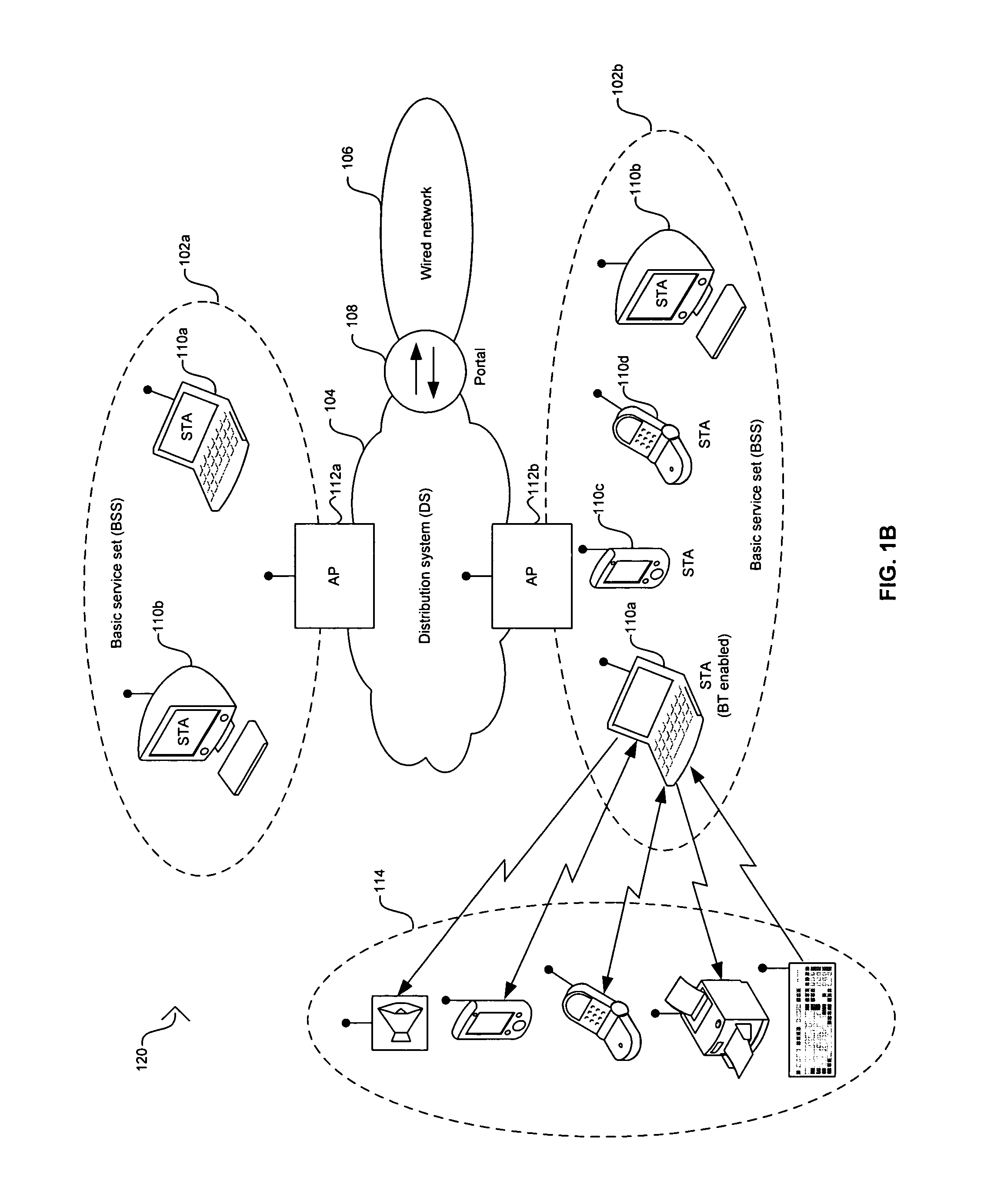

Method and system for antenna and radio front-end topologies for a system-on-a-chip (SOC) device that combines bluetooth and IEEE 802.11 b/g WLAN technologies

Certain embodiments of the invention may be found in a method and system for antenna and radio front-end topologies for a system-on-a-chip (SOC) device that combines Bluetooth and IEEE 802.11 b / g WLAN technologies. A single chip radio device that supports WLAN and Bluetooth technologies receives a WLAN signal in a WLAN processing circuitry of the radio front-end and in a Bluetooth processing circuitry of the radio front-end. Signals generated by the WLAN processing circuitry and the Bluetooth processing circuitry from the received WLAN signal may be combined in a diversity combiner that utilizes selection diversity gain combining or maximal ratio combining (MRC). When a generated signal is below a threshold value, the signal may be dropped from the combining operation. A single antenna usage model may be utilized with the single chip radio device front-end topology to support WLAN and Bluetooth communications.

Owner:AVAGO TECH INT SALES PTE LTD

Heterogeneous integrated high voltage DC/AC light emitter

ActiveUS7221044B2Accelerated dissipationConvenient lightingElectric indicationSemiconductor/solid-state device detailsElectricityEngineering

A single-chip integrated LED particularly adapted for direct use with a high voltage DC or AC power sources comprises a plurality of electrically isolated LEDs on a generally transparent substrate and bonded to electrically conductive elements on a thermally conductive mount. A reflective coating may be applied to the area between LEDs.

Owner:LED LIGHTING

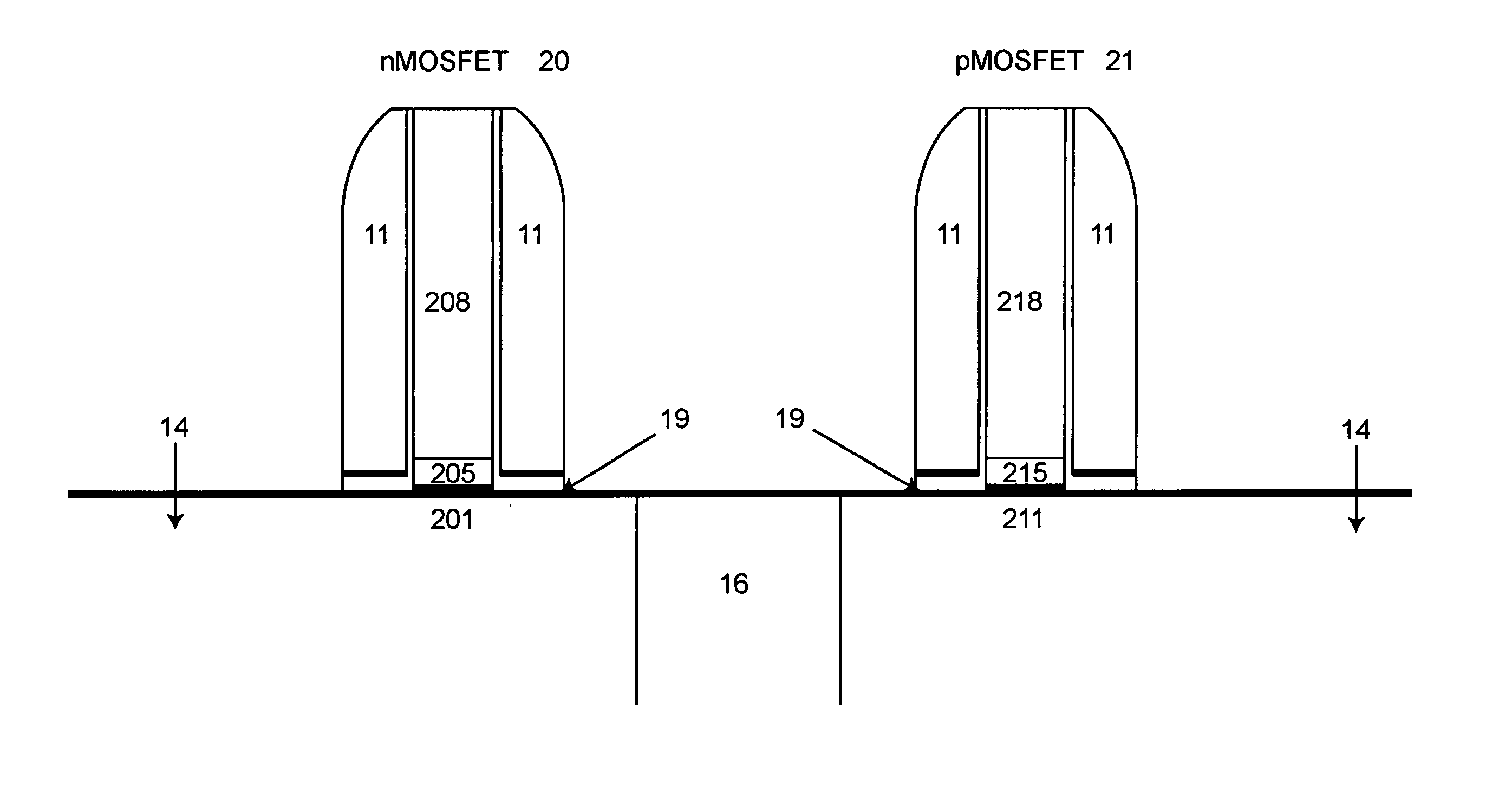

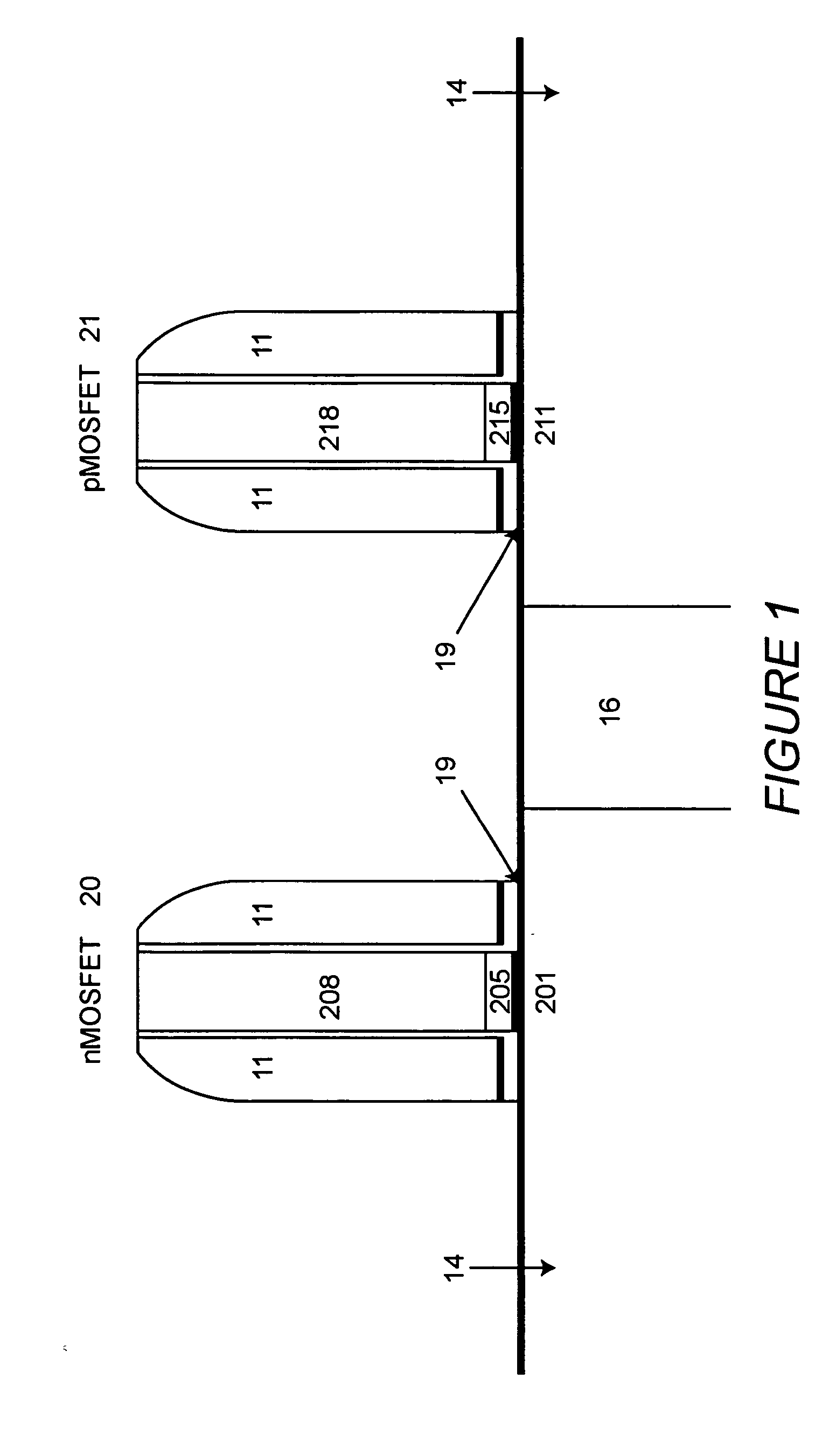

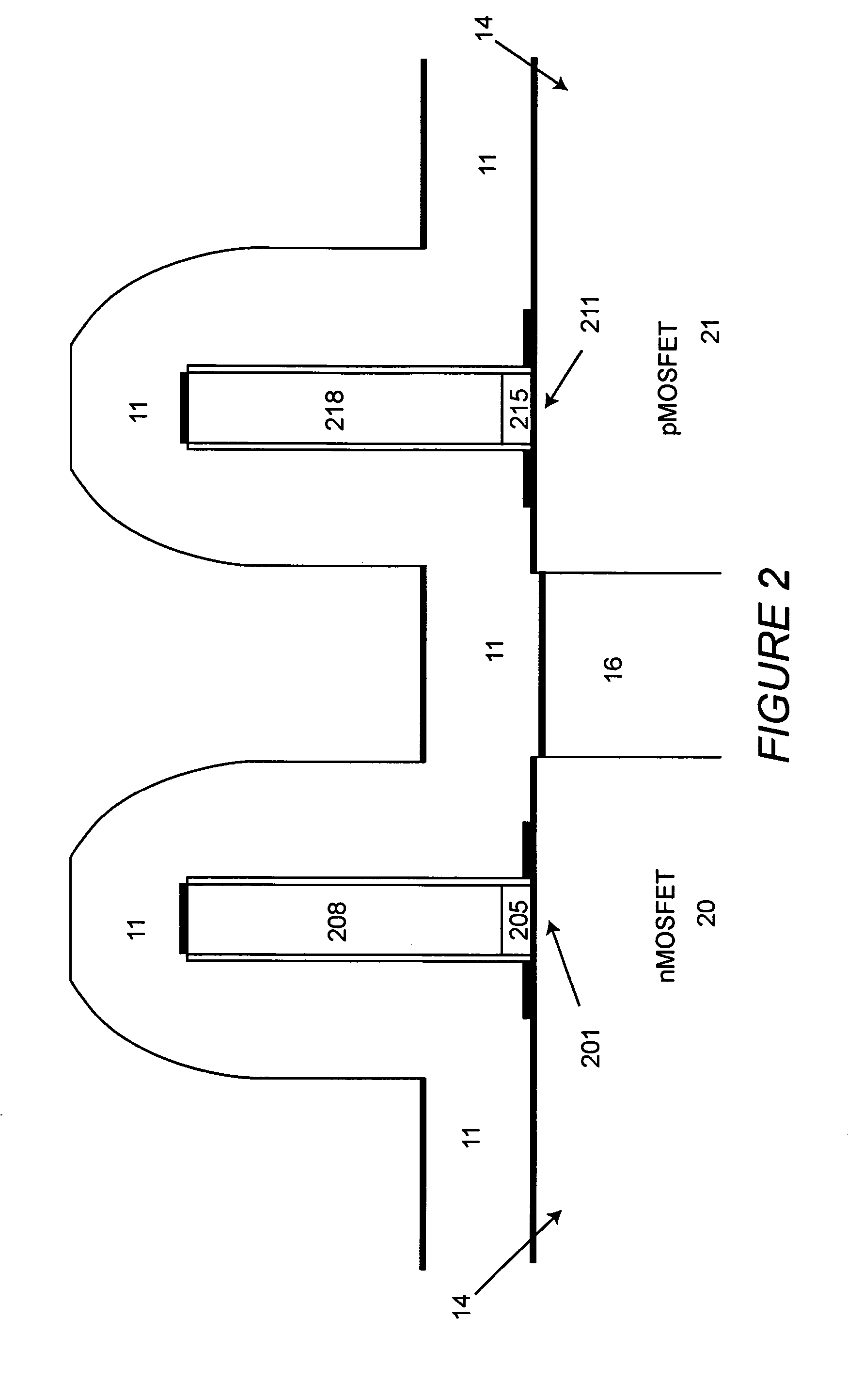

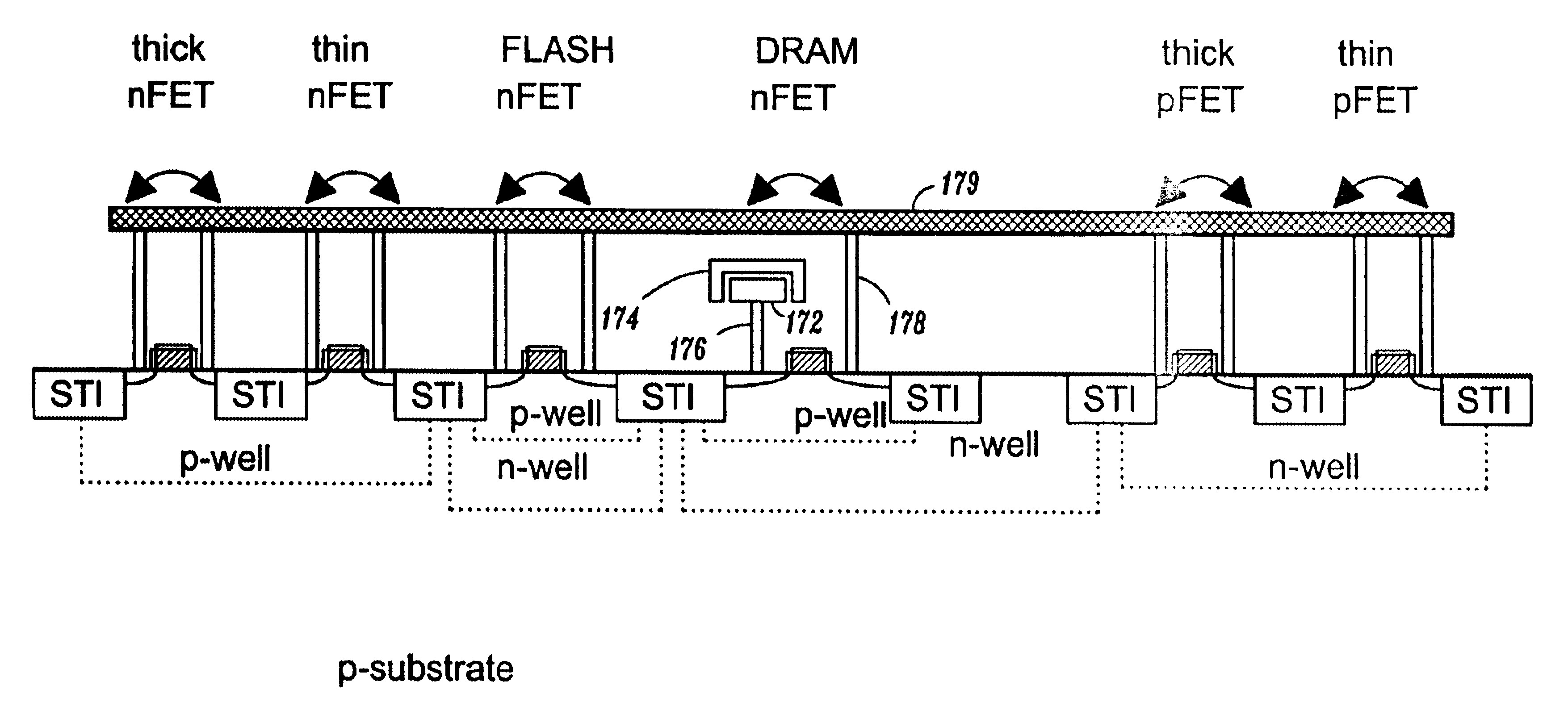

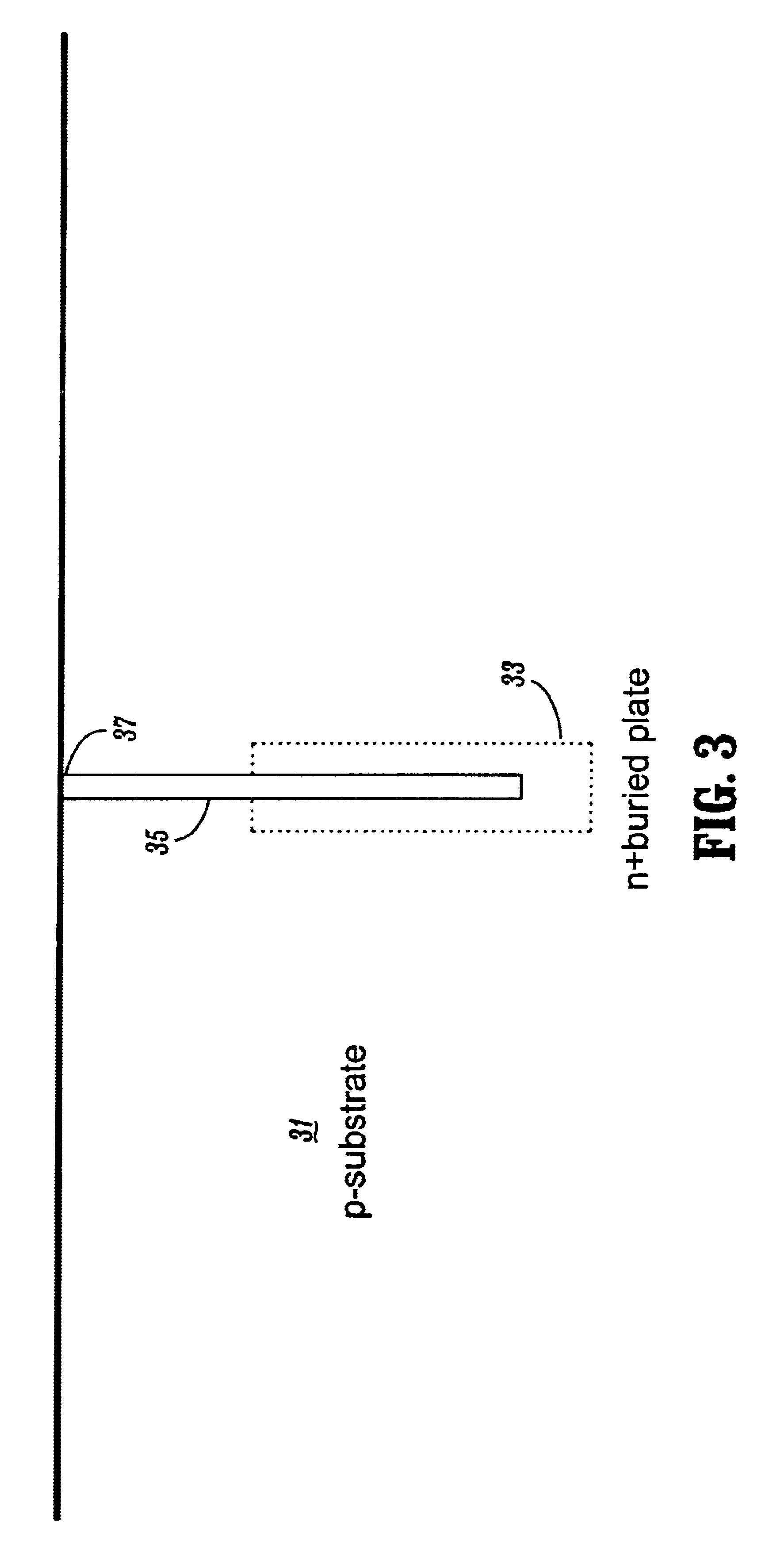

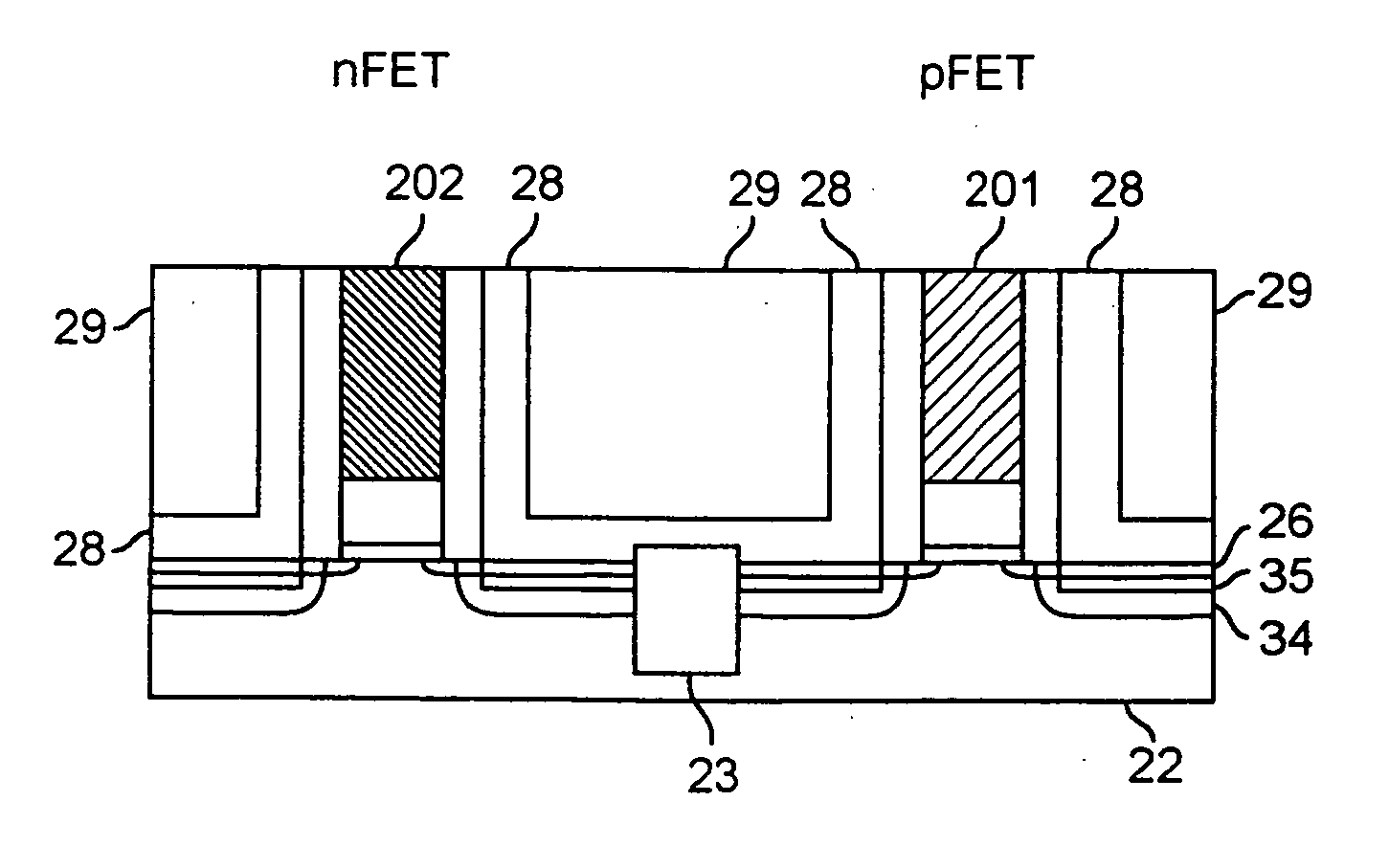

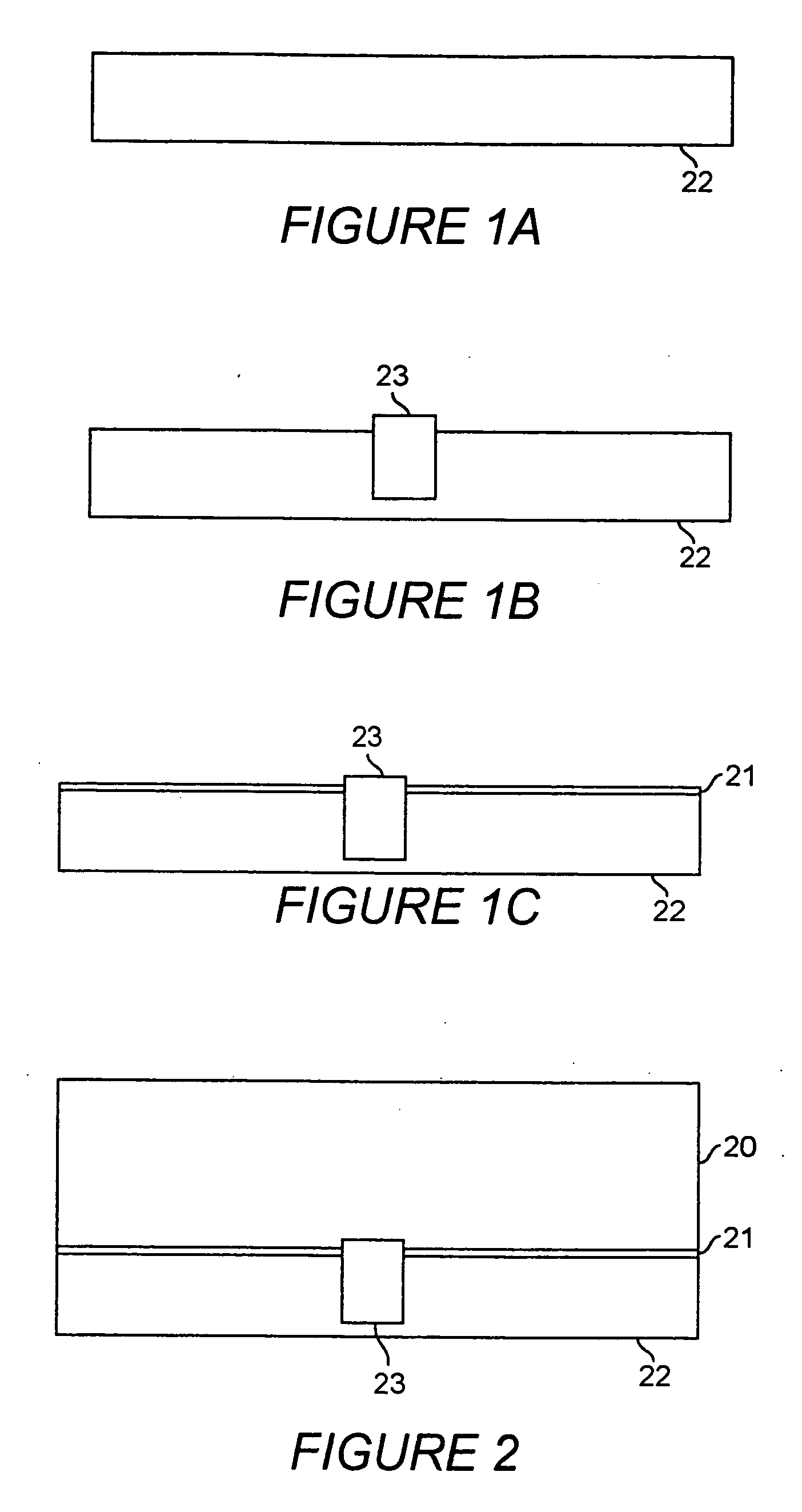

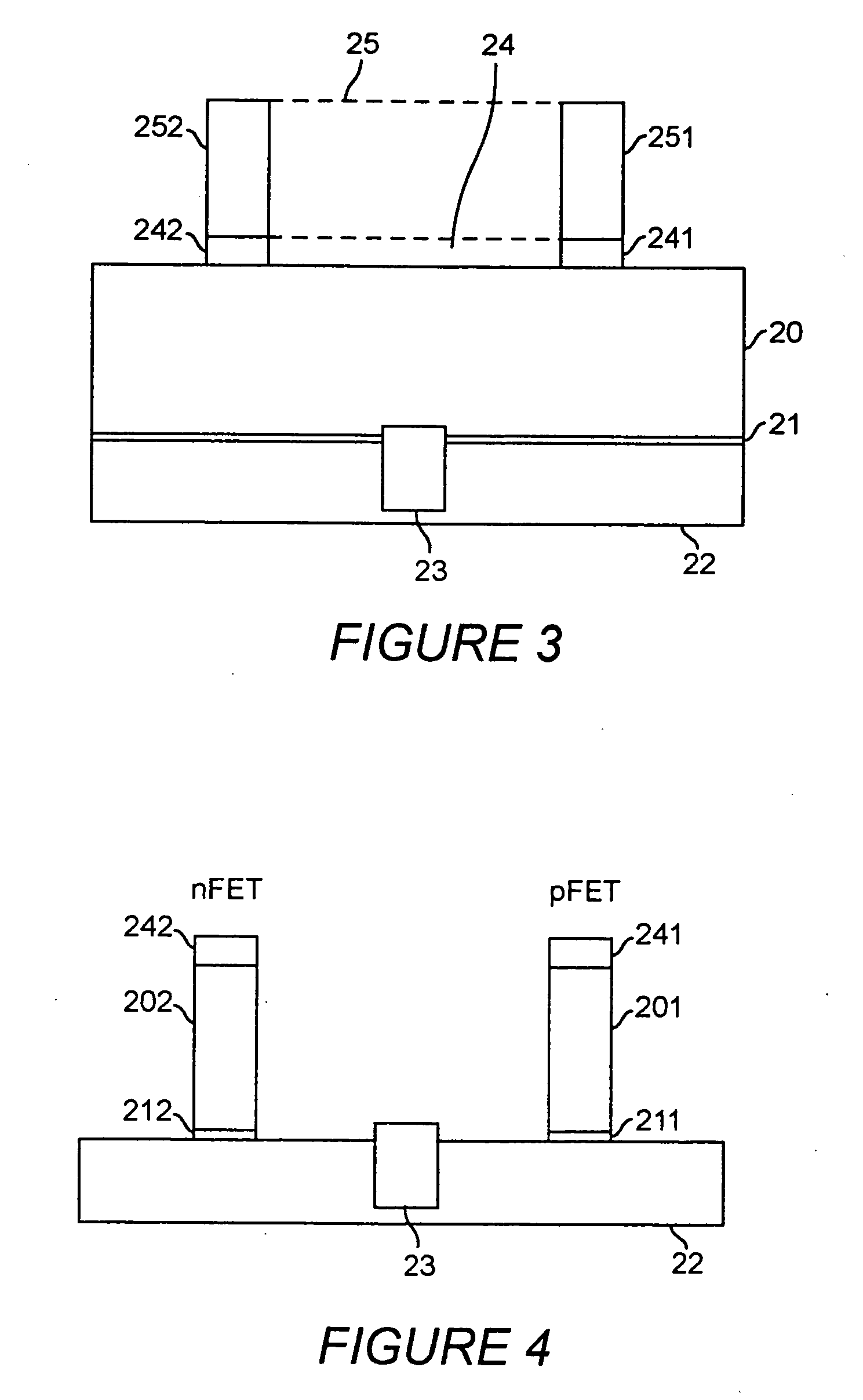

Structure and method to enhance both nFET and pFET performance using different kinds of stressed layers

InactiveUS20050093030A1Improve performanceTransistorSemiconductor/solid-state device detailsCMOSCharge carrier mobility

In producing complementary sets of metal-oxide-semiconductor (CMOS) field effect transistors, including nMOS and pMOS transistors), carrier mobility is enhanced or otherwise regulated through the use of layering various stressed films over either the nMOS or pMOS transistor (or both), depending on the properties of the layer and isolating stressed layers from each other and other structures with an additional layer in a selected location. Thus both types of transistors on a single chip or substrate can achieve an enhanced carrier mobility, thereby improving the performance of CMOS devices and integrated circuits.

Owner:GLOBALFOUNDRIES INC

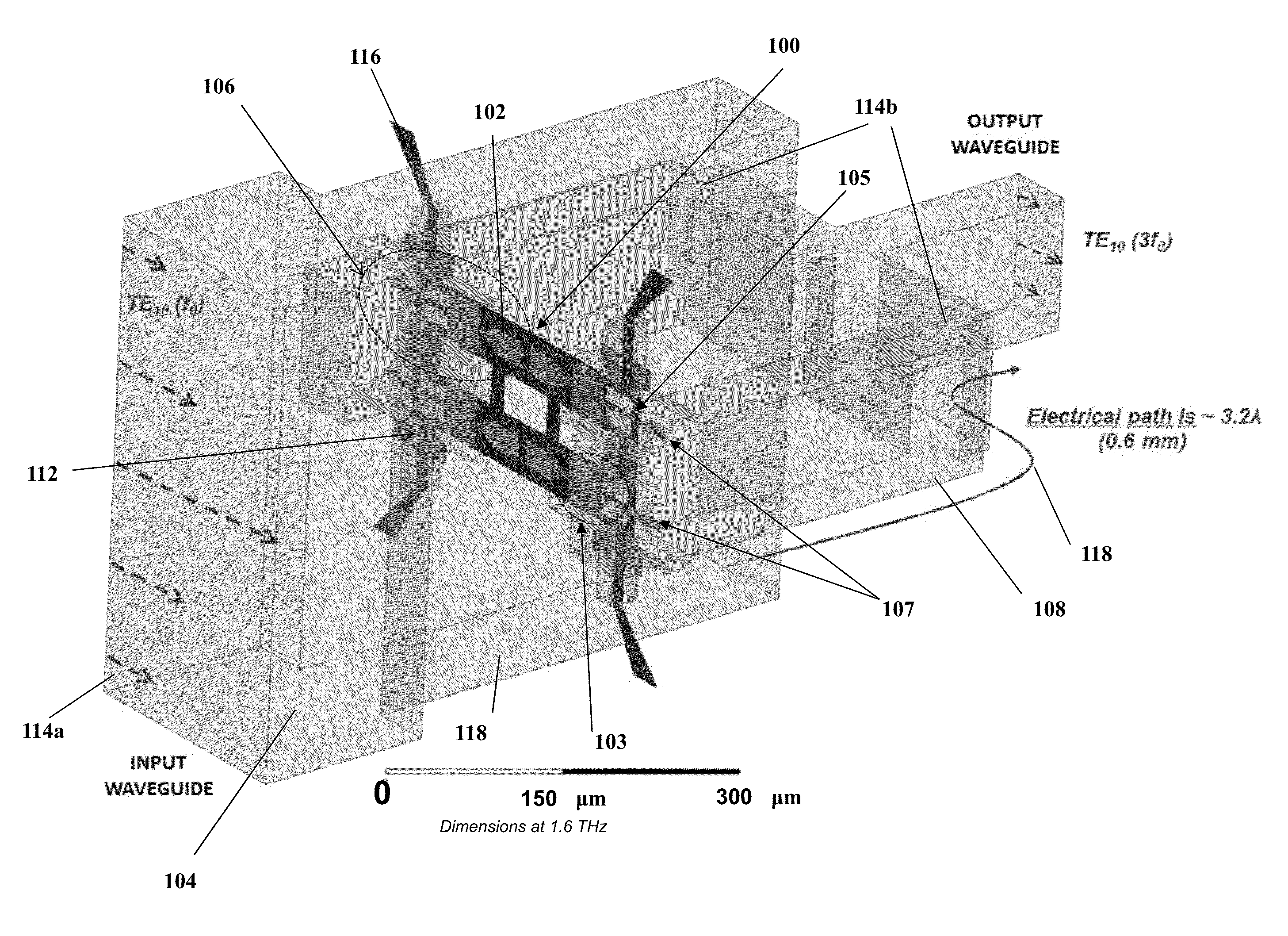

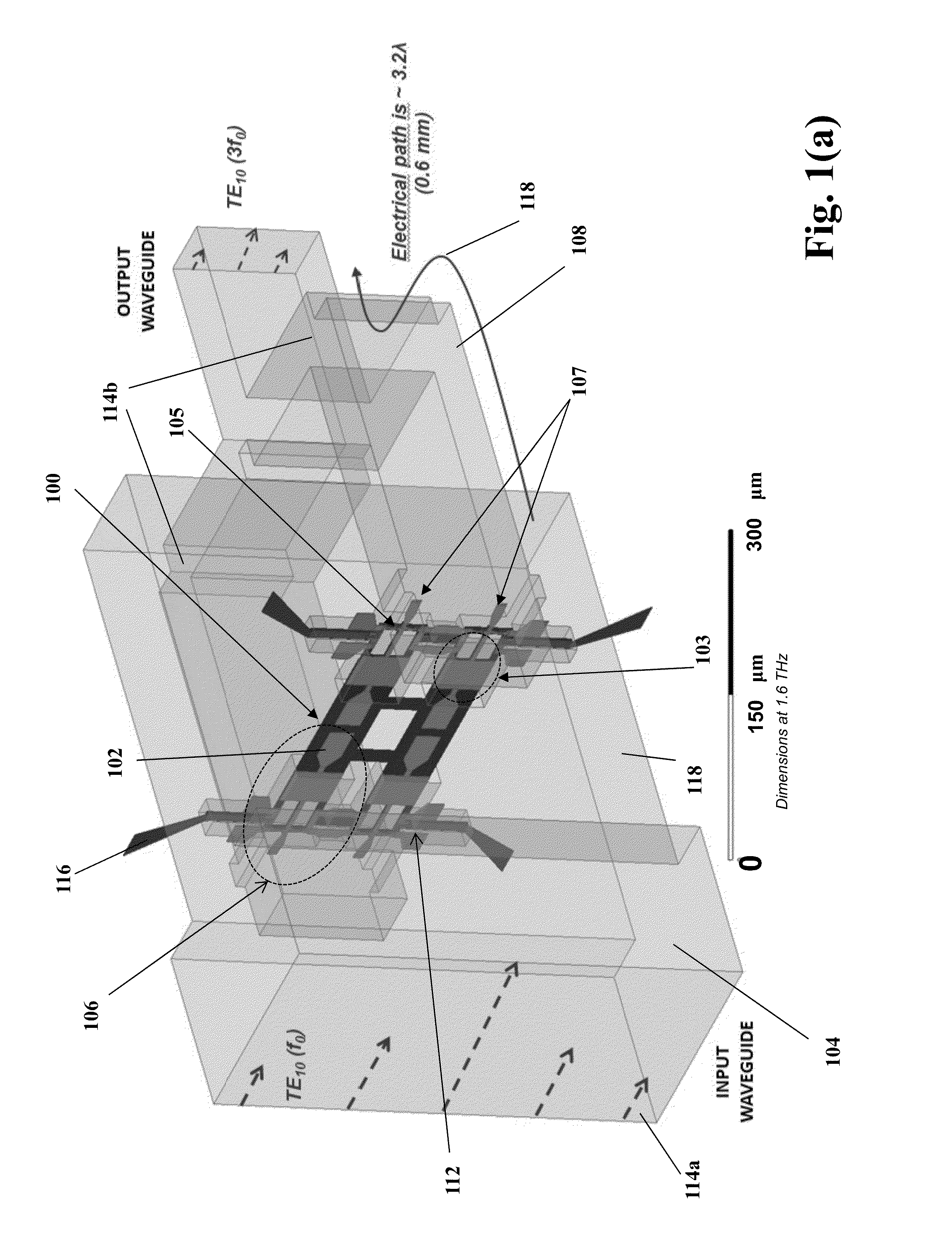

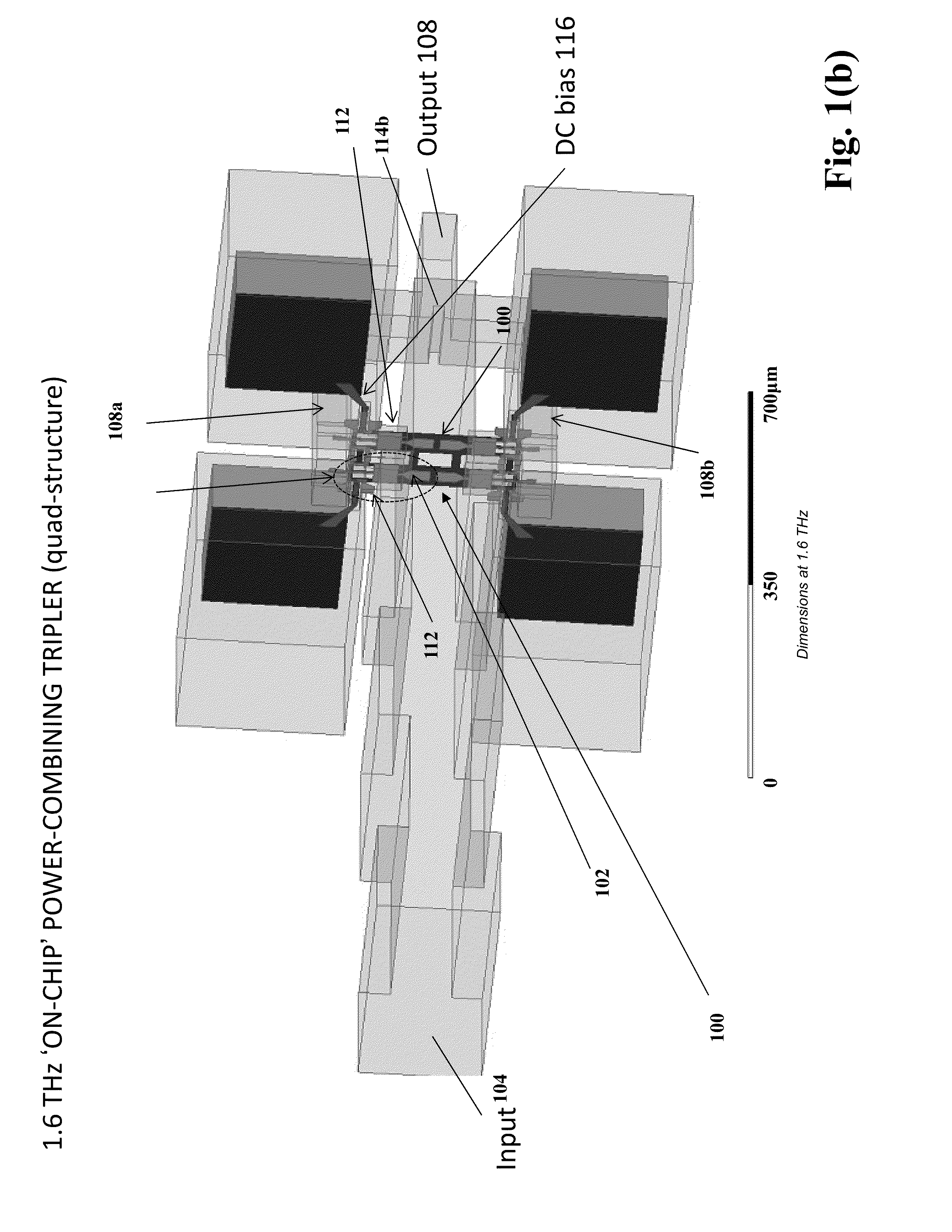

On-chip power-combining for high-power schottky diode based frequency multipliers

ActiveUS9143084B2Split evenlySemiconductor/solid-state device detailsSolid-state devicesHarmonicFrequency multiplier

A novel MMIC on-chip power-combined frequency multiplier device and a method of fabricating the same, comprising two or more multiplying structures integrated on a single chip, wherein each of the integrated multiplying structures are electrically identical and each of the multiplying structures include one input antenna (E-probe) for receiving an input signal in the millimeter-wave, submillimeter-wave or terahertz frequency range inputted on the chip, a stripline based input matching network electrically connecting the input antennas to two or more Schottky diodes in a balanced configuration, two or more Schottky diodes that are used as nonlinear semiconductor devices to generate harmonics out of the input signal and produce the multiplied output signal, stripline based output matching networks for transmitting the output signal from the Schottky diodes to an output antenna, and an output antenna (E-probe) for transmitting the output signal off the chip into the output waveguide transmission line.

Owner:CALIFORNIA INST OF TECH

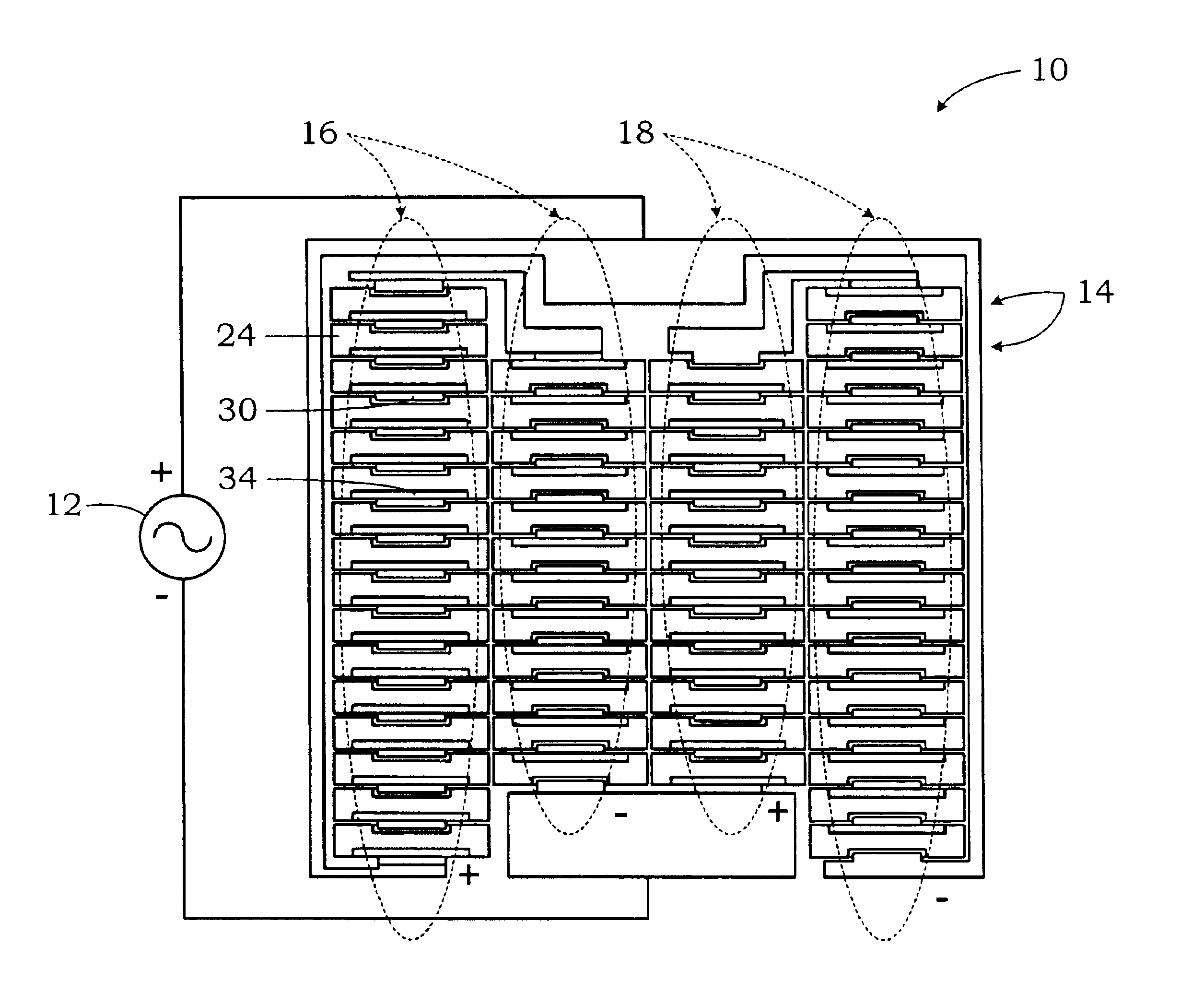

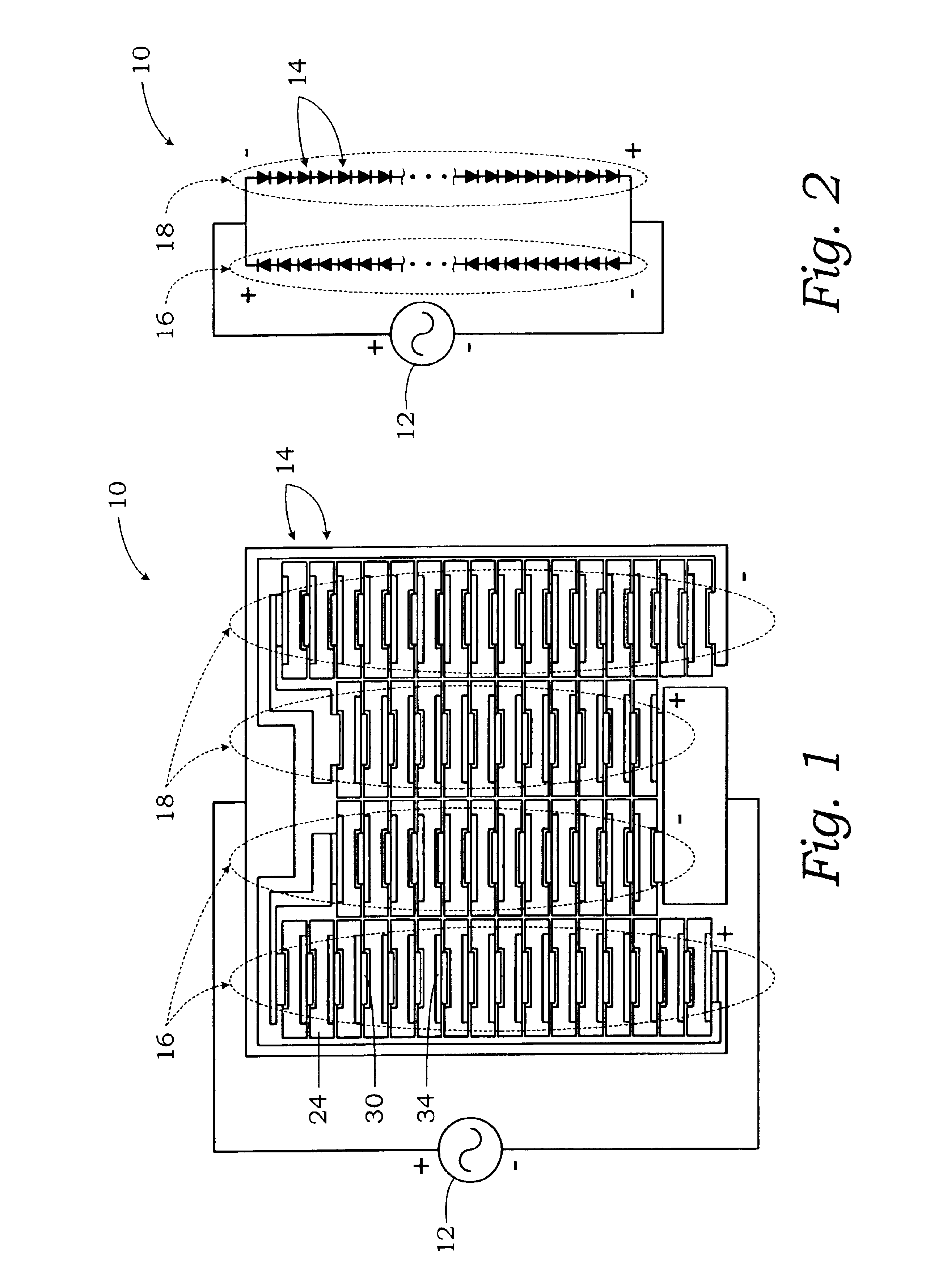

Light emitting diodes for high AC voltage operation and general lighting

InactiveUS7213942B2Improve heat transfer performanceLighting support devicesPoint-like light sourceLed arrayEffect light

A single-chip integrated LED particularly adapted for direct use with a high voltage AC power comprises a plurality of series-connected LEDs arranged in two arrays and flip chip bonded to a transparent substrate. The opposite polarities of the arrays are connected together and then connected to the AC power source. During the positive half of the AC cycle, one array of LEDs is forward biased and energized, while the other array is reverse biased. During the negative half of the AC cycle, the other array of LEDs is forward biased and thus energized, while the first array is reverse biased and thus not energized. The arrays are alternately energized and de-energized at the frequency of the AC power source, and thus the single-chip integrated LED always appears to be energized.

Owner:SEOUL SEMICONDUCTOR

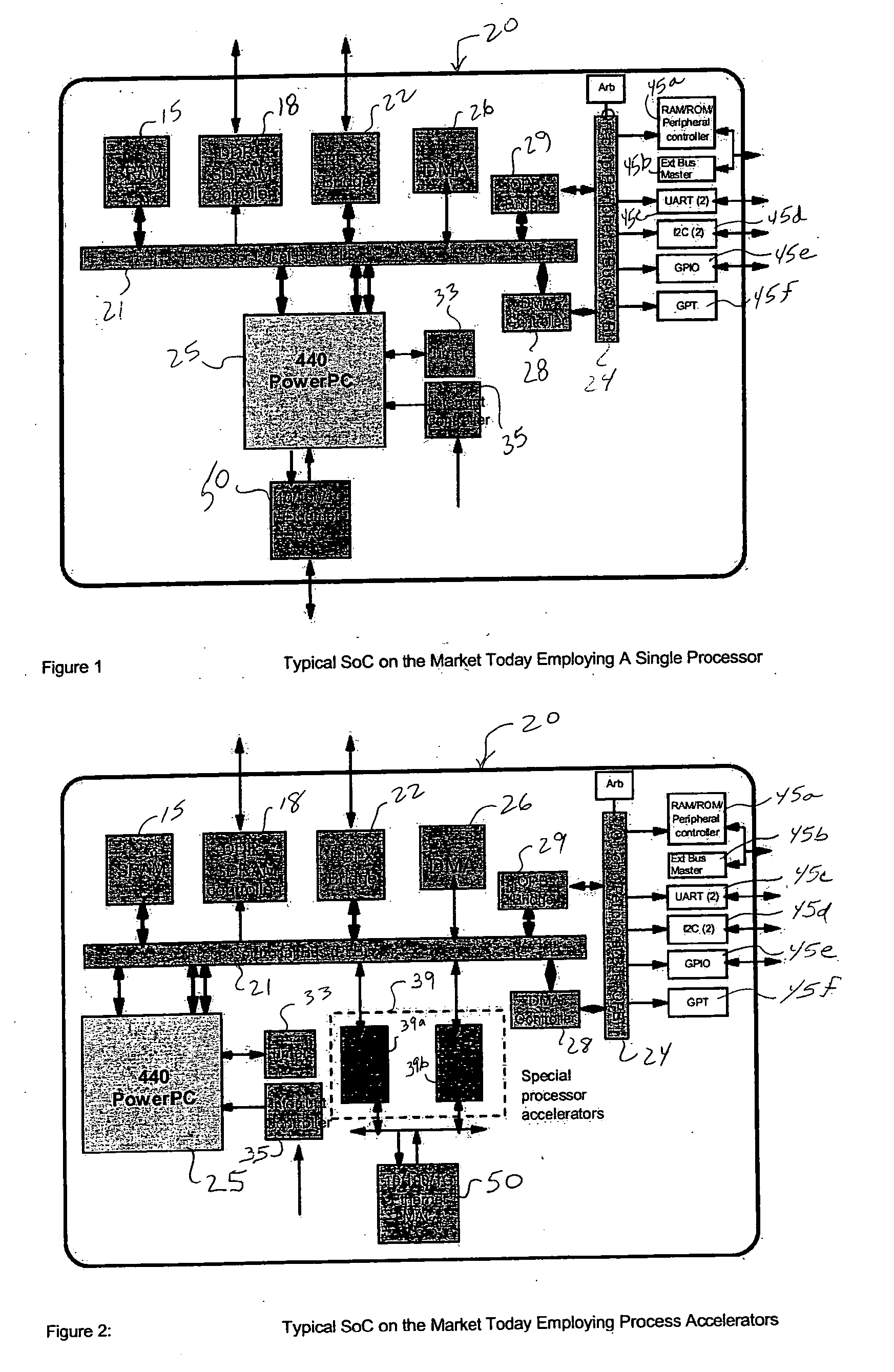

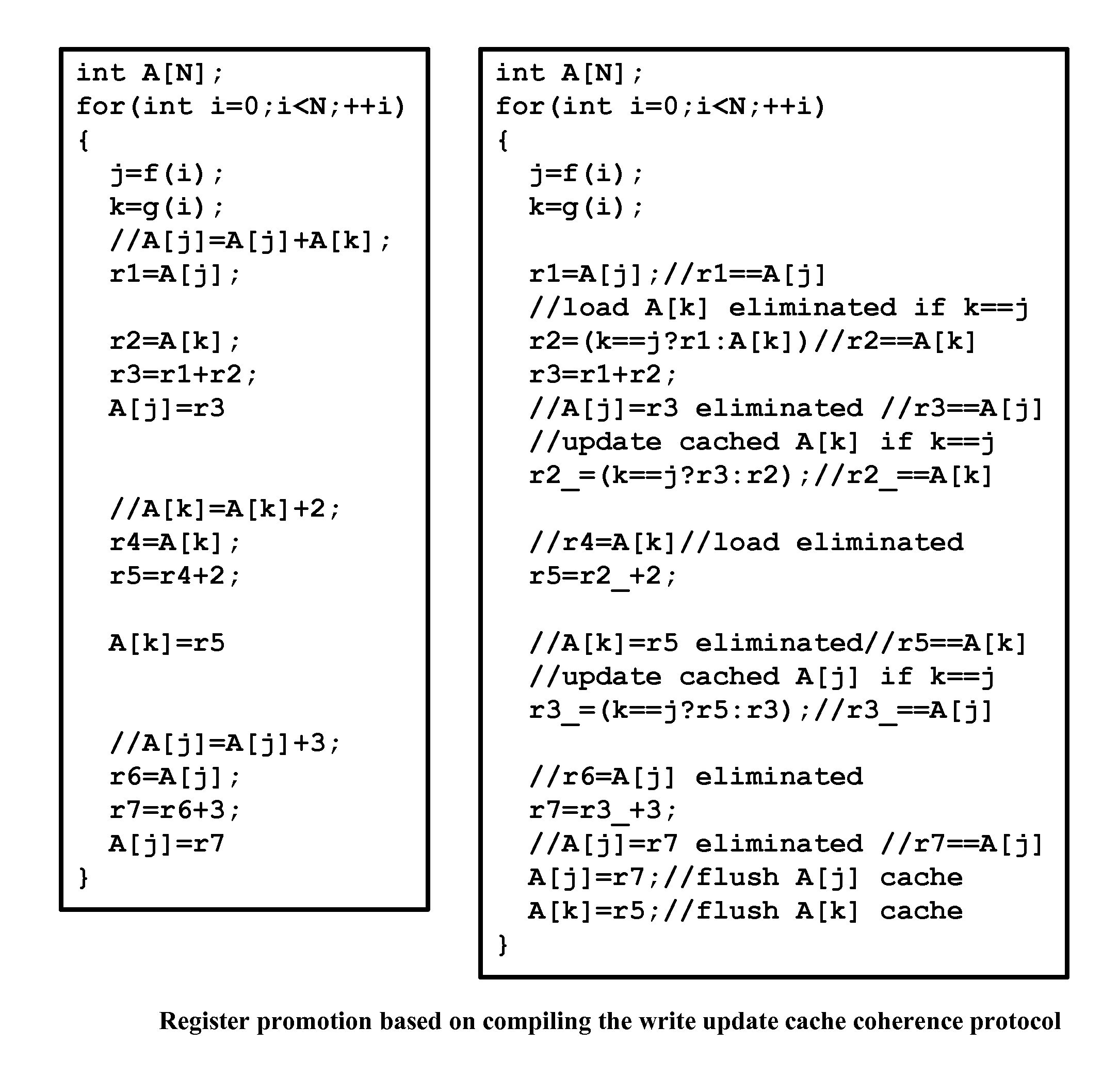

Method and system for converting a single-threaded software program into an application-specific supercomputer

ActiveUS20130125097A1Improve efficiencyLow overhead implementationMemory architecture accessing/allocationTransformation of program codeSupercomputerComputer architecture

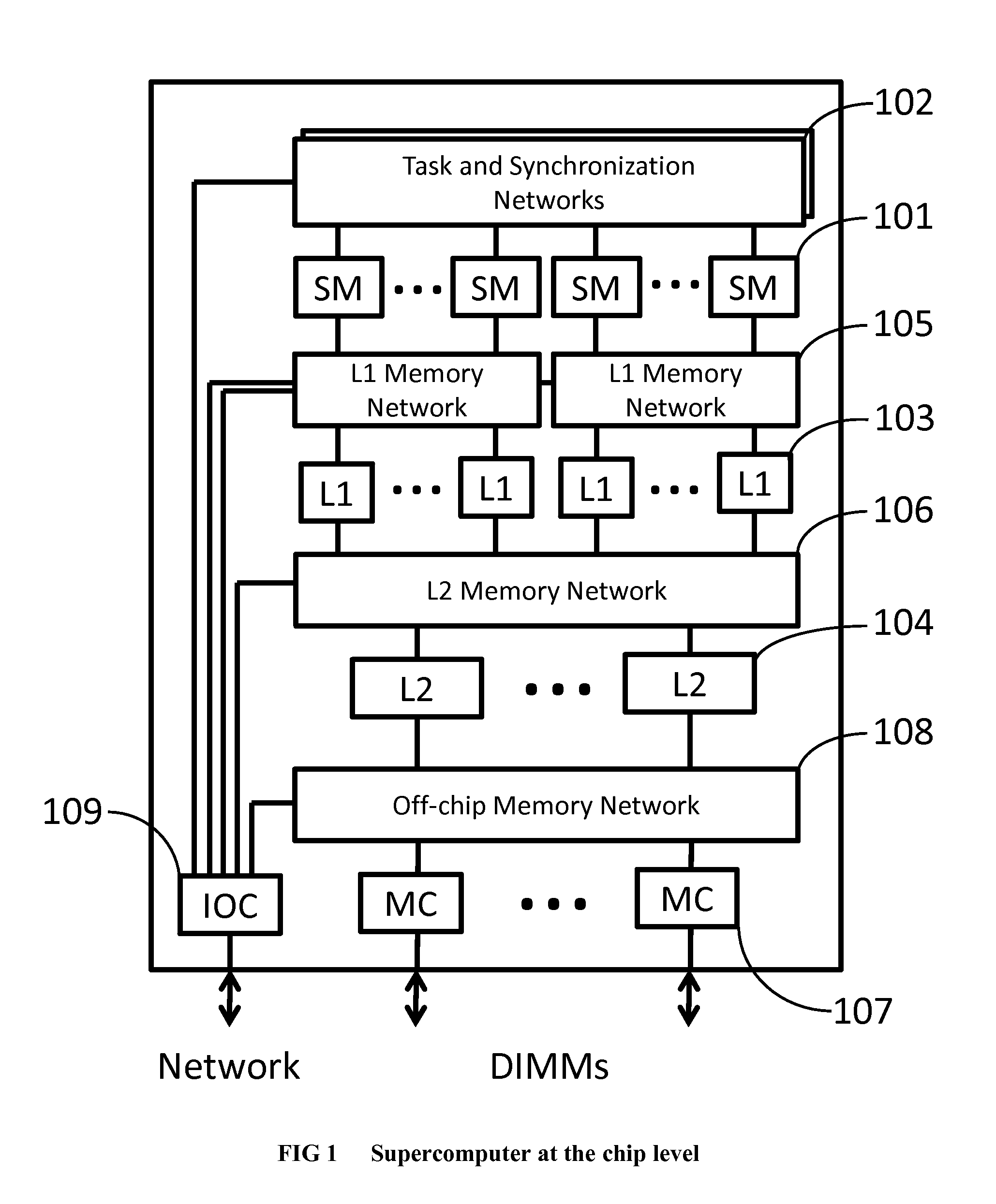

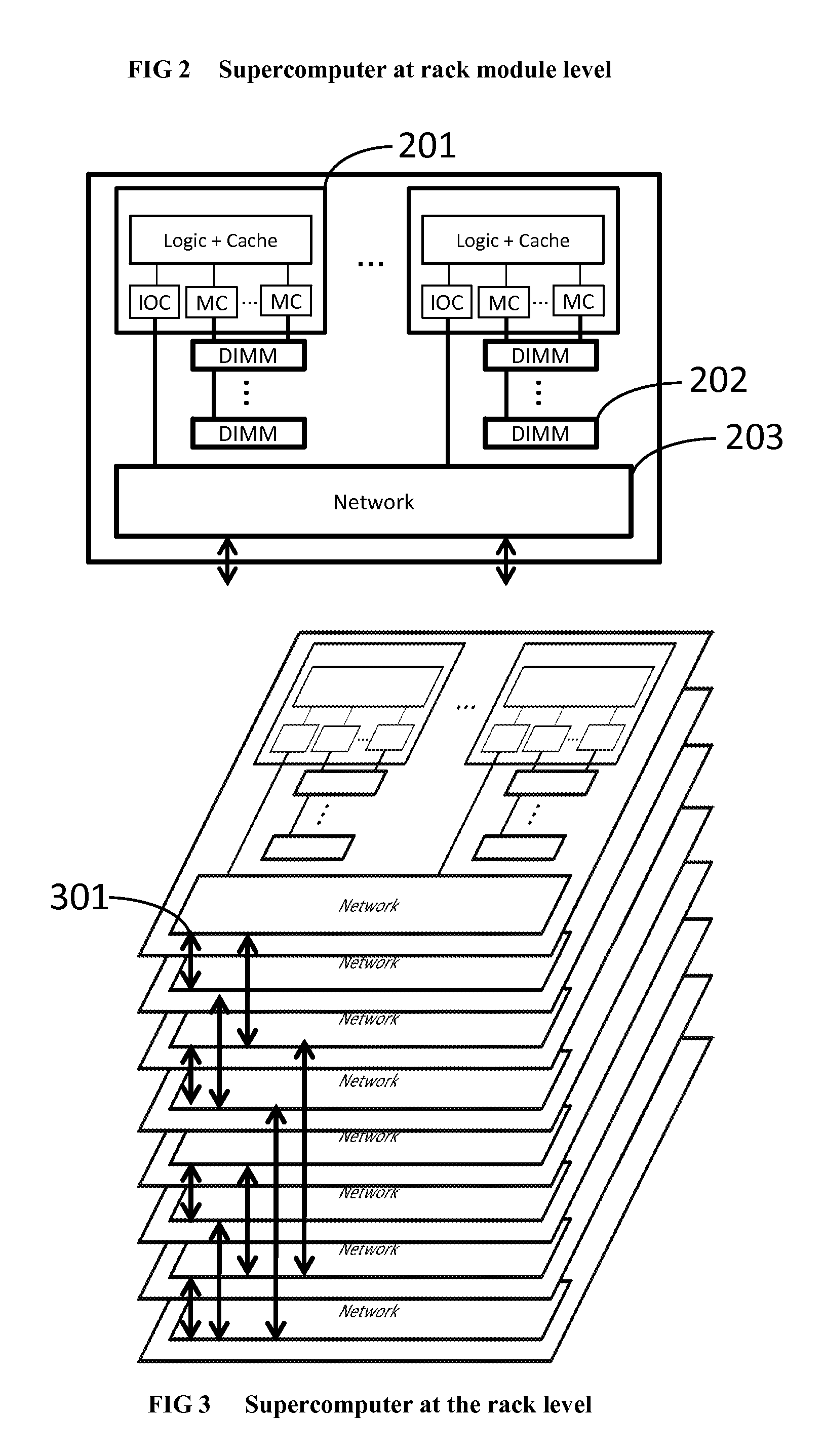

The invention comprises (i) a compilation method for automatically converting a single-threaded software program into an application-specific supercomputer, and (ii) the supercomputer system structure generated as a result of applying this method. The compilation method comprises: (a) Converting an arbitrary code fragment from the application into customized hardware whose execution is functionally equivalent to the software execution of the code fragment; and (b) Generating interfaces on the hardware and software parts of the application, which (i) Perform a software-to-hardware program state transfer at the entries of the code fragment; (ii) Perform a hardware-to-software program state transfer at the exits of the code fragment; and (iii) Maintain memory coherence between the software and hardware memories. If the resulting hardware design is large, it is divided into partitions such that each partition can fit into a single chip. Then, a single union chip is created which can realize any of the partitions.

Owner:GLOBAL SUPERCOMPUTING CORP

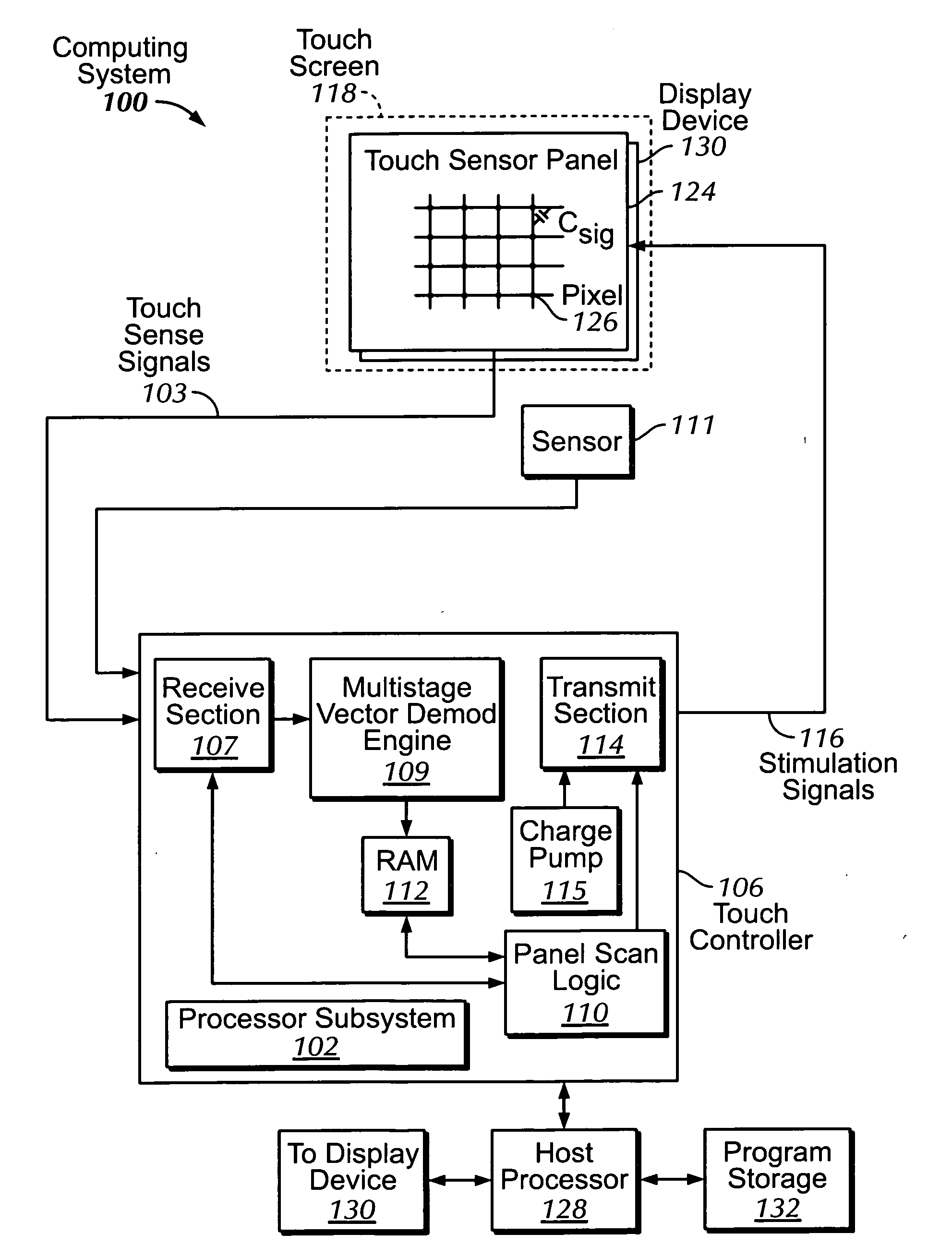

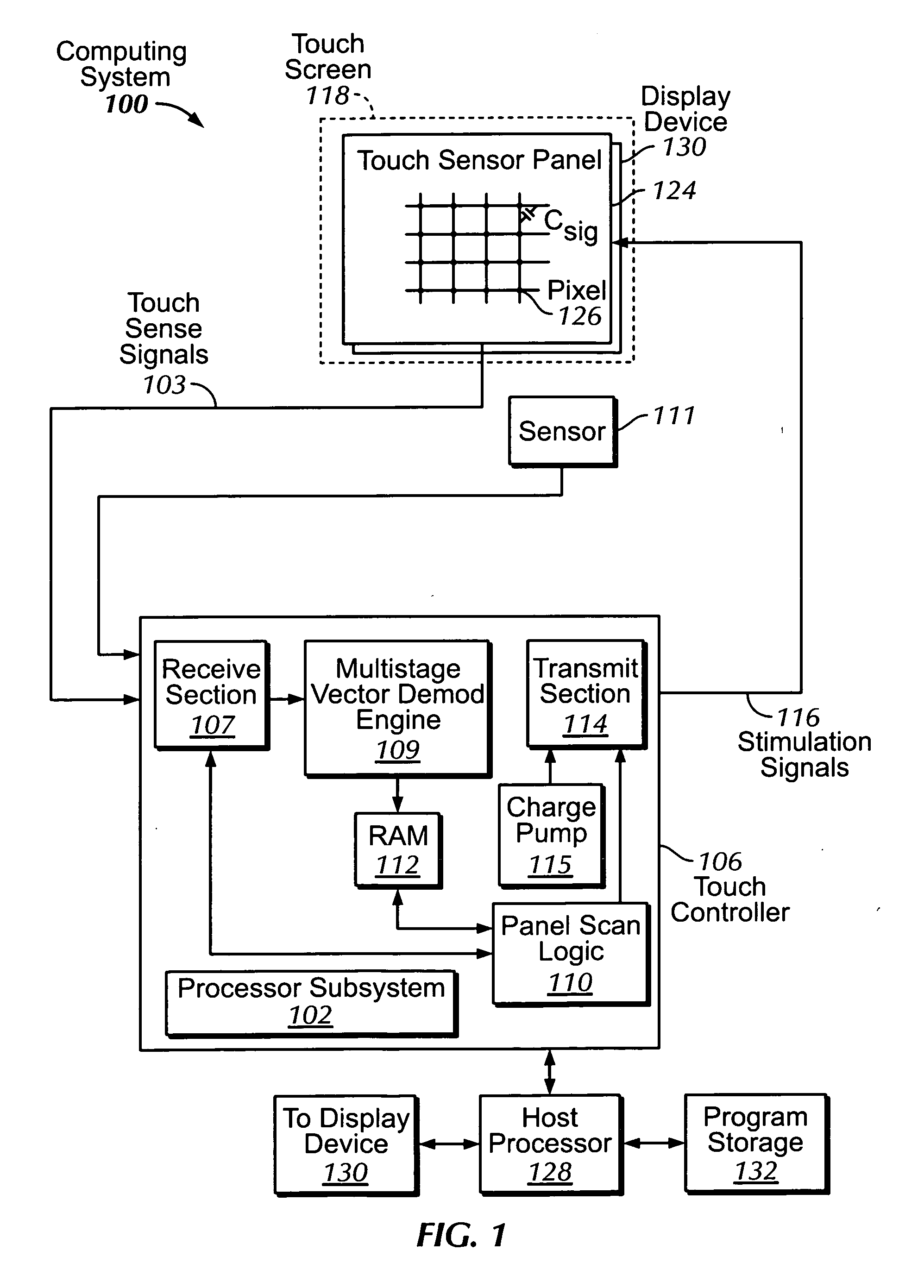

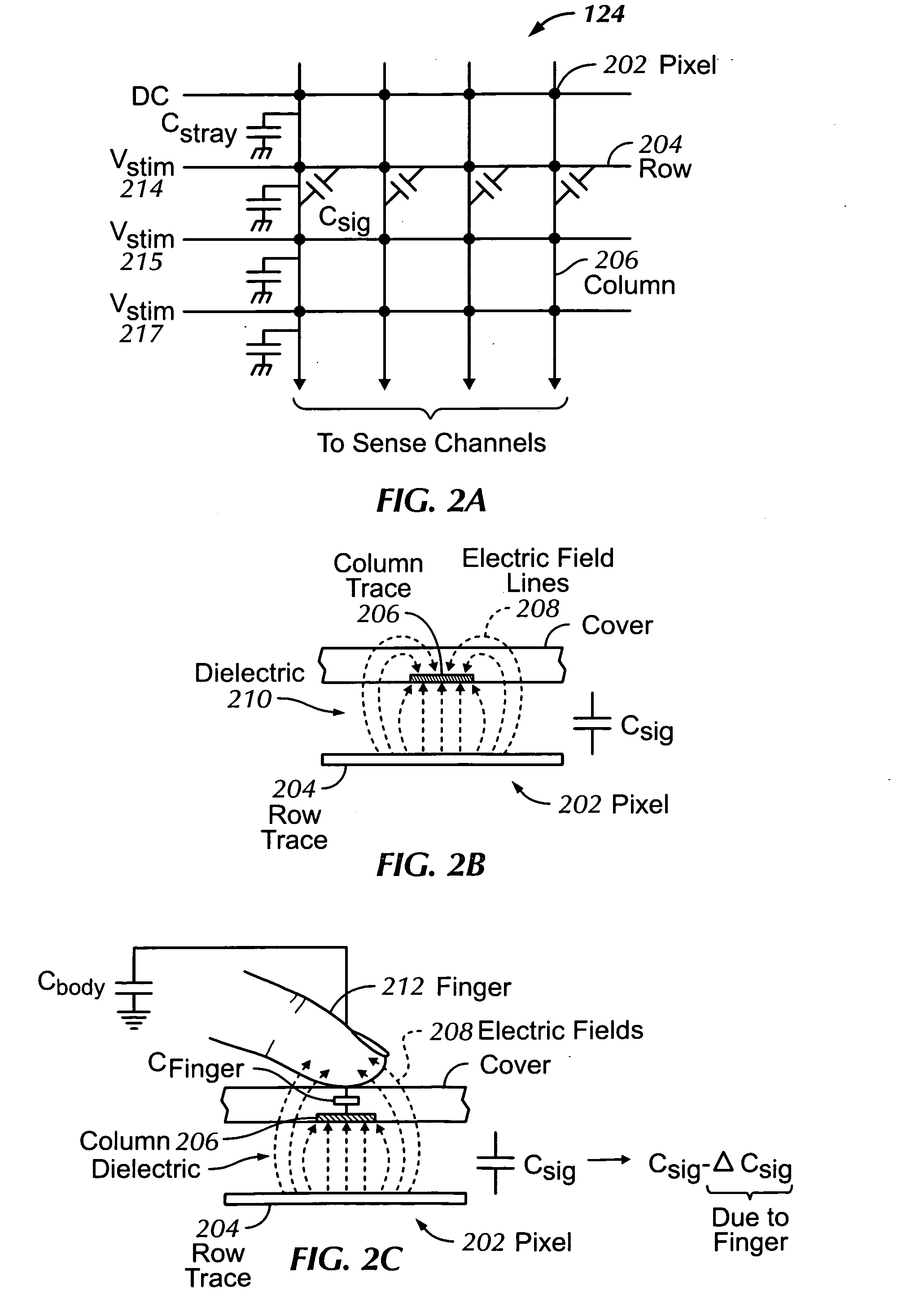

Single-chip multi-stimulus sensor controller

ActiveUS20100059295A1Transmission systemsCathode-ray tube indicatorsSingle chipFrequency demodulation

A multi-stimulus controller for a multi-touch sensor is formed on a single integrated circuit (single-chip). The multi-stimulus controller includes a transmit oscillator, a transmit signal section that generates a plurality of drive signals based on a frequency of the transmit oscillator, a plurality of transmit channels that transmit the drive signals simultaneously to drive the multi-touch sensor, a receive channel that receives a sense signal resulting from the driving of the multi-touch sensor, a receive oscillator, and a demodulation section that demodulates the received sense signal based on a frequency of the receive oscillator to obtain sensing results, the demodulation section including a demodulator and a vector operator.

Owner:APPLE INC

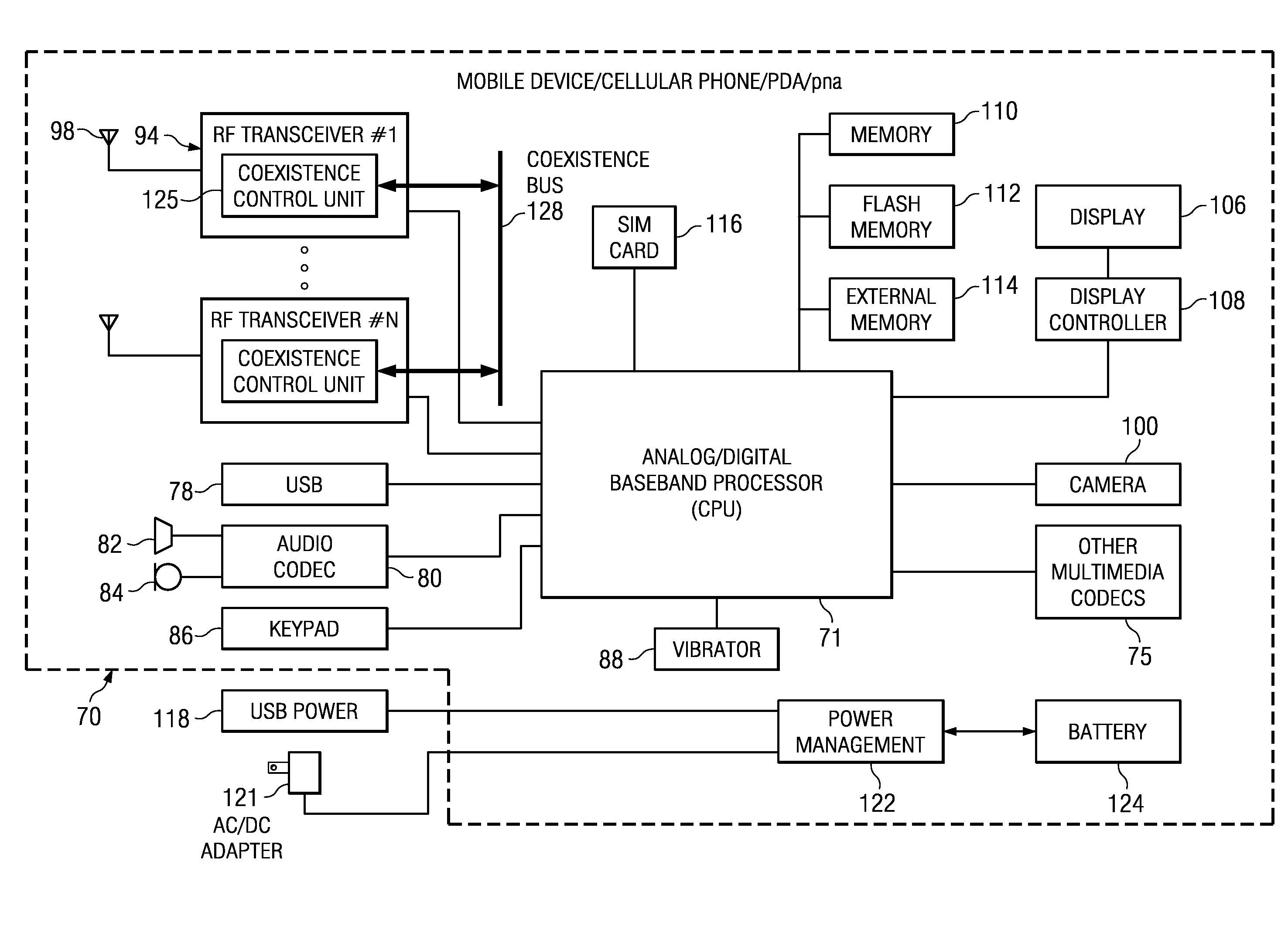

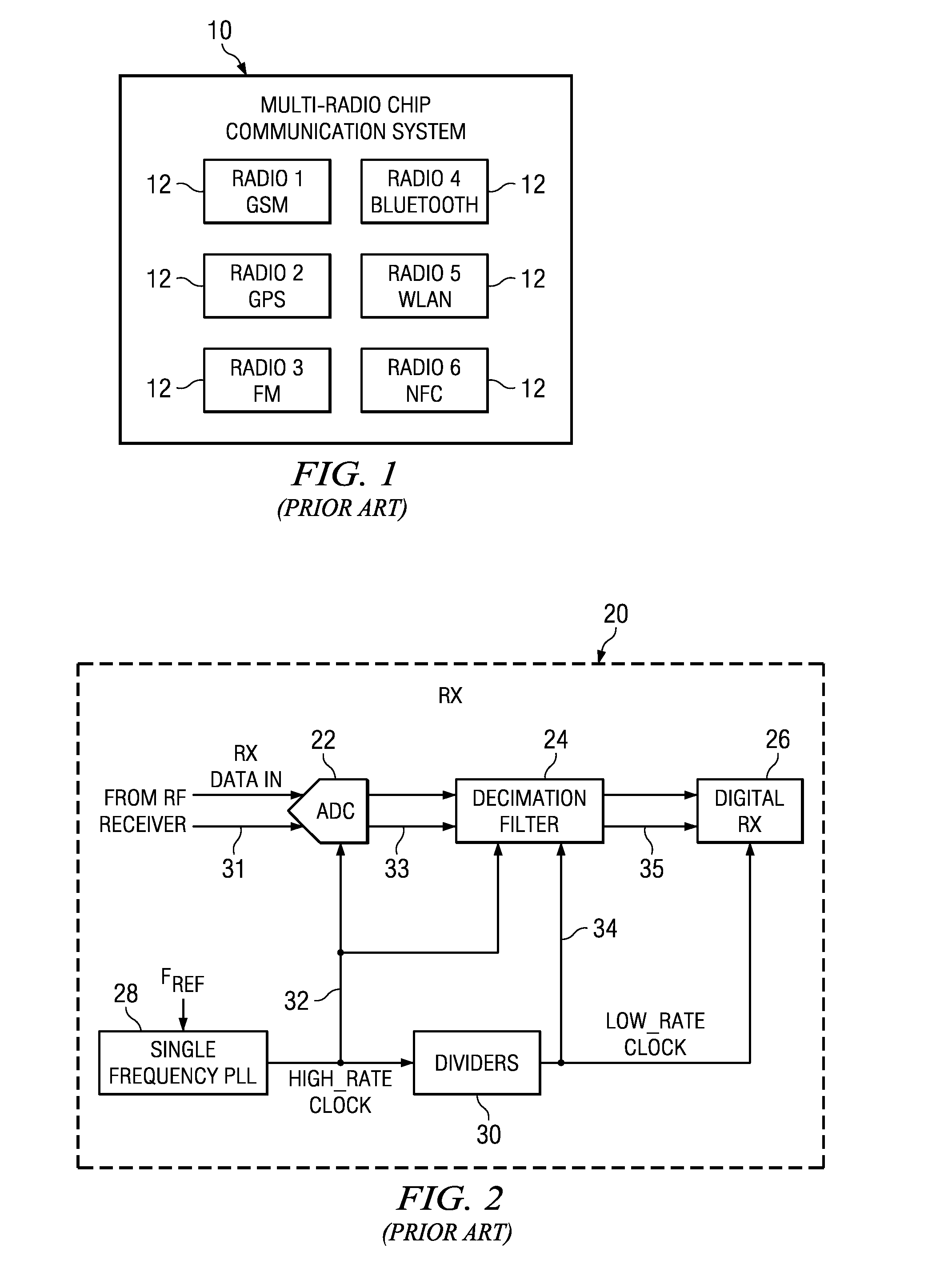

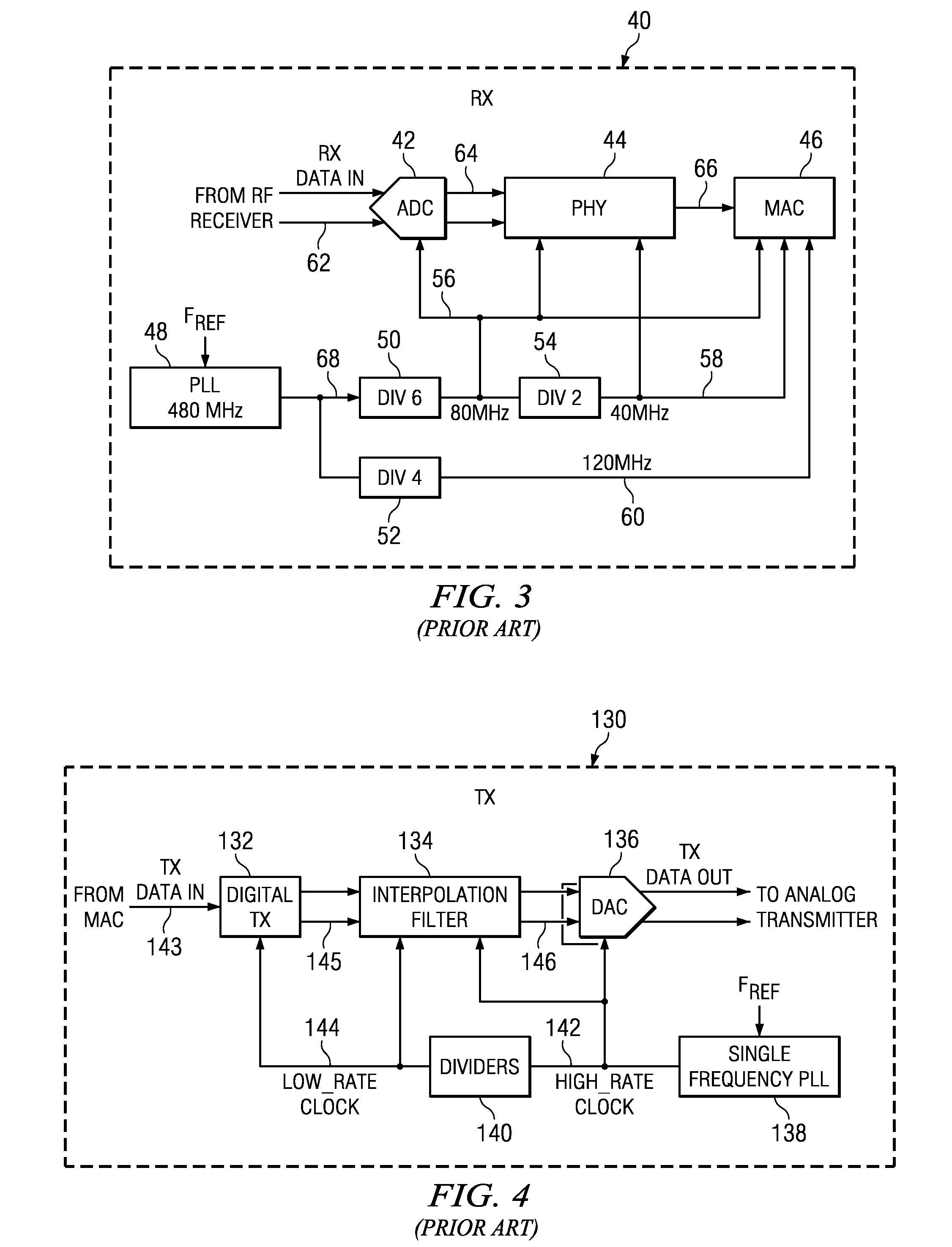

Distributed coexistence system for interference mitigation in a single chip radio or multi-radio communication device

ActiveUS20100137025A1Reduce distractionsAvoid interferenceCross-talk reductionSubstation equipmentTransceiverRadio reception

A novel and useful apparatus for and method of distributed coexistence for mitigating interference in a single chip radio and / or a multi-radio (i.e. multi-transceiver) communications device. The invention enables coexistence ‘friendly’ radio IPs having frequency agility in that they are capable of shifting their clock frequencies thereby avoiding frequency bands of potential victim radios. Frequency agility on the aggressor radio side (rather than by mitigating the effect of interference on the victim radio side) prevents harmonics from the aggressor's clock scheme from falling in the operating frequency band of the victim radio, and in turn causing degradation to its performance. Each aggressor radio, based on information received from other radios, configures the root clock frequency of its RX and / or TX chain clock generation circuits.

Owner:TEXAS INSTR INC

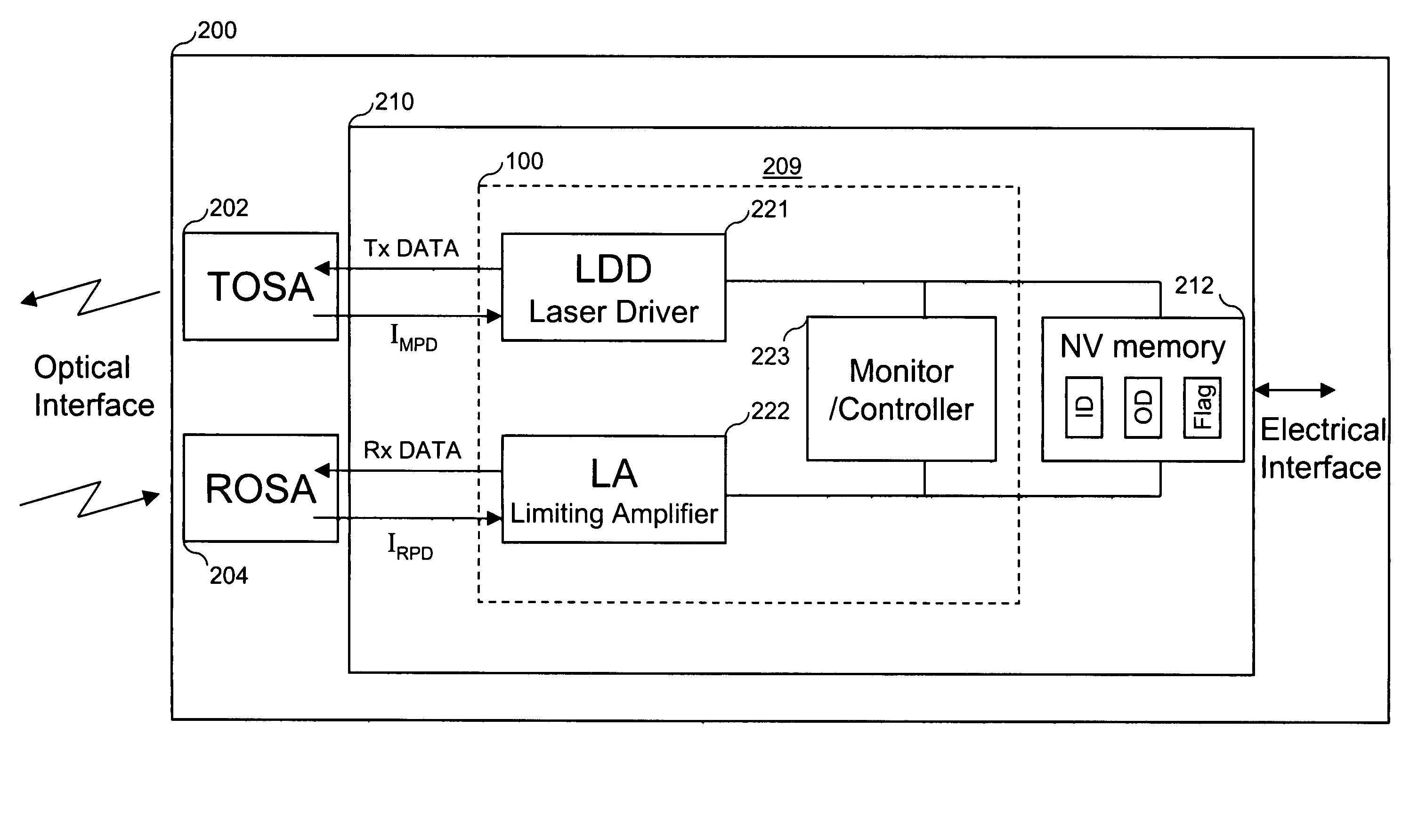

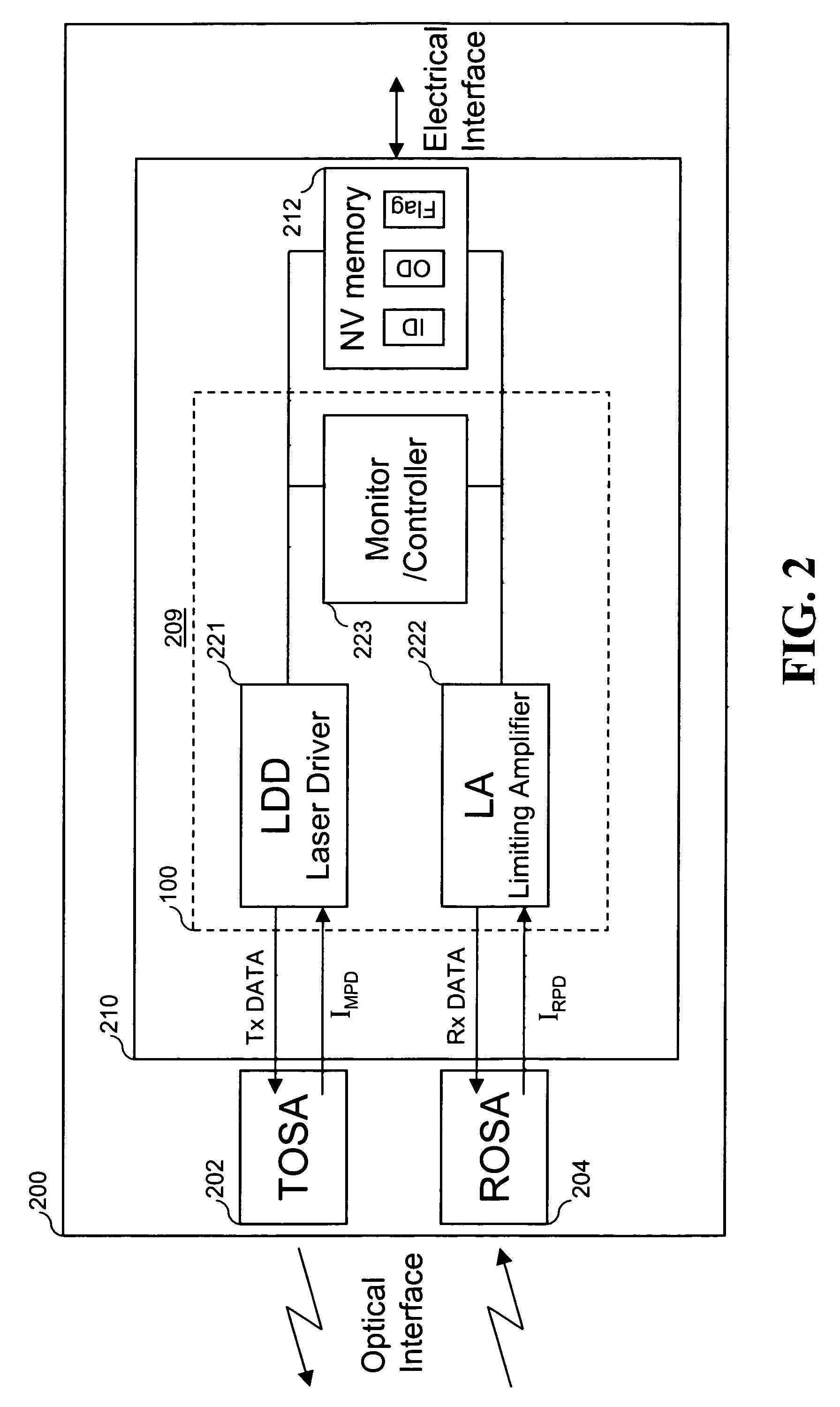

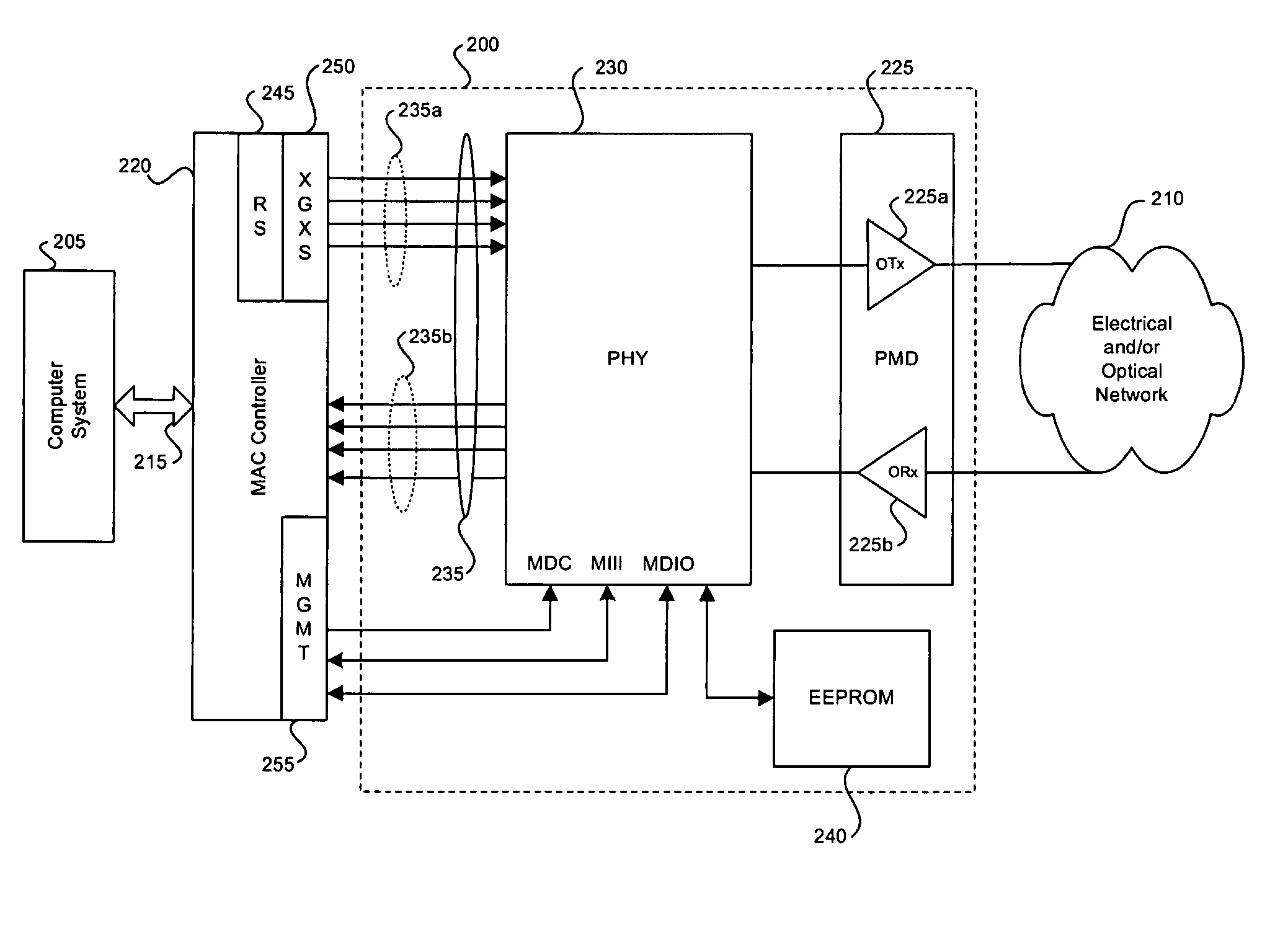

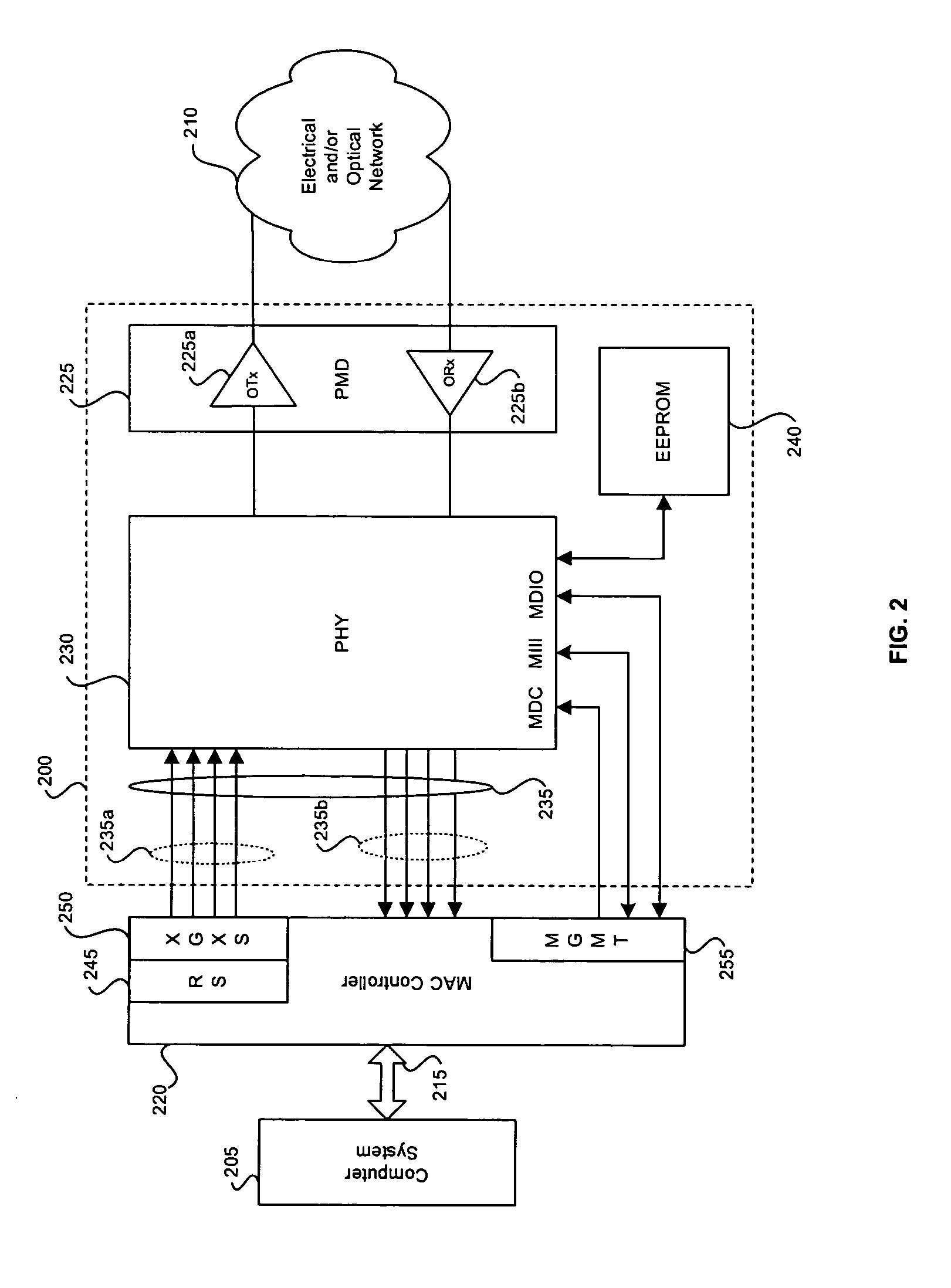

Integrated driving, receiving, controlling, and monitoring for optical transceivers

ActiveUS7215891B1Wide driving flexibilityElectromagnetic transmittersElectromagnetic transceiversTransceiverOpto electronic

An optical transceiver includes a single integrated circuit chip to integrate the drive, receive, control, and monitoring functions of the optical transceiver. The single chip may further have an advance replacement algorithm and monitoring algorithm for the opto-electronic devices of the optical transmitter and receiver to generate flags and / or an advance replacement indication. Methods, apparatus, and systems are disclosed.

Owner:NASA +1

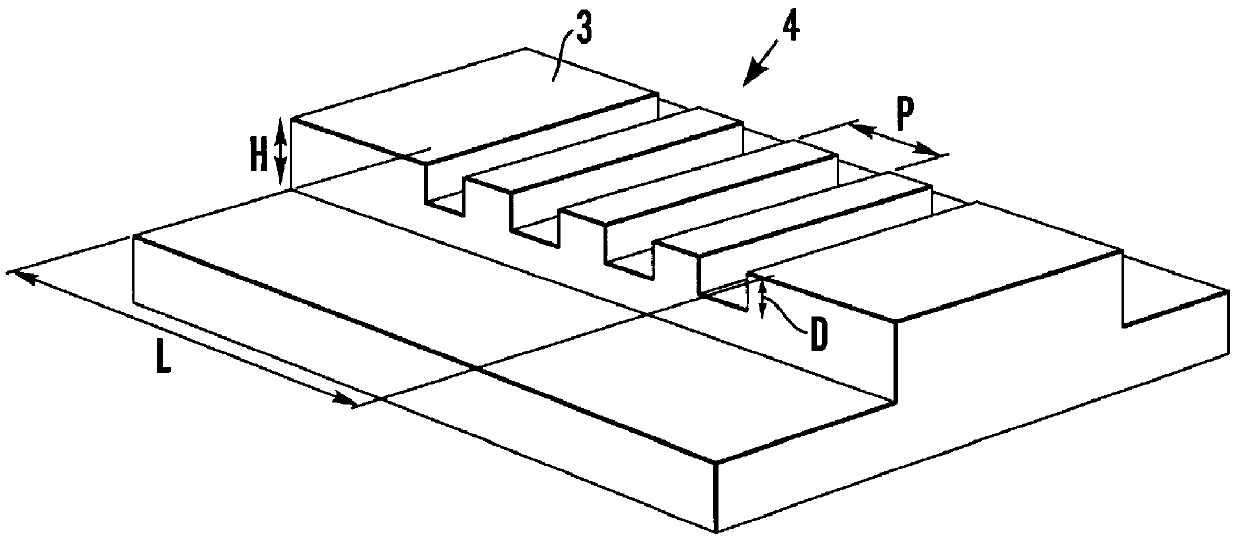

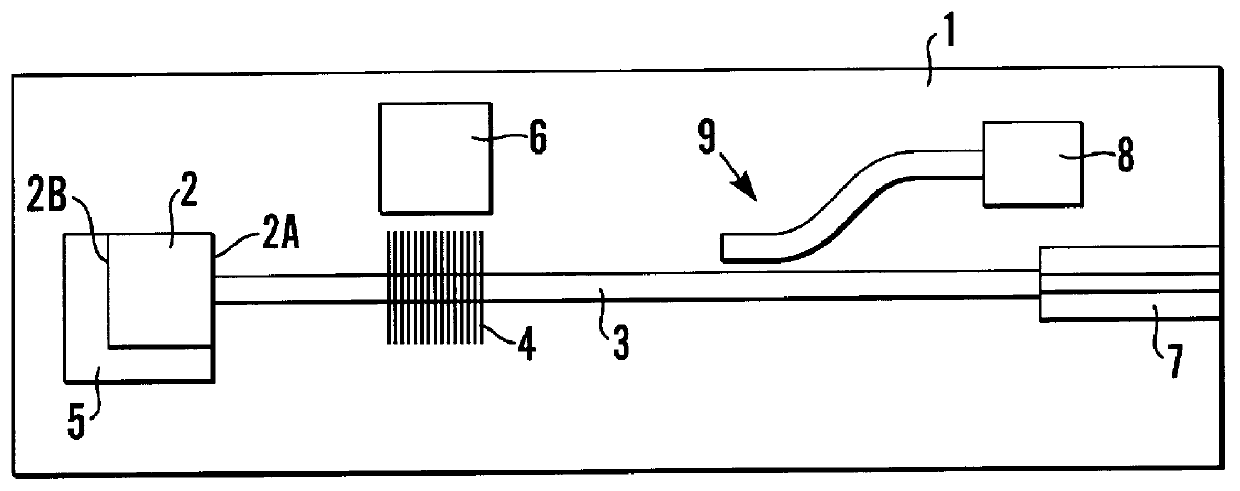

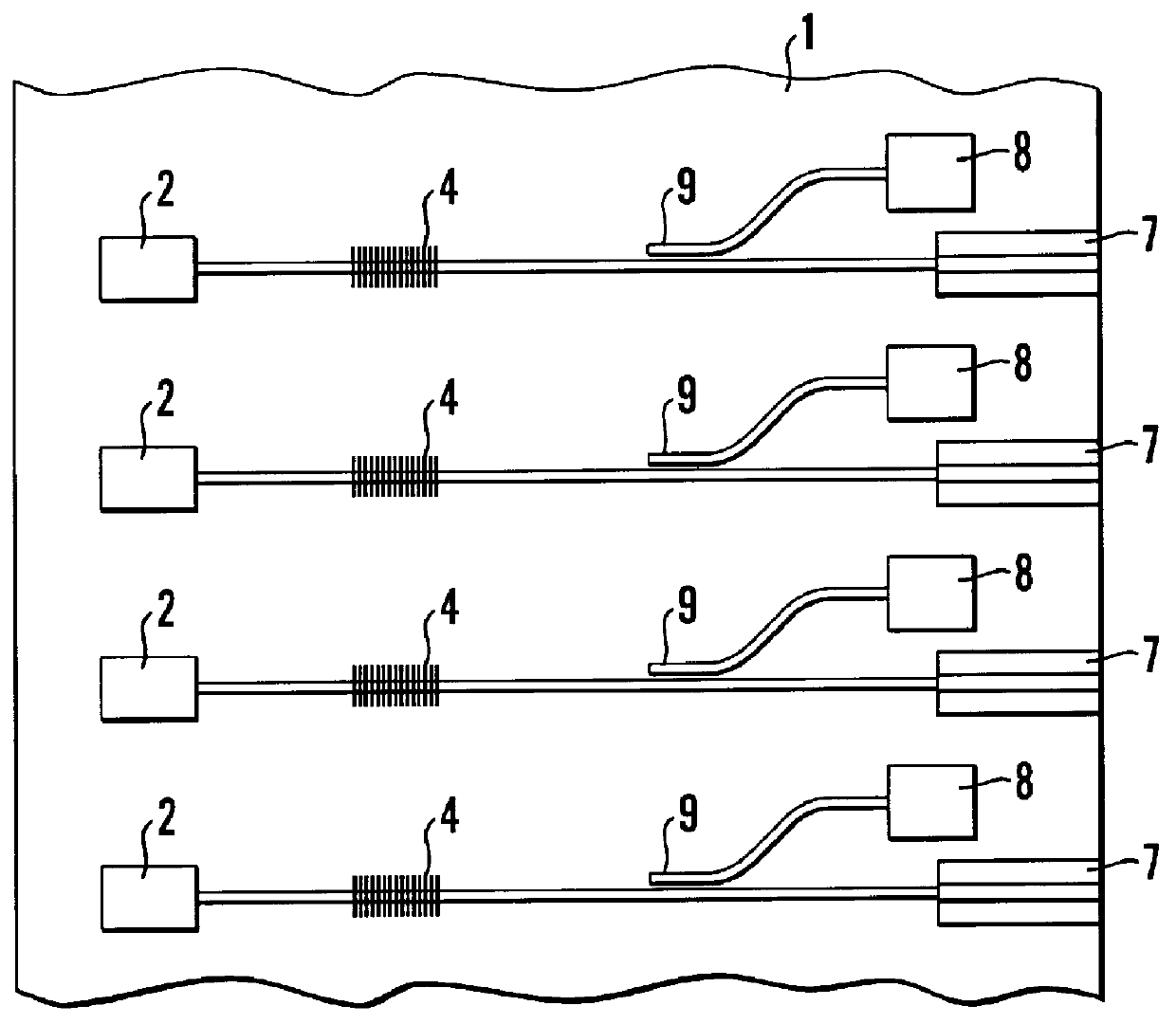

External cavity laser

InactiveUS6101210AAvoid disadvantagesEasy temperature controlLaser optical resonator constructionSemiconductor laser arrangementsTemperature controlGrating

External Cavity Laser An external cavity laser comprising first and second feedback means with an optical gain medium (2) therebetween, one of the feedback means is provided by a grating (4) formed in a silicon waveguide and the other feedback means is provided by a reflective back facet (2B) of the optical gain medium (2). The output wavelength of the laser, at a given temperature, can thus be determined during its manufacture and the laser can be made by mass production techniques. The grating (4) may be thermally isolated to obviate the need for temperature control means (6) to control the temperature of the grating (4). An array of lasers may be provided on a single chip.

Owner:KOTURA

Light emitting diodes for high AC voltage operation and general lighting

InactiveUS6957899B2Non-electric lightingDischarge tube luminescnet screensLed arrayElectrical polarity

A single-chip integrated LED particularly adapted for direct use with a high voltage AC power comprises a plurality of series-connected LEDs arranged in two arrays. The opposite polarities of the arrays are connected together and then connected to the AC power source. During the positive half of the AC cycle, one array of LEDs is forward biased and energized, while the other array is reverse biased. During the negative half of the AC cycle, the other array of LEDs is forward biased and thus energized, while the first array is reverse biased and thus not energized. The arrays are alternately energized and de-energized at the frequency of the AC power source, and thus the single-chip integrated LED always appears to be energized.

Owner:JINGYU LIN +1

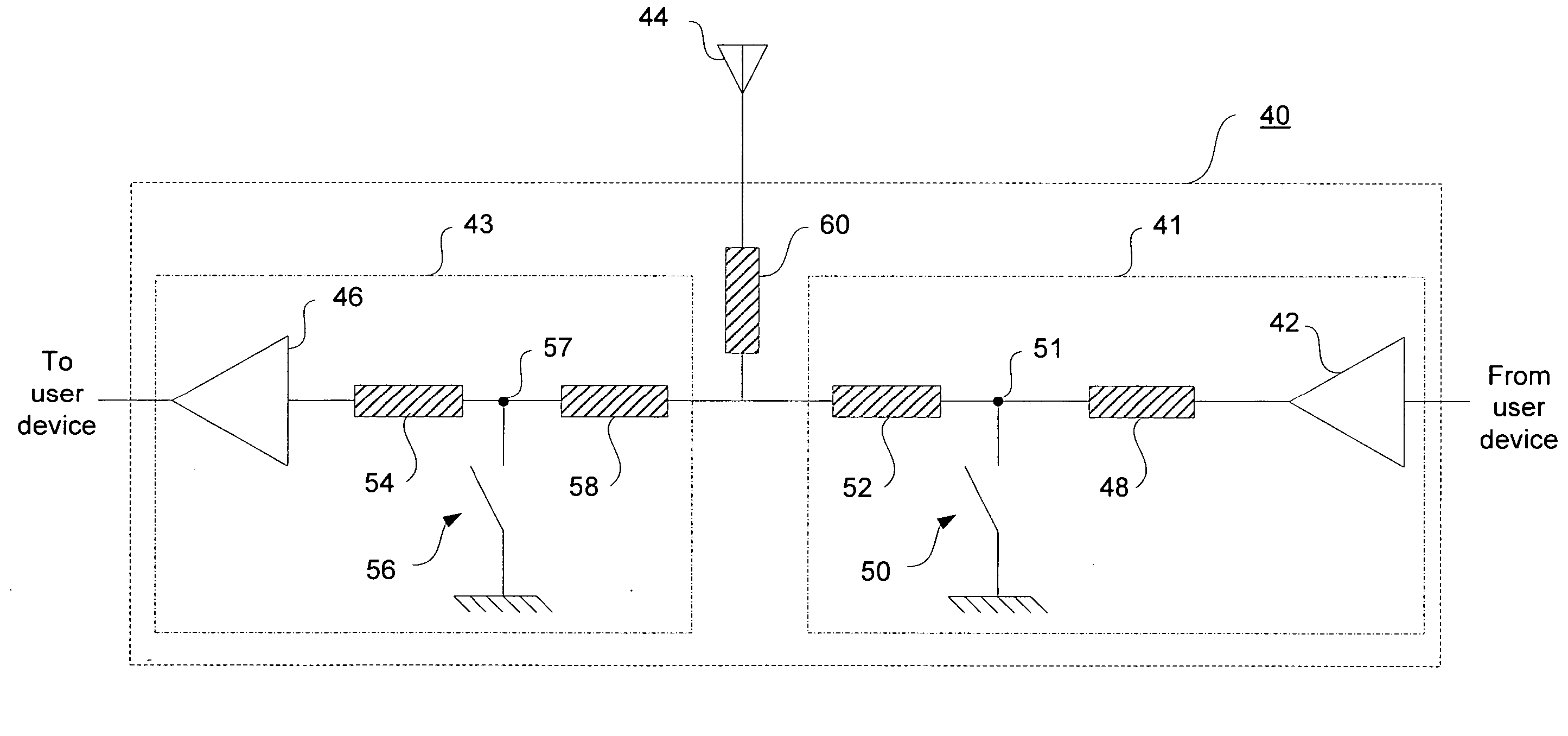

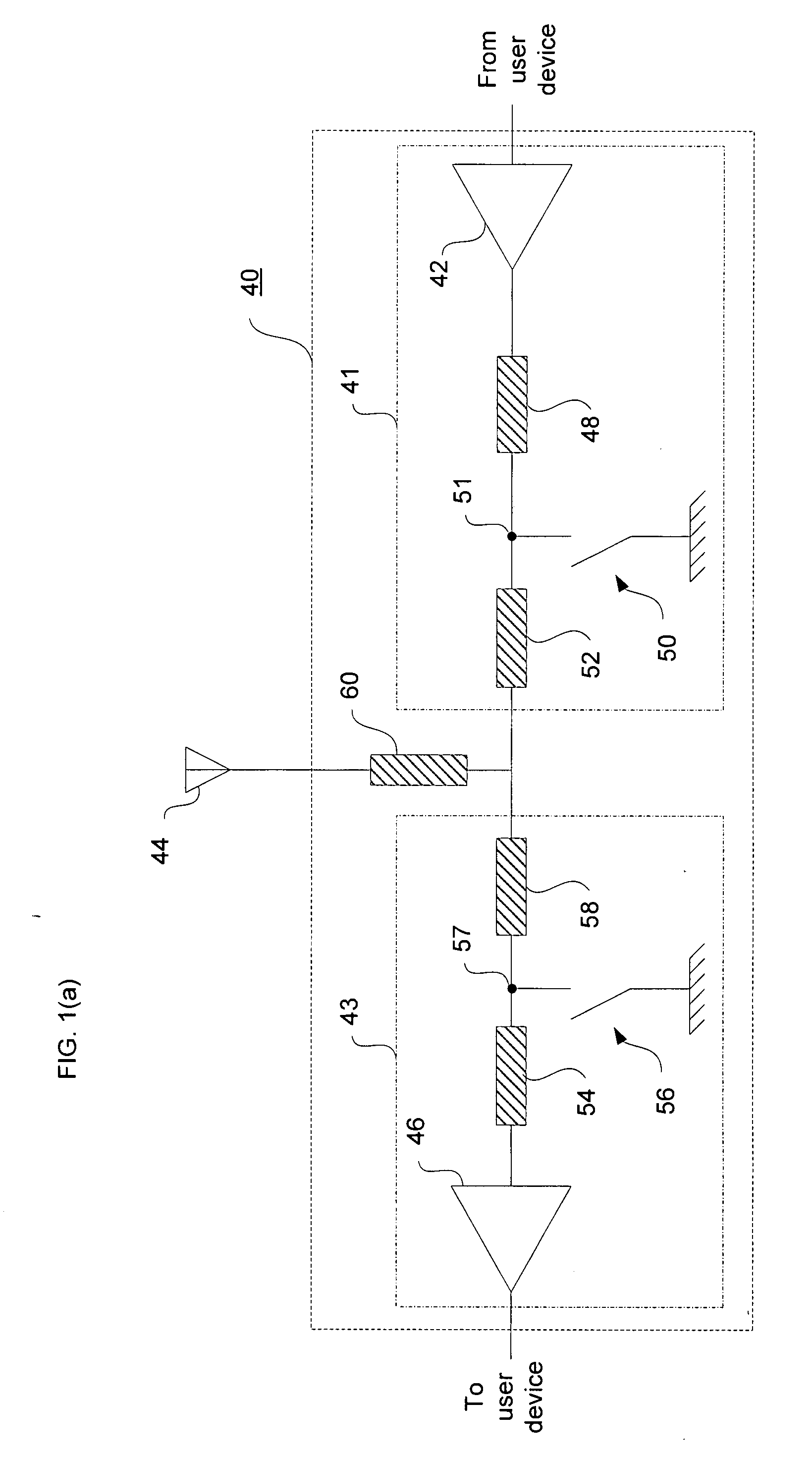

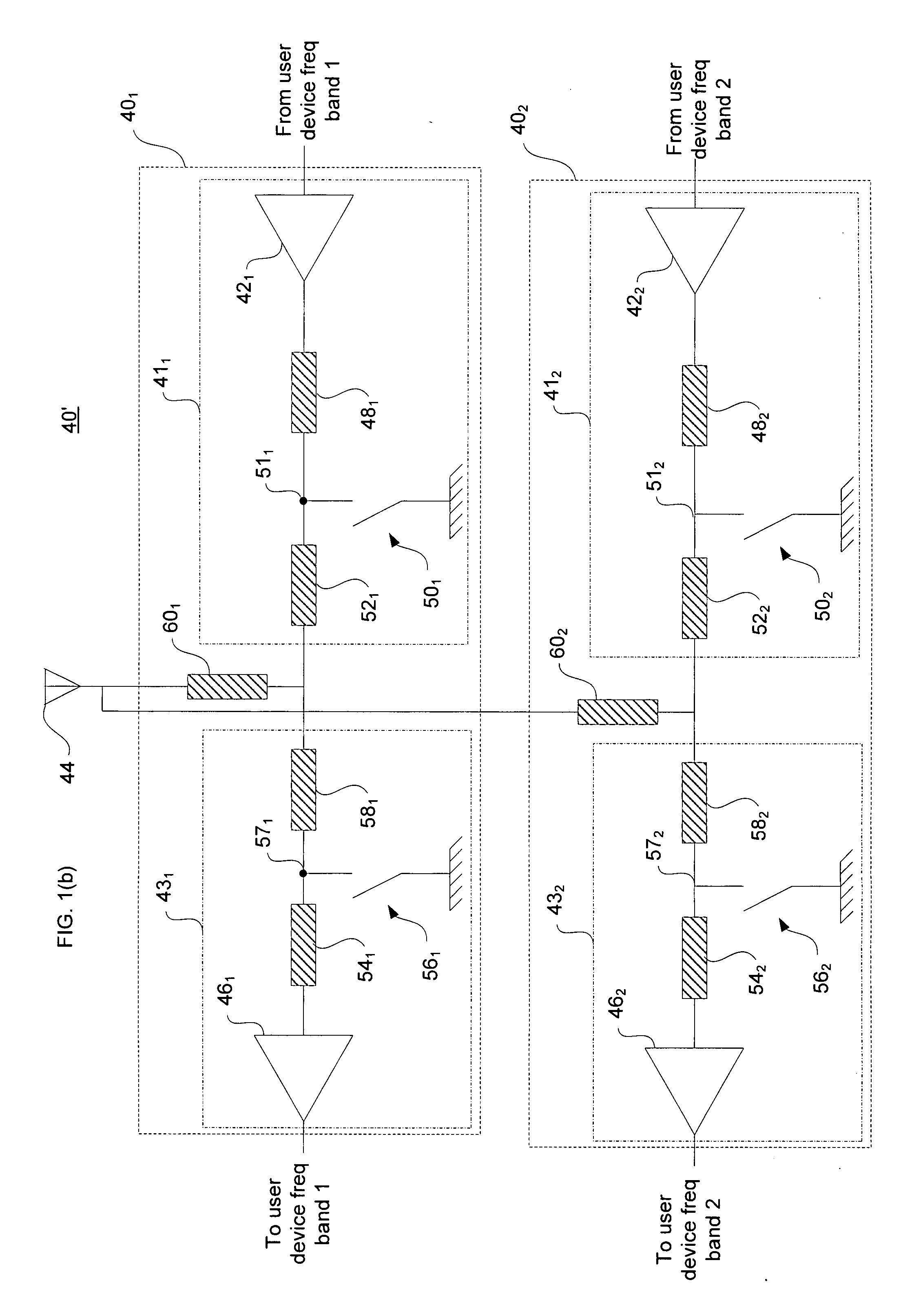

RF transceiver switching system

The present invention relates to transceiver systems and methods which employ shunt switches during transmit and receive operating modes. The shunt switches may be configured with various reactive networks to achieve high or low impedance states at power amplifiers or low noise amplifiers in order to reflect or transmit power along a given path. The shunt switches are designed for protection against excessive voltage swings that would otherwise damage components in the transceiver switching circuit. The switching circuits may be implemented in a single chip architecture, which results in manufacturing efficiencies, lower cost and higher reliability circuits. Single or multi band devices may also be employed.

Owner:RESONANCE SEMICON CORP

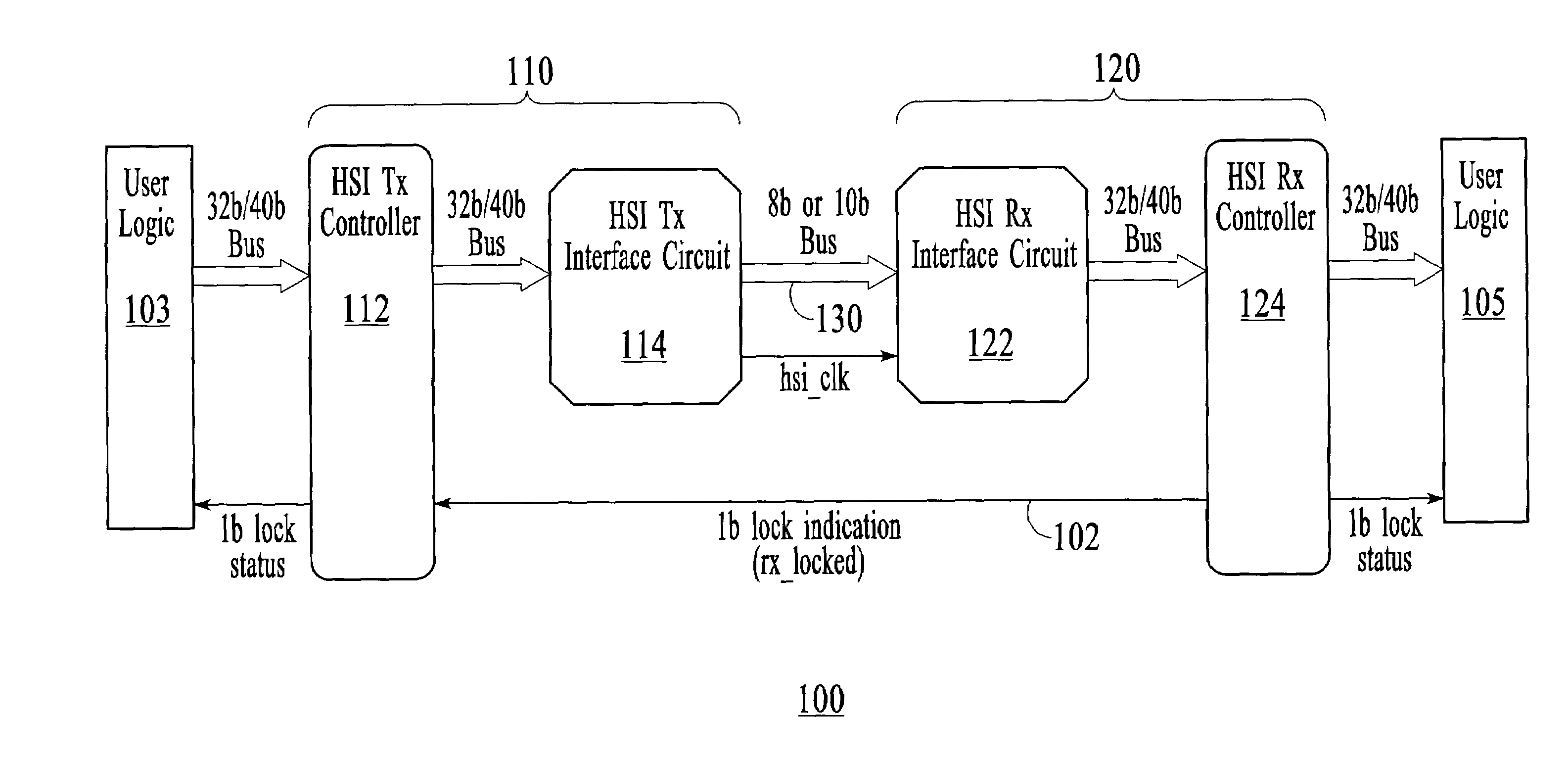

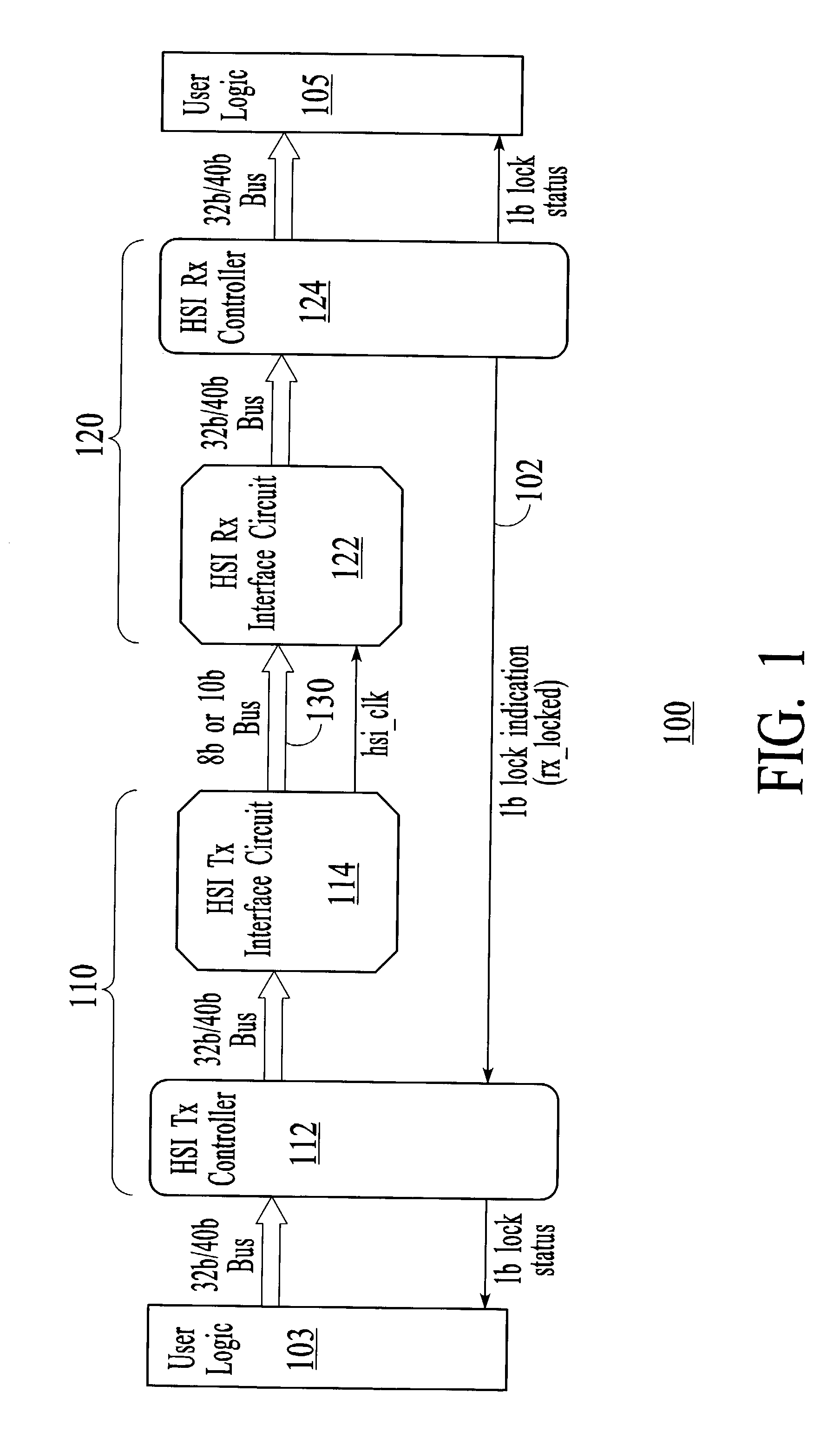

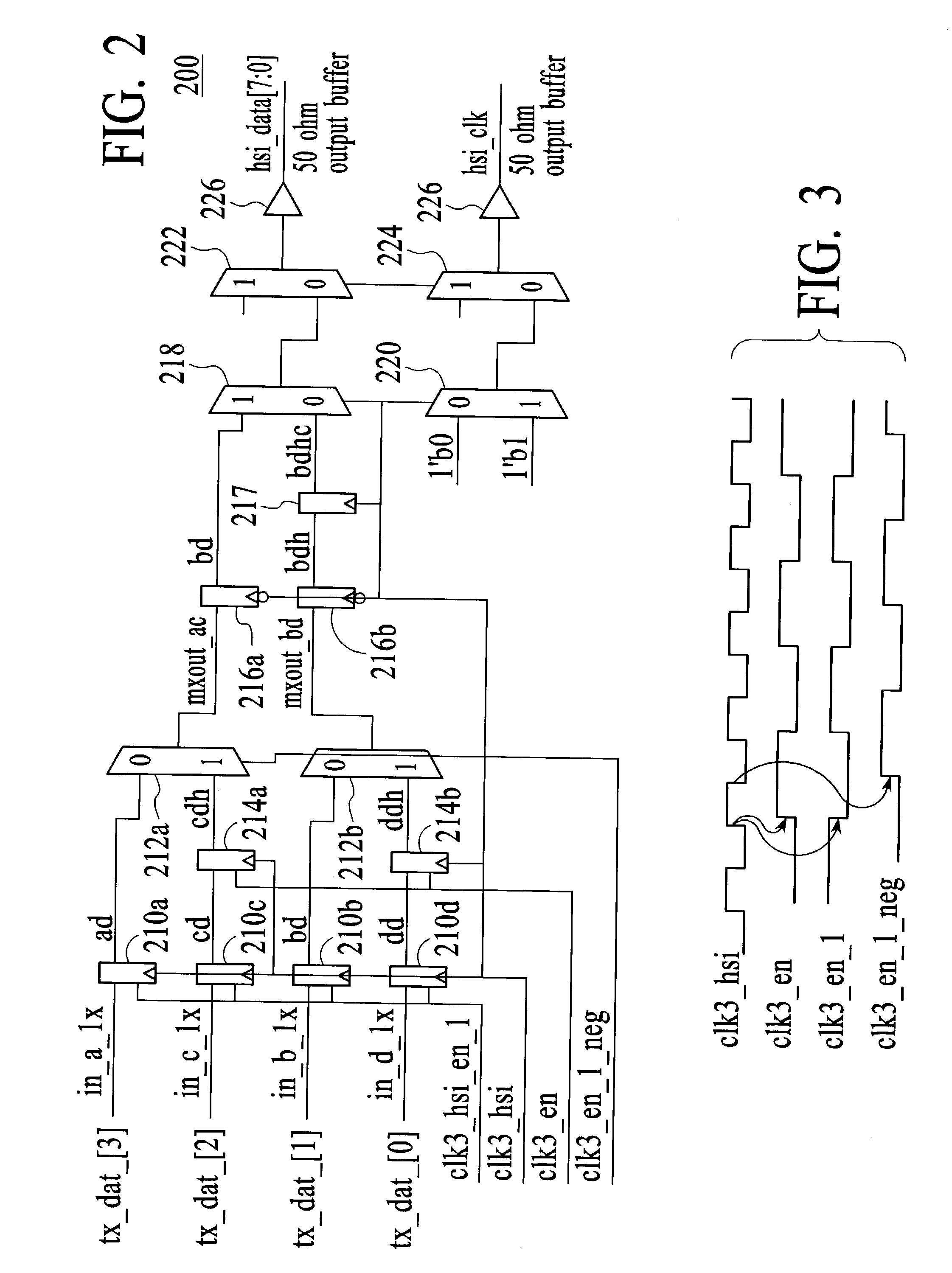

High-speed chip-to-chip communication interface

ActiveUS7180949B2Improve scalabilitySynchronisation information channelsModulated-carrier systemsCommunication interfaceCMOS

A high-speed parallel interface for communicating data between integrated circuits is disclosed. The interface is implemented by a transmitter and receiver pair and a single-ended parallel interconnect bus coupling to the transmitter and receiver pair. As opposed to transmitting small swing signals over differential signal lines, the transmitter transmits data to the receiver at full swing over the single-ended parallel interconnect bus. The invention can be implemented with simple CMOS circuitry that does not consume large die area. Accordingly, many link interfaces can be implemented on a single chip to provide a large data bandwidth.

Owner:RIVERSTONE NETWORKS +1

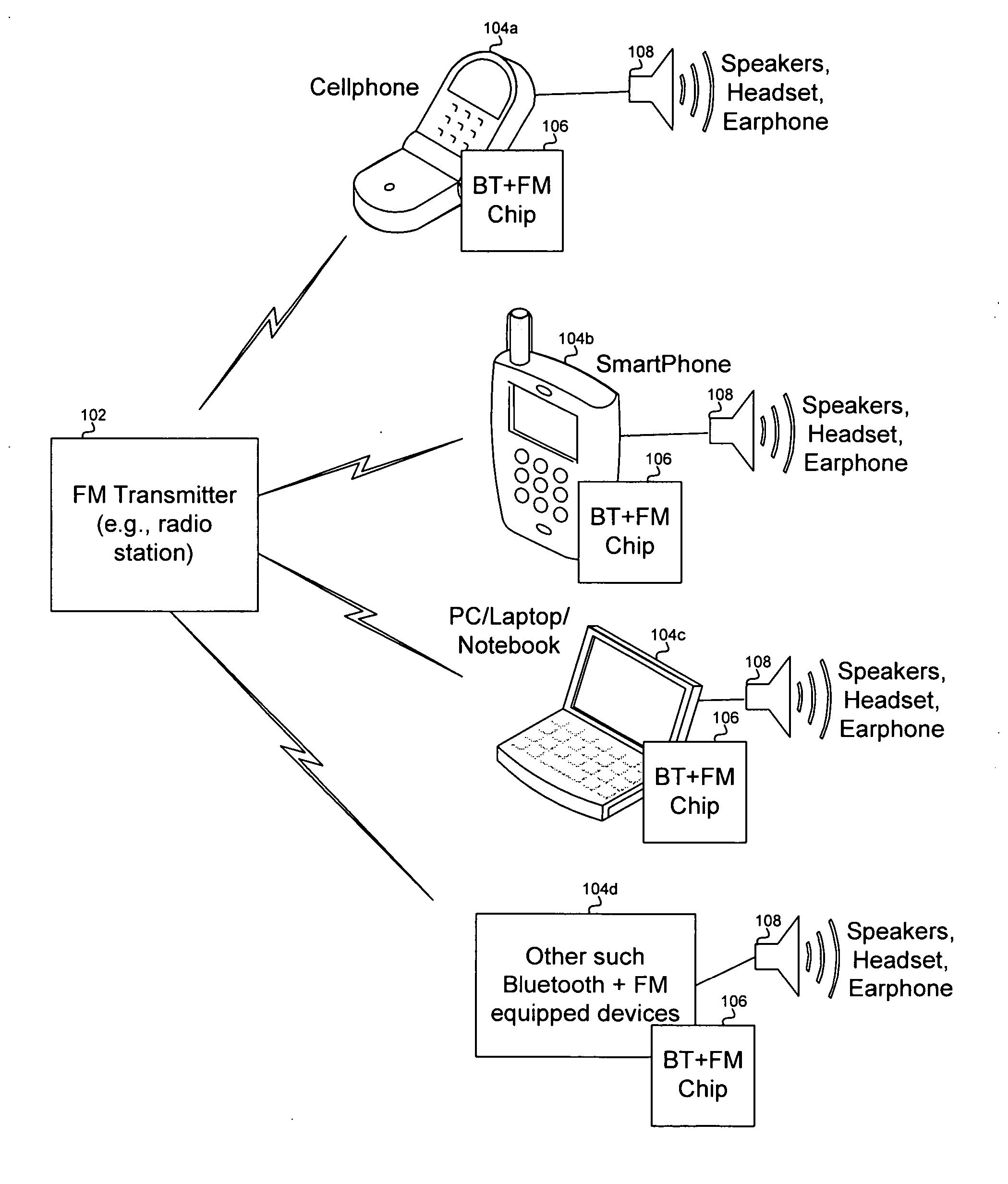

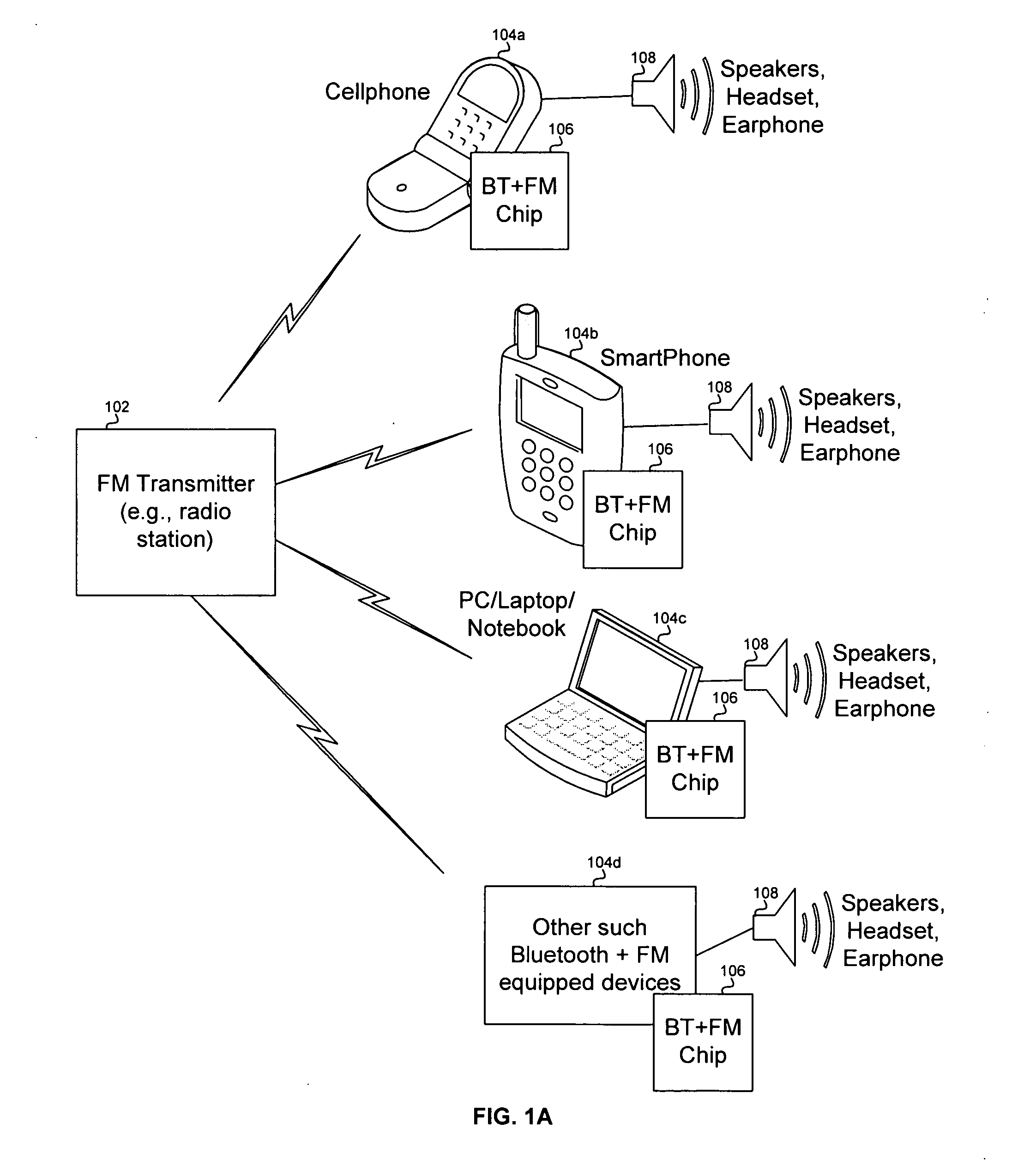

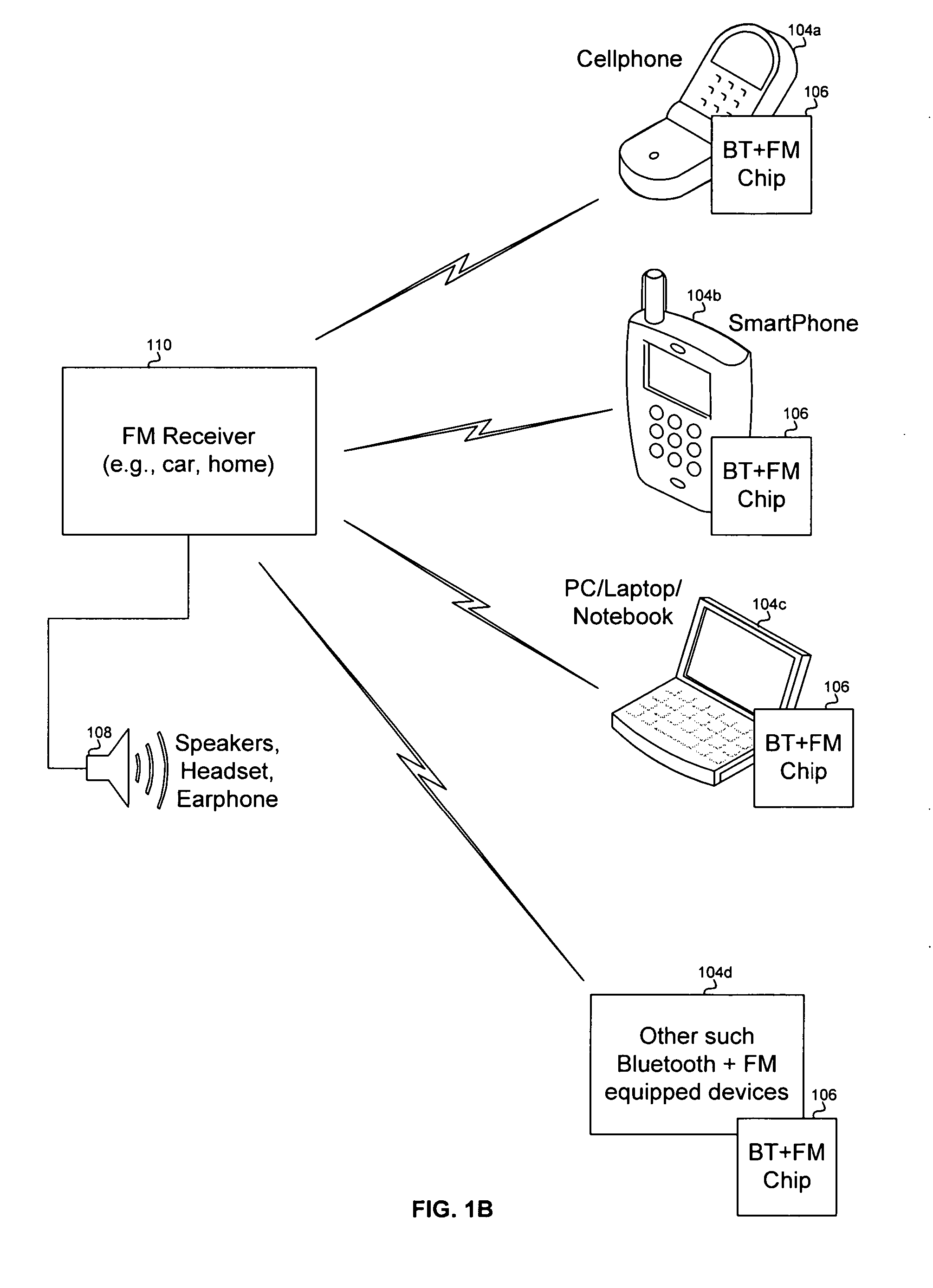

Method and system for a single chip integrated Bluetooth and FM transceiver and baseband processor

A method and system for a single chip integrated Bluetooth and FM transceiver and baseband processor are provided. The single chip may comprise a Bluetooth radio, an FM radio, a processor system, and a peripheral transport unit (PTU). FM data may be received and / or transmitted via the FM radio and Bluetooth data may be received and / or transmitted via the Bluetooth radio. The FM radio may receive radio data system (RDS) data. The PTU may support digital and analog interfaces. A processor in the processor system may time-multiplex processing of FM data and processing of Bluetooth data. The single chip may operate in an FM-only, a Bluetooth-only, and an FM-Bluetooth mode. The single chip may reduce power consumption by disabling portions of the Bluetooth radio during FM-only mode and / or disabling analog circuitry when performing digital processing. Communication between Bluetooth and FM channels may be enabled via the single chip.

Owner:NXP USA INC

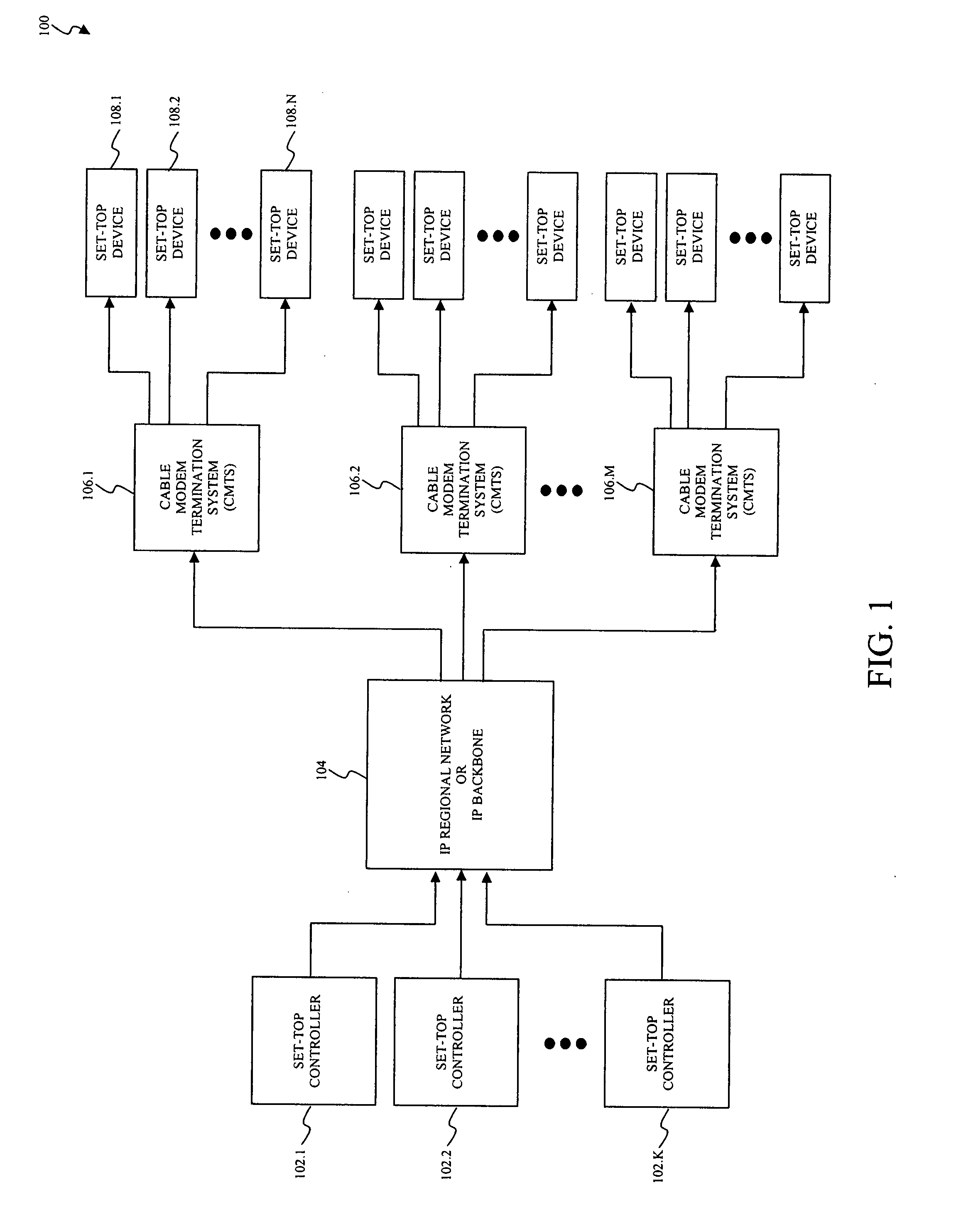

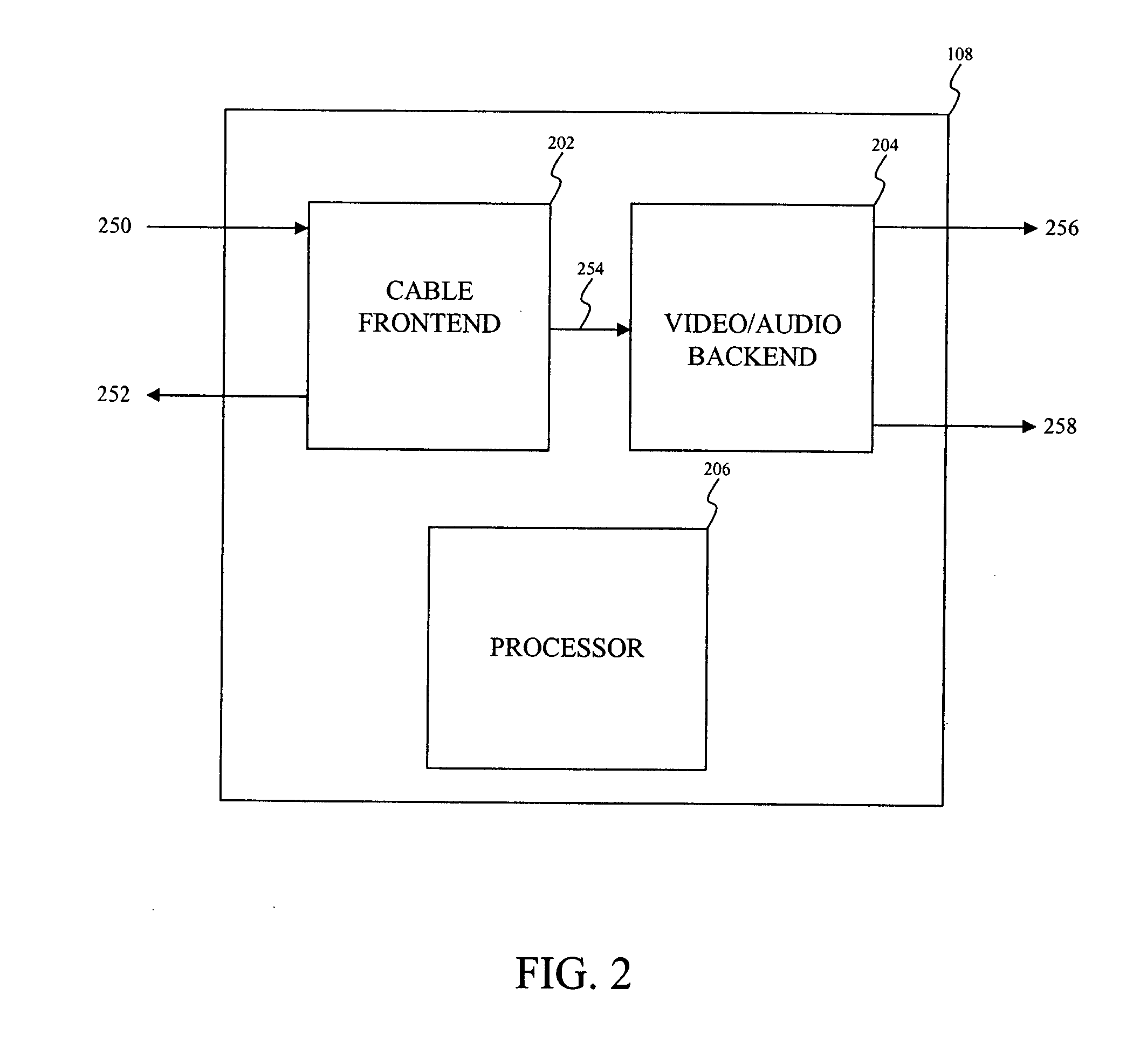

Single chip cable set-top box supporting DOCSIS set-top Gateway (DSG) protocol and high definition advanced video codec (HD AVC) decode

InactiveUS20070294738A1Analogue secracy/subscription systemsTwo-way working systemsModem deviceThe Internet

A single integrated circuit is provided to enable the distribution of voice, video, and / or data services throughout a multimedia distribution network, such as a cable communications network. The single integrated circuit supports both digital and analog television services (e.g., PVR, pay-for-view, EPG, e-commerce, etc.) and computer data services (e.g., telephony, Internet browsing, facsimile, messaging, videoconferencing, etc.). In an embodiment, the single integrated circuit includes three components that constitute a DOCSIS™ compliant cable modem, namely an inband demodulator, an upstream burst modulator, a media access controller, and a microprocessor. In an embodiment, a digital out-of-band demodulator is also included. In another embodiment, the single integrated circuit integrates front-end and backend set-top box functionality in addition to DOCSIS™ cable modem functionality.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

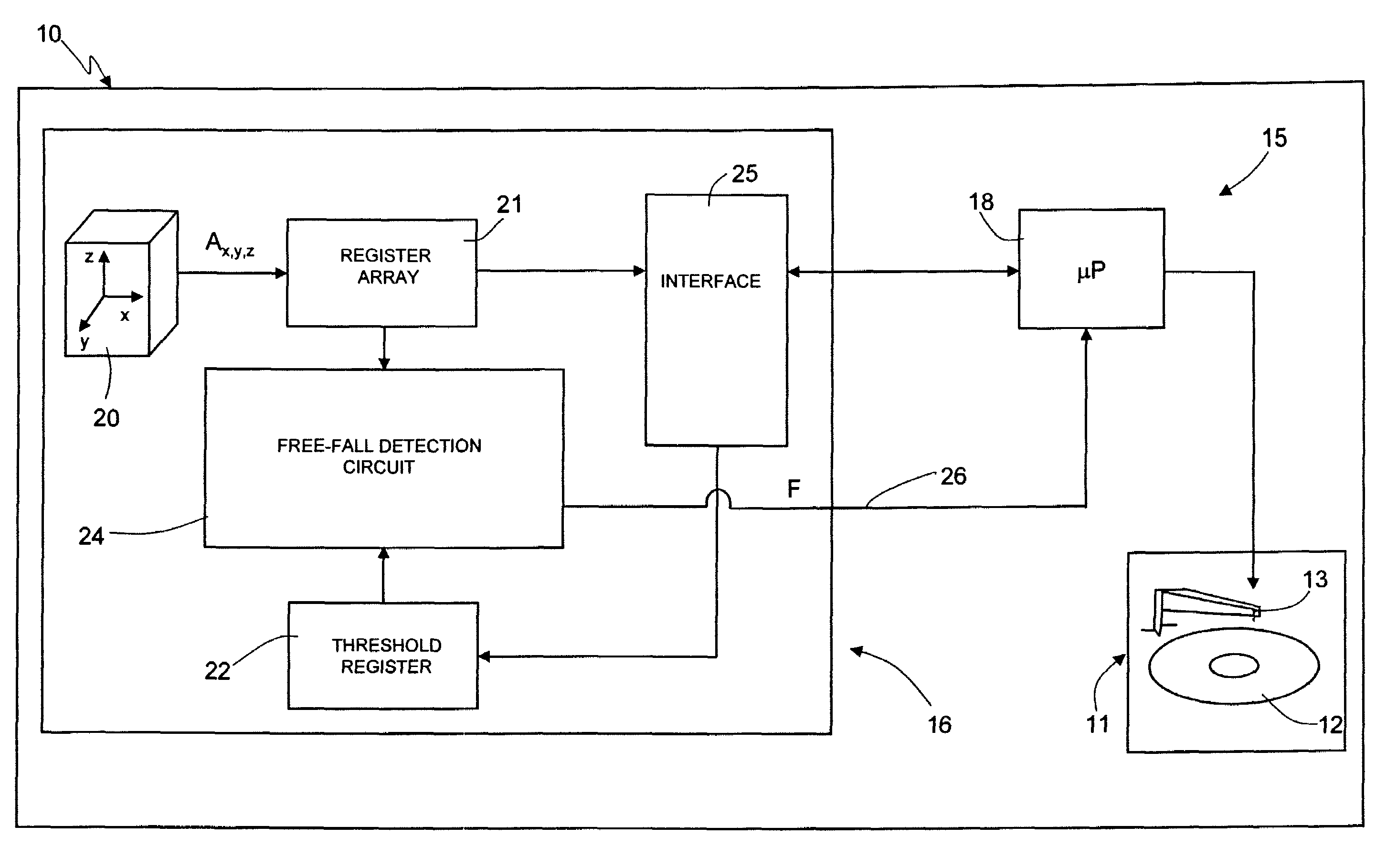

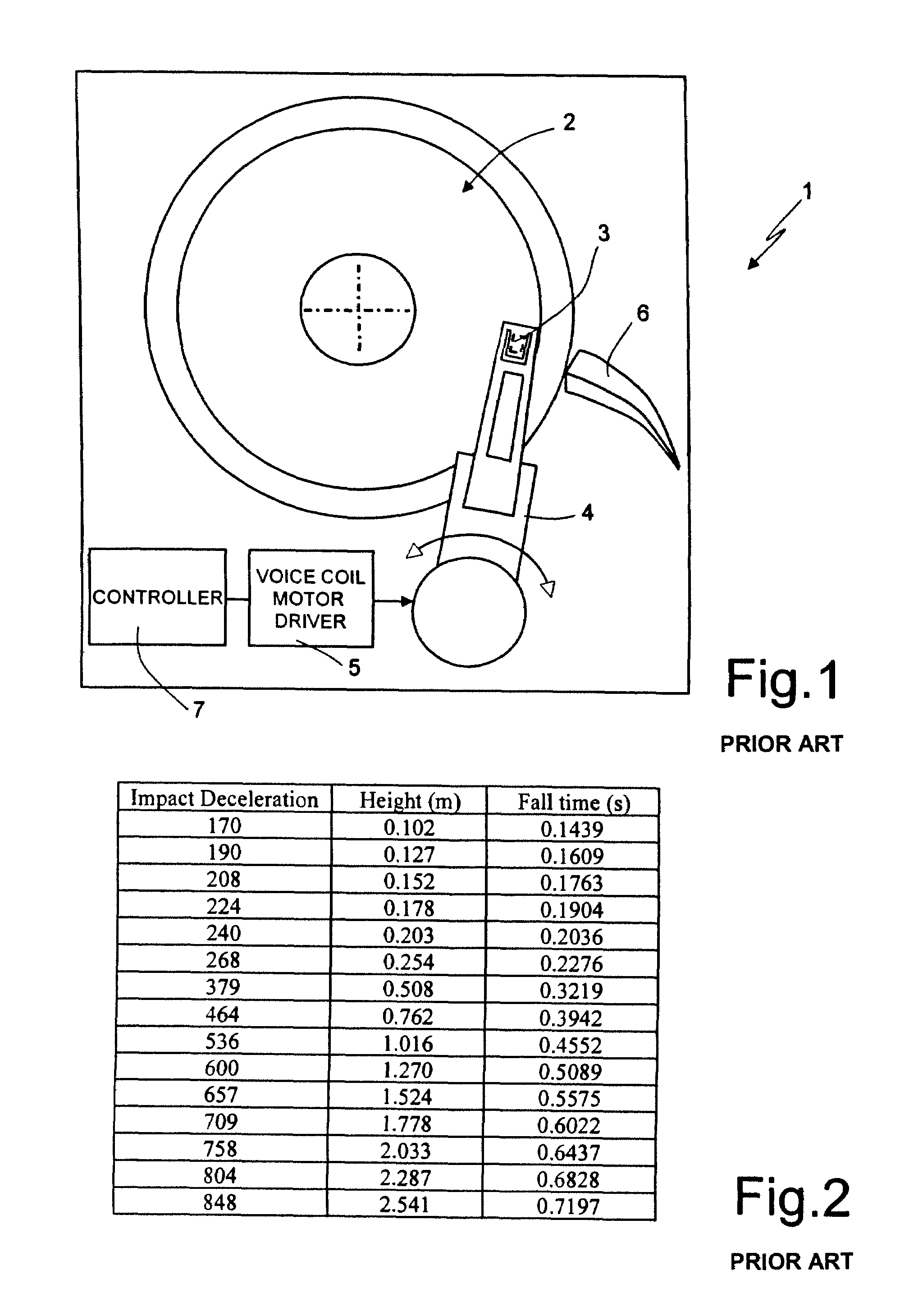

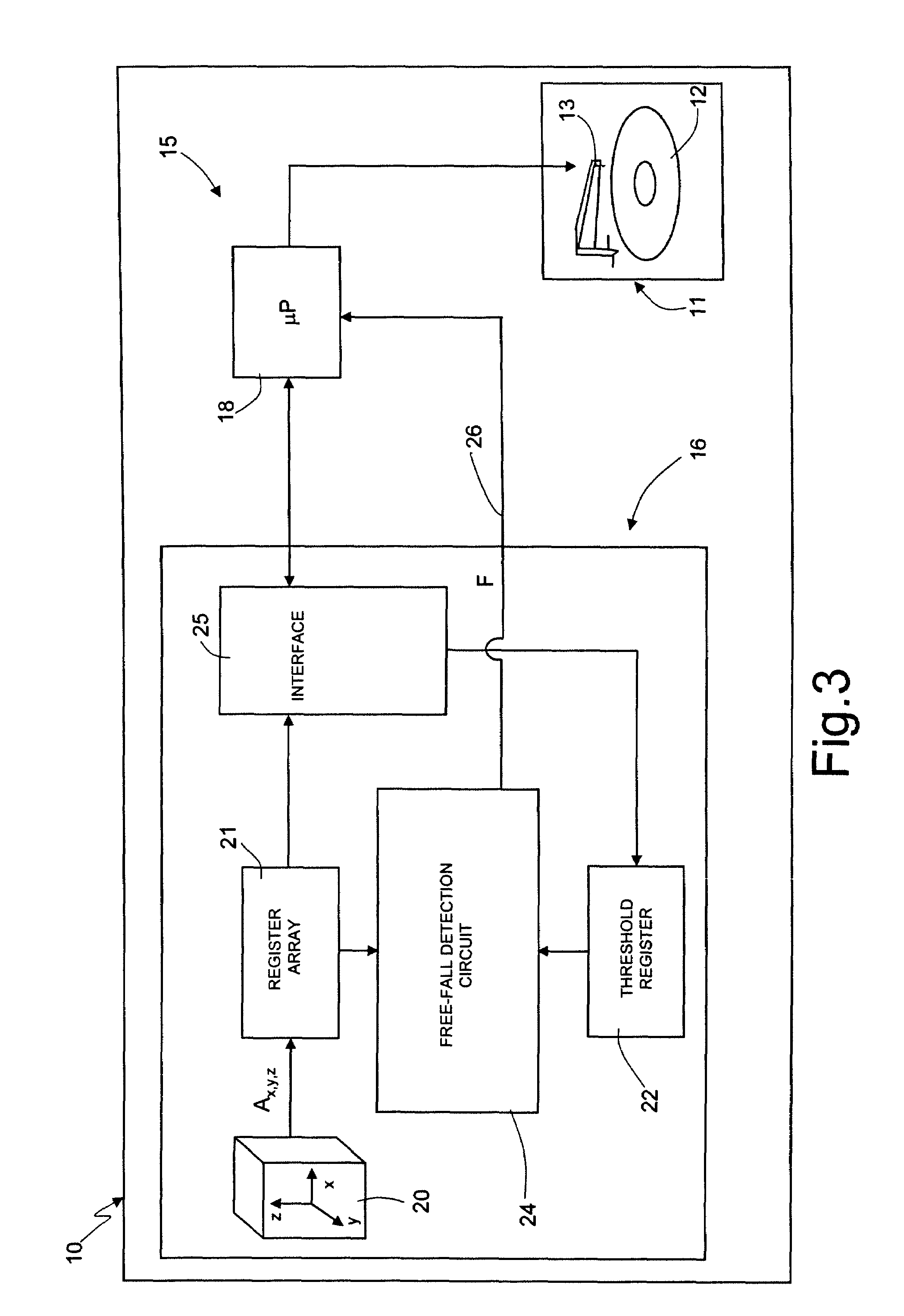

Free-fall detection device and free-fall protection system for a portable electronic apparatus

ActiveUS7450332B2Acceleration measurement using interia forcesDriving/moving recording headsFree fallingEngineering

In an integrated free-fall detection device for a portable apparatus an acceleration sensor generates acceleration signals correlated to the components of the acceleration of the portable apparatus along three detection axes. A dedicated purely hardware circuit connected to the acceleration sensor generates a free-fall detection signal in a continuous way and in real-time. The free-fall detection signal has a first logic value in the event that the acceleration signals are simultaneously lower than a respective acceleration threshold, and is sent to a processor unit of the portable apparatus as an interrupt signal to activate appropriate actions of protection for the portable apparatus. Preferably, the acceleration sensor and the dedicated purely hardware circuit are integrated in a single chip and the acceleration sensor is made as a MEMS.

Owner:STMICROELECTRONICS SRL

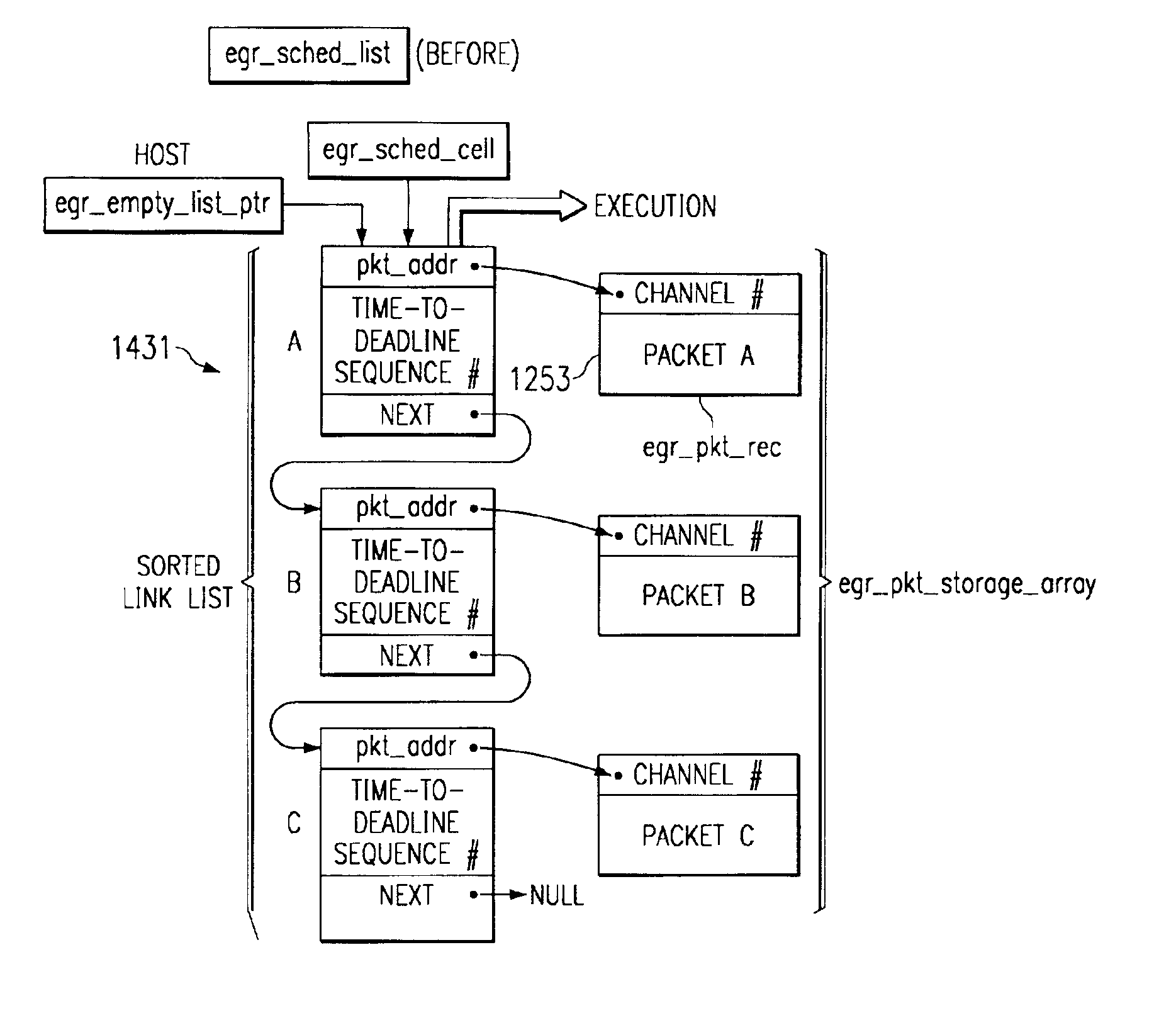

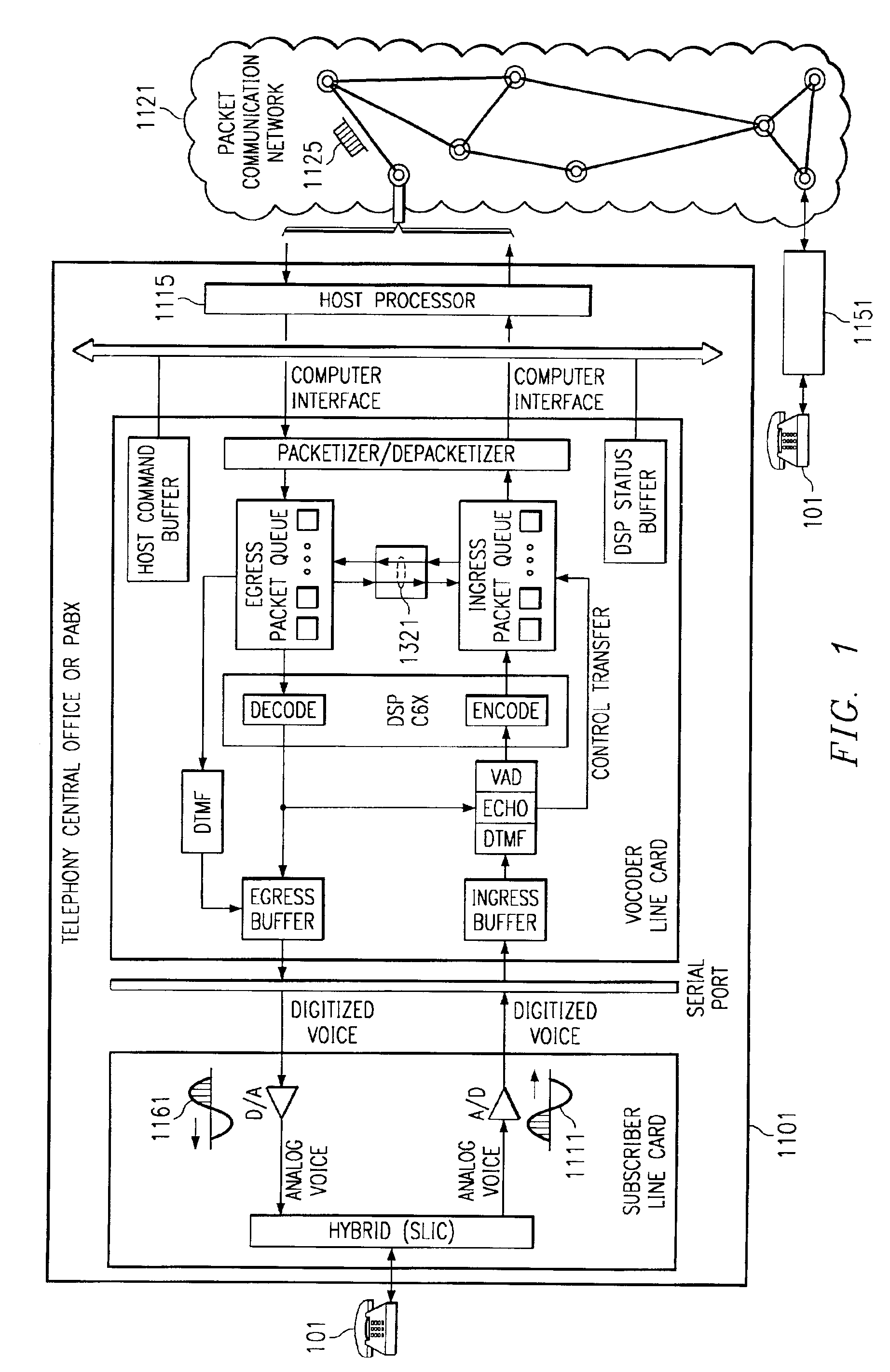

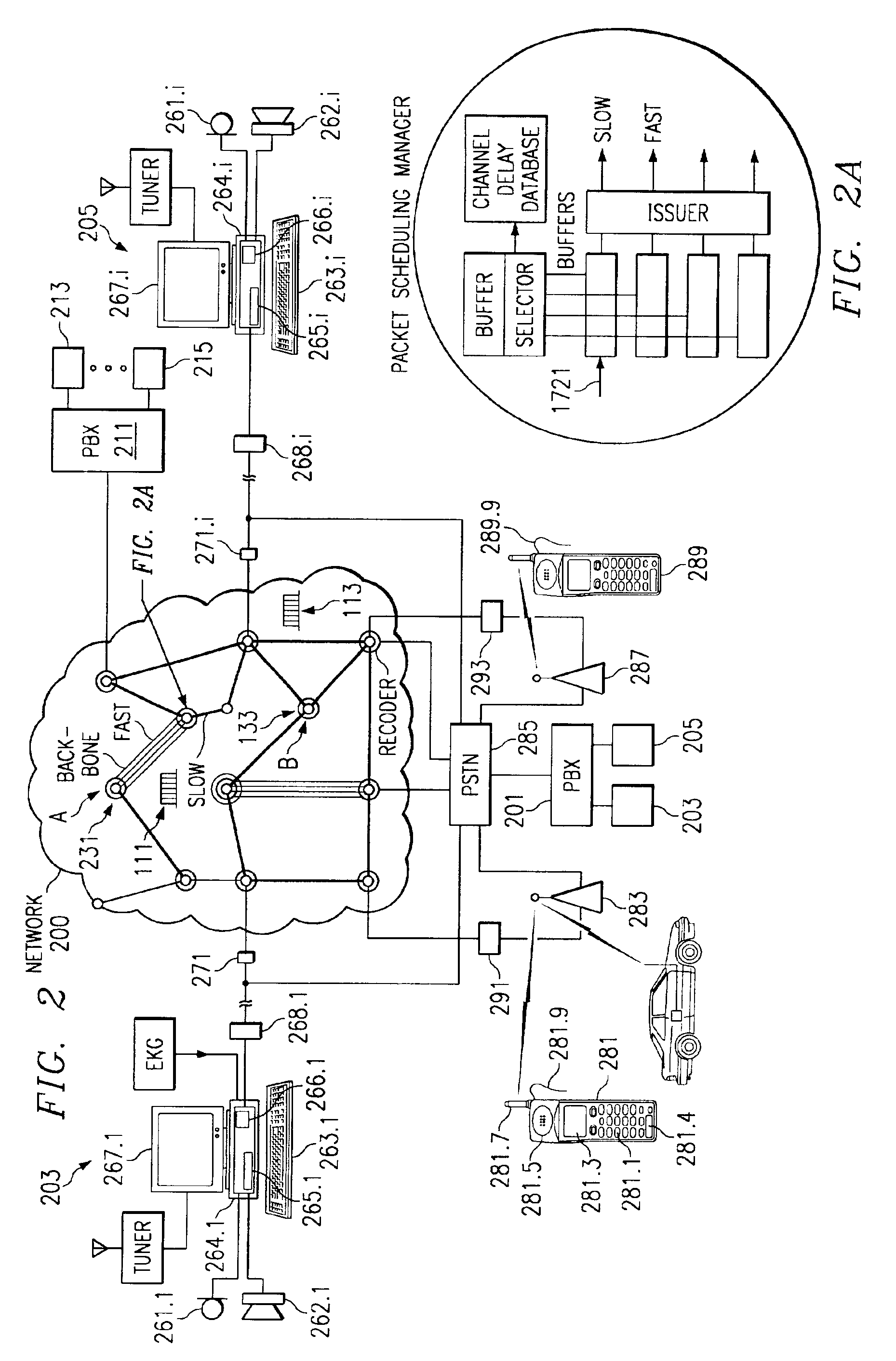

Processing packets based on deadline intervals

A method of processing first and second record packets of real-time information includes computing for each packet a deadline interval and ordering processing of the packets according to the respective deadline intervals. A single-chip integrated circuit has a processor circuit and embedded electronic instructions forming an egress packet control establishing an egress scheduling list structure and operations in the processor circuit that extract a packet deadline intervals, place packets in the egress scheduling list according to deadline intervals; and embed a decoder that decodes the packets according to a priority depending to their deadline intervals.

Owner:TEXAS INSTR INC

An Intelligent Integrated Sensor Of Tire Pressure Monitoring System (TPMS)

InactiveUS20060185429A1Precise size controlAccurate identificationSolid-state devicesTyre measurementsAccelerometerEngineering

A single integrated sensing chip with multi-functions for tire pressure monitor system (TPMS) comprises: a pressure sensor, an accelerometer, a temperature sensor, and an ASIC (Applied Specific Integrated Circuit) that implements signal conditioning and digitalizes pressure output. The accelerometer incorporated for vehicle motion is used to determine centrifugal acceleration or three-axial acceleration of the rotating wheel, and used for the TPMS sensor wake-up from “power down” mode, or when the velocity of the vehicle is higher than certain speed threshold, which is more robust and lower in cost than the mechanical vibration switch and is naturally integrated with the electronic control unit. The accelerometer can be used for regular motion sensing to monitor the dynamic stability. The integrated sensor system can be packaged into one plastic package first, and then surface mounted to the printed circuit board, or the multi-function single chip can be wafer bonded on the wafer level first and diced into many individual chips, with each chip being directly attached on to the printed circuit board by wire bonding or flip-chip assembly.

Owner:WUHAN FINEMEMS

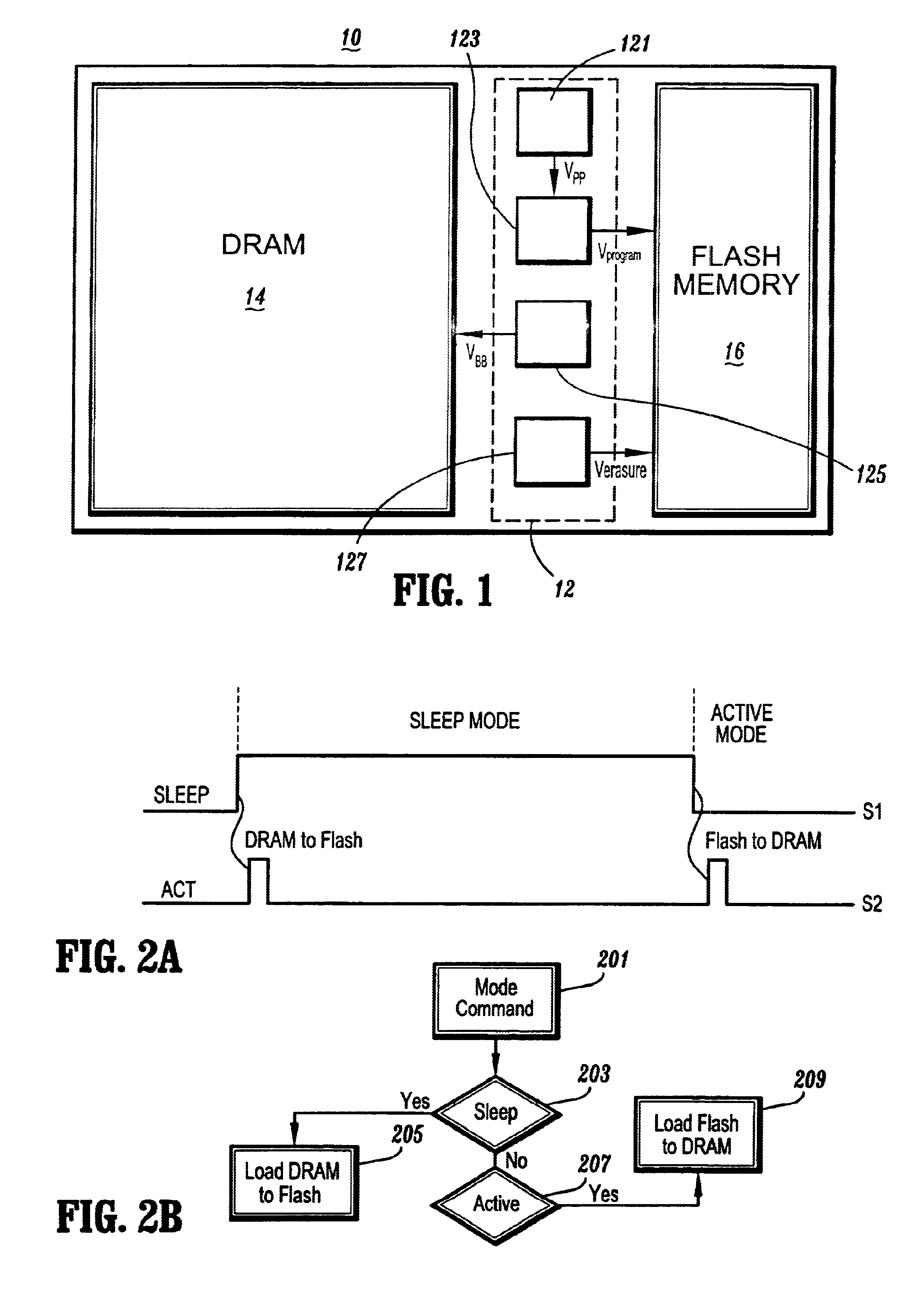

Method of integrating volatile and non-volatile memory cells on the same substrate and a semiconductor memory device thereof

InactiveUS6670234B2Simple processMinimizes stepSolid-state devicesSemiconductor/solid-state device manufacturingSingle chipDram

Owner:GOOGLE LLC

Structure and method to improve channel mobility by gate electrode stress modification

InactiveUS20050245017A1Easily and repeatably formedImprove production yieldTransistorSolid-state devicesCMOSCharge carrier mobility

Owner:GLOBALFOUNDRIES INC

Method and system for power management in a gigabit Ethernet chip

InactiveUS20050097378A1Set clearEnergy efficient ICTPower managementControl registerFinite-state machine

Aspects of the invention for managing power in a single chip device may comprise, an internal finite state machine that, while in a communicating state, determines from within the single chip device whether a power management status is set and / or whether a first power management event is received. If the power management status is set, the finite state machine may transition from the communicating state to a power management event sent state. If the first power management event is received, the finite state machine may transition from the communicating state to a non-communicating state. The first power management event may be a turn off power management event. Furthermore, in instances where the power management status is set, it may be cleared, thereby causing the finite state machine to transition back to the communicating state. One or more power management control registers may be utilized for indicating power management status.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

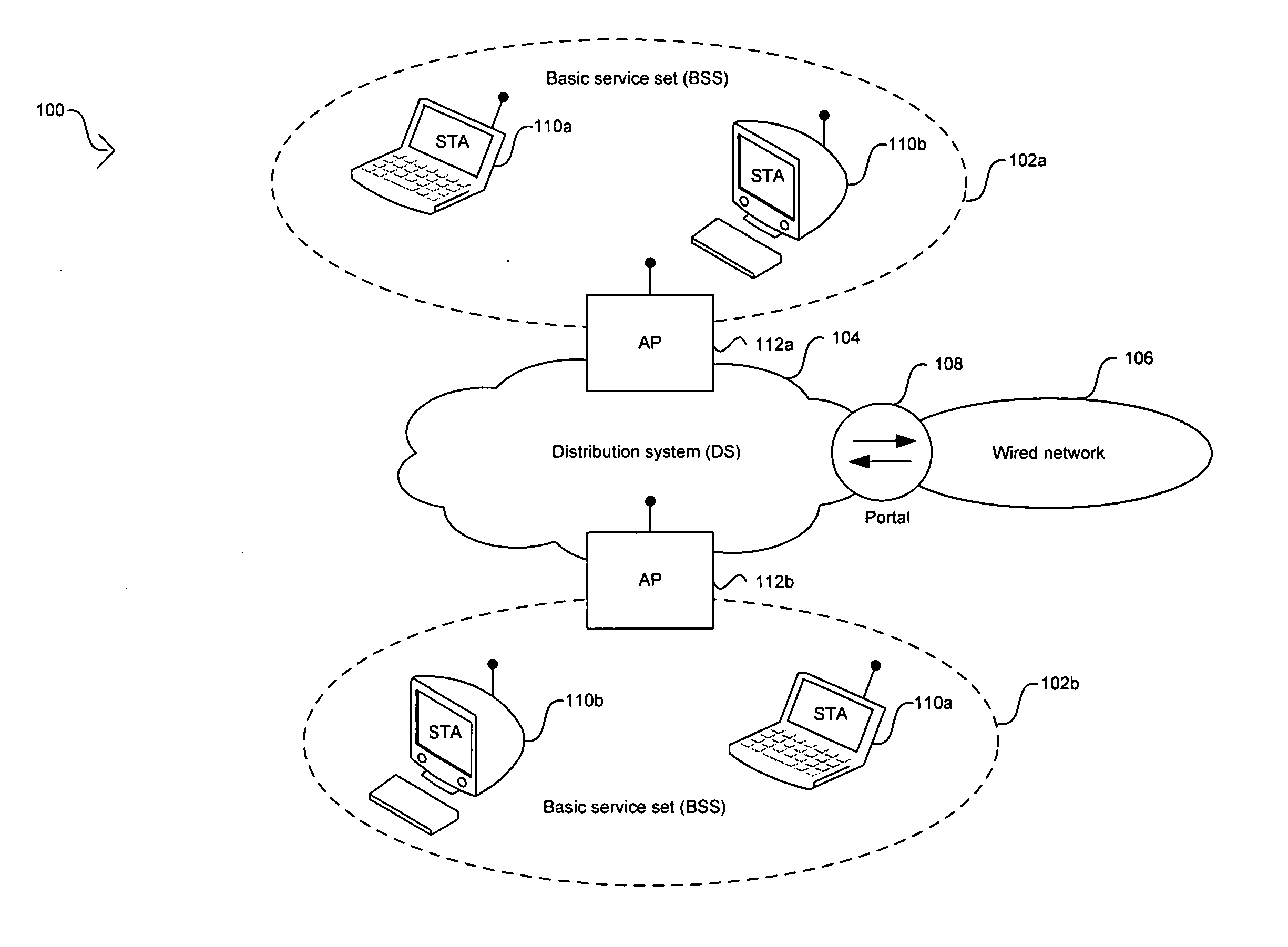

Method and system for collocated IEEE 802.11 B/G WLAN, and BT with FM in coexistent operation

A method and system for collocated IEEE 802.11 b / g WLAN, and Bluetooth (BT) with FM in coexistent operation are provided. A single chip comprising an integrated BT radio and an integrated FM radio in a coexistence station may generate a priority signal to disable WLAN transmissions in a WLAN radio when a BT HV3 frame is available for transmission. When the priority signal is asserted, an exponentially growing retransmission backoff mechanism in the WLAN radio may be disabled. Moreover, when the BT radio and the WLAN radio are enabled for coexistence operation, a WLAN fragmentation threshold in the WLAN radio may be modified based on a WLAN modulation rate and the BT HV3 frame duration. An on-chip processor that time multiplexes FM and Bluetooth data processing may be utilized to control the BT radio operation and the FM radio operation in the single chip.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

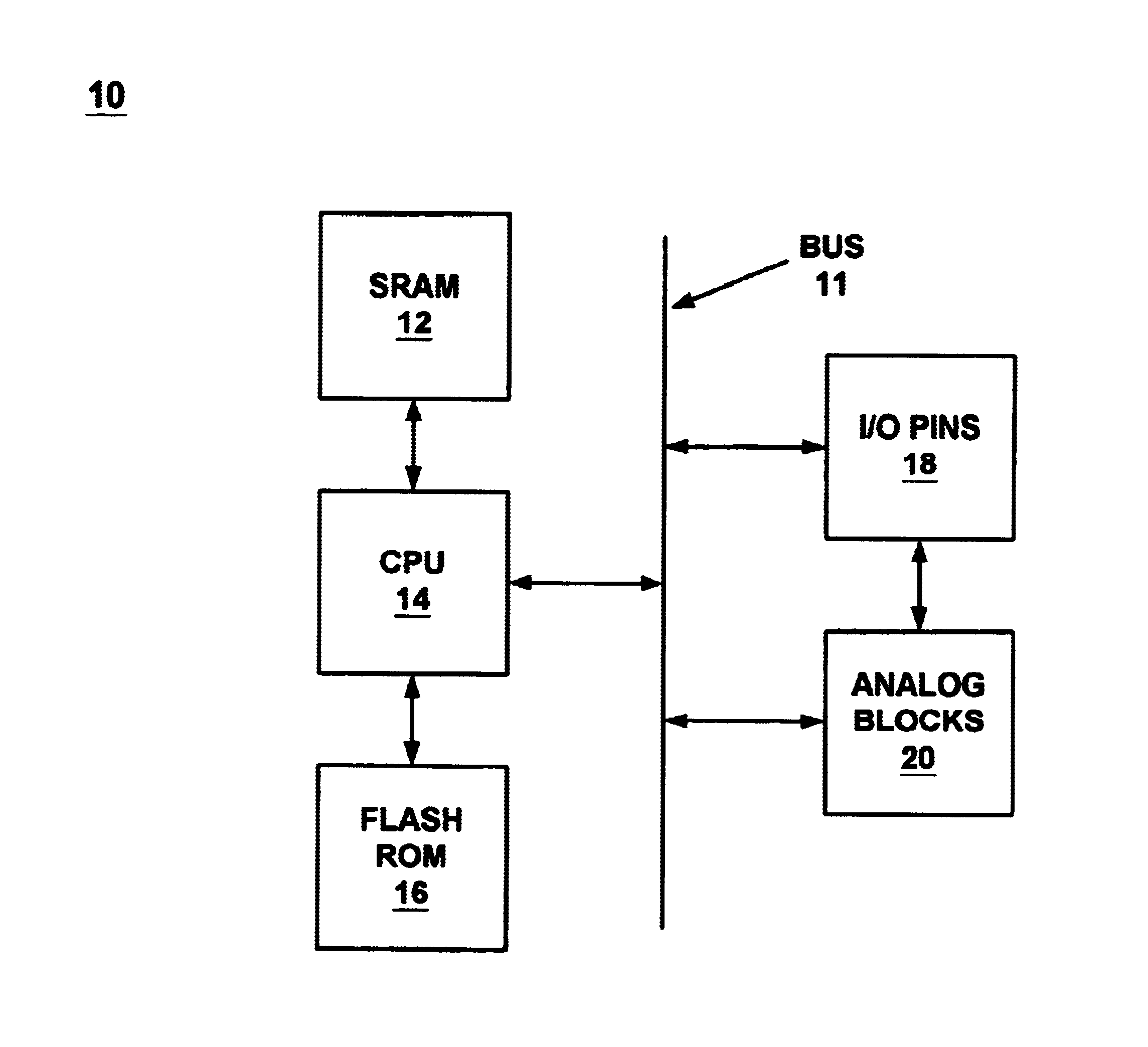

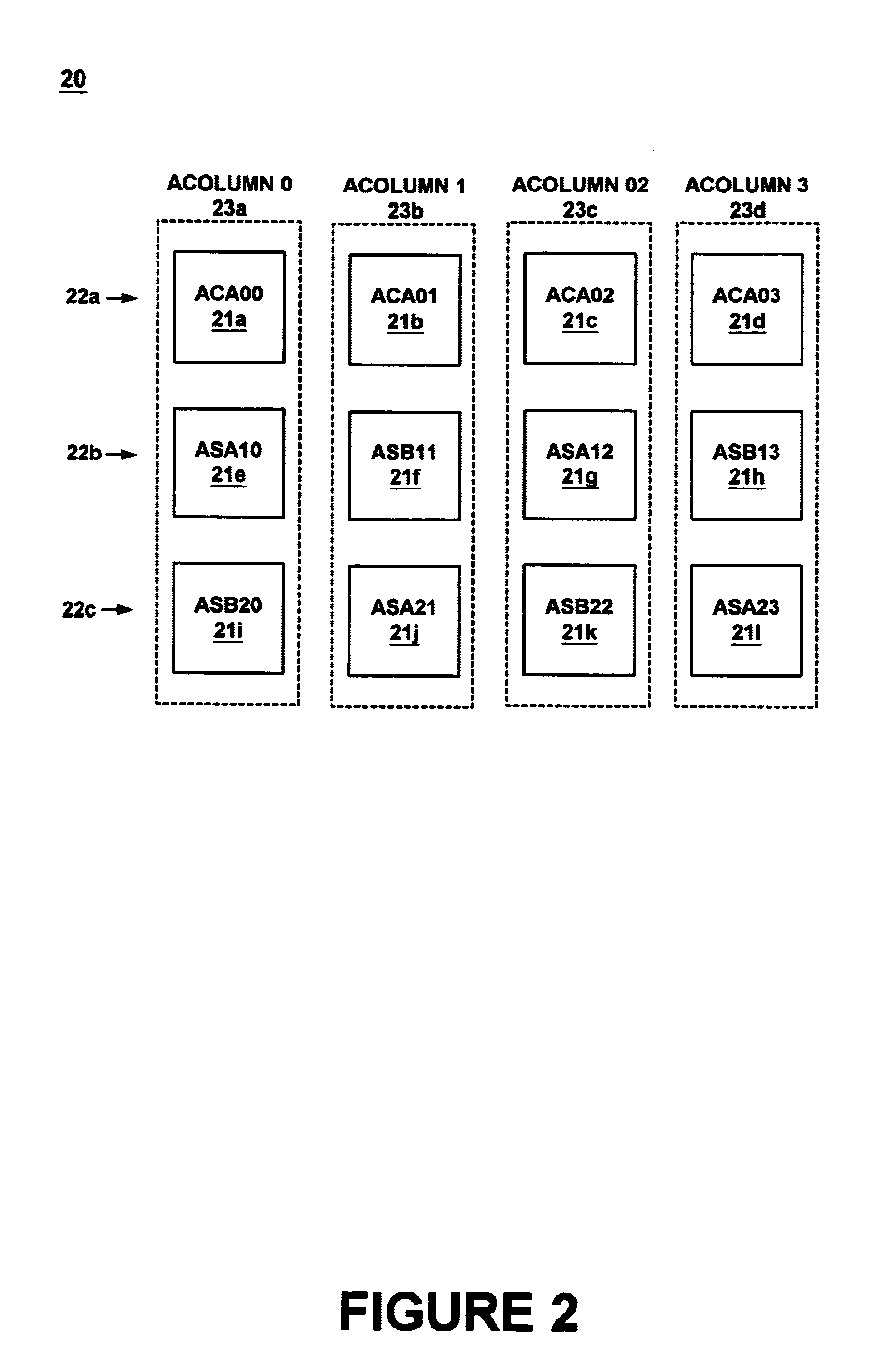

Programmable analog system architecture

InactiveUS6941336B1Shorten development timeReduce expensesProgramming arrangements for electric/magnetic computingElectric pulse generatorElectricityCapacitance

A programmable analog system architecture and method thereof are described. The analog system architecture and method introduce a single chip solution that contains a set of tailored analog blocks and elements that can be configured and reconfigured in different ways to implement a variety of different analog functions. The architecture includes an array of analog blocks, including continuous time blocks and different types of switched capacitor blocks. The analog blocks can be electrically coupled to each other in different combinations to perform different analog functions. Each analog block includes analog elements that have changeable characteristics that can be specified according to the function to be performed. The architecture thereby facilitates the design of customized chips at less time and expense.

Owner:CYPRESS SEMICON CORP