Patents

Literature

654 results about "Logical block addressing" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

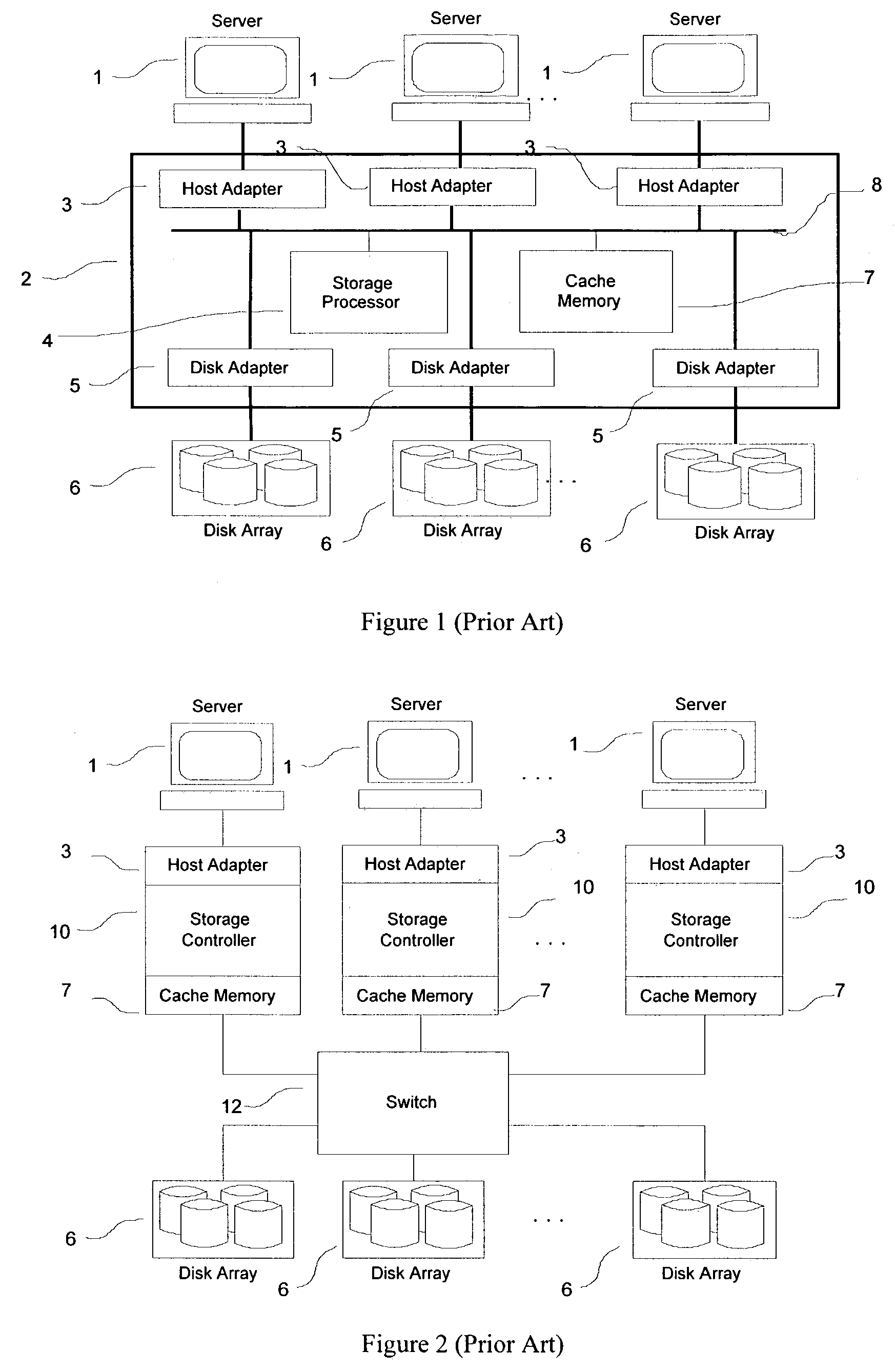

Logical block addressing (LBA) is a common scheme used for specifying the location of blocks of data stored on computer storage devices, generally secondary storage systems such as hard disk drives. LBA is a particularly simple linear addressing scheme; blocks are located by an integer index, with the first block being LBA 0, the second LBA 1, and so on.

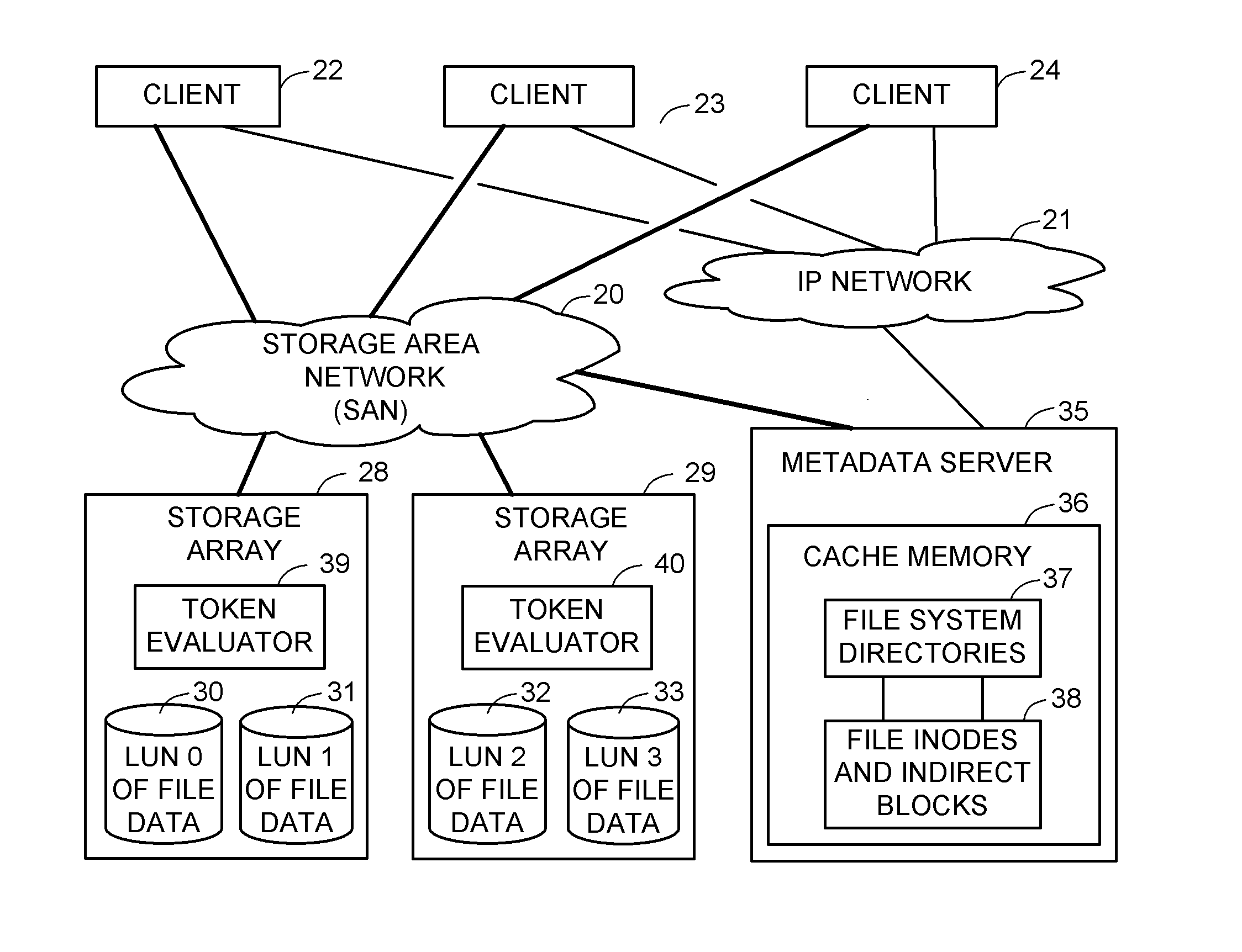

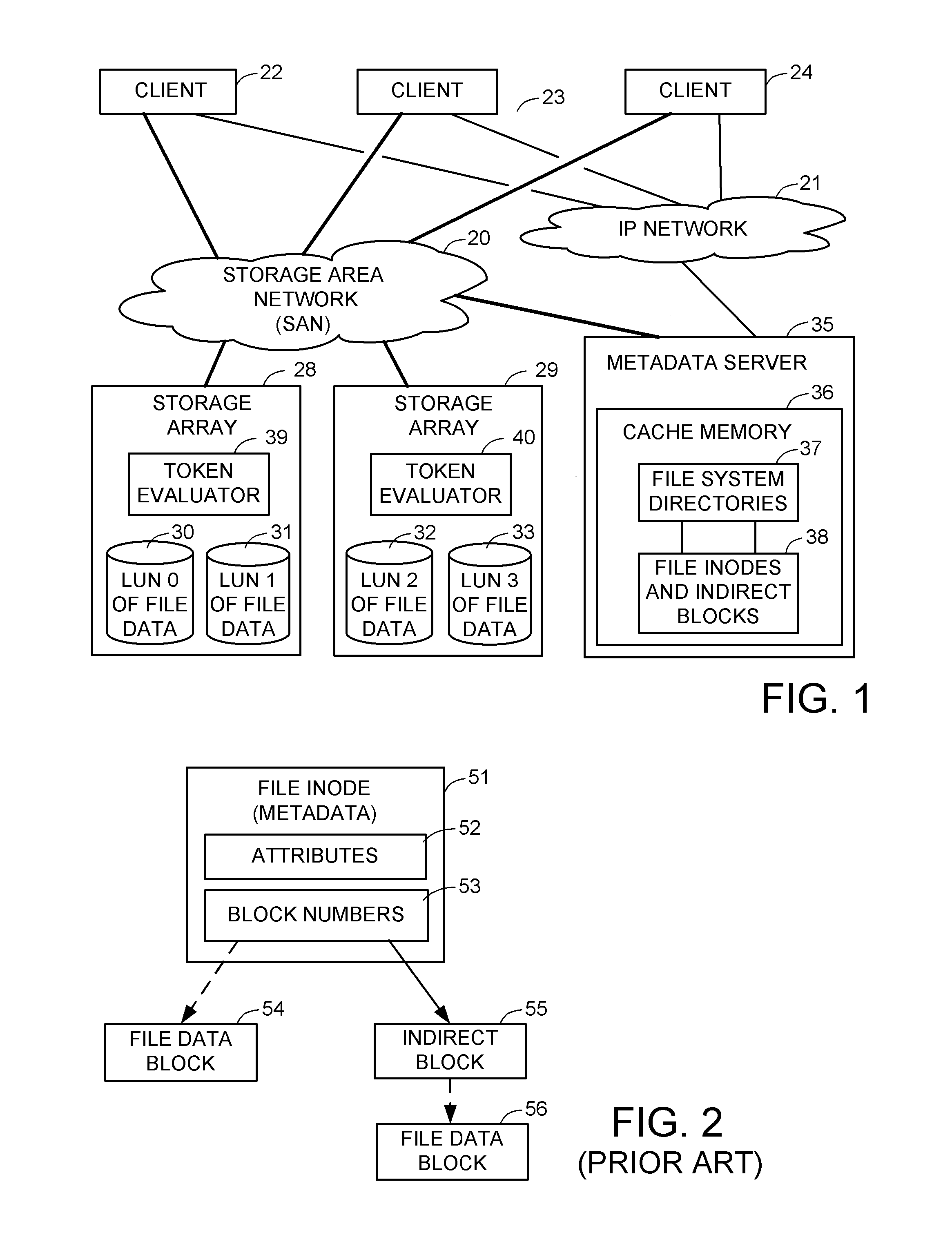

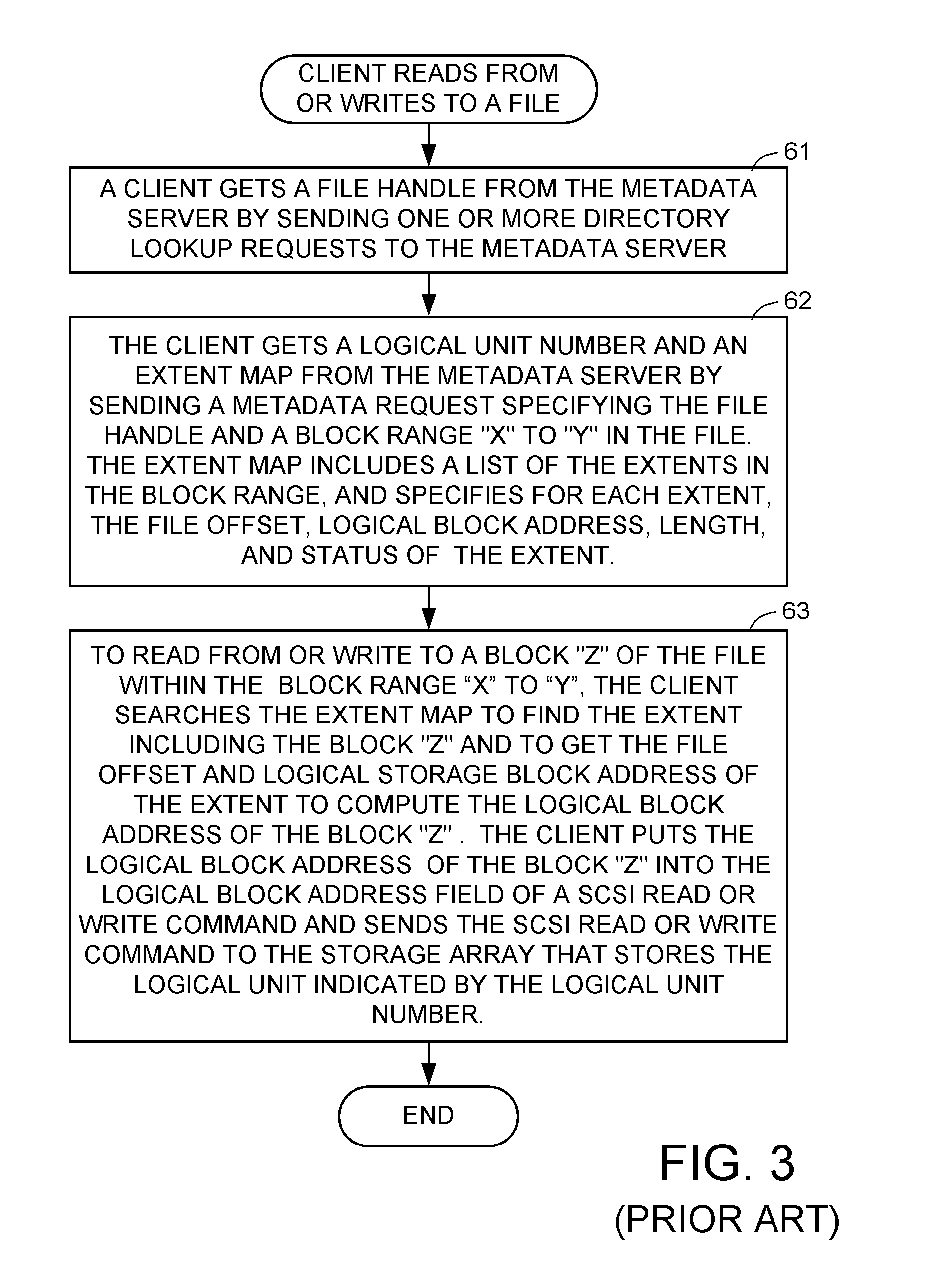

Access control to block storage devices for a shared disk based file system

ActiveUS8086585B1Improve securityChangeDigital data information retrievalDigital data processing detailsSCSILogical block addressing

For enhanced access control, a client includes a token in each read or write command sent to a block storage device. The block storage device evaluates the token to determine whether or not read or write access is permitted at a specified logical block address. For example, the token is included in the logical block address field of a SCSI read or write command. The client may compute the token as a function of the logical block address of a data block to be accessed, or a metadata server may include the token in each block address of each extent reported to the client in response to a metadata request. For enhanced security, the token also is a function of a client identifier, a logical unit number, and access rights of the client to a particular extent of file system data blocks.

Owner:EMC IP HLDG CO LLC

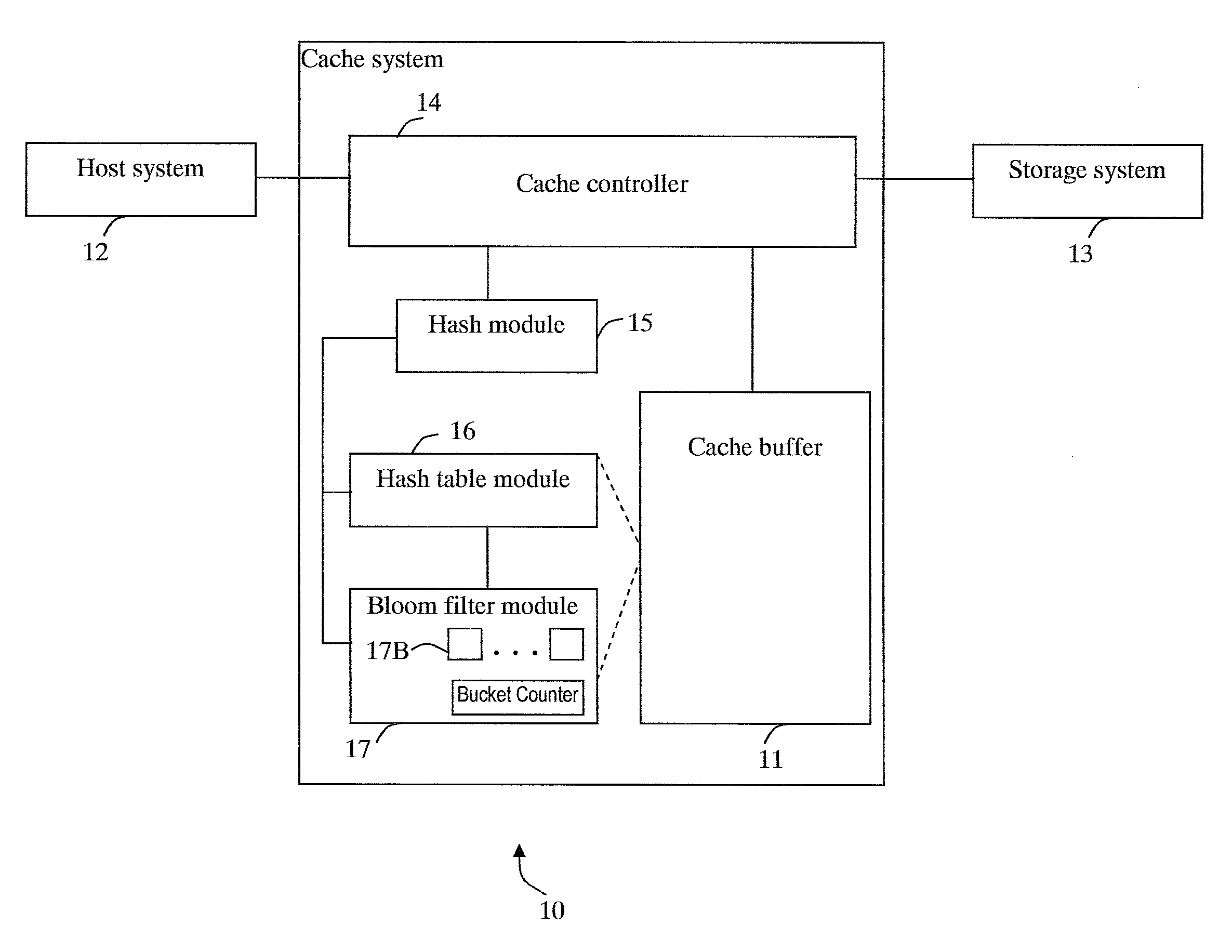

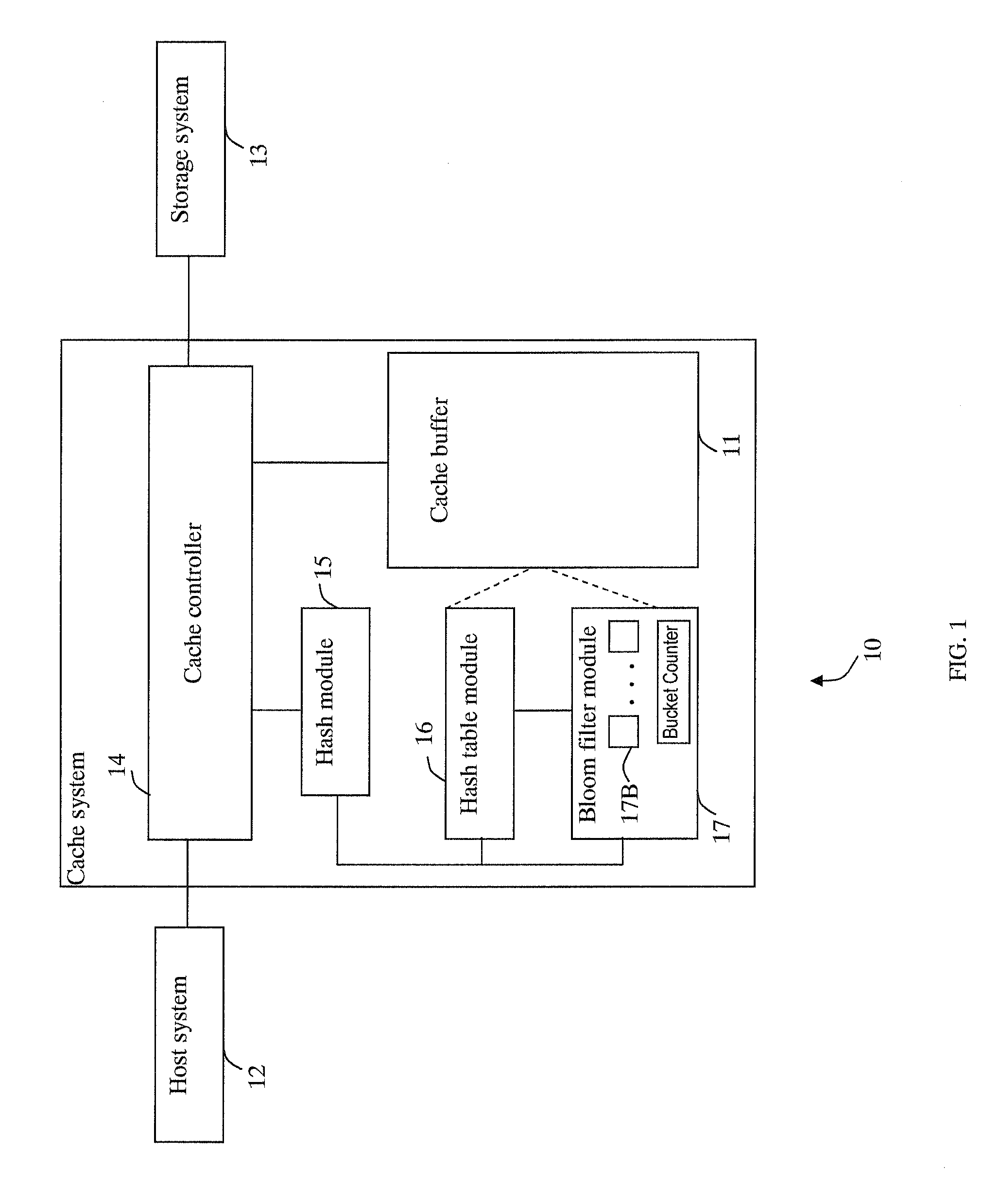

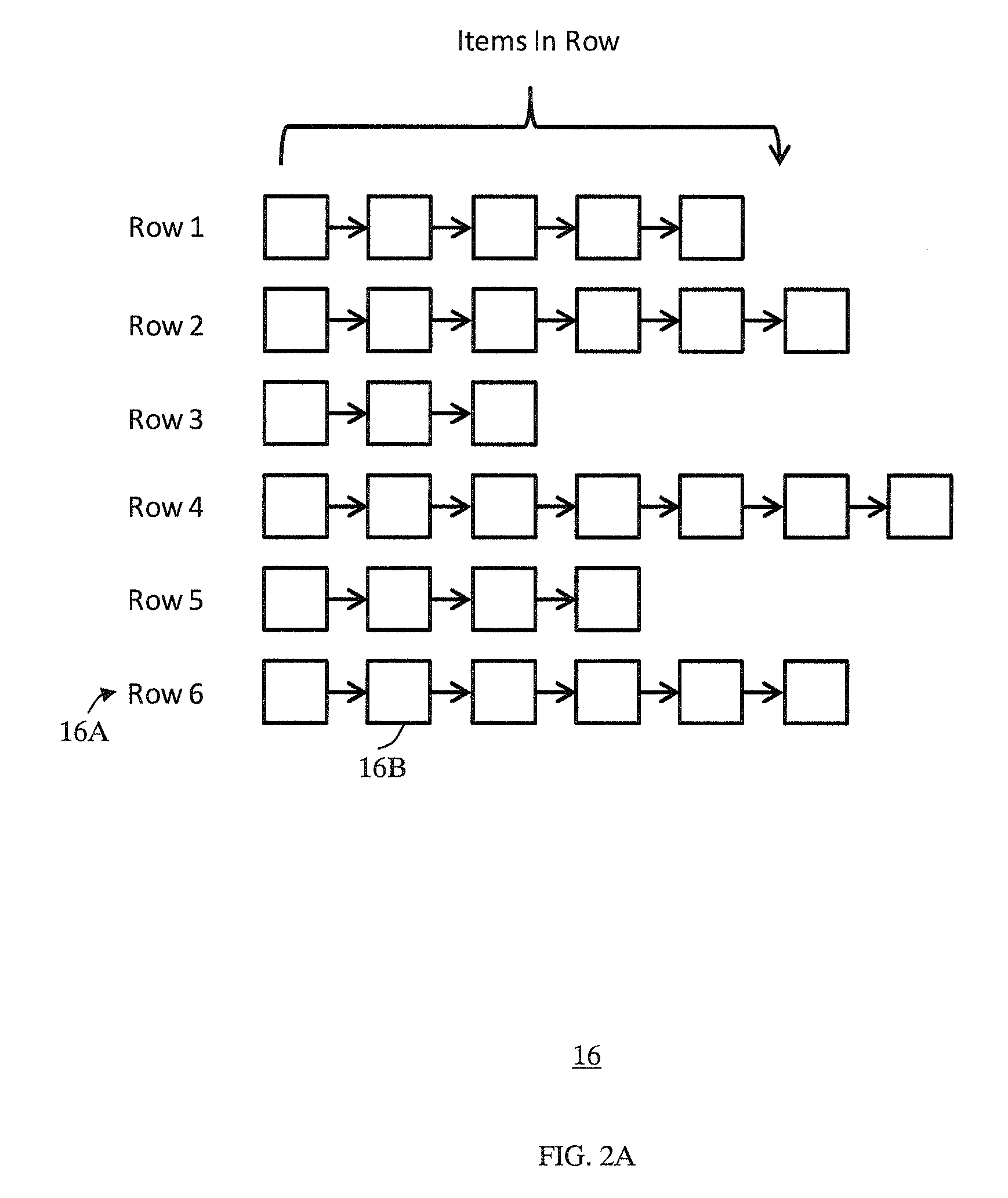

Cache system optimized for cache miss detection

ActiveUS20130326154A1Memory architecture accessing/allocationMemory adressing/allocation/relocationLogical block addressingBloom filter

According to an embodiment of the invention, cache management comprises maintaining a cache comprising a hash table including rows of data items in the cache, wherein each row in the hash table is associated with a hash value representing a logical block address (LBA) of each data item in that row. Searching for a target data item in the cache includes calculating a hash value representing a LBA of the target data item, and using the hash value to index into a counting Bloom filter that indicates that the target data item is either not in the cache, indicating a cache miss, or that the target data item may be in the cache. If a cache miss is not indicated, using the hash value to select a row in the hash table, and indicating a cache miss if the target data item is not found in the selected row.

Owner:SAMSUNG ELECTRONICS CO LTD

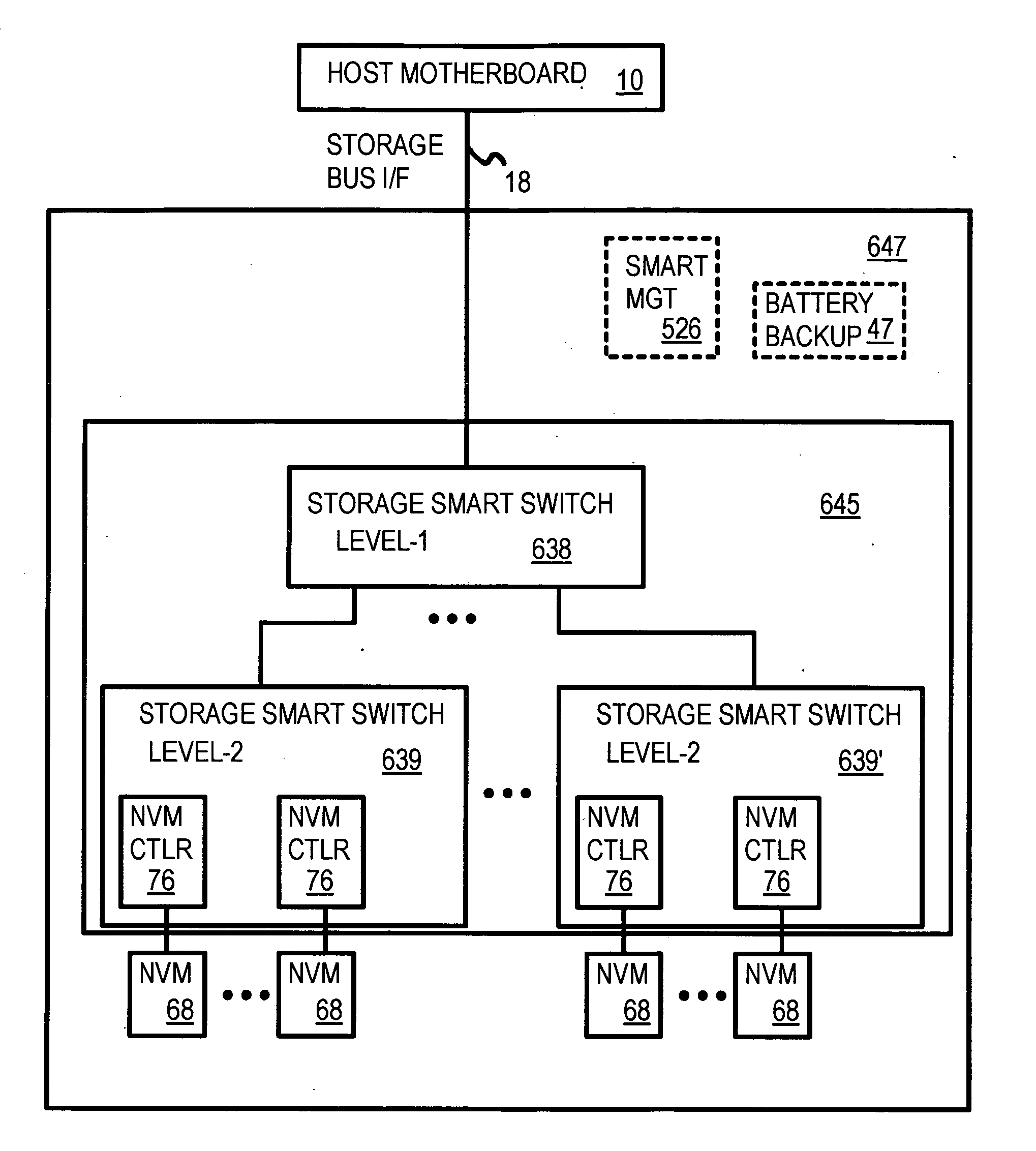

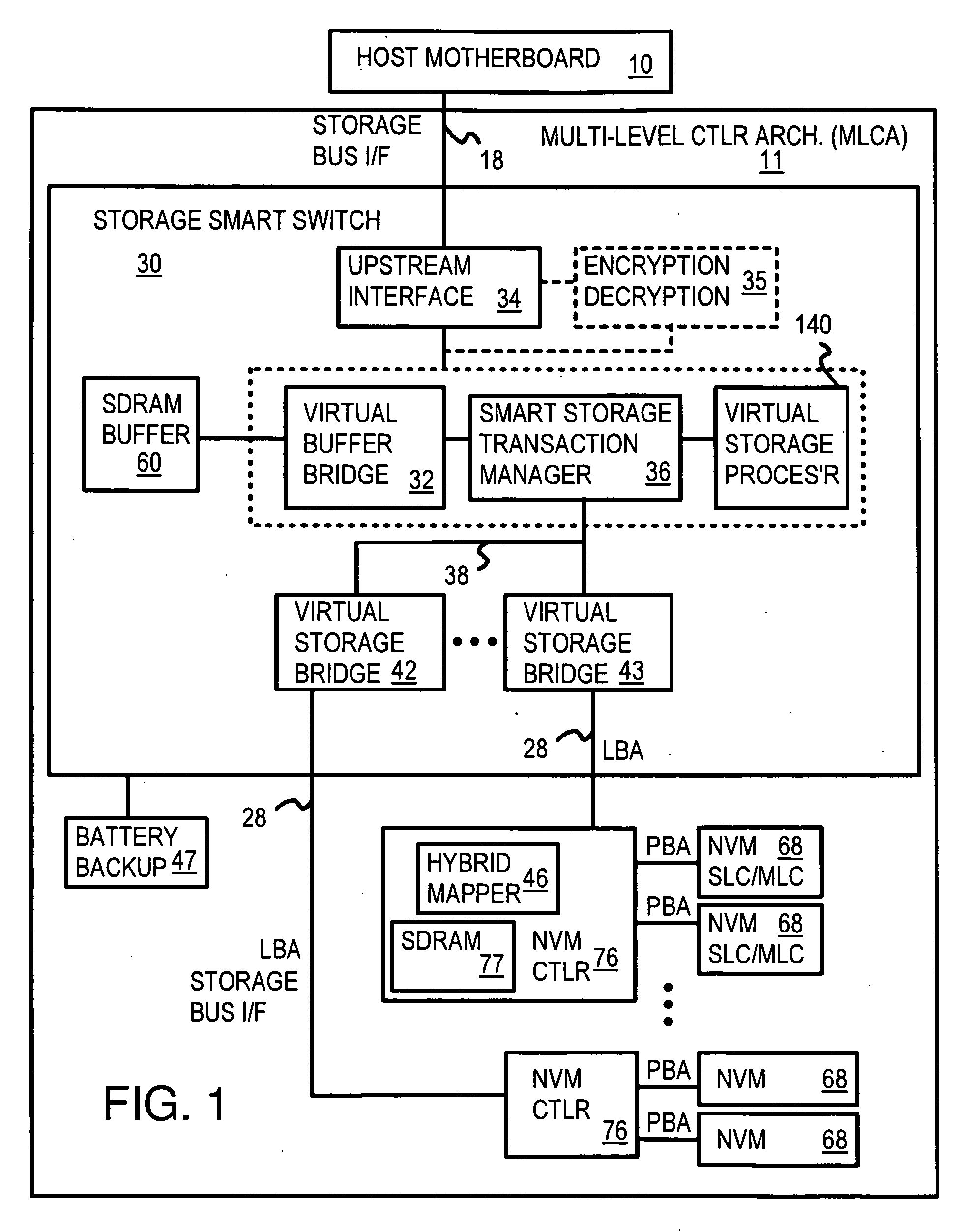

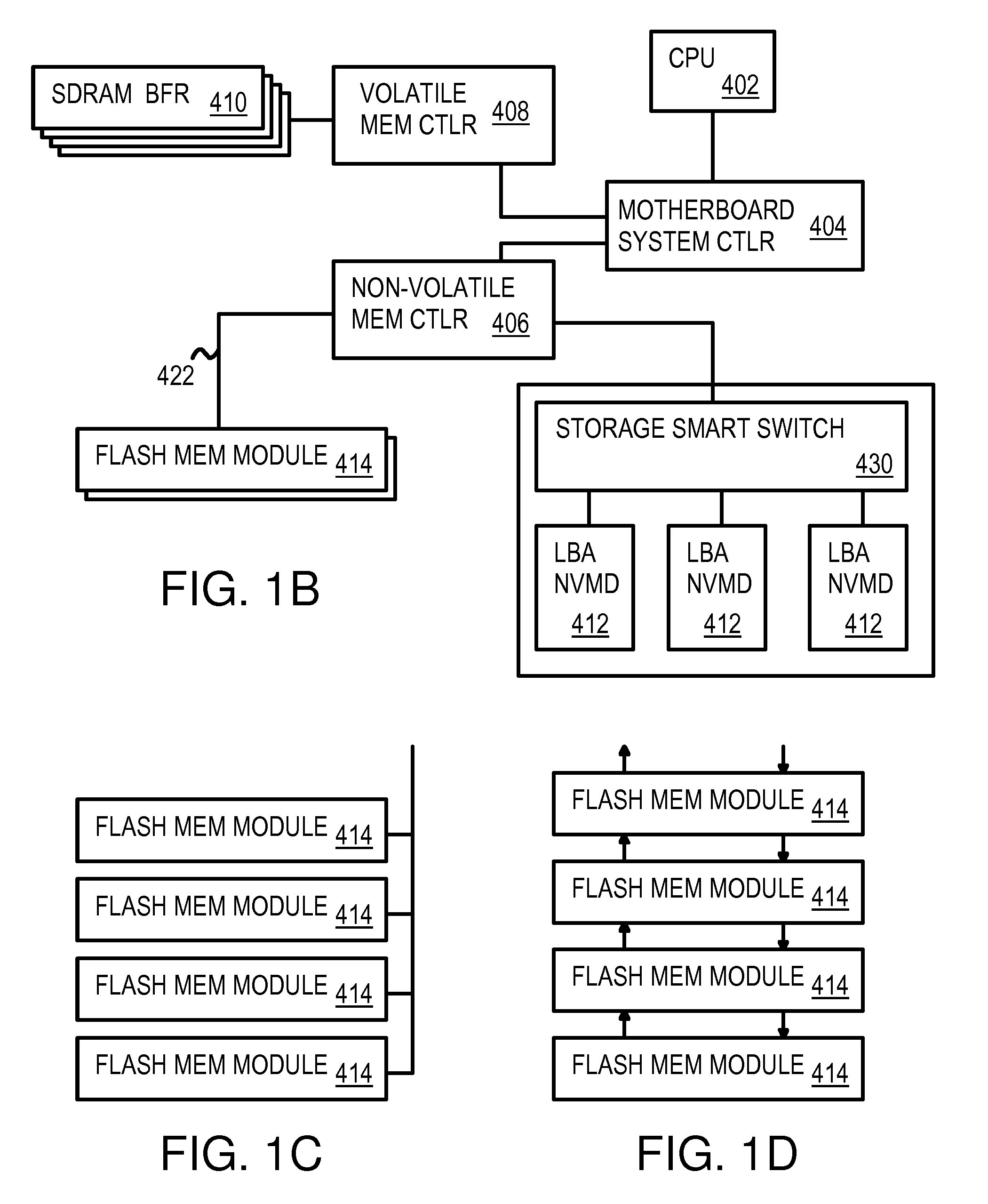

Multi-Level Striping and Truncation Channel-Equalization for Flash-Memory System

InactiveUS20090240873A1Memory architecture accessing/allocationError preventionLogical block addressingData access

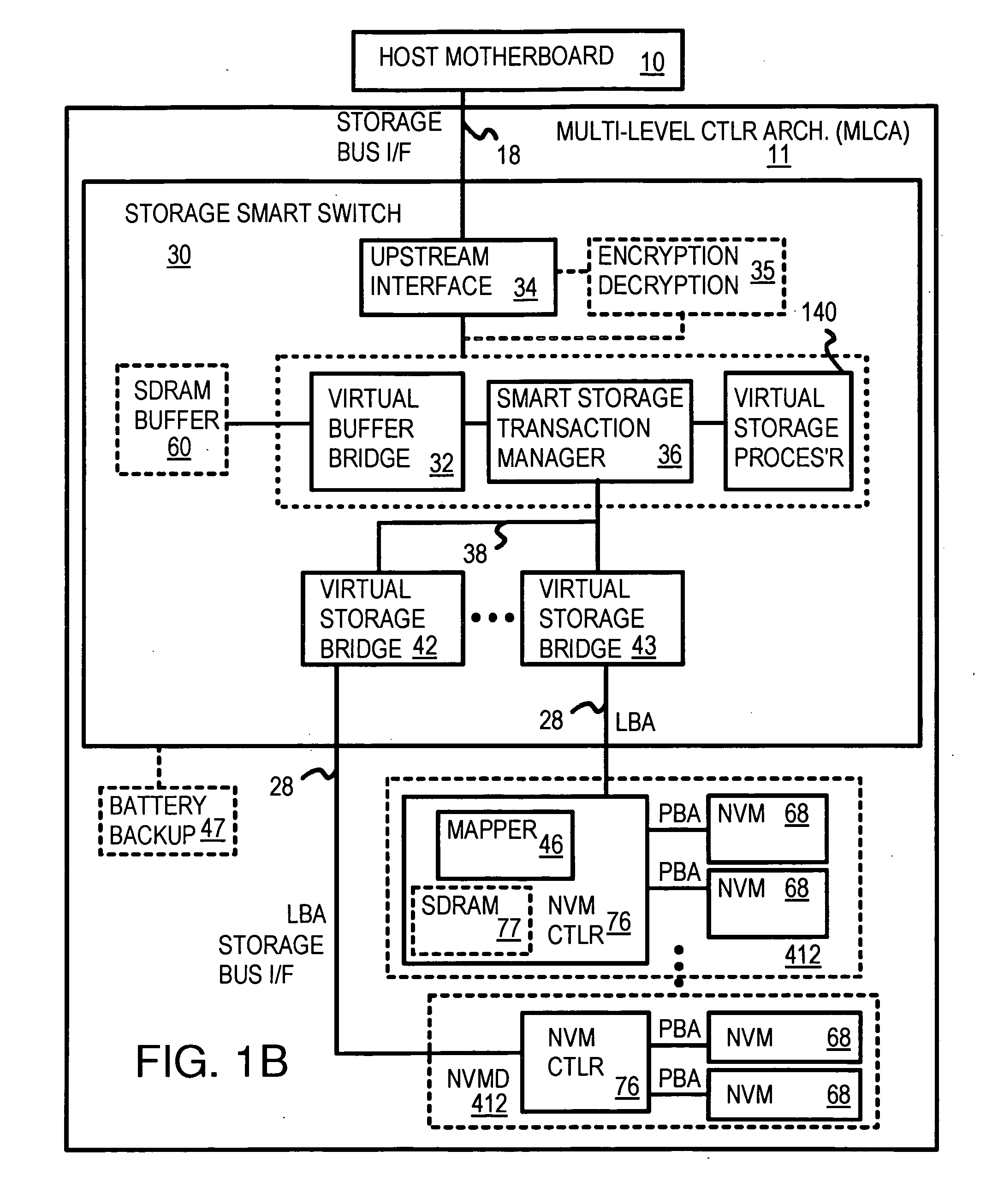

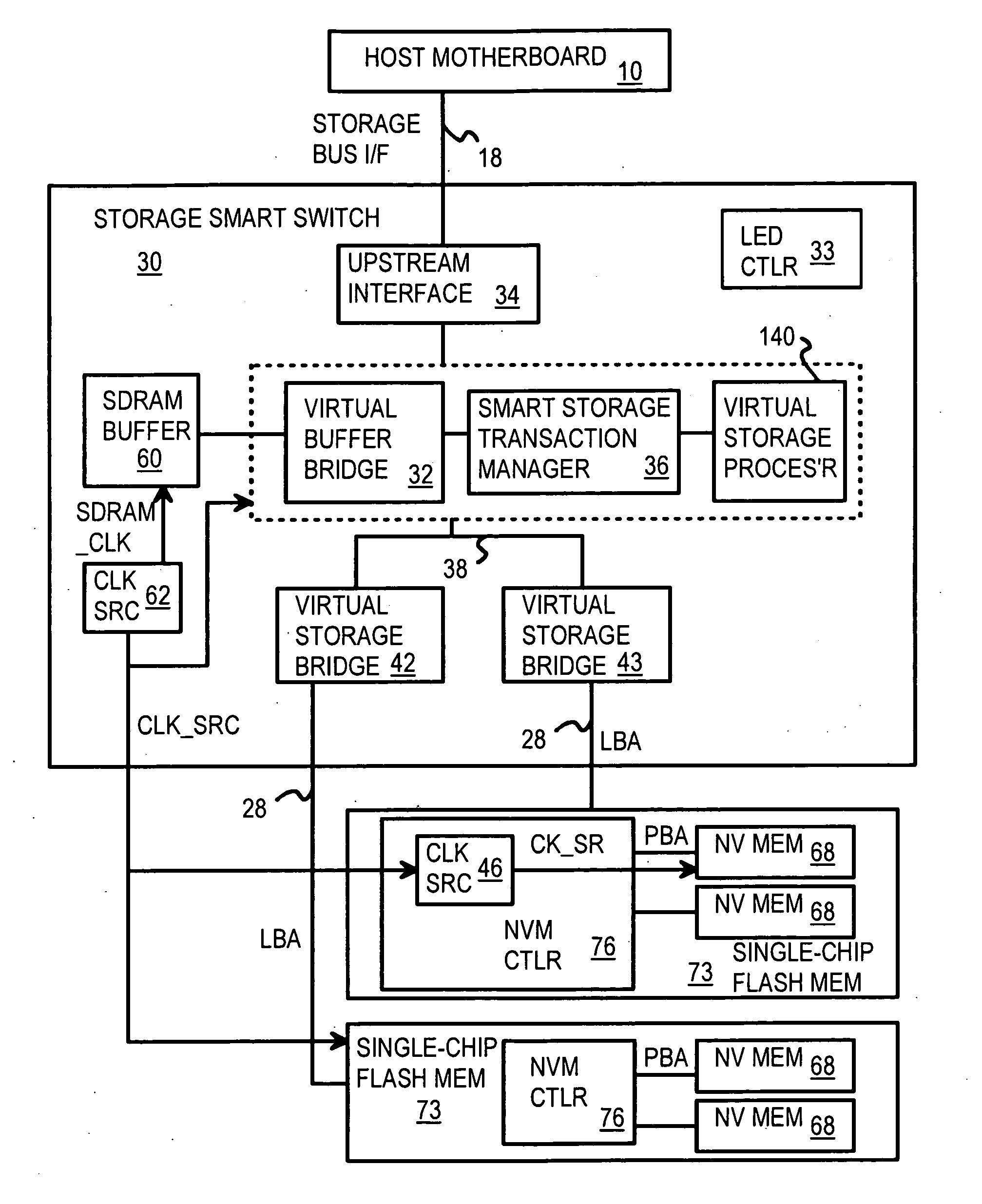

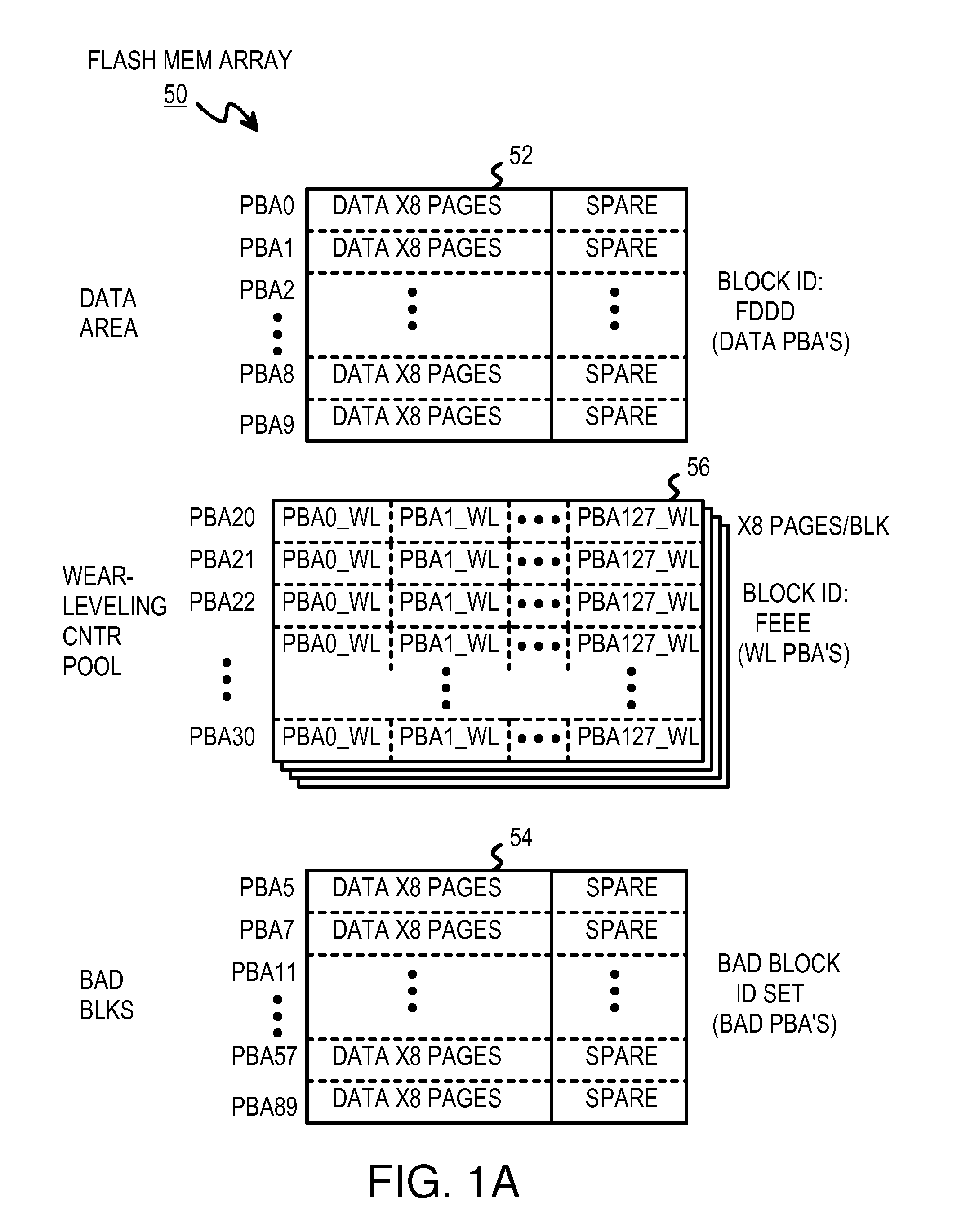

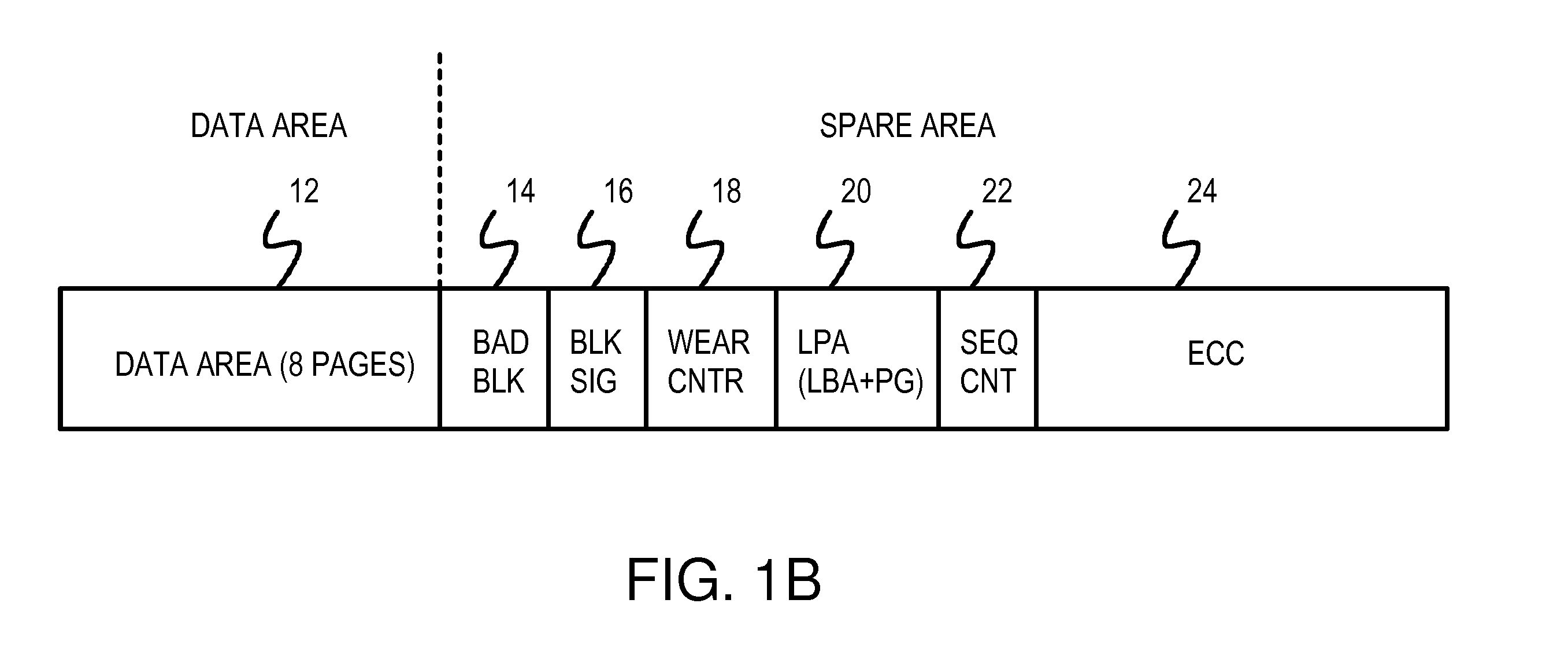

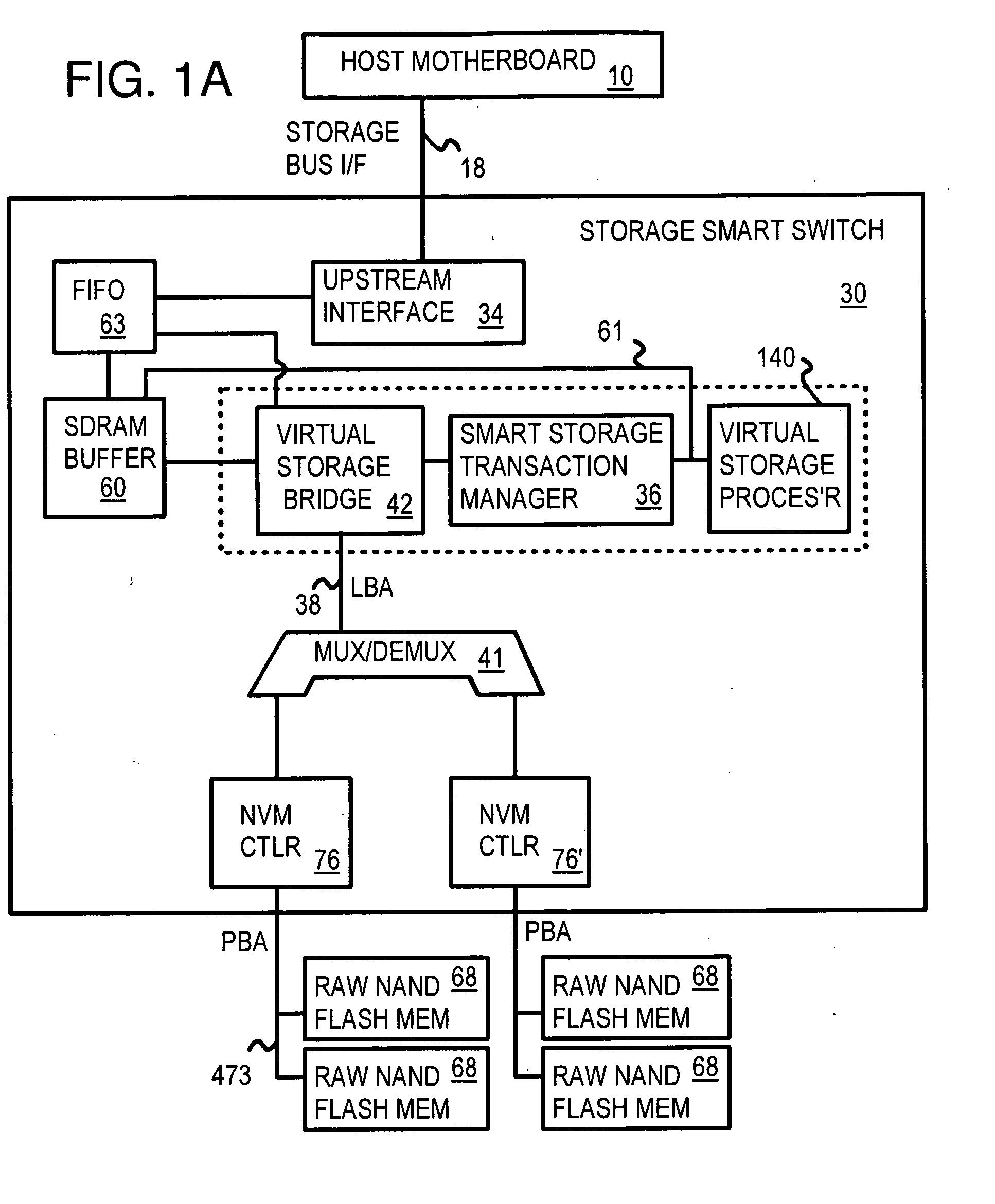

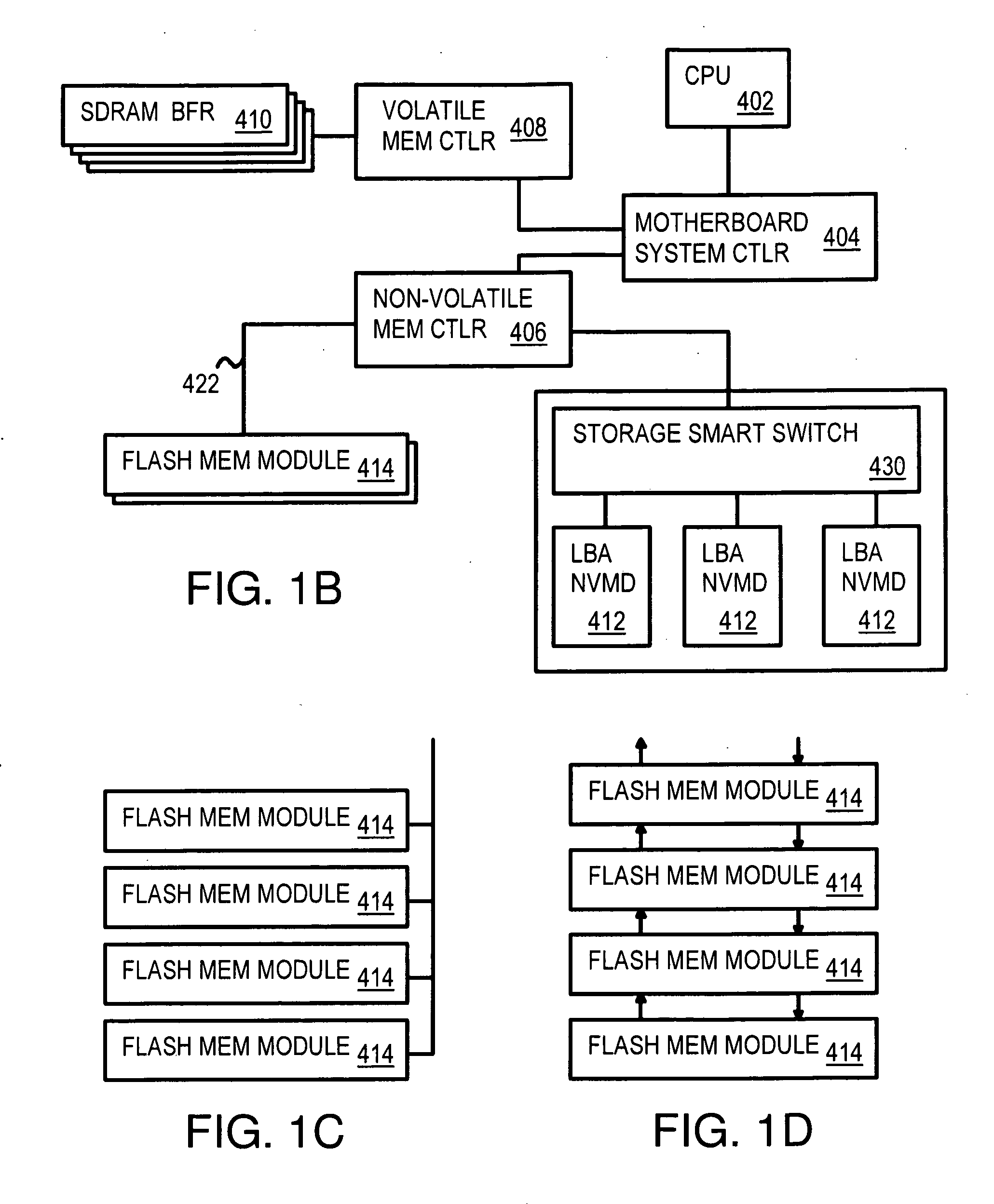

Truncation reduces the available striped data capacity of all flash channels to the capacity of the smallest flash channel. A solid-state disk (SSD) has a smart storage switch salvages flash storage removed from the striped data capacity by truncation. Extra storage beyond the striped data capacity is accessed as scattered data that is not striped. The size of the striped data capacity is reduced over time as more bad blocks appear. A first-level striping map stores striped and scattered capacities of all flash channels and maps scattered and striped data. Each flash channel has a Non-Volatile Memory Device (NVMD) with a lower-level controller that converts logical block addresses (LBA) to physical block addresses (PBA) that access flash memory in the NVMD. Wear-leveling and bad block remapping are preformed by each NVMD. Source and shadow flash blocks are recycled by the NVMD. Two levels of smart storage switches enable three-level controllers.

Owner:SUPER TALENT TECH CORP

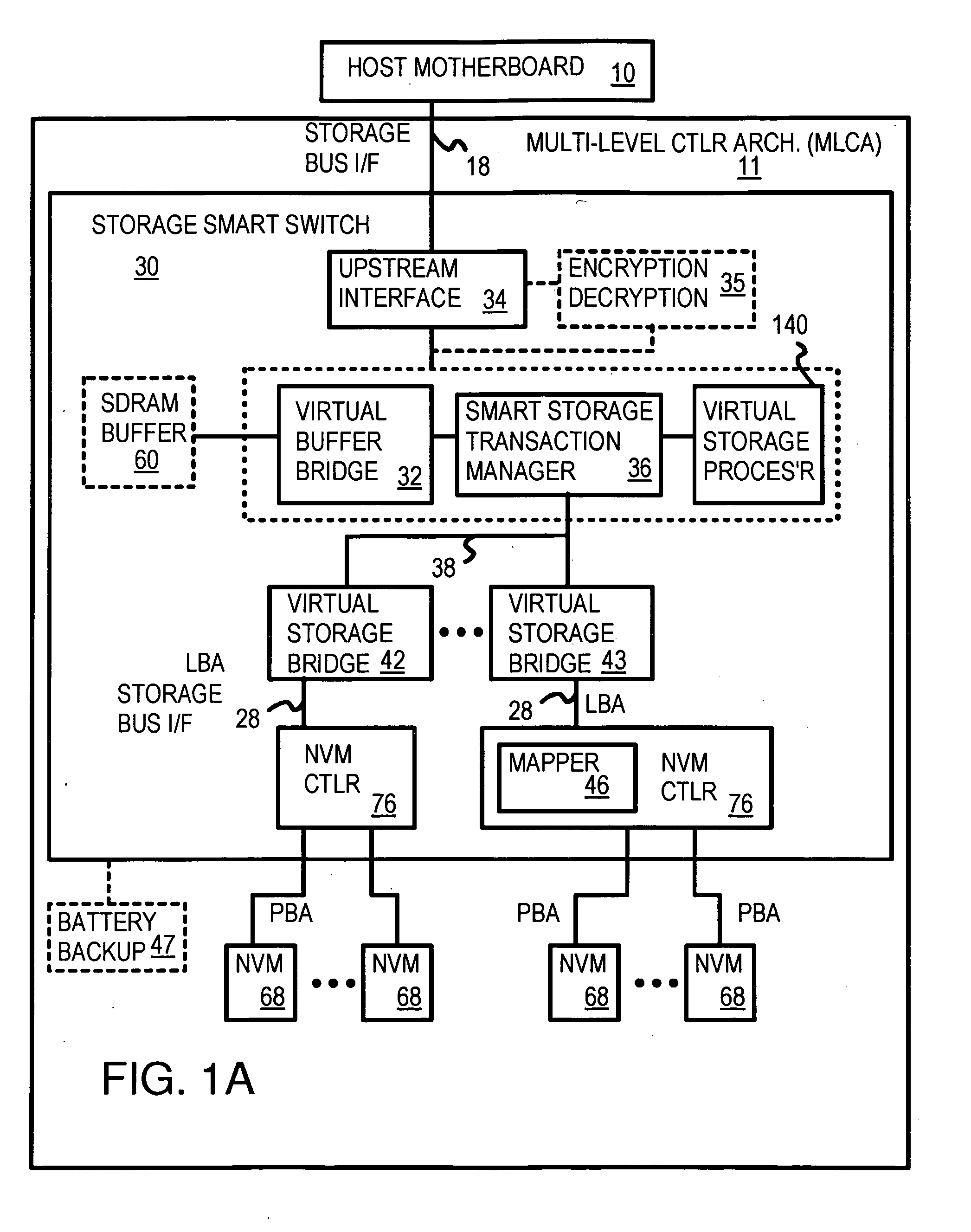

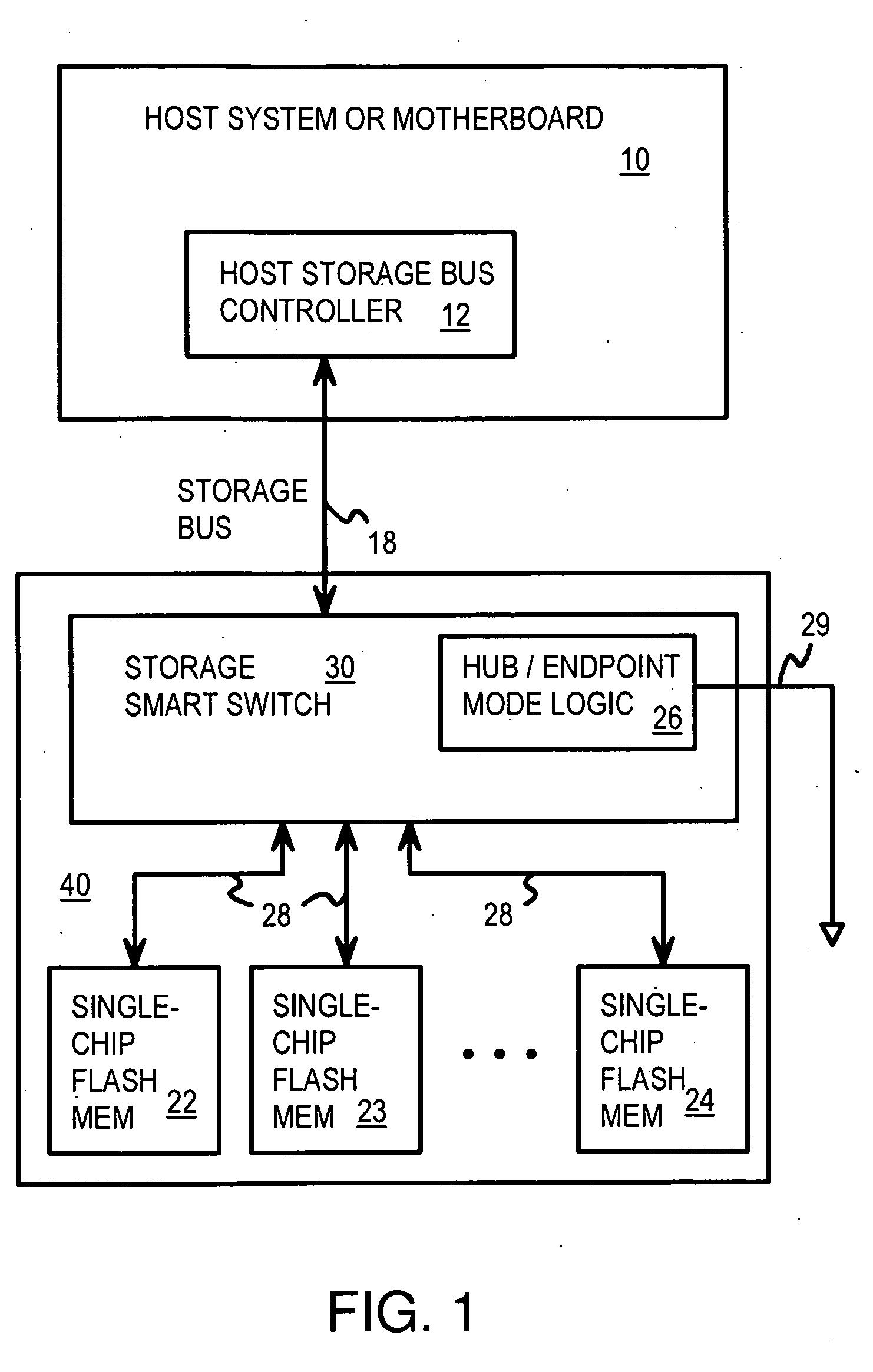

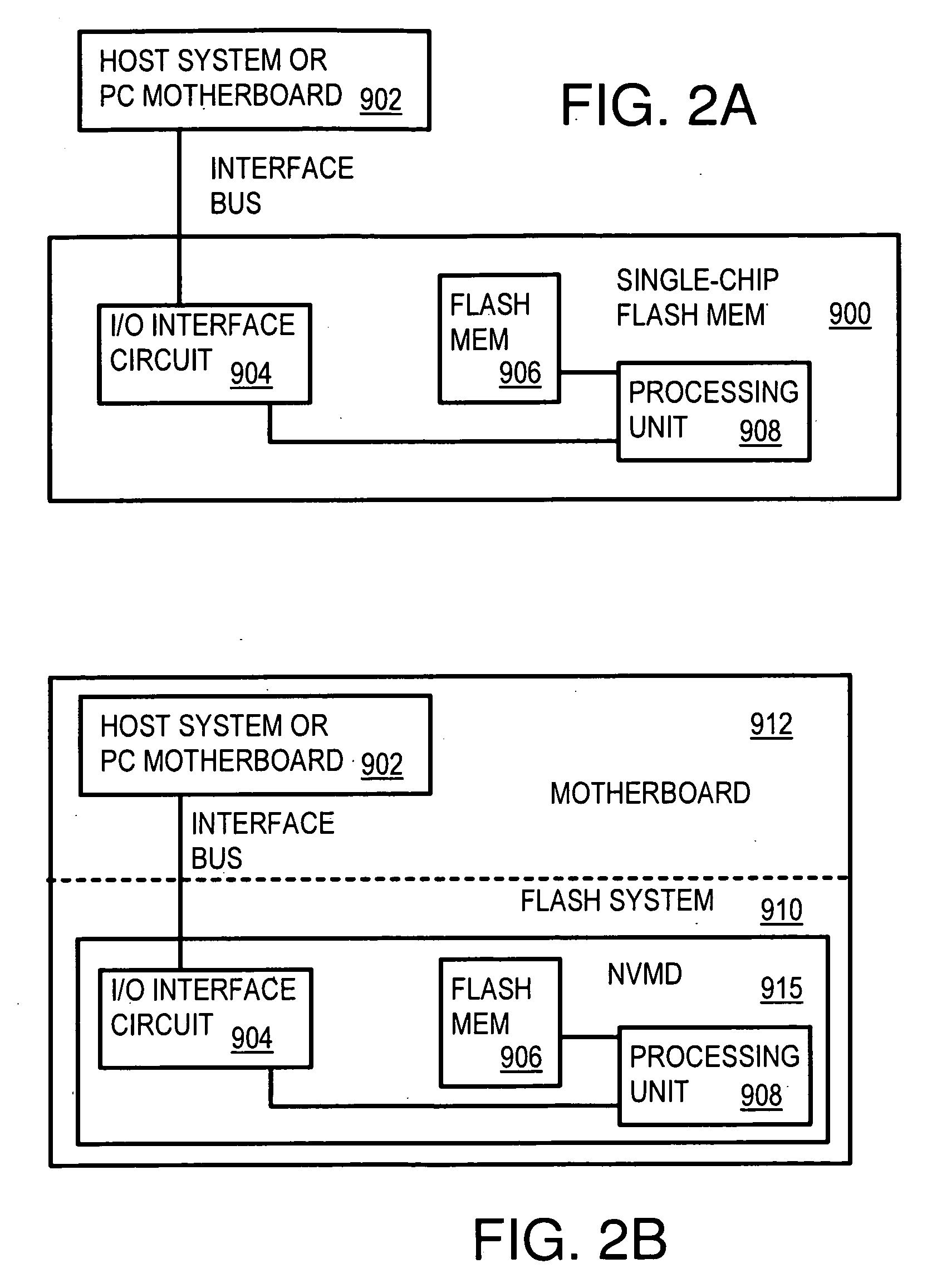

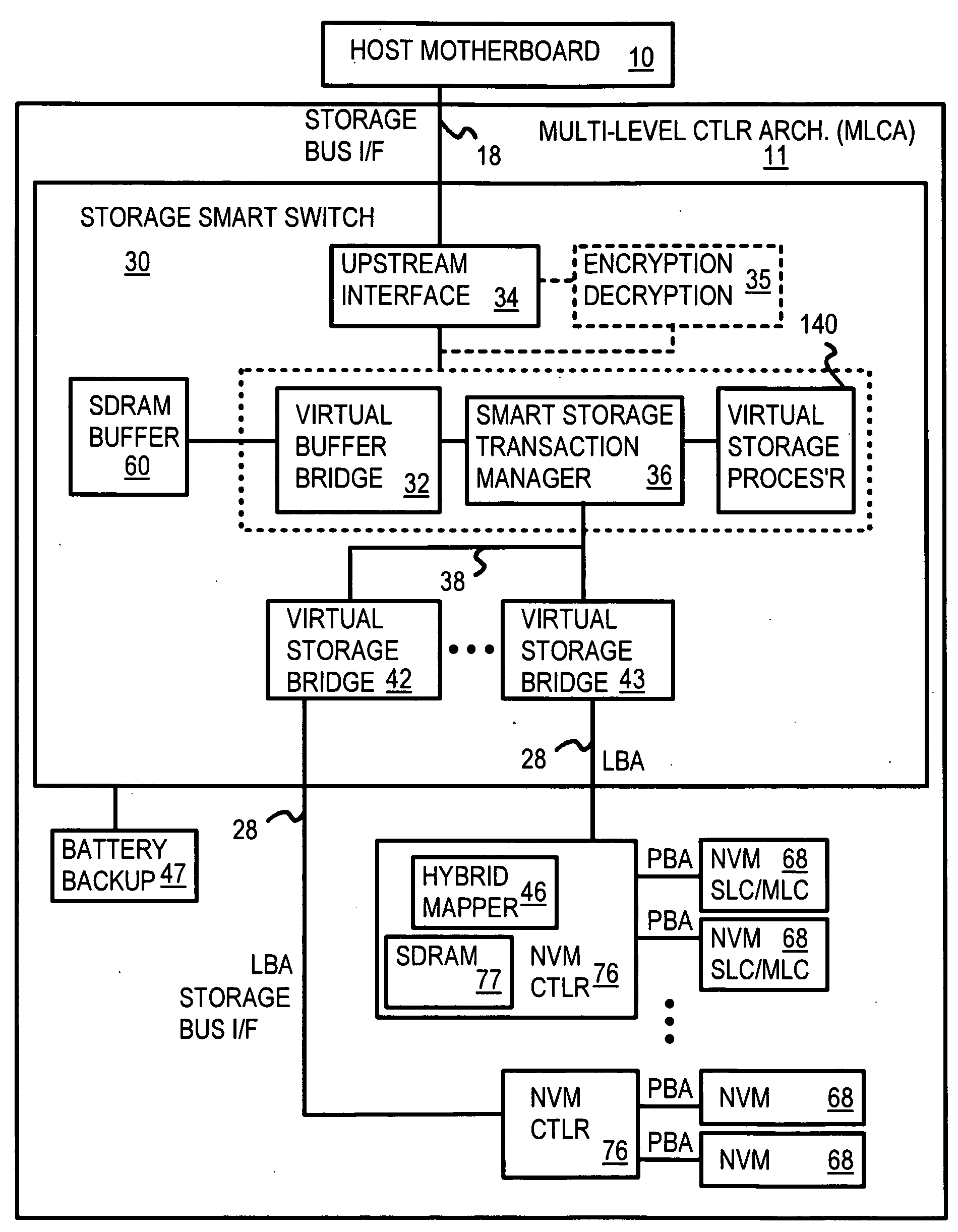

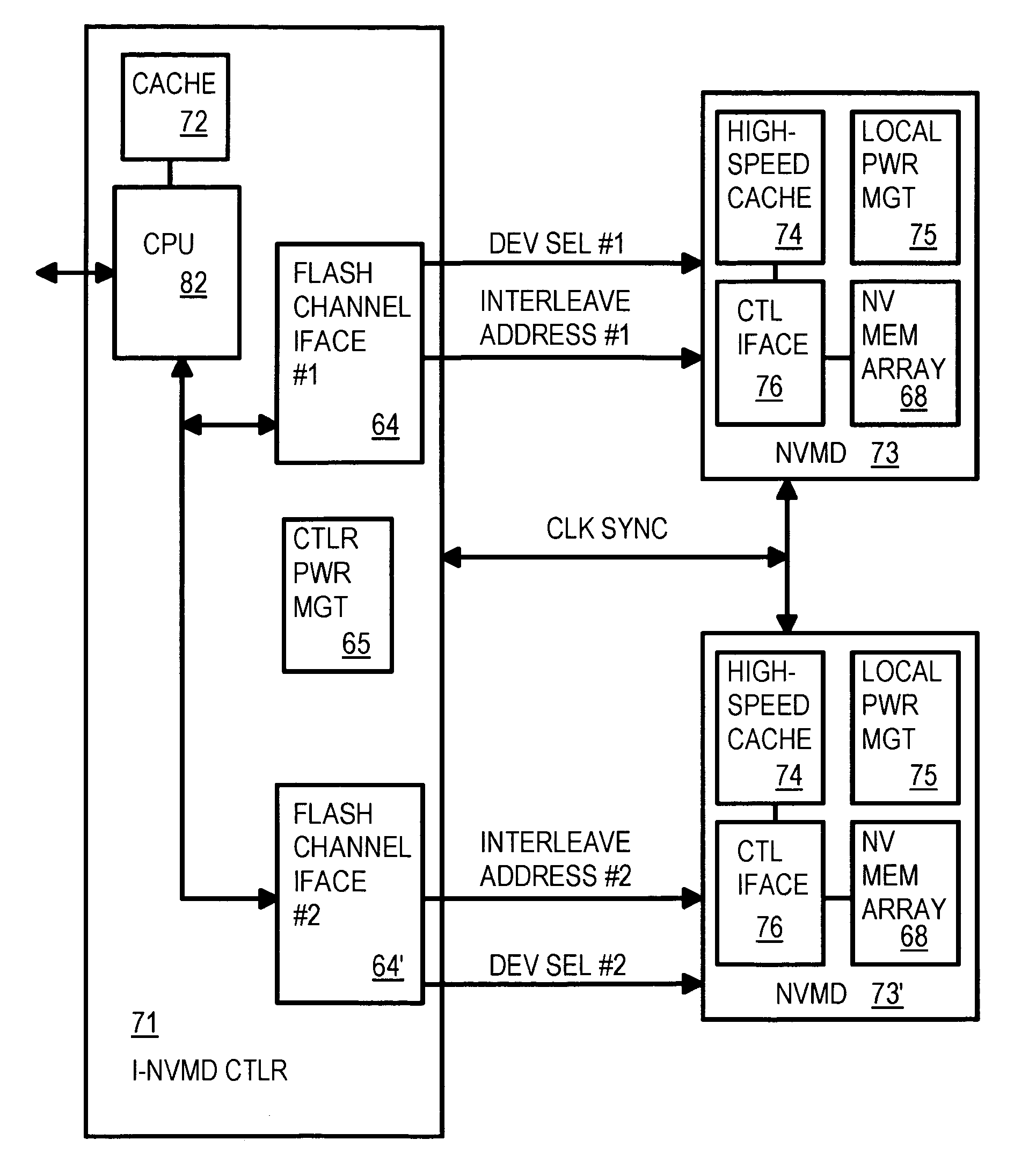

Multi-Level Controller with Smart Storage Transfer Manager for Interleaving Multiple Single-Chip Flash Memory Devices

InactiveUS20080320214A1Memory architecture accessing/allocationMemory adressing/allocation/relocationLogical block addressingSolid-state drive

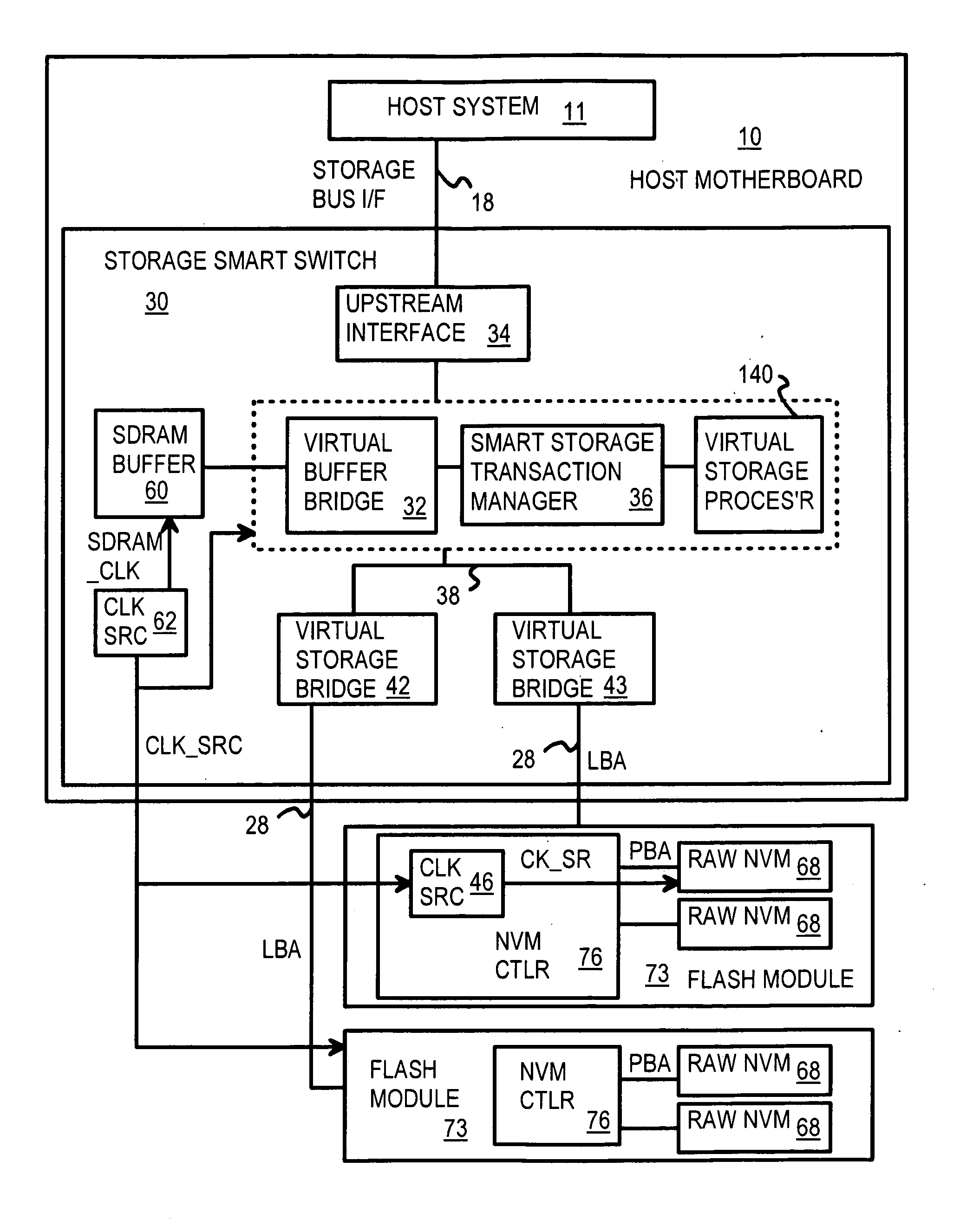

A solid-state disk (SSD) has a smart storage switch with a smart storage transaction manager that re-orders host commands for accessing downstream single-chip flash-memory devices. Each single-chip flash-memory device has a lower-level controller that converts logical block addresses (LBA) to physical block addresses (PBA) that access flash memory blocks in the single-chip flash-memory device. Wear-leveling and bad block remapping are preformed by each single-chip flash-memory device, and at a higher level by a virtual storage processor in the smart storage switch. Virtual storage bridges between the smart storage transaction manager and the single-chip flash-memory devices bridge LBA transactions over LBA buses to the single-chip flash-memory devices. Data striping and interleaving among multiple channels of the single-chip flash-memory device is controlled at a high level by the smart storage transaction manager, while further interleaving and remapping may be performed within each single-chip flash-memory device.

Owner:SUPER TALENT TECH CORP

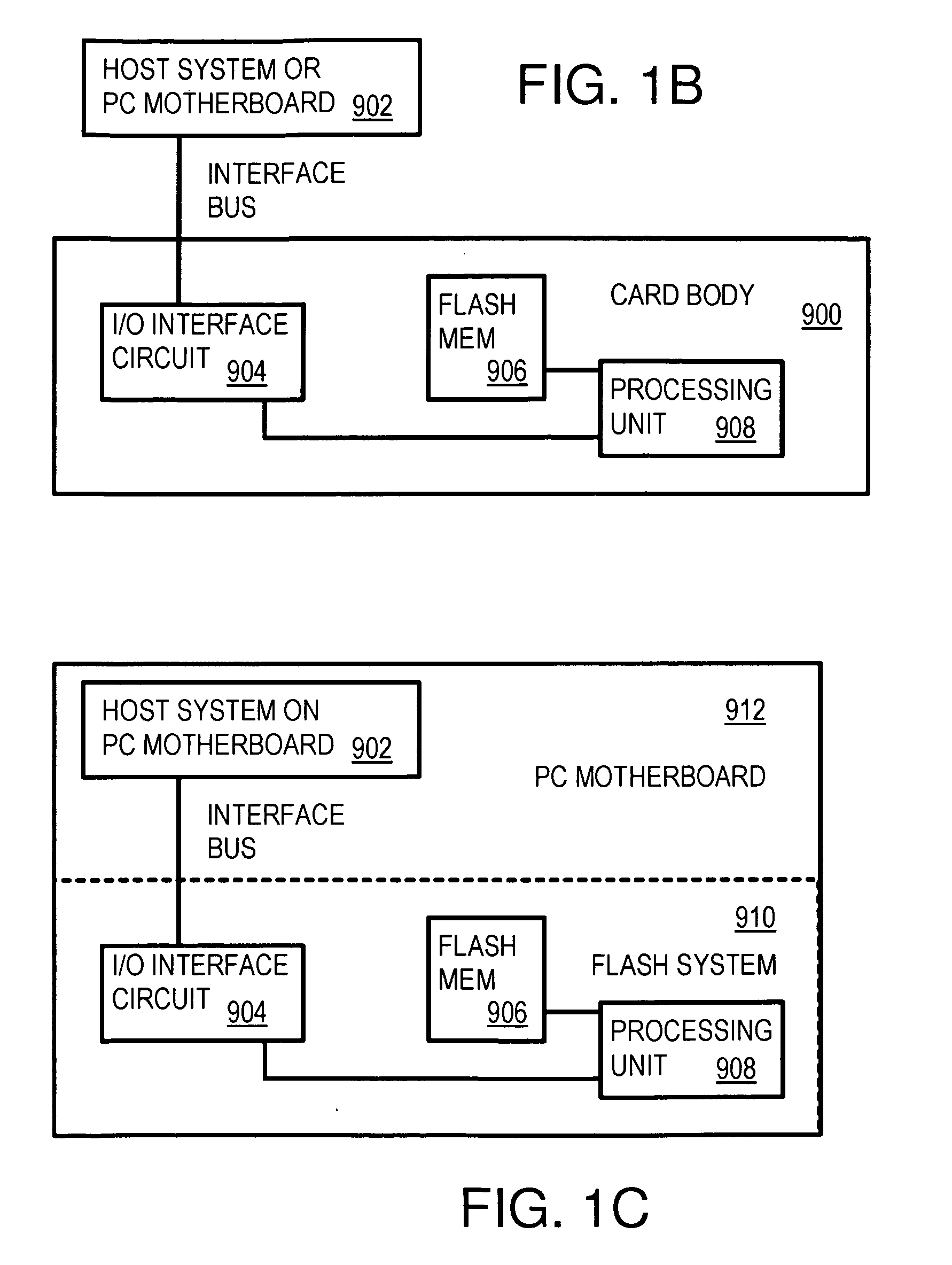

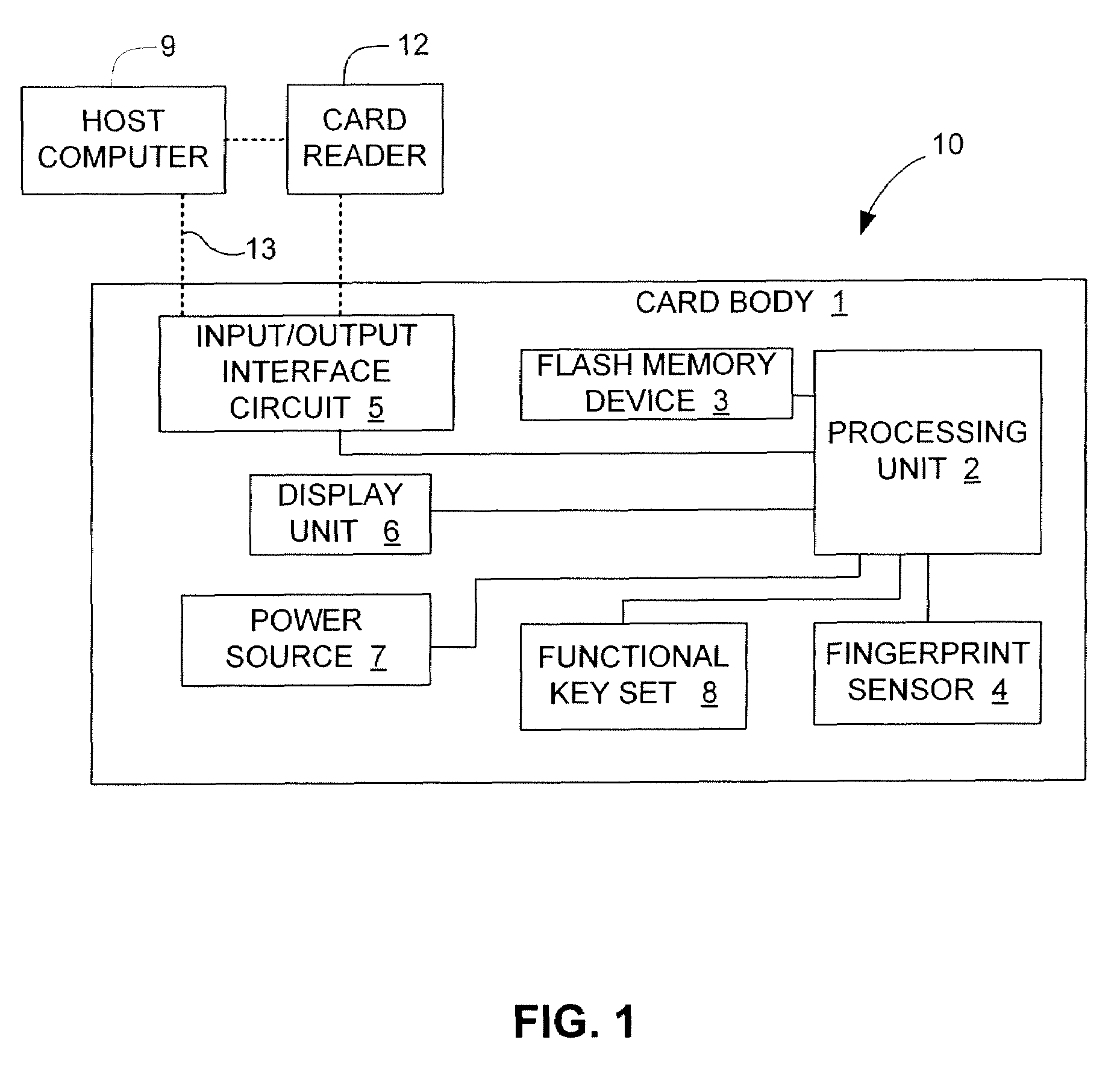

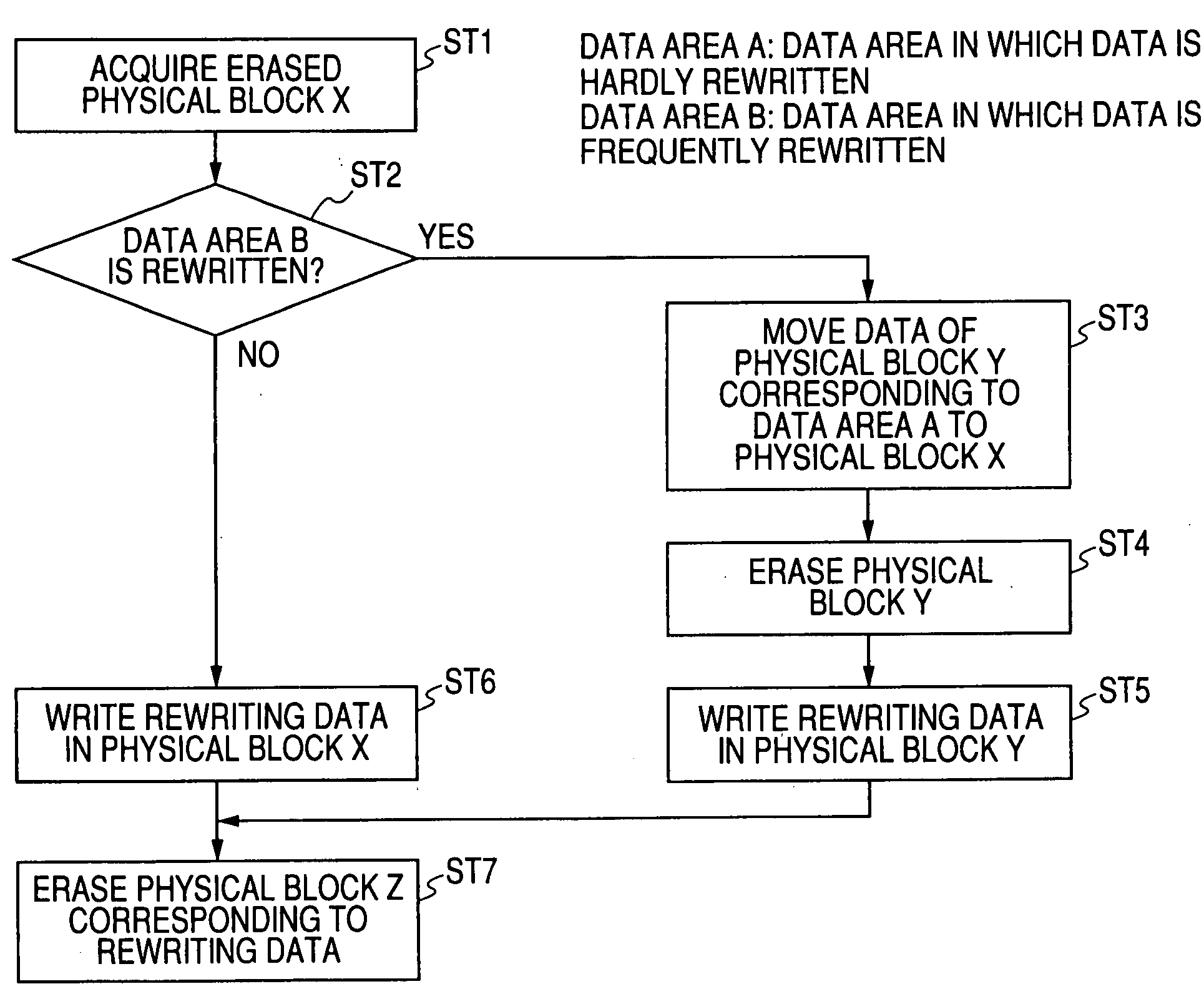

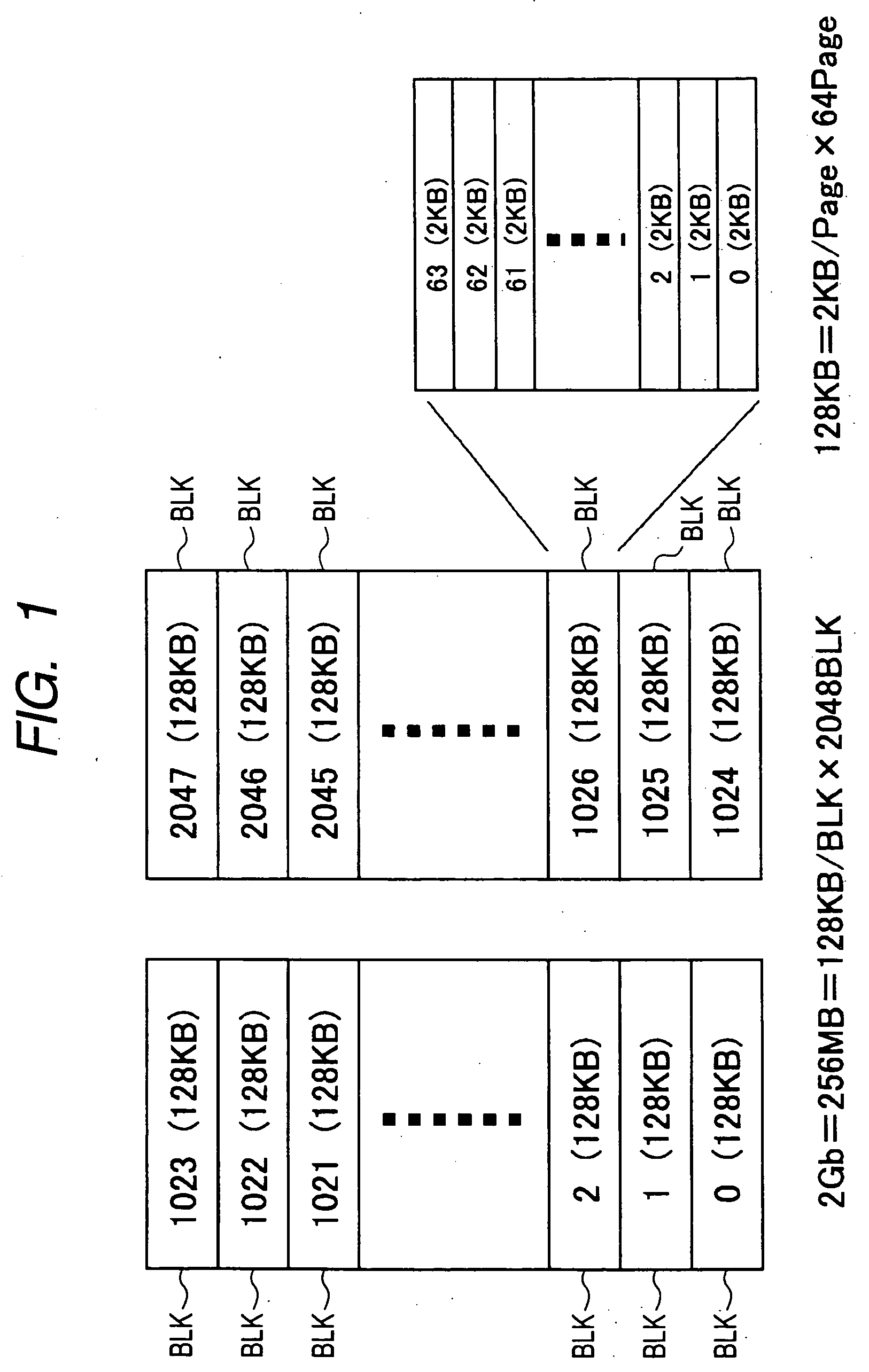

Managing bad blocks in various flash memory cells for electronic data flash card

InactiveUS20080082736A1Small sizeLow costMemory architecture accessing/allocationMemory systemsComputer accessFlash memory controller

An electronic data flash card accessible by a host computer, includes a flash memory controller connected to a flash memory device, and an input-output interface circuit activated to establish a communication with the host. In an embodiment, the flash card uses a USB interface circuit for communication with the host. A flash memory controller includes an arbitrator for mapping logical addresses with physical block addresses, and for performing block management operations including: storing reassigned data to available blocks, relocating valid data in obsolete blocks to said available blocks and reassigning logical block addresses to physical block addresses of said available blocks, finding bad blocks of the flash memory device and replacing with reserve blocks, erasing obsolete blocks for recycling after relocating valid data to available blocks, and erase count wear leveling of blocks, etc. Furthermore, each flash memory device includes an internal buffer for accelerating the block management operations.

Owner:SUPER TALENT ELECTRONICS

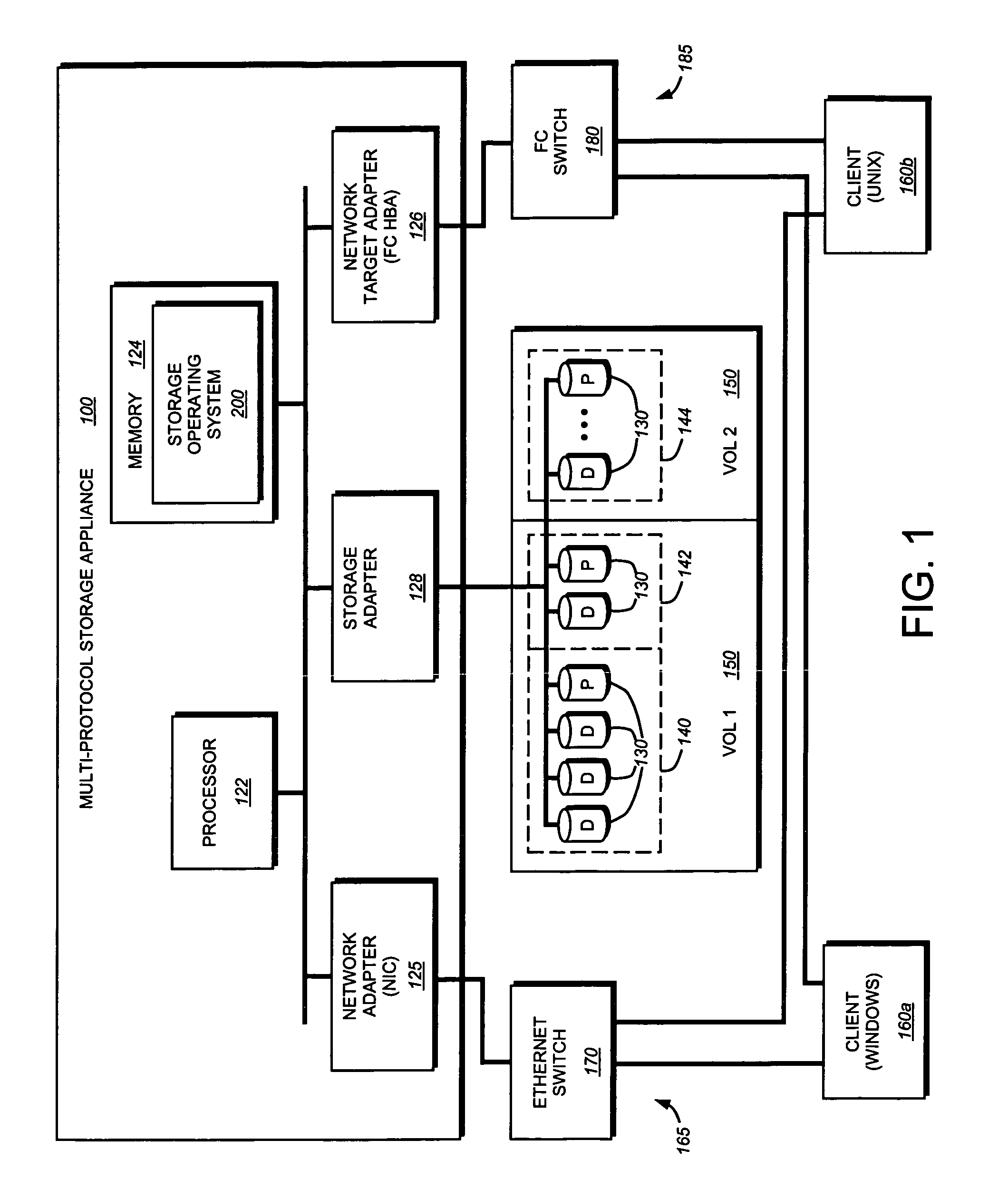

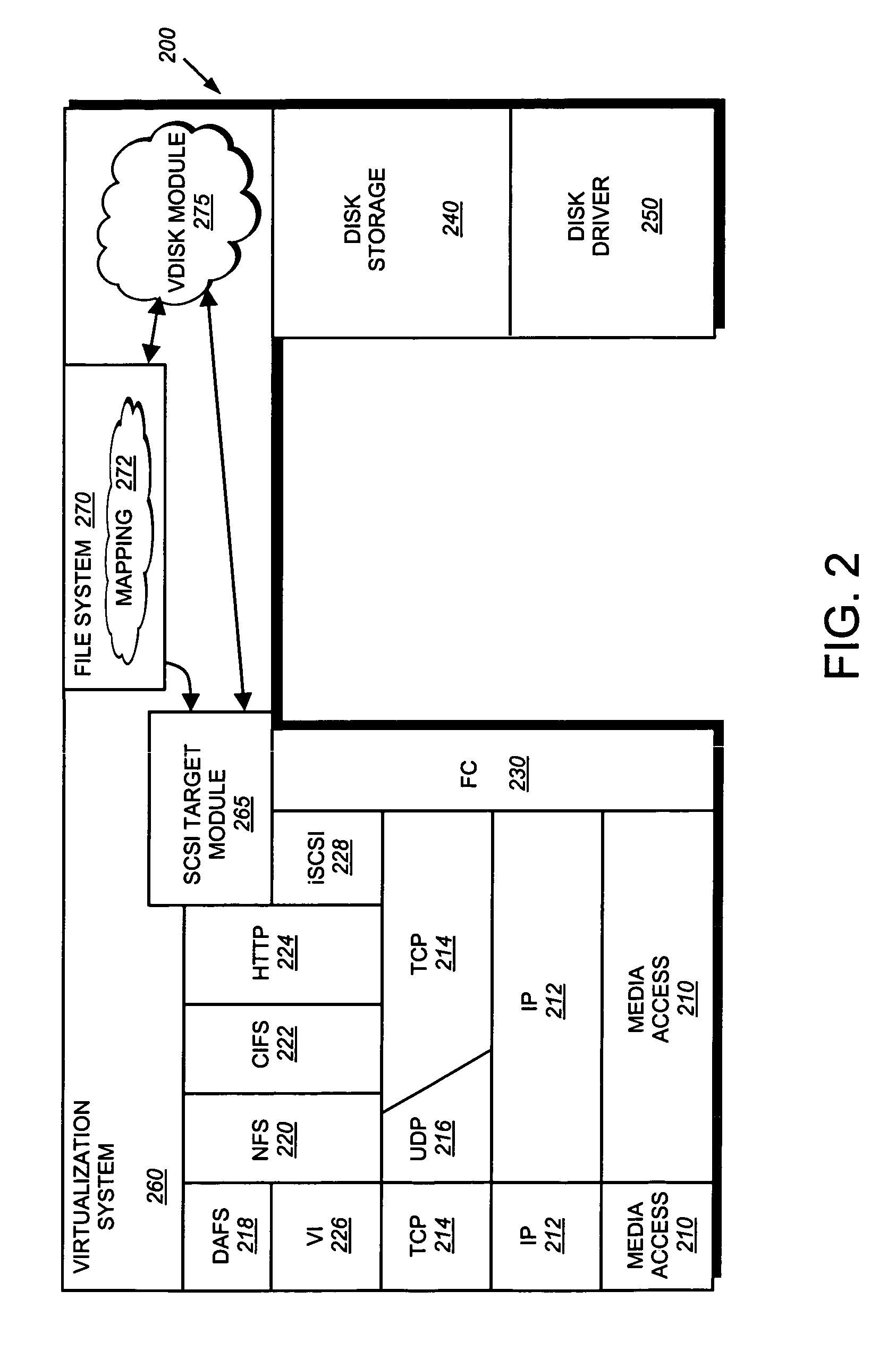

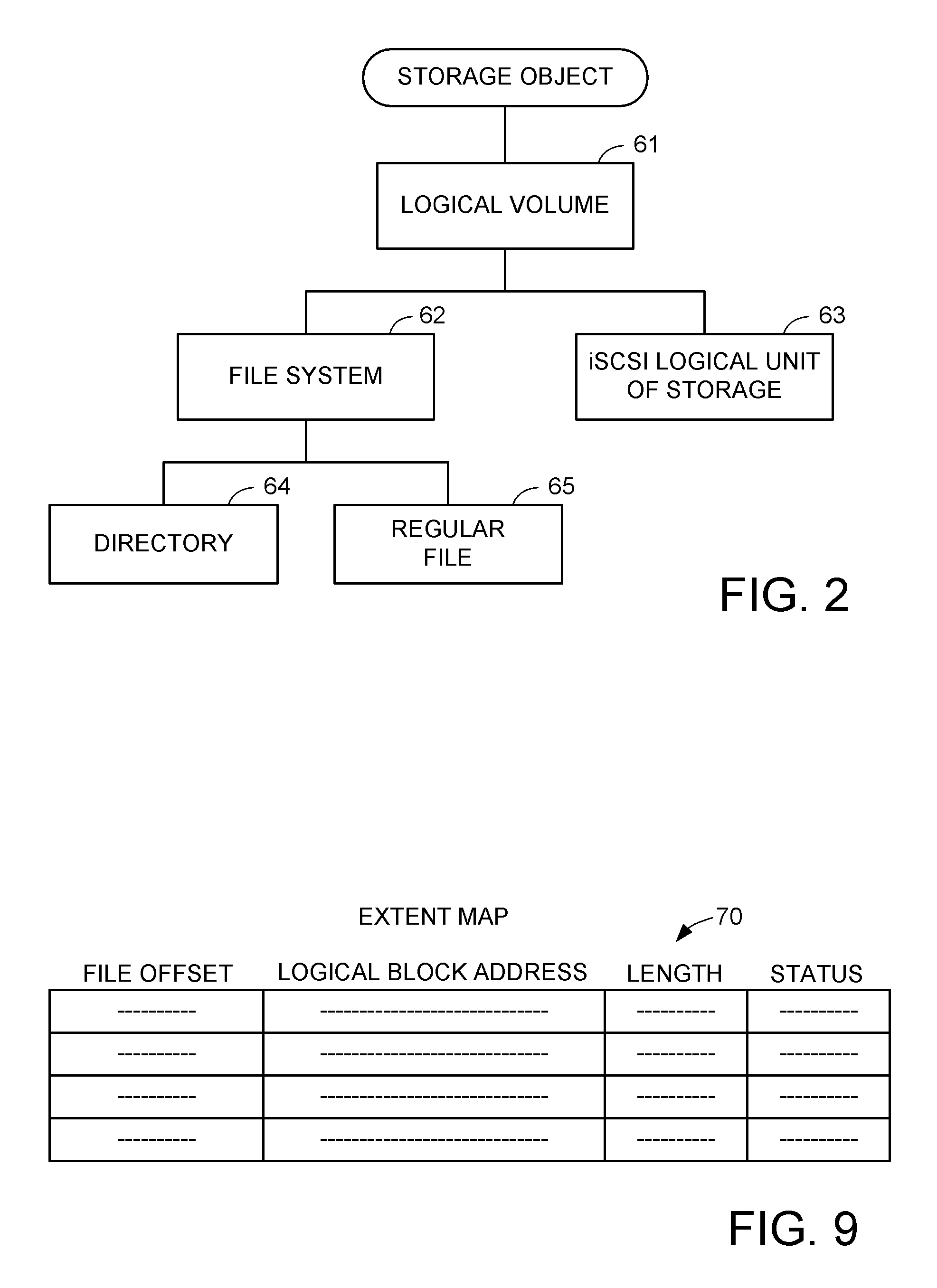

System and method for mapping file block numbers to logical block addresses

ActiveUS7437530B1Improve performanceRaise transfer toMultiple digital computer combinationsTransmissionOperational systemLogical block addressing

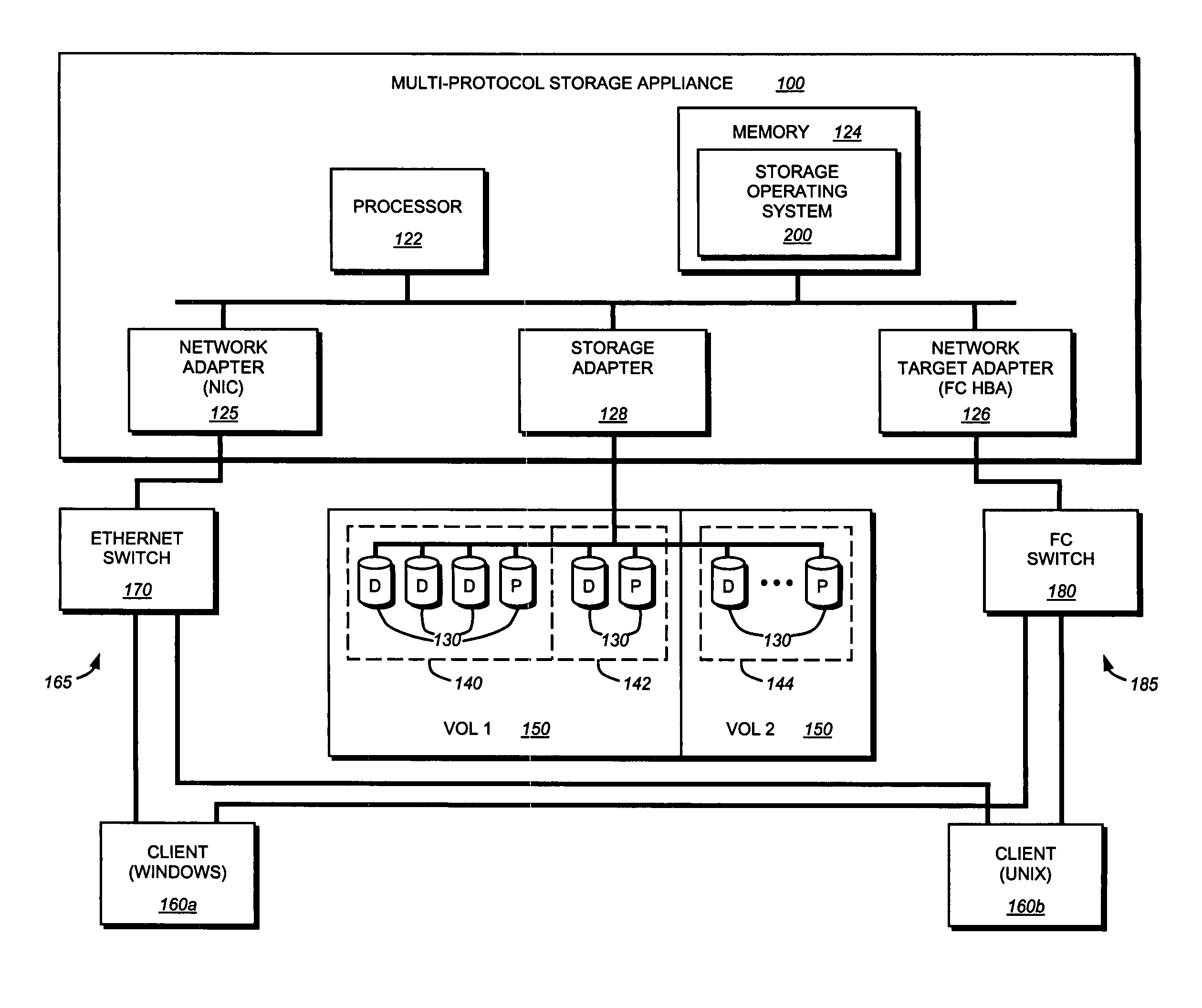

A system and method for mapping file block numbers (FBNs) to logical block addresses (LBAs) is provided. The system and method performs the mapping of FBNs to LBAs in a file system layer of a storage operating system, thereby enabling the use of clients in a storage environment that have not been modified to incorporate mapping tables. As a result, a client may send data access requests to the storage system utilizing FBNs and have the storage system perform the appropriate mapping to LBAs.

Owner:NETWORK APPLIANCE INC

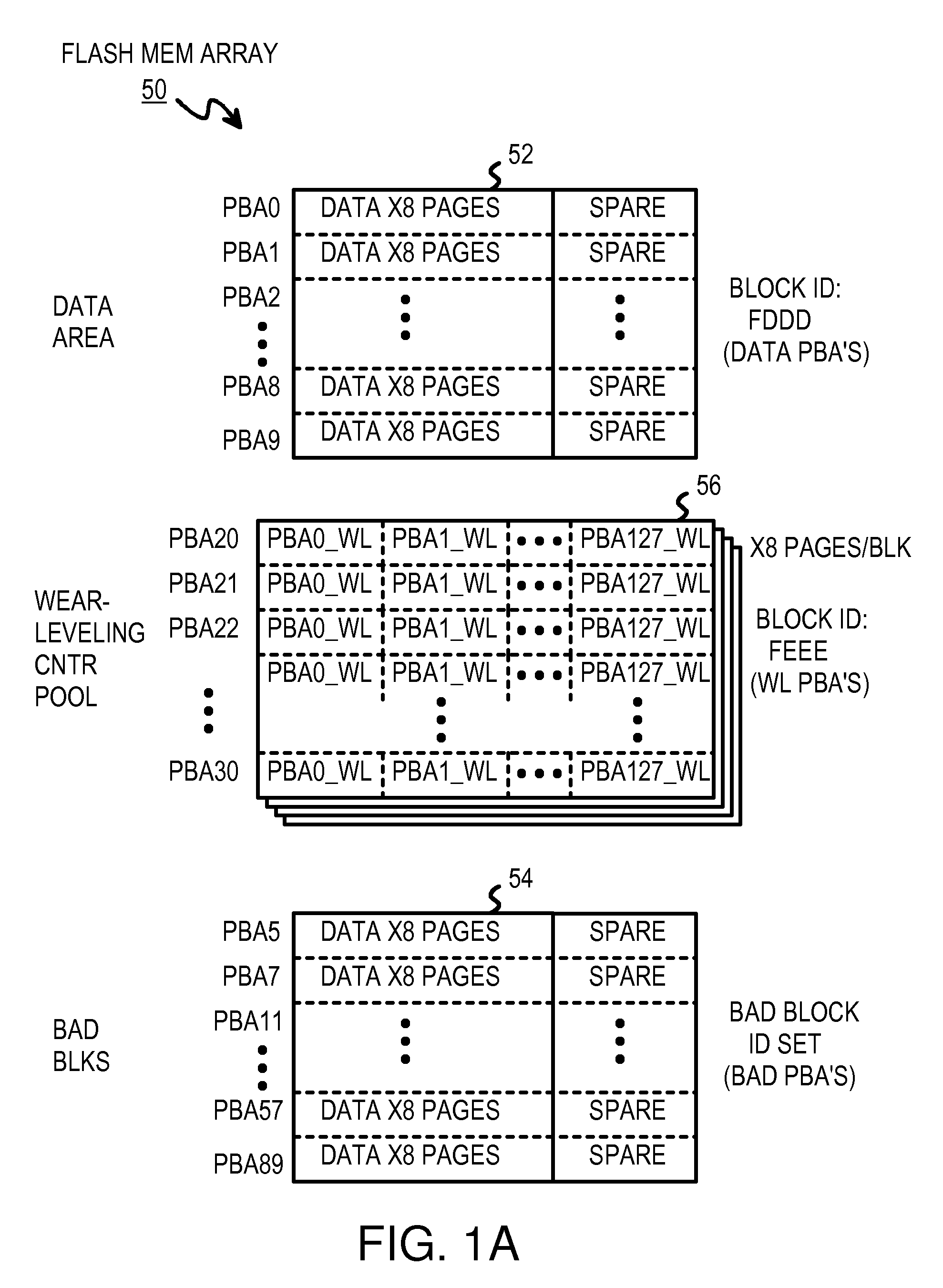

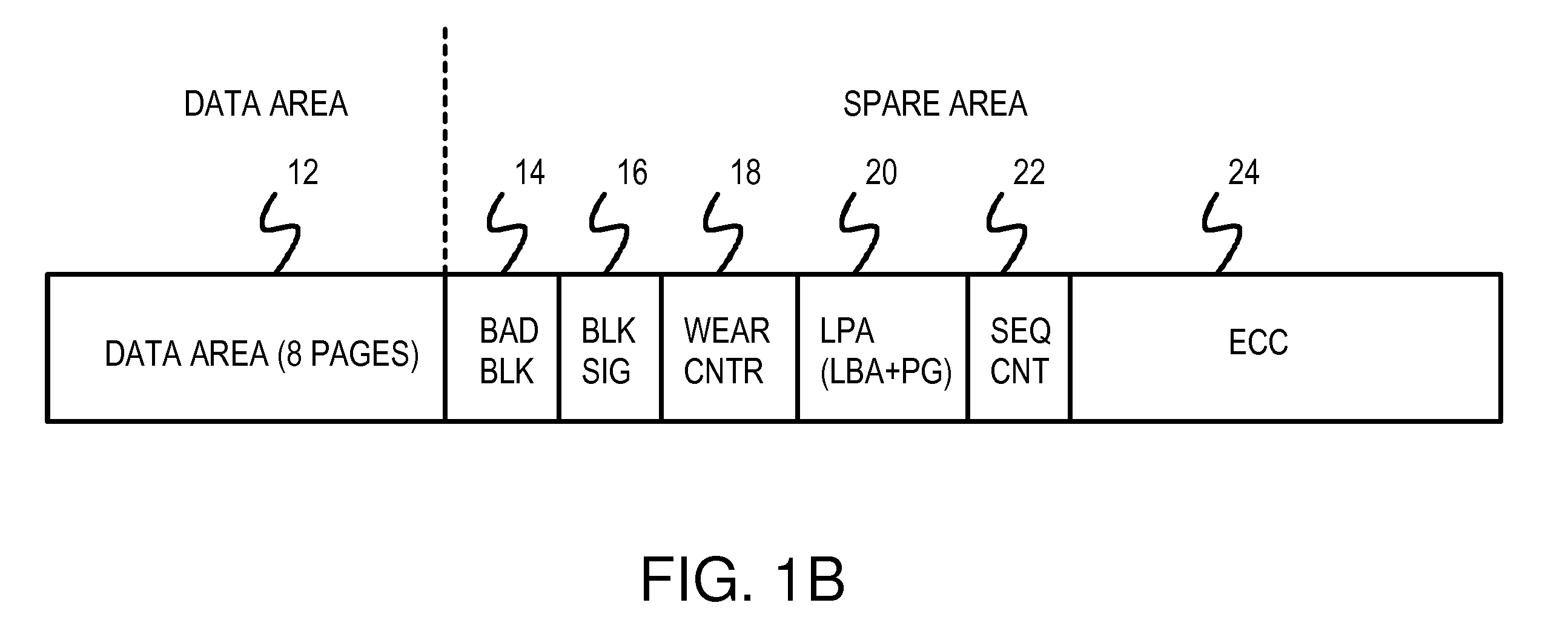

Hybrid 2-Level Mapping Tables for Hybrid Block- and Page-Mode Flash-Memory System

InactiveUS20090193184A1Memory architecture accessing/allocationMemory adressing/allocation/relocationVirtual fieldFrequency counter

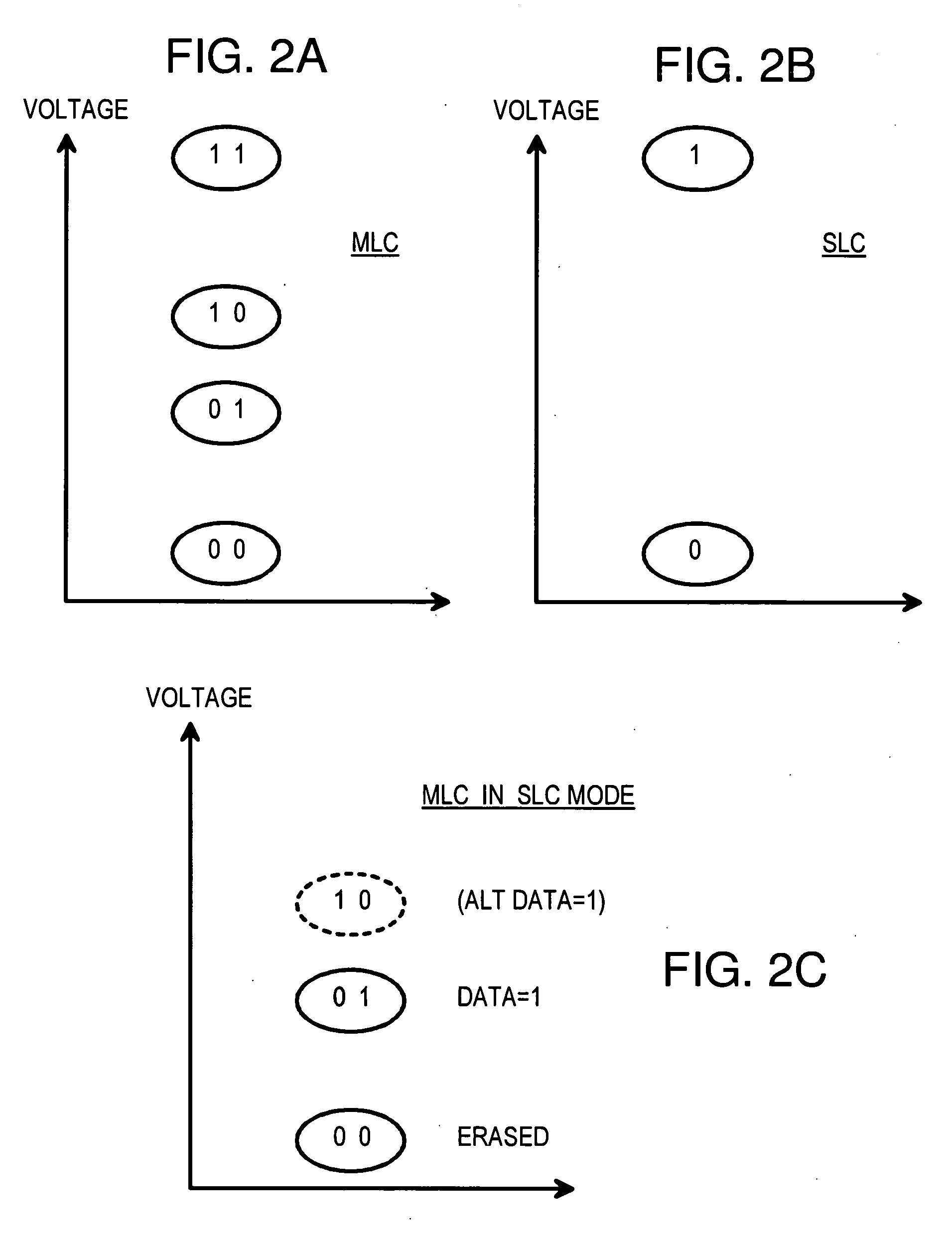

A hybrid solid-state disk (SSD) has multi-level-cell (MLC) or single-level-cell (SLC) flash memory, or both. SLC flash may be emulated by MLC that uses fewer cell states. A NVM controller converts logical block addresses (LBA) to physical block addresses (PBA). Most data is block-mapped and stored in MLC flash, but some critical or high-frequency data is page-mapped to reduce block-relocation copying. A hybrid mapping table has a first-level and a second level. Only the first level is used for block-mapped data, but both levels are used for page-mapped data. The first level contains a block-page bit that indicates if the data is block-mapped or page-mapped. A PBA field in the first-level table maps block-mapped data, while a virtual field points to the second-level table where the PBA and page number is stored for page-mapped data. Page-mapped data is identified by a frequency counter or sector count. SRAM space is reduced.

Owner:SUPER TALENT ELECTRONICS

Method and apparatus for efficient scalable storage management

ActiveUS7181578B1Improve performanceSolve the lack of spaceMemory systemsInput/output processes for data processingHandling systemDatapath

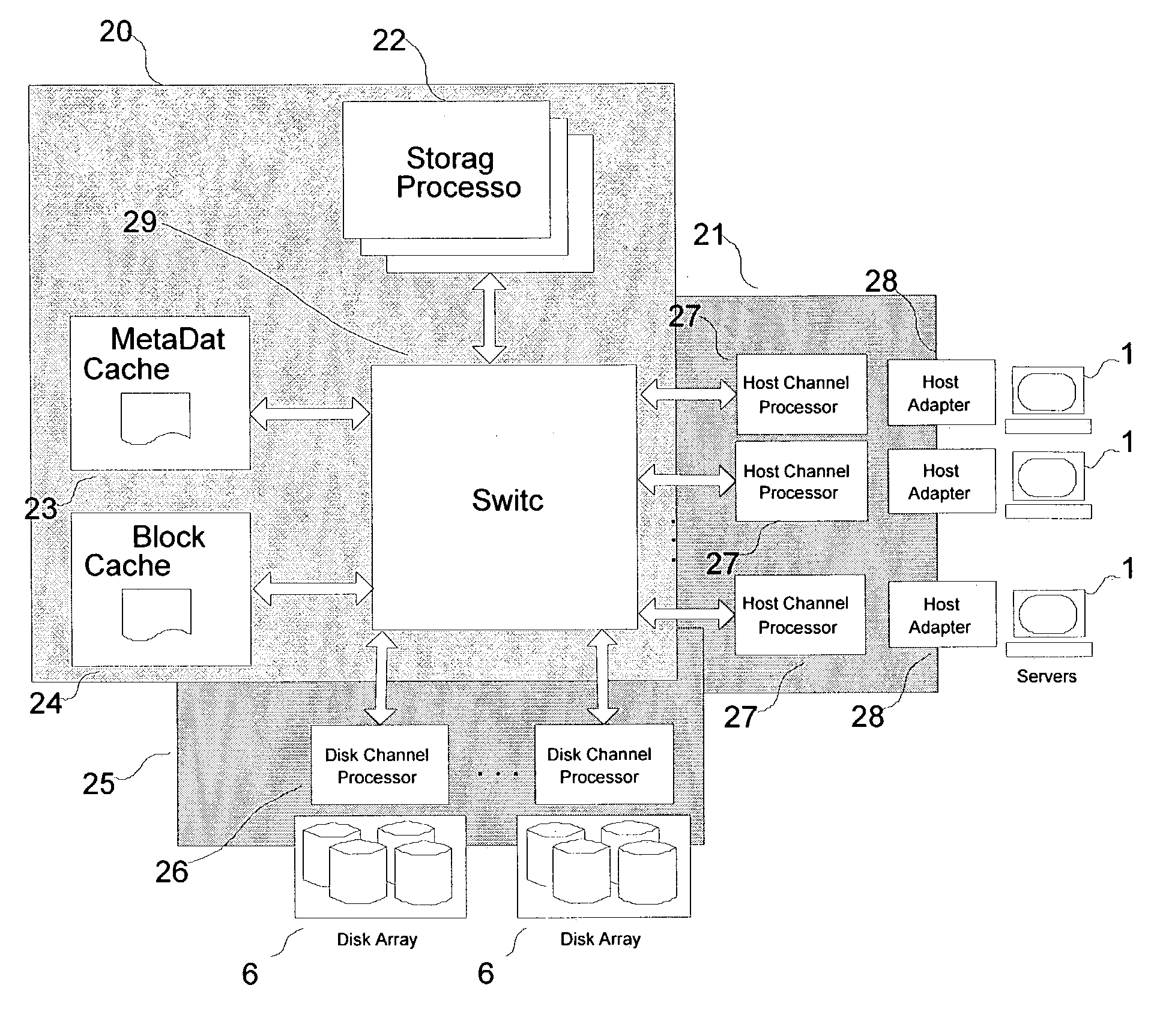

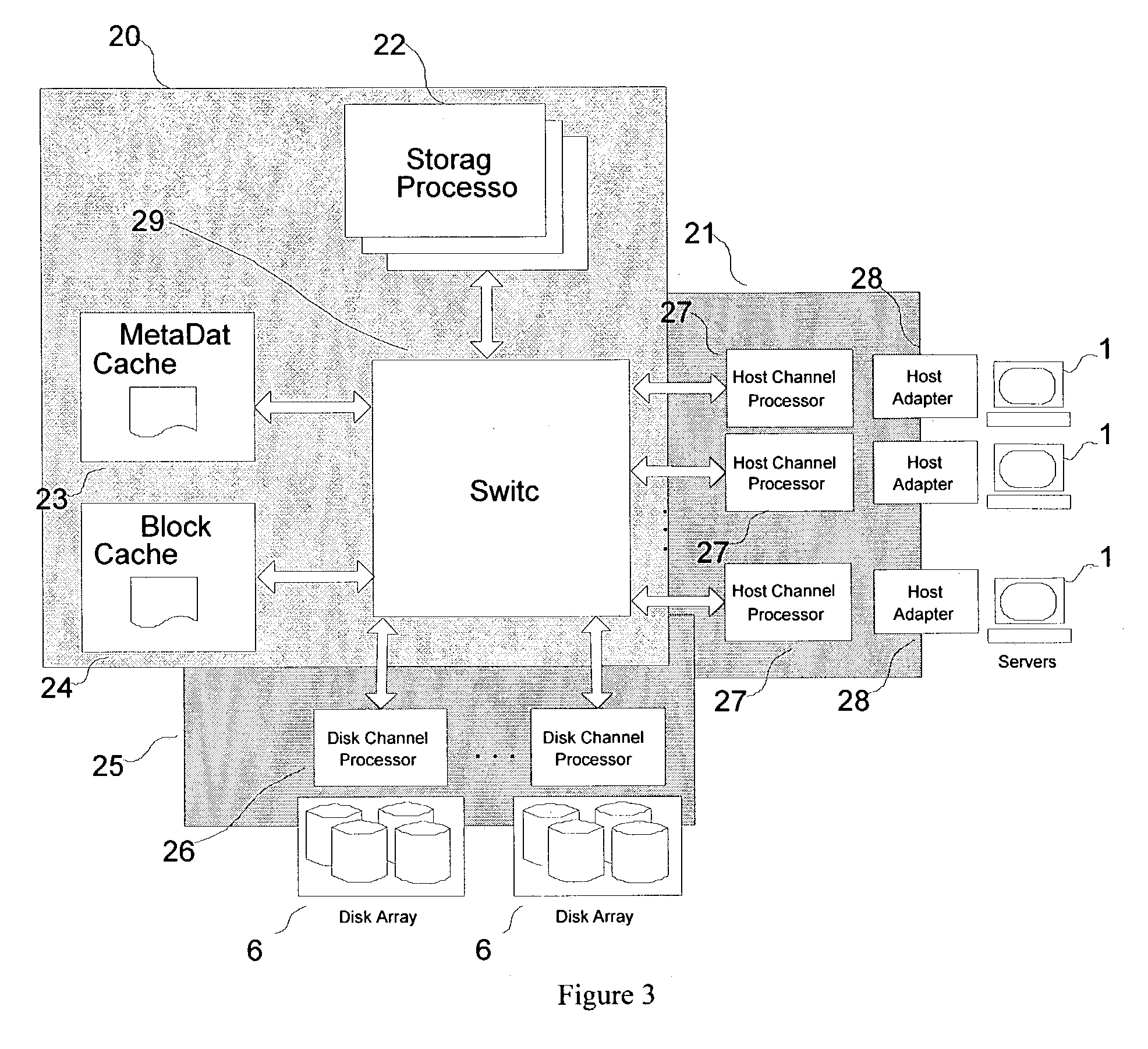

A hybrid centralized and distributed processing system includes a switching device that connects a storage processor to one or more servers through a host channel processor. The switching device also connects the storage processor to one or more storage devices such as disk drive arrays, and to a metadata cache and a block data cache memory. The storage processor processes access request from one or more servers in the form of a logical volume or logical block address and accesses the metadata cache to determine the physical data address. The storage processor monitors the performance of the storage system and performs automatic tuning by reallocating the logical volume, load balancing, hot spot removal, and dynamic expansion of storage volume. The storage processor also provides fault-tolerant access and provides parallel high performance data paths for fail over. The storage processor also provides faster access by providing parallel data paths for, making local copies and providing remote data copies, and by selecting data from a storage device that retrieves the data the earliest.

Owner:COPAN SYST INC +1

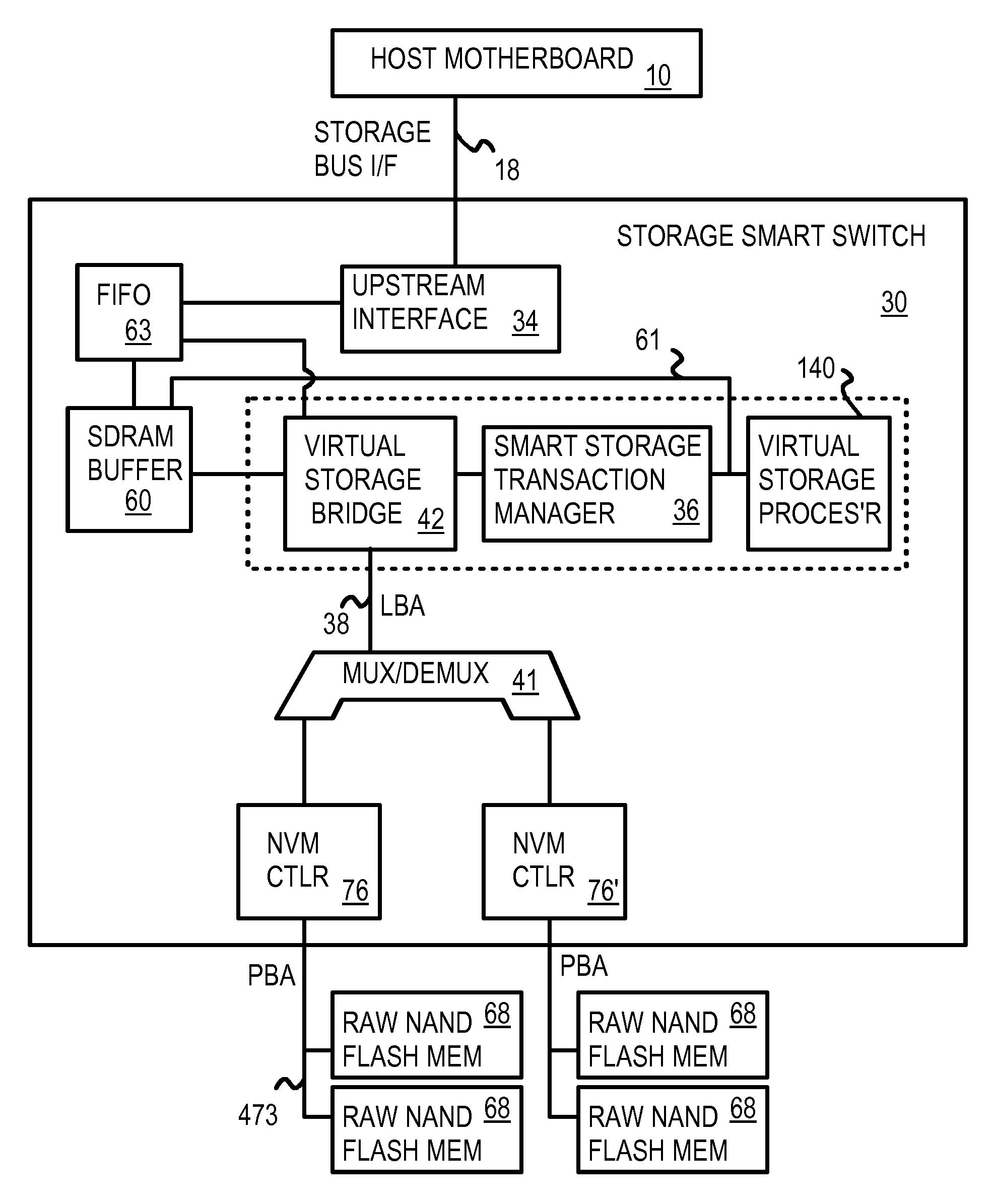

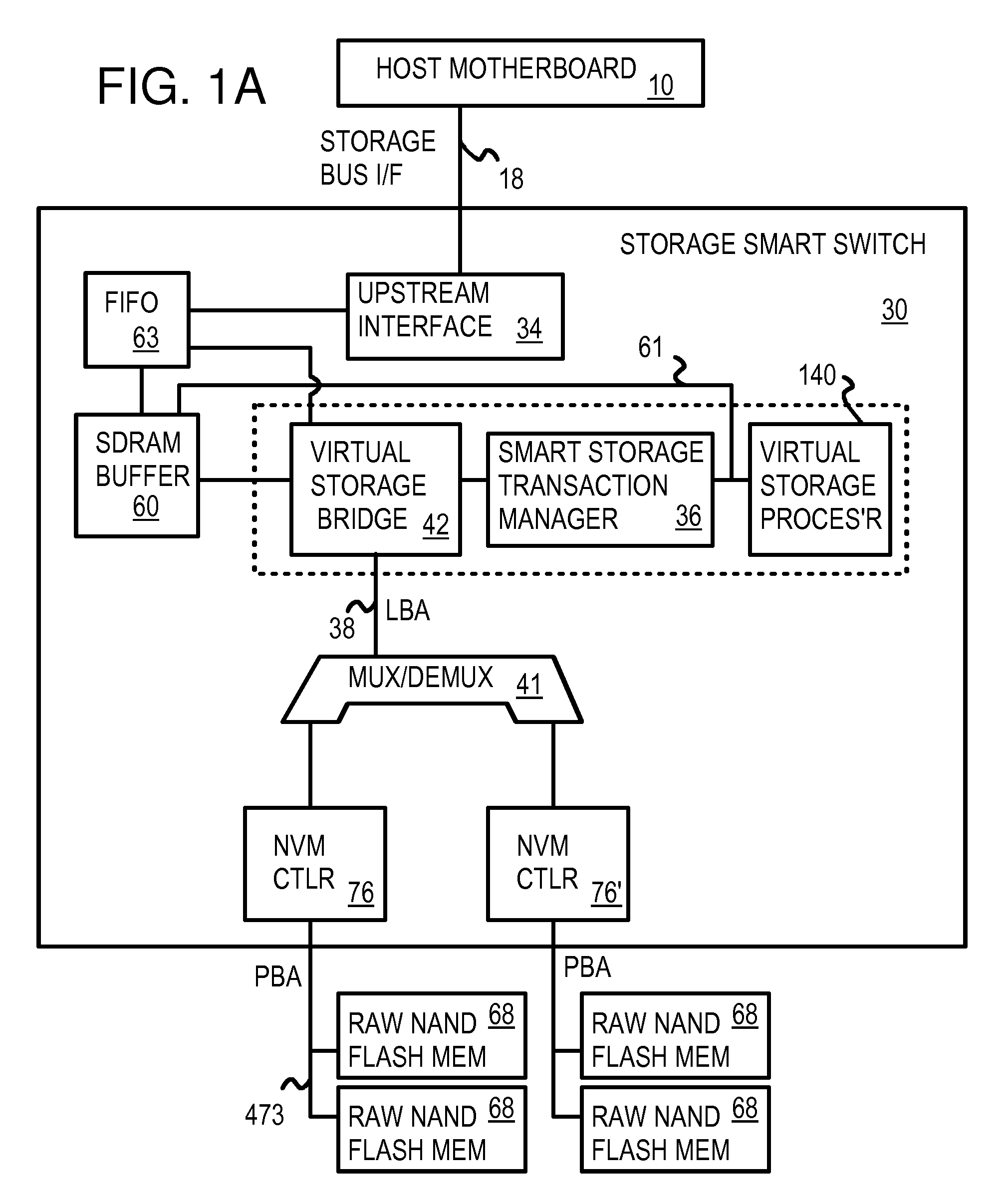

Command Queuing Smart Storage Transfer Manager for Striping Data to Raw-NAND Flash Modules

ActiveUS20090037652A1Memory architecture accessing/allocationMemory adressing/allocation/relocationLogical block addressingHost machine

A flash module has raw-NAND flash memory chips accessed over a physical-block address (PBA) bus by a NVM controller. The NVM controller is on the flash module or on a system board for a solid-state disk (SSD). The NVM controller converts logical block addresses (LBA) to physical block addresses (PBA). Data striping and interleaving among multiple channels of the flash modules is controlled at a high level by a smart storage transaction manager, while further interleaving and remapping within a channel may be performed by the NVM controllers. A SDRAM buffer is used by a smart storage switch to cache host data before writing to flash memory. A Q-R pointer table stores quotients and remainders of division of the host address. The remainder points to a location of the host data in the SDRAM. A command queue stores Q, R for host commands.

Owner:SUPER TALENT TECH CORP

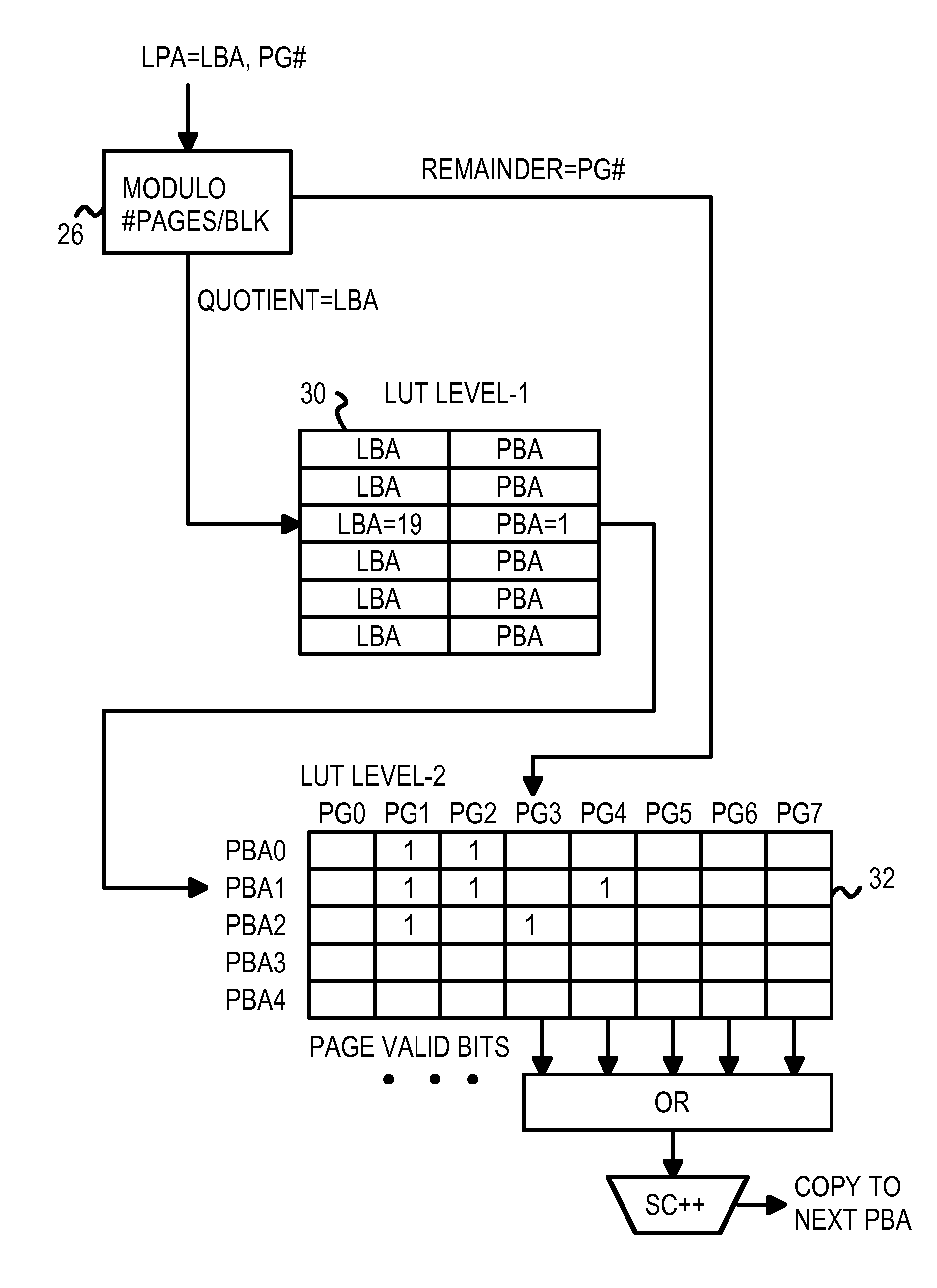

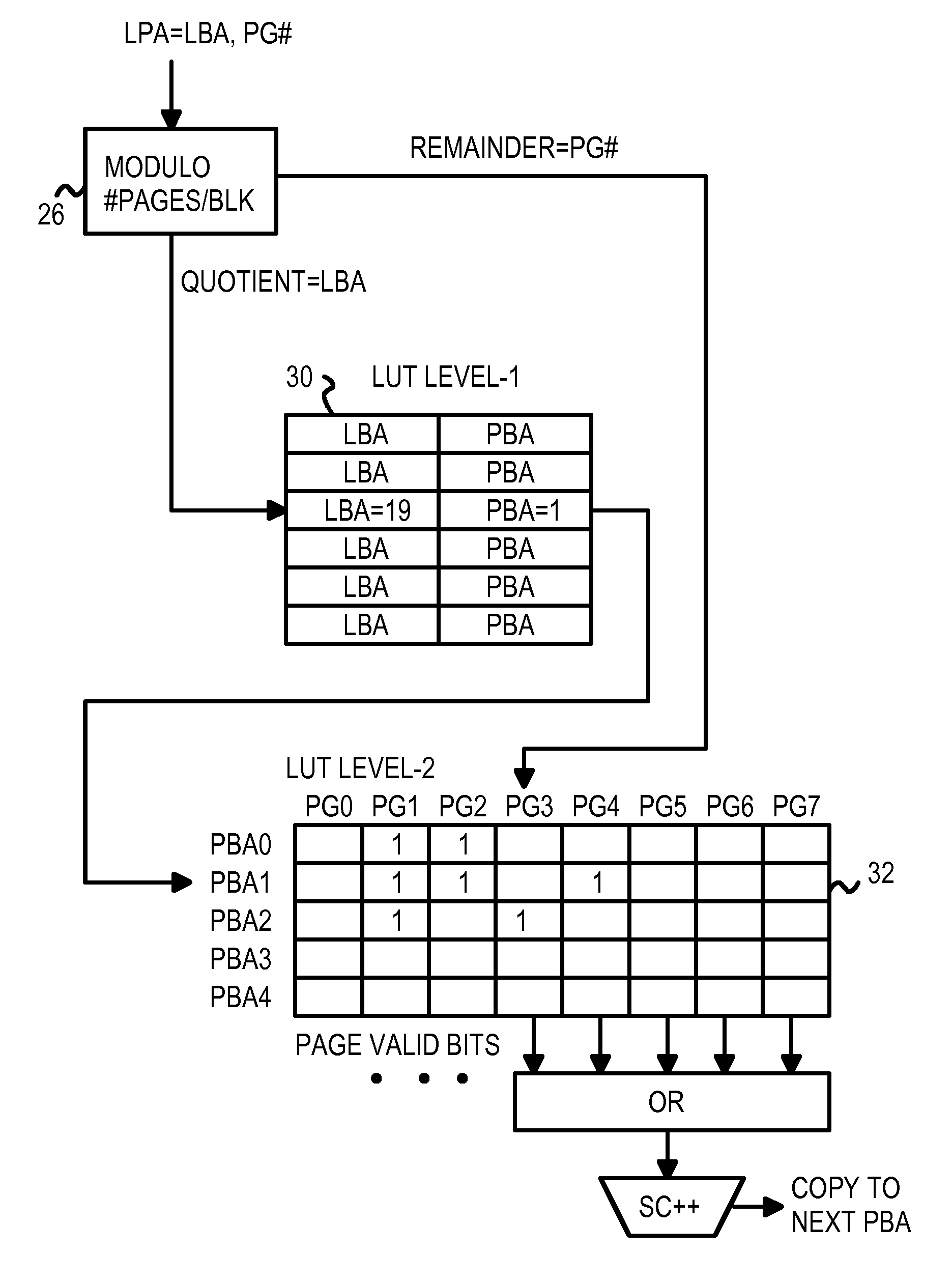

Two-Level RAM Lookup Table for Block and Page Allocation and Wear-Leveling in Limited-Write Flash-Memories

InactiveUS20070204128A1Memory architecture accessing/allocationRead-only memoriesRandom access memoryLogical block addressing

A restrictive multi-level-cell (MLC) flash memory prohibits regressive page-writes. When a regressive page-write is requested, an empty block having a low wear-level count is found, and data from the regressive page-write and data from pages stored in the old block are written to the empty block in page order. The old block is erased and recycled. A two-level look-up table is stored in volatile random-access memory (RAM). A logical page address from a host is divided by a modulo divider to generate a quotient and a remainder. The quotient is a logical block address that indexes a first-level look-up table to find a mapping entry with a physical block address that selects a row in a second-level look-up table. The remainder locates a column in the row in the second-level look-up table. If any page-valid bits above the column pointed to by the remainder are set, the write is regressive.

Owner:SUPER TALENT TECH CORP

Command Queuing Smart Storage Transfer Manager for Striping Data to Raw-NAND Flash Modules

InactiveUS20090204872A1Memory architecture accessing/allocationMemory adressing/allocation/relocationLogical block addressingComputer module

A flash module has raw-NAND flash memory chips accessed over a physical-block address (PBA) bus by a NVM controller. The NVM controller is on the flash module or on a system board for a solid-state disk (SSD). The NVM controller converts logical block addresses (LBA) to physical block addresses (PBA). Data striping and interleaving among multiple channels of the flash modules is controlled at a high level by a smart storage transaction manager, while further interleaving and remapping within a channel may be performed by the NVM controllers. A SDRAM buffer is used by a smart storage switch to cache host data before writing to flash memory. A Q-R pointer table stores quotients and remainders of division of the host address. The remainder points to a location of the host data in the SDRAM. A command queue stores Q, R for host commands.

Owner:SUPER TALENT ELECTRONICS

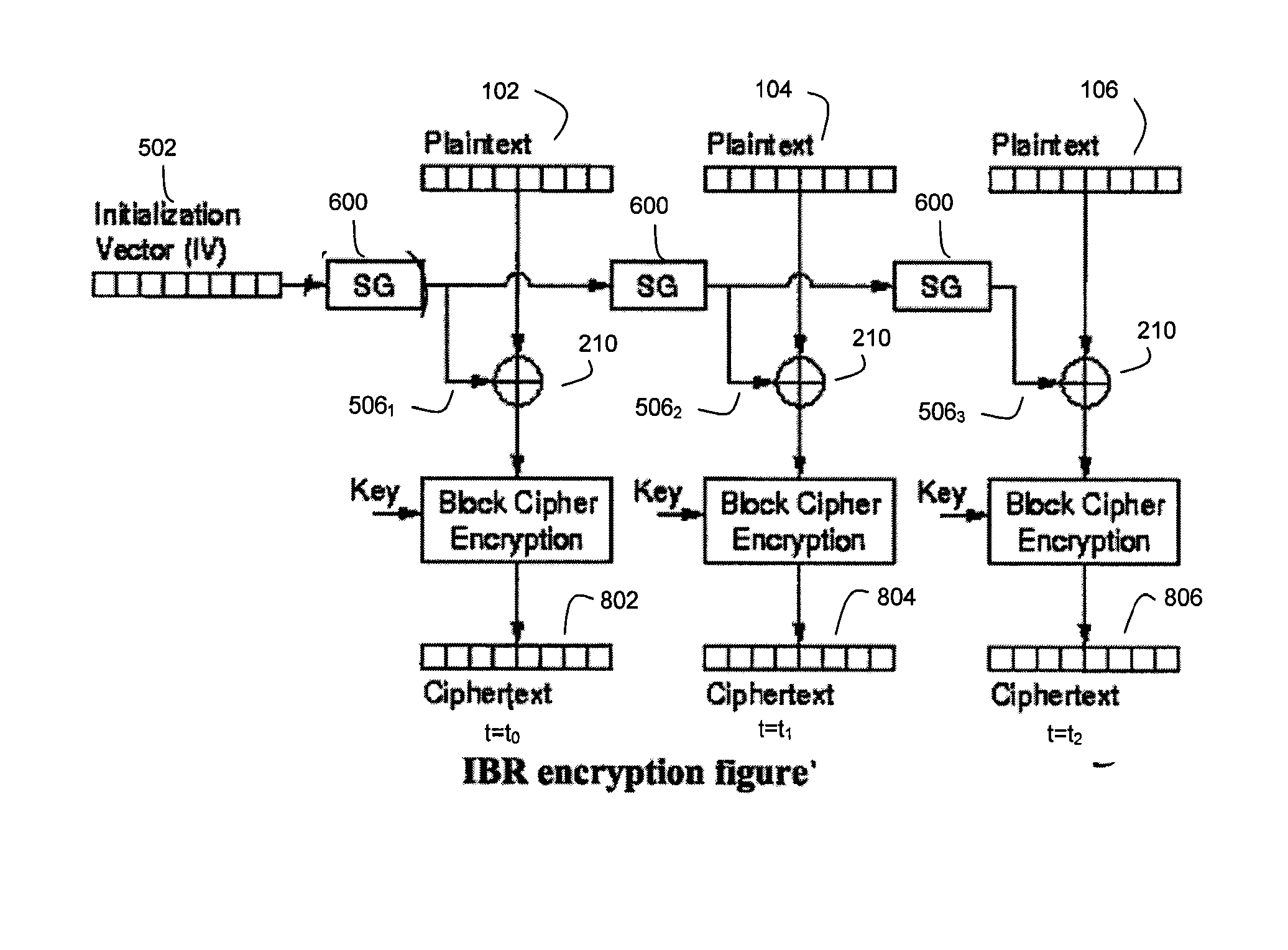

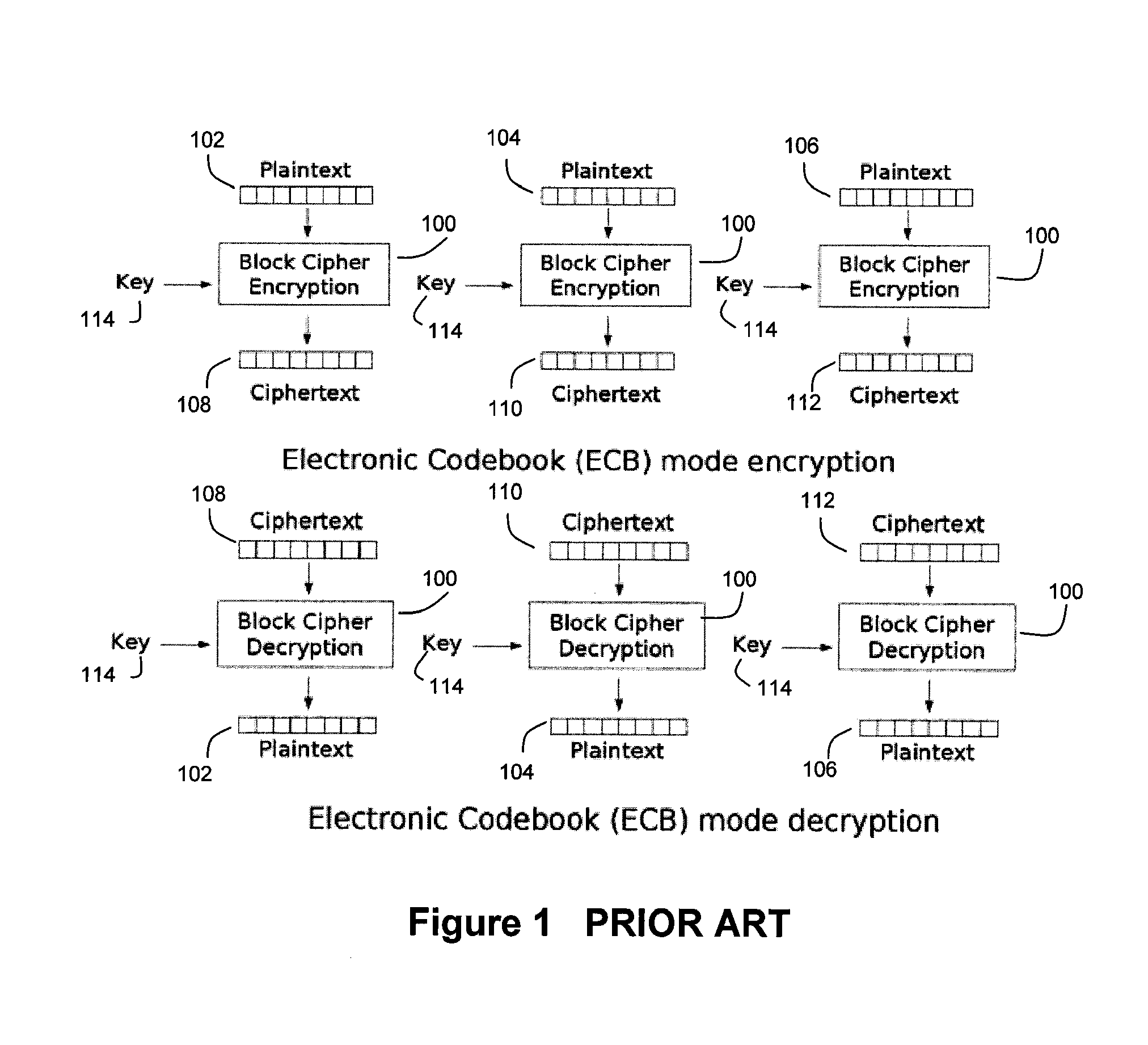

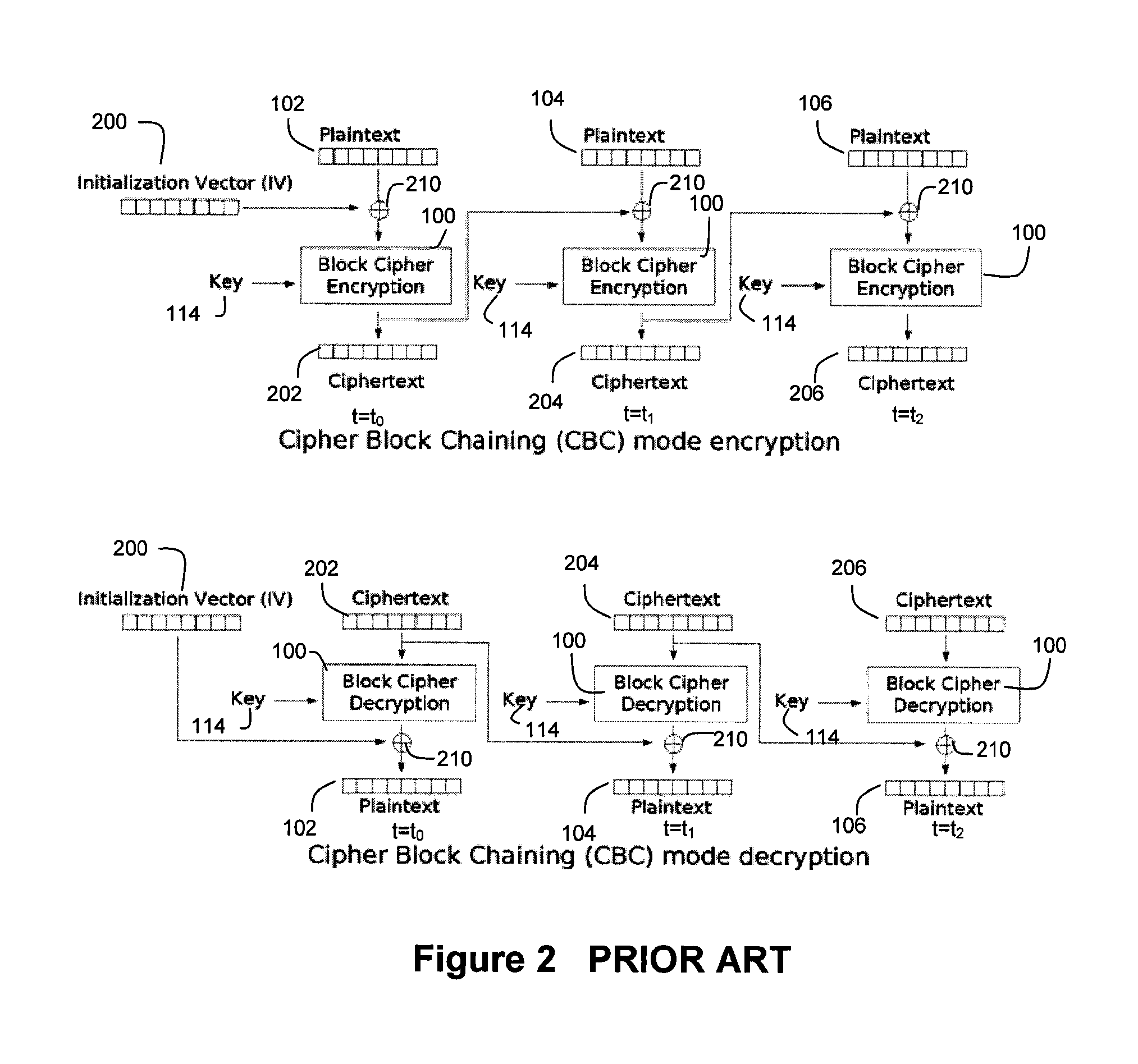

Method and System for High Throughput Blockwise Independent Encryption/Decryption

ActiveUS20070237327A1Computational complexity increaseReduce throughputMultiple keys/algorithms usageSecret communicationData segmentLogical block addressing

An encryption technique is disclosed for encrypting a data segment comprising a plurality of data blocks, wherein the security and throughput of the encryption is enhanced by using blockwise independent bit vectors for reversible combination with the data blocks prior to key encryption. Preferably, the blockwise independent bit vectors are derived from a data tag associated with the data segment. Several embodiments are disclosed for generating these blockwise independent bit vectors. In a preferred embodiment, the data tag comprises a logical block address (LBA) for the data segment. Also disclosed herein is a corresponding decryption technique as well as a corresponding symmetrical encryption / decryption technique.

Owner:IP RESERVOIR

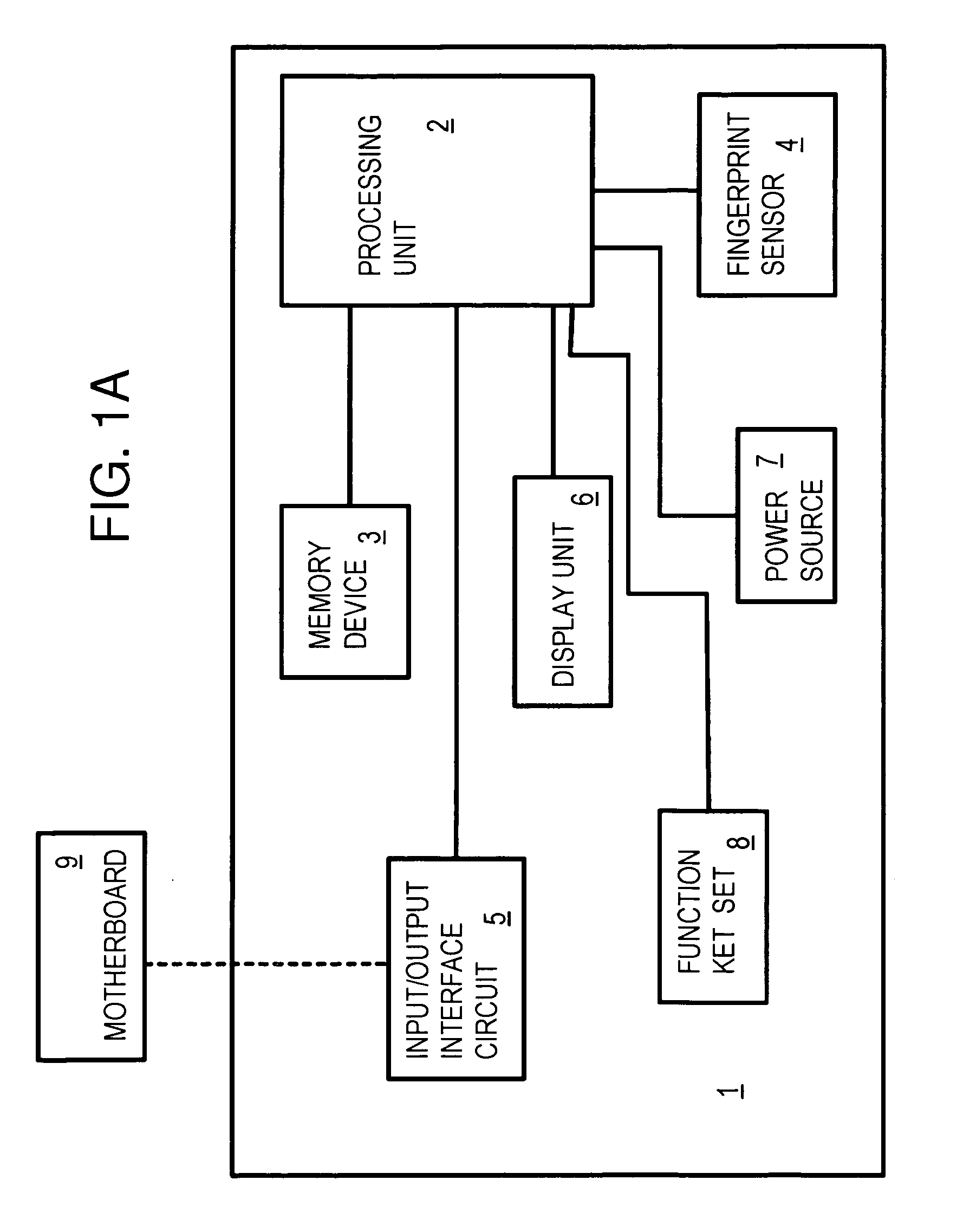

Intelligent Solid-State Non-Volatile Memory Device (NVMD) System With Multi-Level Caching of Multiple Channels

InactiveUS20080235443A1Memory architecture accessing/allocationEnergy efficient ICTPower controllerLogical block addressing

A flash memory system stores blocks of data in Non-Volatile Memory Devices (NVMD) that are addressed by a logical block address (LBA). The LBA is remapped for wear-leveling and bad-block relocation by the NVMD. The NVMD are interleaved in channels that are accessed by a NVMD controller. The NVMD controller has a controller cache that caches blocks stored in NVMD in that channel, while the NVMD also contain high-speed cache. The multiple levels of caching reduce access latency. Power is managed in multiple levels by a power controller in the NVMD controller that sets power policies for power managers inside the NVMD. Multiple NVMD controllers in the flash system may each controller many channels of NVMD. The flash system with NVMD may include a fingerprint reader for security.

Owner:SUPER TALENT TECH CORP

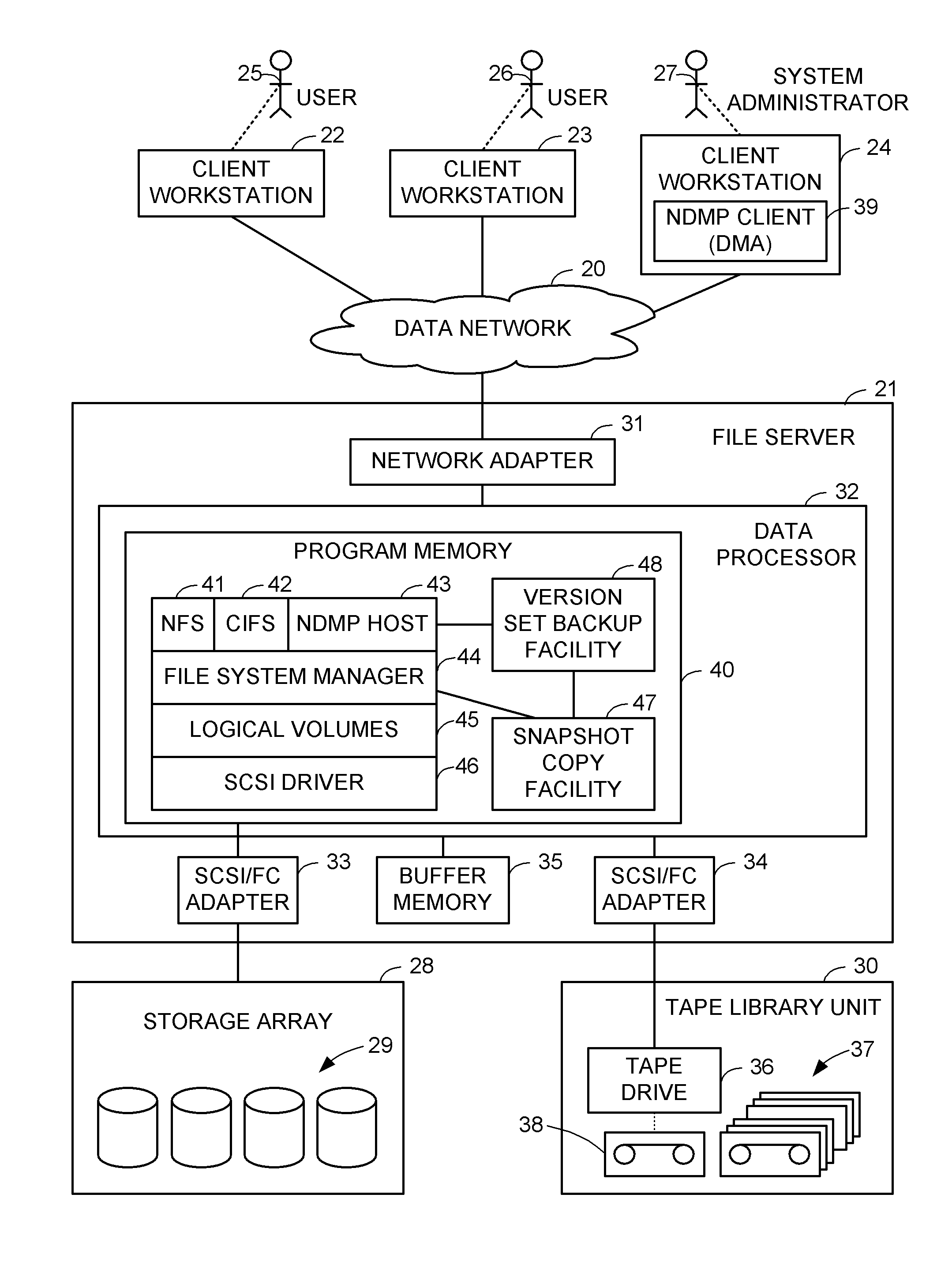

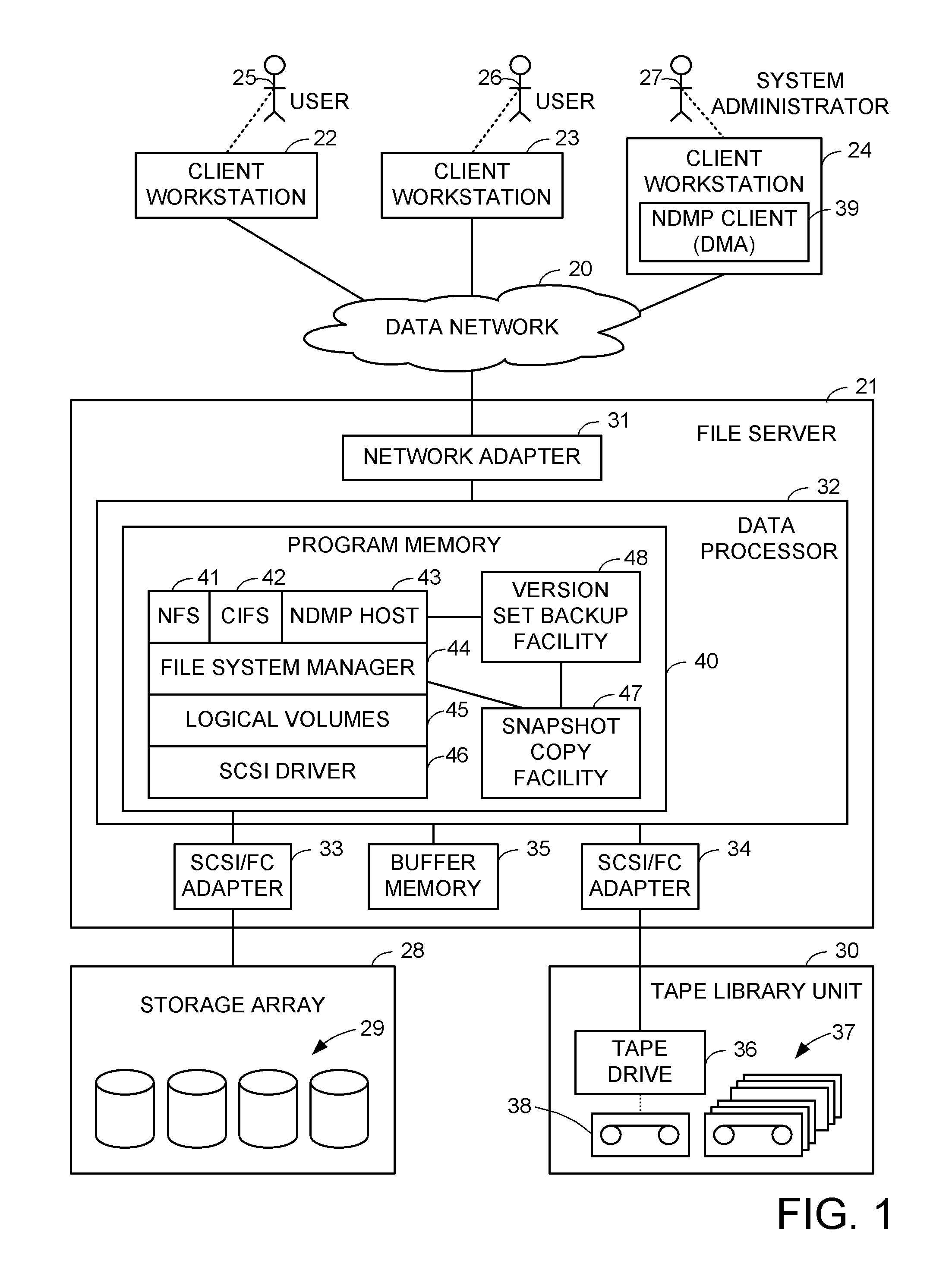

Efficient backup and restore of storage objects in a version set

ActiveUS8099572B1Efficient backupIncrease management costsDigital data processing detailsError detection/correctionLogical block addressingMagnetic tape

The version set backup and restore facility responds to a version set backup request by backing up multiple snapshot copies of a storage object concurrently from a storage array to backup storage media. The version set backup and restore facility responds to a version set restore request by restoring a plurality of snapshot copies of the storage object concurrently from the backup storage media to the storage array. The on-tape backup image of the version set includes variable-length extents of data for each of the multiple snapshot copies of the storage object. The variable-length extents of data for each of the snapshot copies of the storage object are grouped together and ordered in the on-tape backup image by increasing or decreasing logical block address.

Owner:EMC IP HLDG CO LLC

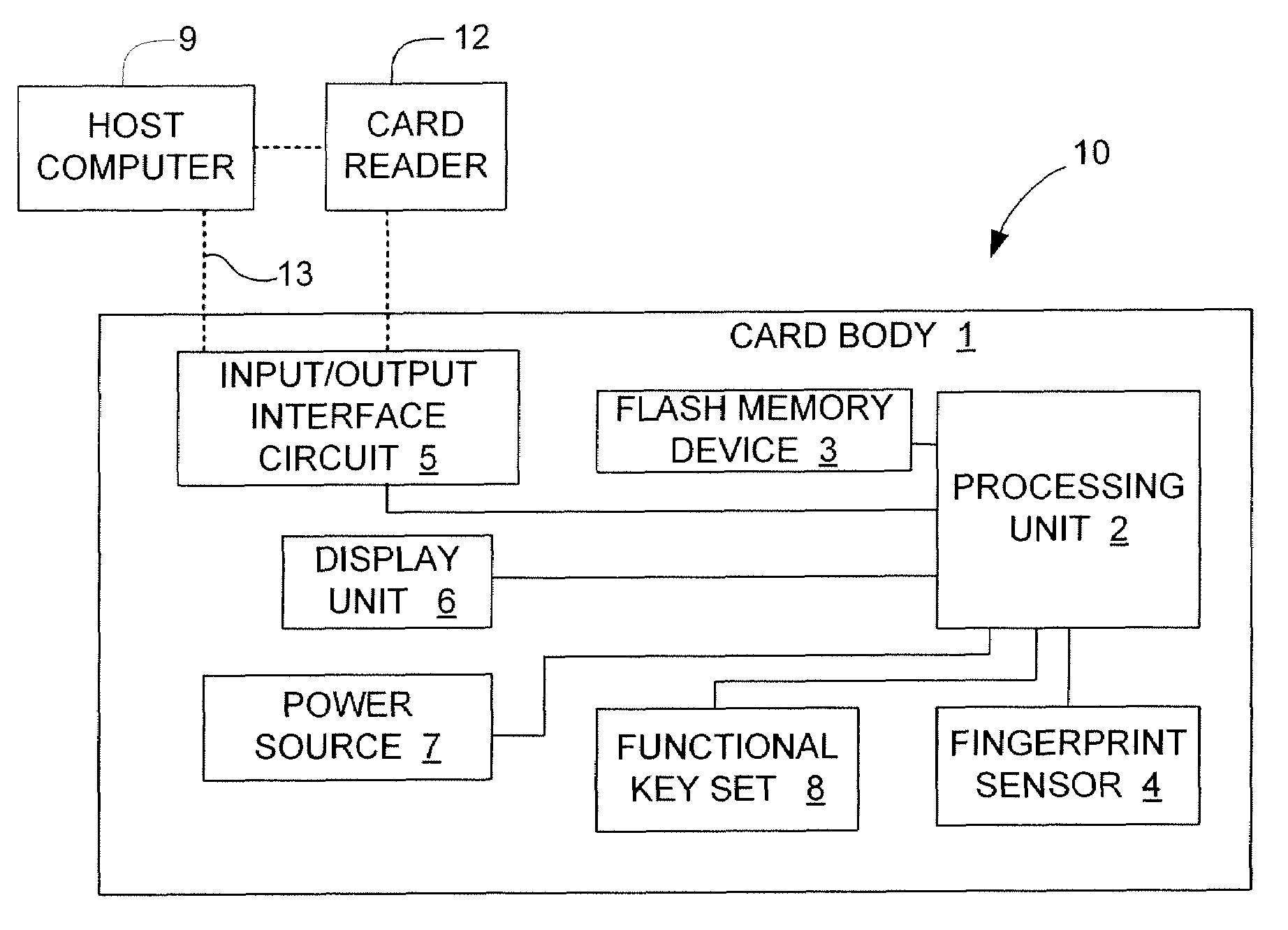

Managing Bad Blocks In Flash Memory For Electronic Data Flash Card

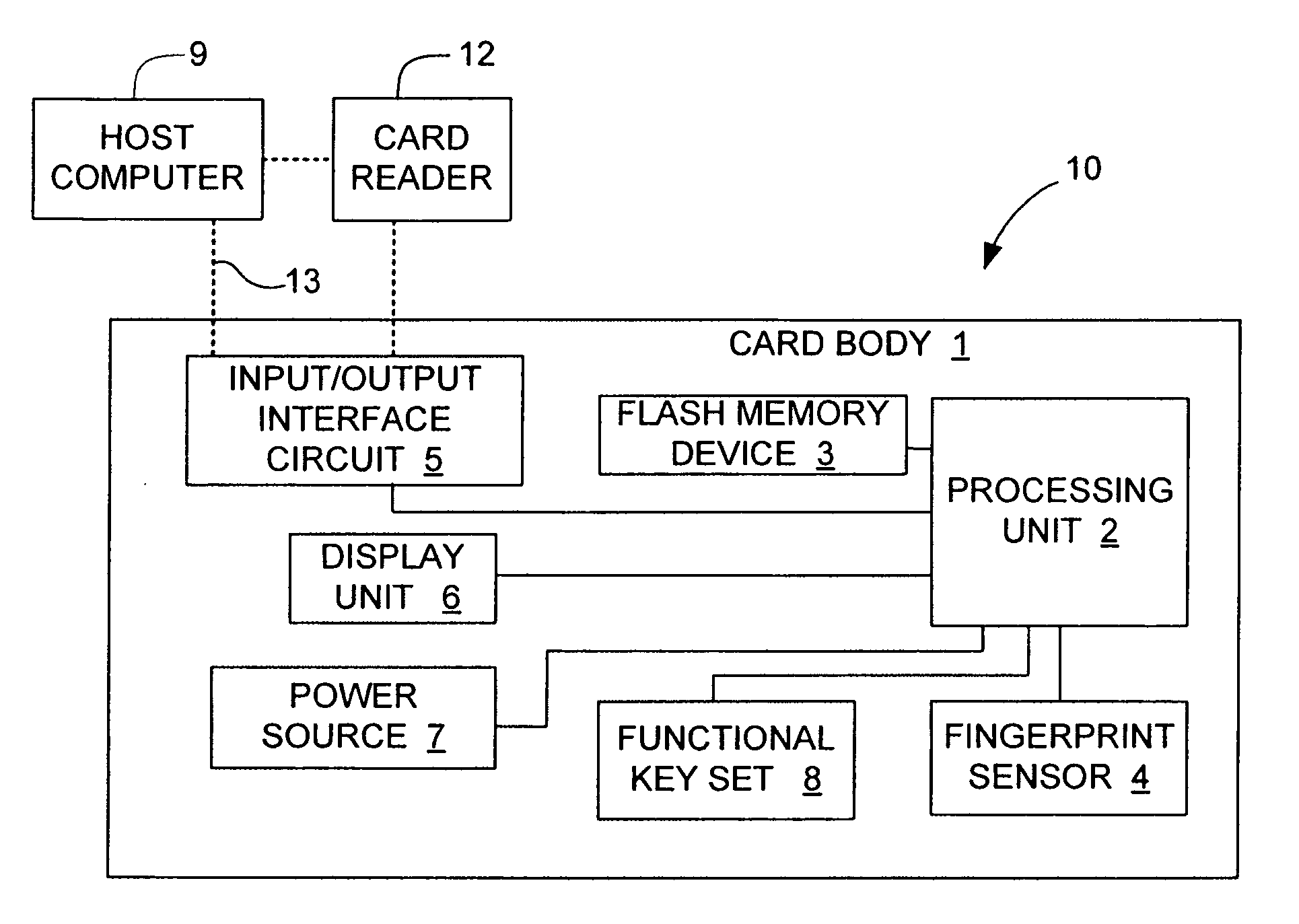

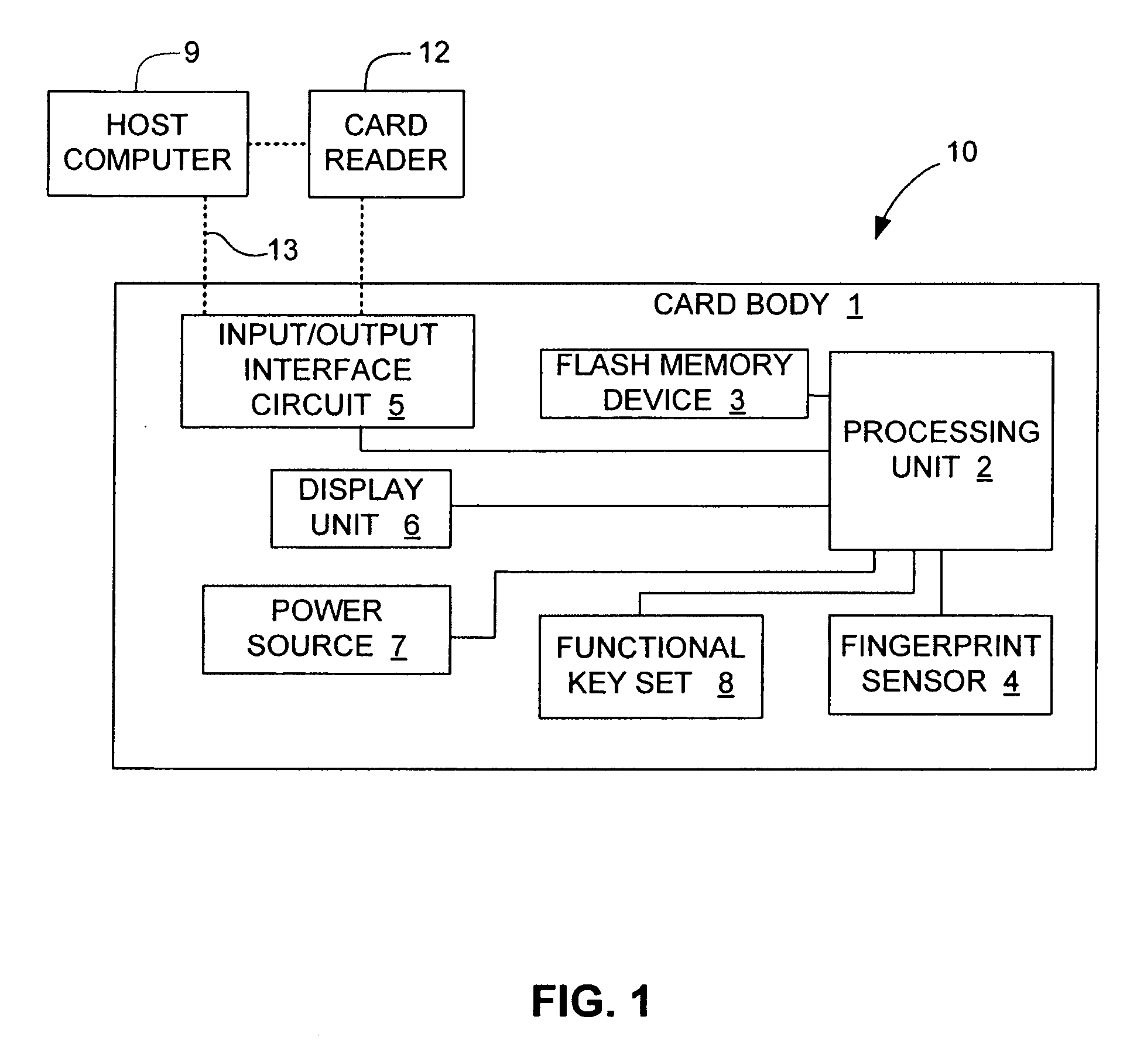

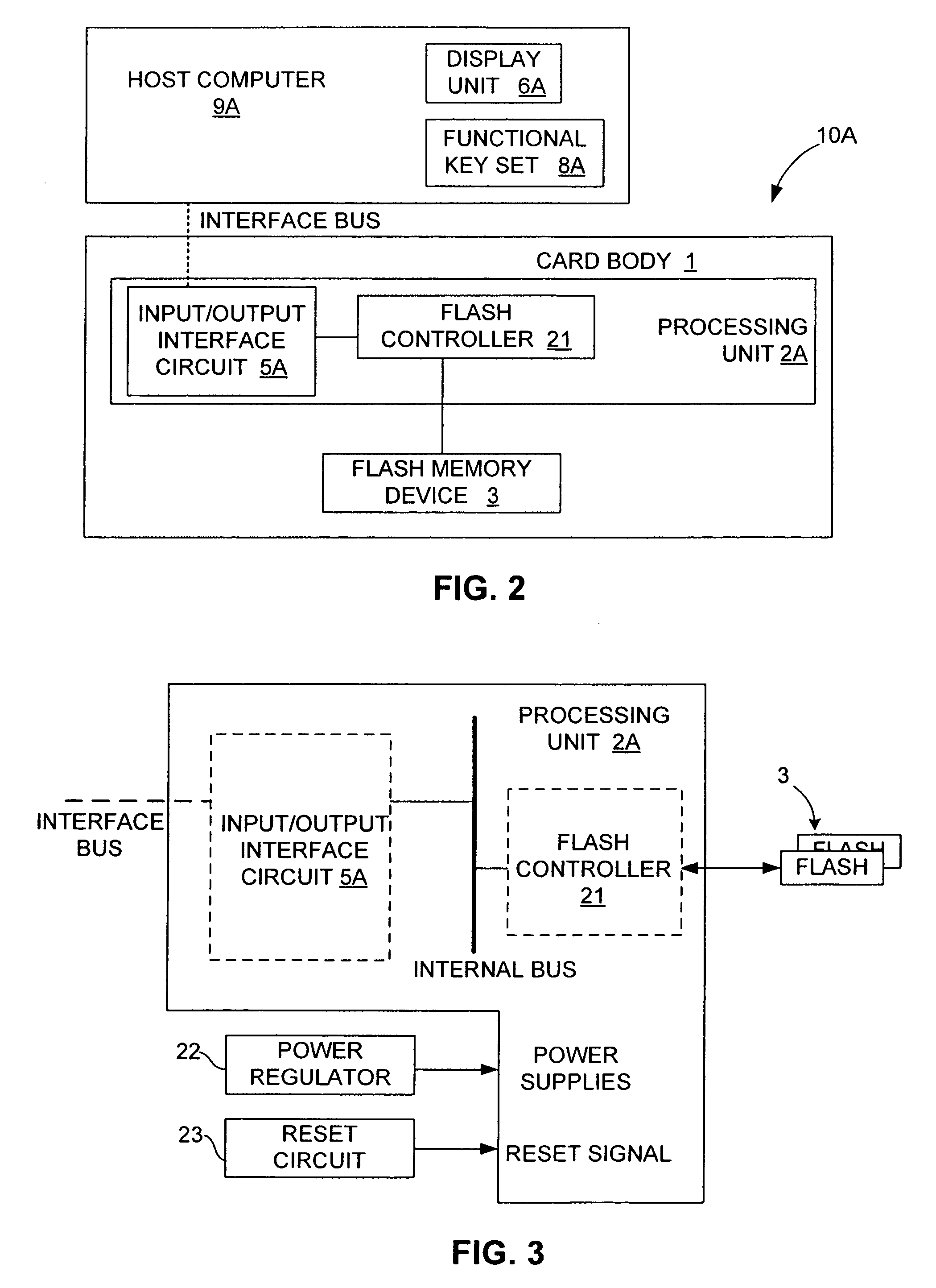

InactiveUS20070283428A1Reduce search timeAvoid congestionDigital data processing detailsUser identity/authority verificationLogical block addressingComputer access

An electronic data flash card accessible by a host computer, includes a flash memory controller connected to a flash memory device, and an input-output interface circuit activated to establish a communication with the host. In an embodiment, the flash card uses a USB interface circuit for communication with the host. A flash memory controller includes an arbitrator for mapping logical addresses with physical block addresses, and for performing block management operations including: storing reassigned data to available blocks, relocating valid data in obsolete blocks to said available blocks and reassigning logical block addresses to physical block addresses of said available blocks, finding bad blocks of the flash memory device and replacing with reserve blocks, erasing obsolete blocks for recycling after relocating valid data to available blocks, and erase count wear leveling of blocks, etc. Furthermore, each flash memory device includes an internal buffer for accelerating the block management operations.

Owner:SUPER TALENT TECH CORP

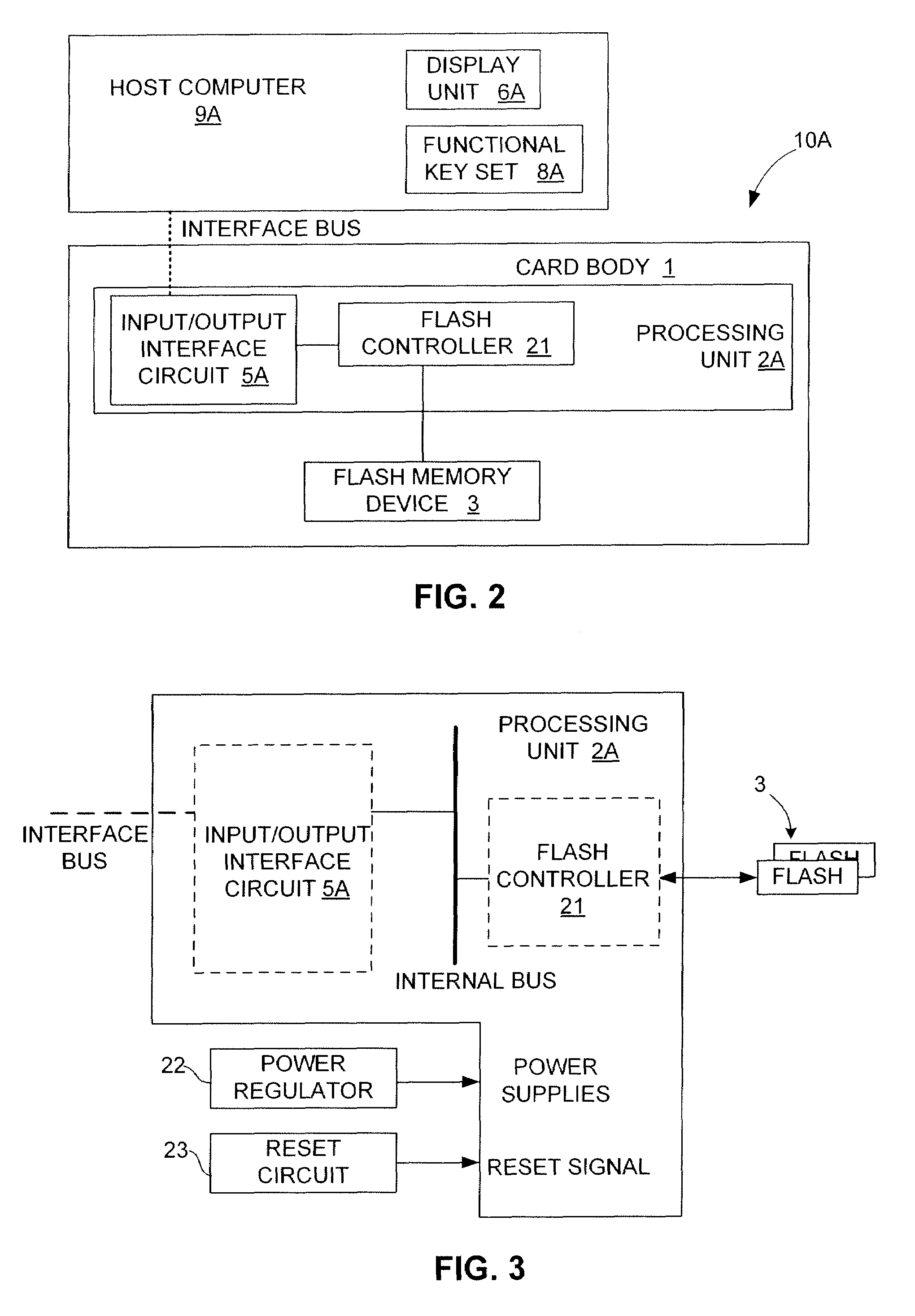

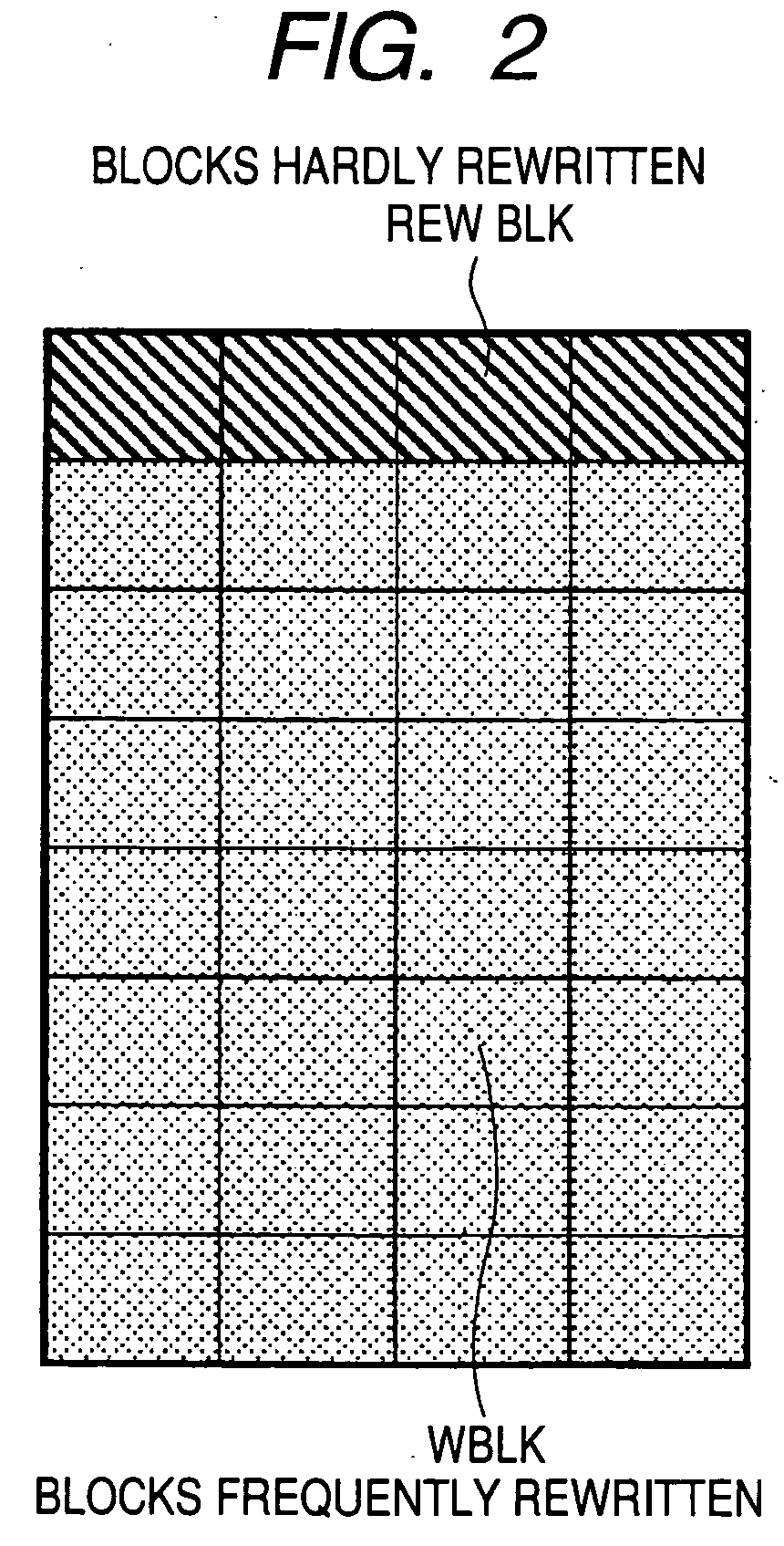

Memory system

ActiveUS20070103992A1Extend effective lifeEasy to controlMemory architecture accessing/allocationRead-only memoriesLogical block addressingSemiconductor storage devices

A memory system including a nonvolatile semiconductor storage device includes: a nonvolatile memory unit that includes a first data area in which data is frequently rewritten and a second data area in which data is hardly rewritten; and a control unit. The control unit sequentially selects logical block addresses in the second data area in which data is hardly rewritten and updates physical block addresses at new rewriting destinations in the first data area in which data is frequently rewritten to physical block addresses corresponding to the logical block addresses selected.

Owner:SONY CORP

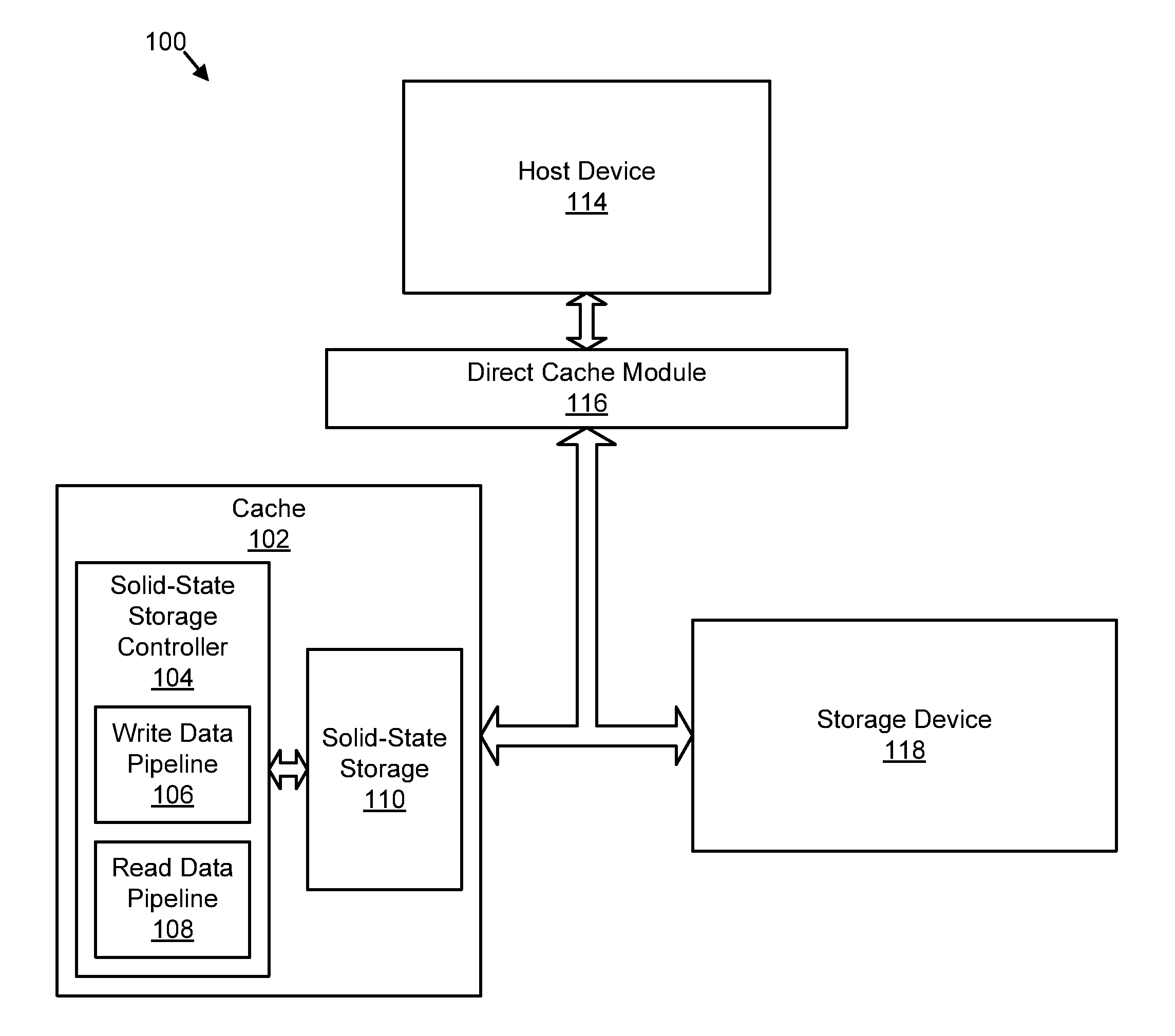

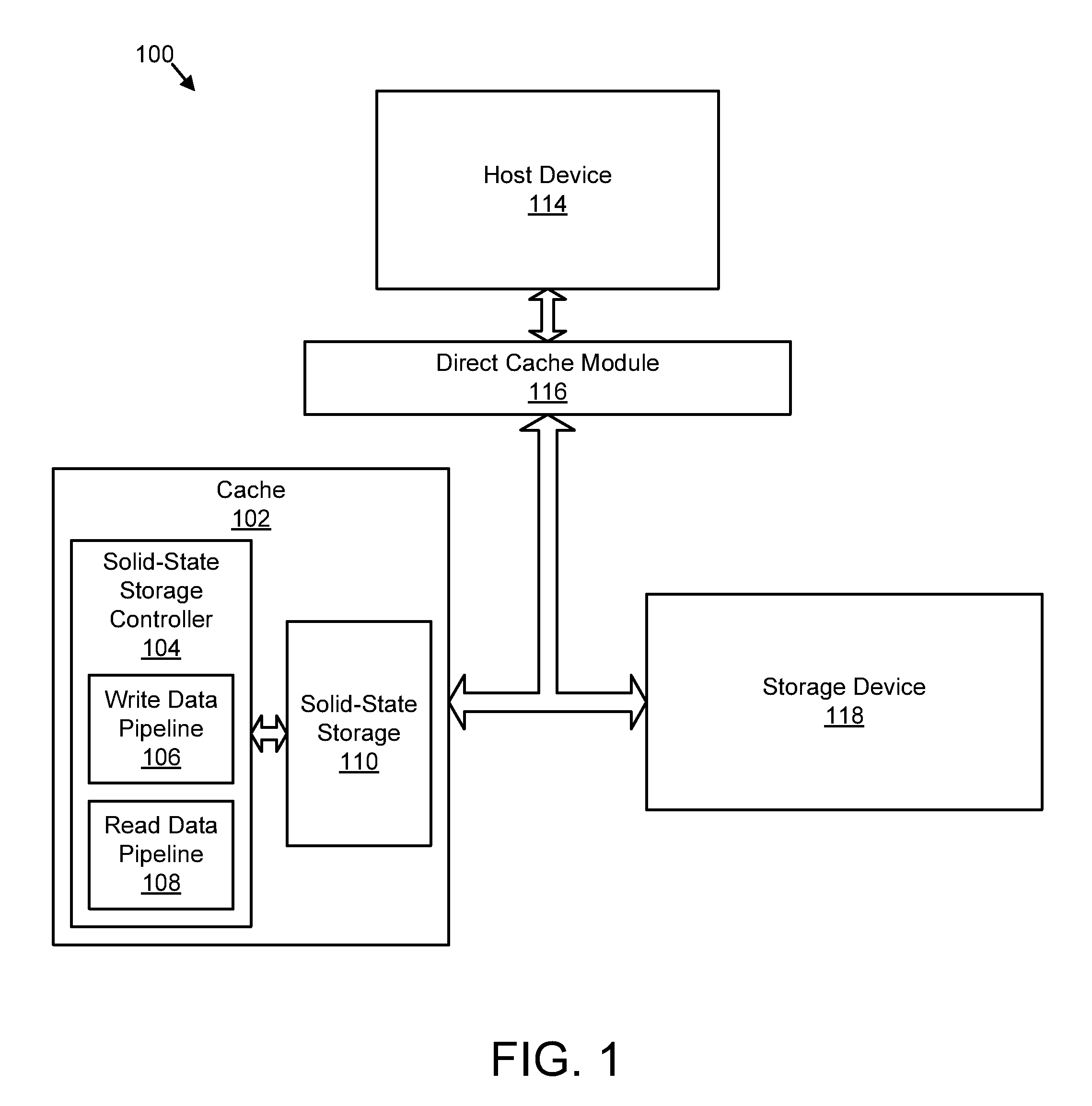

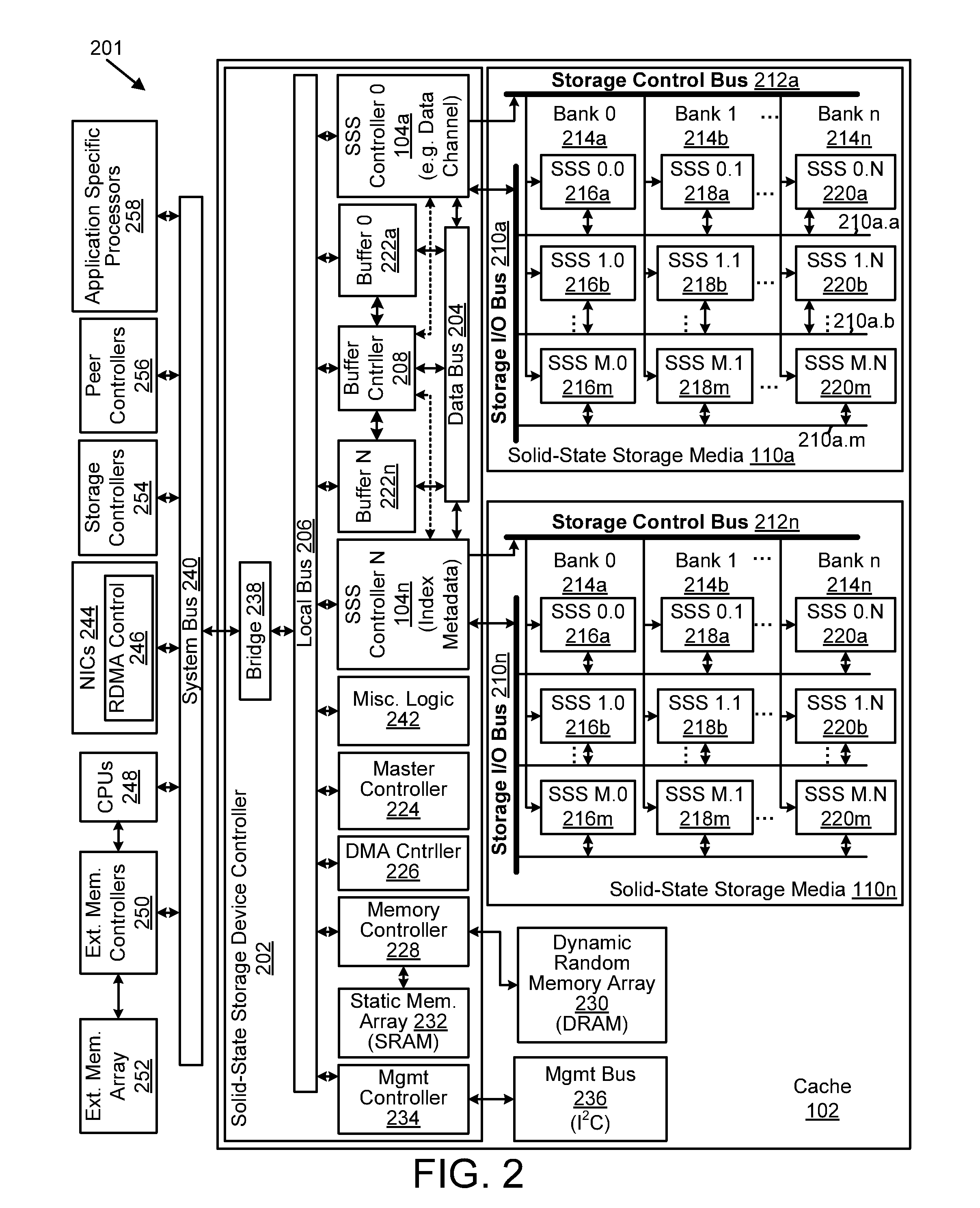

Apparatus, system, and method for caching data

ActiveUS20120210041A1Effective cachingMinimize cache collisionMemory architecture accessing/allocationServersSolid-state storageLogical block addressing

An apparatus, system, and method are disclosed for caching data. A storage request module detects an input / output (“I / O”) request for a storage device cached by solid-state storage media of a cache. A direct mapping module references a single mapping structure to determine that the cache comprises data of the I / O request. The single mapping structure maps each logical block address of the storage device directly to a logical block address of the cache. The single mapping structure maintains a fully associative relationship between logical block addresses of the storage device and physical storage addresses on the solid-state storage media. A cache fulfillment module satisfies the I / O request using the cache in response to the direct mapping module determining that the cache comprises at least one data block of the I / O request.

Owner:SANDISK TECH LLC

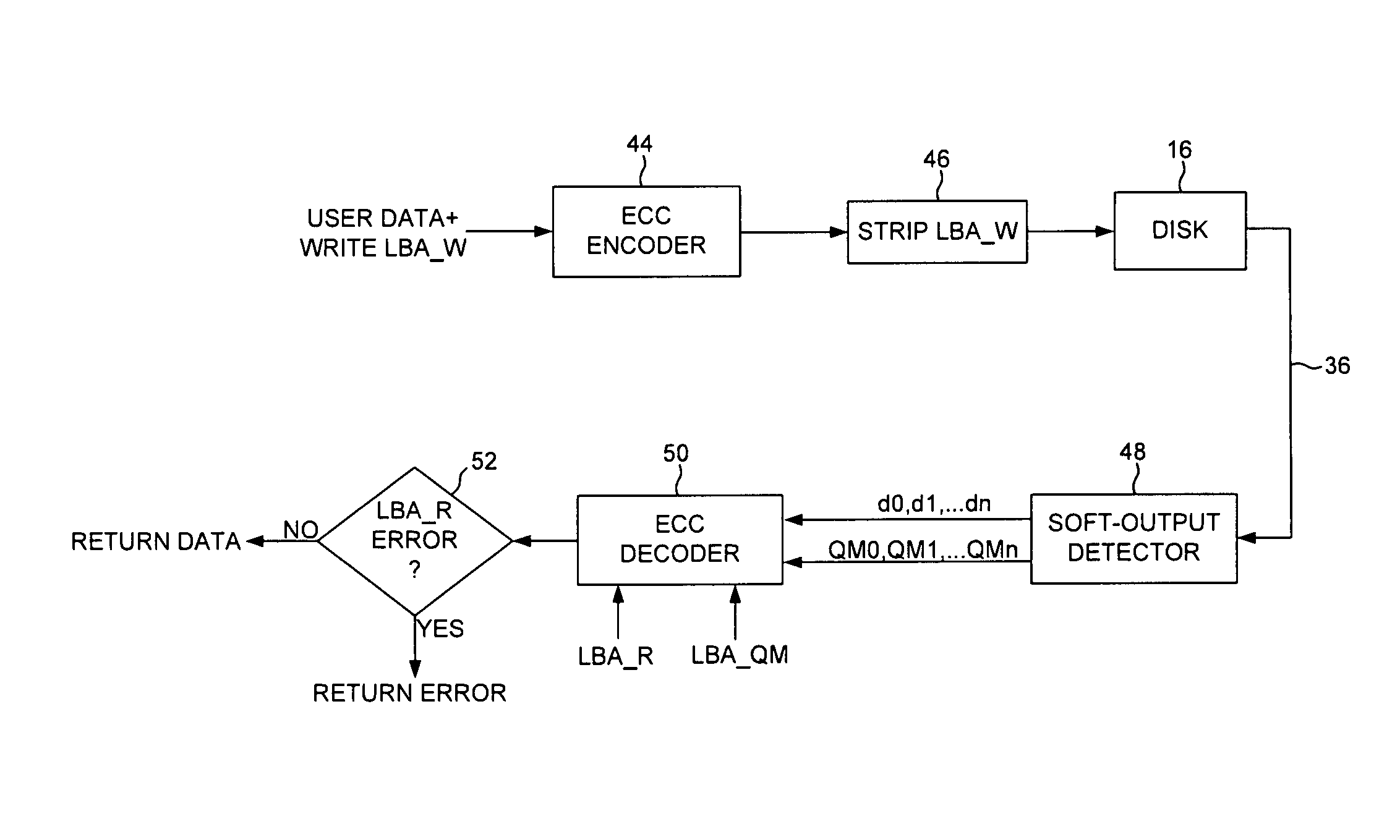

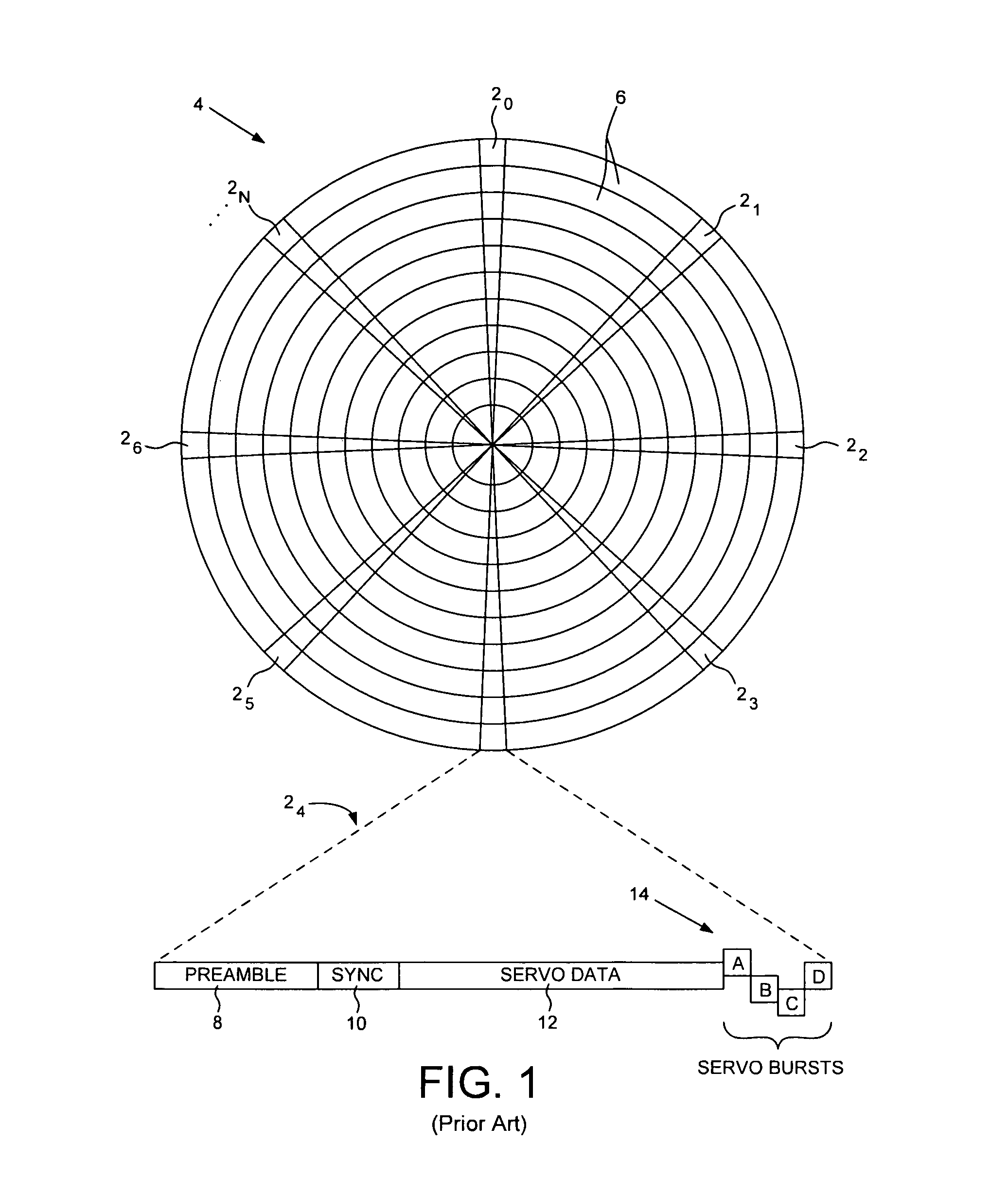

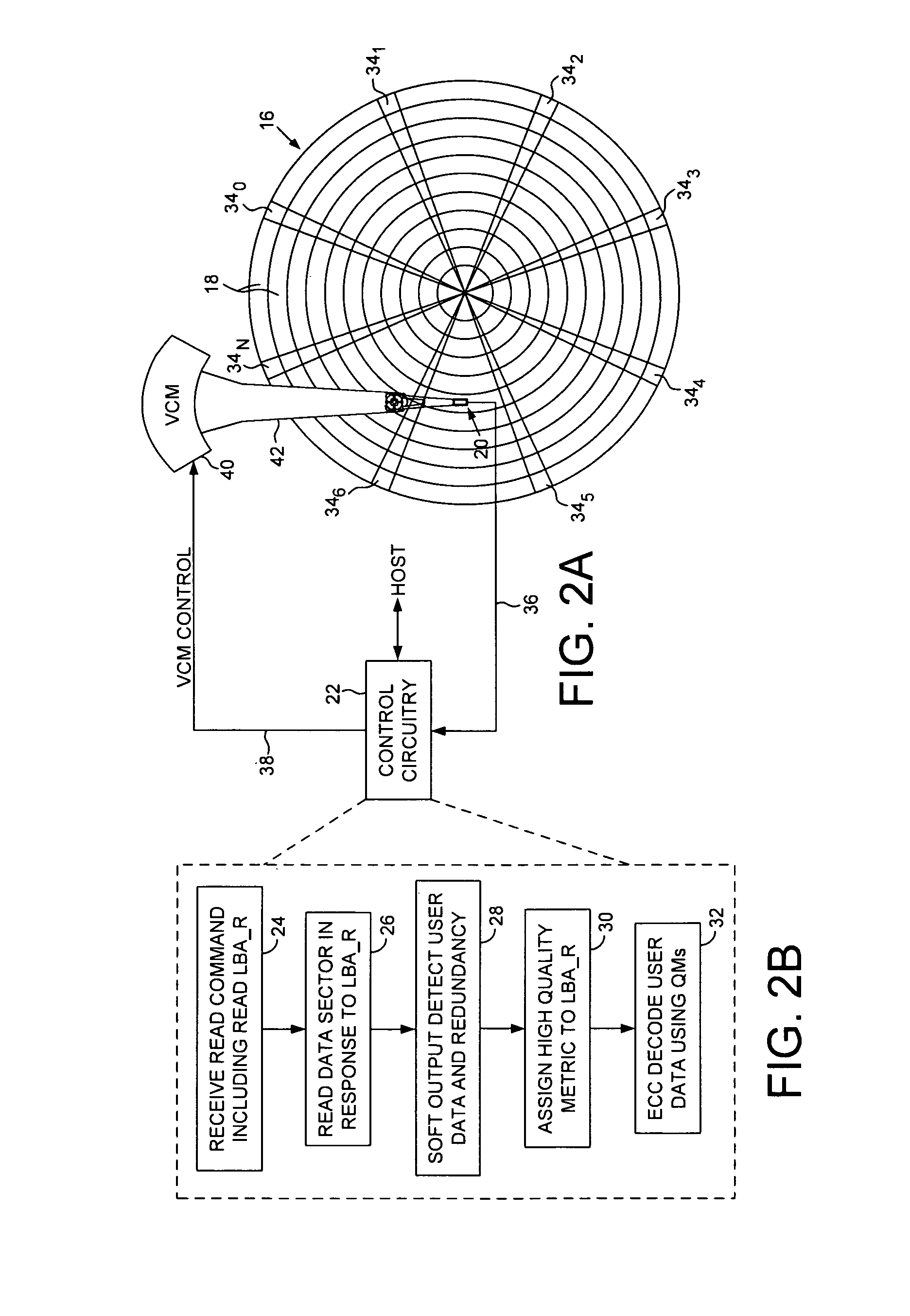

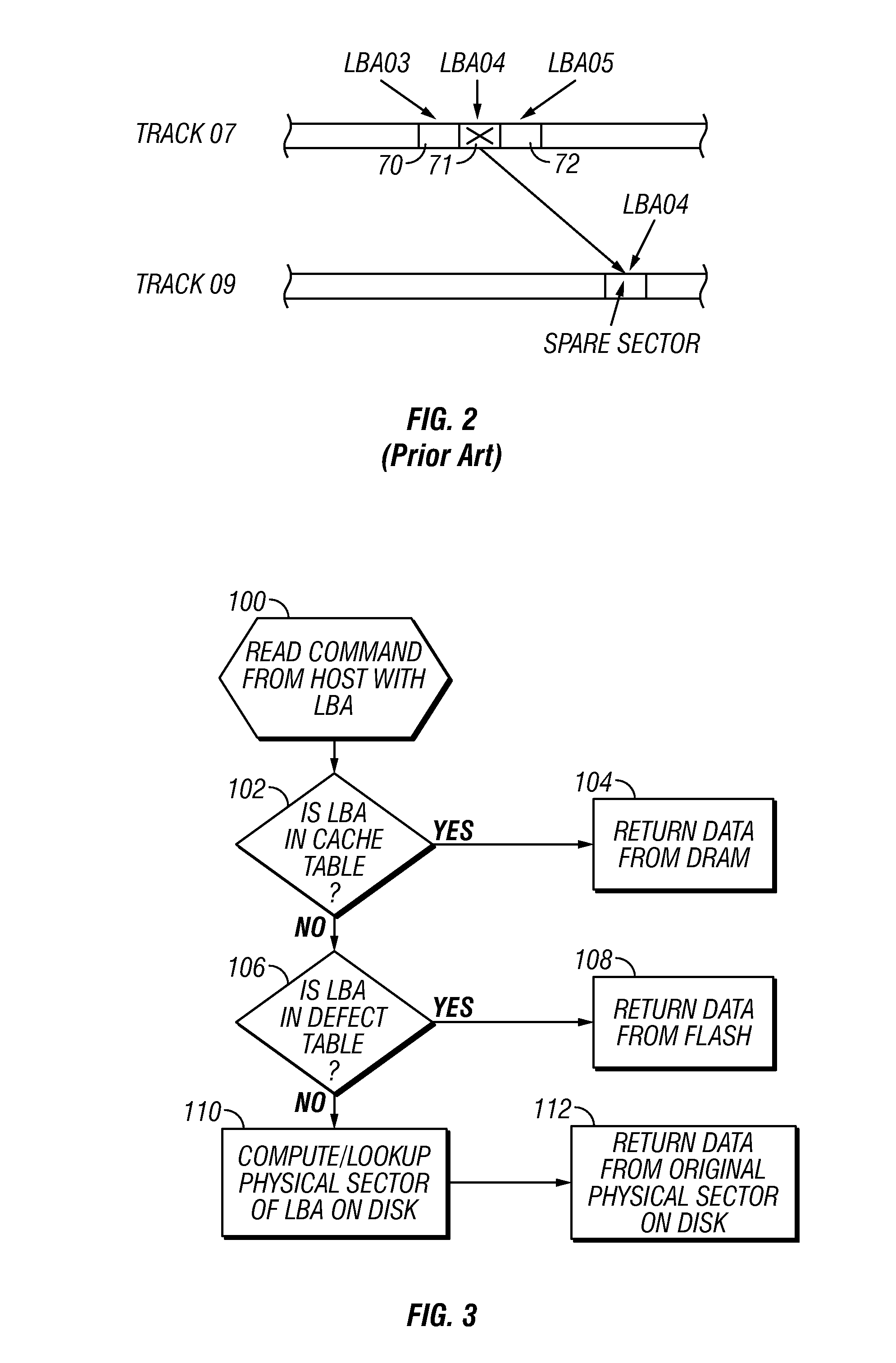

Data storage device employing high quality metrics when decoding logical block address appended to a data sector

ActiveUS8413010B1Data representation error detection/correctionCode conversionLogical block addressingCorrection code

A data storage device is disclosed that receives a read command from a host, wherein the read command comprises a read logical block address (LBA_R). A target data sector is read in response to the LBA_R to generate a read signal. The read signal is processed to detect user data and redundancy data using a soft-output detector that outputs quality metrics for the user data and redundancy data. A high quality metric is assigned to the LBA_R, and errors are corrected in the user data using an error correction code (ECC) decoder in response to the quality metrics output by the soft-output detector and the quality metrics assigned to the LBA_R.

Owner:WESTERN DIGITAL TECH INC

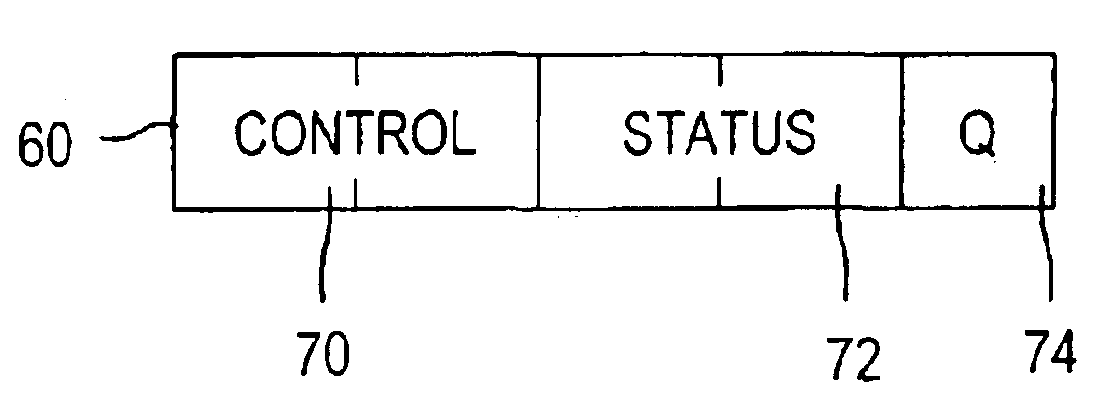

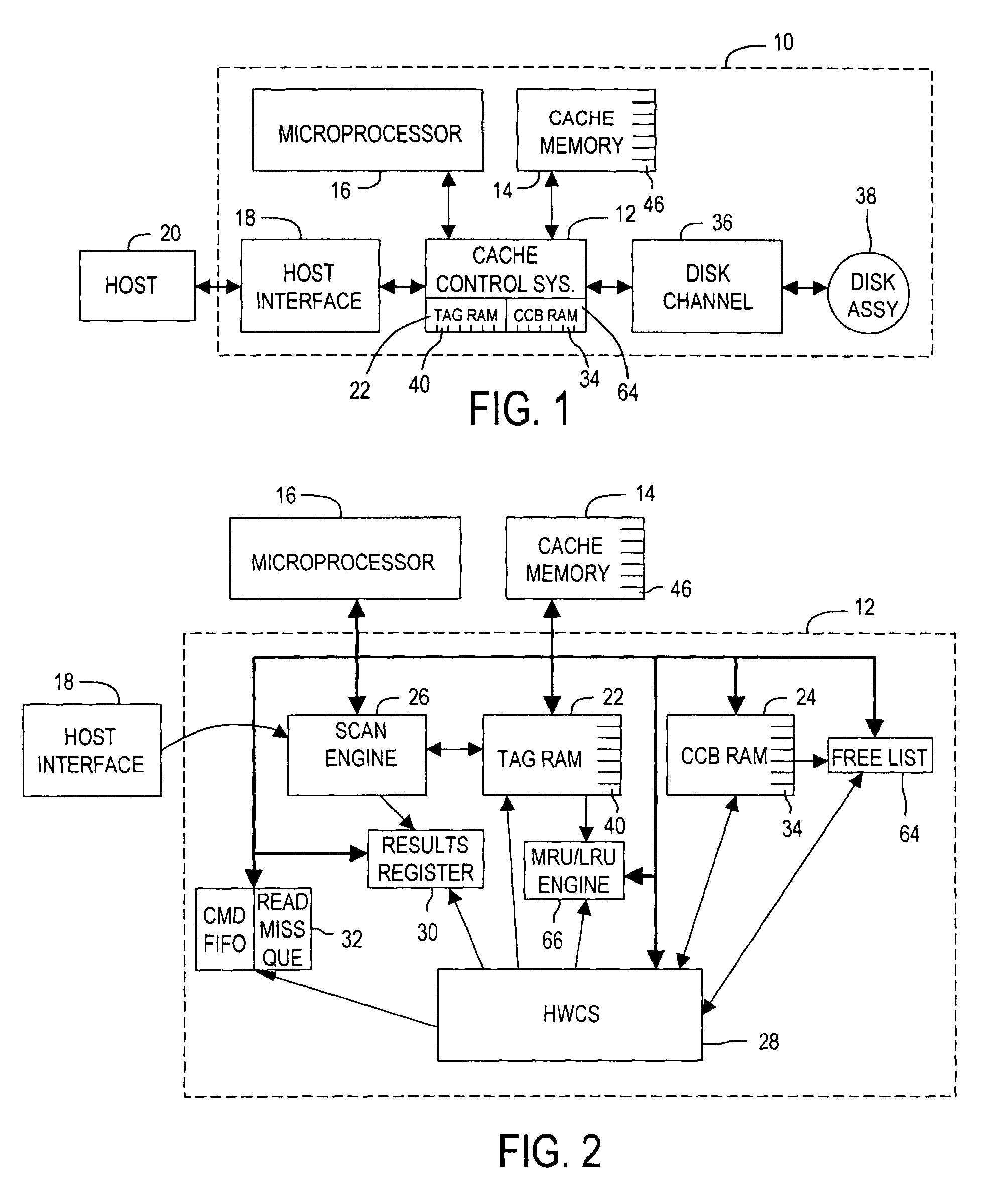

Range-based cache control system and method

InactiveUS6880043B1Memory architecture accessing/allocationMemory adressing/allocation/relocationLogical block addressingControl system

The present invention relates to disk drive having a cache control system that generates scan results that permit response to a host command using existing cached data having a logical block address (LBA) range that overlaps a host command LBA range. The cache control system forms variable length segments of memory clusters in a cache memory for caching disk data in contiguous LBA ranges. The cached LBA ranges are scanned for segments having LBA ranges overlapping with an LBA range of a host command. The cache control system is effective in exploiting any existing overlapping cache data.

Owner:WESTERN DIGITAL TECH INC

Disk drive write verifying unformatted data sectors

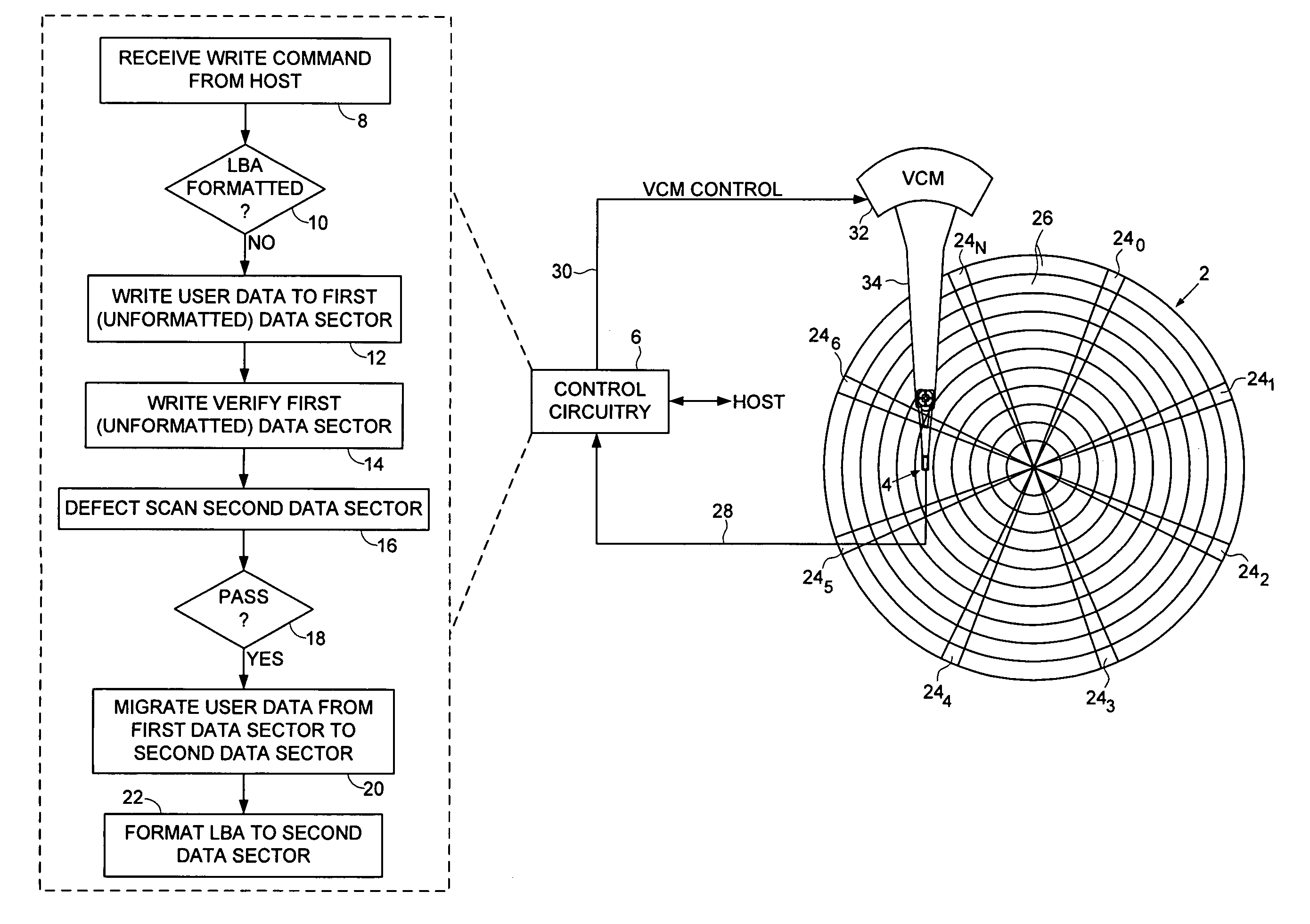

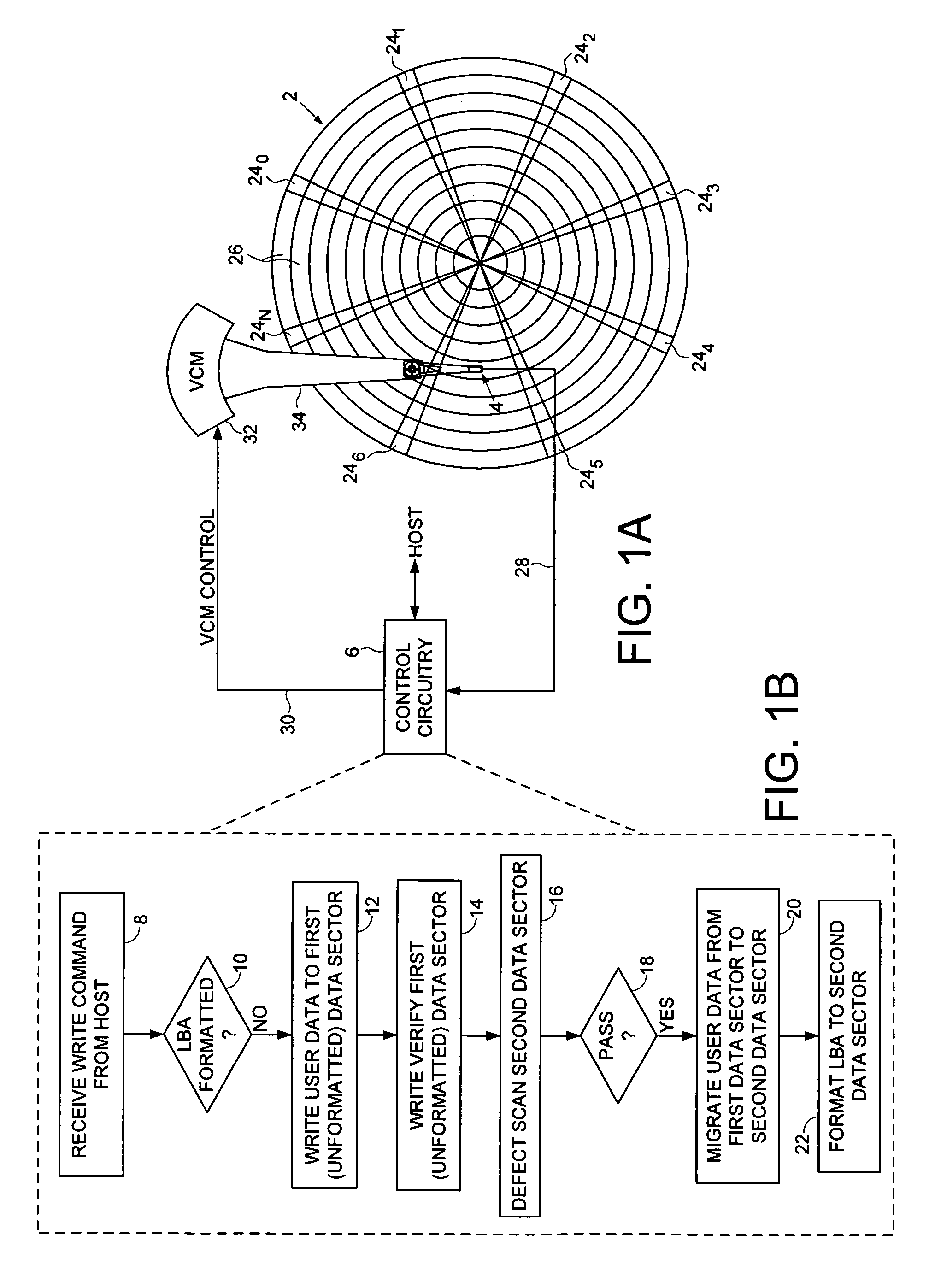

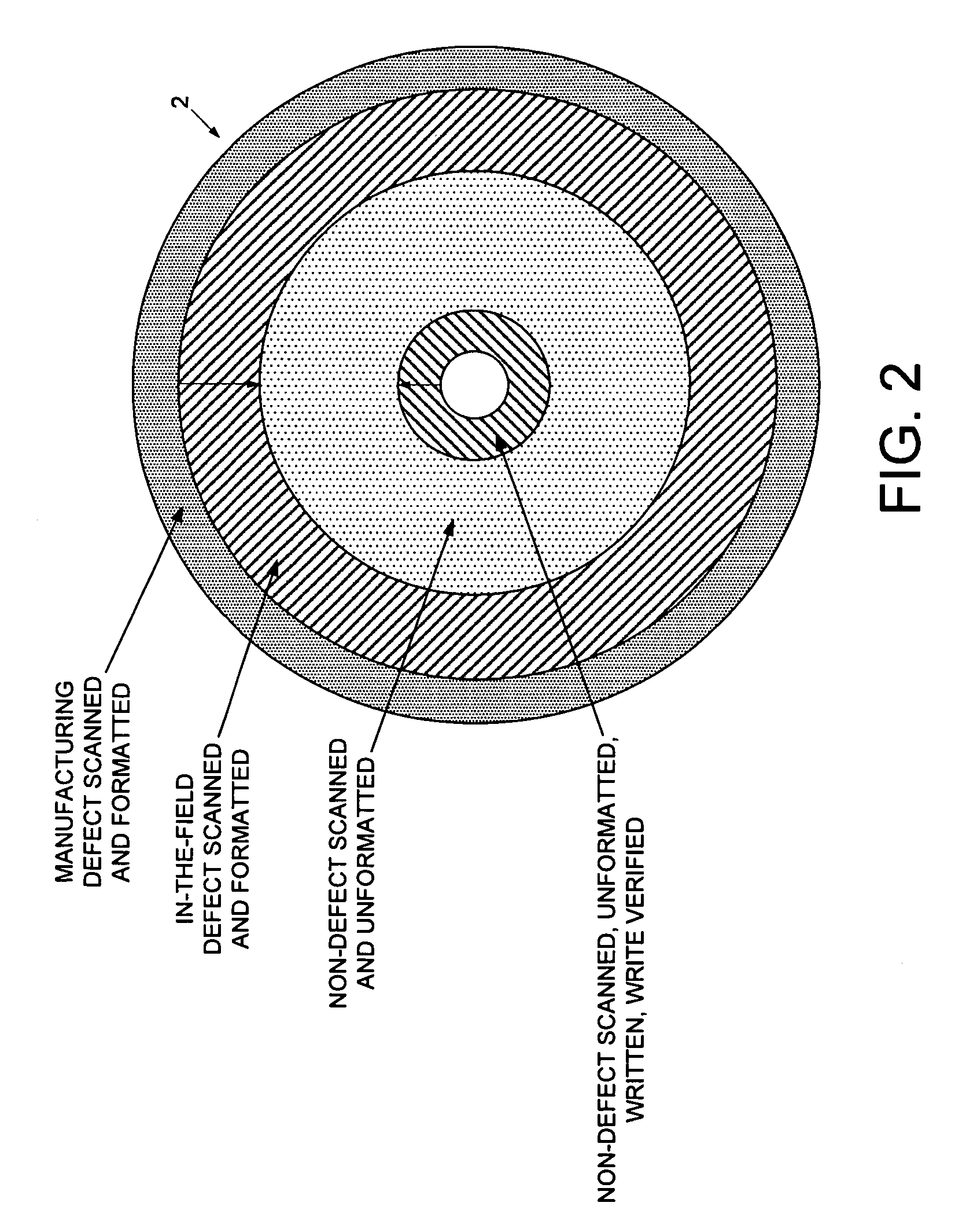

InactiveUS8004785B1Disc-shaped record carriersCopying/moving digital dataLogical block addressingPhysical address

Owner:WESTERN DIGITAL TECH INC

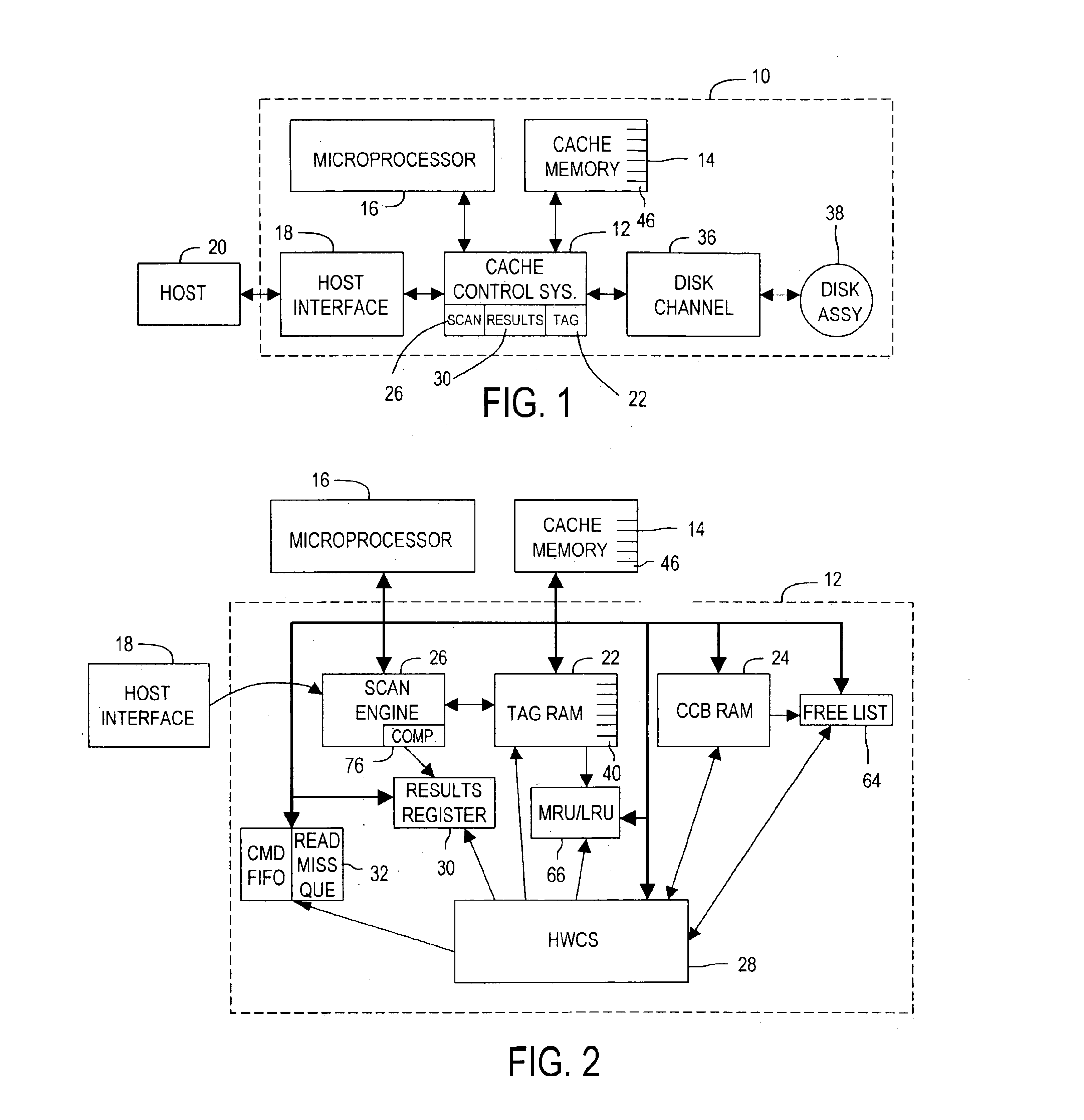

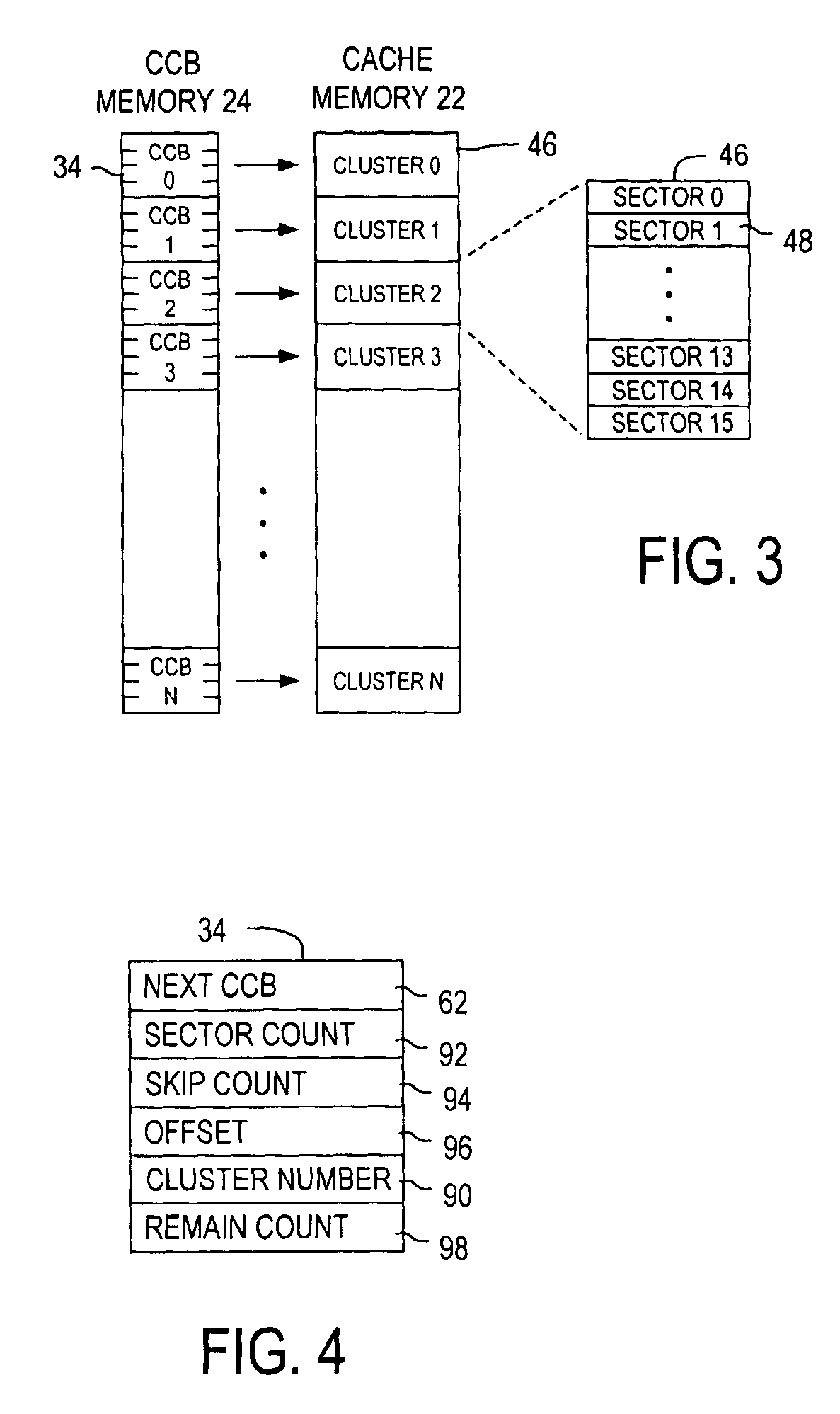

Cluster-based cache memory allocation

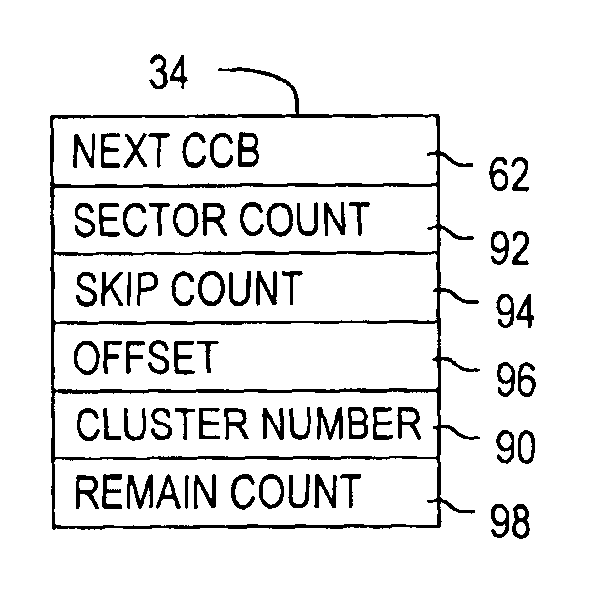

InactiveUS6996669B1Uniform sizeIncrease the lengthMemory architecture accessing/allocationMemory adressing/allocation/relocationLogical block addressingControl system

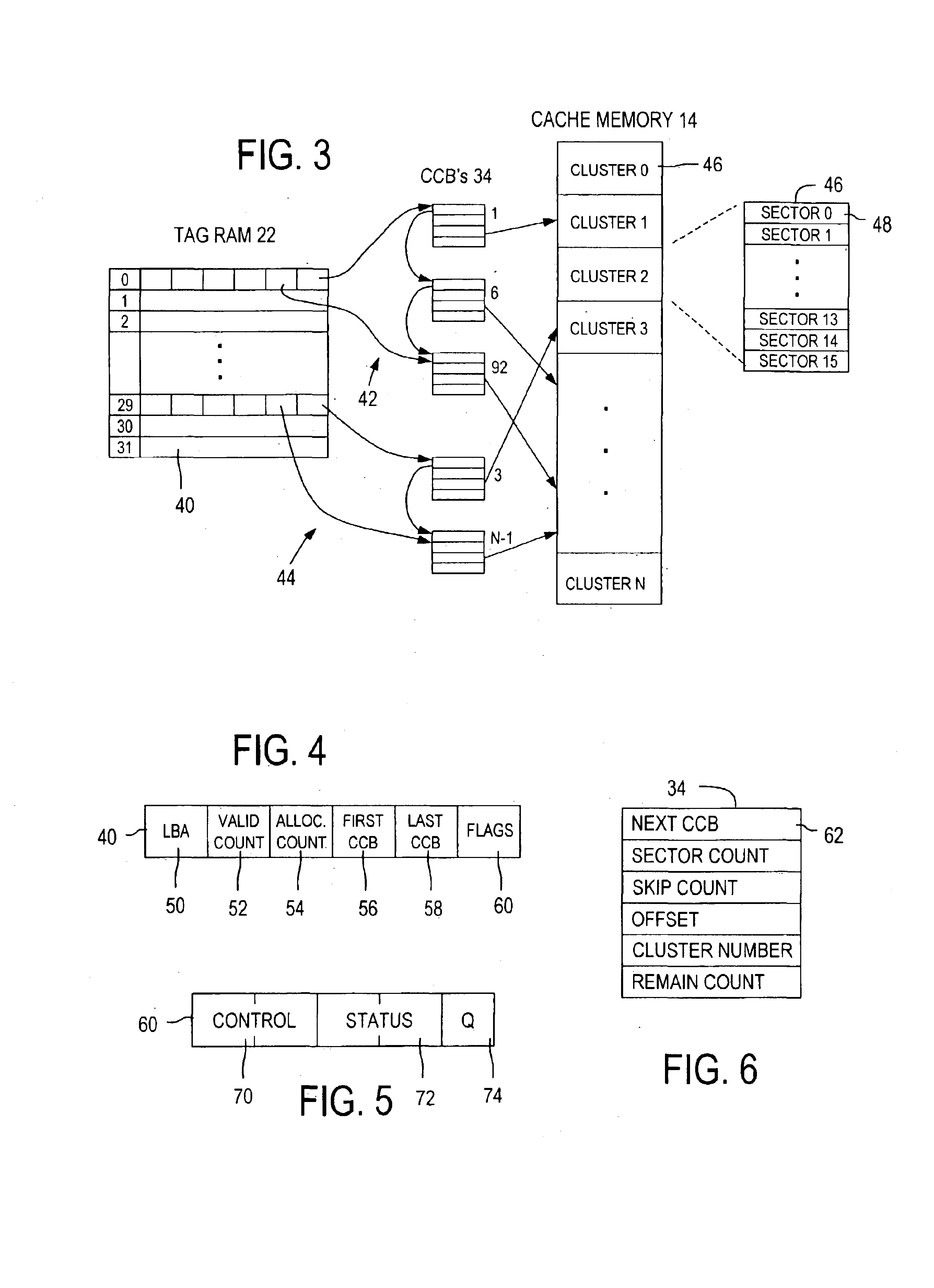

The present invention relates to a disk drive including a cache memory having a plurality of sequentially-ordered memory clusters for caching disk data stored in sectors (not shown) on disks of a disk assembly. The disk sectors are identified by logical block addresses (LBAs). A cache control system of the disk drive comprises a cluster control block memory, having a plurality of cluster control blocks (CCB), and a tag memory 22, having a plurality of tag records, that are embedded within the cache control system. Each CCB includes a cluster segment record with an entry for associating the CCB with a particular memory cluster and for forming variable length segments of the memory clusters without regard to the sequential order of the memory clusters. Each tag record assigns a segment to a continuous range of LBAs and defines the CCBs forming the segment. Each segment of the memory clusters is for caching data from a contiguous range of the logical block addresses. The cache control system efficiently exploits available memory clusters for responding to host commands.

Owner:WESTERN DIGITAL TECH INC

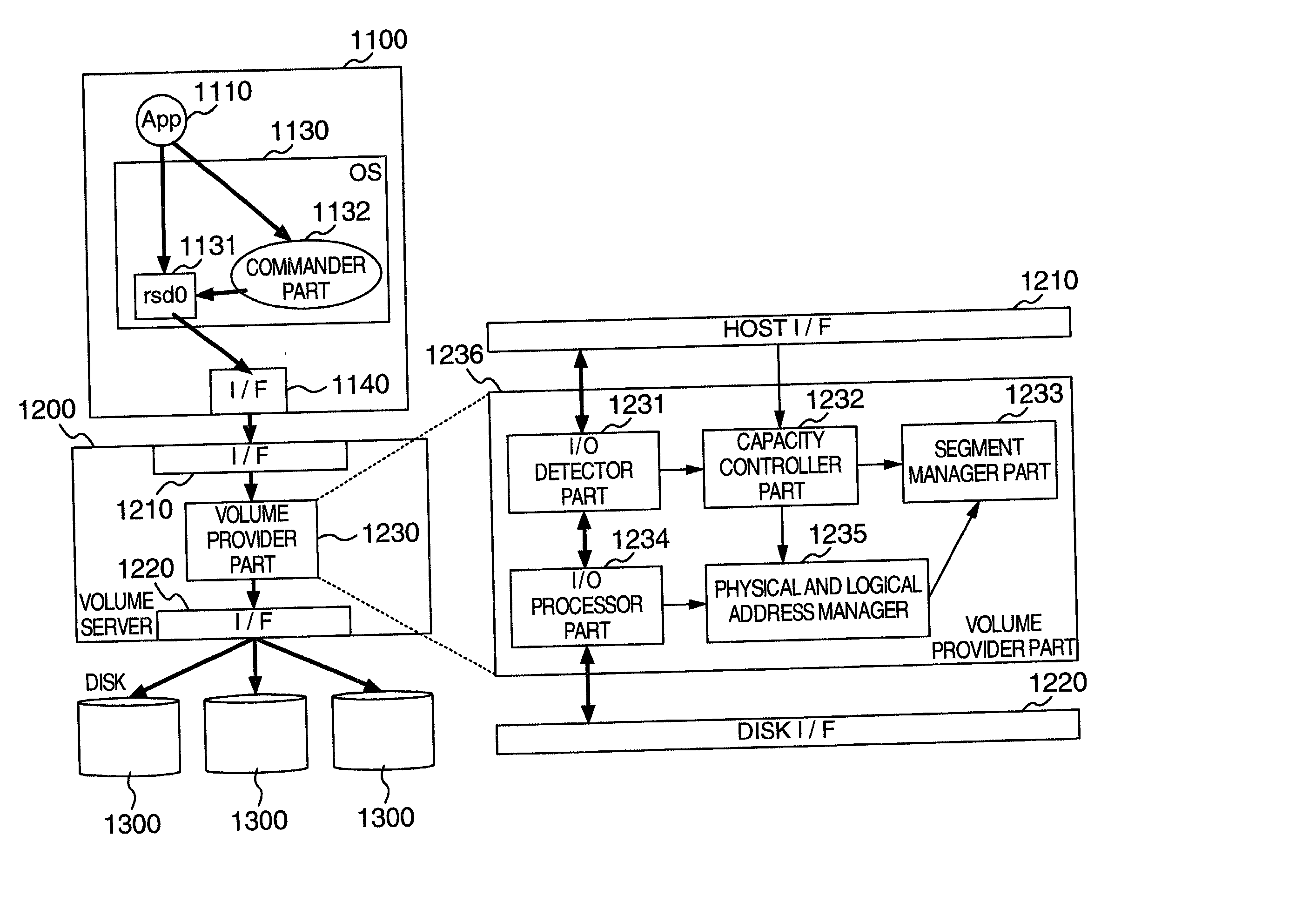

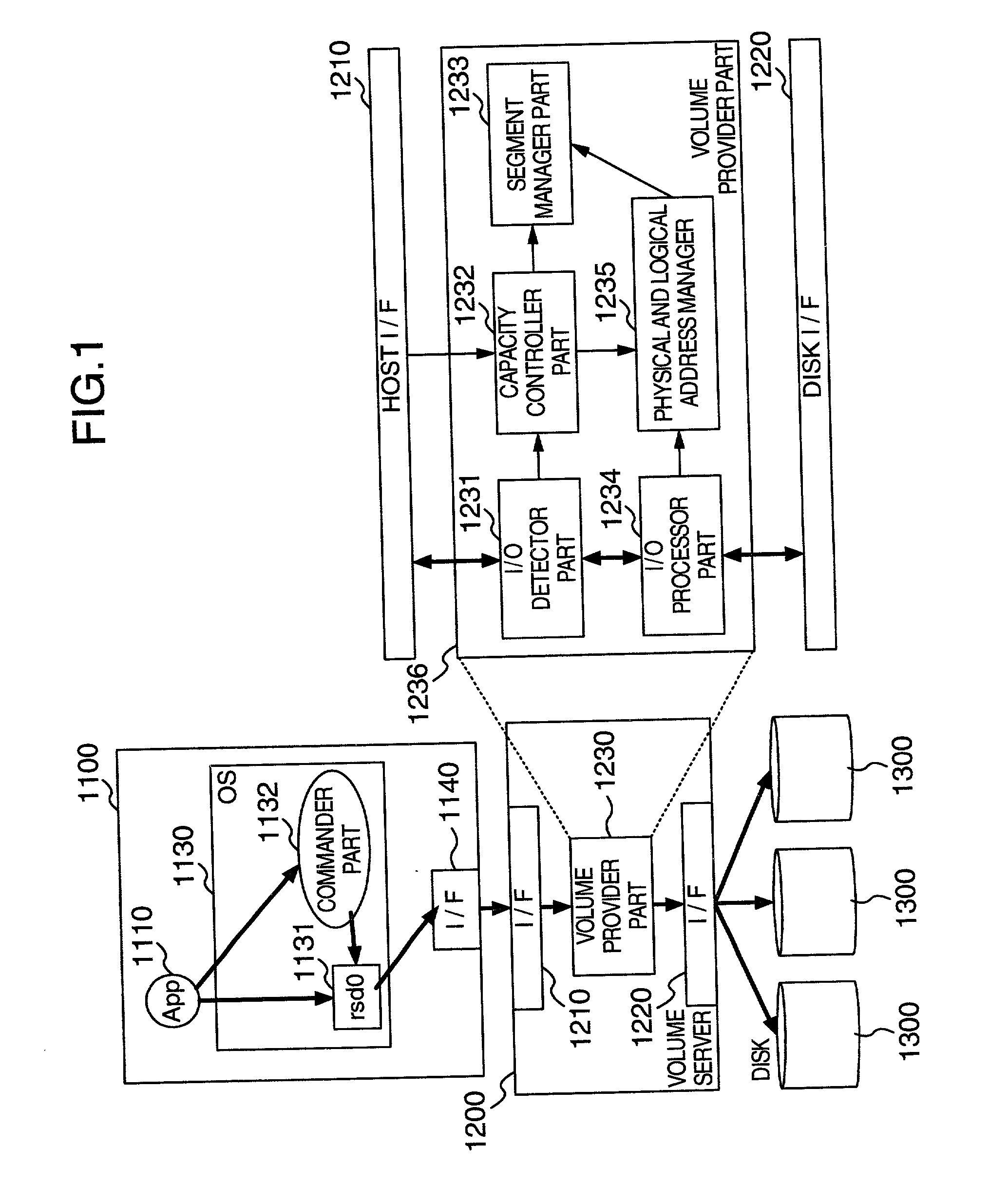

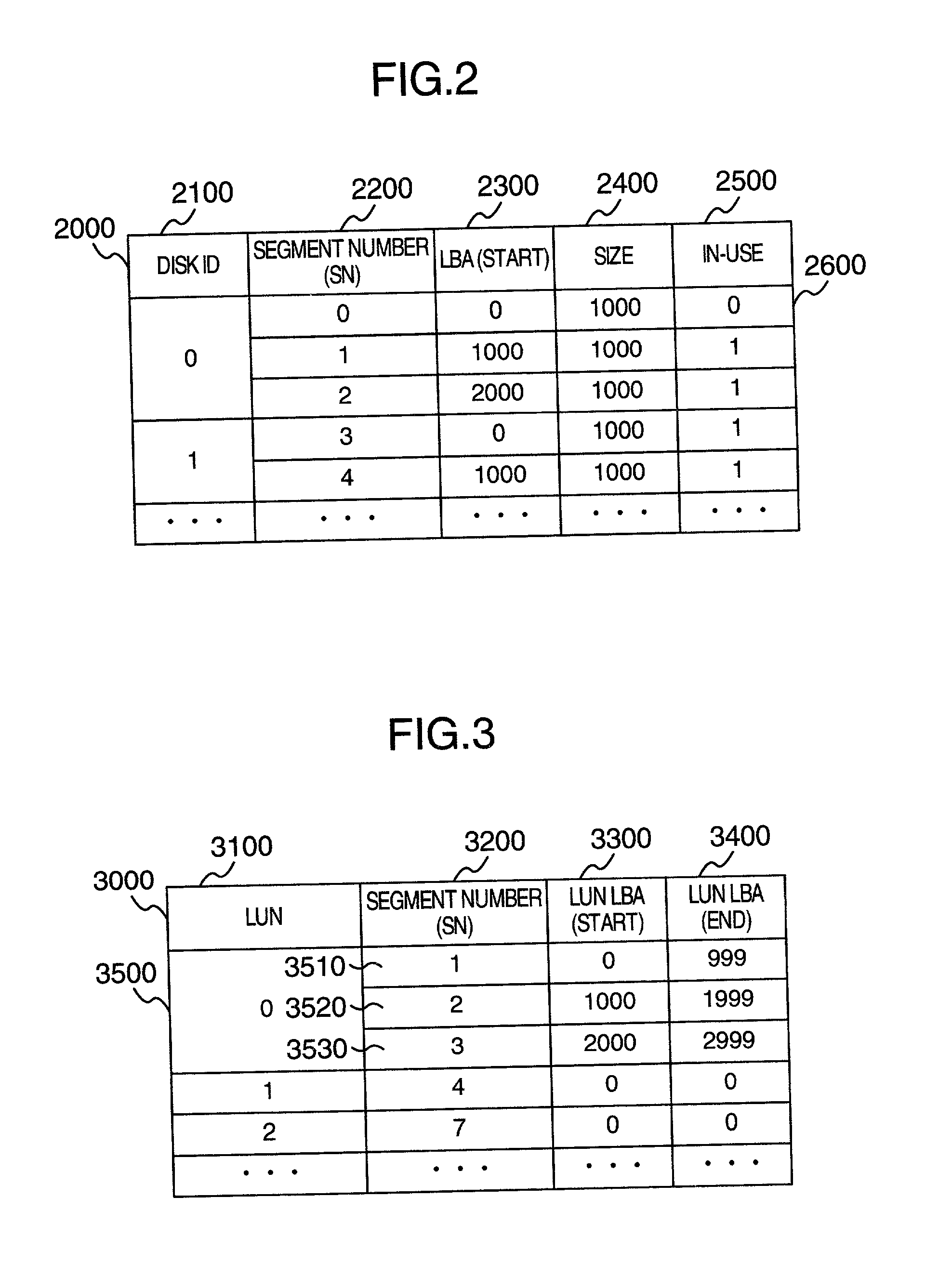

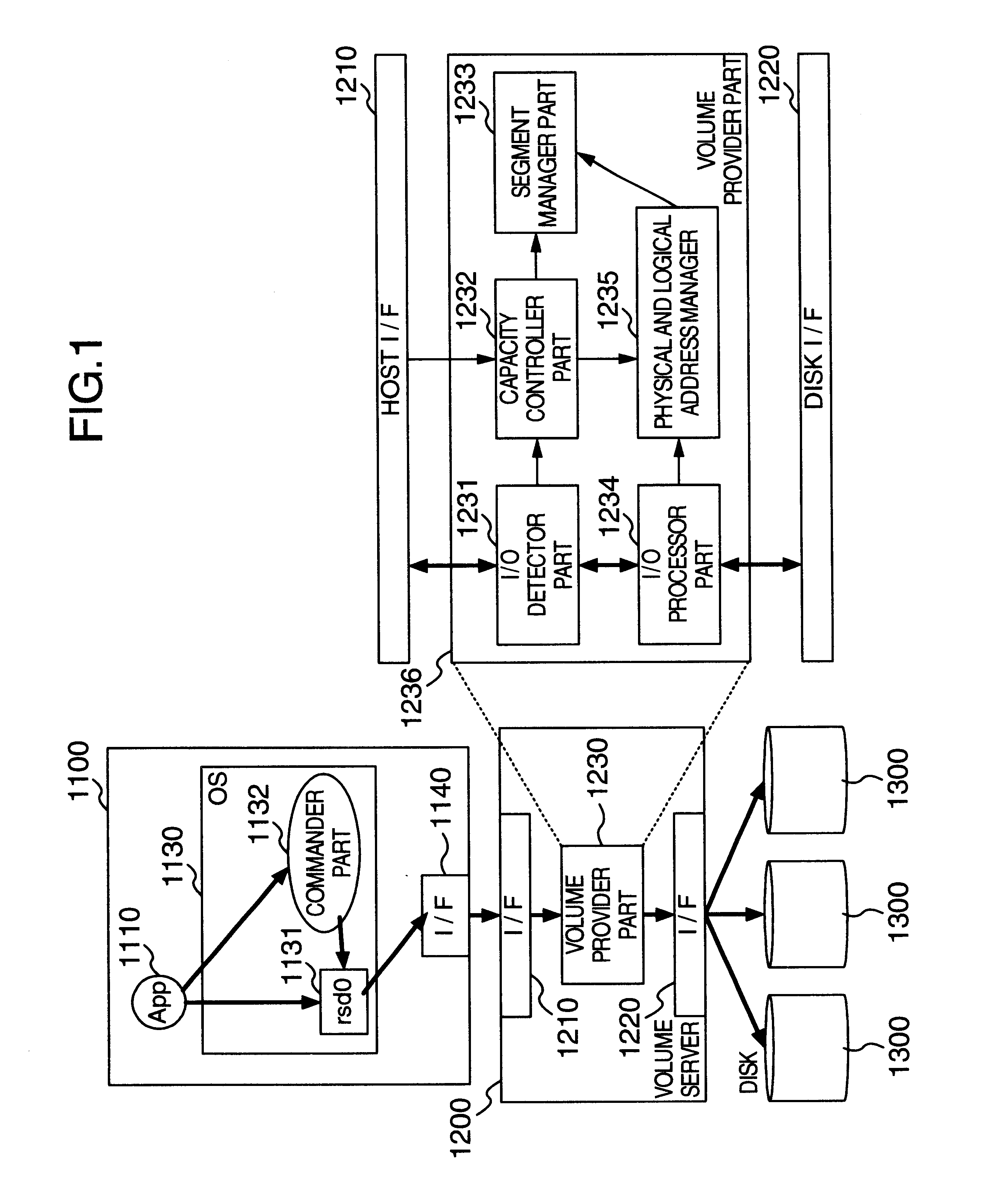

Automated on-line capacity expansion method for storage device

InactiveUS20030009619A1Input/output to record carriersMemory adressing/allocation/relocationLogical block addressingComputerized system

A volume provider unit in a computer system detects a logical block address of a read or write I / O accessing a logical volume of a storage device from a host. According to the logical block address fetched, a storage domain of the logical volume is dynamically expanded. Moreover, the storage domain of the logical volume is reduced or expanded according to an instruction of a logical volume capacity reduction or expansion from a host commander part to a volume server.

Owner:HITACHI LTD

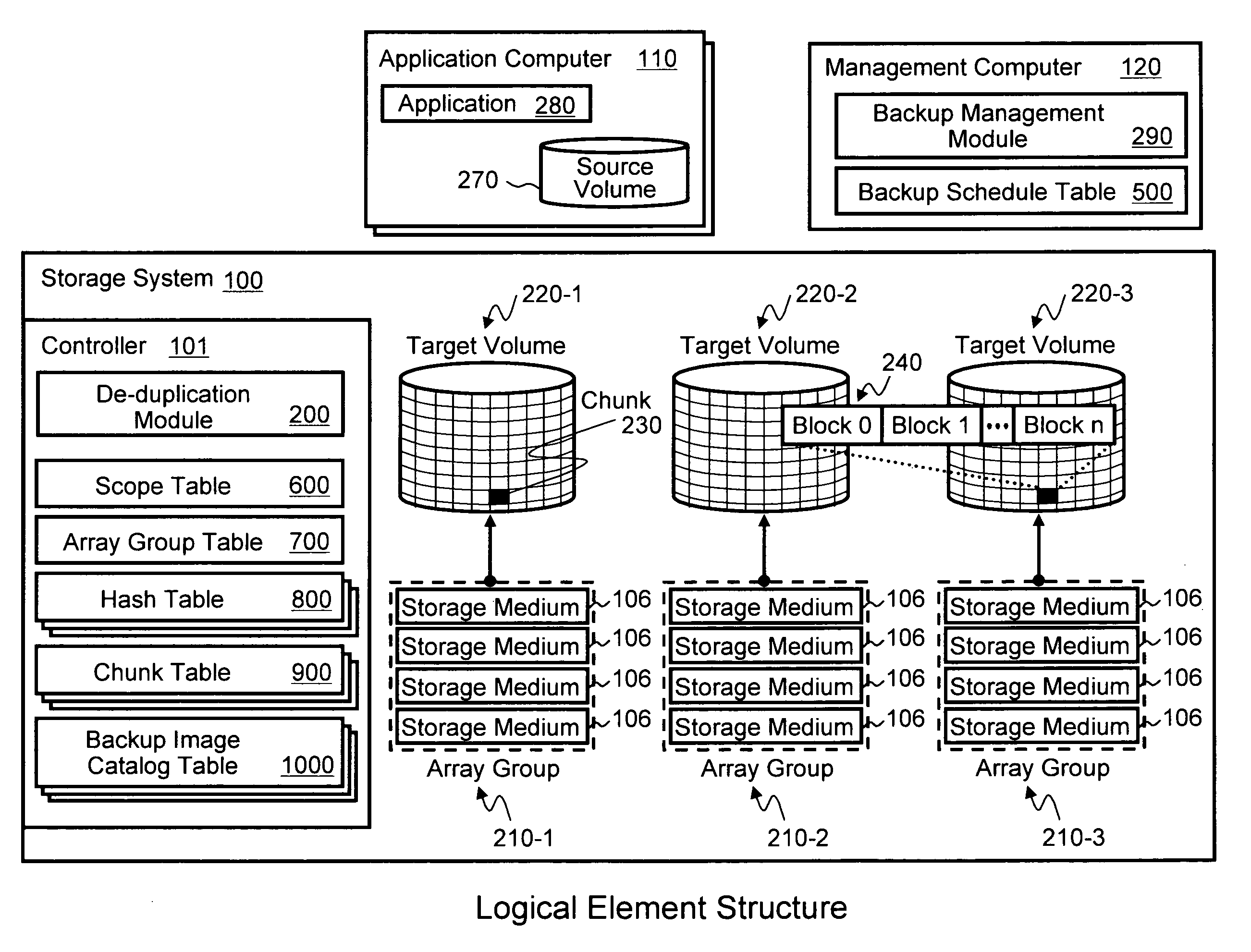

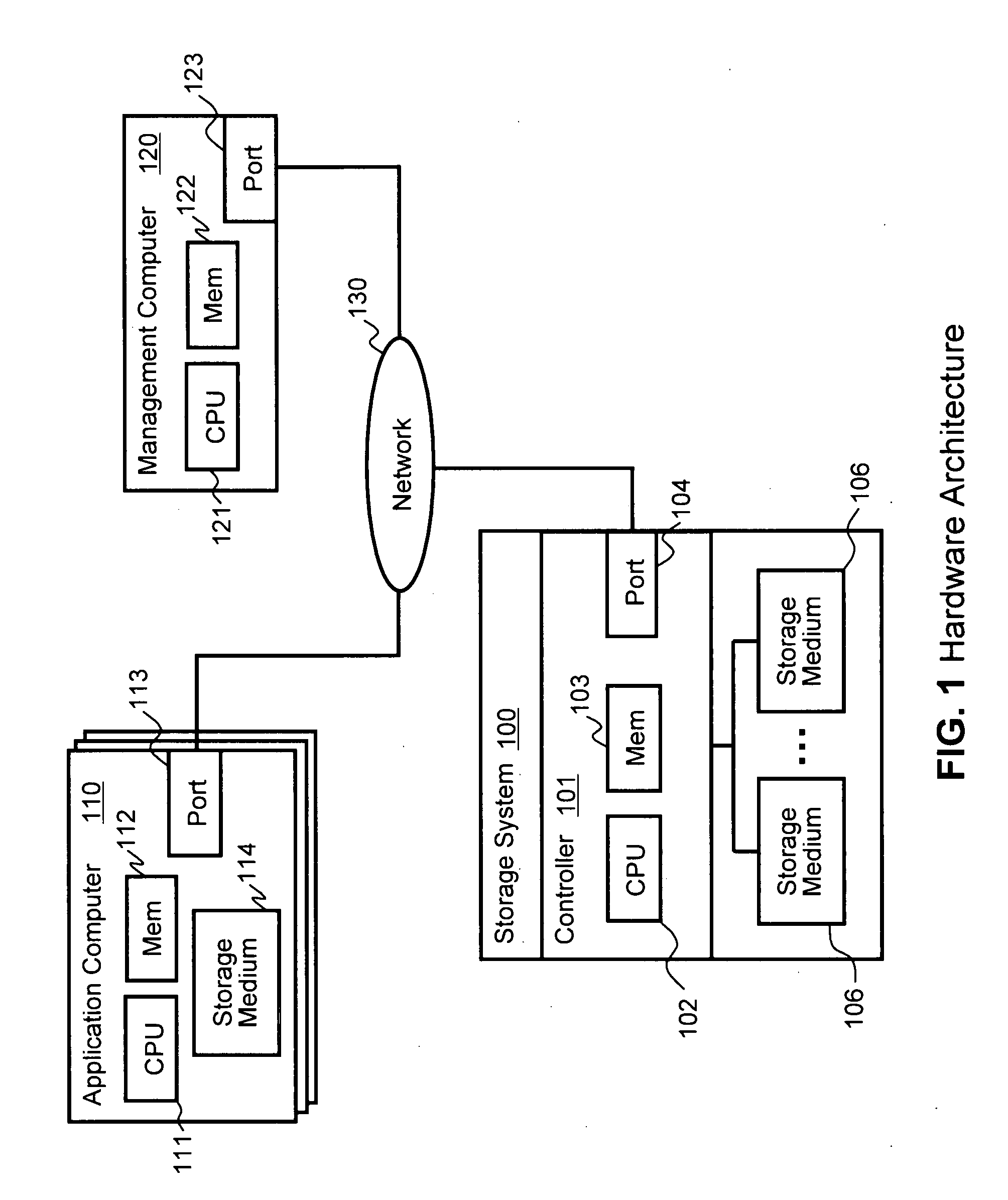

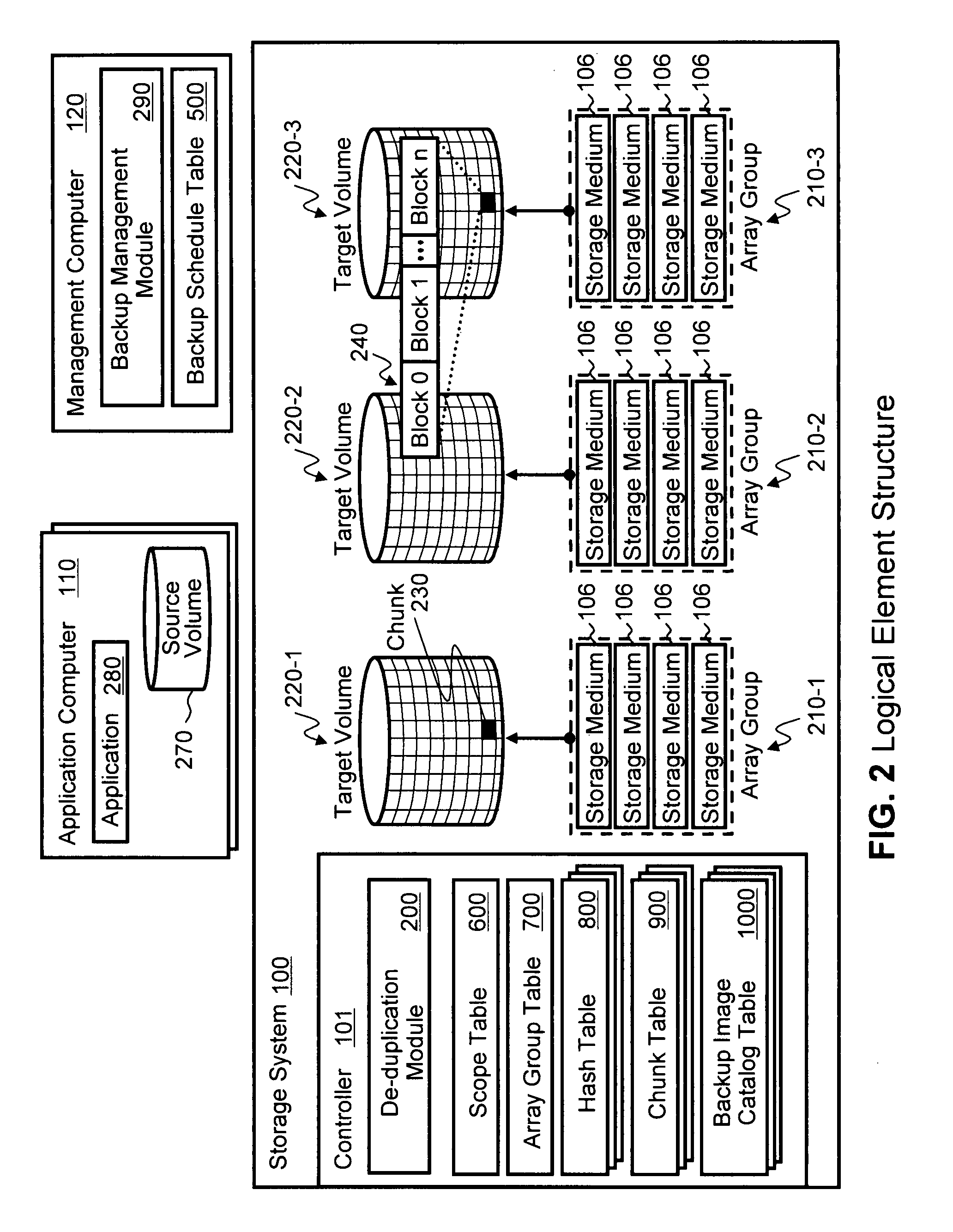

Power efficient data storage with data de-duplication

InactiveUS20090083563A1Energy efficient ICTMemory loss protectionPower efficientLogical block addressing

A storage system includes a first de-duplication scope comprising a first volume, a first table of hash values corresponding to first chunks of data stored on the first volume, and a first table of logical block addresses of where the chunks of data are stored on the first volume. A second de-duplication scope includes similar information for a second volume. The first scope is used for de-duplicating and storing first data from a first data source and the second scope is used for de-duplicating and storing second data from a second data source. First storage mediums that make up the first volume remain powered off while de-duplication and storage of the second data on the second volume takes place, and second storage mediums that make up the second volume remain powered off while de-duplication and storage of the first data takes place, thereby enabling data de-duplication while saving power.

Owner:HITACHI LTD

Two-level RAM lookup table for block and page allocation and wear-leveling in limited-write flash-memories

InactiveUS7660941B2Memory architecture accessing/allocationRead-only memoriesLogical block addressingRandom access memory

A restrictive multi-level-cell (MLC) flash memory prohibits regressive page-writes. When a regressive page-write is requested, an empty block having a low wear-level count is found, and data from the regressive page-write and data from pages stored in the old block are written to the empty block in page order. The old block is erased and recycled. A two-level look-up table is stored in volatile random-access memory (RAM). A logical page address from a host is divided by a modulo divider to generate a quotient and a remainder. The quotient is a logical block address that indexes a first-level look-up table to find a mapping entry with a physical block address that selects a row in a second-level look-up table. The remainder locates a column in the row in the second-level look-up table. If any page-valid bits above the column pointed to by the remainder are set, the write is regressive.

Owner:SUPER TALENT TECH CORP

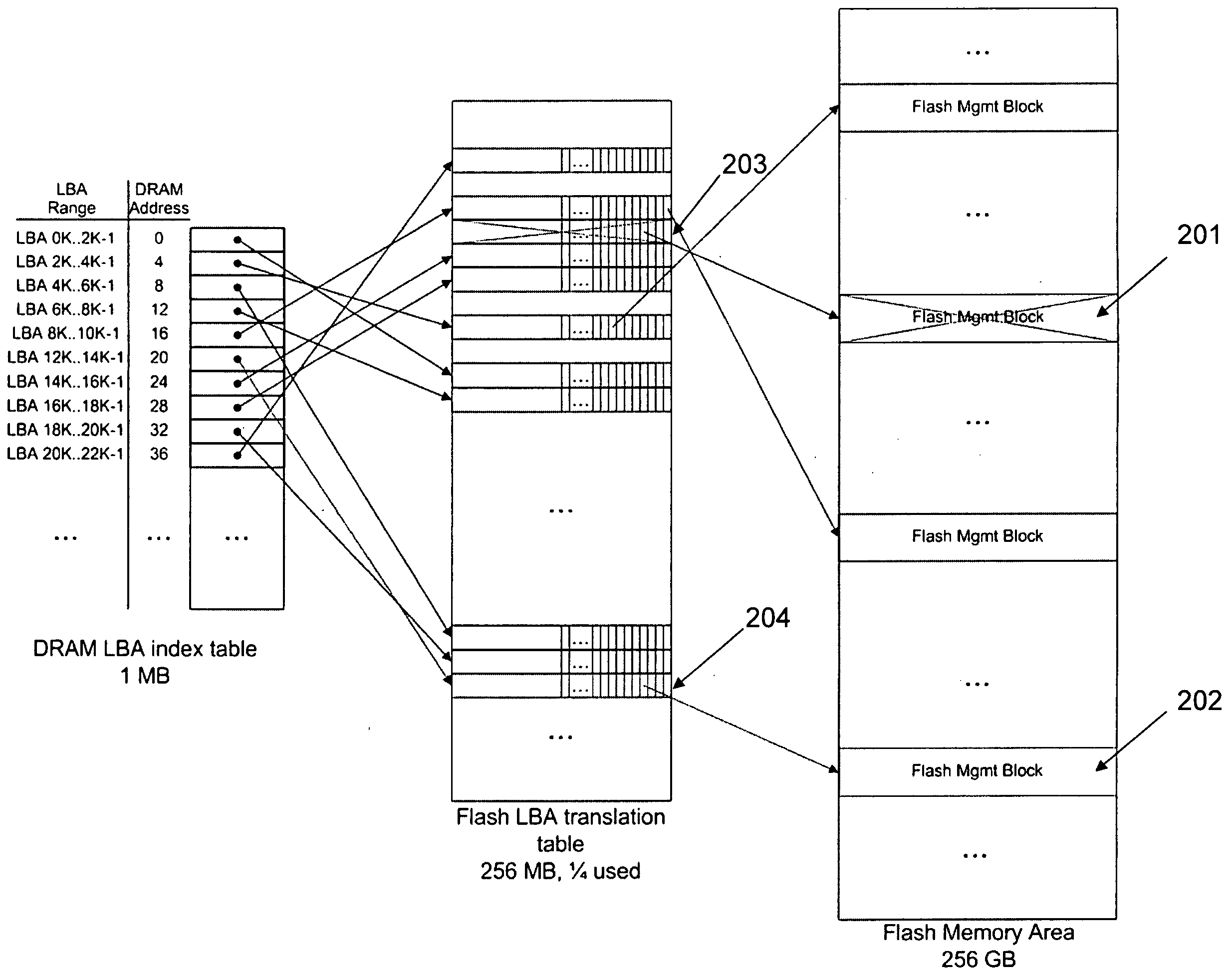

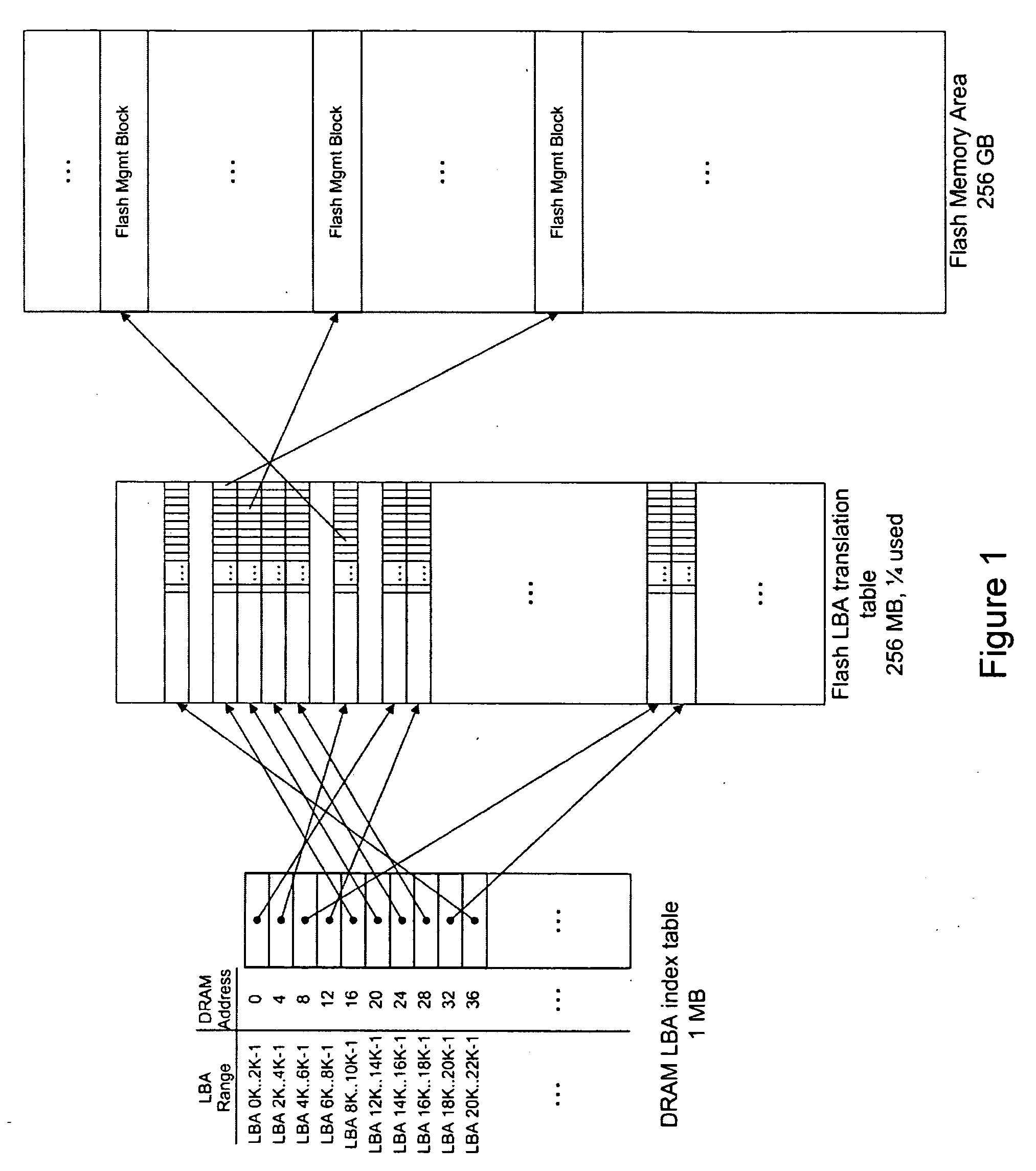

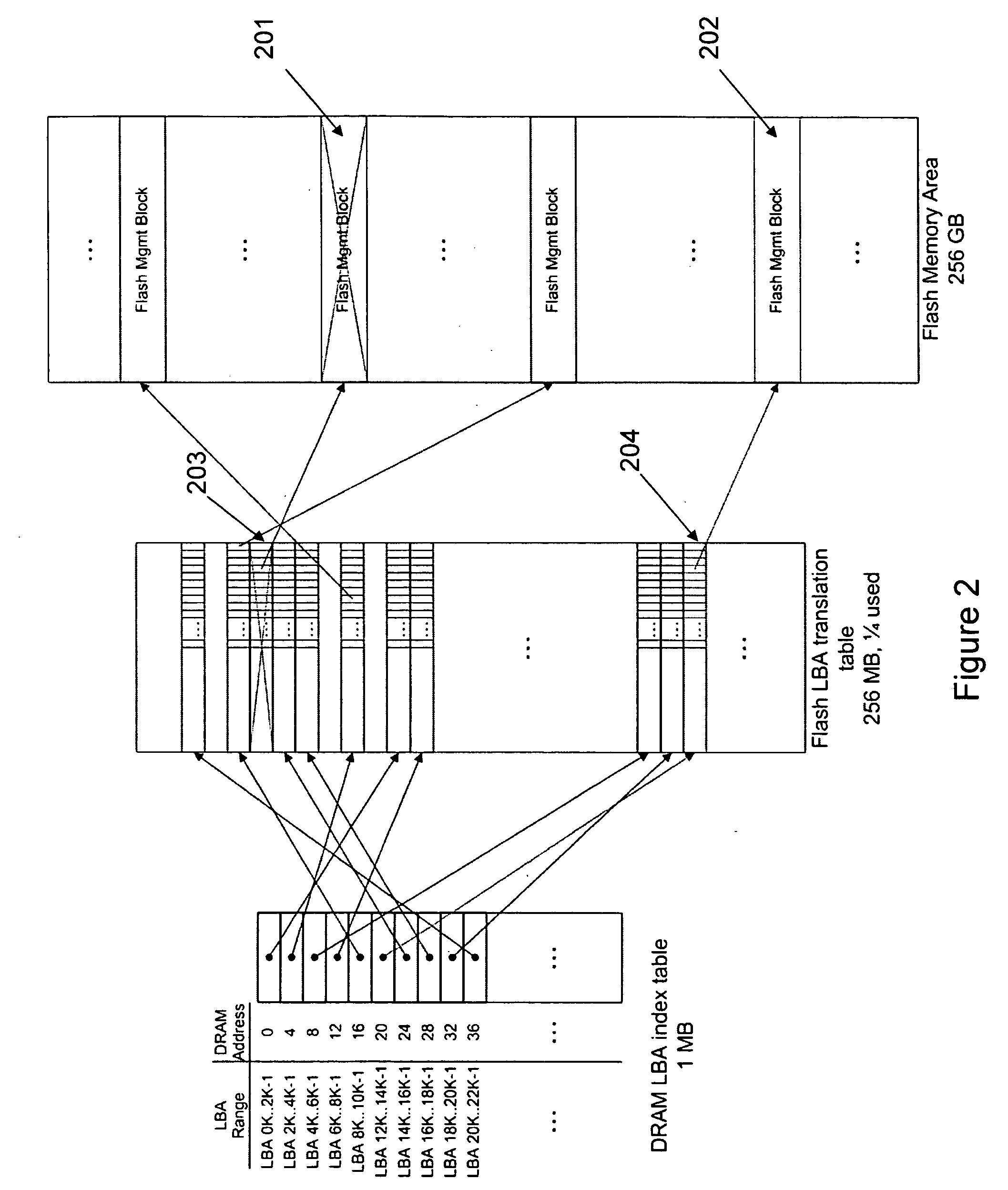

Process and Method for Logical-to-Physical Address Mapping in Solid Sate Disks

ActiveUS20100030999A1Memory architecture accessing/allocationMemory adressing/allocation/relocationMass storageLogical block addressing

An embodiment of the invention relates to a mass storage device including a nonvolatile memory device with a plurality of memory management blocks and an address translation table formed with pointers to locations of the memory management blocks. A volatile memory device is included with an address index table formed with pointers to the pointers to the locations of the memory management blocks. The address index table is stored in the nonvolatile memory upon loss of bias voltage. Changes to the address translation table are accumulated in the volatile memory and written to the address translation table when at least a minimum quantity of the changes has been accumulated. The changes to the logical block address translation table accumulated in the volatile memory are written to a page in the address translation table after prior data in the page has been updated, written to another page, and then erased.

Owner:INFINEON TECH AG

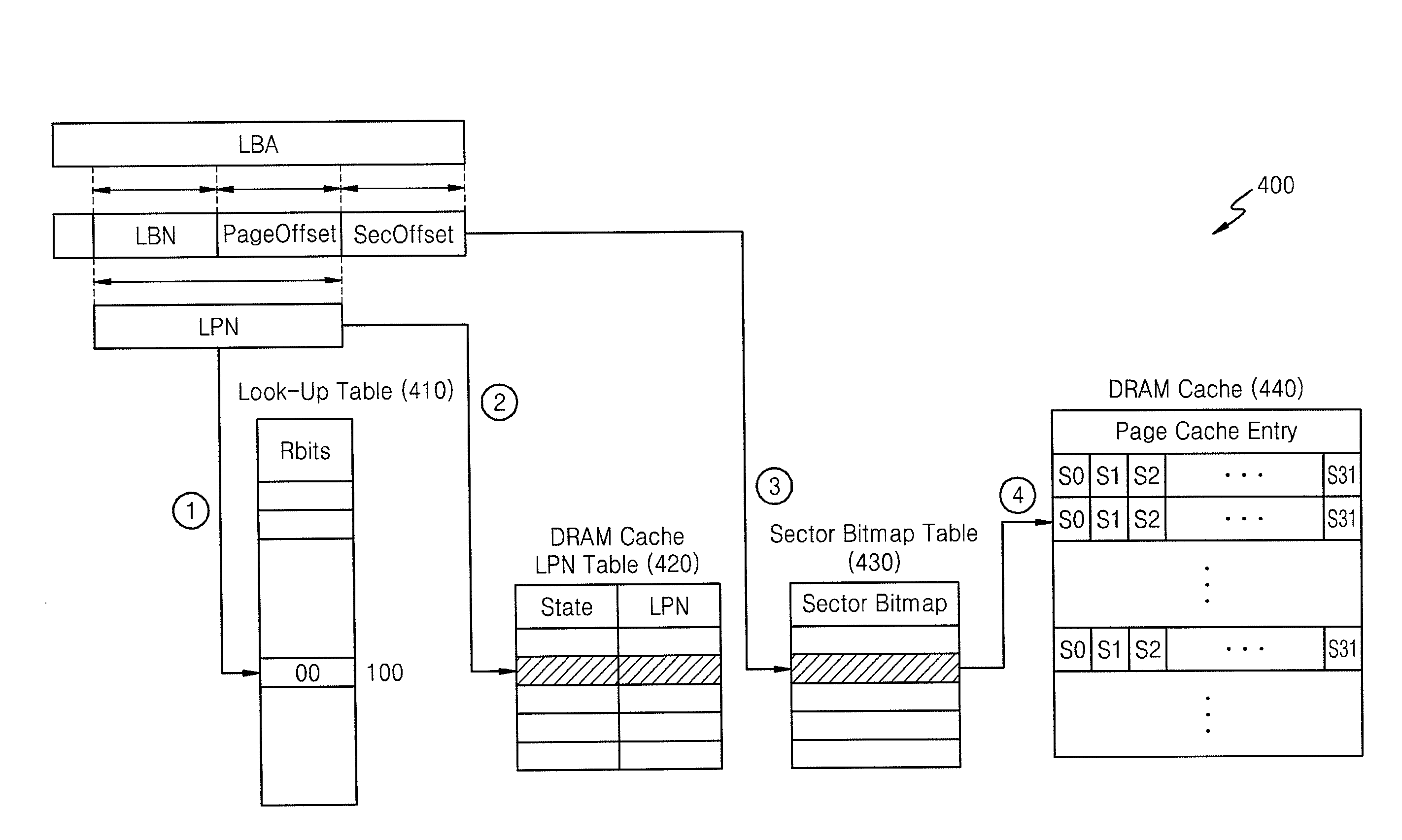

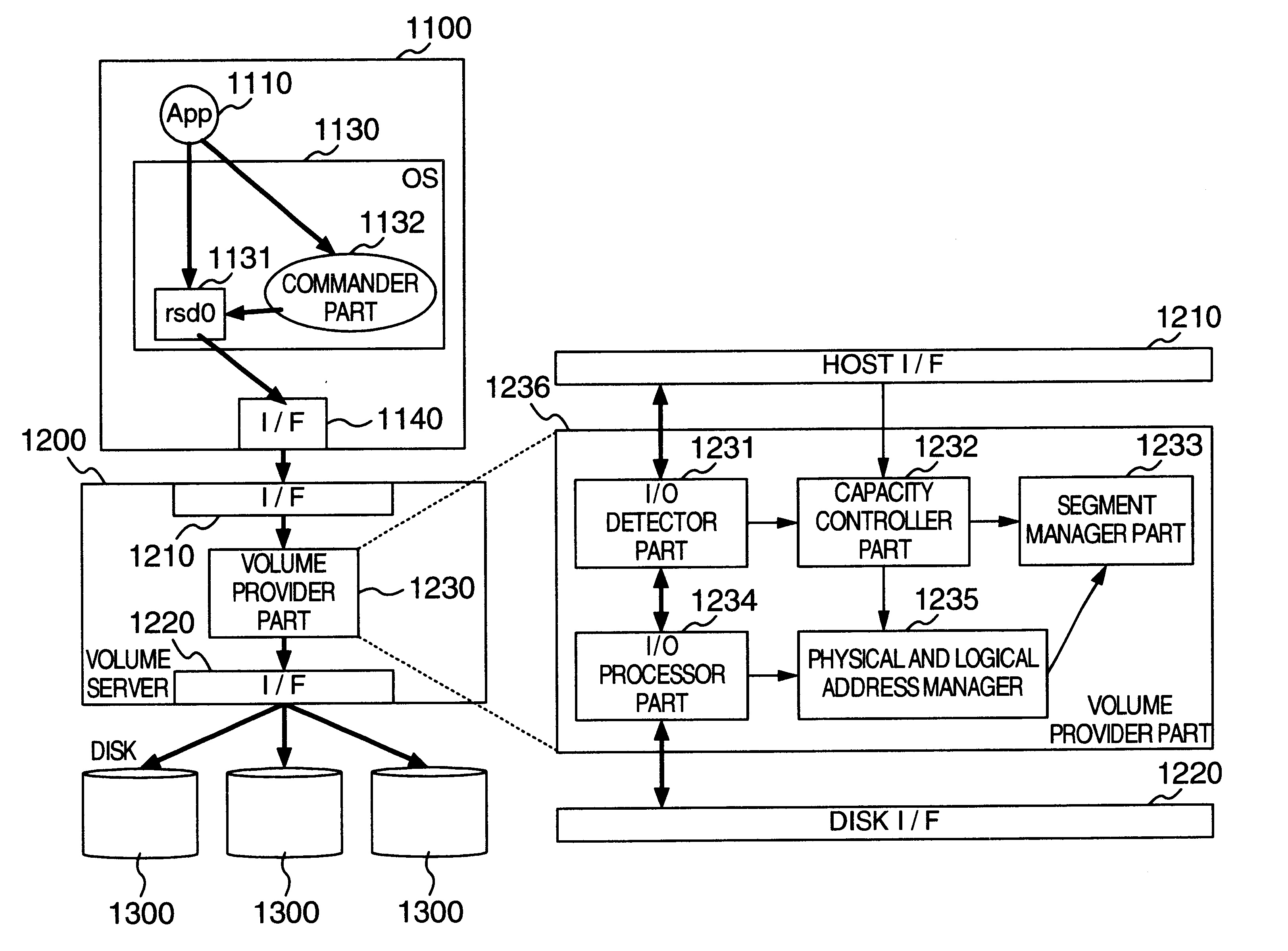

Method for operating buffer cache of storage device including flash memory

InactiveUS20080195801A1Easy to operateMemory architecture accessing/allocationMemory adressing/allocation/relocationLogical block addressingLogic block

Provided is a method for operating a buffer cache which is performed by a storage device including a flash memory. The method includes converting a logical block address requested from a host into a logical page number. A region in which a page corresponding to the logical page number is located is searched for. A physical block address corresponding to the logical block address is generated with reference to a mapping table of the region in which the page corresponding to the logical page number is located. The searching for of the region includes searching for a look-up table having information about a region in which a plurality of pages of the flash memory are located.

Owner:SAMSUNG ELECTRONICS CO LTD

Automated on-line capacity expansion method for storage device

InactiveUS6725328B2Input/output to record carriersMemory adressing/allocation/relocationLogical block addressingComputerized system

A volume provider unit in a computer system detects a logical block address of a read or write I / O accessing a logical volume of a storage device from a host. According to the logical block address fetched, a storage domain of the logical volume is dynamically expanded. Moreover, the storage domain of the logical volume is reduced or expanded according to an instruction of a logical volume capacity reduction or expansion from a host commander part to a volume server.

Owner:HITACHI LTD

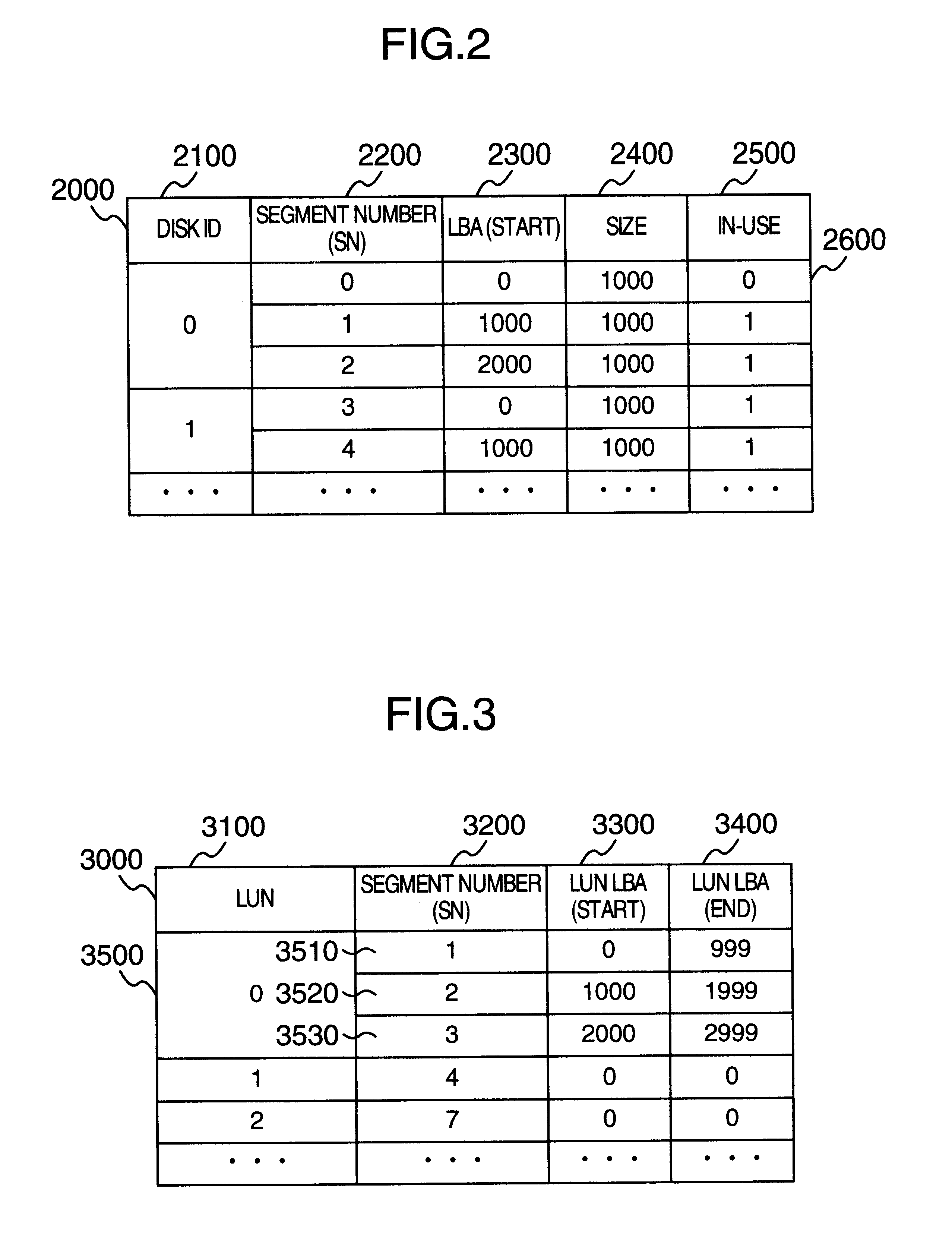

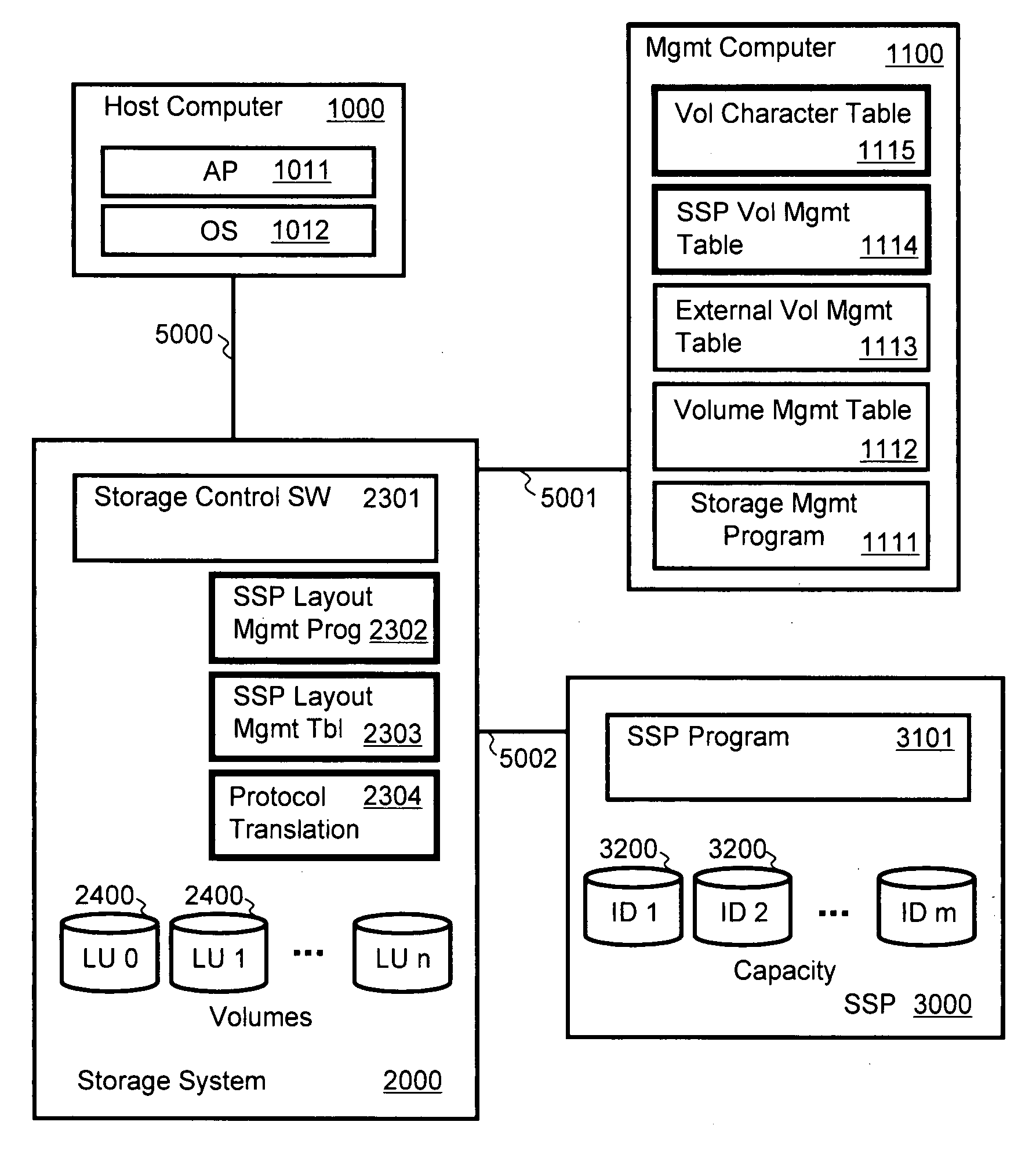

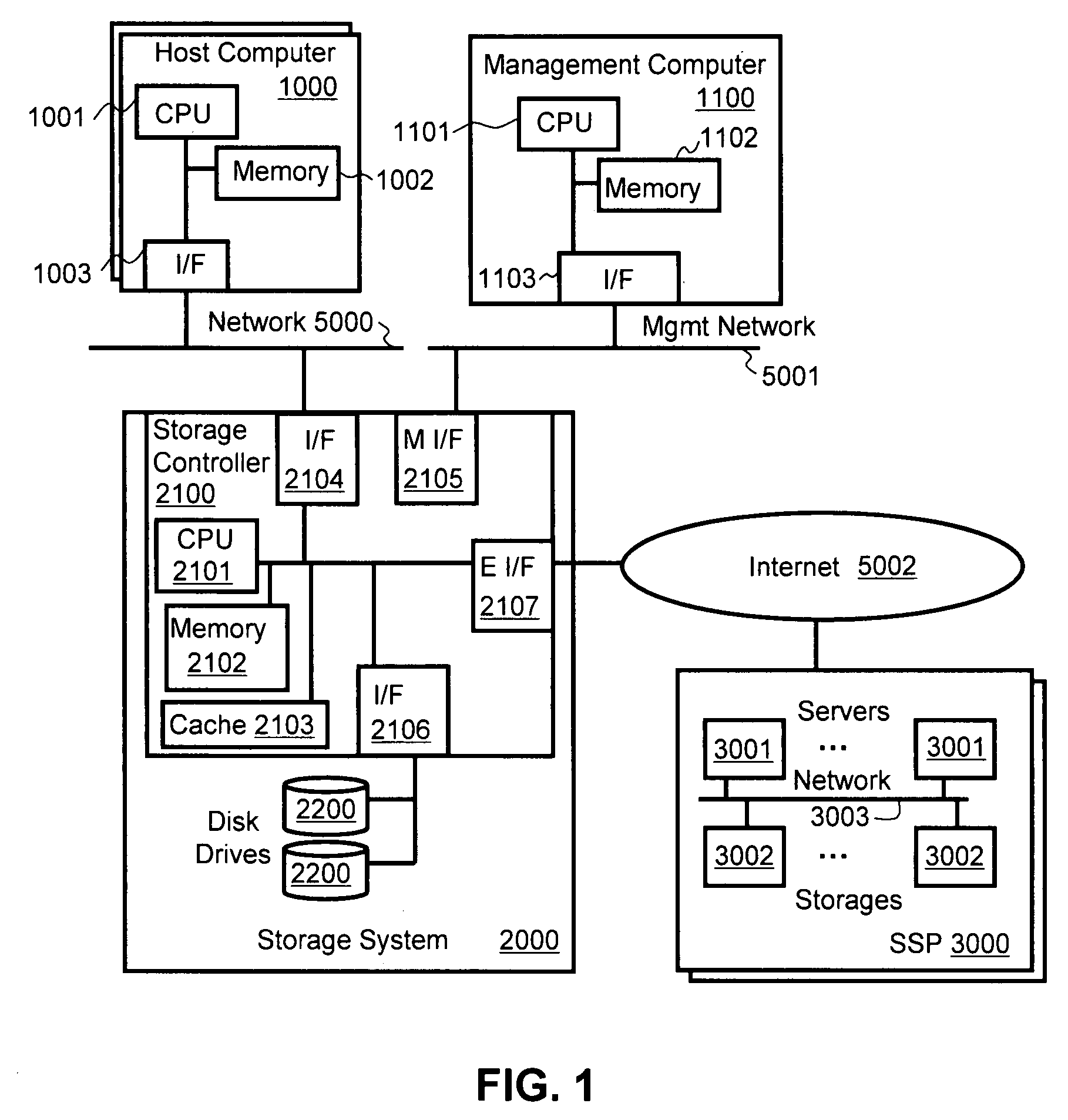

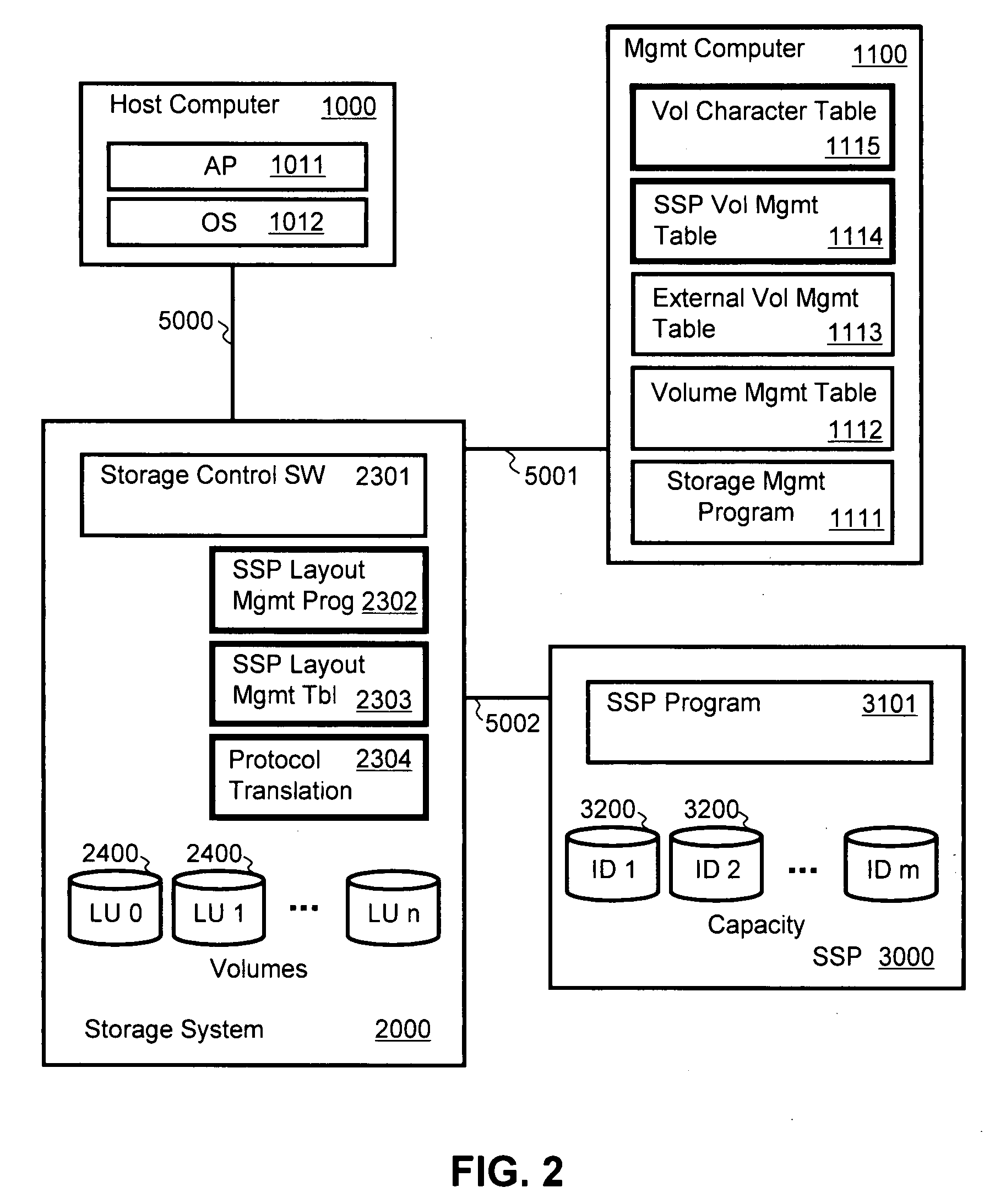

Method and apparatus for storage-service-provider-aware storage system

InactiveUS20090024752A1Error detection/correctionMultiple digital computer combinationsLogical block addressingService provision

A storage system includes a virtual volume configured on a storage controller and mapping to a physical storage capacity maintained at a remote location by a storage service provider (SSP). The storage controller receives an I / O command in a block-based protocol specifying a logical block address (LBA). The storage controller correlates the LBA with a file name of a file stored by the SSP, translates the I / O command to an IP-supported protocol, and forwards the translated I / O command with the file name to the SSP for processing. In the case of a write command, the SSP stores the write data using the specified file name. In the case of a read command, the SSP enables download of data from the specified file name. In an alternative embodiment, a NAS head may replace the storage controller for correlating the LBA with a file name and translating the I / O command.

Owner:HITACHI LTD

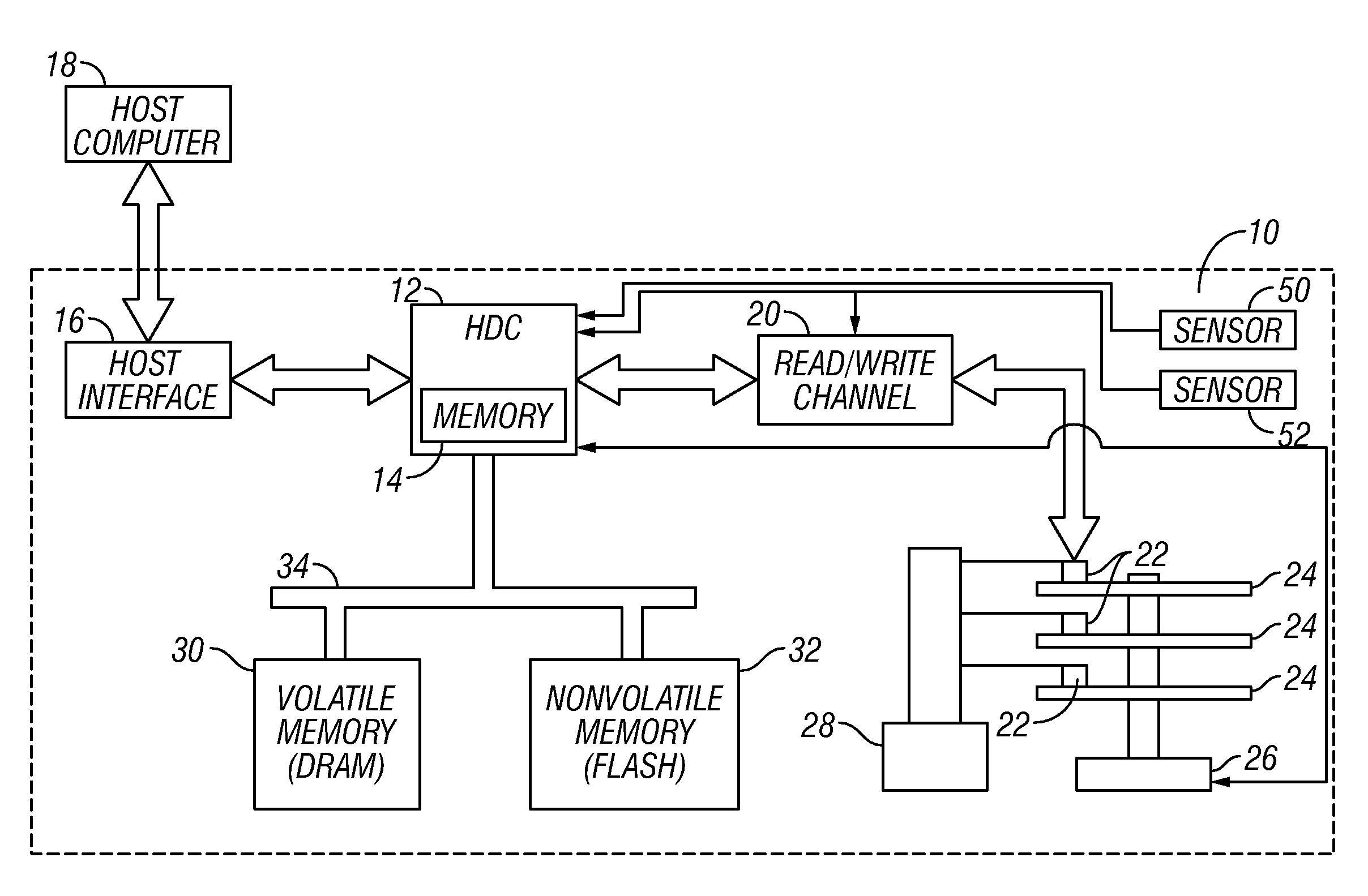

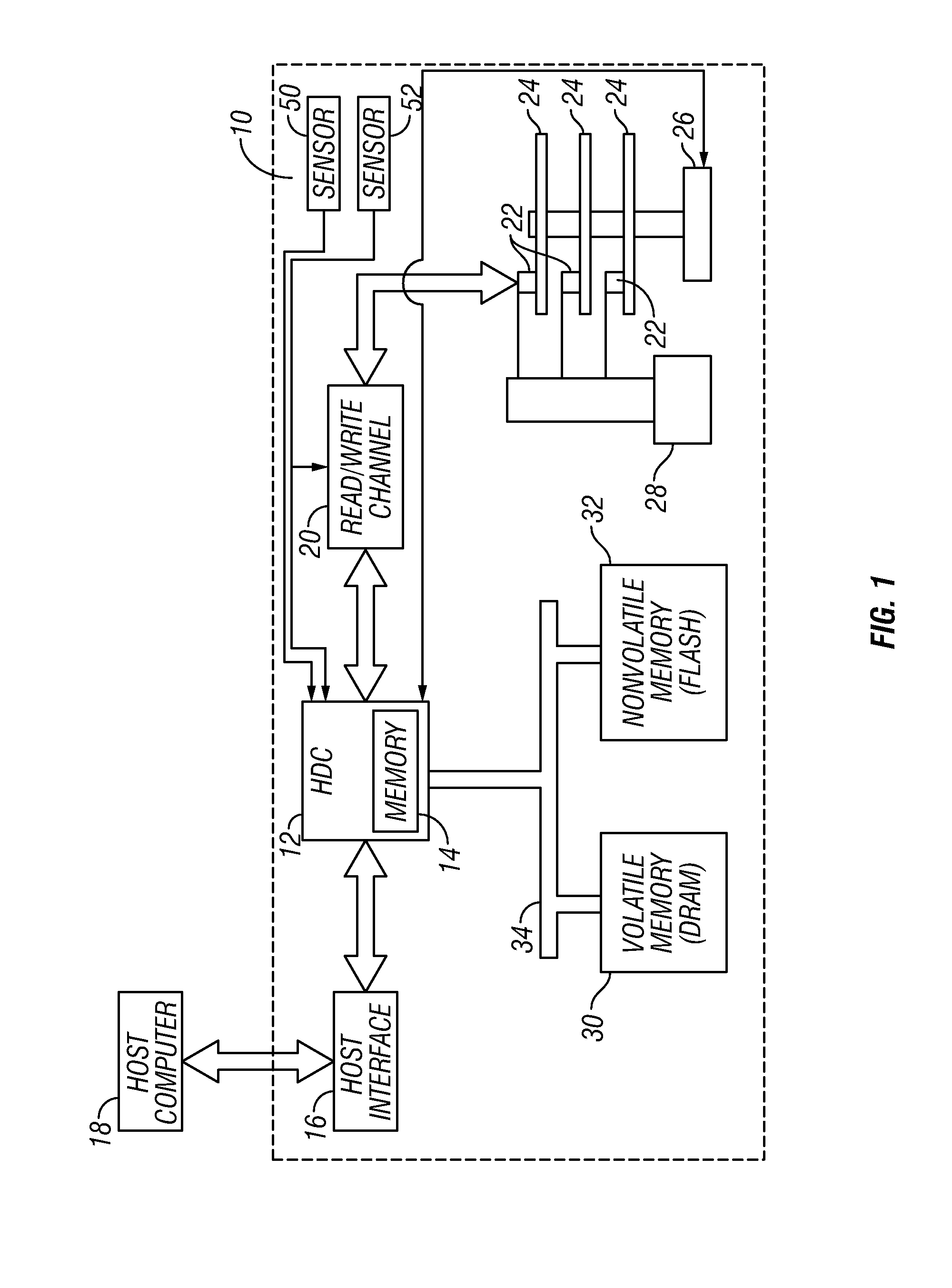

Disk drive with nonvolatile memory for storage of failure-related data

InactiveUS20080130156A1Facilitate repair and re-designLarge storage capacityInput/output to record carriersError detection/correctionDiagnostic programLogical block addressing

Owner:WESTERN DIGITAL TECH INC

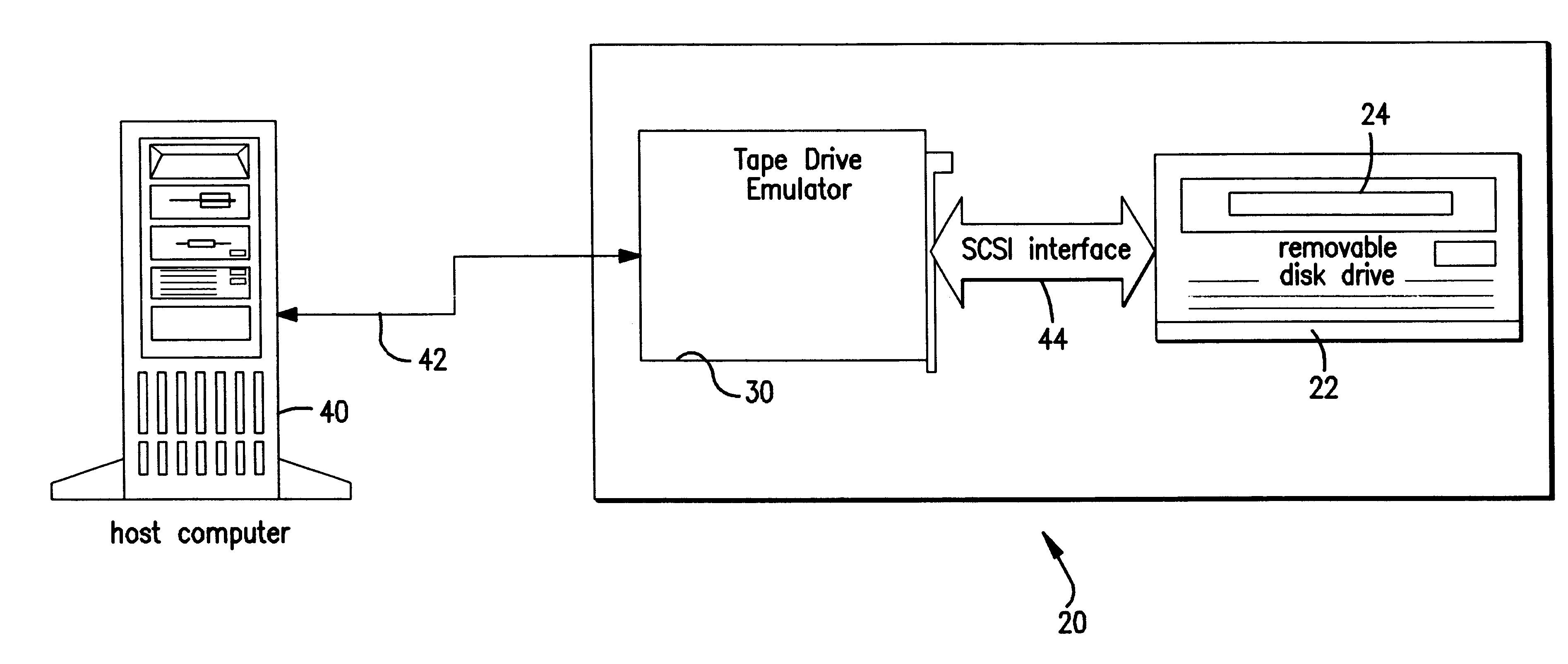

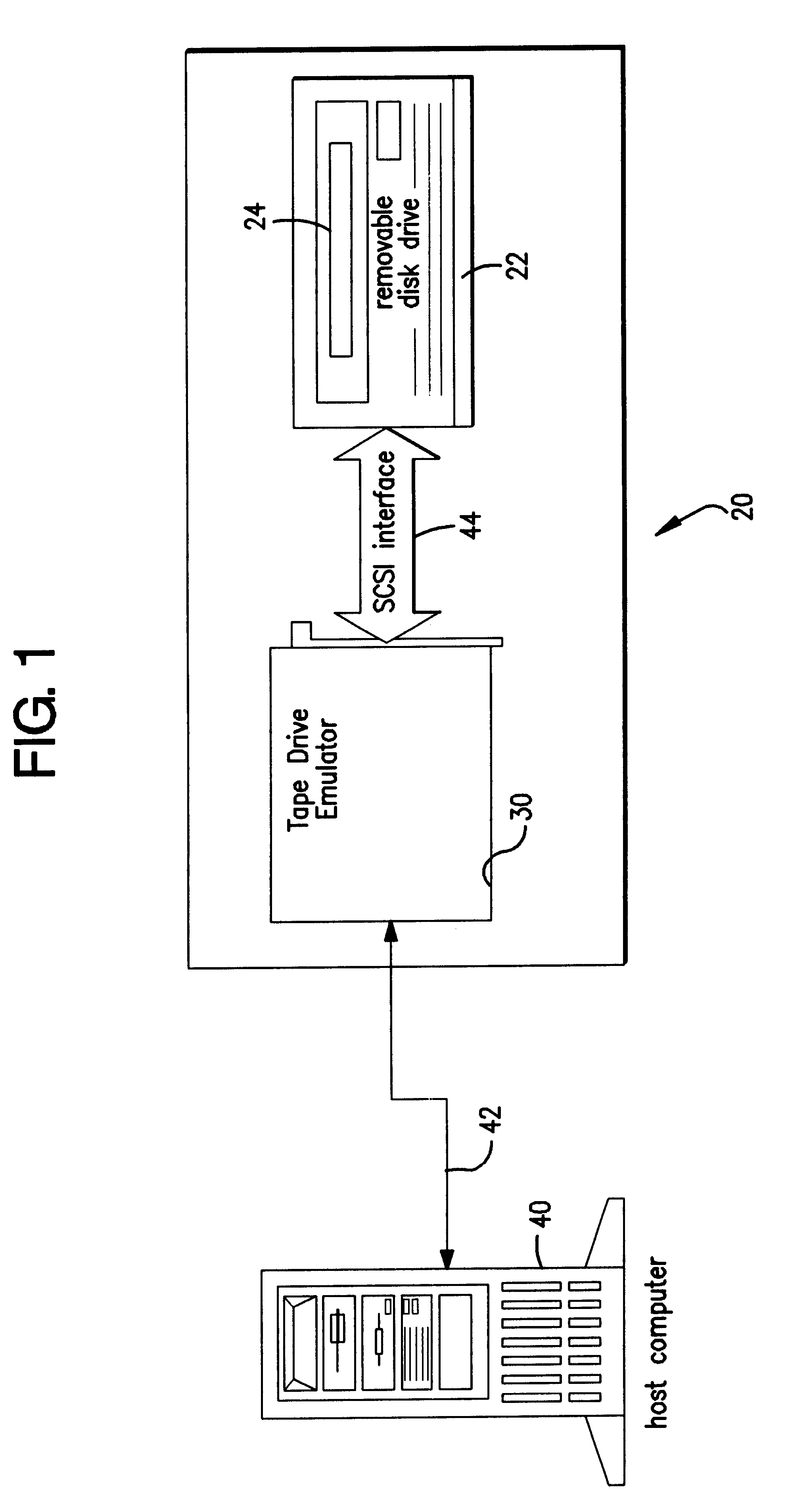

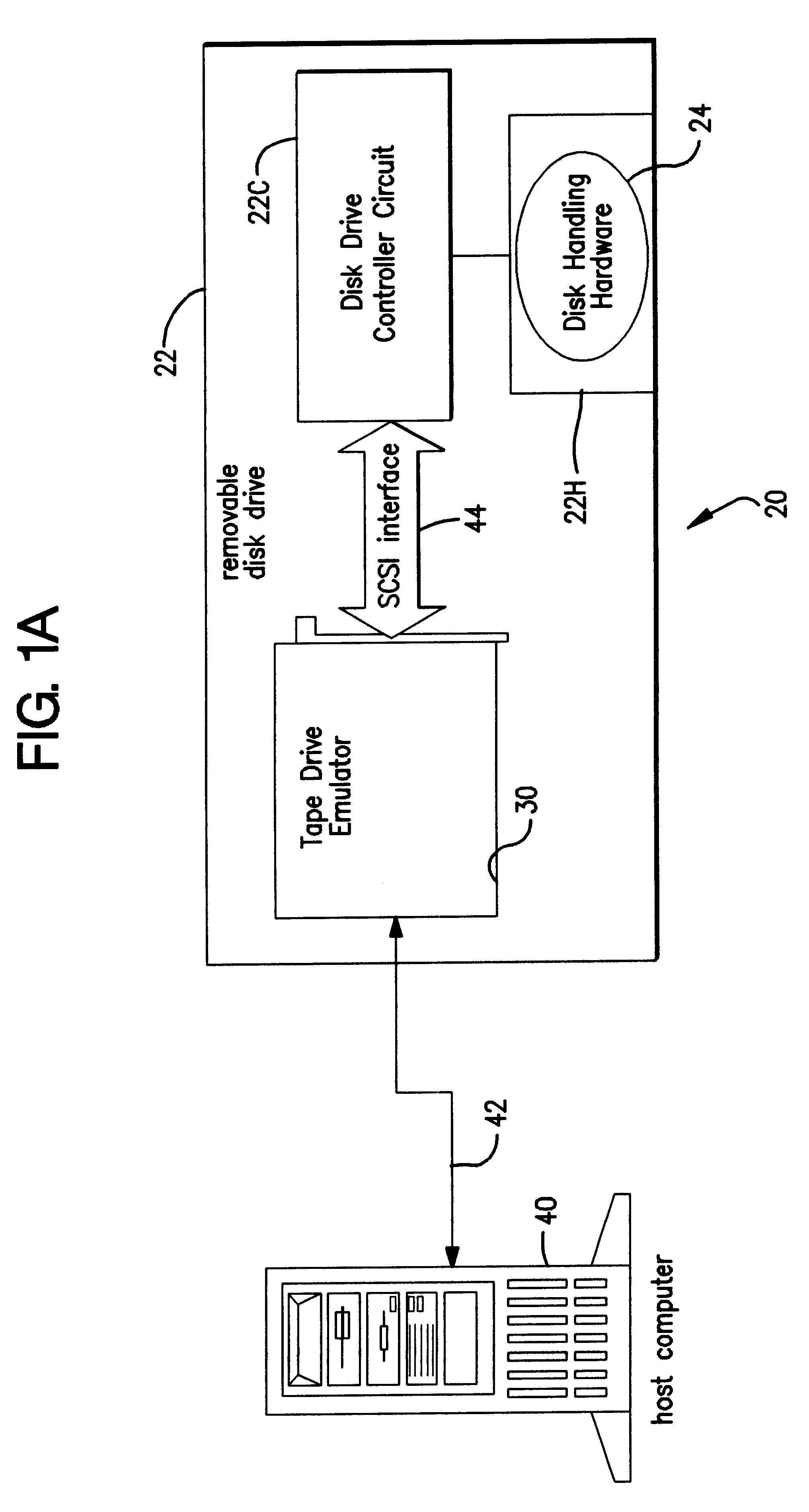

Tape drive emulation by removable disk drive and media formatted therefor

InactiveUS6389503B1Input/output to record carriersRecord information storageData integrityFrame based

A disk drive detects whether a disk inserted therein has a frame-based enhanced formatting. Disks having the frame-based enhanced formatting are readable by enhanced drives, e.g., those with the tape drive emulators. The frame-based enhanced formatting imposes on the data (1) an data organization, imperceptible to disk drive 22, for rendering the data expressible and locatable in a tape drive format, and (2) an additional degree of error correction that provides enhanced data integrity necessary for data backup / restore operations. The detection stems from a secondary formatting operation of the invention in which a format type identification is recorded on the disk. Preferably, the format type identification is recorded as one disk sector at a beginning logical block address of the disk, and forms part of a volume header frame. The volume header frame is followed by a directory comprising one or more directory frames.

Owner:TANDBERG DATA