Patents

Literature

2185results about "Data representation error detection/correction" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

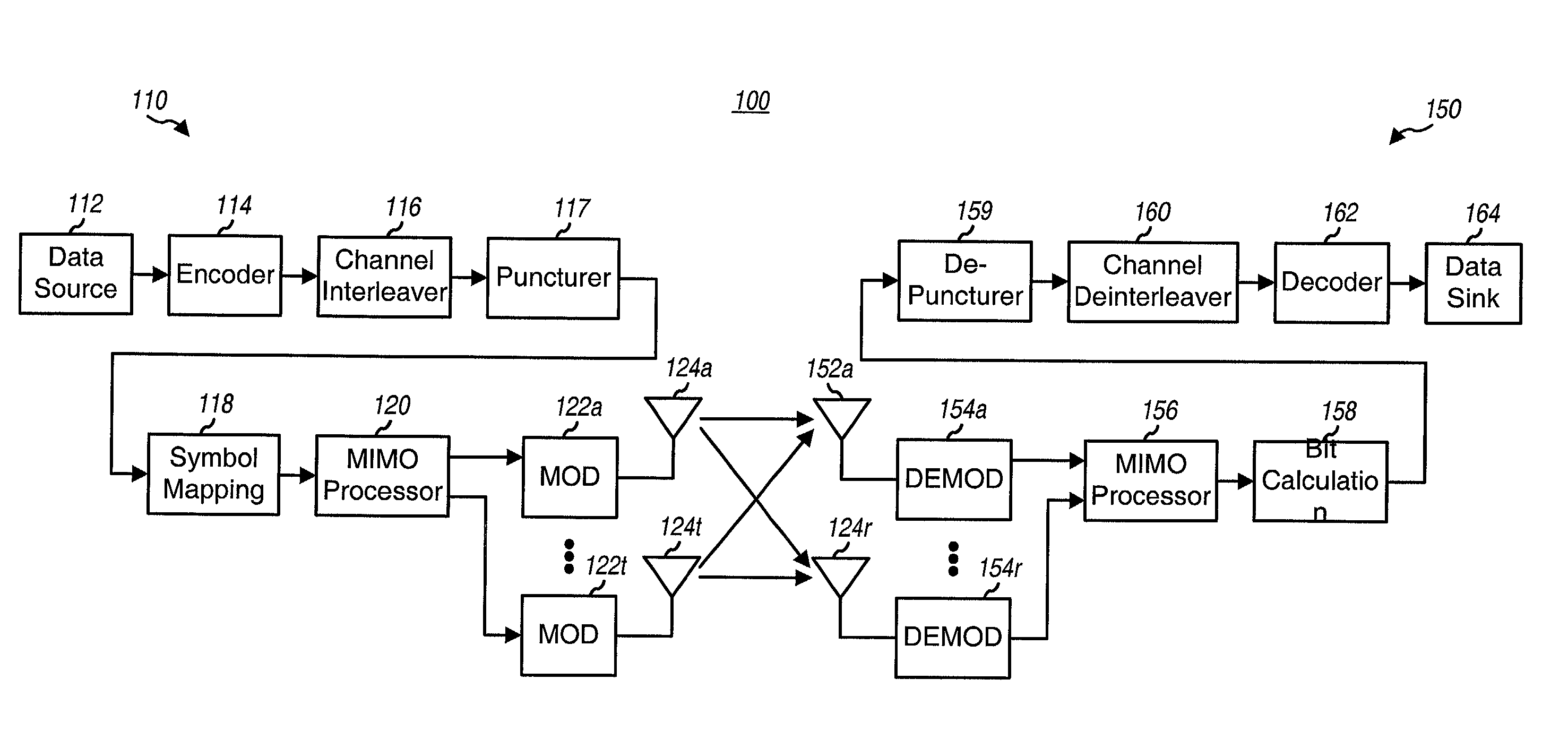

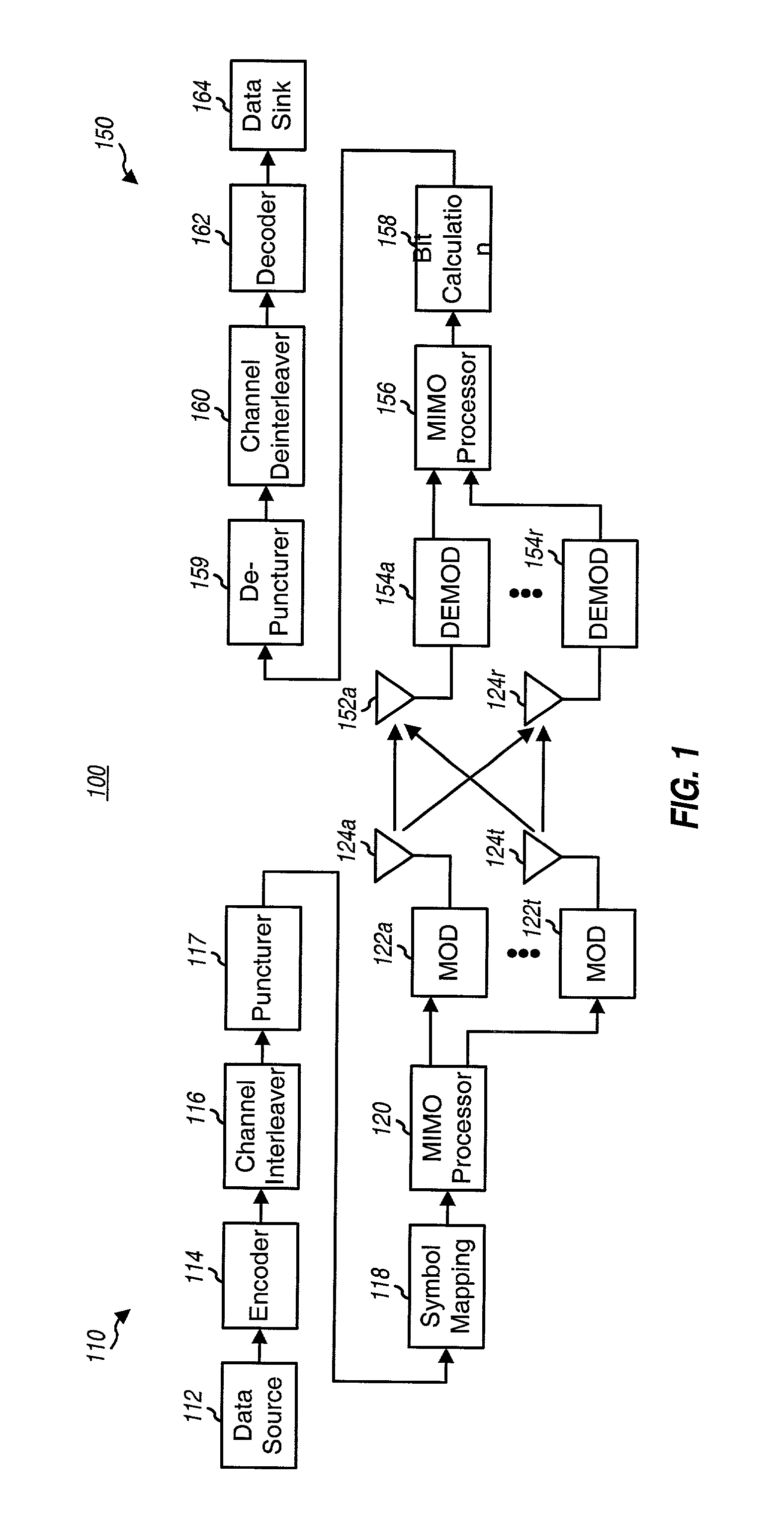

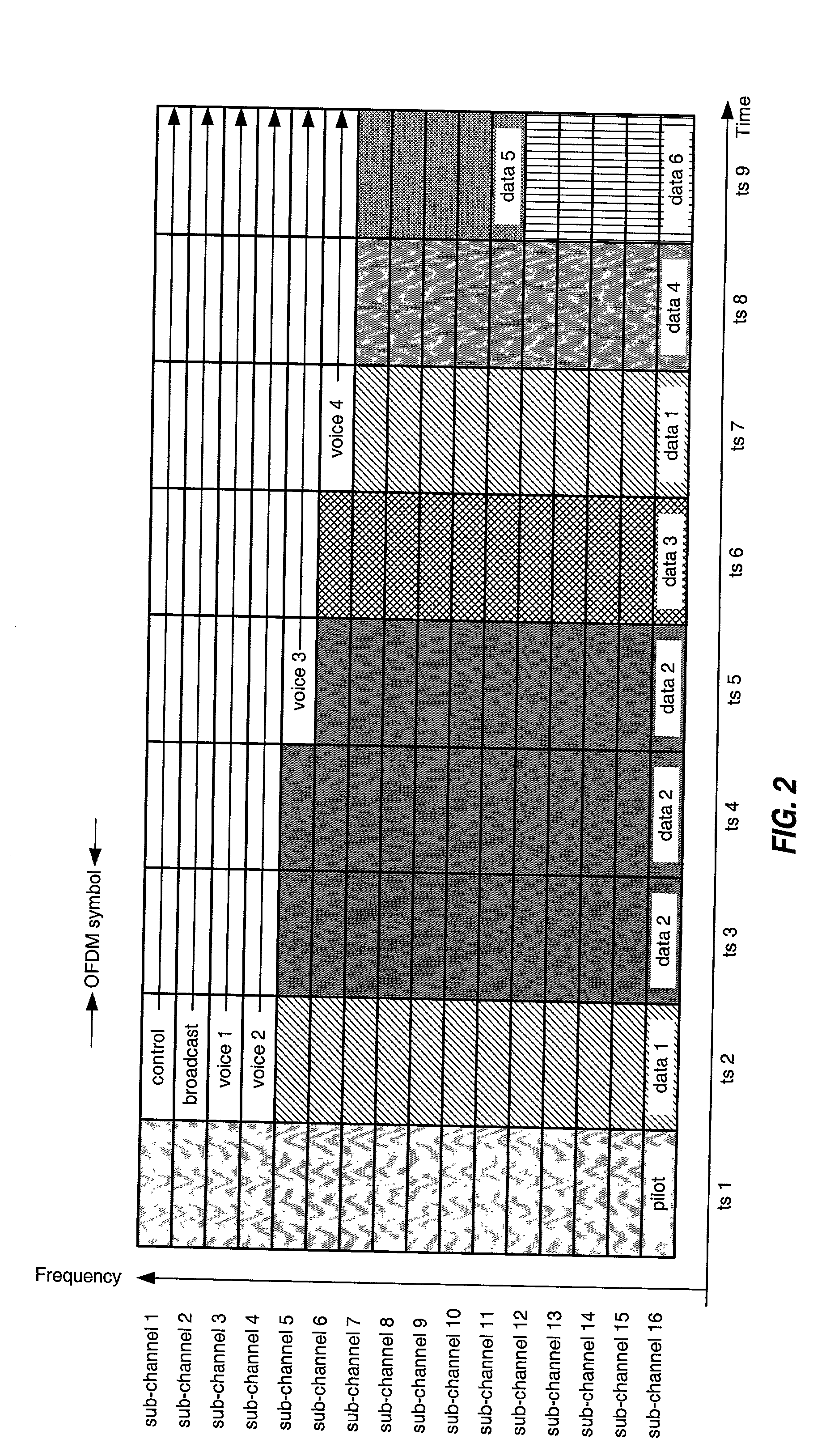

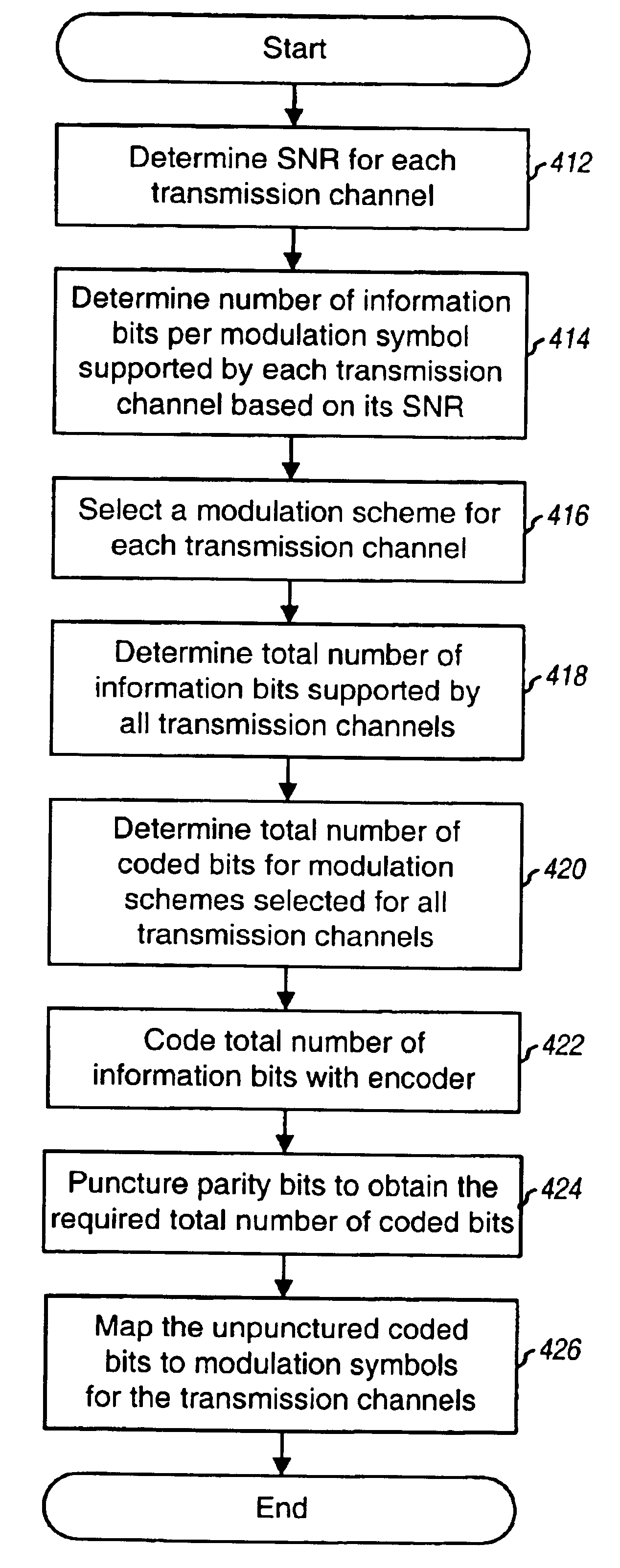

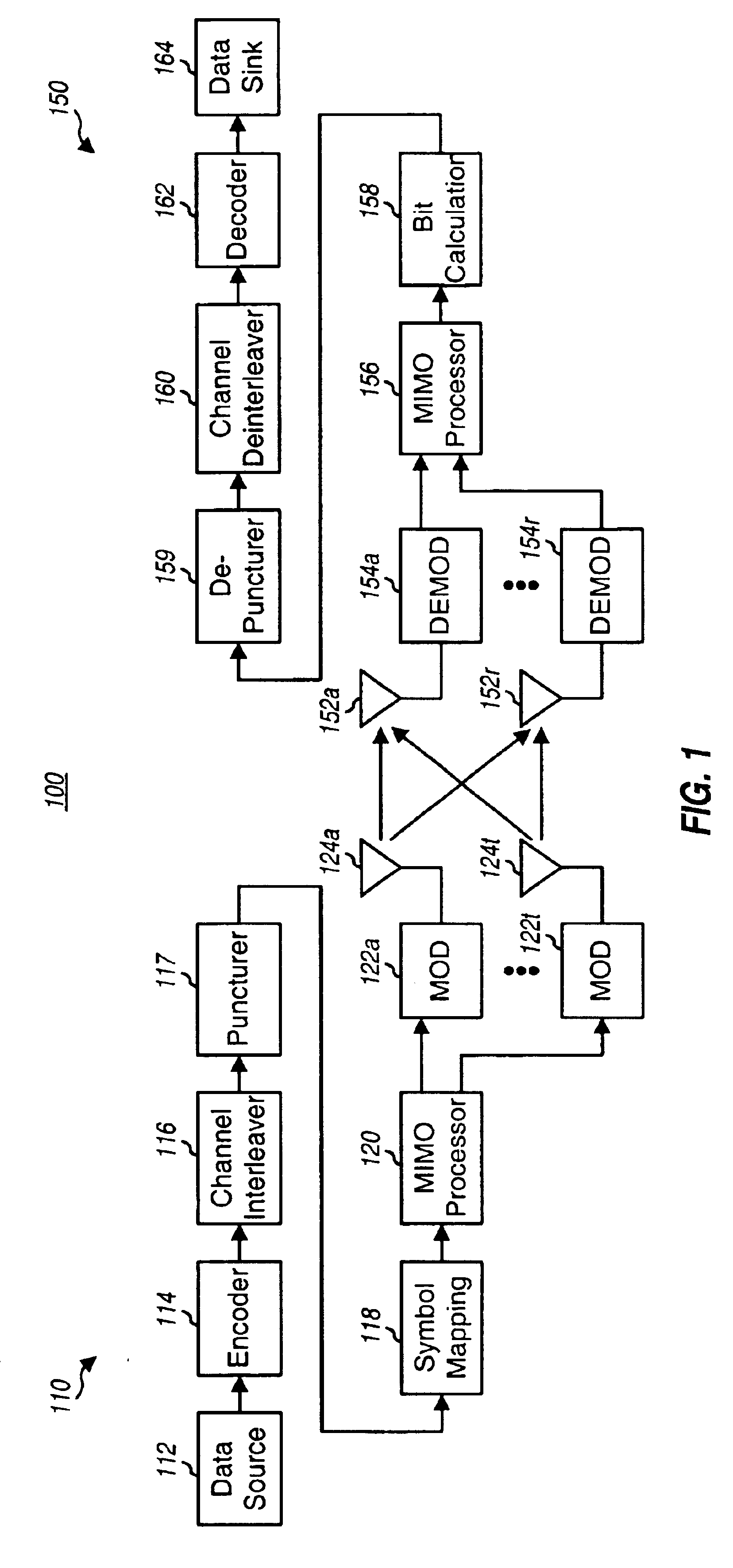

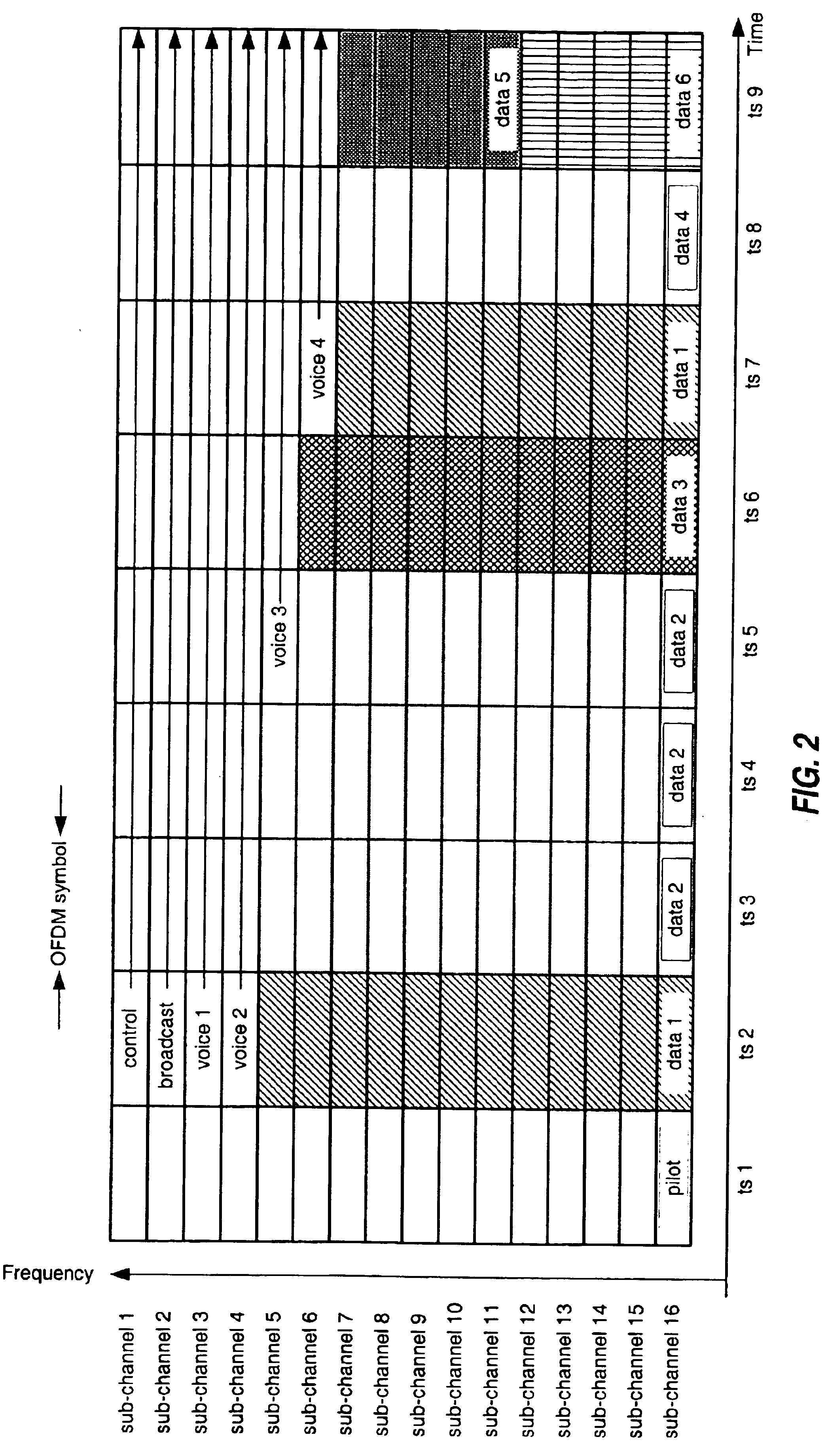

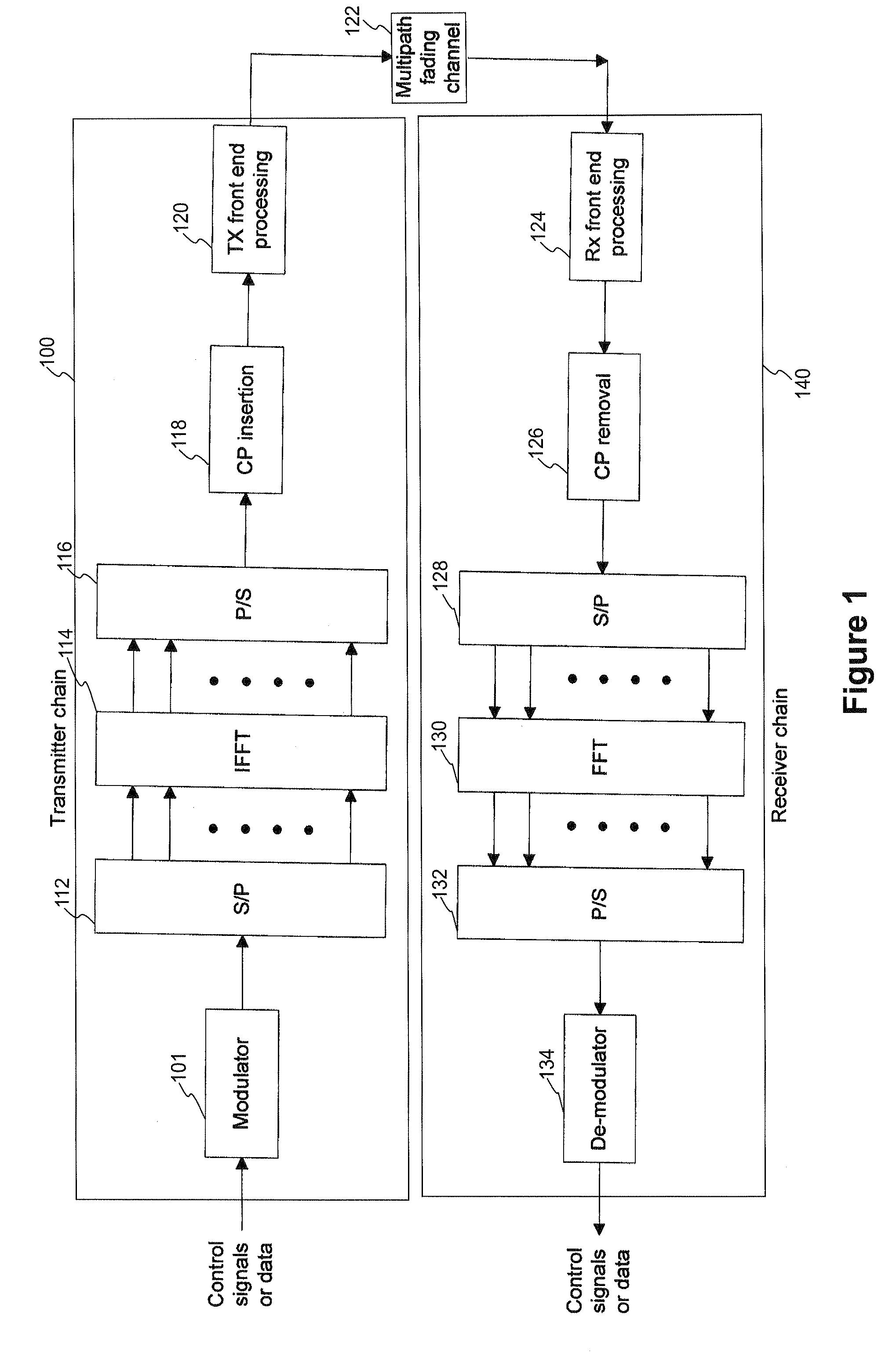

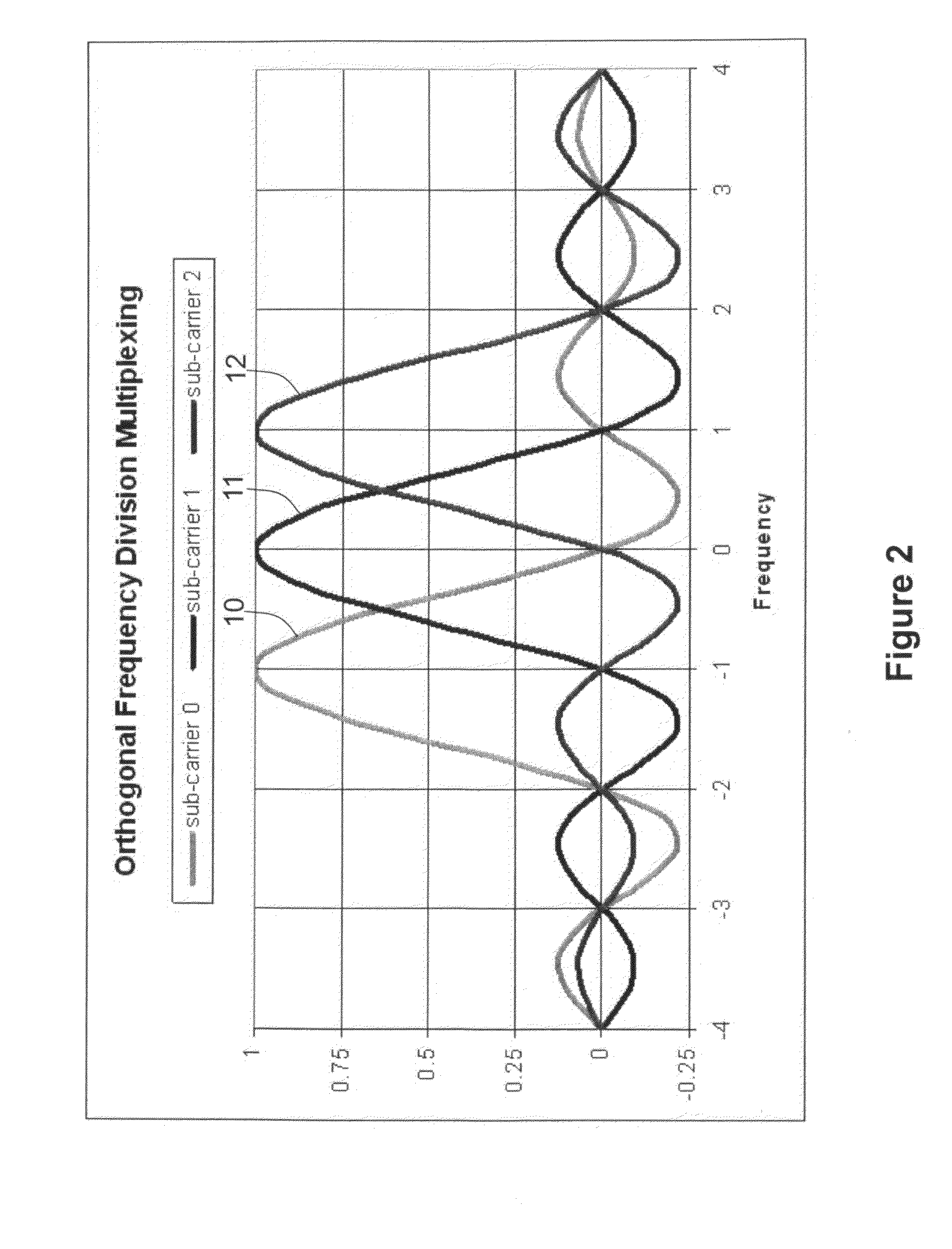

Coding scheme for a wireless communication system

InactiveUS20030043928A1High data transmission reliabilityRemove correlationData representation error detection/correctionColor television with pulse code modulationBase codePre-condition

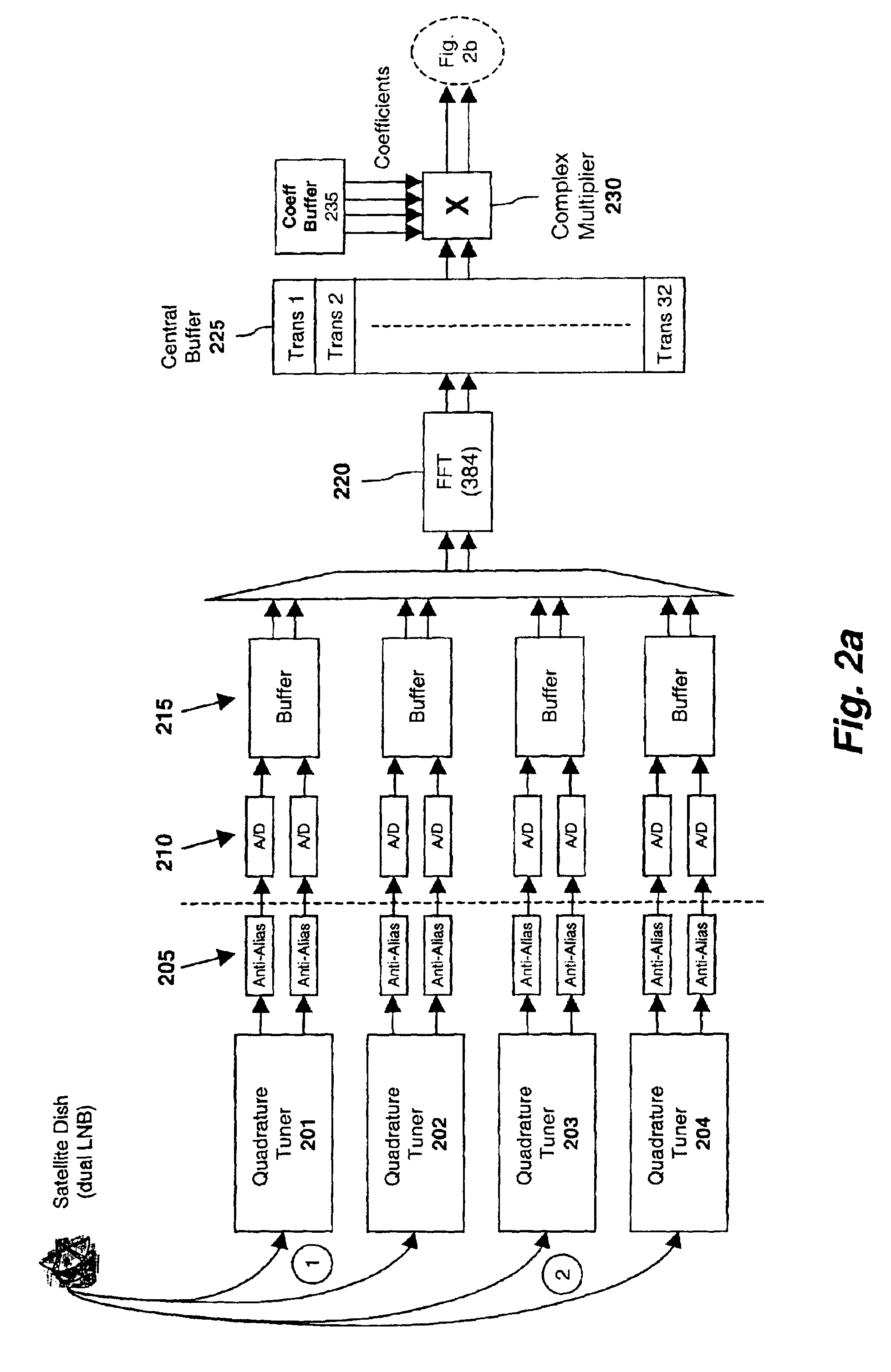

Coding techniques for a (e.g., OFDM) communication system capable of transmitting data on a number of "transmission channels" at different information bit rates based on the channels' achieved SNR. A base code is used in combination with common or variable puncturing to achieve different coding rates required by the transmission channels. The data (i.e., information bits) for a data transmission is encoded with the base code, and the coded bits for each channel (or group of channels with the similar transmission capabilities) are punctured to achieve the required coding rate. The coded bits may be interleaved (e.g., to combat fading and remove correlation between coded bits in each modulation symbol) prior to puncturing. The unpunctured coded bits are grouped into non-binary symbols and mapped to modulation symbols (e.g., using Gray mapping). The modulation symbol may be "pre-conditioned" and prior to transmission.

Owner:QUALCOMM INC

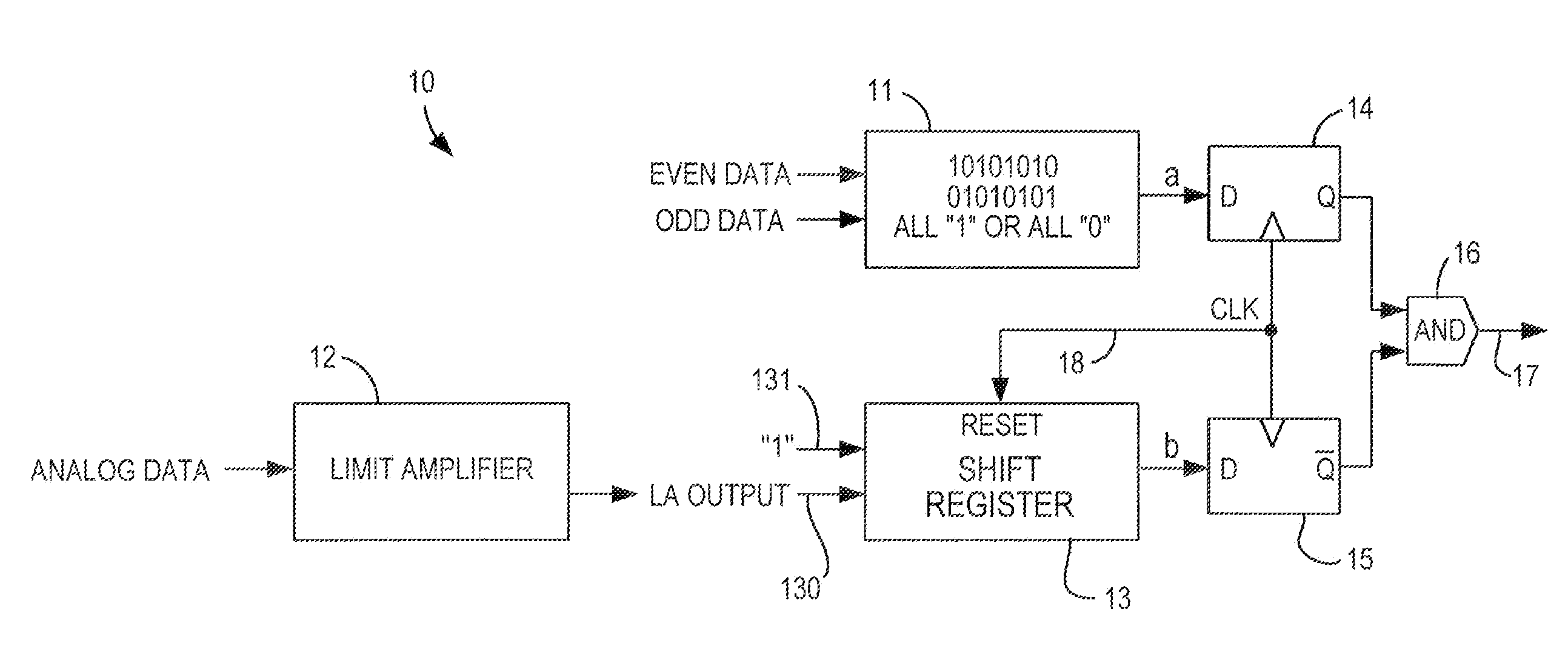

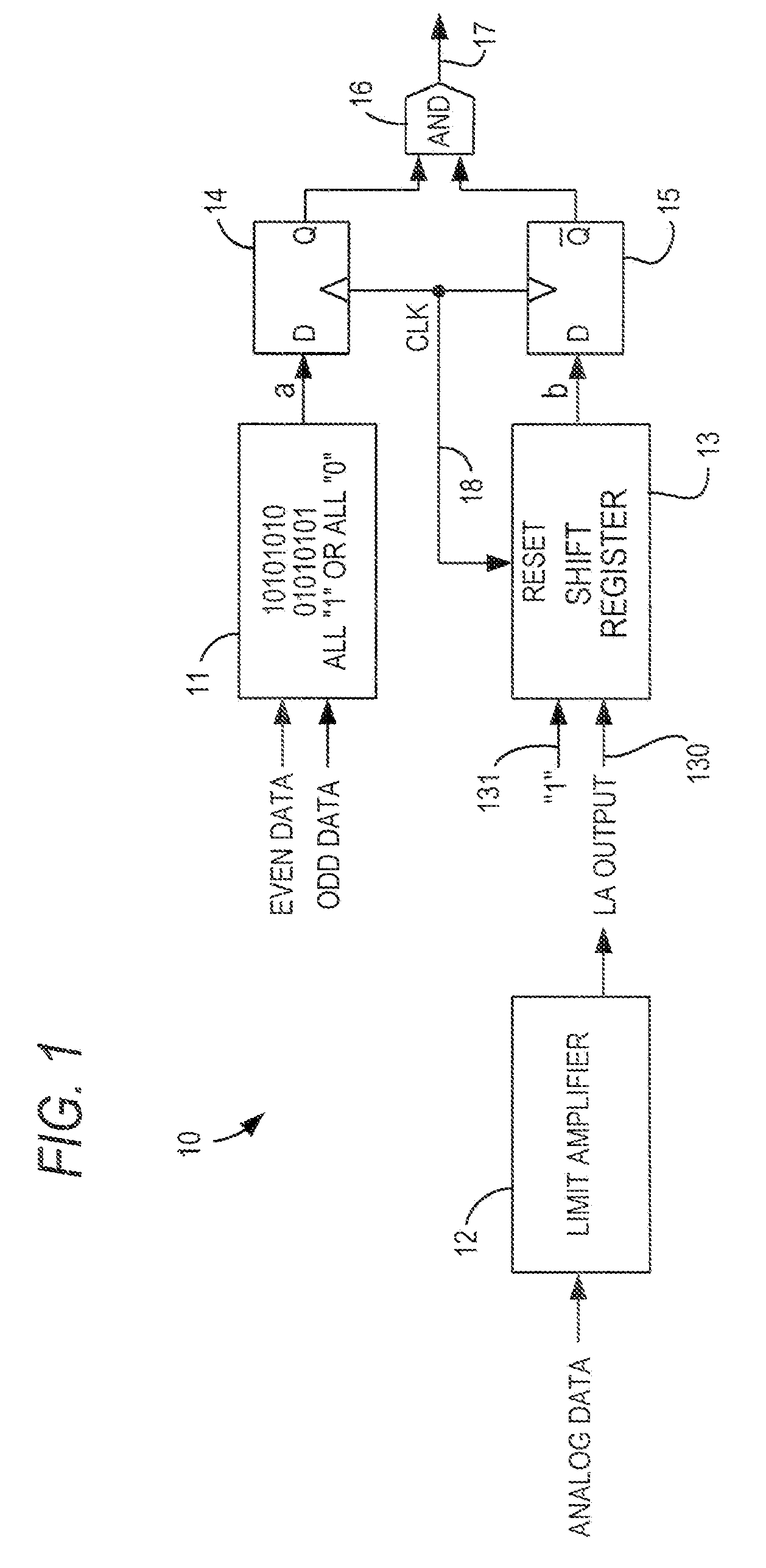

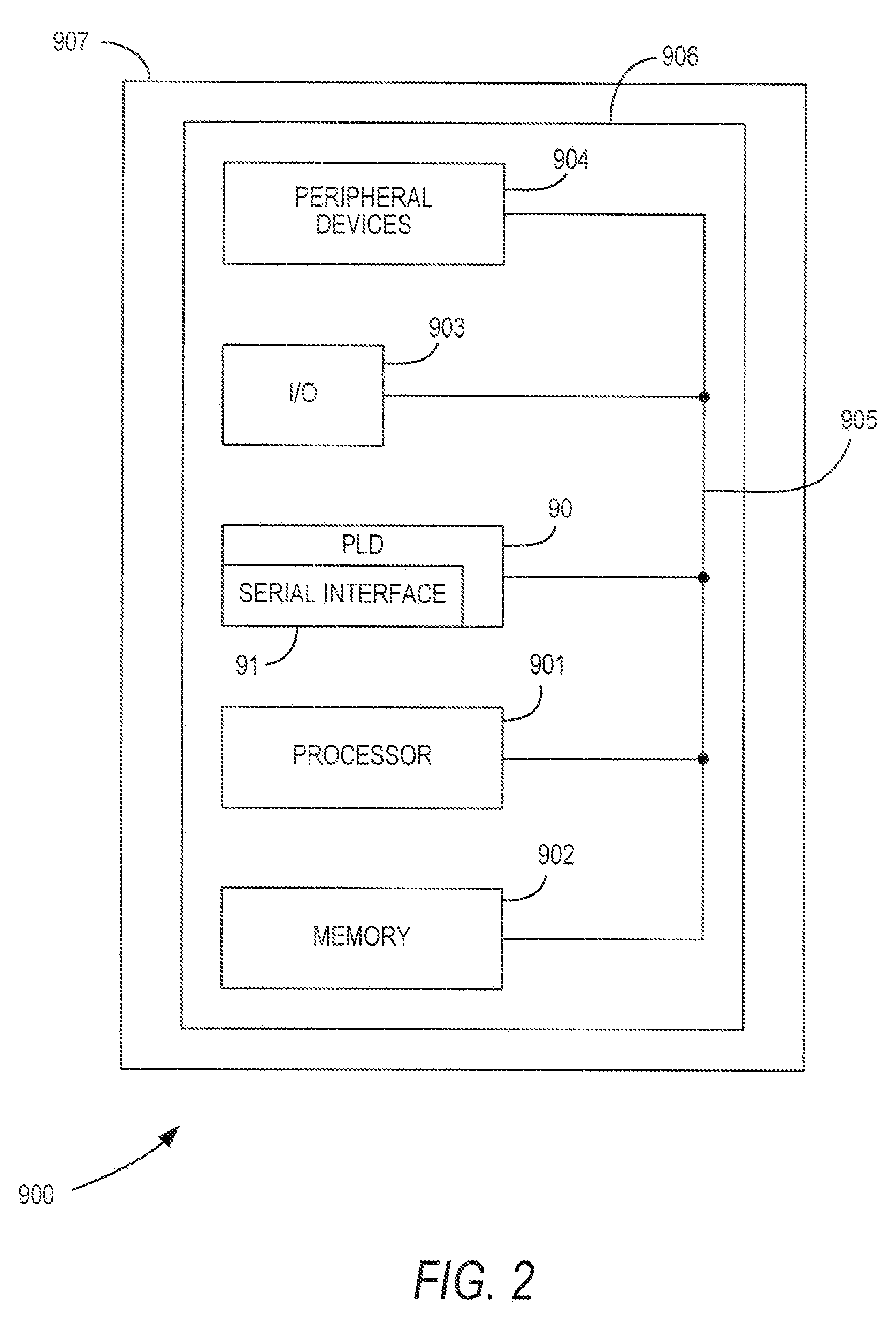

Signal loss detector for high-speed serial interface of a programmable logic device

InactiveUS7996749B2Multiple-port networksData representation error detection/correctionPattern matchingProgrammable logic device

Owner:ALTERA CORP

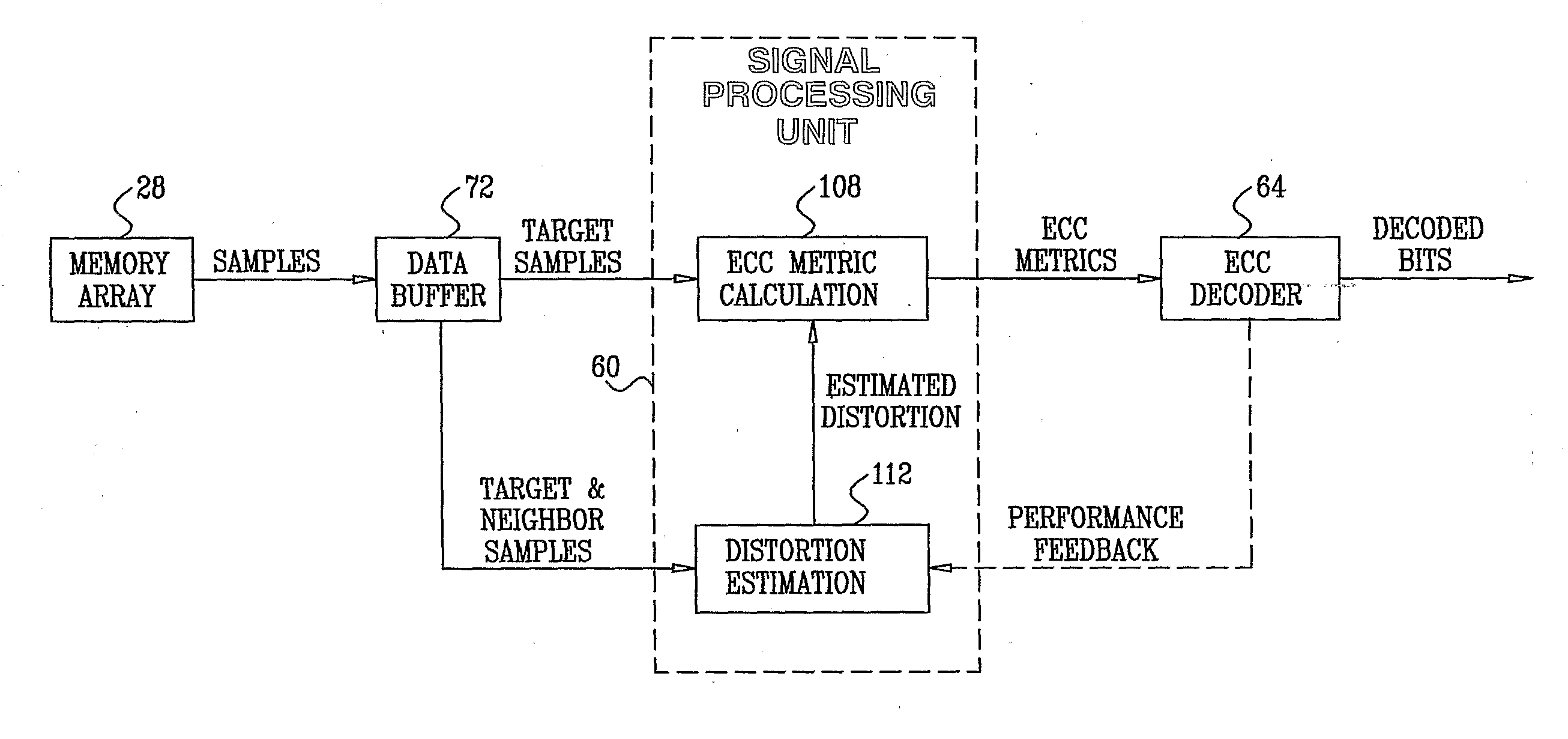

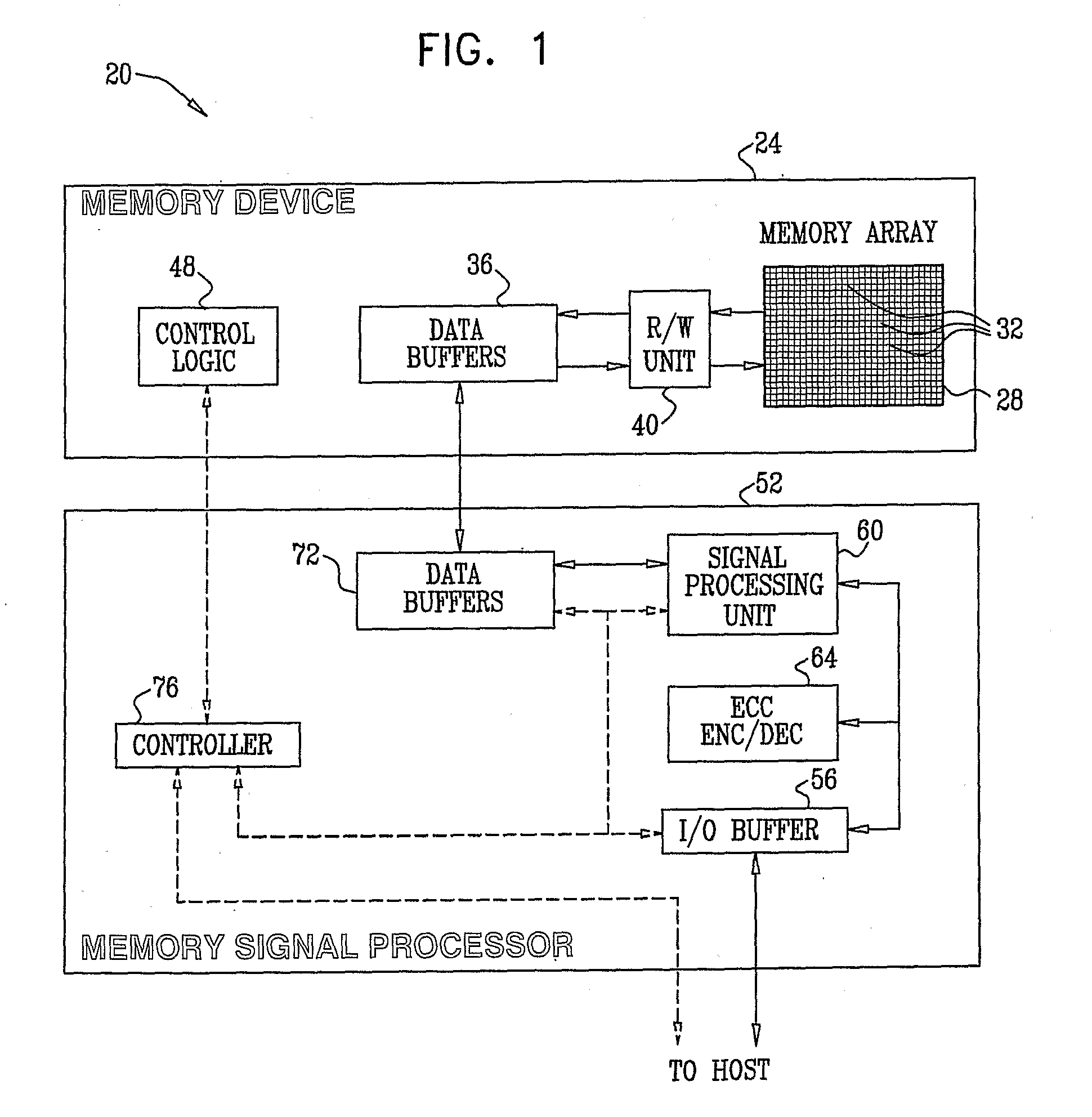

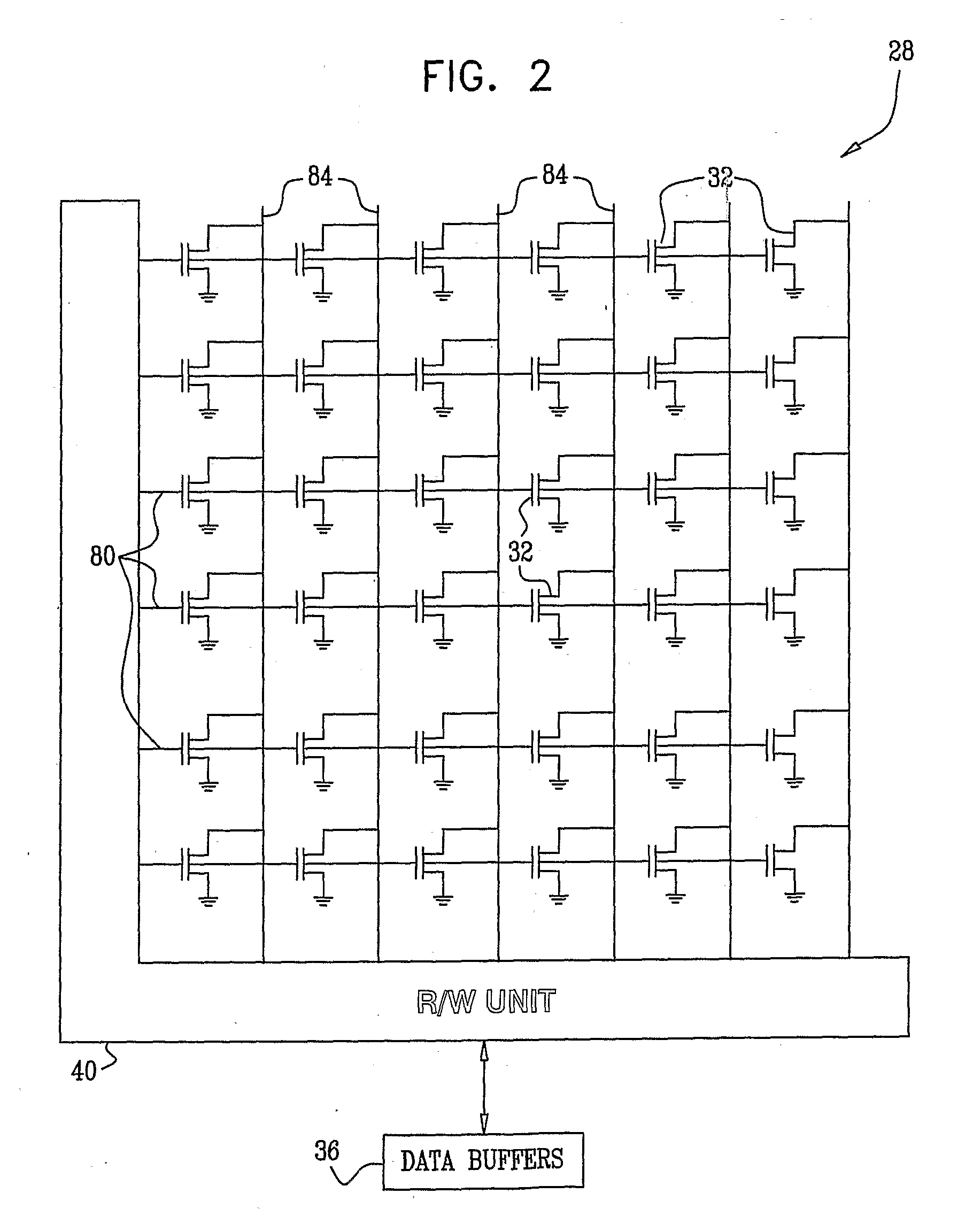

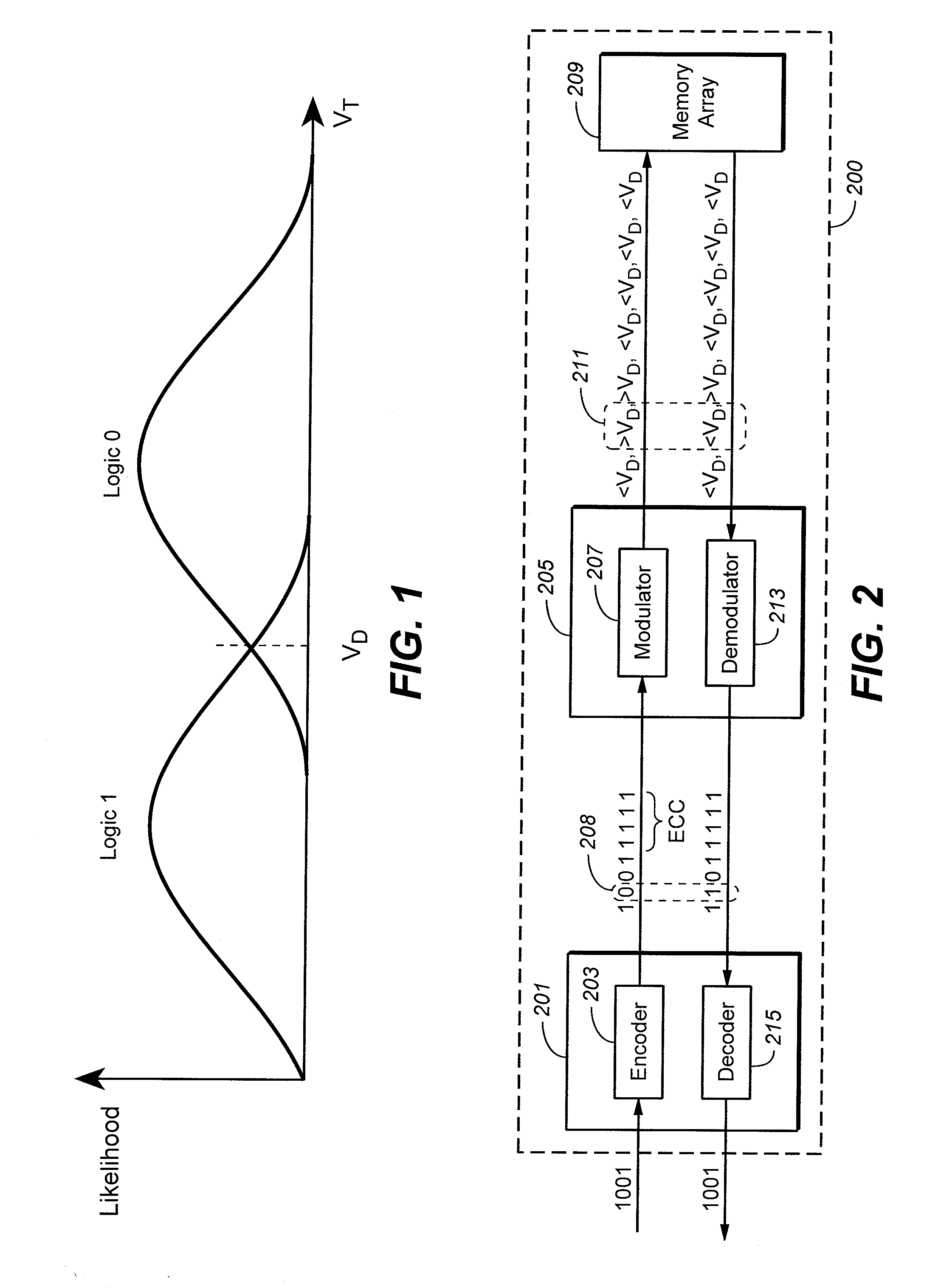

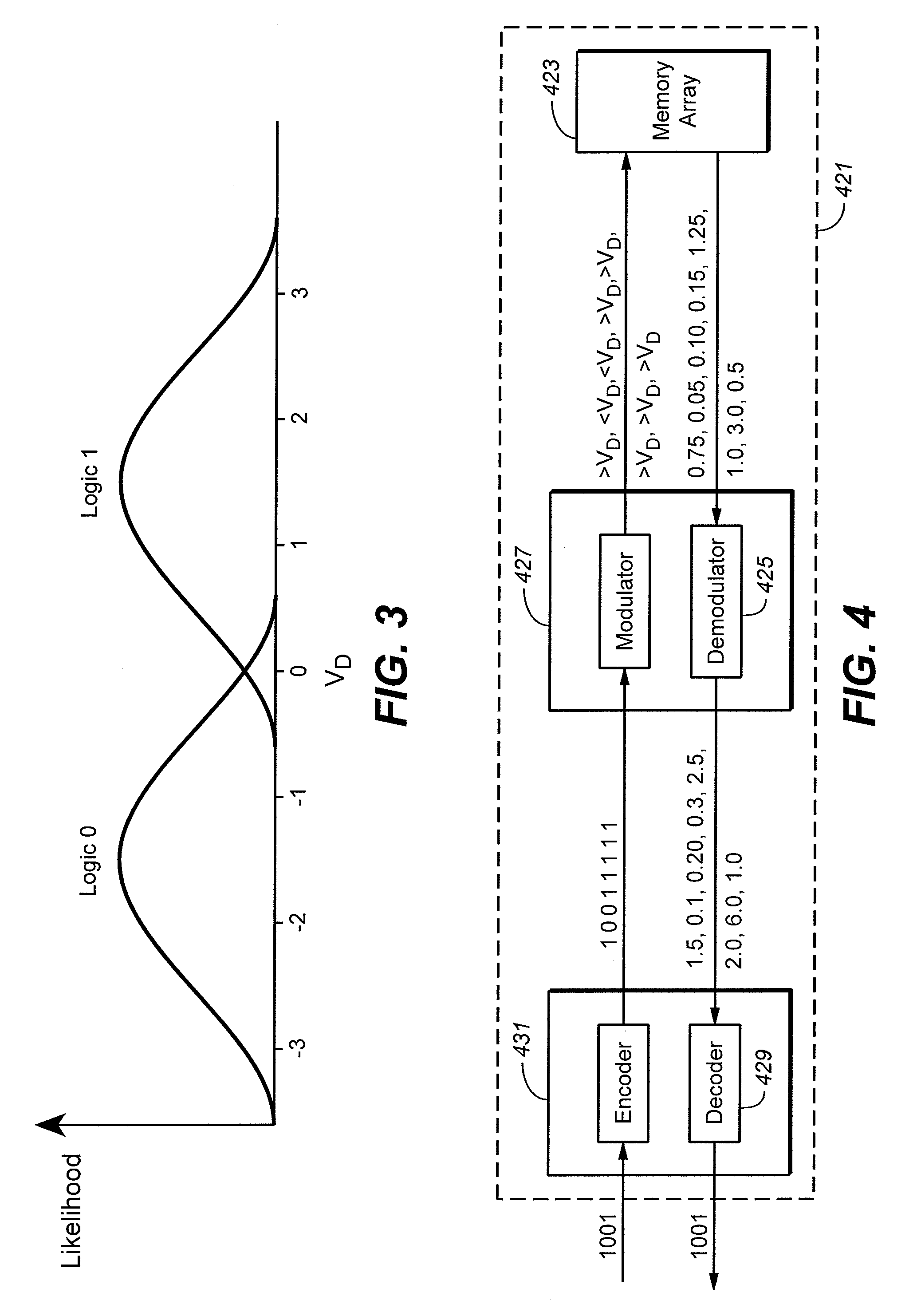

Combined distortion estimation and error correction coding for memory devices

ActiveUS20090024905A1Improve performanceData representation error detection/correctionError detection/correctionCalculation errorDistortion

A method for operating a memory device (24) includes encoding data using an Error Correction Code (ECC) and storing the encoded data as first analog values in respective analog memory cells (32) of the memory device. After storing the encoded data, second analog values are read from the respective memory cells of the memory device in which the encoded data were stored. At least some of the second analog values differ from the respective first analog values. A distortion that is present in the second analog values is estimated. Error correction metrics are computed with respect to the second analog values responsively to the estimated distortion. The second analog values are processed using the error correction metrics in an ECC decoding process, so as to reconstruct the data.

Owner:APPLE INC

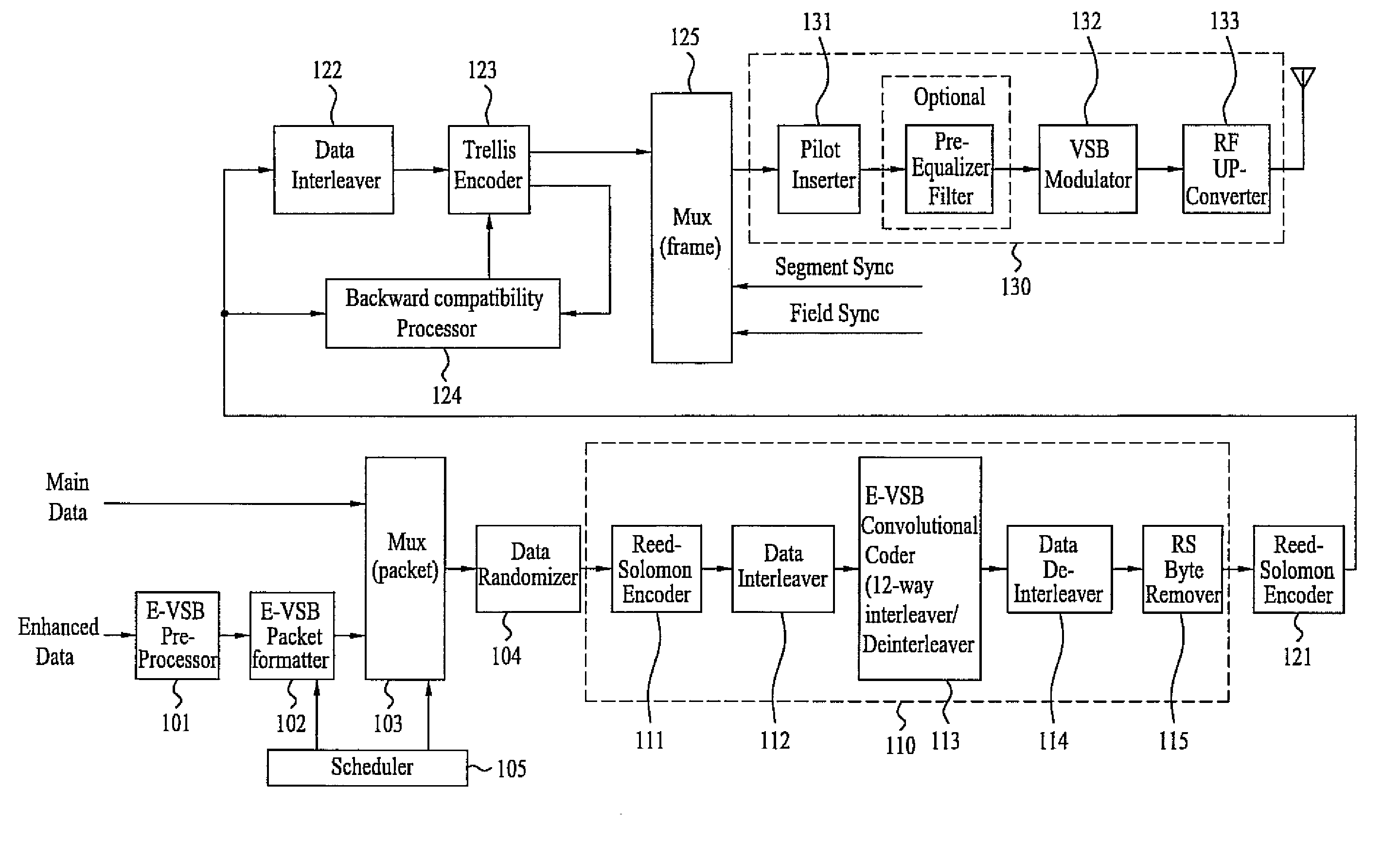

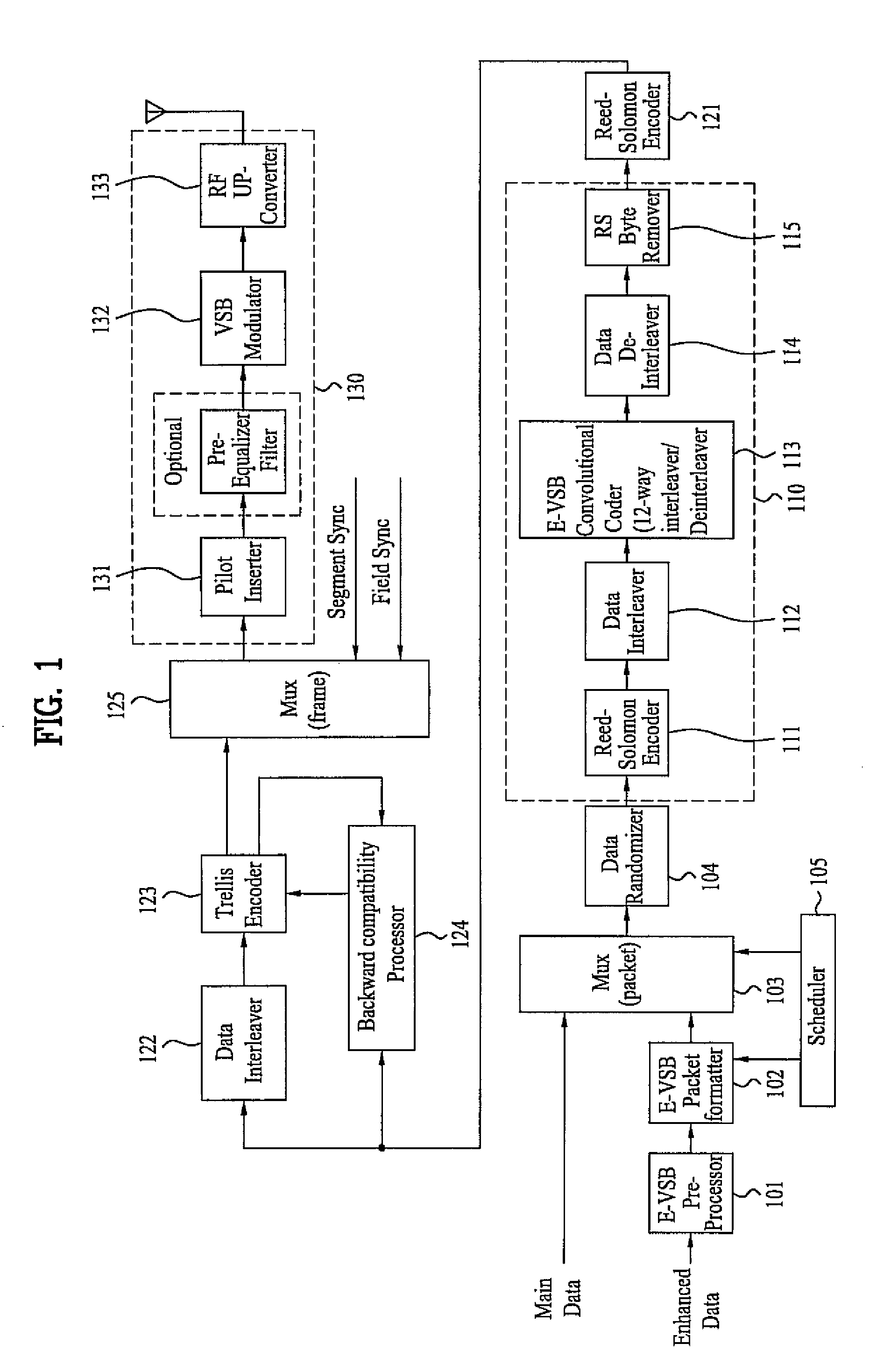

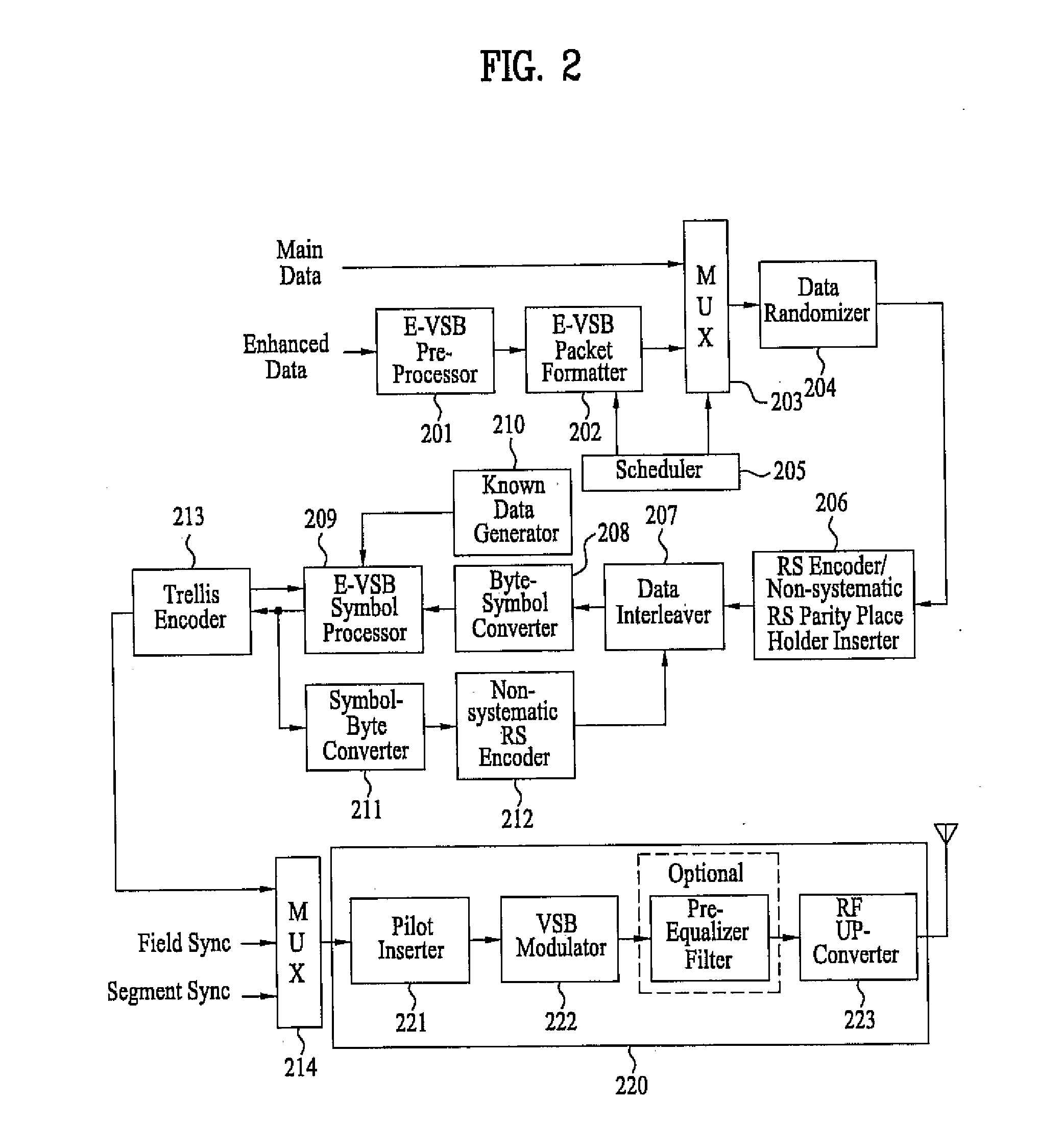

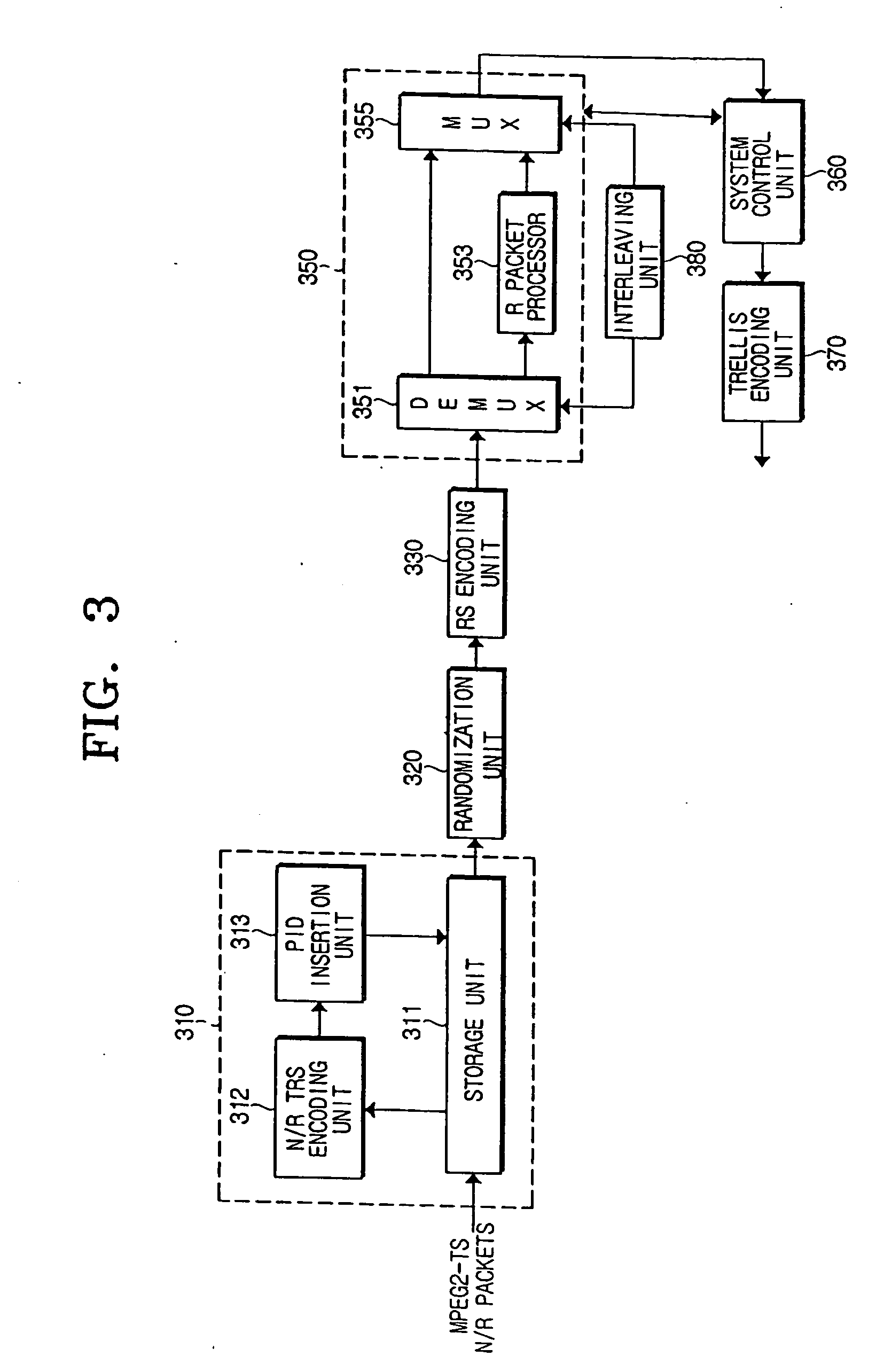

Digital television transmitter/receiver and method of processing data in digital television transmitter/receiver

InactiveUS20070121681A1Robust against noiseTransmit dataData representation error detection/correctionPulse modulation television signal transmissionTime informationMultiplexing

A digital television (DTV) transmitter and a method of processing data in the DTV transmitter / receiver are disclosed. In the DTV transmitter, a pre-processor pre-processes the enhanced data by coding the enhanced data for forward error correction (FEC) and expanding the FEC-coded data. A packet formatter generates one or more groups of enhanced data packets, each enhanced data packet including the pre-processed enhanced data and known data, wherein the data formatter adds burst time information into each group of enhanced data packets. And, a packet multiplexer generates at least one burst of enhanced data by multiplexing the one or more groups of enhanced data packets with at least one main data packet including the main data, each burst of enhanced data including at least one group of enhanced data packets.

Owner:LG ELECTRONICS INC

Coding scheme for a wireless communication system

InactiveUS6961388B2Data representation error detection/correctionColor television with pulse code modulationBase codePre-condition

Coding techniques for a (e.g., OFDM) communication system capable of transmitting data on a number of “transmission channels” at different information bit rates based on the channels' achieved SNR. A base code is used in combination with common or variable puncturing to achieve different coding rates required by the transmission channels. The data (i.e., information bits) for a data transmission is encoded with the base code, and the coded bits for each channel (or group of channels with the similar transmission capabilities) are punctured to achieve the required coding rate. The coded bits may be interleaved (e.g., to combat fading and remove correlation between coded bits in each modulation symbol) prior to puncturing. The unpunctured coded bits are grouped into non-binary symbols and mapped to modulation symbols (e.g., using Gray mapping). The modulation symbol may be “pre-conditioned” and prior to transmission.

Owner:QUALCOMM INC

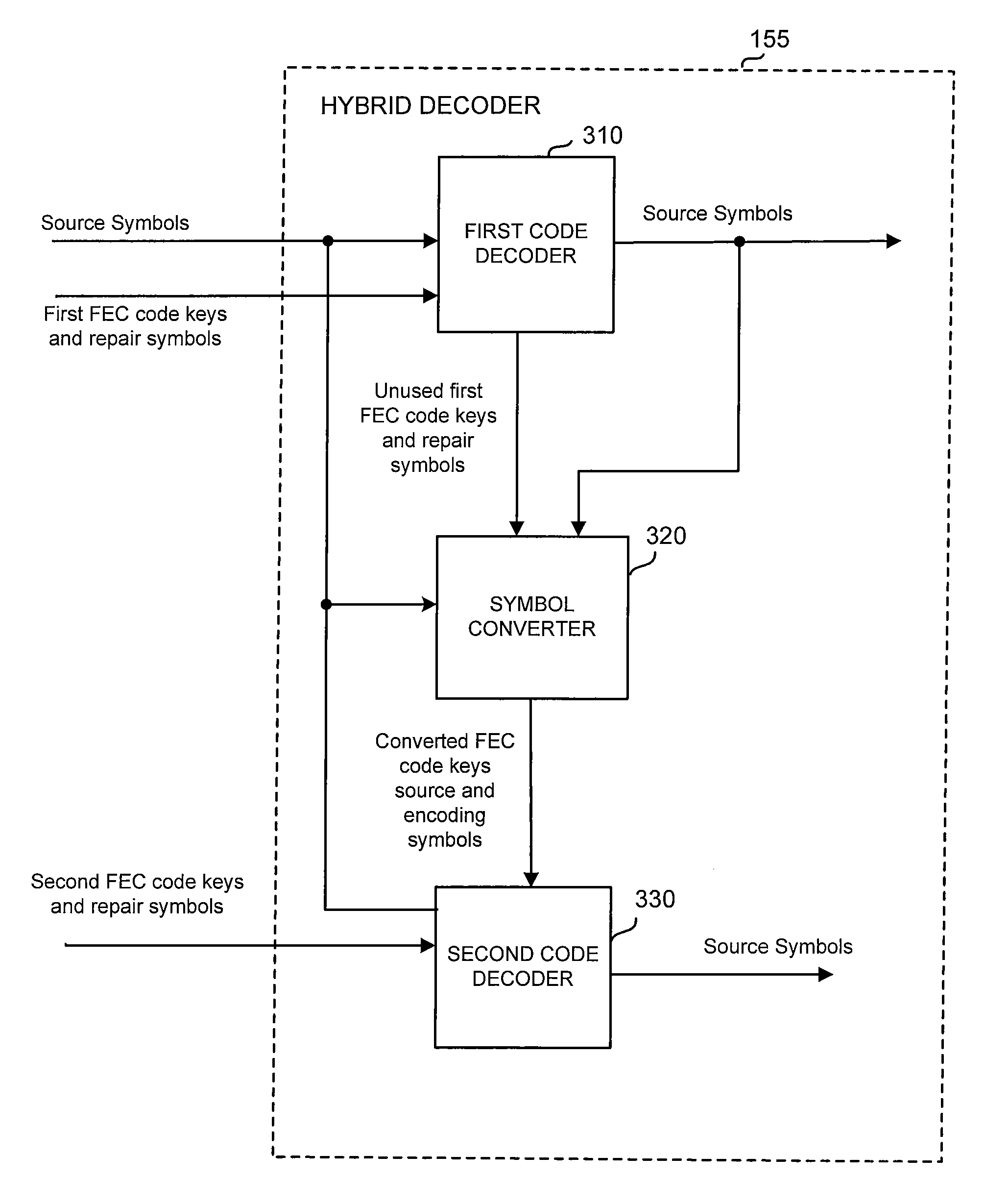

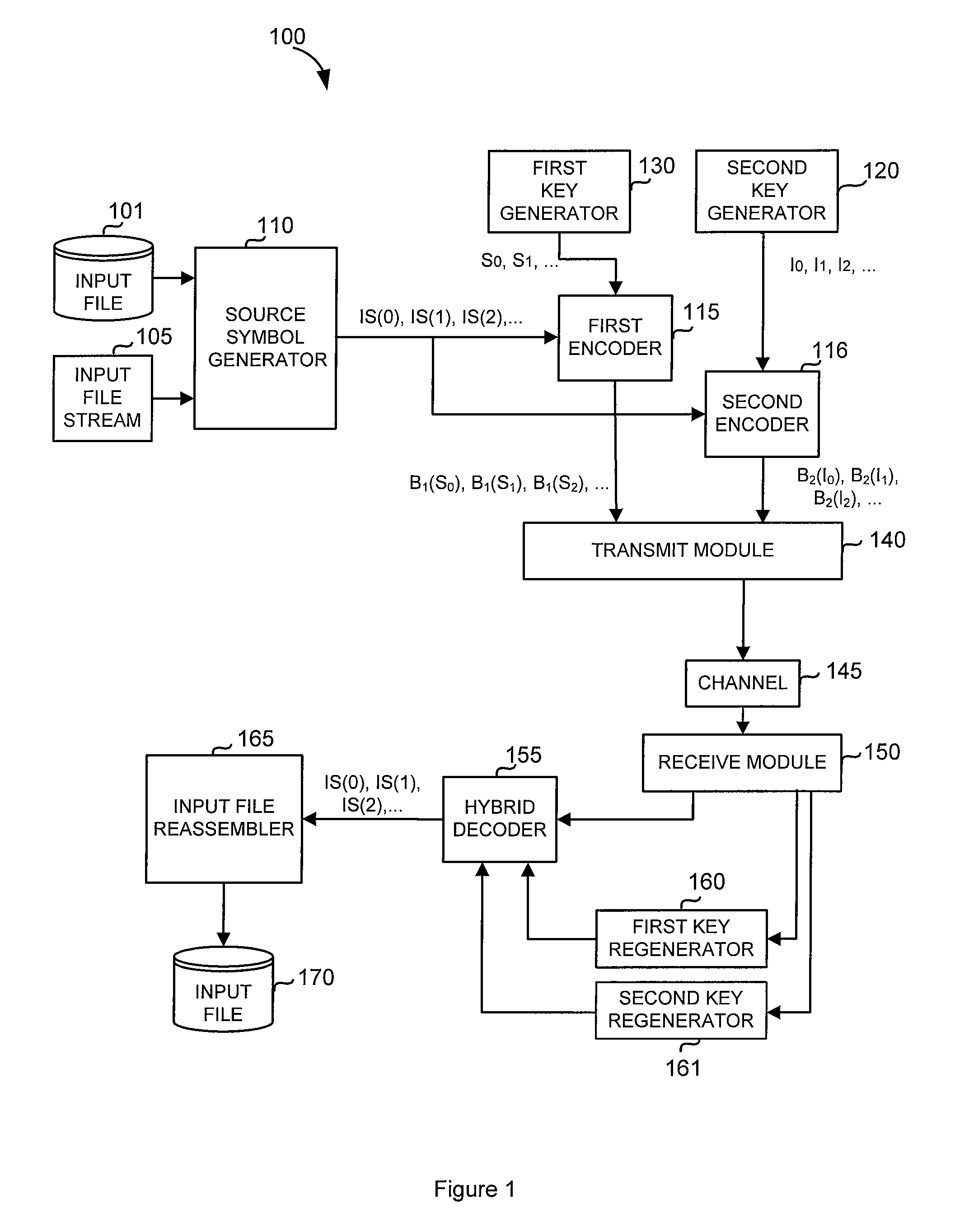

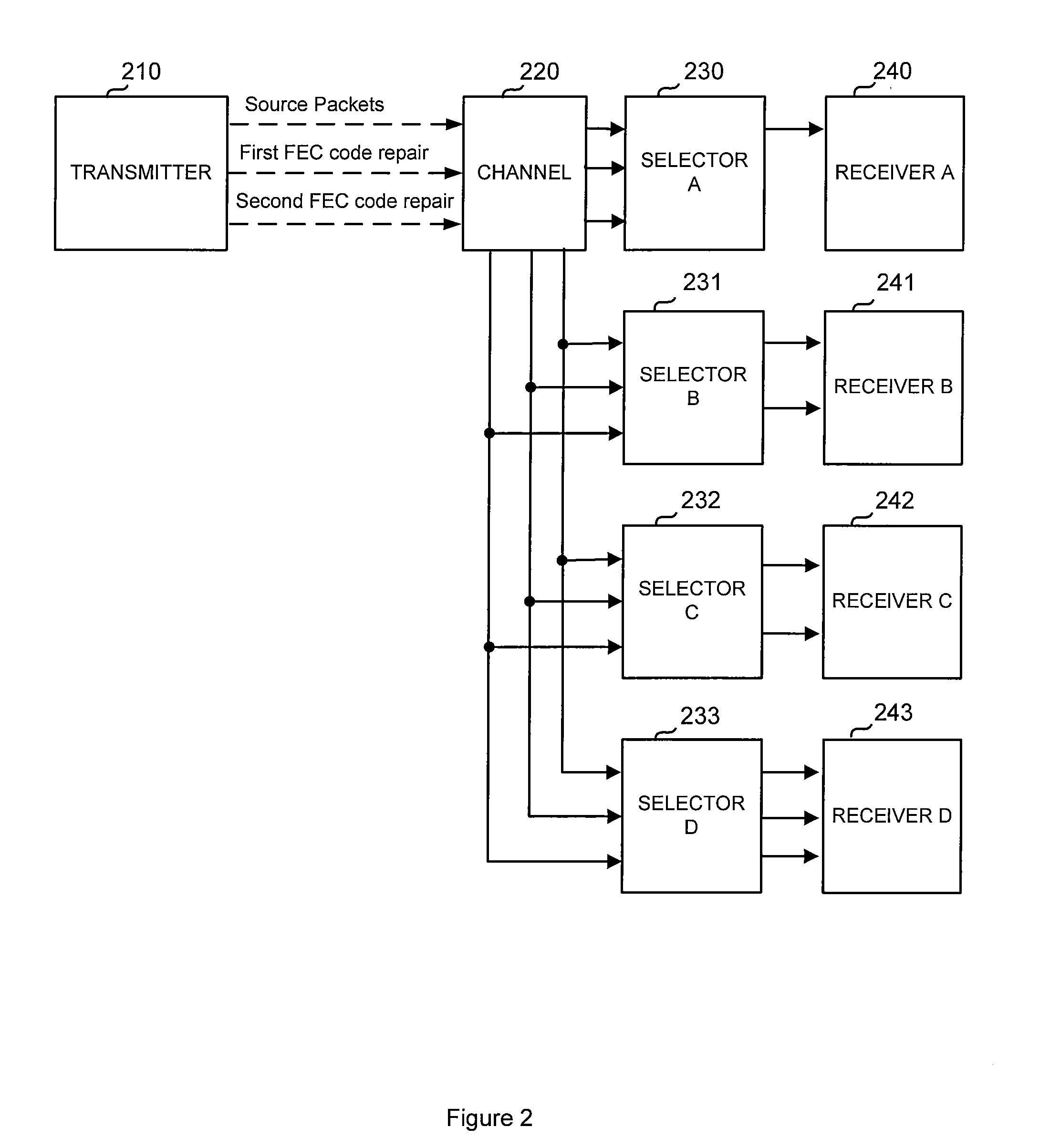

Code generator and decoder for communications systems operating using hybrid codes to allow for multiple efficient users of the communications systems

InactiveUS7971129B2Error protectionImprove errorData representation error detection/correctionError preventionComputer hardwareCommunications system

Owner:QUALCOMM INC

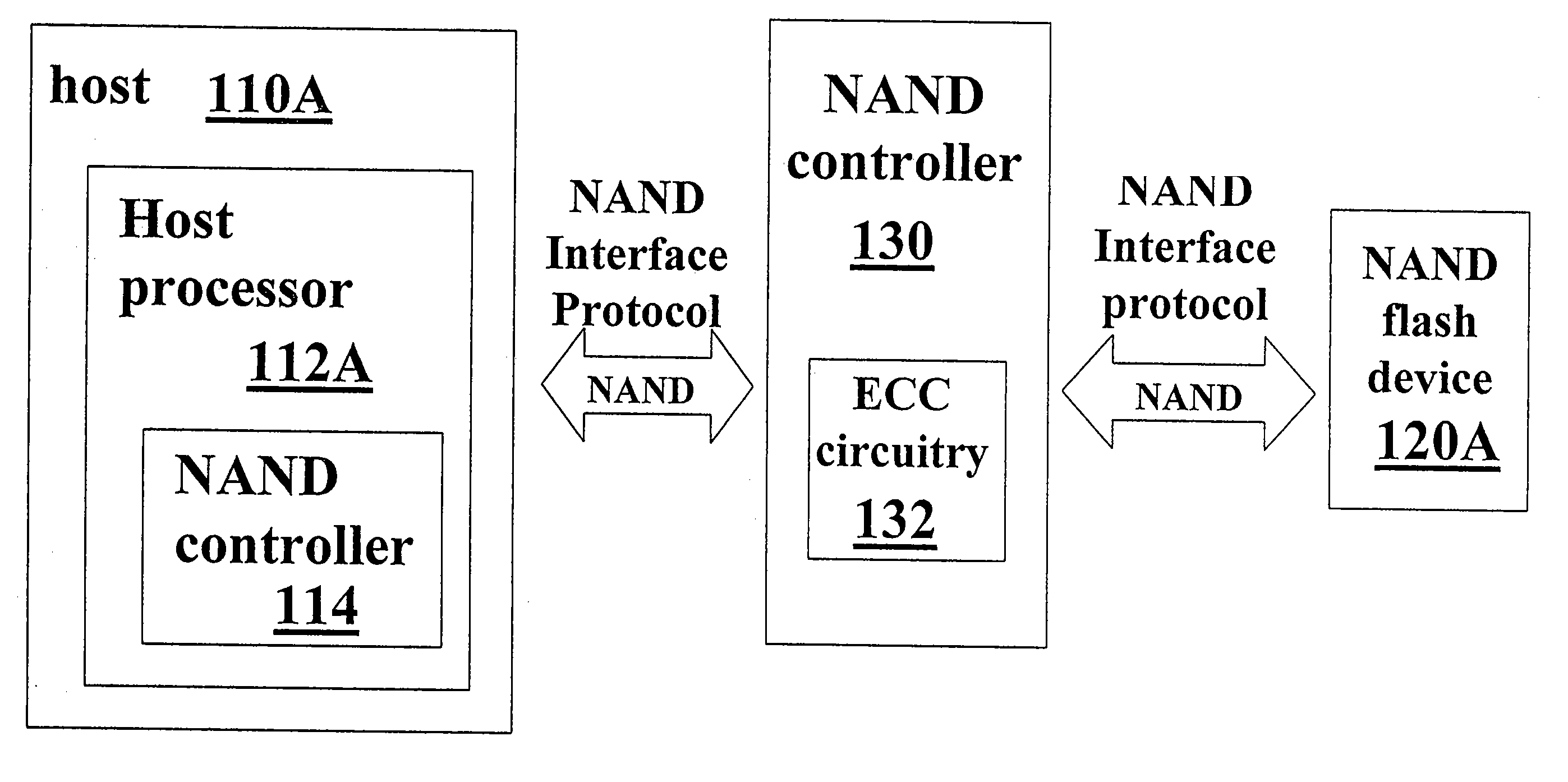

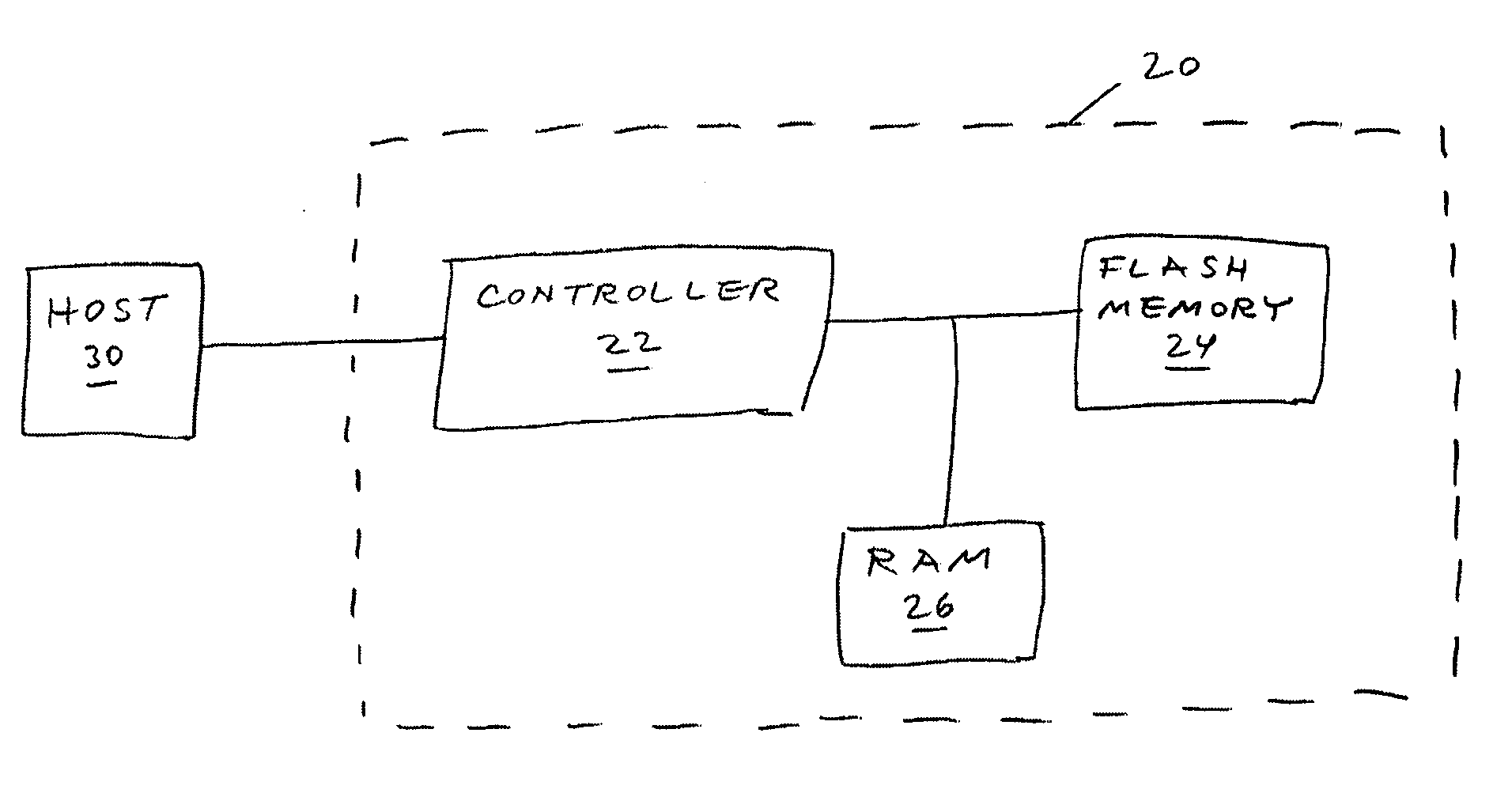

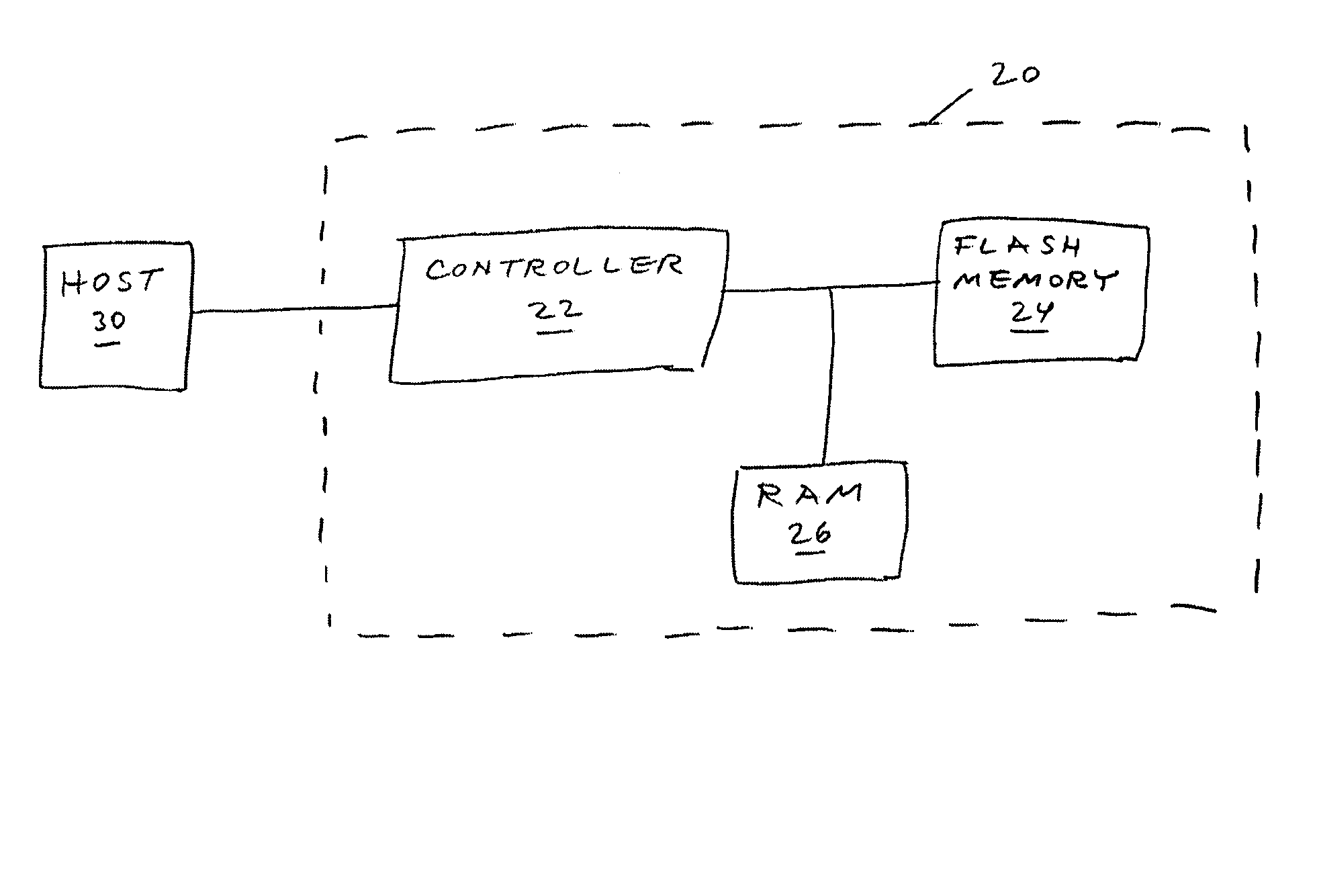

NAND Flash Memory Controller Exporting a NAND Interface

ActiveUS20100023800A1Satisfies needMemory architecture accessing/allocationData representation error detection/correctionHost typeHost machine

A NAND controller for interfacing between a host device and a flash memory device (e.g., a NAND flash memory device) fabricated on a flash die is disclosed. In some embodiments, the presently disclosed NAND controller includes electronic circuitry fabricated on a controller die, the controller die being distinct from the flash die, a first interface (e.g. a host-type interface, for example, a NAND interface) for interfacing between the electronic circuitry and the flash memory device, and a second interface (e.g. a flash-type interface) for interfacing between the controller and the host device, wherein the second interface is a NAND interface. According to some embodiments, the first interface is an inter-die interface. According to some embodiments, the first interface is a NAND interface. Systems including the presently disclosed NAND controller are also disclosed. Methods for assembling the aforementioned systems, and for reading and writing data using NAND controllers are also disclosed.

Owner:INNOVATIVE MEMORY SYST INC

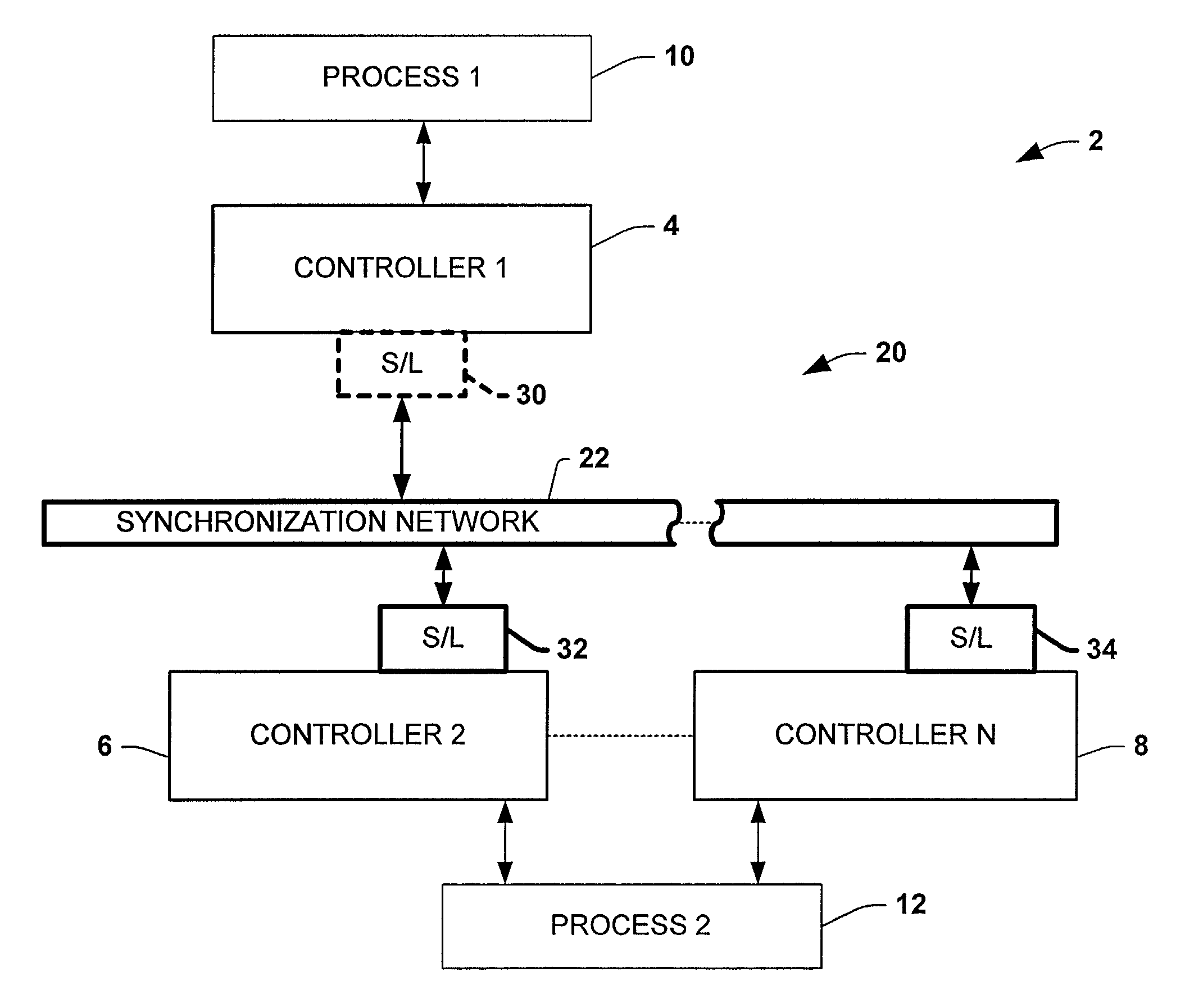

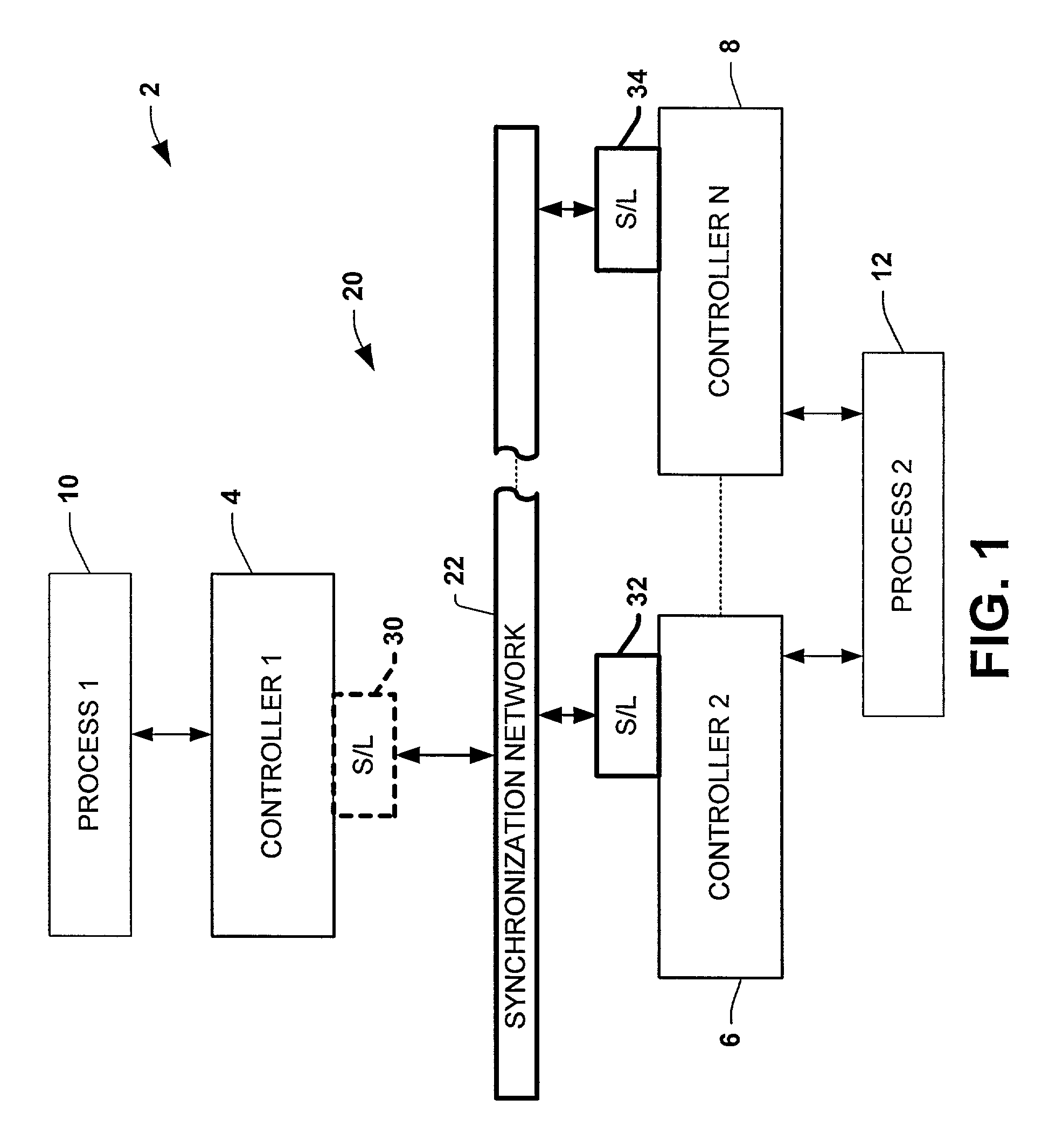

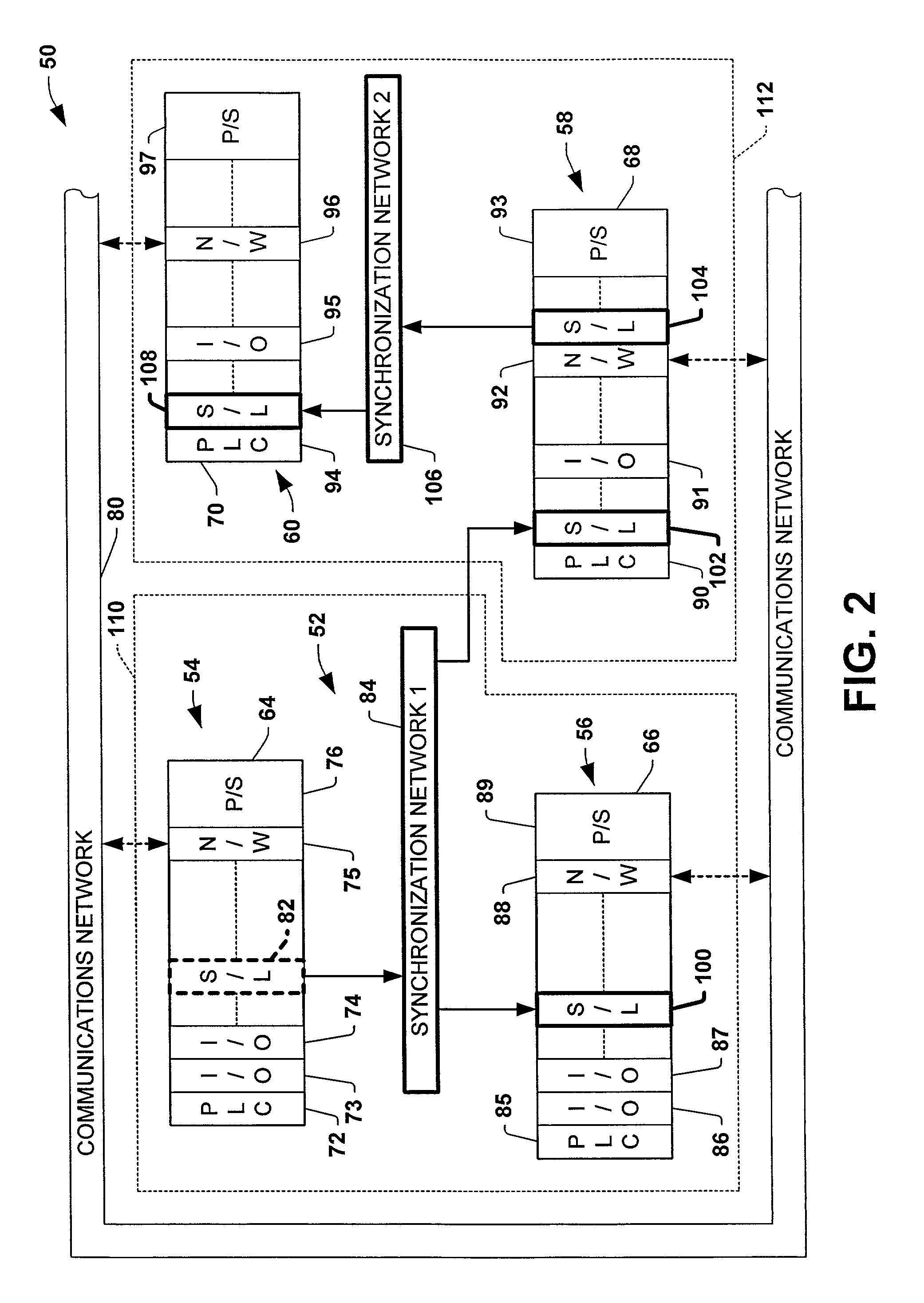

Protocol and method for multi-chassis configurable time synchronization

ActiveUS7007106B1Data representation error detection/correctionCode conversionSynchronous controlControl system

Systems and methods are disclosed for time synchronization of operations in a control system. Synchronization networks and devices are provided for transferring synchronization information between controllers in a distributed or localized control system, which is employed in order to allow operation of such controllers to be synchronized with respect to time. Also disclosed are synchronization protocols and hardware apparatus employed in synchronizing control operations in a control system.

Owner:ROCKWELL TECH

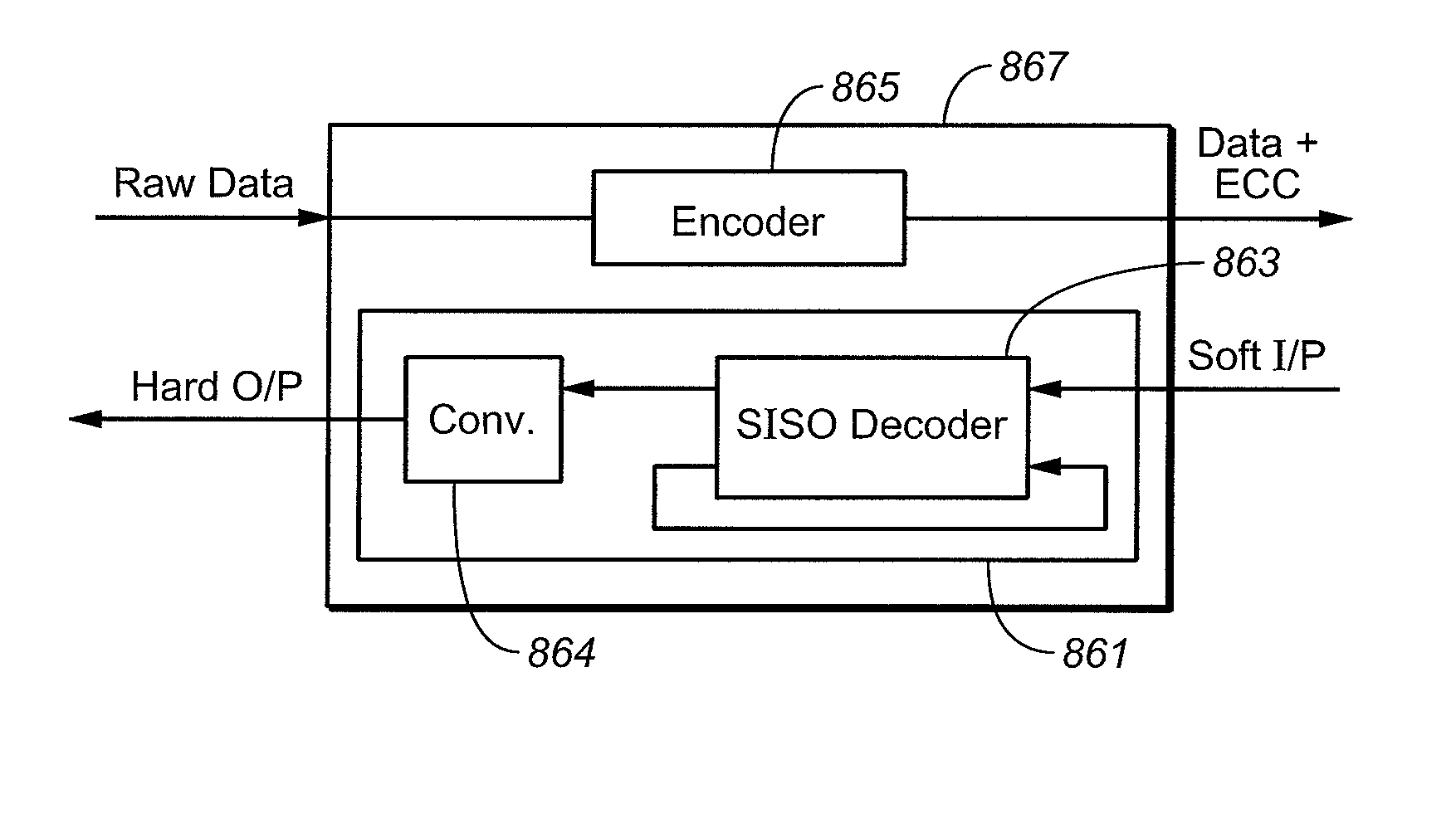

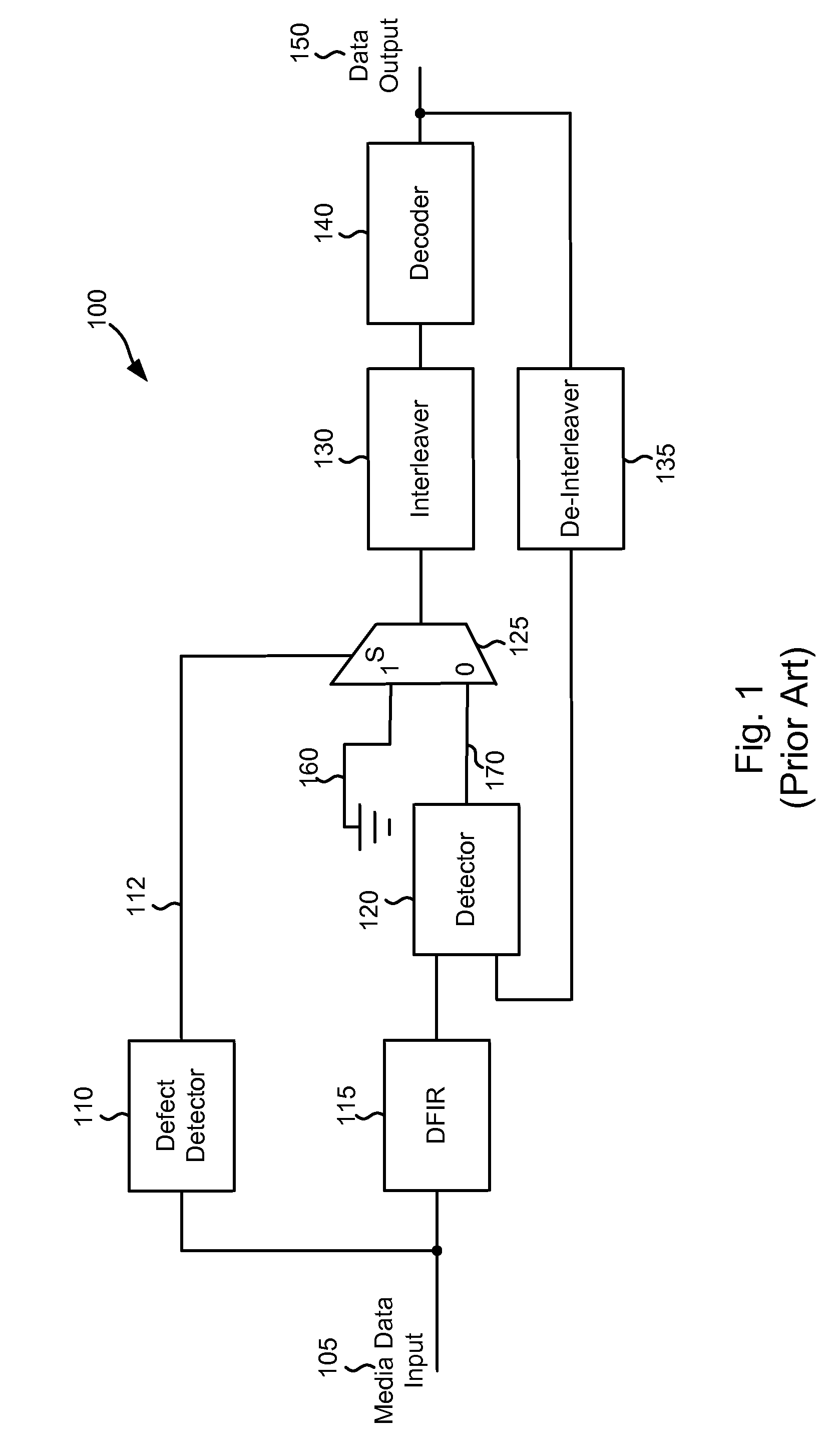

Methods of Soft-Input Soft-Output Decoding for Nonvolatile Memory

ActiveUS20080092026A1Data representation error detection/correctionOther decoding techniquesNon-volatile memoryMemory systems

In a nonvolatile memory system, data is read from a memory array and used to obtain likelihood values, which are then provided to a soft-input soft-output decoder. The soft-input soft-output decoder calculates output likelihood values from input likelihood values and from parity data that was previously added according to an encoding scheme.

Owner:SANDISK TECH LLC

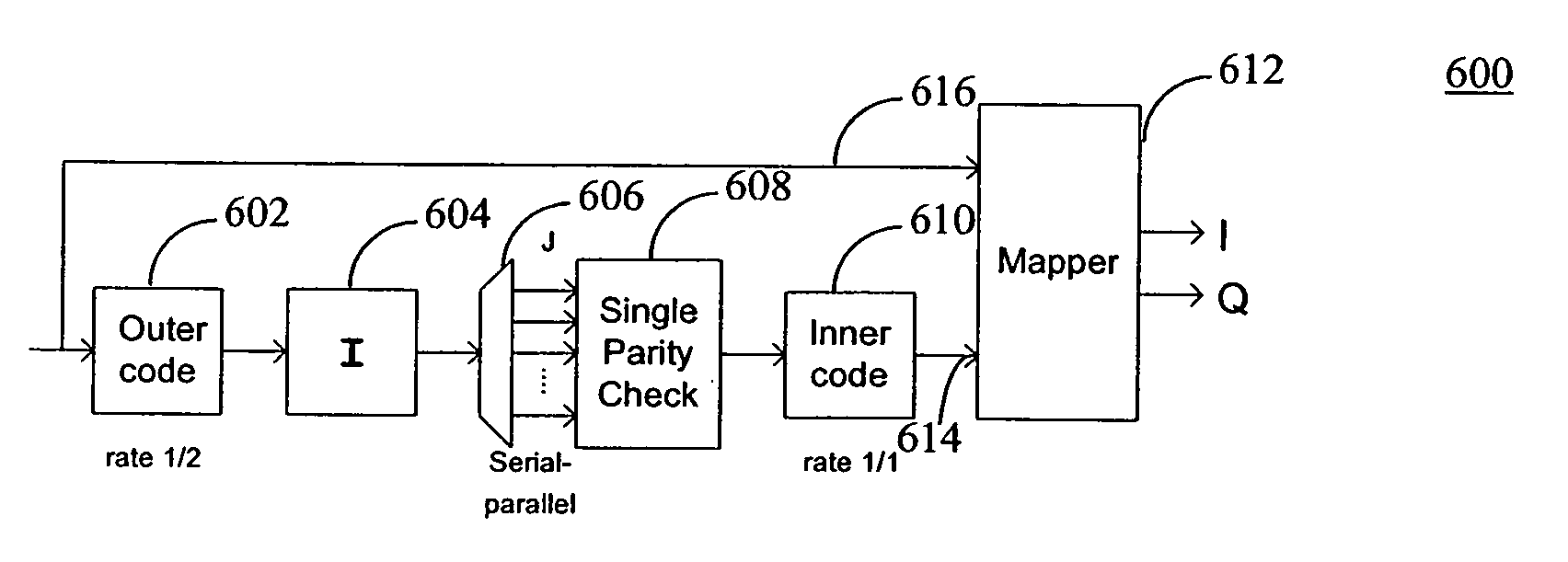

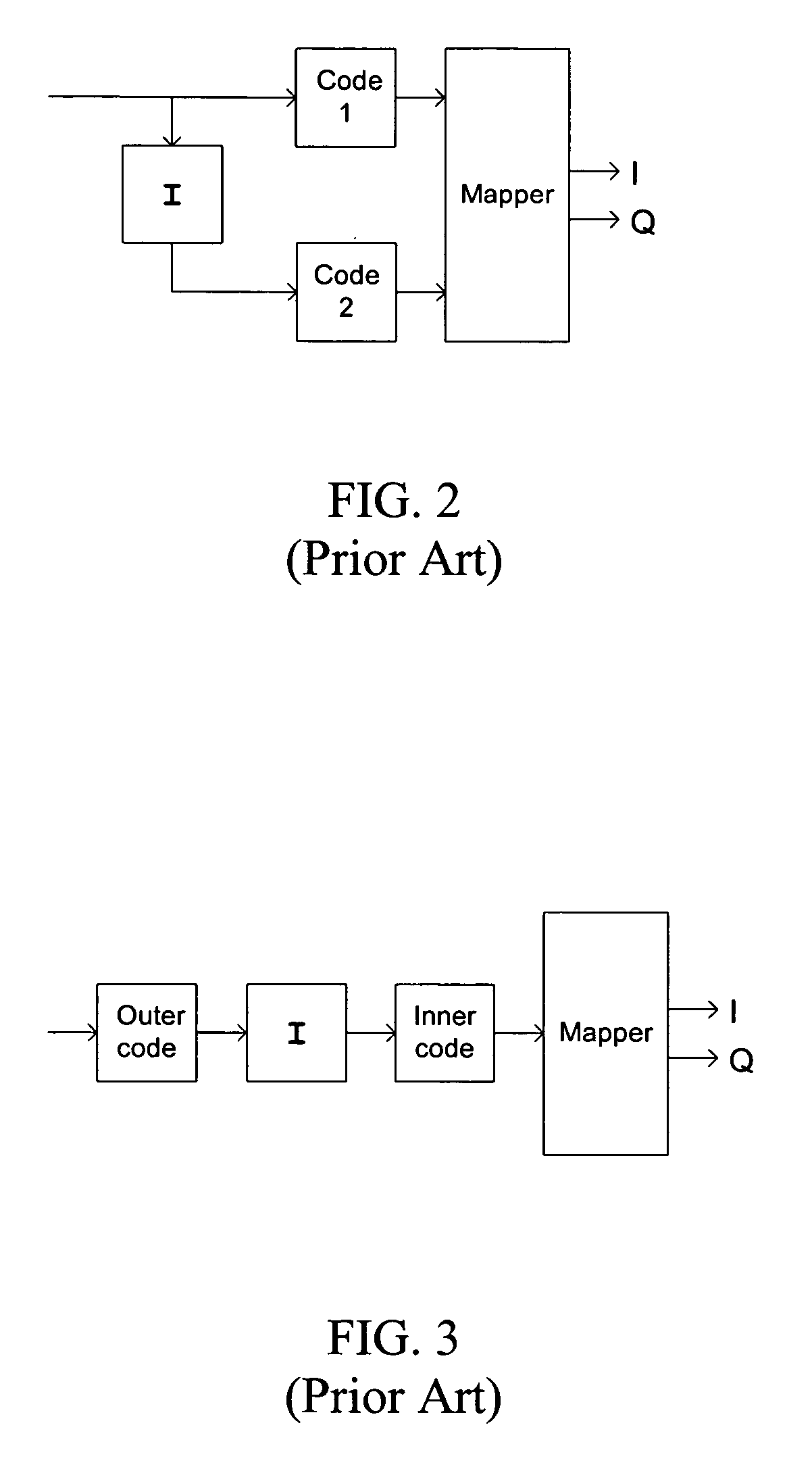

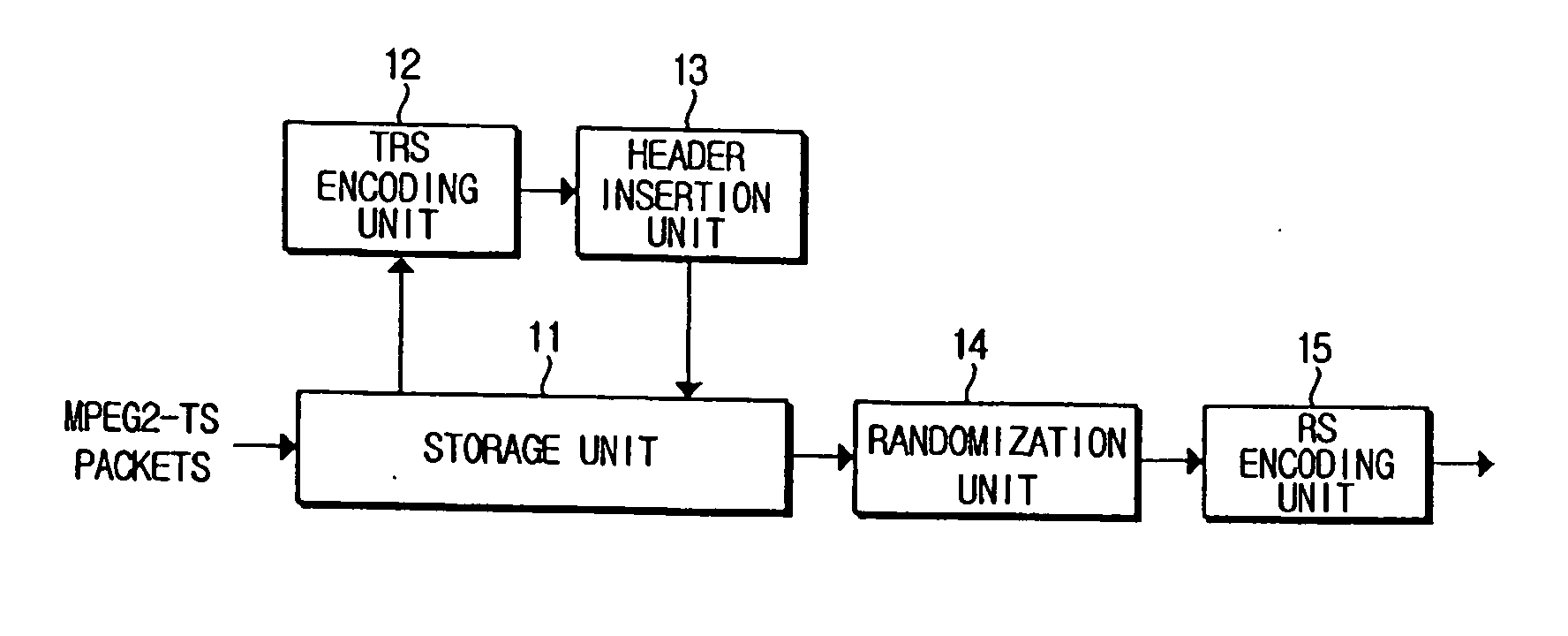

Method and apparatus for communications using improved turbo like codes

ActiveUS20060031737A1Data representation error detection/correctionCode conversionSingle parity checkConvolutional code

Methods, apparatuses, and systems are presented for performing data encoding involving encoding data bits according to an outer convolutional code to produce outer encoded bits, processing the outer encoded bits using an interleaver and a single parity check (SPC) module to produce intermediate bits, encoding the intermediate bits according to an inner convolutional code to produce inner encoded bits, processing the inner encoded bits using a puncture module to produce punctured bits, and combining the data bits and the punctured bits to produce encoded outputs. Methods, apparatuses, and systems are also presented for performing data decoding based on soft channel metrics derived from a channel using various iterative techniques.

Owner:TRELLIS WARE TECH

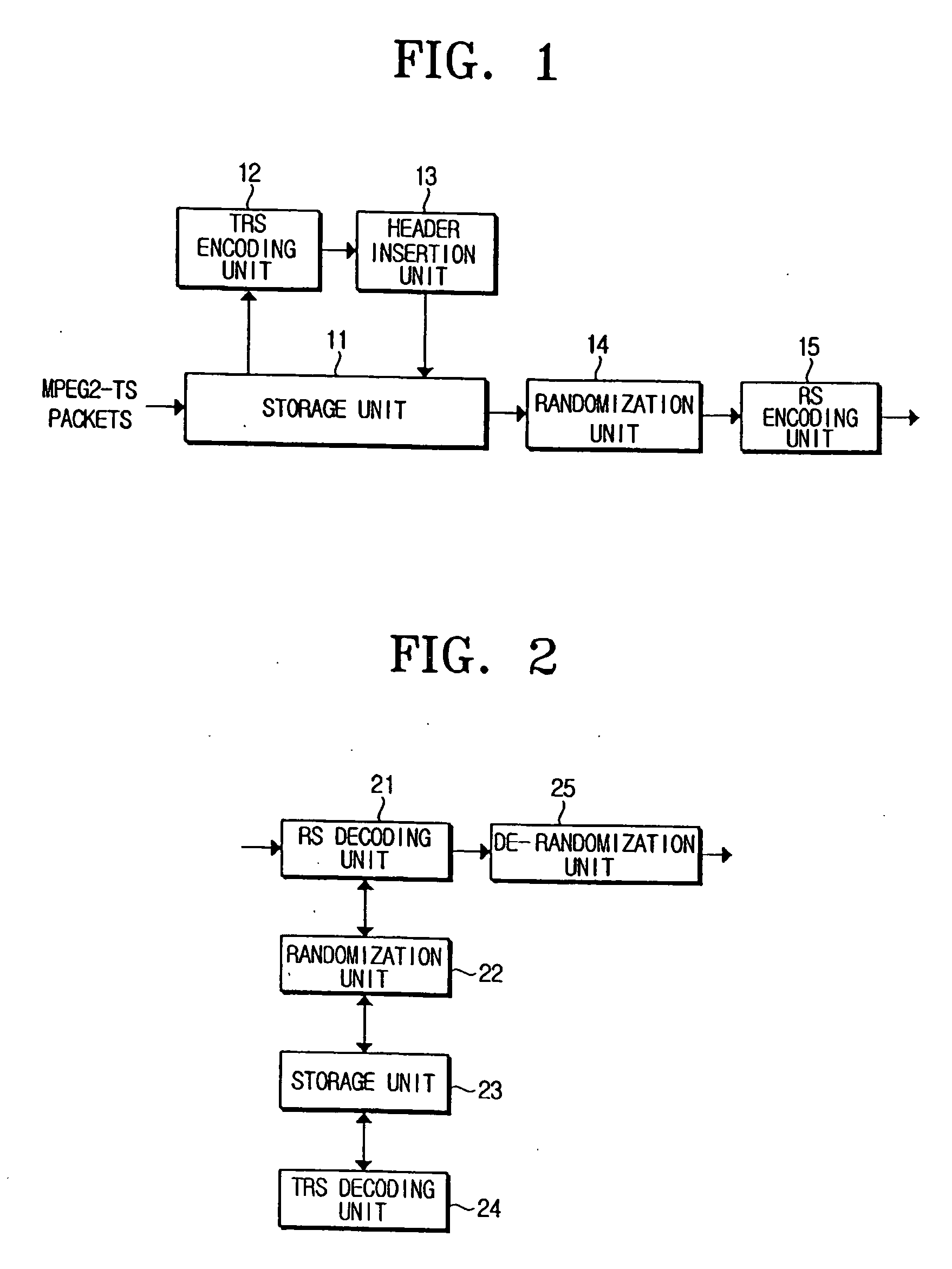

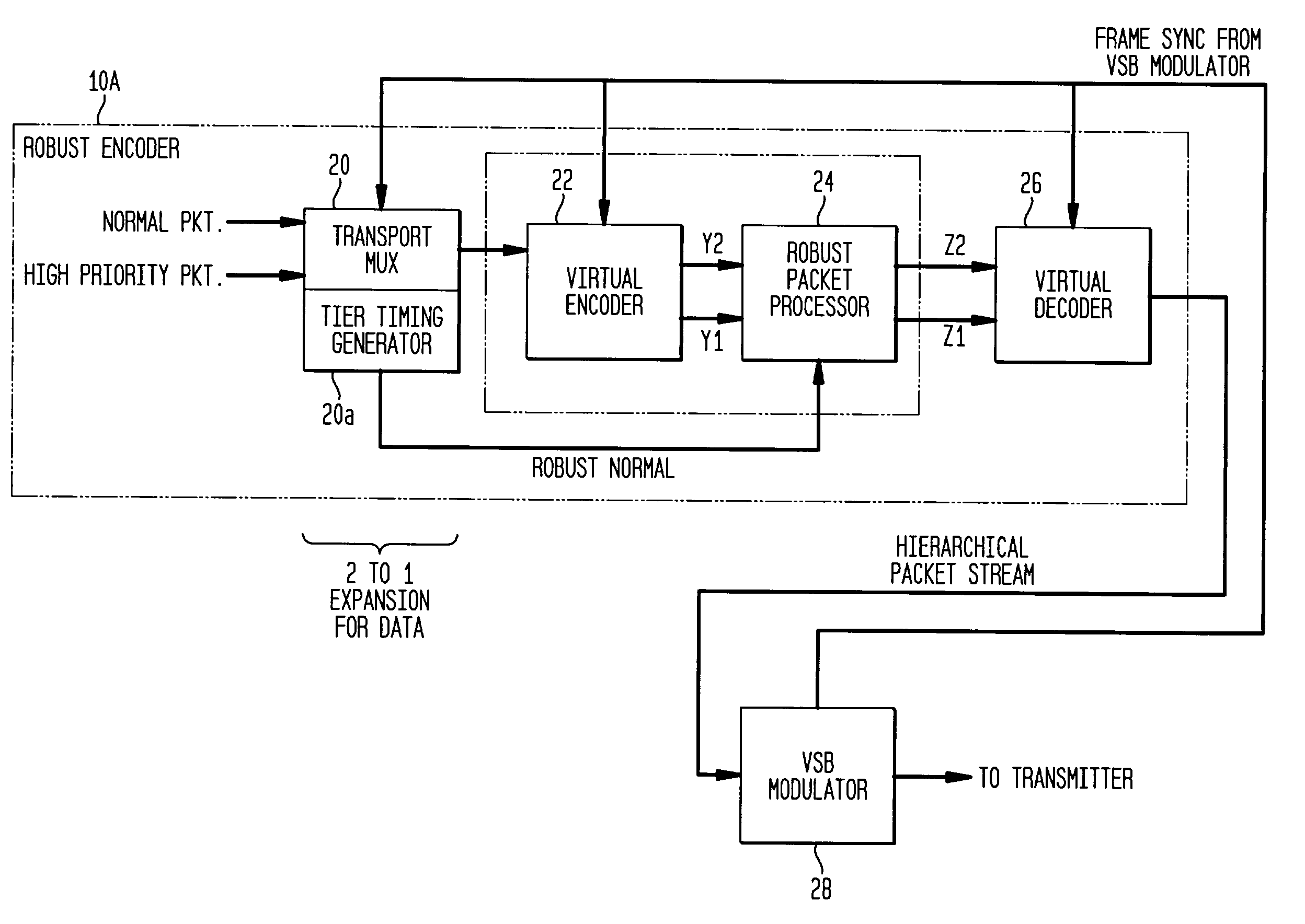

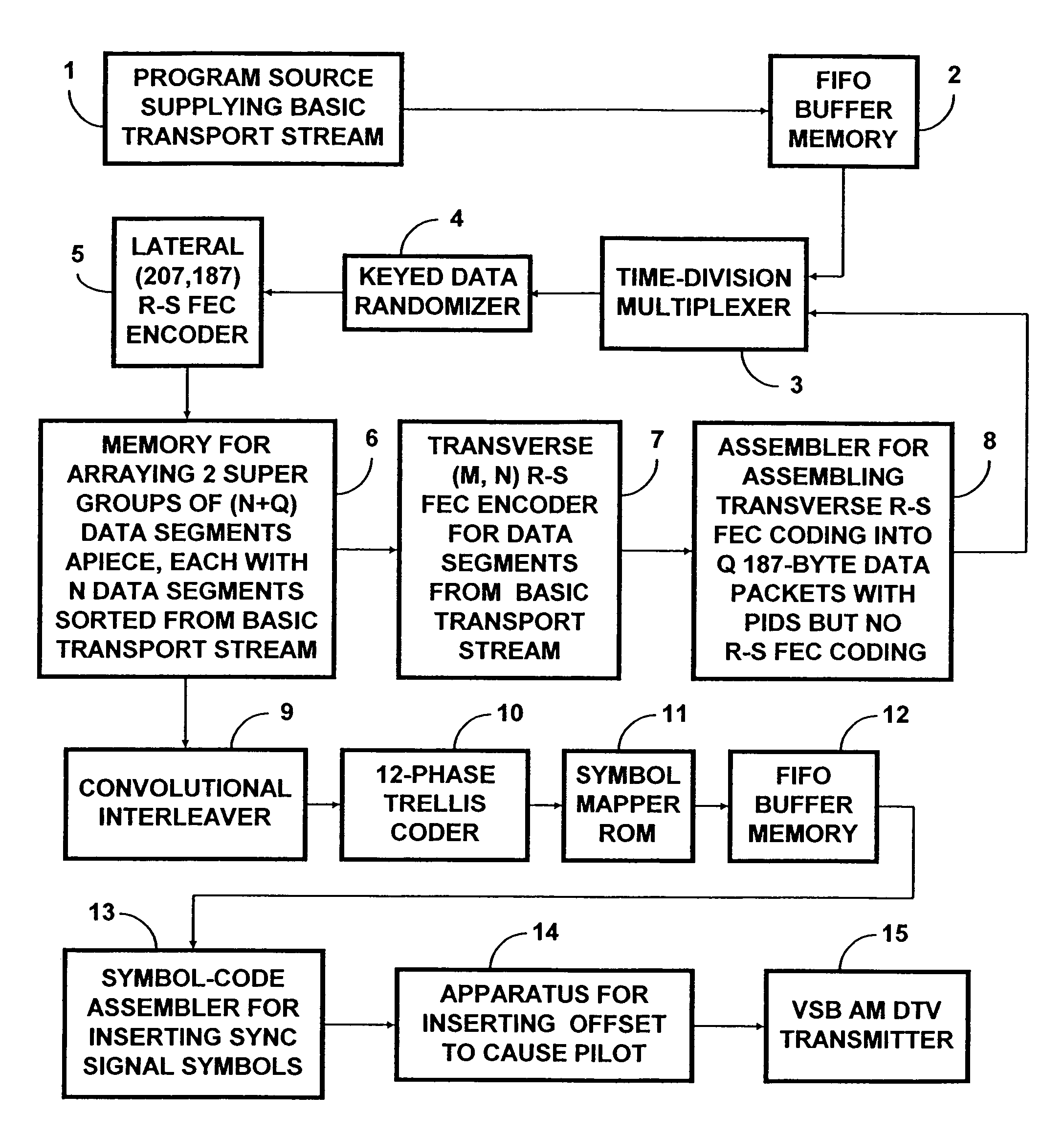

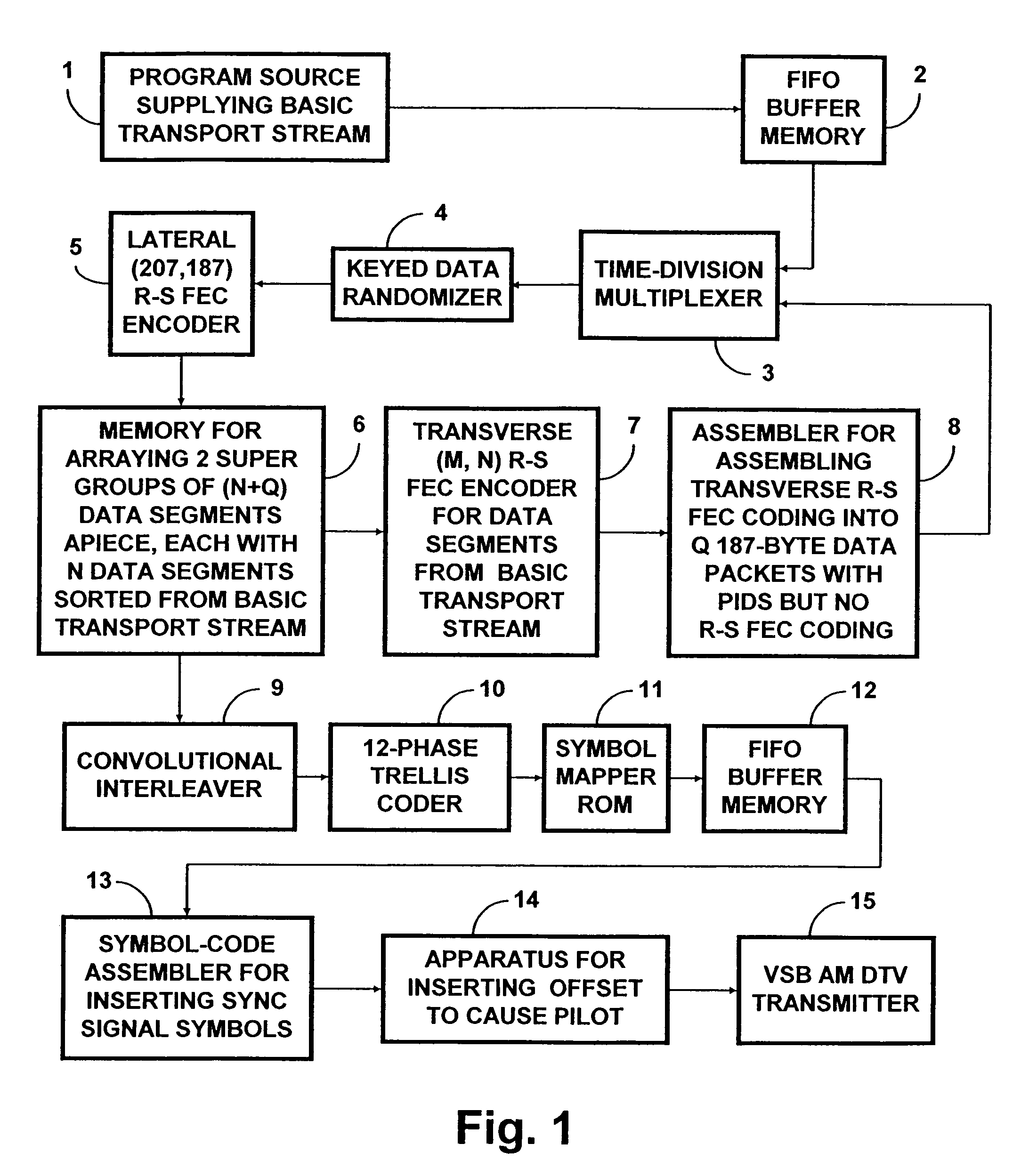

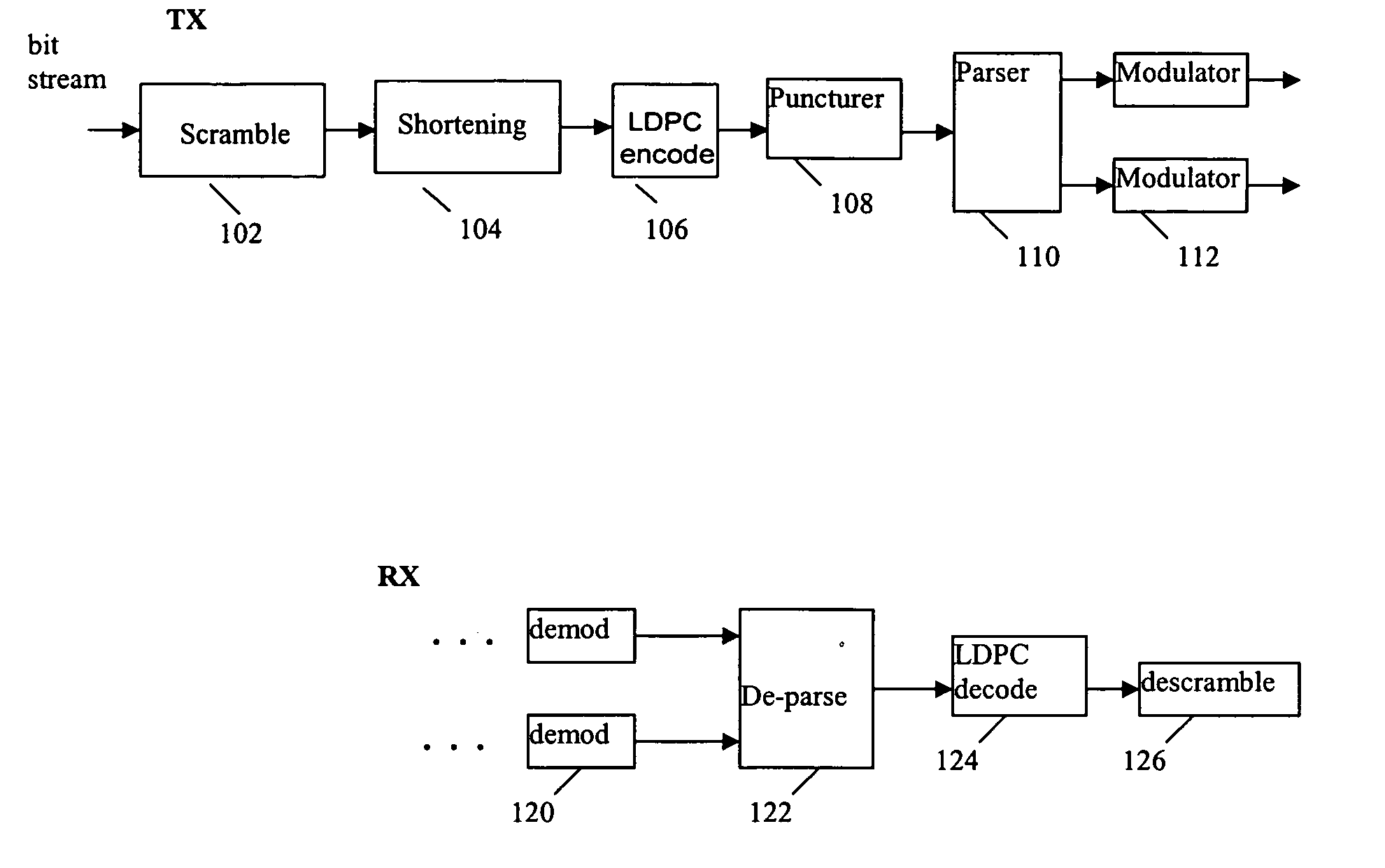

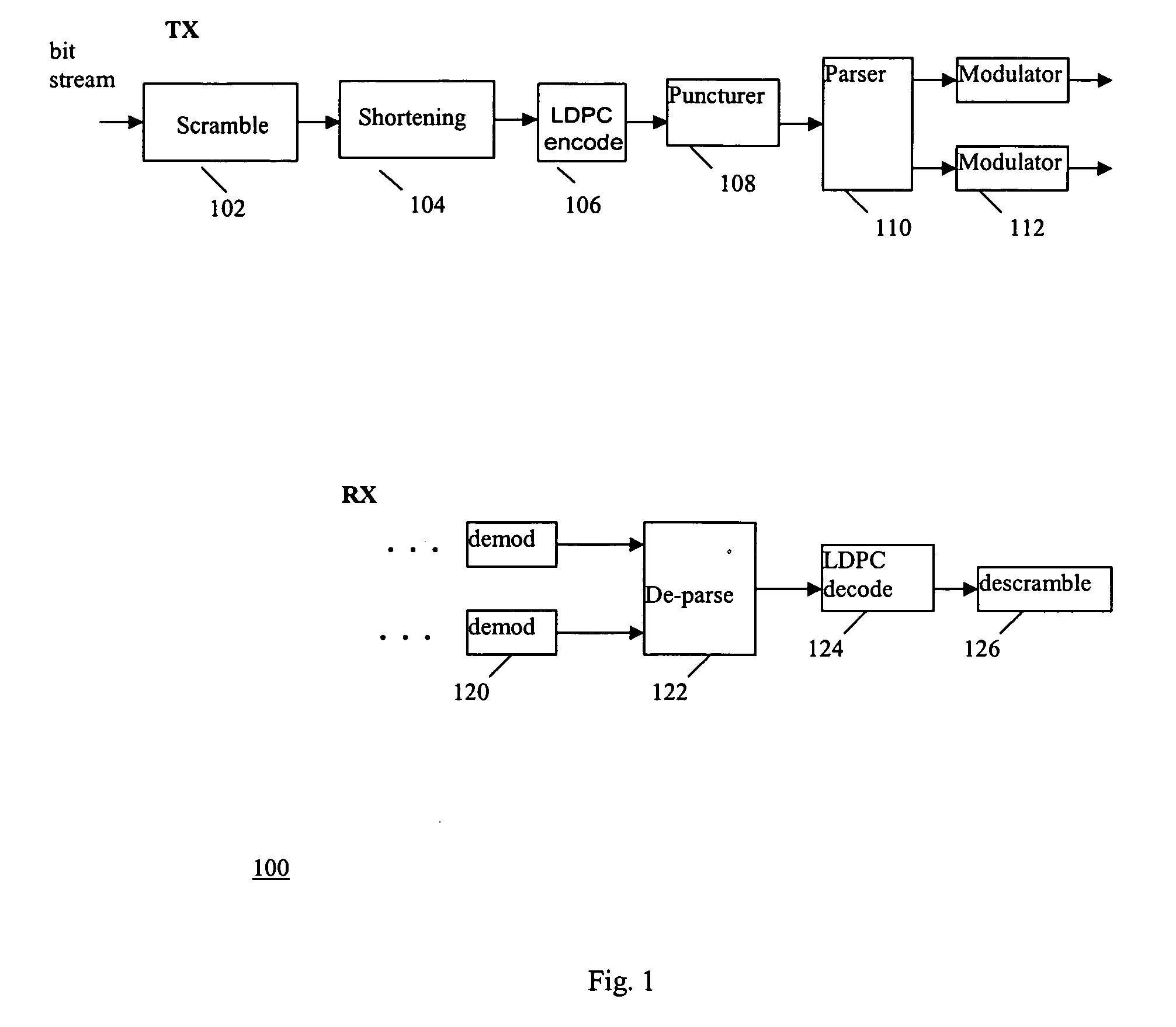

Robust error correction encoding/deconding apparatus and method of digital dual-stream broadcast reception/transmission system

ActiveUS20050097428A1Data representation error detection/correctionPulse modulation television signal transmissionTransfer systemControl data

An error correction encoding and / or decoding apparatus and method of a digital dual-stream broadcast transmission and / or reception system. An error correction encoding apparatus includes a TRS encoding part to apply the transversal encoding to normal data packets and robust data packets and to append parity packets to the normal data packet and robust data packet, a randomization unit to randomize the data packets and the parity packets according to a predetermined pattern, an RS encoding unit to append parities to the randomized data packets and parity packets, a packet format unit to split the data packets and the parity packets into normal data and robust data and to process the normal and robust data, and a system control unit to control the packet format unit. Accordingly, a robust error correction encoding apparatus can be provided for the digital dual-stream broadcast transmission system to which Transversal Reed-Solomon (TRS) encoding is applied.

Owner:SAMSUNG ELECTRONICS CO LTD

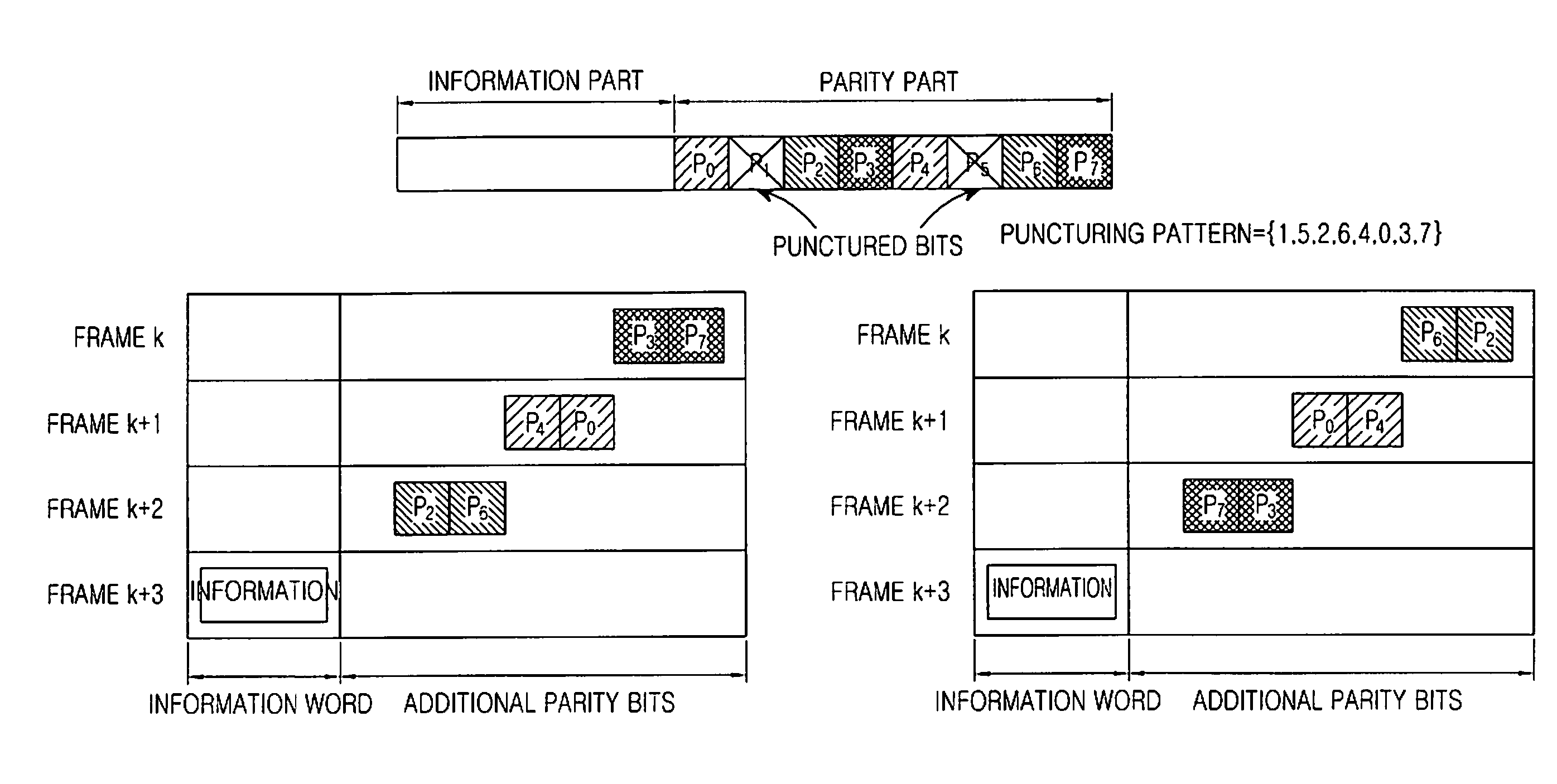

Method and apparatus for transmitting and receiving data in a communication system

ActiveUS20110119568A1Data representation error detection/correctionCode conversionCommunications systemComputer science

A method is provided for transmitting data, which improves a diversity effect in a communication system. The method includes transmitting an information word including a codeword in a (k+s)-th frame, generating s groups based on parity bits obtained by encoding the information word, and transmitting the s groups in s frames preceding the (k+s)-th frame, in a distributed manner.

Owner:SAMSUNG ELECTRONICS CO LTD

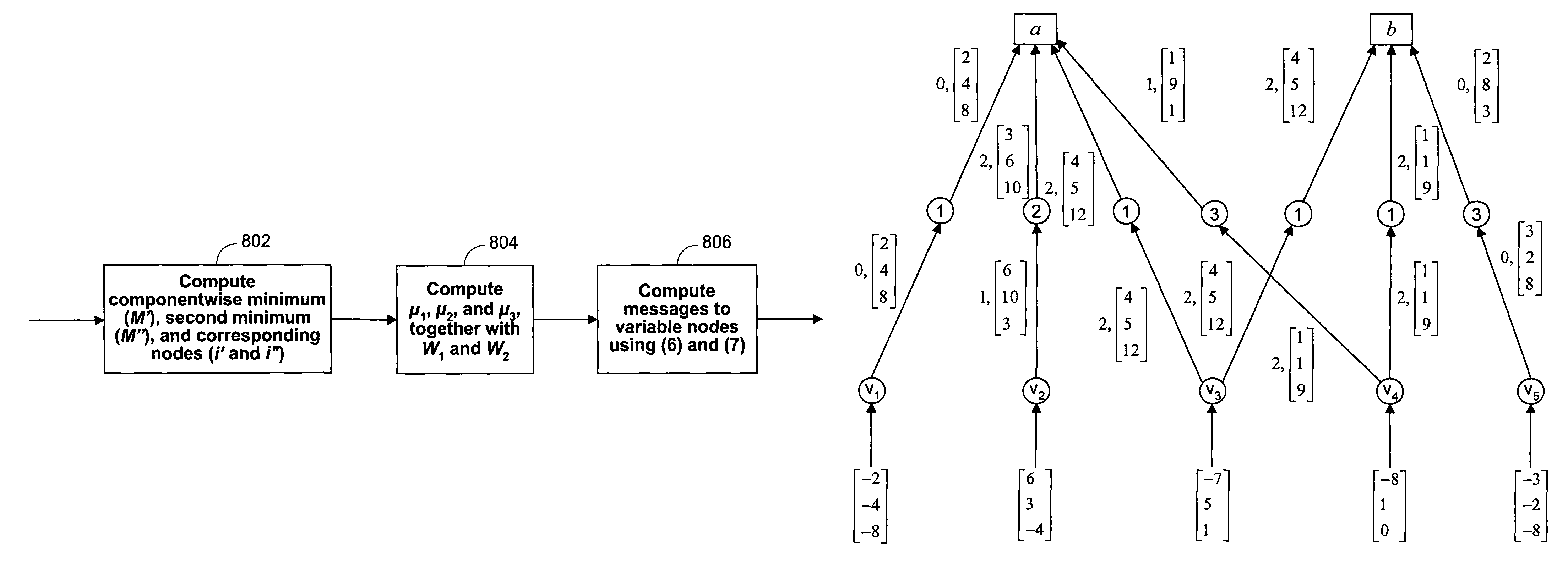

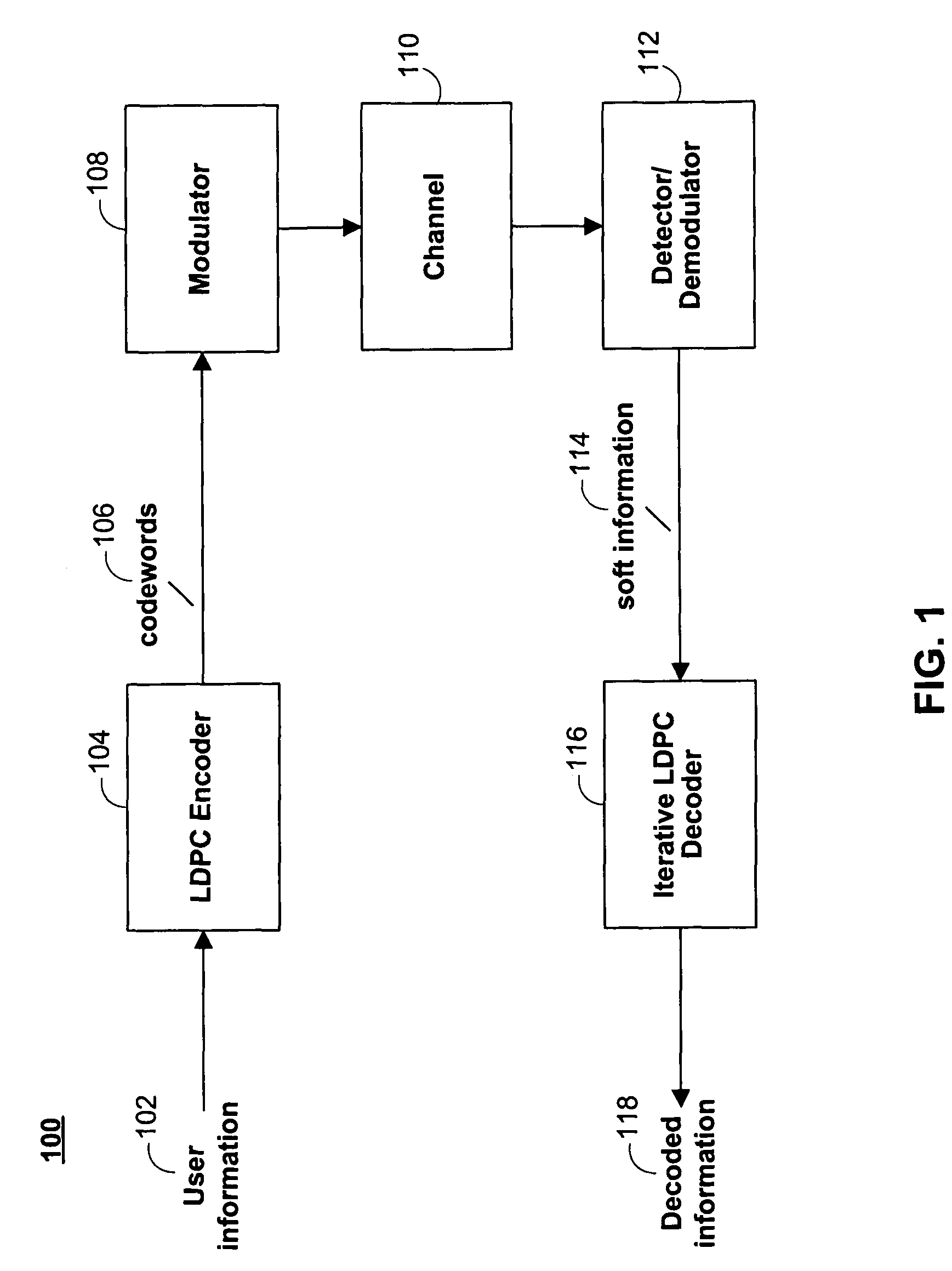

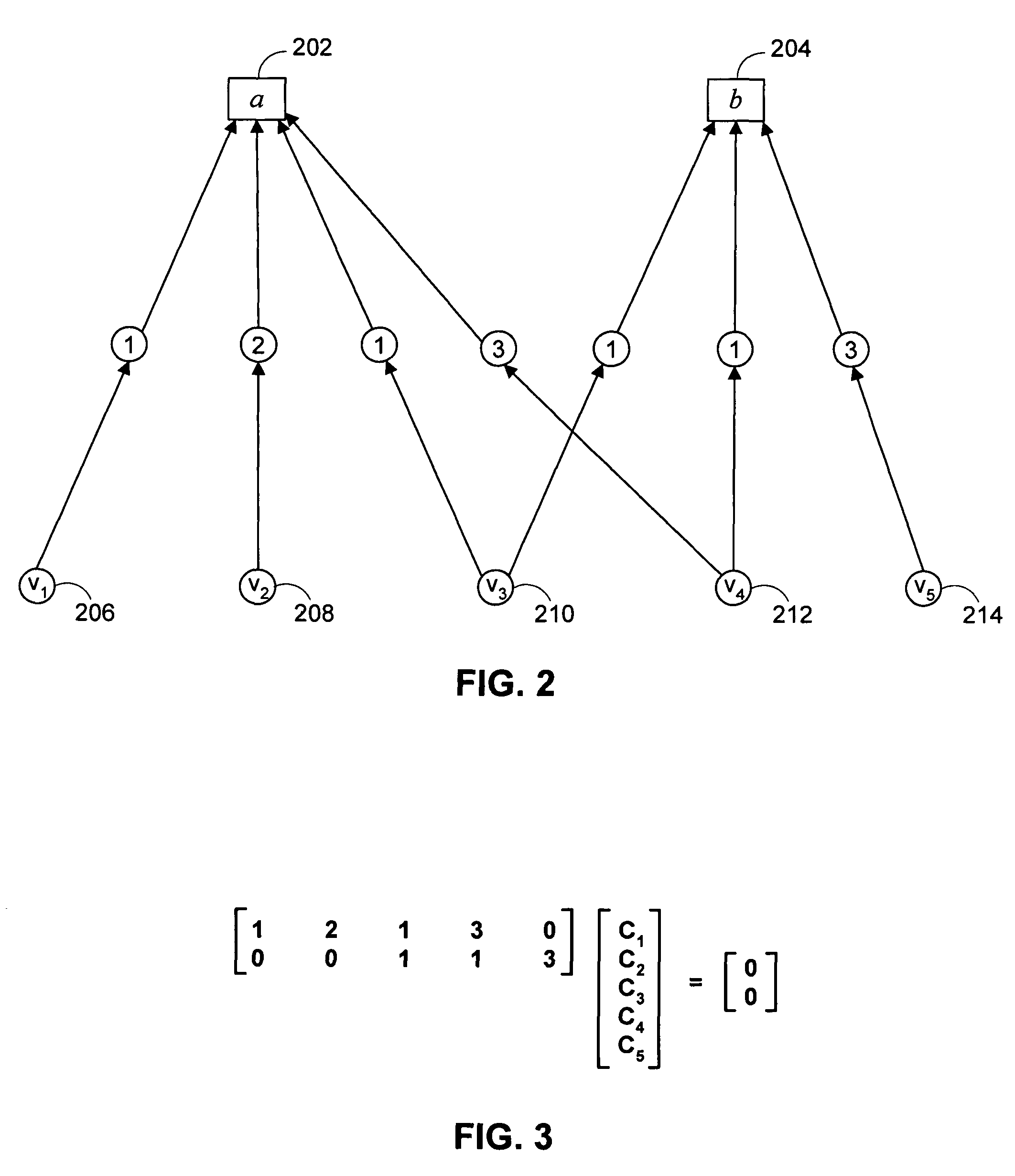

Reduced-complexity decoding of parity check codes

ActiveUS7752523B1Less resourcesData representation error detection/correctionCode conversionRound complexityTheoretical computer science

The disclosed technology provides a less resource intensive way to decode a parity check code using a modified min-sum algorithm. For a particular parity check constraint that includes n variable nodes, an LDPC decoder can compute soft information for one of the variable nodes based on combinations of soft information from other variable nodes, wherein each combination includes soft information from at most a number d of other variable nodes. In one embodiment, soft information from one of the other variable nodes is used in a combination only if it corresponds to a non-most-likely value for the other variable node.

Owner:MARVELL ASIA PTE LTD

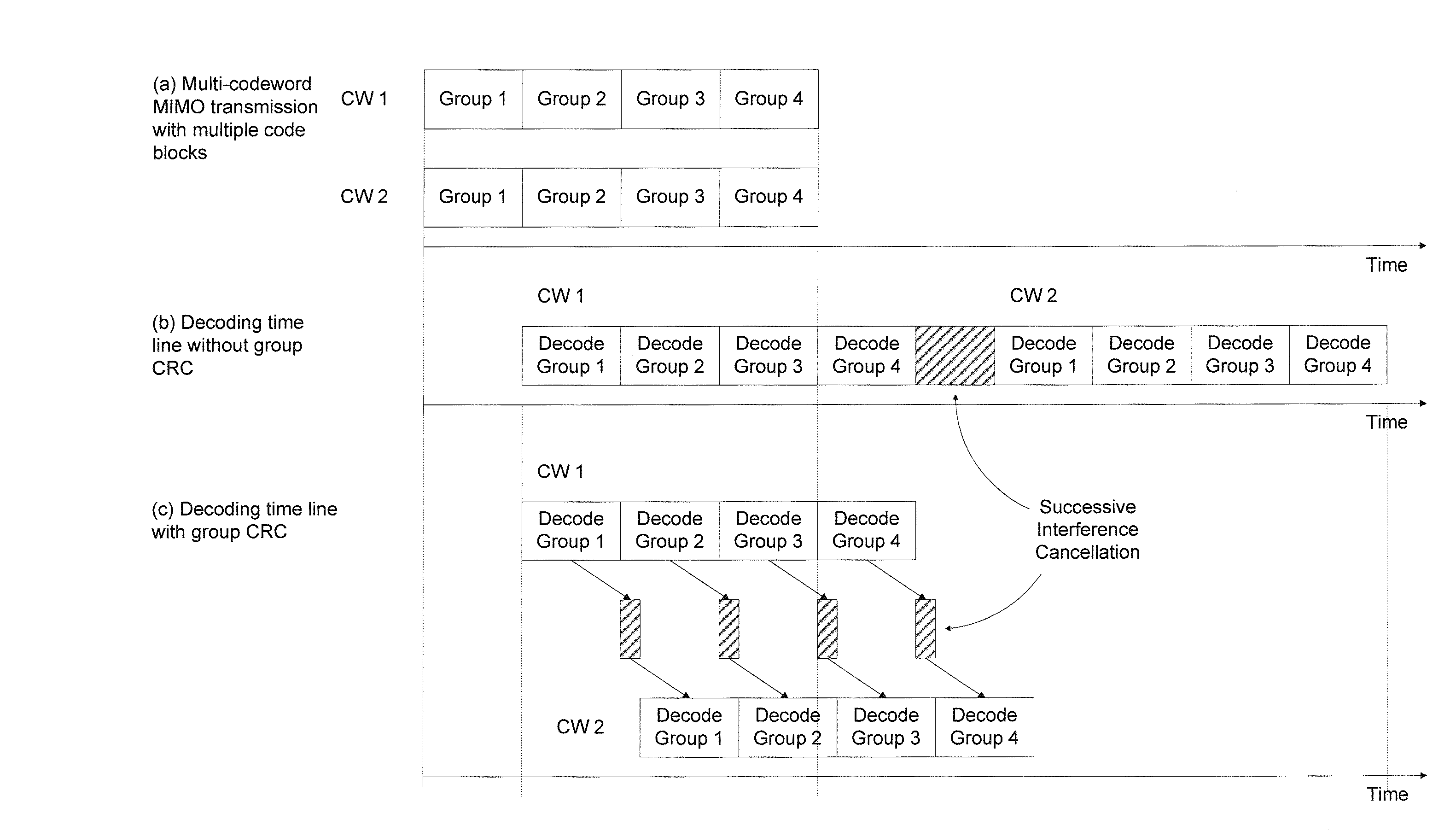

Methods and apparatus to improve performance and enable fast decoding of transmissions with multiple code blocks

ActiveUS20080225965A1Data representation error detection/correctionError preventionCoding blockResource element

Owner:SAMSUNG ELECTRONICS CO LTD

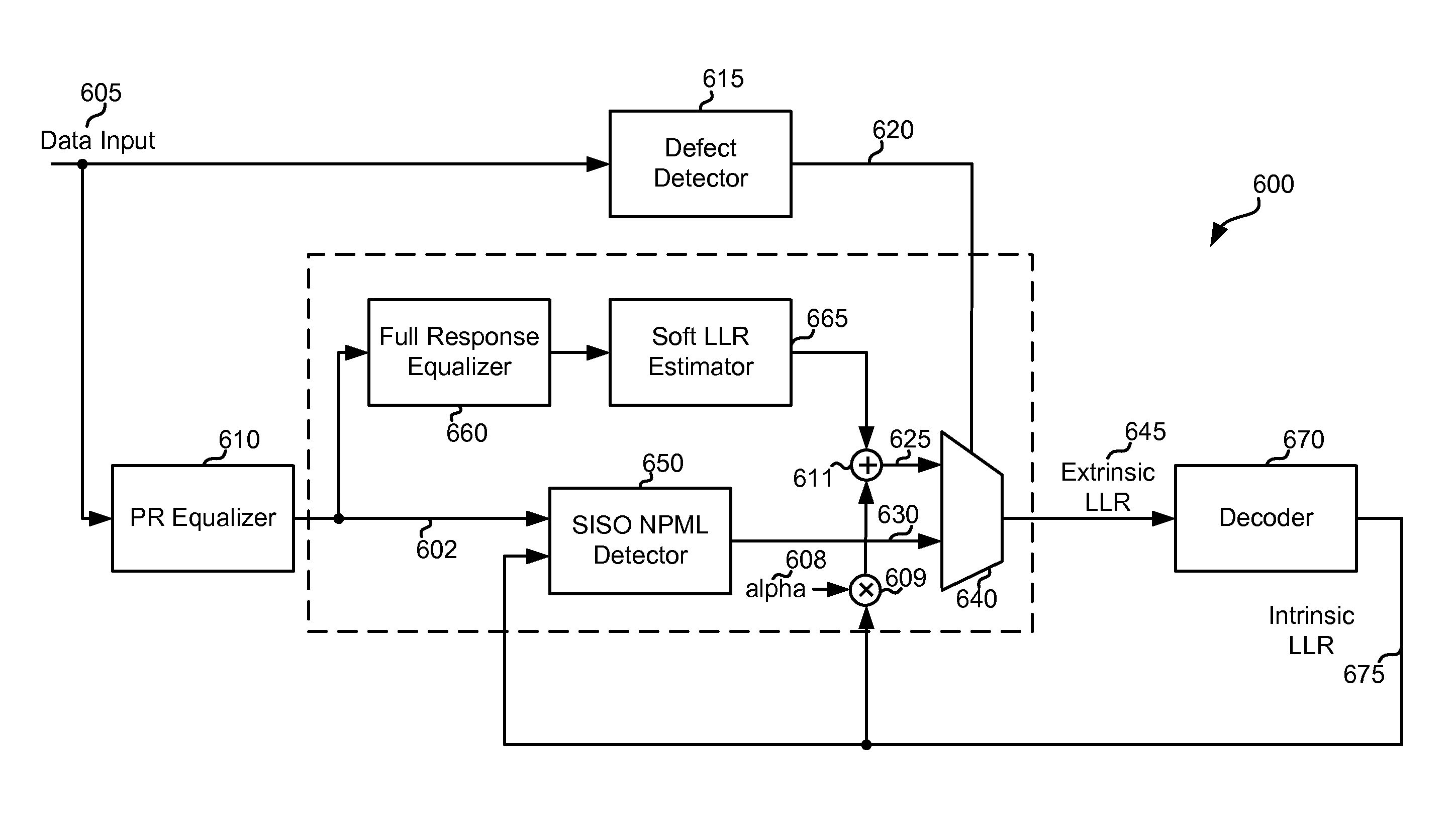

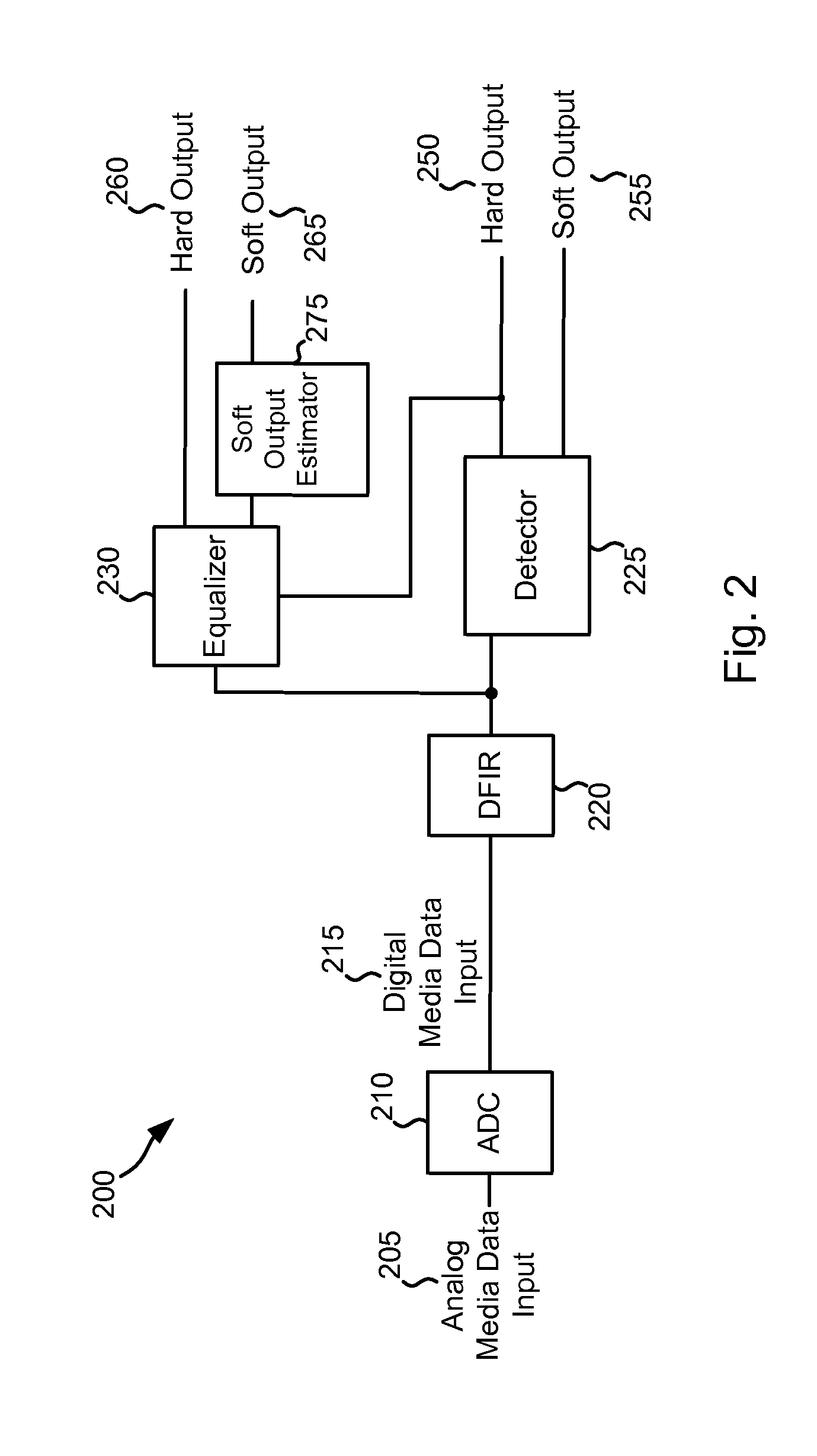

Systems and Methods for Using Intrinsic Data for Regenerating Data from a Defective Medium

ActiveUS20090235146A1Error prevention/detection by using return channelData representation error detection/correctionMultiplexerData recovery

Various embodiments of the present invention provide systems and methods for data regeneration. For example, a system for data regeneration is disclosed that includes a data input derived from the medium. A data detector and a data recovery system receive the data input. The data detector provides a first soft output, and the data recovery system provides a second soft output. The first soft output and the second soft output are provided to a multiplexer. A media defect detector performs a media defect detection process, and provides a defect flag that indicates whether the data input is derived form a defective portion of the medium. The defect flag is provided to the multiplexer where it is used to select whether the first soft output or the second soft output is provides as an extrinsic output.

Owner:AVAGO TECH INT SALES PTE LTD

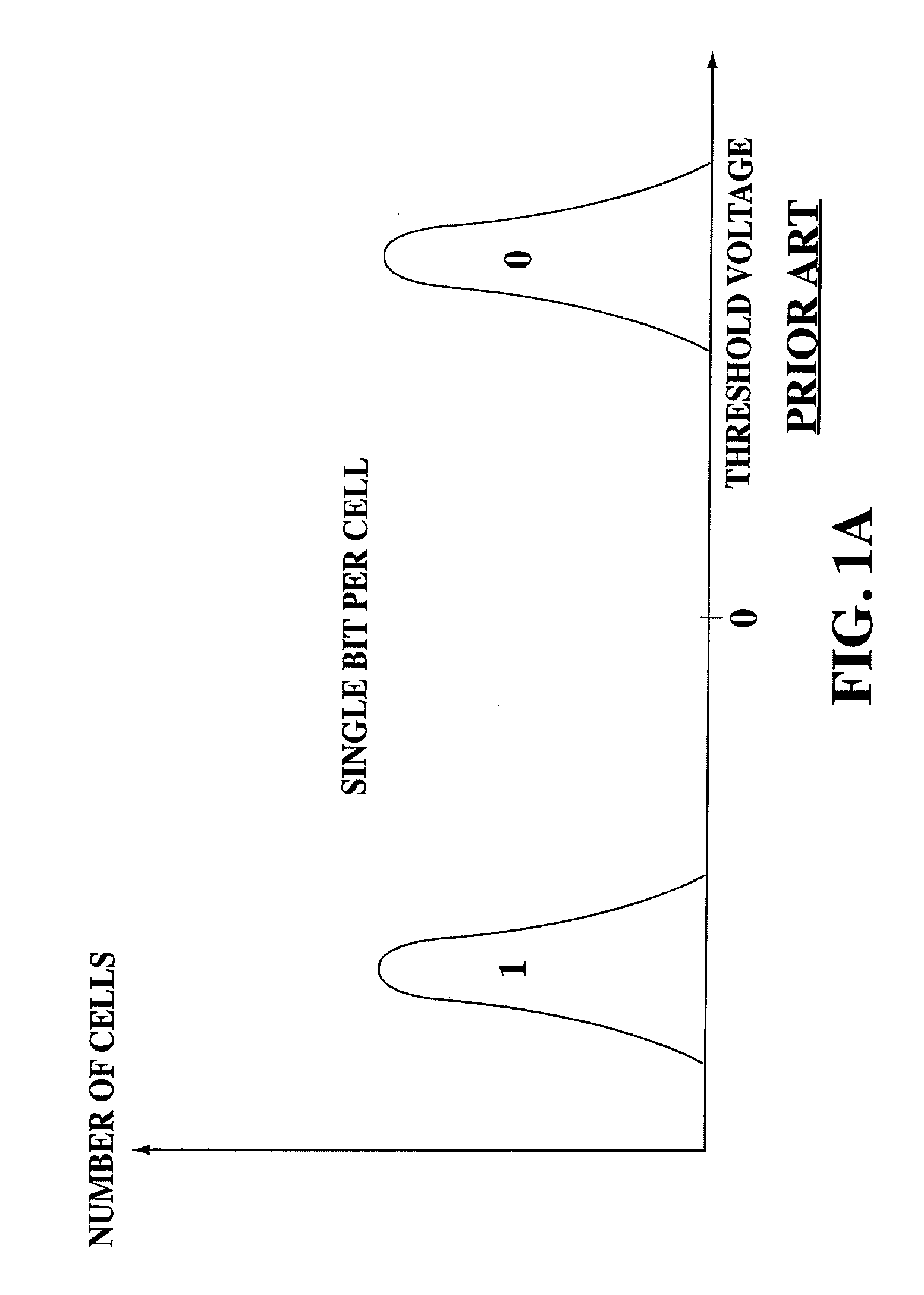

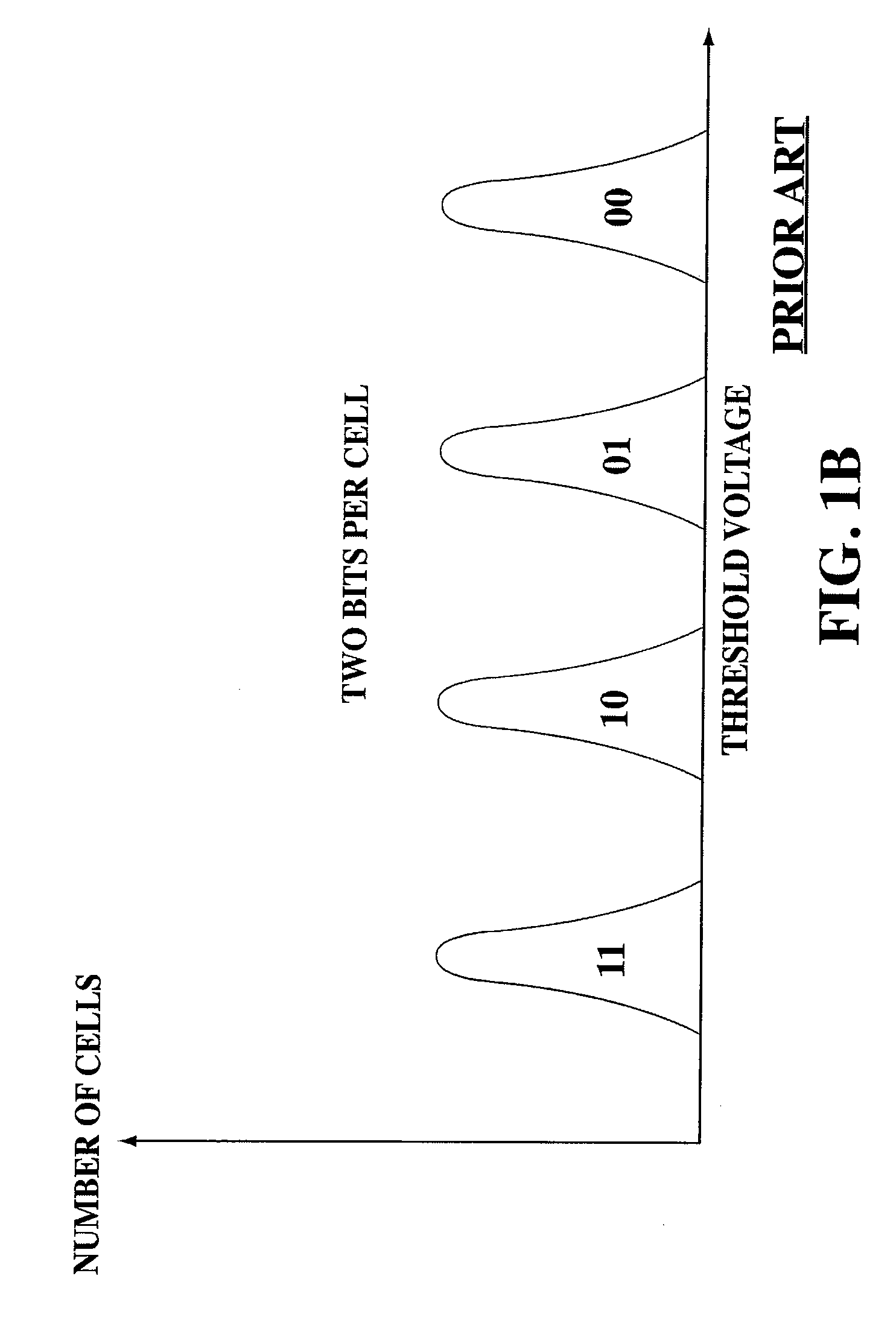

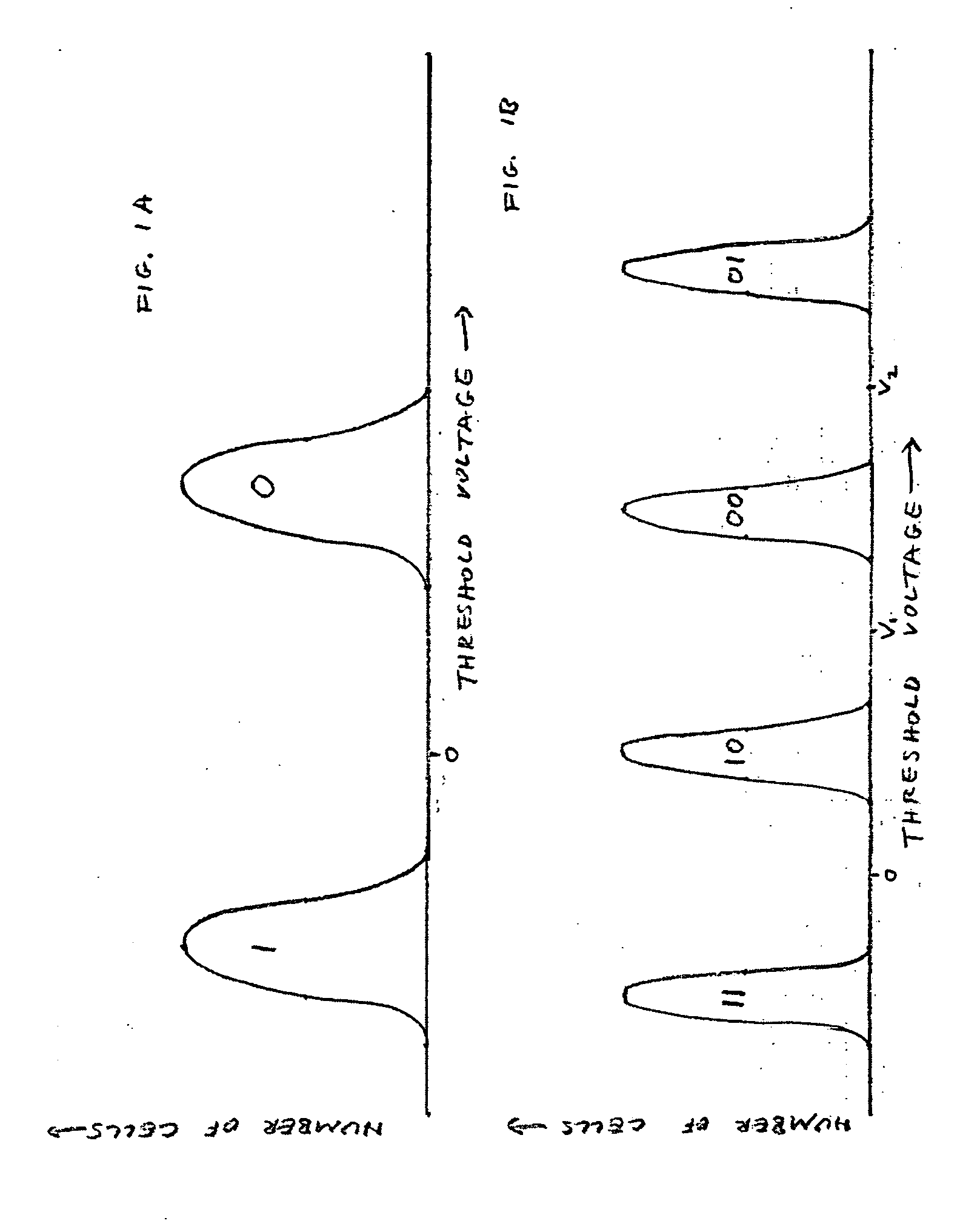

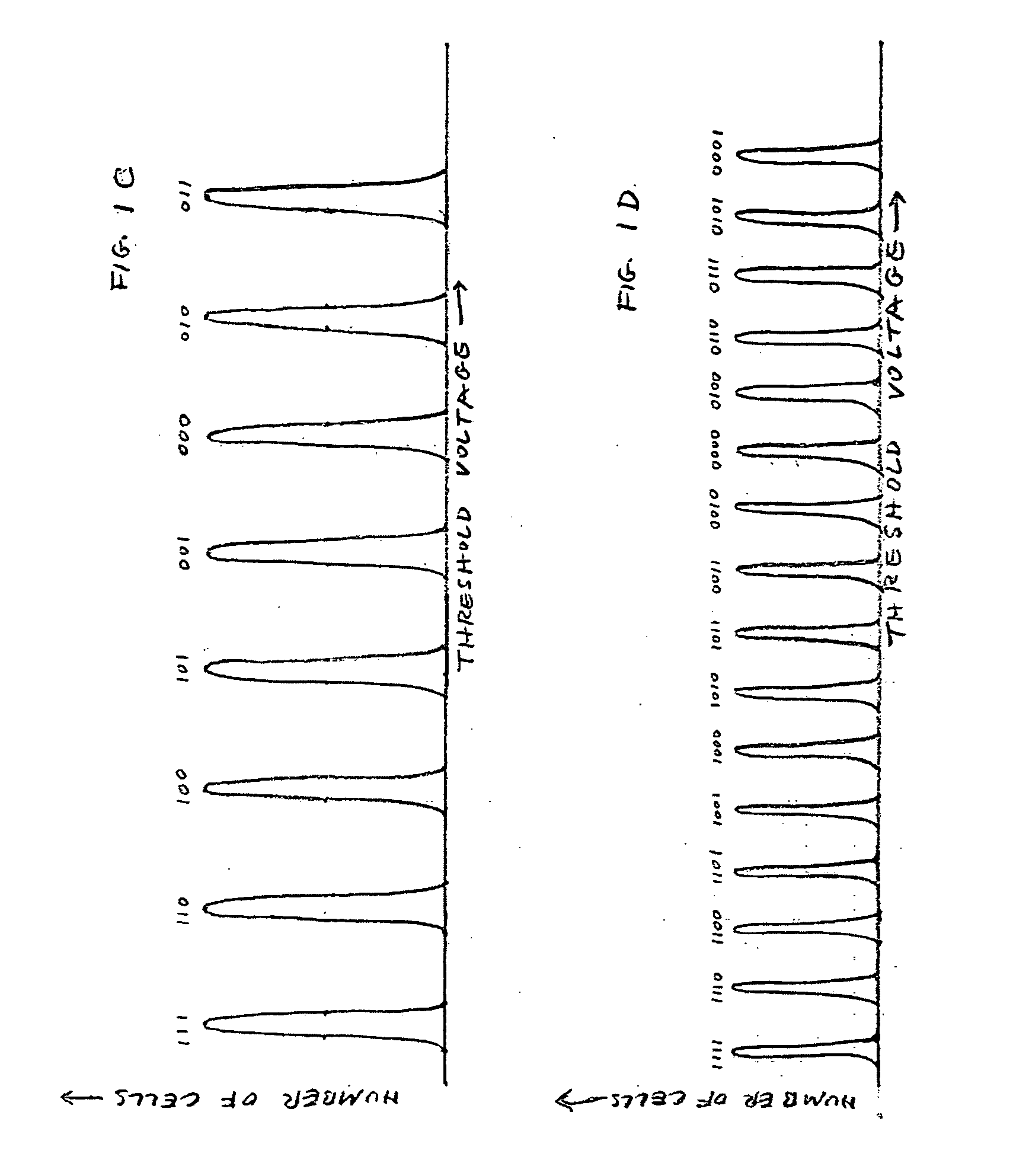

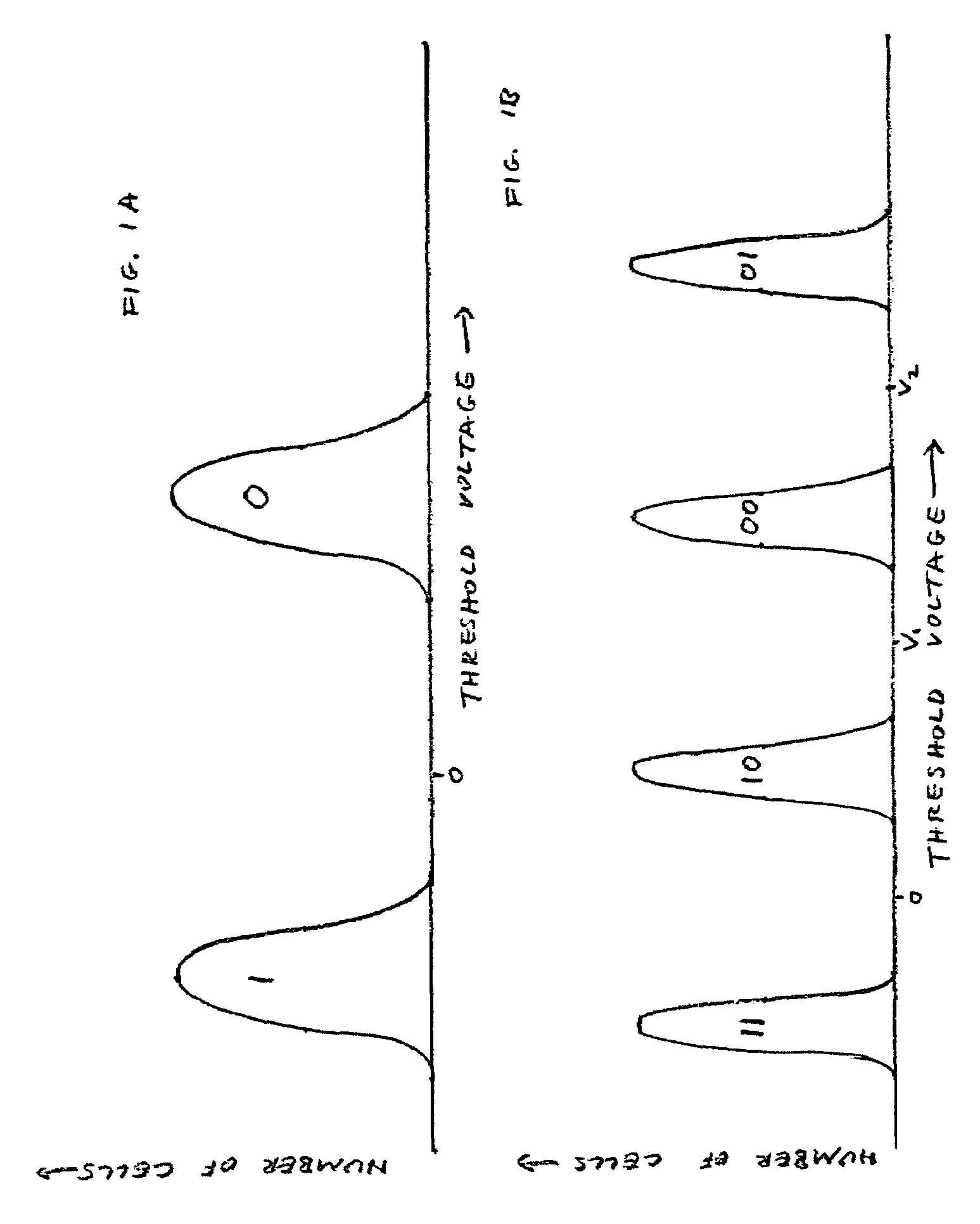

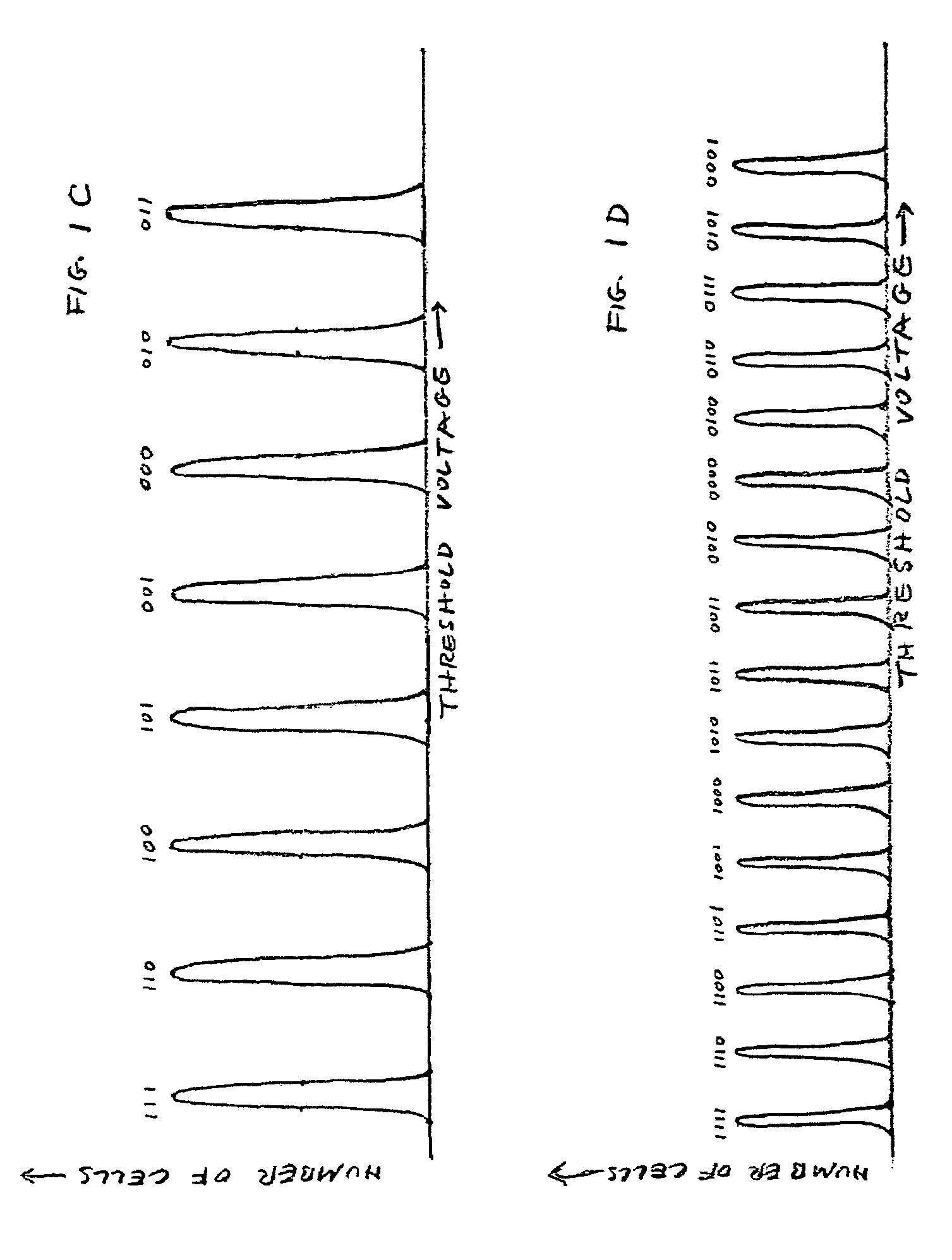

Method of error correction in a multi-bit-per-cell flash memory

InactiveUS20080010581A1Practical to useData representation error detection/correctionError detection/correctionFlash memory

Data are encoded as a systematic or nonsystematic codeword that is stored in a memory such as a flash memory. A representation of the codeword is read from the memory. A plurality of bits related to the representation of the codeword is decoded iteratively. The plurality of bits could be, for example, part or all of the representation of the codeword itself or part or all of the results of preliminary processing of part or all of the representation of the codeword.

Owner:RAMOT AT TEL AVIV UNIV LTD

Apparatus and method for saturating decoder values

InactiveUS7073118B2Television system detailsData representation error detection/correctionSign bitSignomial

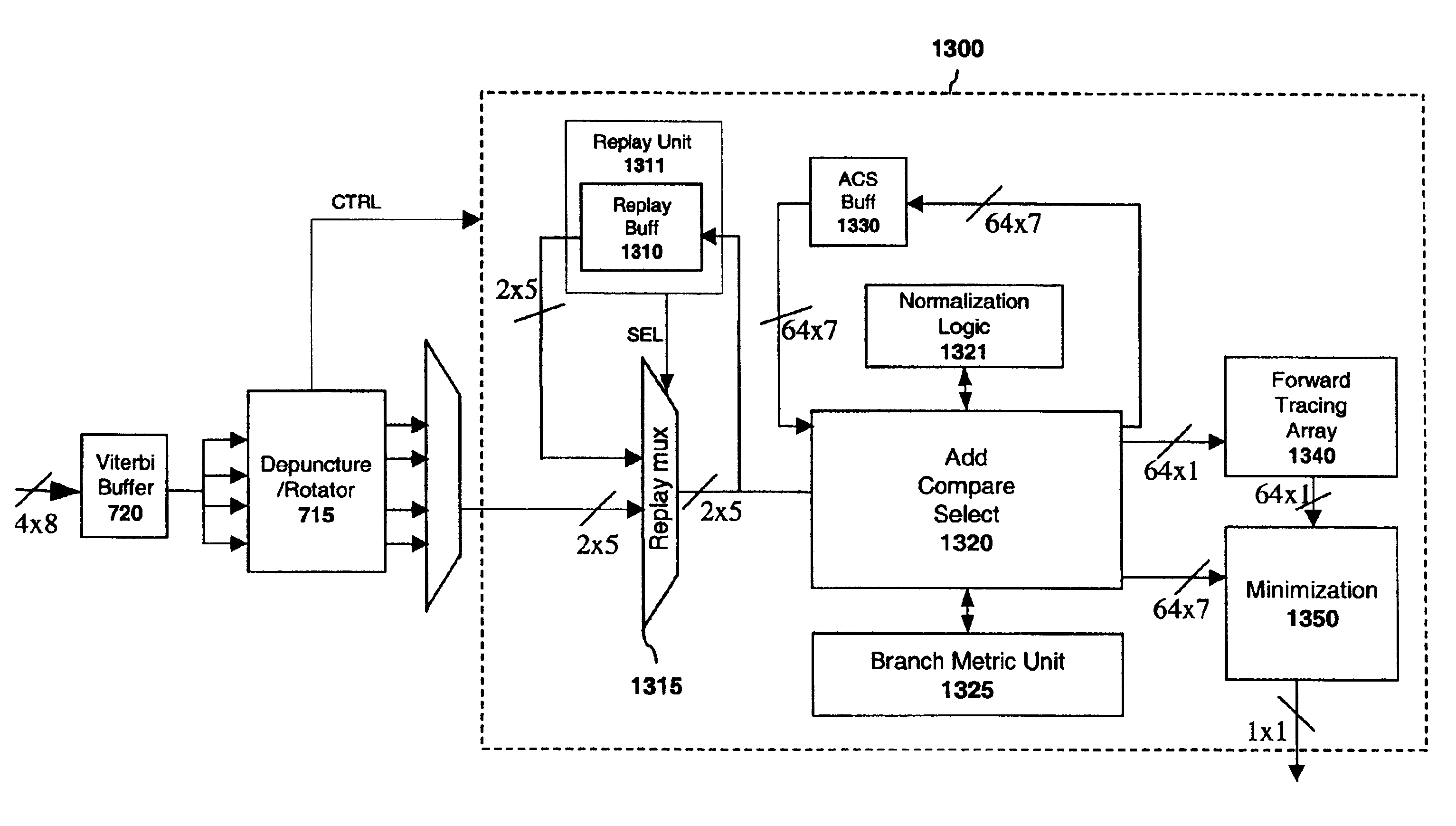

In one embodiment of the invention, during add-compare-select computations, the output of the adders is guaranteed to be a positive value because the only time normalization logic subtracts a normalization amount is when all accumulators are greater than the normalization amount. As such, the detection of overflow is greatly simplified. Overflow in the add-compare-select unit may be indicated simply by the value of the most significant bit (“MSB”) (i.e., the sign bit) of the result. If the MSB of the result of the adder is set then, in one embodiment, the output of the adder gets forced the maximum possible value given the number of bits. For example, this value will be forced to 7h7f if the value is represented by 7-bits. That is to say, if an overflow is detected, then the accumulator is saturated to the maximum value.

Owner:ARRIS ENTERPRISES LLC

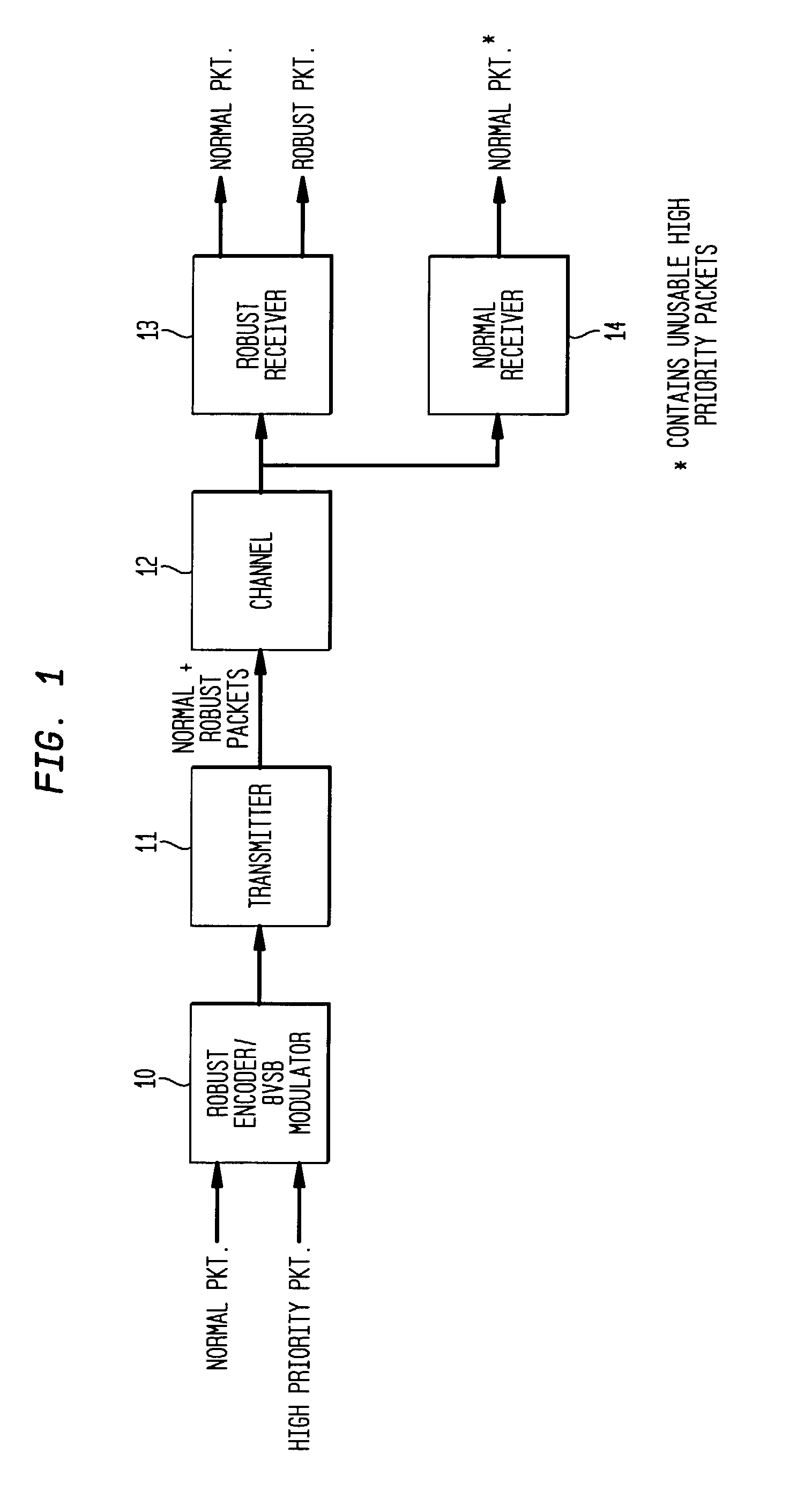

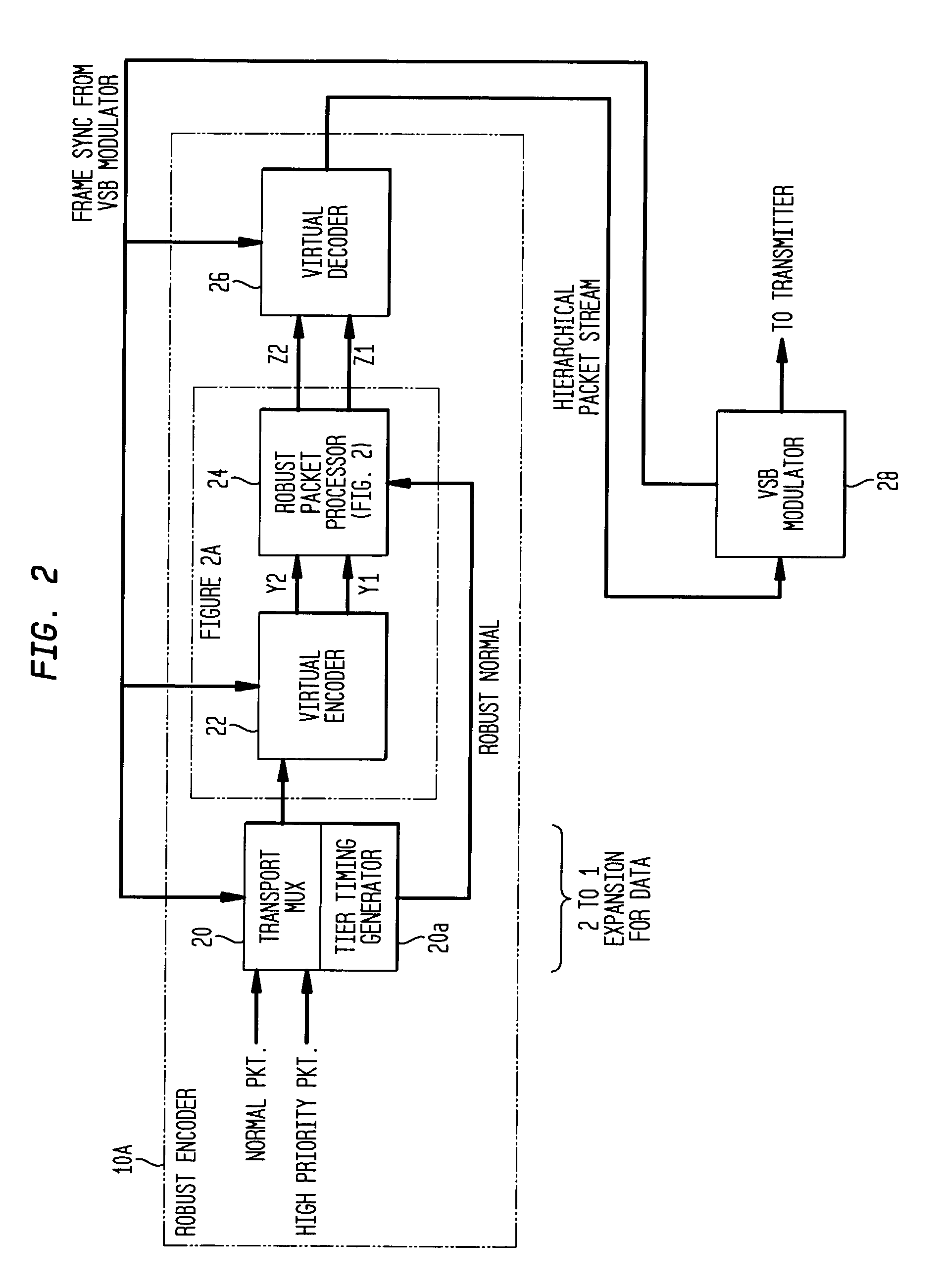

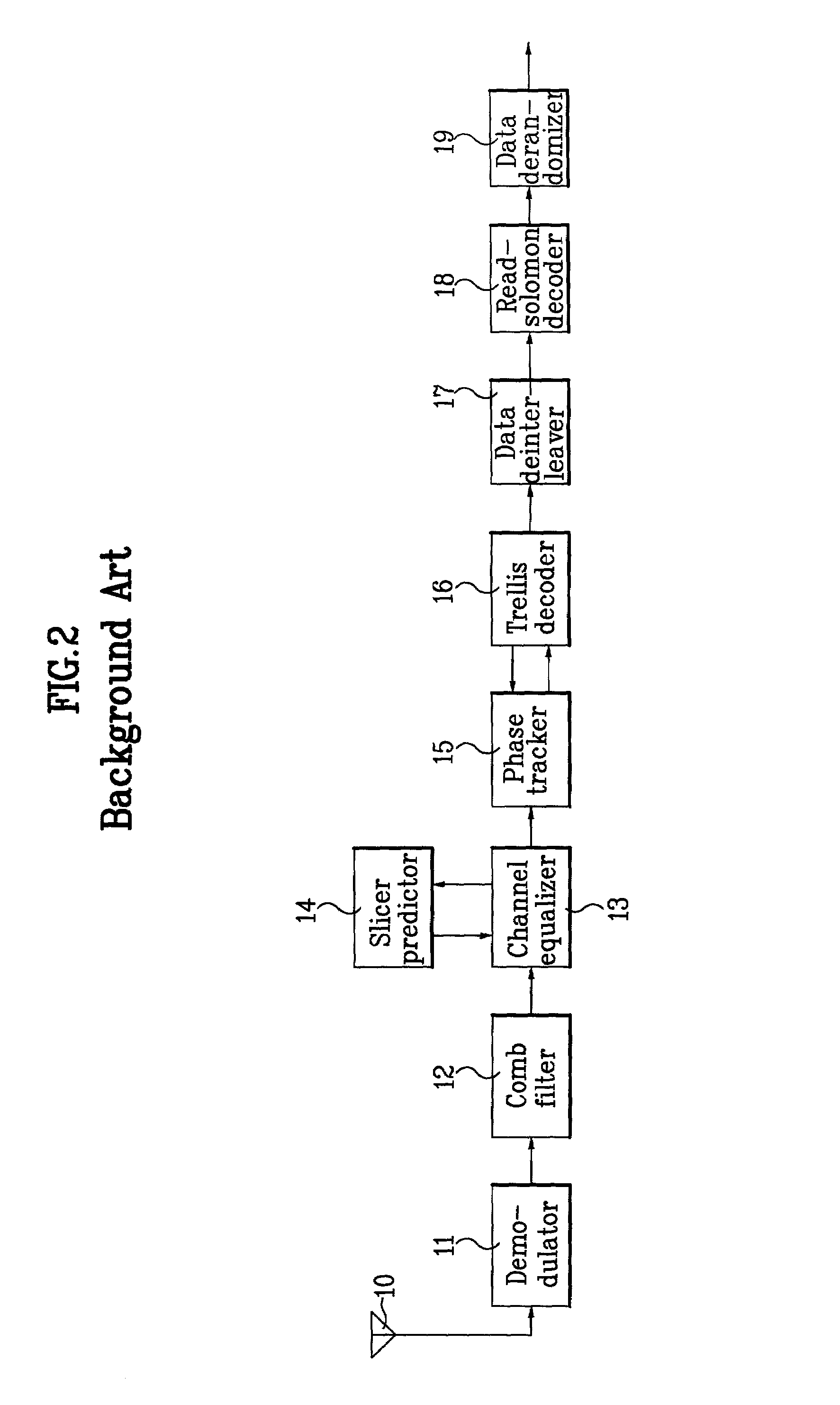

Receiver for robust data extension for 8VSB signaling

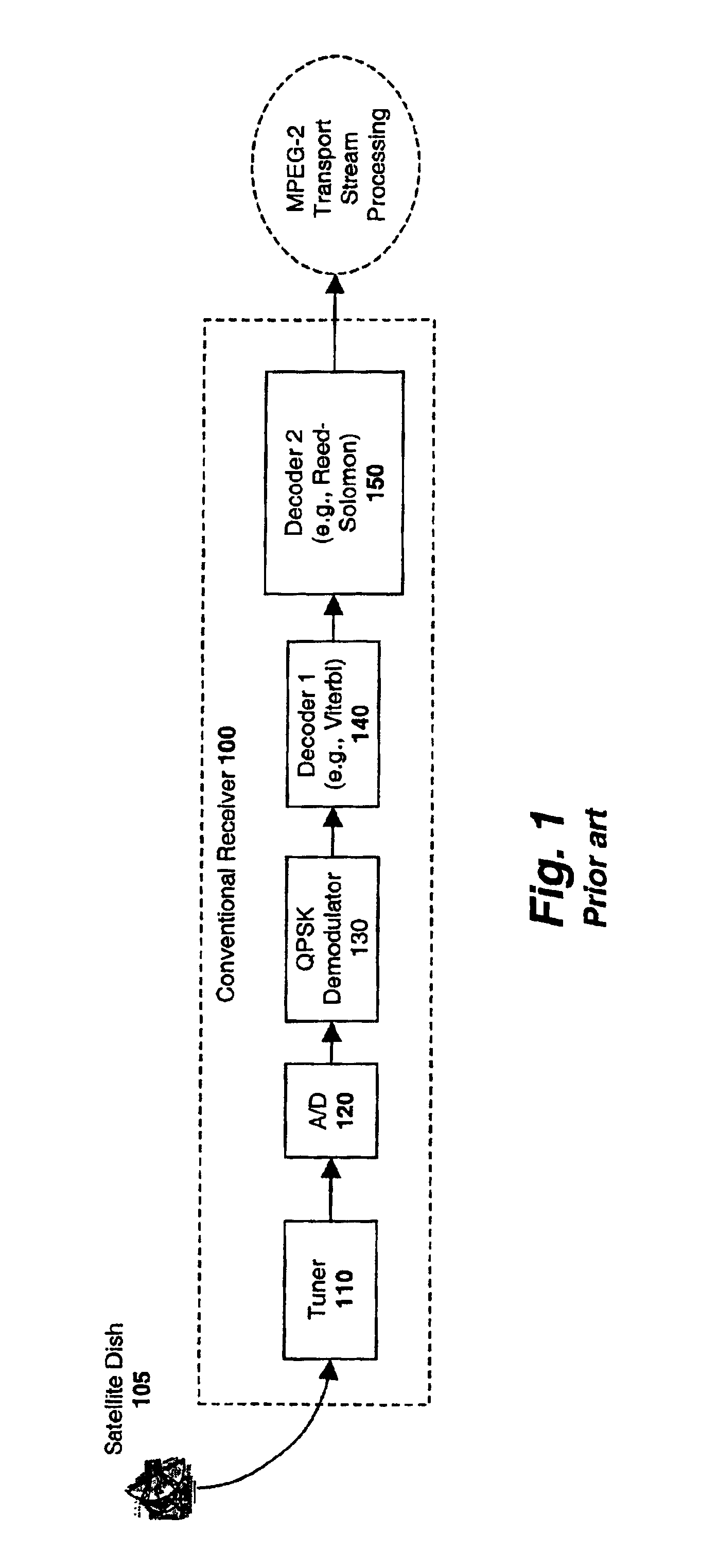

InactiveUS7194047B2Robust of serviceImprove performanceData representation error detection/correctionBroadcast specific applicationsDigital televisionCarrier recovery

A robust data extension, added to a standard 8VSB digital television signal, is used to improve the performance of a digital television receiver. Robust data packets are encoded at a 1 / 3-trellis rate as compared to normal data packets that are encoded at a 2 / 3-trellis rate. In addition to delivery of robust data for mobile applications, the redundant robust data packets also improve the performance of the receiver in the normal tier of service. In particular, the robust data packets improve the performance of the receiver equalizer filter in the presence of rapidly changing transient channel conditions such as dynamic multipath for both robust data packets and normal data packets. The robust data packets improve the performance of the carrier recovery loop and the symbol timing recovery loop. Backward compatibility with existing receivers is maintained for 1) 8VSB signaling, 2) trellis encoding and decoding, 3) Reed Solomon encoding and decoding, and 4) MPEG compatibility.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

Robust signal transmission in digital television broadcasting

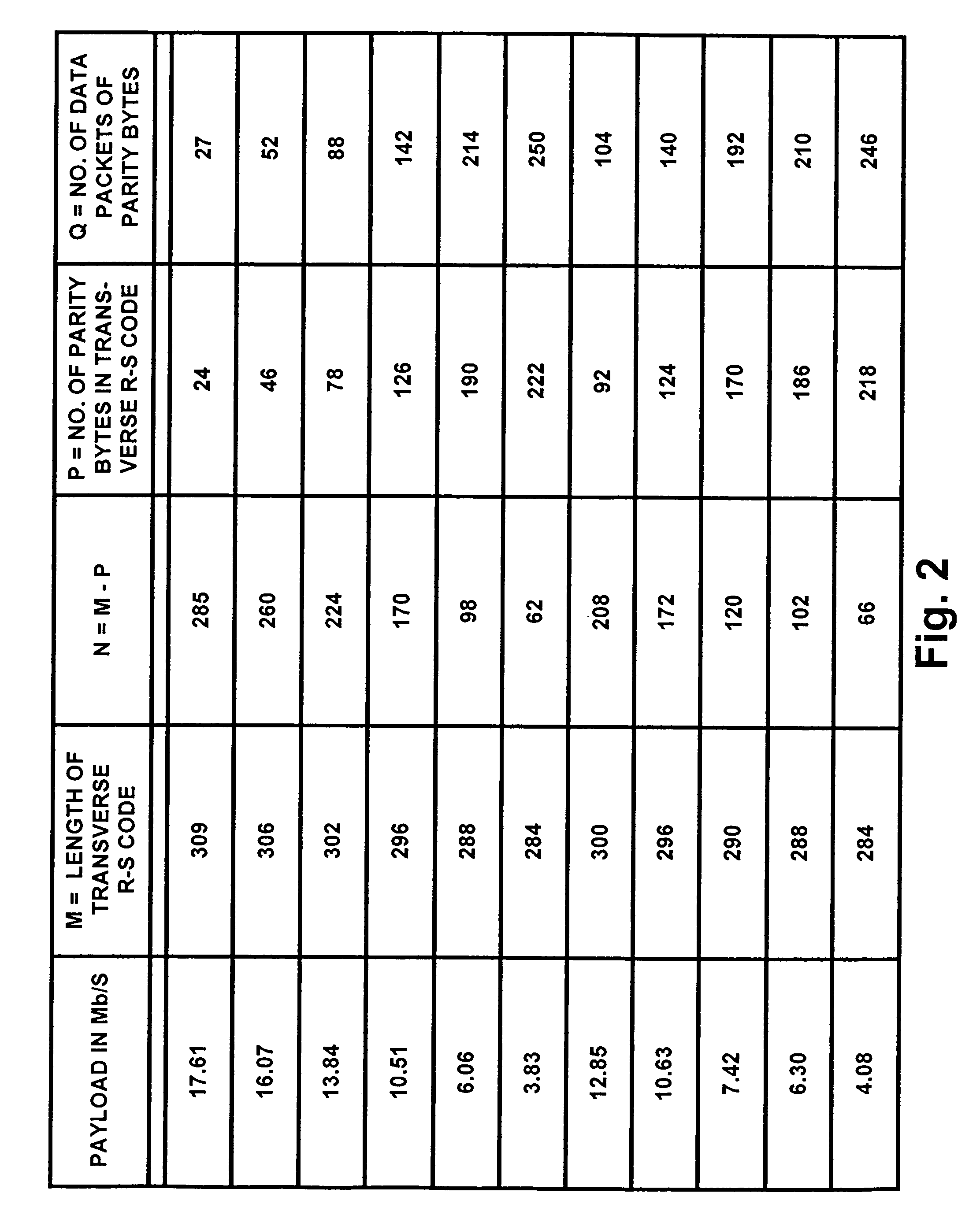

ActiveUS7197685B2Improve the level ofReduce signal to noise ratioTelevision system detailsData representation error detection/correctionData segmentData field

A data field of transmitted digital television signals includes a first set of A / 53-compliant data segments that convey payload information and further includes a second set of A / 53-compliant data segments that contain parity bytes for transverse Reed-Solomon forward-error-correction coding of the data contained within the first set of A / 53-compliant data segments. A digital television receiver uses the parity bytes in the second set of A / 53-compliant data segments to implement transverse Reed-Solomon forward-error-correction decoding that corrects byte errors in the data contained in the first set of A / 53-compliant data segments.

Owner:SAMSUNG ELECTRONICS CO LTD

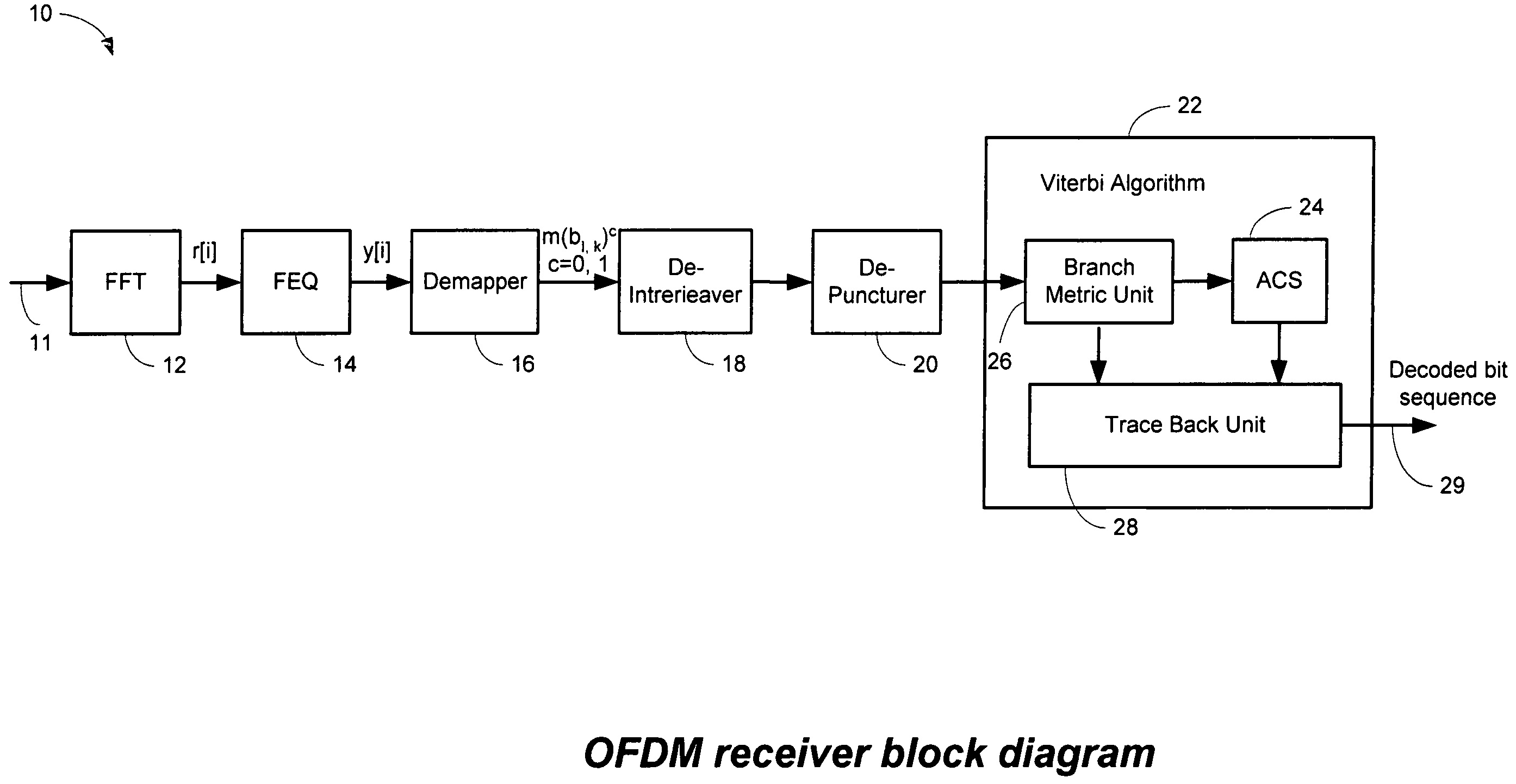

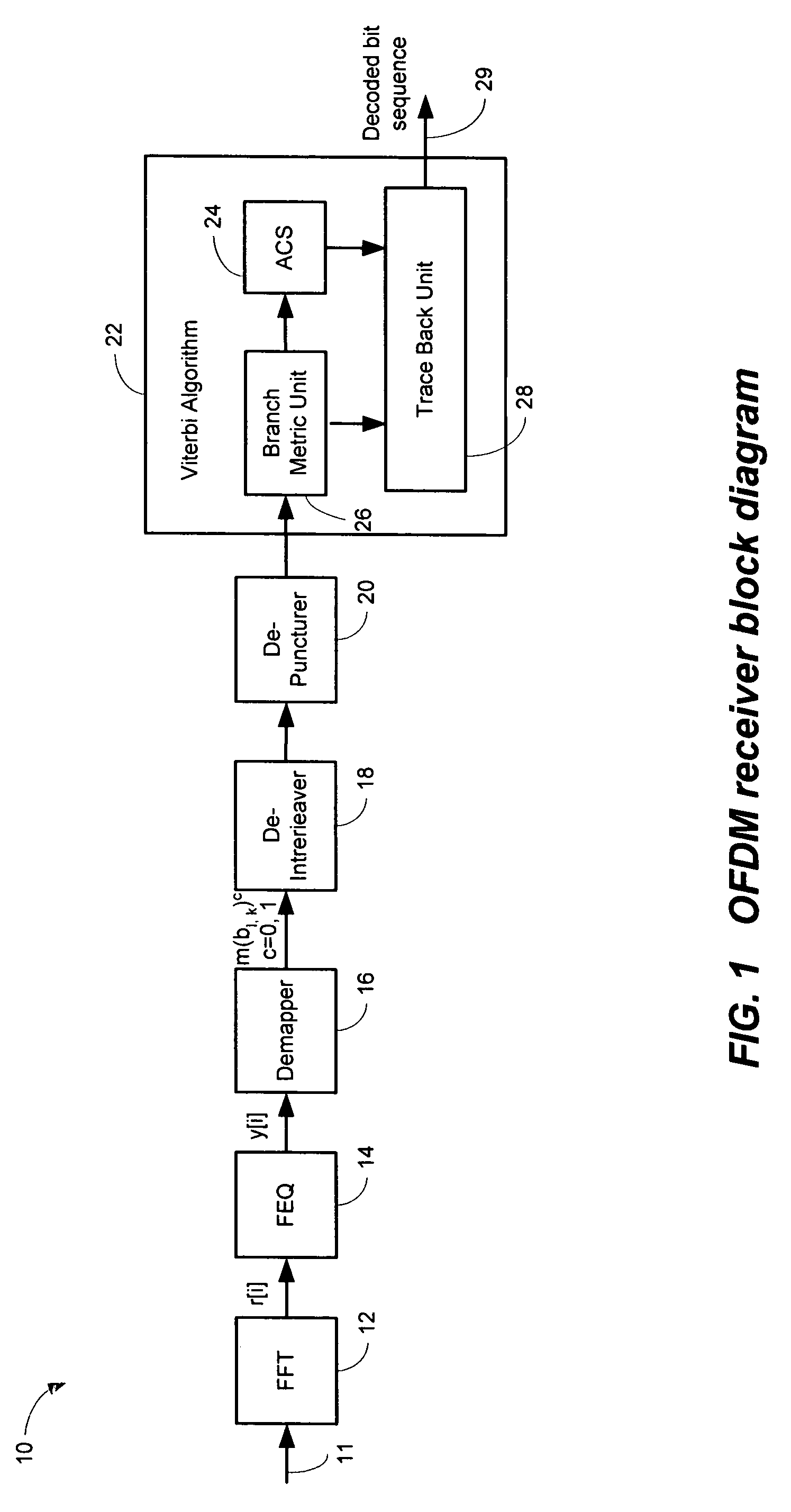

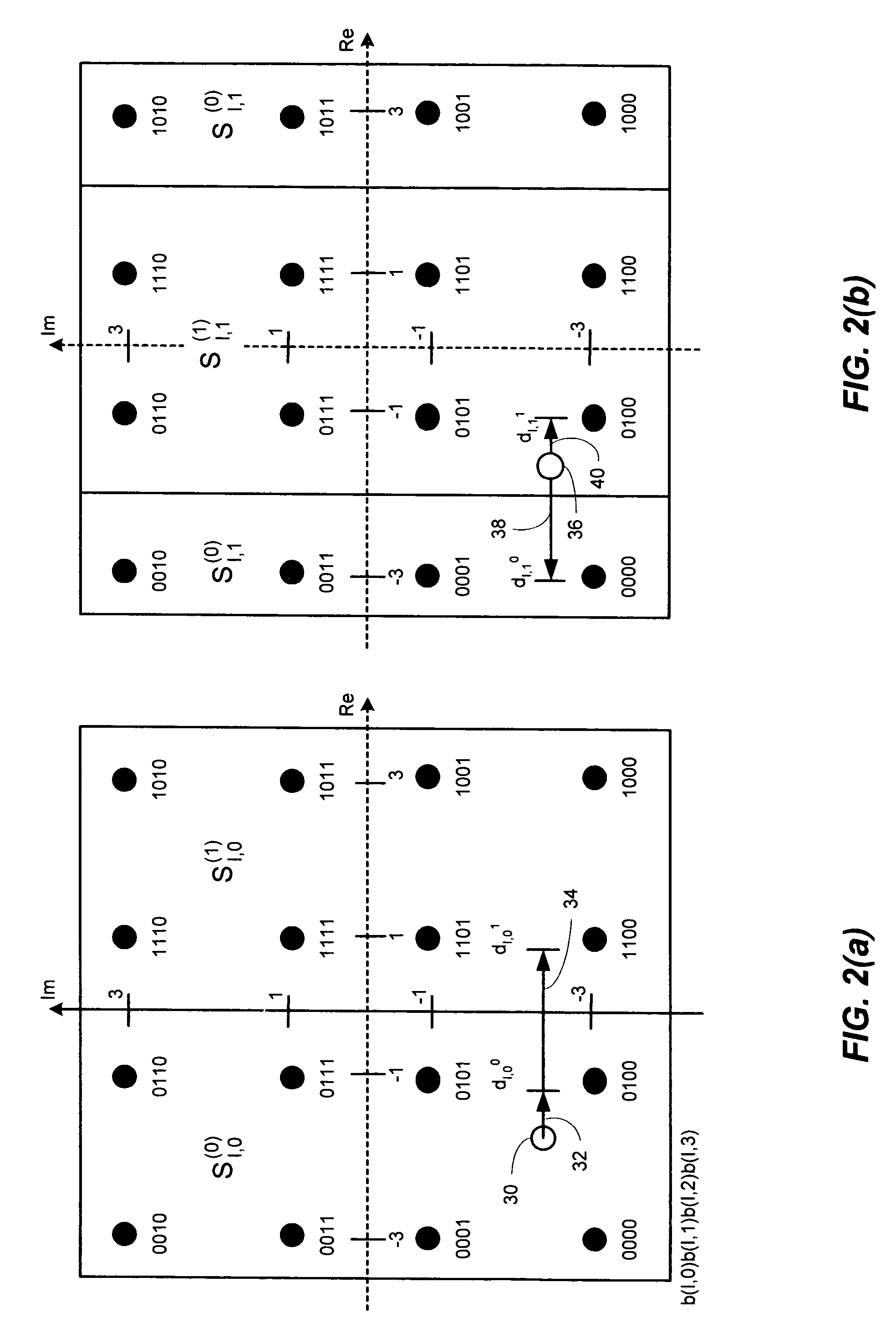

Efficient soft decision demapper to minimize viterbi decoder complexity

InactiveUS7313750B1Improve performanceSmall sizeData representation error detection/correctionOther decoding techniquesViterbi decoderComputer science

A receiver system that receives signals and has a demapper device that is responsive to an equalizer output and generates a demapper output including one or more bit metrics. The receiver system also generates equalizer output, and the demapper uses distance measure to calculate bit metrics. The receiver system uses demapper output to generate a processed output. The receiver system further includes a convolutional decoder which is responsive to the processed output, and subsequently generates a decoded bit sequence, as well as uses the processed output to generate one or more path metrics. The convolutional decoder uses bit metrics and path metrics to the decode processed output, to generate a decoded bit sequence. The receiver system uses the distance measure to reduce the size of the bit metrics and the size of the path metrics to improve the performance of said convolutional decoder.

Owner:MEDIATEK INC

Method of error correction in a multi-bit-per-cell flash memory

InactiveUS7533328B2Data representation error detection/correctionError detection/correctionFlash memory

Data are encoded as a systematic or nonsystematic codeword that is stored in a memory such as a flash memory. A representation of the codeword is read from the memory. A plurality of bits related to the representation of the codeword is decoded iteratively. The plurality of bits could be, for example, part or all of the representation of the codeword itself or part or all of the results of preliminary processing of part or all of the representation of the codeword.

Owner:RAMOT AT TEL AVIV UNIV LTD

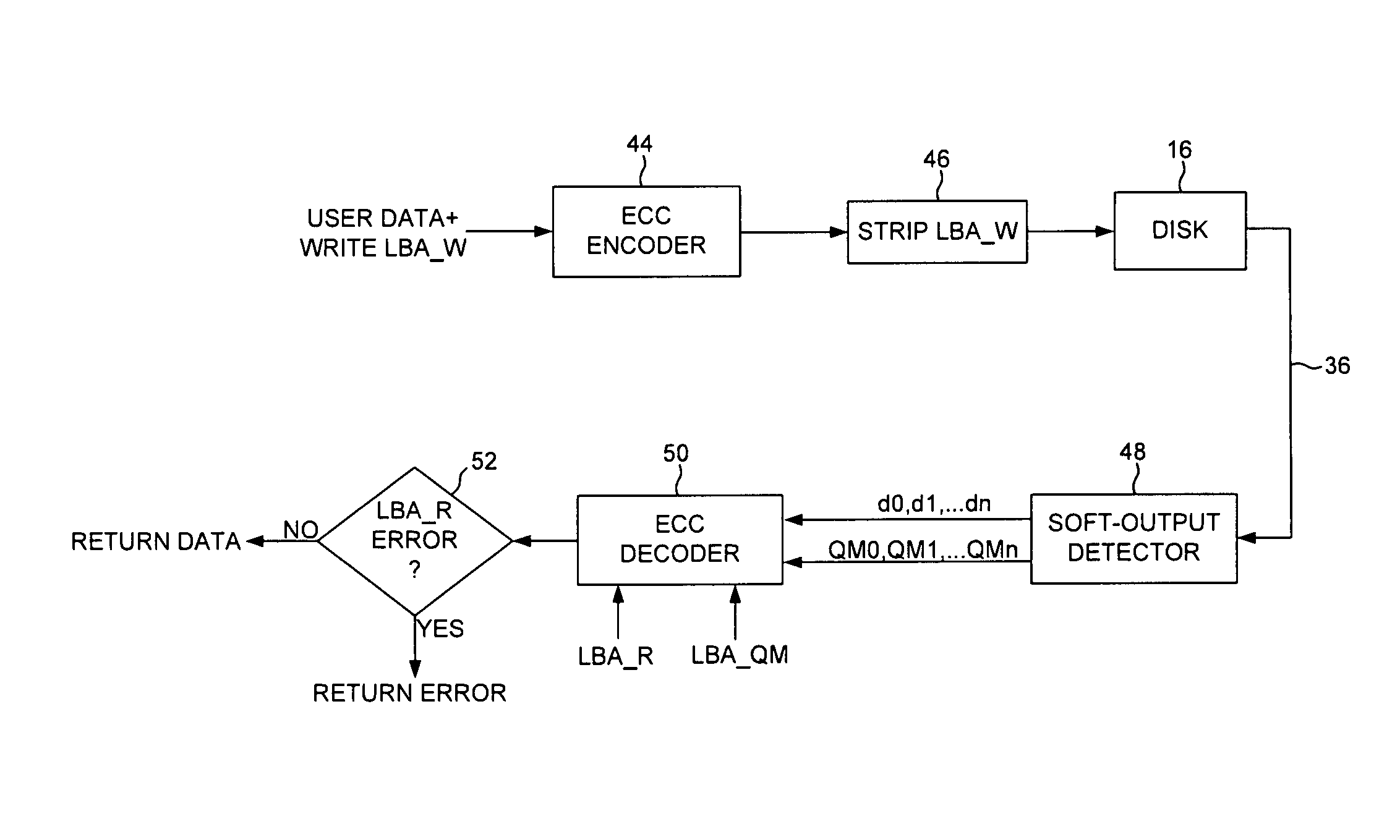

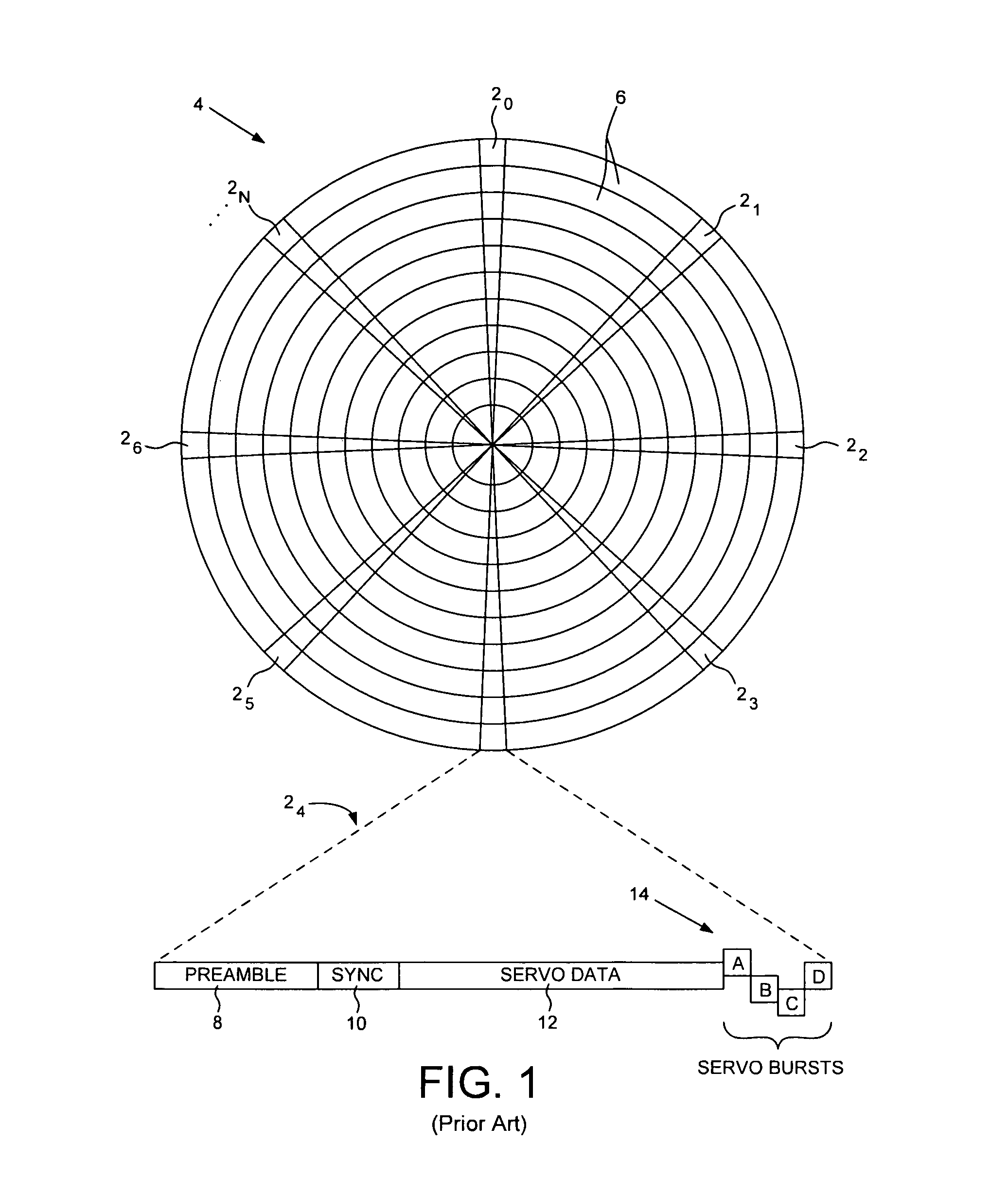

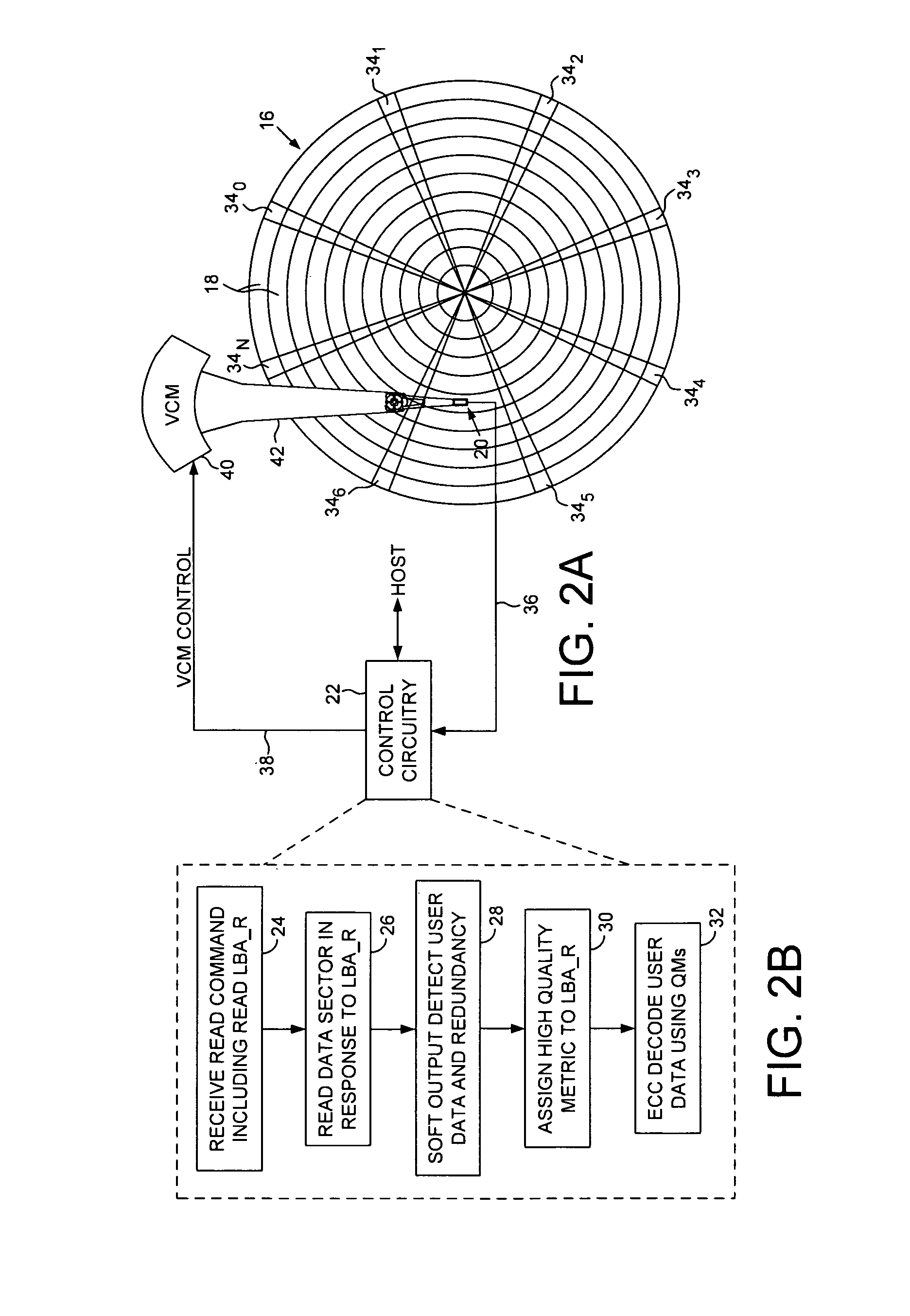

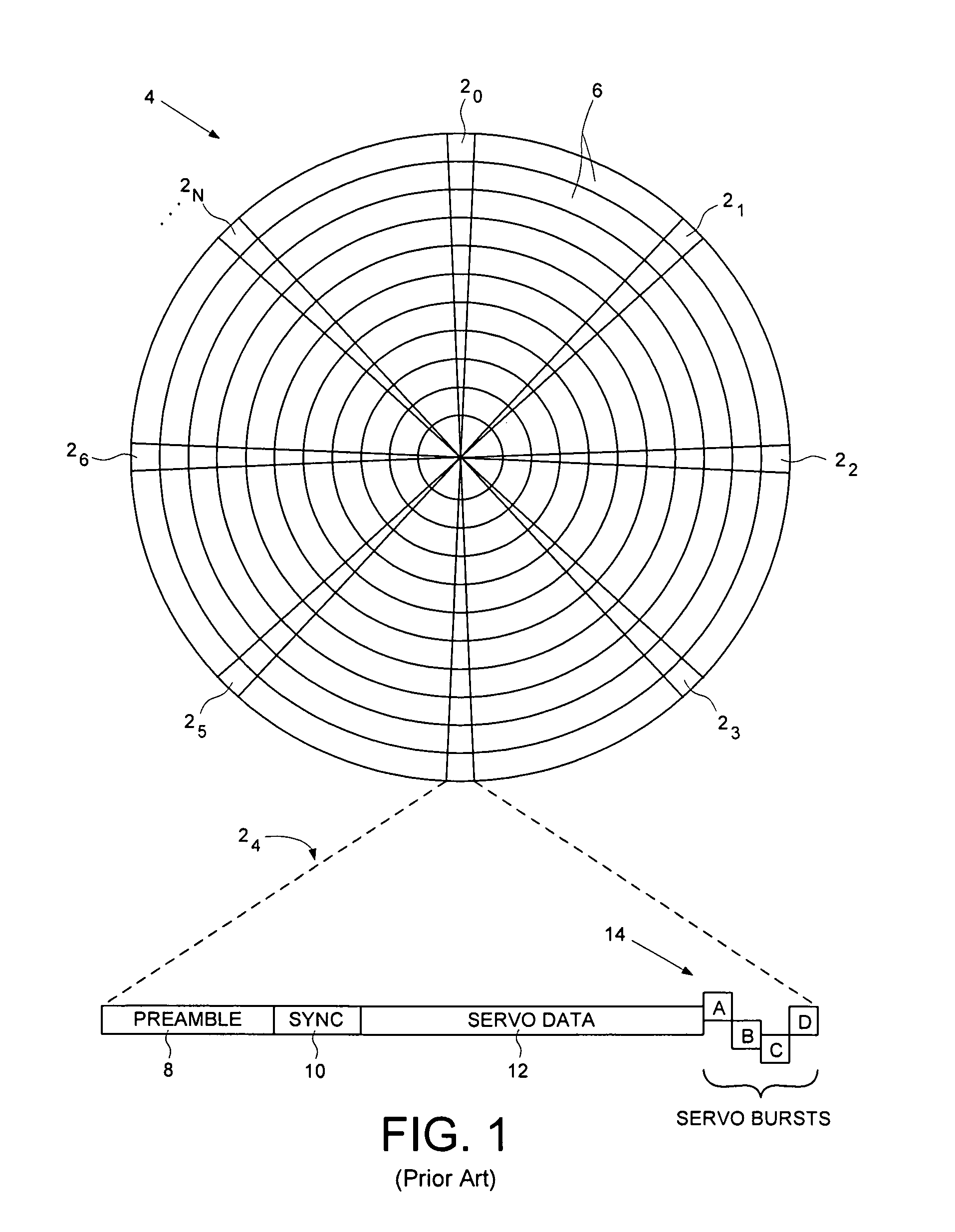

Data storage device employing high quality metrics when decoding logical block address appended to a data sector

ActiveUS8413010B1Data representation error detection/correctionCode conversionLogical block addressingCorrection code

A data storage device is disclosed that receives a read command from a host, wherein the read command comprises a read logical block address (LBA_R). A target data sector is read in response to the LBA_R to generate a read signal. The read signal is processed to detect user data and redundancy data using a soft-output detector that outputs quality metrics for the user data and redundancy data. A high quality metric is assigned to the LBA_R, and errors are corrected in the user data using an error correction code (ECC) decoder in response to the quality metrics output by the soft-output detector and the quality metrics assigned to the LBA_R.

Owner:WESTERN DIGITAL TECH INC

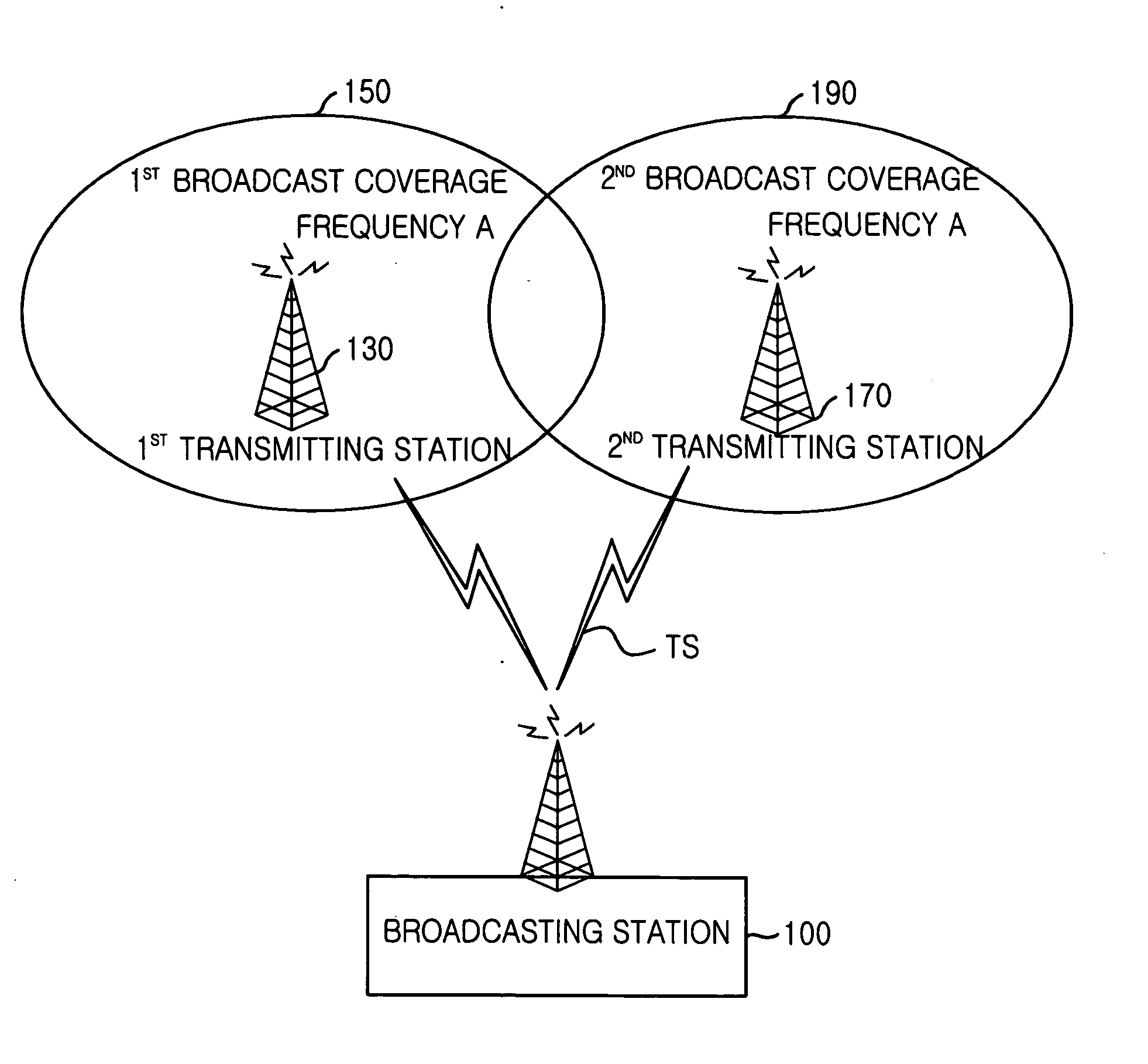

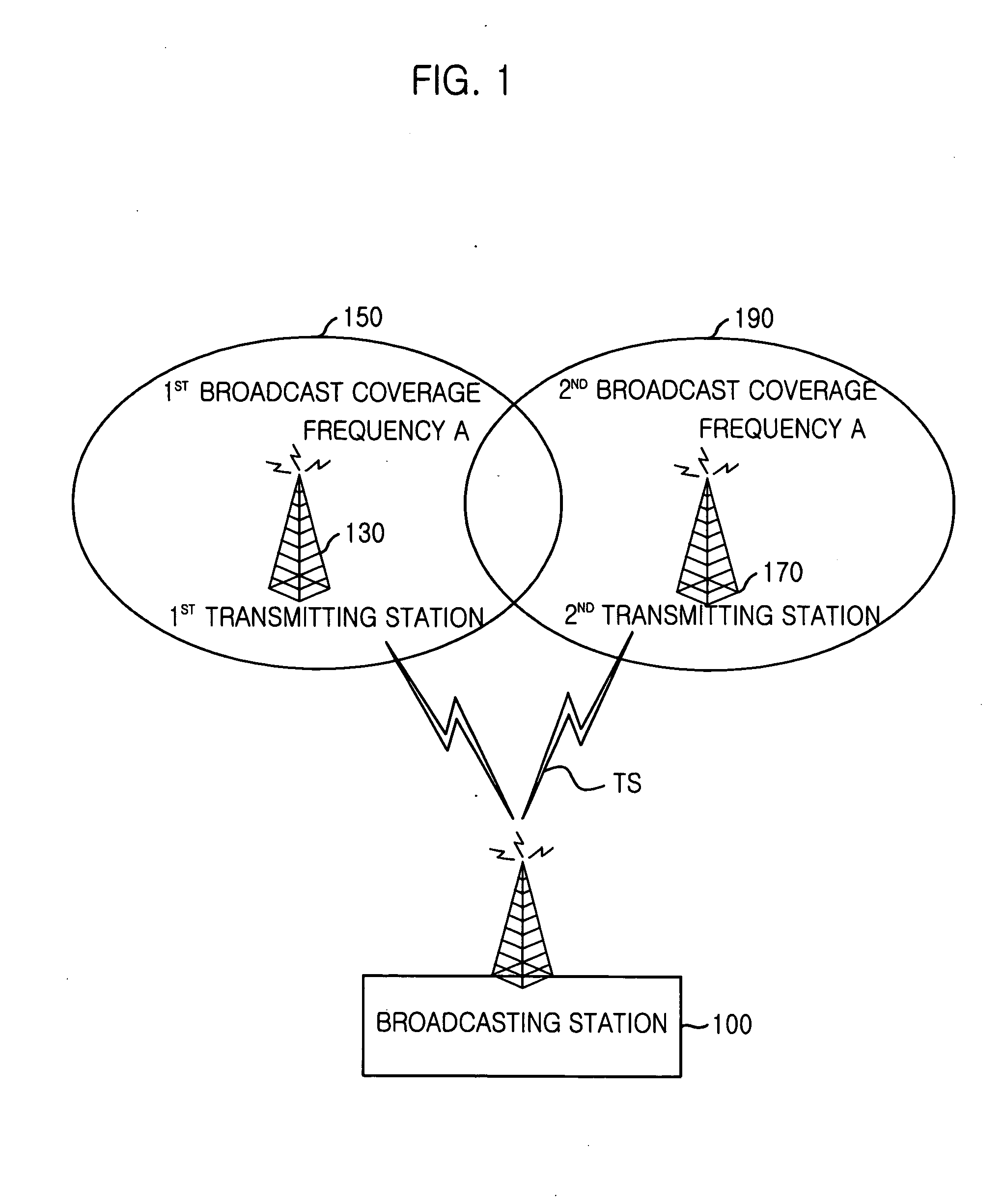

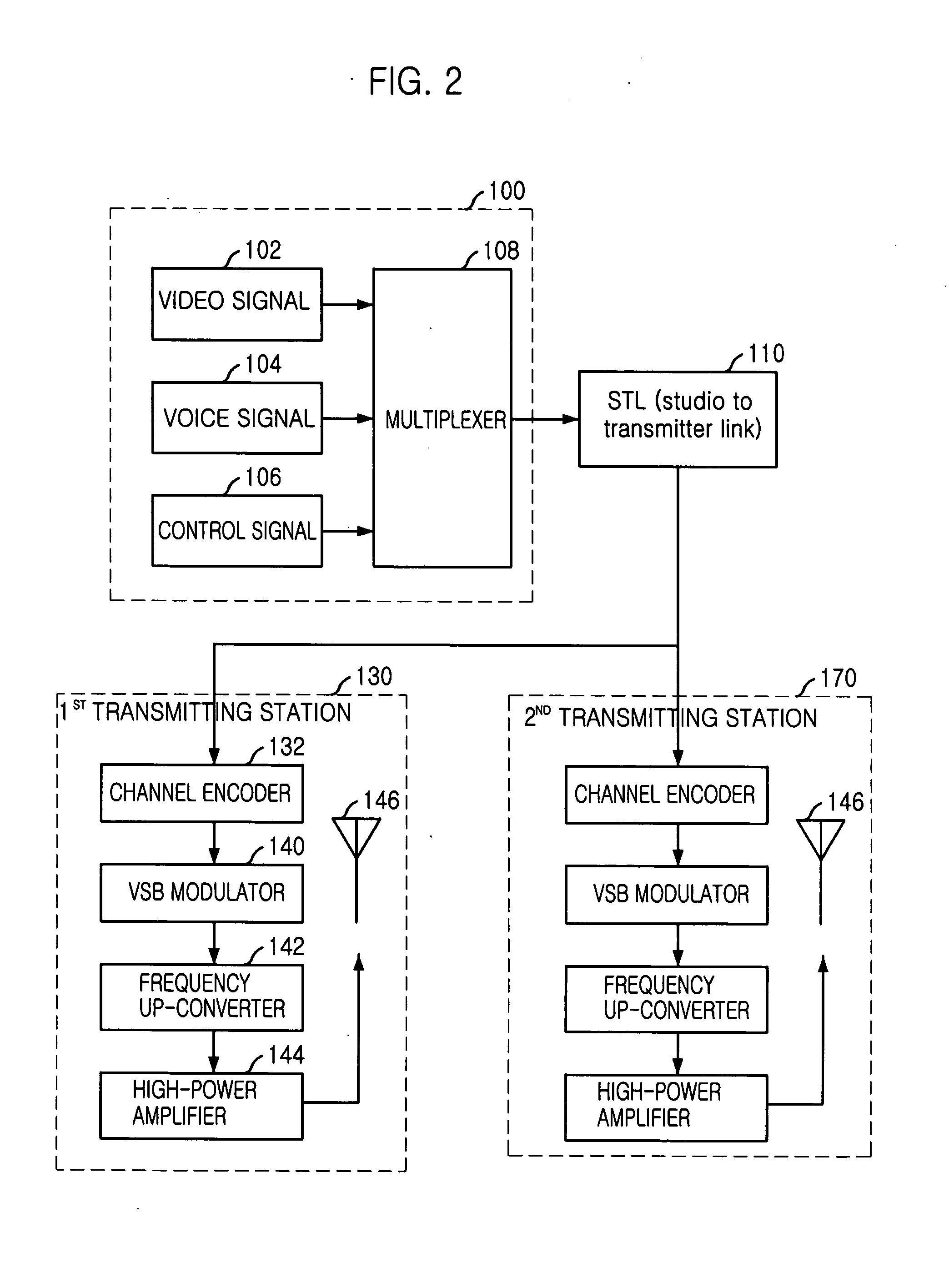

System and method for providing terrestrial digital broadcasting service using single frequency network

InactiveUS20060253890A9Television system detailsData representation error detection/correctionMultiplexingInit

Provided is a system and method for terrestrial digital broadcasting service using a single frequency network without additional equipment. The system and method synchronizes input signals into transmitting stations by inserting a transmission synchronization signal into a header of TS periodically, and solves the problematic ambiguity of the trellis encoder by including a trellis encoder switching unit separately and initializing a memory of the trellis encoder. The terrestrial digital broadcasting system includes: a broadcasting station for multiplexing video, voice and additional signals into transport stream (TS) and transmitting the TS to the transmitting stations and a transmitting stations for receiving the TS and broadcast the TS to receiving stations through a single frequency network

Owner:ELECTRONICS & TELECOMM RES INST

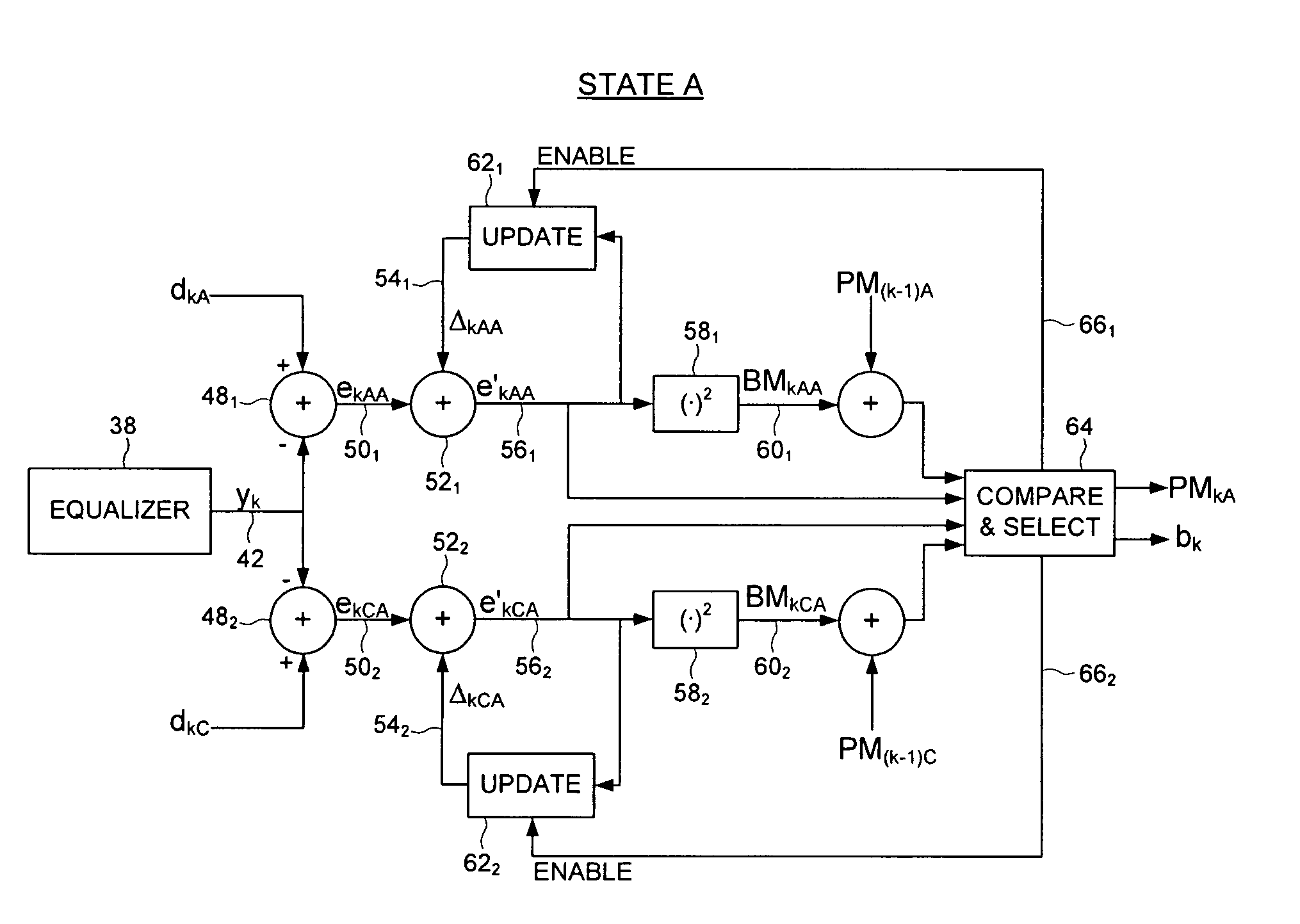

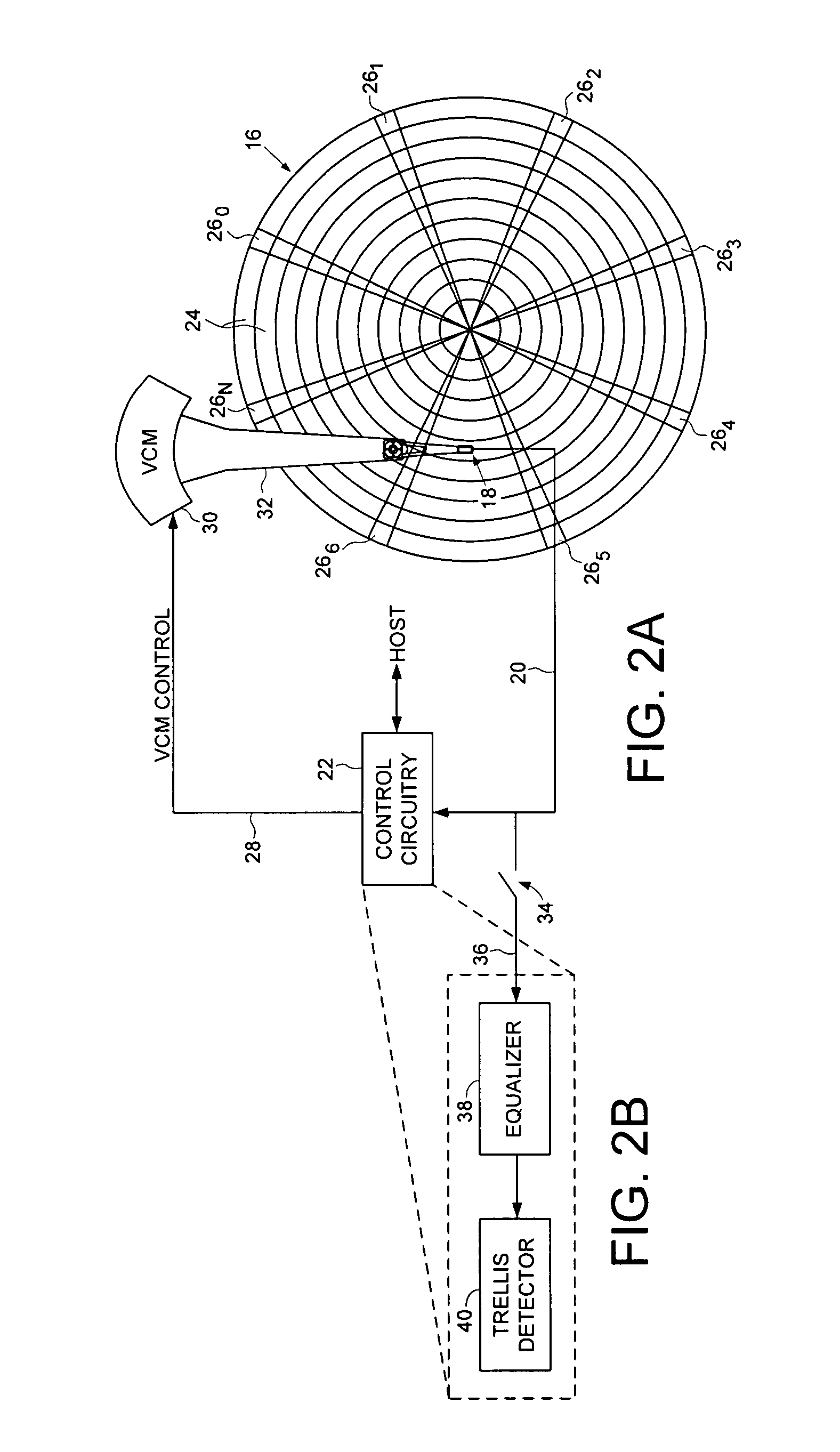

Disk drive comprising a trellis detector having a read signal whitener in the ACS circuit

InactiveUS8201066B1Modification of read/write signalsData representation error detection/correctionComputer scienceData sequences

A disk drive is disclosed comprising a disk, a head actuated over the disk to generate a read signal, and a trellis detector for detecting an estimated data sequence from the read signal. The trellis detector comprises a sampling device operable to sample the read signal to generate a sequence of signal sample values, and a plurality of add / compare / select (ACS) circuits each corresponding to a state in a trellis. Each ACS circuit comprises a first and second branch metric calculators for computing first and second branch metrics in response to first and second errors adjusted in response to first and second deltas that compensate for a distortion in the read signal.

Owner:WESTERN DIGITAL TECH INC

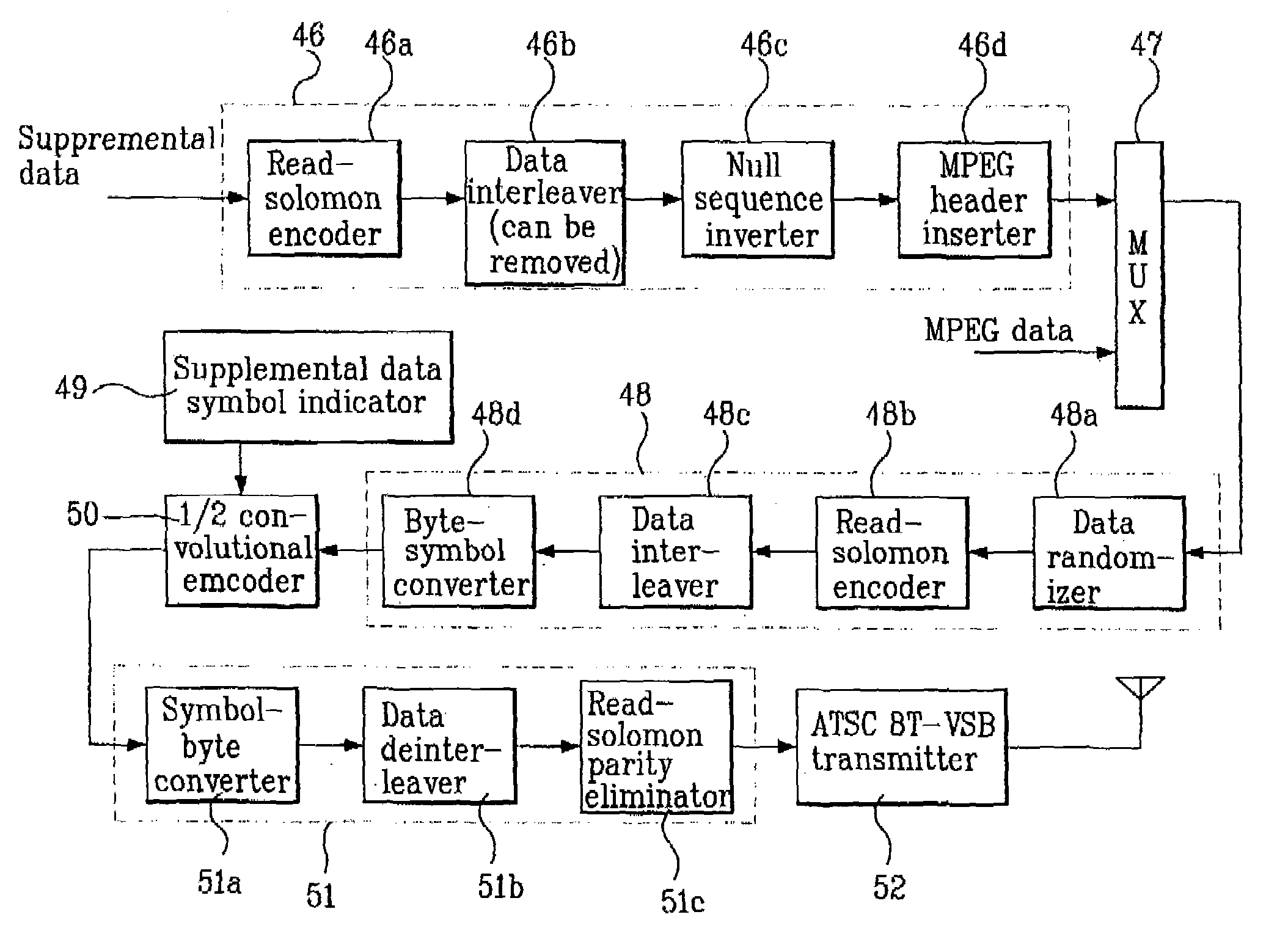

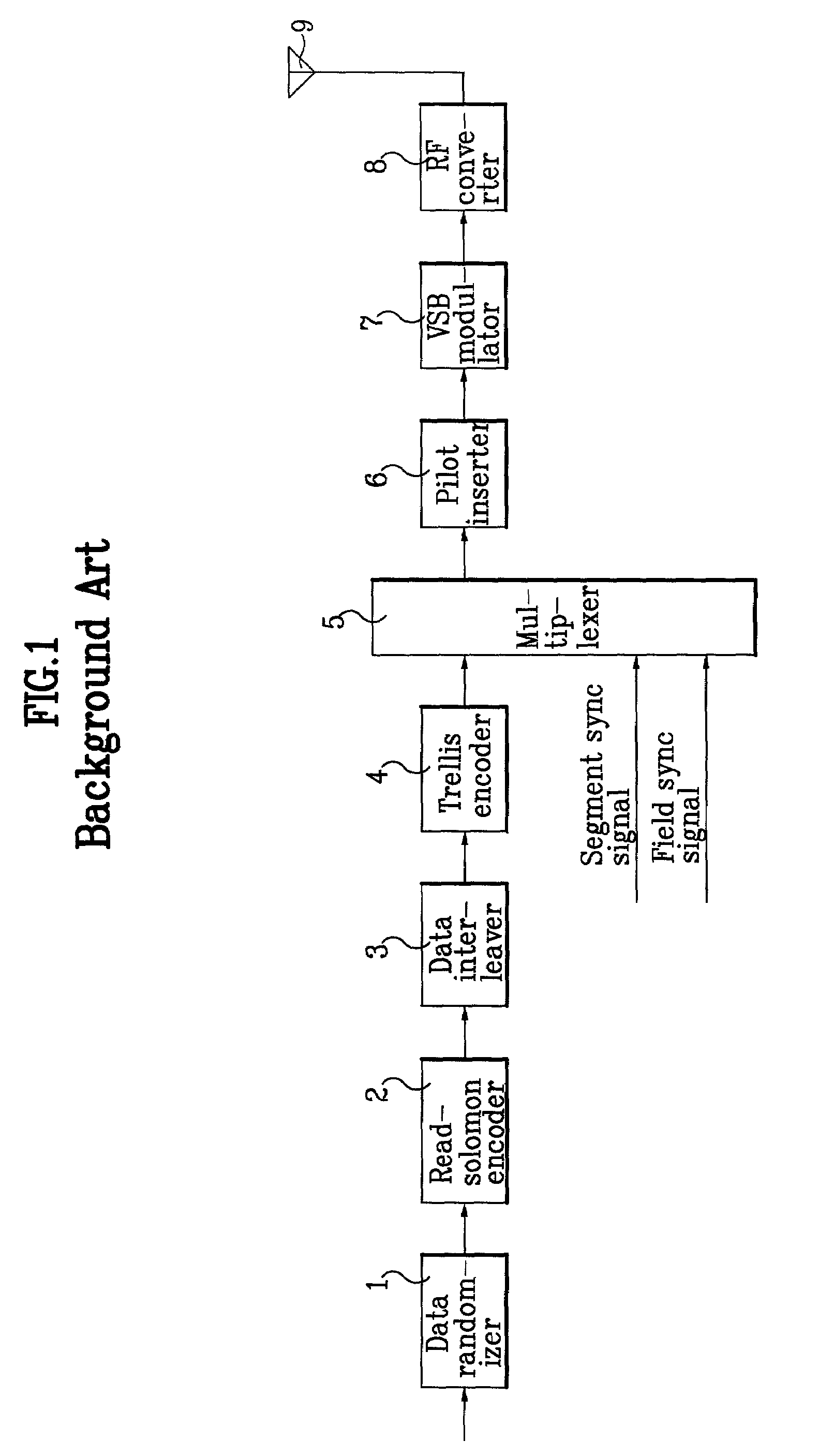

Digital VSB transmission system

InactiveUS6980603B2Noise robustData representation error detection/correctionCode conversionNoise levelComputer science

A digital VSB transmission system in disclosed. The system is compatible with the existing ATSC 8T-VSB receiver and able to transmit additional supplemental data as well as MPEG image / sound data. It initially encodes the information bit of the supplemental data with a ½ encoding rate in order to produce a parity bit and sends the parity bit together with the information bit. Therefore, both of the MPEG image / sound data and the supplemental data can be transmitted properly even through a channel having a high ghost and / or noise level. Particularly, it can significantly improve performances of the slicer predictor and trellis decoder of the VSB receiver.

Owner:LG ELECTRONICS INC

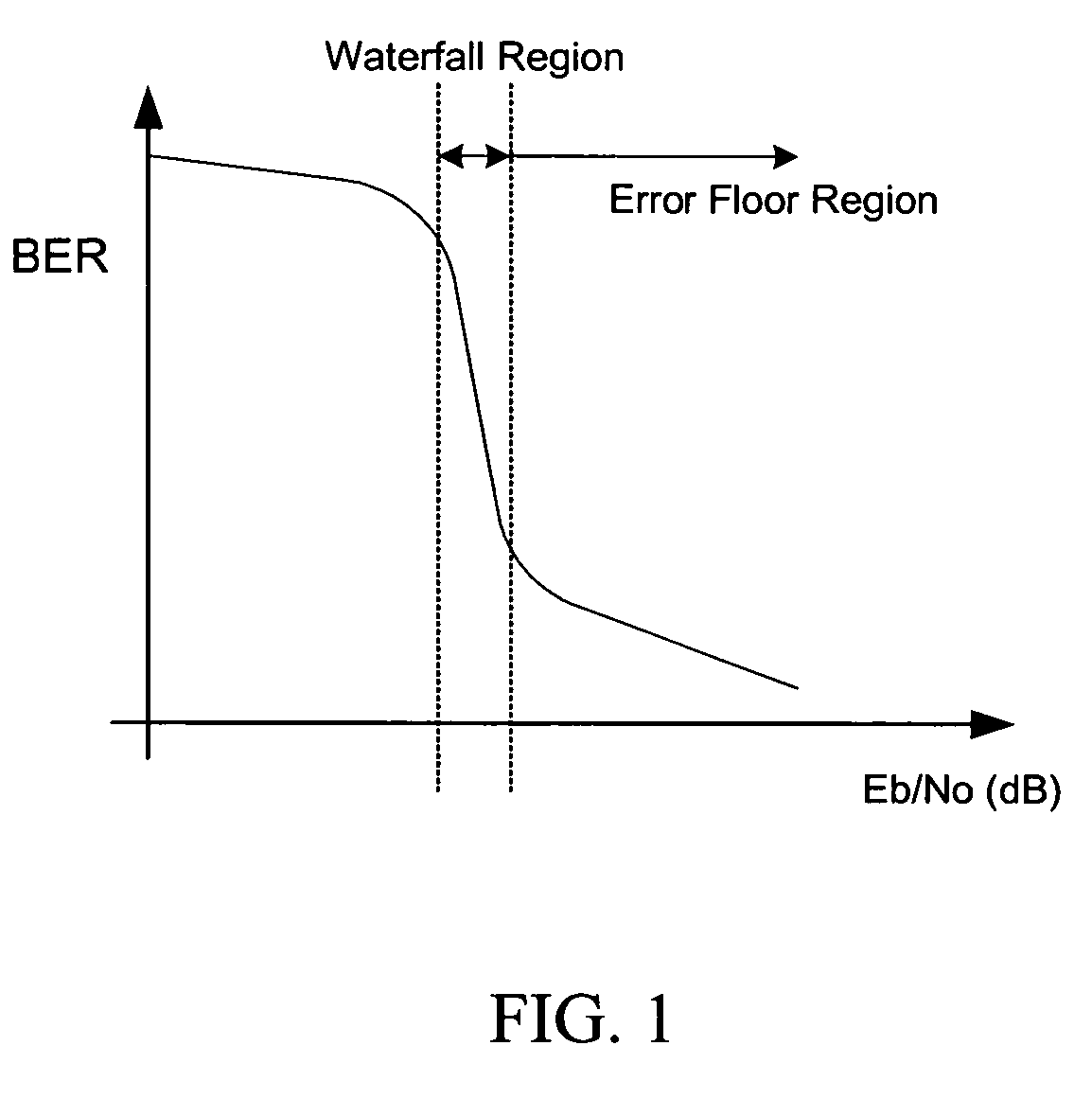

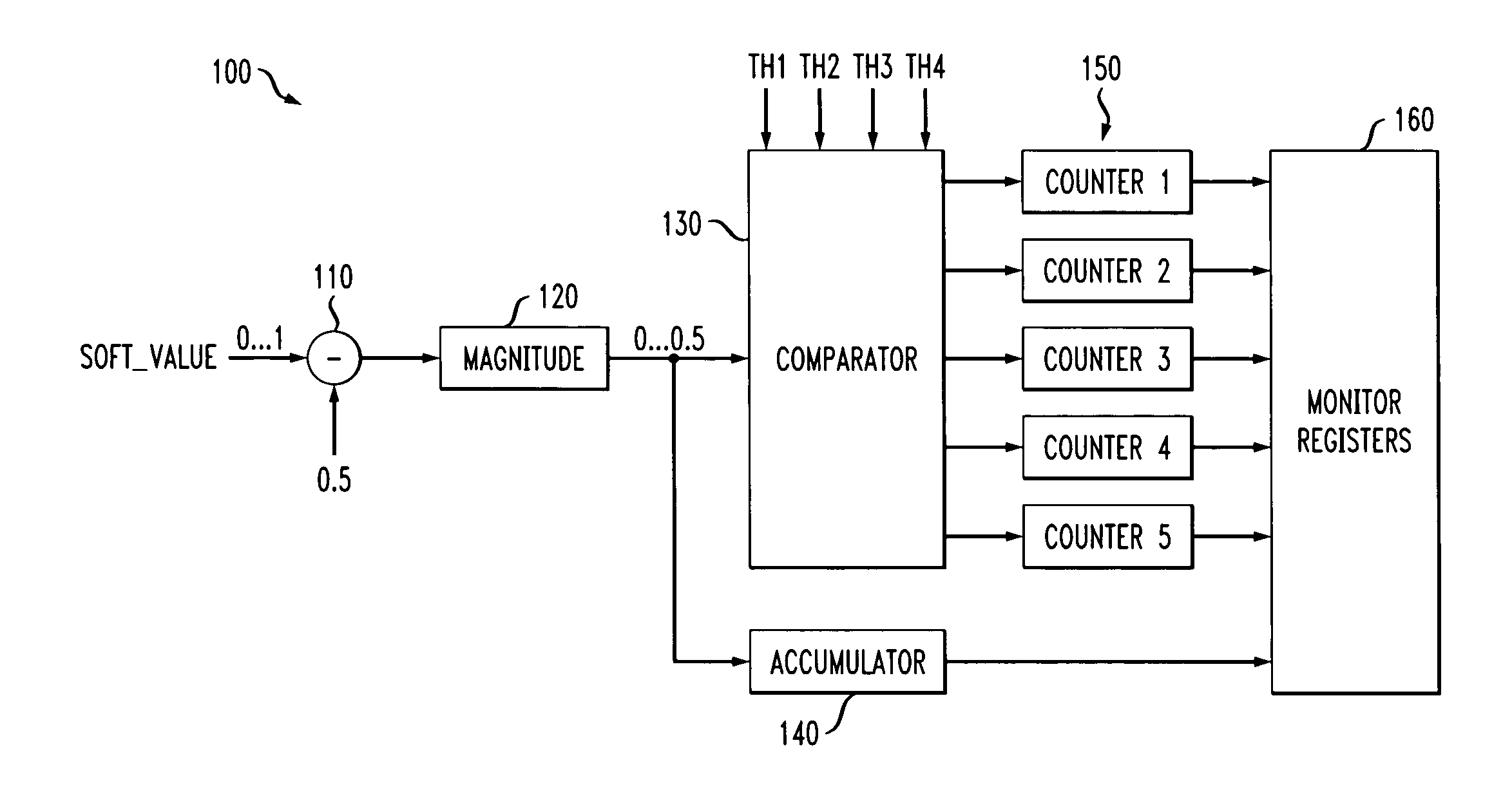

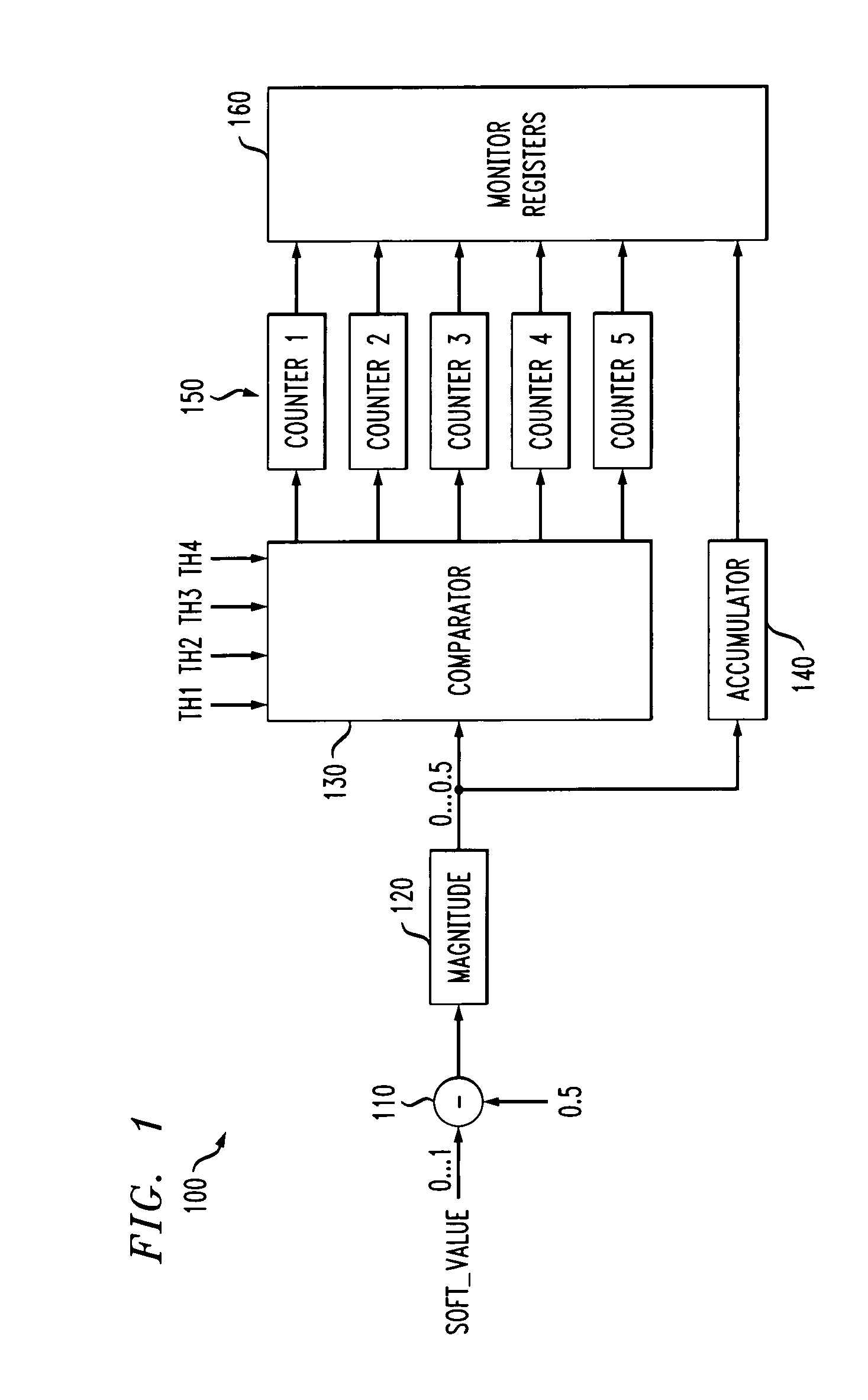

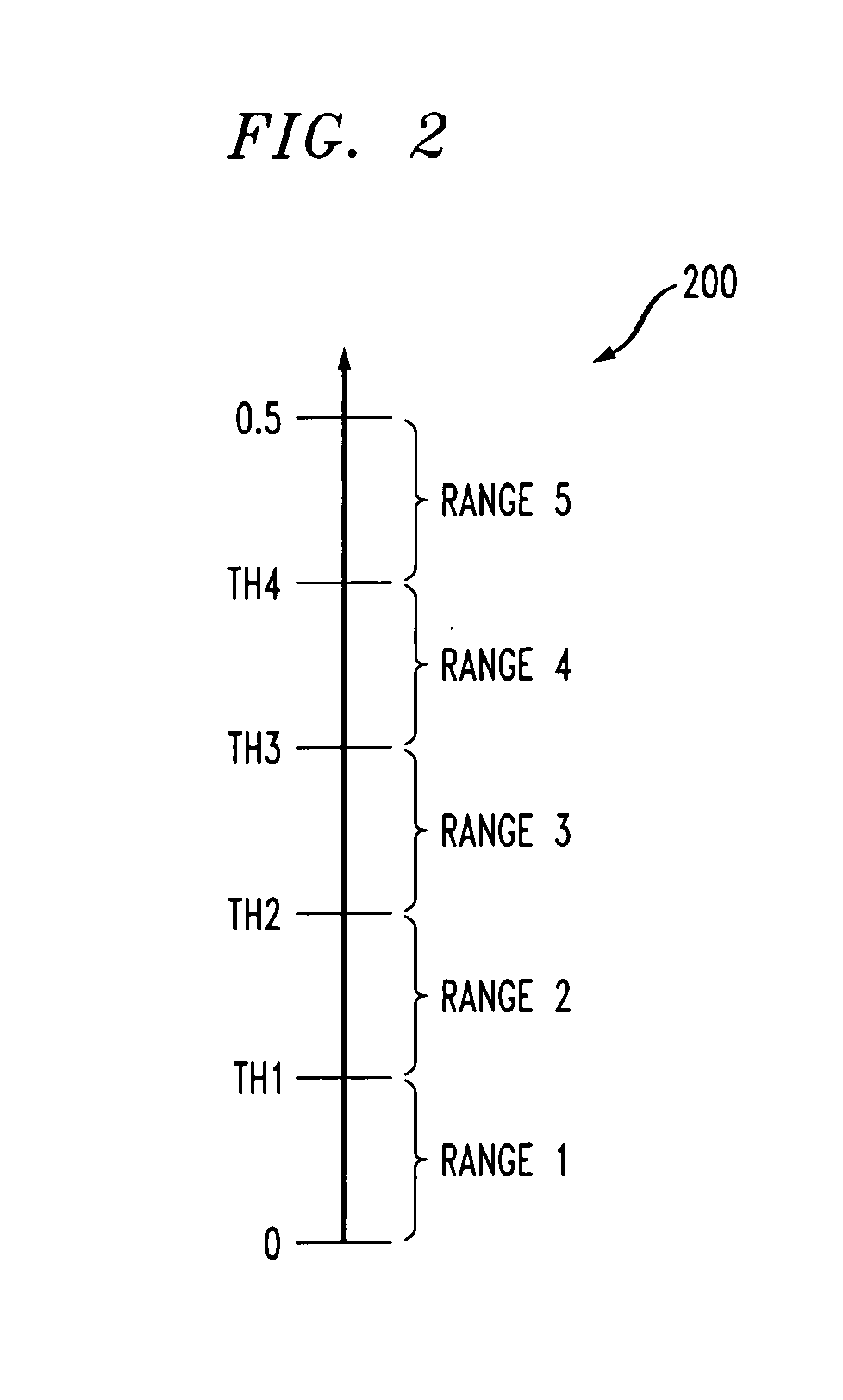

Method and apparatus for evaluating performance of a read channel

ActiveUS20060195772A1Less timeData representation error detection/correctionOther error detection/correction/protectionLogitLog likelihood

Methods and apparatus are provided for measuring the performance of a read channel. A number of detection techniques, such as SOVA and maximum-a-posteriori (MAP) detectors, produce a bit decision and a corresponding reliability value associated with the bit decision. The reliability value associated with the bit decision may be expressed, for example, in the form of log likelihood ratios (LLRs). The reliability value can be monitored and used as a performance measure. The present invention provides a channel performance measure that generally correlates directly to the BER but can be collected in less time.

Owner:AVAGO TECH INT SALES PTE LTD

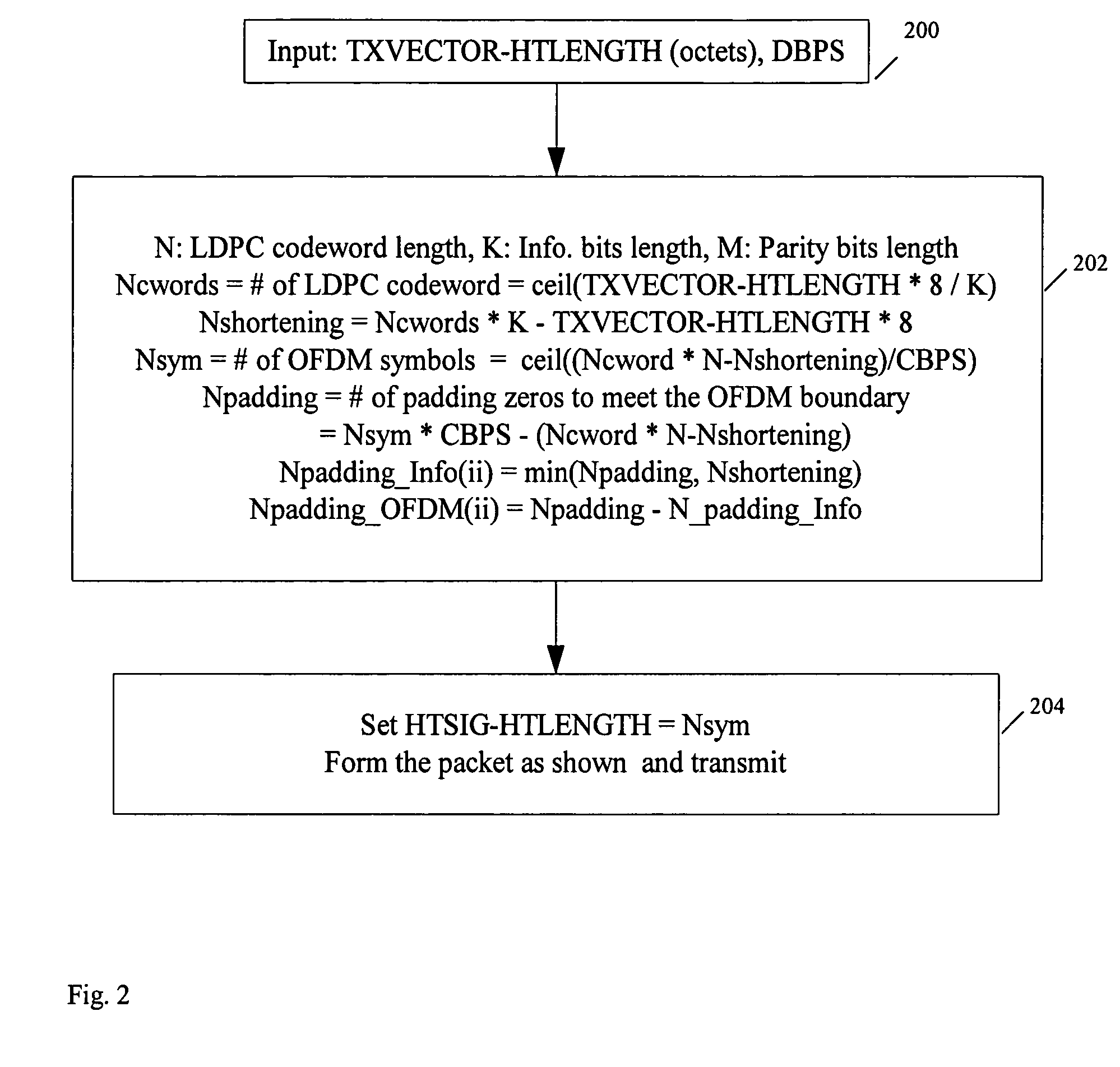

LDPC concatenation rules for IEEE 802.11n system with packets length specified in OFDM symbols

InactiveUS20070143655A1Data representation error detection/correctionError preventionByteConcatenation

A method of concatenation for LDPC encoding in an OFDM wireless system selects codewords based on the data packet payload size, wherein the payload size is the number of transmitted information bits in octets. For low transmission rates, shortening and puncturing across all codewords within the packet is applied to minimize OFDM symbol padding. For high transmission rates, only shortening across all codewords within the packet is applied to minimize OFDM symbol padding.

Owner:SAMSUNG ELECTRONICS CO LTD

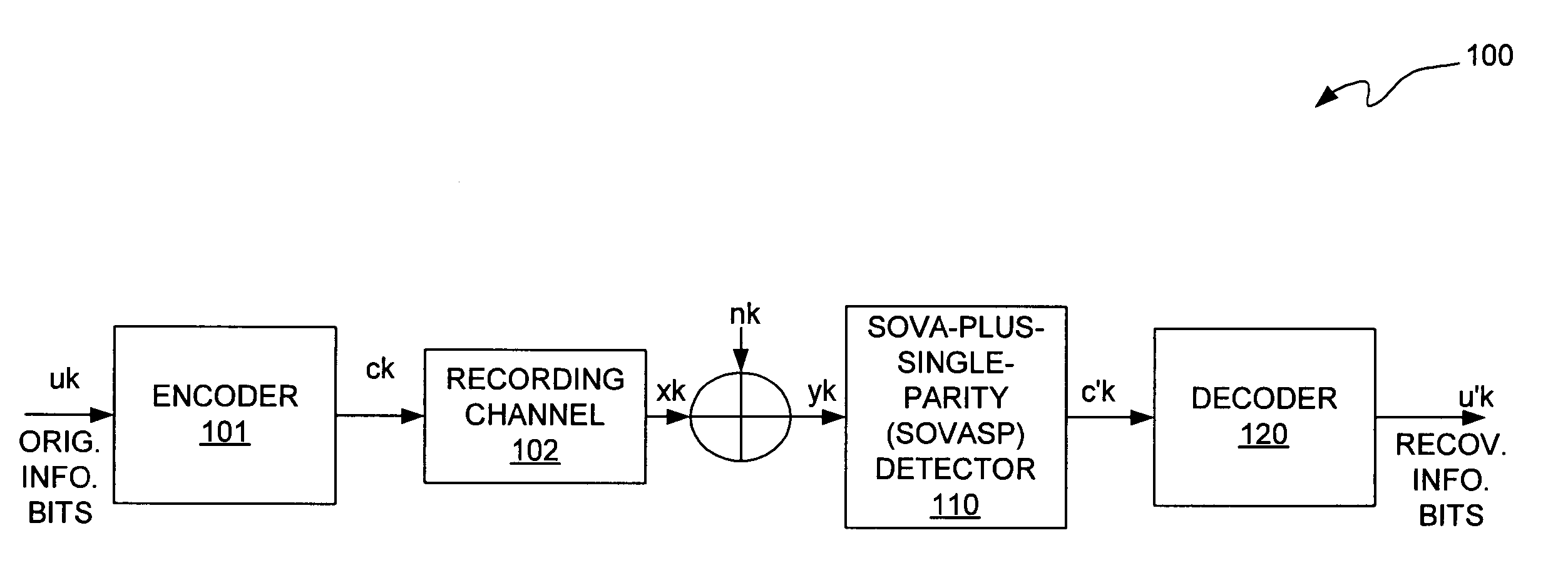

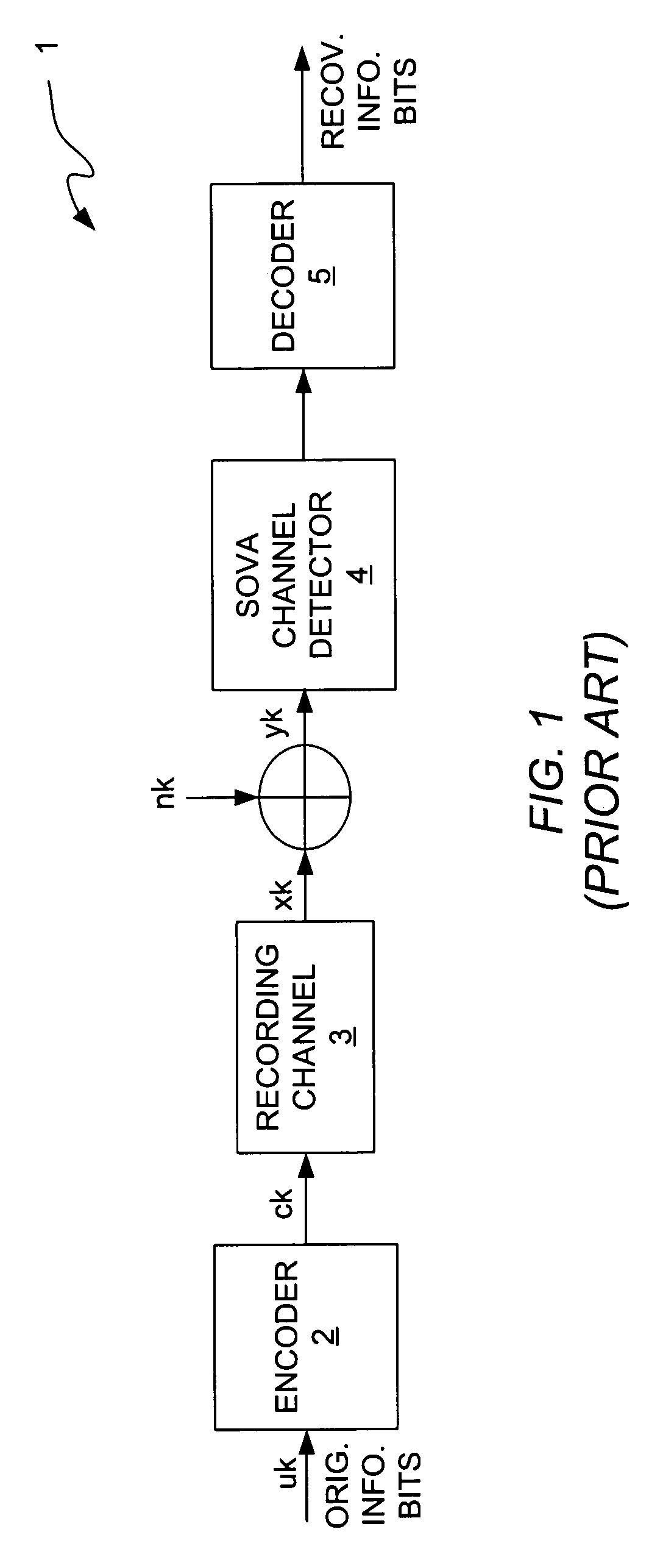

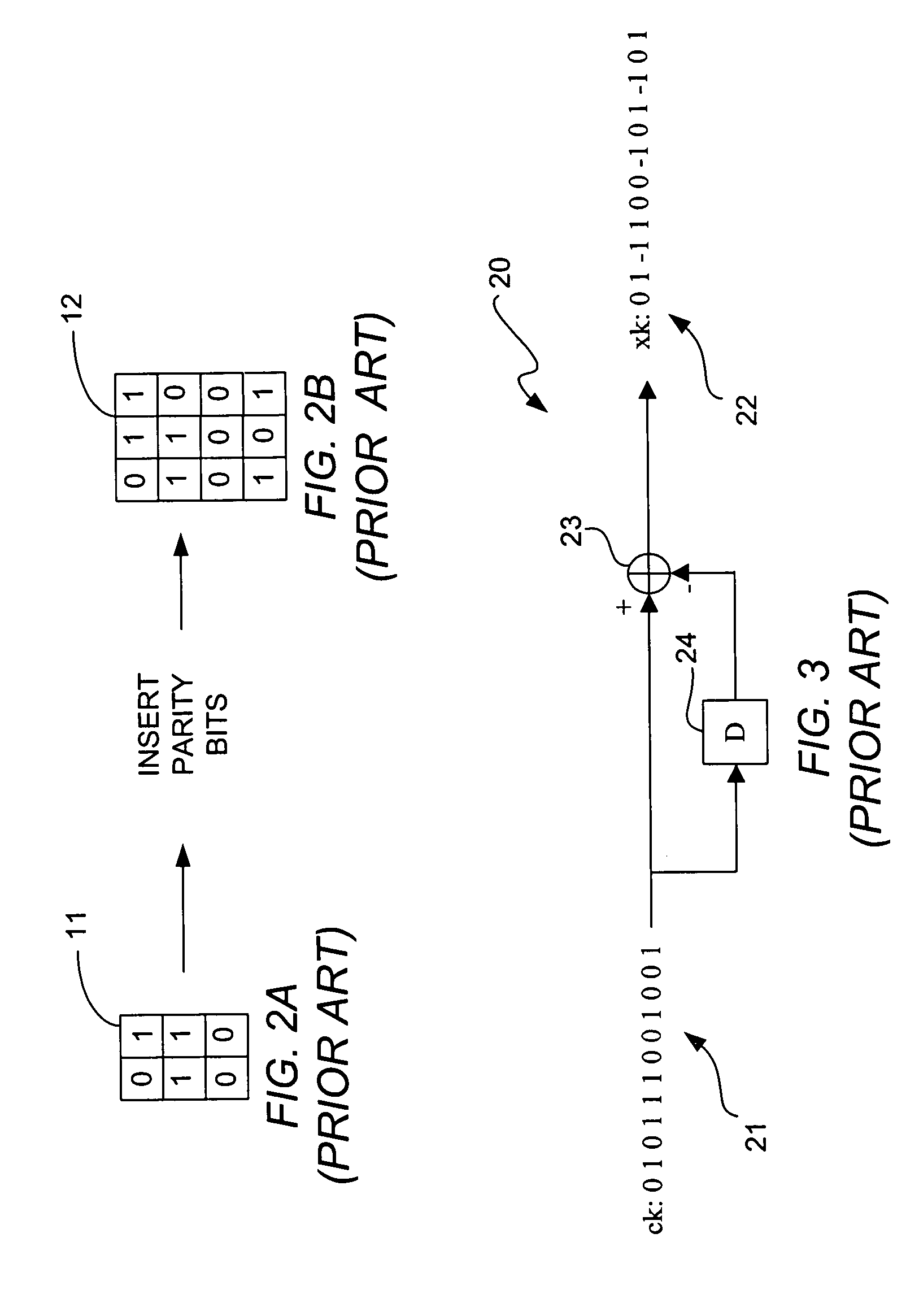

Data detection and decoding system and method

ActiveUS20060168493A1Data representation error detection/correctionOther decoding techniquesSingle parity checkAlgorithm

A data detection and decoding system includes a SOVA channel detector that uses single parity (SOVASP) to improve the accuracy with which the detector estimates bits. Each column or row read back from the read channel constitutes a code word and each code word is encoded to satisfy single parity. Because the SOVASP channel detector detects whether each code word satisfies single parity, it is unnecessary to use both a column decoder and a row decoder in the channel decoder. Either the row decoder or the column decoder can be eliminated depending on whether bits are read back on a column-by-column basis or on a row-by-row basis. This reduction in components reduces hardware complexity and improves system performance. The output of the row or column decoder is received by a second detector that processes the output received from the decoder to recover the original information bits.

Owner:AVAGO TECH INT SALES PTE LTD

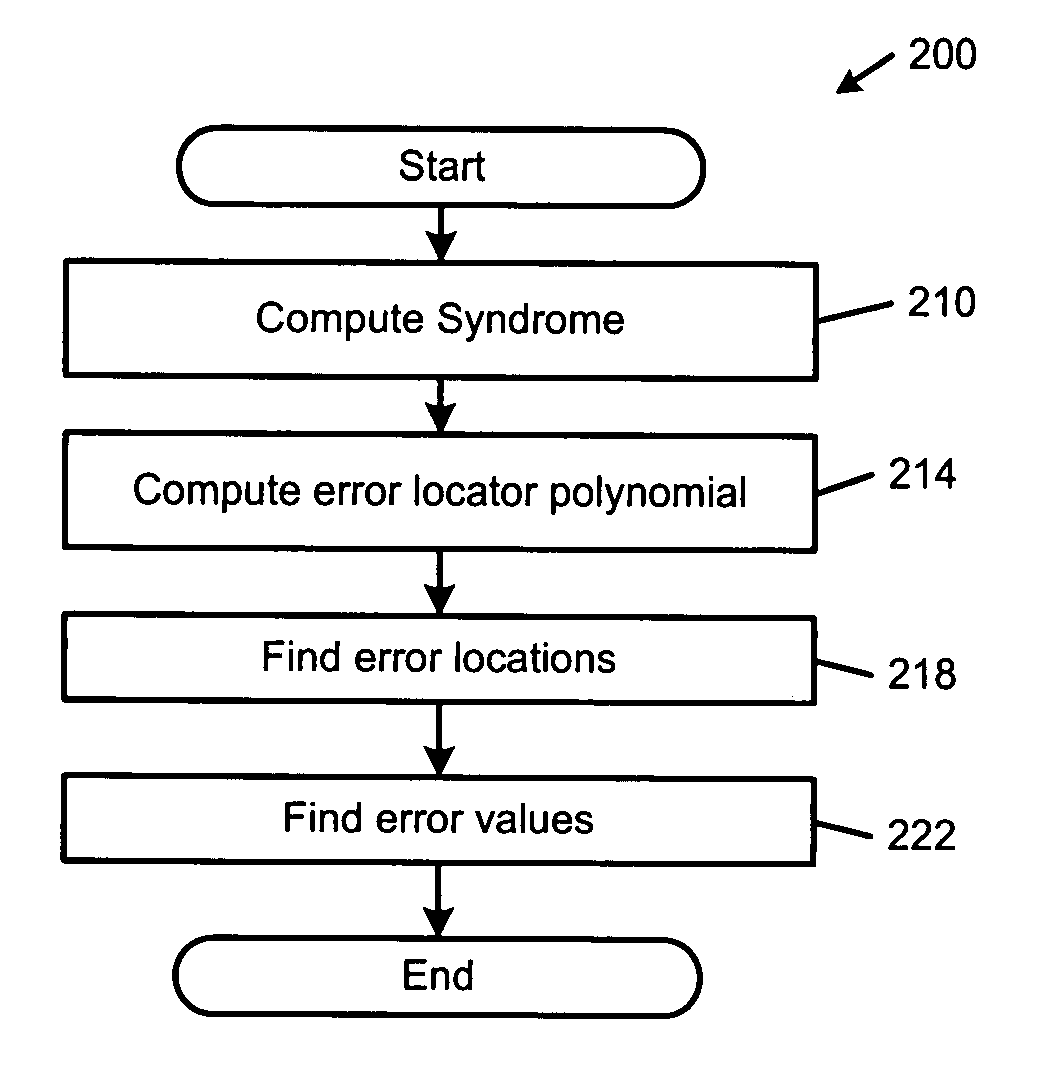

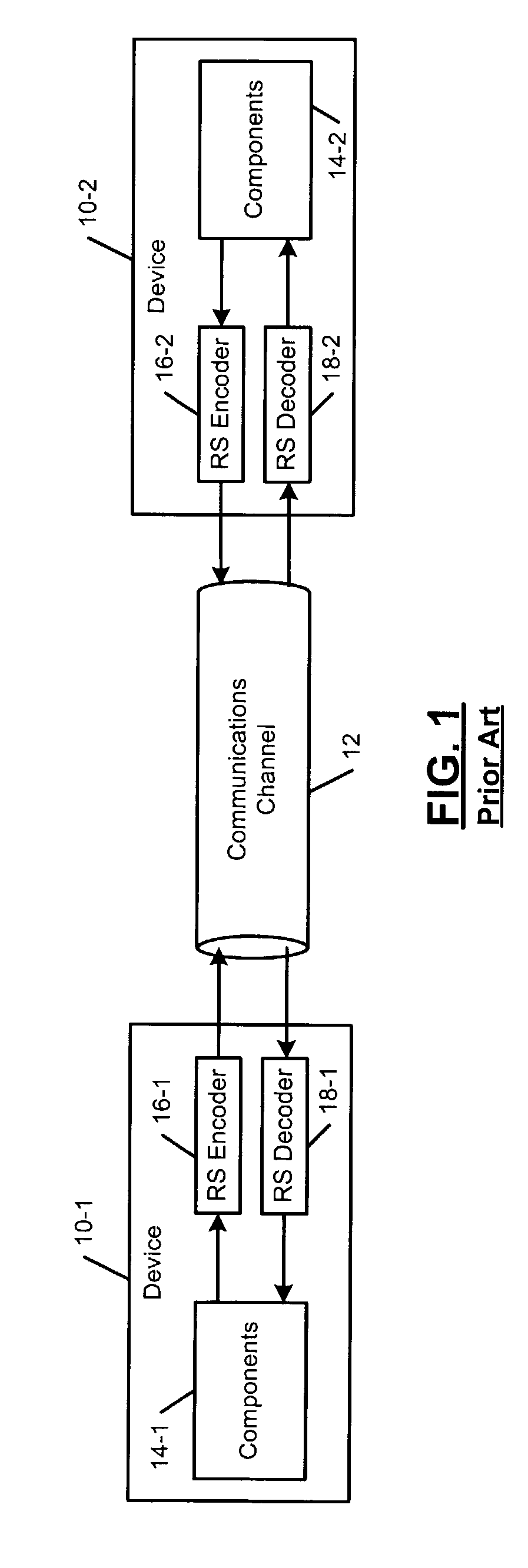

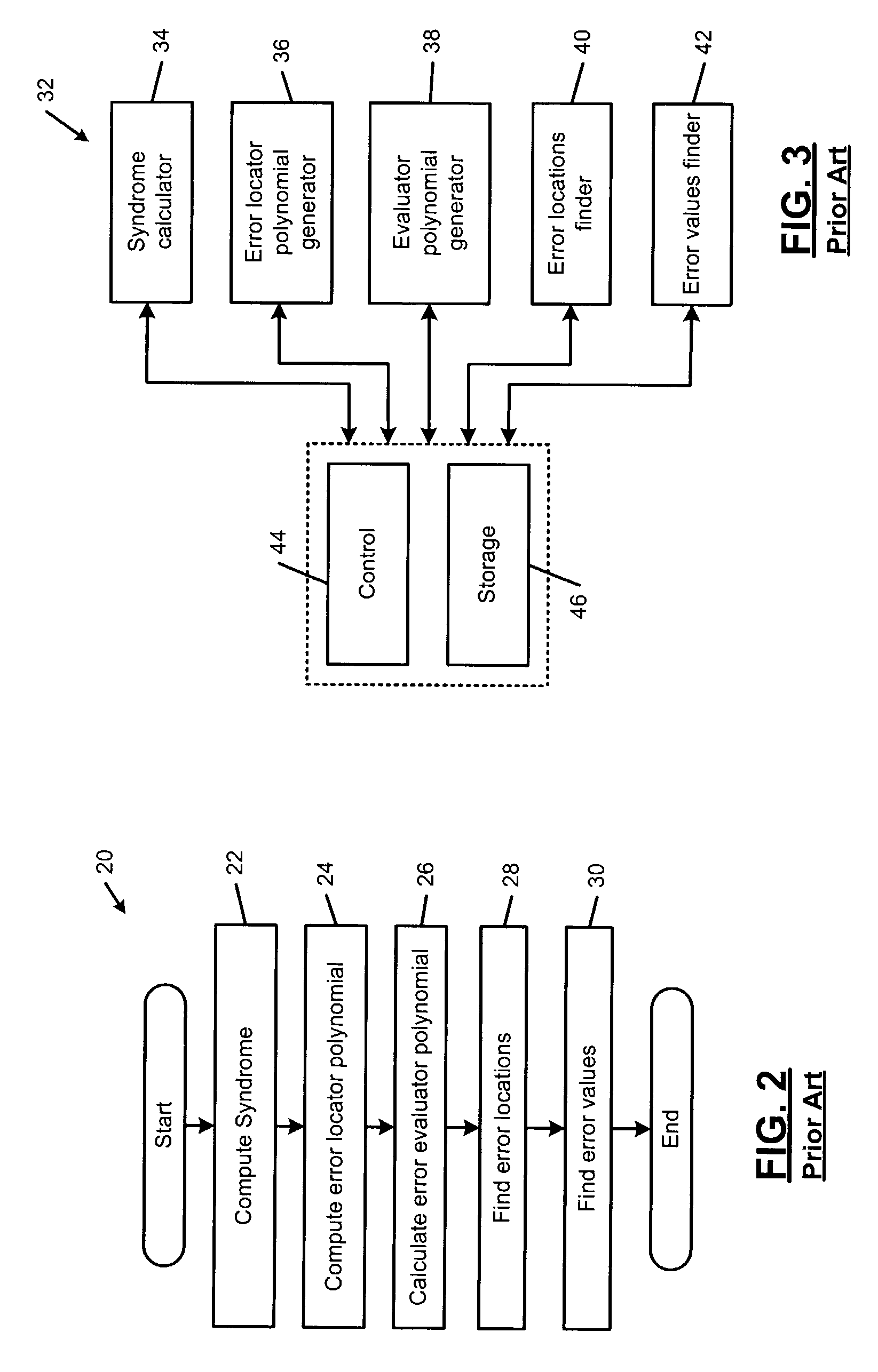

Error evaluator for inversionless Berlekamp-Massey algorithm in Reed-Solomon decoders

ActiveUS7010739B1Data representation error detection/correctionCode conversionError locationReed solomon decoder

An error correcting Reed-Solomon decoder includes a syndrome calculator that calculates syndrome values. An error locator polynomial generator communicates with the syndrome calculator and generates an error locator polynomial. An error location finder communicates with at least one of the syndrome calculator and the error locator polynomial generator and generates error locations. An error values finder communicates with at least one of the syndrome calculator, the error location finder and the error locator polynomial generator and generates error values using an error value relationship that is not based on the traditional error evaluator polynomial. The error locator polynomial generator is an inversionless Berlekamp-Massey algorithm (iBMA), which calculates an error locator polynomial and a scratch polynomial. The error value relationship is based on the error locator polynomial and the scratch polynomial.

Owner:MARVELL ASIA PTE LTD

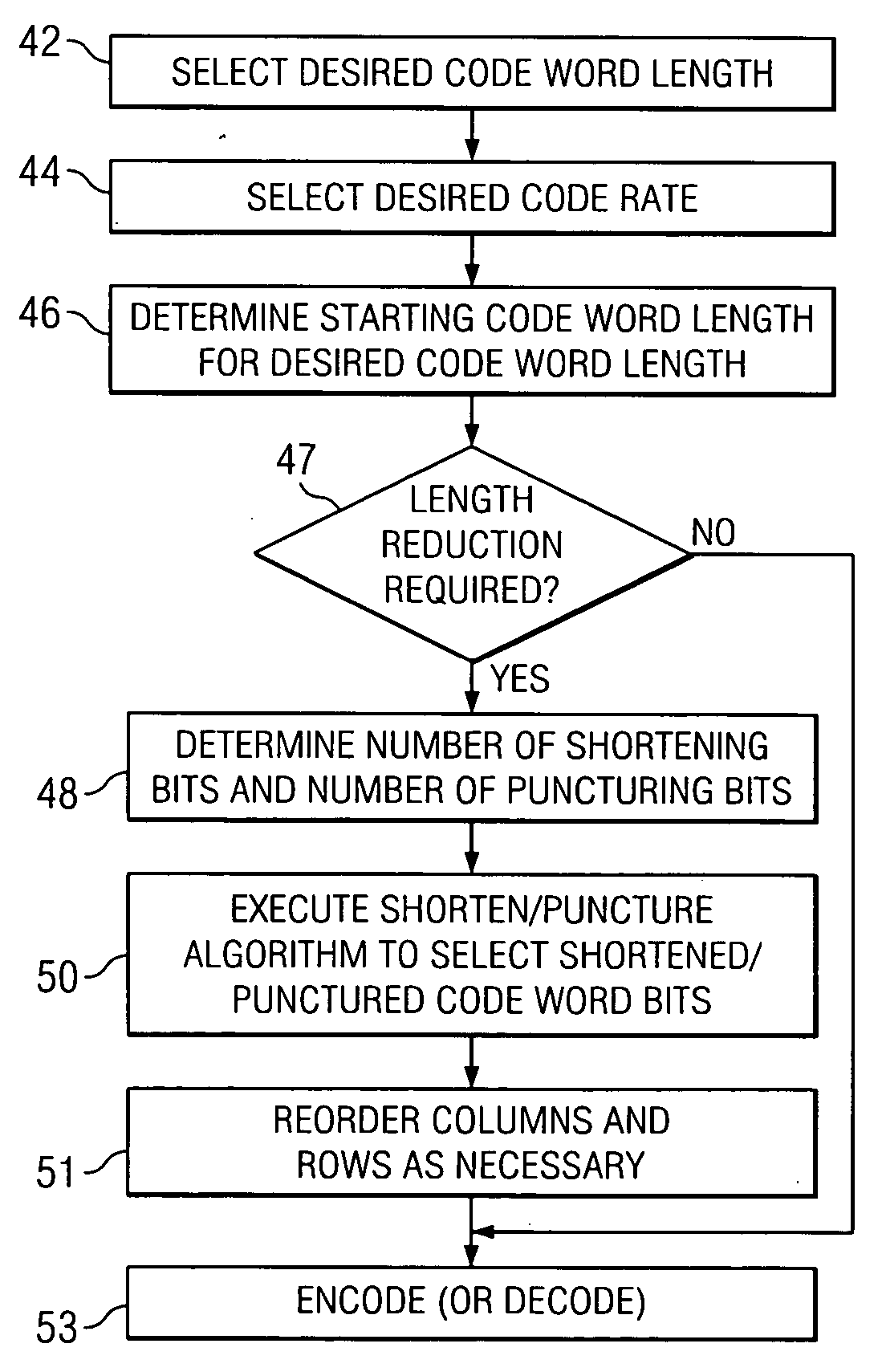

Simplified decoding using structured and punctured LDPC codes

ActiveUS20060123277A1Improve performanceAvoid interferenceData representation error detection/correctionError preventionProgramming languageTransceiver

A communications transceiver for transmitting and receiving coded communications, with the coding corresponding to a low-density parity check code, is disclosed. A set of available code word lengths and code rates are to be supported by the transceiver. These available code word lengths and code rates are implemented as a subset of starting code word lengths, which are length-reduced by shortening and puncturing selected bit positions in the starting code word length to attain the desired one of the available code word lengths and code rates. The bit positions to be shortened and punctured are selected in a manner that avoids interference between the shortened and punctured bit positions, and that attains excellent code performance.

Owner:TEXAS INSTR INC

Popular searches

Modulated-carrier systems Color television with bandwidth reduction Color television details Diversity/multi-antenna systems Television signal transmission by single/parallel channels Orthogonal multiplex Transmission path multiple use Baseband systems Delay line applications Single output arrangements