Patents

Literature

302results about "Other error detection/correction/protection" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Error detection and rejection for a diagnostic testing system

ActiveUS20080254544A1Minimize impactError preventionTransmission systemsMeasurement deviceComputer science

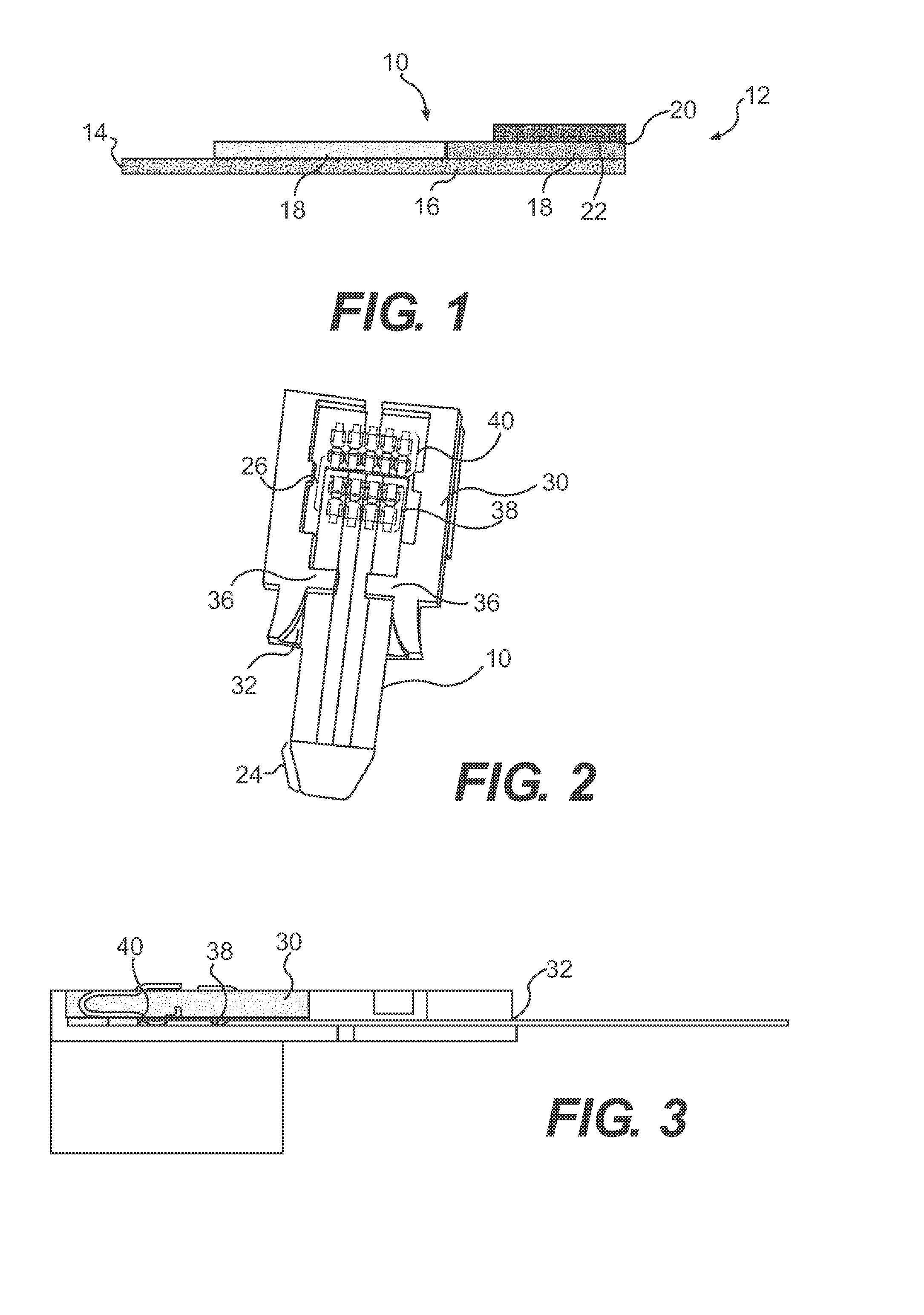

A system for measuring a property of a sample is provided. The system comprises a diagnostic measuring device having a memory and a diagnostic test strip for collecting the sample. The strip has embedded thereon a pattern representative of at least first data and second data, the first data being data representing at least one of parameters related to measuring the property, codes usable for calibration of the diagnostic measuring device, or parameters indicating proper connection between the measuring device and the test strip and the second data usable for detecting and rejecting potential errors affecting the proper measurement of the property.

Owner:TRIVIDIA HEALTH

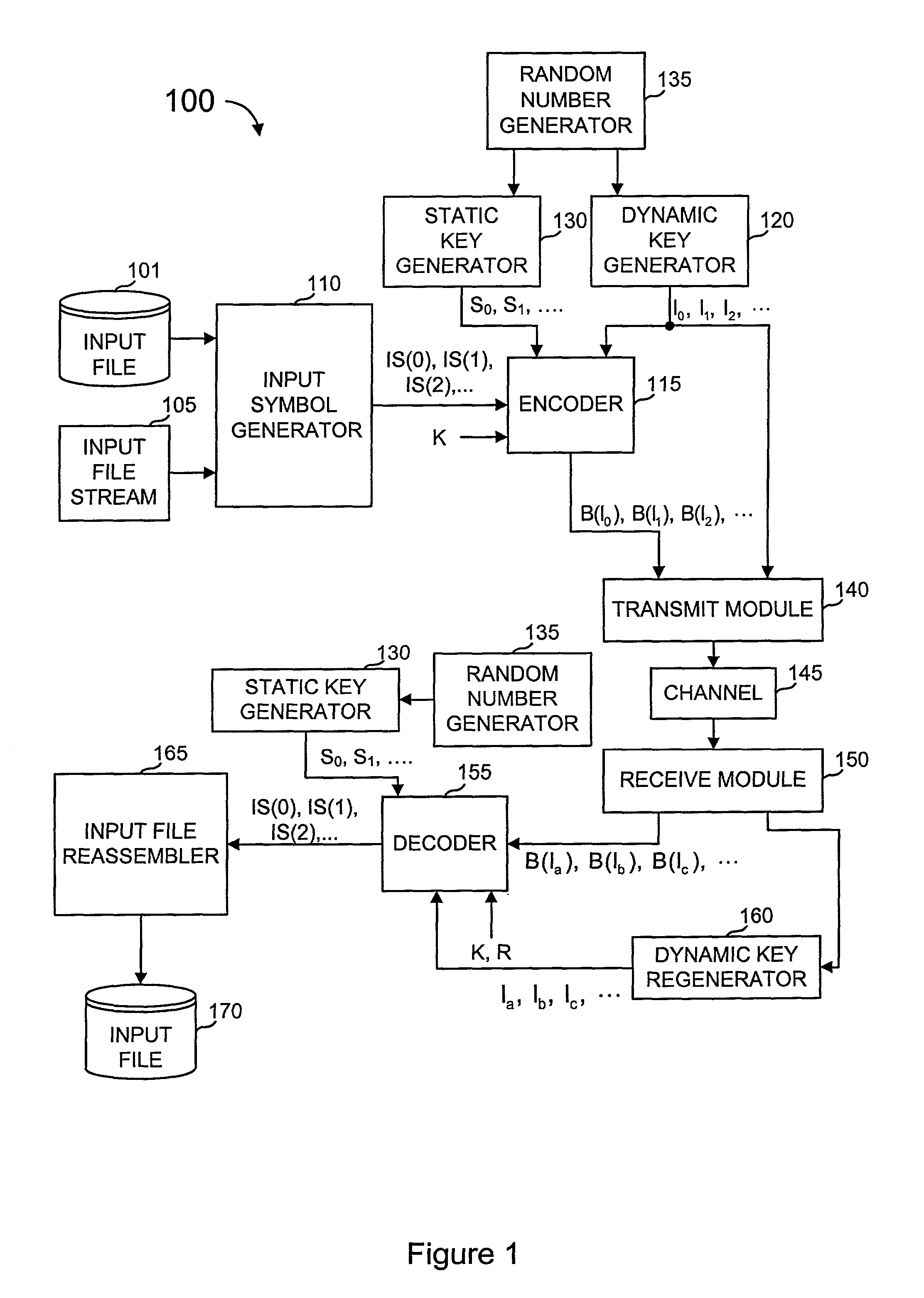

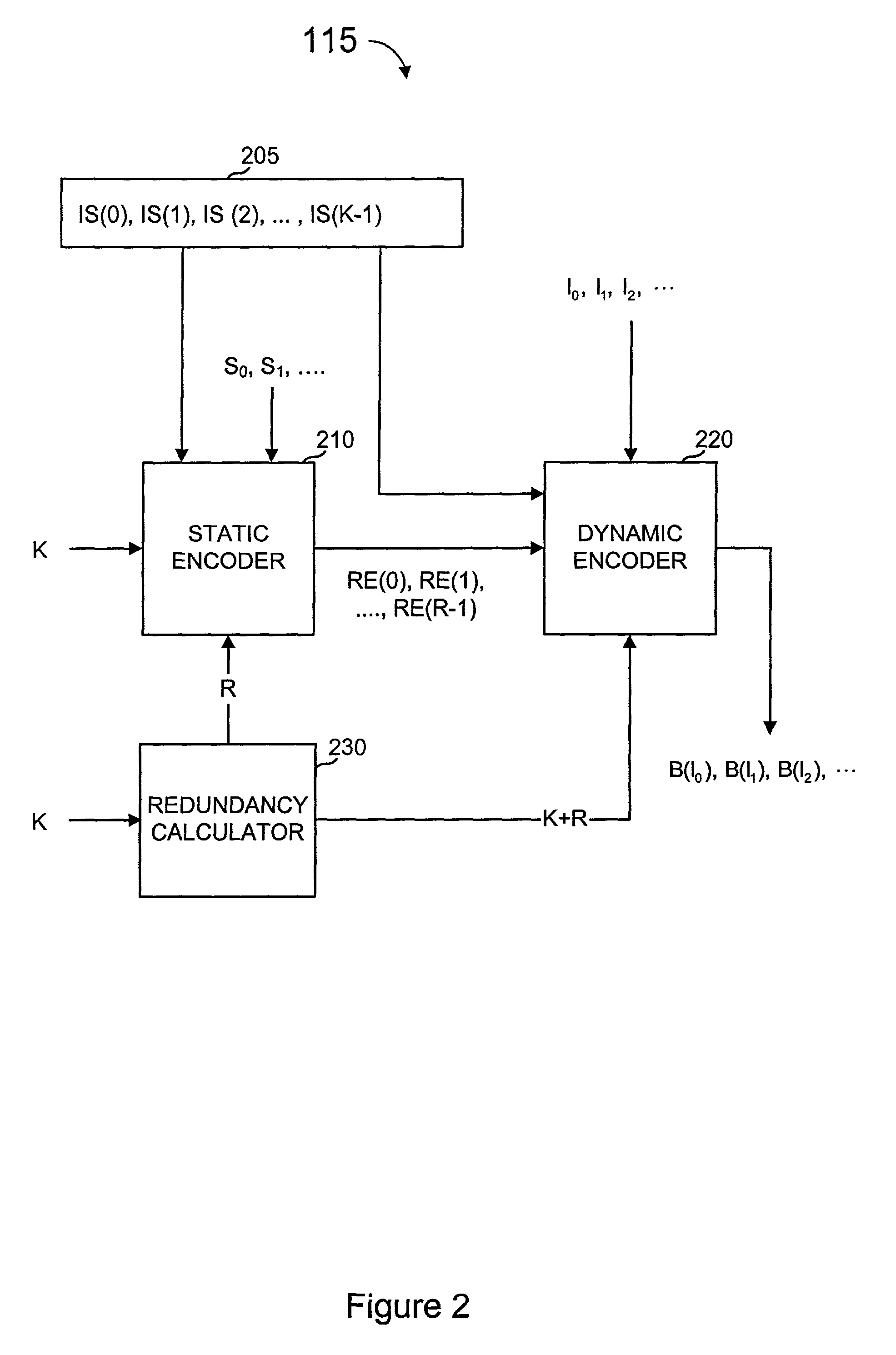

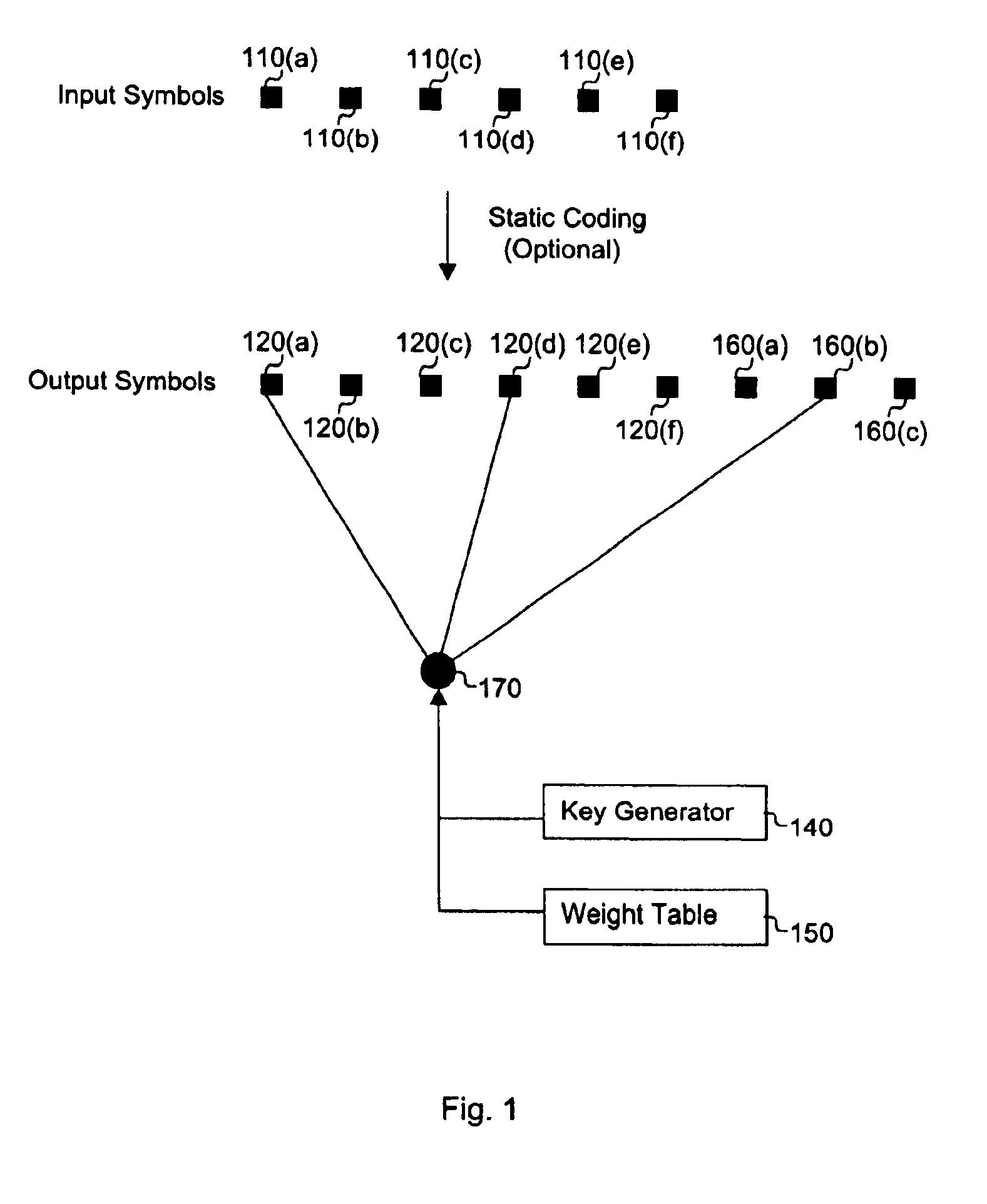

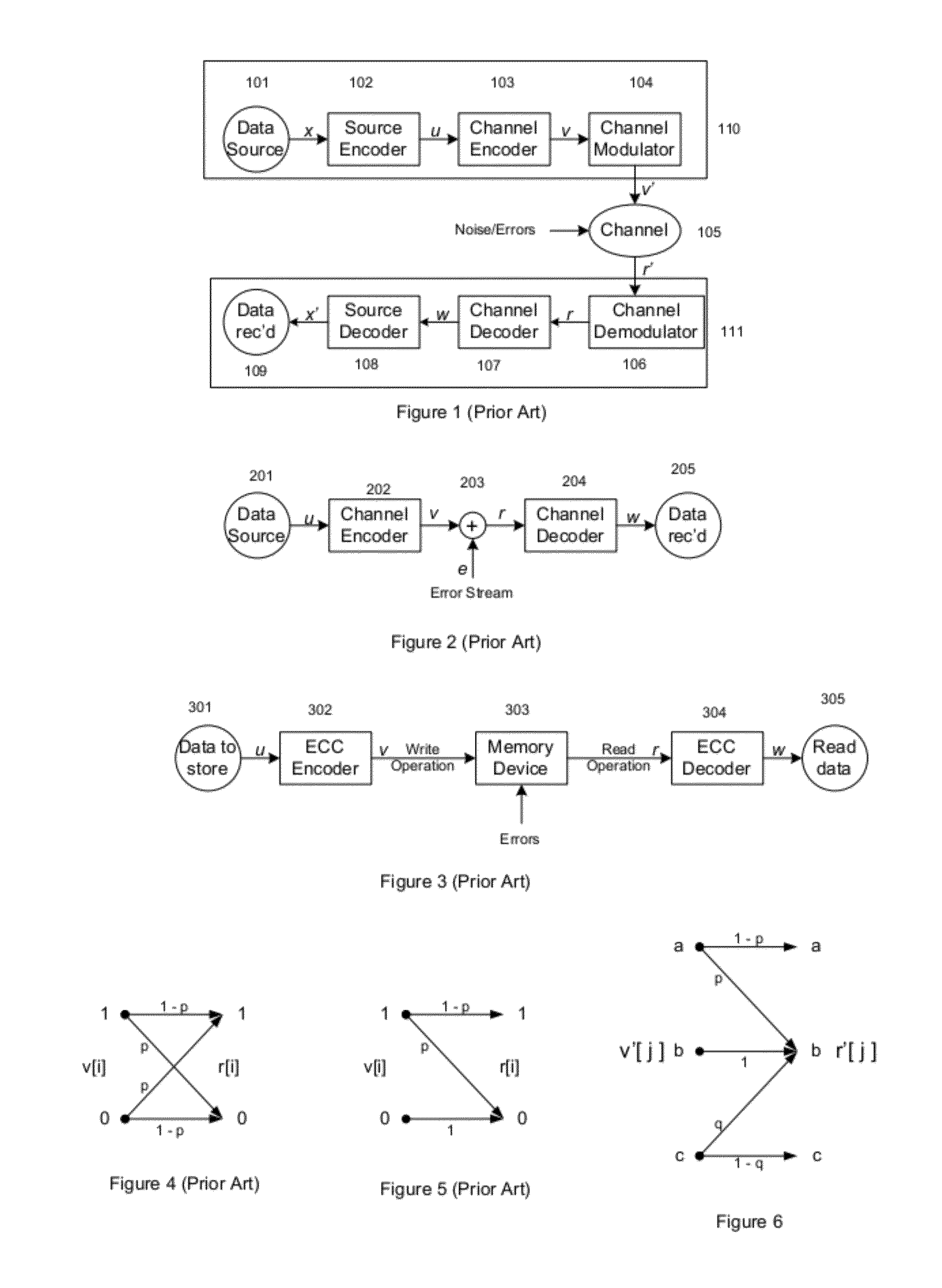

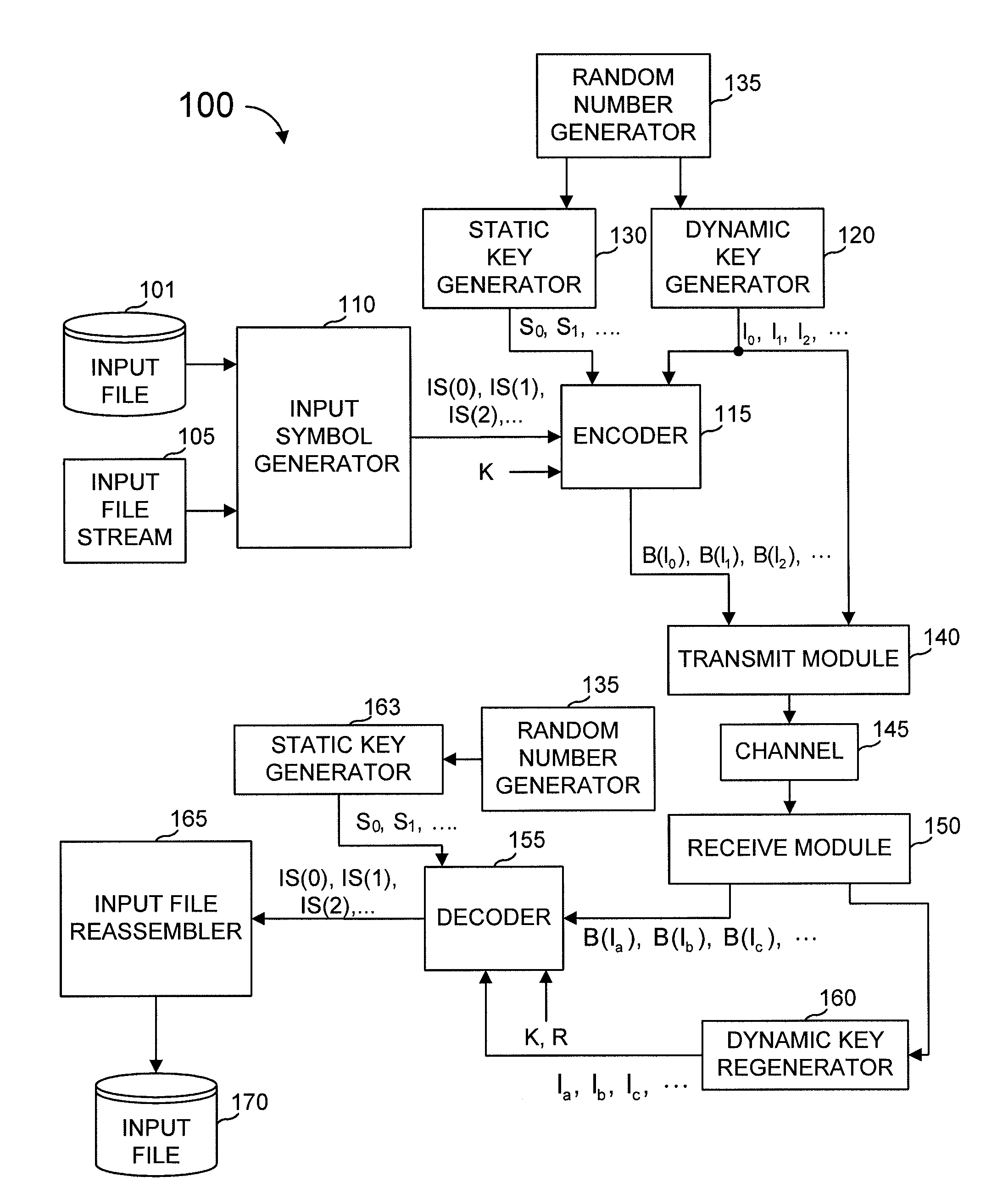

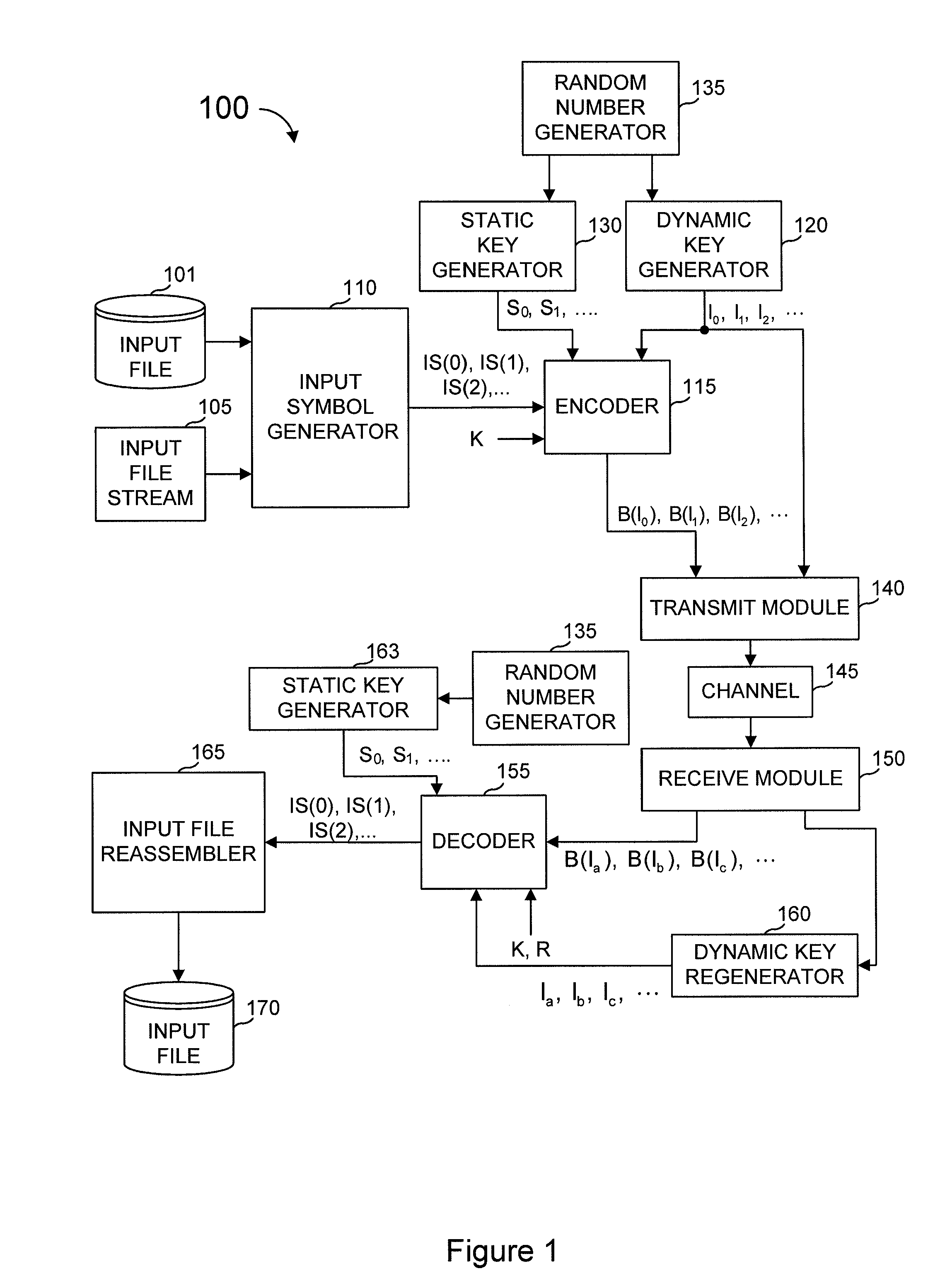

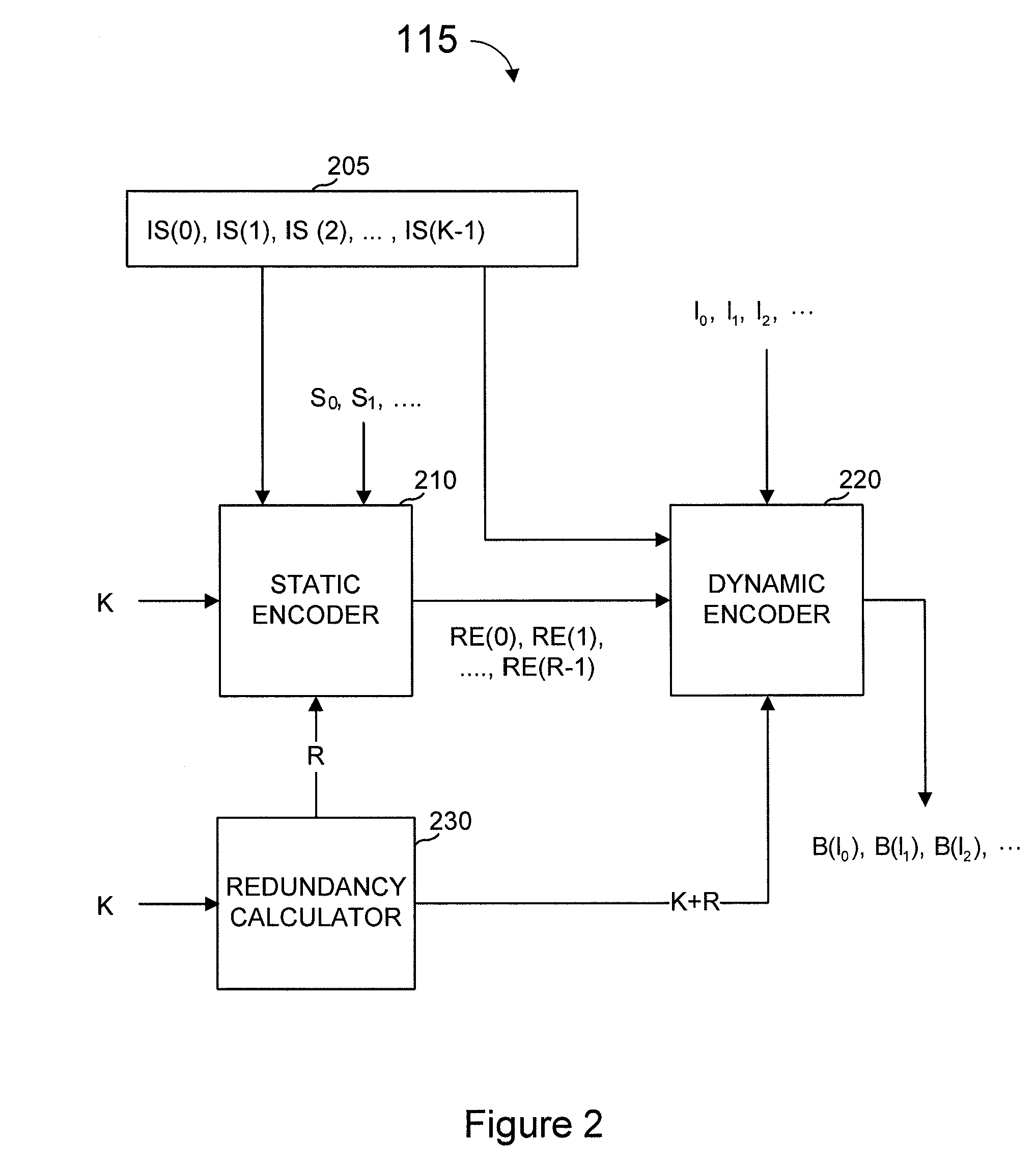

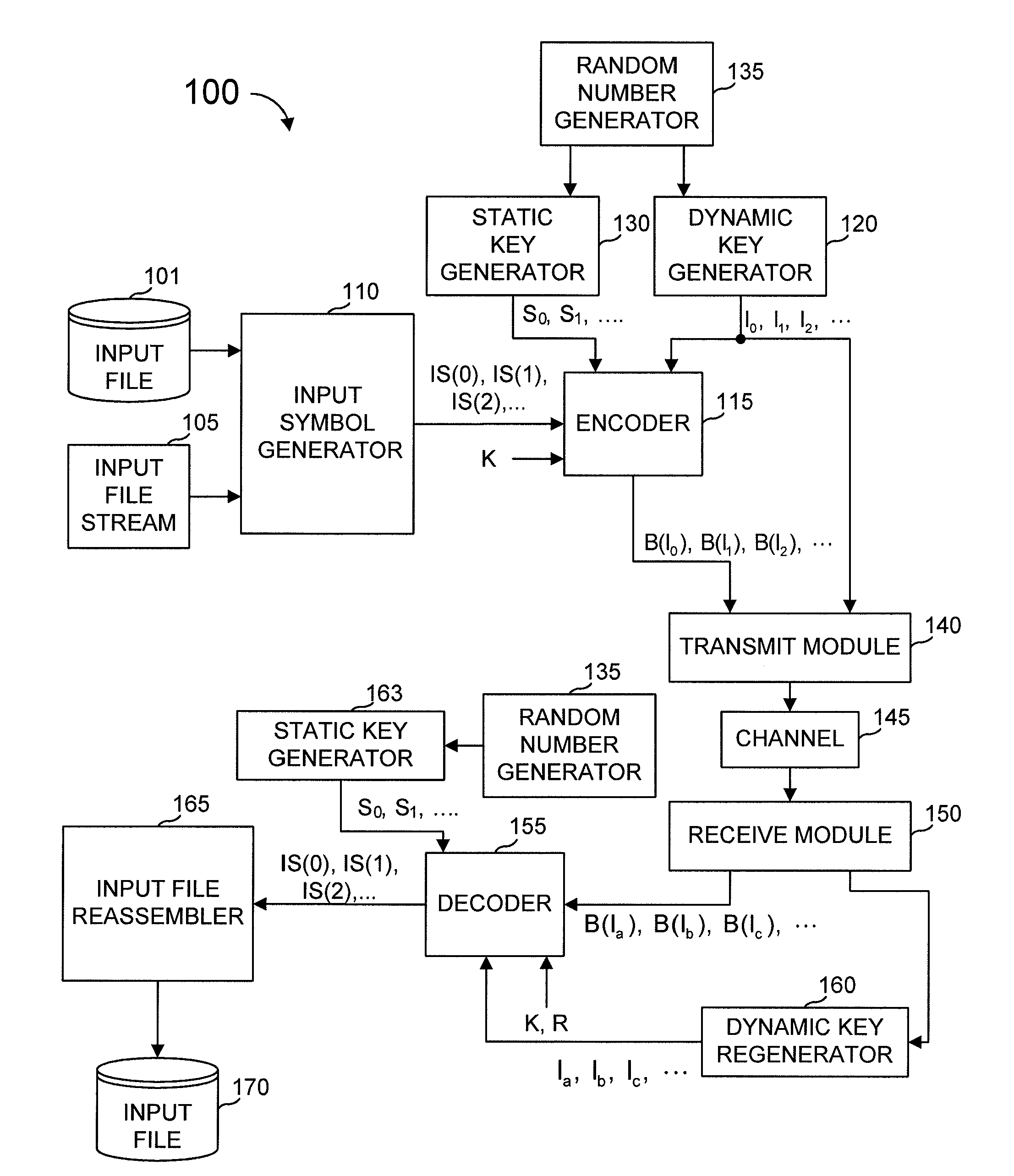

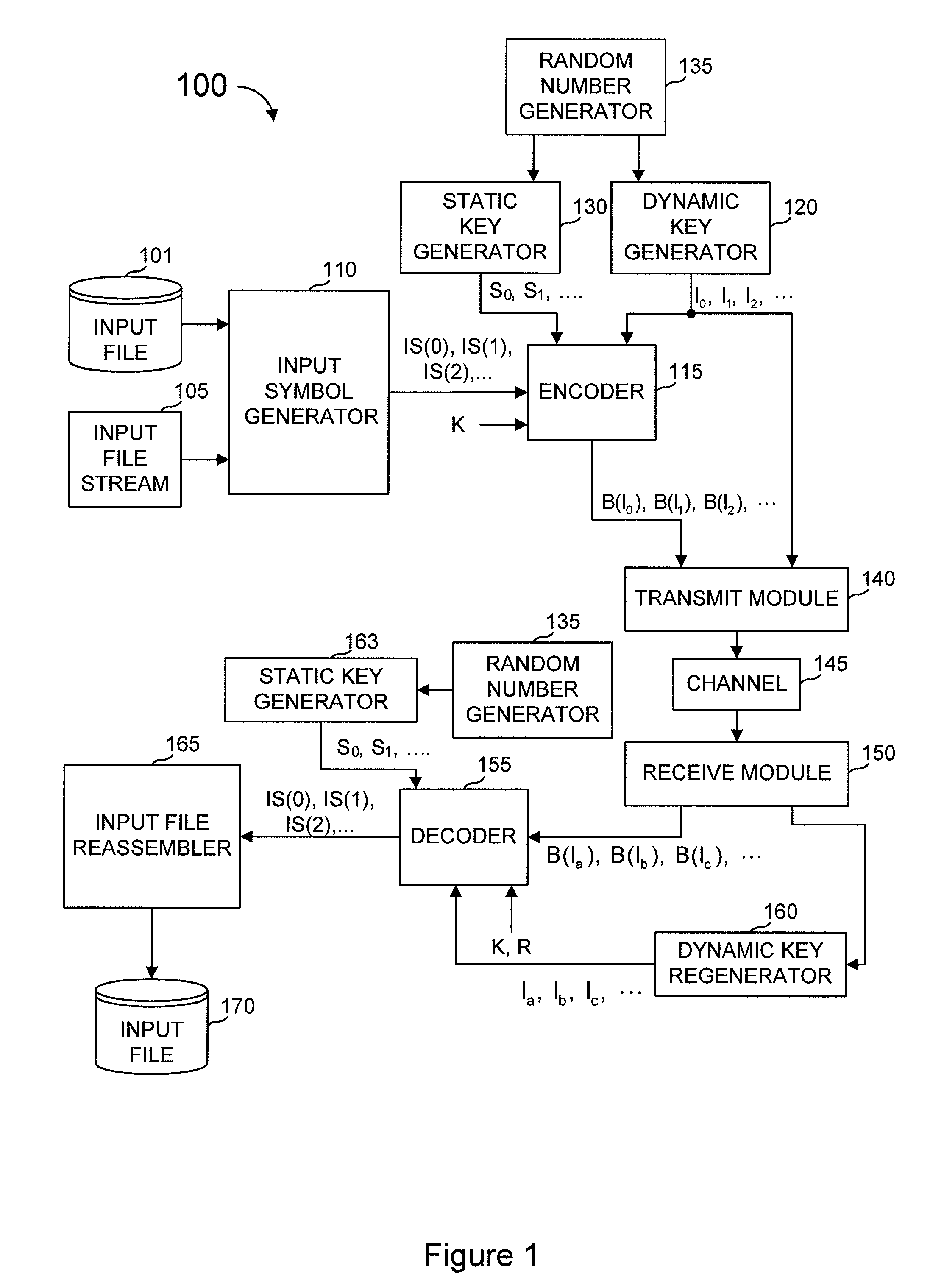

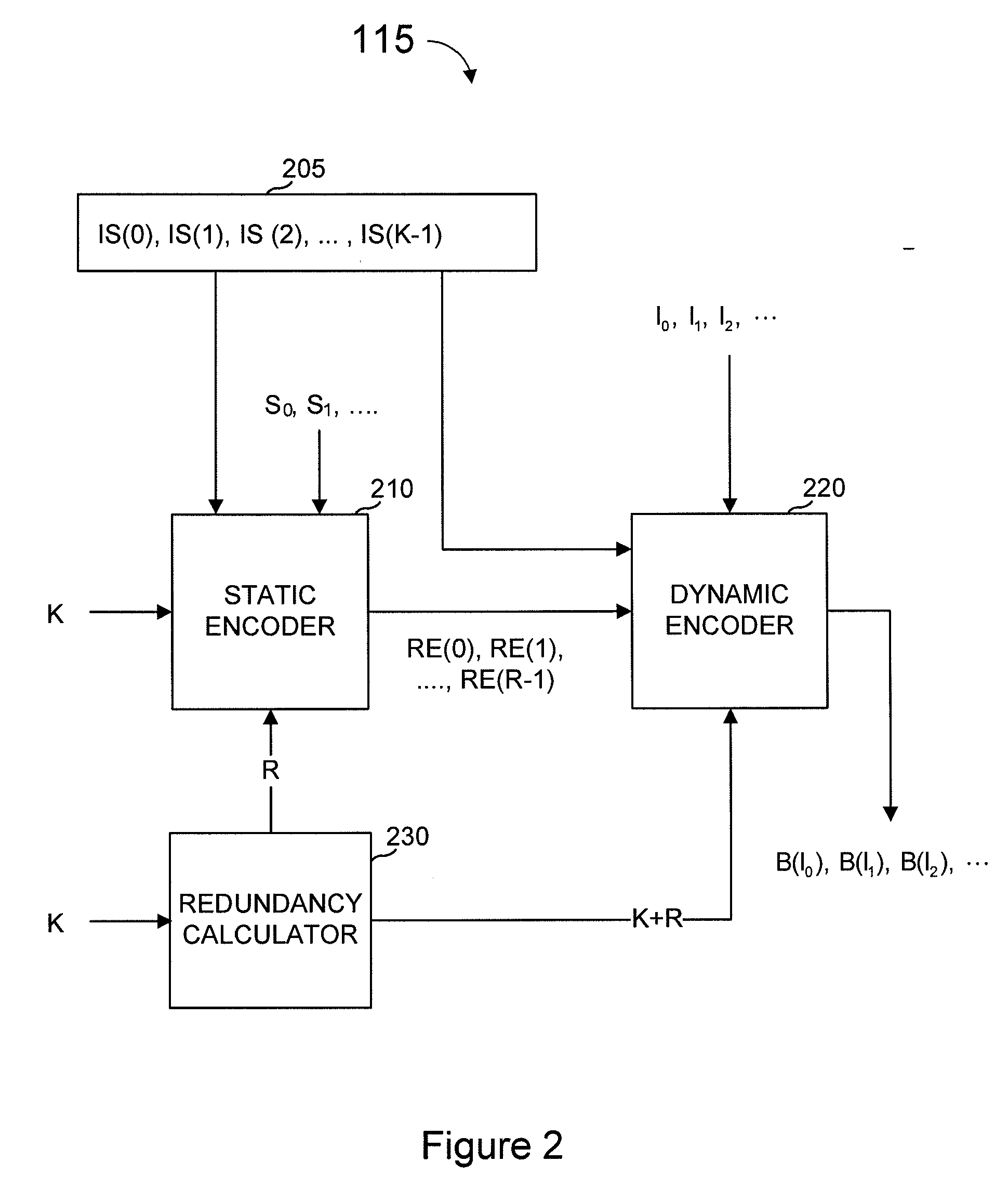

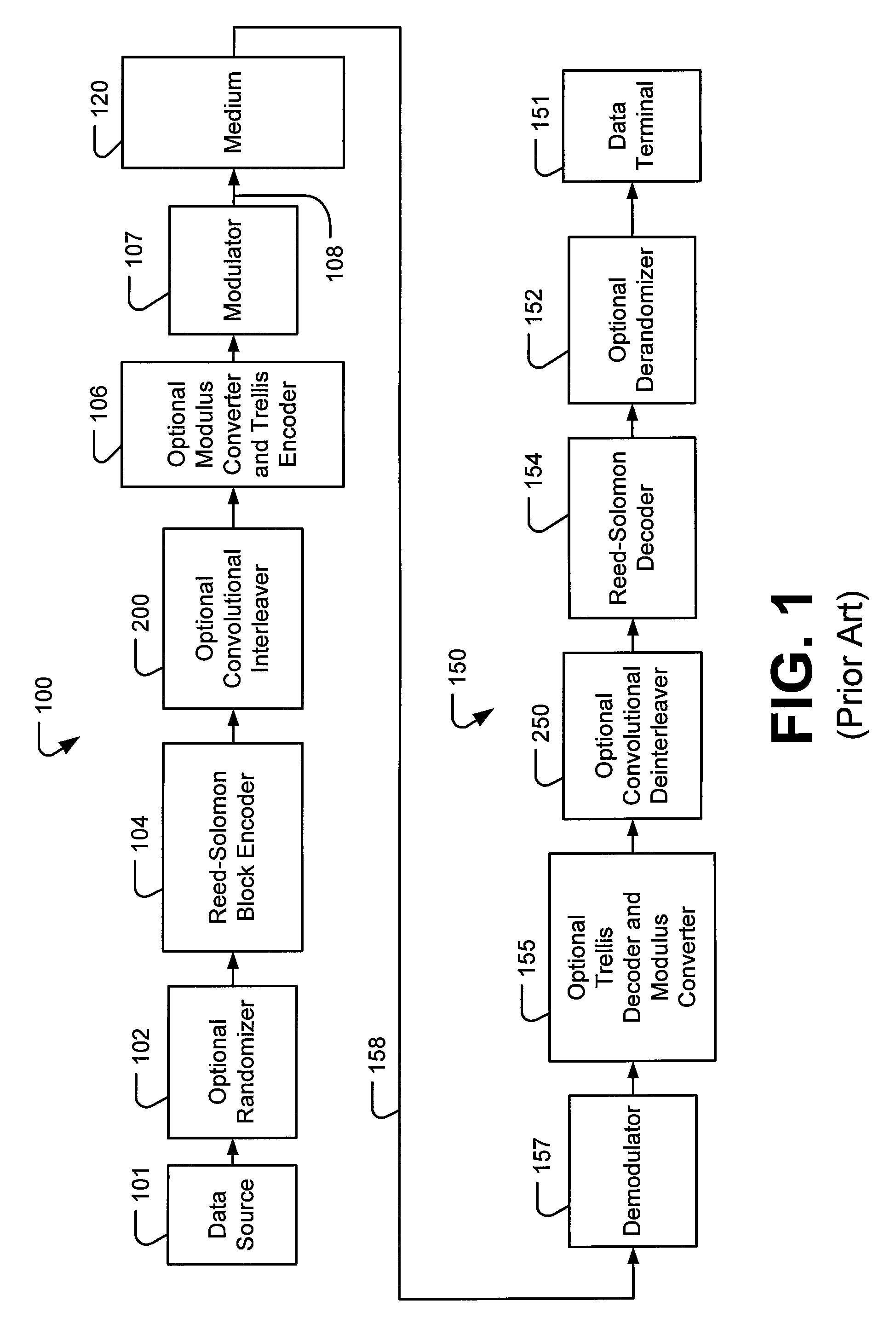

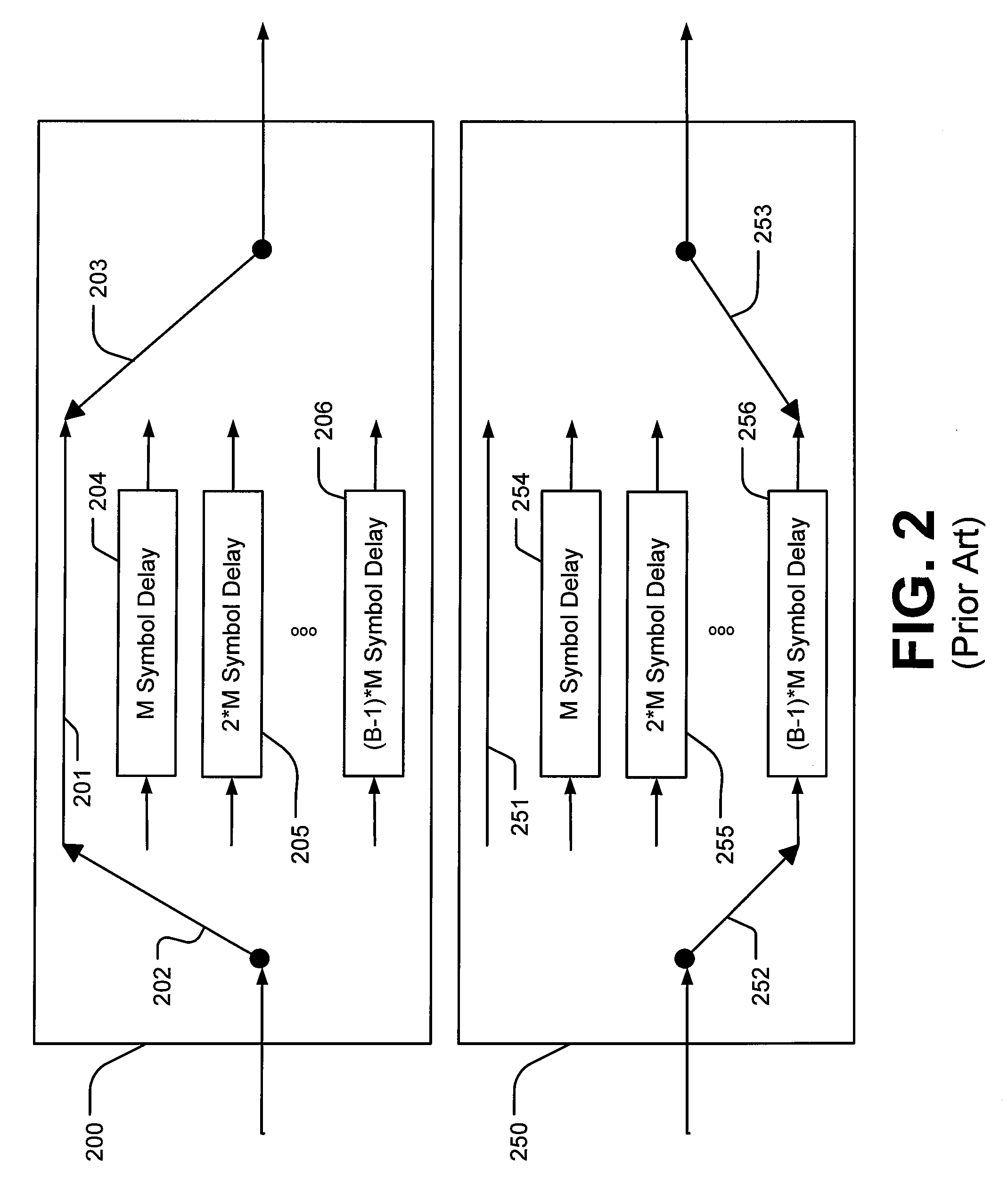

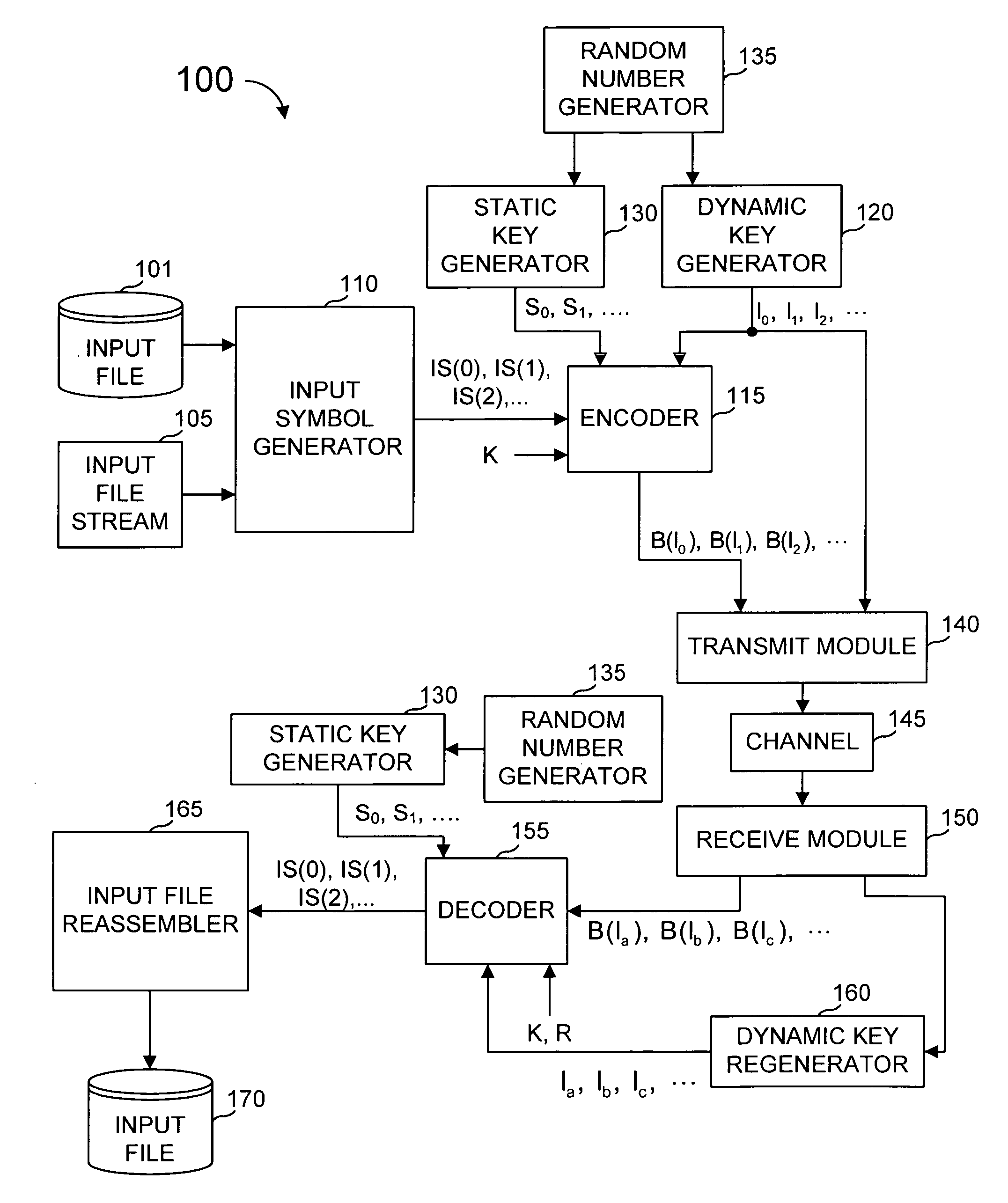

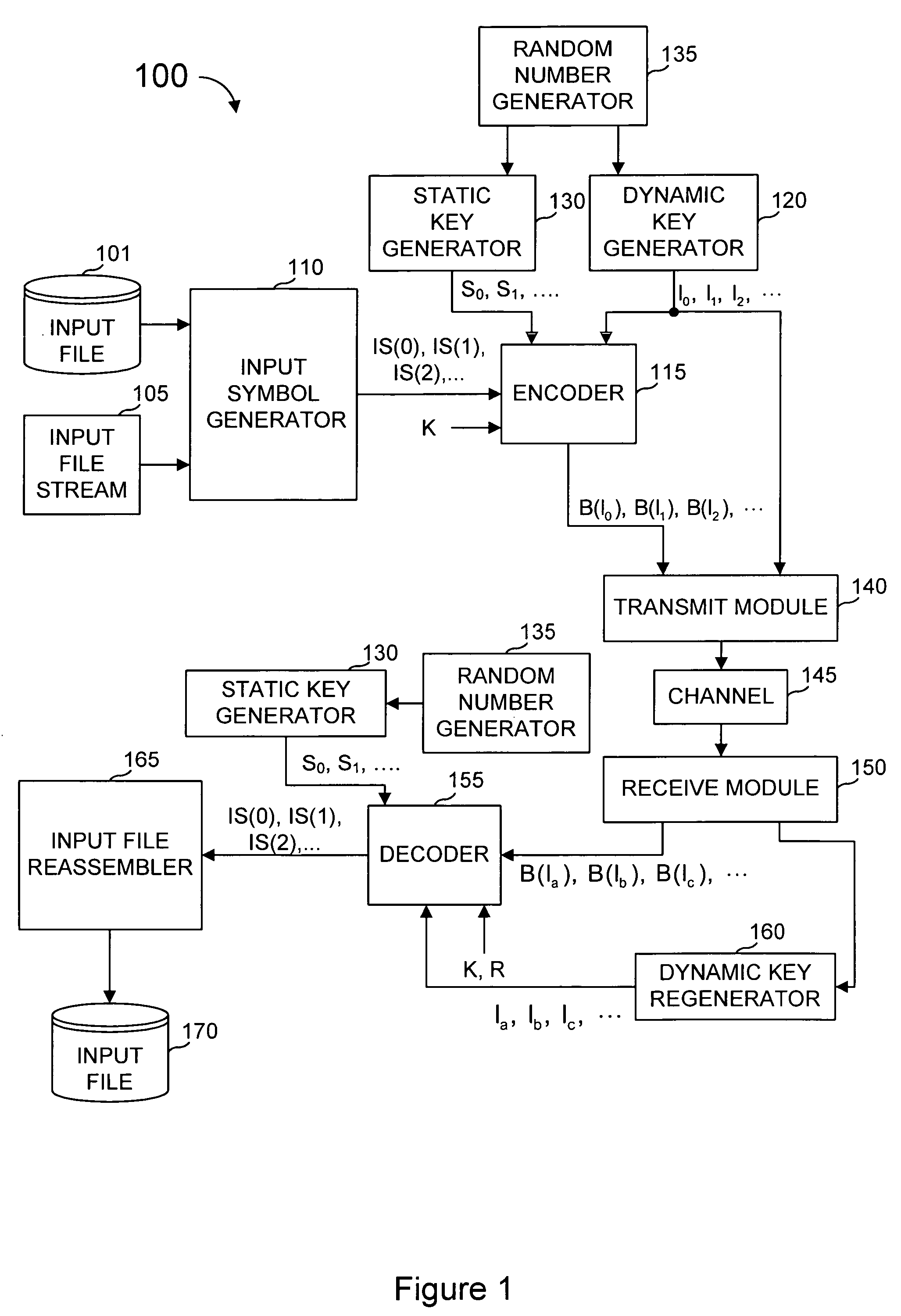

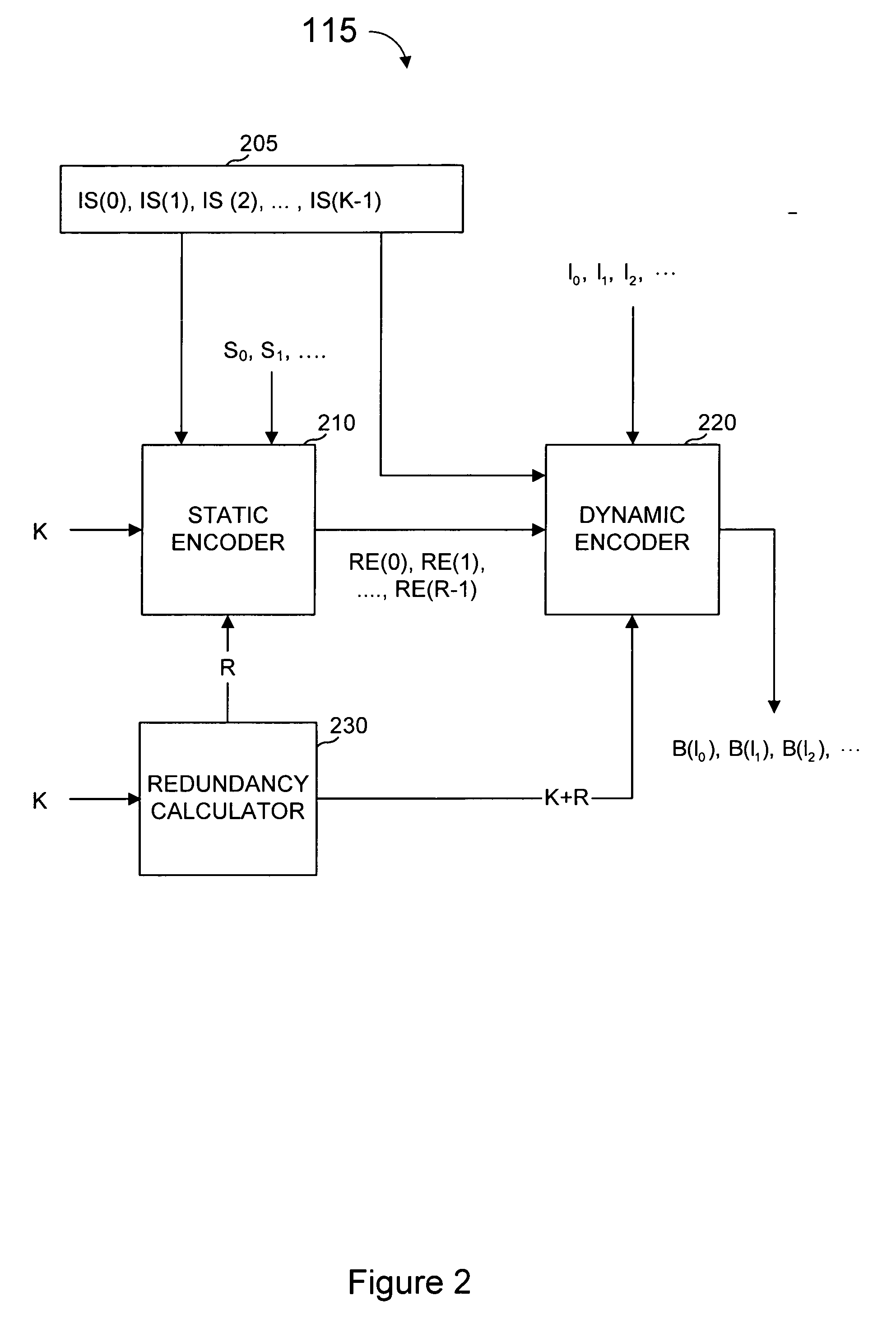

Multi-stage code generator and decoder for communication systems

InactiveUS7068729B2Reduce expensesOther decoding techniquesOther error detection/correction/protectionCommunications systemOrder set

Owner:QUALCOMM INC

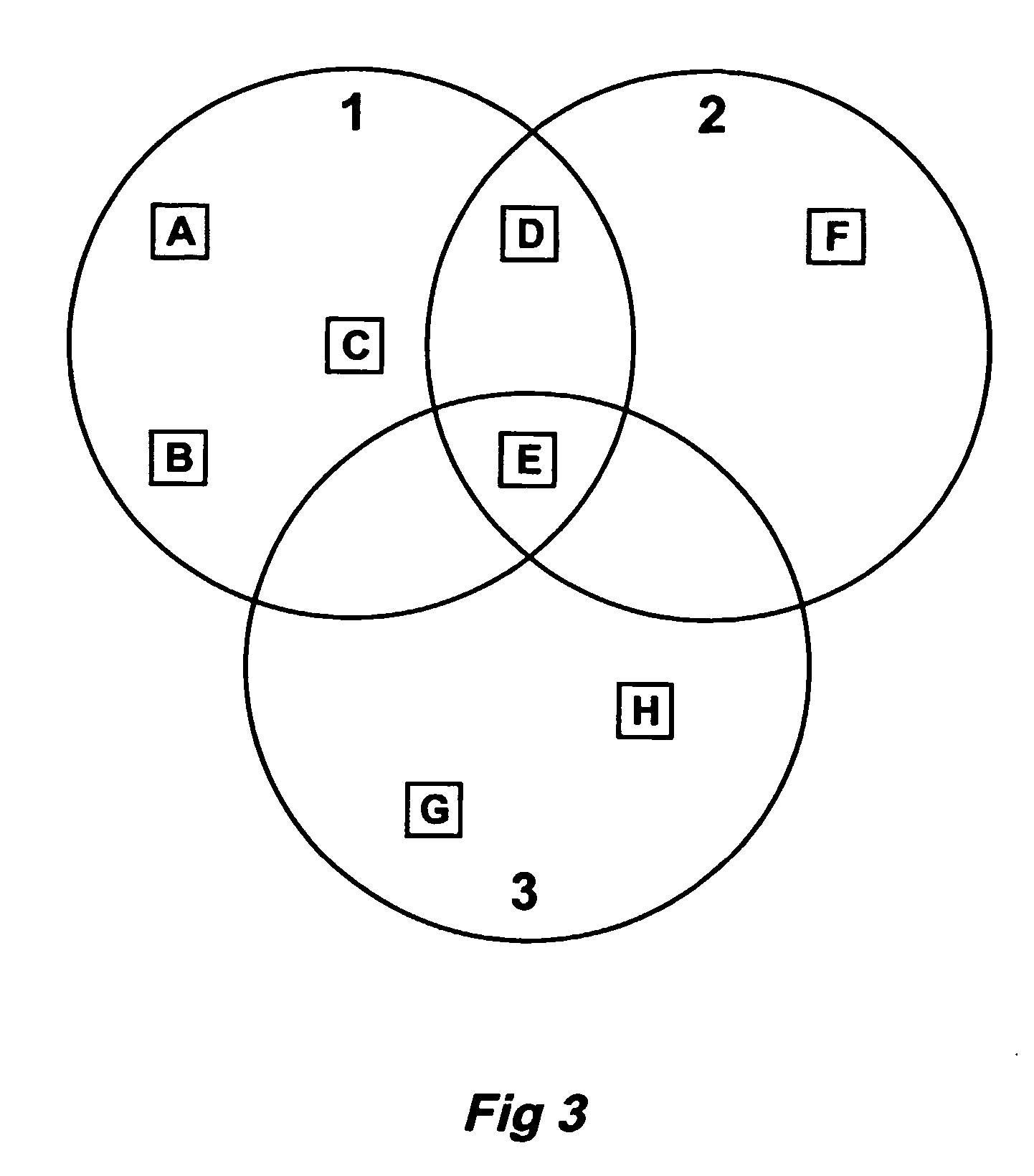

Method for checking an m out of n code

InactiveUS20140230055A1Inhibit outputReliably recognizeMemory loss protectionError detection/correctionProgramming languageReducer

A method and a circuit system for checking an m out of n code are provided. The method uses a code checker, to which at least one code reducer is assigned, a reduction of the code word width to in each case half being carried out using the at least one code reducer until a 1 out of x (x=n / 2, n / 4, n / 8 . . . ) code or another code which is not reducible further in this way is provided, each step of the code reducer additionally being connected to different bits of a counter, the 1 out of x code or the code which is not further reducible being checked and additionally the signal pairs of each step being checked.

Owner:ROBERT BOSCH GMBH

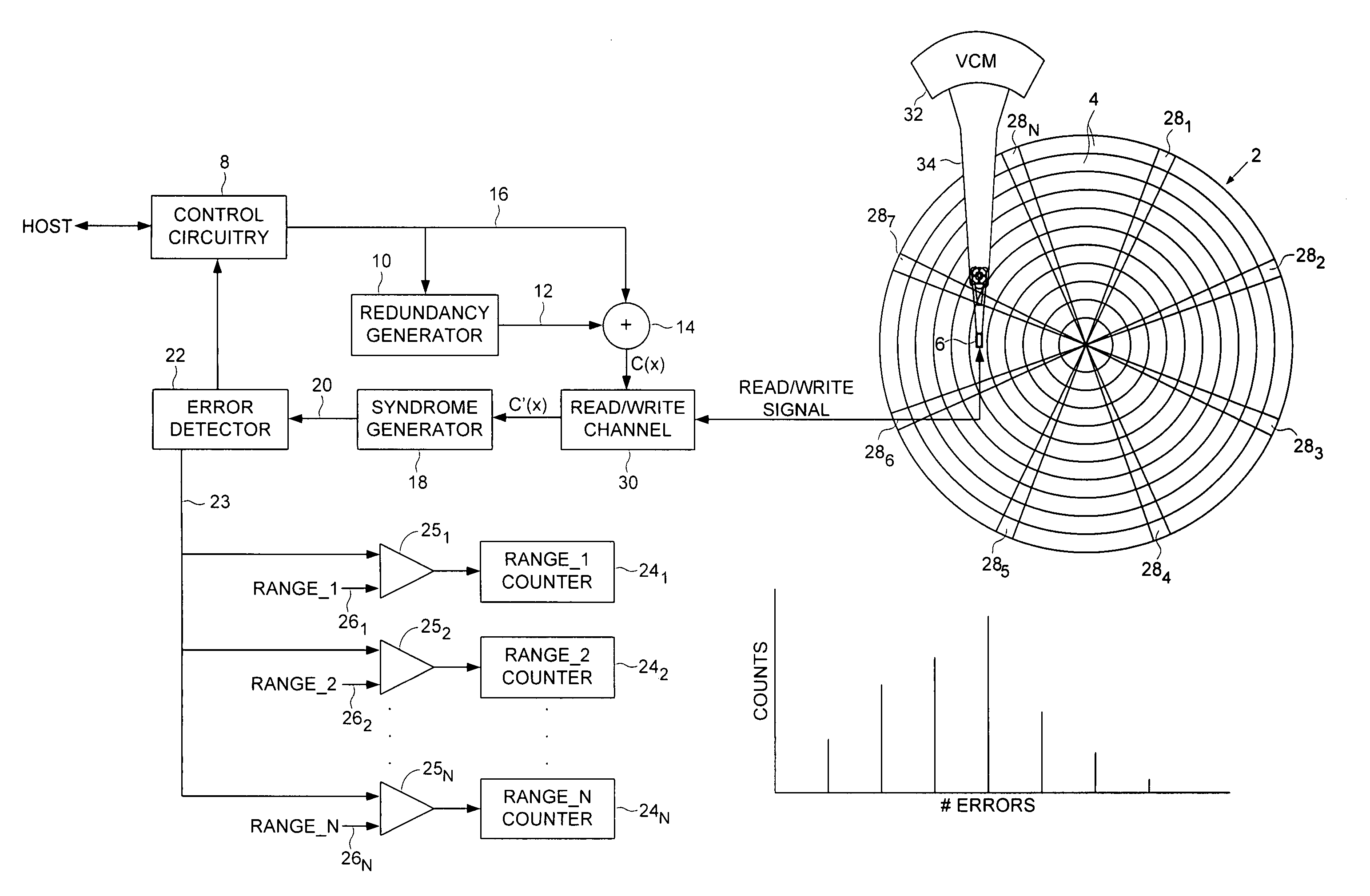

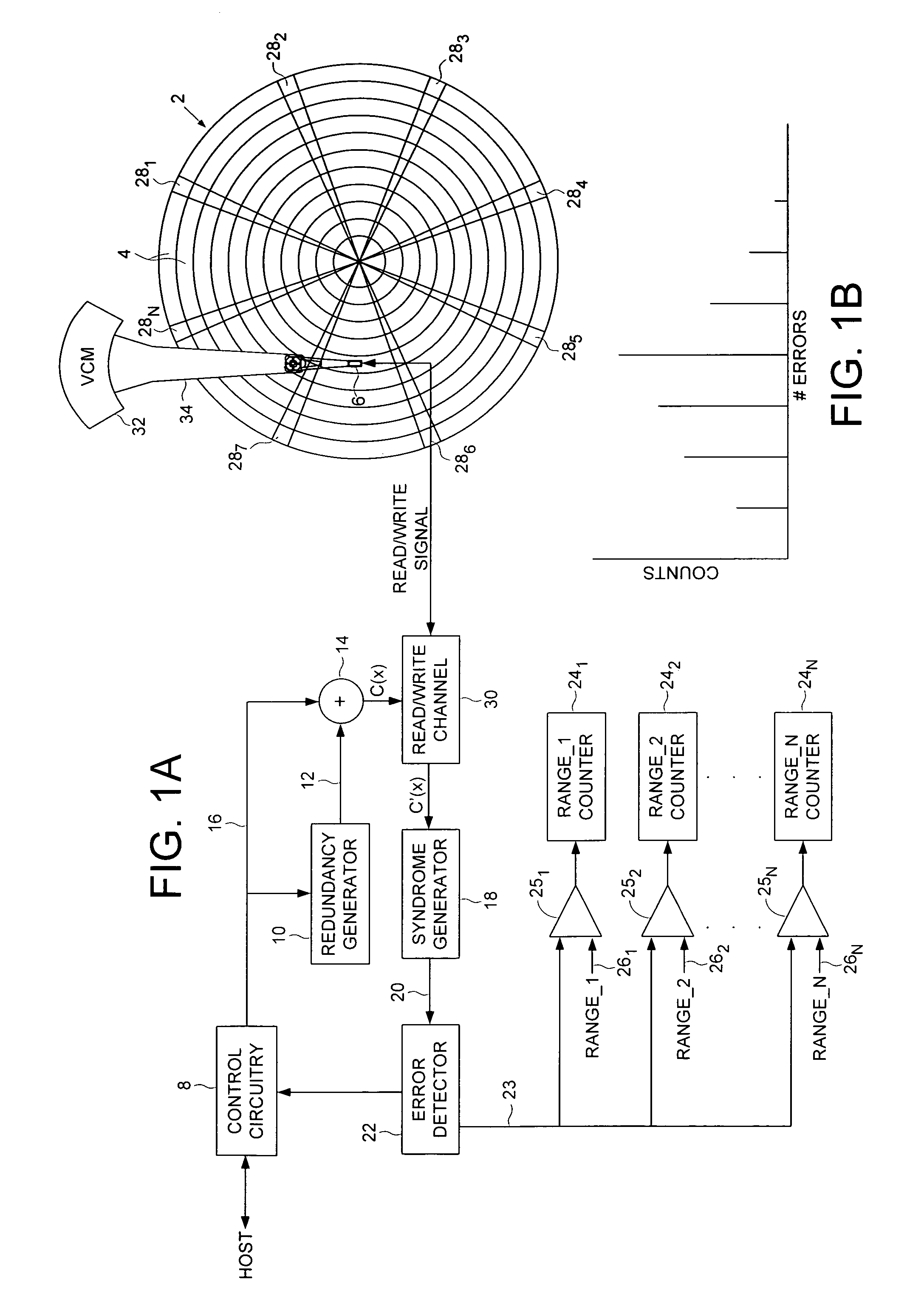

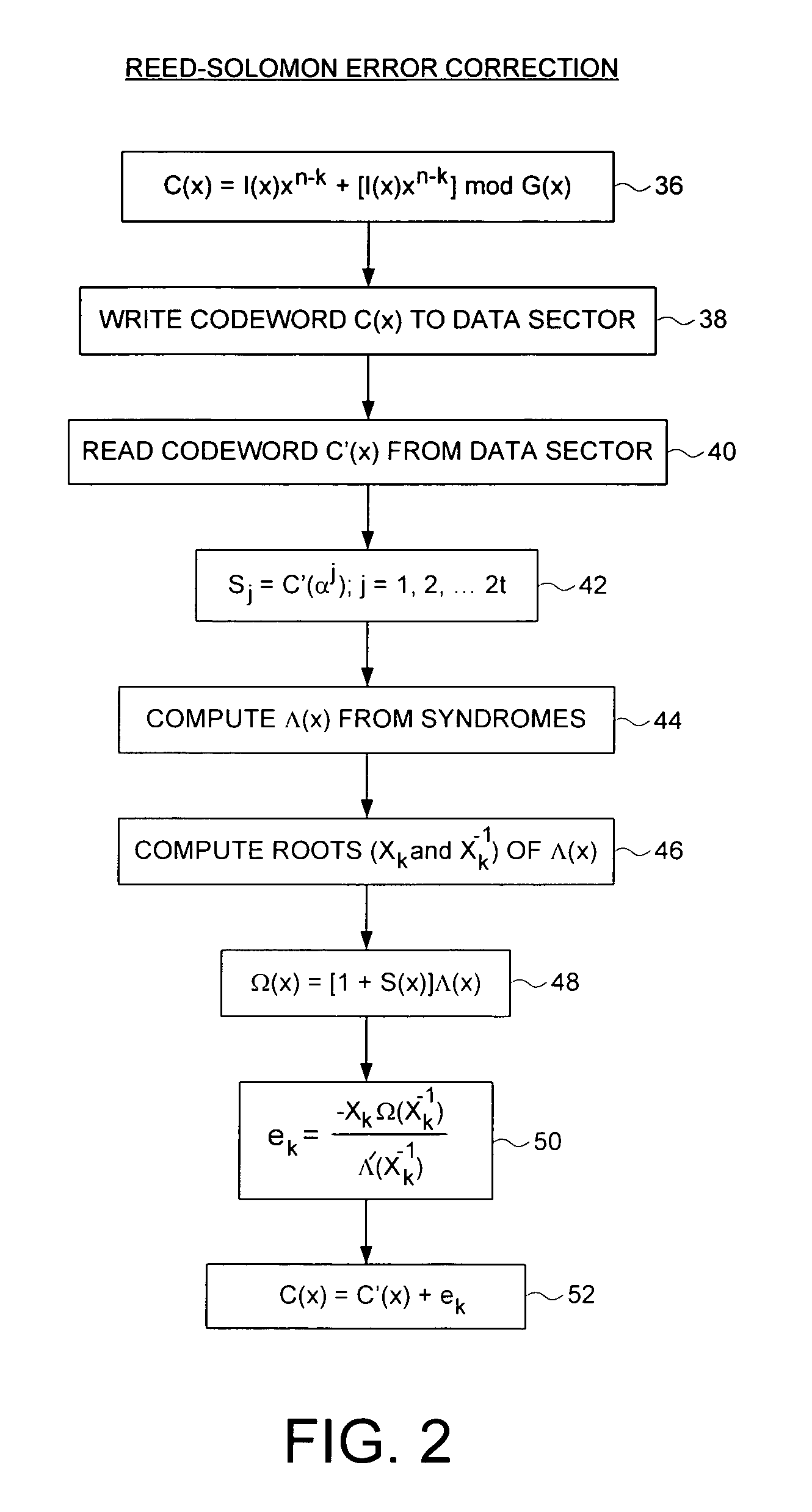

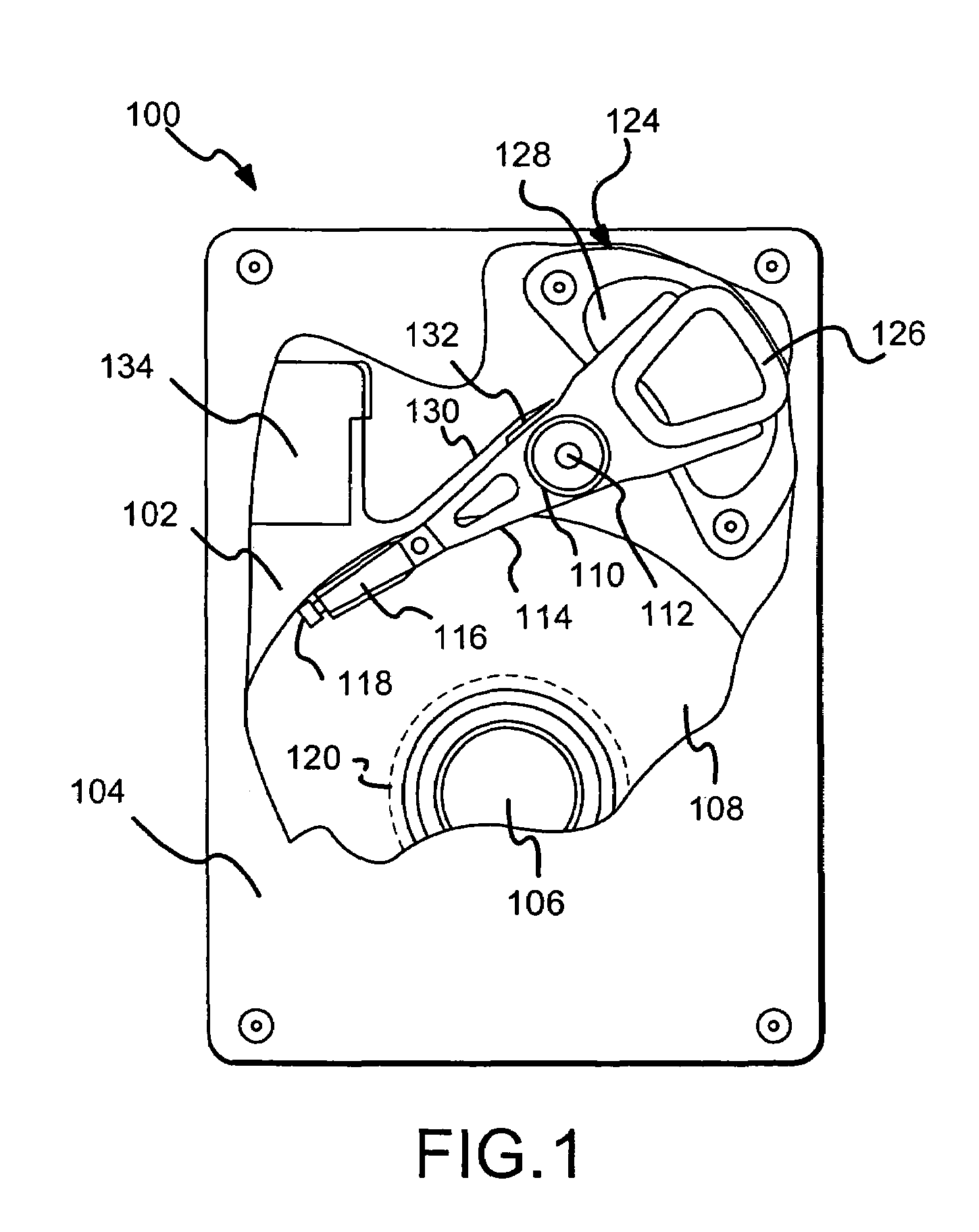

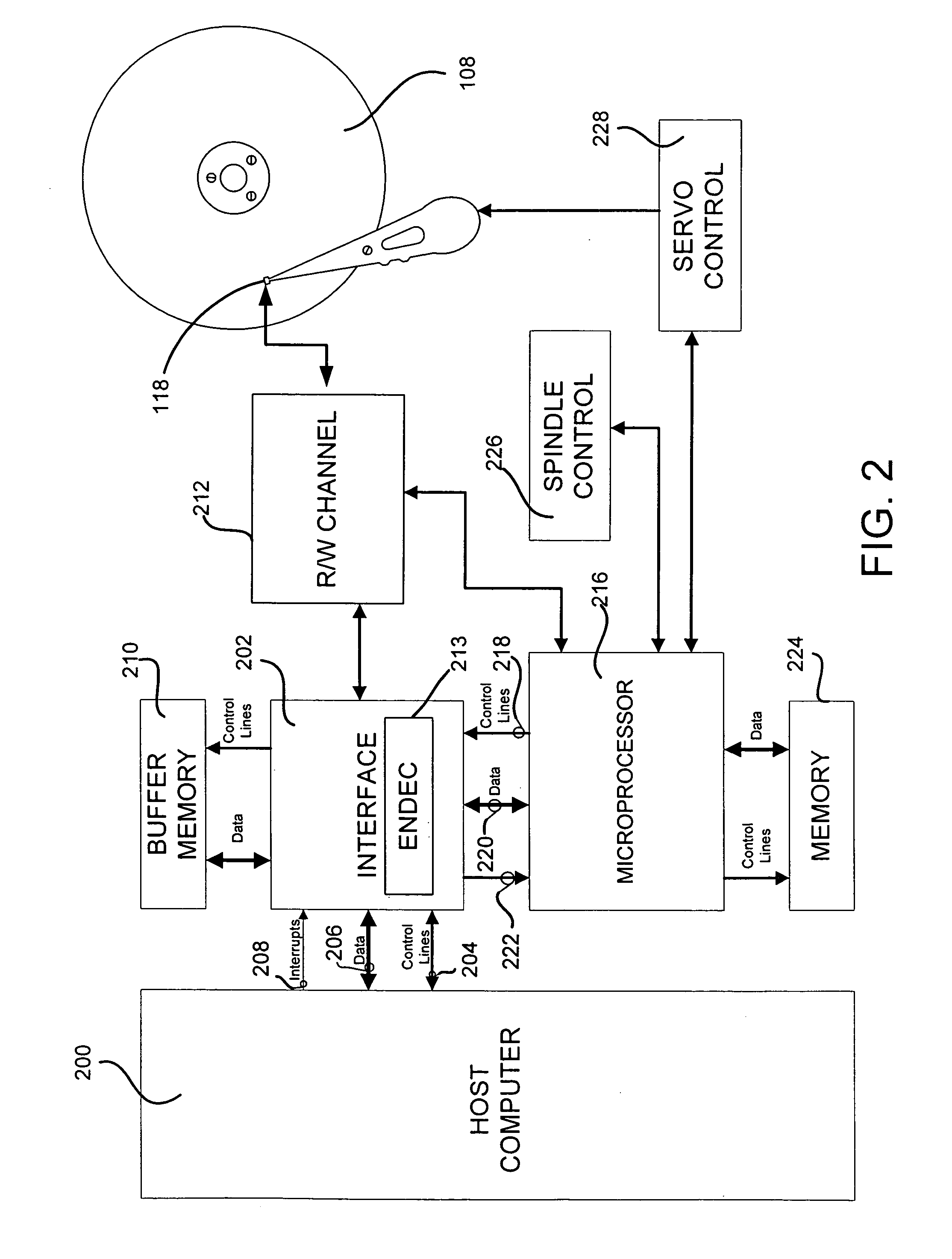

Disk drive employing error threshold counters to generate an ECC error distribution

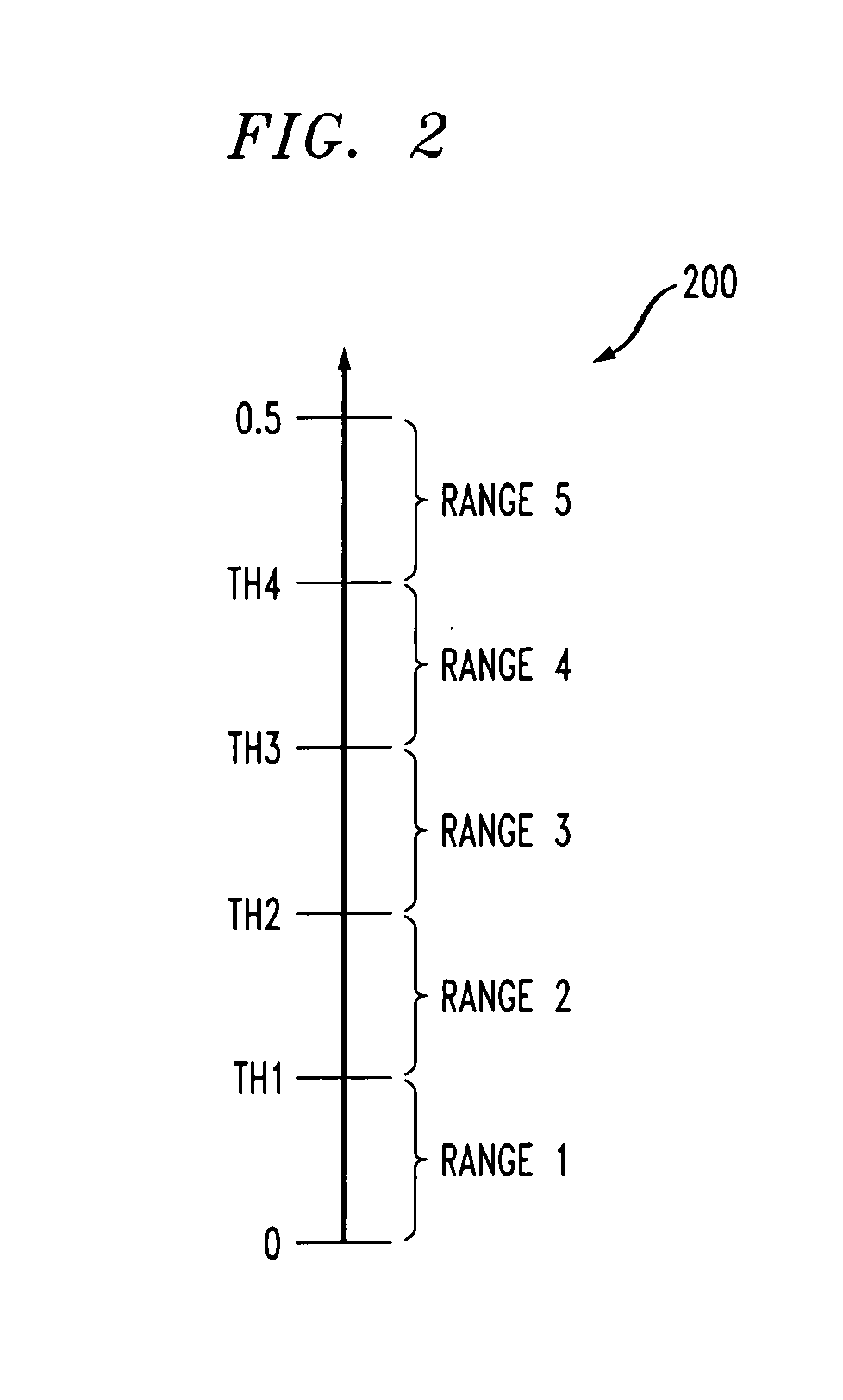

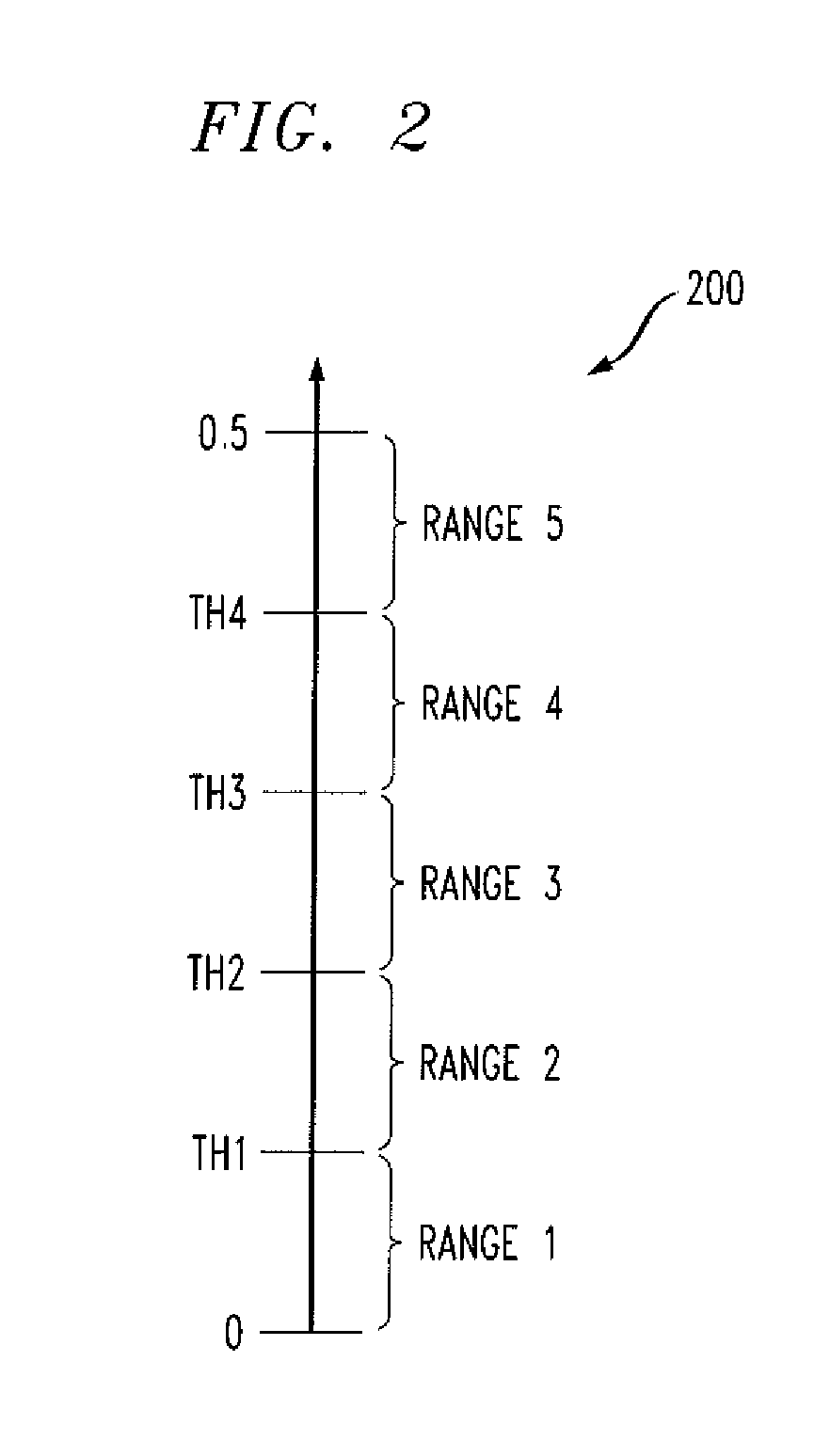

A disk drive is disclosed comprising a head actuated over a disk. A redundancy generator generates a plurality of redundancy symbols appended to user data to form a codeword C(x) written to a selected data sector on the disk. During a read operation, a syndrome generator generates a plurality of error syndromes in response to a received codeword C′(x) generated by reading the selected data sector. An error detector, responsive to the error syndromes, detects a number of errors in the received codeword C′(x), and a plurality of counters count a number of times the number of errors falls within a predetermined plurality of ranges to thereby provide a distribution of the errors. The error distribution is used, for example, for selecting a track density or ECC depth, or for failure prediction or defect mapping.

Owner:WESTERN DIGITAL TECH INC

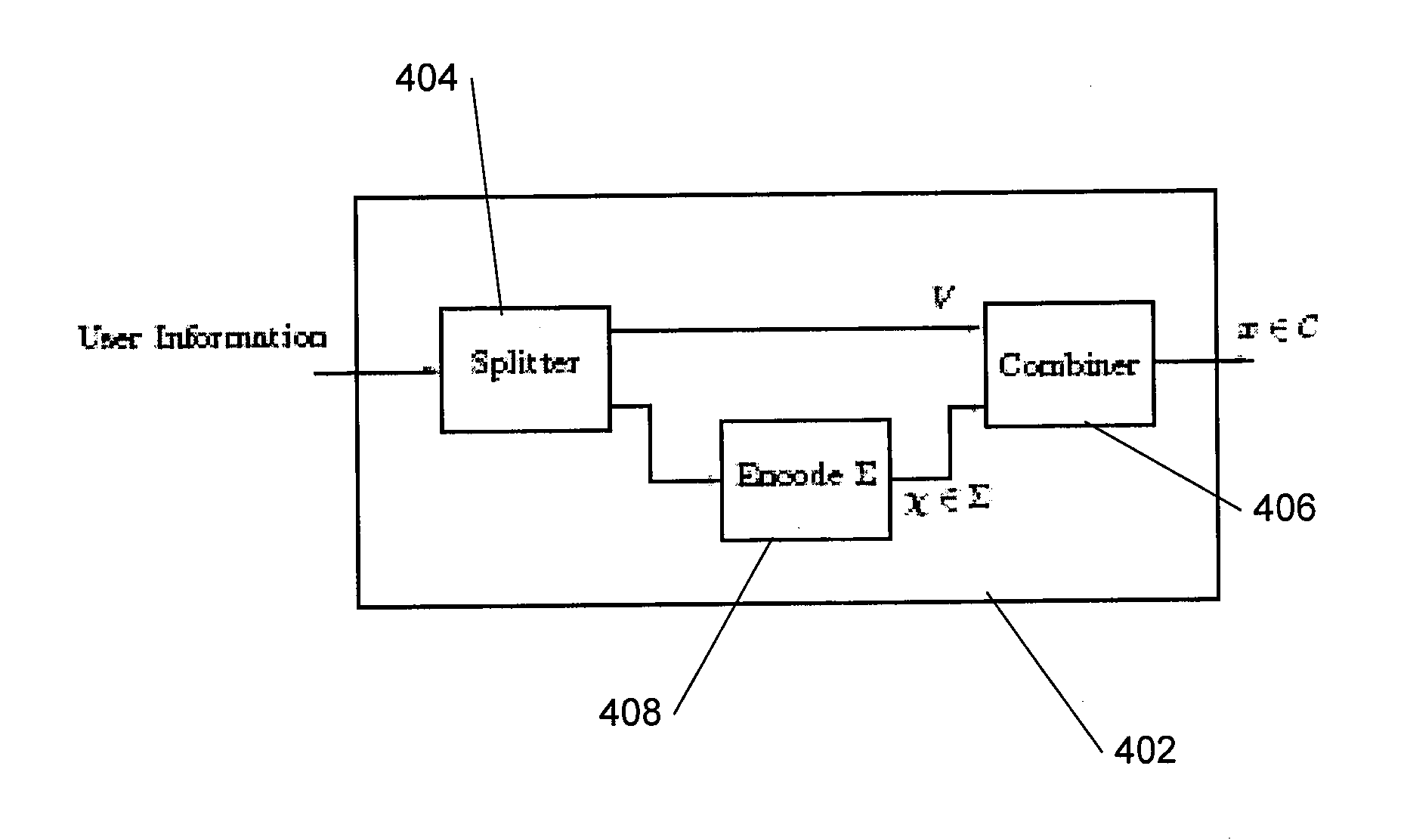

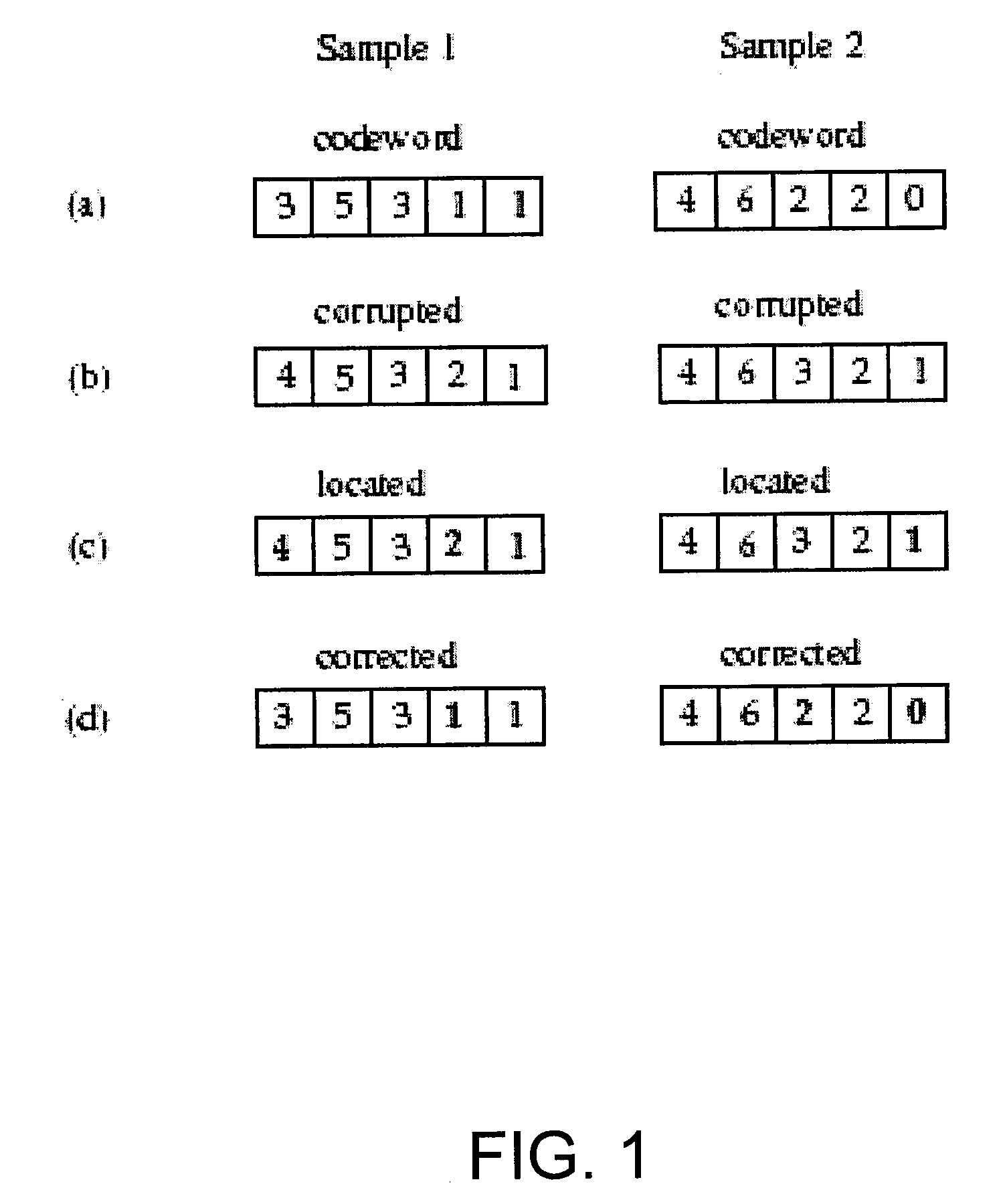

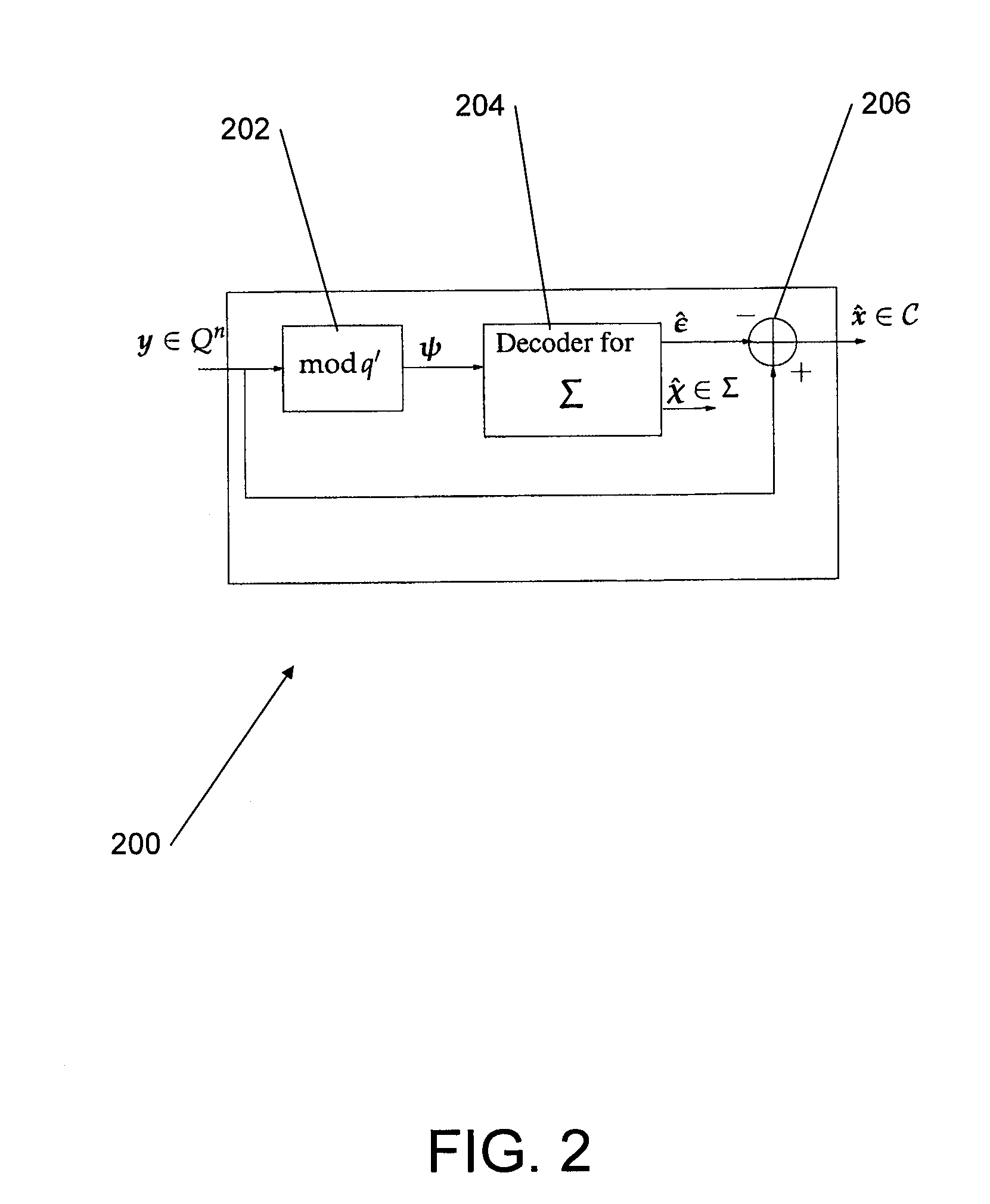

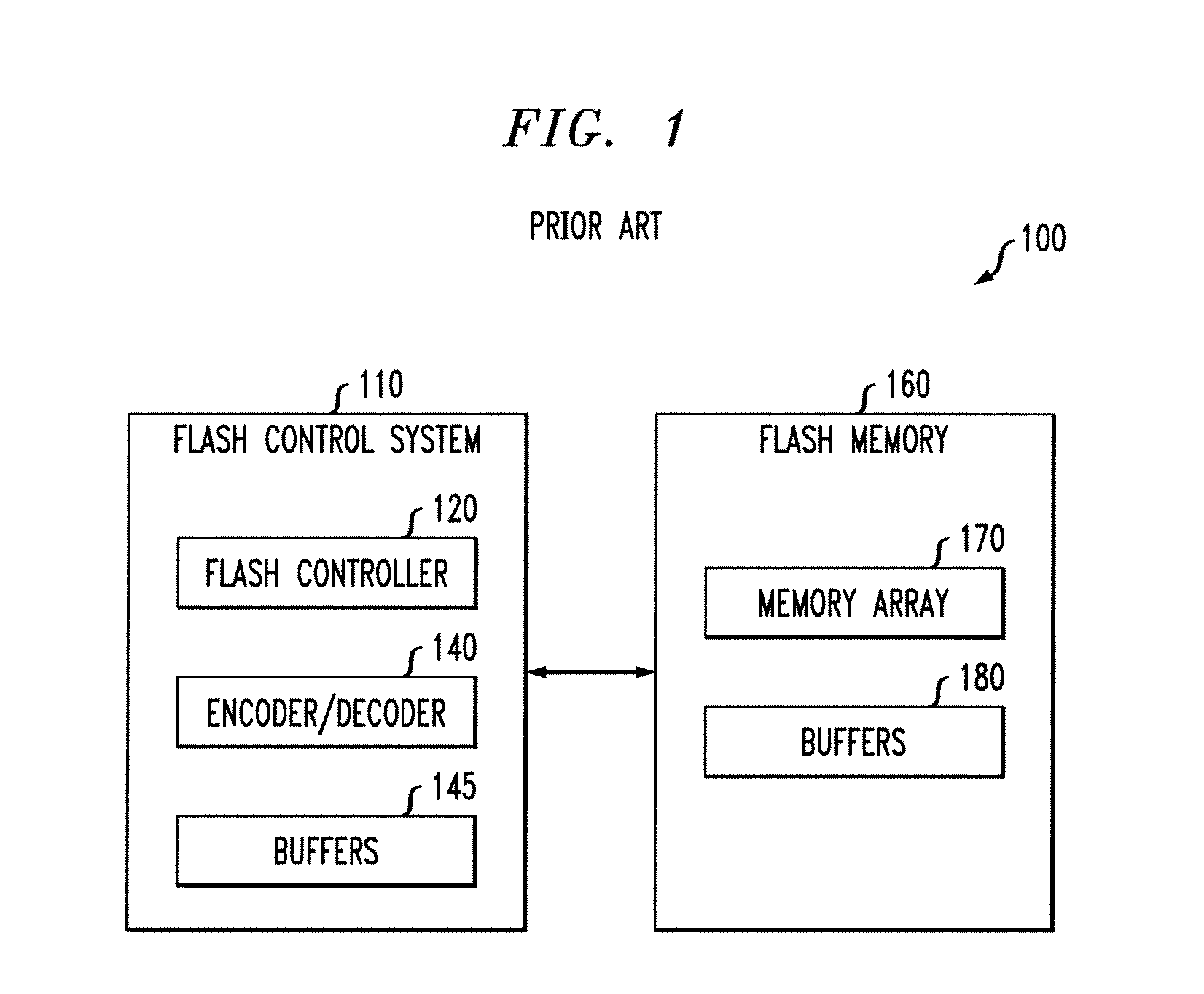

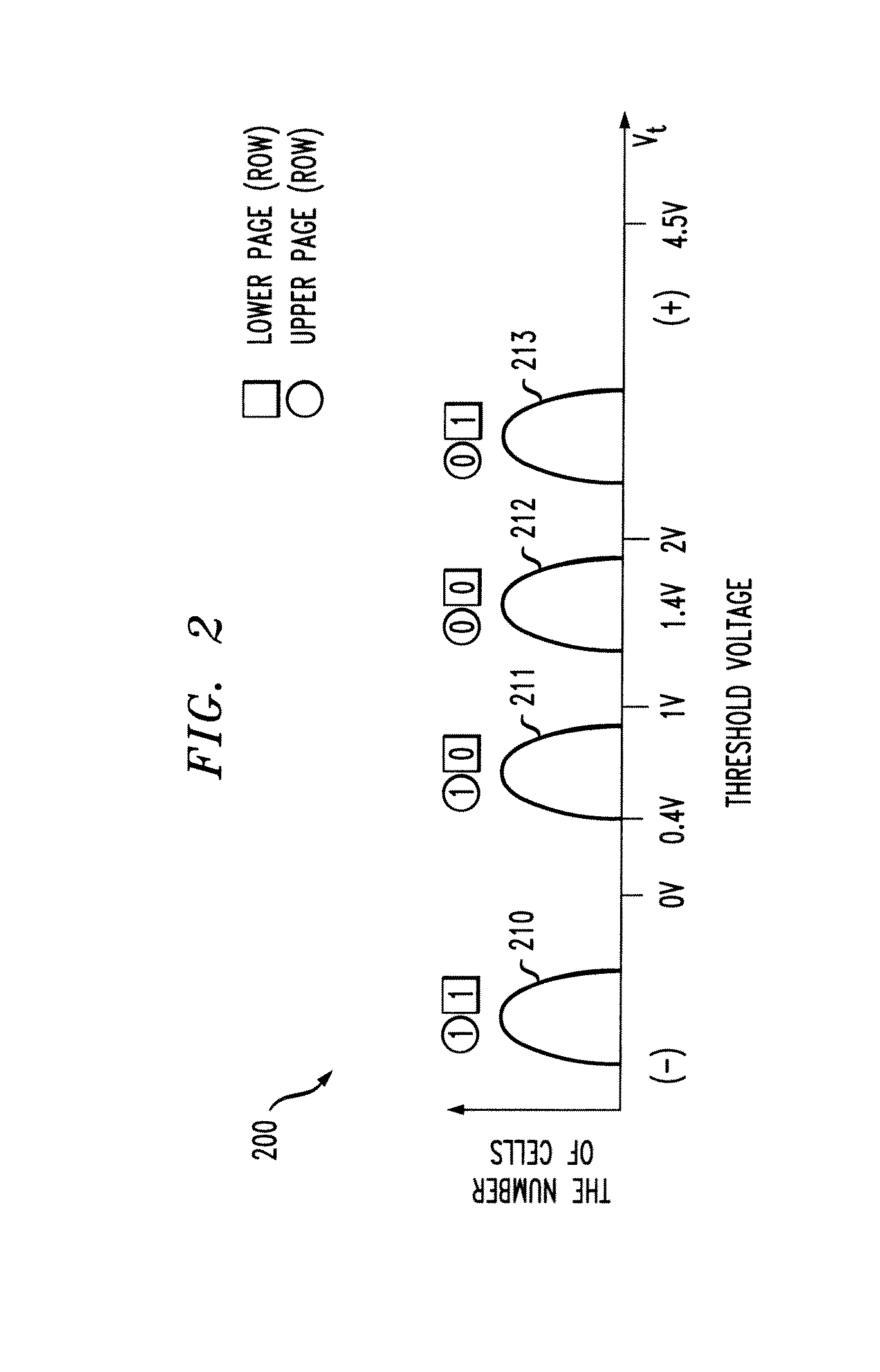

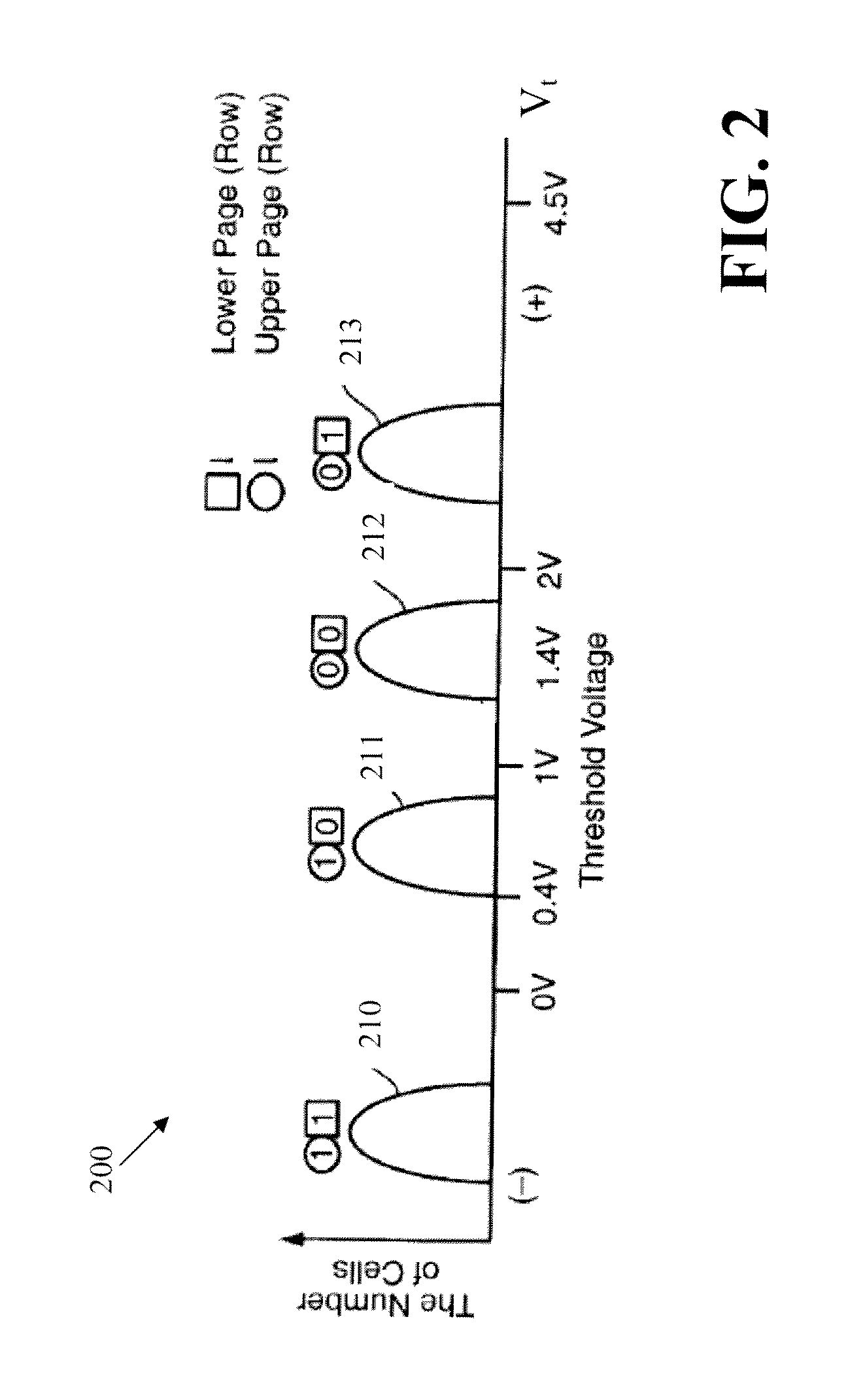

Codes For Limited Magnitude Asymetric Errors In Flash Memories

ActiveUS20080168320A1Increase speedReach levelError preventionTransmission systemsReduced sizeErrors and residuals

Error correction is tailored for the use of an ECC for correcting asymmetric errors with low magnitude in a data device, with minimal modifications to the conventional data device architecture. The technique permits error correction and data recovery to be performed with reduced-size error correcting code alphabets. For particular cases, the technique can reduce the problem of constructing codes for correcting limited magnitude asymmetric errors to the problem of constructing codes for symmetric errors over small alphabets. Also described are speed up techniques for reaching target data levels more quickly, using more aggressive memory programming operations.

Owner:CALIFORNIA INST OF TECH

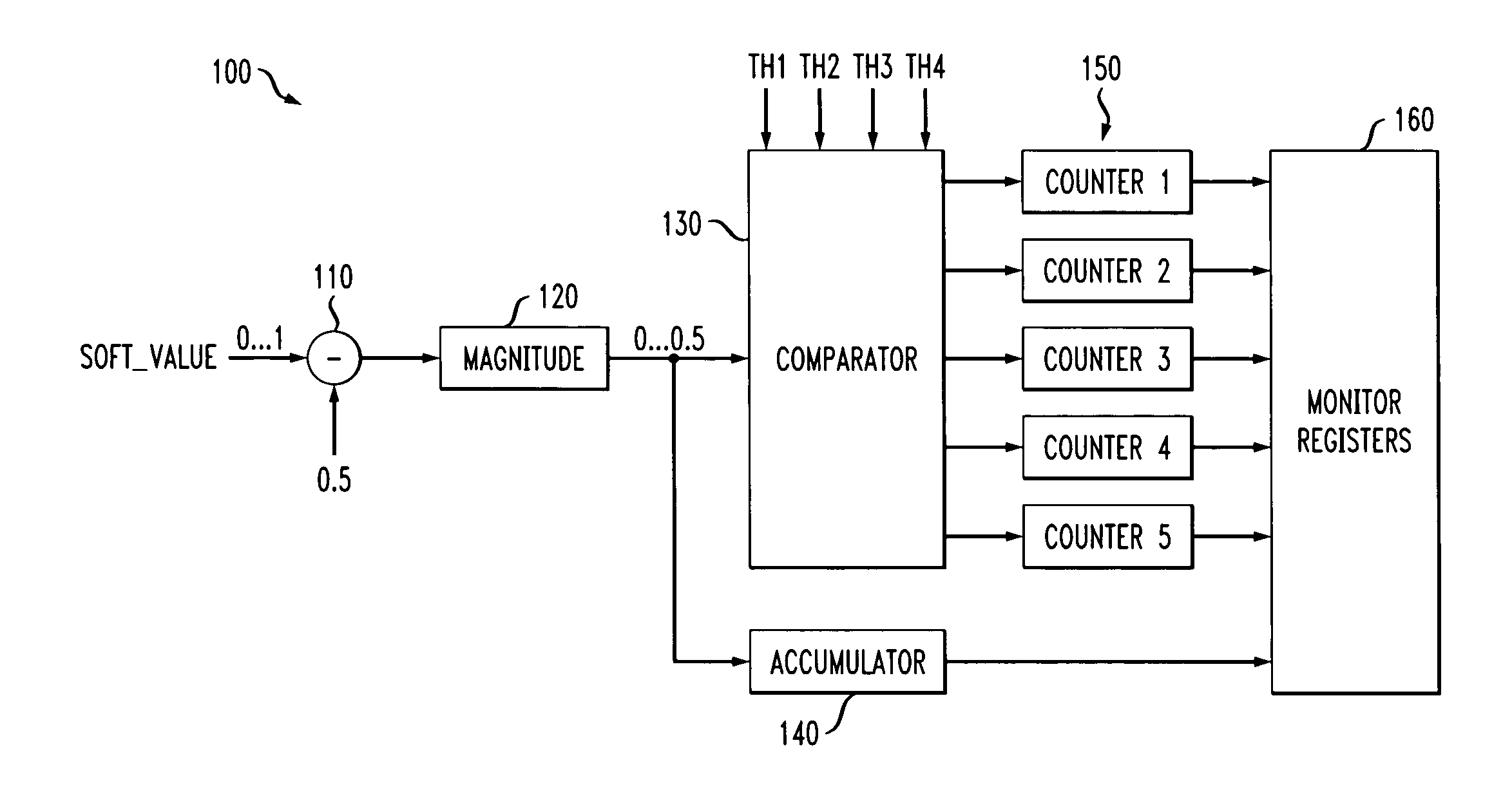

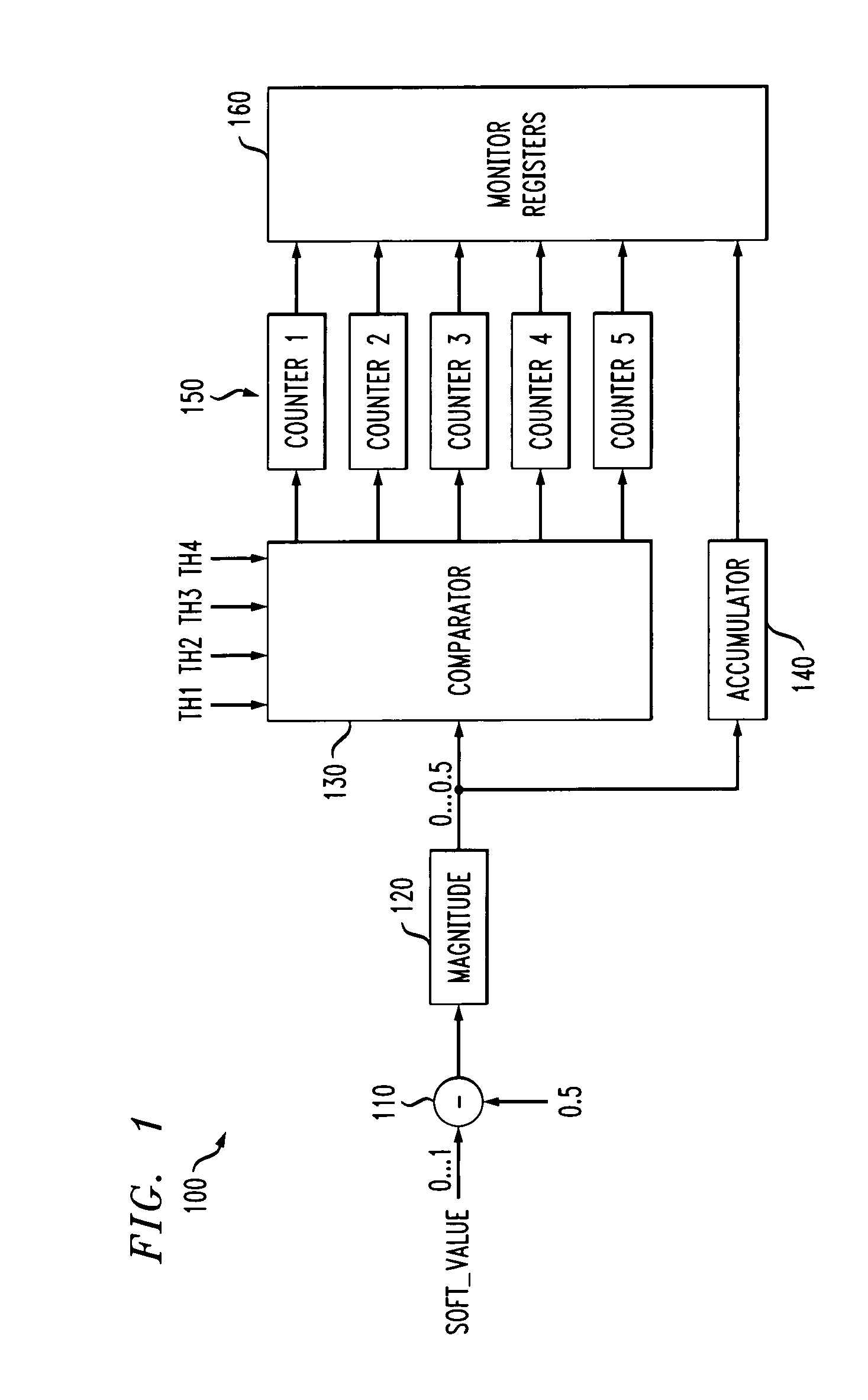

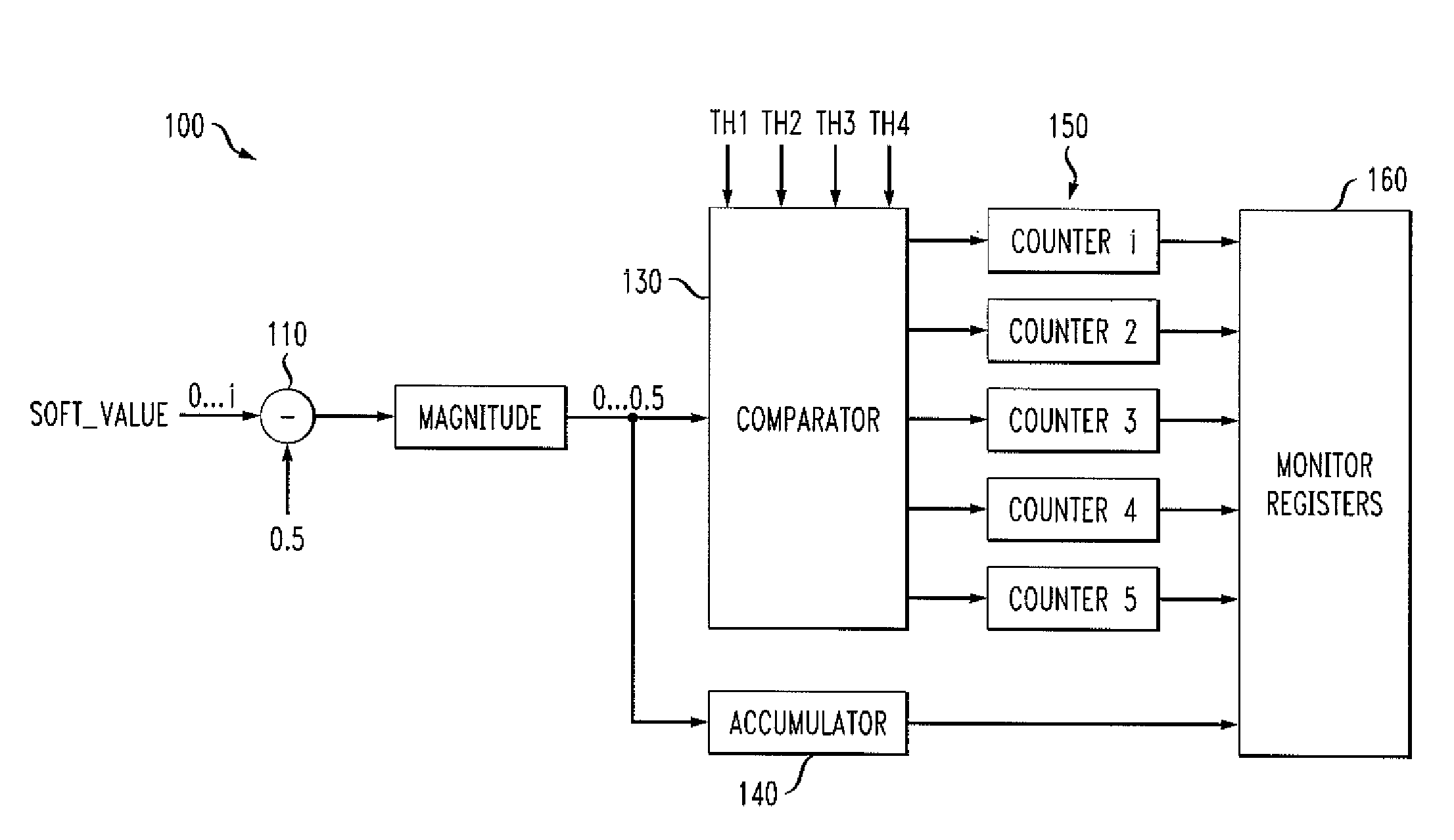

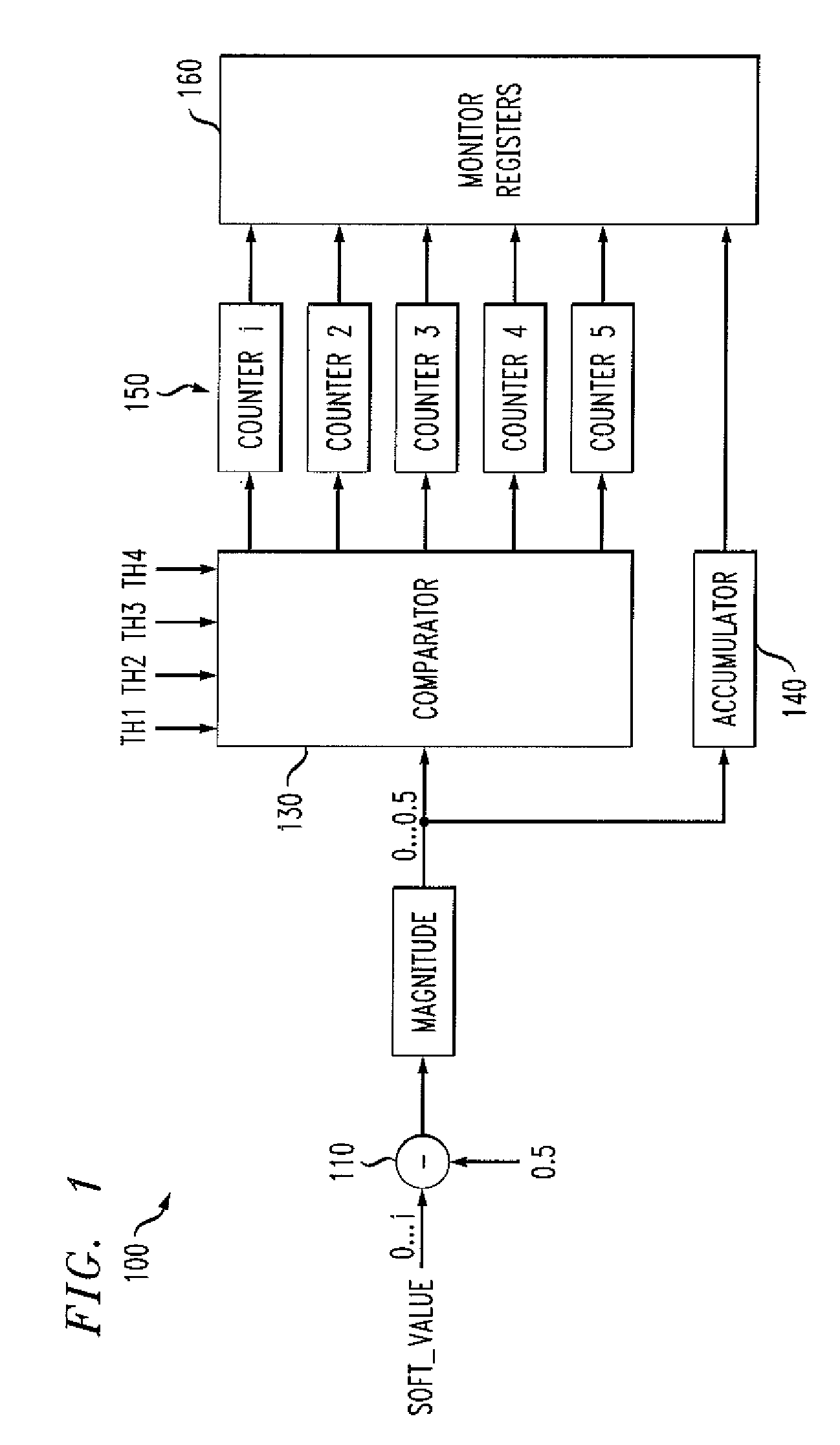

Method and apparatus for evaluating performance of a read channel

ActiveUS20060195772A1Less timeData representation error detection/correctionOther error detection/correction/protectionLogitLog likelihood

Methods and apparatus are provided for measuring the performance of a read channel. A number of detection techniques, such as SOVA and maximum-a-posteriori (MAP) detectors, produce a bit decision and a corresponding reliability value associated with the bit decision. The reliability value associated with the bit decision may be expressed, for example, in the form of log likelihood ratios (LLRs). The reliability value can be monitored and used as a performance measure. The present invention provides a channel performance measure that generally correlates directly to the BER but can be collected in less time.

Owner:AVAGO TECH INT SALES PTE LTD

Systems and processes for decoding chain reaction codes through inactivation

InactiveUS6856263B2Error prevention/detection by using return channelOther decoding techniquesAlgorithmChain reaction

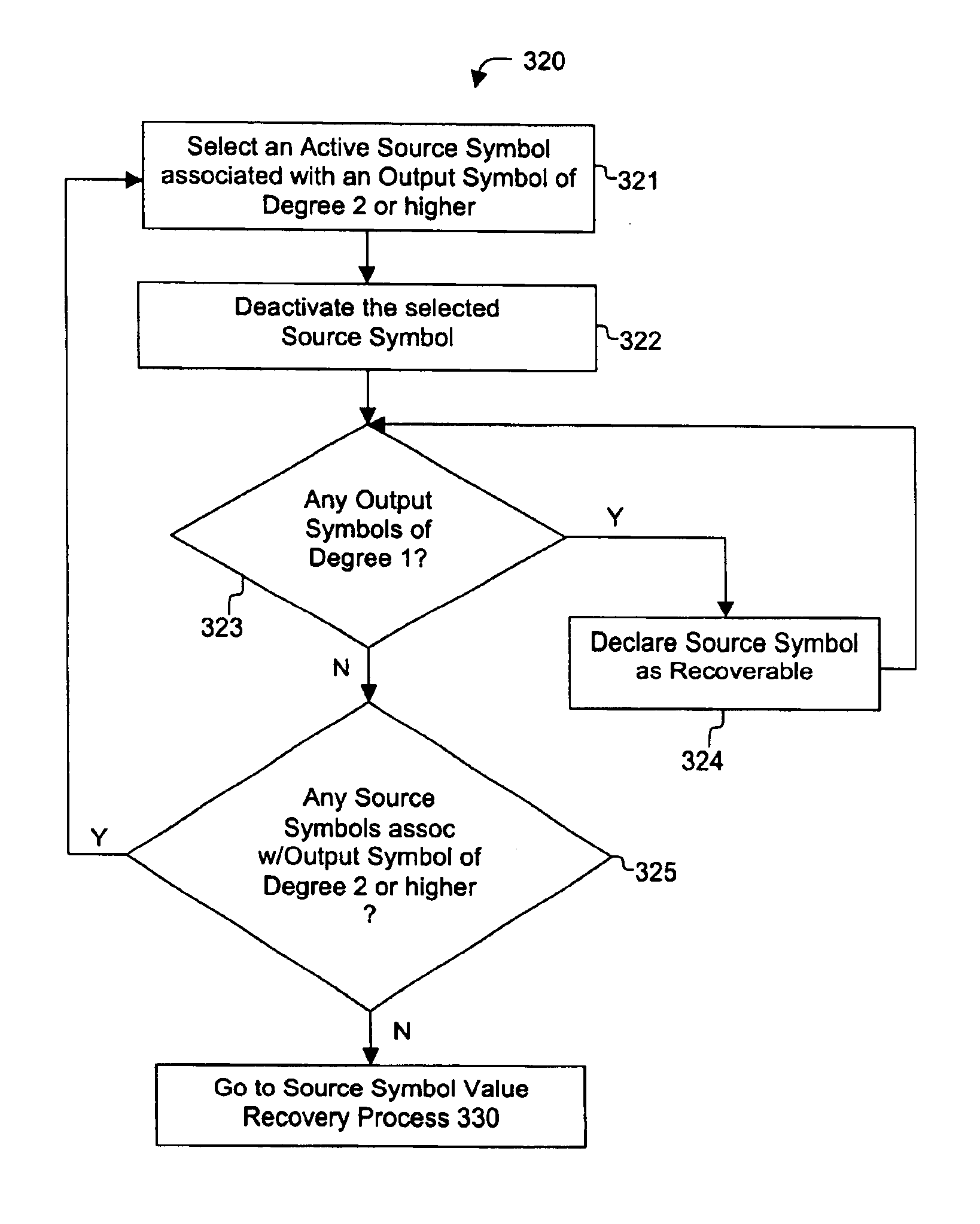

A method for processing a chain reaction codes includes first selecting a source symbol which is associated an output symbol of degree two or higher (i.e., an output symbol which is itself associated with two or more input symbols), and subsequently deactivating the selected source symbol in an attempt to produce an output symbol of degree one. The inactivation process can be repeated either successively until an output symbol of degree one is identified, and / or whenever the decoding process is unable to locate an output symbol of degree one.

Owner:QUALCOMM INC

Error detection and correction codes for channels and memories with incomplete error characteristics

InactiveUS8429495B2Efficient error-correcting codeOther error detection/correction/protectionCode conversionParallel computingErrors and residuals

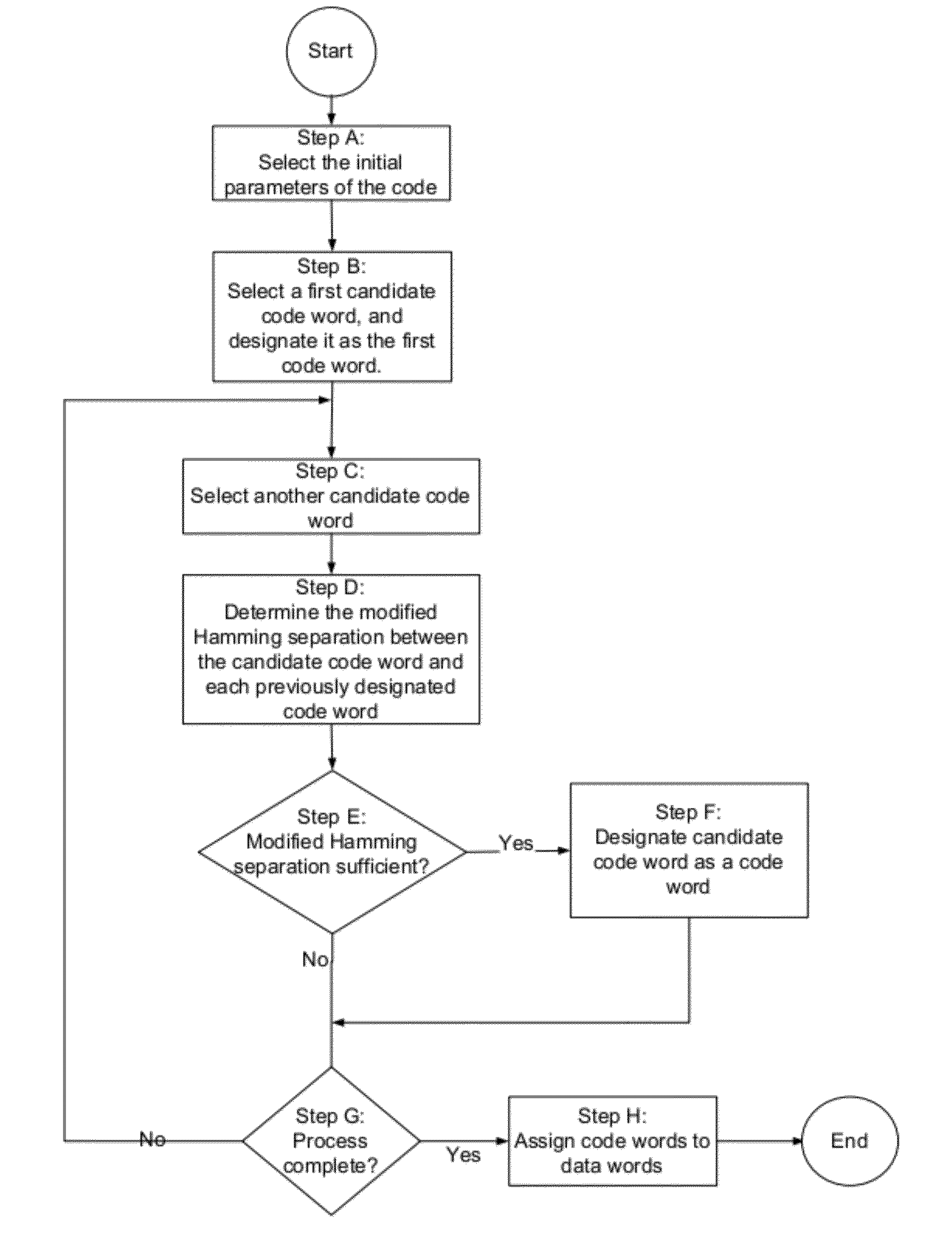

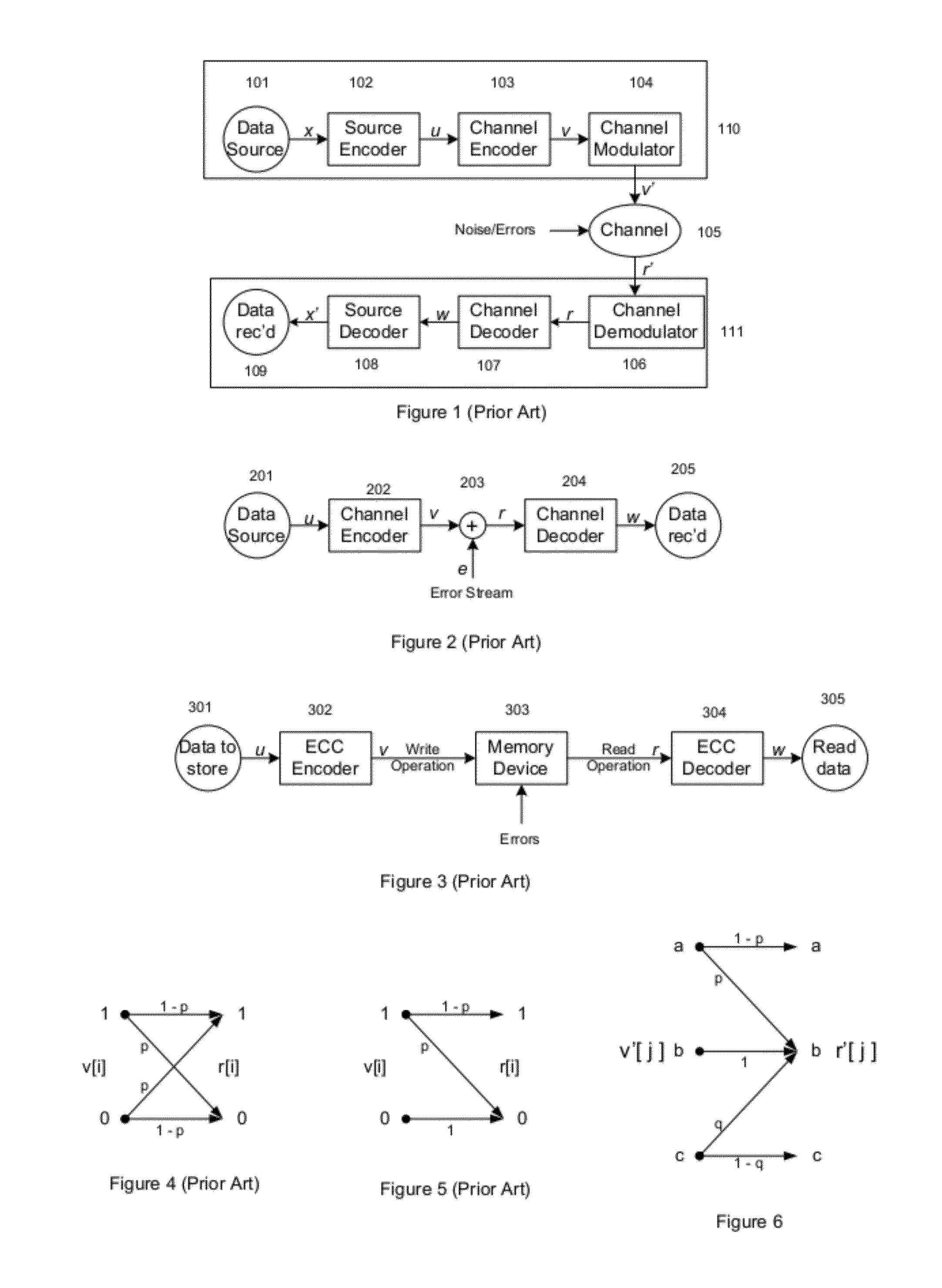

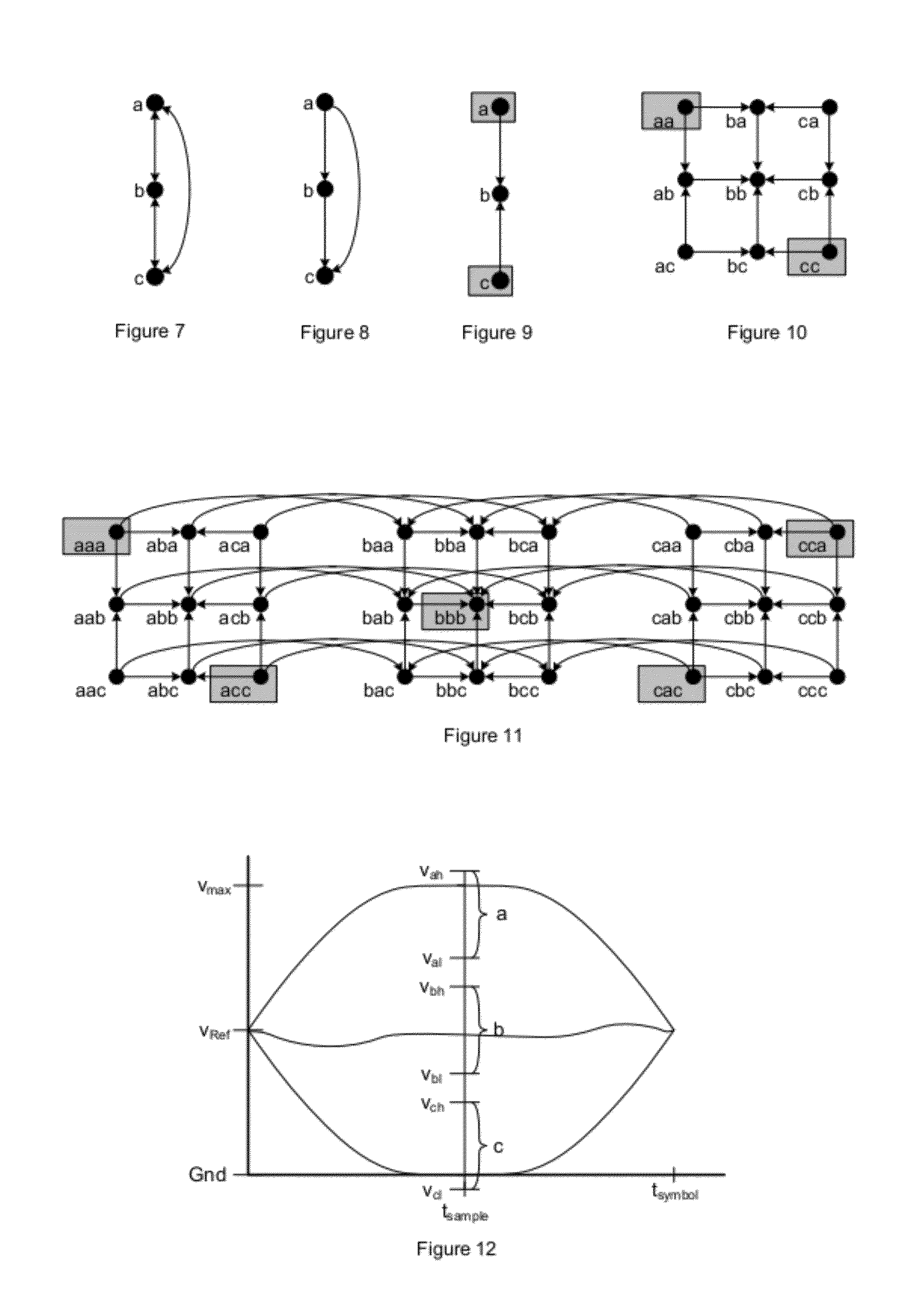

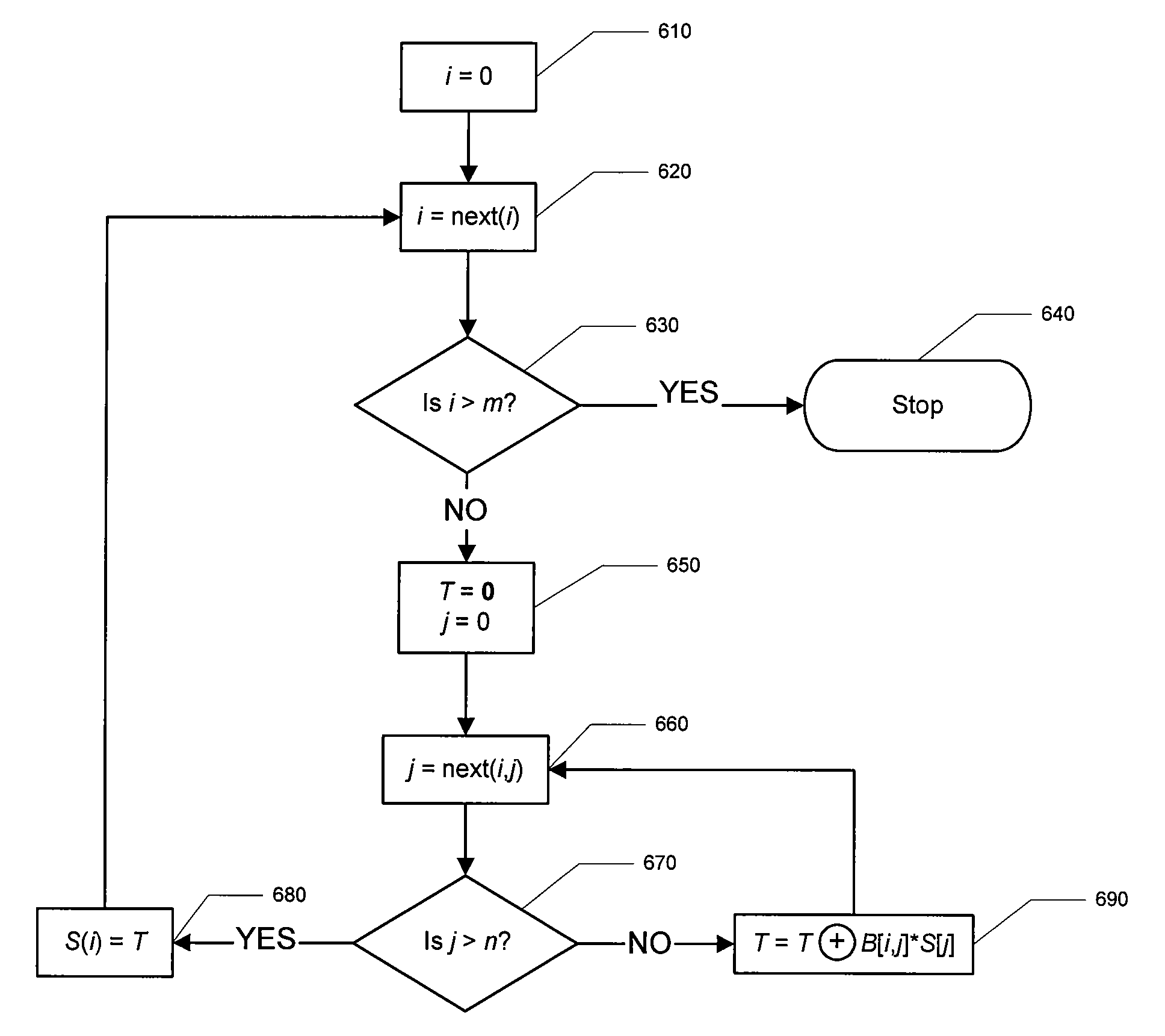

A channel has a first and a second end. The first end of the channel is coupled to a transmitter. The channel is capable of transmitting symbols selected from a symbol set from the first end to the second end. The channel exhibits incomplete error introduction properties. A code comprises a set of code words. The elements of the set of code words are one or more code symbols long. The code symbols are members of the symbol set. The minimum modified Hamming separation between the elements of the set of code words in light of the error introduction properties of the channel is greater than the minimum Hamming distance between the elements of the set of code words. A memory device, a method of using the channel, and a method of generating the code are also described.

Owner:CONVERSANT INTPROP MANAGEMENT INC

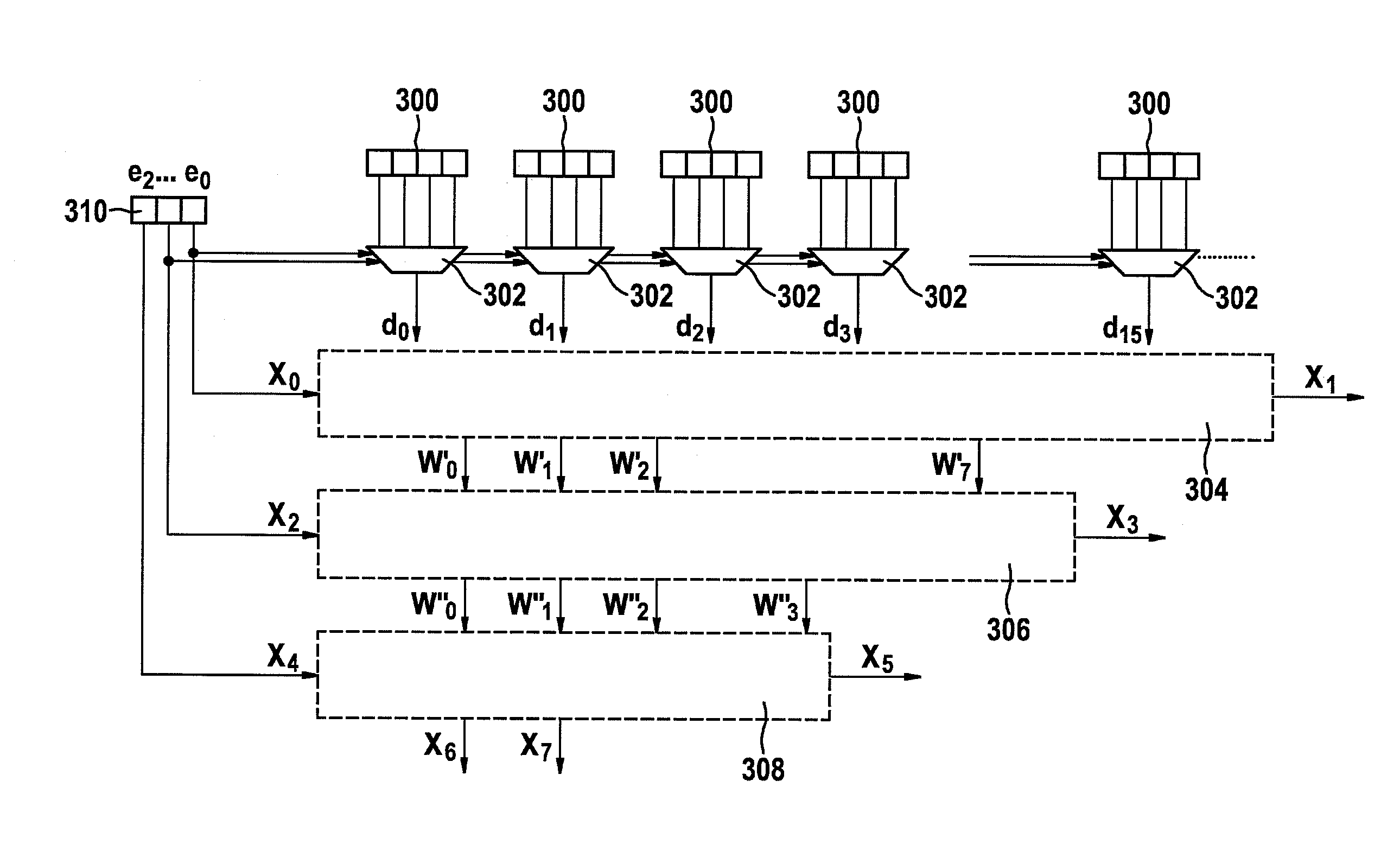

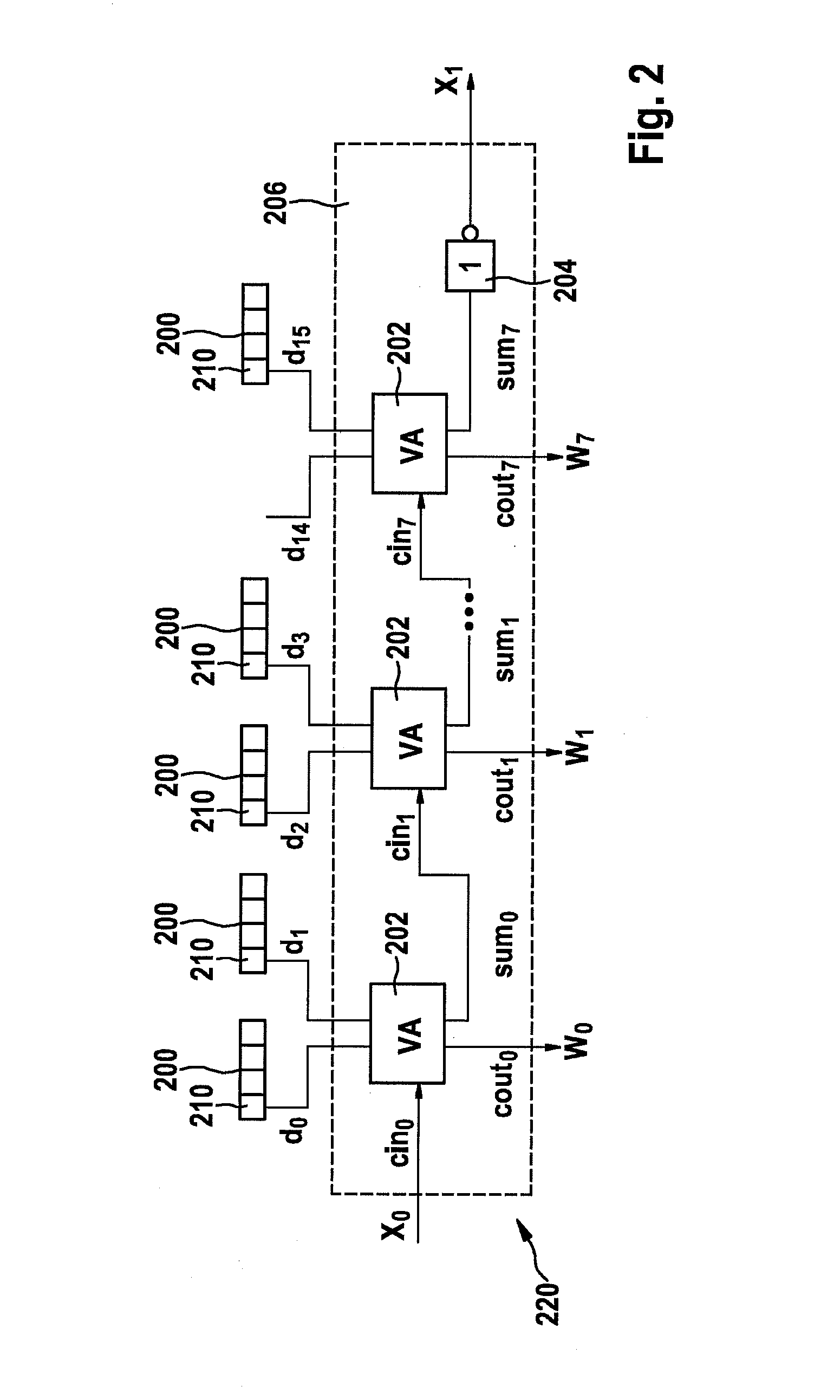

Method and apparatus for fast encoding of data symbols according to half-weight codes

ActiveUS7721184B2Reduce expensesOther error detection/correction/protectionCode conversionHigh densityAlgorithm

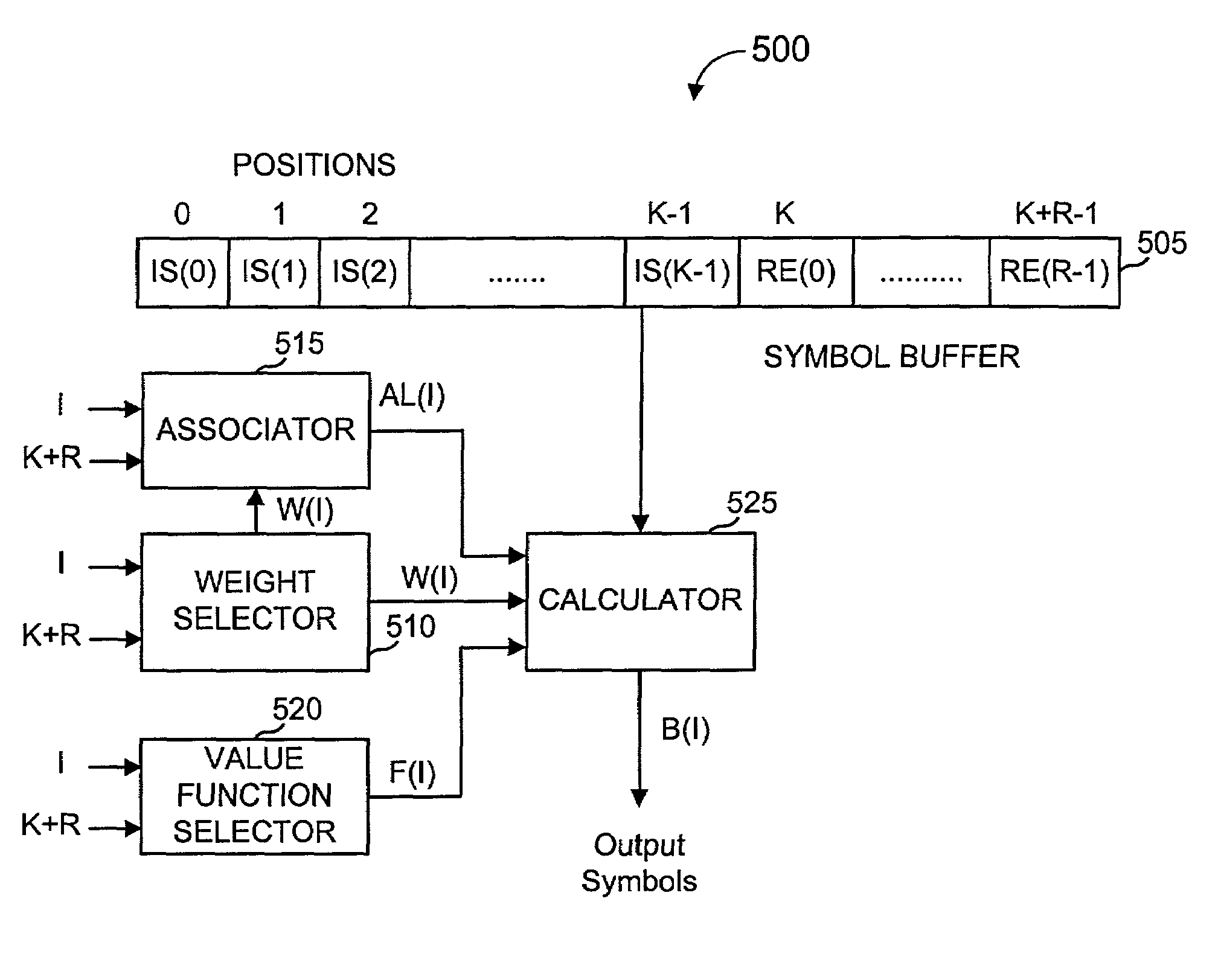

Efficient methods for encoding and decoding Half-Weight codes are disclosed and similar high density codes are disclosed. The efficient methods require at most 3·(k−1)+h / 2+1 XORs of symbols to calculate h Half-Weight symbols from k source symbols, where h is of the order of log(k).

Owner:QUALCOMM INC

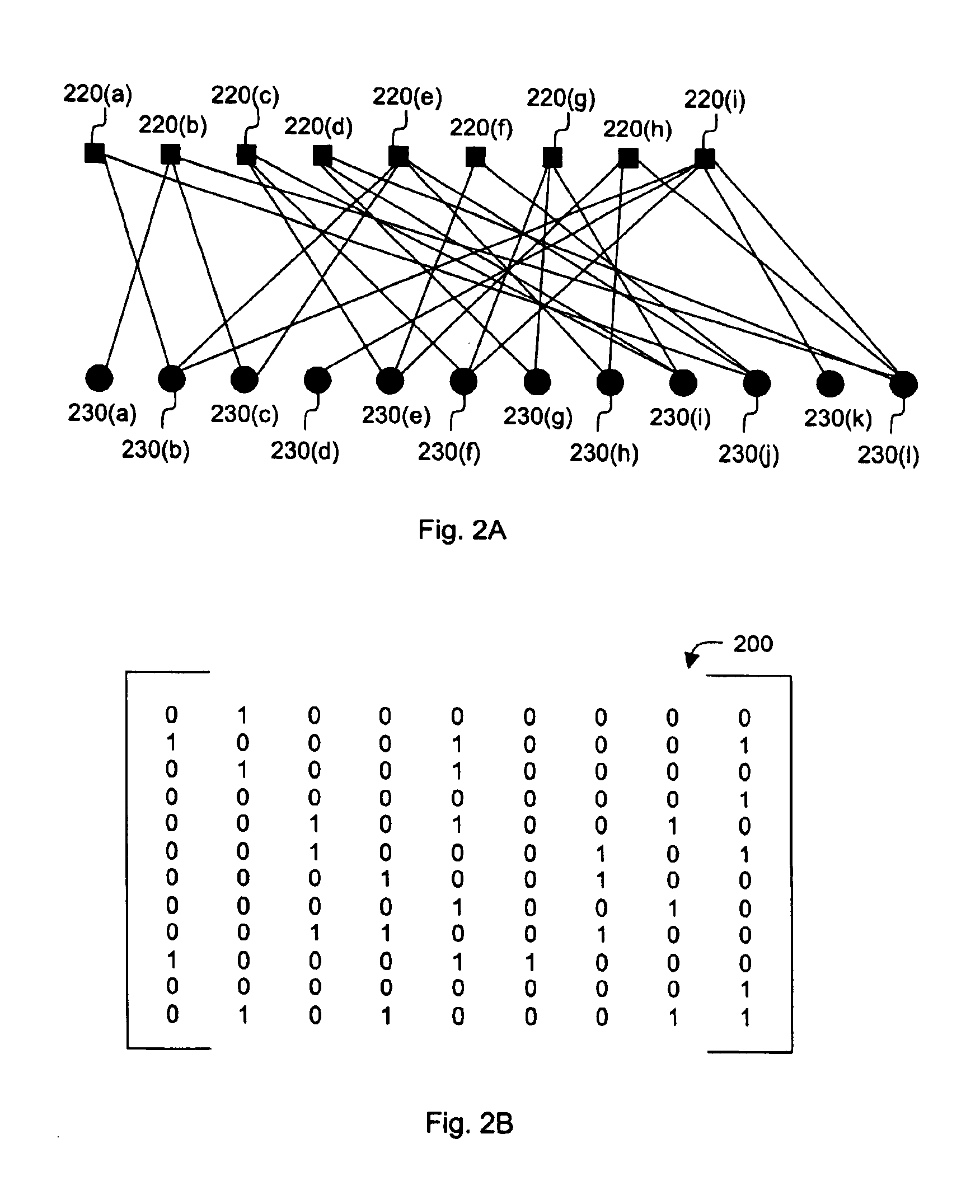

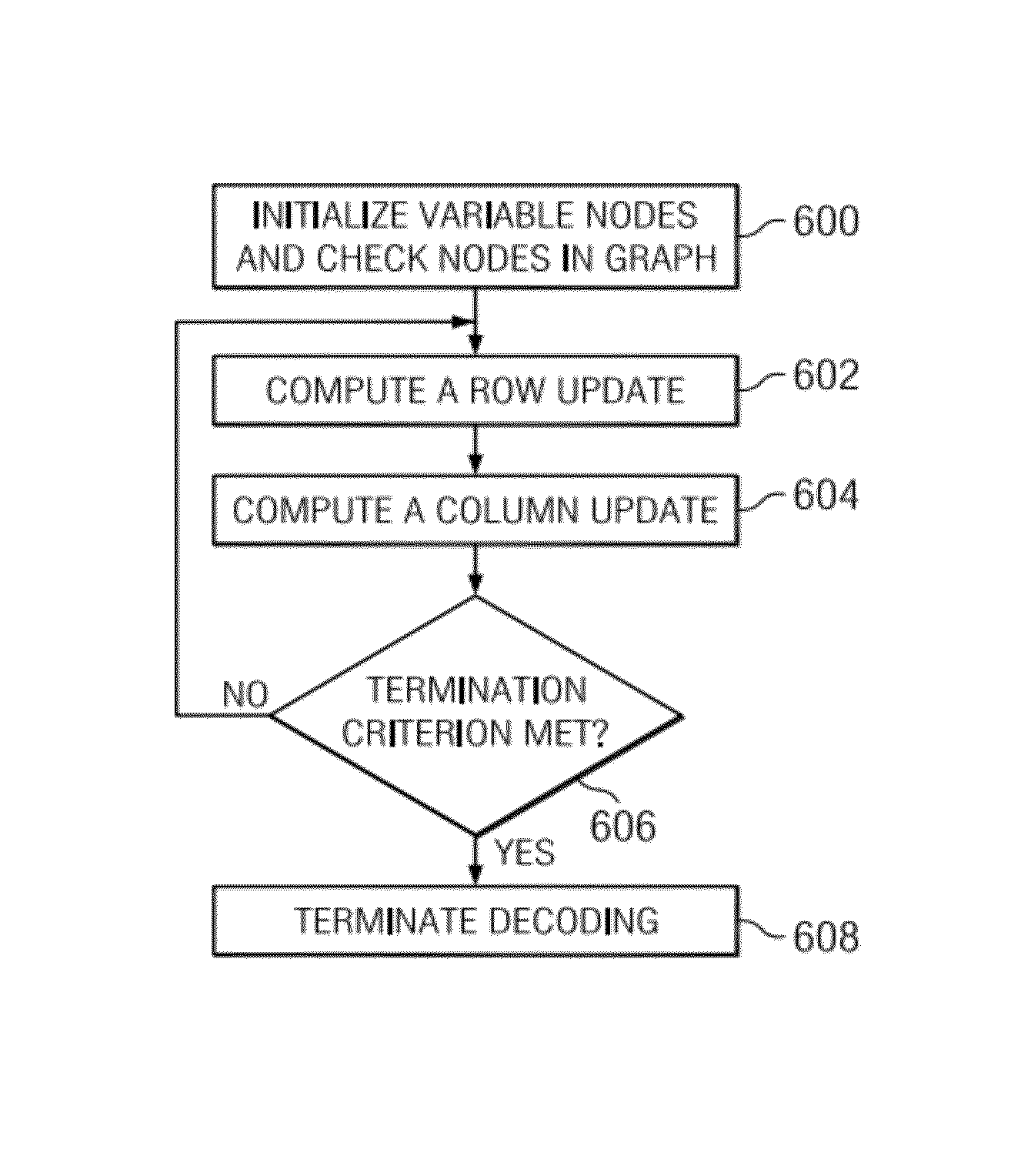

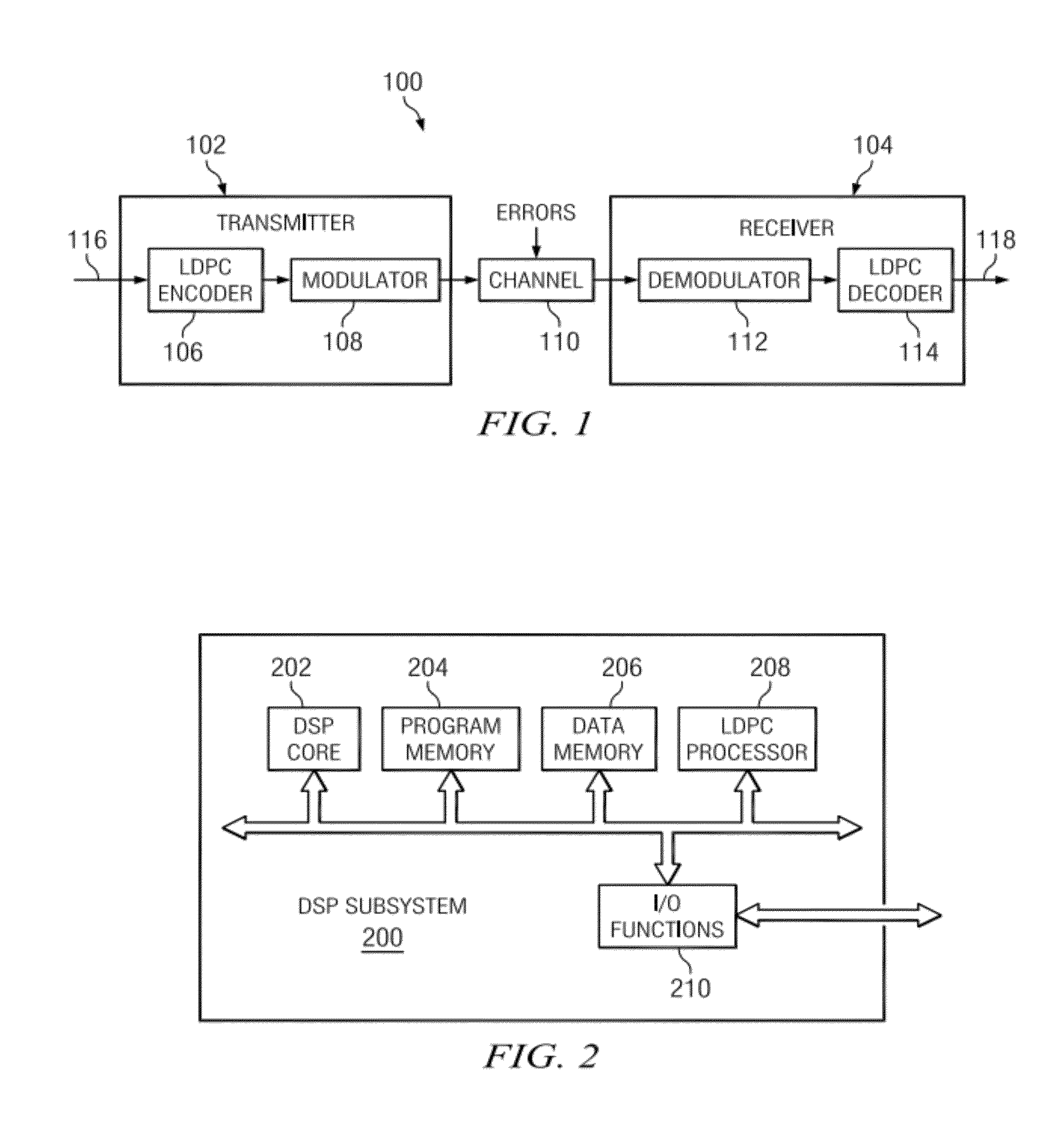

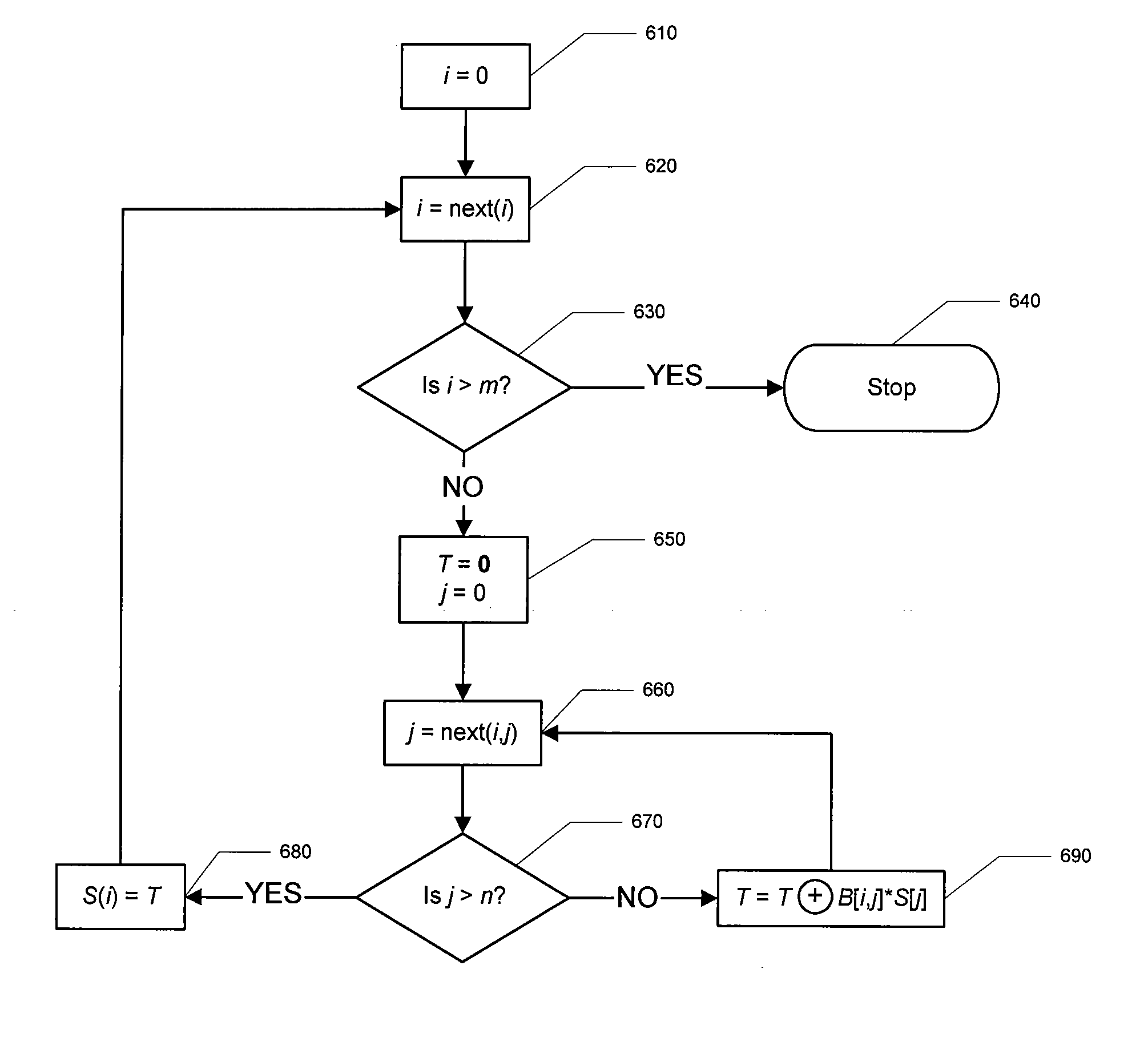

Method and system for decoding low density parity check codes

ActiveUS8392789B2Data representation error detection/correctionOther error detection/correction/protectionGraphicsData stream

A method for decoding a codeword in a data stream encoded according to a low density parity check (LDPC) code having an m×j parity check matrix H by initializing variable nodes with soft values based on symbols in the codeword, wherein a graph representation of H includes m check nodes and j variable nodes, and wherein a check node m provides a row value estimate to a variable node j and a variable node j provides a column value estimate to a check node m if H(m,j) contains a 1, computing row value estimates for each check node, wherein amplitudes of only a subset of column value estimates provided to the check node are computed, computing soft values for each variable node based on the computed row value estimates, determining whether the codeword is decoded based on the soft values, and terminating decoding when the codeword is decoded.

Owner:TEXAS INSTR INC

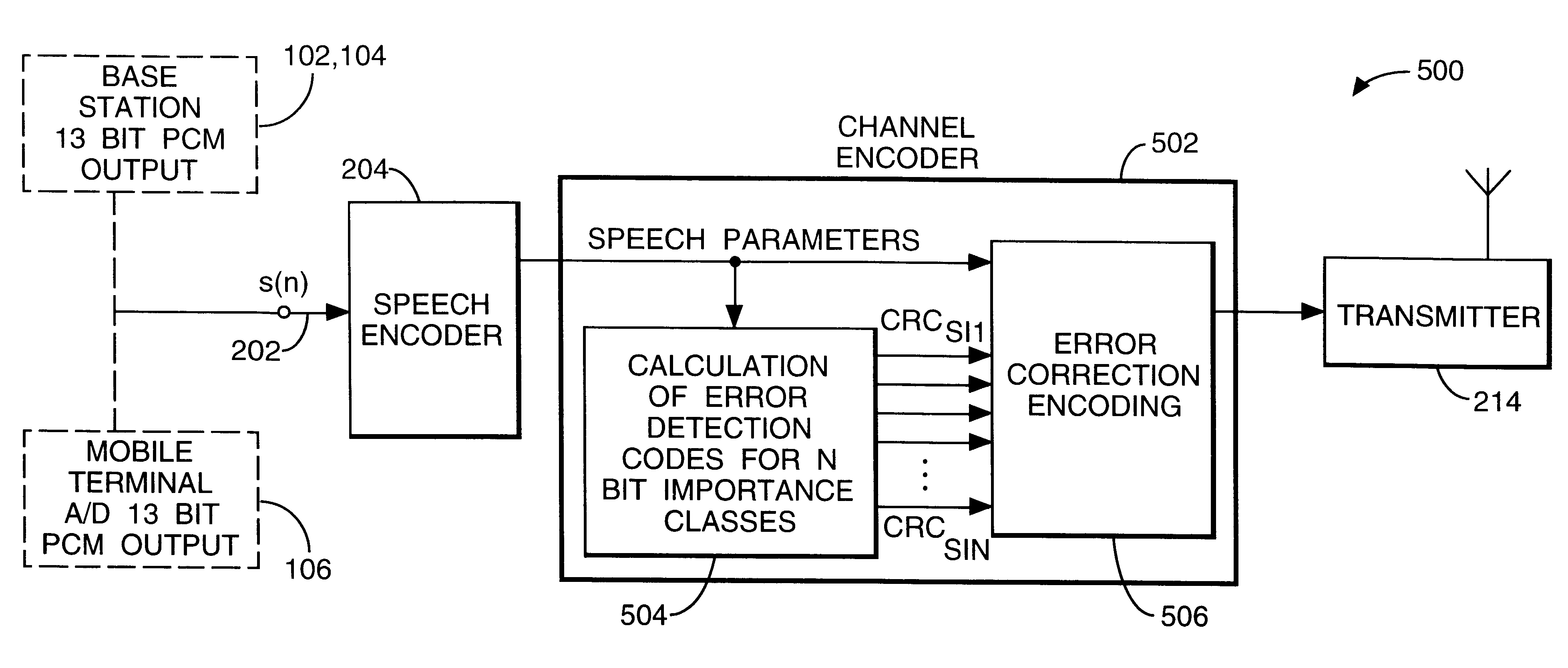

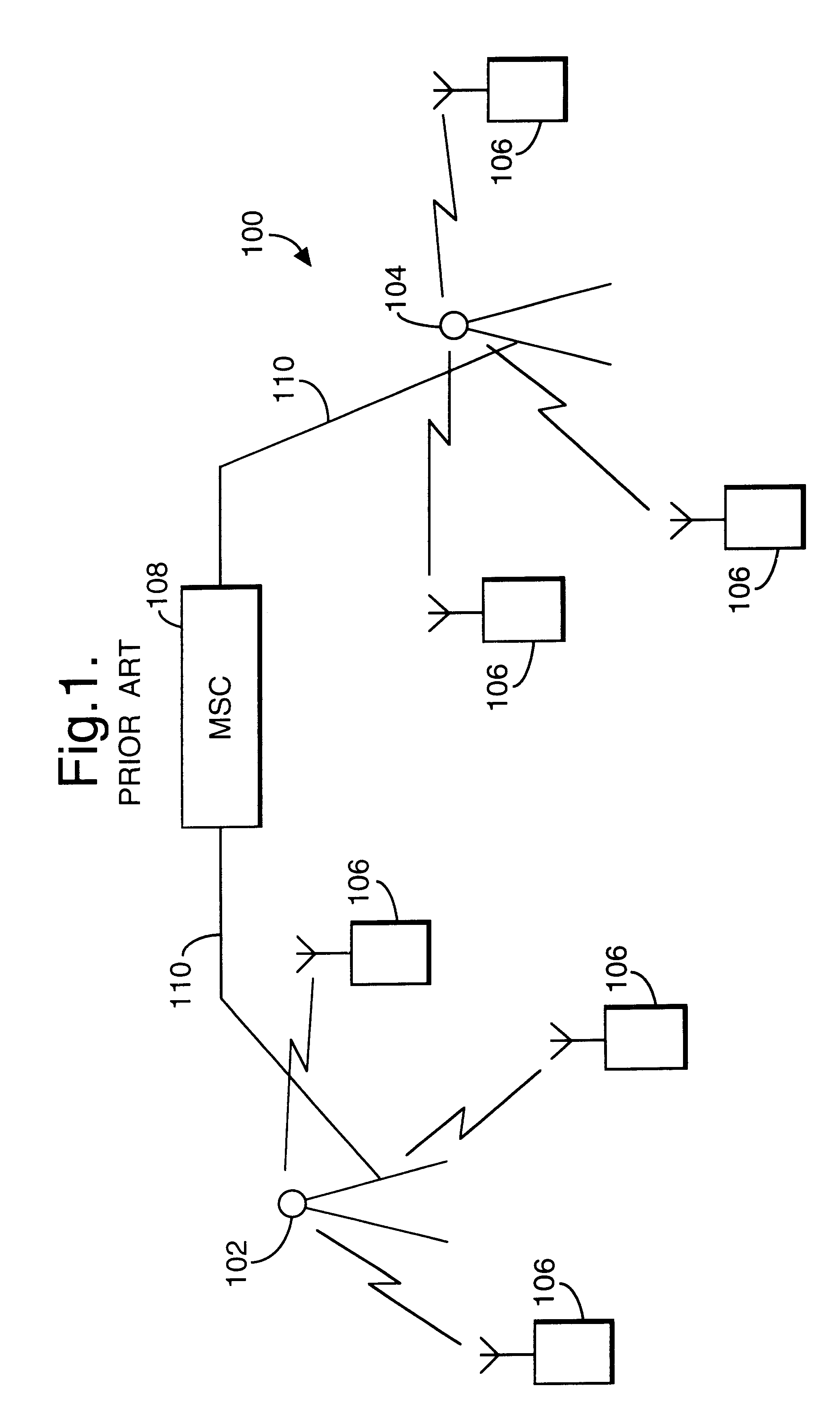

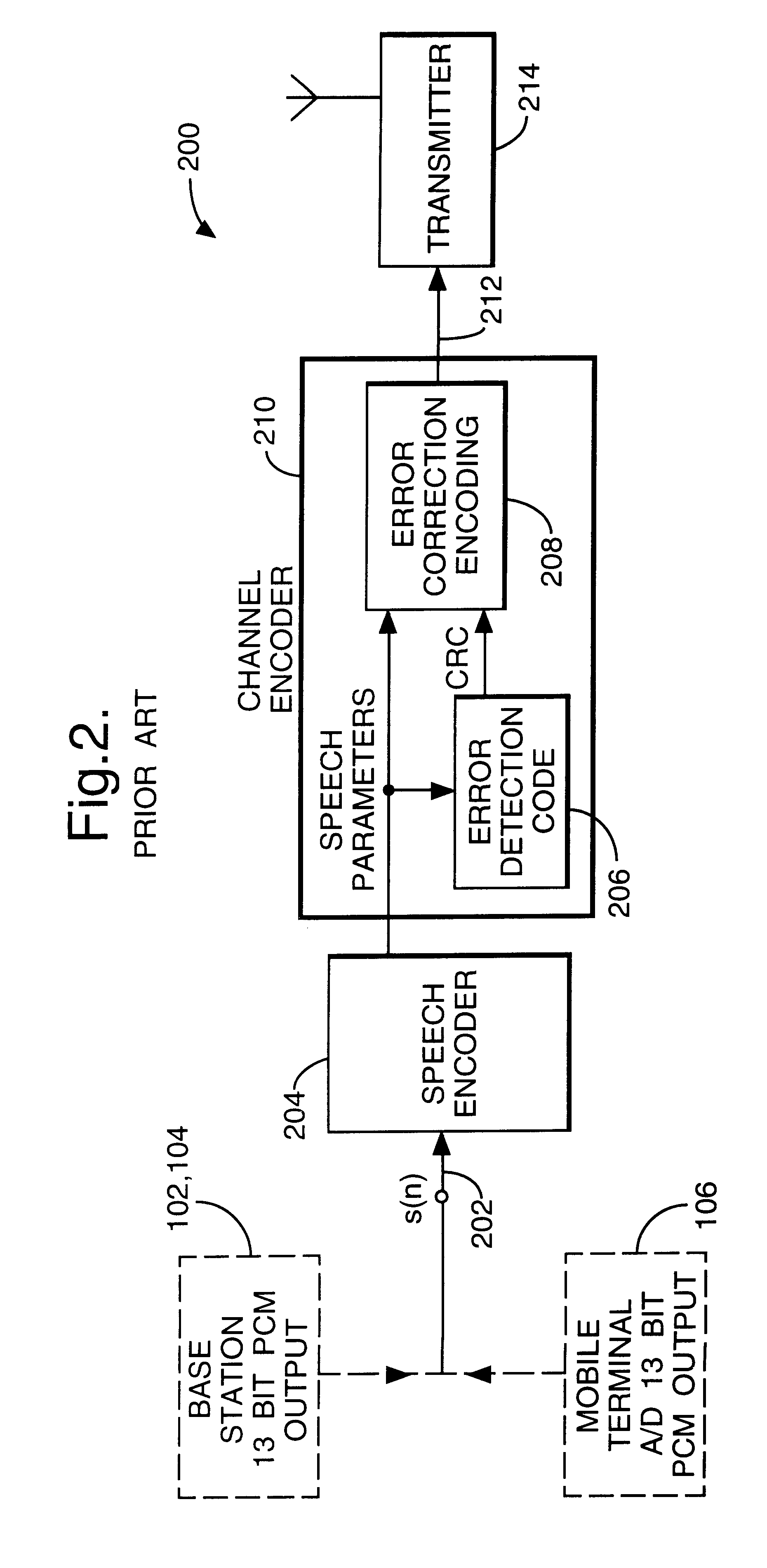

Method and apparatus for error detection in digital communications

InactiveUS6170073B1Accurate detectionImprove voice qualityError preventionOther error detection/correction/protectionData qualityComputer science

An encoder encodes digital signals representative of data by classifying the digital signals into first and second classes indicative of their influence on data quality and subjects them to error detection encoding capable of generating at least two error detection codes which respectively correspond to the first and second classes. A decoder receives the encoded digital signals classified into first and second digital signal classes, decodes the error detection codes, and generates error signals, corresponding to the respective digital signal classes, from which the quality of the received digital signals is estimated and the utility of the received digital signals is determined.

Owner:INTELLECTUAL VENTURES I LLC

Method and apparatus for fast encoding of data symbols according to half-weight codes

InactiveUS20090307565A1Reduce expensesOther error detection/correction/protectionCode conversionHigh densityTheoretical computer science

Efficient methods for encoding and decoding Half-Weight codes are disclosed and similar high density codes are disclosed. The efficient methods require at most 3·(k−1)+h / 2+1 XORs of symbols to calculate h Half-Weight symbols from k source symbols, where h is of the order of log(k).

Owner:QUALCOMM INC

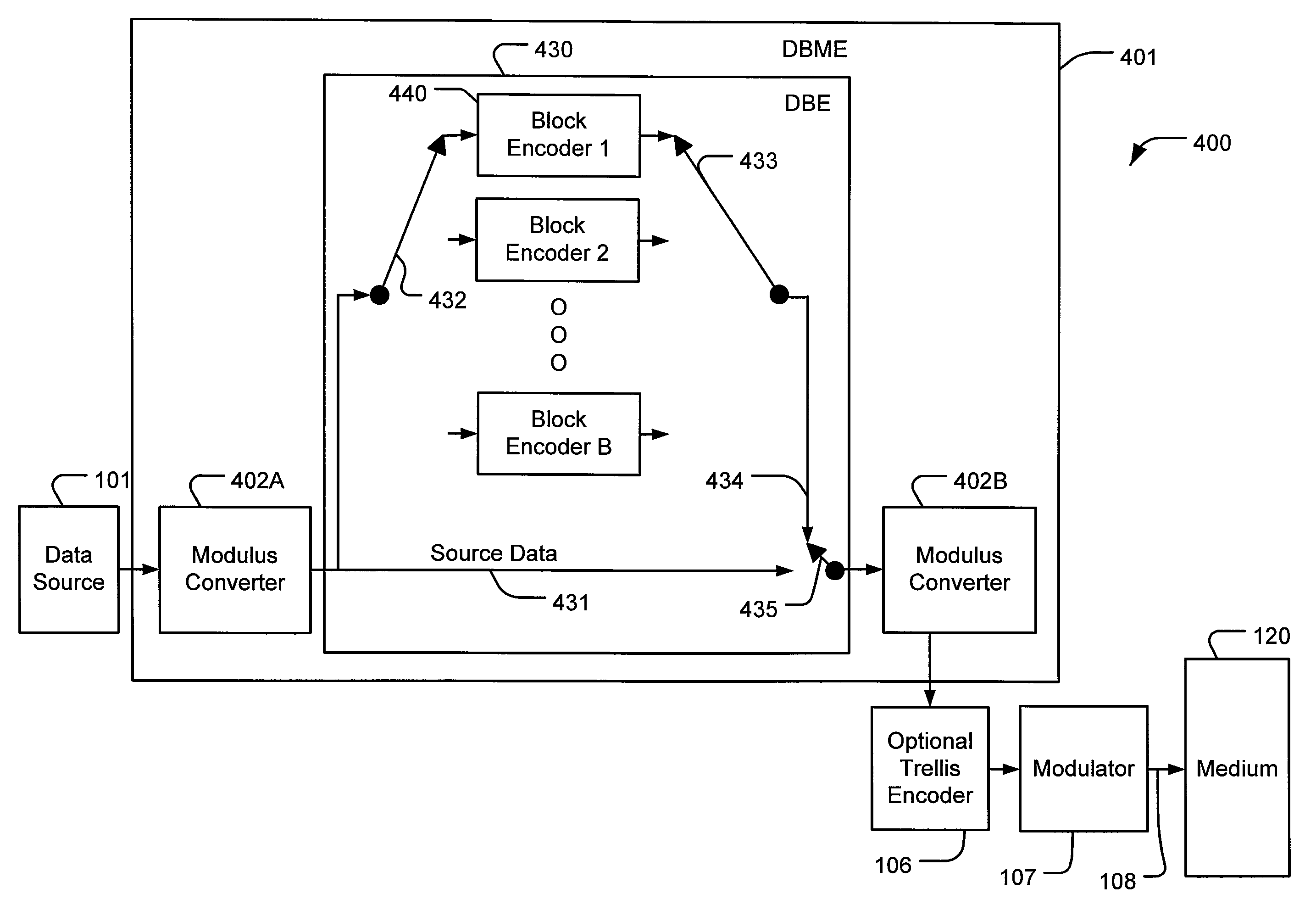

Block Modulus Coding (BMC) Systems and Methods for Block Coding with Non-Binary Modulus

InactiveUS20090204877A1Reduce memory requirementsFacilitate interleavingData representation error detection/correctionOther error detection/correction/protectionCommunications systemBlock code

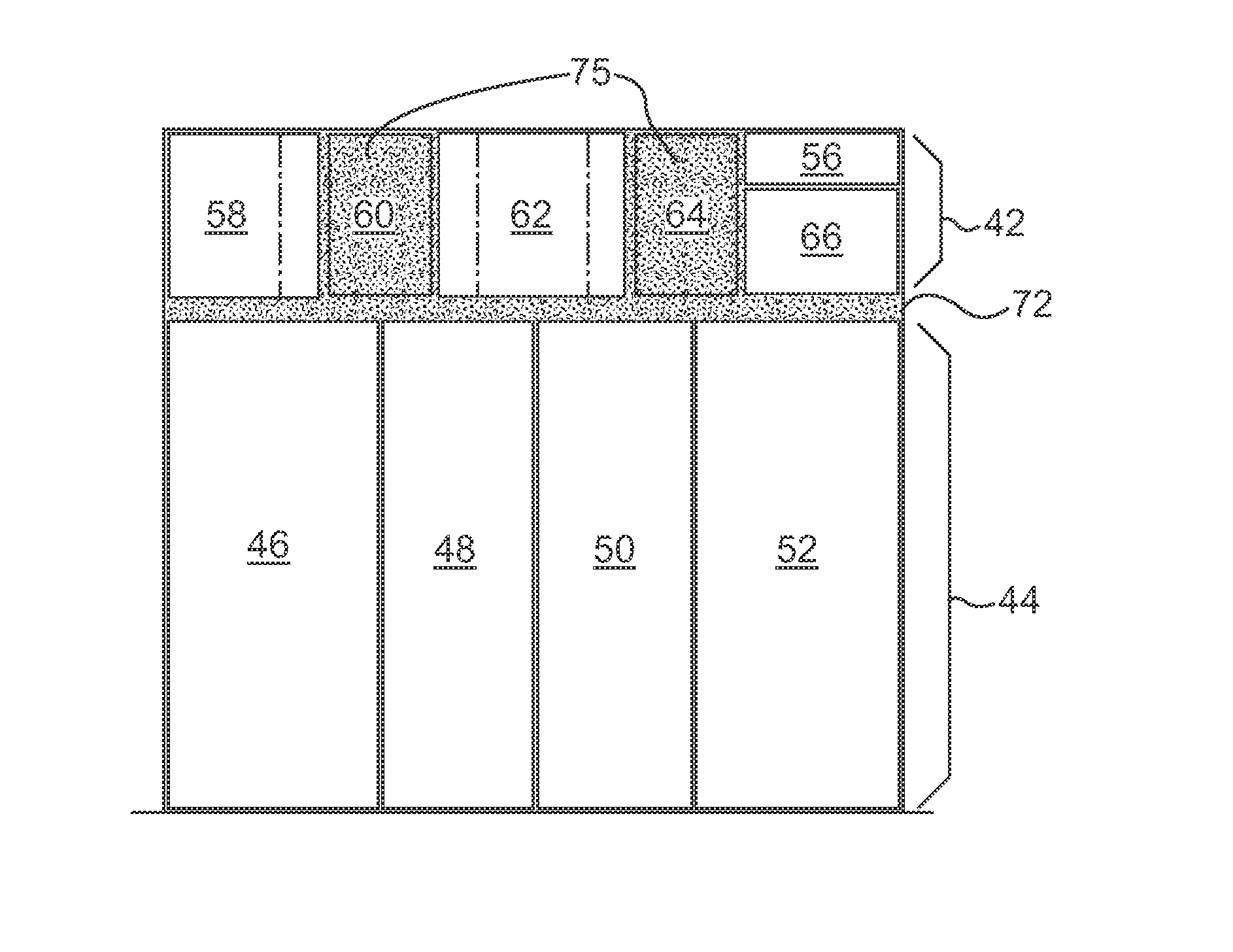

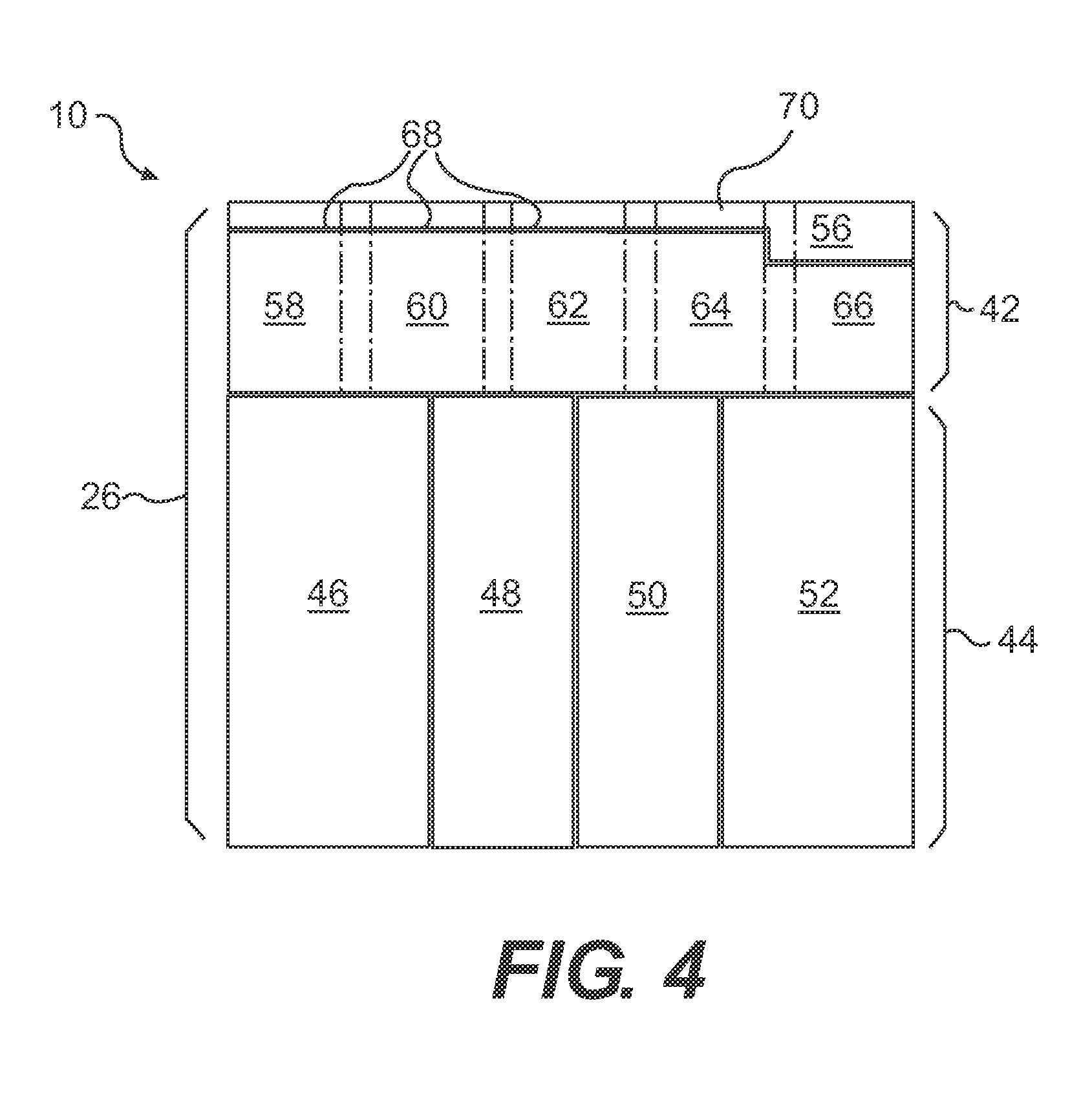

Block modulus coding (BMC) systems implement block coding on non-binary modulus m symbols, where m is greater than 2. BMC systems can be used for, among other things, forward error correction (FEC) of source data in communication systems or parity backup for error correction of source data in storage systems where the source data is represented by non-binary symbols that may be corrupted by burst errors. The block coding is preferably performed using a distributed arrangement of block encoders or decoders. A distributed block modulus encoder (DBME) encodes sequential source data symbols of modulus m with a plurality of sequential block encoders to produce interleaved parity codewords. The codewords utilize modulus m symbols where the medium can reliably resolve m symbol states. The interleaved parity codewords enable decoding of error-corrected source data symbols of modulus m with a distributed block modulus decoder (DBMD) that utilizes a plurality of sequential block decoders to produce the error-corrected source data symbols.

Owner:SUNRISE IP

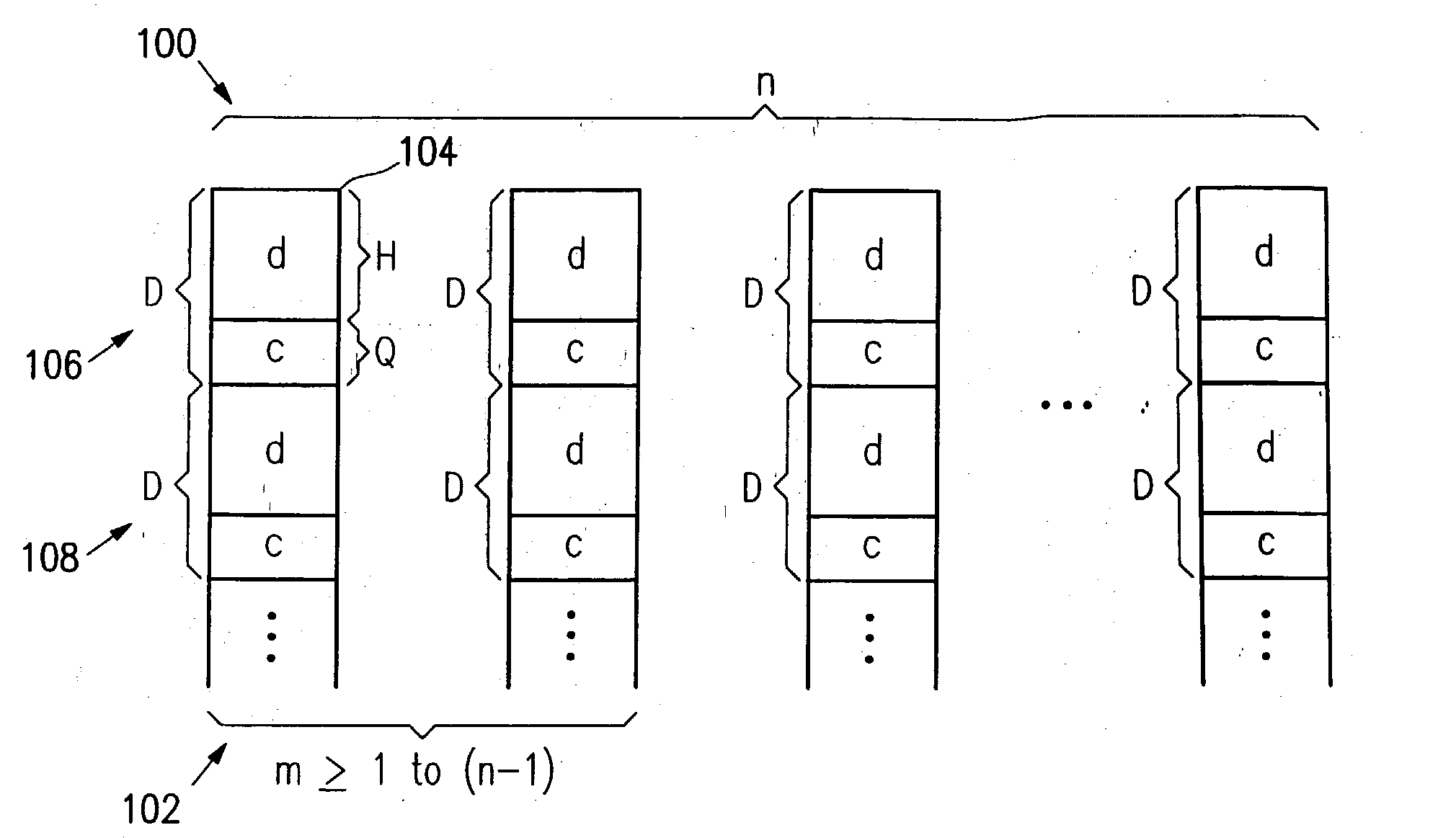

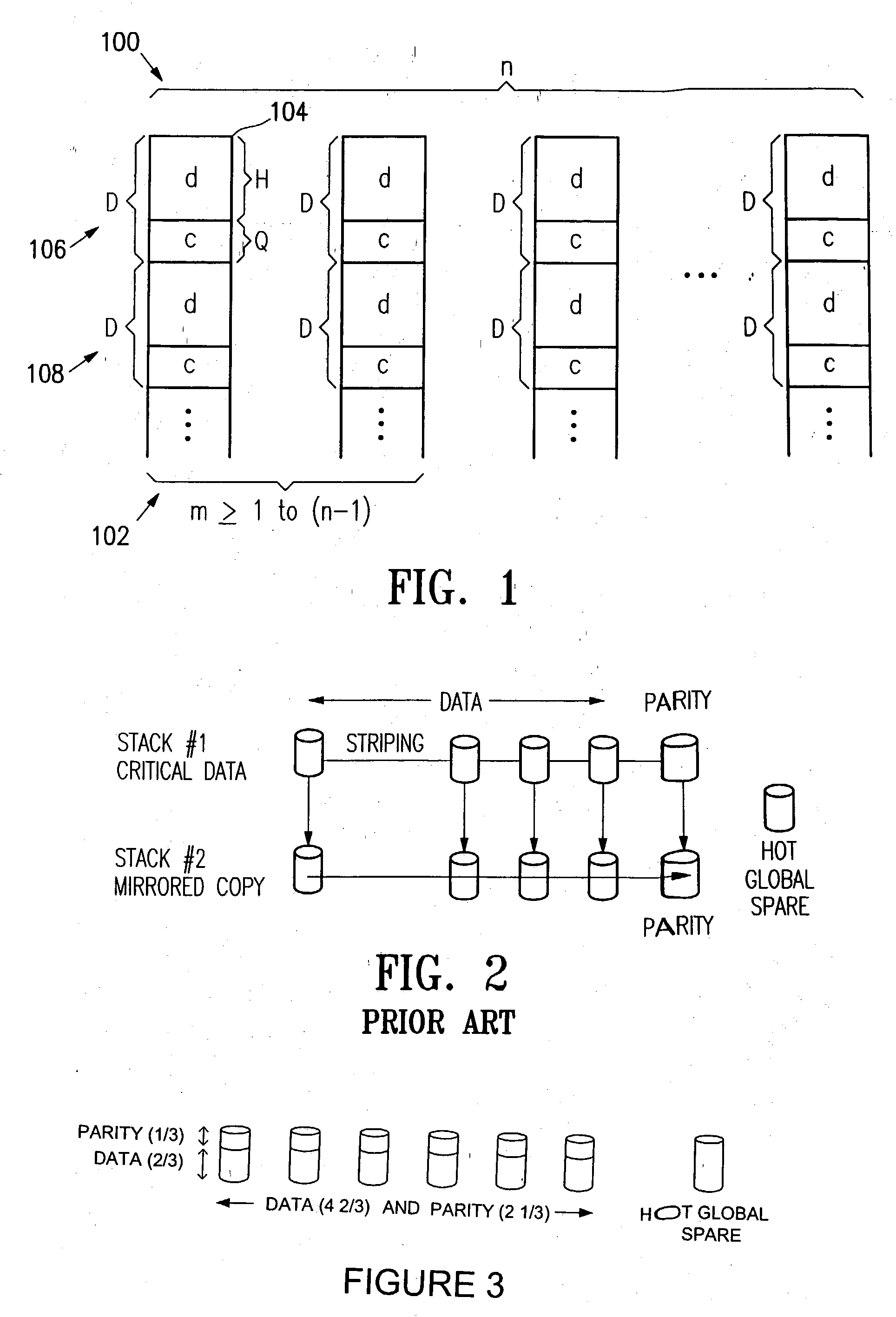

Data redundancy methods and apparatus

Method and apparatus for providing data recovery in a one or multiple disk loss situation in a RAID5 like system. A data storage apparatus has a plurality of n disks storing data comprising a plurality of n data groupings stored across the plurality of n disks. Each one of the n data groupings comprises a data portion and a redundancy portion. The size of the data portion relative to the redundancy portion is as H to Q, where H / Q<(n-m) / m, where m is the maximum number of disks that may be lost at any given time. Advantageously, the n data portions are recoverable from any and all combinations of n-m data grouping(s) on n-m disk(s) when the other m data grouping(s) are unavailable, where 1<=m<n.

Owner:TANDBERG DATA

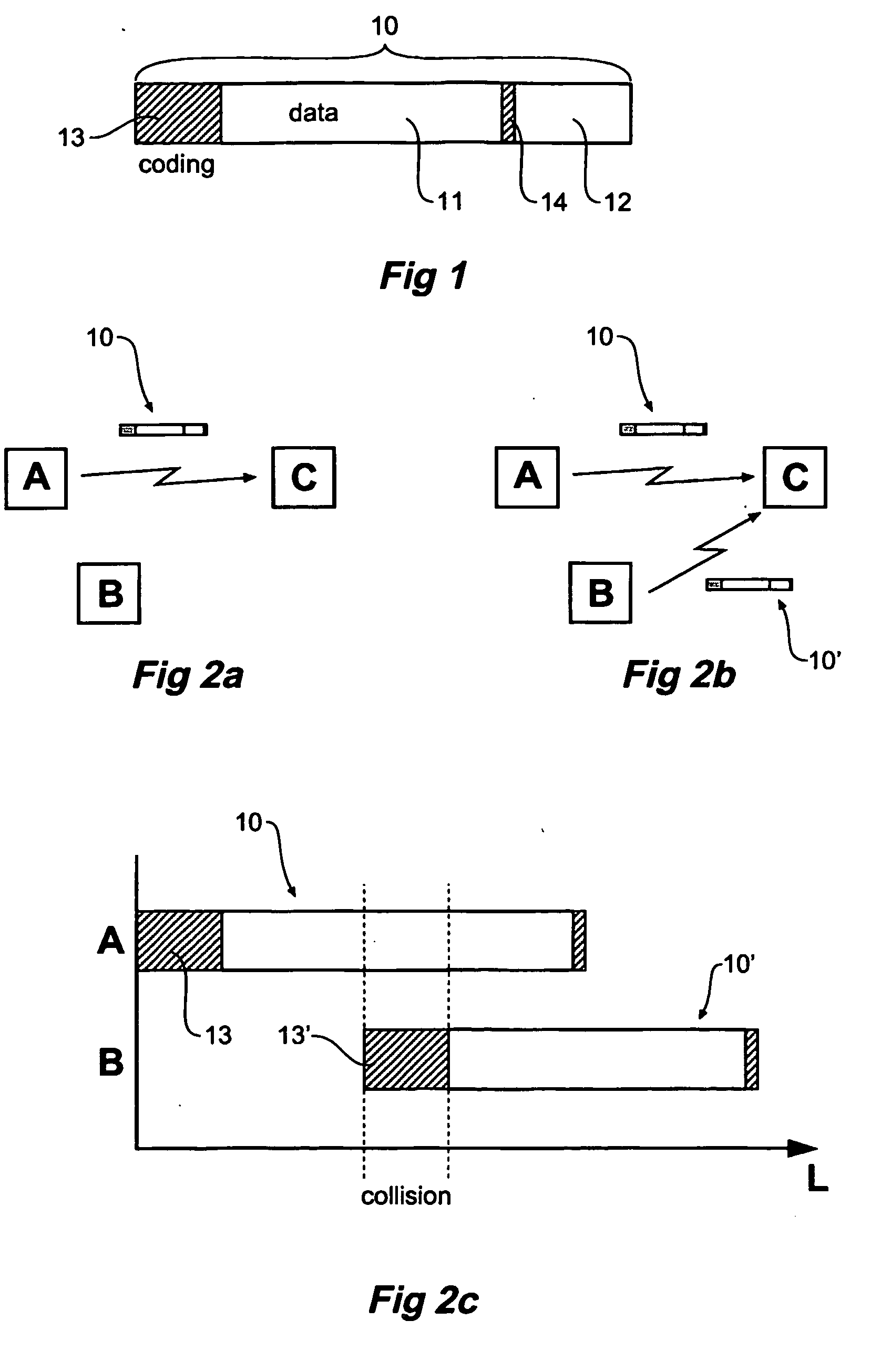

Collision detection in a non-dominant bit radio network communication system

InactiveUS20060192697A1Error prevention/detection by using return channelFrequency-division multiplex detailsNetwork variableTransceiver

A communications system and protocol for use in a non-dominant bit radio network. The radio network includes transceivers which communicate with other transceivers to allow network variables to be shared by all transceivers. The protocol allows the network to handle collisions between competing transmissions from different transceivers. The protocol also handles communications between transceivers that are out of transmitting range of each other.

Owner:CLIPSAL INTEGRATED SYST

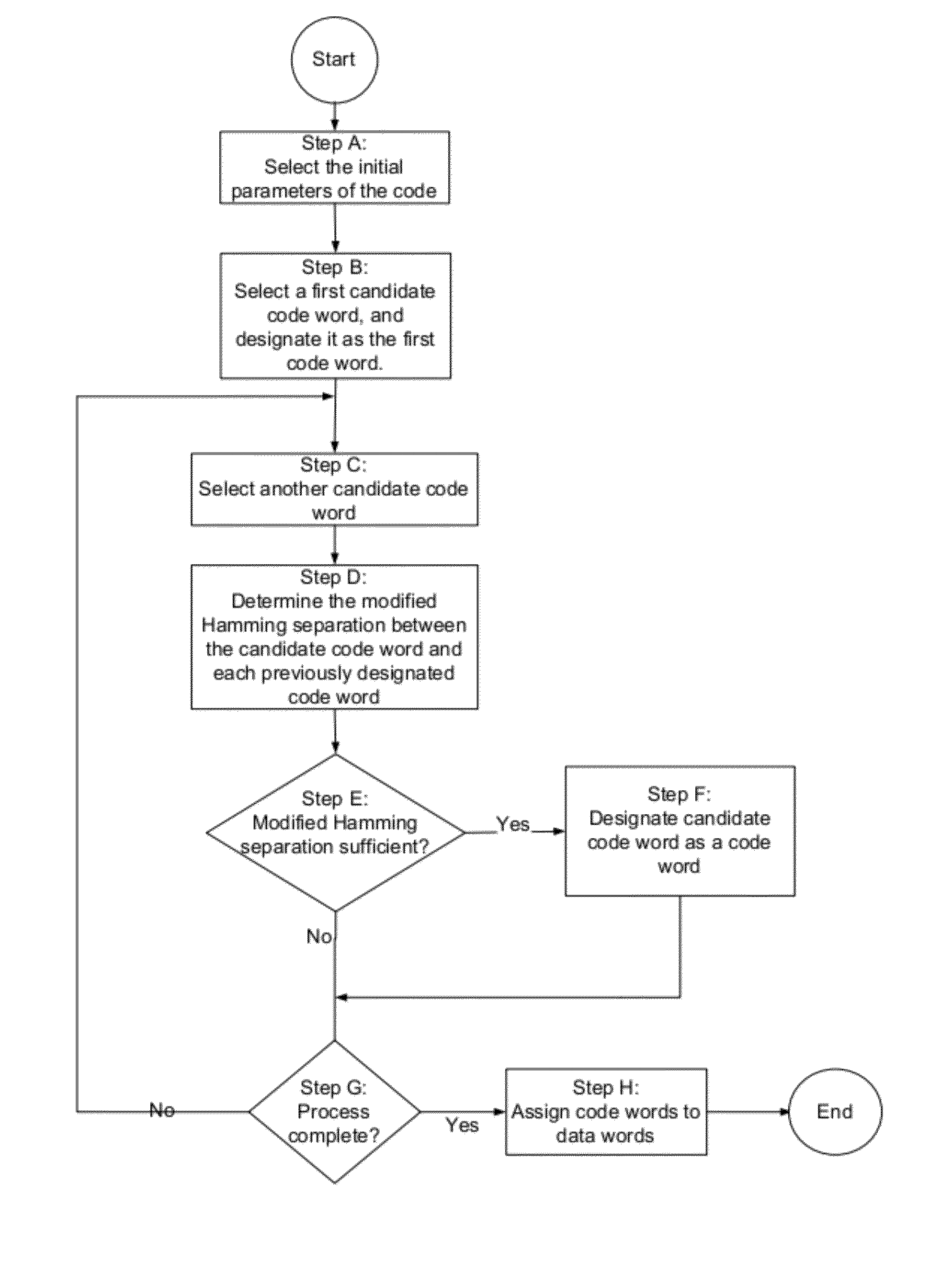

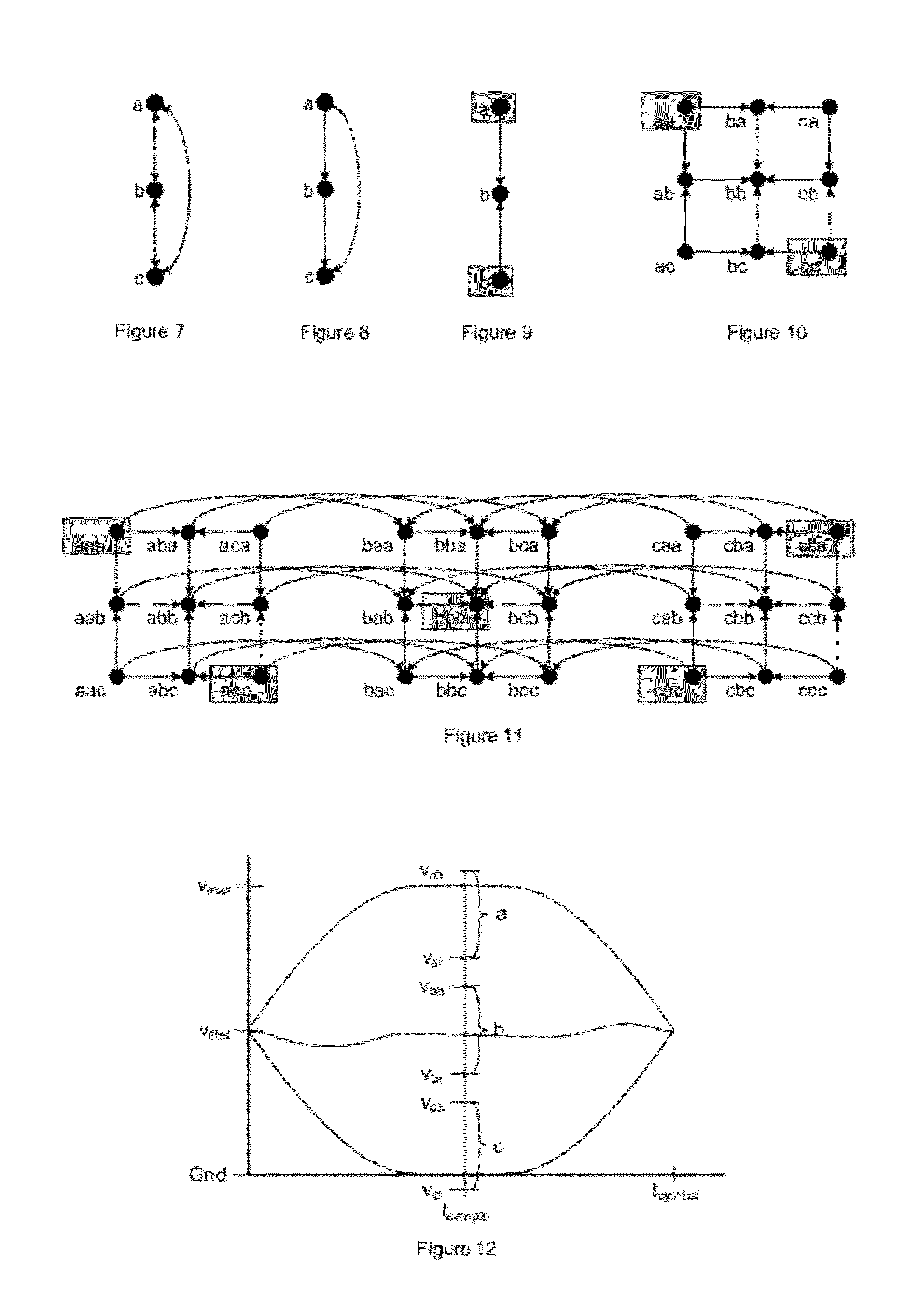

Error detection and correction codes for channels and memories with incomplete error characteristics

InactiveUS20120096330A1Efficient error-correcting codeOther error detection/correction/protectionCode conversionParallel computingHamming distance

A channel has a first and a second end. The first end of the channel is coupled to a transmitter. The channel is capable of transmitting symbols selected from a symbol set from the first end to the second end. The channel exhibits incomplete error introduction properties. A code comprises a set of code words. The elements of the set of code words are one or more code symbols long. The code symbols are members of the symbol set. The minimum modified Hamming separation between the elements of the set of code words in light of the error introduction properties of the channel is greater than the minimum Hamming distance between the elements of the set of code words. A memory device, a method of using the channel, and a method of generating the code are also described.

Owner:CONVERSANT INTPROP MANAGEMENT INC

In-place transformations with applications to encoding and decoding various classes of codes

InactiveUS7644335B2Reduce running timeLess time accessing memoryError preventionOther decoding techniquesComputer hardwareMemory form

In an encoder for encoding symbols of data using a computing device having memory constraints, a method of performing a transformation comprising loading a source block into memory of the computing device, performing an intermediate transformation of less than all of the source block, then replacing a part of the source block with intermediate results in the memory and then completing the transformation such that output symbols stored in the memory form a set of encoded symbols. A decoder can perform decoding steps in an order that allows for use of substantially the same memory for storing the received data and the decoded source block, performing as in-place transformations. Using an in-place transformation, a large portion of memory set aside for received data can be overwritten as that received data is transformed into decoded source data without requiring a similar sized large portion of memory for the decoded source data.

Owner:QUALCOMM INC

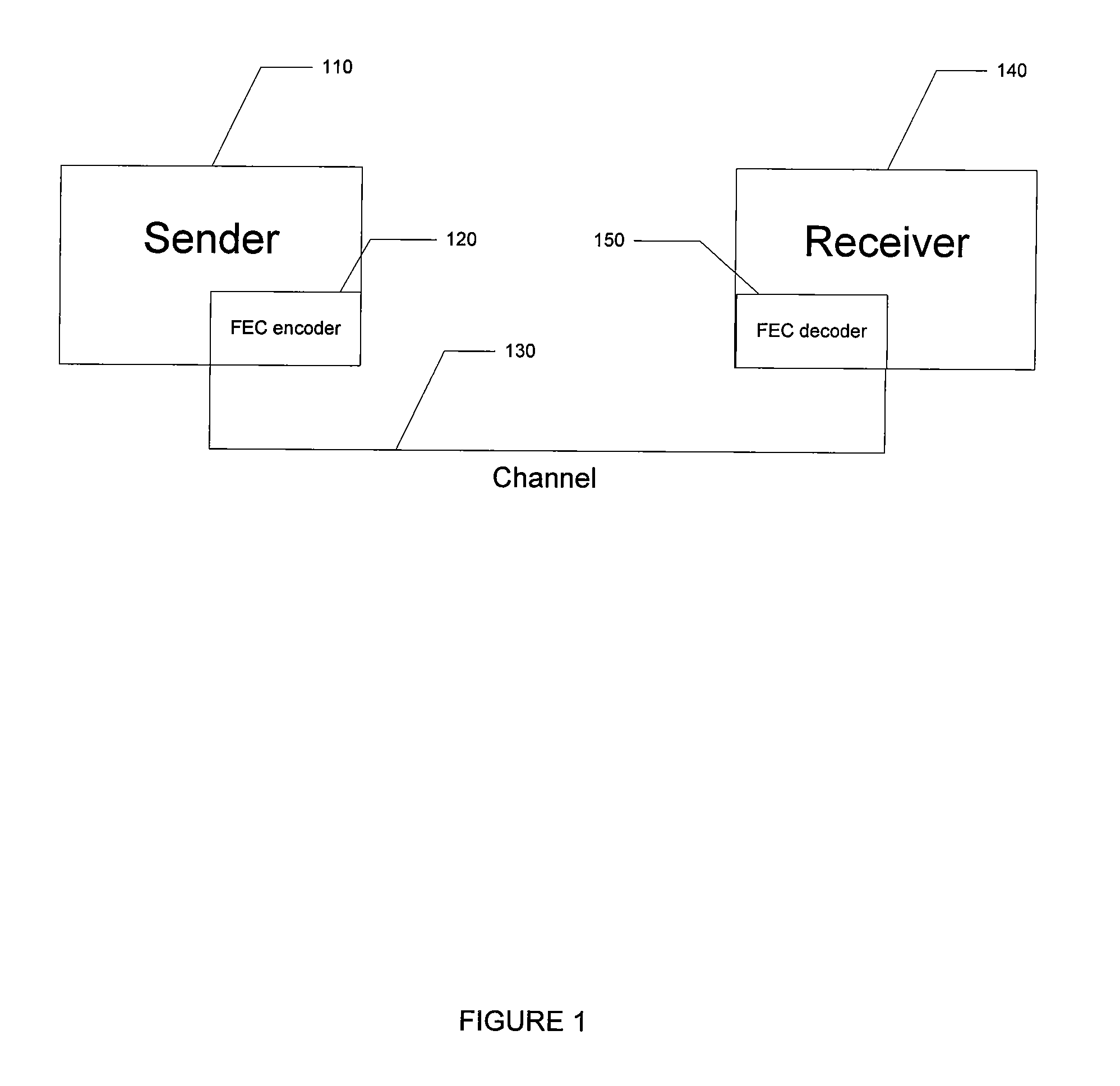

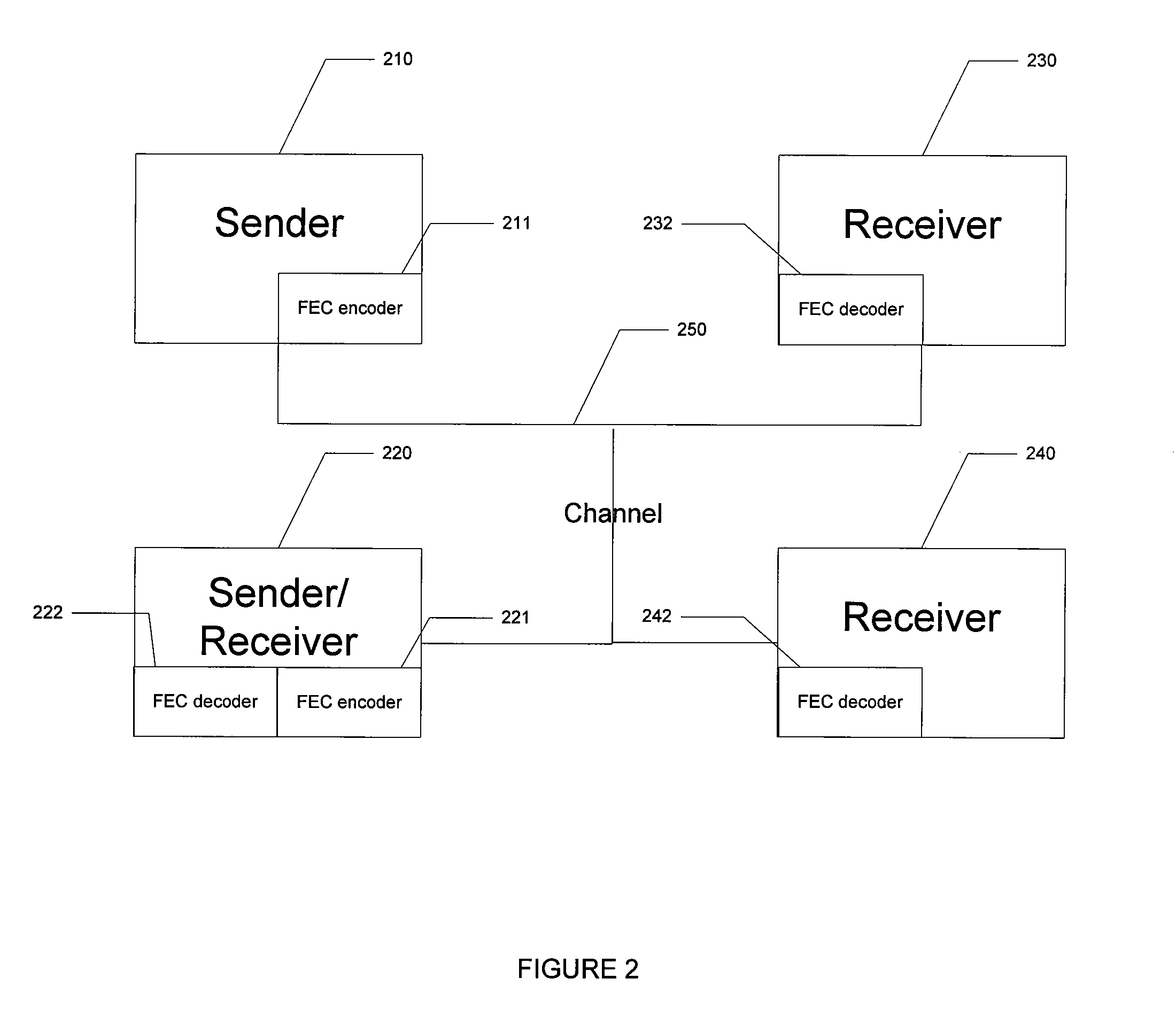

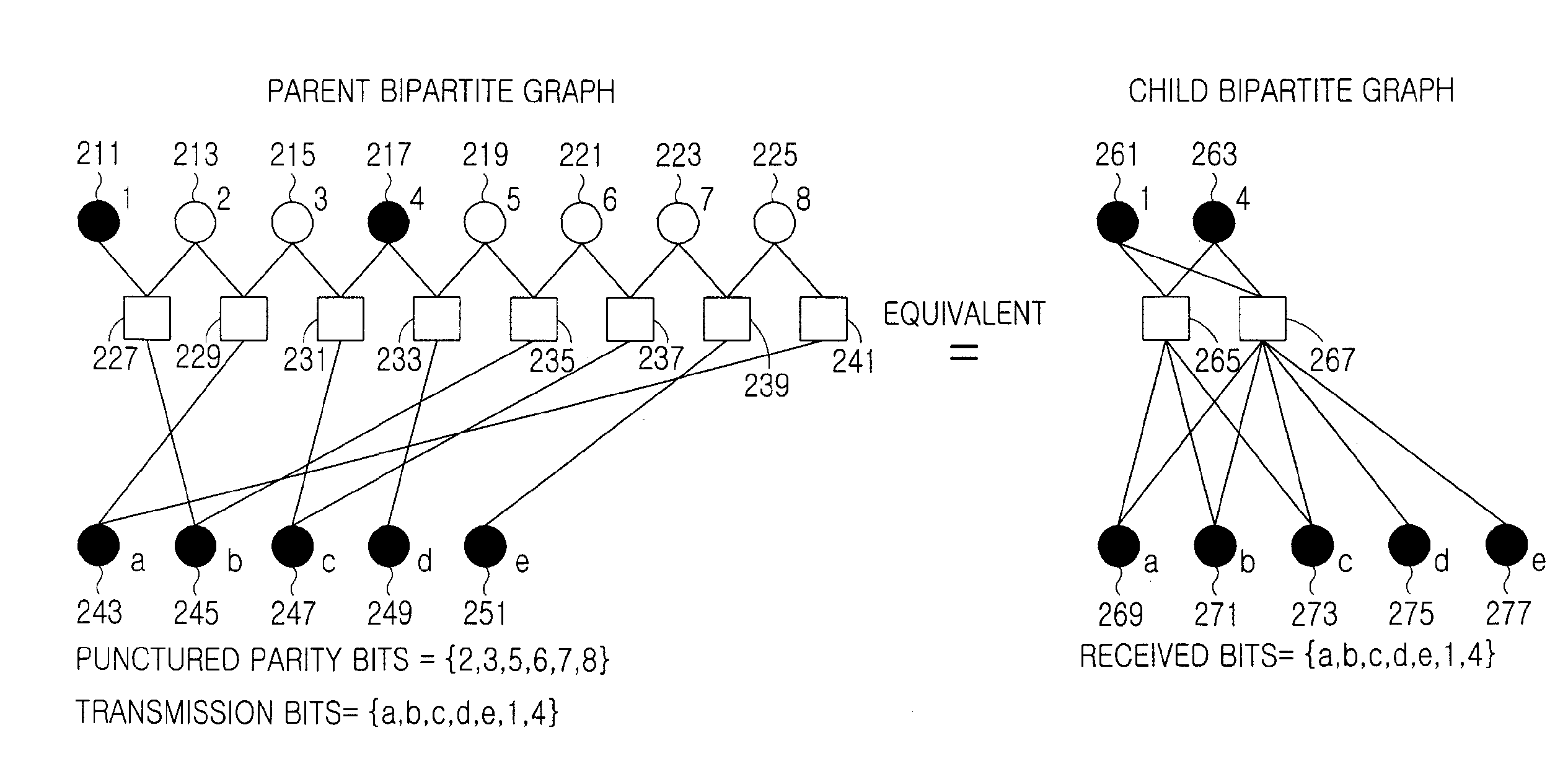

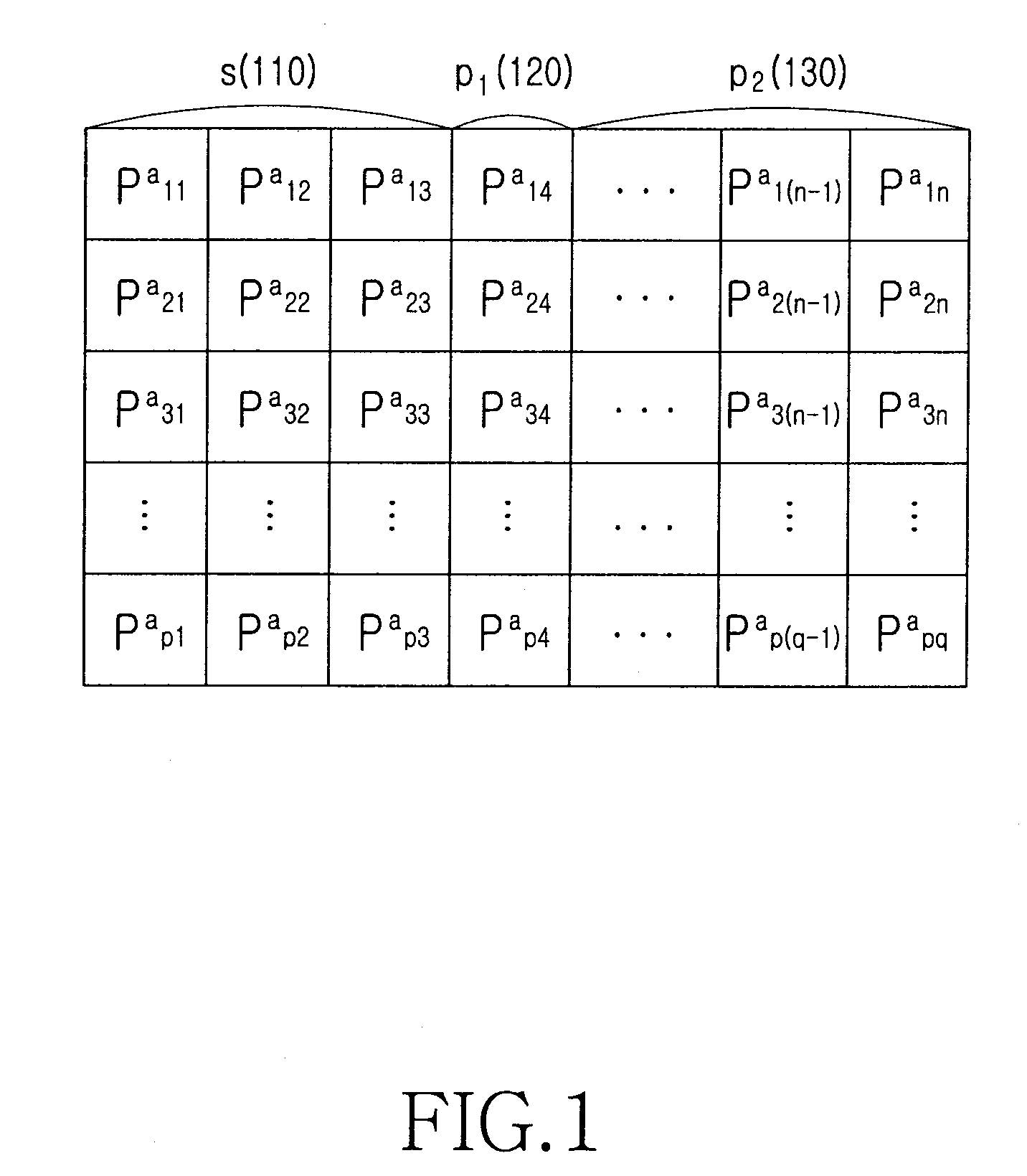

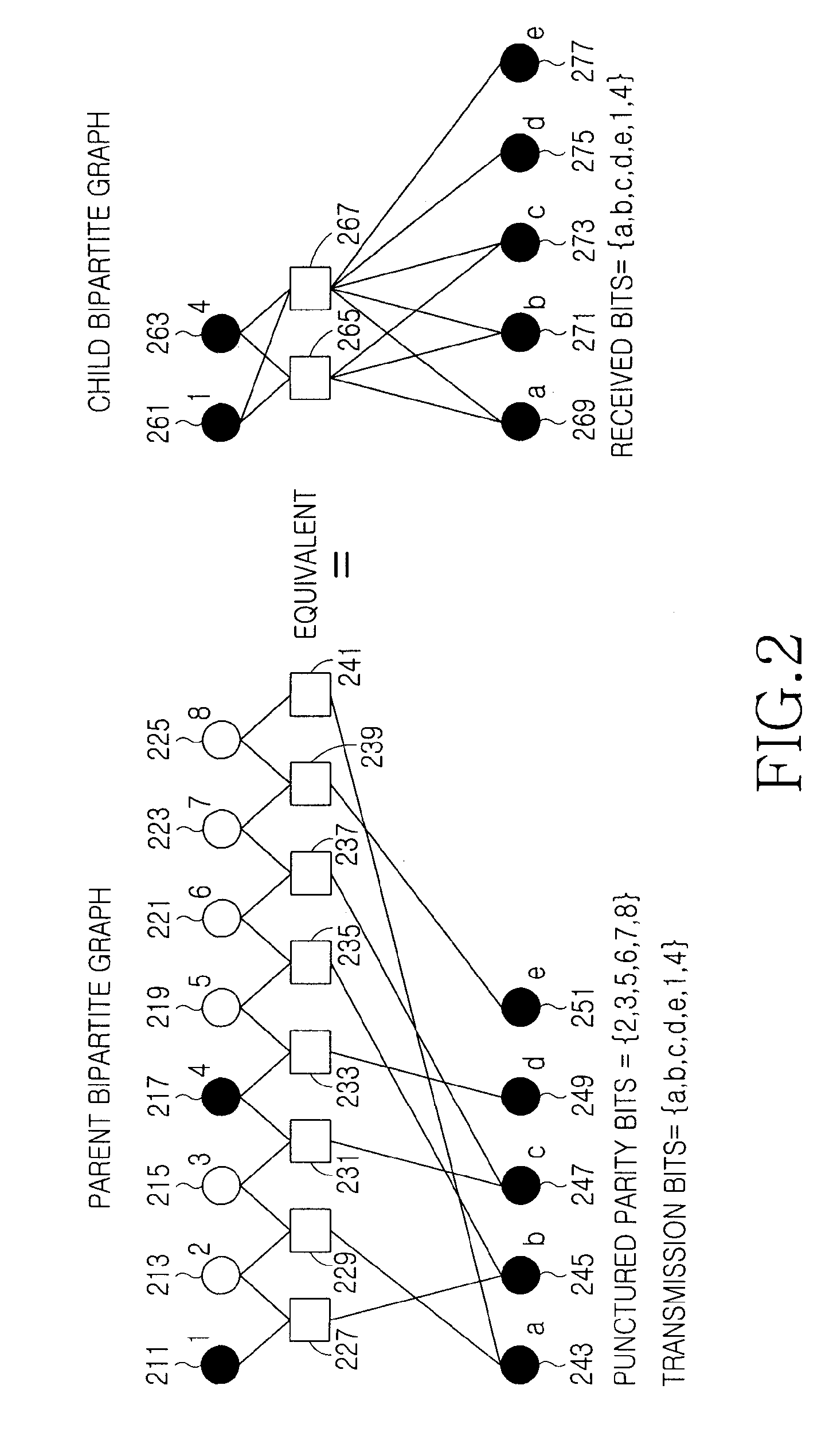

Apparatus and method to transmit/receive signal in a communication system

InactiveUS20080059862A1Other error detection/correction/protectionError correction/detection using multiple parity bitsCommunications systemParity-check matrix

An apparatus and method for transmitting / receiving a signal in a communication system are provided. A signal reception apparatus of a communication system receives a signal and generates a child Low Density Parity Check (LDPC) codeword vector by decoding the received signal according to a child parity check matrix supporting a first coding rate. The child LDPC codeword vector includes an information vector including A (A≧1) information bits, and when the first coding rate is equal to a coding rate for a case where D (D≧1) parity bits are punctured among B (B≧1)+C (C≧1) parity bits included in a parent LDPC codeword vector generated by encoding the information vector according to a parent parity check matrix supporting a second coding rate, a child bipartite graph corresponding to the child parity check matrix is generated such that a parent bipartite graph corresponding to the parent parity check matrix corresponds to an edge merge scheme.

Owner:SAMSUNG ELECTRONICS CO LTD

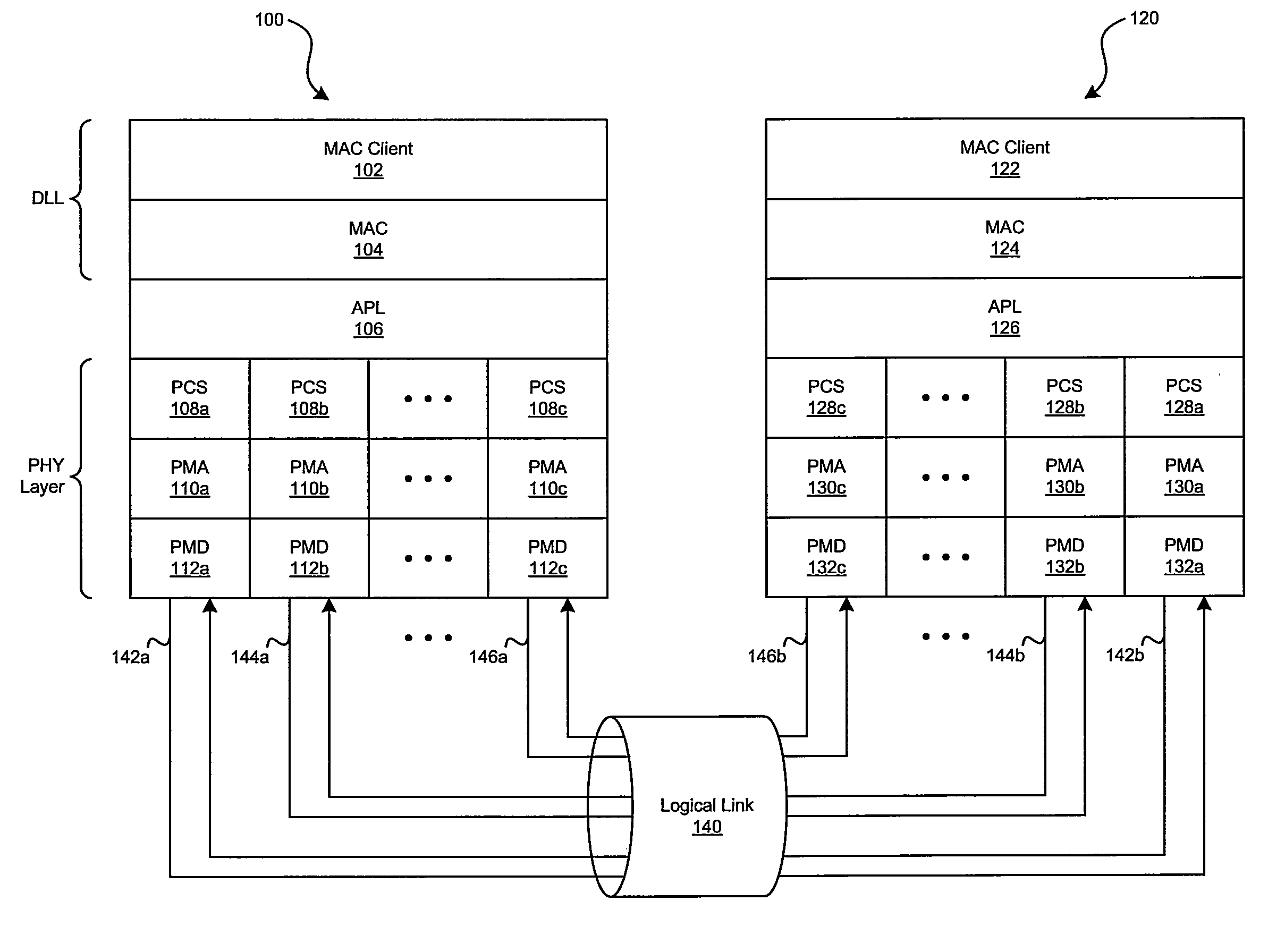

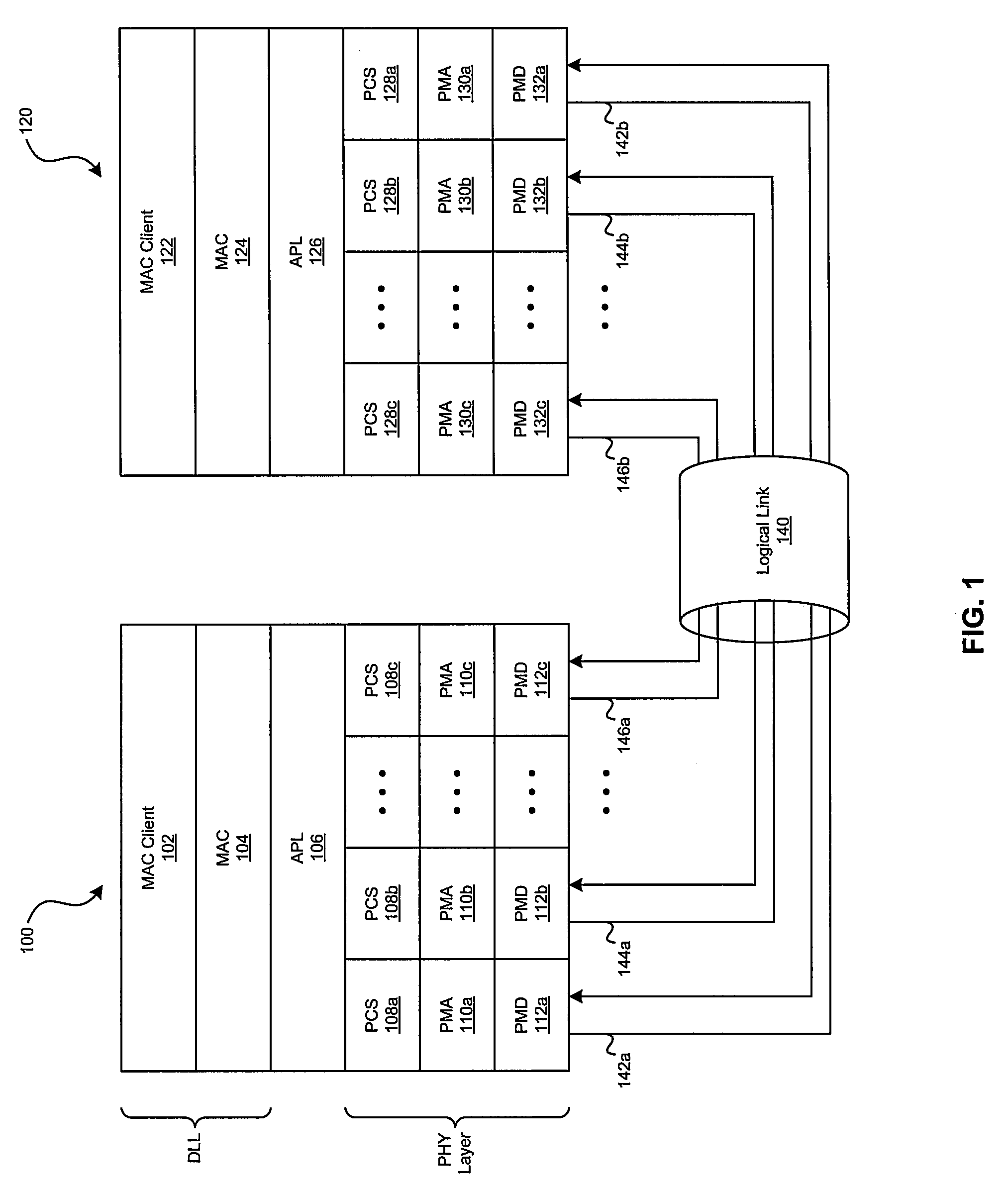

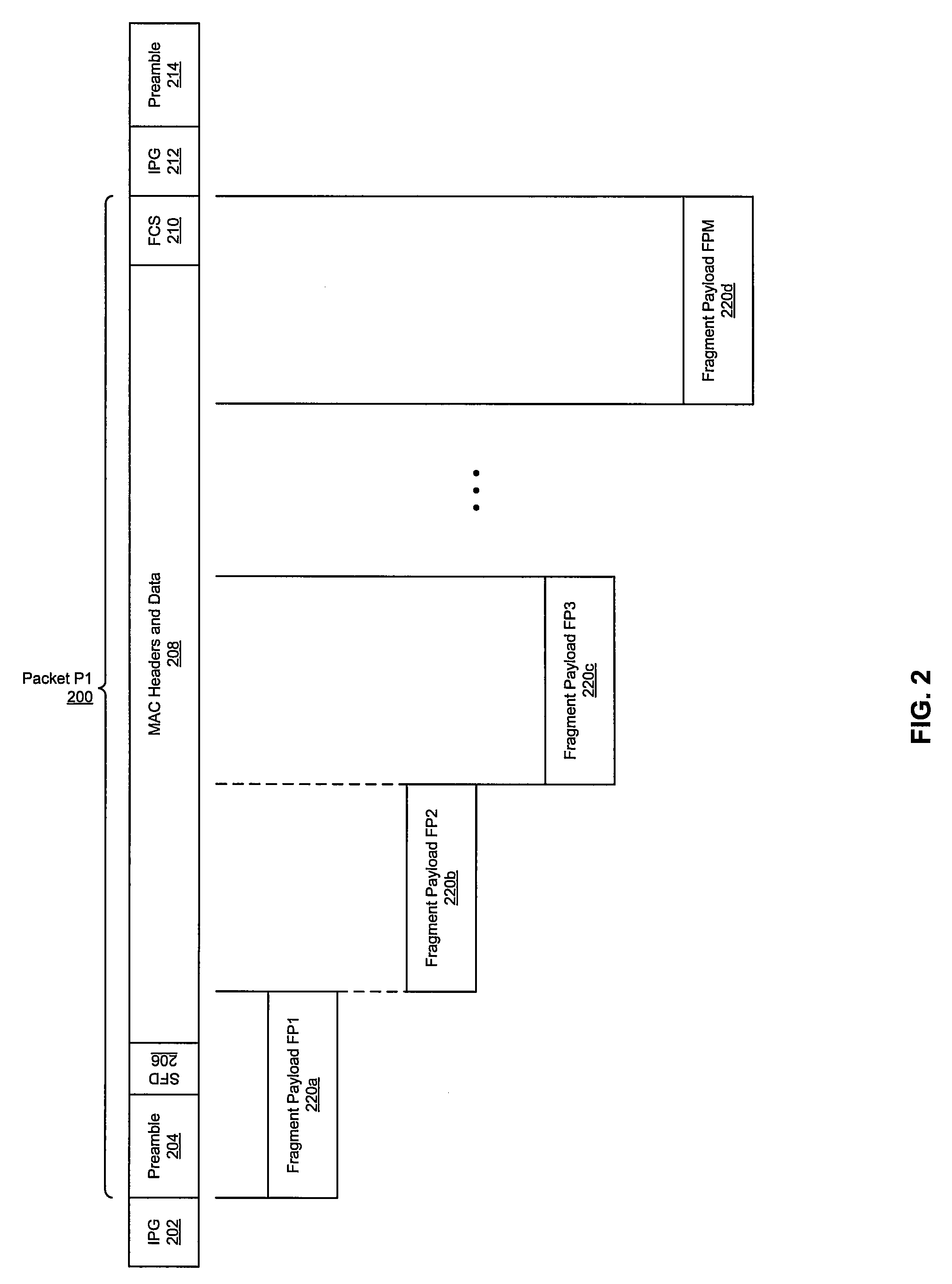

Method and system for physical layer aggregation

Aspects of a system for physical layer aggregation may include one or more switch ICs and / or physical (PHY) layer ICs that enable reception of data packets via a medium access control (MAC) layer protocol entity. Each of the received data packets may be fragmented into a plurality of fragment payloads. Each of the plurality of fragment payloads may be sent to a PHY layer protocol entity instance a physical layer protocol entity instance selected from a plurality of physical layer protocol entity instances.

Owner:AVAGO TECH INT SALES PTE LTD

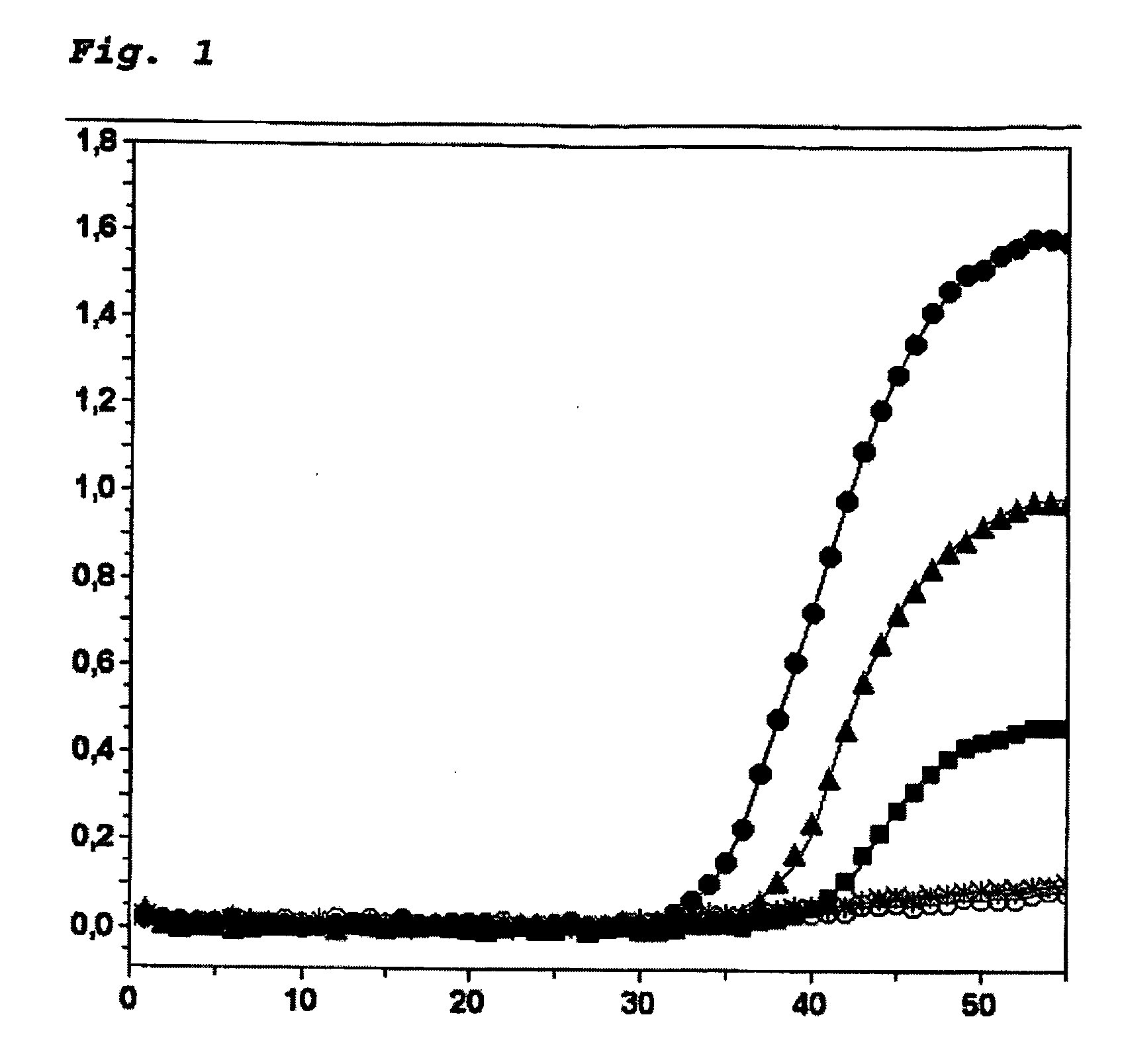

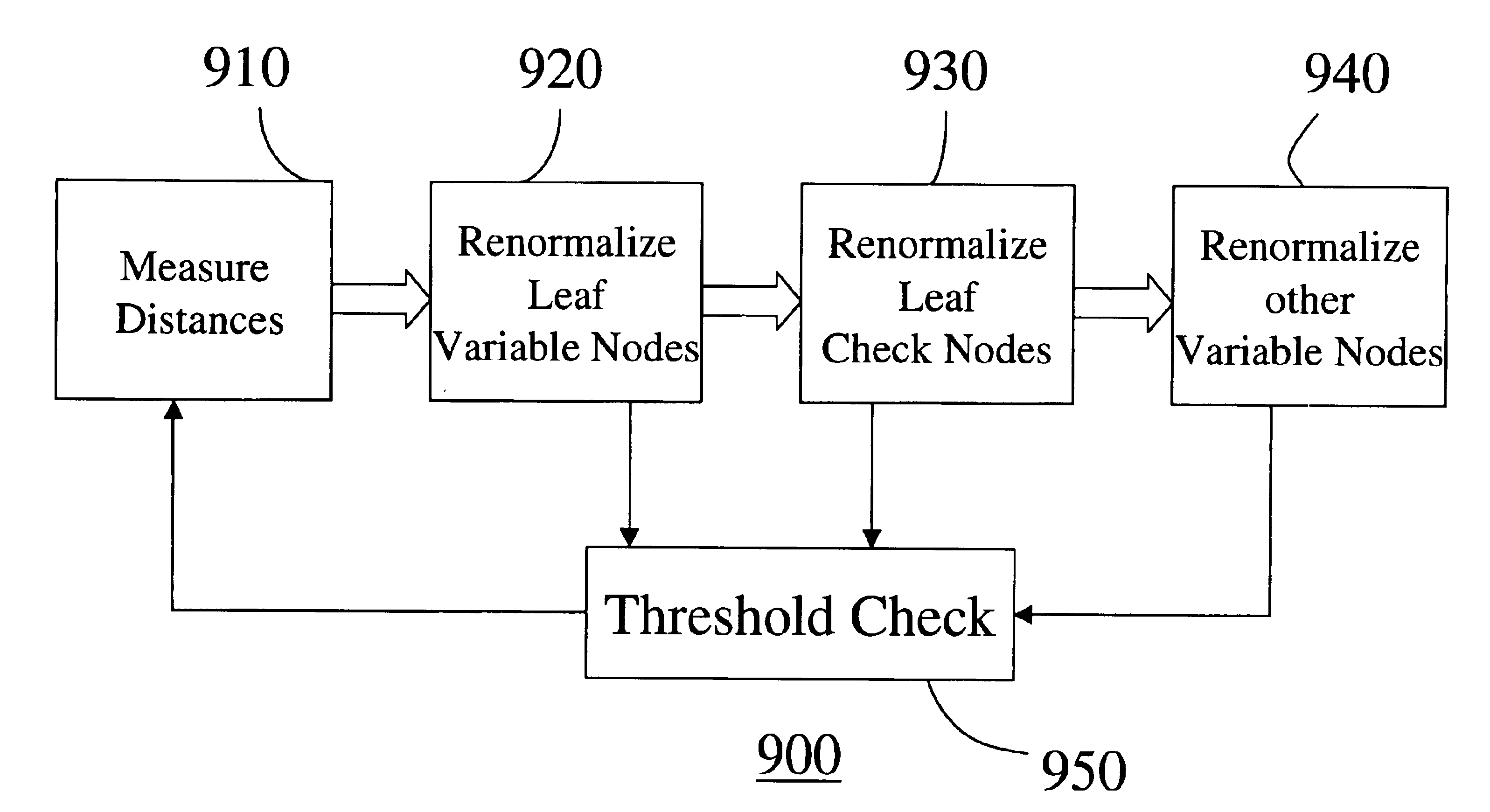

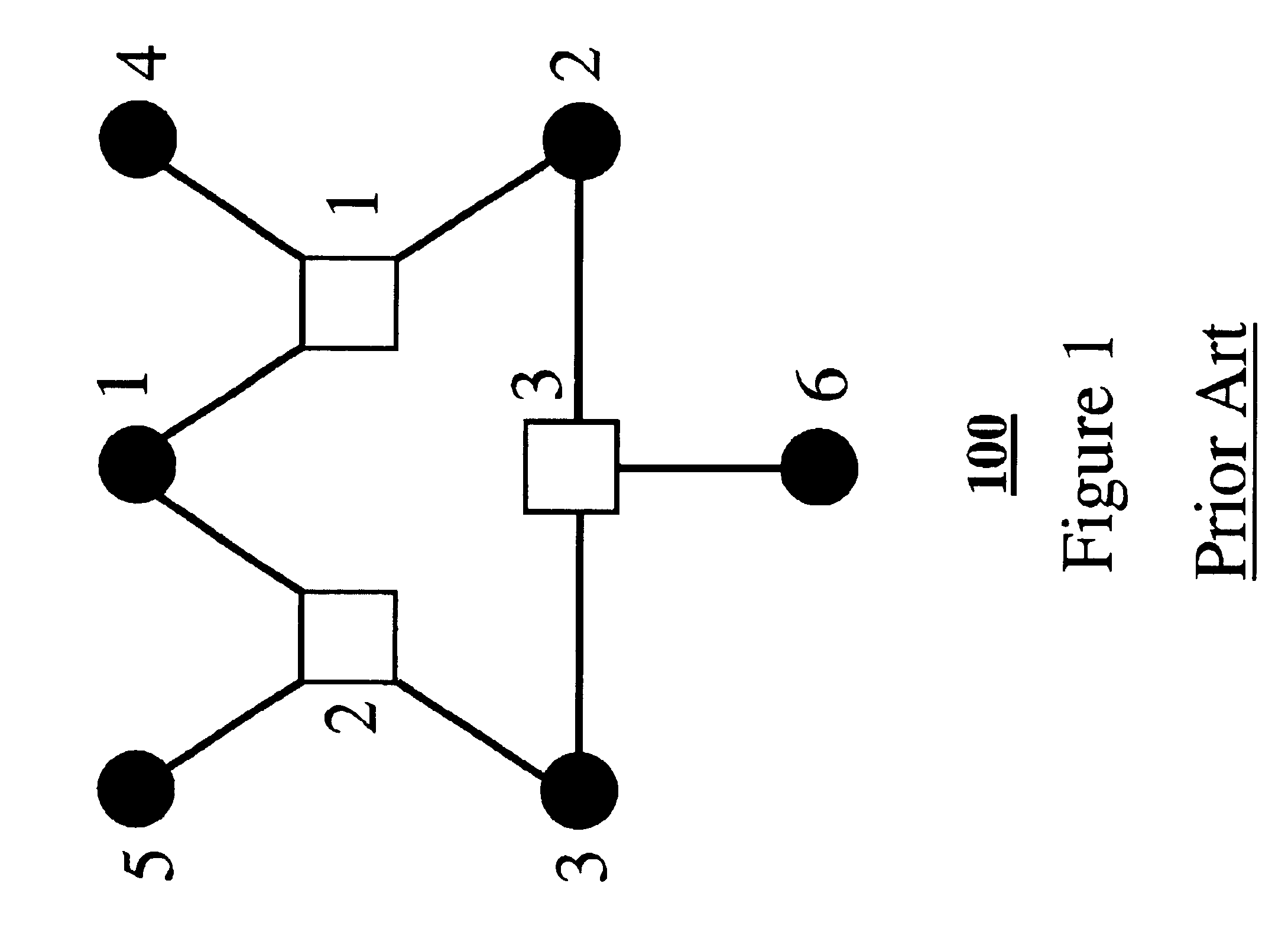

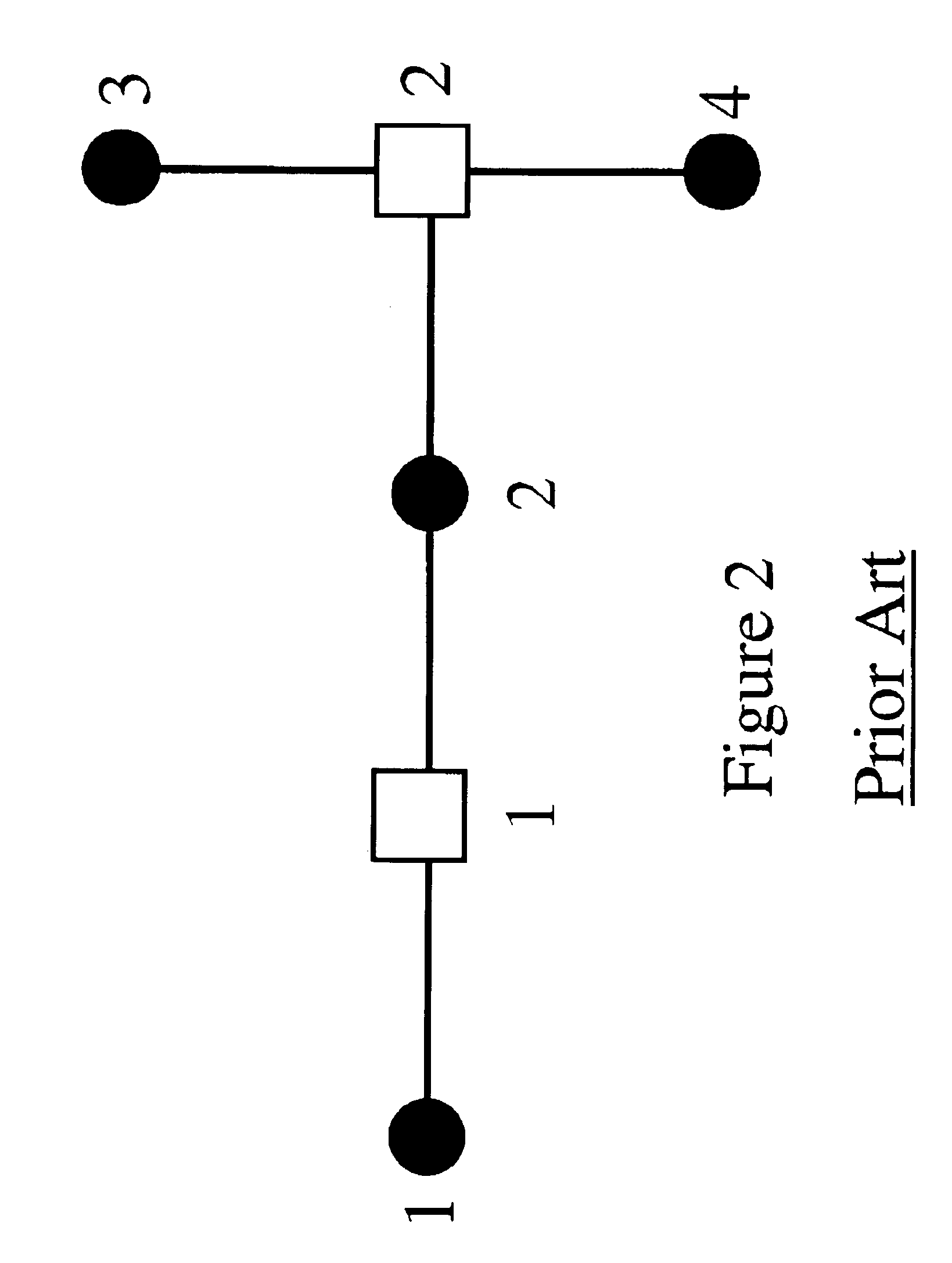

Evaluating and optimizing error-correcting codes using a renormalization group transformation

InactiveUS6857097B2Improve performanceCorrect operation testingOther decoding techniquesRenormalizationParity-check matrix

A method evaluates an error-correcting code for a data block of a finite size. An error-correcting code is defined by a parity check matrix, wherein columns represent variable bits and rows represent parity bits. The parity check matrix is represented as a bipartite graph. A single node in the bipartite graph is iteratively renormalized until the number of nodes in the bipartite graph is less than a predetermine threshold. During the iterative renormalization, a particular variable node is selected as a target node, and a distance between the target node and every other node in the bipartite graph is measured. Then, if there is at least one leaf variable node, renormalize the leaf variable node farthest from the target node, otherwise, renormalize a leaf check node farthest from the target node, and otherwise renormalize a variable node farthest from the target node and having fewest directly connected check nodes. By evaluating many error-correcting codes according to the method, an optimal code according to selected criteria can be obtained.

Owner:MITSUBISHI ELECTRIC RES LAB INC

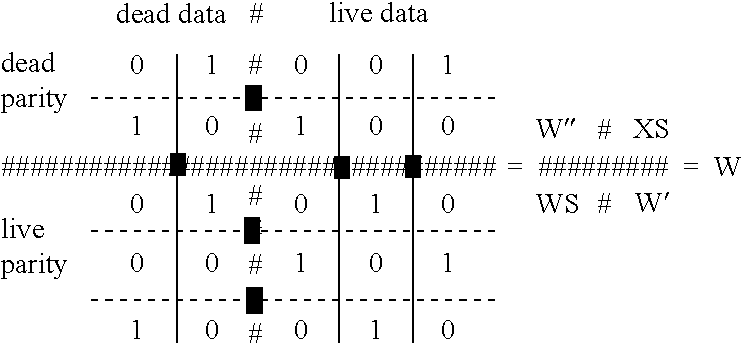

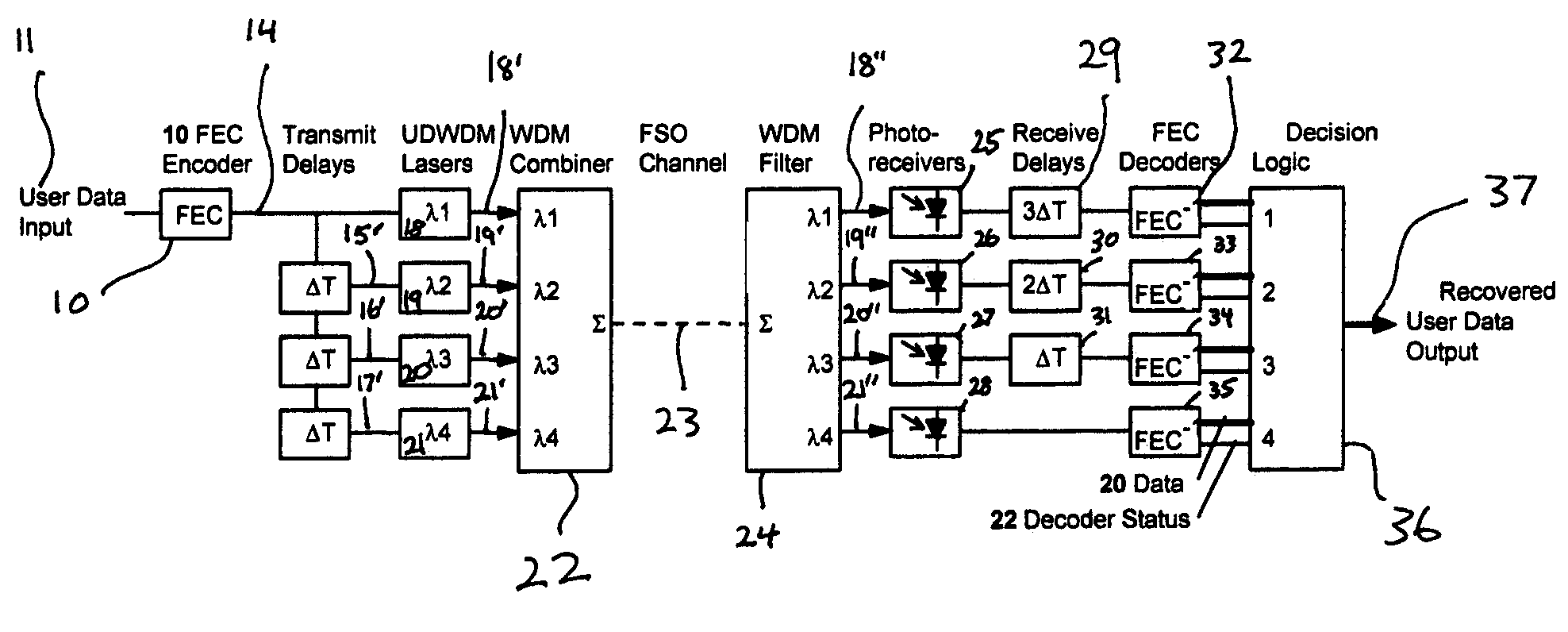

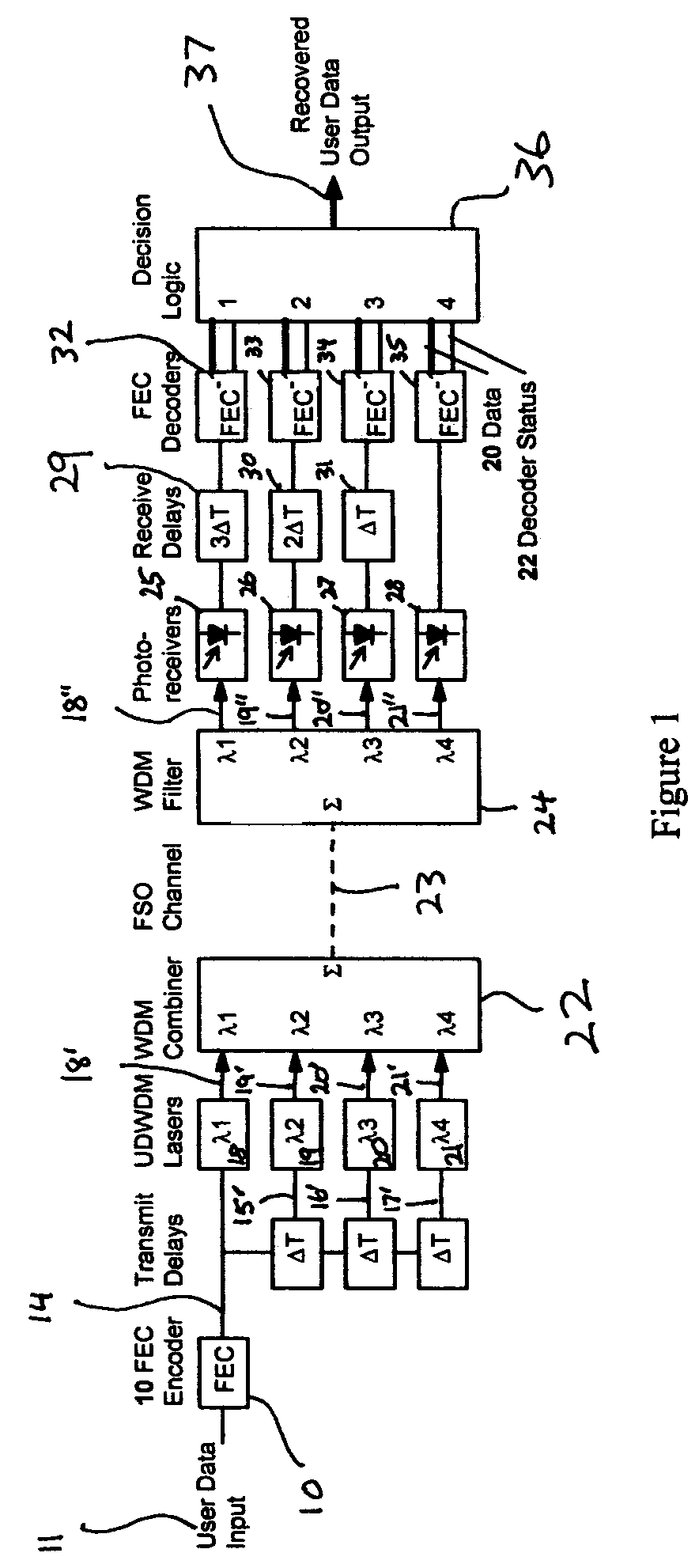

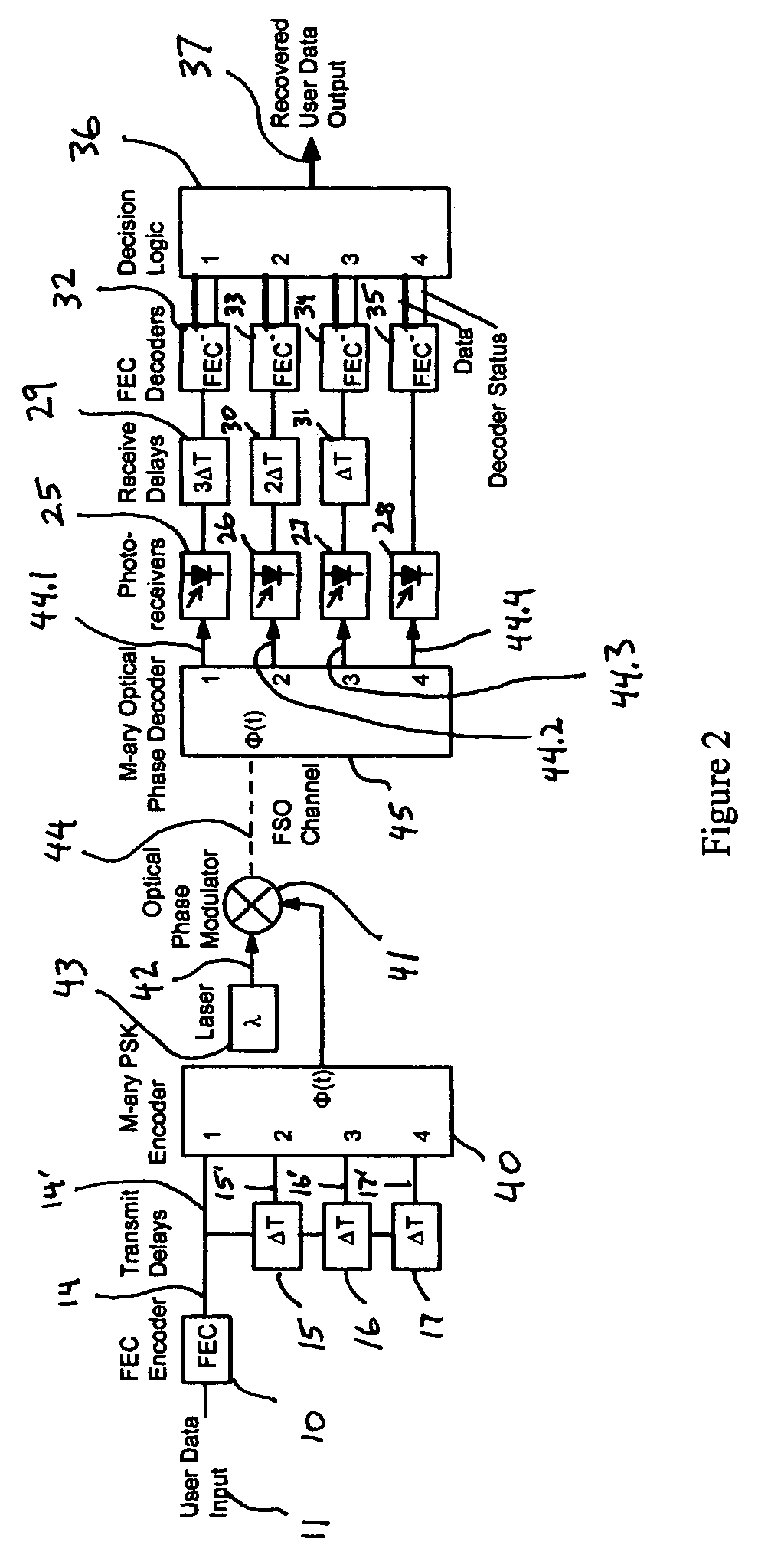

Fade-resistant forward error correction method for free-space optical communications systems

InactiveUS7277644B2Improve spectral efficiencyWide-bandwidth and secure connectionError preventionOther error detection/correction/protectionCommunications systemForward error correction

Free-space optical (FSO) laser communication systems offer exceptionally wide-bandwidth, secure connections between platforms that cannot other wise be connected via physical means such as optical fiber or cable. However, FSO links are subject to strong channel fading due to atmospheric turbulence and beam pointing errors, limiting practical performance and reliability. We have developed a fade-tolerant architecture based on forward error correcting codes (FECs) combined with delayed, redundant, sub-channels. This redundancy is made feasible though dense wavelength division multiplexing (WDM) and / or high-order M-ary modulation. Experiments and simulations show that error-free communications is feasible even when faced with fades that are tens of milliseconds long. We describe plans for practical implementation of a complete system operating at 2.5 Gbps.

Owner:LAWRENCE LIVERMORE NAT SECURITY LLC

Method and apparatus for evaluating performance of a read channel

ActiveUS7730384B2Data representation error detection/correctionOther error detection/correction/protectionDependabilityLog likelihood

Methods and apparatus are provided for measuring the performance of a read channel. A number of detection techniques, such as SOVA and maximum-a-posteriori (MAP) detectors, produce a bit decision and a corresponding reliability value associated with the bit decision. The reliability value associated with the bit decision may be expressed, for example, in the form of log likelihood ratios (LLRs). The reliability value can be monitored and used as a performance measure. The present invention provides a channel performance measure that generally correlates directly to the BER but can be collected in less time.

Owner:AVAGO TECH INT SALES PTE LTD

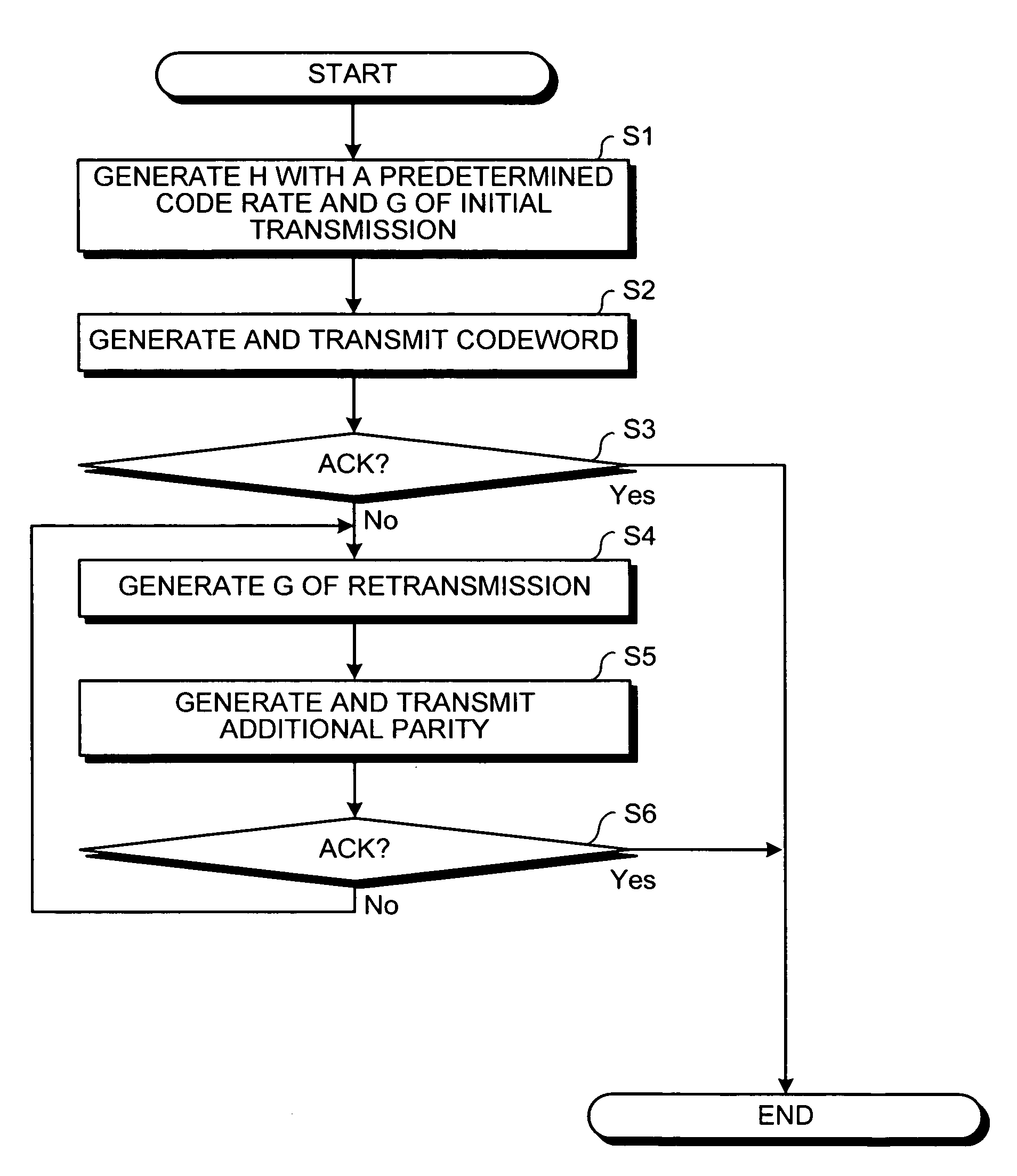

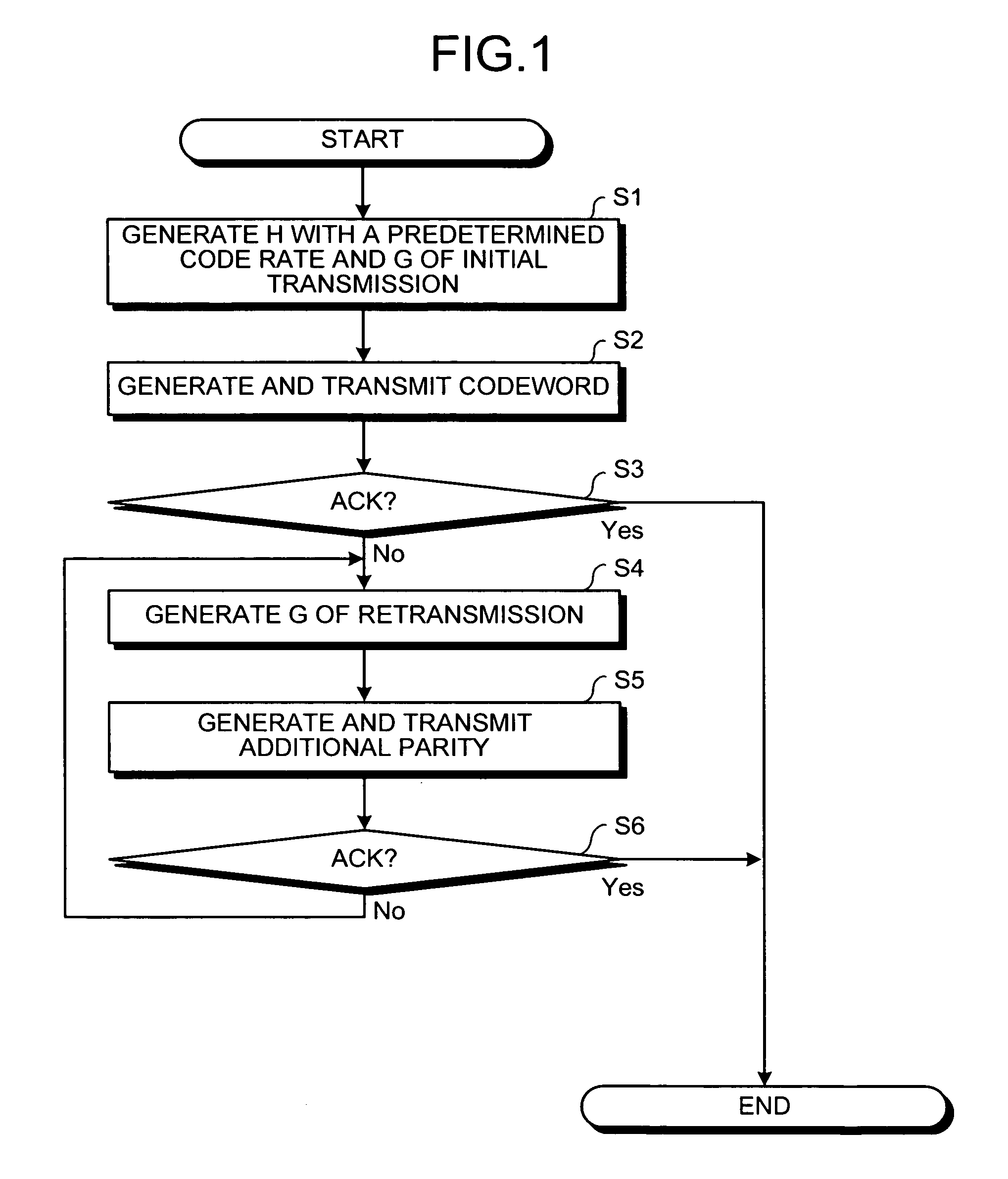

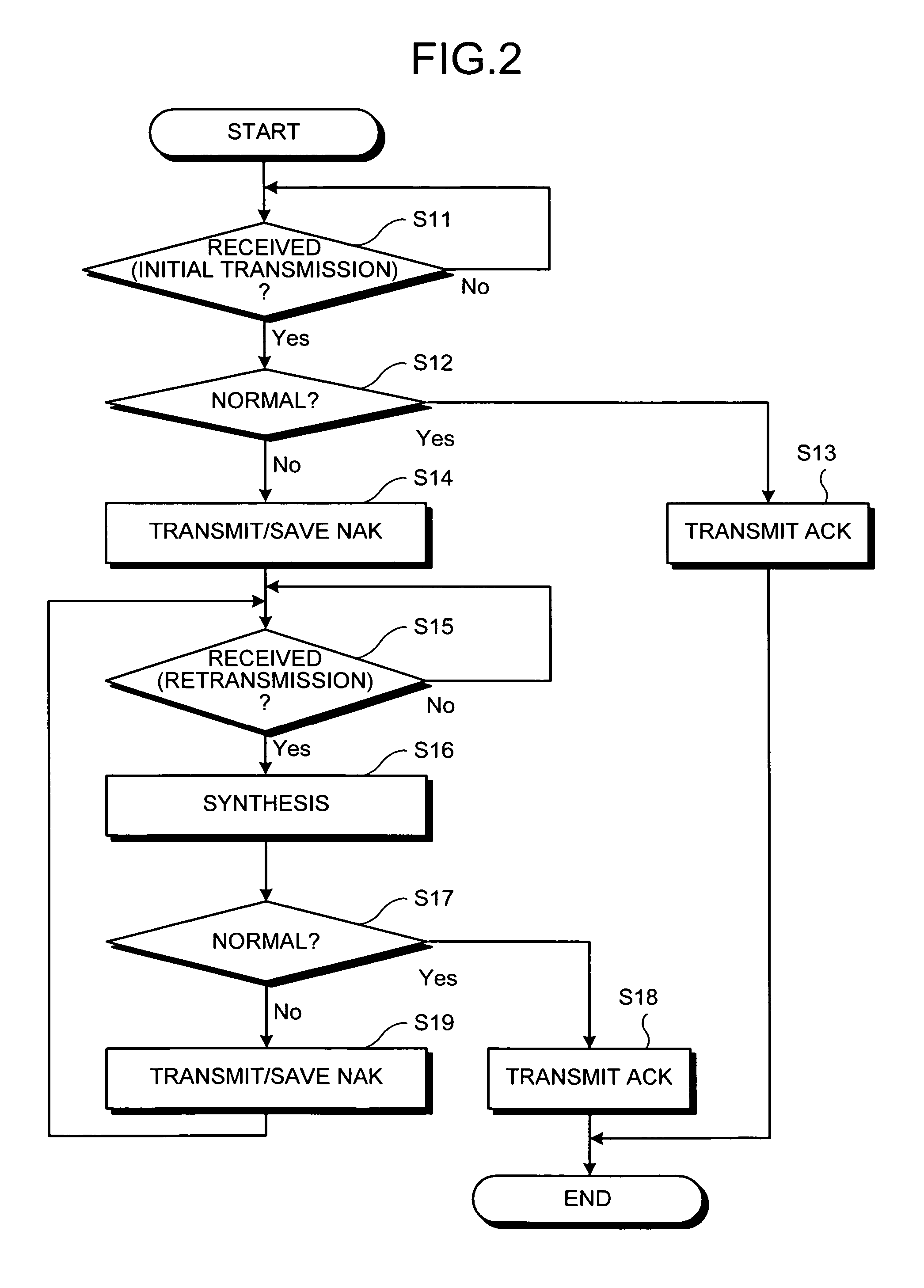

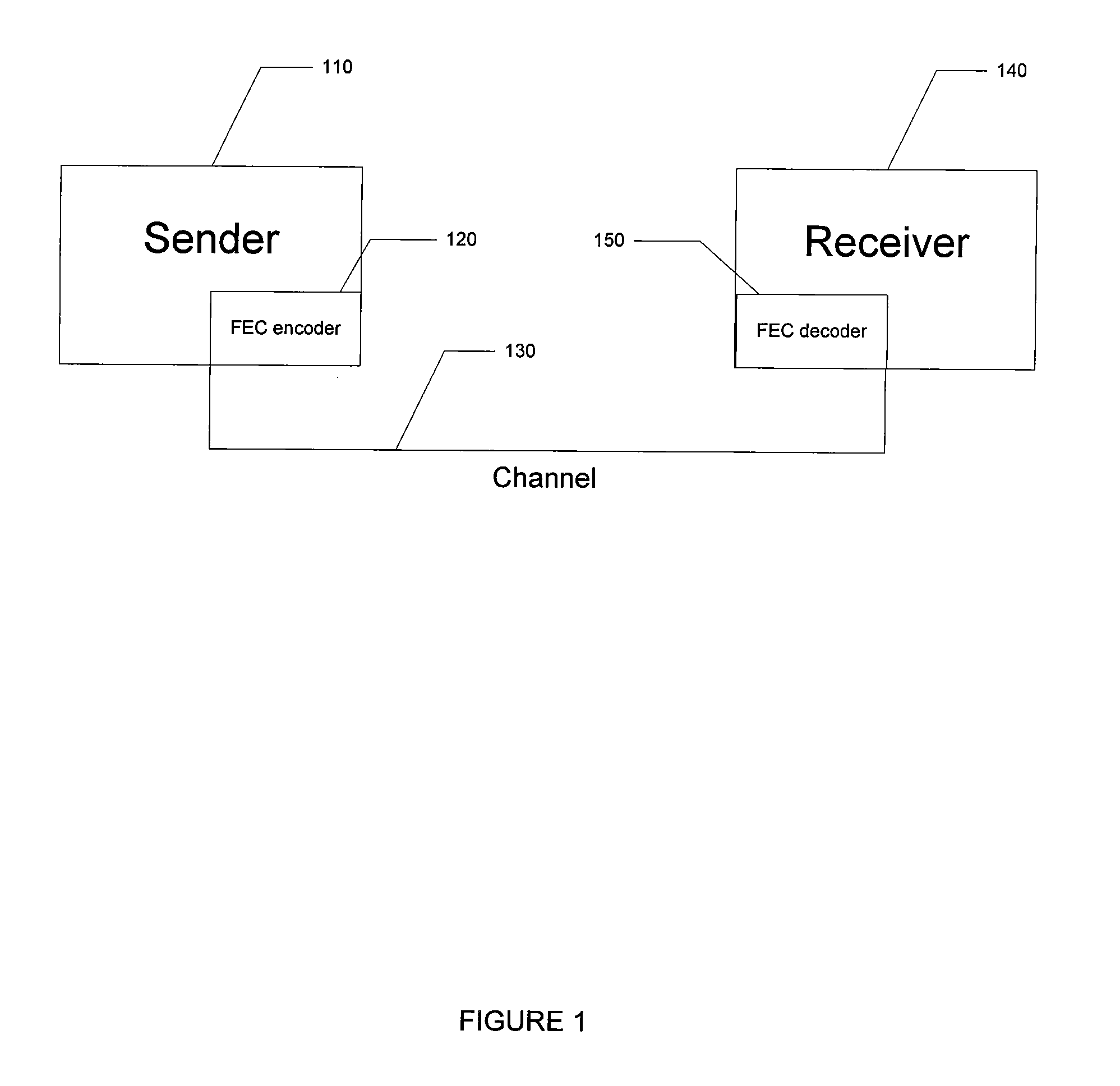

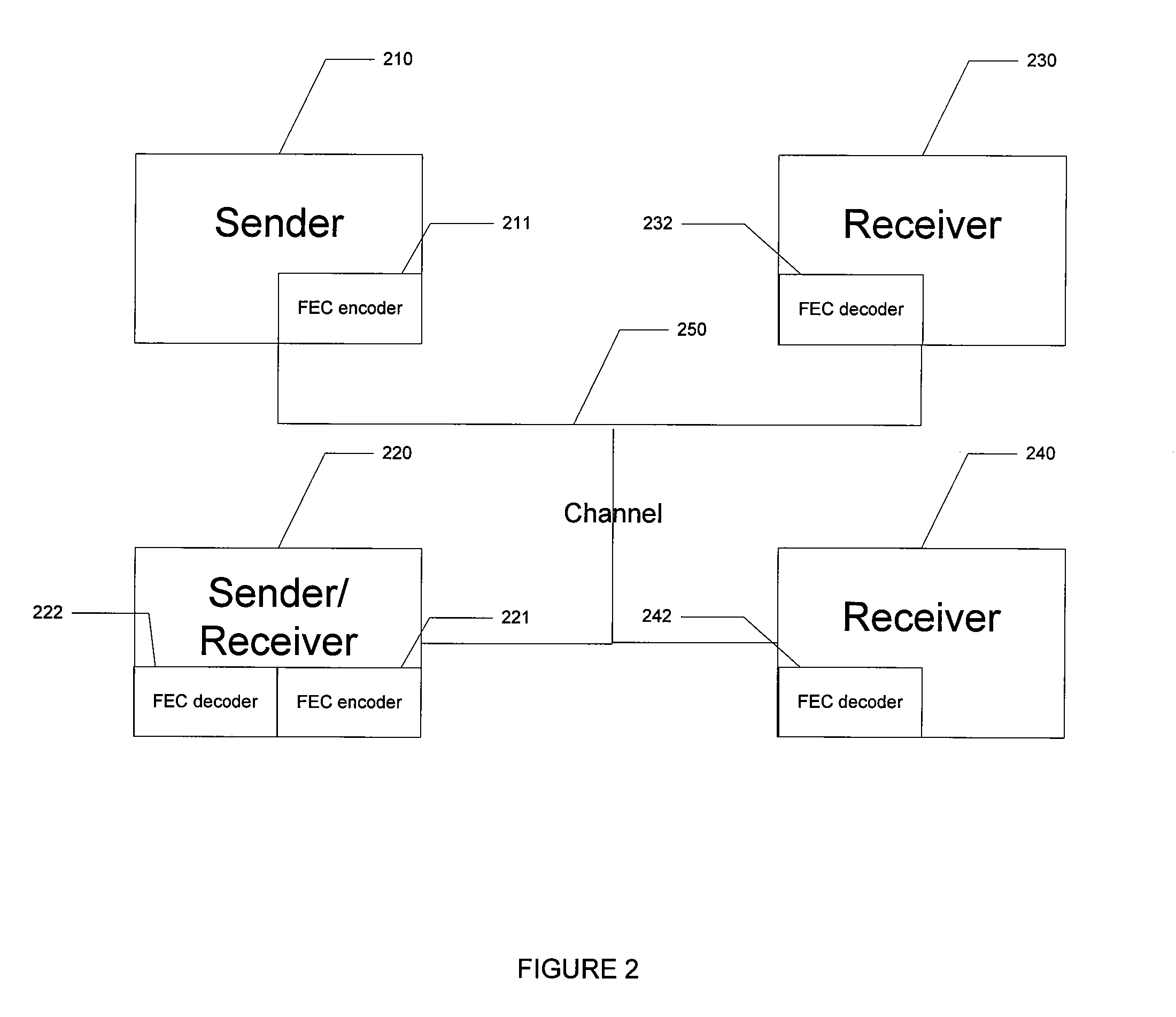

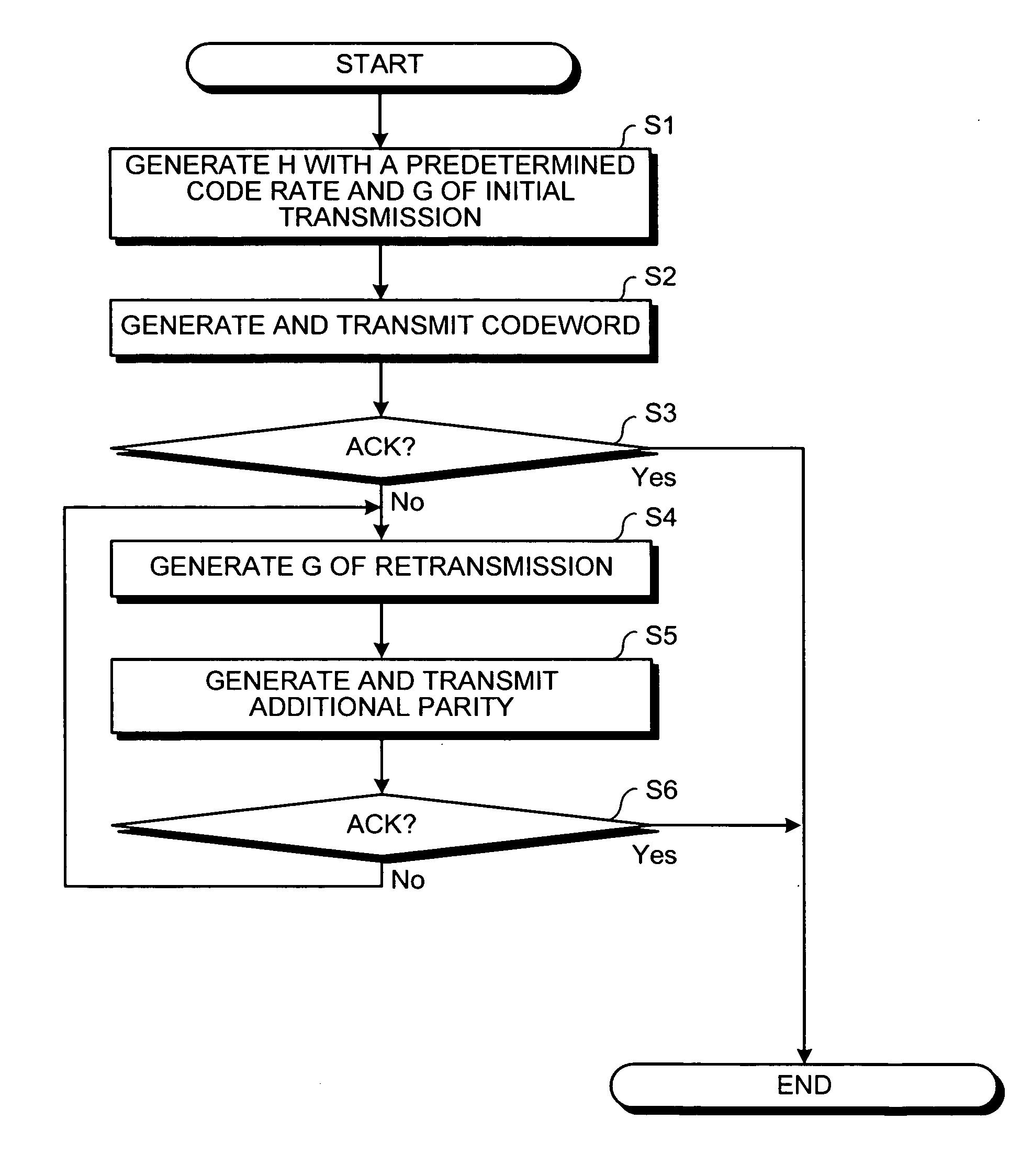

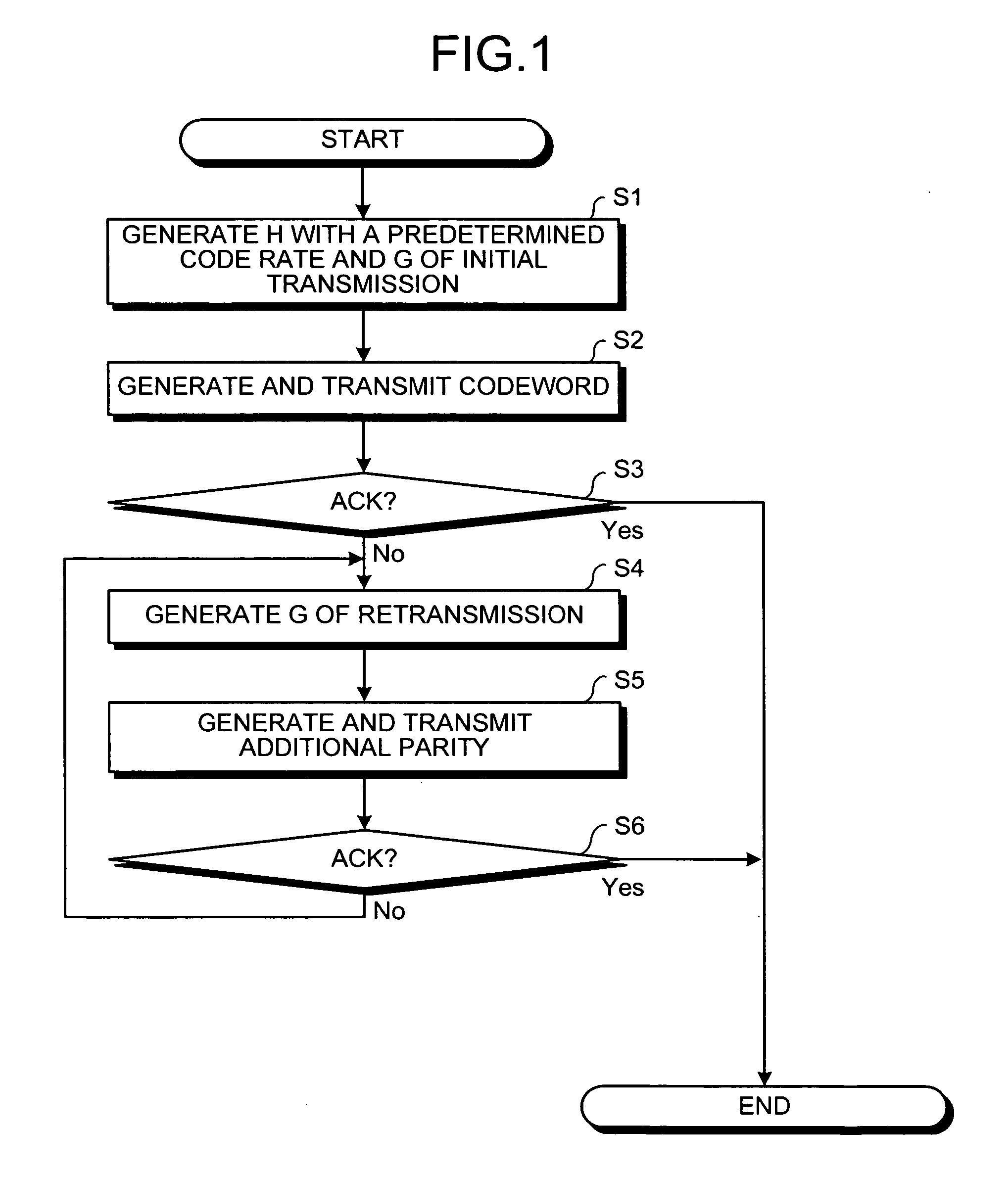

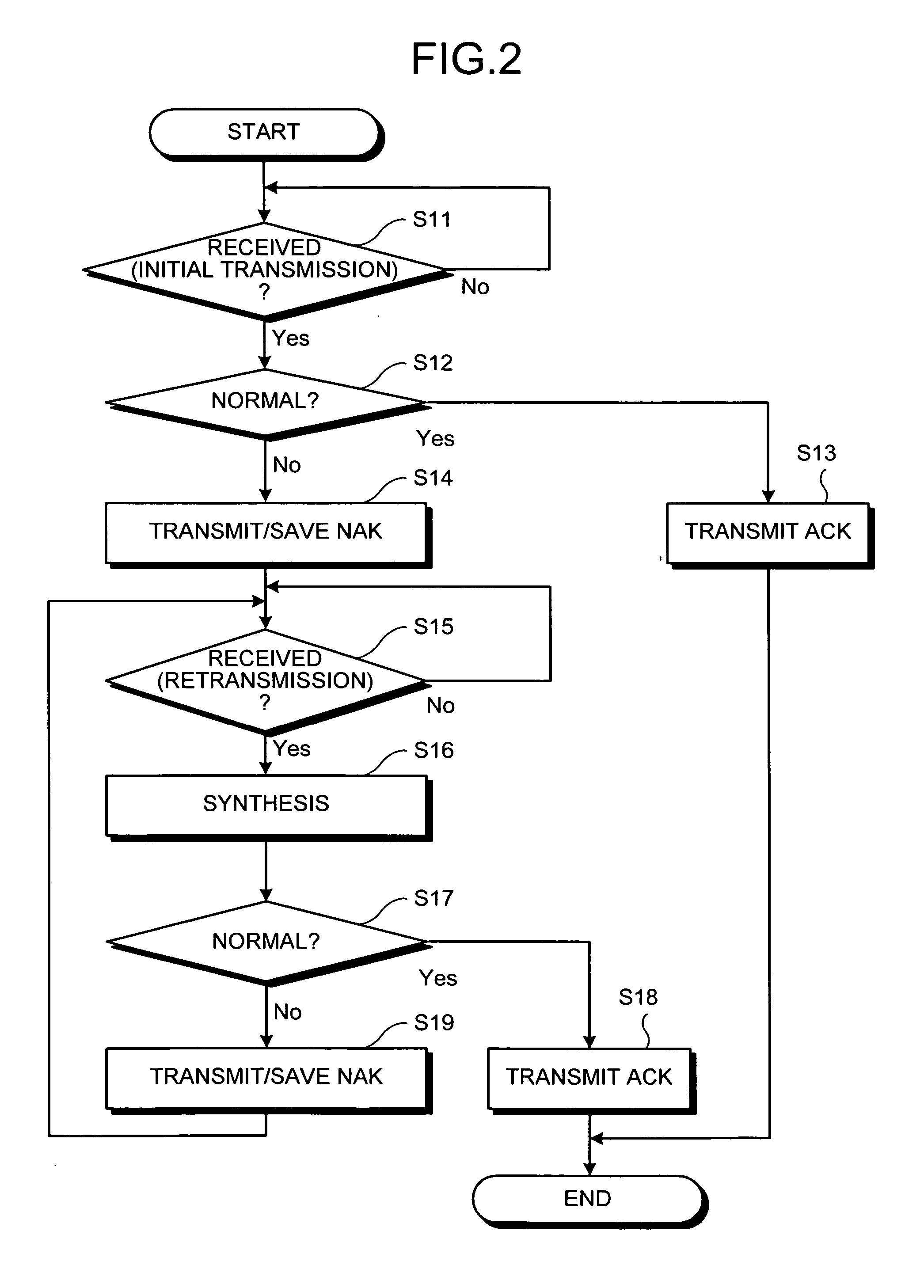

Retransmission control method and communications device

InactiveUS7600173B2Reduce rateError prevention/detection by using return channelTransmission systemsComputer hardwareParity-check matrix

A retransmission control method comprising: generating N parity check matrices; generating a generator matrix containing a check symbol generator matrix contained in the first parity check matrix; transmitting the codeword generated by using the generator matrix to another communications device; generating, when the communications device receives a NAK in response to the codeword, a first additional parity by using the second parity check matrix; and retransmitting the first additional parity to the another communications device.

Owner:MITSUBISHI ELECTRIC CORP

Method and apparatus for fast encoding of data symbols according to half-weight codes

ActiveUS20060036930A1Lower computational expenseReduce expensesOther error detection/correction/protectionCode conversionHigh densityTheoretical computer science

Efficient methods for encoding and decoding Half-Weight codes are disclosed and similar high density codes are disclosed. The efficient methods require at most 3·(k−1)+h / 2+1 XORs of symbols to calculate h Half-Weight symbols from k source symbols, where h is of the order of log(k).

Owner:QUALCOMM INC

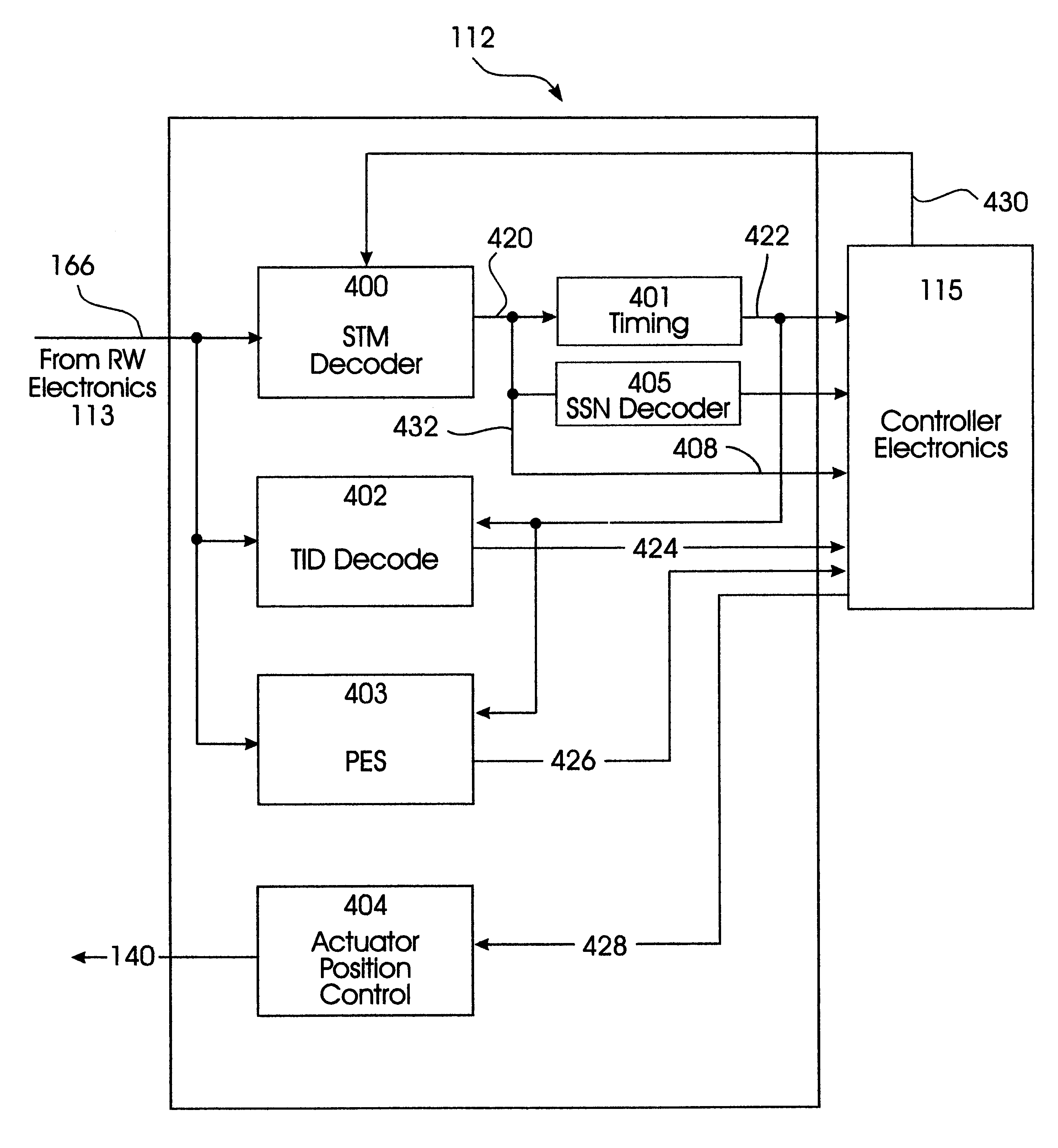

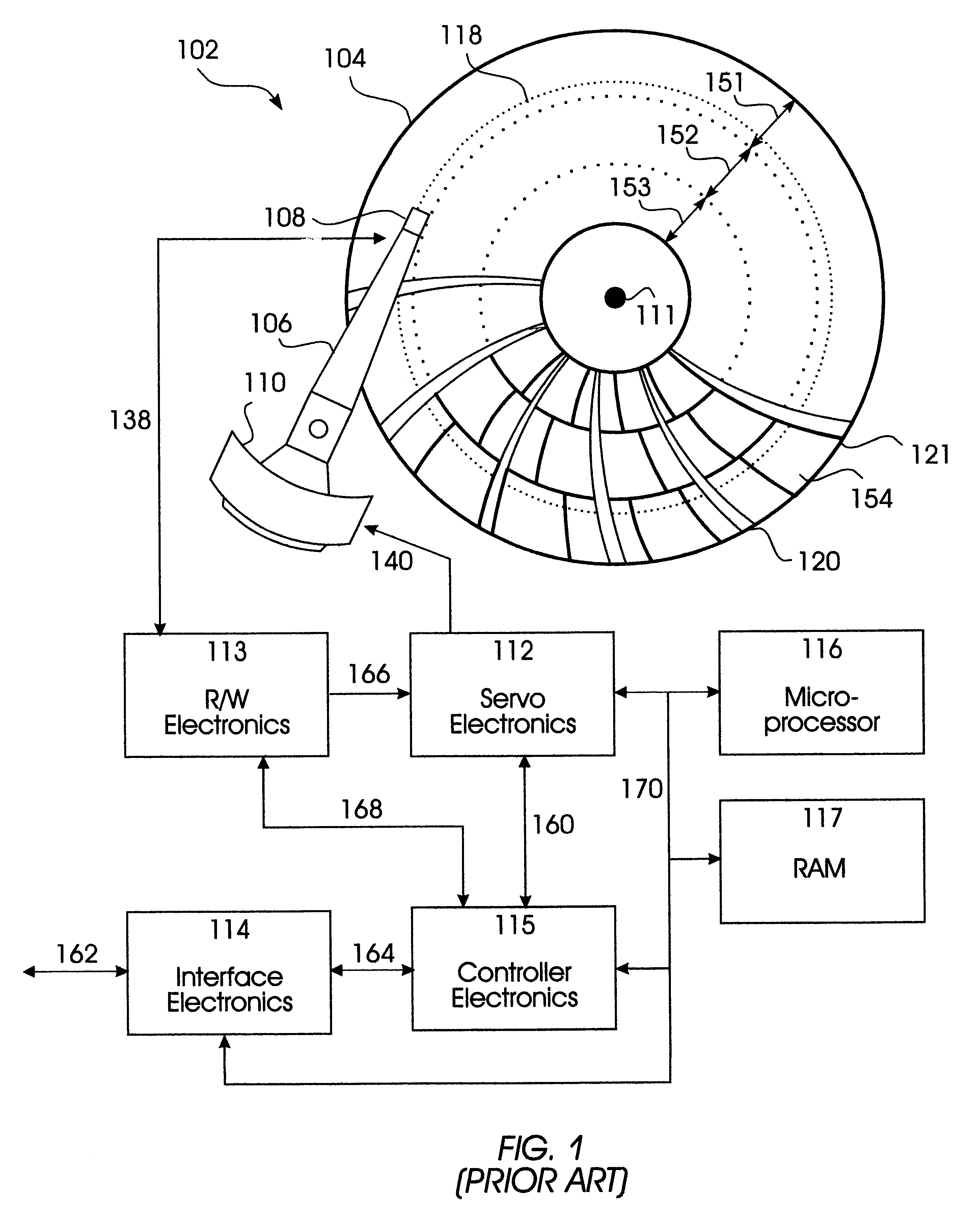

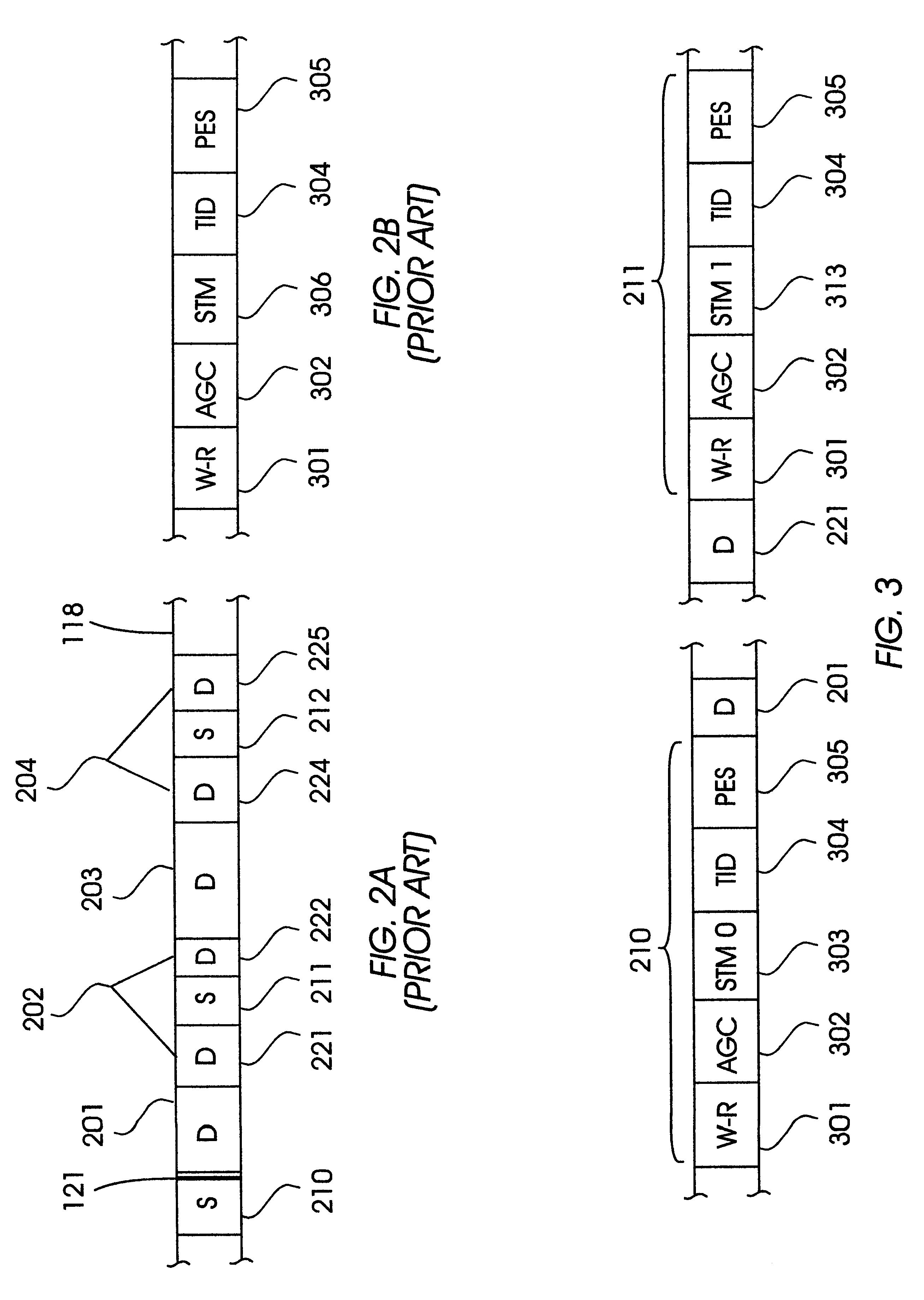

Disk drive with sector numbers encoded by sequences of sector types

InactiveUS6288861B1Disc-shaped record carriersOther error detection/correction/protectionControl theoryHamming distance

A magnetic recording disk drive has head positioning servo sectors with servo sector numbers (SSNs) that are not recorded on the disk. The SSNs are encoded through the use of multiple servo sector types that are arranged in a specific sequence around the data tracks. The different servo sector types are identified by unique types of servo timing marks (STMs), which are used to locate the servo sectors. The SSNs that are used to identify the servo sectors on the track form a set or code of m fixed n-bit patterns. A SSN is determined when the STM types read from n sequential servo sectors match one of the fixed SSN pattems. A set or code of m servo sectors, where each servo sector is identified by a unique SSN pattern having length n, is denoted as an (m,n,d) code, where d is referred to as the minimum Hamming distance of the code. The Hamming distance between two patterns refers to the number of locations that are different between the two pattems.

Owner:IBM CORP

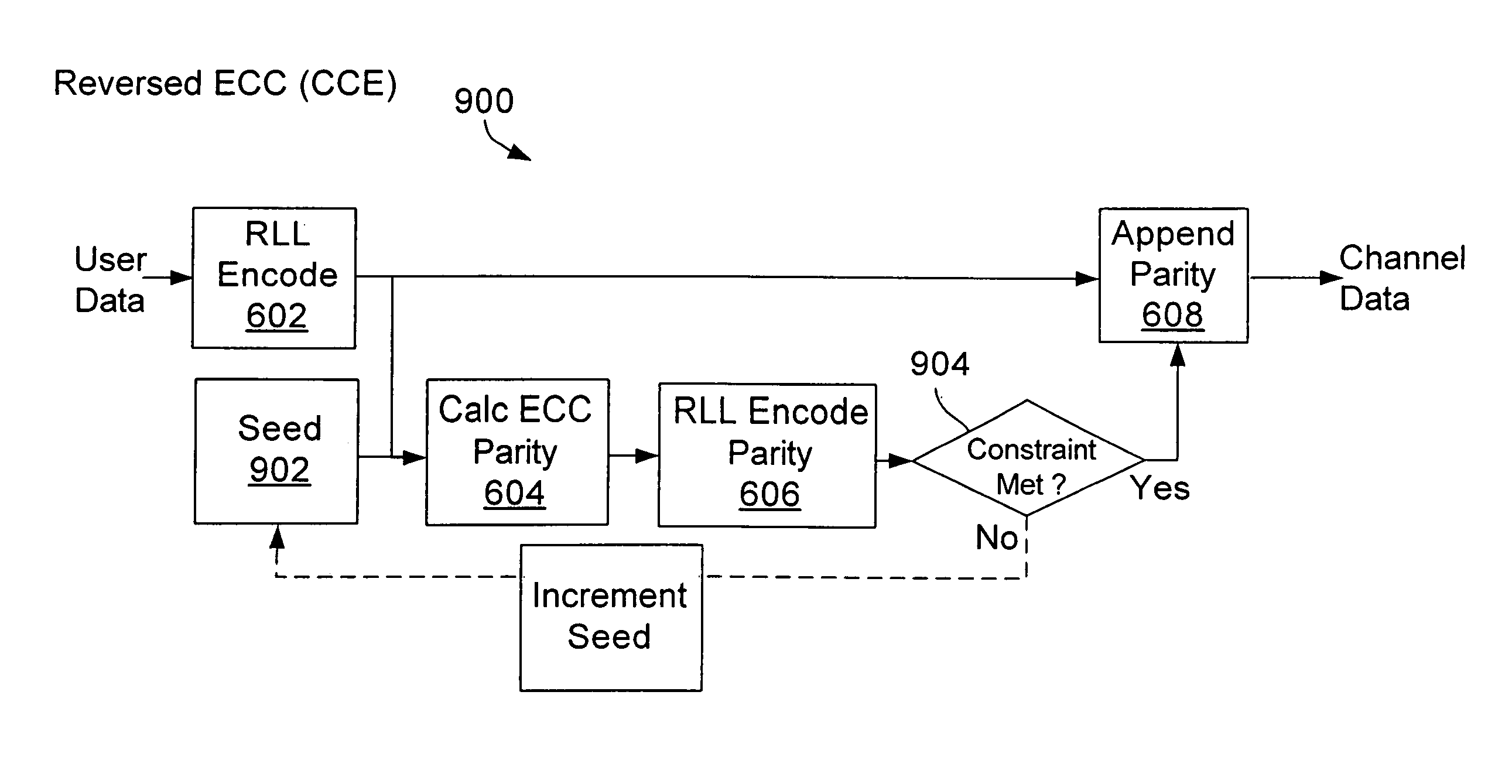

Reverse error correction coding with run length limited constraint

ActiveUS7174485B2Error detection/correctionOther error detection/correction/protectionComputer hardwareForward error correction

A method and apparatus for communicating data is provided. The data is encoded in accordance with a run length limited (RLL) code. A seed is appended to the RLL encoded data. The seed can be used to alter the error correction code (ECC) parity to meet an RLL constraint.

Owner:SEAGATE TECH LLC

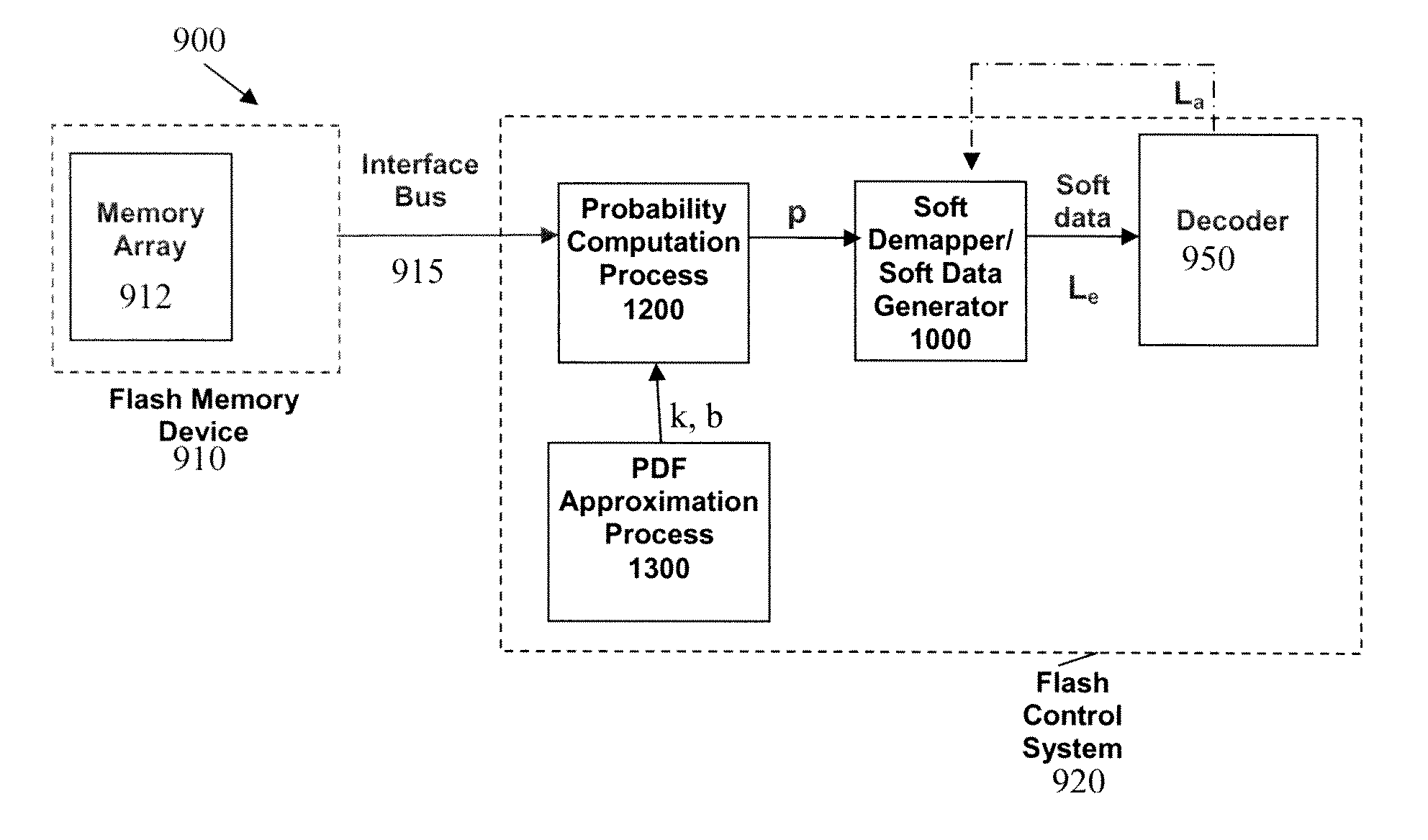

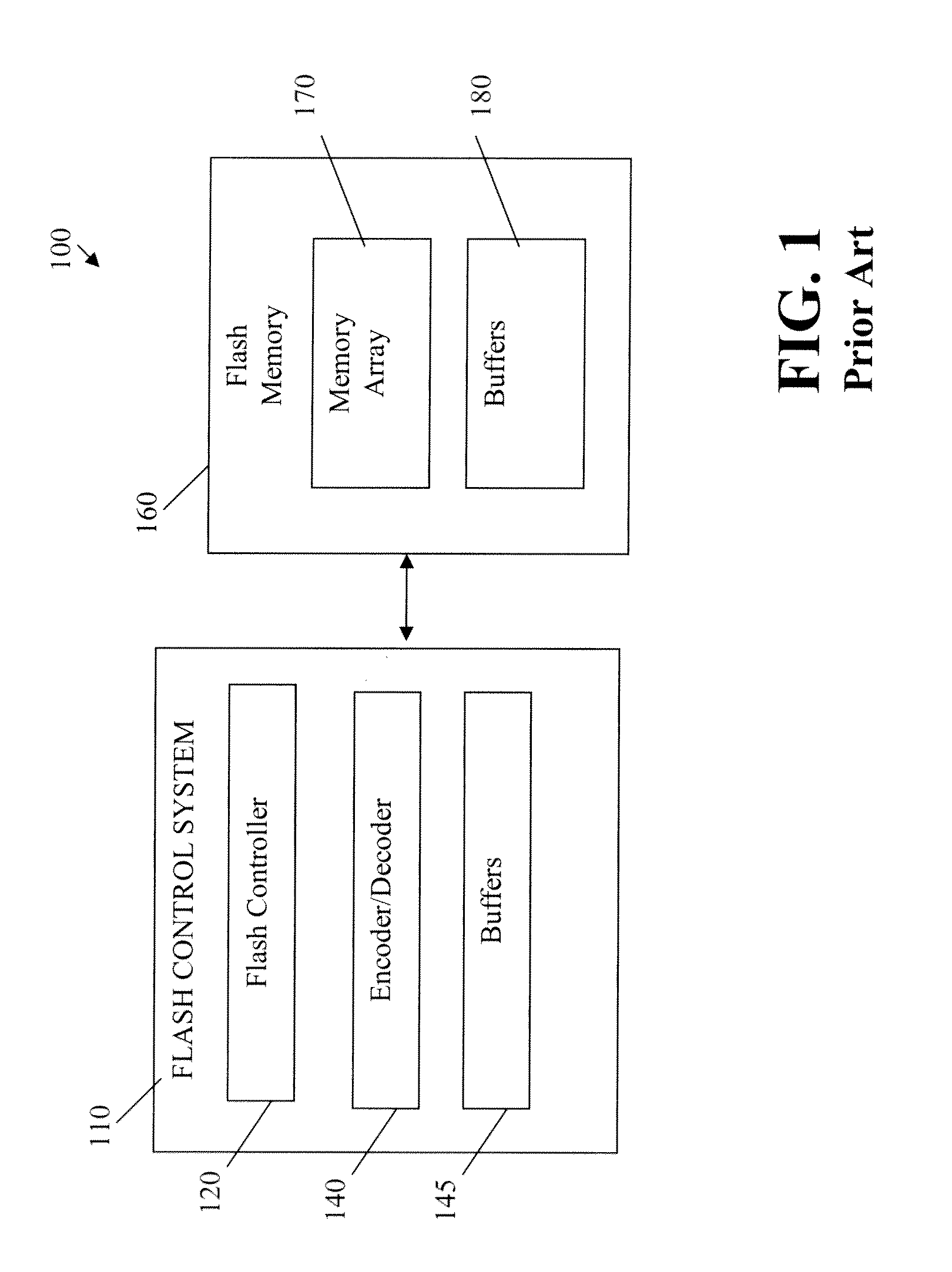

Methods and apparatus for computing soft data or log likelihood ratios for received values in communication or storage systems

ActiveUS8775913B2Other decoding techniquesOther error detection/correction/protectionCommunications systemEngineering

Owner:AVAGO TECH INT SALES PTE LTD

In-place transformations with applications to encoding and decoding various classes of codes

InactiveUS20060280254A1Reduce running timeLess time accessing memoryError preventionOther decoding techniquesComputer hardwareTerm memory

In an encoder for encoding symbols of data using a computing device having memory constraints, a method of performing a transformation comprising loading a source block into memory of the computing device, performing an intermediate transformation of less than all of the source block, then replacing a part of the source block with intermediate results in the memory and then completing the transformation such that output symbols stored in the memory form a set of encoded symbols. A decoder can perform decoding steps in an order that allows for use of substantially the same memory for storing the received data and the decoded source block, performing as in-place transformations. Using an in-place transformation, a large portion of memory set aside for received data can be overwritten as that received data is transformed into decoded source data without requiring a similar sized large portion of memory for the decoded source data.

Owner:QUALCOMM INC

Retransmission Control Method And Communications Device

InactiveUS20070277082A1Reduce code rateImprove featuresError prevention/detection by using return channelTransmission systemsComputer hardwareParity-check matrix

A retransmission control method comprising: generating N parity check matrices; generating a generator matrix containing a check symbol generator matrix contained in the first parity check matrix; transmitting the codeword generated by using the generator matrix to another communications device; generating, when the communications device receives a NAK in response to the codeword, a first additional parity by using the second parity check matrix; and retransmitting the first additional parity to the another communications device.

Owner:MITSUBISHI ELECTRIC CORP

Methods and apparatus for computing soft data or log likelihood ratios for received values in communication or storage systems

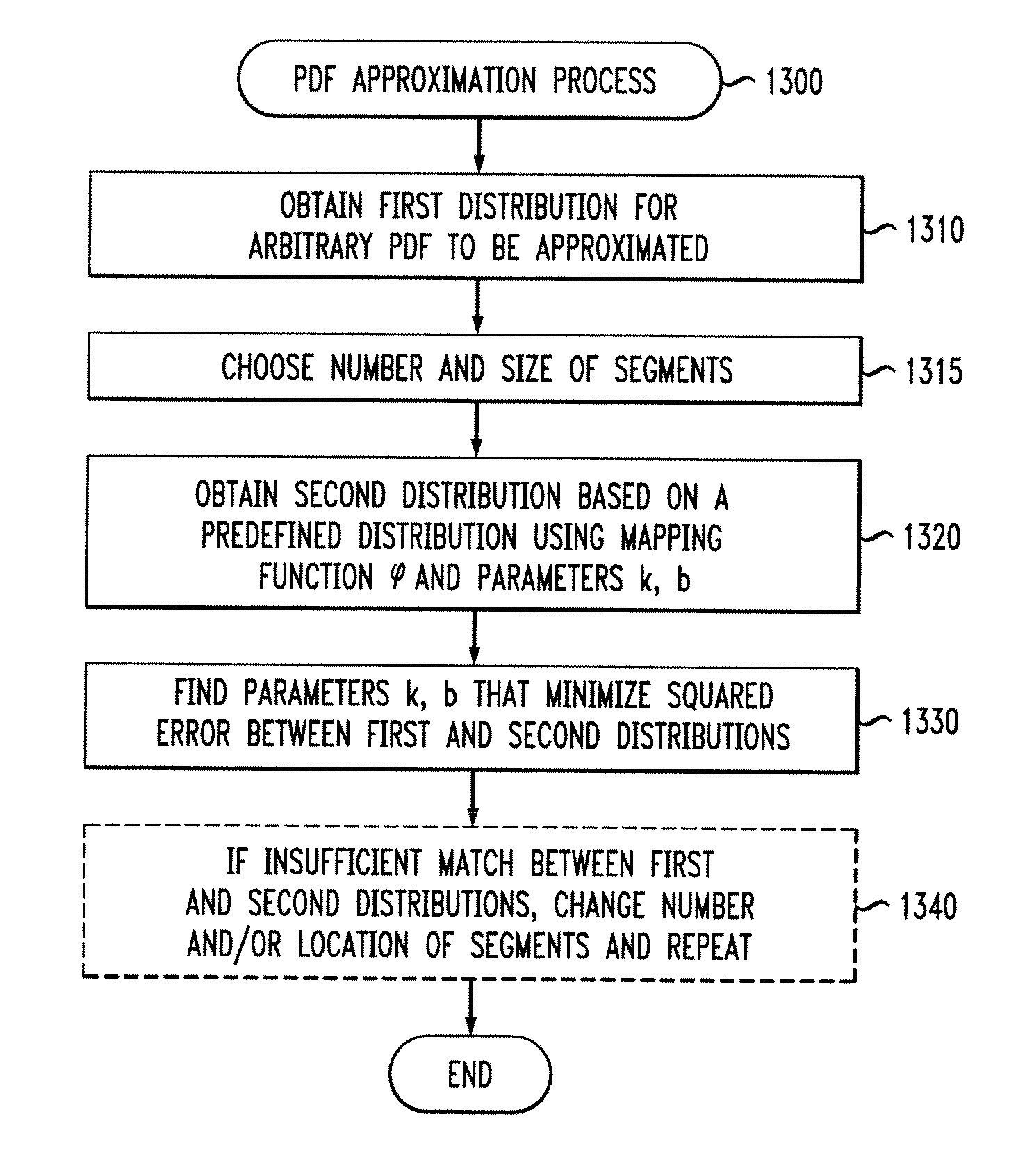

ActiveUS20110246859A1Other decoding techniquesOther error detection/correction/protectionCommunications systemSoft data

Methods and apparatus are provided for computing soft data or log likelihood ratios for received values in communication or storage systems. Soft data values or log likelihood ratios are computed for received values in a communication system or a memory device by obtaining at least one received value; identifying a segment of a function corresponding to the received value, wherein the function is defined over a plurality of segments, wherein each of the segments has an associated set of parameters; and calculating the soft data value or log likelihood ratio using the set of parameters associated with the identified segment. The computed soft data values or log likelihood ratios are optionally provided to a decoder.

Owner:AVAGO TECH INT SALES PTE LTD