Patents

Literature

2791results about "Error correction/detection by combining multiple code structures" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

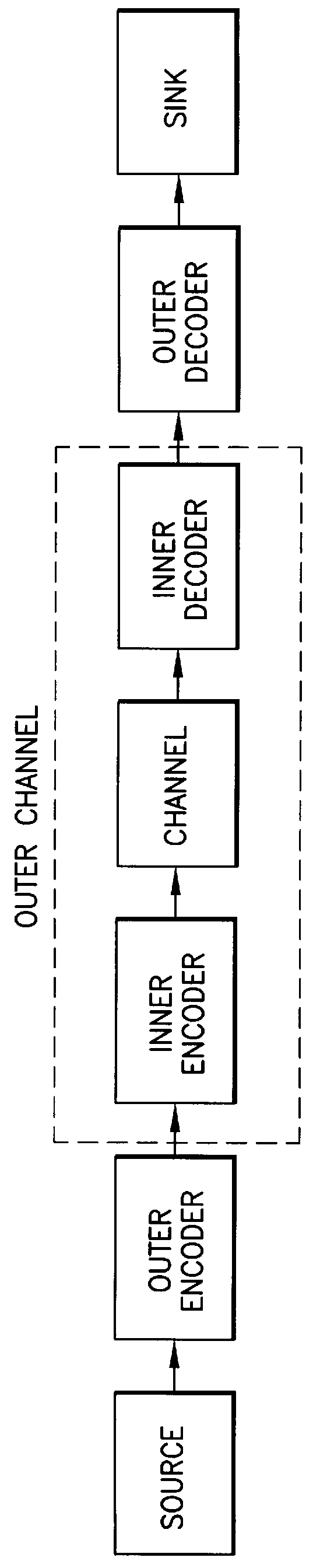

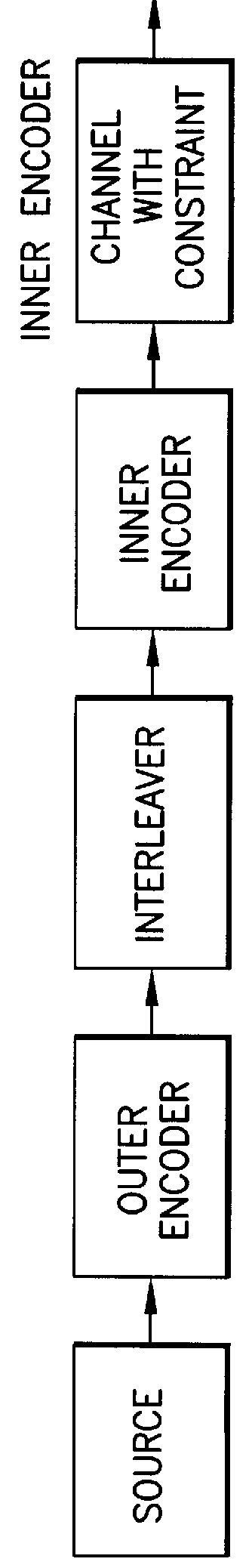

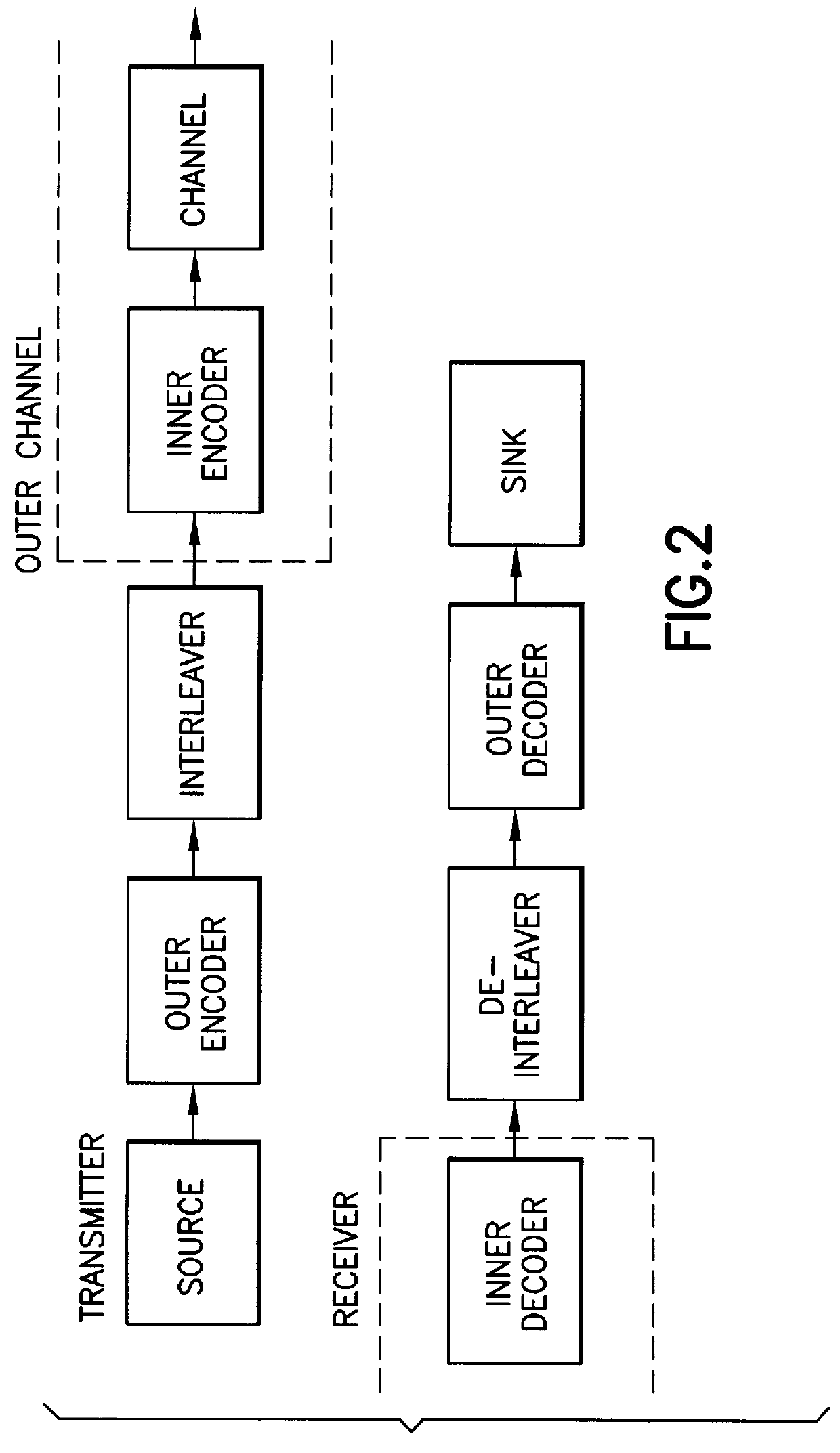

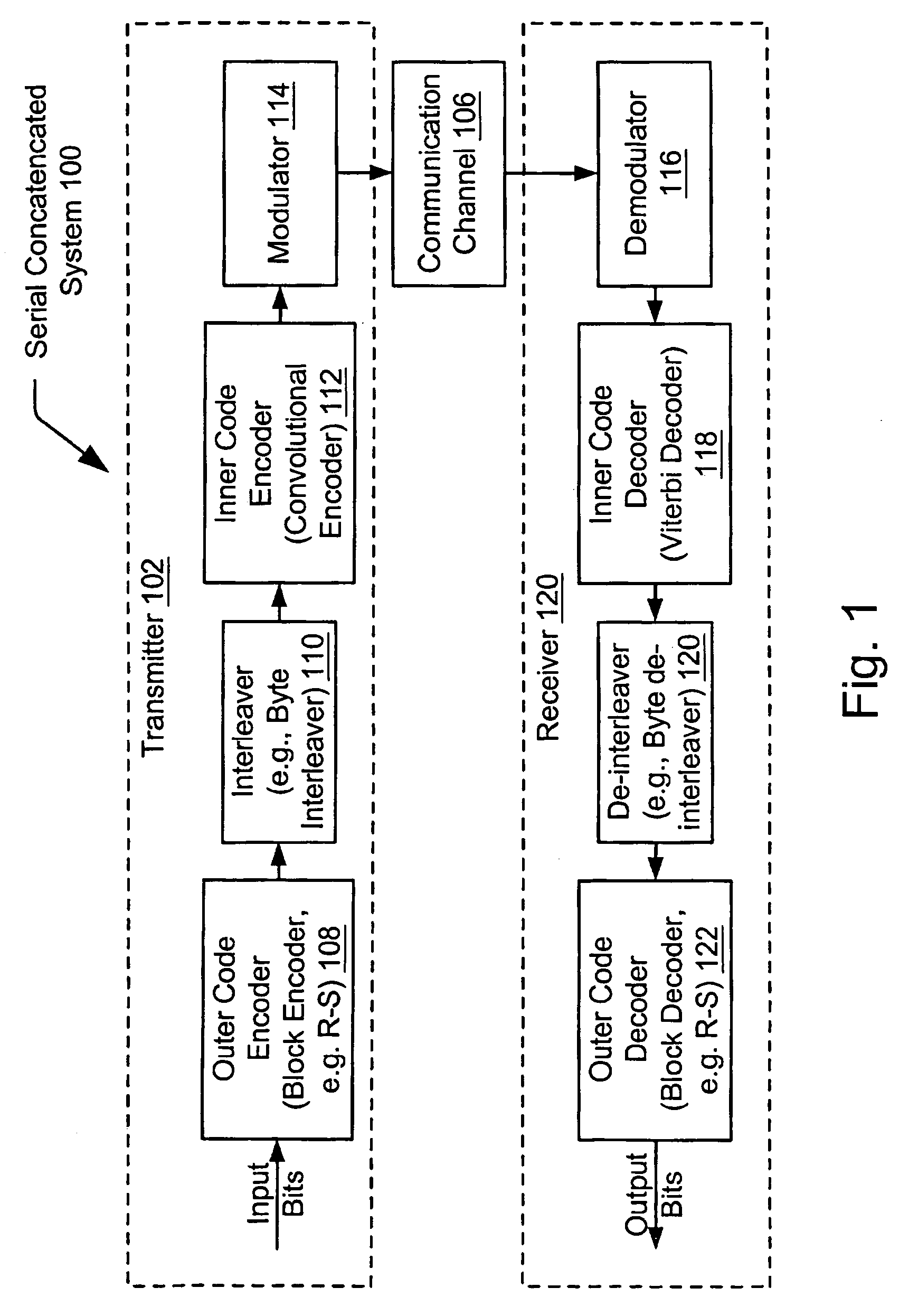

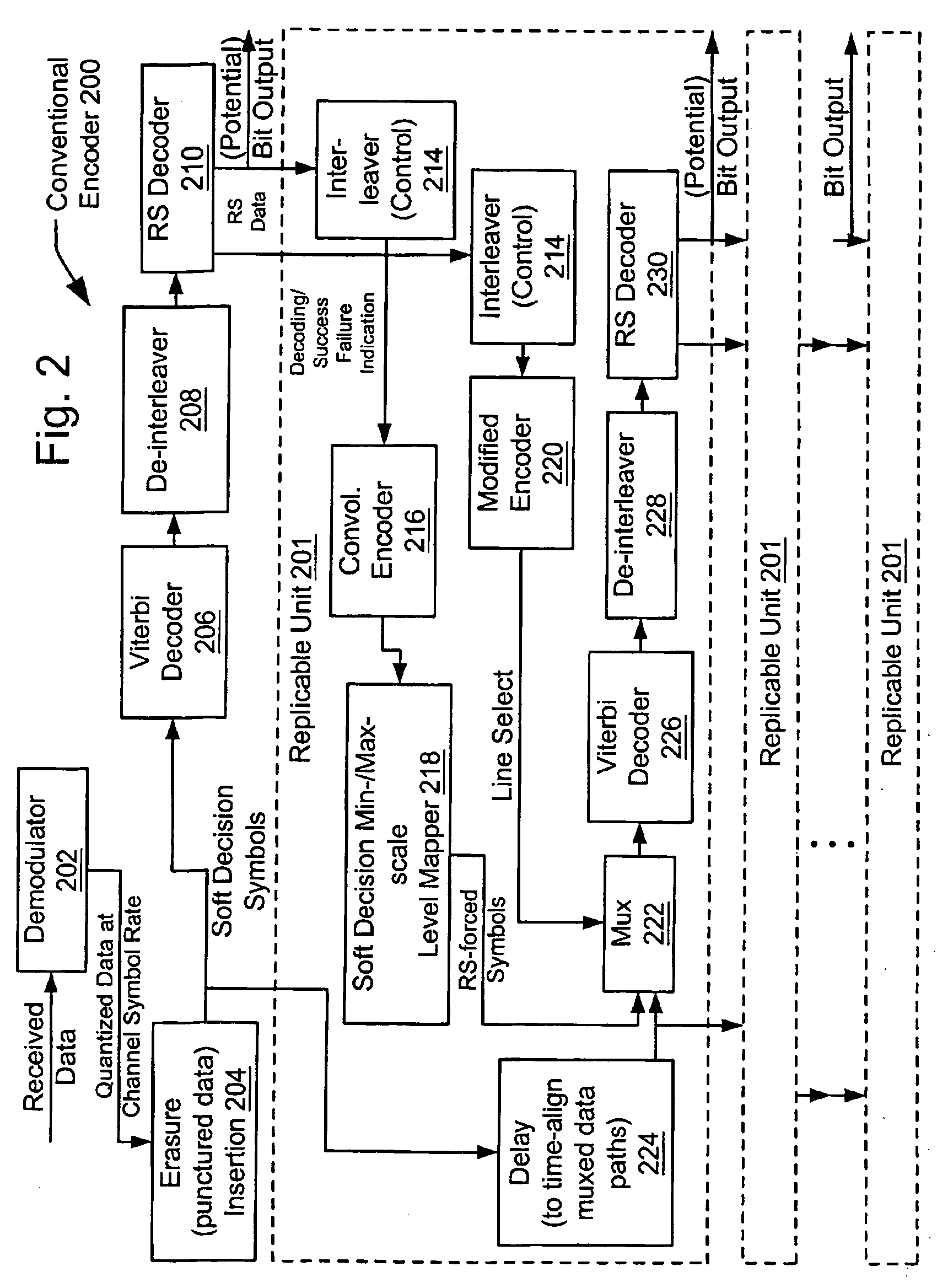

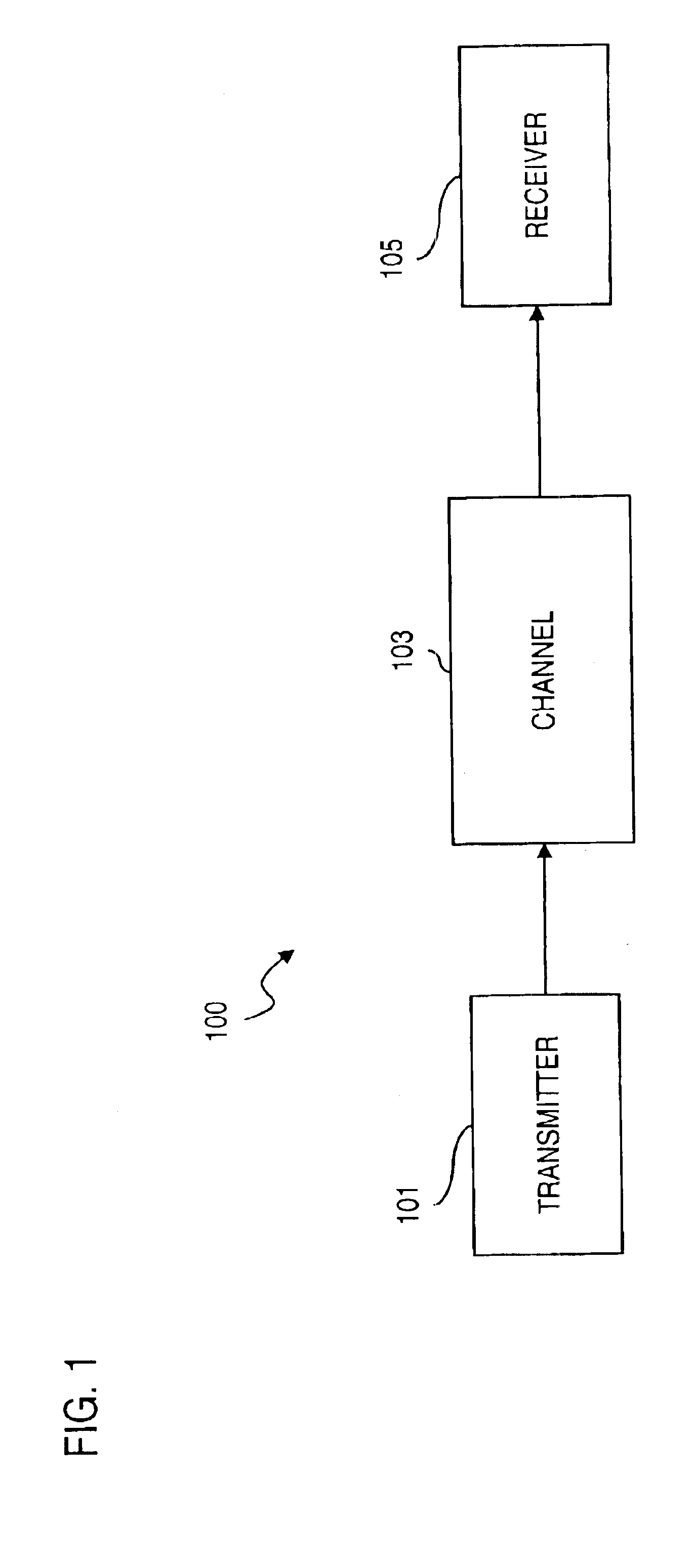

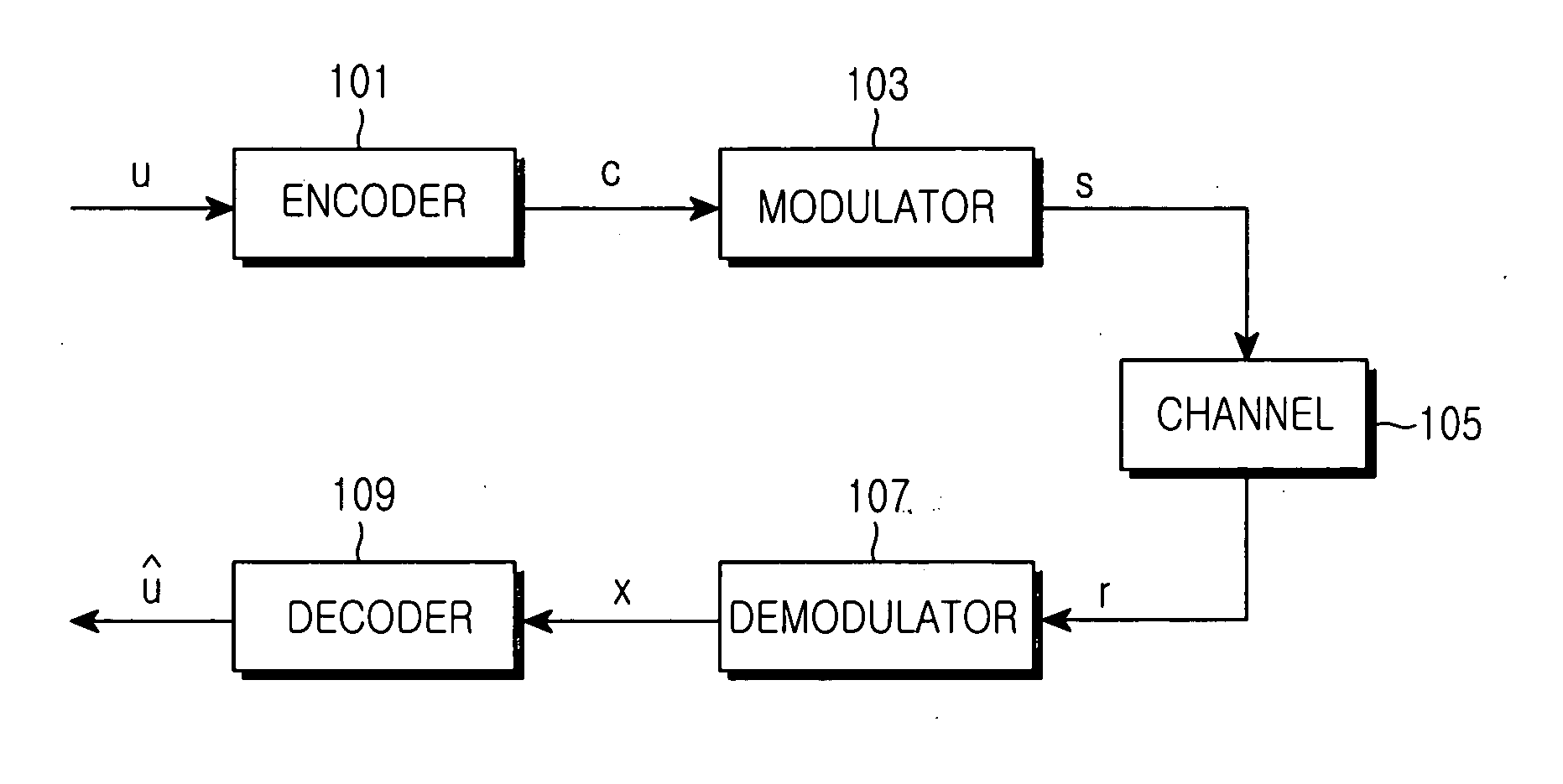

System and method for error correcting a received data stream in a concatenated system

A received signal is first converted into a digital sequence that may contain "erasures" (or ambiguity symbols) as well as errors. Then iterative decoding is applied in order to eliminate or reduce the erasures. This decoding procedure works effectively with the associated transmitter that adopts a concatenation of an outer coder, a permutation and an inner coder. The principal of the invention is also applicable to a system in which the inner coder is replaced by a "digital modulator" that introduces some constraint, or a channel that introduces some memory such as partial response signaling, intersymbol interference or multipath propagation. The invention can be applied to many existing systems while maintaining "backward compatibility" in the sense that the transmitter side need not be modified.

Owner:THE TRUSTEES FOR PRINCETON UNIV

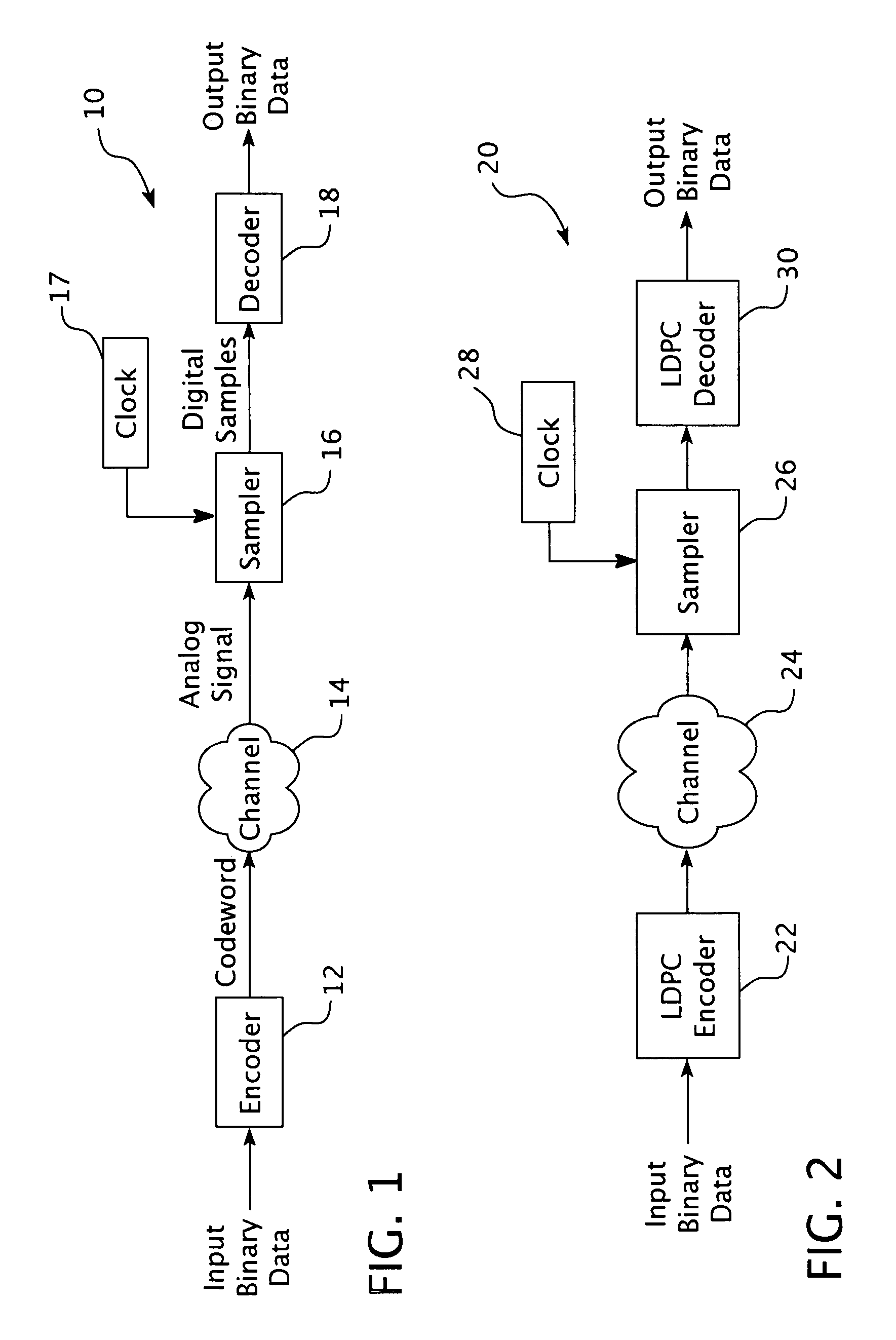

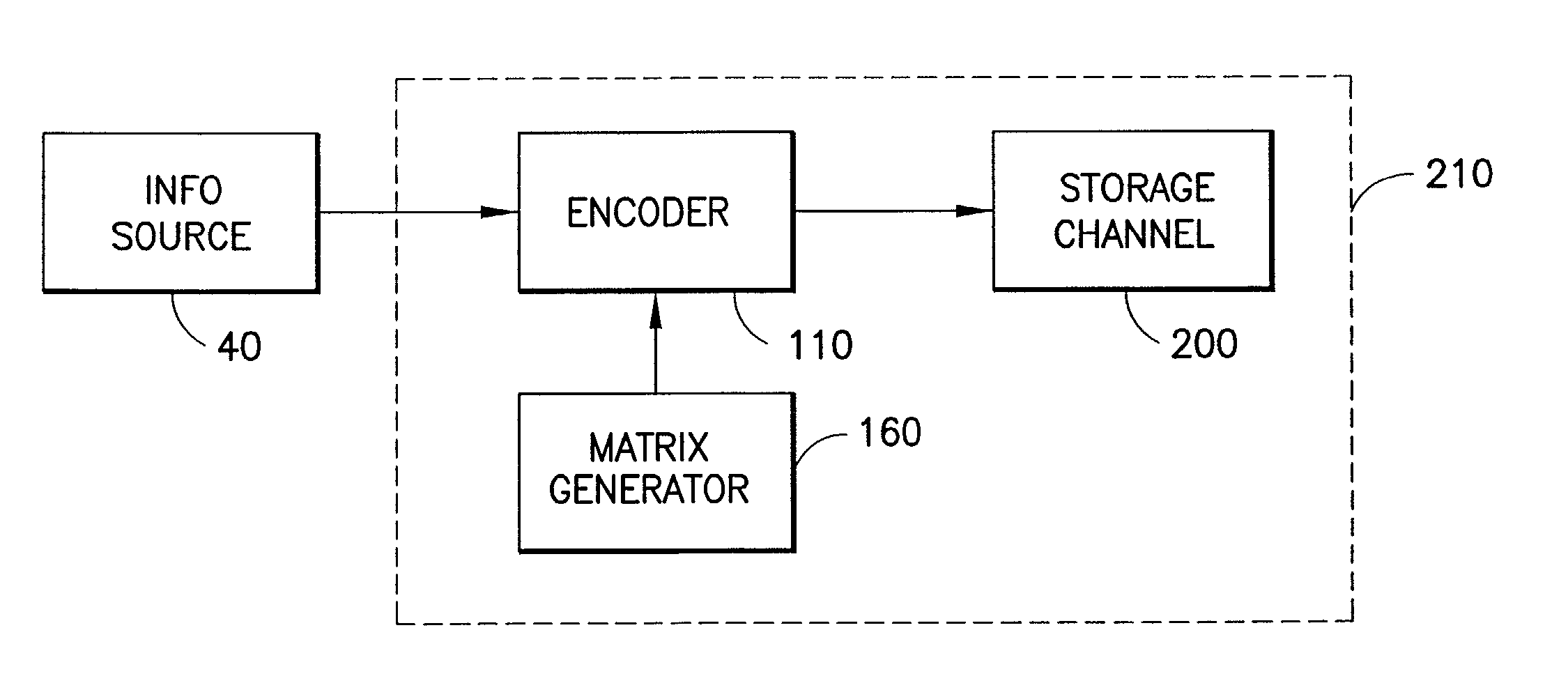

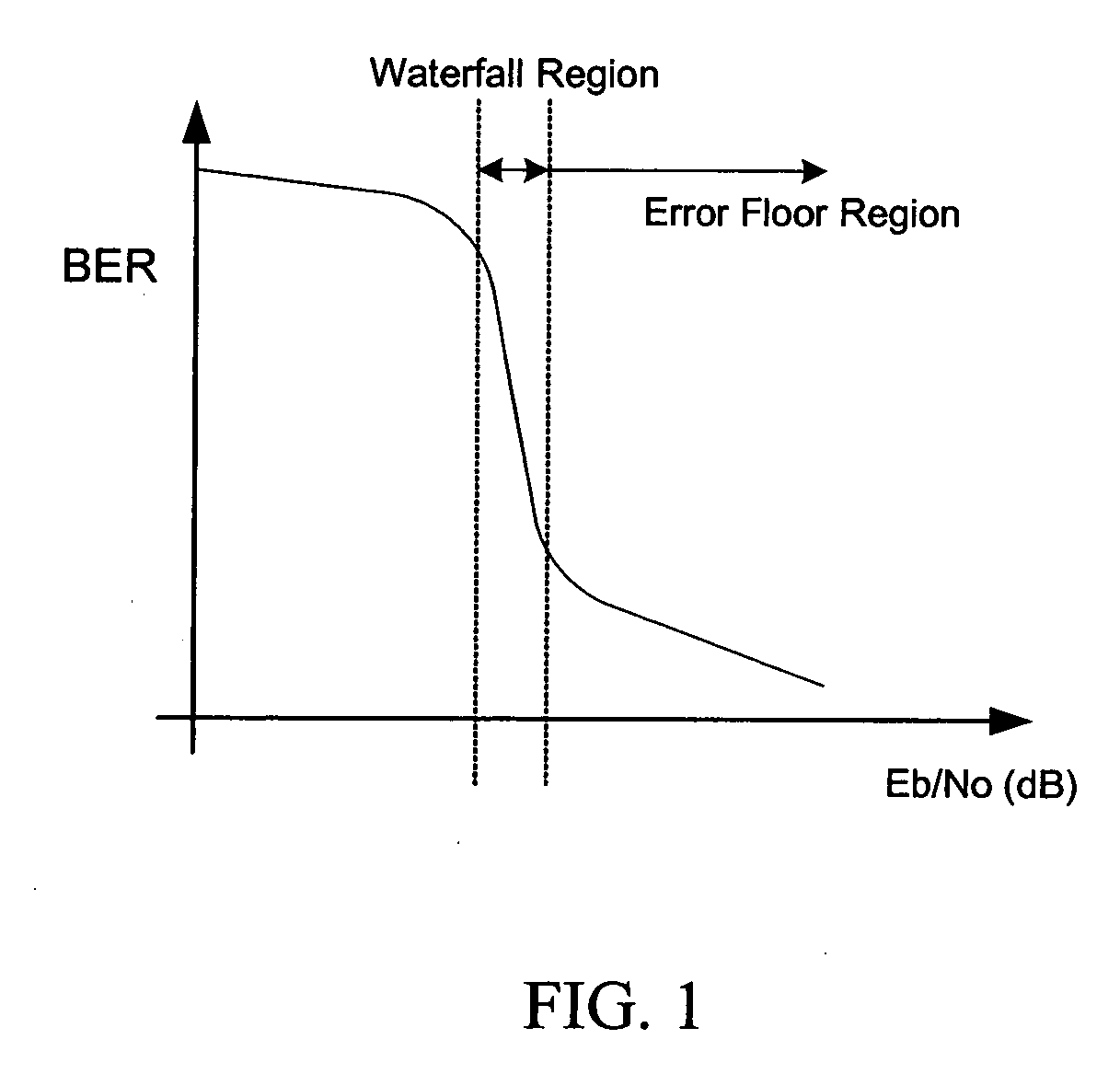

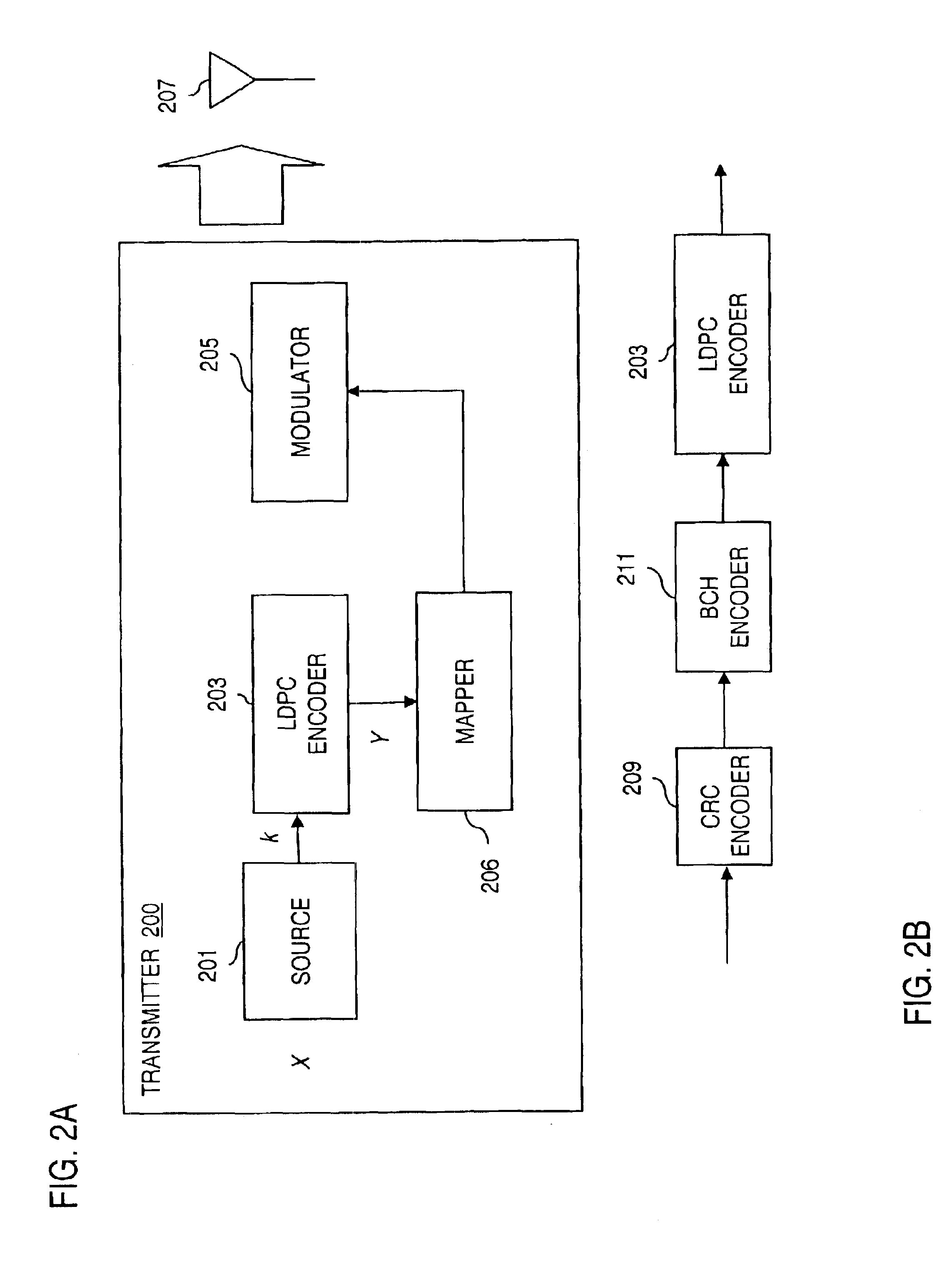

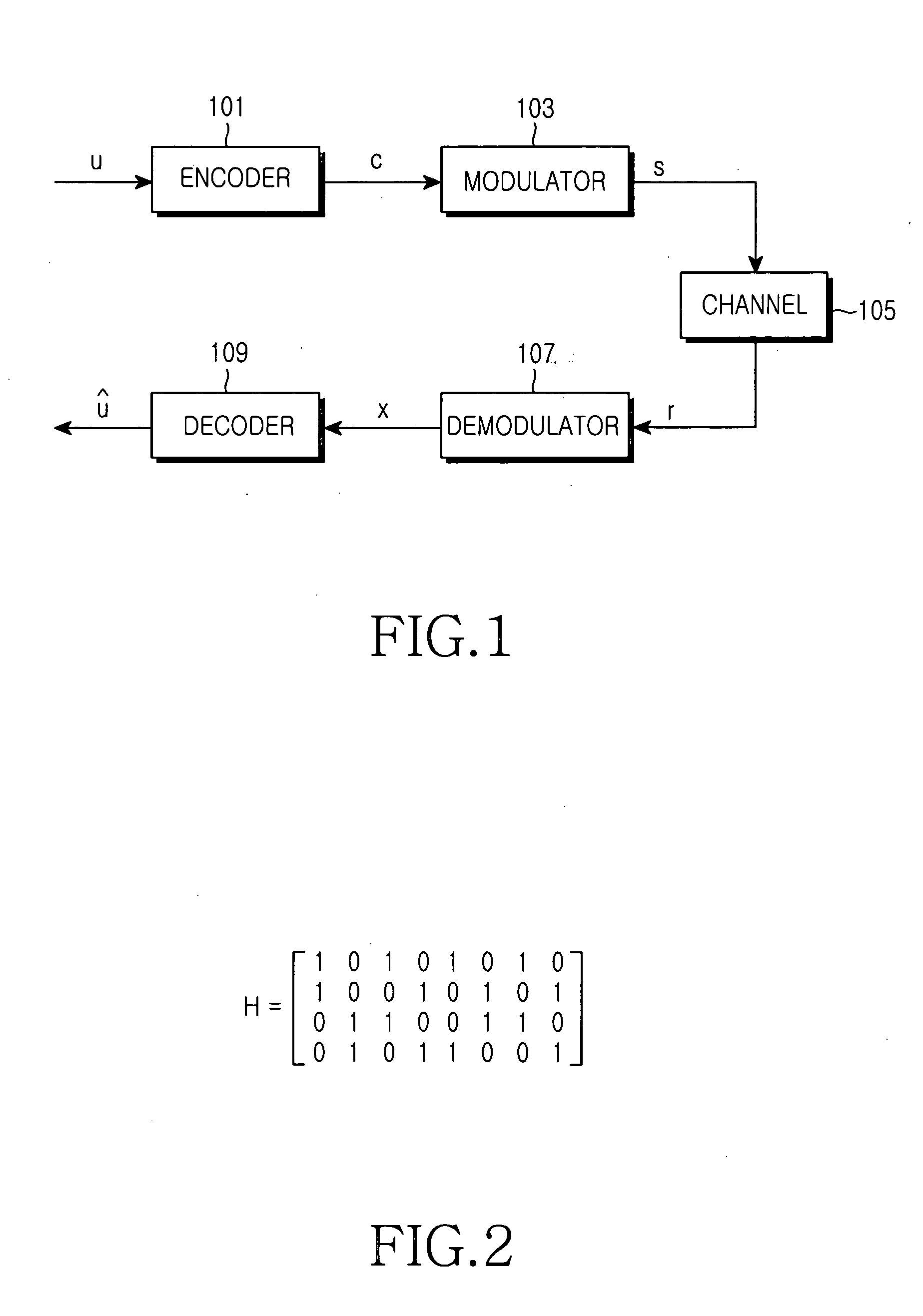

Method and apparatus for low density parity check encoding of data

InactiveUS6895547B2Improve performanceError preventionError detection/correctionTheoretical computer scienceParity-check matrix

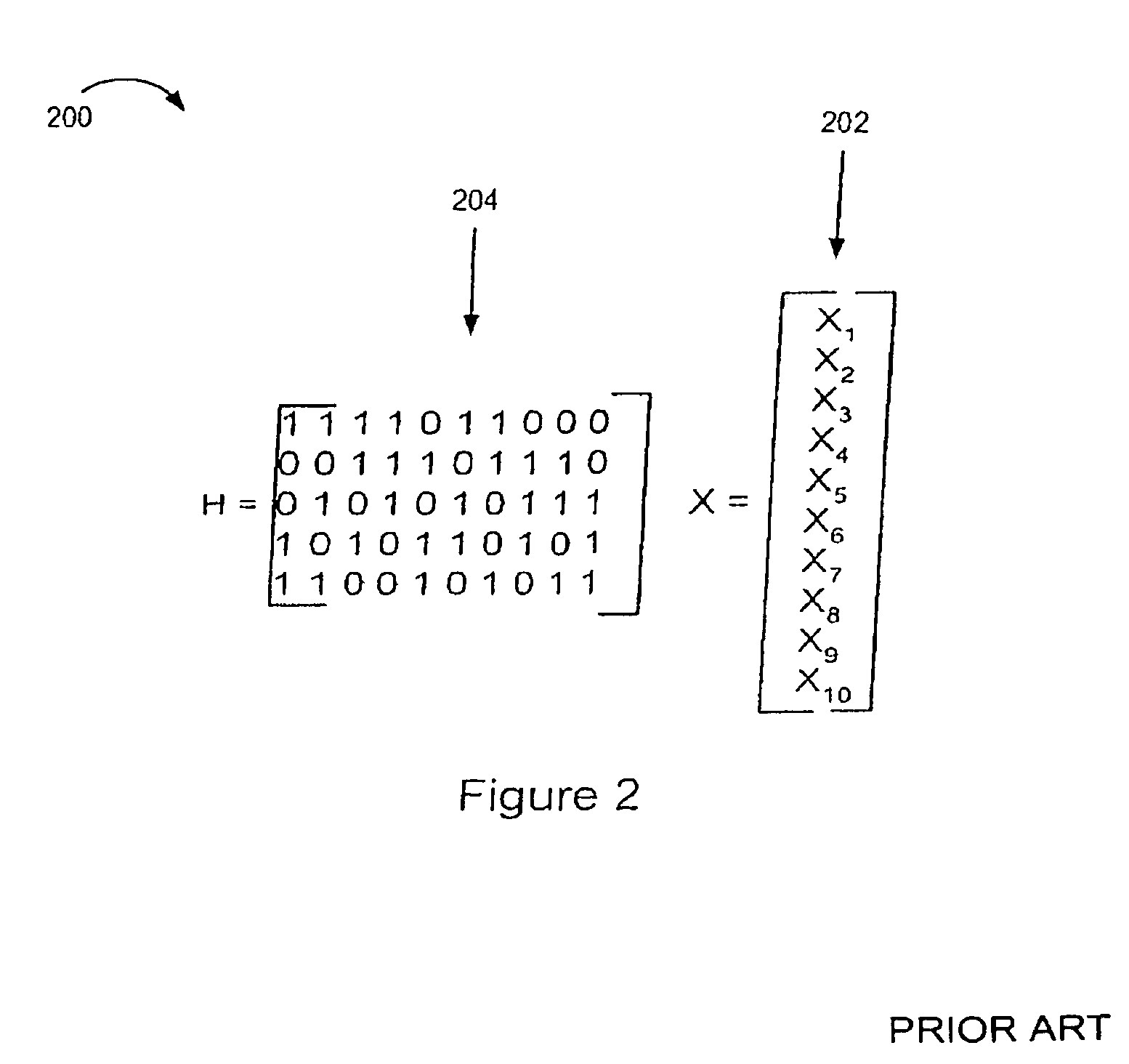

A method for low-density parity-check (LDPC) encoding of data comprises defining a first M×N parity check matrix; generating, based on the first parity check matrix, a second parity check matrix having an M×M triangular sub-matrix; and, mapping the data into an LDPC code word based on the second parity check matrix. The method is particularly useful for data communications applications, but may also be employed in other applications such as, for example, data storage.

Owner:GLOBALFOUNDRIES US INC

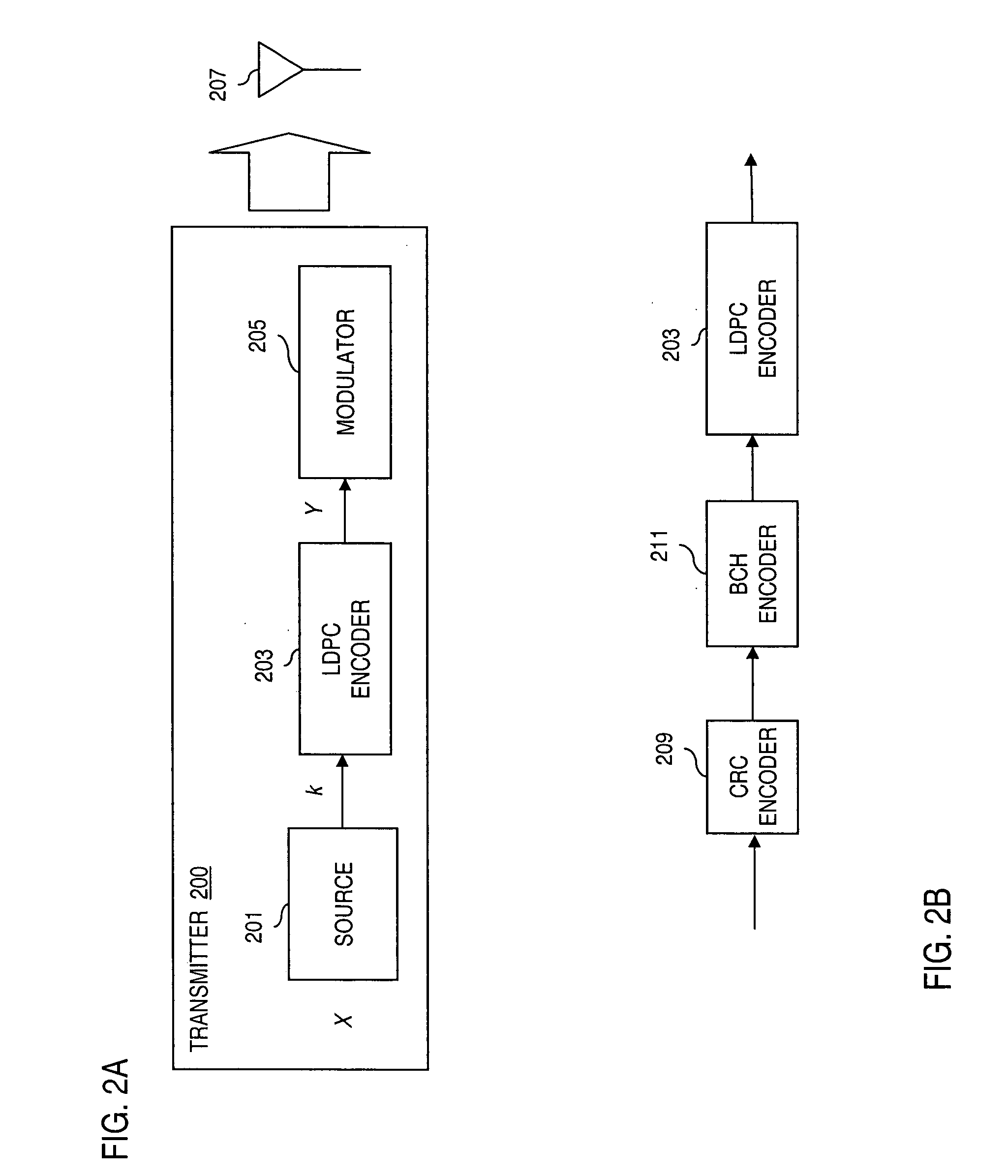

Method and system for providing low density parity check (LDPC) encoding

ActiveUS7191378B2Readily apparentInterconnection arrangementsError correction/detection using LDPC codesAlgorithmParity-check matrix

An approach is provided for a method of encoding structure Low Density Parity Check (LDPC) codes. Memory storing information representing a structured parity check matrix of Low Density Parity Check (LDPC) codes is accessed during the encoding process. The information is organized in tabular form, wherein each row represents occurrences of one values within a first column of a group of columns of the parity check matrix. The rows correspond to groups of columns of the parity check matrix, wherein subsequent columns within each of the groups are derived according to a predetermined operation. An LDPC coded signal is output based on the stored information representing the parity check matrix.

Owner:DTVG LICENSING INC

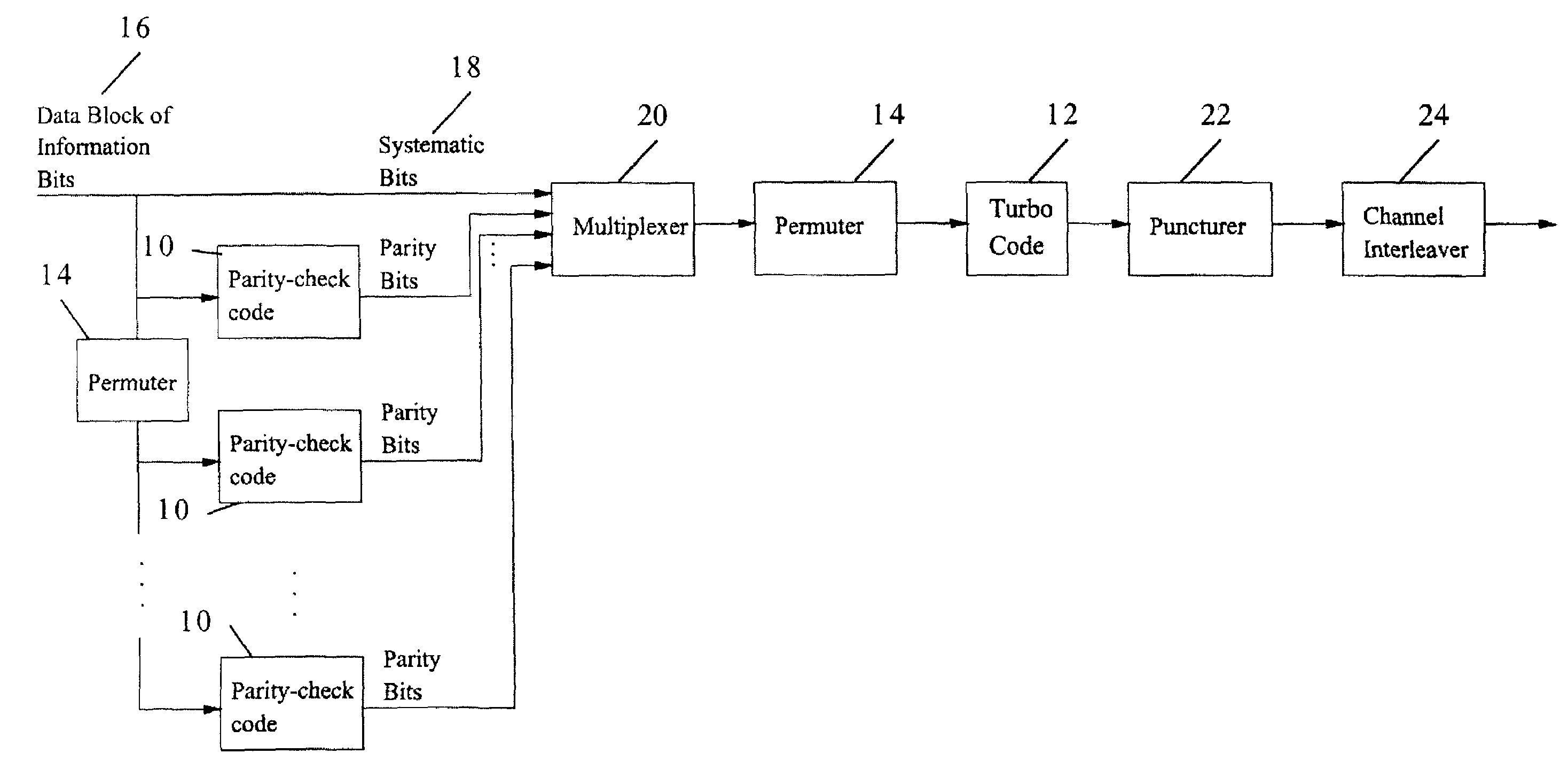

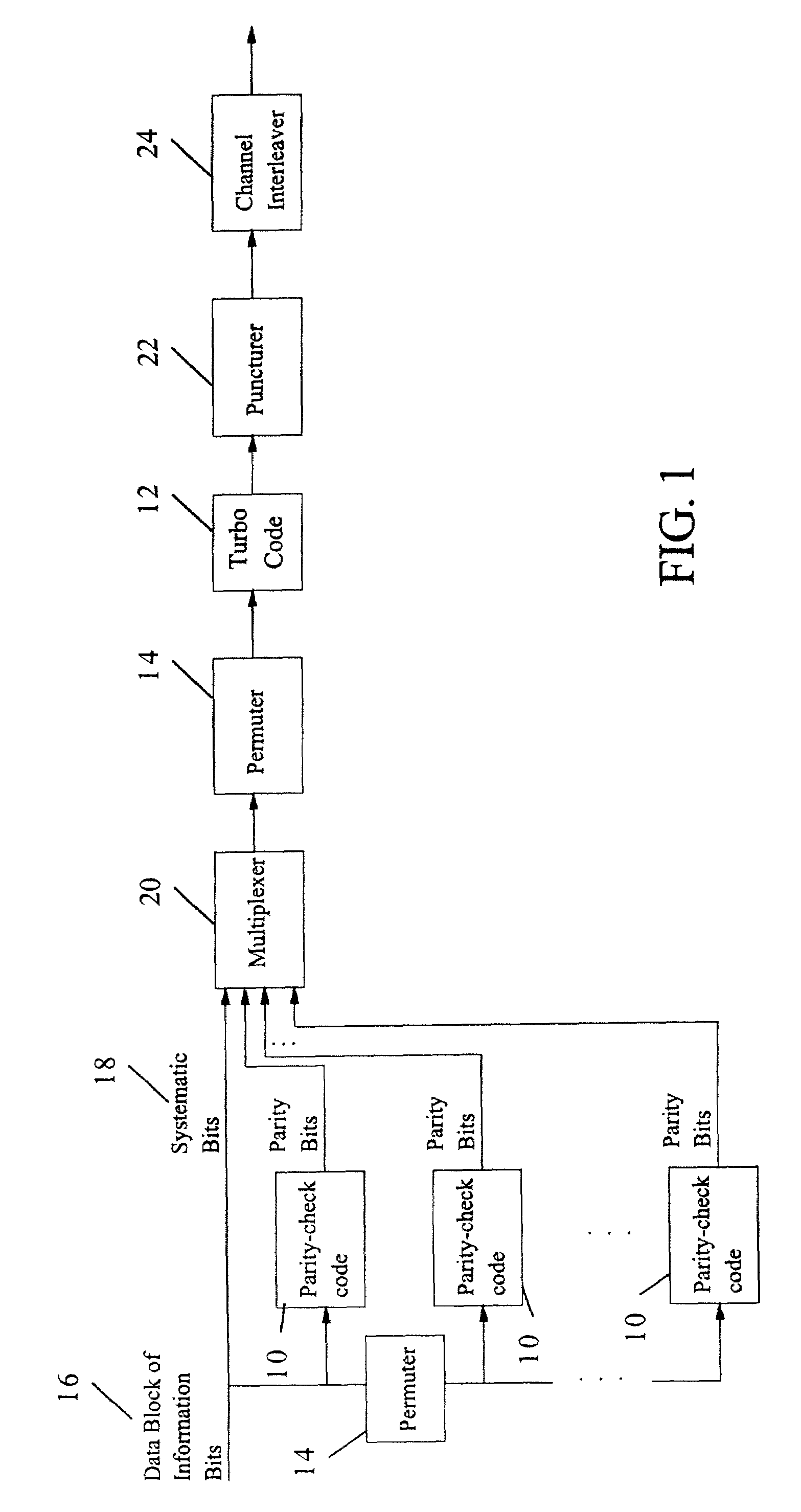

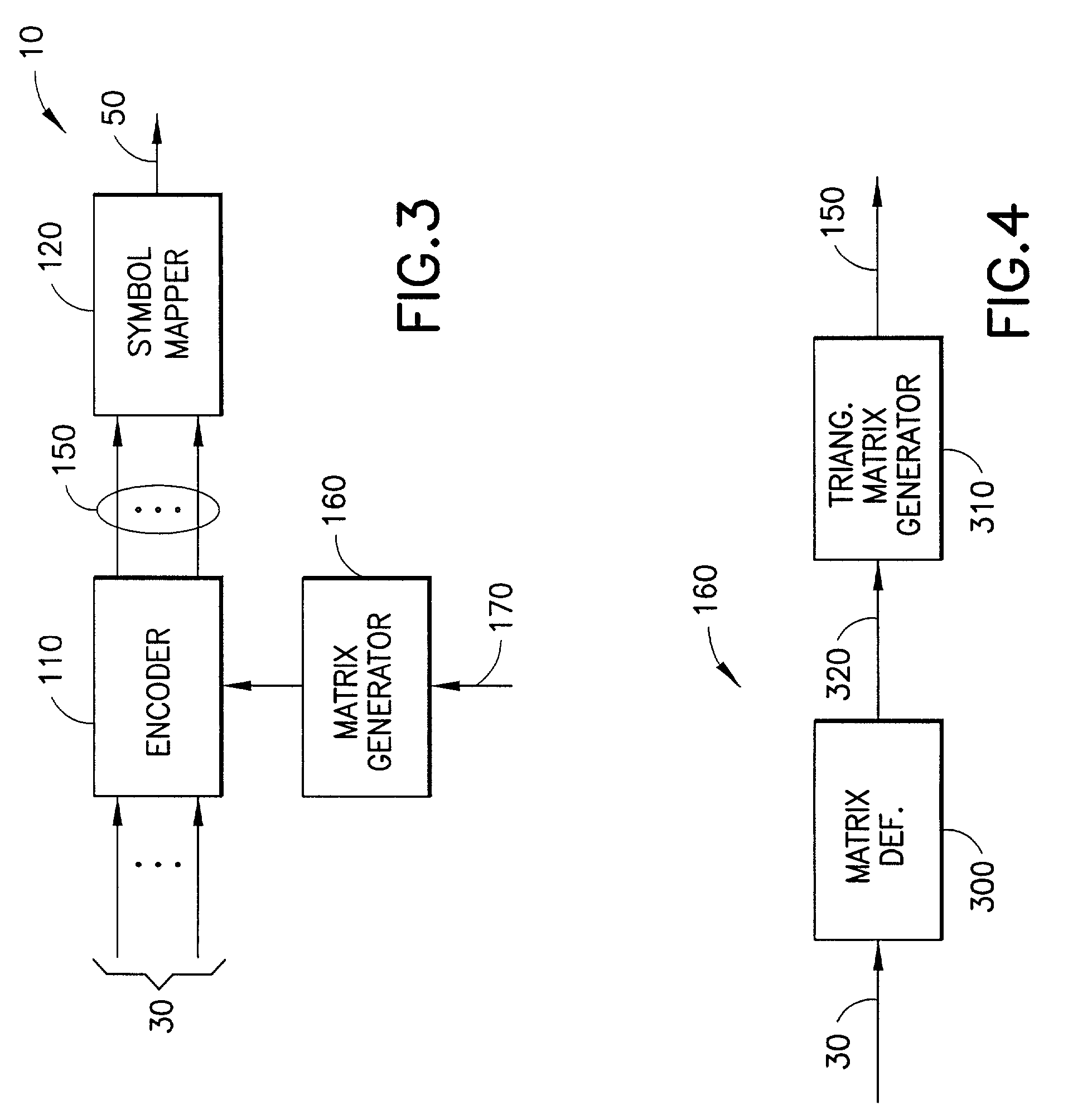

Method and coding means for error-correction utilizing concatenated parity and turbo codes

InactiveUS7093179B2Reduction in rateImprove overall utilizationError preventionError detection/correctionParallel computingTurbo coded

A method and apparatus for encoding and decoding data using an overall code comprising an outer parity-check and an inner parallel concatenated convolutional, or turbo code. The overall code provides error probabilities that are significantly lower than can be achieved by using turbo codes alone. The output of the inner code can be punctured to maintain the same turbo code rate as the turbo code encoding without the outer code. Multiple parity-check codes can be concatanated either serially or in parallel as outer codes. Decoding can be performed with iterative a posteriori probability (APP) decoders or with other decoders, depending on the requirements of the system. The parity-check code can be applied to a subset of the bits to achieve unequal error protection. Moreover, the techniques presented can be mapped to higher order modulation schemes to achieve improved power and bandwidth efficiency.

Owner:FLORIDA UNIV OF A FLORIDA +1

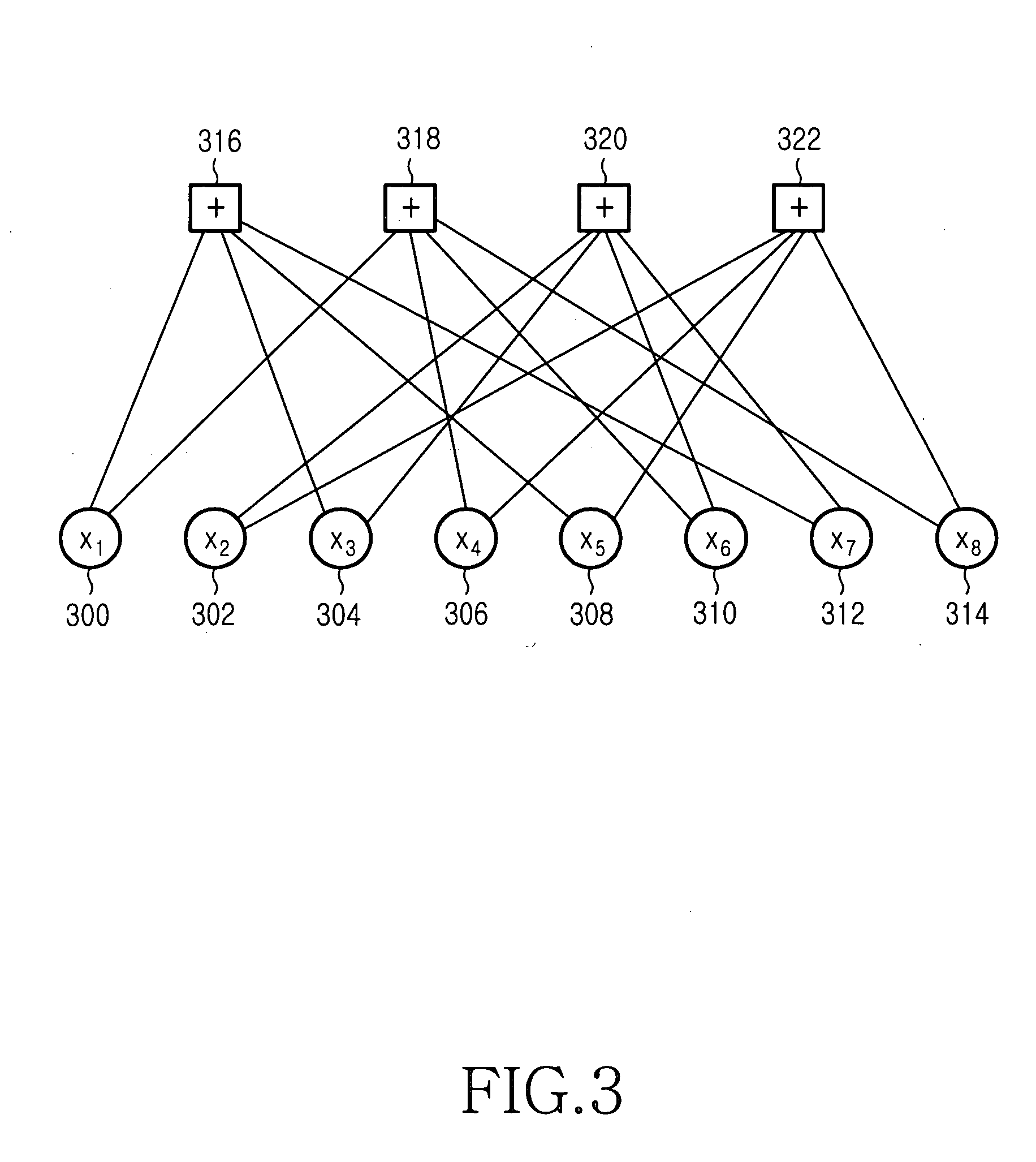

Encoding method using a low density parity check code with a column weight of two

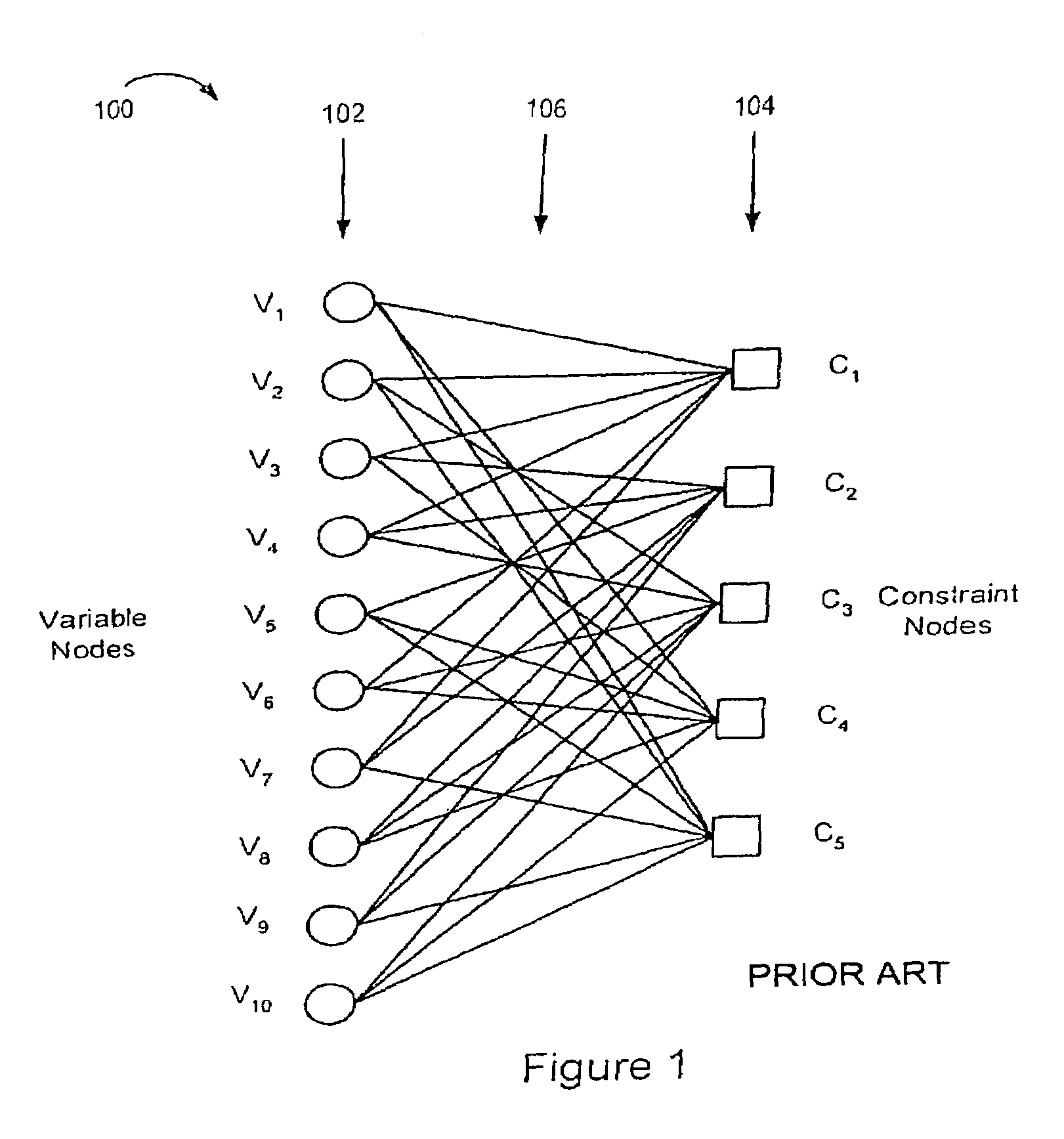

ActiveUS7058873B2Facilitate the processOther decoding techniquesError correction/detection using multiple parity bitsTanner graphCommunications system

A method for communicating binary data and a digital communication system are presented. According to one embodiment, the method includes encoding a message word by multiplying the message word with a generator matrix, wherein the generator matrix multiplied by the transpose of a parity check matrix for a low density parity check code yields a null set, and wherein the parity check matrix has a column weight of two. Additionally disclosed is an encoding scheme based on a three-tier Tanner graph having a girth of twelve.

Owner:CARNEGIE MELLON UNIV

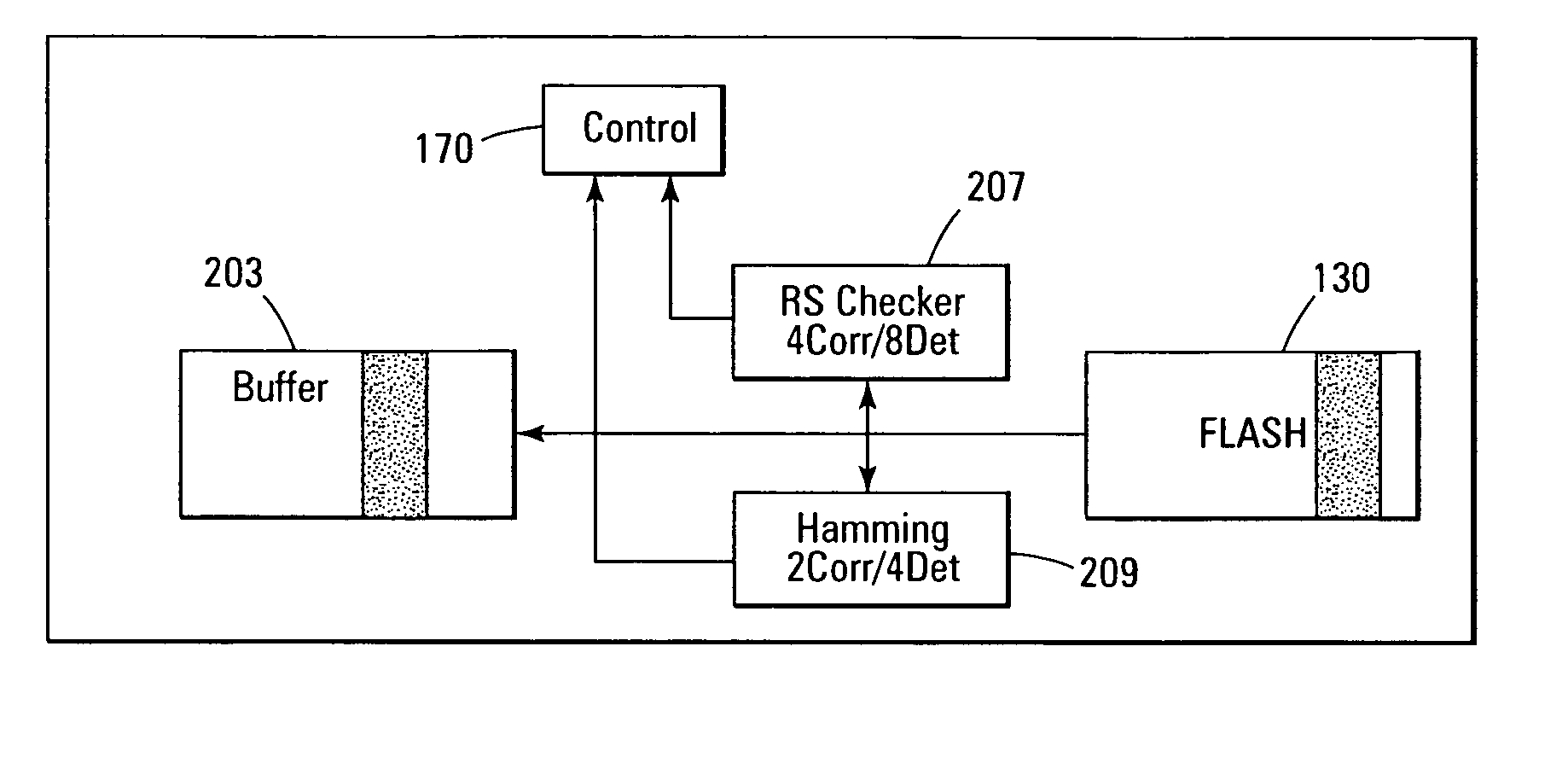

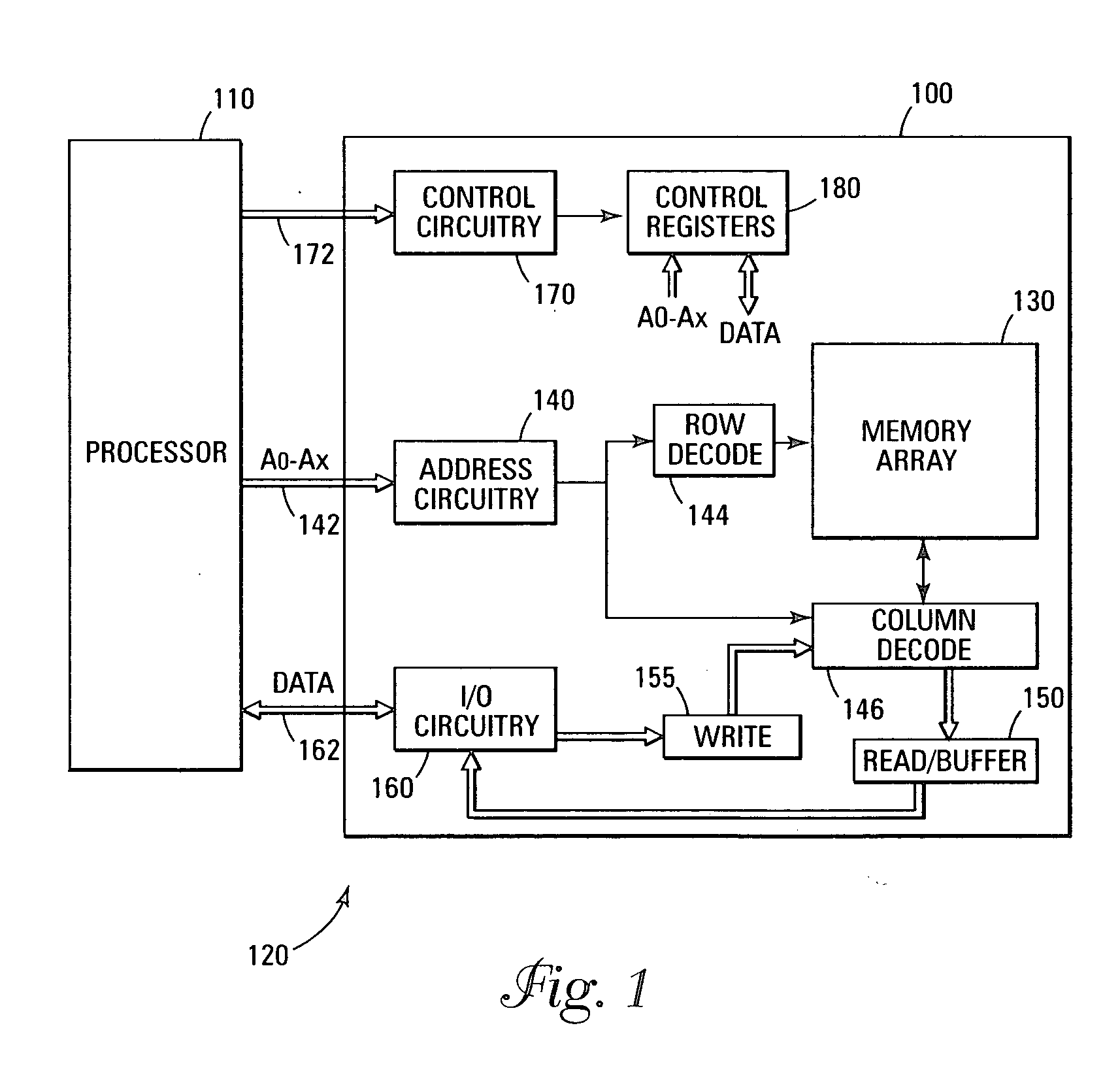

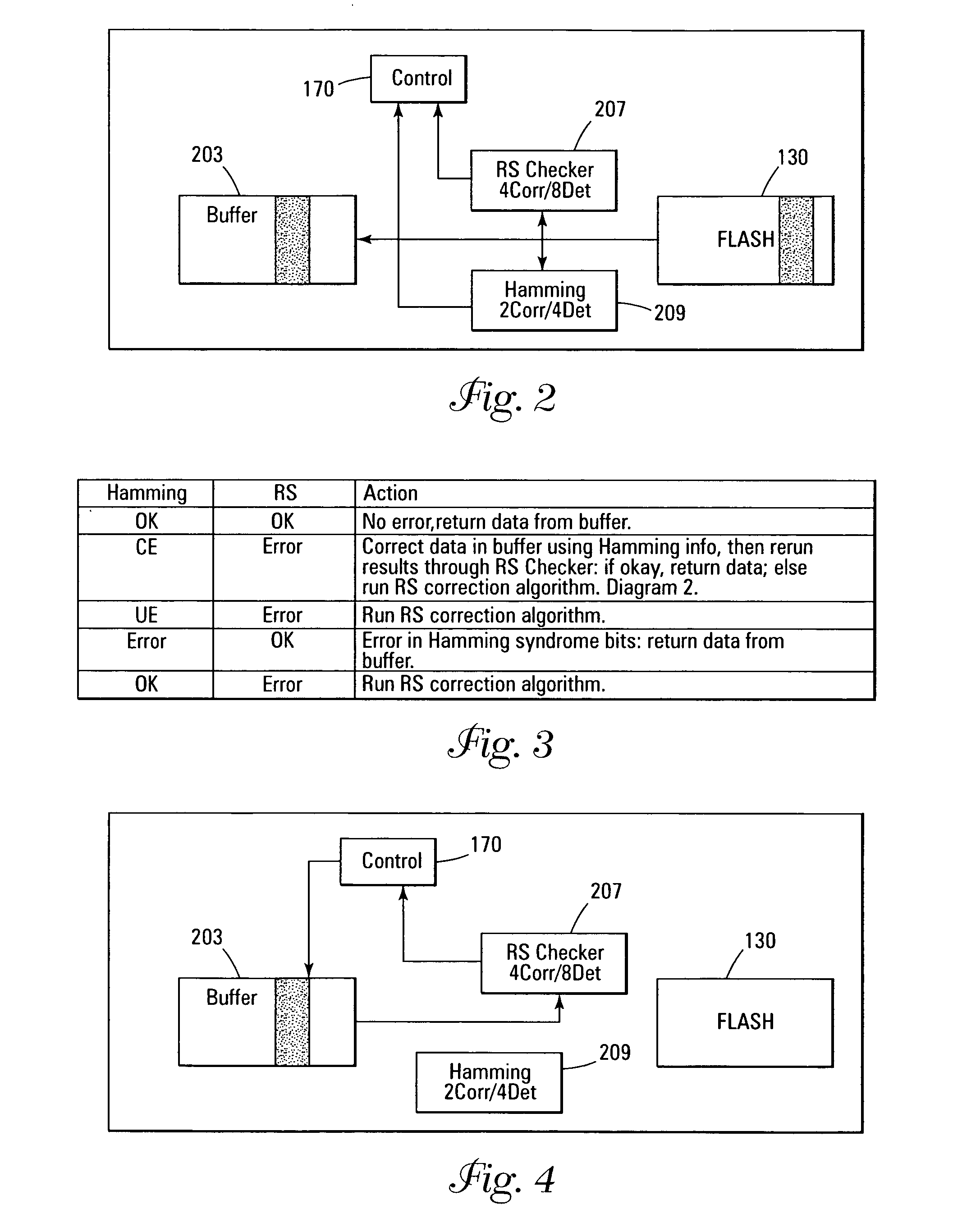

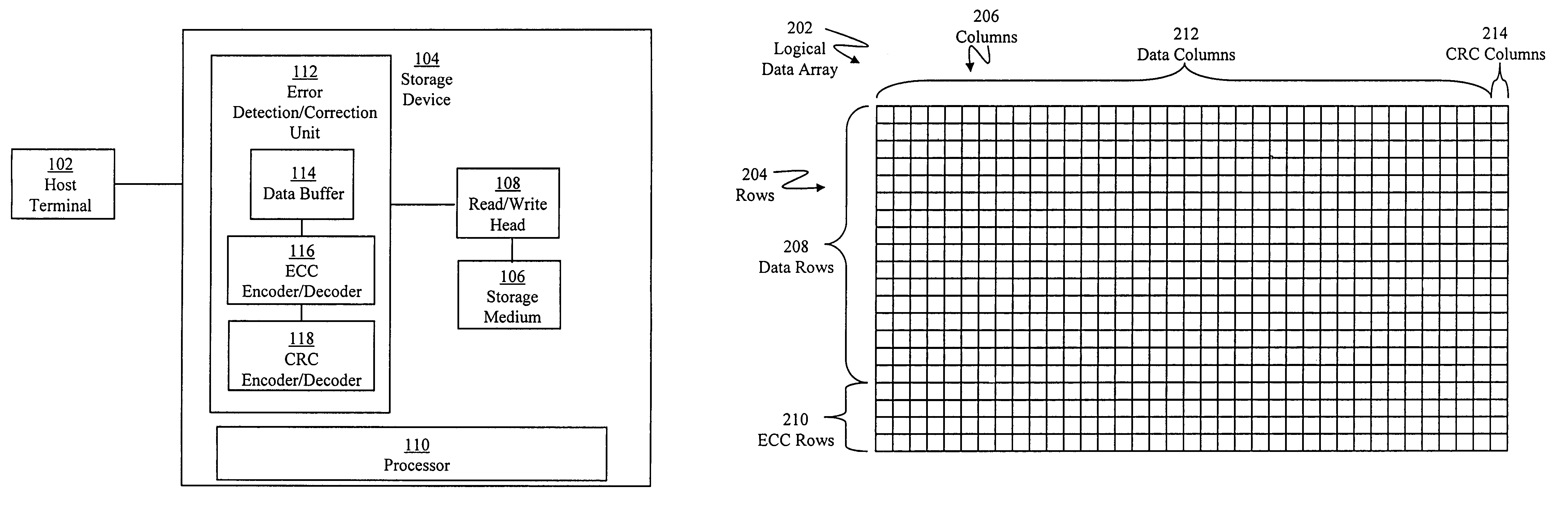

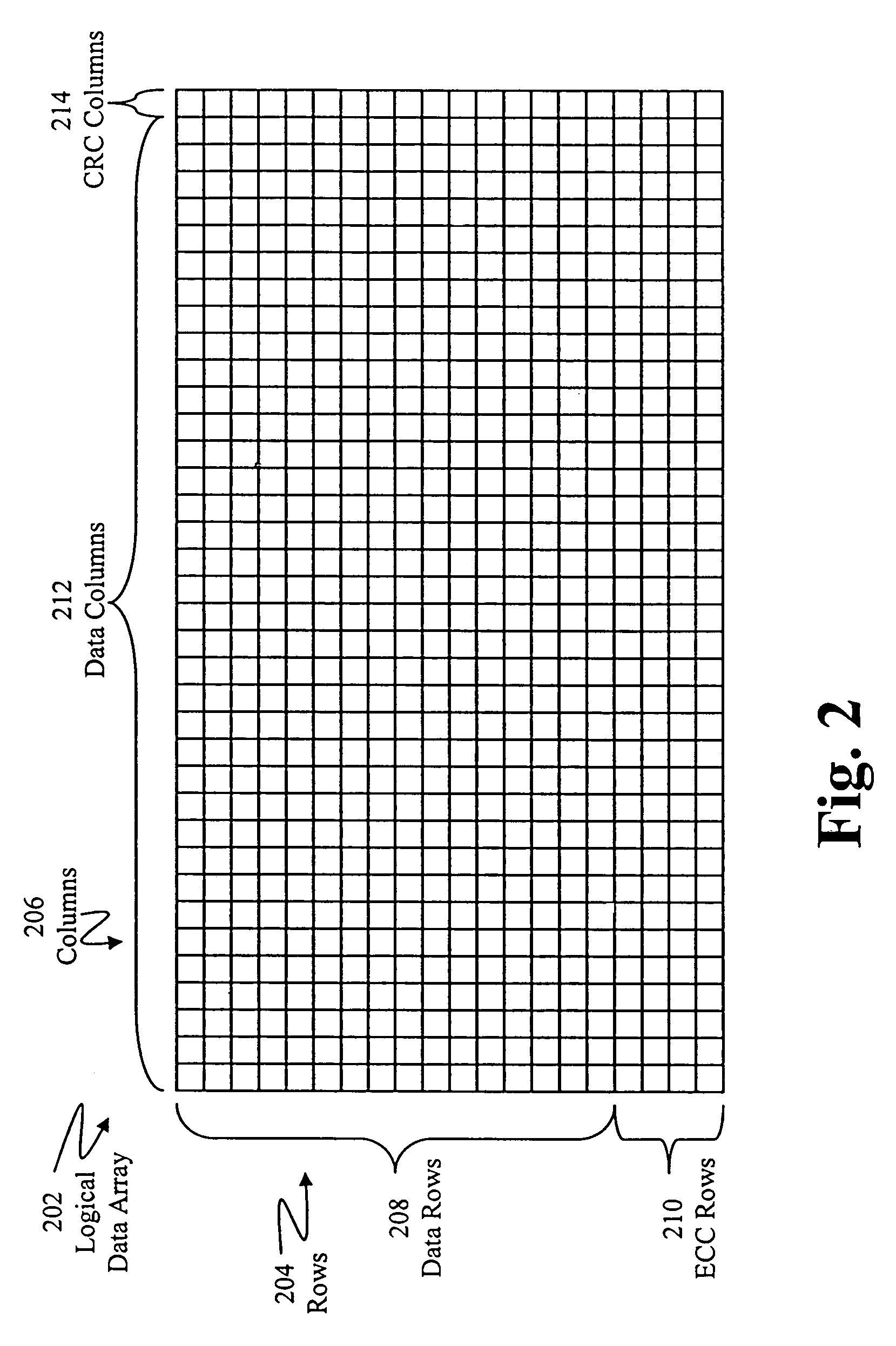

Error detection and correction scheme for a memory device

ActiveUS20050172207A1Code conversionError correction/detection by combining multiple code structuresHamming codeCorrection code

Data is read from a memory array. Before being stored in a data buffer, a Hamming code detection operation and a Reed-Solomon code detection operation are operated in parallel to determine if the data word has any errors. The results of the parallel detection operations are communicated to a controller circuit. If an error is present that can be corrected by the Hamming code correction operation, this is performed and the Reed-Solomon code detection operation is performed on the corrected word. If the error is uncorrectable by the Hamming code, the Reed-Solomon code correction operation is performed on the word.

Owner:MICRON TECH INC

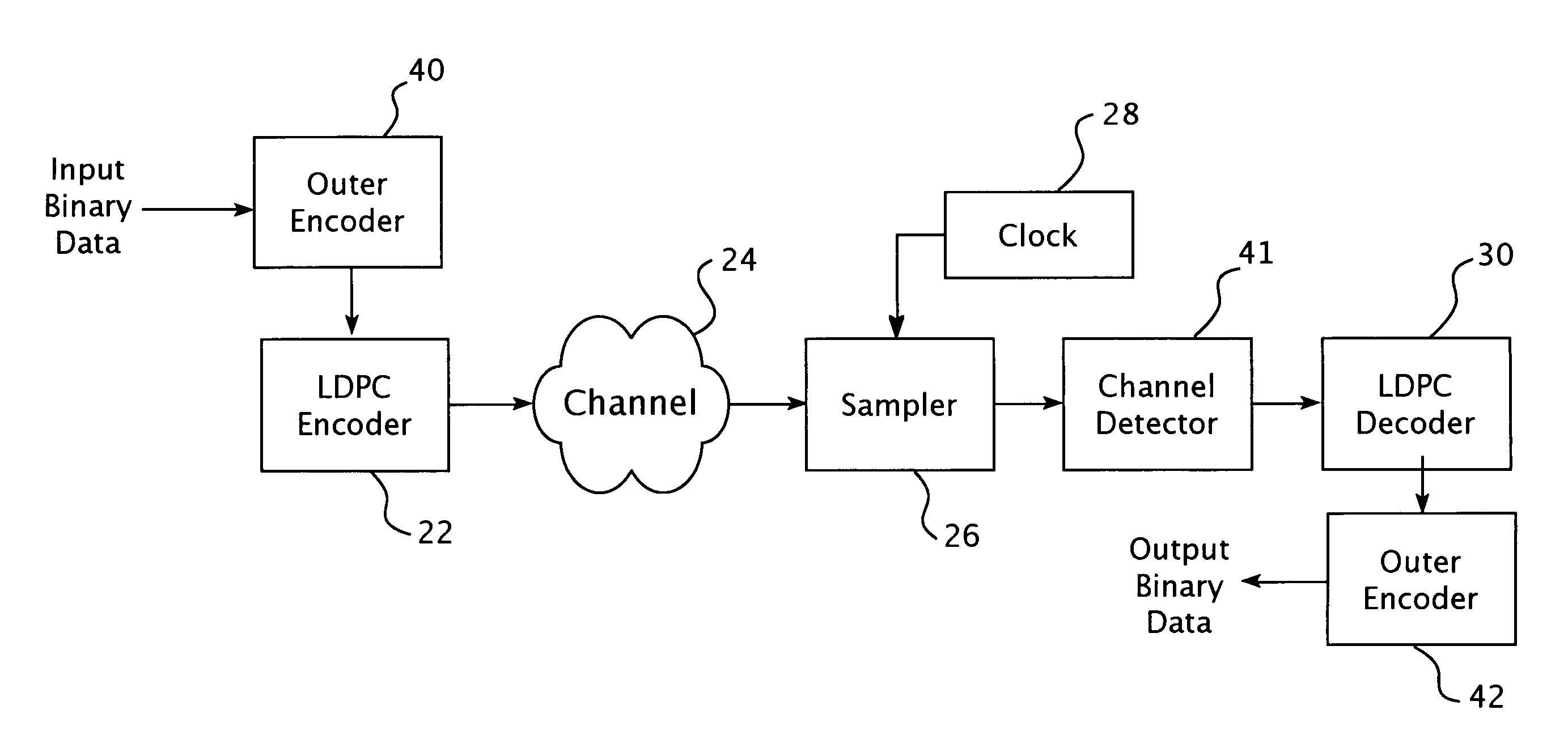

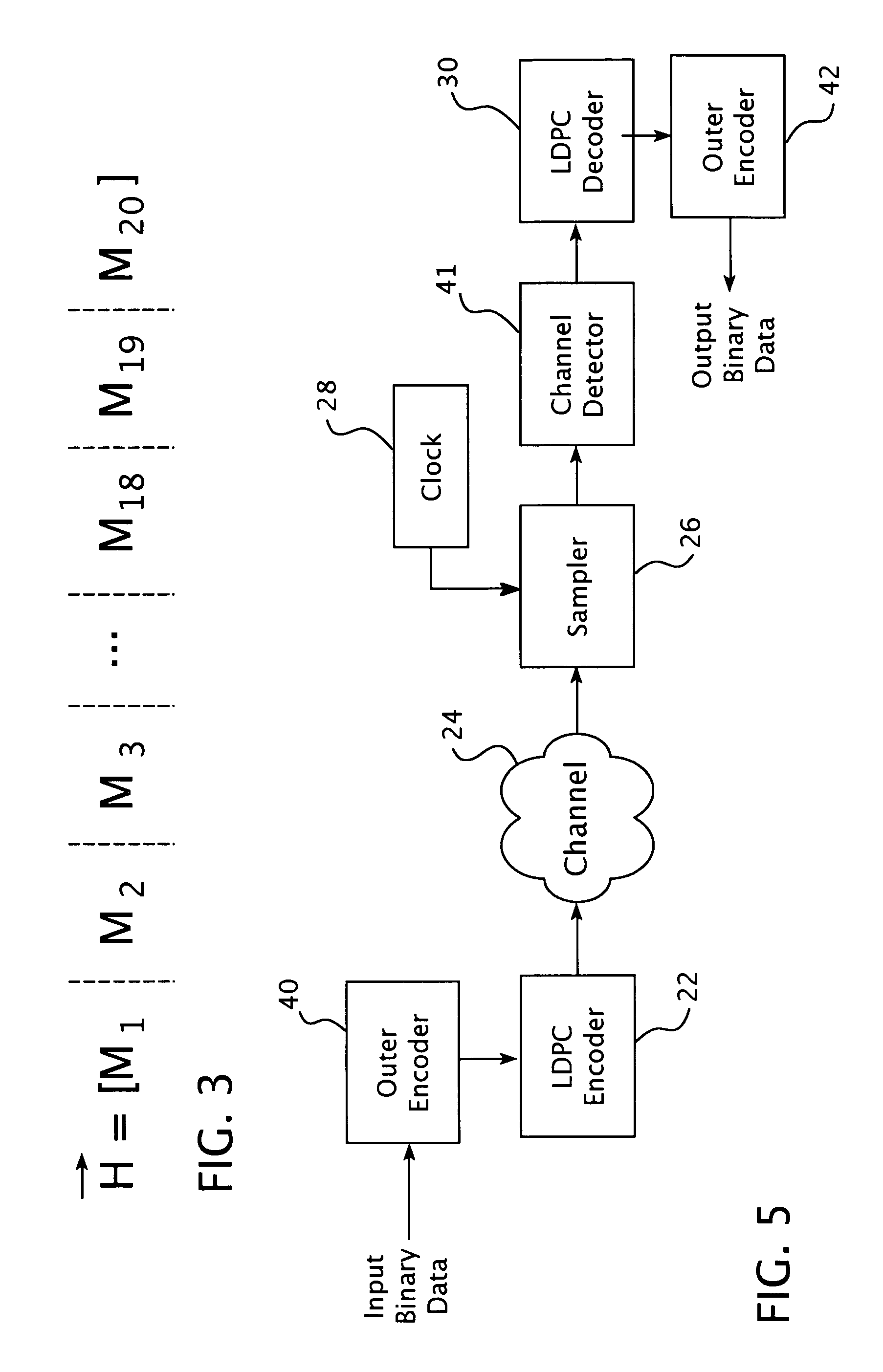

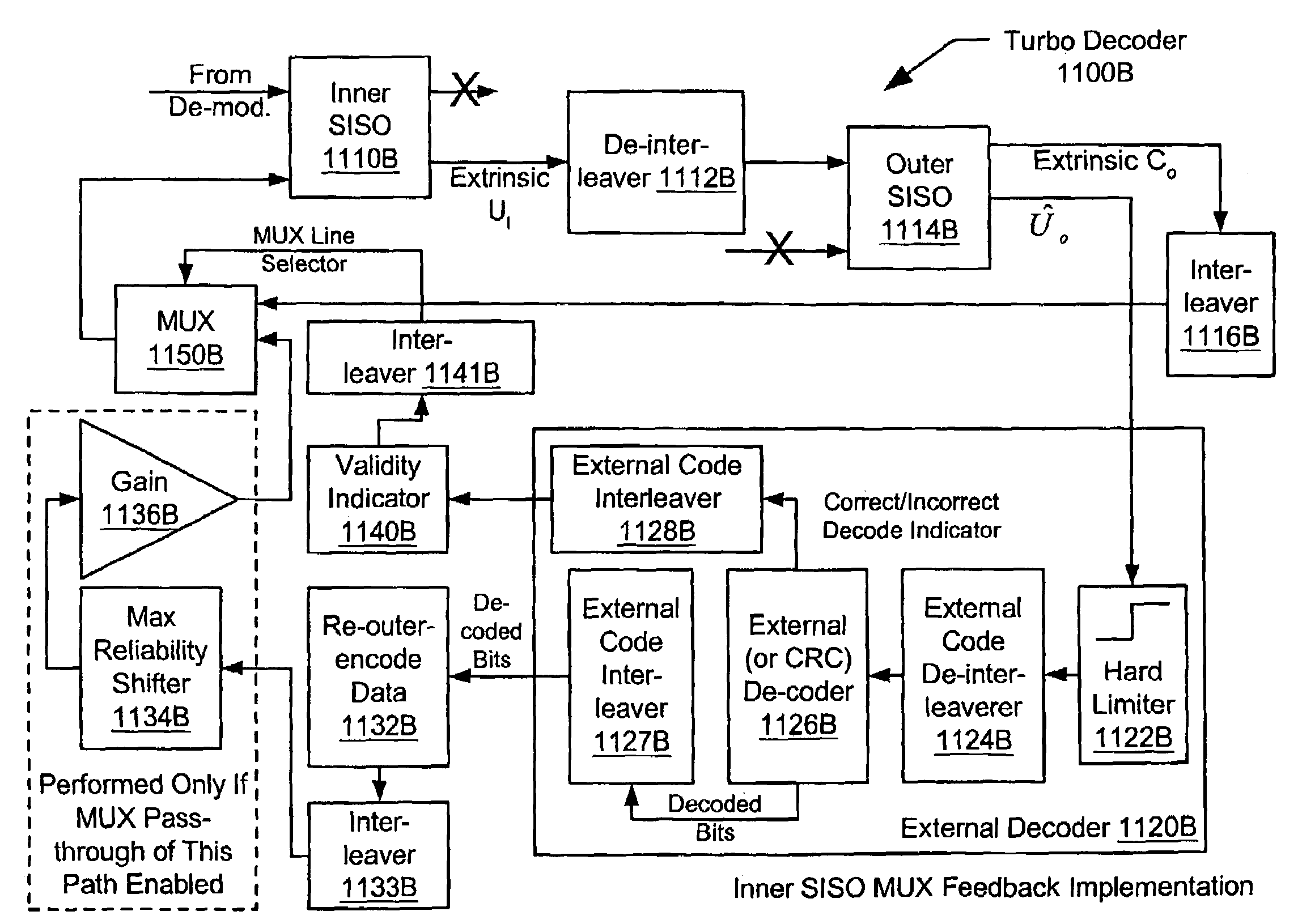

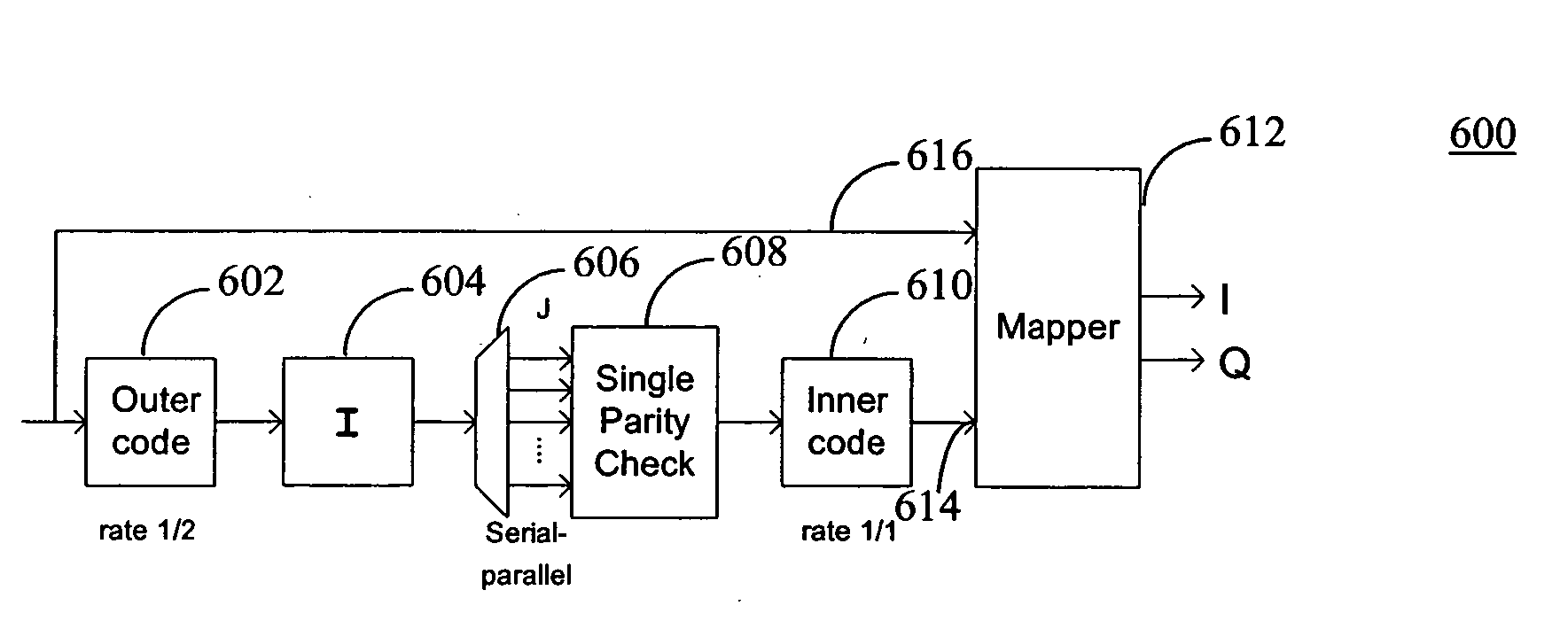

Iterative decoder employing multiple external code error checks to lower the error floor

InactiveUS7310768B2Code conversionError correction/detection by combining multiple code structuresError checkDegree of certainty

Owner:ENTROPIC COMM INC

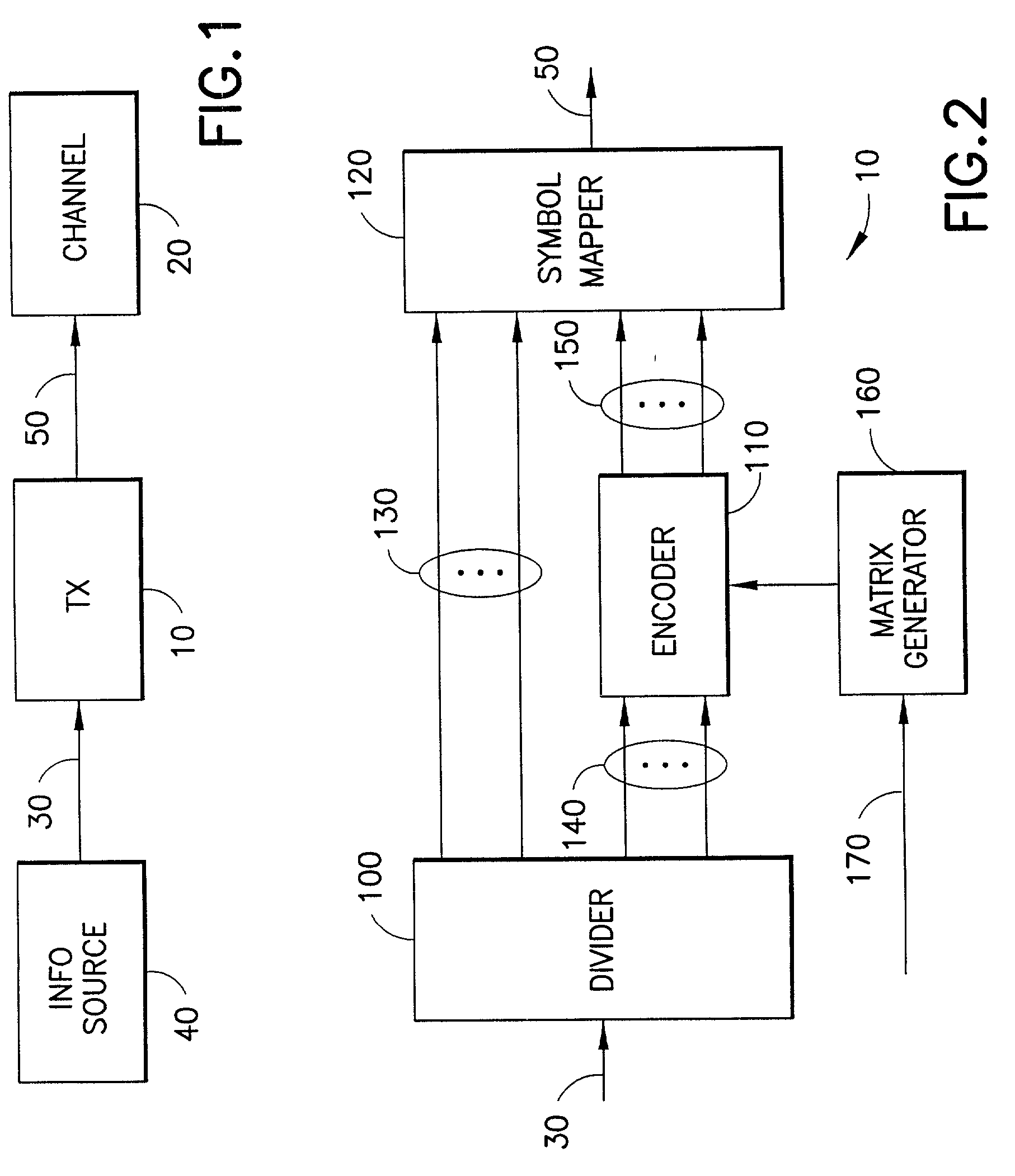

Multi-stage code generator and decoder for communication systems

InactiveUS7068729B2Reduce expensesOther decoding techniquesOther error detection/correction/protectionCommunications systemOrder set

Owner:QUALCOMM INC

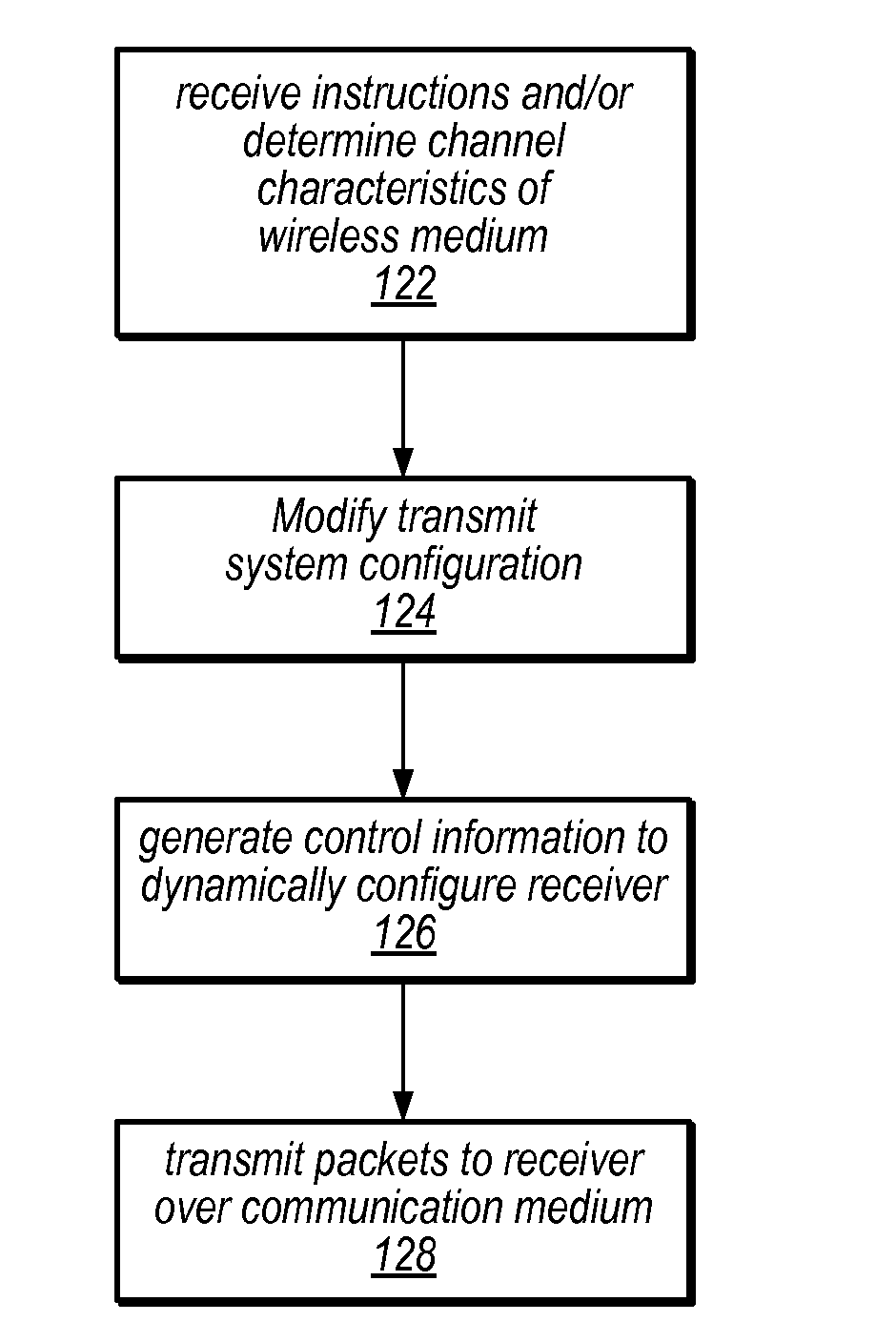

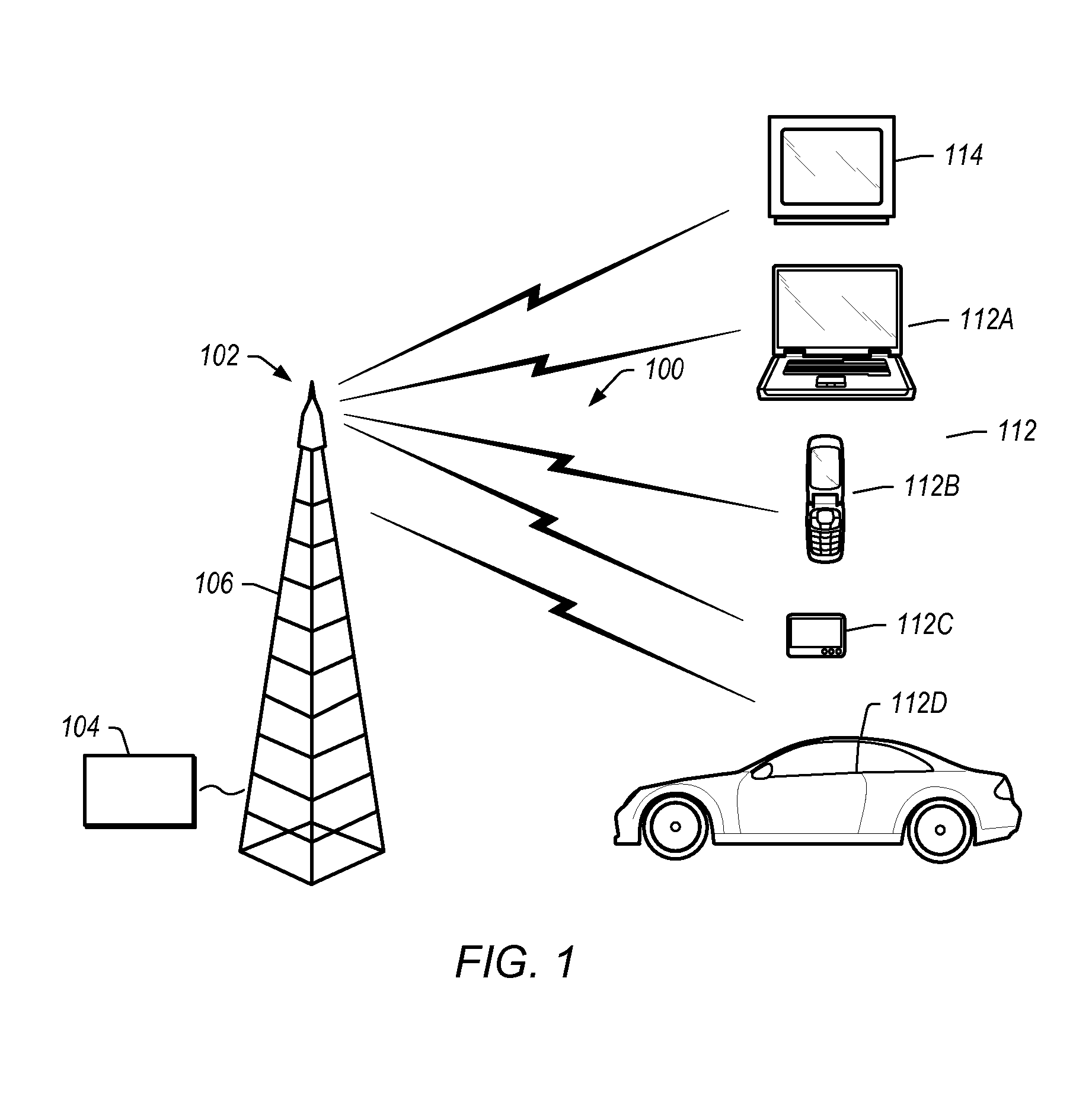

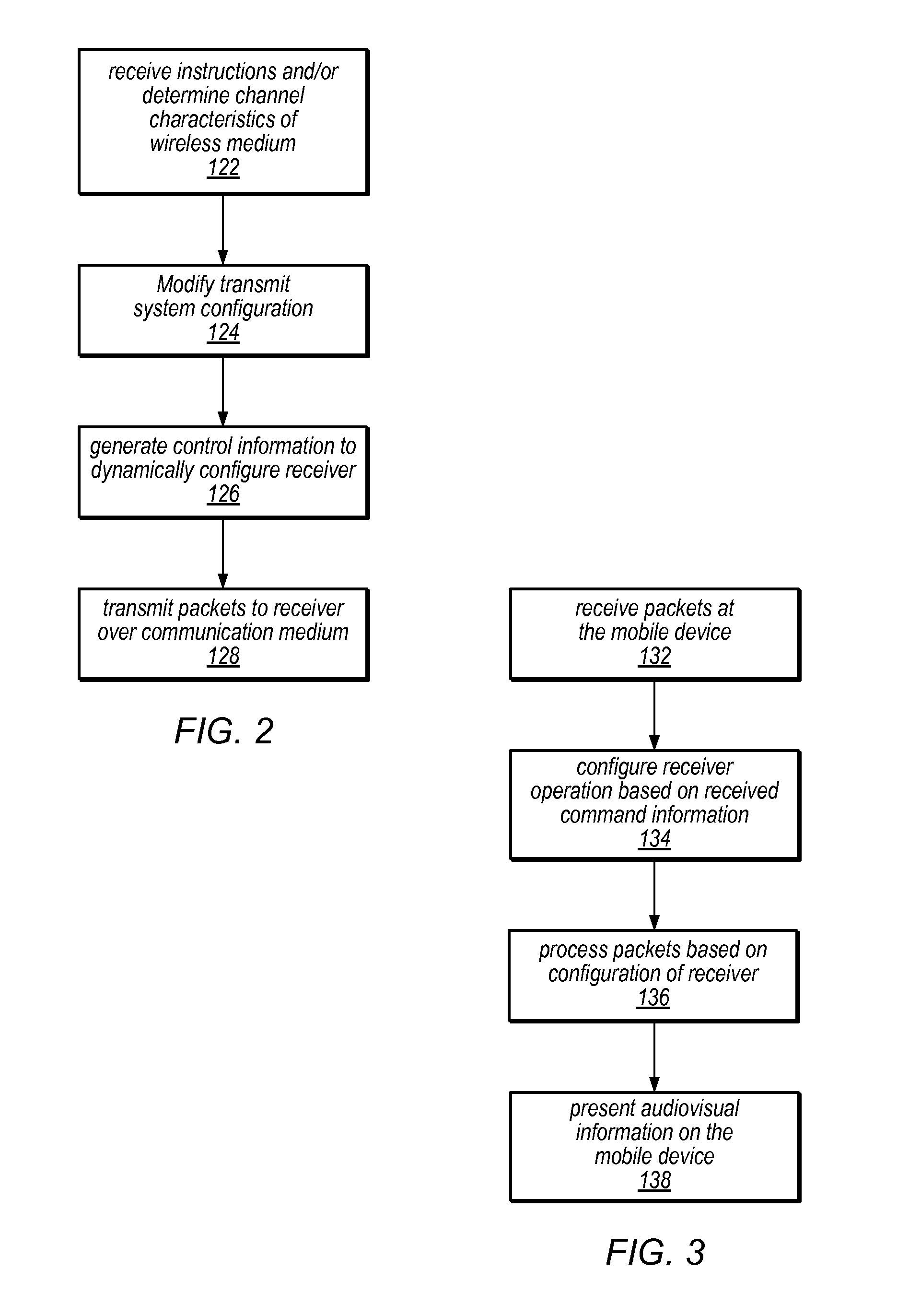

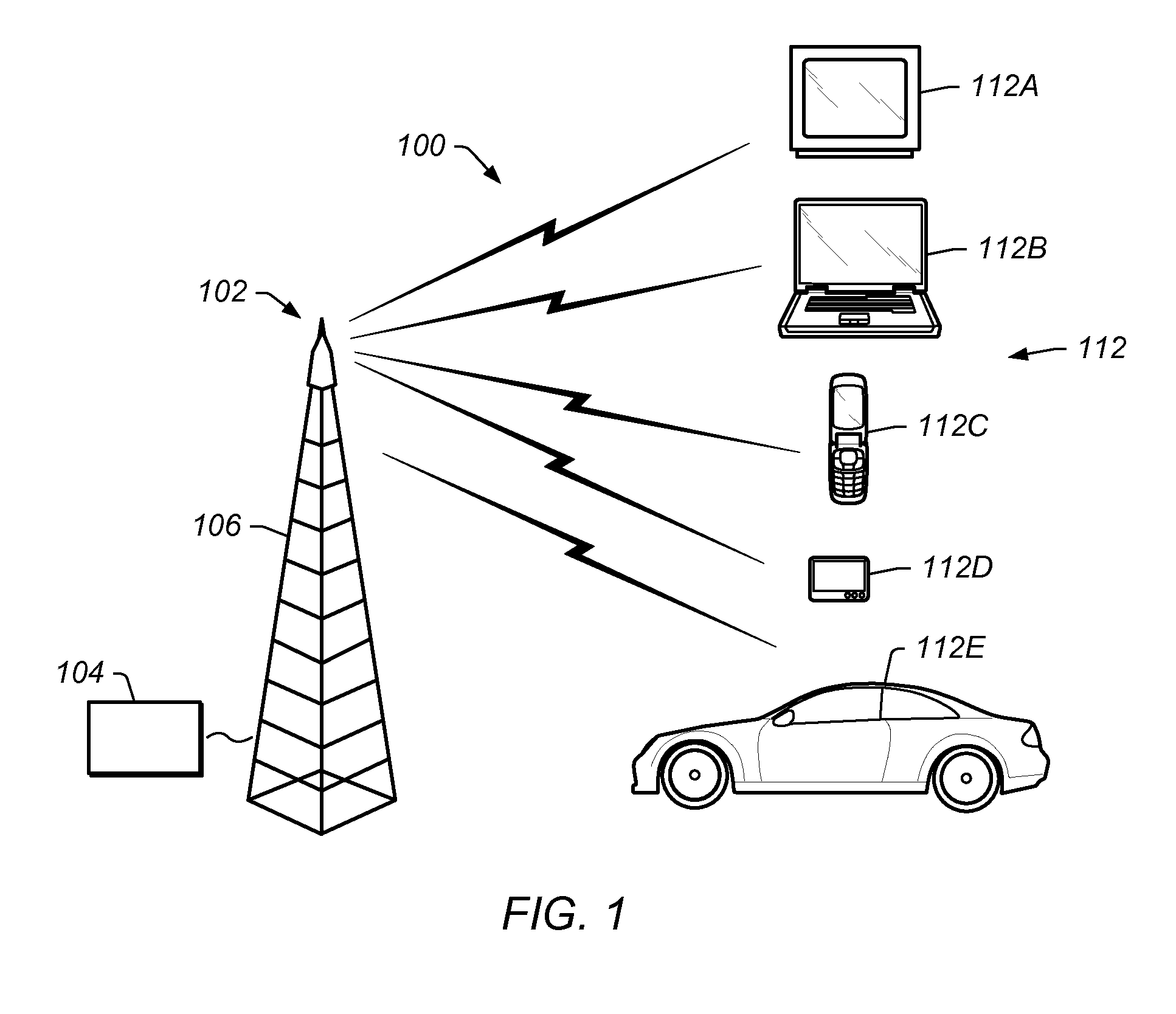

Mobile television broadcast system

ActiveUS20090013356A1Efficiently specifiedFunction increaseCode conversionError correction/detection by combining multiple code structuresCurrent channelSystem configuration

A digital television broadcast system with transmission and / or reception of digital television signals for improved mobile reception. The communication layers in the transmit and receive portions of the transmission system can be dynamically modified, e.g., based on usage patterns or current channel characteristics. The transmission system also provides for cross layer control, whereby parameters in various of the communication layers are analyzed to determine appropriate updates to the system configuration.

Owner:COHERENT LOGIX

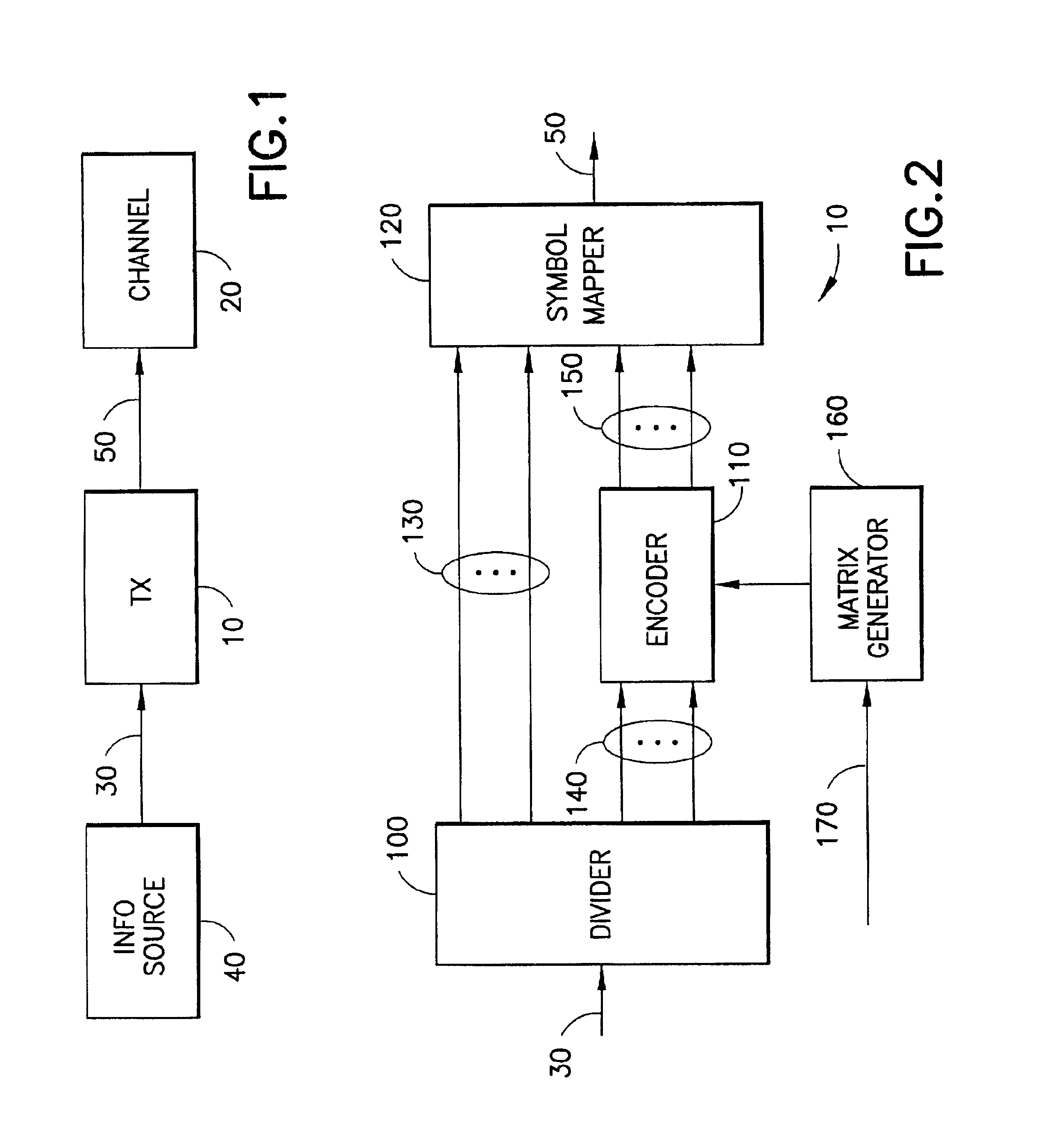

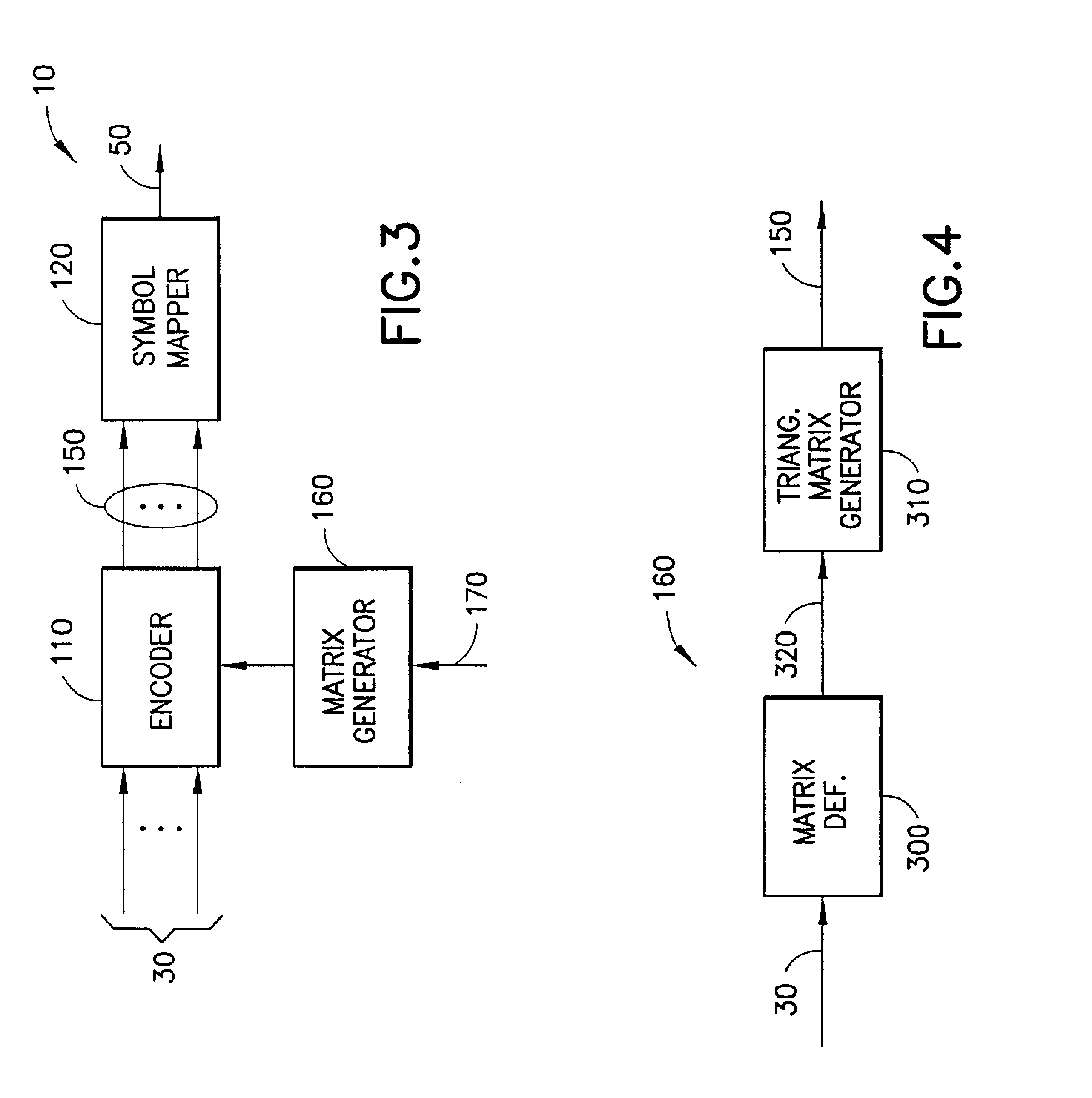

Method and apparatus for low density parity check encoding of data

InactiveUS20030037298A1Improve performanceError preventionError detection/correctionParity-check matrixTheoretical computer science

A method for low-density parity-check (LDPC) encoding of data comprises defining a first MxN parity check matrix; generating, based on the first parity check matrix, a second parity check matrix having an MxM triangular sub-matrix; and, mapping the data into an LDPC code word based on the second parity check matrix. The method is particularly useful for data communications applications, but may also be employed in other applications such as, for example, data storage.

Owner:GLOBALFOUNDRIES US INC

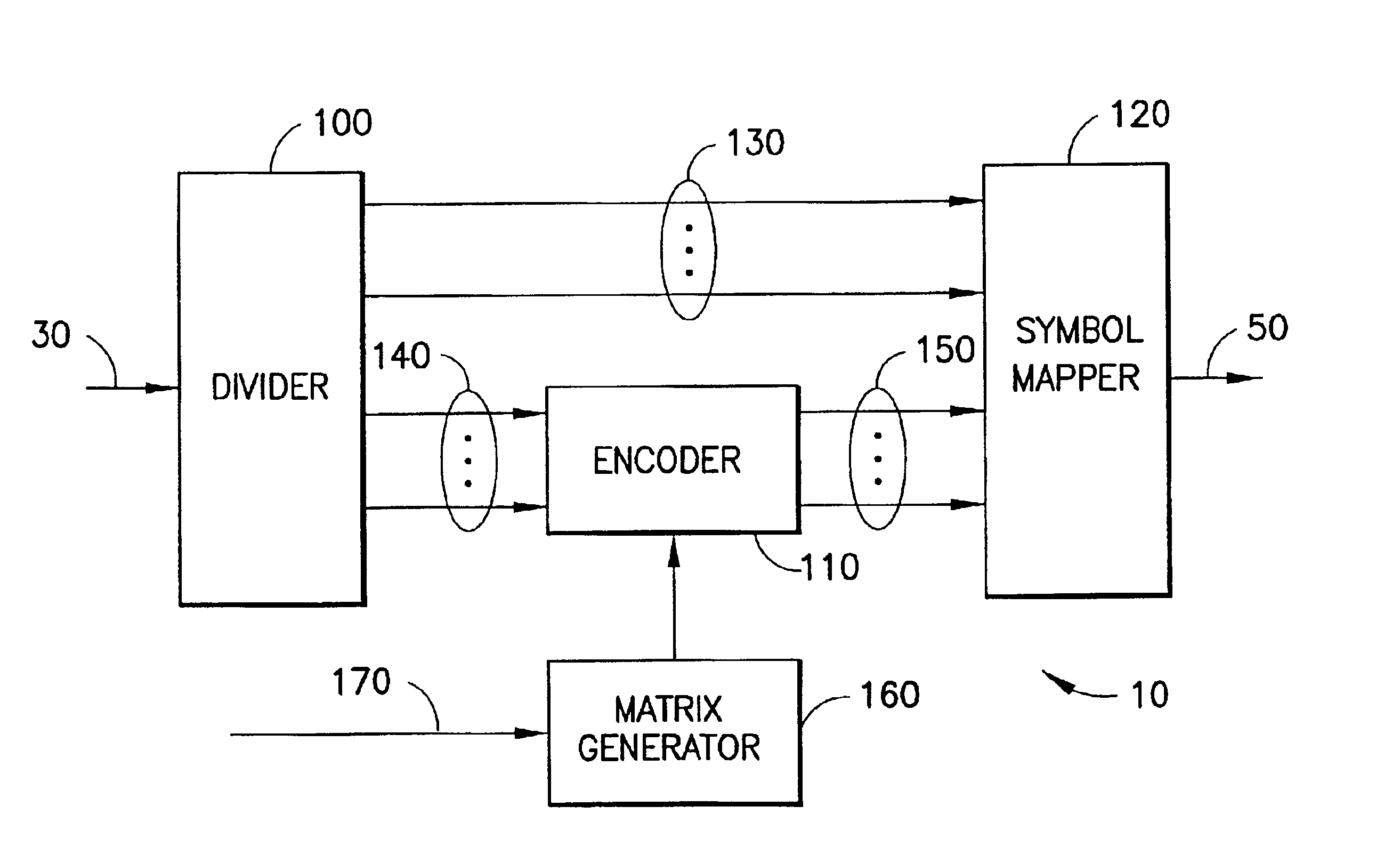

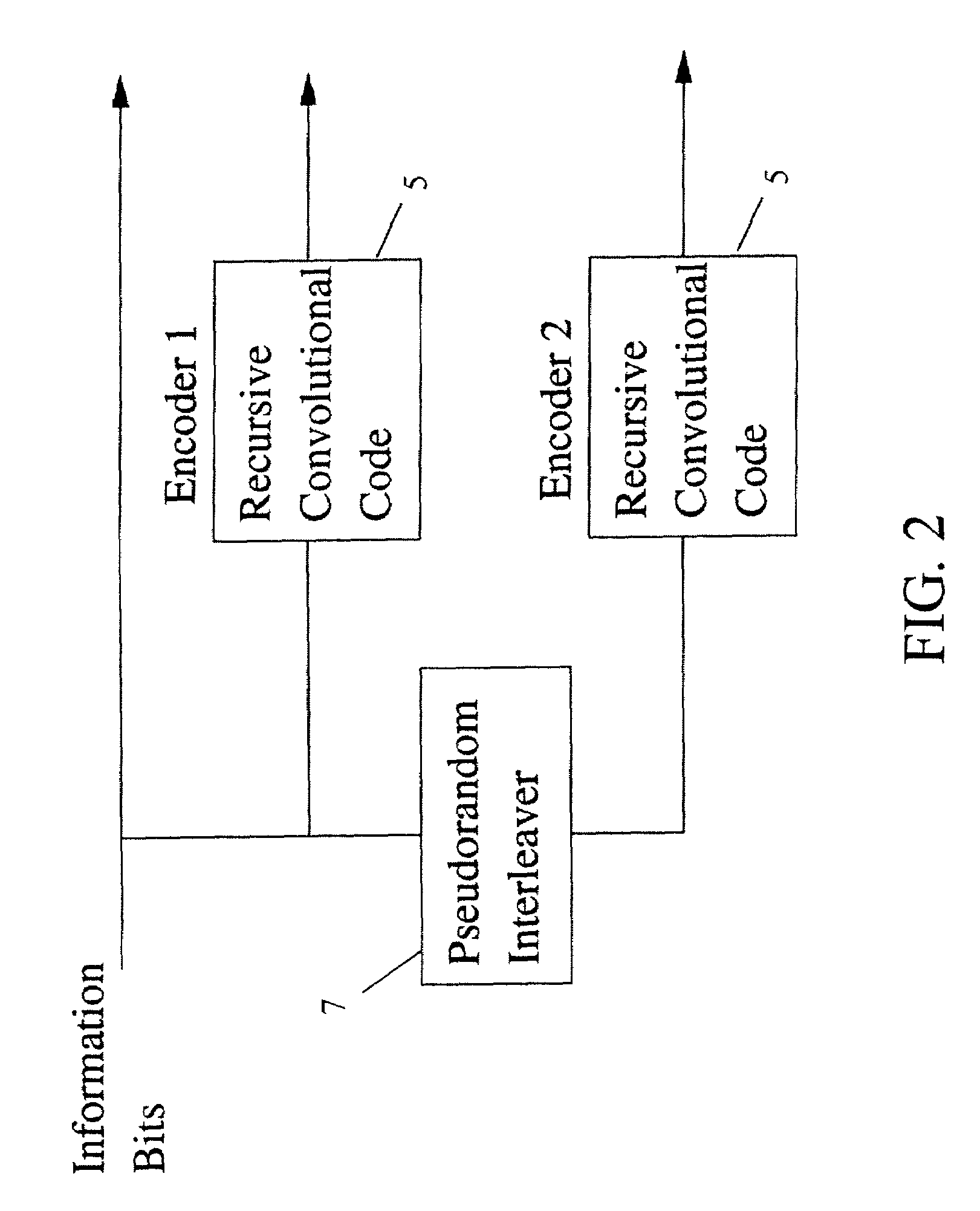

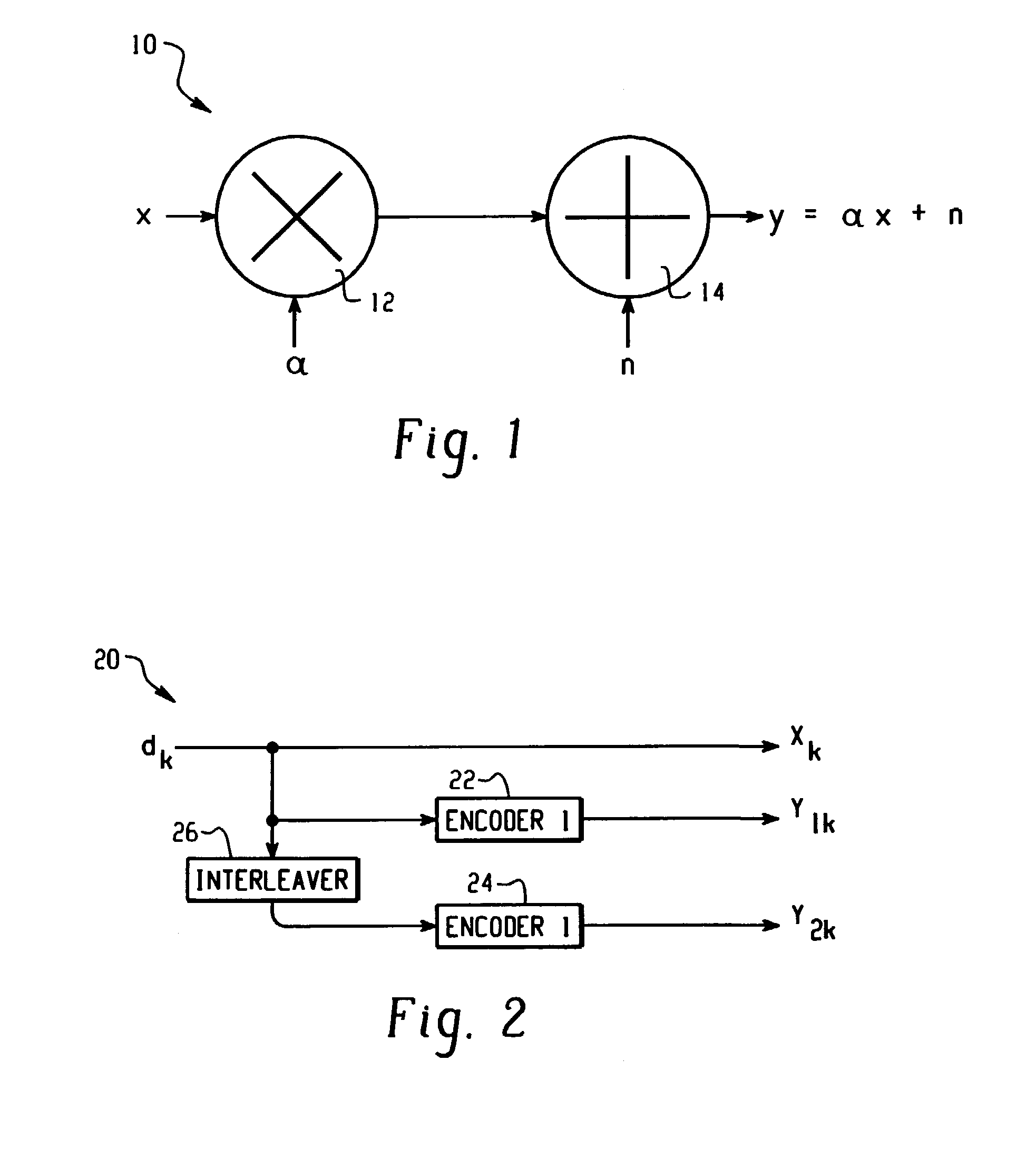

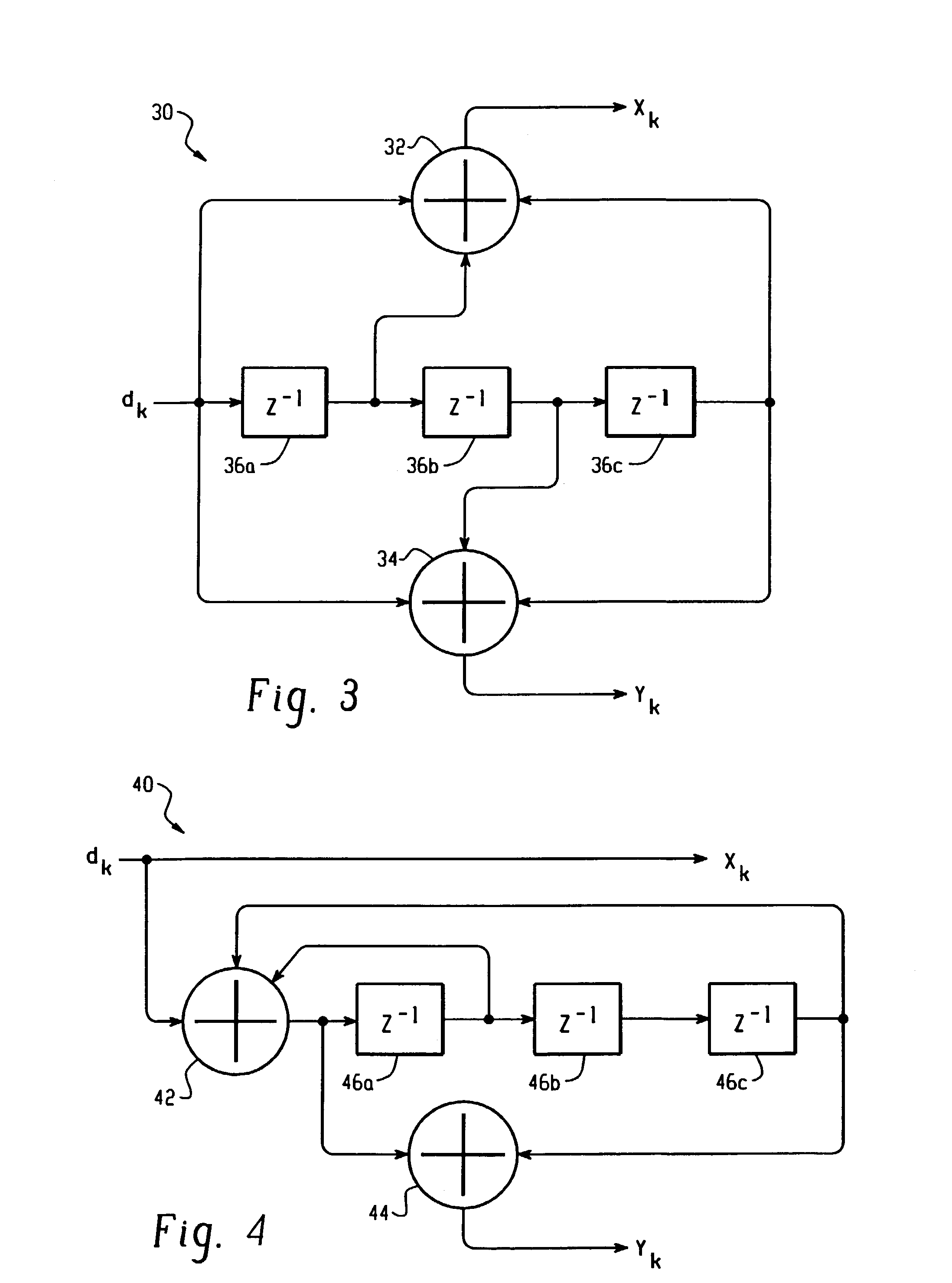

Method and apparatus for communications using turbo like codes

The present invention relates to methods, apparatuses, and systems for performing data encoding involving encoding data bits according to an outer convolutional code to produce outer encoded bits processing the outer encoded bits using an interleaver and a logical unit to produce intermediate bits, wherein the logical unit receives a first number of input bits and produces a second number of corresponding output bits, the second number being less than the first number, and wherein the logical unit takes each of the first number of input bits into account in producing the second number of output bits, encoding the intermediate bits according to an inner convolutional code to produce inner encoded bits, wherein the inner convolutional code is characterized by at least two states, and combining the data bits and the inner encoded bits to produce encoded outputs.

Owner:TRELLIS WARE TECH

Hybrid automatic repeat request system and method

InactiveUS7000174B2Uniform puncturingError prevention/detection by using return channelTransmission systemsTheoretical computer scienceLow density

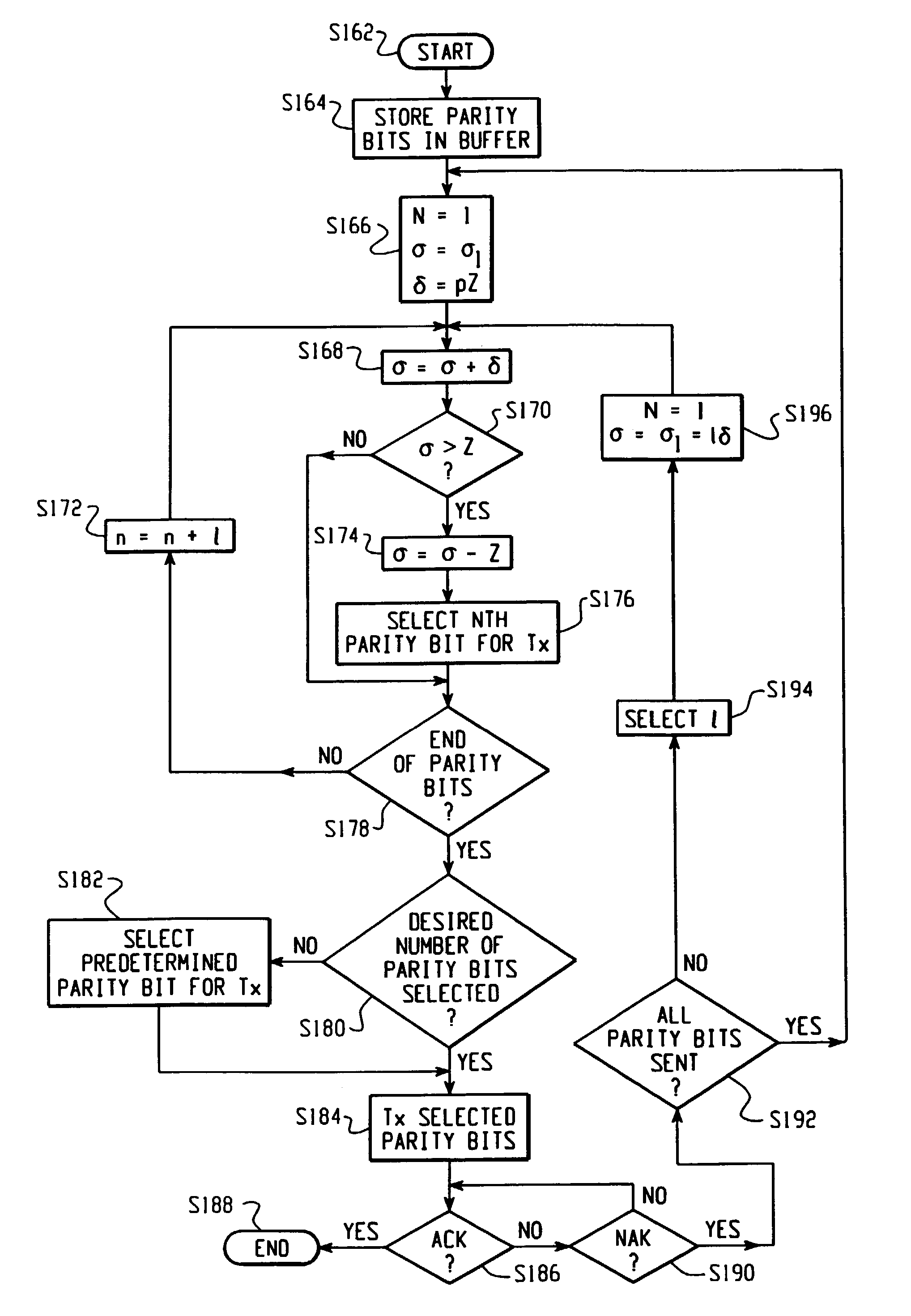

A data communication method and system for uniform arbitrary puncturing of parity bits generated by an encoder. The parity bits are stored in a buffer, and an a-bit accumulator is incremented to a predetermined initial value. For each parity bit in the buffer, the following steps are performed: the accumulator is incremented by a predetermined increment value, and if the accumulator overflows, the parity bit is selected for transmission. The predetermined initial value and the predetermined increment value are selected to achieve a desired amount of puncturing. In a further hybrid automatic repeat request (HARQ) communication method and system, the parity bits are generated by a low density parity check (LDPC) coder.

Owner:MALIKIE INNOVATIONS LTD

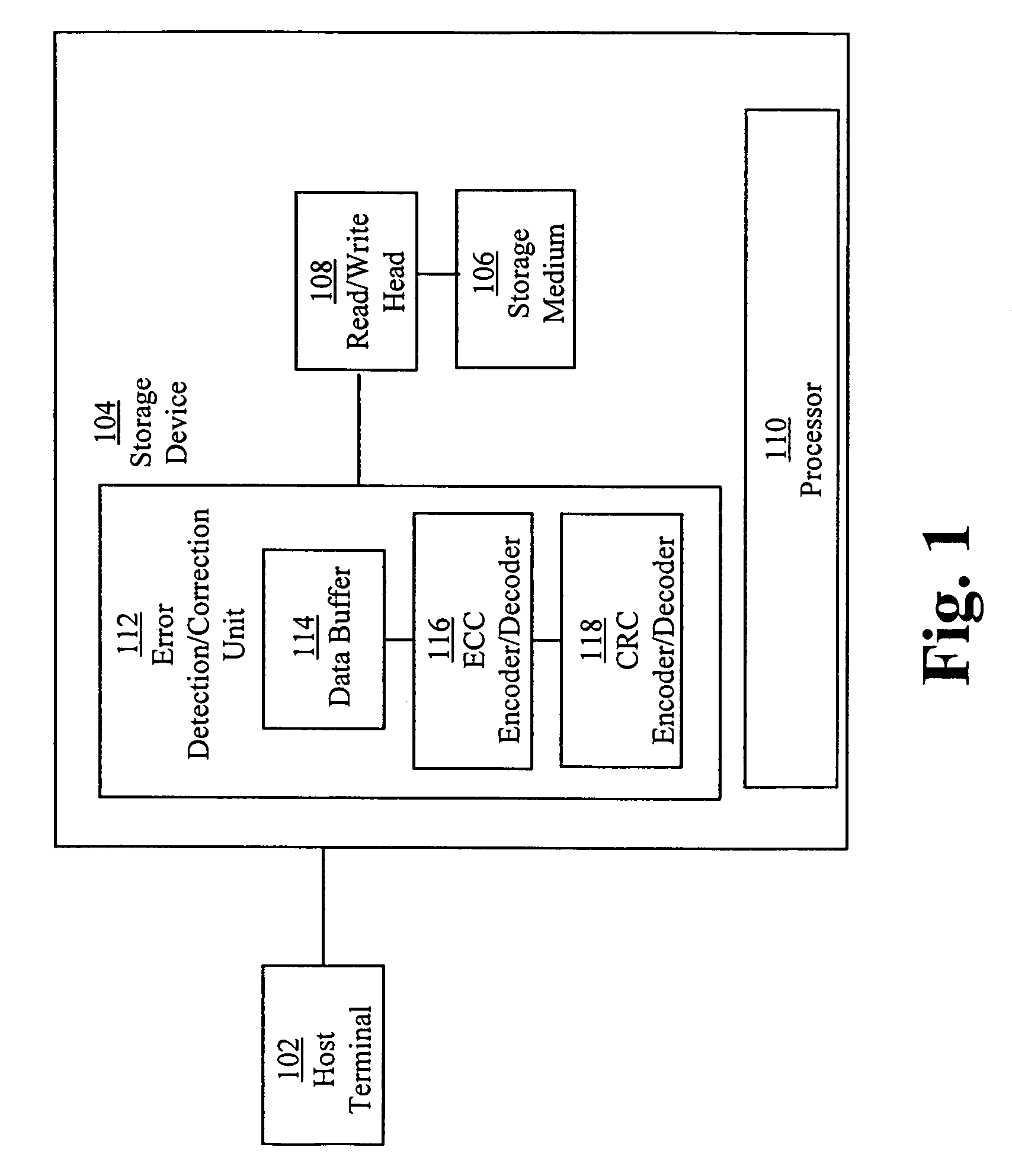

Extended error correction codes

Errors in data retrieved from a storage medium are verified by retrieving a plurality of data blocks from the storage medium. A data set having data from multiple data blocks is selected, where the data set includes a plurality of rows corresponding to the data bocks and a row has data from a data block corresponding to the row. One or more error correction codes (ECCs) are retrieved from the storage medium, where the one or more ECCs correspond to the data set. A plurality of check sums are retrieved from the storage medium, where a check sum corresponds to a data block. Data blocks retrieved from the storage medium having errors are identified using the check sums corresponding to the data blocks. When the number of data blocks identified as having errors is greater than the number of ECCs for the data set, a first set of rows in the data set corresponding to the data blocks identified as having errors is selected, where the number of rows in the first set of rows is equal to the number of ECCs for the data set and less than the number of data blocks identified as having errors. Data for the first set of rows are generated using the ECCs for the data set, and the rows corresponding to the data blocks identified as having errors are verified based on the generated data for the first set of rows.

Owner:QUANTUM CORP

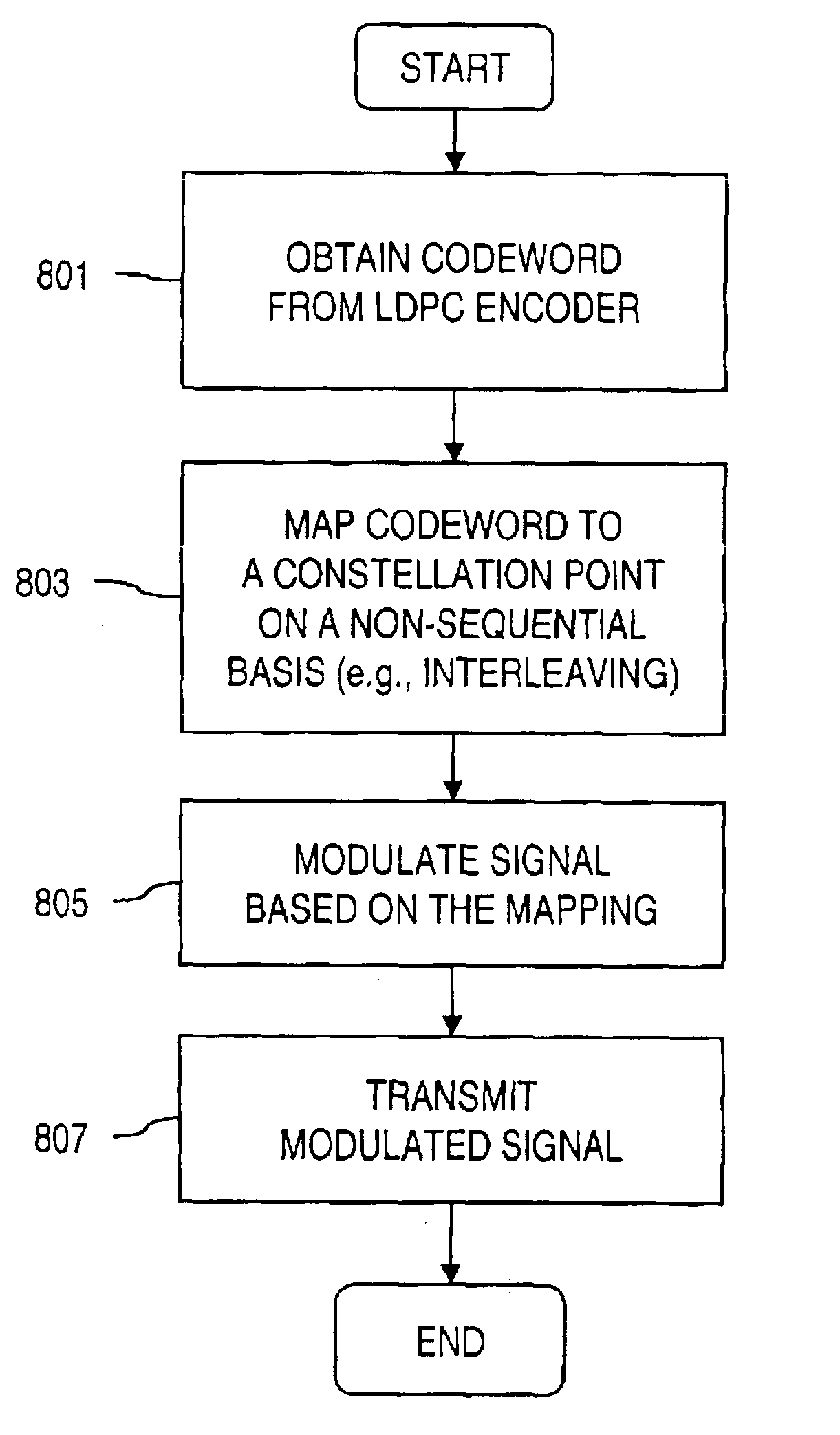

Bit labeling for amplitude phase shift constellation used with low density parity check (LDPC) codes

InactiveUS6963622B2Improve performanceError correction/detection using LDPC codesCode conversionParity-check matrixEngineering

An approach is provided for bit labeling of a signal constellation. A transmitter generates encoded signals using, according to one embodiment, a structured parity check matrix of a Low Density Parity Check (LDPC) code. The transmitter includes an encoder for transforming an input message into a codeword represented by a plurality of set of bits. The transmitter includes logic for mapping non-sequentially (e.g., interleaving) one set of bits into a higher order constellation (Quadrature Phase Shift Keying (QPSK), 8-PSK, 16-APSK (Amplitude Phase Shift Keying), 32-APSK, etc.), wherein a symbol of the higher order constellation corresponding to the one set of bits is output based on the mapping.

Owner:DTVG LICENSING INC

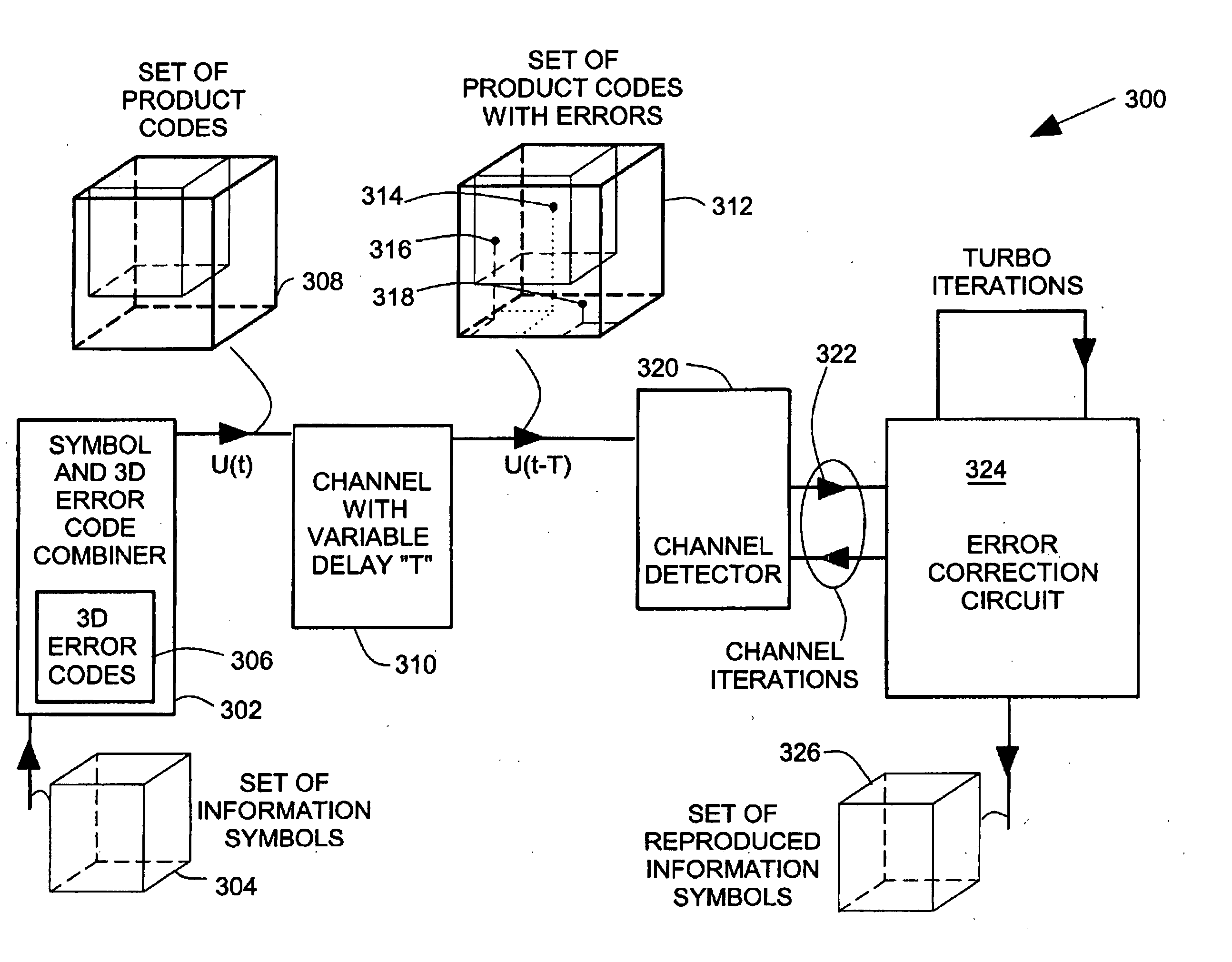

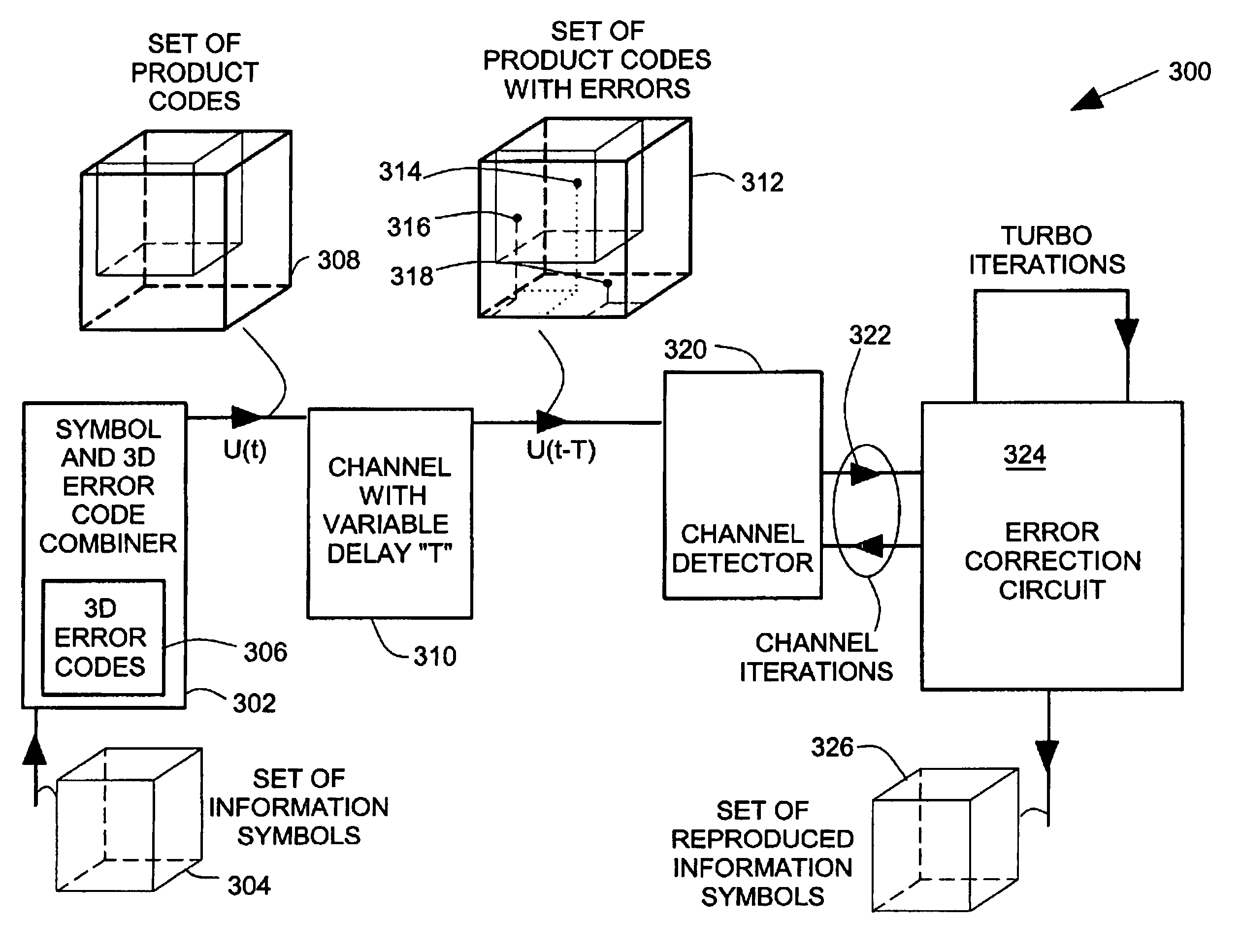

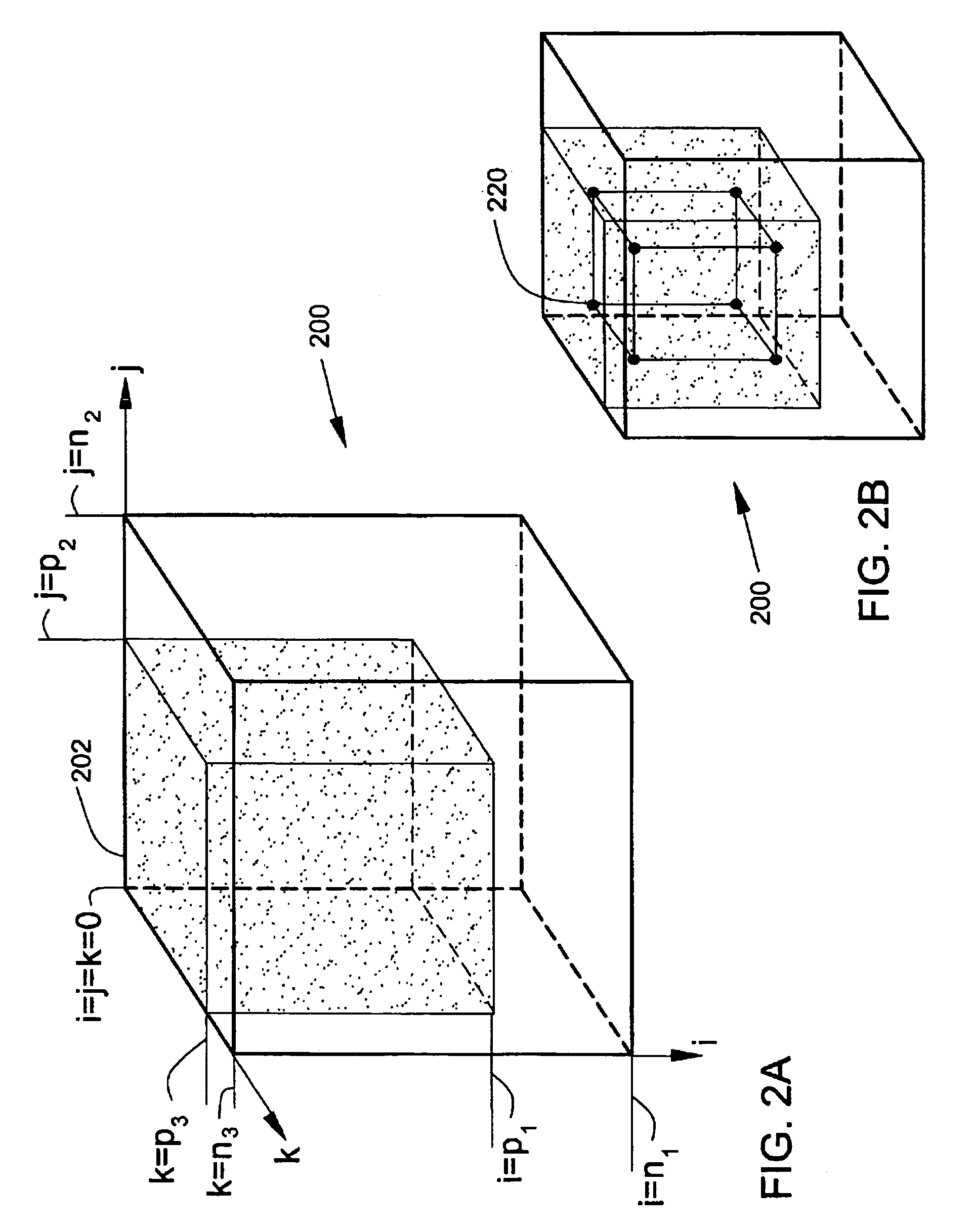

Data communication system with multi-dimensional error-correction product codes

InactiveUS20050273688A1Reduce errorsCode conversionError correction/detection by combining multiple code structuresCommunications systemMulti dimensional

A data communication system has a combiner circuit that combines a set of information symbols with error correction codes and that generates a set of product codes that are at least three dimensional. A communication channel receives the set of product codes and provides the set of product codes with errors after a channel delay. A channel detector receives the set of product codes with the errors and generates a channel detector output. An error correction circuit receives the channel detector output and iteratively removes the errors to provide a set of reproduced information symbols with a reduced number of the errors.

Owner:SEAGATE TECH LLC

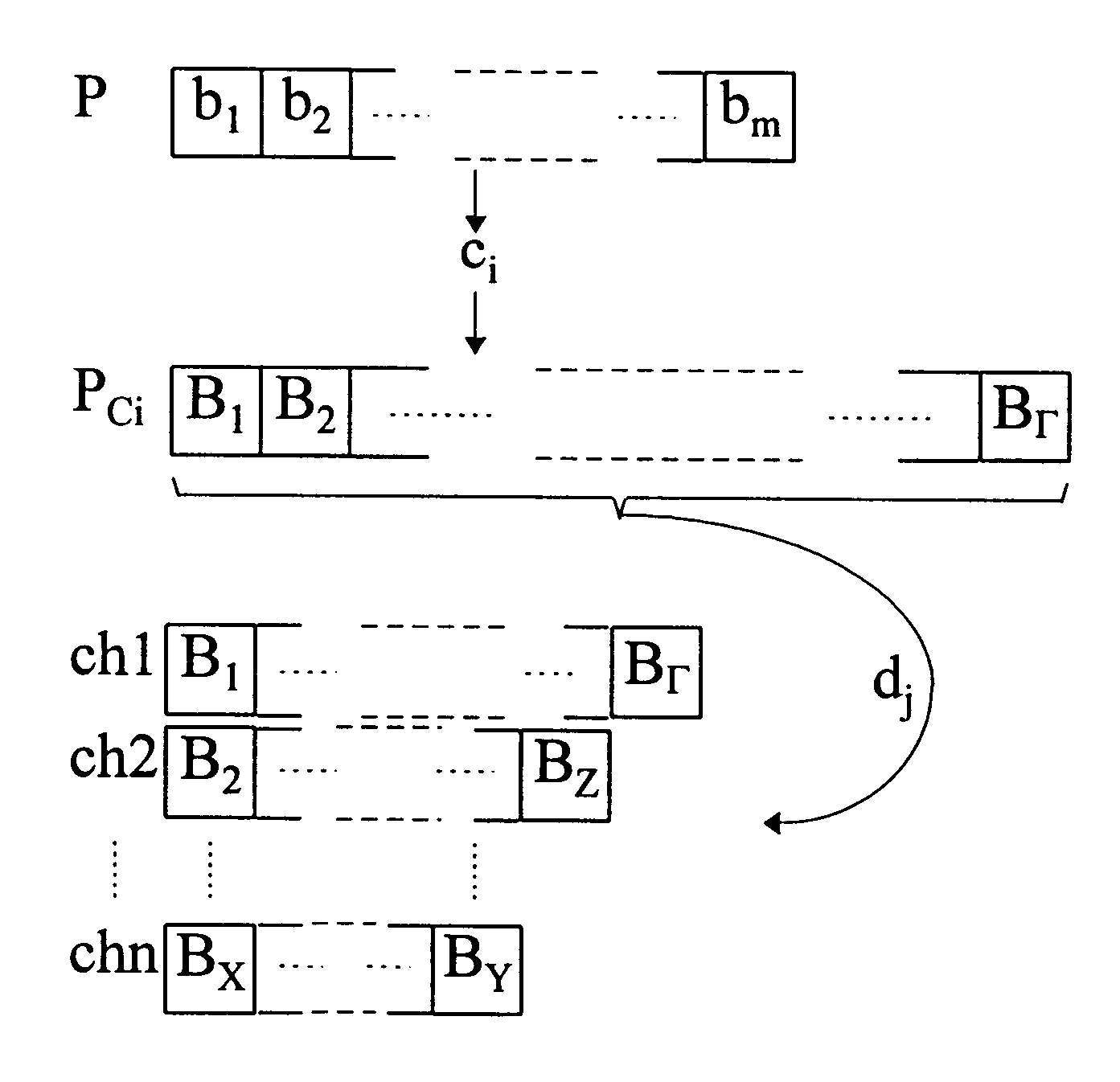

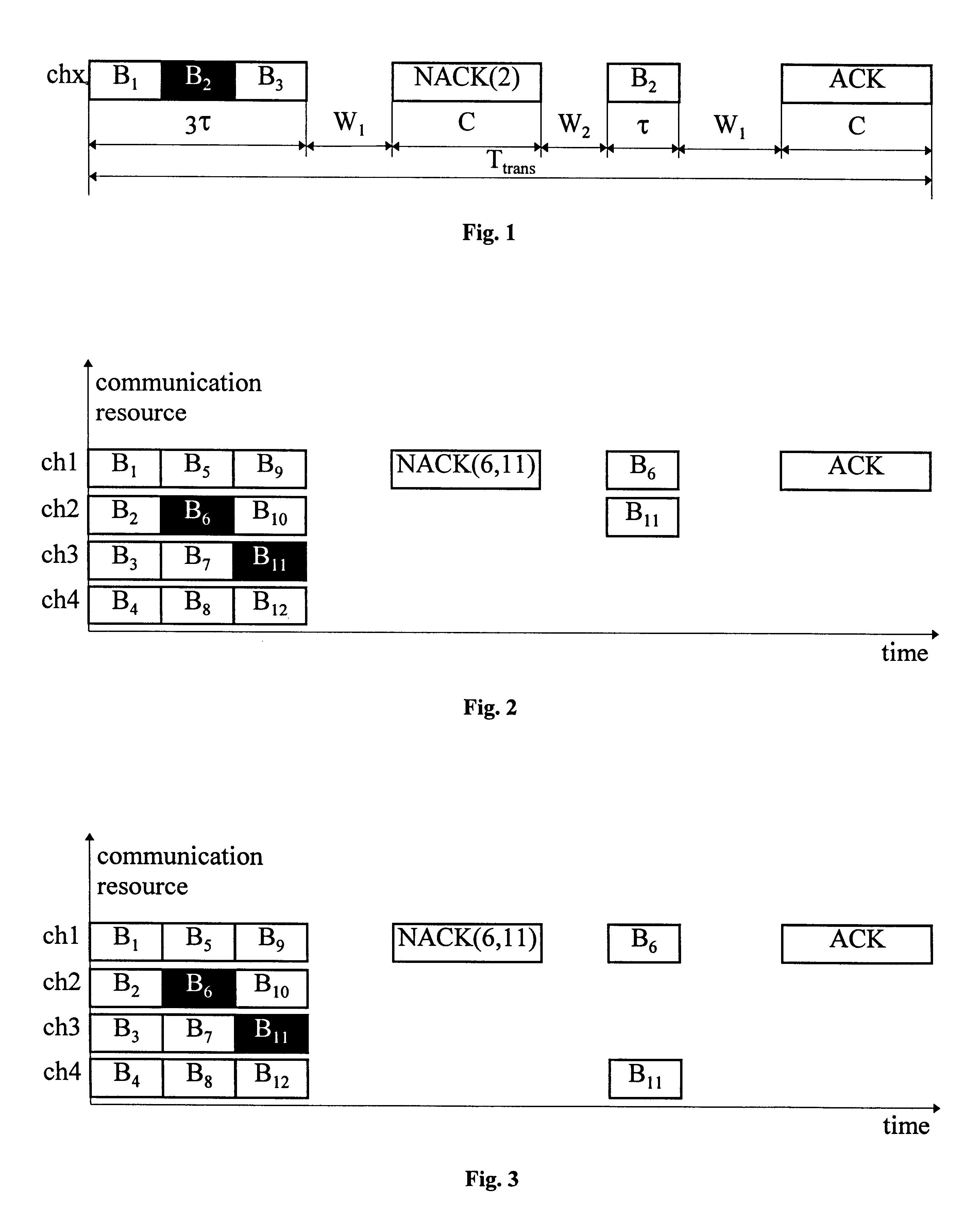

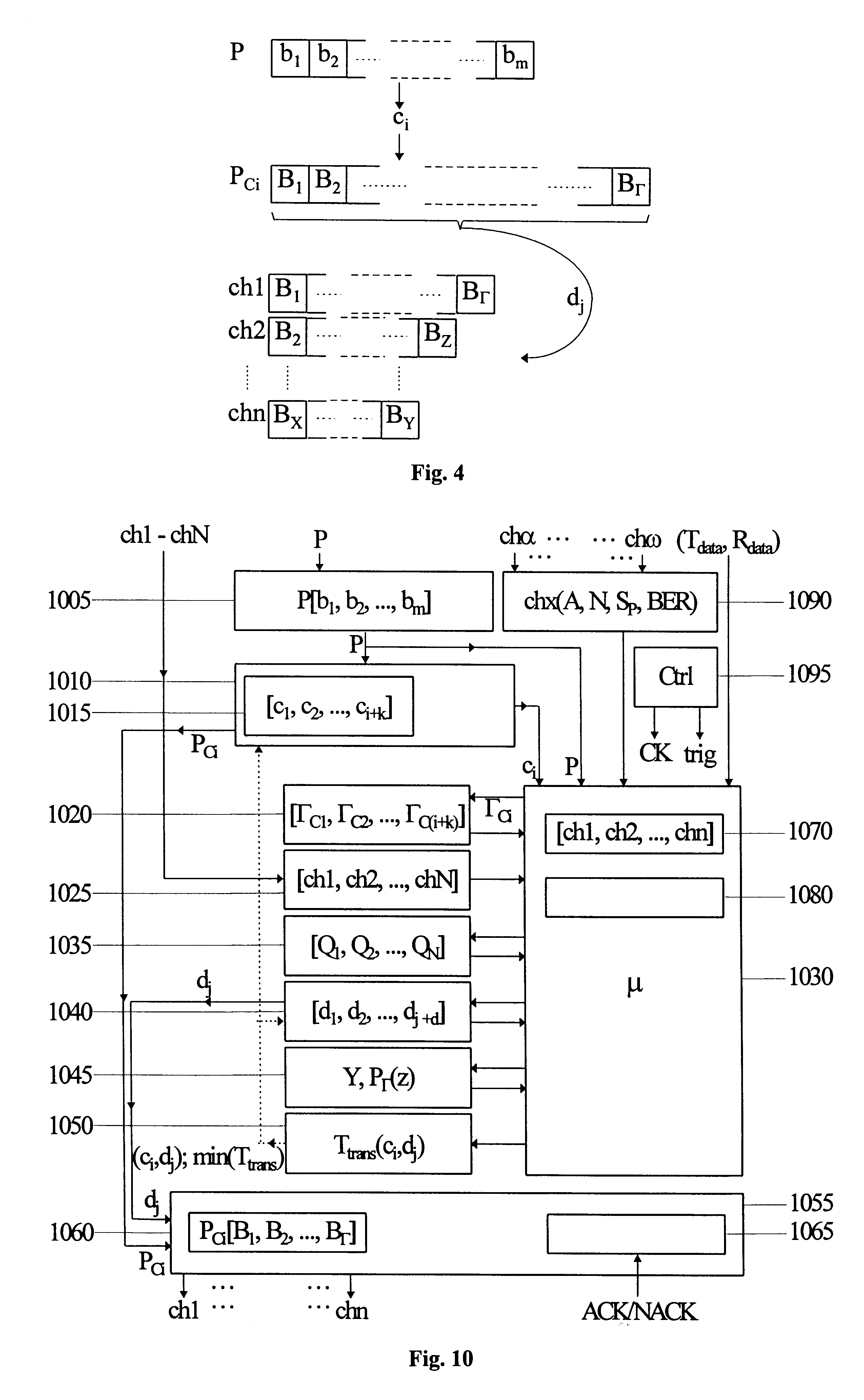

Digital telecommunication system with selected combination of coding schemes and designated resources for packet transmission based on estimated transmission time

InactiveUS6363425B1Quantity minimizationAir interface efficientlyError prevention/detection by using return channelCode conversionForward error correctionMajorization minimization

The present invention relates to a method and an arrangement for communicating packet information in a digital telecommunications system. Through the invention is selected a set of designated communication resources (ch1-chn) from an available amount of resources. Every packet (P) is forward error correction encoded into an encoded packet (Pci), via one of at least two different coding schemes (ci), prior to being transmitted to a receiving party, over the designated communication resources (ch1-chn). An estimated transmission time is calculated for all combinations of coding scheme (ci) and relevant distribution (dj) of the encoded data blocks (B1-BΓ), in the encoded packet (Pci) over the set of designated communication resources (ch1-chn), and the combination (ci,dj) is selected, which minimises the estimated transmission time.

Owner:TELEFON AB LM ERICSSON (PUBL)

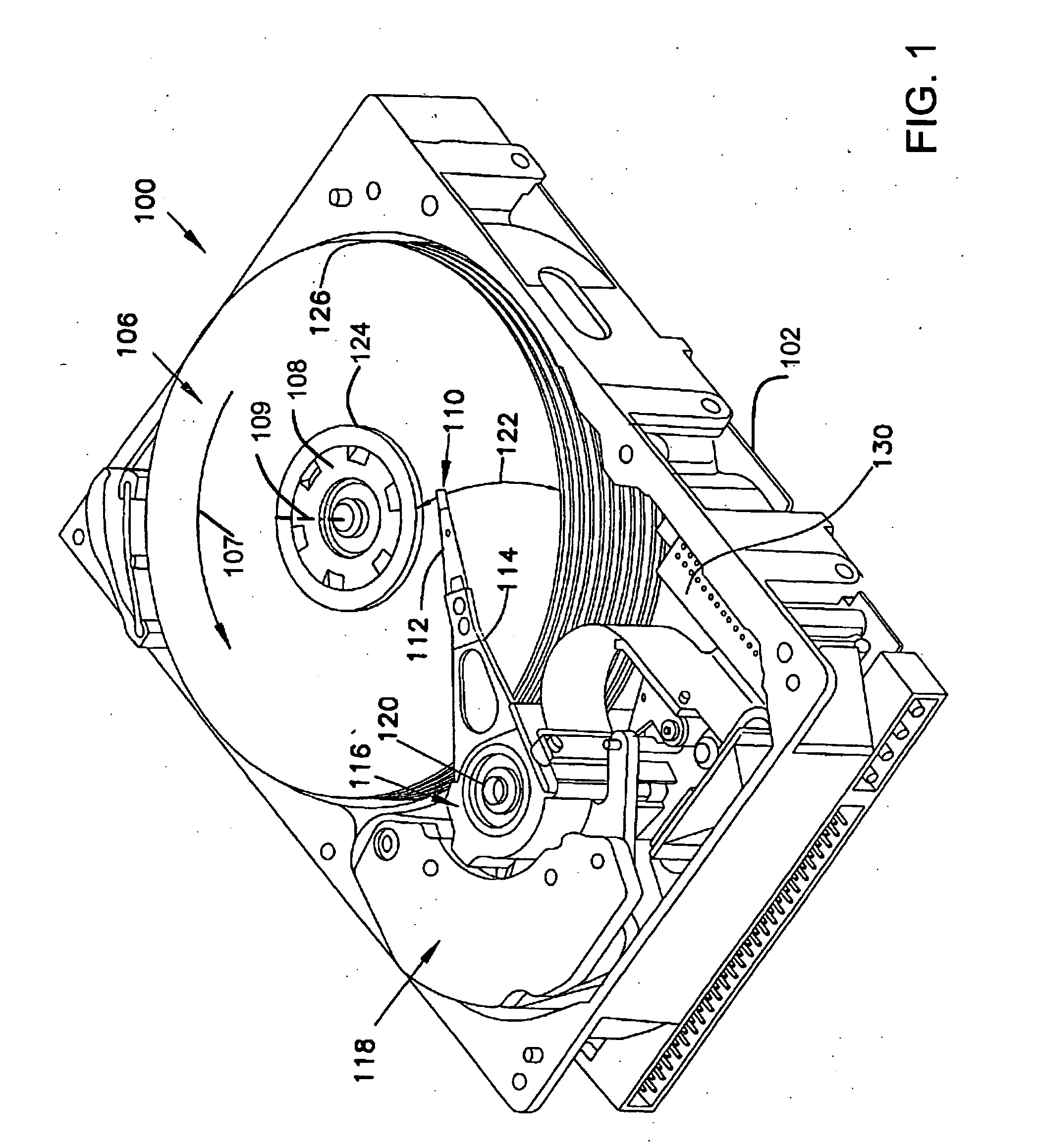

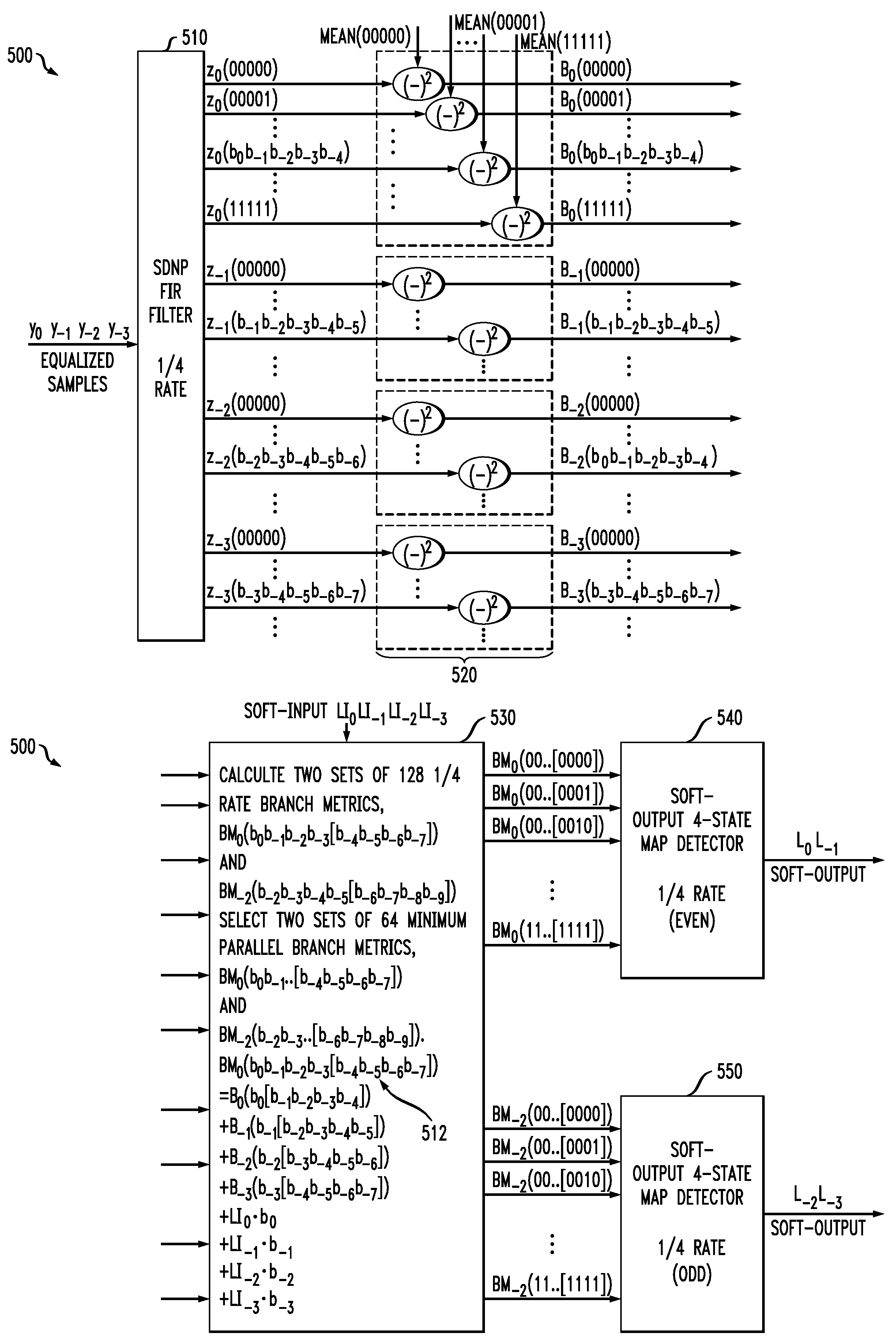

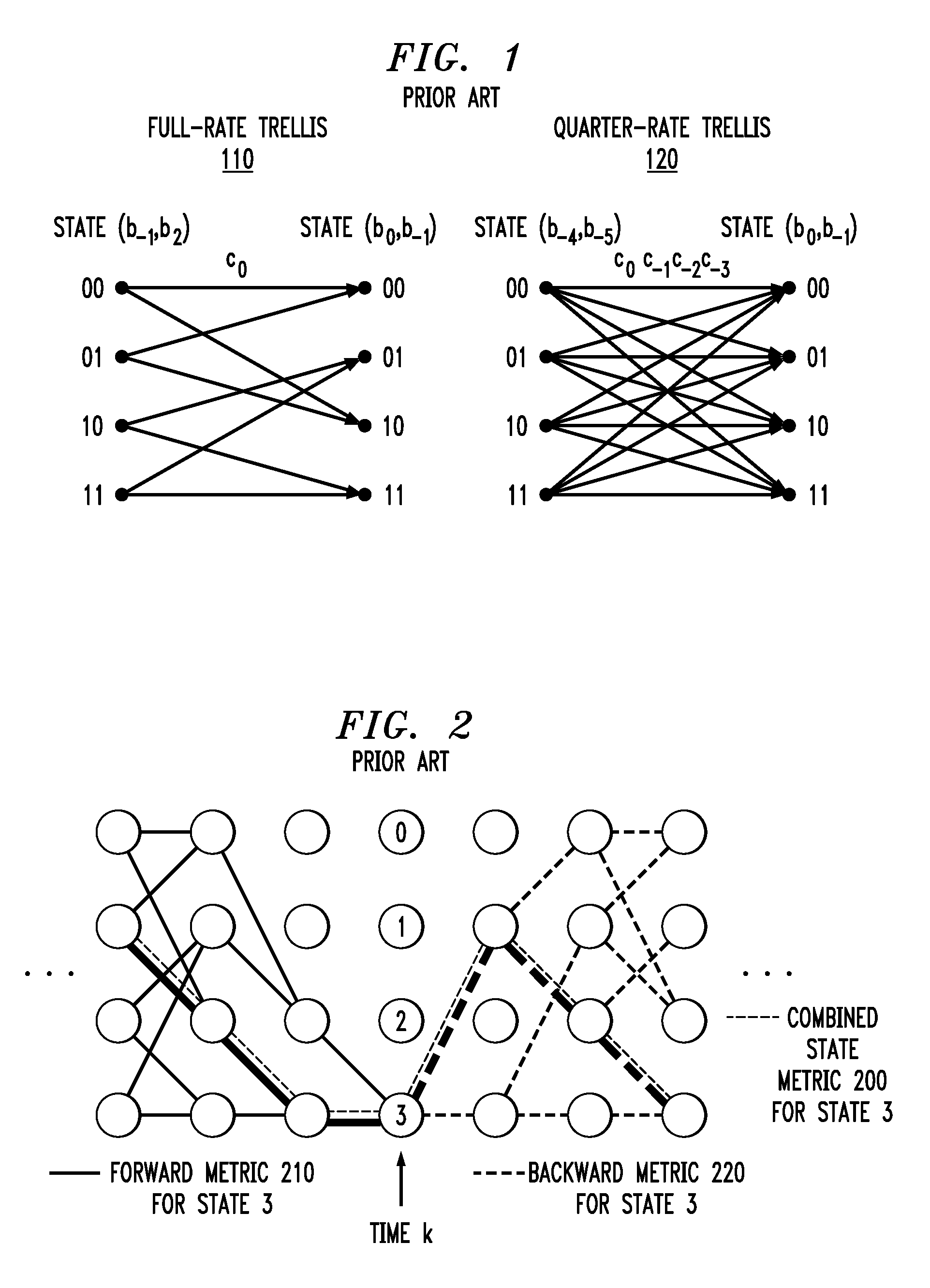

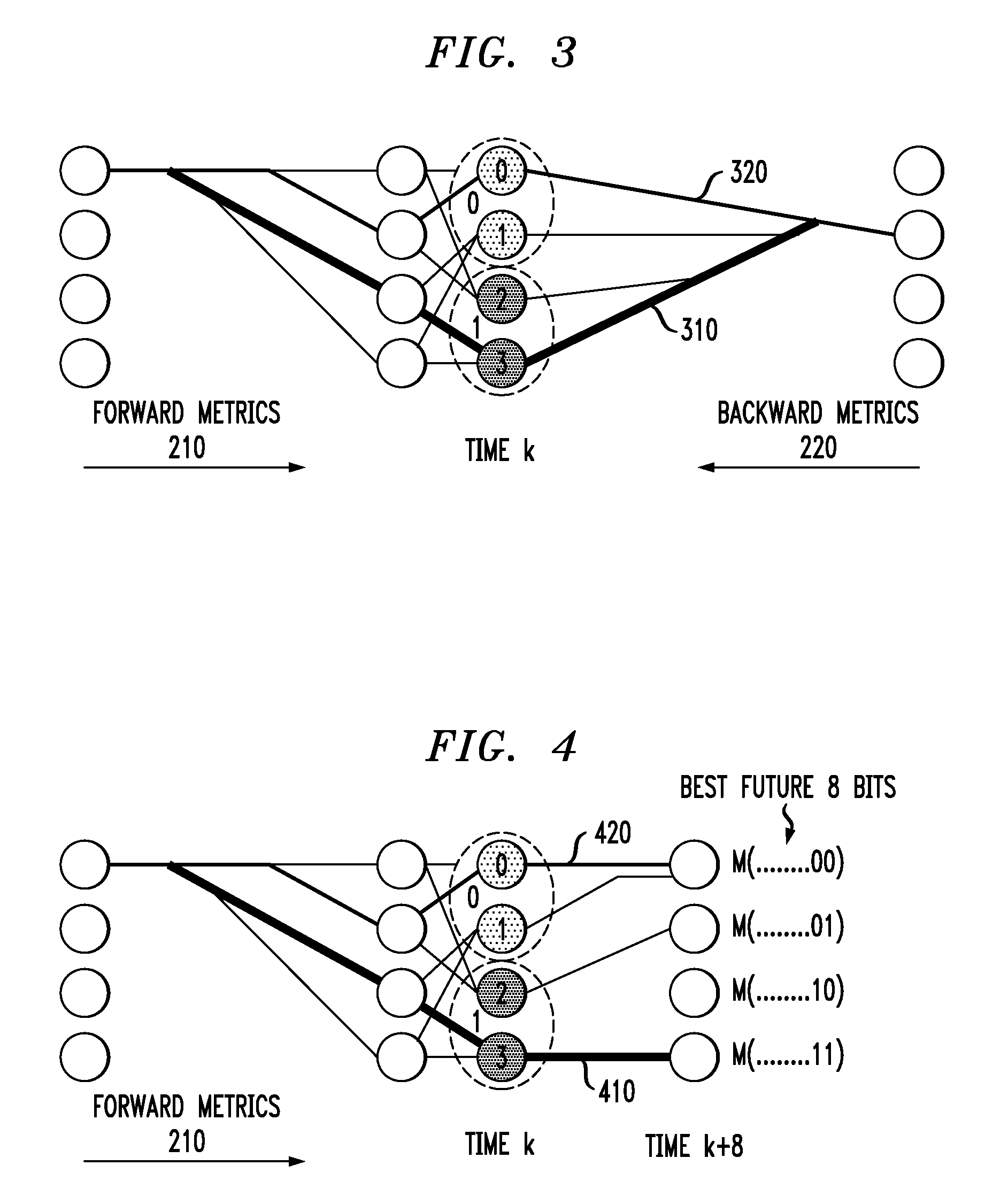

Methods and Apparatus for Map Detection with Reduced Complexity

ActiveUS20090185643A1Reduce complexityDependence moreDriving/moving recording headsError preventionLog likelihoodComputer science

Methods and apparatus are provided for high-speed, low-power, high-performance channel detection. A soft output channel detector is provided that operates at a rate of 1 / N and detects N bits per 1 / N-rate clock cycle. The channel detector comprises a plurality, D, of MAP detectors operating in parallel, wherein each of the MAP detectors generates N / D log-likelihood ratio values per 1 / N-rate clock cycle and wherein at least one of the plurality of MAP detectors constrains each of the bits. The log-likelihood ratio values can be merged to form an output sequence. A single MAP detector is also provided that comprises a forward detector for calculating forward state metrics; a backward detector for calculating backward state metrics; and a current branch detector for calculating a current branch metric, wherein at least two of the forward detector, the backward detector and the current branch detector employ different trellis structures.

Owner:AVAGO TECH INT SALES PTE LTD

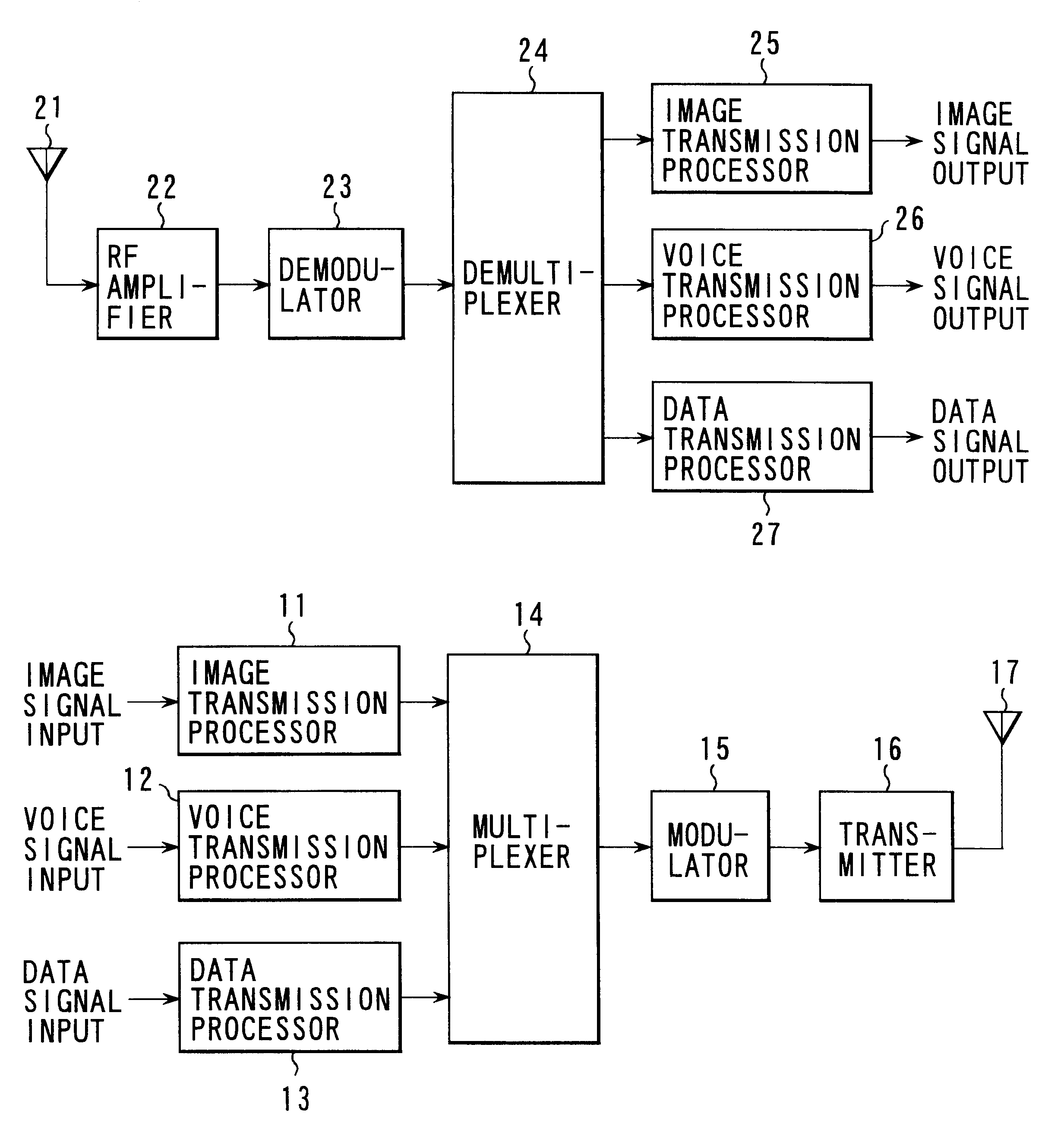

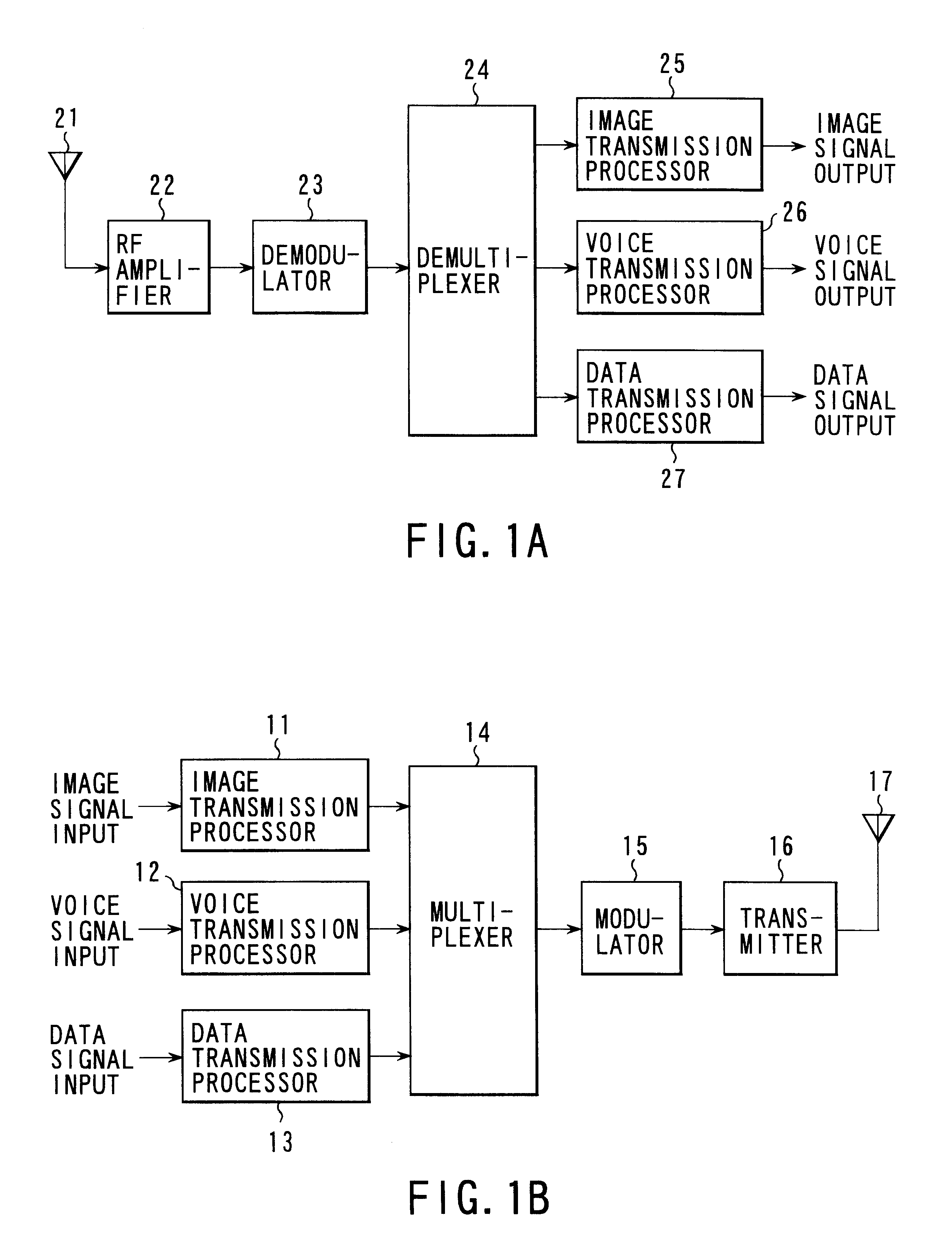

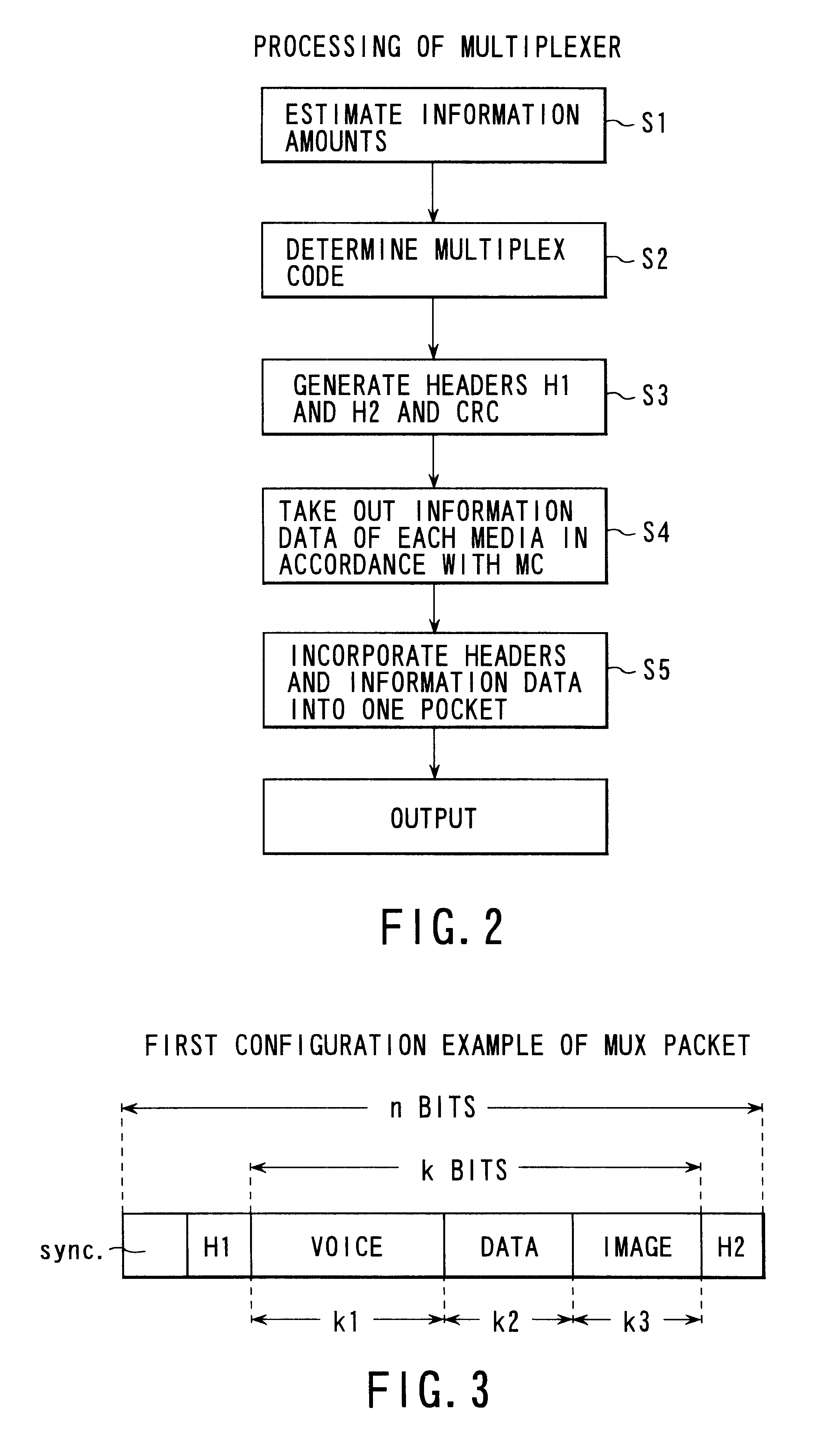

Information data multiplex transmission system, its multiplexer and demultiplexer and error correction encoder and decoder

InactiveUS6490243B1Reduce the probability of packet lossAccurate readingData representation error detection/correctionPulse modulation television signal transmissionMultiplexingMultiplexer

A multiplexing unit on the transmitting side estimates information amounts supplied from respective signal processing units, determines a multiplex code on the basis of respective information amounts, derives a parity of the first determined multiplex code to form a second multiplex code, adds a CRC to each of the multiplex codes to generate two headers H1 and H2, takes out information data of respective media according to the multiplex codes, incorporates the information data into a packet together with the two headers H1 and H2, and outputs the packet. If error correction of H1 is impossible on the receiving side, error correction decoding is conducted by using the header H2. If error correction of H2 is also impossible, error correction decoding is conducted collectively for H1 and H2.

Owner:KK TOSHIBA

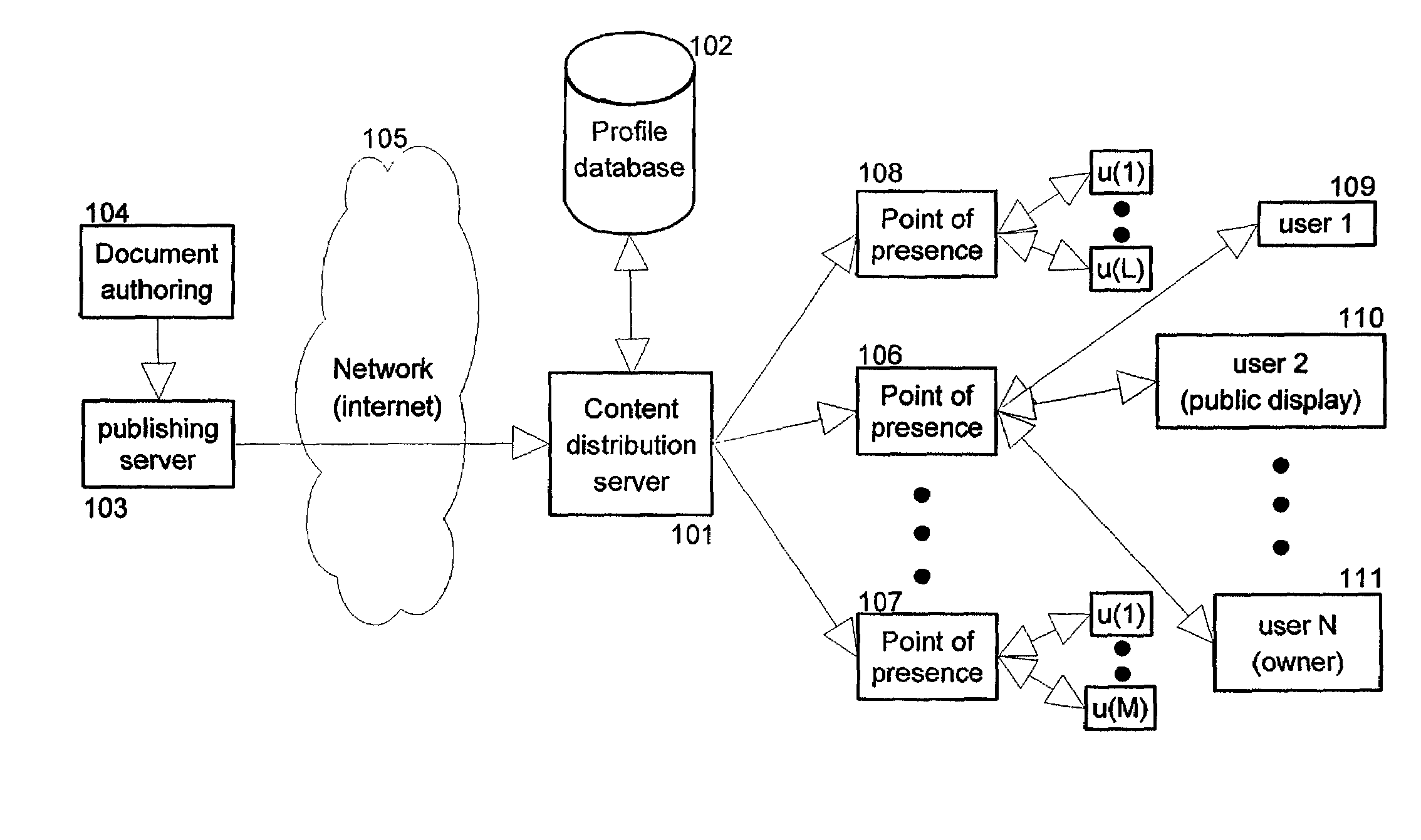

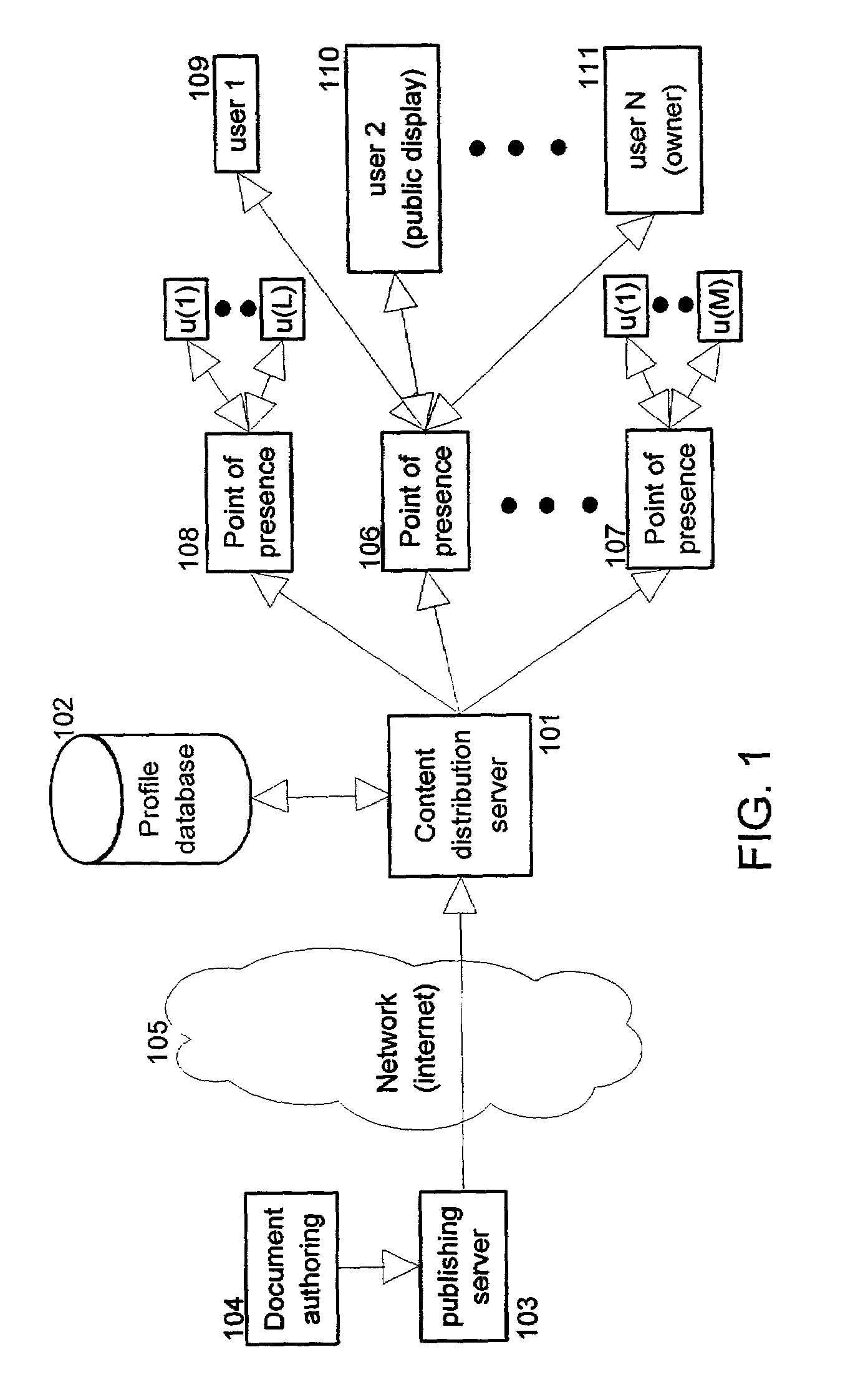

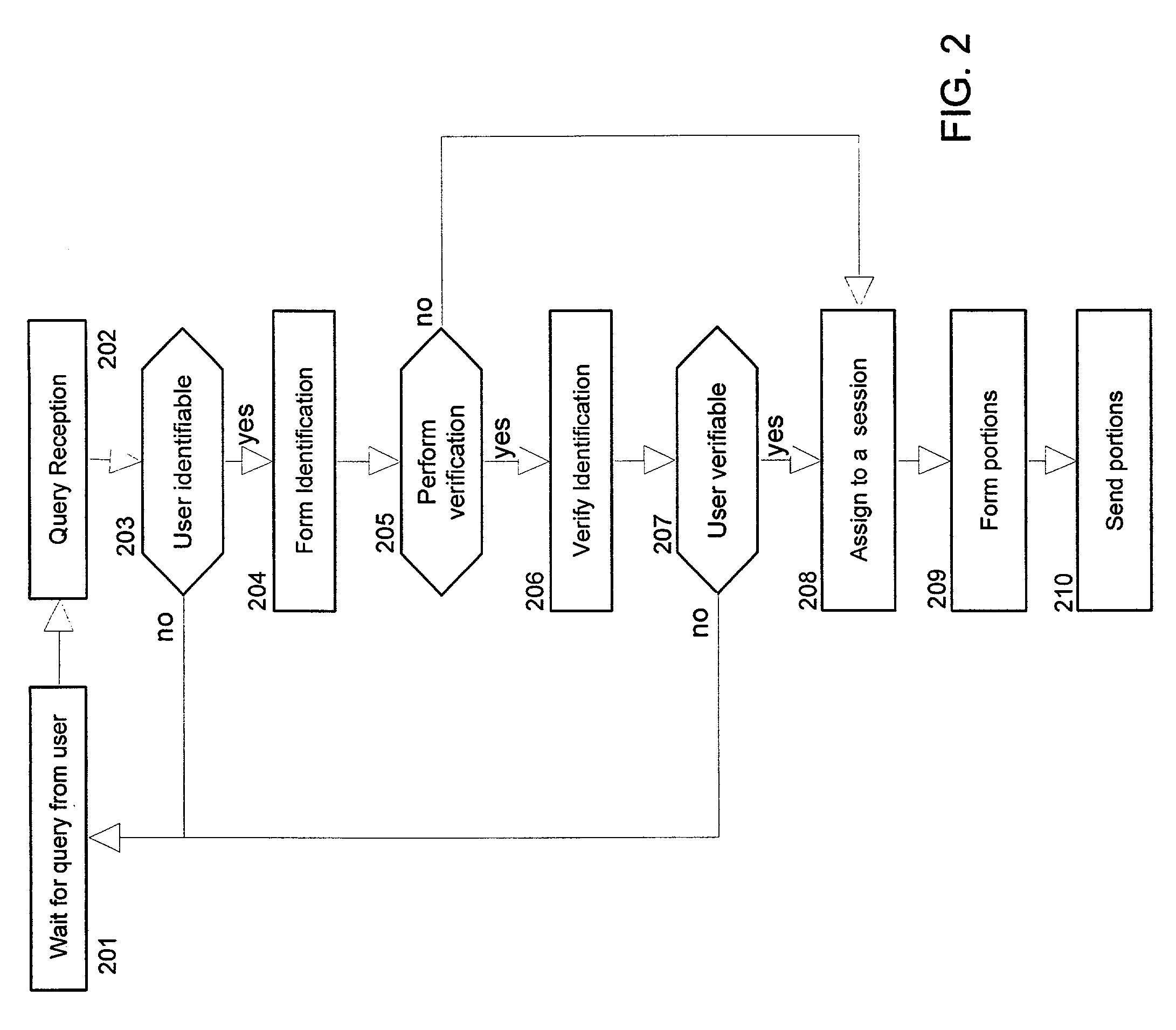

Information content distribution based on privacy and/or personal information

InactiveUS7162451B2Protect user privacyData representation error detection/correctionError preventionContent distributionPublic place

The present invention provides methods and apparatus to protect user privacy while accessing information in public places, using both public and personal devices. This is achieved by employing a mechanism that prevents private information from being displayed on public devices. Instead, this type of information is made available only to a user's personal device(s) that the user carries and / or trusts. An example embodiment of the invention shows relevant parts of the information content, referred to also as information documents or simply documents, to multiple devices based on privacy level and user preferences. Embodiments of the present invention also provide personalized services based on privacy levels defined by users. These users can for example be customers of a retail store. The service provided is sometimes also based on user history of accessing information documents. It permits personalized information to be sent to a customer's personal device.

Owner:IBM CORP

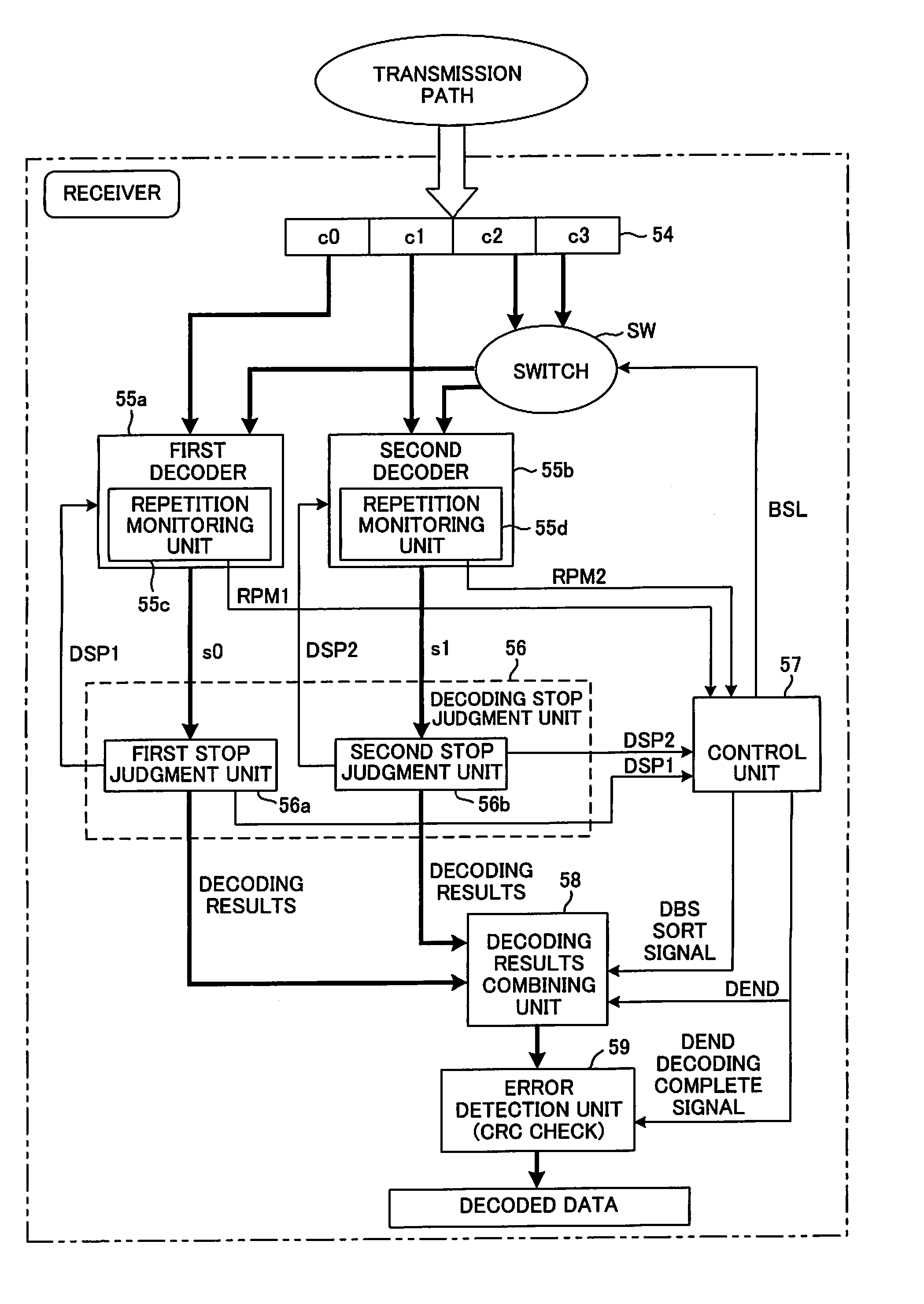

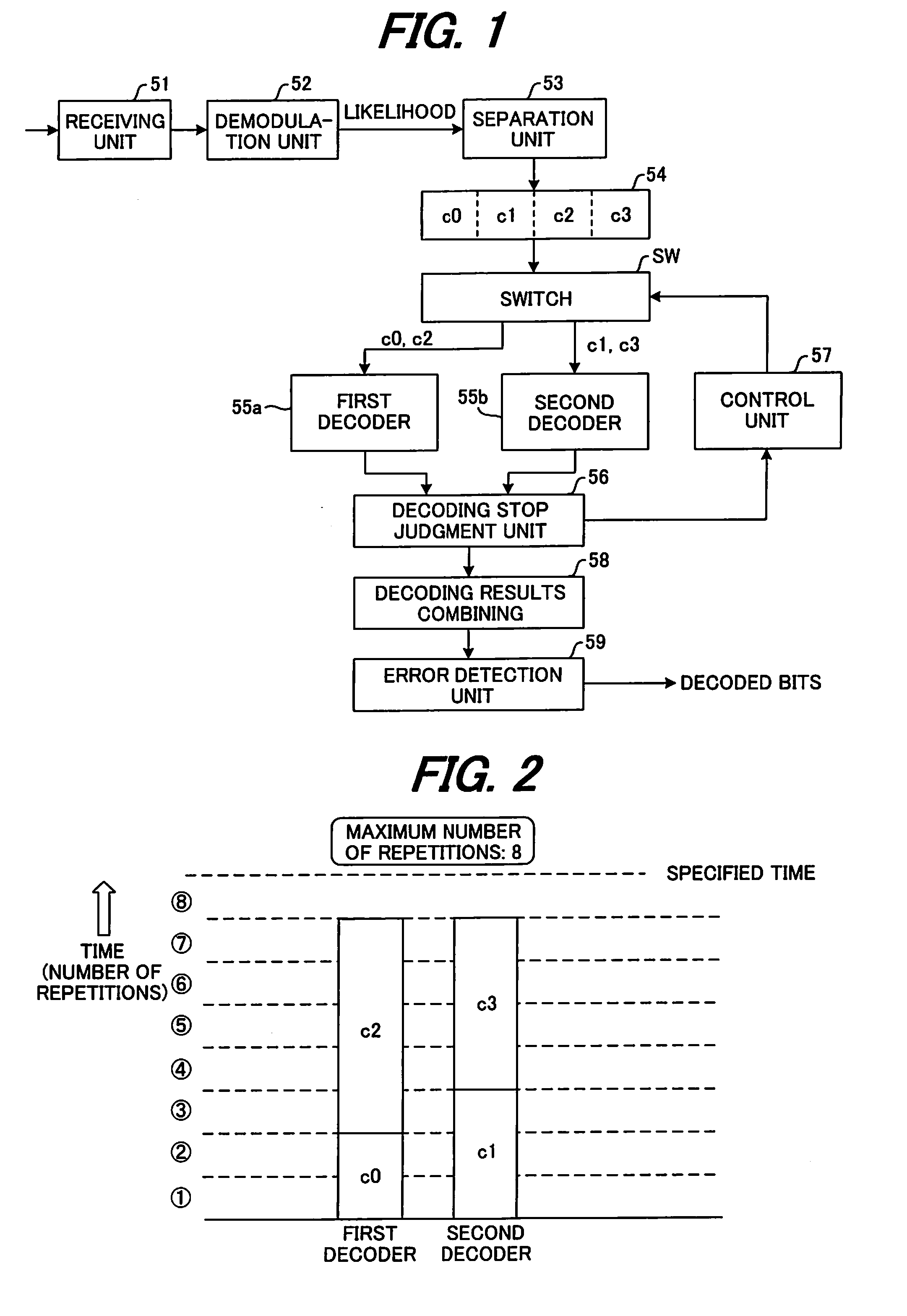

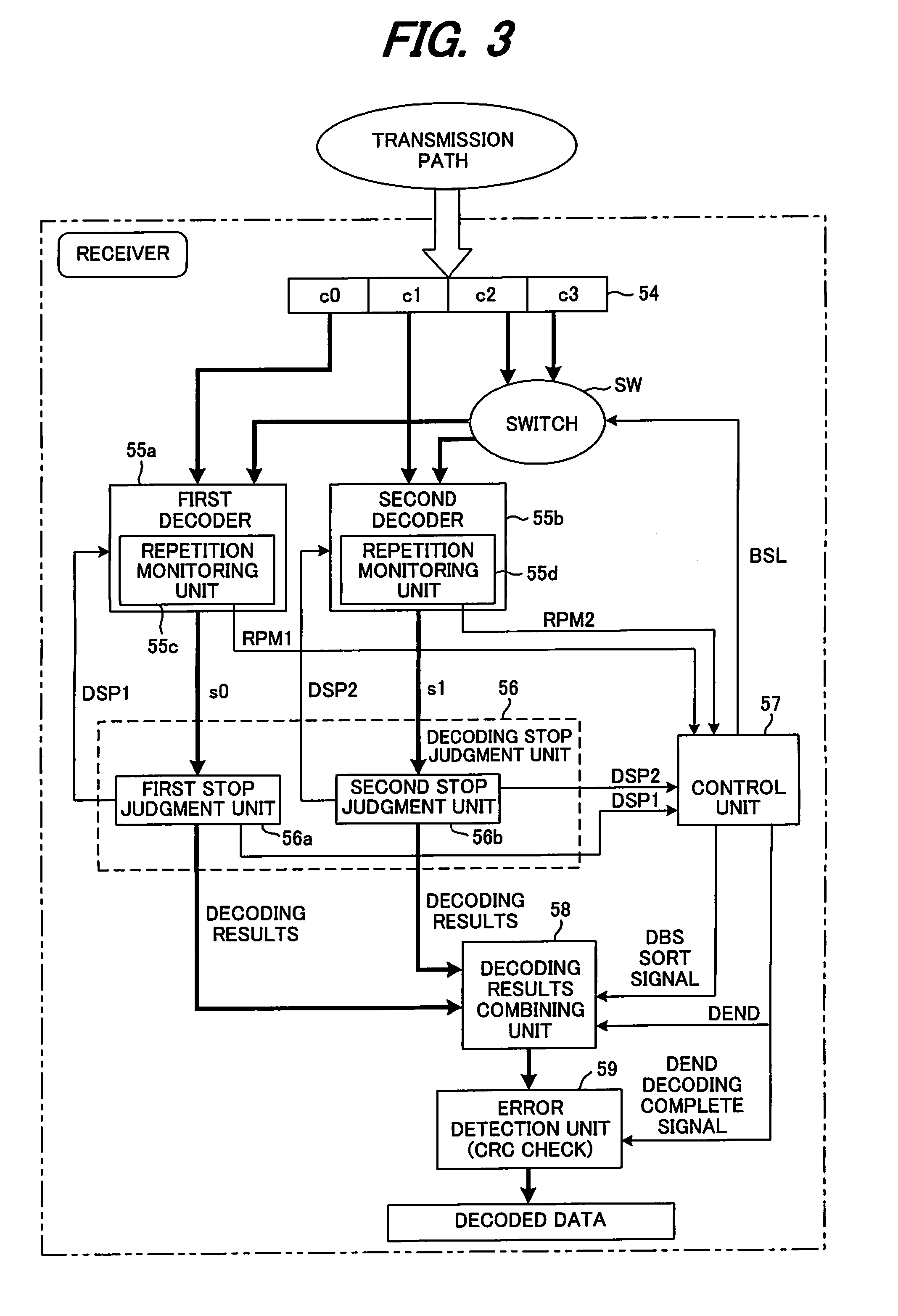

Receiving device and decoding method thereof

InactiveUS20090132893A1Avoid mistakesReduce the numberOther decoding techniquesCode conversionComputer hardwareDecoding methods

A receiving device in a communication system that separates one frame of information bits into plural blocks, performs turbo encoding of the information bits of each block and transmits the result, and decodes the encoded information bits, where the receiving device includes plural decoders number of which is less than the number of blocks per frame. Each decoder performs a decoding process on encoded information bits of each block that have been expressed by likelihood, when a condition for stopping decoding is met, executes the decoding process of encoded information bits of another block for which decoding has not yet been performed. When the condition for stopping decoding has been met for all block before the number of times decoding has been performed for each decoder reaches a preset maximum number of repetitions, the decoding results of all the blocks are serially combined, an error detection process is executed, and when no error is detected, the decoding results are output.

Owner:FUJITSU LTD

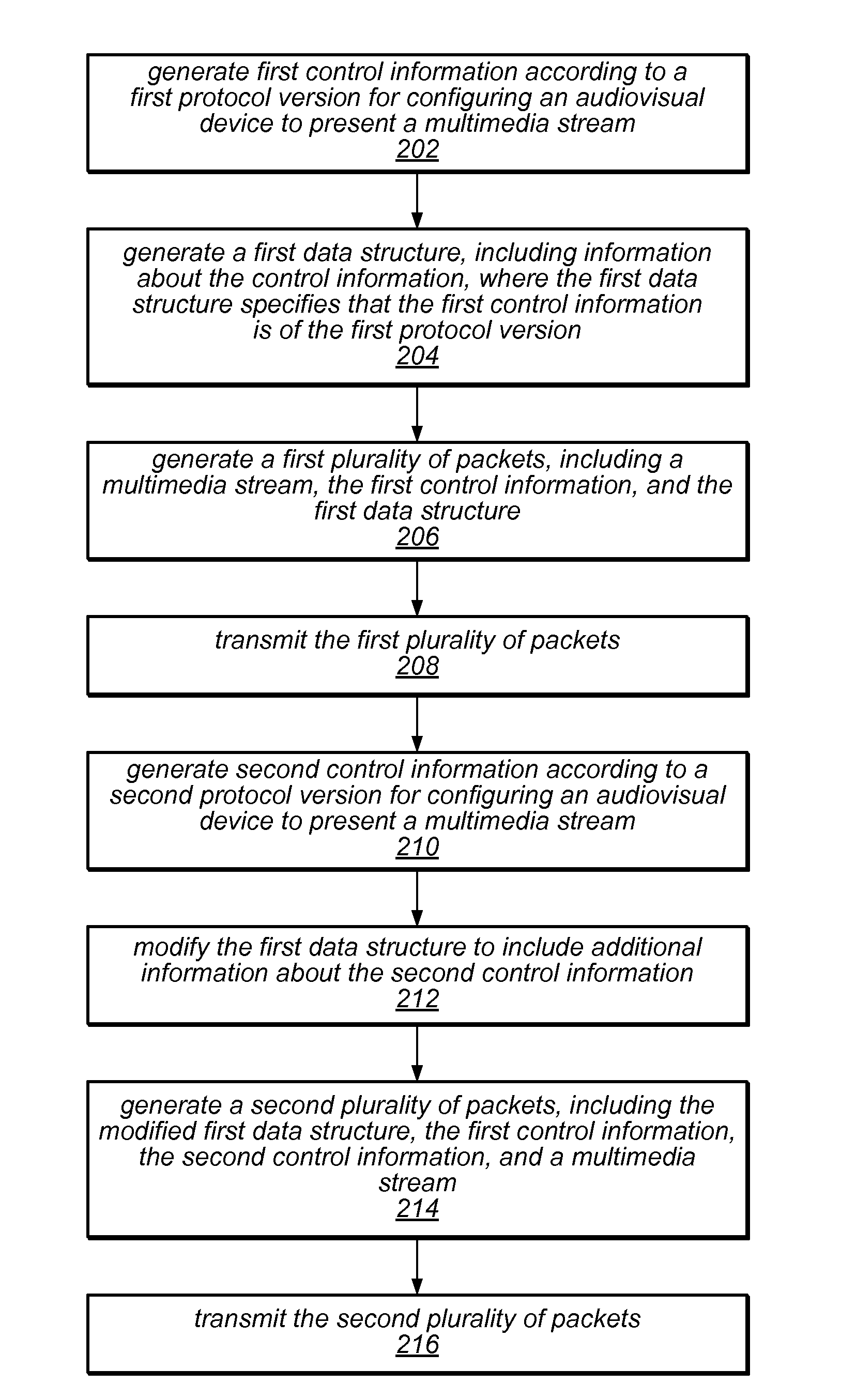

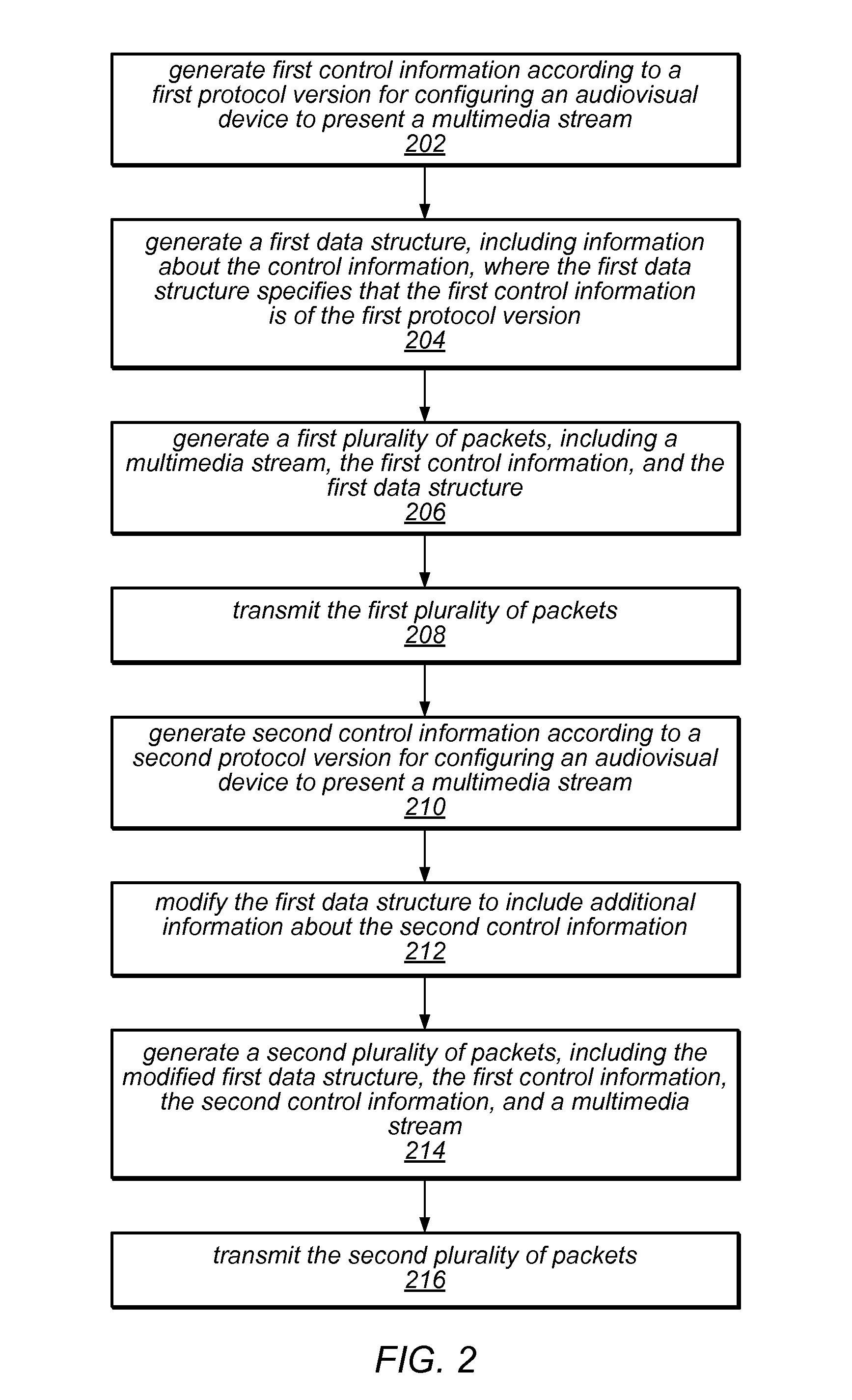

Transmitting and Receiving Control Information for Use with Multimedia Streams

ActiveUS20090260041A1Generate efficientlyUniform lengthCode conversionError correction/detection by combining multiple code structuresMultimedia streamsComputer network

First control information, generated according to a first protocol version, for configuring an audiovisual device to present a multimedia stream, may be generated. A first data structure specifying that the first control information is of the first protocol version may be generated. A plurality of packets, including a multimedia stream, the first control information, and the first data structure, may be generated and transmitted. Second control information, generated according to a second protocol version, for configuring an audiovisual device to present a multimedia stream, may be generated. The first data structure may be modified to include information about the second control information. A second plurality of packets, including the modified first data structure, the first control information, a multimedia stream specified by the first control information, the second control information, and a multimedia stream specified by the second control information, may be generated.

Owner:COHERENT LOGIX

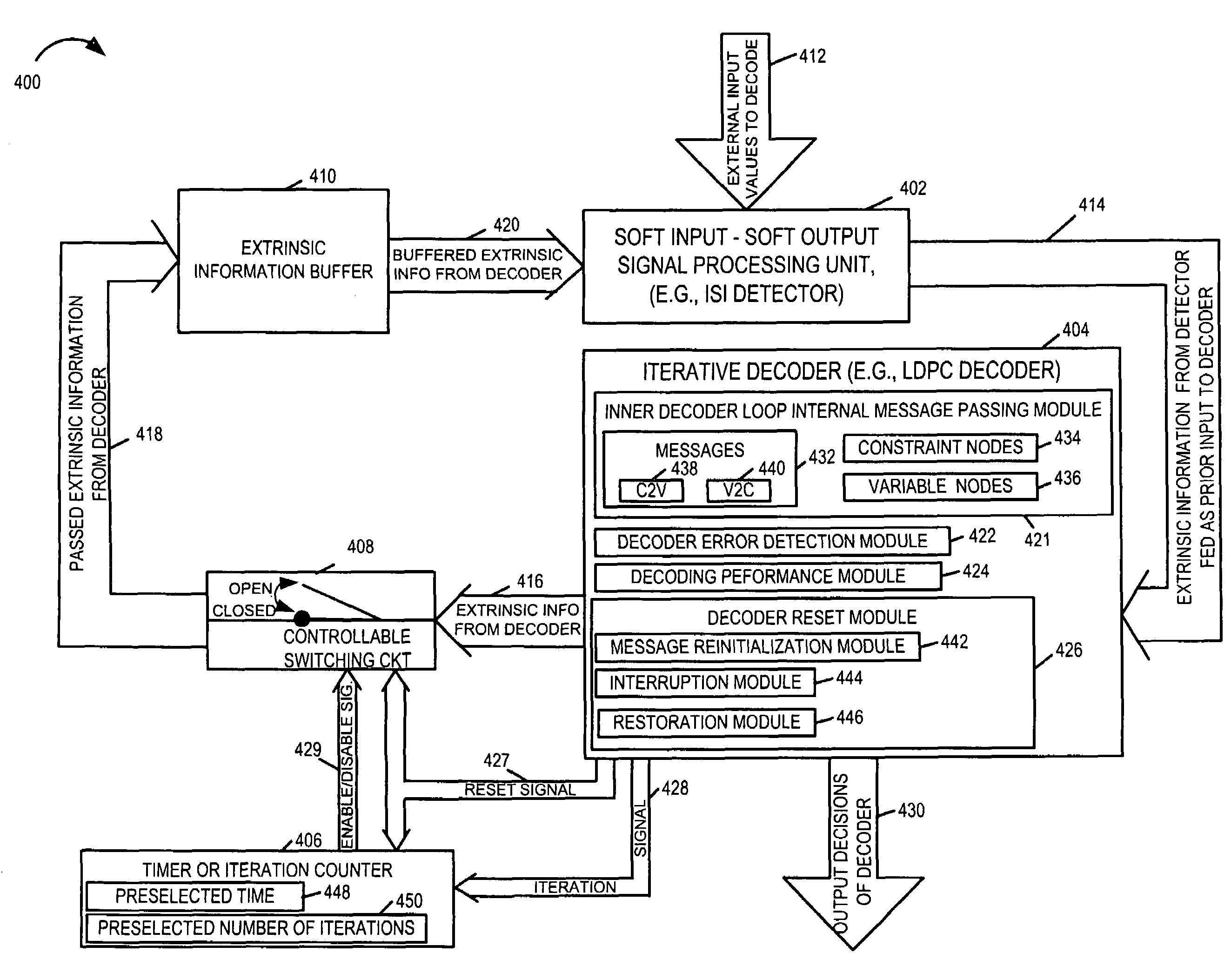

Methods and apparatus for reducing error floors in message passing decoders

ActiveUS7237181B2Reduce the numberReduce quality problemsError preventionError correction/detection using multiple parity bitsComputer hardwareEdge states

An iterative message passing decoder, e.g., an LDPC decoder, operating in conjunction with a soft input-soft output signal processing unit, e.g., an ISI detector, has an error floor performance region influenced by the decoder's sub-optimal message passing nature. Error floor reduction is achieved by a simple message re-initialization mechanism. Decoder edge states, e.g., constraint to variable node messages in decoder memory, are reinitialized, e.g., for an iteration, during the decoding after soft values provided by signal processing unit have improved. During the message re-initialization and for some subsequent amount of iterative decoder processing, extrinsic information fed back from the decoder to the signal processing unit and / or soft values delivered to the decoder from the signal processing unit, in an outer communications loop, is temporarily frozen, e.g., using a switch and a buffer. Then, the outer communications loop is restored as the decoding continues, achieving improved decoding performance.

Owner:QUALCOMM INC

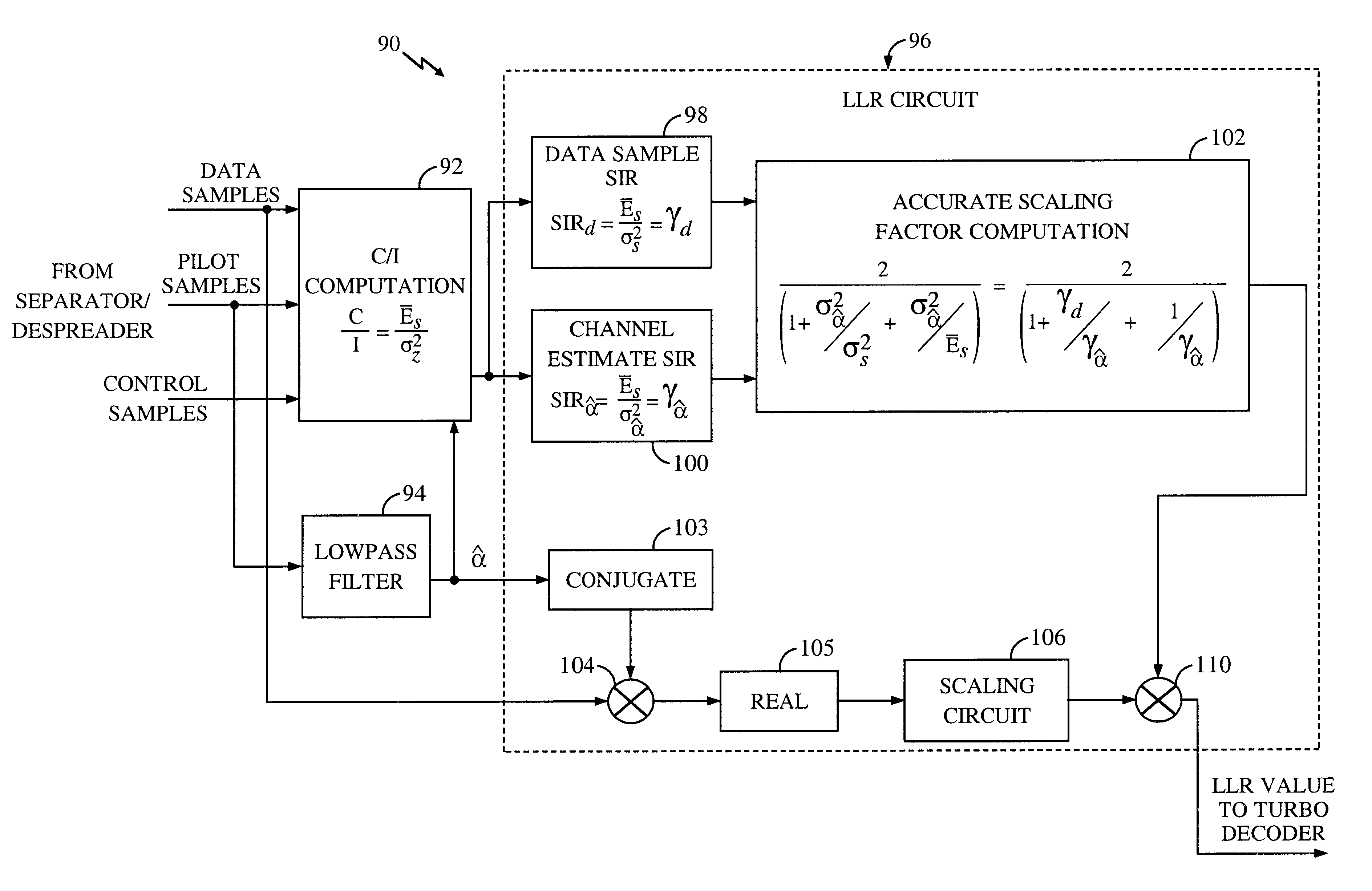

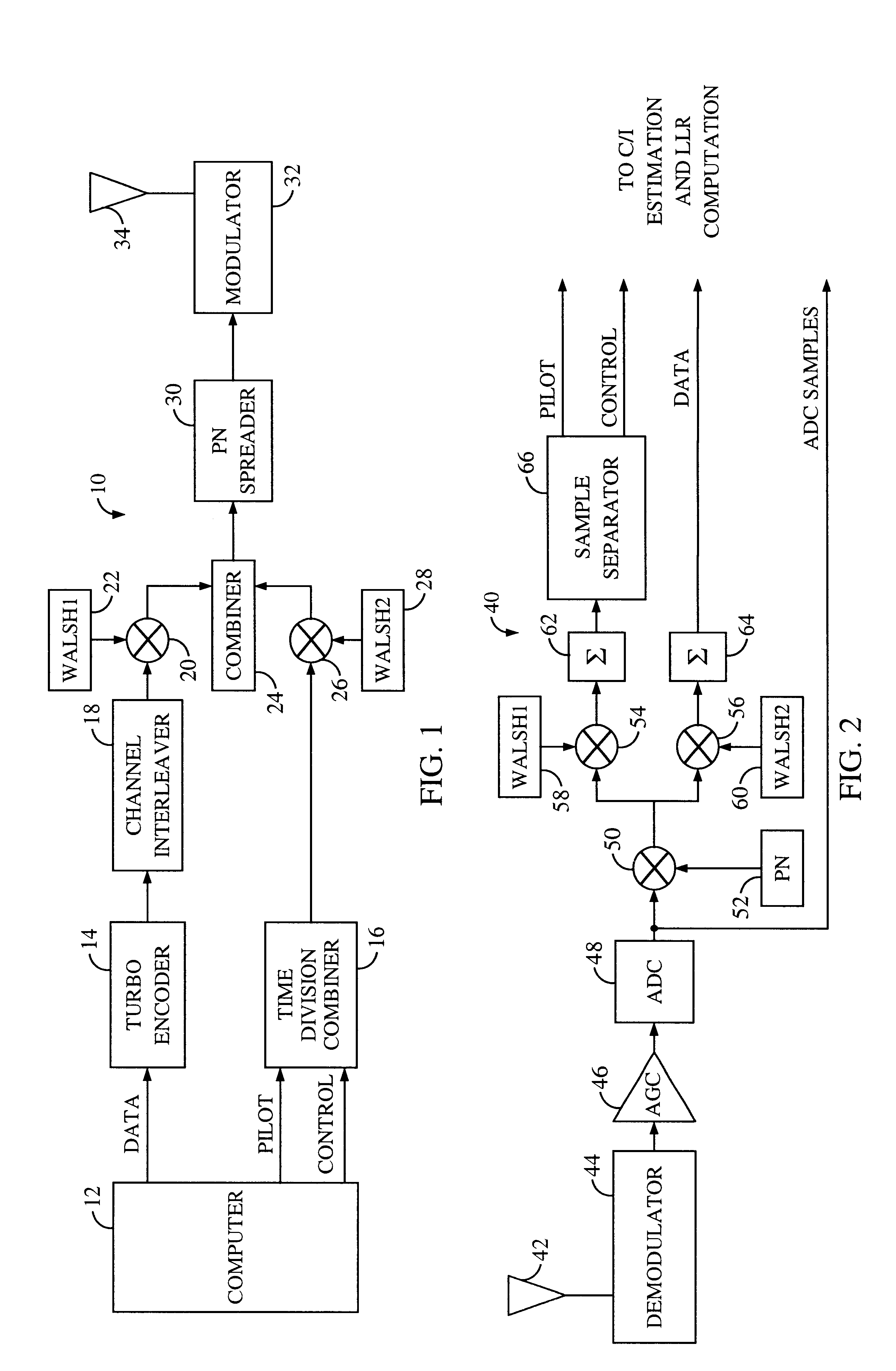

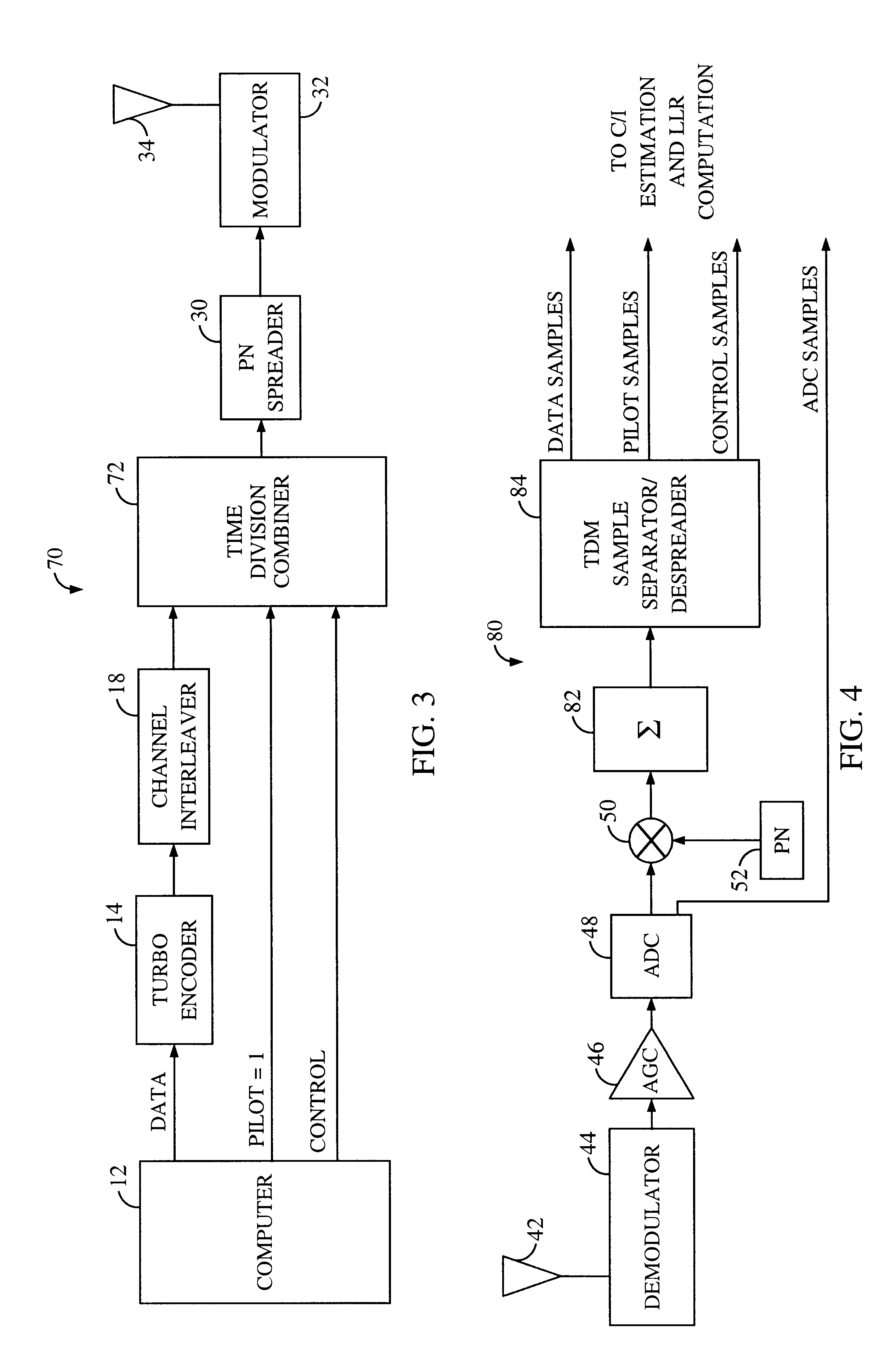

System and method for performing accurate demodulation of turbo-encoded signals via pilot assisted coherent demodulation

InactiveUS6377607B1Error detection/prevention using signal quality detectorError correction/detection using convolutional codesTransceiverInterference ratio

An efficient telecommunications receiver system for accurately decoding a received composite signal having a data signal component and a pilot signal component. The receiver system includes a first circuit for receiving the composite signal and extracting a pilot signal and a data signal from received composite signal. A second circuit calculates a log-likelihood ratio as a function of a channel estimate based on the pilot signal. A third circuit scales the log-likelihood ratio by a predetermined log-likelihood ratio scaling factor and provides an accurate log-likelihood value in response thereto. A fourth circuit decodes the received composite signal based on the accurate log-likelihood value and the data signal. In a specific embodiment, the pilot signal and the data signal comprise pilot samples and data samples, respectively. The third circuit includes a carrier signal-to-interference ratio circuit for computing a first signal-to-interference ratio and a second signal-to-interference ratio based partly on the pilot signal. The first signal-to-interference ratio is based on the data samples, and the second signal-to-interference ratio is based on the pilot samples. The first signal-to-noise ratio and the second signal-to-noise ratio provide input to a circuit for computing the predetermined log-likelihood ratio scaling factor that is included in the third circuit. In a more specific embodiment, the first circuit includes a despreader for despreading the received composite signal in accordance with a predetermined spreading function and providing a despread signal in response thereto. The spreading function is a pseudo noise sequence or a Walsh function. The first circuit further includes a decovering circuit that extracts the pilot signal and the data signal from the despread signal. In the illustrative embodiment, the accurate receiver system further includes a circuit for generating a rate and / or power control message and transmitting the rate and / or power control message to an external transceiver in communication with the efficient receiver system.

Owner:QUALCOMM INC

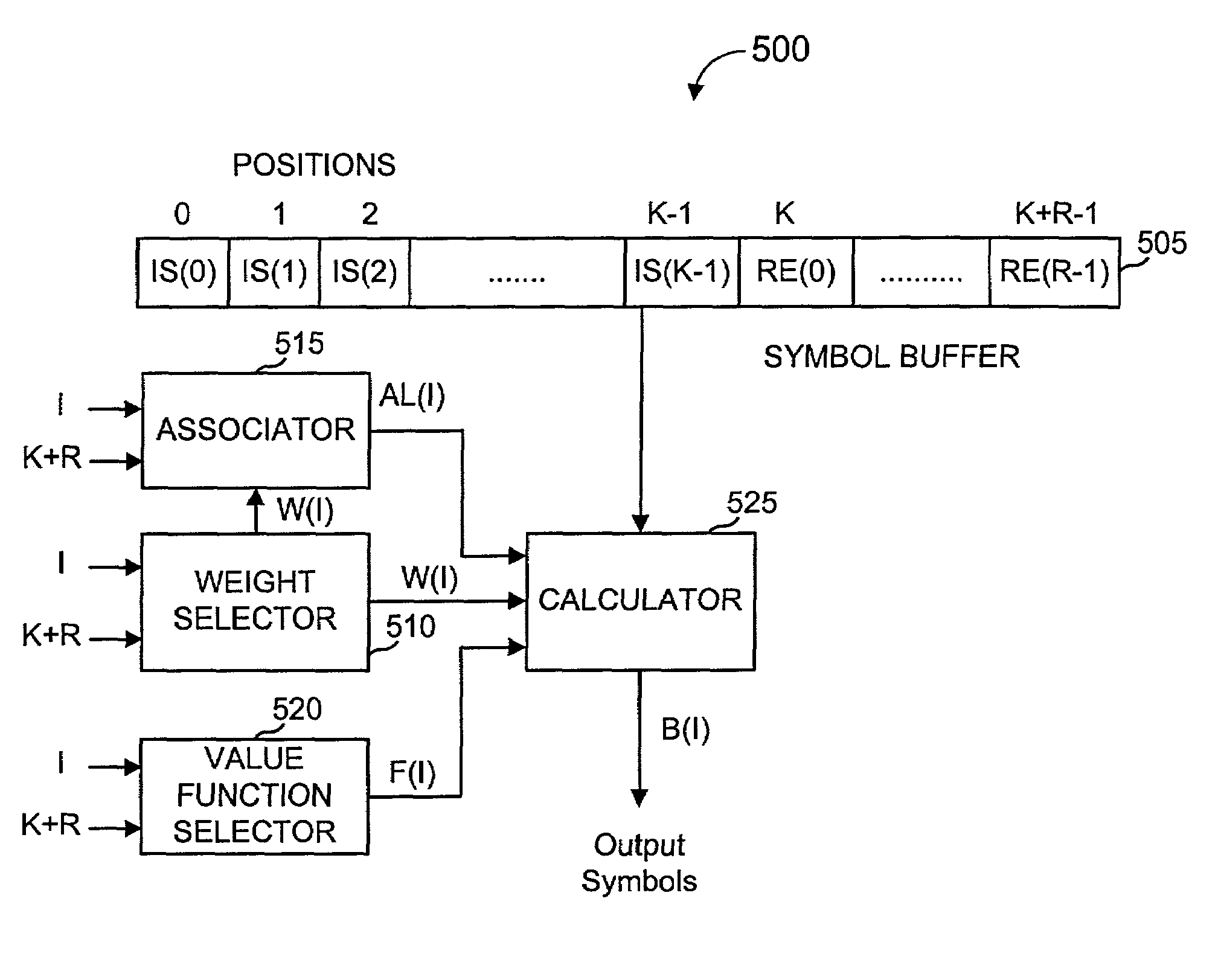

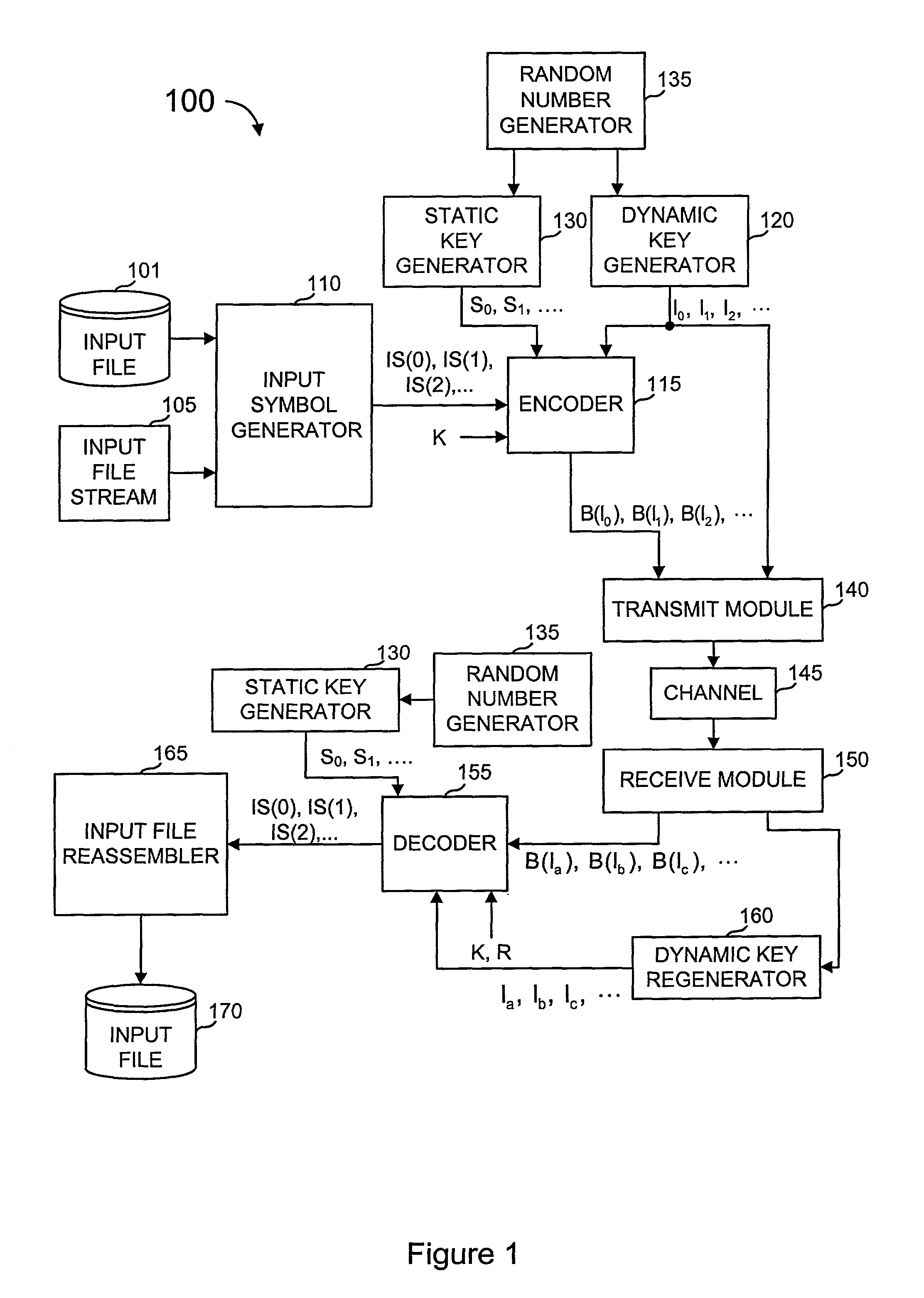

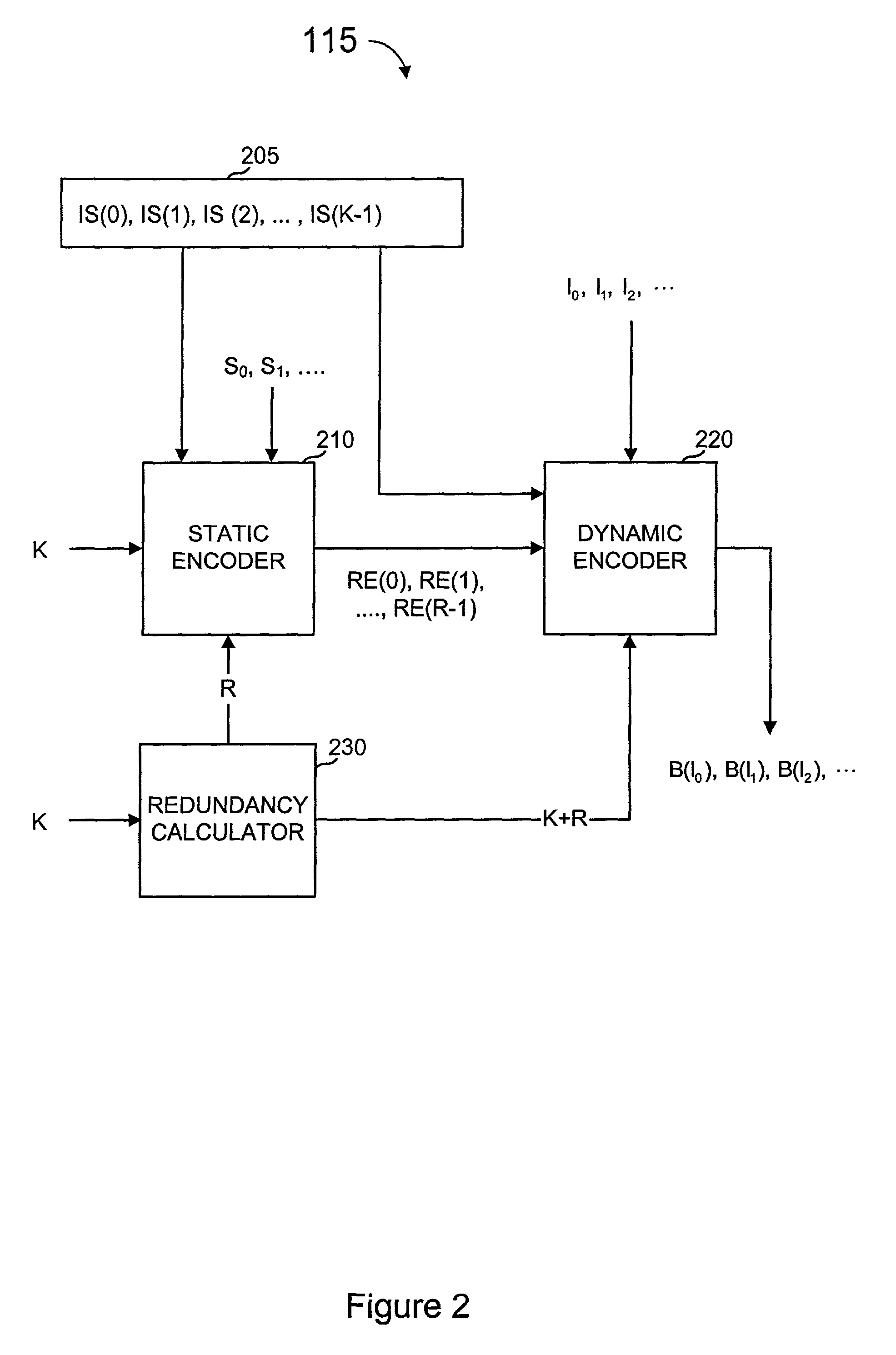

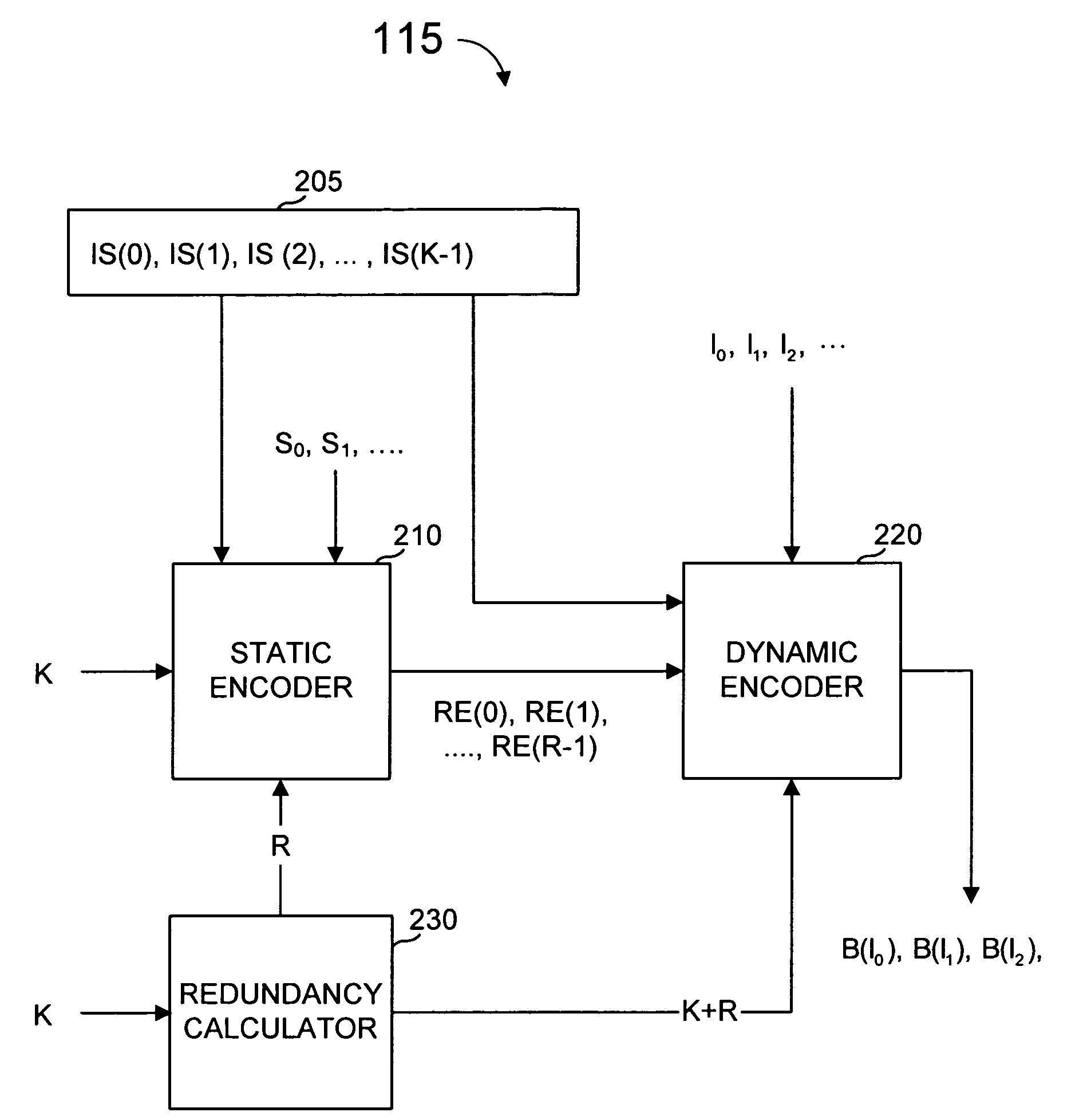

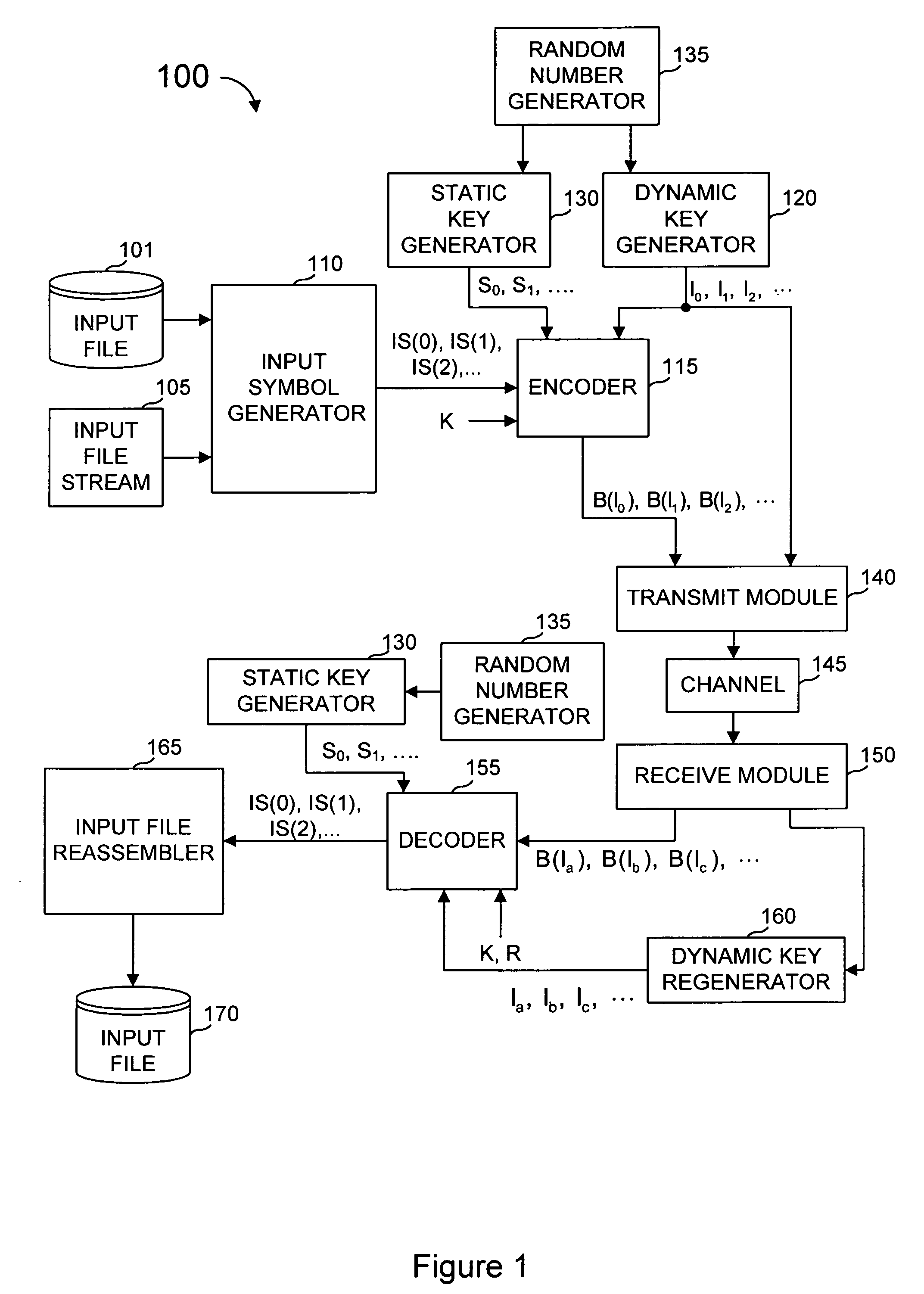

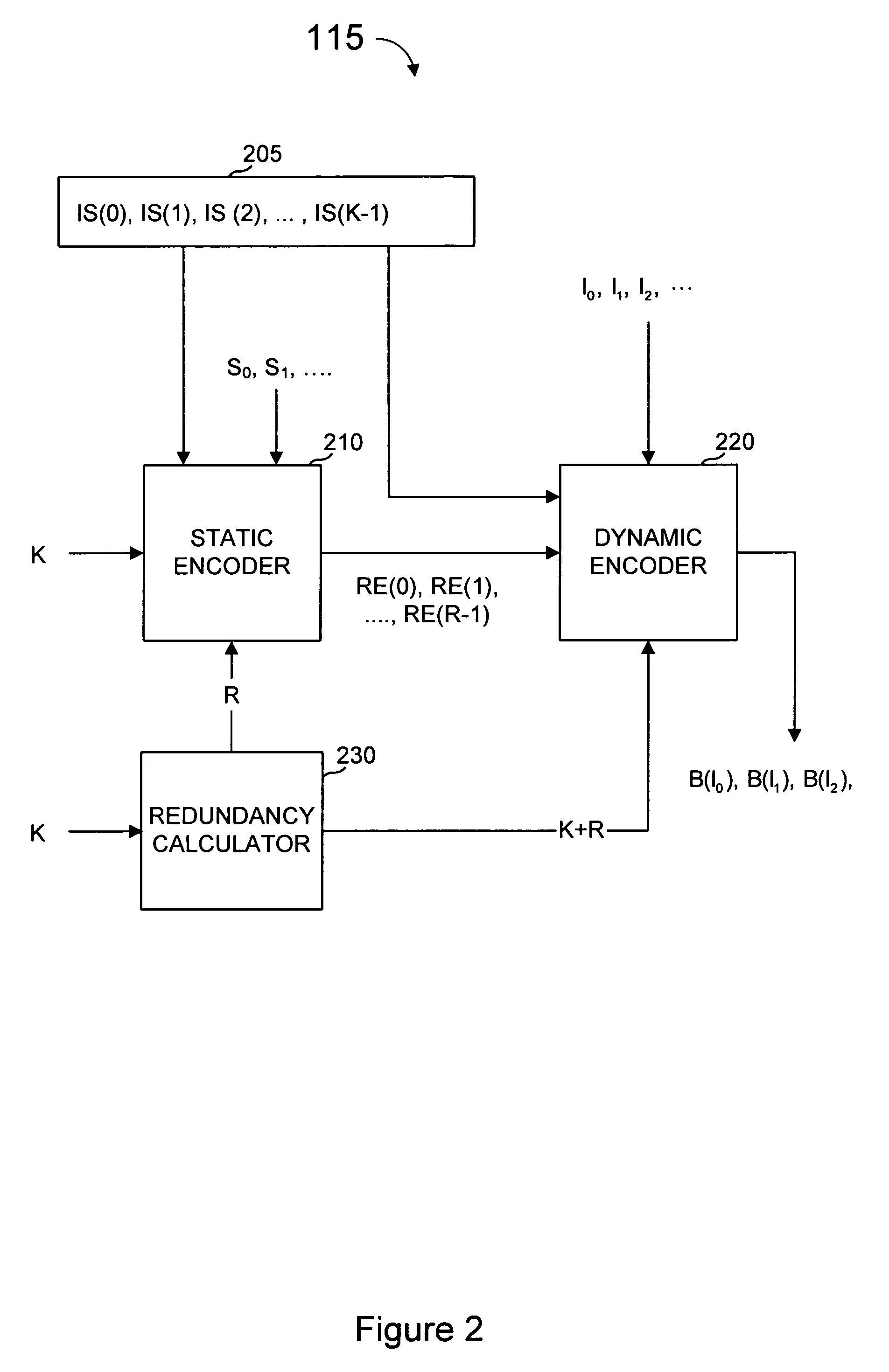

File download and streaming system

Owner:QUALCOMM INC

Channel coding/decoding apparatus and method using a parallel concatenated low density parity check code

InactiveUS20050149841A1Reduce complexityError prevention/detection by using return channelError detection/correctionComputer hardwareLow-density parity-check code

A parallel concatenated low density parity check (LDPC) code having a variable code rate is provided by generating, upon receiving information bits, a first component LDPC code according to the information bits, interleaving the information bits according to a predetermined interleaving rule, and generating a second component LDPC code according to the interleaved information bits. With use of the parallel concatenated LDPC code, a mobile communication system can use a Hybrid Automatic Retransmission Request (HARQ) scheme and an Adaptive Modulation and Coding (AMC) scheme without restriction.

Owner:SAMSUNG ELECTRONICS CO LTD

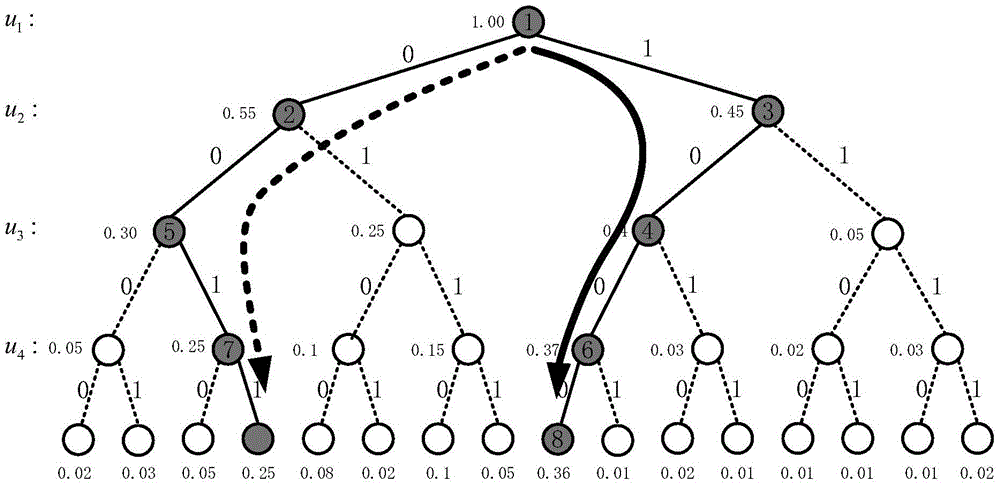

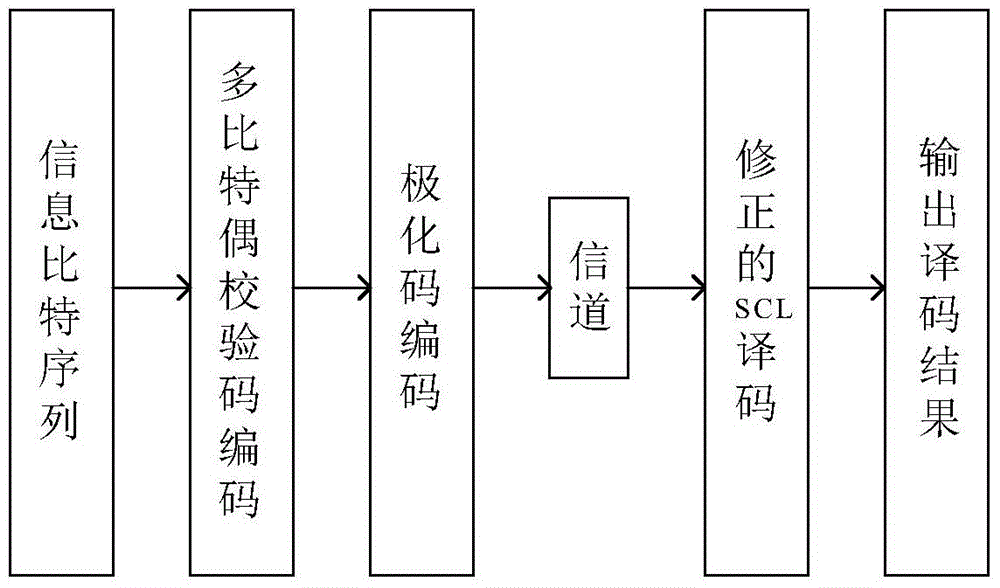

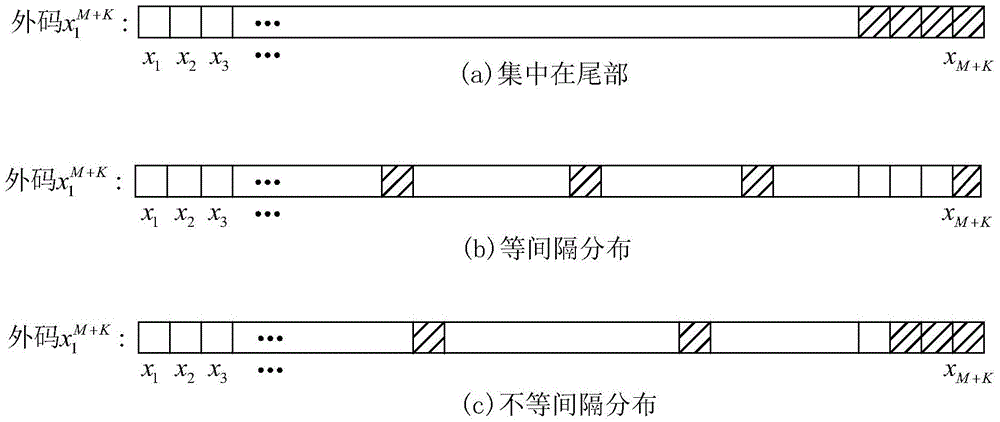

Polarization code and multi-bit even parity check code cascaded error correction coding method

ActiveCN105680883AImprove error correction performanceBreakthrough in error correction performanceCode conversionError correction/detection by combining multiple code structuresComputer hardwareError correction coding

The invention discloses a polarization code and multi-bit even parity check code cascaded error correction coding method. The method comprises the steps: a transmitting end encoder utilizes a multi-bit even parity check code as an outer code, and utilizes a polarization code as an inner code; a receiving end decoder decodes by utilizing a modified successive cancellation list (SCL) decoding algorithm. On the aspect of error correction performance, comparing with the prior art utilizing middle-short code length non-cascaded polarization codes of the SCL decoding algorithm, the polarization code and multi-bit even parity check code cascaded error correction coding method has the advantages that frame error rate performance of a system can be remarkably improved, and a maximum likelihood bound (ML Bound), which cannot be broken through by the SCL decoding algorithm, can be remarkably broken through. On the aspect of engineering realization, according to the polarization code and multi-bit even parity check code cascaded error correction coding method, the outer code utilizes the multi-bit even parity check code, which is simple to code; the modified SCL decoding algorithm is utilized to decode, bit decision and even parity check are combined to be carried out in a decoding process, and compared with the original SCL decoding algorithm, the method provided by the invention does not increase the decoding complexity, and facilitates the engineering realization.

Owner:HUAZHONG UNIV OF SCI & TECH

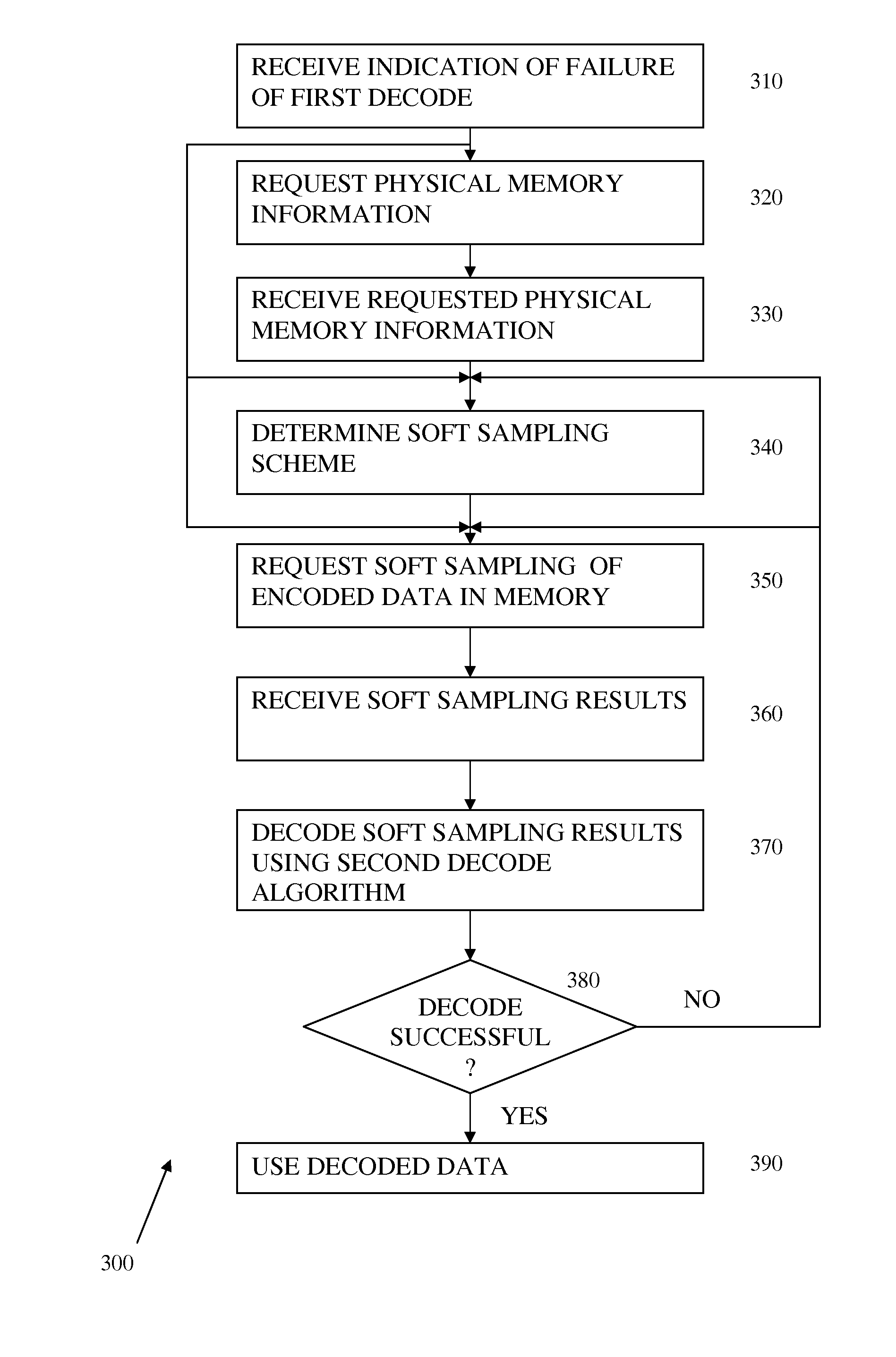

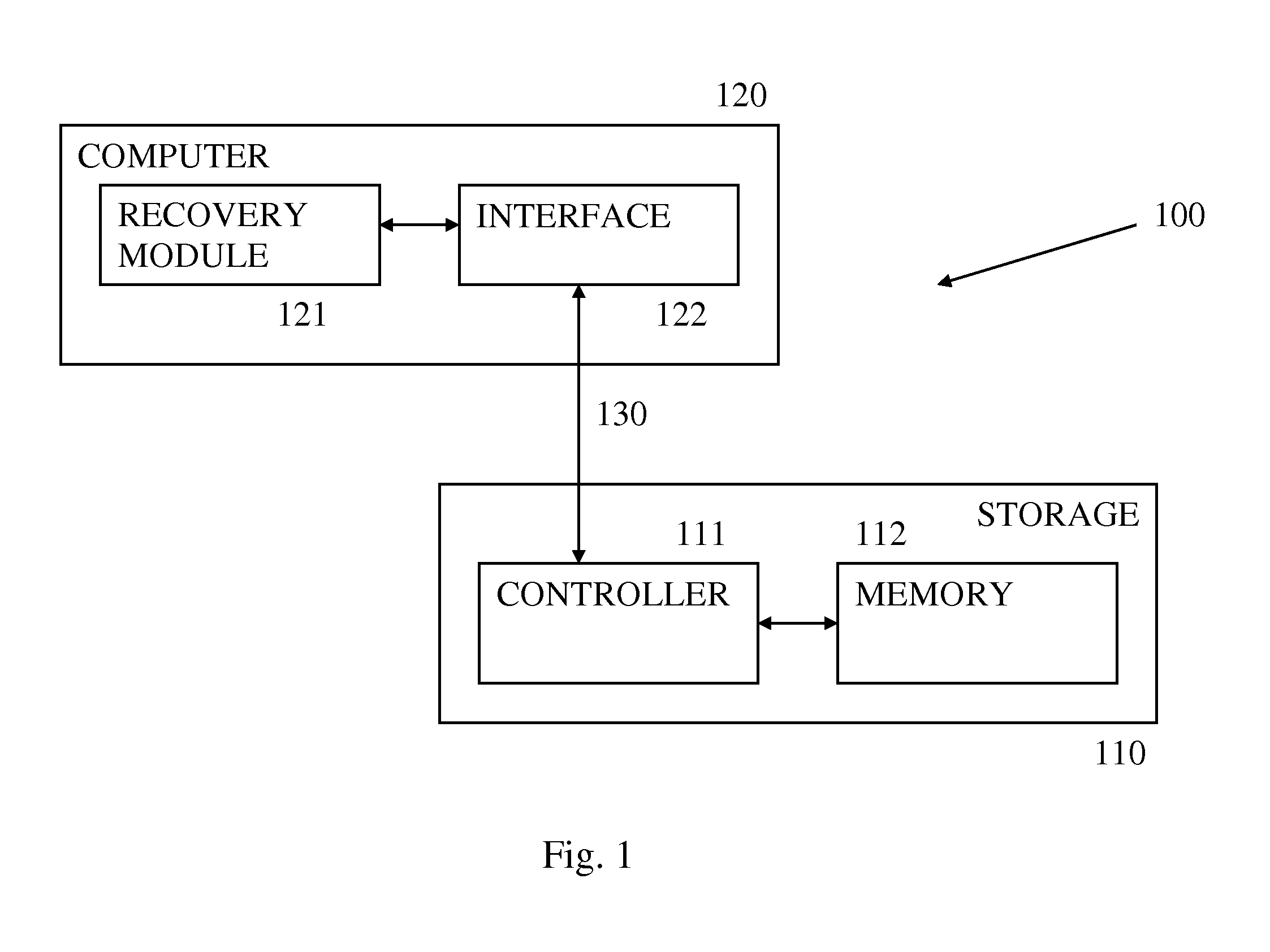

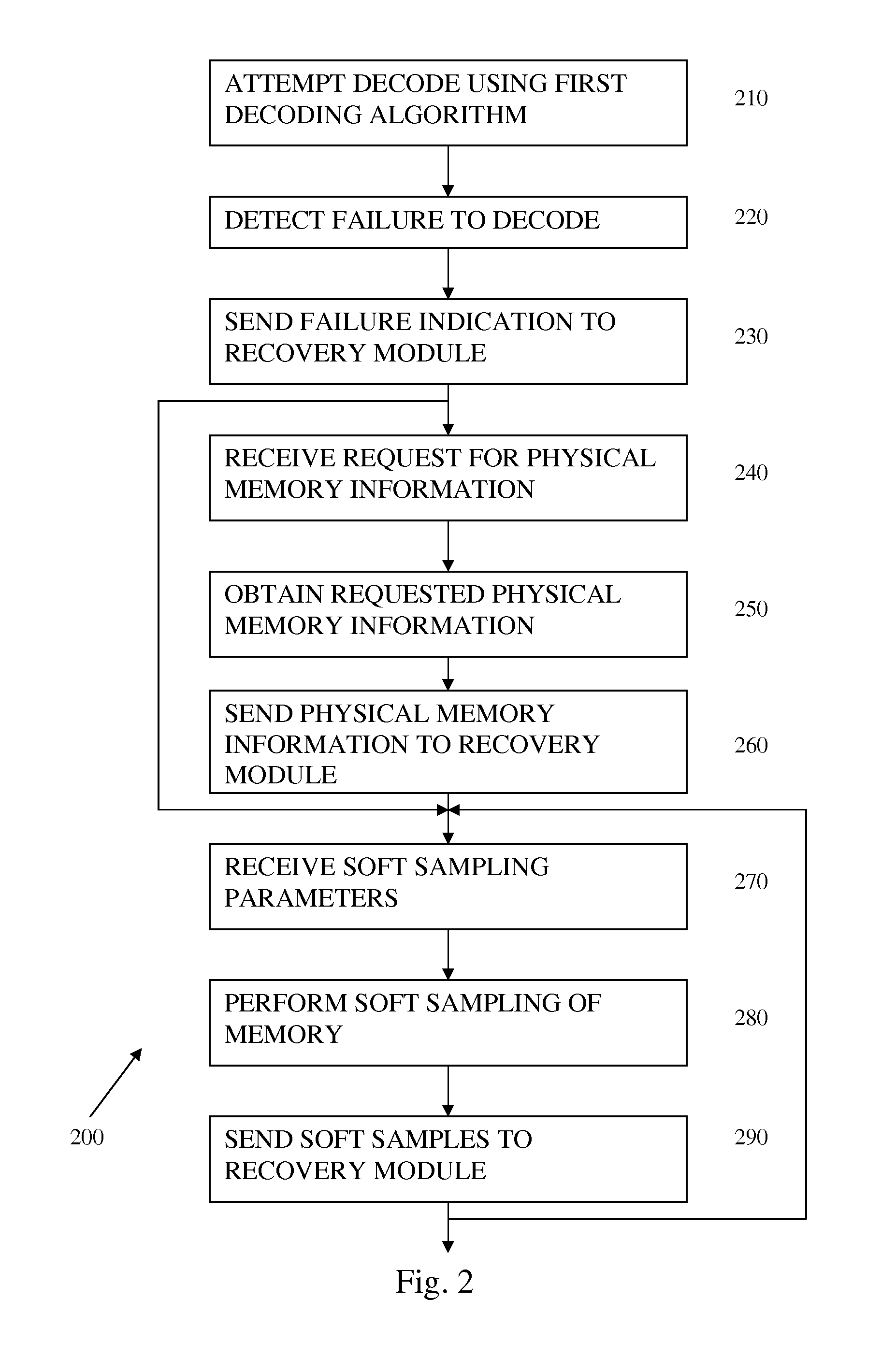

System and method for restoring damaged data programmed on a flash device

A system and a method for restoring damaged data programmed on a memory, such as a Flash memory, including detecting a failure of a memory controller to successfully decode encoded data using a first decoding algorithm, performing soft sampling of the encoded data to provide soft samples of the encoded data, applying, for example, by a computer coupled to the memory controller, a second decoding algorithm on the soft samples of the encoded data. The second decoding algorithm may have an error correction capability exceeding an error correction capability of the first decoding algorithm

Owner:AVAGO TECH INT SALES PTE LTD

Data communication system with multi-dimensional error-correction product codes

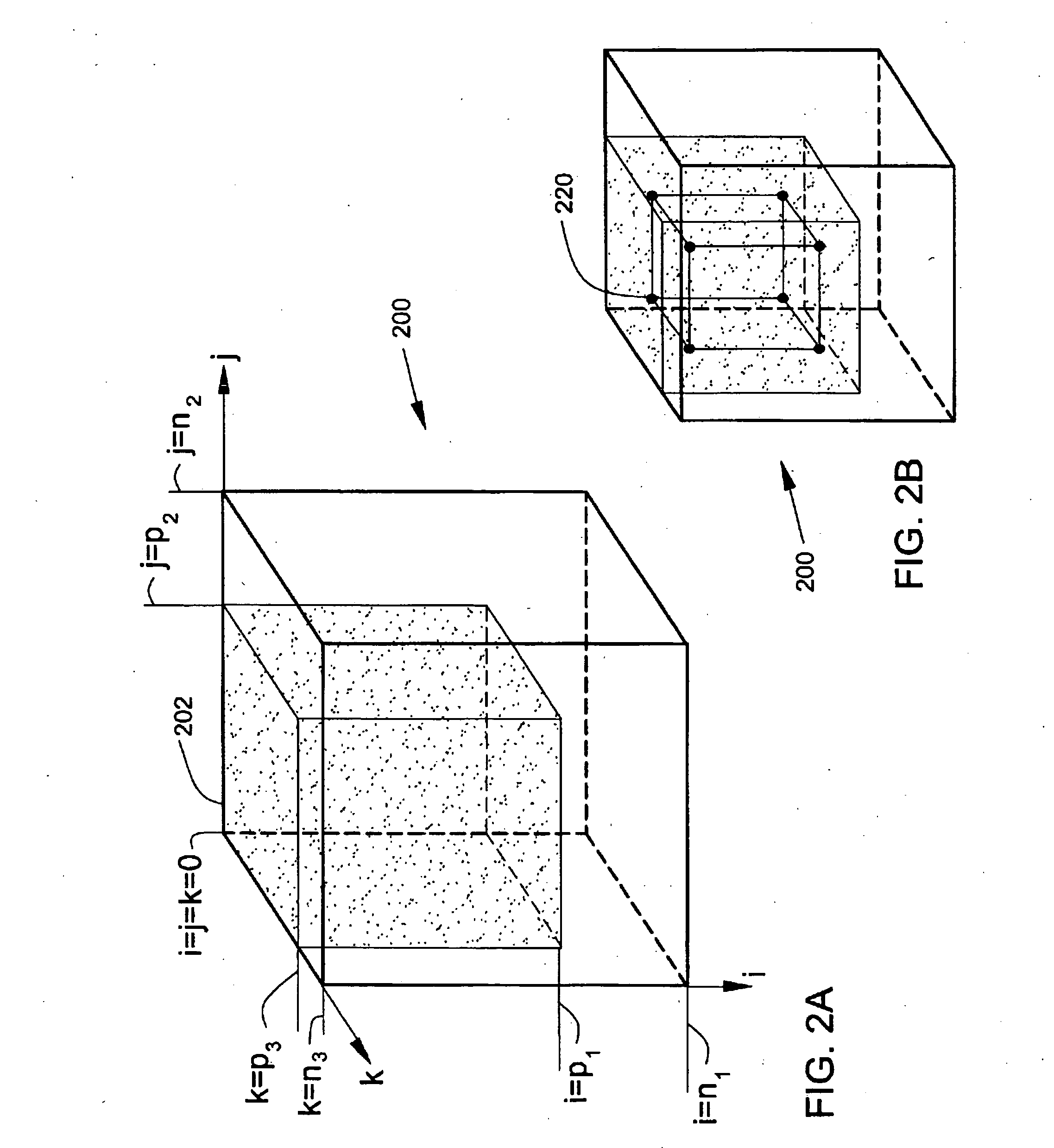

InactiveUS7415651B2Reduce errorsCode conversionError correction/detection by combining multiple code structuresCommunications systemMulti dimensional

A data communication system has a combiner circuit that combines a set of information symbols with error correction codes and that generates a set of product codes that are at least three dimensional. A communication channel receives the set of product codes and provides the set of product codes with errors after a channel delay. A channel detector receives the set of product codes with the errors and generates a channel detector output. An error correction circuit receives the channel detector output and iteratively removes the errors to provide a set of reproduced information symbols with a reduced number of the errors.

Owner:SEAGATE TECH LLC

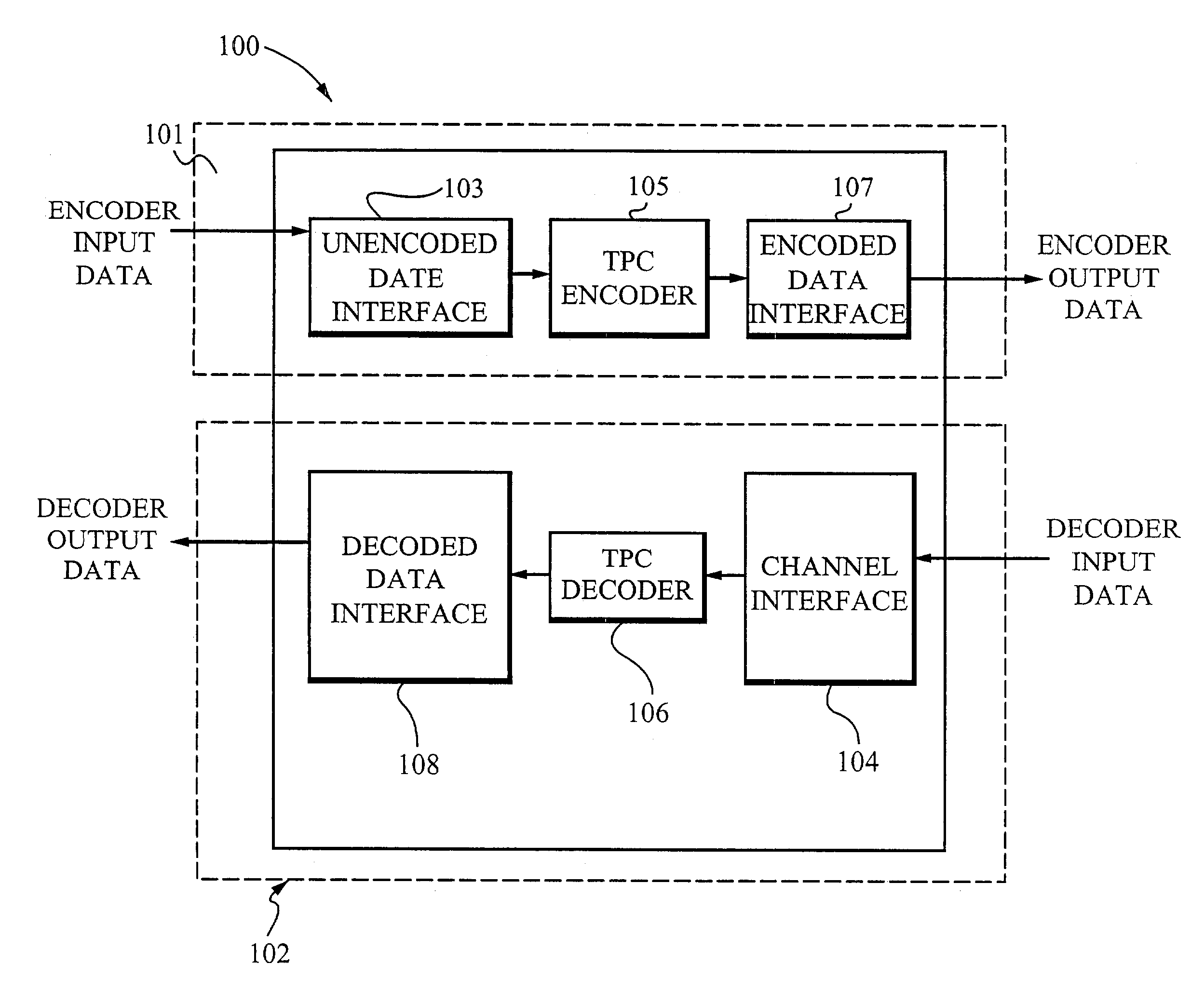

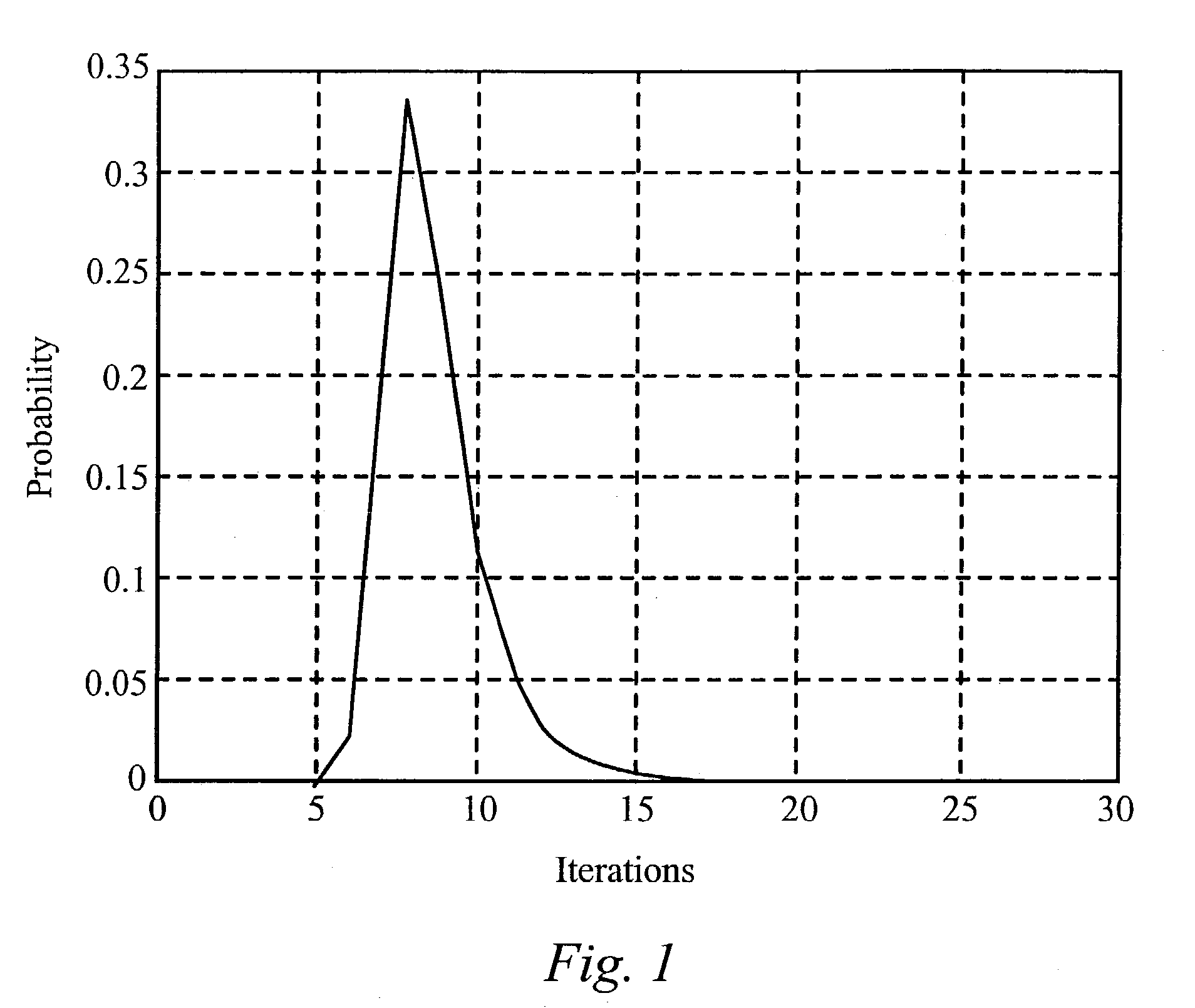

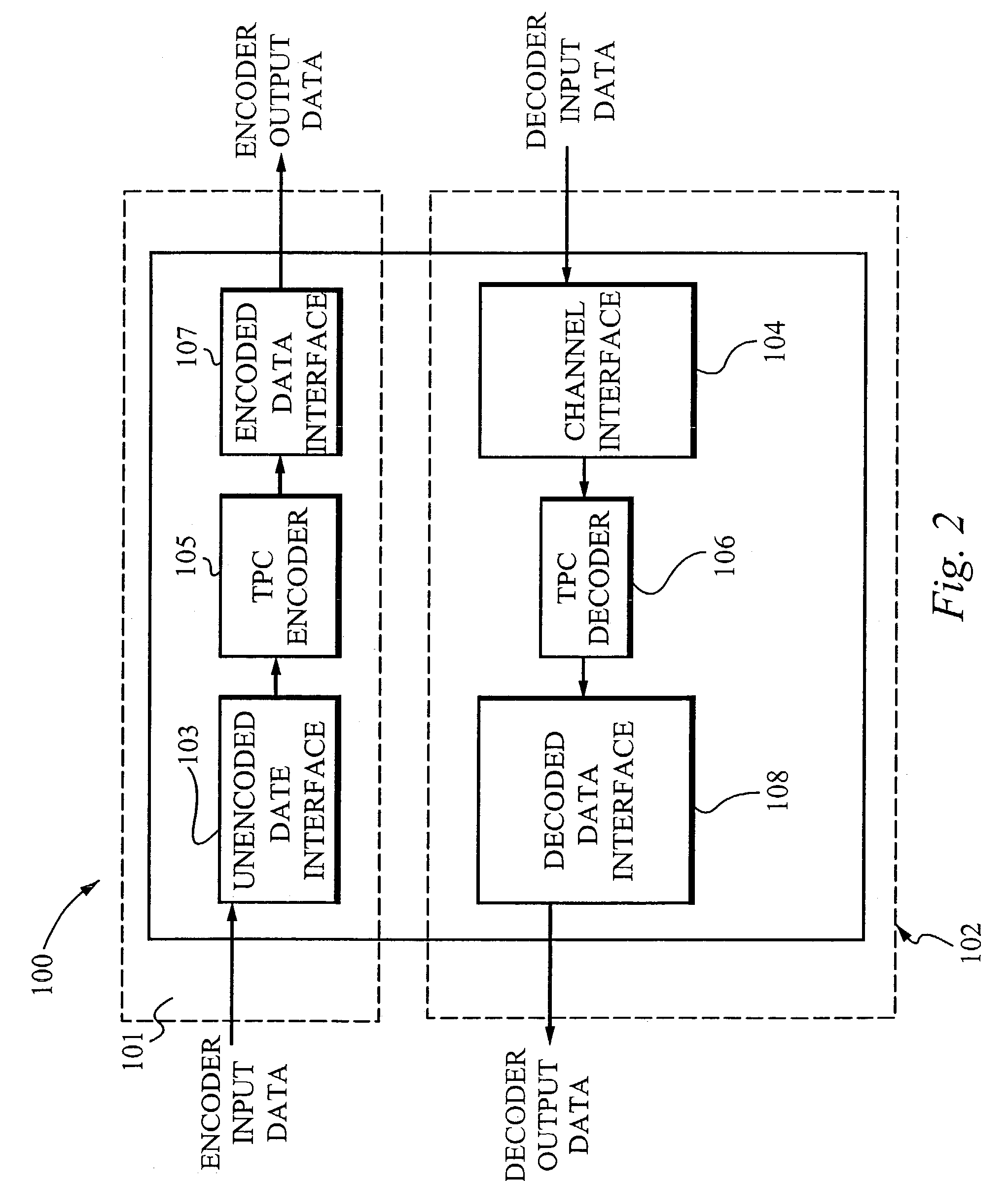

Enhanced turbo product code decoder system utilizing a codeword organization method

InactiveUS7039846B2Error preventionOther decoding techniquesMemory addressTheoretical computer science

A method and apparatus for decoding a linear block encoded string of information bits comprising: converting the string into a plurality of codewords. Performing hard and soft decisions on each codeword to generate a hard and soft decision vector. Computing the syndrome and finding the location of the two minimum values by Galois Field Arithmetic. Designating these values LOW1 and LOW2 and xoring with a Nc1, thus generating Nc2. Swapping Nc1 with Nc2 and determining the lowest soft decision value, Min1 and a next lowest value, Min2. The two bit locations creating Min1 are designated as MinA and MinB. MinA being replaced with Min2 minus the value MinA. MinB being replaced with Min2 minus the value at MinB. Generating an output codeword by subtracting Min1 from all other bit locations values and 2's complementing all soft values with 0 in their location. Creating the new soft value vector. Some embodiments include a system and method that organizes an encoded codeword. The encoded codeword has several codeword bits. The method receives the encoded codeword, assigns multiple codeword bits to at least one memory address in a plurality of memory addresses, and iteratively decodes the received codeword by utilizing the plurality of memory addresses in a predetermined order. The predetermined order is based on a dimension of the received codeword.

Owner:COMTECH TELECOMM CORP

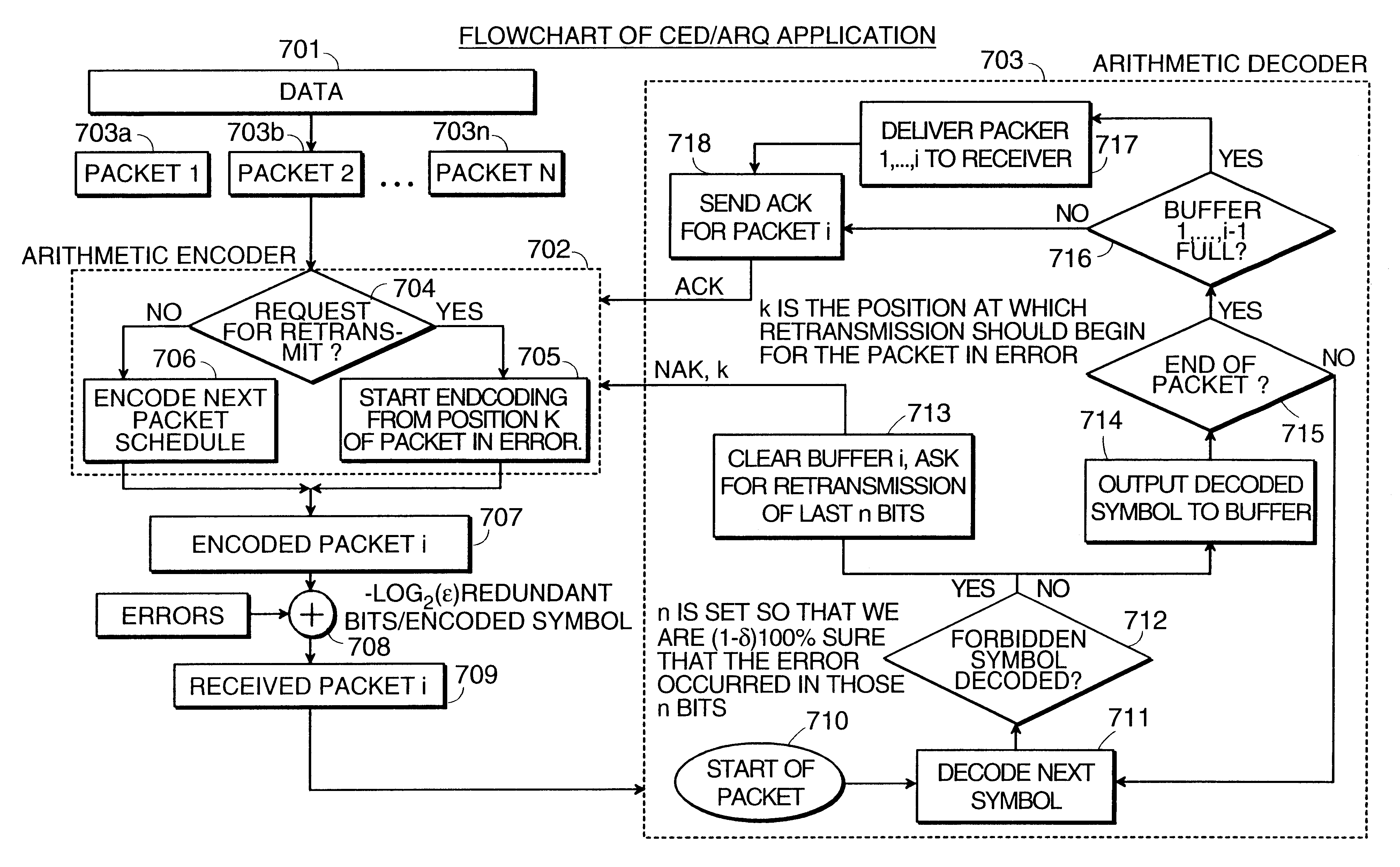

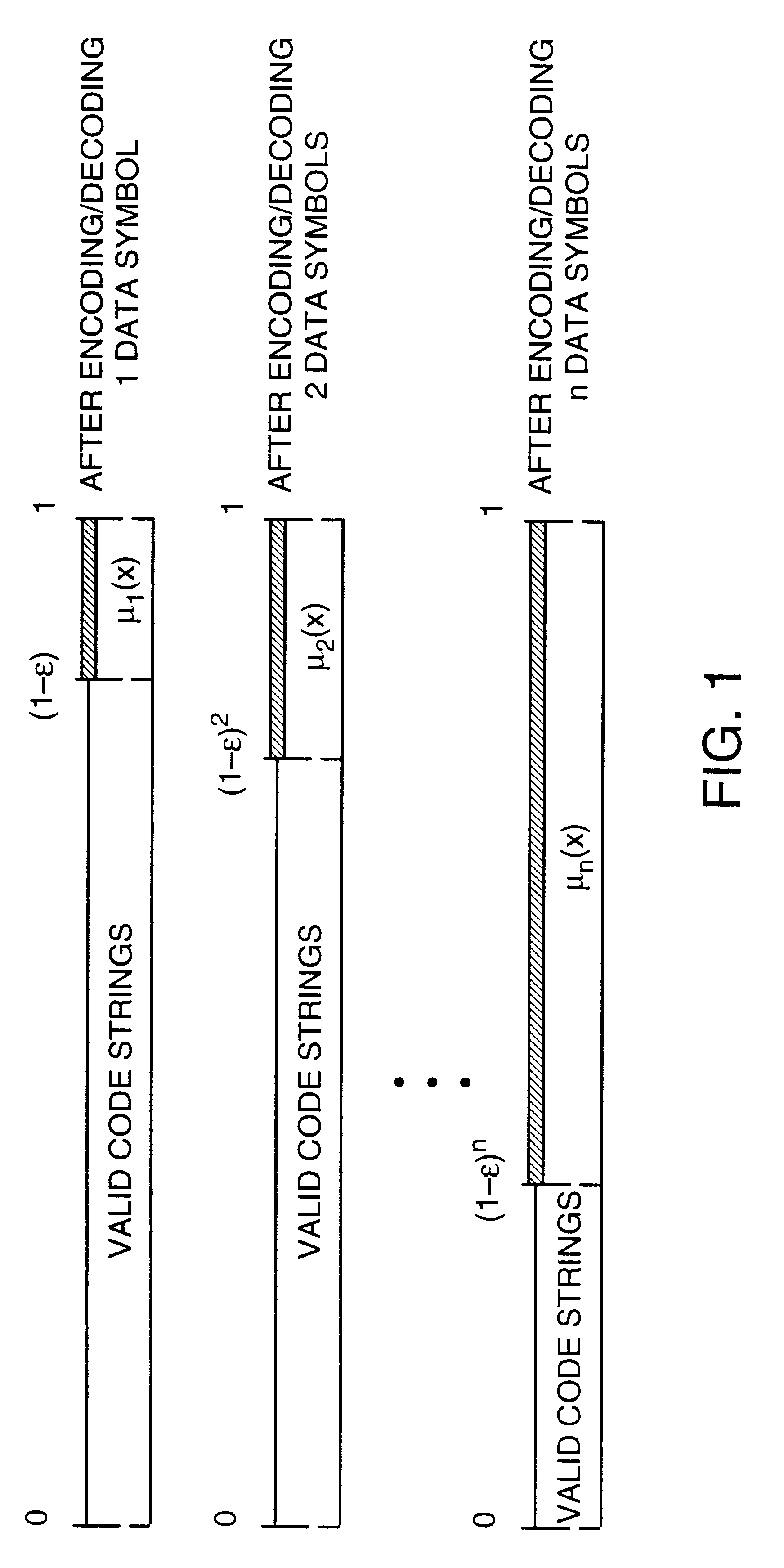

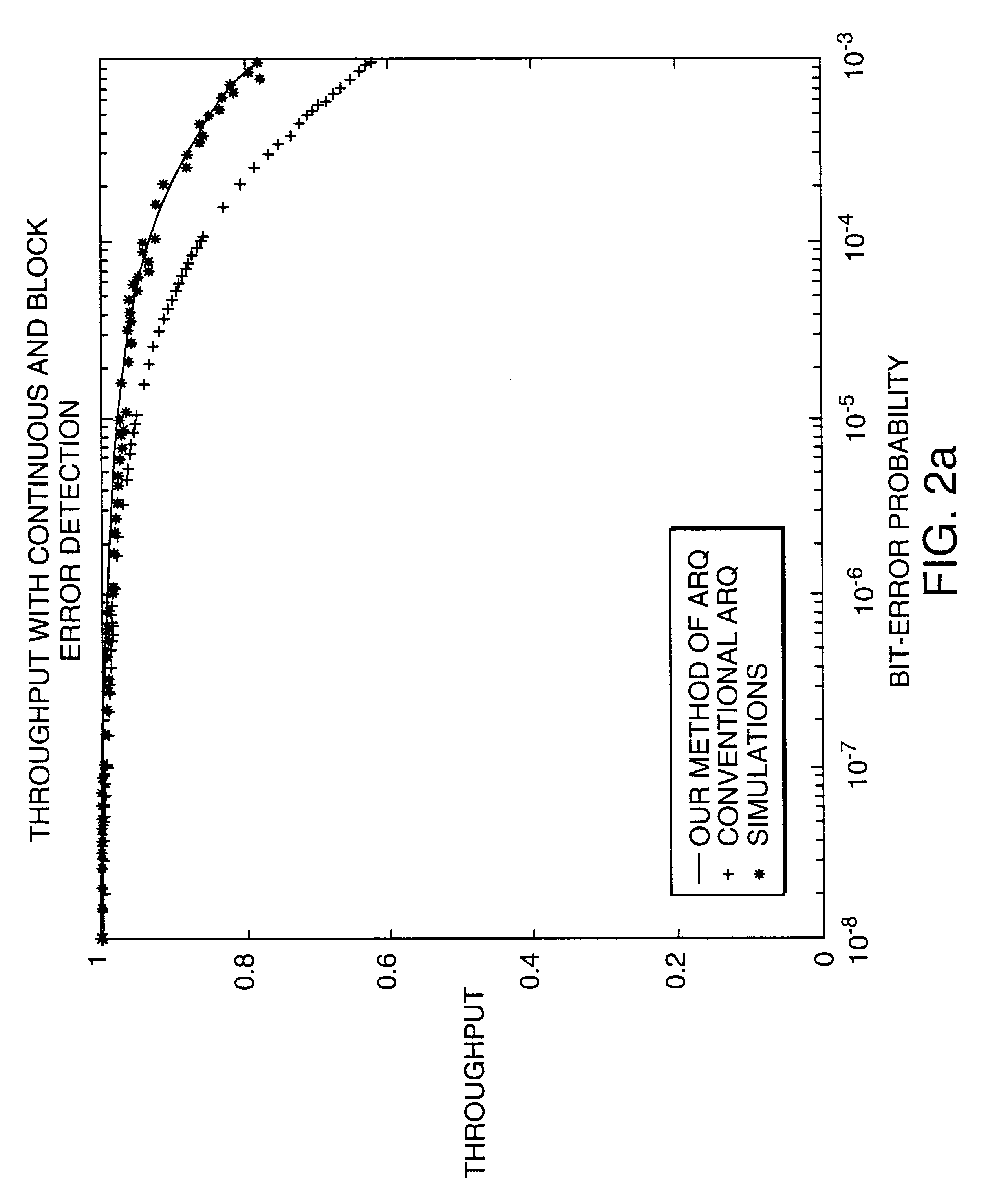

Data transmission using arithmetic coding based continuous error detection

InactiveUS6418549B1Error prevention/detection by using return channelTransmission systemsAutomatic repeat requestTrade offs

Method and apparatus for image transmission using arithmetic coding, based on continuous error detection uses a controlled amount of added redundancy. A continuous error detection scheme is provided, wherein there is a trade-off between the amount of added redundancy and the time needed to detect an error once it occurs. Herein, there is no need for the cyclic redundancy check (CRC) to wait until an entire block of data has been received and processed before an error can be detected. The invention can be used to great advantage both in the automatic repeat request (ARQ) and other concatenated coding schemes. Errors in the received bit stream are detected by introducing added redundancy, e.g., a forbidden symbol, in the arithmetic coding operation. The forbidden symbol is never intended to be encoded. The redundancy error causes loss of synchronization, which is used to detect errors. If a forbidden symbol gets decoded, it means that an error has occurred. In this invention, there is direct control over the amount of redundancy added vs. the amount of time it takes to detect an error. For image compression systems, by using the invention and ARQ, only one device would suffice both for source compression and channel coding.

Owner:MERU NETWORKS