Patents

Literature

14535 results about "Multiplexer" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In electronics, a multiplexer (or mux), also known as a data selector, is a device that selects between several analog or digital input signals and forwards it to a single output line. A multiplexer of 2ⁿ inputs has n select lines, which are used to select which input line to send to the output. Multiplexers are mainly used to increase the amount of data that can be sent over the network within a certain amount of time and bandwidth.

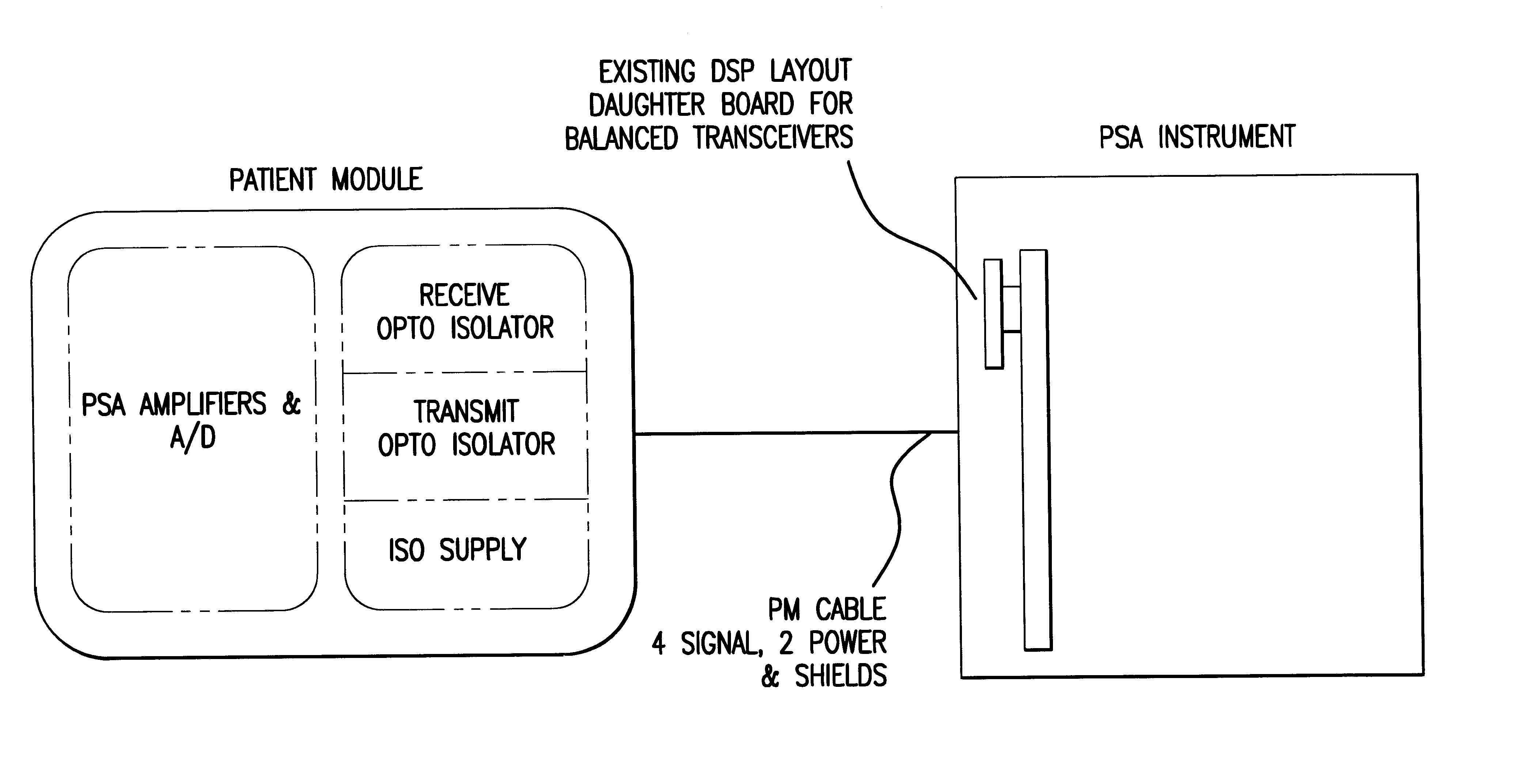

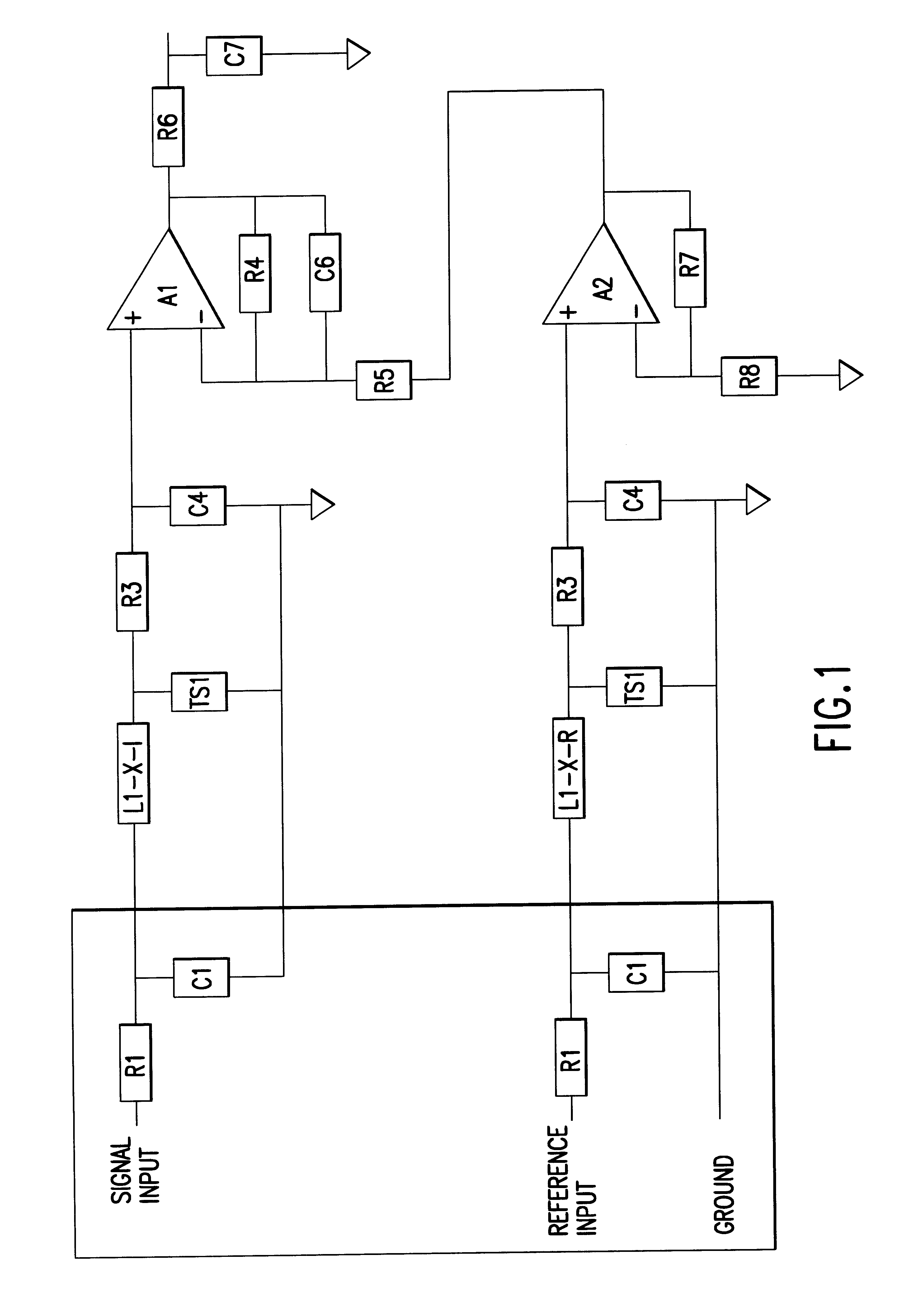

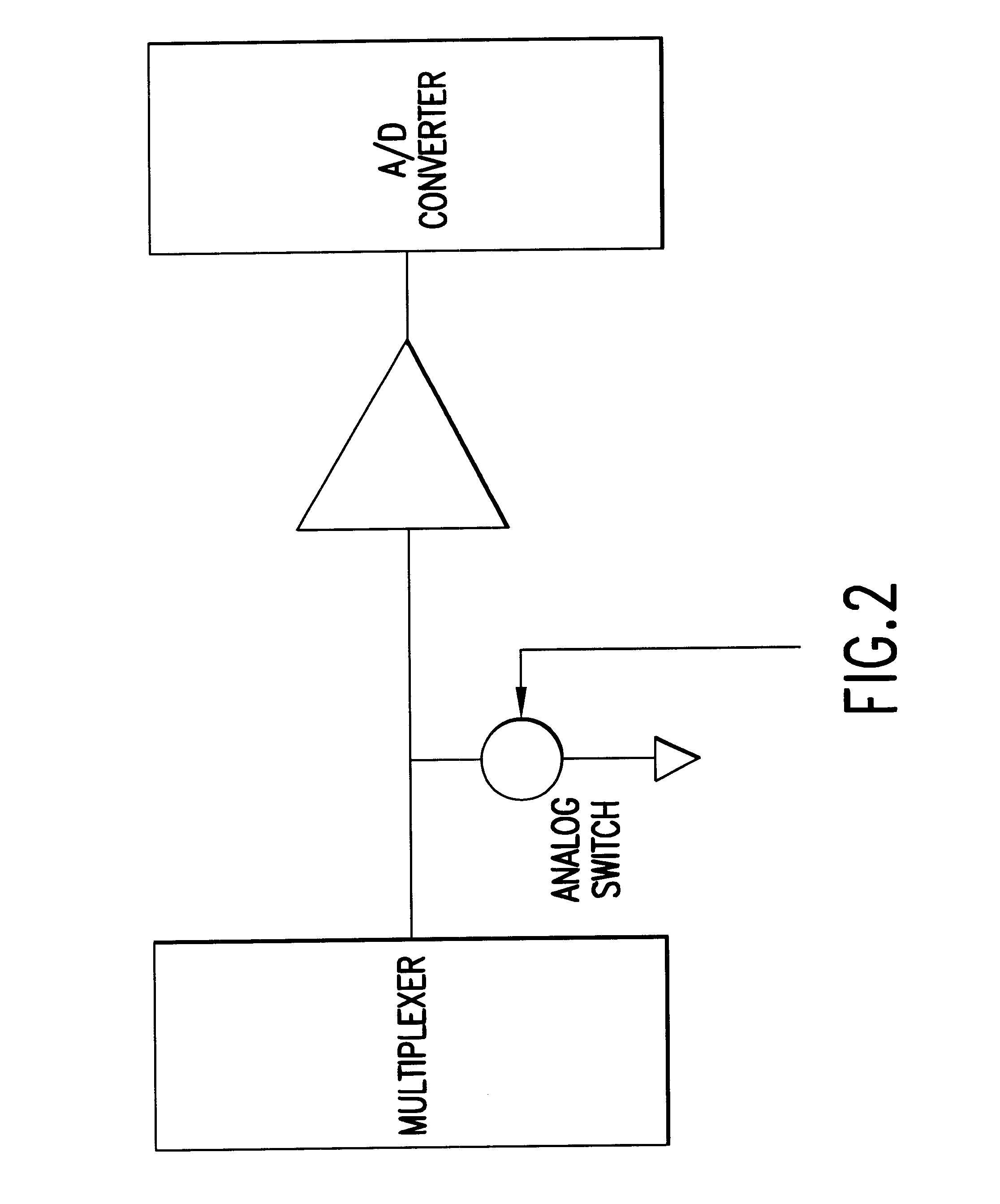

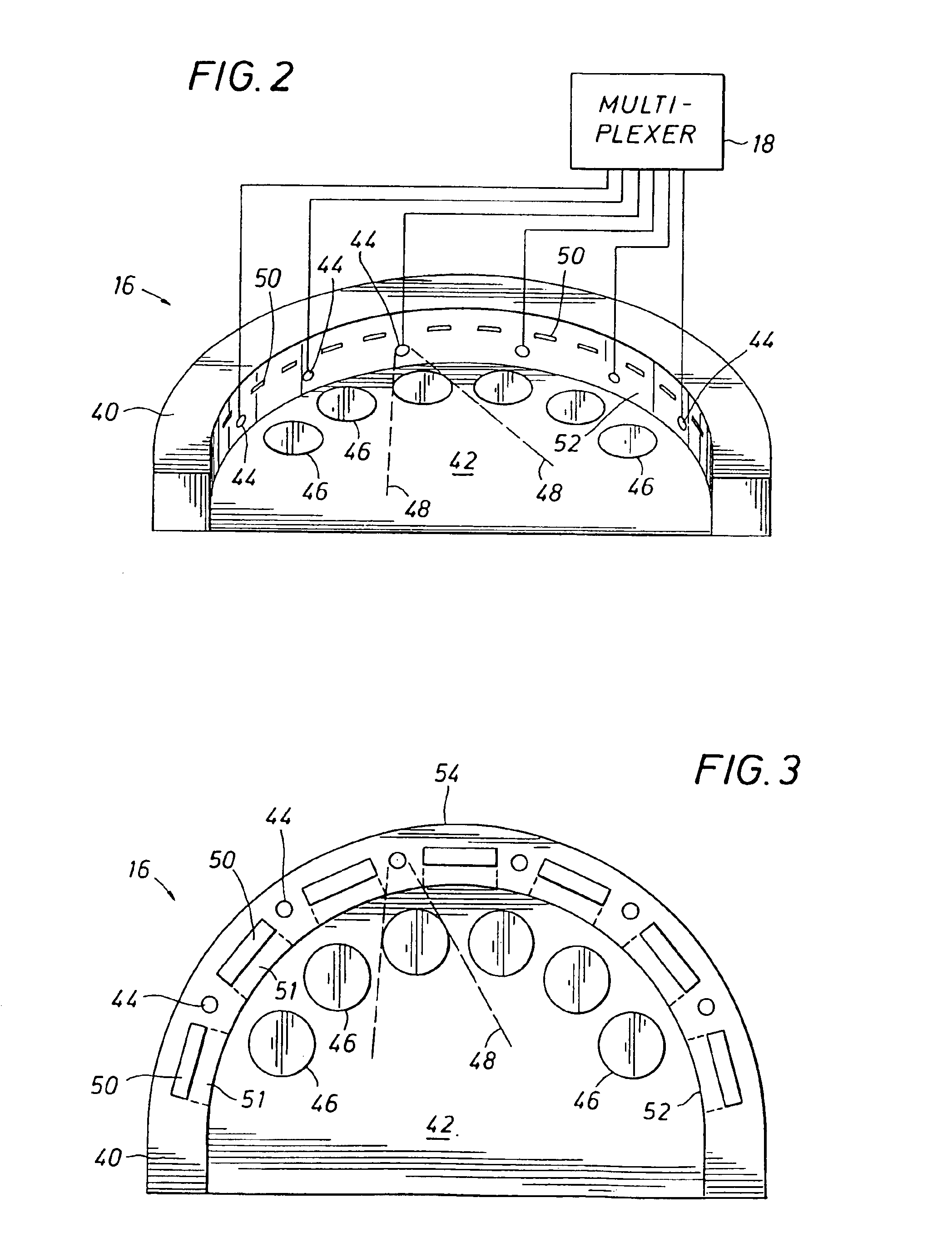

Module for acquiring electroencephalograph signals from a patient

InactiveUS6430437B1Good techniqueEliminate artifactsElectroencephalographyPloughsAudio power amplifierMultiplexer

A patient module comprising an 8 channel EEG pre-amplifier whose signal acquisition and processing characteristics are optimized for use in the operating room and intensive care unit. This patient module comprises at least an optimized multistage input filter, an optimized input stage circuit topography, ultra-isolation, oversampling, a multiplexer inter-sample charge dump, and high performance low-frequency-enhanced shielding.

Owner:JPMORGAN CHASE BANK NA

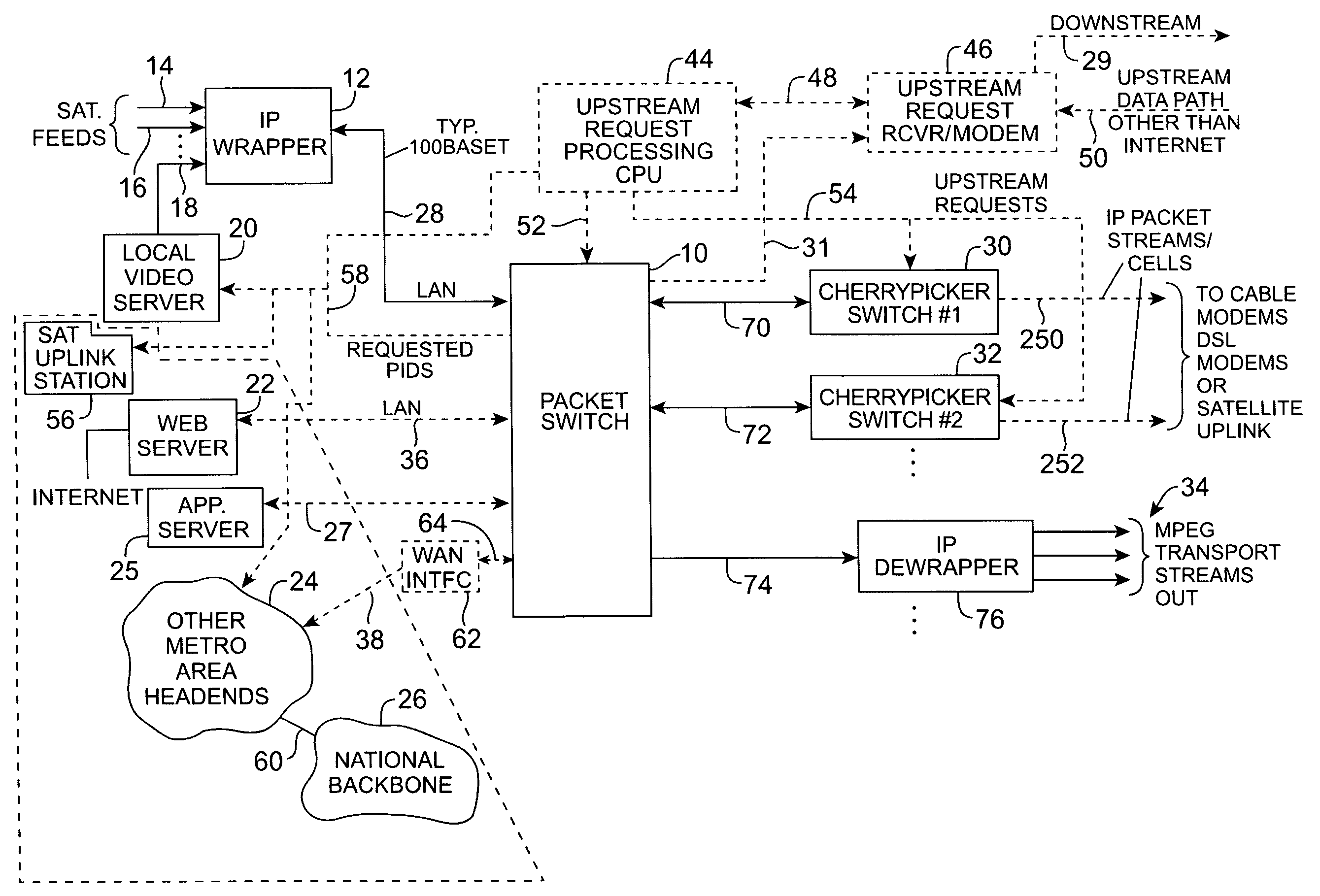

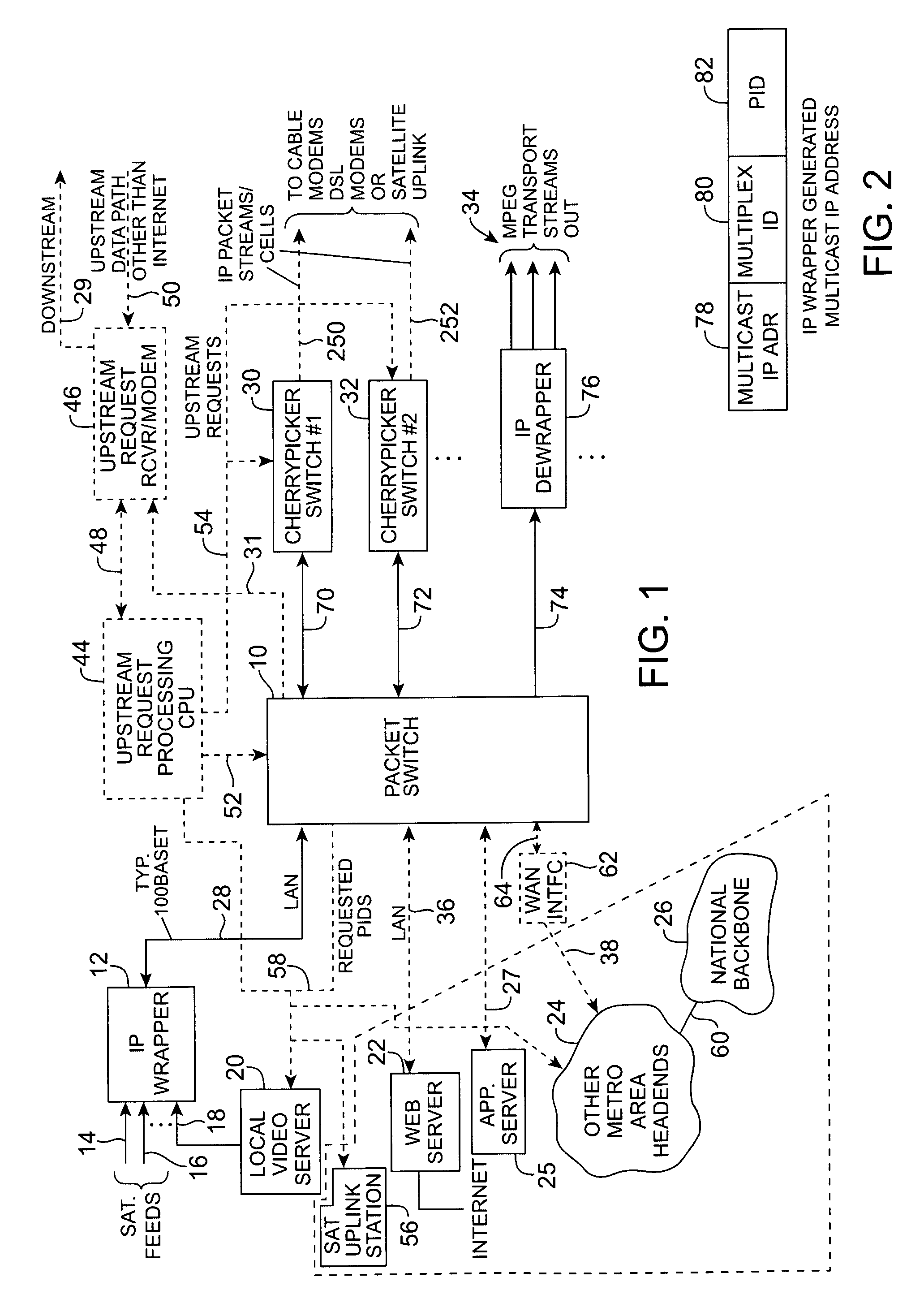

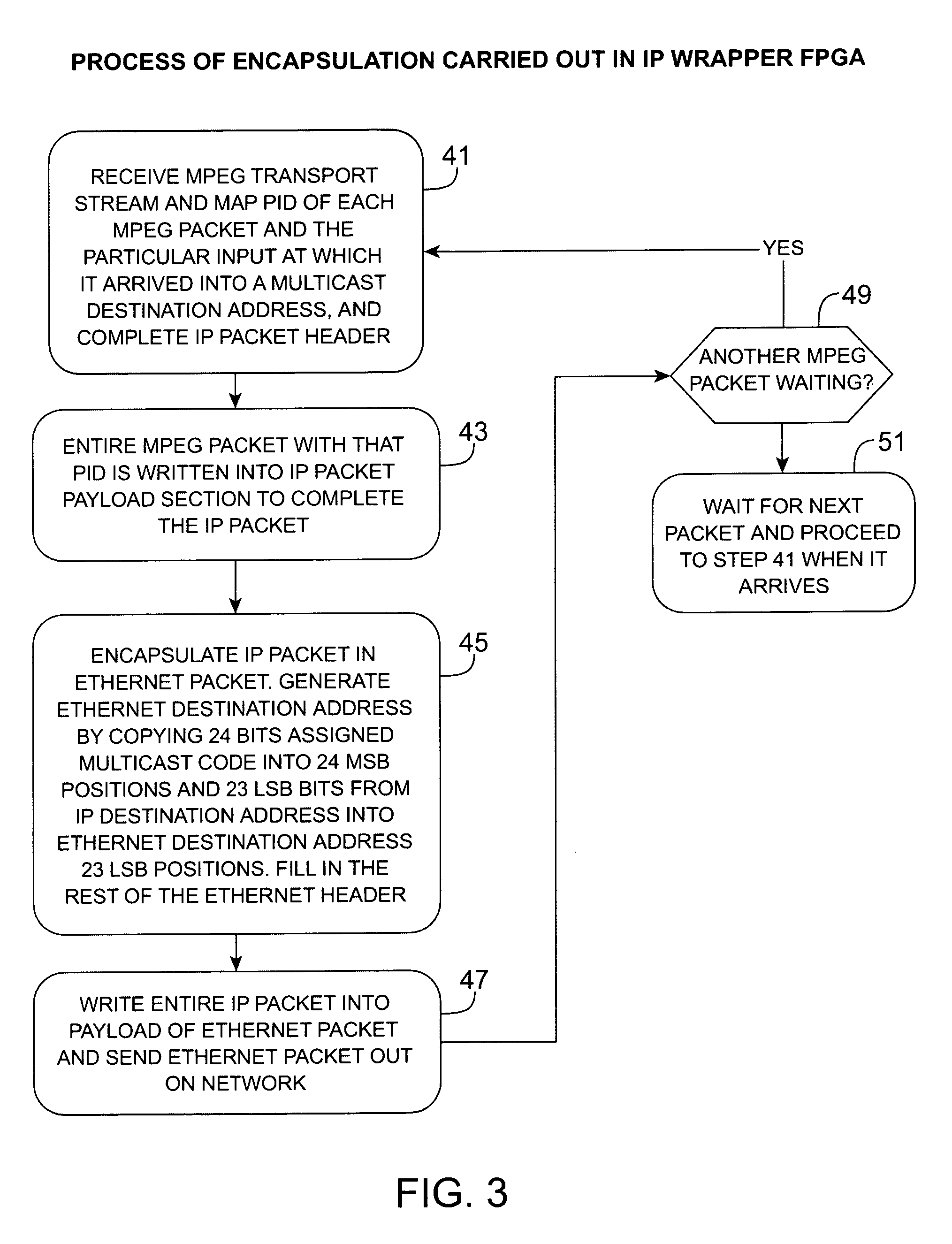

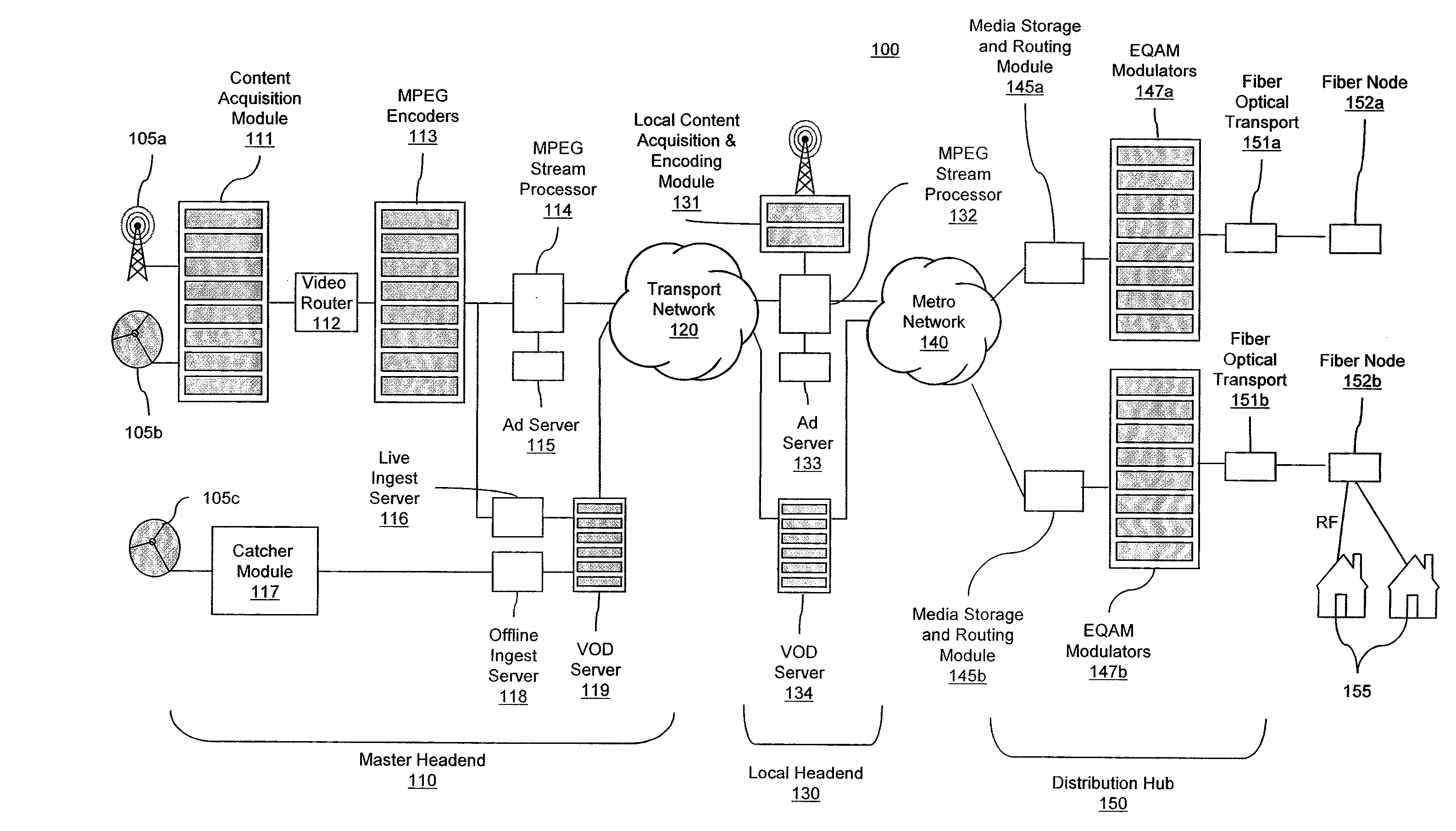

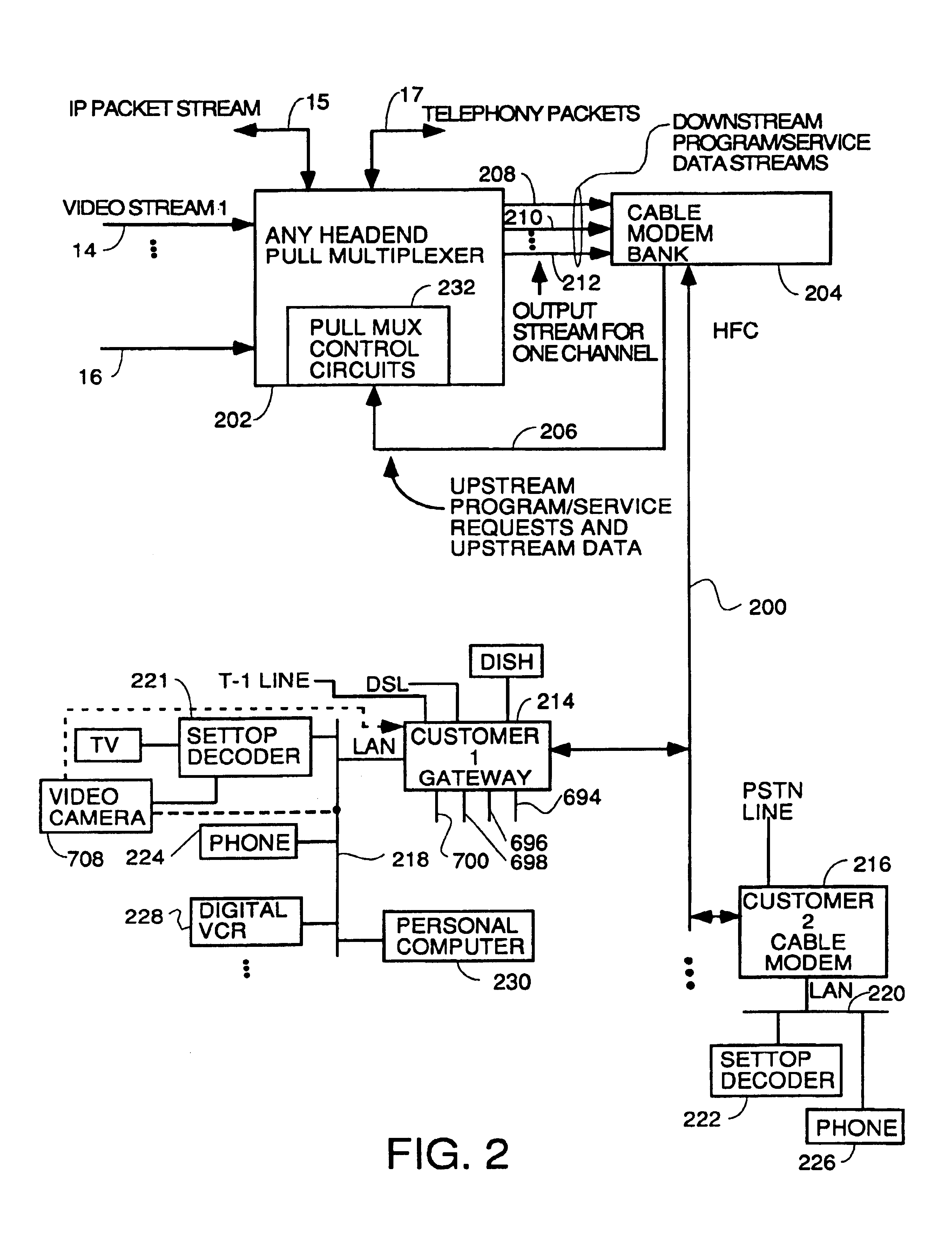

Headend cherrypicker multiplexer with switched front end

InactiveUS7039048B1Low costEasily scaledBroadband local area networksTime-division multiplexMPEG transport streamModem device

A headend or central office or satellite uplink facility for receiving upstream video-on-demand requests and MPEG transport streams containing video program data and packetizing said video data into TCP / IP or UDP / IP packets and LAN packets and routing them through a switch to one or more cherrypicker multiplexers. Each cherrypicker multiplexer receives LAN packets, depacketizes the MPEG data, partially or fully decompresses the data and recompresses the data to another smaller bandwidth, and repacketizes the data into MPEG packets or TCP / IP or UDP / IP packets. The repacketized TCP / IP or UDP / IP packets are transmitted directly to the customer as TCP / IP or UDP / IP packet data. MPEG packets generated by the cherrypicker multiplexer are, optionally, encapsulated in LAN packets addressed to an IP dewrapper circuit. There, they are depacketized back to MPEG packets and transmitted to the appropriate transmitter or modem for transmitting to a customer. Internet data and data from application servers, referred to as iData, can also be transmitted to customers through the cherrypicker multiplexers or a downstream modem, and upstream iData can be received through the modem.

Owner:GOOGLE TECH HLDG LLC

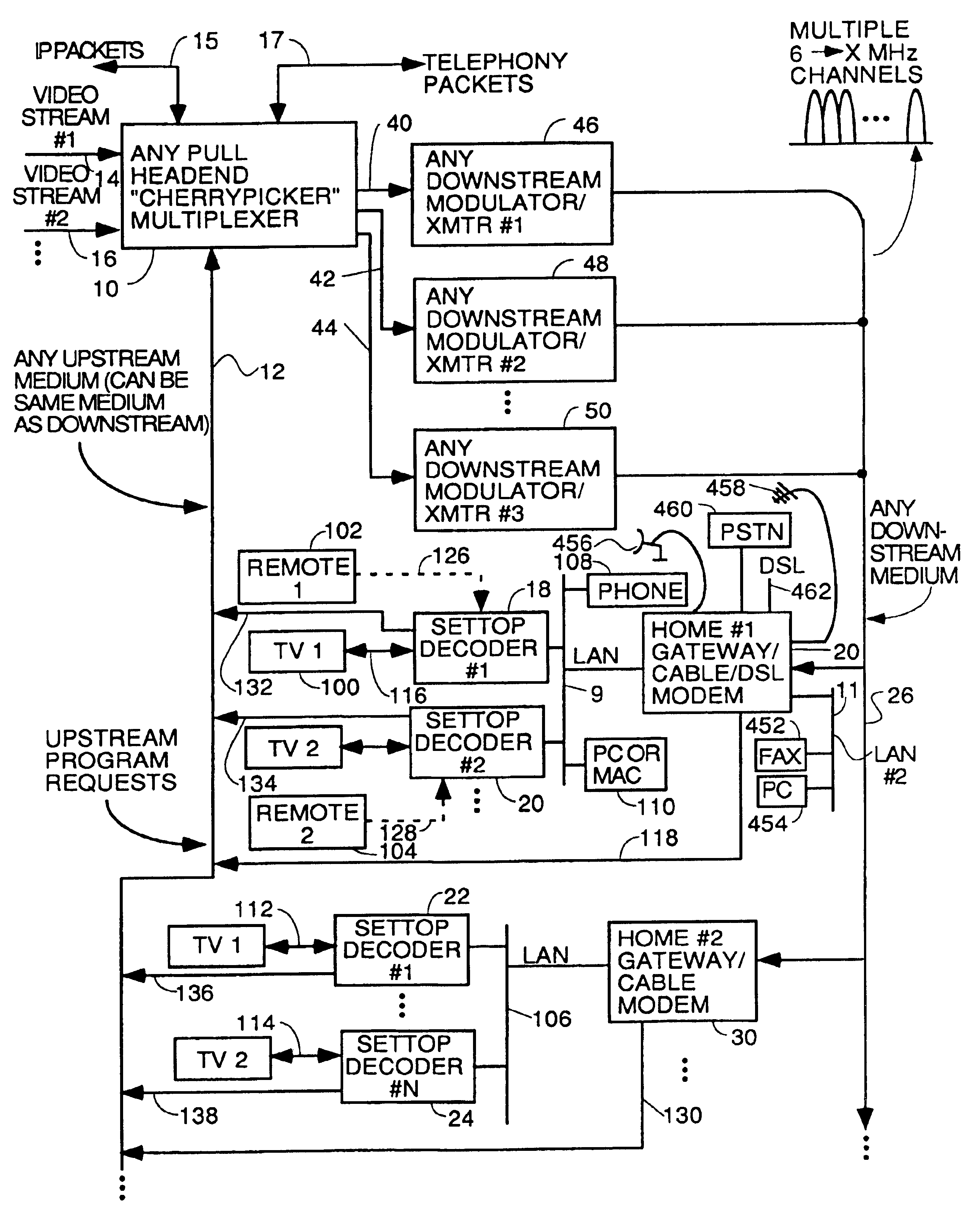

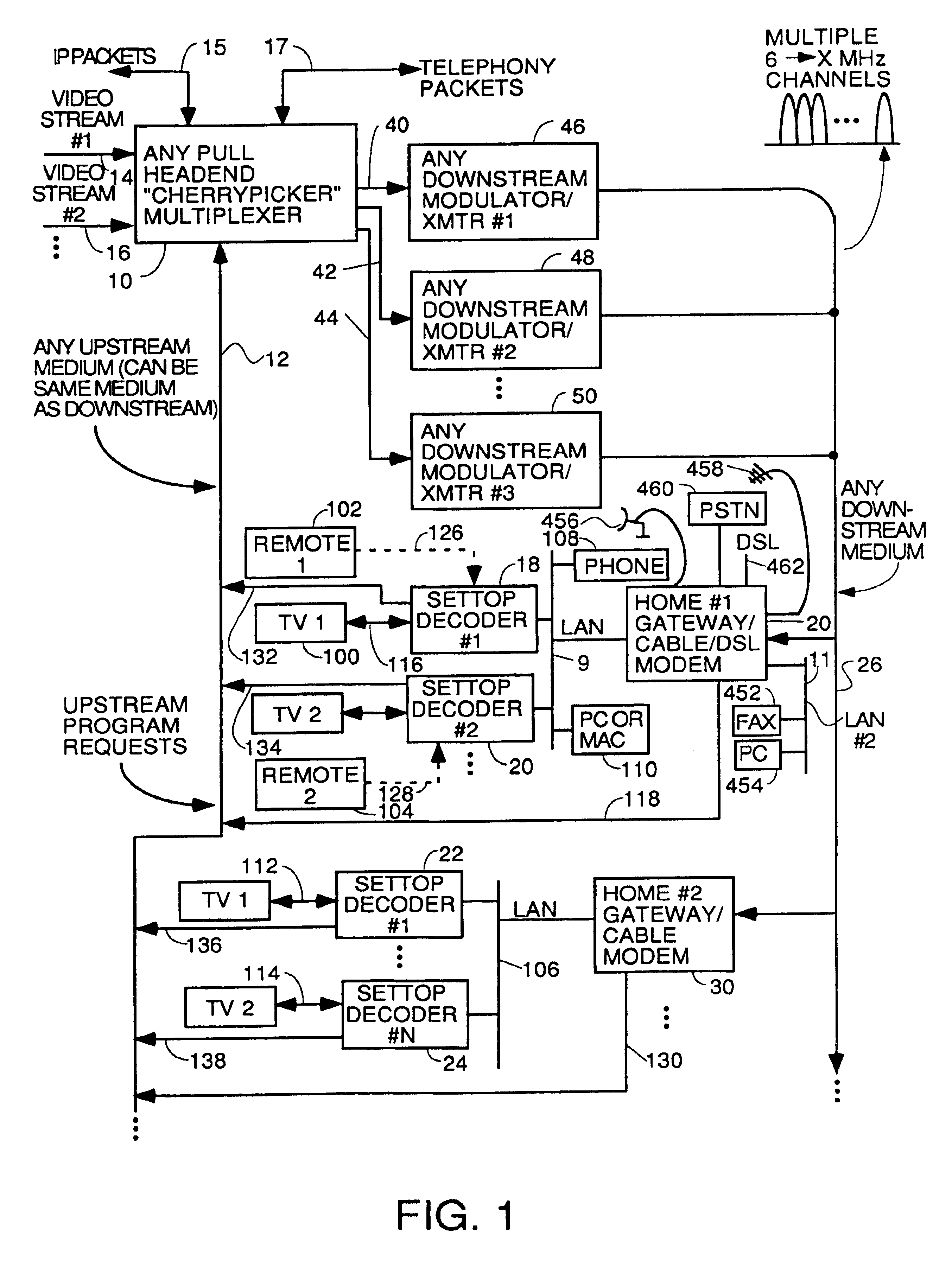

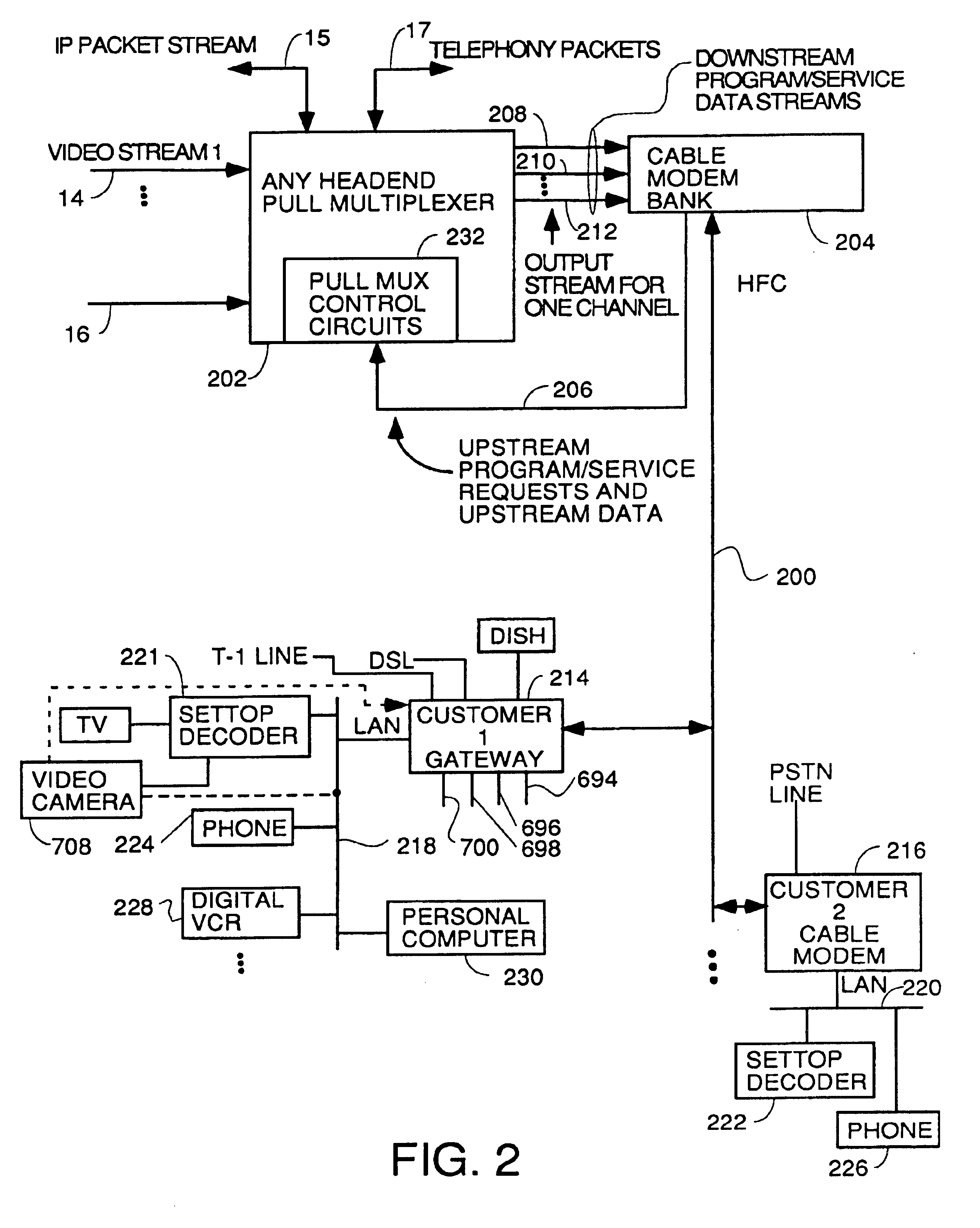

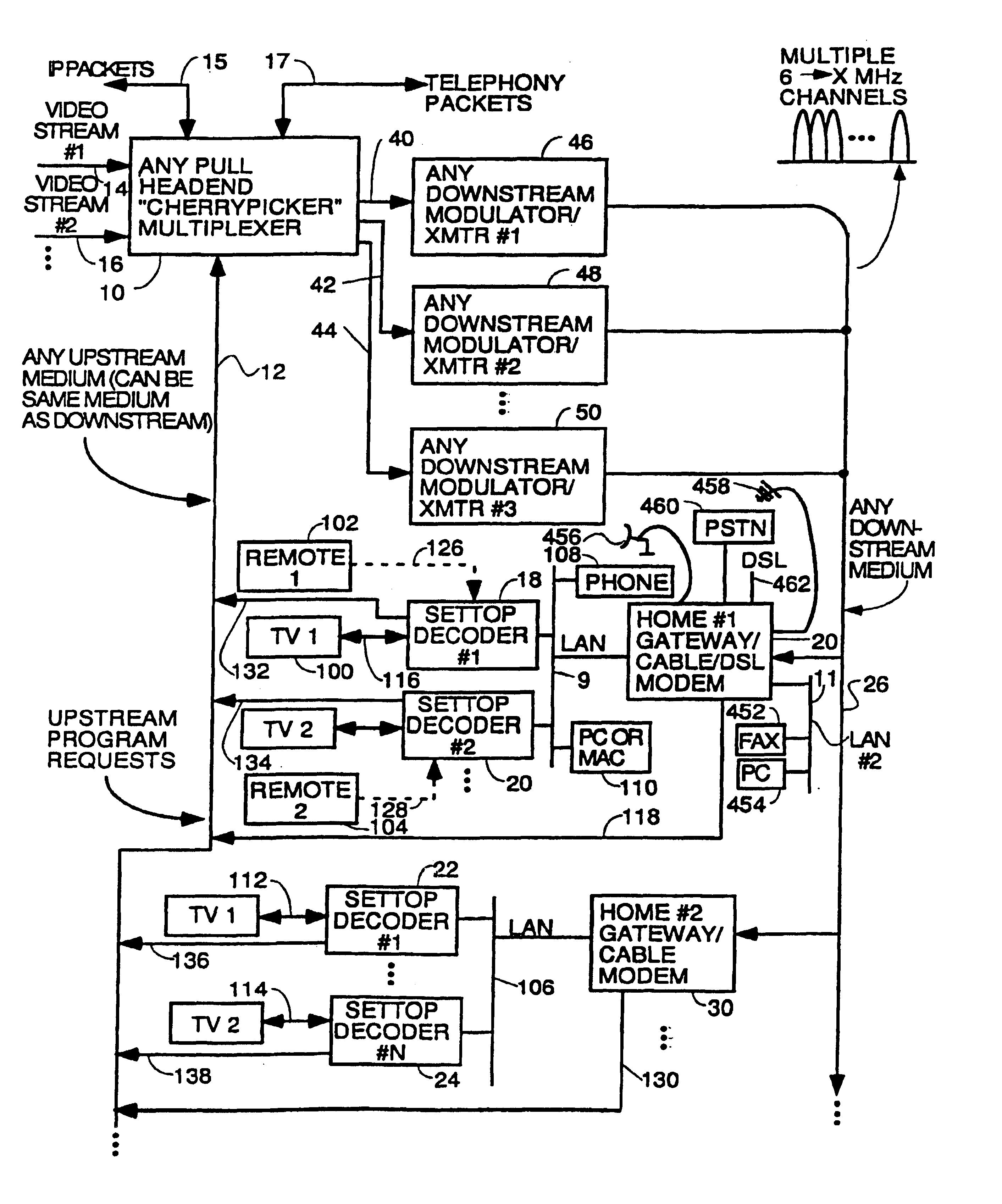

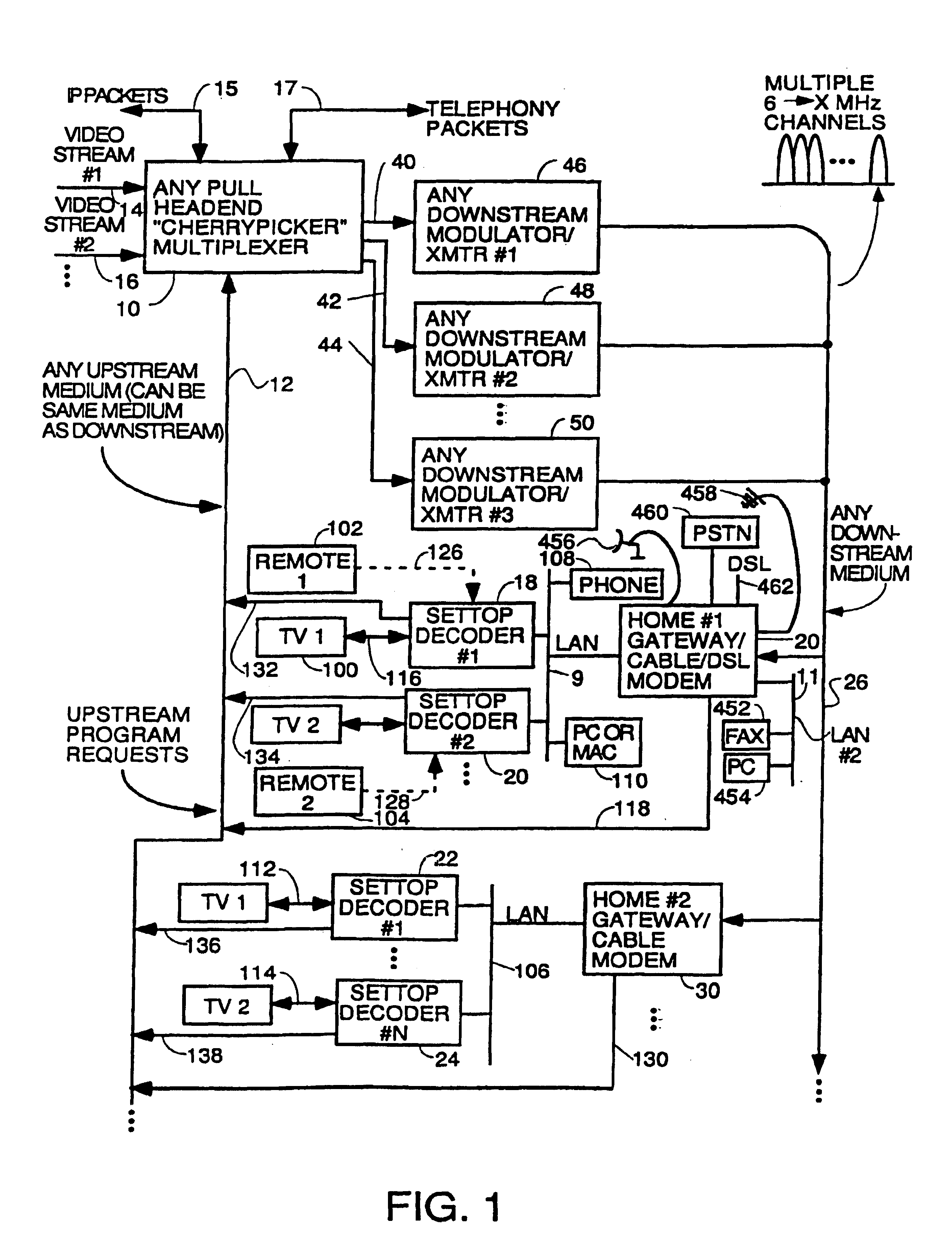

Home network for receiving video-on-demand and other requested programs and services

InactiveUS6889385B1Reduce quality problemsReduce bandwidth consumptionBroadband local area networksAnalogue secracy/subscription systemsVideocassette recorderTransceiver

A system for providing video-on-demand service, broadband internet access and other broadband services over T-carrier systems including a pull multiplexer cherrypicker at the head end is disclosed. The pull multiplexer receives upstream requests and cull out MPEG or other compressed video packets, IP packets and other data packet types to satisfy the requests or to send pushed programming downstream. The downstream can be DSL or HFC. Each customer has a cable modem, DSL modem or a gateway which interfaces multiple signal sources to a LAN to which settop decoders, digital phones, personal computers, digital FAX machines, video cameras, digital VCRs etc. can be attached. Each gateway can coupled the LAN to a DSL line or HFC through a cable modem or a satellite dish through a satellite transceiver. A PSTN and conventional TV antenna interface is also provided.

Owner:GOOGLE TECHNOLOGY HOLDINGS LLC

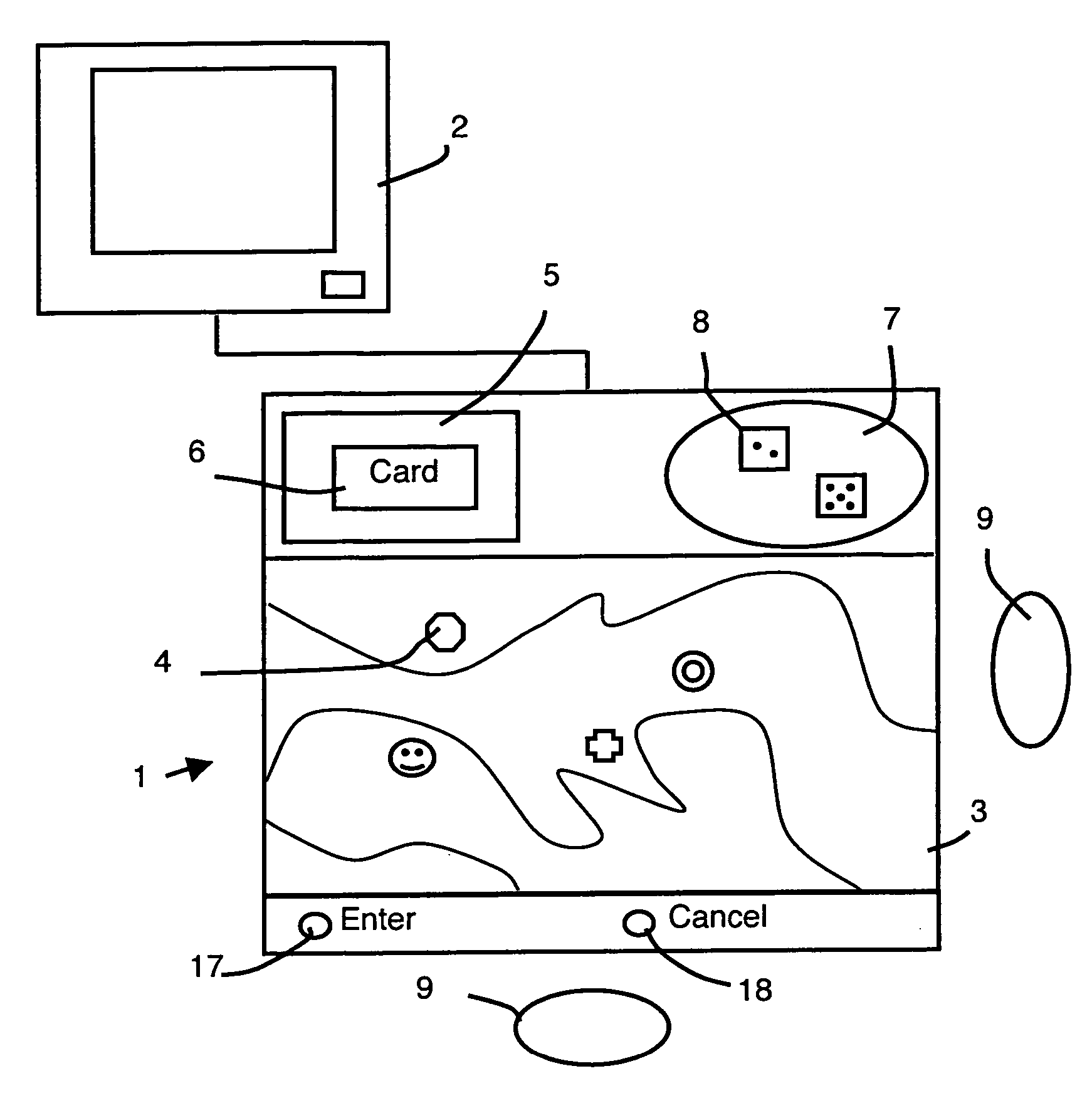

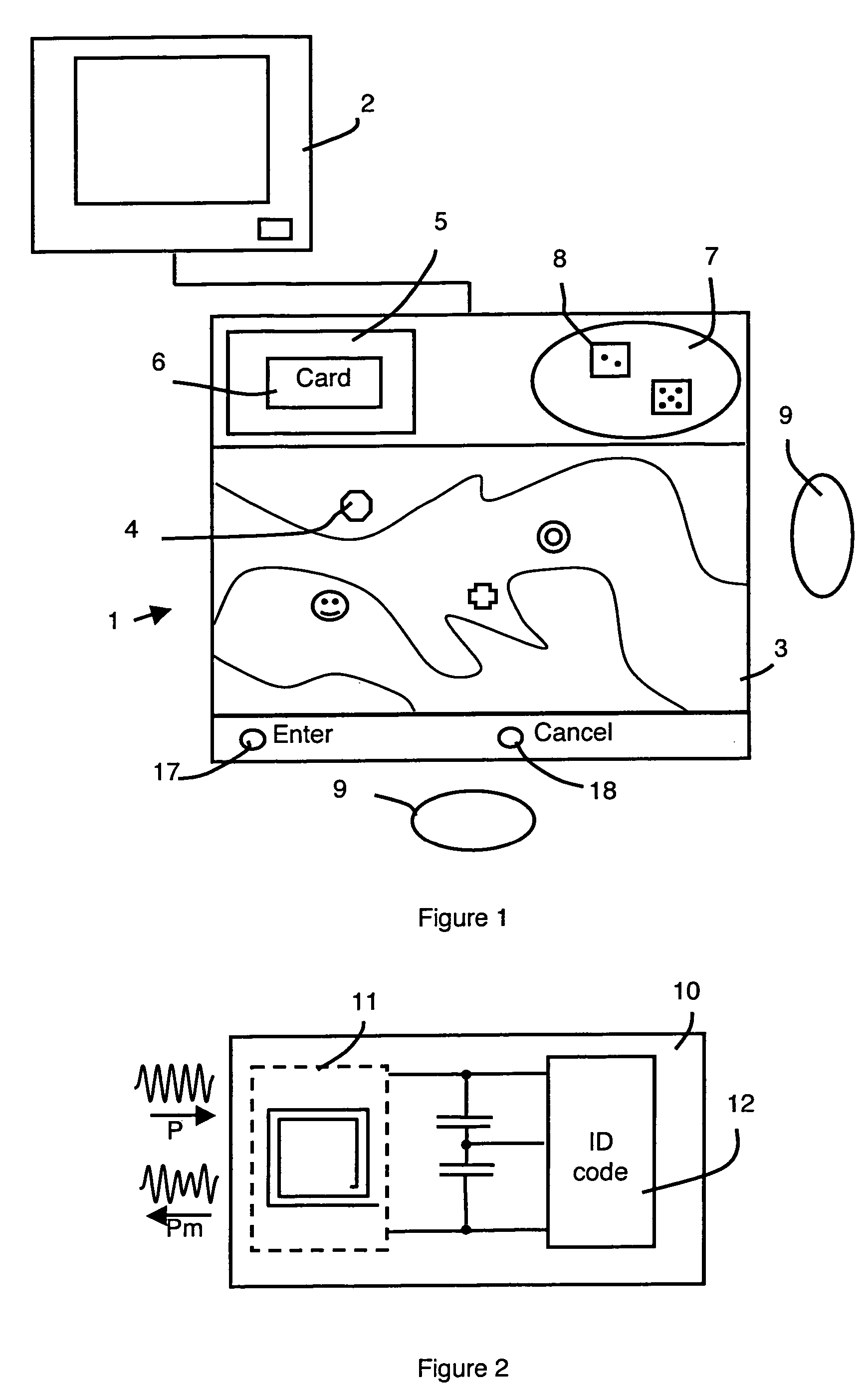

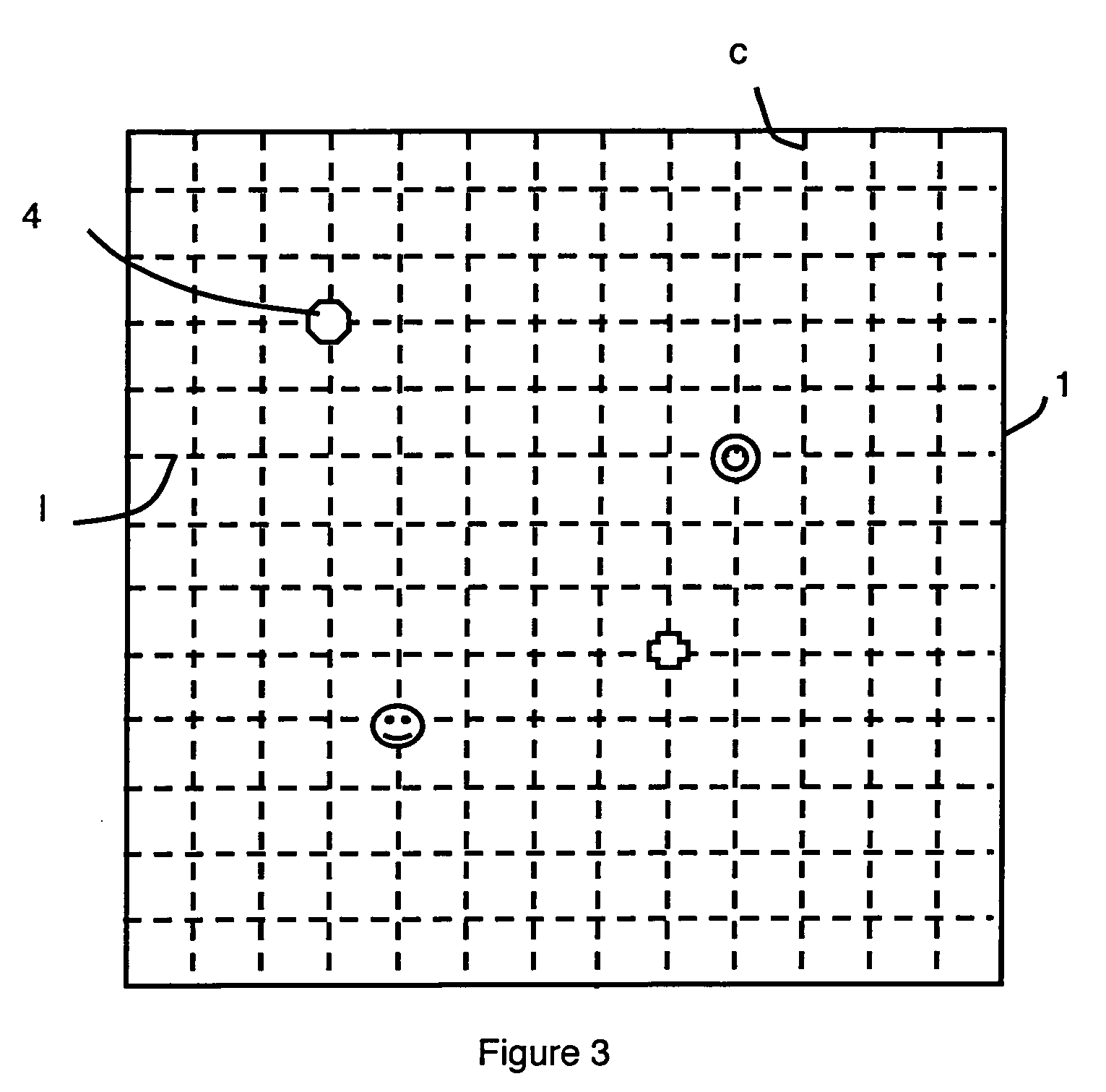

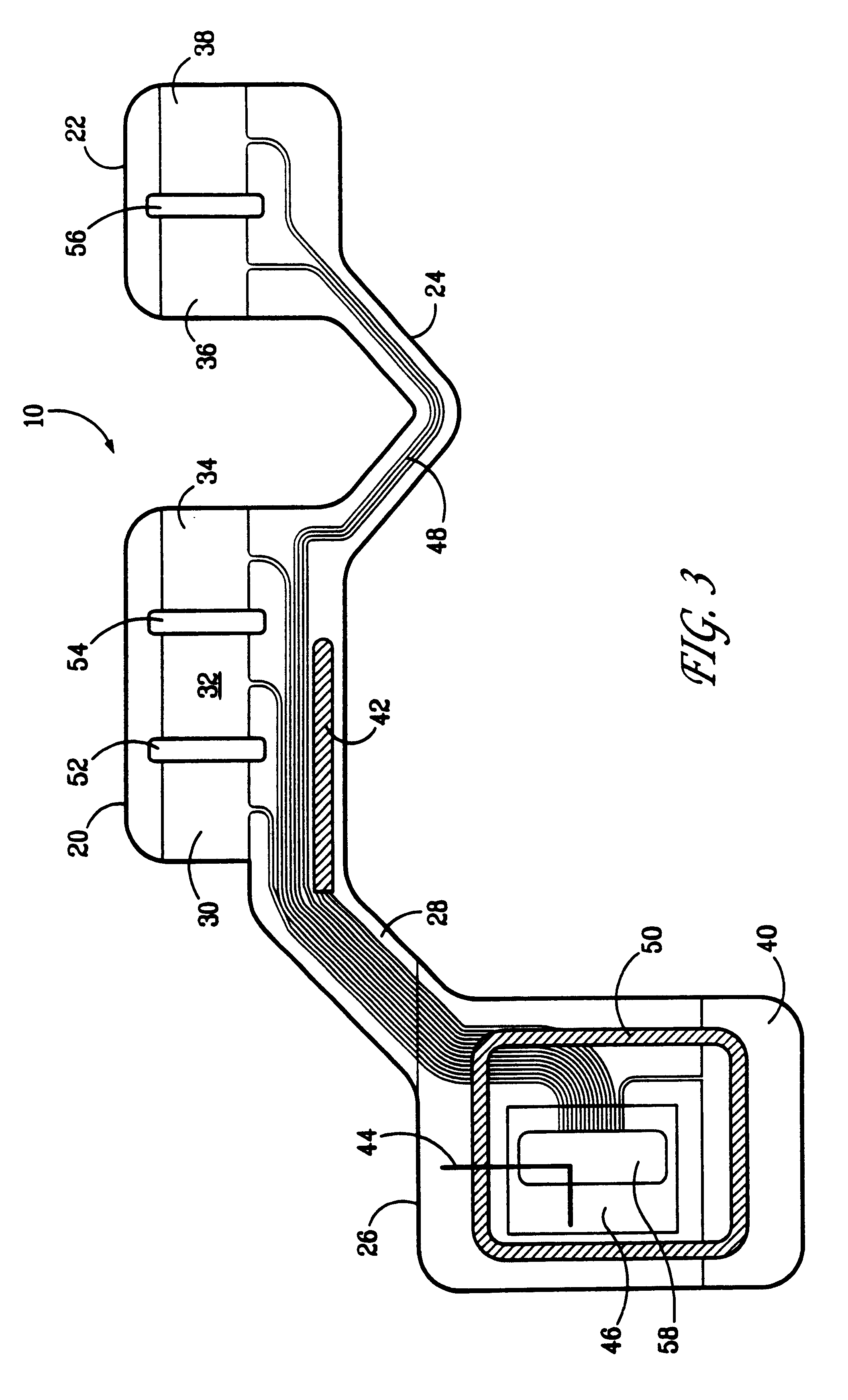

Electronic educational game set having communicating elements with a radio-frequency tag

InactiveUS20060246403A1Short response timeLower average response timeBoard gamesInput/output processes for data processingEducational gamePersonal identification number

The invention relates to a game set which comprises communicating elements, in the form of pieces, figurines, cards or dice, each having a radio-frequency tag provided with an individual identification code. A game board comprises a digital processing circuit which is connected to a plurality of antennas, arranged such as to form a sensor matrix, for detecting the presence, type and position of the communicating elements. Radio-frequency readers are respectively connected to m corresponding input / output terminals of the digital processing circuit. Each radio-frequency reader is connected to an associated group of antennas, preferably by means of a corresponding multiplexer. The game board may consist of a removable assembly of basic boards, each comprising a basic digital processing circuit which is connected to the antennas of the corresponding basic board.

Owner:FRANCE TELECOM SA

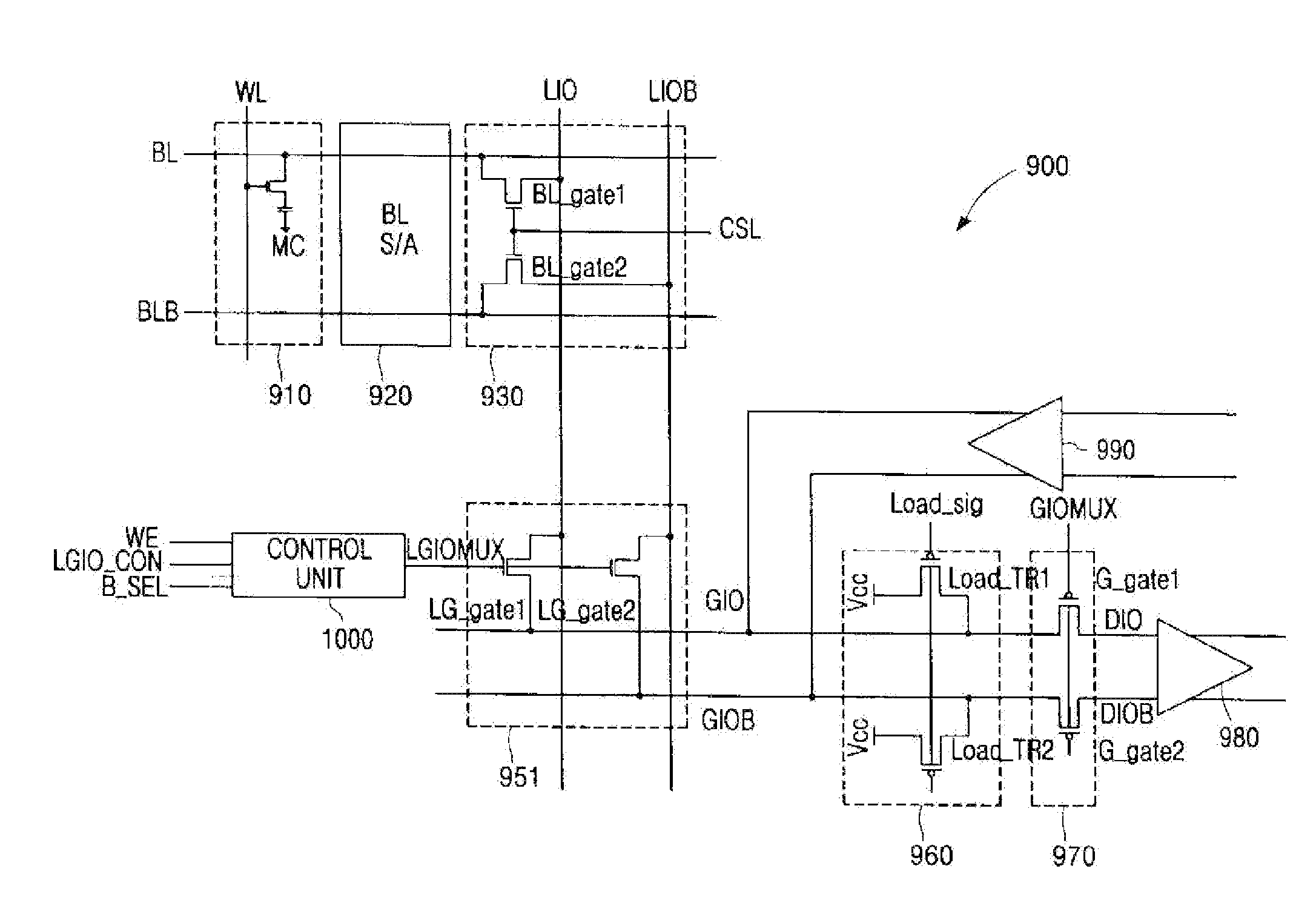

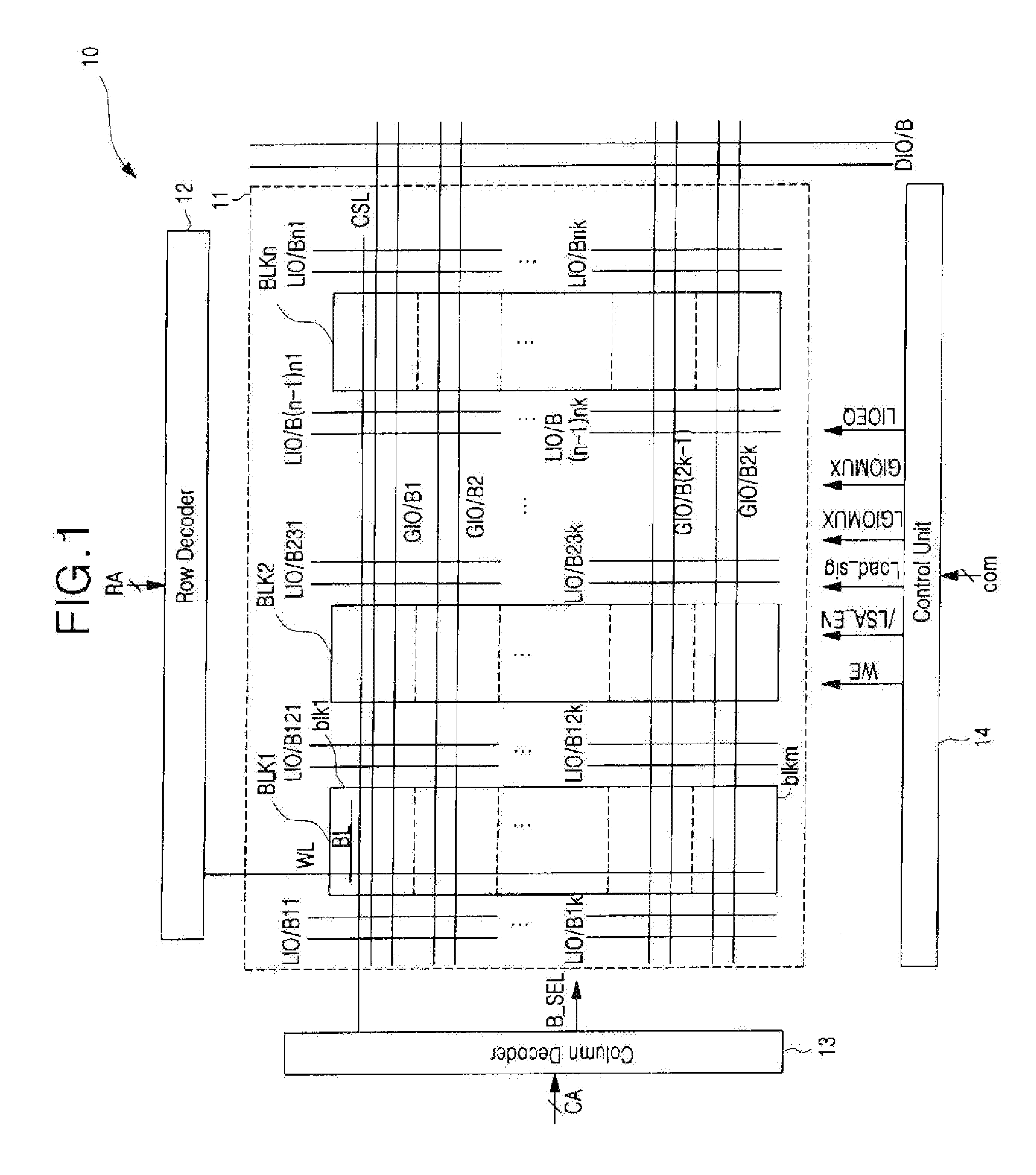

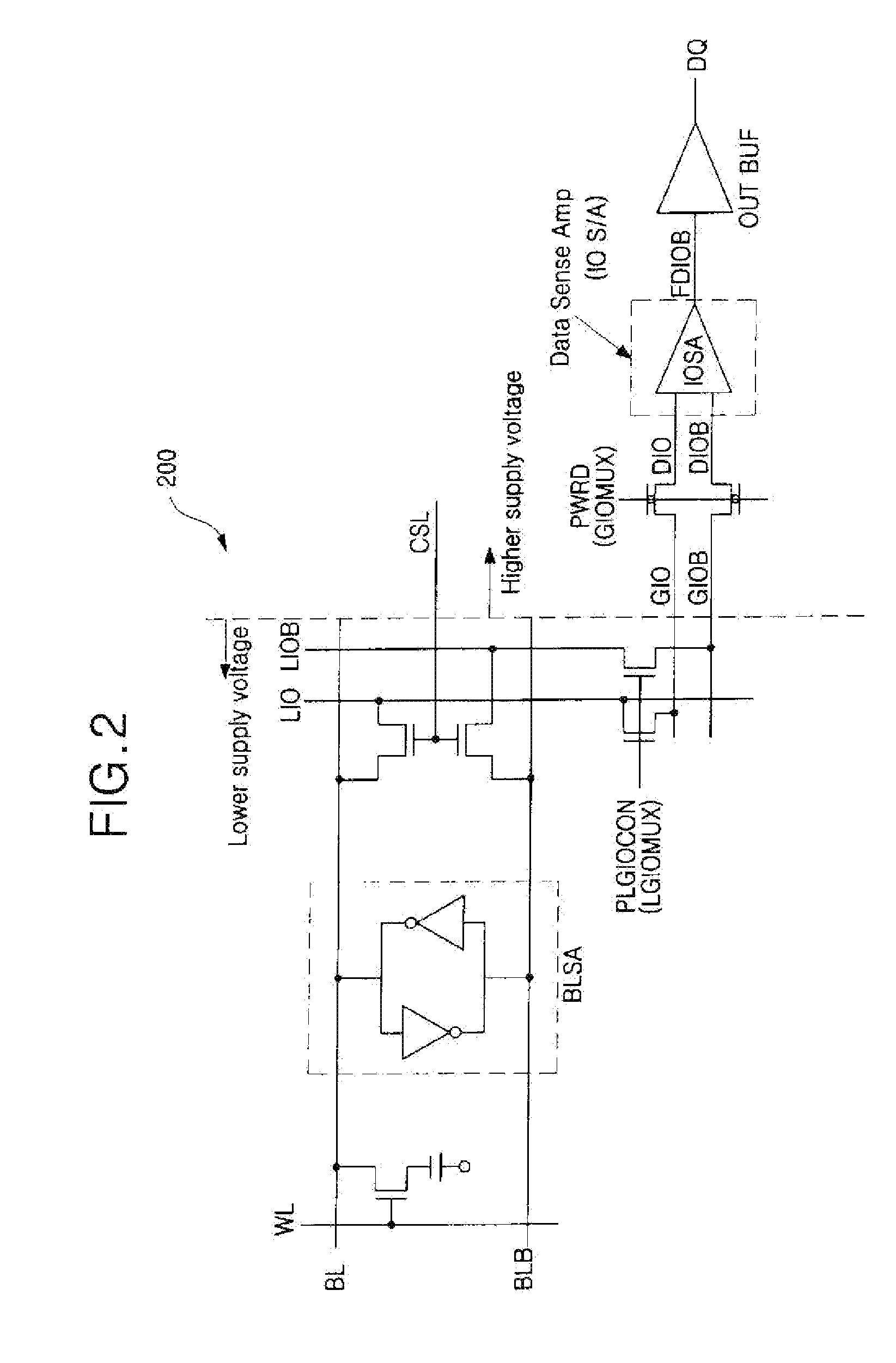

Memory device with separate read and write gate voltage controls

A circuit and method are provided for controlling the gate voltage of a transistor acting between local and global input / output lines of a memory device, the circuit including a local input / output line, a local from / to global input / output multiplexer in signal communication with the local input / output line, a global input / output line in signal communication with the local from / to global input / output multiplexer, and a local from / to global input / output controller having an input node and an output node, the input node disposed for receiving a signal indicative of an input or output operation, and the output node in signal communication with a gate of the local from / to global input / output multiplexer for providing a gate signal of a first or second level in the presence of the output operation, and a gate signal of a third level in the presence of the input operation.

Owner:SAMSUNG ELECTRONICS CO LTD

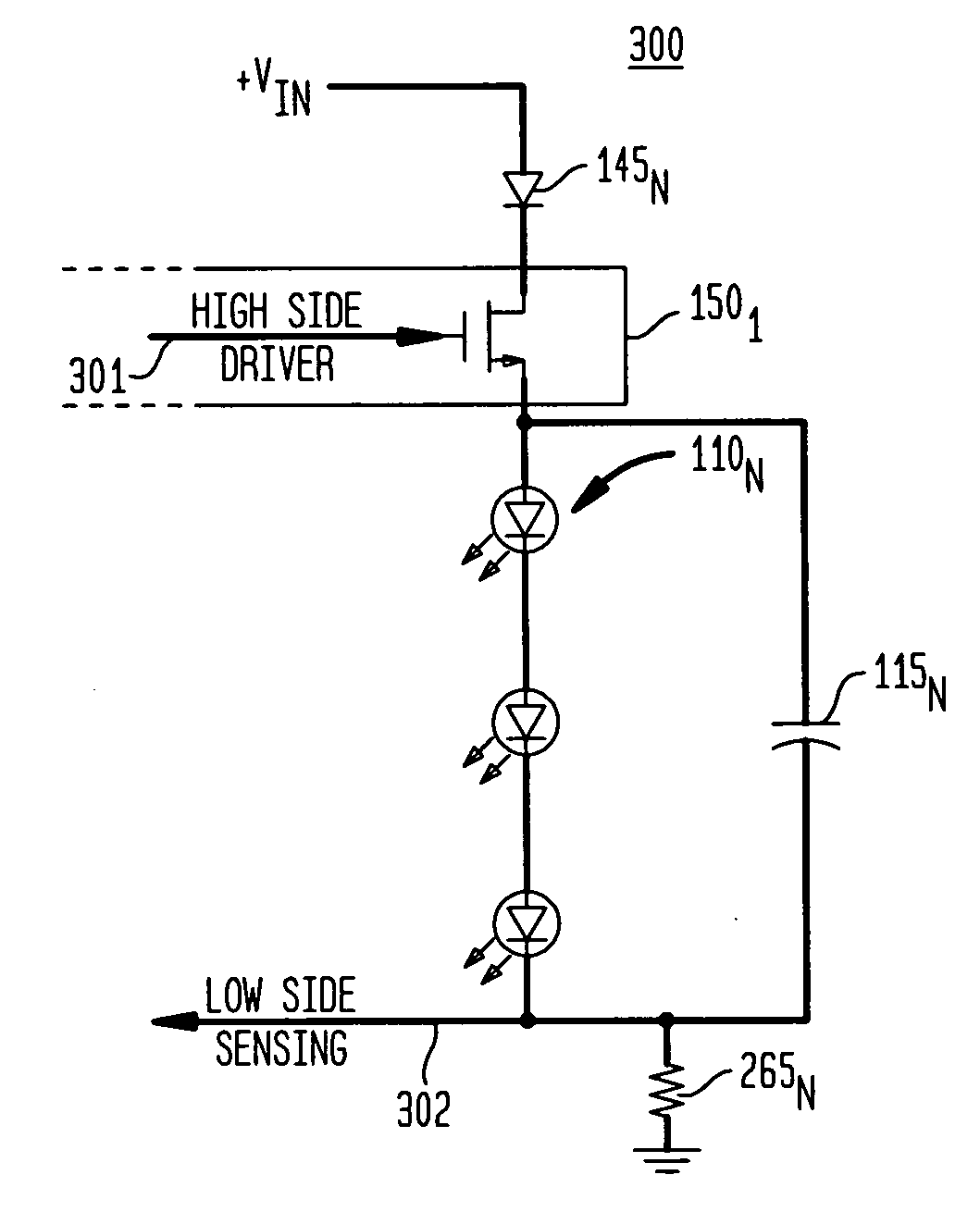

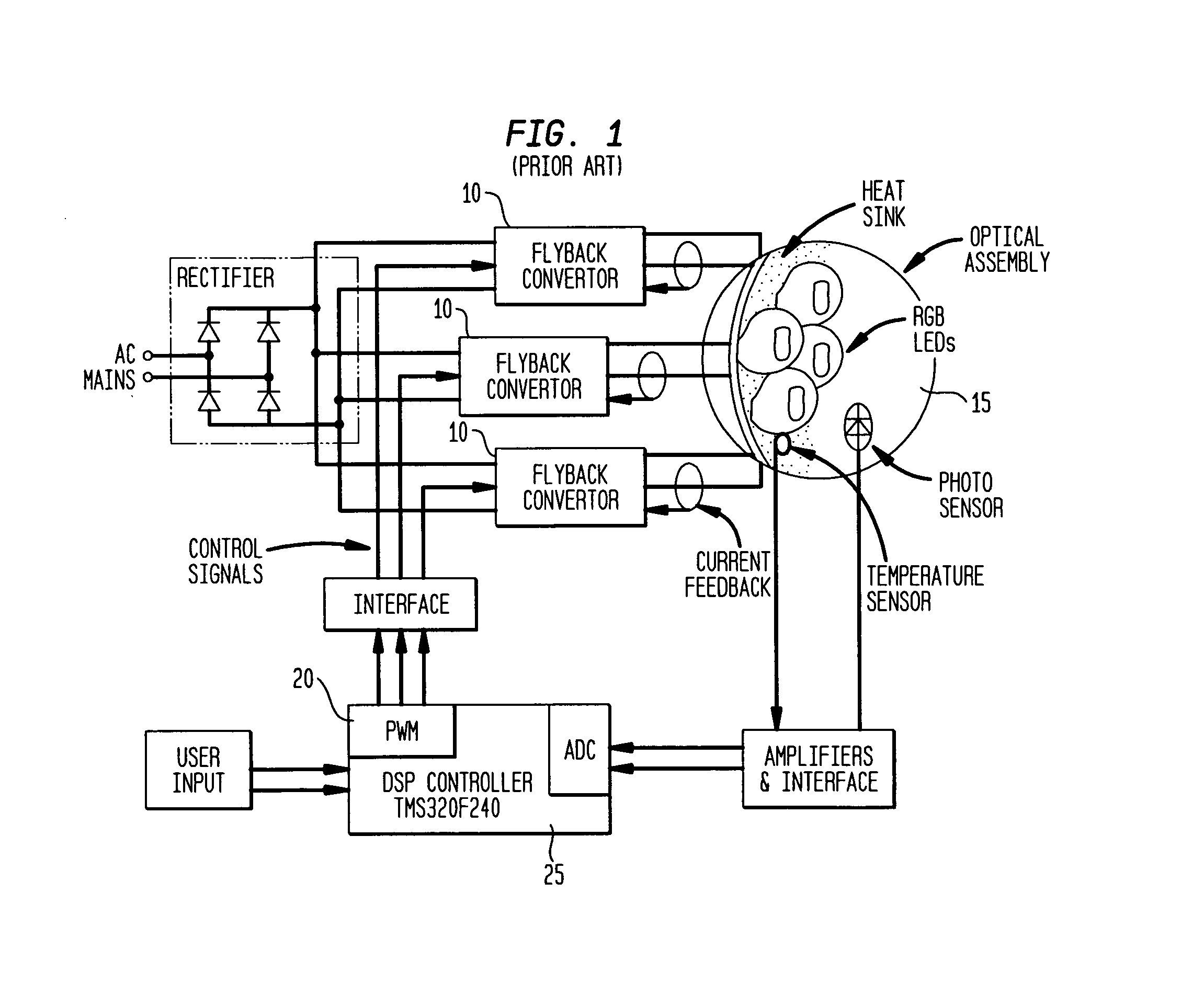

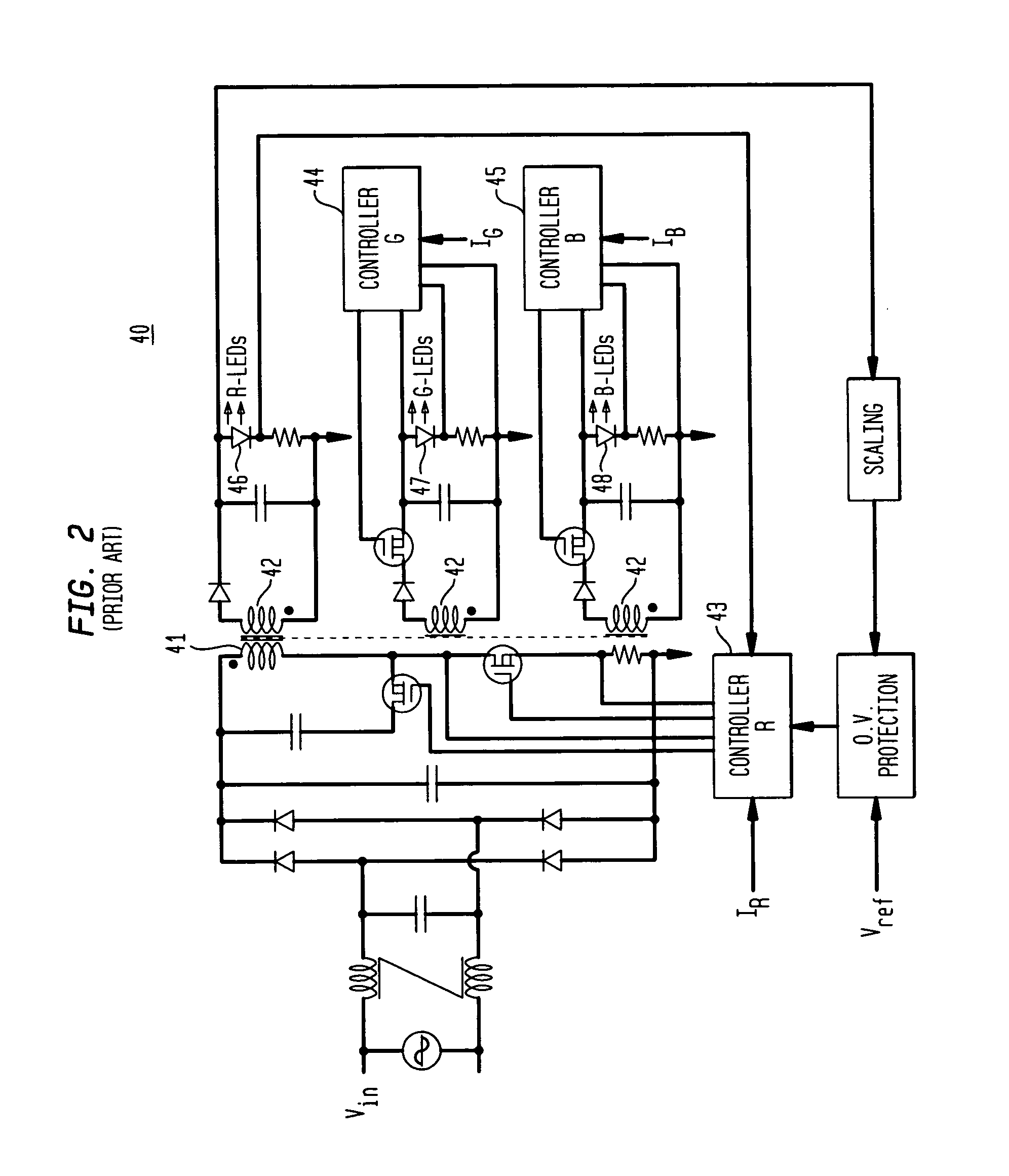

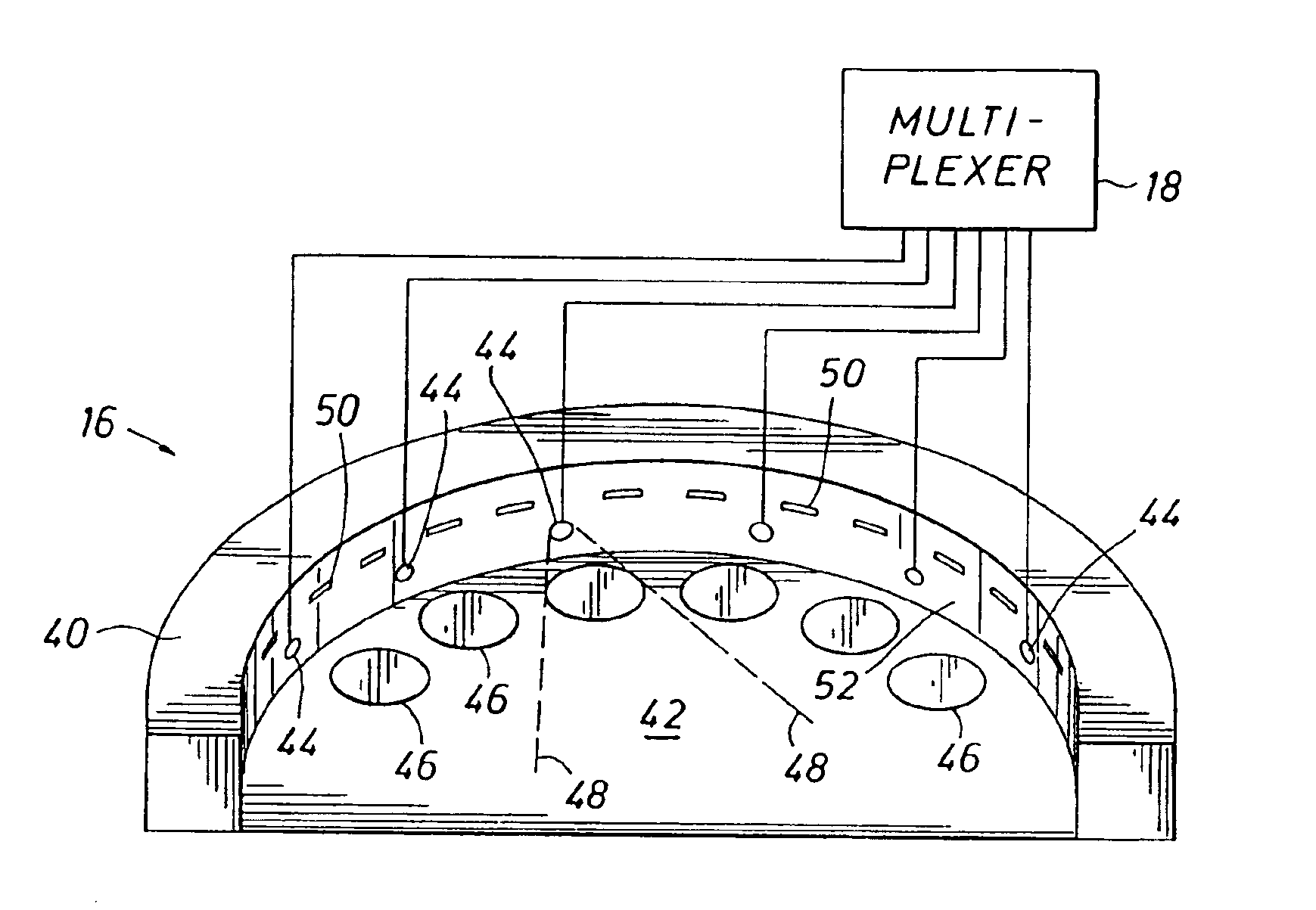

Time division modulation with average current regulation for independent control of arrays of light emitting diodes

ActiveUS20080116818A1Low costFast response timeElectrical apparatusElectroluminescent light sourcesSwitched currentAverage current

Exemplary apparatus, method and system embodiments provide for separately and independently sourcing current to a series of light emitting diodes of a plurality of series of light-emitting diodes. An exemplary apparatus comprises a power converter which generates a current, a first multiplexer, and a controller. The controller provides for sequential and separate switching of the current through the first multiplexer to each of the series of light-emitting diodes for a corresponding period of time. An average current provided by the power converter is determined as substantially equal to a sum of the corresponding currents through the plurality of series of light-emitting diodes. A total period for switching current to all of the series of light-emitting diodes is also determined. A corresponding time period for switching current to a selected corresponding series of light-emitting diodes is substantially equal to a proportion of the total period determined as a ratio of the corresponding current for the selected corresponding series of light-emitting diodes to the average current provided by the power converter.

Owner:CHEMTRON RES

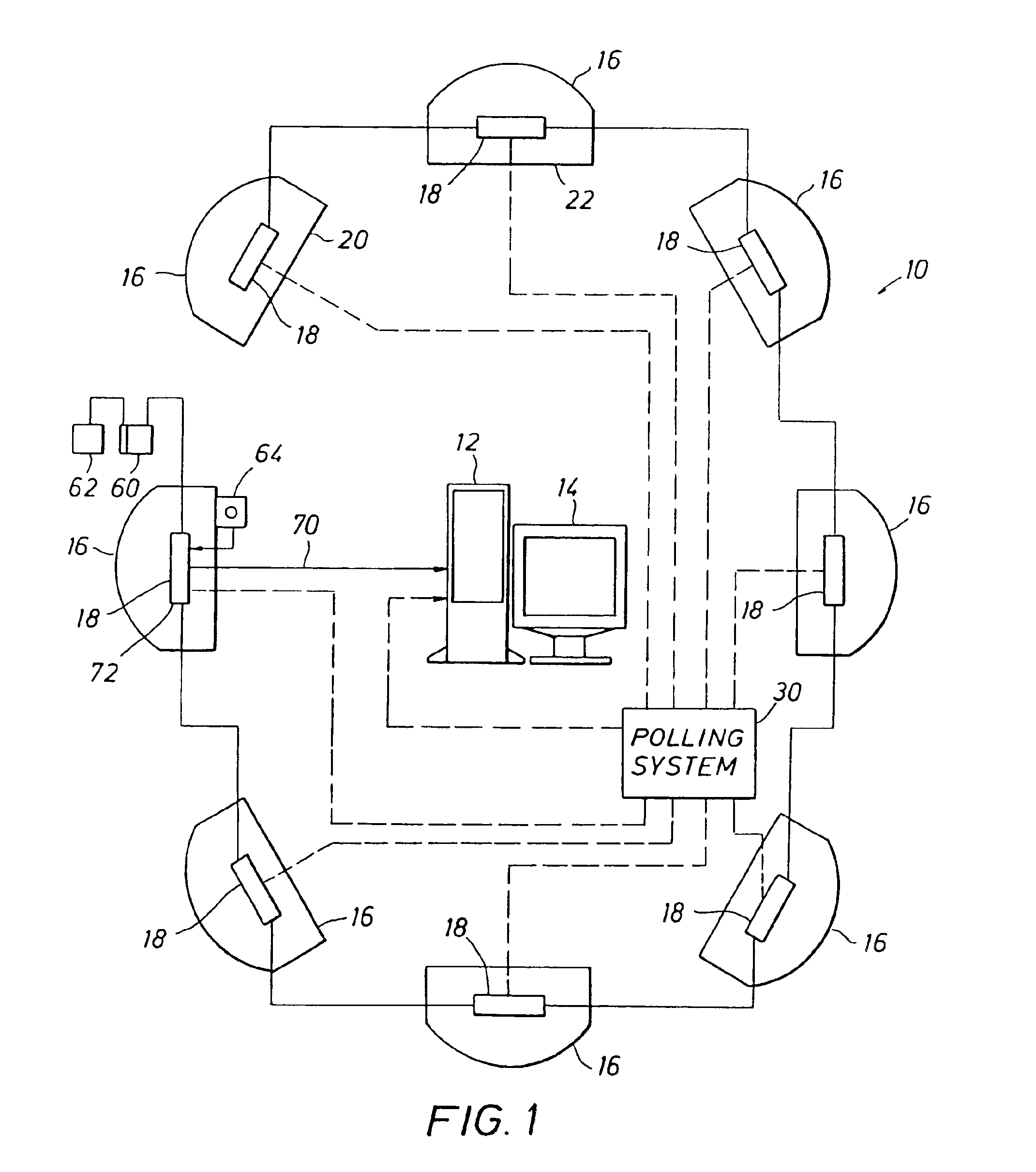

Automated wagering recognition system

InactiveUS6848994B1Eliminate spurious signalAvoid shadow effectColor television detailsClosed circuit television systemsMultiplexerComputer graphics (images)

A system and method for acquiring and analyzing the bets at a plurality of locations at a plurality of tables is provided. The system includes a gaming table with a raised platform, underneath which is positioned a video camera for each of the wagering locations on the table. The video cameras one each table are coupled together into a multiplexer, and the multiplexers from the plurality of tables are coupled together and into a central computer. The system and method thus eliminate the labor intensive and often inaccurate technique of tracking the gambling habits of patrons at the gaming tables.

Owner:GENESIS GAMING SOLUTIONS

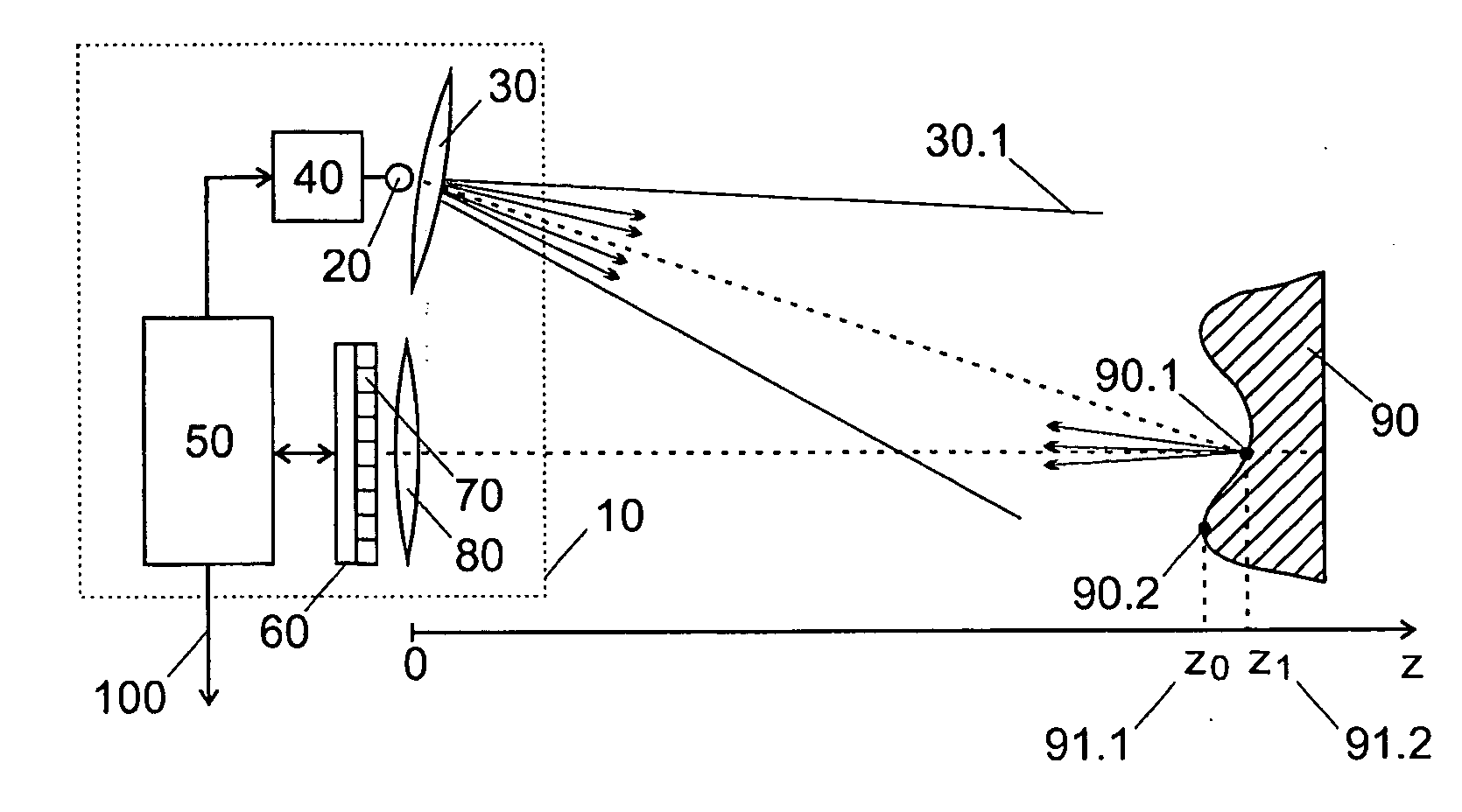

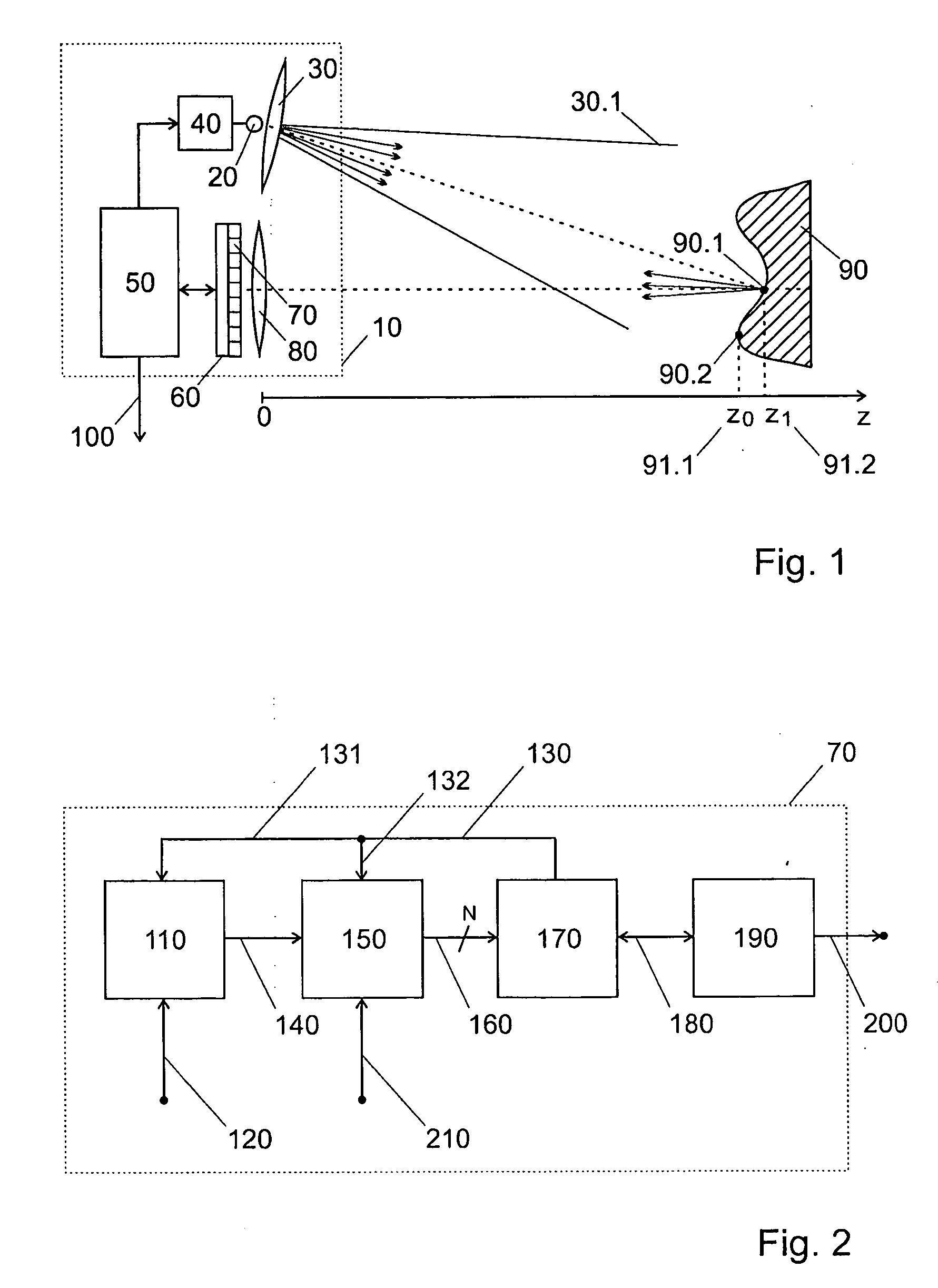

Method and arrangement for measuring the distance to an object

ActiveUS20070182949A1Low costHigh resolutionOptical rangefindersHeight/levelling measurementMultiplexerPhotonics

Arrangement (10) for measuring the distance to an object, comprising: a photonic source for illuminating said object using a continuous modulated photonic wave, a solid-state image sensor, comprising an array of avalanche photodiodes and a plurality of circuits for processing signals output by said avalanche photodiodes to yield data depending on the photonic wave reflected by said object onto said photodiodes. The circuit may comprise a multiplexer at the pixel level arranged so as to accumulate the signal output by the avalanche photodiode during different sub-periods in different storage devices.

Owner:ECOLE POLYTECHNIQUE FEDERALE DE LAUSANNE (EPFL)

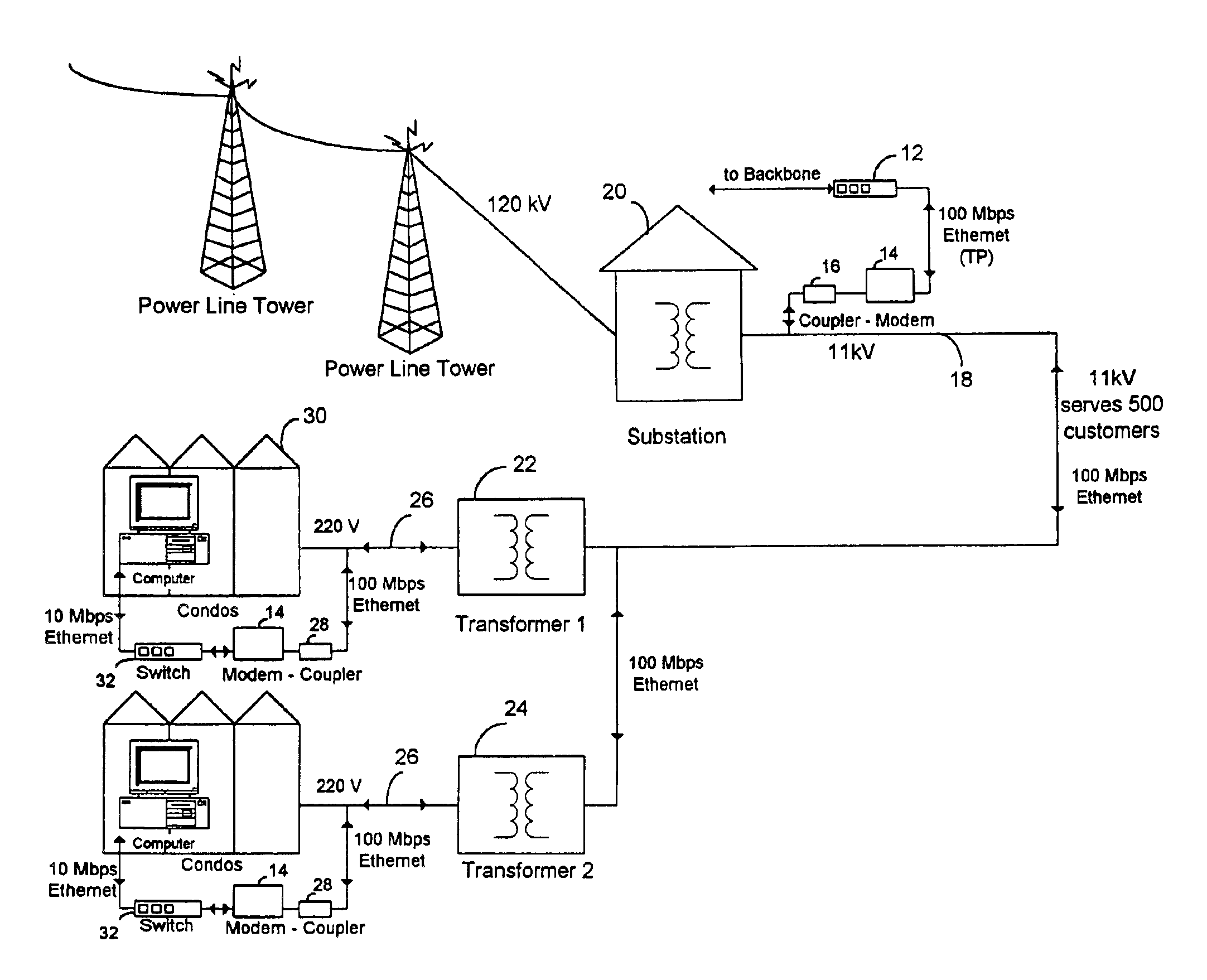

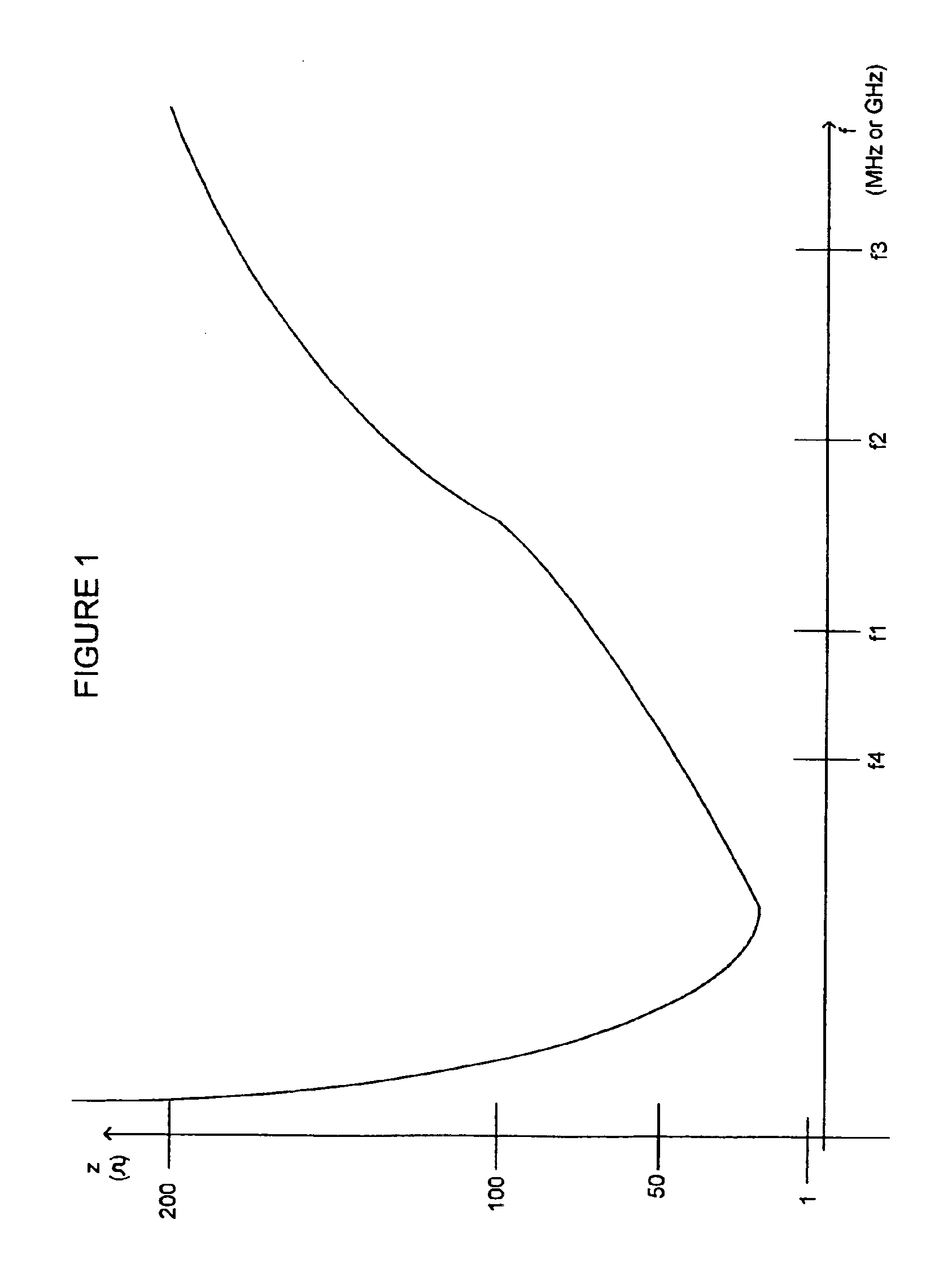

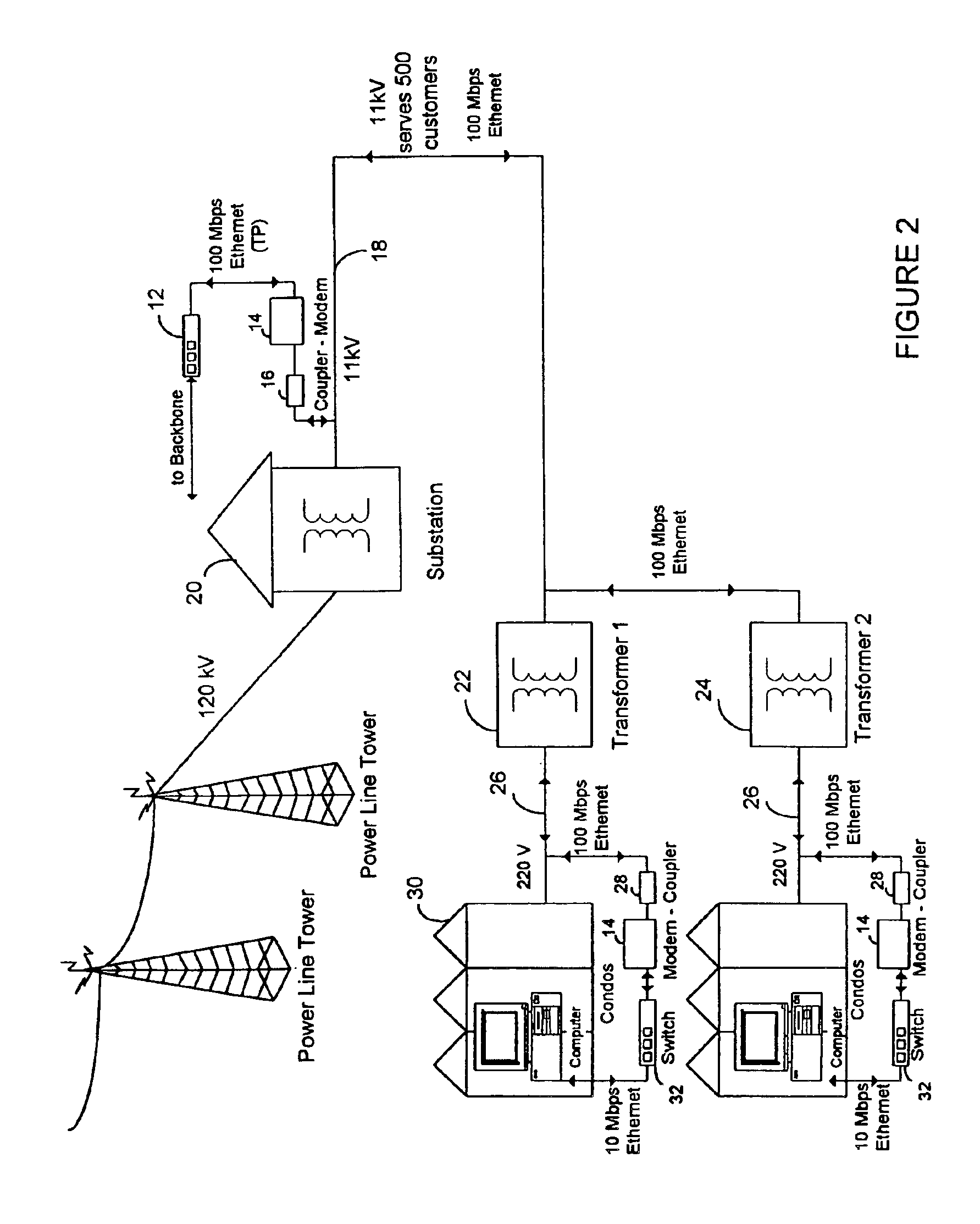

High frequency network multiplexed communications over various lines using multiple modulated carrier frequencies

InactiveUS6922135B2Substantial phase distortionMultiple-port networksPowerline communication systemsCapacitanceModem device

An apparatus is provided for high frequency multiplexed electrical line communication for cable TV, telephone, internet, security and other control applications over the mid and low voltage power lines and directly through the transformers. The apparatus includes a transmitter, a receiver, a modem, a multiplexer and multiple couplers at each of two or more locations along an electrical line. The couplers have capacitive circuits serially connected with an air-core or dielectric-core transformer. The capacitive circuits resonate with the transformer at a preselected frequency. The coupler eliminates noise and is matched to the characteristic impedance of the line at the preselected frequency, which linearizes communication on the line and allows high speed data and voice communication over long distances. Multiple modulators and demodulators are used to produce multiple modulated carrier frequencies.

Owner:SATIUS

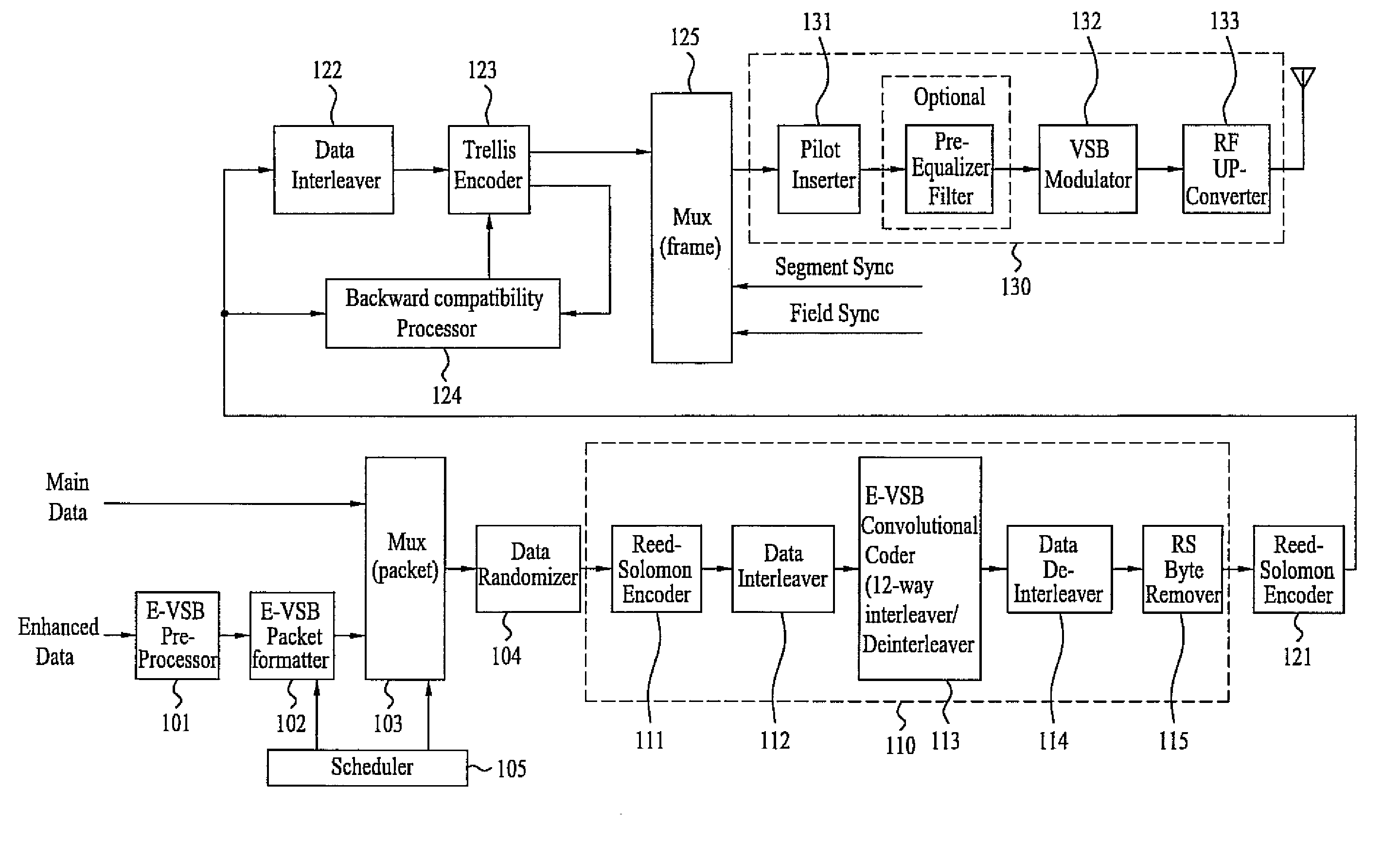

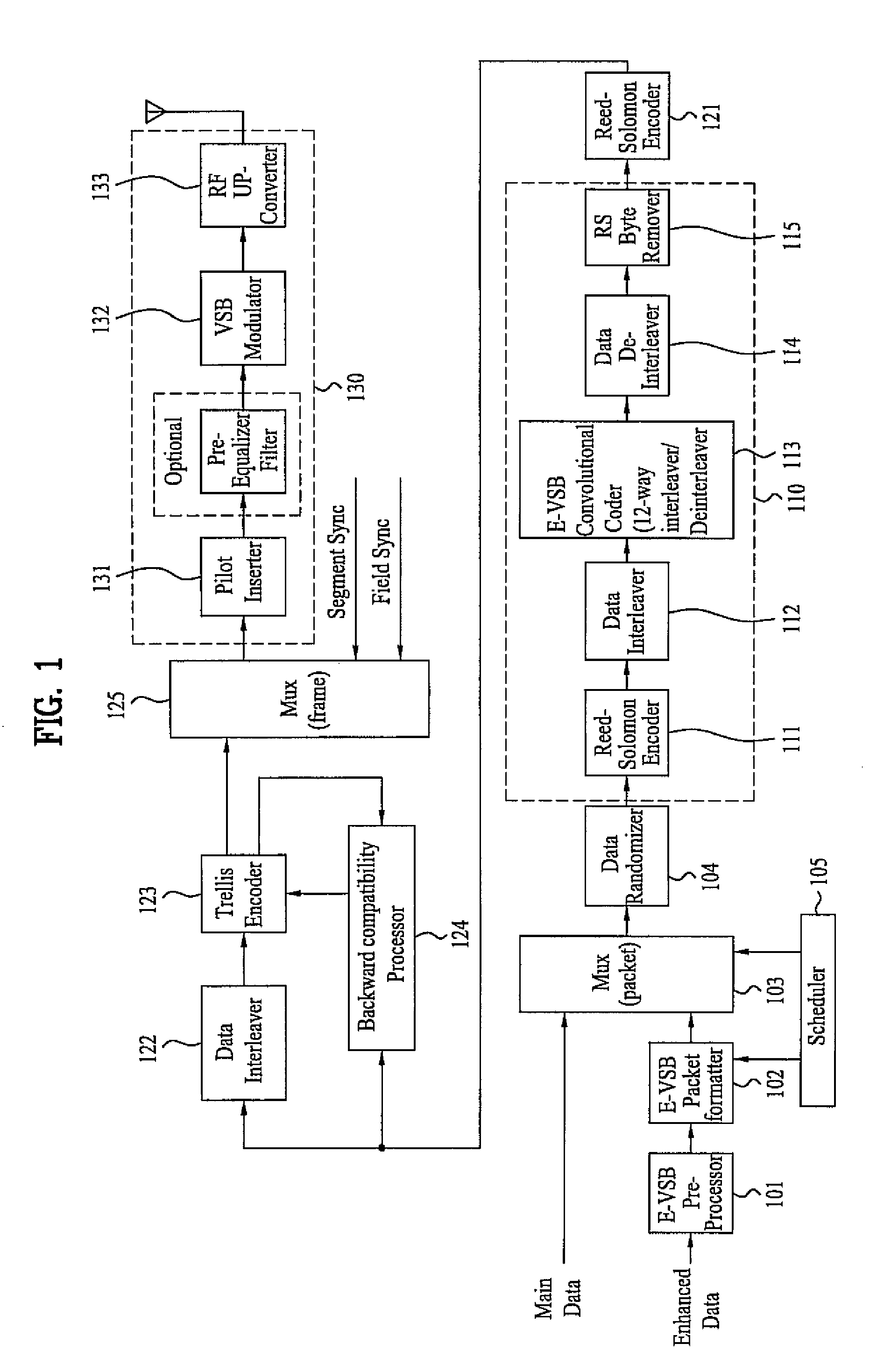

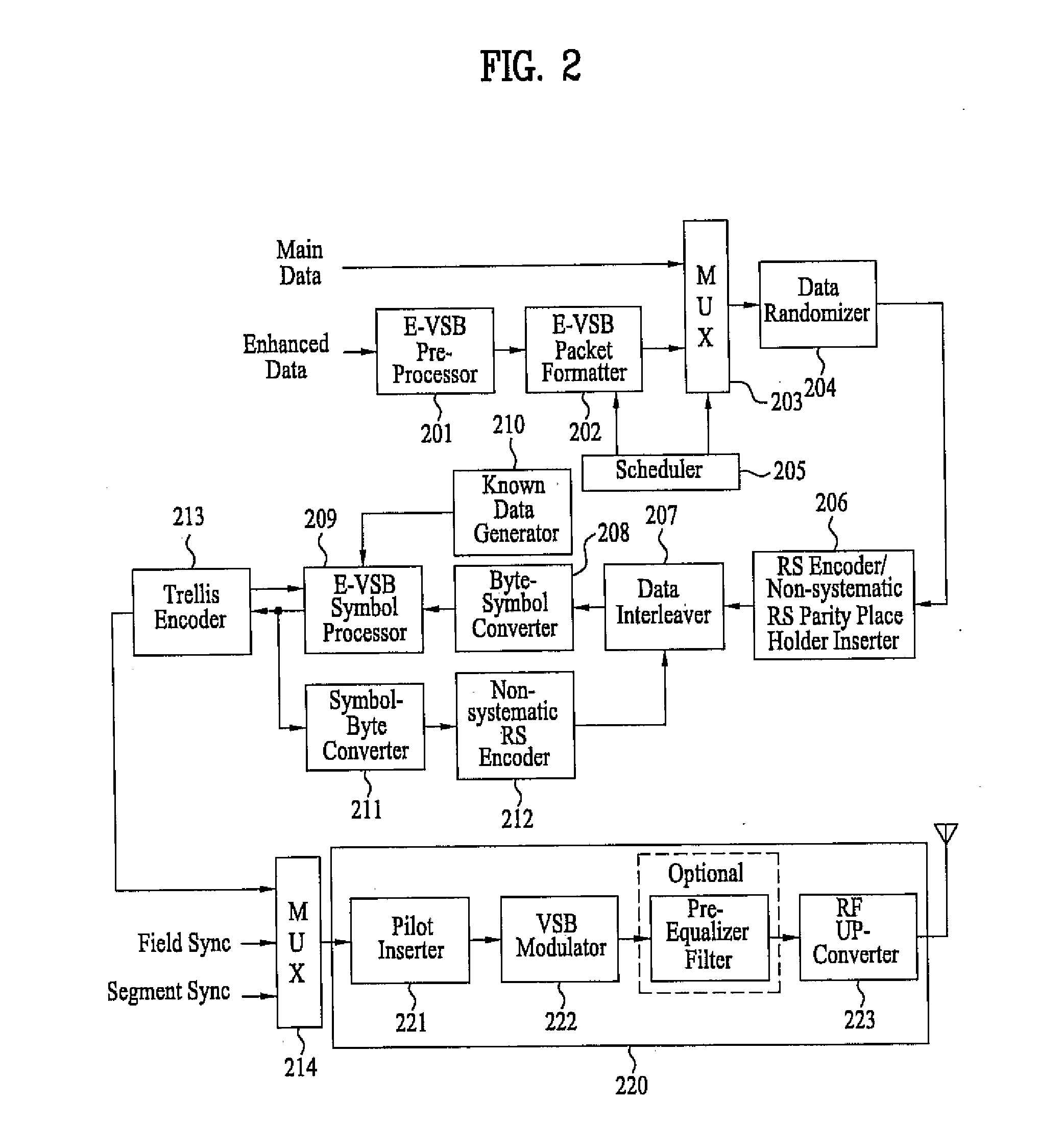

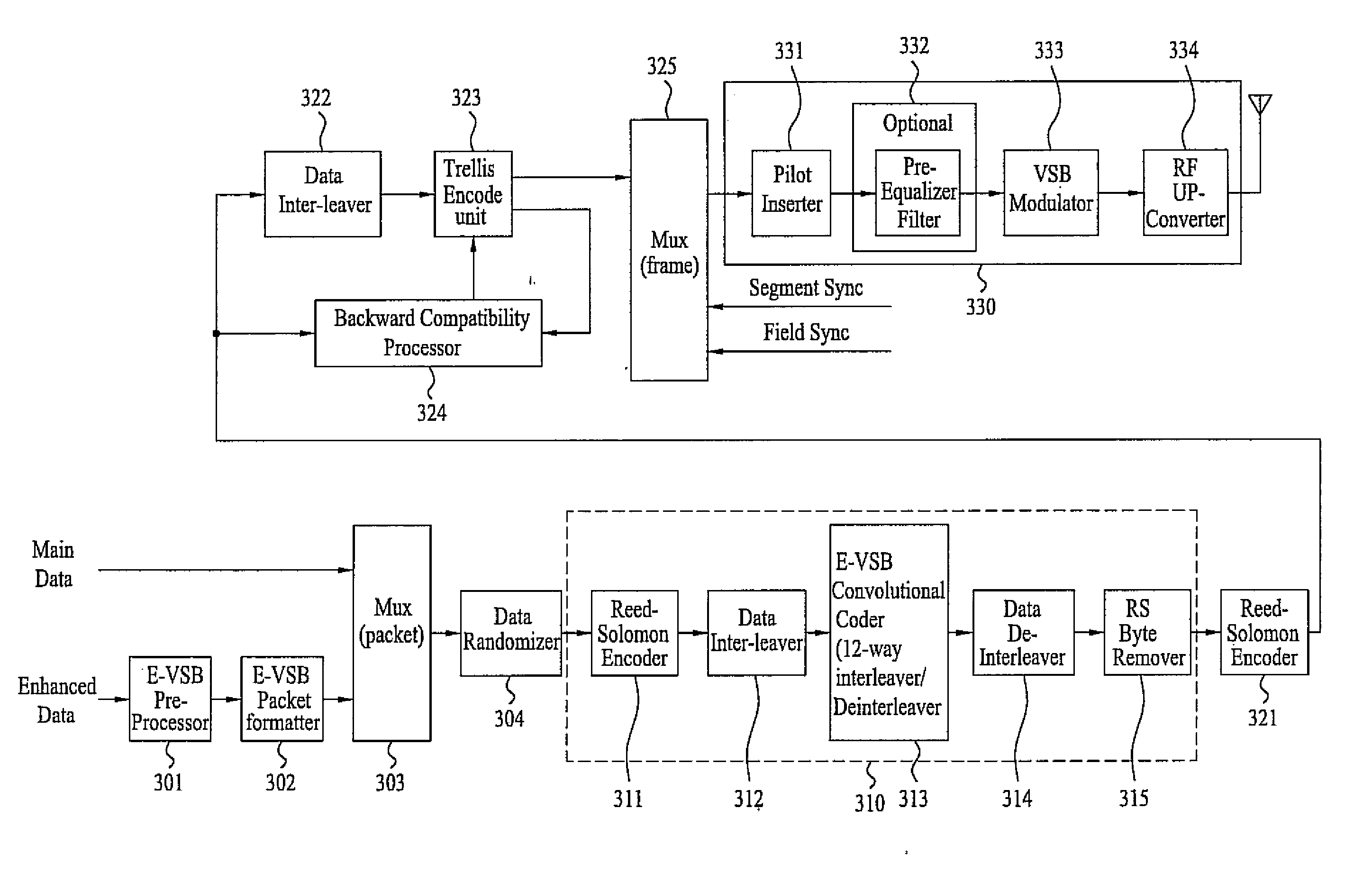

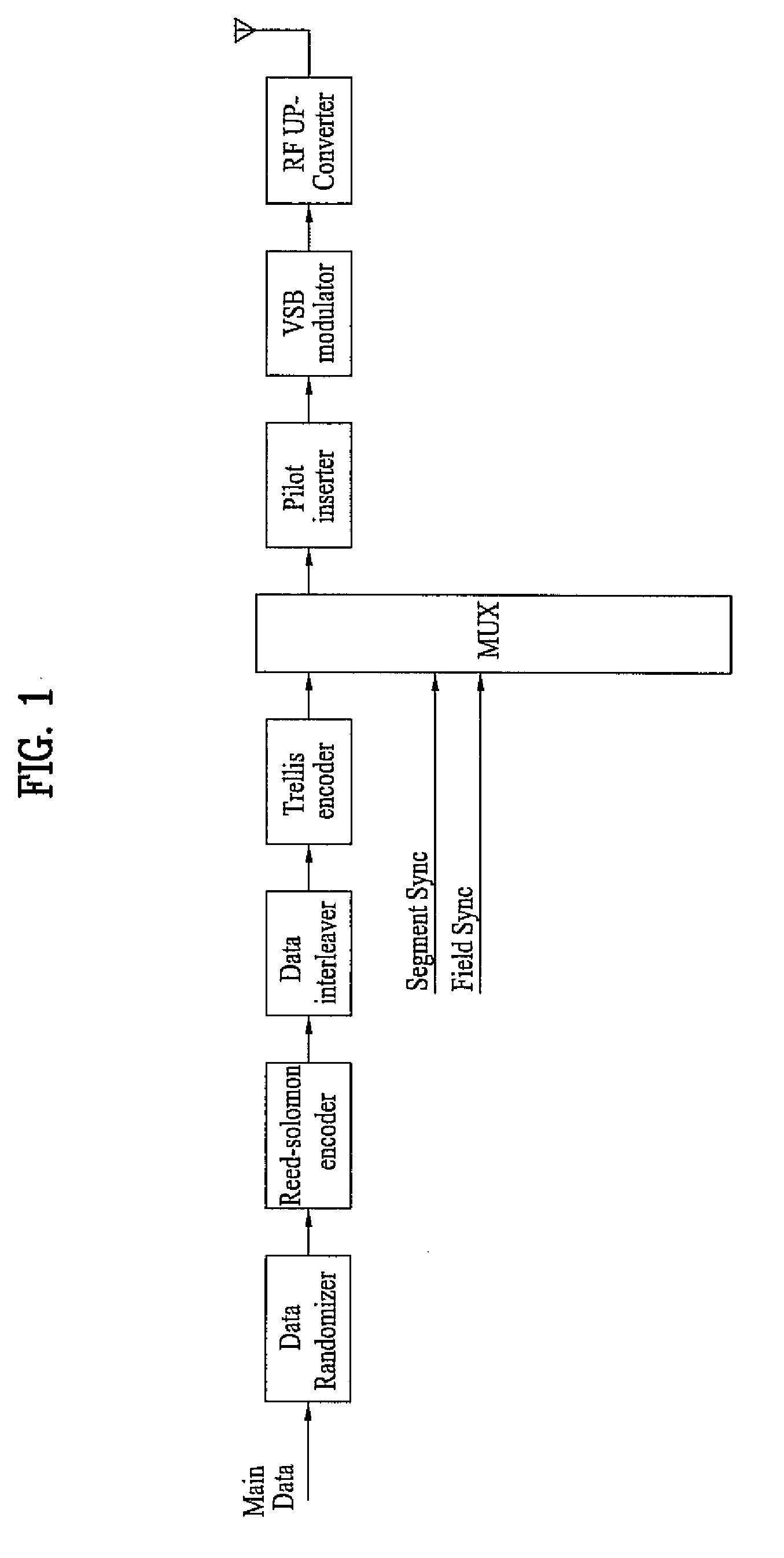

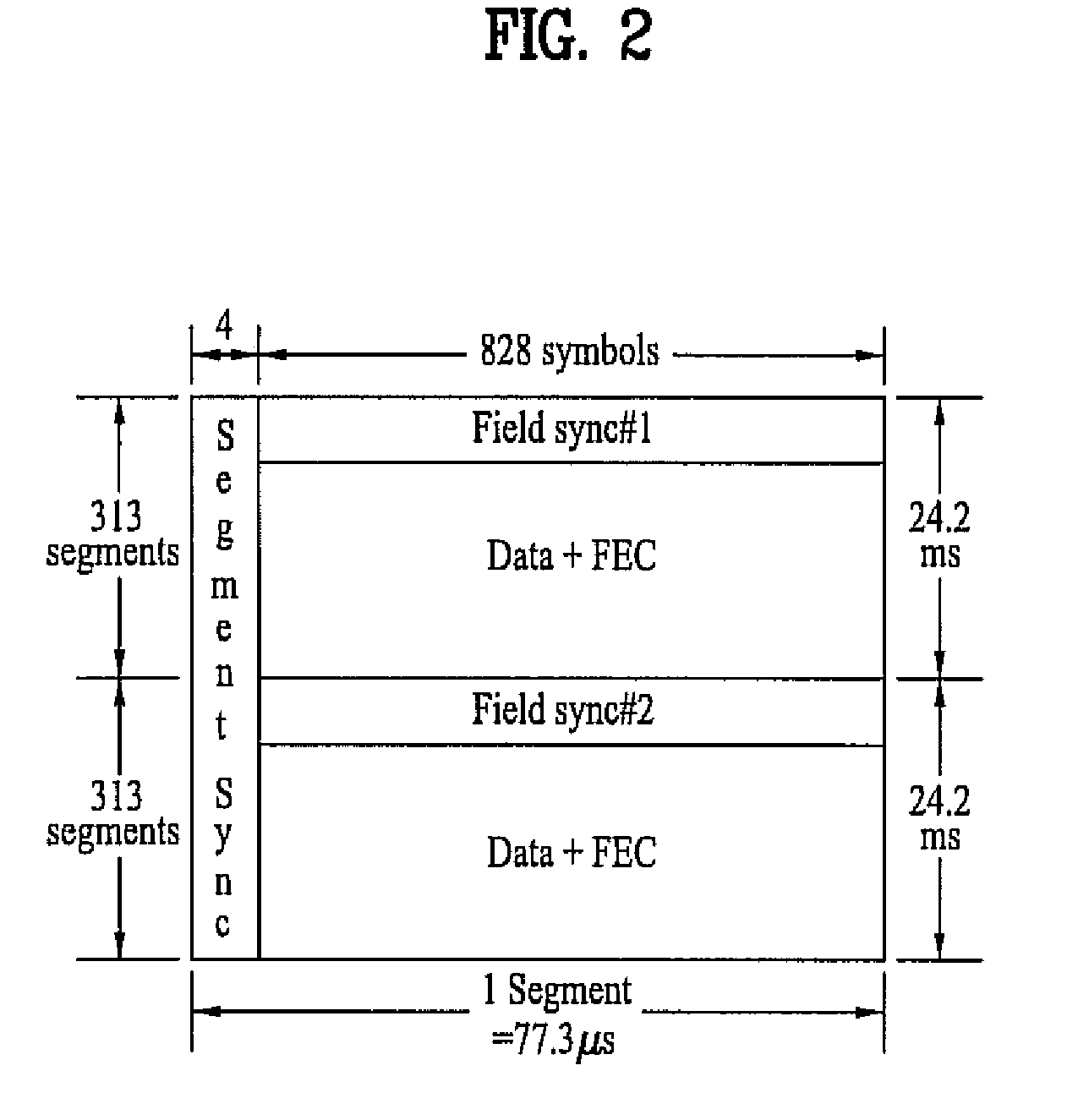

Digital television transmitter/receiver and method of processing data in digital television transmitter/receiver

InactiveUS20070121681A1Robust against noiseTransmit dataData representation error detection/correctionPulse modulation television signal transmissionTime informationMultiplexing

A digital television (DTV) transmitter and a method of processing data in the DTV transmitter / receiver are disclosed. In the DTV transmitter, a pre-processor pre-processes the enhanced data by coding the enhanced data for forward error correction (FEC) and expanding the FEC-coded data. A packet formatter generates one or more groups of enhanced data packets, each enhanced data packet including the pre-processed enhanced data and known data, wherein the data formatter adds burst time information into each group of enhanced data packets. And, a packet multiplexer generates at least one burst of enhanced data by multiplexing the one or more groups of enhanced data packets with at least one main data packet including the main data, each burst of enhanced data including at least one group of enhanced data packets.

Owner:LG ELECTRONICS INC

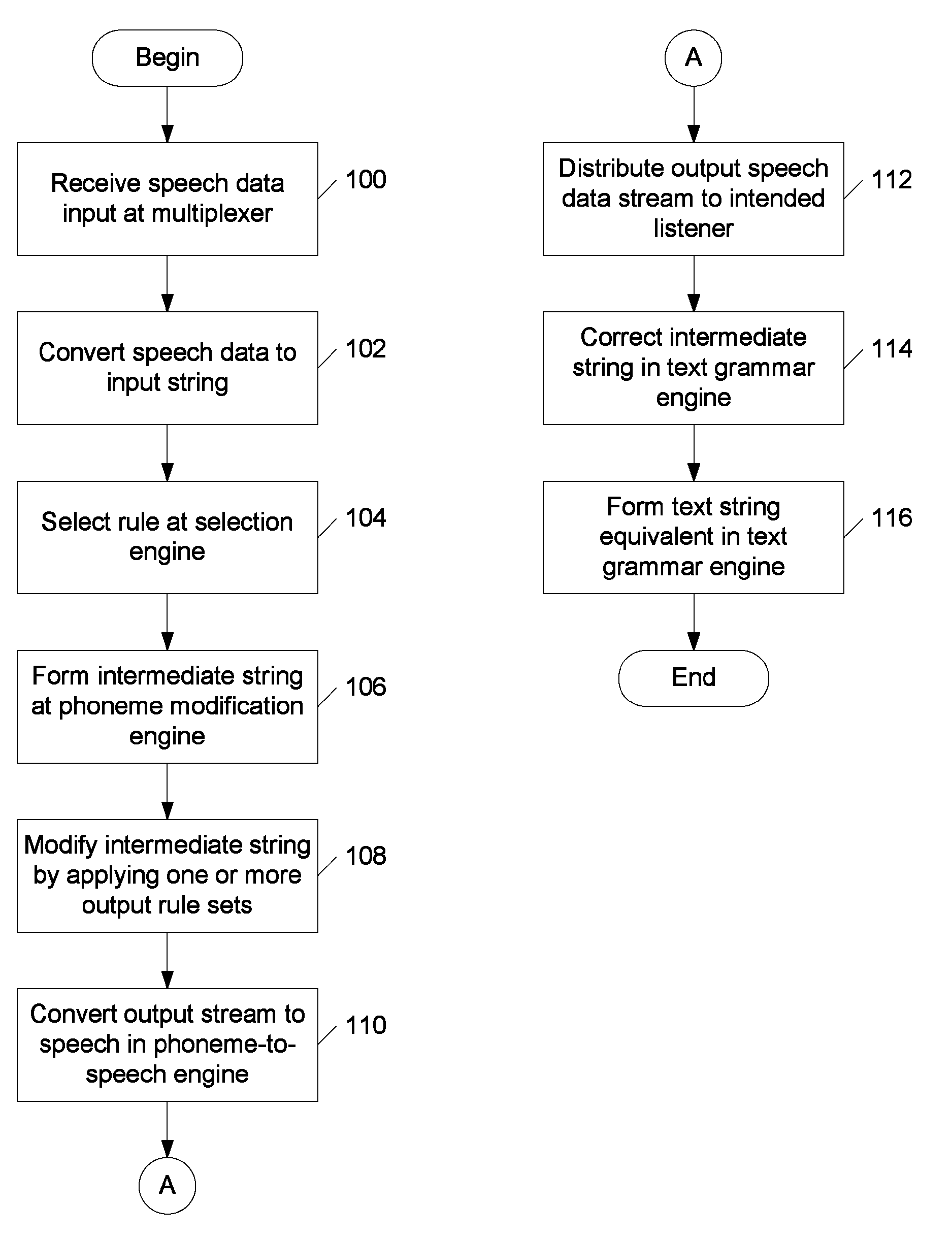

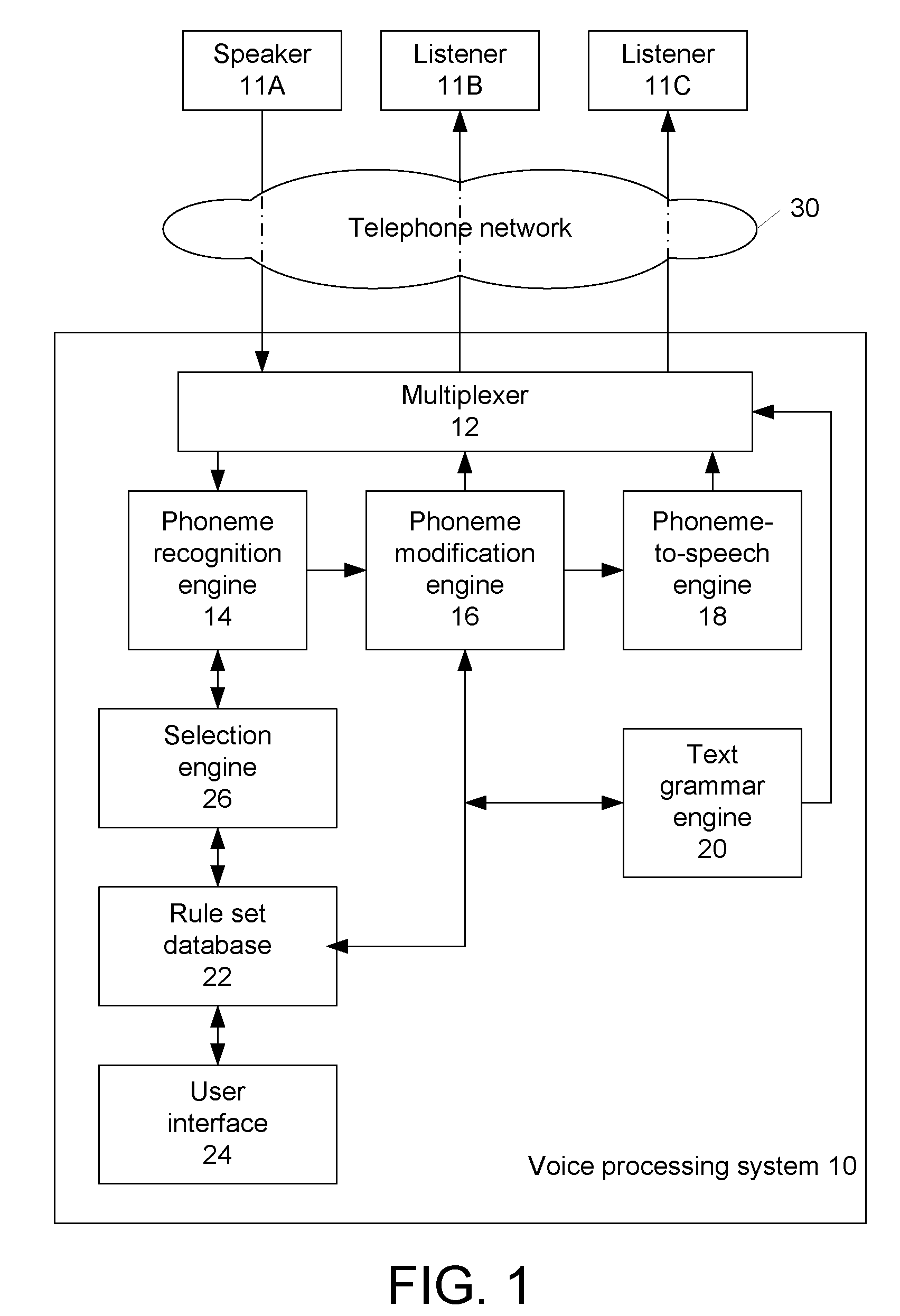

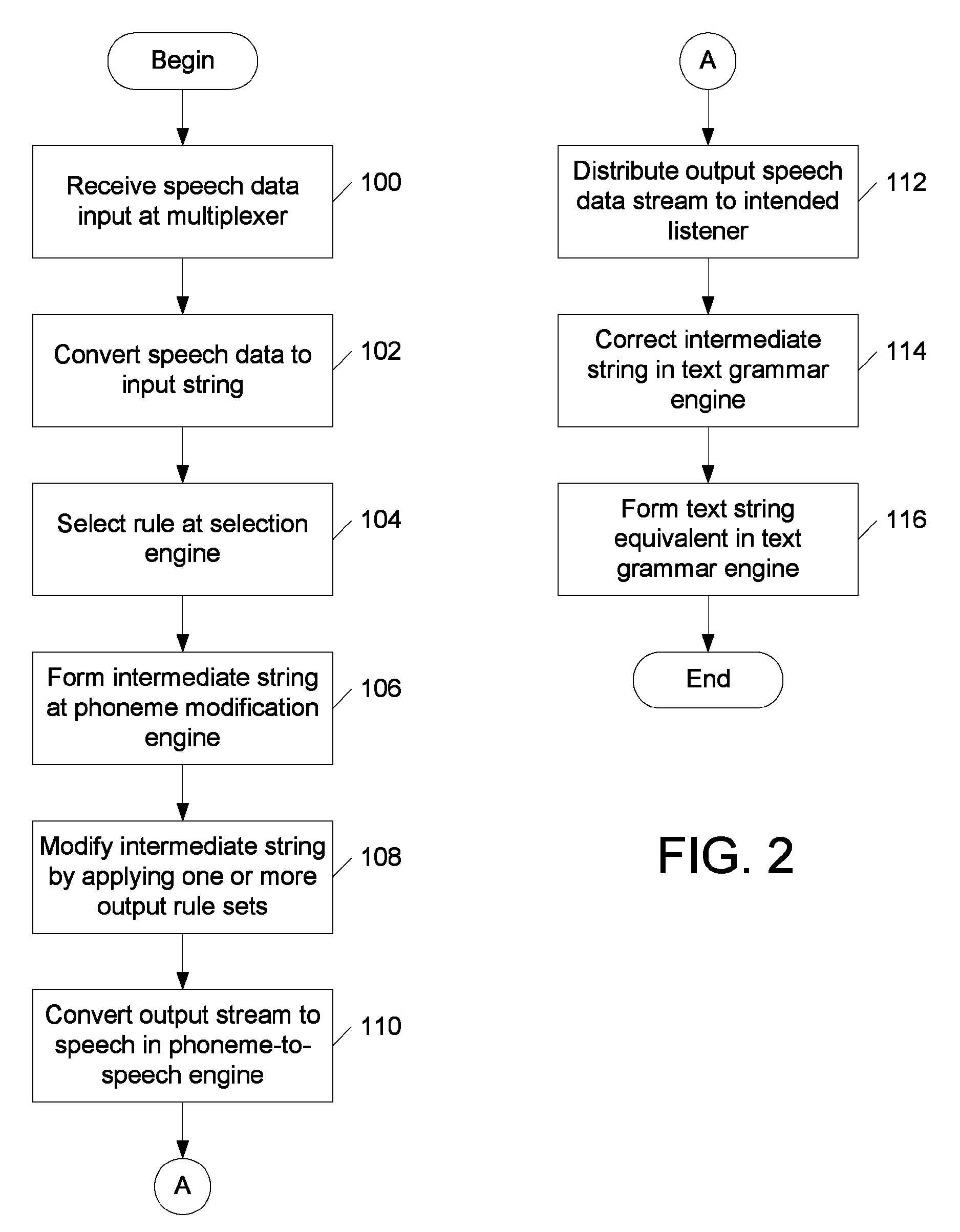

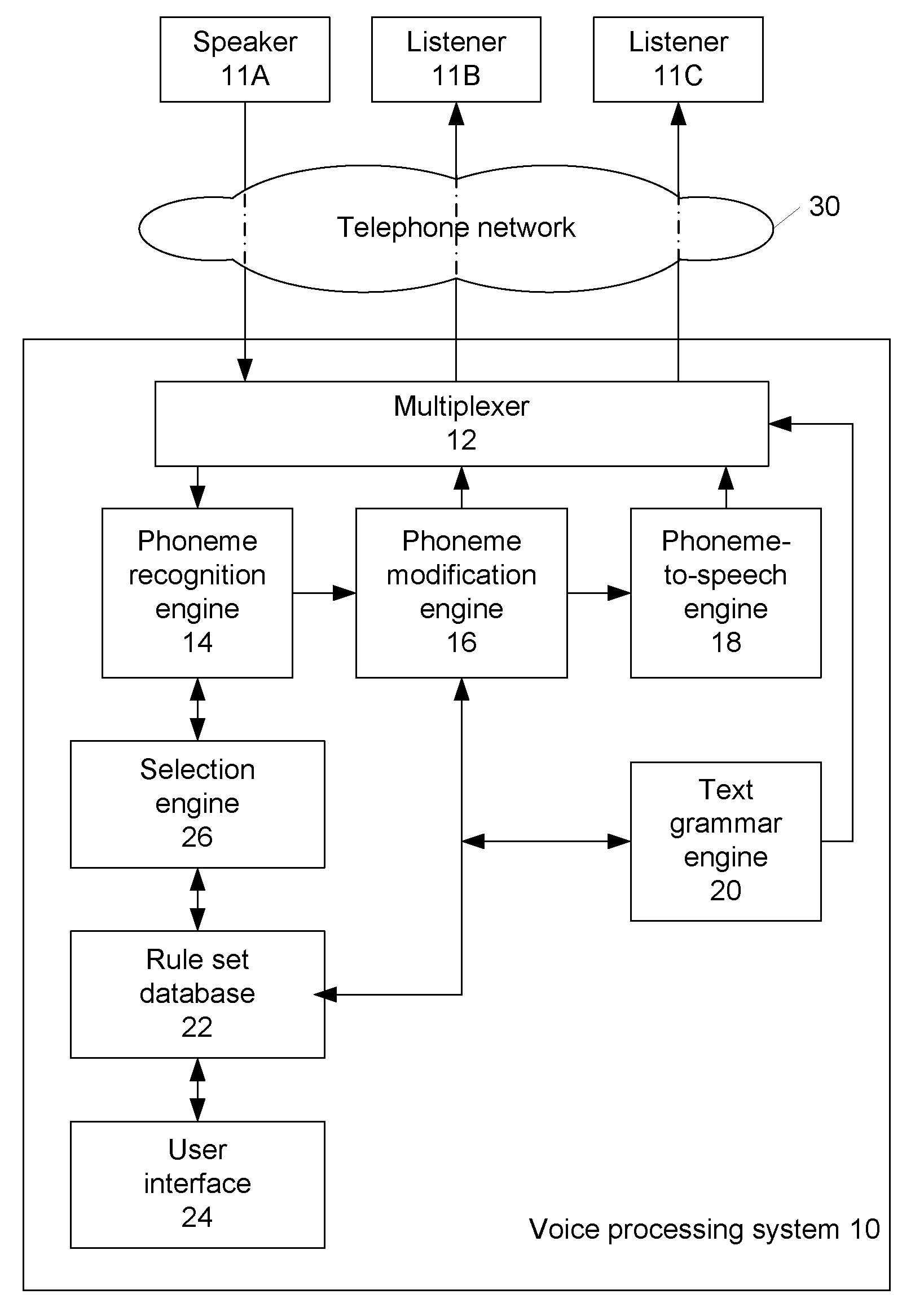

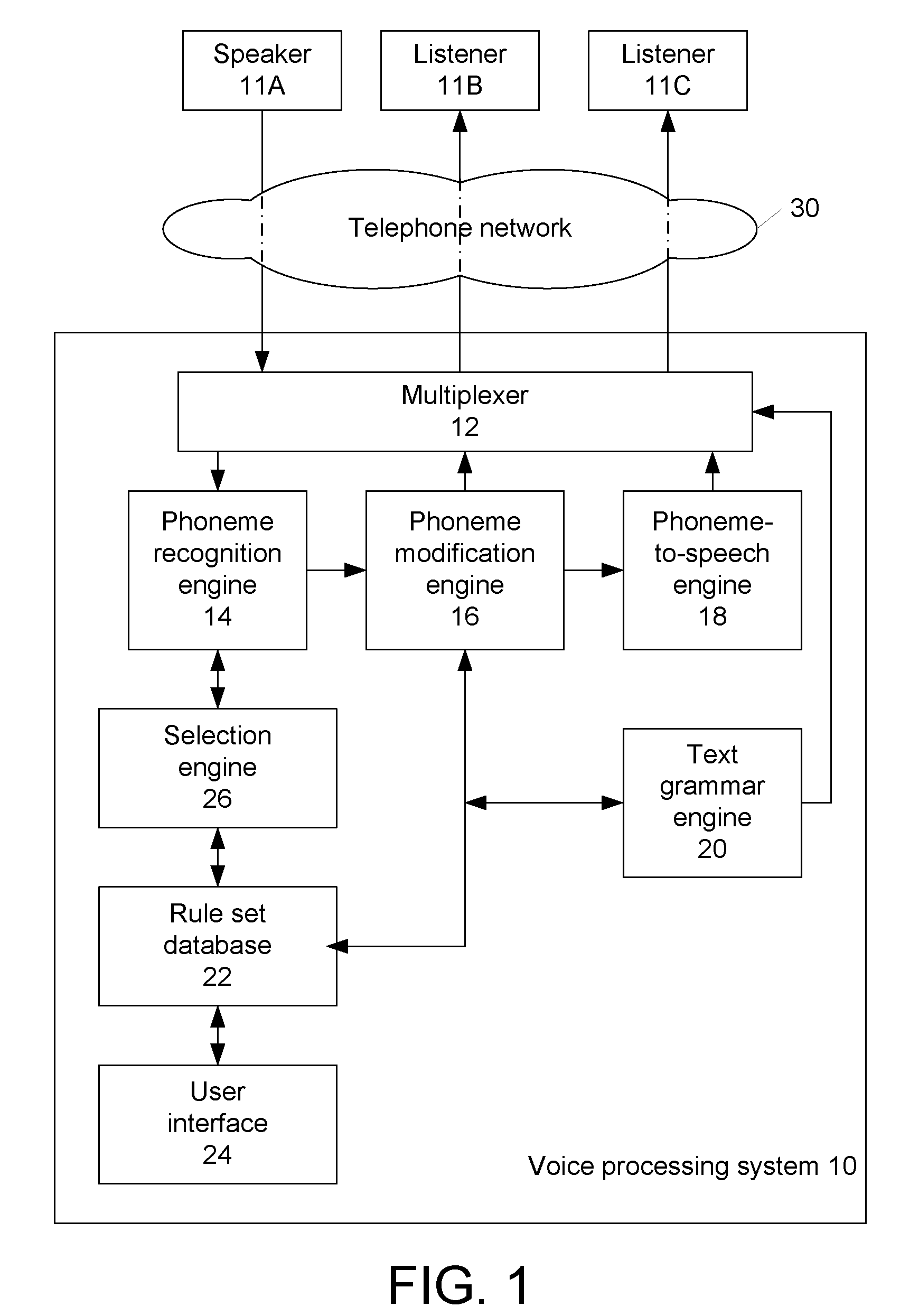

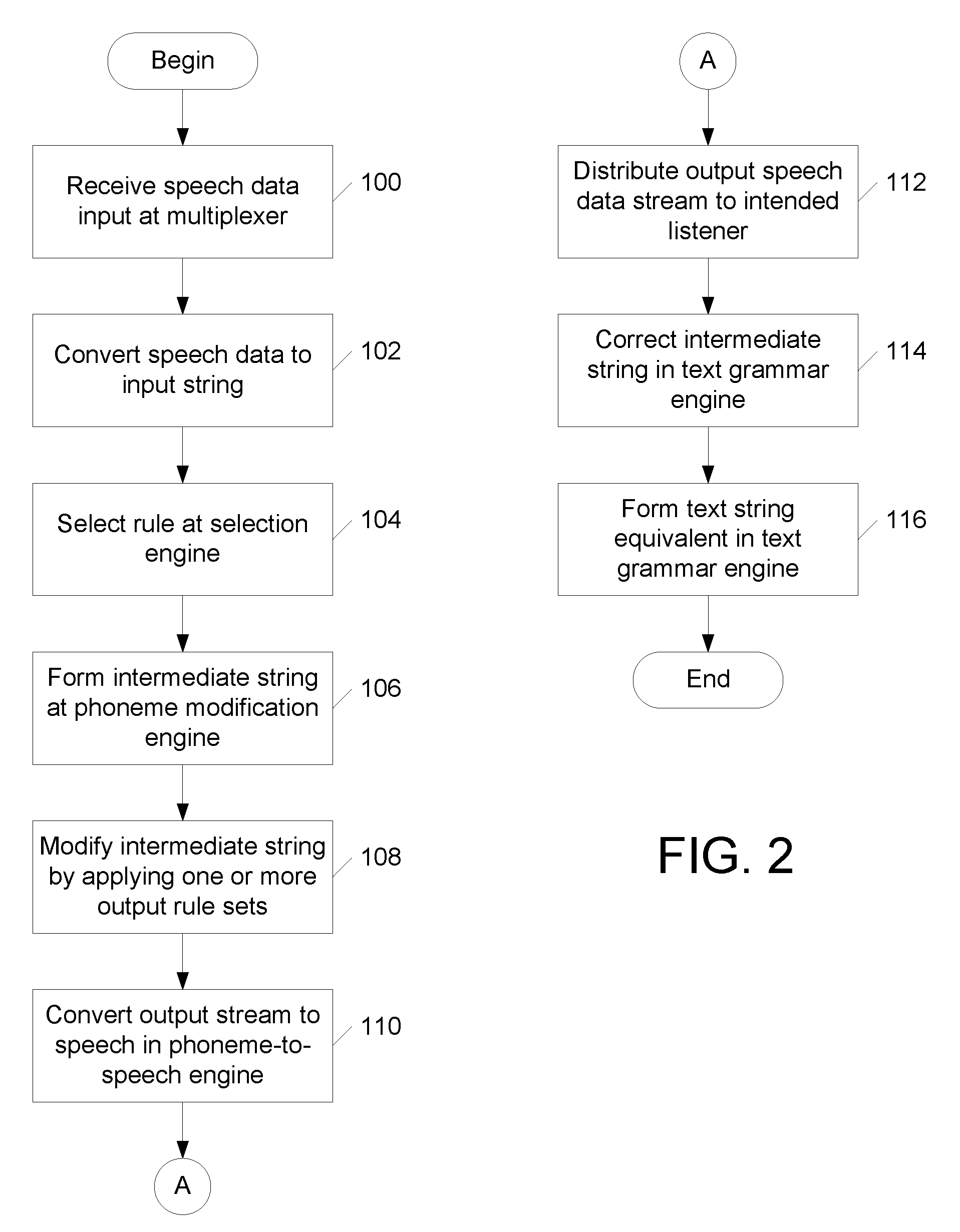

Phonetic decoding and concatentive speech synthesis

A speech processing system includes a multiplexer that receives speech data input as part of a conversation turn in a conversation session between two or more users where one user is a speaker and each of the other users is a listener in each conversation turn. A speech recognizing engine converts the speech data to an input string of acoustic data while a speech modifier forms an output string based on the input string by changing an item of acoustic data according to a rule. The system also includes a phoneme speech engine for converting the first output string of acoustic data including modified and unmodified data to speech data for output via the multiplexer to listeners during the conversation turn.

Owner:CERENCE OPERATING CO

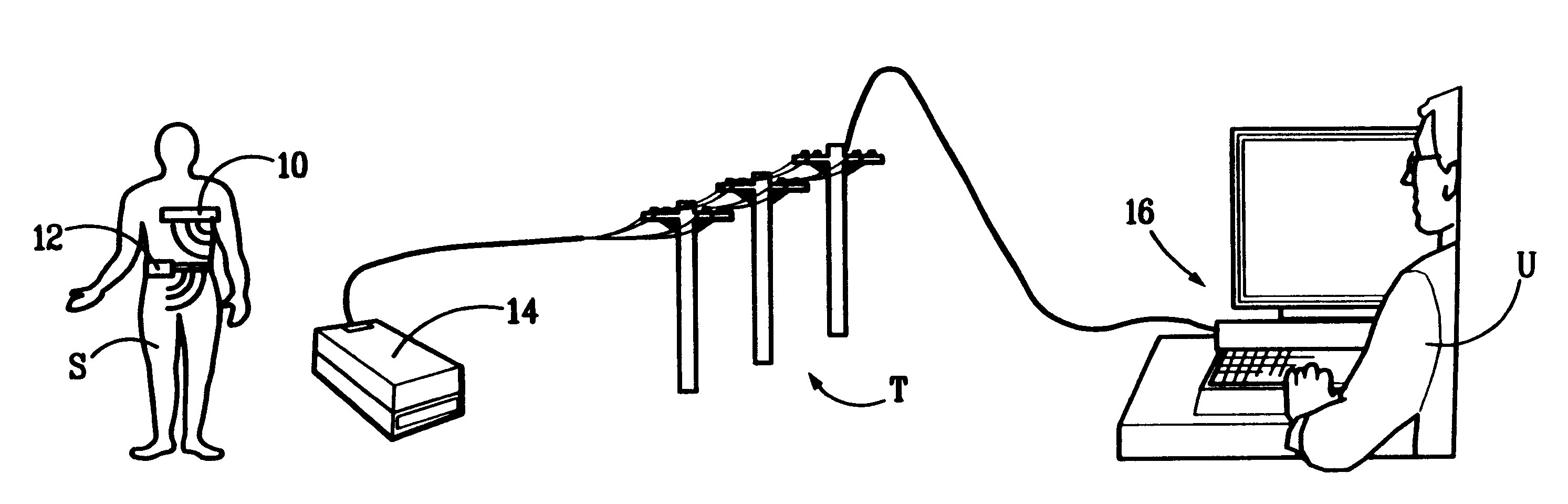

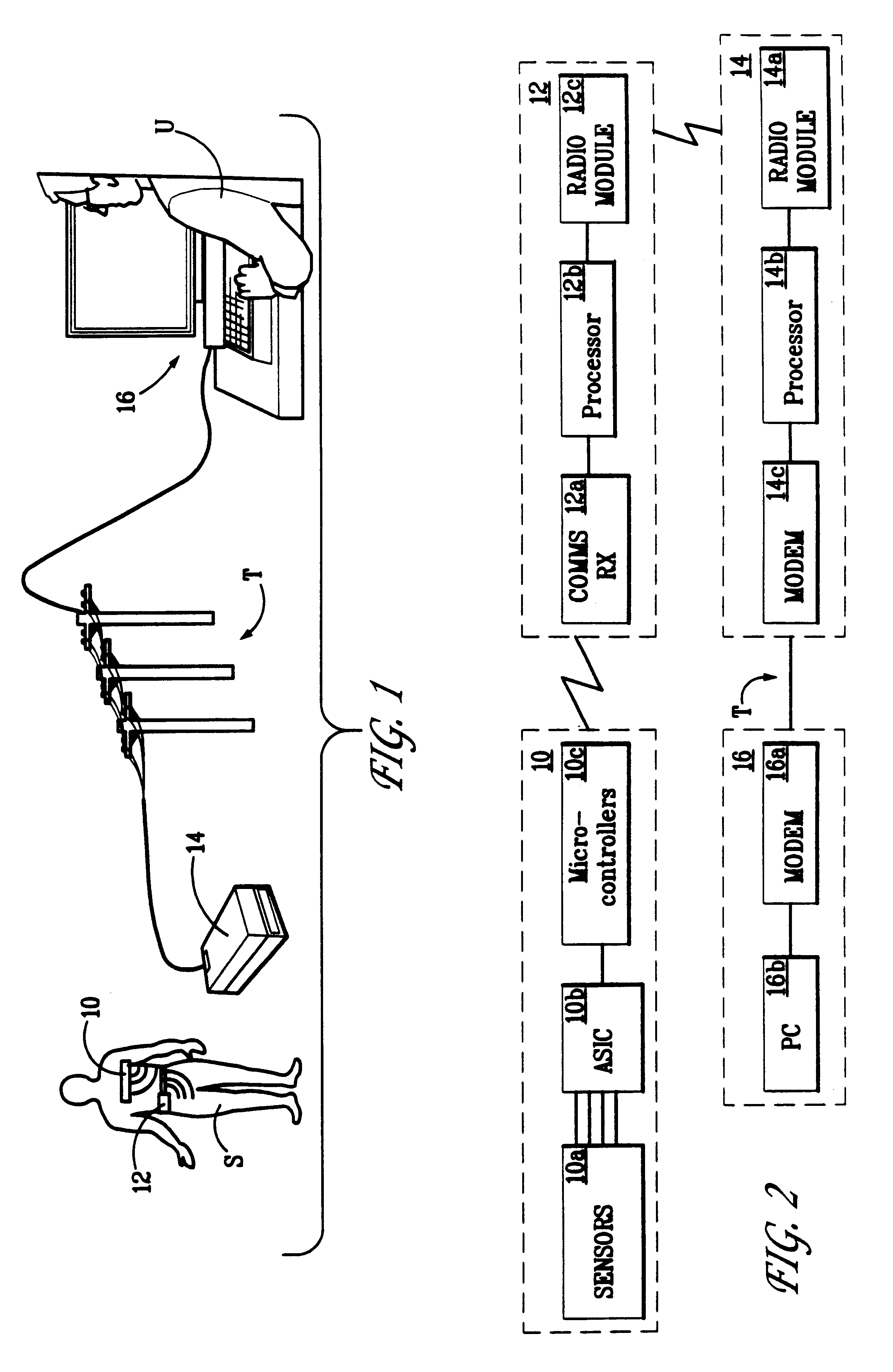

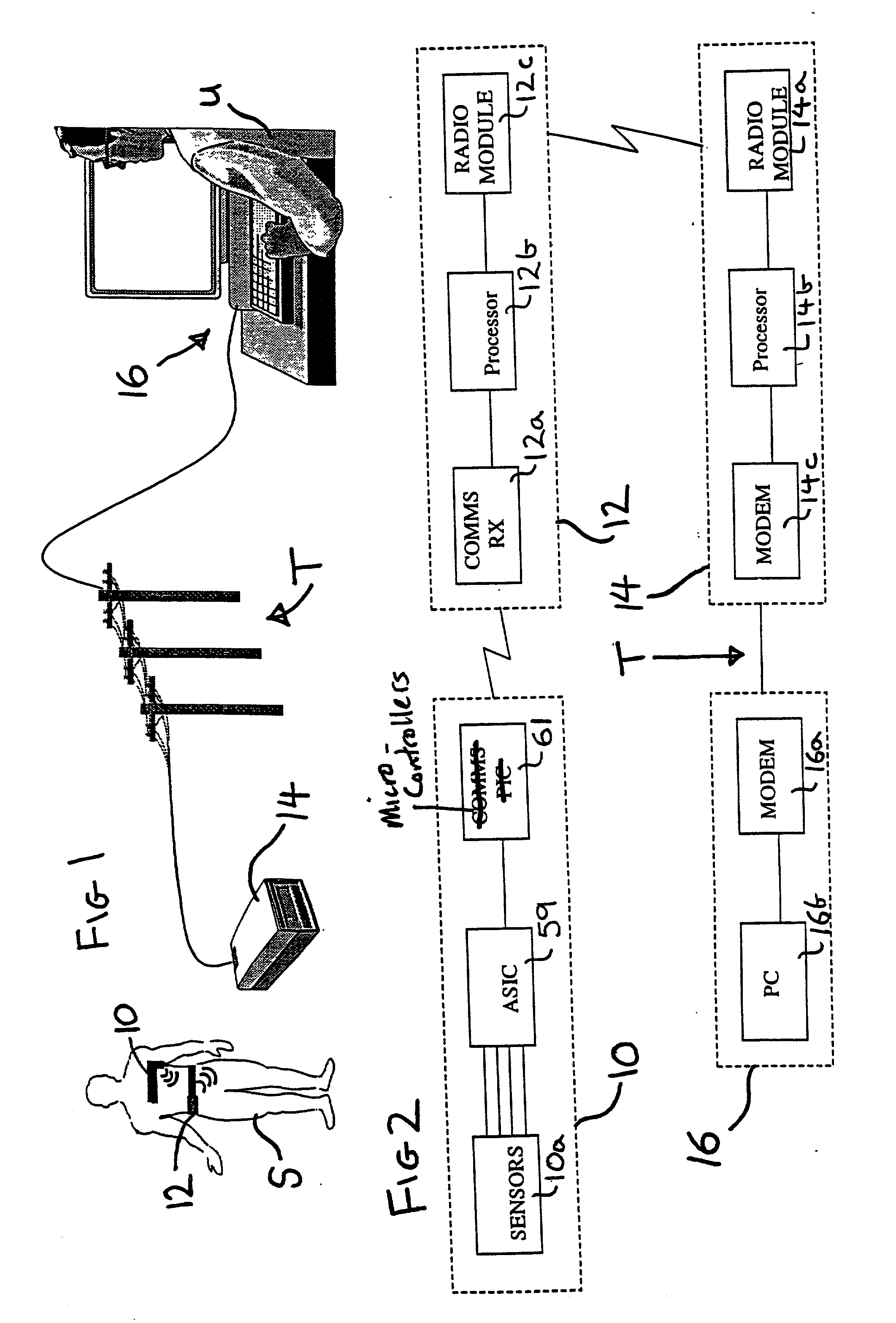

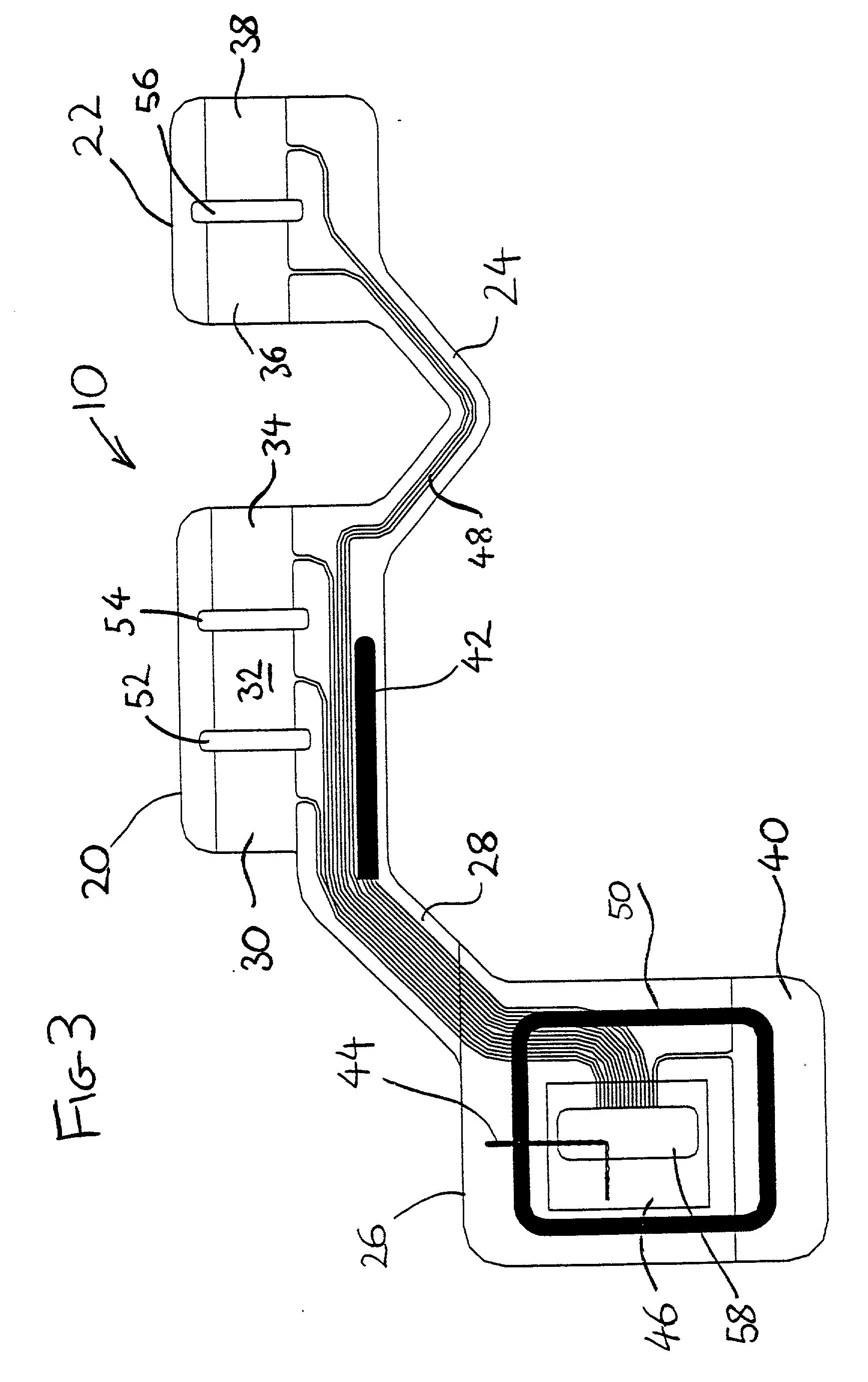

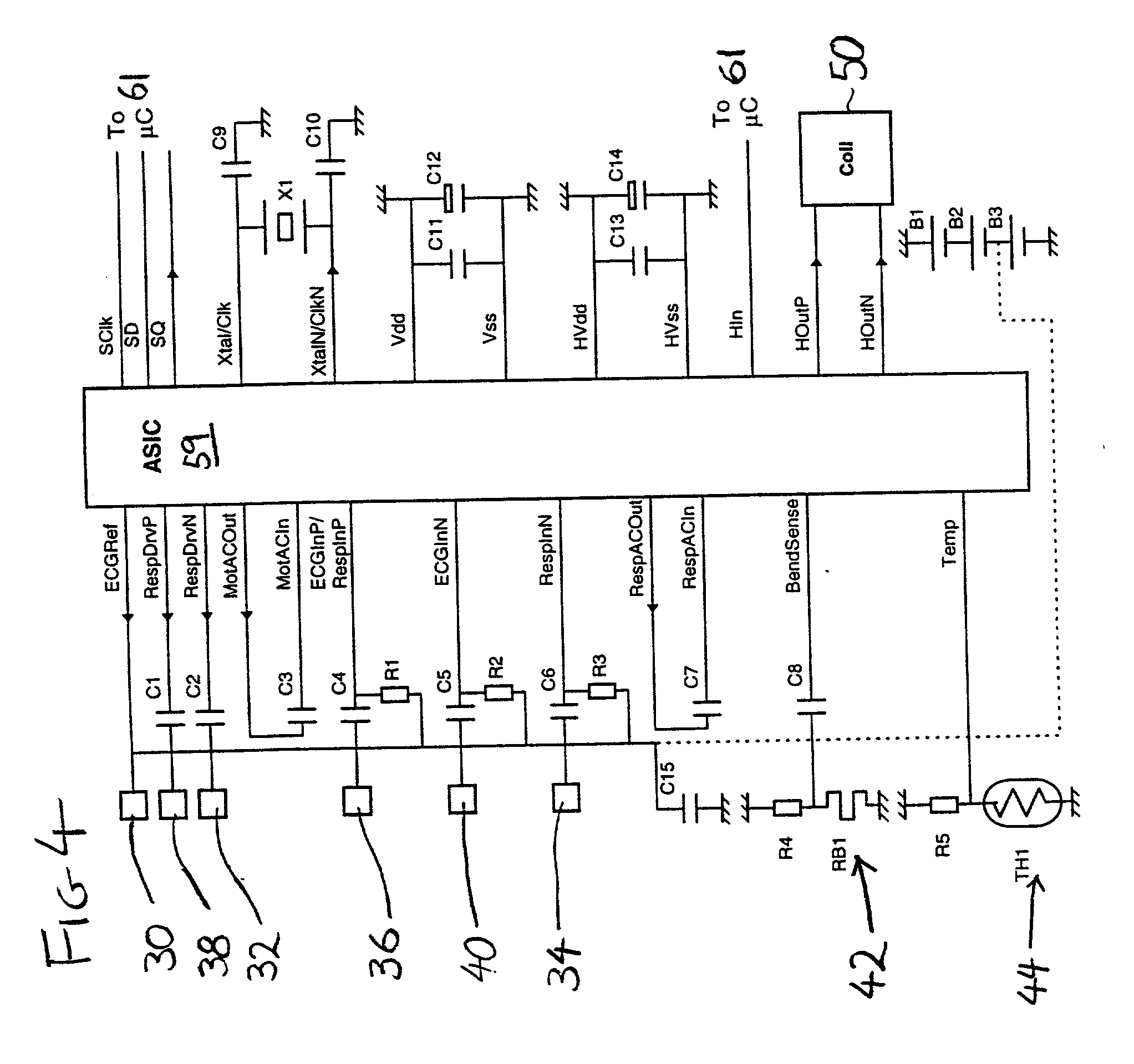

Physiological sensor array

InactiveUS6494829B1Efficient low powered transfer of dataImprove power efficiencyElectric signal transmission systemsElectrocardiographySensor arrayMultiplexer

A physiological sensor device for attachment to a mammalian subject comprising an output transmitter, at least two physiological sensors each for sensing one of the subject's physiological parameters, and a controller operably in communication with the physiological sensors which controller communicates a signal comprising data representative of both the sensed physiological parameters to the output transmitter which operably transmits the signal to a remote location, wherein the controller comprises a multiplexer which operably switches the data from both the physiological sensors into a serial output signal. Respiration may be detected by a bend sensor including an elongate member and an electrical component mounted thereon which electrical component has an electrical property which varies in dependence on the extent of bending of the elongate member. Other parameters such as temperature and full waveform ECG may also be measured.

Owner:CLEARPATH PARTNERS

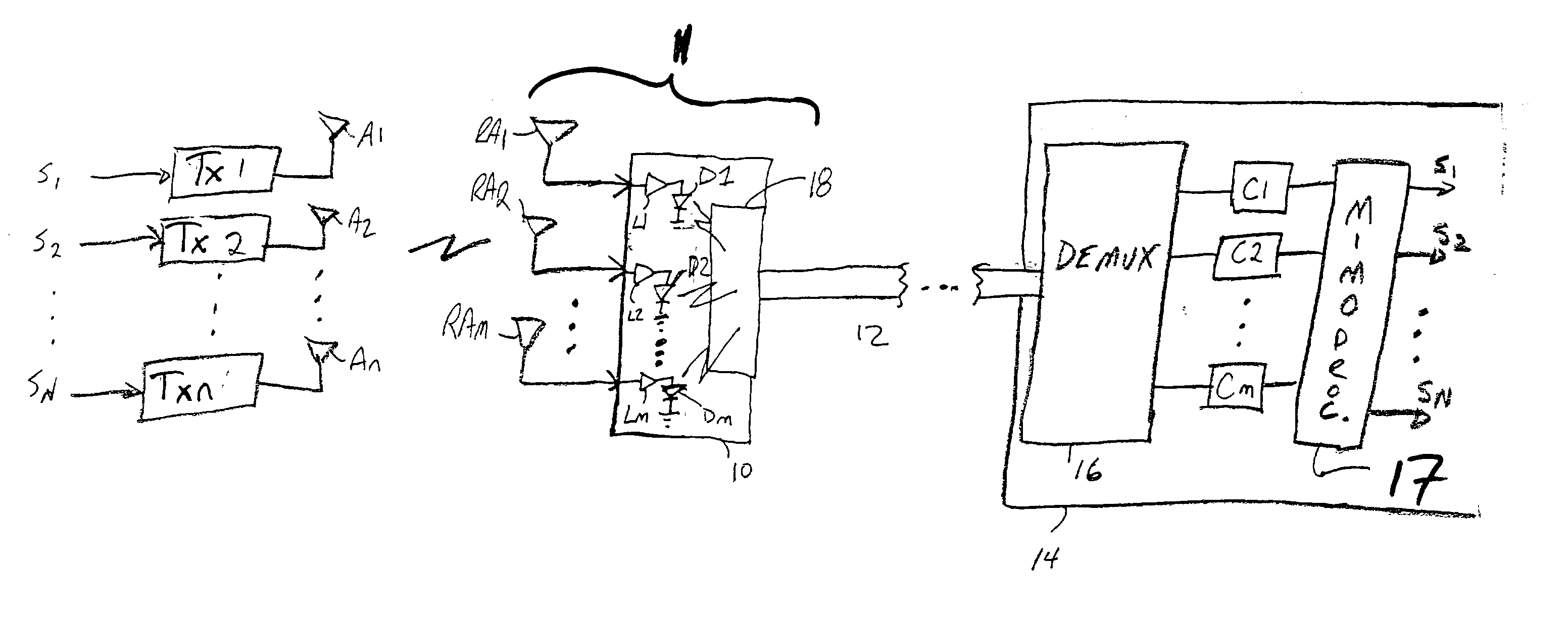

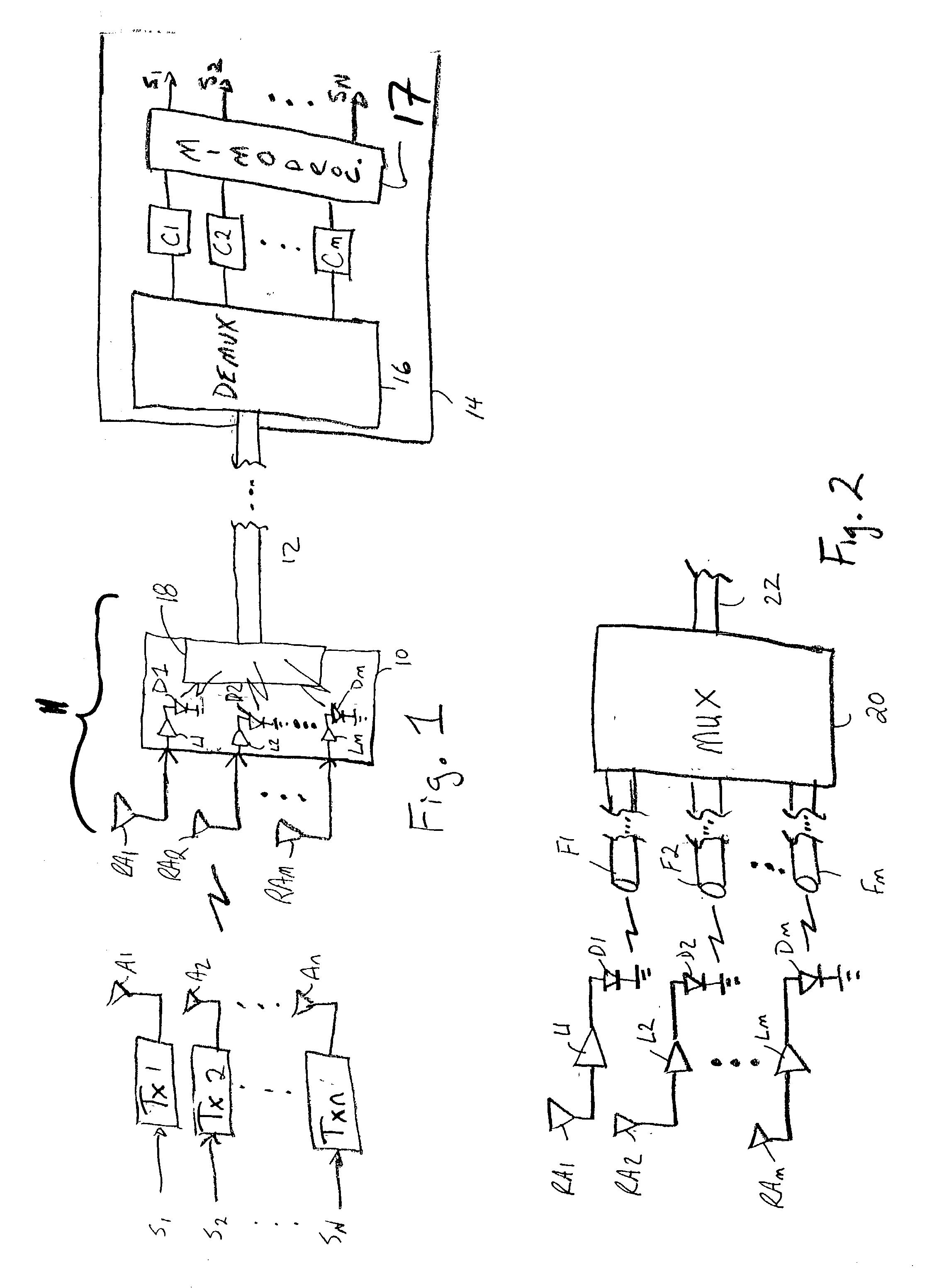

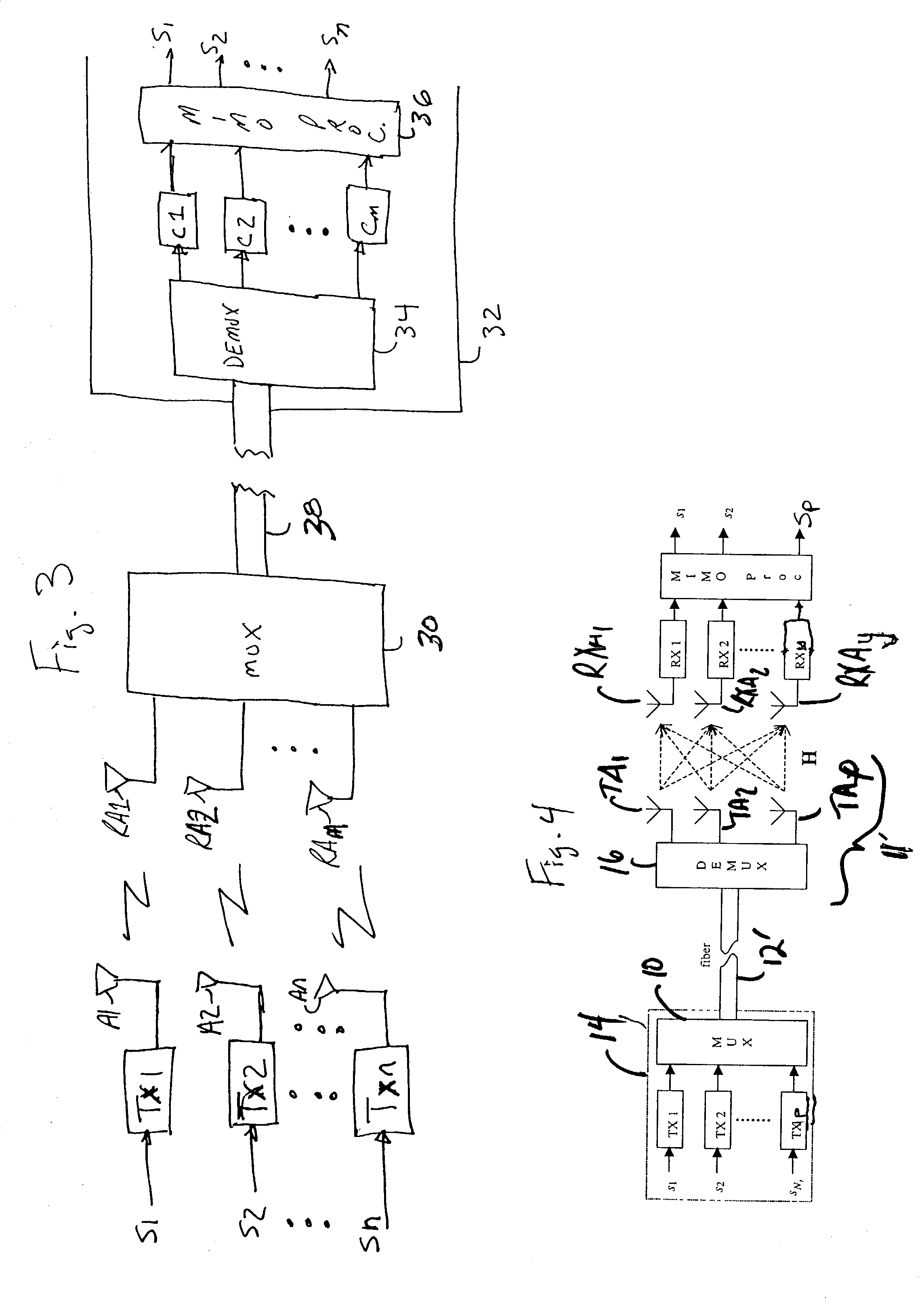

System for transporting multiple radio frequency signals of a multiple input, multiple output wireless communication system to/from a central processing base station

InactiveUS20040017785A1Spatial transmit diversityWavelength-division multiplex systemsMultiplexingElectrical conductor

The system includes, at least first and second antennas receiving first and second radio frequency signals, and a multiplexing system converting the first and second radio frequency signals to first and second optical signals and multiplexing the first and second optical signals for transmission over the optical fiber. A central processing base station is adapted for connection to the optical fiber. The central processing base station demultiplexes the first and second optical signals from the optical fiber, converts the first and second optical signals into the first and second radio frequency signals, and processes the first and second radio frequency signals to obtain information signals. In another embodiment, a conductor such as a coaxial cable replaces the optical fiber, and the multiplexer multiplexes the first and second radio frequency signals onto the conductor. In a further embodiment, the central processing base station uses the same techniques to send signals to an access point for transmission.

Owner:AGERE SYST INC

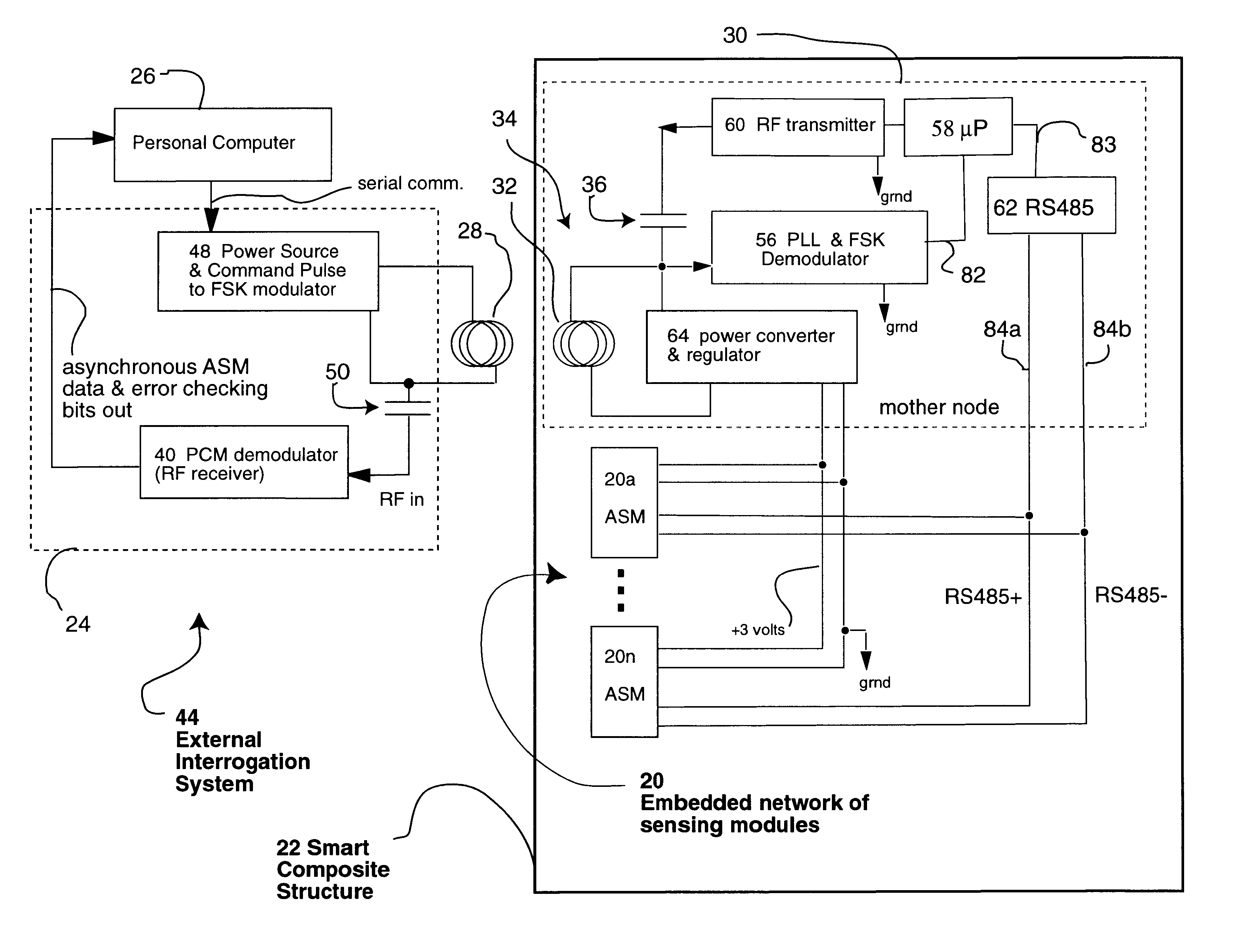

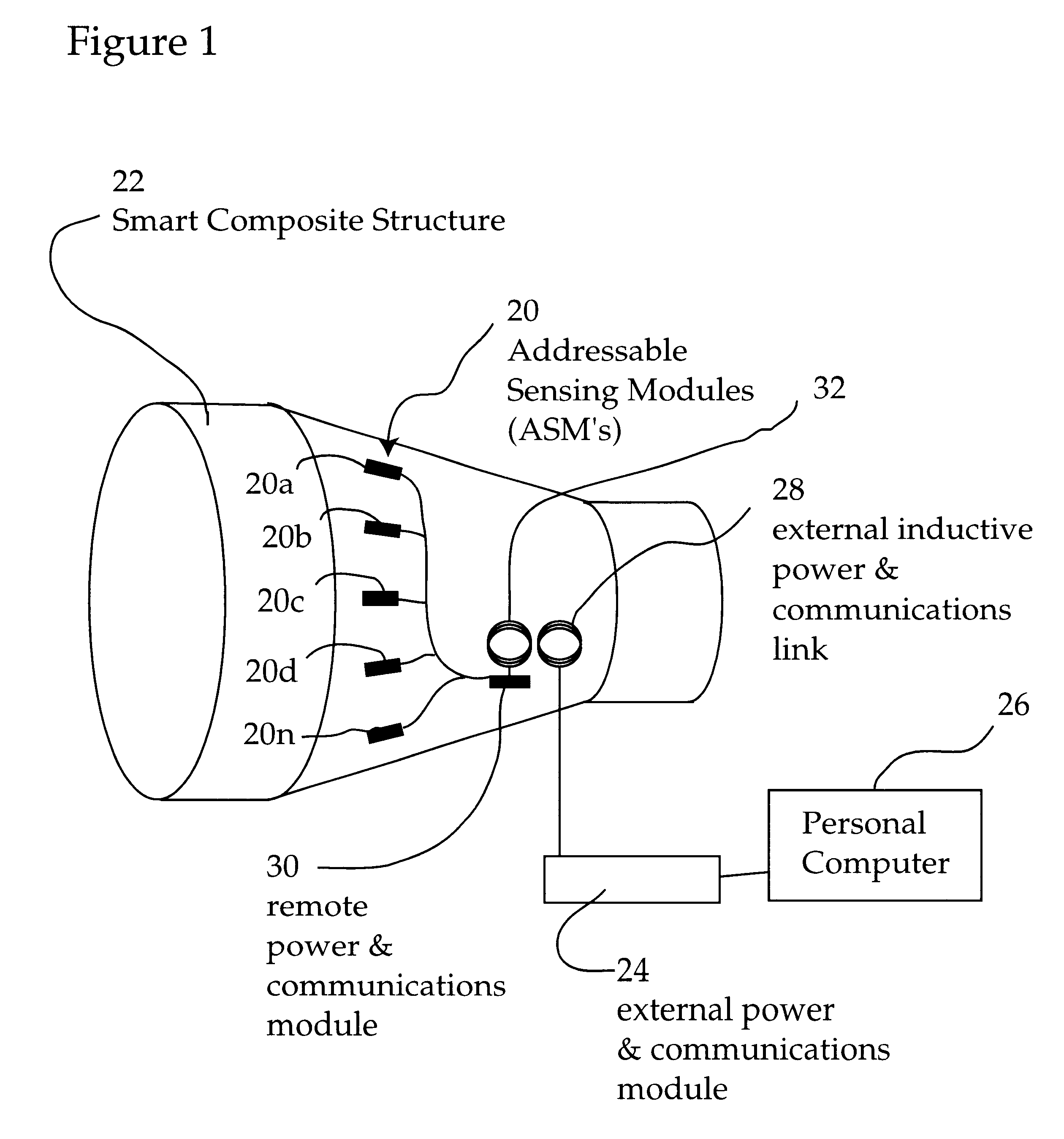

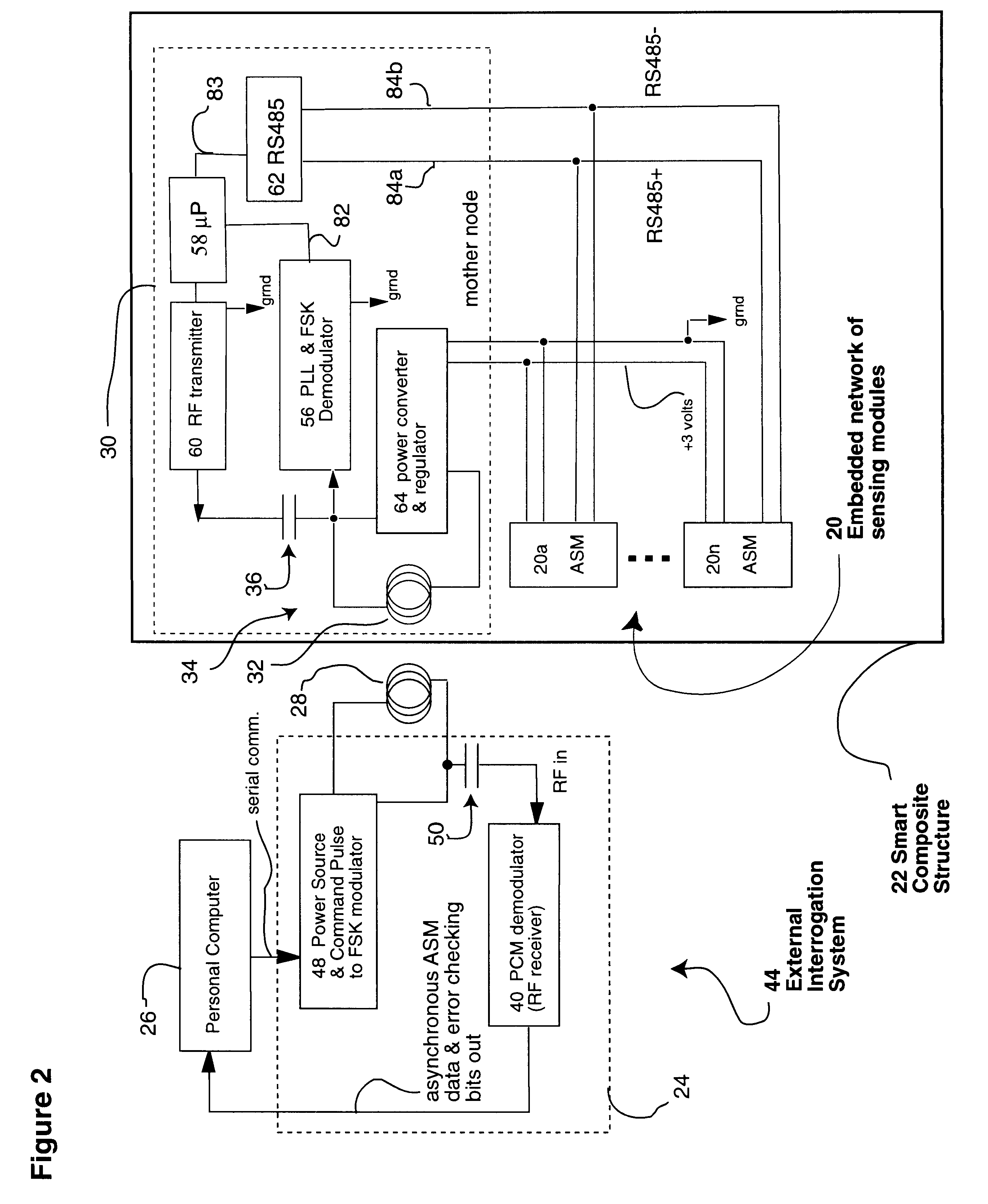

System for remote powering and communication with a network of addressable, multichannel sensing modules

InactiveUS6529127B2Low costElectric signal transmission systemsDigital data processing detailsError checkingInstrumentation amplifier

A multidrop network of multichannel, addressable sensing modules (ASM's), to be embedded within a composite structure, remotely powered, and interrogated by a personal computer through a non-contacting inductive link. Each ASM contains a microprocessor with non-volatile memory, multiplexer, programmable gain and filter instrumentation amplifier, and sigma delta analog to digital converter (all housed in two thin surface mount packages). An embedded mothernode includes circuitry for power and data reception (into the structure), and data transmission (back out of the structure). The external interrogation system communicates into the network of ASM's by modulating the AC waveform that delivers power to the embedded electronics. Once addressed, each ASM powers up its programmable (gain & filter) sensing channels (3 full differential or 5 pseudo differential) and data conversion elements. Sensed data are pulse code modulated, including error checking, which serially modulate an RF carrier for wireless transmission out of the composite to the interrogating computer. These advanced, micro-miniature sensing networks may be applied to a wide variety of military, medical, & civil structures.

Owner:LORD CORP

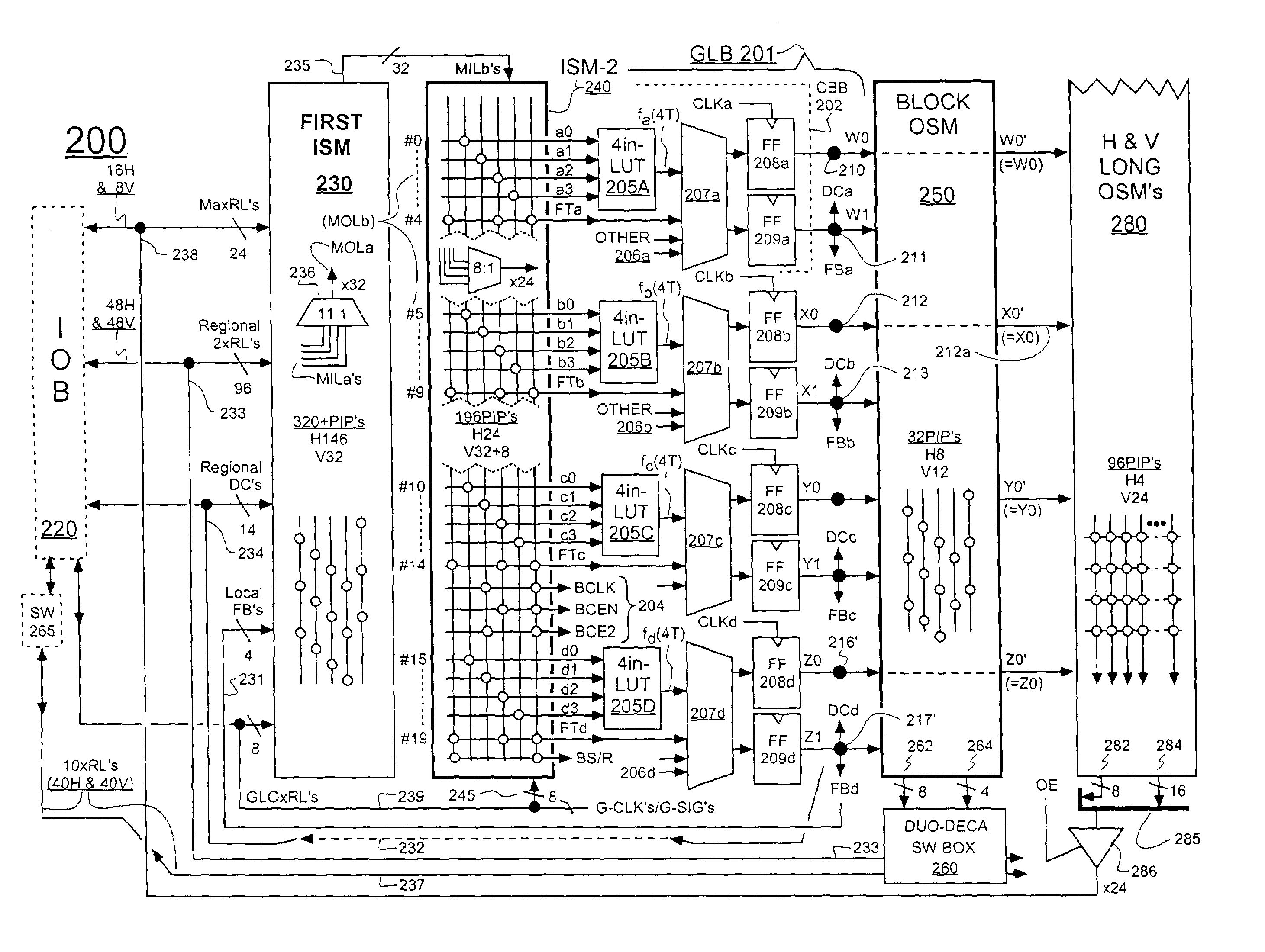

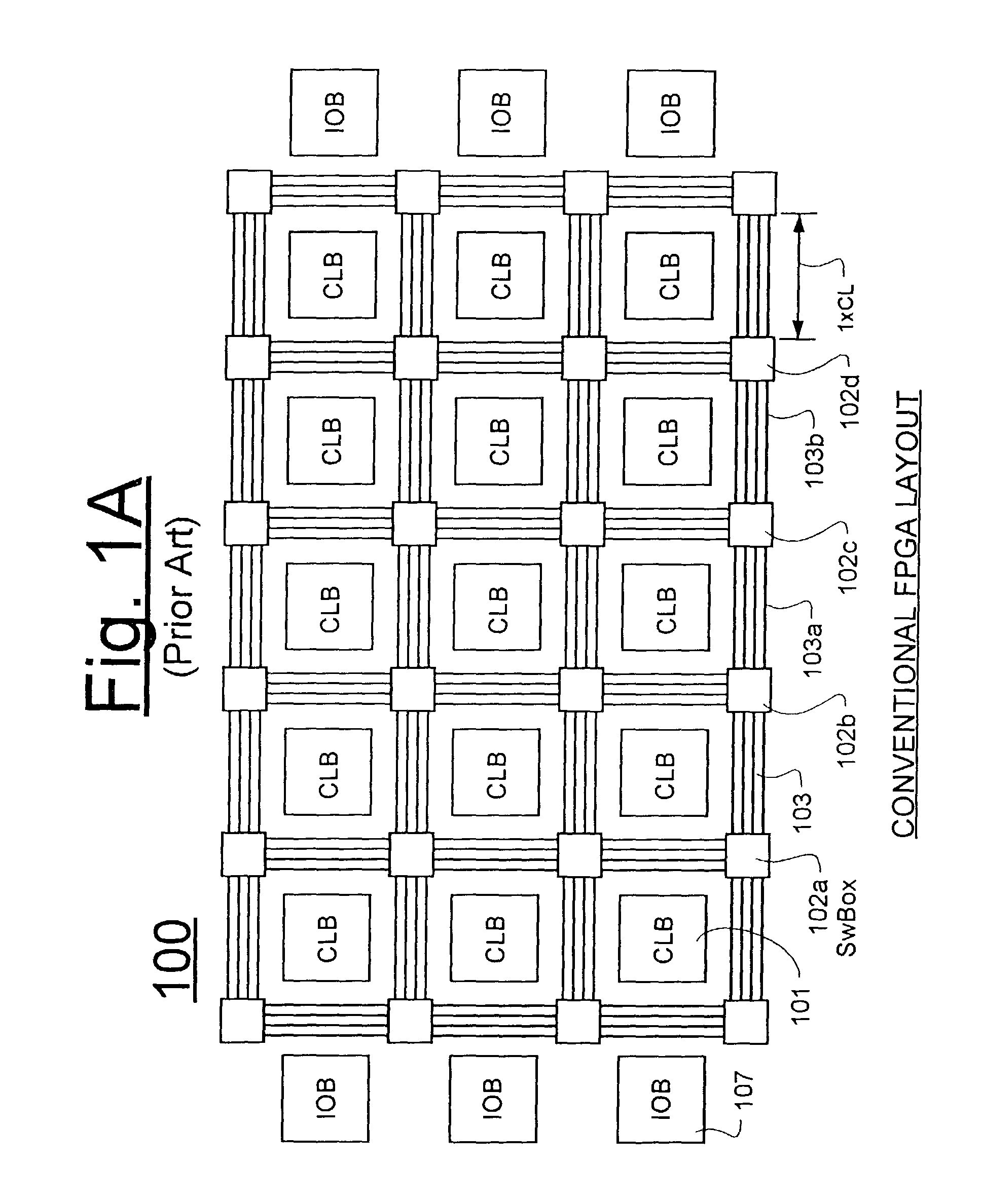

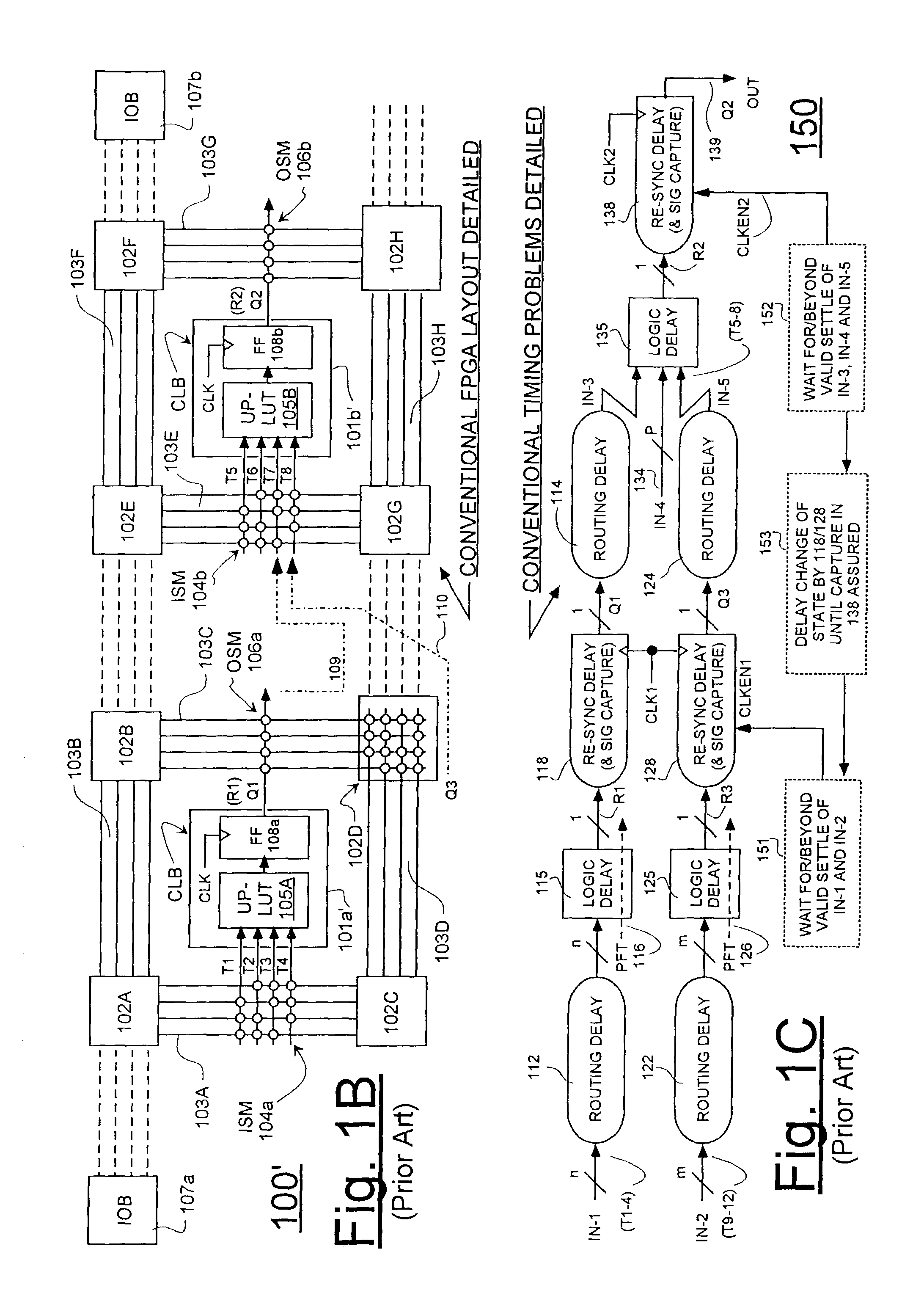

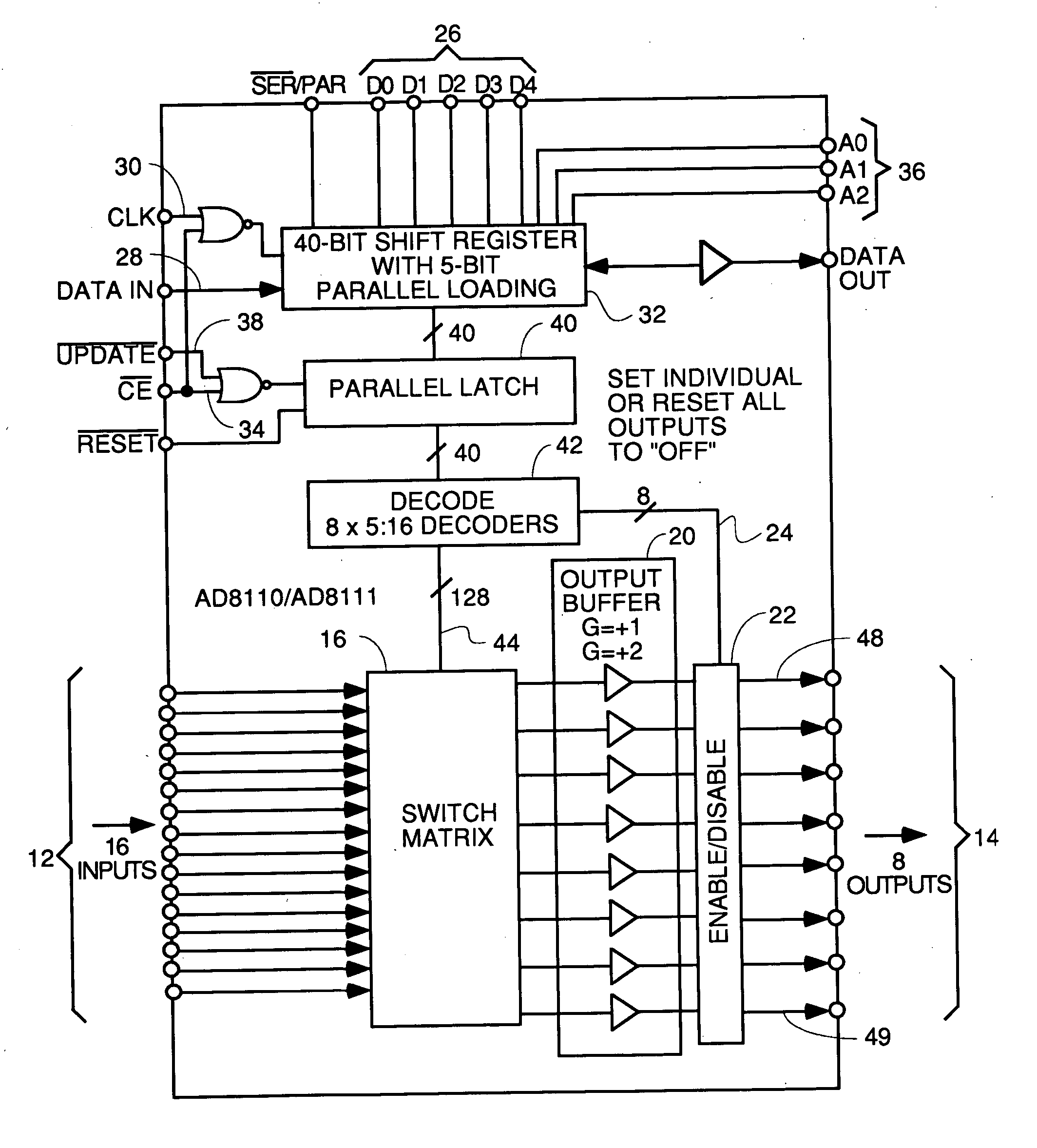

FPGA with register-intensive architecture

ActiveUS7028281B1Minimize resourceReduce consumptionSolid-state devicesCAD circuit designProcessor registerMultiplexer

Field programmable gate arrays (FPGA's) may be structured in accordance with the disclosure to have a register-intensive architecture that provides, for each of plural function-spawning LookUp Tables (e.g. a 4-input, base LUT's) within a logic block, a plurality of in-block accessible registers. A register-feeding multiplexer means may be provided for allowing each of the plural registers to equivalently capture and store a result signal output by the corresponding, base LUT of the plural registers. Registerable, primary and secondary feedthroughs may be provided for each base LUT so that locally-acquired input signals of the LUT may be fed-through to the corresponding, in-block registers for register-recovery purposes without fully consuming (wasting) the lookup resources of the associated, base LUT. A multi-stage, input switch matrix (ISM) may be further provided for acquiring and routing input signals from adjacent, block-interconnect lines (AIL's) and / or block-intra-connect lines (e.g., FB's) to the base LUT's and / or their respective, registerable feedthroughs. Techniques are disclosed for utilizing the many in-block registers and / or the registerable feedthroughs and / or the multi-stage ISM's for efficiently implementing various circuit designs by appropriately configuring such register-intensive FPGA's.

Owner:LATTICE SEMICON CORP

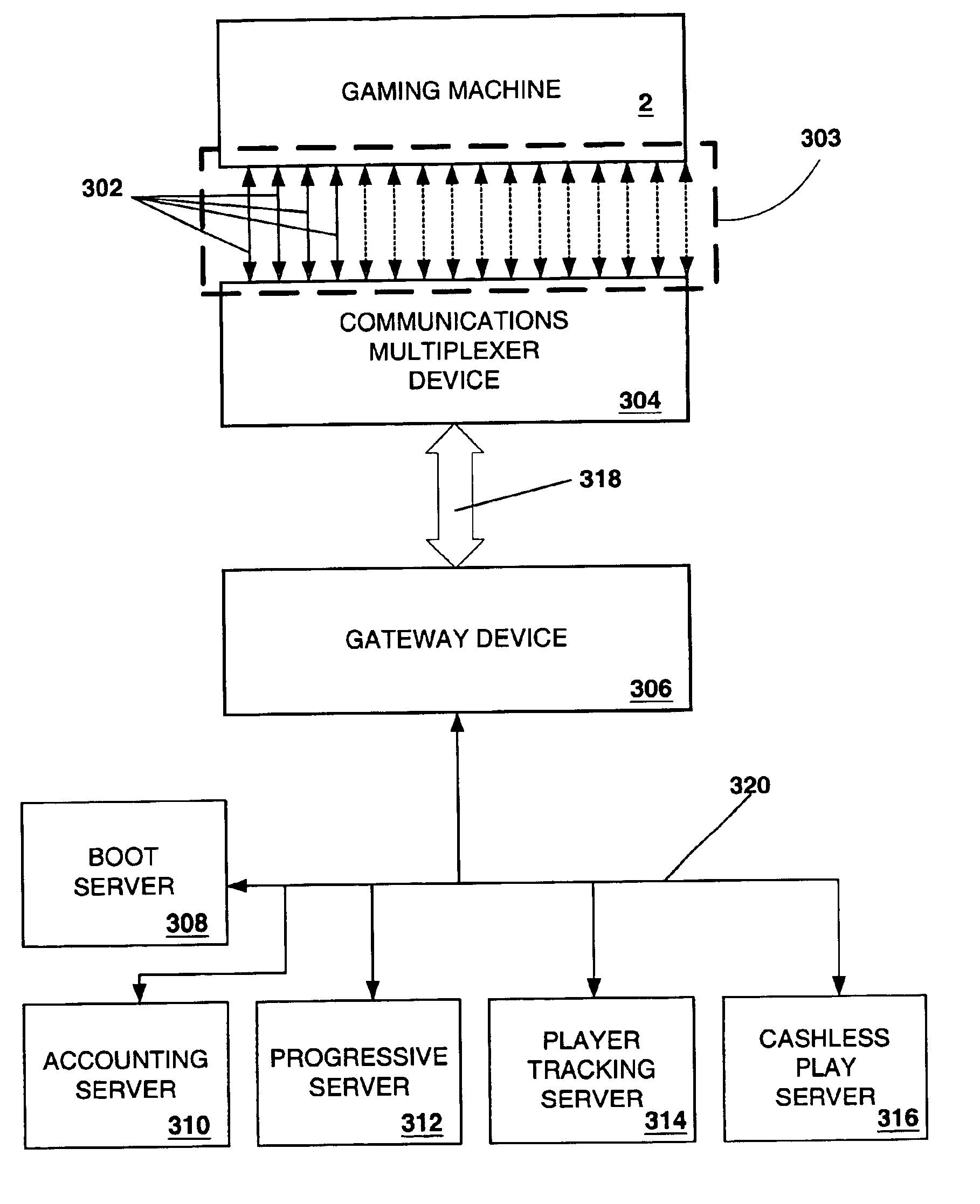

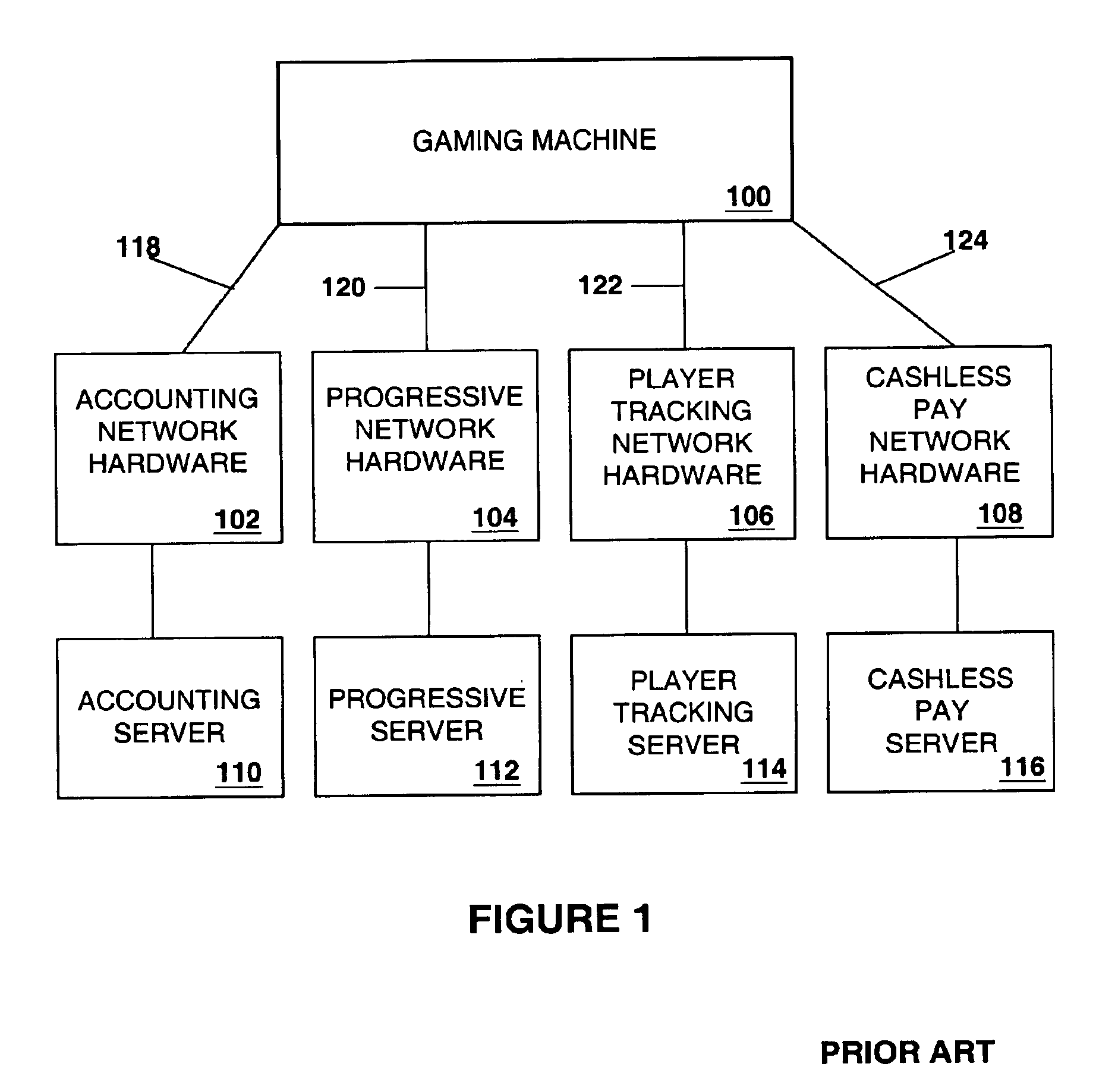

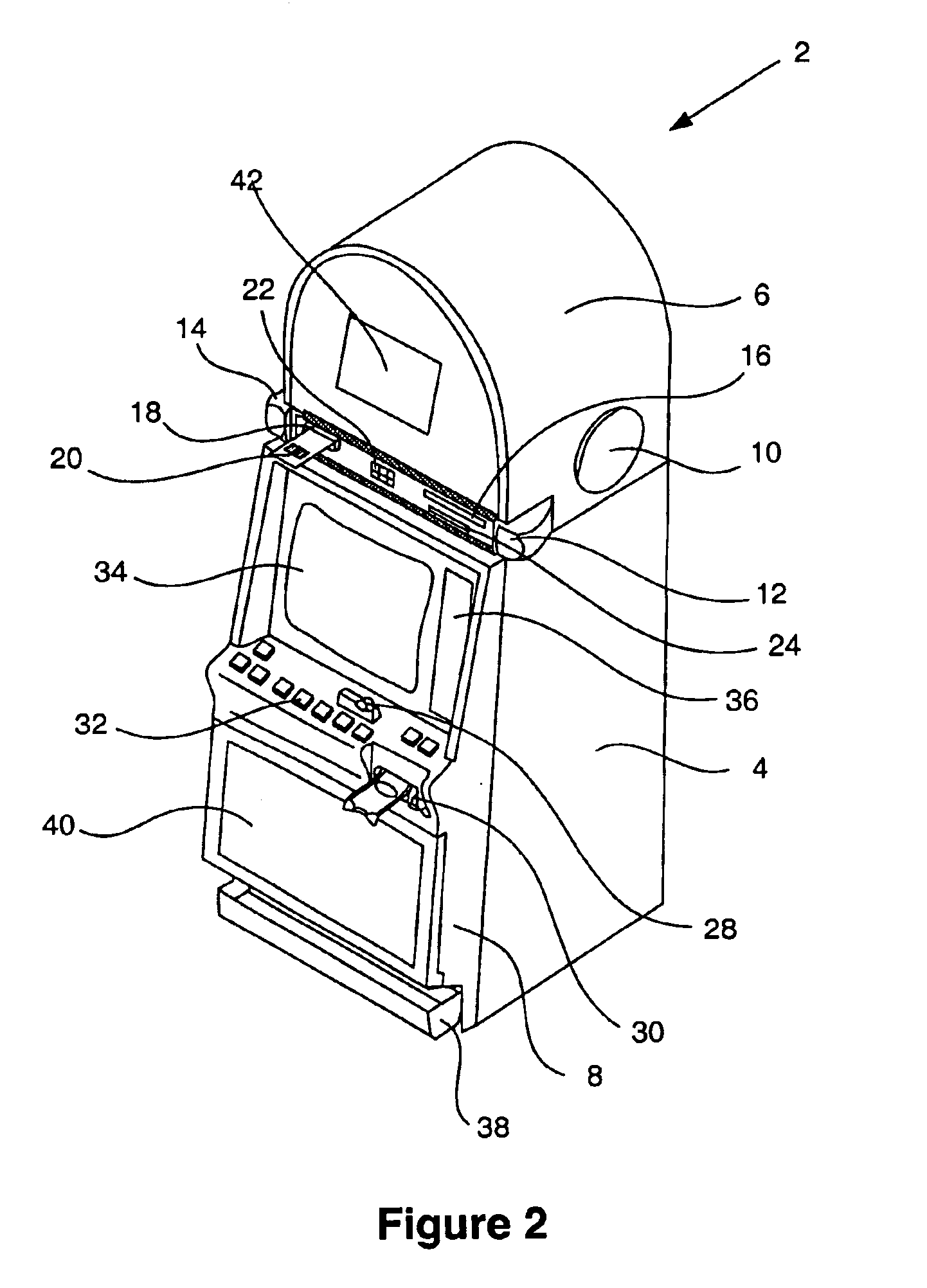

Multi-system gaming terminal communication device

InactiveUS6875110B1Metabolism disorderApparatus for meter-controlled dispensingMultiplexingMultiplexer

A gaming machine with a communication multiplexer device that allows communications between the gaming machine and one or more game service servers all within a single network interface is described. The single network interface may be a wireless or wired network interface. The communication multiplexer device converts messages in native communication protocols used by the gaming machine to a network communication protocol such as TCP / IP for transmission over the single wired or wireless network interface. The communication multiplexer is designed such that the gaming machine may receive messages that have been transmitted using the native communication protocols without modifying regulated gaming software on the gaming machine.

Owner:IGT

Digital television transmitter and method of coding data in digital television transmitter

InactiveUS20070071110A1Enhance decoding functionImprove reception qualityPicture reproducers using cathode ray tubesCode conversionMultiplexingMultiplexer

A digital television (DTV) transmitter and a method of coding data in the DTV transmitter method are disclosed. A pre-processes enhanced data by coding the enhanced data for forward error correction (FEC) and expanding the FEC-coded enhanced data. A data formatter generates enhanced data packets including the pre-processed enhanced data and inserting known data to at least one of the enhanced data packets. A first multiplexer multiplexes main data packets with the enhanced data packets, and a data randomizer randomizes the multiplexed data packets. A Reed-Solomon (RS) encoder RS-codes the randomized data packets by adding first parity data, and a data interleaver interleaves the RS-coded data packets. A trellis encoder trellis-encodes the interleaved data packets, wherein the trellis encoder may be initialized when a known data sequence is inputted thereto.

Owner:LG ELECTRONICS INC

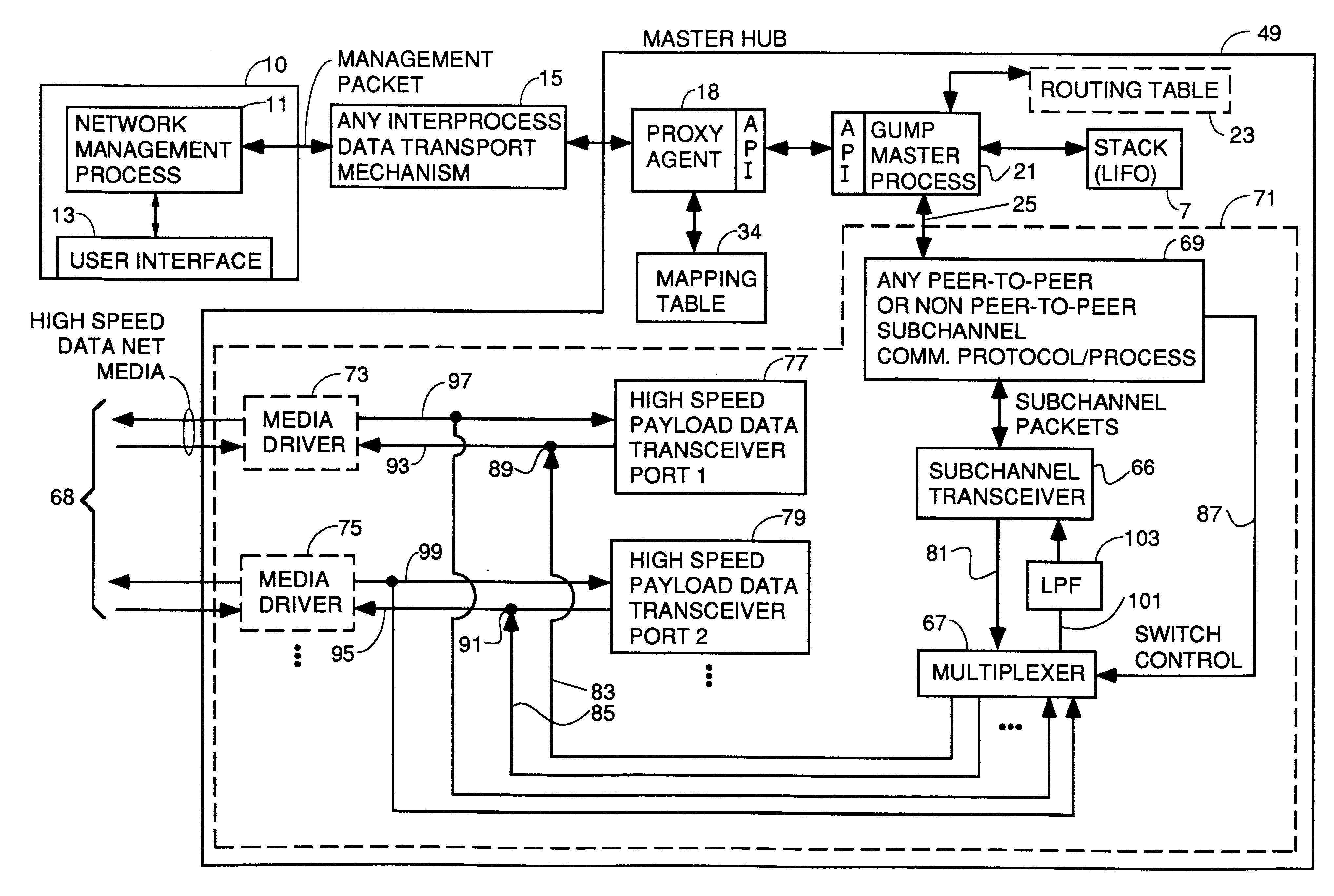

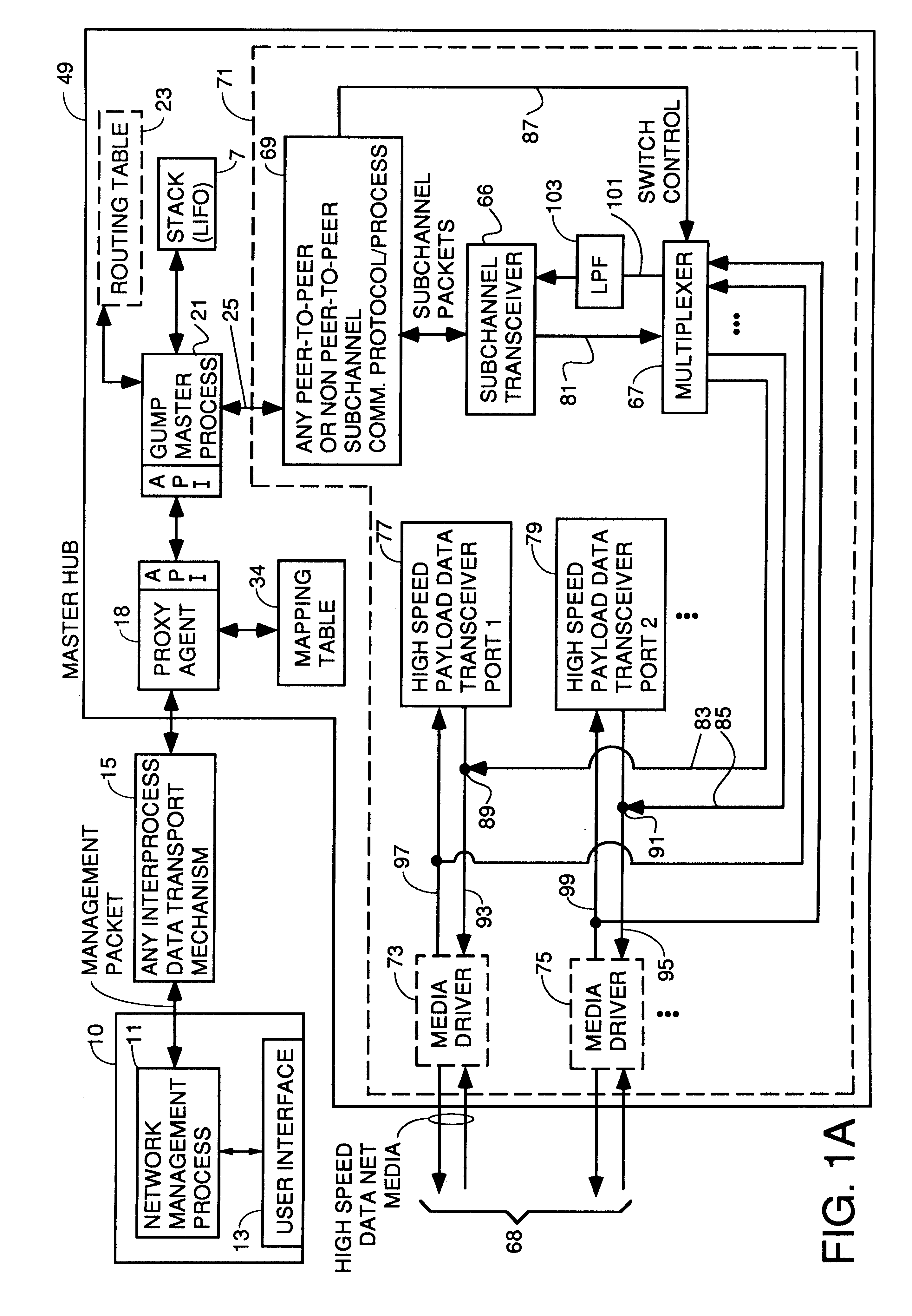

Apparatus and method for unilateral topology discovery in network management

A system for reducing the cost of network managment by using a proxy agent and subchannel communications so fewer SNMP licenses and fewer protocol stacks are needed. Subchannel communication is achieved in a plurality of different embodiments. Embodiments having single subchannel transceivers, multiple transceivers, single multiplexer and multiple multiplexers are disclosed. An NMS process using routing table CRC to automatically detect when the NMS topology information is incorrect and automated topology discovery is disclosed. A process for automated discovery of redundant cables during automated topology discovery is disclosed.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

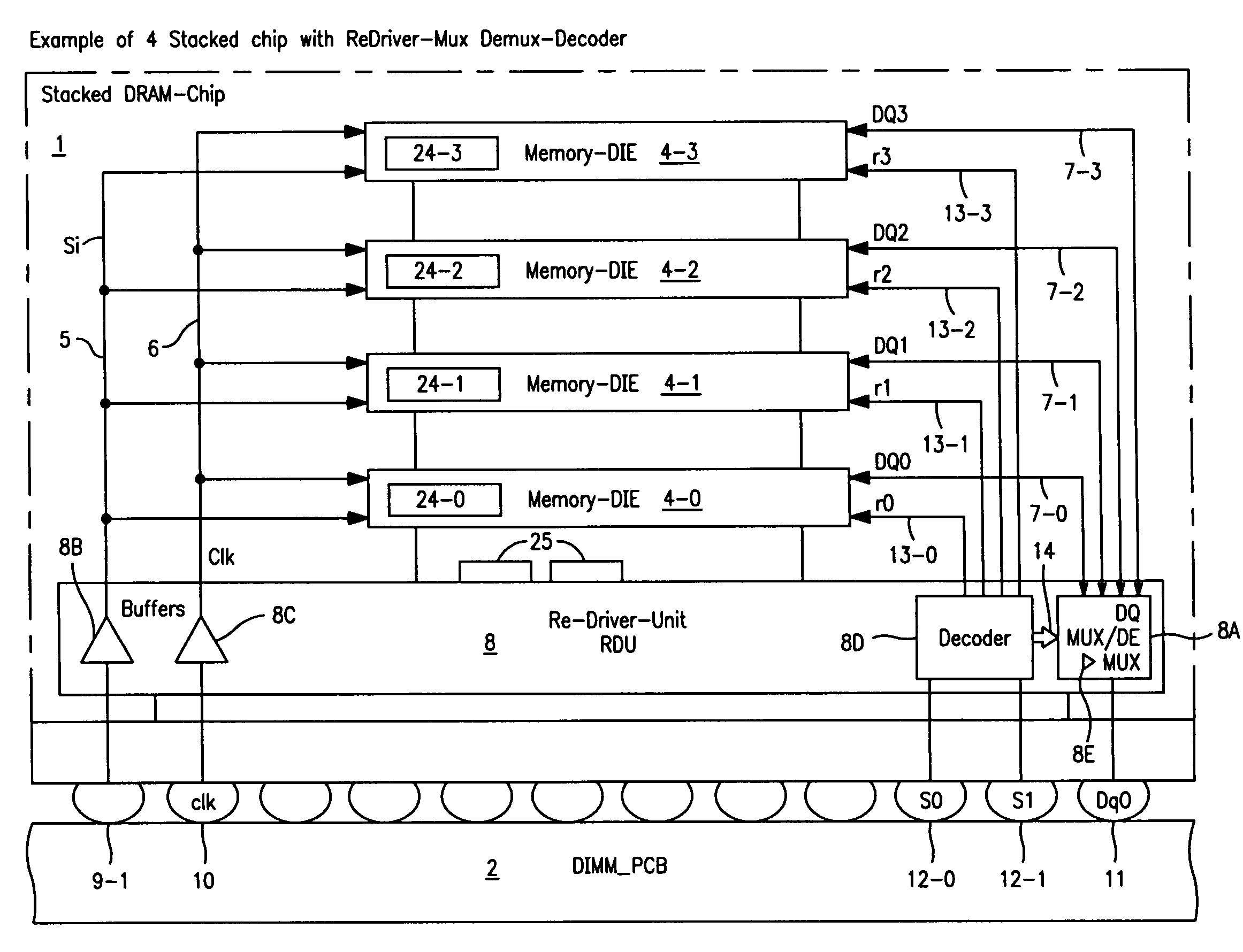

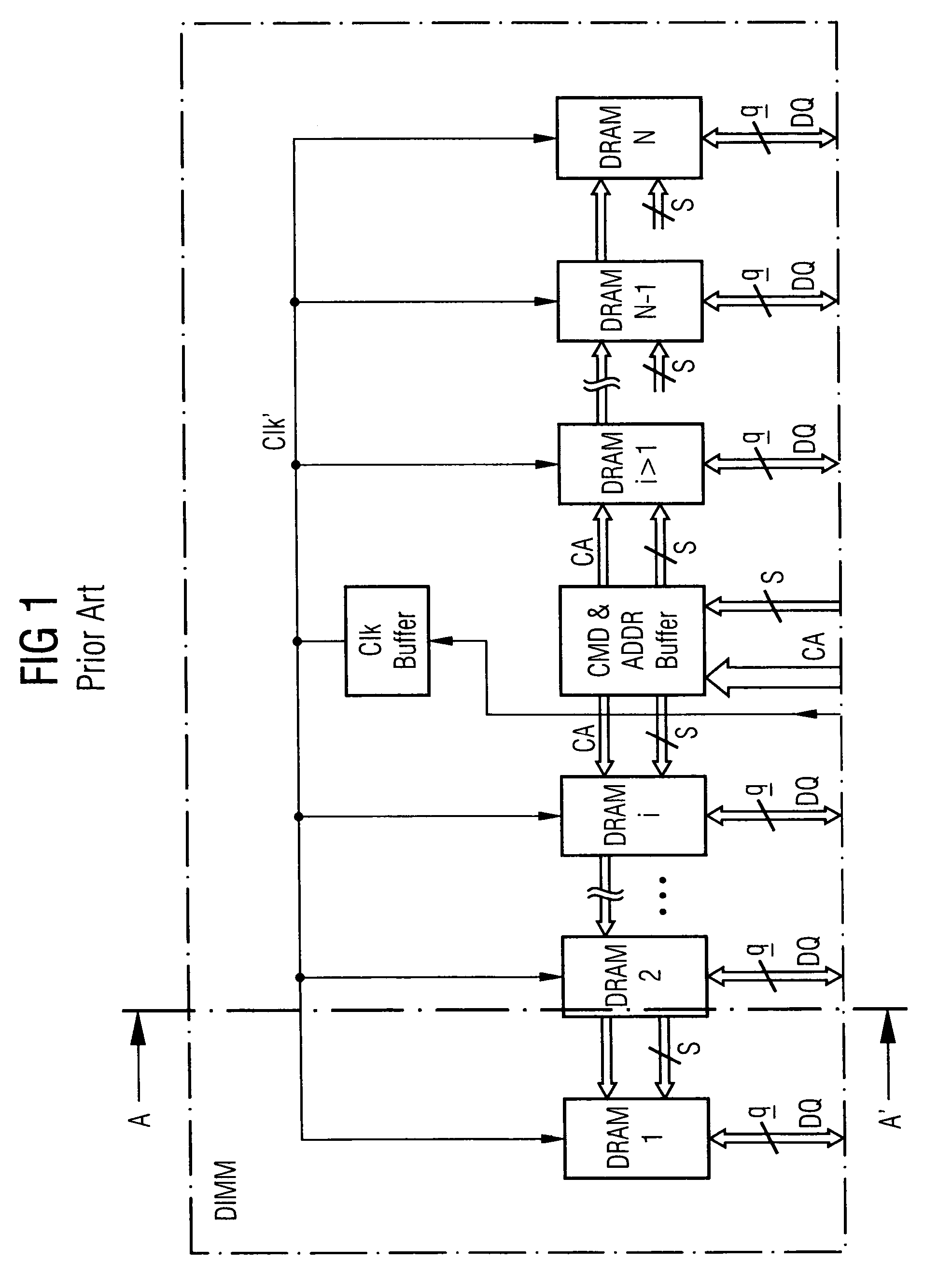

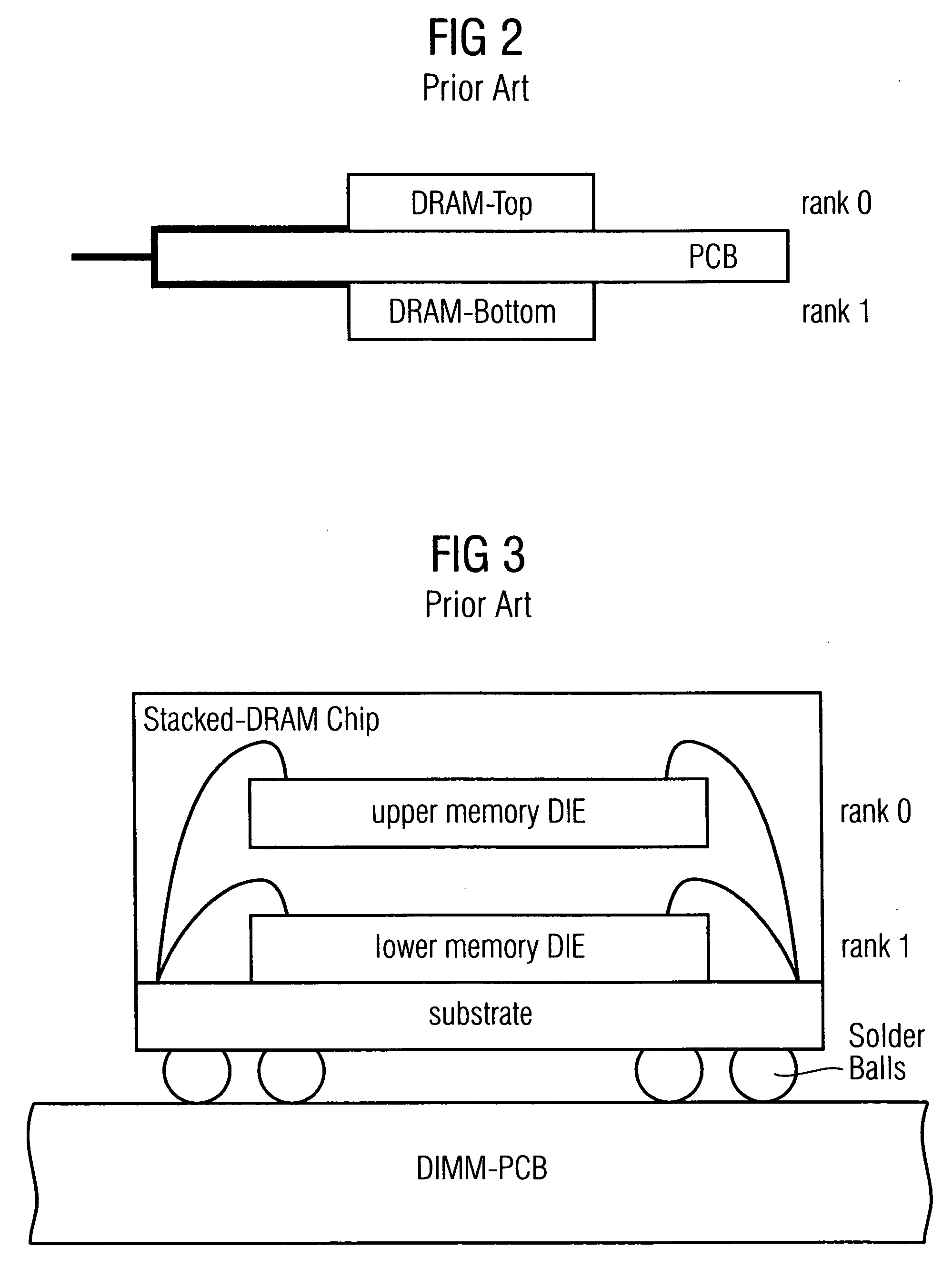

Stacked DRAM memory chip for a dual inline memory module (DIMM)

ActiveUS7200021B2Increase the number ofSmall sizeSemiconductor/solid-state device detailsNanoinformaticsInternal memoryMemory chip

A stacked DRAM memory chip for a Dual In Line Memory Module (DIMM) is disclosed. According to one aspect, the DRAM memory chip comprises at least four stacked DRAM memory dies. Further, the memory dies are each selectable by a corresponding internal memory rank signal. Each memory die comprises an array of memory cells. A common internal address bus is provided for addressing the memory cells and is connected to all stacked DRAM memory dies. Internal data buses are provided for writing data into the memory cells and reading data out of the memory cells of the DRAM memory dies. An integrated redriving unit comprises buffers for all internal address lines provided for driving external address signals applied to address pads of the DRAM memory chip. A multiplexer / demultiplexer switches the internal data lines of the selected DRAM memory die. A memory rank decoder selects a corresponding memory die.

Owner:POLARIS INNOVATIONS LTD

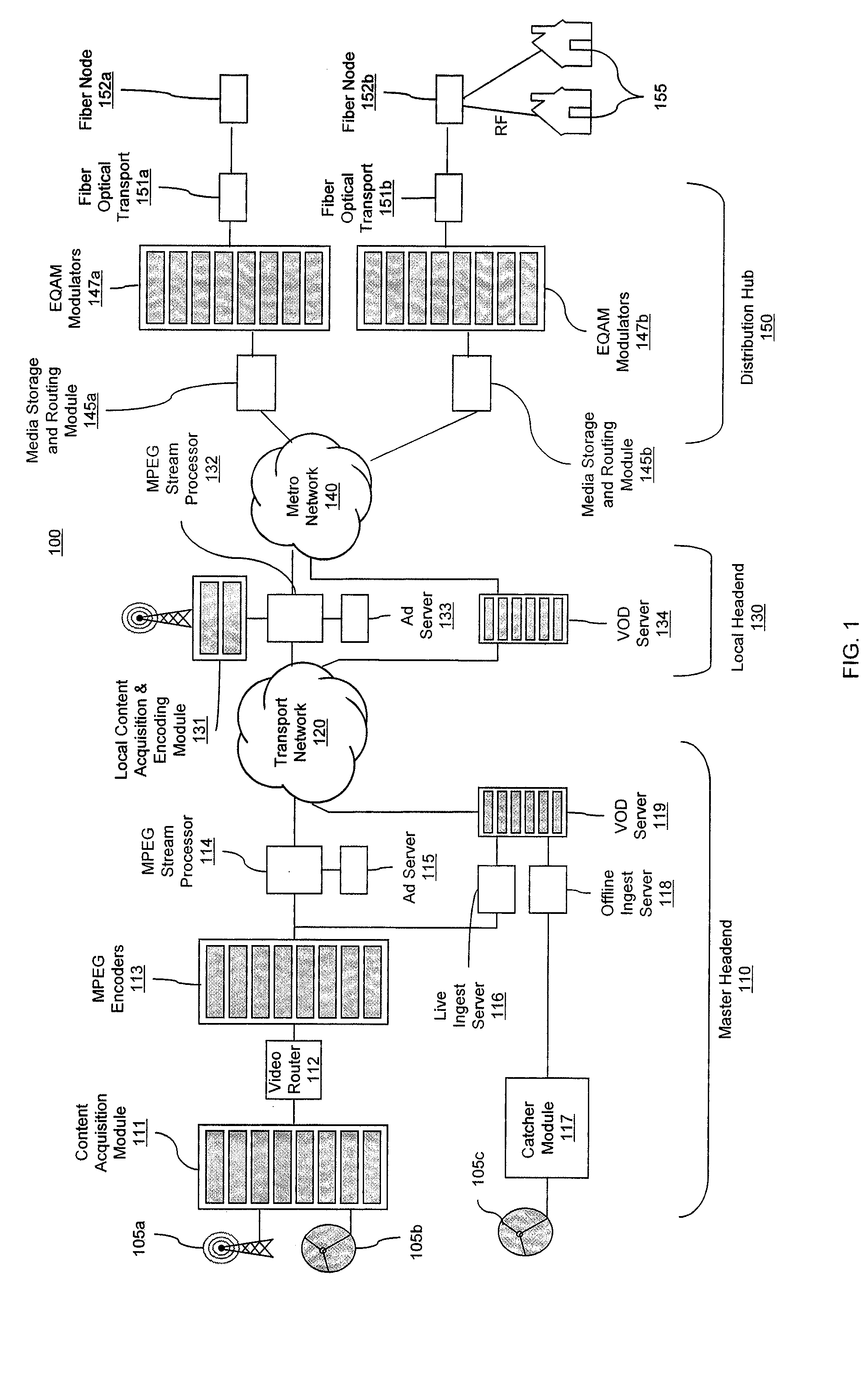

Video Delivery Module

InactiveUS20090083813A1Easy to useLow costAnalogue secracy/subscription systemsTwo-way working systemsVideo transmissionMultiplexer

Described herein are techniques, including methods and systems, including computer program products, for a video delivery module. A broadcast program and a video-on-demand program are ingested by a video delivery module. At least a portion of the broadcast program and at least a portion of the video-on-demand program are stored. The broadcast program, the video-on-demand program, or both are delivered as a unicast video stream to a first single subscriber through a multiplexer connected to a plurality of subscribers.

Owner:AKAMAI TECH INC

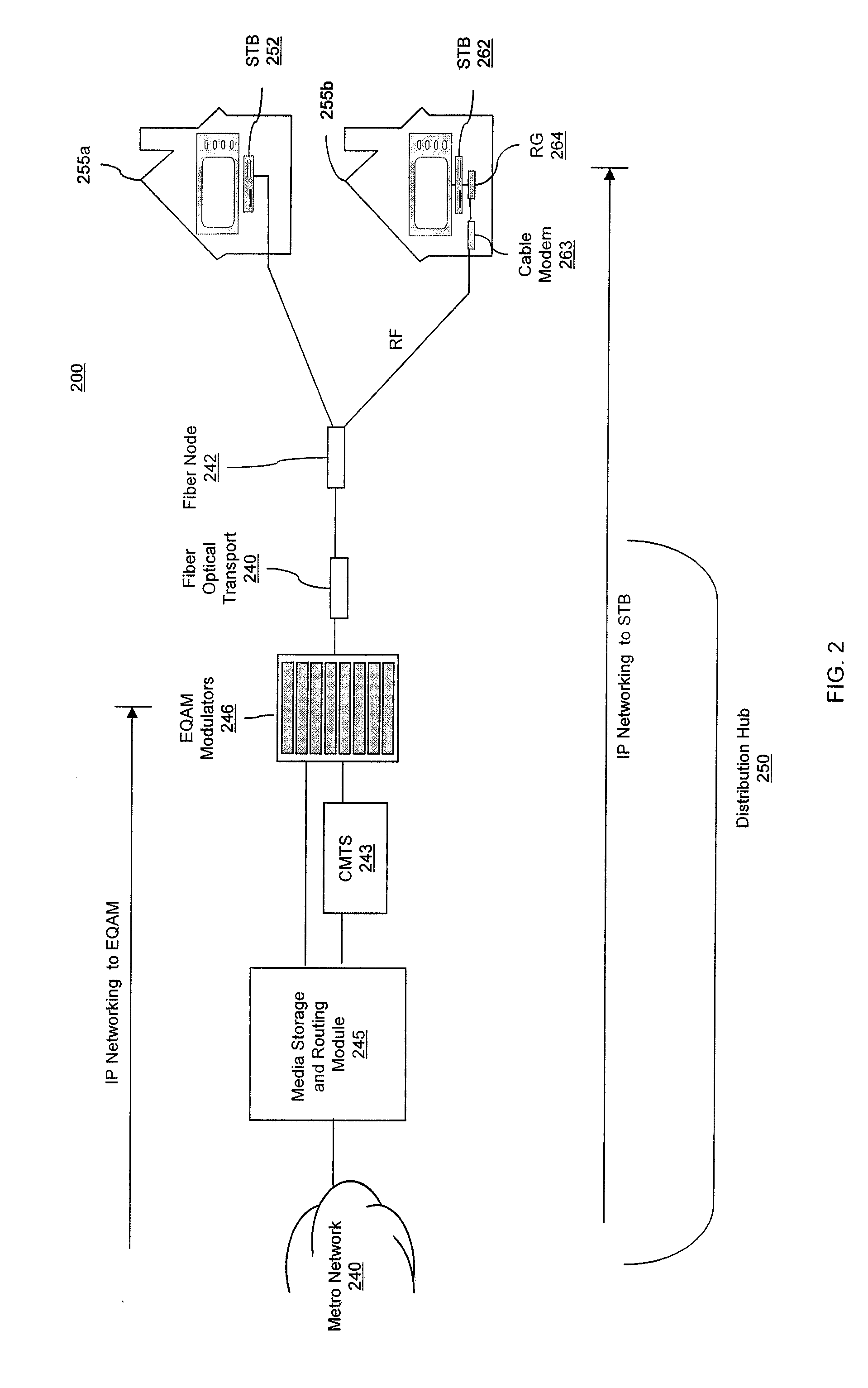

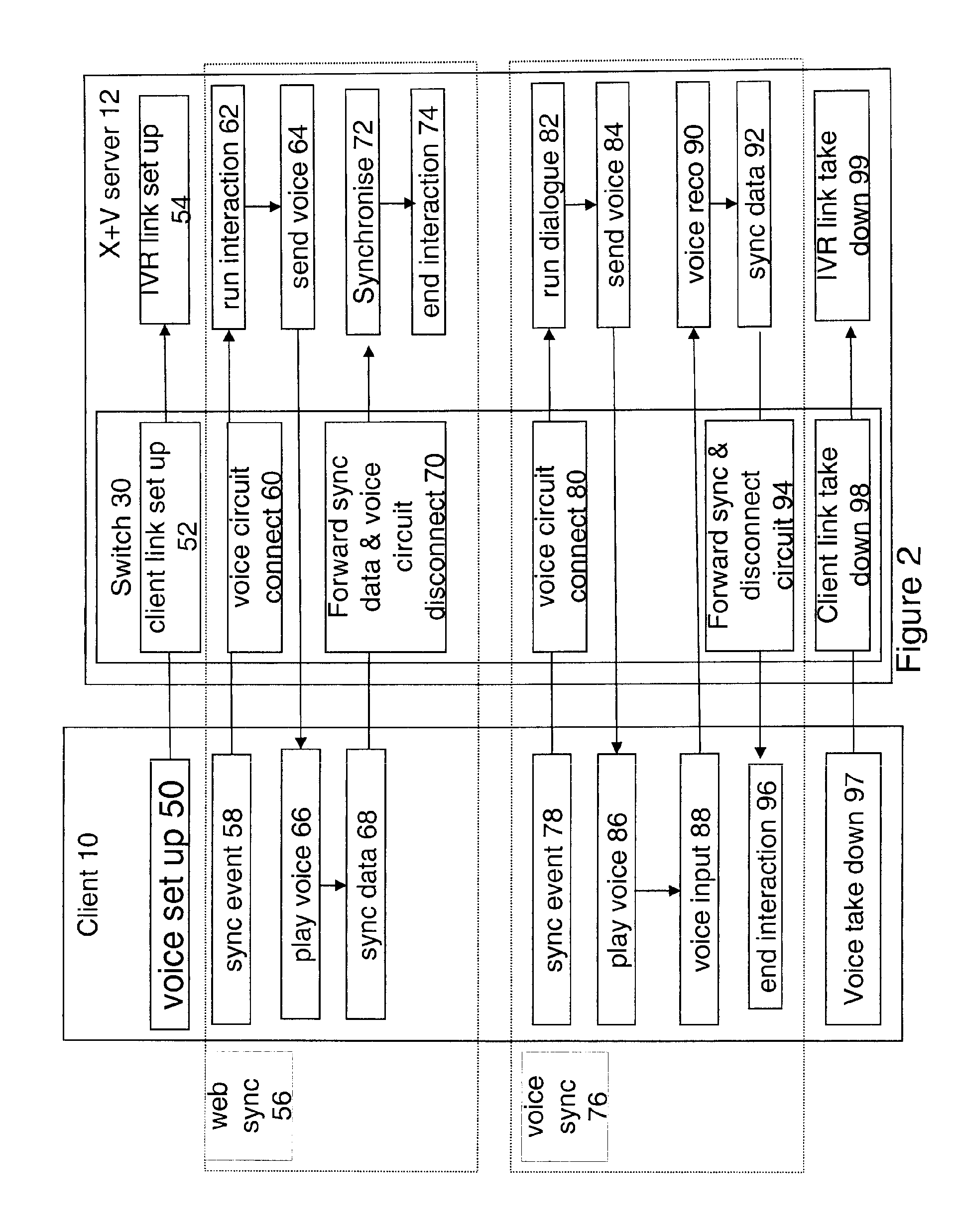

Method and Apparatus For Multimodal Voice and Web Services

InactiveUS20090144428A1No setup overheadReduce latencyError preventionFrequency-division multiplex detailsMultiplexerWeb service

This invention is based on being able to locate a voice server, temporarily allocate it, send it the audio of you saying “When is flight 683 due to arrive?”, getting the results of what you said back in the browser, and deallocating the voice server for use by the next person talking into their browser. Voice channels and IVR ports are initially set up by a switch and the IVR using conventional audio protocols. The Voice channels are not initially connected to the client. The switch handles the allocation and deallocation of IVR voice channels without having to communication further with the IVR. A user indicates (usually by pressing a PTT button) to the client device that he wishes to initiate a voice interaction during an X+V session. This translates to a request on the CTRL channel to synchronise the XHTML and VXML forms which the embodiment uses as a trigger for the VXML browser to execute a conversational turn. The multiplexer intercepts this control command and connects the virtual voice circuit between the device and an existing open but unattached voice port. The virtual circuit is connected without having to set up an RTP channel. The CTRL signal is then forwarded to the interaction manager so that the conversation can take place. At the end of the conversation the virtual circuit is disconnected.

Owner:IBM CORP

Phonetic decoding and concatentive speech synthesis

A speech processing system includes a multiplexer that receives speech data input as part of a conversation turn in a conversation session between two or more users where one user is a speaker and each of the other users is a listener in each conversation turn. A speech recognizing engine converts the speech data to an input string of acoustic data while a speech modifier forms an output string based on the input string by changing an item of acoustic data according to a rule. The system also includes a phoneme speech engine for converting the first output string of acoustic data including modified and unmodified data to speech data for output via the multiplexer to listeners during the conversation turn.

Owner:CERENCE OPERATING CO

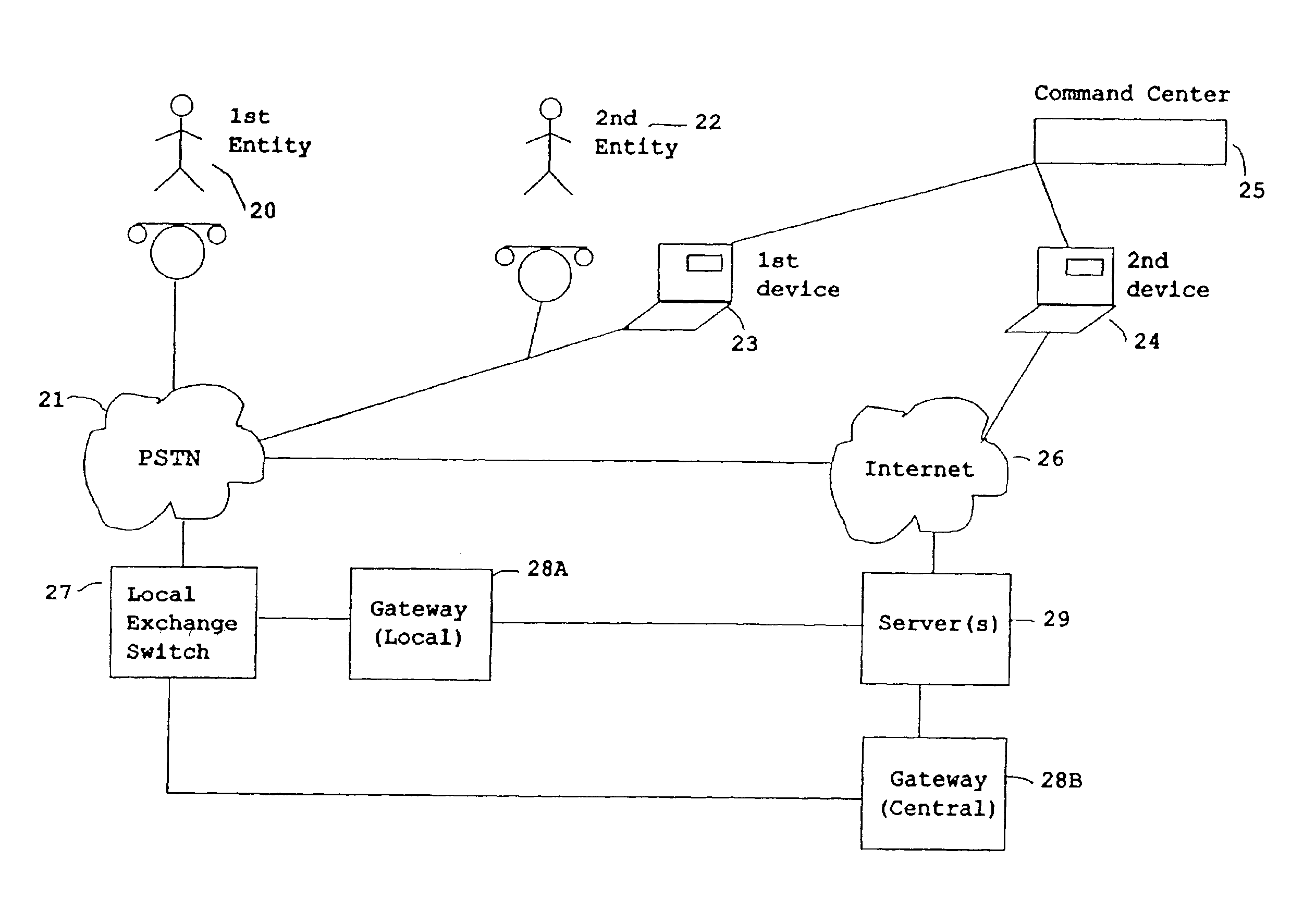

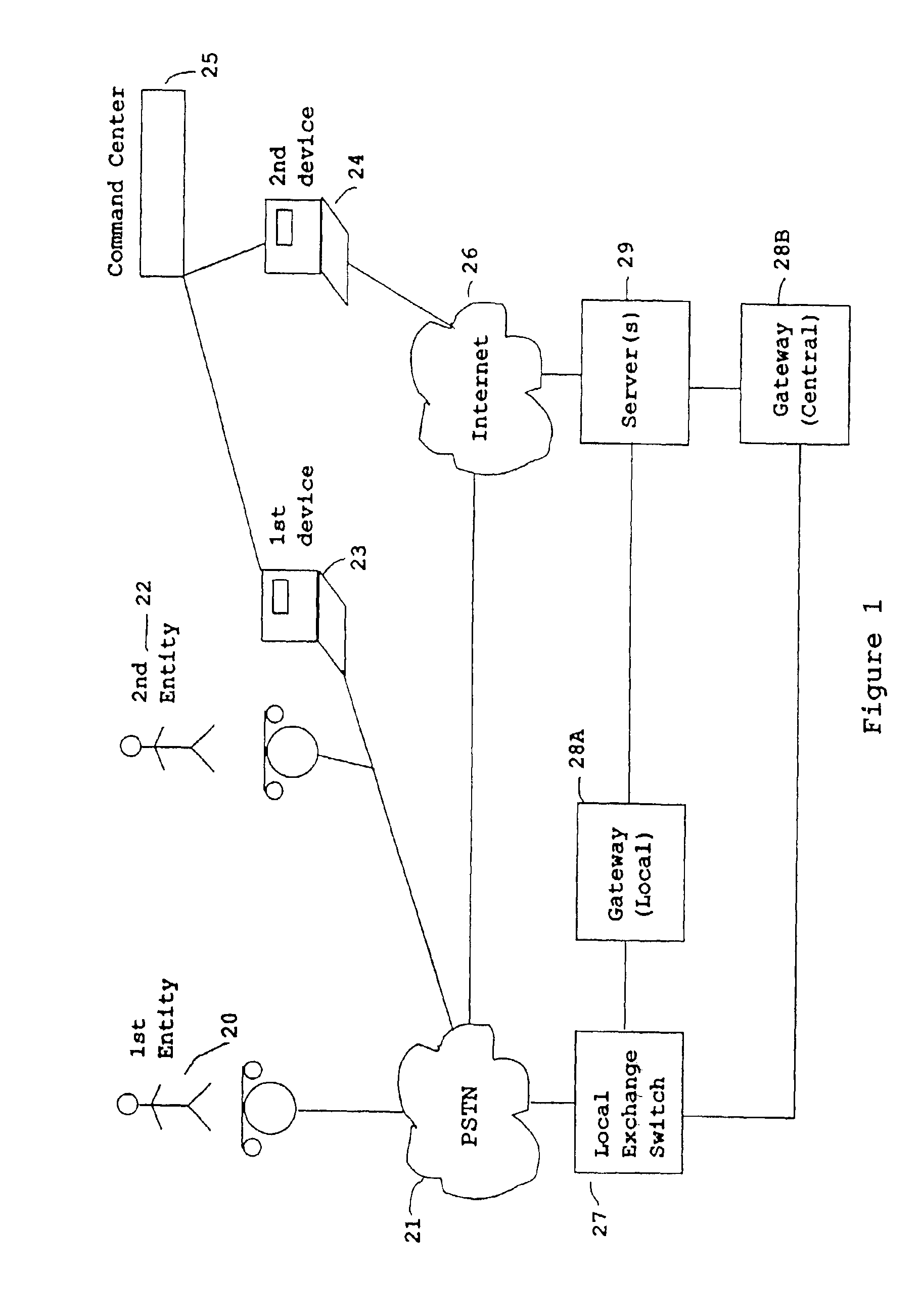

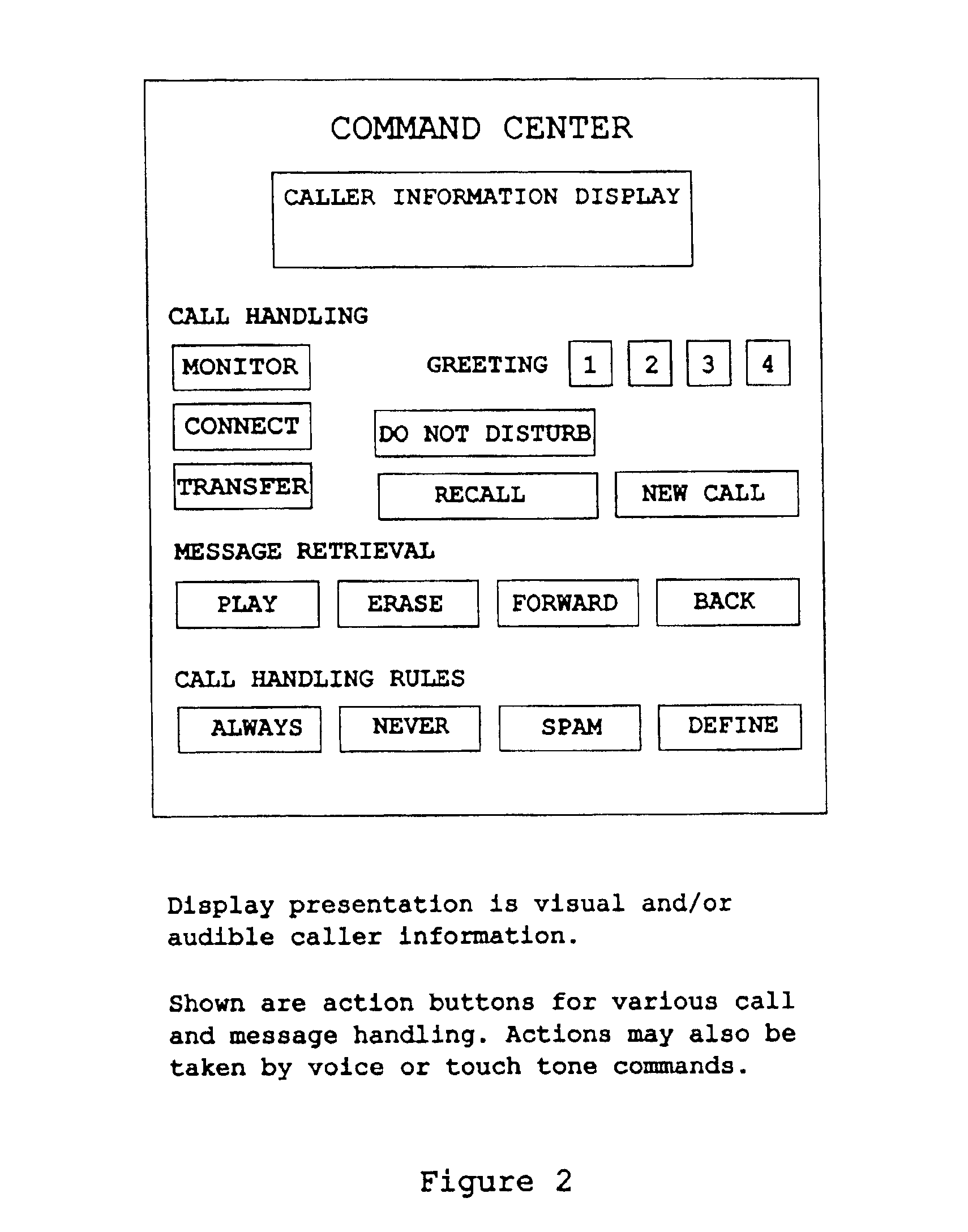

Method and apparatus for providing expanded telecommunications service

InactiveUS6898275B2Add featureAutomatic call-answering/message-recording/conversation-recordingSpecial service for subscribersTelecommunications linkMultiplexer

System and method for putting control of incoming telephone calls in the hands of subscribers with the aid of computer software and the Internet. In effect, a very efficient multiplexer is provided that does not require a change in the behavior of the called party or the calling party. This system permits the called party to hear a spoken message by the calling party in real time, and the content of the spoken message permits the called party to decide how to handle the call. The system adaptively learns and captures the rules of the called party for handling calls, and learns which callers the called party always wishes to talk to. The system uses special control software on the called party's computer which is connected to the Internet. The system employs a central server in which all of the required intelligence is resident. Audio signals are exchanged via non-data channels provided by the telephone companies and by the Internet. Either a very simple Internet busy pick-up is provided, or a very complex messaging system is provided, as desired. A feature is the monitoring and screening of incoming calls before deciding how to handle them. Another feature is the capturing and storage of the decision making profile.

Owner:CALLWAVE COMM

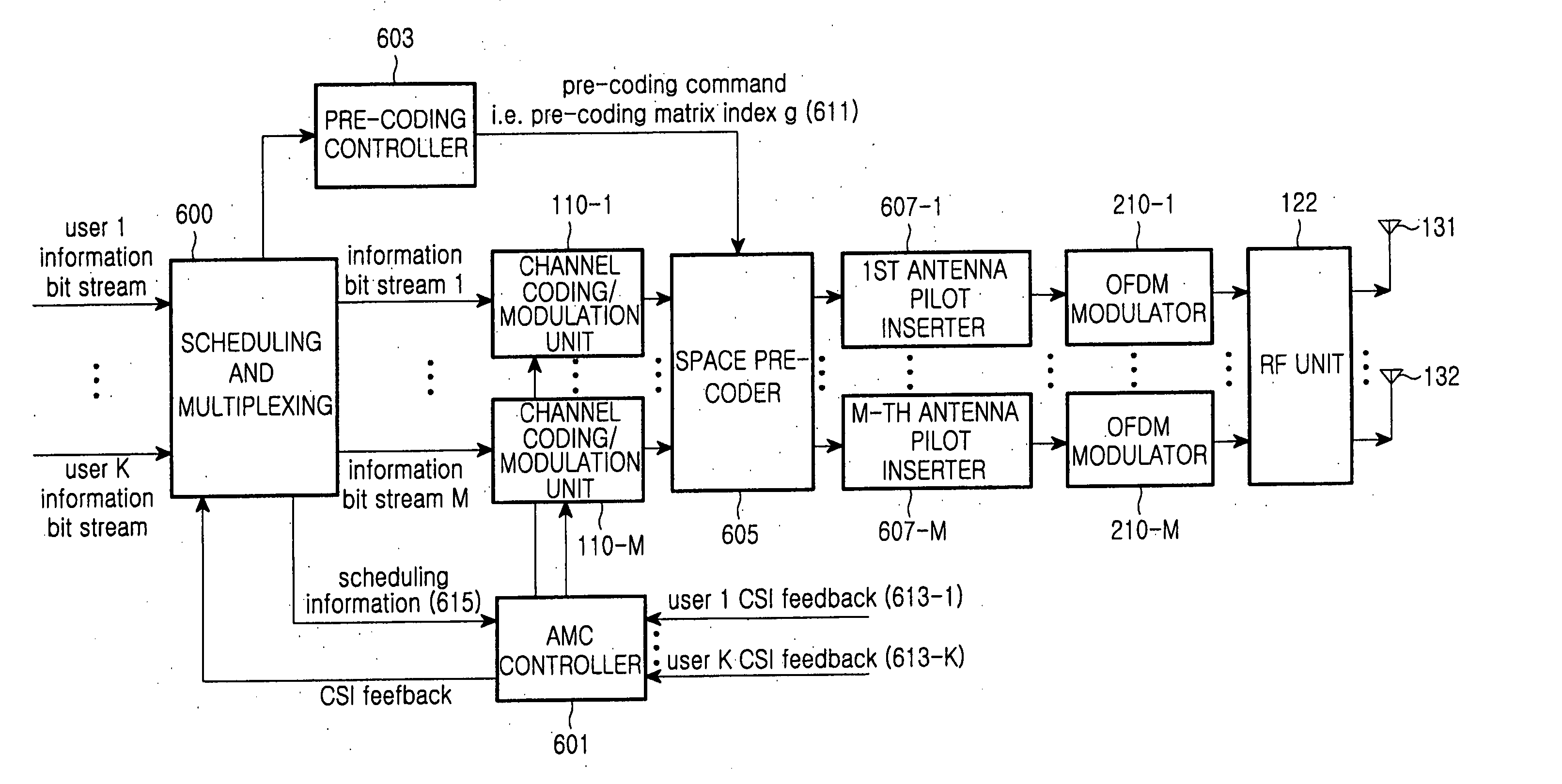

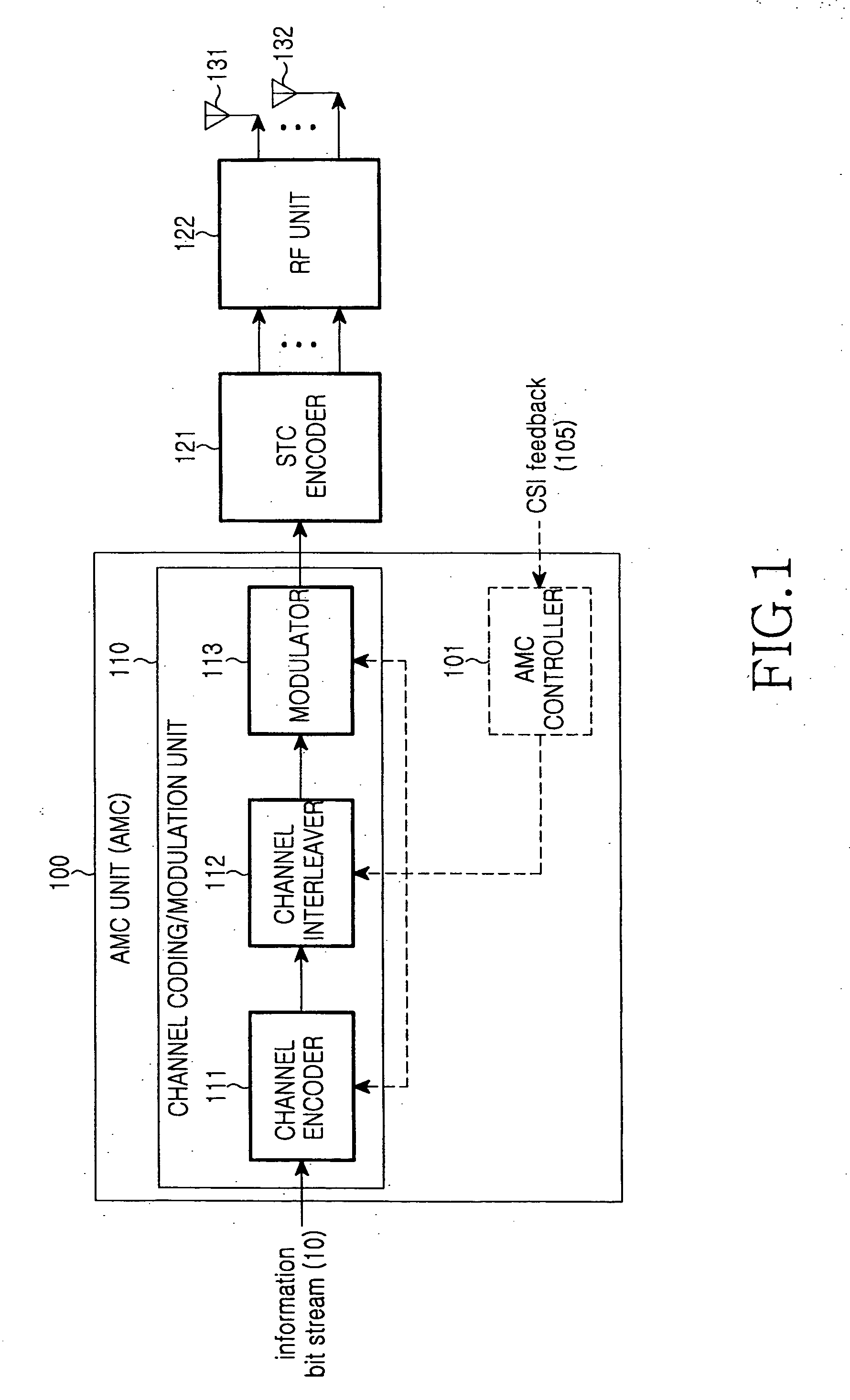

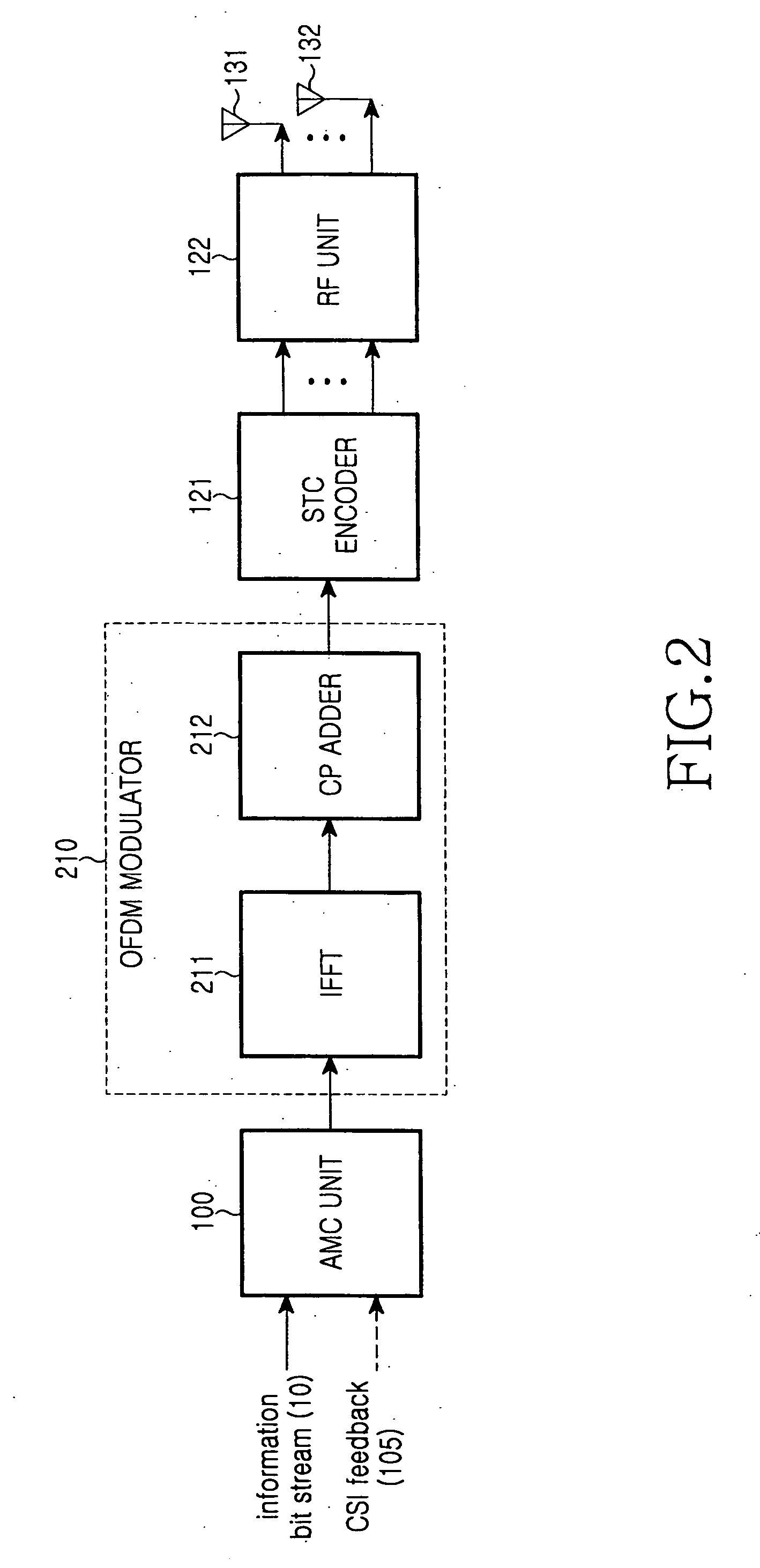

Apparatus and method for transmitting/receiving data in a multi-antenna communication system

ActiveUS20070104283A1Increase system capacityData augmentationSpatial transmit diversitySecret communicationChannel state informationMultiplexing

An apparatus for transmitting data in a base station of a wireless communication system that transmits data depending on channel status information fed back from terminals and uses a plurality of antennas. Based on the channel status information, a scheduler determines a terminal to which the base station will transmit data, determines antennas via which the base station will transmit data among the plurality of antennas, and determines a space pre-coding method. A multiplexer multiplexes transmission data into a plurality of data streams according to the number of the determined antennas. A modulation and coding unit performs modulation and coding on each of the data streams. A pre-coding controller outputs a matrix select signal for selecting one of a plurality of space pre-coding matrixes according to the space pre-coding method. A space pre-coder spatial-codes each of the coded streams with the matrix selected based on the matrix select signal. An OFDM modulator performs OFDM modulation on each of the spatial-coded streams. An RF unit transmits each of the OFDM-modulated streams via an associated antenna.

Owner:SAMSUNG ELECTRONICS CO LTD

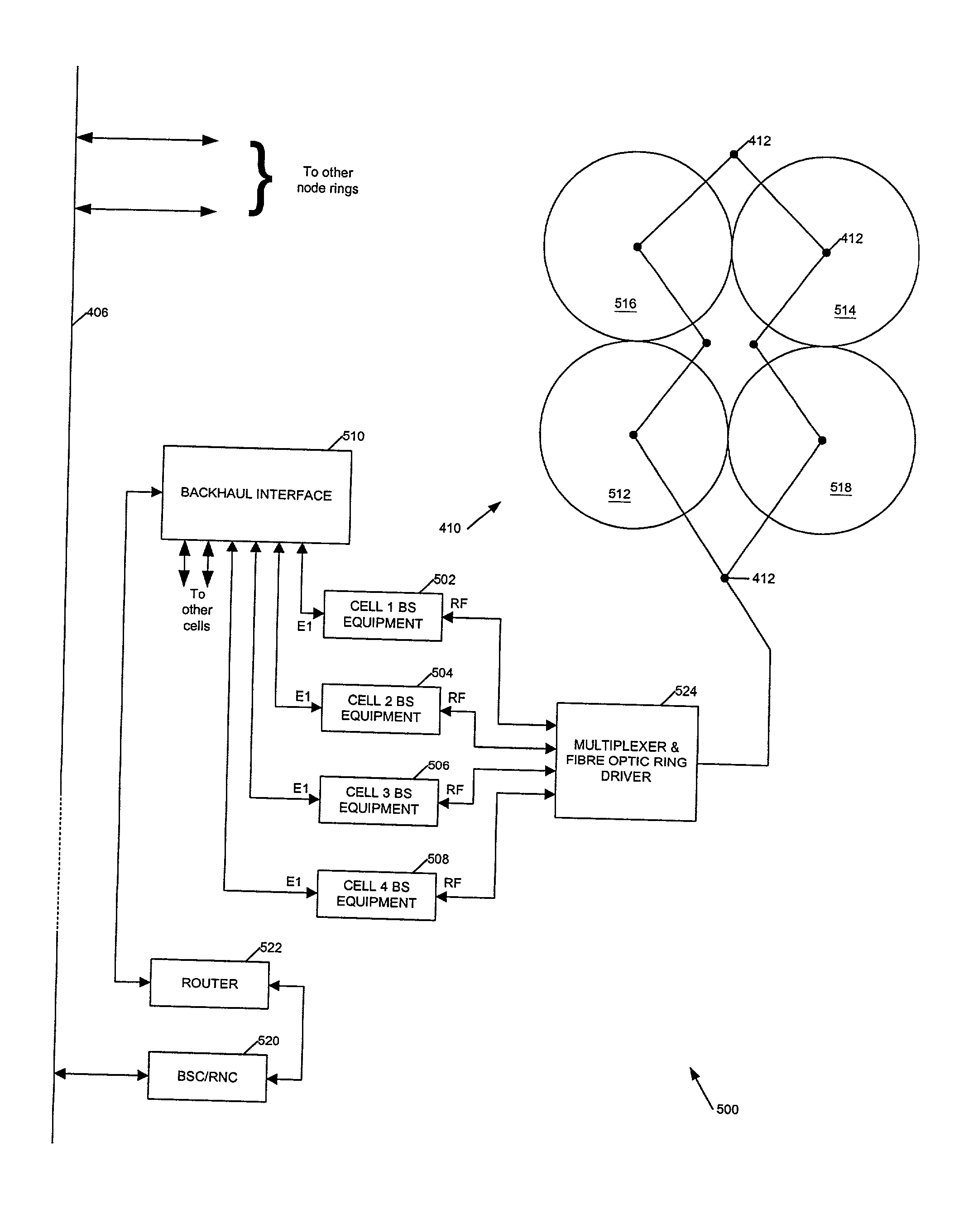

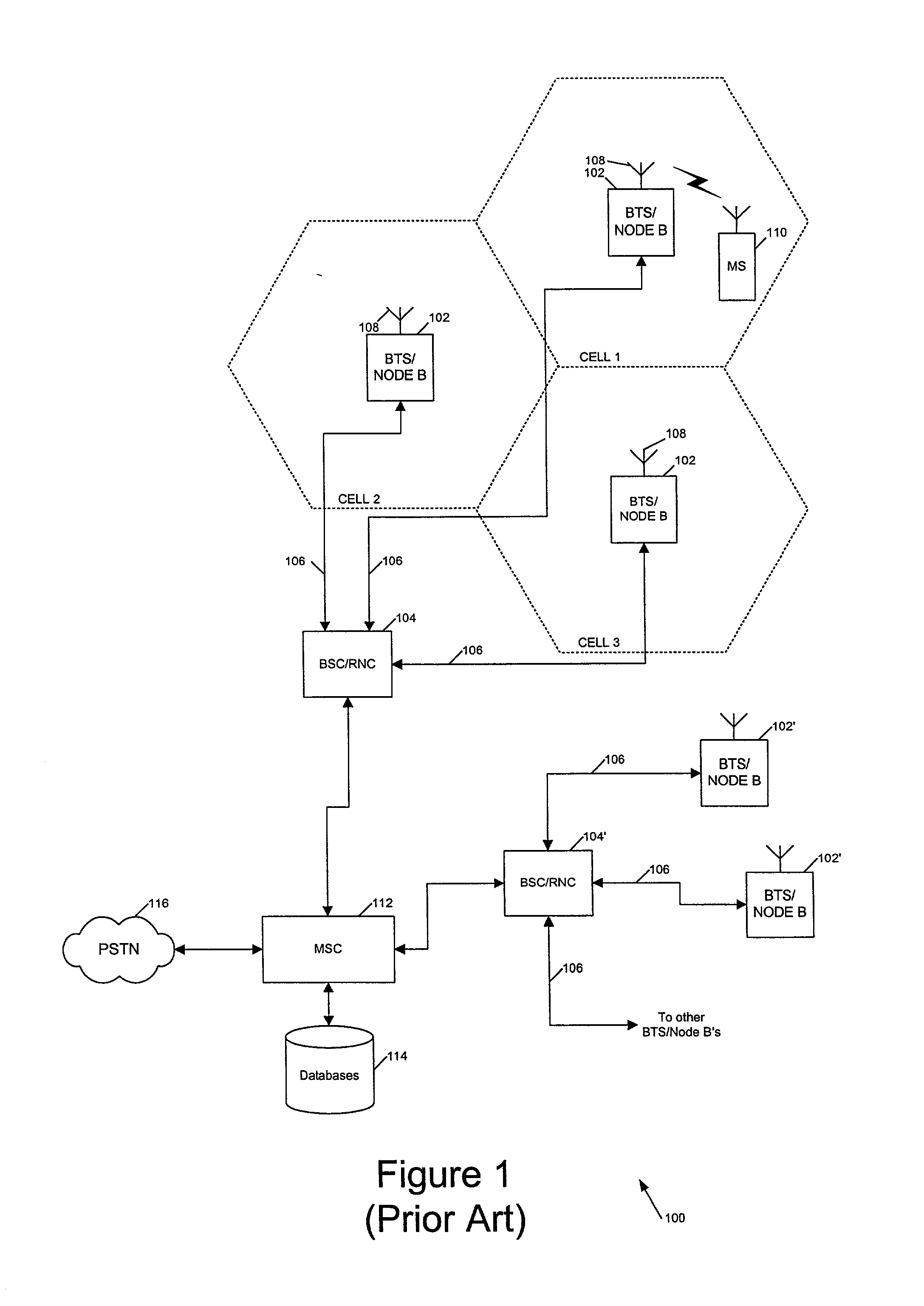

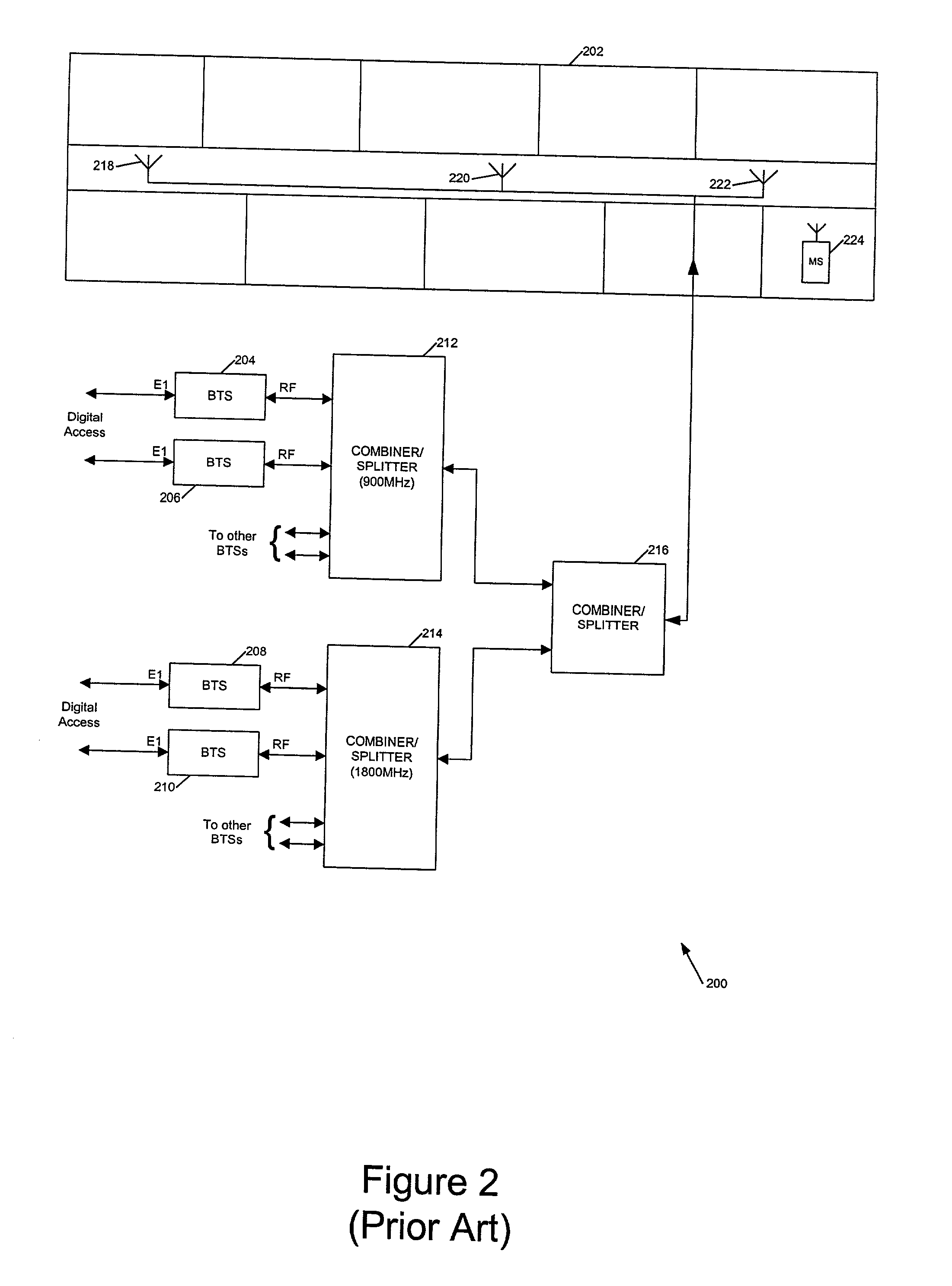

Signal transmission systems

Signal transmission systems for second and third generation mobile communications networks are described. A signal distribution system comprises a plurality of rf transmitters for serving a plurality of network cells. The system is characterised by a multiplexer coupled to the transmitters for multiplexing the transmitter outputs, a signal transporter for transporting the multiplexed signals to each of the network cells, and a multiplexed signal receiver at each cell for selecting and receiving a signal from a transmitter serving the cell. The invention also provides a complementary signal reception system, and corresponding methods. Preferably, the multiplexed signals are transported over a fibre optic network such as an existing cable TV network. The system simplifies the deployment of network infrastructure for third generation mobile communications systems.

Owner:NTL GROUP

Process for supplying video-on-demand and other requested programs and services from a headend

InactiveUS7089577B1Reduce quality problemsReduce bandwidth consumptionTwo-way working systemsSelective content distributionTransceiverT-carrier

A system for providing video-on-demand service, broadband internet access and other broadband services over T-carrier systems including a pull multiplexer cherrypicker at the head end is disclosed. The pull multiplexer receives upstream requests and cull out MPEG or other compressed video packets, IP packets and other data packet types to satisfy the requests or to send pushed programming downstream. The downstream can be DSL or HFC. Each customer has a cable modem, DSL modem or a gateway which interfaces multiple signal sources to a LAN to which settop decoders, digital phones, personal computers, digital FAX machines, video cameras, digital VCRs etc. can be attached. Each gateway can coupled the LAN to a DSL line or HFC through a cable modem or a satellite dish through a satellite transceiver. A PSTN and conventional TV antenna interface is also provided.

Owner:GOOGLE TECH HLDG LLC

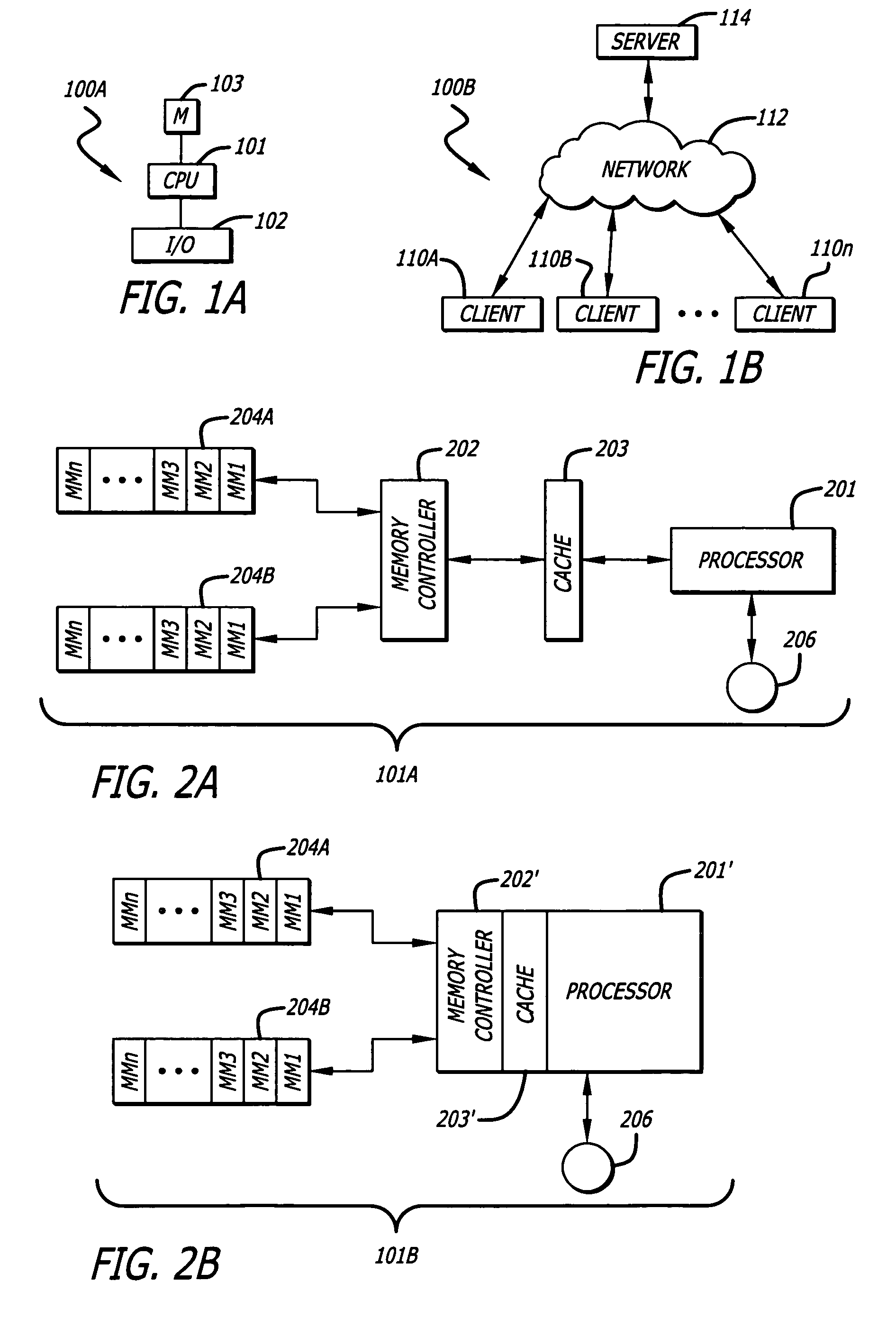

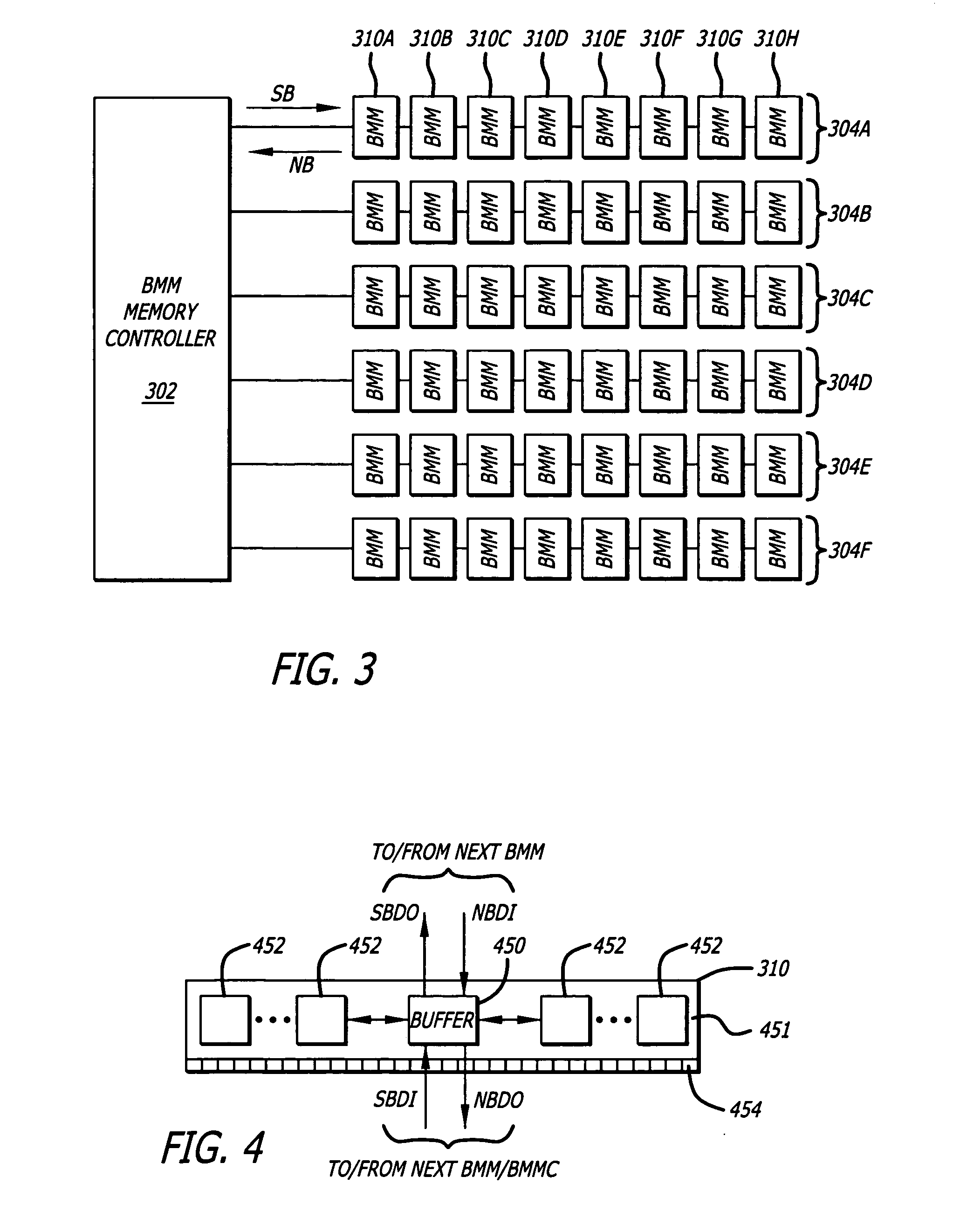

Memory buffers for merging local data from memory modules

InactiveUS20060195631A1Input/output for user-computer interactionDigital data processing detailsShift registerMultiplexing

An integrated circuit to serialize local data and selectively merge it with serialized feed-through data into a serial data stream output that includes a parallel-in-serial-out (PISO) shift register, a multiplexer, and a transmitter. The PISO shift register serializes parallel data on a local data bus into serialized local data. The multiplexer selectively merges serialized local data and feed-through data into a serial data stream. The transmitter drives the serial data stream onto a serial data link. In another embodiment of the invention, a method for a memory module includes receiving an input serial data stream; merging local frames of data and feed-through frames of data together into an output serial data stream in response to a merge enable signal; and transmitting the output serial data stream on a northbound data output to a next memory module or a memory controller. Other embodiments of the invention are disclosed and claimed.

Owner:INTEL CORP

Physiological sensor array

InactiveUS20010047127A1Efficient low powered transfer of dataReduce power lossElectric signal transmission systemsElectrocardiographySensor arrayMultiplexer

A physiological sensor device for attachment to a mammalian subject comprising an output transmitter, at least two physiological sensors each for sensing one of the subject's physiological parameters, and a controller operably in communication with the physiological sensors which controller communicates a signal comprising data representative of both the sensed physiological parameters to the output transmitter which operably transmits the signal to a remote location, wherein the controller comprises a multiplexer which operably switches the data from both the physiological sensors into a serial output signal. In a preferred embodiment, respiration is detected by a bend sensor including an elongate member and an electrical component mounted thereon which electrical component has an electrical property which varies in dependence on the extent of bending of the elongate member. Other parameters such as temperature and full waveform ECG may also be measured.

Owner:CLEARPATH PARTNERS

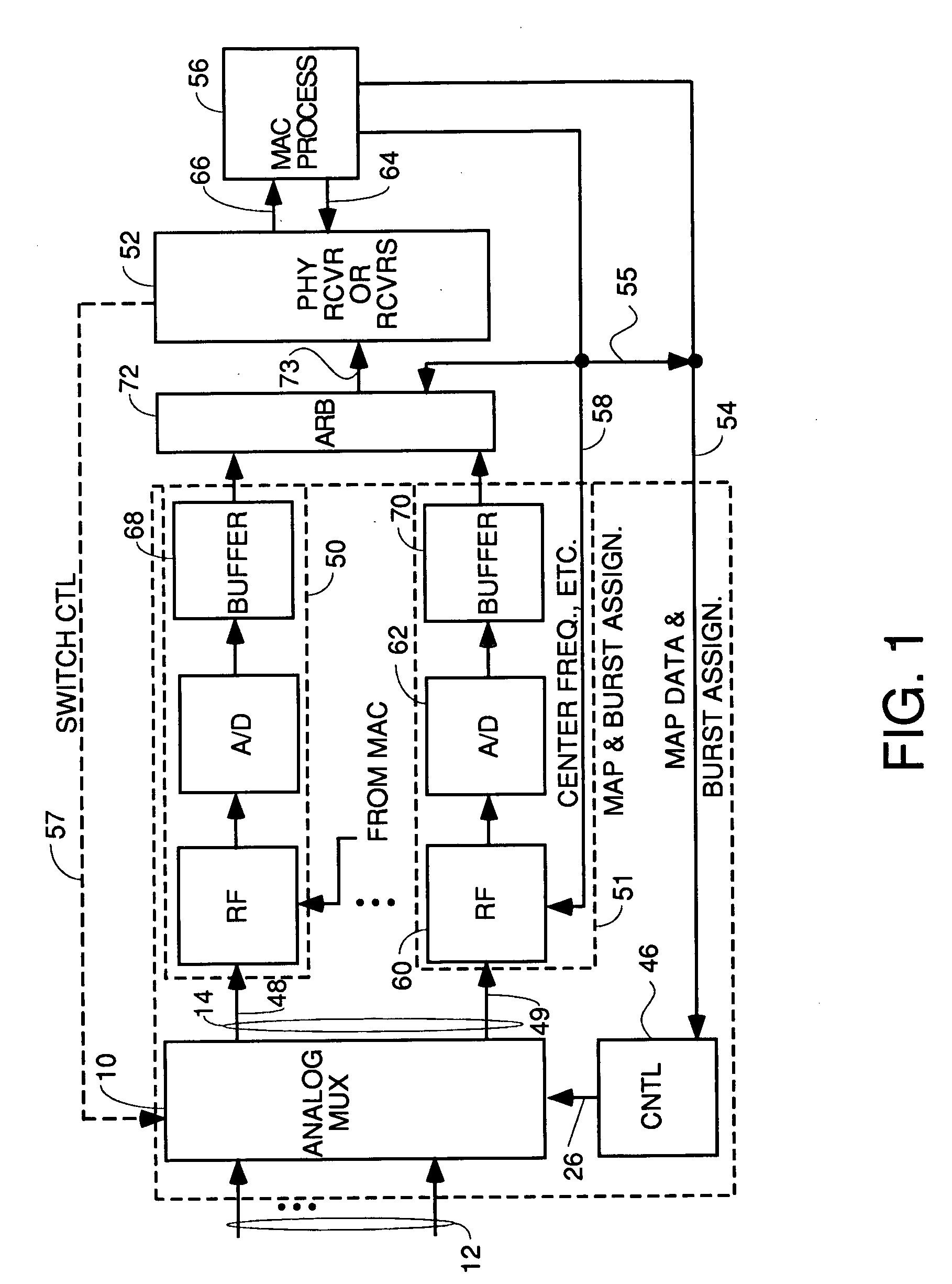

Upstream only linecard with front end multiplexer for CMTS

InactiveUS20050010958A1Easy to addMaximize Utilization EfficiencyMultiplex system selection arrangementsBroadband local area networksCrossbar switchMultiplexer

An upstream line card including a digital or analog multiplexer front end circuit for a Cable Modem Termination System. Each upstream line card has only upstream receivers and allows a CMTS to share one or a handful of receiver chips to receive and recover data from a larger number of input cables coupled to the front end multiplexer. A control circuit for the multiplexer uses MAP data and burst assignment data and upstream mini-slot counts for each of the input cables to determine when a burst is about to arrive on a cable and cause appropriate switching by the multiplexer or crossbar switch. In some embodiments, there is only one RF channel circuit coupled to the output of the multiplexer, so the multiplexer is controlled to couple the input cable upon which the burst is expected to the single RF channel. In other embodiments, there are multiple RF channels coupled to the inputs of the multiplexer so the multiplexer is controlled to connect each input cable on which a burst is expected to an available RF channel. In some embodiments, the sample data generated by each RF channel is buffered and an arbiter picks one burst at a time for application to the input of a CMTS receiver or doles out bursts to different receivers. In other embodiments, no buffers or arbiter are used, and each RF channel has its own dedicated CMTS receiver.

Owner:GOOGLE TECH HLDG LLC

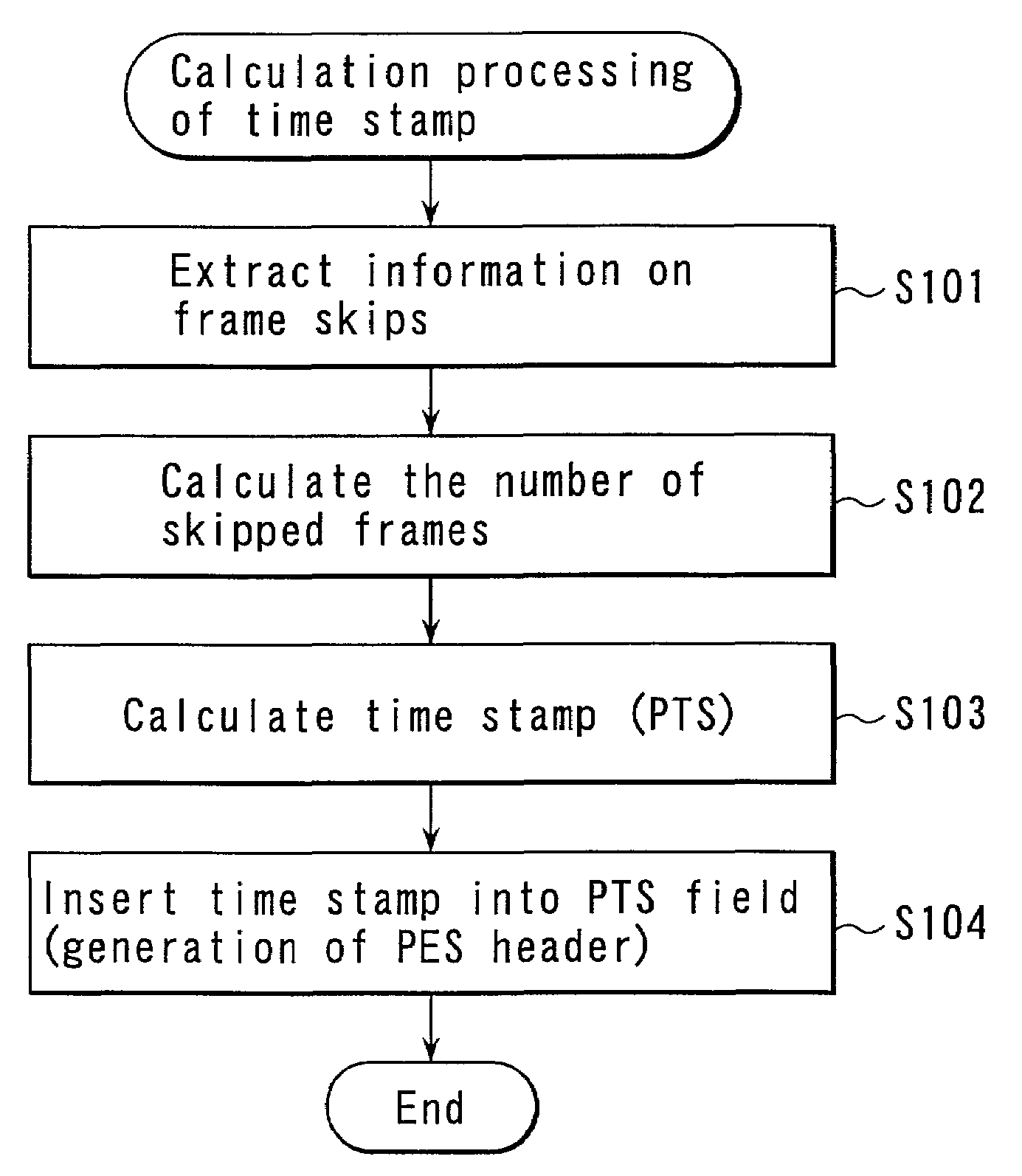

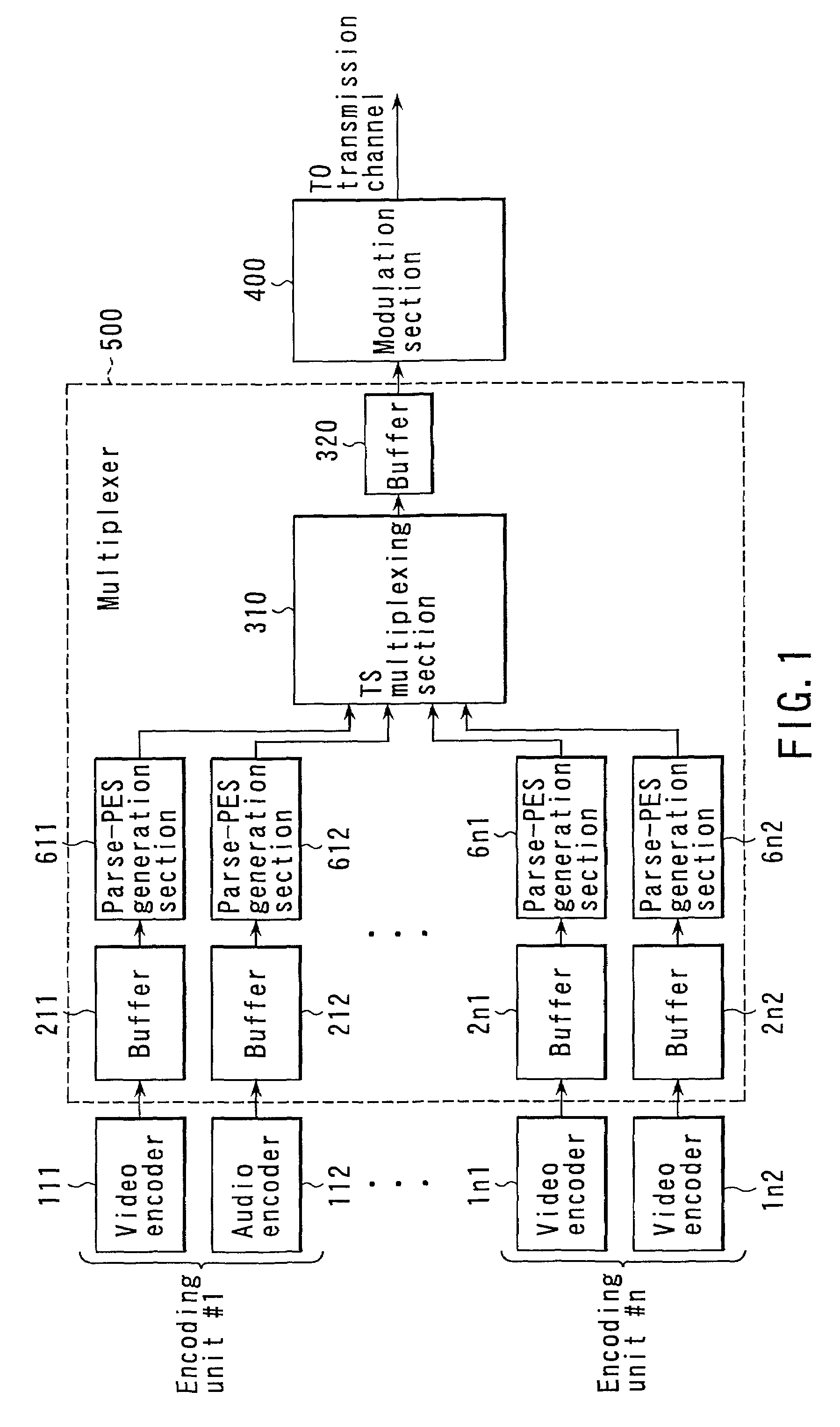

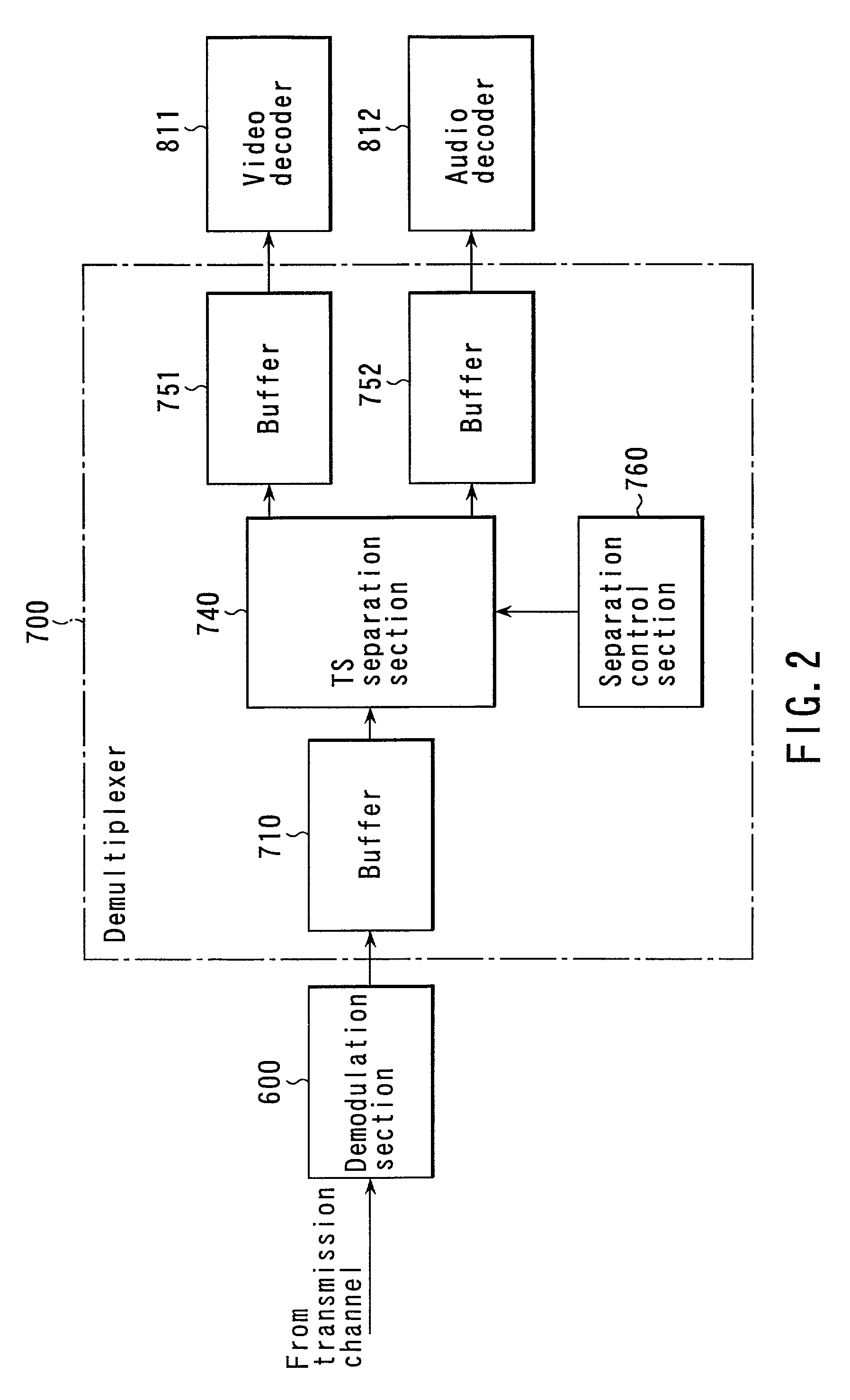

Multiplexer, multimedia communication apparatus and time stamp generation method

InactiveUS6987767B2Accurate detectionReduce processing burdenTime-division multiplexData switching by path configurationMultiplexerTransmission channel

In order to allow the generation of a time stamp in consideration of a frame skip even in the case where the frame skip is generated, a PES generation section of a multiplexer detects the number of skipped frames by analyzing elementary video streams output from a video encoder to determine a PTS on the basis of the time difference between frames calculated on the basis of the number of skipped frames. Then, a frame to which a PTS is to be placed with the above stream analysis is cut out to insert the PTS into a PES header of this frame to be transmitted to the transmission channel.

Owner:KK TOSHIBA