Patents

Literature

39825 results about "Low voltage" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In electrical engineering low voltage is a relative term, the definition varying by context. Different definitions are used in electric power transmission and distribution, and electrical safety codes define "low voltage" circuits that are exempt from the protection required at higher voltages. These definitions vary by country and specific codes or regulations.

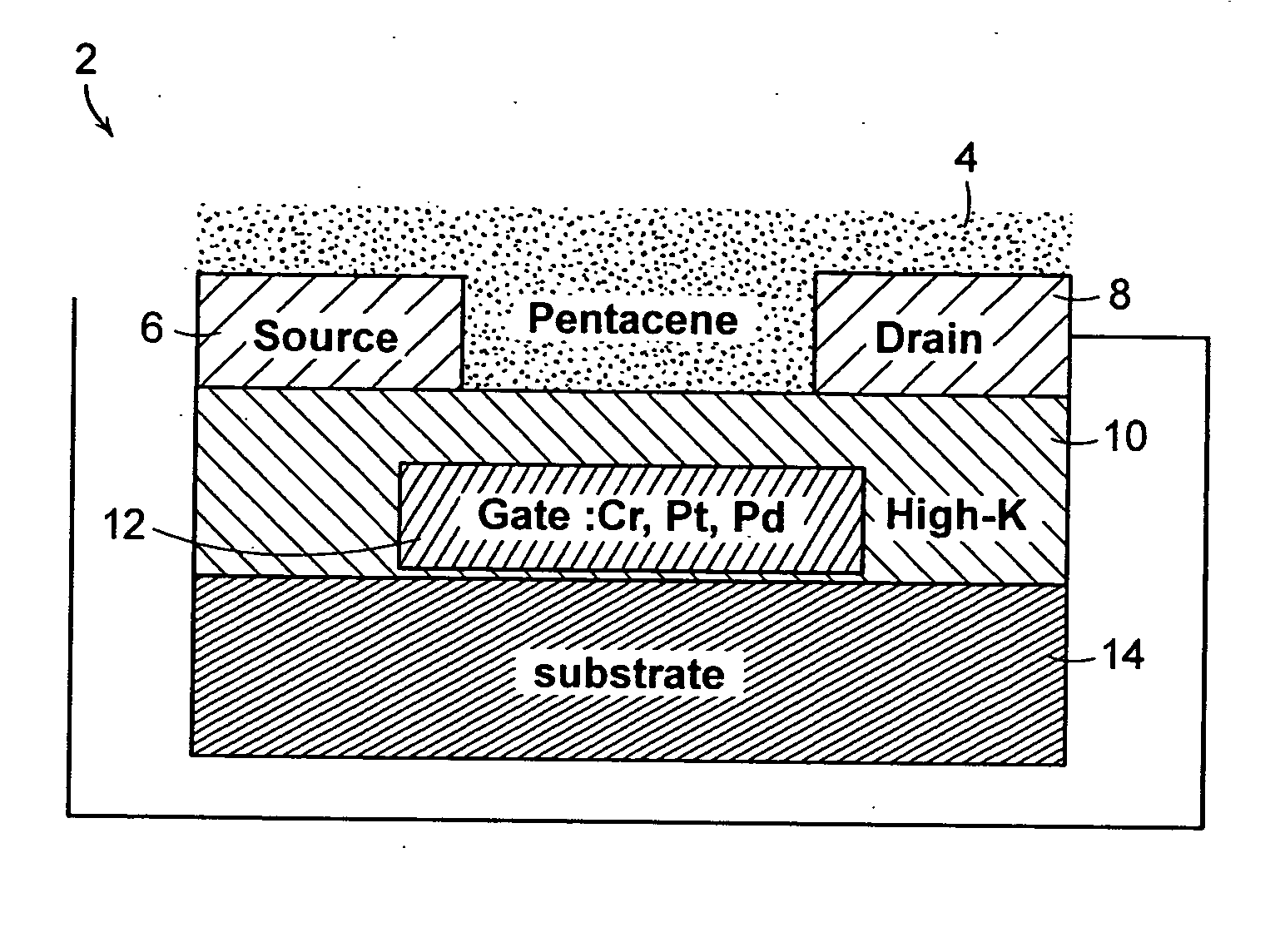

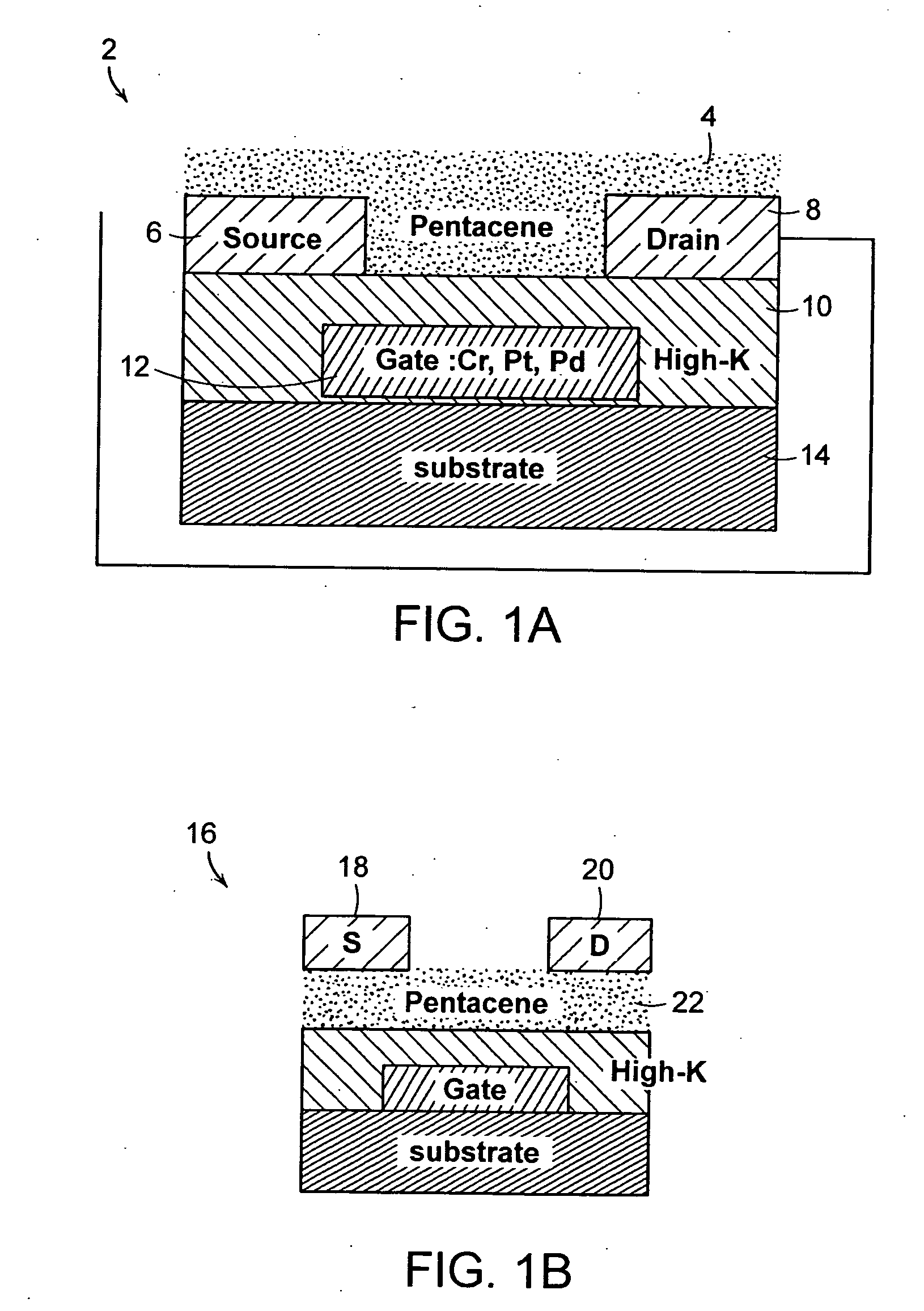

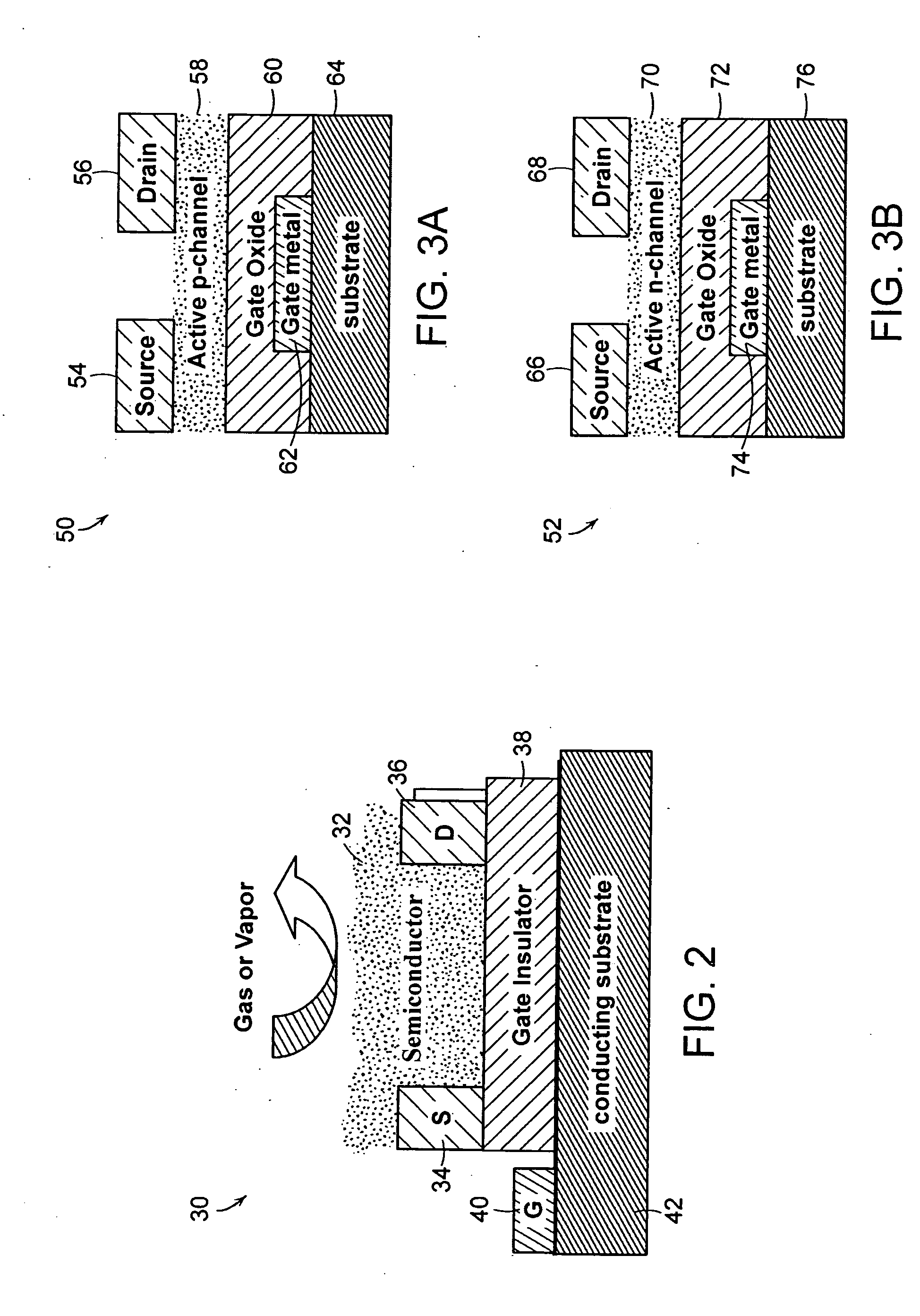

Low voltage flexible organic/transparent transistor for selective gas sensing, photodetecting and CMOS device applications

A thin film transistor (TFT) includes a source electrode, a drain electrode, and a gate electrode. A gate insulator is coupled to the source electrode, drain electrode, and gate electrode. The gate insulator includes room temperature deposited high-K materials so as to allow said thin film transistor to operate at low operating voltage.

Owner:MASSACHUSETTS INST OF TECH

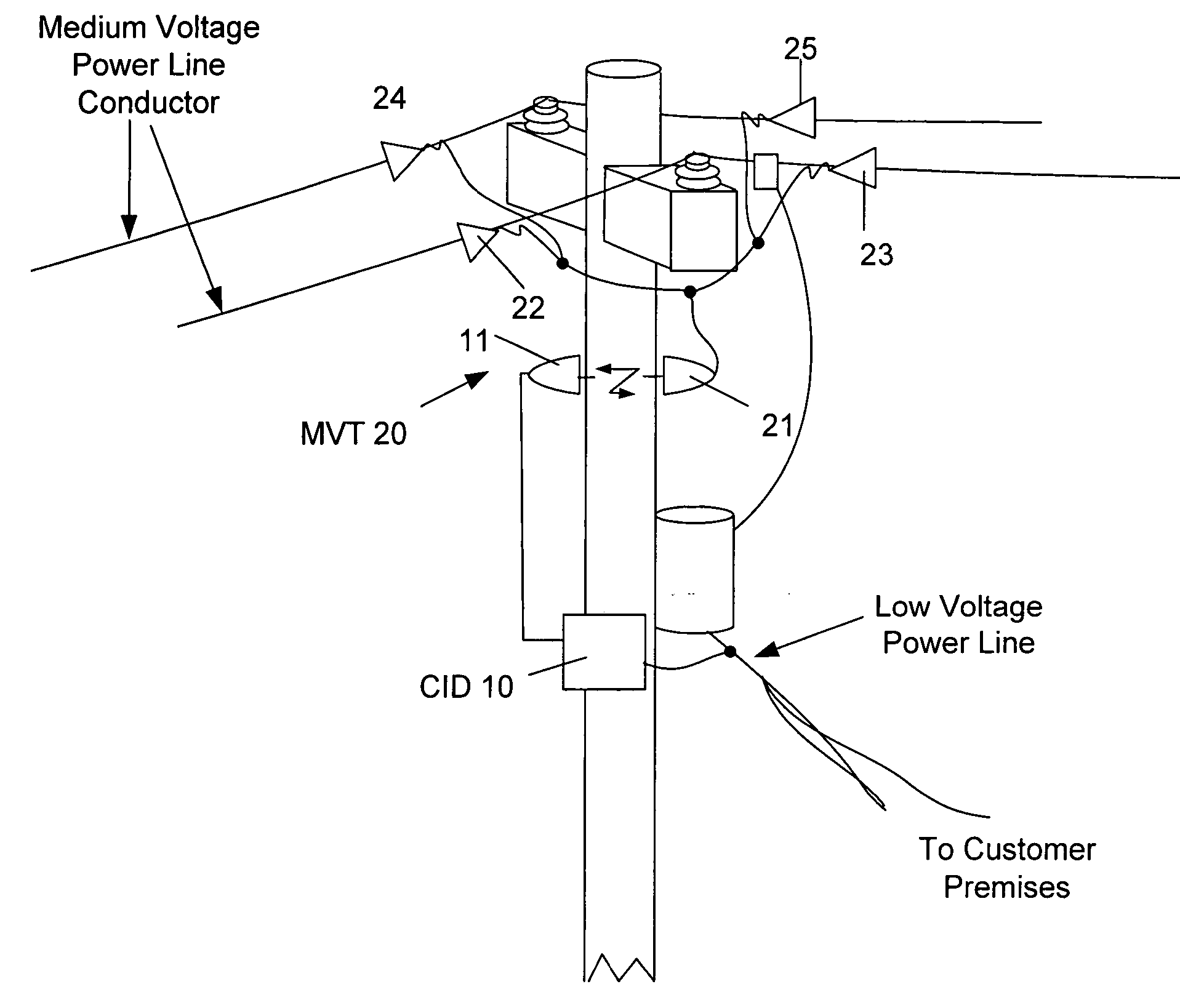

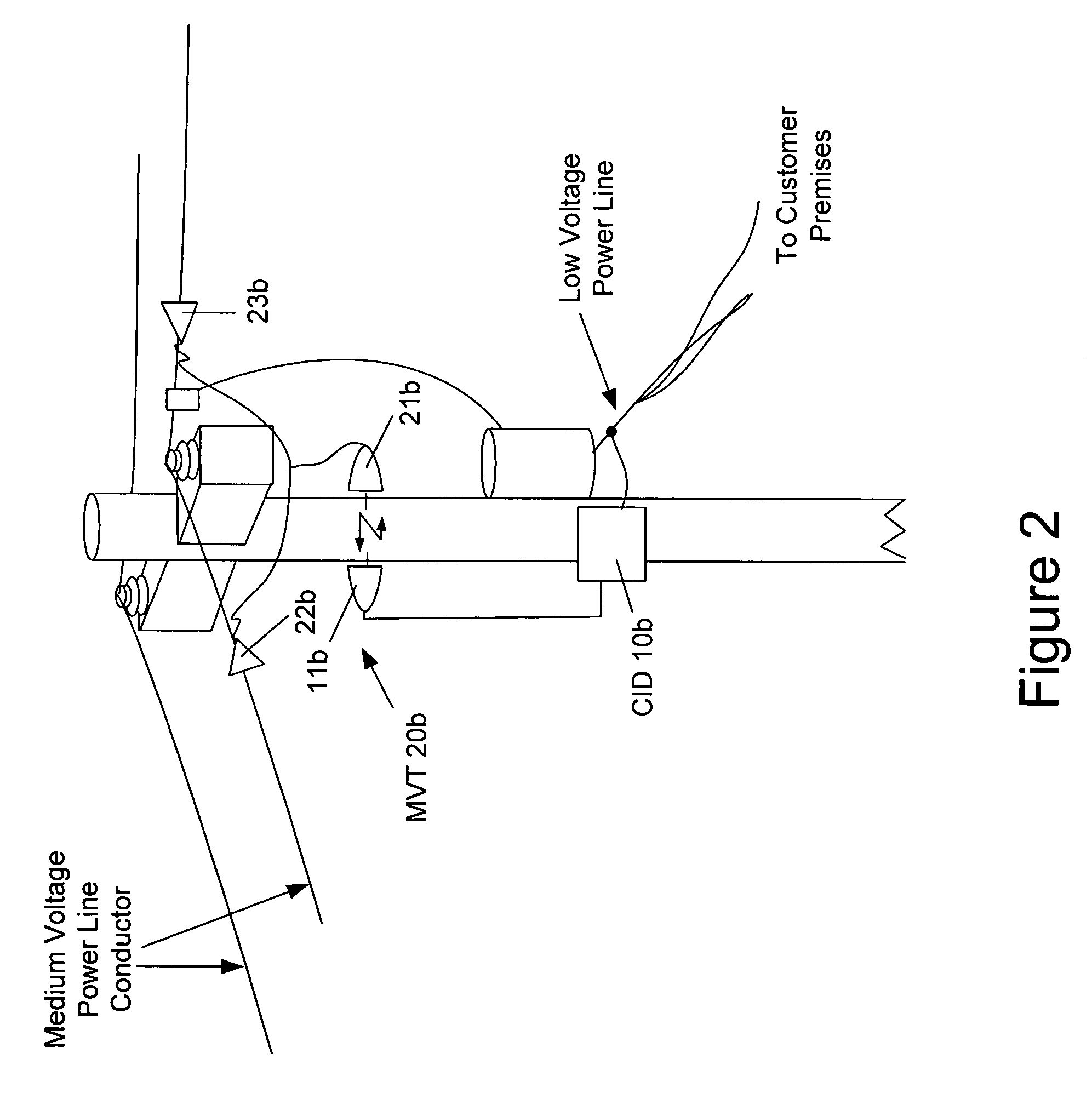

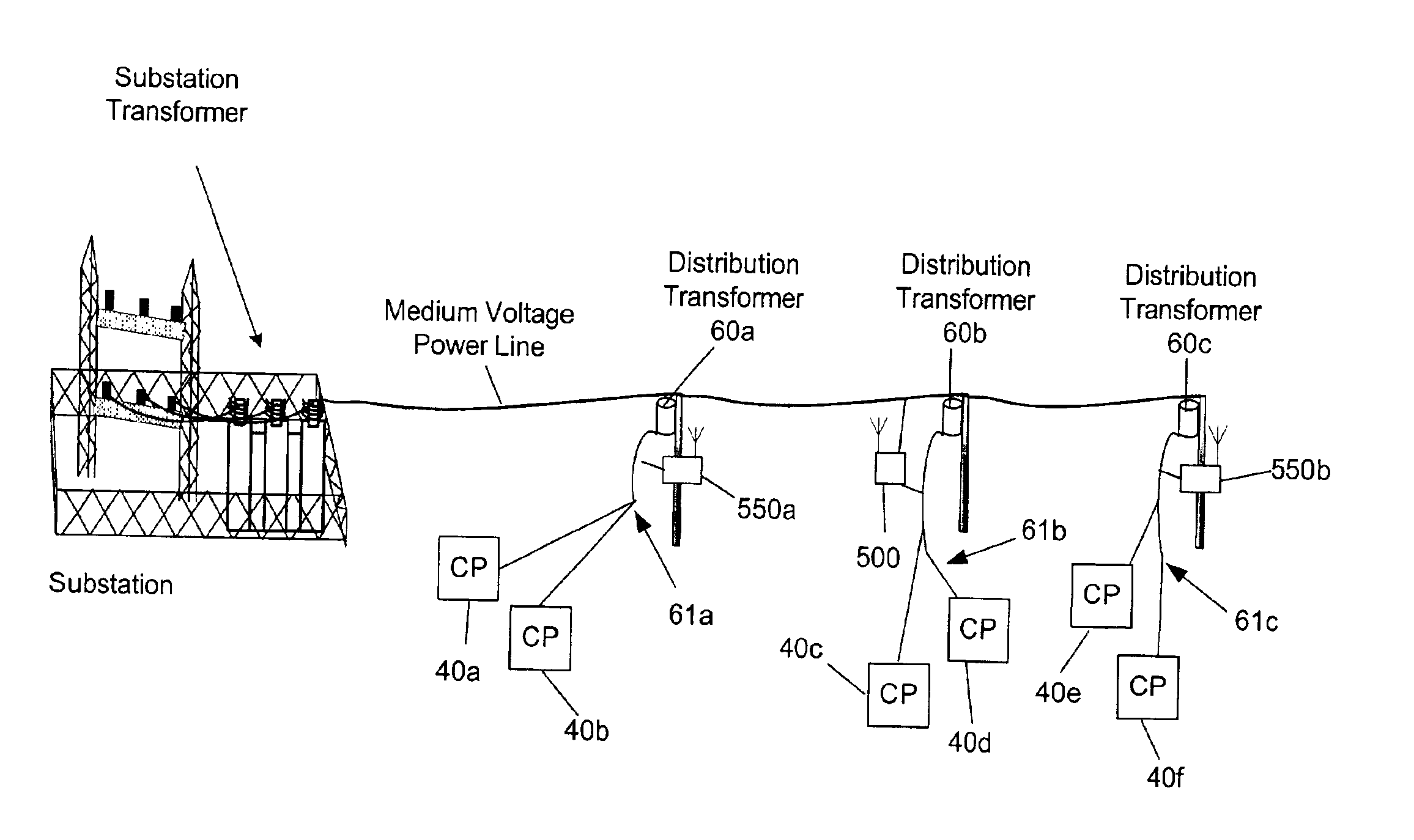

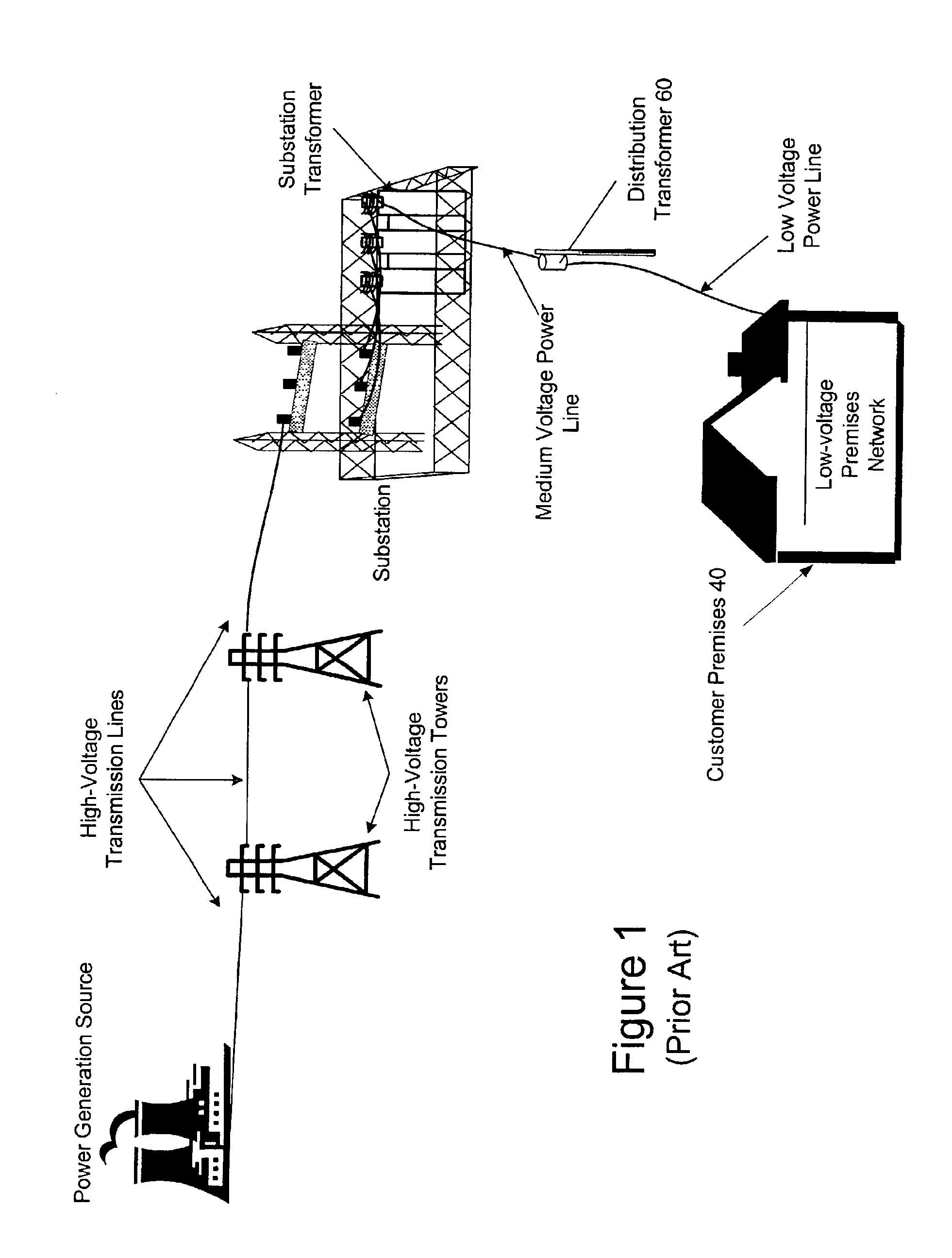

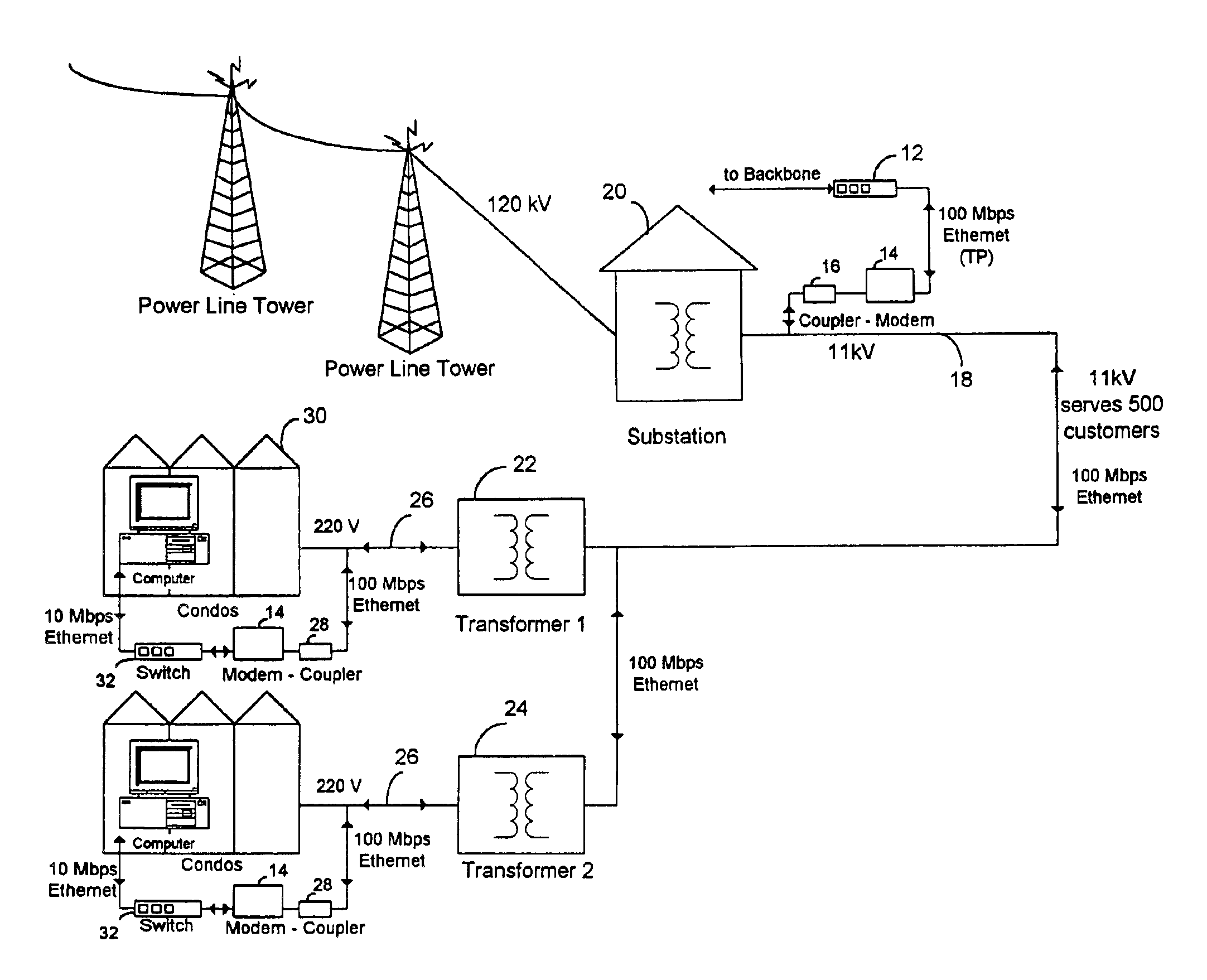

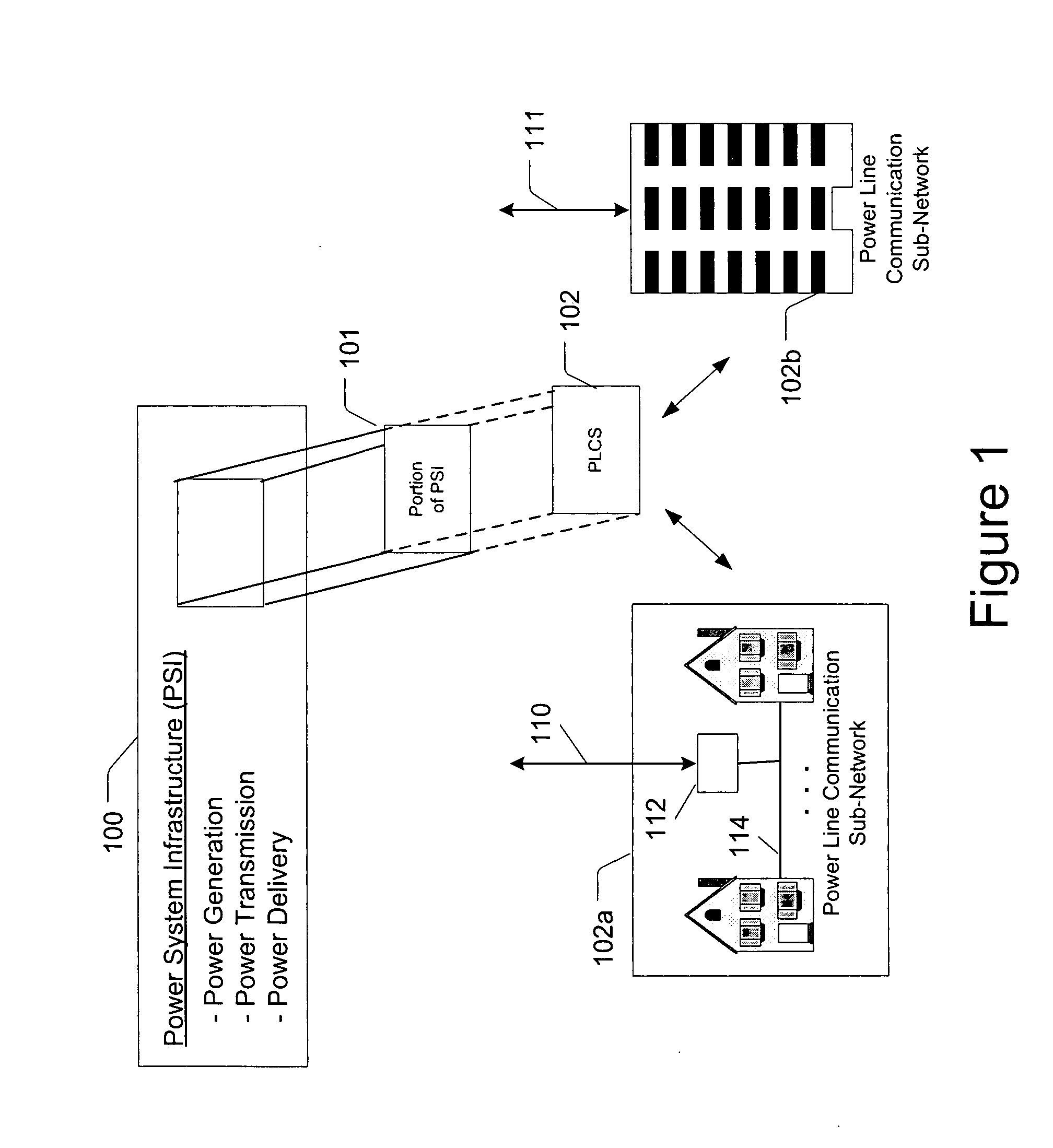

Surface wave power line communications system and method

InactiveUS20050111533A1Electric signal transmission systemsInterconnection arrangementsCommunication interfaceCommunications system

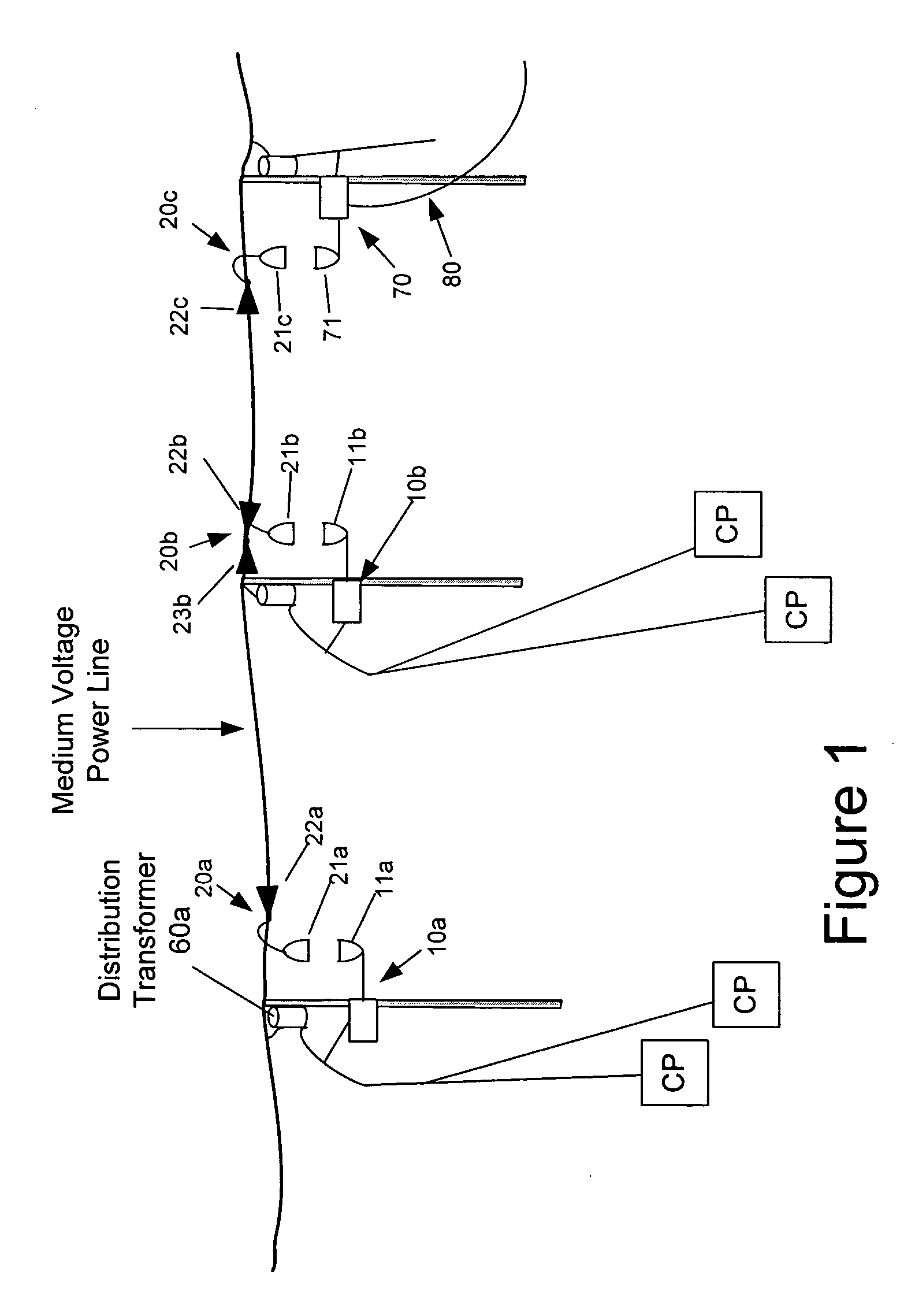

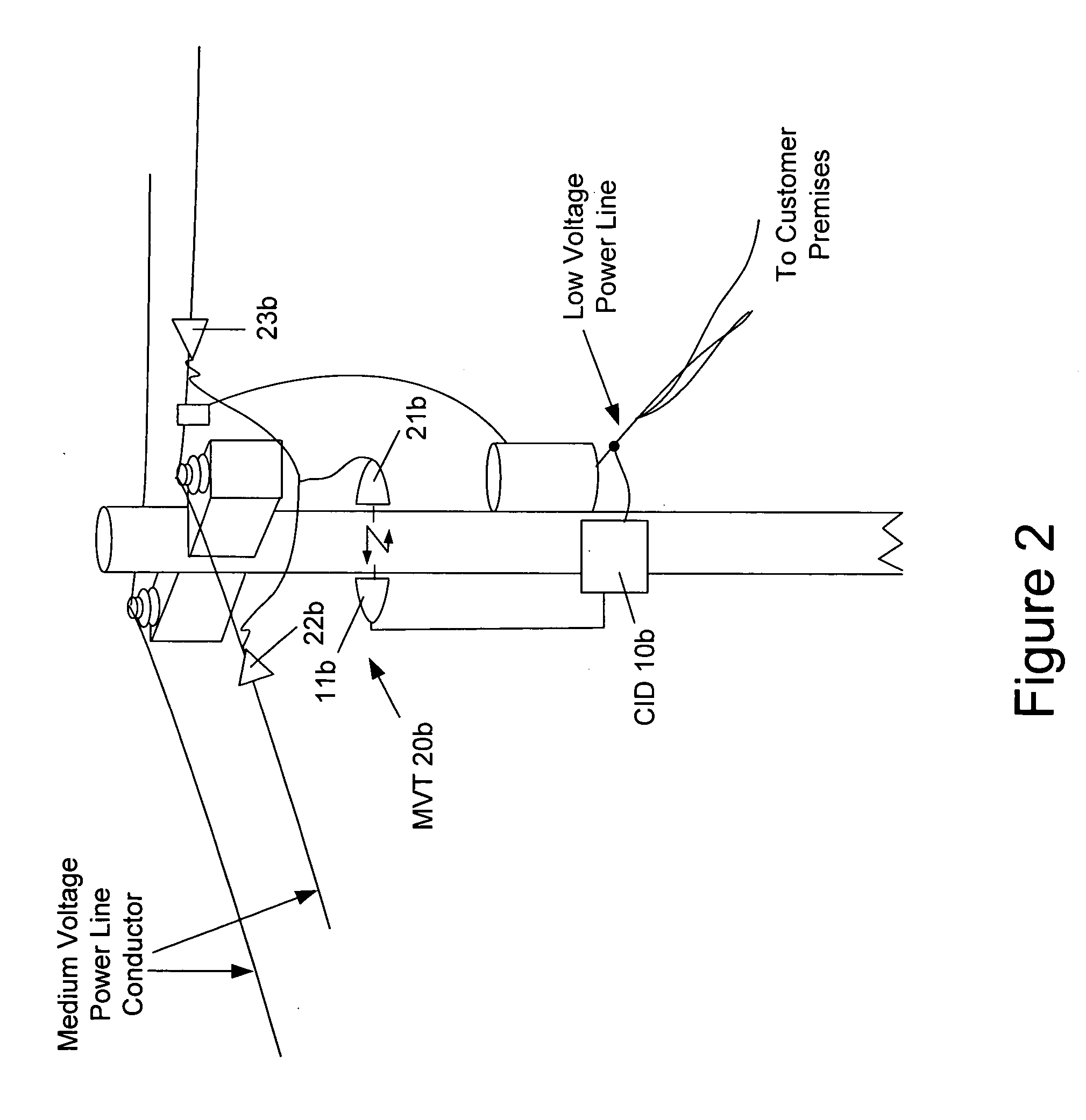

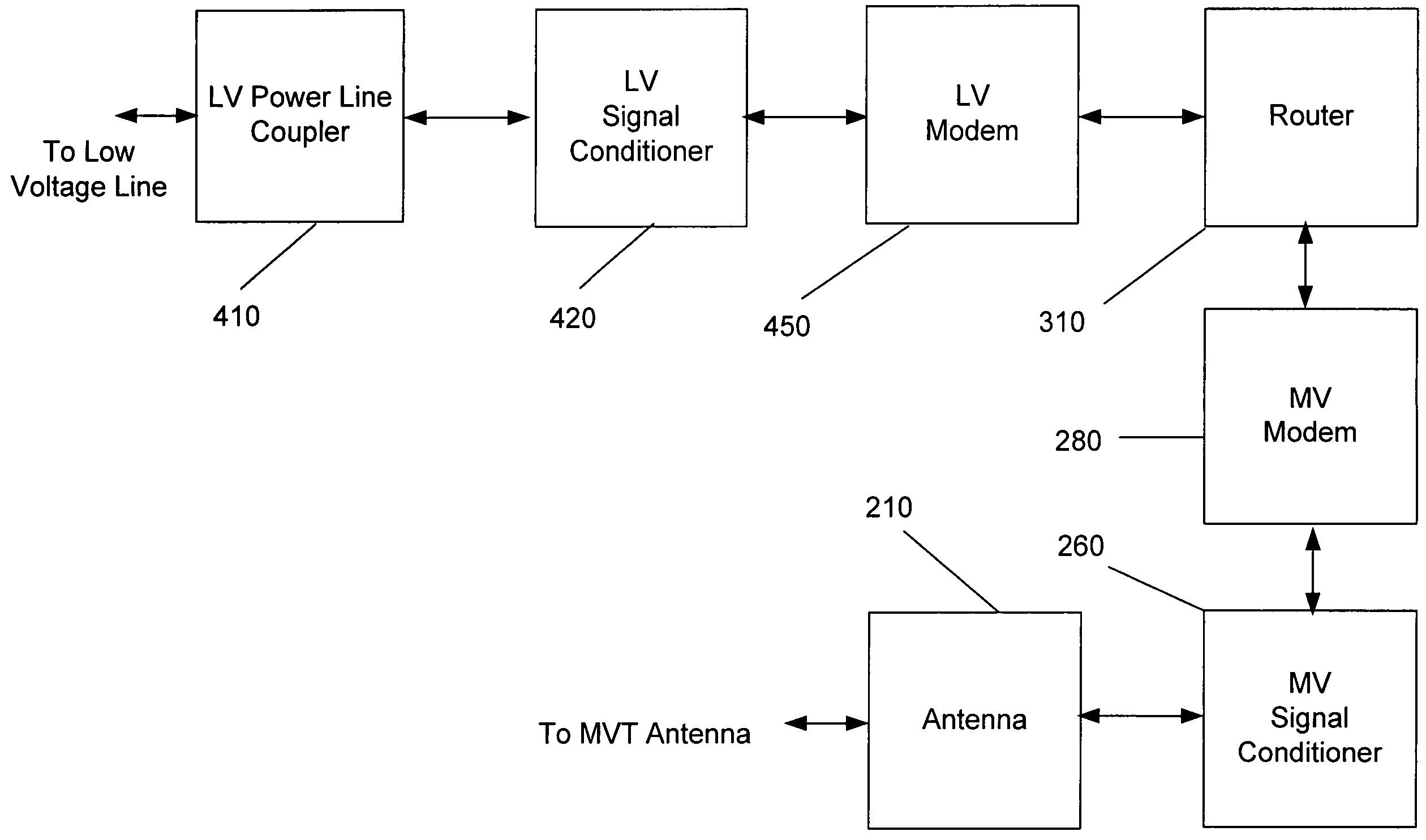

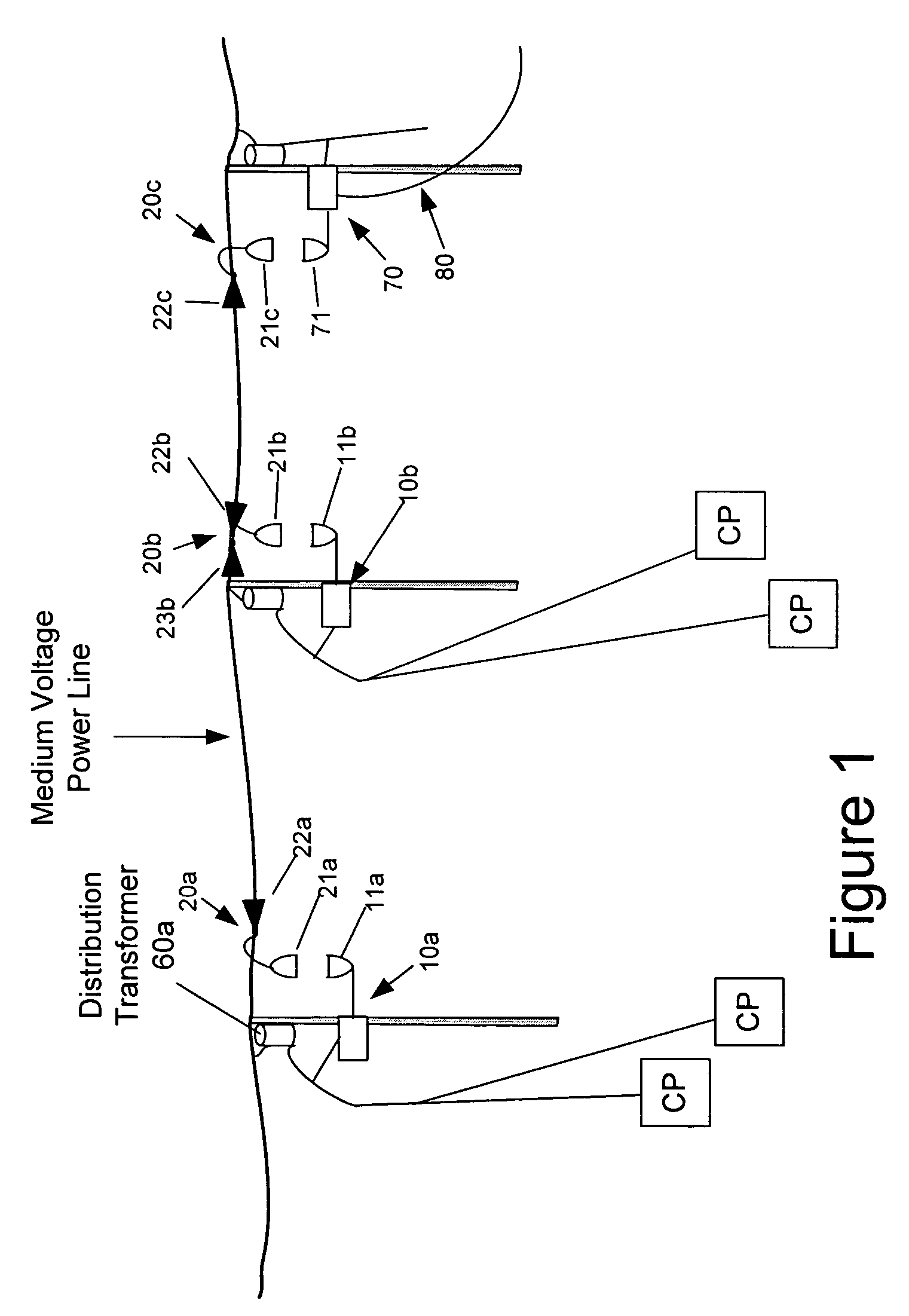

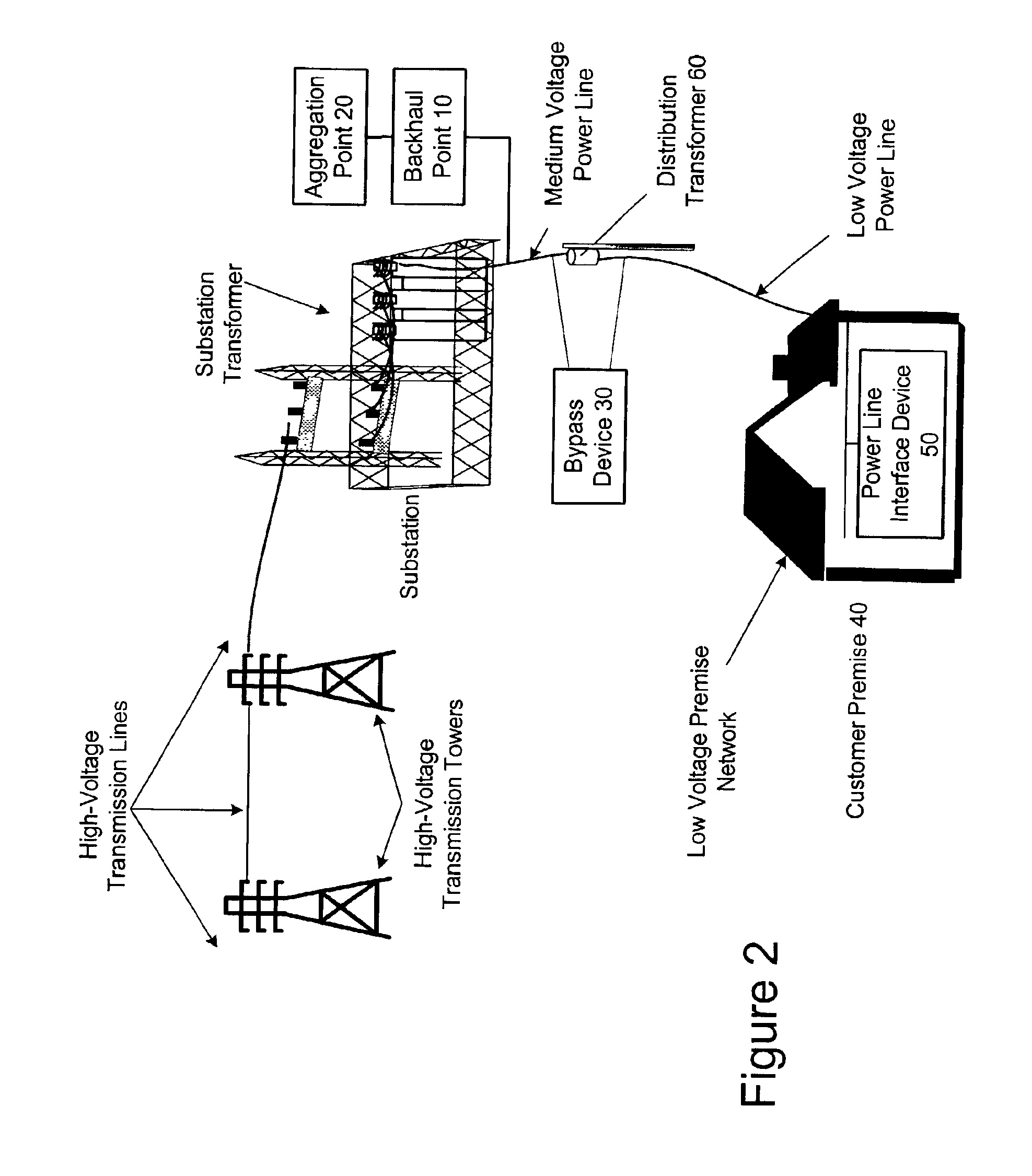

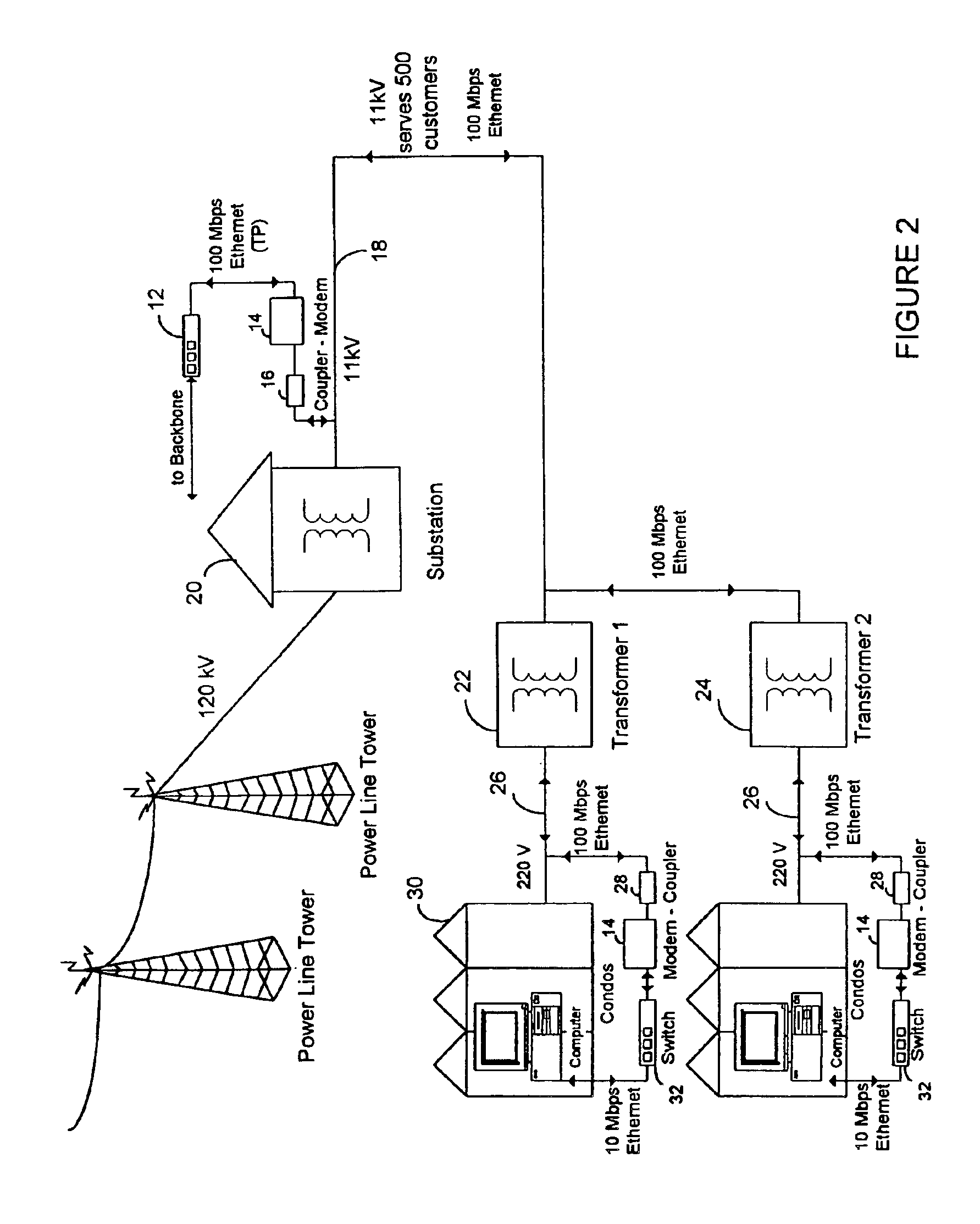

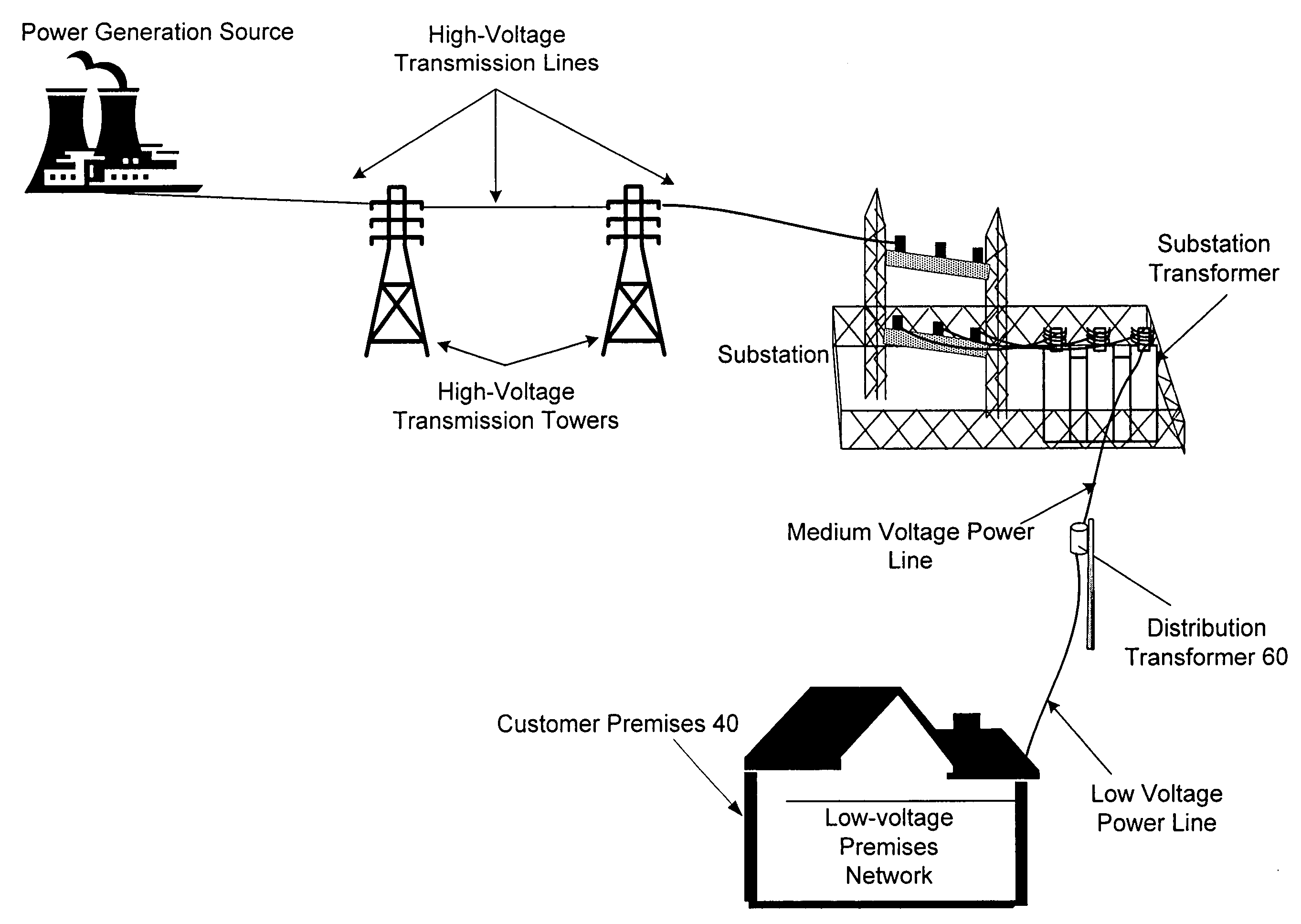

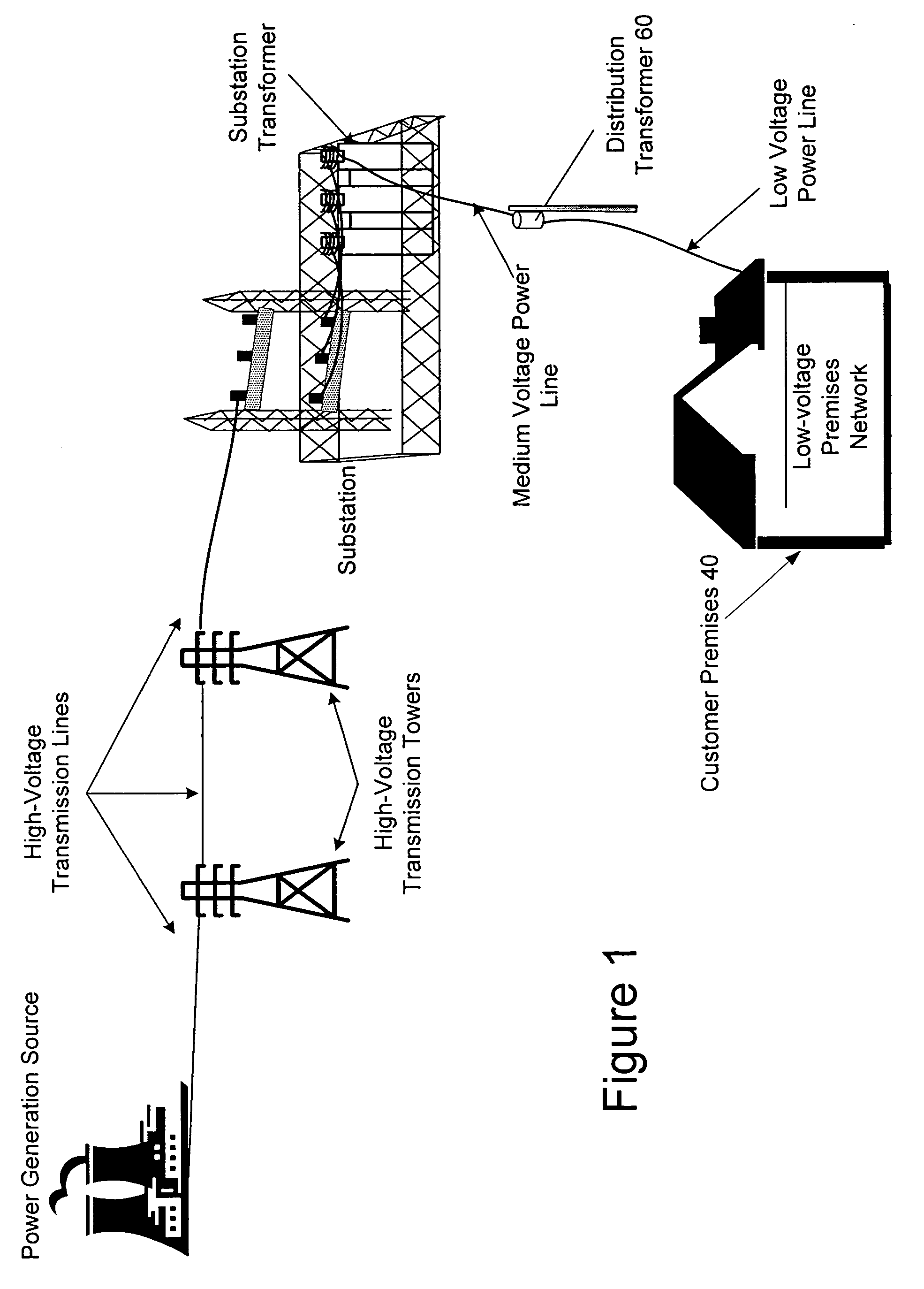

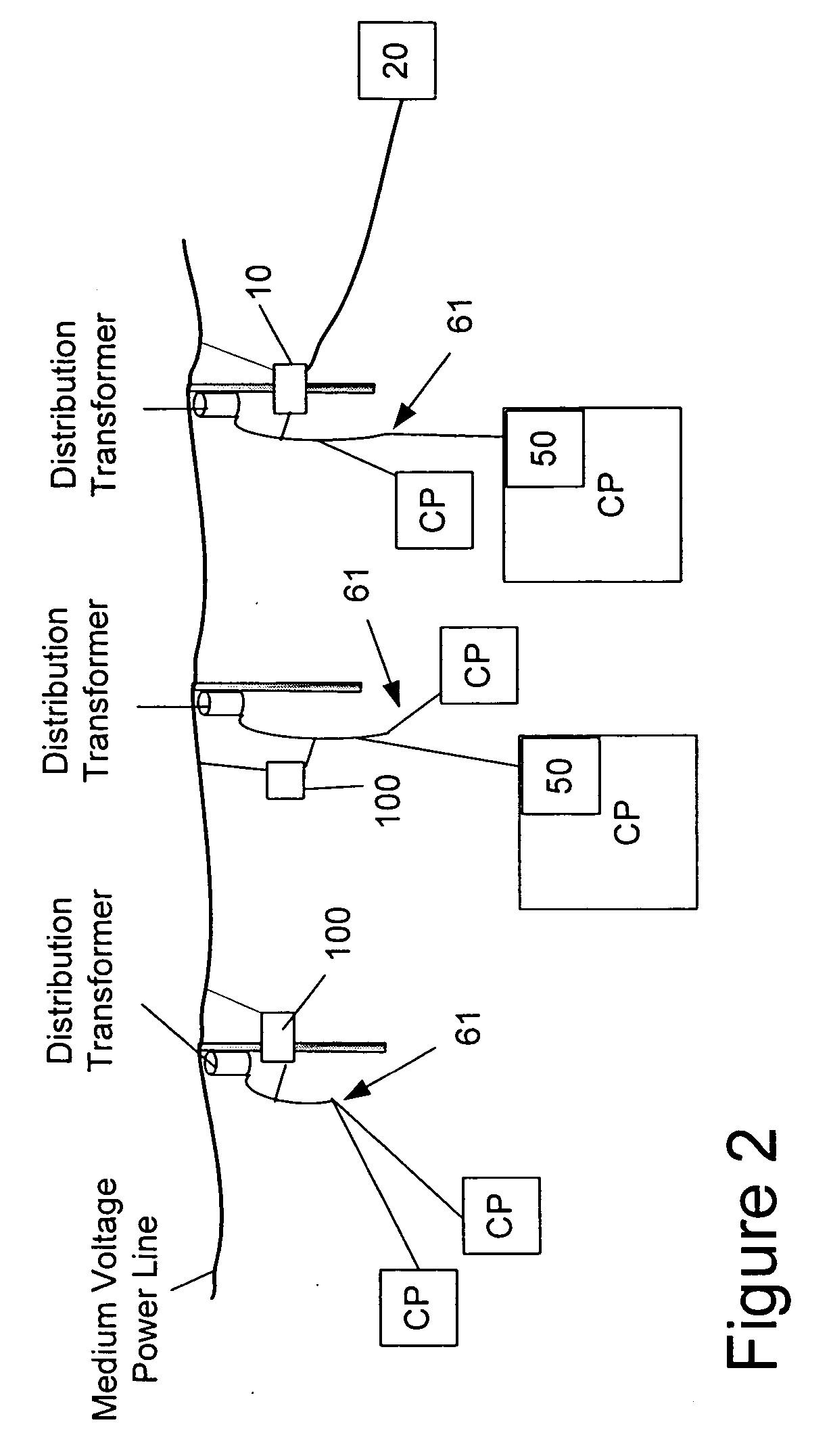

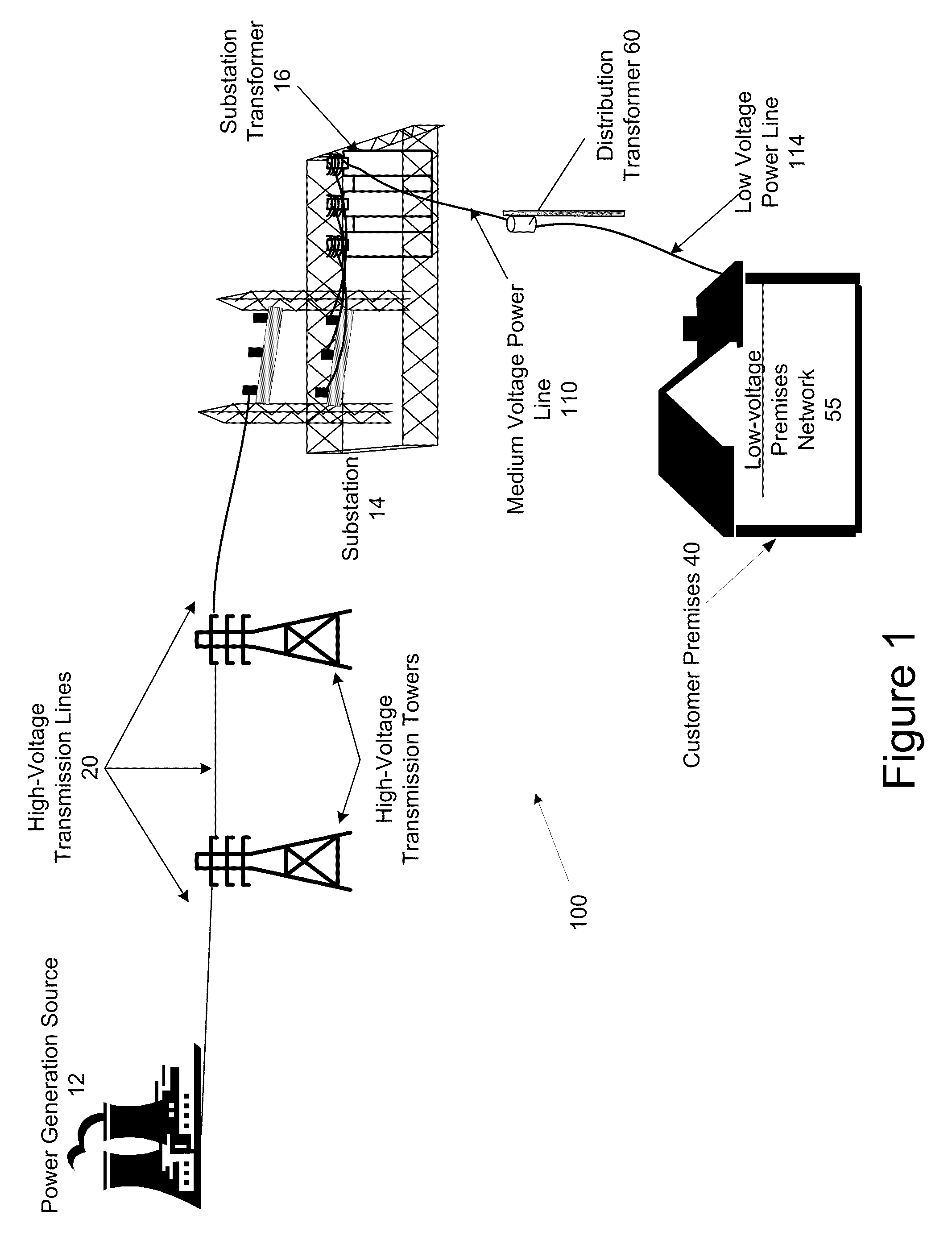

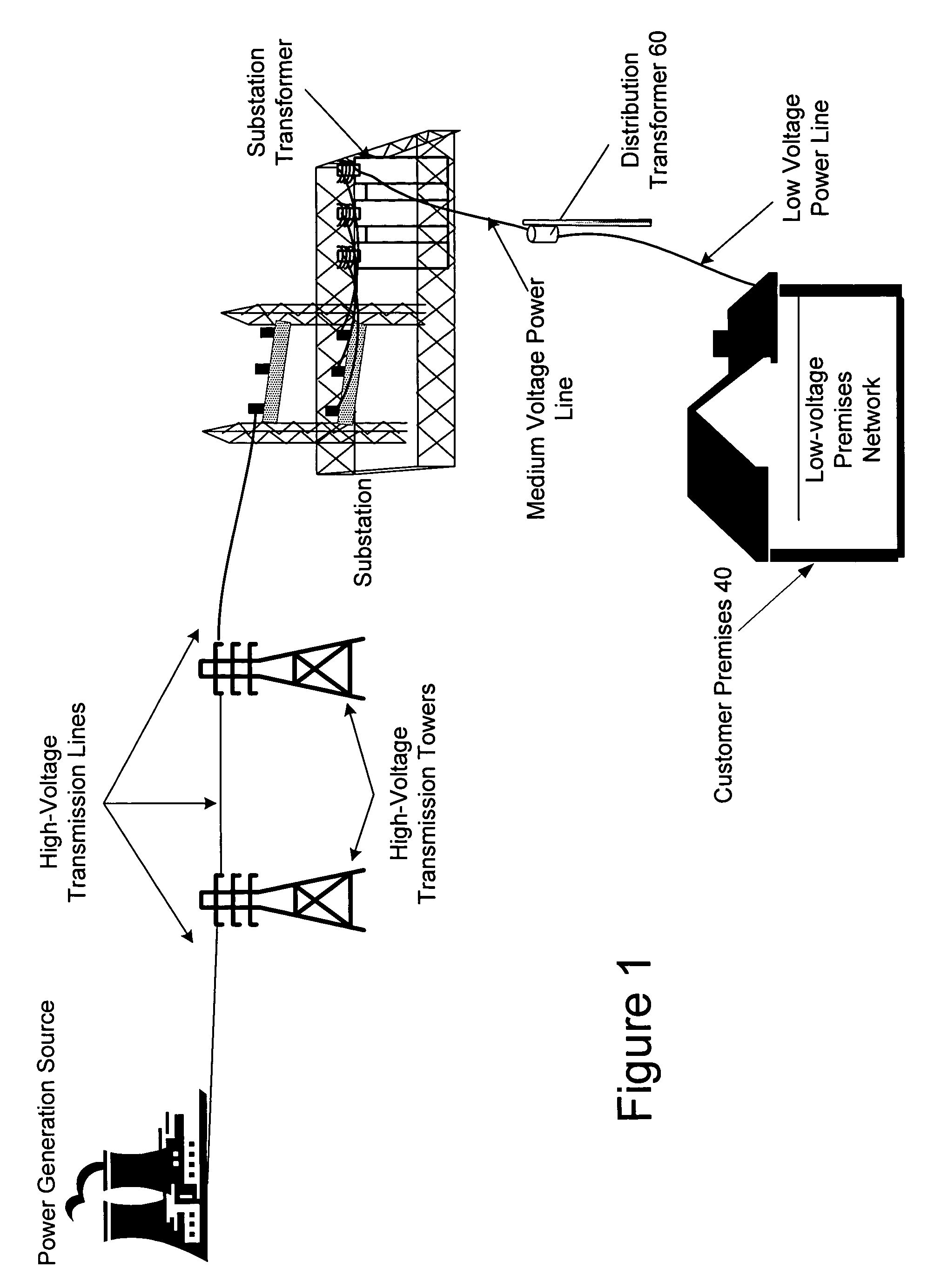

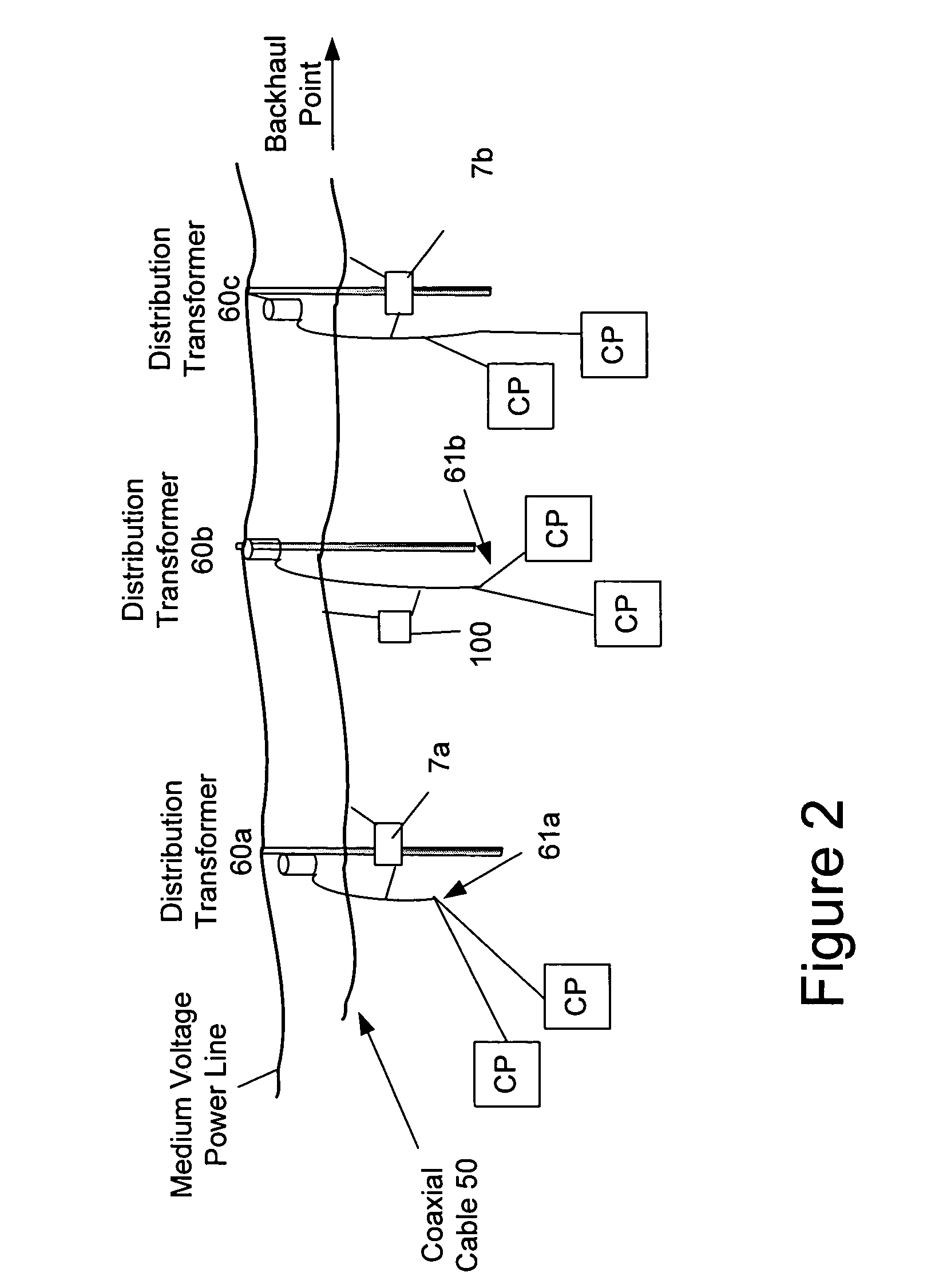

The present invention provides a system for operating a power line communications system that employs surface wave communications and conducted communications. The system is comprised of a plurality of network elements, which may take the form of repeaters, communication interface devices, backhaul devices, medium voltage transducers, distribution points, aggregation points, and others. In one embodiment, surface waves are communicated over the medium voltage power lines and the conducted communications are communicated via the low voltage power lines to and from customer premises.

Owner:CURRENT TECH

Surface wave power line communications system and method

InactiveUS7280033B2Electric signal transmission systemsInterconnection arrangementsCommunication interfaceCommunications system

The present invention provides a system for operating a power line communications system that employs surface wave communications and conducted communications. The system is comprised of a plurality of network elements, which may take the form of repeaters, communication interface devices, backhaul devices, medium voltage transducers, distribution points, aggregation points, and others. In one embodiment, surface waves are communicated over the medium voltage power lines and the conducted communications are communicated via the low voltage power lines to and from customer premises.

Owner:CURRENT TECH

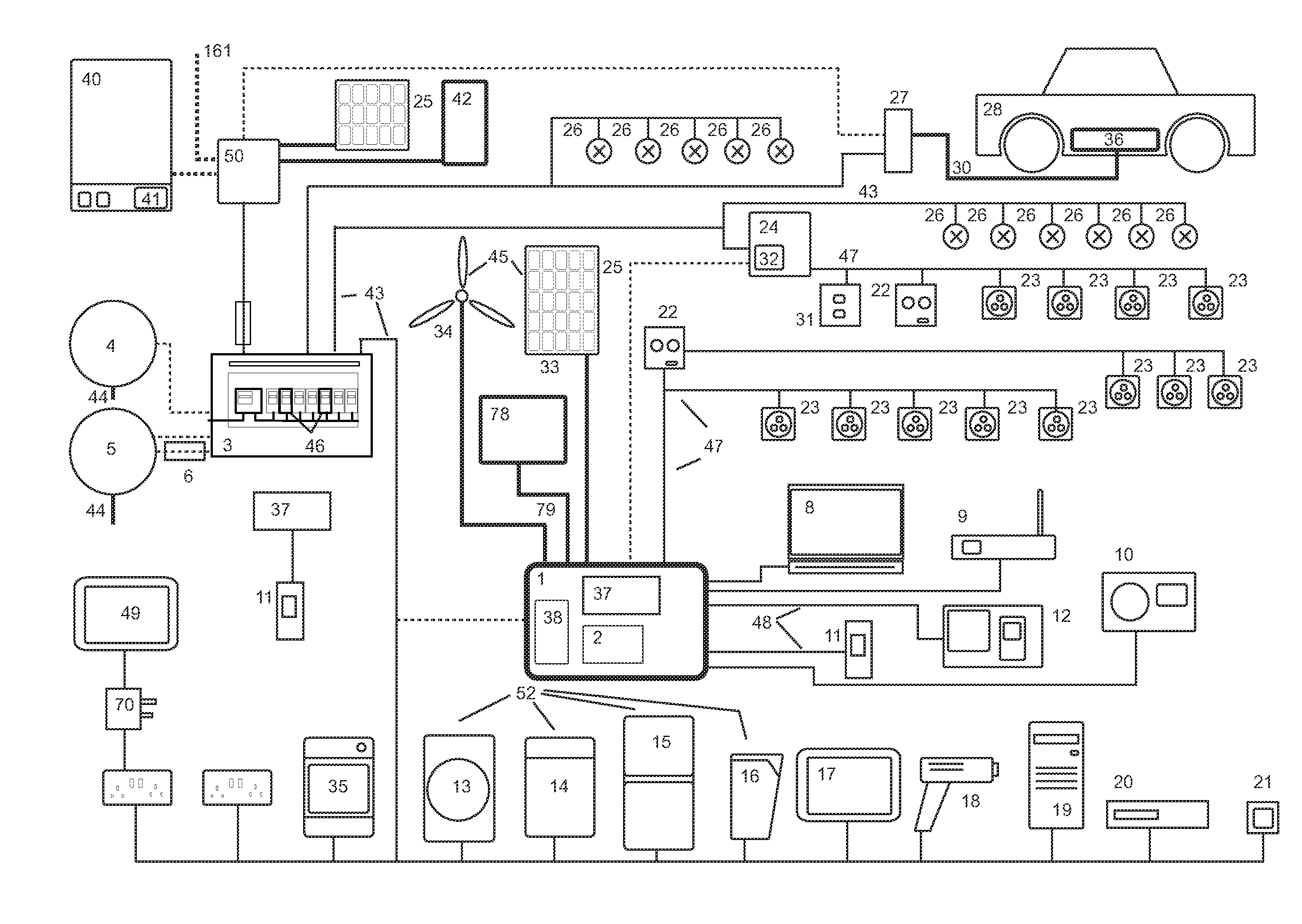

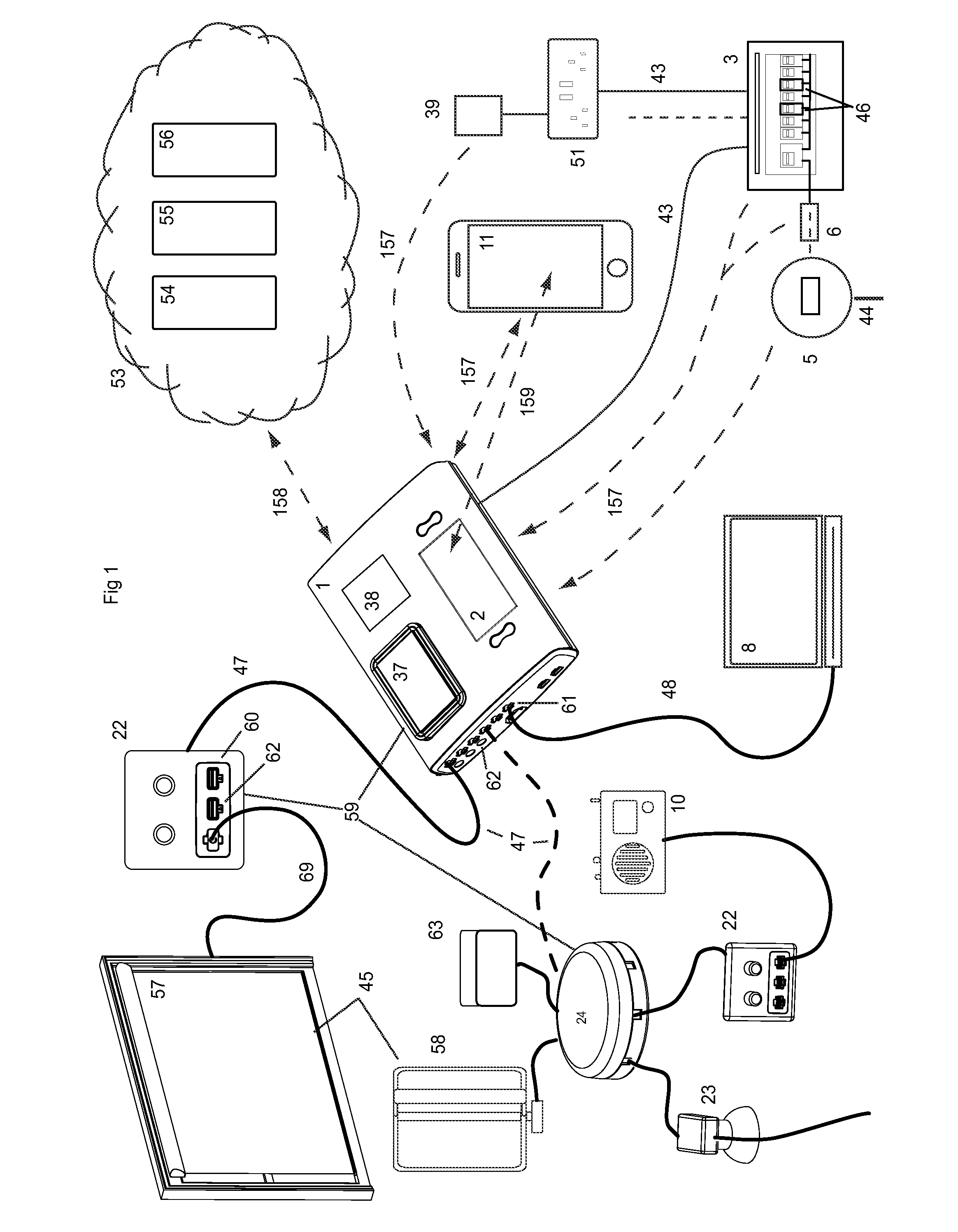

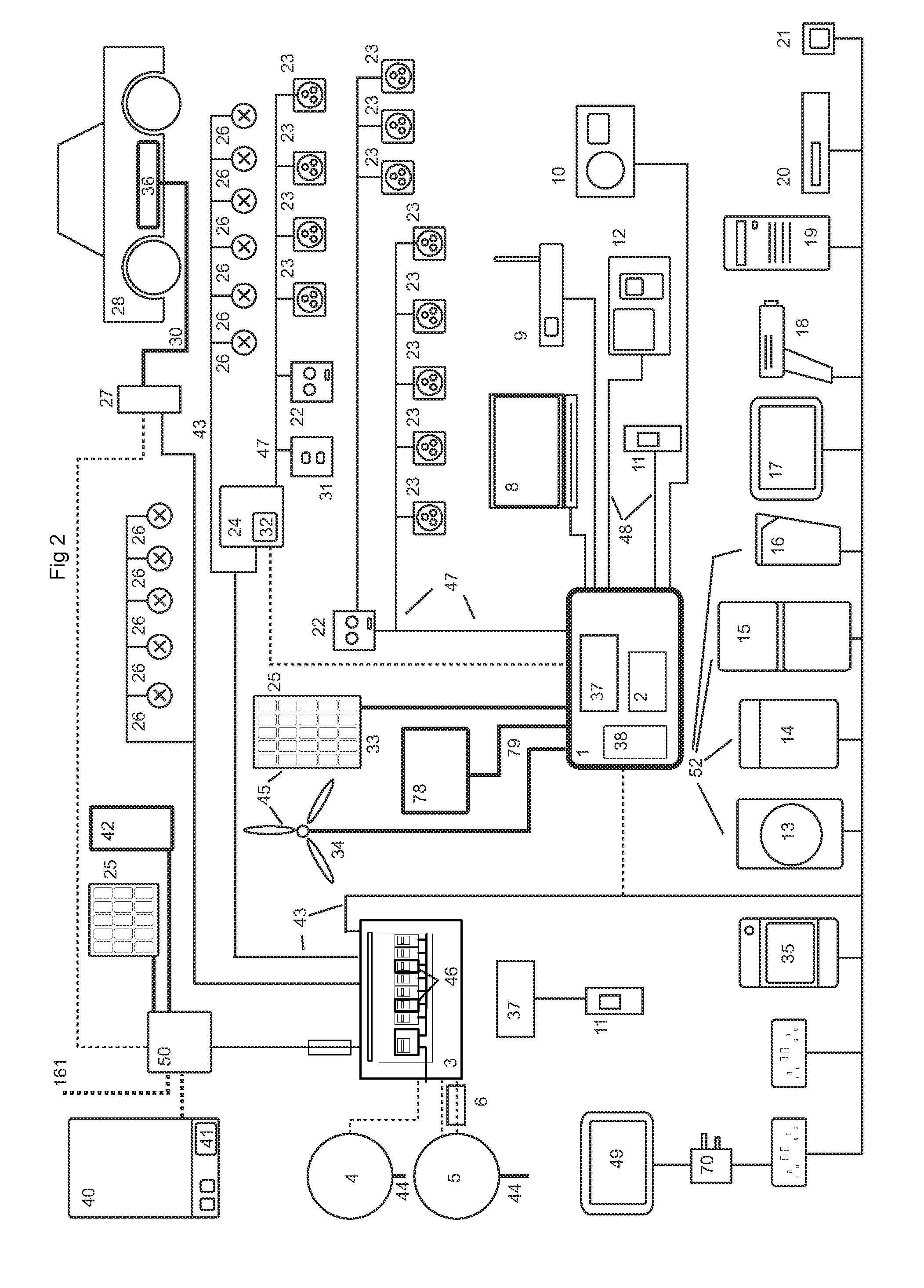

Systems, devices and methods for electricity provision, usage monitoring, analysis, and enabling improvements in efficiency

ActiveUS20100076615A1Facilitating in changing their energy usage behaviourEasy to installPhotovoltaic monitoringLevel controlLight equipmentRenewable technologies

The invention relates generally to systems, devices and methods for the efficient use of utilities, more particularly to the distribution and provision of electricity supply at appropriate voltages, monitoring and usage by end devices, and to facilitating consumers in changing their energy usage behaviour, and to adopt and easily install appropriate sustainable, energy efficient or renewable technologies. Said end devices typically including traditional electric, electronic and lighting appliances requiring AC or DC power provision or low voltage DC power via AC / DC converters.

Owner:MOIXA ENERGY HLDG

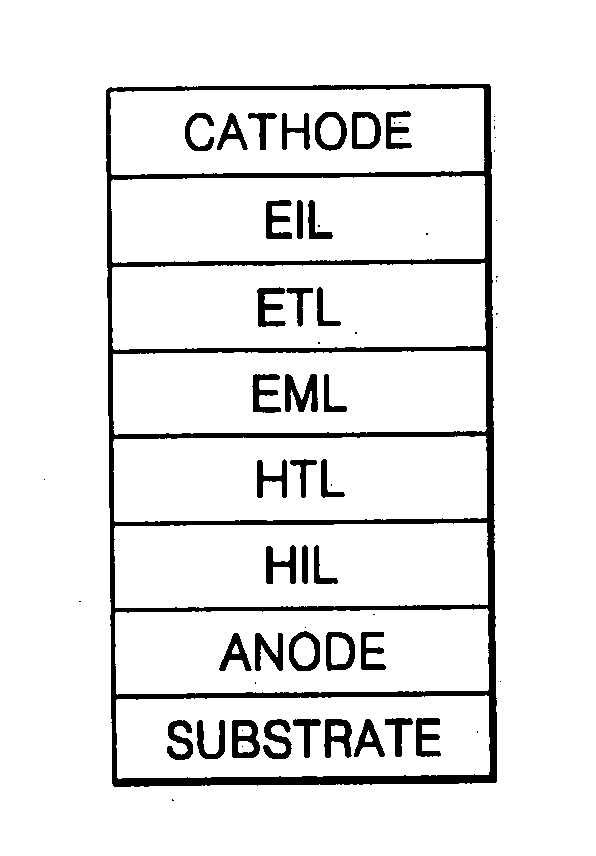

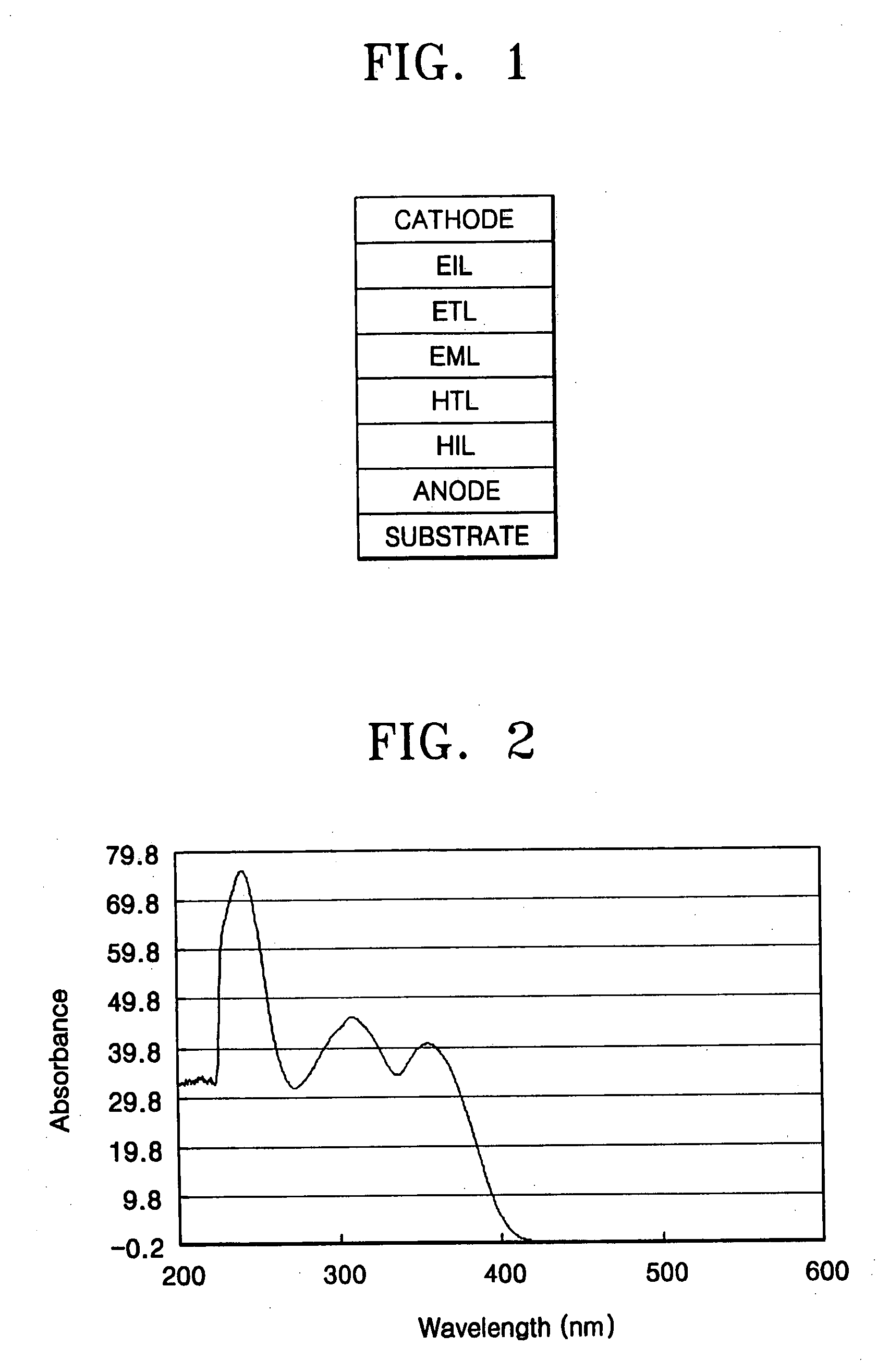

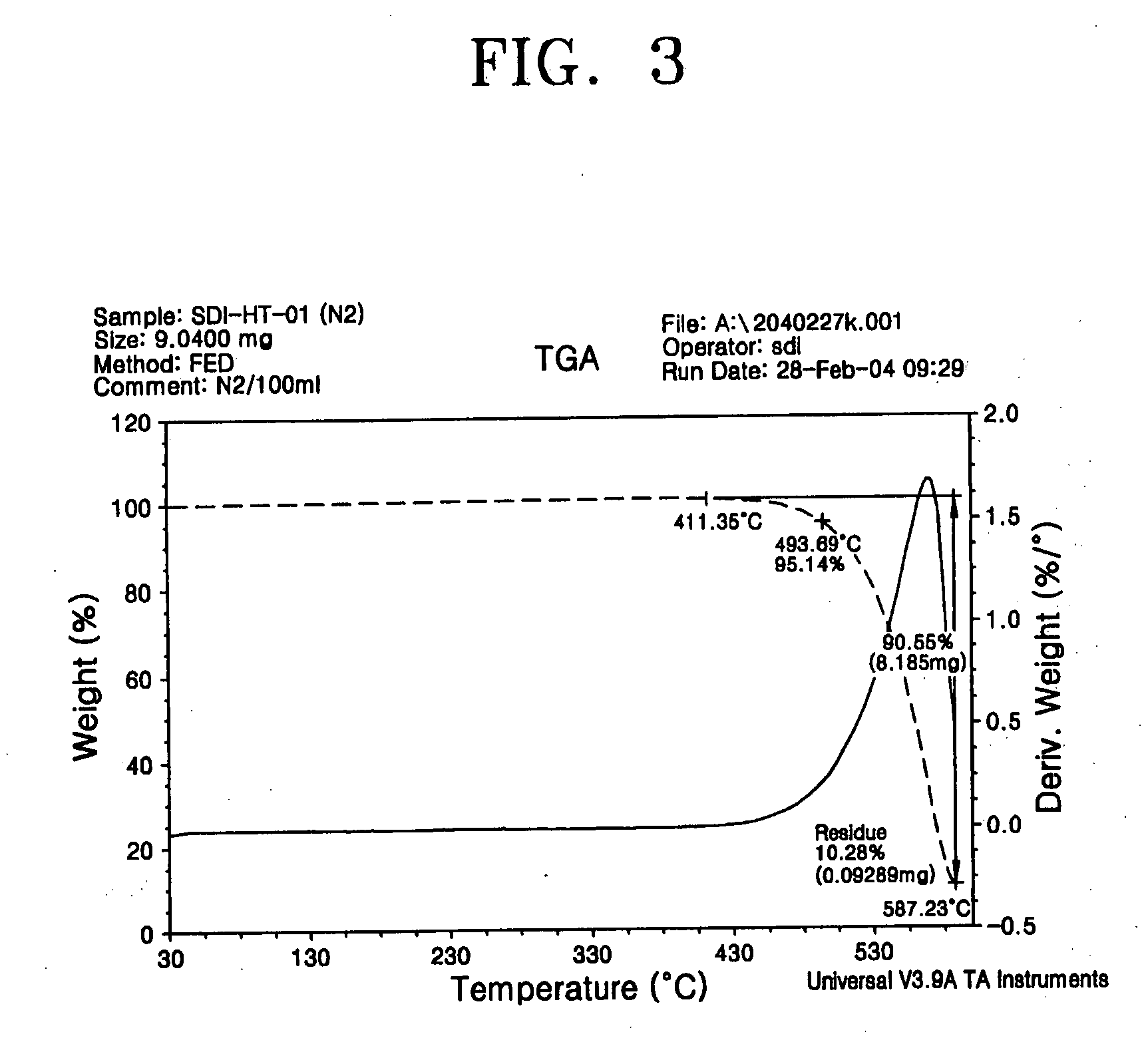

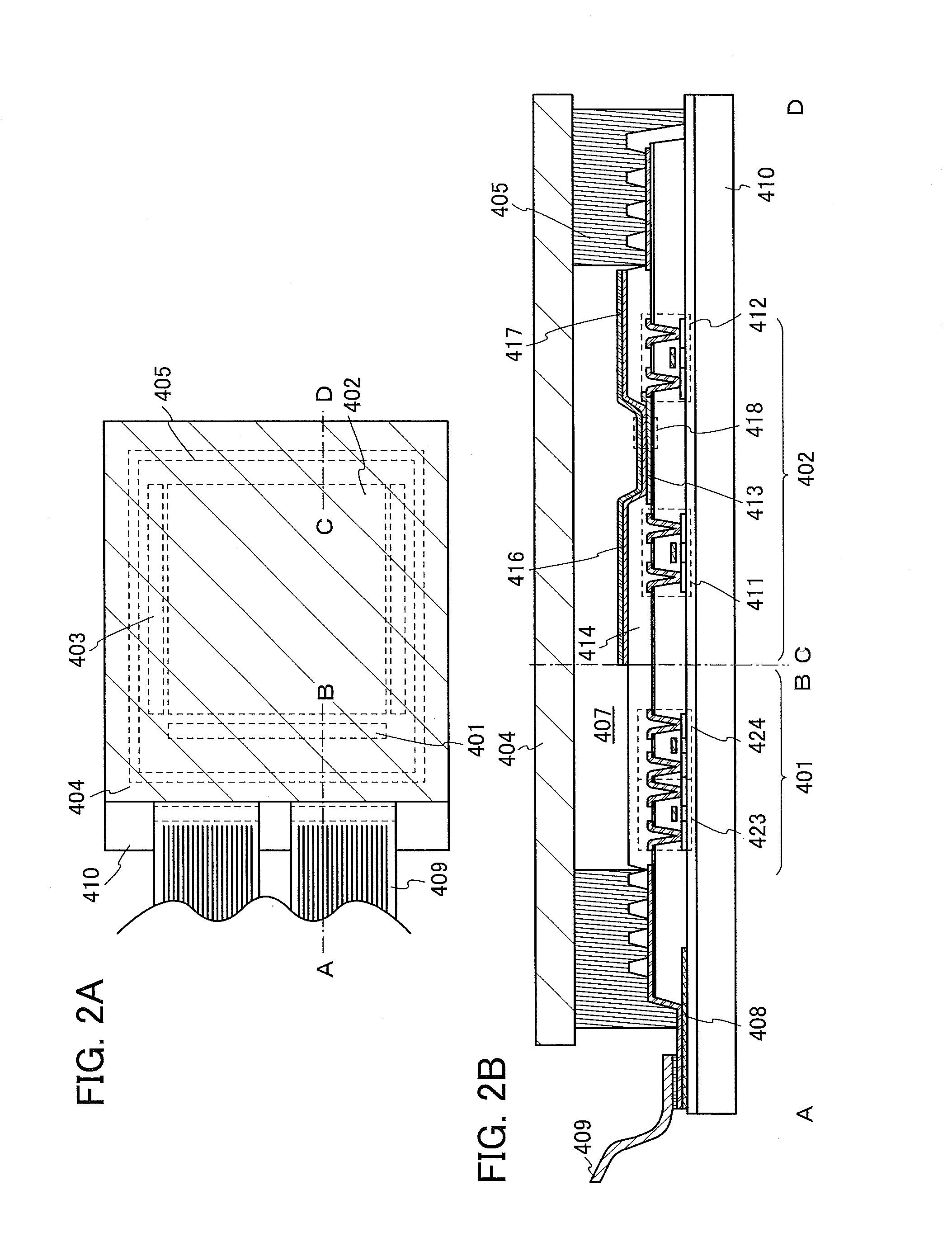

Phenylcarbazole-based compound and organic electroluminescent device employing the same

ActiveUS20080107919A1High glass transition temperatureElectric stabilityOrganic chemistryDischarge tube luminescnet screensCarbazoleLow voltage

A phenylcarbazole-based compound is represented by Formula 1, and has superior electric properties and charge transport abilities, and thus is useful as a hole injection material, a hole transport material, and / or an emitting material which is suitable for fluorescent and phosphorescent devices of all colors, including red, green, blue, and white colors. The phenylcarbazole-based compound is synthesized by reacting carbazole with diamine. The organic electroluminescent device manufactured using the phenylcarbazole-based compound has high efficiency, low voltage, high luminance, and a long lifespan.

Owner:SAMSUNG DISPLAY CO LTD

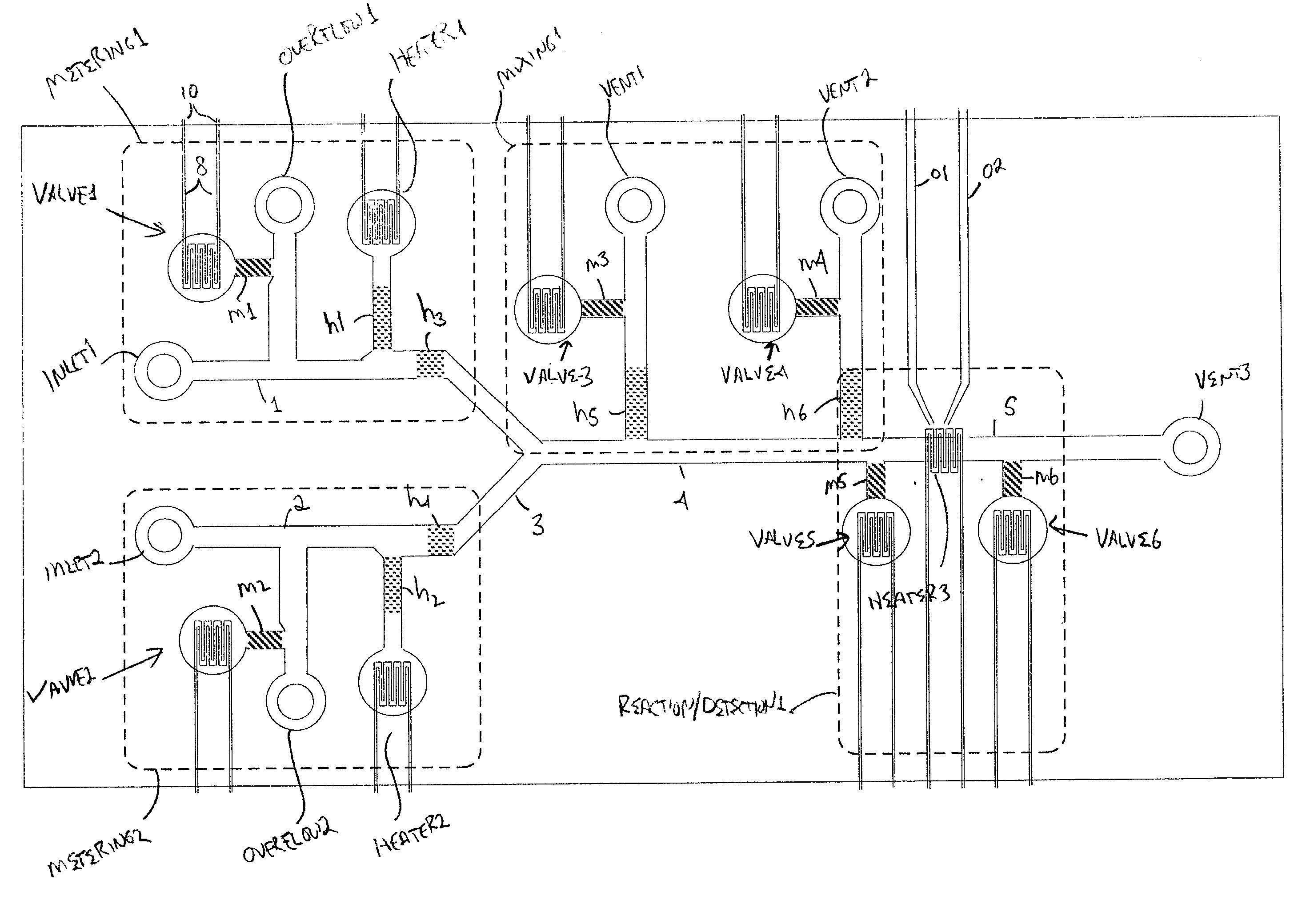

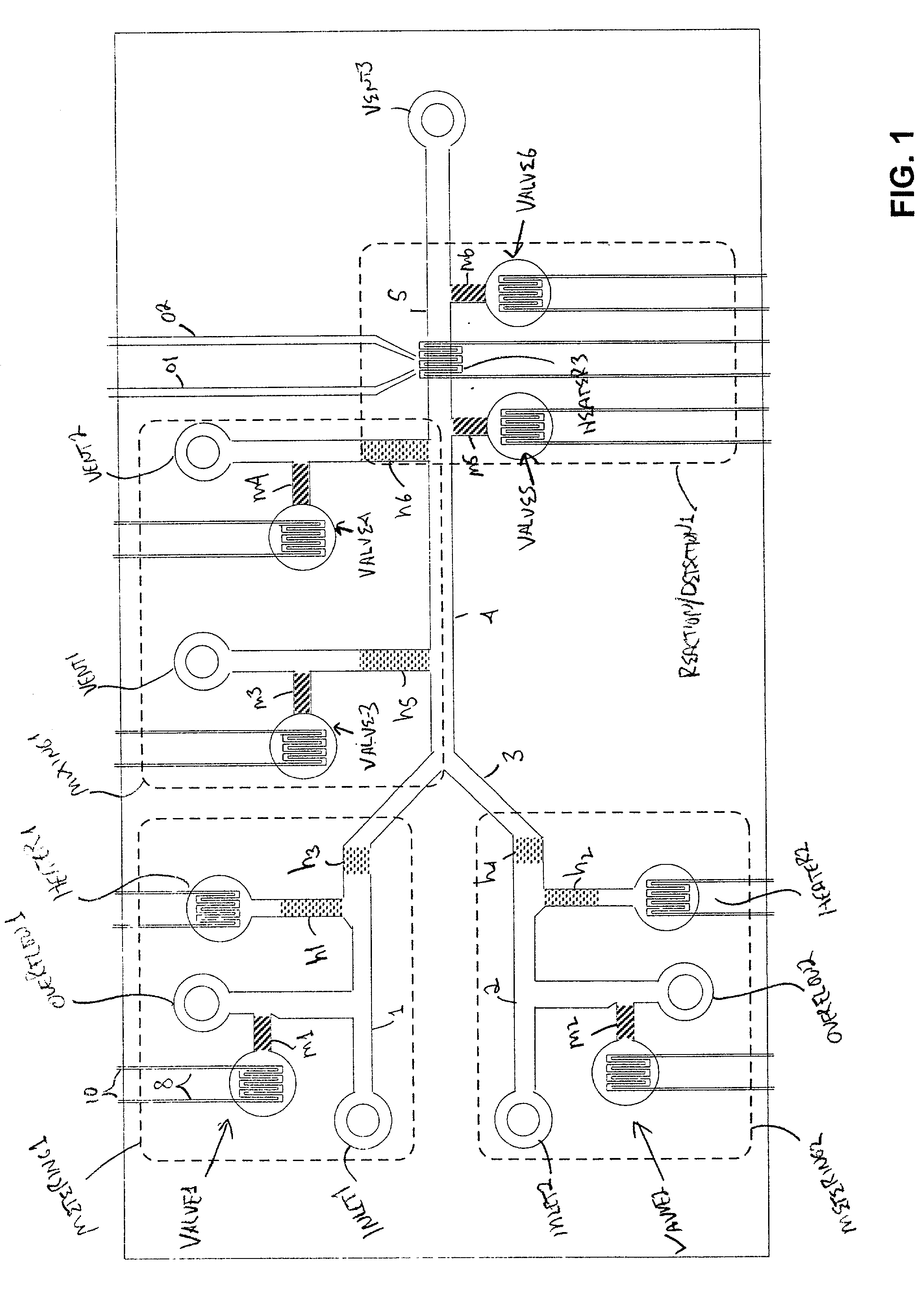

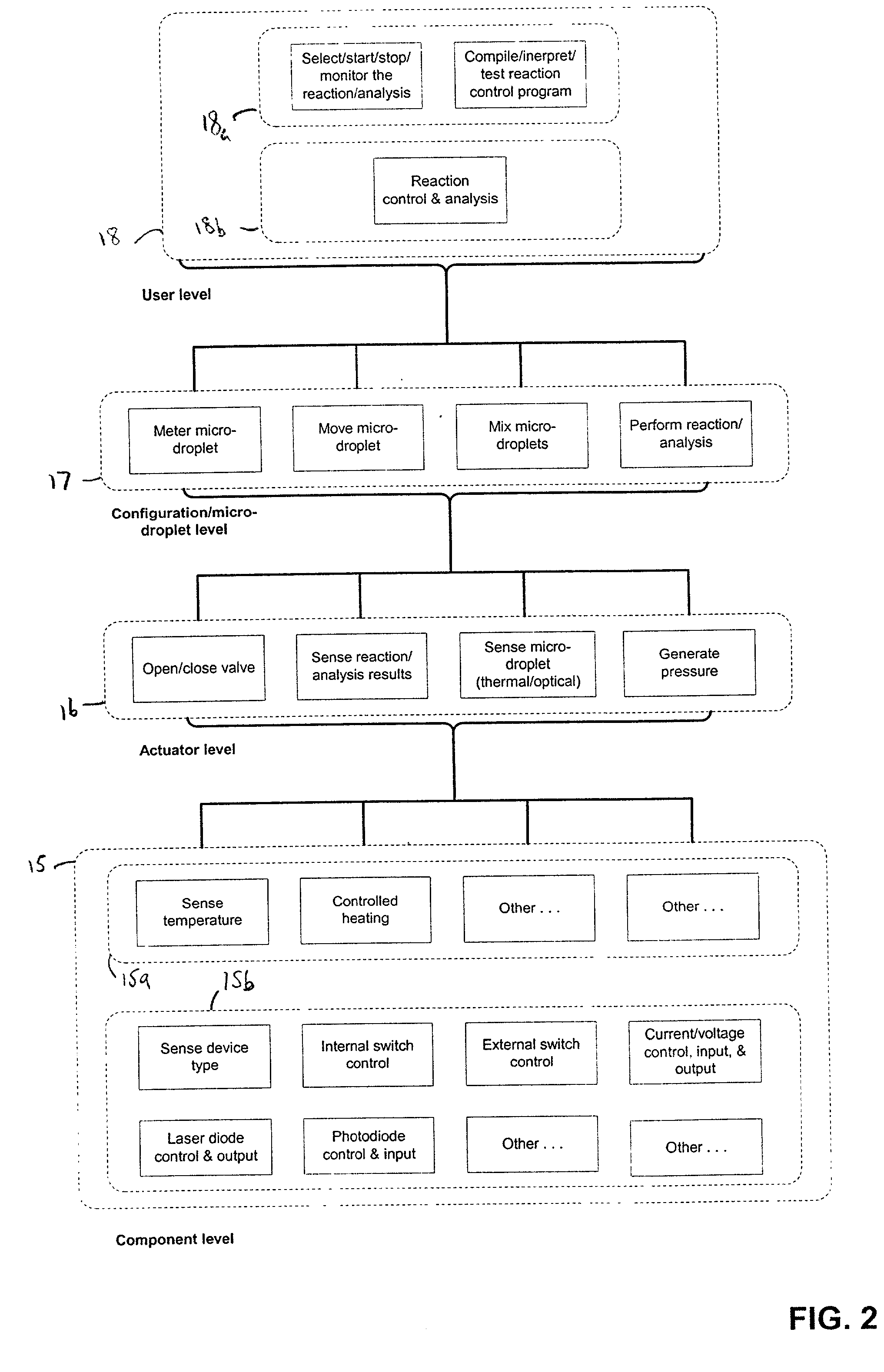

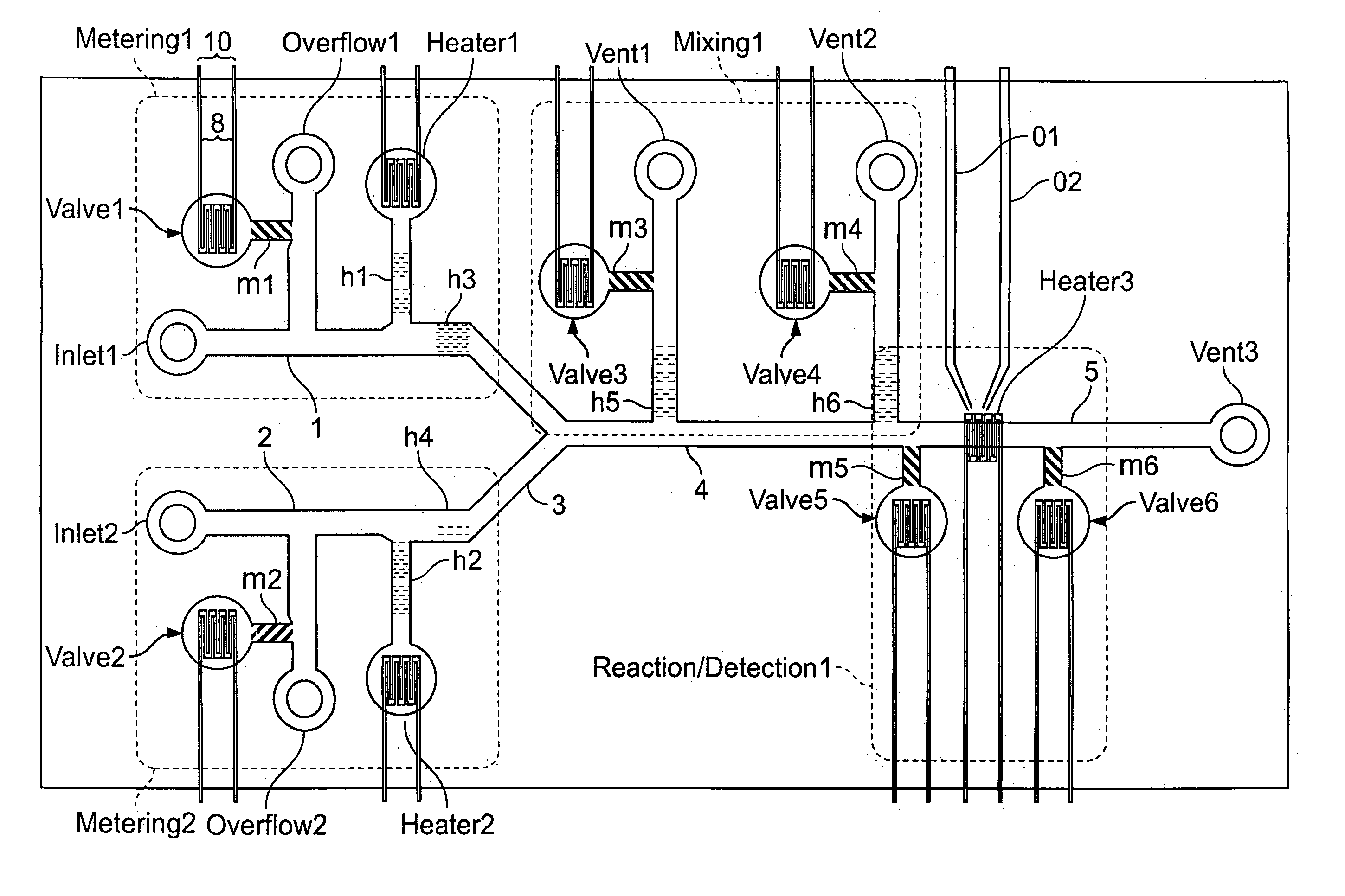

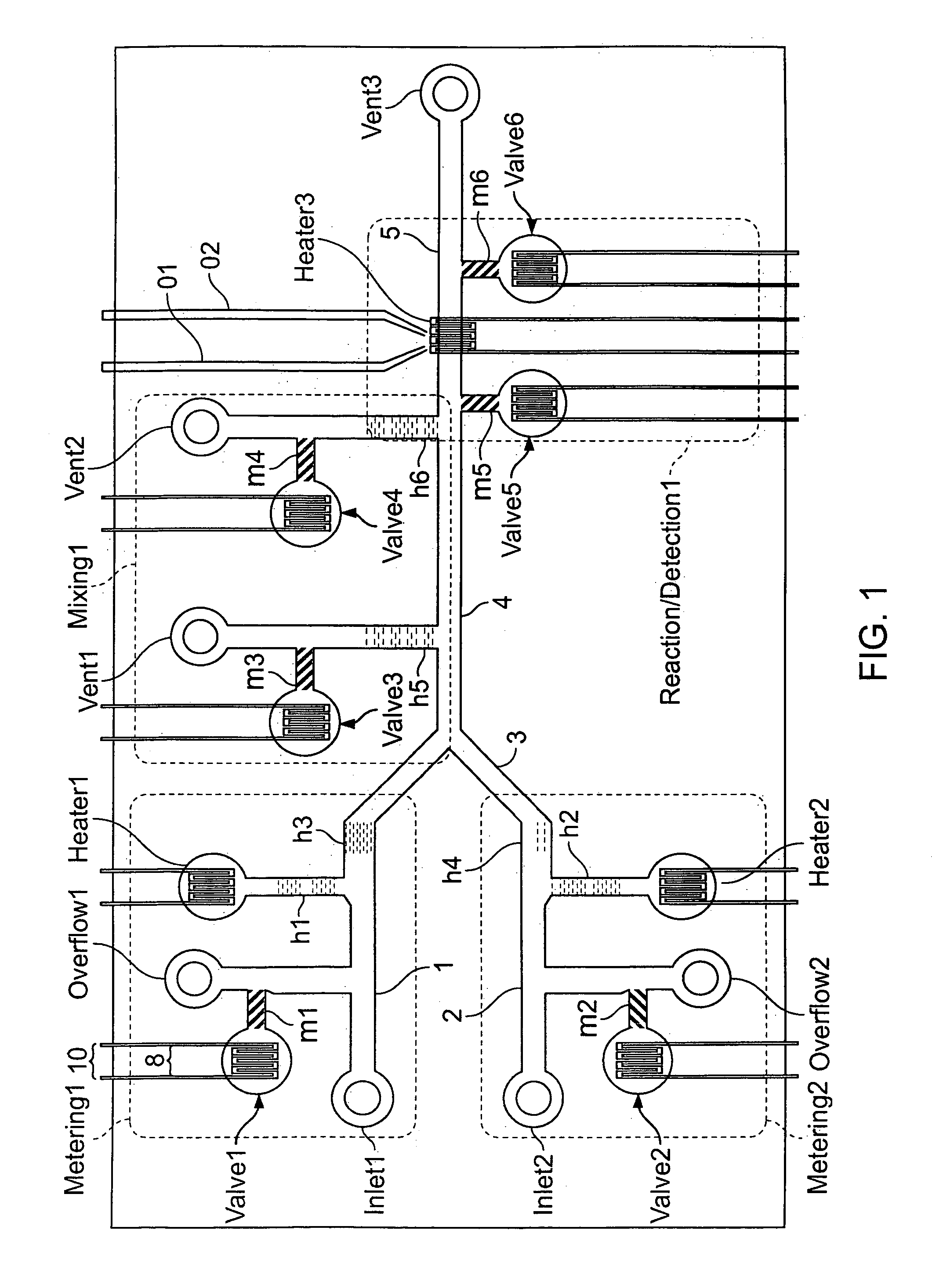

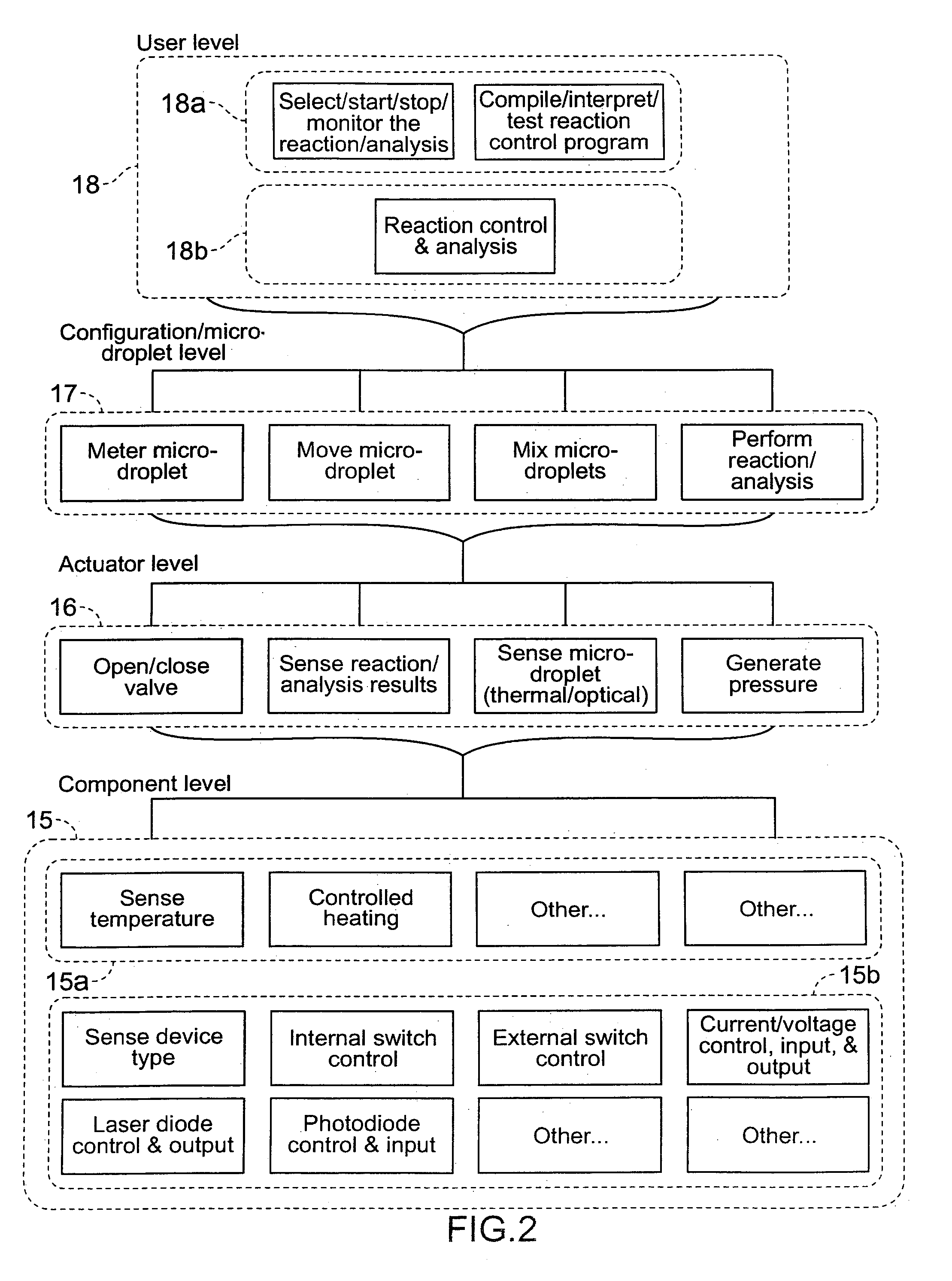

Methods and systems for control of microfluidic devices

InactiveUS20020143437A1Overcome deficienciesFixed microstructural devicesVolume/mass flow measurementControl systemLow voltage

The present invention provides control methods, control systems, and control software for microfluidic devices that operate by moving discrete micro-droplets through a sequence of determined configurations. Such microfluidic devices are preferably constructed in a hierarchical and modular fashion which is reflected in the preferred structure of the provided methods and systems. In particular, the methods are structured into low-level device component control functions, middle-level actuator control functions, and high-level micro-droplet control functions. Advantageously, a microfluidic device may thereby be instructed to perform an intended reaction or analysis by invoking micro-droplet control function that perform intuitive tasks like measuring, mixing, heating, and so forth. The systems are preferably programmable and capable of accommodating microfluidic devices controlled by low voltages and constructed in standardized configurations. Advantageously, a single control system can thereby control numerous different reactions in numerous different microfluidic devices simply by loading different easily understood micro-droplet programs.

Owner:HANDYLAB

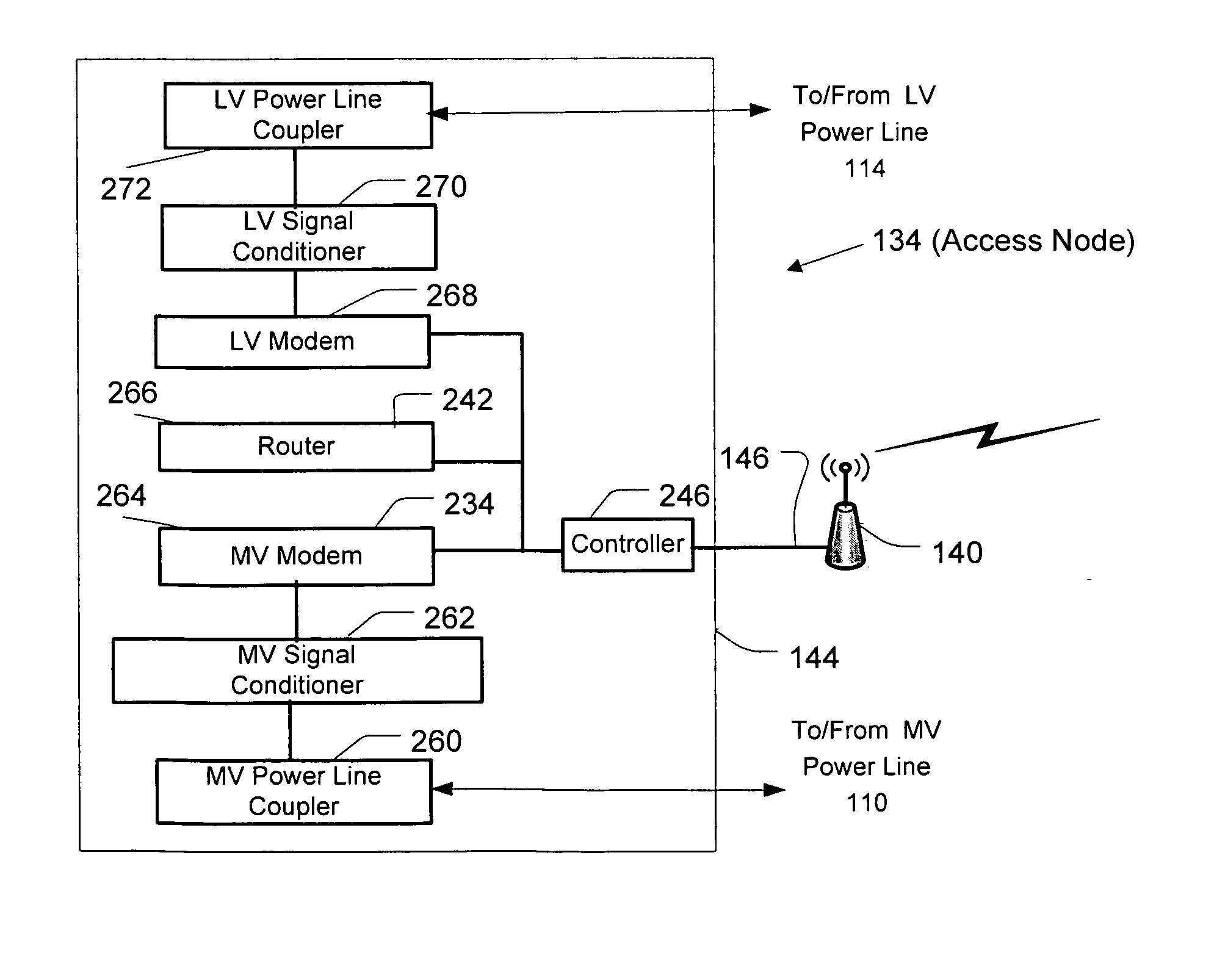

Power line communication system and method of using the same

InactiveUS6965302B2Electric signal transmission systemsWireless systems/telephoneCommunications systemWireless transceiver

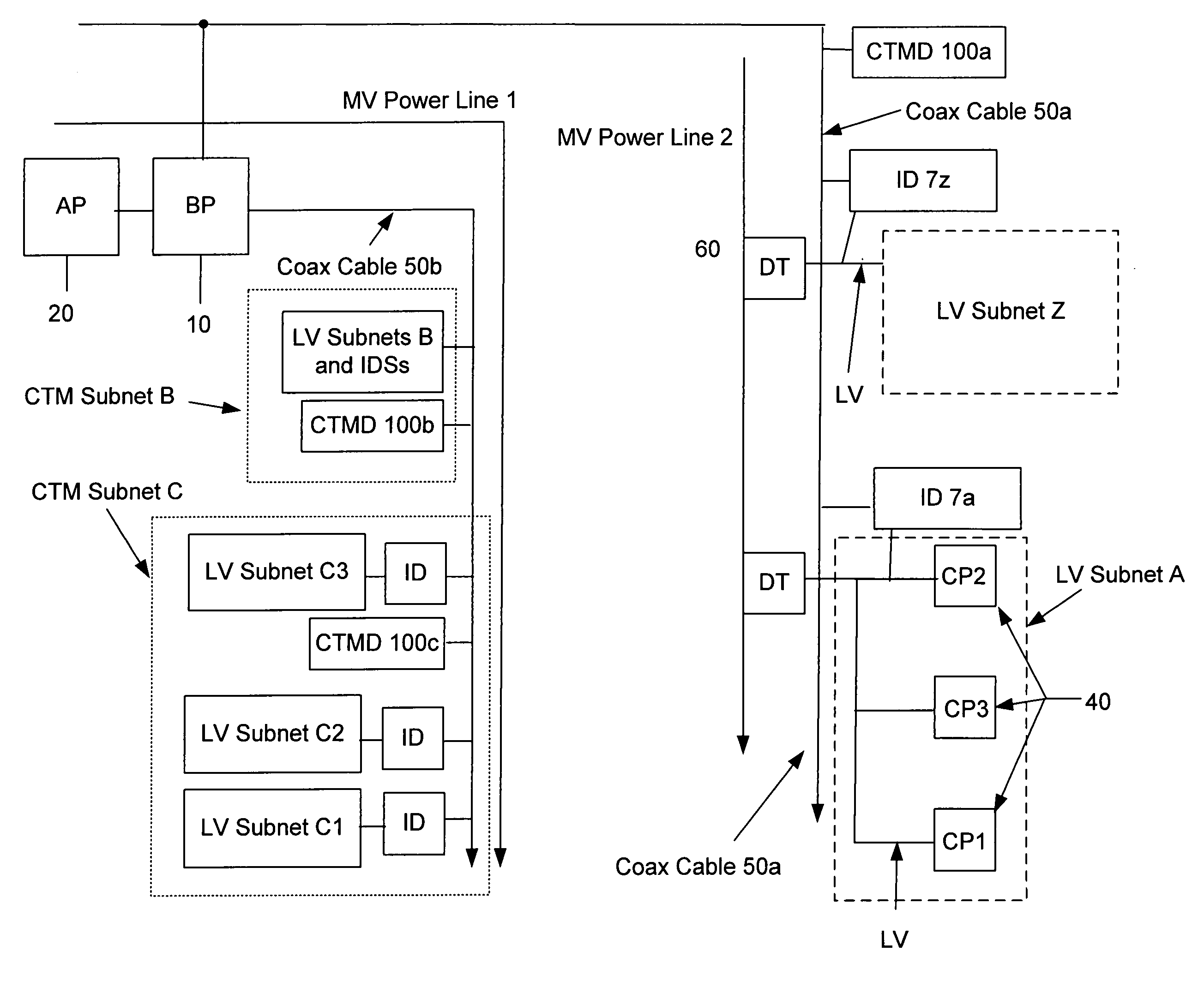

The communication system of one embodiment is for communicating data through a power distribution system having a medium voltage power line and low voltage power line and comprises a first device comprising a first wireless transceiver, a first modem in communication with the first wireless transceiver and the medium voltage power line. The system may also comprise a second device comprising a second wireless transceiver in wireless communication with the first wireless transceiver; and a second modem in communication with the second wireless transceiver and the low voltage power line.

Owner:CURRENT TECH

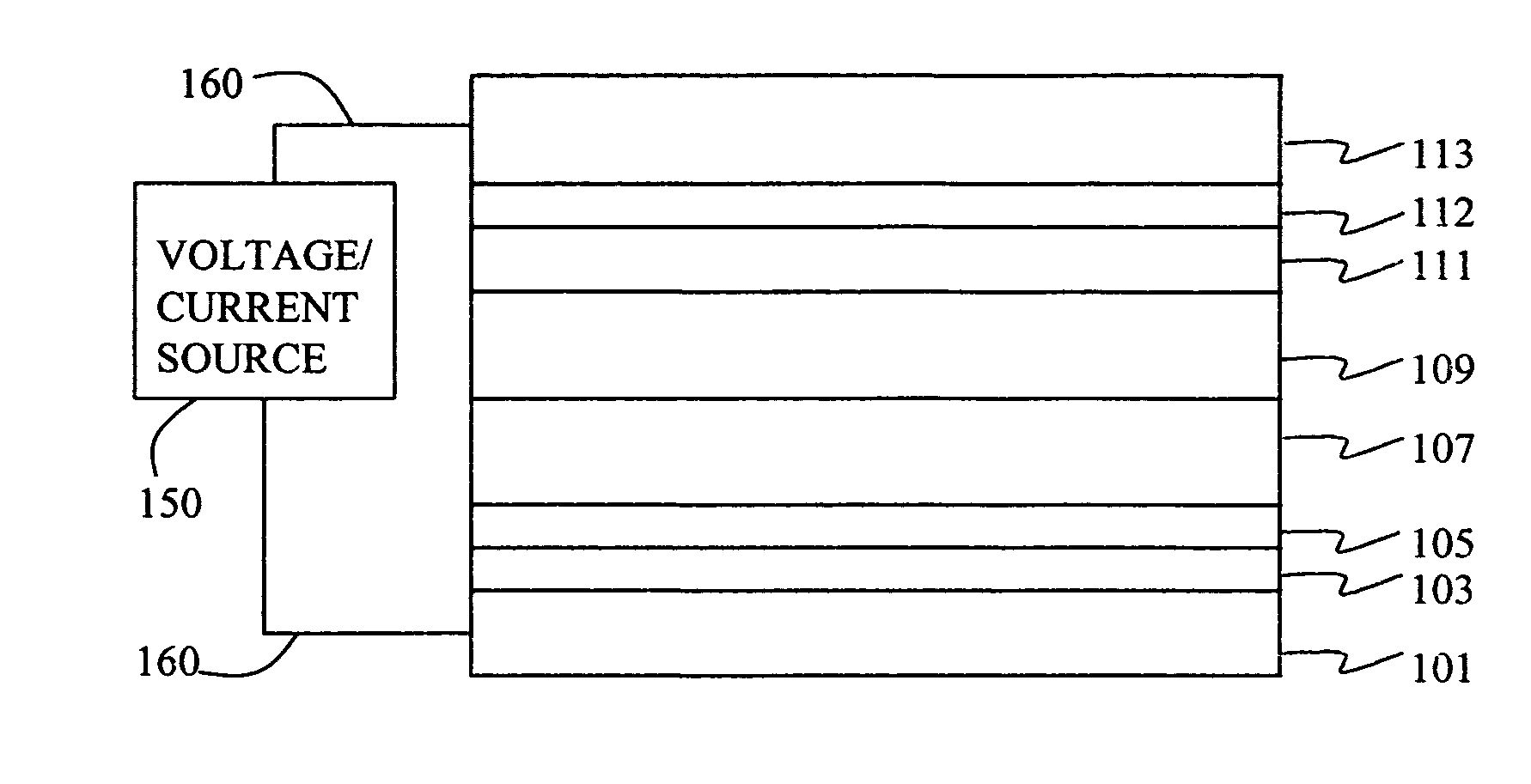

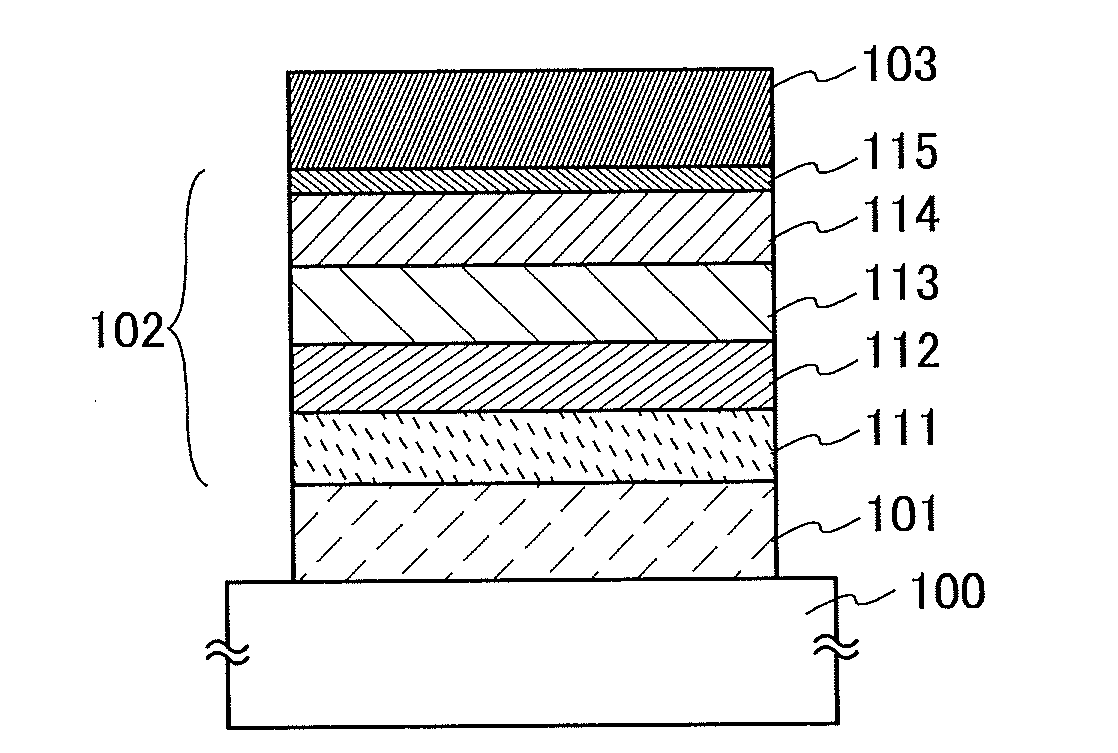

SOI stacked DRAM logic

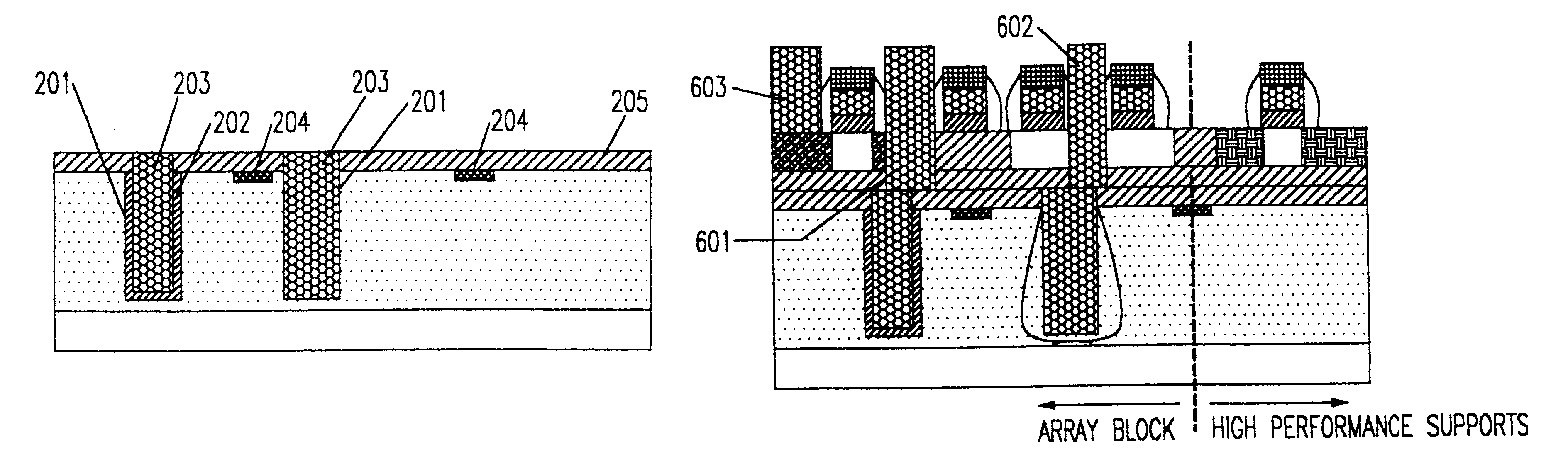

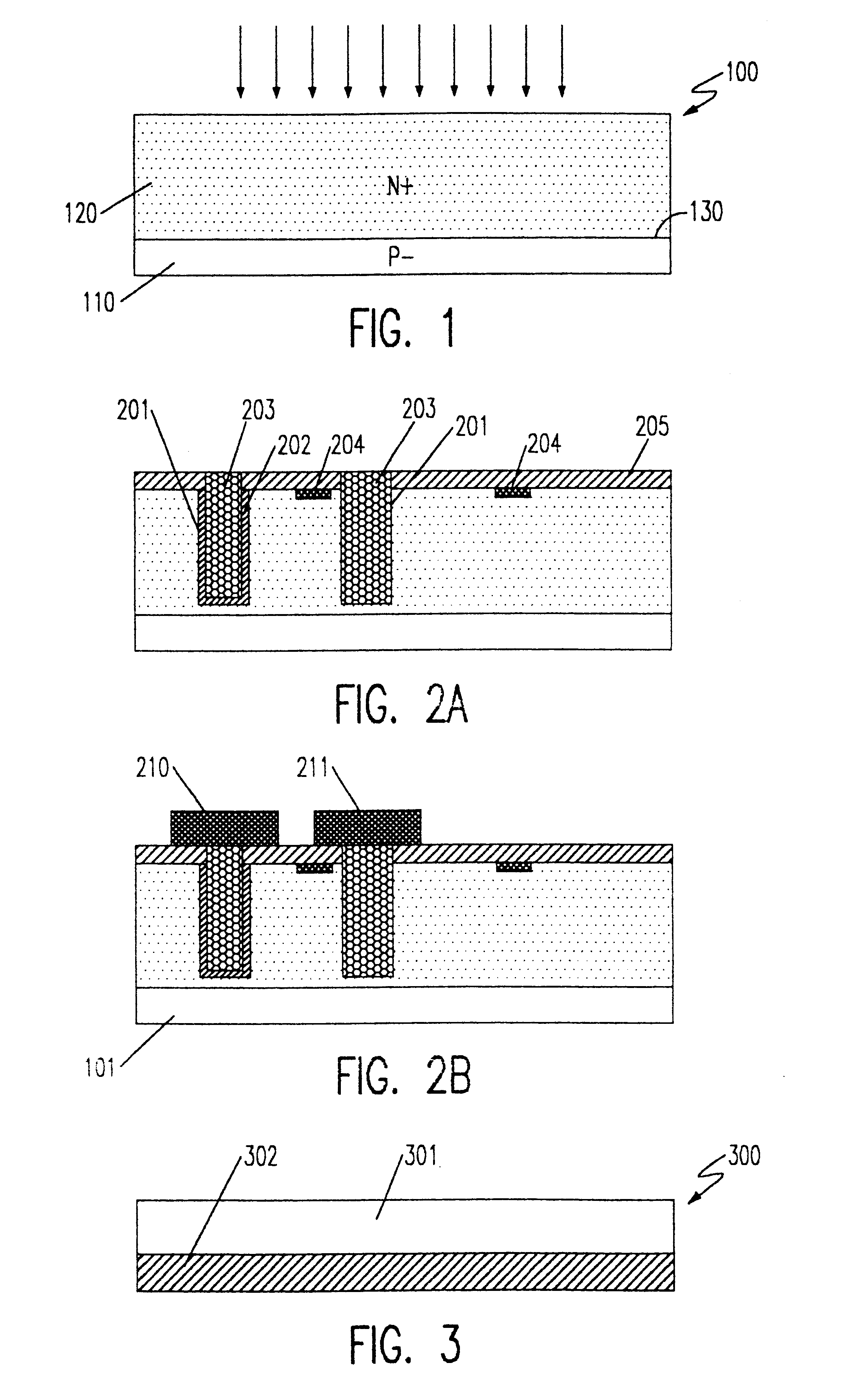

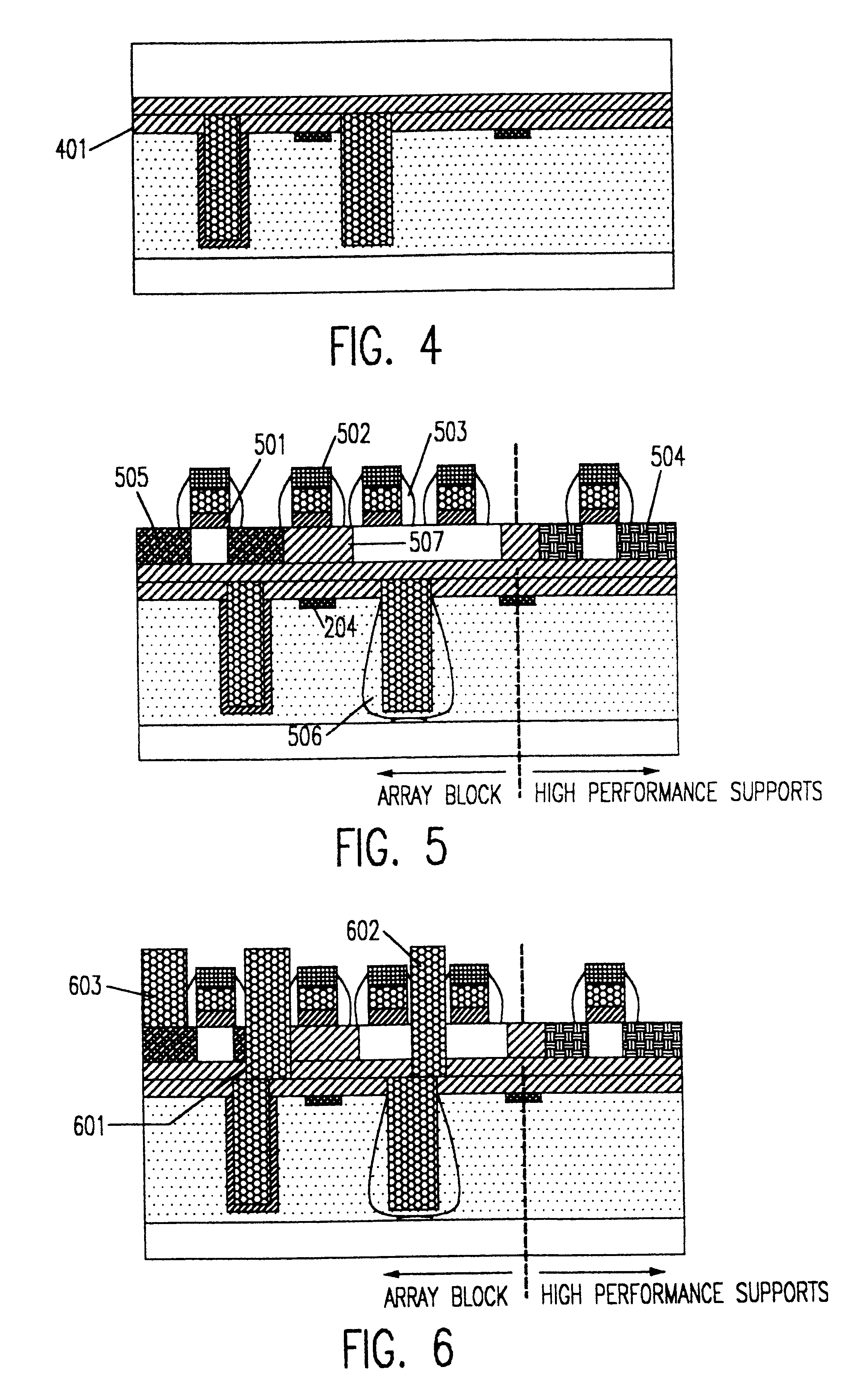

A composite, layered, integrated circuit formed by bonding of insulator layers on wafers provides for combination of otherwise incompatible technologies such as trench capacitor DRAM arrays and high performance, low power, low voltage silicon on insulator (SOI) switching transistors and short signal propagation paths between devices formed on respective wafer layers of a chip. In preferred embodiments, an SOI wafer is formed by hydrophilic bonding of a wafer over an integrated circuit device and then cleaving a layer of the second wafer away using implanted hydrogen and low temperature heat treatment. Further wafers of various structures and compositions may be bonded thereover and connections between circuit elements and connection pads in respective wafers made using short vias that provide fast signal propagation as well as providing more numerous connections than can be provided on chip edges.

Owner:INT BUSINESS MASCH CORP

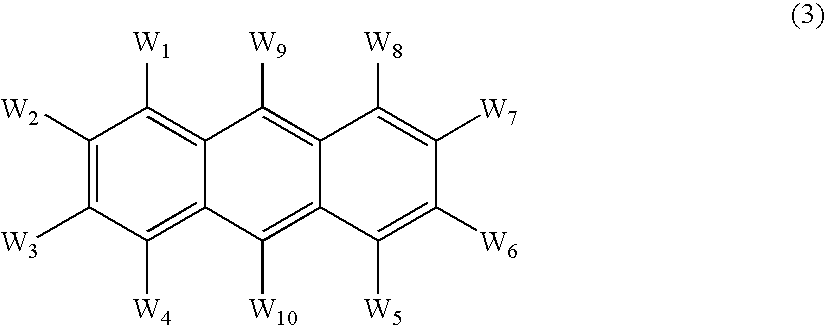

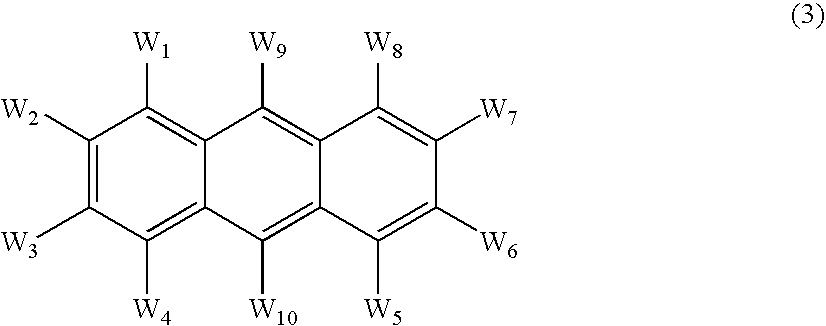

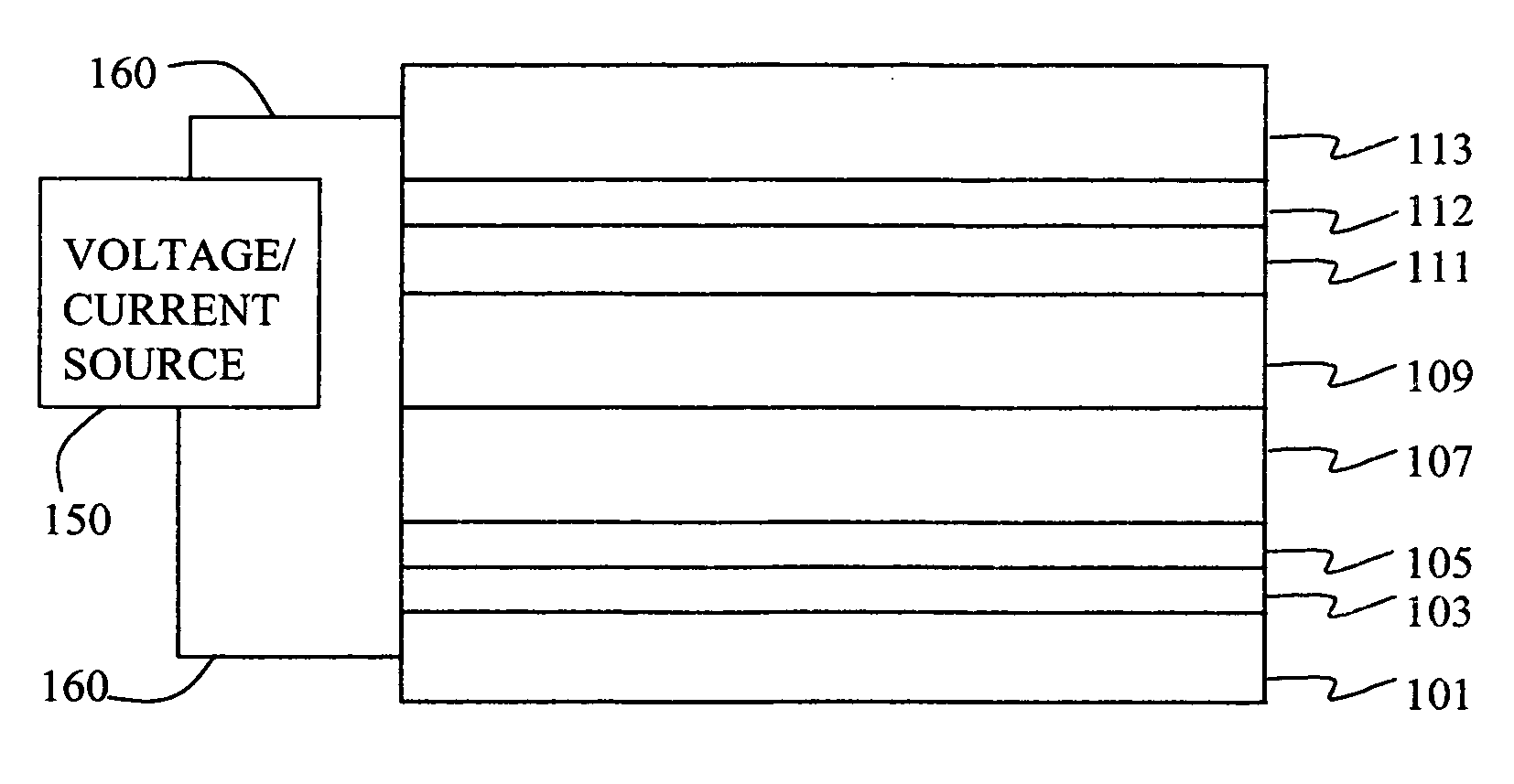

Organic element for low voltage electroluminescent devices

InactiveUS20070092753A1Reduce the driving voltageIncrease brightnessDischarge tube luminescnet screensLamp detailsAnthraceneHydrogen

An OLED device comprises a cathode, a light emitting layer and an anode, in that order, wherein (i) the light-emitting layer comprises up to 10 volume % of a light emitting compound and at least one anthracene host compound of Formula (3): wherein W1-W10 independently represents hydrogen or an independently selected substituent, and (ii) a further layer located between the cathode and the light emitting layer, contains (a) 10-volume % or more of an anthracene compound of Formula (3) and (b) at least one salt or complex of an element selected from Group IA, IIA, IIIA and IIB of the Periodic Table. Such devices exhibit reduced drive voltage while maintaining good luminance.

Owner:EASTMAN KODAK CO

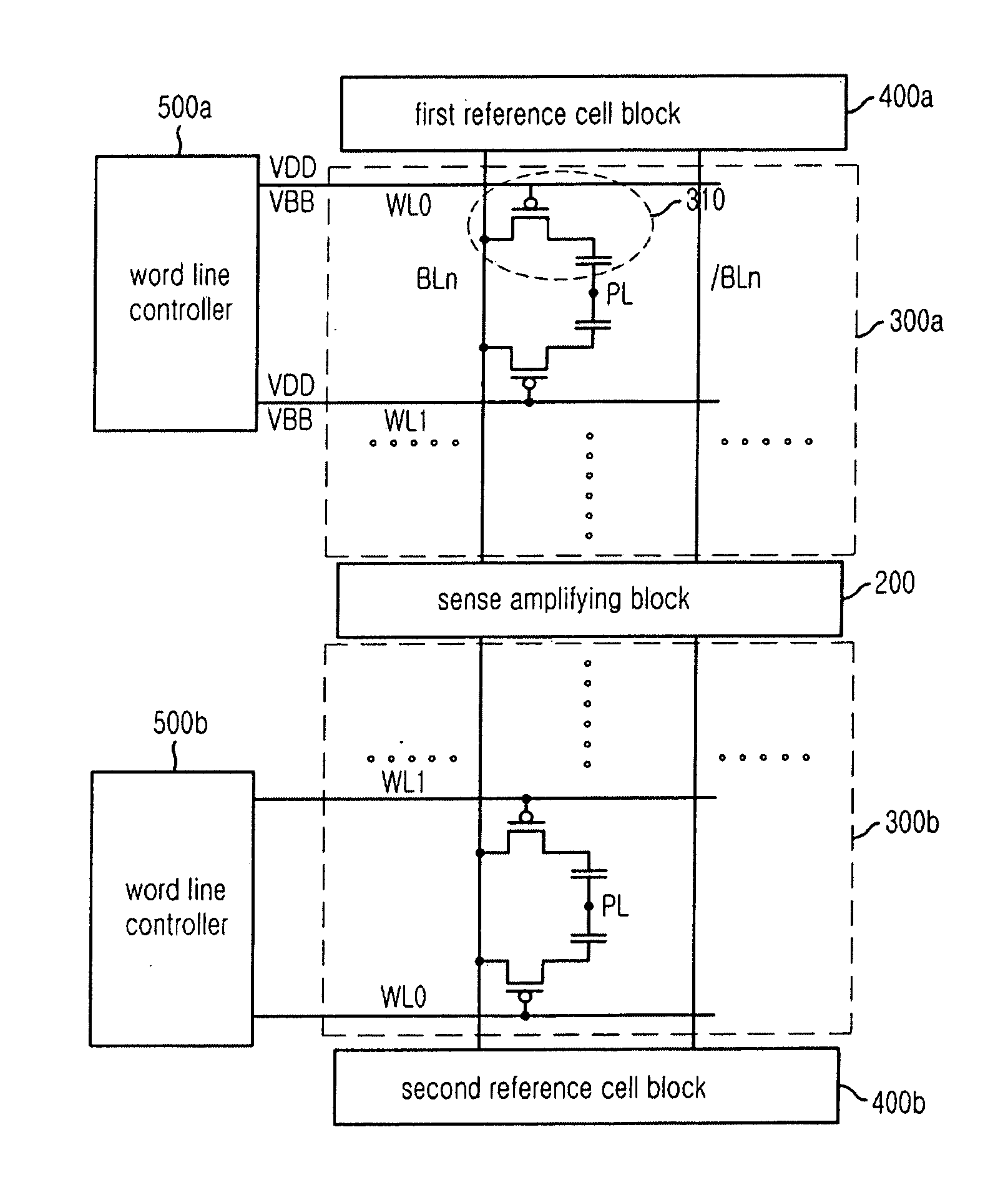

Semiconductor memory device for low voltage

A semiconductor memory device includes a first cell array including a plurality of unit cells and a bit line sense amplifying unit for sensing and amplifying data signals stored in the unit cells. Each unit cell is provided with a PMOS transistor and a capacitor. Therefore, the semiconductor memory device efficiently operates with low voltage without any degradation of operation speed.

Owner:SK HYNIX INC

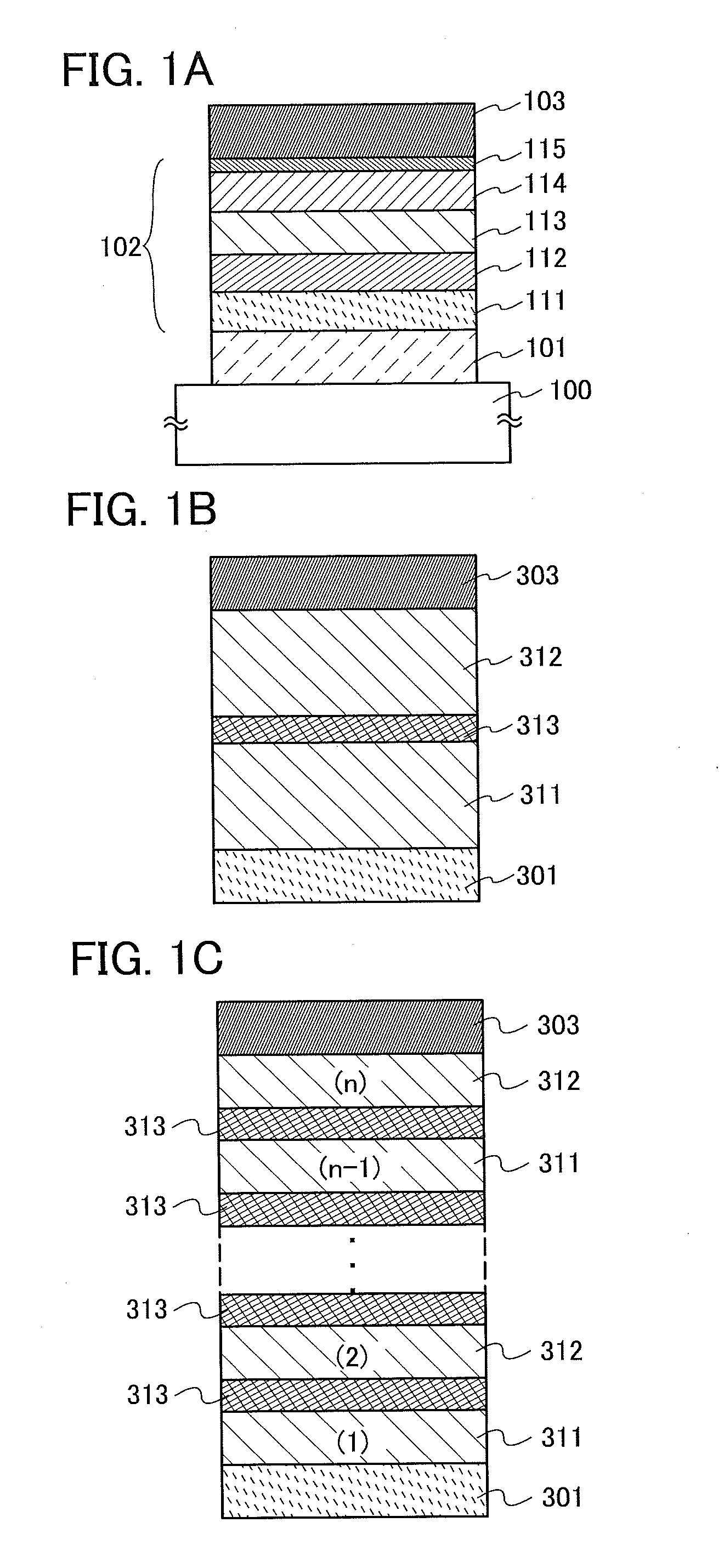

Light-Emitting Element, Light-Emitting Device, Electronic Appliance, and Lighting Device

InactiveUS20140183503A1Reduce the driving voltageImprove current efficiencyOrganic chemistrySolid-state devicesLow voltageQuinoline

Disclosed is a light-emitting element having high emission efficiency, capable of driving at low voltage, and showing a long lifetime. The light-emitting element contains a compound between a pair of electrodes, and the compound is configured to give a first peak of m / z around 202 and a second peak of m / z around 227 in a mass spectrum. The first and second peaks are product ions of the compound and possess compositions of C16H9 and C17H10N, respectively, which are derived from a dibenzo[f,h]quinoline unit.

Owner:SEMICON ENERGY LAB CO LTD

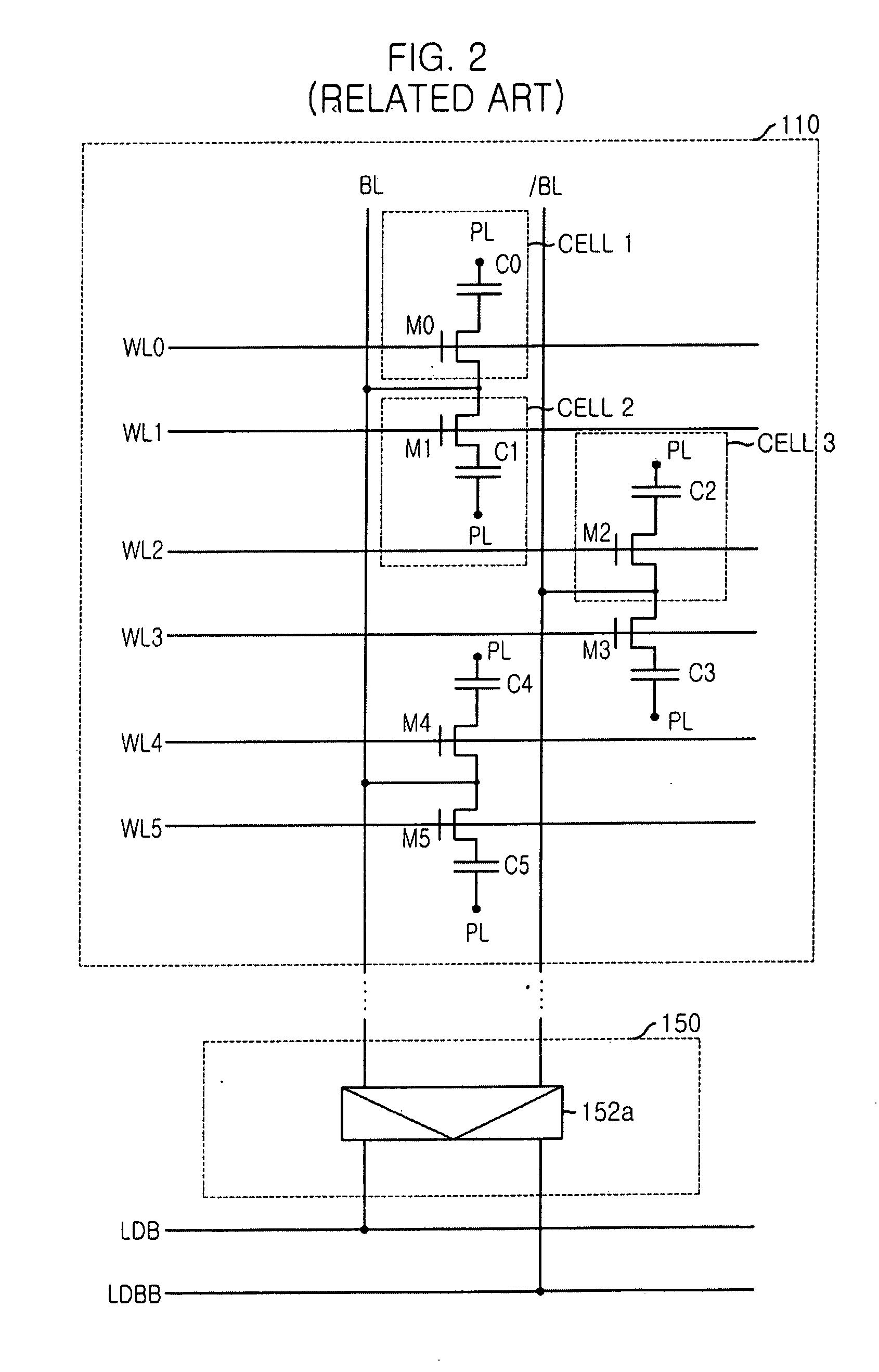

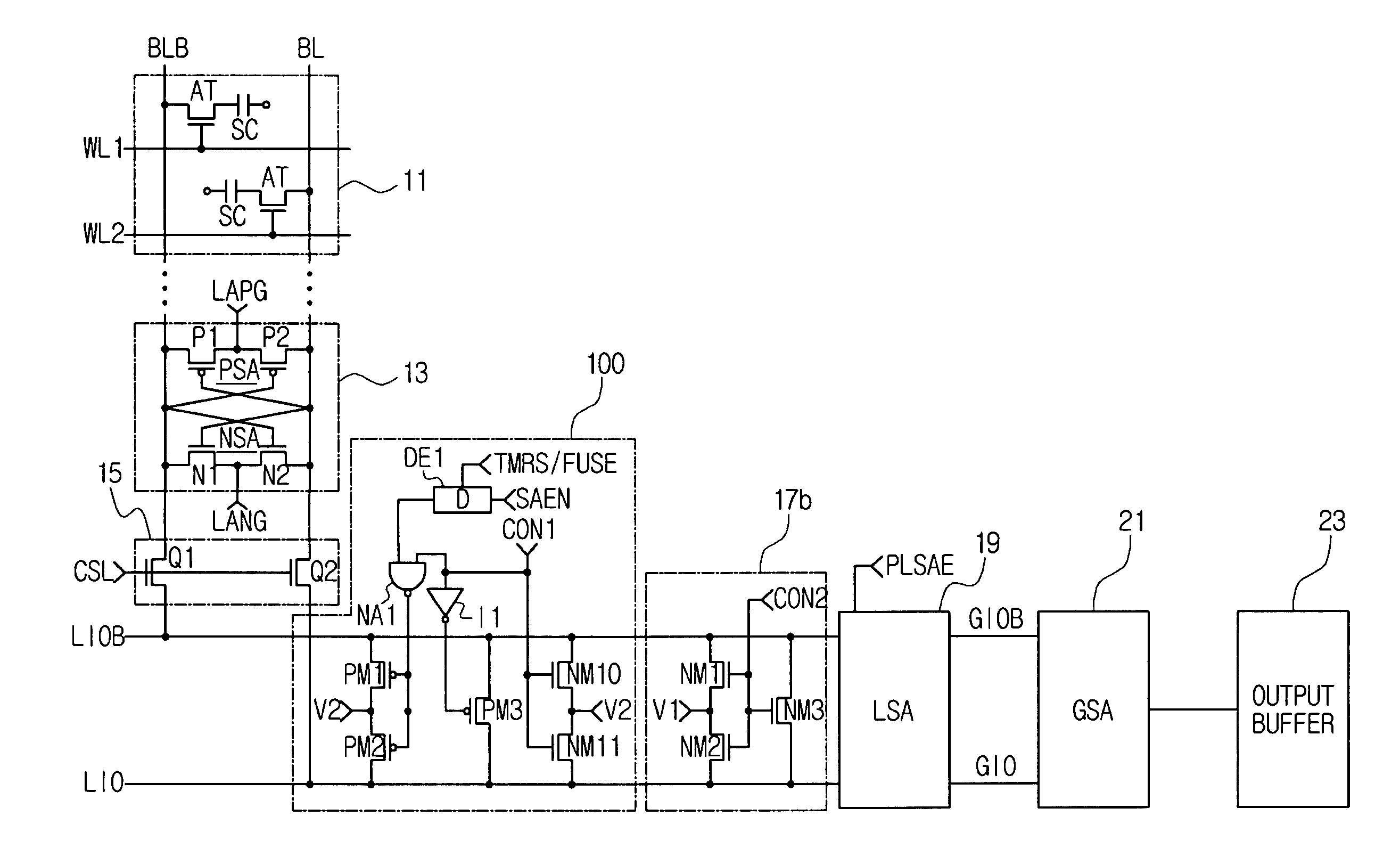

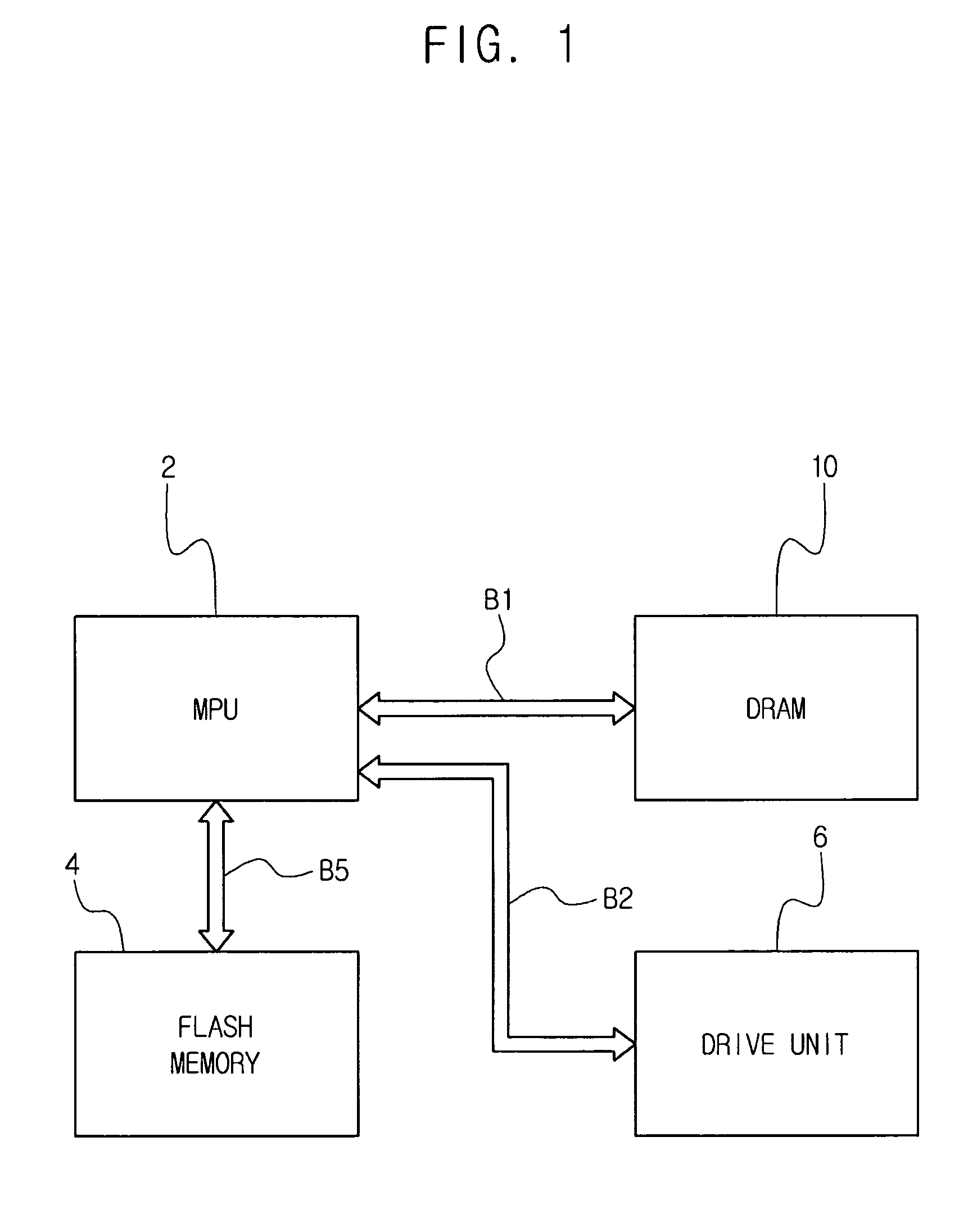

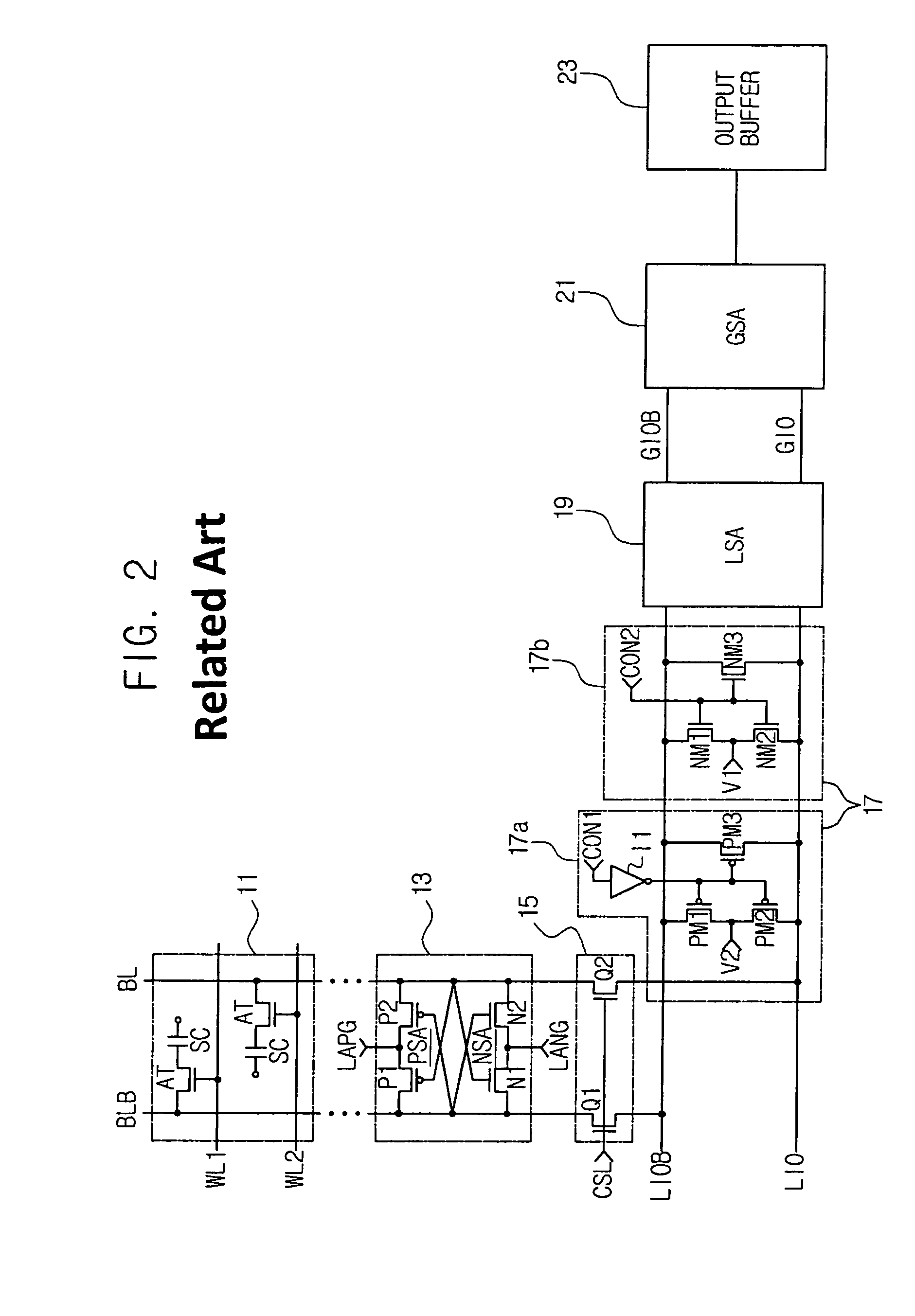

Semiconductor memory device adopting improved local input/output line precharging scheme

A semiconductor memory device capable of preventing or minimizing bit line disturbance and performing a low-voltage high-speed operation includes a read data path circuit including a bit line sense amplifier, a local input / output line sense amplifier, a column selecting unit to operationally connect bit lines connected to the bit line sense amplifier to local input / output lines connected to the local input / output line sense amplifier in response to a column selection signal, and a local input / output line precharging unit to precharge the pair of local input / output lines by a first precharging unit, equalizing the pair of local input / output lines by an equalizing unit, and to precharge the local input / output lines by a second precharging unit following an elapsed time after the bit line sense amplifier is activated, while the column selection is deactivated.

Owner:SAMSUNG ELECTRONICS CO LTD

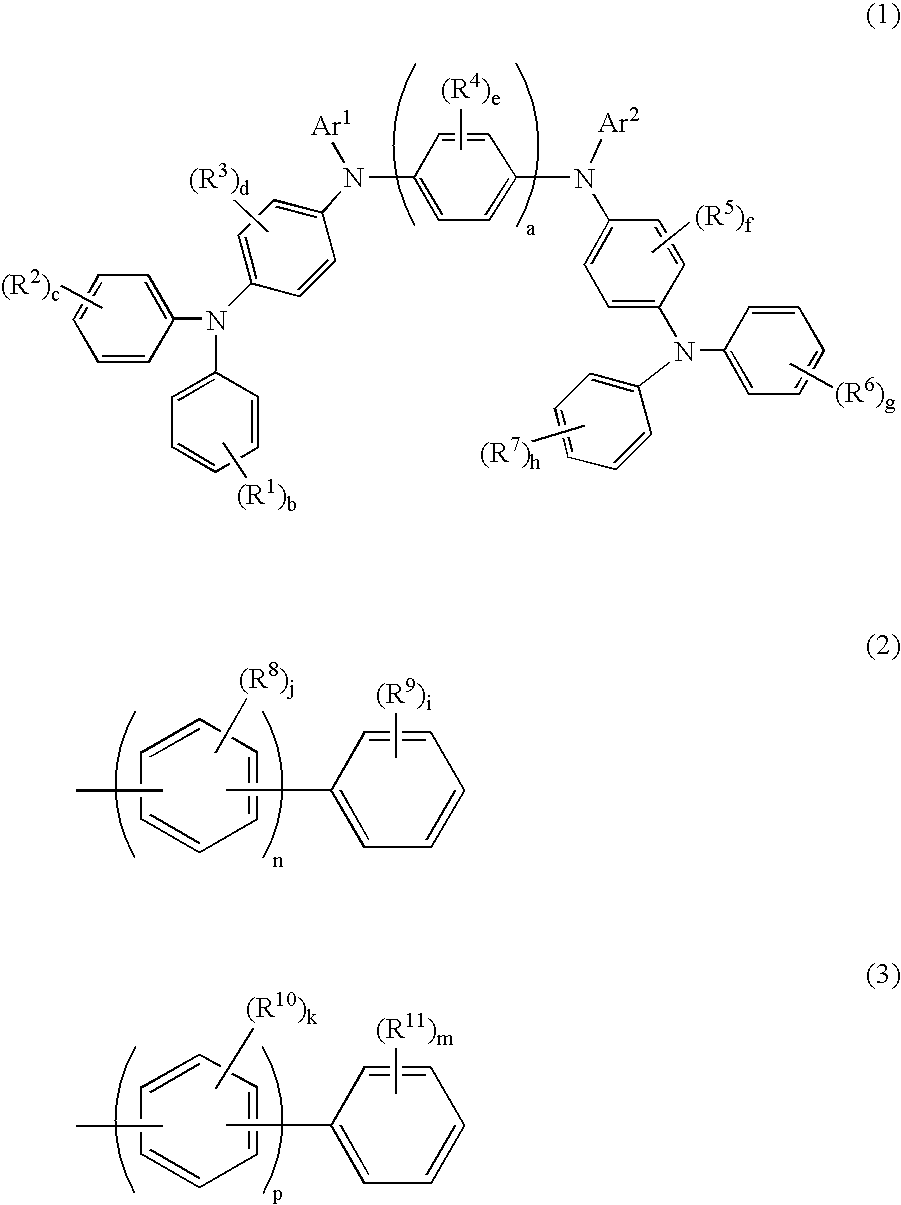

Aromatic amine derivative and organic electroluminescence device using the same

InactiveUS20080145707A1Small increase in driving voltageSolution to short lifeOrganic chemistryLayered productsArylHydrogen atom

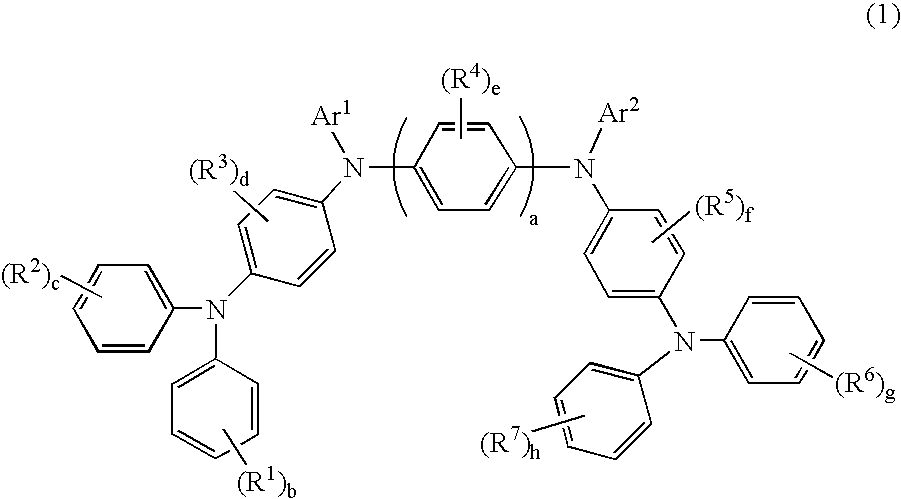

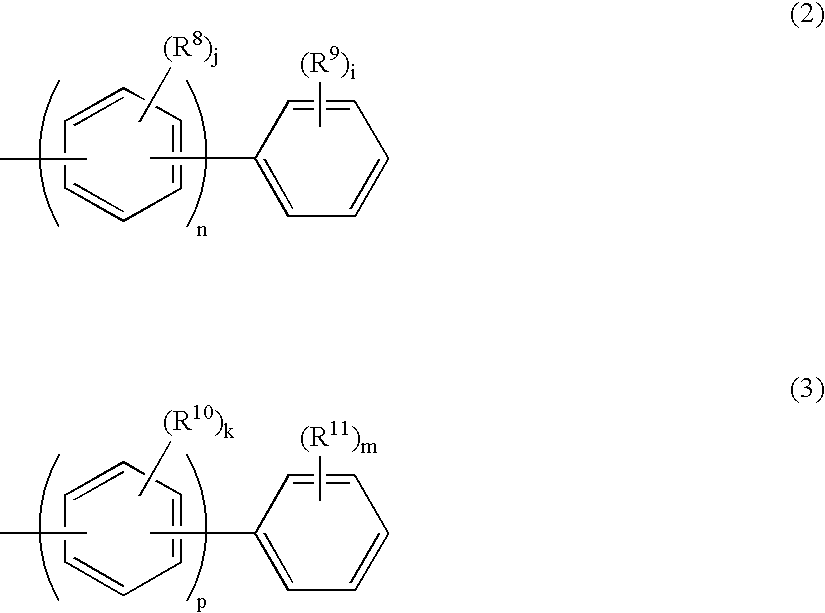

The present invention provides a novel aromatic amine derivative enabling to obtain an organic electroluminescence device which is driven under a low voltage, exhibits small increase in the driving voltage after continuous driving for a long time and has a long life. The amine derivative is represented by the following general formula (1). In the formula, R1 to R7 each represent, for example, hydrogen atom or a substituted or unsubstituted aryl group having 5 to 50 nuclear carbon atoms; a represents an integer of 1 or greater; b, c, g and h each represent an integer of 1 to 5, and d, e and f each represent an integer of 1 to 4; and Ar1 and Ar2 represent a group represented by following general formulae (2) and (3), respectively, and the groups represented by Ar1 and Ar2 are not same with each other. R8 to R11 each represent, for example, hydrogen atom; and i and m each represent an integer of 1 to 5, j and k each represent an integer of 1 to 4, n and p each represent an integer of 0 or greater, and n≠p.

Owner:IDEMITSU KOSAN CO LTD

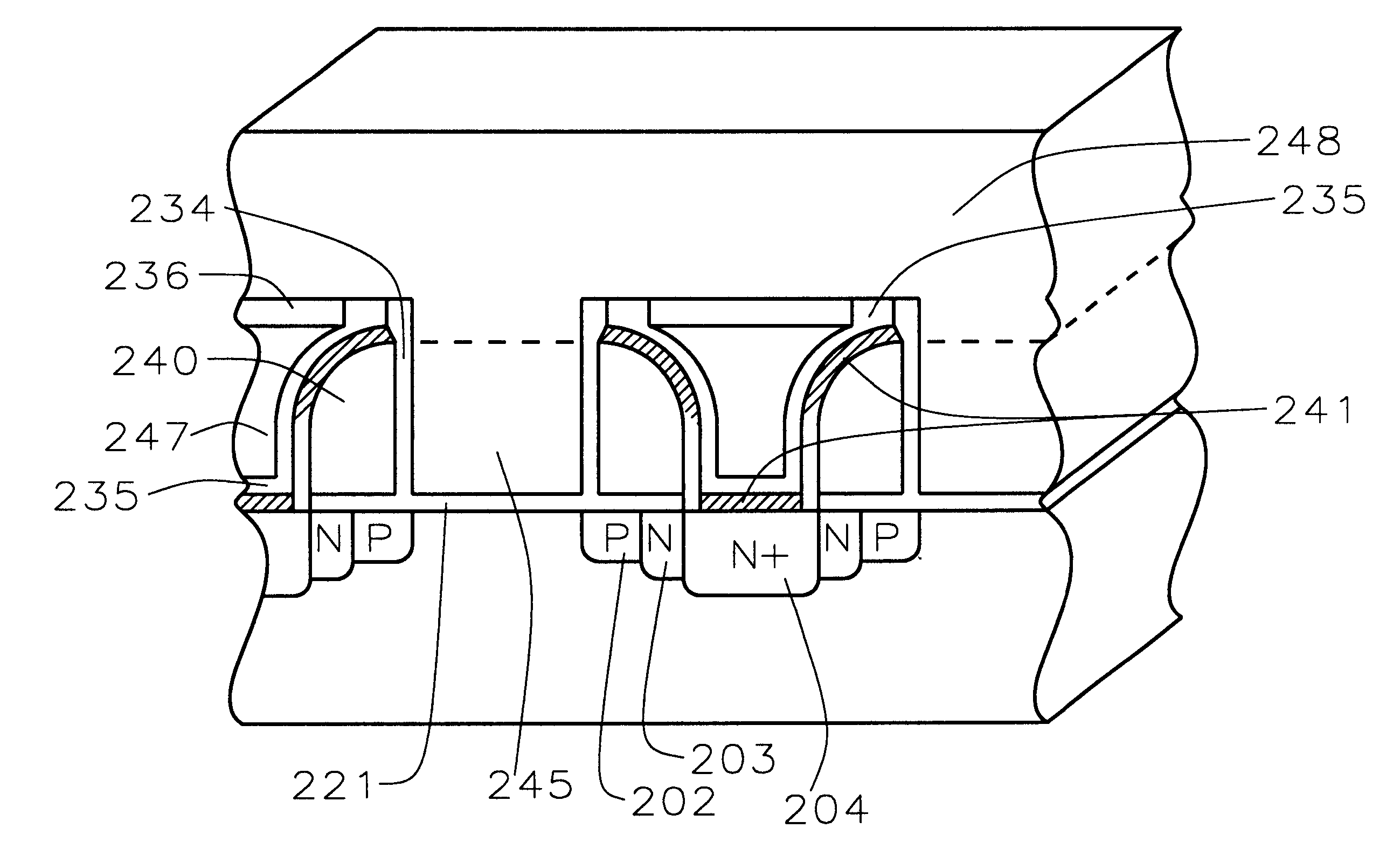

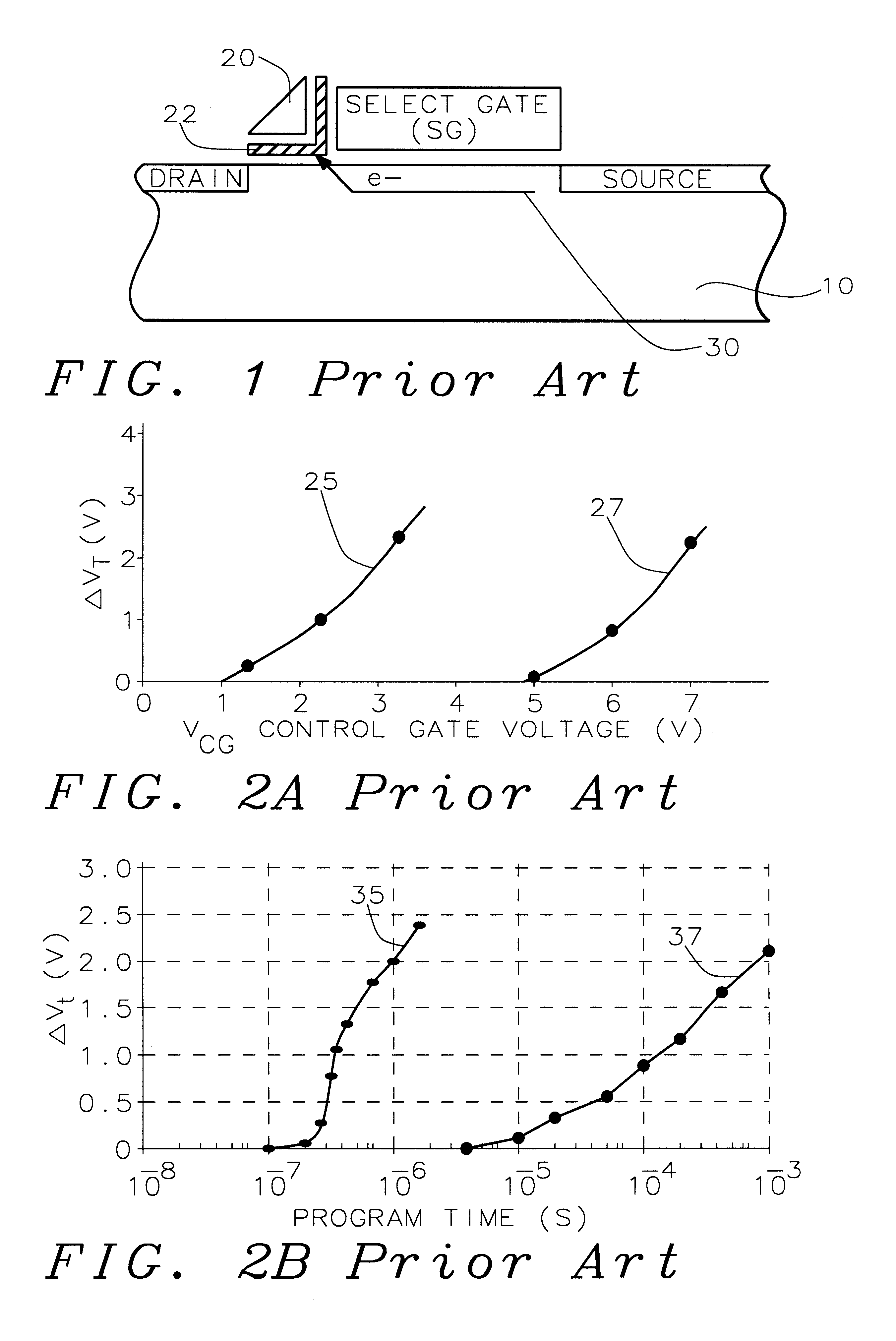

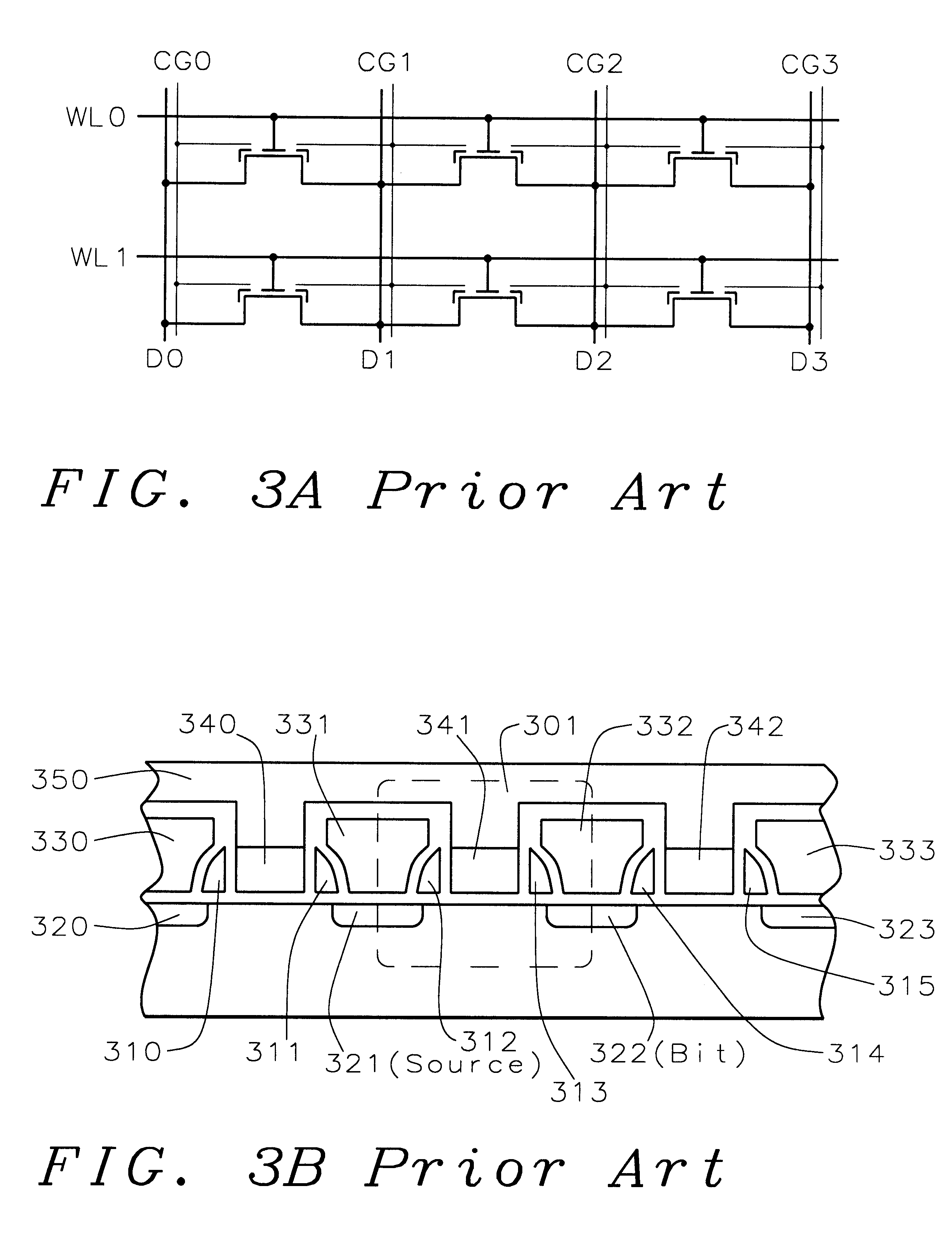

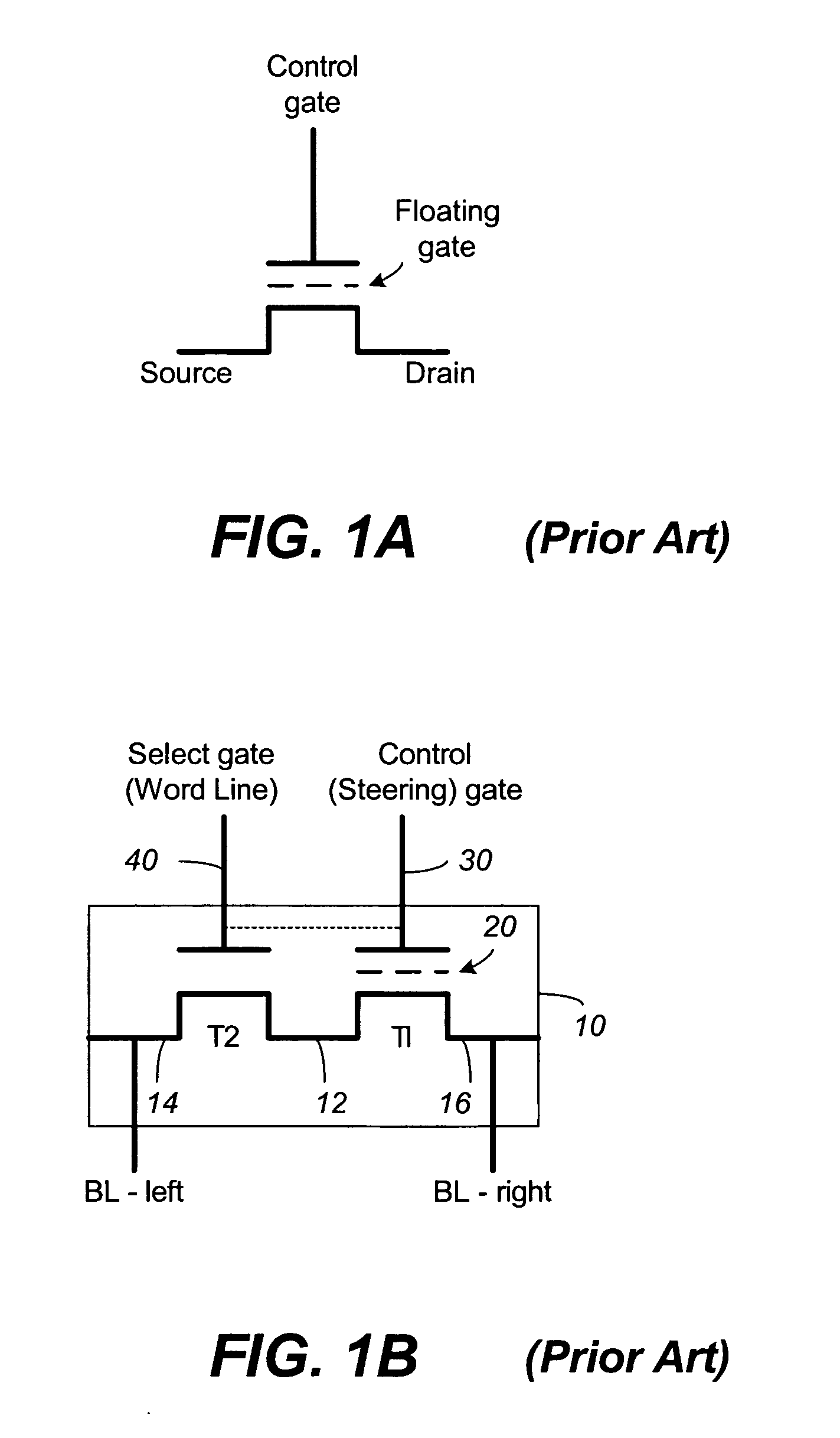

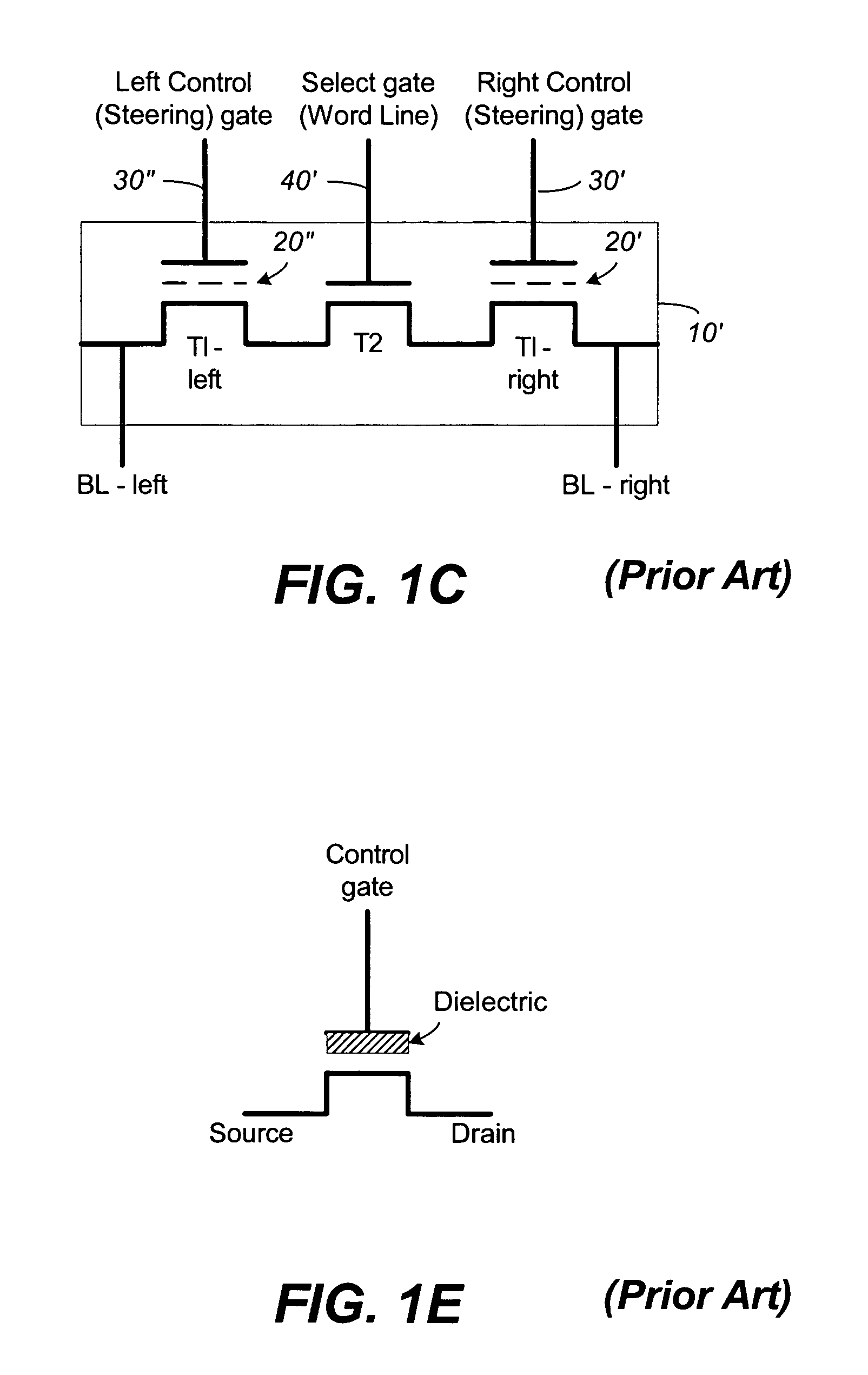

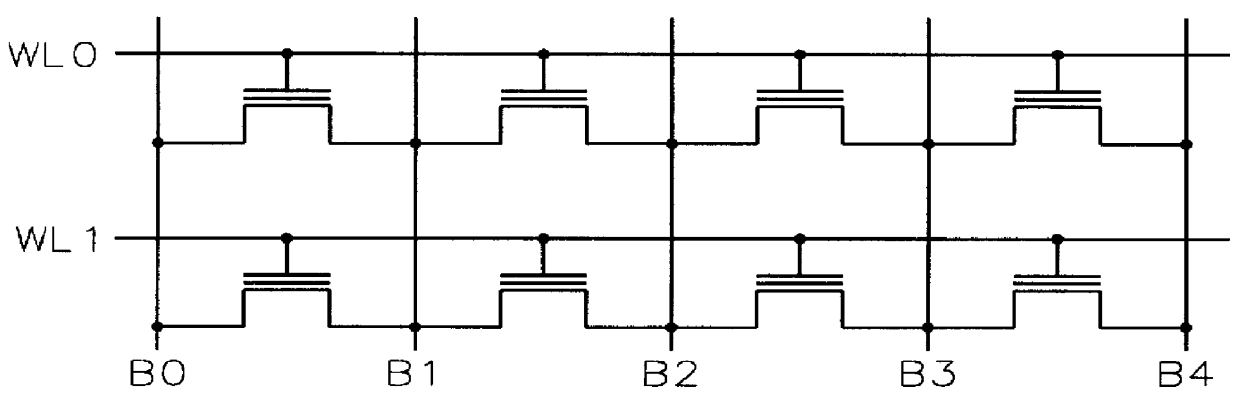

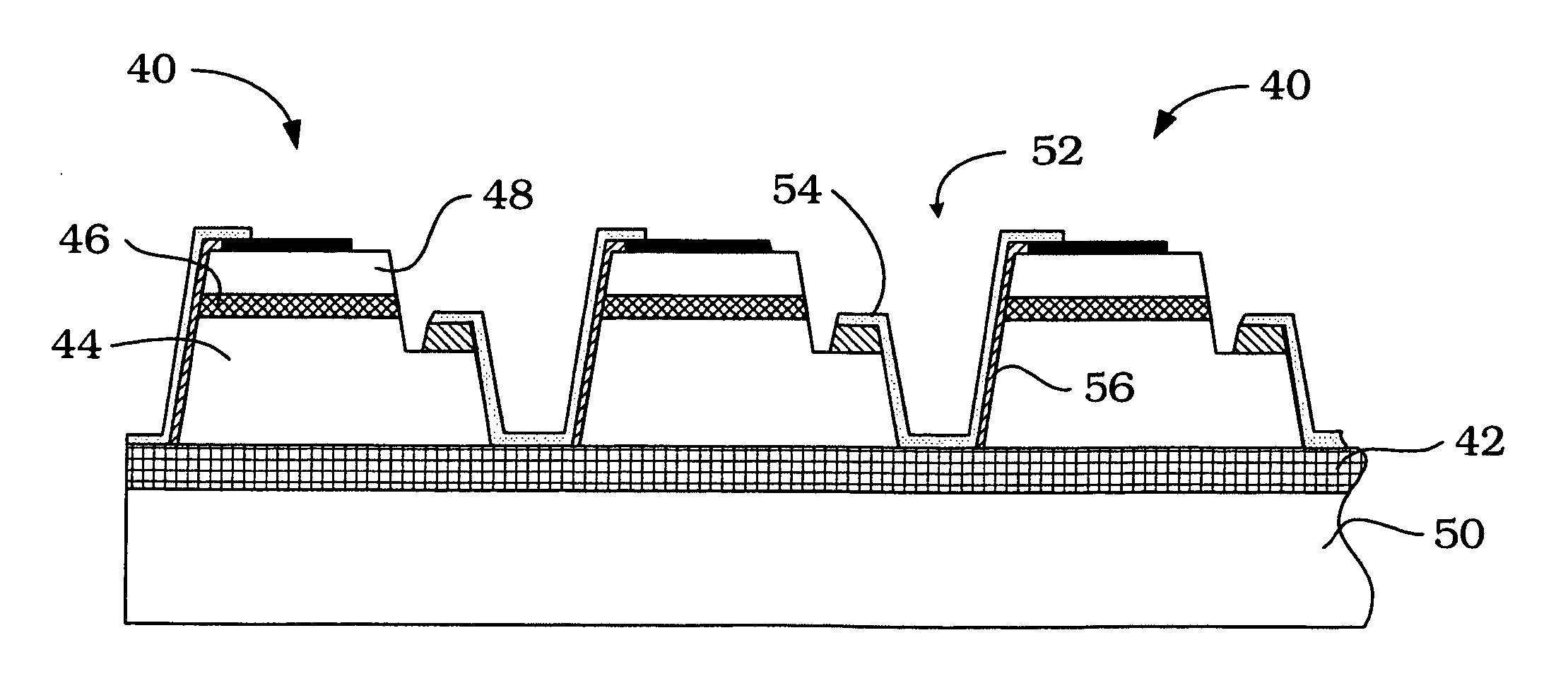

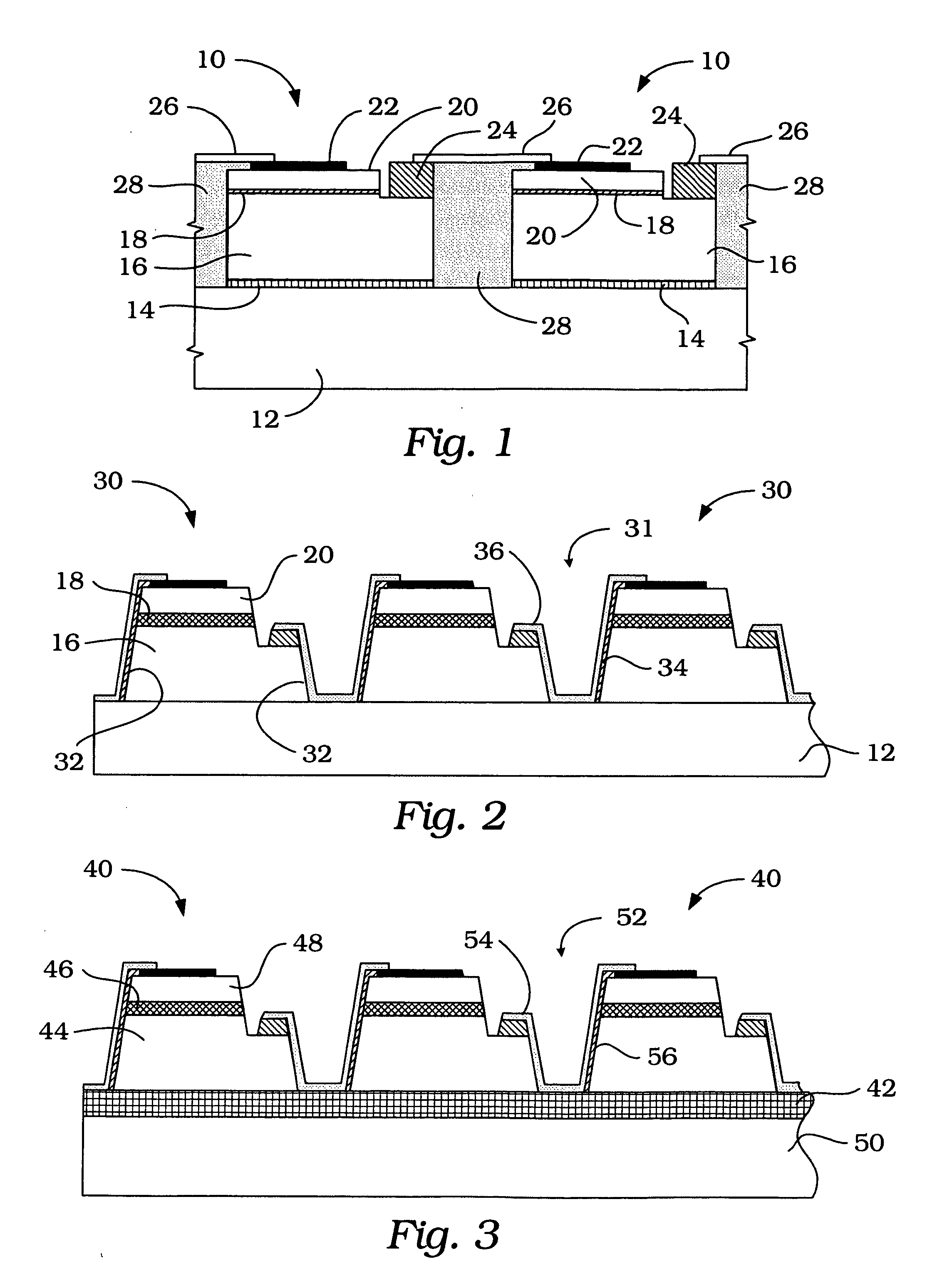

Process for making and programming and operating a dual-bit multi-level ballistic MONOS memory

A fast low voltage ballistic program, ultra-short channel, ultra-high density, dual-bit multi-level flash memory is described with a two or three polysilicon split gate side wall process. The structure and operation of this invention is enabled by a twin MONOS cell structure having an ultra-short control gate channel of less than 40nm, with ballistic injection which provides high electron injection efficiency and very fast program at low program voltages of 3~5V. The cell structure is realized by (i) placing side wall control gates over a composite of Oxide-Nitride-Oxide (ONO) on both sides of the word gate, and (ii) forming the control gates and bit diffusion by self-alignment and sharing the control gates and bit diffusions between memory cells for high density. Key elements used in this process are: 1) Disposable side wall process to fabricate the ultra short channel and the side wall control gate with or without a step structure, and 2) Self-aligned definition of the control gate over the storage nitride and the bit line diffusion, which also runs in the same direction as the control gate. The features of fast program, low voltage, ultra-high density, dual-bit, multi-level MONOS NVRAM of the present invention include: 1) Electron memory storage in nitride regions within an ONO layer underlying the control gates, 2) high density dual-bit cell in which there are two nitride memory storage elements per cell, 3) high density dual-bit cell can store multi-levels in each of the nitride regions, 4) low current program controlled by the word gate and control gate, 5) fast, low voltage program by ballistic injection utilizing the controllable ultra-short channel MONOS, and 6) side wall control poly gates to program and read multi-levels while masking out memory storage state effects of the unselected adjacent nitride regions and memory cells. The ballistic MONOS memory cell is arranged in the following array: each memory cell contains two nitride regions for one word gate, and ½ a source diffusion and ½ a bit diffusion. Control gates can be defined separately or shared together over the same diffusion. Diffusions are shared between cells and run in parallel to the side wall control gates, and perpendicular to the word line.

Owner:HALO LSI INC

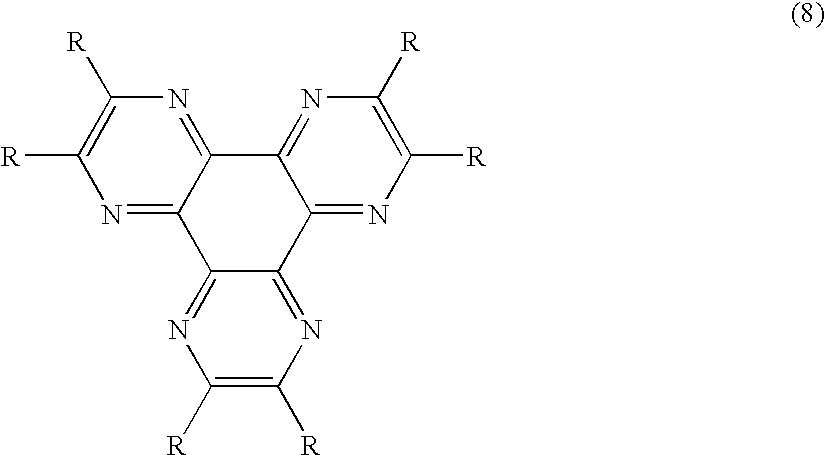

Organic element for low voltage electroluminescent devices

InactiveUS20070092755A1Reduce the driving voltageIncrease brightnessDischarge tube luminescnet screensLamp detailsHydrogenLow voltage

An OLED device comprises a cathode, a light emitting layer and an anode, in that order, and comprises; (i) a further layer located between the cathode and the light emitting layer, containing (a) 10 vol % or more of a carbocyclic fused ring aromatic compound, and (b) at least one salt or complex of a Group IA, IIA, IIIA and IIB element of the Periodic Table, and (ii) an additional layer, located between the anode and the light emitting layer, containing a compound of Formula (8) wherein: each R independently represents hydrogen or an independently selected substituent, at least one R representing an electron-withdrawing substituent having a Hammett's sigma para value of at least 0.3. Such devices exhibit reduce drive voltage while maintaining good luminance.

Owner:EASTMAN KODAK CO

Memory sensing circuit and method for low voltage operation

InactiveUS7046568B2Large capacityImprove performanceRead-only memoriesDigital storageBit lineAudio power amplifier

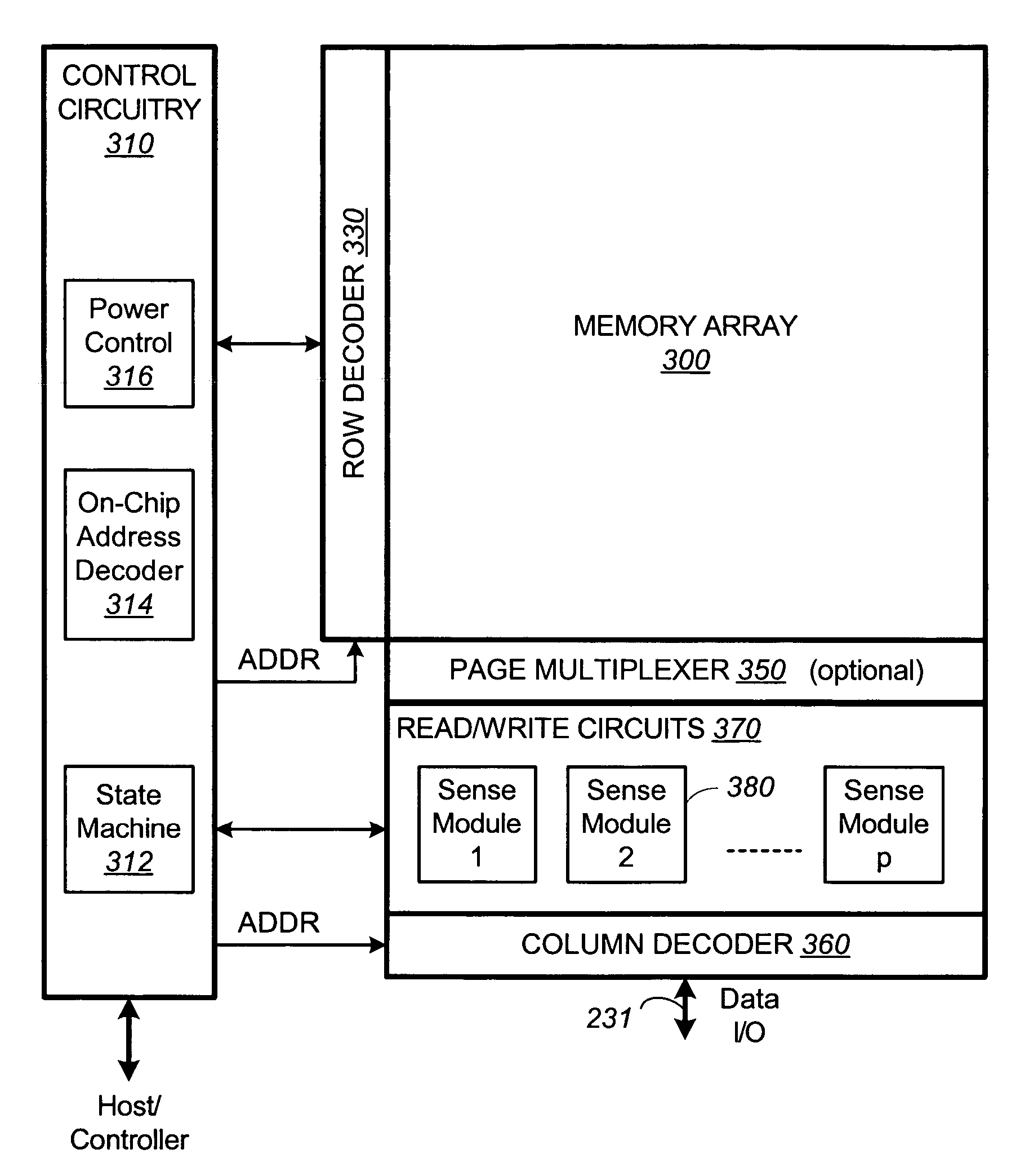

A sensing module operates with a sense amplifier sensing a conduction current of a memory cell via a coupled bit line under constant voltage condition in order to minimize bit-line to bit-line coupling. The rate of discharge of a dedicated capacitor as measured by a change in the voltage drop there across in a predetermined period is used to indicate the magnitude of the conduction current. The voltage cannot drop below a minimum level imposed by a circuit for maintaining the constant voltage condition on the bit line. A voltage shifter is used to boost the voltage during the discharge and to unboost the voltage after the discharge, so that the change in voltage drop properly reflects the rate of discharge without running into the minimum level.

Owner:SANDISK TECH LLC

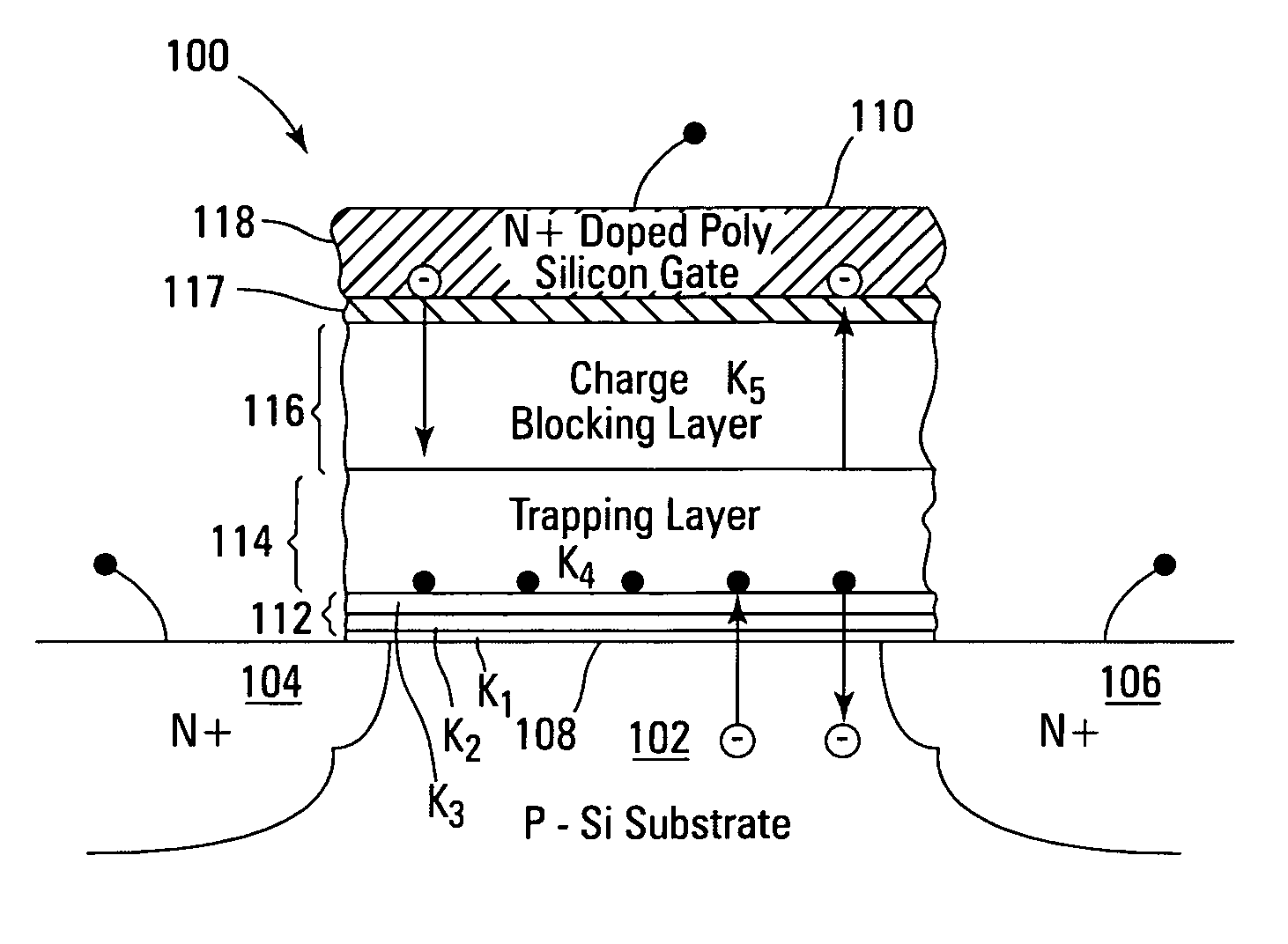

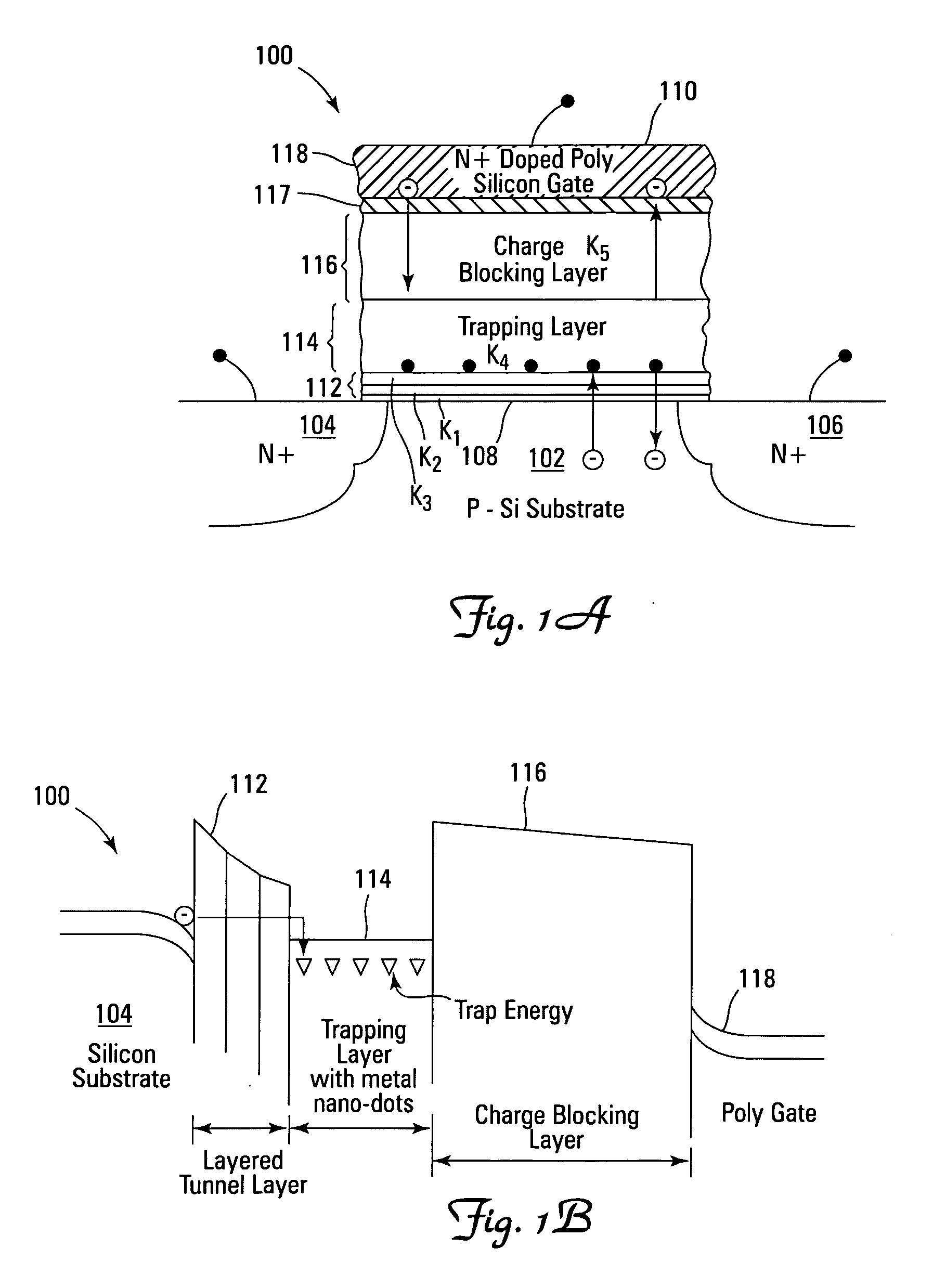

Novel low power non-volatile memory and gate stack

ActiveUS20060261401A1High charge blocking barrierExcellent charge retentionTransistorNanoinformaticsCharge retentionLow voltage

Non-volatile memory devices and arrays are described that facilitate the use of band-gap engineered gate stacks with asymmetric tunnel barriers in reverse and normal mode floating node memory cells in NOR or NAND memory architectures that allow for direct tunnel programming and erase, while maintaining high charge blocking barriers and deep carrier trapping sites for good charge retention. The low voltage direct tunneling program and erase capability reduces damage to the gate stack and the crystal lattice from high energy carriers, reducing write fatigue and enhancing device lifespan. The low voltage direct tunnel program and erase capability also enables size reduction through low voltage design and further device feature scaling. Memory cells of the present invention also allow multiple bit storage. These characteristics allow memory device embodiments of the present invention to operate within the definition of a universal memory, capable of replacing both DRAM and ROM in a system.

Owner:MICRON TECH INC

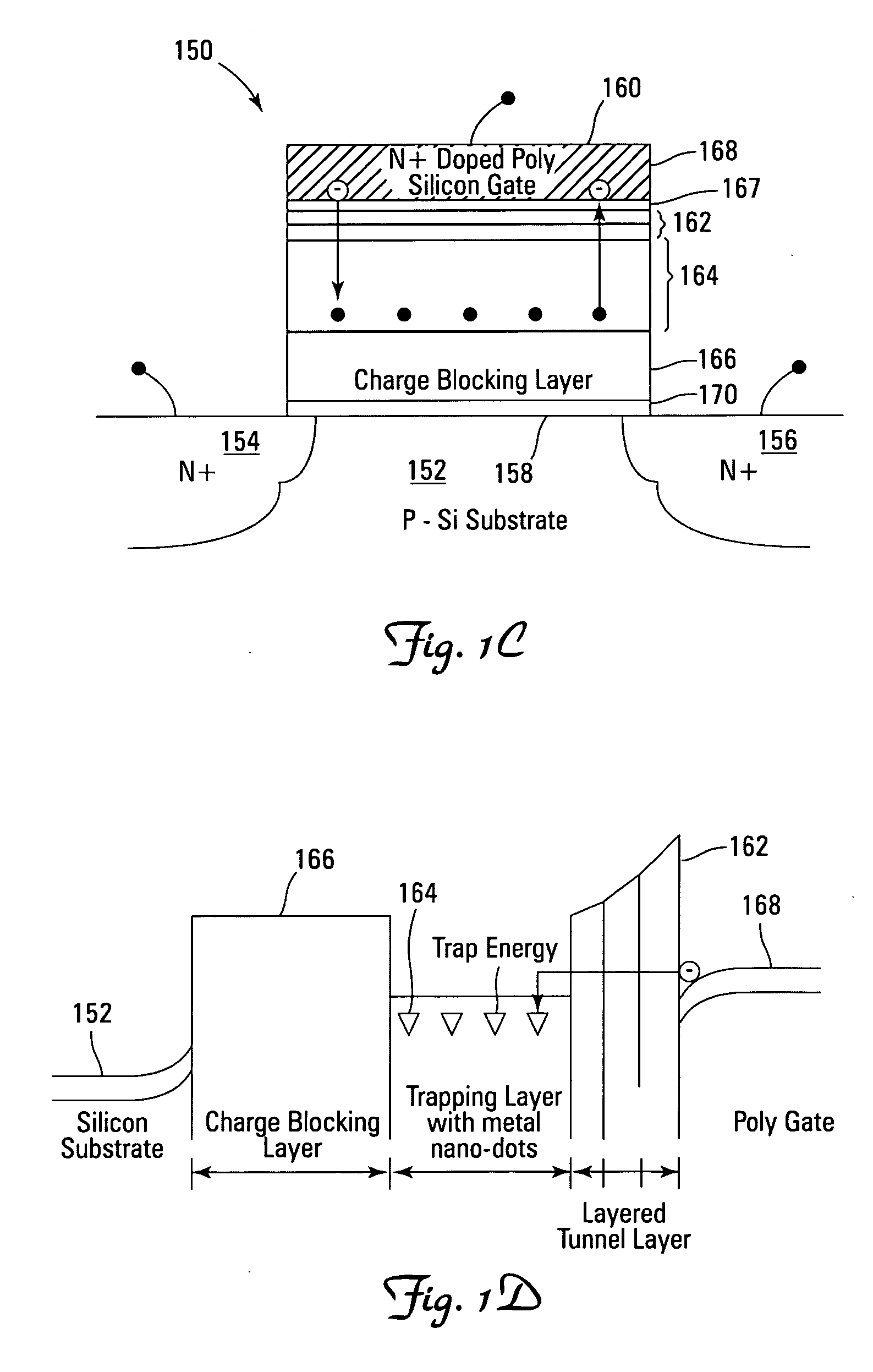

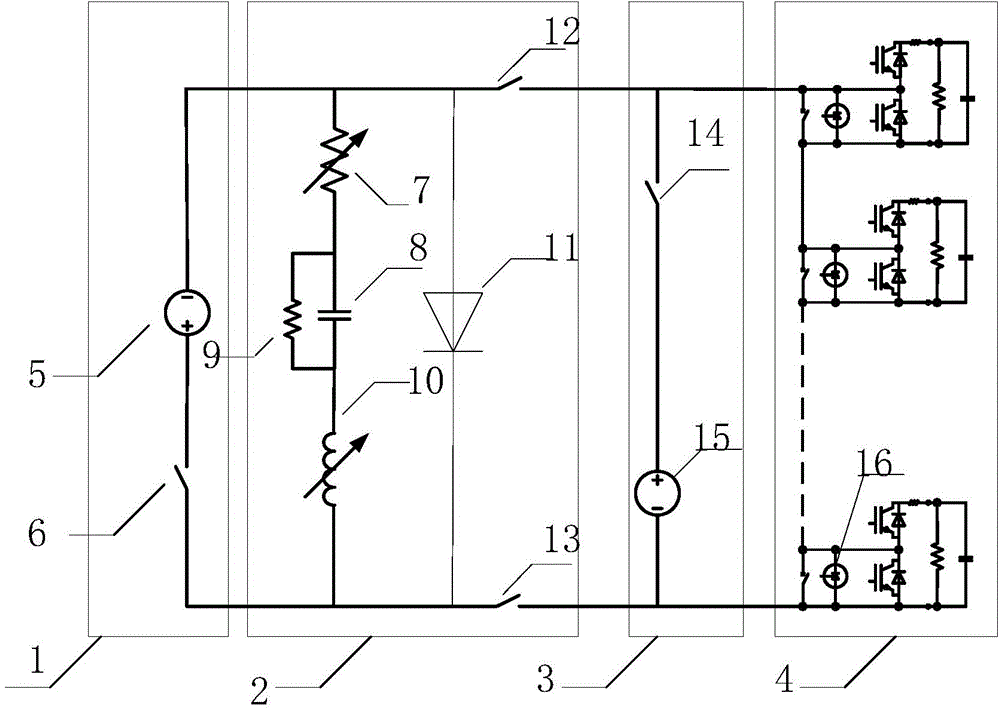

Short circuit simulation test circuit and test method thereof

Owner:NR ELECTRIC CO LTD +1

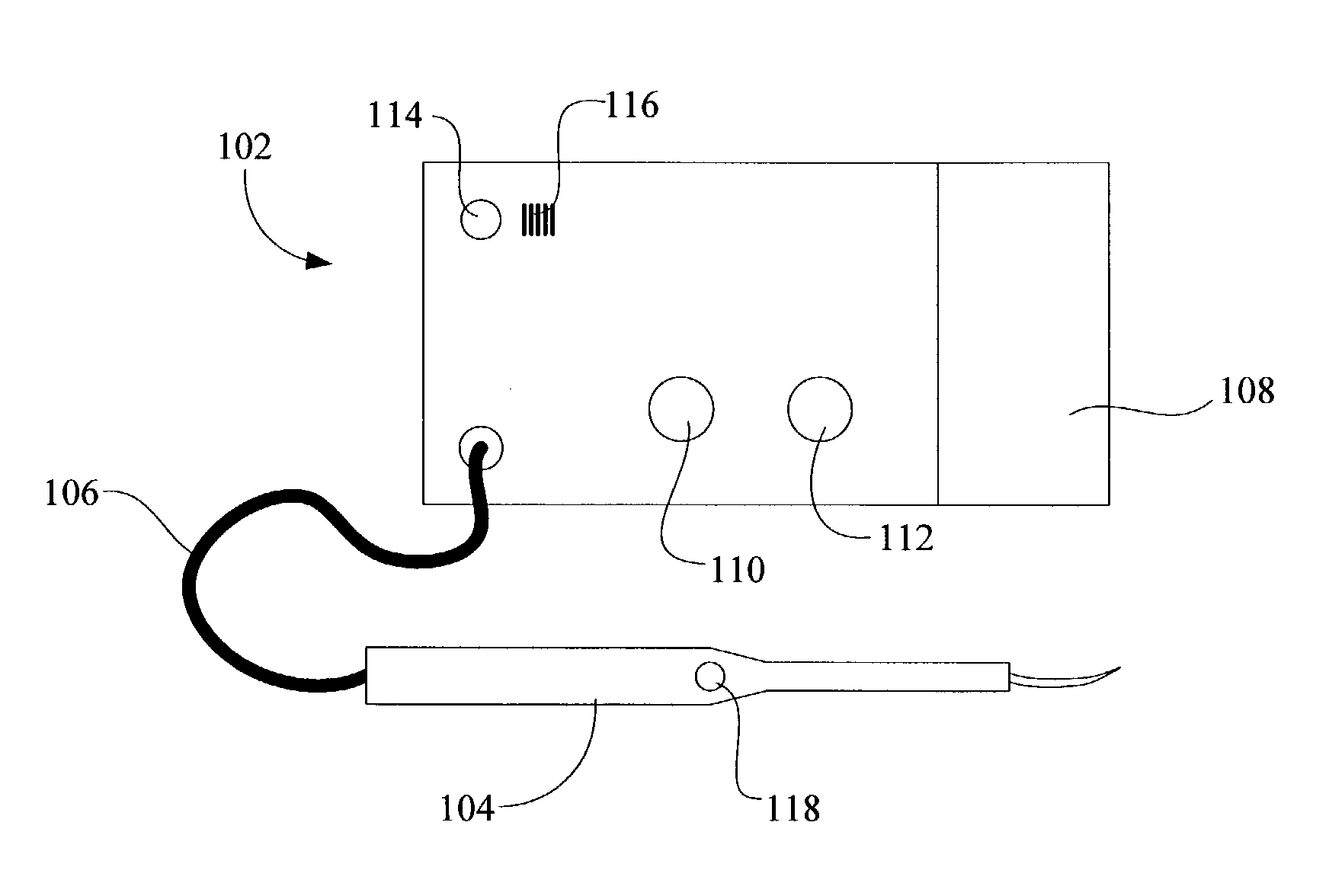

Portable ultrasonic scalpel/cautery device

A portable ultrasonic scalpel / cautery device is disclosed. According to one embodiment of the present invention, the ultrasonic surgical instrument includes a low voltage battery-powered ultrasonic generator and a handheld ultrasonic surgical instrument. The battery-powered ultrasonic generator generates an ultrasonic signal having a frequency of about 55 kHz.

Owner:SONTRA MEDICAL

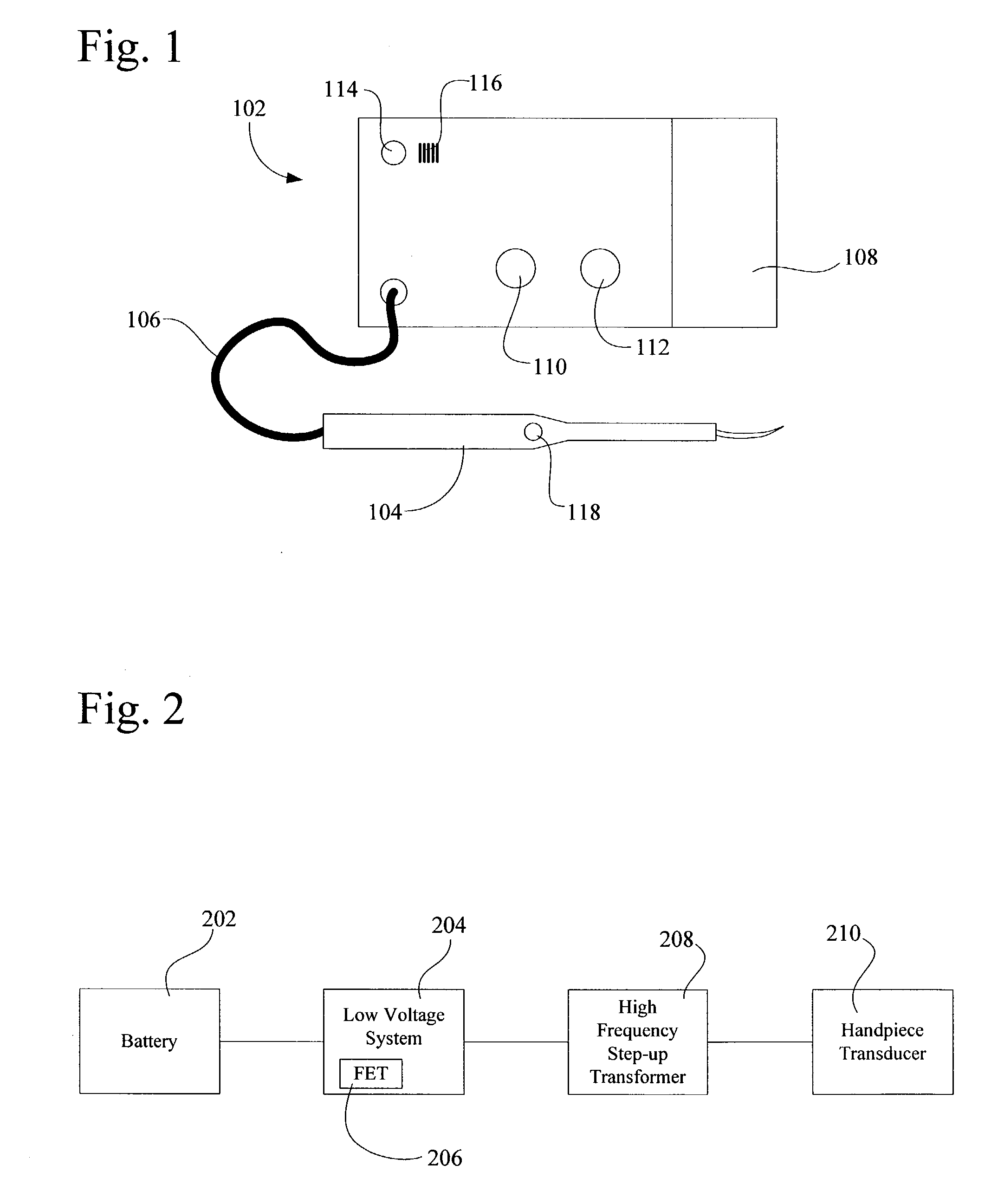

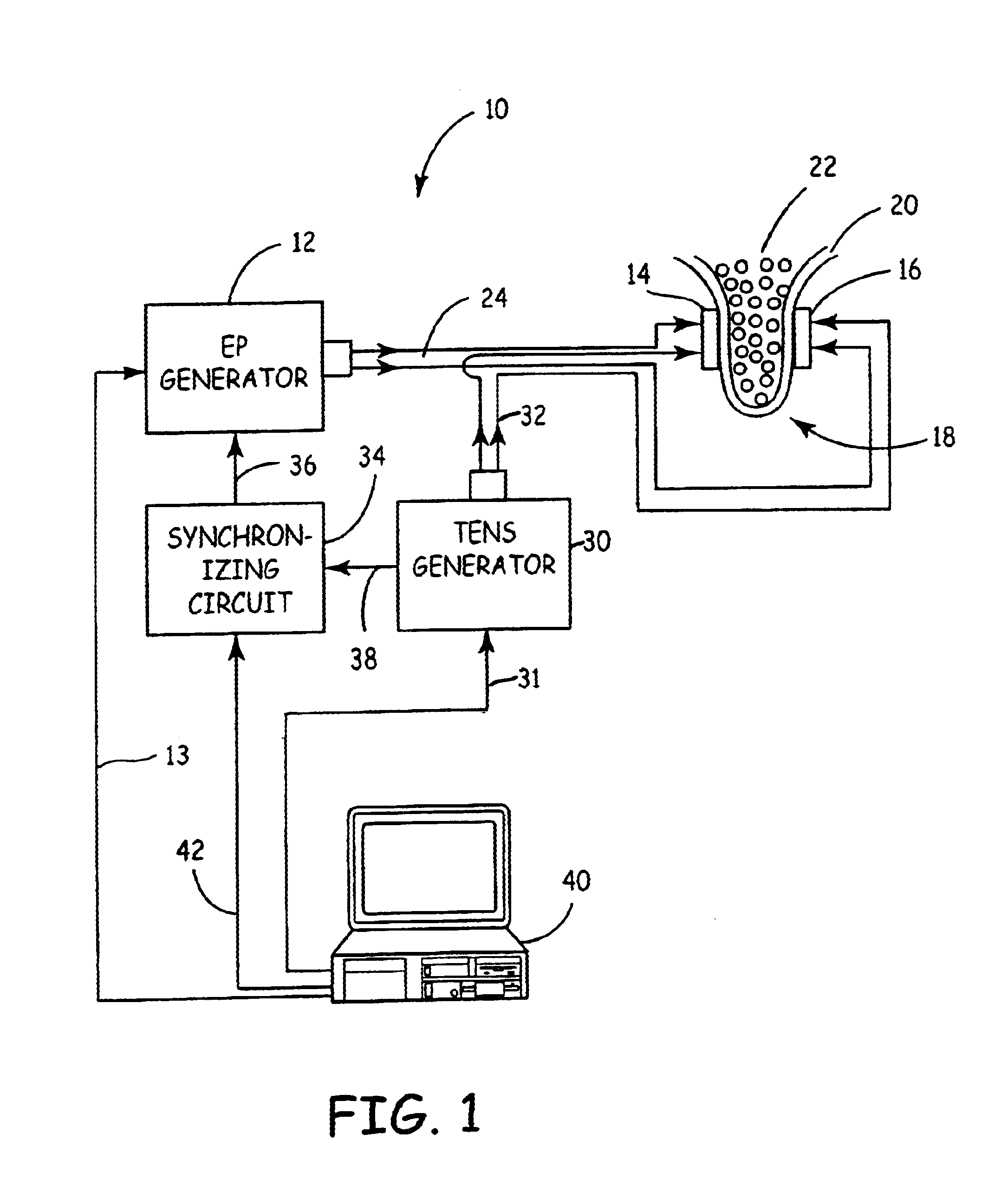

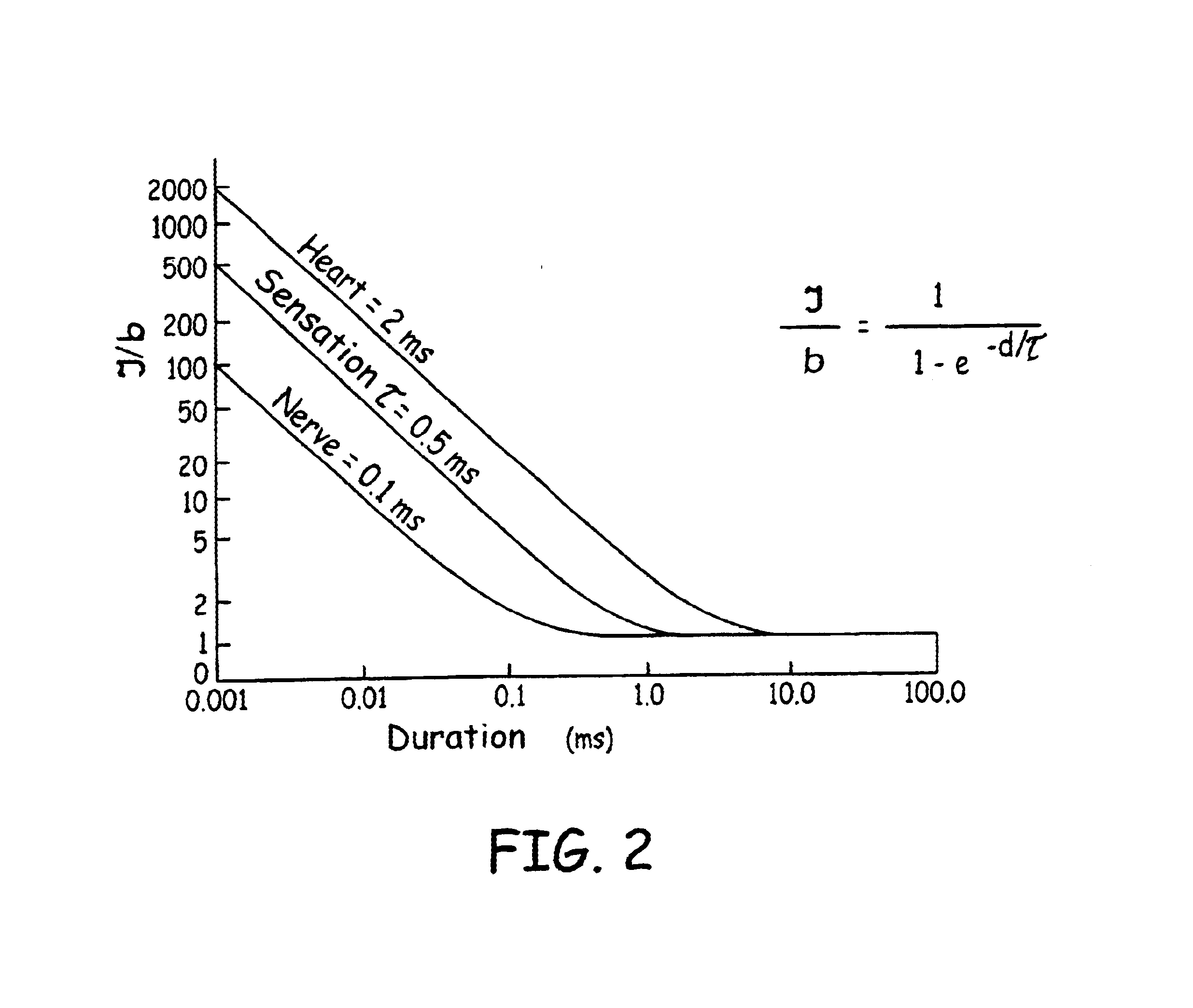

Apparatus and method for reducing subcutaneous fat deposits by electroporation with improved comfort of patients

InactiveUS6697670B2Improve comfortReducing subcutaneous fat depositsElectrotherapyElectricityReduced subcutaneous fat

An apparatus and method for non-invasive treatment in lieu of cosmetic surgery is disclosed. The apparatus comprises a combination of a high and low voltage pulse generators connected to two or more electrodes placed on a treatment site of the patient's body. High voltage pulses, delivered to the electrodes, create an electric field that kills subcutaneous fat cells. Low voltage pulses, delivered to the same or individual electrodes provide transcutaneous electrical nerve stimulation (TENS), blocking the signals of discomfort or pain that may arise from the high voltage pulsing.

Owner:ANGIODYNAMICS INC

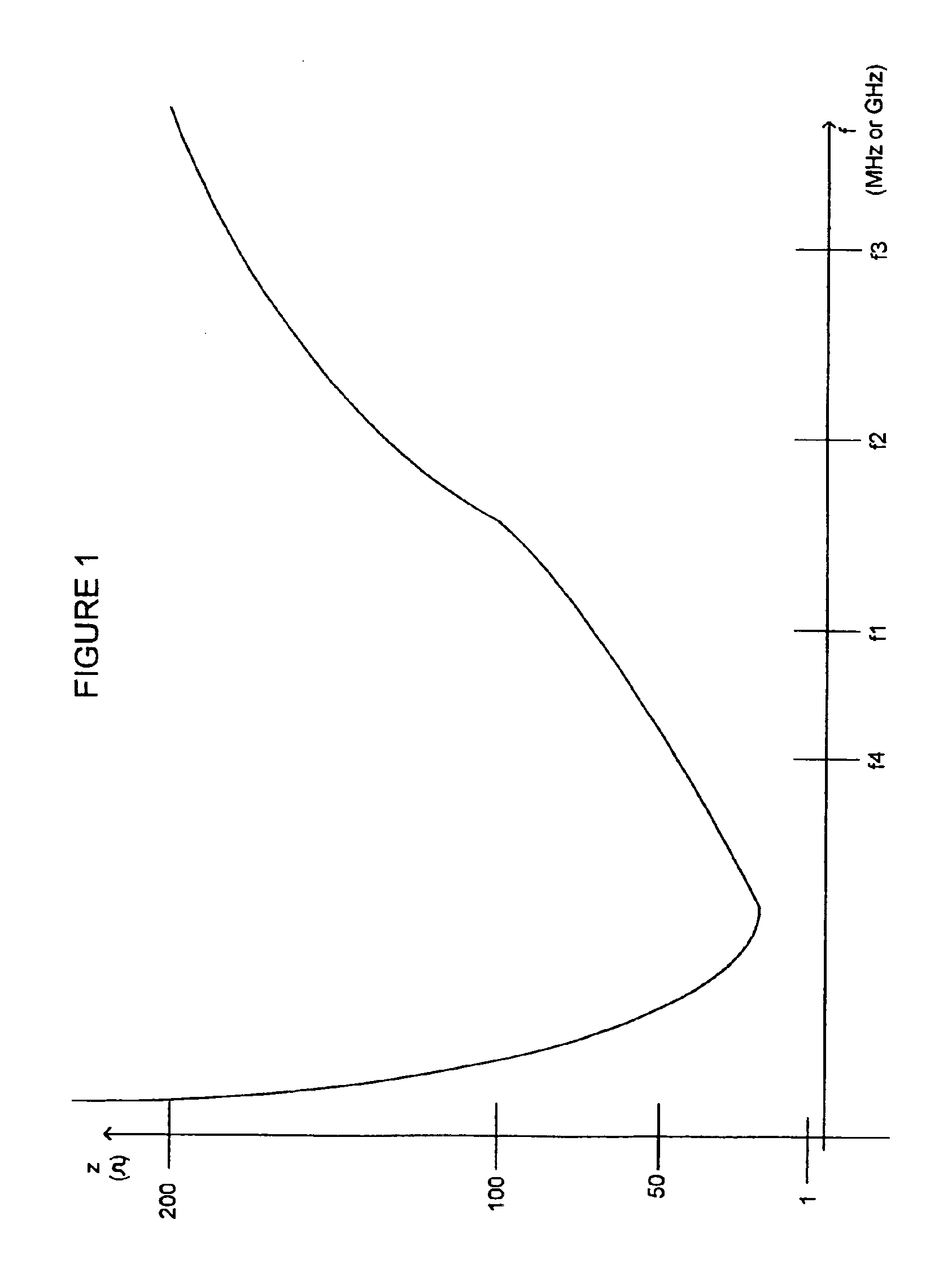

High frequency network multiplexed communications over various lines using multiple modulated carrier frequencies

InactiveUS6922135B2Substantial phase distortionMultiple-port networksPowerline communication systemsCapacitanceModem device

An apparatus is provided for high frequency multiplexed electrical line communication for cable TV, telephone, internet, security and other control applications over the mid and low voltage power lines and directly through the transformers. The apparatus includes a transmitter, a receiver, a modem, a multiplexer and multiple couplers at each of two or more locations along an electrical line. The couplers have capacitive circuits serially connected with an air-core or dielectric-core transformer. The capacitive circuits resonate with the transformer at a preselected frequency. The coupler eliminates noise and is matched to the characteristic impedance of the line at the preselected frequency, which linearizes communication on the line and allows high speed data and voice communication over long distances. Multiple modulators and demodulators are used to produce multiple modulated carrier frequencies.

Owner:SATIUS

Power line communication rate limiting system and method

InactiveUS20070002771A1Rate limiting quality of service (QoS) controlError preventionTransmission systemsQuality of serviceRate limiting

A power line communications device that may provide rate limiting and quality of service control is provided. The device may include a first modem in communication with one or more user devices via a low voltage power line subnet and a second modem communicatively coupled to a second communications medium. The device also may include a controller in communication with the first and second modems and a computer readable medium encoded with instructions to control the operation of the controller. The controller may rate limit data to and / or from a destination and / or source based one or more parameters such as the destination address, the source address, the type of data, temporal parameters, and other criteria. In addition, the controller may implement QoS for data and transmit QoS parameters to power line modems to allow the power line modems to perform QoS.

Owner:CURRENT TECH

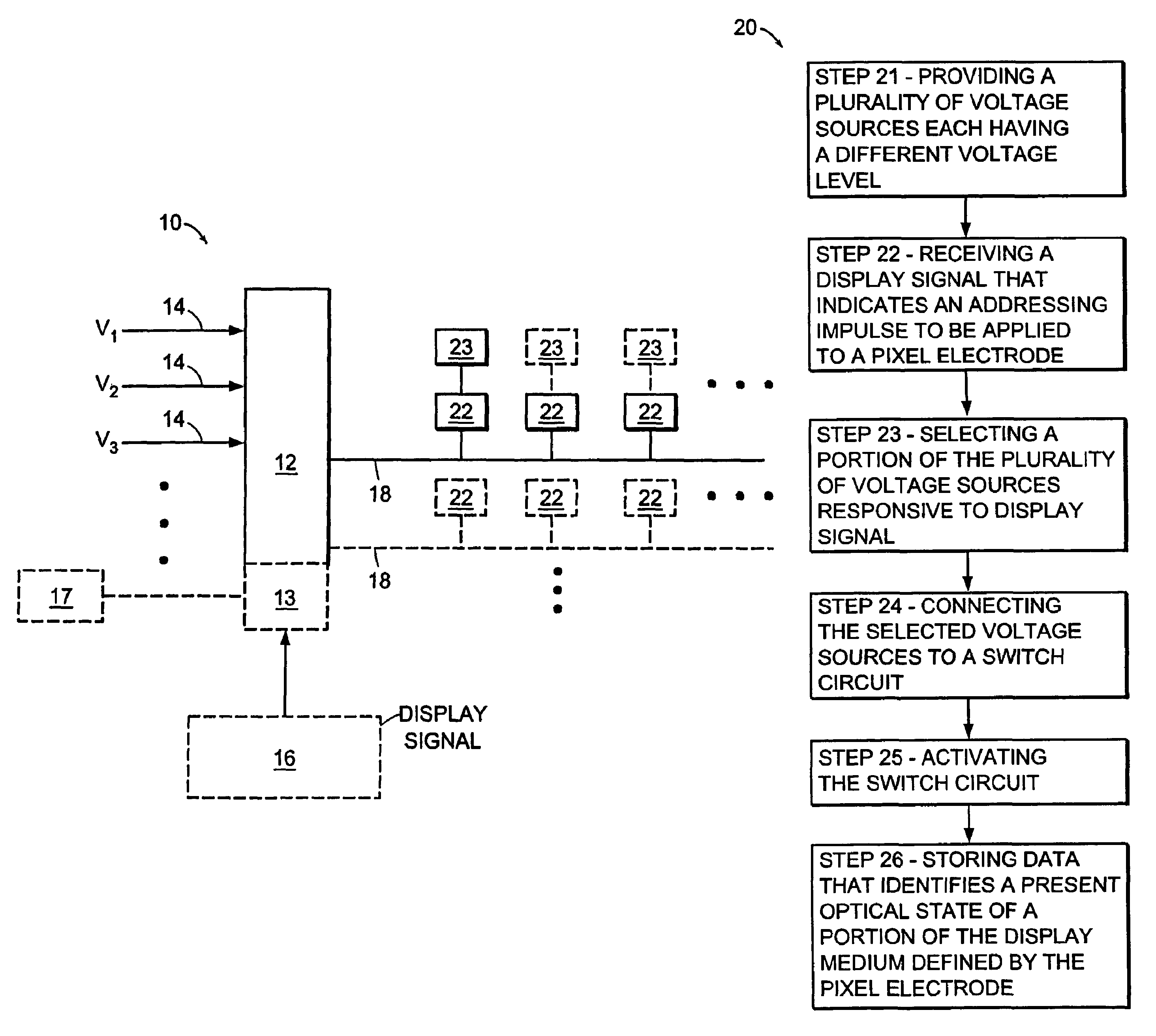

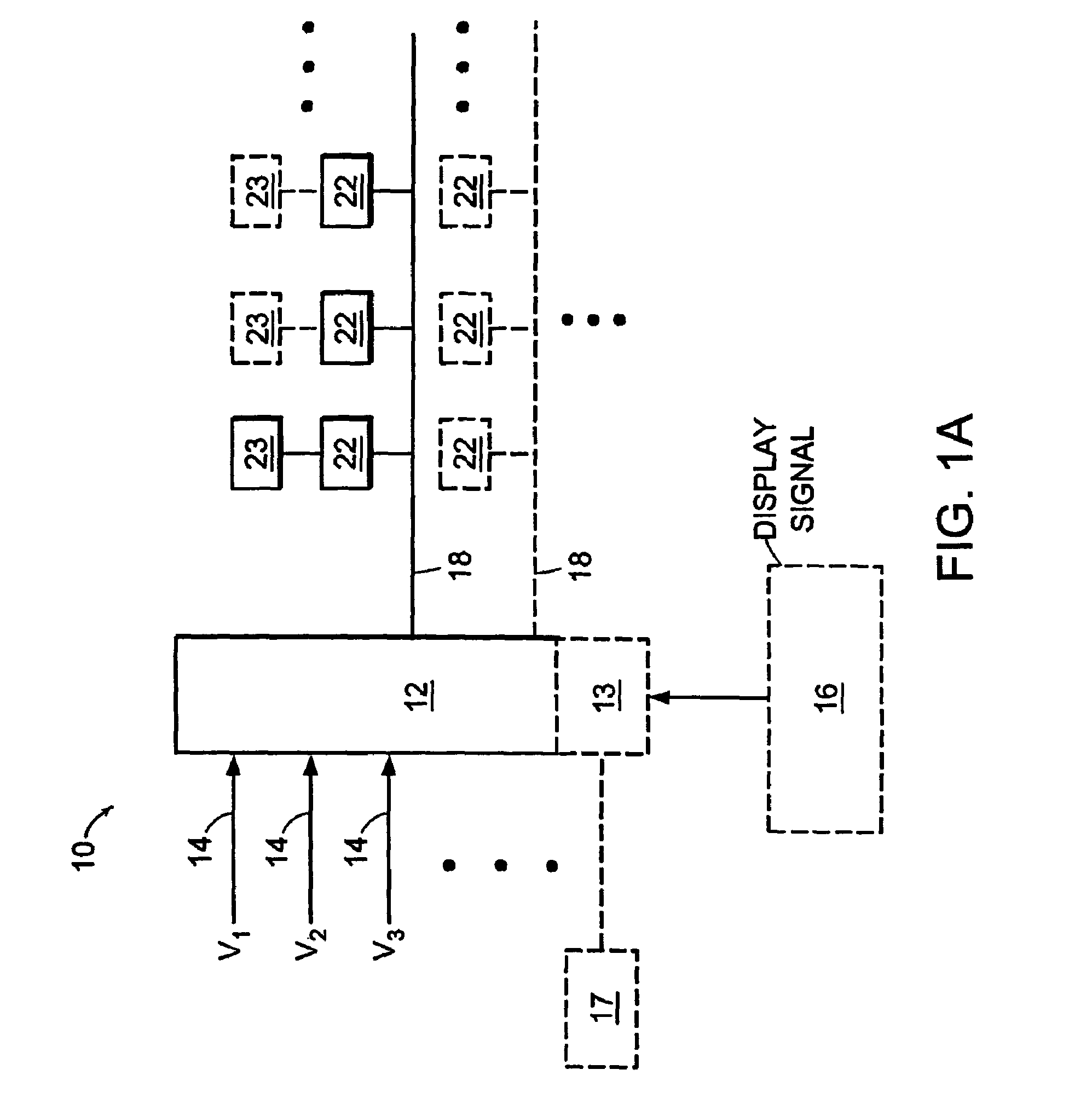

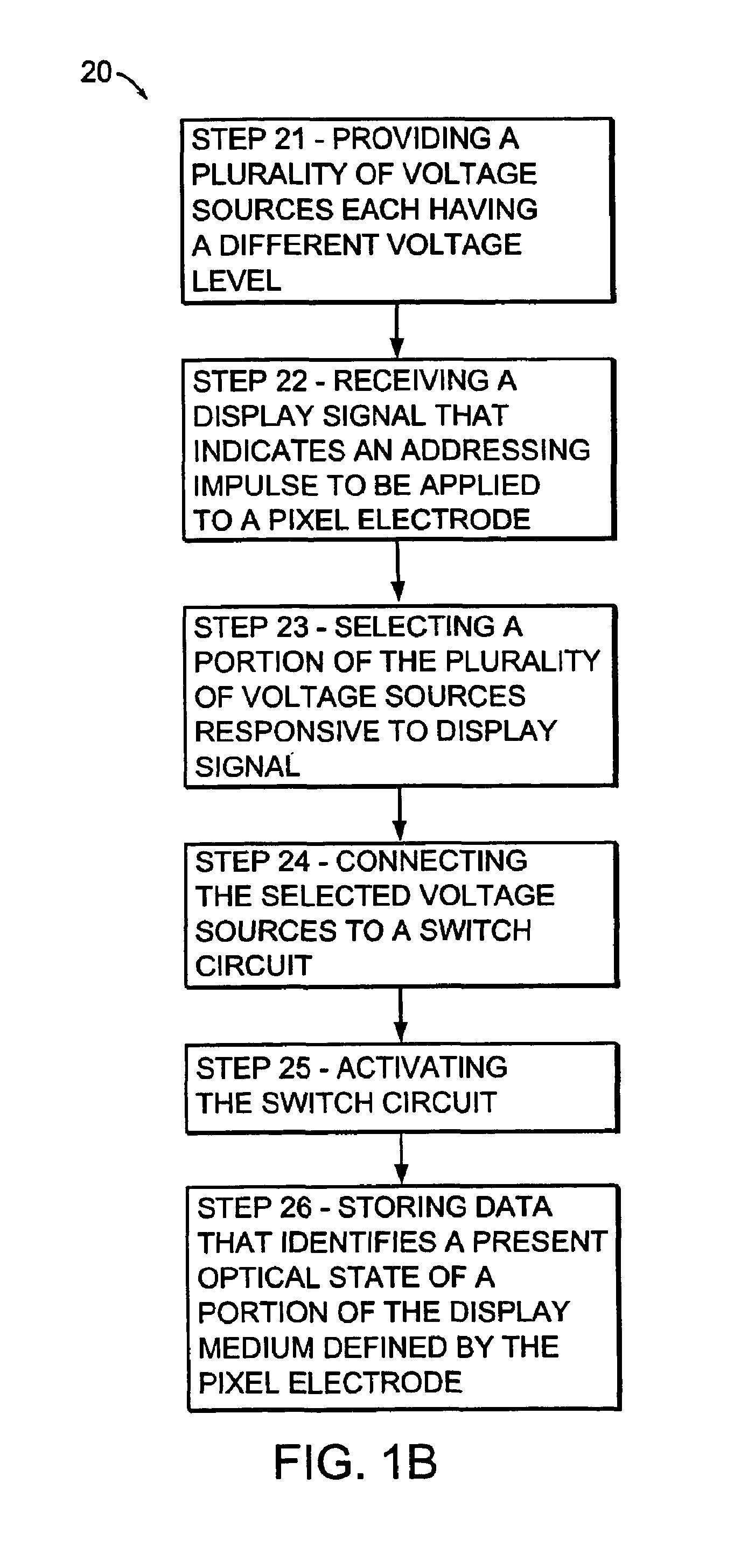

Voltage modulated driver circuits for electro-optic displays

ActiveUS8125501B2Low implementation costFaster design timeCathode-ray tube indicatorsInput/output processes for data processingElectricityDriver circuit

A method and system for applying addressing voltages to pixels of a display involves receiving input data. The input data includes an indication of an addressing voltage impulse to be applied to a pixel via an electrode. One or more voltage sources are selected, to provide the addressing voltage impulse. The one or more voltage sources each have a pre-selected voltage, The selected one or more voltage sources are electrically connected to an electrode to apply the addressing voltage impulse to the pixel. The invention also provides a method of driving an electro-optic display which uses an intermediate image of reduced bit depth, and a method of driving an electro-optic display which uses a limited number of differing drive voltages, with higher voltage pulses being used before lower voltage pulses.

Owner:E INK CORPORATION

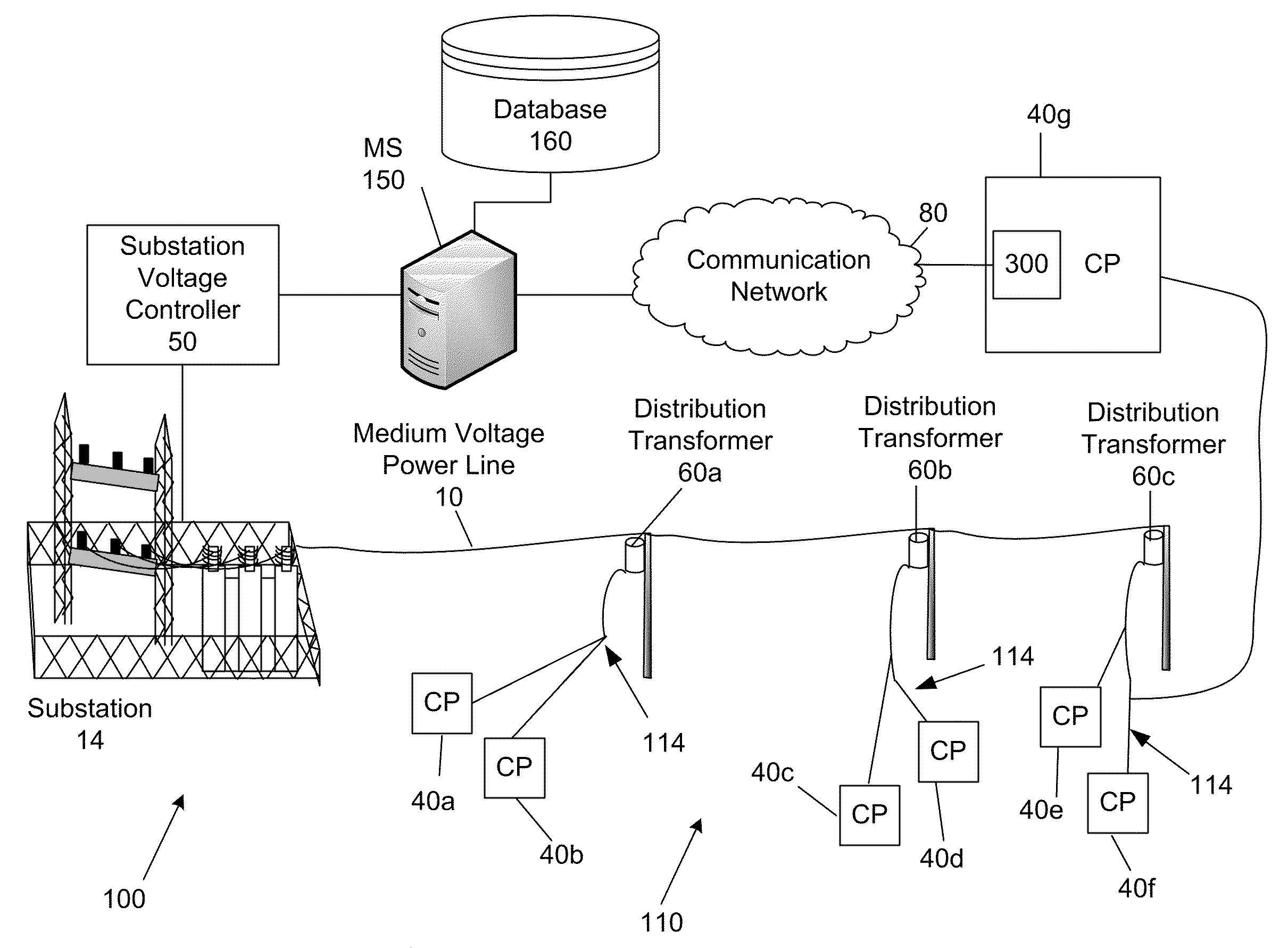

System and Method for Providing Voltage Regulation in a Power Distribution System

InactiveUS20090265042A1Mechanical power/torque controlDc network circuit arrangementsLow voltageDistribution power system

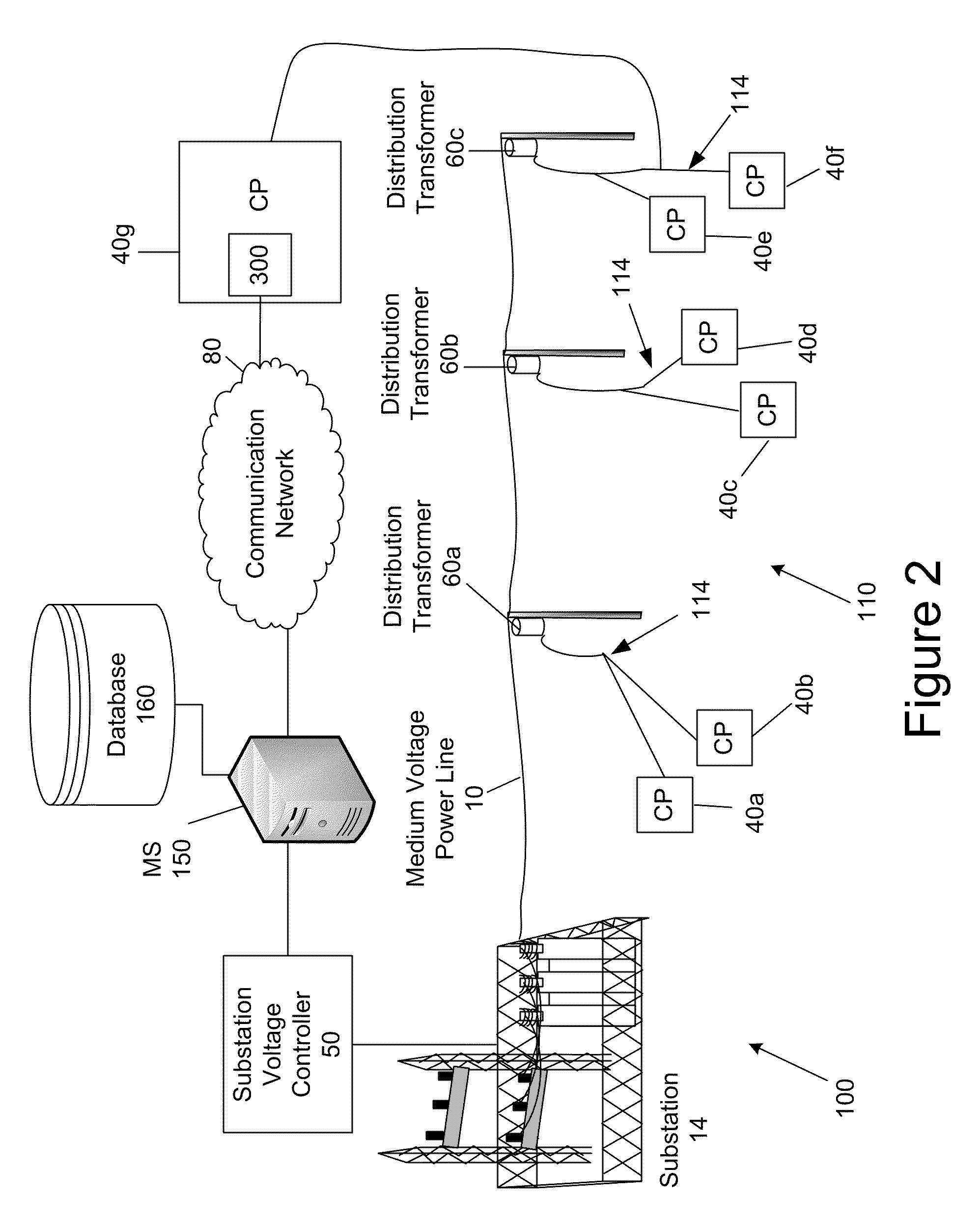

A system and method of regulating the voltage of the power supplied to a plurality of power customers via a power distribution system that includes low voltage power lines and medium voltage power lines is provided. In one embodiment, the method includes measuring the voltage of a plurality of low voltage power lines at a plurality locations in the power distribution system with a plurality of voltage monitoring devices; with the plurality of voltage monitoring devices, transmitting voltage data in real time to a remote computer system; receiving, with the computer system, the real time voltage data of the voltage measured from the voltage monitoring devices; comparing, with the computer system, the real time voltage data with a first threshold value; and if the real time voltage data is beyond the first threshold value, transmitting with the computer system a first voltage adjustment instruction to a voltage control device configured to adjust the voltage supplied to a low voltage power line.

Owner:S&C ELECTRIC

Power line communication system and method of operating the same

InactiveUS7098773B2Electric signal transmission systemsOne-port networksCommunications systemCoaxial cable

Owner:CURRENT TECH

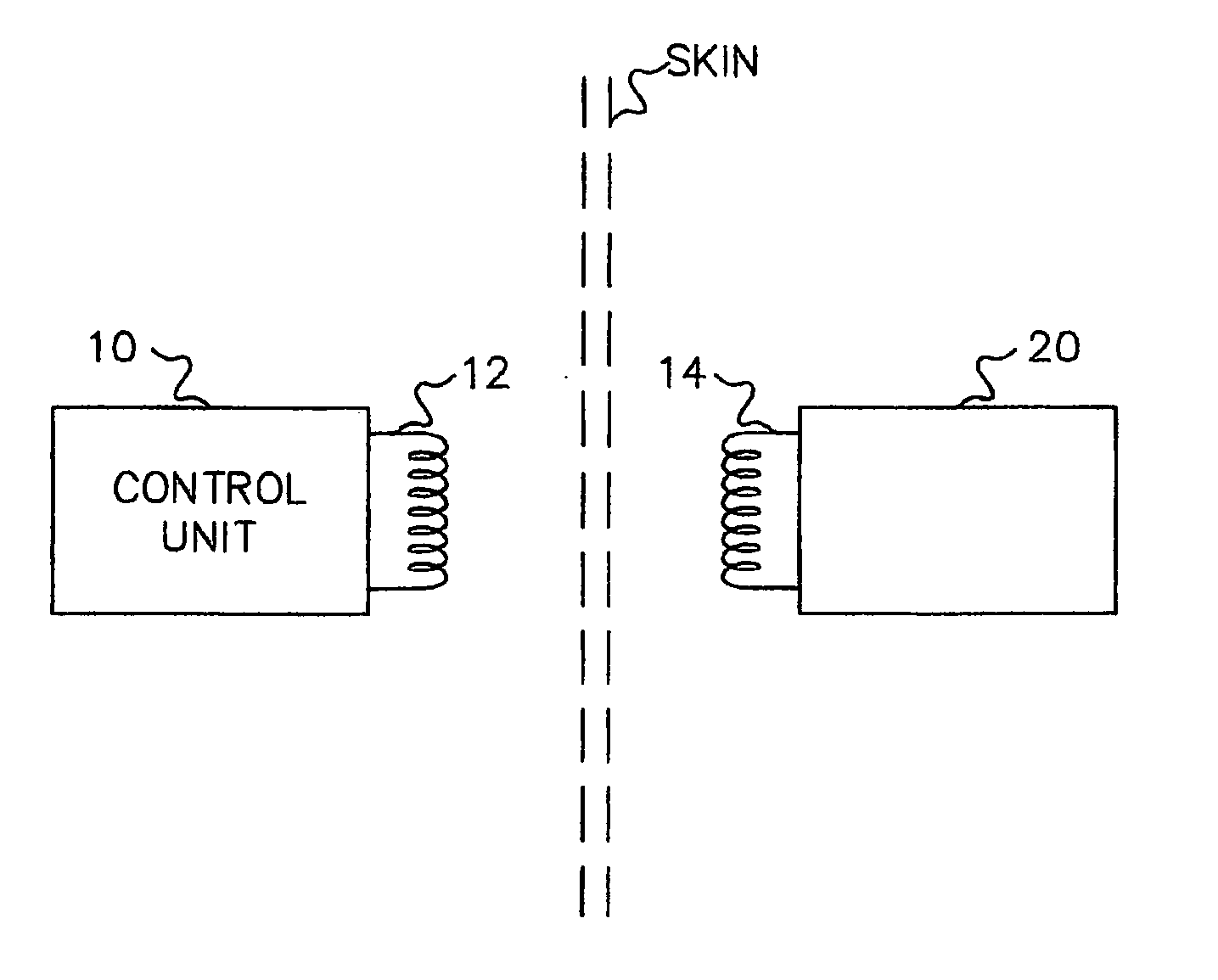

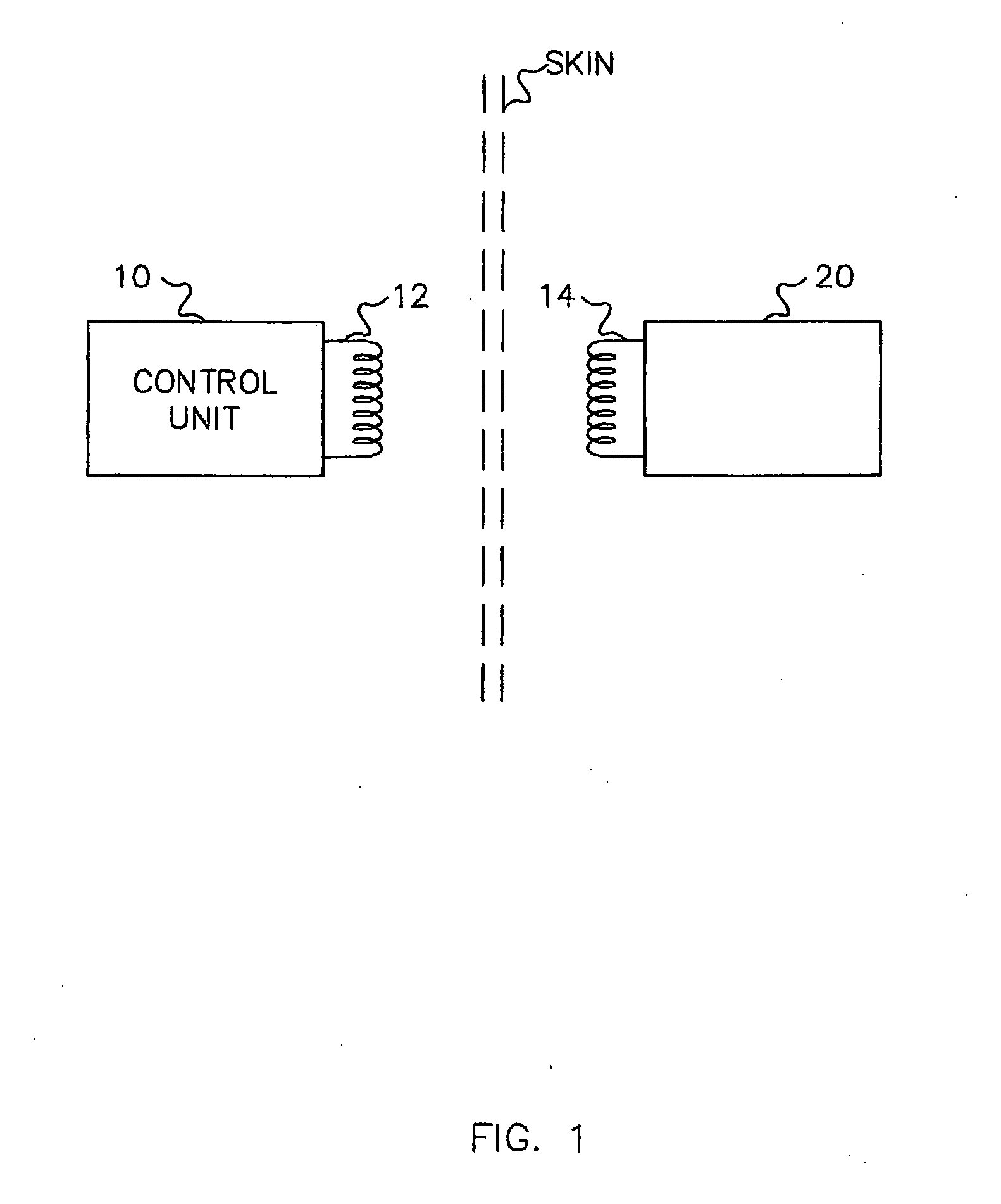

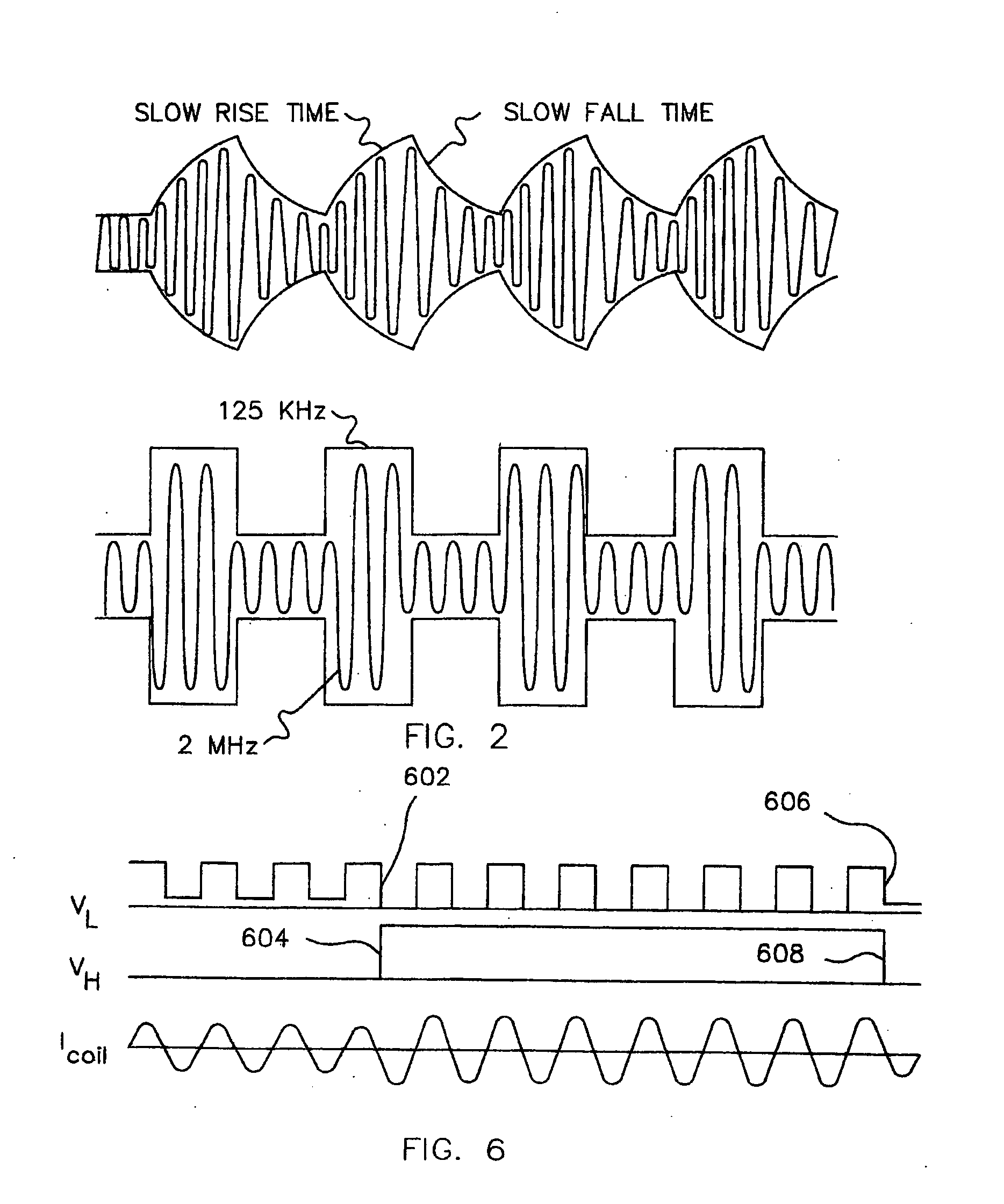

Method and apparatus for efficient power/data transmission

A system, method and power / data transmission device comprising a coil having a high Q, a low-voltage driver and a high-voltage driver switchably coupled to the coil. The low-voltage driver and the high-voltage driver are controlled by a microcontroller and switch at about the same time thereby providing a modulated data signal for transmission. Furthermore, the system includes at least one implantable microstimulator coupled to the transmission device.

Owner:ALFRED E MANN FOUND FOR SCI RES

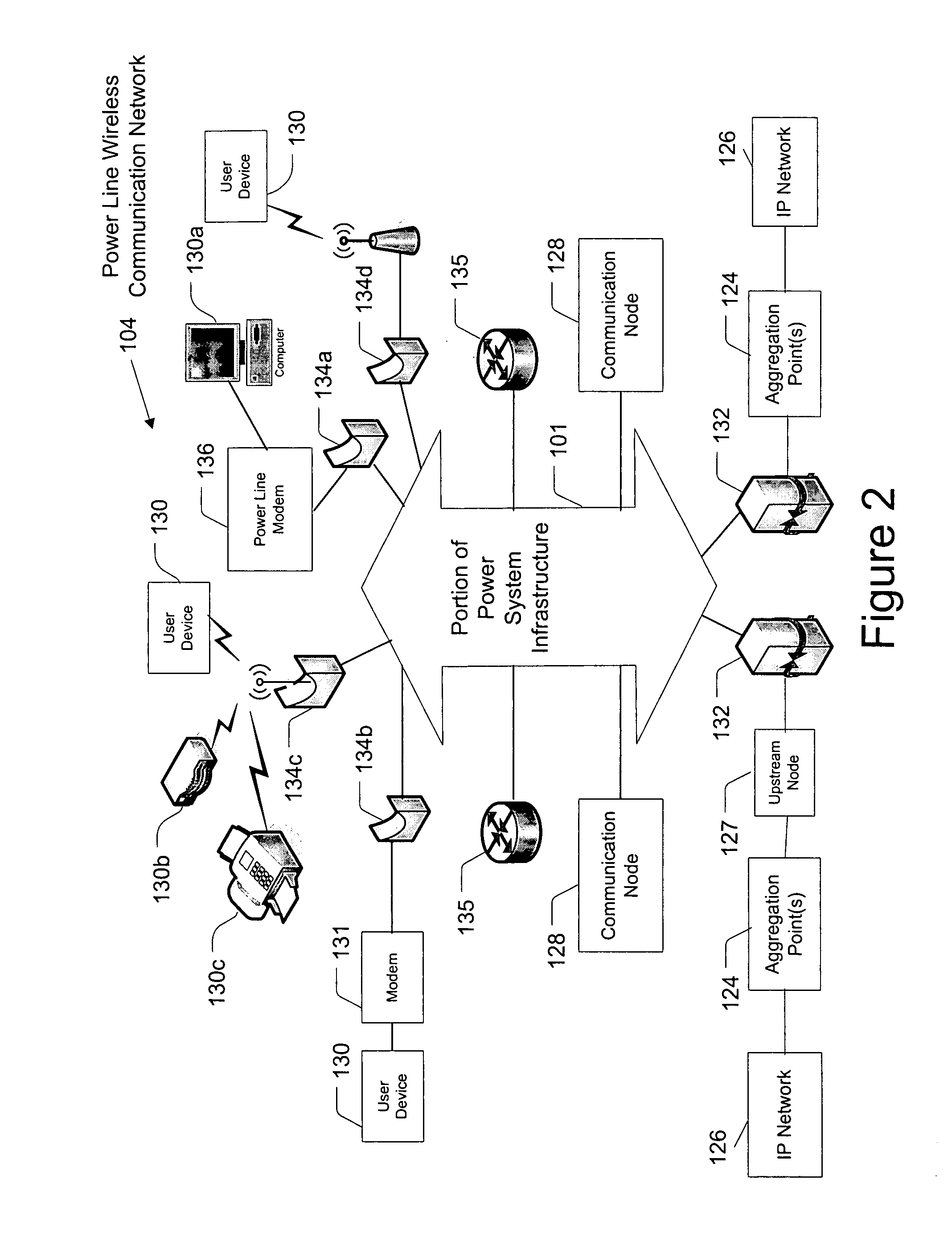

Hybrid power line wireless communication network

InactiveUS20070201540A1Wireless systems/telephoneLock network applicationsCommunications systemLow voltage

A hybrid power line wireless communication system may include an access controller and plurality of communication nodes that each may include a wireless access point coupled to a power line communication device. The wireless access points may provide wireless broadband communications to one or more user devices while the power line communication devices may provide low voltage power line broadband communications. The access controller remotely manages the wireless access points by sending control messages to the communication nodes. Control messages may traverse a power line, a non-power line medium, and / or a wireless medium. Control messages may include information relating to encryption parameters, transmission power levels, communication channels, access control, and other such parameters.

Owner:CURRENT TECH

Methods and systems for control of microfluidic devices

InactiveUS7010391B2Easy programmingSludge treatmentFixed microstructural devicesControl systemLow voltage

Owner:HANDYLAB

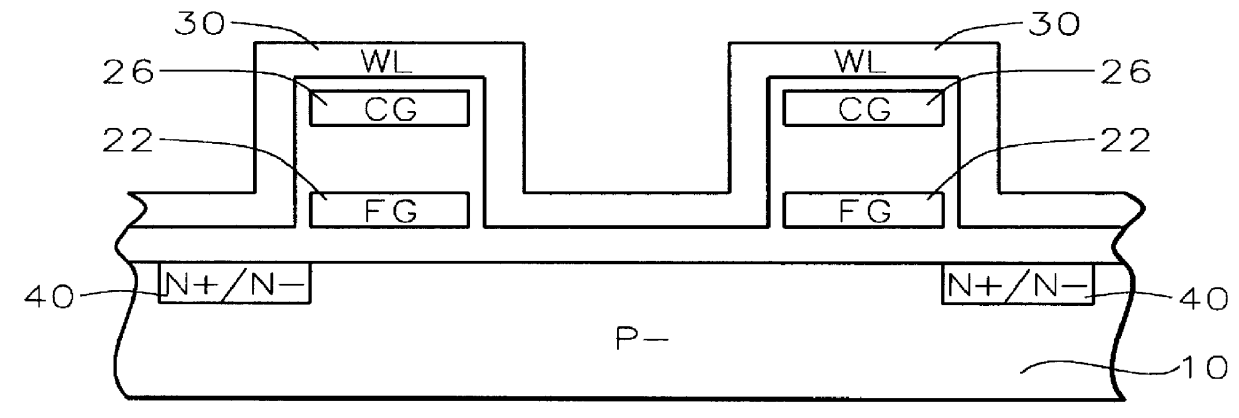

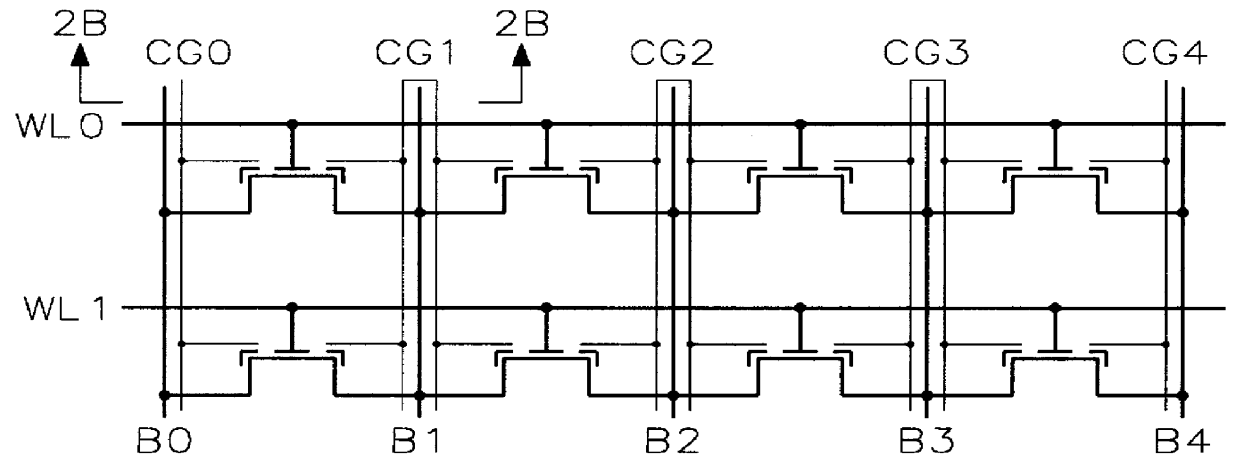

Process for making and programming and operating a dual-bit multi-level ballistic flash memory

An fast program, ultra-high density, dual-bit, multi-level flash memory process, which can be applied to a ballistic step split gate side wall transistor, or to a ballistic planar split gate side wall transistor, which enables program operation by low voltage requirement on the floating gate during program is described. Two side wall floating gates are paired with a single word line select gate, and word lines are arranged to be perpendicular both the bit lines and control gate lines. Two adjacent memory cells on the same word line do not require an isolation region. Also, the isolation region between adjacent memory cells sharing the same bitline is defined by the minimum lithography feature, utilizing a self align fill technique. Adjacent memory cells on the same word line share bitline diffusion as well as a third poly control gate. Control gates allow program and read access to the individual floating gate. In addition to the dual-bit nature of the cell, density can be even further improved by multi-level storage. In one embodiment, the dual multi-level structure is applied to the ballistic step split gate side wall transistor. In a second embodiment, the dual multi-level structure is applied to the ballistic planar split gate side wall transistor. Both types of ballistic transistors provide fast, low voltage programming. The control gates are used to override or suppress the various threshold voltages on associated floating gates, in order to program to and read from individual floating gates. The targets for this non-volatile memory array are to provide the capabilities of high speed, low voltage programming (band width) and high density storage.

Owner:HALO LSI DESIGN & DEVICE TECH

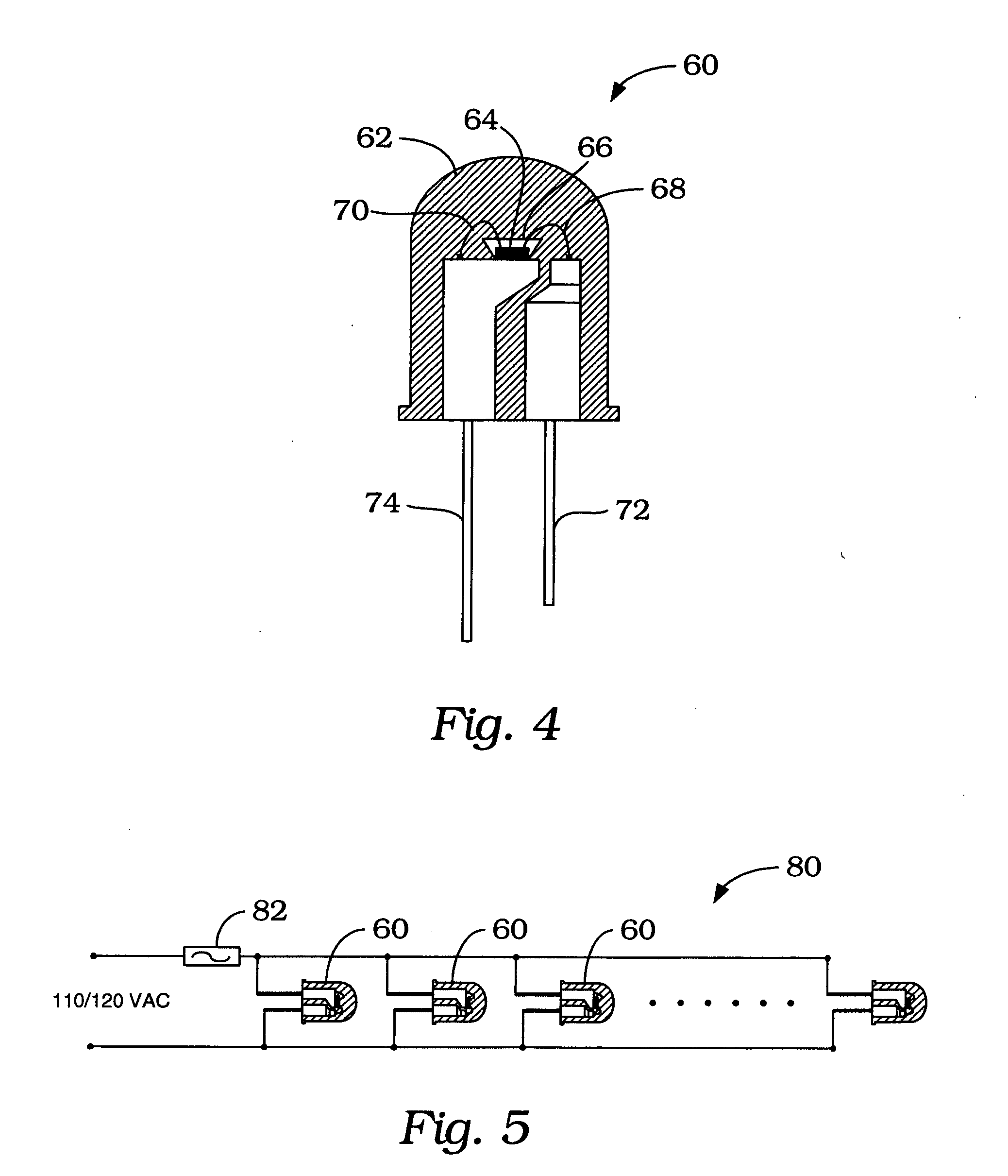

Micro-LED based high voltage AC/DC indicator lamp

ActiveUS20060169993A1Similar power consumptionImprove reliabilitySolid-state devicesSemiconductor devices for light sourcesLow voltageEngineering

An AC / DC indicator lamp based on an array of micro-LEDs may be powered by a standard high voltage AC or DC power source. The indicator lamp has a low power consumption. The micro-LEDs are serially connected on a substrate with the total device area and power consumption compatible with a standard DC low voltage LED. A plurality of indicator lamps may be connected together in parallel to present a string of indicator lamps.

Owner:LED LIGHTING