Semiconductor memory device for low voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0081] Hereinafter, a semiconductor memory device in accordance with the present invention will be described in detail referring to the accompanying drawings.

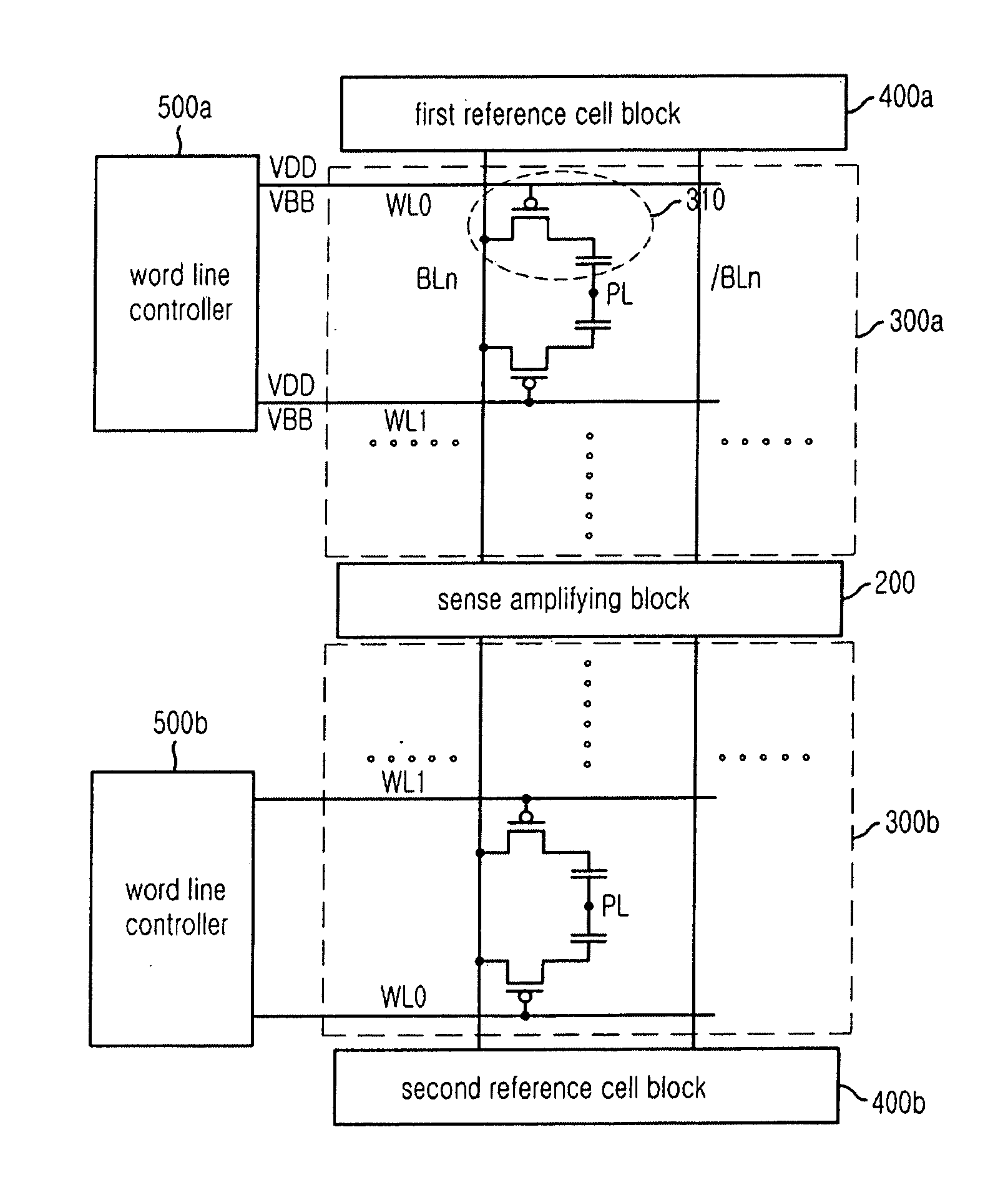

[0082]FIG. 7 is a block diagram showing a semiconductor memory device in accordance with an embodiment of the present invention.

[0083] As shown, the semiconductor memory device includes a plurality of cell arrays, e.g., 300a and 300b, a plurality of sense amplifying blocks, e.g., 200. The semiconductor memory device further includes word line controllers, e.g., 500a and 500b, and reference cell blocks, e.g., 400a and 400b, corresponding to the cell arrays.

[0084] In detail, each cell array, e.g., 300a, includes a plurality of unit cells, e.g., 310, each provided with a PMOS transistor and a capacitor. The PMOS transistor included in each unit cell connected to a corresponding word line WL0 and WL1, driven based on a low voltage VBB and a power supply voltage VDD.

[0085] The word line controller 500a and 500b, determines a vol...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More