Patents

Literature

639 results about "Address decoder" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

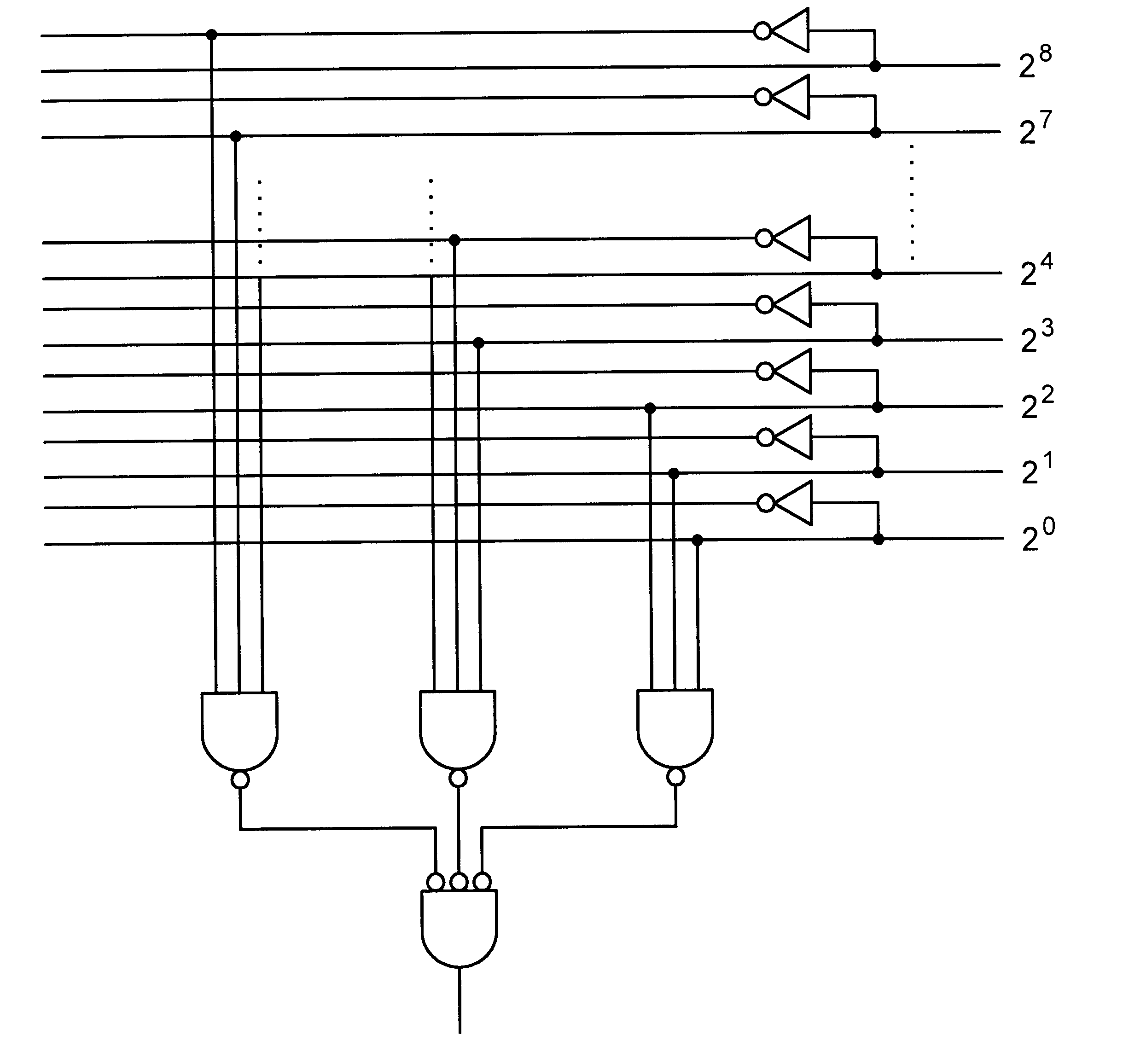

In digital electronics, an address decoder is a binary decoder that has two or more inputs for address bits and one or more outputs for device selection signals. When the address for a particular device appears on the address inputs, the decoder asserts the selection output for that device. A dedicated, single-output address decoder may be incorporated into each device on an address bus, or a single address decoder may serve multiple devices.

Drive circuit for display device

InactiveUS6344843B1Reduce scan timeRun at high speedCathode-ray tube indicatorsInput/output processes for data processingAddress decoderGray level

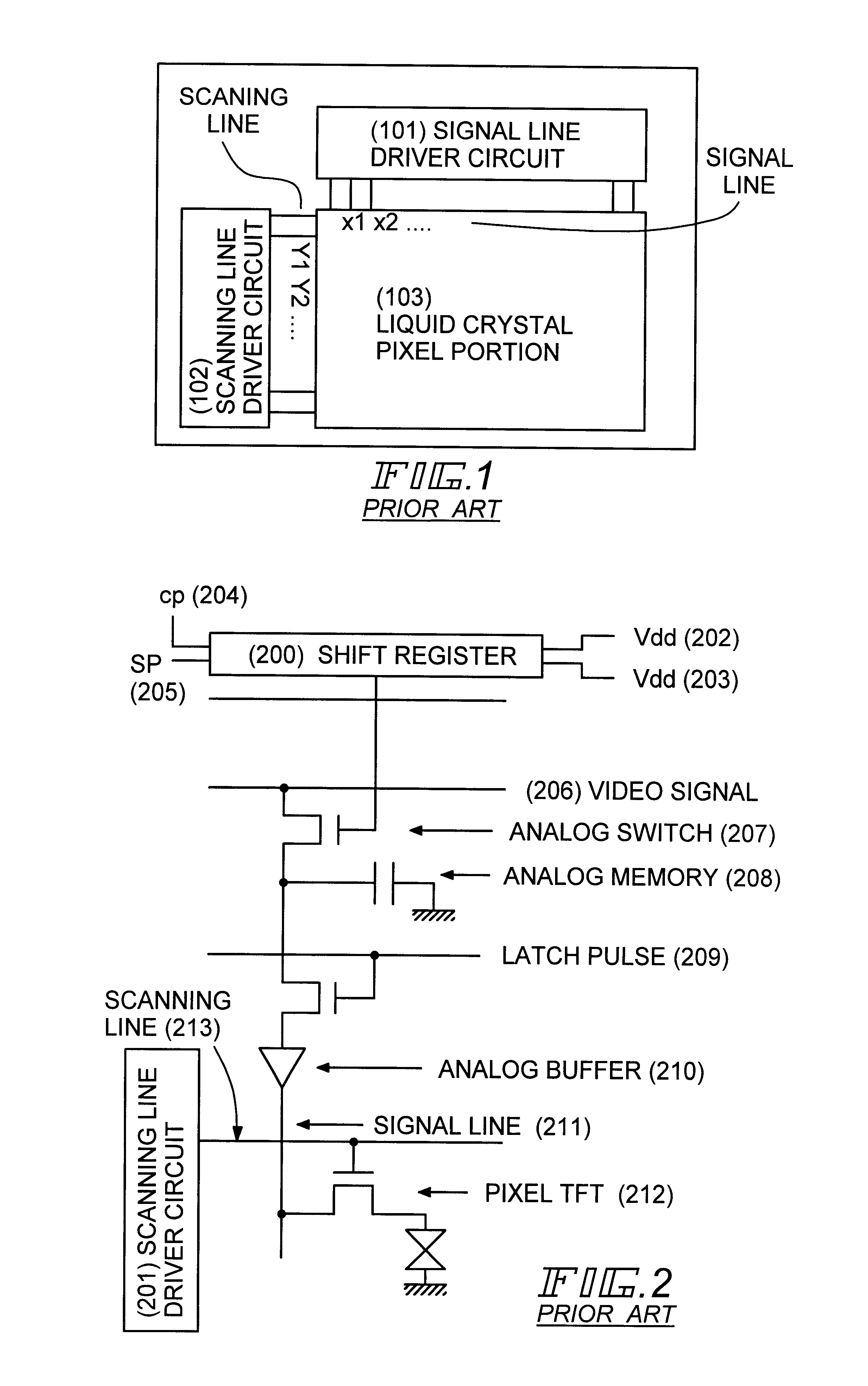

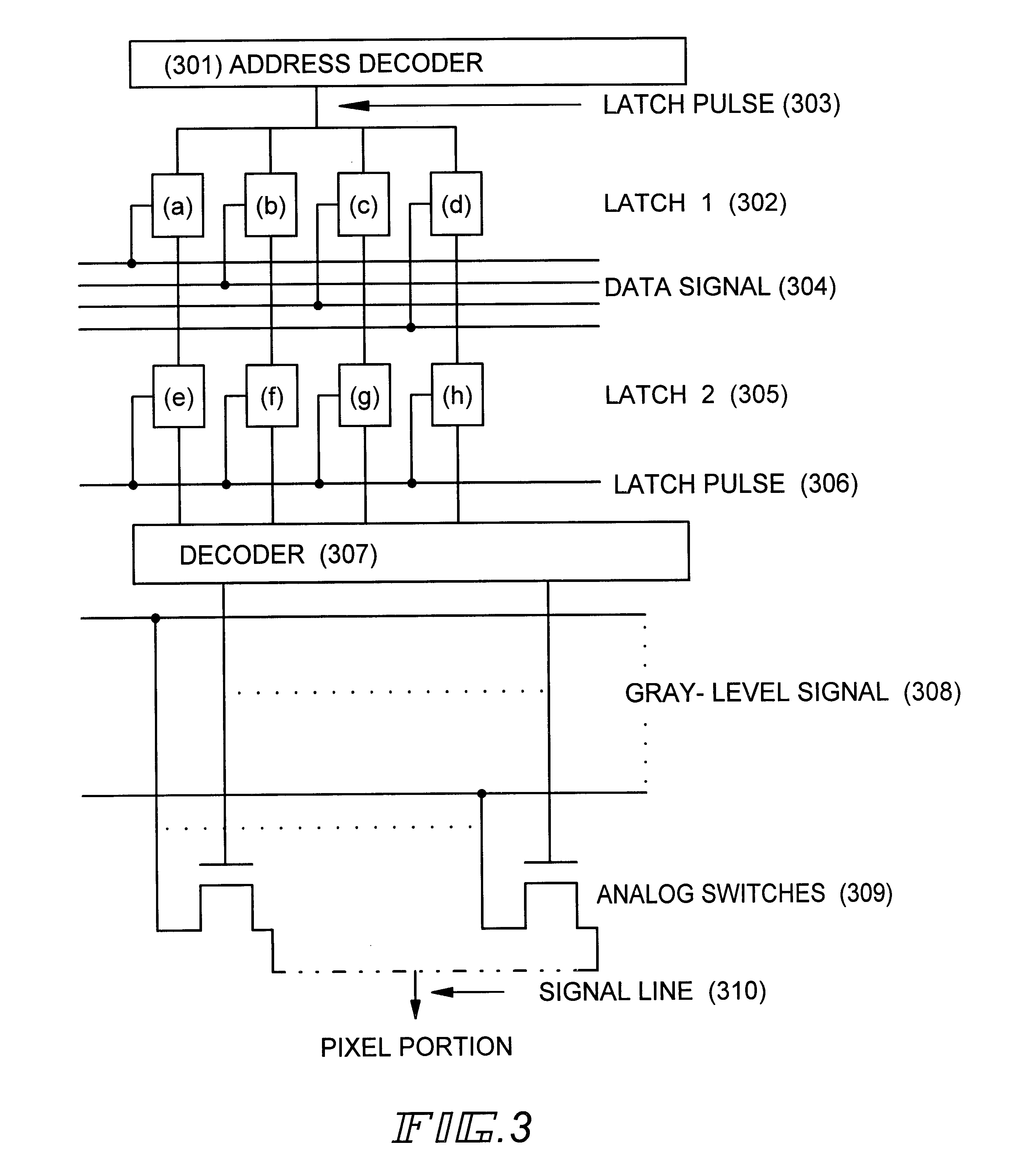

A driver circuit for use in an active matrix display having switching devices at pixels. The driver circuit uses no shift registers. Random access to signal lines or scanning lines can be obtained. The display quality is improved. The production yield is improved. Also, lower electric power consumption and higher-speed operation can be accomplished. Data about gray levels assumes the form of digital values and is supplied to the driver circuit. The signal lines or scanning lines are selected by an address decoder circuit.

Owner:SEMICON ENERGY LAB CO LTD

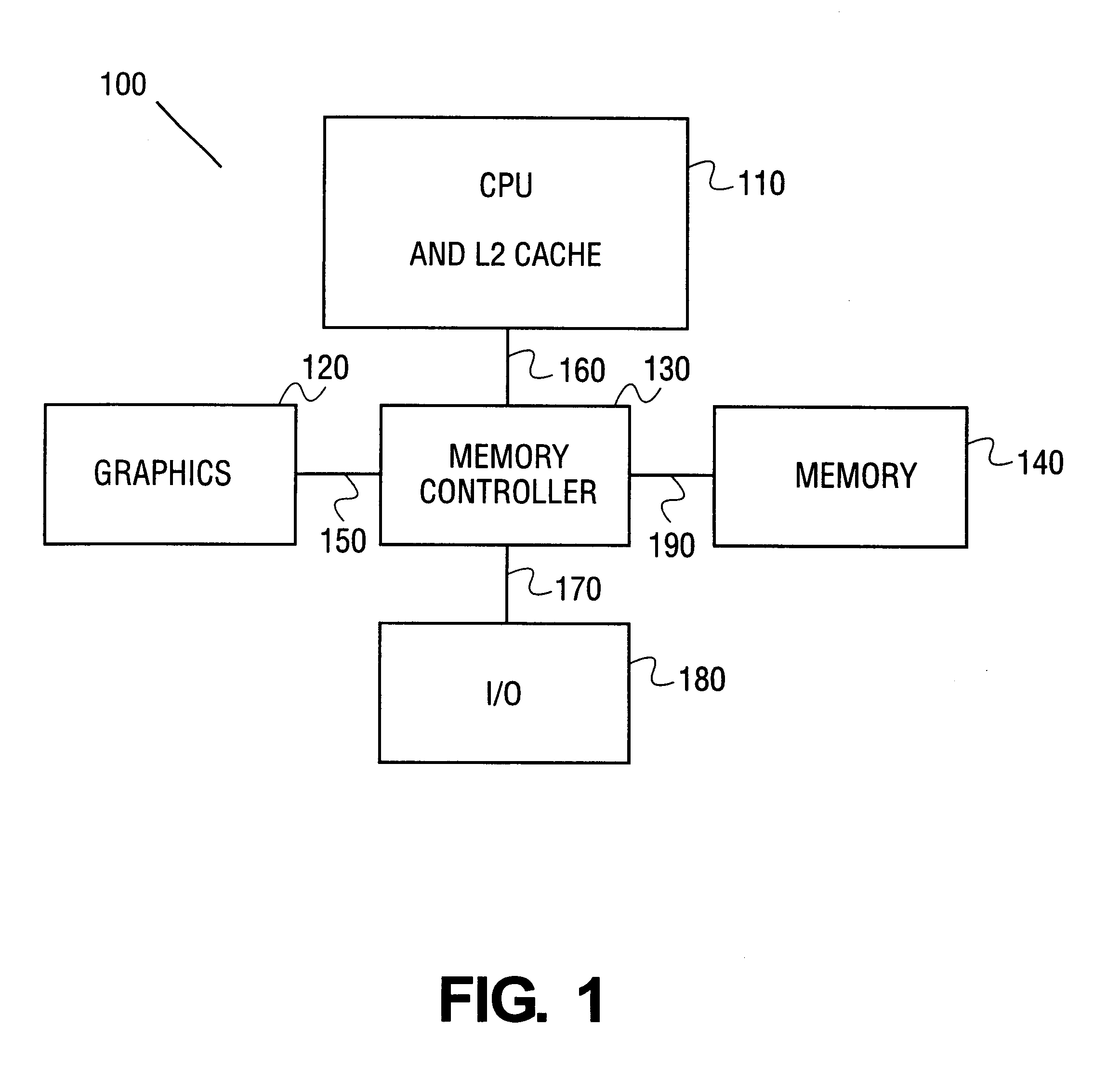

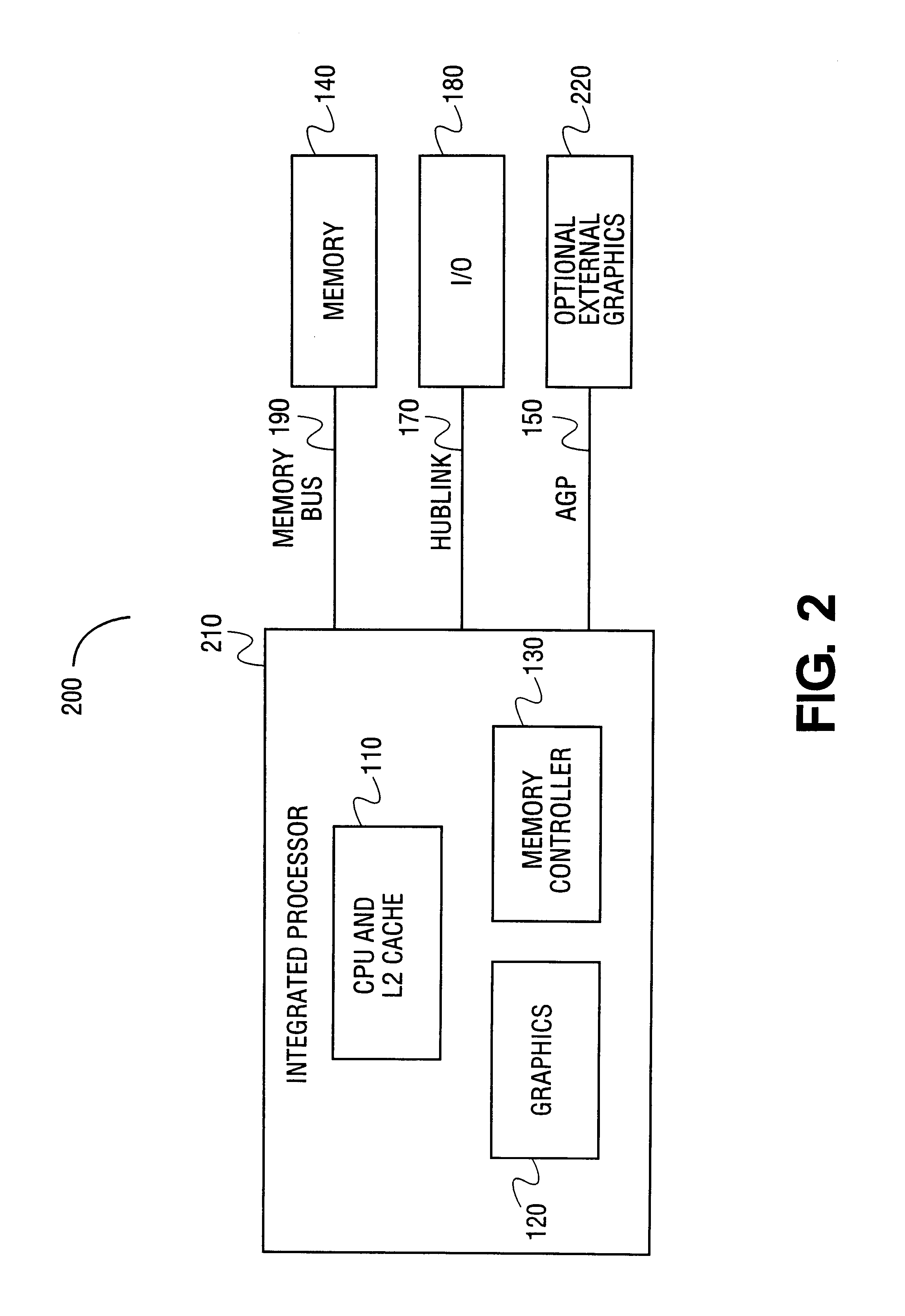

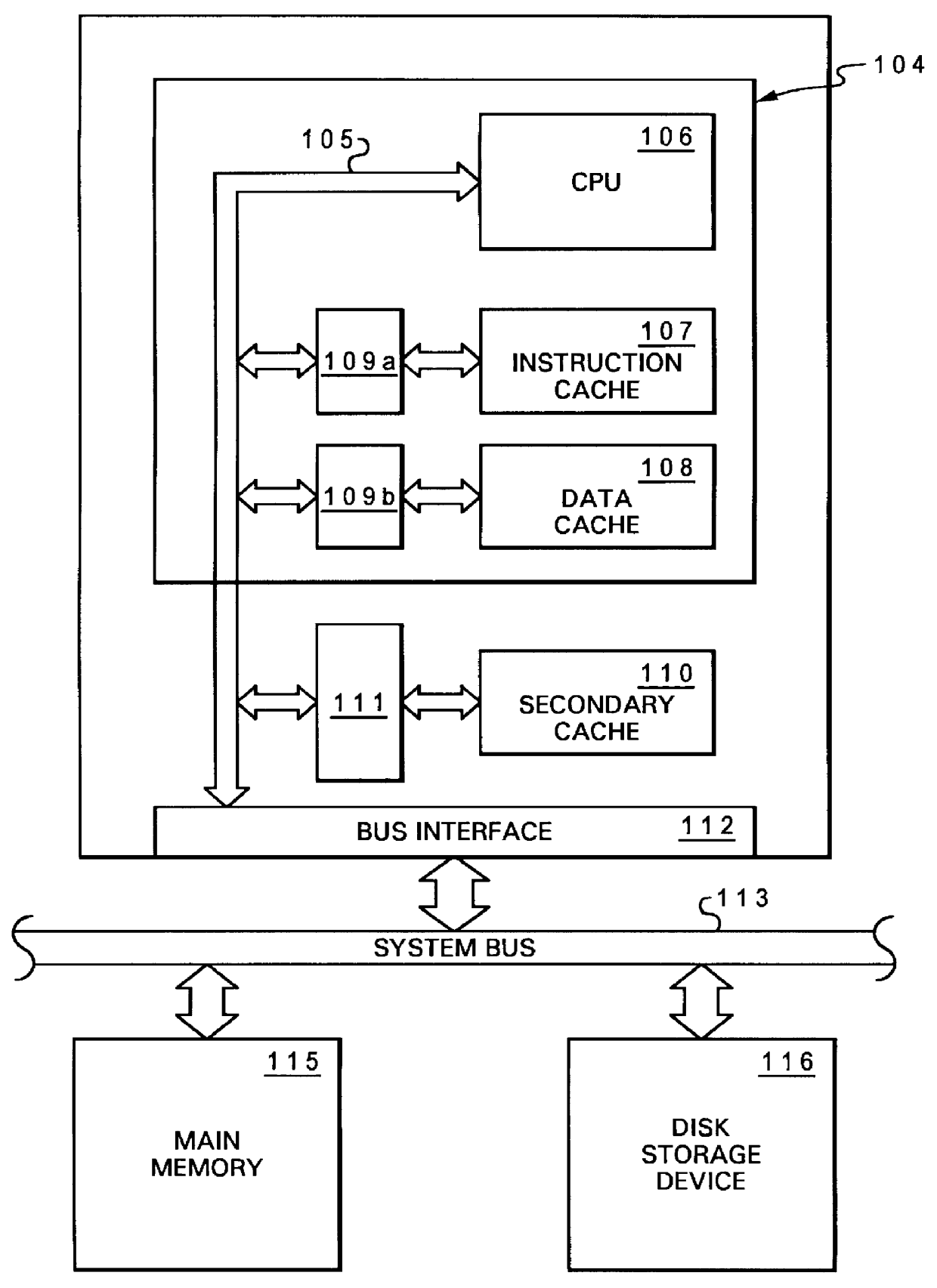

Opportunistic sharing of graphics resources to enhance CPU performance in an integrated microprocessor

InactiveUS6842180B1Memory architecture accessing/allocationMemory adressing/allocation/relocationGraphicsAddress decoder

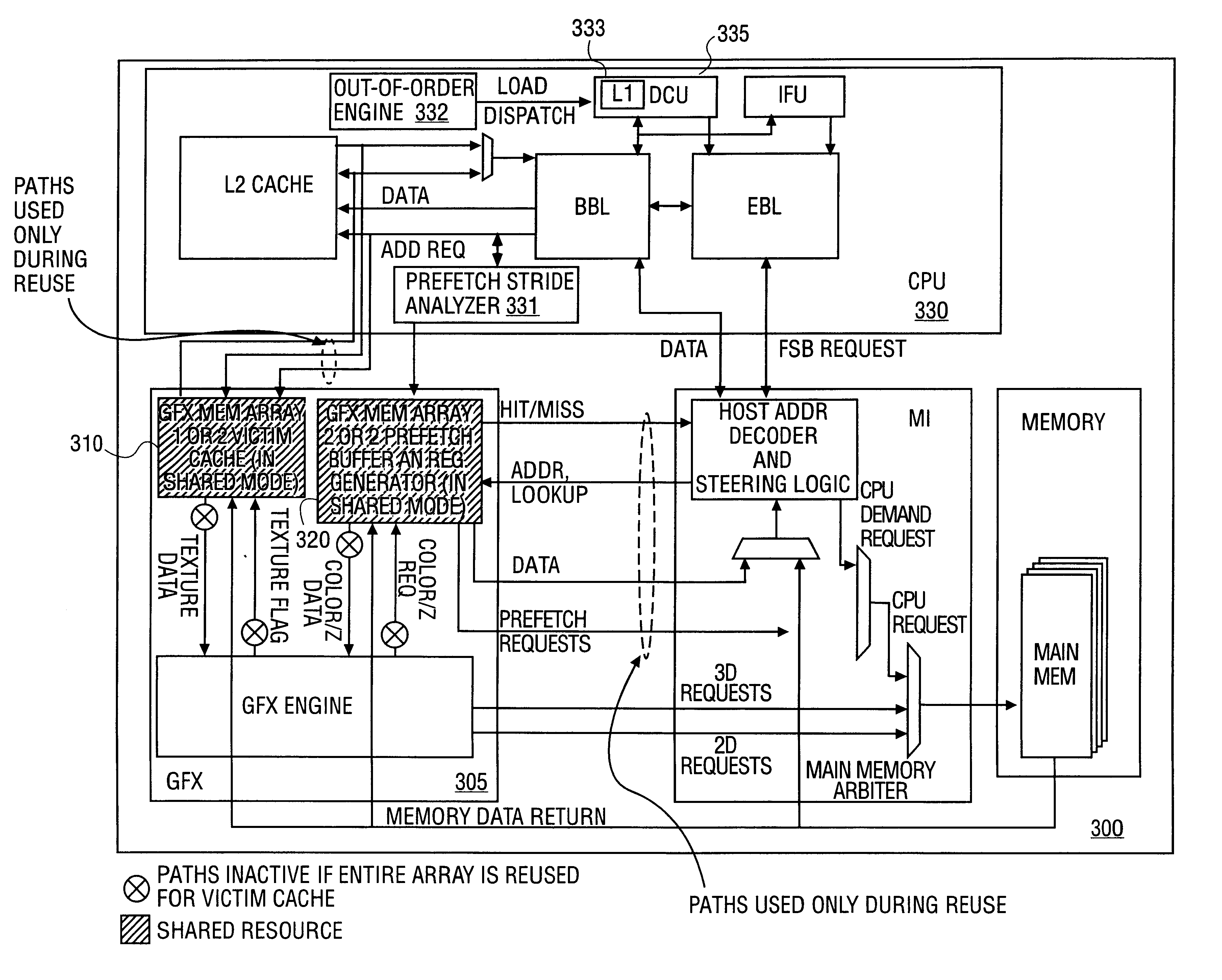

An electronic device that has an integrated central processing unit (CPU) including a pre-fetch stride analyzer and an out-of-order engine is provided. The electronic device also has a graphics engine, having graphics memory, that is coupled to the integrated CPU. A main memory that is coupled to a memory controller is provided. The memory controller is also coupled to the CPU and the graphics engine. The device has a host address decoder coupled to the integrated CPU. A front side bus (FSB) is provided that is coupled to the integrated CPU and the host address decoder. Also provided is a plurality of memory components. Accordingly, either the plurality of memory components or the graphics memory can be shared to perform alternate memory functions. Additionally, a method is provided that determines allocation availability between memory components in an integrated computer processing unit. The method also shares an available memory component as a pre-fetch buffer and another available memory component as a victim cache.

Owner:INTEL CORP

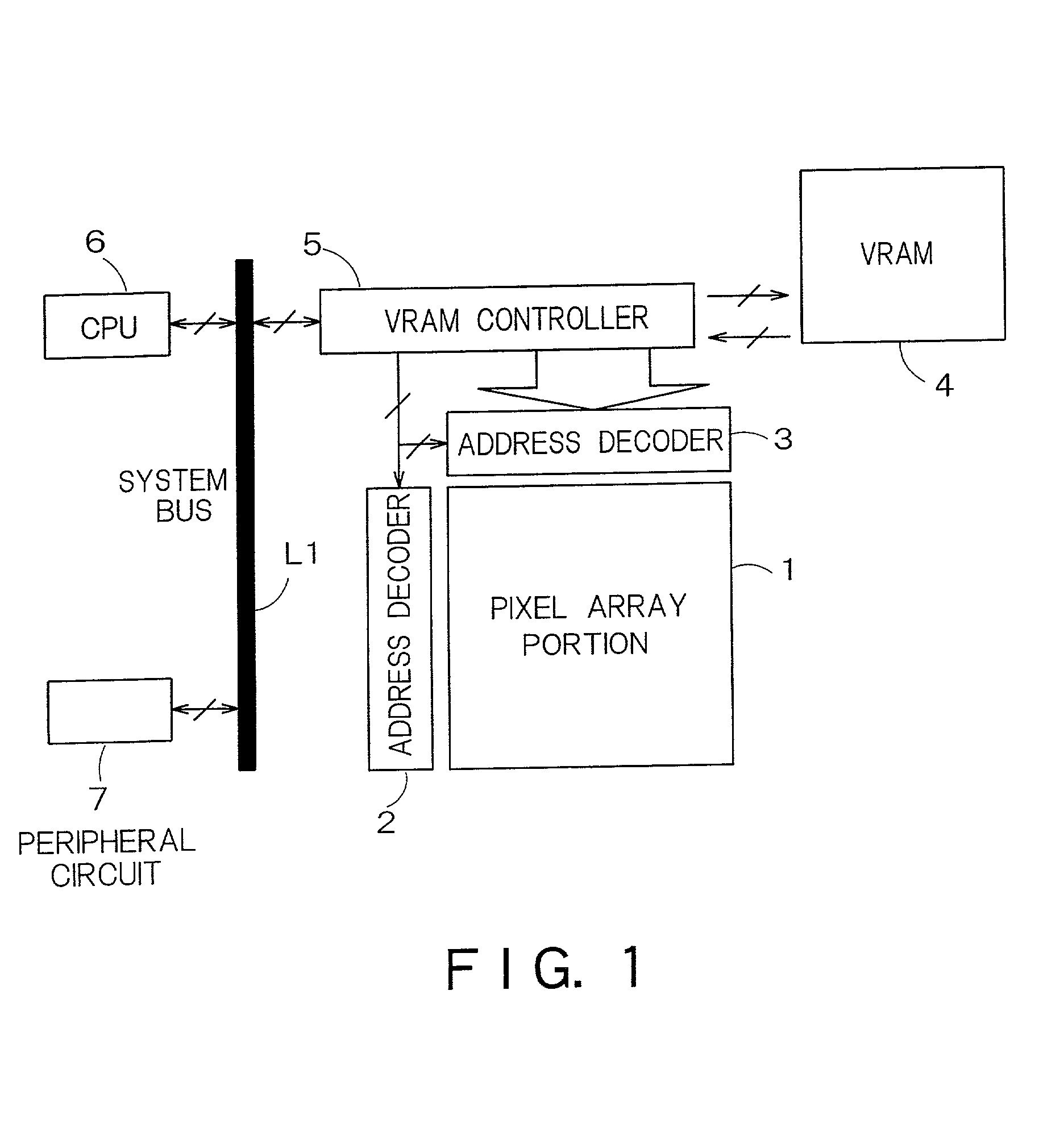

Display apparatus and driving method thereof

InactiveUS20020075211A1Static indicating devicesNon-linear opticsAddress decoderLiquid-crystal display

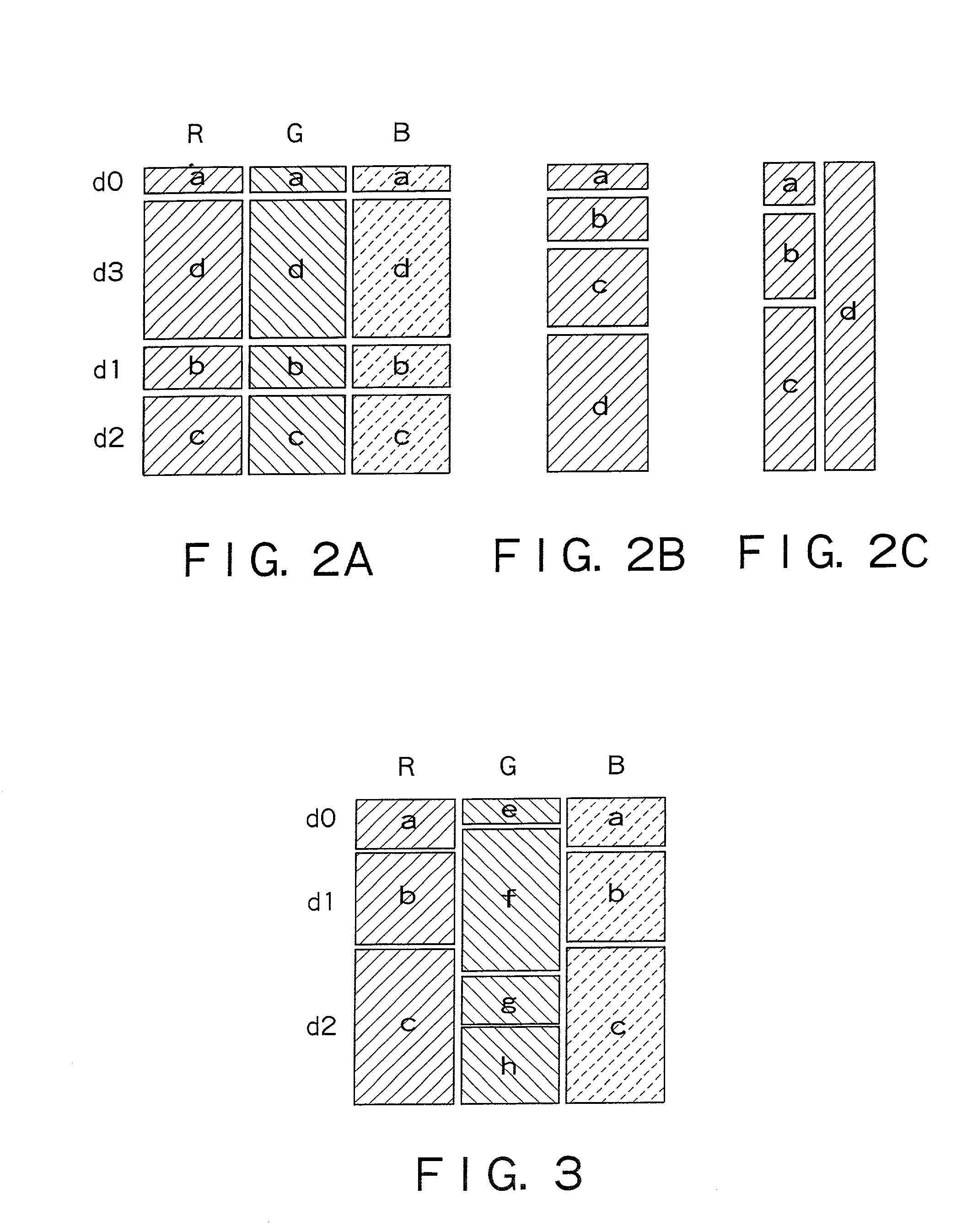

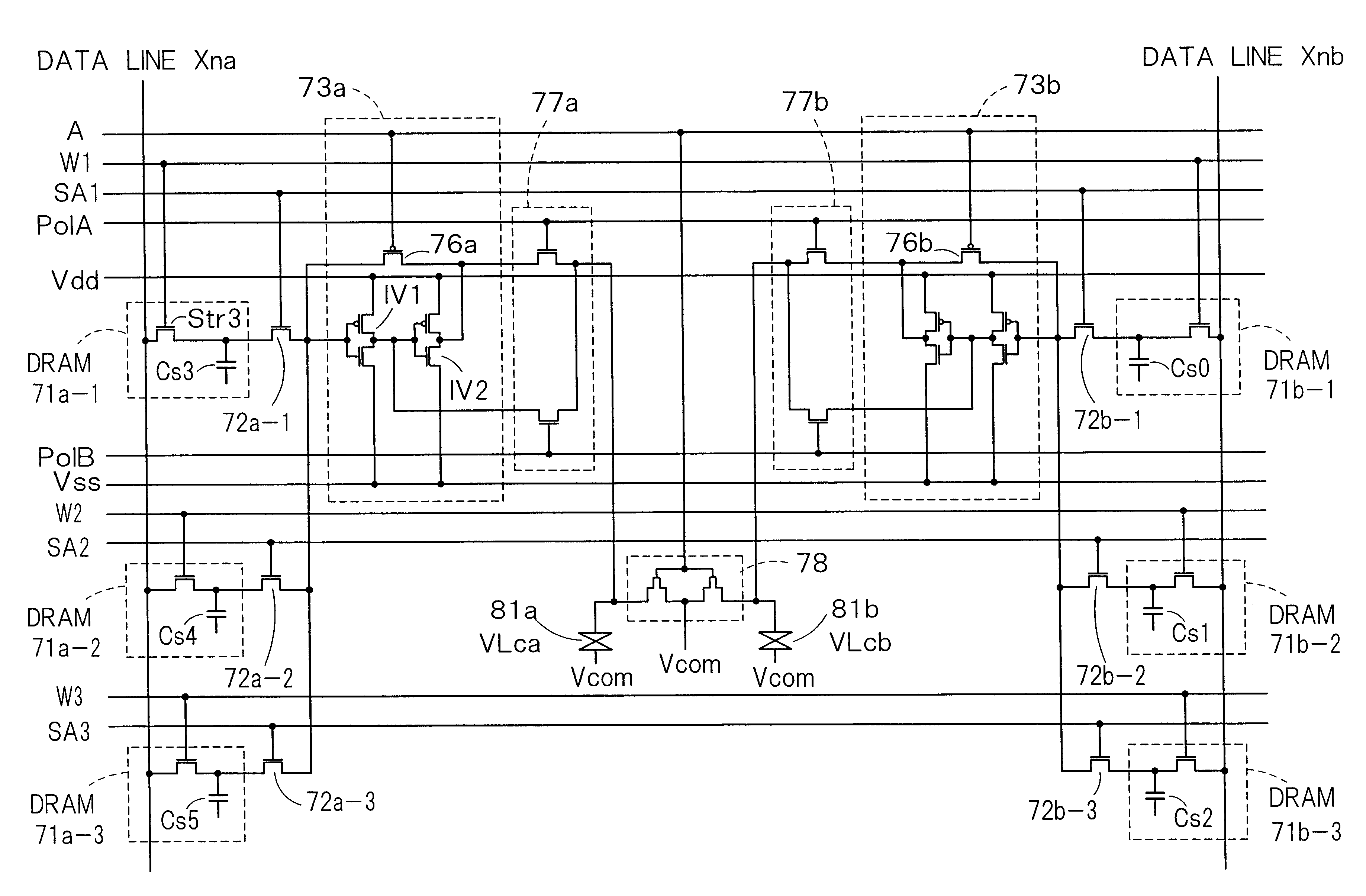

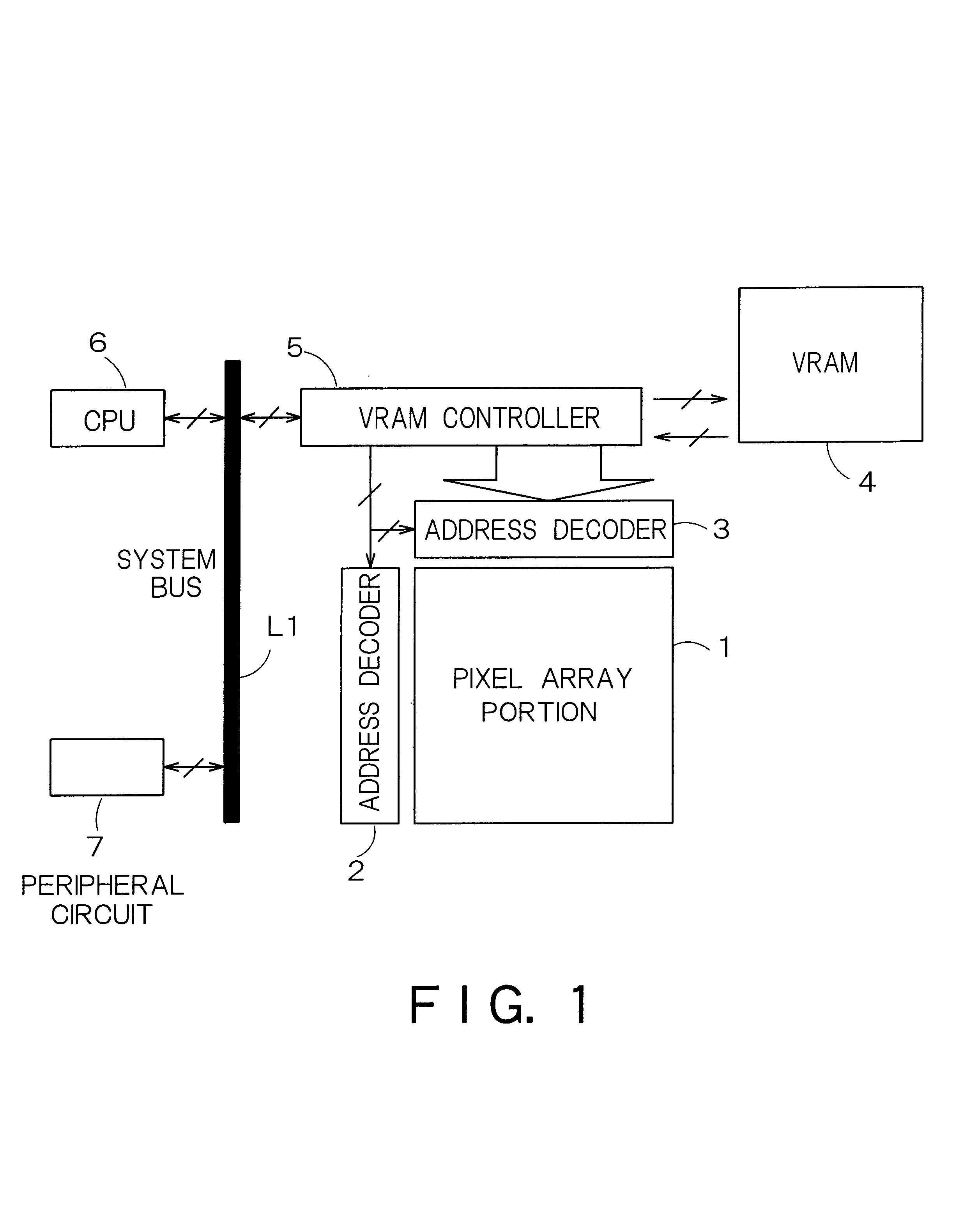

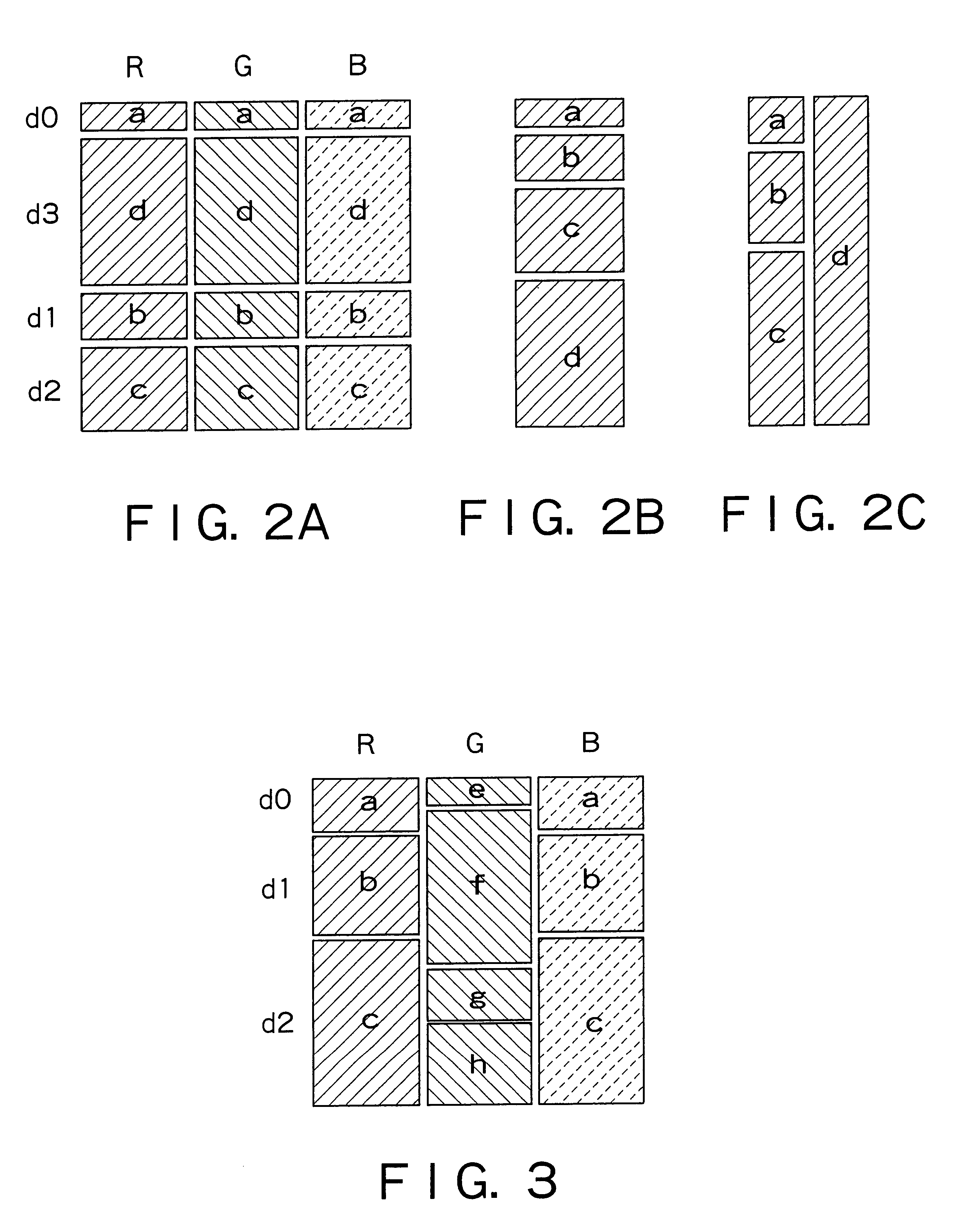

A liquid crystal display device which can reduce power consumption and can be miniaturized. The liquid crystal display device according to the present invention includes a pixel array portion, an address decoder, a display memory (VRAM), and a VRAM controller, and transmits / receives a signal to / from a CPU and a peripheral circuit through a system bus. The pixel array portion has an area gradation pixel structure in which each pixel is composed of a plurality of one-bit memories. The entire pixel array portion is divided into pixel blocks each of which consists of a plurality of pixels, and the one-bit memory is rewritten in units of block. The one-bit memory has a double-word line structure.

Owner:JAPAN DISPLAY CENTRAL CO LTD

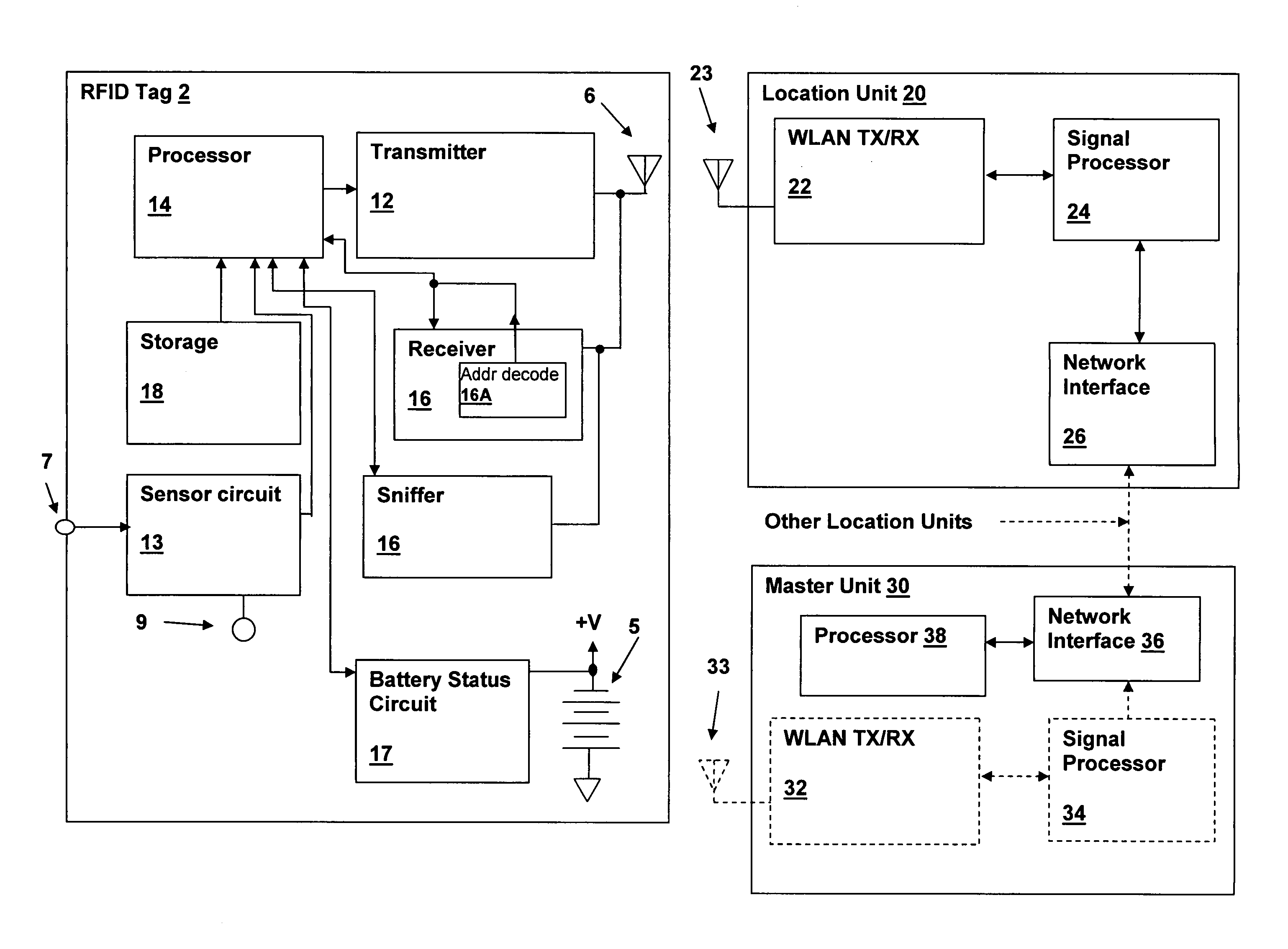

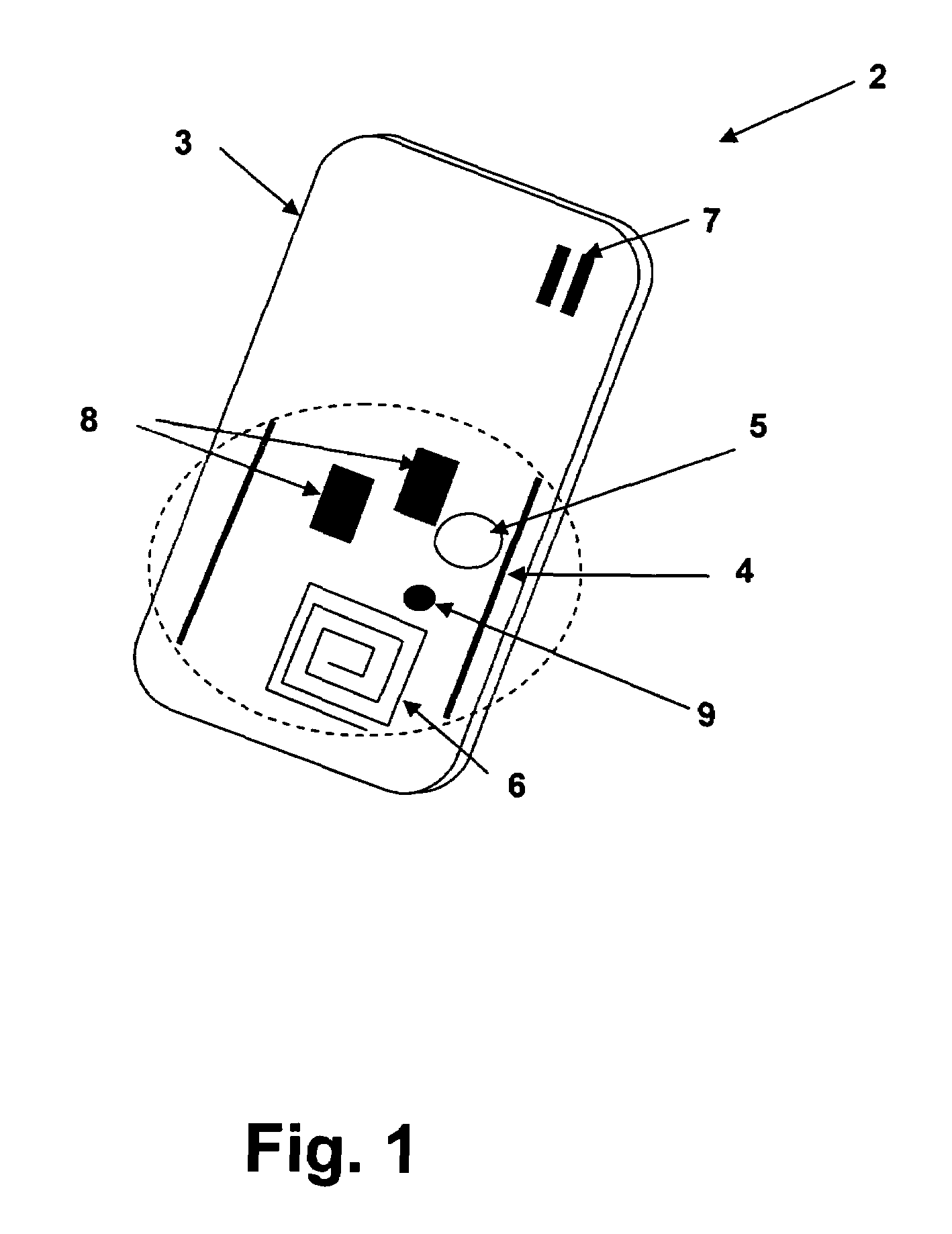

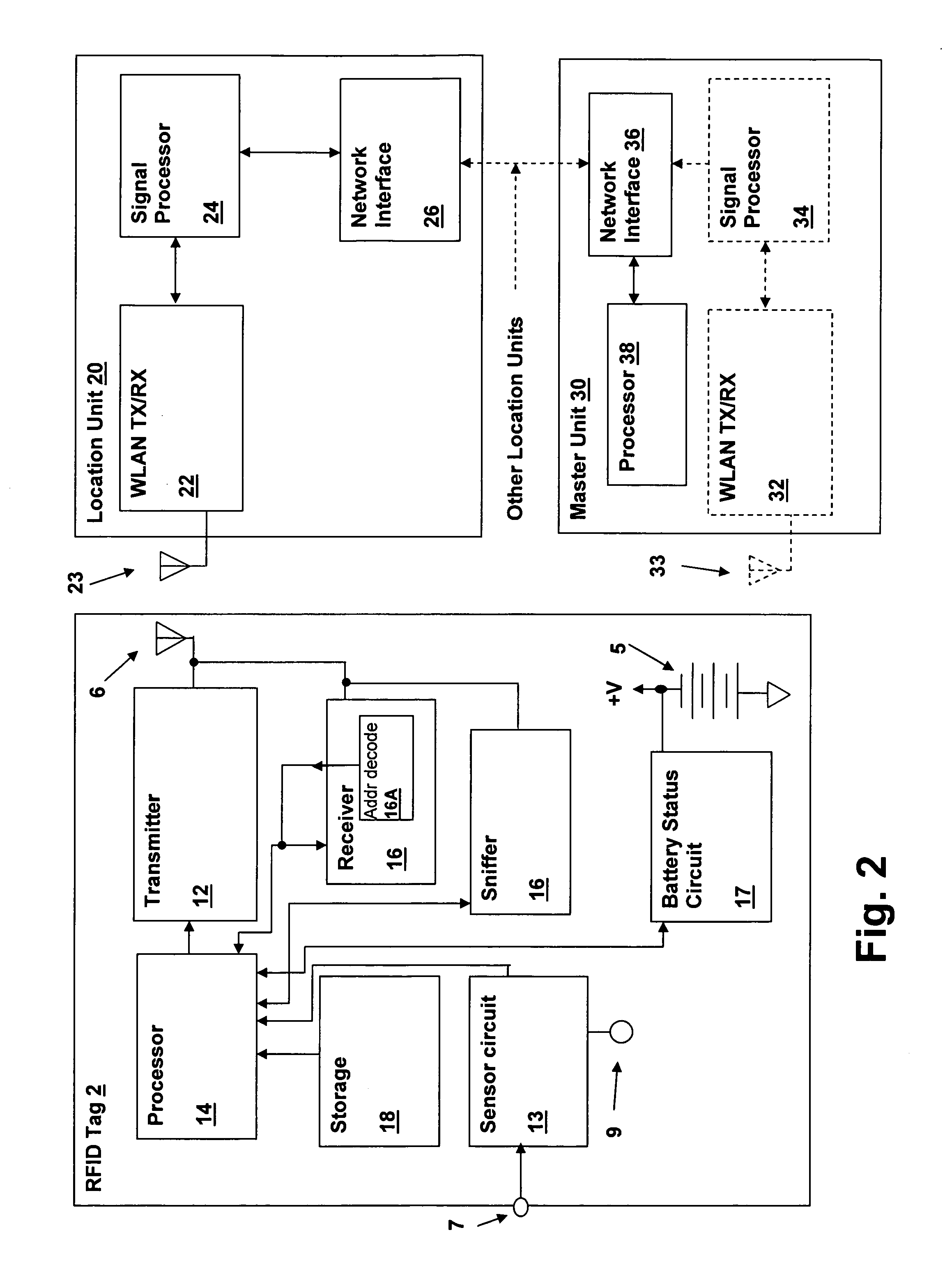

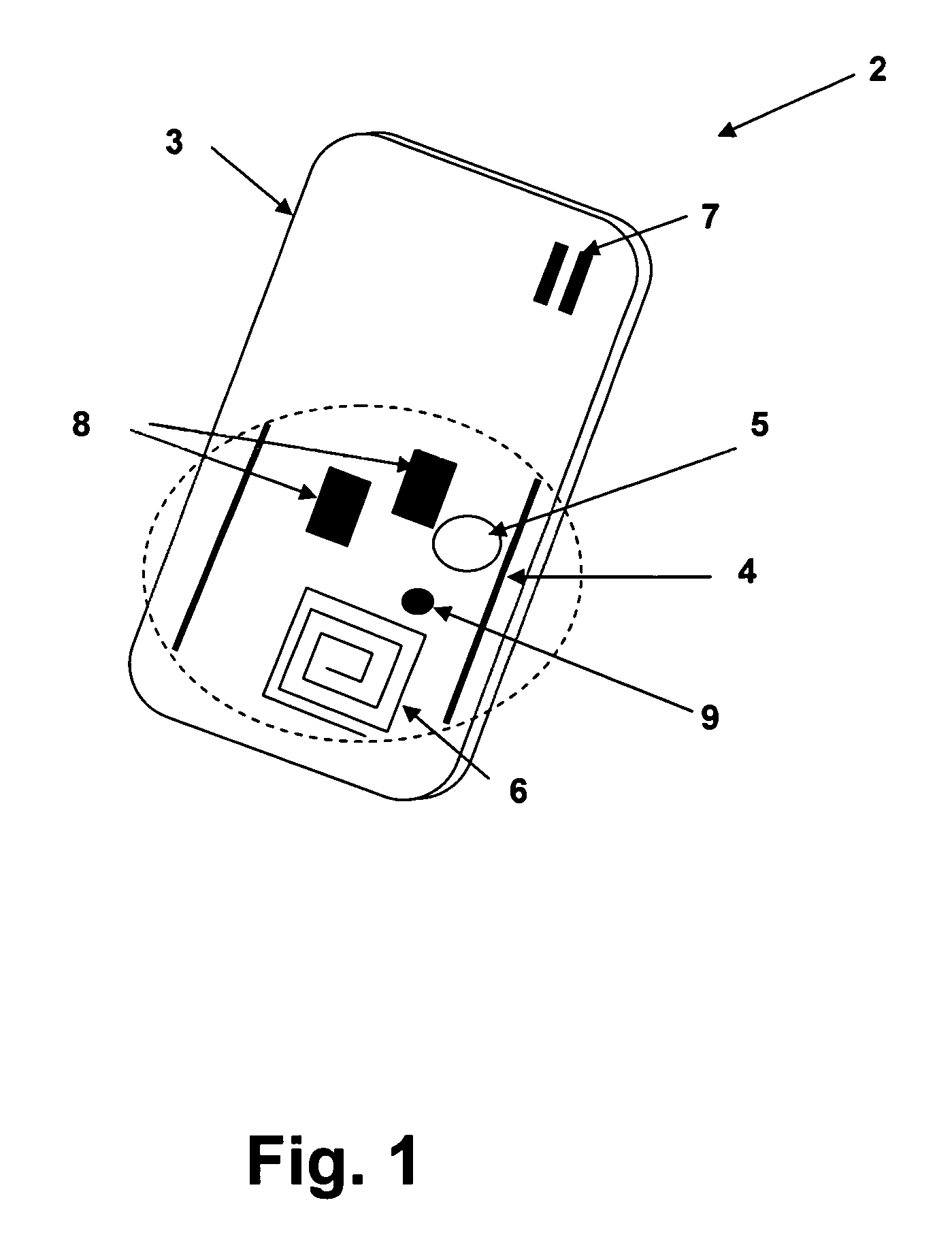

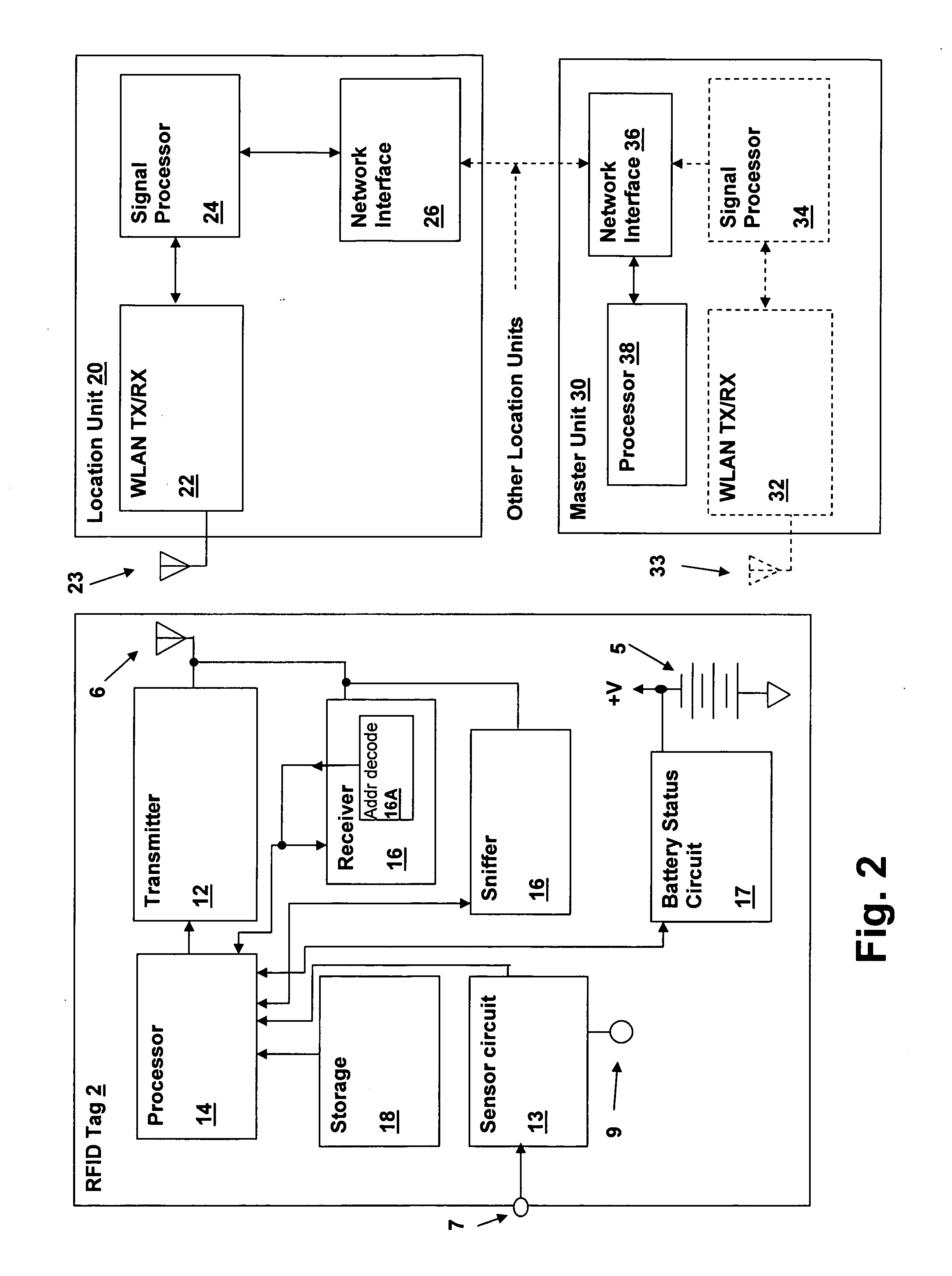

Radio-frequency identification (RFID) tag employing unique reception window and method therefor

InactiveUS7295115B2Frequency-division multiplex detailsPosition fixationAddress decoderRadio frequency

Owner:AEROSCOUT

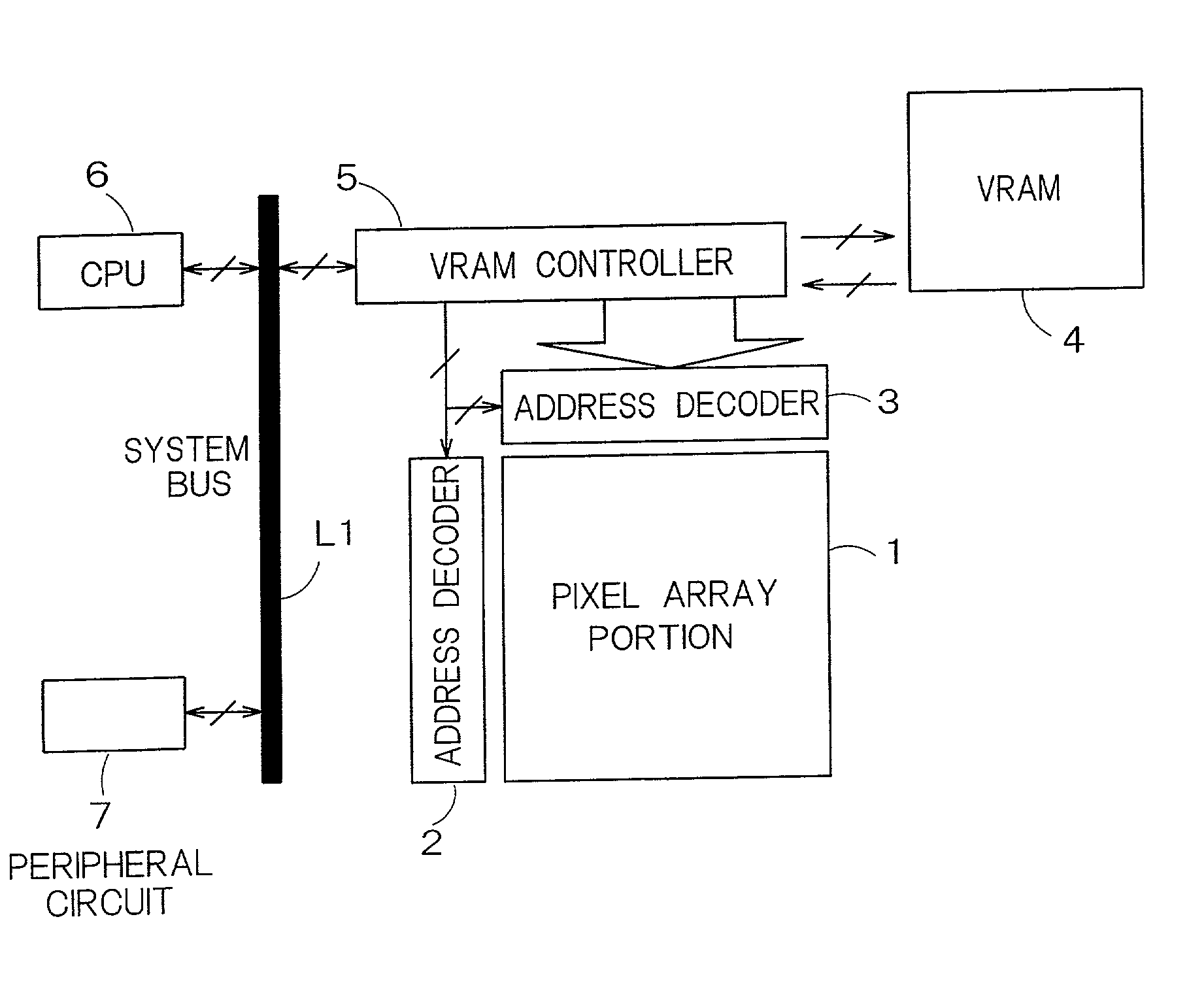

Display device and driving method thereof

InactiveUS6873320B2Reduce consumptionSmall sizeCathode-ray tube indicatorsNon-linear opticsAddress decoderLiquid-crystal display

A liquid crystal display device which can reduce power consumption and can be miniaturized. The liquid crystal display device according to the present invention includes a pixel array portion, an address decoder, a display memory (VRAM), and a VRAM controller, and transmits / receives a signal to / from a CPU and a peripheral circuit through a system bus. The pixel array portion has an area gradation pixel structure in which each pixel is composed of a plurality of one-bit memories. The entire pixel array portion is divided into pixel blocks each of which consists of a plurality of pixels, and the one-bit memory is rewritten in units of block. The one-bit memory has a double-word line structure.

Owner:KK TOSHIBA

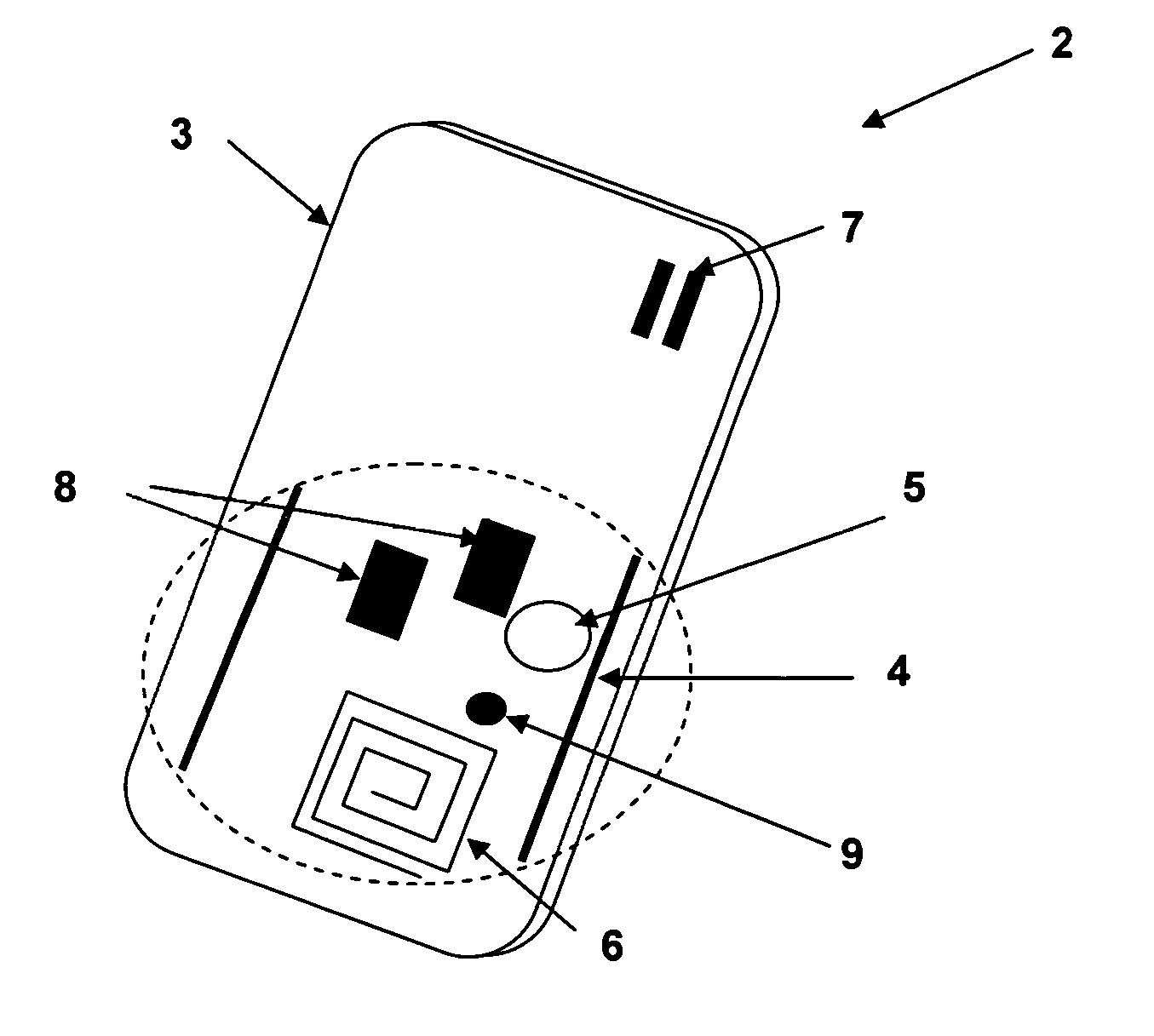

Radio-frequency identification (RFID) tag employing unique reception window and method therefor

InactiveUS20050156711A1Frequency-division multiplex detailsPosition fixationAddress decoderWireless lan

A radio-frequency identification (RFID) tag employing a unique reception window and method for operating the tag system provides low-power operation for enhanced tag battery life, while providing addressable tags that can receive commands and data from the system, which can be a wireless local area network (WLAN) incorporating location finding for locating the tags. Interference with other tags and other transmitters is prevented by either using a sniffer circuit to determine that no network transmission is in progress, or by using a special non-interfering coding sequence. A receiver within the tag is operated for a predetermined period of time after a periodic transmission is made from the tag, and an address decoder determines if the tag is being addressed. The receiver can receive data and / or commands after being addressed and is shutdown if the window time elapses, the tag is not addressed, or at the completion of data / command transfer.

Owner:AEROSCOUT

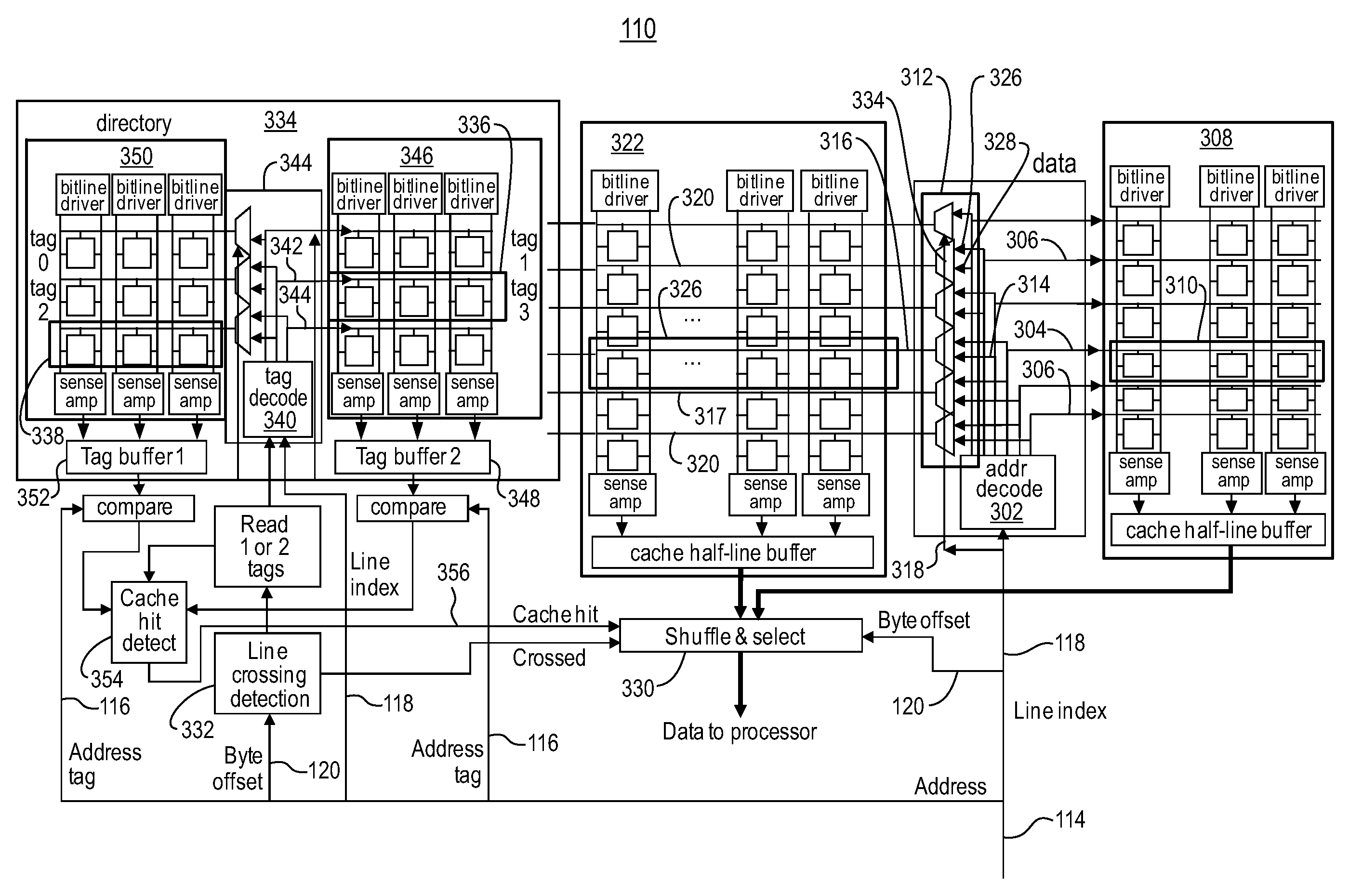

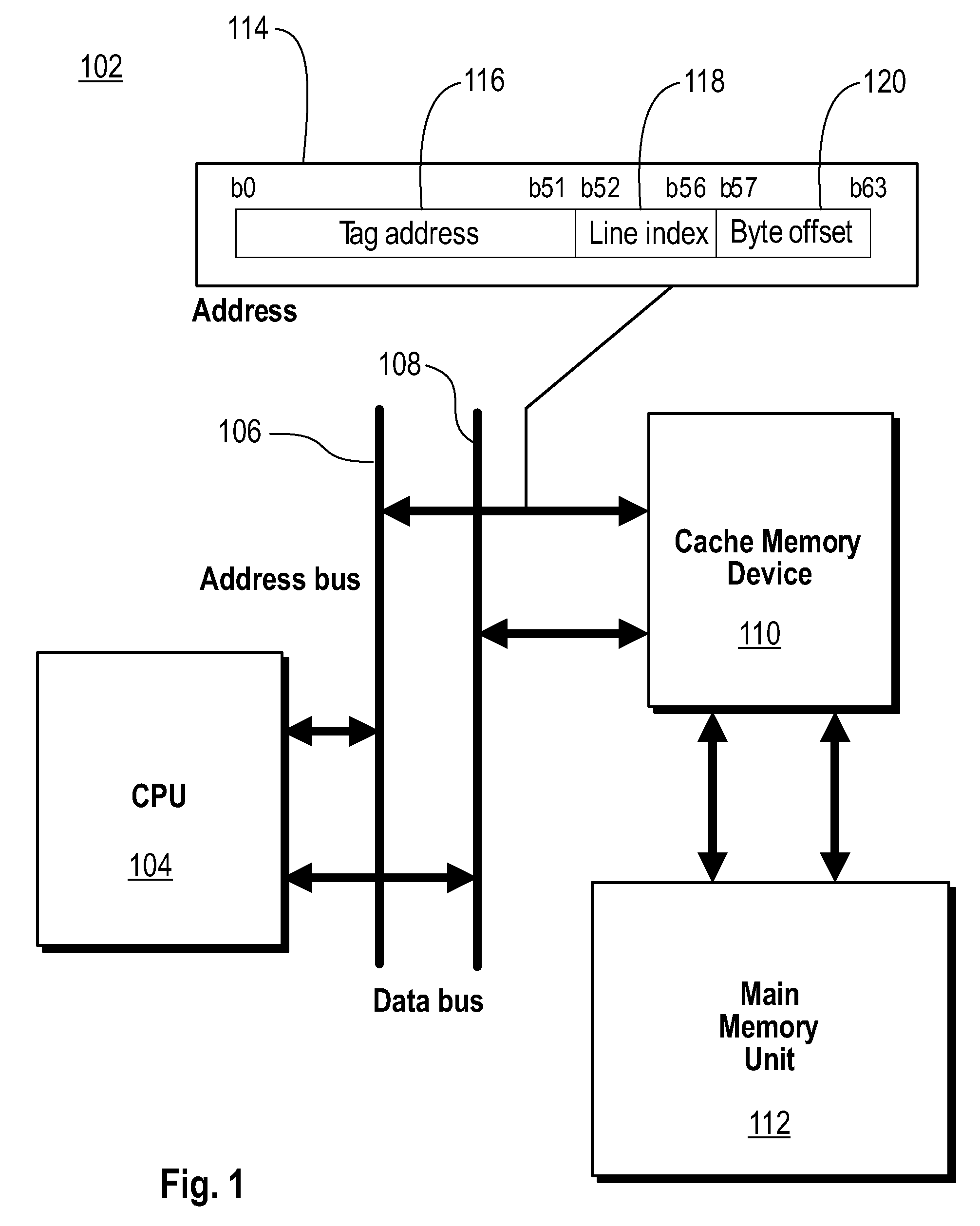

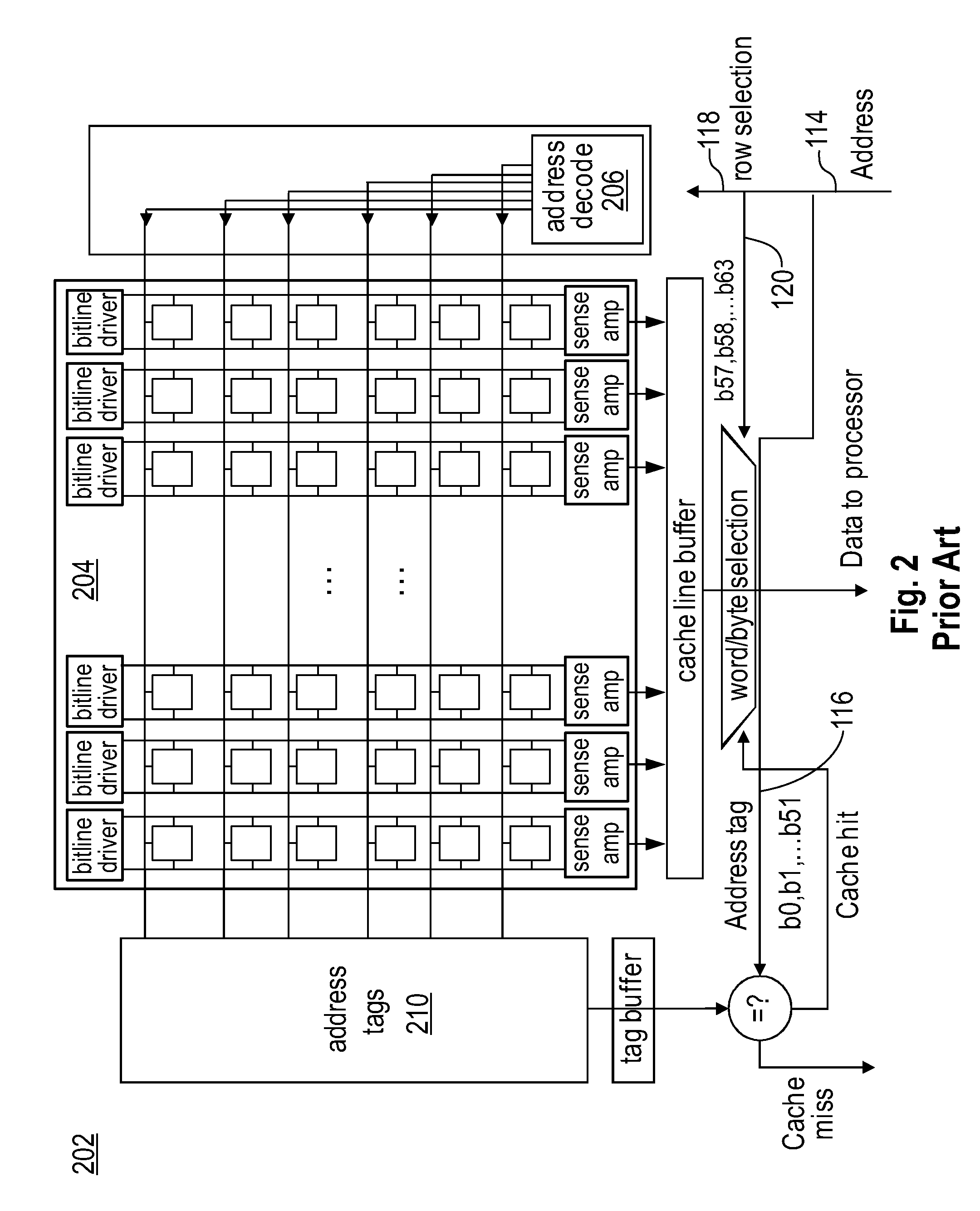

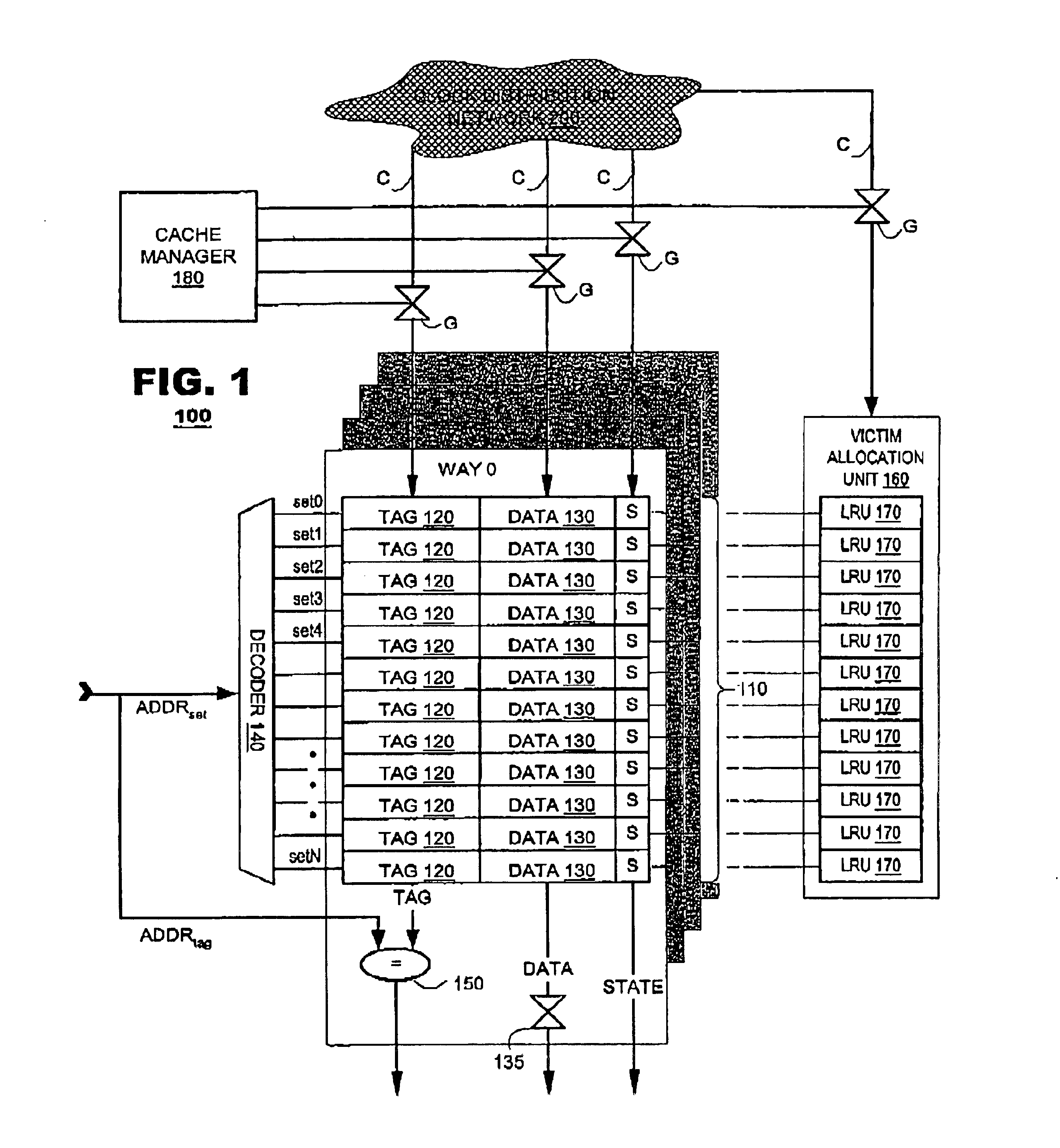

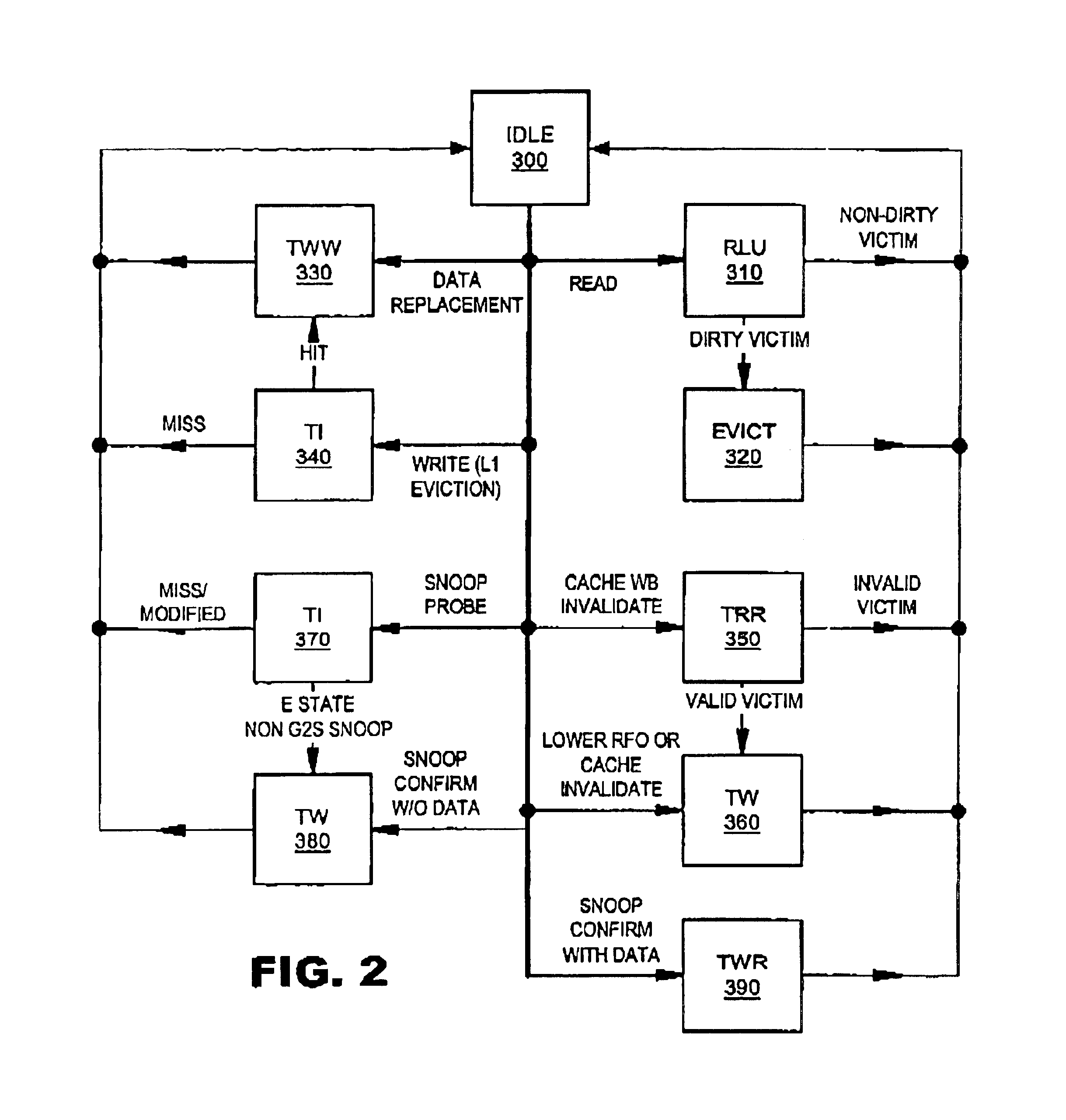

High performance unaligned cache access

A cache memory device and method for operating the same. One embodiment of the cache memory device includes an address decoder decoding a memory address and selecting a target cache line. A first cache array is configured to output a first cache entry associated with the target cache line, and a second cache array coupled to an alignment unit is configured to output a second cache entry associated with the alignment cache line. The alignment unit coupled to the address decoder selects either the target cache line or a neighbor cache line proximate the target cache line as an alignment cache line output. Selection of either the target cache line or a neighbor cache line is based on an alignment bit in the memory address. A tag array cache is split into even and odd cache lines tags, and provides one or two tags for every cache access.

Owner:IBM CORP

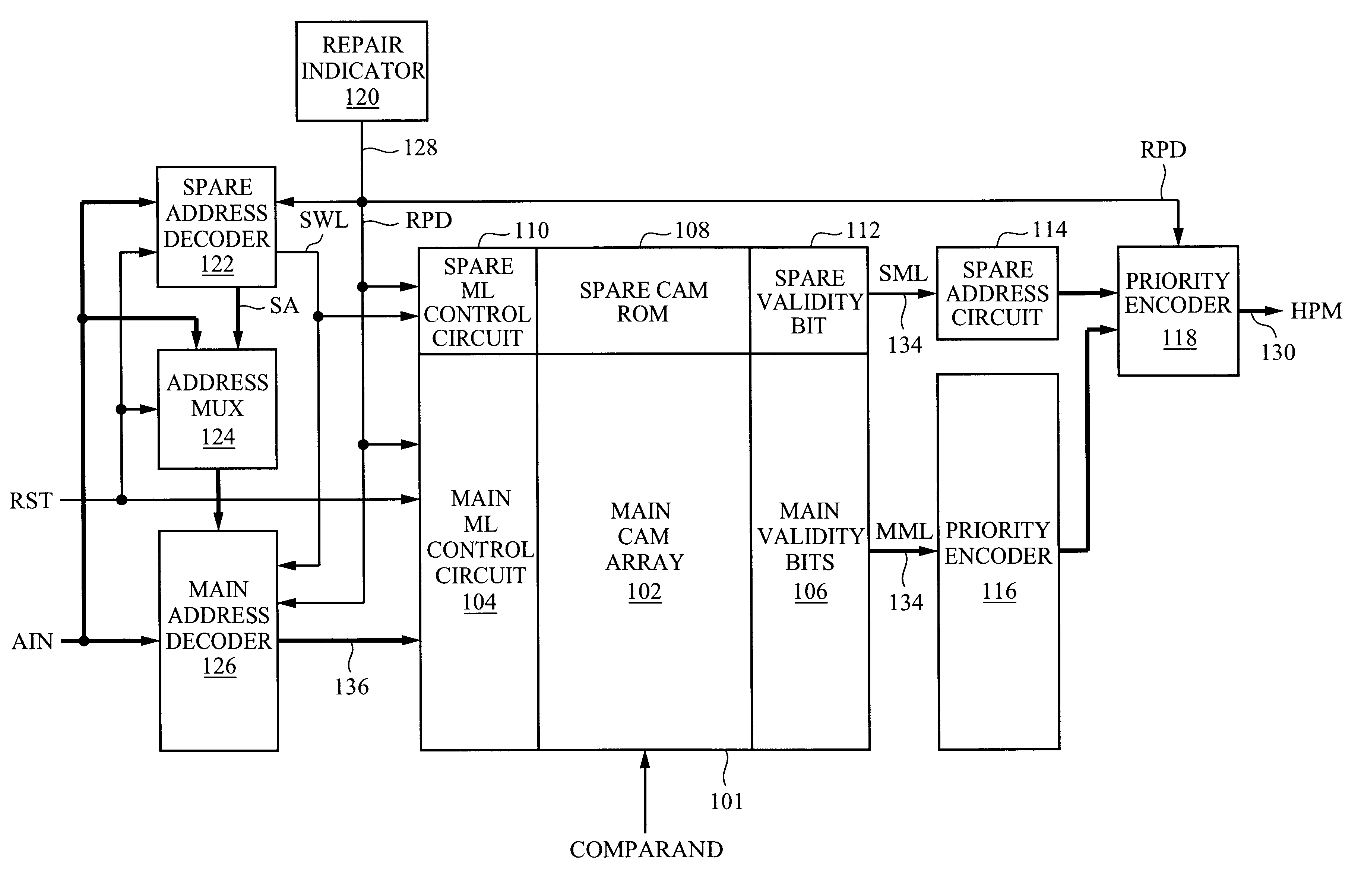

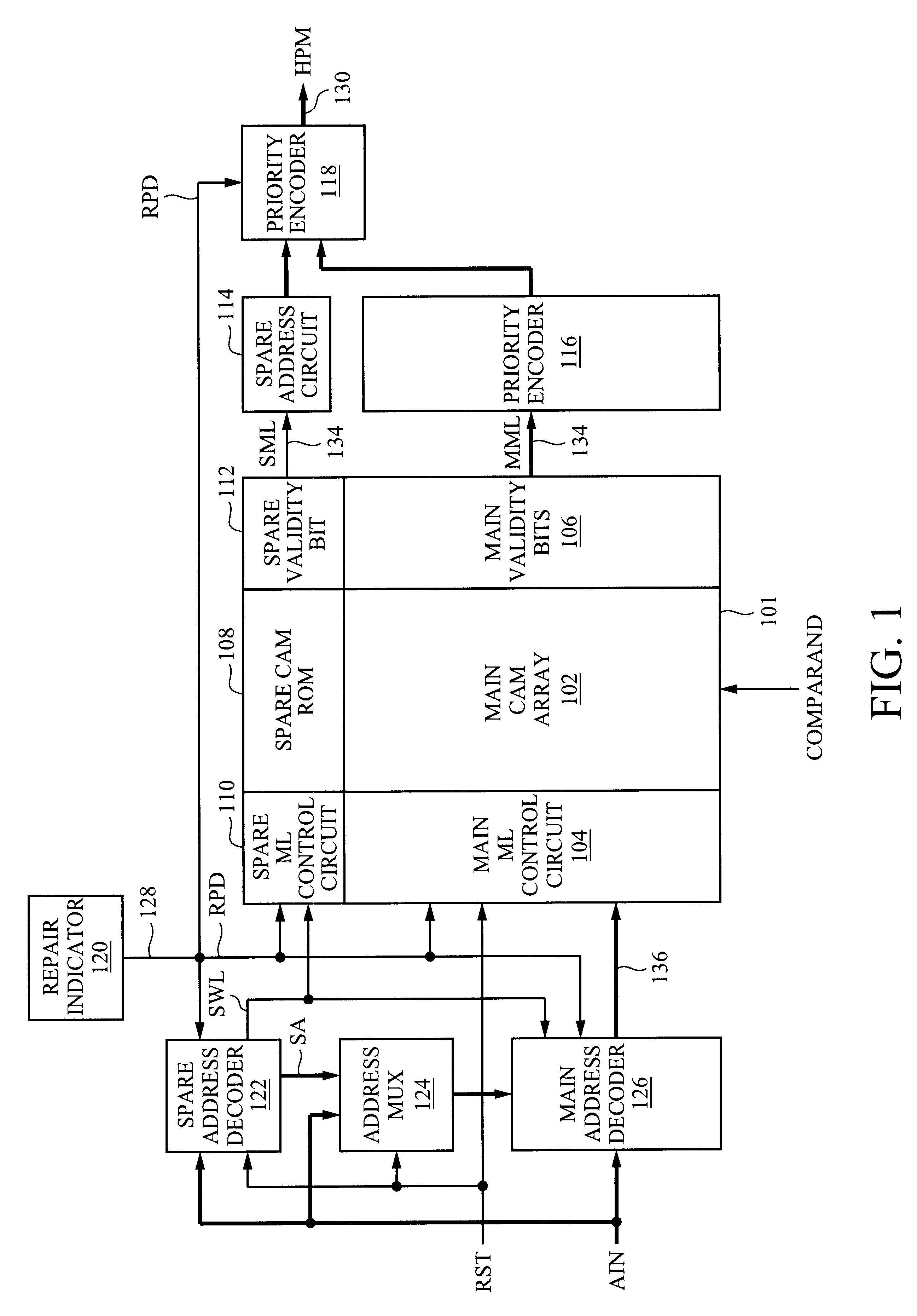

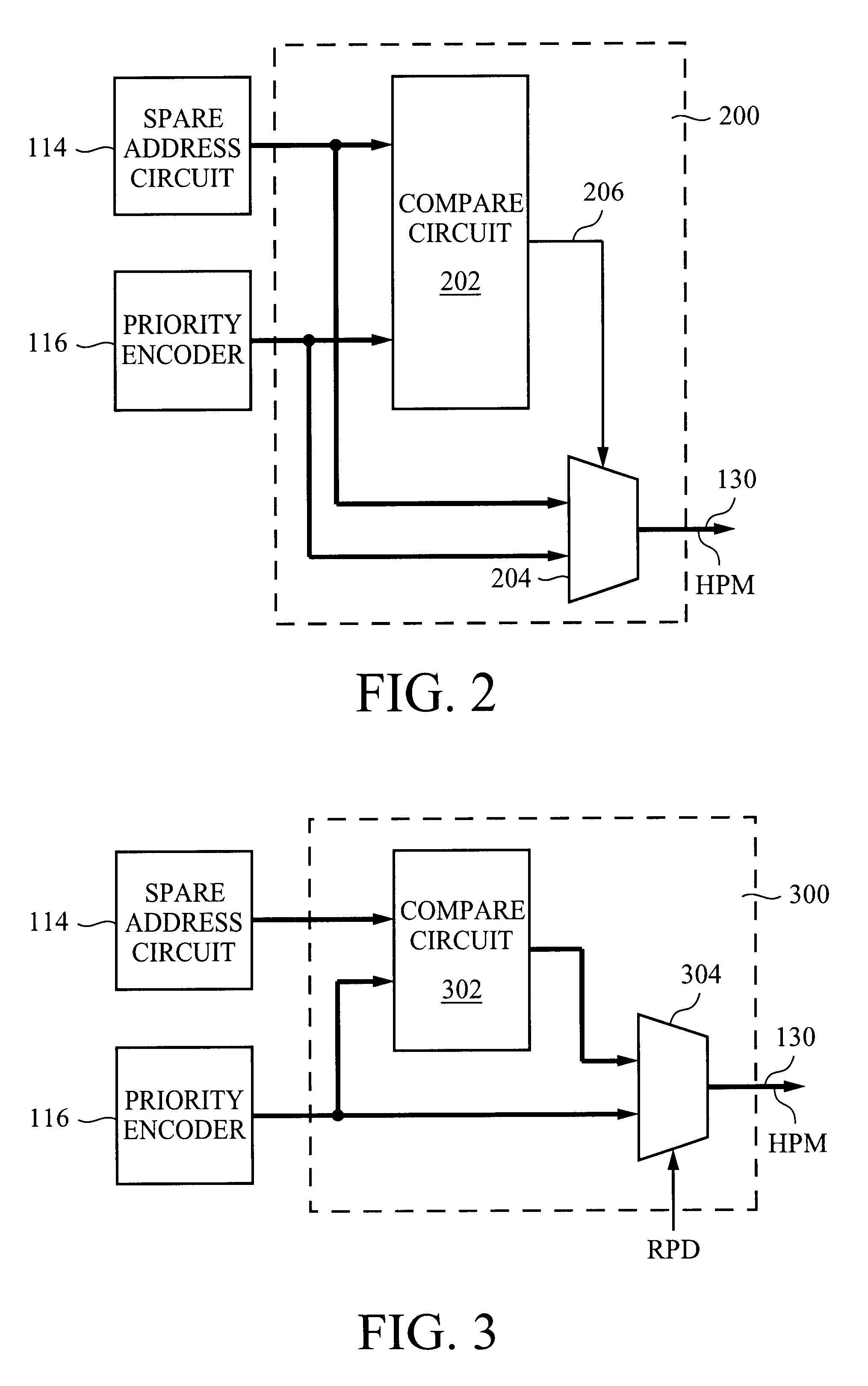

Row redundancy in a content addressable memory

A CAM device that allows defective rows in one CAM block to be functionally replaced by spare rows from any CAM block in the device. In some embodiments, the CAM device includes a main address decoder, a plurality of CAM blocks, a corresponding plurality of spare address decoders, and a block select circuit. In one embodiment, each CAM block includes a main CAM array having a plurality of rows of CAM cells each coupled to a corresponding word line, and a spare row of CAM cells coupled to a spare word line. Each spare row may be used to functionally replace a defective row in the same CAM block or in any other CAM block by programming the address of the defective row into the corresponding spare address decoder.

Owner:AVAGO TECH INT SALES PTE LTD

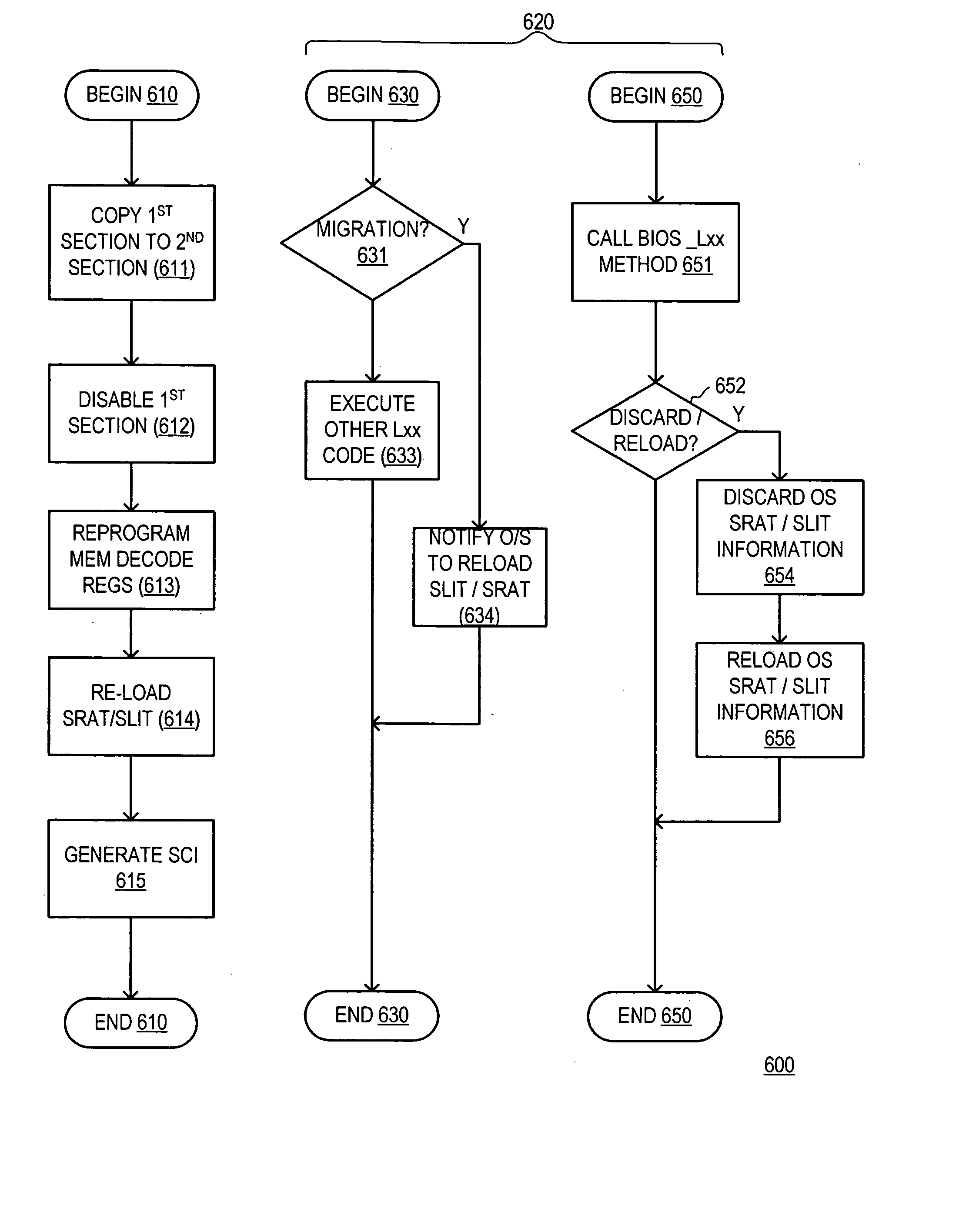

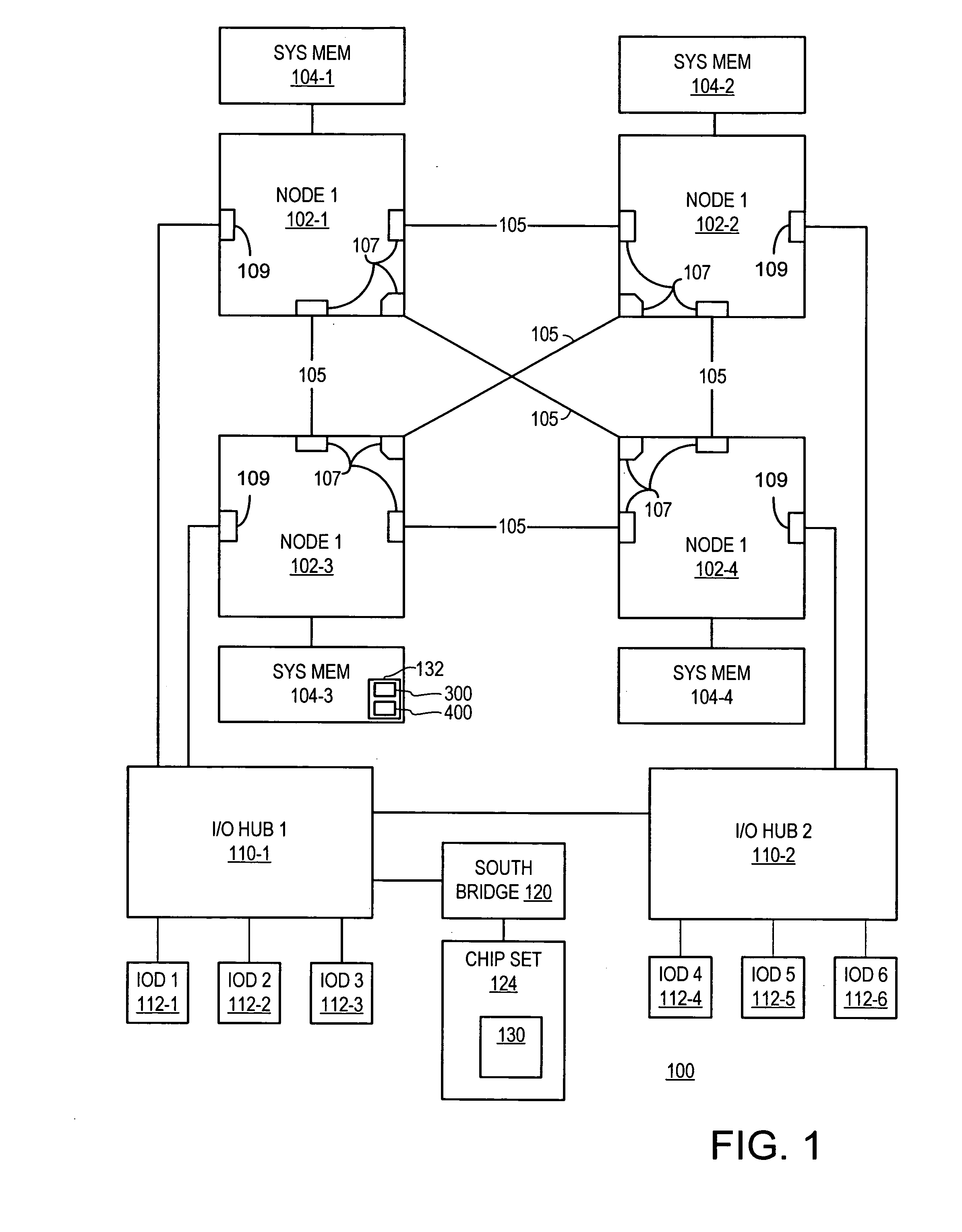

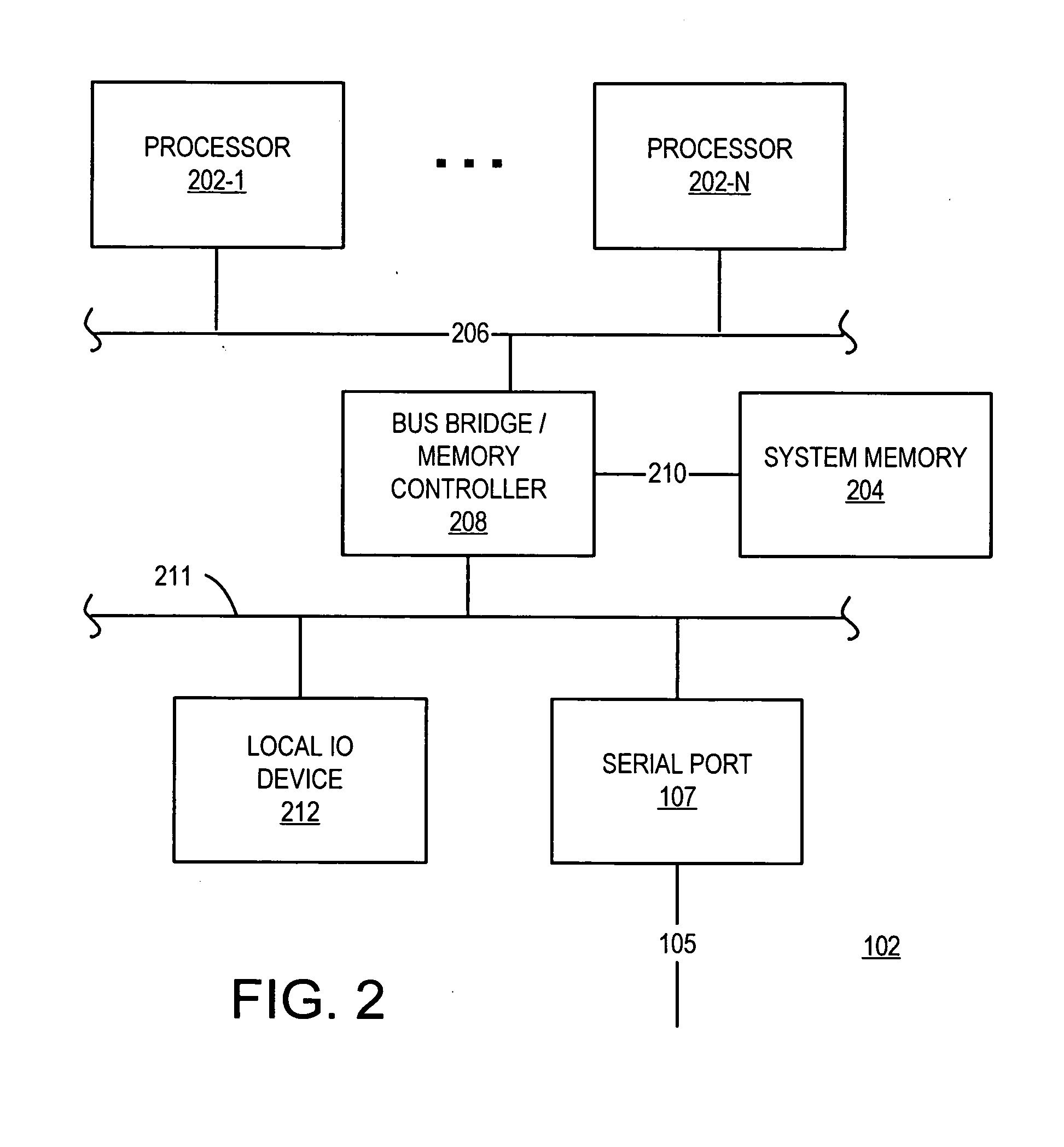

Modifying node descriptors to reflect memory migration in an information handling system with non-uniform memory access

An information handling system includes a first node and a second node. Each node includes a processor and a local system memory. An interconnect between the first node and the second node enables a processor on the first node to access system memory on the second node. The system includes affinity information that is indicative of a proximity relationship between portions of system memory and the system nodes. A BIOS module migrates a block from one node to another, reloads BIOS-visible affinity tables, and reprograms memory address decoders before calling an operating system affinity module. The affinity module modifies the operating system visible affinity information. The operating system then has accurate affinity information with which to allocate processing threads so that a thread is allocated to a node where memory accesses issued by thread are local accesses.

Owner:DELL PROD LP

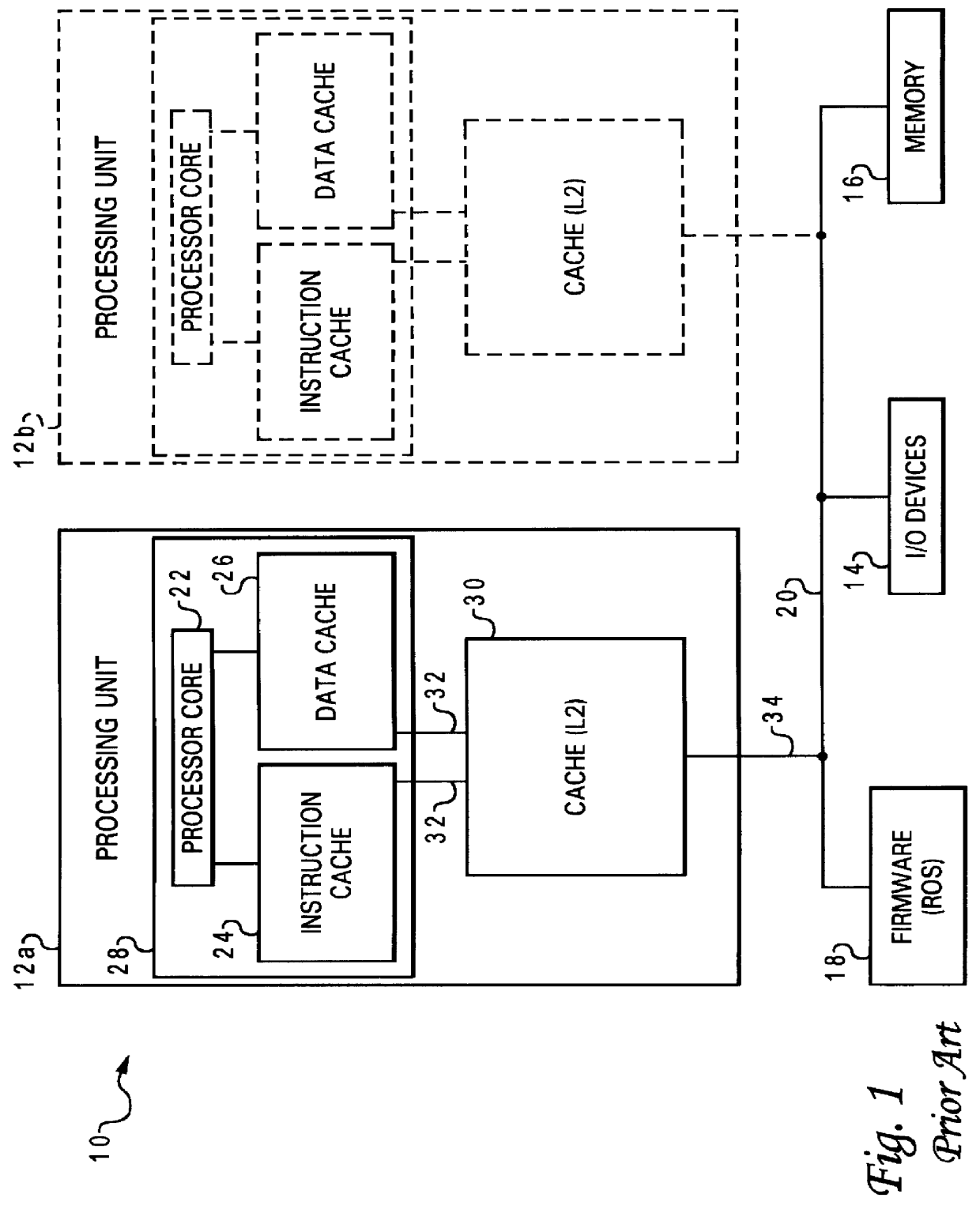

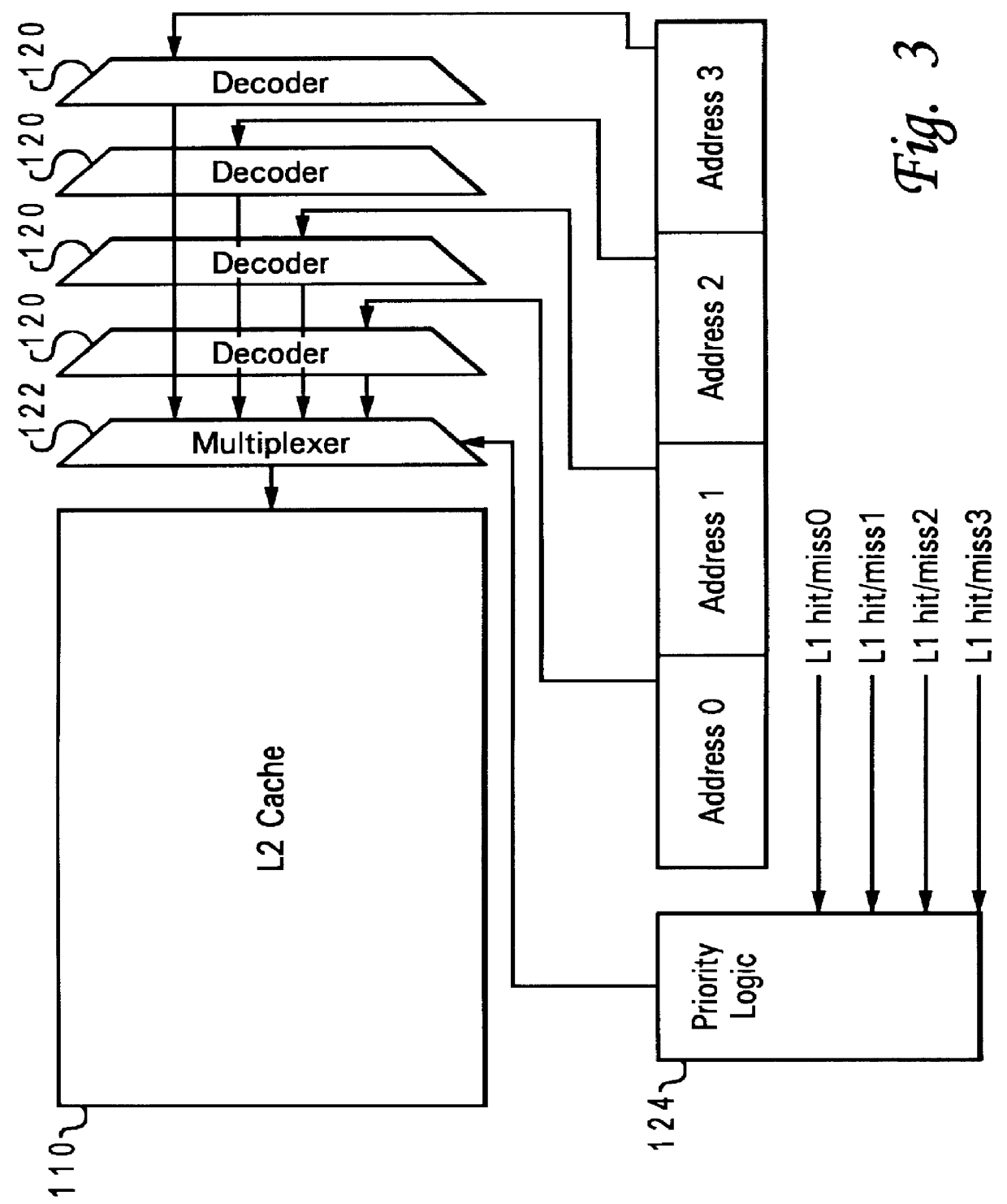

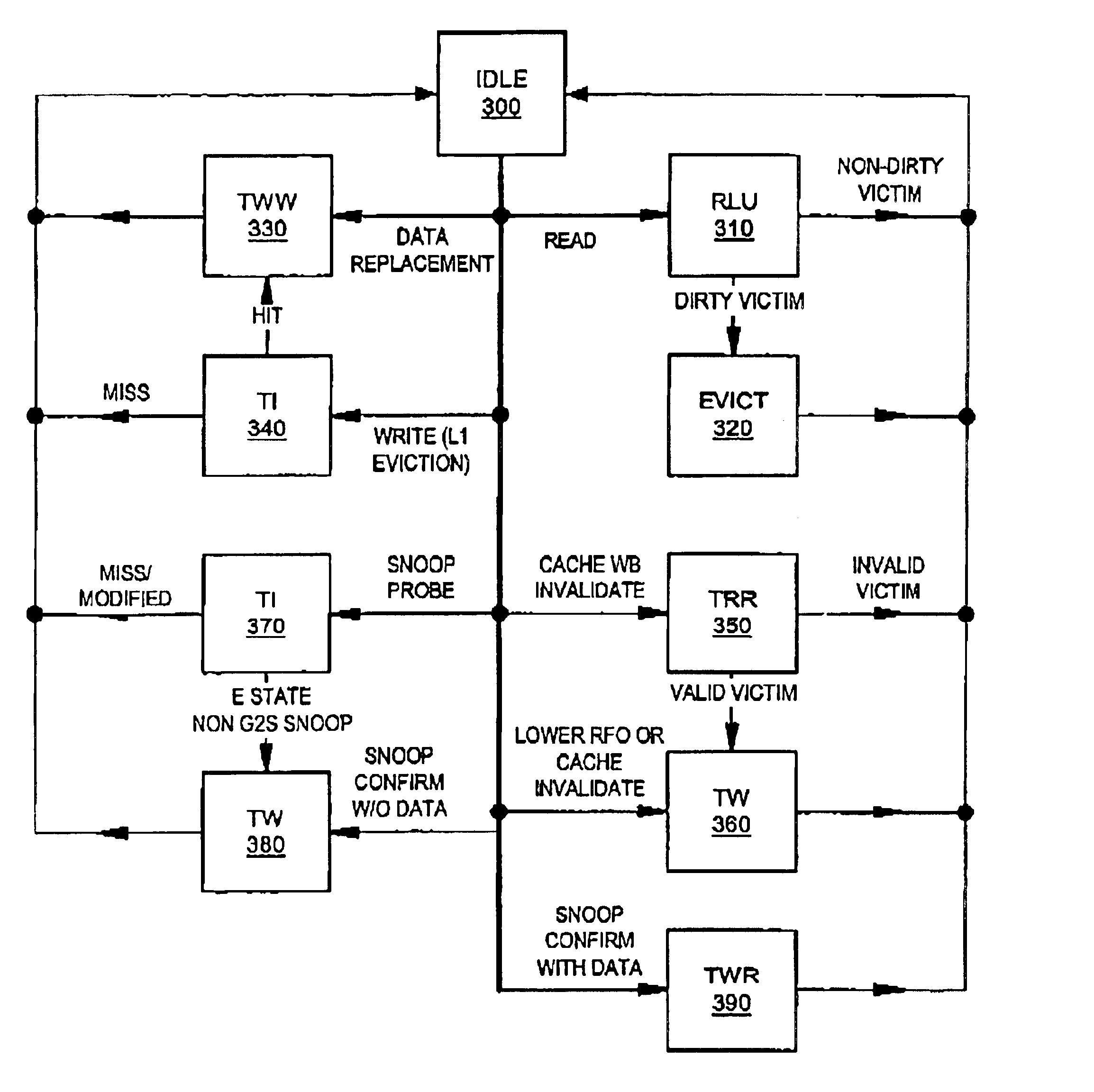

Multiple level cache memory with overlapped L1 and L2 memory access

A method of providing simultaneous, or overlapped, access to multiple cache levels to reduce the latency penalty for a higher level cache miss. A request for a value (data or instruction) is issued by the processor, and is forwarded to the lower level of the cache before determining whether a cache miss of the value has occurred at the higher level of the cache. In the embodiment wherein the lower level is an L2 cache, the L2 cache may supply the value directly to the processor. Address decoders are operated in parallel at the higher level of the cache to satisfy a plurality of simultaneous memory requests. One of the addresses (selected by priority logic based on hit / miss information from the higher level of the cache) is gated by a multiplexer to a plurality of memory array word line drivers of the lower level of the cache. Some bits in the address which do not require virtual-to-real translation can be immediately decoded.

Owner:IBM CORP

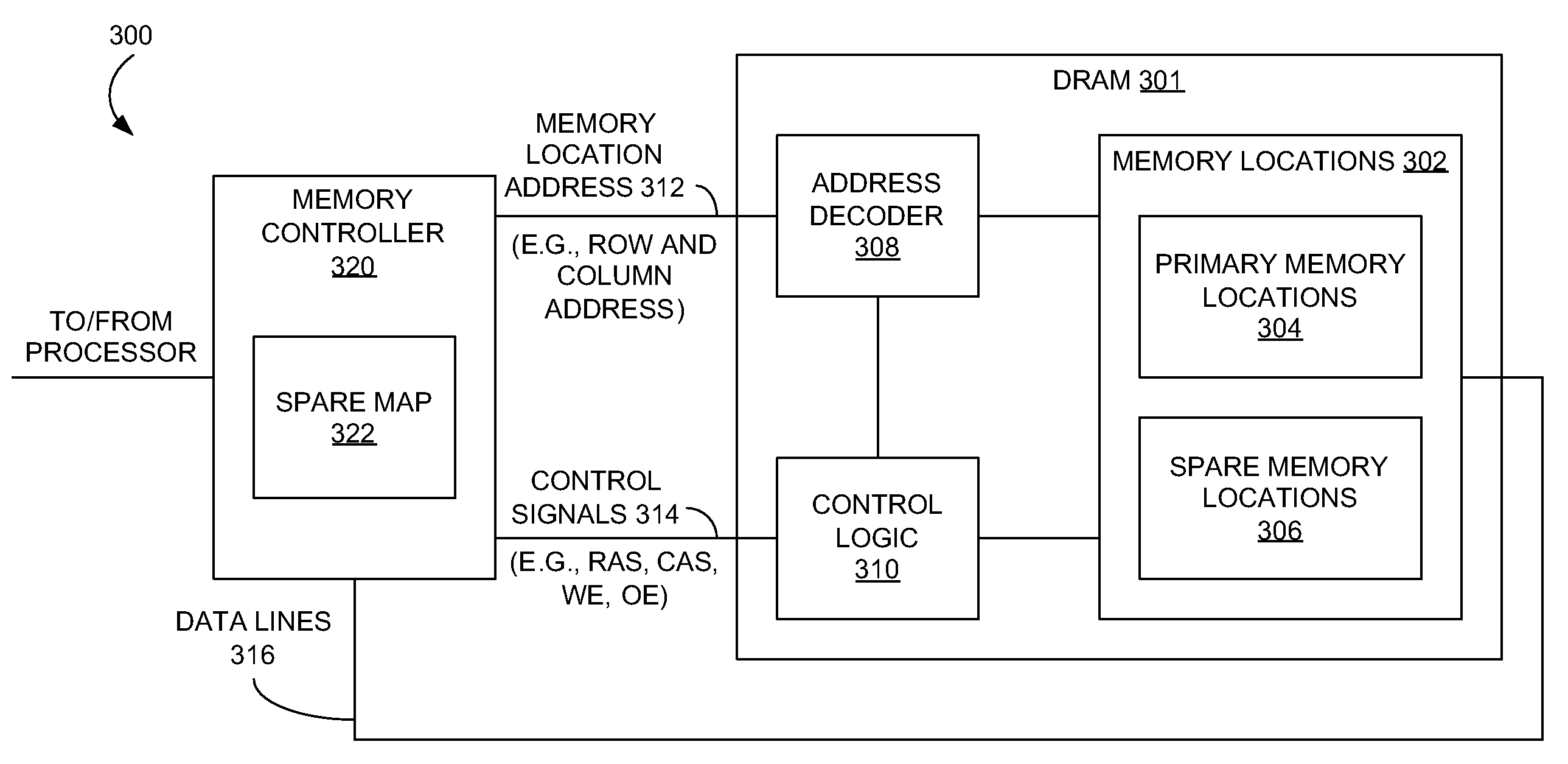

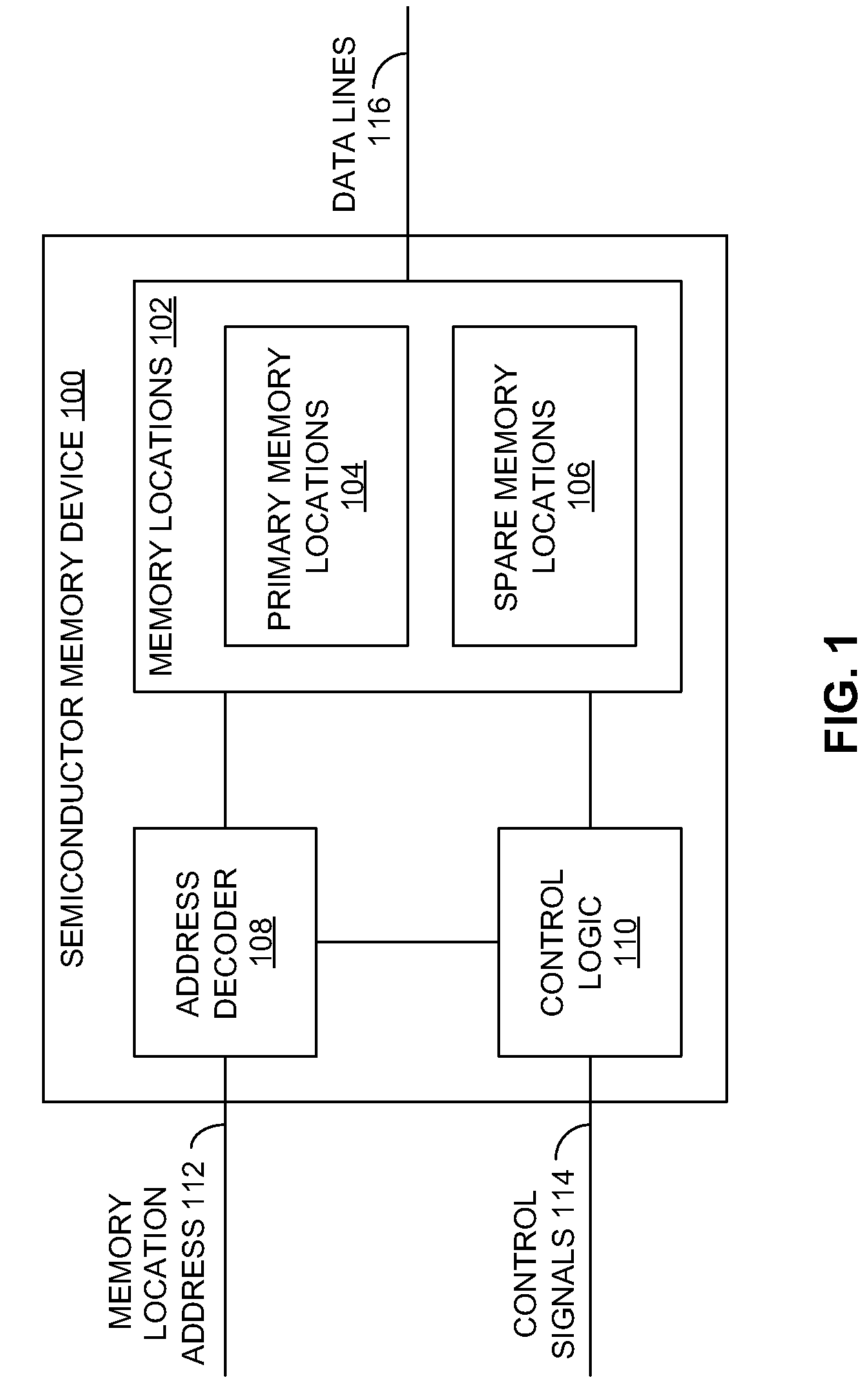

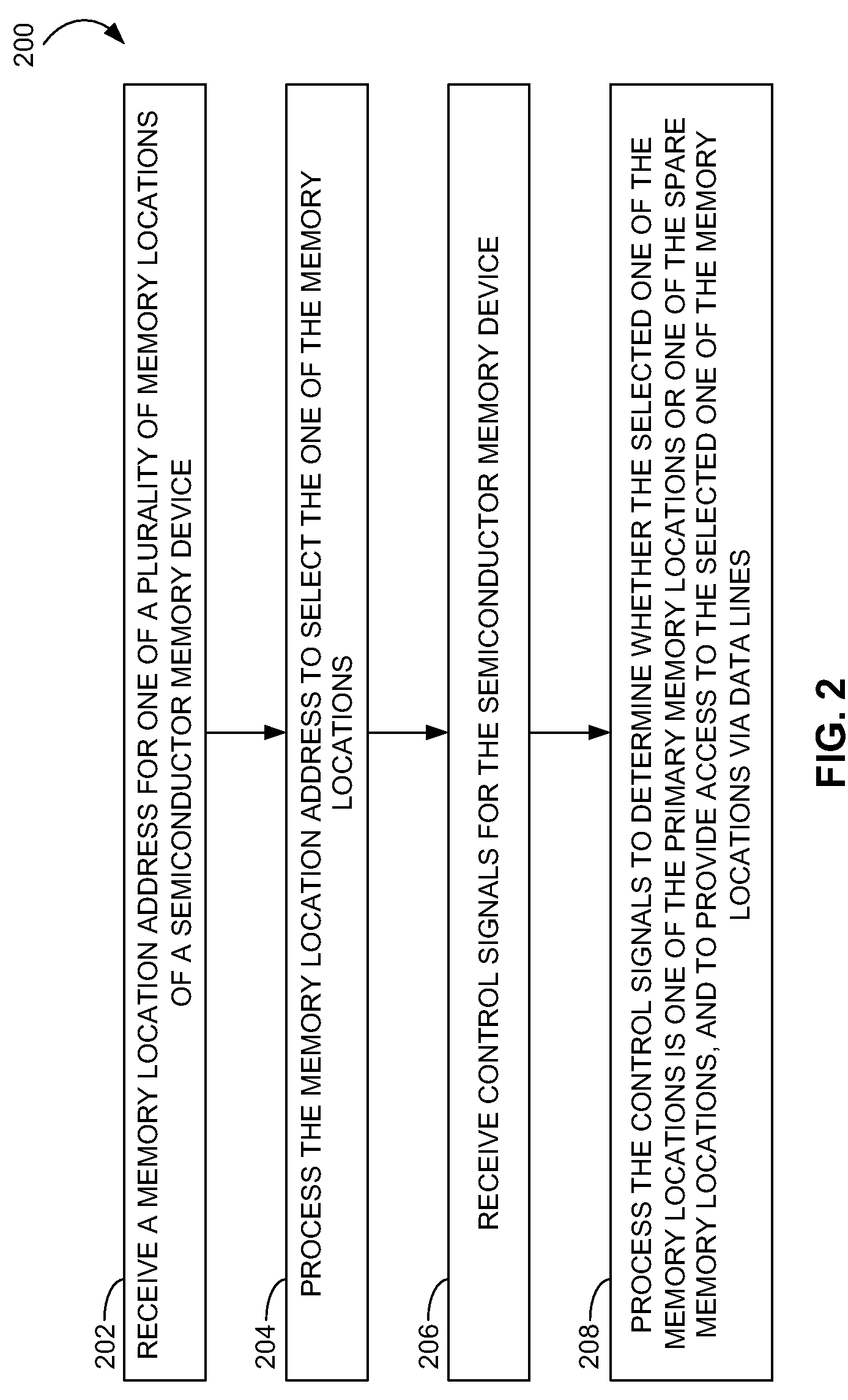

Semiconductor memory device and system providing spare memory locations

A semiconductor memory device having a plurality of memory locations is presented. The plurality of memory locations includes a plurality of primary memory locations and a plurality of spare memory locations. The device includes an address decoder configured to receive a memory location address and process the address to select one of the memory locations. The device further includes control logic configured to receive control signals and process the control signals to determine whether the selected one of the memory locations is one of the primary memory locations or one of the spare memory locations, and to provide access to the selected one of the memory locations via data lines.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

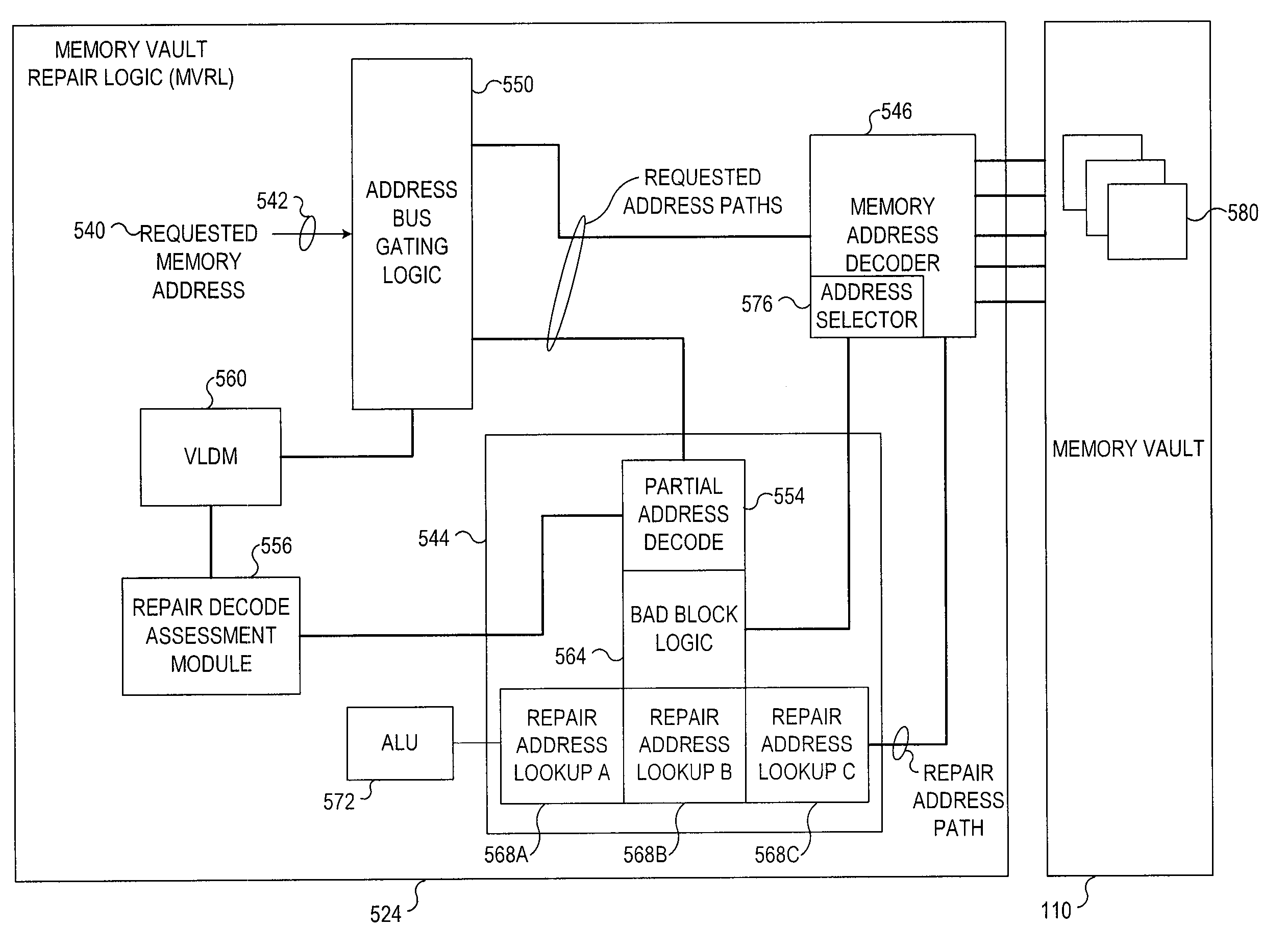

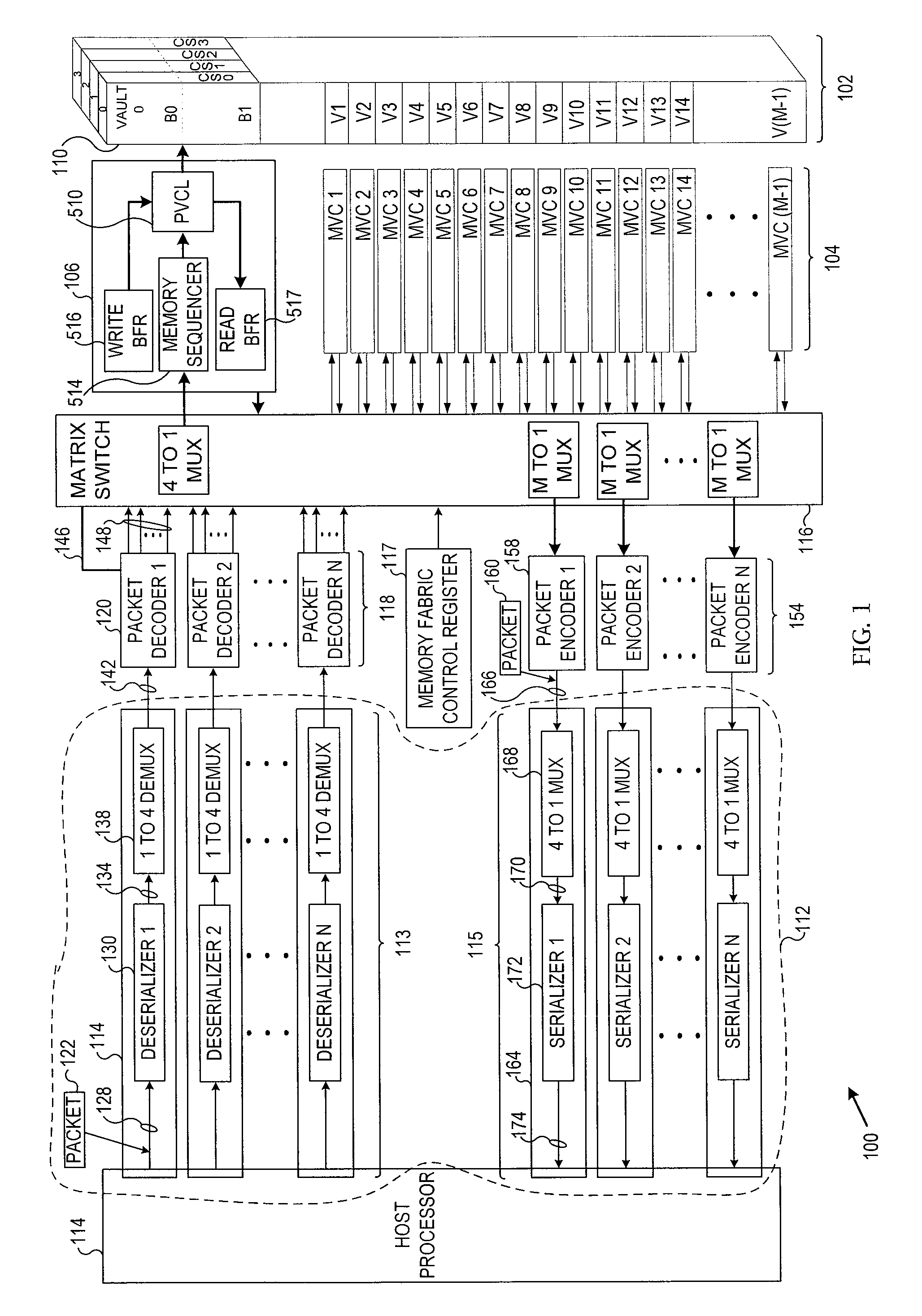

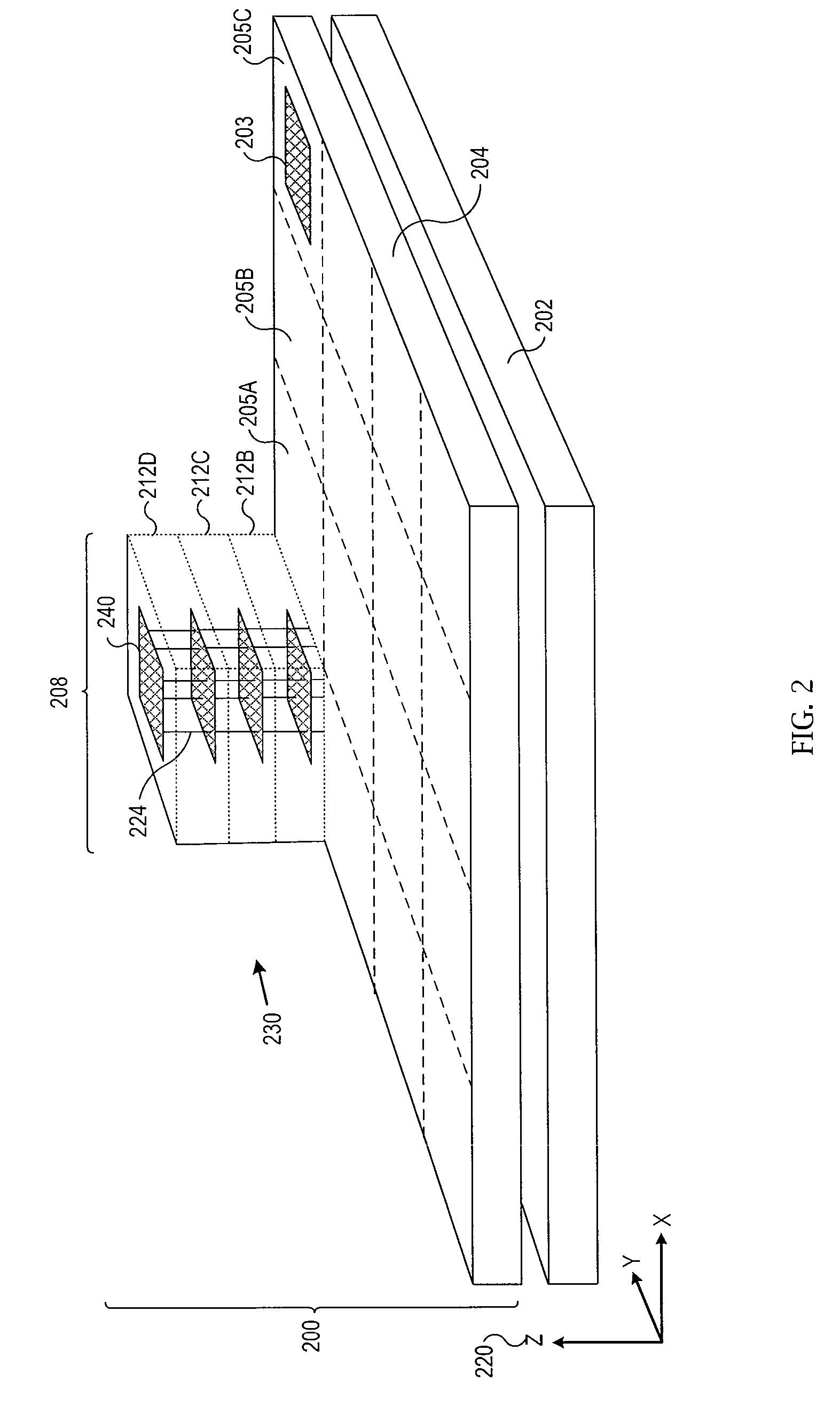

Switched interface stacked-die memory architecture

ActiveUS20100110745A1Efficient power electronics conversionDigital storageMemory addressAddress decoder

Systems and methods disclosed herein include those that may receive a memory request including a requested memory address and may send the memory request directly to an address decoder associated with a stacked-die memory vault without knowing whether a repair address is required. If a subsequent analysis of the memory request shows that a repair address is required, an in-process decode of the requested memory address can be halted and decoding of the repair address initiated.

Owner:MICRON TECH INC

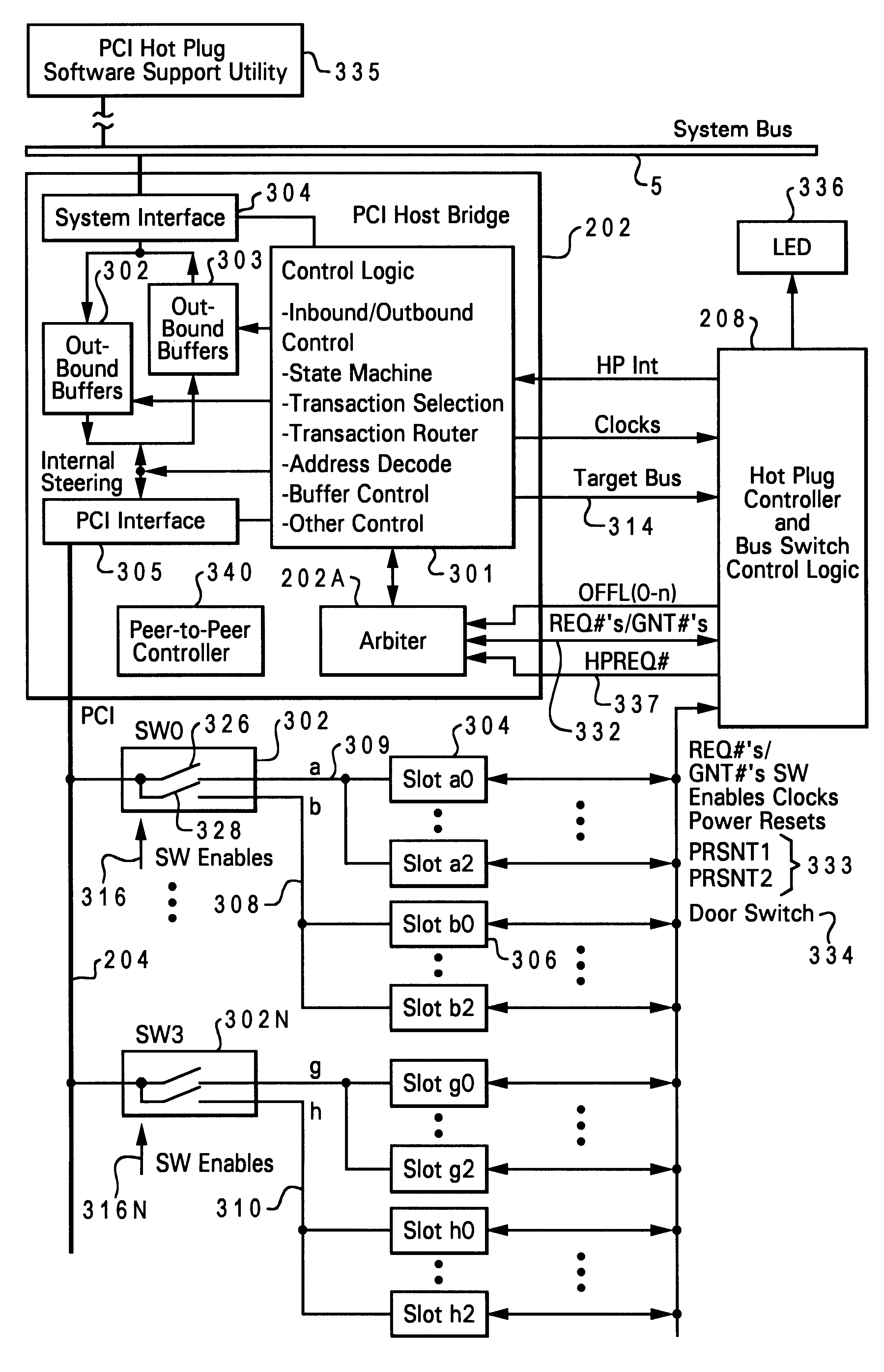

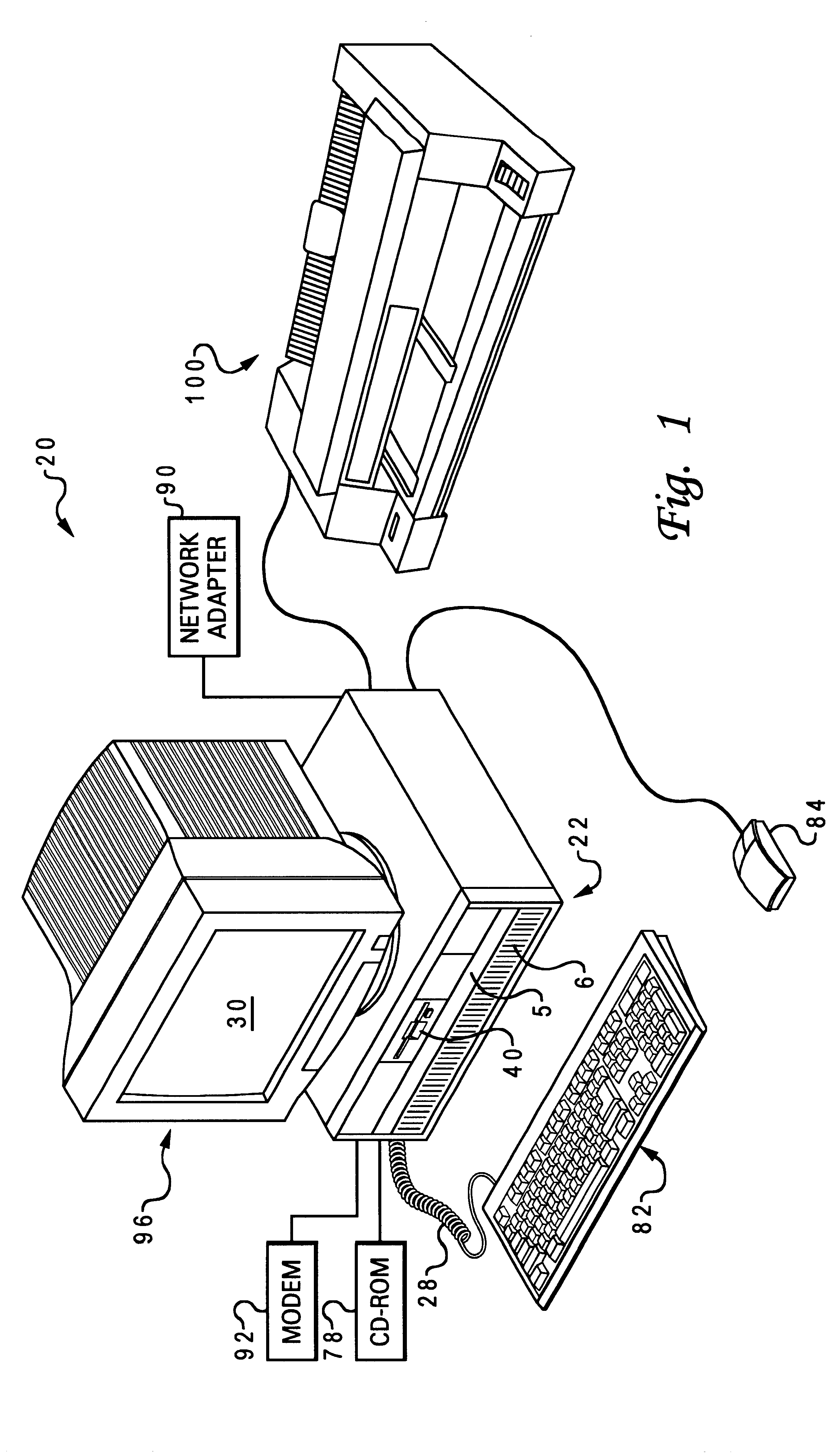

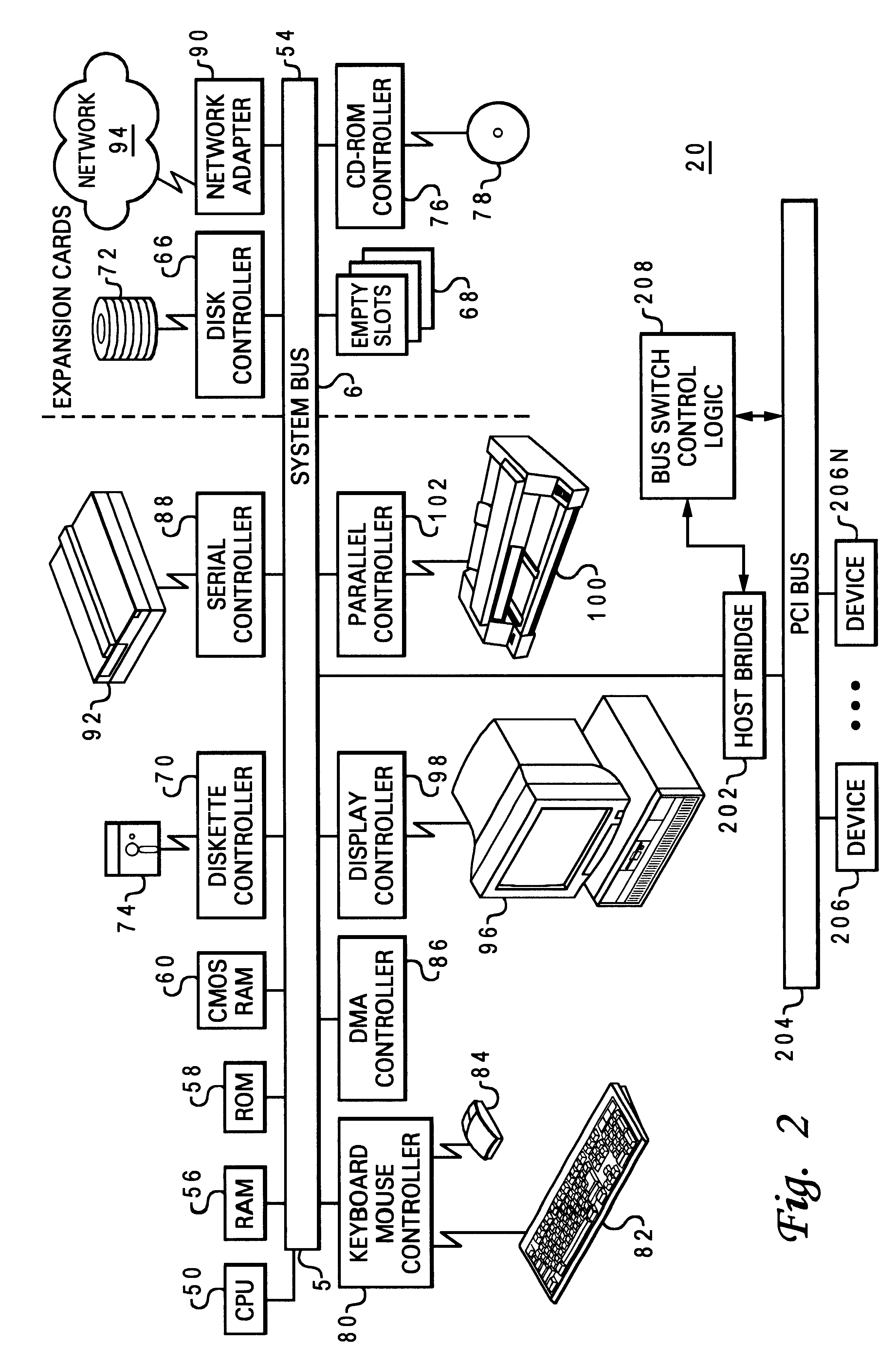

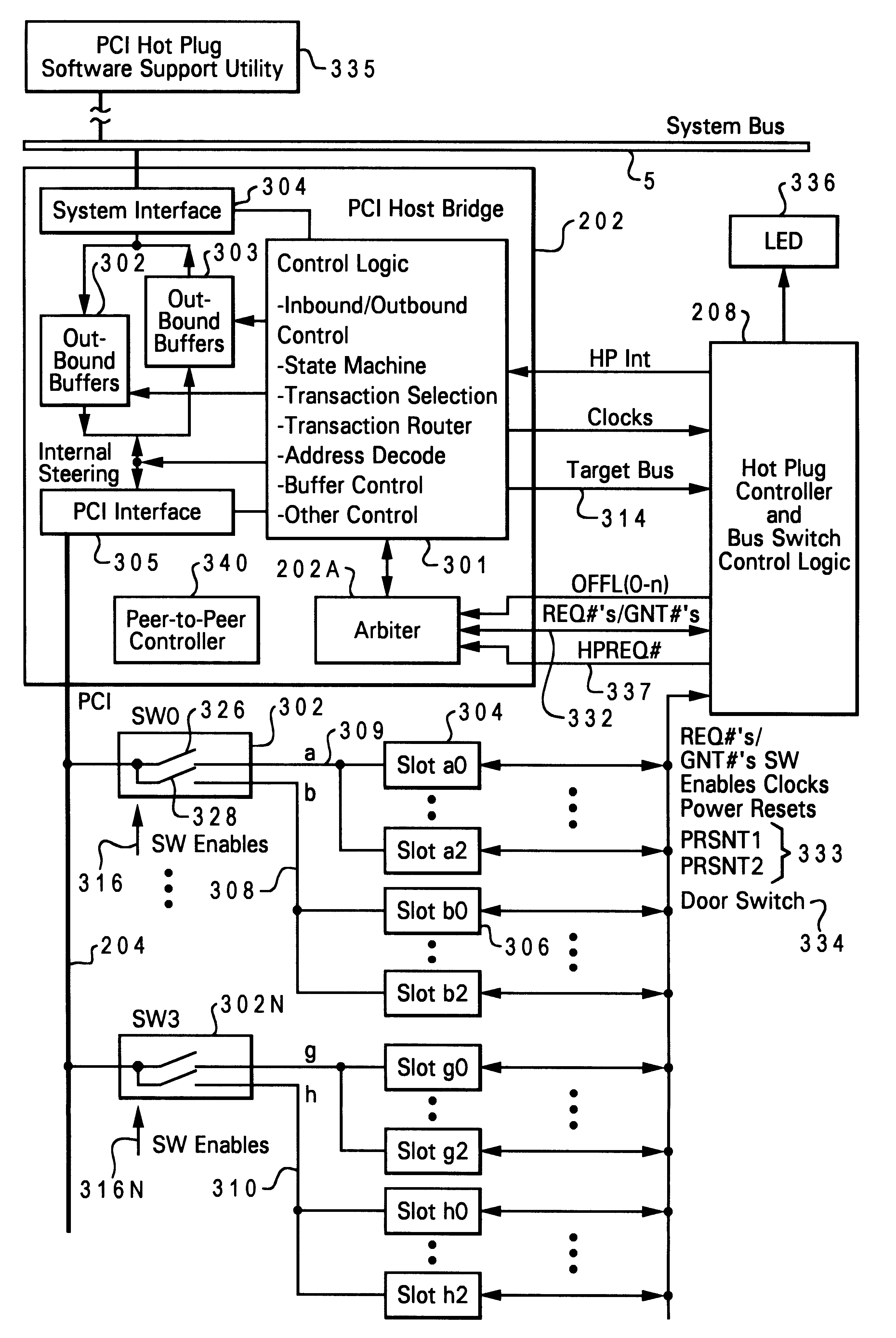

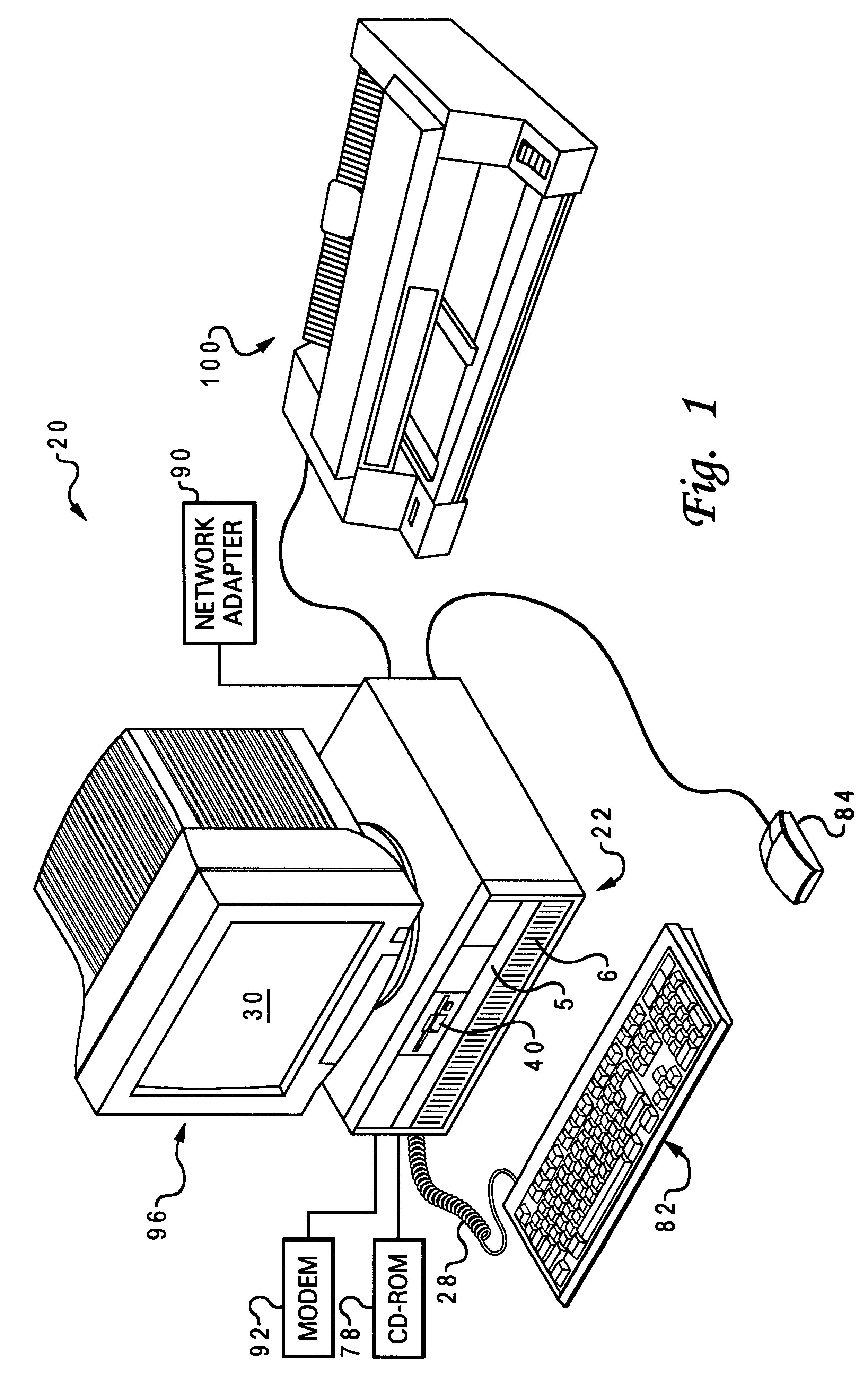

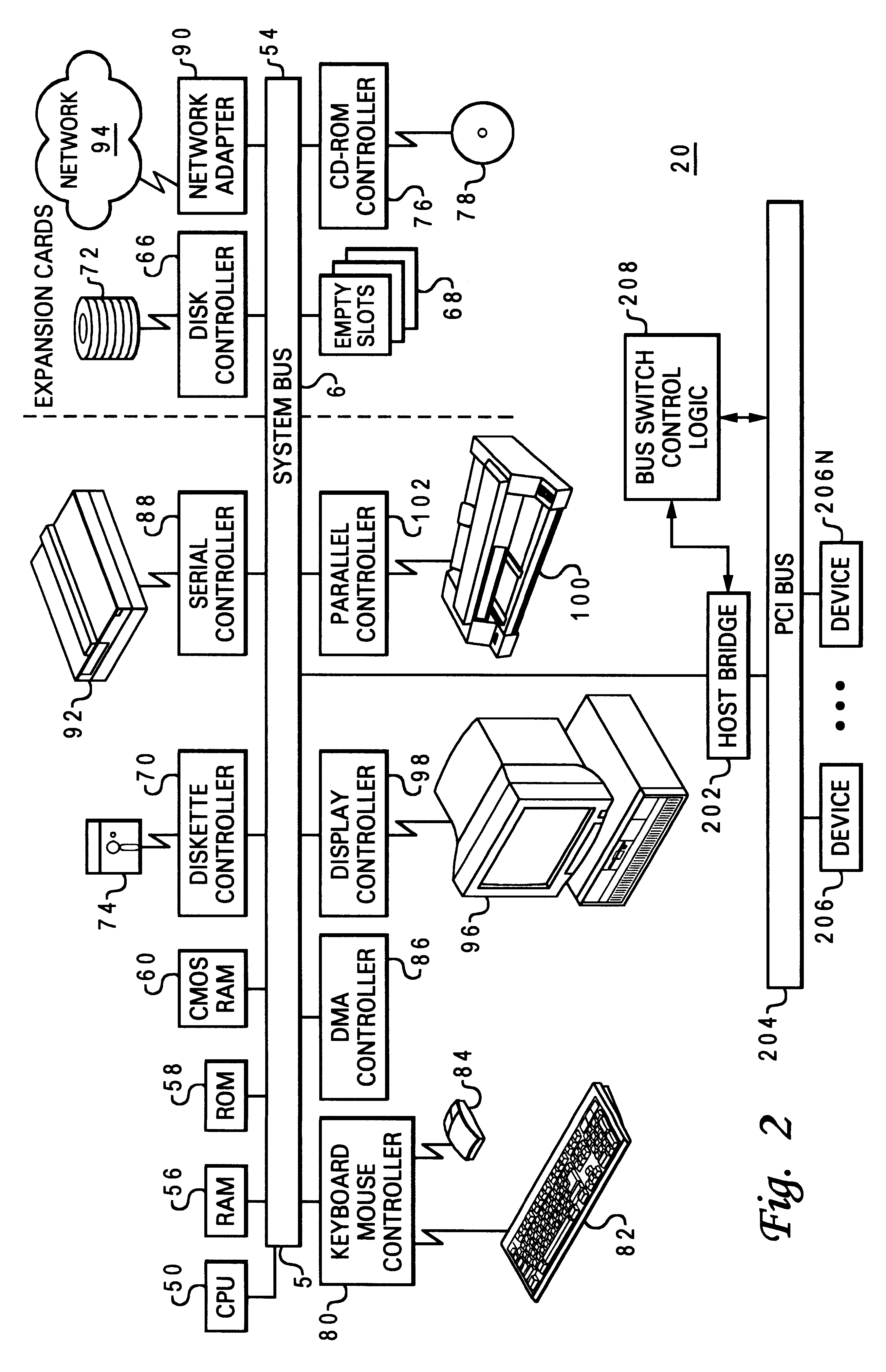

Method and system for providing hot plug of adapter cards in an expanded slot environment

InactiveUS6338107B1Component plug-in assemblagesElectric digital data processingAddress decoderMethod selection

A method of providing an interconnection between one or more peripheral devices and a system bus of a computer system selectively establishes and removes a connection from a primary peripheral bus to a secondary peripheral buses, and determines a target from among the one or more peripheral devices when a bus bridge is a master of the primary peripheral bus, using an address decoder. Access to and from the primary peripheral bus is controlled using an arbiter to select a master for the primary peripheral bus from among the one or more peripheral devices, to allow both (i) selective establishing and removing of a connection from the primary peripheral bus to one of the secondary peripheral buses in response to the selection of the master, and (ii) isolating of the master prior to establishing the connection to the secondary peripheral bus. Hot Plug Control Logic and Switch Control Logic in conjunction with the arbiter allows Hot Plug support along with the expanded slot environment.

Owner:IBM CORP

Low power cache architecture

InactiveUS6845432B2Memory architecture accessing/allocationEnergy efficient ICTAddress decoderOptical Module

In a processor cache, cache circuits are mapped into one or more logical modules. Each module may be powered down independently of other modules in response to microinstructions processed by the cache. Power control may be applied on a microinstruction-by-microinstruction basis. Because the microinstructions determine which modules are used, power savings may be achieved by powering down those modules that are not used. A cache layout organization may be modified to distribute a limited number of ways across addressable cache banks. By associating fewer than a total number of ways to a bank (for example, one or two ways), the size of memory clusters within the bank may reduced. The reduction in this size of the memory cluster reduces the power needed for an address decoder to address sets within the bank.

Owner:INTEL CORP

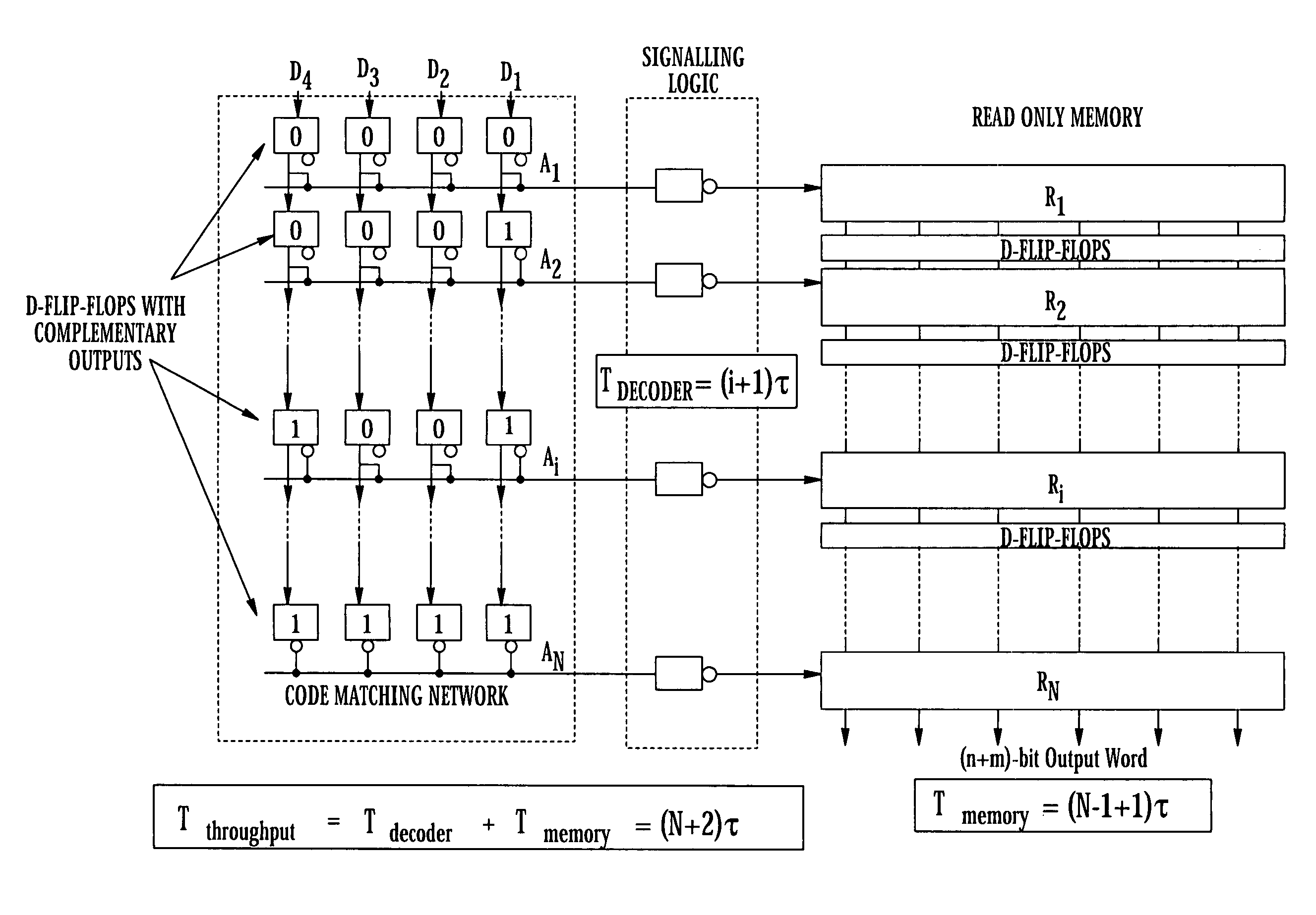

Superconducting circuit for high-speed lookup table

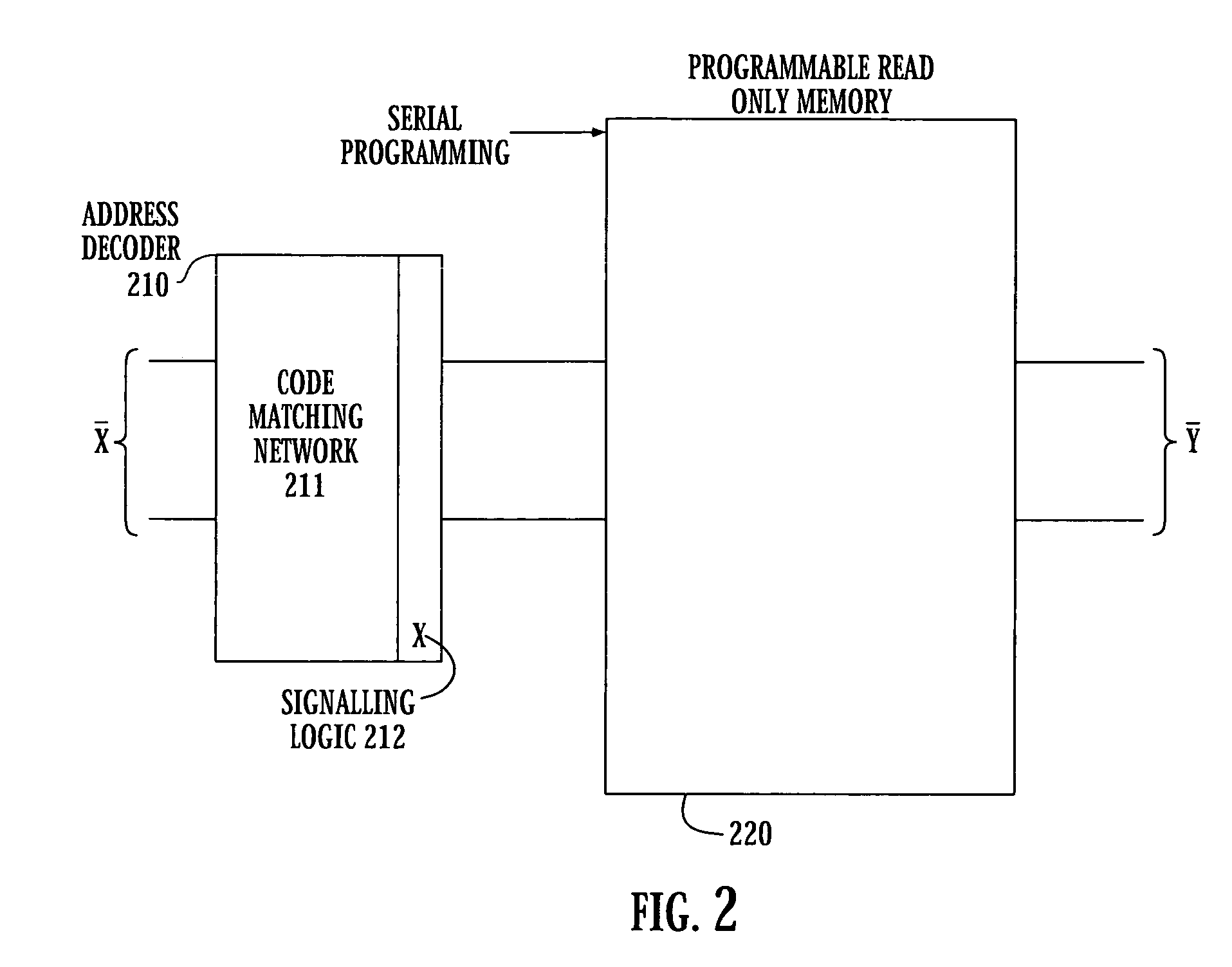

ActiveUS7443719B2Superconductors/hyperconductorsRead-only memoriesProgrammable read-only memoryReprogramming

A high-speed lookup table is designed using Rapid Single Flux Quantum (RSFQ) logic elements and fabricated using superconducting integrated circuits. The lookup table is composed of an address decoder and a programmable read-only memory array (PROM). The memory array has rapid parallel pipelined readout and slower serial reprogramming of memory contents. The memory cells are constructed using standard non-destructive reset-set flip-flops (RSN cells) and data flip-flops (DFF cells). An n-bit address decoder is implemented in the same technology and closely integrated with the memory array to achieve high-speed operation as a lookup table. The circuit architecture is scalable to large two-dimensional data arrays.

Owner:SEEQC INC

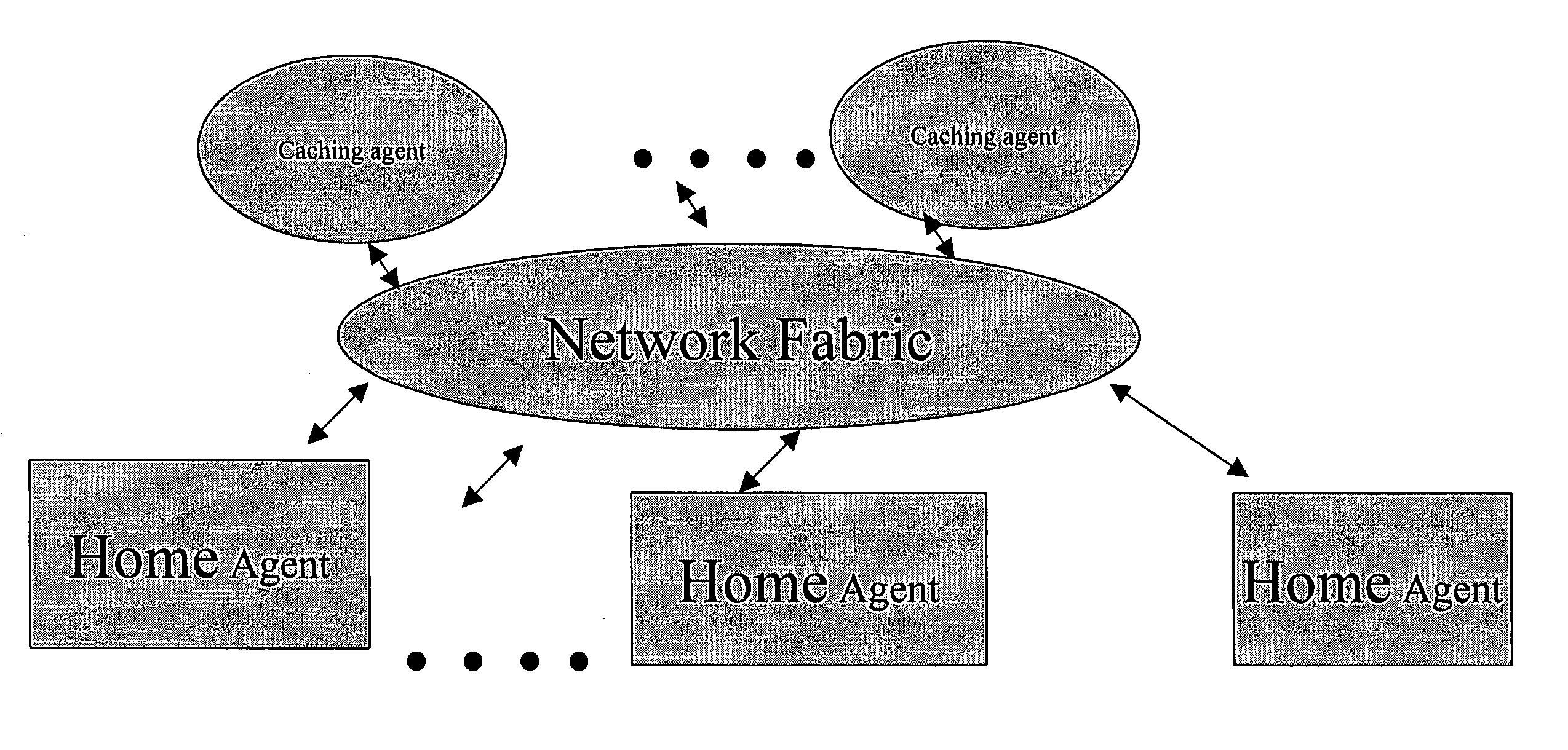

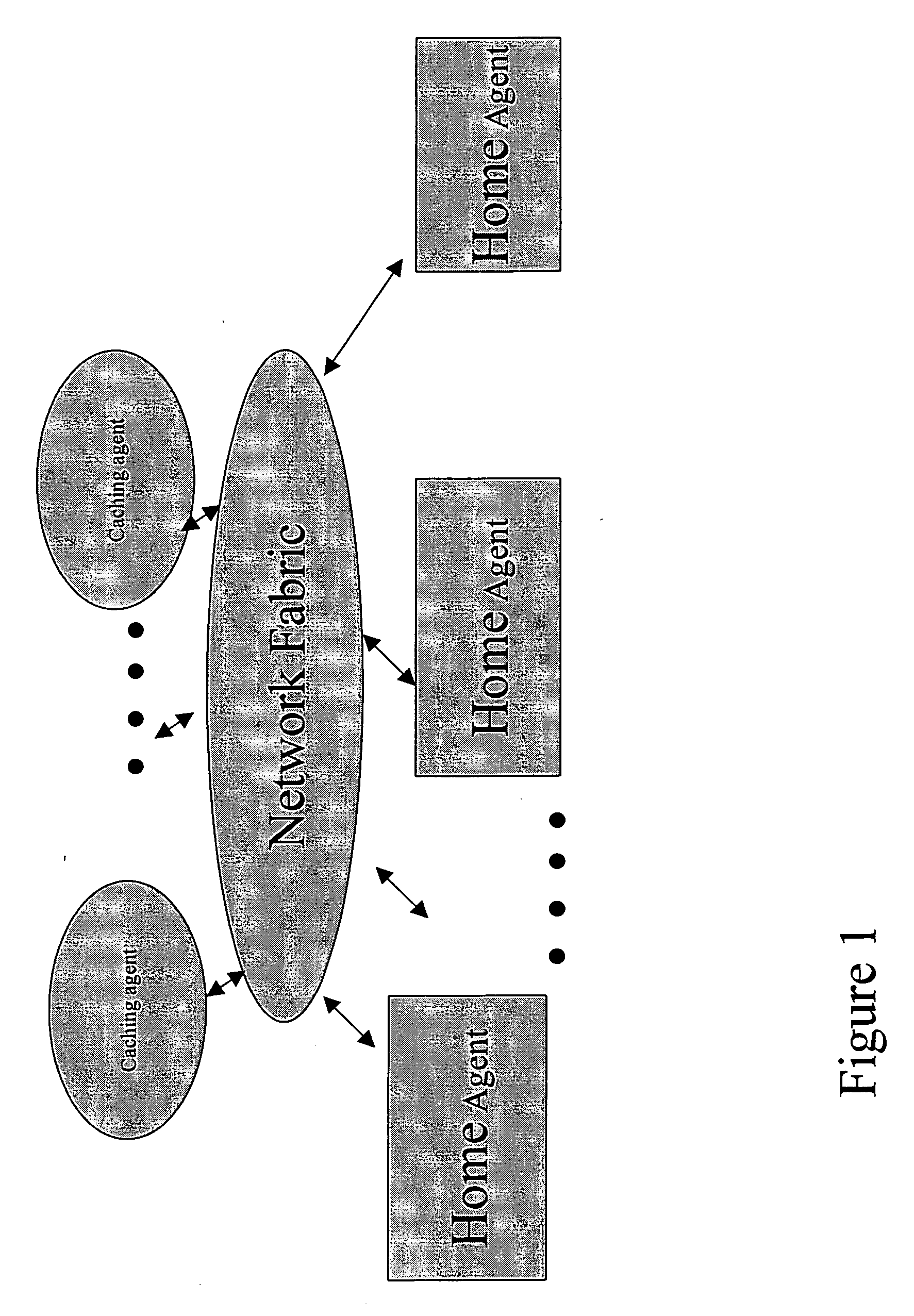

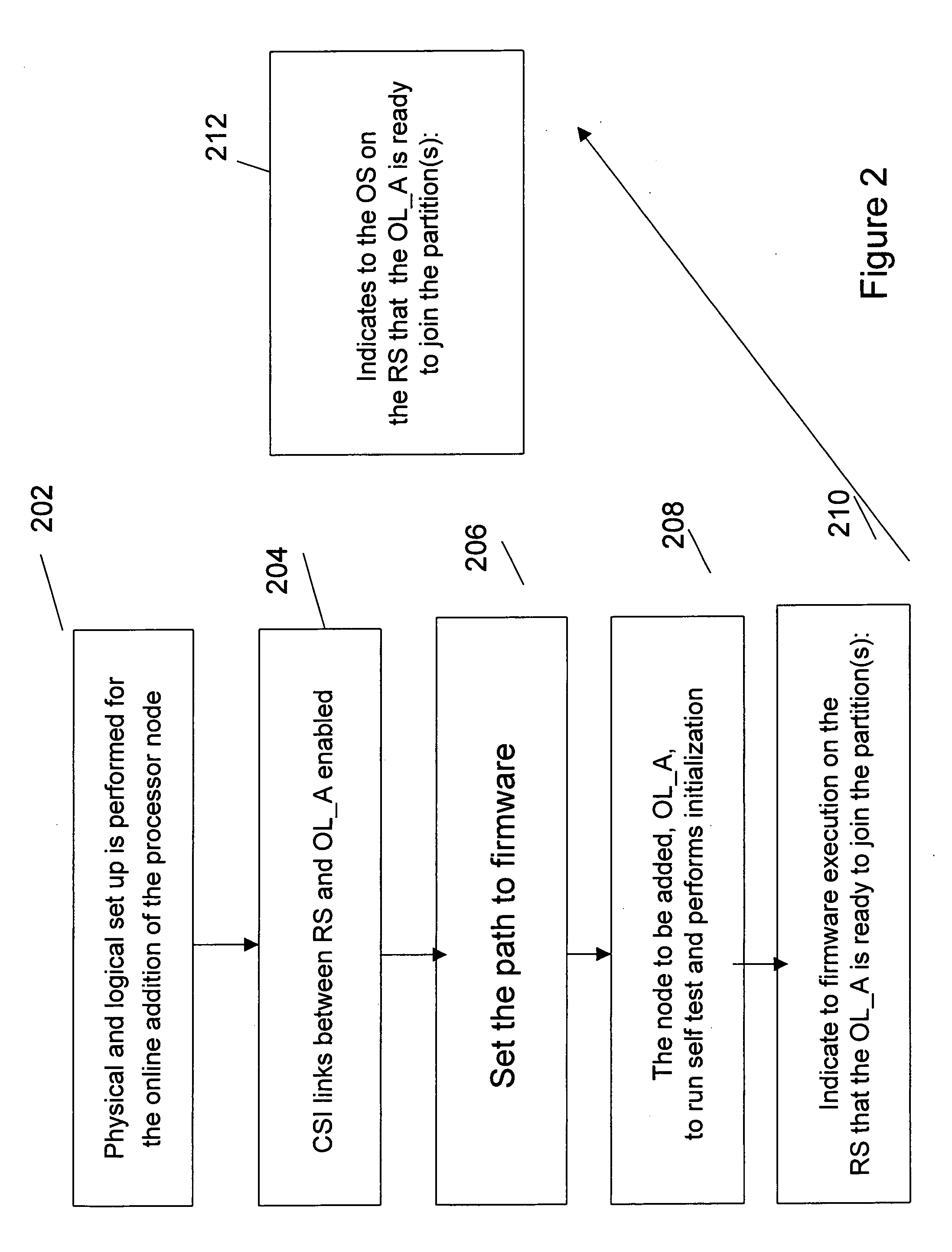

Method, system, and apparatus for dynamic reconfiguration of resources

InactiveUS20060184480A1Facilitates dynamic allocationResource allocationDigital computer detailsAddress decoderRouting table

A dynamic reconfiguration to include on-line addition, deletion, and replacement of individual modules of to support dynamic partitioning of a system, interconnect (link) reconfiguration, memory RAS to allow migration and mirroring without OS intervention, dynamic memory reinterleaving, CPU and socket migration, and support for global shared memory across partitions is described. To facilitate the on-line addition or deletion, the firmware is able to quiesce and de-quiesce the domain of interest so that many system resources, such as routing tables and address decoders, can be updated in what essentially appears to be an atomic operation to the software layer above the firmware.

Owner:INTEL CORP

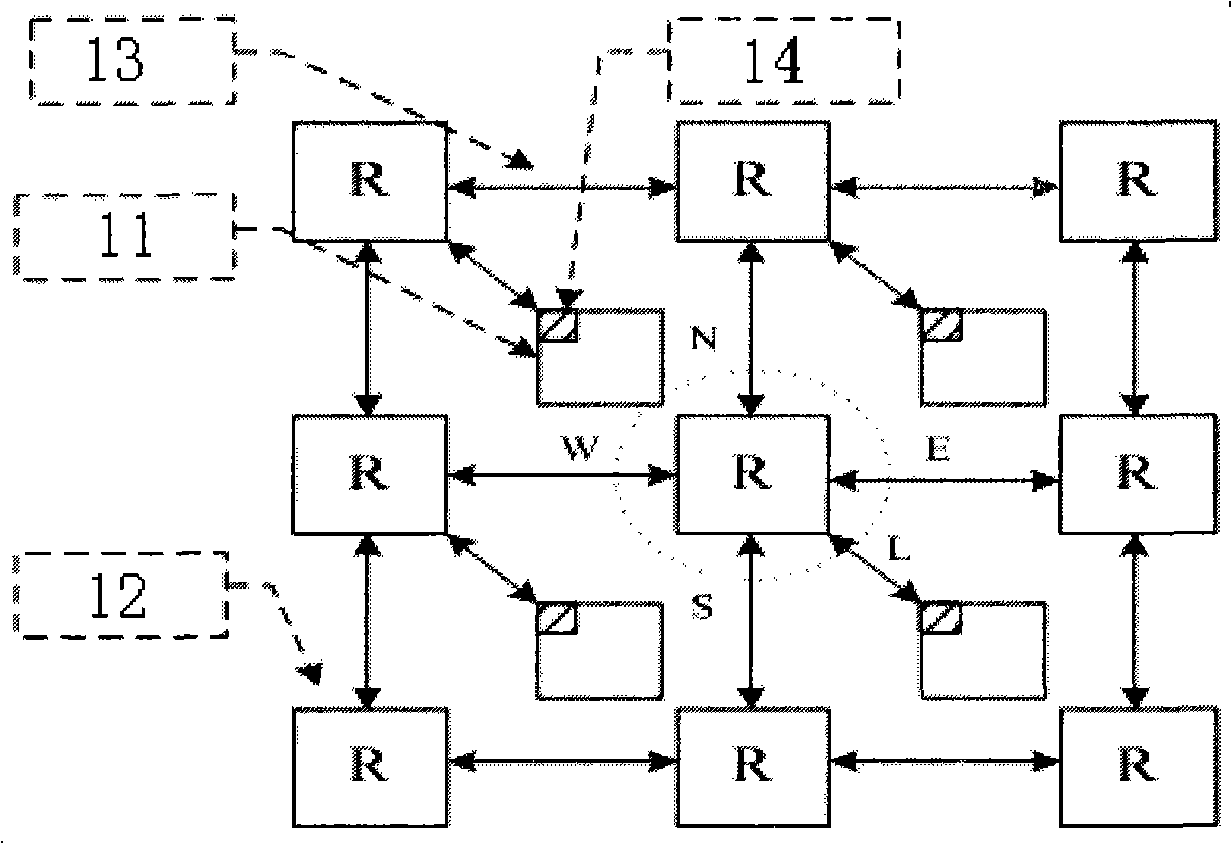

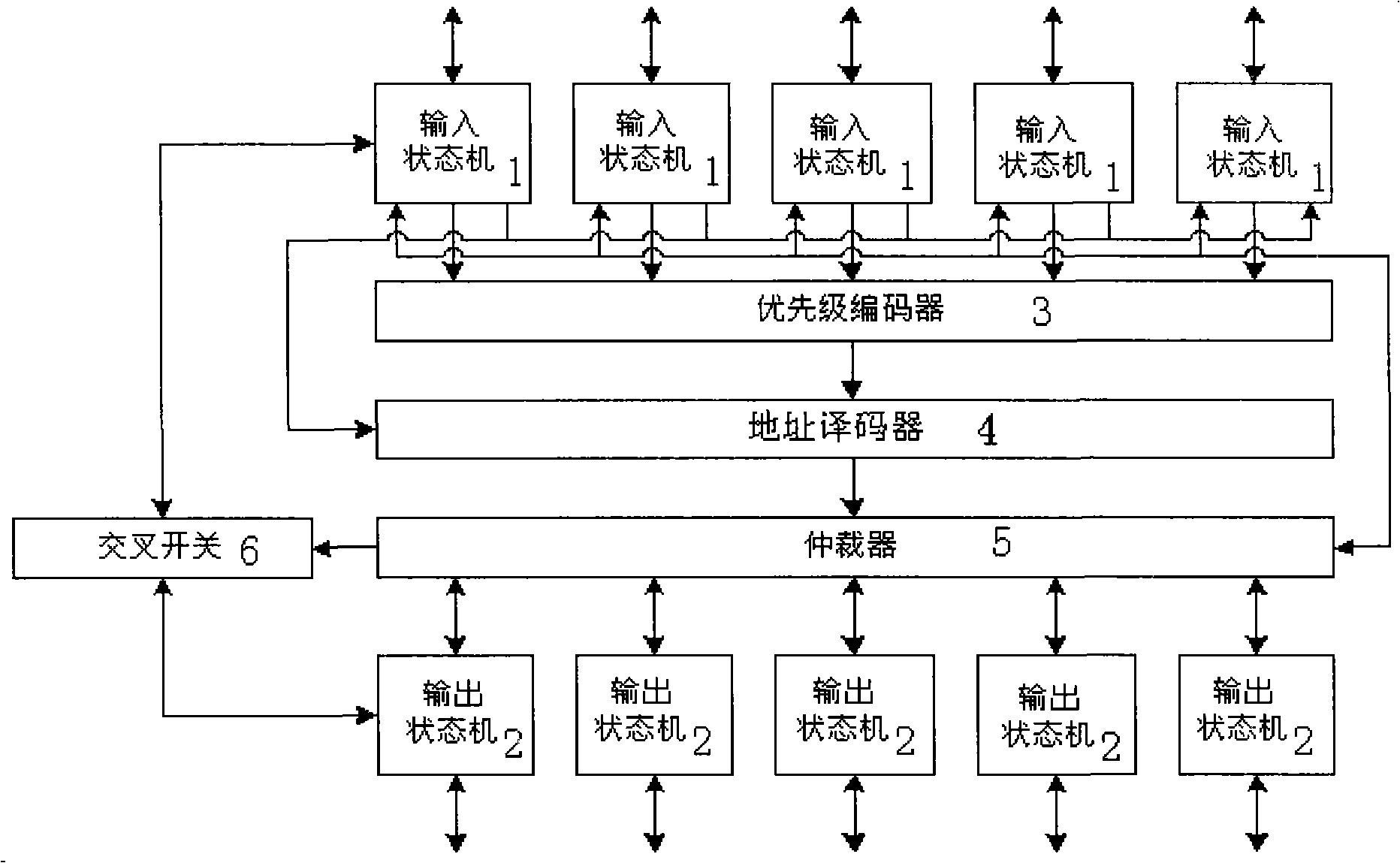

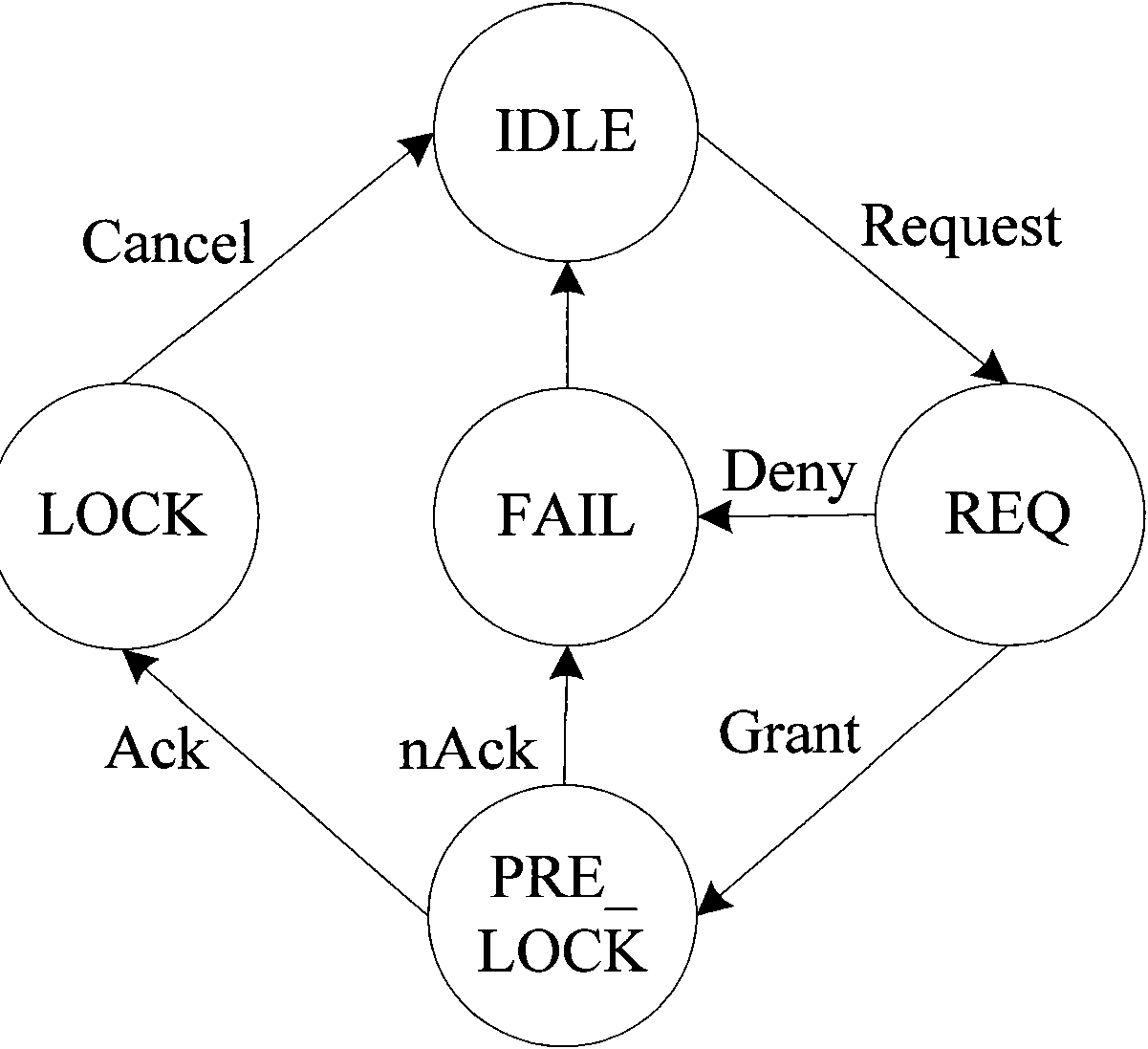

Router and transmission method thereof on packet-circuit switching chip

InactiveCN101778049AReduce transmission delayEasy to implementData switching networksAddress decoderCrossbar switch

The invention discloses a router and a transmission method thereof on a packet-circuit switching chip forming networks on chips. An input state device in the router controls the work state of an input channel and transmits received requisite signals to a priority encoder; the priority encoder encodes the request signals according to the set fixed priority and transforms input target node address signals to route direction signals by an address decoder to be output; an arbiter receives decoding results of the address decoder, outputs interconnected signals of an input port and an output port and occupation signals of the input port according the sequence of the fixed priority and the occupation condition of the ports until selecting a proper route to reach the target node; and a crossbar switch receives the interconnected signals output by the arbiter and realizes the correct interconnection between the input port and the output port. The invention has the advantages of little resource consumption and small transmission time delay. The invention is suitable for forming networks on chips with high performance, and can be applied to complicated systems on chips adopting on-chip network structure.

Owner:NANJING UNIV +1

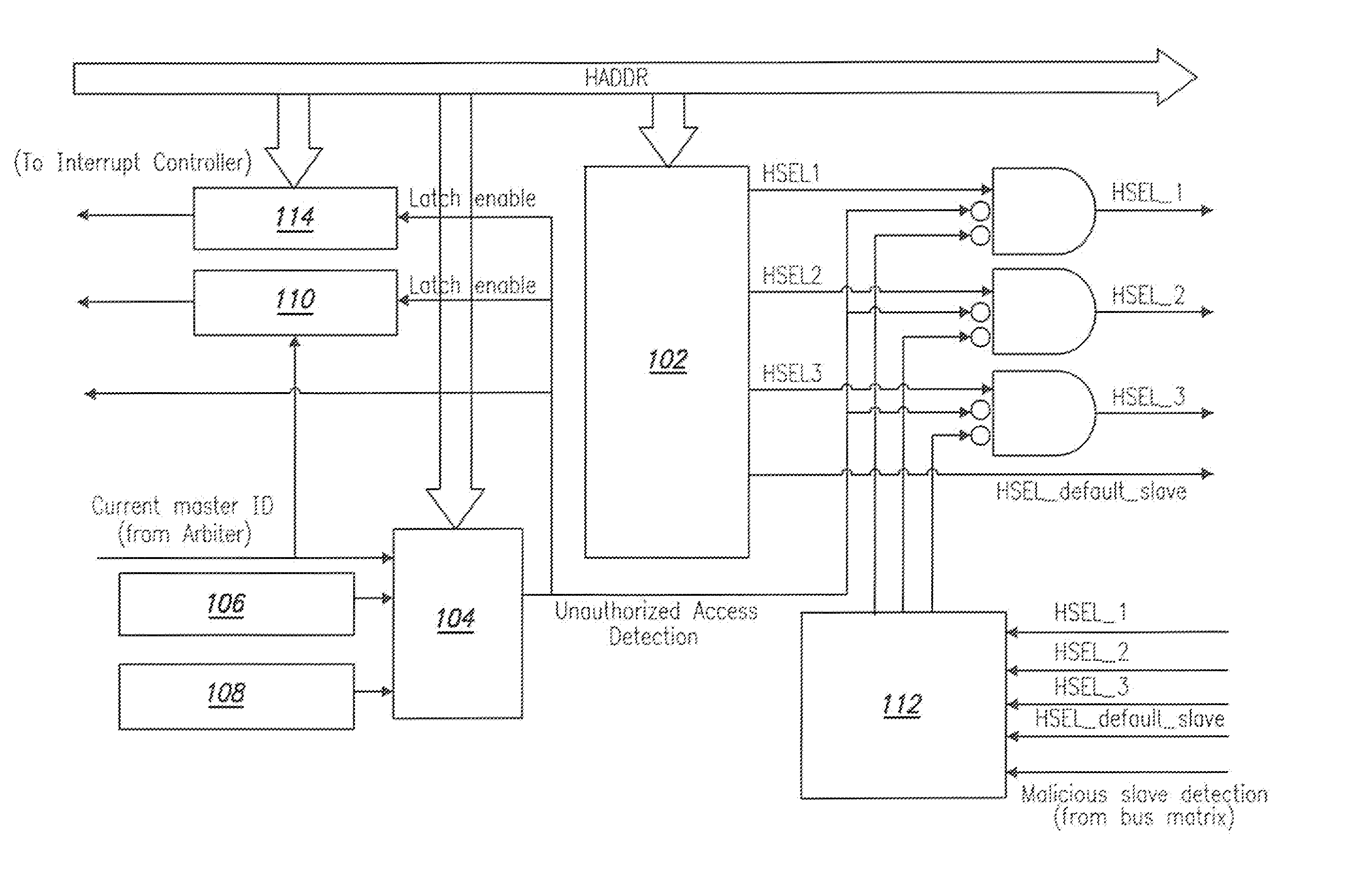

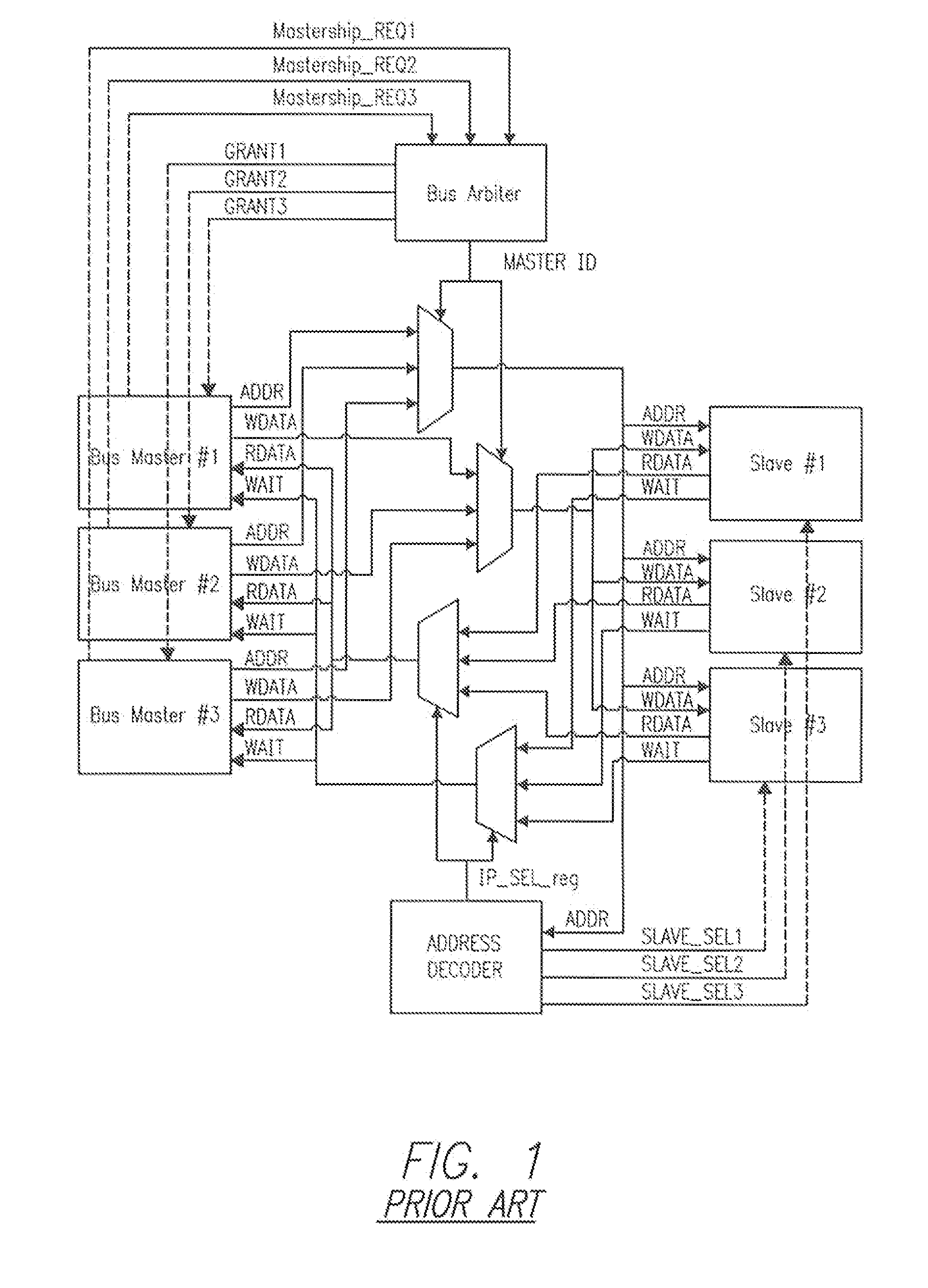

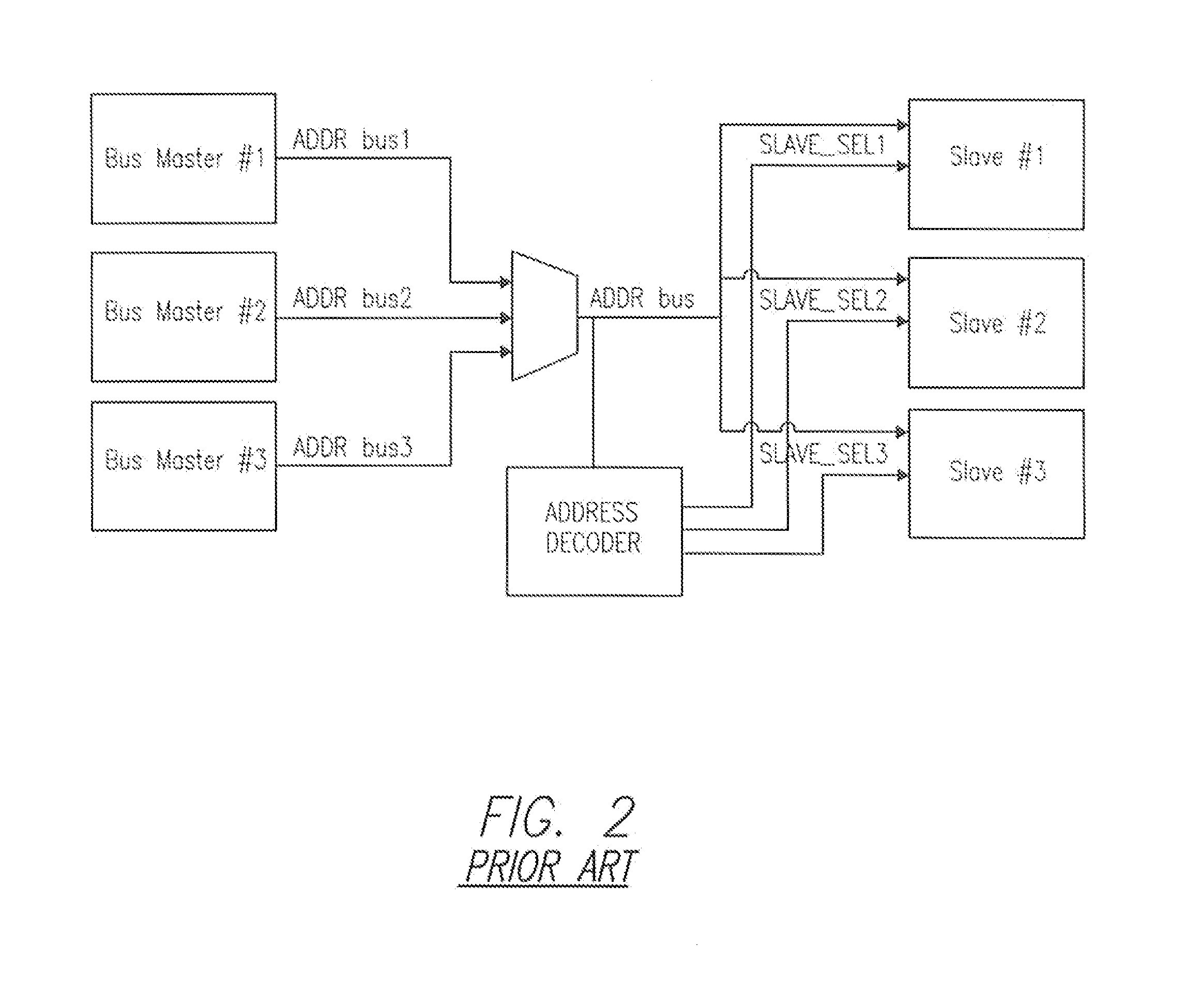

Trojan-Resistant Bus Architecture and Methods

InactiveUS20110225651A1Low costProtection attackMemory loss protectionError detection/correctionAddress decoderAttack

A method of securing bus architecture from a Trojan attack. A restricted address access detector generates an unauthorized access detection, signal when a master ID signal is within a restricted range. The unauthorized access detection signal disables the requested slave select signal, and the address decoder instead outputs a default slave select signal. A counter determines the duration of a lock signal from a master, and a comparator activates a malicious bus lock signal if the lock signal duration exceeds a threshold. The master mask register forcibly gates the lock signal upon receipt of the malicious bus lock signal. If the duration of a wait request from a slave exceeds a maximum duration register value, a comparator activates a malicious wait detection signal to disable the wait request signal. The method might include storing identifying information about the malicious master and storing a slave ID corresponding to the malicious slave.

Owner:RGT UNIV OF CALIFORNIA

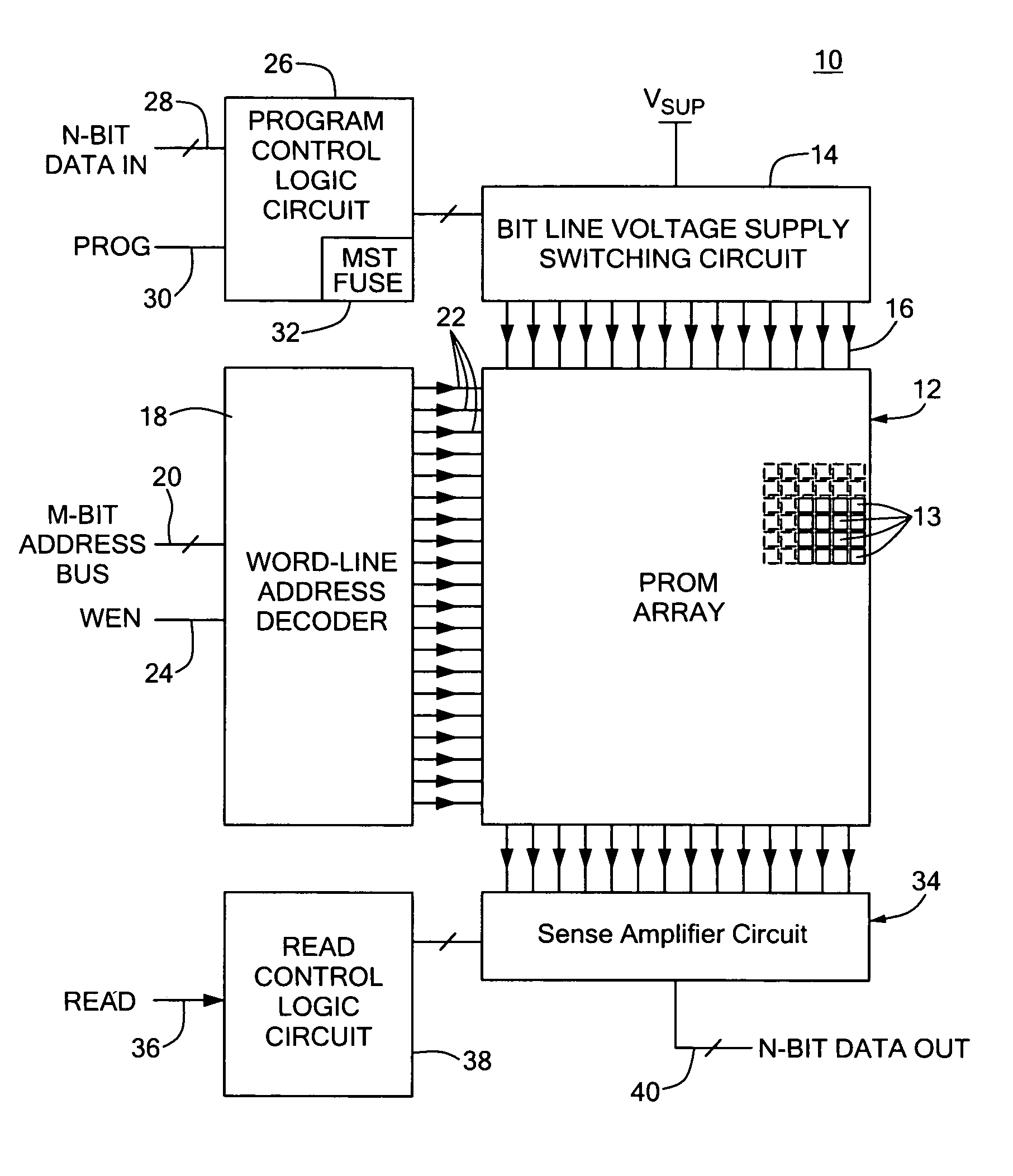

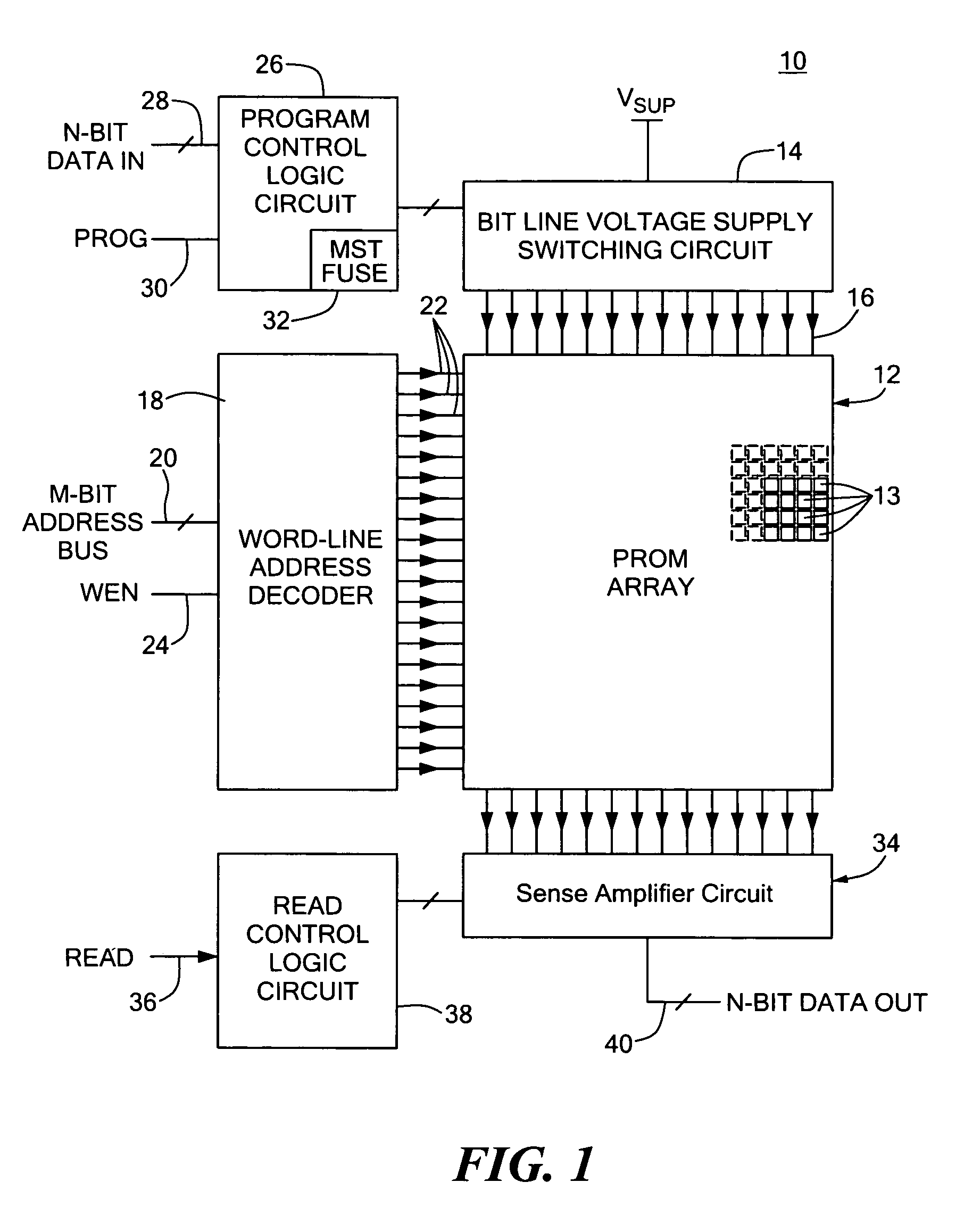

Programmable semi-fusible link read only memory and method of margin testing same

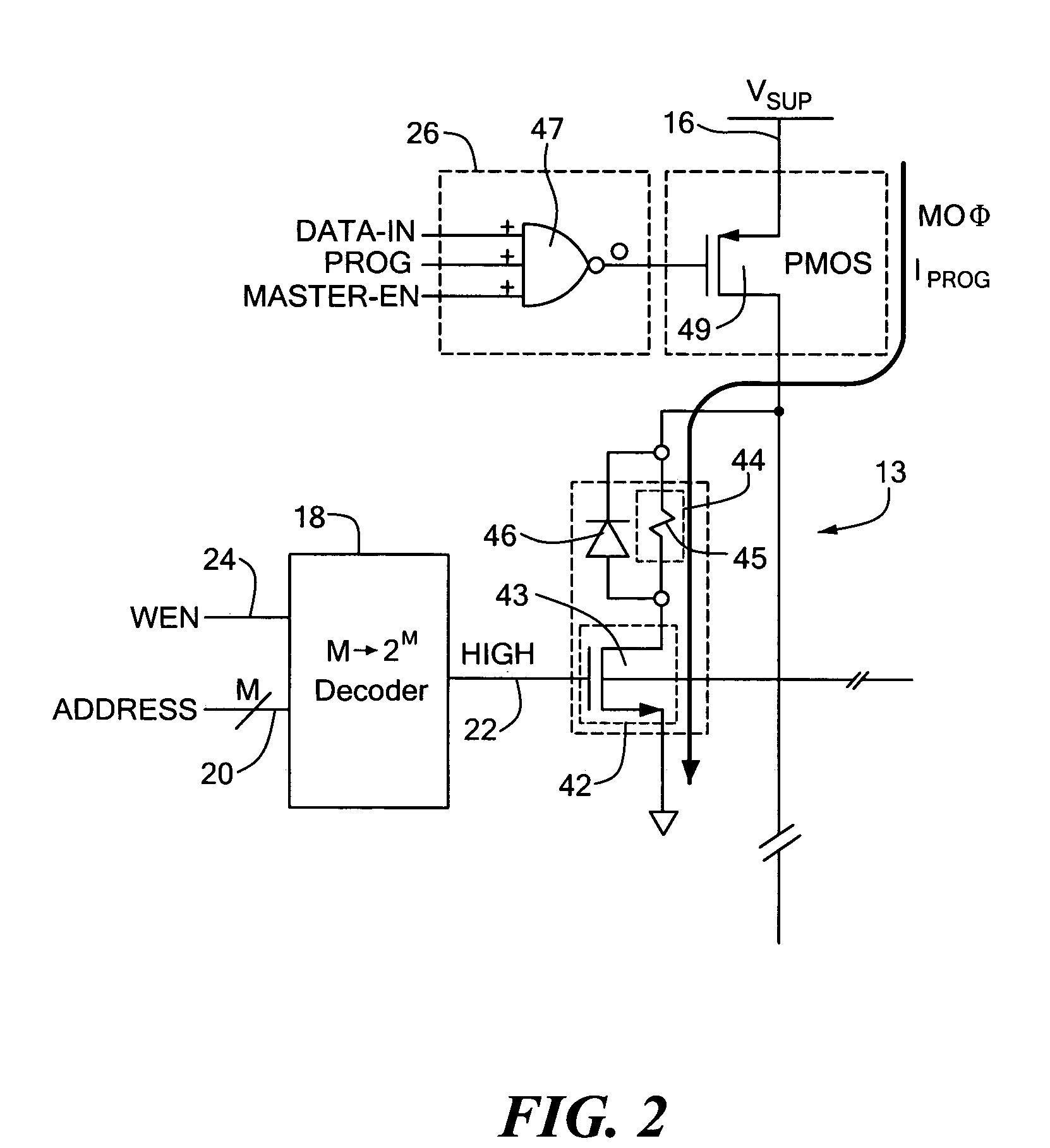

ActiveUS7136322B2Lower average currentNot destructive of surrounding featureRead-only memoriesDigital storageProgrammable read-only memoryHemt circuits

A programmable read only memory includes a matrix of semi-fusible link memory cells, each including a semi-fusible link having an intact impedance and a blown impedance; a bit line voltage supply switching circuit for applying a current to at least one selected bit line; a word line address decoder for selecting a word line; and a program control logic circuit for blowing the semi-fusible links in the memory cells identified by the intersection of the selected word and bit lines; a method is disclosed of testing programmed and unprogrammed read only memory.

Owner:ANALOG DEVICES INC

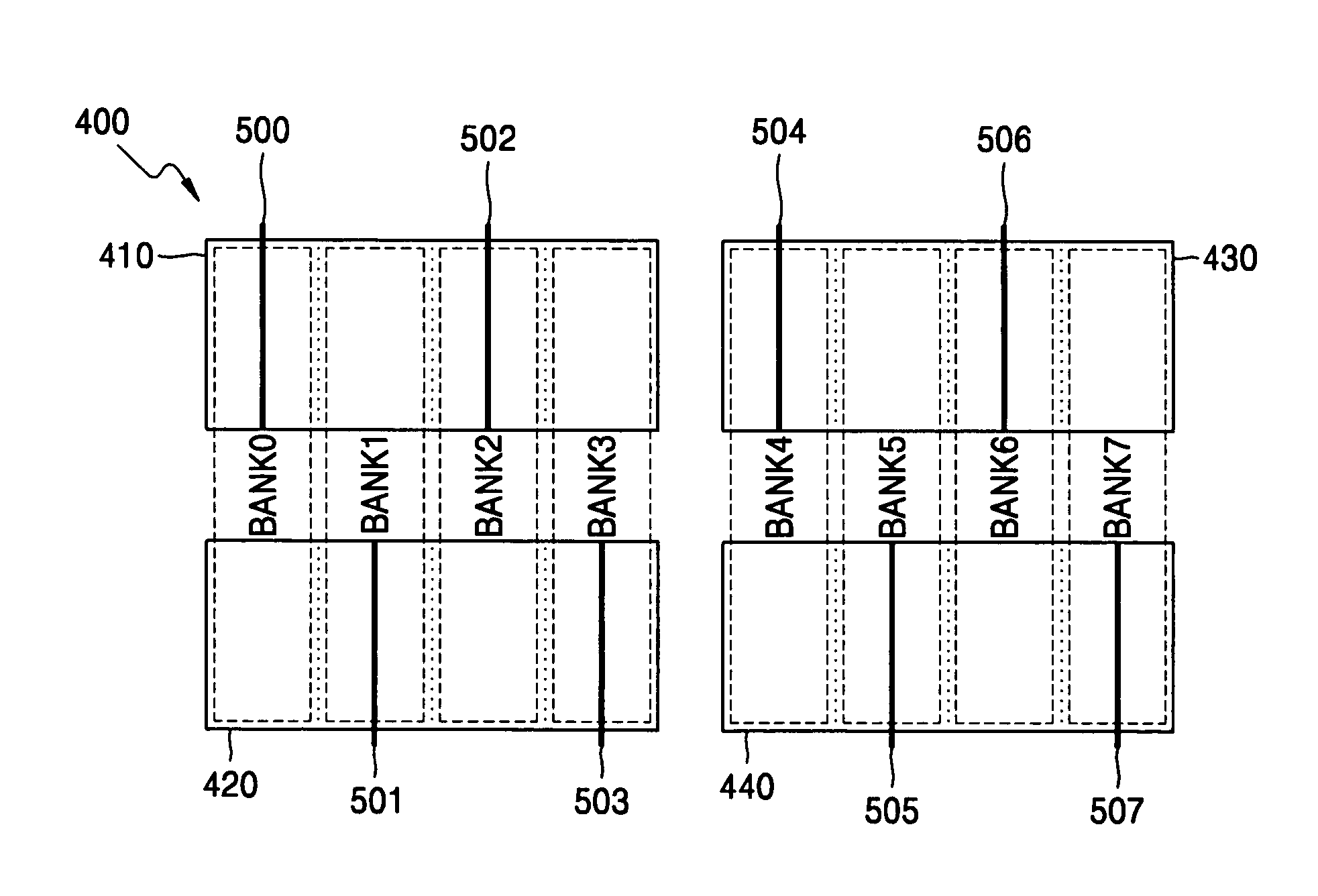

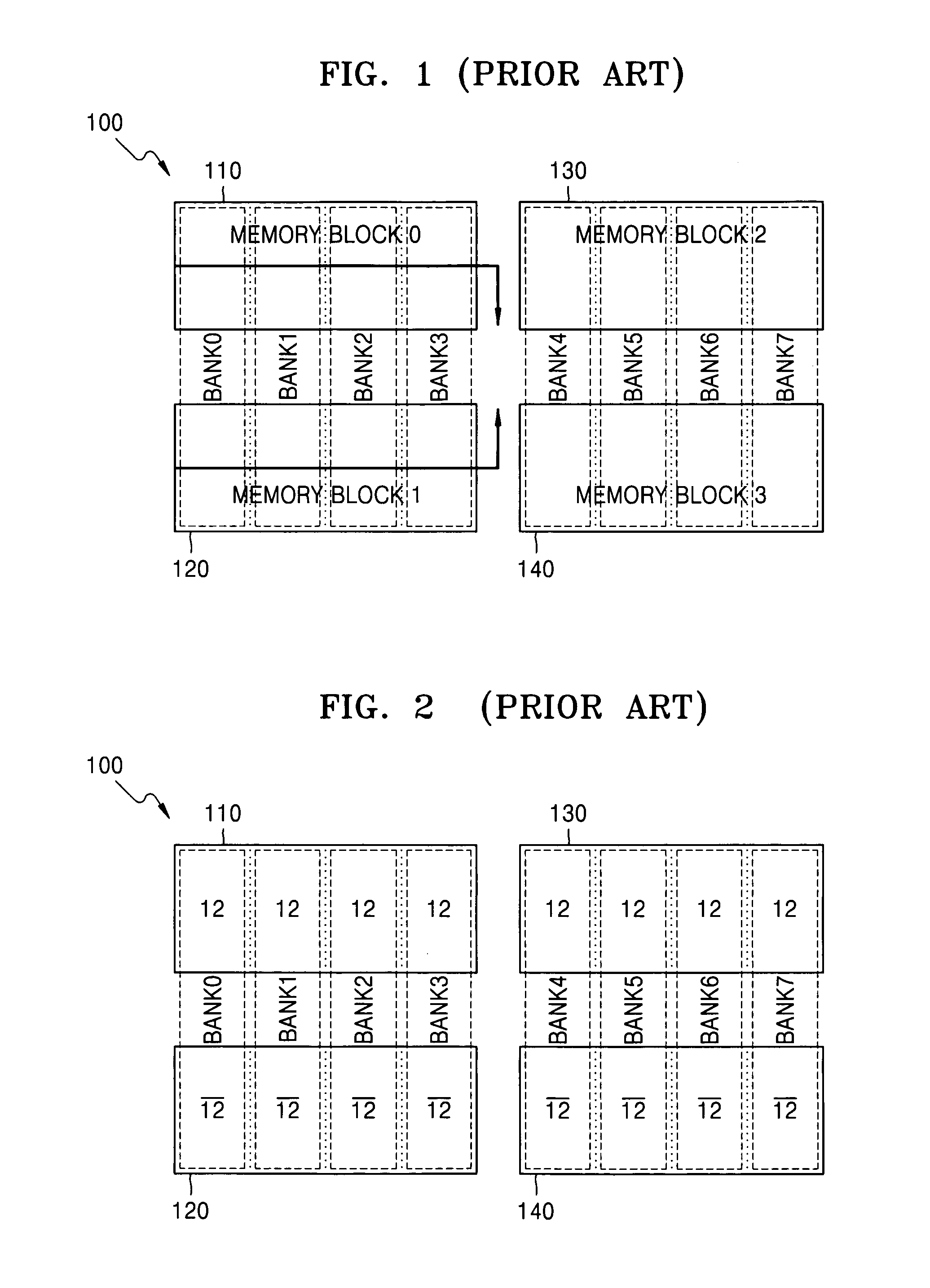

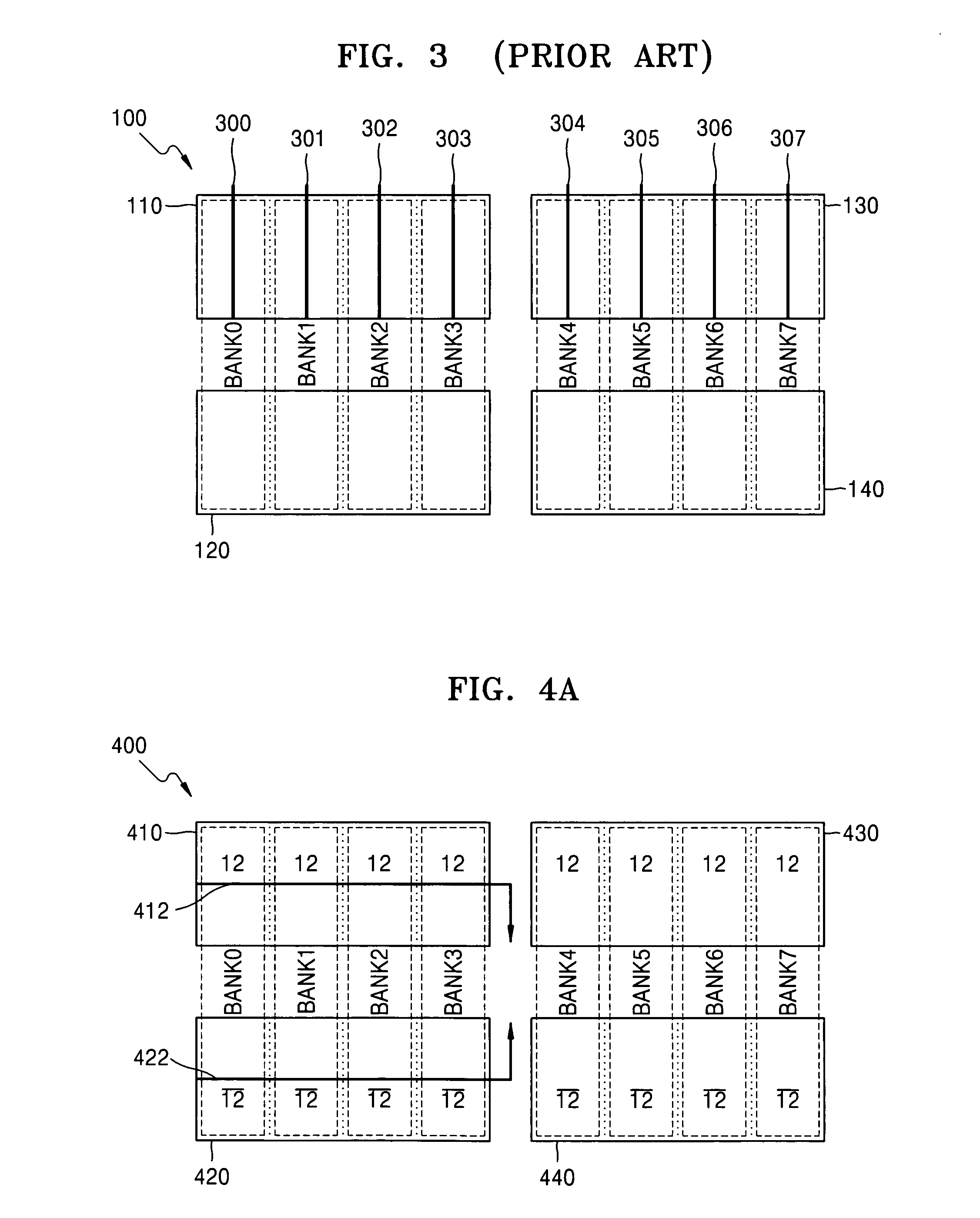

Address coding method and address decoder for reducing sensing noise during refresh operation of memory device

An address coding method, which is performed by a memory device including a plurality of banks each being shared by at least two memory blocks, includes: activating adjacent banks shared by at least two memory blocks during a refresh operation of the memory device, and enabling the refresh operation in each bank alternately between the at least two memory blocks. The method includes activating adjacent banks shared by the at least two memory blocks during another operation of the memory device, and enabling the another operation in each bank alternately between the at least two memory blocks.

Owner:SAMSUNG ELECTRONICS CO LTD

Method and system for PCI slot expansion via electrical isolation

A method of providing an interconnection between one or more peripheral devices and a system bus of a computer system selectively establishes and removes a connection from a primary peripheral bus to a secondary peripheral buses, and determines a target from among the one or more peripheral devices when a bus bridge is a master of the primary peripheral bus, using an address decoder. Access to and from the primary peripheral bus is controlled using an arbiter to select a master for the primary peripheral bus from among the one or more peripheral devices, to allow both (i) selective establishing and removing of a connection from the primary peripheral bus to one of the secondary peripheral buses in response to the selection of the master, and (ii) isolating of the master prior to establishing the connection to the secondary peripheral bus.

Owner:IBM CORP

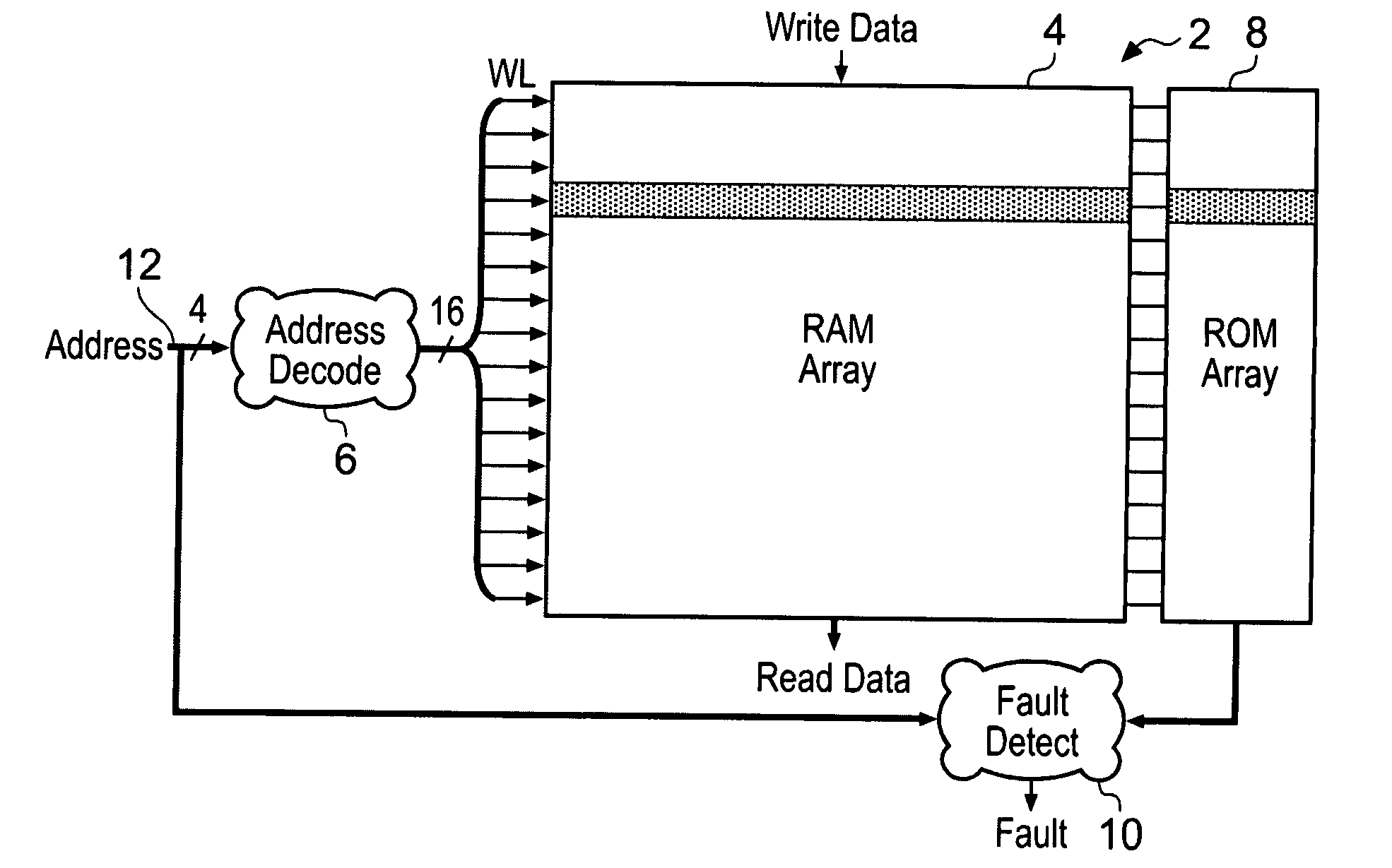

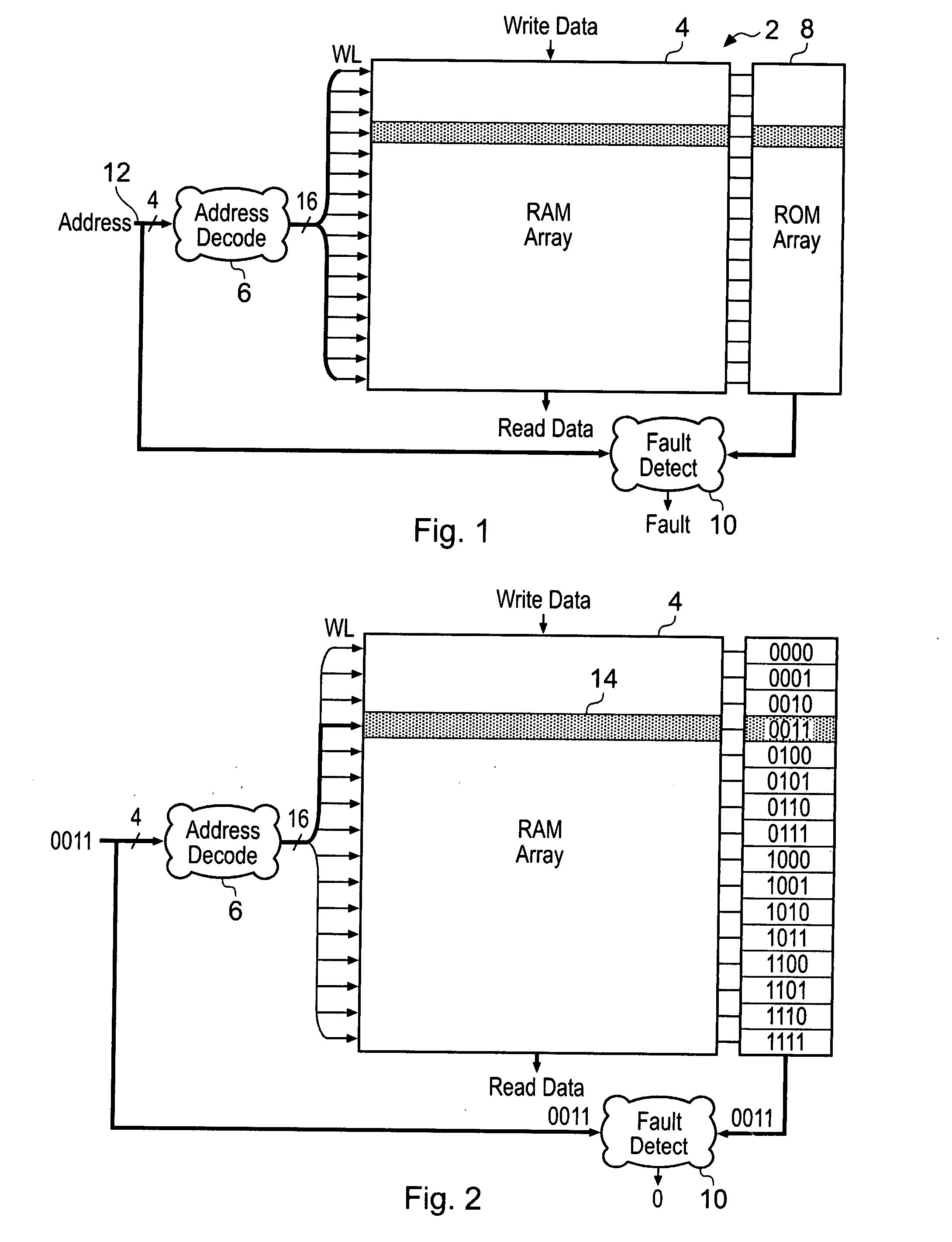

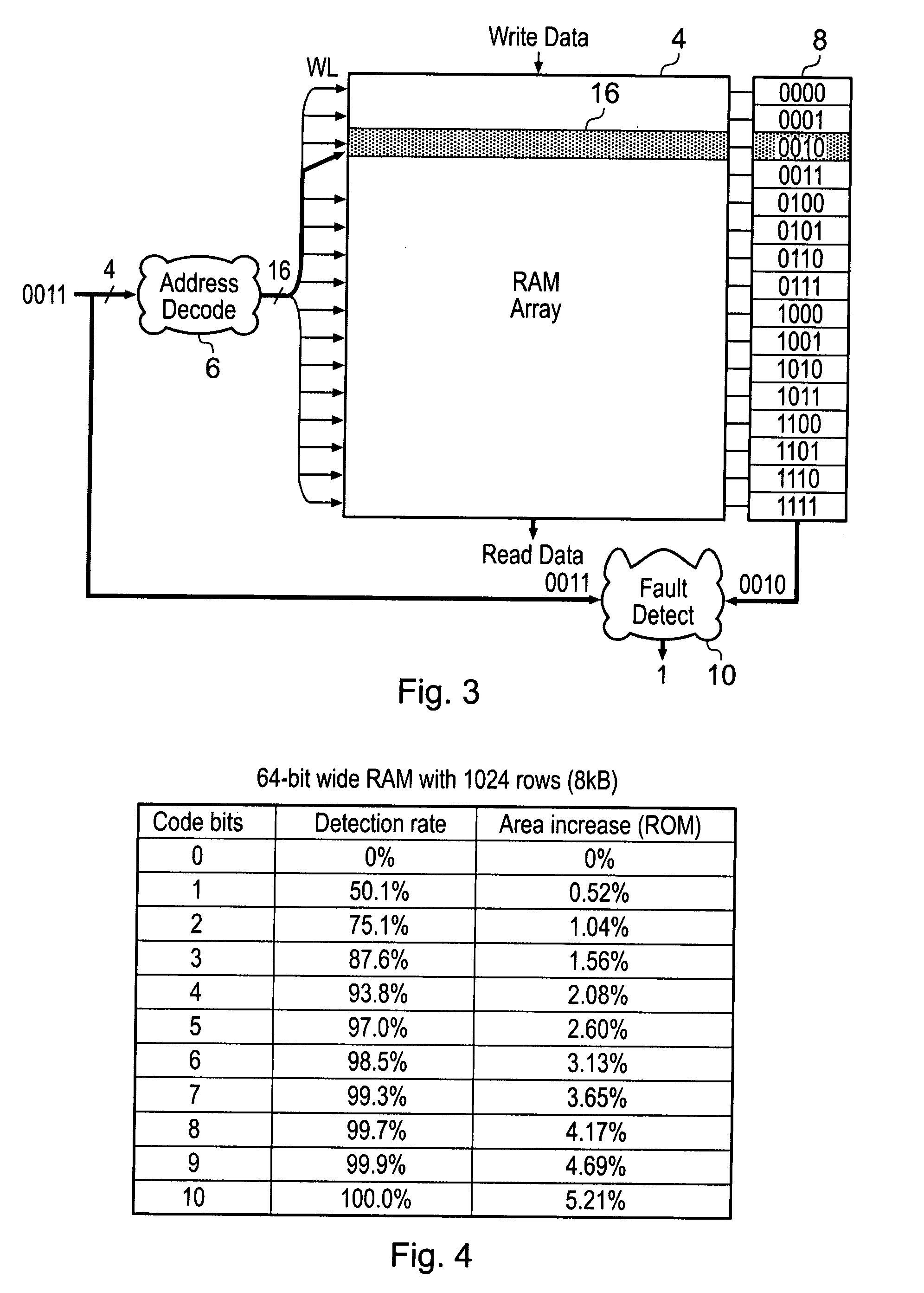

Detection of address decoder faults

InactiveUS20090037782A1Reduce overheadEfficient storageError detection/correctionStatic storageAddress decoderStorage cell

A memory 2 is formed having an array of memory cells 4 arranged in rows 14. An address decoder 6 generates a word line signal WL in response to an input address to select one of the rows of memory cells for access. The word line signal also accesses address identifying data associated with the row of memory cells being accessed. This address identifying data is compared with the input address by fault detection circuitry 10. If a mismatch is detected, then this indicates a fault within the address decoder 6.

Owner:ARM LTD

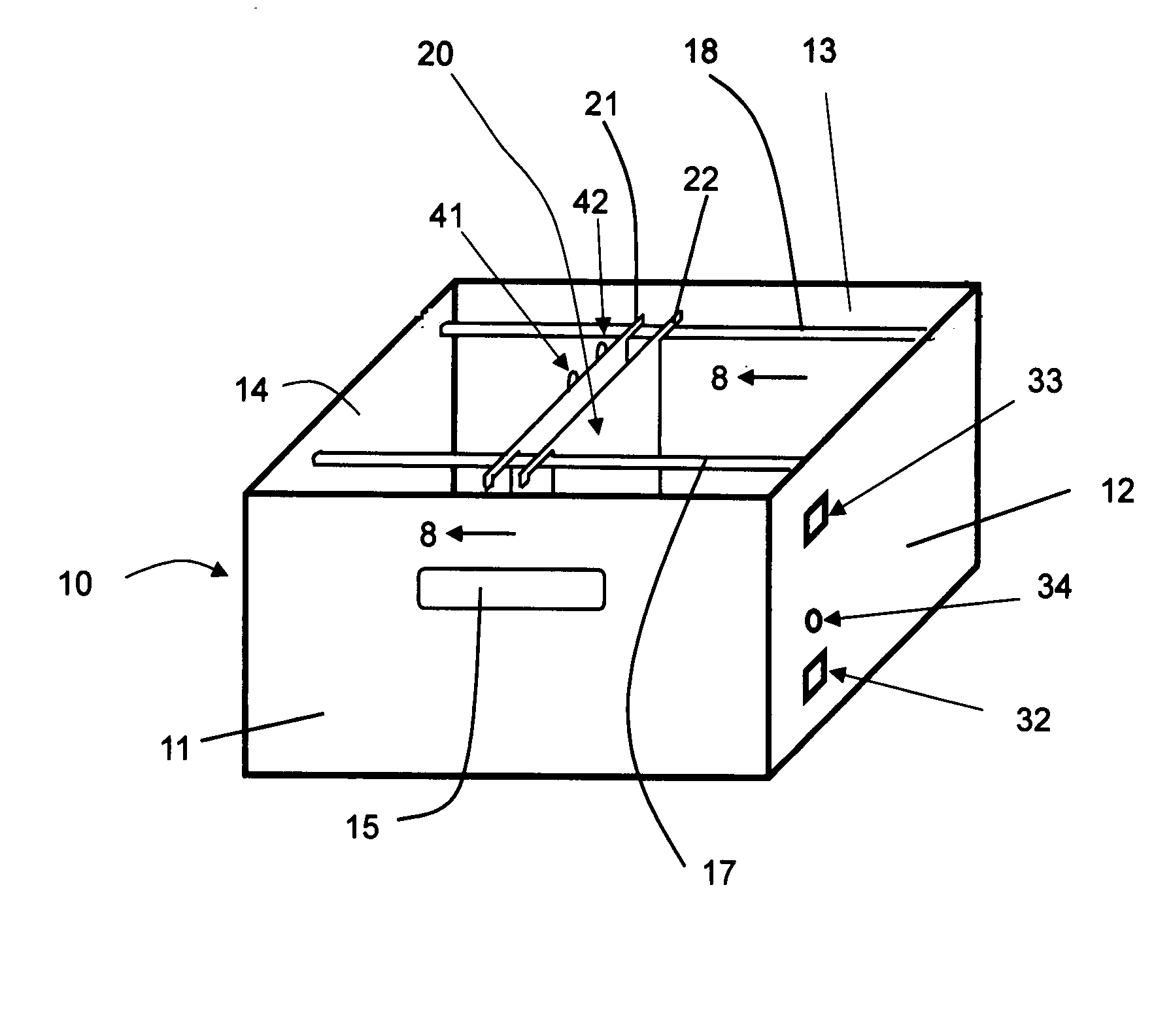

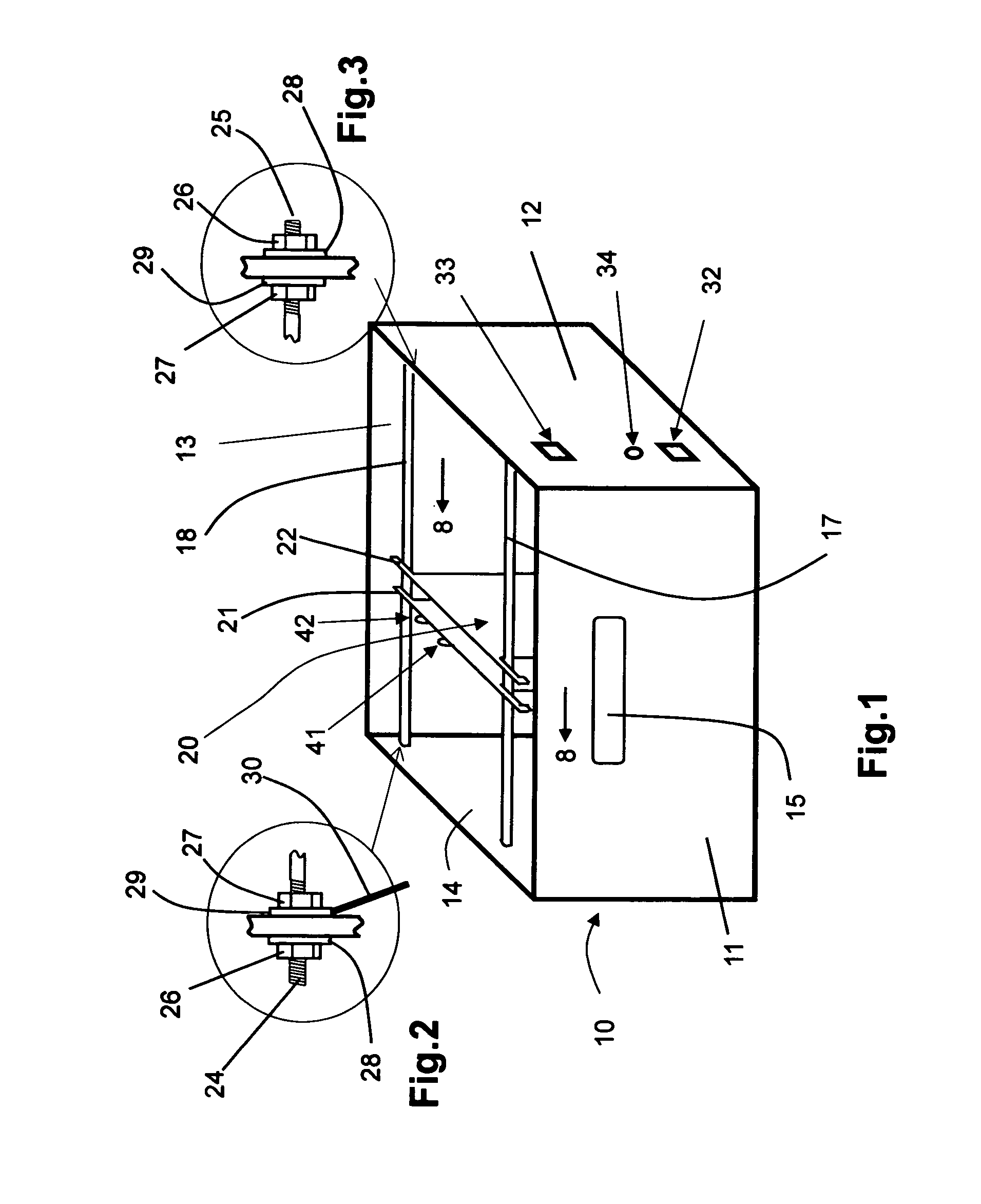

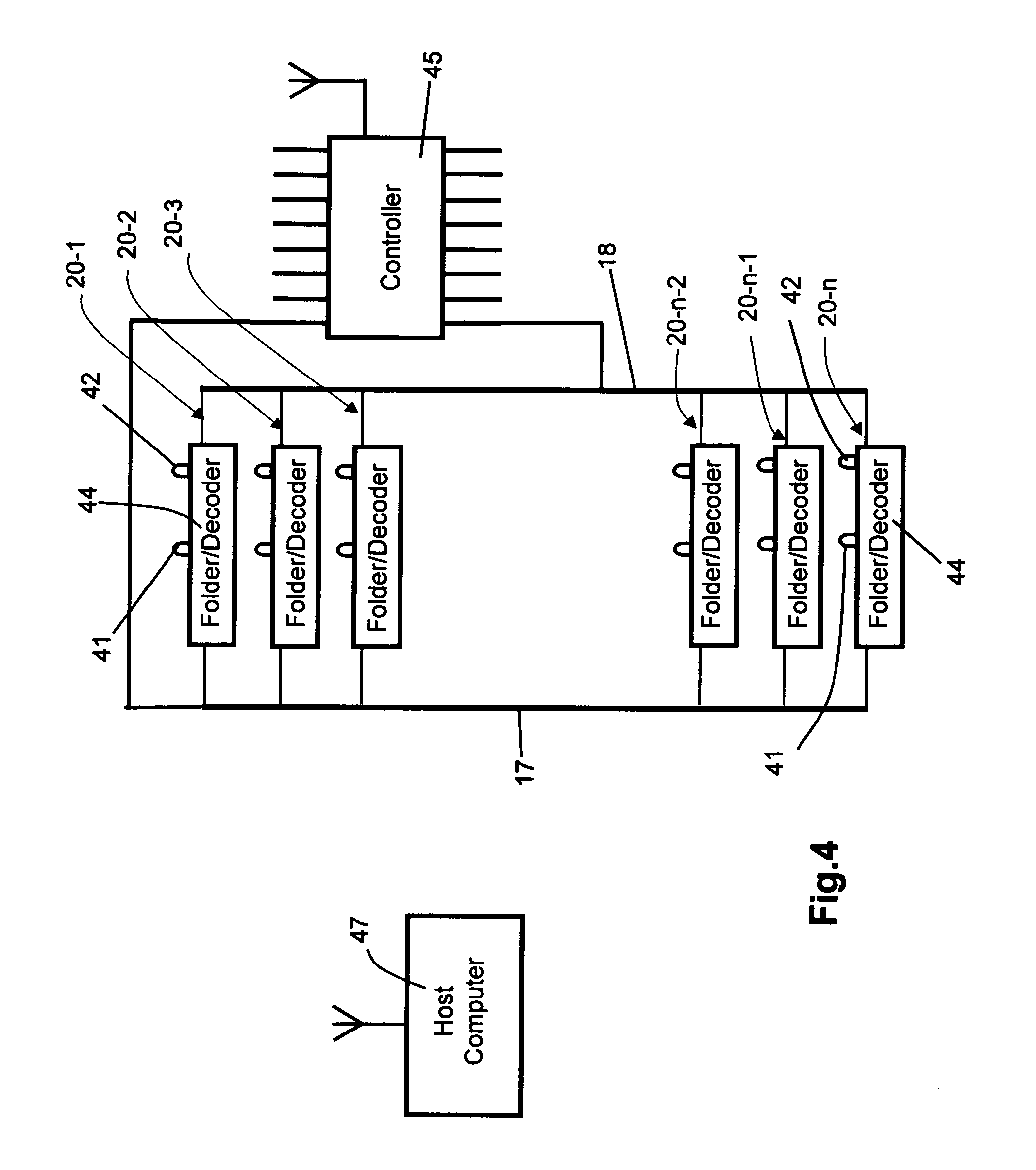

Storage container for electronically addressable file folders and documents

A storage container for use in a documents management system with remote location of file folders positioned on support members mounted between walls of the storage container. The support members are electrically connected to an electrical input connector which supplies file folder search signals to the container and receives response signals from address decoder circuits located in each file folder removably received in the container. Each container has an electrical output connector which can be connected to the electrical input connector of another container so that several containers can be connected to one another. Each container can be removably installed in a file cabinet drawer and electrically connected to the file drawer conductive rails to communicate with a file cabinet based file management system.

Owner:IMICRODATA

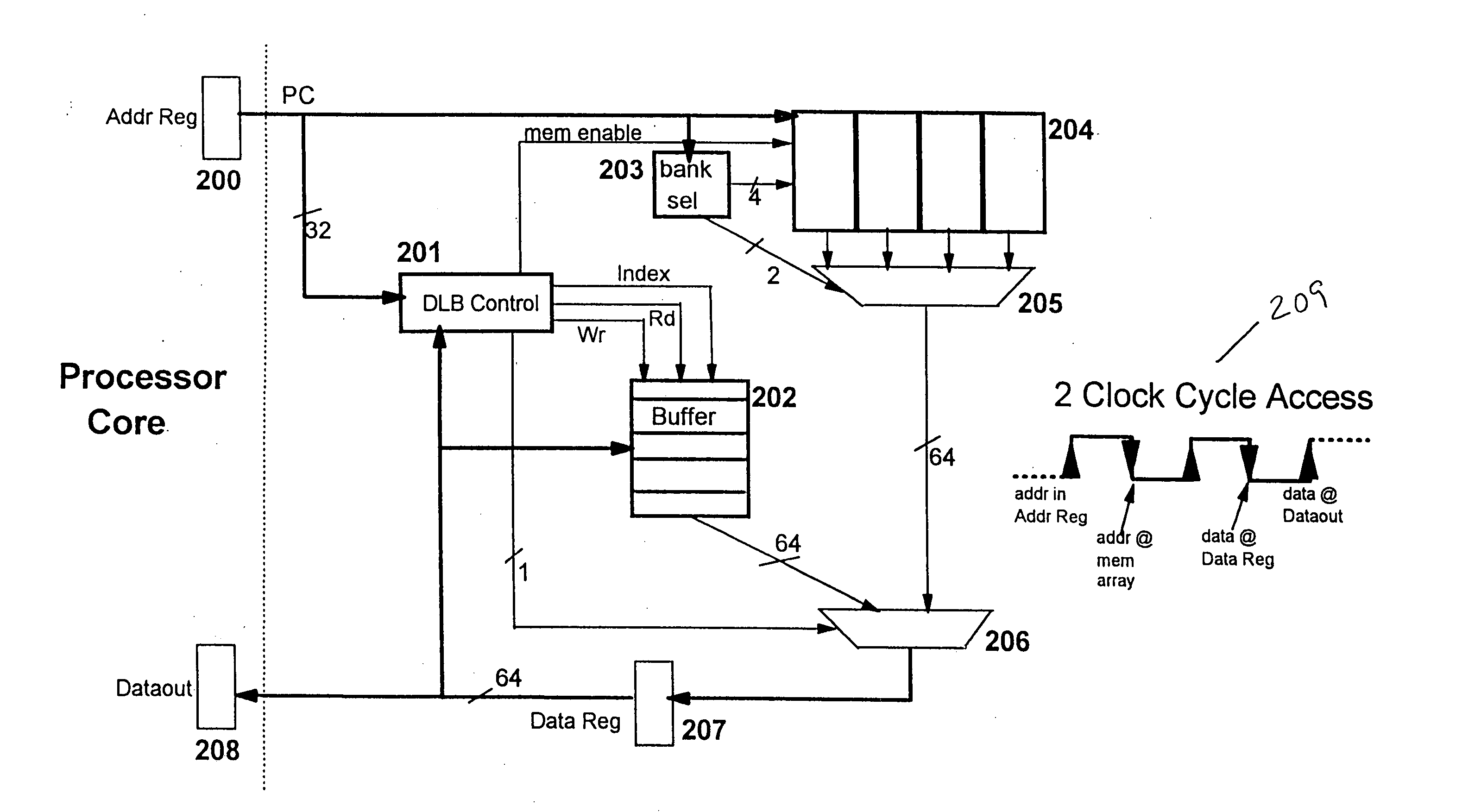

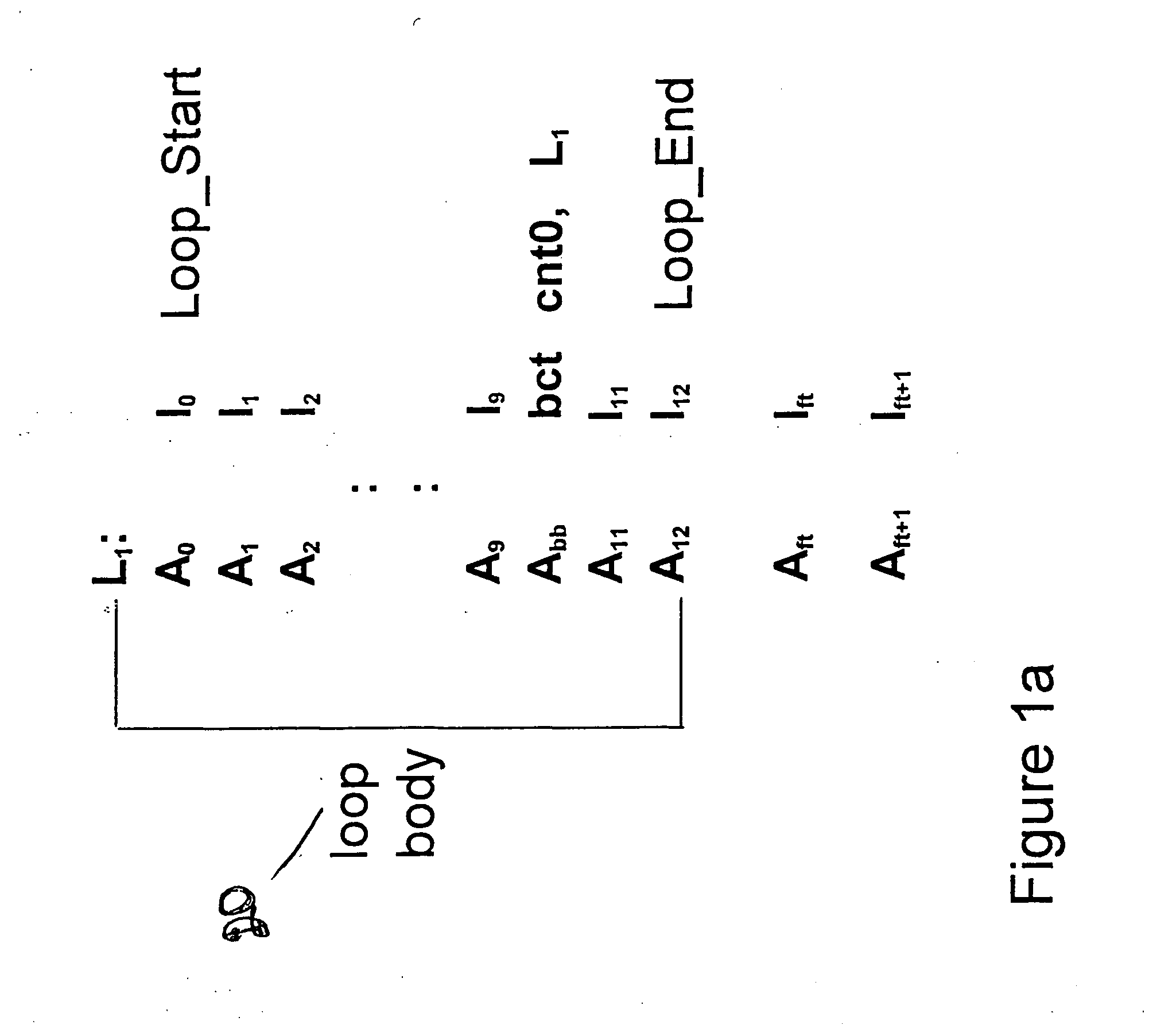

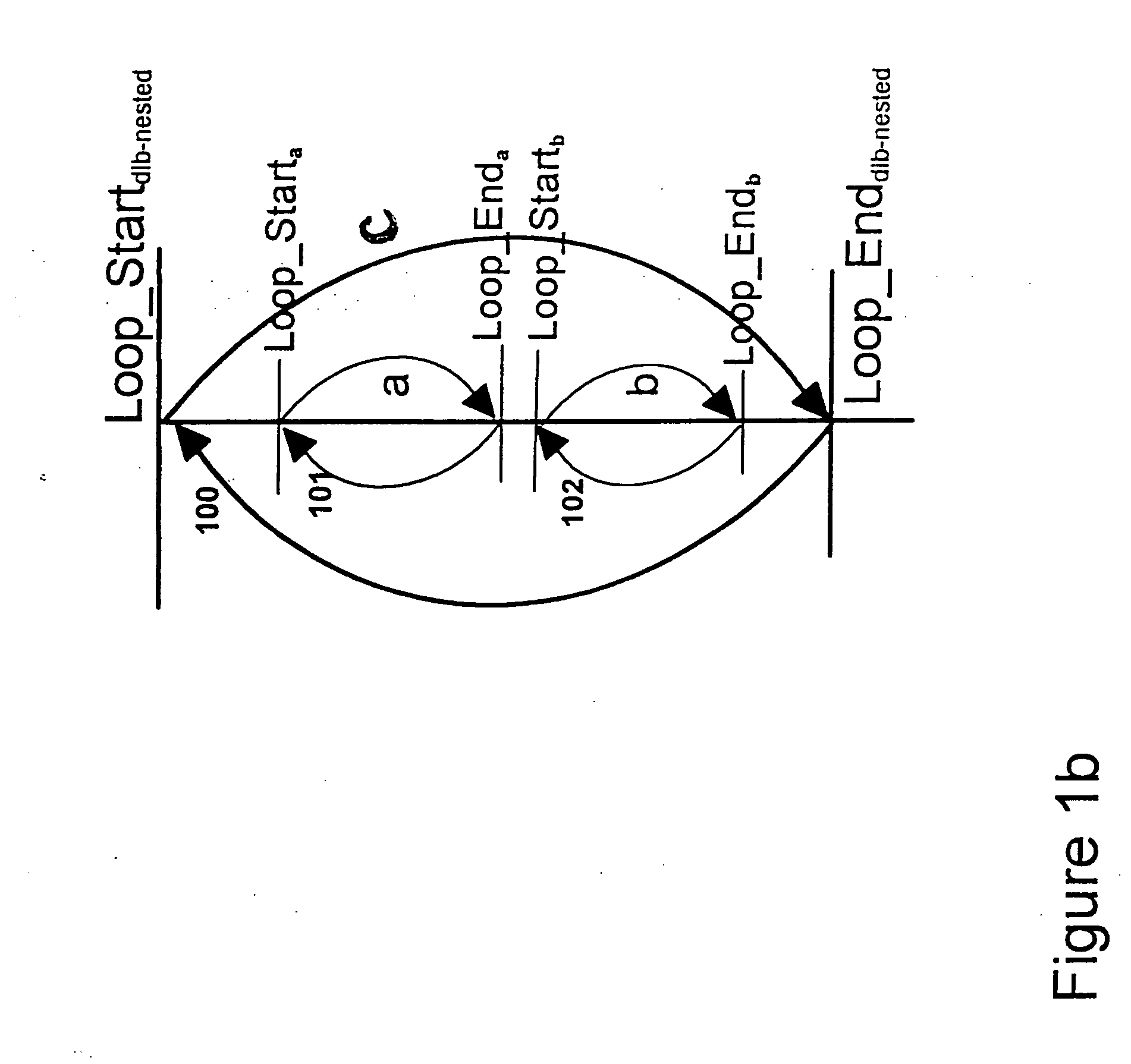

System and method for instruction memory storage and processing based on backwards branch control information

InactiveUS20050015537A1Easy to manageMemory adressing/allocation/relocationDigital computer detailsProcessing InstructionAddress decoder

A system for instruction memory storage and processing in a computing device having a processor, the system is based on backwards branch control information and comprises a dynamic loop buffer (DLB) which is a tagless array of data organized as a direct-mapped structure; a DLB controller having a primary memory unit partitioned into a plurality of banks for controlling the state of the instruction memory system and accepting a program counter address as an input, the DLB controller outputs distinct signals. The system further comprises an address register located in the memory of the computing device, it is a staging register for the program counter address and an instruction fetch process that takes two cycles of the processor clock; and a bank select unit for serving as a program counter address decoder to accept the program counter address and to output a bank enable signal for selecting a bank in a primary memory unit, and a decoded address for access within the selected bank.

Owner:IBM CORP

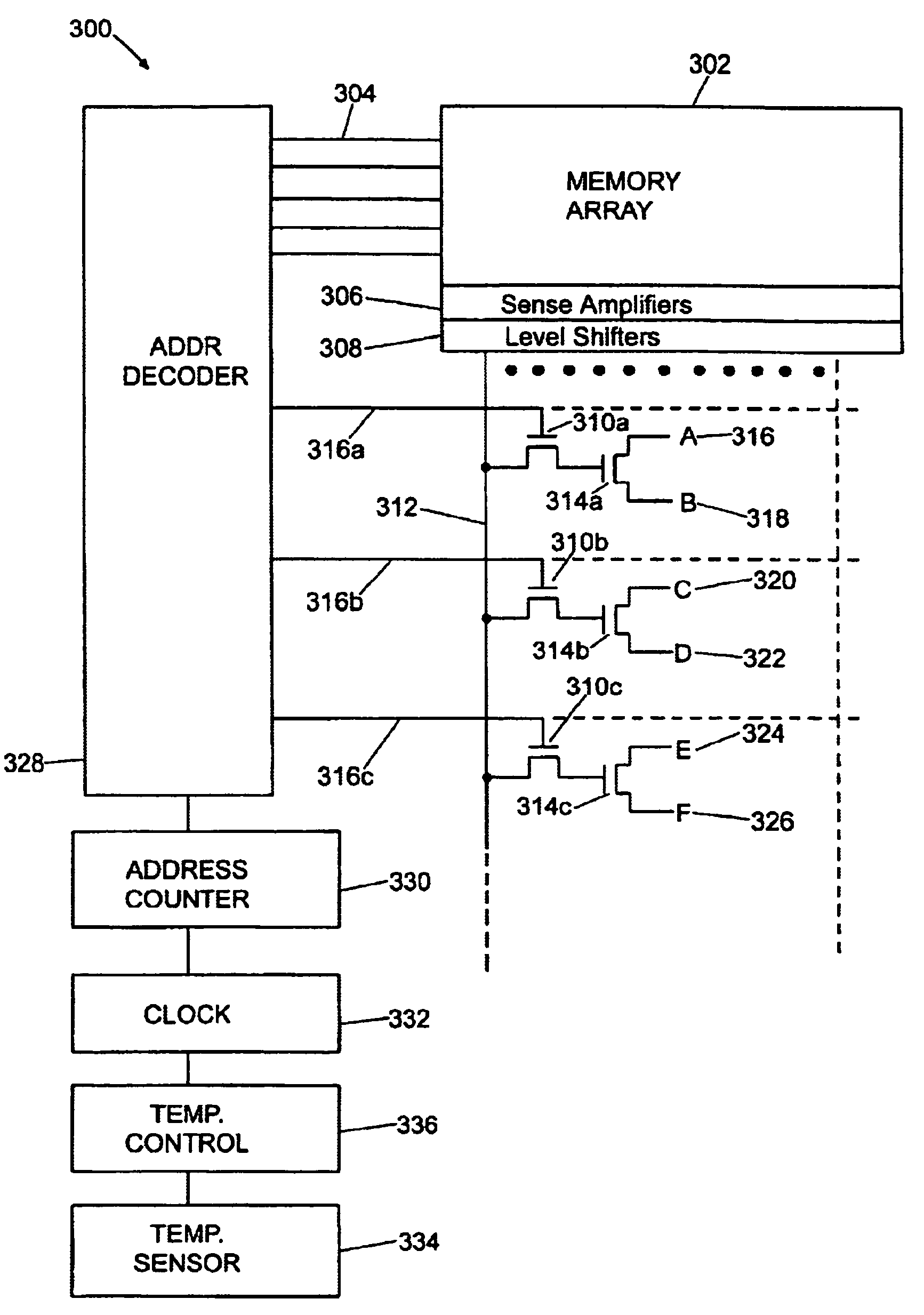

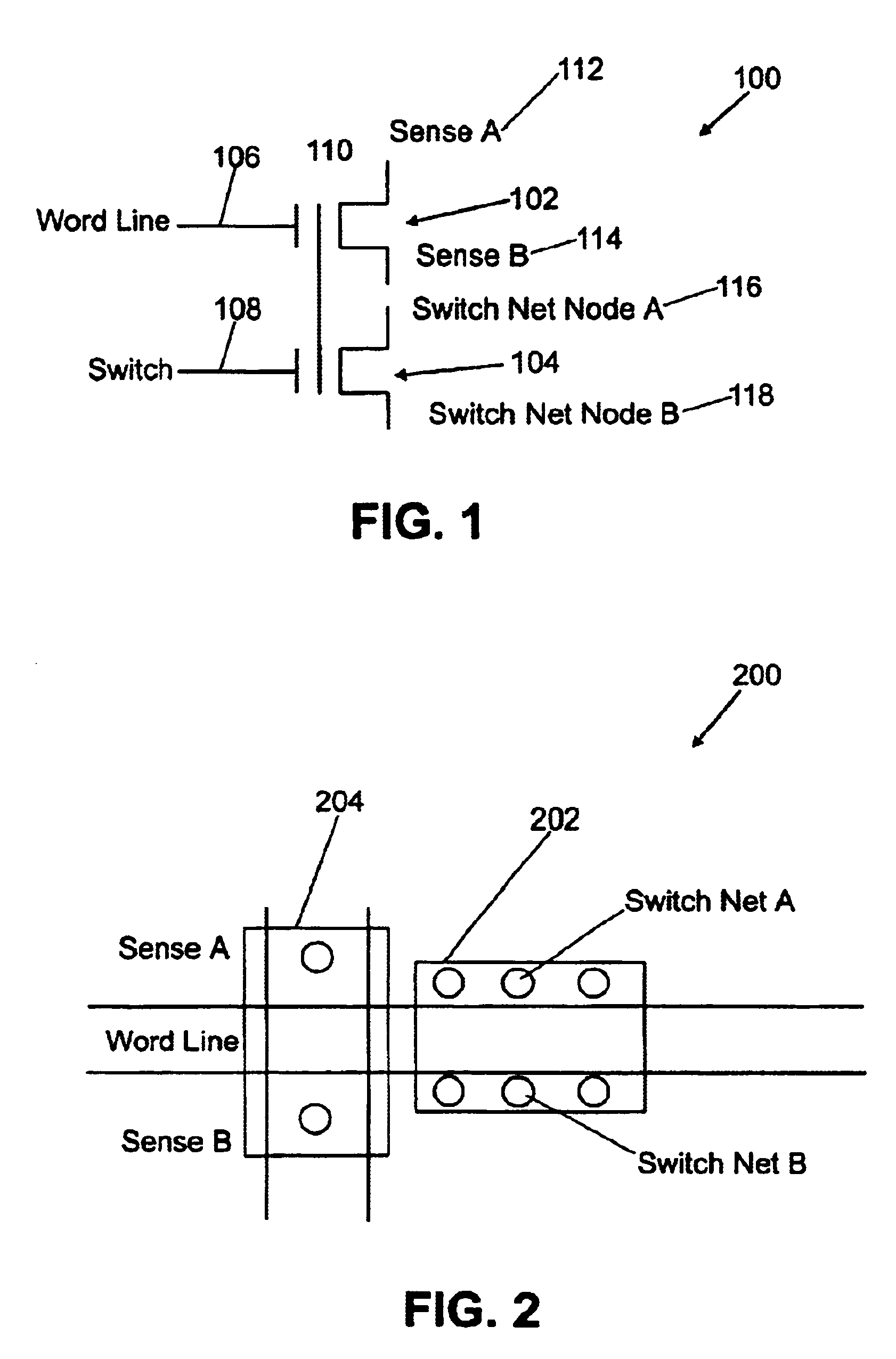

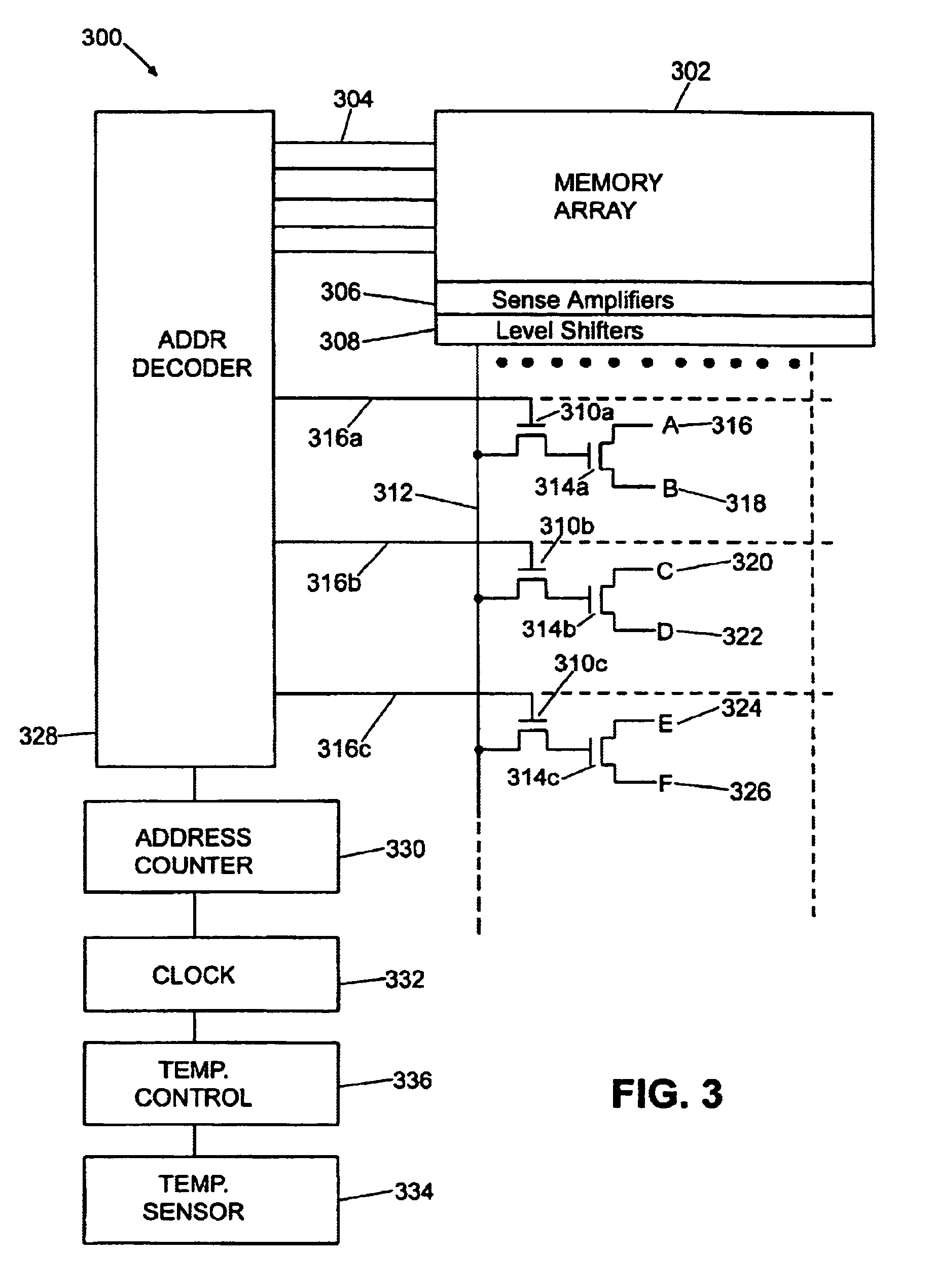

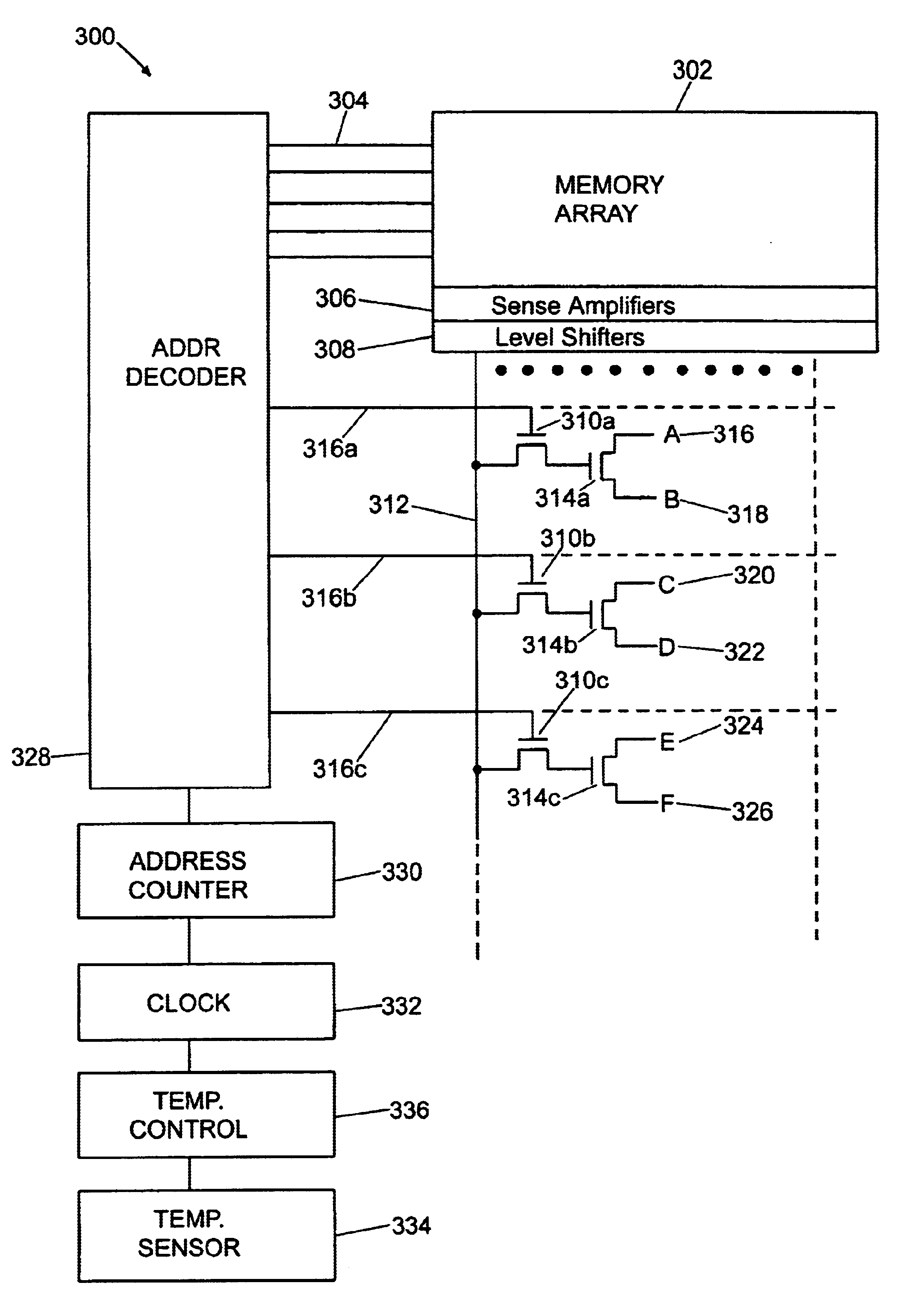

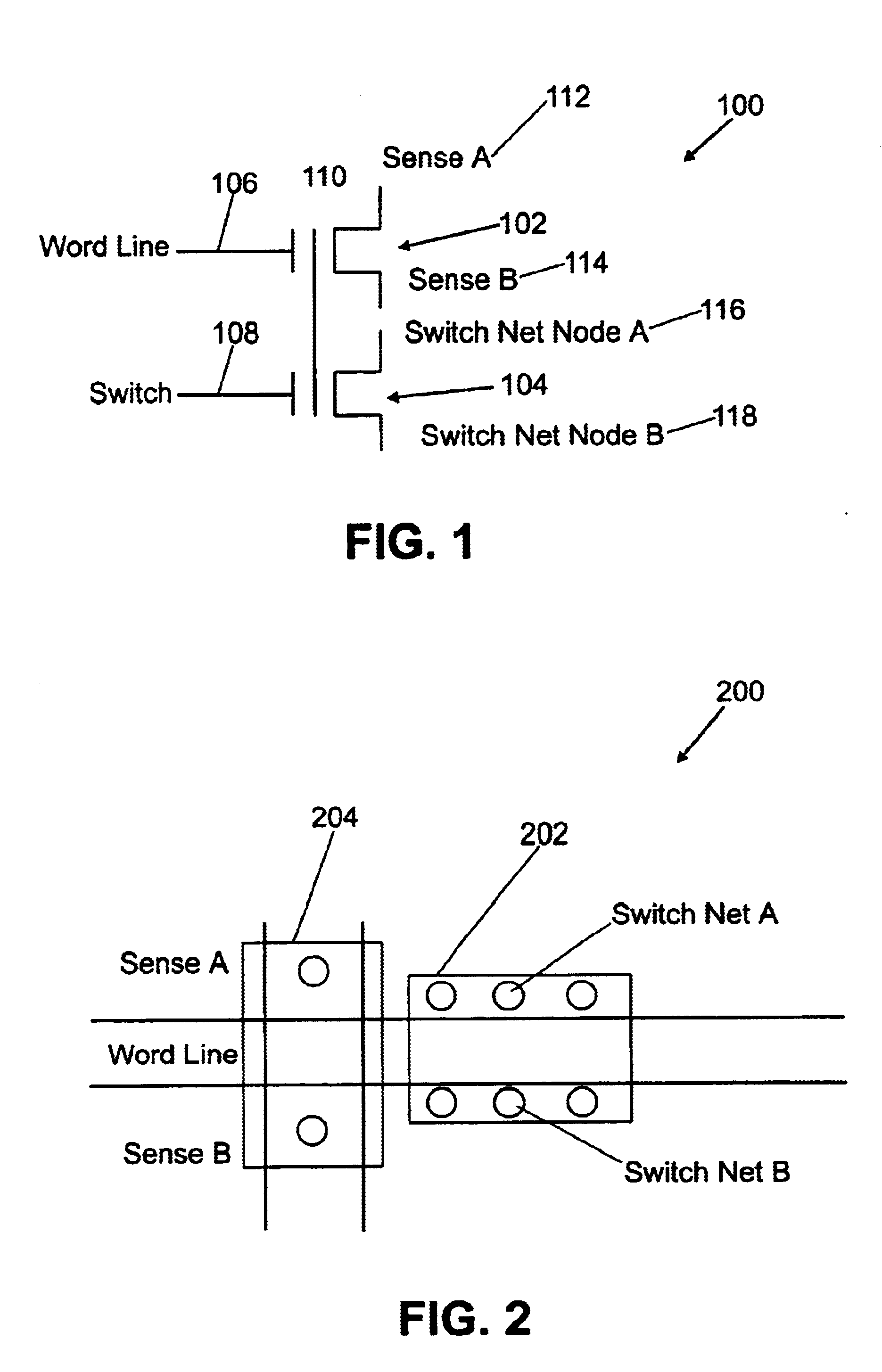

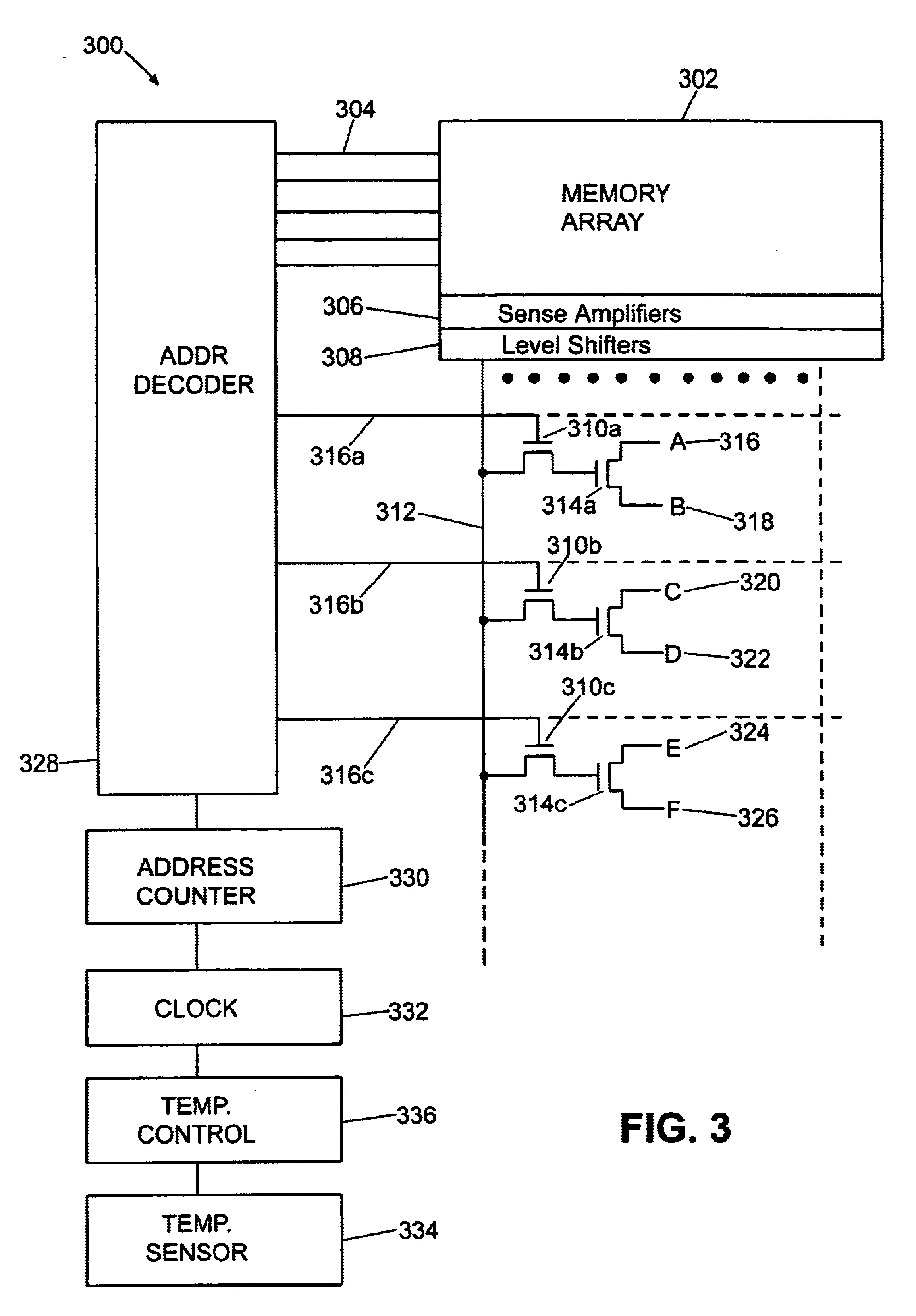

Flash/dynamic random access memory field programmable gate array

A method for providing a circuit for selectively interconnecting N pairs of nodes in an integrated circuit device comprising: providing a memory array having a plurality of wordlines and a plurality of bitlines; providing a plurality of dynamic random access memory wordlines; providing a separate switch for each pair of nodes in the integrated circuit, each switch associated with a unique combination of one of the plurality of bitlines and one of the plurality of dynamic random access memory wordlines, each switch including a refresh transistor and a switching transistor; and providing an address decoder having at least N distinct states for supplying signals to the plurality of wordlines and the plurality of dynamic random access memory wordlines.

Owner:ACTEL CORP

Flash/dynamic random access memory field programmable gate array

A circuit for selectively interconnecting two nodes in an integrated circuit device includes a memory array having a plurality of wordlines and a plurality of bitlines. A refresh transistor has a source coupled to one of the plurality of bitlines, a control gate coupled to a dynamic random access memory wordline and a drain. A switching transistor has a gate coupled to the drain of the refresh transistor, a source coupled to a first one of the nodes and a drain coupled to a second one of the nodes. An address decoder for supplies periodic signals to the wordlines and the dynamic random access memory wordline.

Owner:MICROSEMI SOC

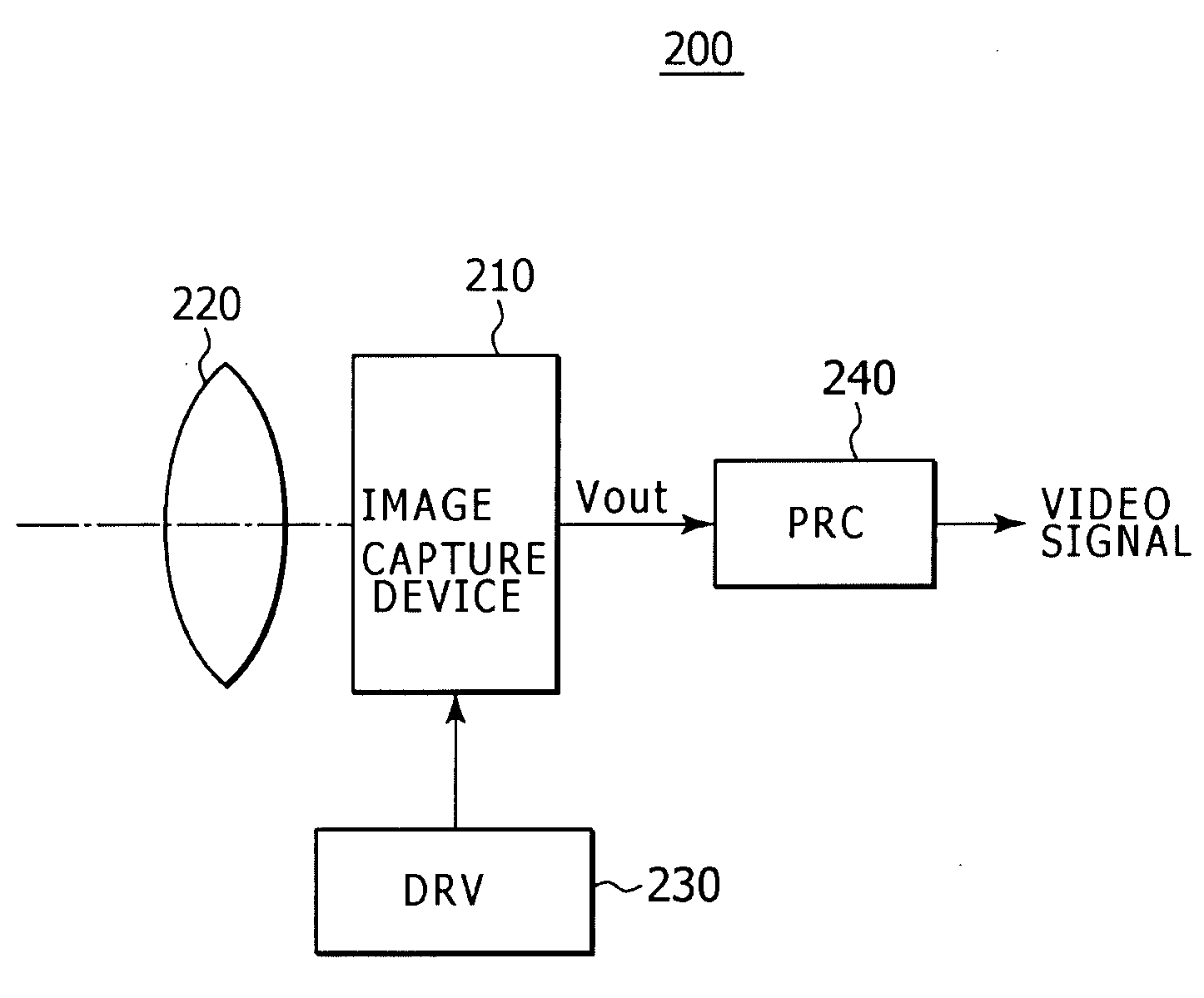

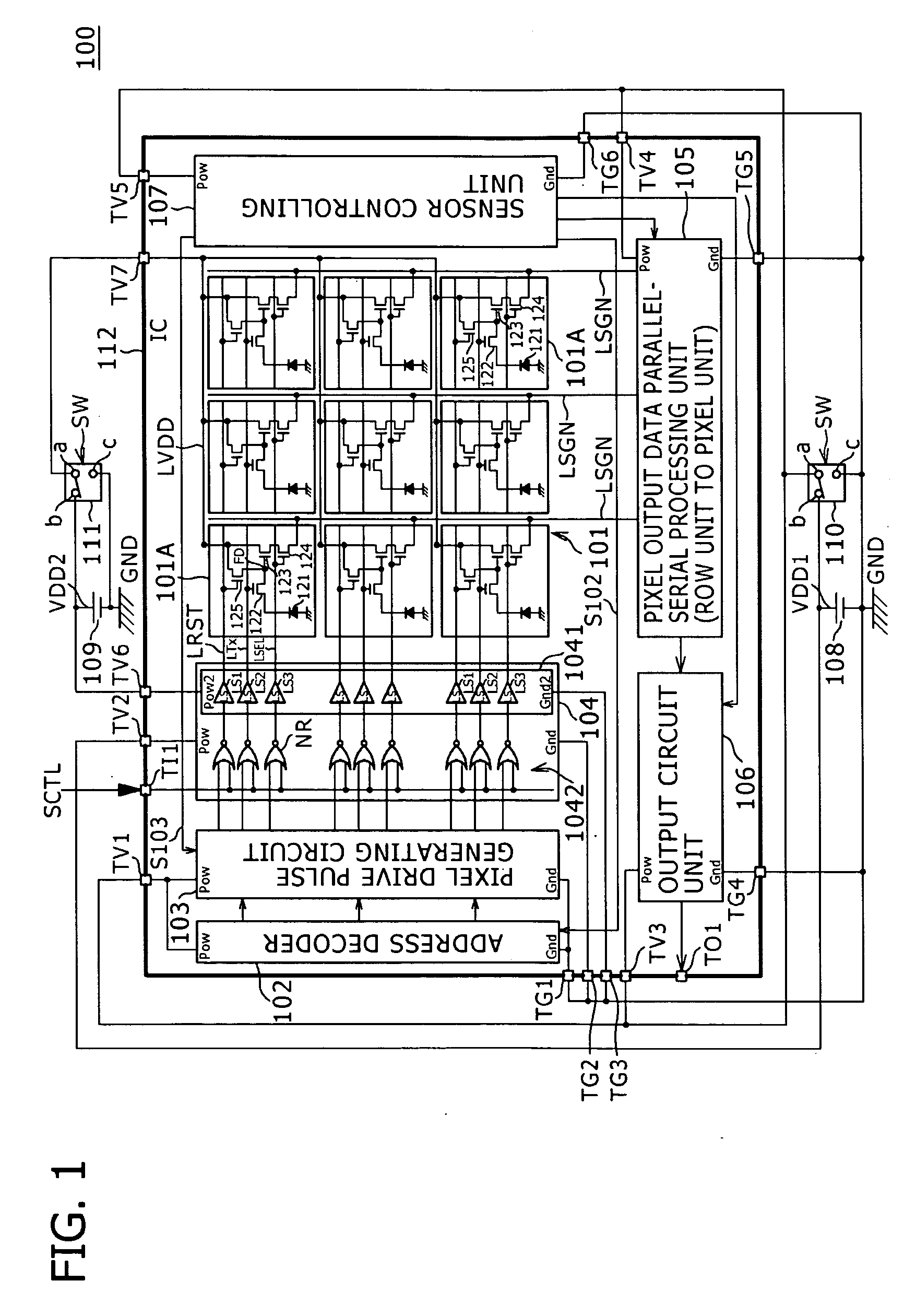

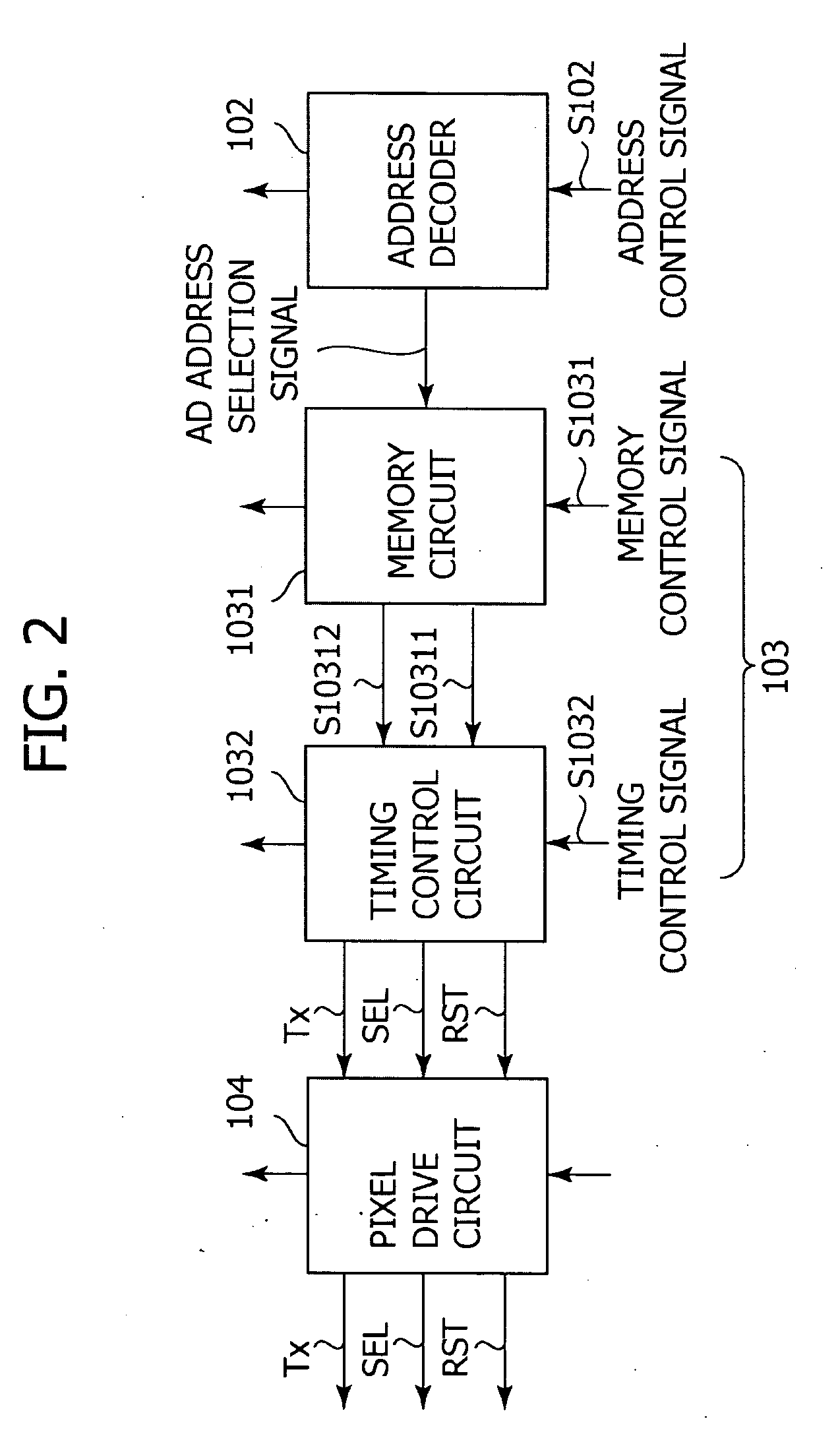

Pixel drive circuit, image capture device, and camera system

InactiveUS20090086049A1Image quality of image is not loweredEnhance the imageTelevision system detailsTelevision system scanning detailsAddress decoderCharge discharge

A pixel drive circuit includes a plurality of pixel circuits each including a photoelectric converting unit for converting an incident light into an electric charge and accumulating the converted electric charge, the plurality of pixel circuits being arranged in a matrix shape, an address decoder for selecting the pixel circuits to be controlled which are arranged on an identical line, a storage circuit for storing operation information to be executed by the pixel circuits selected by the address decoder, and a control circuit for controlling an operation of the pixel circuits selected by the address decoder in accordance with a storage state of the storage circuit. The control circuit controls a charge discharging operation of discharging an electric charge remaining in the photoelectric converting unit of each of the pixel circuits. The storage circuit holds the storage state until the charge discharging operation is completed.

Owner:SONY CORP

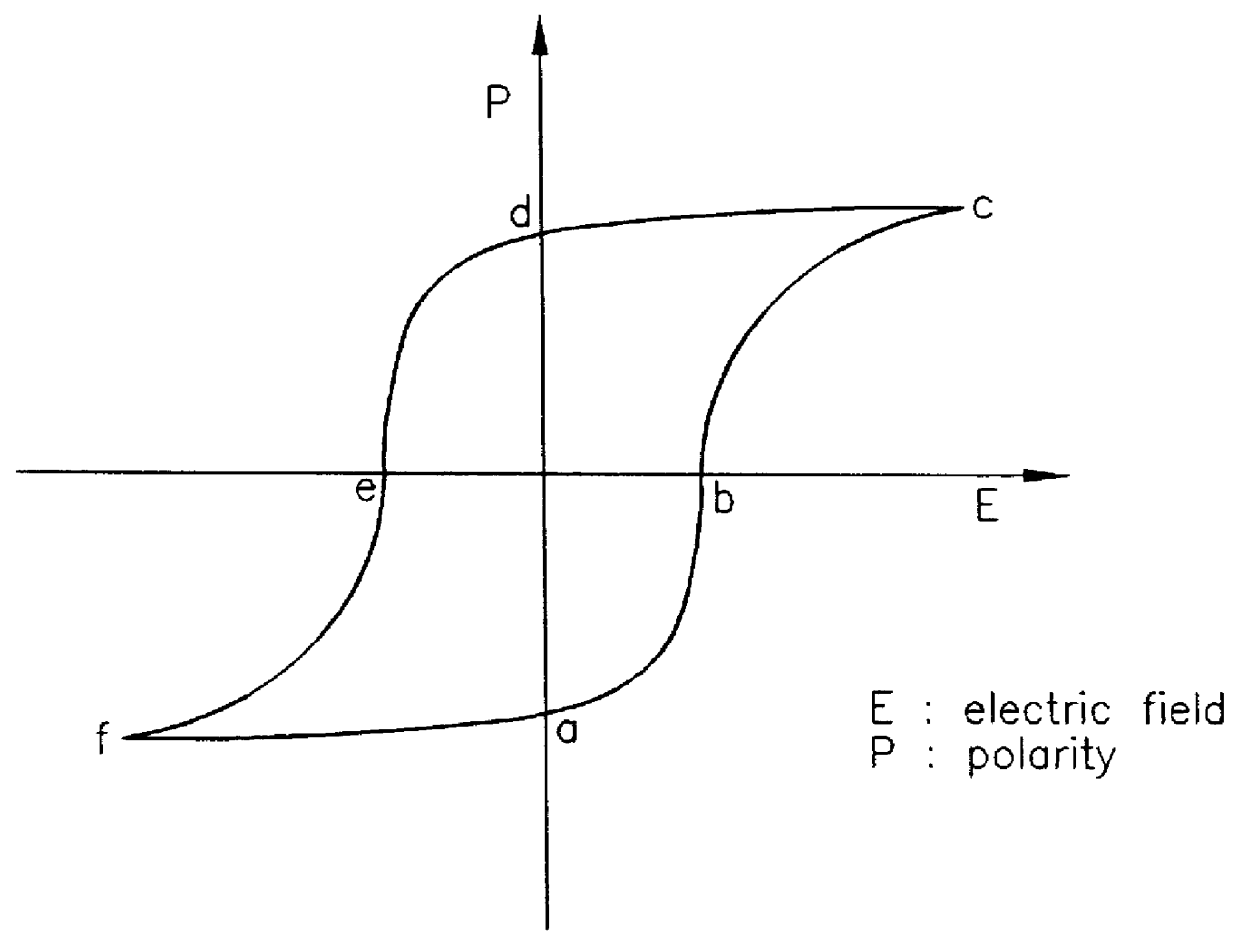

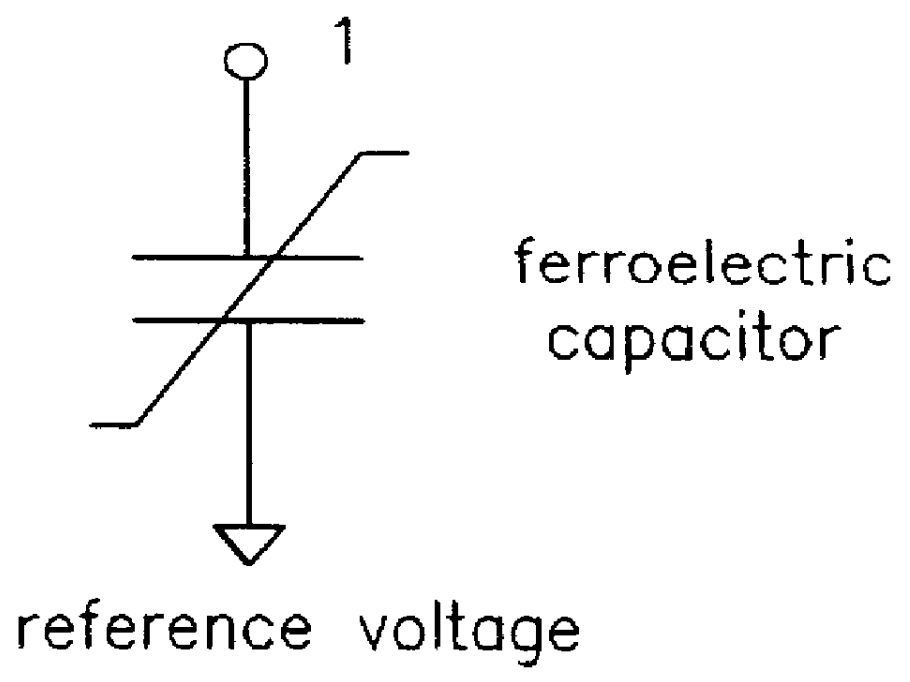

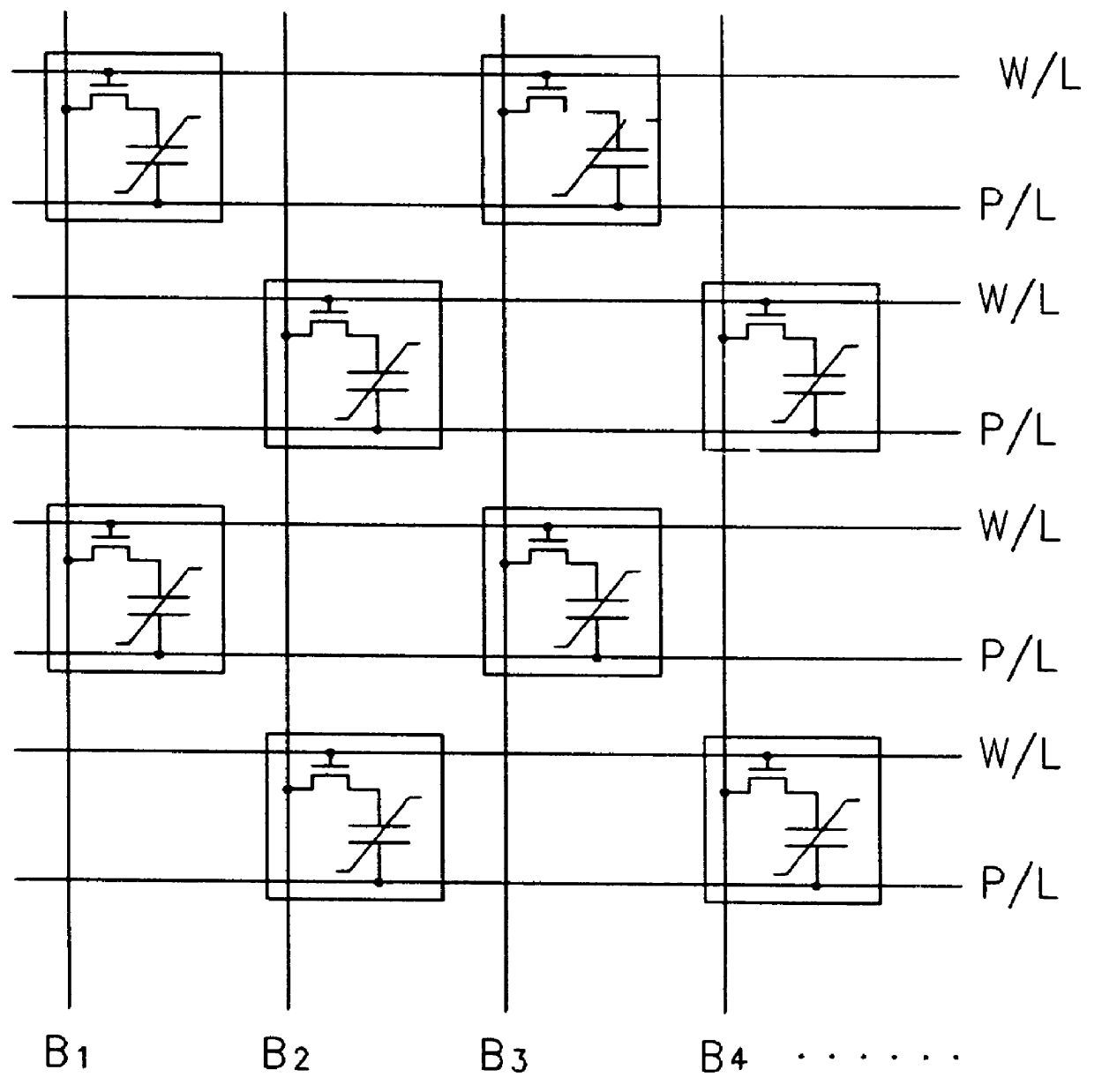

SWL ferroelectric memory and circuit for driving the same

A split wordline ferroelectric memory does not utilize plate lines and a circuit for driving the same is disclosed. The memory including unit cell arrays and each array has a plurality of split wordlines (SWLs) arranged in a first direction at fixed intervals, and a plurality of bitlines arranged in a second direction vertical to each of the SWLs at fixed intervals. A ferroelectric unit memory cell is arranged in each pair of adjacent two SWLs and adjacent two bitlines. The circuit includes a post X-decoder for receiving and decoding X and Z-addresses for controlling a cell array block operative, a global control pulse generator for providing a control pulse required for data write or read in response to a CSBpad signal received externally, a local control pulse generator for receiving the control pulse from the global control pulse generator and providing a control signal required for data write and read, an SWL cell array block for storage of data, an SWL driver for driving the SWL cell array block in response to control signals from the post X-decoder and the local control pulse generator, a Y-address decoder for decoding a Y-address signal received externally, a column controller for controlling columns in response to the control signal from the local control pulse generator and a decoded signal from the Y-address decoder, and a sense amplifier and I / O controller for sensing / recording a data from / to the SWL cell array block.

Owner:HYUNDAI ELECTRONICS IND CO LTD

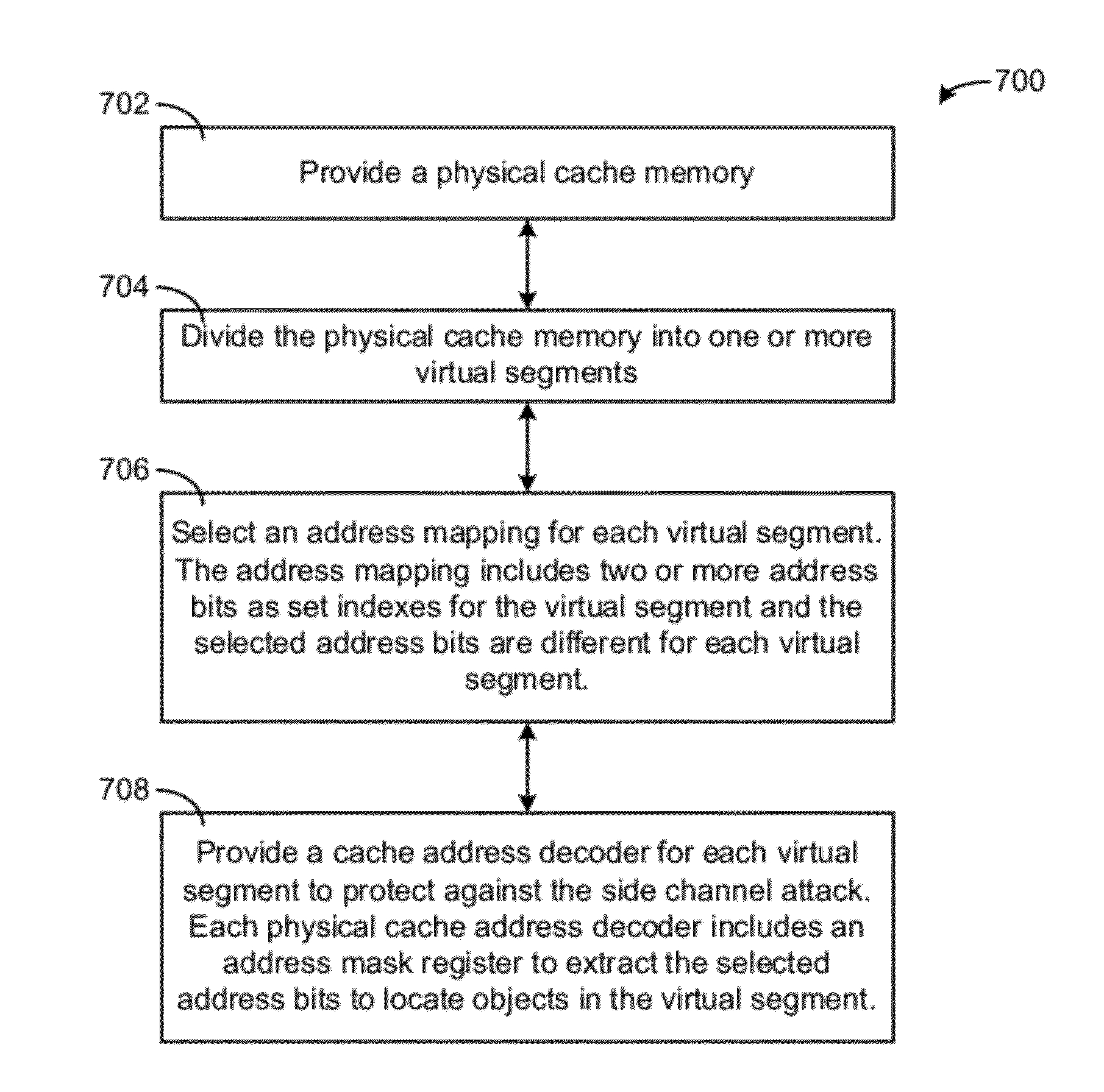

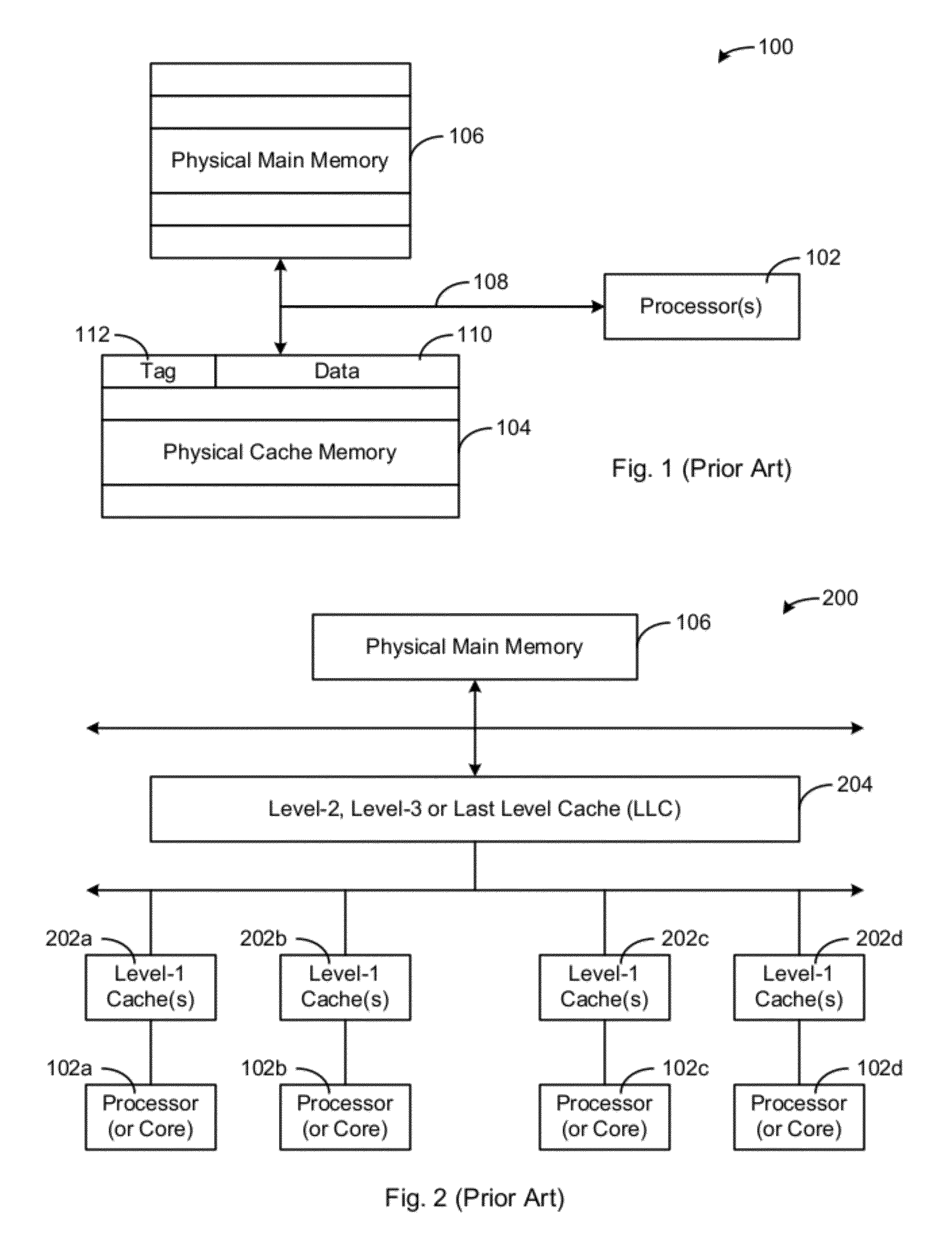

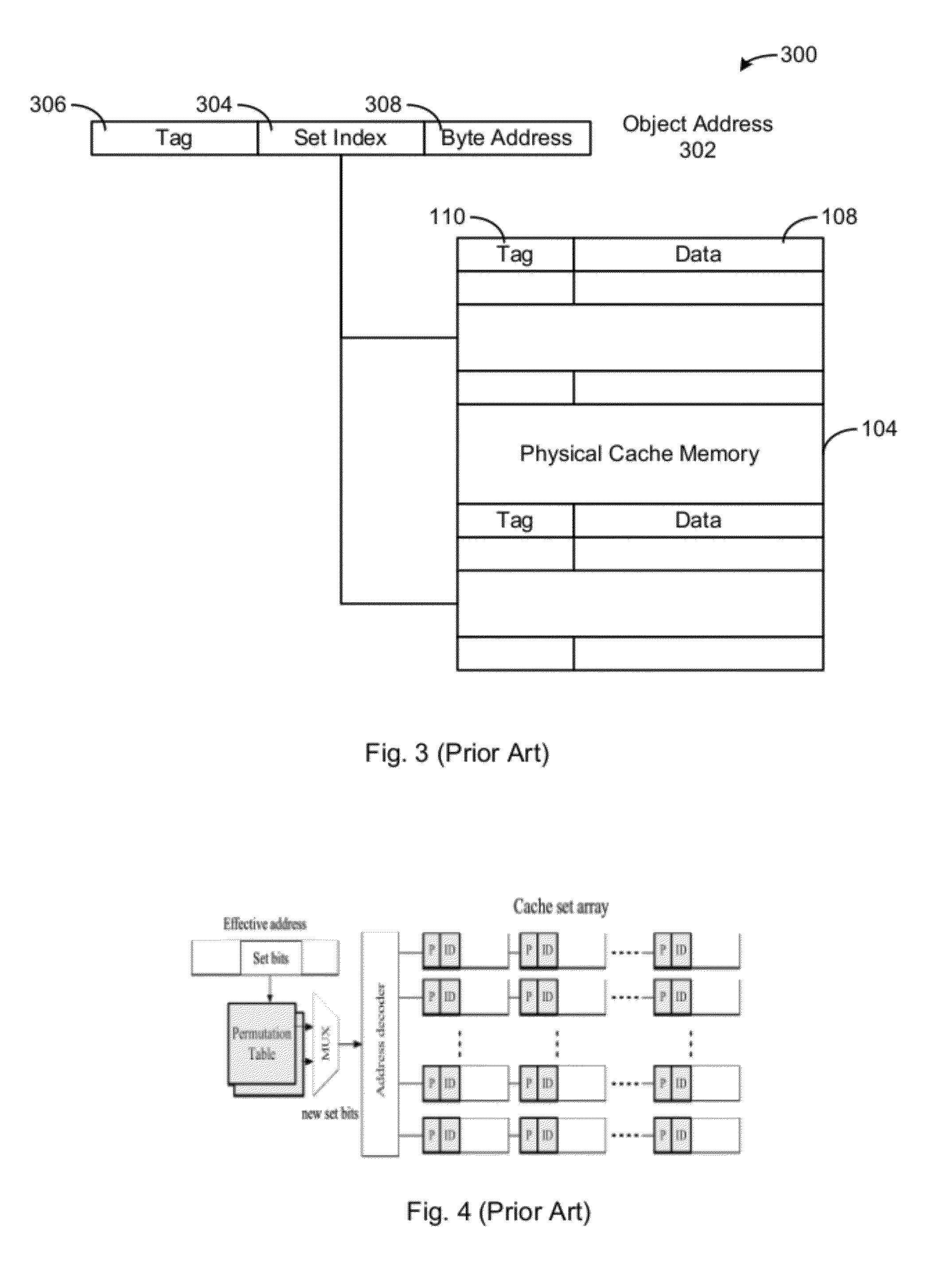

Method and apparatus for improving computer cache performance and for protecting memory systems against some side channel attacks

ActiveUS20120297110A1Increase profitReduce probabilityMemory architecture accessing/allocationMemory adressing/allocation/relocationAddress decoderParallel computing

A physical cache memory that is divided into one or more virtual segments using multiple circuits to decode addresses is provided. An address mapping and an address decoder is selected for each virtual segment. The address mapping comprises two or more address bits as set indexes for the virtual segment and the selected address bits are different for each virtual segment. A cache address decoder is provided for each virtual segment to enhance execution performance of programs or to protect against the side channel attack. Each physical cache address decoder comprises an address mask register to extract the selected address bits to locate objects in the virtual segment. The foregoing can be implemented as a method or apparatus for protecting against a side channel attack.

Owner:UNIVERSITY OF NORTH TEXAS

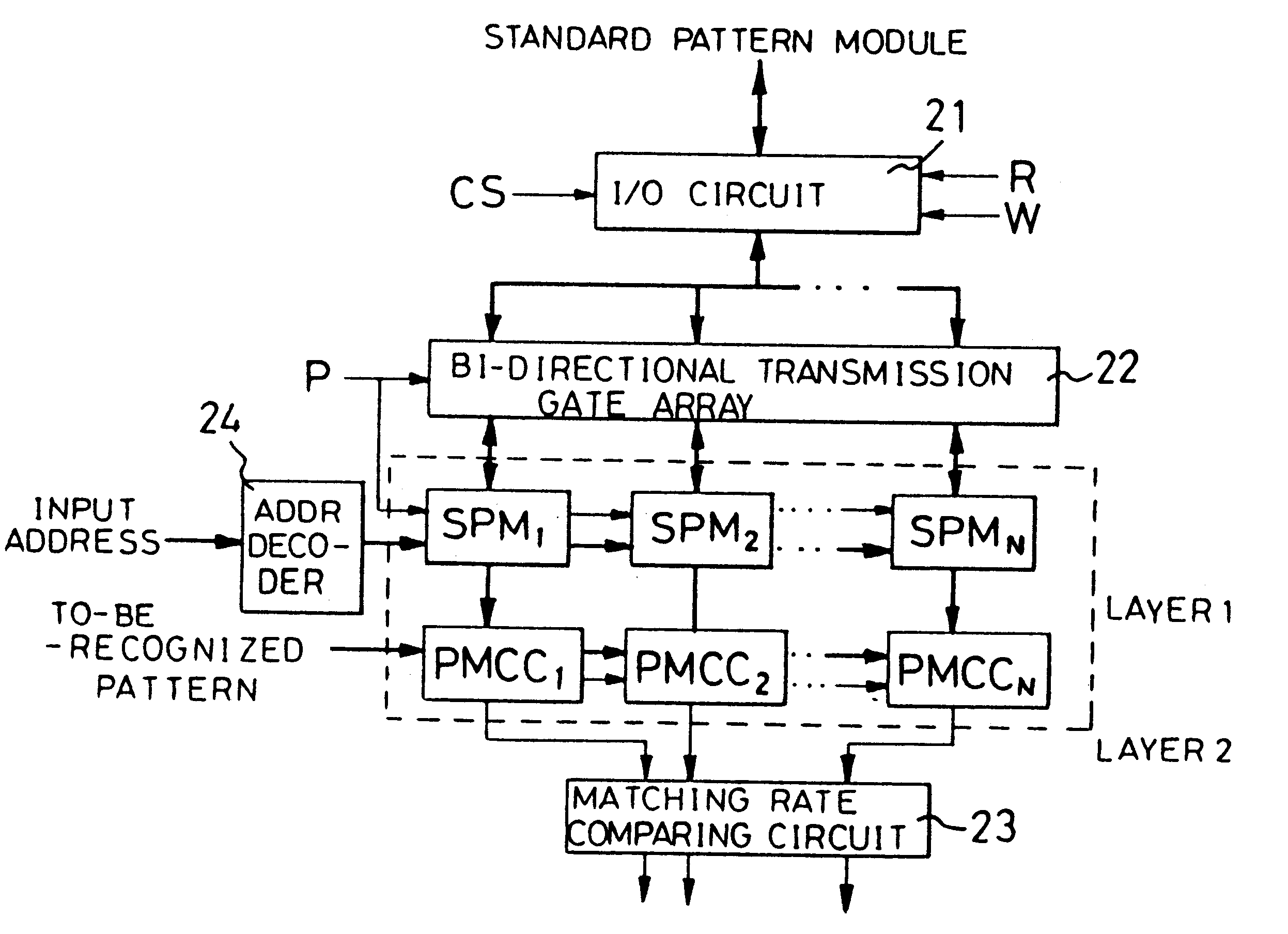

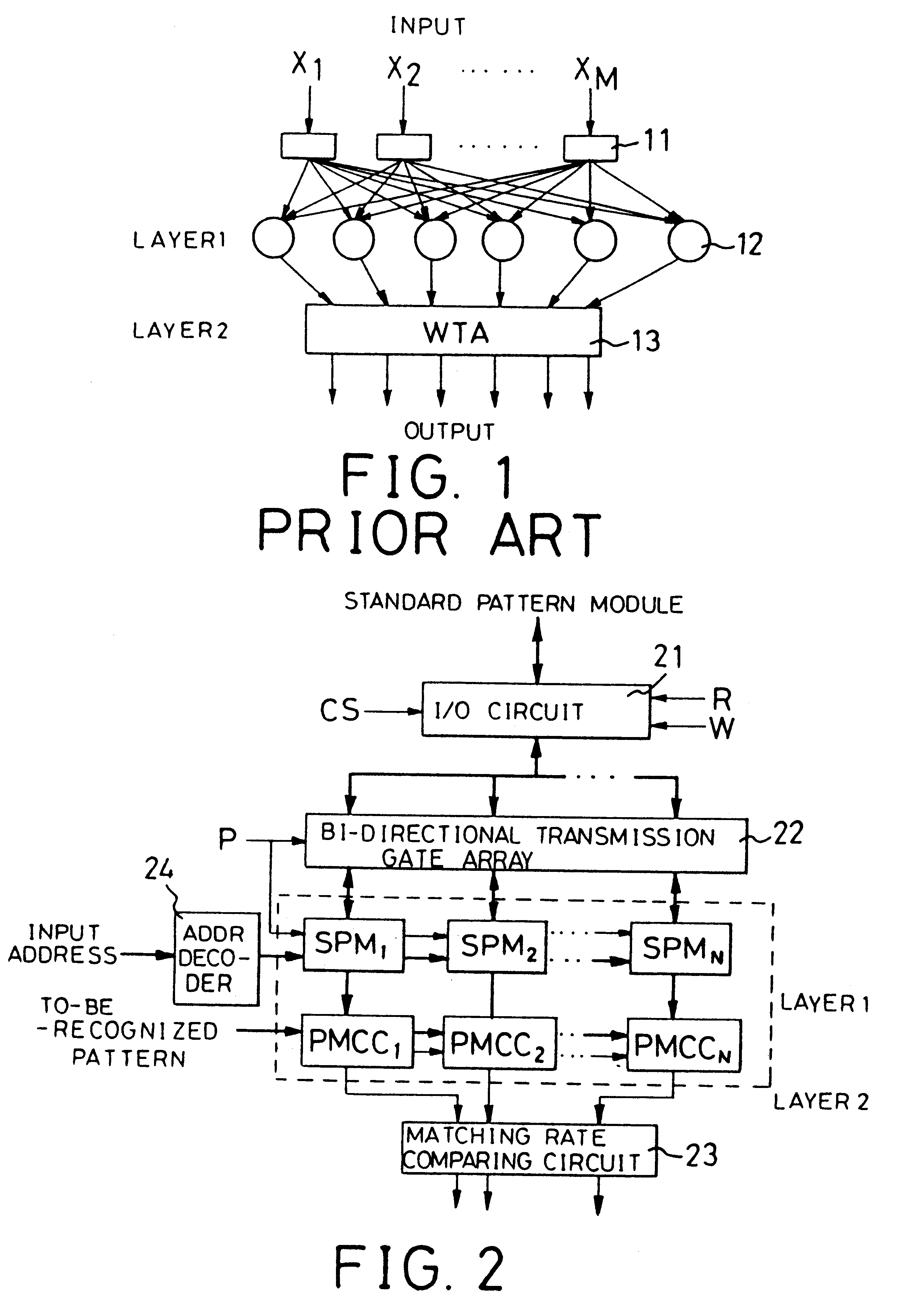

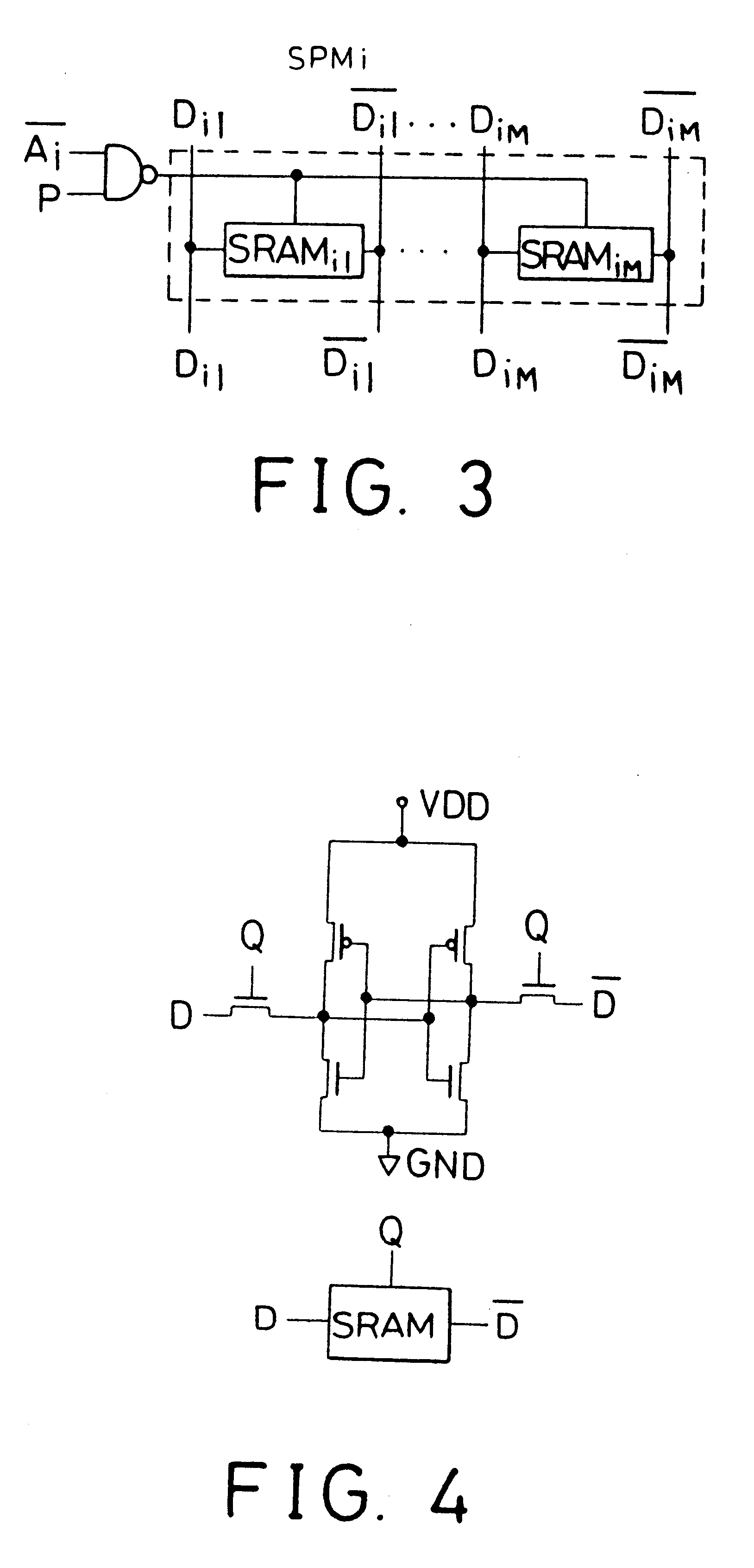

Programmable and expandable hamming neural network circuit

InactiveUS6341275B1Digital computer detailsCharacter and pattern recognitionAddress decoderTransmission gate

A Hamming neural network circuit which can be programmed and expanded is disclosed. The Hamming neural network includes an I / O circuit for inputting and outputting a plurality of standard patterns. A bi-directional transmission gate array is connected to the I / O circuit and controlled by a programming signal for transmitting the standard patterns. A plurality of standard pattern memory units is connected to the bi-directional transmission gate array for storing the plurality of standard patterns respectively. An address decoder is connected to the plurality of standard pattern memory units for addressing one of the plurality of standard pattern memory units. A plurality of pattern matching calculation circuit units are respectively connected to the plurality of standard pattern memory units for generating a plurality of matching rates between a to-be-recognized pattern and the plurality of standard patterns. An expandable matching rate comparing circuit is provided for comparing and sorting said plurality of matching rates.

Owner:WINBOND ELECTRONICS CORP