Patents

Literature

3531results about "Component plug-in assemblages" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Method of manufacturing a semiconductor package

InactiveUS7185426B1Printed circuit assemblingSemiconductor/solid-state device detailsElectrical conductorSemiconductor package

A semiconductor package including top-surface terminals for mounting another semiconductor package provides a three-dimensional circuit configuration that can provide removable connection of existing grid-array packages having a standard design. A semiconductor die is mounted on an electrically connected to a circuit substrate having terminals disposed on a bottom side for connection to an external system. The die and substrate are encapsulated and vias are laser-ablated or otherwise formed through the encapsulation to terminals on the top surface of the substrate that provide a grid array mounting lands to which another grid array semiconductor package may be mounted. The bottom side of the vias may terminate and electrically connect to terminals on the substrate, terminals on the bottom of the semiconductor package (through terminals) or terminals on the top of the semiconductor die. The vias may be plated, paste-filled, filled with a low melting point alloy and may have a conical profile for improved plating performance.

Owner:AMKOR TECH SINGAPORE HLDG PTE LTD

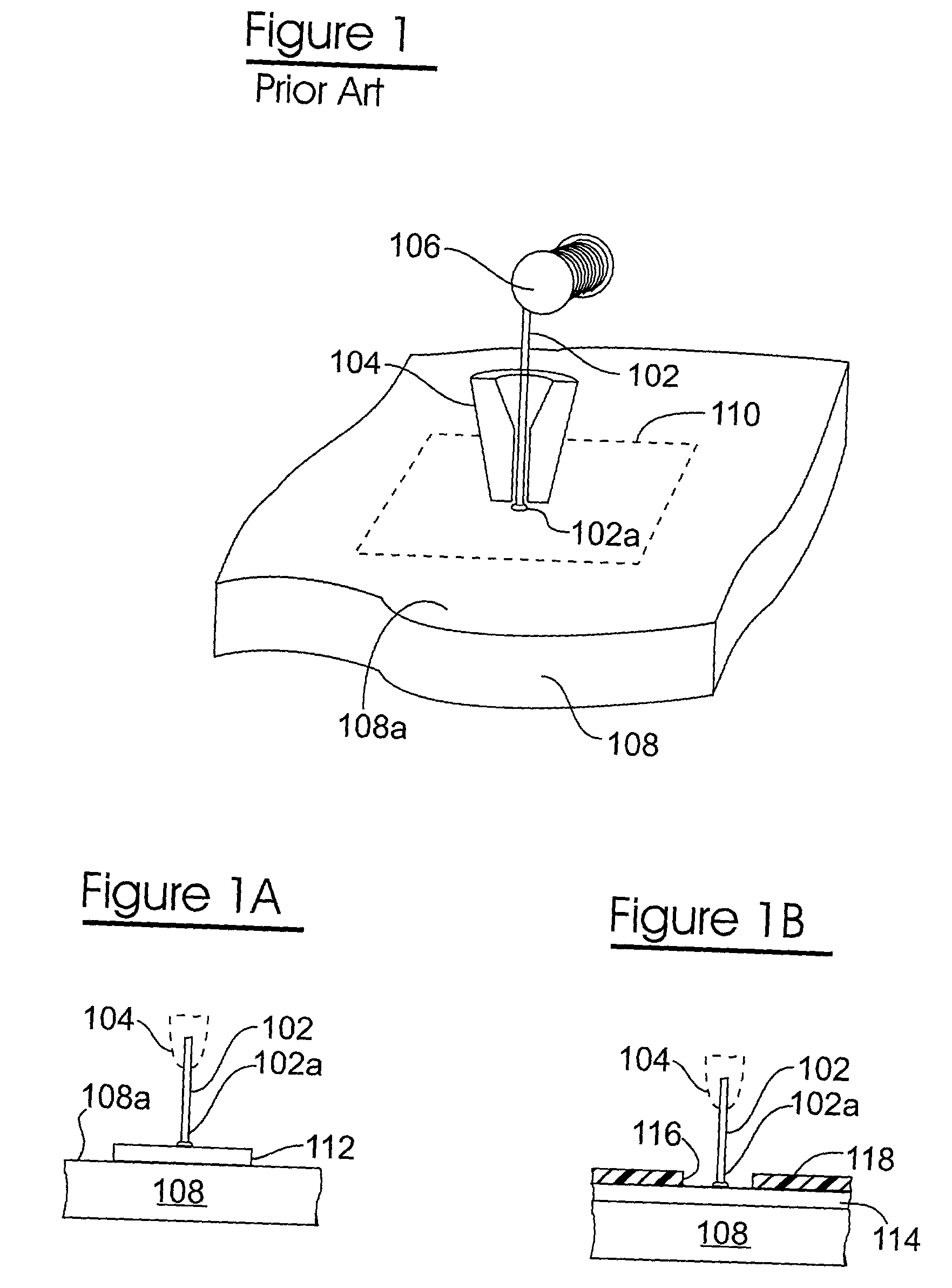

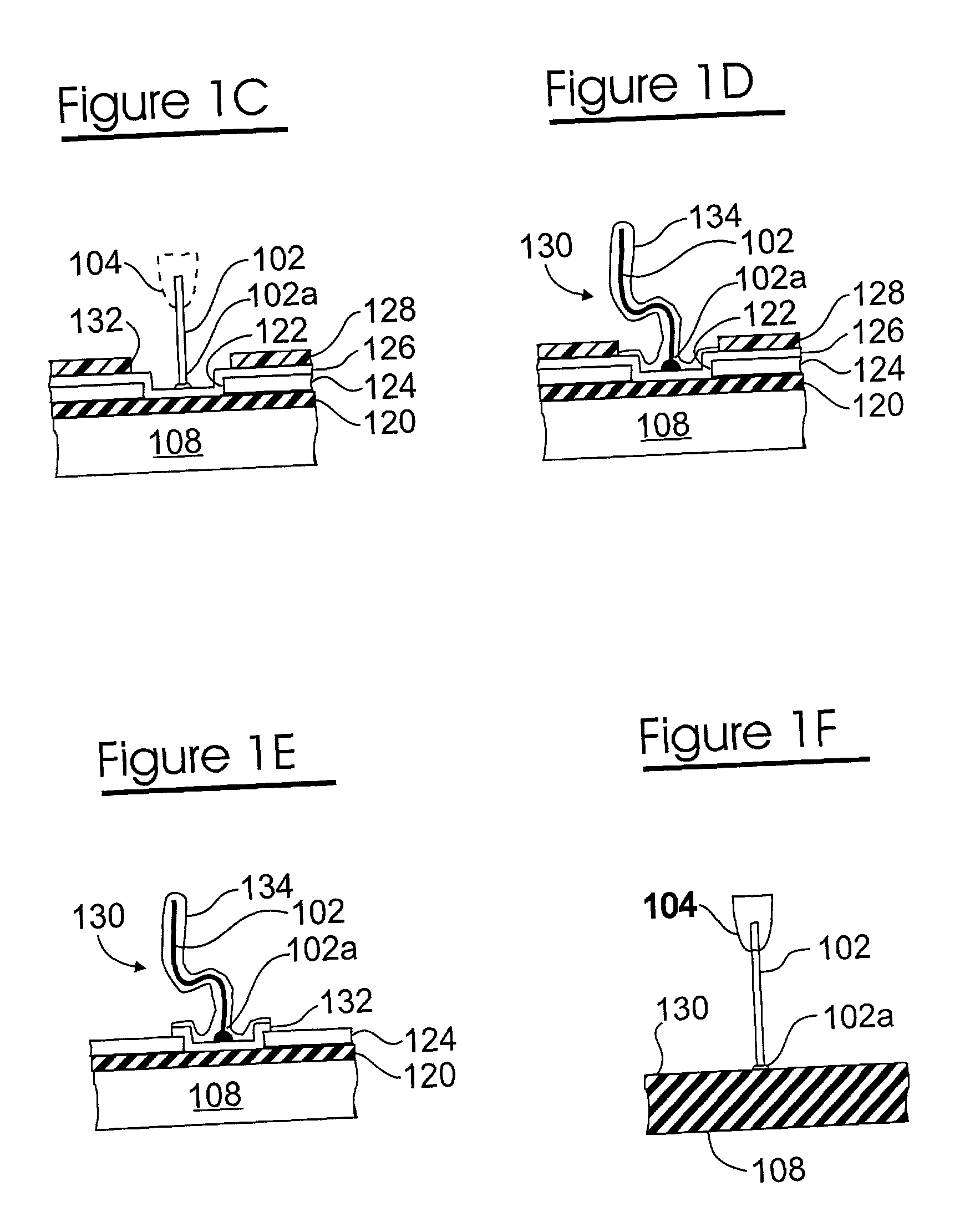

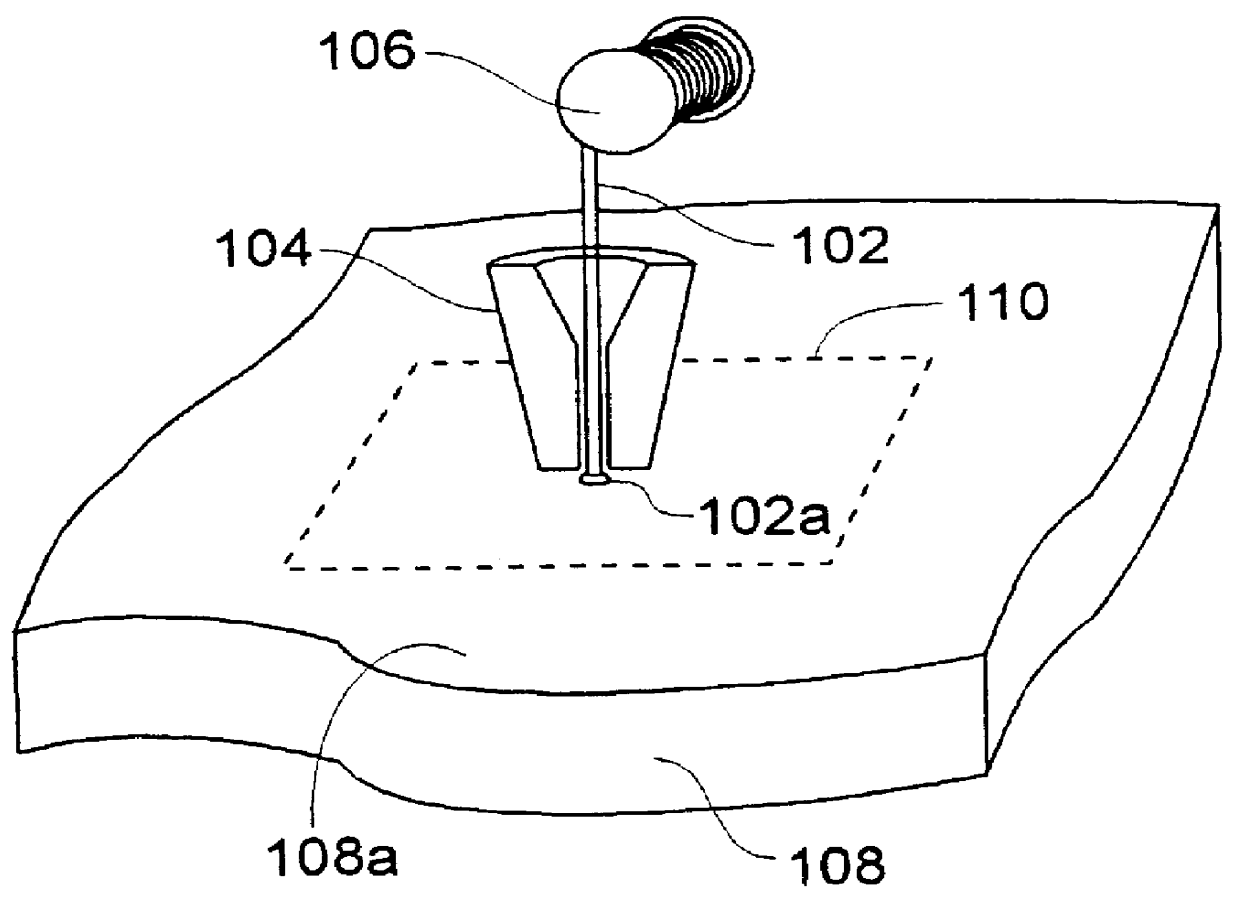

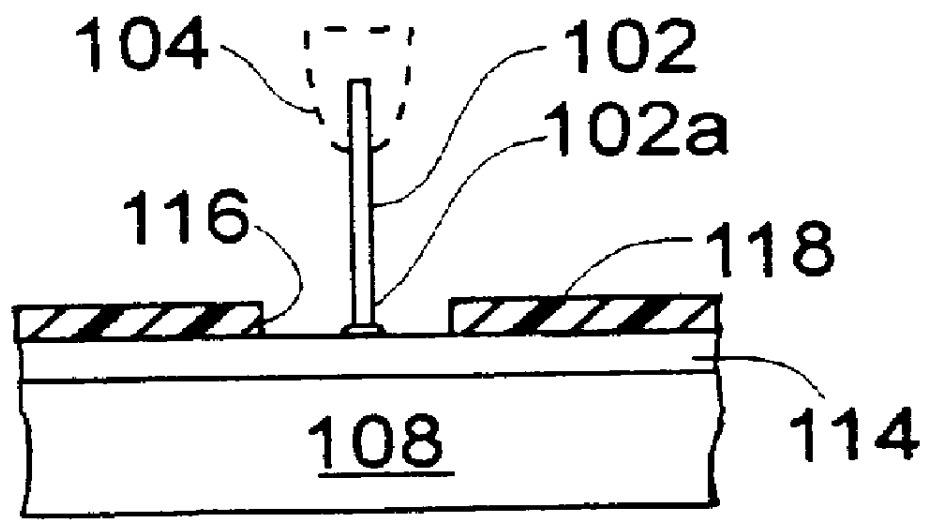

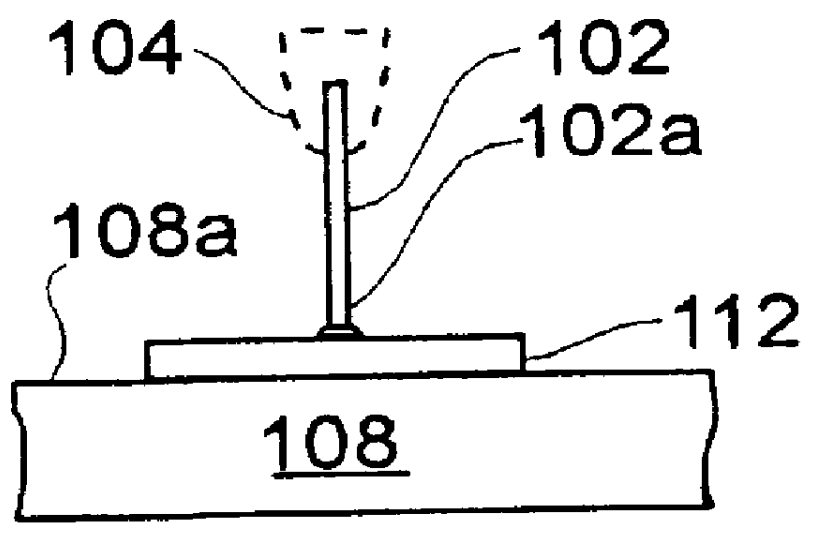

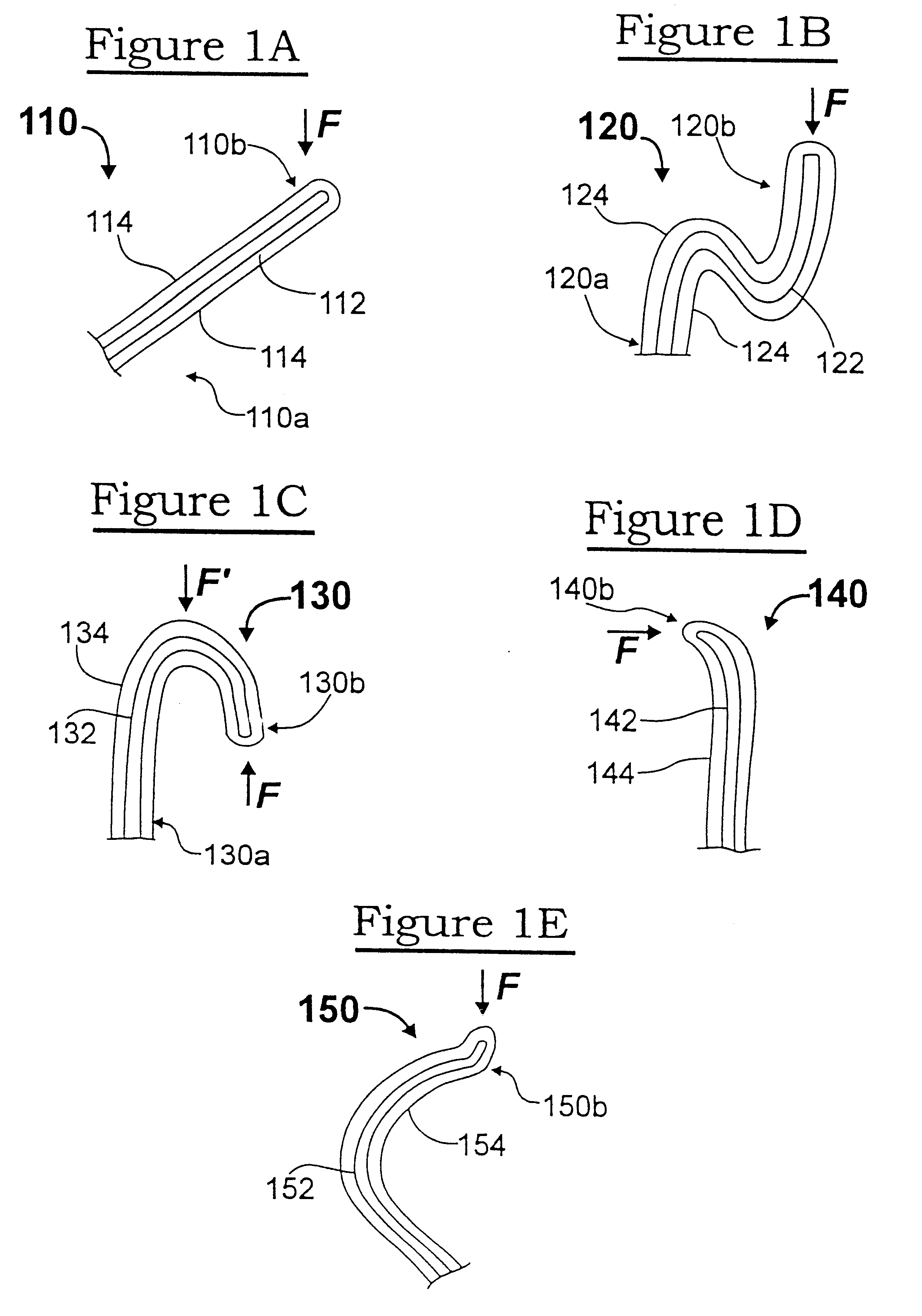

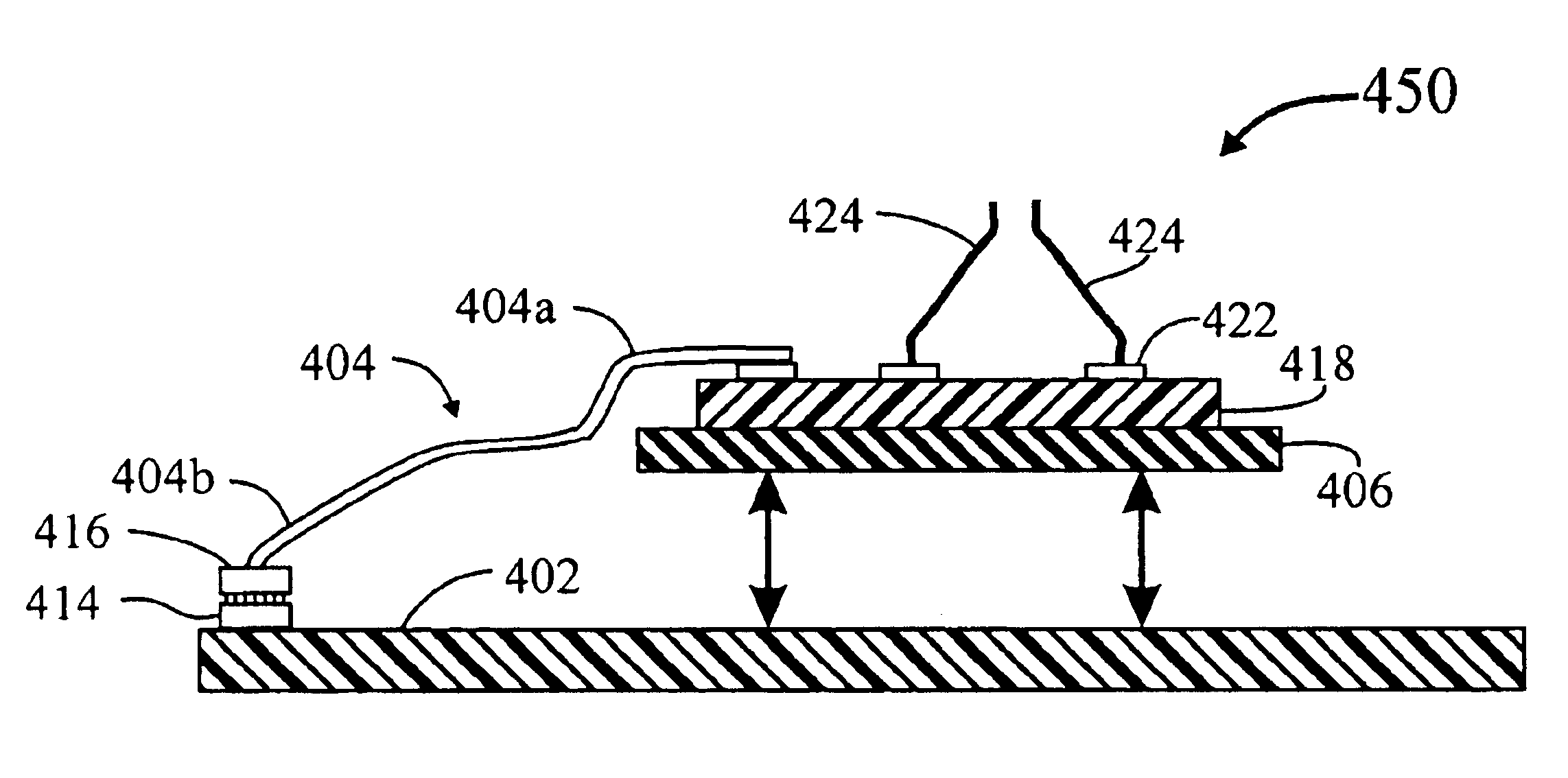

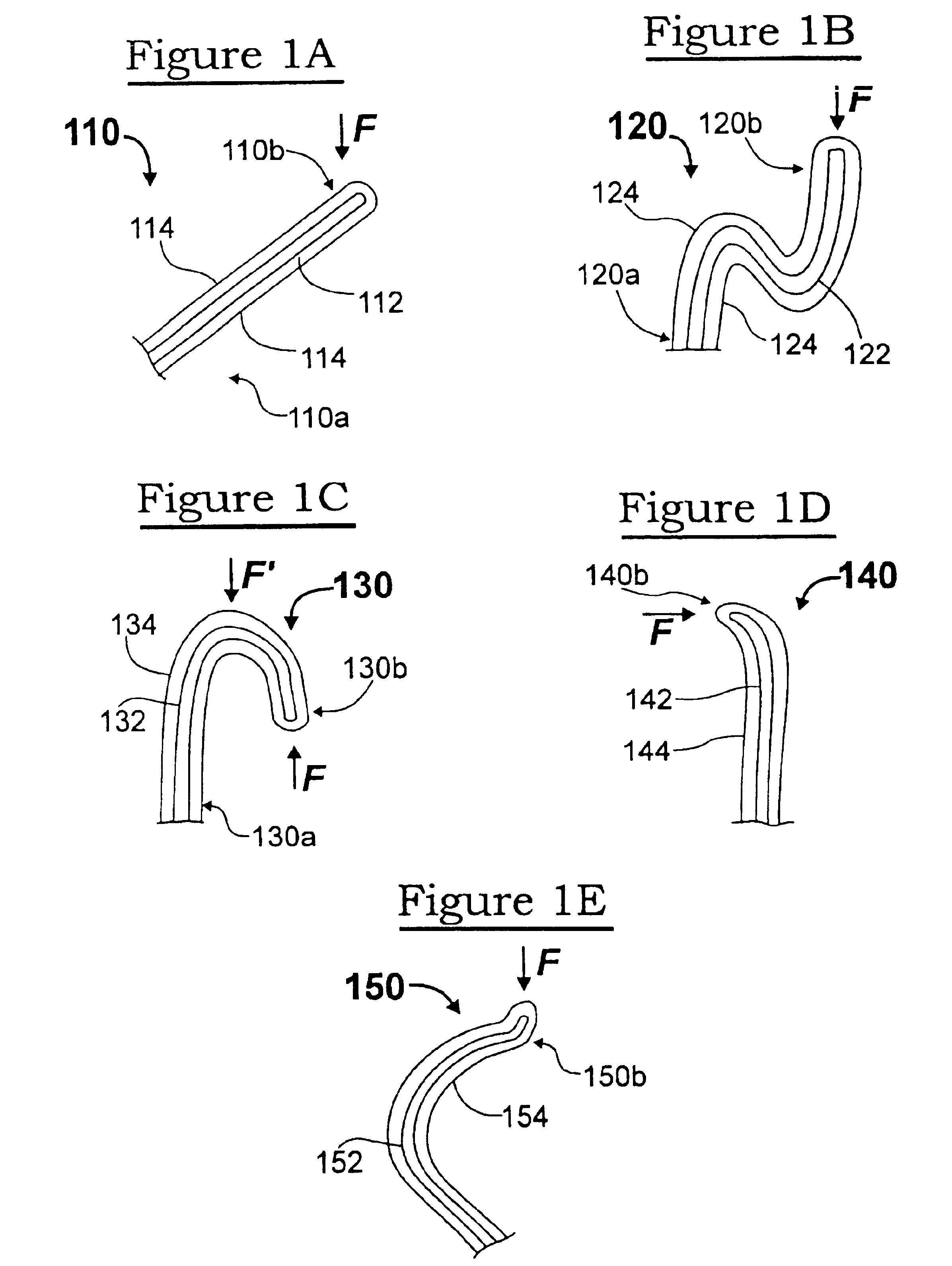

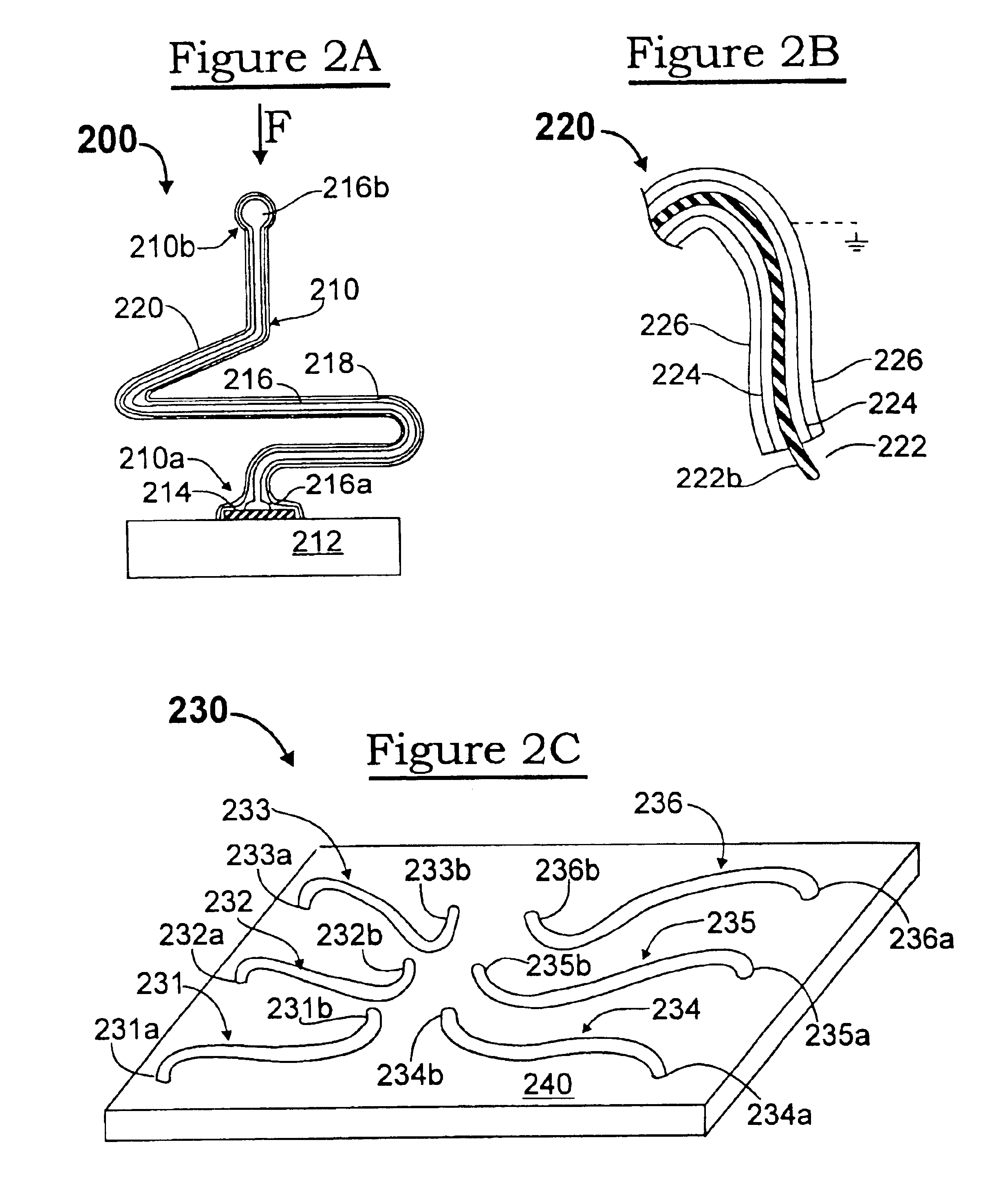

Resilient contact structures formed and then attached to a substrate

InactiveUS20020117330A1Simple technologyCoupling device connectionsSemiconductor/solid-state device testing/measurementEngineeringTopography

Owner:FORMFACTOR INC

Method of modifying the thickness of a plating on a member by creating a temperature gradient on the member, applications for employing such a method, and structures resulting from such a method

InactiveUS6110823ASimple technologyTrend downSemiconductor/solid-state device testing/measurementFinal product manufactureEngineeringElectronic component

Contact structures exhibiting resilience or compliance for a variety of electronic components are formed by bonding a free end of a wire to a substrate, configuring thw wire into a wire stem having a springable shape, serving thw wire stem, and overcoating the wire stem with at least one layer of a material chosen primarily for its structural (resiliency, compliance) characteristics. A variety of techniques for configuring, serving, and overcoating the wire stem are disclosed. In an exemplary embodiment, a free end of a wire stem is bonded to a contact area on a substrate, the wire stem is configured to ahve a springable shape, the wire stem is served to be free-standing by an electrical discharge, and the free-standing wire stem is overcoating by plating.

Owner:FORMFACTOR INC

Method and apparatus for a semiconductor package for vertical surface mounting

InactiveUS6291894B1Electrically conductive connectionsDigital data processing detailsDevice materialSurface mounting

A method for packaging a semiconductor device includes connecting a plurality of wire leads to a corresponding plurality of electrical connection pads on the semiconductor device, covering at least a portion of the semiconductor device and at least a portion of each of the wire leads with an encapsulating material, and removing a portion of the encapsulating material and a portion of each of the wire leads to form a packaged semiconductor device wherein each of the wire leads has an exposed portion only at an end. The invention also includes a packaged semiconductor device having an integrated circuit device with a plurality of electrical connection pads, a plurality of wire leads coupled to the plurality of electrical connection pads, and a covering of encapsulating material covering at least a portion of the integrated circuit device and covering each of the wire leads, wherein each of the wire leads has an exposed end. The present invention contemplates wire bonding and encapsulation of individual die as well as multiple die on a single wafer.

Owner:MICRON TECH INC

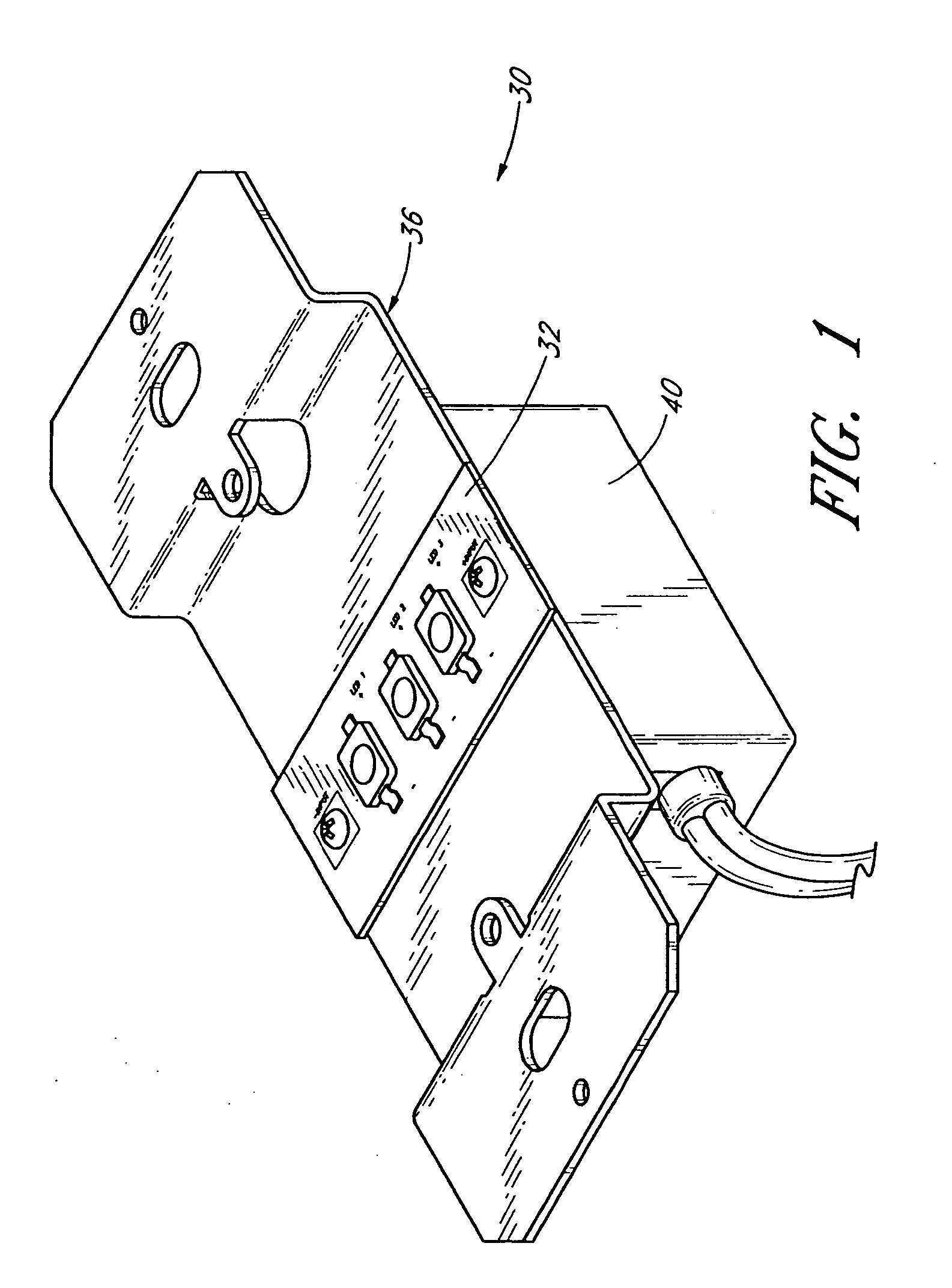

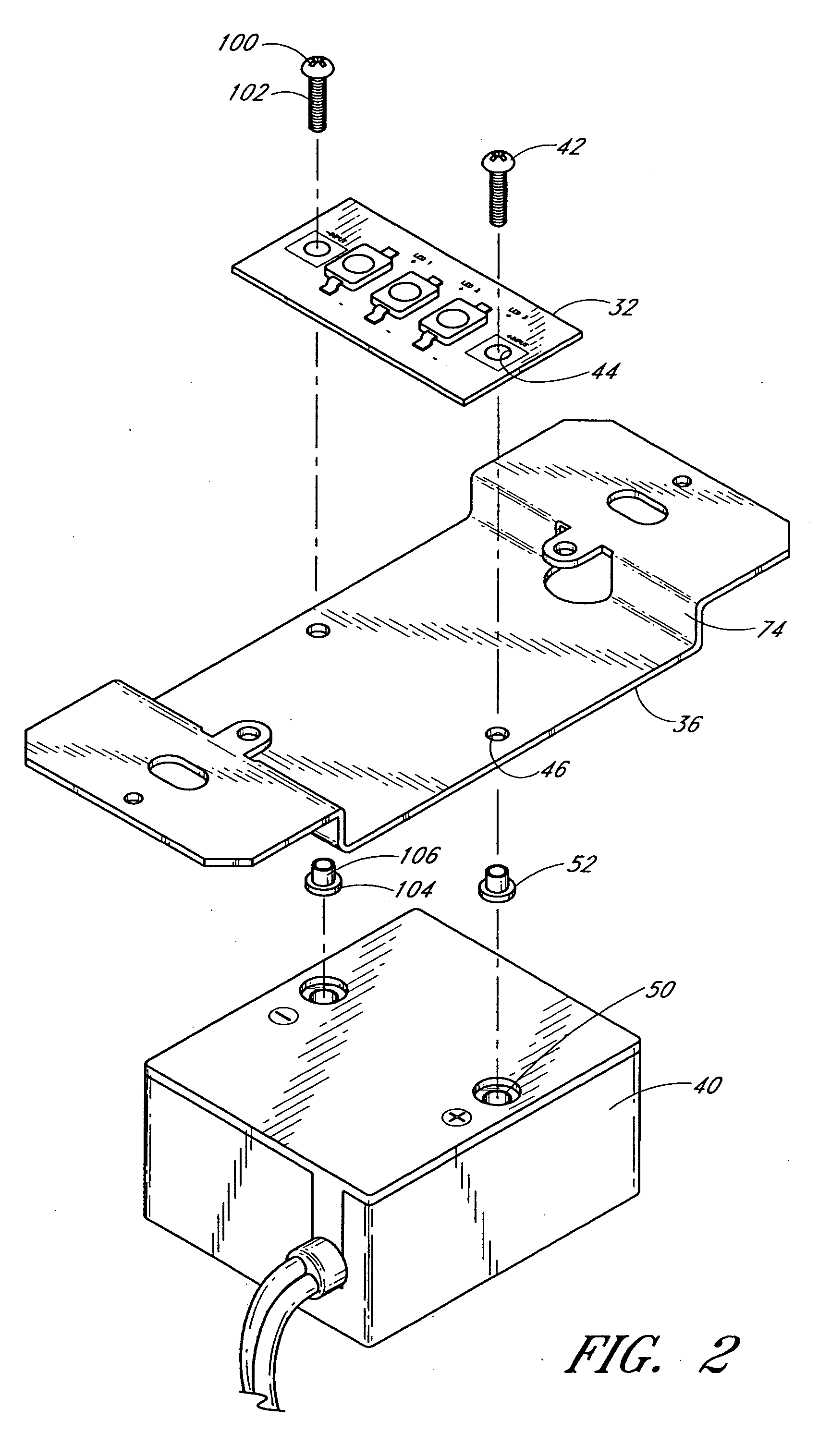

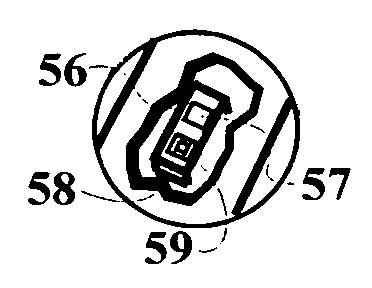

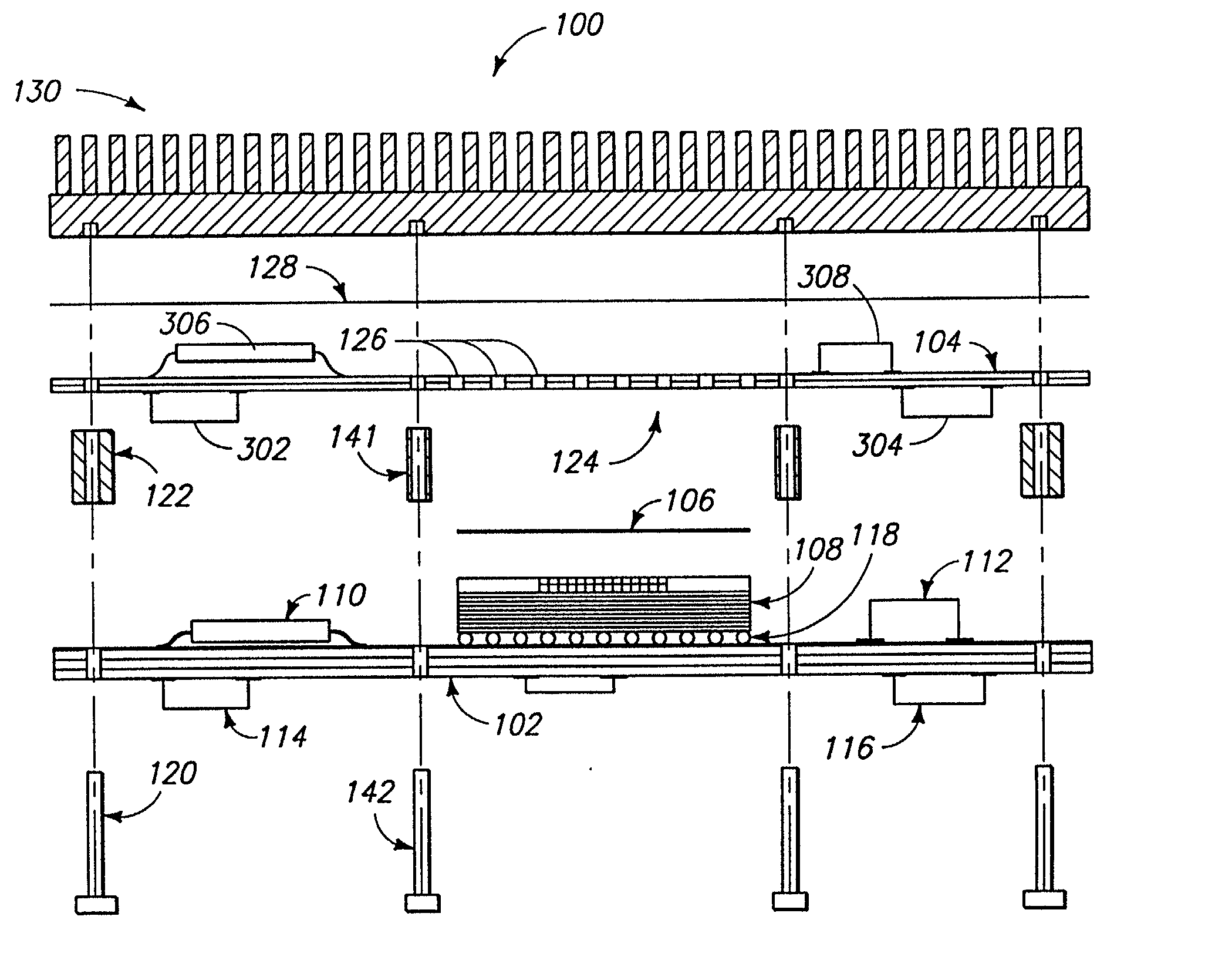

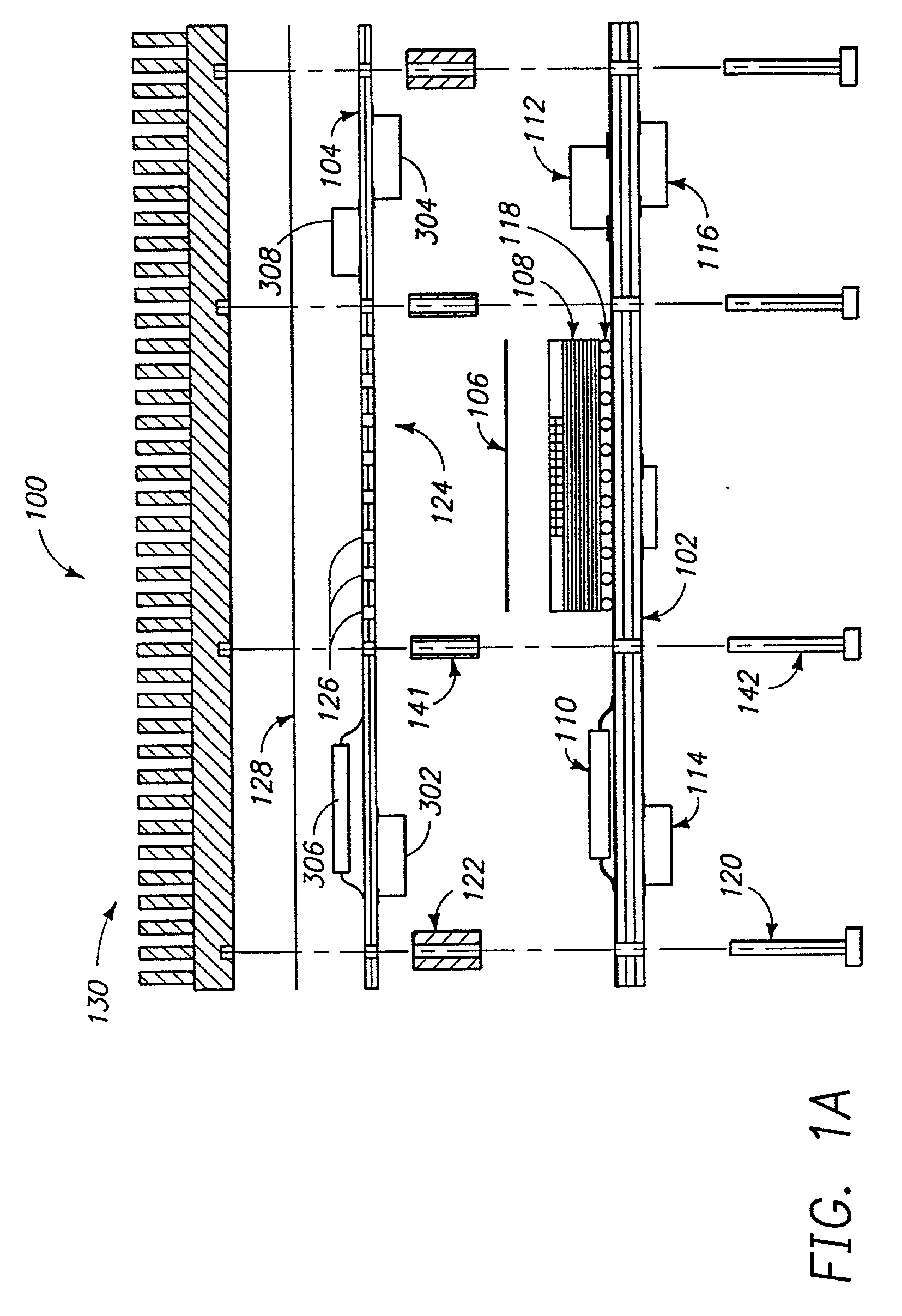

LED-based luminaire

InactiveUS20070041220A1Maximize lighting effectivenessLow costCoupling device connectionsPlanar light sourcesEffect lightEngineering

An LED-based luminaire includes a driver configured to convert line voltage into a desired power configuration. Elongate fasteners attach one or more LED-based lighting modules to a mount member and also to energized poles of the power driver. The fasteners communicate electrical energy from the power driver to the lighting module. In one embodiment, the mount member functions as a heat sink, and it includes a bumpy surface coating having a texture with sufficient feature heights to enhance heat transfer between the heat sink and the surrounding environment.

Owner:DIAMOND CREEK CAPITAL LLC

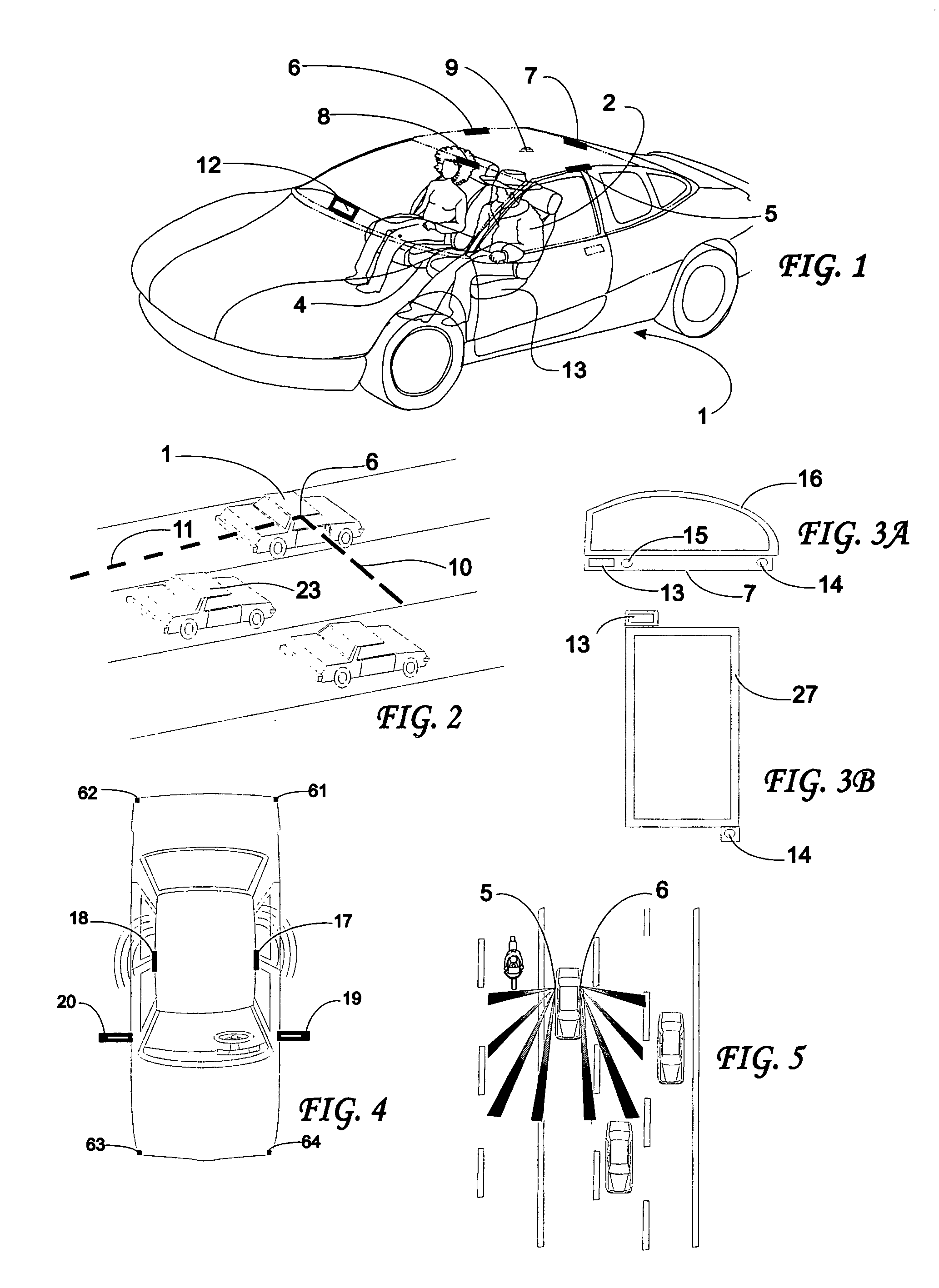

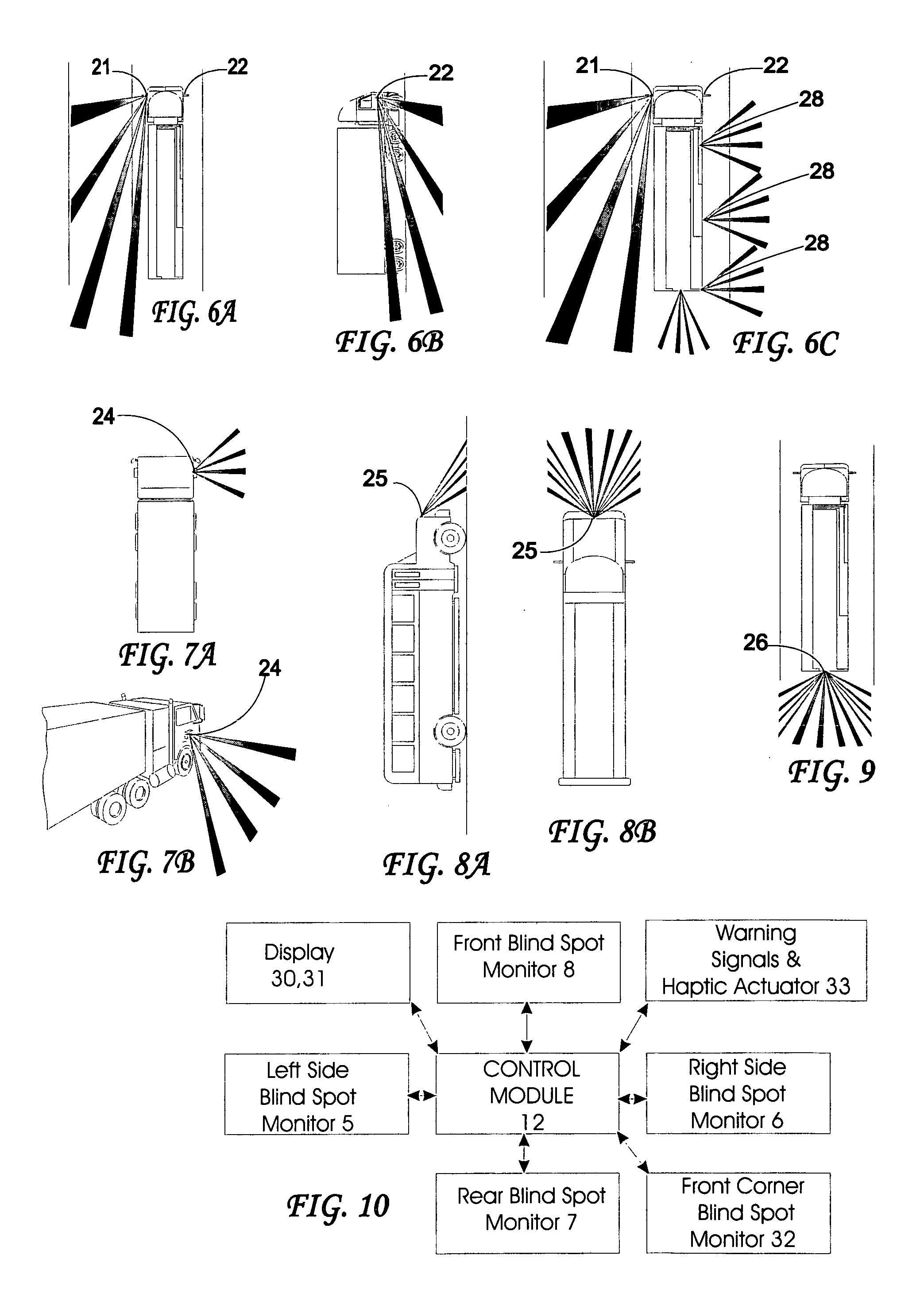

Vehicular impact reactive system and method

InactiveUS20050278098A1Reduce number and severityDigital data processing detailsAnti-collision systemsEngineeringReactive system

System and method for reacting to an expected impact involving a vehicle including an anticipatory sensor system for determining that an impact involving the vehicle is about to occur prior to the impact and an impact responsive system coupled to the sensor system and actuated after its determination of the expected impact. The sensor system includes wave receivers spaced apart from one another, each receiving waves generated by, modified by, or reflected from a common object exterior of the vehicle. The impact responsive system attempts to reduce the potential harm resulting from the impact and can be a protection apparatus which protects a vehicular occupant or a pedestrian, such as one including an airbag and an inflator for inflating the airbag.

Owner:AMERICAN VEHICULAR SCI

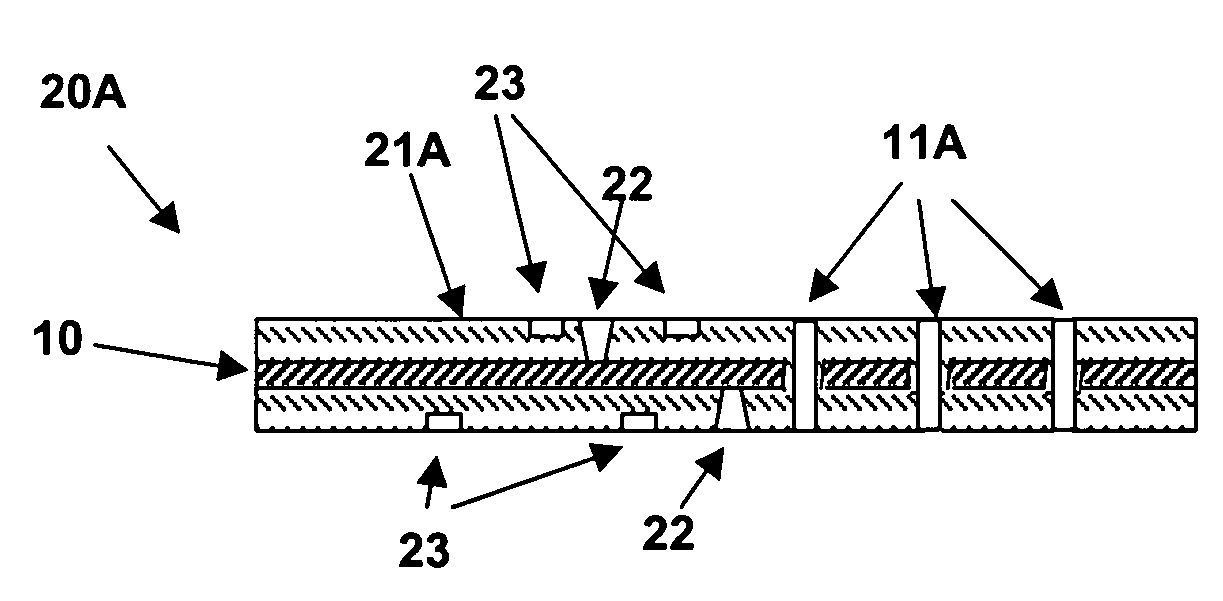

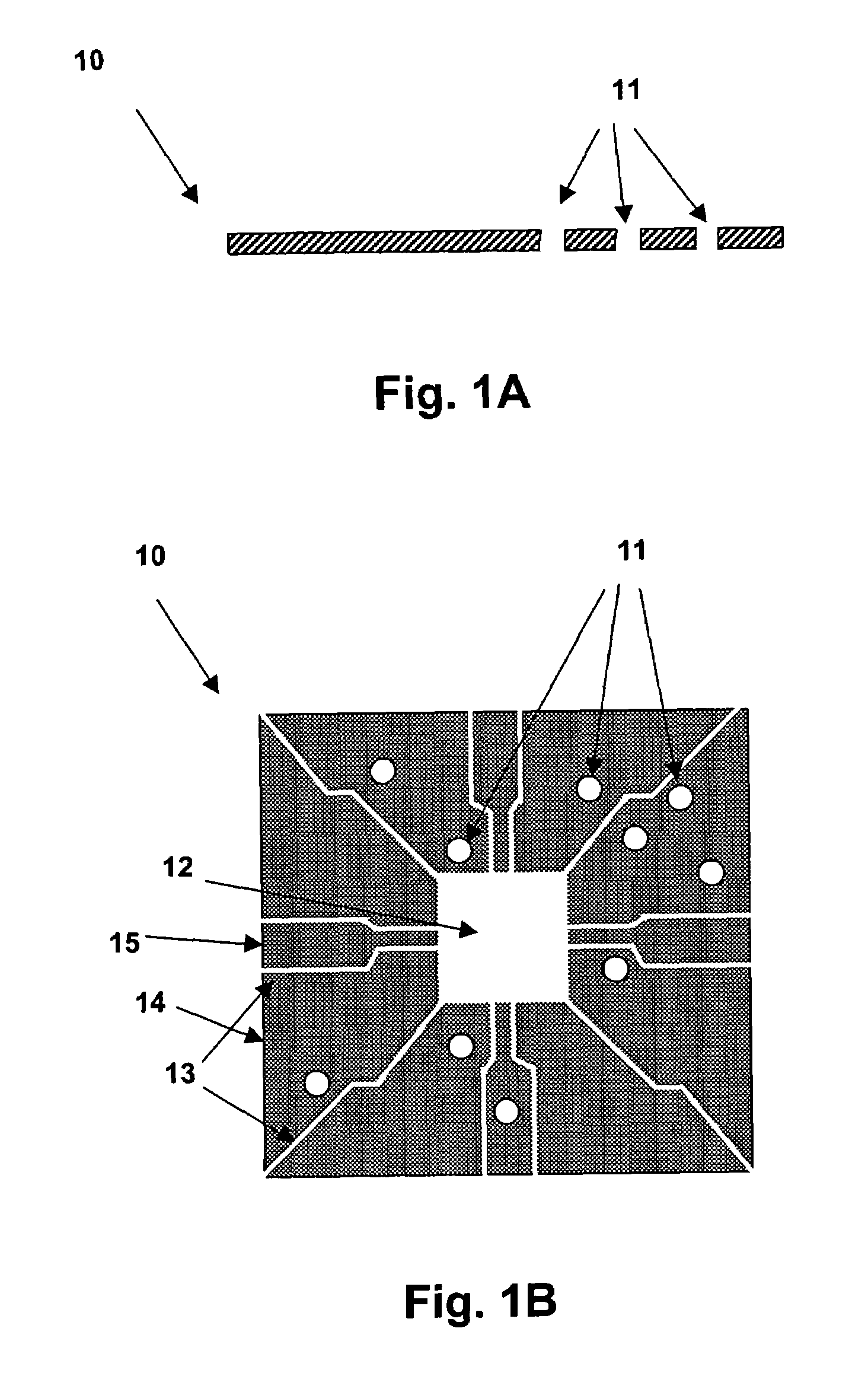

Integrated circuit substrate having laser-embedded conductive patterns and method therefor

InactiveUS6930256B1Printed electric component incorporationSemiconductor/solid-state device detailsScreen printingHigh density

An integrated circuit substrate having laser-embedded conductive patterns provides a high-density mounting and interconnect structure for integrated circuits. Conductive patterns within channels on the substrate provide interconnects that are isolated by the channel sides. A dielectric material is injection-molded or laminated over a metal layer that is punched or etched. The metal layer can provide one or more power planes within the substrate. A laser is used to ablate channels on the surfaces of the outer dielectric layer for the conductive patterns. The conductive patterns are electroplated or paste screen-printed and an etchant-resistive material is applied. Finally, a plating material can be added to exposed surfaces of the conductive patterns. An integrated circuit die and external terminals can then be attached to the substrate, providing an integrated circuit having a high-density interconnect.

Owner:AMKOR TECH SINGAPORE HLDG PTE LTD

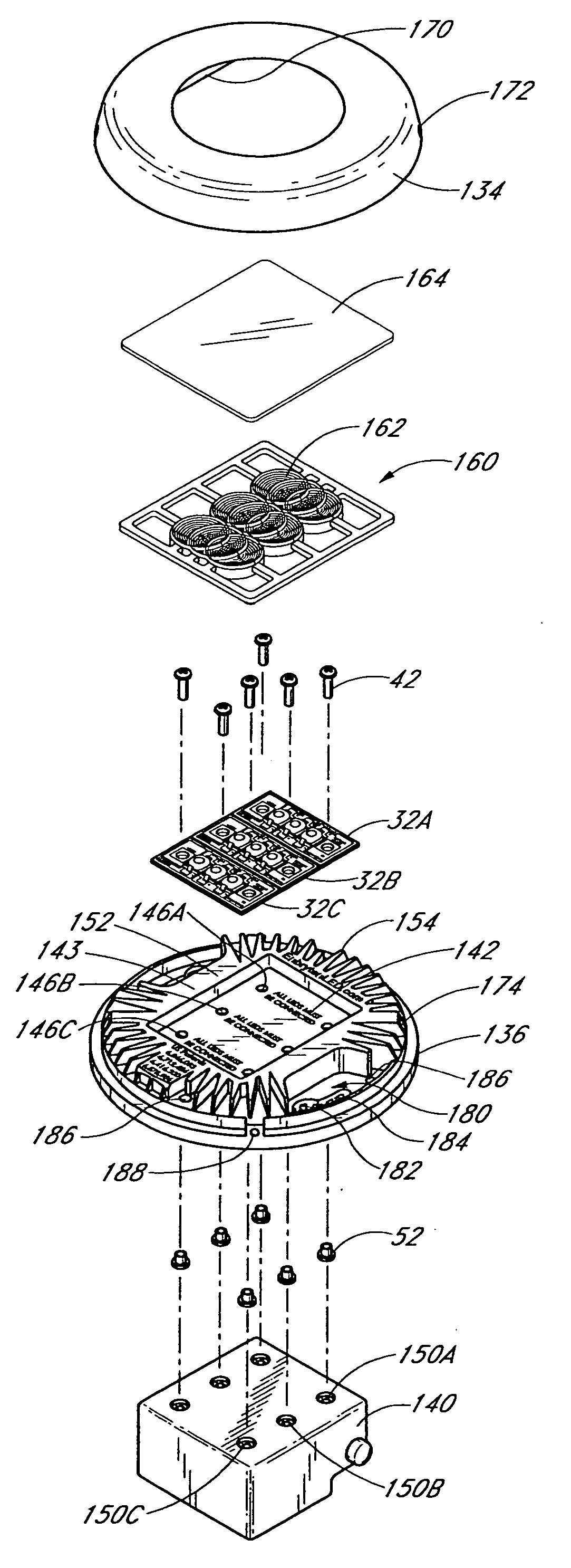

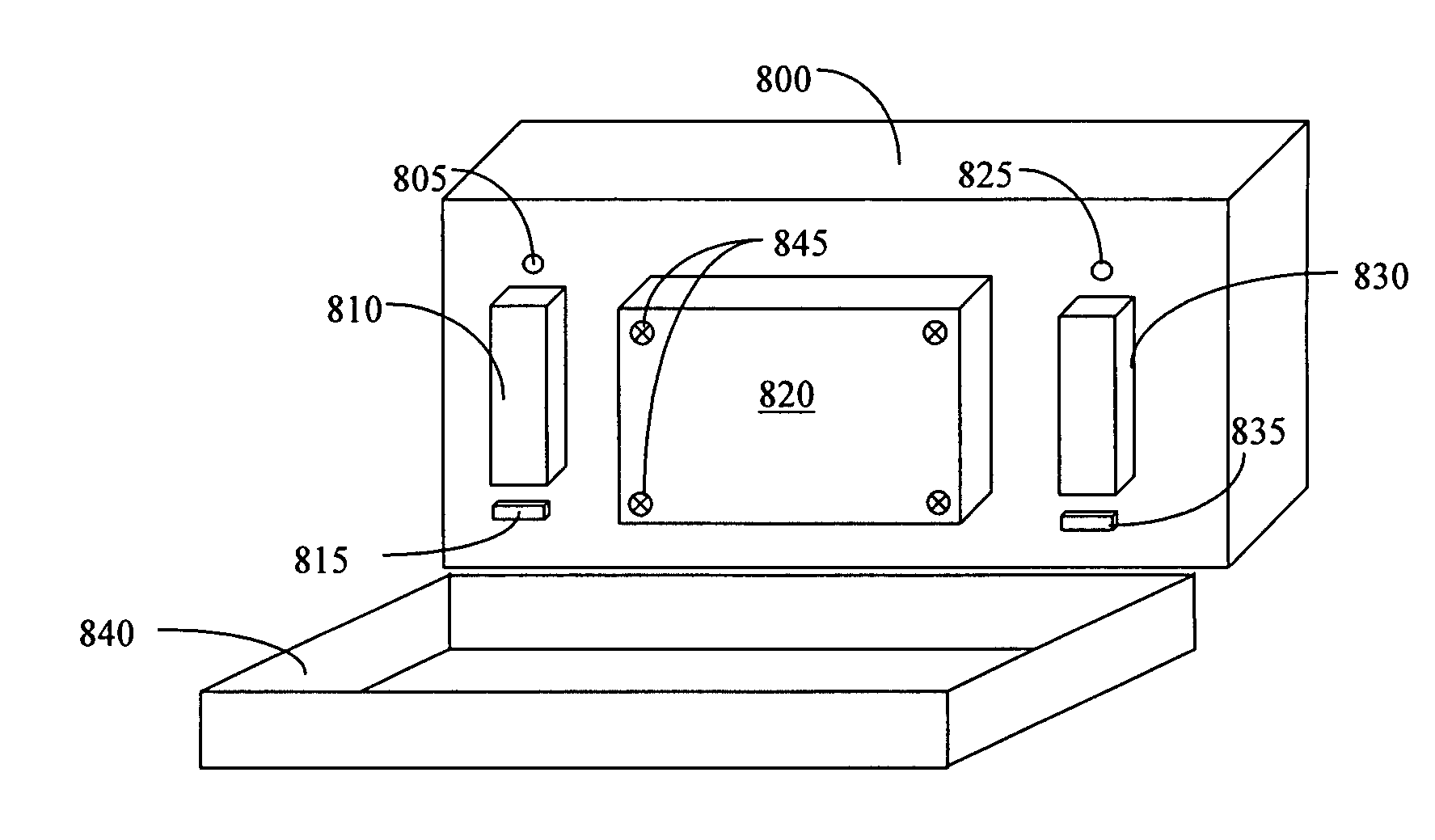

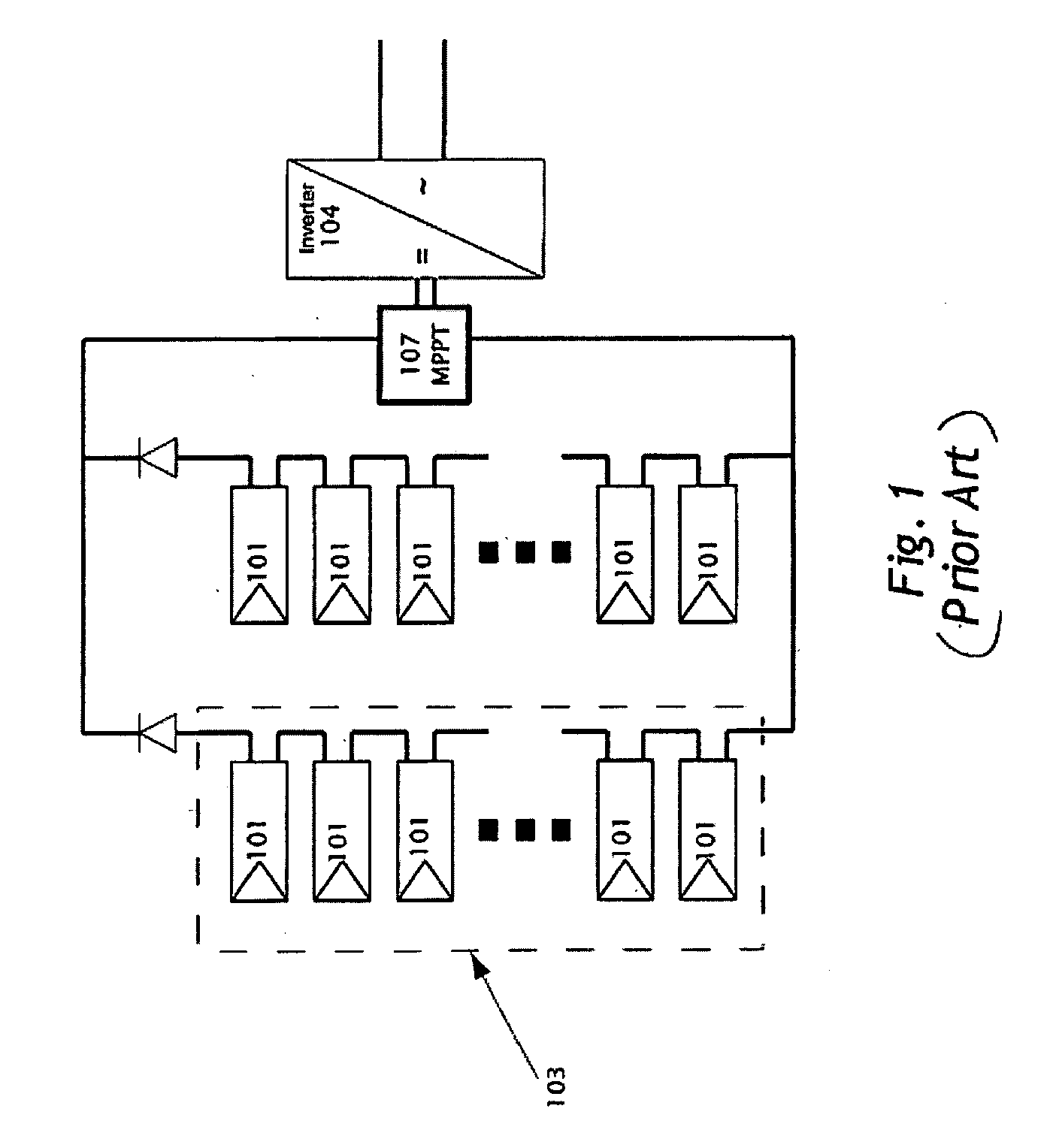

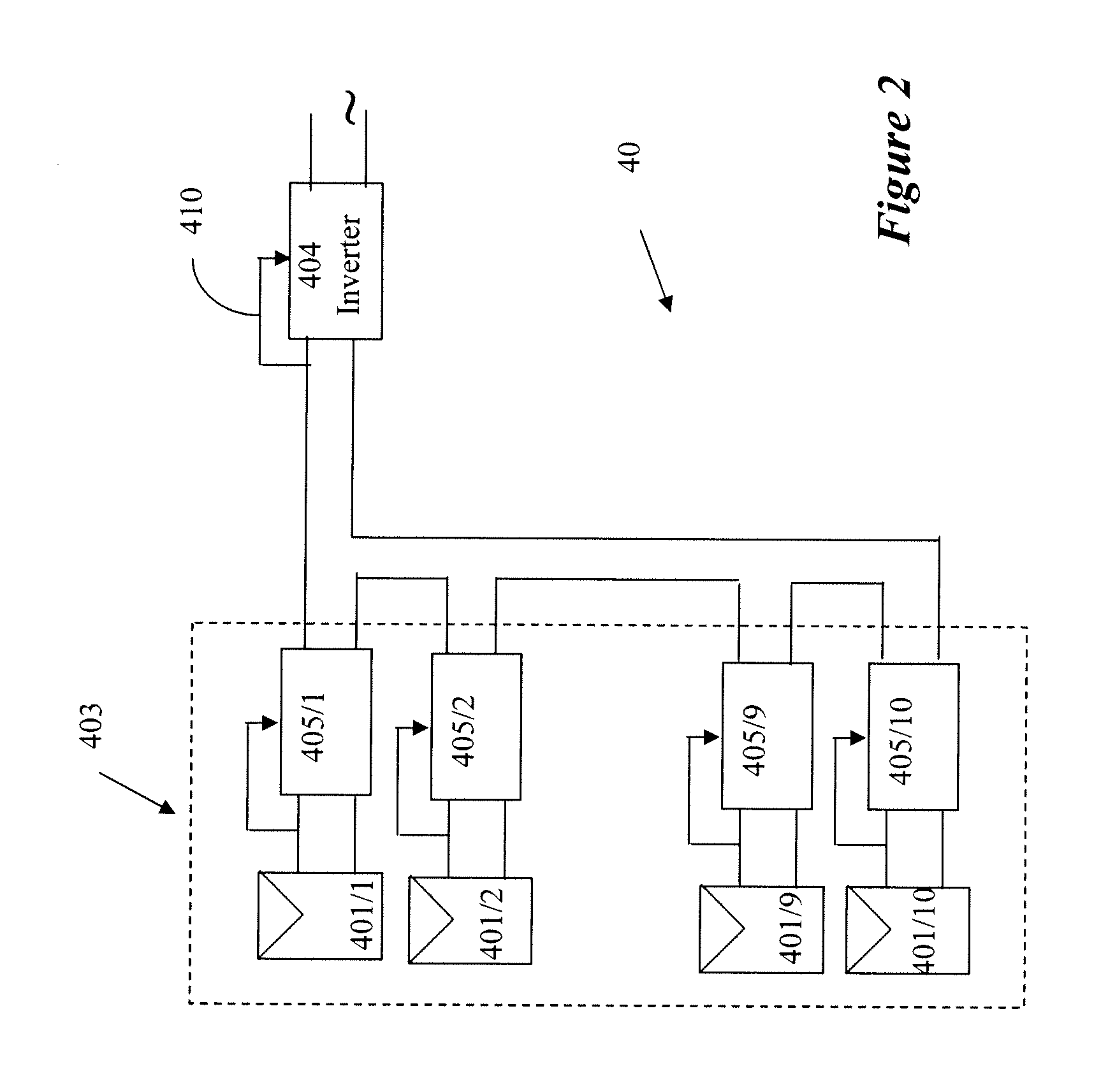

Removal component cartridge for increasing reliability in power harvesting systems

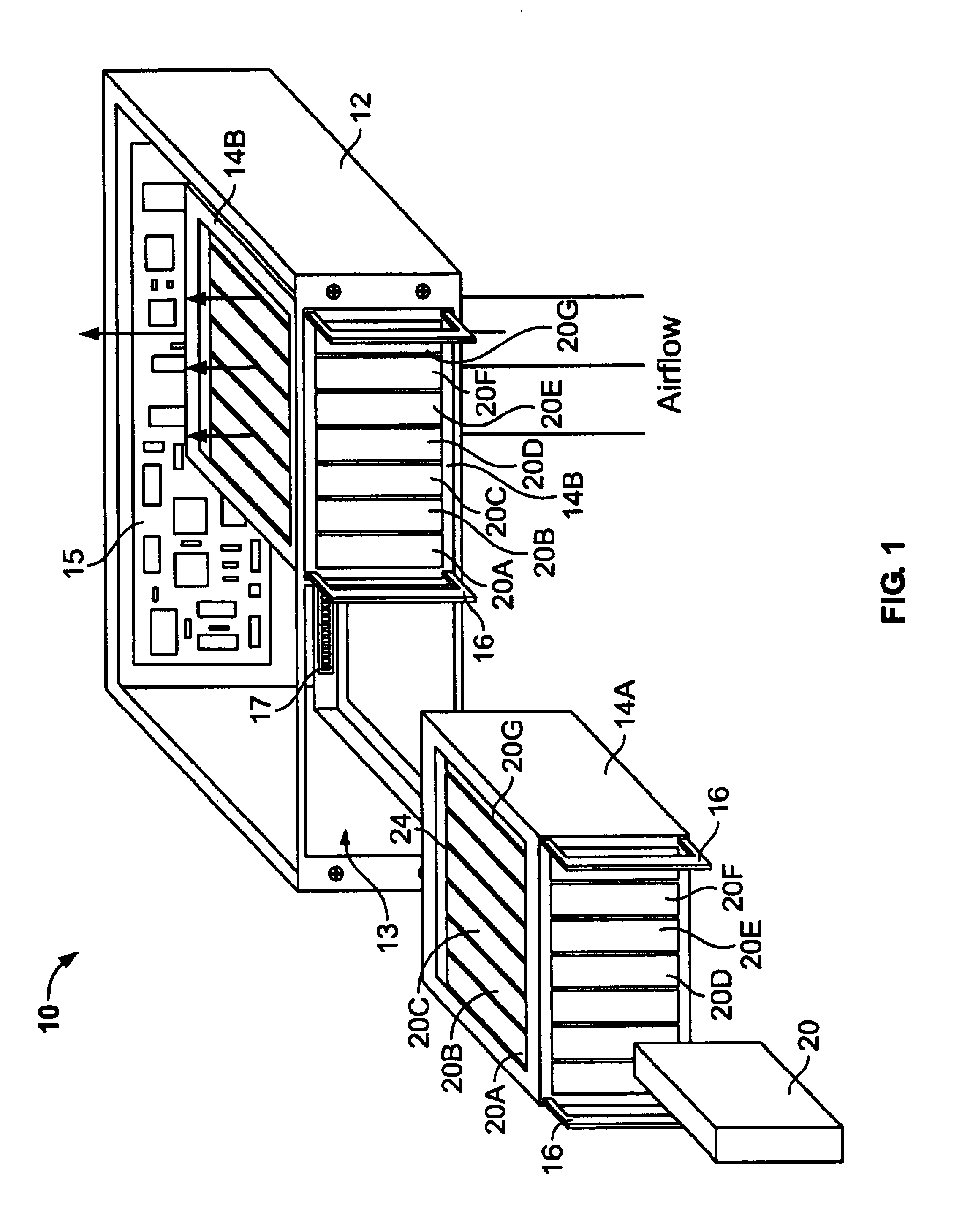

InactiveUS20080144294A1Simplifies diagnosisSimple repairPrinted circuit board receptaclesComponent plug-in assemblagesEngineeringElectric power

Owner:SOLAREDGE TECH LTD

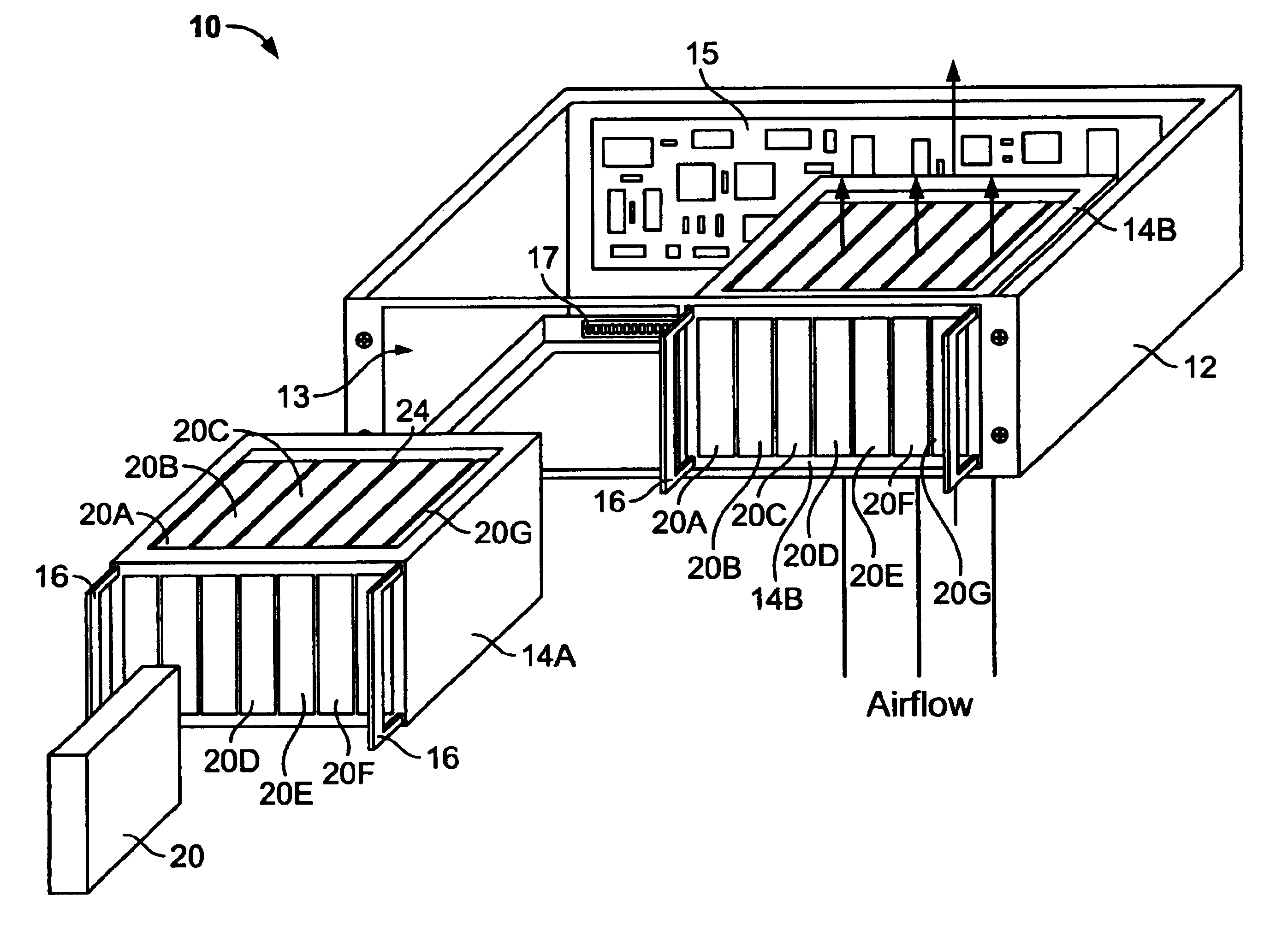

Removable disk storage array emulating tape library having backup and archive capability

InactiveUS6957291B2Enhance system functionsLow costInput/output to record carriersError detection/correctionData connectionHard disc drive

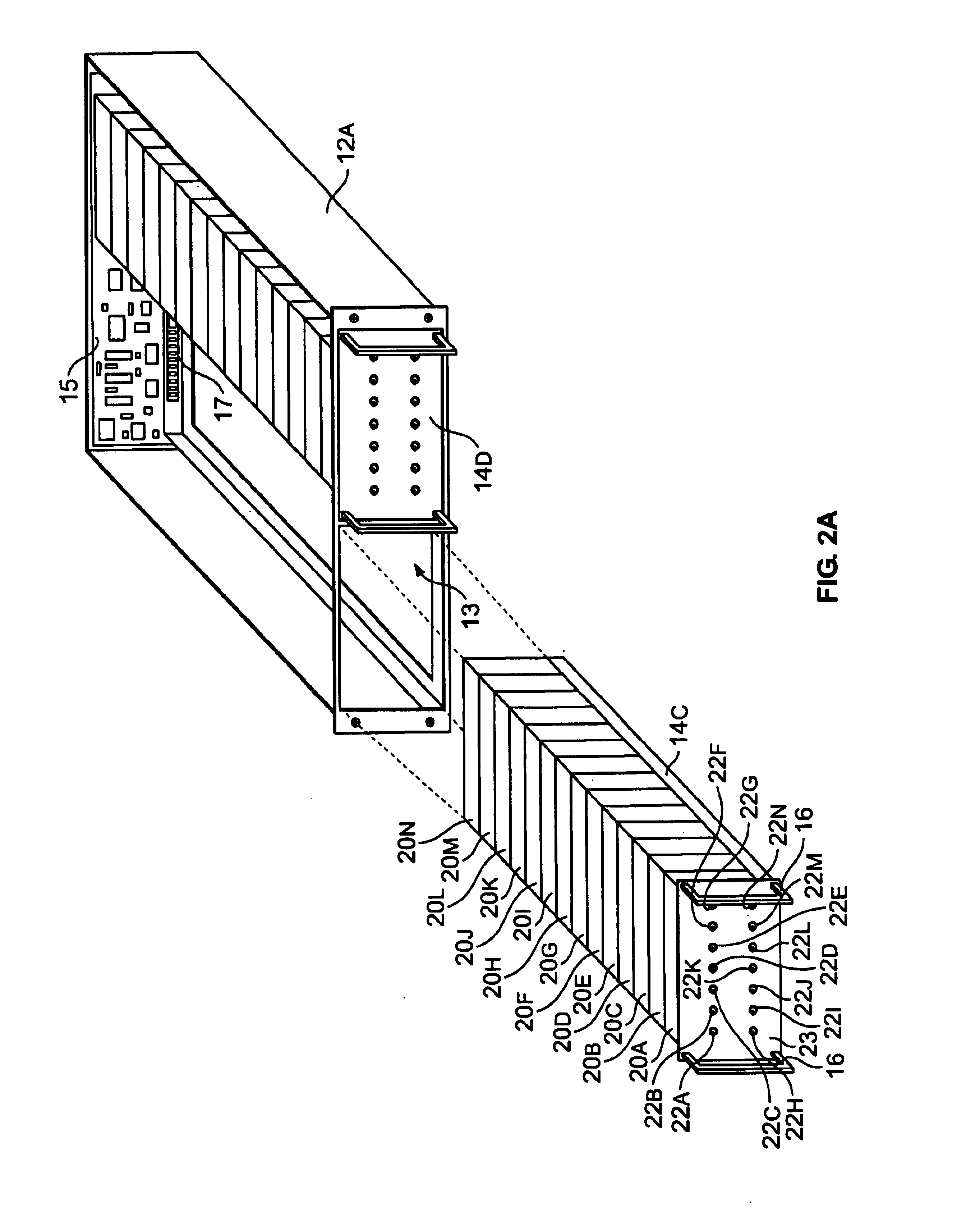

A hard disk drive based data archive system emulating a tape archive system includes a hot pluggable multi-drive magazine having a housing for holding a plurality of hard disk drives, each drive connected to receive power and data from the magazine in a controlled fashion, and at least one magazine receiving system for physically receiving the magazine and for thereupon providing power, data and control connections to the magazine, such that when the magazine is received within the magazine receiving system, the hard disk drives selectively receive power and data connections via the magazine and receiving system from a host computer. The magazine may be hot-disconnected from an active computing system environment and removed to an archive rack wherein each disk drive is periodically checked to ensure functionality and to provide some limited-bandwidth data retrieval functions via a network connection to the archive rack. A file mark structure enables a disk drive in the magazine to emulate functionality of a tape cartridge.

Owner:QUANTUM CORP

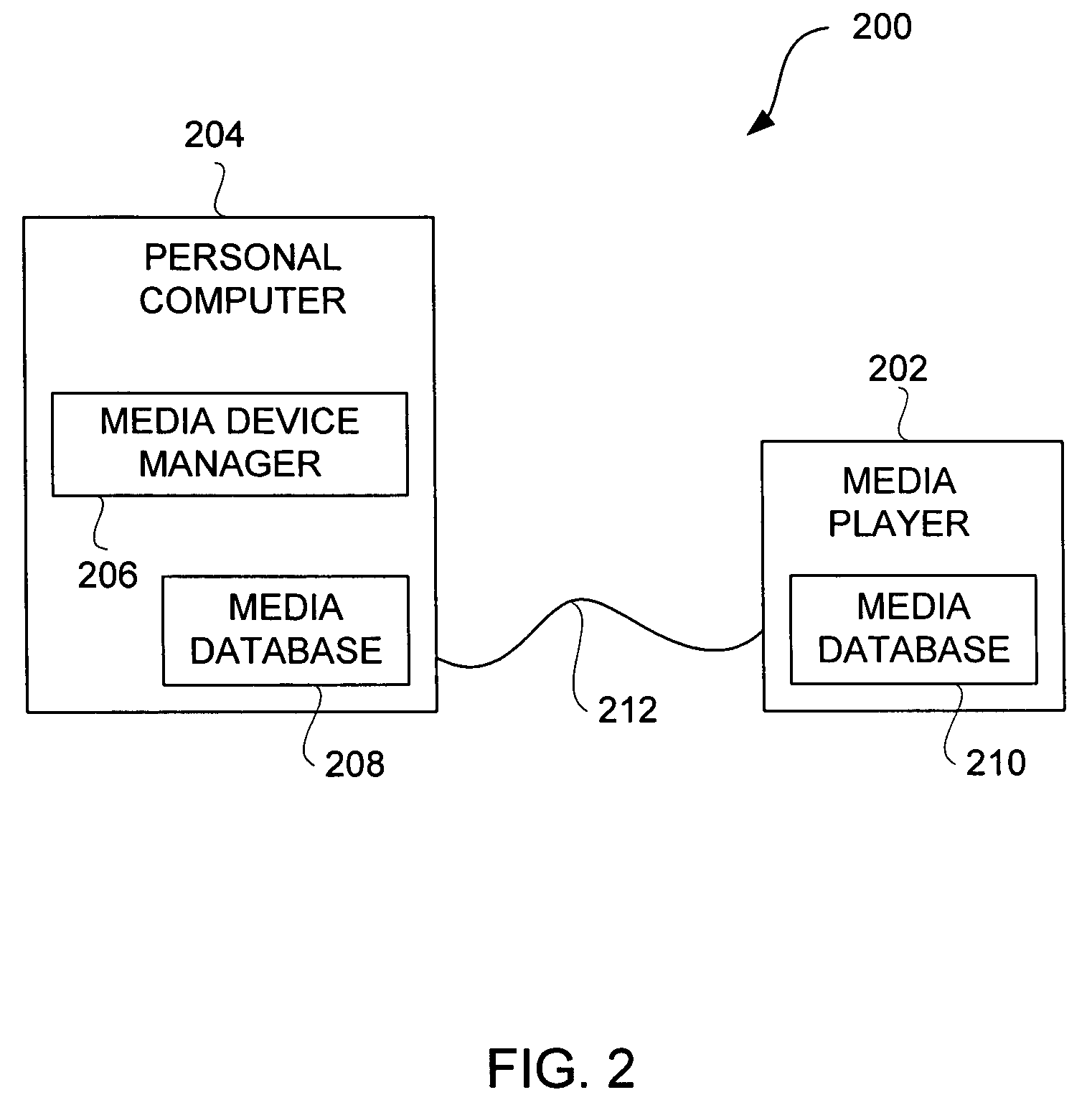

Hot unpluggable media storage device

InactiveUS7146437B2Simple technologyInput/output to record carriersComponent plug-in assemblagesFile systemData storing

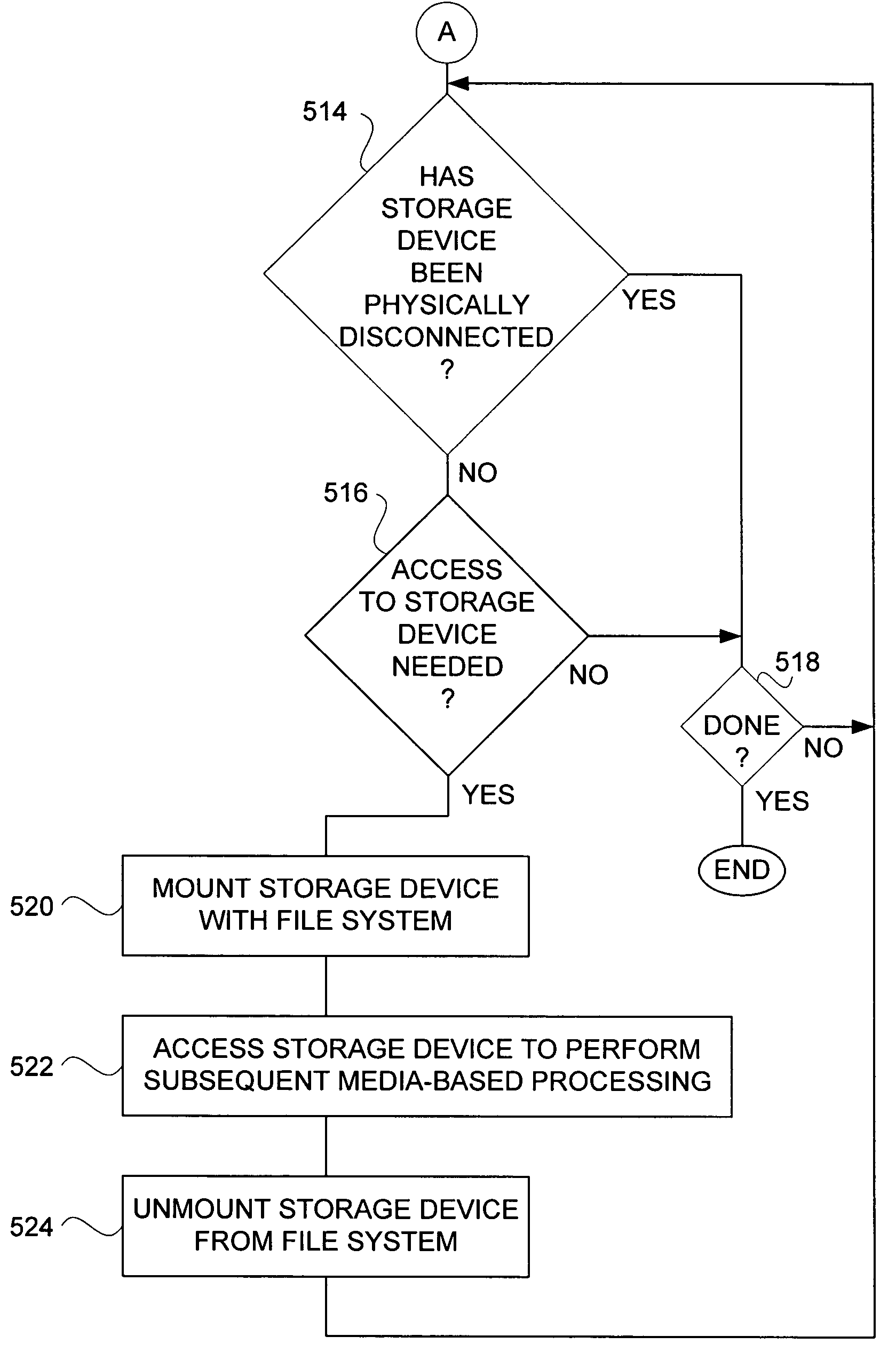

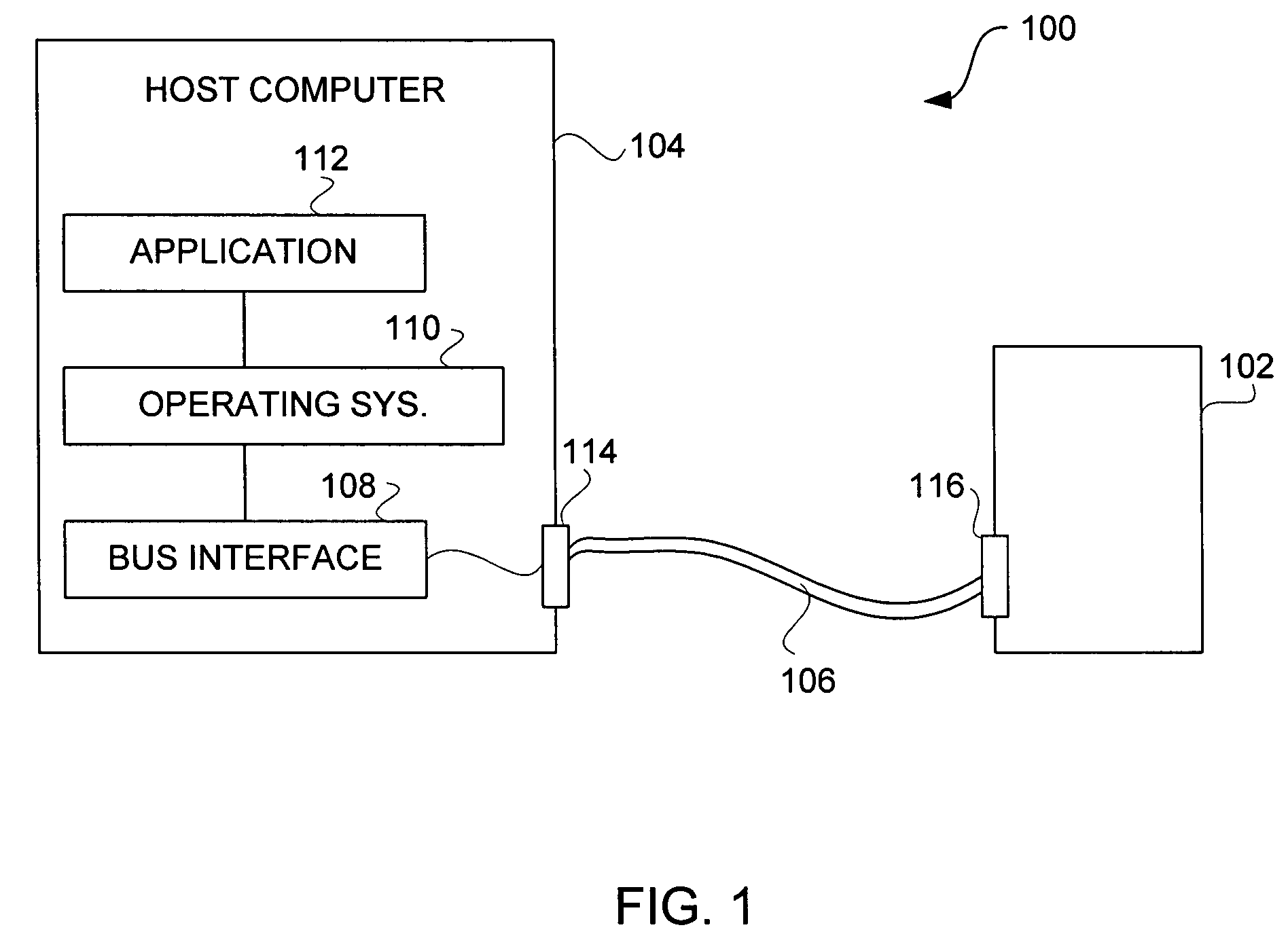

Improved techniques for rendering a peripheral device removable (e.g., unpluggable) are disclosed. According to one aspect of the invention, the peripheral device is rendered removable from a host computer without preparatory user actions. In effect, the peripheral device can be automatically prepared for removal in the event that its user removes (unplugs) it from its host computer. According to another aspect of the invention, the peripheral device includes a data storage device that is mounted to a file system of the other computer when the other computer desires access to the data storage device. Otherwise, the data storage device is normally unmounted so that if the peripheral device were to be removed (e.g., unplugged) no harm or damage to data stored therein would occur. These aspects of the invention can be utilized alone or in combination with one another. The invention is particularly well suited for peripheral devices that are media players which are “hot” unpluggable without detrimental consequences.

Owner:APPLE INC

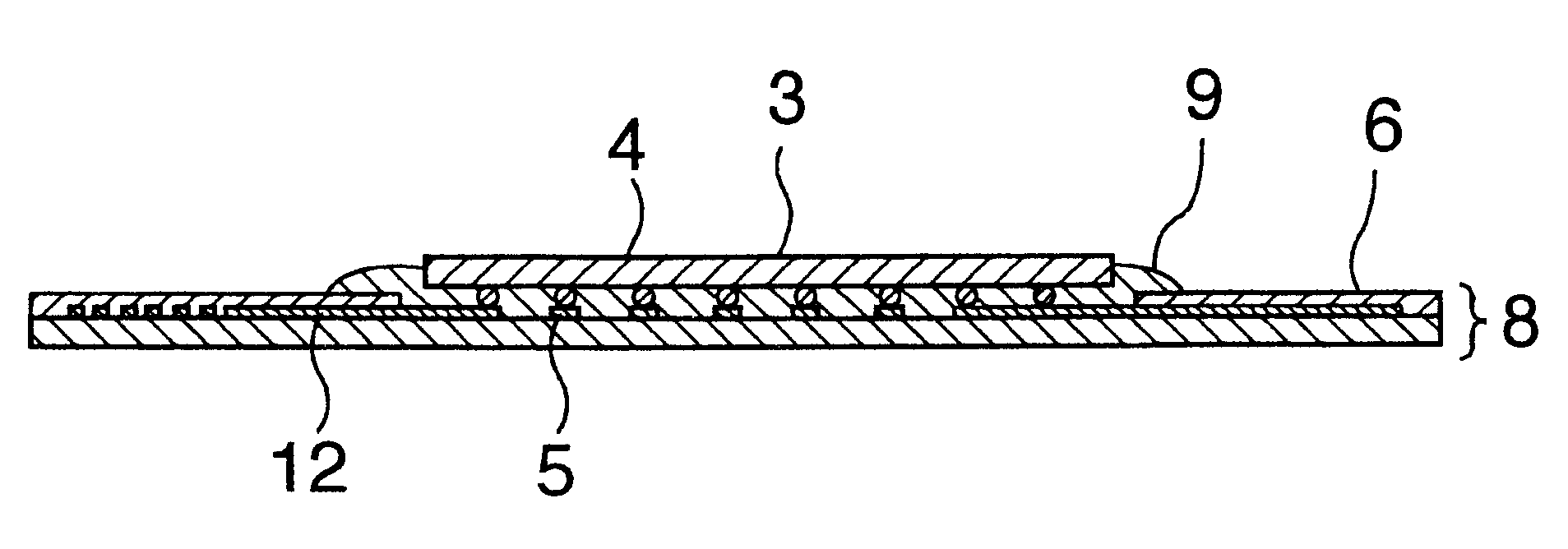

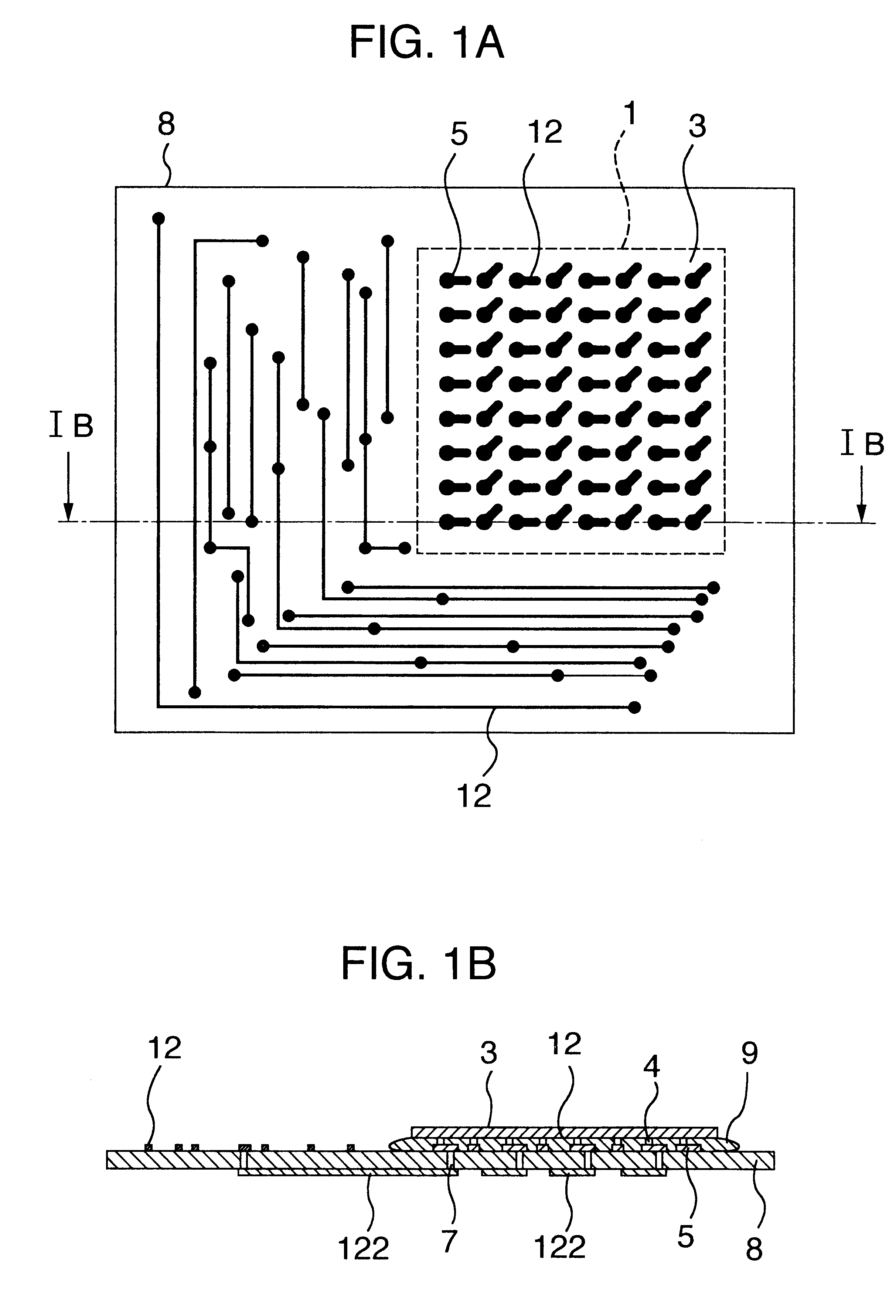

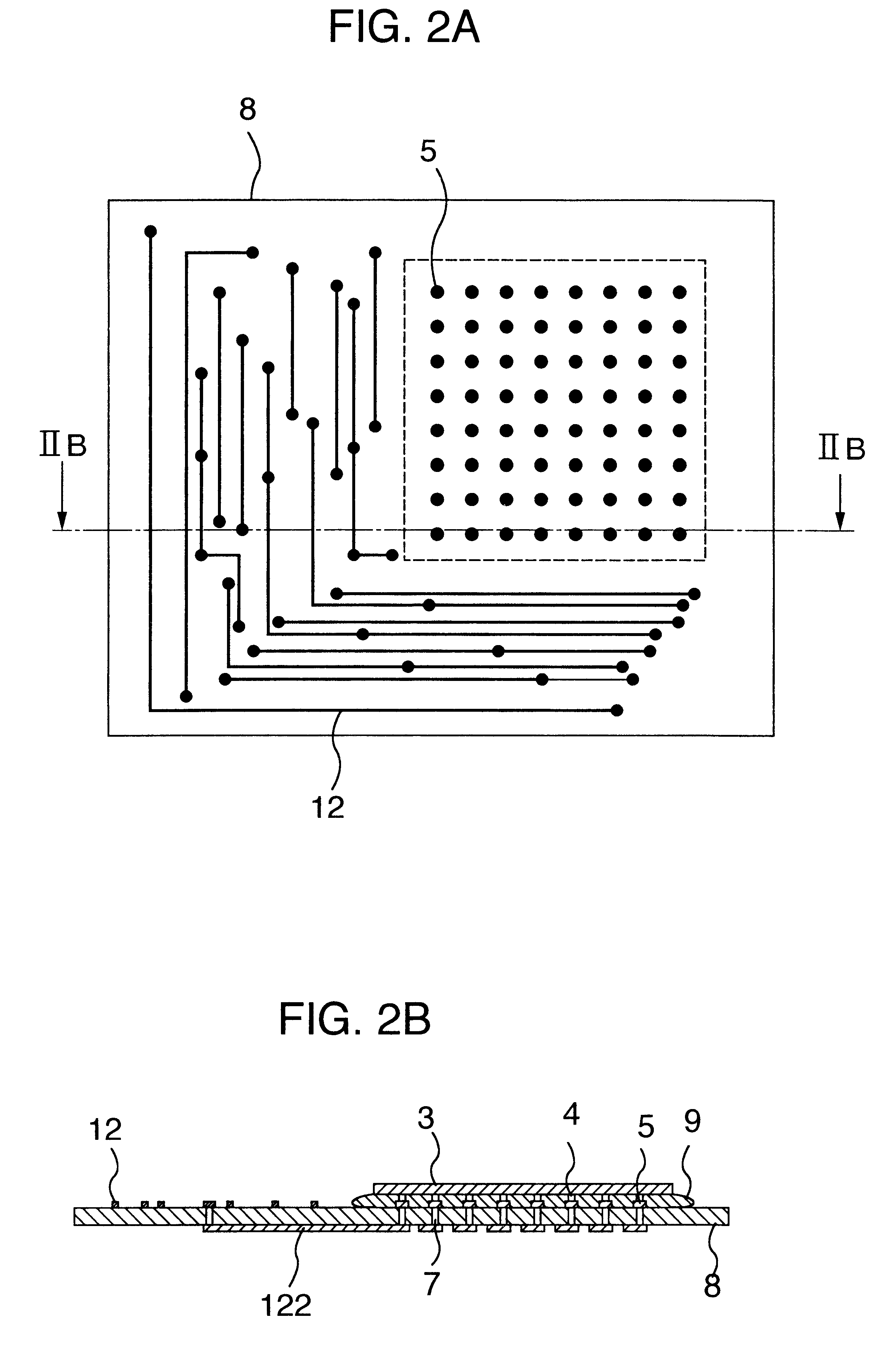

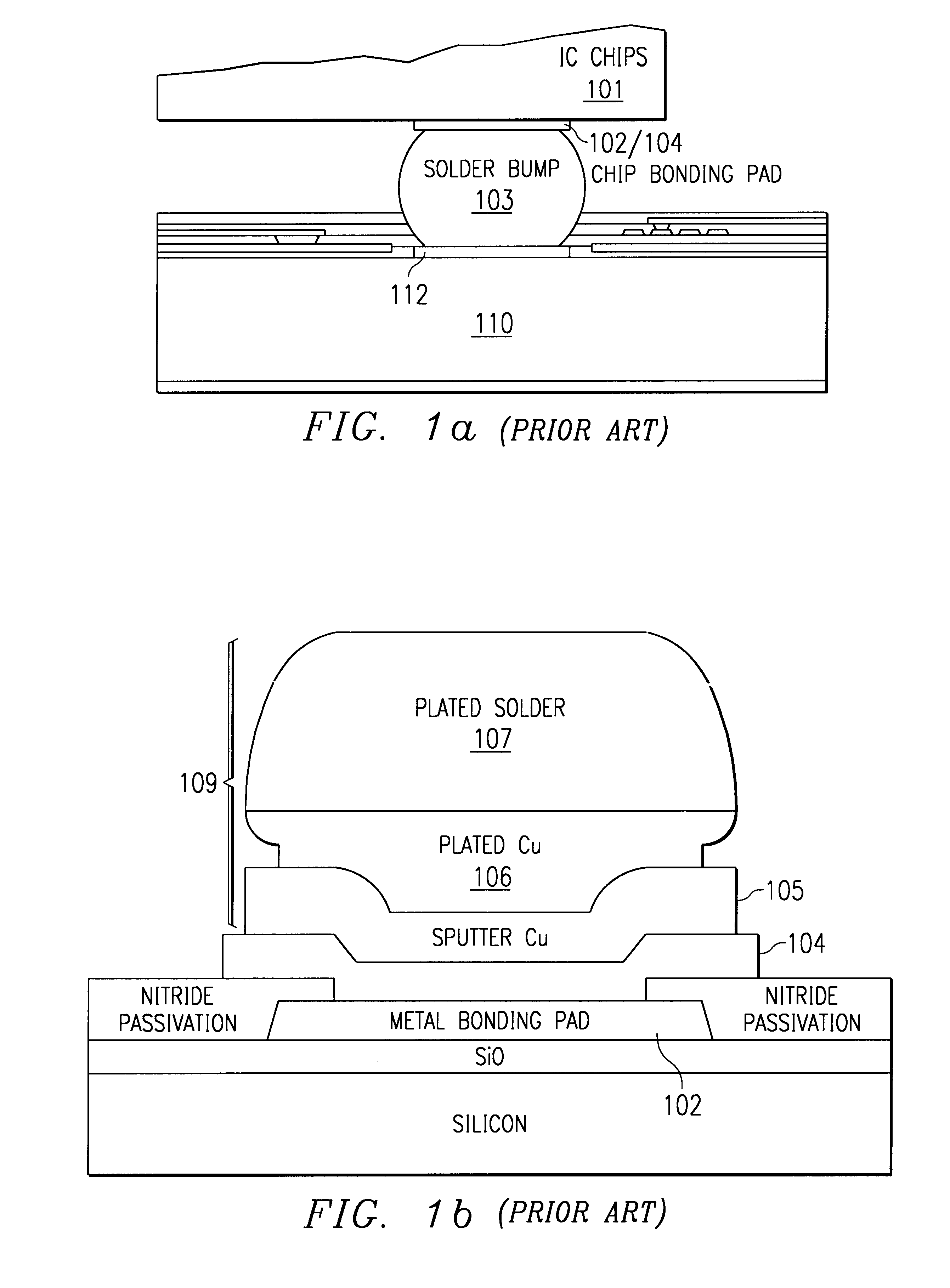

Substrate for mounting semiconductor chips

InactiveUS6281450B1Improve connection reliabilityImprove batch productivitySemiconductor/solid-state device detailsSolid-state devicesProduction rateElectrical conductor

A substrate for mounting a semiconductor chip having bumps using an adhesive thereon, said substrate being, for instance, provided with an insulating coating having an opening in the semiconductor chip mounting area so that the wiring conductors will not be exposed to the substrate surface near the boundary of the semiconductor chip mounting area, is improved in connection reliability and has high mass productivity.

Owner:HITACHI CHEM CO LTD

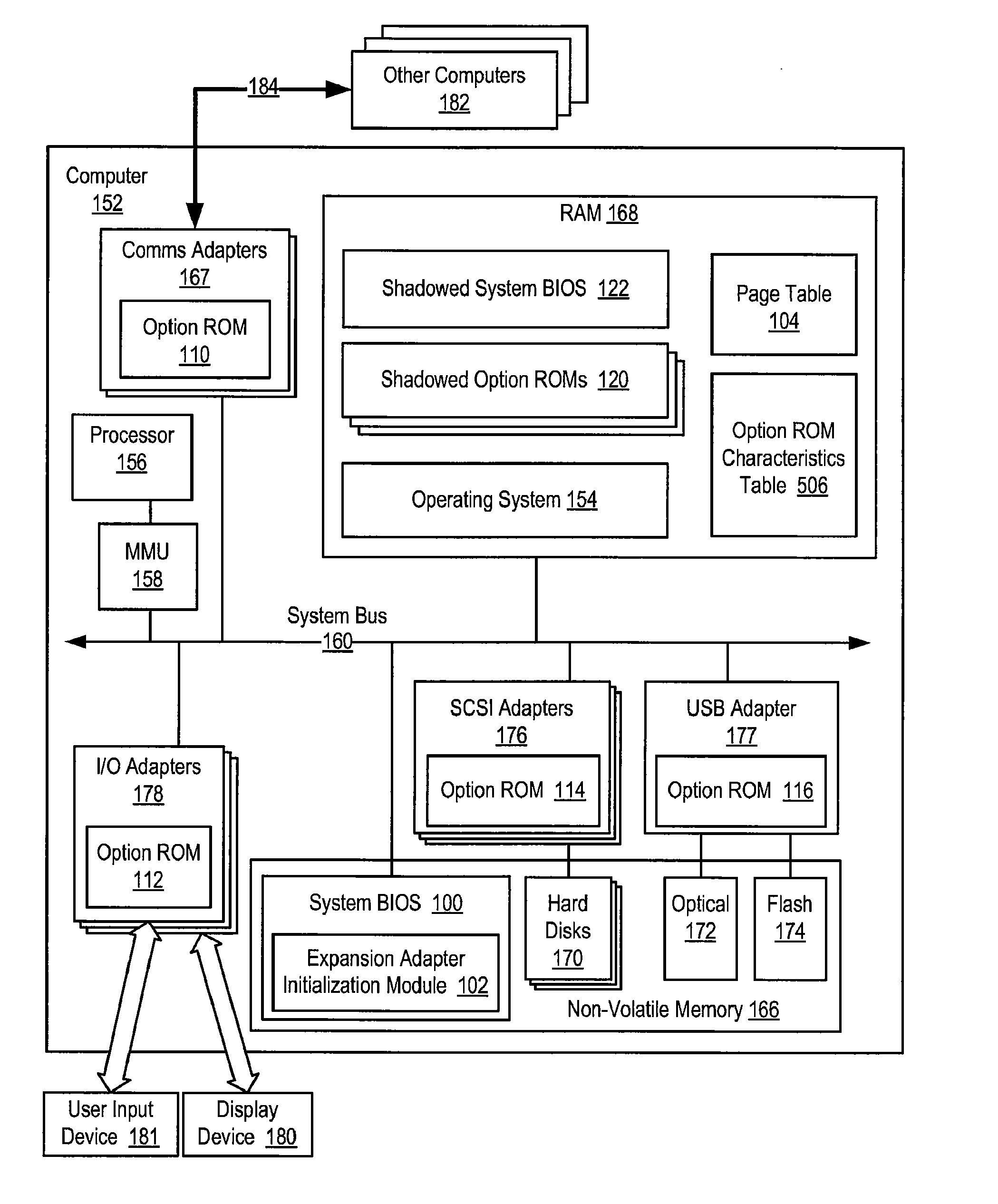

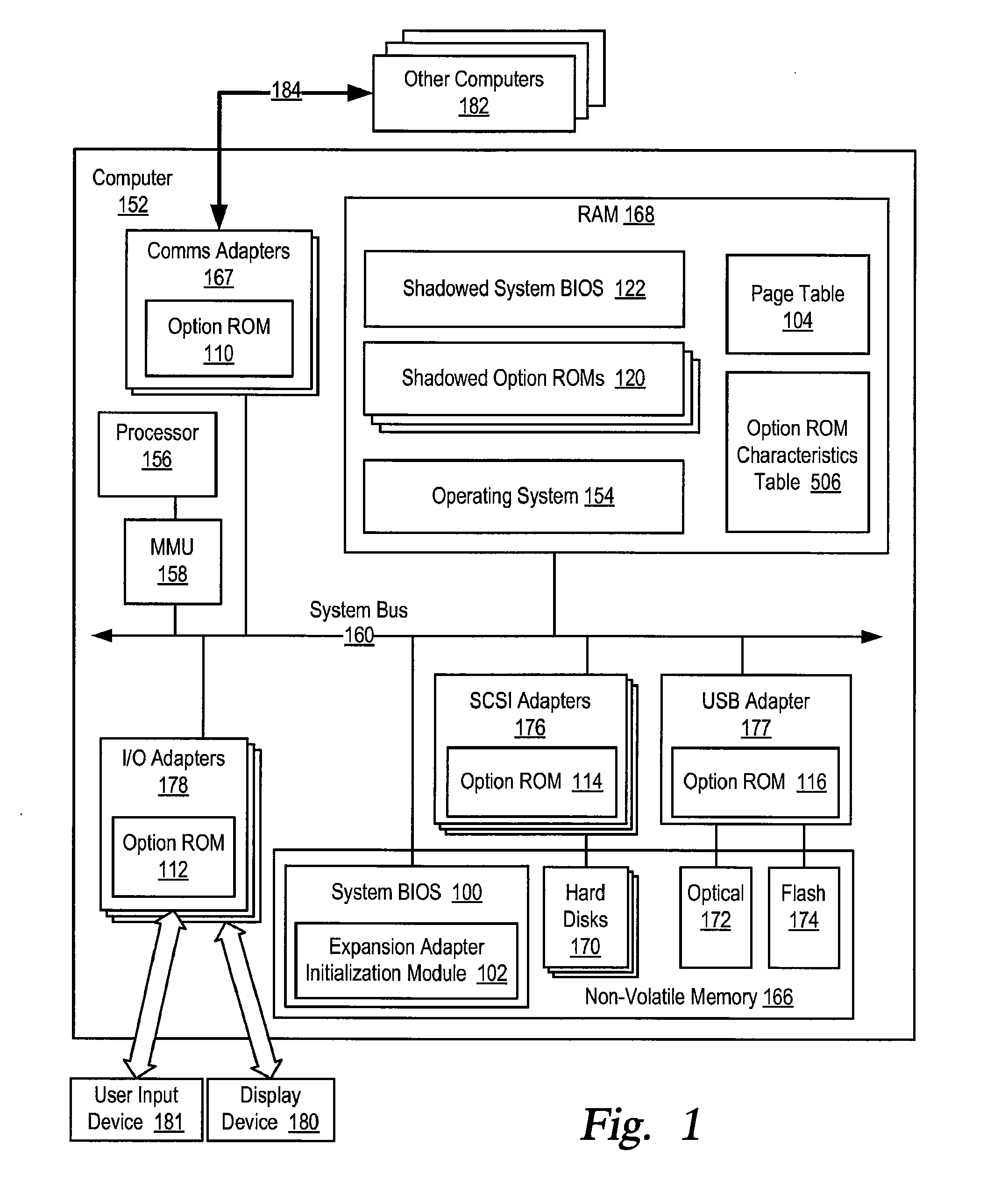

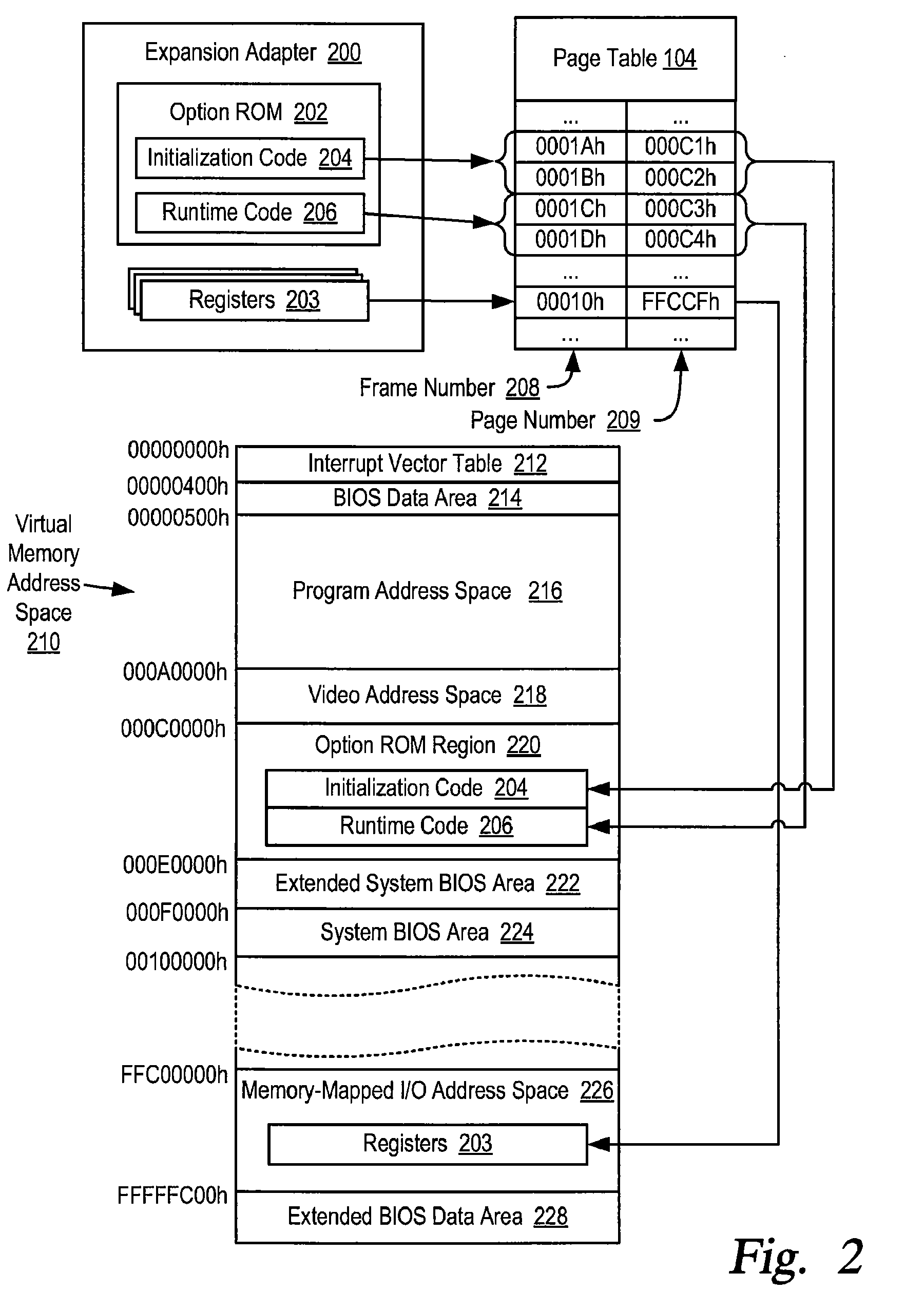

Structure for initializing expansion adpaters installed in a computer system having similar expansion adapters

A design structure embodied in a machine readable storage medium for at designing, manufacturing, and / or testing a design is disclosed for initializing expansion adapters installed in a computer system having similar expansion adapters that include detecting an expansion adapter installed in a computer system having a plurality of expansion adapters, the detected expansion adapter having an option ROM containing initialization code, identifying similar expansion adapters installed in the computer system that correspond to the detected expansion adapter, each of the identified similar expansion adapters having an option ROM containing initialization code, disabling the option ROM of each of the identified similar expansion adapters, and initializing the plurality of expansion adapters installed in the computer system without executing the initialization code of the identified similar expansion adapters.

Owner:IBM CORP

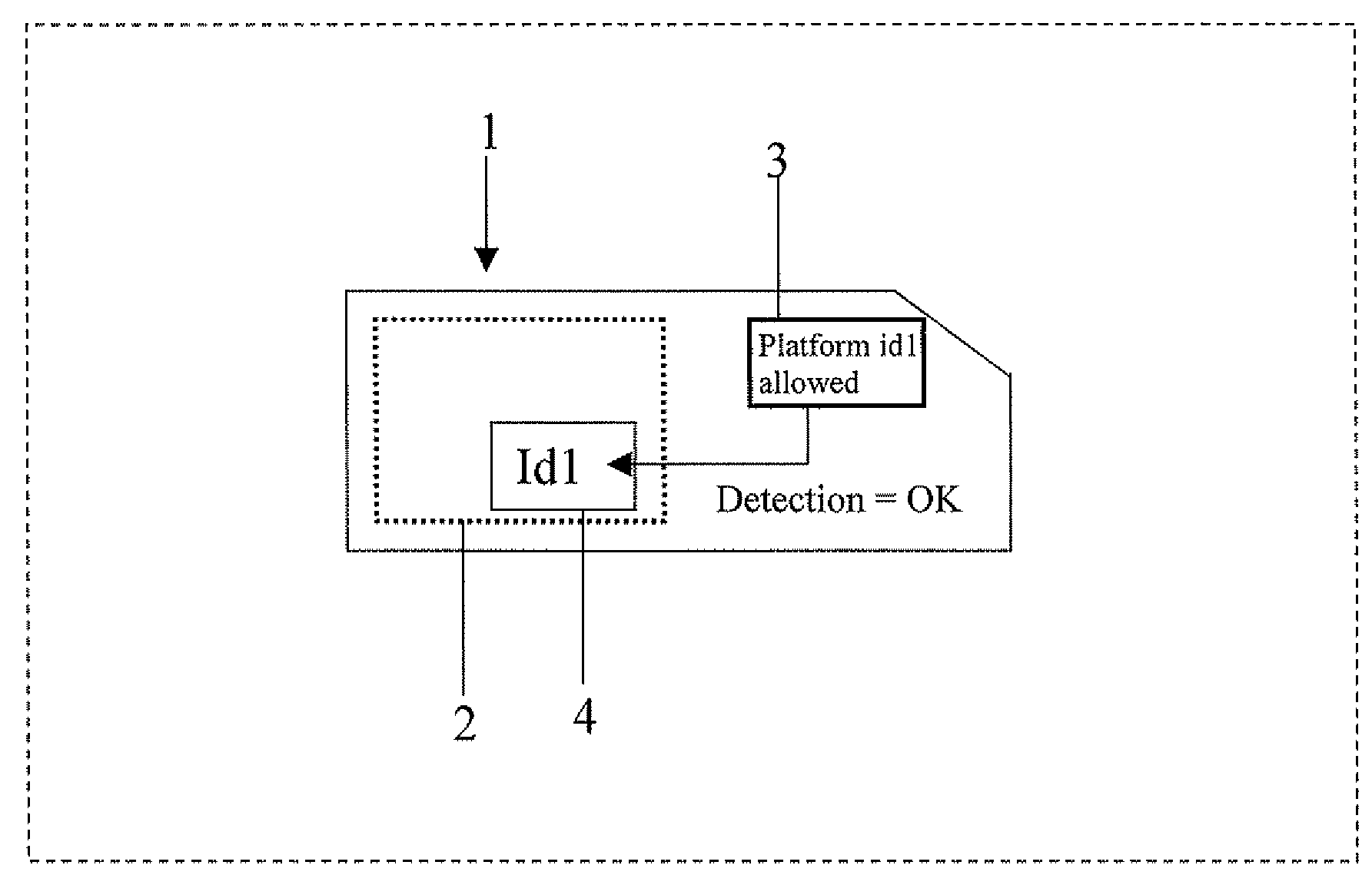

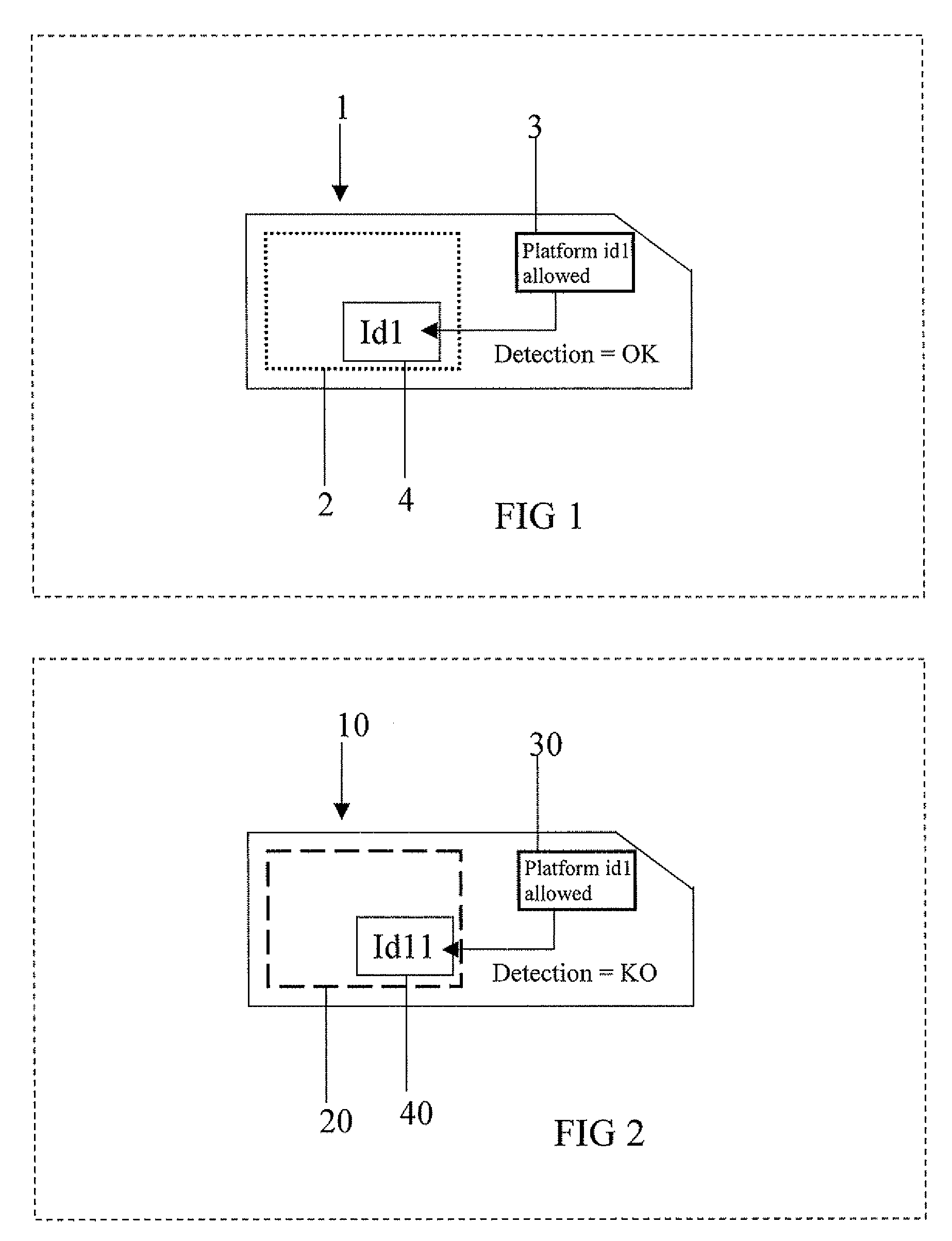

Method for controlling the execution of an applet for an IC card

ActiveUS20080288699A1Preventing executionAvoid business lossInternal/peripheral component protectionComponent plug-in assemblagesOperating systemJava Card

A method for controlling the execution of an applet for an IC Card including a java card platform, includes a phase for downloading the applet inside the IC Card, a phase for executing the applet through the java card platform and a phase for storing an identification platform number inside a memory portion of the IC Card. The phase for executing the applet has a first step for detecting the identification platform number to perform the phase for executing the applet with or without restrictions, respectively if the identification platform number is not or is detected by the step for detecting. The applet is a java card applet or a SIM toolkit applet.

Owner:STMICROELECTRONICS INT NV

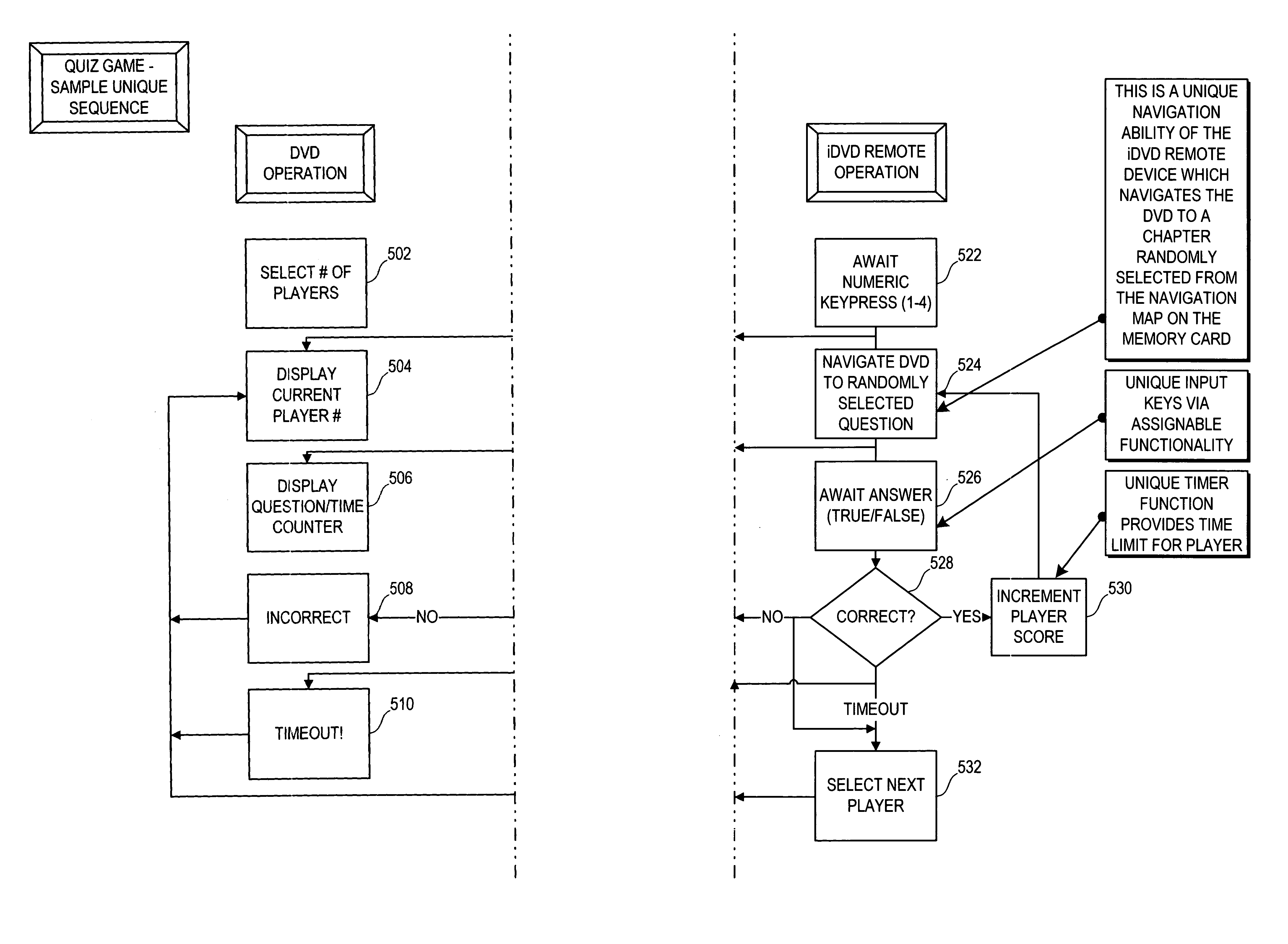

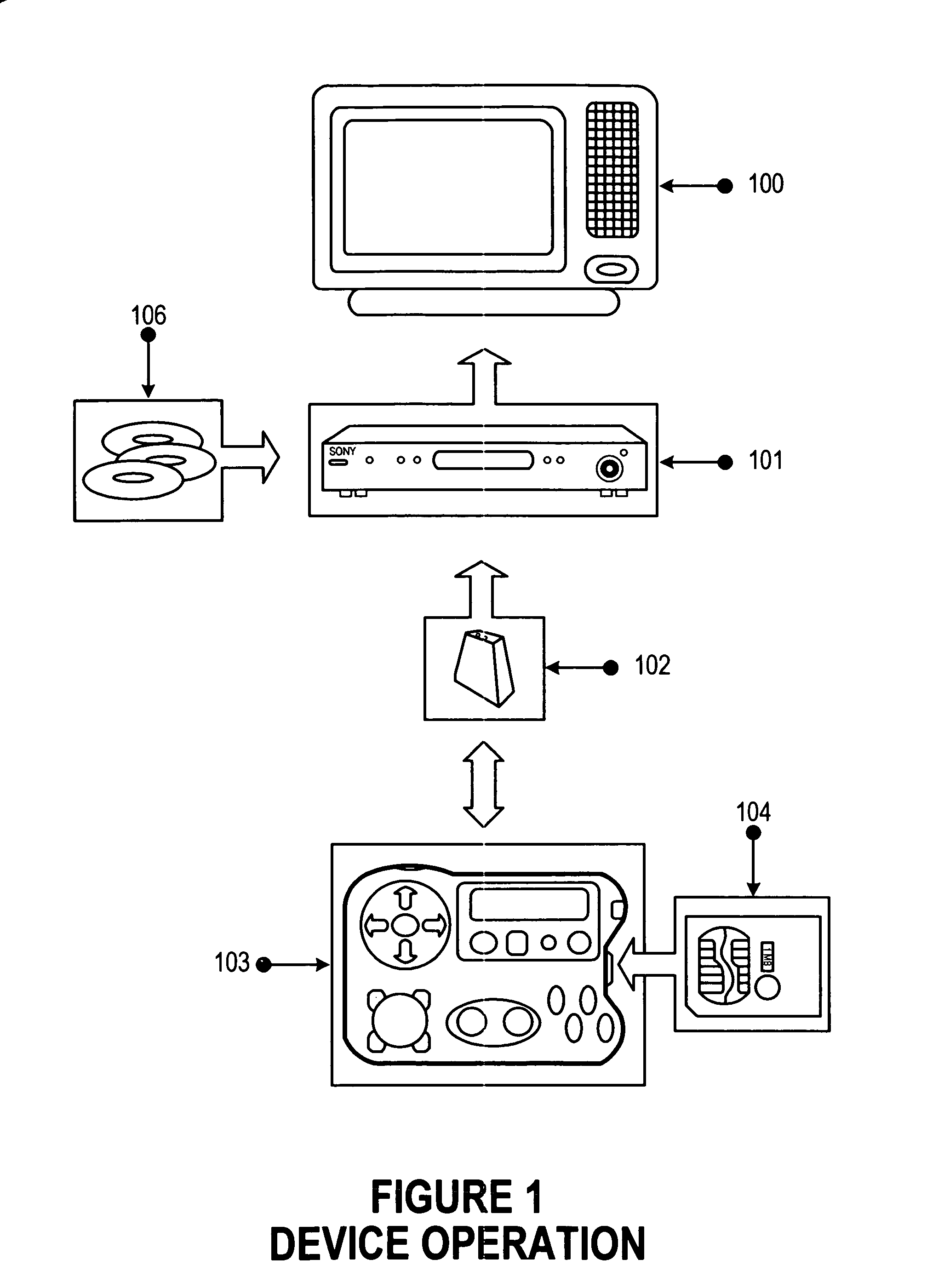

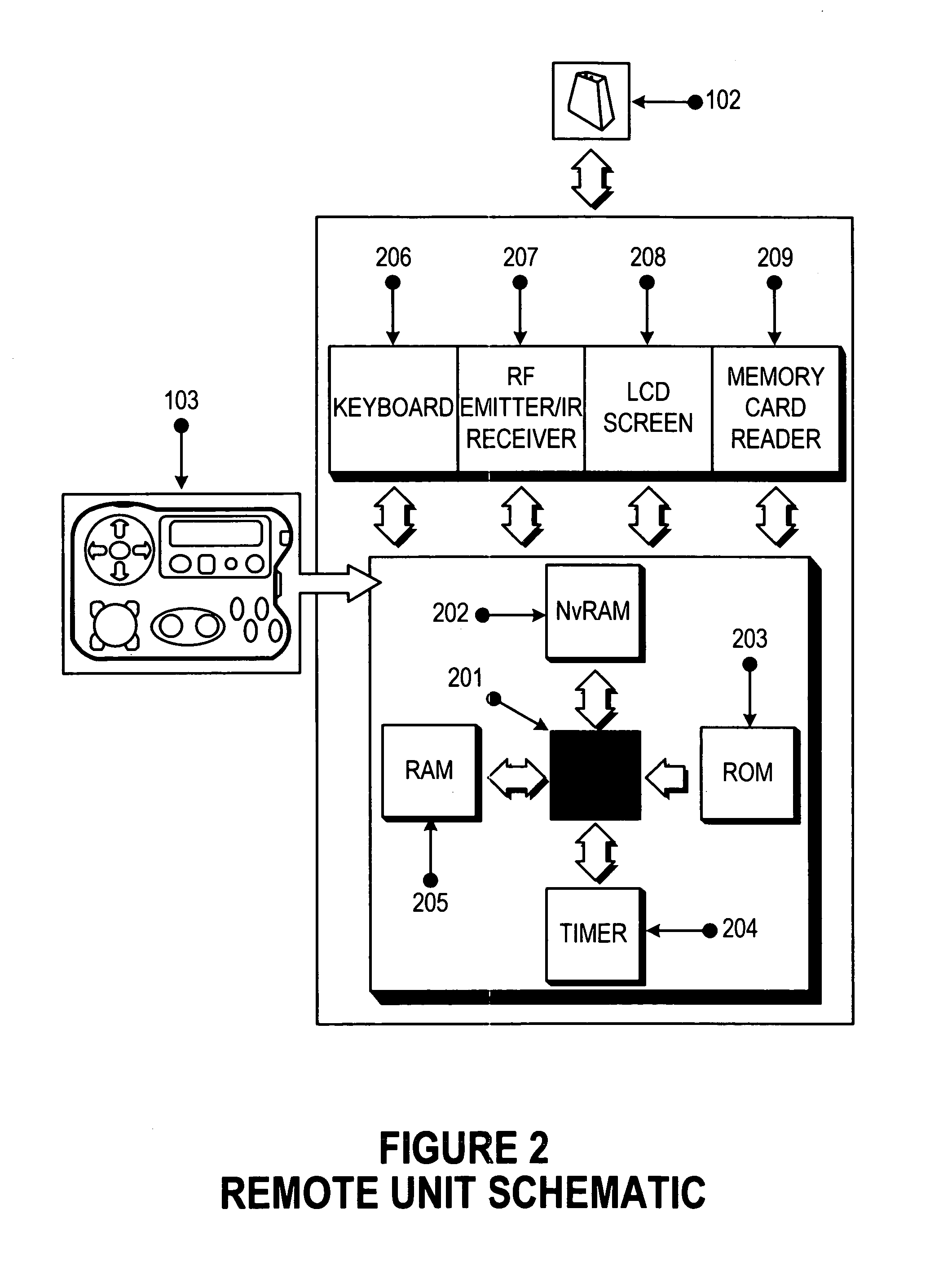

Remote control for providing interactive DVD navigation based on user response

InactiveUS7003598B2Improve the level ofTelevision system detailsDigital data processing detailsDigital videoComputer graphics (images)

A game control unit includes a computer processor for executing game logic stored on a removable memory device. Rich, audiovisual content for the interactive gaming experience is provided on a digital video disk (DVD) in small clips which are selectively played back in a standard DVD player under control of the game control unit. Specifically, the game control unit mimics standard remote control signals to control playback of the audiovisual content by the DVD player.

Owner:BRIGHT ENTERTAINMENT

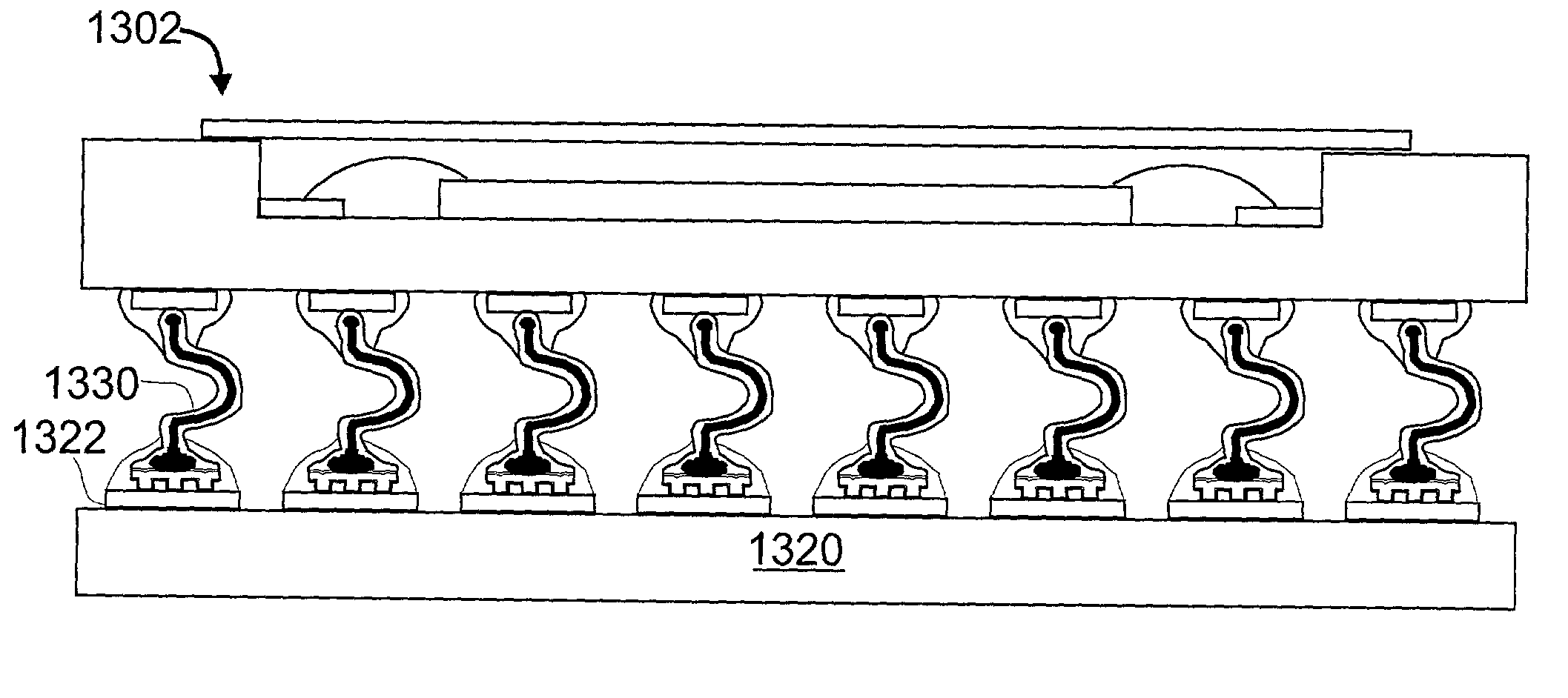

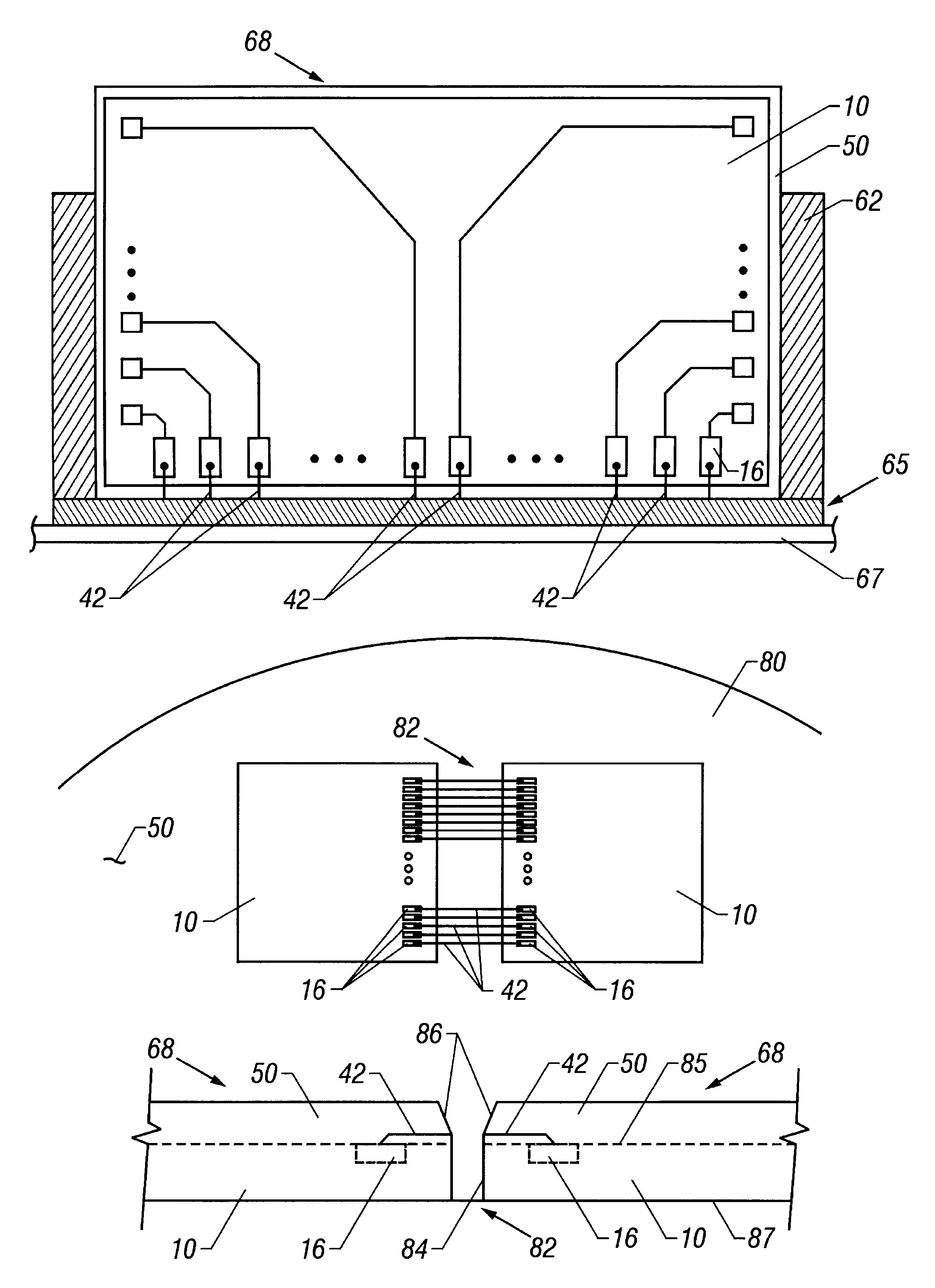

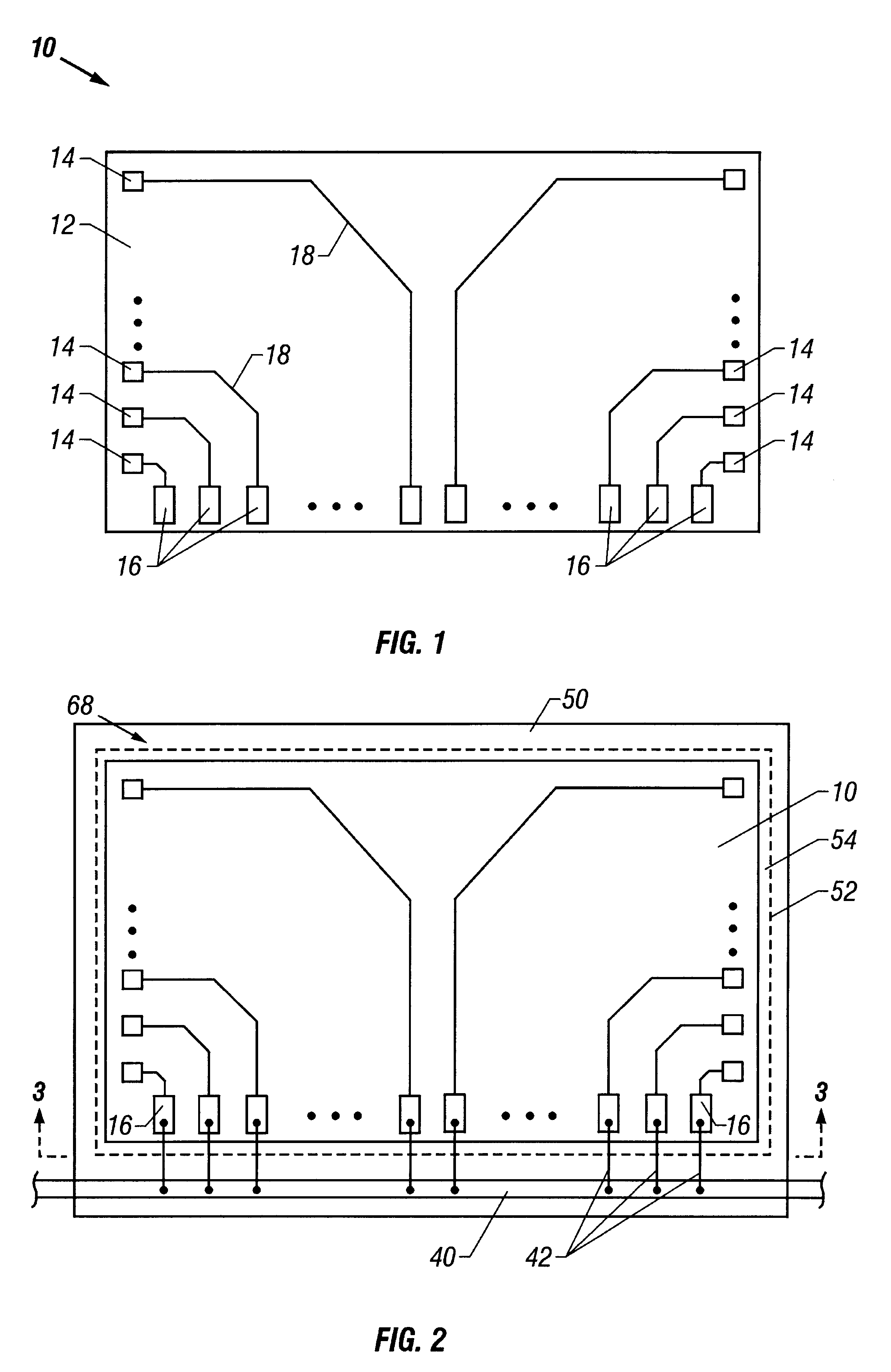

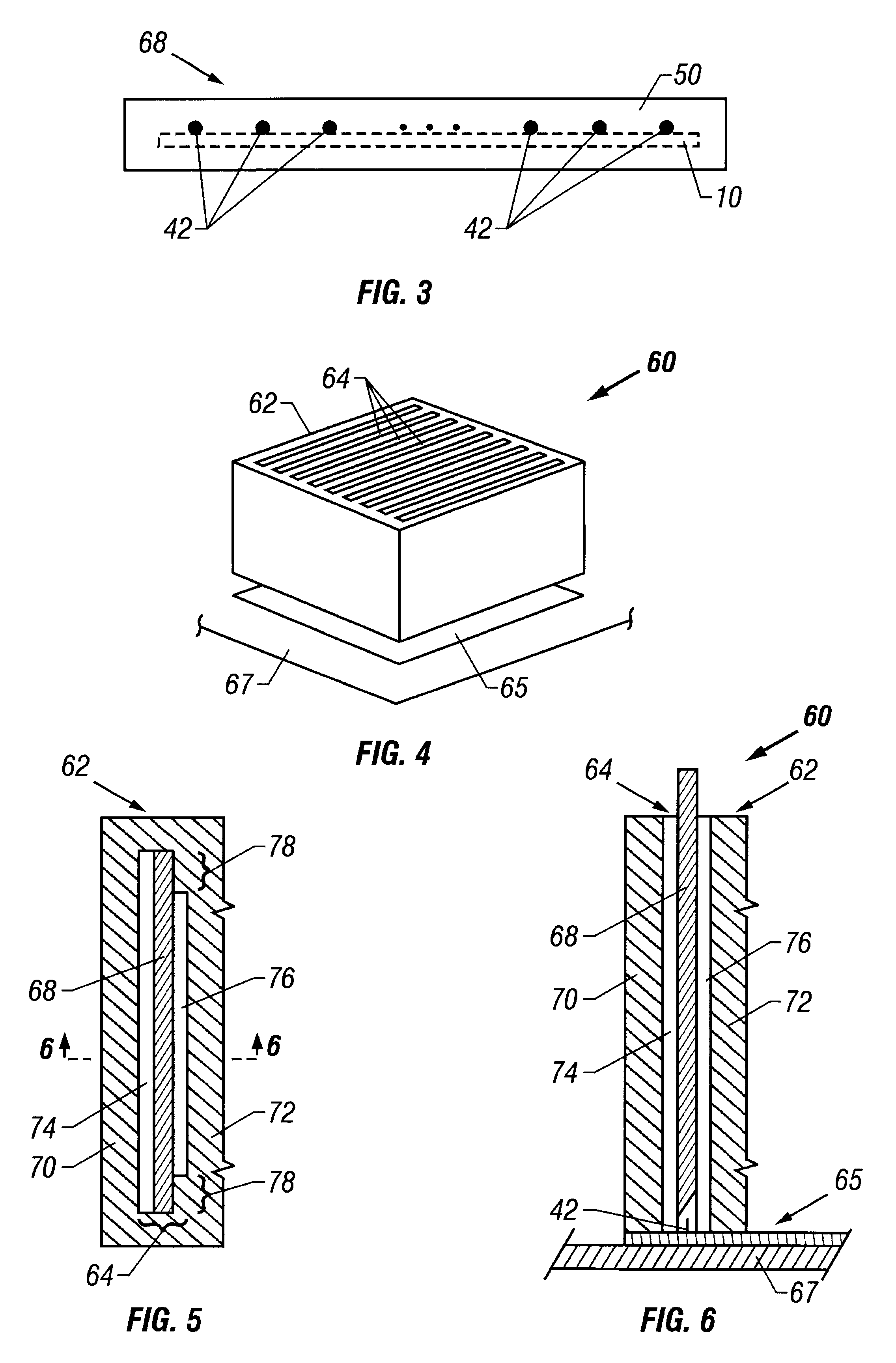

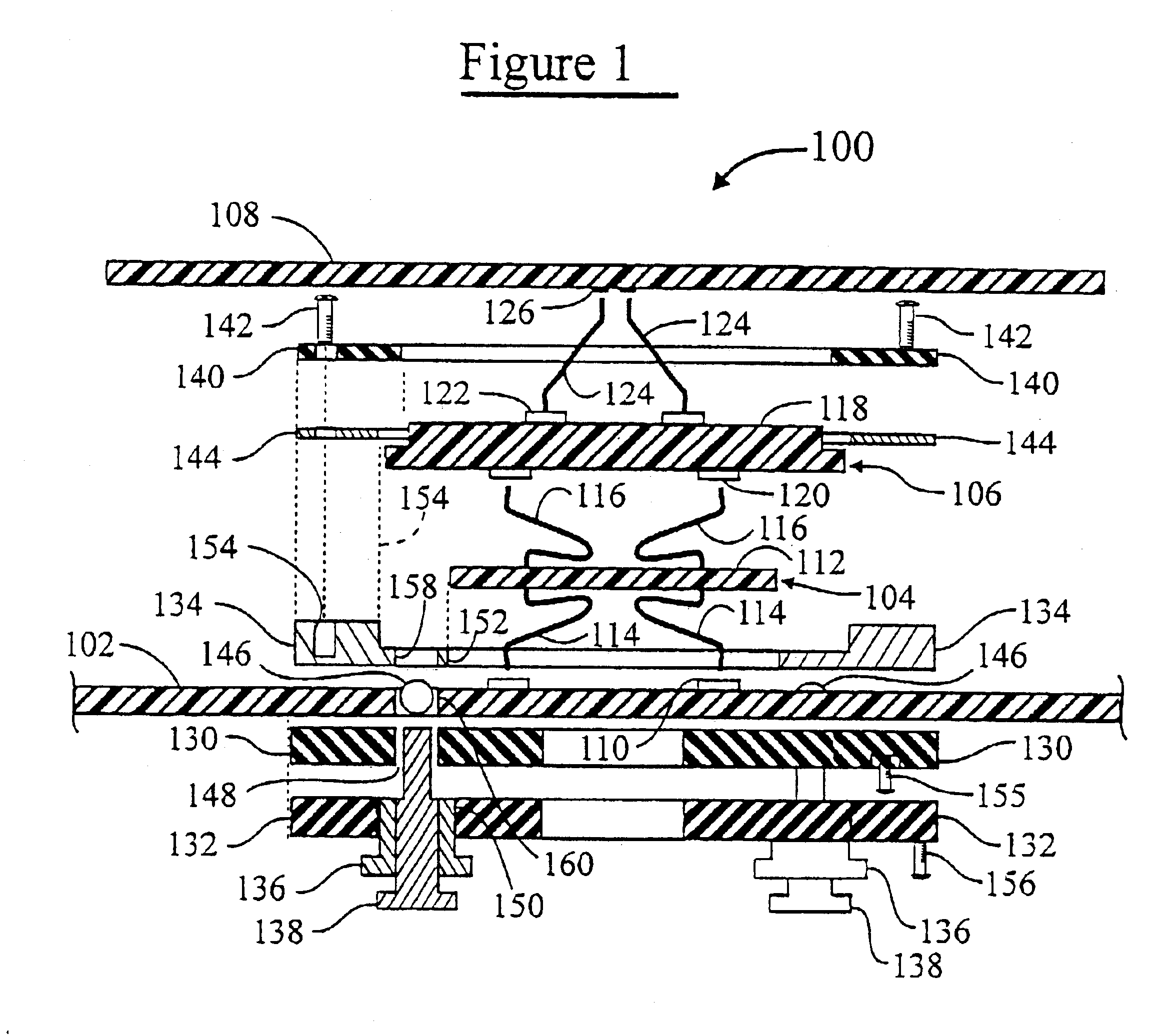

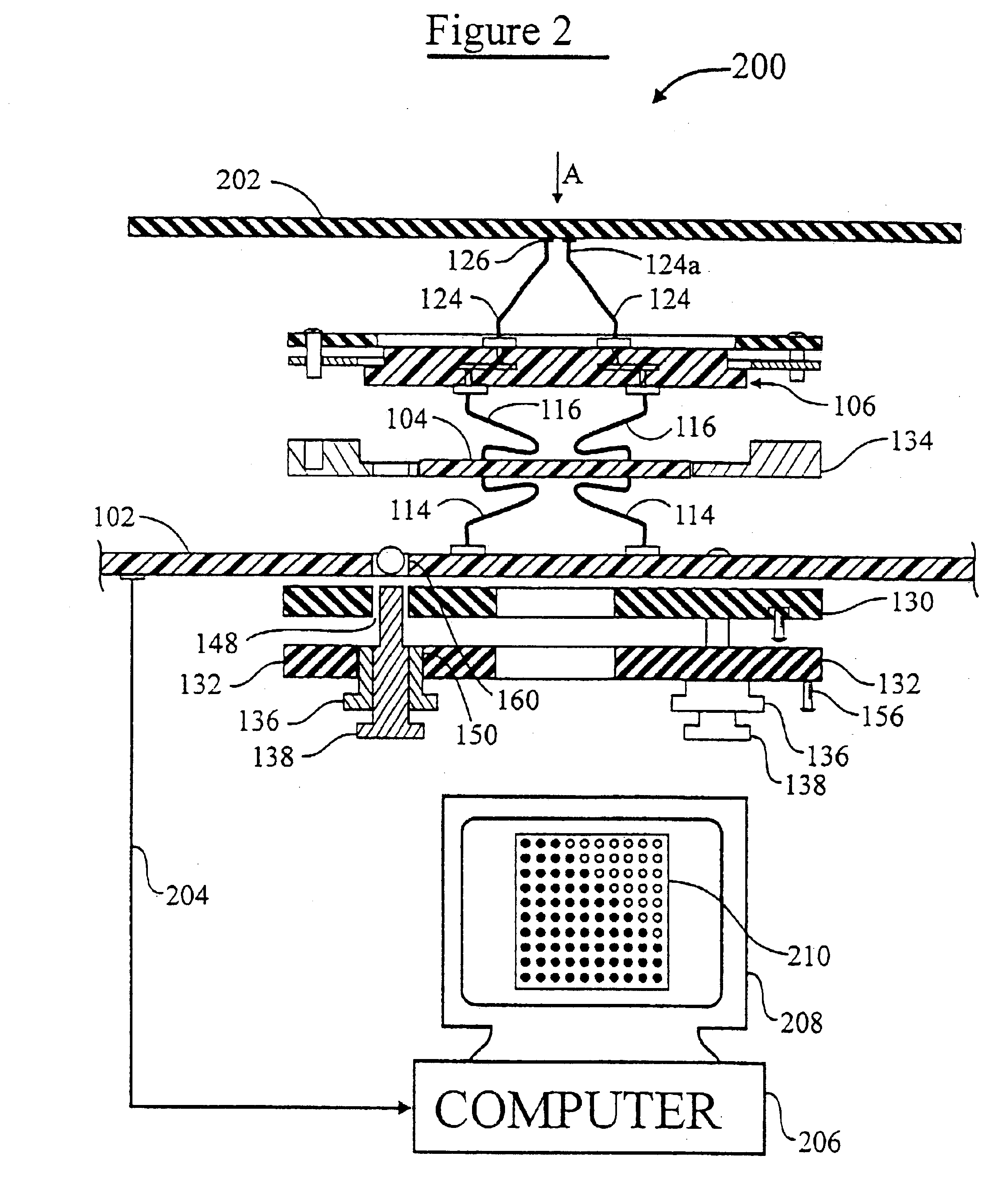

Probe card assembly and kit, and methods of using same

InactiveUS6246247B1Easy to disassembleEffective shieldingSemiconductor/solid-state device testing/measurementFinal product manufactureElectricityProbe card

A probe card assembly includes a probe card, a space transformer having resilient contact structures (probe elements) mounted directly thereto (i.e., without the need for additional connecting wires or the like) and extending from terminals on a surface thereof, and an interposer disposed between the space transformer and the probe card. The space transformer and interposer are "stacked up" so that the orientation of the space transformer, hence the orientation of the tips of the probe elements, can be adjusted without changing the orientation of the probe card. Suitable mechanisms for adjusting the orientation of the space transformer, and for determining what adjustments to make, are disclosed. The interposer has resilient contact structures extending from both the top and bottom surfaces thereof, and ensures that electrical connections are maintained between the space transformer and the probe card throughout the space transformer's range of adjustment, by virtue of the interposer's inherent compliance. Multiple die sites on a semiconductor wafer are readily probed using the disclosed techniques, and the probe elements can be arranged to optimize probing of an entire wafer. Composite interconnection elements having a relatively soft core overcoated by a relatively hard shell, as the resilient contact structures are described.

Owner:FORMFACTOR INC

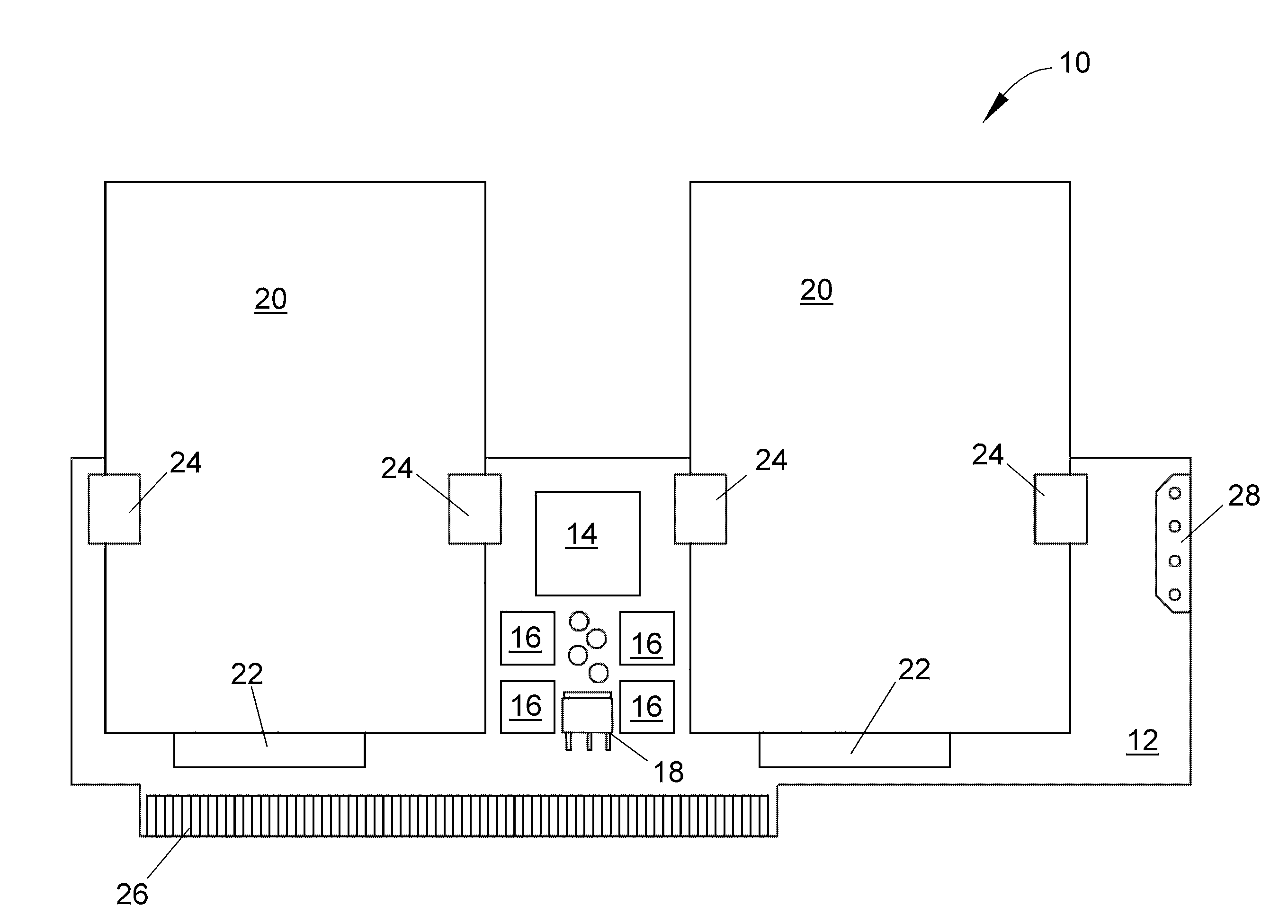

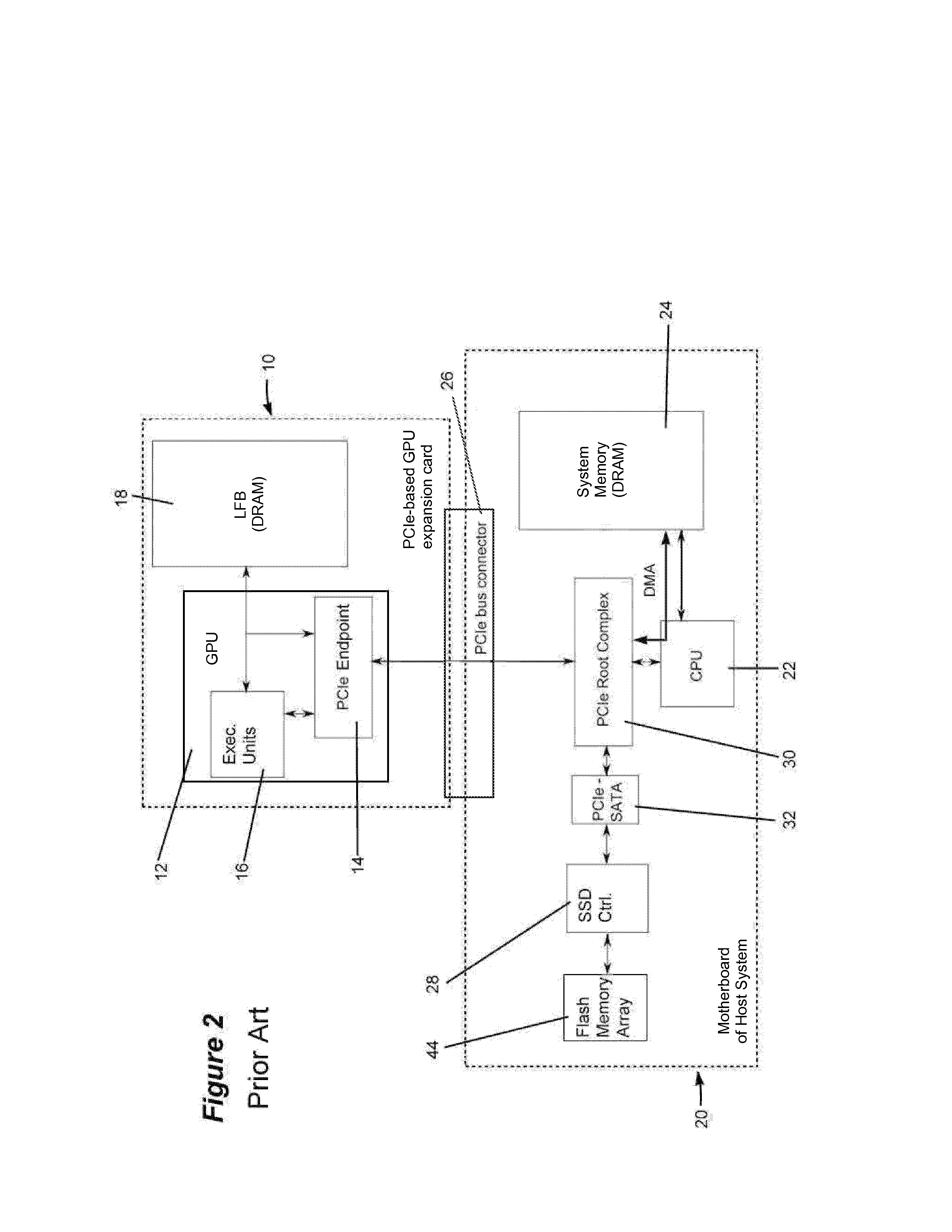

Mass storage system and method using hard disk and solid-state media

ActiveUS20110320690A1Minimal degradationReduce access latencyMemory architecture accessing/allocationError detection/correctionPrinted circuit boardSolid state memory

Methods and systems for mass storage of data over two or more tiers of mass storage media that include nonvolatile solid-state memory devices, hard disk devices, and optionally volatile memory devices or nonvolatile MRAM in an SDRAM configuration. The mass storage media interface with a host through one or more PCIe lanes on a single printed circuit board.

Owner:KIOXIA CORP

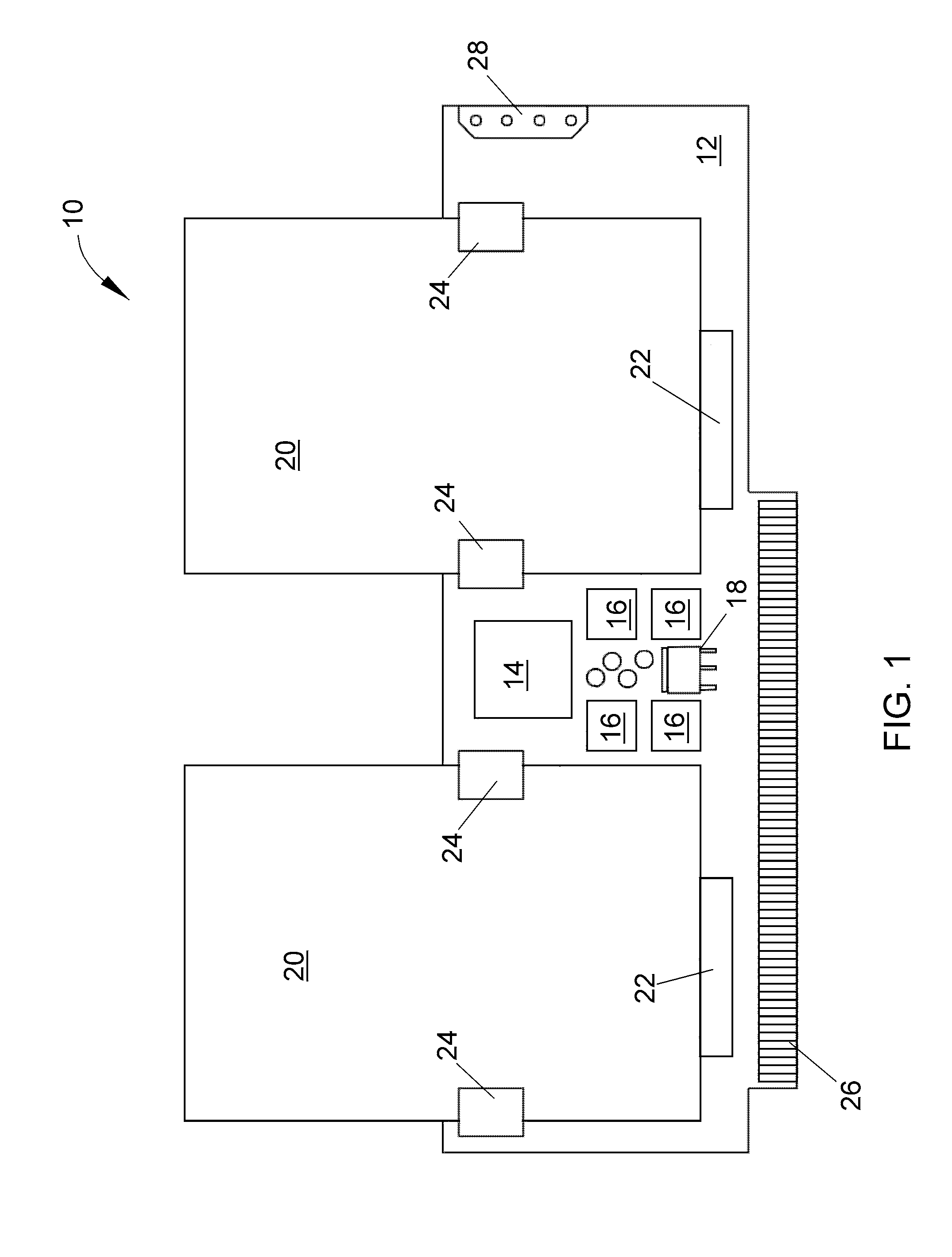

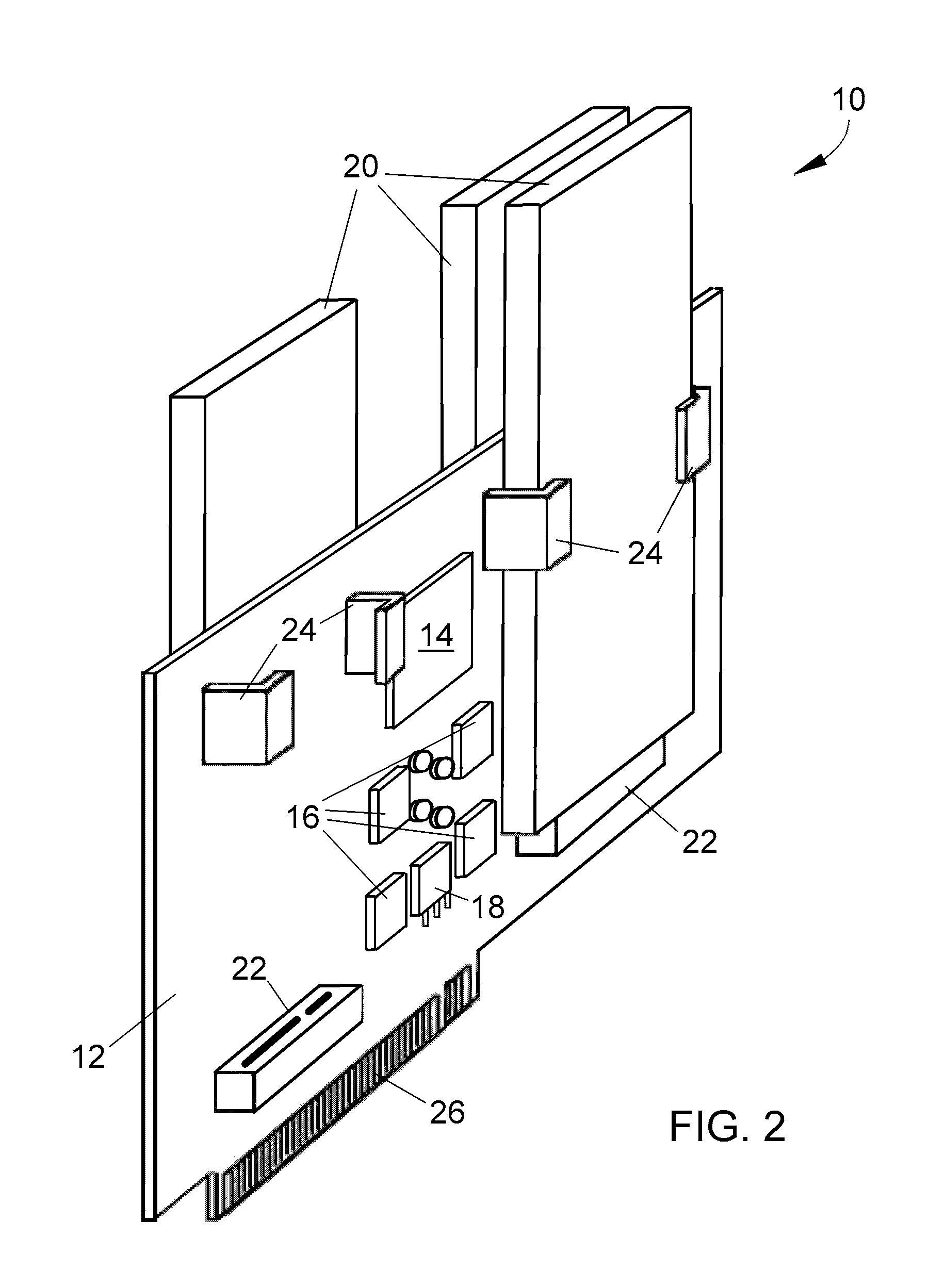

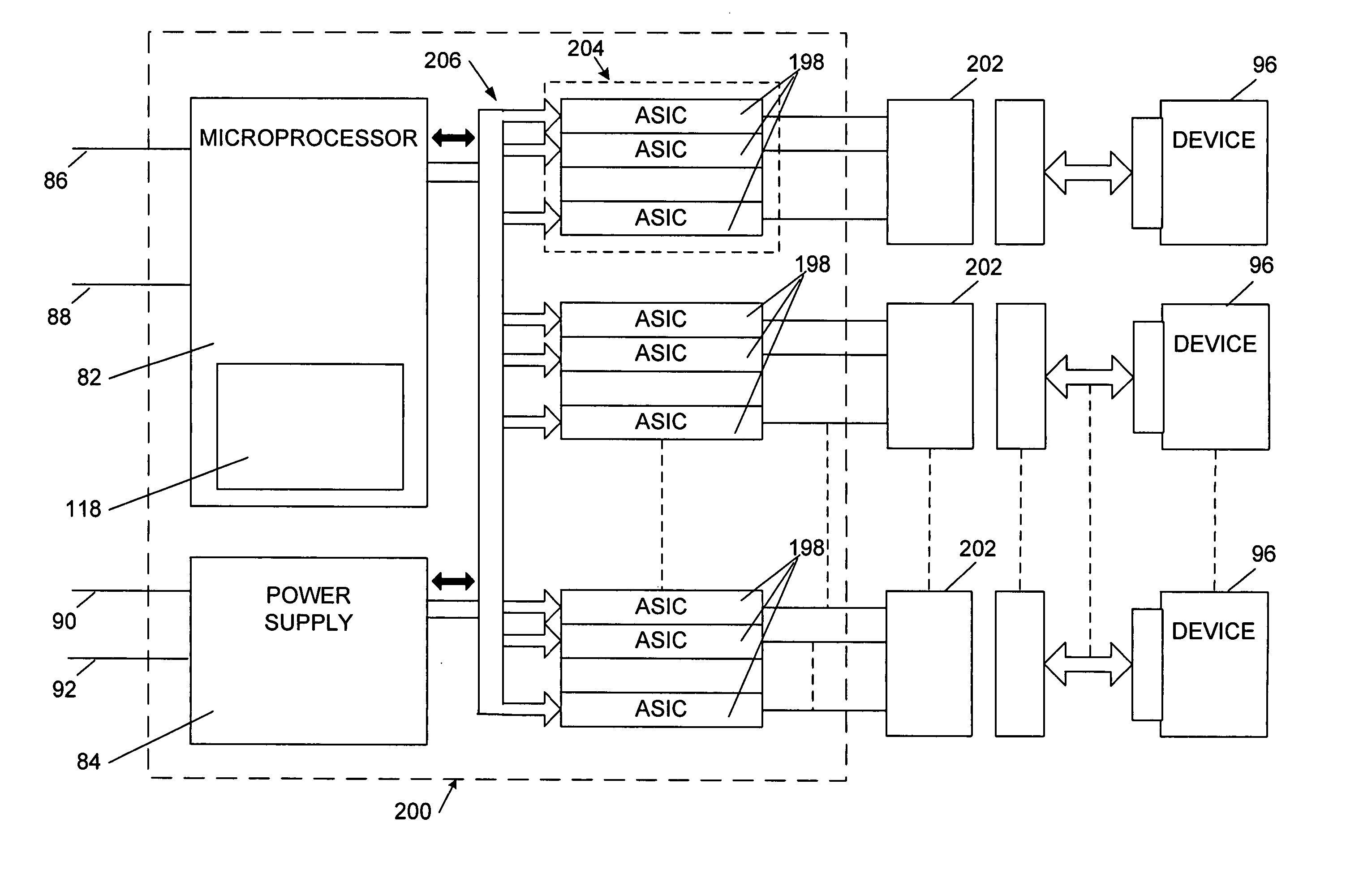

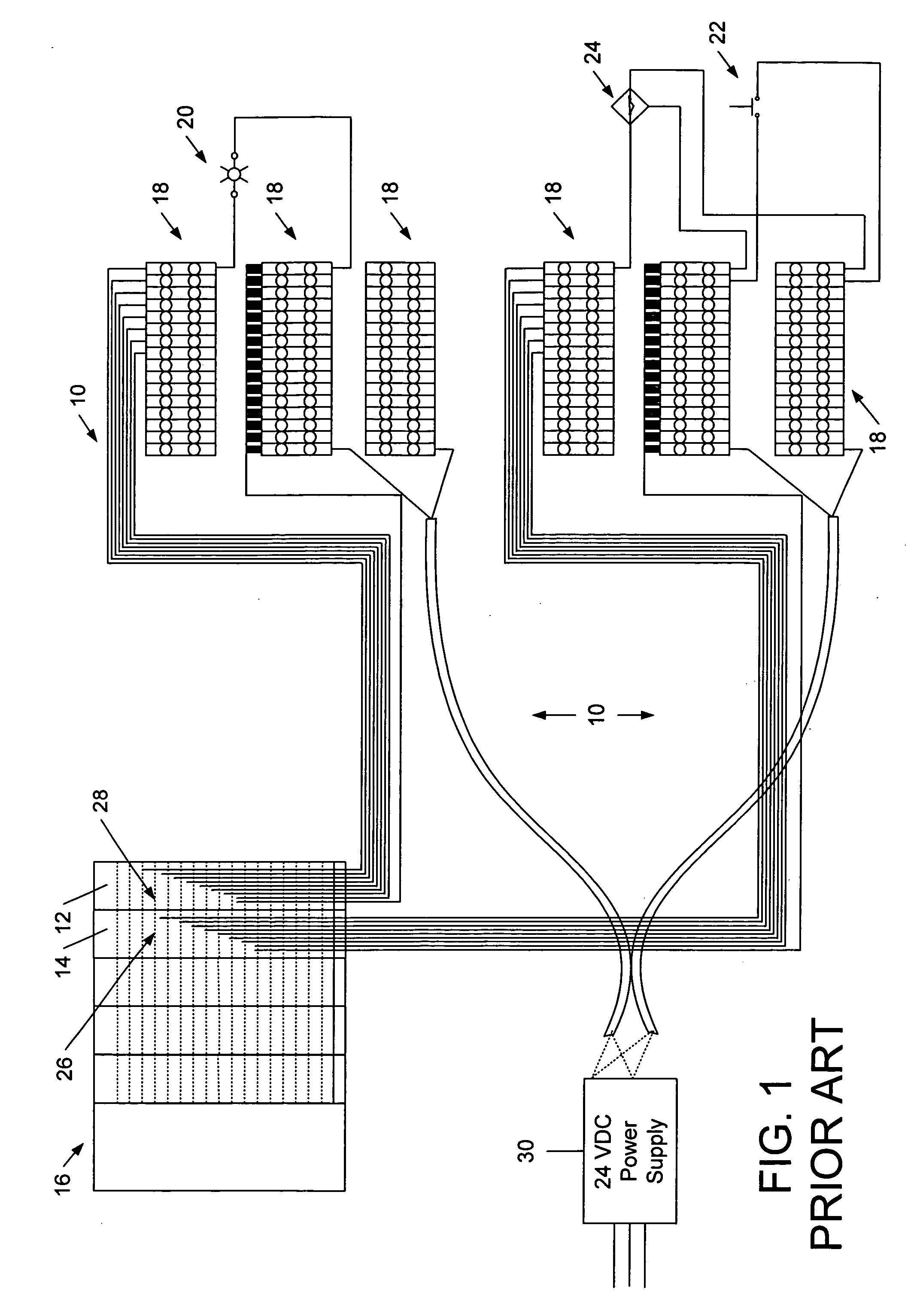

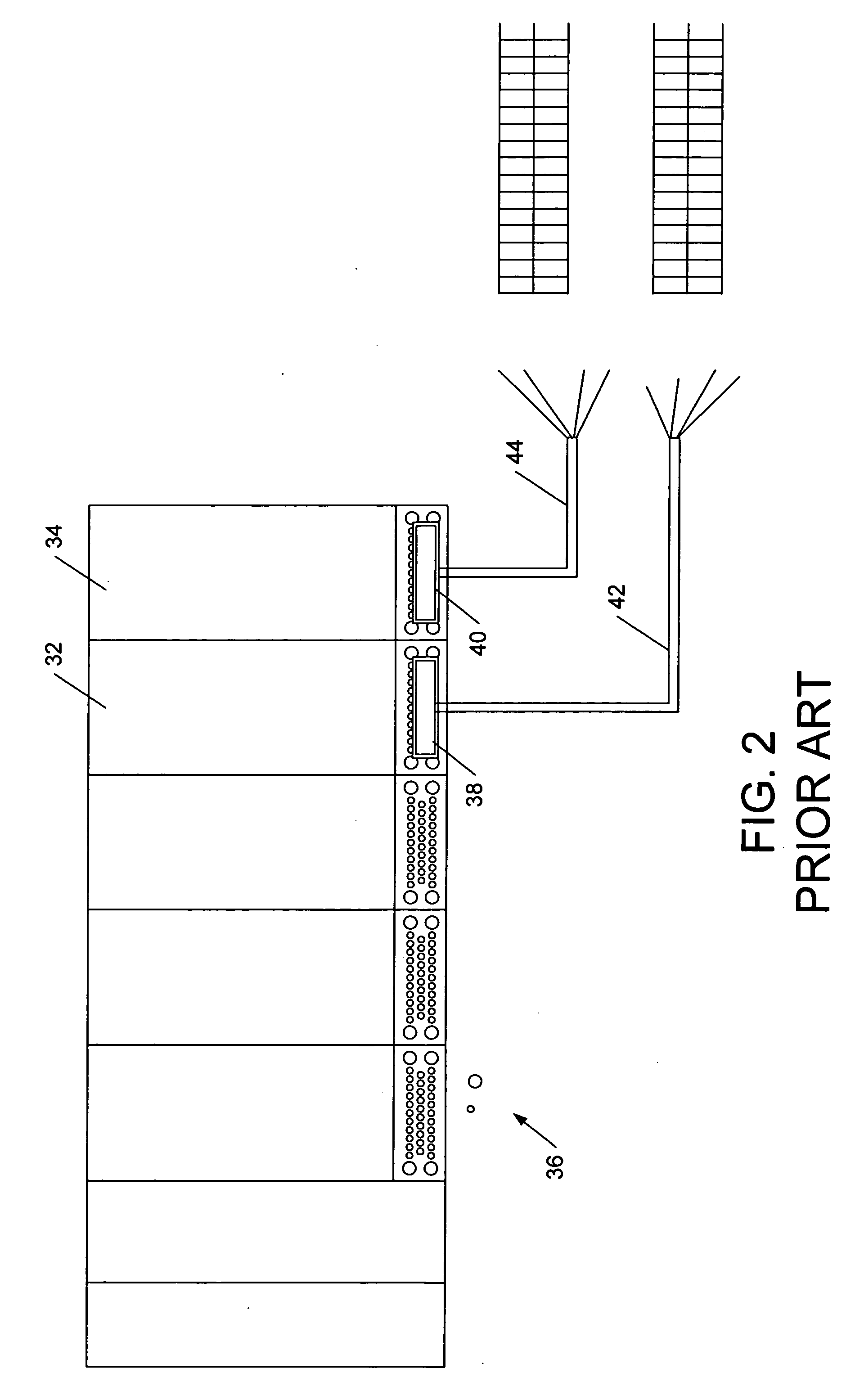

System for programmed control of signal input and output to and from cable conductors

InactiveUS20060155900A1Reduced Routing ComplexityReduce in quantityProgramme controlDigital data processing detailsElectrical conductorInterconnection

An input / output module for implementing directions from a controller for sending and receiving signals to and from devices. The input / output module includes a microprocessor for communication with, and receiving programming from the controller. The input / output module further includes device communication connectors, each having number of pins, each pin for interconnection with a cable conductor to a device. The input / output module has an ASIC for each of the pins, providing a controlled interface with the corresponding pin. Each ASIC has interconnection apparatus, selectable by the microprocessor for providing a particular interface with the pin served by the ASIC.

Owner:X 10

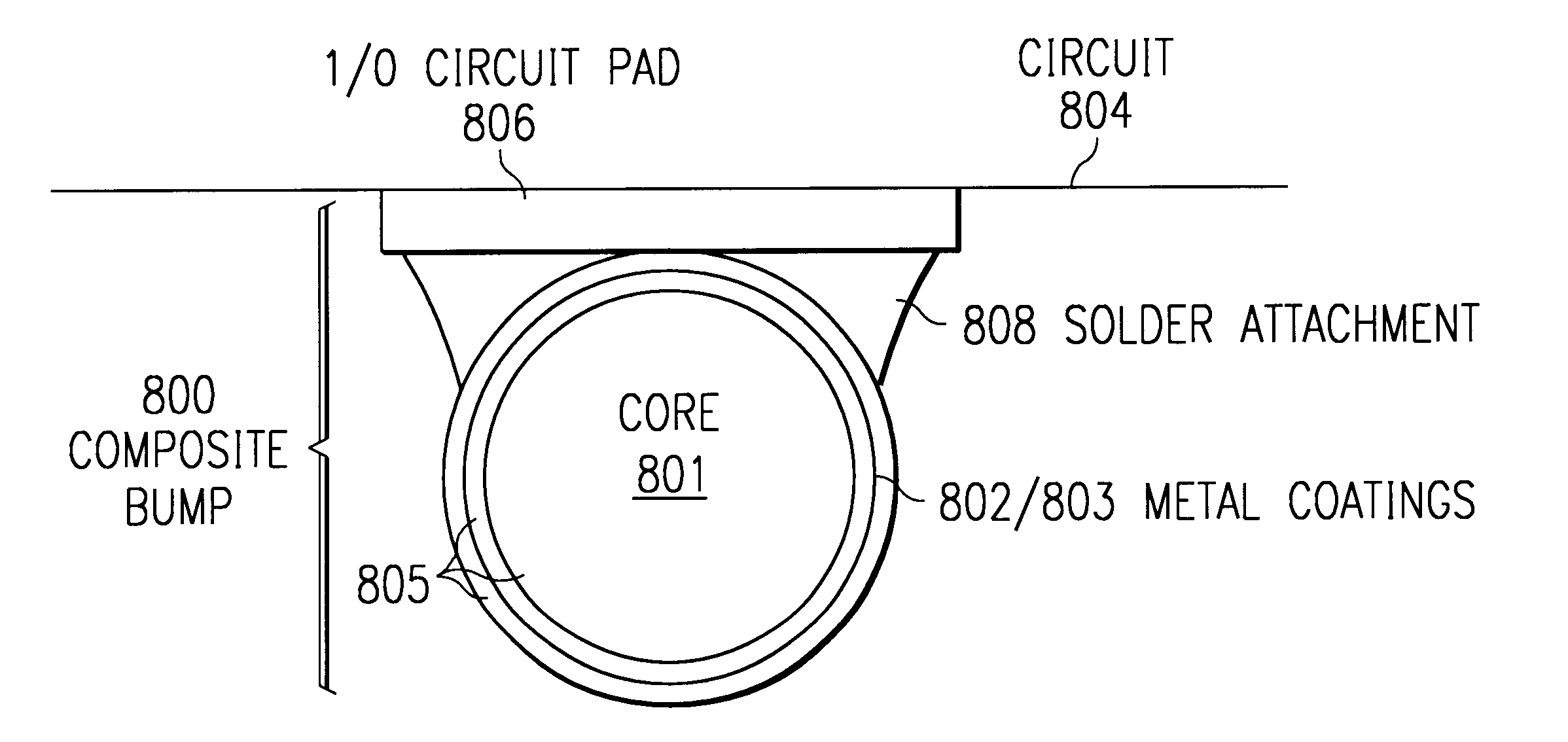

Composite connection structure and method of manufacturing

InactiveUS6337445B1Improve reliability and performanceImprove thermal conductivityPrinted circuit assemblingFinal product manufactureContact padSolder paste

A bump connection structure and a method of attachment to integrated circuits or packages is provided which comprises a prefabricated core structure coated with solderable metal layers to form a composite bump. Said composite bump is aligned to contact pads of the chip or package which have been coated with solder paste, and the assembly heated to form a metallurgical bond. The prefabricated core structures are comprised of metal, plastic or ceramic of the size and dictated by package standards. The connection structure is preferably lead free.

Owner:TEXAS INSTR INC

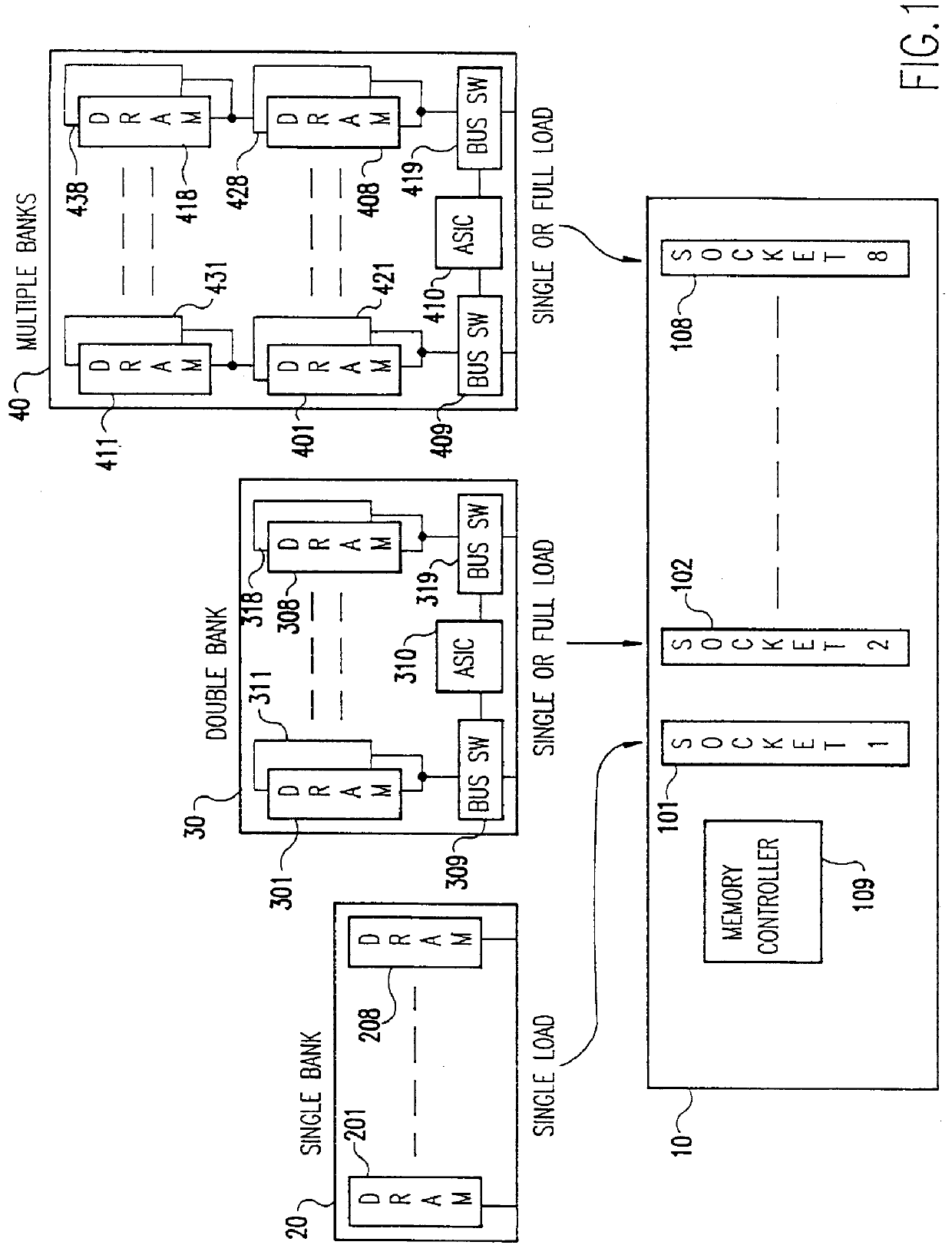

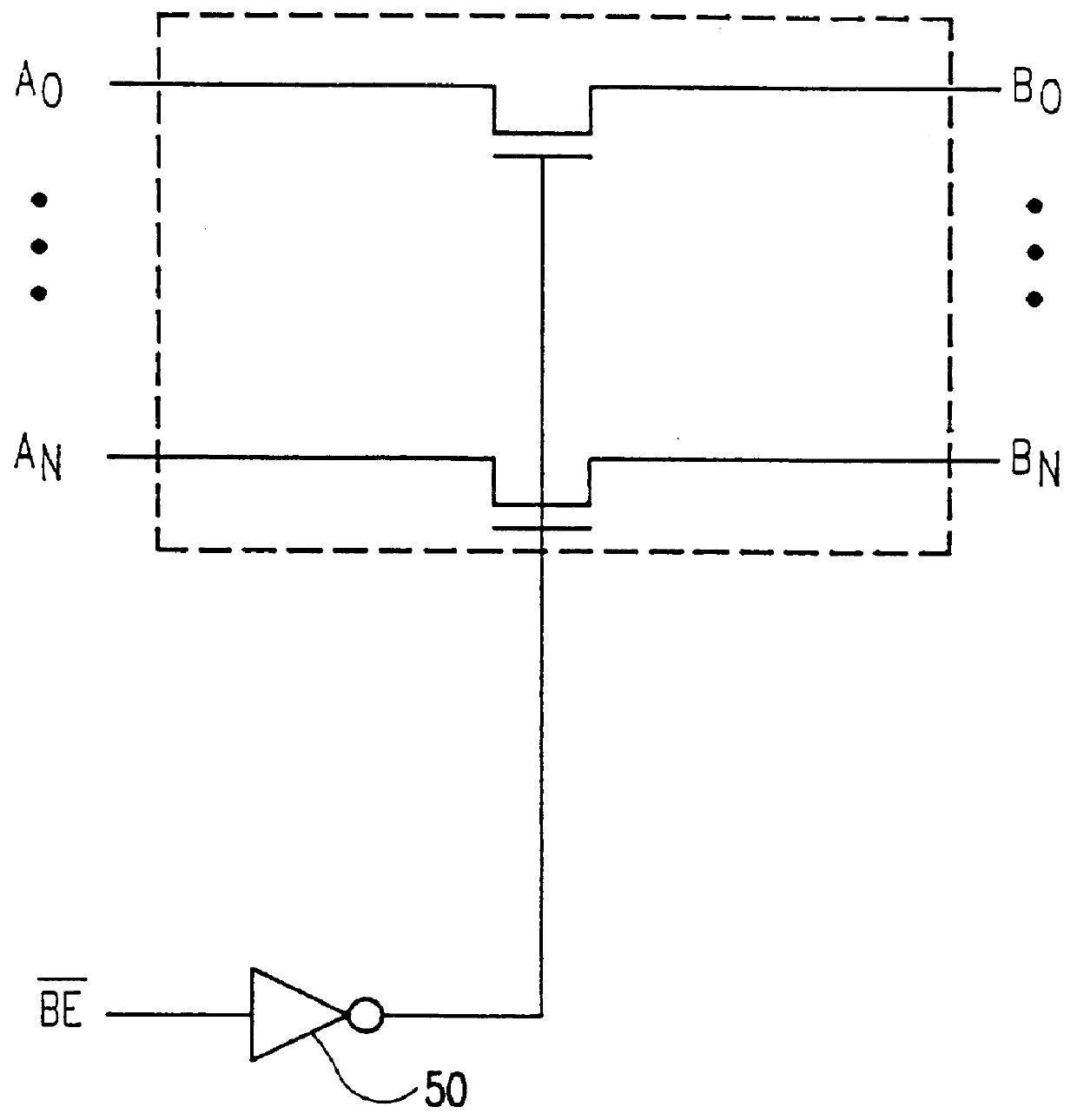

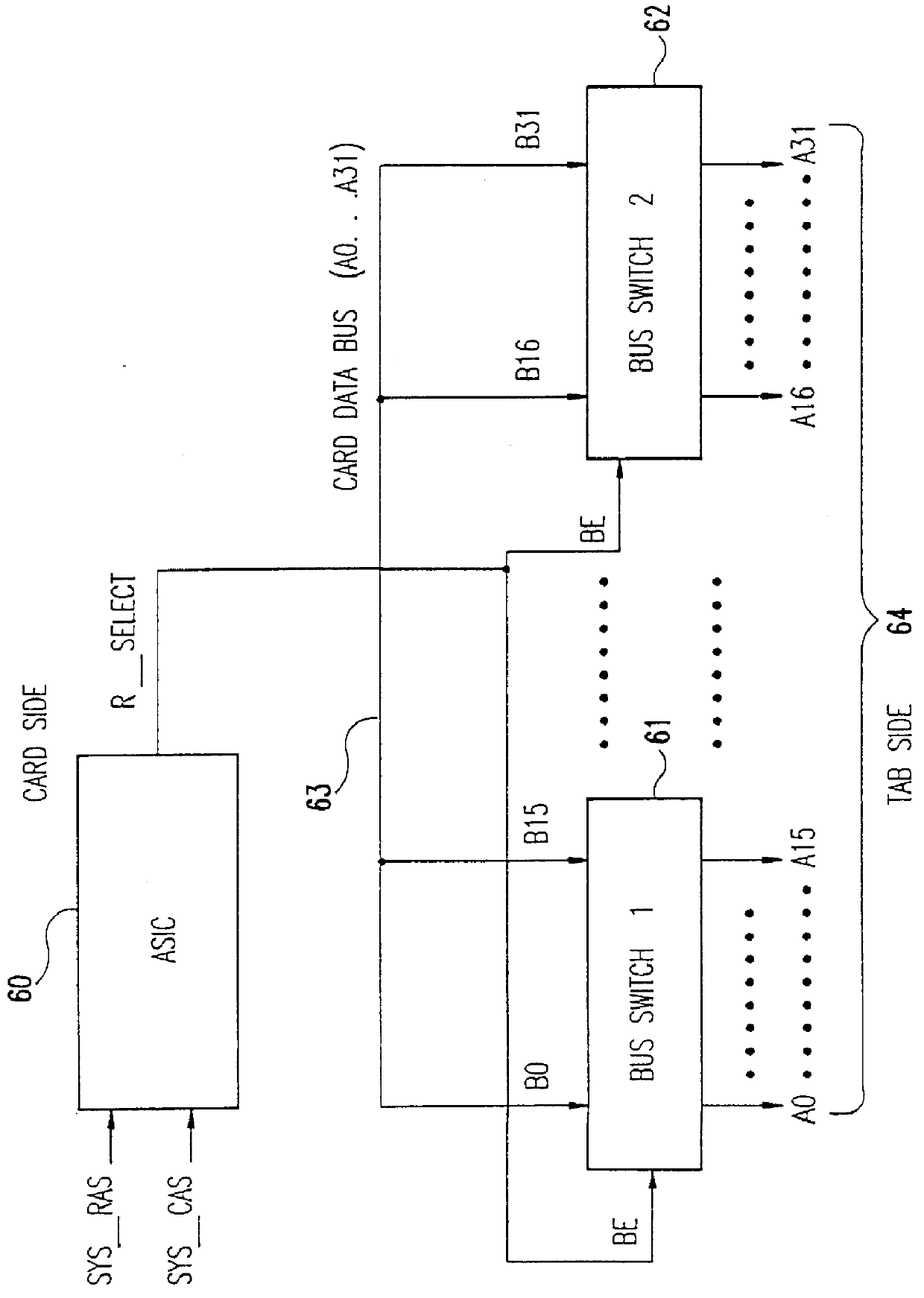

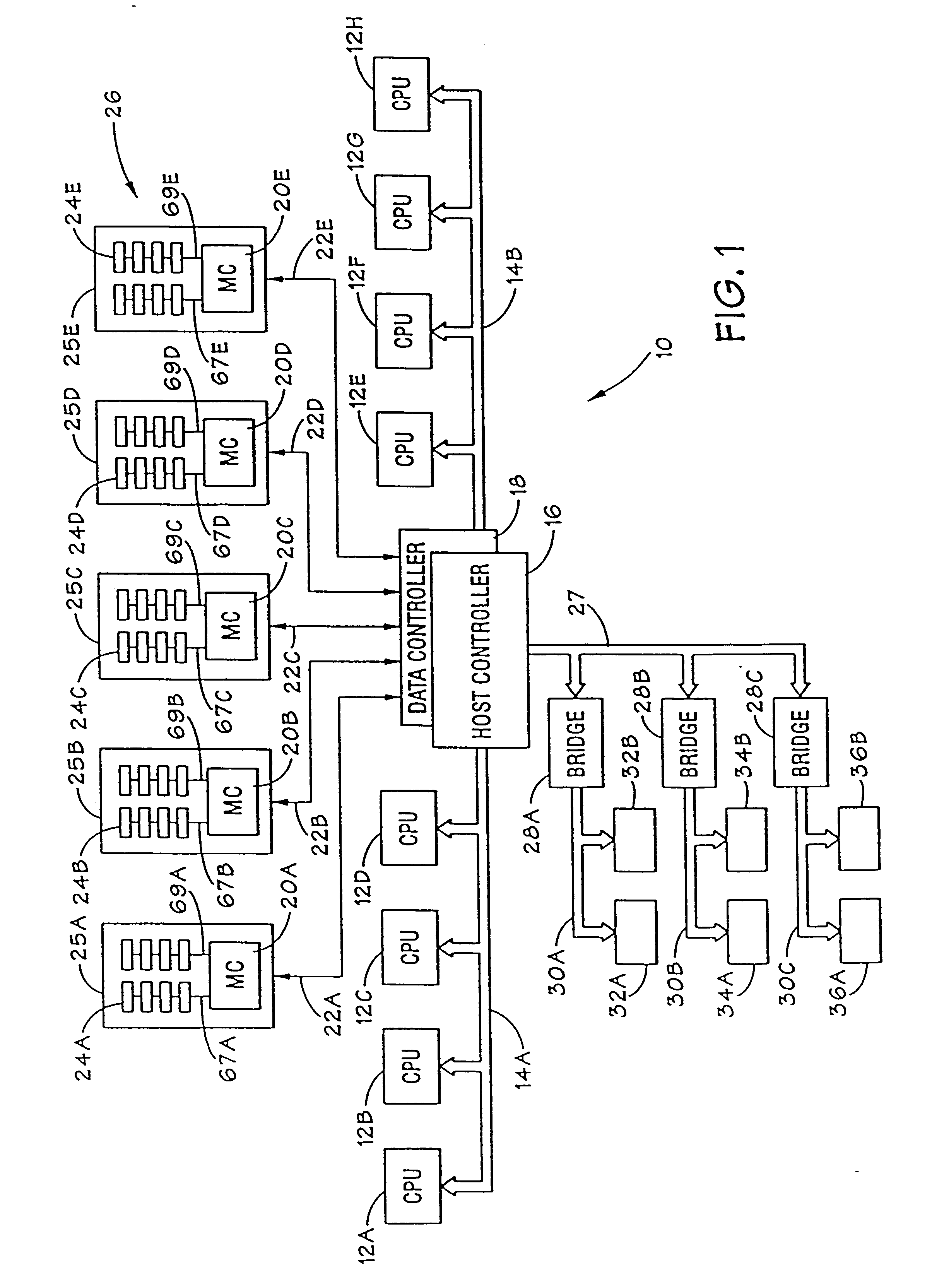

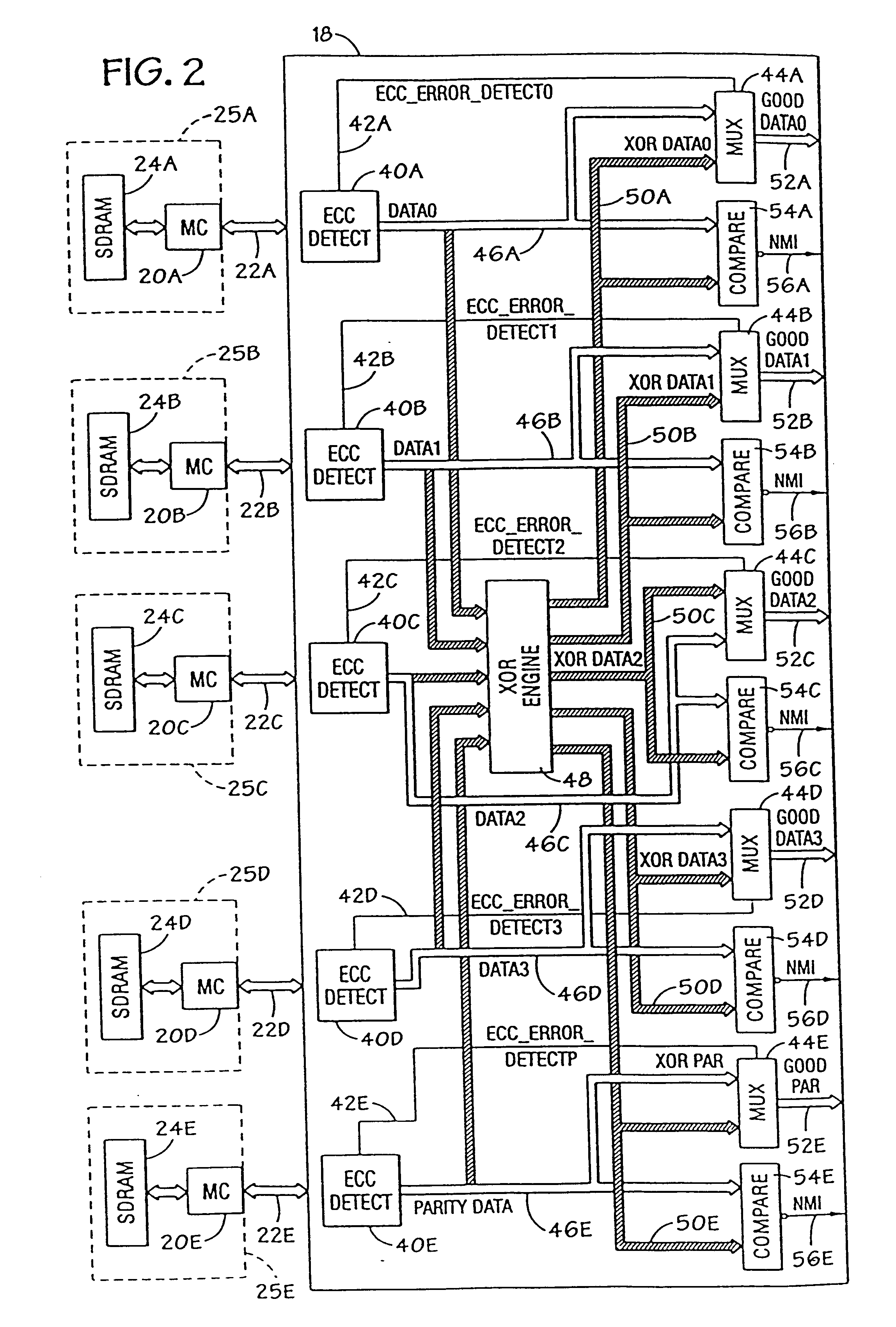

High density memory module with in-line bus switches being enabled in response to read/write selection state of connected RAM banks to improve data bus performance

InactiveUS6070217AMaximize memory densityReduce signal reflectionMemory adressing/allocation/relocationSolid-state devicesCapacitanceBiological activation

Data line loading on high density modules with multiple DRAMs is minimized permitting the maximum memory density of systems of otherwise limited density to be increased without an ensuing performance degradation due to data line capacitive loading. First the single or dual in-line memory module (SIMM or DIMM) includes in-line bus switches. The bus switches are between the SIMM or DIMM module tabs (system) and random access memory devices (RAM) and are either in a high impedance (off) or active state depending on the READ / WRITE state of the RAM. When in the high impedance state, the effective loading of the module is that of the bit switch device. The logic for determining the READ / WRITE state may be embedded in an application specific integrated circuit (ASIC) that monitors bus activity and controls activation of the bus switches, be provided by a memory controller or, generated by the RAM itself. The bus switches are active when the RAM is performing a read or a write and inactive otherwise. The RAM is Fast Page Mode (FPM) and Extended Data Output (EDO) or Synchronous DRAM (SDRAM).

Owner:IBM CORP

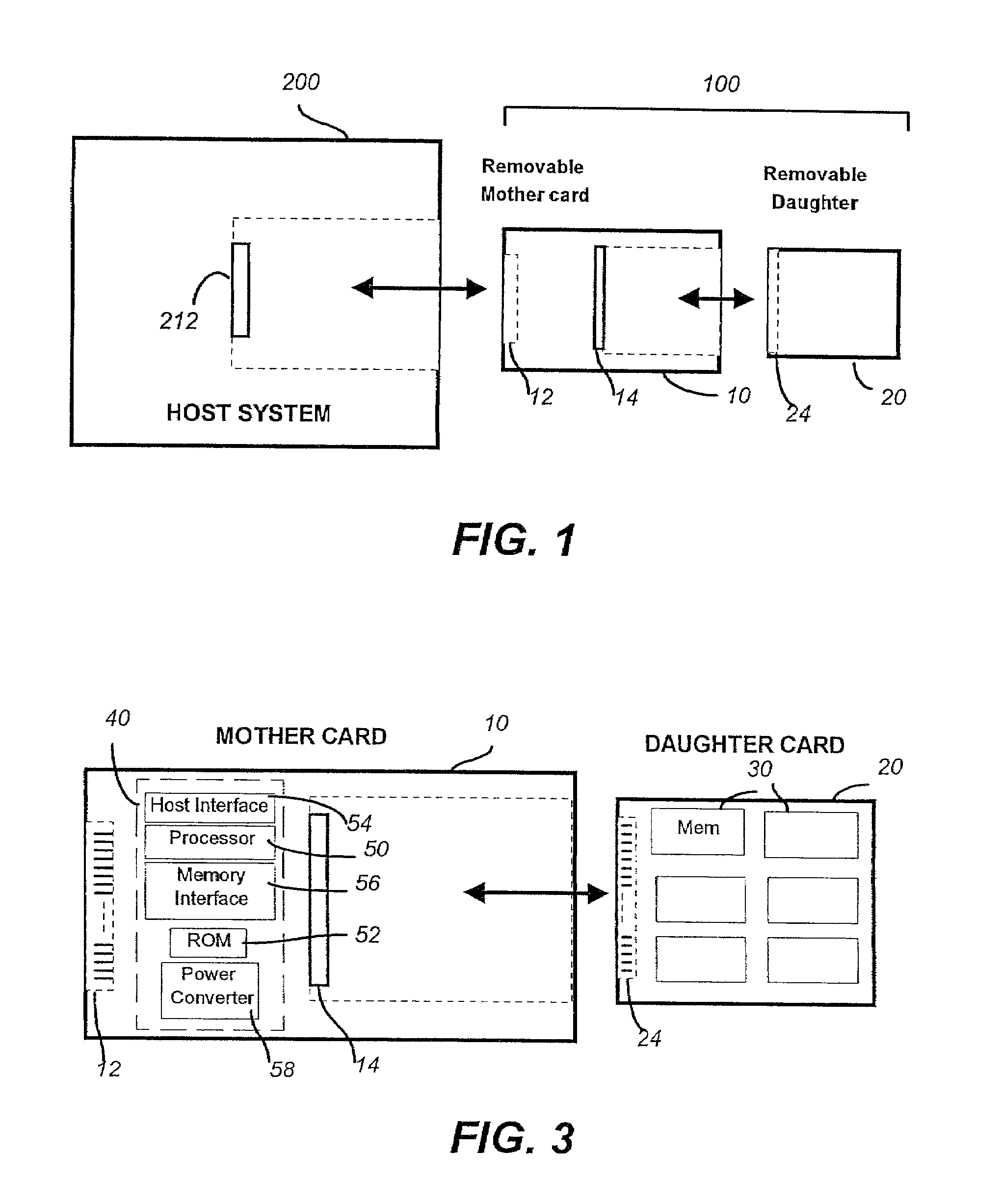

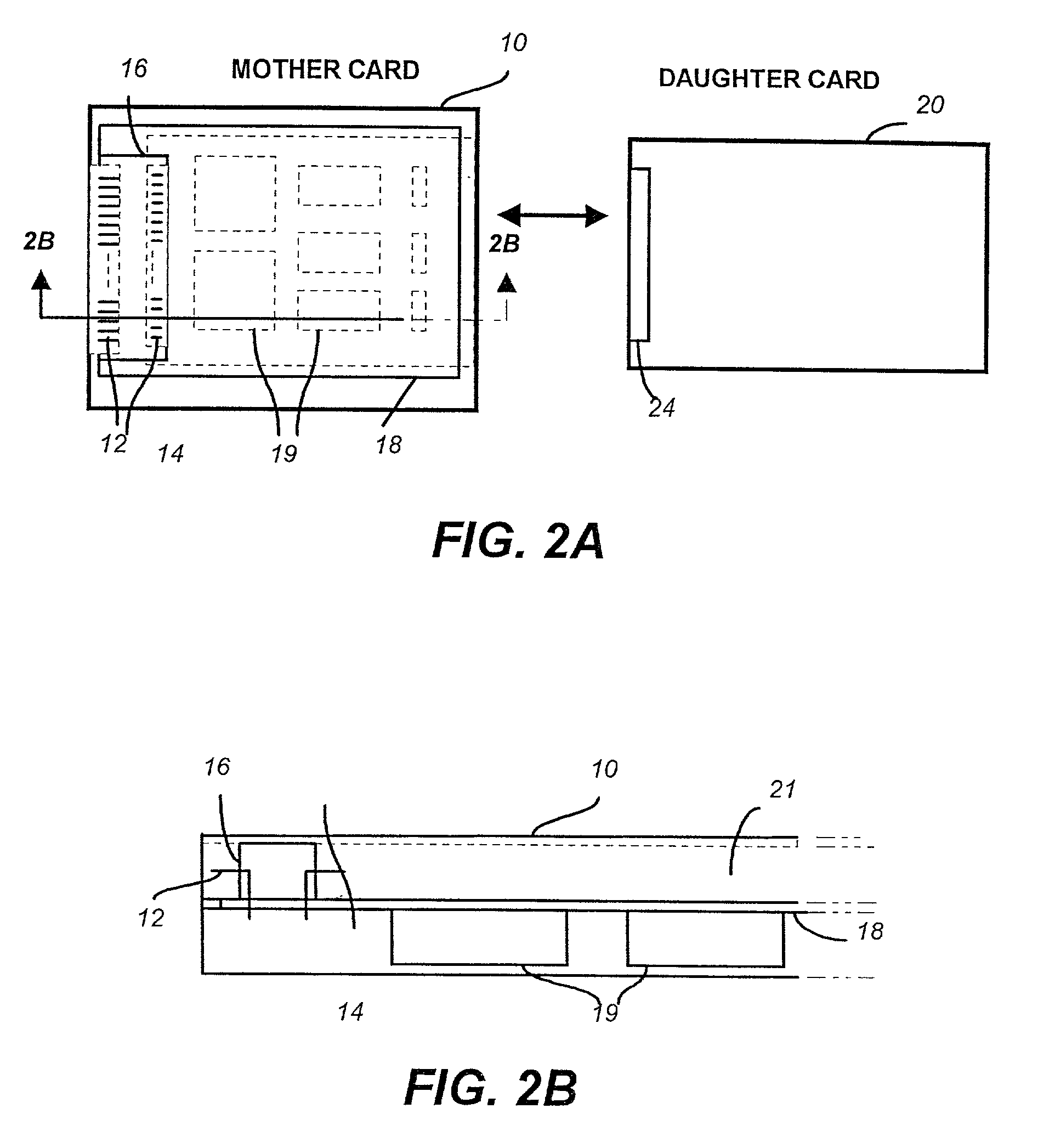

Removable mother/daughter peripheral card

InactiveUS7137011B1Add and decrease memory capacityMore cost-effective memory systemCoupling device connectionsSubstation/switching arrangement detailsFloppy diskDaughterboard

A peripheral card having a Personal Computer (“PC”) card form factor and removably coupled externally to a host system is further partitioned into a mother card portion and a daughter card portion. The daughter card is removably coupled to the mother card. In the preferred embodiment, a low cost flash “floppy” is accomplished with the daughter card containing only flash EEPROM chips and being controlled by a memory controller residing on the mother card. Other aspects of the invention includes a comprehensive controller on the mother card able to control a predefined set of peripherals on daughter cards connectable to the mother card; relocation of some host resident hardware to the mother card to allow for a minimal host system; a mother card that can accommodate multiple daughter cards; daughter cards that also operates directly with hosts having embedded controllers; daughter cards carrying encoded data and information for decoding it; and daughter cards with security features.

Owner:SANDISK TECH LLC

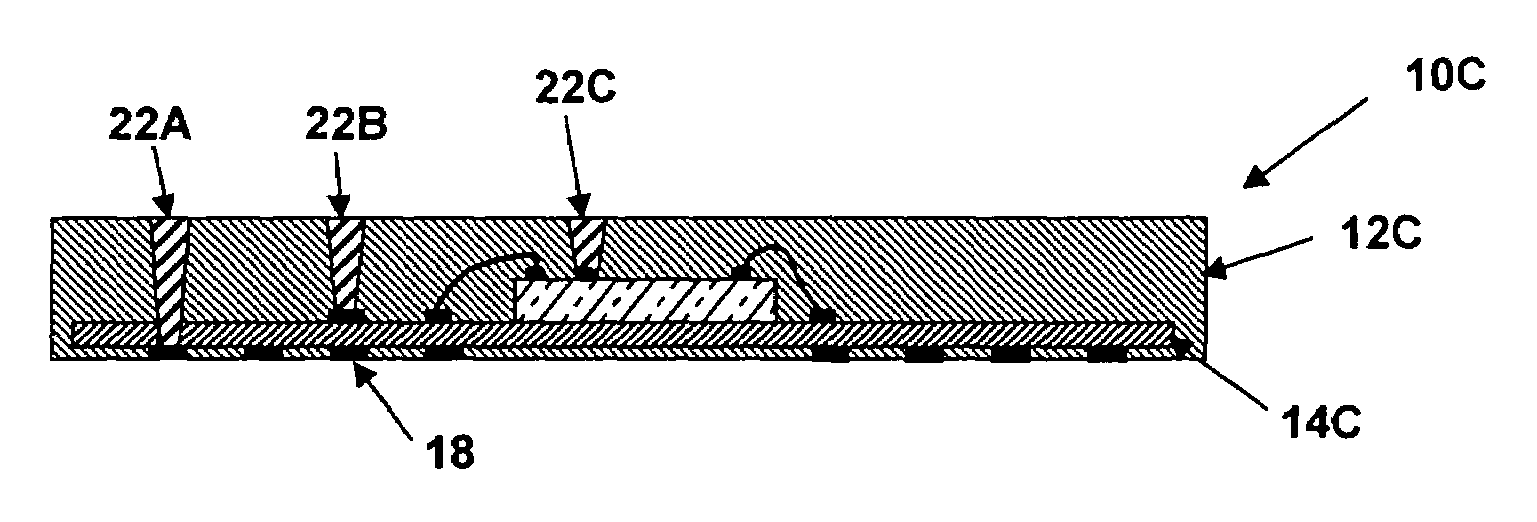

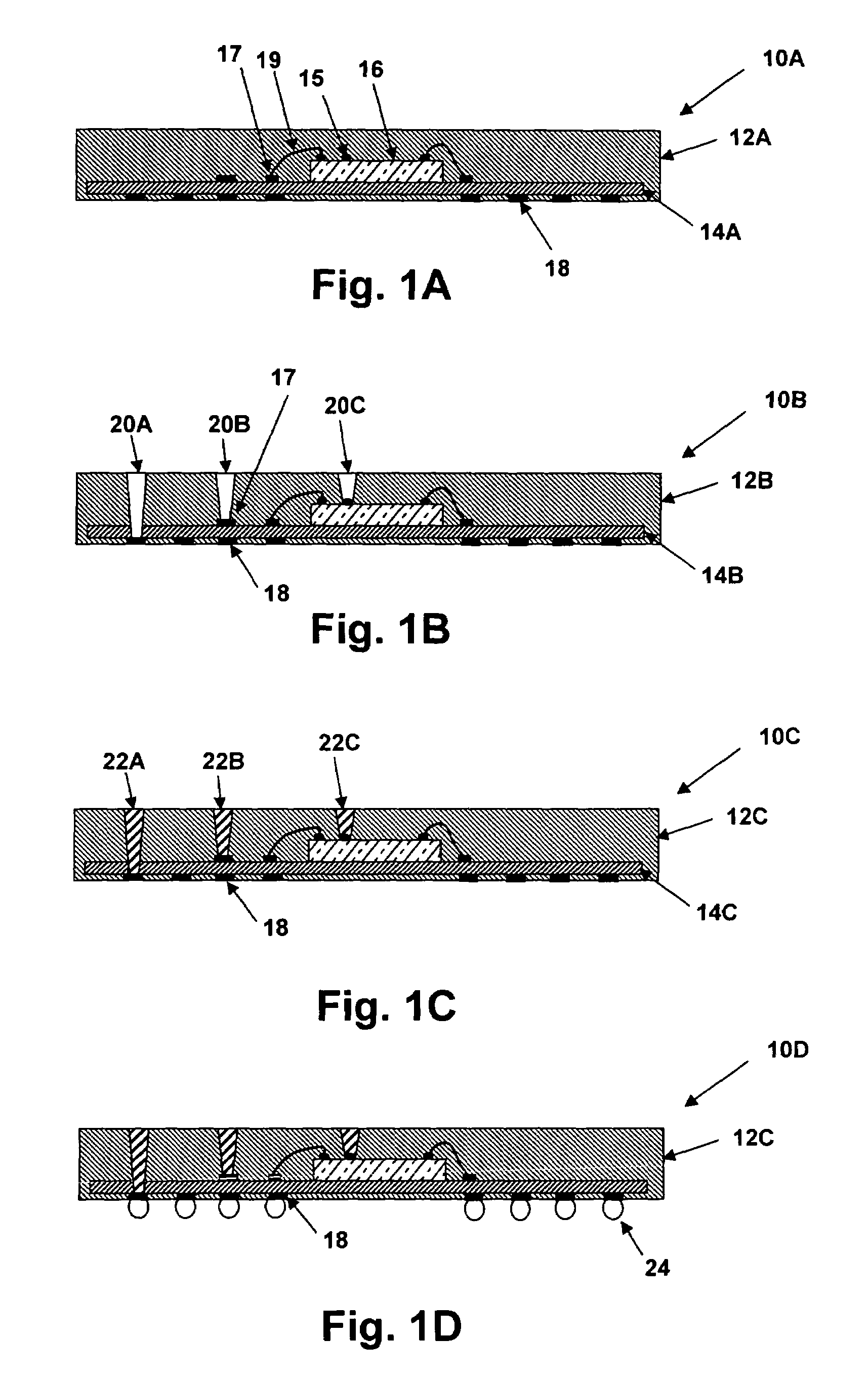

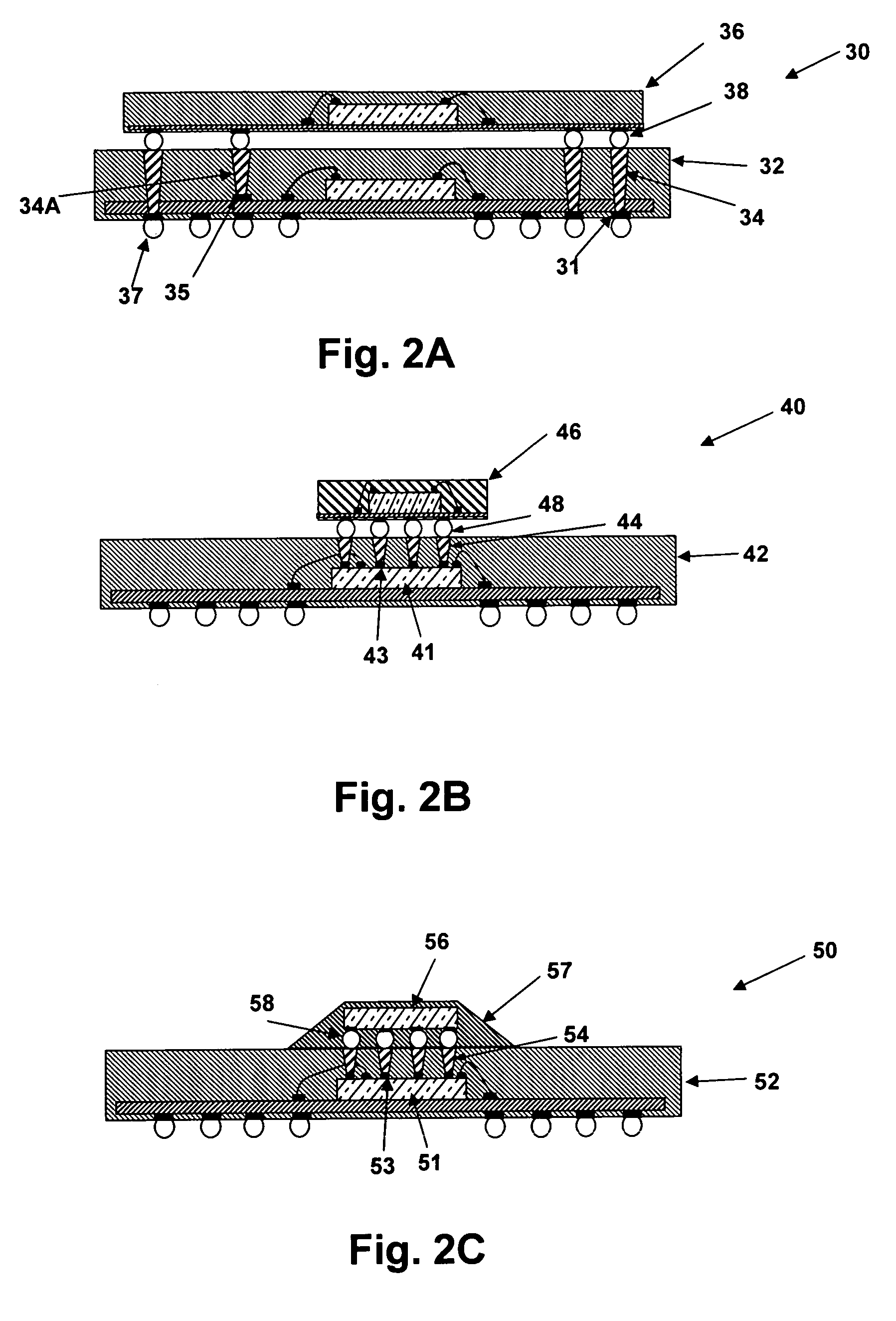

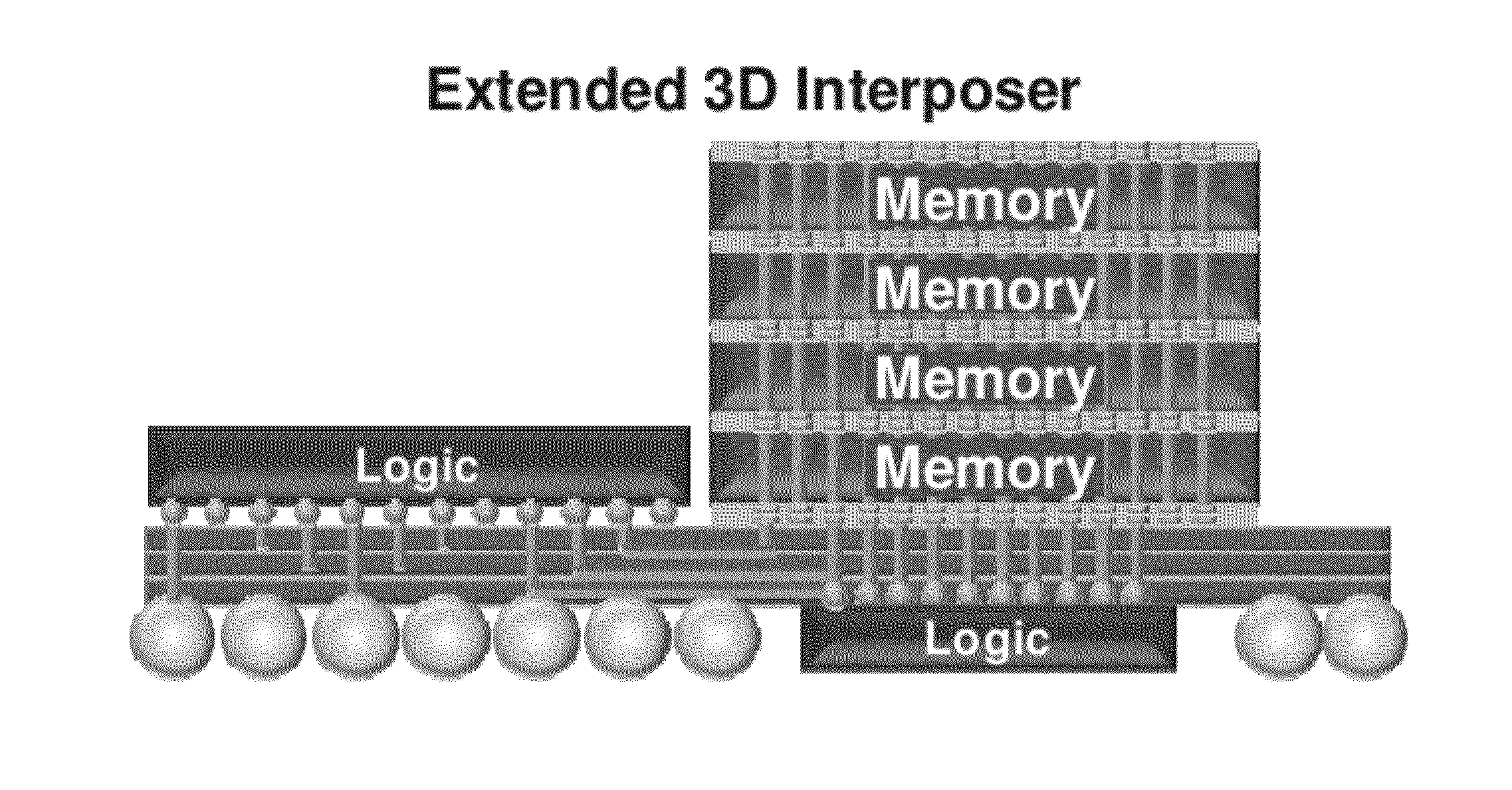

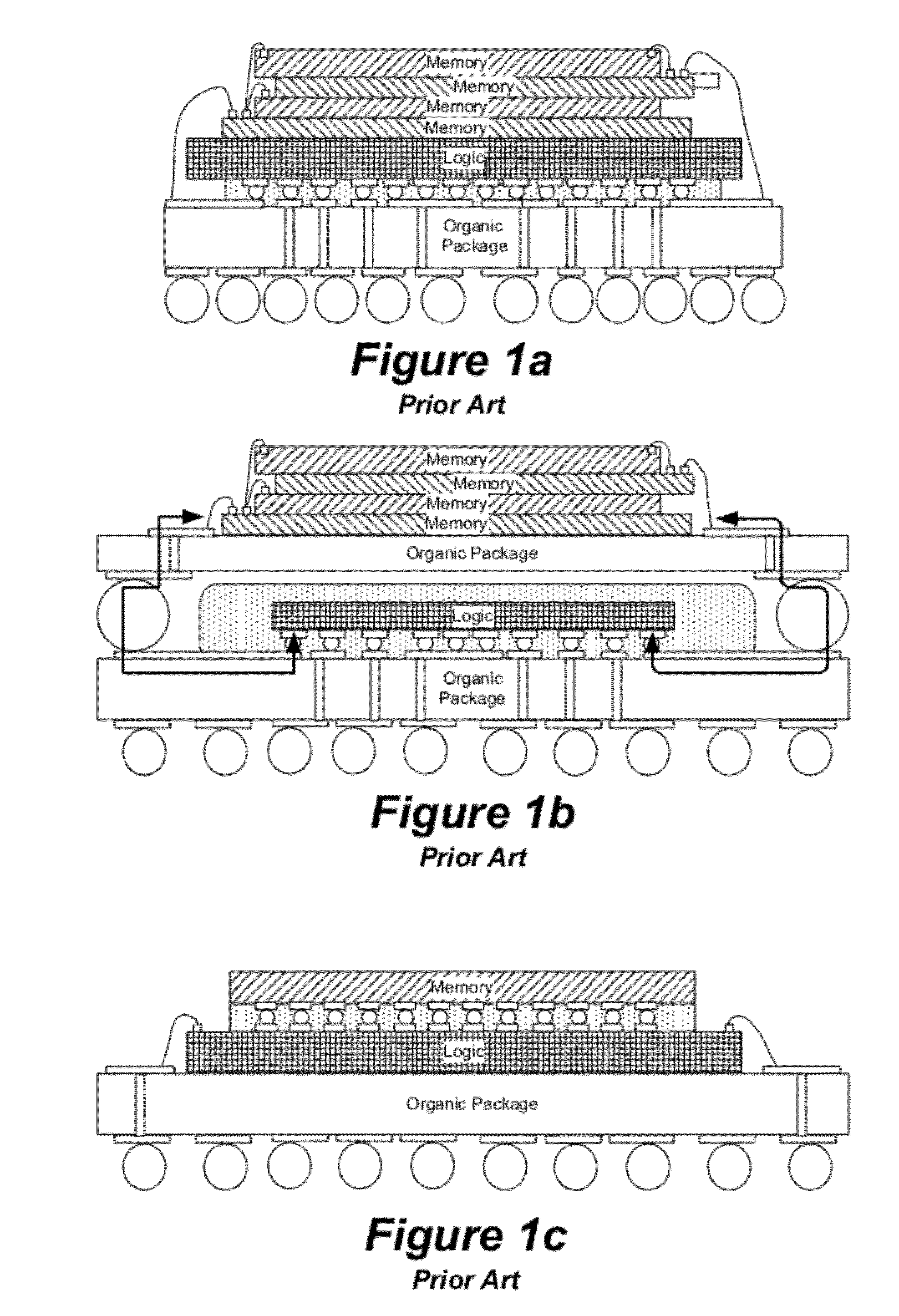

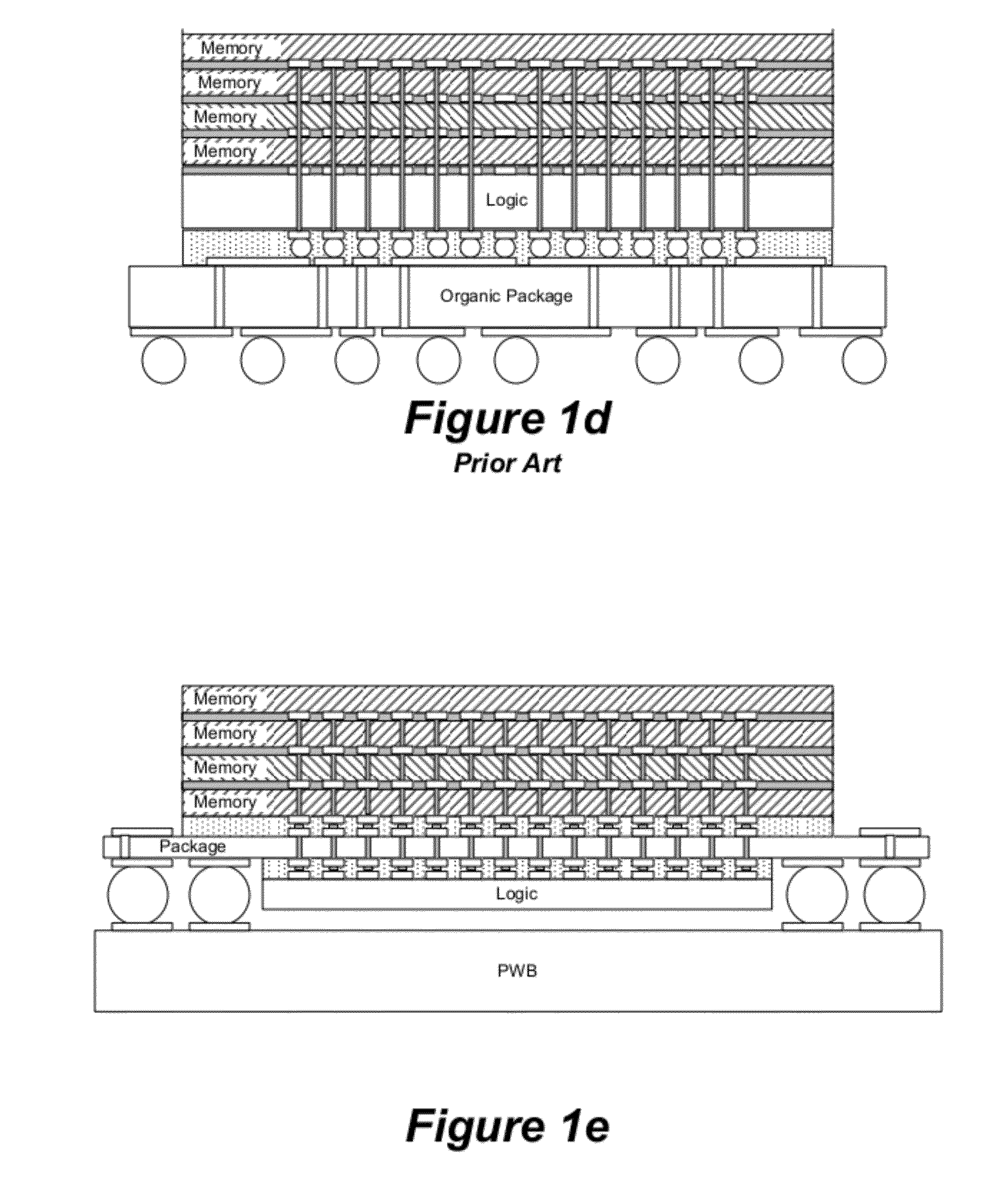

Ultra-thin interposer assemblies with through vias

ActiveUS20120106117A1Semiconductor/solid-state device detailsPrinted circuit aspectsGraphicsElectricity

A 3D interconnect structure comprising an ultra-thin interposer having a plurality of ultra-high density of through-via interconnections defined therein. The 3D interposer electrically connects first and second electronic devices in vertical dimension and has the same or similar through-via density as the first or second electronic devices it connects. The various embodiments of the interconnect structure allows 3D ICs to be stacked with or without TSVs and increases bandwidth between the two electronic devices as compared to other interconnect structures of the prior art. Further, the interconnect structure of the present invention is scalable, testable, thermal manageable, and can be manufactured at relatively low costs. Such a 3D structure can be used for a wide variety of applications that require a variety of heterogeneous ICs, such as logic, memory, graphics, power, wireless and sensors that cannot be integrated into single ICs.

Owner:GEORGIA TECH RES CORP

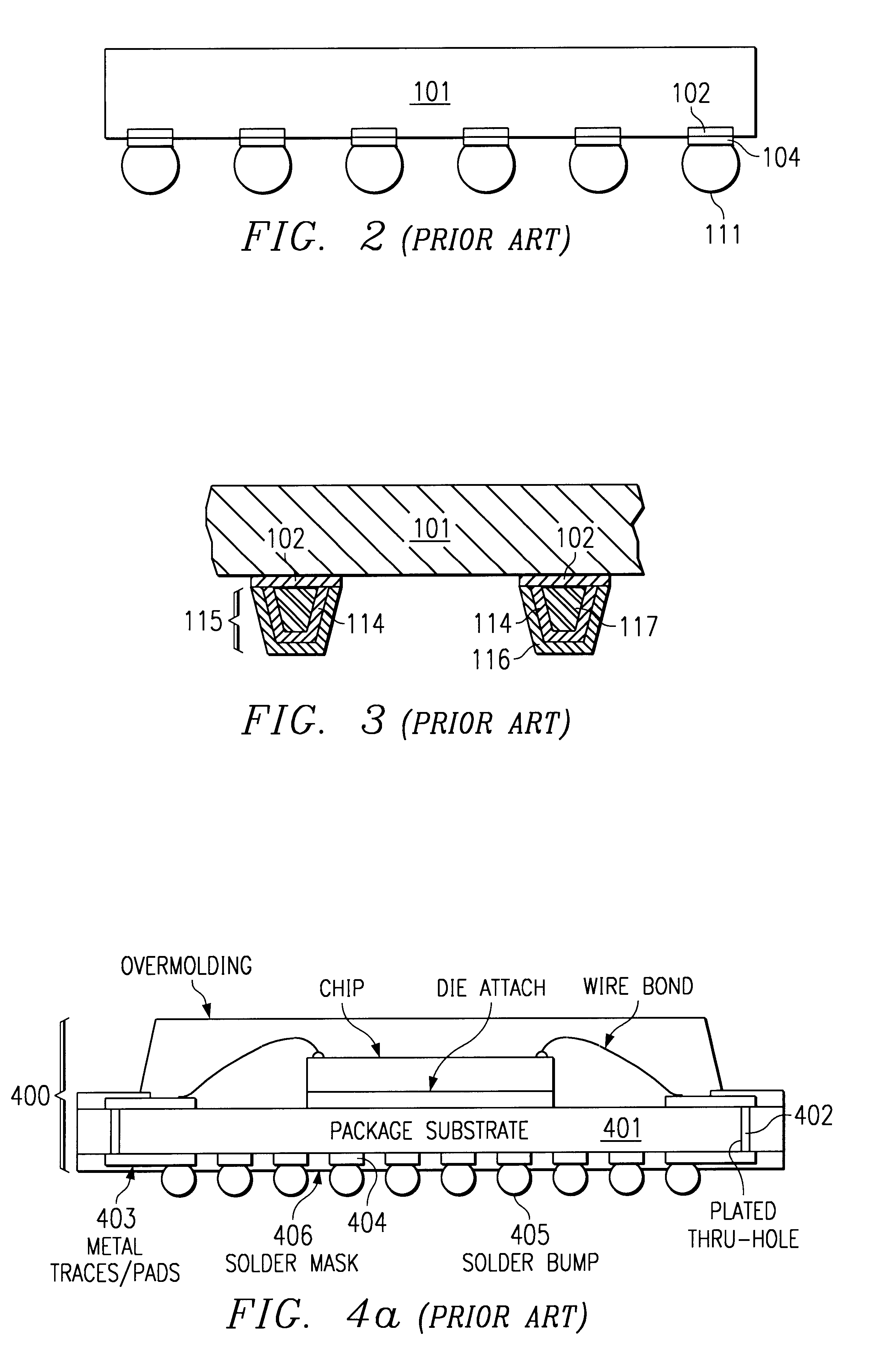

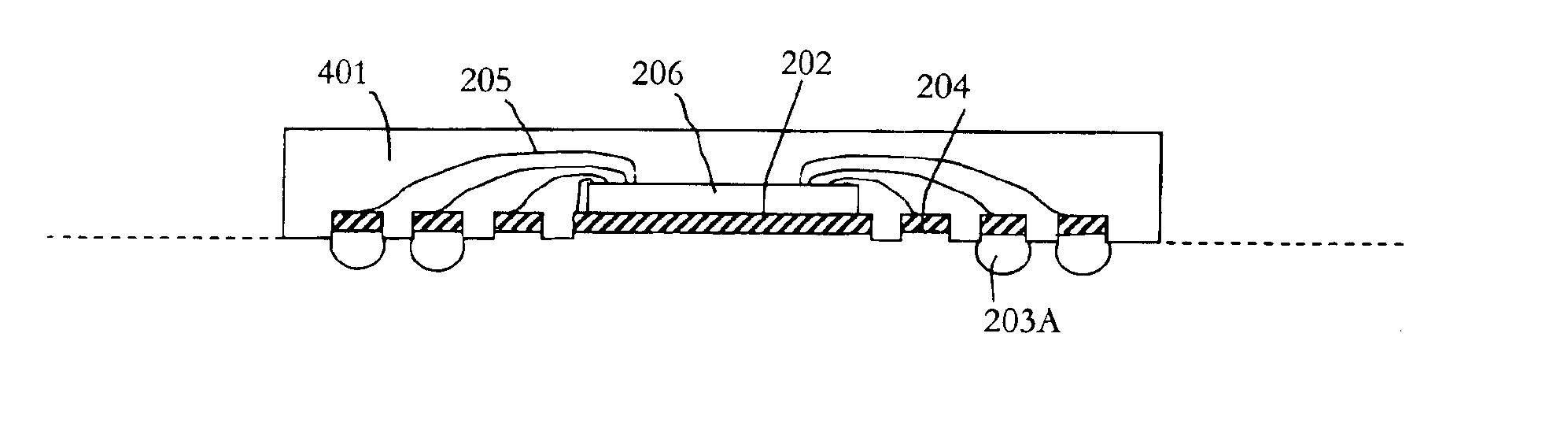

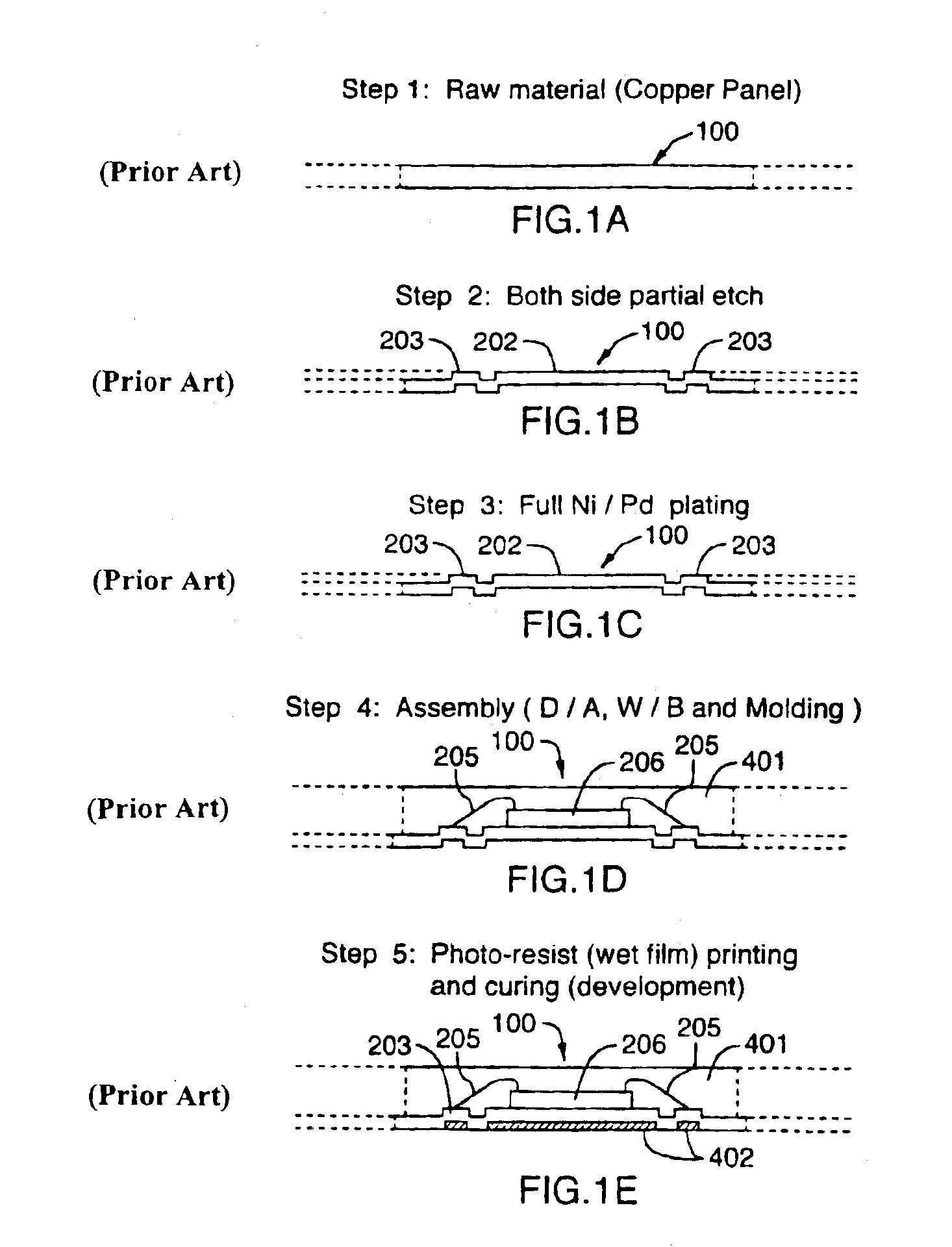

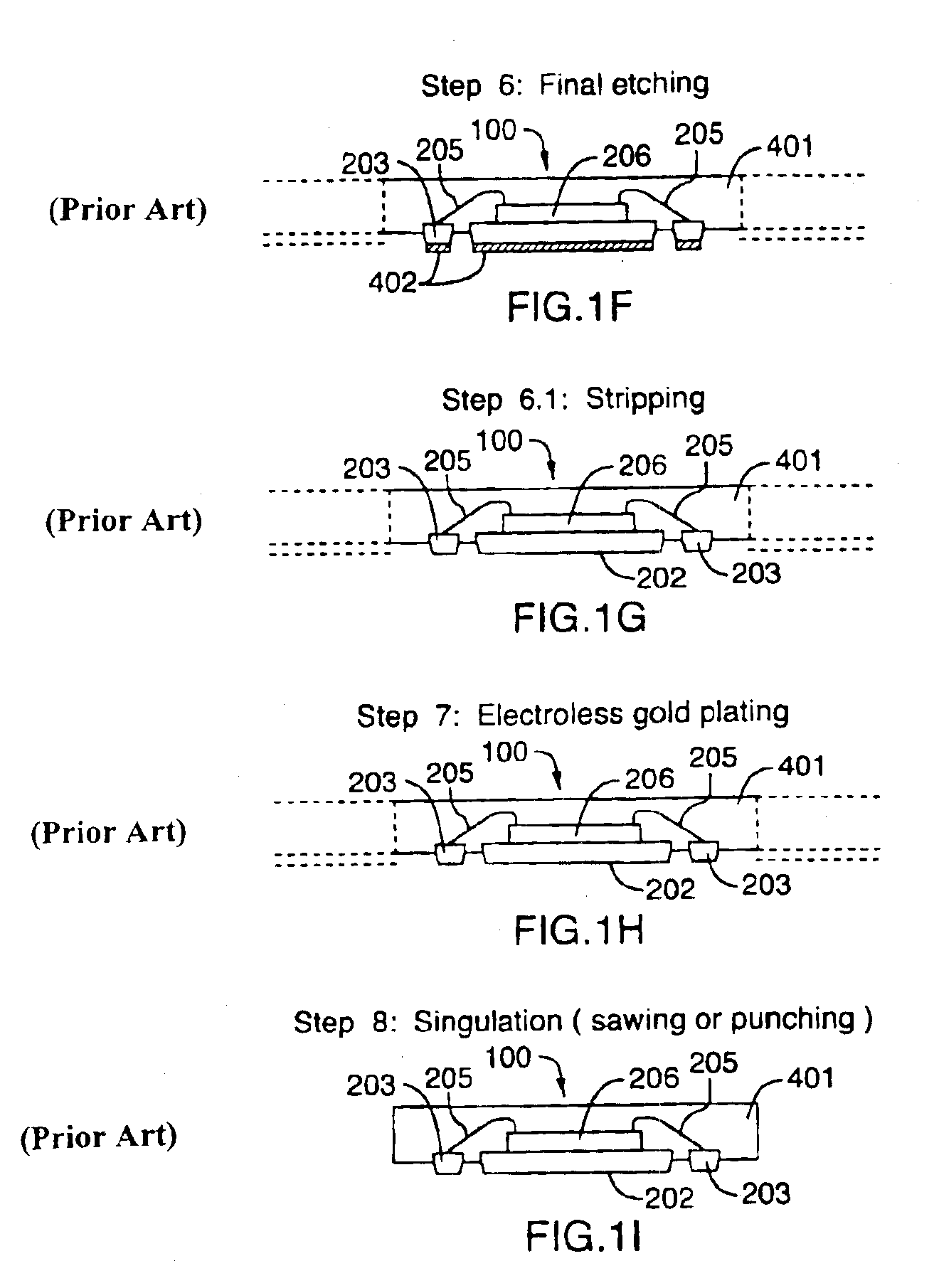

Leadless plastic chip carrier with etch back pad singulation

InactiveUS6933594B2Improve interlockEasy alignmentSemiconductor/solid-state device detailsSolid-state devicesEtchingPunching

A leadless plastic chip carrier is constructed by half etching one or both sides of the package design onto a leadframe strip so as to create unique design features such as power and / or ground ring surrounding the die attach pad, interlocking rivet head construction for the contact pads, and an interlocking pattern for the die attach pad. After wire bonding and molding, a further etching is performed to isolate and expose contact pads. Singulation of individual chip packages from the leadframe strip is then performed by saw singulation or die punching.

Owner:UTAC HEADQUARTERS PTE LTD

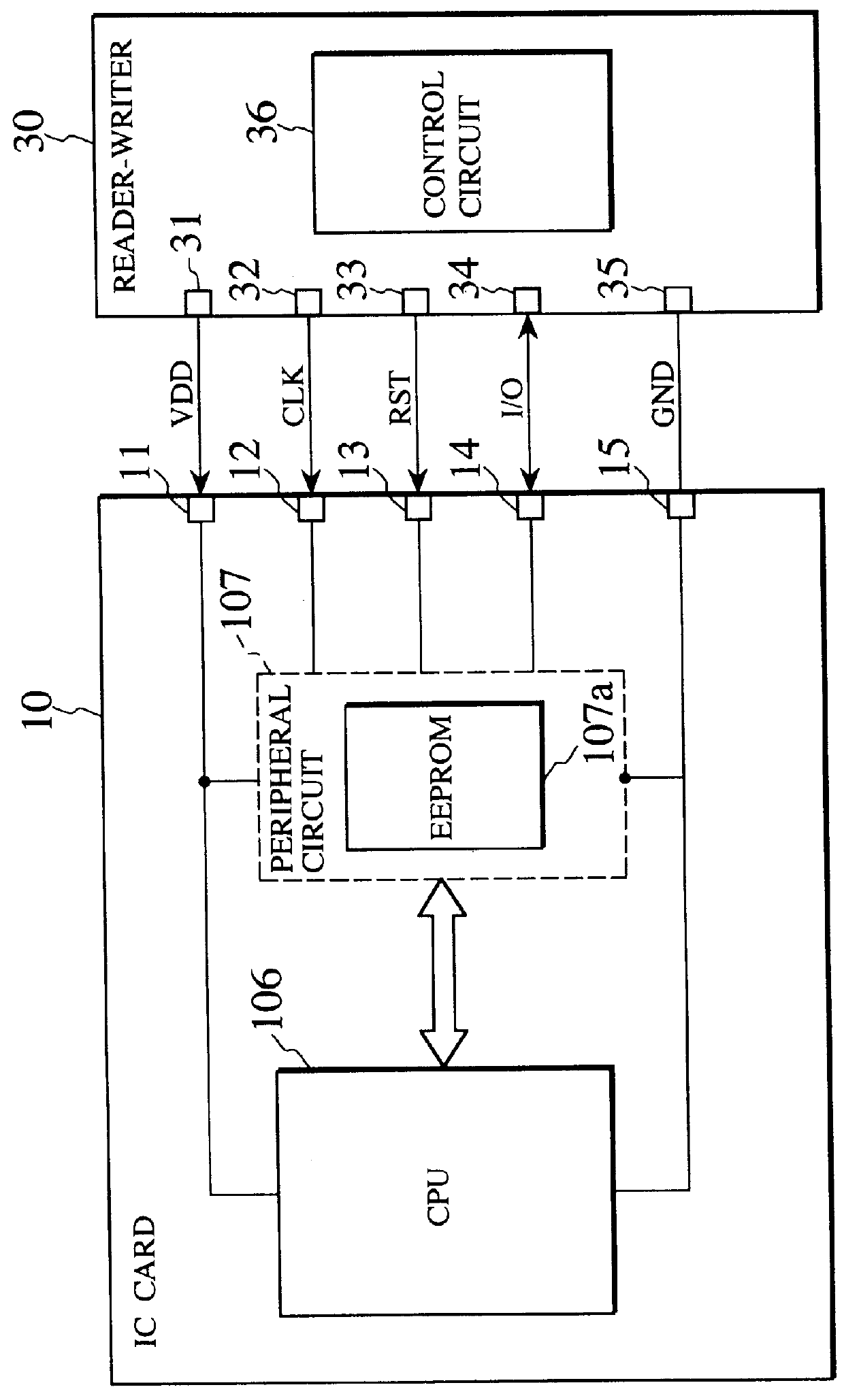

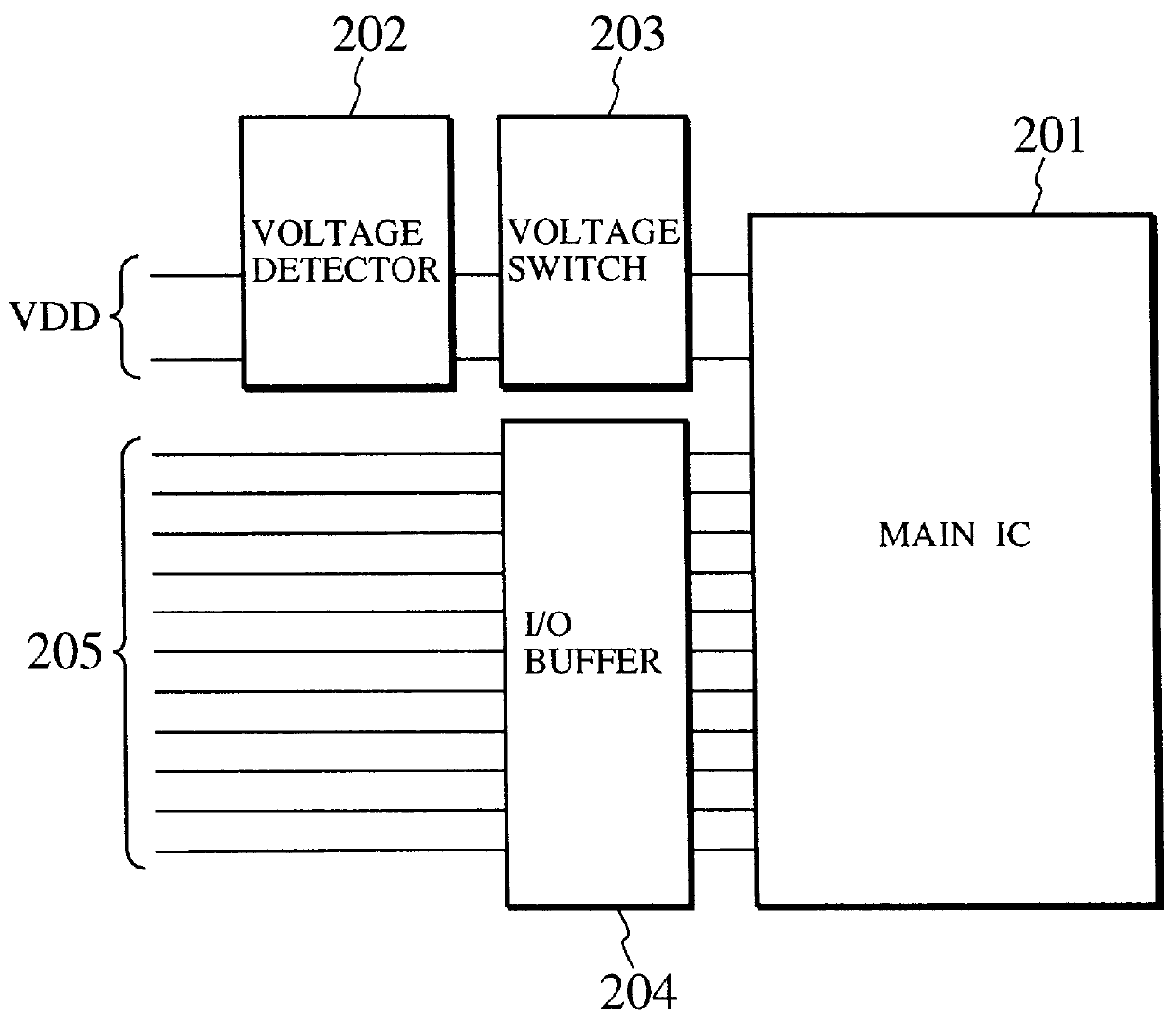

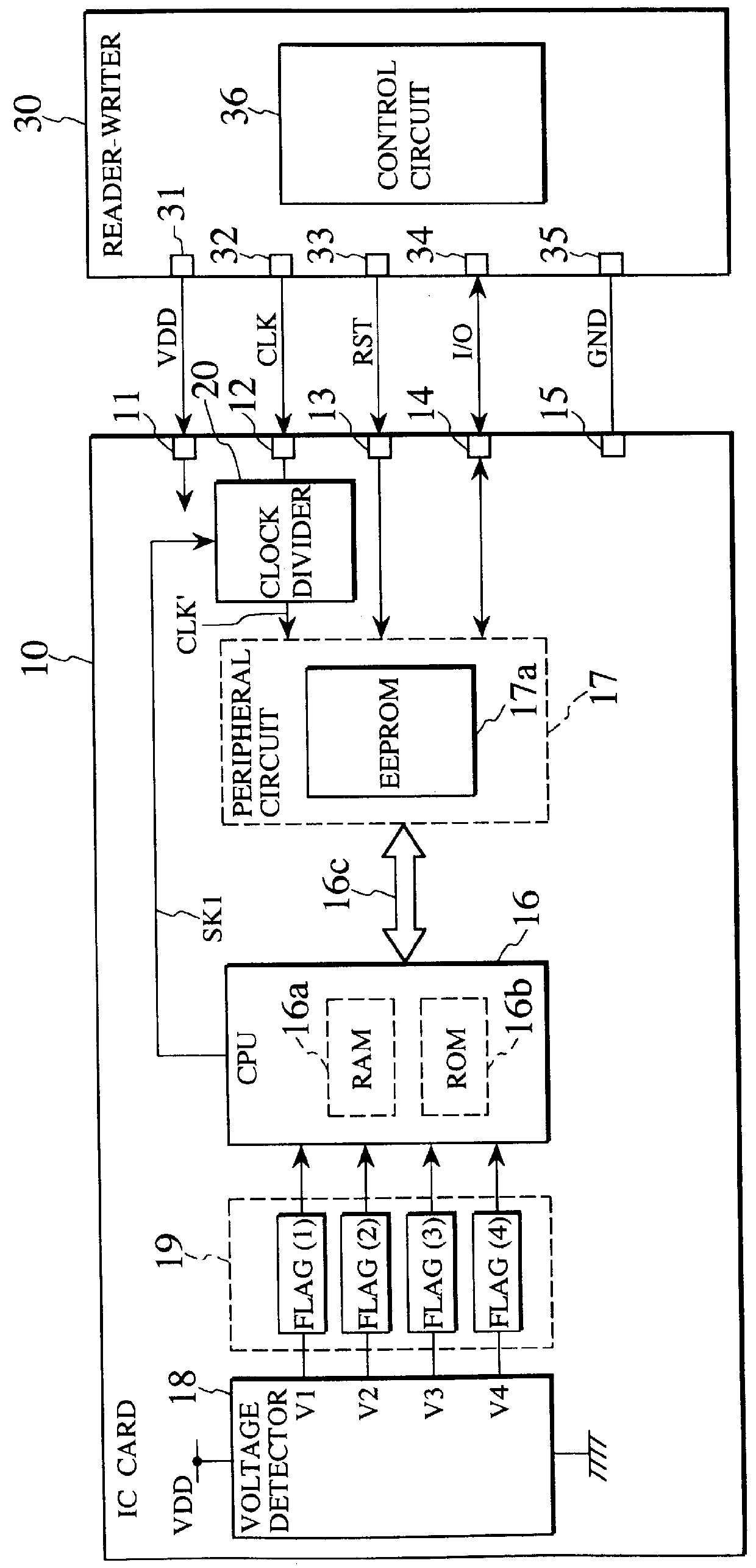

IC card compatible with different supply voltages, IC card system comprising the same, and IC for the IC card

InactiveUS6035357AMemory record carrier reading problemsCo-operative working arrangementsEngineeringPeripheral

An IC card has a peripheral circuit and a CPU. The peripheral circuit has a memory for storing data. The CPU controls various operations including an access operation of the memory. The IC card receives a supply voltage and a clock signal from an external unit. The IC card has a detector for detecting the supply voltage, a tester for testing the detected supply voltage, and an adjuster for adjusting the peripheral circuit according to a result of the voltage test. With these arrangements, the IC card stably operates on a wide range of supply voltages and is capable of coping with a fluctuation in the supply voltage. The tester may be incorporated in the CPU as one of functions thereof or may be realized by hardware that is arranged outside the CPU. The IC card and external unit constitute an IC card system.

Owner:KK TOSHIBA

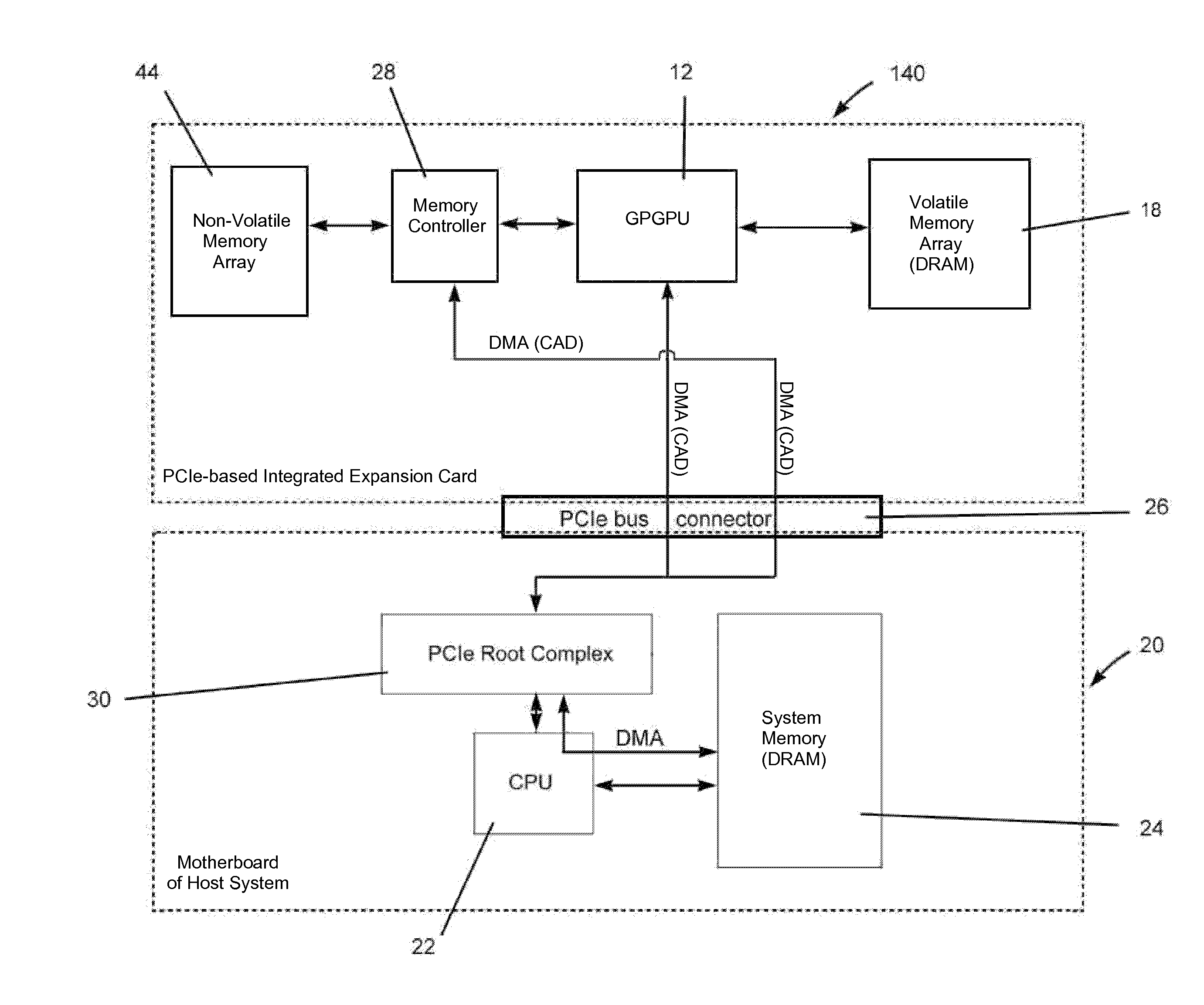

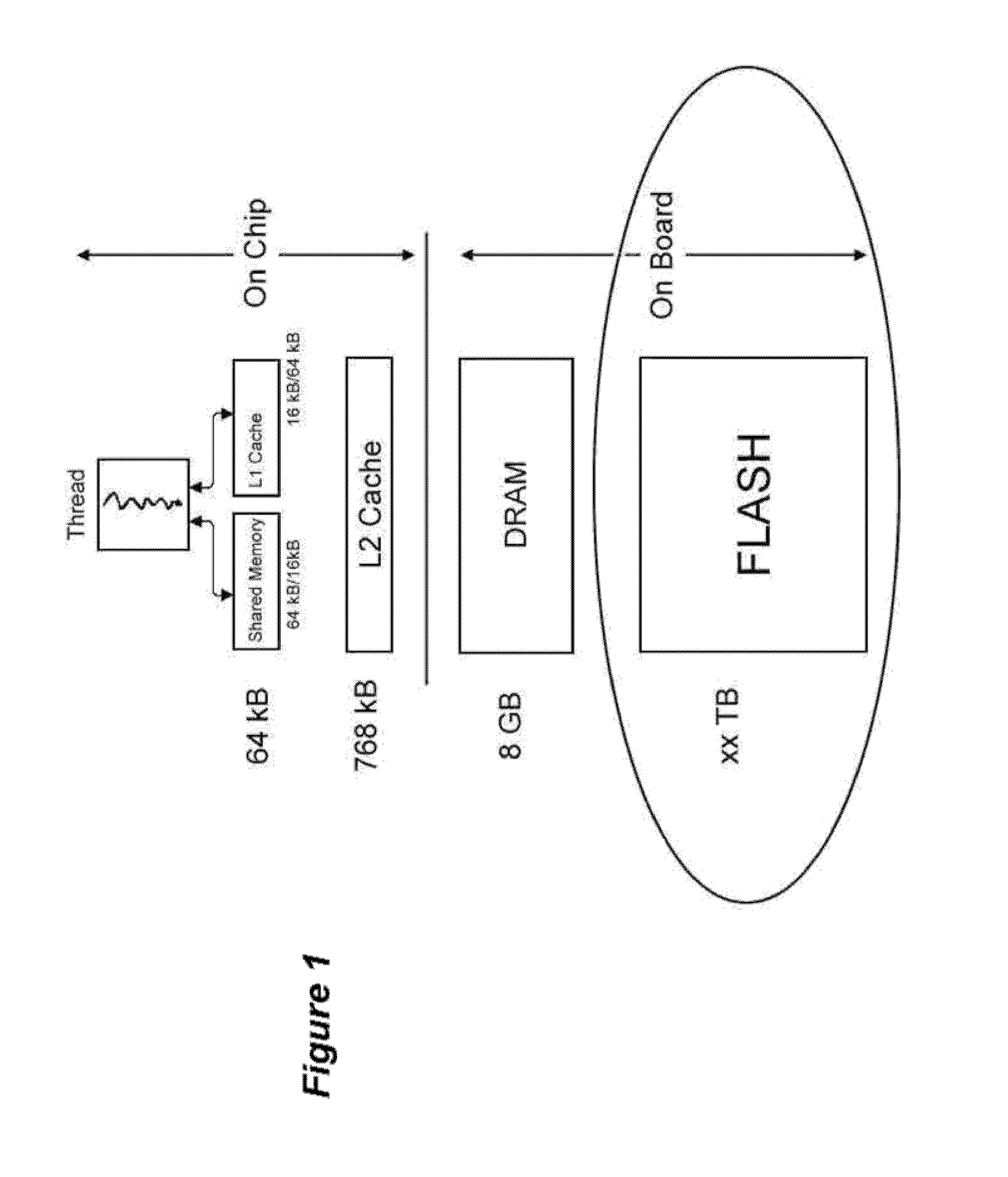

Integrated storage/processing devices, systems and methods for performing big data analytics

ActiveUS20140129753A1Faster throughputComponent plug-in assemblagesElectric digital data processingGeneral purposeGraphics

Architectures and methods for performing big data analytics by providing an integrated storage / processing system containing non-volatile memory devices that form a large, non-volatile memory array and a graphics processing unit (GPU) configured for general purpose (GPGPU) computing. The non-volatile memory array is directly functionally coupled (local) with the GPU and optionally mounted on the same board (on-board) as the GPU.

Owner:KIOXIA CORP

Probe card assembly

InactiveUS6838893B2Easy to disassembleEffective shieldingSemiconductor/solid-state device testing/measurementFinal product manufactureProbe cardTransformer

In a probe card assembly, a series of probe elements can be arrayed on a silicon space transformer. The silicon space transformer can be fabricated with an array of primary contacts in a very tight pitch, comparable to the pitch of a semiconductor device. One preferred primary contact is a resilient spring contact. Conductive elements in the space transformer are routed to second contacts at a more relaxed pitch. In one preferred embodiment, the second contacts are suitable for directly attaching a ribbon cable, which in turn can be connected to provide selective connection to each primary contact. The silicon space transformer is mounted in a fixture that provides for resilient connection to a wafer or device to be tested. This fixture can be adjusted to planarize the primary contacts with the plane of a support probe card board.

Owner:FORMFACTOR INC

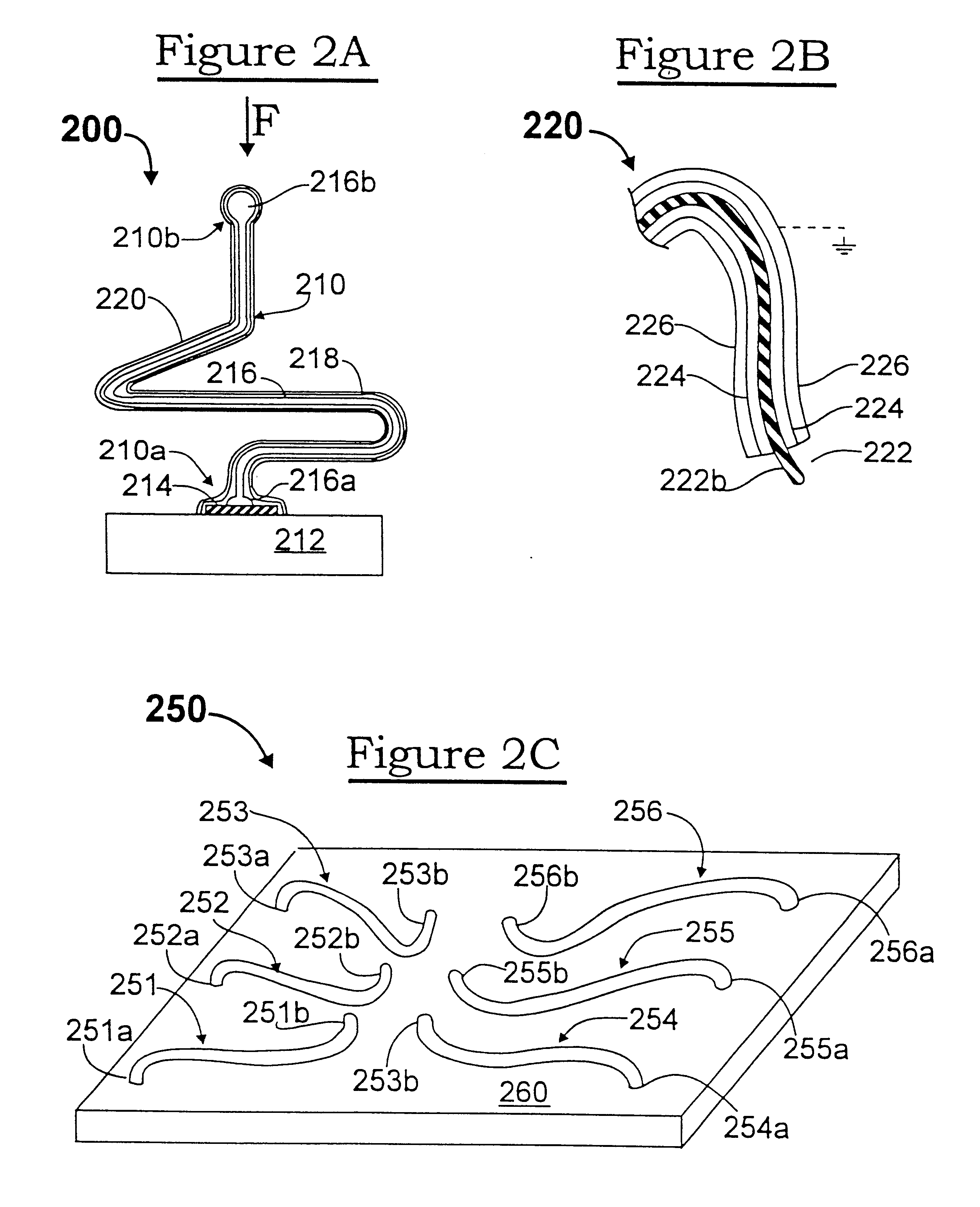

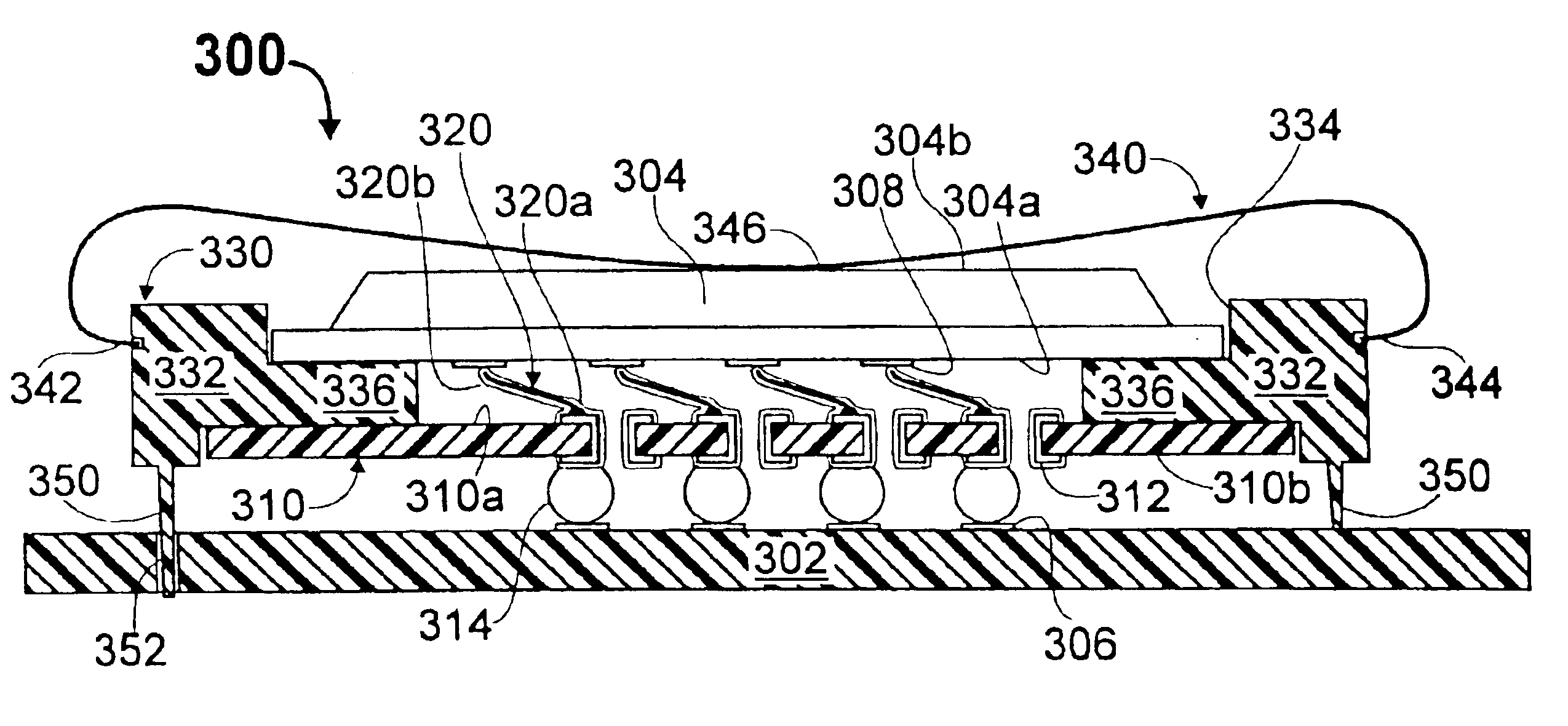

Methods of removably mounting electronic components to a circuit board, and sockets formed by the methods

InactiveUS6913468B2Easy to disassembleEffective shieldingSemiconductor/solid-state device testing/measurementFinal product manufactureSurface mountingSolder ball

Surface-mount, solder-down sockets are described which permit electronic components such as semiconductor packages to be releasably mounted to a circuit board. Generally, the socket includes resilient contact structures extending from a top surface of a support substrate, and solder-ball (or other suitable) contact structures disposed on a bottom surface of the support substrate. Composite interconnection elements are described for use as the resilient contact structures disposed atop the support substrate. In use, the support substrate is soldered down onto the circuit board, the contact structures on the bottom surface of the support substrate contacting corresponding contact areas on the circuit board. In any suitable manner, selected ones of the resilient contact structures atop the support substrate are connected, via the support substrate, to corresponding ones of the contact structures on the bottom surface of the support substrate.

Owner:FORMFACTOR INC

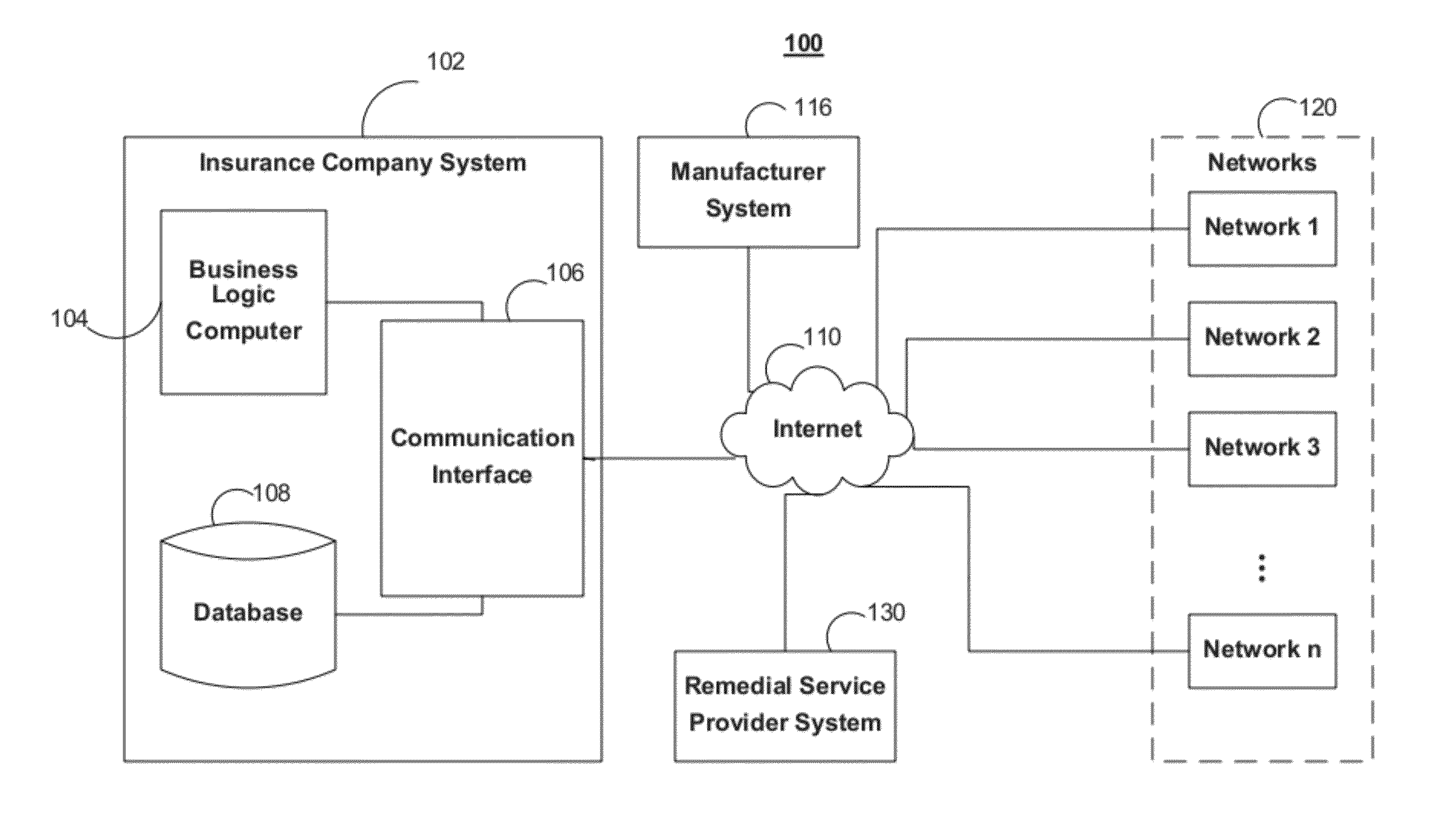

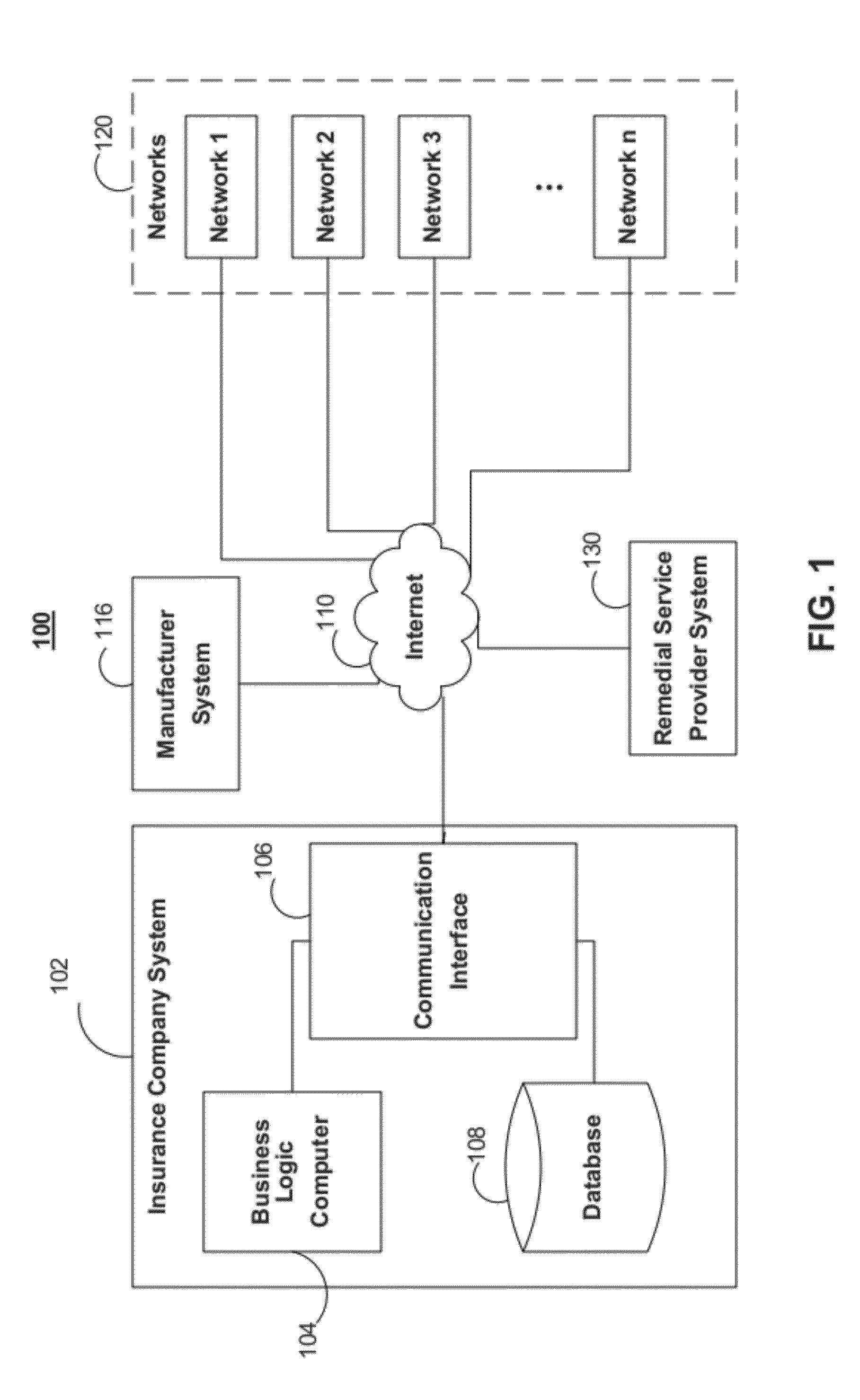

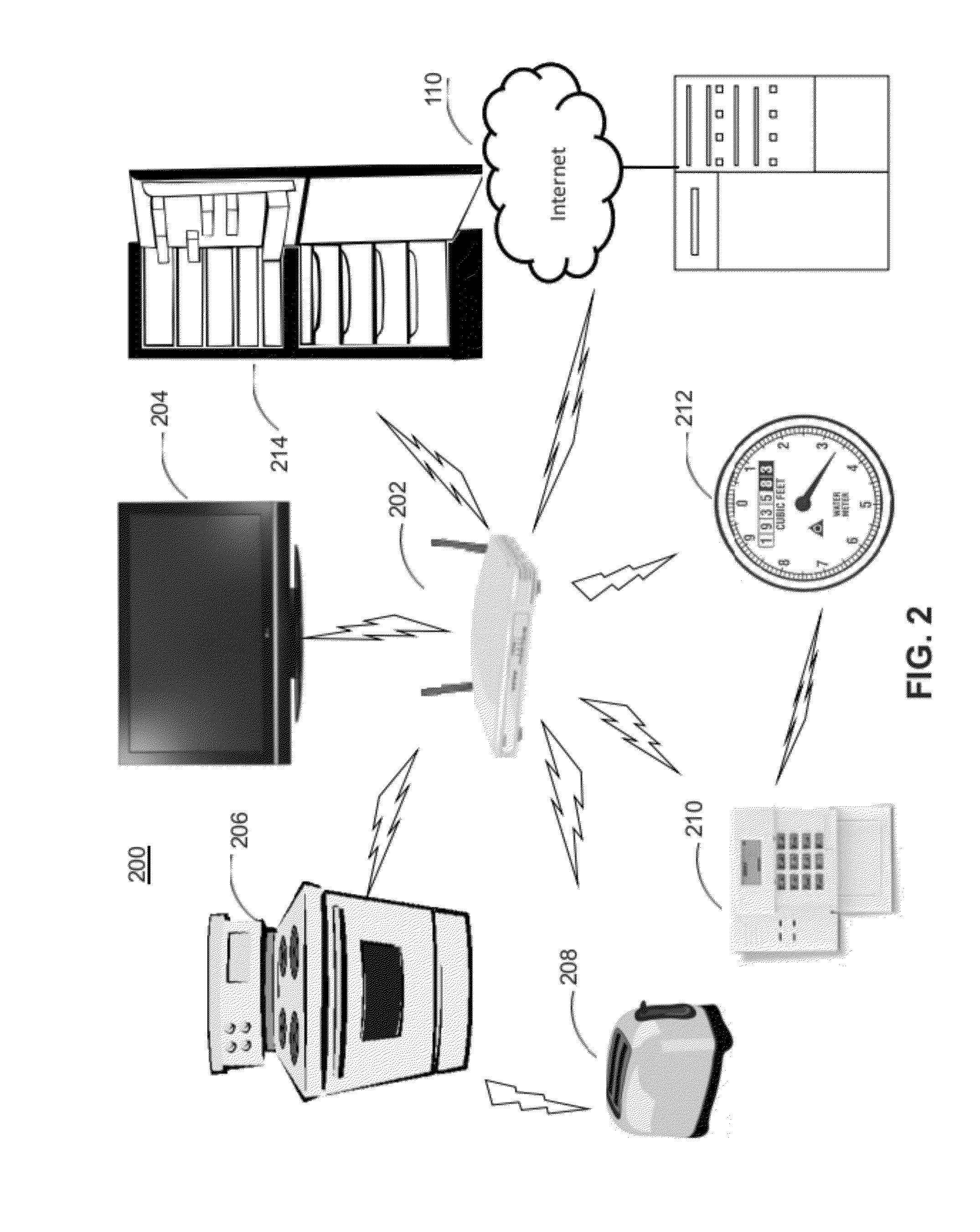

System and method for active insurance underwriting using intelligent ip-addressable devices

A system and method are disclosed herein for maintaining an inventory of assets located at an insured property covered under an insurance policy based on data received from IP-addressable devices located at the property. The system includes an inventory database for storing inventory information about assets located at an insured property, a communication interface for receiving registration and operational data associated with an IP-addressable device, and a business logic computer. The business logic computer creates a data structure for storing inventory information about assets located at the insured property in the inventory database for each insured property. The business logic computer determines, for the insured property, the inventory information about the insured property's assets based on registration and operational data received from its IP-addressable devices located at the property. The business logic computer stores the insured property's inventory information in its associated data structure in the inventory database.

Owner:HARTFORD FIRE INSURANCE

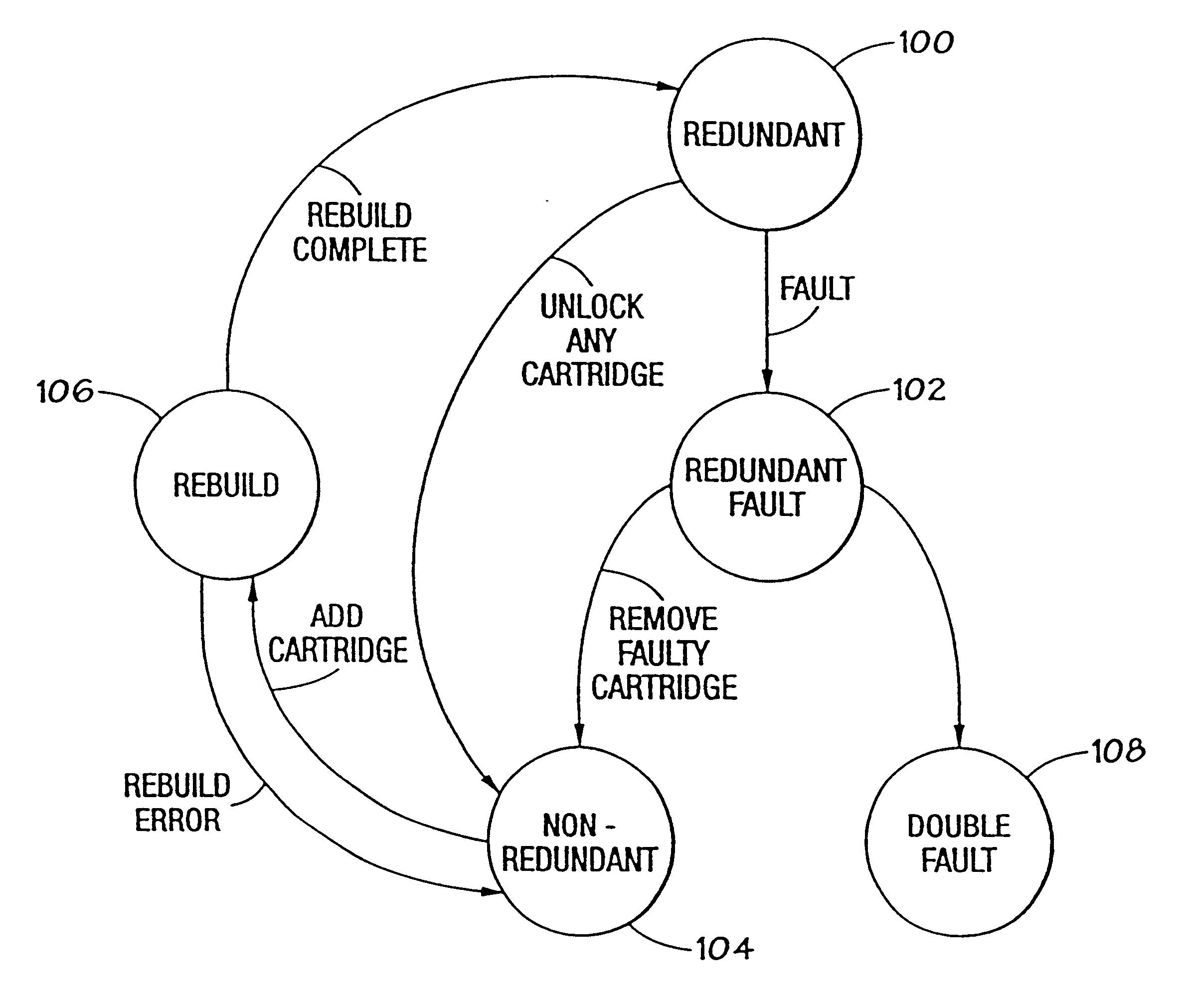

Memory module resync

A technique for resynchronizing a memory system. More specifically, a technique for resynchronizing a plurality of memory segments in a redundant memory system after a hot-plug event. After a memory cartridge is hot-plugged into a system, the memory cartridge is synchronized with the operational memory cartridges such that the memory system can operate in lock step. A refresh counter in each memory cartridge is disabled to generate a first refresh request to the corresponding memory segments in the memory cartridge. After waiting a period of time to insure that regardless of what state each memory cartridge is in when the first refresh request is initiated all cycles have been completely executed, each refresh counter is re-enabled, thereby generating a second refresh request. The generation of the second refresh request to each of the memory segments provides synchronous operation of each of the memory cartridges.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

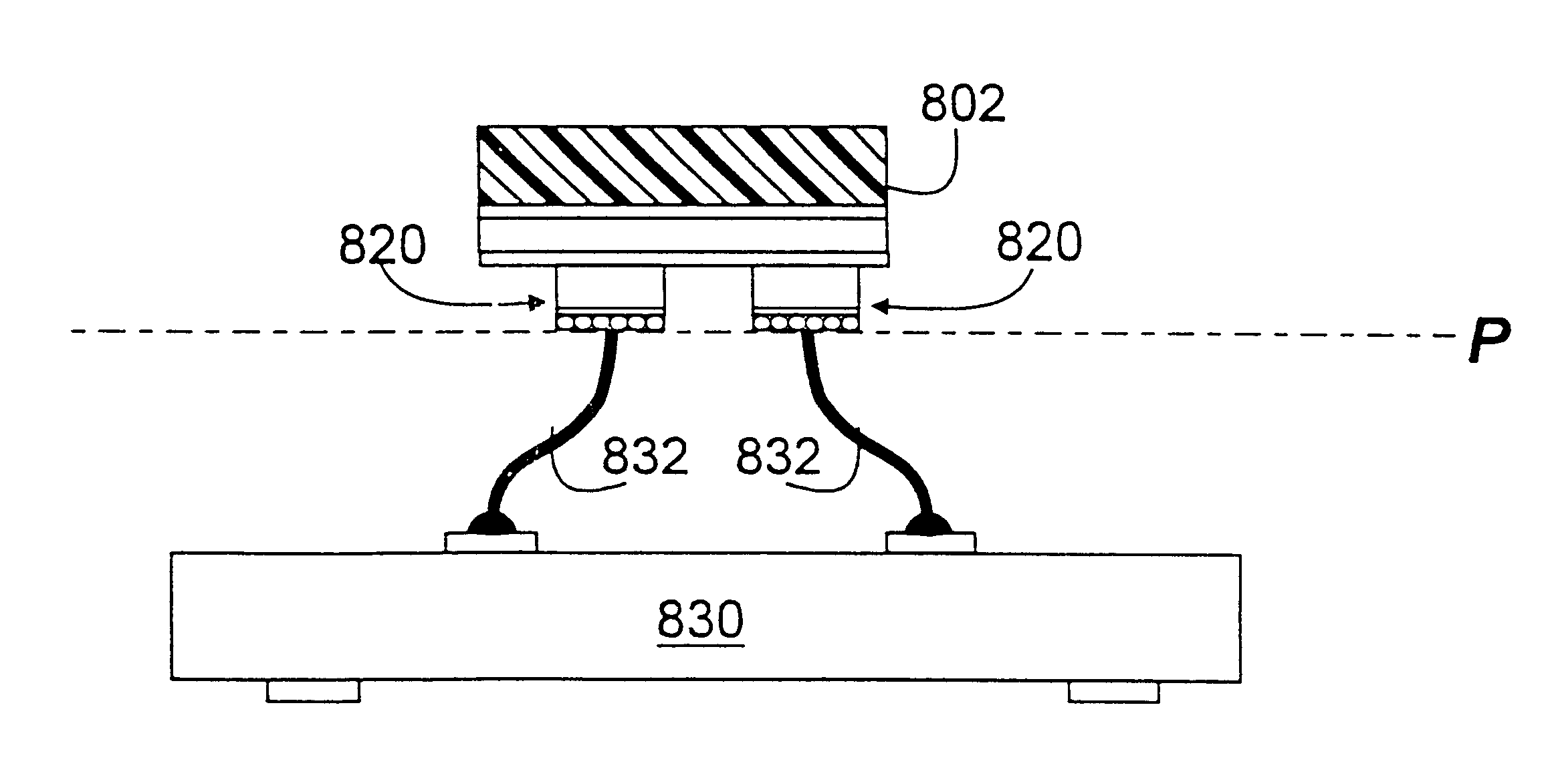

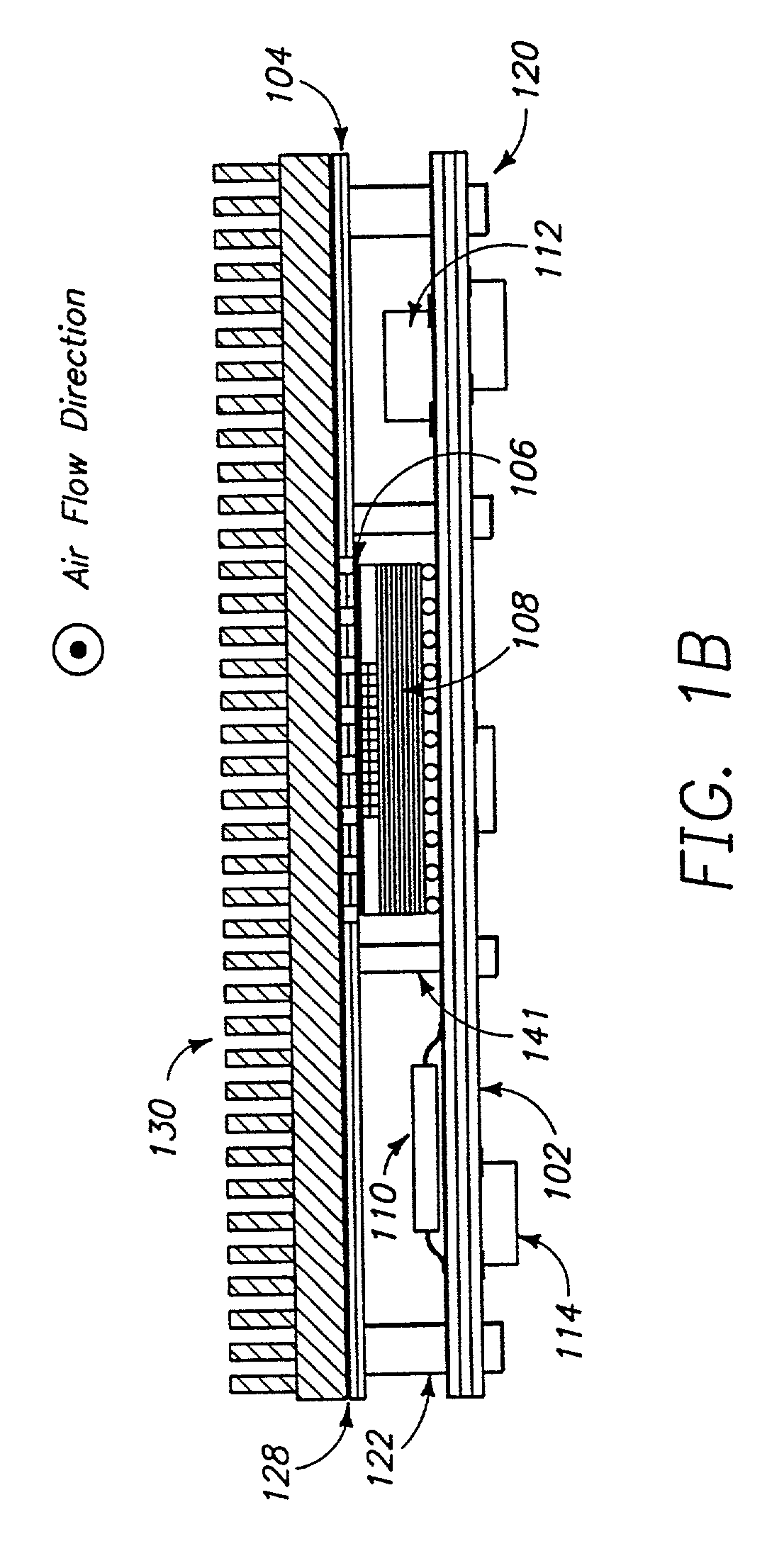

Inter-circuit encapsulated packaging

InactiveUS20020008963A1Semiconductor/solid-state device detailsSolid-state devicesThermal energyHeat spreader

A modular circuit board assembly is disclosed. The modular circuit board assembly comprises a substrate, a circuit board, and a component, disposed between the circuit board and the substrate, the component physically and electrically coupled to the substrate. In one embodiment, the circuit board also comprises an aperture allowing for the transmission of thermal energy from the component to a heat sink. In still another embodiment of the invention, the heat sink includes a mesa having surface features cooperatively interacting with surface features on the component or members mounted on the component to provide for location and / or retention.

Owner:INCEP TECH