Patents

Literature

11034 results about "Surface mounting" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

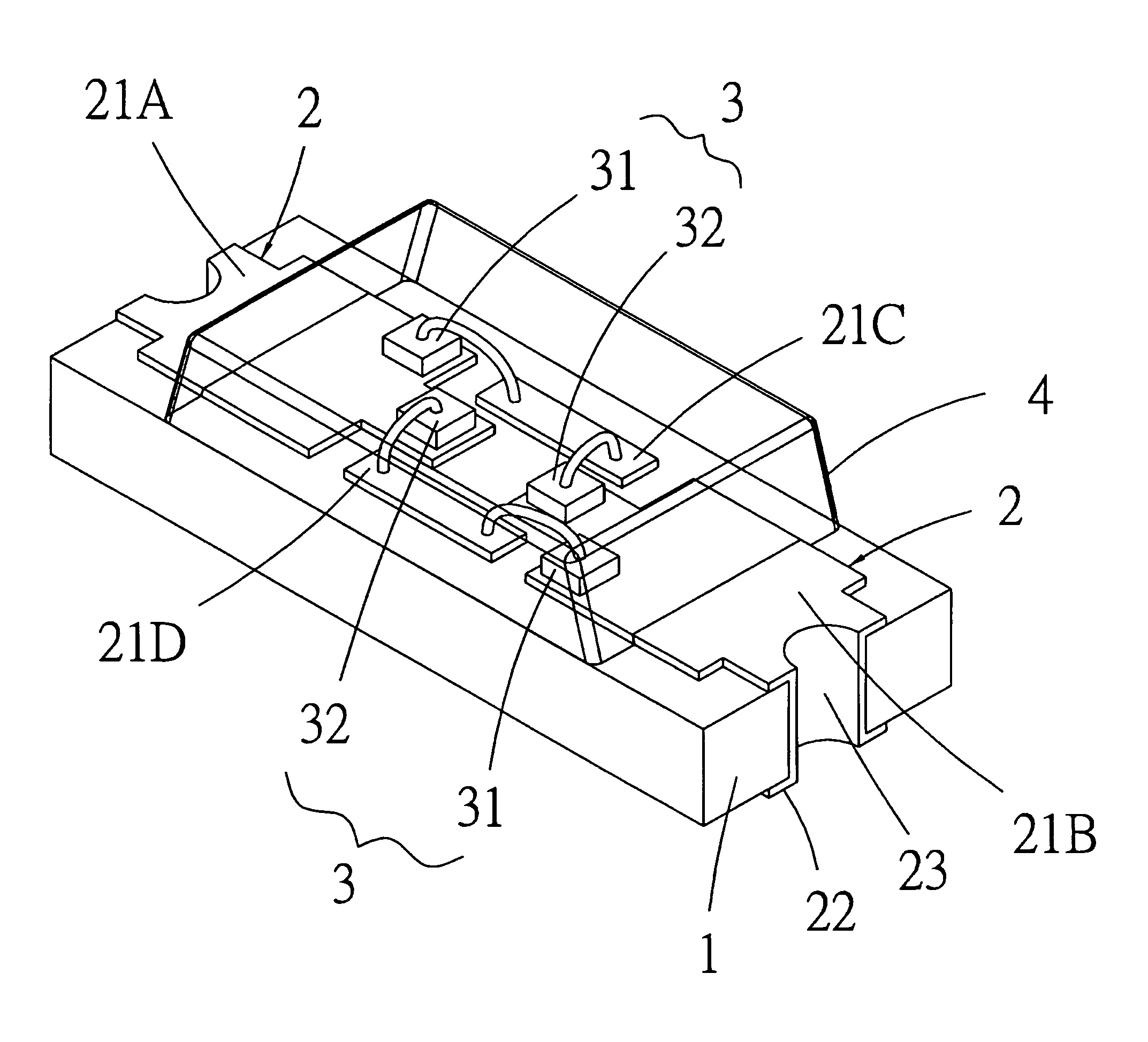

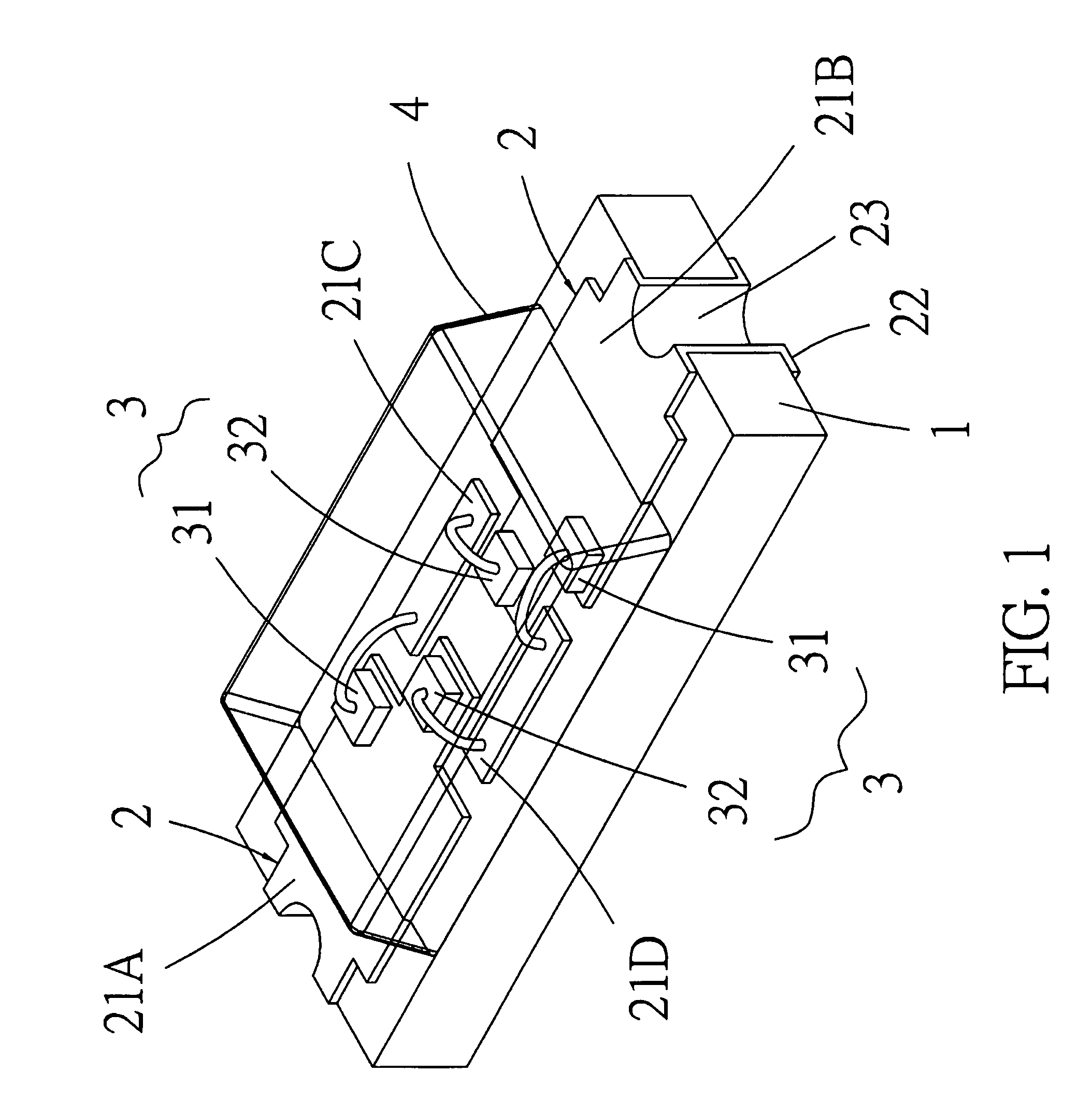

Polarless surface mounting light emitting diode

A polarless surface mounting light emitting diode comprises a substrate; an upper surface of the substrate being etched with four independent metal thin film blocks; a lower surface of the substrate being formed with two independent metal thin film blocks; two ends of the substrate being formed with electroplated through holes; a plurality of metal thin films adhered upon the upper and lower surfaces of the substrate; two light emitting assemblies, each light emitting assembly being formed by a chip resistor and a chip light emitting diode; and a package layer. The connection of the polarless surface mounting light emitting diode of the present invention is not limited by the polarity. Any end of the polarless surface mounting light emitting diode can be connected to positive electrode or negative electrode.

Owner:LIN PETER P W

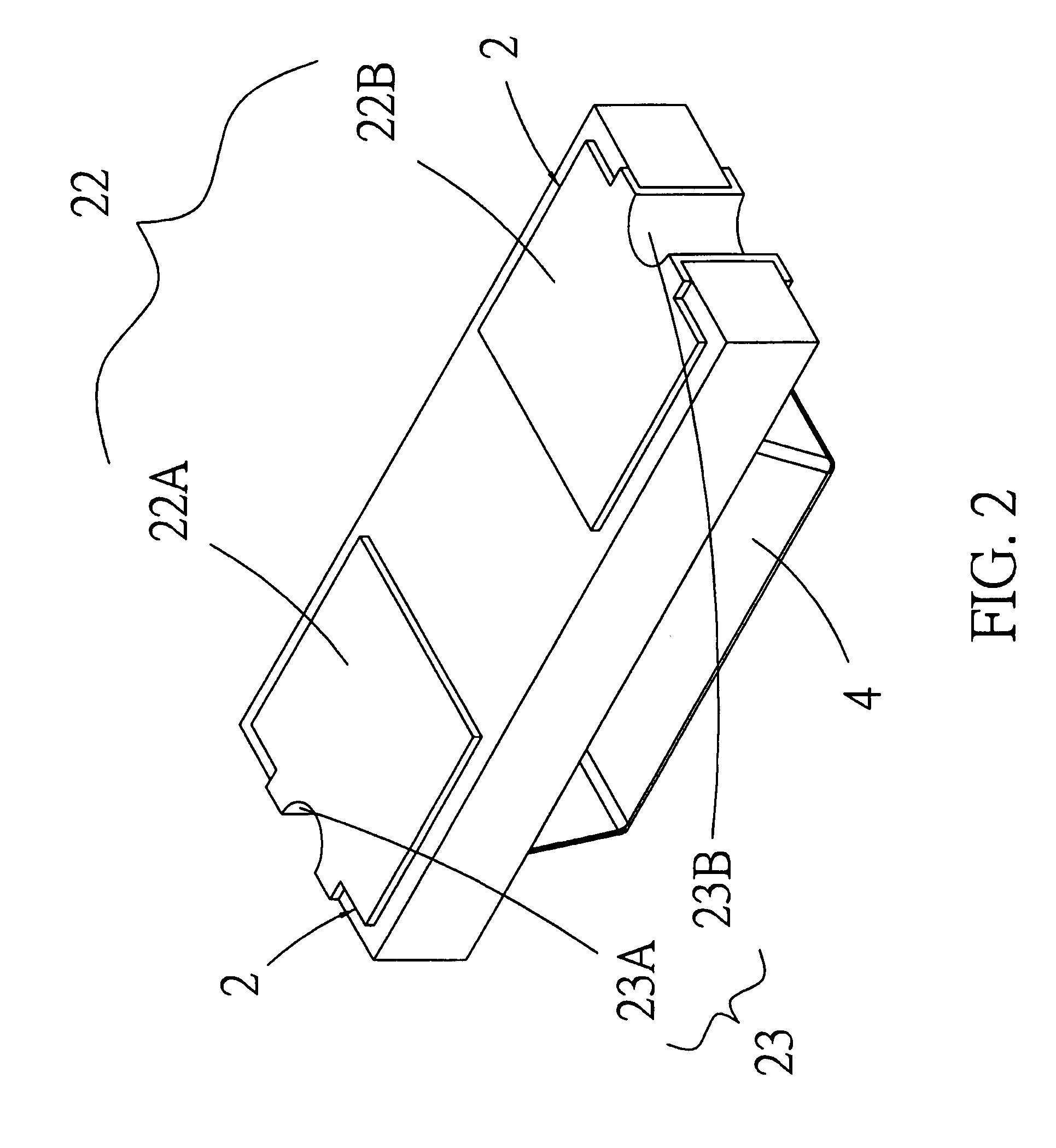

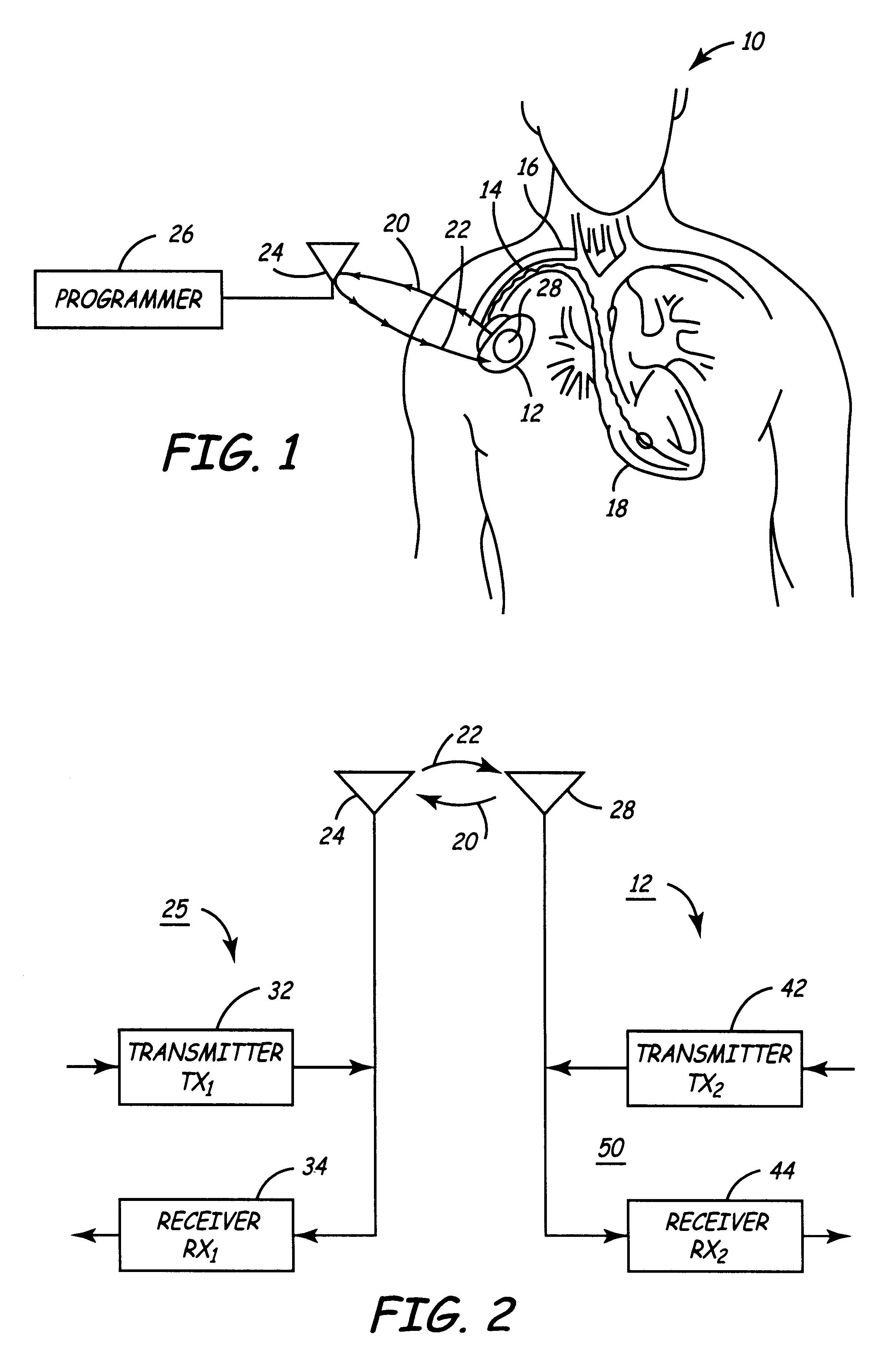

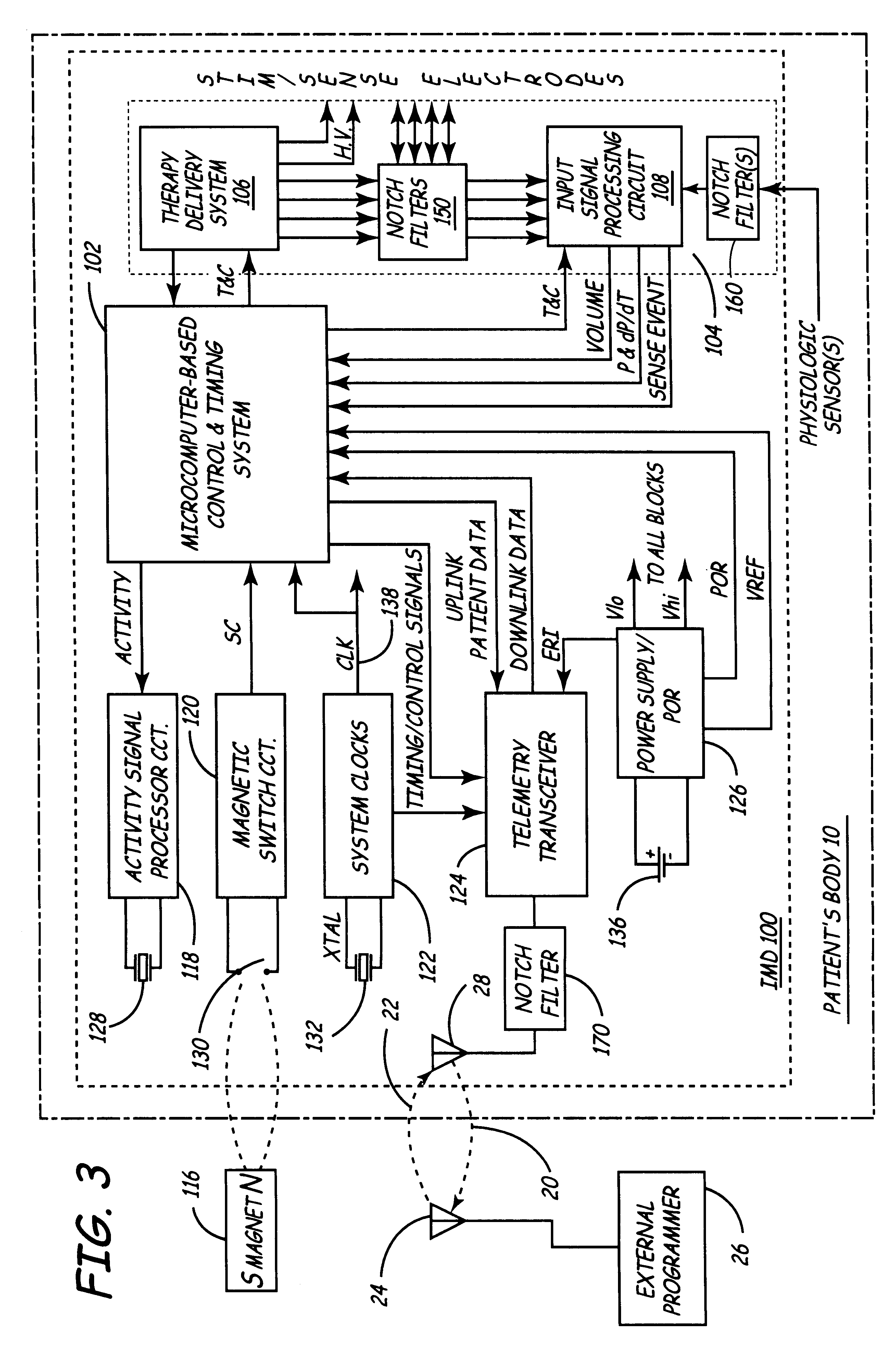

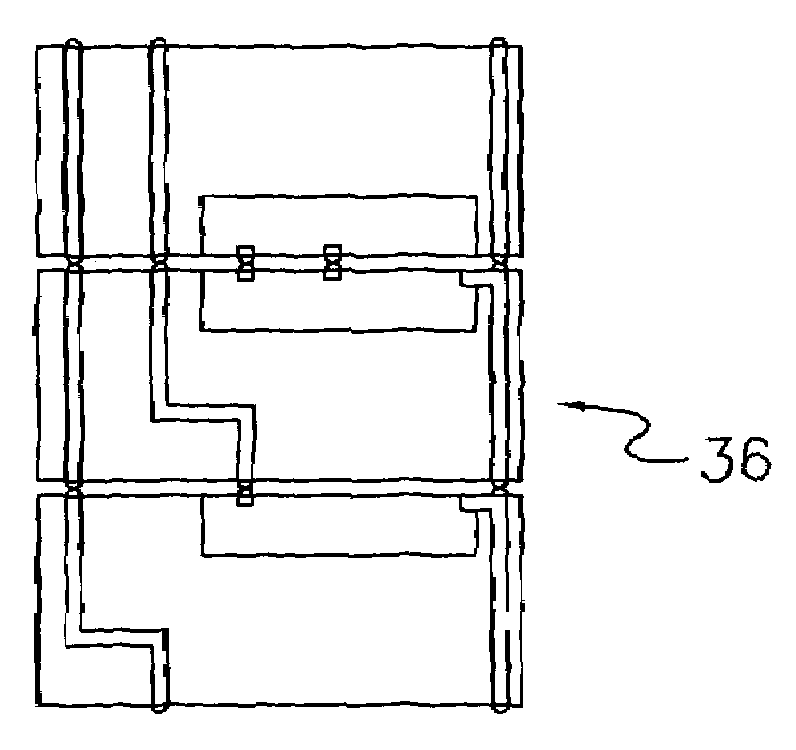

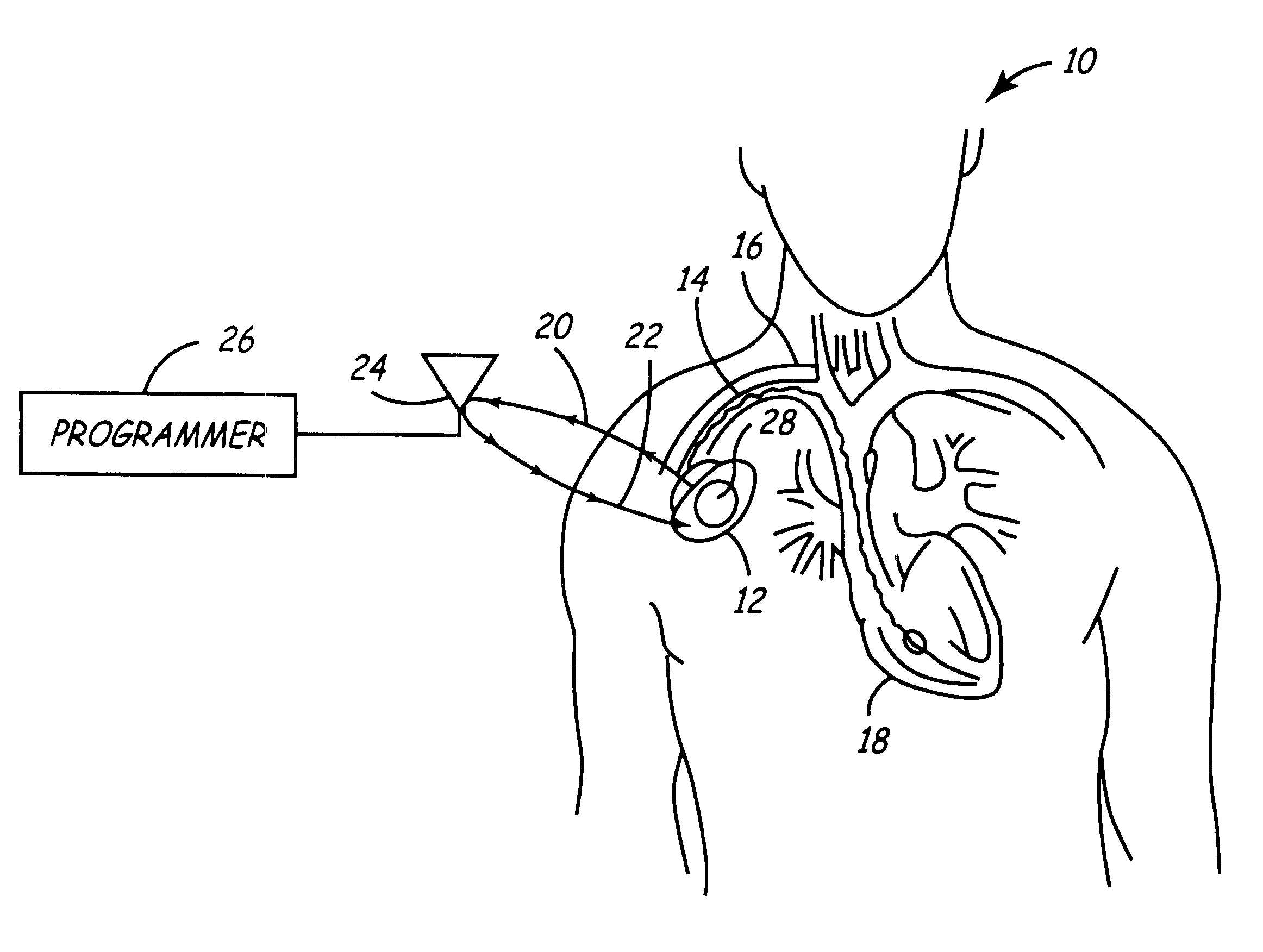

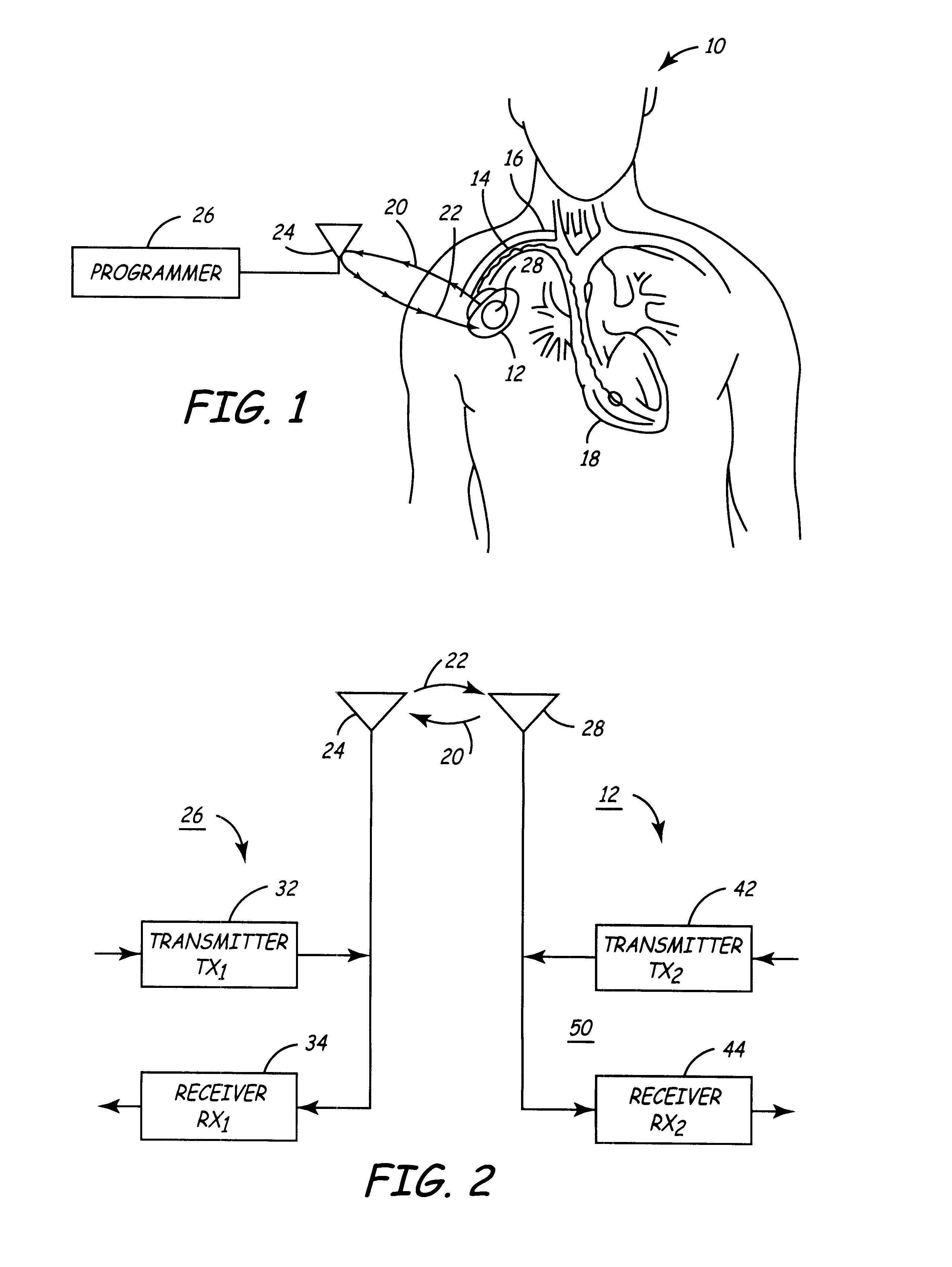

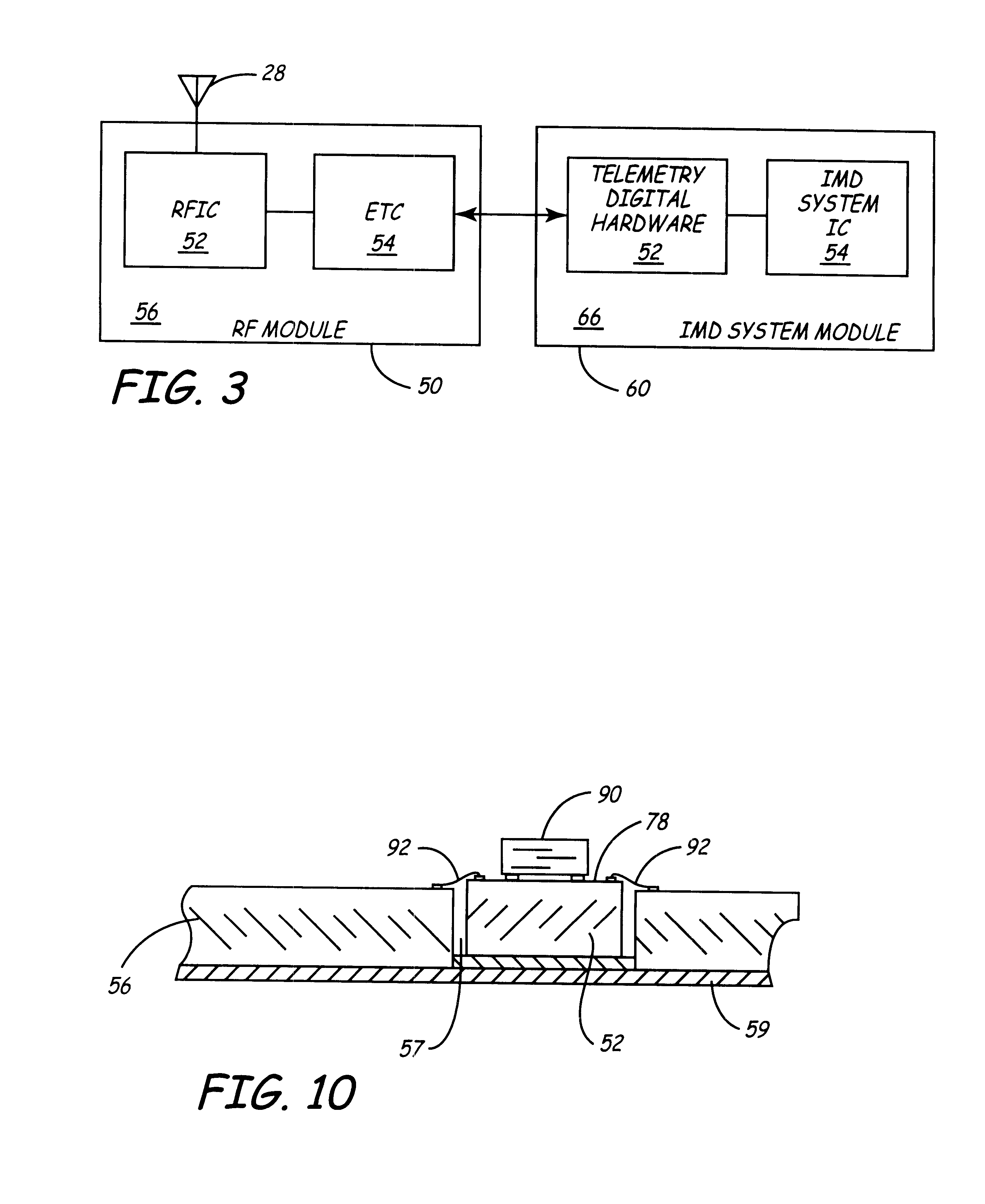

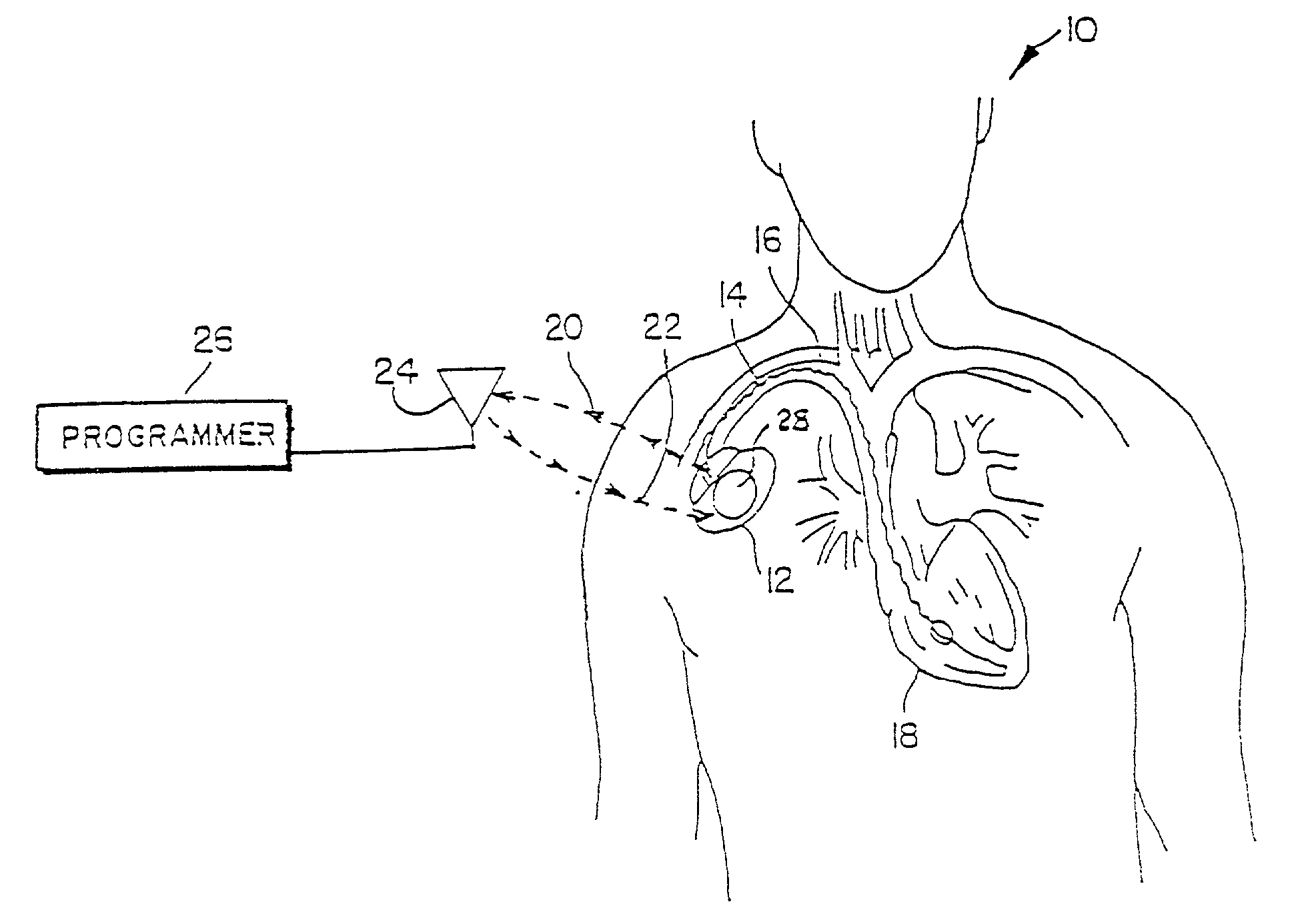

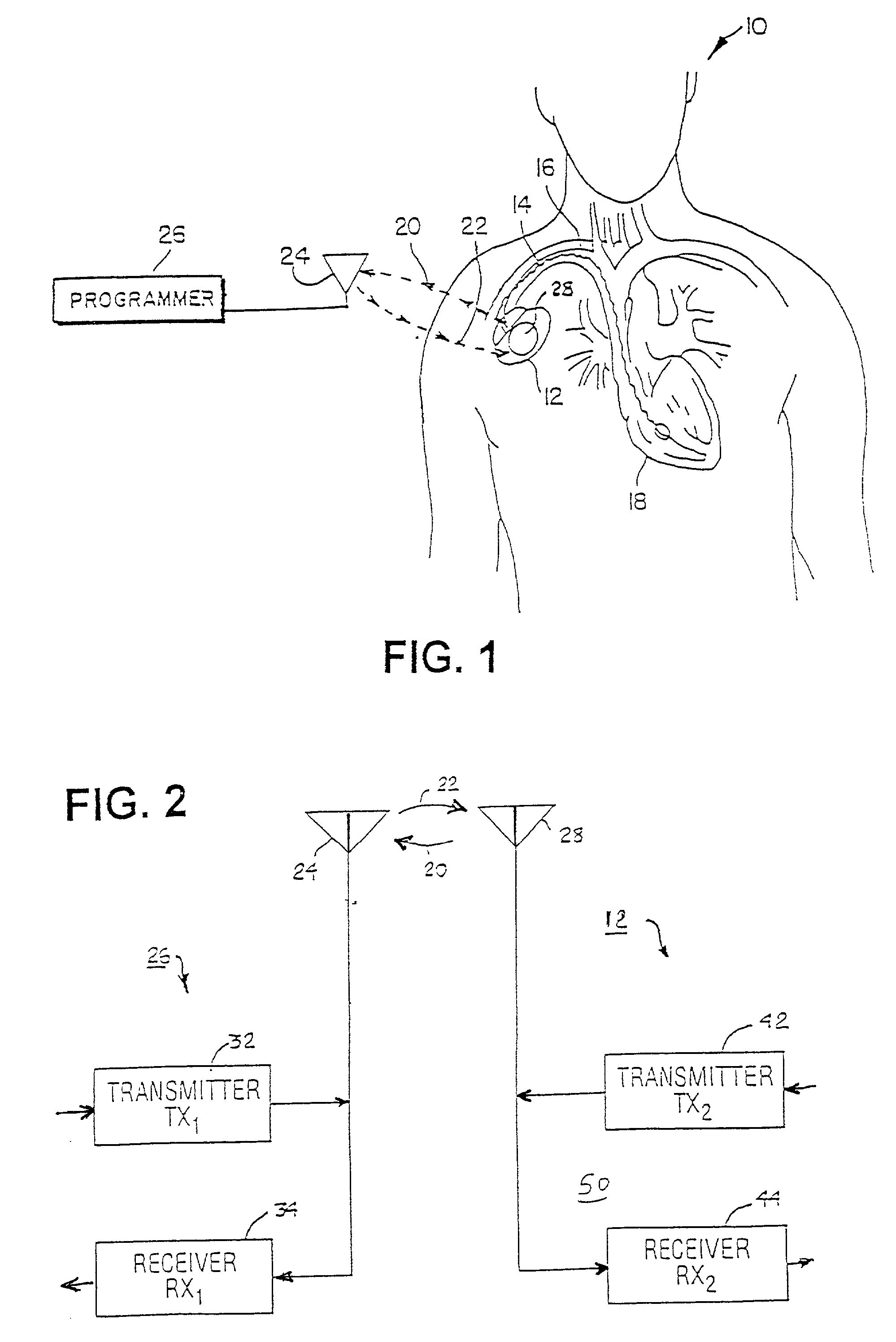

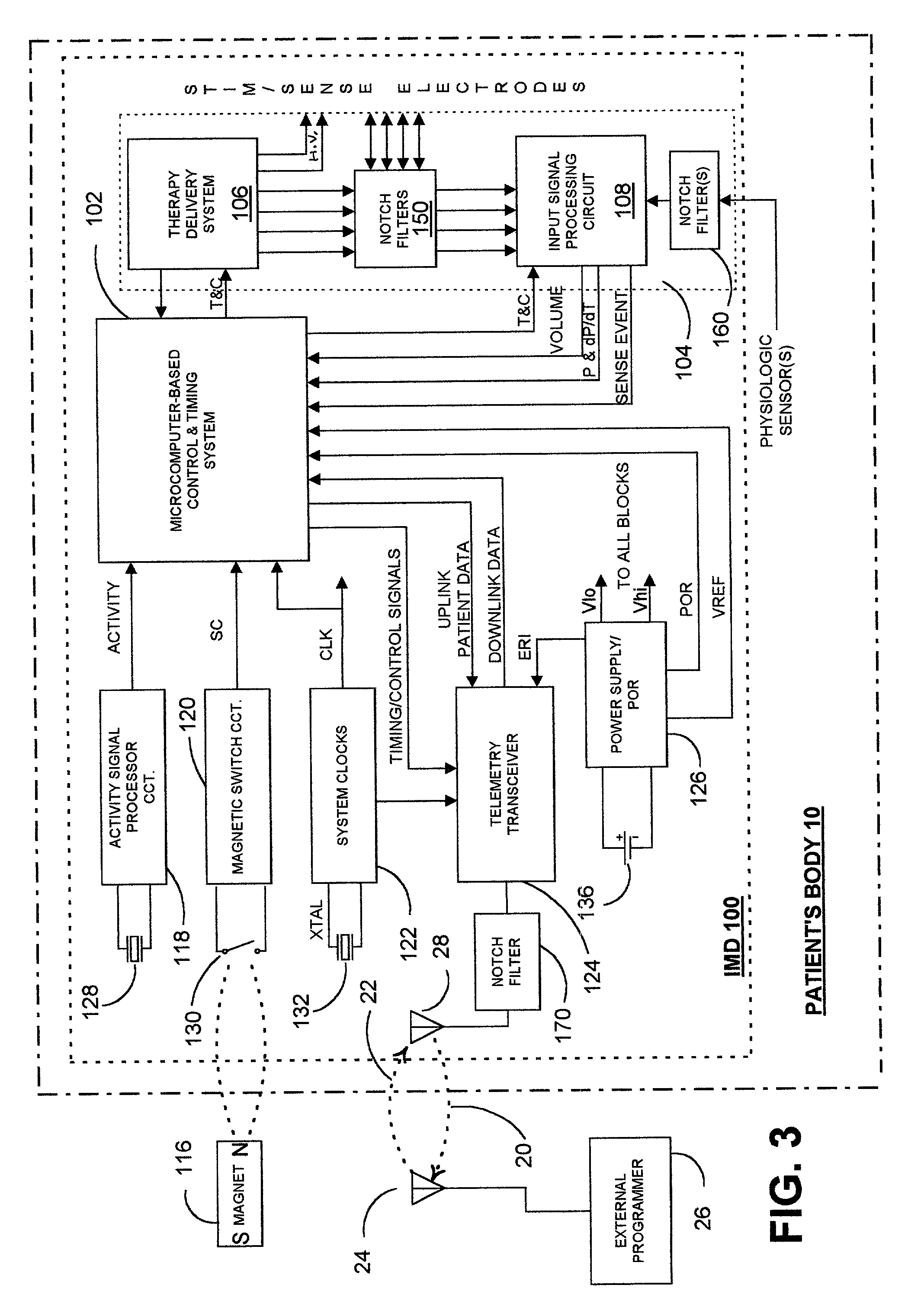

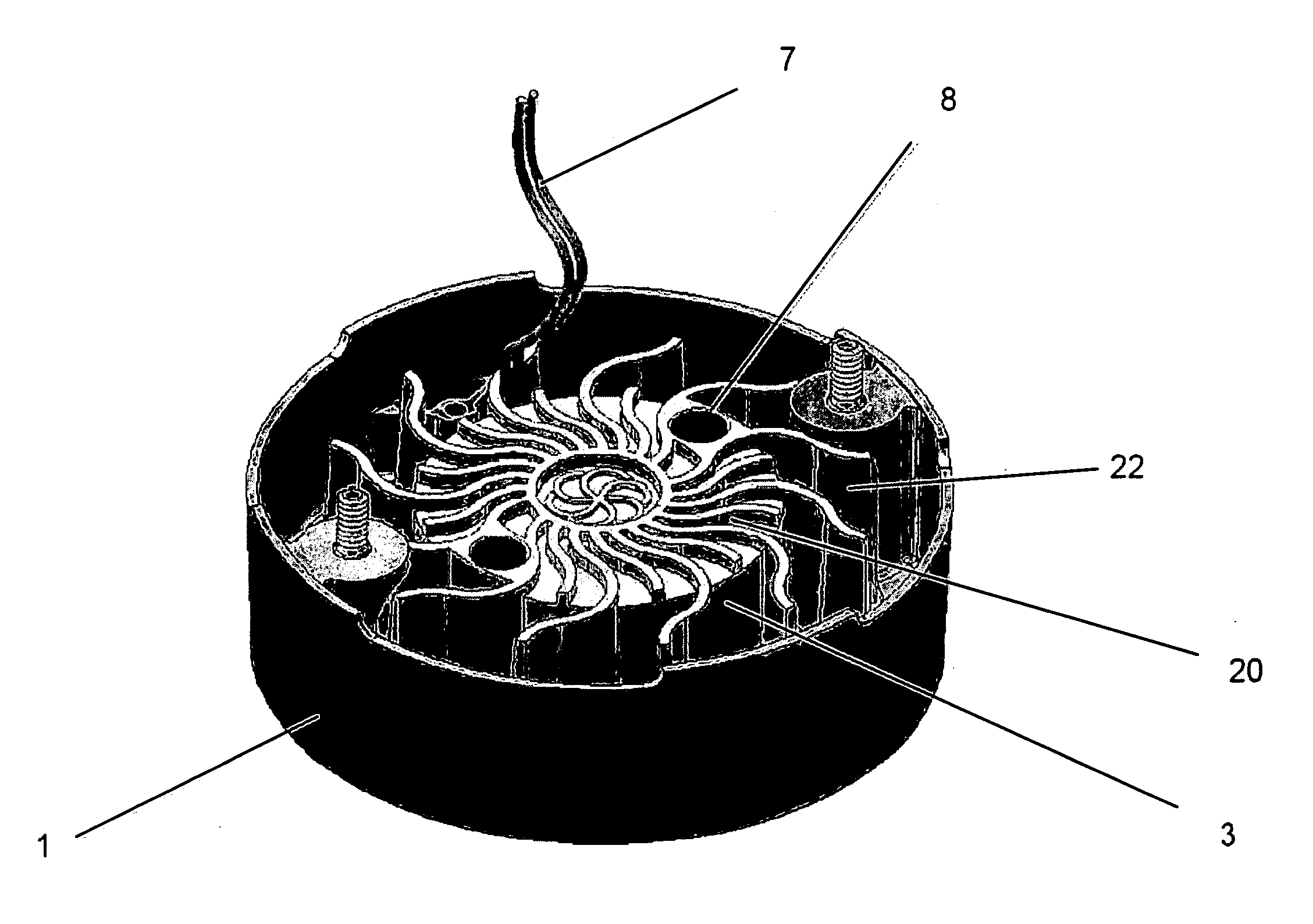

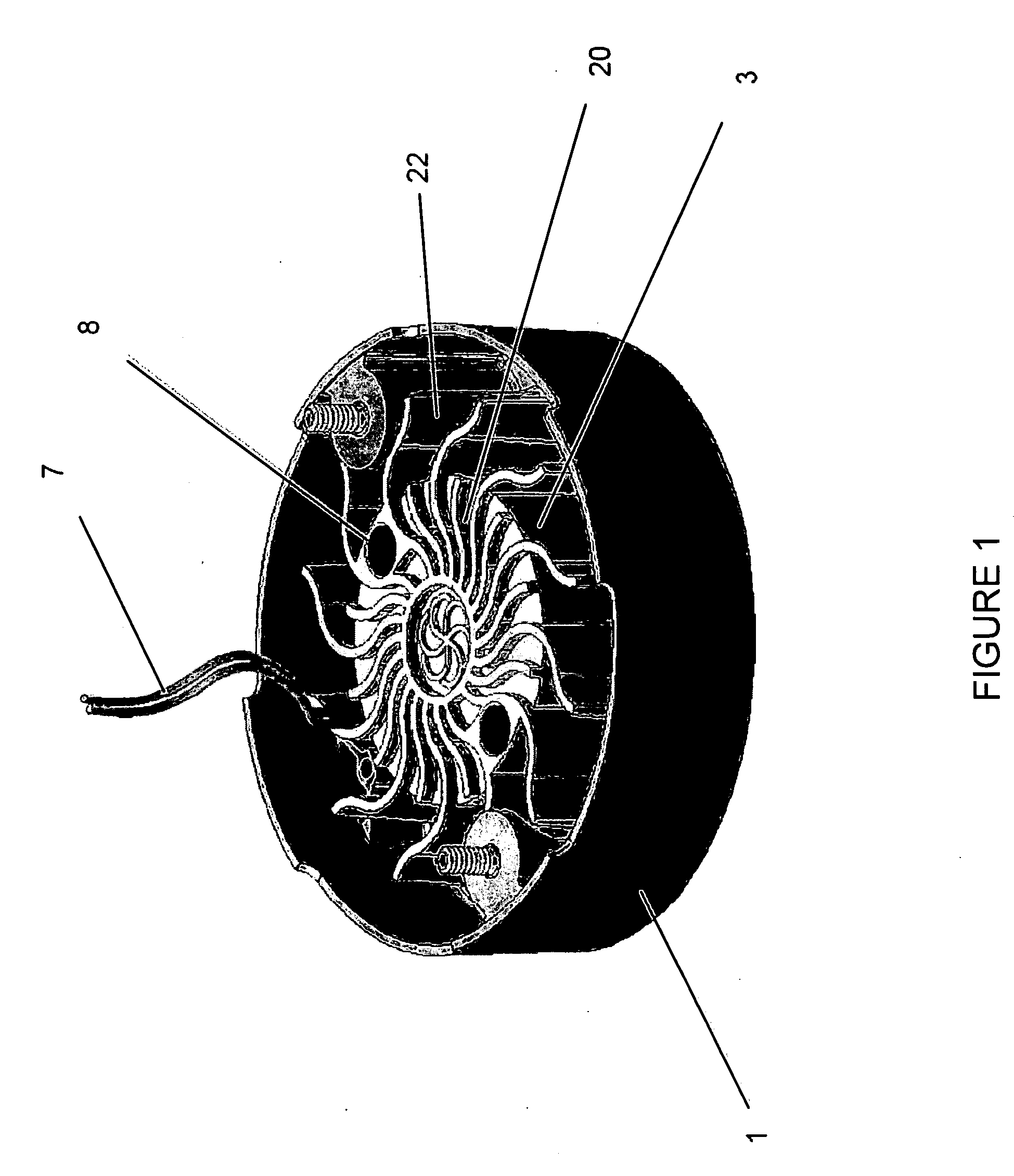

Implantable medical device incorporating integrated circuit notch filters

Implantable medical devices (IMDs) having sense amplifiers for sensing physiologic signals and parameters, RF telemetry capabilities for uplink transmitting patient data and downlink receiving programming and interrogation commands to and from an external programmer or other medical device are disclosed. At least one IC chip and discrete components have a volume and dimensions that are optimally minimized to reduce its volumetric form factor. Miniaturization techniques include forming notch filters of MEMS structures or forming discrete circuit notch filters by one or more of: (1) IC fabricating inductors into one or more IC chips mounted to the RF module substrate; (2) mounting each IC chip into a well of the RF module substrate and using short bonding wires to electrically connect bond pads of the RF module substrate and the IC chip; and (3) surface mounting discrete capacitors over IC chips to reduce space taken up on the RF module substrate. The IC fabricated inductors are preferably fabricated as planar spiral wound conductive traces formed of high conductive metals to reduce trace height and width while maintaining low resistance, thereby reducing parasitic capacitances between adjacent trace side walls and with a ground plane of the IC chip. The spiral winding preferably is square or rectangular, but having truncated turns to eliminate 90° angles that cause point-to-point parasitic capacitances. The planar spiral wound conductive traces are further preferably suspended over the ground plane of the IC chip substrate by micromachining underlying substrate material away to thereby reduce parasitic capacitances.

Owner:MEDTRONIC INC

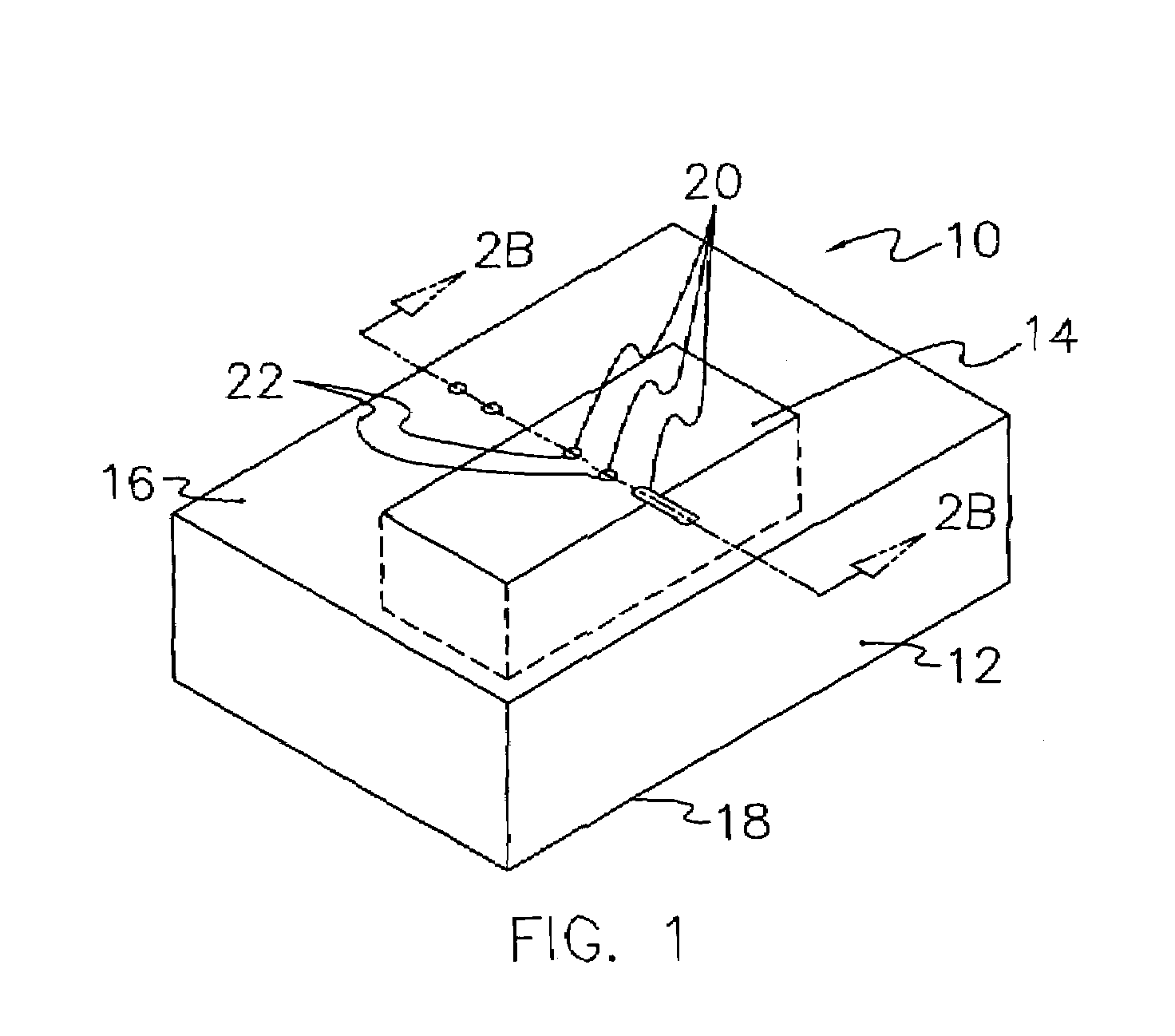

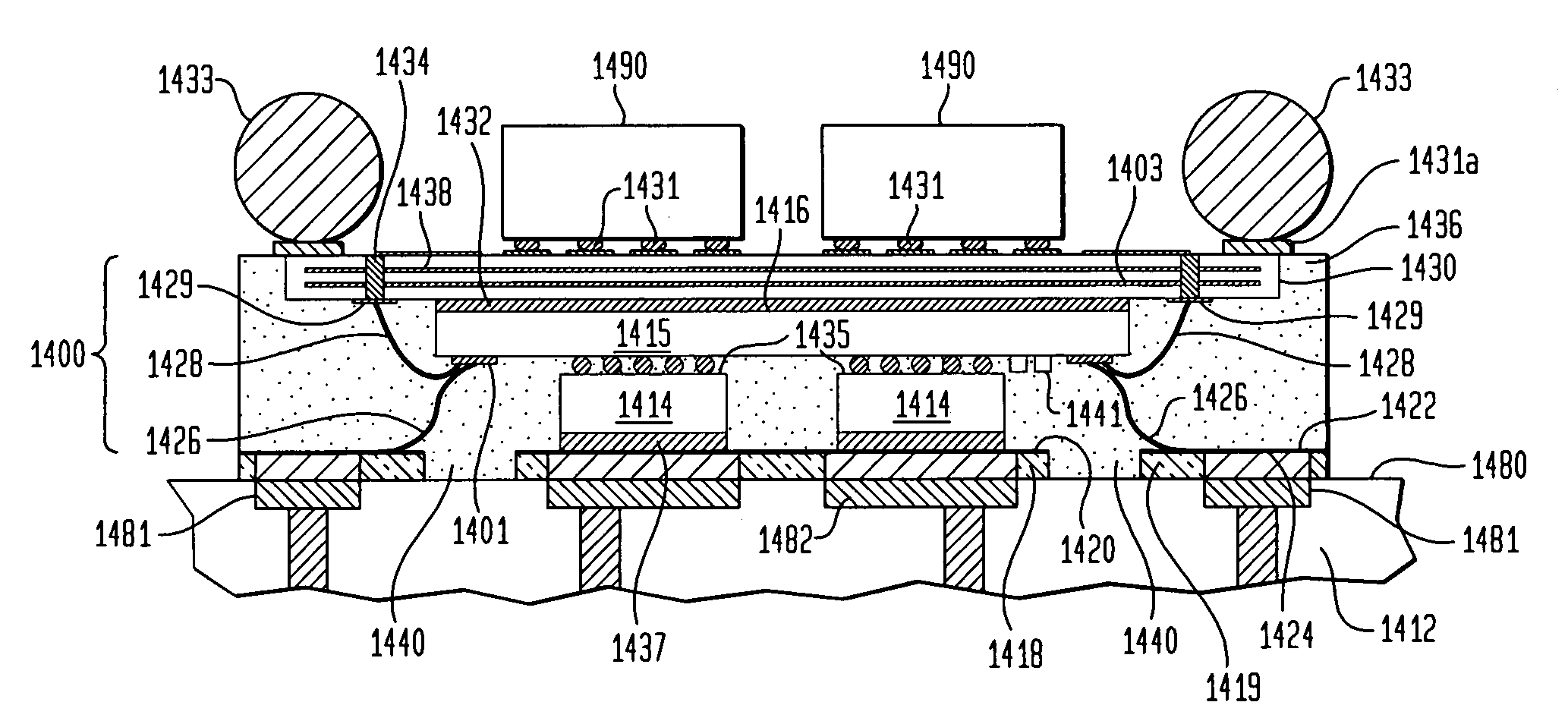

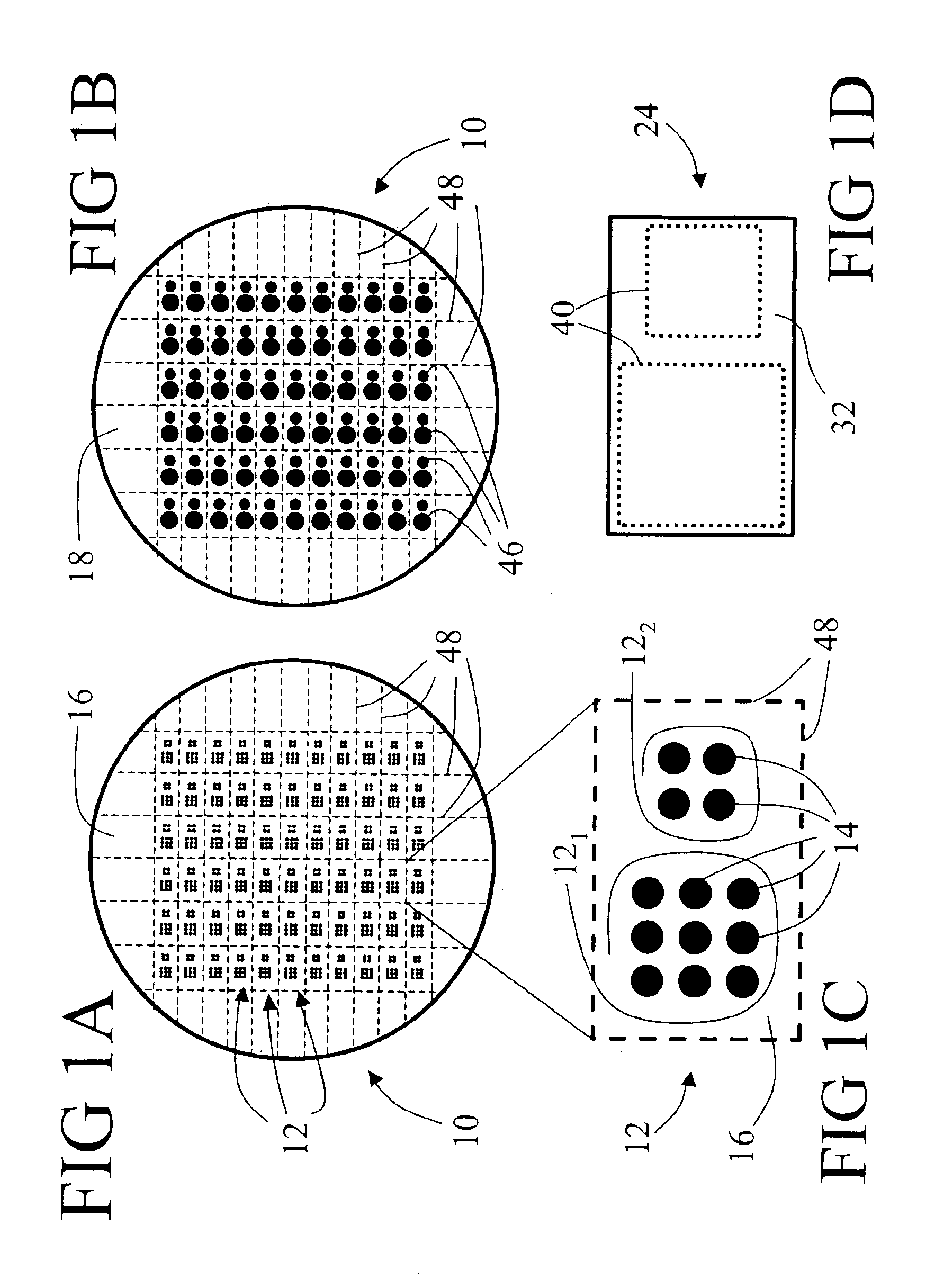

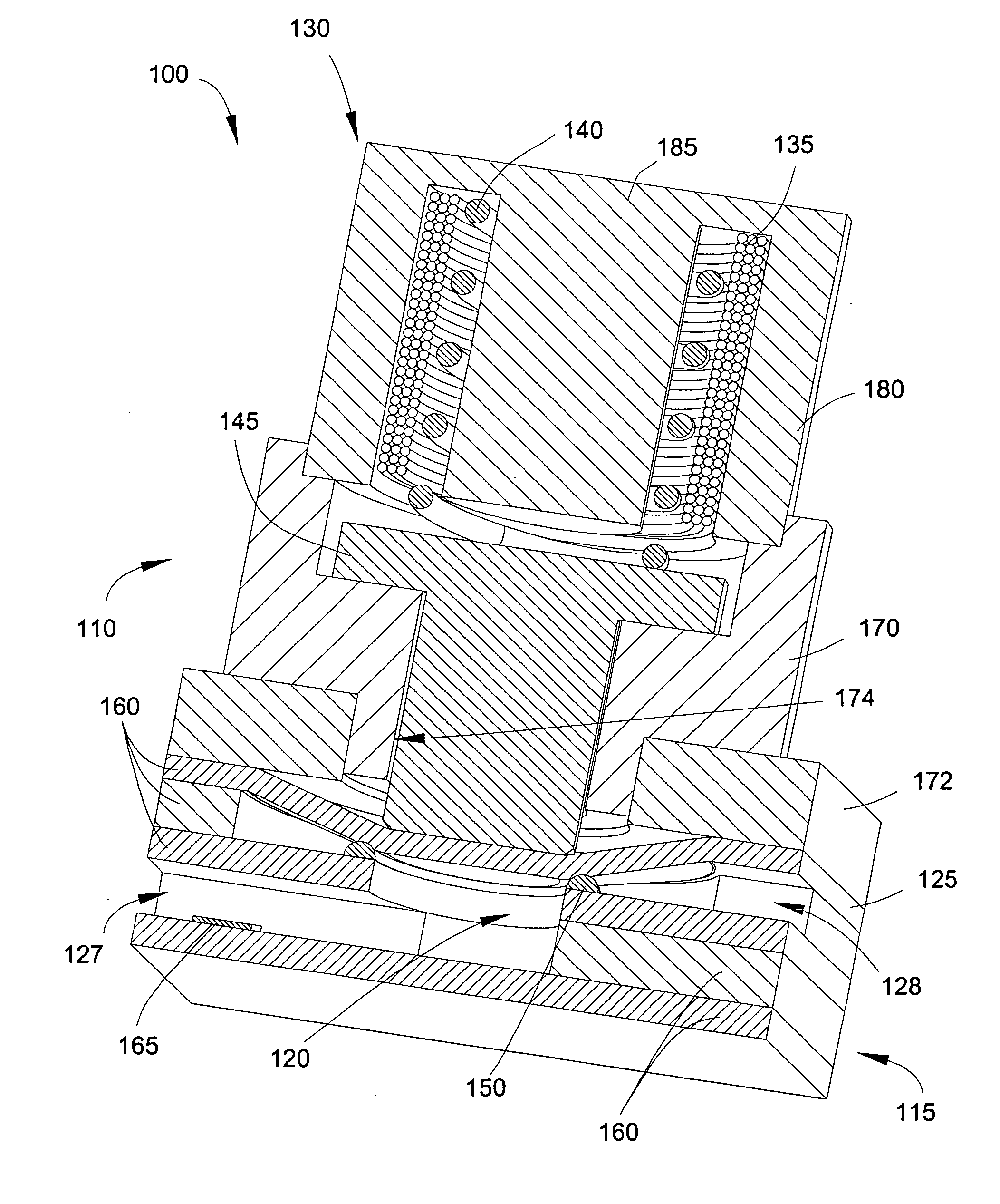

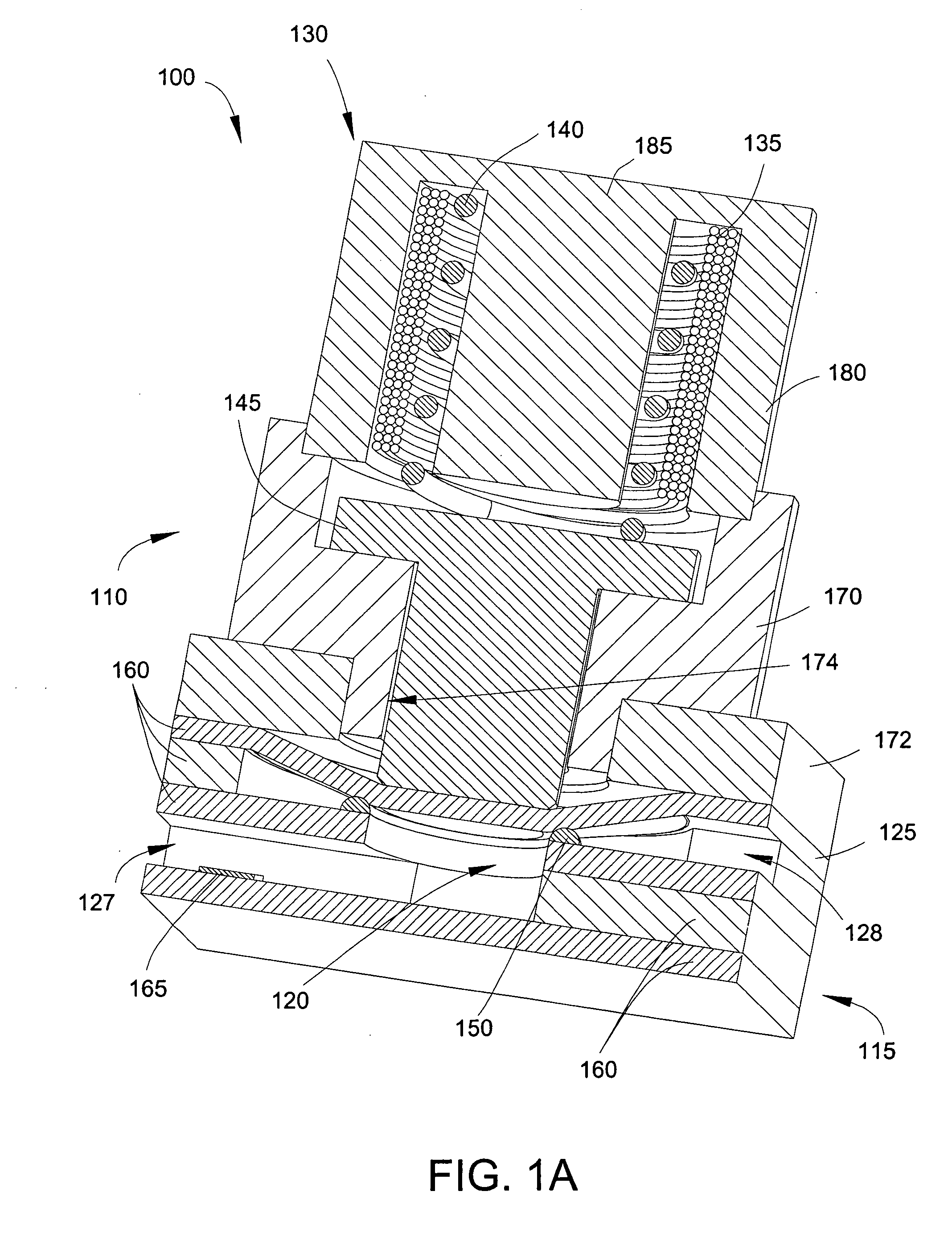

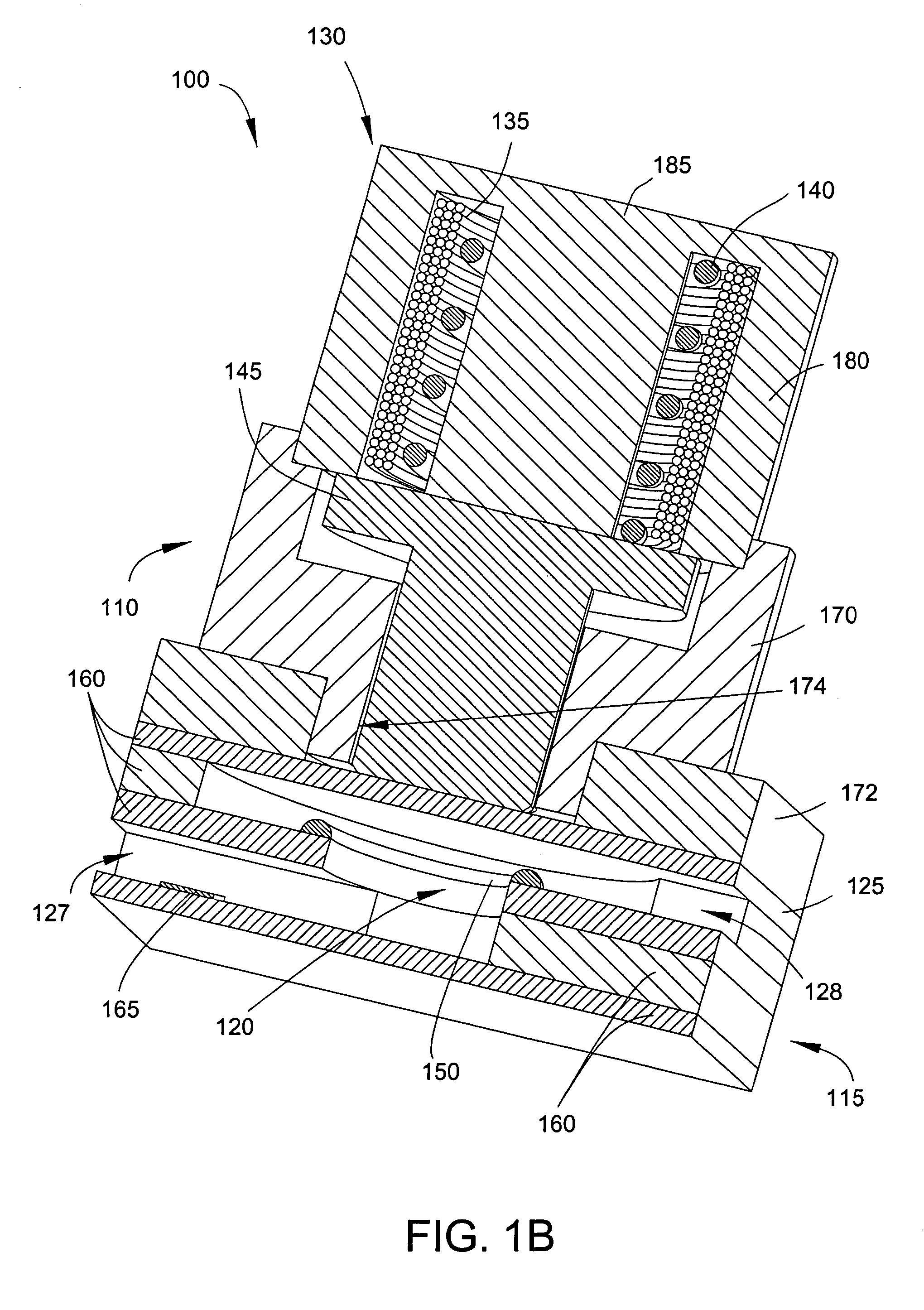

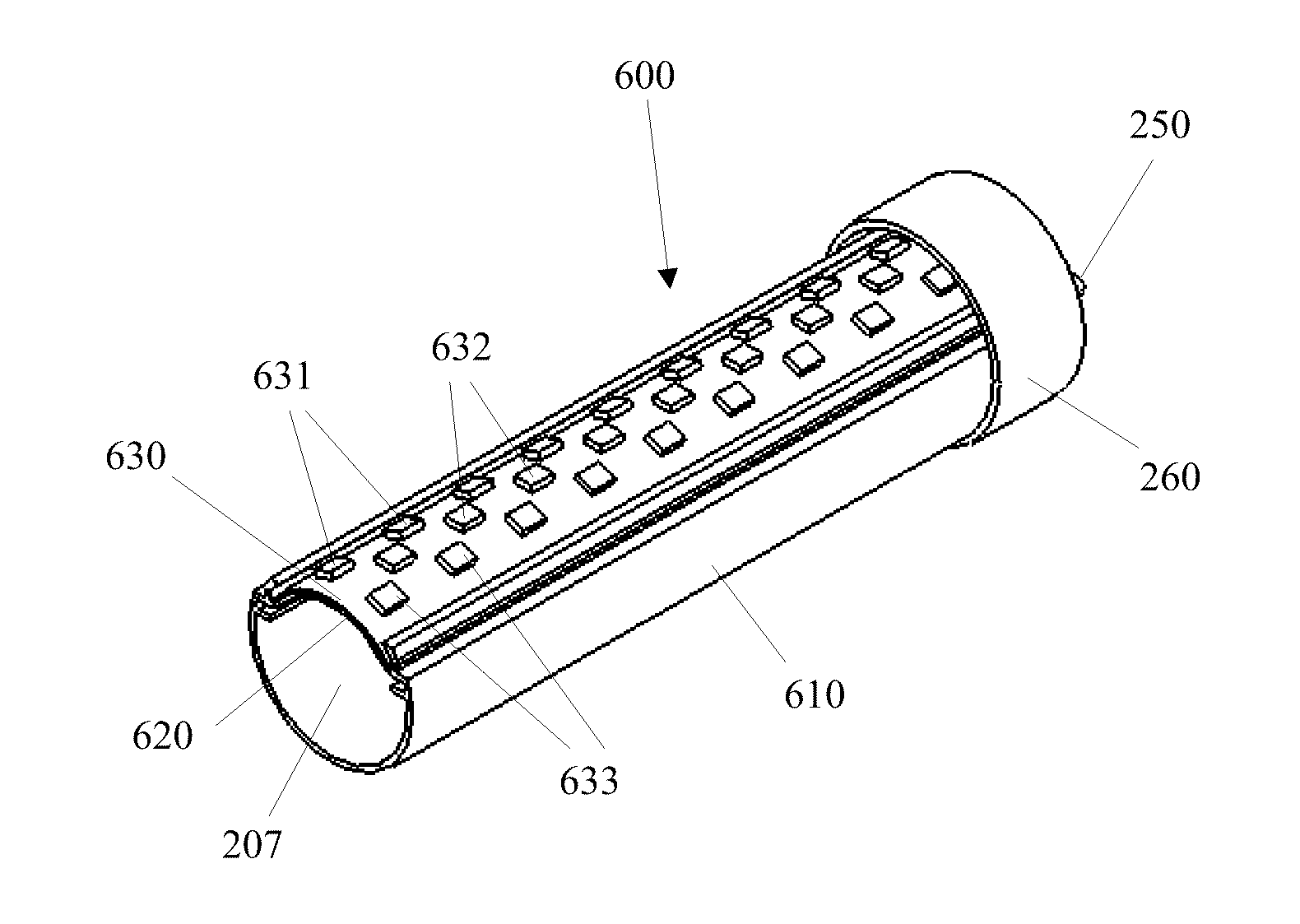

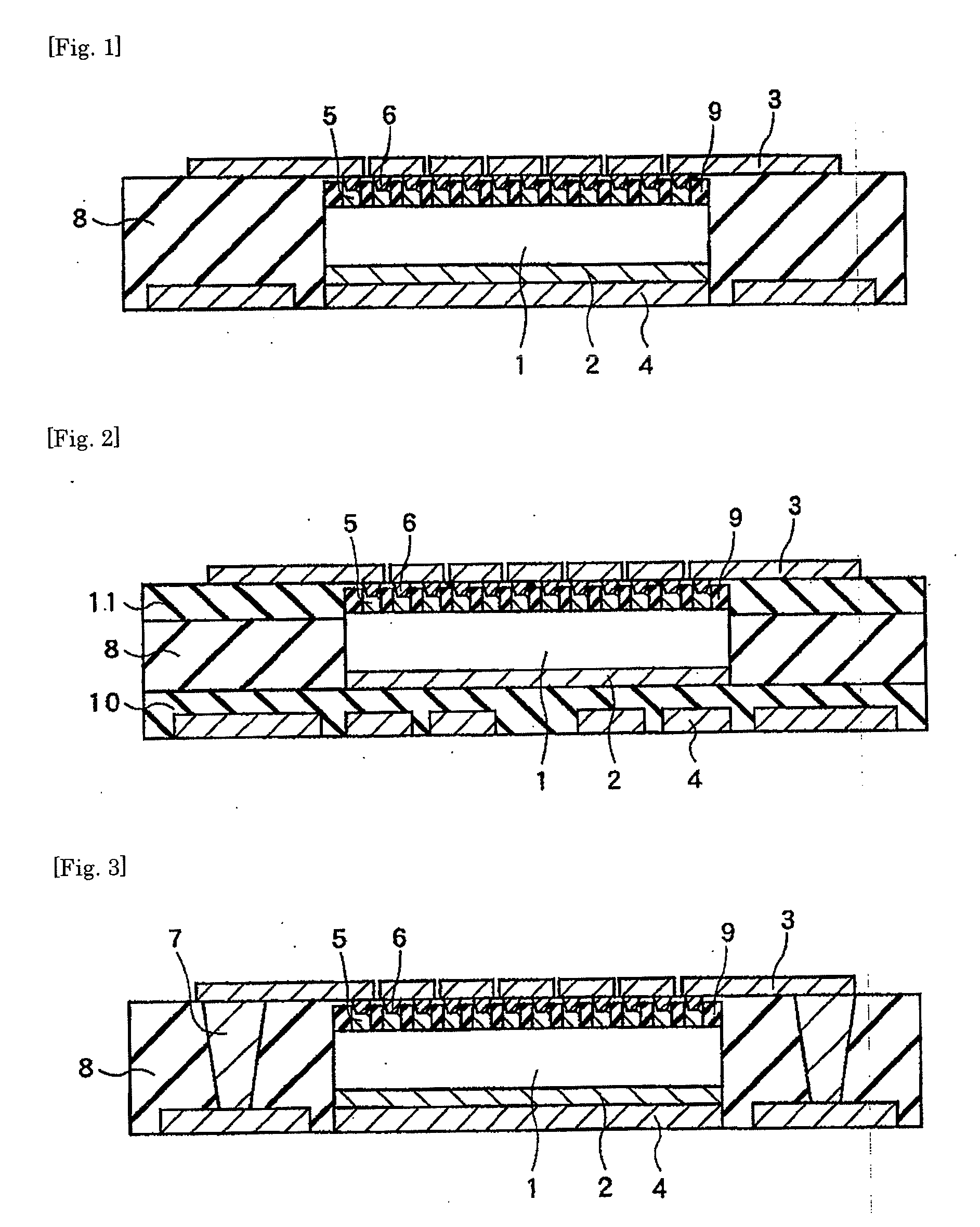

Space-saving packaging of electronic circuits

InactiveUS7071546B2Simplifies electrical connectionsMinimized volumeSemiconductor/solid-state device detailsSolid-state devicesInterior spaceSurface mounting

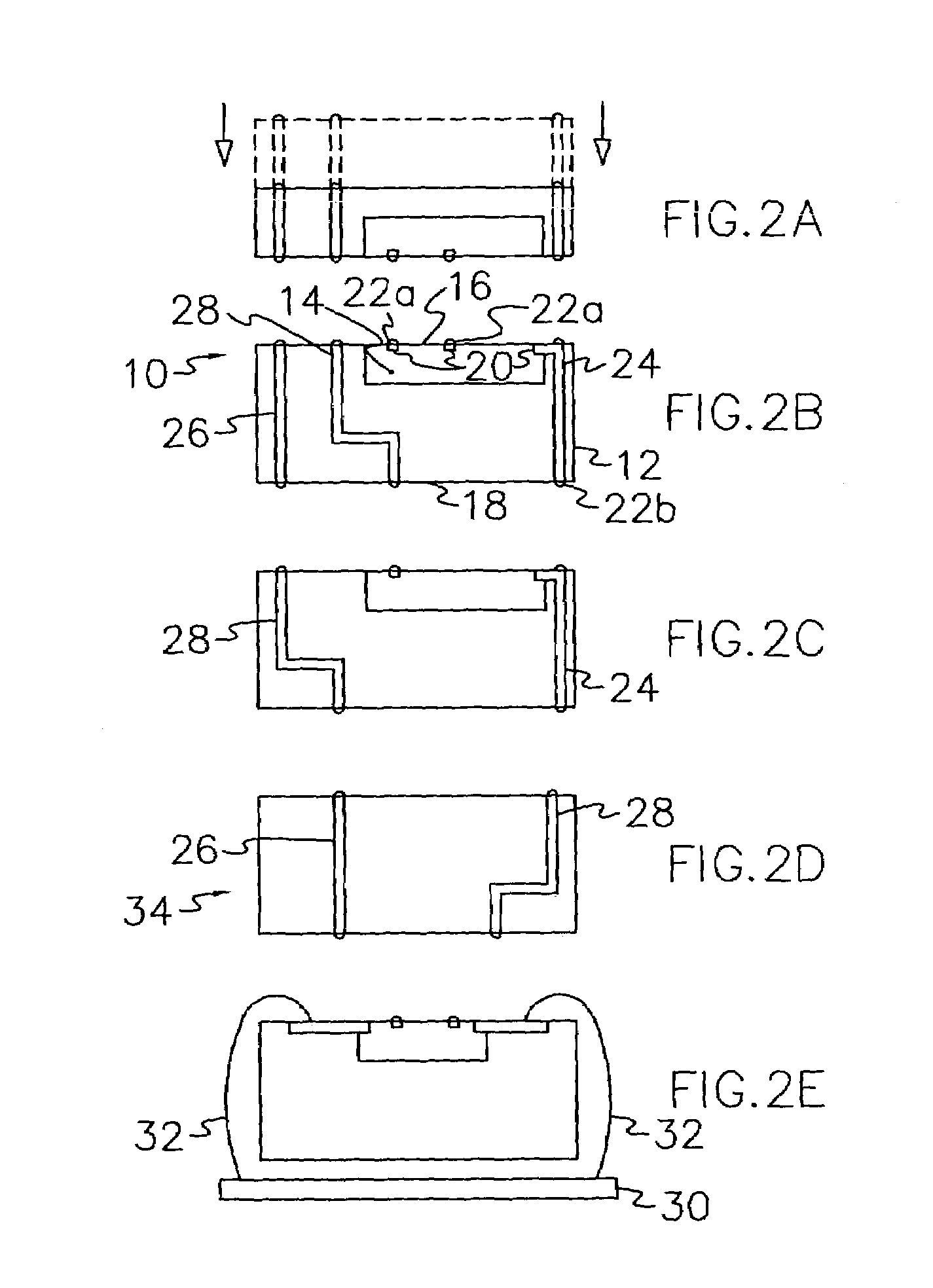

An apparatus and packaging method for stacking a plurality of integrated circuit substrates, i.e., substrates having integrated circuits formed as integral portions of the substrates, which provides interconnection paths through the substrates to simplify electrical connections between the integrated circuits while facilitating minimization of the volume and customization of the three dimensional package size to conform to the available internal space within a housing, e.g., one used in an implantabie device where package volume is at a premium. Furthermore, an internal cavity can be created by the stacked formation that is suitable for mounting of a surface mount device, e.g., a crystal or the like.

Owner:ALFRED E MANN FOUND FOR SCI RES

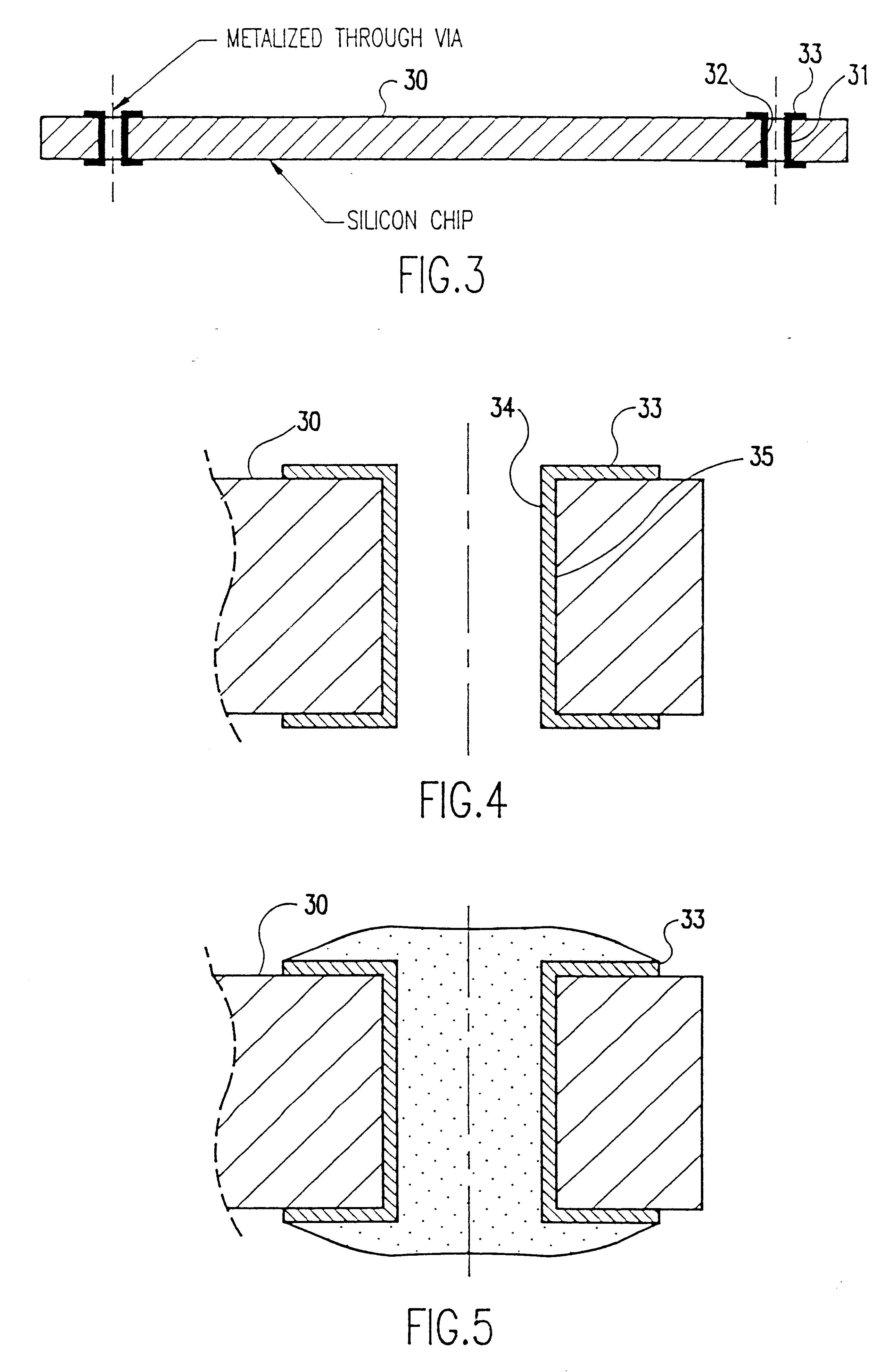

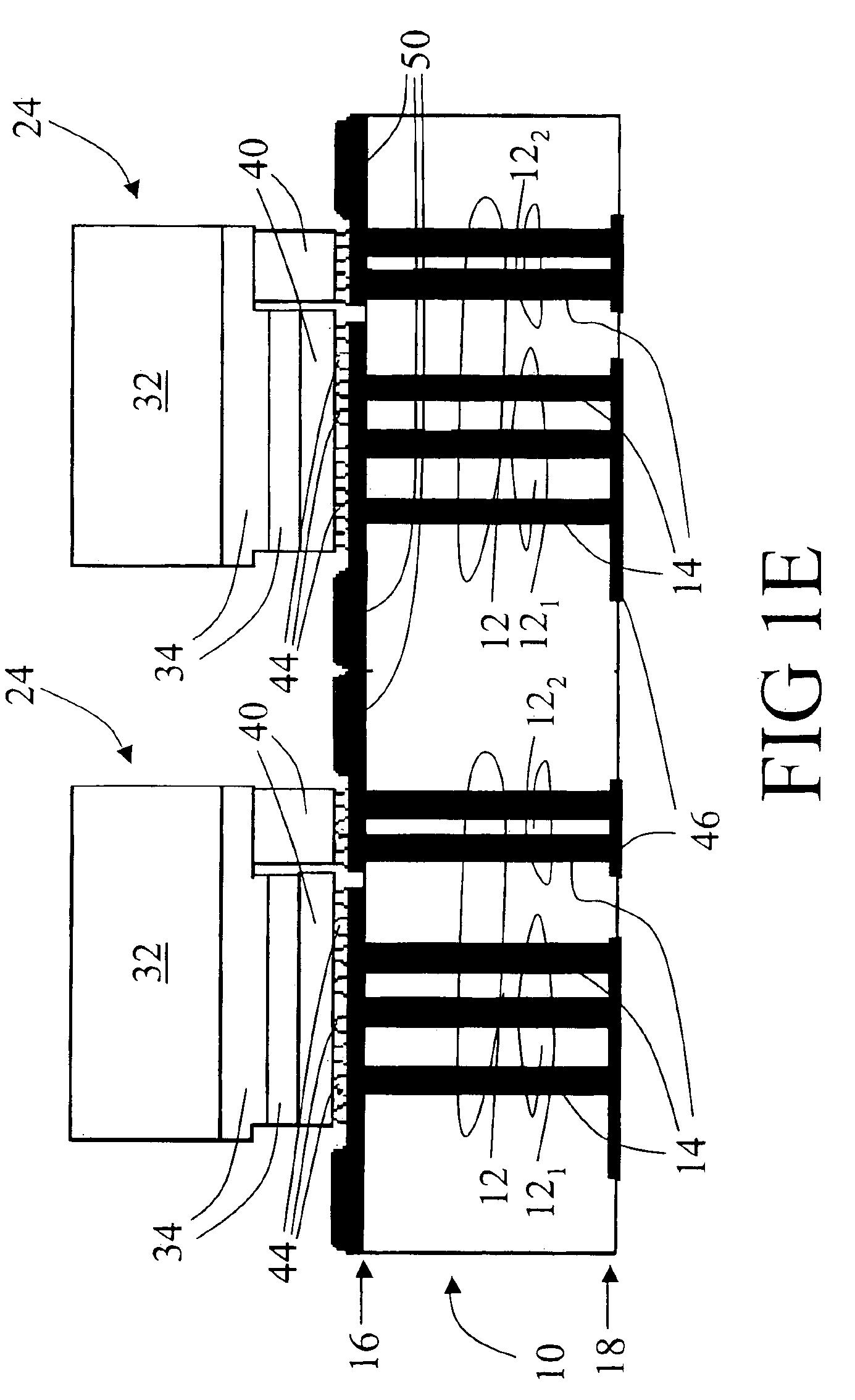

High density integrated circuit packaging with chip stacking and via interconnections

InactiveUS6236115B1Reduced connection exposureLarge capacitySemiconductor/solid-state device detailsSolid-state devicesEngineeringThermal expansion

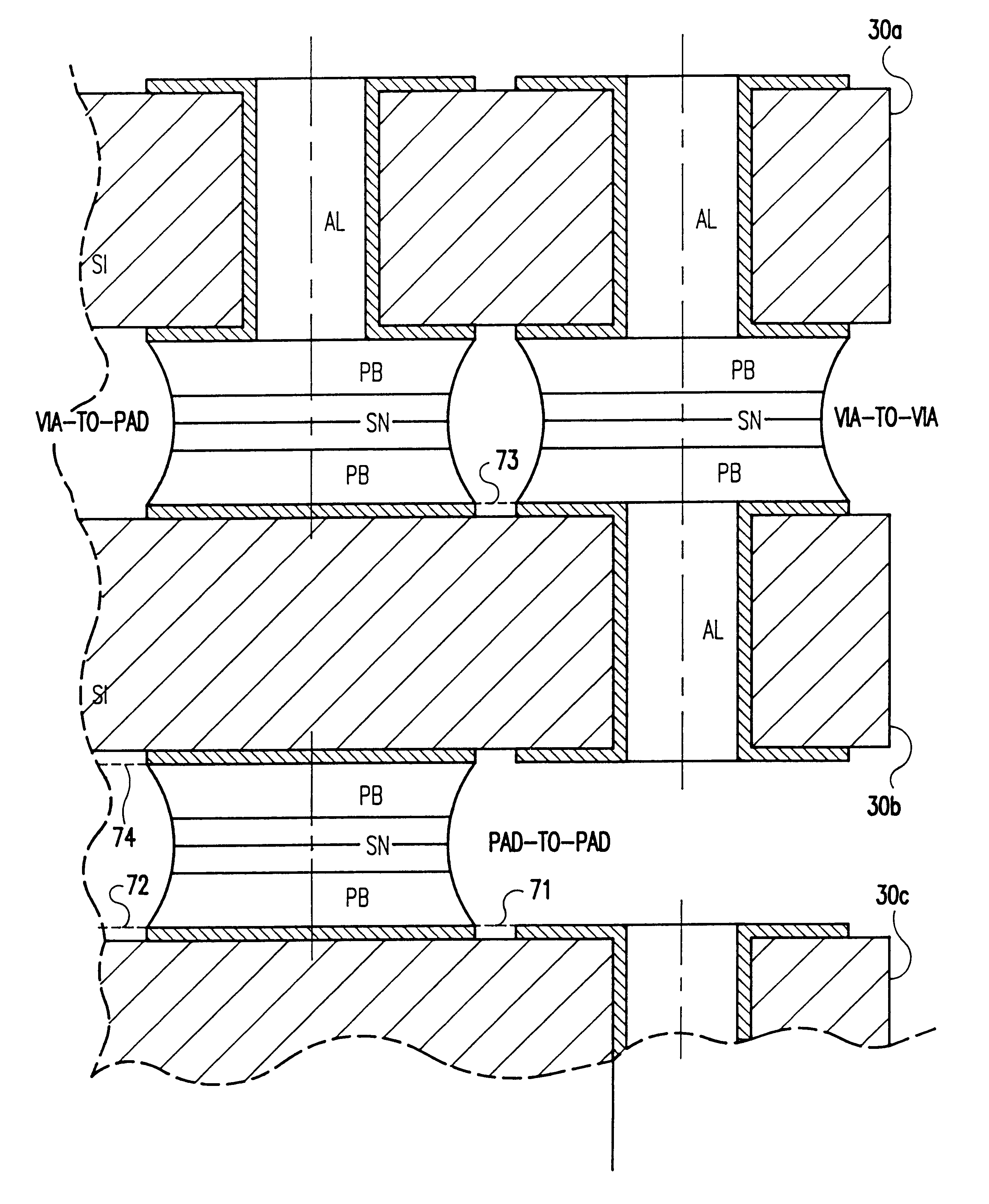

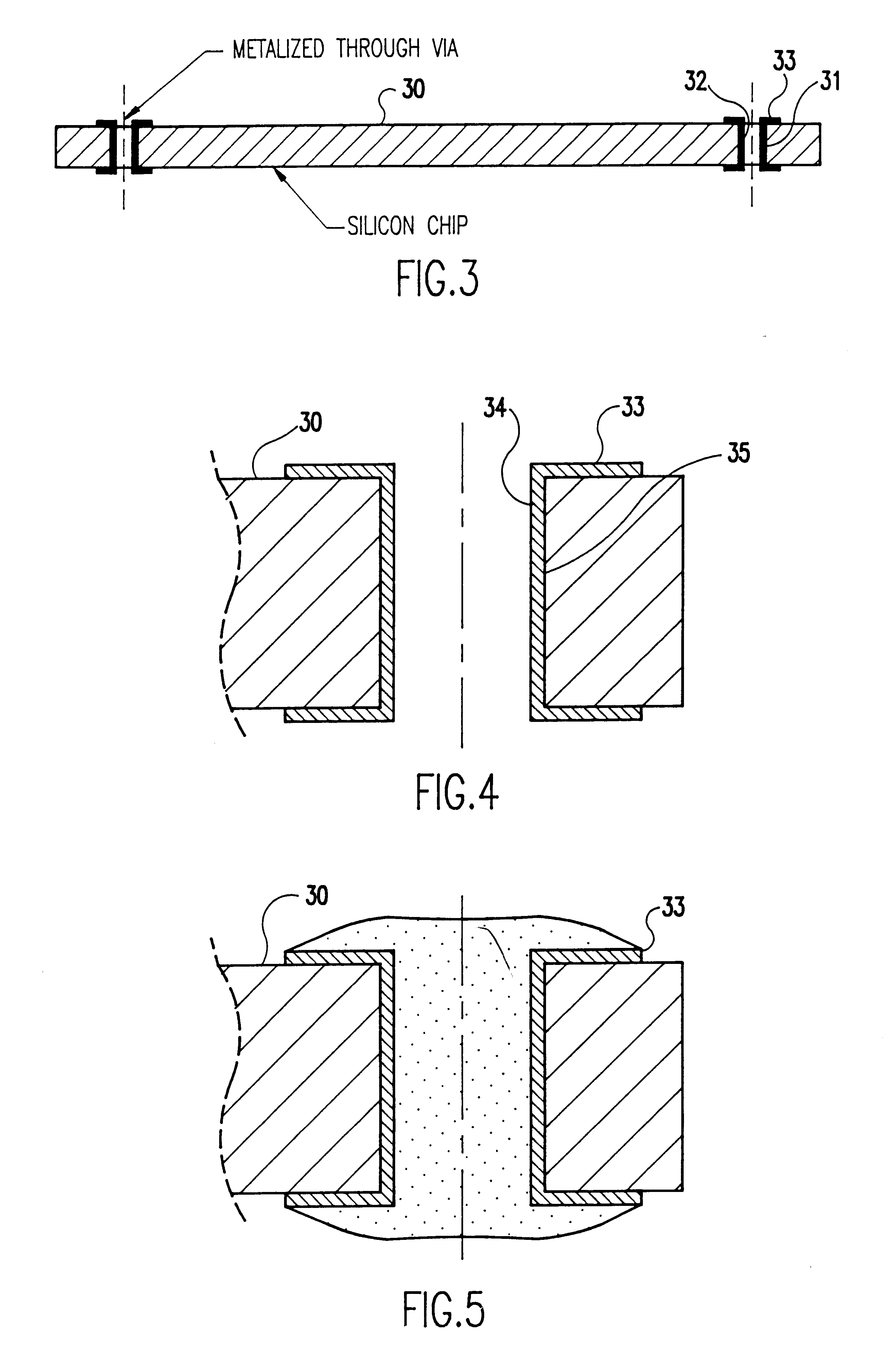

Chip stacks with decreased conductor length and improved noise immunity are formed by laser drilling of individual chips, such as memory chips, preferably near but within the periphery thereof, and forming conductors therethrough, preferably by metallization or filling with conductive paste which may be stabilized by transient liquid phase (TLP) processes and preferably with or during metallization of conductive pads, possibly including connector patterns on both sides of at least some of the chips in the stack. At least some of the chips in the stack then have electrical and mechanical connections made therebetween, preferably with electroplated solder preforms consistent with TLP processes. The connections may be contained by a layer of resilient material surrounding the connections and which may be formed in-situ. High density circuit packages thus obtained may be mounted on a carrier by surface mount techniques or separable connectors such as a plug and socket arrangement. The carrier may be of the same material as the chip stacks to match coefficients of thermal expansion. High-density circuit packages may also be in the form of removable memory modules in generally planar or prism shaped form similar to a pen or as a thermal conduction module.

Owner:INT BUSINESS MASCH CORP

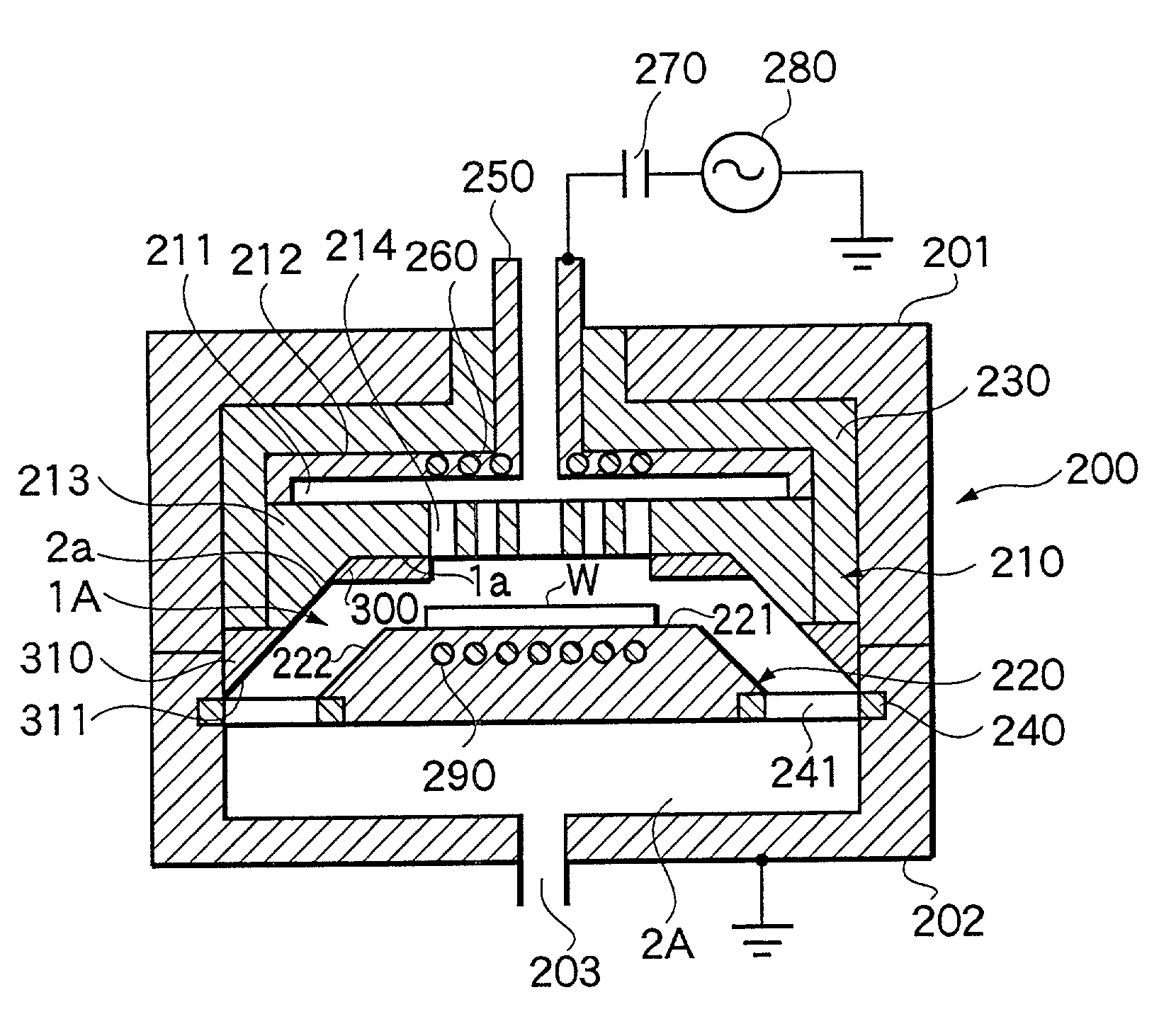

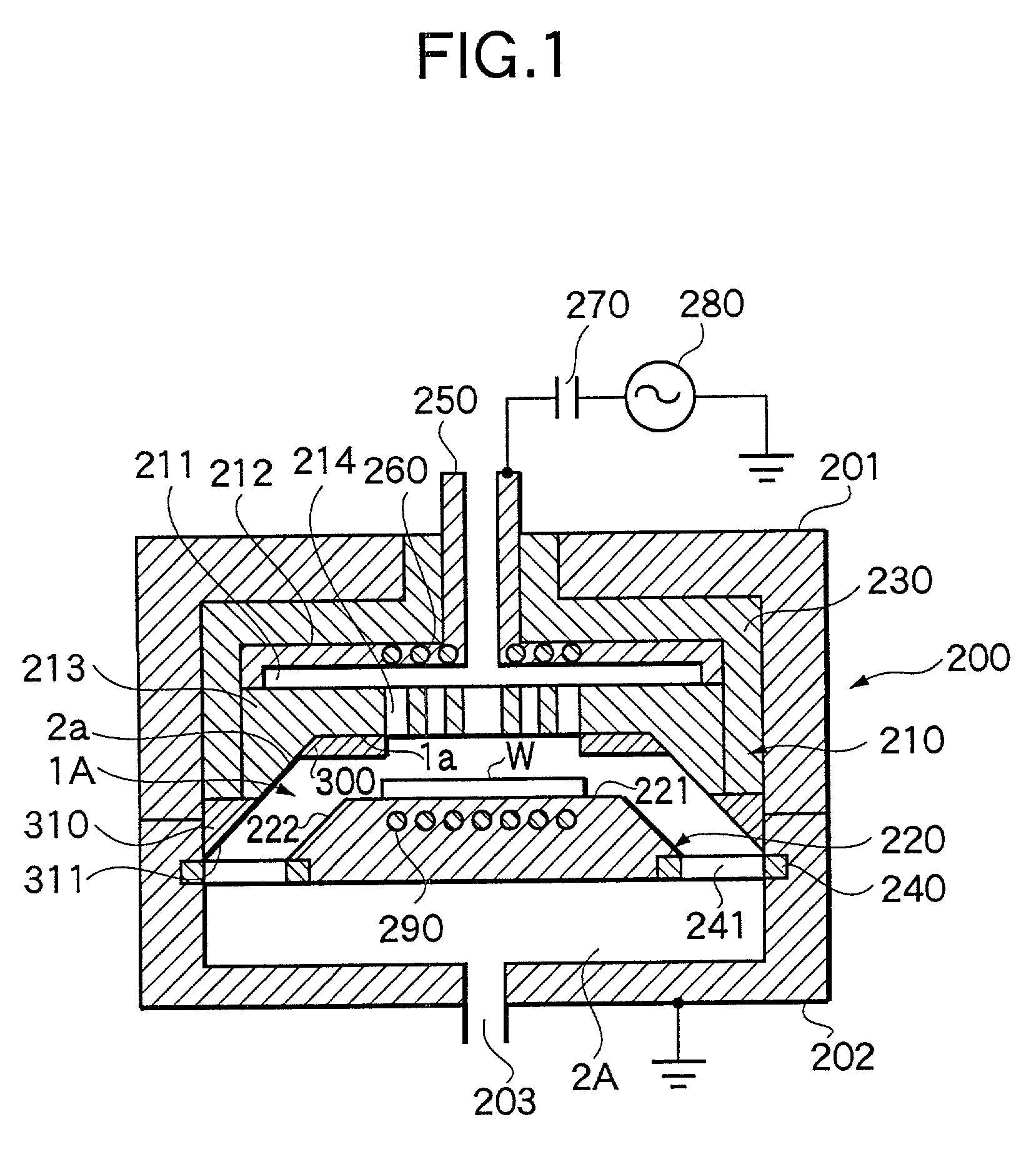

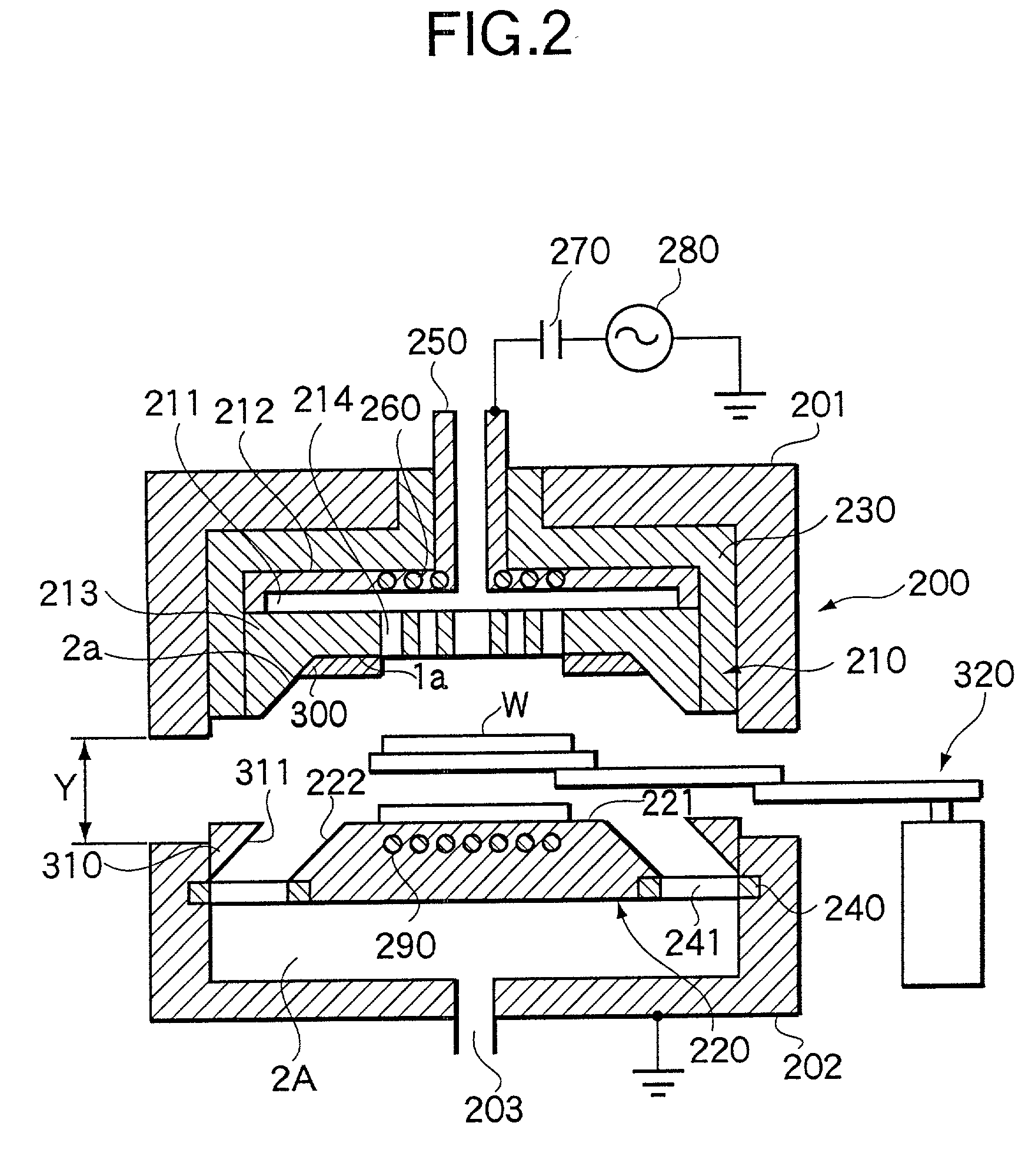

Plasma CVD device

InactiveUS20030205202A1Reduce the amount requiredIncrease productionElectric discharge tubesSemiconductor/solid-state device manufacturingSurface mountingEngineering

It is an object of the present invention to provide a plasma CVD device in which it is possible to inhibit the formation of particles resulting from the adhesion of reaction by-products of poor adhesive strength around the upper electrode. The plasma CVD device has a vacuum container 200, an upper electrode 210 and a lower electrode 220. The edge of the gas dispersion plate 213 of the upper electrode 210 is formed in the shape of an upturned bowl, the edge of which extends below the upper surface of the treatment substrate W mounted on the substrate-mounting surface 221 of the lower electrode 220.

Owner:KOKUSA ELECTRIC CO LTD

High frequency chip packages with connecting elements

InactiveUS7176506B2Reduce packaging costsLow impedance connectionImpedence networksSemiconductor/solid-state device detailsFlexible circuitsSurface mounting

A radio frequency chip package is formed by assembling a connecting element such as a circuit board or flexible circuit tape having chips thereon with a bottom plane element such as a lead frame incorporating a large thermally-conductive plate and leads projecting upwardly from the plane of the plate. The assembly step places the rear surfaces of the chips on the bottom side of the connecting element into proximity with the thermal conductor and joins the conductive traces on the connecting element with the leads. The resulting assembly is encapsulated, leaving terminals at the bottom ends of the leads exposed. The encapsulated assembly may be surface-mounted to a circuit board. The leads provide robust electrical connections between the connecting element and the circuit board.

Owner:TESSERA INC

Method and apparatus for a semiconductor package for vertical surface mounting

InactiveUS6291894B1Electrically conductive connectionsDigital data processing detailsDevice materialSurface mounting

A method for packaging a semiconductor device includes connecting a plurality of wire leads to a corresponding plurality of electrical connection pads on the semiconductor device, covering at least a portion of the semiconductor device and at least a portion of each of the wire leads with an encapsulating material, and removing a portion of the encapsulating material and a portion of each of the wire leads to form a packaged semiconductor device wherein each of the wire leads has an exposed portion only at an end. The invention also includes a packaged semiconductor device having an integrated circuit device with a plurality of electrical connection pads, a plurality of wire leads coupled to the plurality of electrical connection pads, and a covering of encapsulating material covering at least a portion of the integrated circuit device and covering each of the wire leads, wherein each of the wire leads has an exposed end. The present invention contemplates wire bonding and encapsulation of individual die as well as multiple die on a single wafer.

Owner:MICRON TECH INC

High density integrated circuit packaging with chip stacking and via interconnections

InactiveUS6187678B1Reduced connection exposureLarge capacitySemiconductor/solid-state device detailsSolid-state devicesThermal expansionPrism

Chip stacks with decreased conductor length and improved noise immunity are formed by laser drilling of individual chips, such as memory chips, preferably near but within the periphery thereof, and forming conductors therethrough, preferably by metallization or filling with conductive paste which may be stabilized by transient liquid phase (TLP) processes and preferably with or during metallization of conductive pads, possibly including connector patterns on both sides of at least some of the chips in the stack. At least some of the chips in the stack then have electrical and mechanical connections made therebetween, preferably with electroplated solder preforms consistent with TLP processes. The connections may be contained by a layer of resilient material surrounding the connections and which may be formed in-situ. High density circuit packages thus obtained may be mounted on a carrier by surface mount techniques or separable connectors such as a plug and socket arrangement. The carrier may be of the same material as the chip stacks to match coefficients of thermal expansion. High-density circuit packages may also be in the form of removable memory modules in generally planar or prism shaped form similar to a pen or as a thermal conduction module.

Owner:IBM CORP

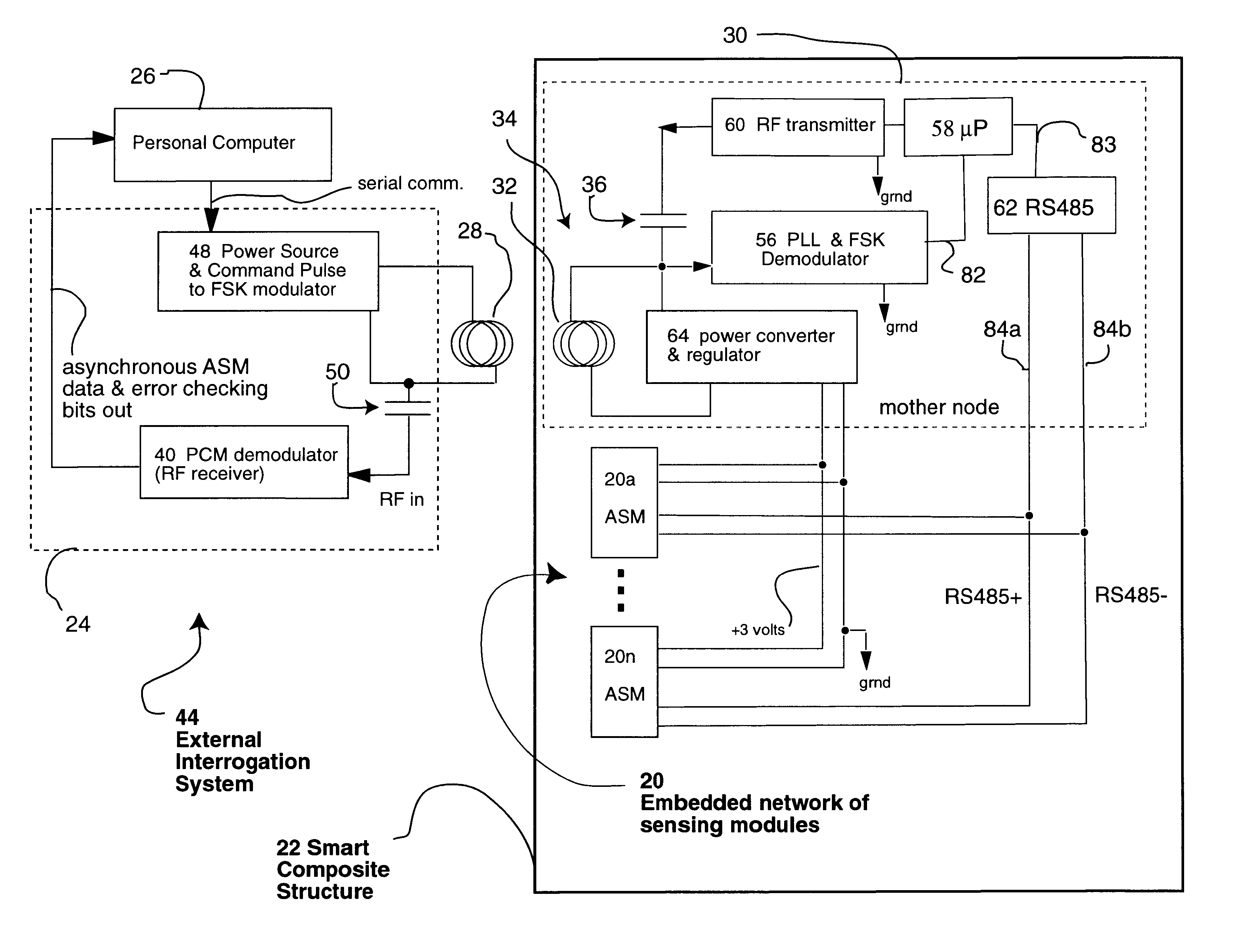

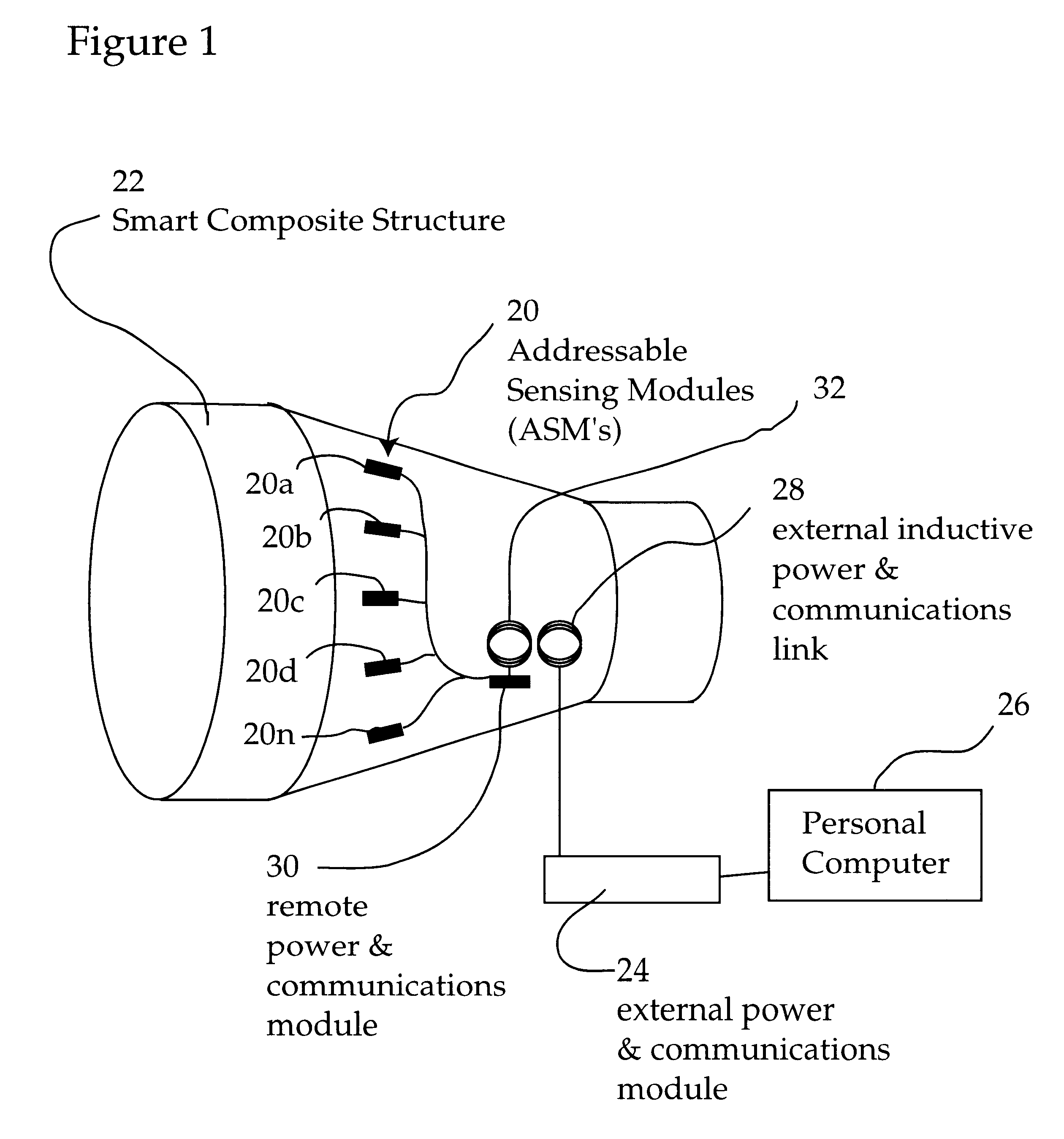

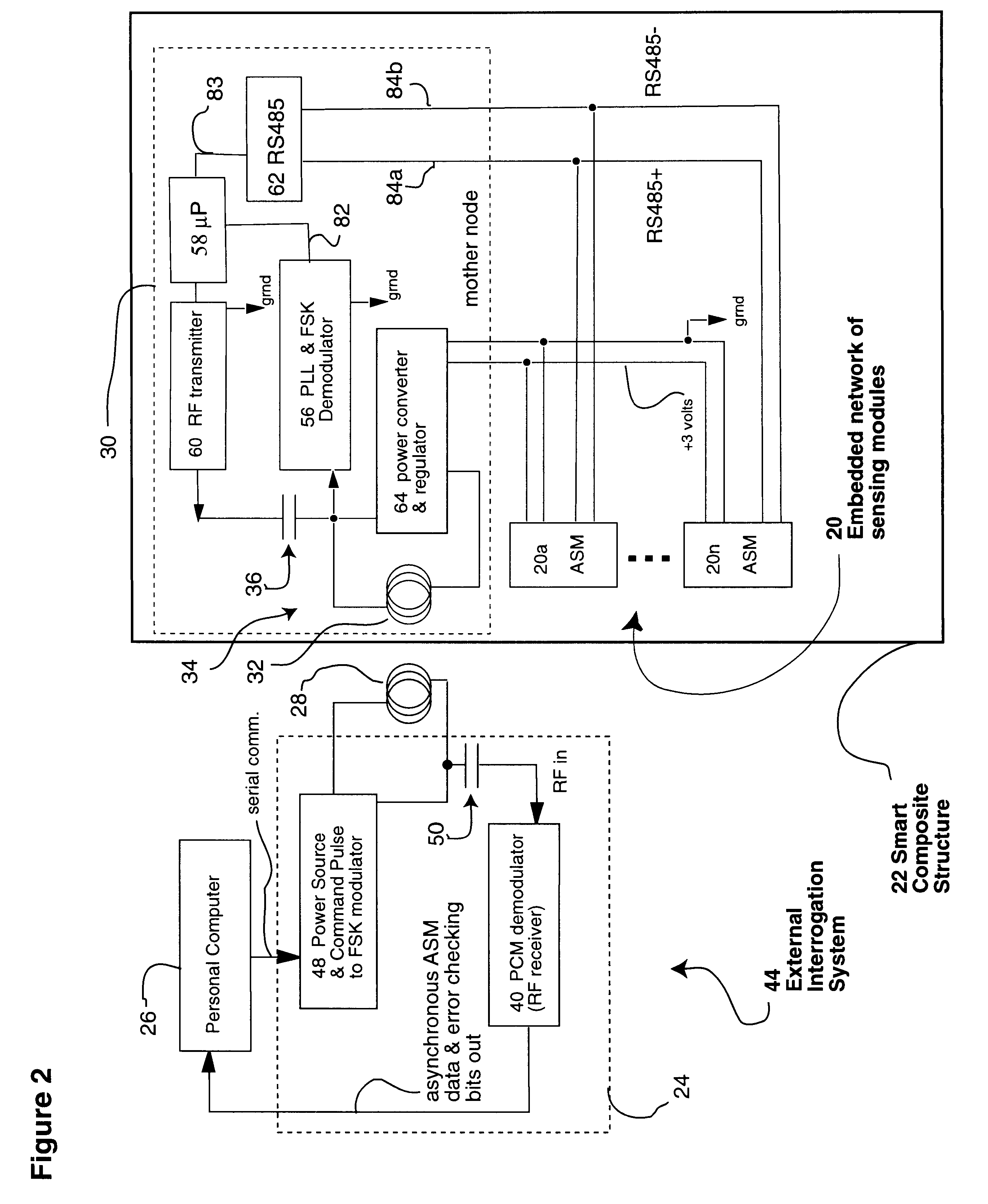

System for remote powering and communication with a network of addressable, multichannel sensing modules

InactiveUS6529127B2Low costElectric signal transmission systemsDigital data processing detailsError checkingInstrumentation amplifier

A multidrop network of multichannel, addressable sensing modules (ASM's), to be embedded within a composite structure, remotely powered, and interrogated by a personal computer through a non-contacting inductive link. Each ASM contains a microprocessor with non-volatile memory, multiplexer, programmable gain and filter instrumentation amplifier, and sigma delta analog to digital converter (all housed in two thin surface mount packages). An embedded mothernode includes circuitry for power and data reception (into the structure), and data transmission (back out of the structure). The external interrogation system communicates into the network of ASM's by modulating the AC waveform that delivers power to the embedded electronics. Once addressed, each ASM powers up its programmable (gain & filter) sensing channels (3 full differential or 5 pseudo differential) and data conversion elements. Sensed data are pulse code modulated, including error checking, which serially modulate an RF carrier for wireless transmission out of the composite to the interrogating computer. These advanced, micro-miniature sensing networks may be applied to a wide variety of military, medical, & civil structures.

Owner:LORD CORP

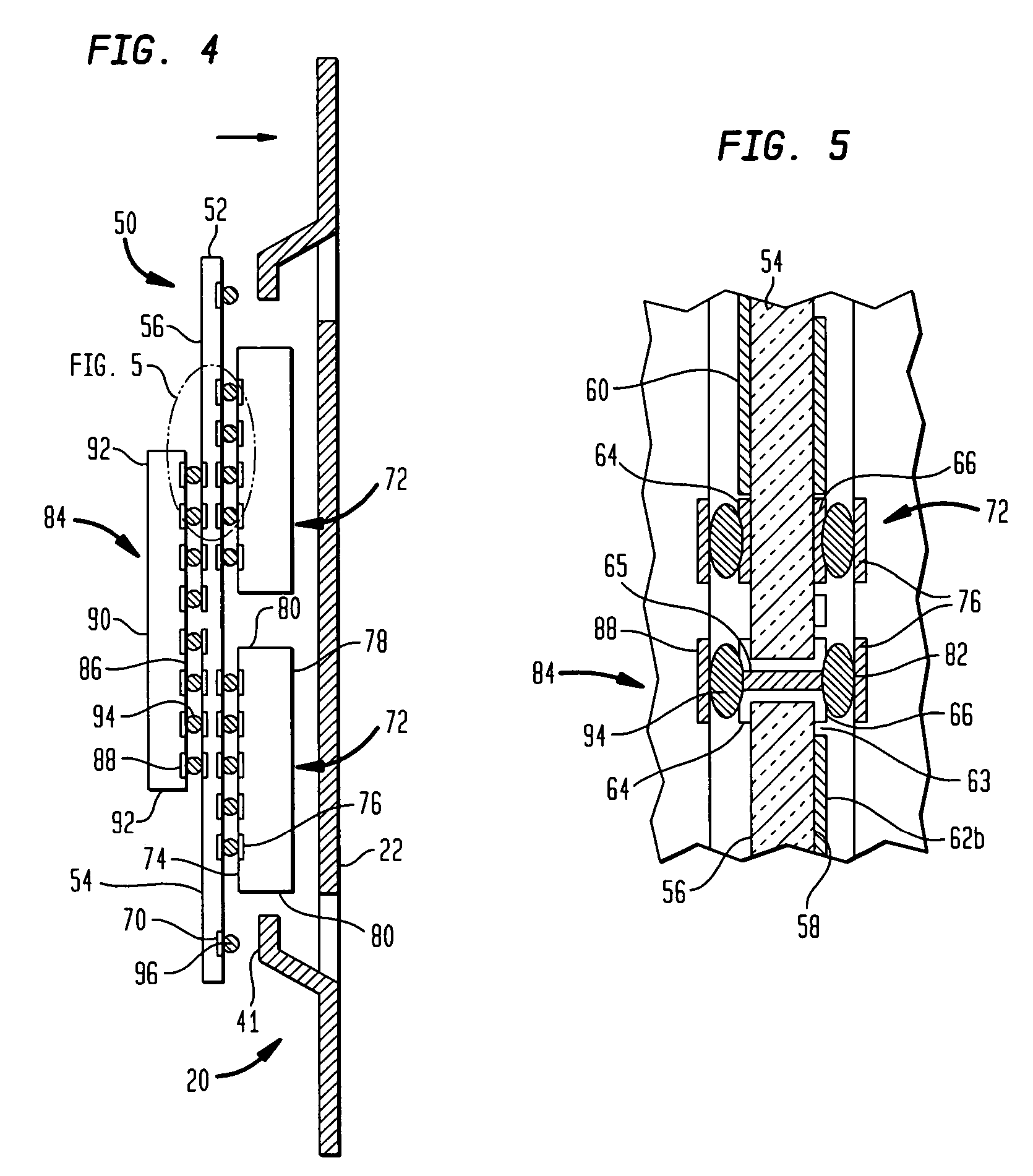

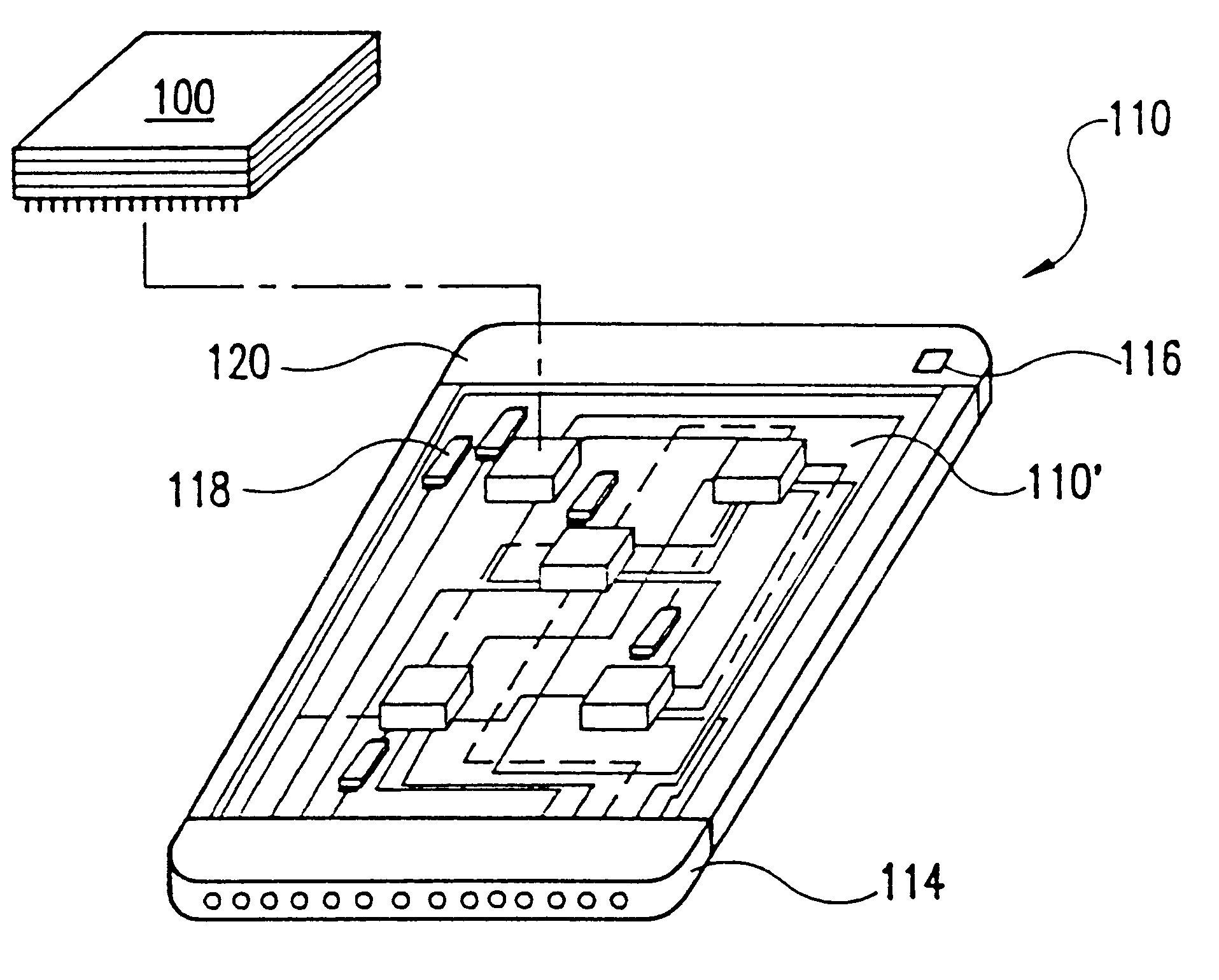

Implantable medical device incorporating miniaturized circuit module

Implantable medical devices (IMDS) having RF telemetry capabilities for uplink transmitting patient data and downlink receiving programming commands to and from an external programmer having an improved RF module configured to occupy small spaces within the IMD housing to further effect the miniaturization thereof. An RF module formed of an RF module substrate and at least one IC chip and discrete components has a volume and dimensions that are optimally minimized to reduce its volumetric form factor. Miniaturization techniques include: (1) integrating inductors into one or more IC chips mounted to the RF module substrate; (2) mounting each IC chip into a well of the RF module substrate and using short bonding wires to electrically connect bond pads of the RF module substrate and the IC chip; and (3) surface mounting discrete capacitors over IC chips to reduce space taken up on the RF module substrate. The integrated inductors are preferably fabricated as planar spiral wound conductive traces formed of high conductive metals to reduce trace height and width while maintaining low resistance, thereby reducing parasitic capacitances between adjacent trace side walls and with a ground plane of the IC chip. The spiral winding preferably is square or rectangular, but having truncated turns to eliminate 90° angles that cause point-to-point parasitic capacitances. The planar spiral wound conductive traces are further preferably suspended over the ground plane of the RF module substrate by micromachining underlying substrate material away to thereby reduce parasitic capacitances.

Owner:MEDTRONIC INC

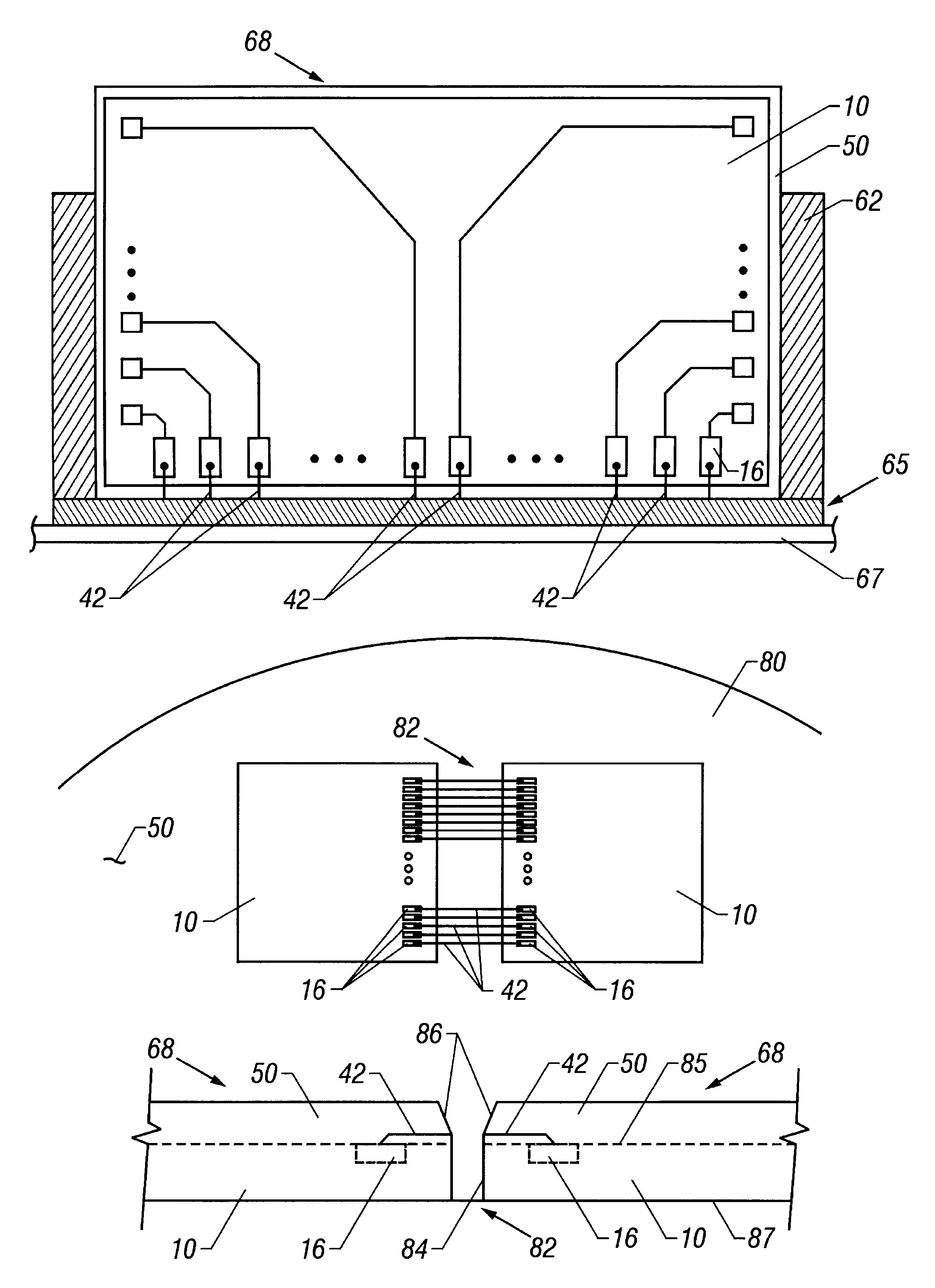

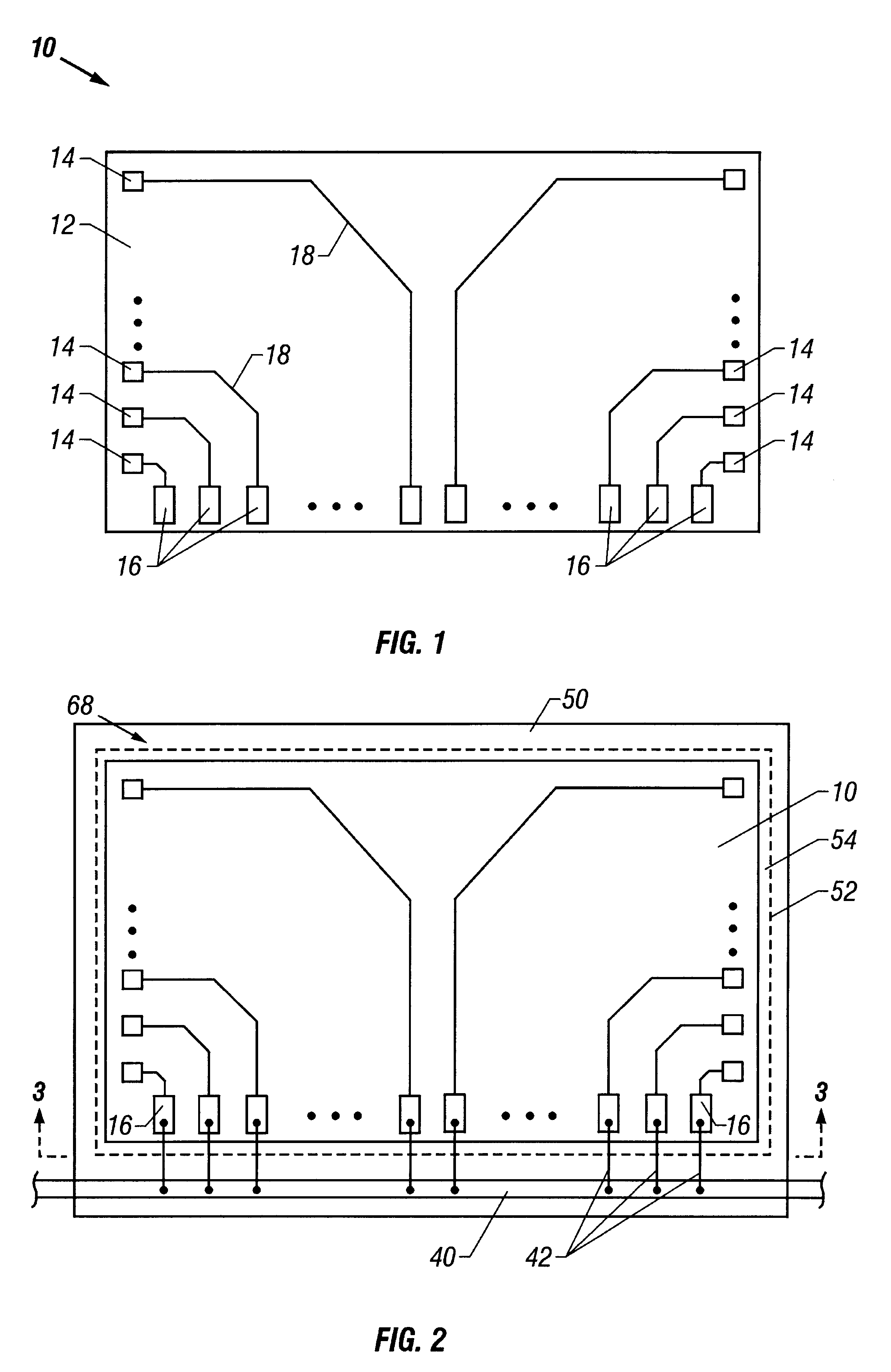

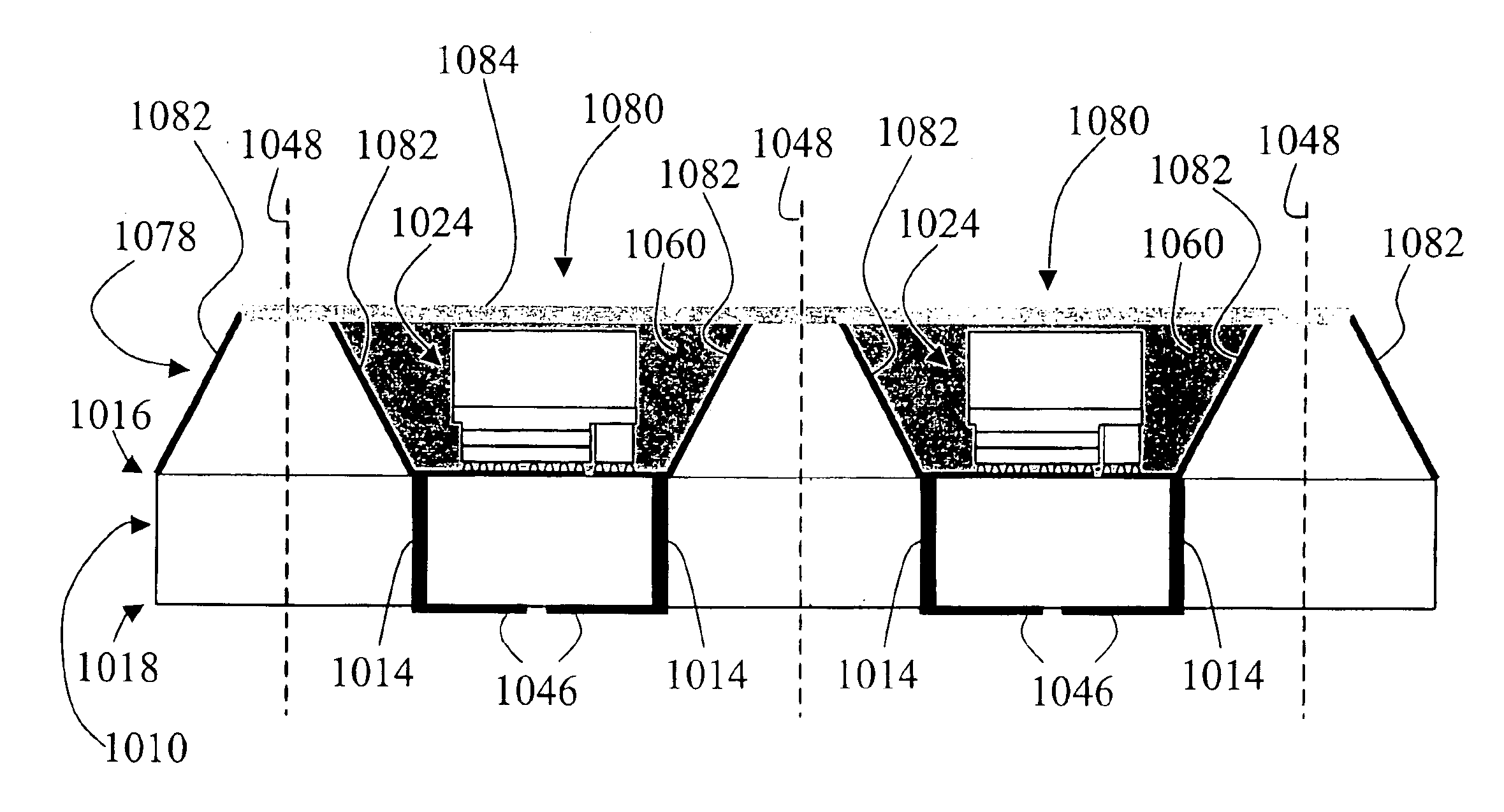

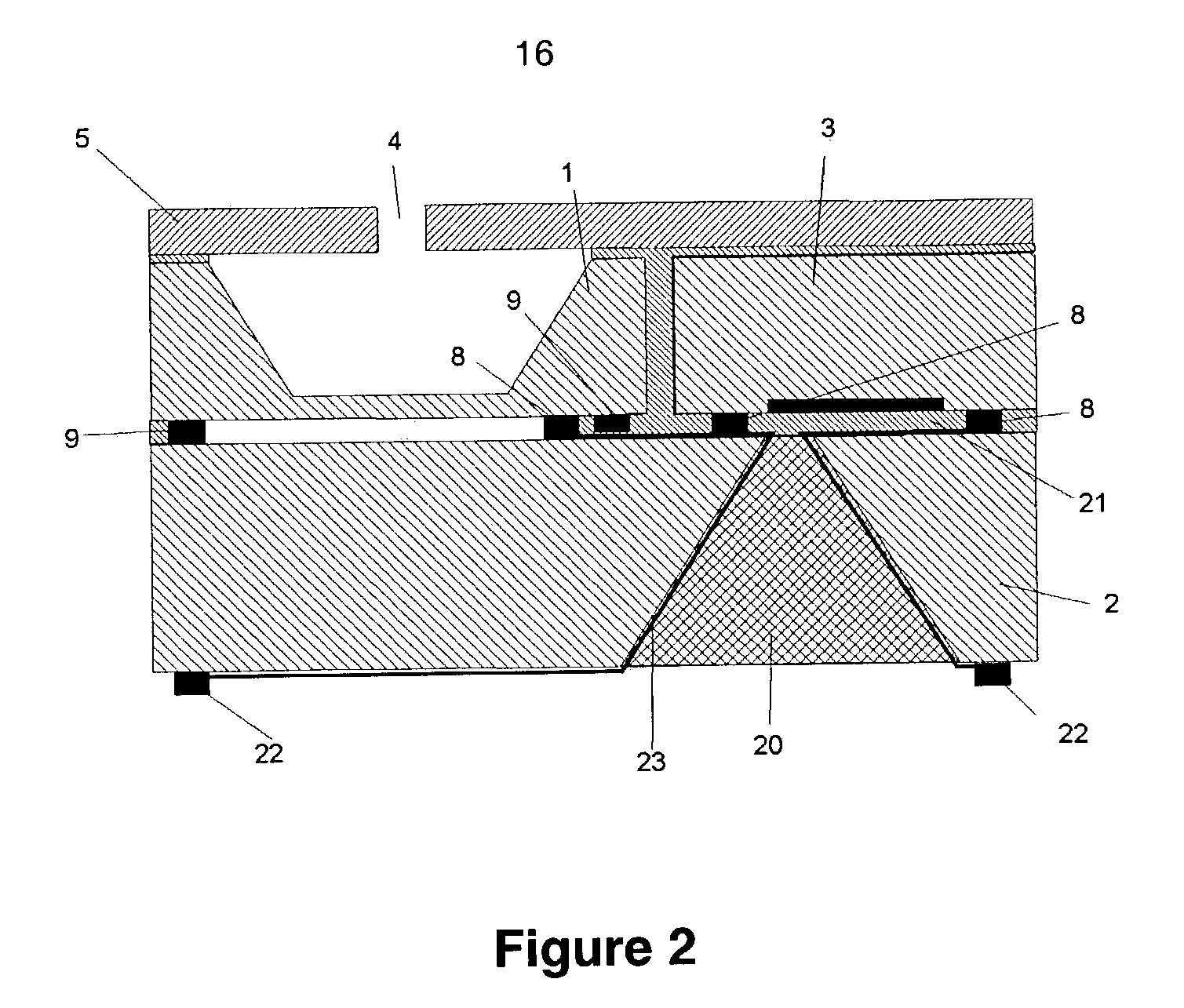

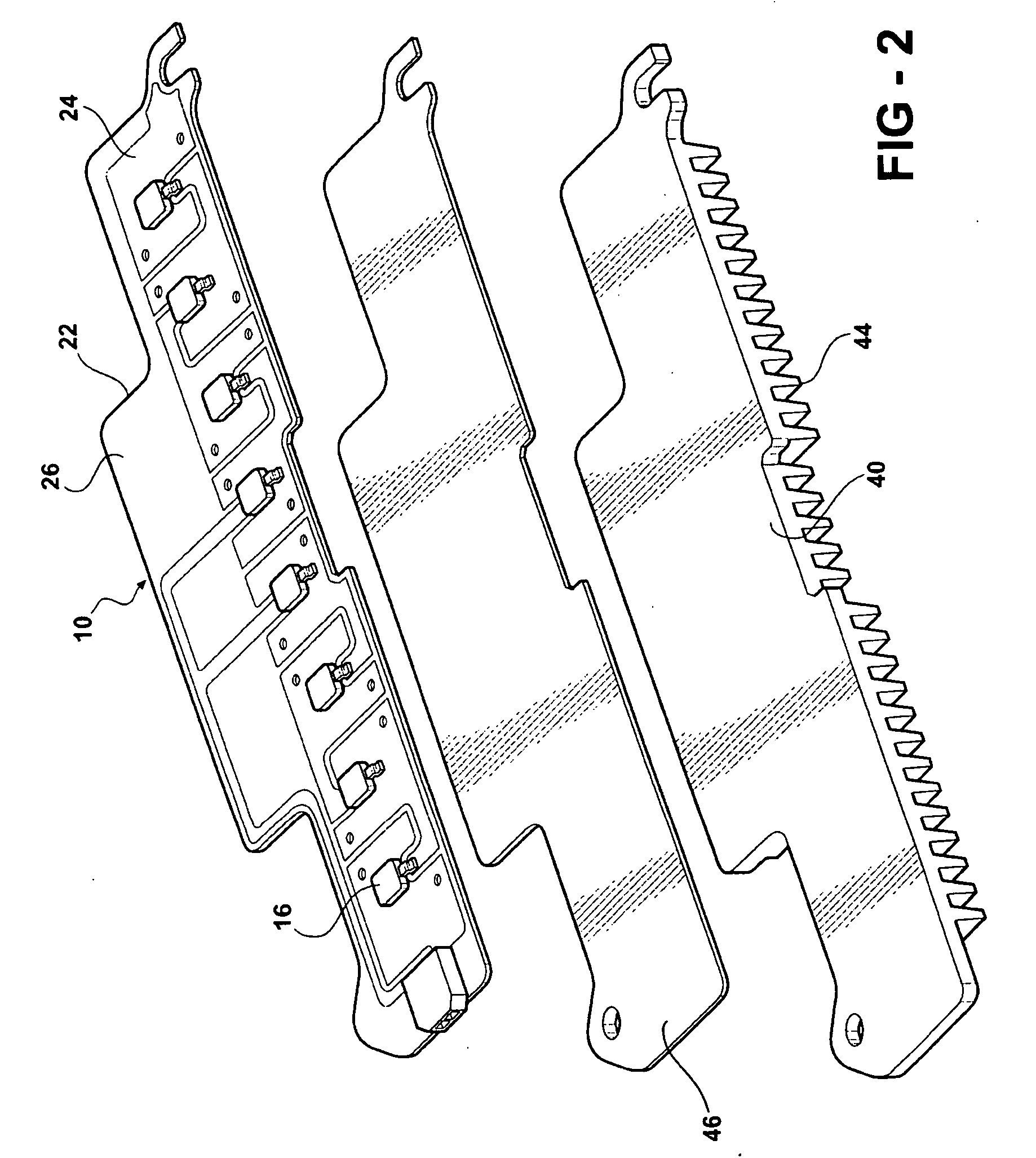

LED power package

InactiveUS6964877B2Solid-state devicesSemiconductor/solid-state device manufacturingSurface mountingEngineering

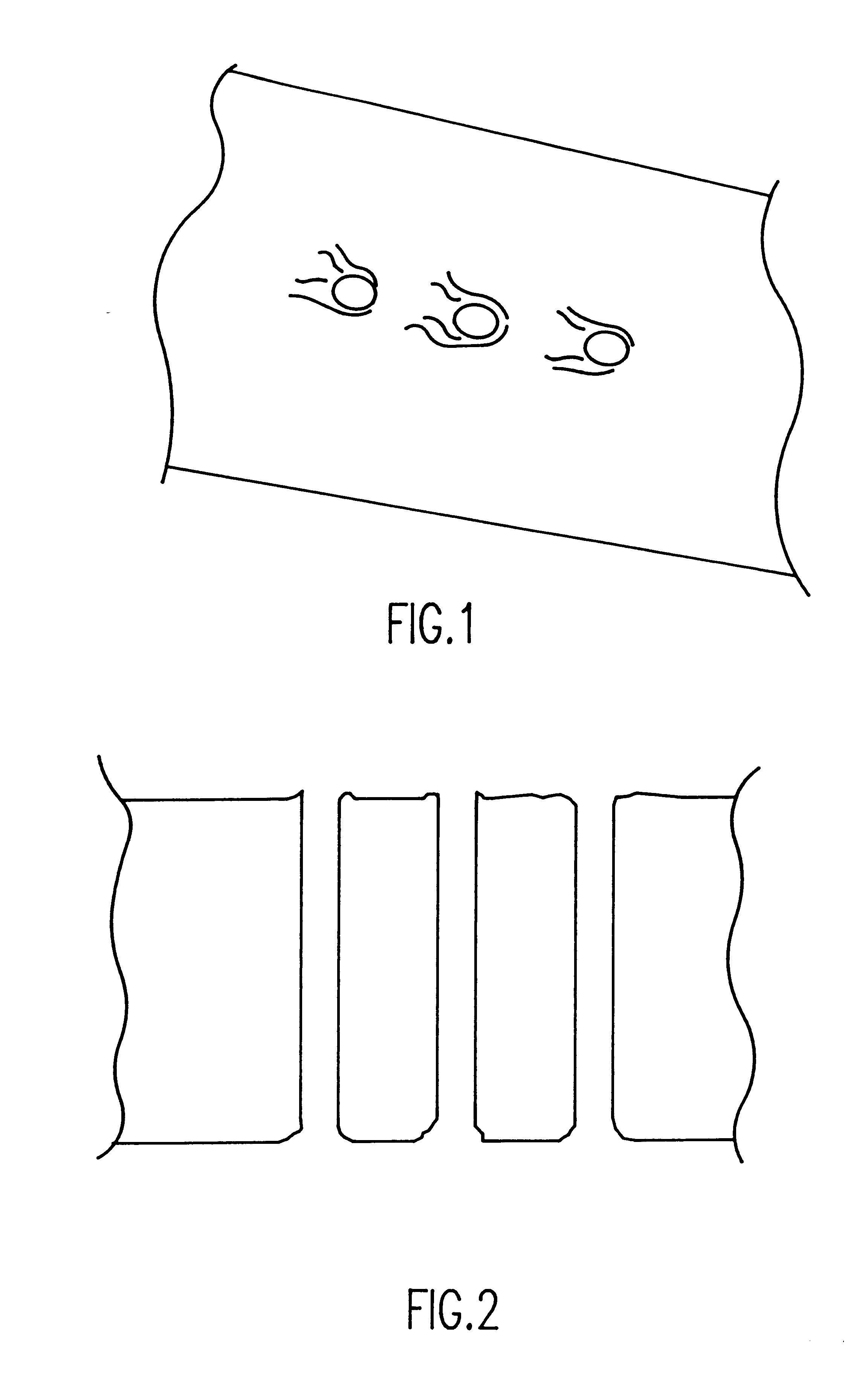

Surface mount light emitting diode (LED) packages each contain a light emitting diode (LED) die (24). A plurality of arrays of openings are drilled into an electrically insulating sub-mount wafer (10). A metal is applied to the drilled openings to produce a plurality of via arrays (12). The LED dice (24) are flip-chip bonded onto a frontside (16) of the sub-mount wafer (10). The p-type and n-type contacts of each flip-chip bonded LED (24) electrically communicate with a solderable backside (18) of the sub-mount wafer (10) through a via array (12). A thermal conduction path (10, 12) is provided for thermally conducting heat from the flip-chip bonded LED dice (24) to the solderable backside (18) of the sub-mount wafer (10). Subsequent to the flip-chip bonding, the sub-mount wafer (10) is separated to produce the surface mount LED packages.

Owner:PROLIGHT OPTO TECH

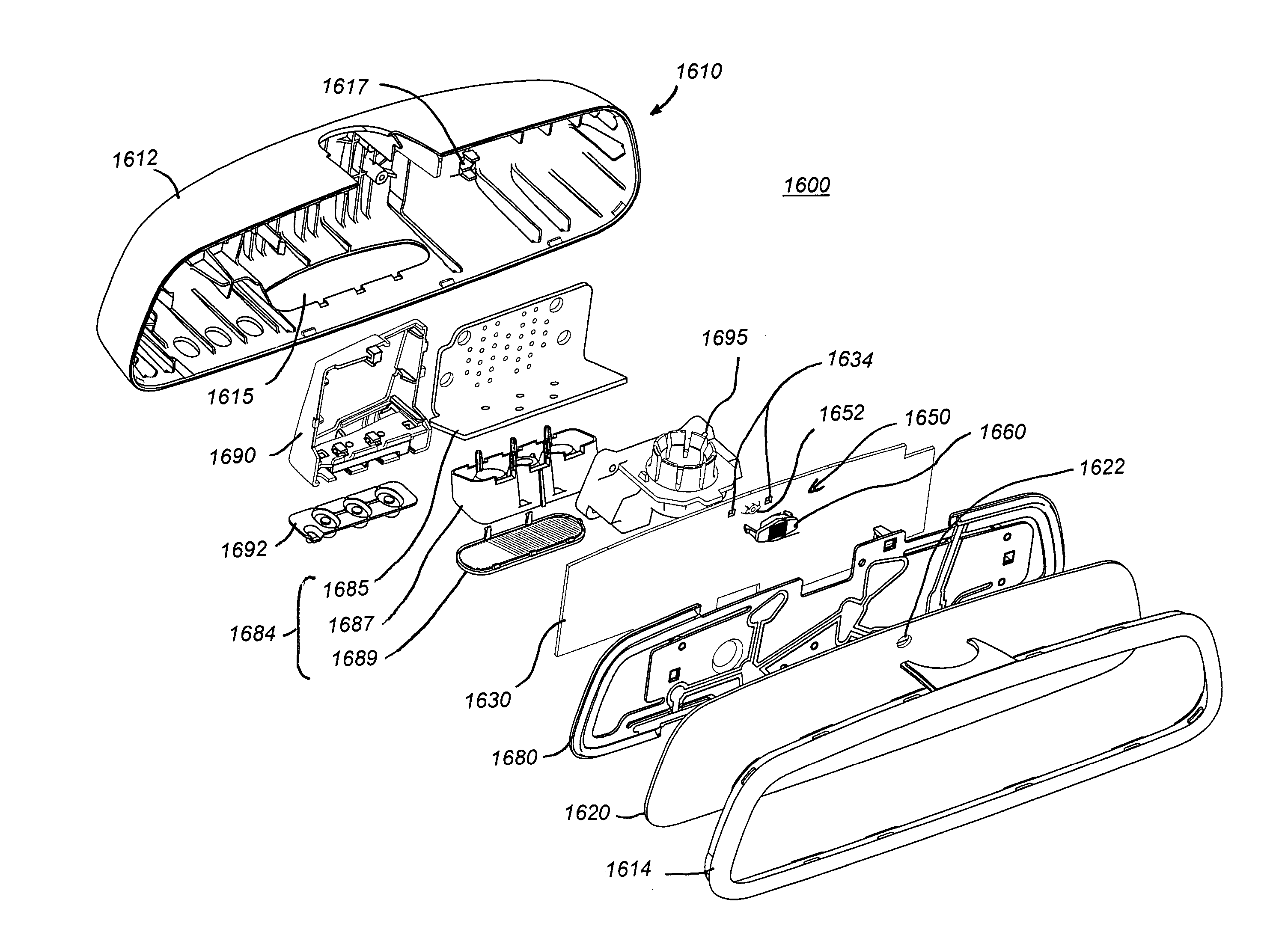

Dimmable rearview assembly having a glare sensor

Owner:GENTEX CORP

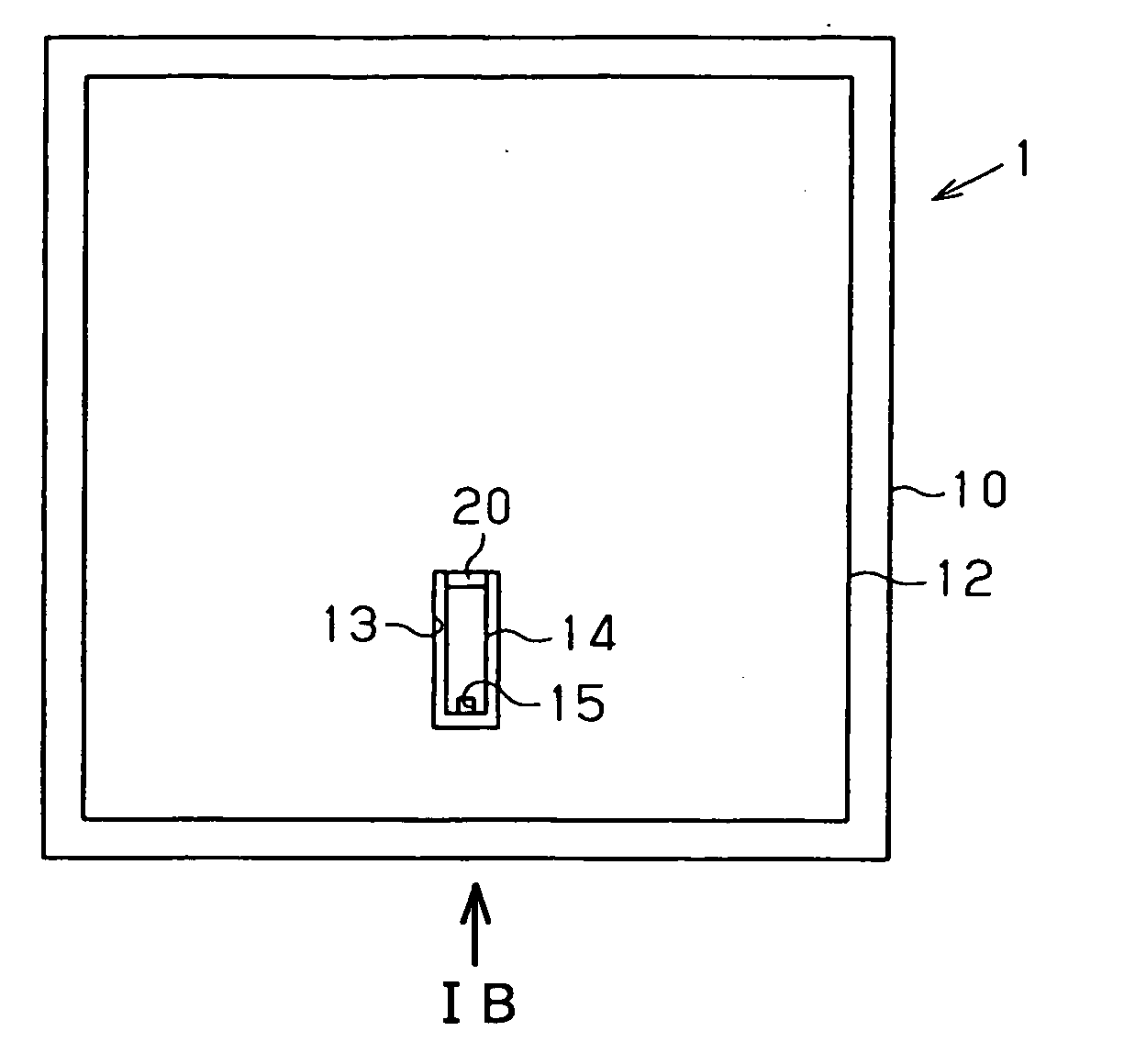

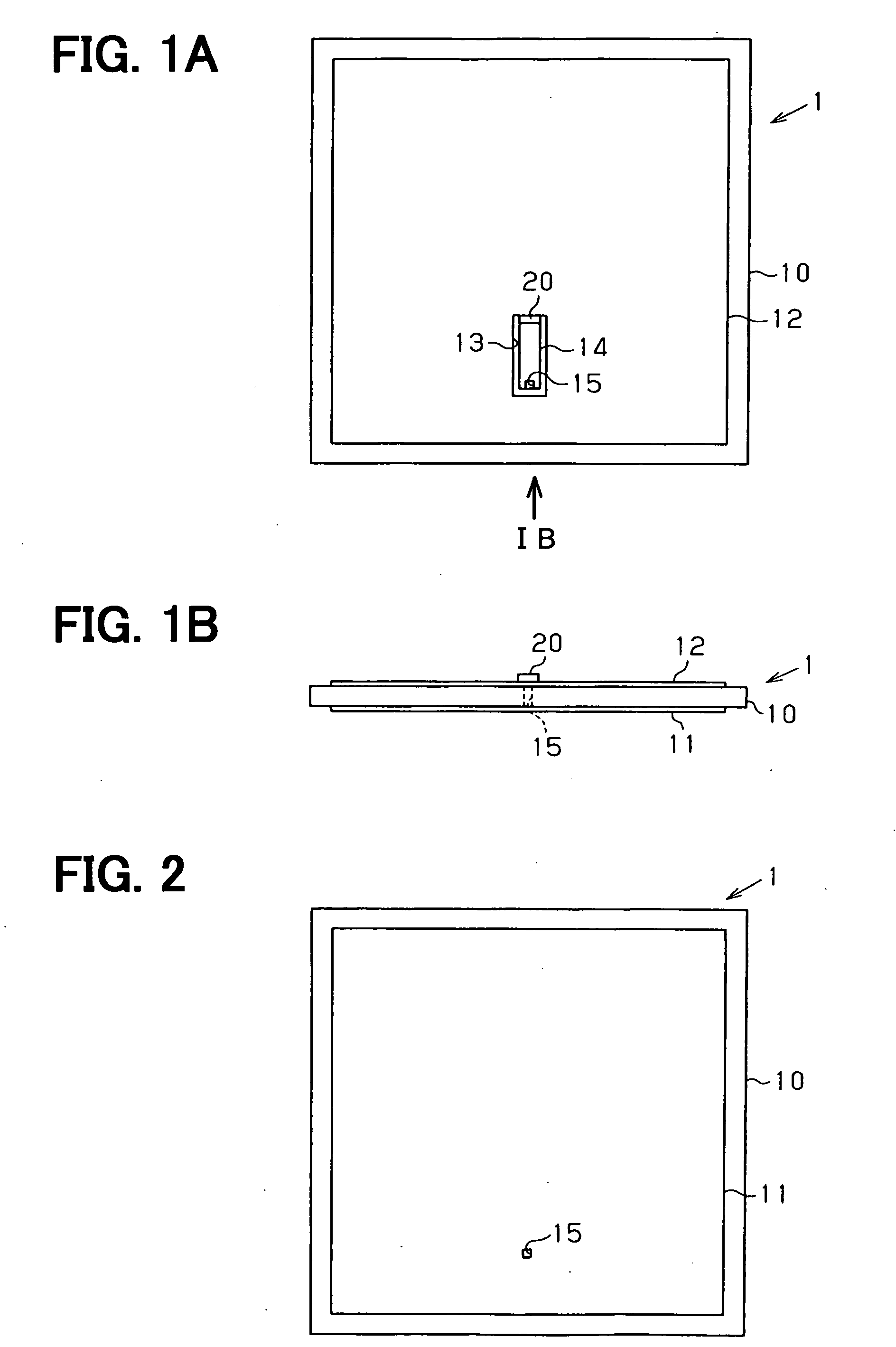

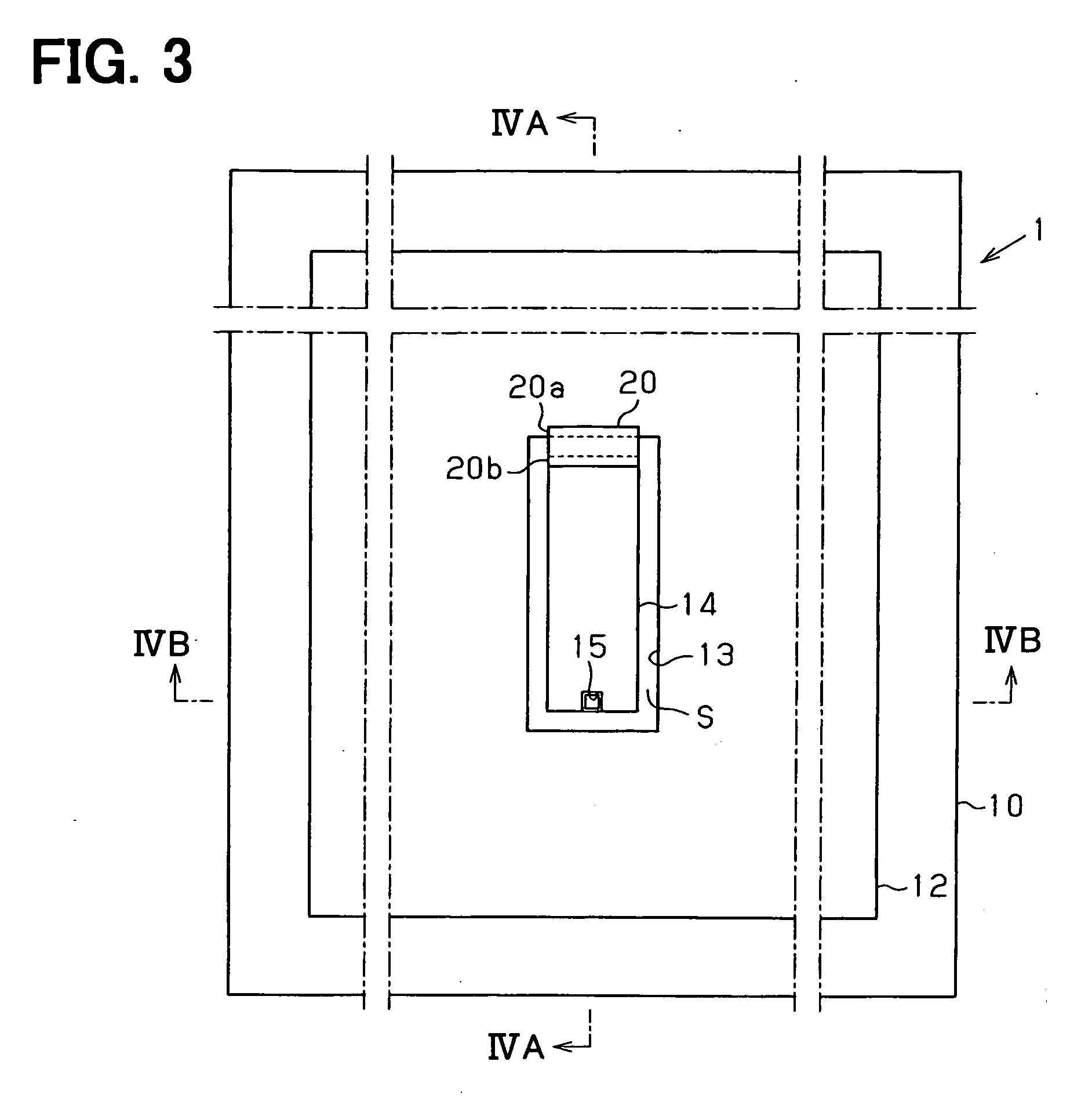

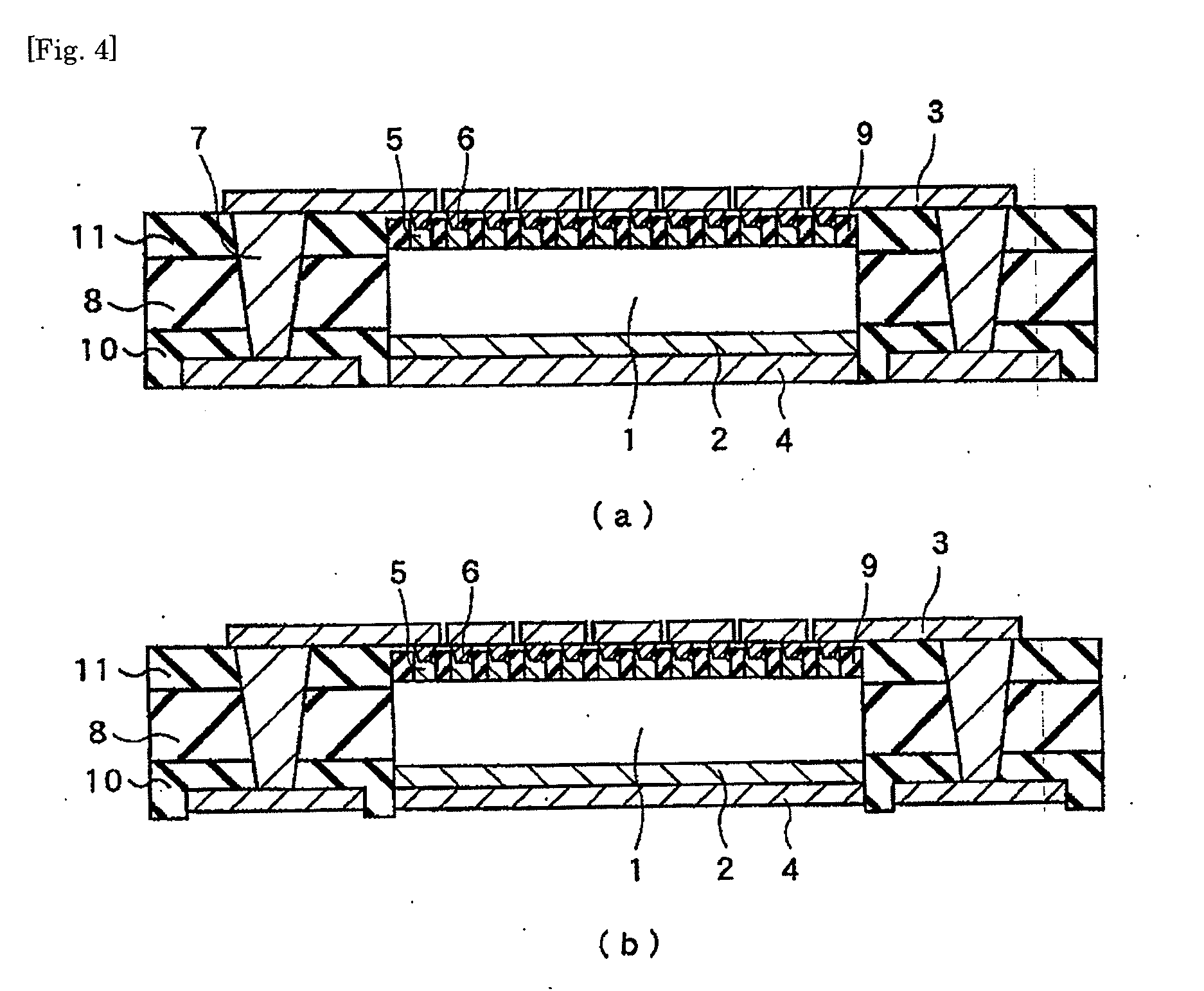

IC tag and IC tag attachment structure

InactiveUS20060145872A1Wide directivityImpedance matchingSemiconductor/solid-state device detailsSolid-state devicesSurface mountingMetal

A first metal plate for transmission and a second metal plate for transmission are closely-attached to a first surface and a second surface of a dielectric body, respectively. An outer edge of the first metal plate substantially symmetrically faces an outer edge of the second metal plate via the dielectric body. A metal plate for matching is arranged inside a hole formed on the second metal plate, with a slit formed with an inner wall of the hole, and is fixed to the dielectric body. The metal plate for matching is electrically connected to the first metal plate via a through hole penetrating the dielectric body. An IC chip is surface-mounted to connect the second metal plate with the metal plate for matching.

Owner:DENSO CORP

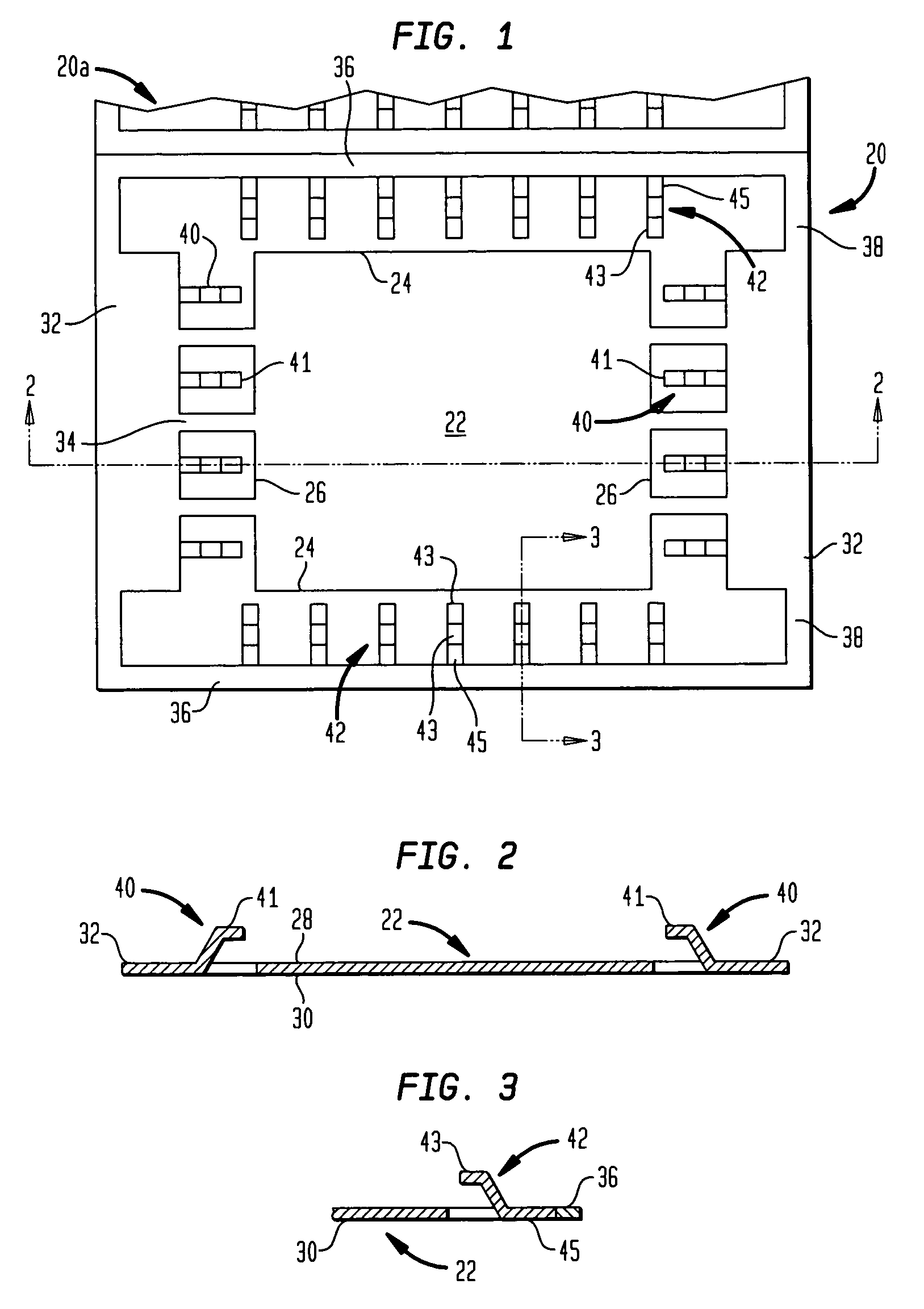

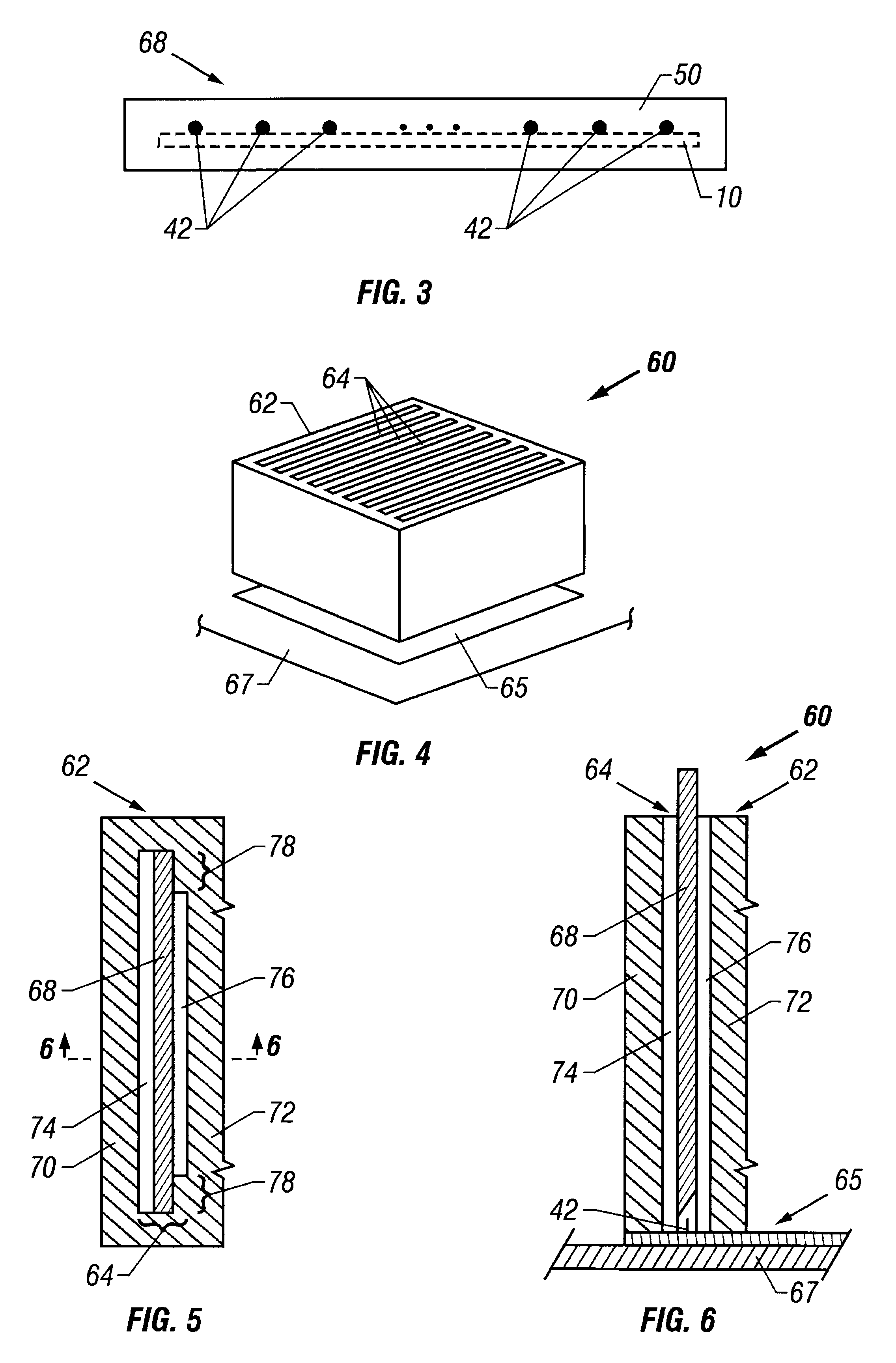

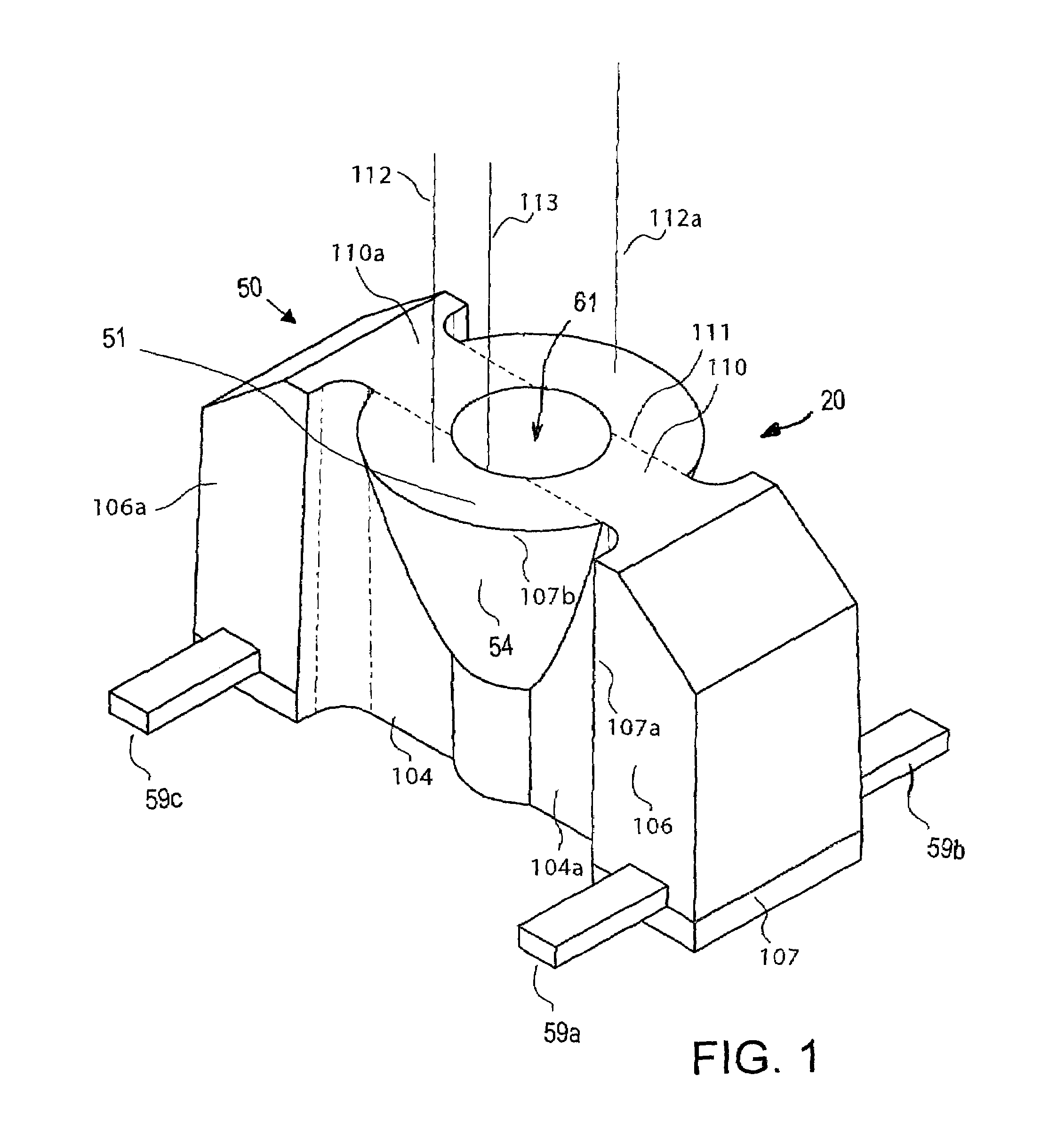

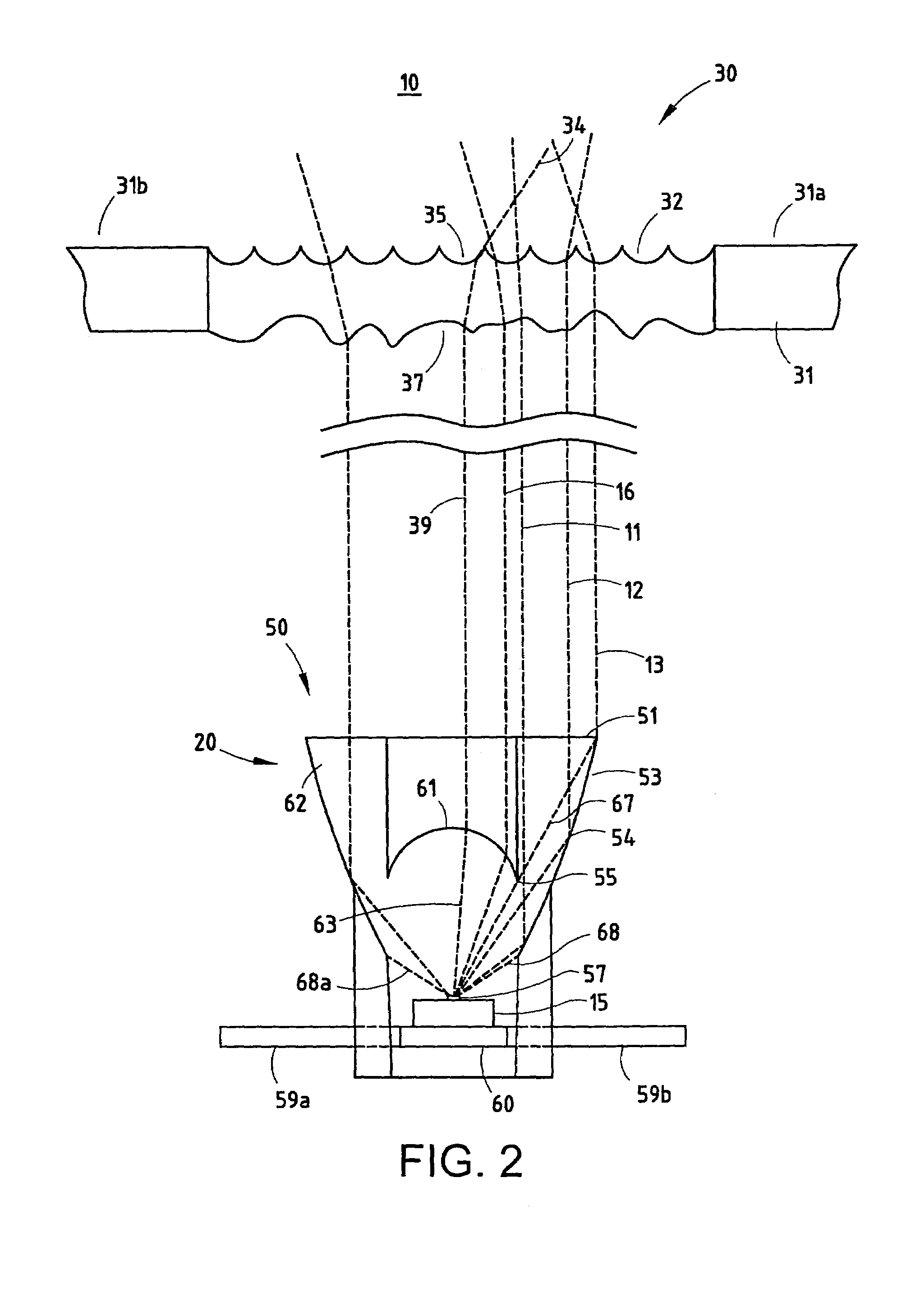

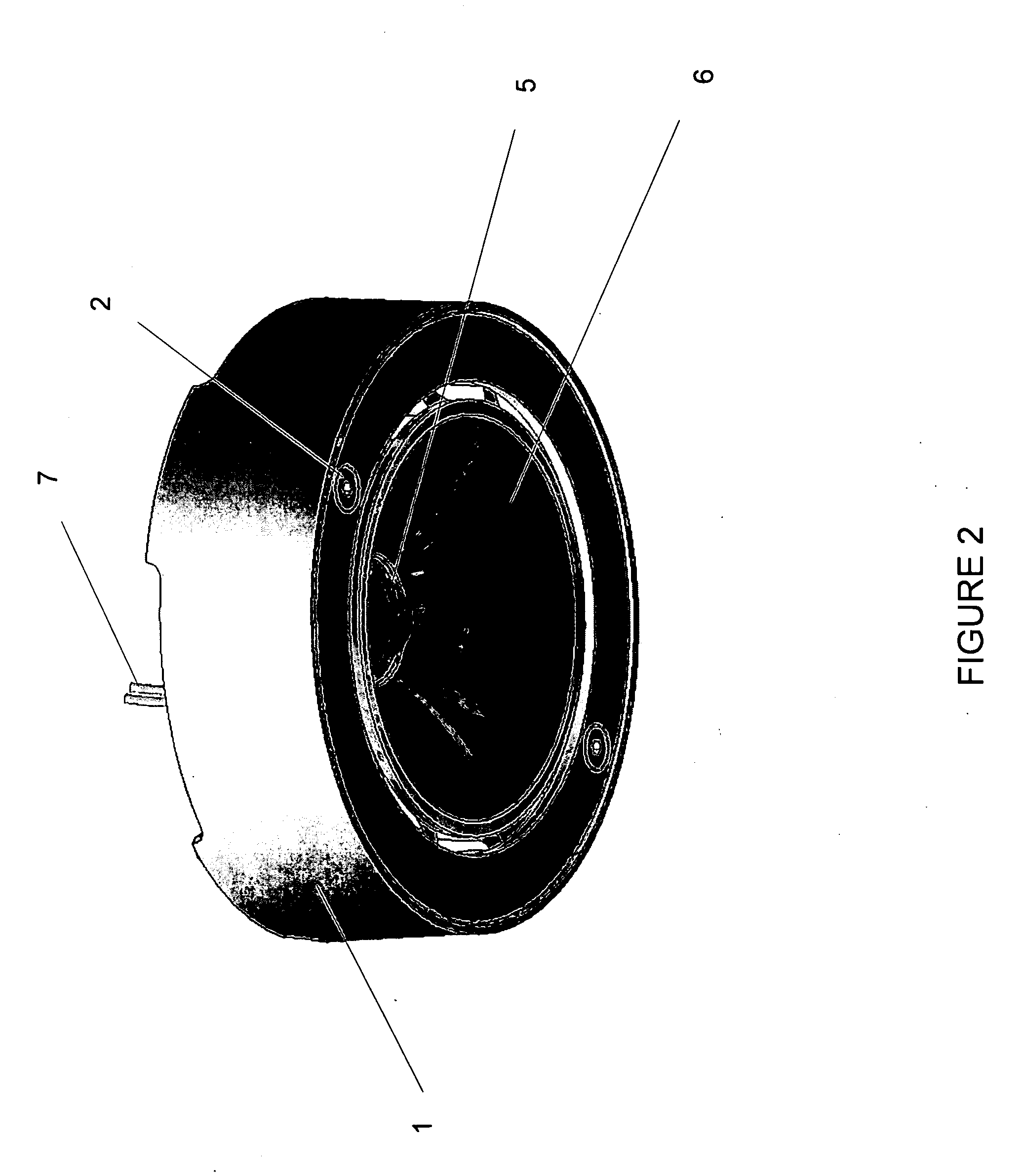

Surface mountable transducer system

InactiveUS7221767B2Established economically and reliablySuitable for mass productionSemiconductor electrostatic transducersElectrostatic transducer microphonesSurface mountingElectrical connection

The present invention relates to a surface mountable acoustic transducer system, comprising one or more transducers, a processing circuit electrically connected to the one or more transducers, and contact points arranged on an exterior surface part of the transducer system. The contact points are adapted to establish electrical connections between the transducer system and an external substrate, the contact points further being adapted to facilitate mounting of the transducer system on the external substrate by conventional surface mounting techniques.

Owner:BALLY TECHNOLOGIES +1

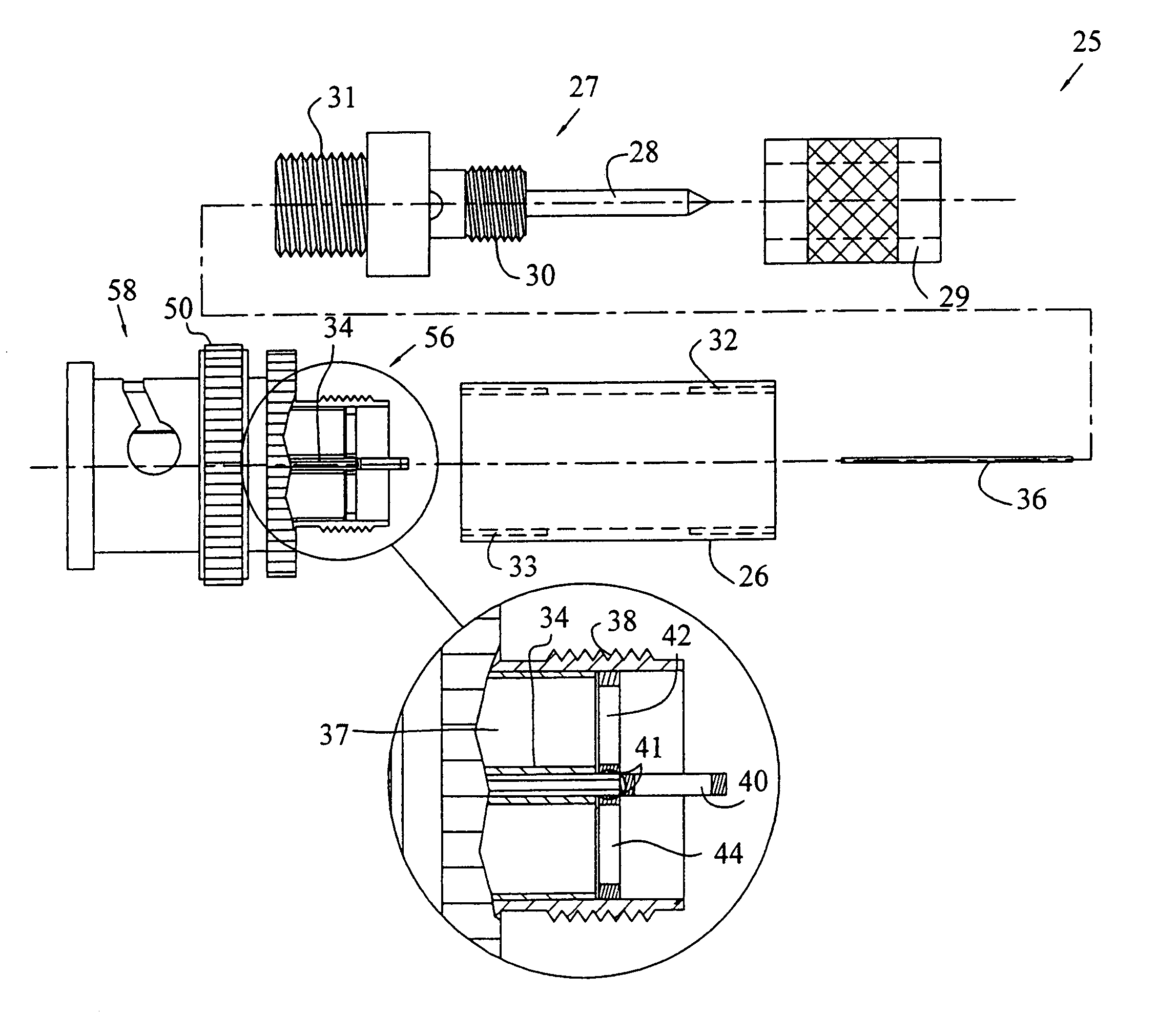

Electromagnetically-actuated microfluidic flow regulators and related applications

InactiveUS20050238506A1Minimize power consumptionEasy to operateFlexible member pumpsMedical devicesSurface mountingClosed loop

A variable, closed-loop apparatus for regulating a microfluidic flow that employs a low-power deflection assembly, which is surface-mounted over a flexible membrane overlying a chamber integrated into a microfabricated platform. A flexible membrane, moveable between two positions, sealingly overlies the chamber. One of the positions of the membrane restricts the flow through the chamber to a greater degree than the other position. A deflection assembly disposed on the substrate over the membrane unidirectionally deflects the membrane, thereby regulating the flow through the chamber.

Owner:CHARLES STARK DRAPER LABORATORY

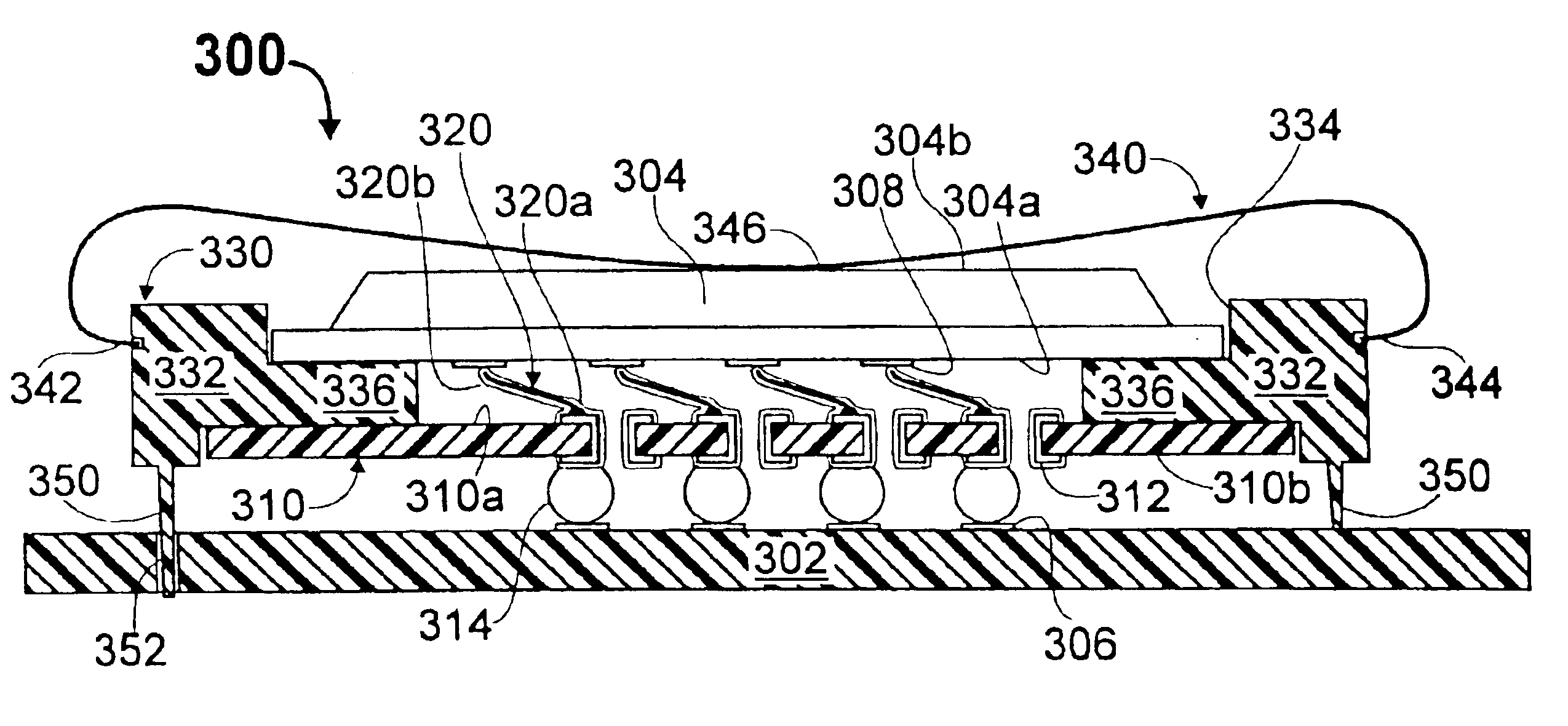

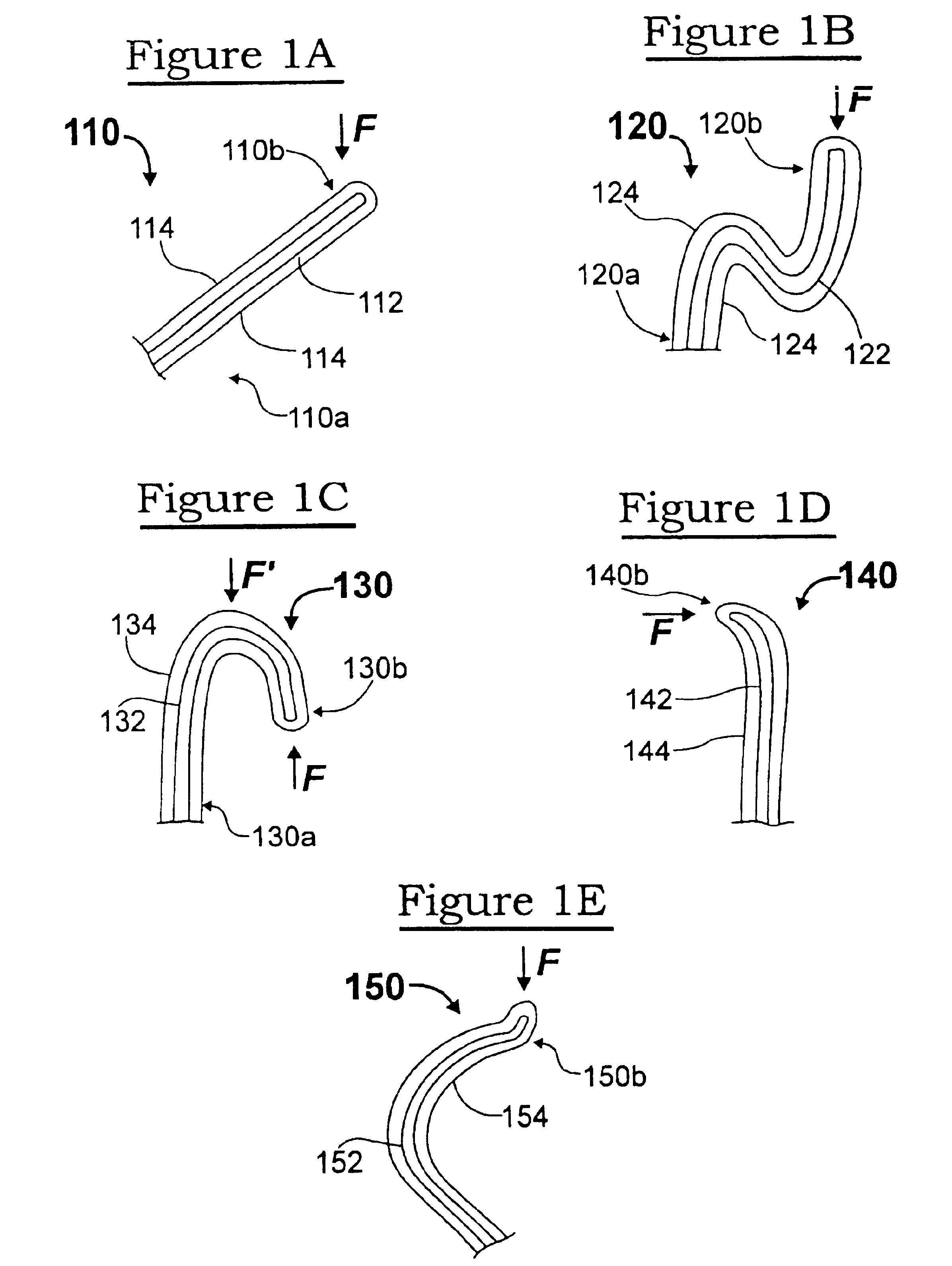

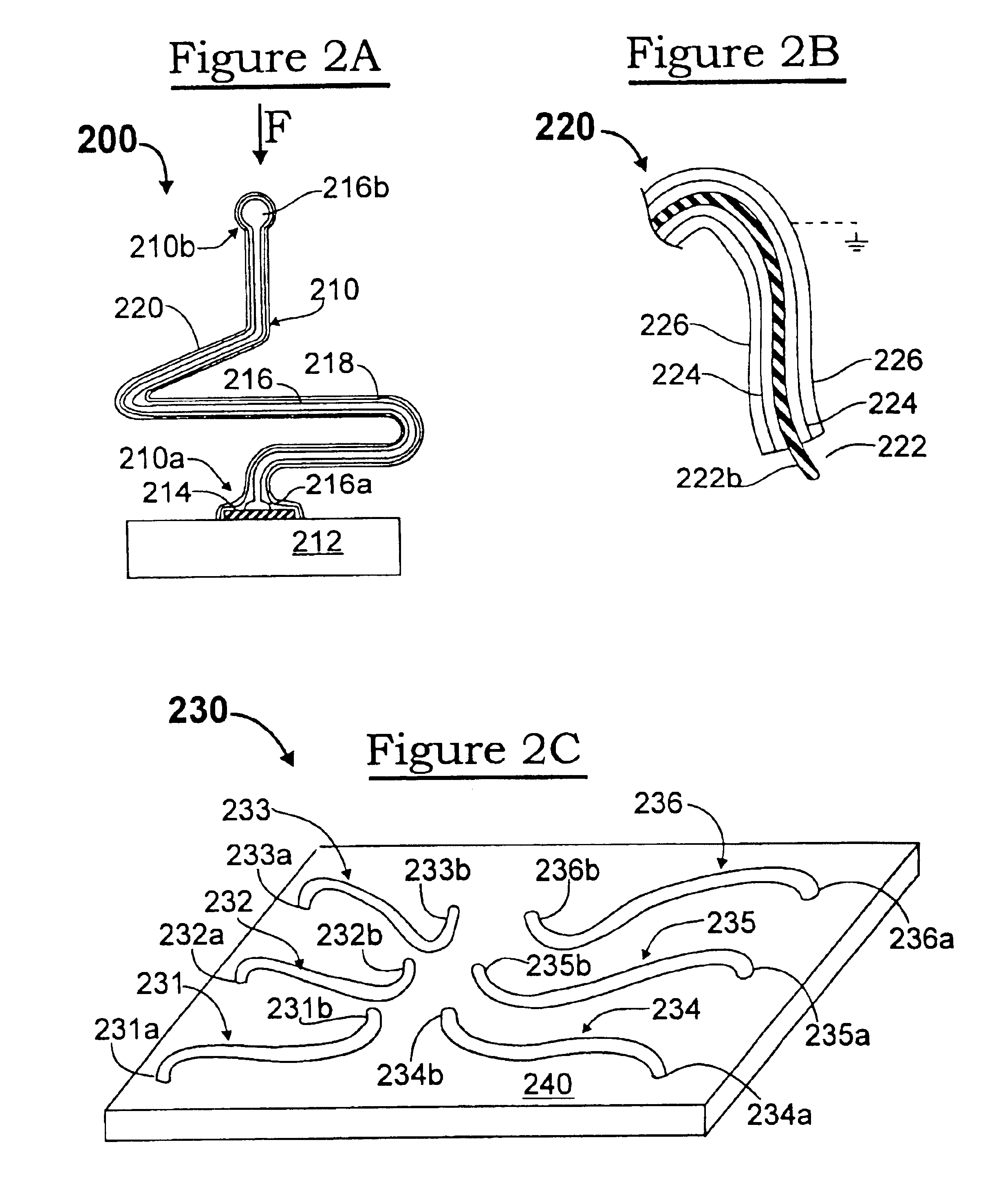

Methods of removably mounting electronic components to a circuit board, and sockets formed by the methods

InactiveUS6913468B2Easy to disassembleEffective shieldingSemiconductor/solid-state device testing/measurementFinal product manufactureSurface mountingSolder ball

Surface-mount, solder-down sockets are described which permit electronic components such as semiconductor packages to be releasably mounted to a circuit board. Generally, the socket includes resilient contact structures extending from a top surface of a support substrate, and solder-ball (or other suitable) contact structures disposed on a bottom surface of the support substrate. Composite interconnection elements are described for use as the resilient contact structures disposed atop the support substrate. In use, the support substrate is soldered down onto the circuit board, the contact structures on the bottom surface of the support substrate contacting corresponding contact areas on the circuit board. In any suitable manner, selected ones of the resilient contact structures atop the support substrate are connected, via the support substrate, to corresponding ones of the contact structures on the bottom surface of the support substrate.

Owner:FORMFACTOR INC

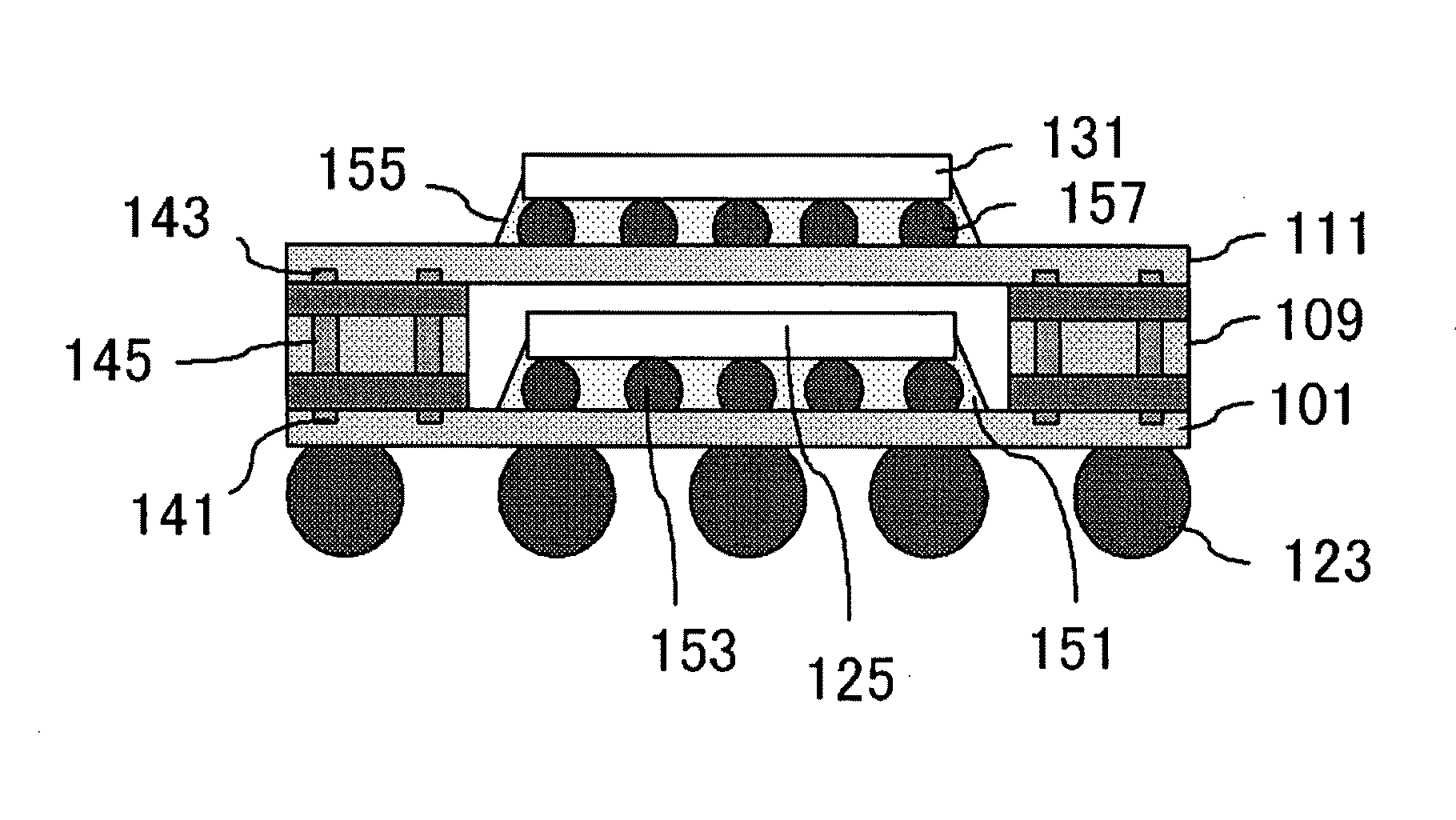

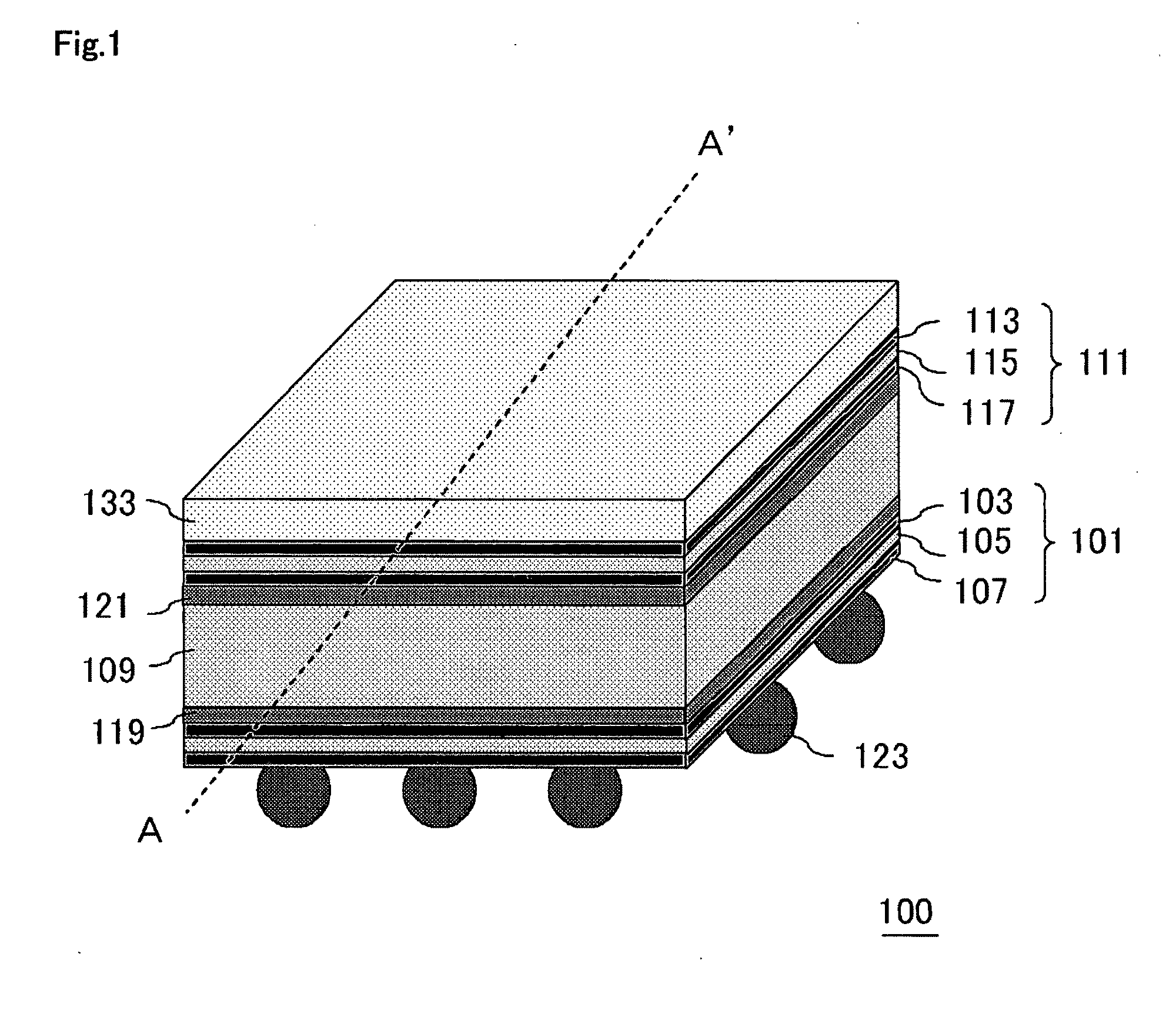

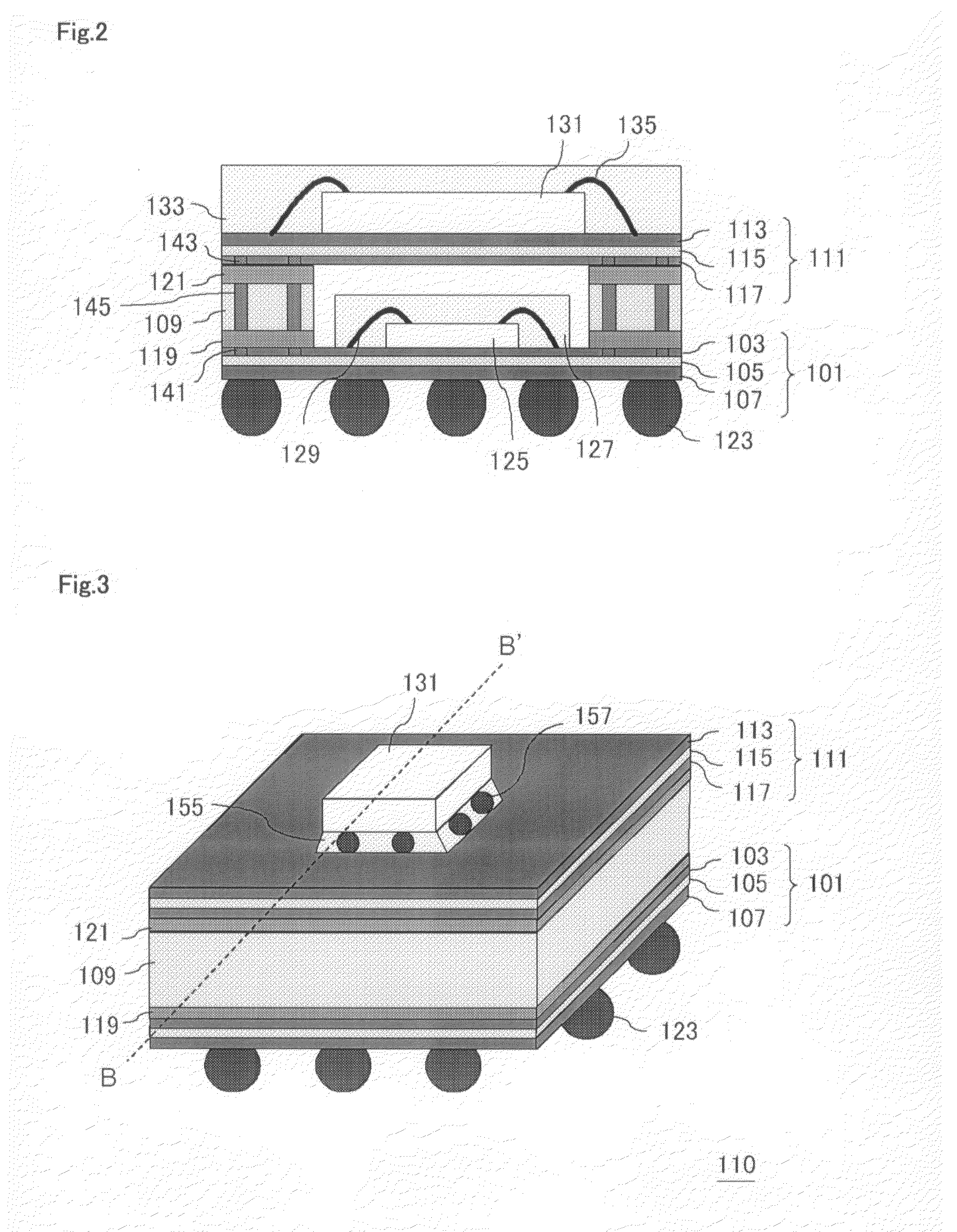

Semiconductor Device and Method for Manufacturing Semiconductor Device

InactiveUS20090243065A1Improve joint reliabilityLower elastic modulusSemiconductor/solid-state device detailsSolid-state devicesSurface mountingSemiconductor chip

A semiconductor device (100) comprises a first resin substrate (101) on which a first semiconductor chip (125) is mounted a surface thereof; a second resin substrate (111) on which a second semiconductor chip (131) is mounted on a surface thereof; and a resin base material (109), joined to a front surface of the first resin substrate (101) and to a back surface of the second resin substrate (111), so that these surfaces are electrically connected. The resin base material (109) is disposed in a circumference of the first resin substrate (101) in the surface of the first resin substrate (101). Further, the first semiconductor chip (125) is disposed in a space section provided among the first resin substrate (101), the second resin substrate (111) and the resin base material (109) in the surface of the first resin substrate (101).

Owner:SUMITOMO BAKELITE CO LTD

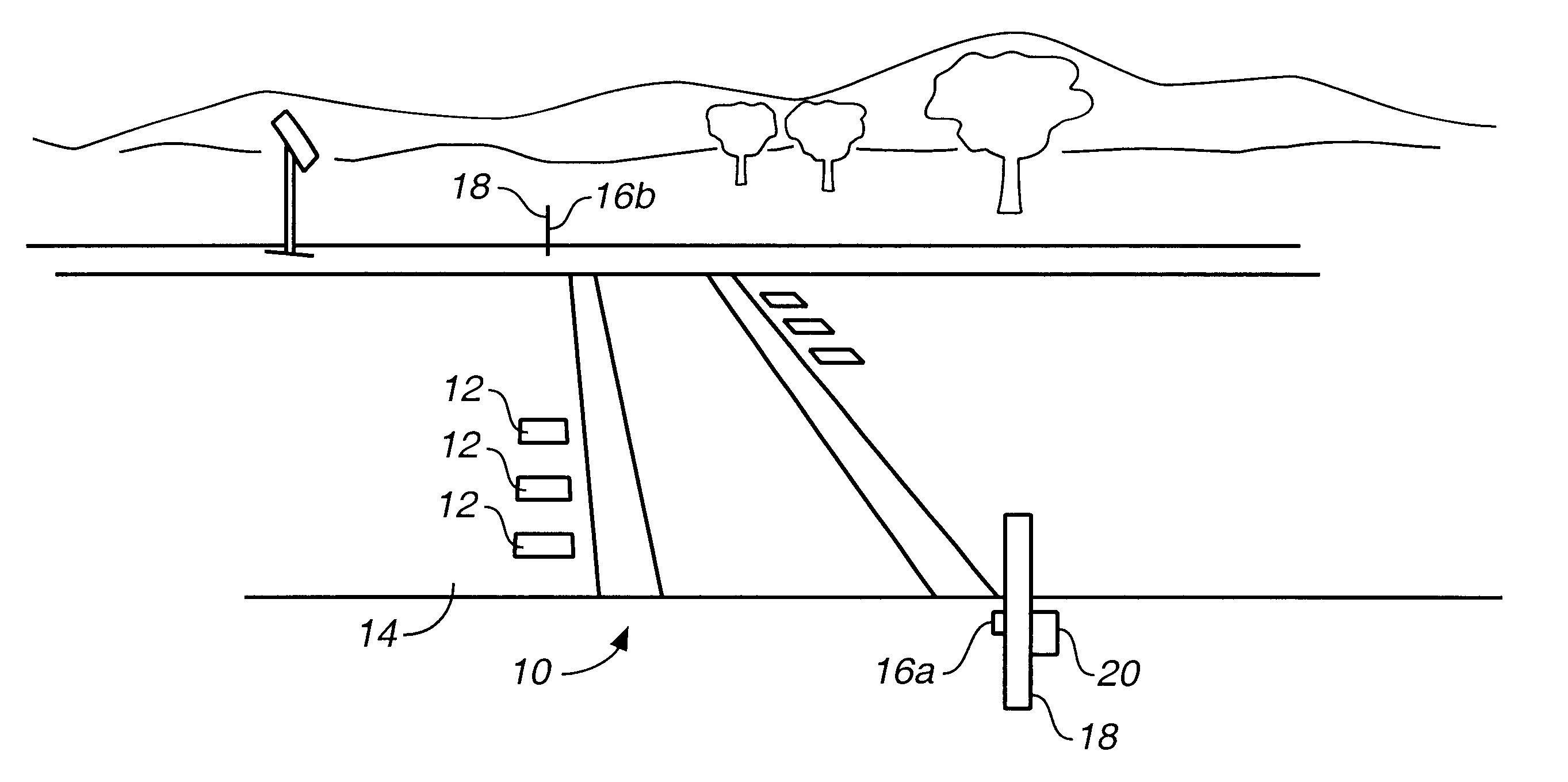

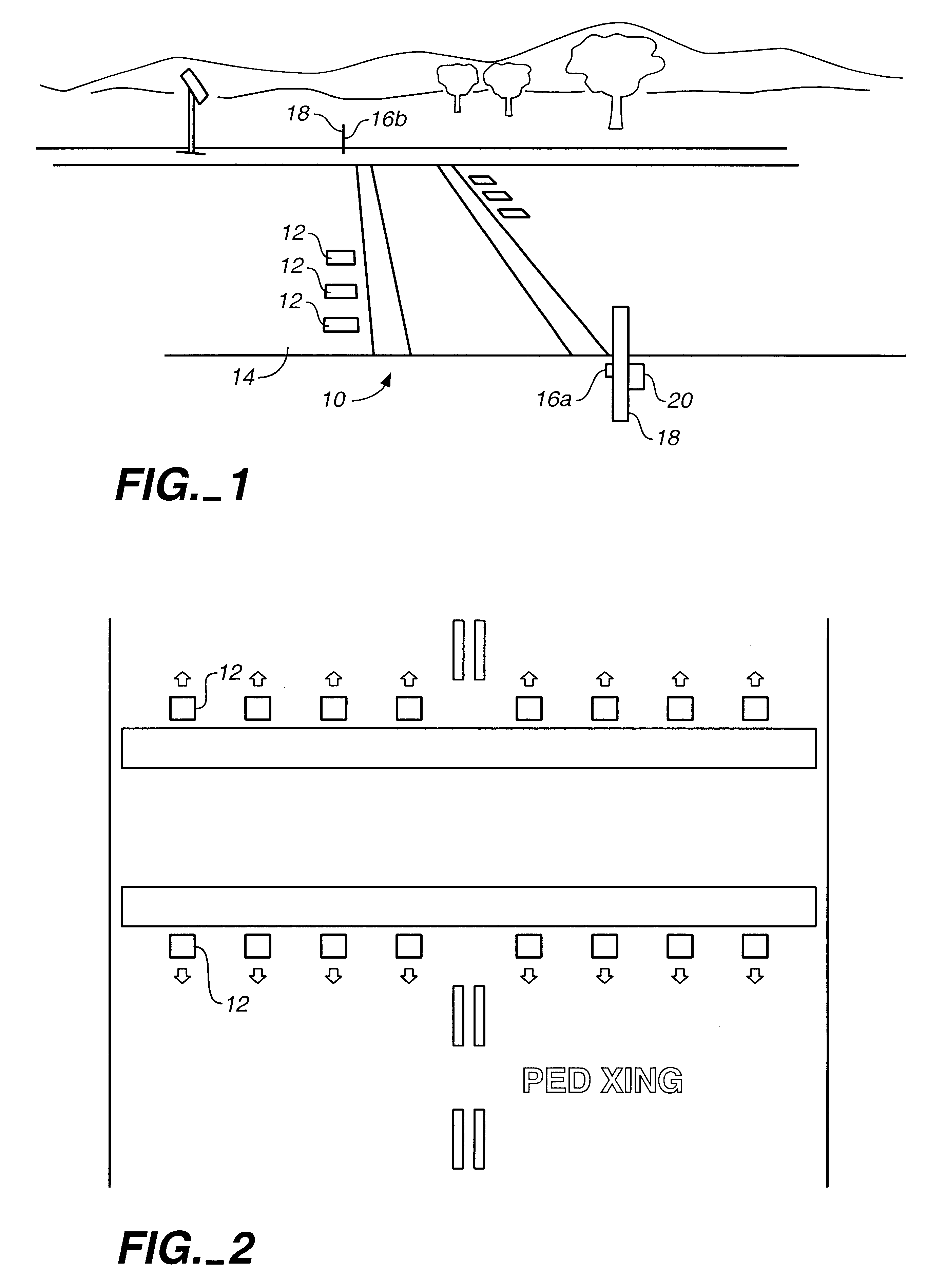

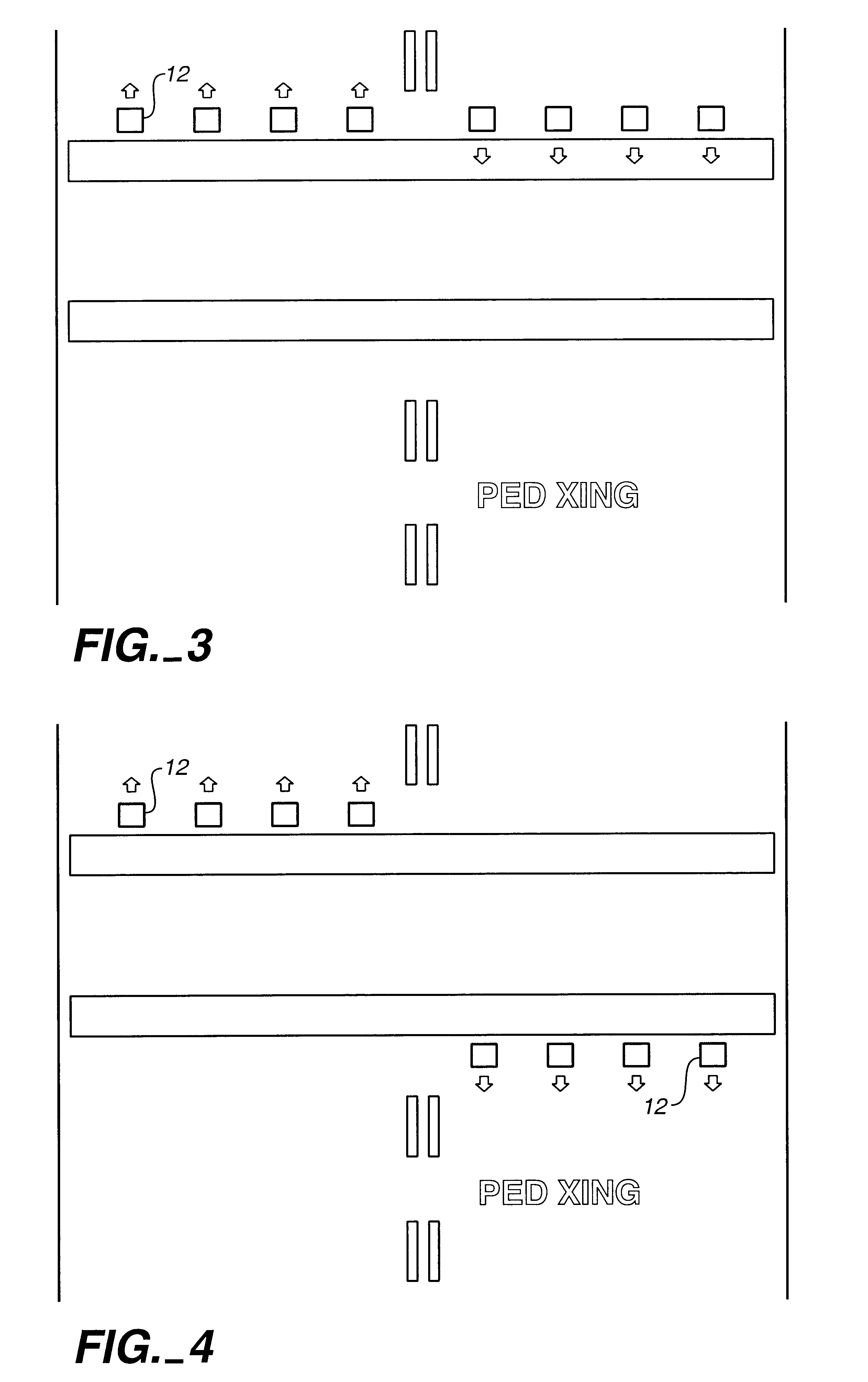

Pedestrian crosswalk signal apparatus-pedestrian crosswalk

InactiveUS6384742B1Low costEasy to installControlling traffic signalsPortable emergency signal deviceSurface mountingWarning system

A traffic warning system which alerts approaching vehicle traffic to the presence of a pedestrian in a crosswalk. The system includes a plurality of surface mounted lights partially embedded in and placed across a roadway. The lights are activated by the pedestrian, either by manual switch or by a sensor, before he enters the crosswalk. Once activated, the flashing lights warn drivers of approaching vehicles that the pedestrian may have entered the crosswalk, and that caution should be exercised.

Owner:LIGHTGUARD SYST

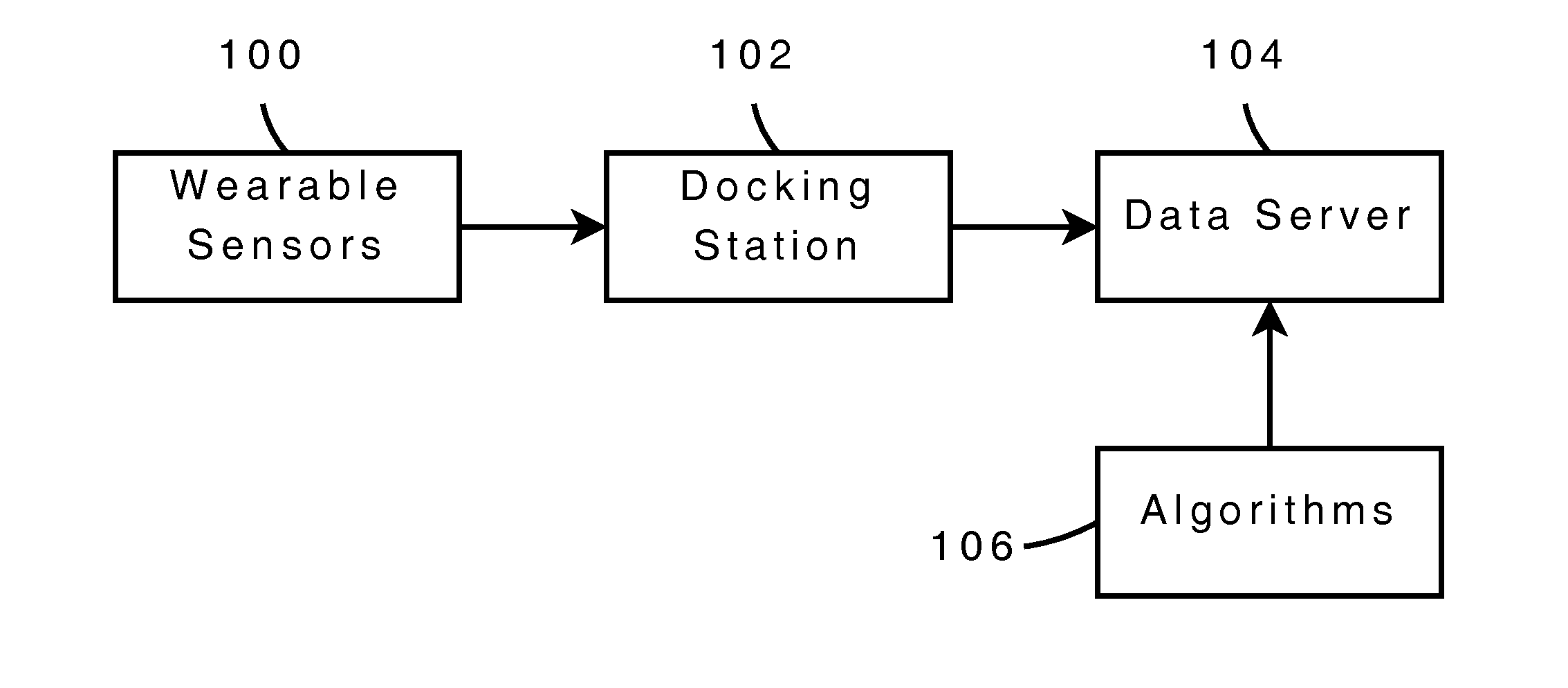

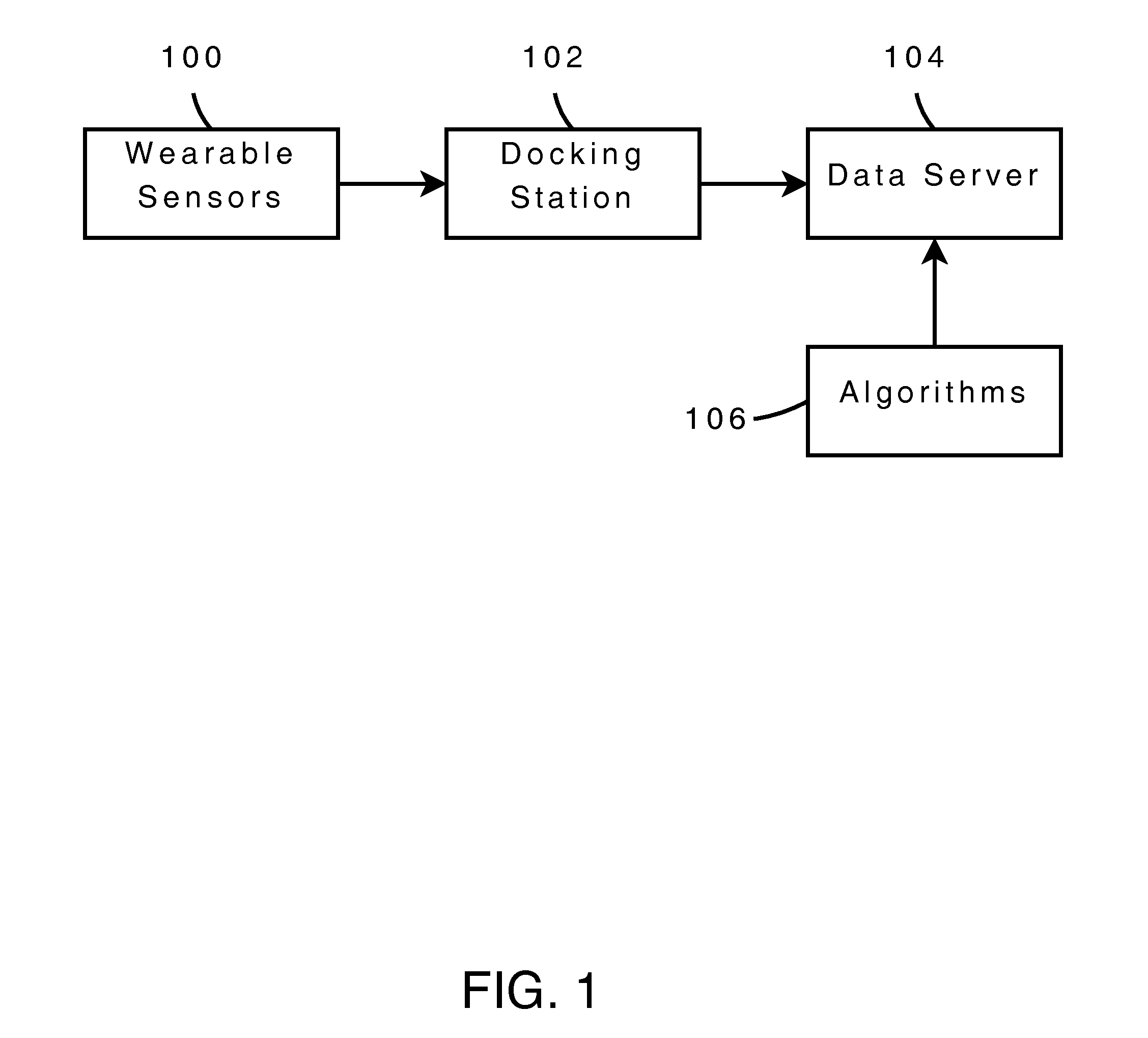

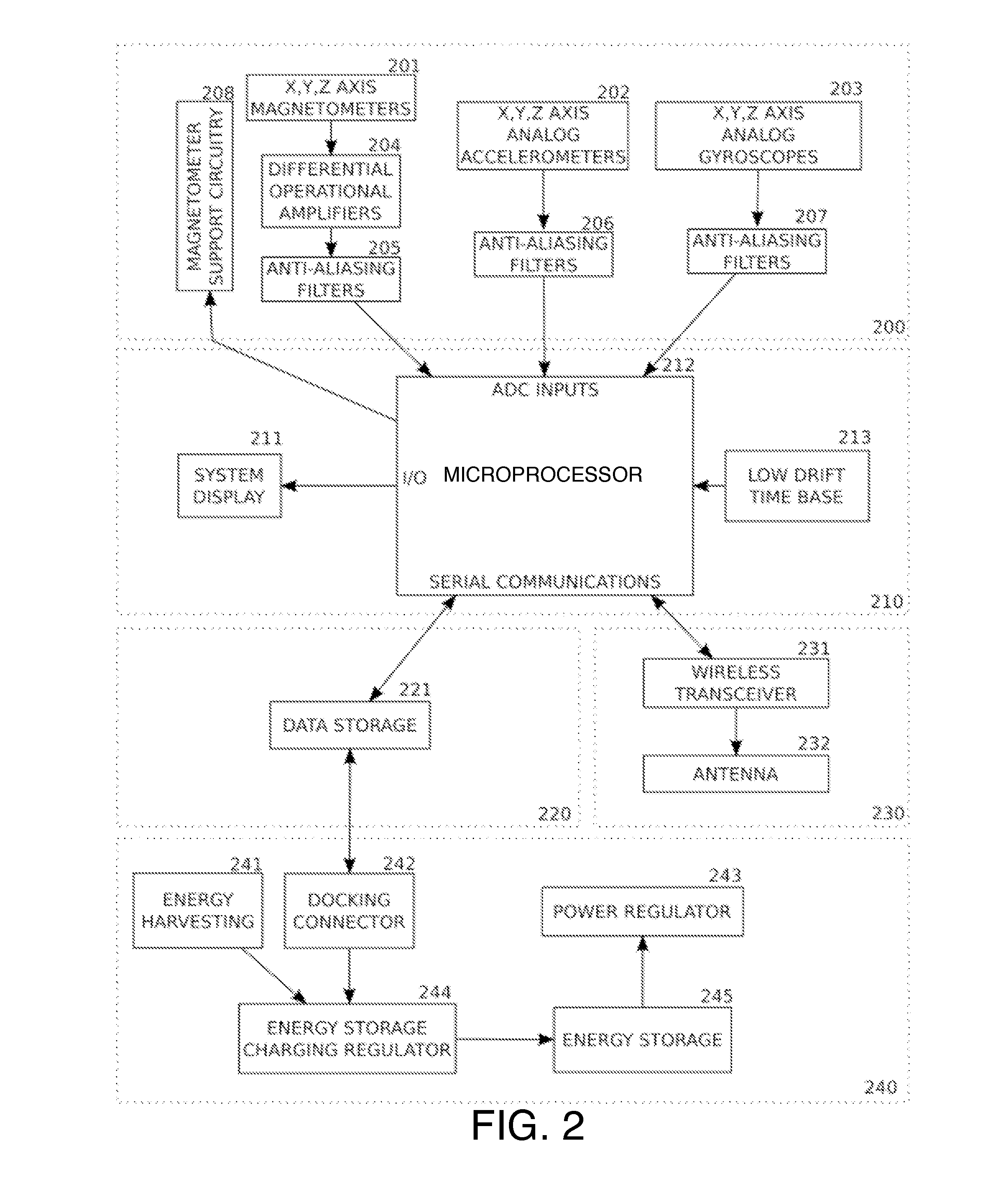

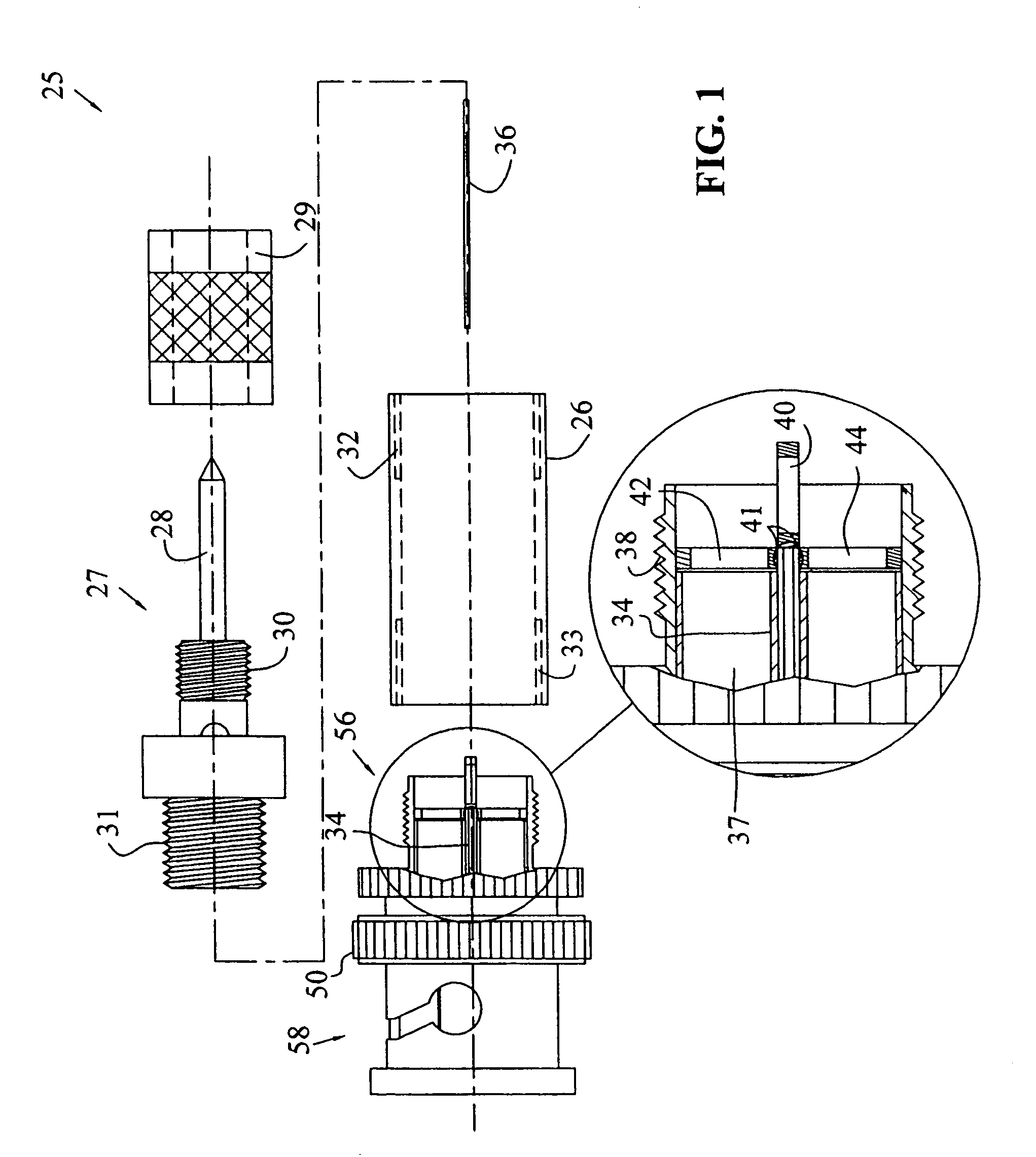

System and Apparatus for Continuous Monitoring of Movement Disorders

Disclosed embodiments include a complete system and platform which allows for continuous monitoring of movement disorders during normal daily activities in the clinic, home, and other normal daily environments. The system comprises: 1) a wearable apparatus for continuous monitoring of movement disorders, 2) a docking station, 3) a web server, and 4) methods for statistical analysis that generate movement impairment measures. Disclosed embodiments include a wearable movement monitoring apparatus comprising of (a) a sensor module including a plurality of low power micro-electromechanical systems kinematics sensors; (b) a microprocessor module including a low power microcontroller configured for device control, device status, and device communication; (c) a data storage module including a solid state local storage medium; (d) a wireless communication module including a low power surface mount transceiver and an integrated antenna; and (e) a power and docking module including a battery, an energy charging regulator circuit, and a docking connector.

Owner:WEARABLES IP HLDG LLC

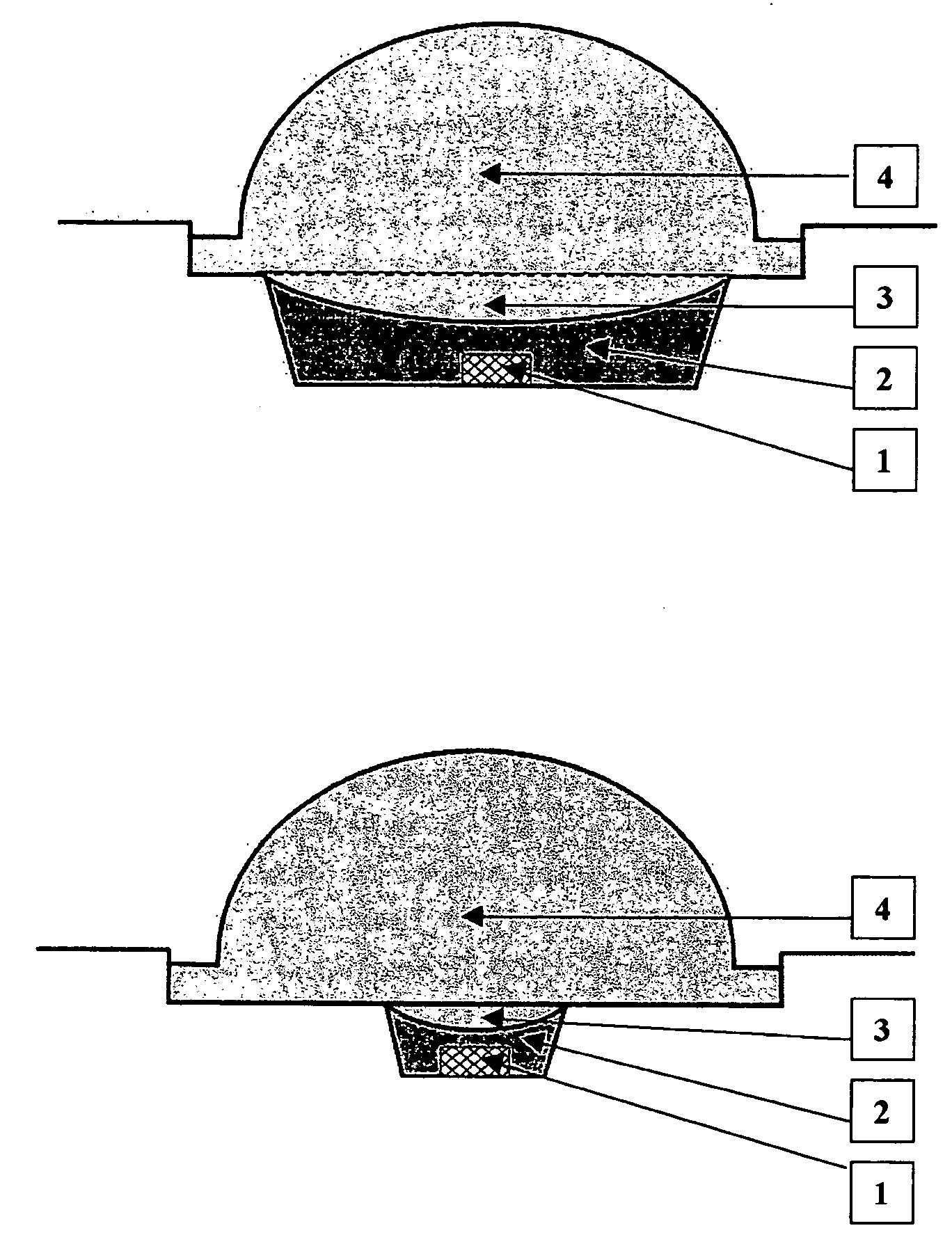

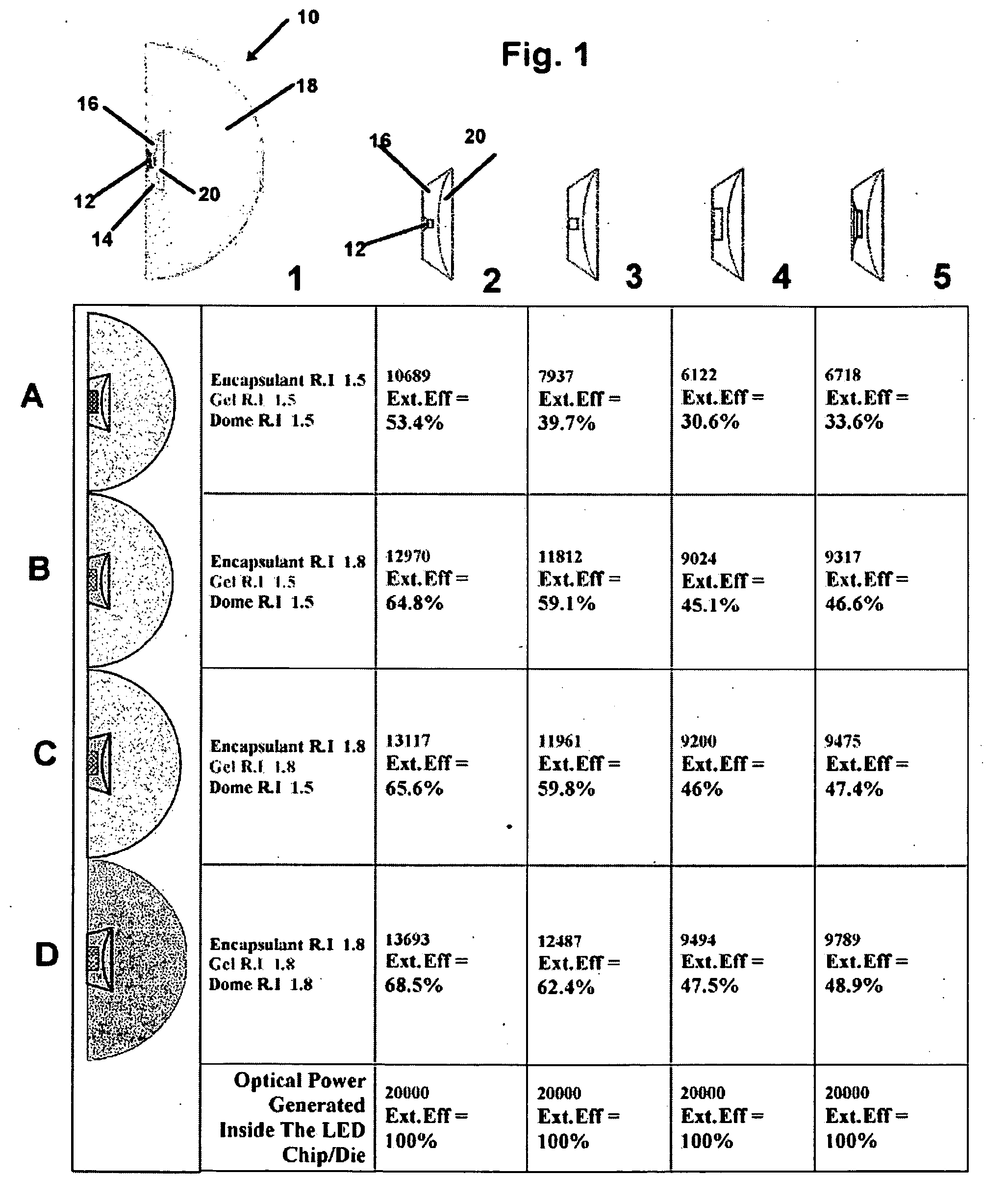

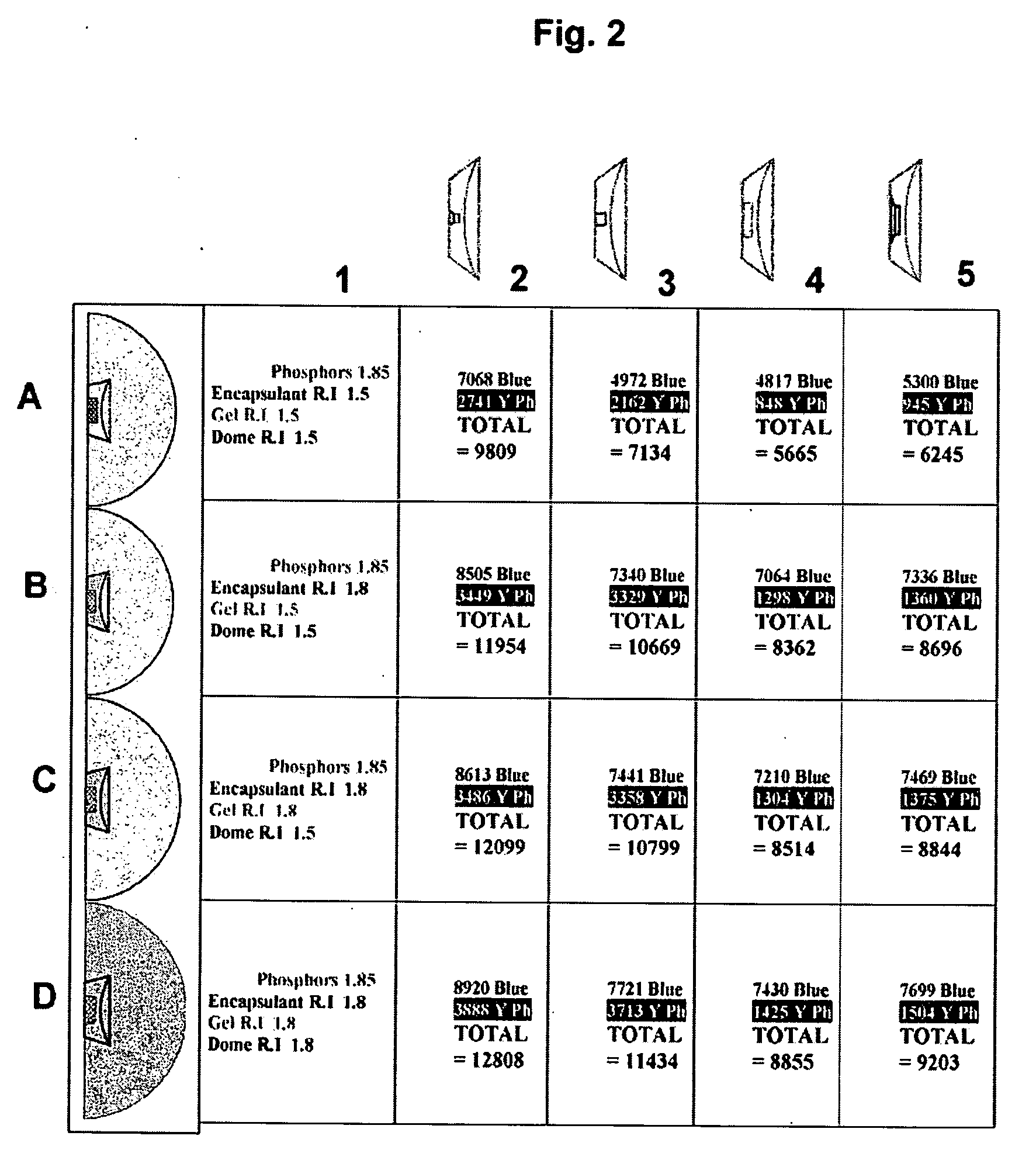

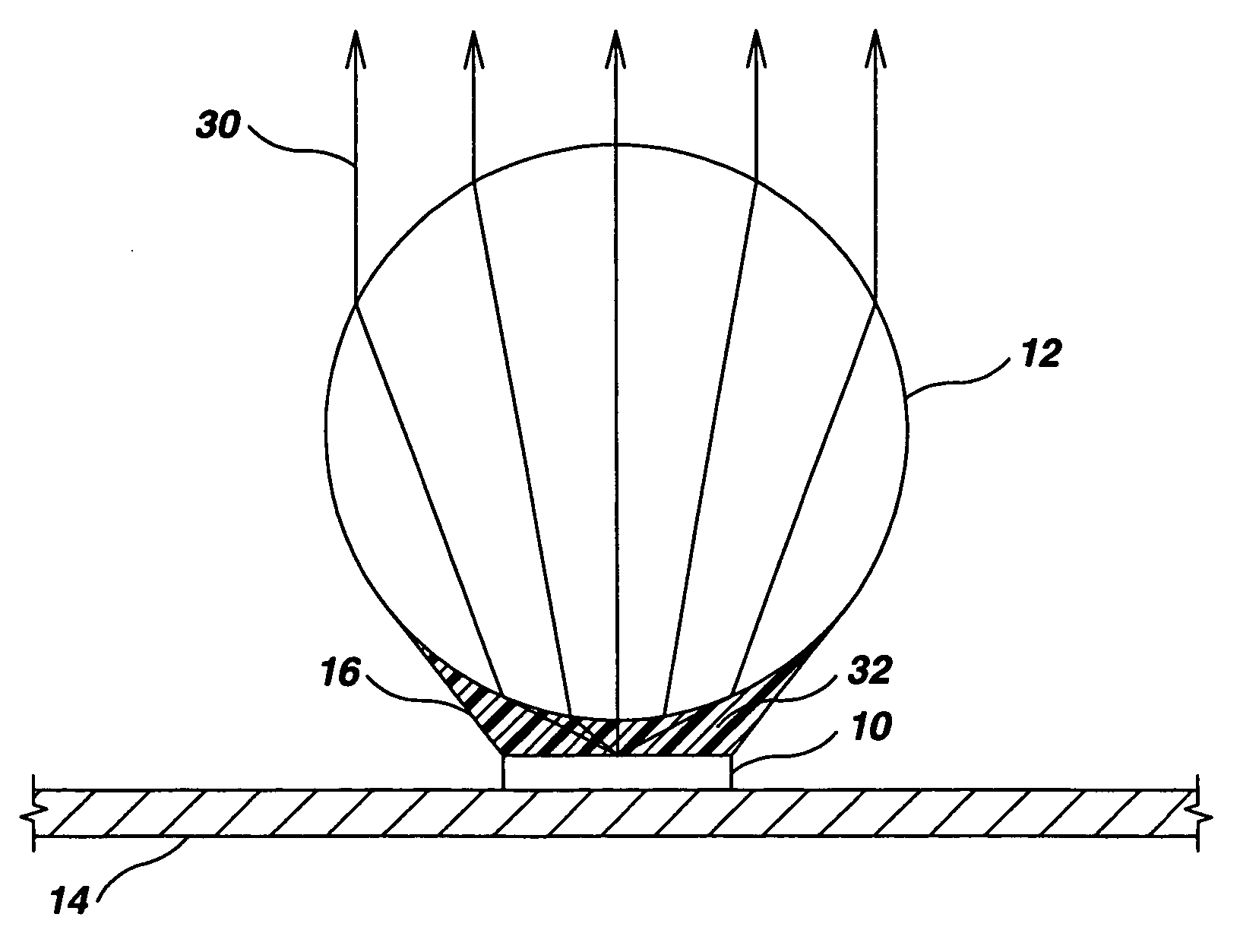

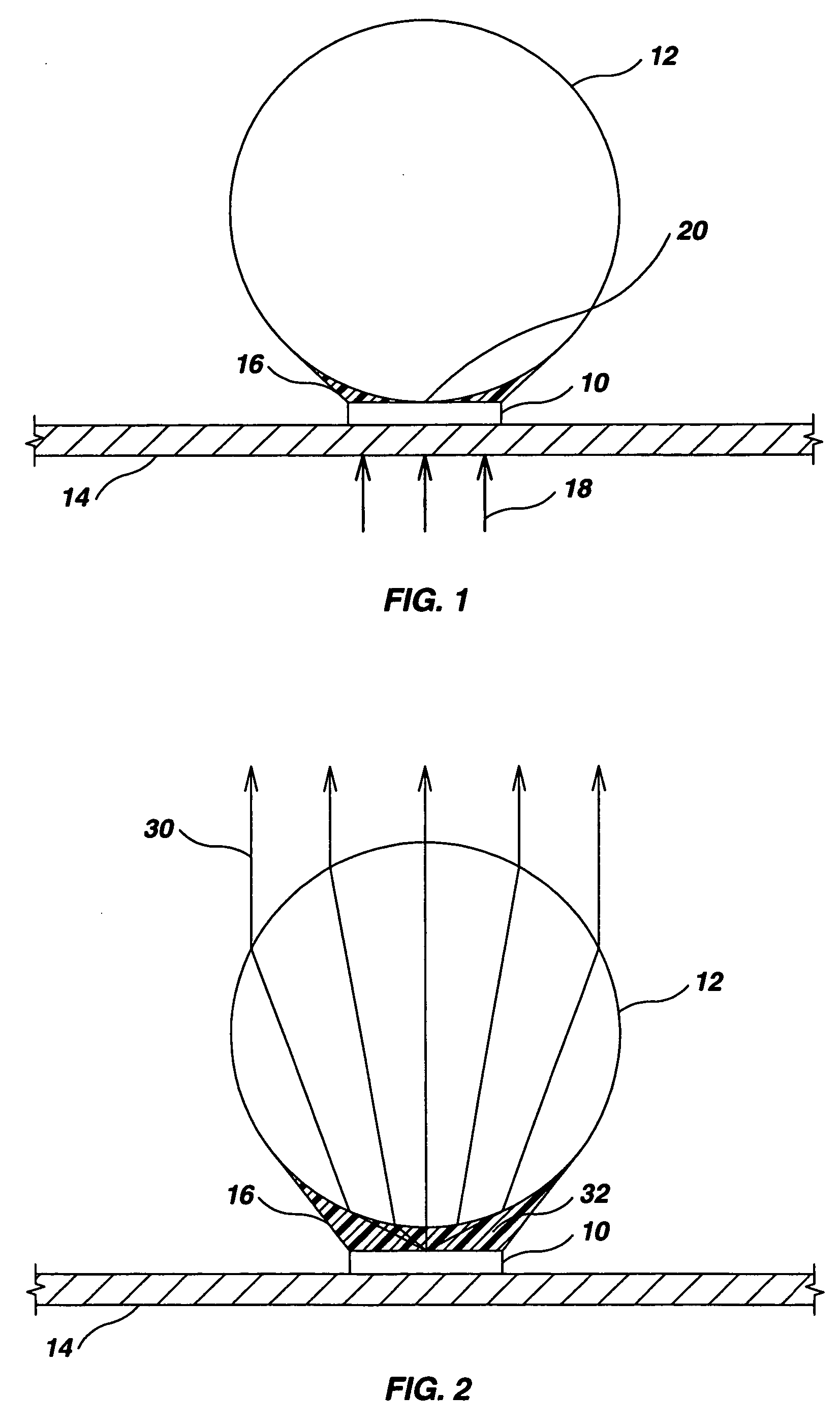

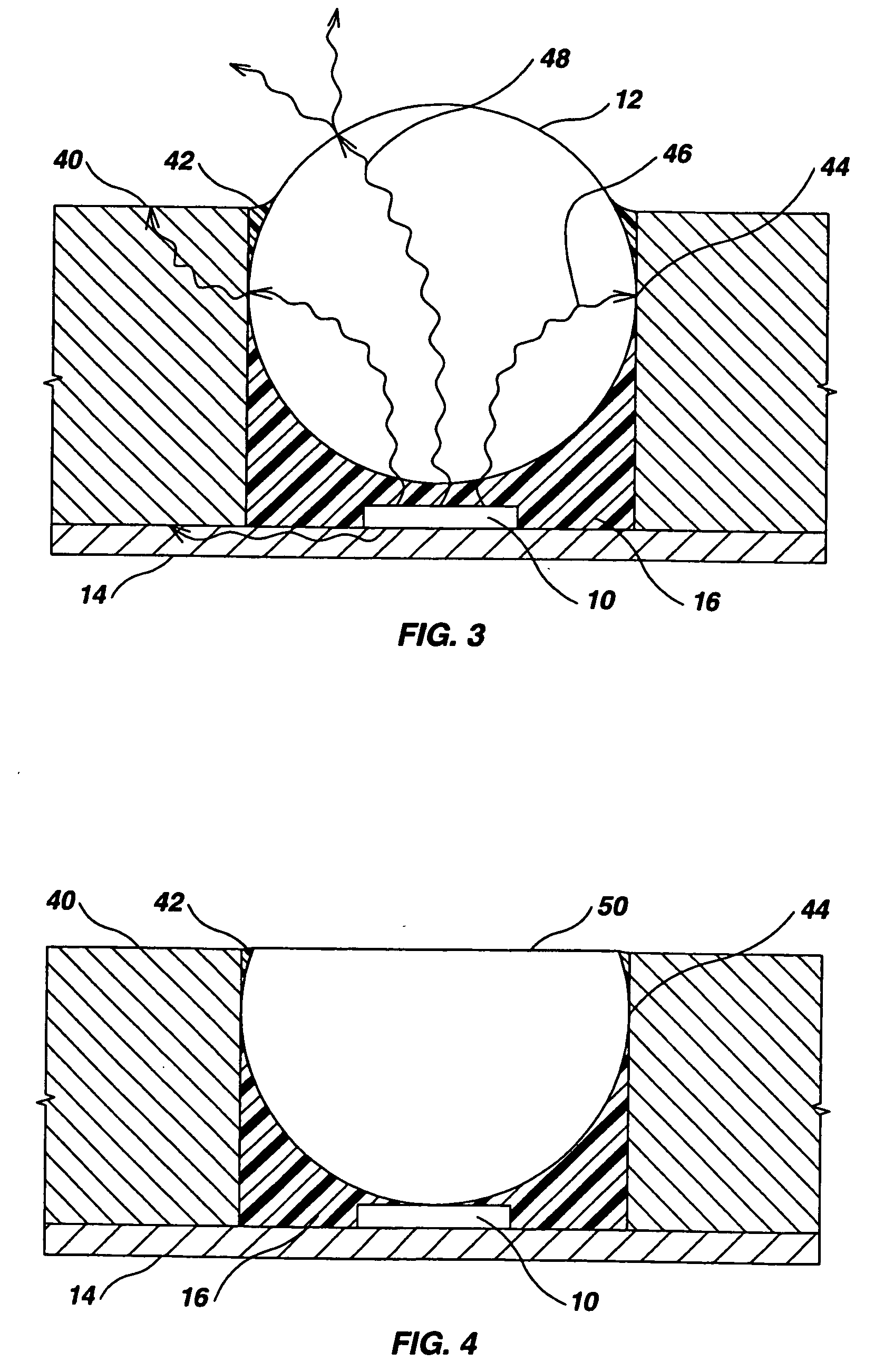

Light efficient packaging configurations for LED lamps using high refractive index encapsulants

InactiveUS20060255353A1High refractive indexImprove optical efficiencyMechanical apparatusPoint-like light sourceSurface mountingRefractive index

Light efficient packaging configurations for LED lamps using high refractive index encapsulants. The packaging configurations including dome (bullet) shaped LED's, SMD (surface mount device) LED's and a hybrid LED type, including a dome mounted within a SMD package. In another embodiment used with SMD LED devices a relatively small semi-hemispherical “blob” of HRI encapsulant surrounds the LED chip with the remainder of the SMD cavity filled with conventional encapsulant. The packaging configurations increase the LED's light emission efficiency at a reasonable cost and in a commercially viable manner, by maximizing the light efficiency while minimizing the amount of high refractive index encapsulant used.

Owner:TASKAR NIKHIL R +3

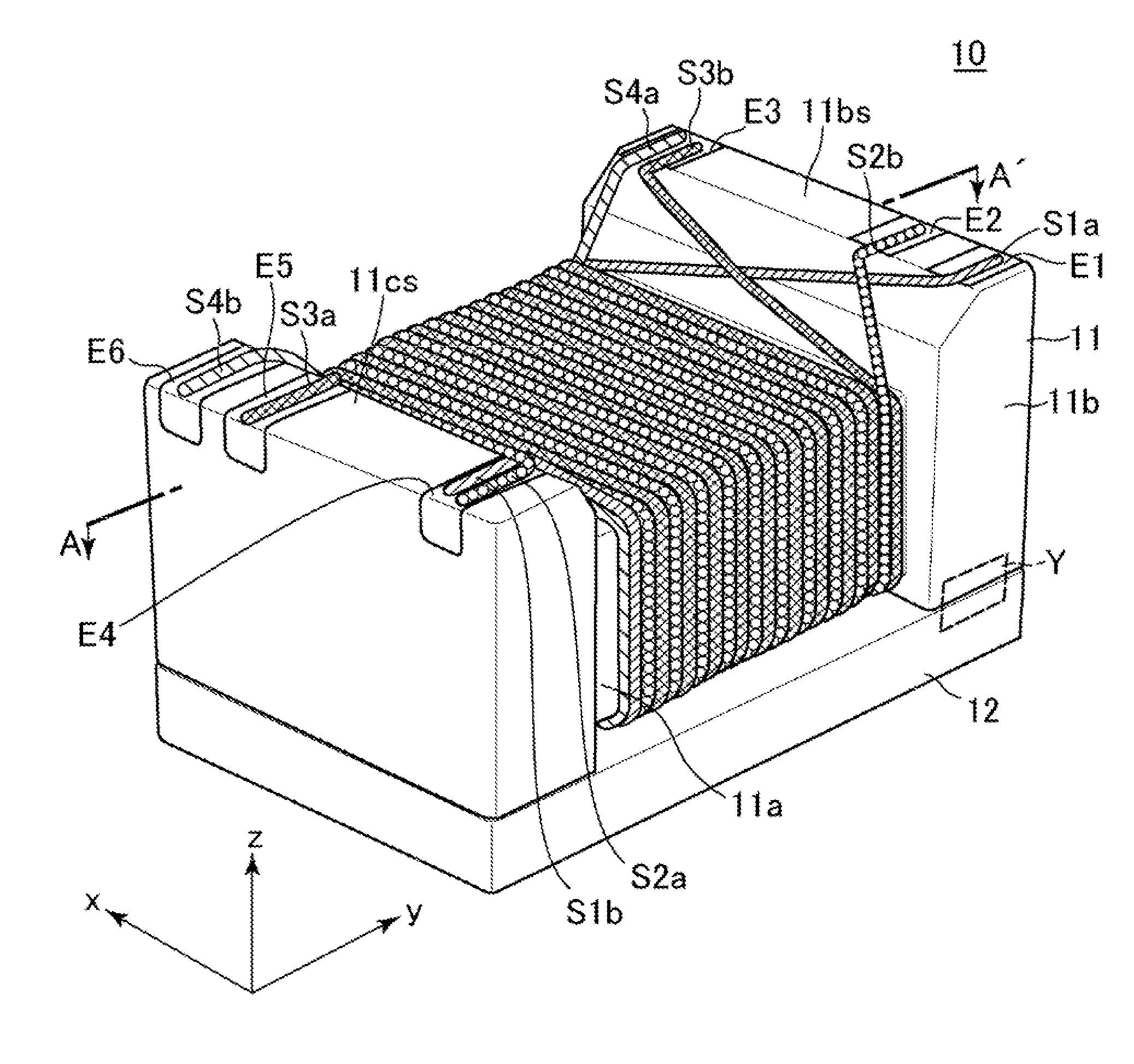

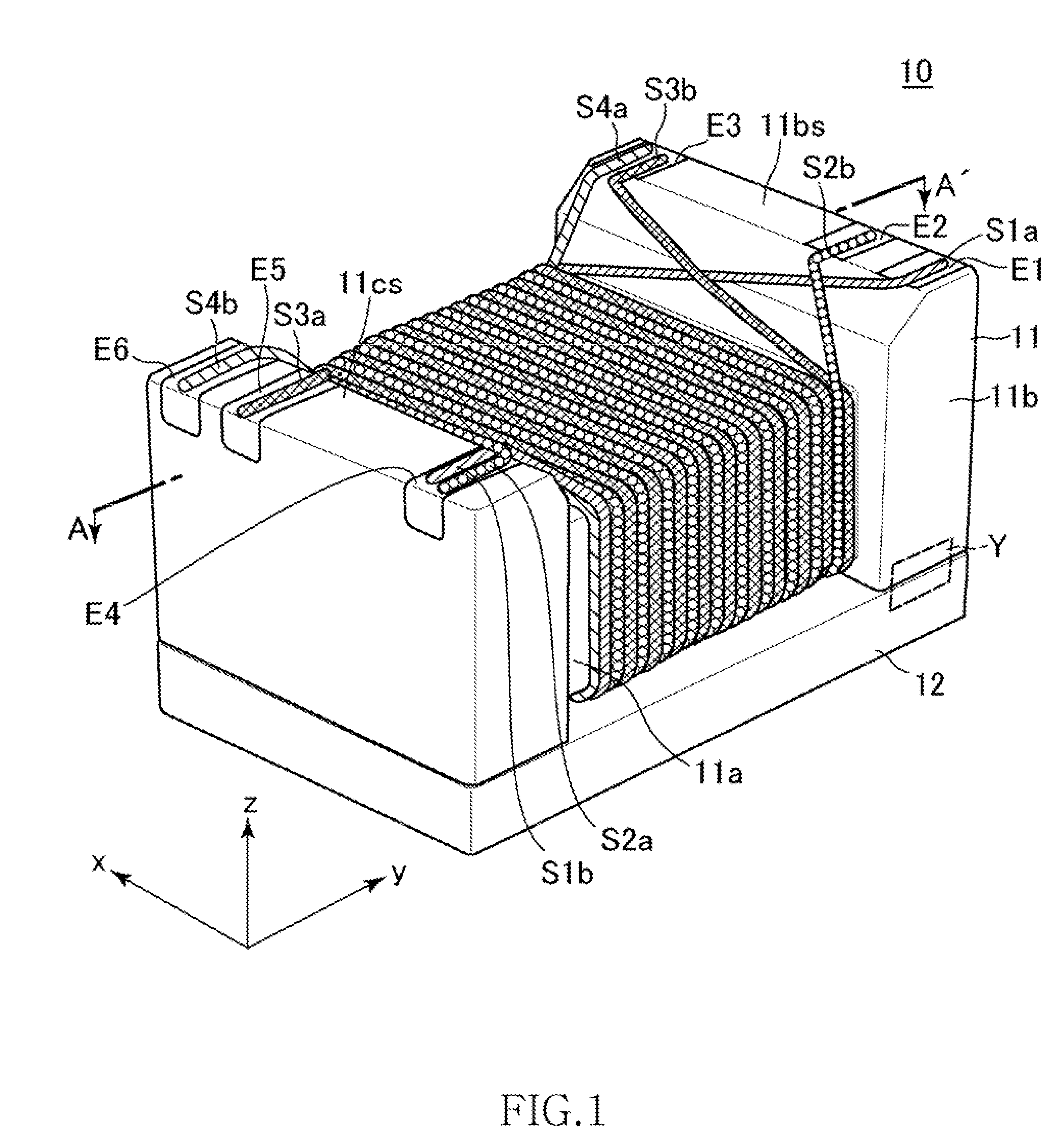

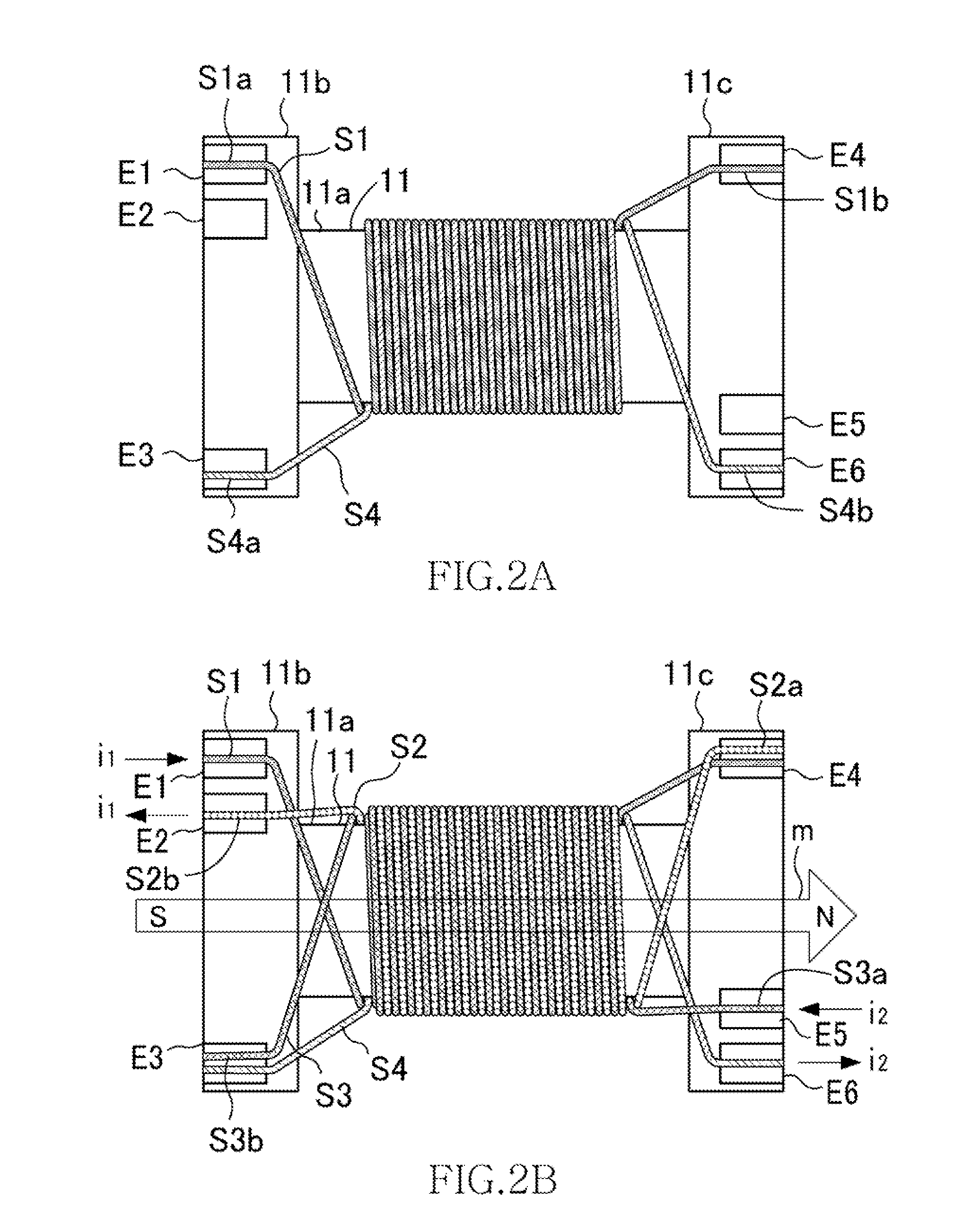

Surface mount pulse transformer and method and apparatus for manufacturing the same

ActiveUS20100109827A1Short working hoursShorten the timeTransformers/inductances casingsTransformers/inductances coils/windings/connectionsSurface mountingEngineering

A surface mount pulse transformer has a drum type core including a core and first and second flanges disposed on both ends of the core and installed on a substrate and a primary winding wire and a secondary winding wire wound around the core and provided with an intermediate tap, respectively, wherein first and second terminal electrodes being connected to each of both ends of the primary winding wire and a third terminal electrode for connecting being connected to the intermediate tap of the secondary winding wire are disposed on the surface of the first flange and a fourth terminal electrode being connected to the intermediate tap of the primary winding wire and fifth and sixth terminal electrodes being connected to each of both ends of the secondary winding wire are disposed on the surface of the second flange.

Owner:TDK CORPARATION

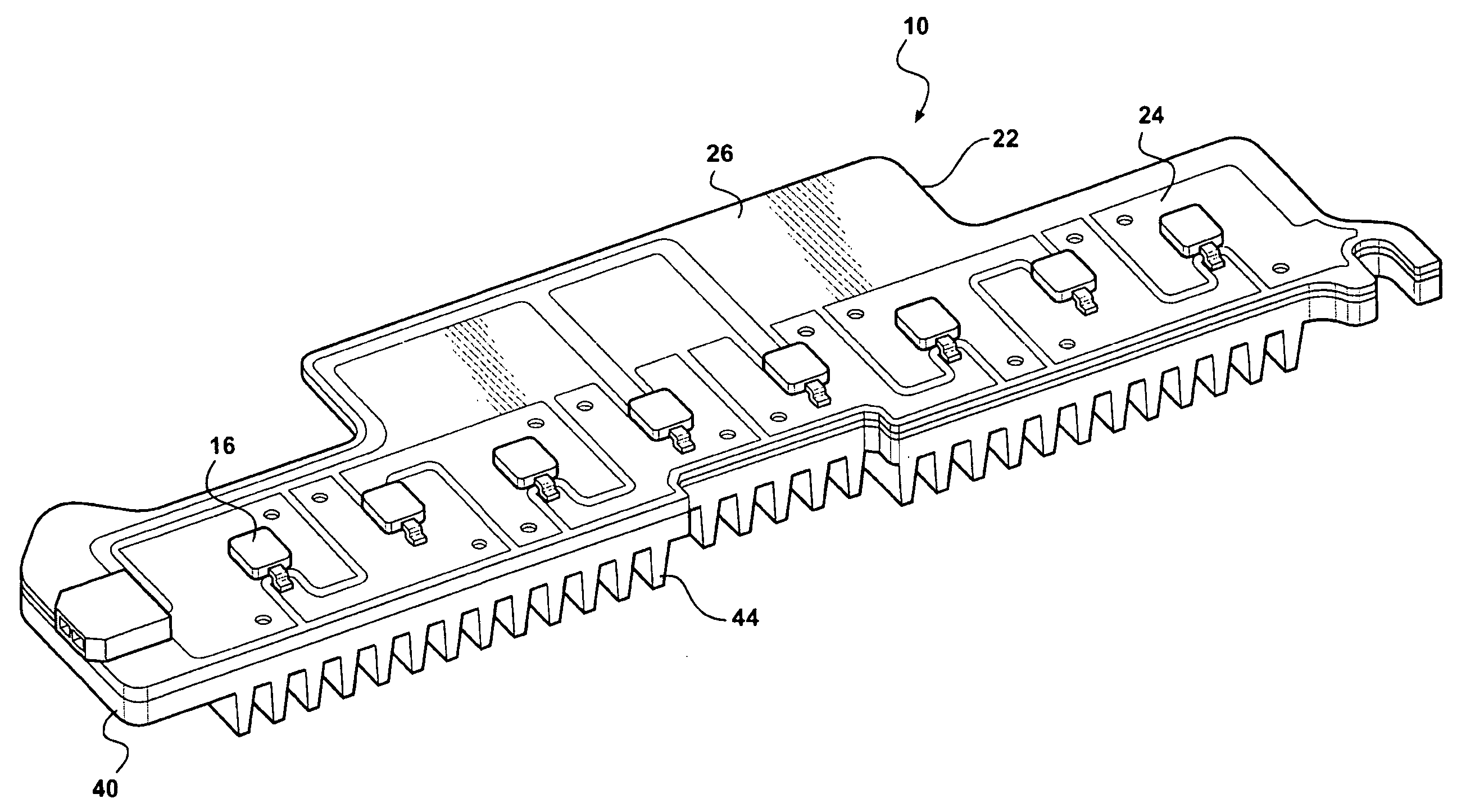

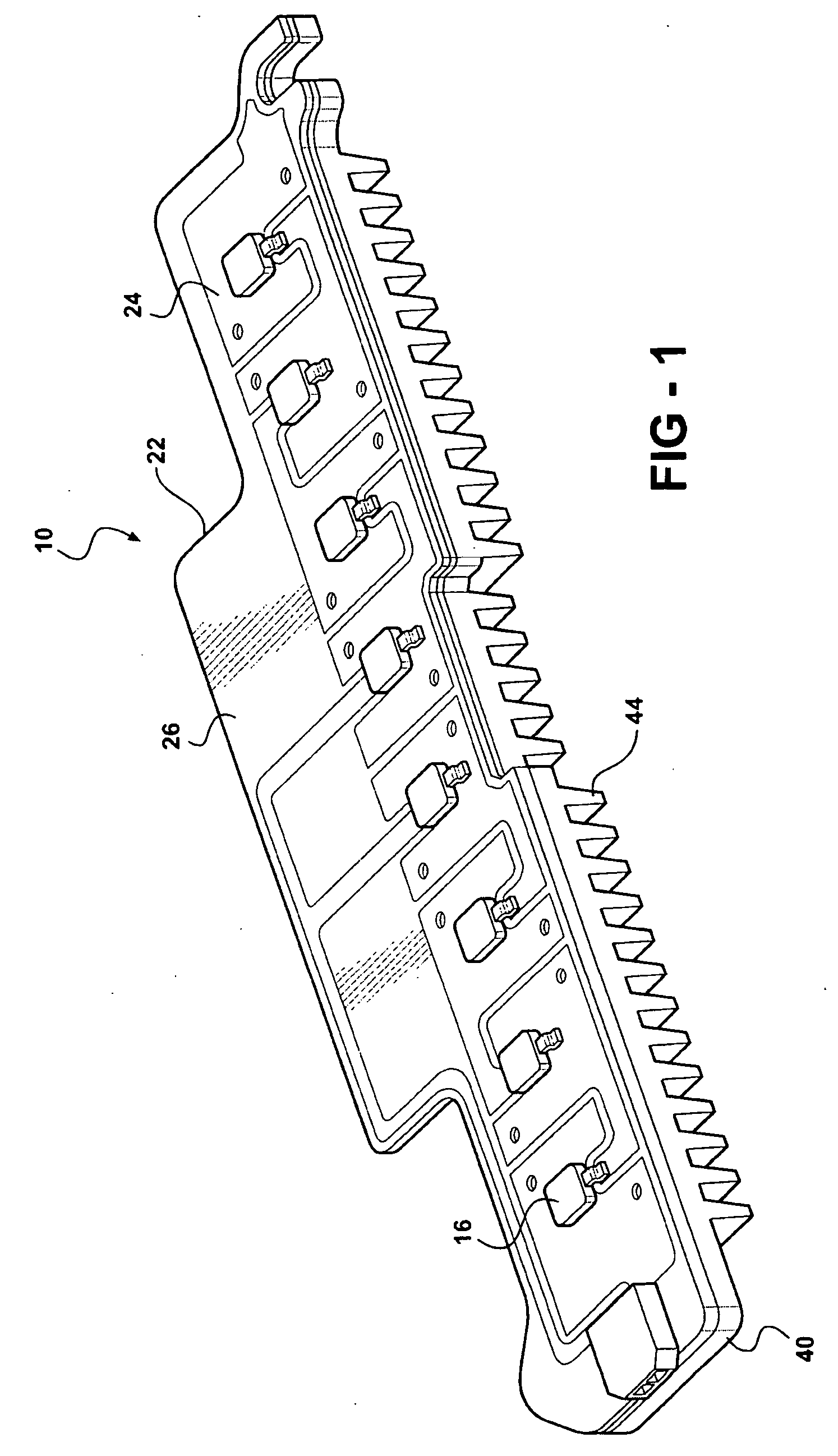

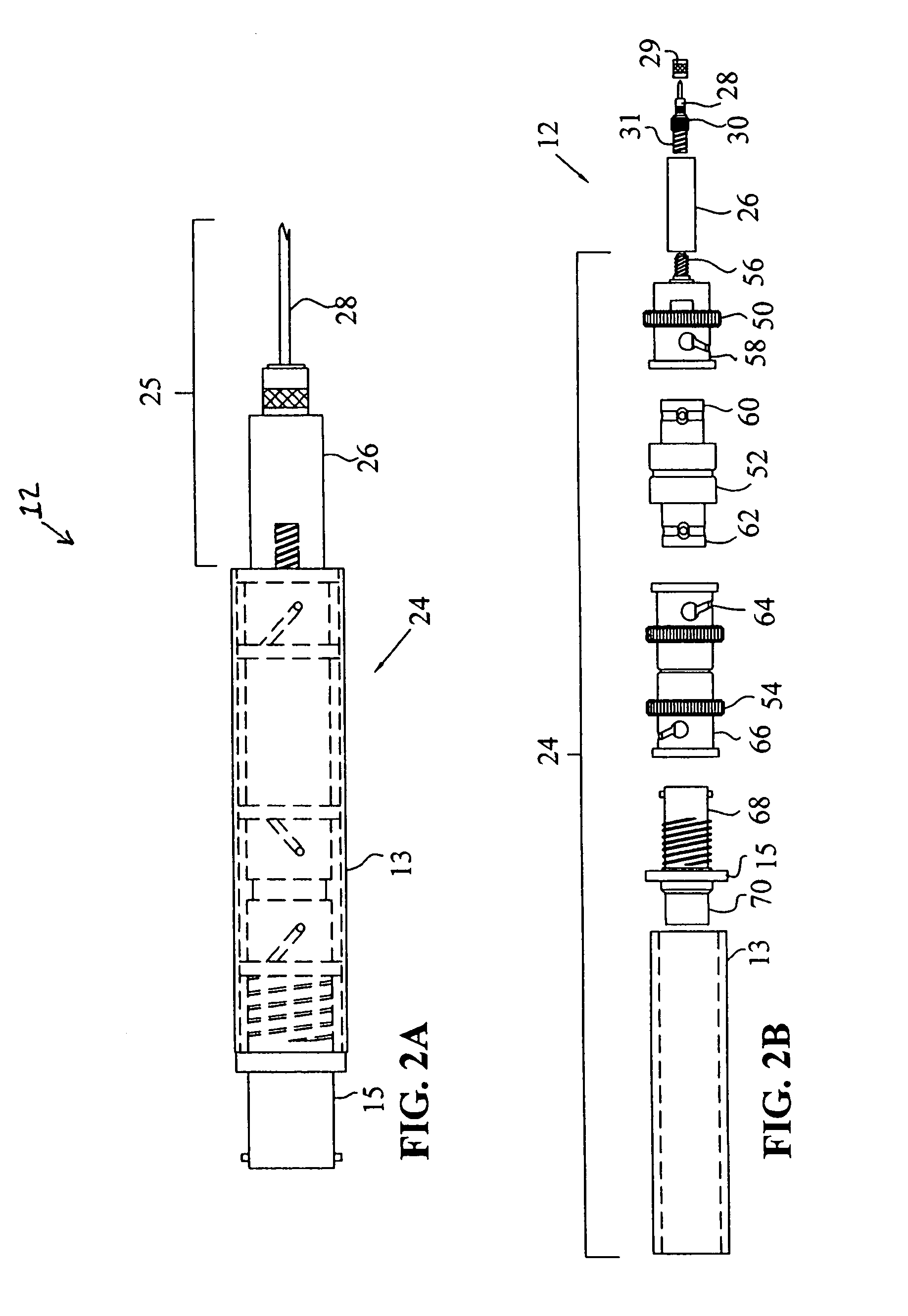

LED light module assembly

ActiveUS20060181878A1Point-like light sourceLighting heating/cooling arrangementsSurface mountingFlexible circuits

An LED light module assembly for use with high power, high light output LED's includes a thin flexible circuit board with surface mounted LED's and other electronic components which is attached to a metal heat sink using a layer of a thermally conductive adhesive, such as a thermally conductive epoxy adhesive. A conduction path is provided from the LED carrier through the flexible circuit board by the incorporation of one or more thermally conductive vias in the region of the attachment pad used to bond the LED to the flexible circuit board. These vias provide a conduction path from the back side of the LED carrier through the circuit board to the thermally conductive adhesive and heat sink. The LED light module assembly has the capacity to dissipate between about 10-14 W of power without exceeding a maximum LED junction temperature of about 125° C.

Owner:FEDERAL MOGUL WORLD WIDE LLC

Ultra-broadband differential voltage probes

ActiveUS7015709B2Reduce parasitic inductanceError minimizationElectrical testingMeasurement leads/probesElectricityElectrical conductor

Passive balanced probes are disclosed for use with a signal analysis device. The probes are very low cost relative to typical commercially available probes and provide an extremely flat response over a frequency range of approximately 0 to at least 1.5 gigahertz. The probes include a probe body constructed primarily from conventional components, a first surface mount resistor electrically connected between a probe tip and a center conductor, and two surface mount resistors electrically connected and parallel between the center conductor and a conductive shield. The probes further include a coaxial cable for connection to an instrument combiner or other instrument connection device.

Owner:APTIV TECH LTD

Implantable medical device incorporating integrated circuit notch filters

Implantable medical devices (IMDs) having sense amplifiers for sensing physiologic signals and parameters, RF telemetry capabilities for uplink transmitting patient data and downlink receiving programming and interrogation commands to and from an external programmer or other medical device are disclosed. At least one IC chip and discrete components have a volume and dimensions that are optimally minimized to reduce its volumetric form factor. Miniaturization techniques include forming notch filters of MEMS structures or forming discrete circuit notch filters by one or more of: (1) IC fabricating inductors into one or more IC chips mounted to the RF module substrate; (2) mounting each IC chip into a well of the RF module substrate and using short bonding wires to electrically connect bond pads of the RF module substrate and the IC chip; and (3) surface mounting discrete capacitors over IC chips to reduce space taken up on the RF module substrate. The IC fabricated inductors are preferably fabricated as planar spiral wound conductive traces formed of high conductive metals to reduce trace height and width while maintaining low resistance, thereby reducing parasitic capacitances between adjacent trace side walls and with a ground plane of the IC chip. The spiral winding preferably is square or rectangular, but having truncated turns to eliminate 90° angles that cause point-to-point parasitic capacitances. The planar spiral wound conductive traces are further preferably suspended over the ground plane of the IC chip substrate by micromachining underlying substrate material away to thereby reduce parasitic capacitances.

Owner:MEDTRONIC INC

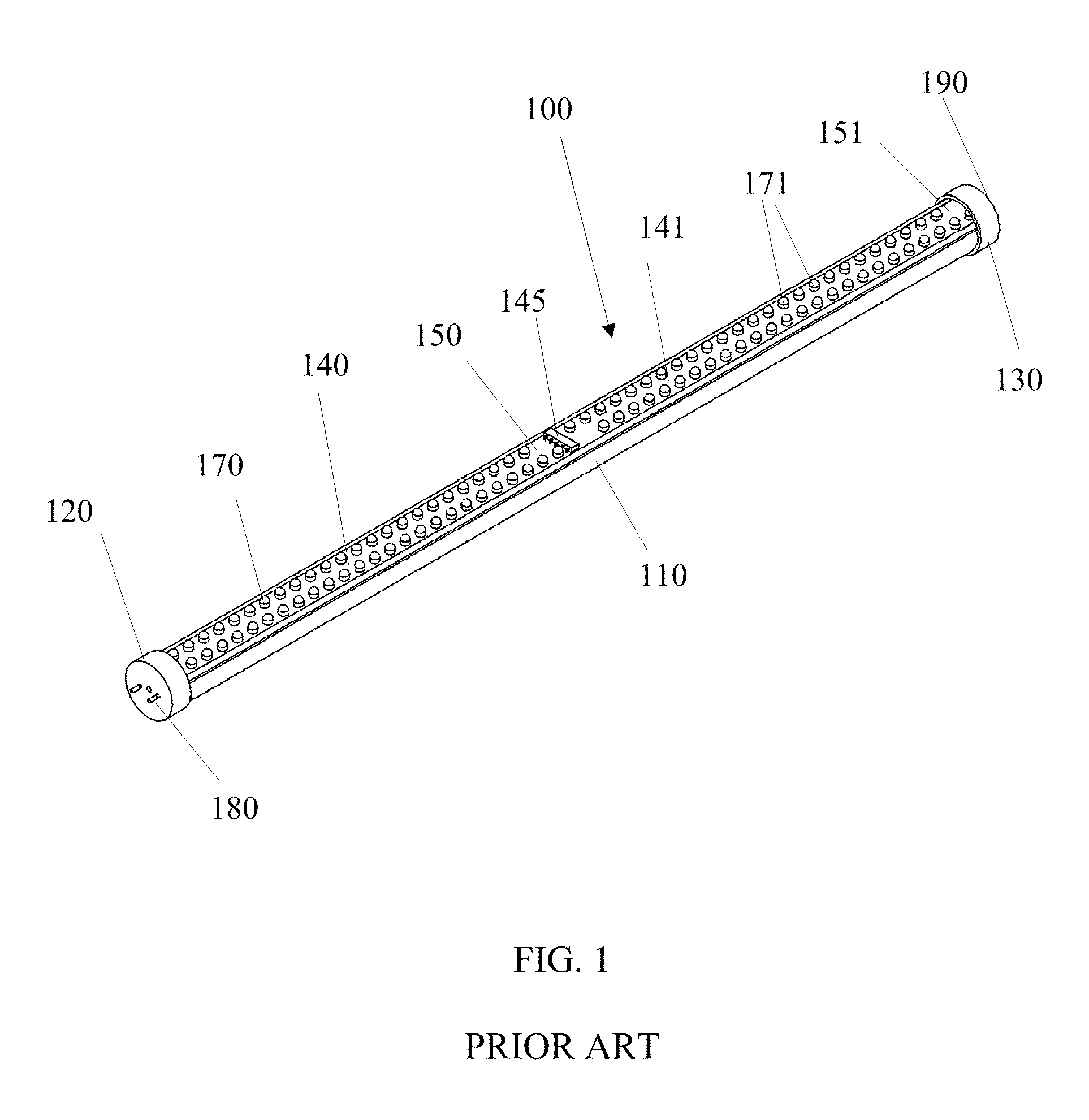

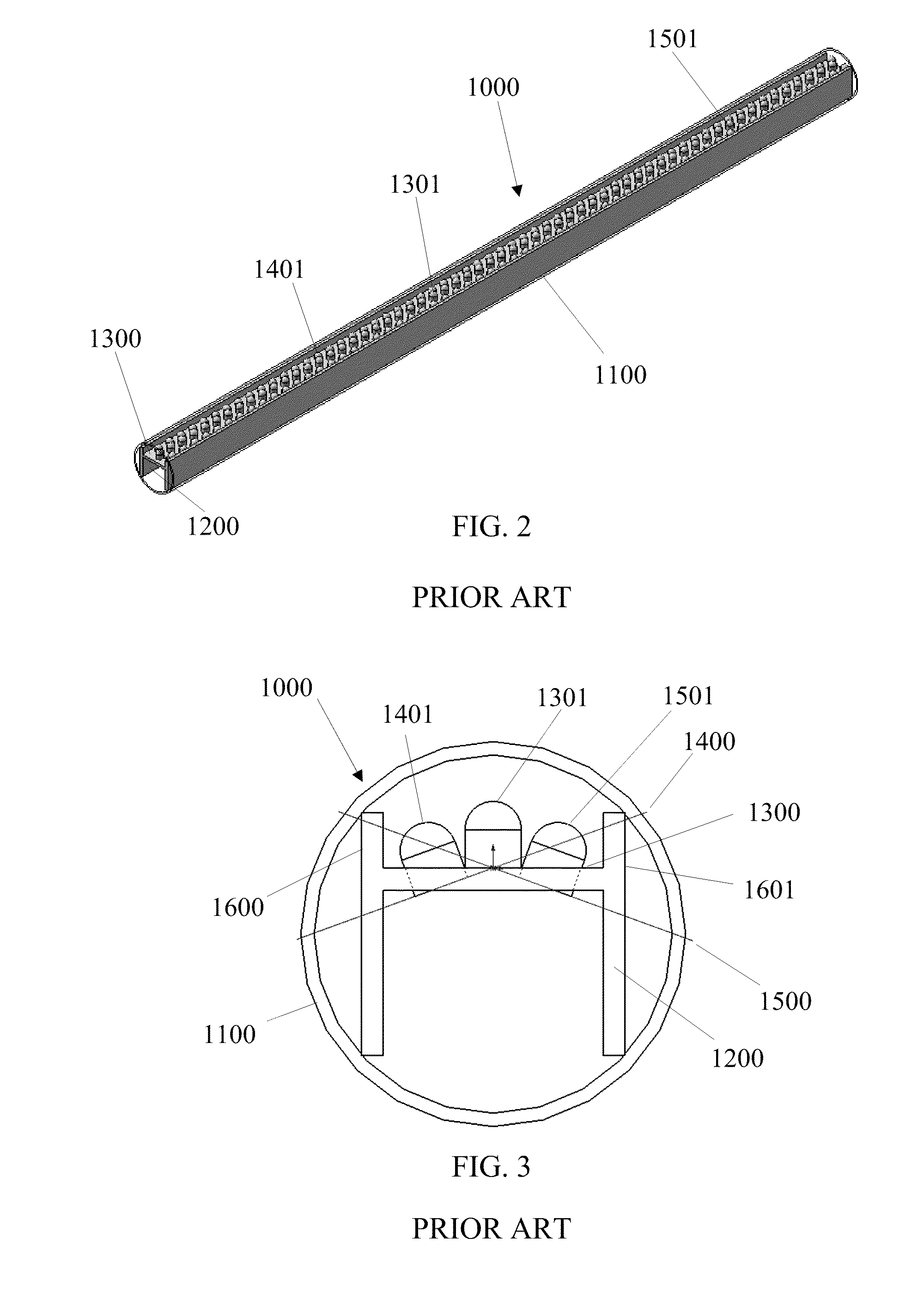

Linear solid-state lighting with broad viewing angle

ActiveUS20110176297A1Energy lossLighting support devicesPoint-like light sourceSmart lightingSurface mounting

A linear light-emitting diode (LED)-based solid-state device comprising a curved surface to hold a flexible printed circuit board with multiple linear arrays of surface mount LEDs provides lighting applications with a broad viewing angle over 180° along the radial direction. On each of the two lamp bases of the lamp, a shock-protection switch is mounted to prevent shock hazard during re-lamping.

Owner:ALEDDRA INC

LED illumination devices

A lens element has a curved surface mounted adjacent an LED for improving the light transmission efficiency and the dispersal pattern of radiation emitted by the LED.

Owner:DEEPSEA POWER & LIGHT

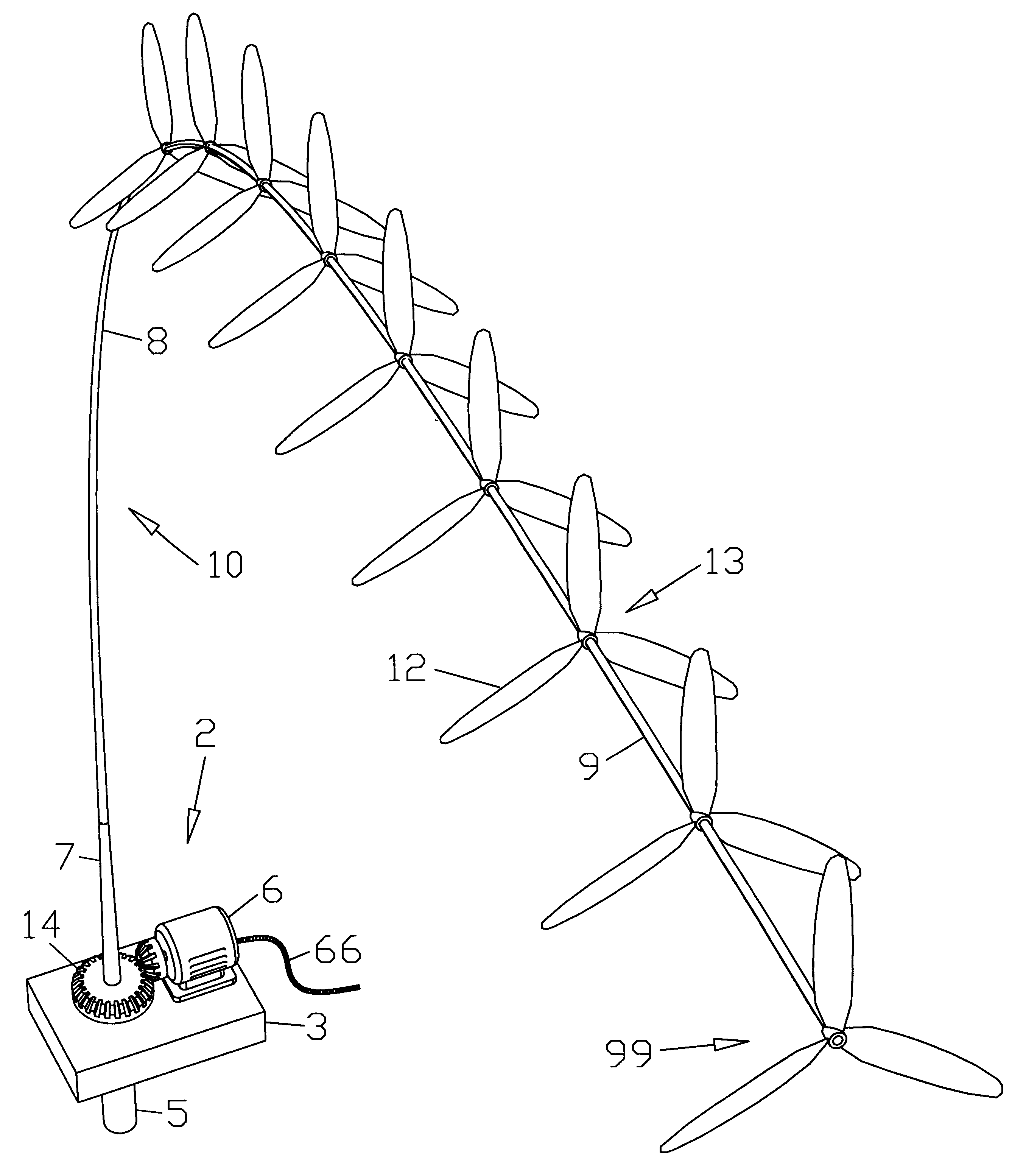

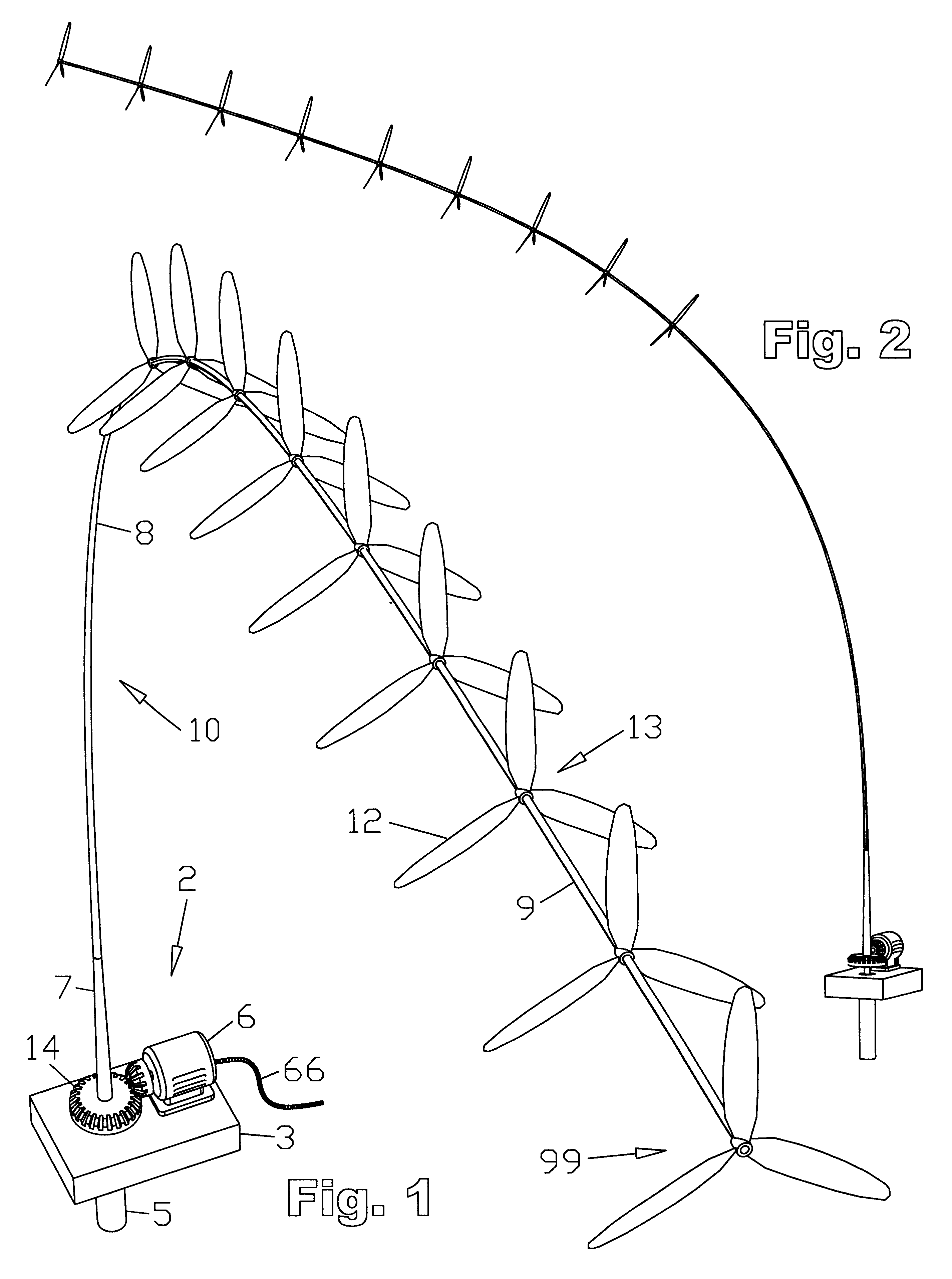

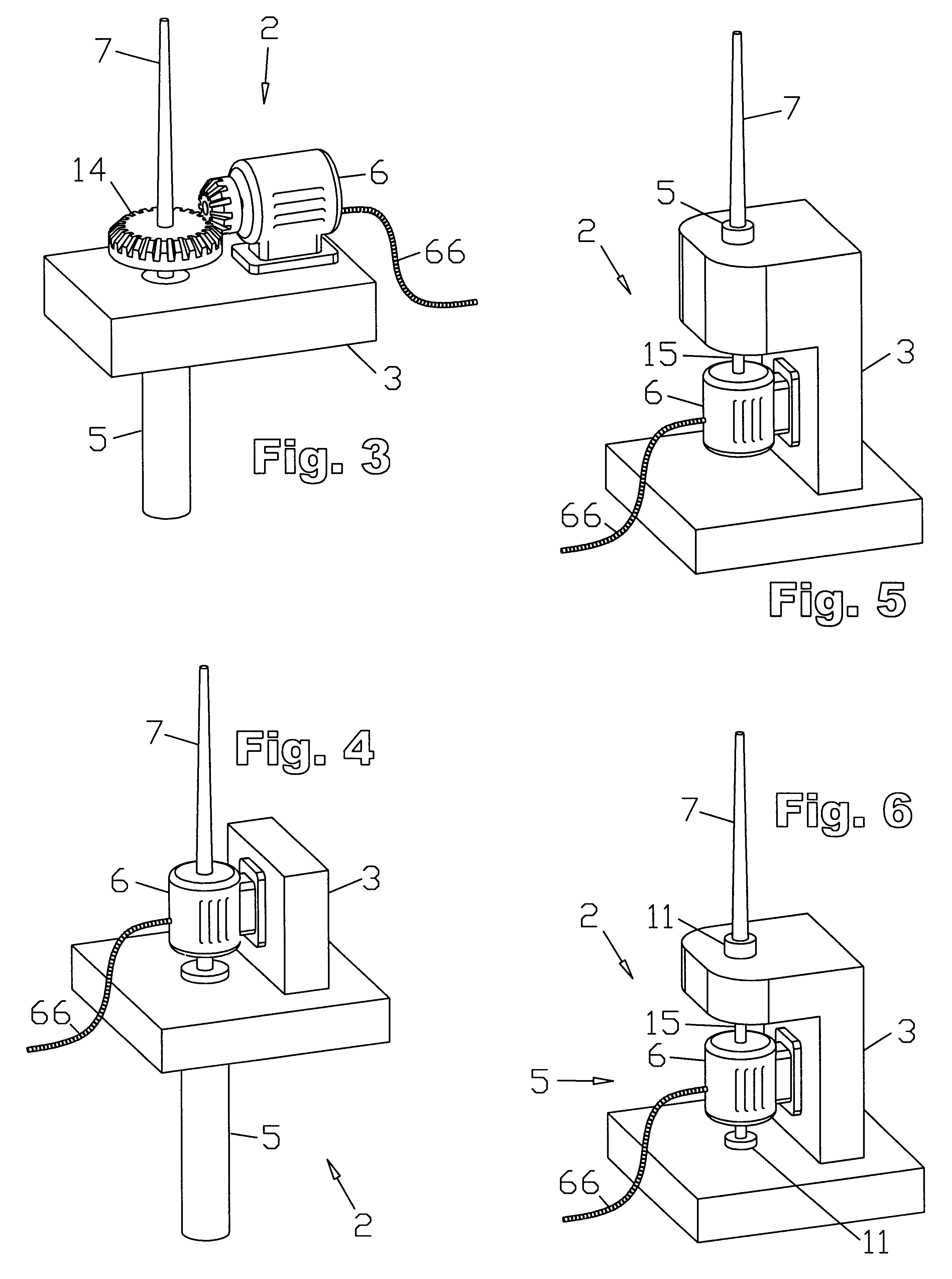

Serpentine wind turbine

Multiple horizontal axis type rotors are coaxially attached along the upper section of an elongate torque transmitting tower / driveshaft, The tower / driveshaft projects upward from a cantilevered bearing means, and is bent downwind, until the rotors become sufficiently aligned with the wind to rotate the entire tower / driveshaft, Power is drawn from the shaft at the base. Surface mount, subsurface mount, and marine installations, including a sailboat, are disclosed. Blade-to-blade lashing, and vertical axis rotor blades may also be included. Vertical and horizontal axis type rotor blades may be interconnected along the length of the tower / driveshaft to form a structural lattice, and the central shaft may even be eliminated. Aerodynamic lifting bodies or tails, buoyant lifting bodies, buoyant rotor blades, and methods of influencing the tilt of the rotors, can help elevate the structure. This wind turbine can have as few as one single moving part.

Owner:SELSAM DOUGLAS SPRIGGS

LED light fixture

InactiveUS20090034261A1Point-like light sourceElectric circuit arrangementsSurface mountingEngineering

An LED light fixture with enhanced thermal management. The fixture may be in a surface-mounted or a recessed configuration. The LED is attached with thermally-conductive material, such as thermal transfer tape, to a heat sink or housing. The heat sink may comprise a number of cooling fins to radiate heat, as well as a number of openings to promote cooling air flow. A variety of reflector assemblies can be used for different optical and aesthetic configurations. One or more lenses may be used.

Owner:GROVE DOUGLAS

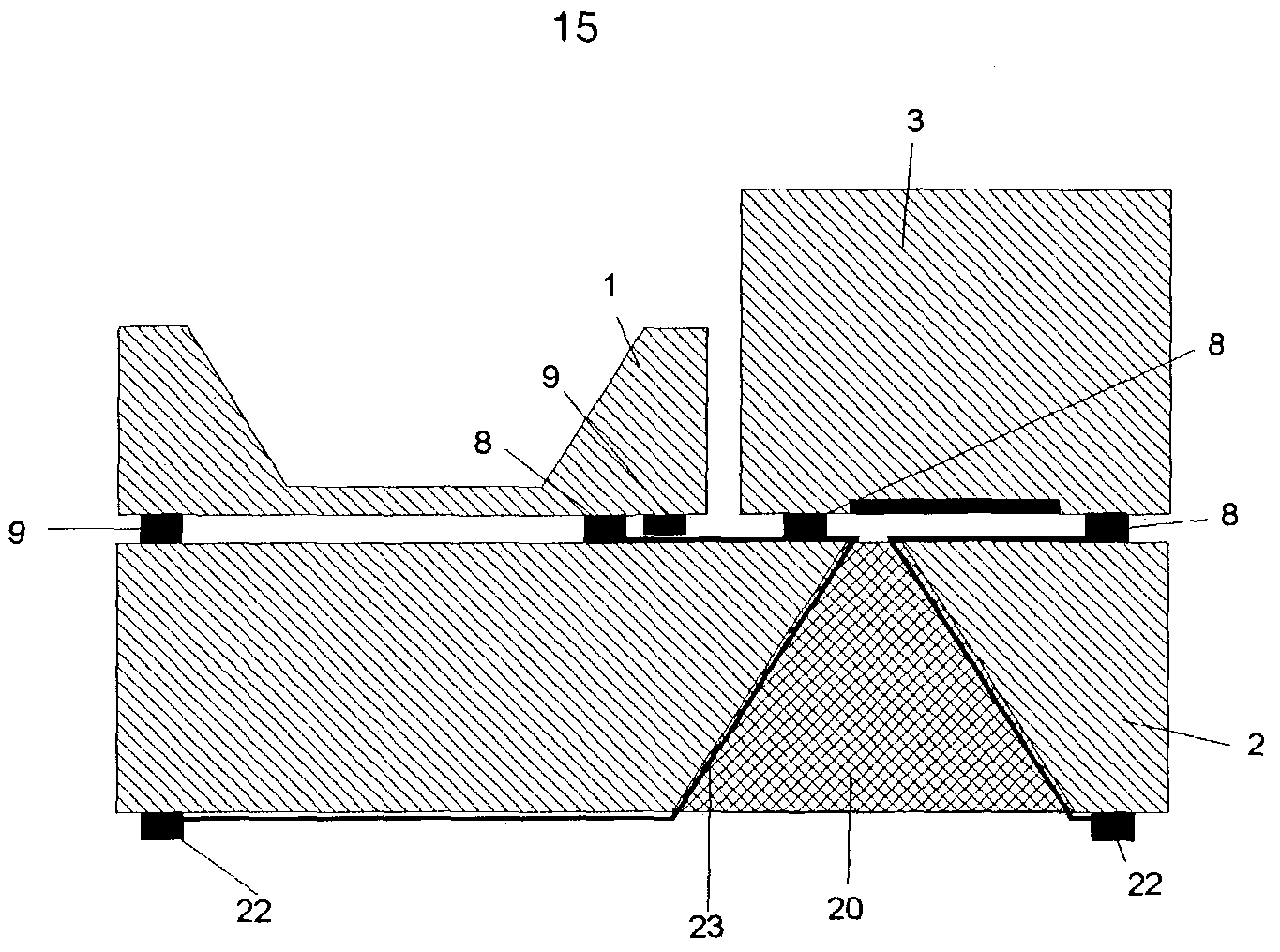

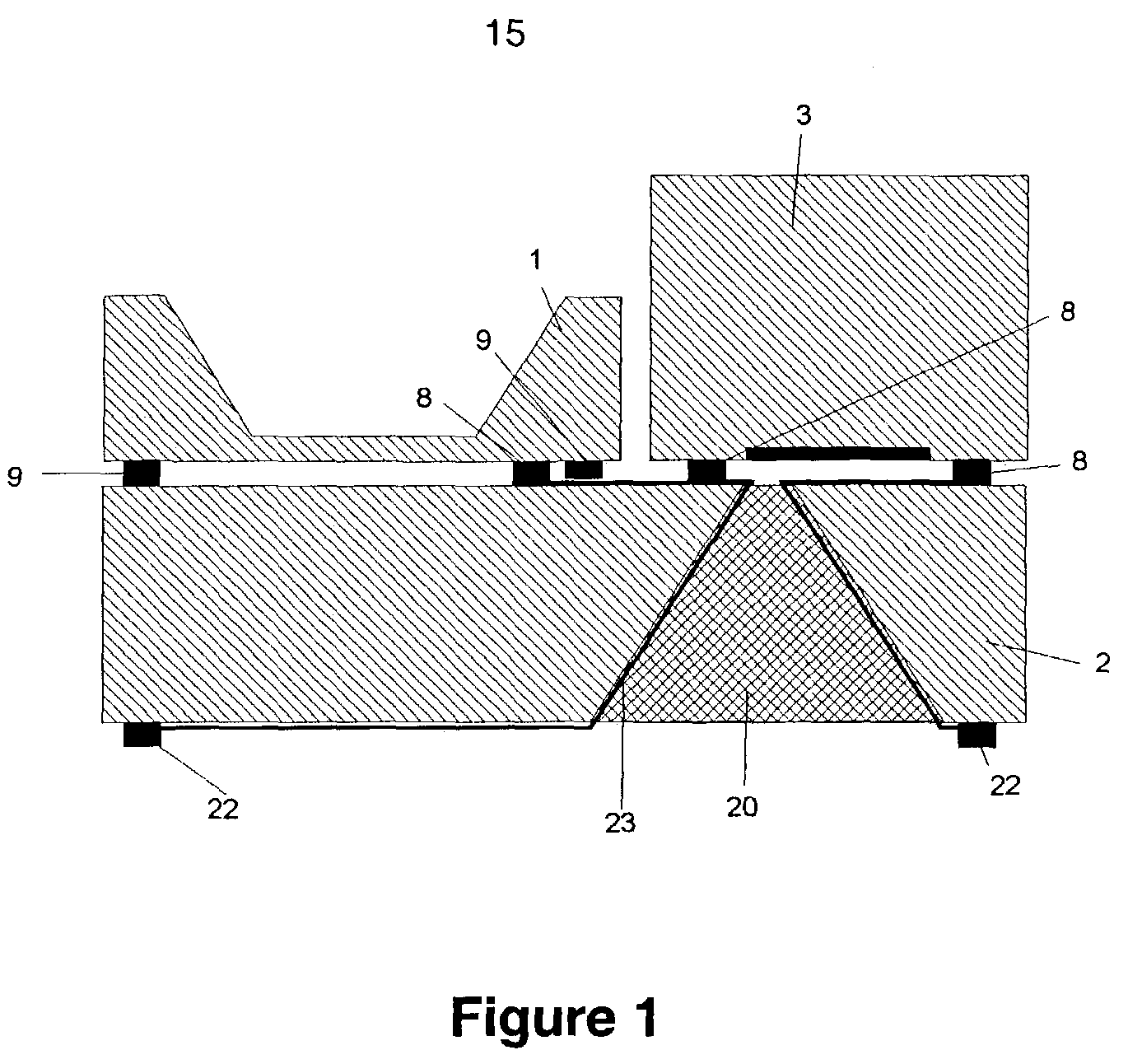

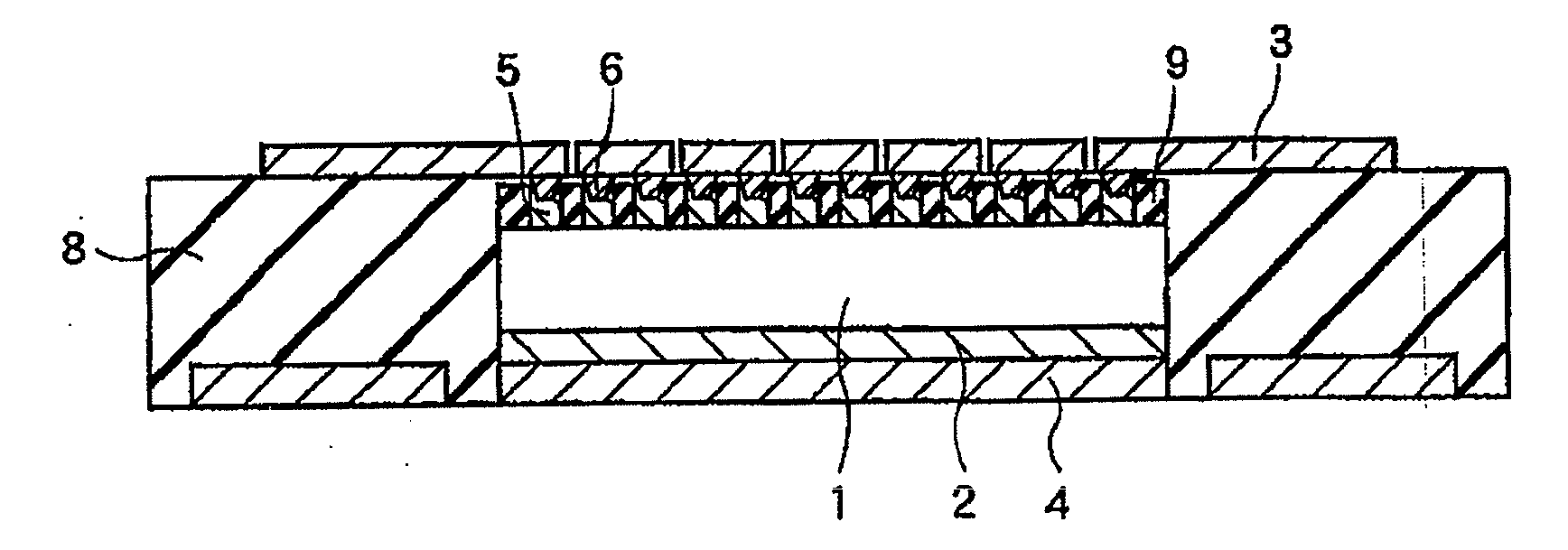

Circuit substrate, an electronic device arrangement and a manufacturing process for the circuit substrate

InactiveUS20100044845A1Improve workabilityImprove reliabilitySemiconductor/solid-state device detailsPrinted circuit aspectsResistSurface mounting

[Problem to be Solved] There are provided a circuit substrate, an electronic device arrangement and a manufacturing process for the circuit substrate which enable to directly implement the surface mounting and so on of electronic components on the conductive wiring without forming solder resist, and also which enable to enhance high speed transmission characteristics and to enlarge wiring rule for the electrode terminal of the function element to be contained therein, and to implement with excellent workability and reliability when connecting the electronic device.[Solution] A circuit substrate comprisinga function element 1 with an electrode terminal 5 a base member containing the function element 1 therein and having at least one layer of a conductive wiring formed on its front side face and rear side face respectively, anda via 6 connecting the electrode terminal 5 with the conductive wiring 3 formed on the base member, wherein the conductive wiring formed on either one of the front side face and the rear side face of the base member is arranged such that a surface exposed outside from the base member is in the same plane with or inside a surface of the base member on which the conductive wiring is formed.

Owner:NEC CORP

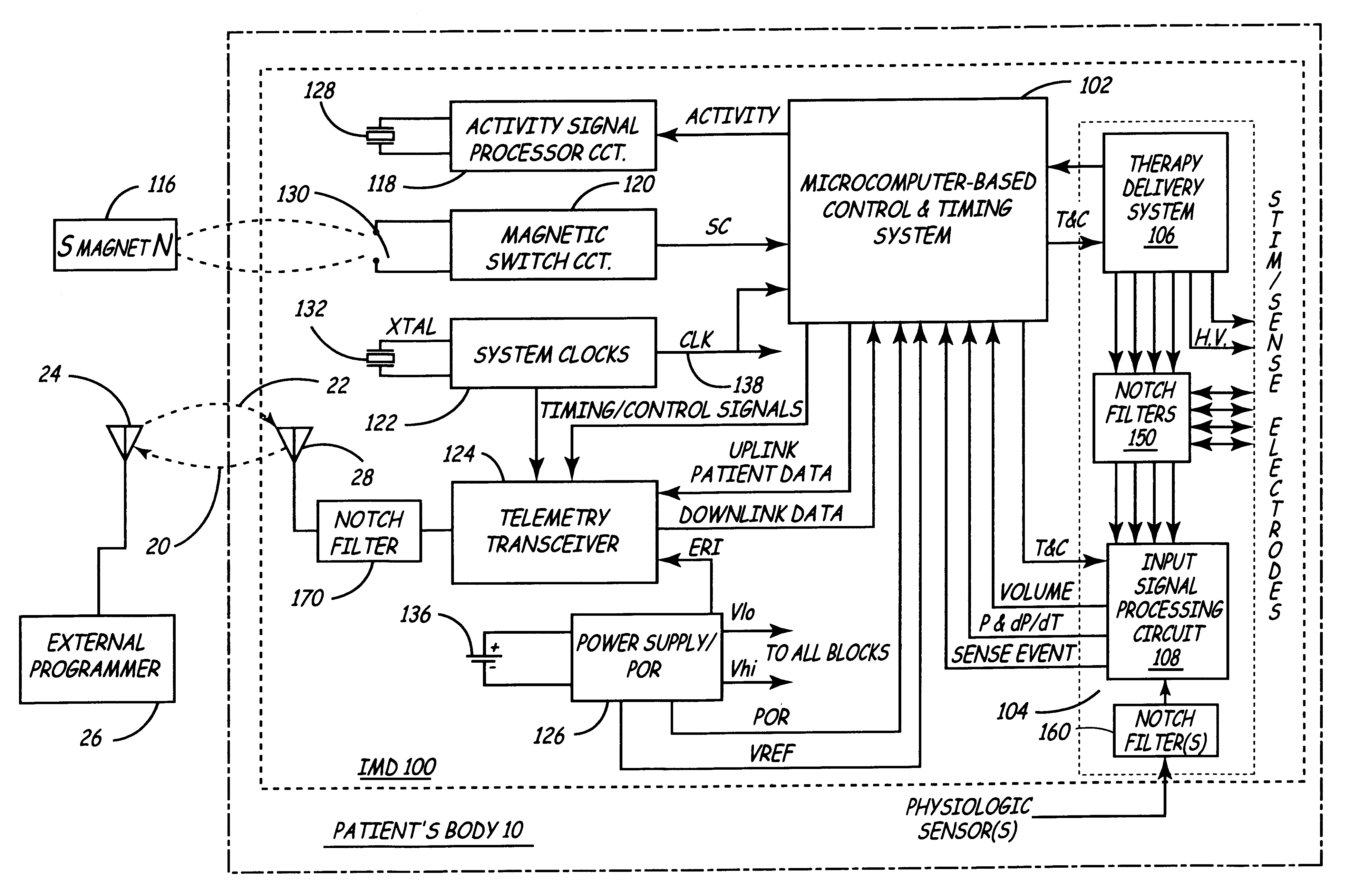

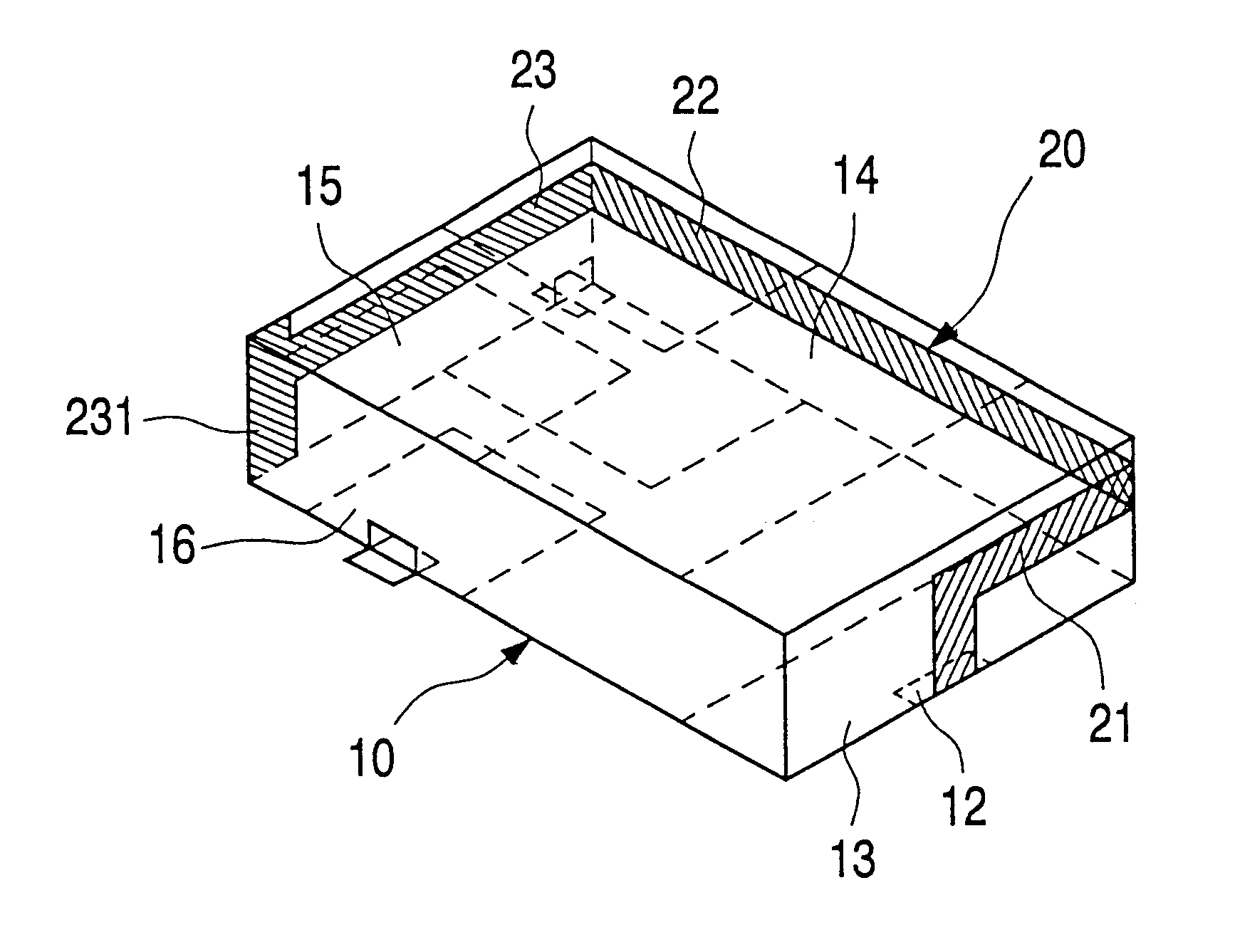

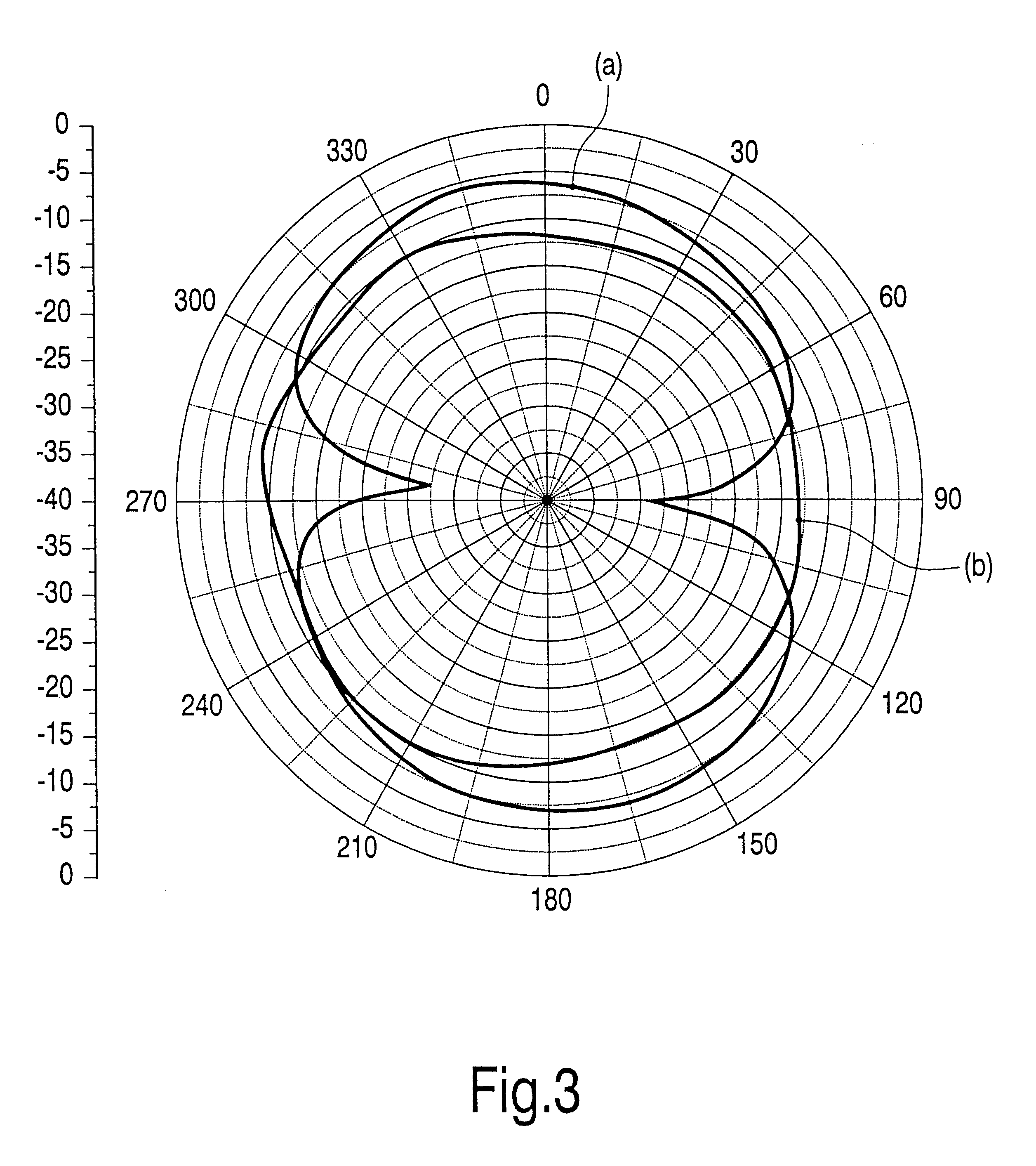

Miniaturized microwave antenna

InactiveUS6680700B2Reduce antenna sizeSmall sizeSimultaneous aerial operationsAntenna supports/mountingsElectrical conductorEngineering

A miniaturized antenna is described with at least a ceramic substrate (10) and a metallization, particularly designed for use in the high-frequency and microwave ranges. The antenna is characterized in that the metallization is a surface metallization which is formed by a feed terminal (12) for electromagnetic energy to be radiated, by at least a first metallization structure (30), and by a conductor track (20) extending along at least part of the circumference of the substrate (10), which track connects the feed terminal to the at least one first metallization structure (30), which first metallization structure (30) comprises a first conductor track portion (31) extending from a side of the substrate lying opposite the feed terminal (12) towards the feed terminal and a first metallization pad (32). The antenna can be provided on a printed circuit board by surface mounting and has a great impedance and radiation bandwidth, so that it is particularly suitable for use in mobile telephones operating in the GSM and UMTS bands.

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV