Patents

Literature

633 results about "Programmer" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A programmer (hardware), device programmer, chip programmer, device burner, or PROM writer is a piece of electronic equipment that arrange written software to configure programmable non-volatile integrated circuits, called programmable devices. The target devices include; PROM, EPROM, EEPROM, Flash memory, eMMC, MRAM, FeRAM, NVRAM, PLD, PLA, PAL, GAL, CPLD, FPGA, and MCU. These are terminologies in the field of computer hardware.

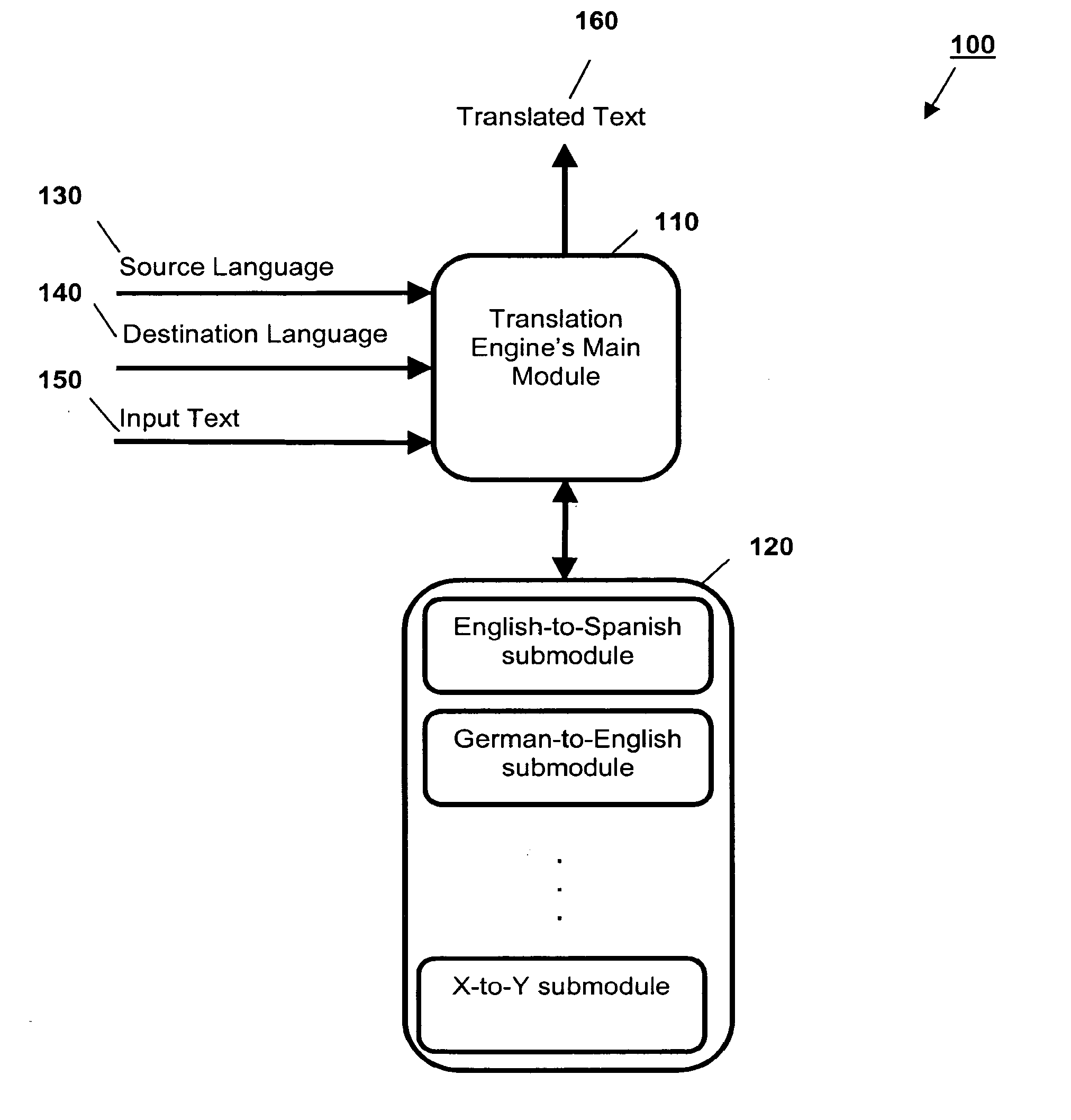

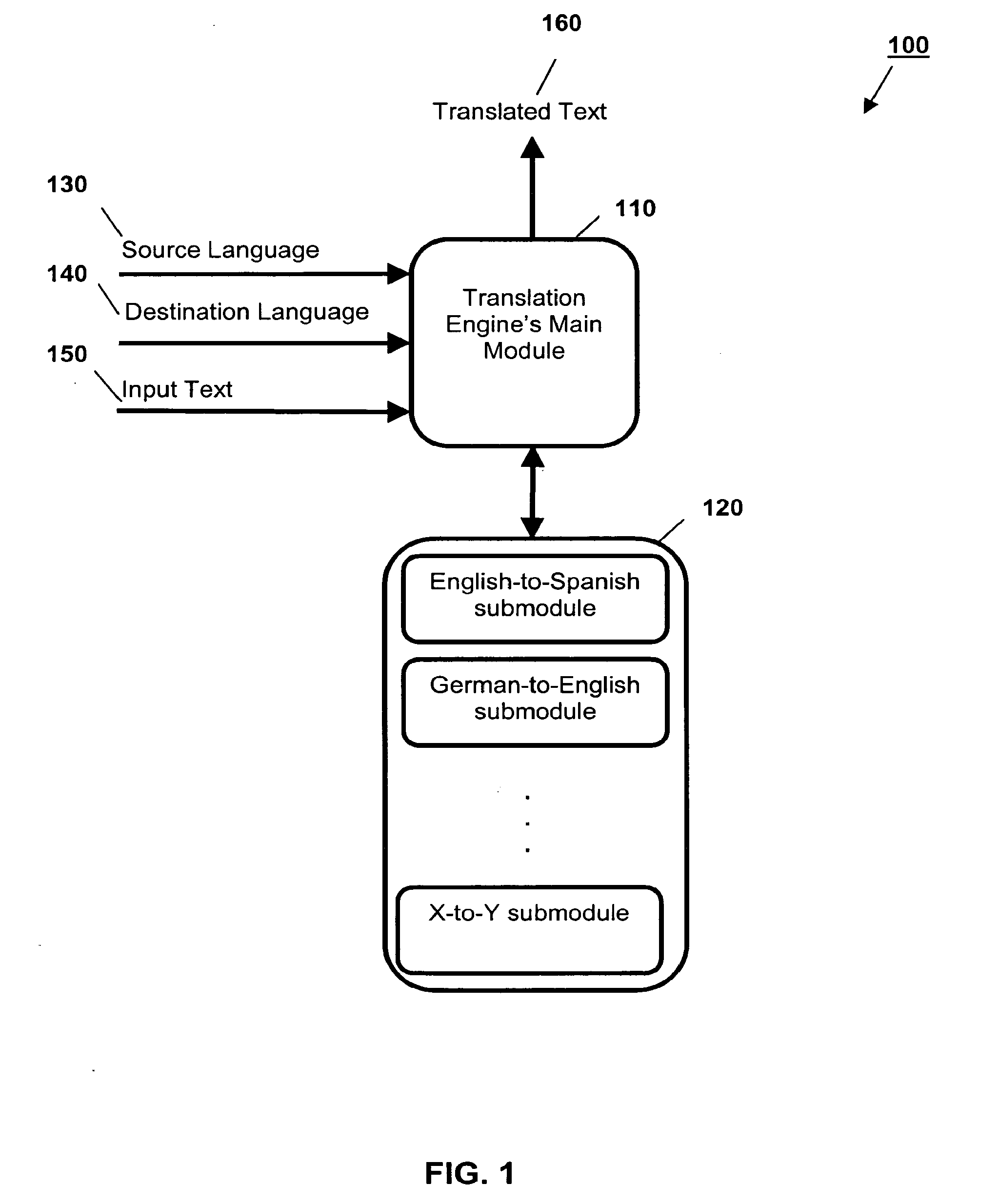

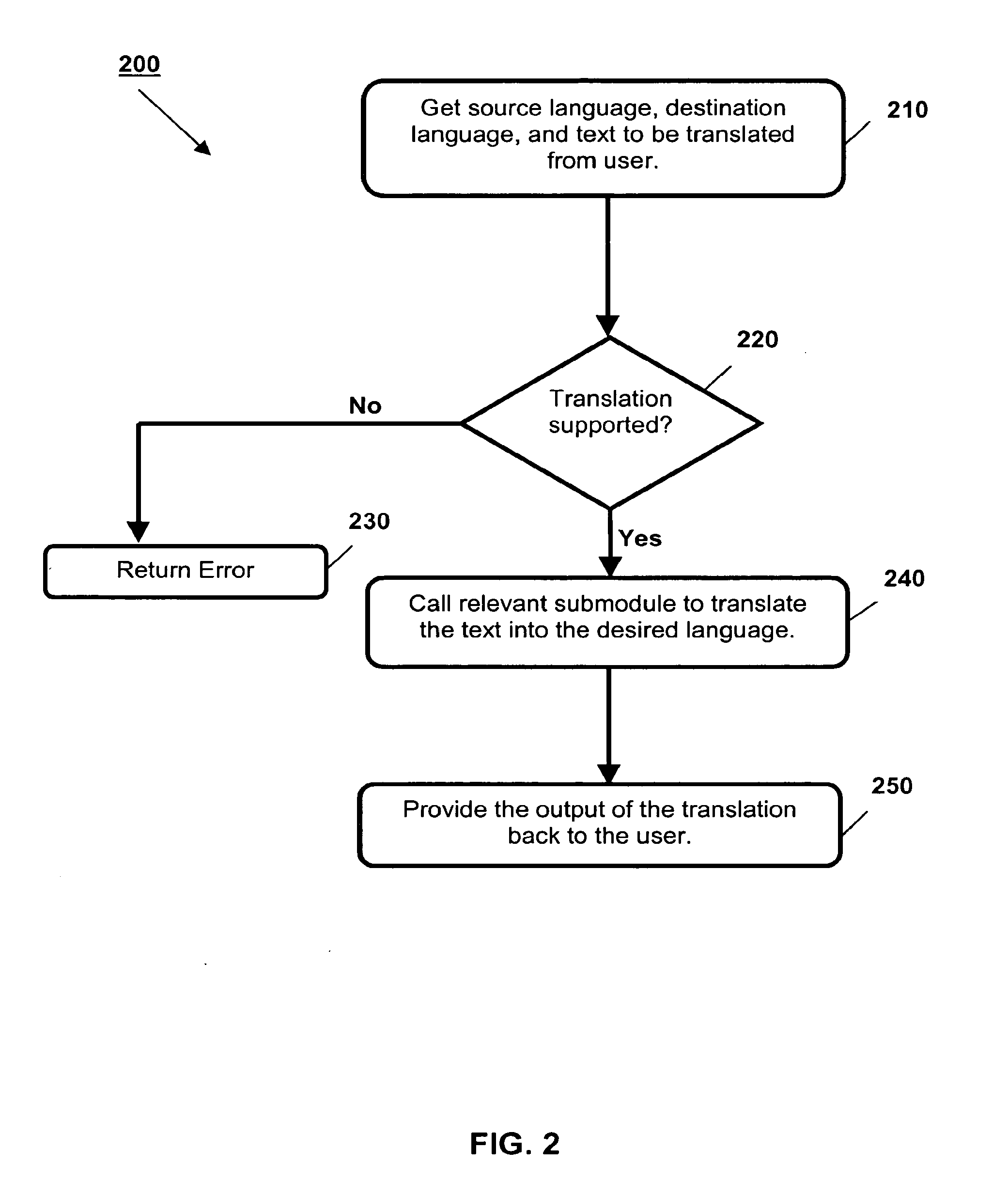

Computer Program Product and Computer System for Language-Enhanced Programming Tools

InactiveUS20090240485A1Natural language translationSpecial data processing applicationsGraphicsGraphical user interface

Statements of a computer program expressed using a first source natural language are made meaningful to a programmer familiar with a second target natural language. The first source natural language of the computer program is determined from the programmer, or through analysis, and the second target natural language desired by the programmer is selected. Textual constructs may be parsed, with reference to stored coding conventions to determine meaningful lexical tokens. Such tokens are translated with a translation engine, and displayed to the programmer, desirably using a graphical user interface feature of an integrated development environment (IDE) for computer programming in a particular programming language.

Owner:IBM CORP

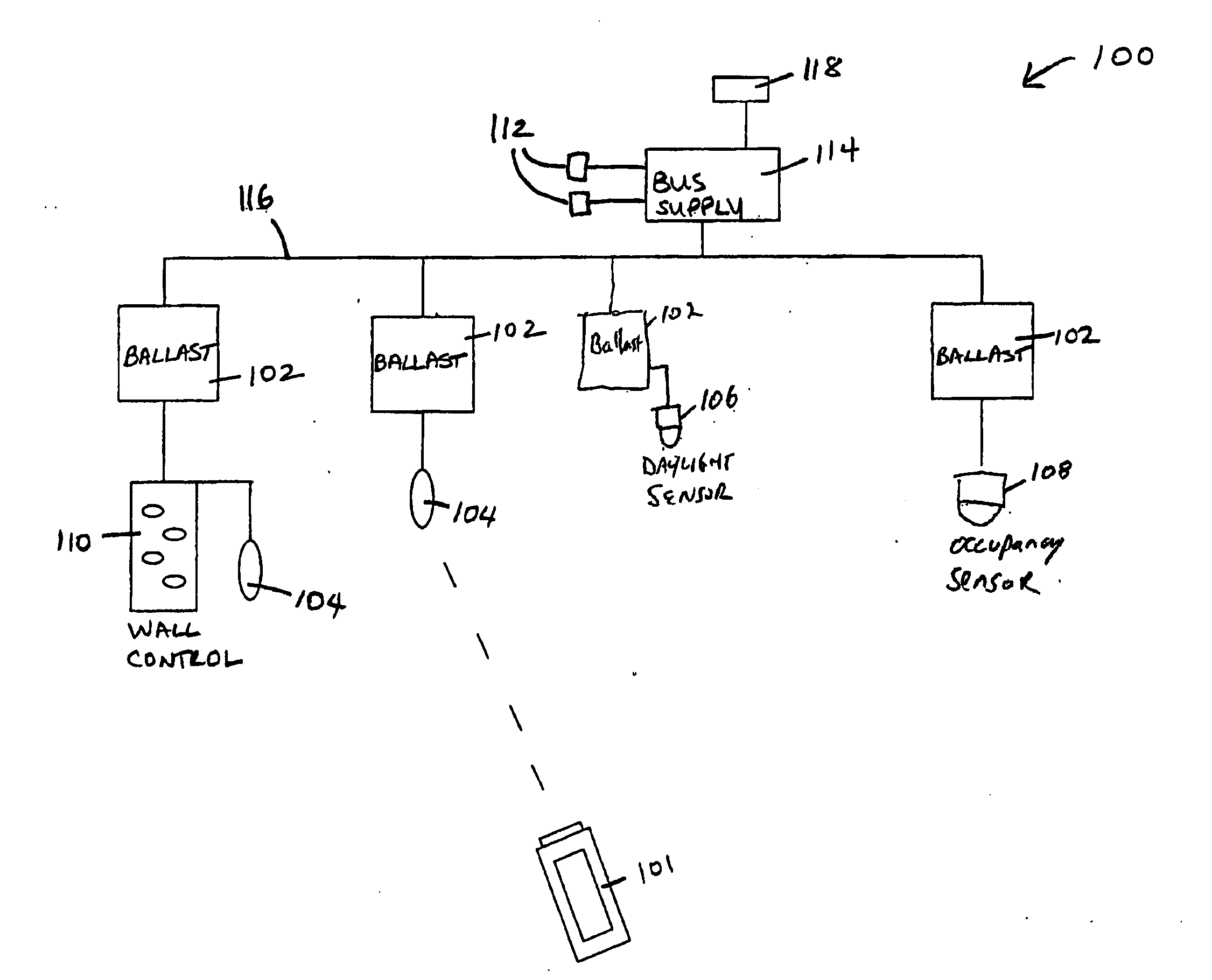

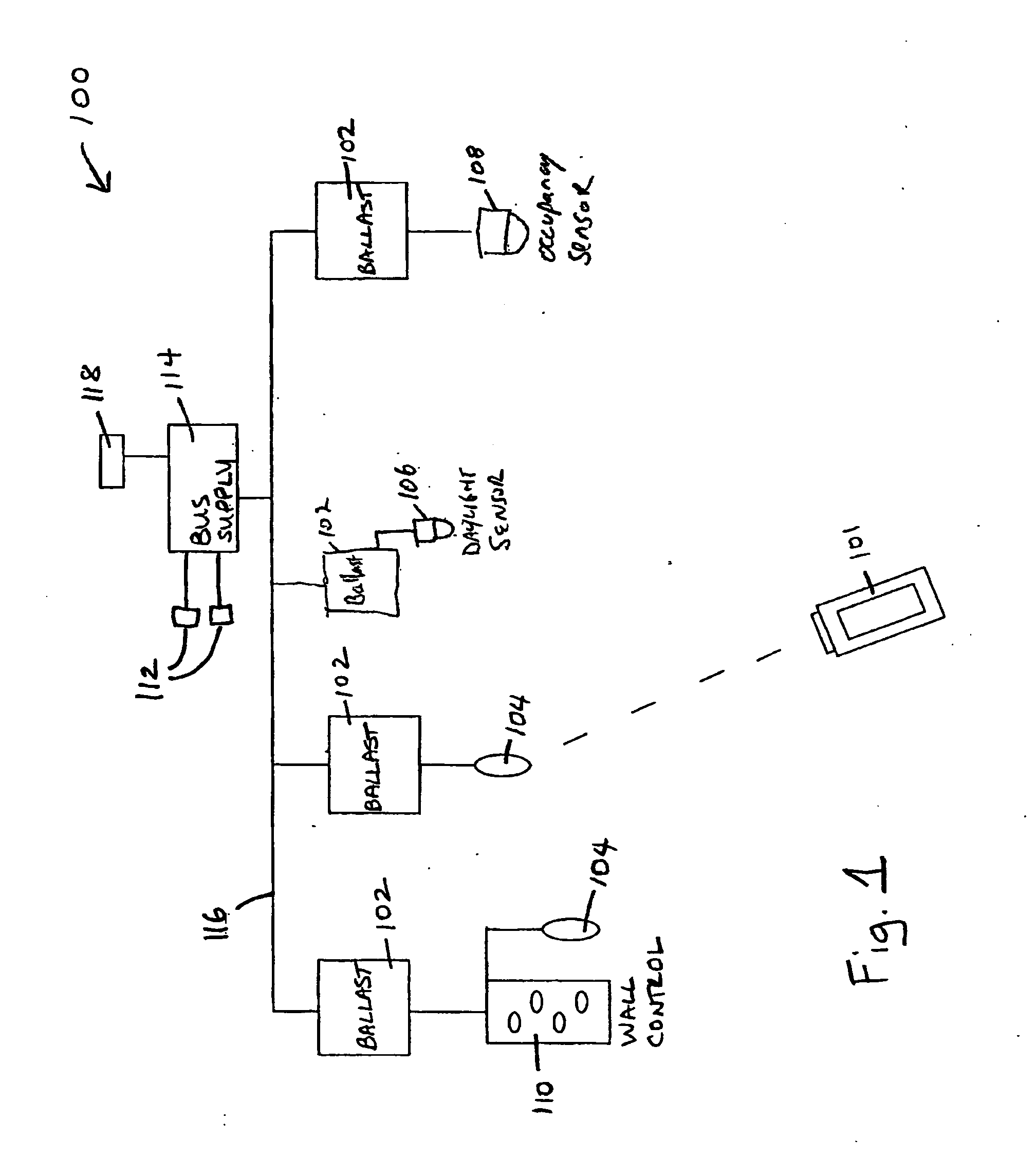

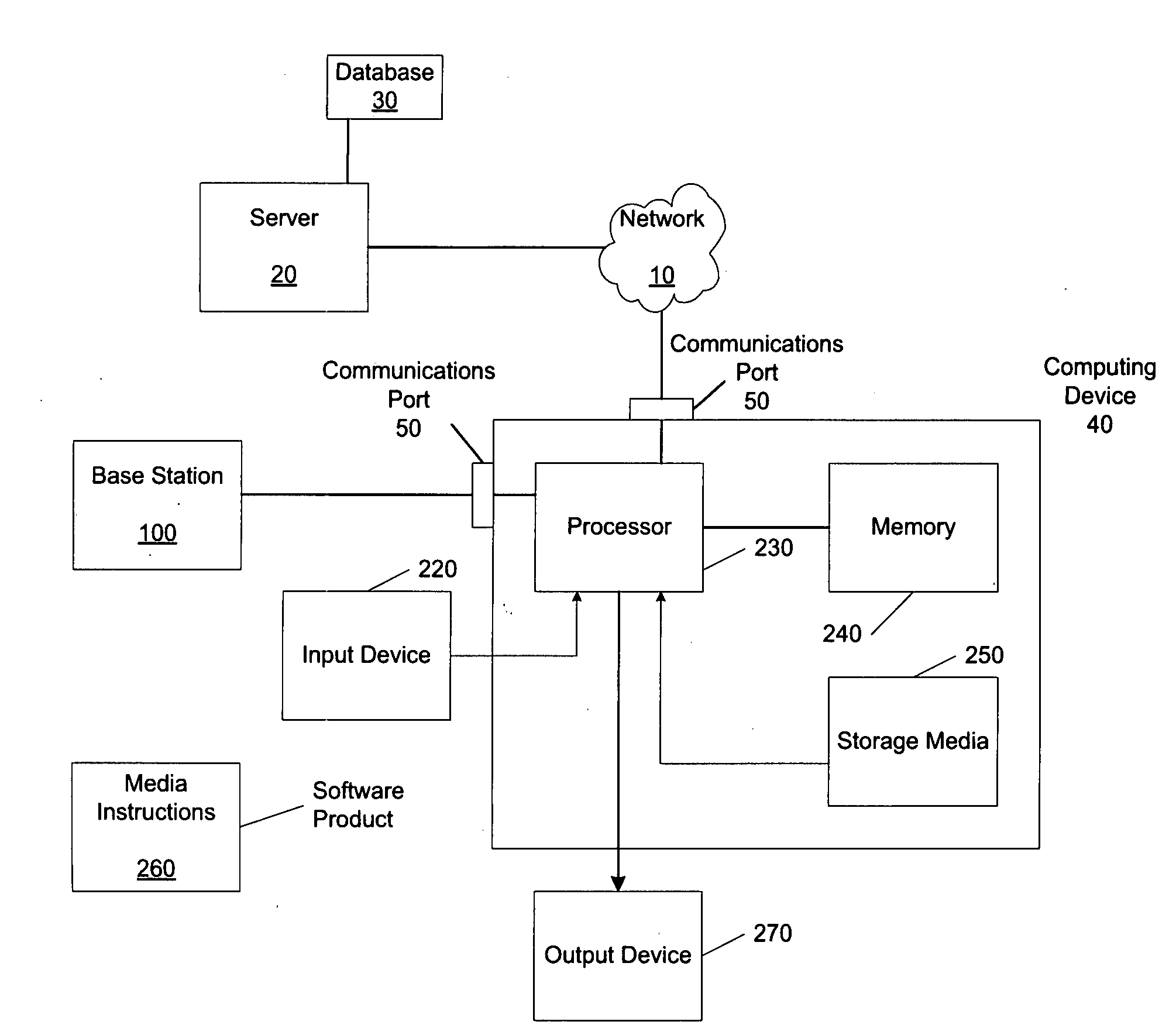

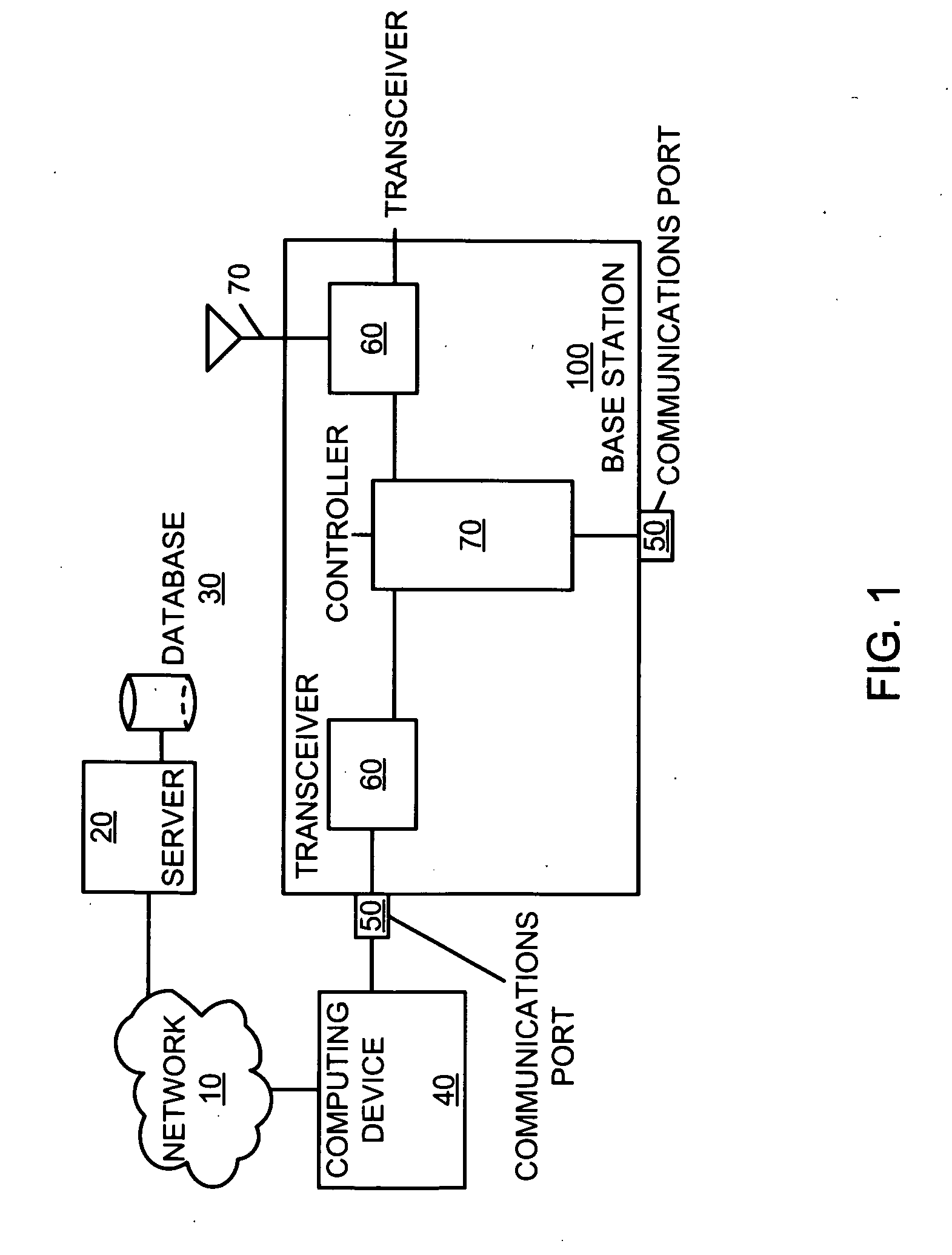

Handheld programmer for lighting control system

ActiveUS20060202851A1Electric signal transmission systemsElectrical apparatusHand heldCommunications receiver

The invention regards a system and method for using a handheld programming device to configure a lighting control system wirelessly. In one embodiment, at least one device configured with a processing section is installed in the lighting control system. A communications receiver that is operable to receive a signal from the handheld programming device is also installed in the lighting control system, wherein the signal includes an instruction for configuring the lighting control system. Further, the signal is wirelessly sent from the handheld programming device to the communications receiver, and the instruction is transmitted from the communications receiver to a device in the system. The instruction functions to configure the lighting control system.

Owner:LUTRON TECH CO LLC

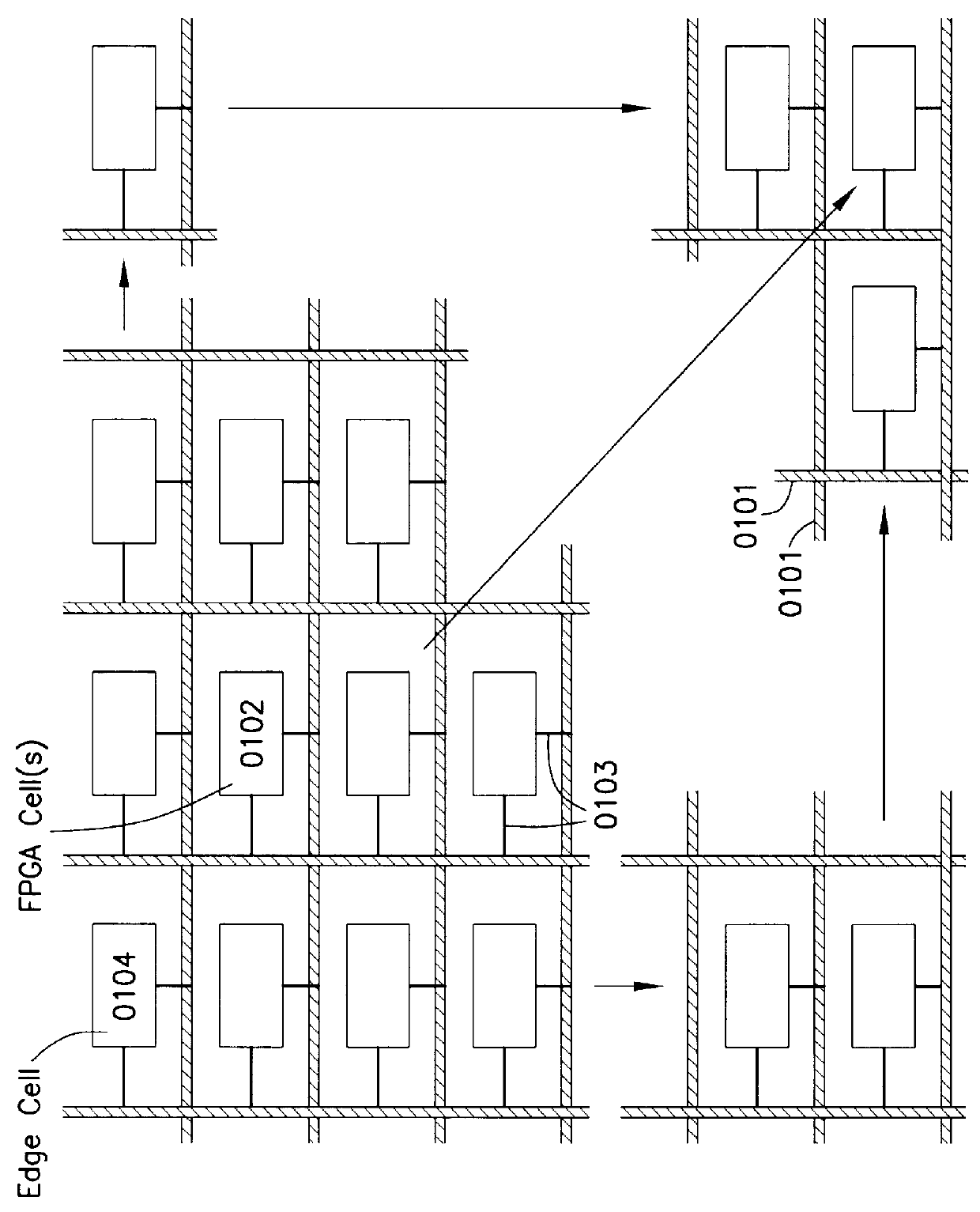

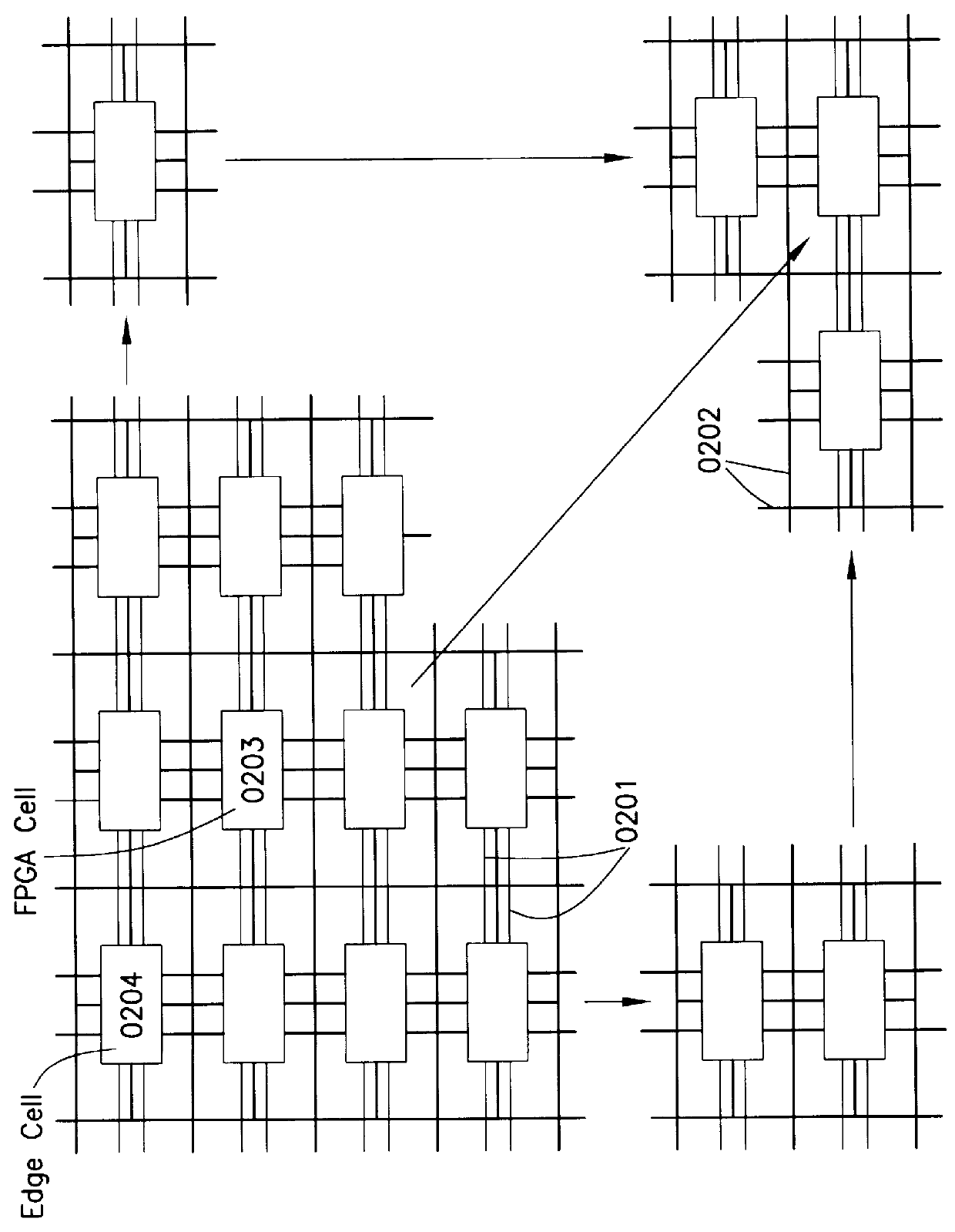

I/O and memory bus system for DFPs and units with two- or multi-dimensional programmable cell architectures

InactiveUS6119181ADigital storageArchitecture with single central processing unitComputer architectureMemory bus

A uniform bus system is provided which operates without any special consideration by a programmer. Memories and peripheral may be connected to this bus system without any special measures. Likewise, units may be cascaded with the help of the bus system. The bus system combines a number of internal lines, and leads them as a bundle to terminals. The bus system control is predefined and does not require any influence by the programmer. Any number of memories, peripherals or other units can be connected to the bus system.

Owner:SCIENTIA SOL MENTIS AG

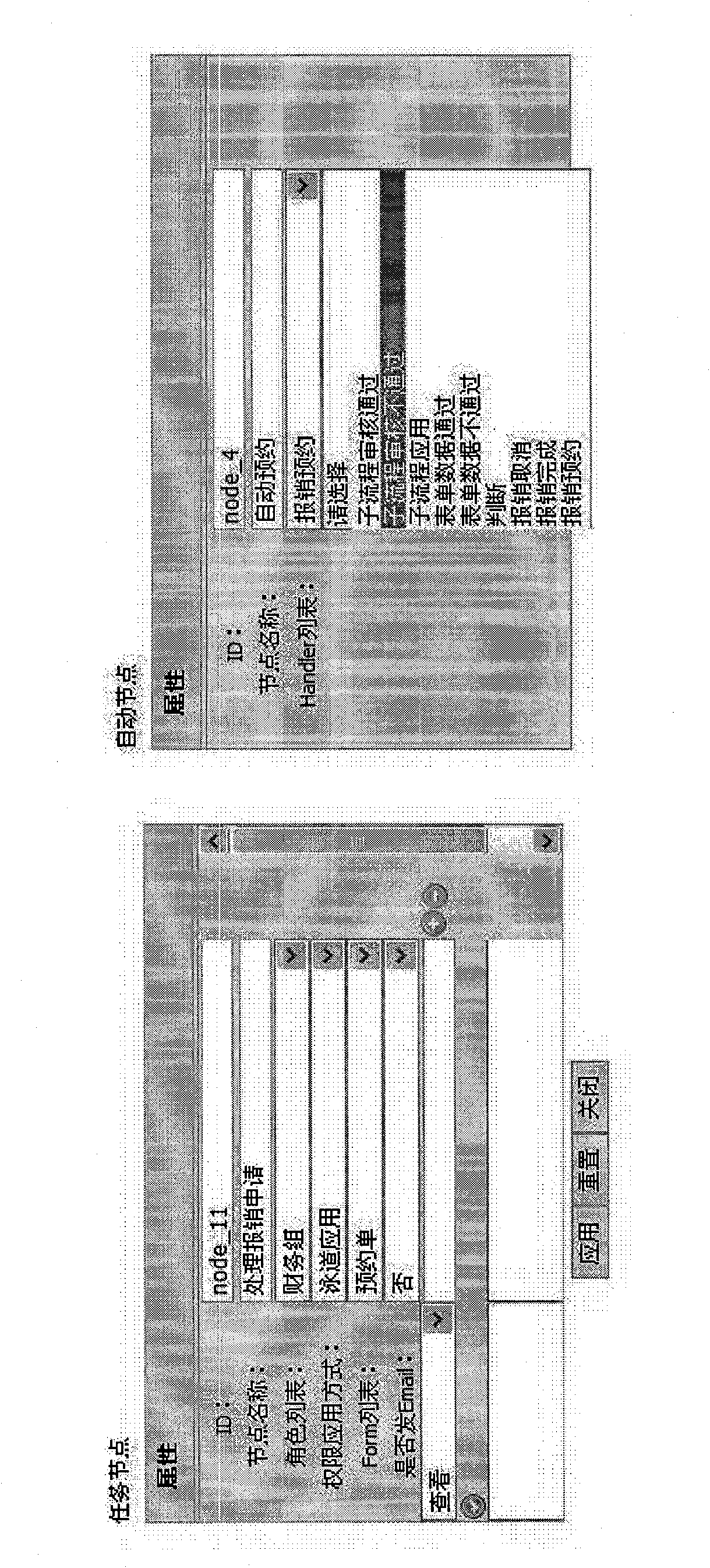

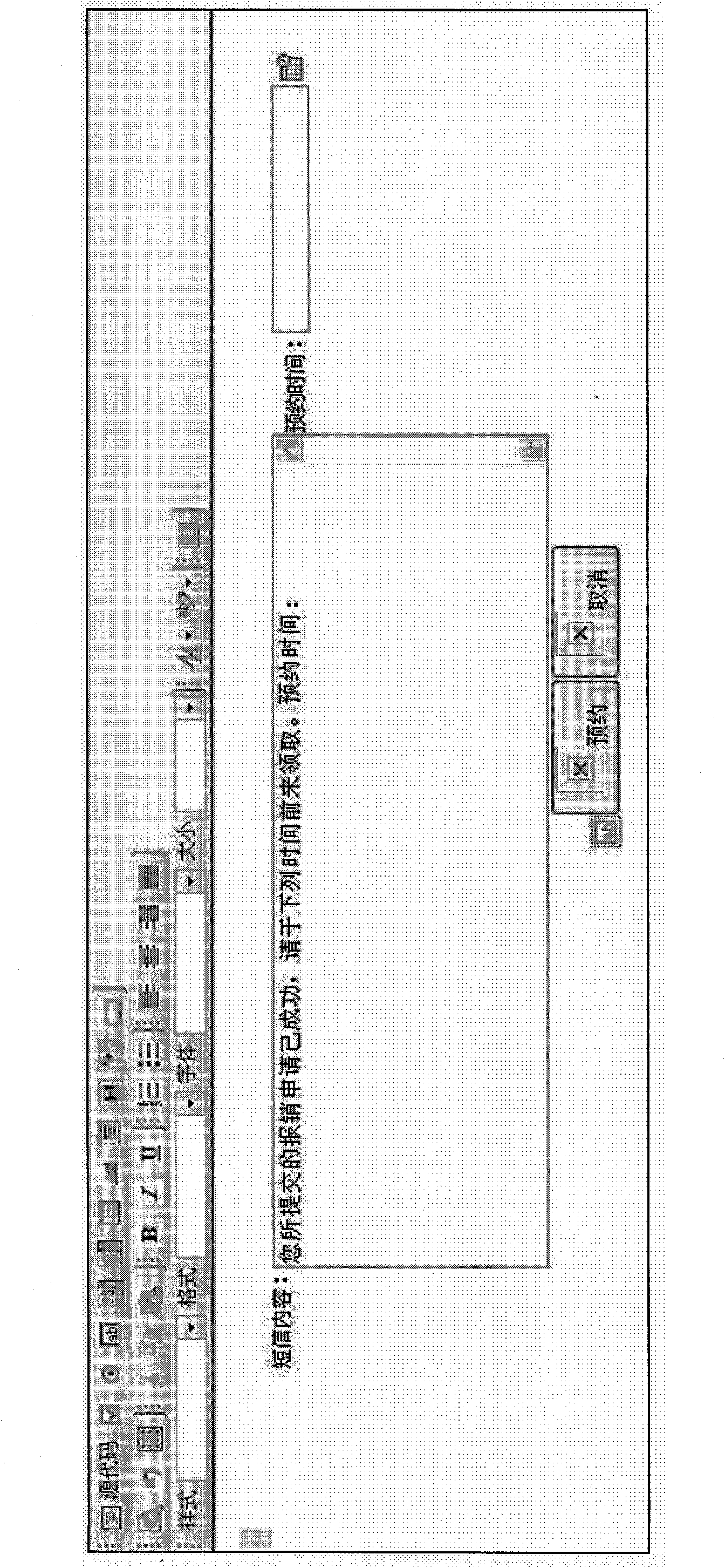

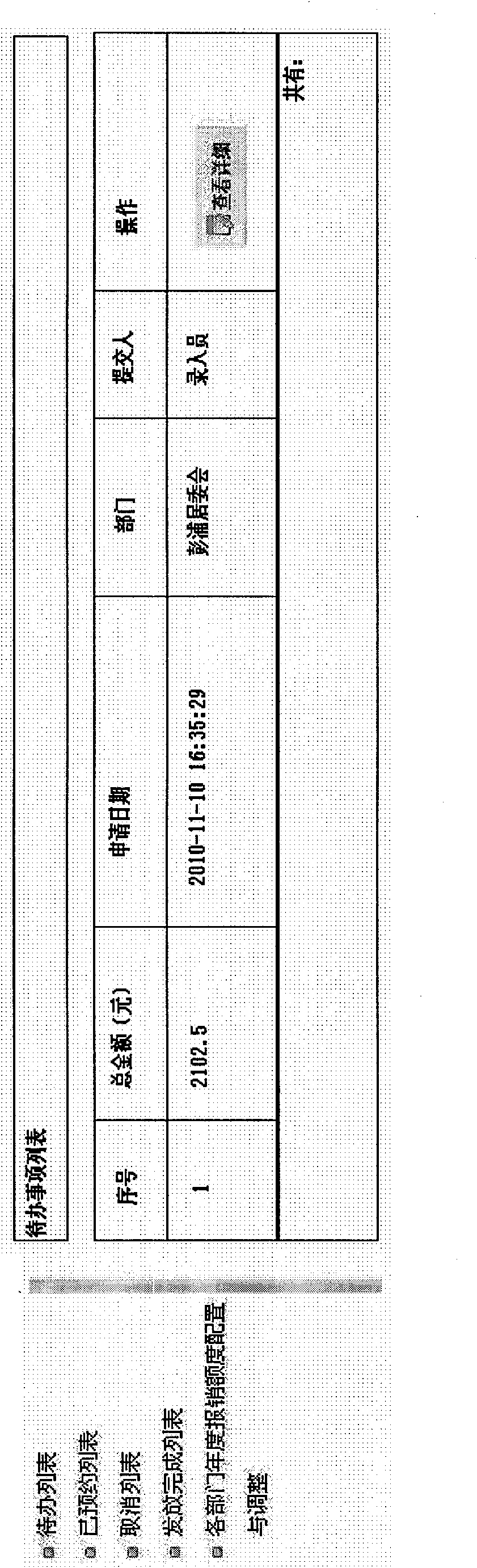

Workflow realization method and workflow system capable of customizing flow in user-defined manner

InactiveCN102486730AImprove and optimize business processesImprove work efficiencyResourcesSpecific program execution arrangementsSystem administratorFilling-in

The invention provides a workflow realization method capable of customizing a flow in a user-defined manner. The method comprises the following steps of: establishing a WYSIWYG (What You See Is What You Get) webpage flow editor; drawing a flow diagram by a system manager; starting a platform program and generating an operation code so as to generate a corresponding workflow operation program; filling in a system by a terminal user, submitting a form, and triggering and starting the workflow working program; and sequentially operating all the flows by the system until the flows are finished. The invention further provides a workflow system capable of customizing the flow in the user-defined manner and the workflow system comprises a defining module, an analyzing module, a workflow engine module, a flow execution module and a database module. According to the invention, the problem that the existing workflows need to be modified by programmers or a modification tool is separated from a user is solved; and the workflow realization method and the workflow system have the advantages of easiness of modification and maintenance, time conservation and cost conservation.

Owner:SHANGHAI XIEXUN SOFTWARE

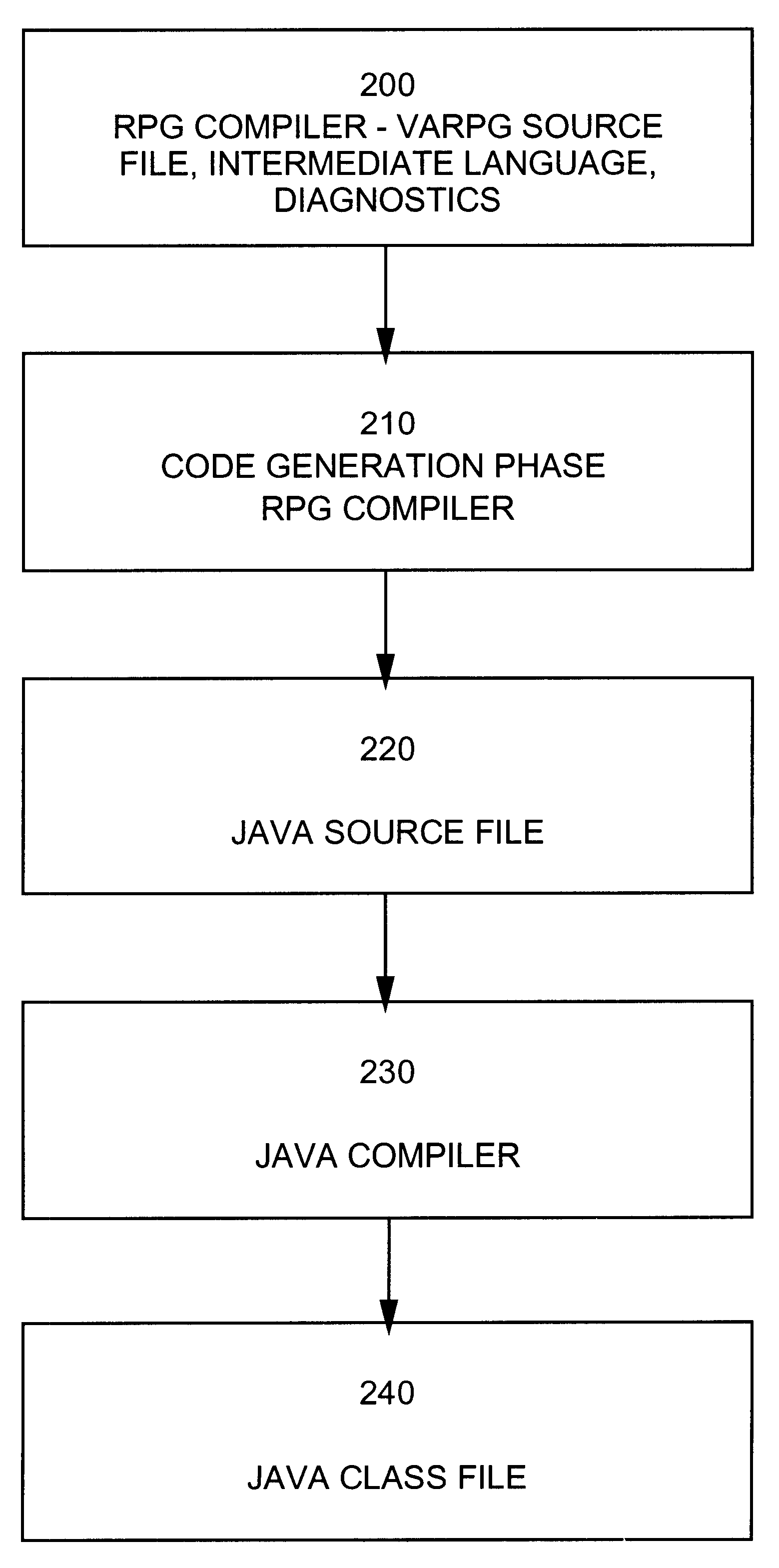

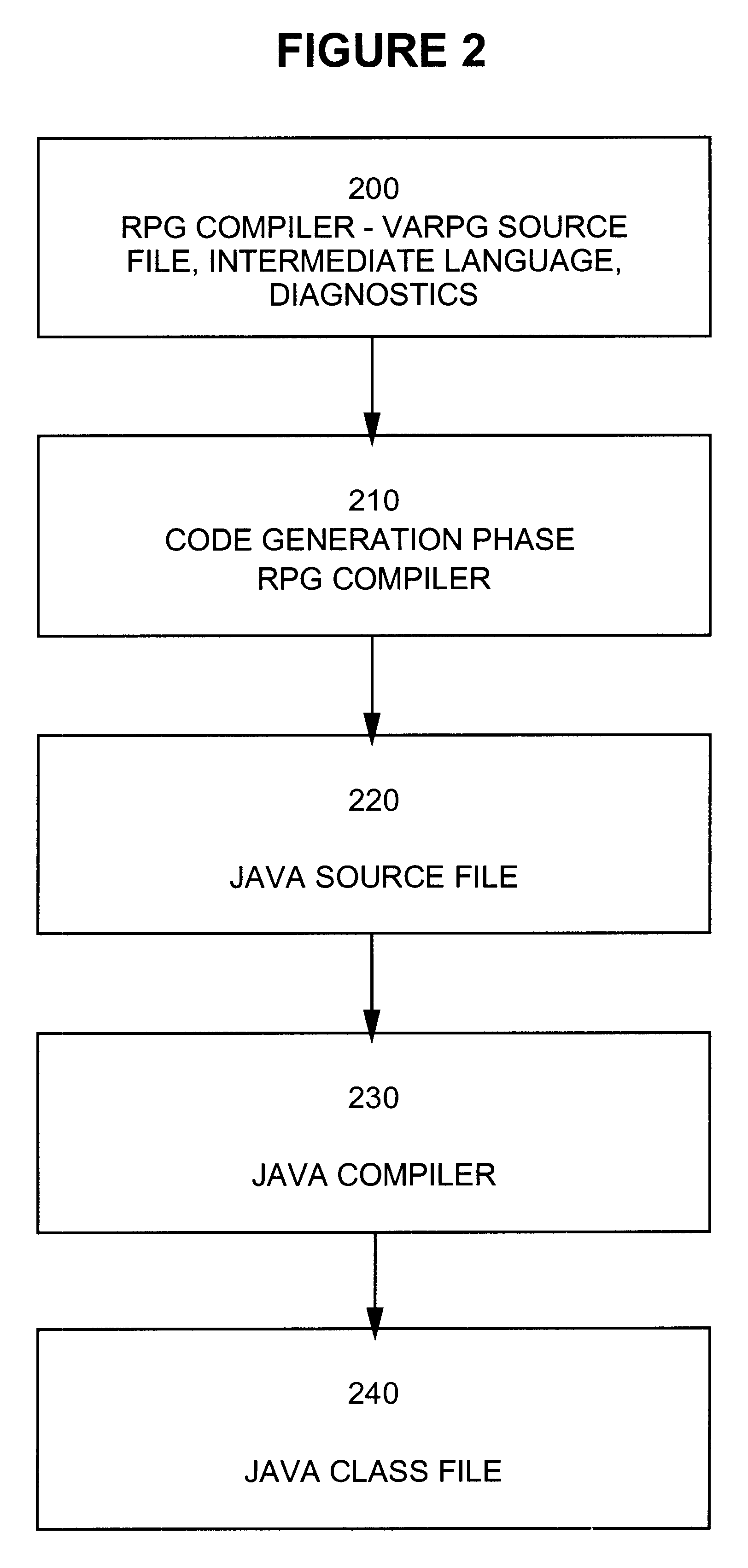

Report program language source code translation to object-oriented language source code which emulates report program language behavior

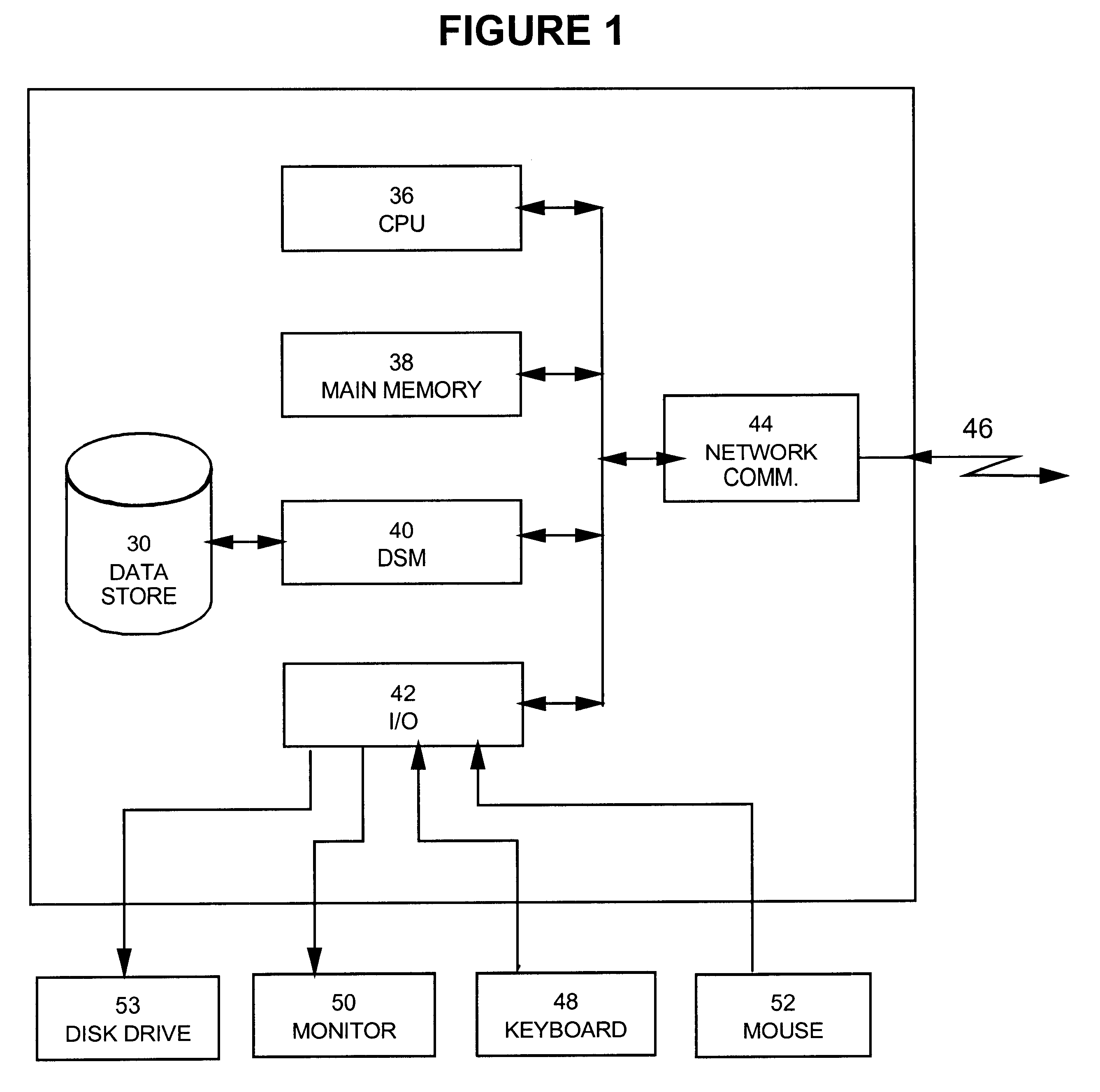

InactiveUS6467079B1Specific program execution arrangementsMemory systemsThe InternetApplication software

A computer-implemented method in which report program language is converted to object-oriented source code, such as Java, using the report program language compiler. The object-oriented source code emulates the behaviour of the report program language, such as VARPG. Applications written in RPG are converted to Java and therefore can run on every platform for which a Java virtual machine exists. RPG programmers now have the ability to write internet applications. Java applications and applets can be written in RPG and existing RPG applications can be converted to Java applets.

Owner:IBM CORP

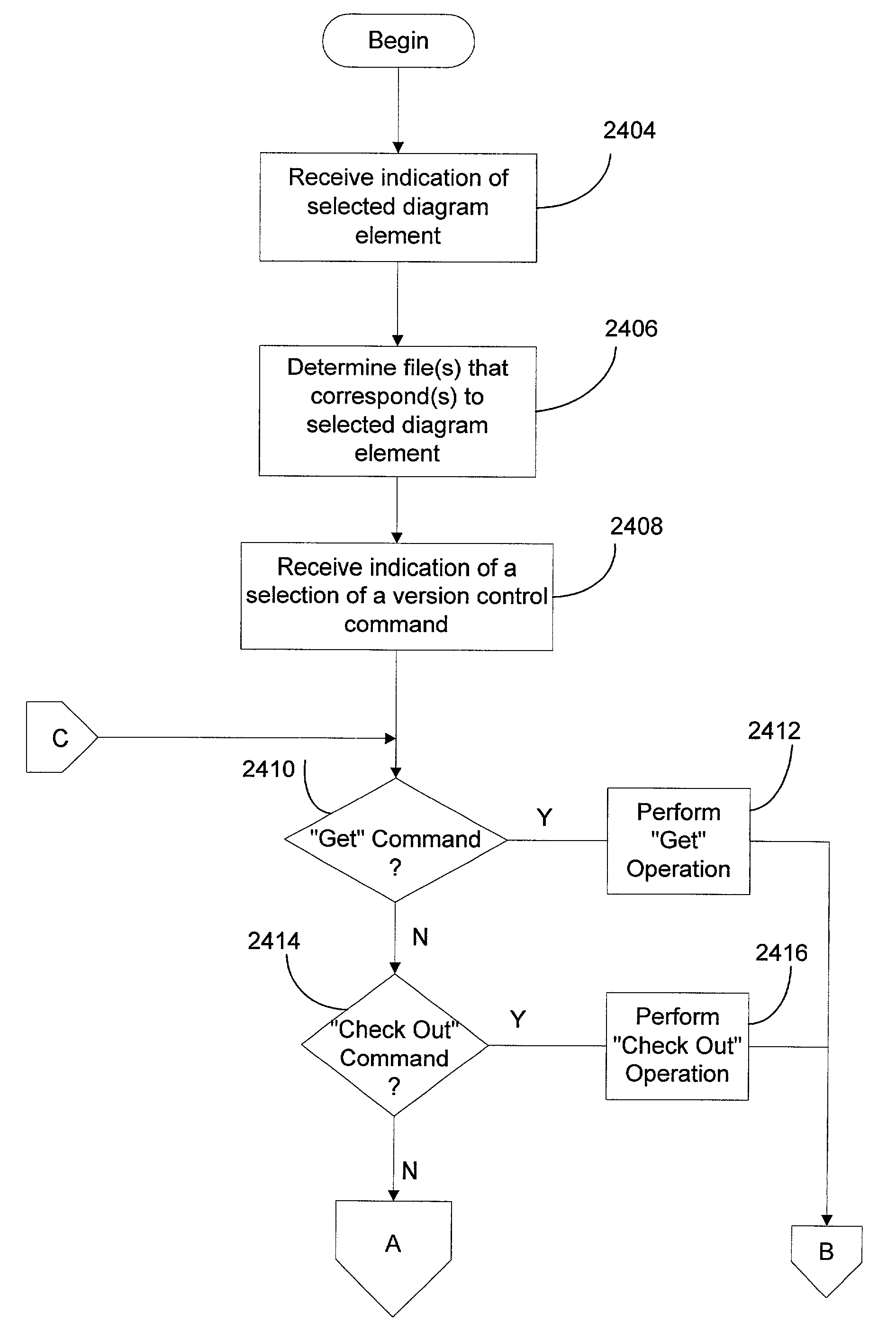

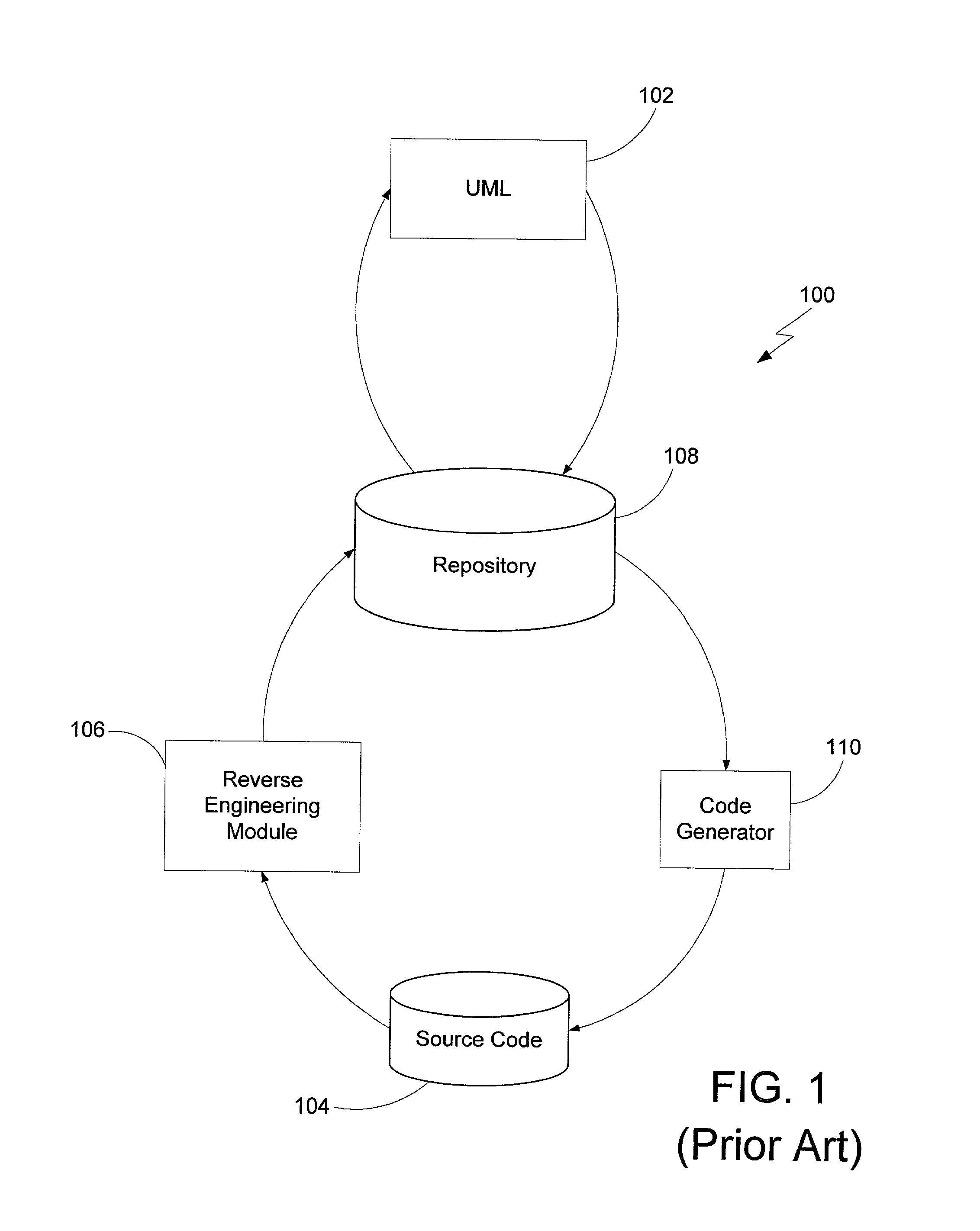

Diagrammatic control of software in a version control system

InactiveUS6993759B2Overcome limitationEasy to useVersion controlReverse engineeringSoftware developmentControl system

Methods and systems consistent with the present invention provide an improved software development tool that includes a version control system that permits multiple programmers to work simultaneously on a single software project by maintaining a central repository containing a master copy of a software project and by managing versions of the software project that the programmers make through the development process. The improved software development tool enables a programmer to interact with the version control system by interacting with a diagram or diagram element that corresponds to a project, package, diagram, or class, thus facilitating the use of the version control system.

Owner:BORLAND

Online Interactive Game System And Methods

An apparatus, system, and methods, for an online entertainment system are provided. In one embodiment, an apparatus is provided that allows for universal control of games. In some embodiments, the games are hosted at an online portal, which contains a software module allowing a game programmer to specify a controller mapping. When a particular game is selected by a user, the mapping is sent to the local computer. Once installed, the mapping file maps commands received from a controller to specific actions within the game. This Abstract is provided for the sole purpose of complying with the Abstract requirement rules that allow a reader to quickly ascertain the subject matter of the disclosure contained herein. This Abstract is submitted with the explicit understanding that it will not be used to interpret or to limit the scope or the meaning of the claims.

Owner:PATENT CATEGORY

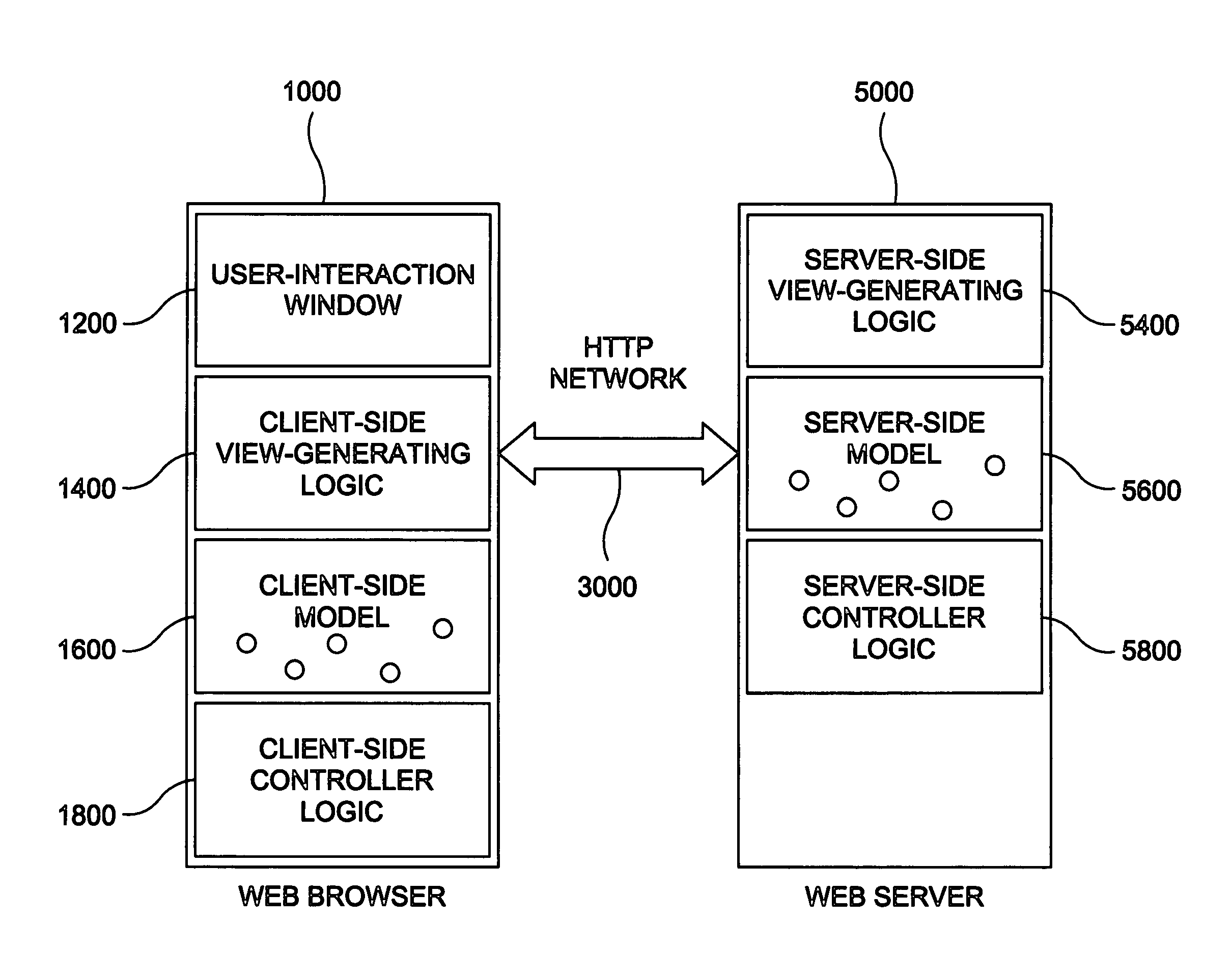

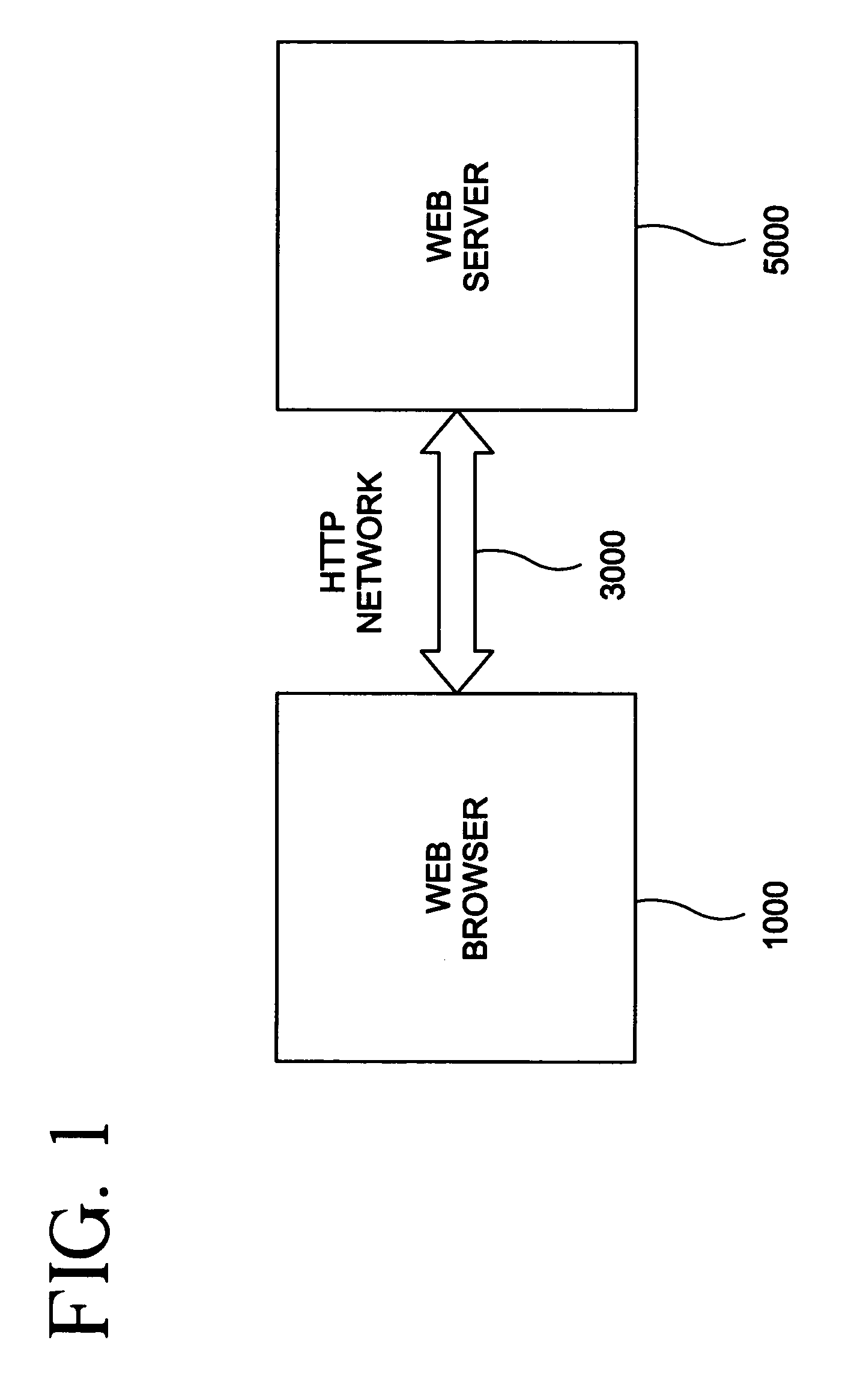

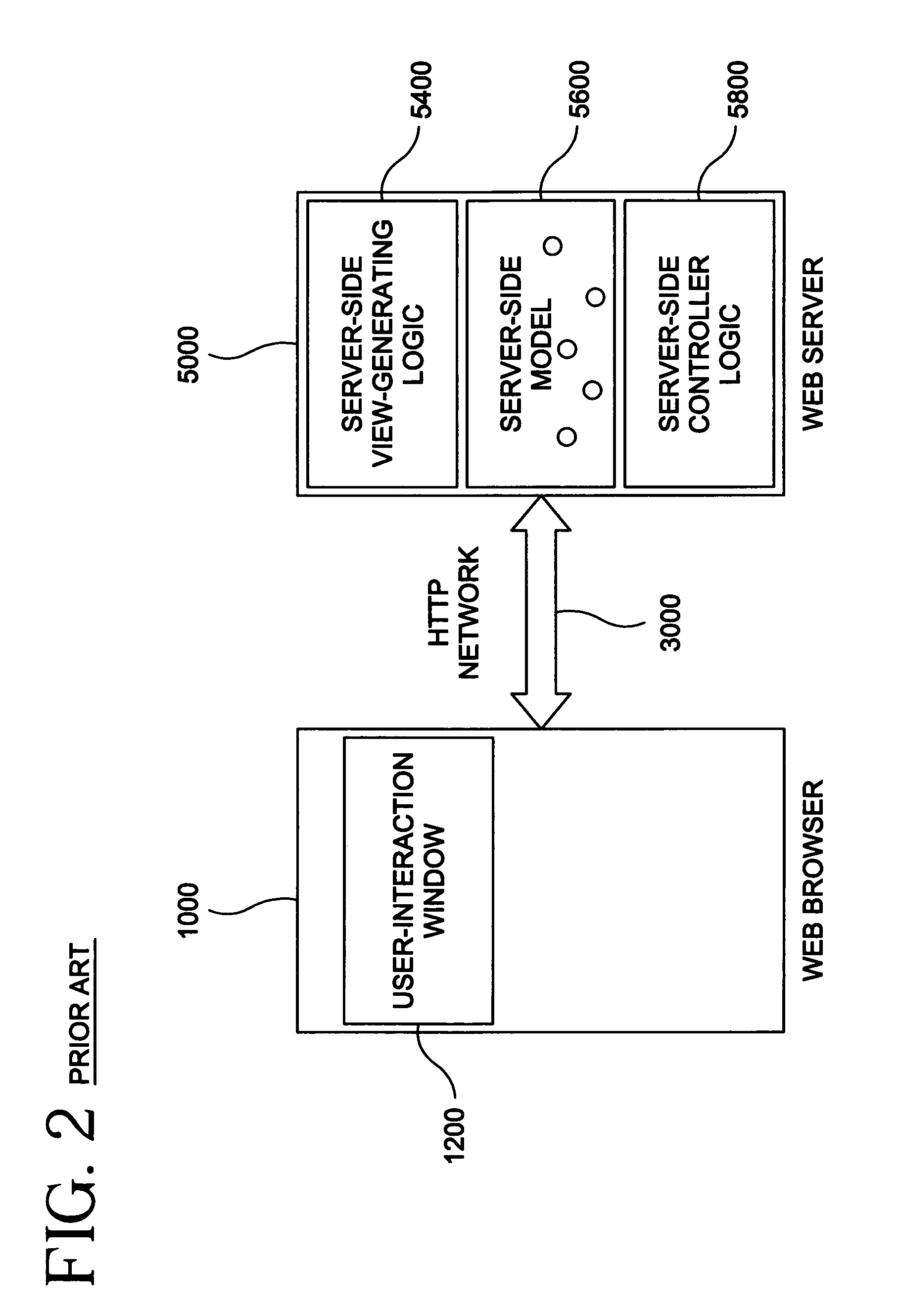

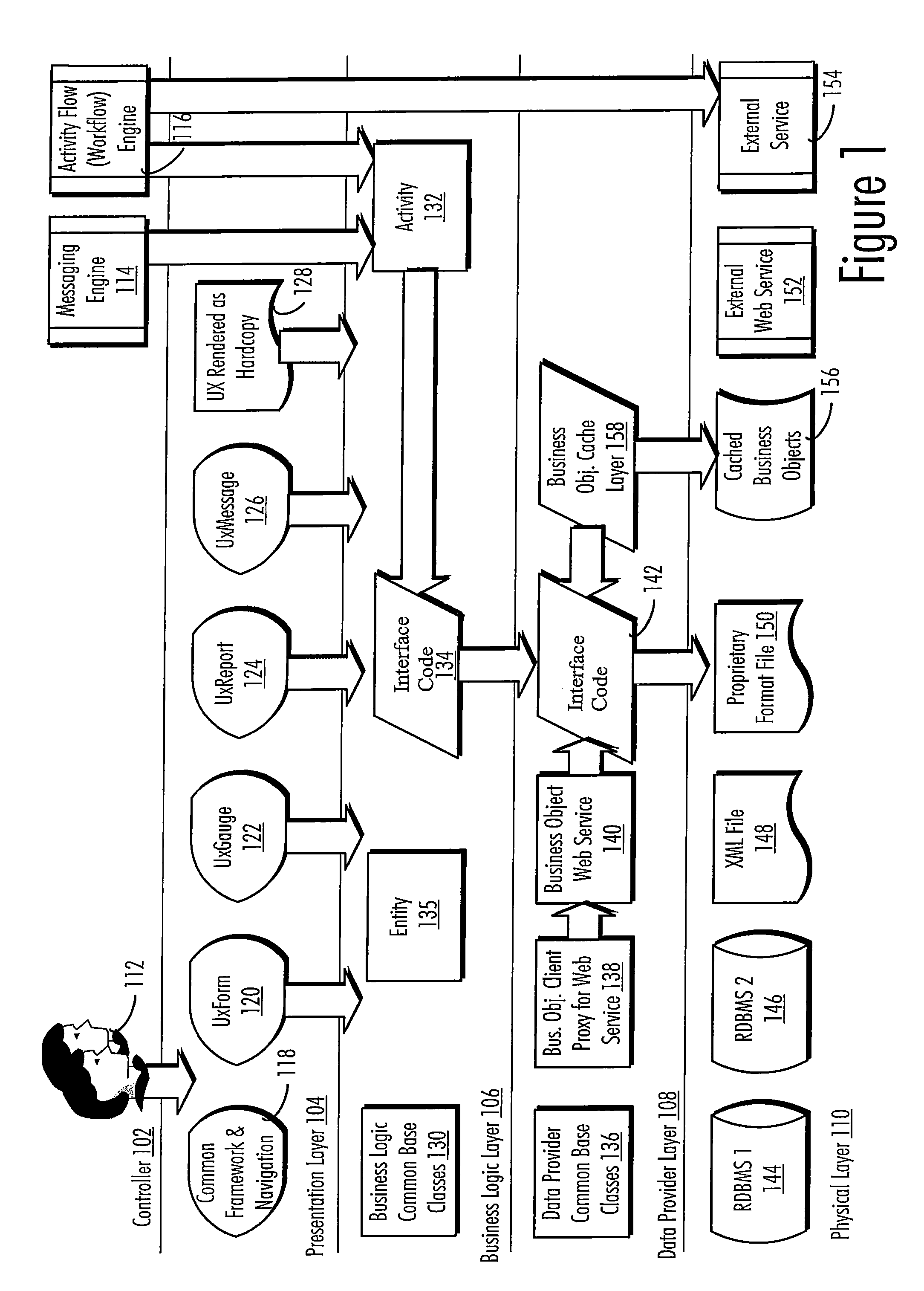

Methods and apparatus for reducing the number of server interactions in network-based applications using a dual-MVC approach

InactiveUS7702719B1Improve performanceReduce developmentInterprogram communicationMultiple digital computer combinationsComputer scienceClient machine

In accordance with a dual-MVC (Model-View-Controller) approach of the invention, the client machine maintains part of the Model, eliminating many round-trips to the server. The invention provides an implementation approach for constructing the frame(s) contained in the client's browser software to allow it to be refreshed locally. The invention addresses development and maintenance by specifying a library of functions that a programmer can use to construct the View and Controller on the client machine. When part of the Model is maintained on the client, the client has the ability to respond to user interaction without paying the performance penalty of continually interacting with the server.

Owner:IBM CORP

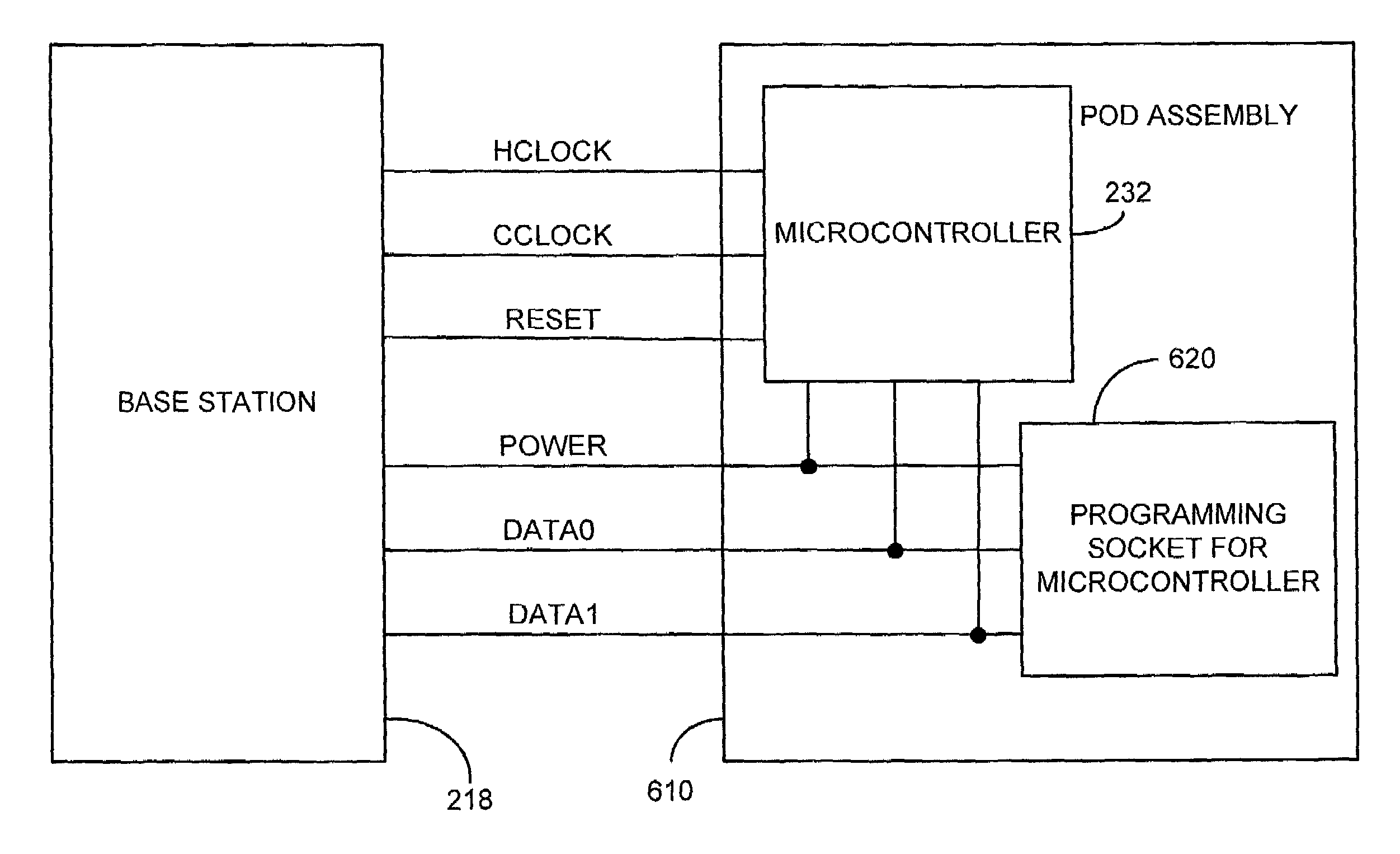

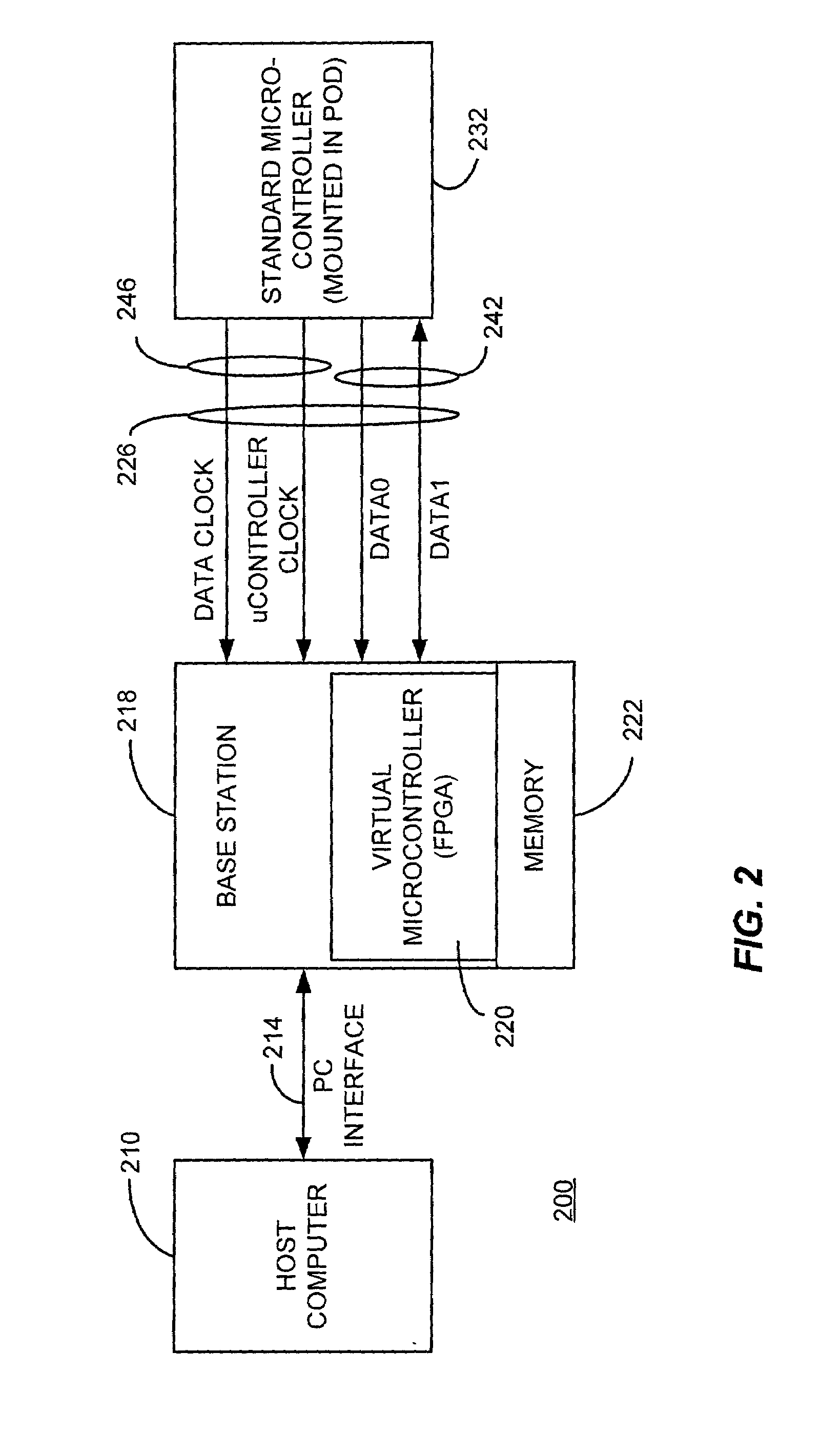

Combined in-circuit emulator and programmer

InactiveUS7089175B1Error detection/correctionSoftware simulation/interpretation/emulationMicrocontrollerProgramming process

A combined in-circuit emulation system and device programmer. A pod assembly used in an in-circuit emulation system has both a real microcontroller used in the In-Circuit Emulation and debugging process as well as a socket that accommodates a microcontroller to be programmed (a program microcontroller). Programming can be carried out over a single interface that is shared between the microcontroller and the program microcontroller and which is also used to provide communication between the real microcontroller and the In-Circuit Emulation system to carry out emulation functions. In order to assure that the emulation microcontroller does not interfere with the programming process for a microcontroller placed in a programming socket, a special sleep mode is implemented in the emulation microcontroller. This sleep mode is activated by a process that takes place at power on in which the a reset line is released with a specified data line held in a logic high state.

Owner:CYPRESS SEMICON CORP

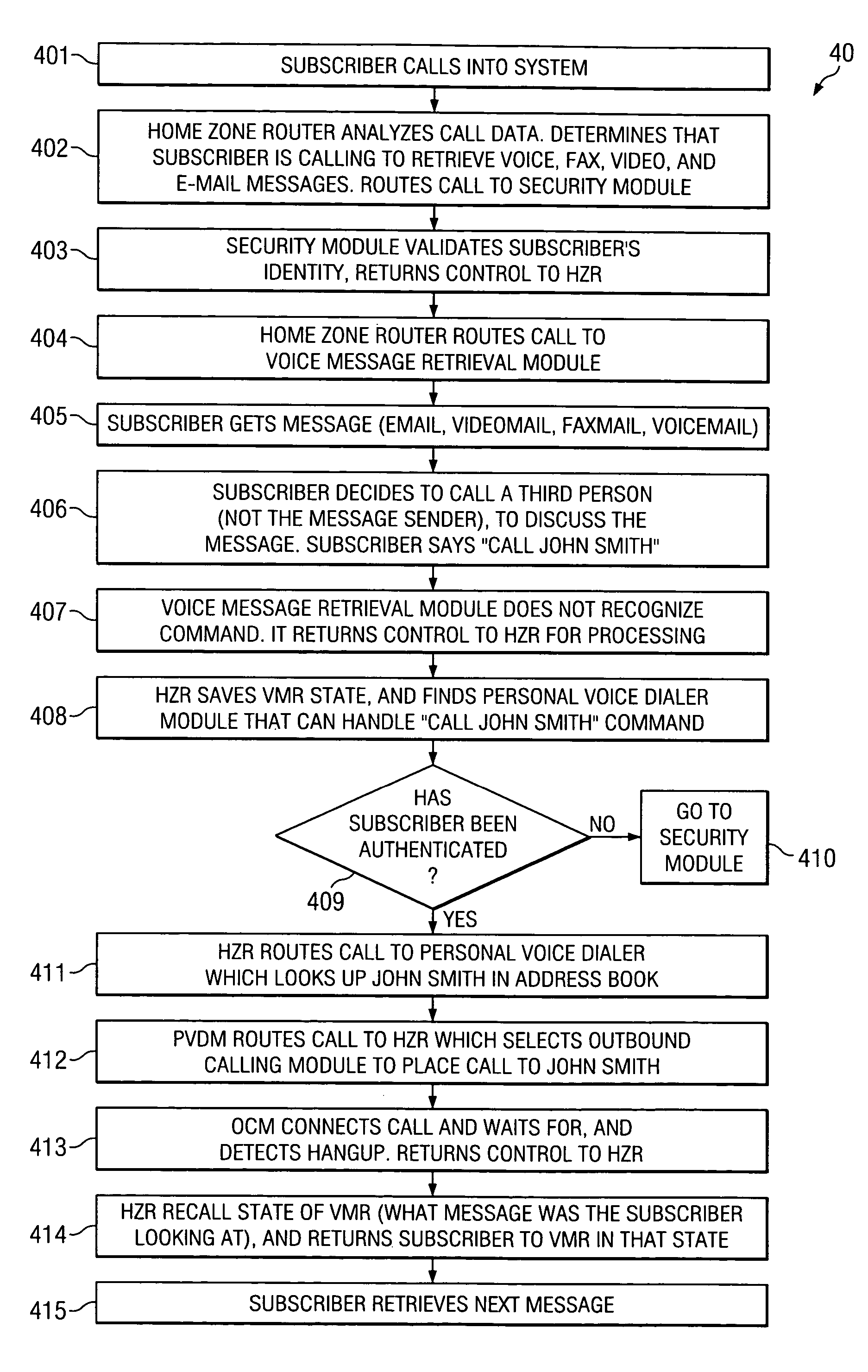

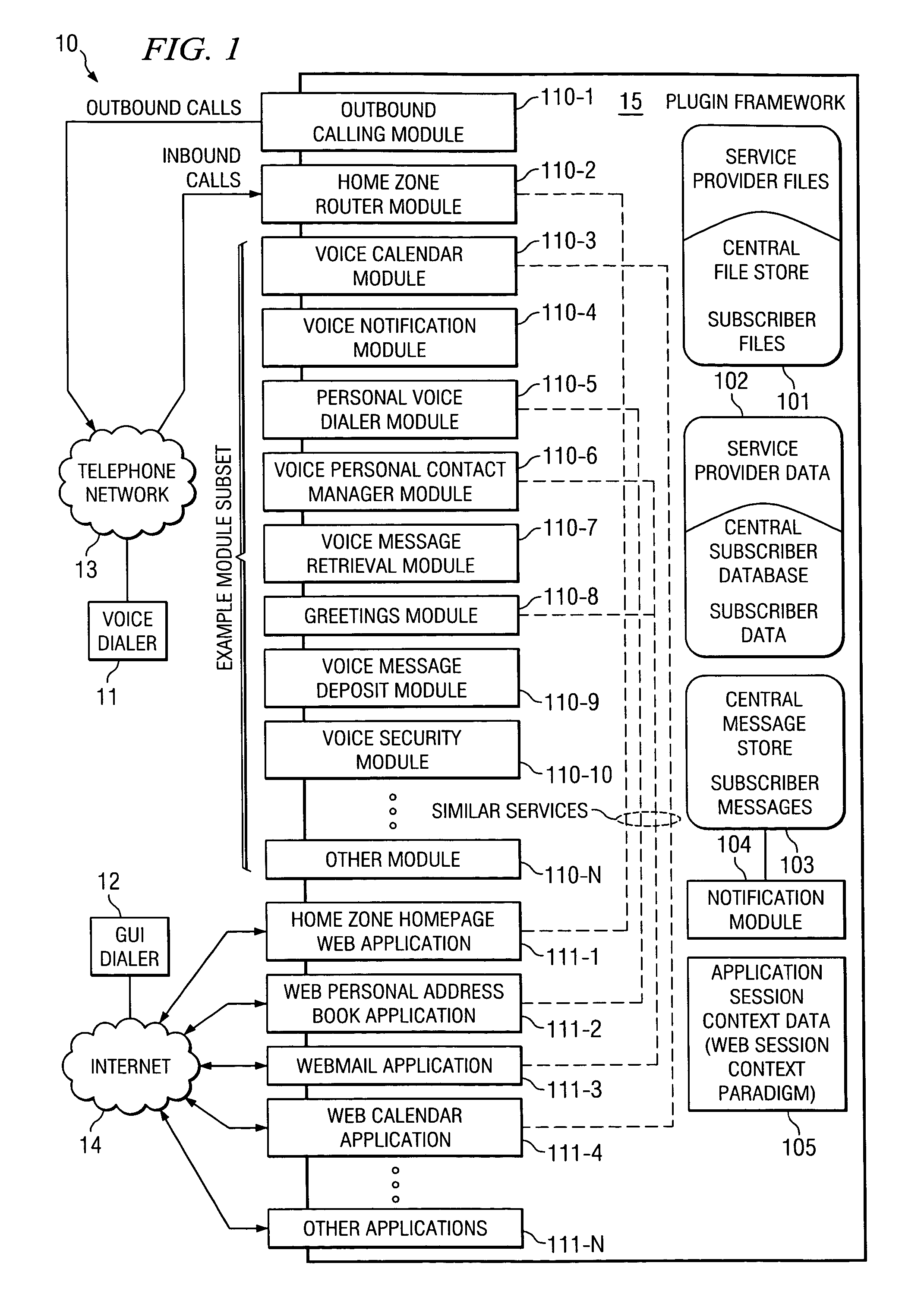

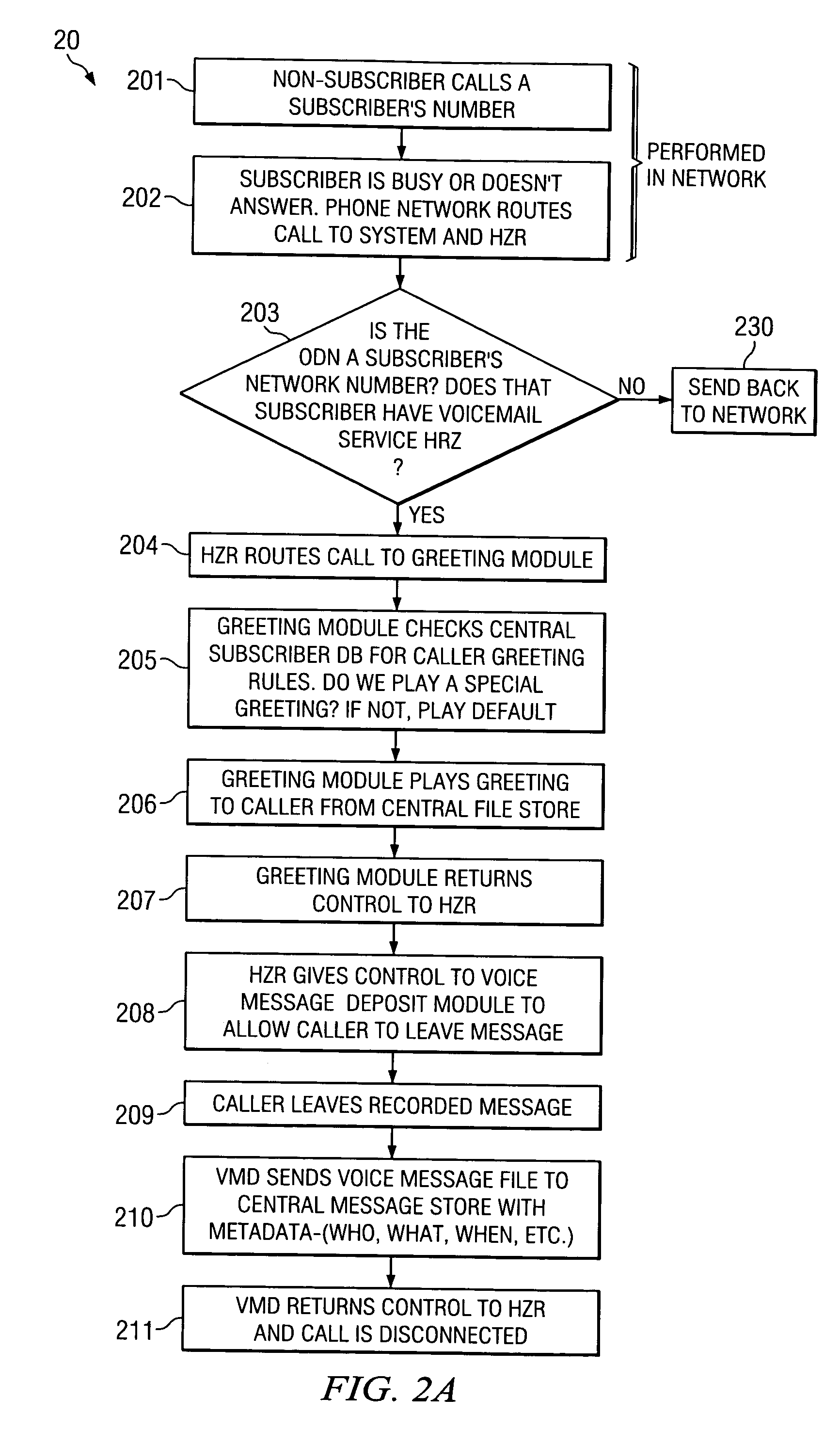

System and method for inheritance of advertised functionality in a user interactive system

InactiveUS20070043569A1Wide range of functionsSpeech analysisAutomatic exchangesSpecific functionDatabase

Systems and methods are described for use in user interactive systems (UIS) so that multiple disparate applications can cooperate to provide broad functionality to users. These systems and methods allow applications to advertise their ability to handle specific functions. This allows applications developed independently to co-exist within the same call session and provide a seamless user experience. A system framework controls the UIS's primary navigational menus, which are automatically updated when new applications are plugged in to the framework. This allows users (assuming they have the proper permissions) to access new applications as soon as they are added, without requiring programmers to manually re-design menus.

Owner:INTERVOICE A NEVADA COMPOSED OF AS ITS SOLE GENERAL PARTNER INTERVOICE GP

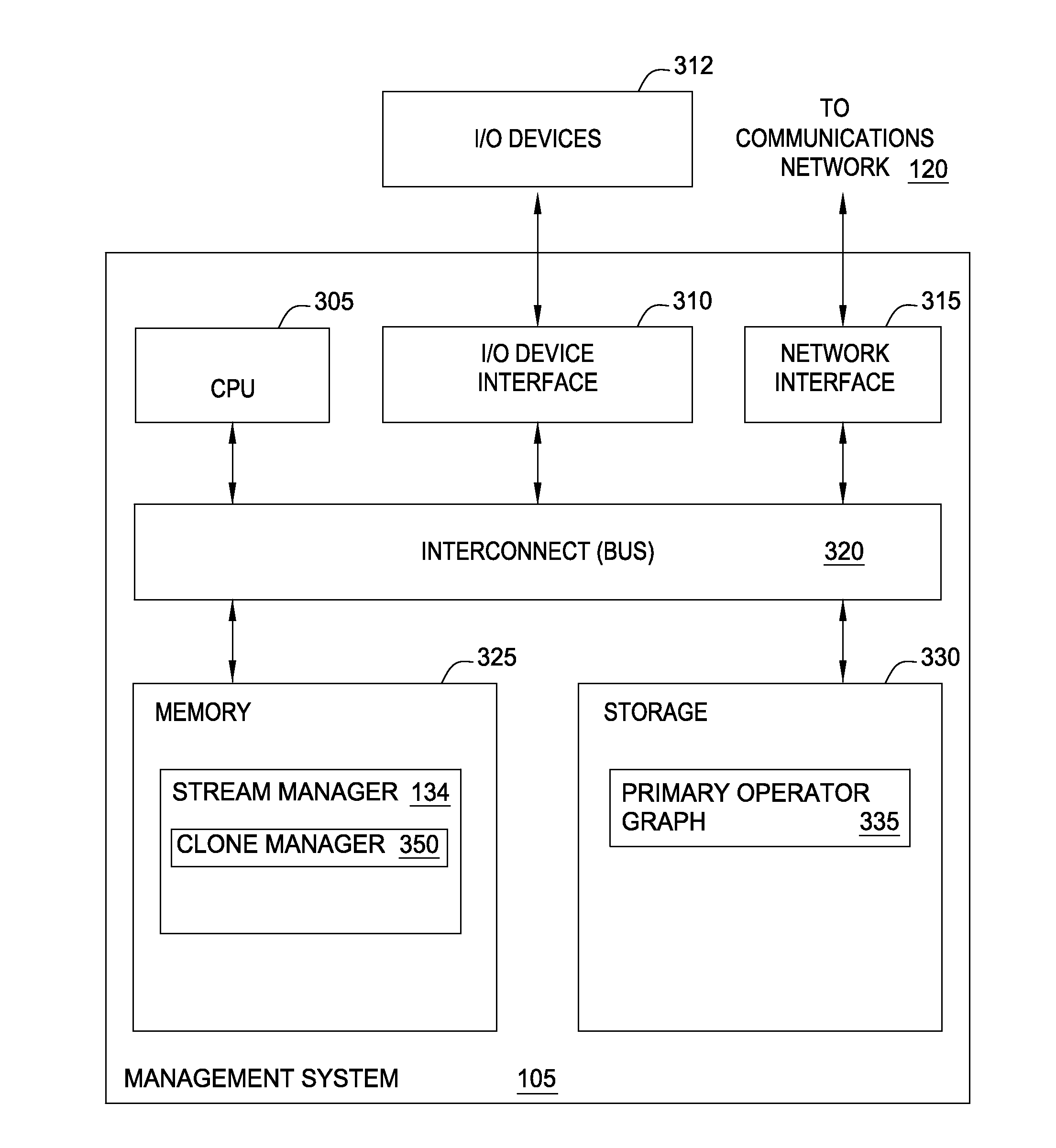

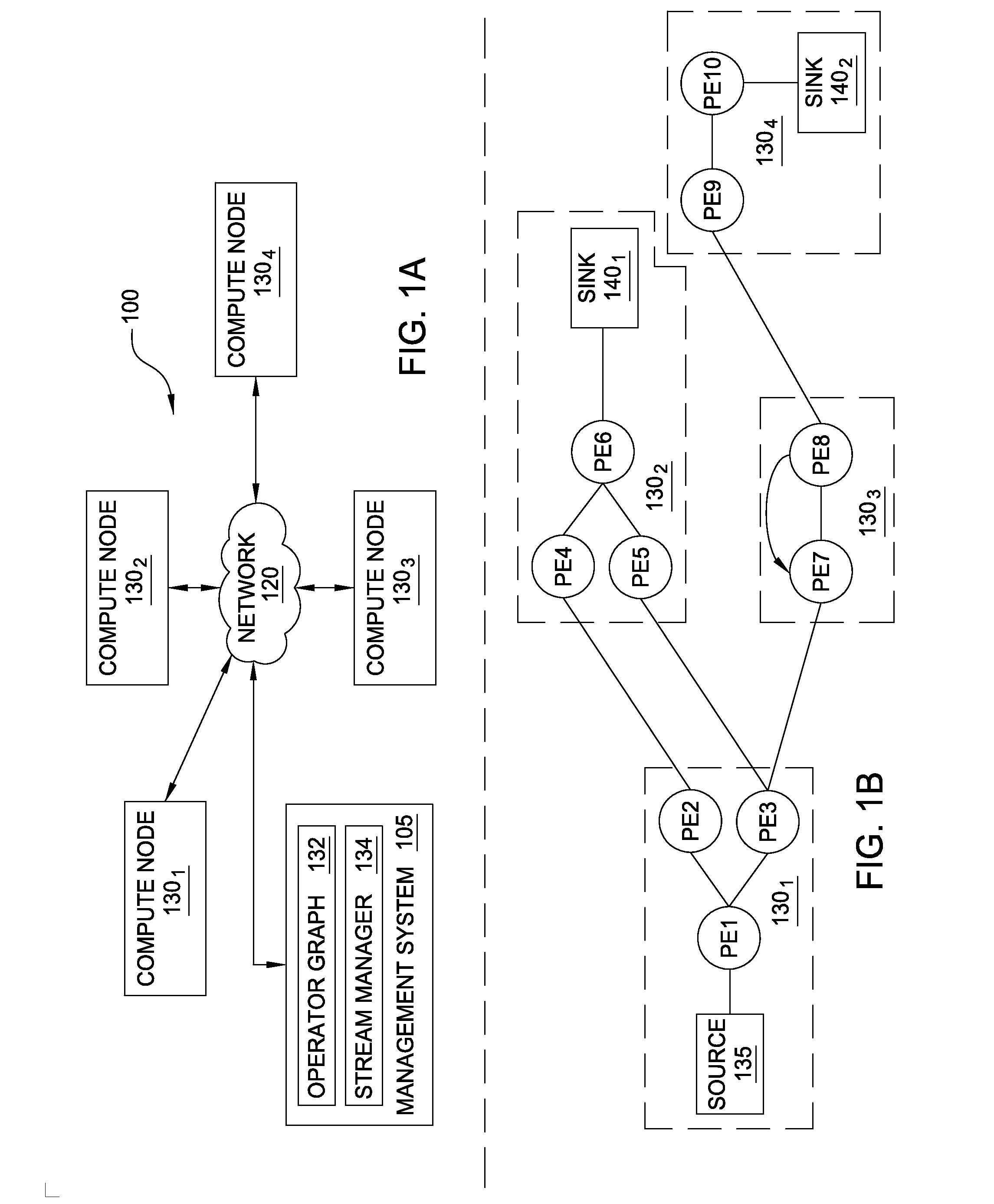

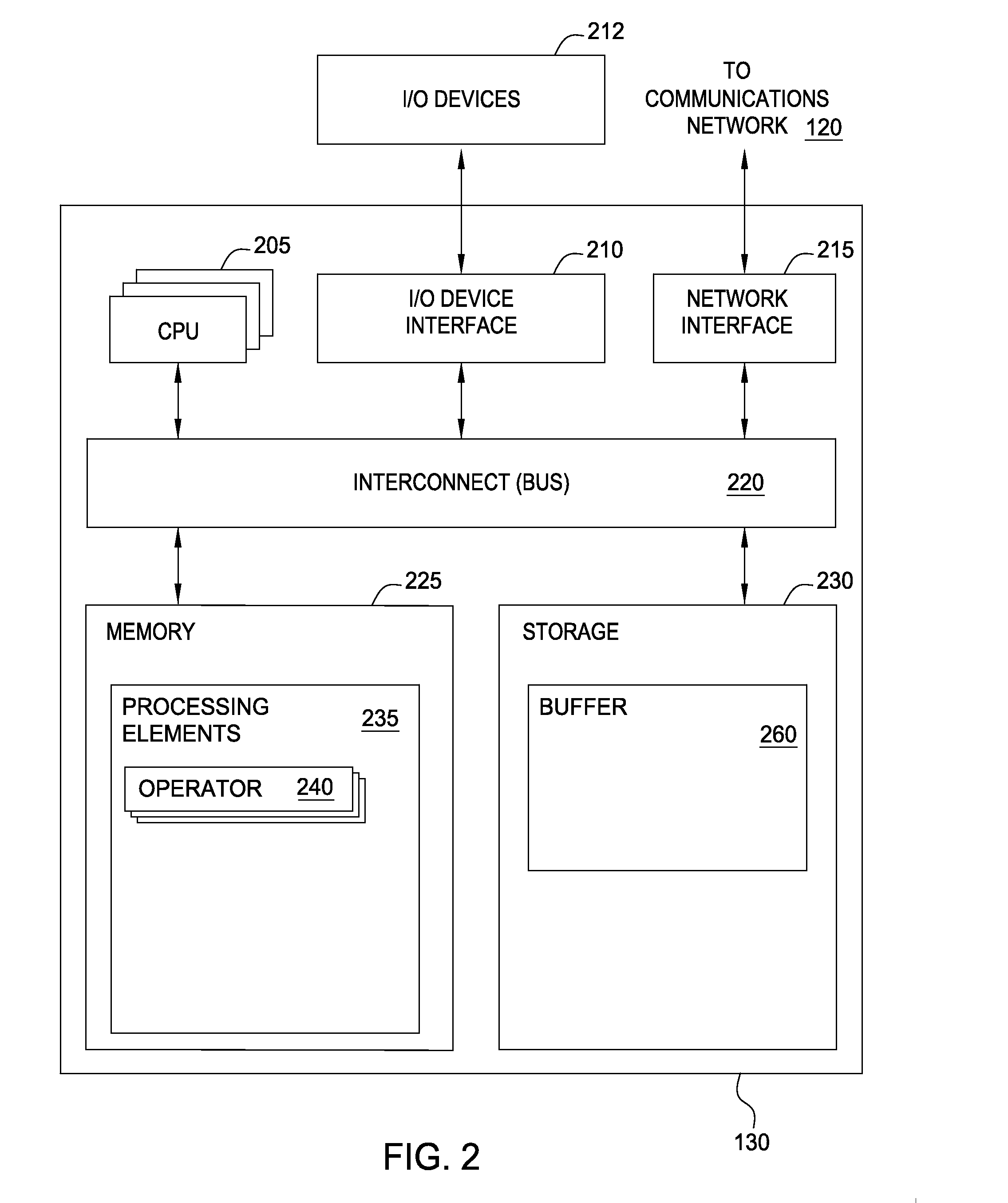

Processing element management in a streaming data system

InactiveUS20130198318A1Multiple digital computer combinationsSpecific program execution arrangementsStreaming dataPathPing

Stream applications may inefficiently use the hardware resources that execute the processing elements of the data stream. For example, a compute node may host four processing elements and execute each using a CPU. However, other CPUs on the compute node may sit idle. To take advantage of these available hardware resources, a stream programmer may identify one or more processing elements that may be cloned. The cloned processing elements may be used to generate a different execution path that is parallel to the execution path that includes the original processing elements. Because the cloned processing elements contain the same operators as the original processing elements, the data stream that was previously flowing through only the original processing element may be split and sent through both the original and cloned processing elements. In this manner, the parallel execution path may use underutilized hardware resources to increase the throughput of the data stream.

Owner:IBM CORP

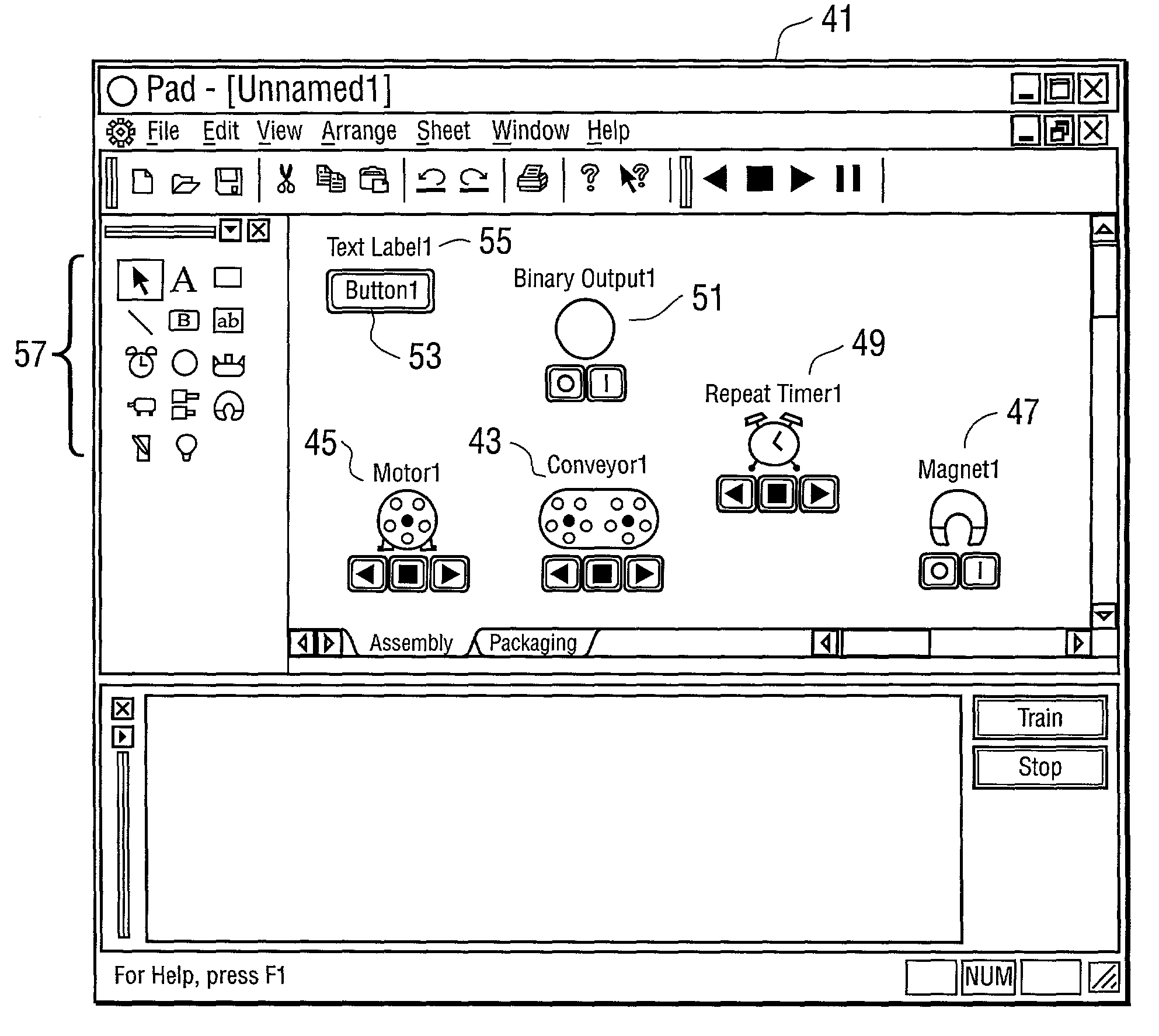

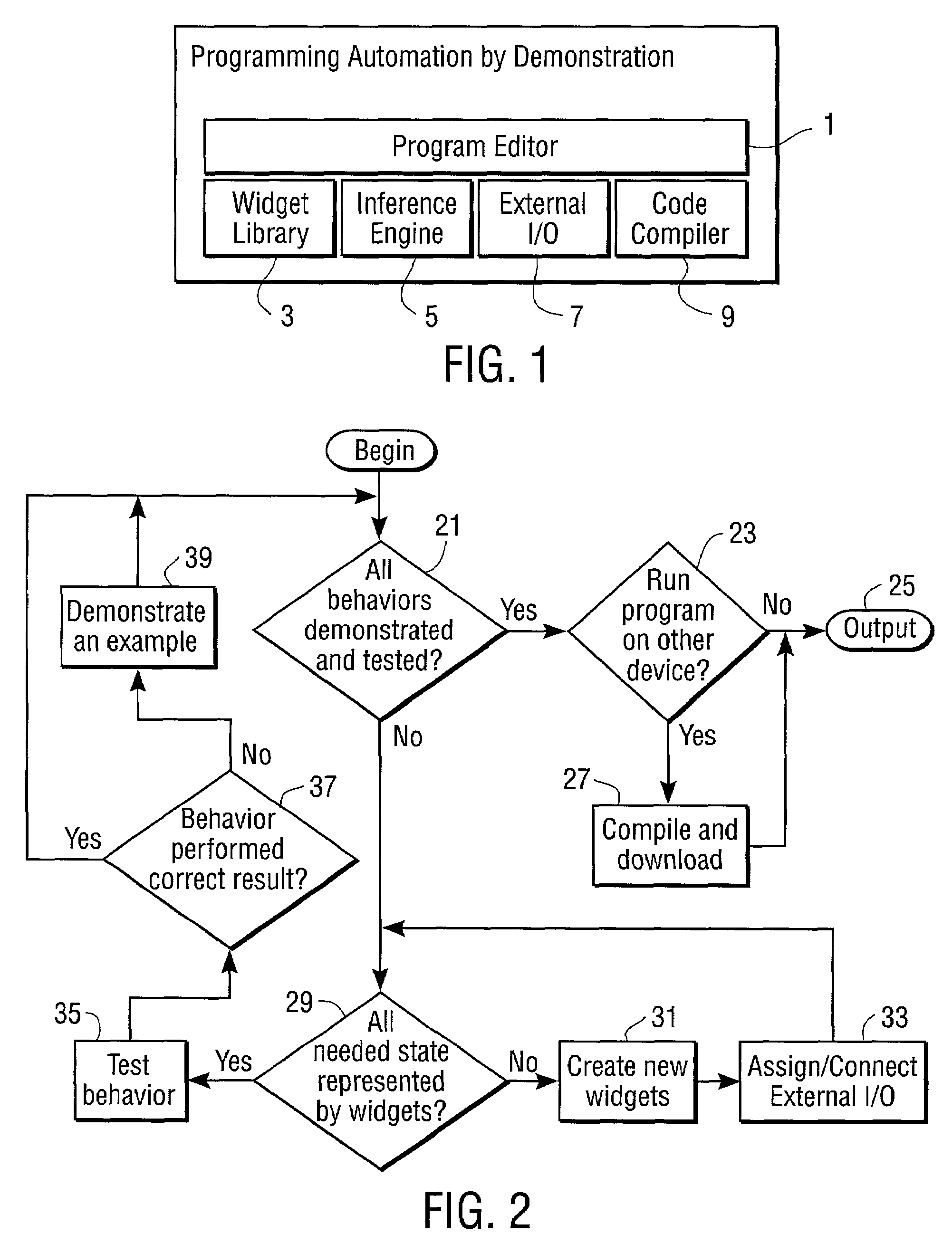

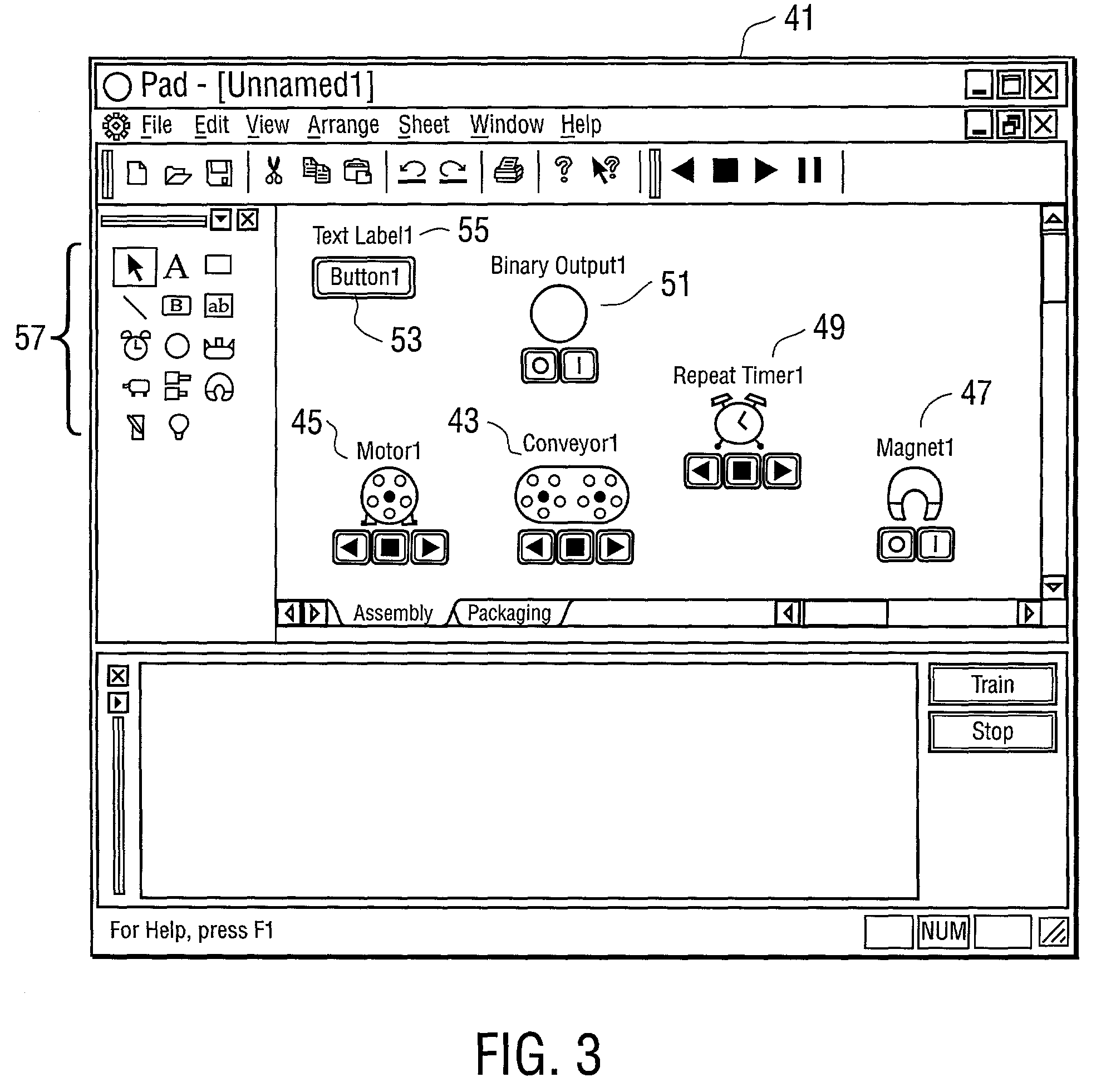

Programming automation by demonstration

InactiveUS7505817B2Easy to implementImprove automationComputer controlSimulator controlGraphicsProgramming by demonstration

A system for programming automation by demonstration where a control program may be created or modified through the process of demonstrating desired behavior using graphical representations (or widgets) of physical, programming, and user interface elements. Widgets have state, or properties, and may also have inherent events associated with them or indirect events that are generated through the demonstration process. The general process of demonstration consists of providing several individual example behaviors. Complete behavior, and thus the resultant code, is generated through inferencing from a number of individual example behaviors. The process of programming automation by demonstration reduces the complexity of the programming task and thereby greatly simplifies the workload of the control programmer, allowing the programmer to concentrate more on the specific automation application at hand rather than on the particulars of the programming language or tools. The invention may be applied to a wide range of automation applications, from home and building automation to industrial automation, and may be practiced by novice and expert-level users.

Owner:SIEMENS CORP

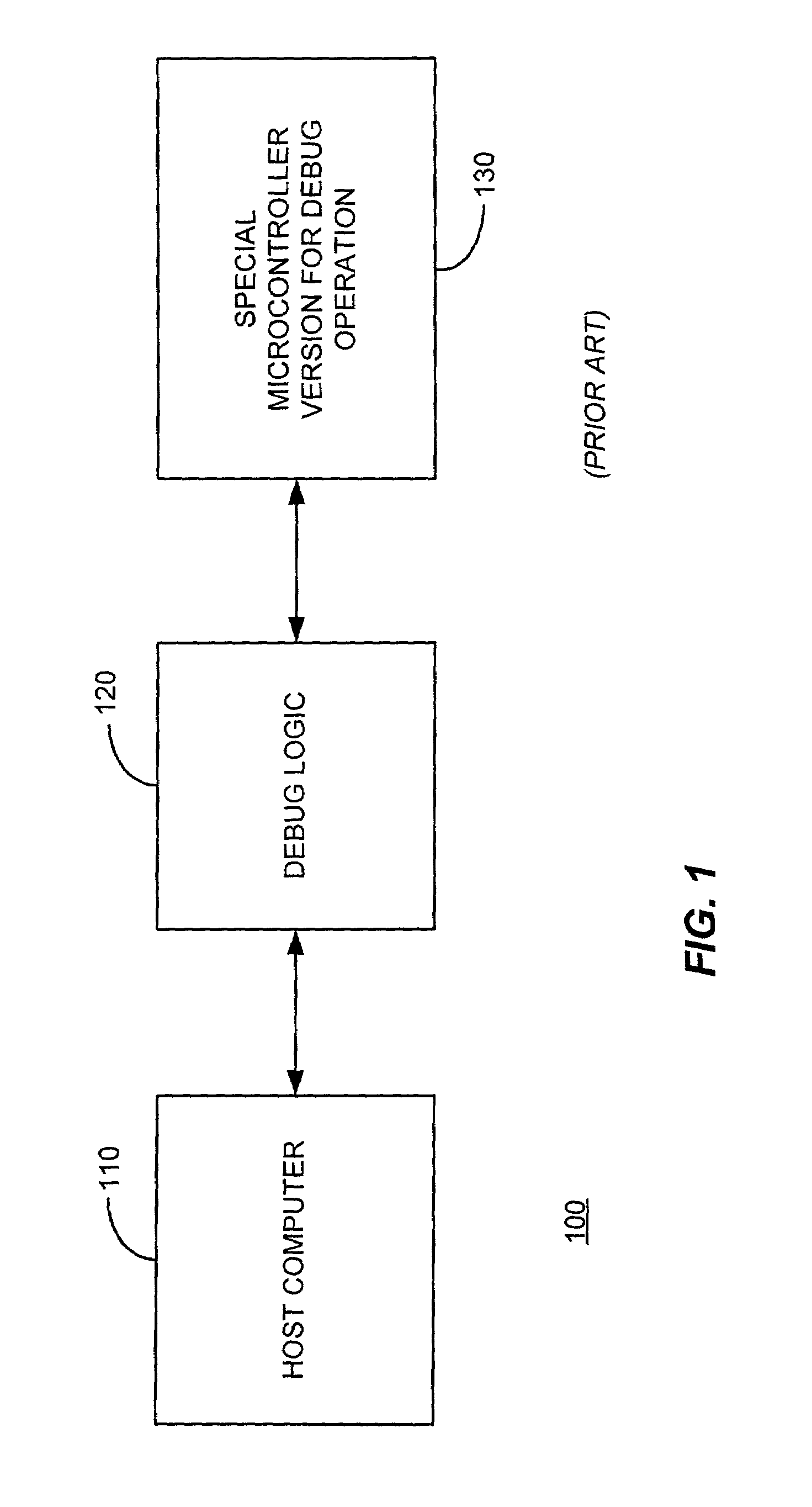

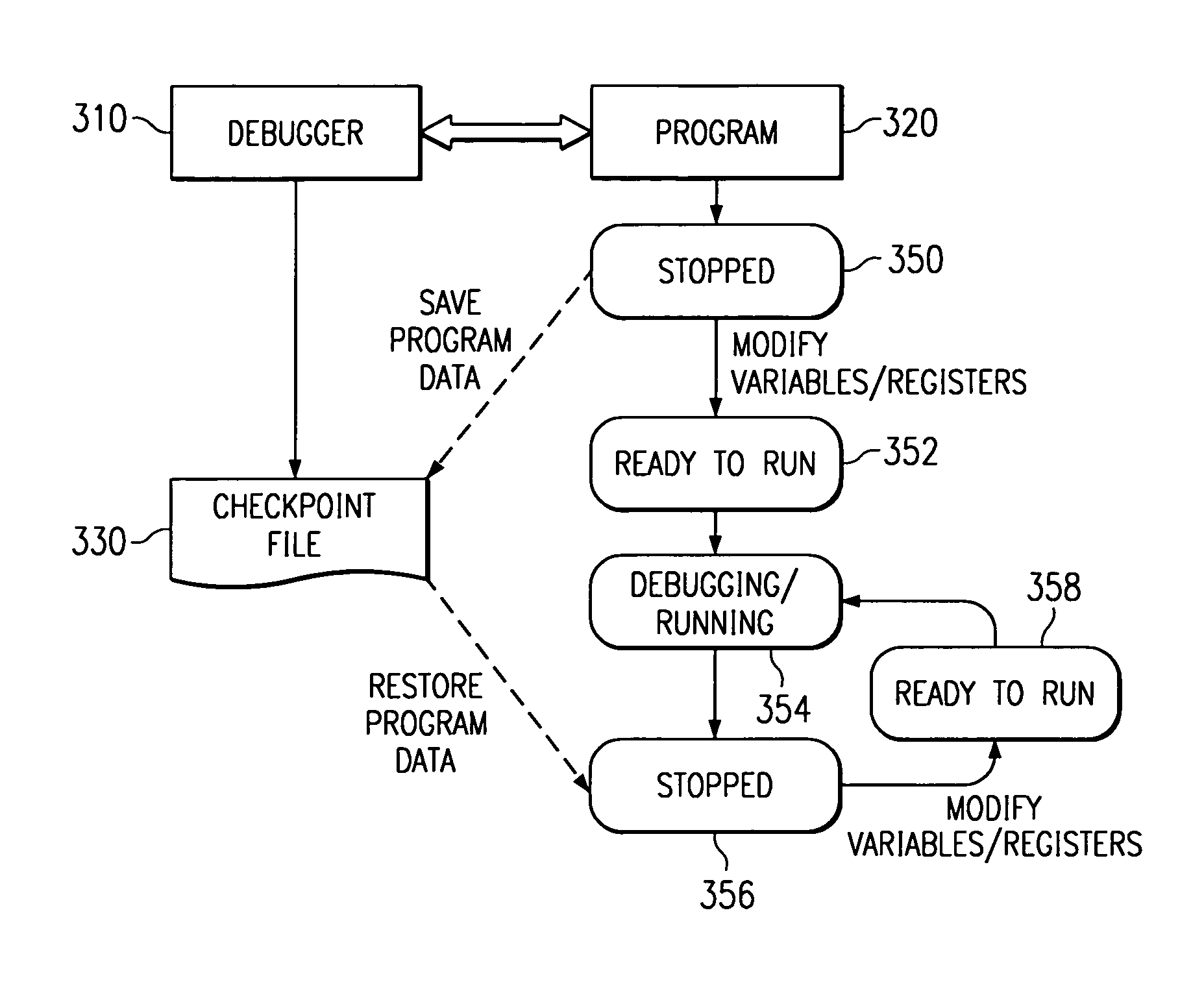

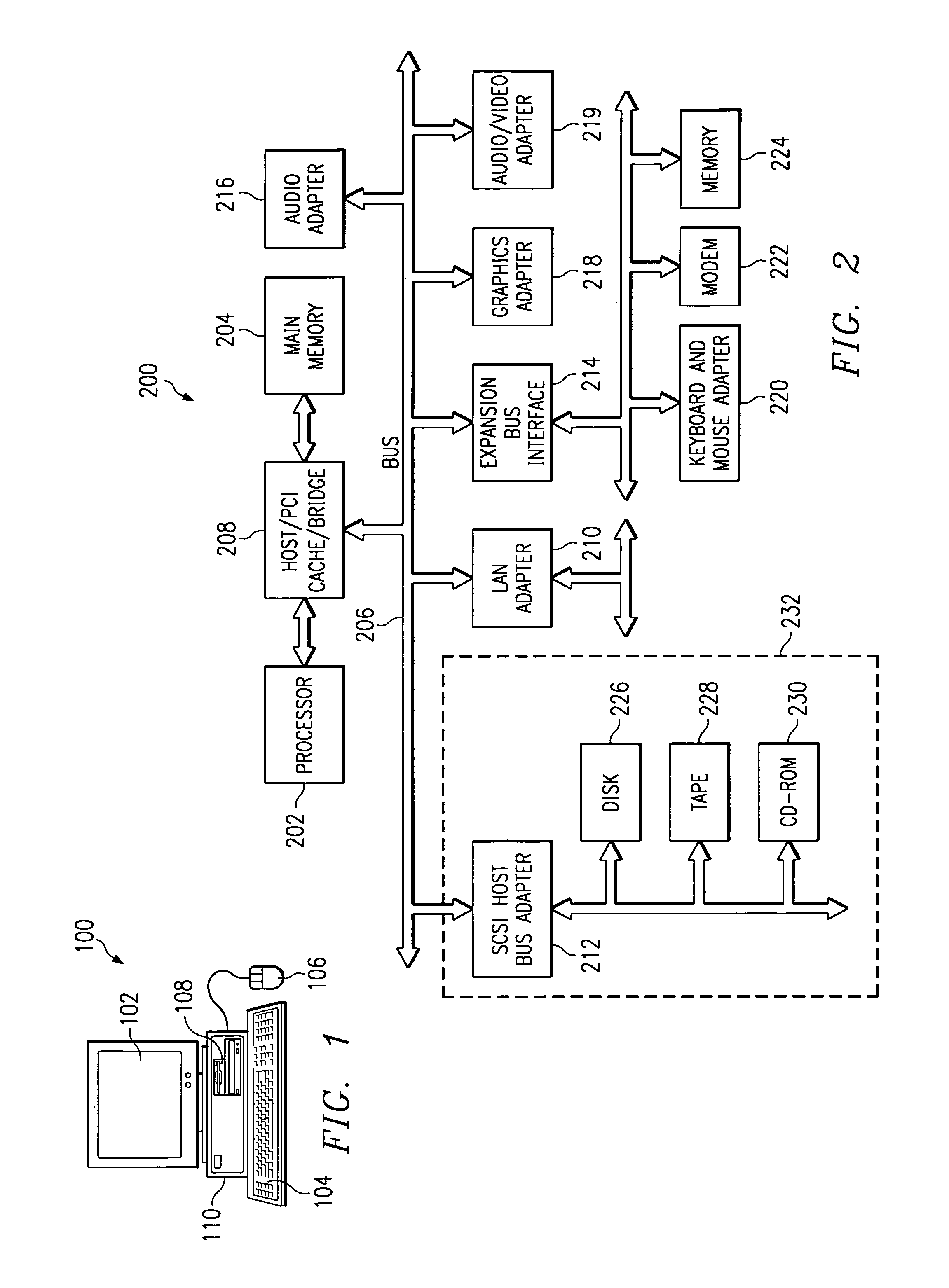

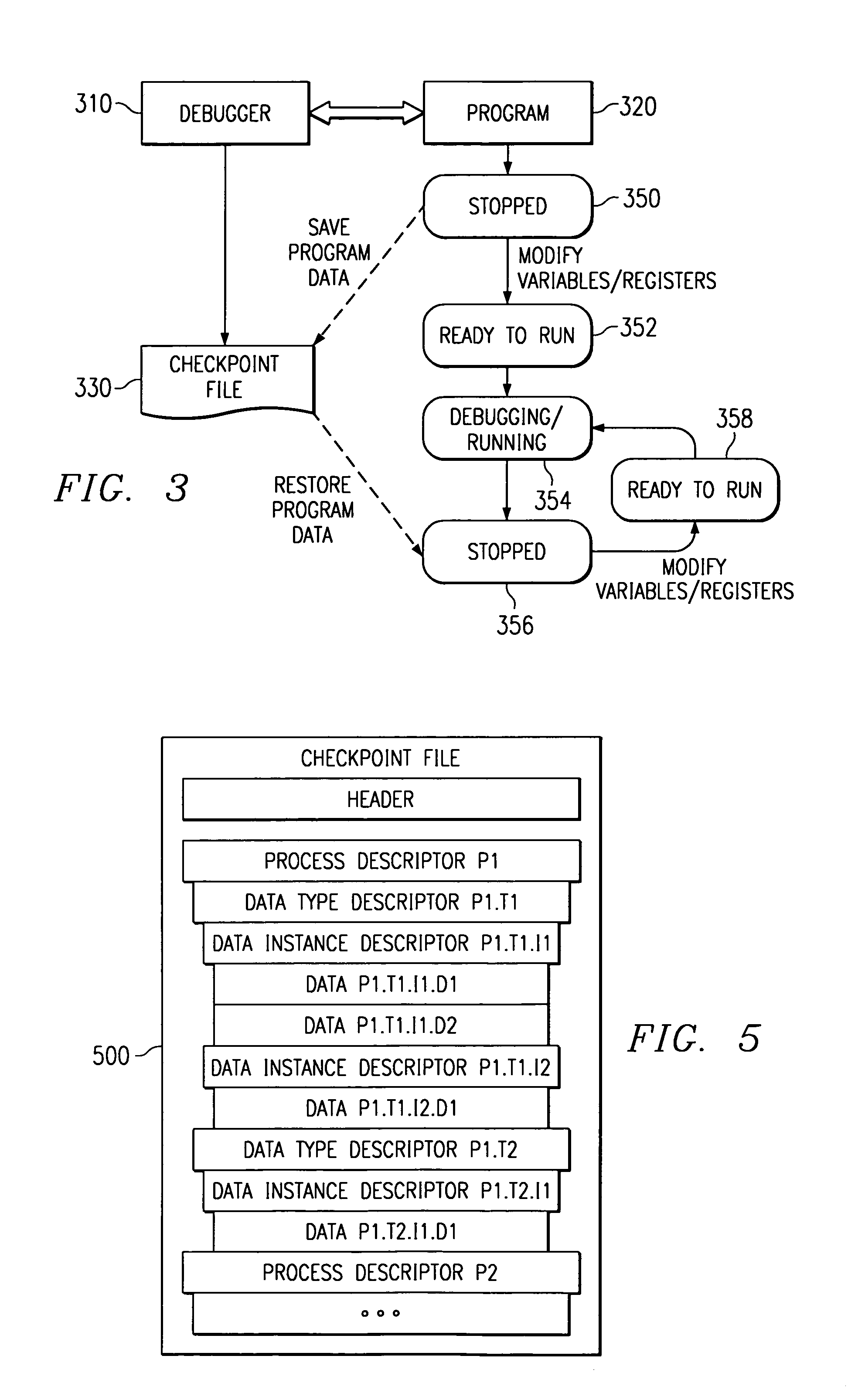

Method and apparatus to debug a program from a predetermined starting point

InactiveUS6981243B1Error detection/correctionSpecific program execution arrangementsComputer hardwareProcessor register

A method and apparatus allow a programmer to repeatedly debug a program from the same starting point. The entire process state of the process can be saved at any time in the course of a debugging session to a disk file, called the checkpoint file. Now registers or memory may be modified, if necessary, and the program may be brought back to the same starting point where the state had been previously saved by resuming from the checkpoint file. The method and apparatus allow the state of all the programs to be saved multiple times and resumed from any one of those states. The debugging of a problem is considerably facilitated by not having to start from scratch to debug the problem as the last saved state of the program can be used to start the debugging.

Owner:IBM CORP

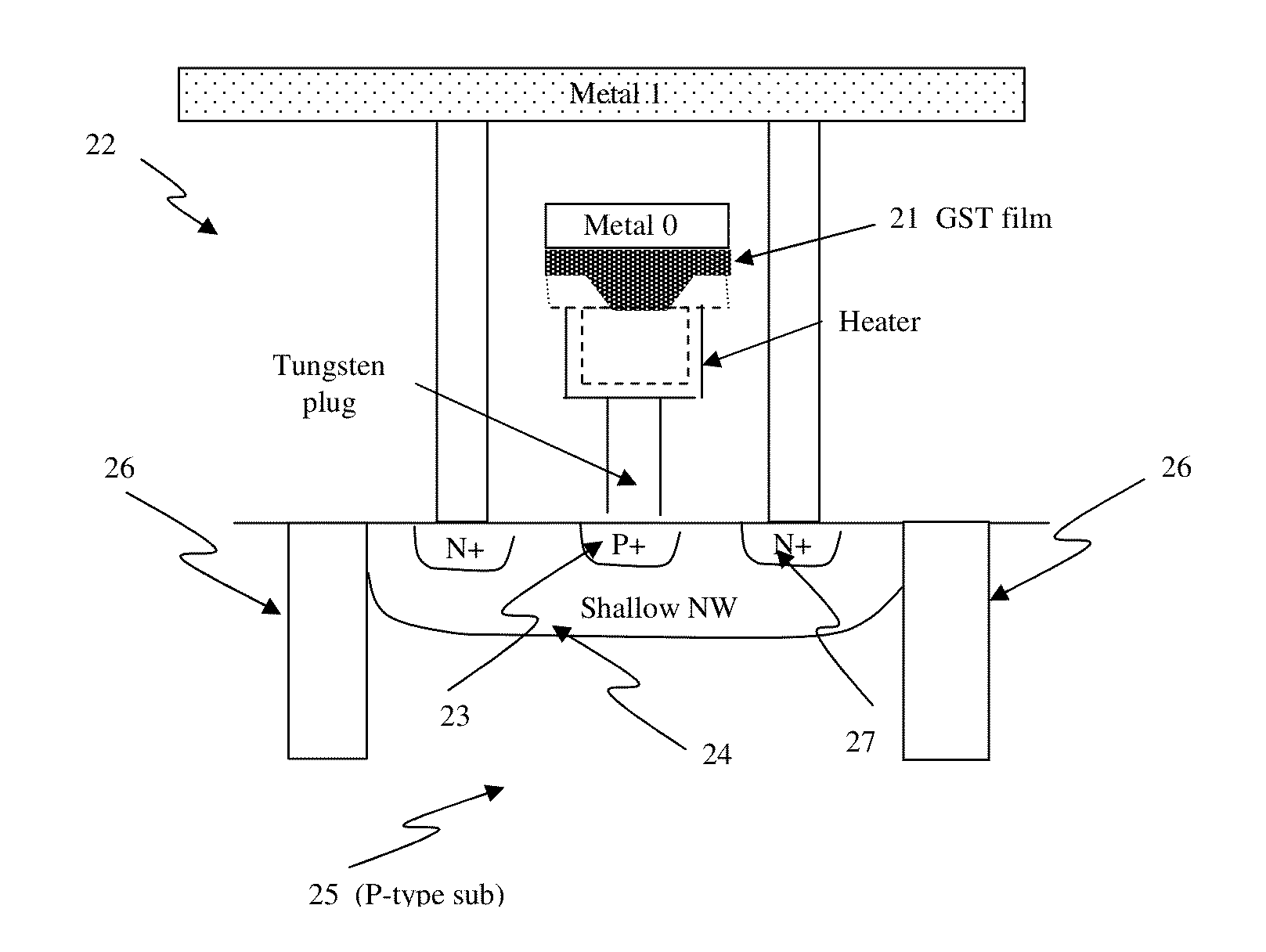

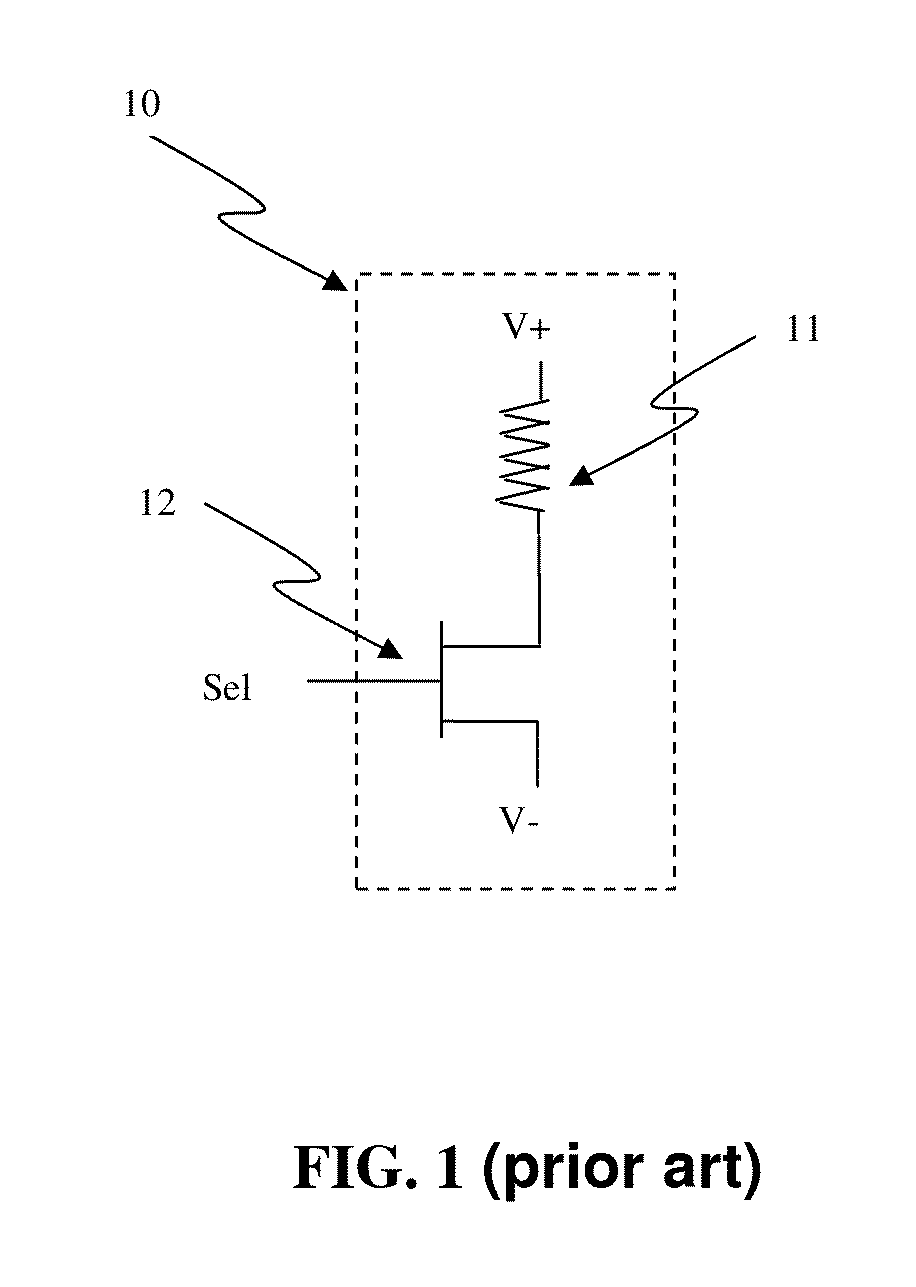

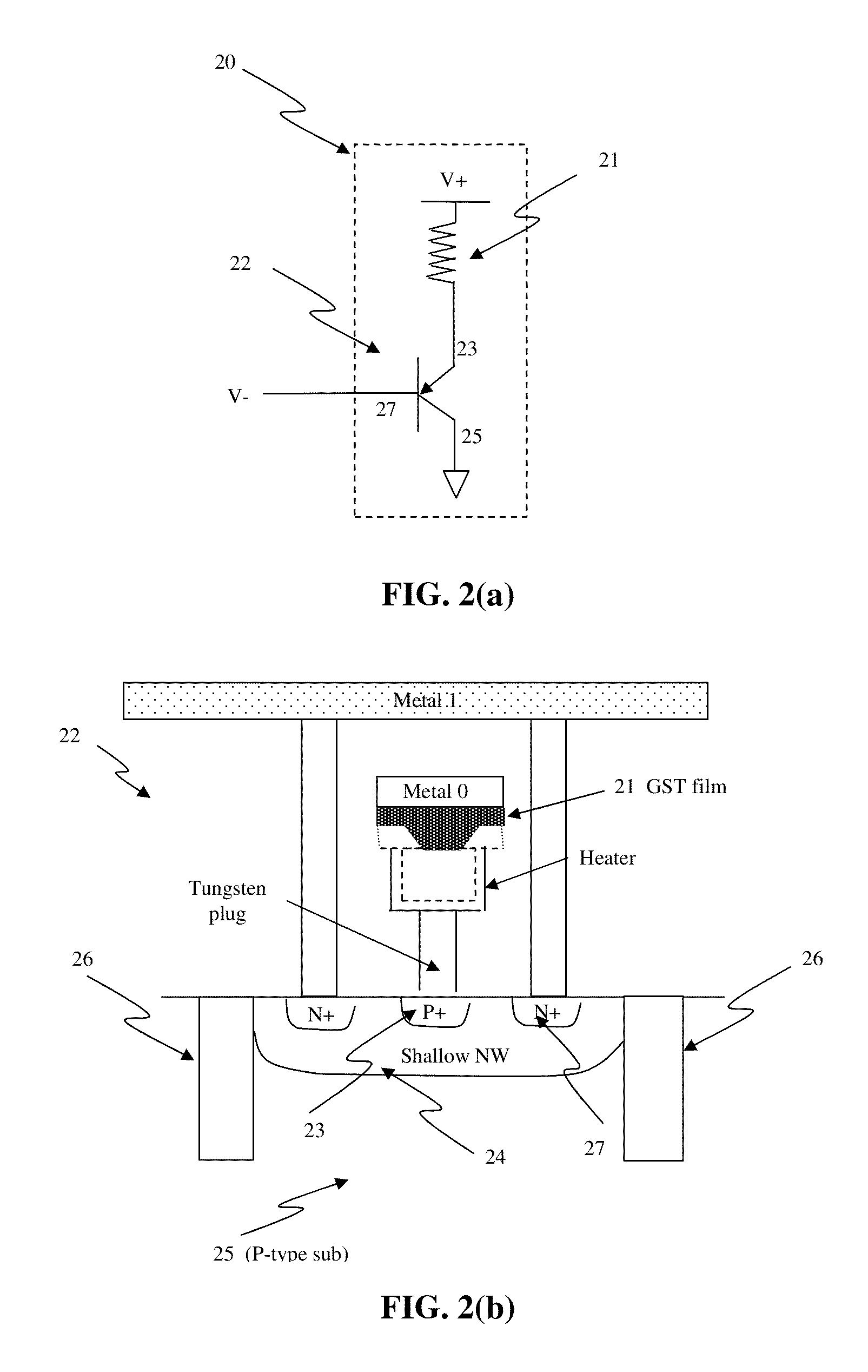

Ccircuit and system of using junction diode as program selector for metal fuses for one-time programmable devices

Junction diodes fabricated in standard CMOS logic processes can be used as program selectors for One-Time Programmable (OTP) devices. An OTP device can have at least one OTP element coupled to at least one diode in a memory cell. With a metal fuse is used by the OTP element, at least one contact and / or a plurality of vias can be built (possibly with use of one or more jumpers) in the program path to generate more Joule heat to assist with programming. The jumpers are conductive and can be formed of metal, metal gate, local interconnect, polymetal, etc. The metal fuse can also have an extended area that is longer than required by design rules for enhanced programmability. The OTP element can be polysilicon, silicided polysilicon, silicide, polymetal, metal, metal alloy, local interconnect, thermally isolated active region, CMOS gate, or combination thereof.

Owner:ATTOPSEMI TECH CO LTD

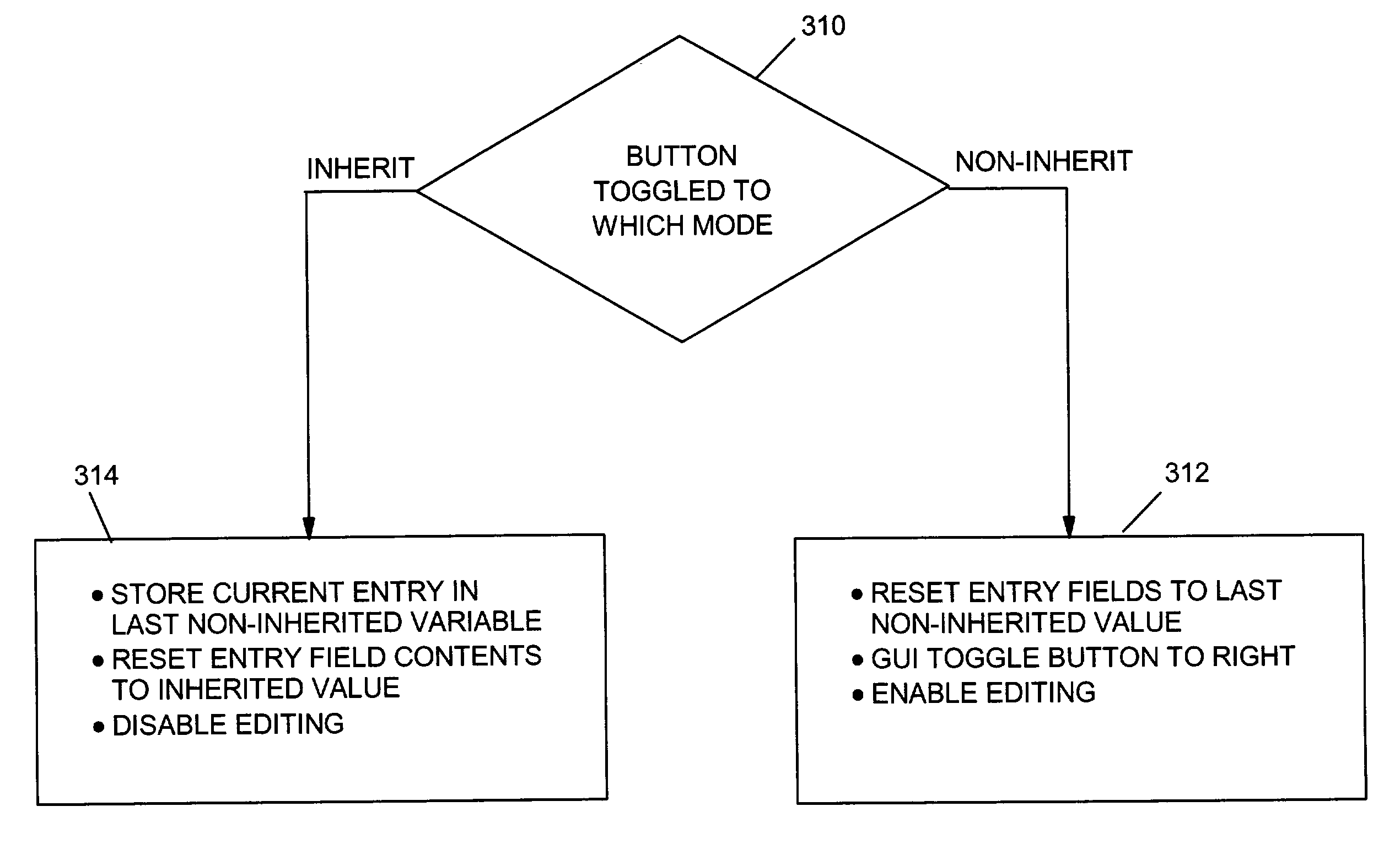

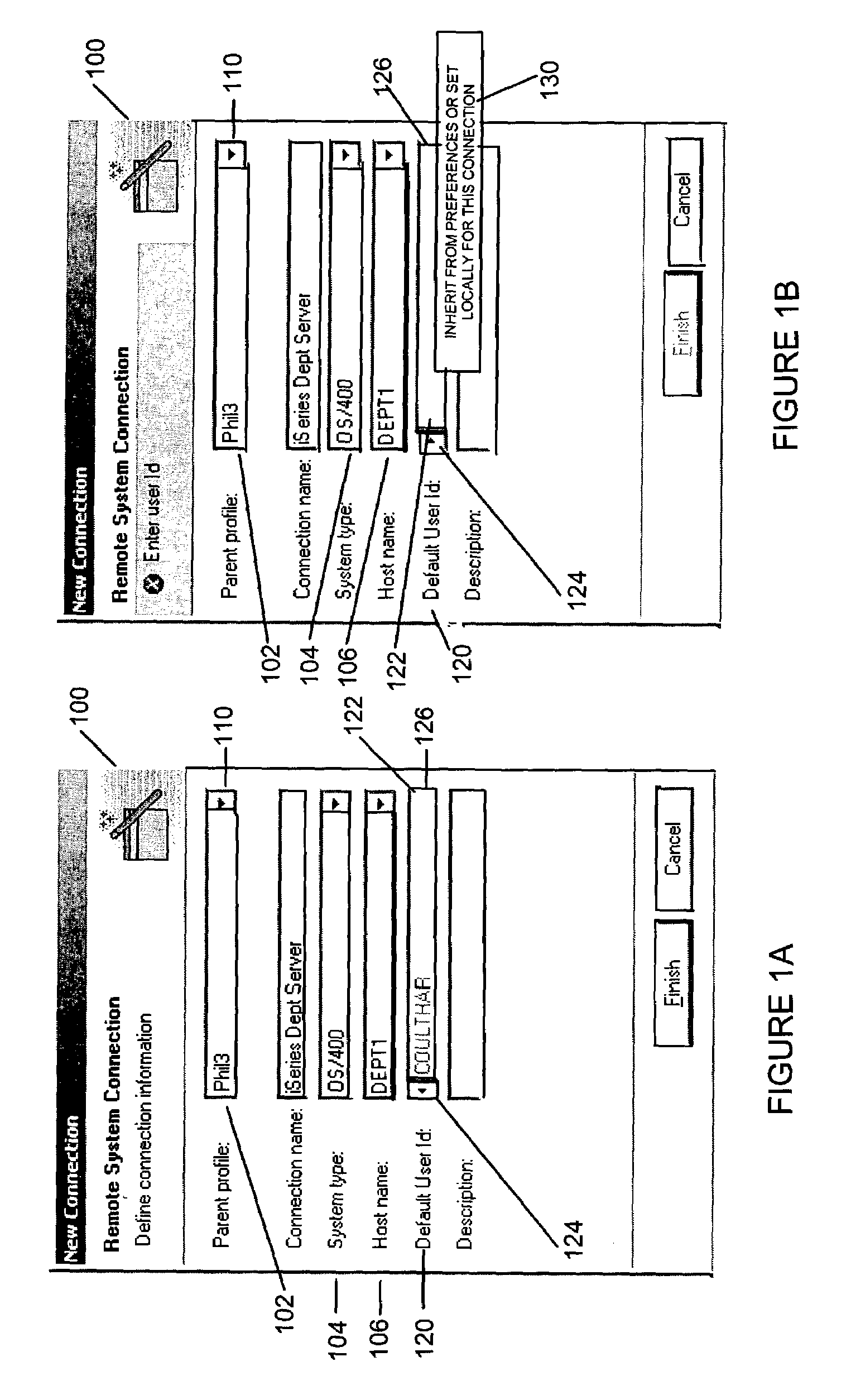

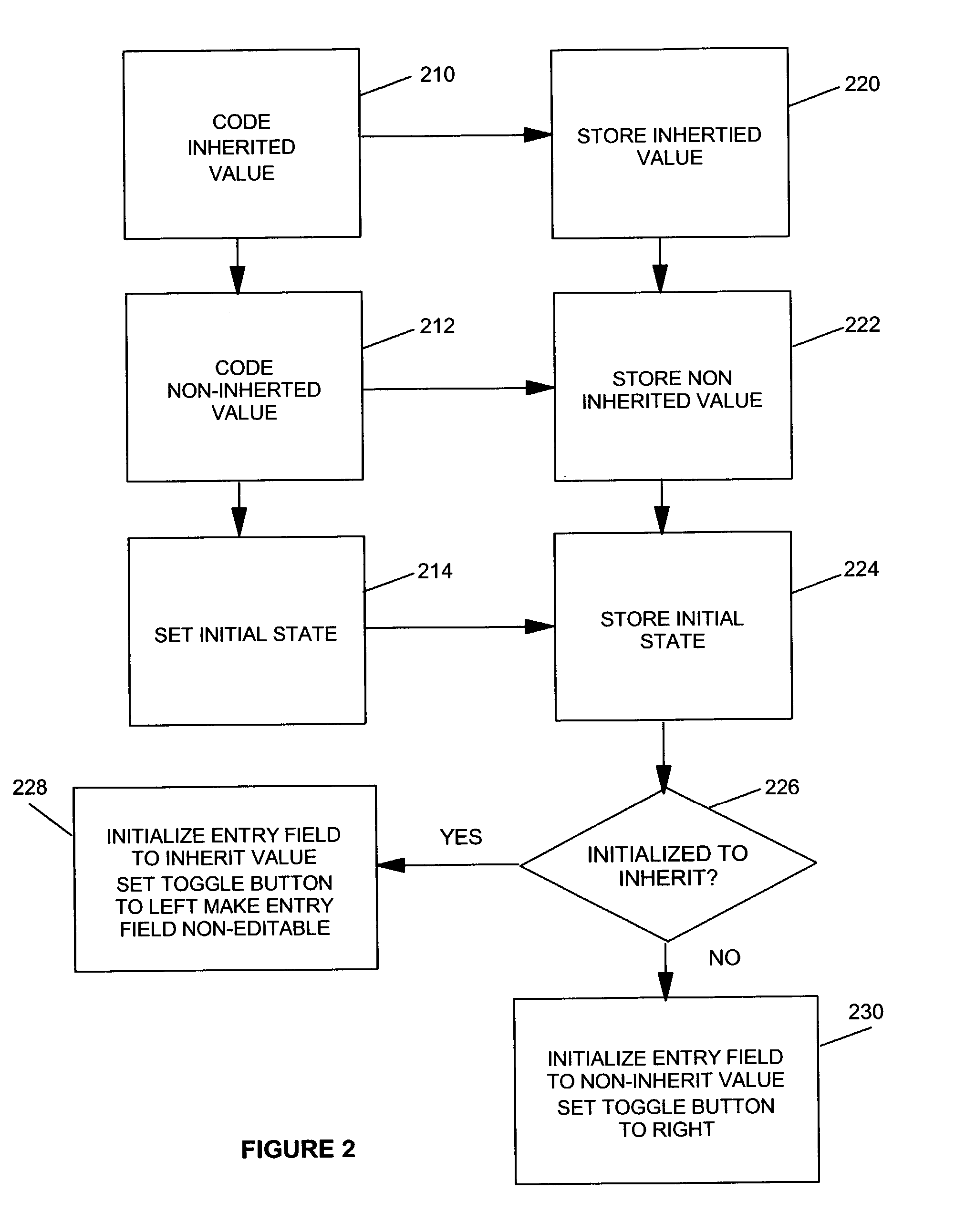

Toggleable widget for a user interface

InactiveUS7107546B2Program controlSpecial data processing applicationsHuman–computer interactionUser interface

A composite interface widget for toggleable entry fields that minimizes real estate and allows the entry field to toggle between a special kind of input that is either a predefined value or a value specified by the user. The widget presents a local or noninherited state which enables the widget to have an entry field with editing capability; alternatively, the widget offers an inherit state having a read-only entry field that displays a present input string. The user is given a small concise button or other icon to toggle between the two states. The programmer specifies the initial state, the string to display in the inherit mode, and the initial value for the local or noninherit mode. The programmer can subsequently query if the user chose the inherit mode or chose the local mode and, if so, what local value was entered.

Owner:IBM CORP

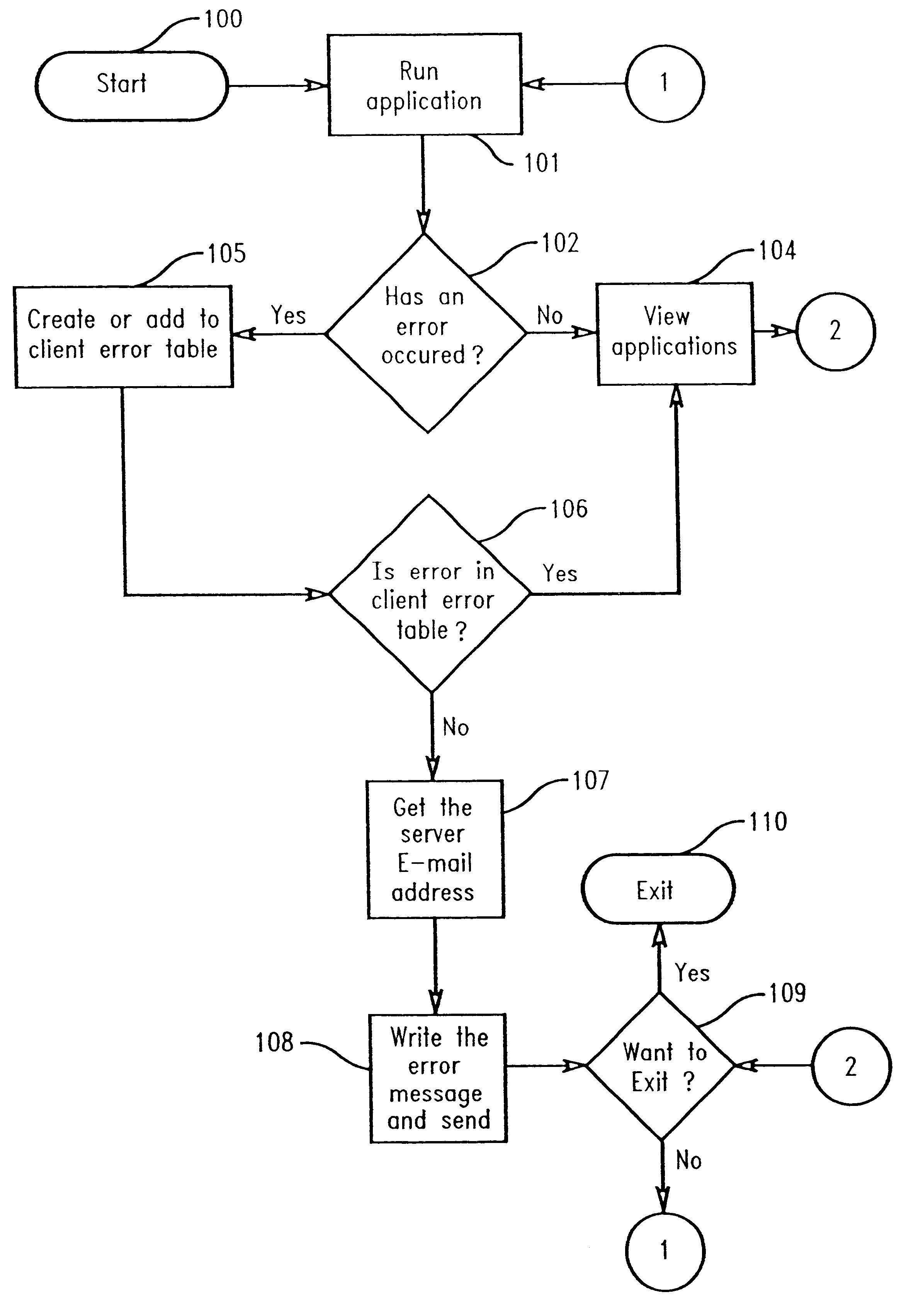

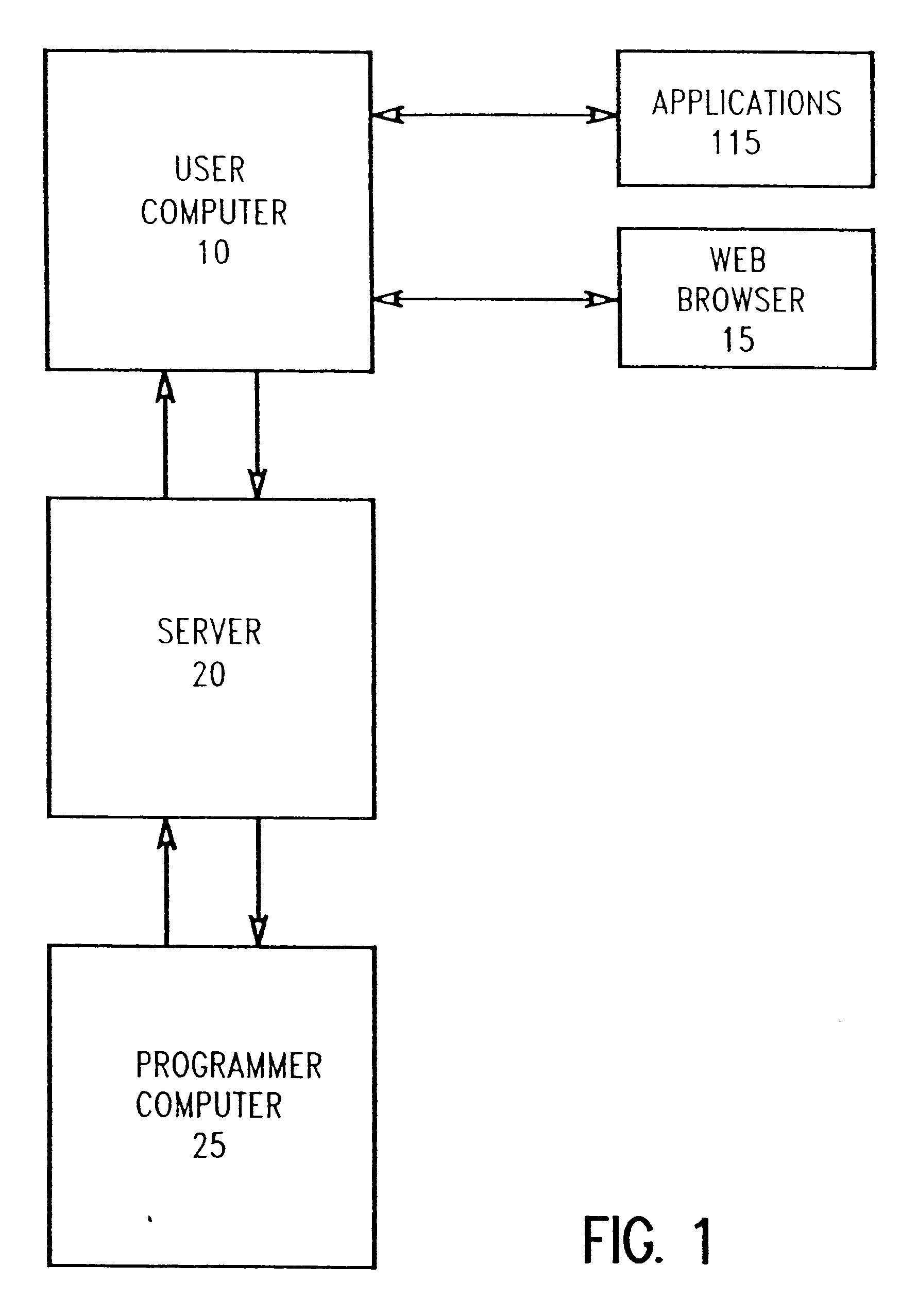

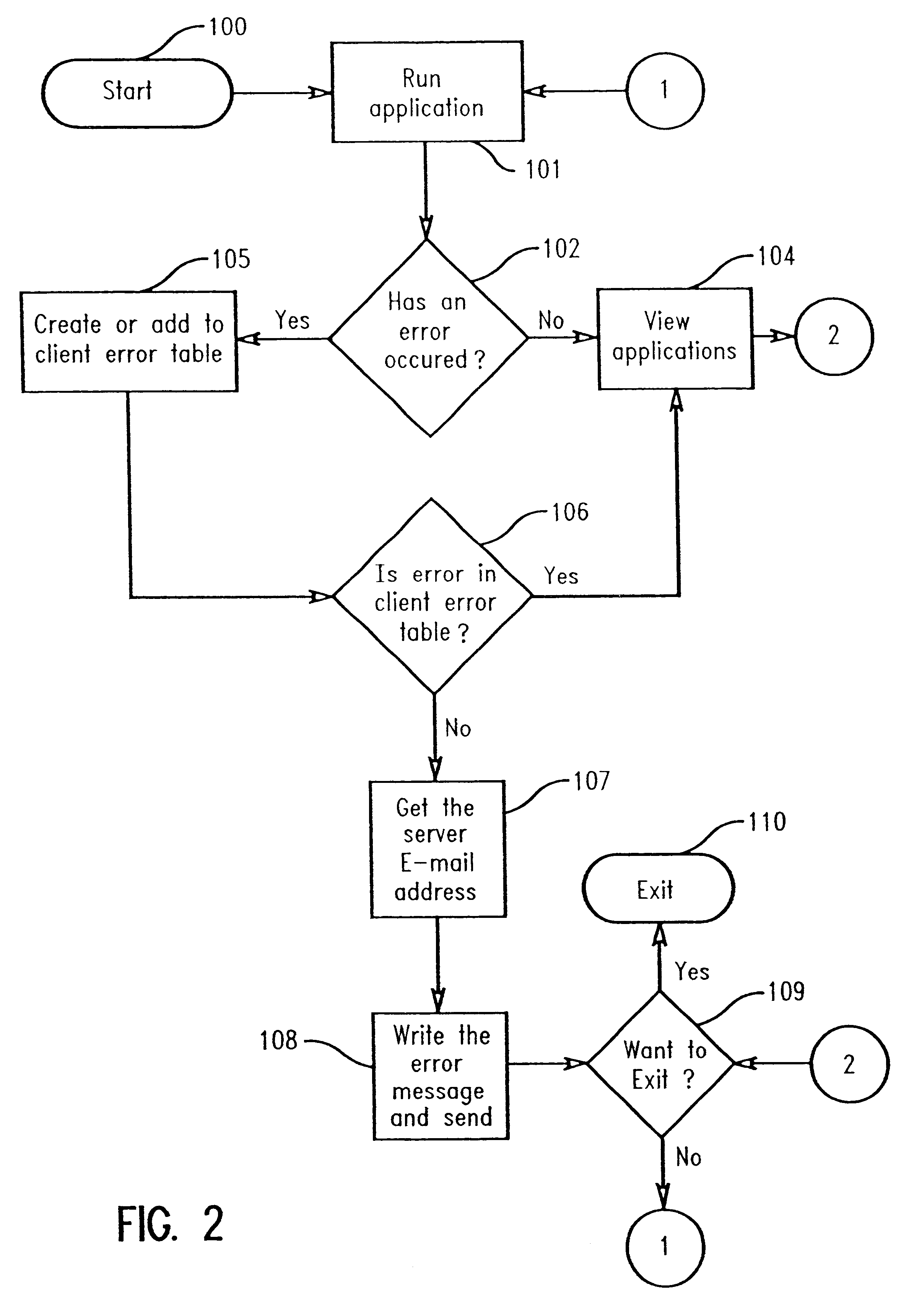

Web browser program feedback system

A method and apparatus for providing feedback to a programmer of a web based application notifying the programmer of application errors encountered by an end user of the application. A user error table is created to log application errors when a user computer is running the web based application. The present invention searches the user error table to determine whether an application error has occurred and only those errors which occur for a first time are forwarded to a server responsible for collecting the programmer's e-mail. A server error table is created to log those error messages received by the server and only those error messages which are unique are forwarded to the programmer. The programmer does not receive duplicate error messages relating to the same error and can use the feedback provided by the present invention to correct the application in subsequent versions. Error messages are filtered at the user computer level and at the server level such that the programmer will receive error messages for a particular programming error only once. The programmer is not inundated with multiple error messages relating to the same error by multiple users. Most preferably, the present invention is a computer program product incorporating known source code containing the means for providing feedback to the programmer of application errors stored on a server accessible to users who can download the application onto their user computers.

Owner:IBM CORP

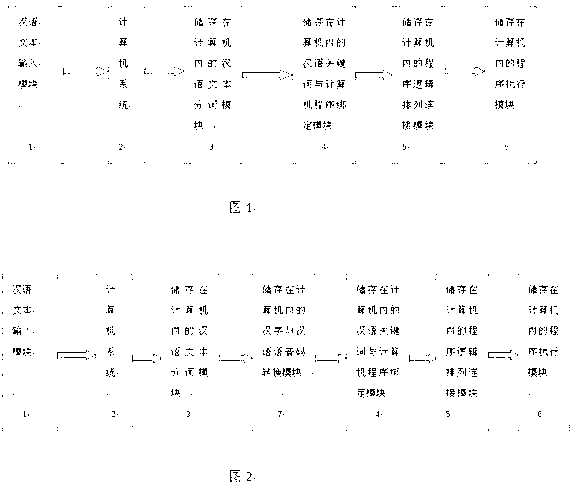

Device for calling computer program to run by utilizing Chinese text

InactiveCN103279190ARealize intelligent controlEasy to callInput/output for user-computer interactionGraph readingInformation processingAutomatic control

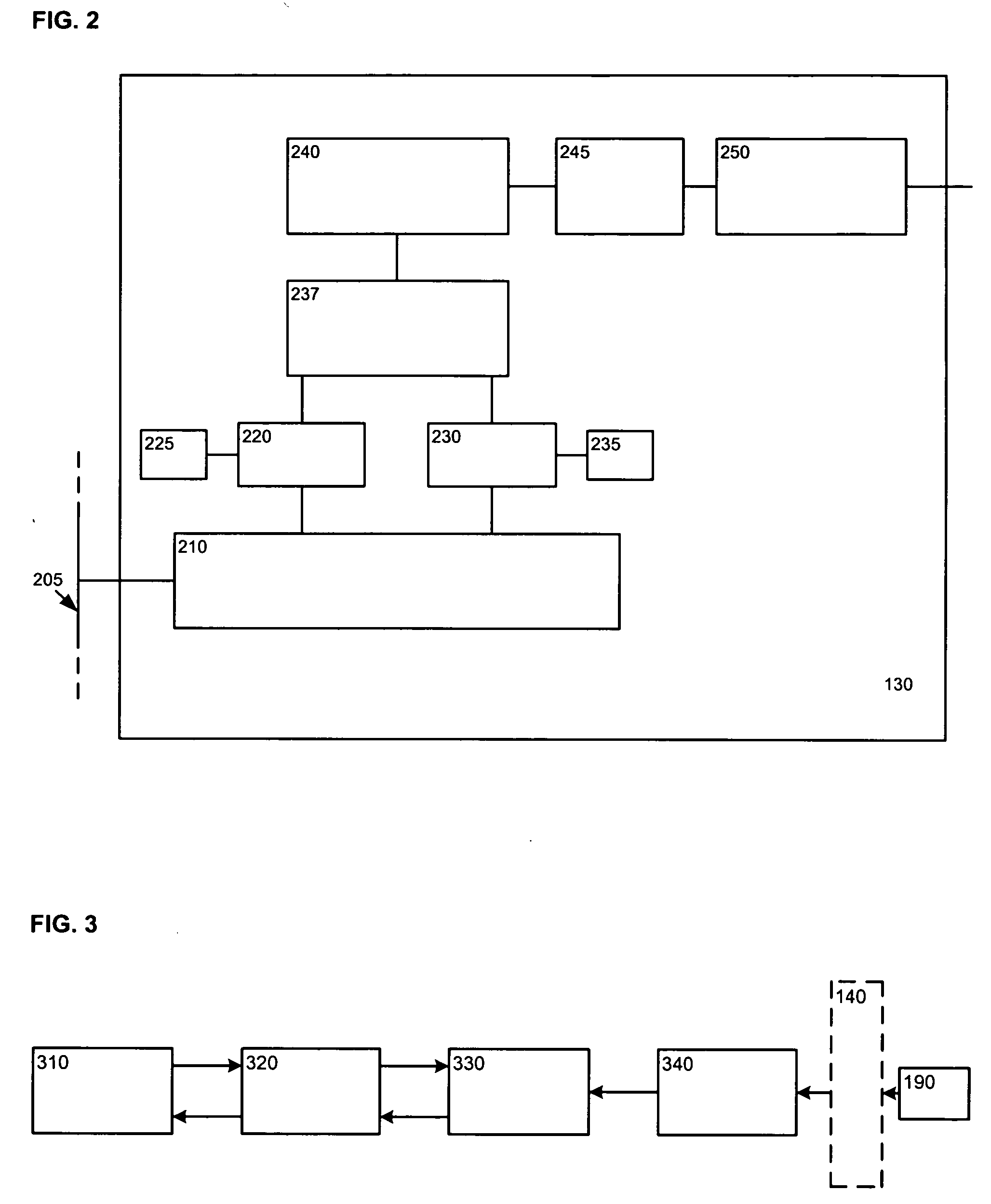

The technical scheme relates to a device for calling a computer program to run by utilizing a Chinese text and belongs to the field of computer man-machine conversation automatic control technologies. The device for calling the computer program to run by utilizing the Chinese text comprises a Chinese text input module (1), a computer system (2), a Chinese text word segmentation module (3), a Chinese character and Chinese speech code conversion module (7), a computer program module (4) which is pre-stored in a computer and bound with input Chinese speech codes or keywords in Chinese characters, a program logic arranging and connecting module (5) which arranges bound programs according to a logic sequence of execution, and a program execution module (6) stored in the computer, and the above modules are sequentially connected in series according to an information processing sequence of the computer. By means of the device for calling the computer program to run by utilizing the Chinese text, a non-computer programmer can call the computer program to run by utilizing Chinese natural language.

Owner:QINGHAI HANLA INFORMATION SCI & TECH CO LTD

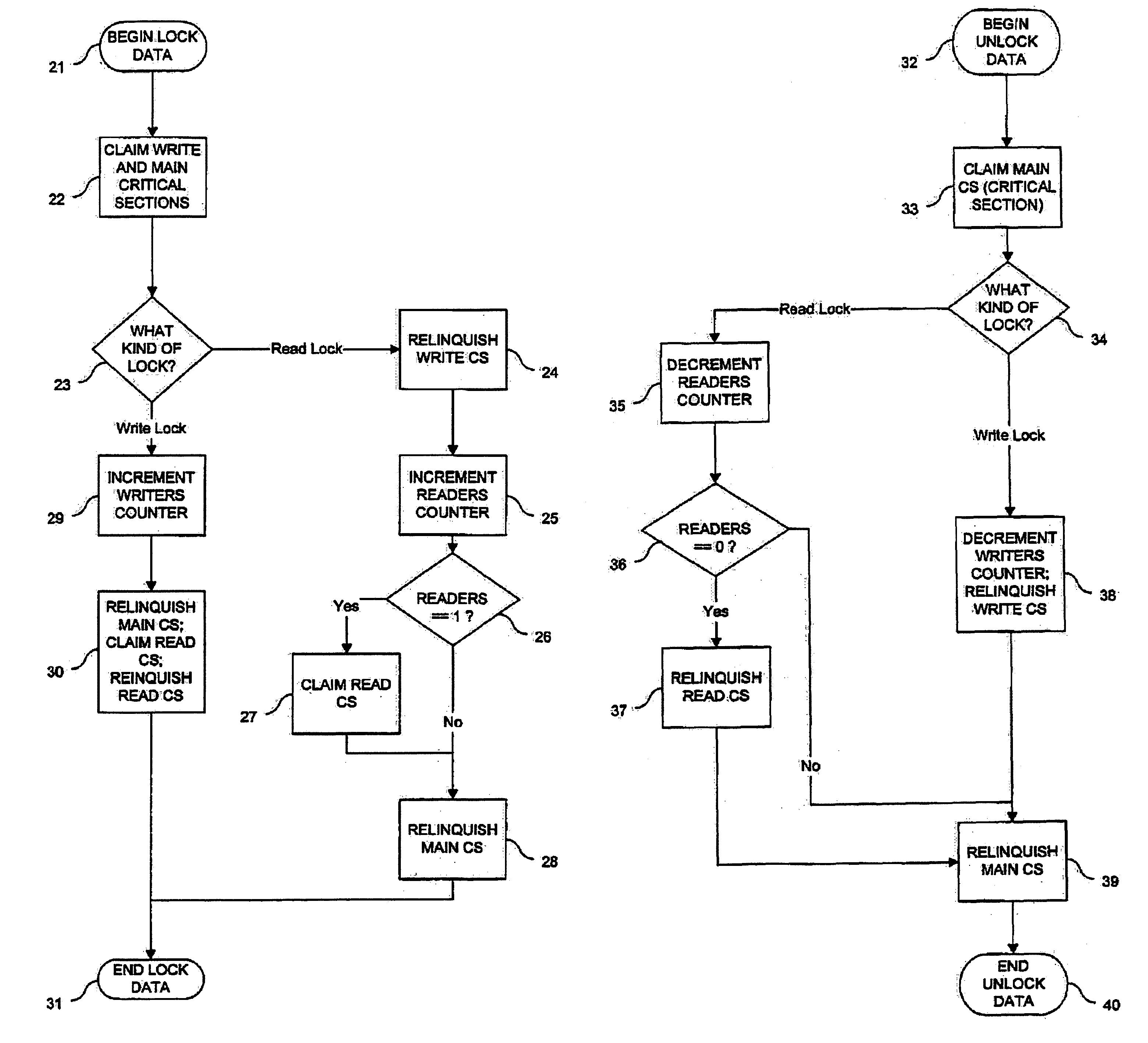

Architecture for a read/write thread lock

InactiveUS7188344B1Minimizing chanceMultiprogramming arrangementsMemory systemsComputer architectureCritical section

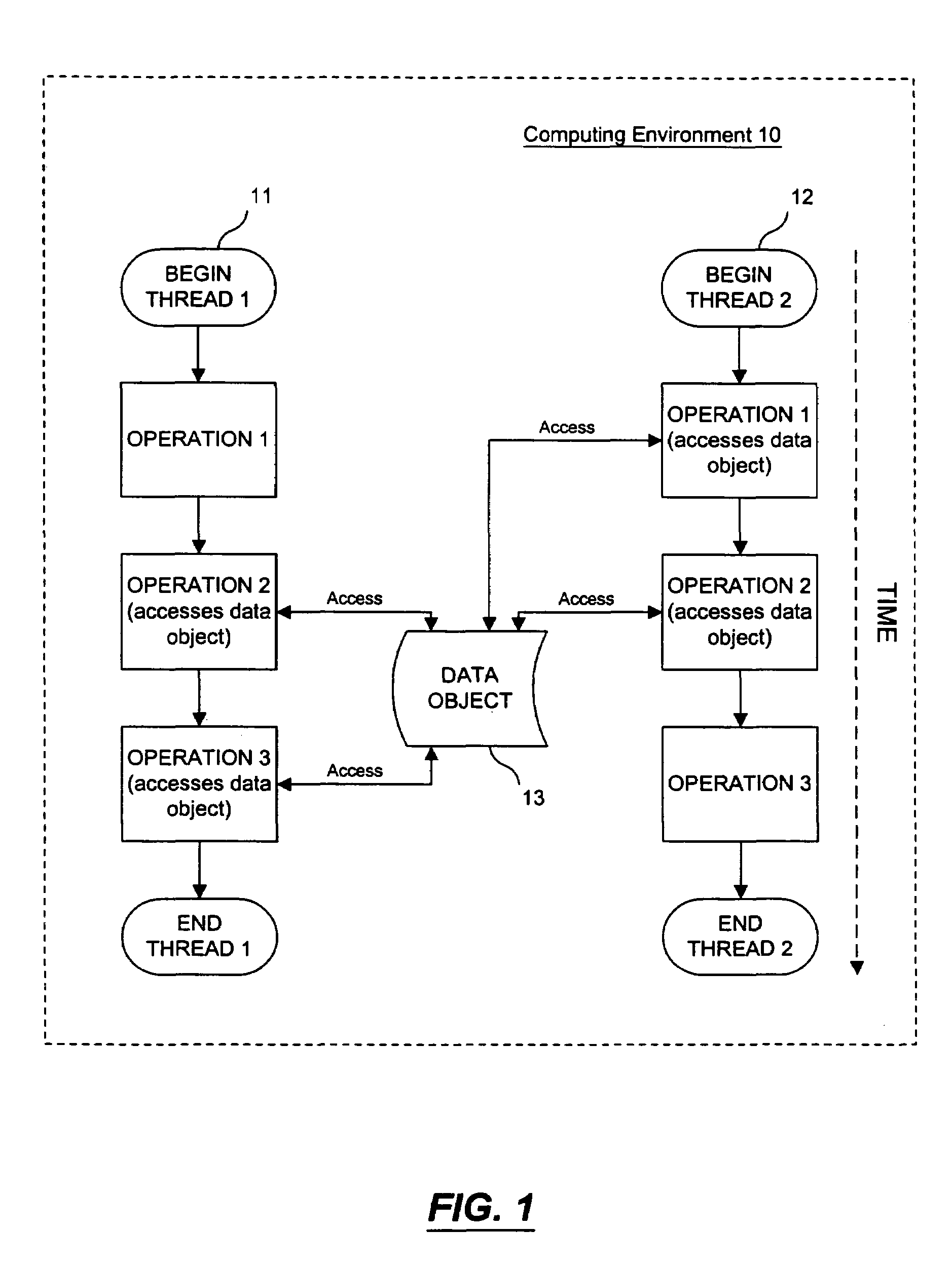

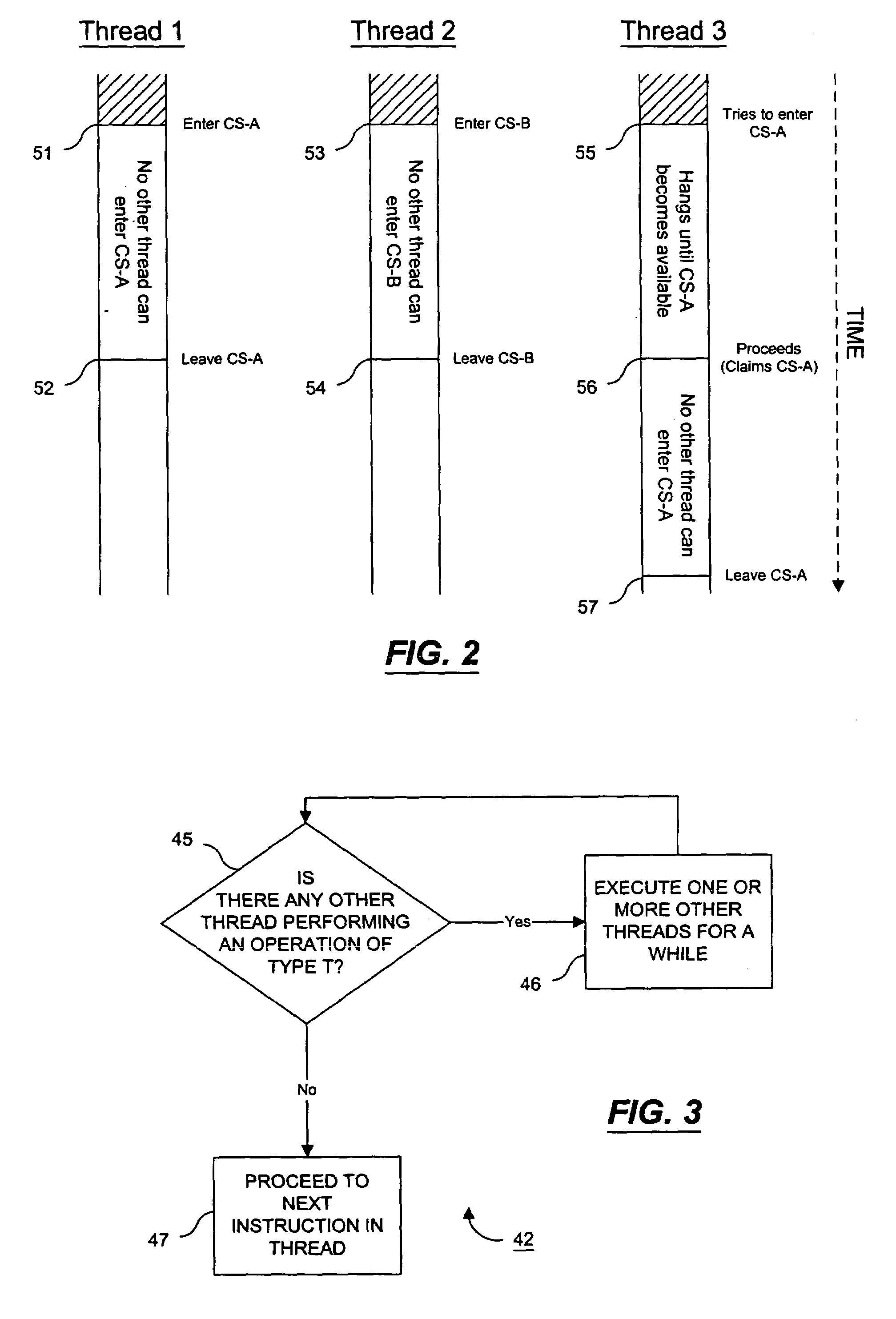

An architecture for a read / write thread lock is provided for use in a computing environment where several sets of computer instructions, or “threads,” can execute concurrently. The disclosed thread lock allows concurrently-executing threads to share access to a resource, such as a data object. The thread lock allows a plurality of threads to read from a resource at the same time, while providing a thread exclusive access to the resource when that thread is writing to the resource. The thread lock uses critical sections to suspend execution of other threads when one thread needs exclusive access to the resource. Additionally, a technique is provided whereby the invention can be deployed as constructors and destructors in a programming language, such as C++, where constructors and destructors are available. When the invention is deployed in such a manner, it is possible for a programmer to issue an instruction to lock a resource, without having to issue a corresponding unlock instruction.

Owner:UNISYS CORP

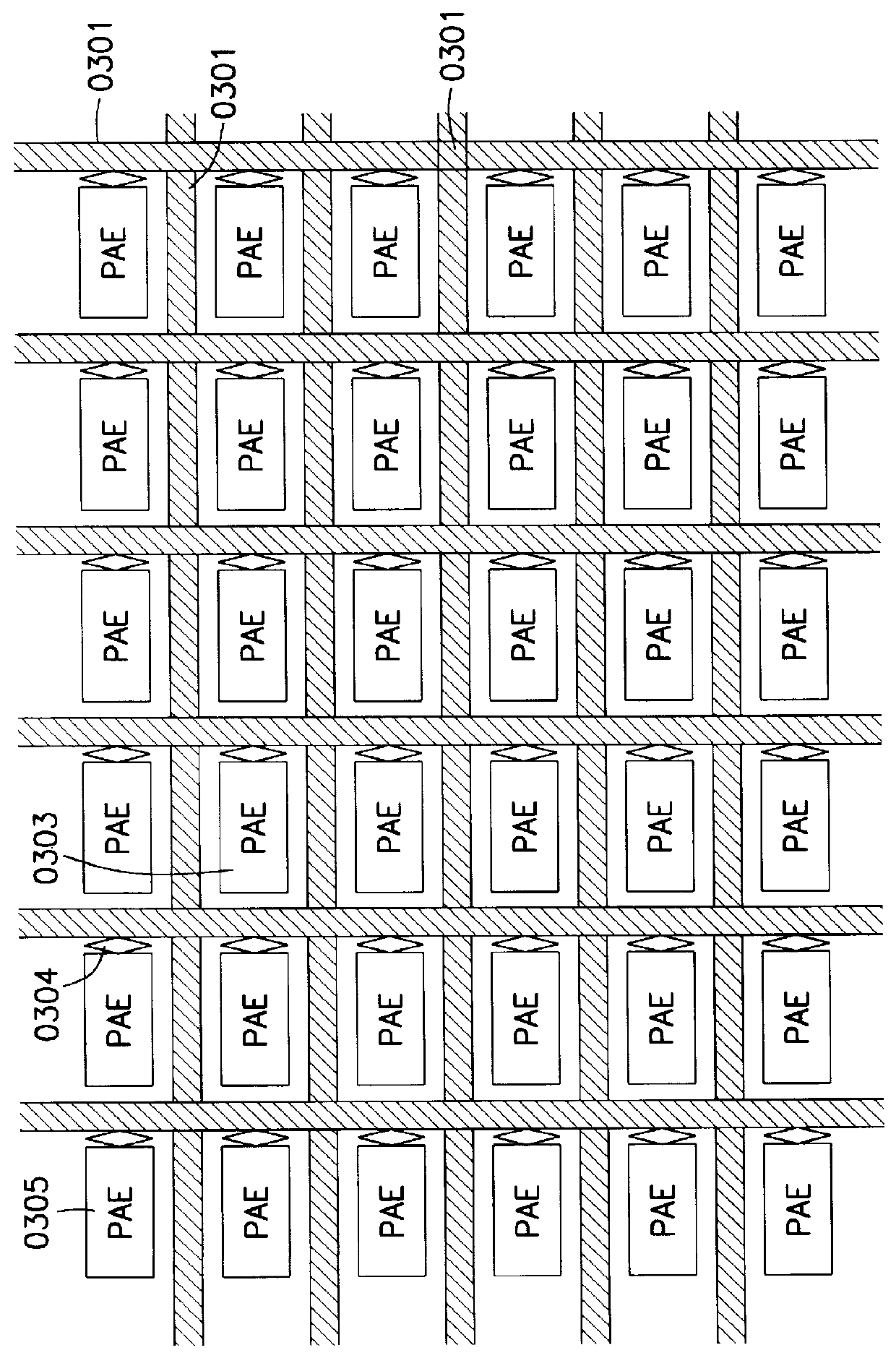

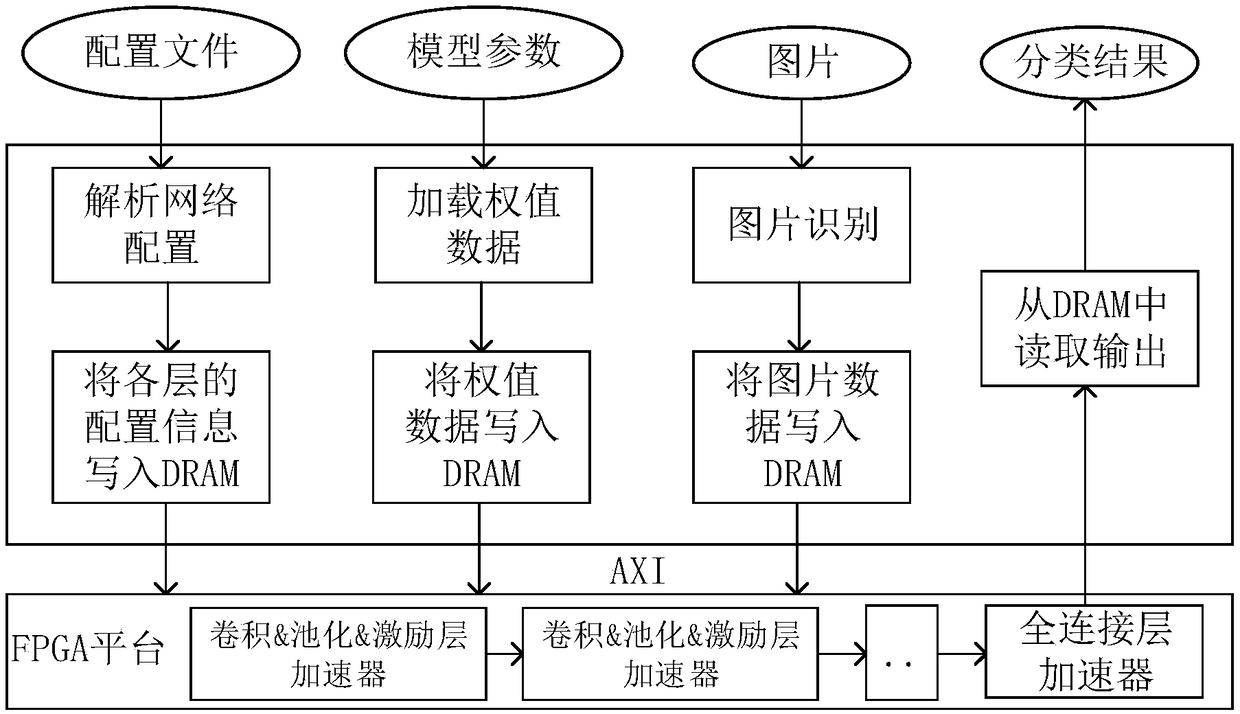

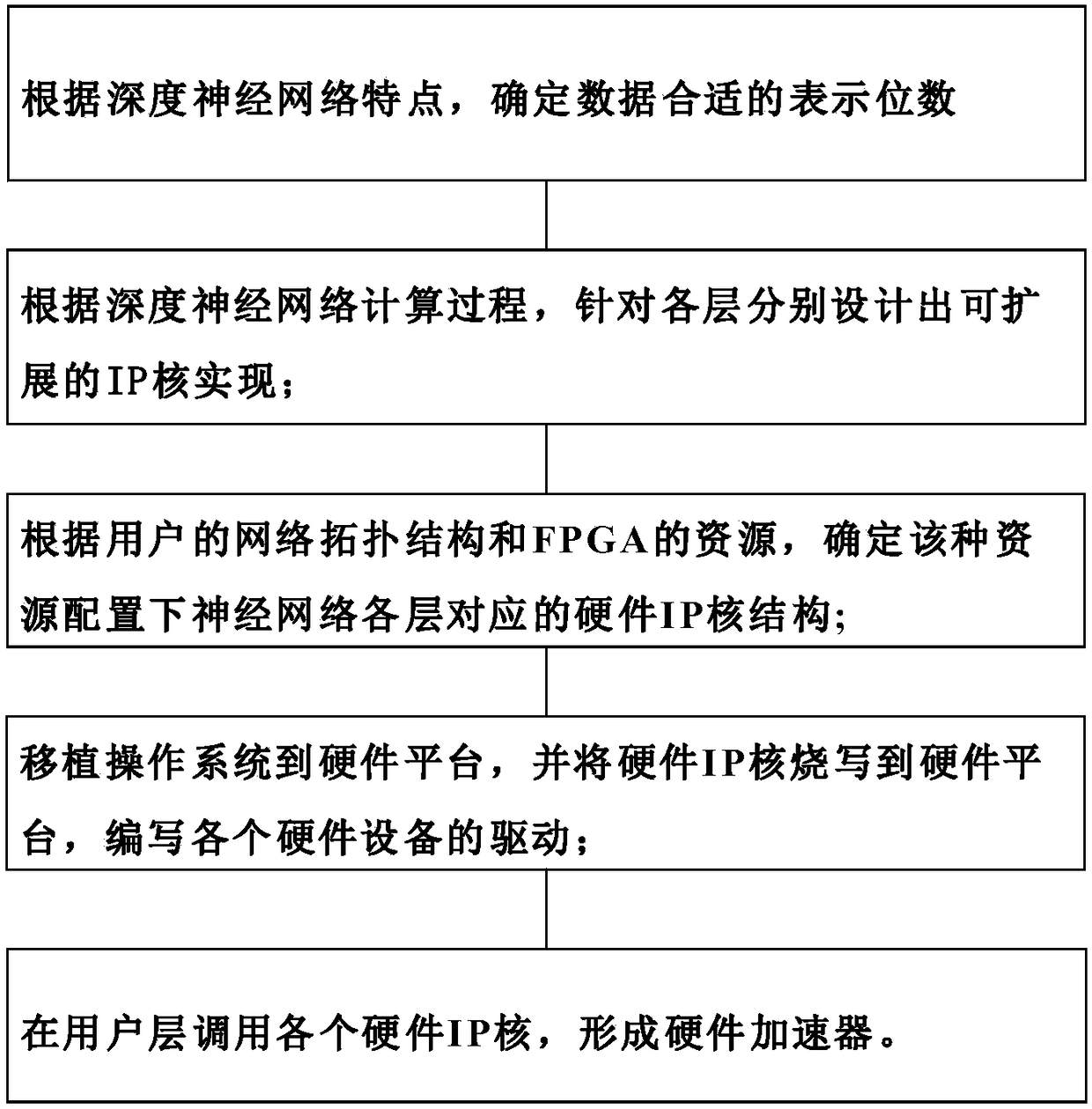

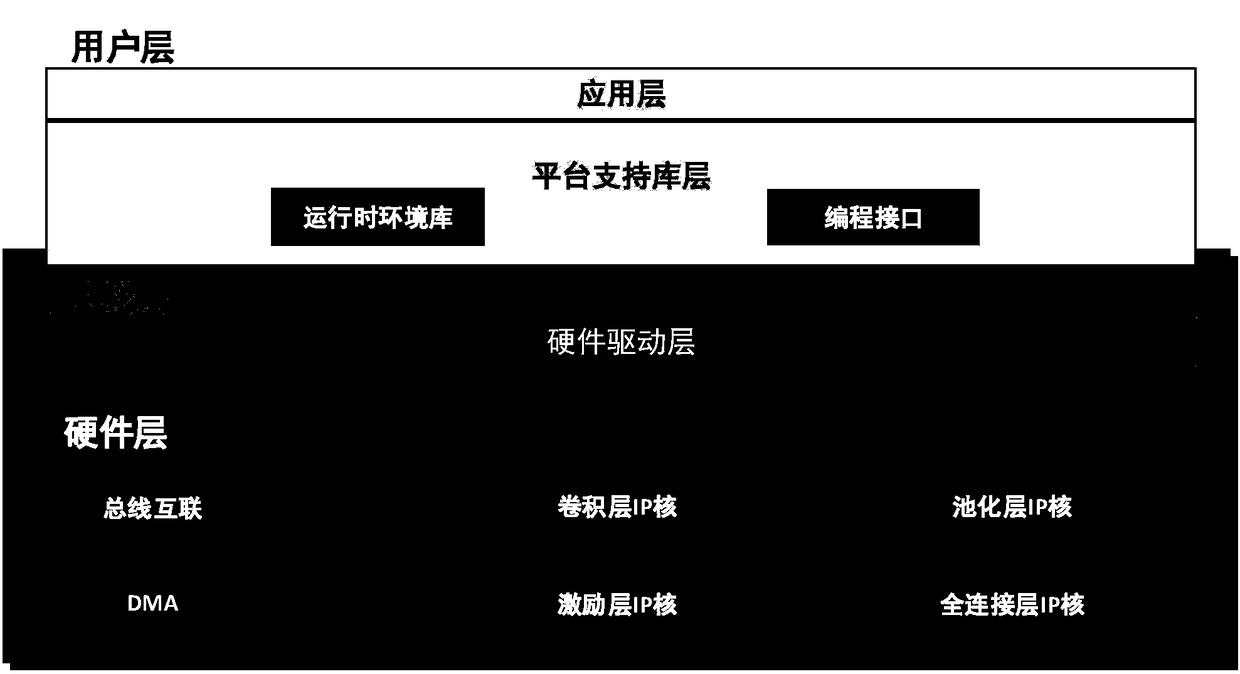

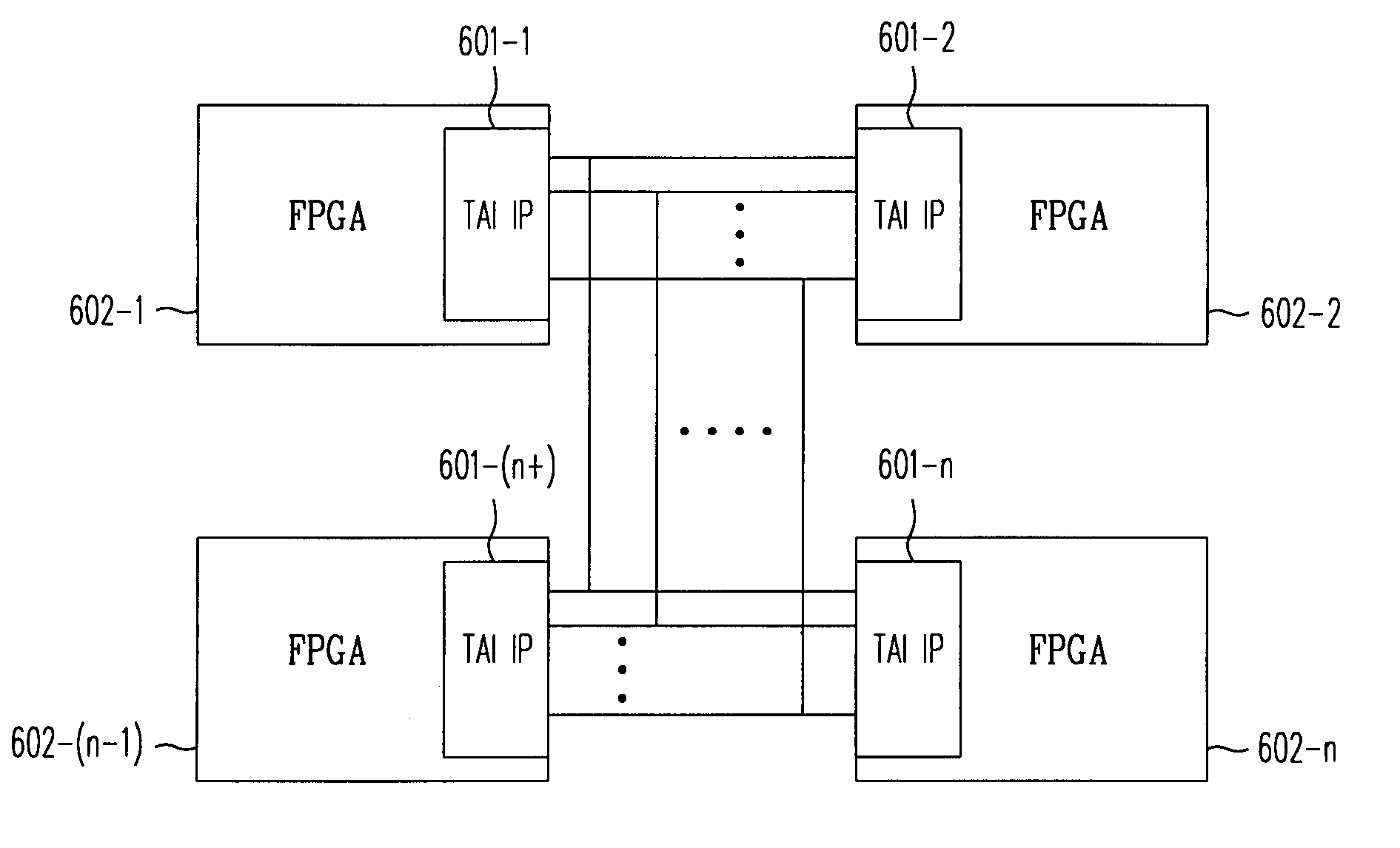

Deep neural network acceleration platform based on FPGA

The present invention discloses a deep neural network acceleration platform based on an FPGA. The platform comprises a general-purpose processor, an FPGA and a DRAM. The general-purpose processor is configured to analyze neural network configuration information and weight data and write the neural network configuration information and the weight data into the DRAM, the FPGA reads the configurationinformation from the DRAM to generate an FPGA accelerator, the general-purpose processor is configured to read in image information and write the image information into the DRAM, the FPGA acceleratorreads the image data from the DRAM and starts to calculate and writes a calculation result into the DRAM, and finally, the general-purpose processor reads a classification result from the DRAM. The accelerator allows each layer to be deployed on a FPGA chip at the same time, allows each layer to operate in a streamline mode, allows programmers having no hardware knowledge to utilize existing FPGAresources to easily obtain good performances.

Owner:苏州中科瀚海高工科技有限公司

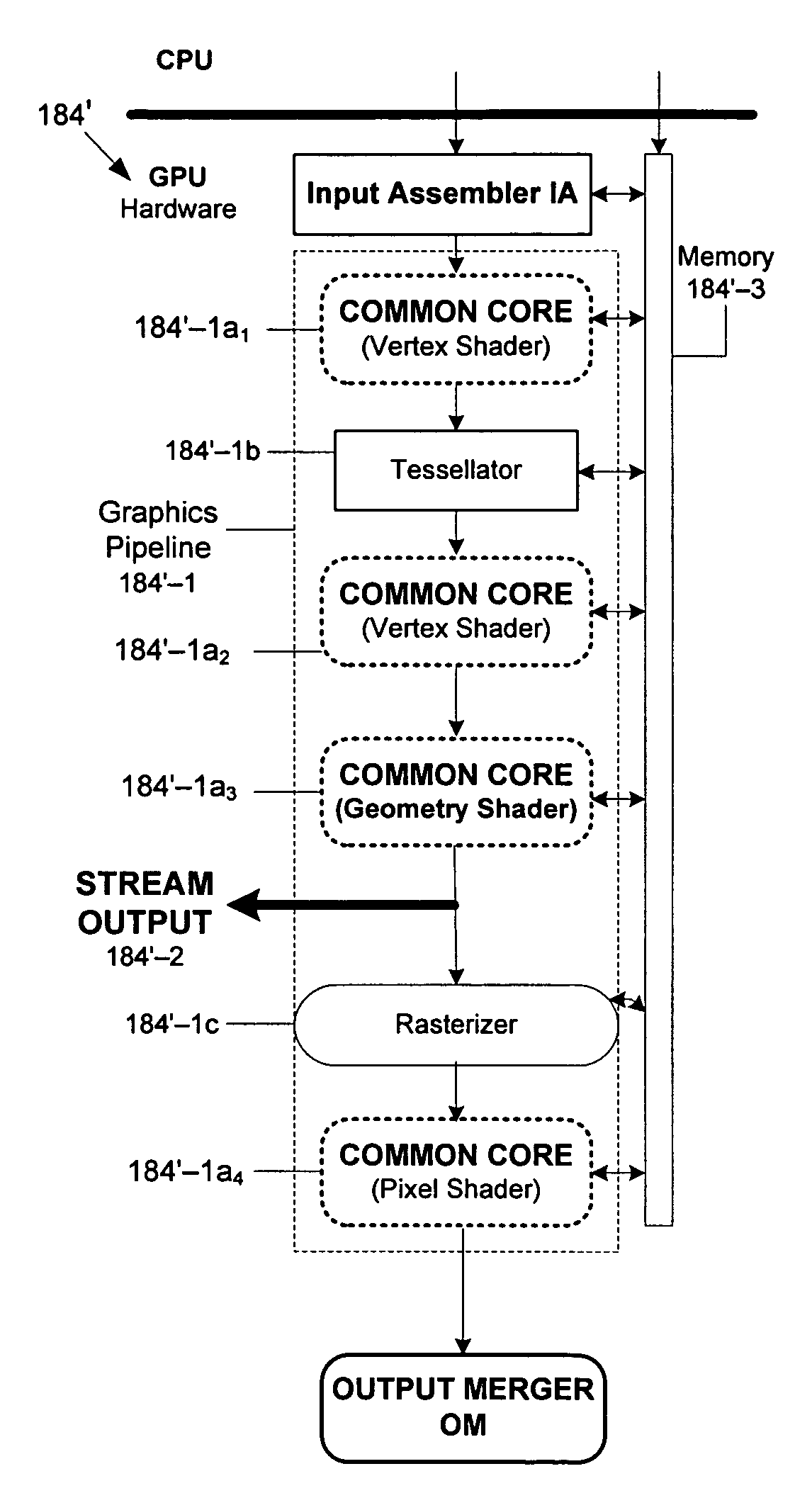

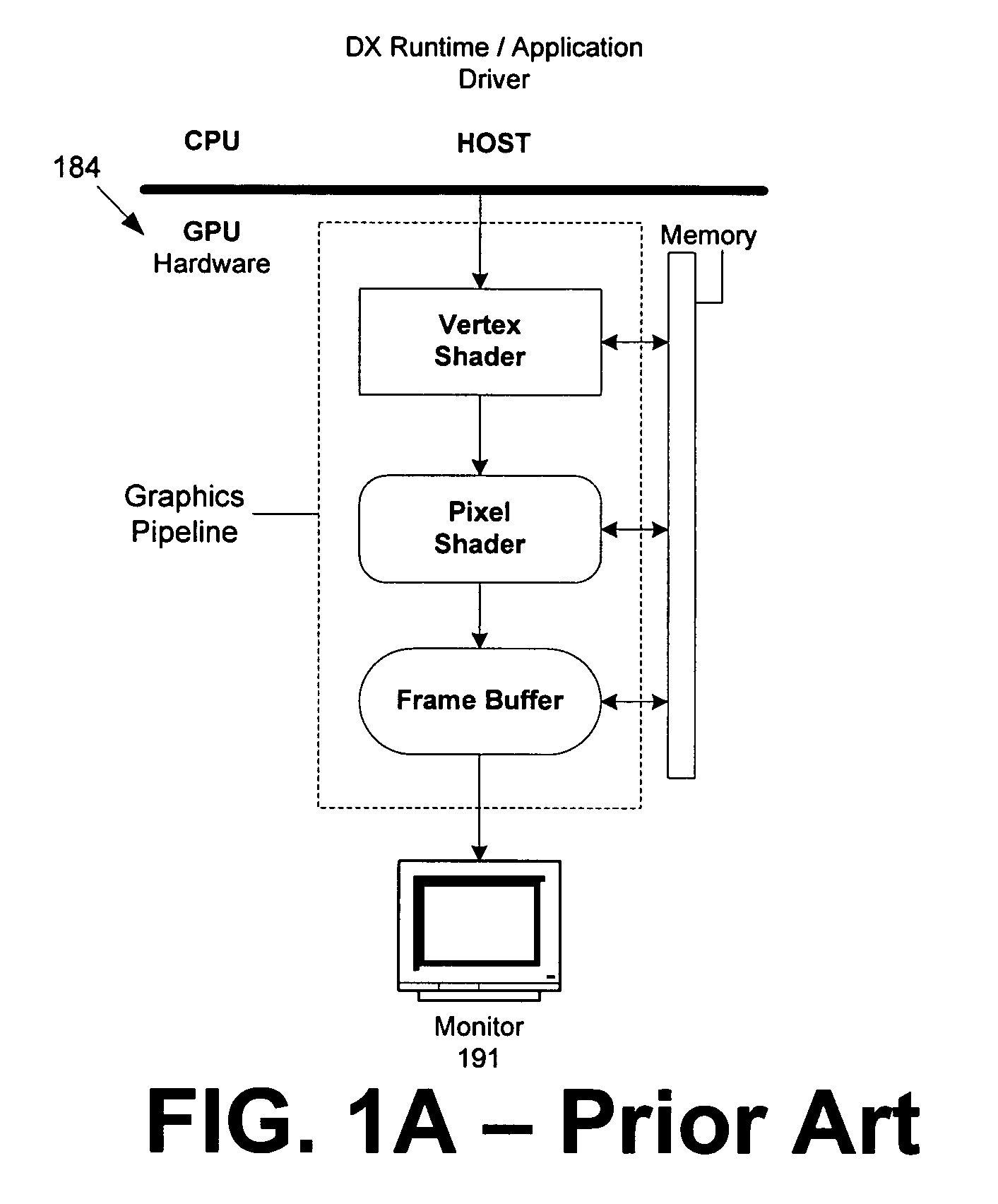

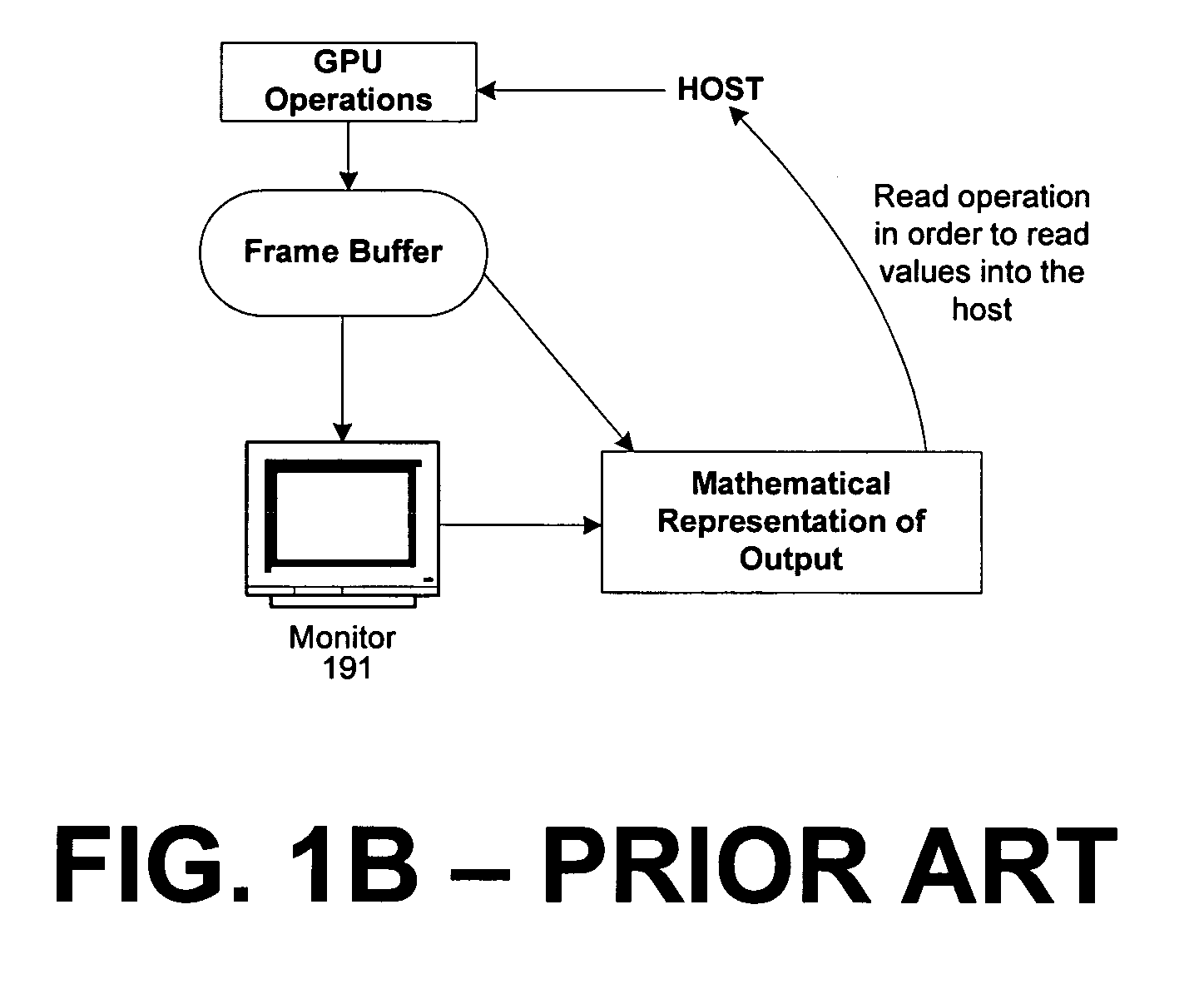

Systems and methods for providing an enhanced graphics pipeline

ActiveUS7671862B1Cathode-ray tube indicatorsMultiple digital computer combinationsGraphicsParallel computing

An enhanced graphics pipeline is provided that enables common core hardware to perform as different components of the graphics pipeline, programmability of primitives including lines and triangles by a component in the pipeline, and a stream output before or simultaneously with the rendering a graphical display with the data in the pipeline. The programmer does not have to optimize the code, as the common core will balance the load of functions necessary and dynamically allocate those instructions on the common core hardware. The programmer may program primitives using algorithms to simplify all vertex calculations by substituting with topology made with lines and triangles. The programmer takes the calculated output data and can read it before or while it is being rendered. Thus, a programmer has greater flexibility in programming. By using the enhanced graphics pipeline, the programmer can optimize the usage of the hardware in the pipeline, program vertex, line or triangle topologies altogether rather than each vertex alone, and read any calculated data from memory where the pipeline can output the calculated information.

Owner:MICROSOFT TECH LICENSING LLC

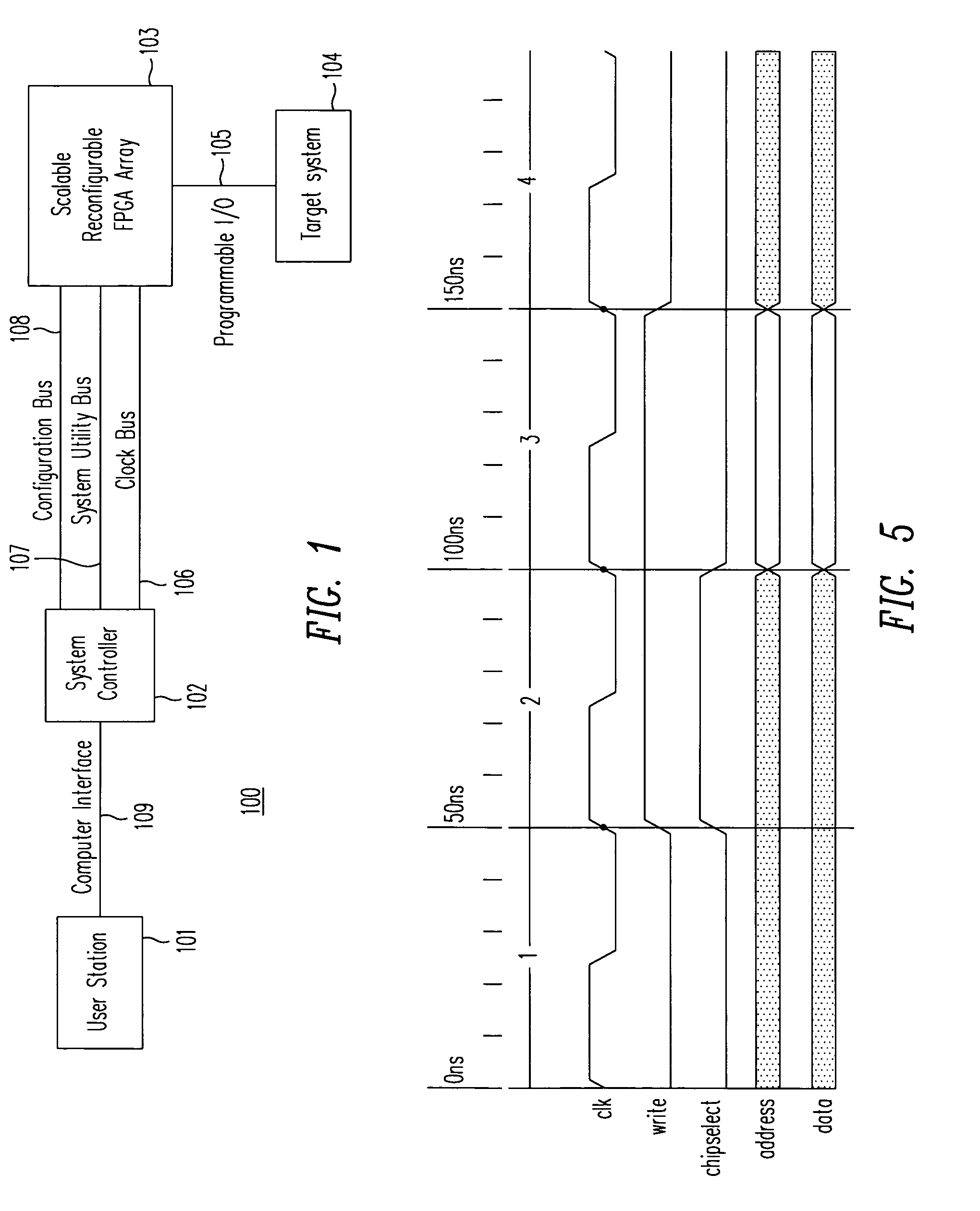

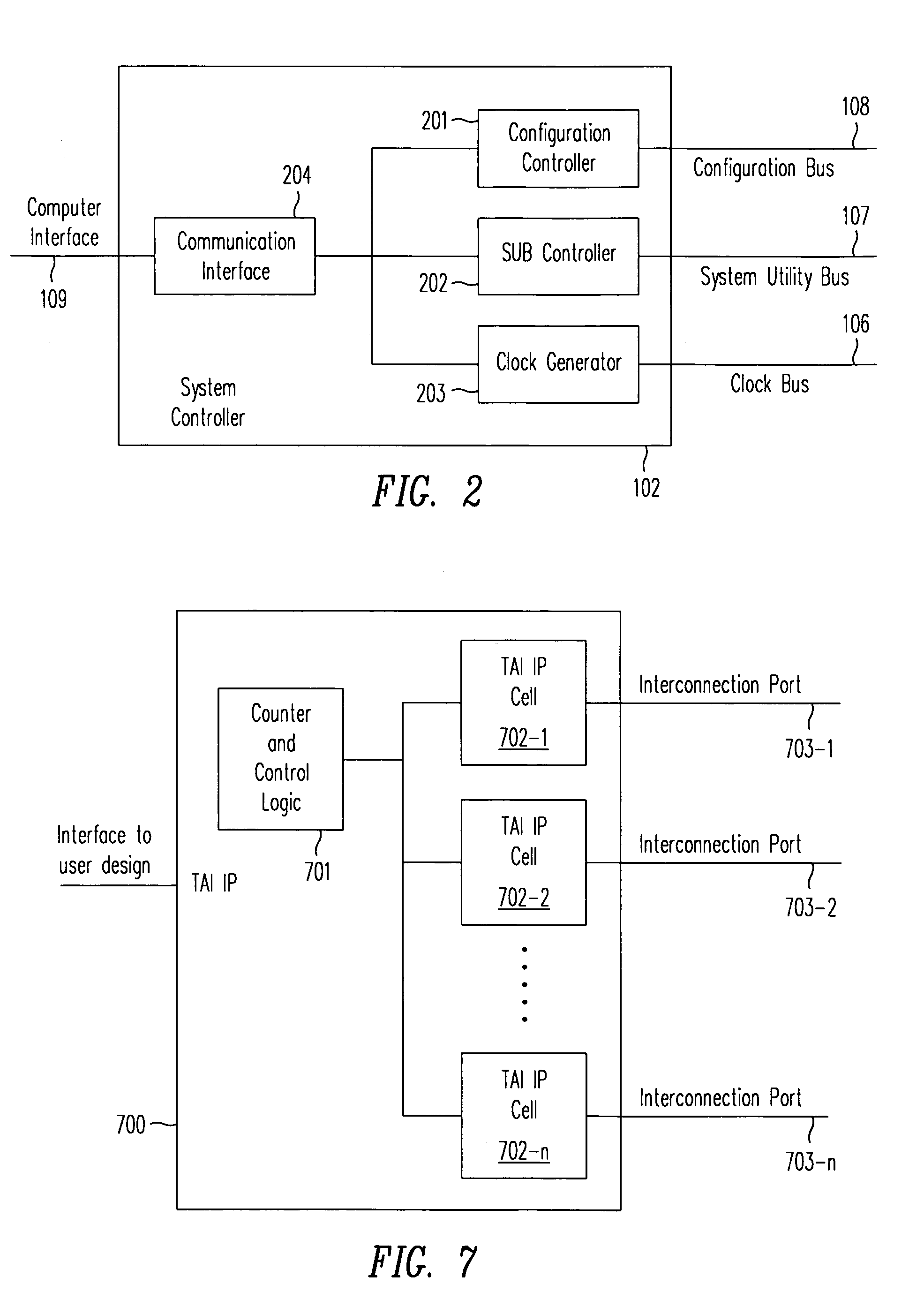

Scalable reconfigurable prototyping system and method

ActiveUS7353162B2Electronic circuit testingAnalogue computers for electric apparatusThird partyComputer architecture

A method and a system provide a reconfigurable platform for designing and emulating a user design. The method and system facilitates design and emulation of a system-on-a-chip type user design. The netlist of a user design may be included with netlists from customized or optimized third party circuits in an emulation using a platform including a number of field programmable devices. Various customized circuits for specific development activities, such as debugging, performance analysis, and simulator linkage may be configured to interact with the user design.

Owner:S2C LTD

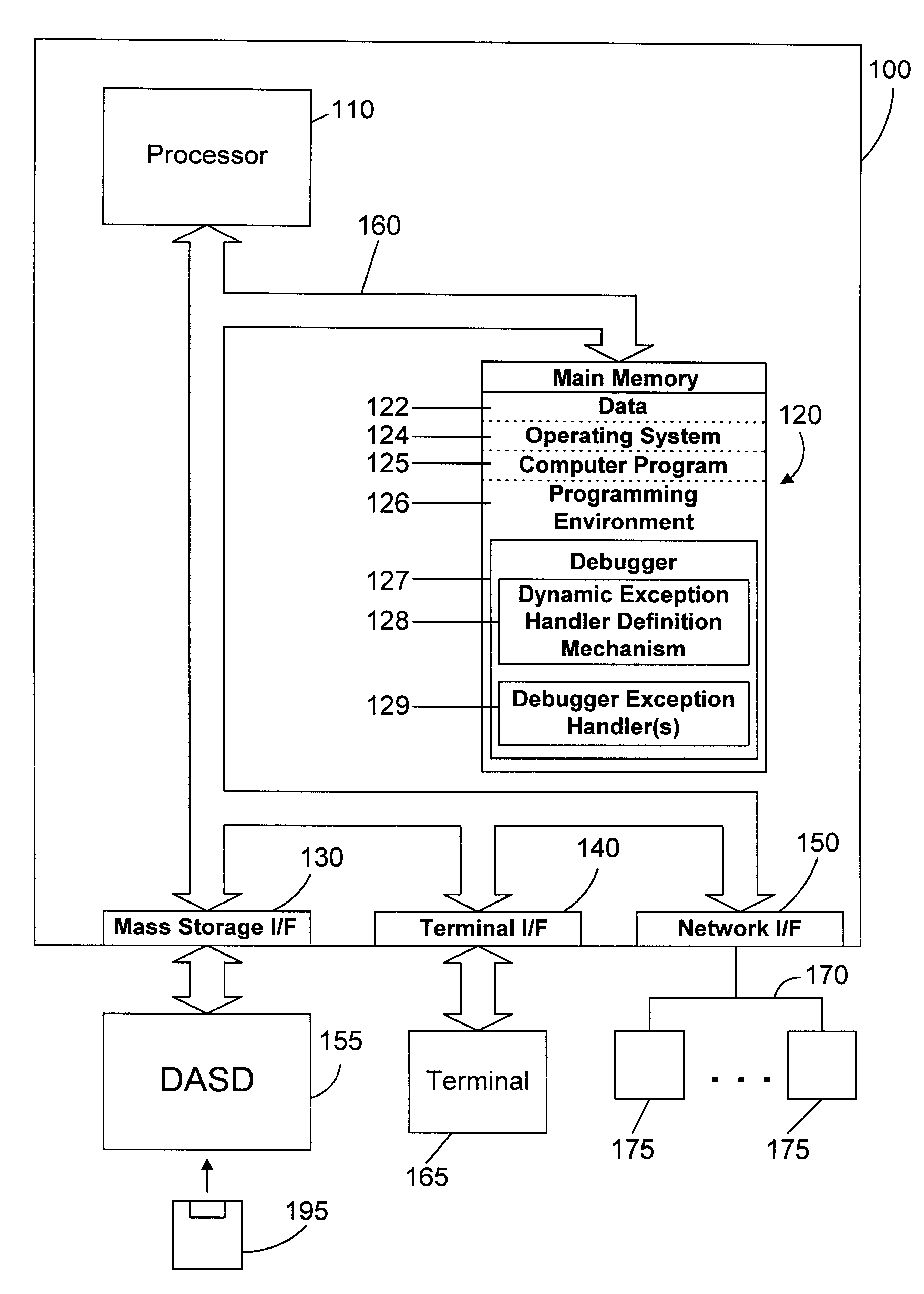

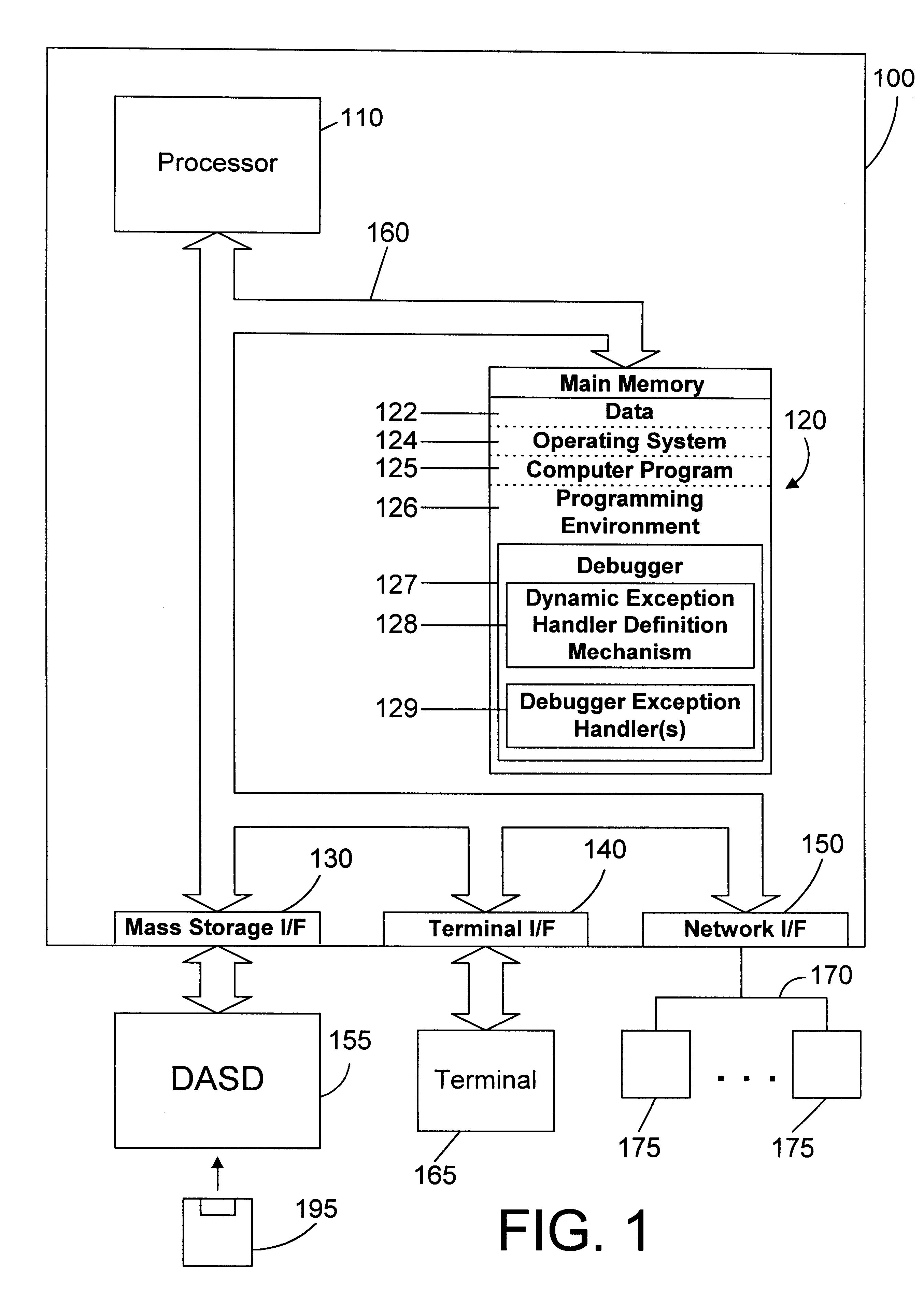

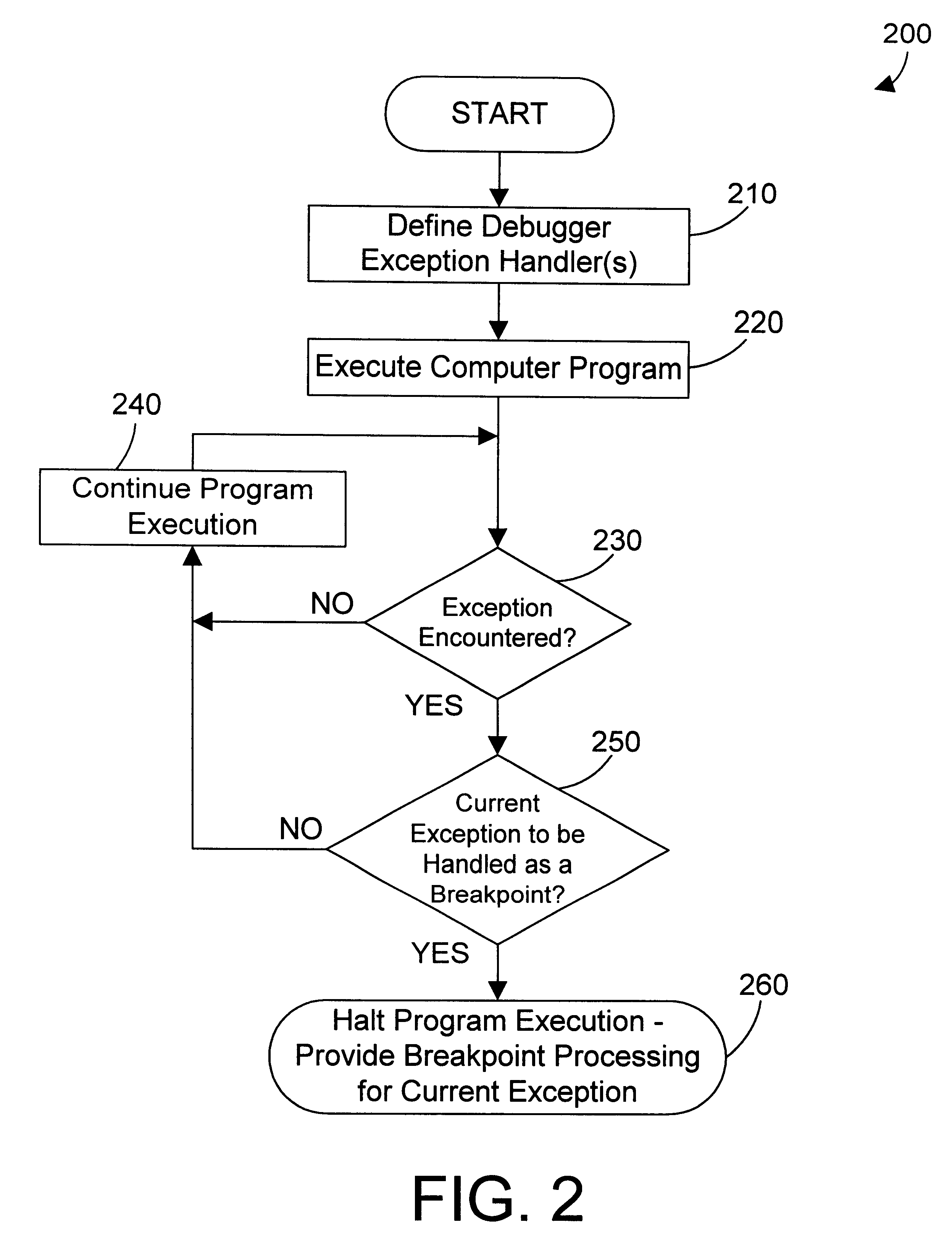

Apparatus and method for dynamically defining exception handlers in a debugger

An apparatus and method allow dynamically defining exception handlers in a debugger and breaking only when one of the dynamically-defined exception handlers is called. In this manner a programmer can define special exception handlers referred to herein as debugger exception handlers that correspond to exceptions of interest while debugging, and can thus distinguish between exceptions that are expected (and therefore handled) in a computer program and exceptions that signal a bug in the computer program during debugging.

Owner:IBM CORP

Bit synchronization for high-speed serial device testing

ActiveUS20060245291A1Difficult for be differenceElectronic circuit testingError detection/correctionComputer hardwareComputer science

An apparatus for testing electronic devices employs a programmable device to adjust the timing of the strobes such that the strobes sample the bit stream from a device under test at or near the center of the bit position. The strobe time adjustment is performed based on pairs of strobe readings made around a number of different bit positions. The programmable device examines the pairs of strobe reading made around each of the different bit positions to determine whether or not a bit transition has occurred there. The programmable device selects the bit positions around which a bit transition has not occurred as eye candidates, and defines the center of the largest contiguous region of eye candidates as the center of the bit position.

Owner:CREDENCE SYSTEMS

Instruction support for performing montgomery multiplication

Techniques are disclosed relating to a processor including instruction support for performing a Montgomery multiplication. The processor may issue, for execution, programmer-selectable instruction from a defined instruction set architecture (ISA). The processor may include an instruction execution unit configured to receive instructions including a first instance of a Montgomery-multiply instruction defined within the ISA. The Montgomery-multiply instruction is executable by the processor to operate on at least operands A, B, and N residing in respective portions of a general-purpose register file of the processor, where at least one of operands A, B, N spans at least two registers of general-purpose register file. The instruction execution unit is configured to calculate P mod N in response to receiving the first instance of the Montgomery-multiply instruction, where P is the product of at least operand A, operand B, and R̂−1.

Owner:ORACLE INT CORP

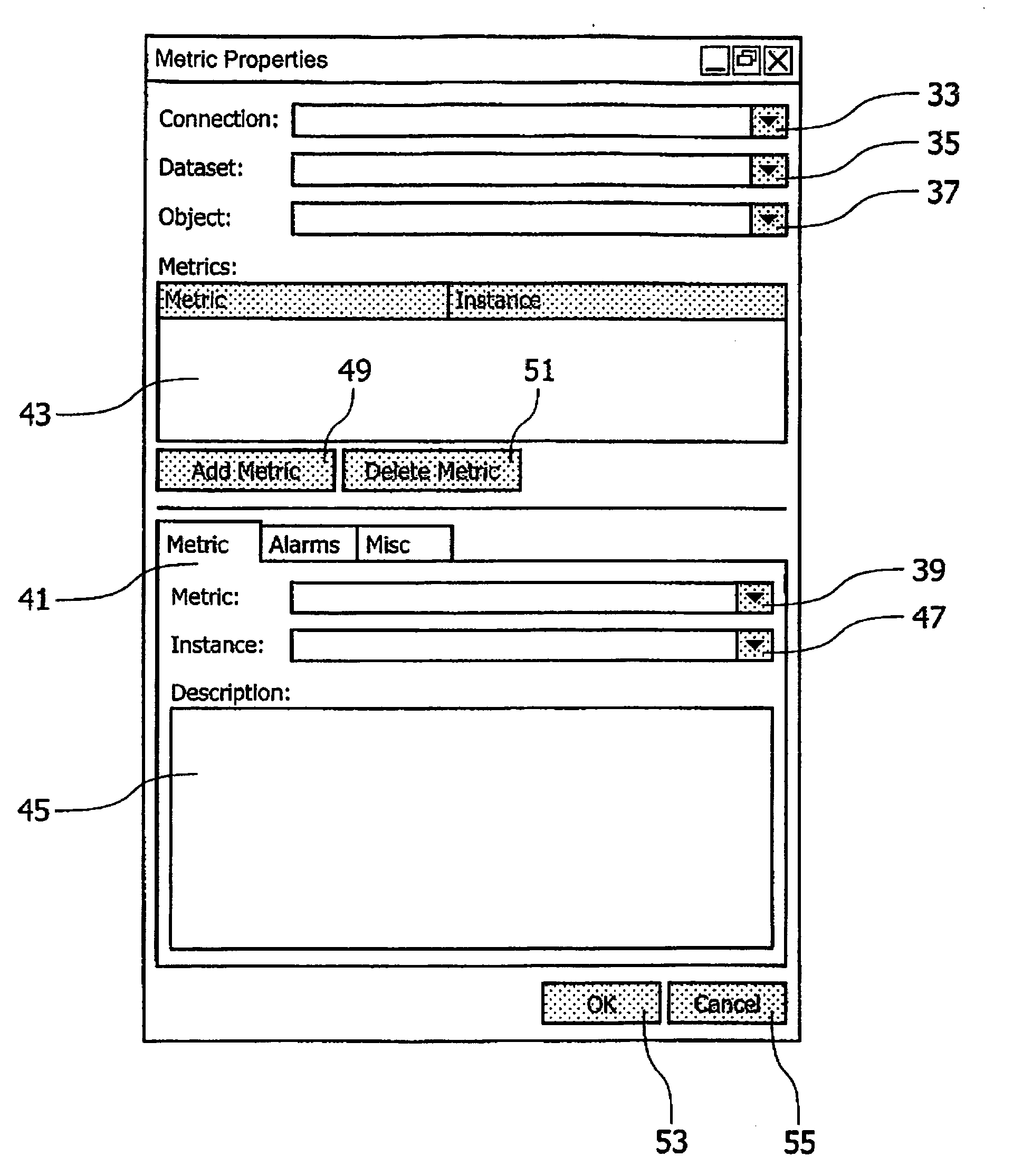

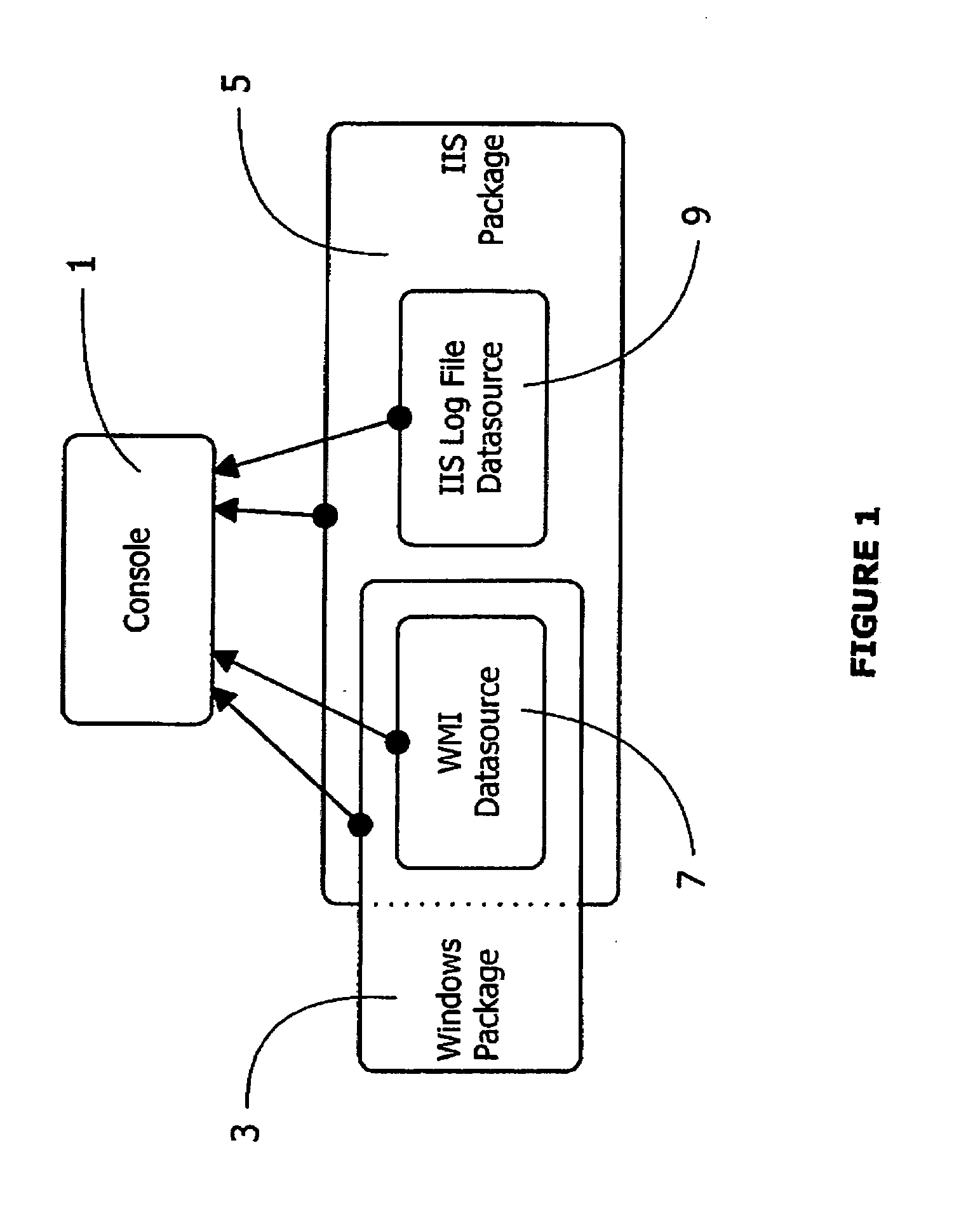

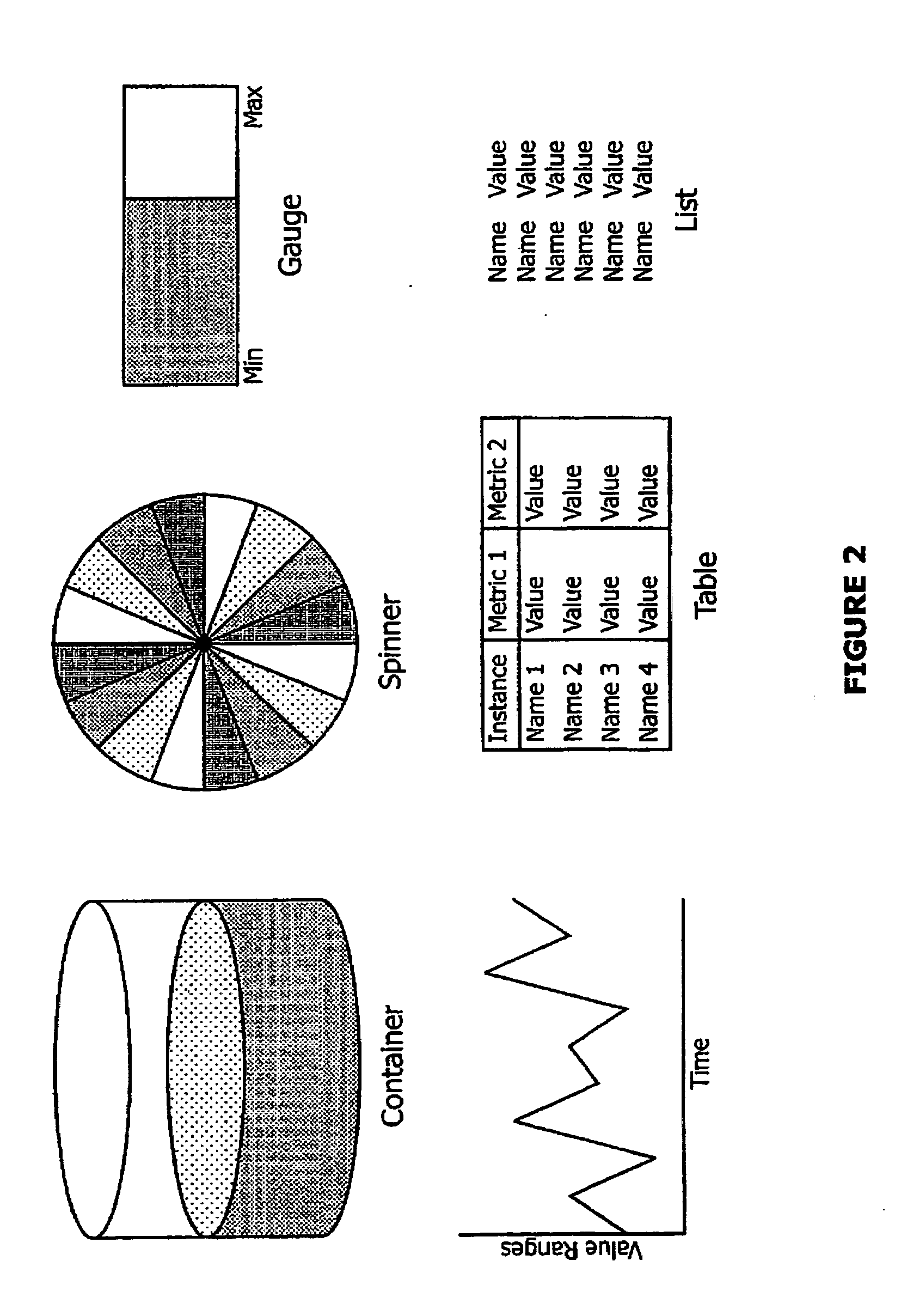

Monitoring performance of a computer system

InactiveUS20070079243A1Error detection/correctionDigital computer detailsOn-screen displayComputer program

A computer program is provided for monitoring the performance or state of a computer system or of an application operable within the computer system or of a computer hardware device in the computer system. The program permits a screen display to be provided of one or more visual components that represent specific system, application or hardware information required to be displayed, as determined by a system administrator, programmer, or like person. The program permits a metric chosen by that person to be assigned to the visual component. This then enables that person or another person such as a user to be provided with a snap shot view of the performance.

Owner:THIRDEYE HLDG

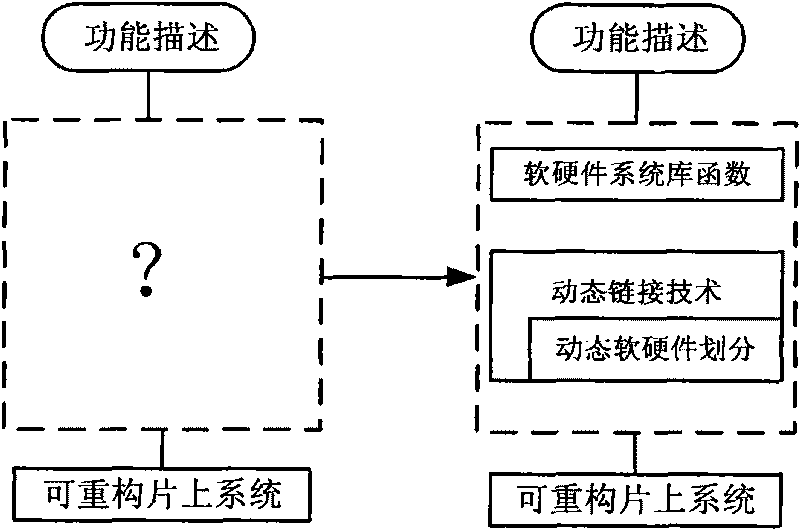

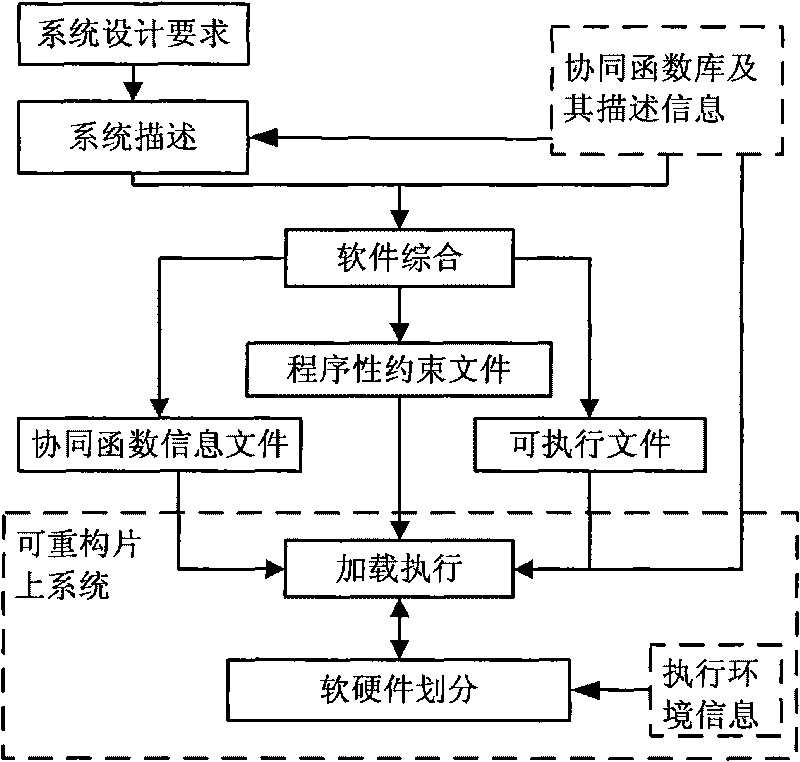

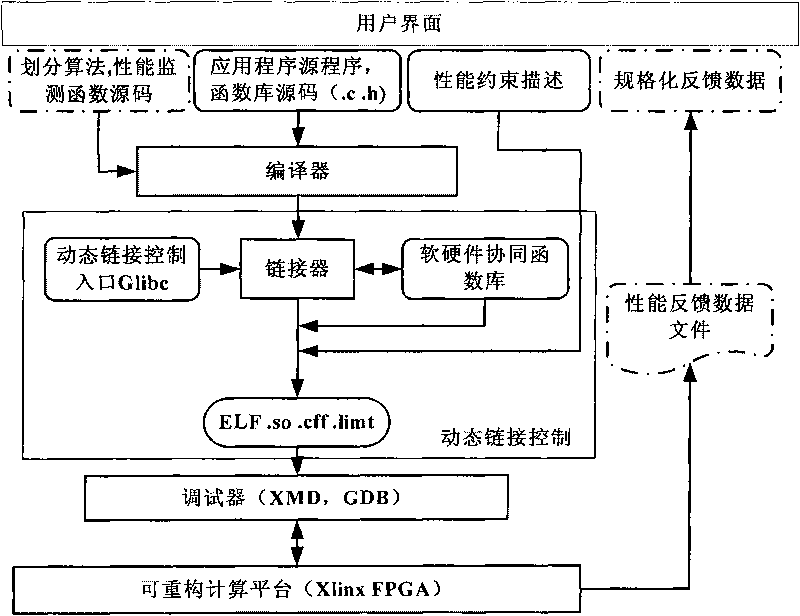

Procedure level software and hardware collaborative design automatized development method

InactiveCN101763265AIncrease profitEasy to divideSpecific program execution arrangementsHigh-level programming languageHardware implementations

The invention provides a procedure level software and hardware collaborative design automatized development method, which is characterized in that the method comprises the following steps: step 1, using high level languages to complete the system function description which comprises the transfer of the software and hardware collaborative functions; step 2, dynamically dividing the software and hardware functions; step 3, linking and executing the step; and step 4, judging and ending the step (judging whether the execution of all functions is completed, ending the step if the execution of all functions is completed, and otherwise, returning parameters used for dividing to the second step to enter a next circulation). The invention uses the procedure level software and hardware uniform programming model for shielding the difference realized by bottom layer hardware to realize the goal of transparent effect of reconstruction devices on program users. The programming model encapsulates the hardware accelerator into C Language functions for bringing convenience for the programming by users, and in addition, the dynamic software and hardware division during the operation is supported, so the division is transparent to programmers, and the utilization rate of reconstruction resources is improved.

Owner:HUNAN UNIV

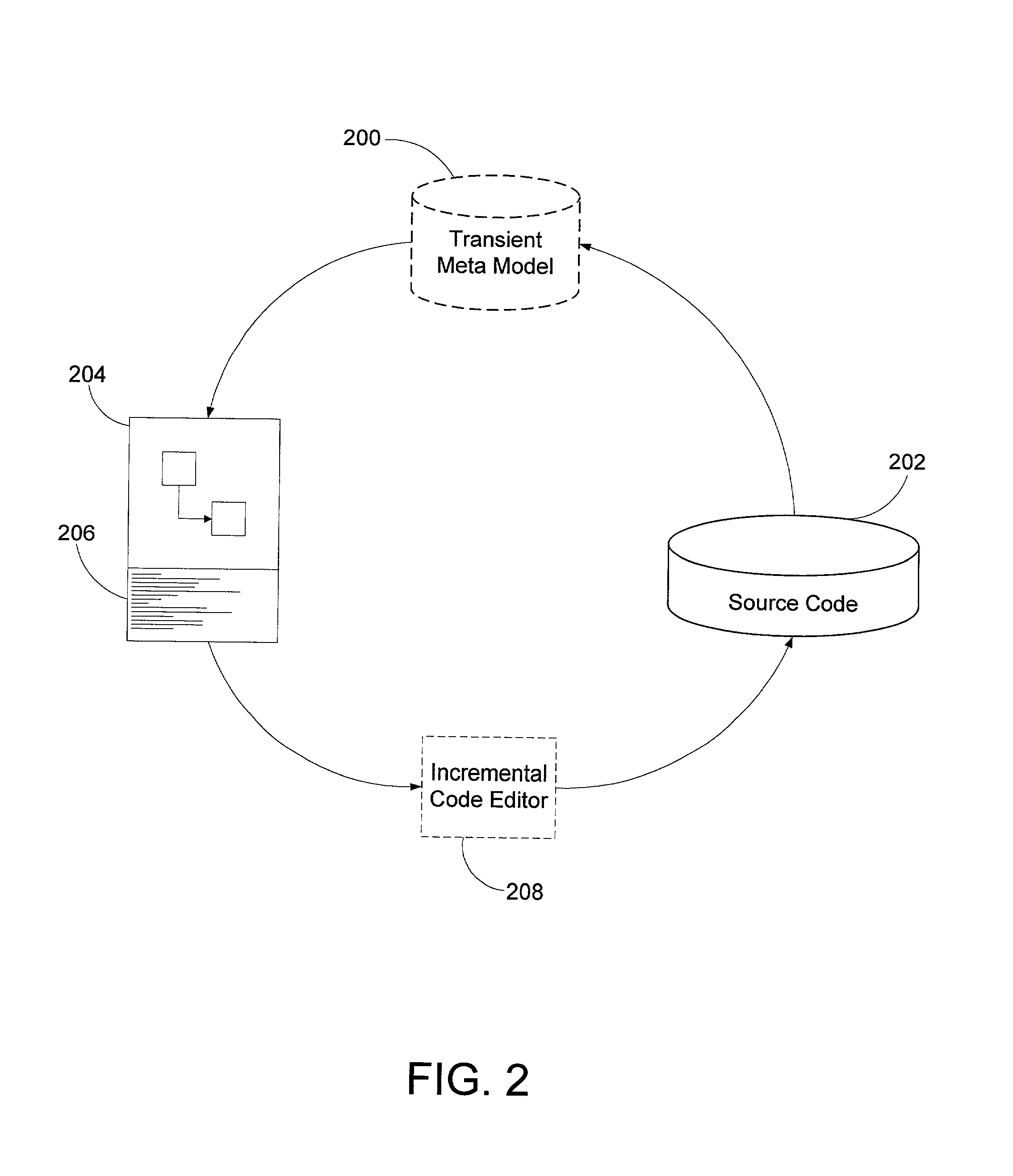

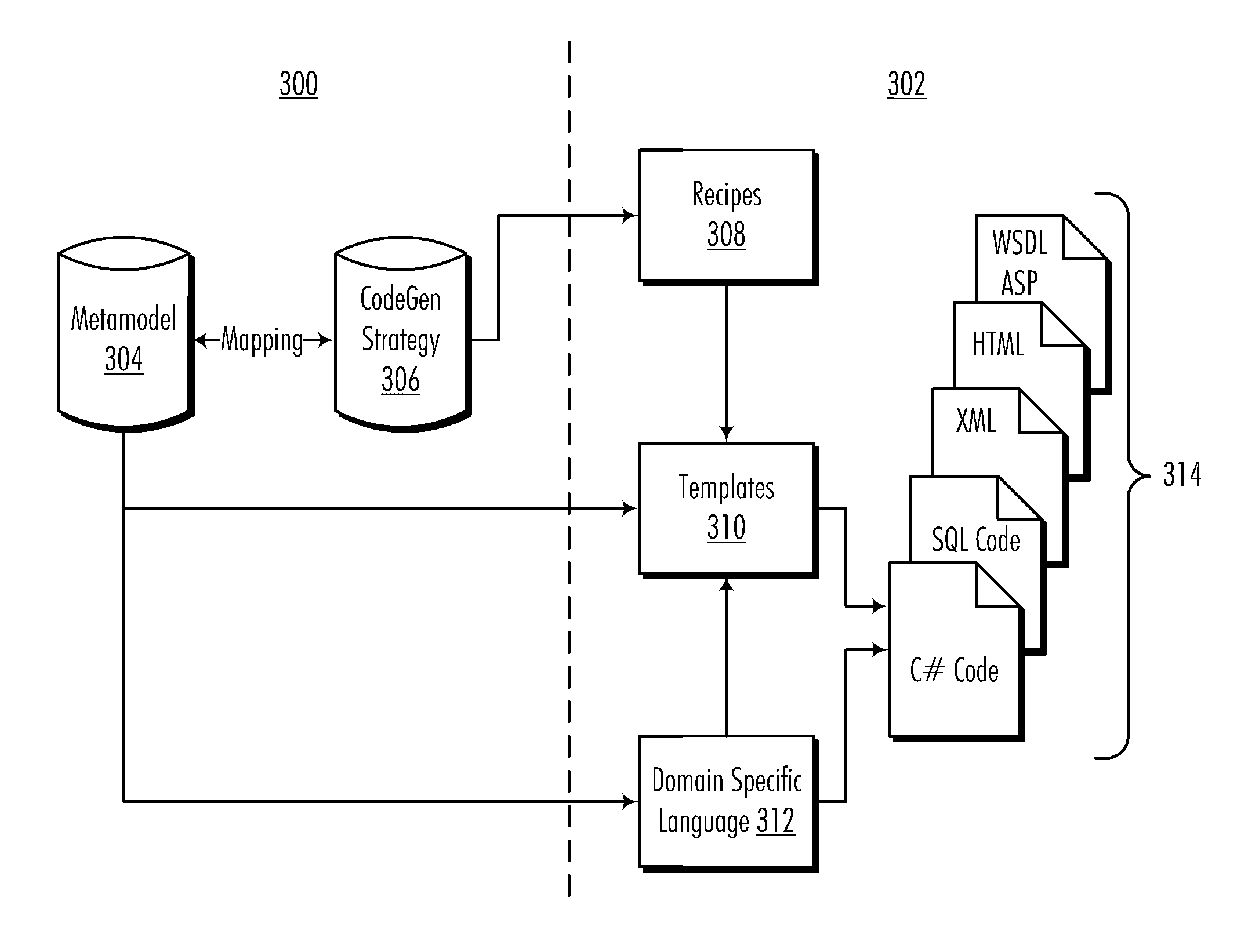

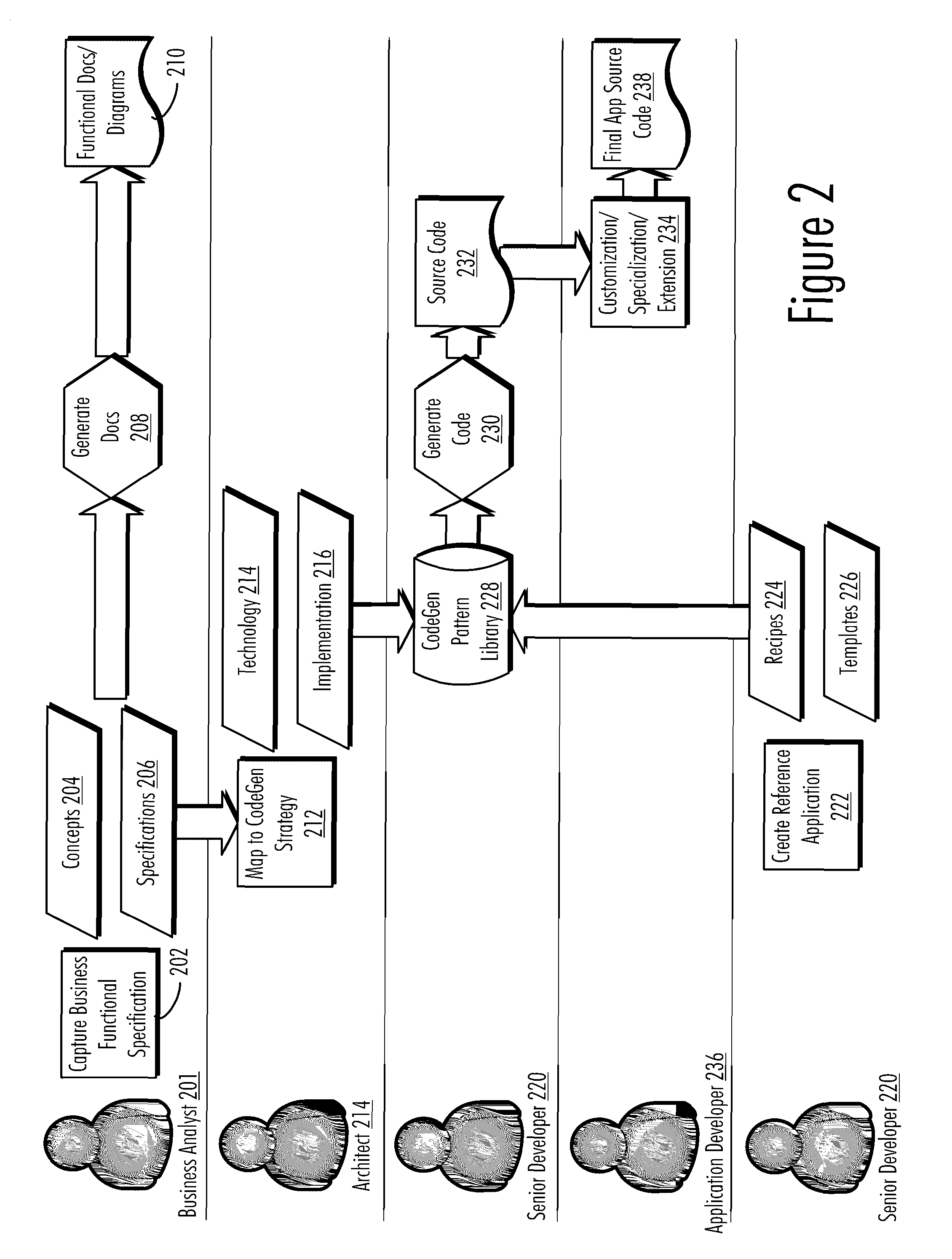

Enterprise-scale application development framework utilizing code generation

A method, computer program product, and data processing system for managing and automating the development of large-scale software systems are disclosed. A preferred embodiment allows for the creation of a metamodel defining the functionality and structure of a software system. The metamodel may be defined according to input from developers or analysts. Additionally, database schemata, web services definitions, and other pertinent legacy metadata may be automatically imported into the metamodel to facilitate compatibility and / or functional comparability with legacy software systems. Specifications contained within the metamodel are then mapped to one or more code generation strategies. The code generation strategies identify and / or define patterns for the generation of source code that implements the specifications and behavior in the metamodel. Source code is generated according to the code generation strategies, which may then be modified as needed by a human programmer, and compiled into one or more executable applications.

Owner:BARCELLONA JON

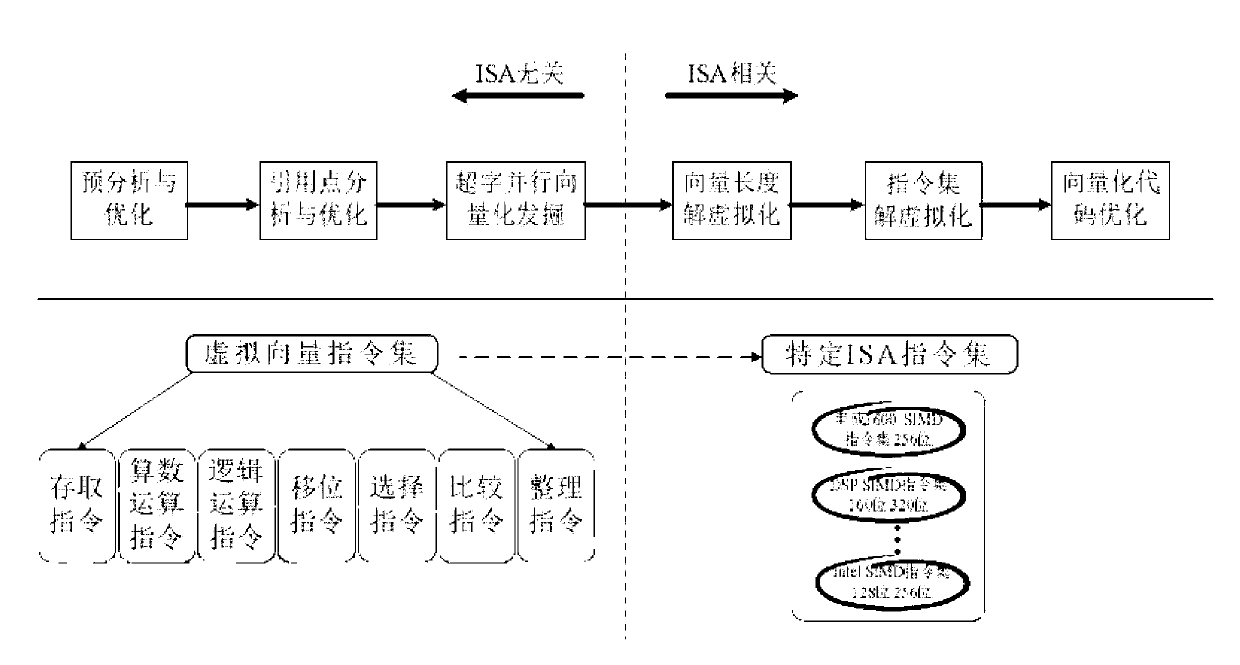

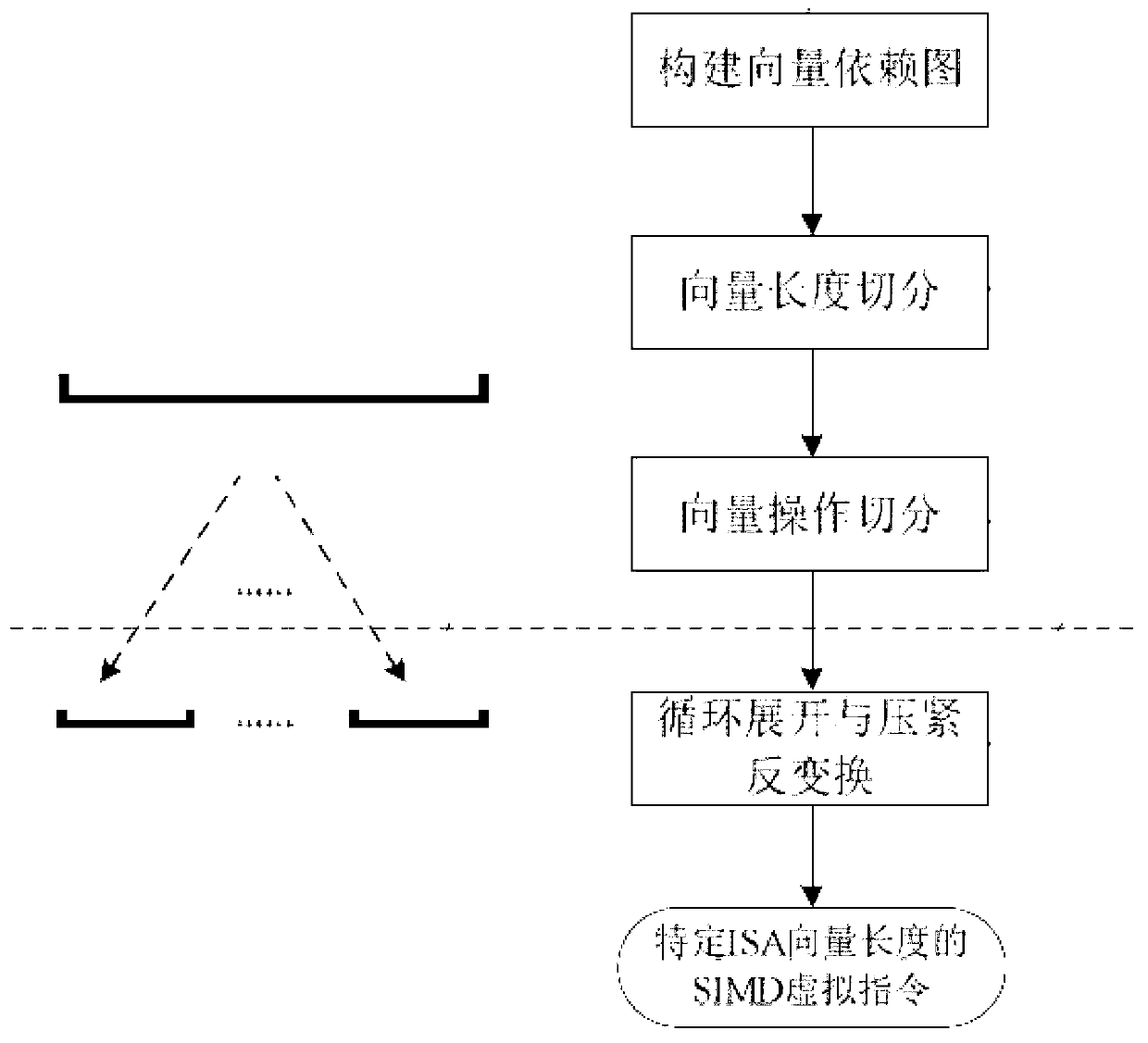

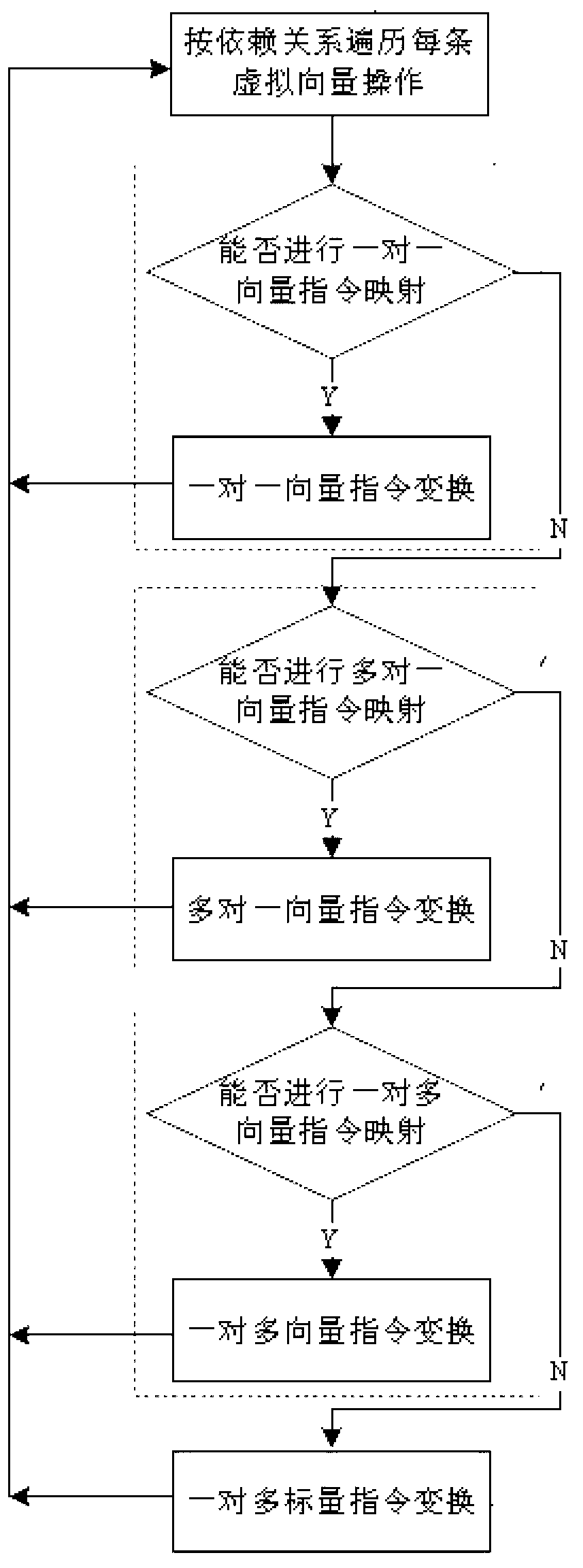

Automatic vectorizing method for heterogeneous SIMD expansion components

InactiveCN103279327AImprove execution efficiencyProgram controlMemory systemsVirtualizationPerformance computing

The invention relates to the field of high-performance computing automatic parallelization, in particular to an automatic vectorizing method for heterogeneous SIMD expansion components. The automatic vectorizing method is suitable for the heterogeneous SIMD expansion components with different vector quantity lengths and different vector quantity instruction sets, a set of virtual instruction sets are designed, and an input C and a Fortran program can be converted into an intermediate representation of virtual instructions under an automatic vectorizing unified framework. The virtual instruction sets are automatically converted into vectorizing codes for the heterogeneous SIMD expansion components through solving virtualization of the vector quantity lengths and solving virtualization of the instruction sets so that a programmer can be free from complex manual vectorizing coding work. The vectorizing method is combined with relative optimizing methods, vectorizing recognition is carried out from different granularities, mixing parallelism of a circulation level and a basic block level is explored to the greatest extent through conventional optimization and invocation point optimization, the redundancy optimization is carried out on generated codes through the analysis about striding data dependence of a basic block, and executing efficiency of a program is effectively improved.

Owner:THE PLA INFORMATION ENG UNIV

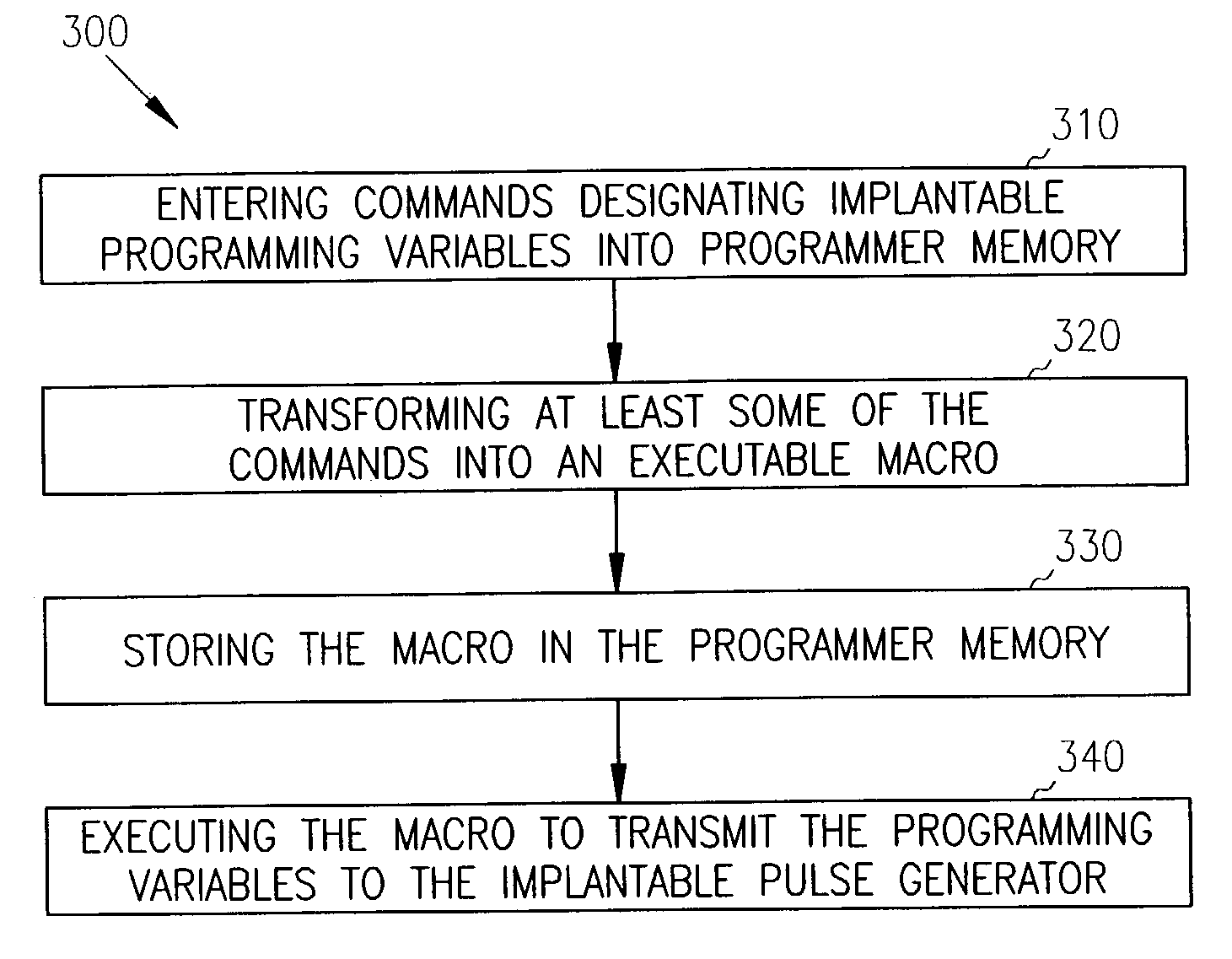

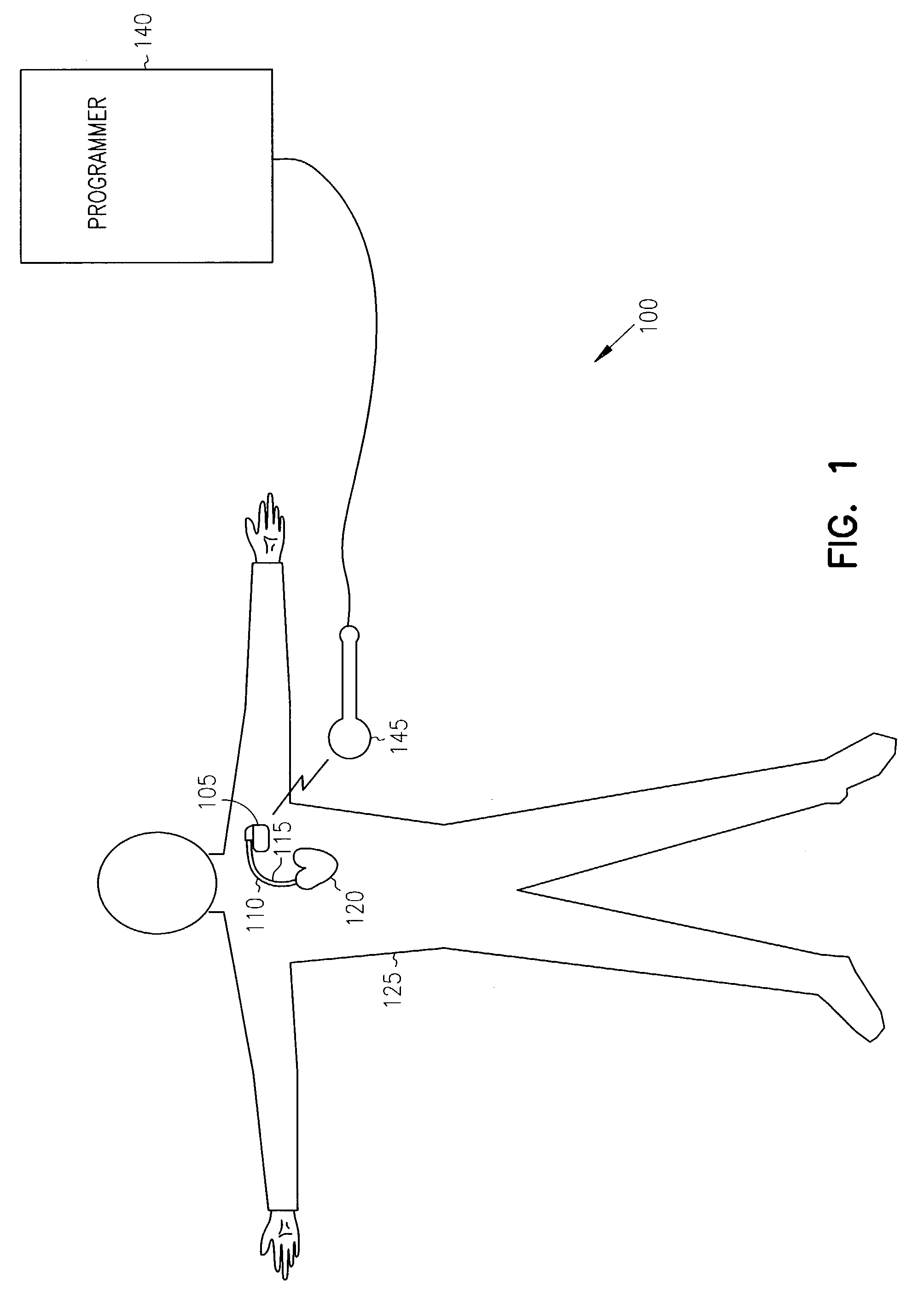

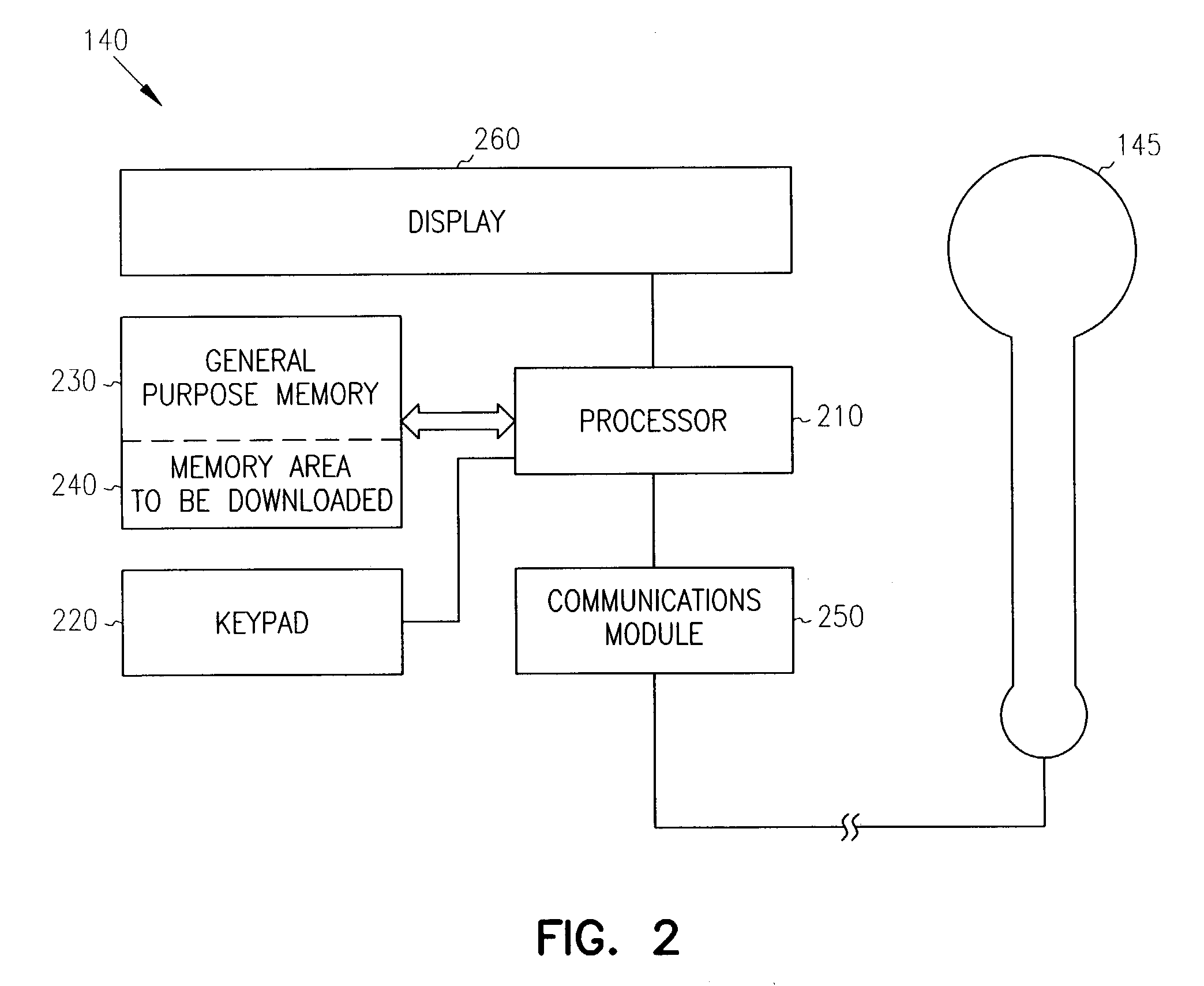

Recordable macros for pacemaker follow-up

A device and method for programming an implantable pulse generator. In one embodiment, commands are entered designating implantable pulse generator programming variables into programmer memory. At least some of the commands are transformed into an executable macro. The macro is stored in the programmer memory. The macro is executed to transmit the programming variables to the implantable pulse generator.

Owner:CARDIAC PACEMAKERS INC

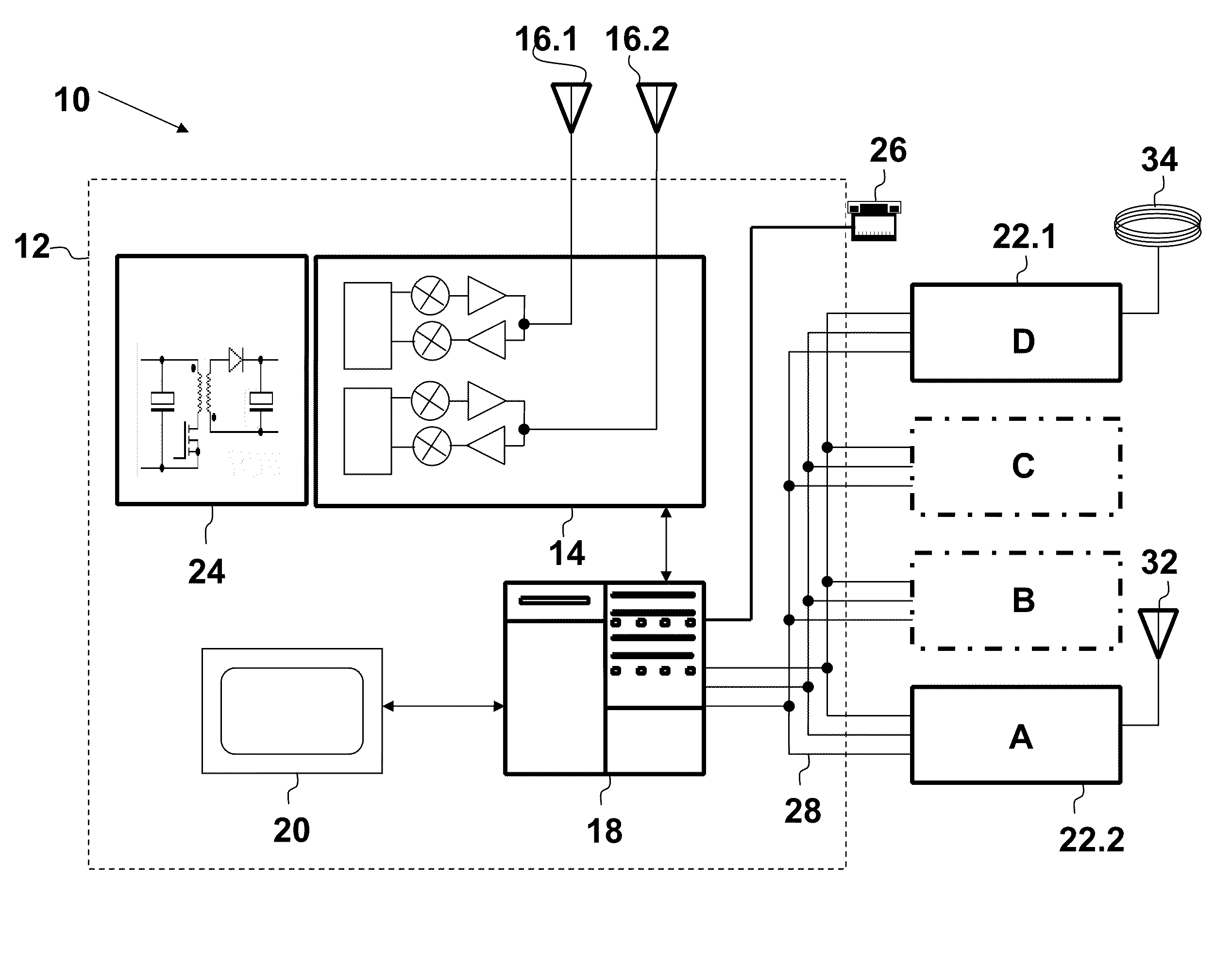

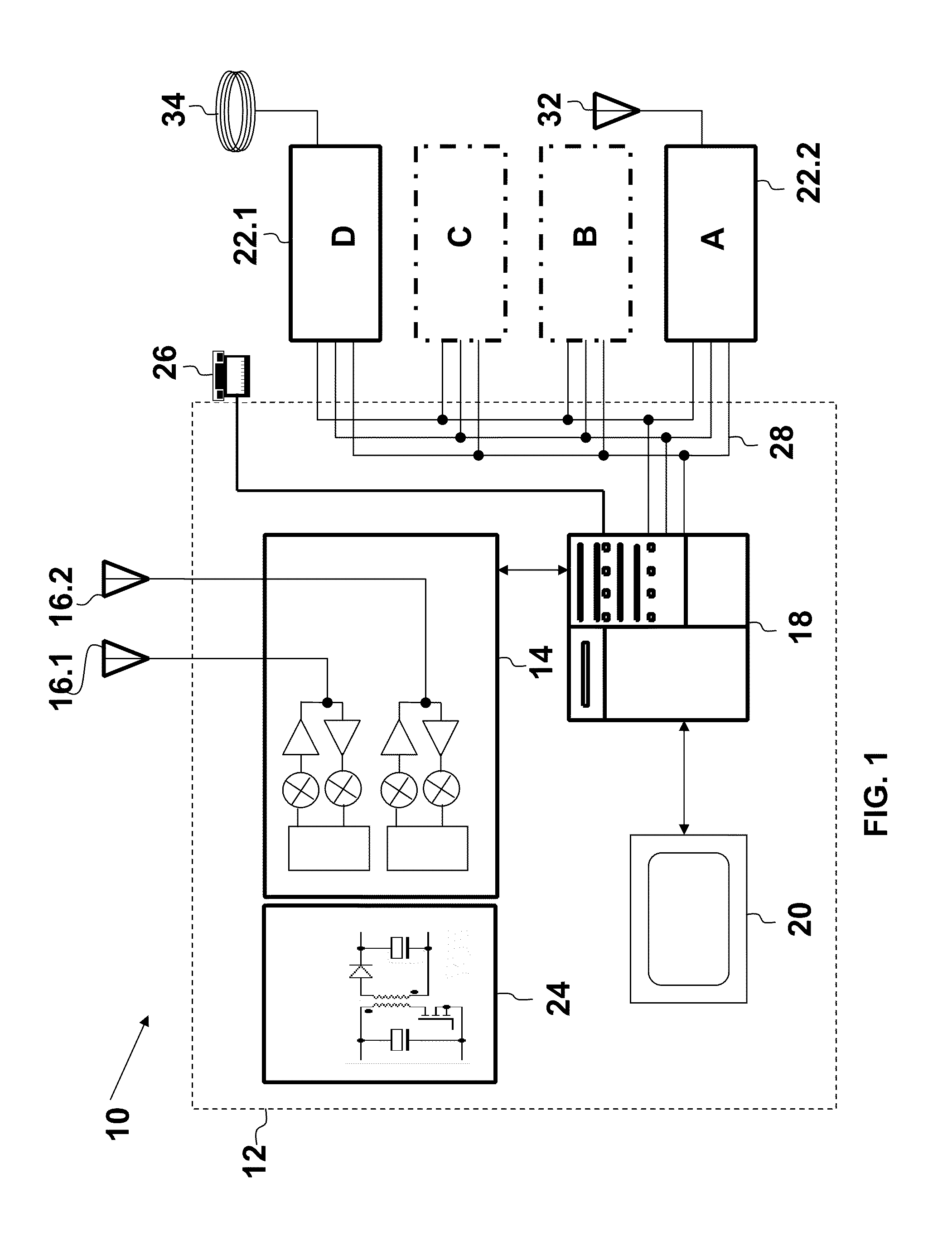

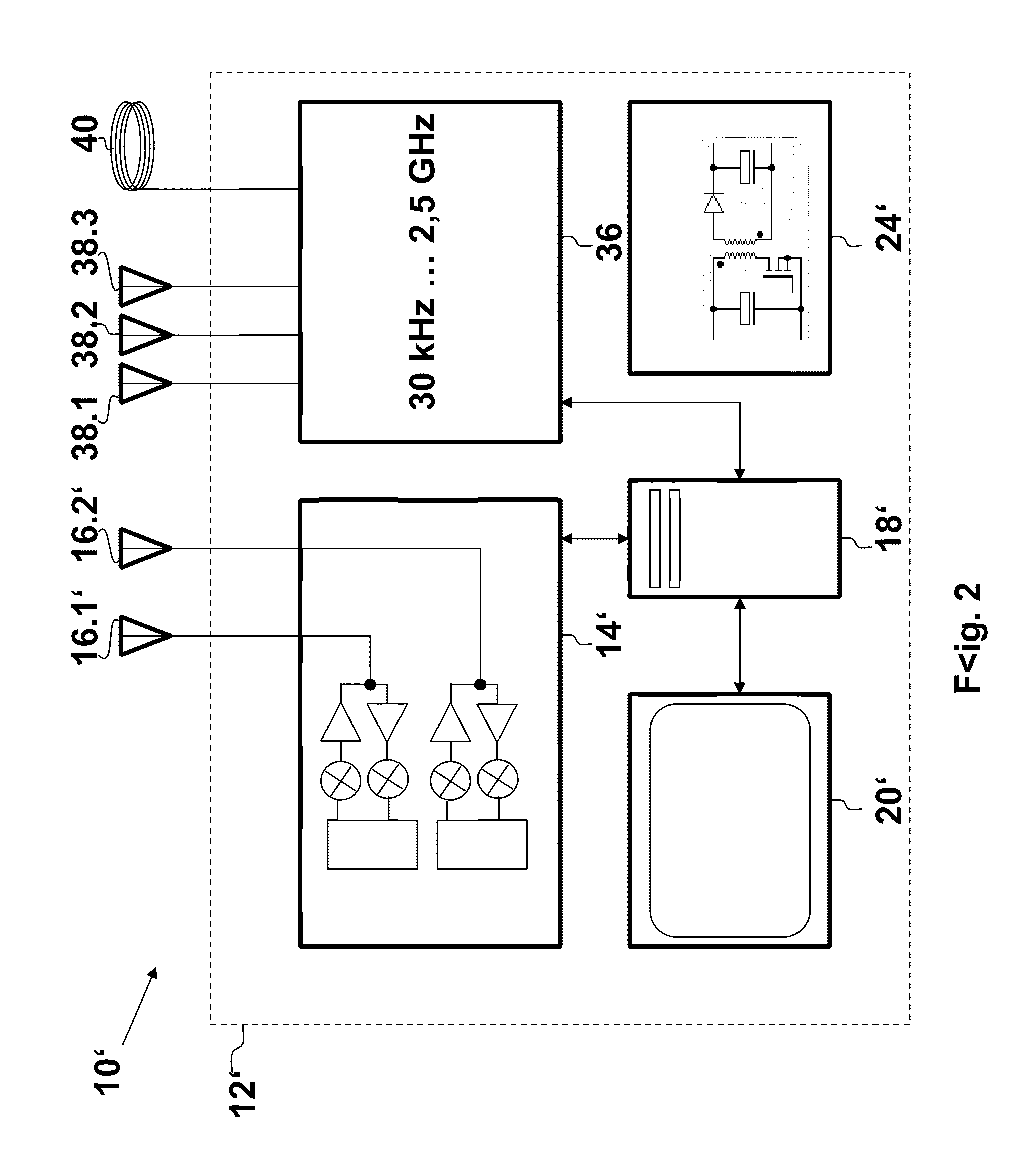

Modular universal programming device

InactiveUS20100114242A1ElectrotherapyInput/output processes for data processingHuman–machine interfaceDisplay device

A universal programming device for individualized patient medical devices such as implants has an RF transceiver (transmitter / receiver), a control unit, and a man-machine interface (or a connection for a man-machine interface). The RF transceiver is configured to receive and transmit data in the MICS frequency band. The control unit is connected to the transceiver and has preconfigured software interfaces, such that the programming device can be expanded by addition of control software modules. The preconfigured software interfaces define a uniform interface for triggering the transceiver, which the control software modules can access. The man-machine interface, e.g., a keyboard and / or a display (and / or the connection for such a man-machine interface) is connected to the control unit.

Owner:BIOTRONIK SE & CO KG