Patents

Literature

18036 results about "Processing element" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A processing element is an element which performs a specific processing requirement or business logic on the message. It can be one of a wide range of operations, such as filtering using conditional branching, transformation, flow control, scope handling such as a transactional scope, and many more.

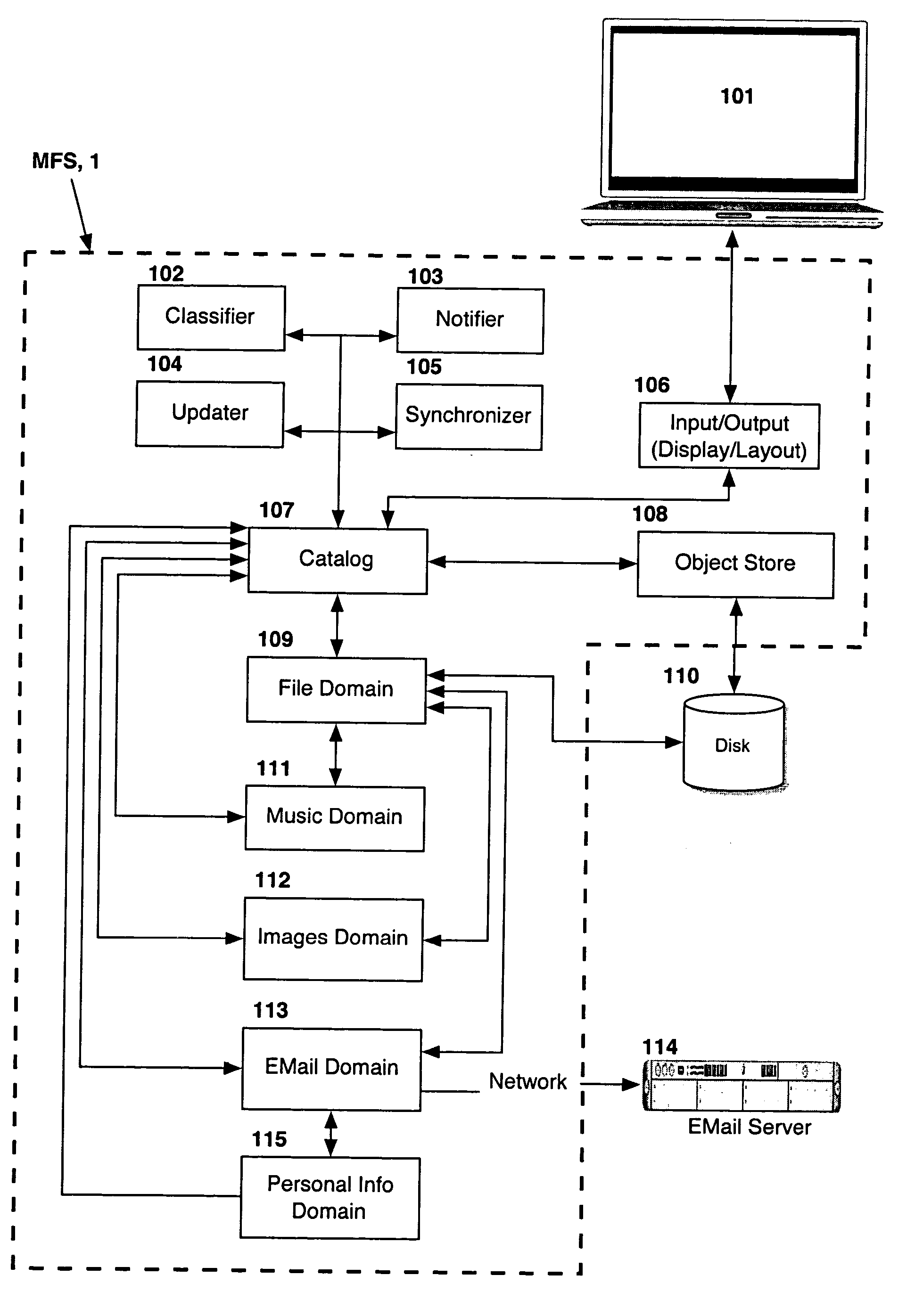

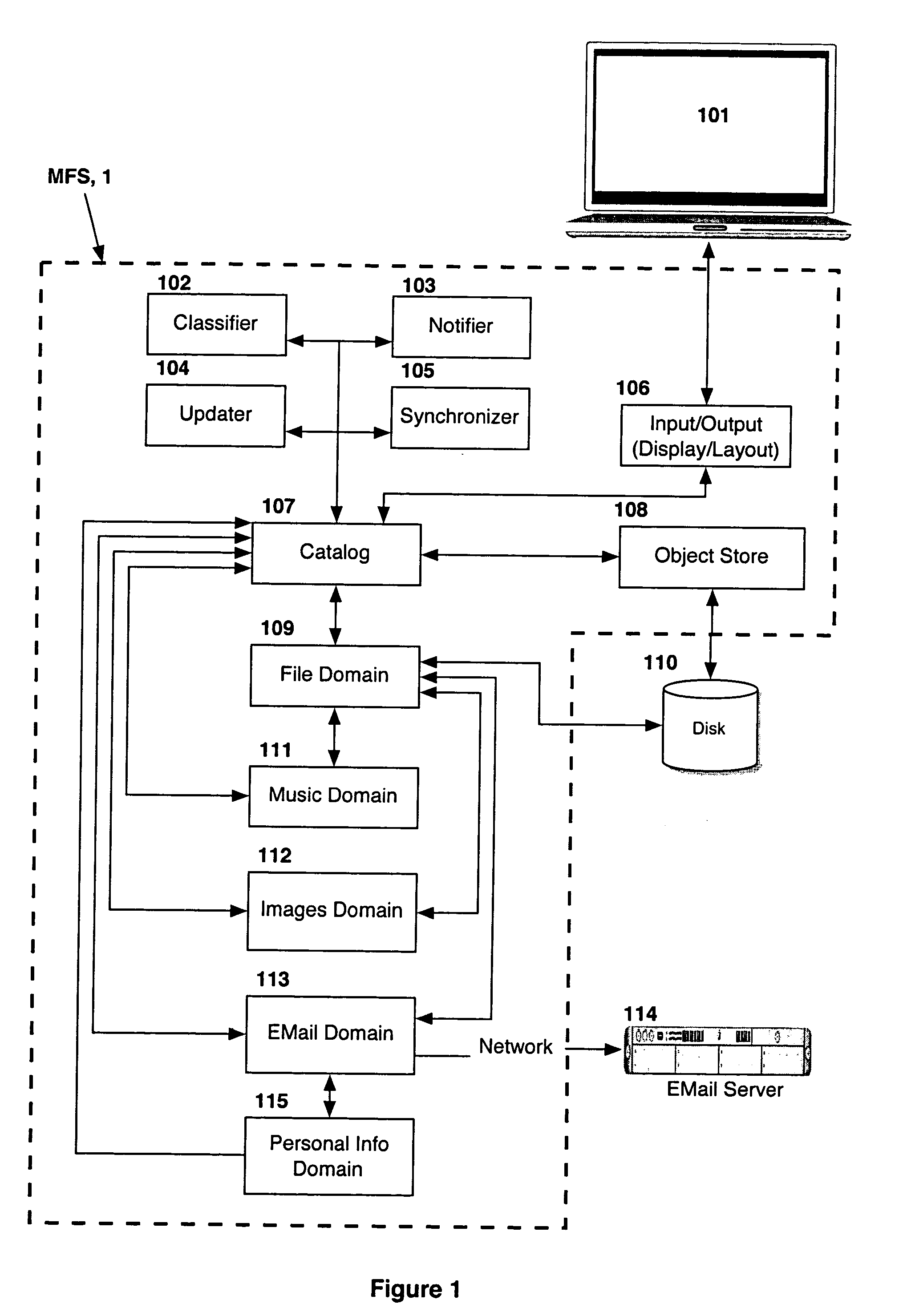

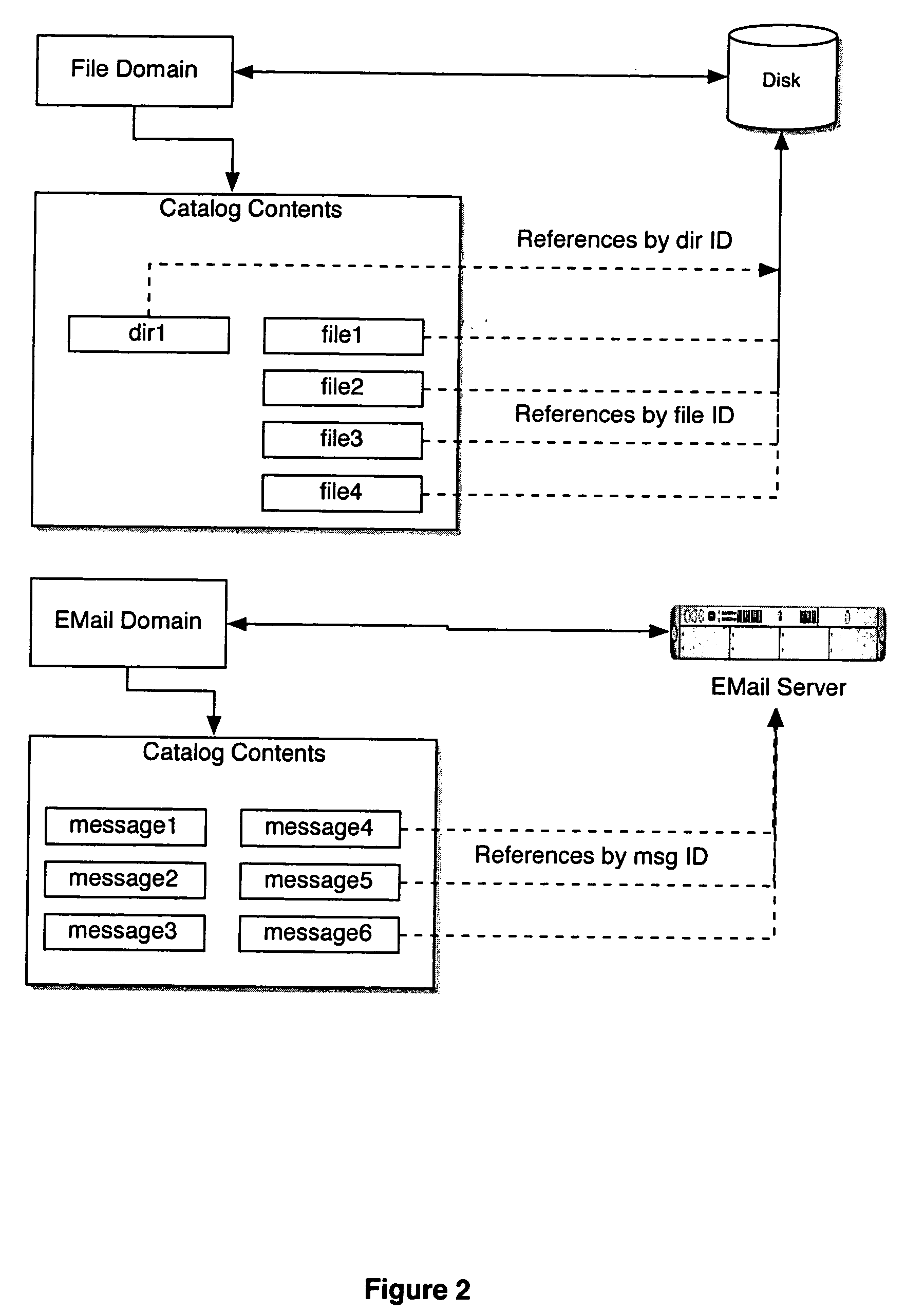

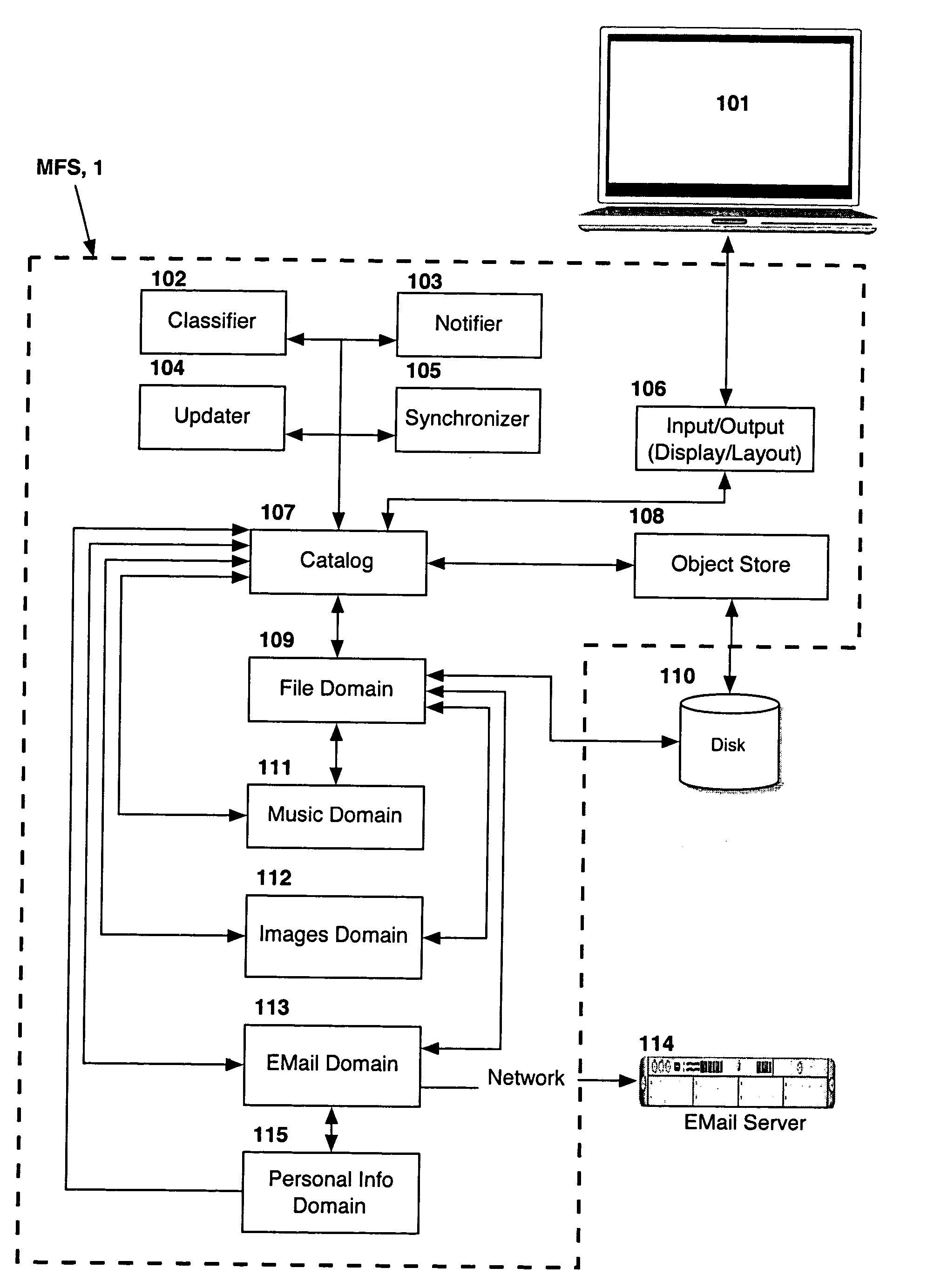

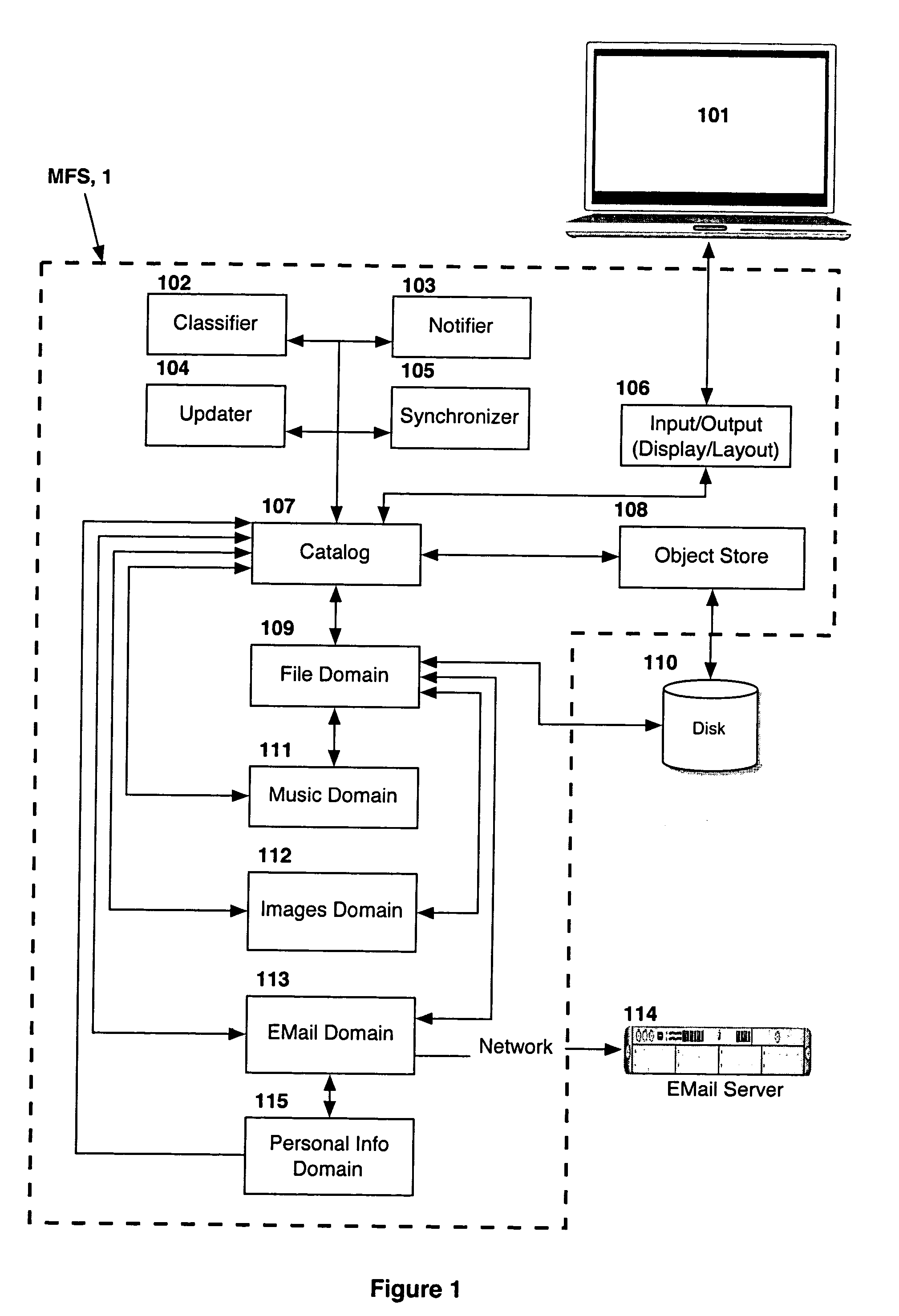

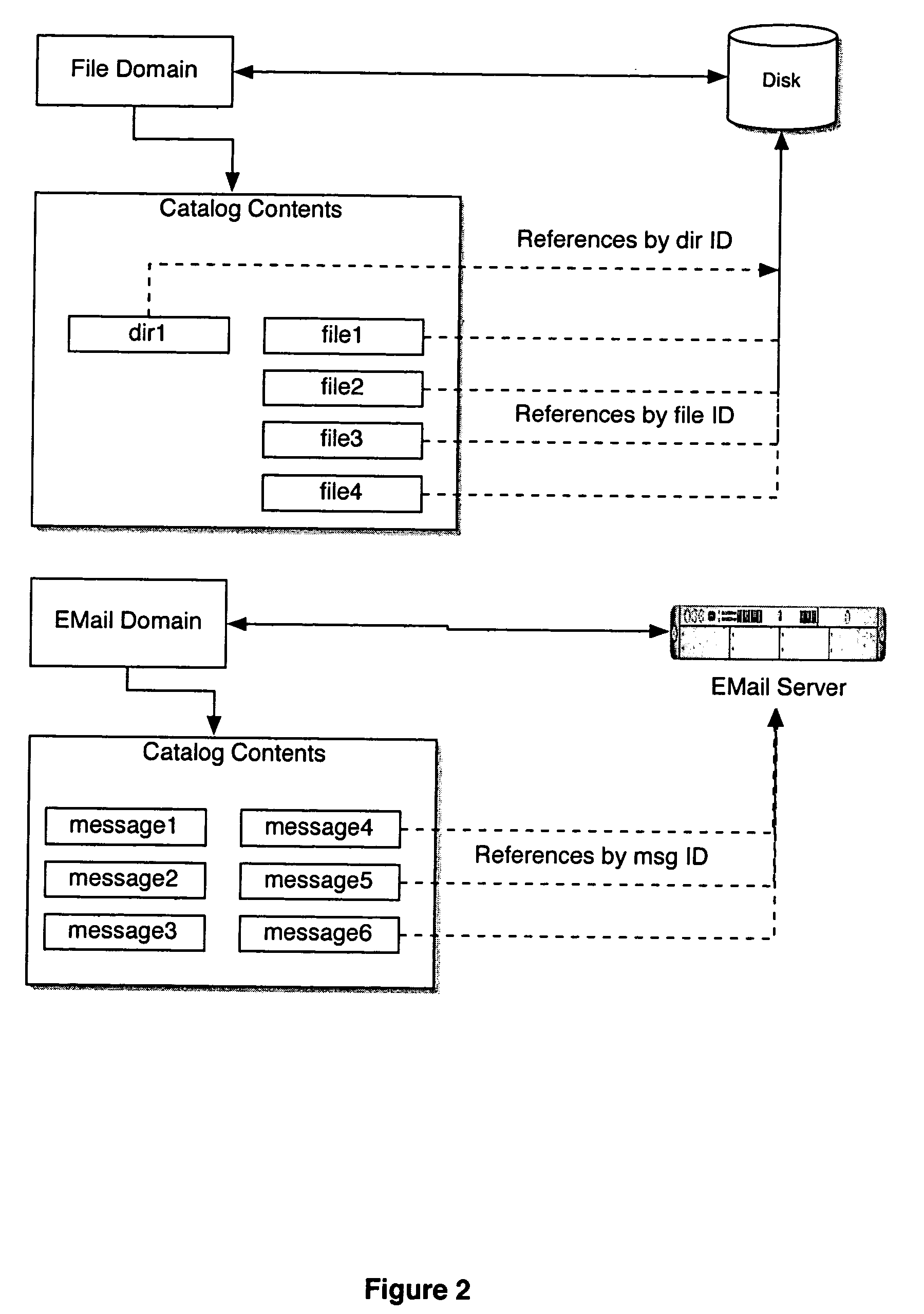

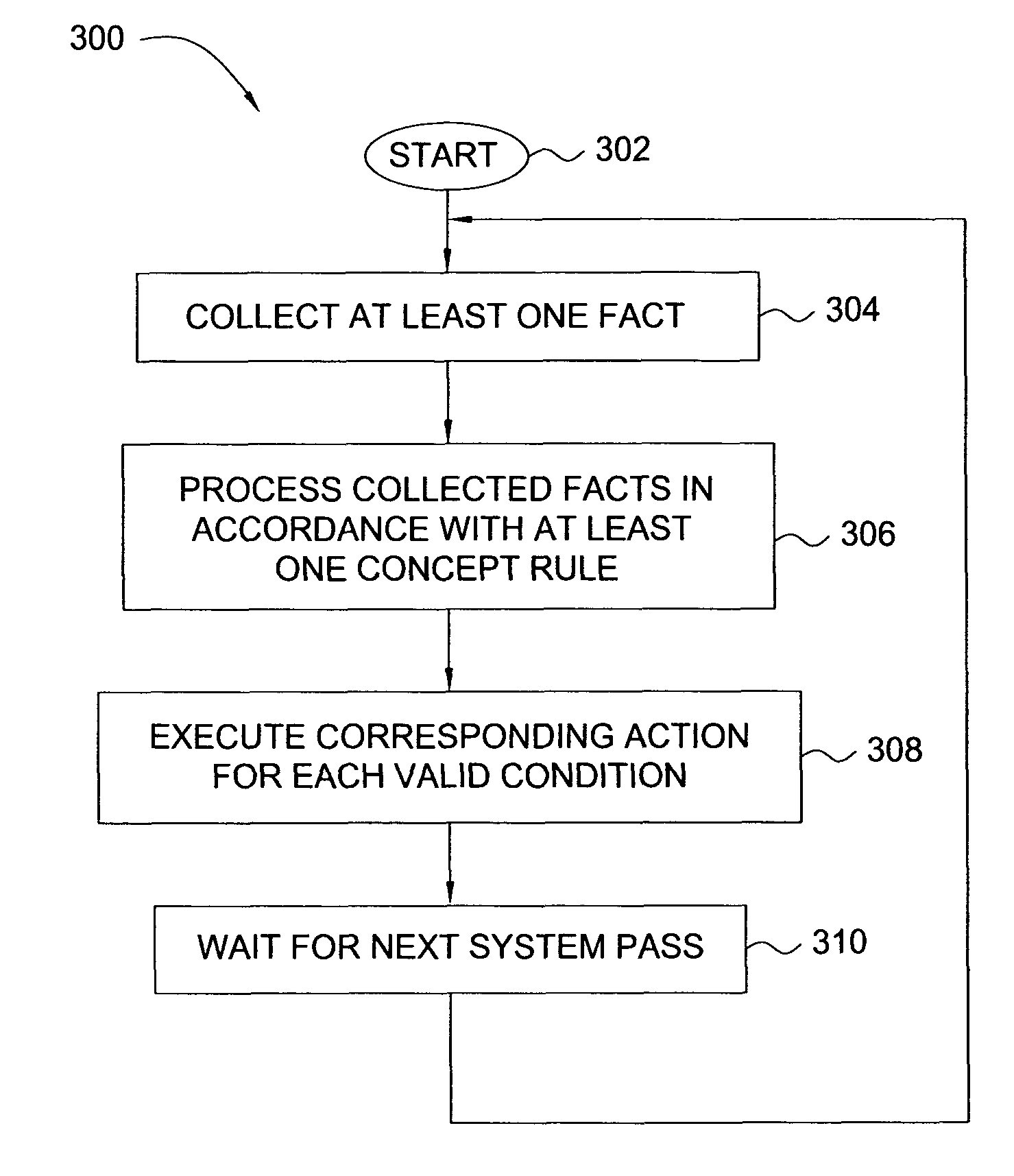

Computer system for automatic organization, indexing and viewing of information from multiple sources

ActiveUS20040177319A1Efficient storageMultimedia data indexingFile access structuresComputer data processingData processing

A computer data processing system including a central processing unit configured with a novel integrated computer control software system for the management of data objects including dynamic and automatic organization, linking, finding, cross-referencing, viewing and retrieval of multiple objects regardless of nature or source. The inventive system provides underlying component architecture having an object-oriented database structure and a metadata database structure which is unique in storing only one instance of each object while linking the object to multiple collections and domains by unique metadata links for the grouping into and retrieval from any of the collections. The system employs configurable, extensible attribute / properties of data objects in metadata format, and a truly user-friendly configurable interface that facilitates faster, more unified, comprehensive, useful and meaningful information management. Additional features include a sticky path object hierarchy viewing system, key phrase linking, viewing by reference, and drag-and-drop relationship link creation.

Owner:EHIERARCHY LLC

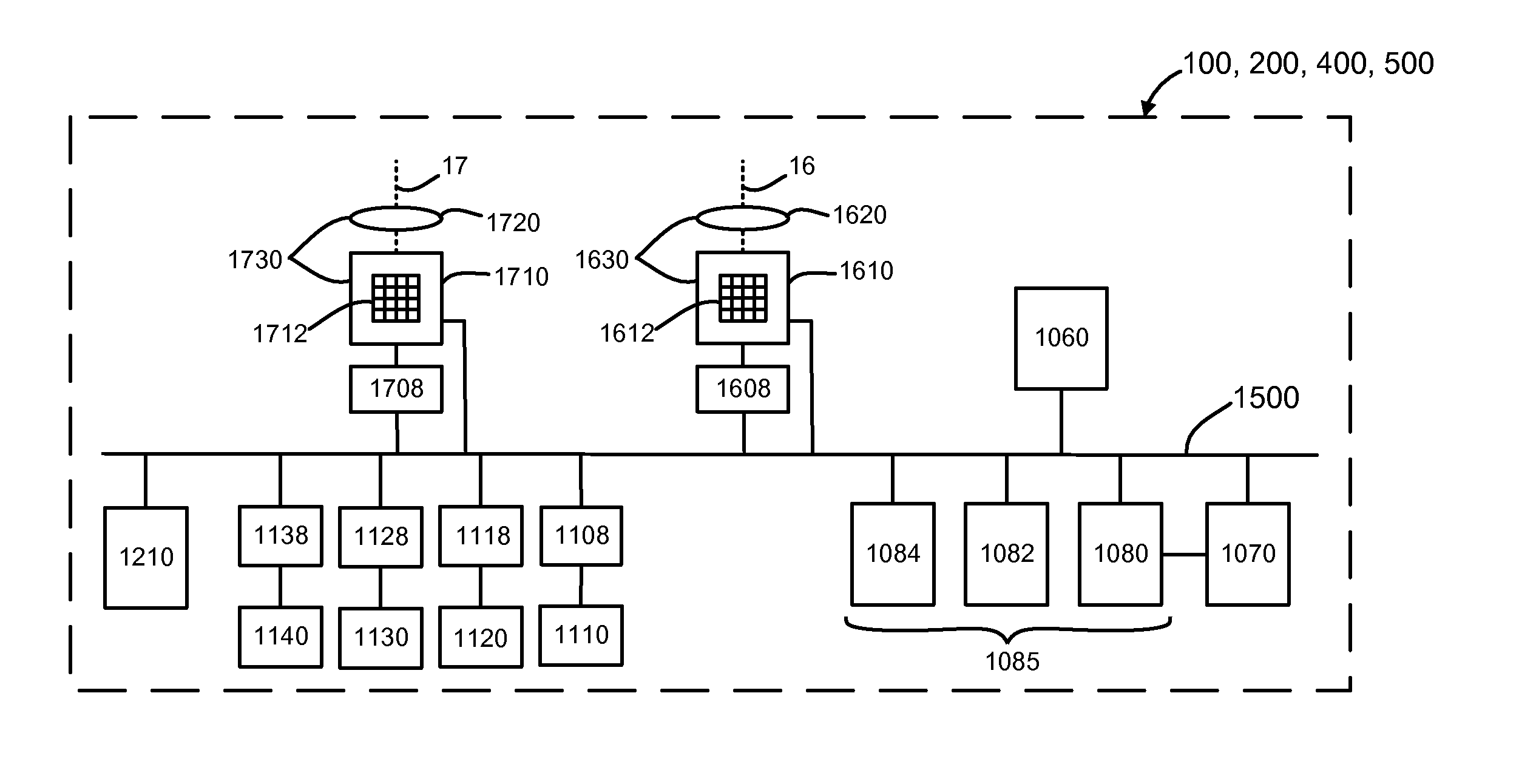

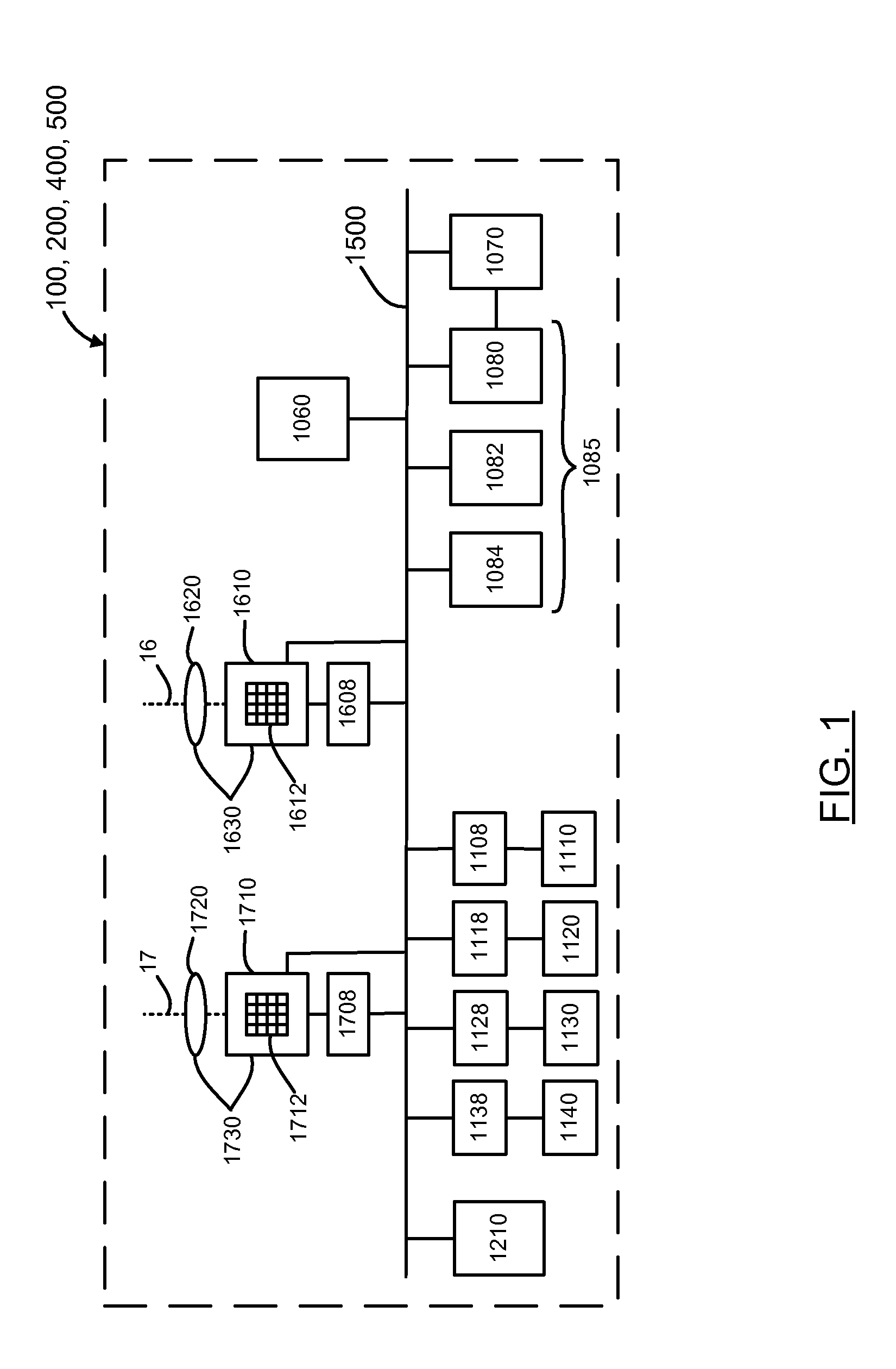

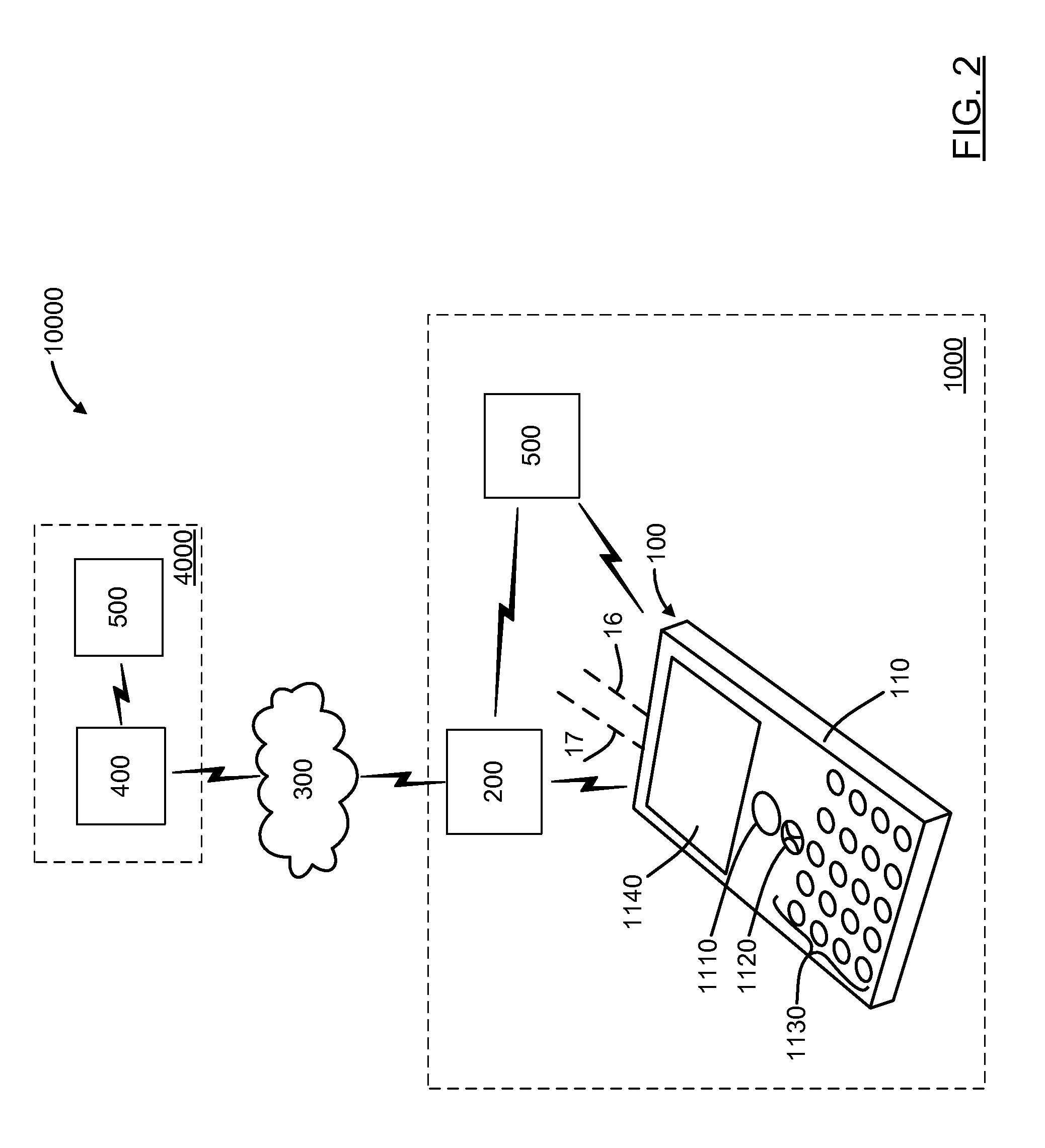

System operative to adaptively select an image sensor for decodable indicia reading

A decodable indicia reading system can be provided for use in locating and decoding a bar code symbol represented within a frame of image data. The system can comprise a central processing unit (CPU), a memory communicatively coupled to the CPU, and two or more image sensors communicatively coupled to the CPU or to the memory. The system can be configured to select an image sensor for indicia reading by cycling through available image sensors to detect an image sensor suitable for an attempted indicia reading operation by comparing a measured parameter value to a pre-defined sensor-specific threshold value. The system can be further configured to select the first suitable or the best suitable image sensor for the attempted decodable indicia reading operation based upon the comparison result. The system can be further configured to notify the system operator which image sensor has been selected. The system can be further configured to obtain a decodable indicia image by the selected image sensor.

Owner:HAND HELD PRODS

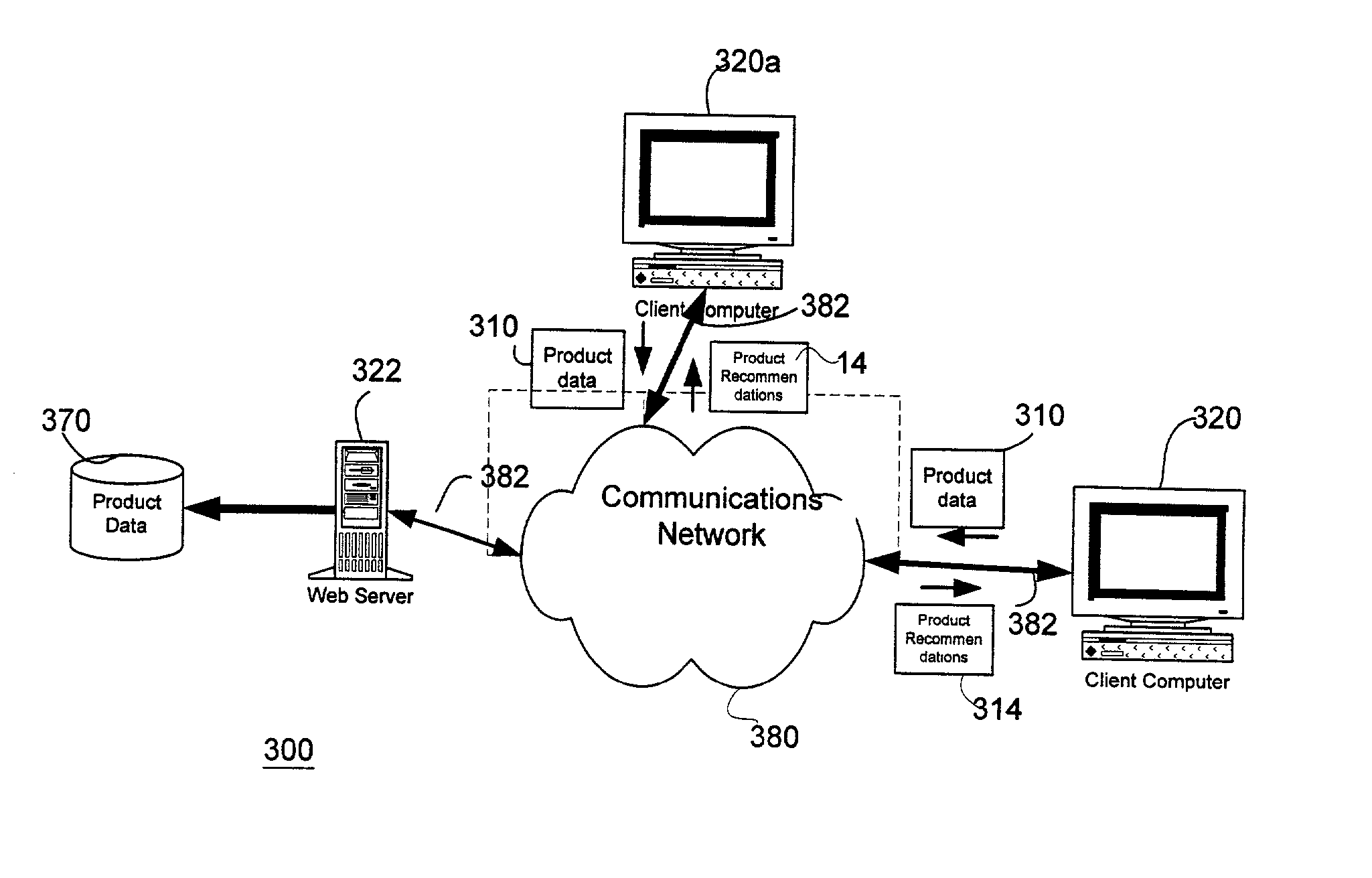

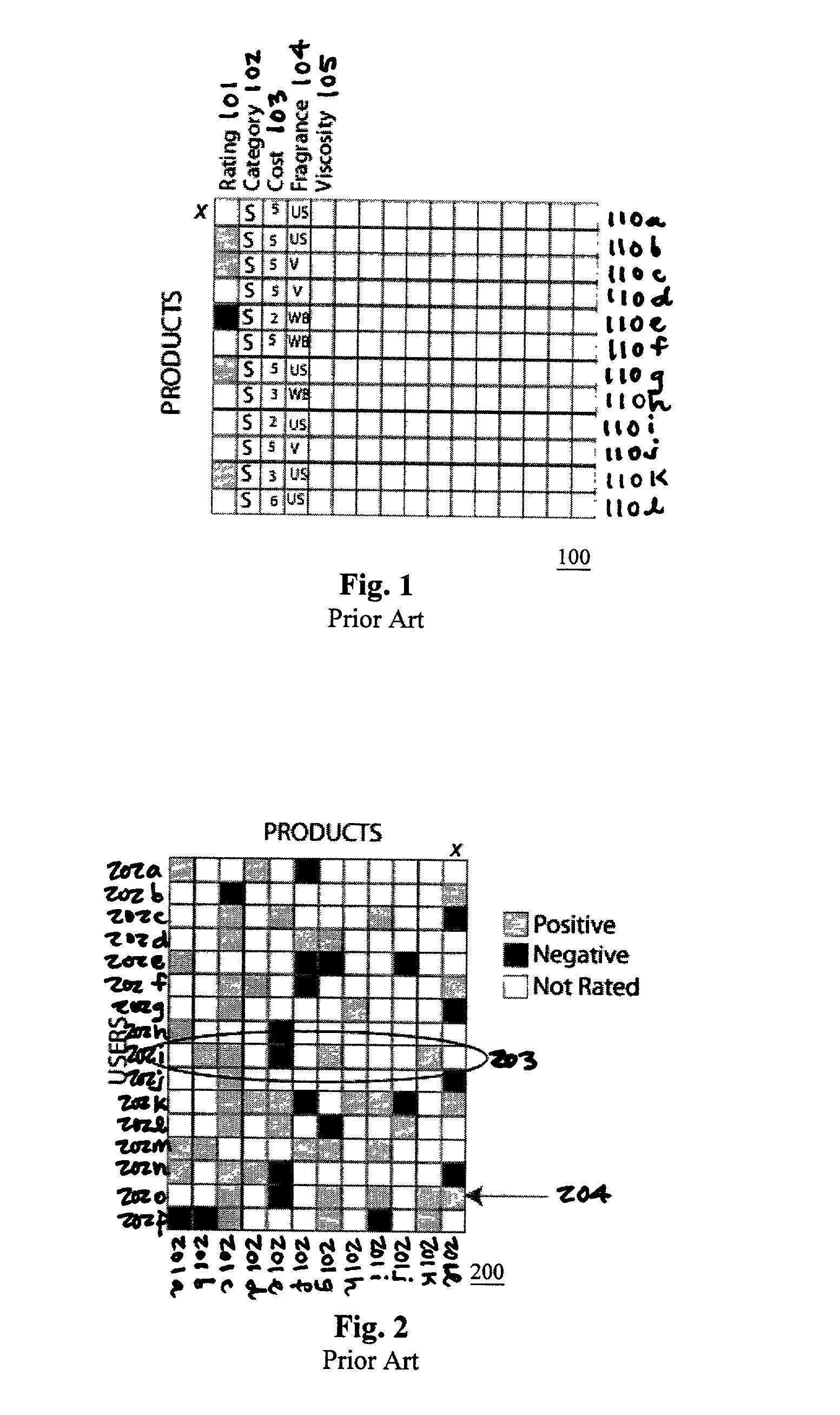

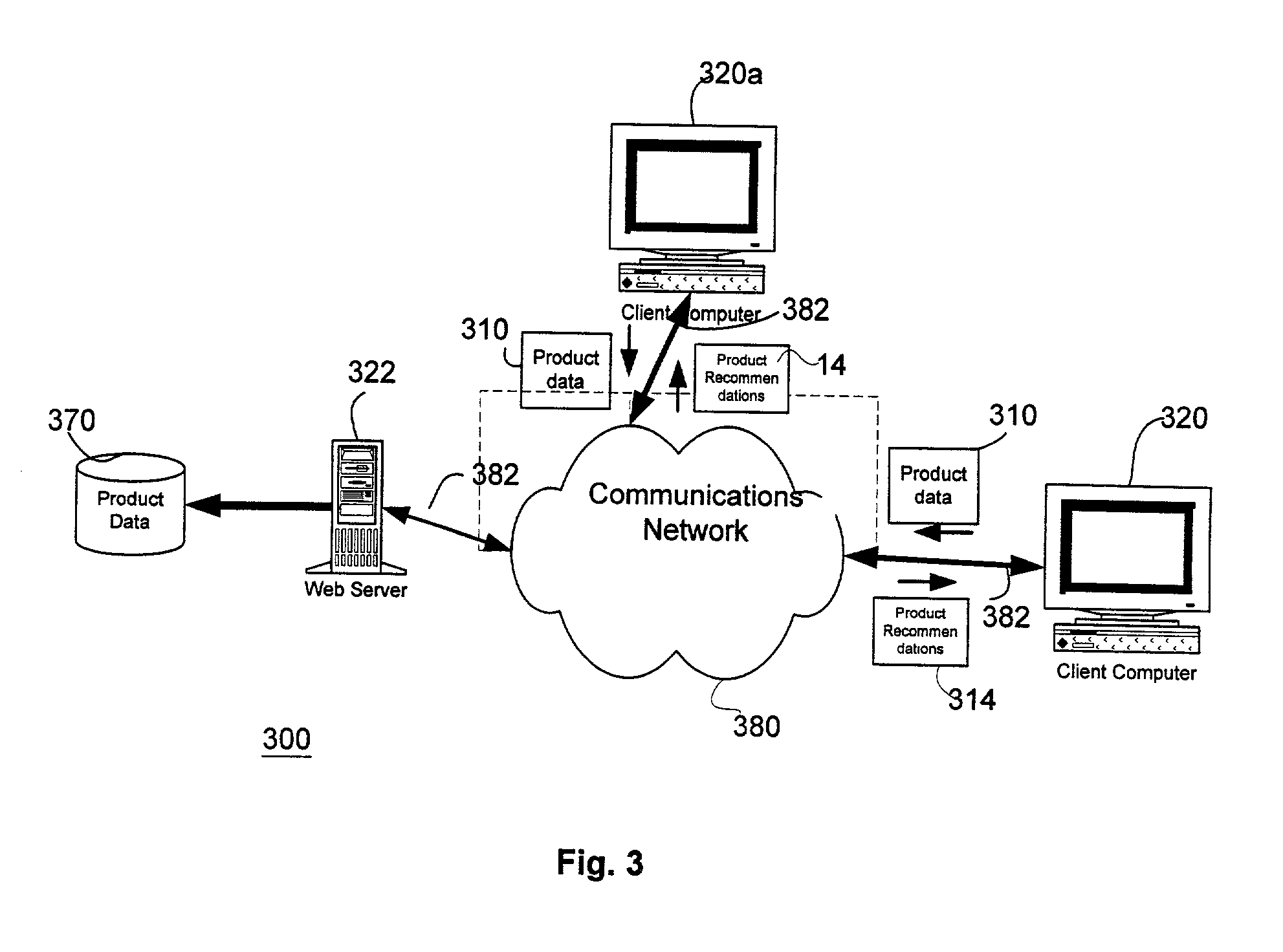

Intelligent performance-based product recommendation system

ActiveUS20020161664A1Accurately predict product performanceAccurately consumer preferenceSpecial data processing applicationsMarketingThe InternetProcessing element

Systems and methods of utilizing communications networks and multivariate analysis to predict or recommend optimal products from a predefined population of commercially available products are disclosed. The recommendations are based on intelligence contained in processing elements and subjective and / or objective product information received from consumers or input to the systems as part of their initial setup. The output of the systems comprise sets of products that they predict the consumer will prefer and / or perform well for the problem or concern identified by the consumer. The performance and preference predictions are a function of consumer problems and product responsiveness patterns. Objective product information is generally obtained with diagnostic instruments. Data measured with the diagnostic instruments may be communicated to the data processing portions of the invention via the Internet. The outputs of the data processing portion of the system may be presented to consumers via the Internet as well.

Owner:JOHNSON & JOHNSON CONSUMER COPANIES

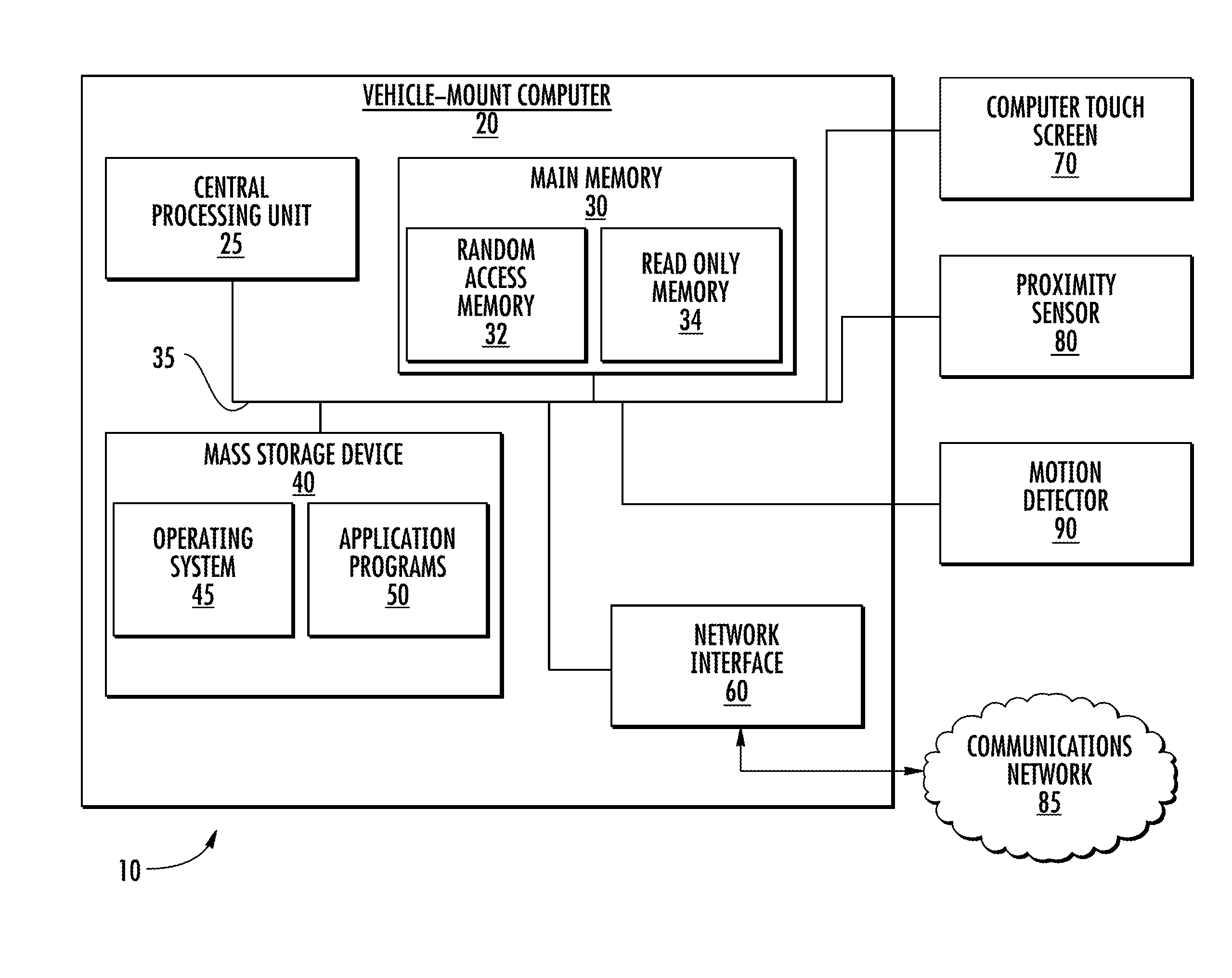

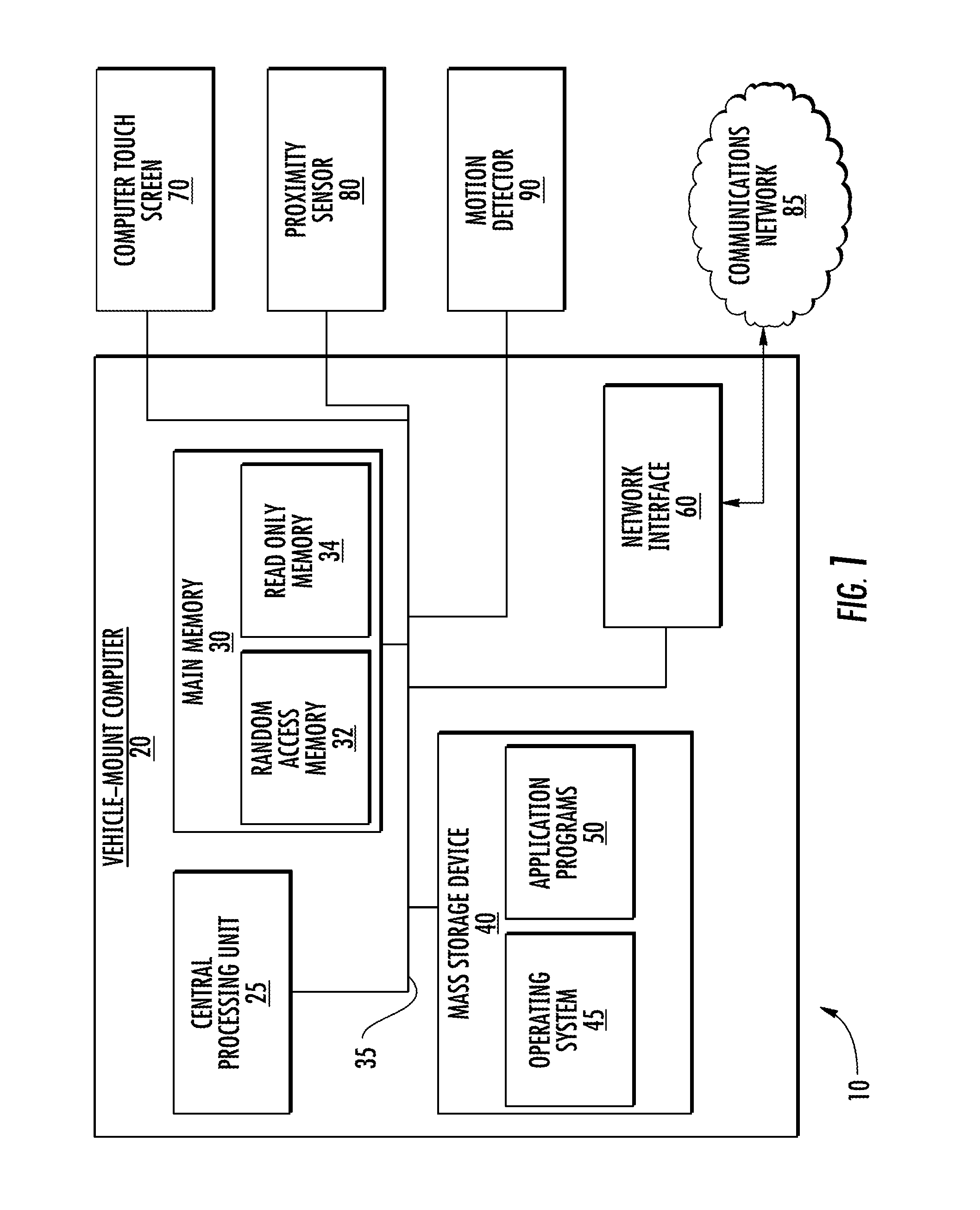

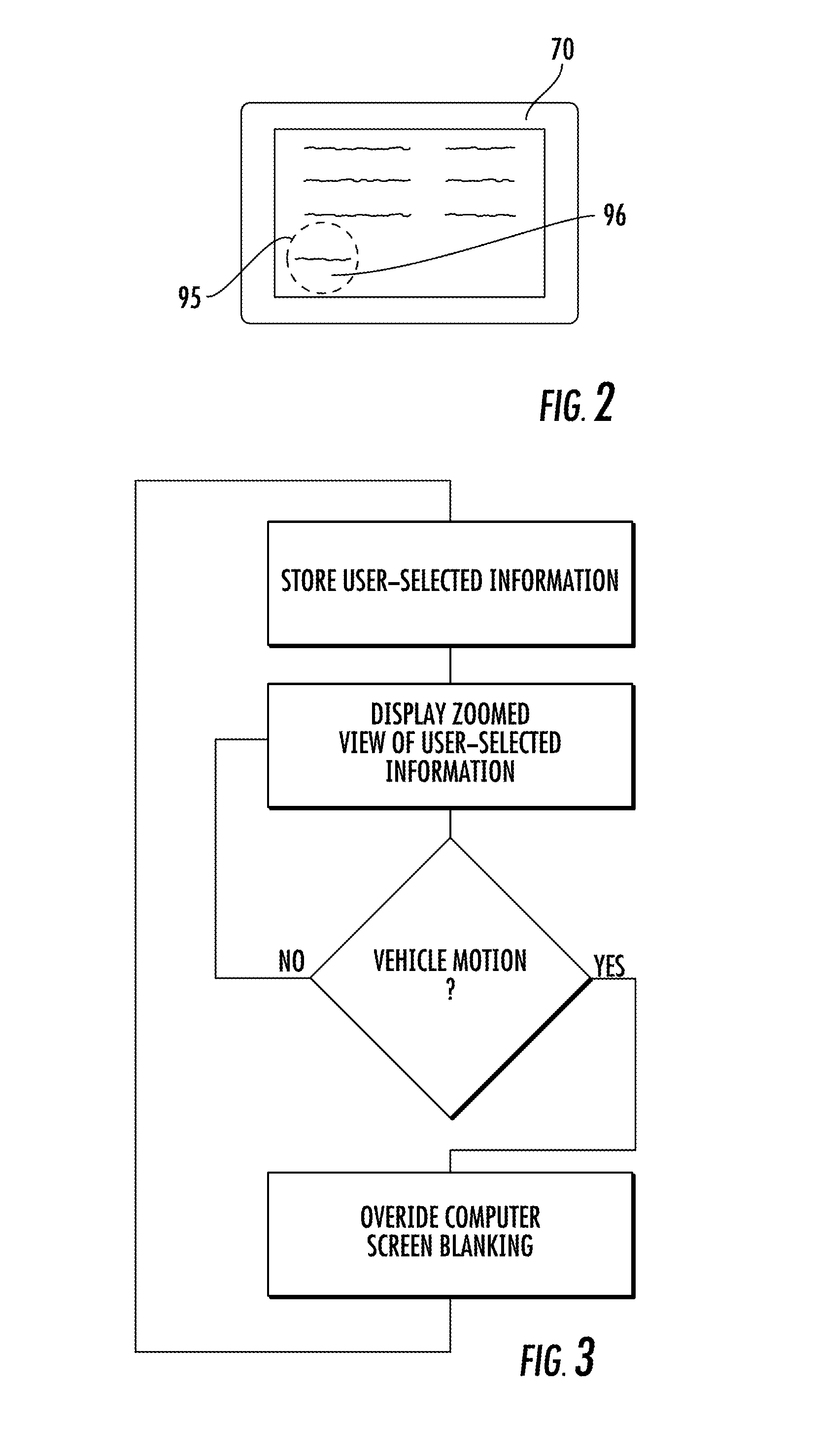

System and method for display of information using a vehicle-mount computer

ActiveUS8918250B2Input/output for user-computer interactionDashboard fitting arrangementsMotion detectorProximity sensor

A system and method displays information using a vehicle-mount computer. The system includes (i) a computer touch screen for inputting and displaying information; (ii) a motion detector for detecting vehicle motion; (iii) a proximity sensor for detecting proximity to an item; and (vi) a vehicle-mount computer in communication with the computer touch screen, the motion detector, and proximity sensor, the vehicle-mount computer including a central processing unit and memory. The vehicle-mount computer's central processing unit is configured to store information associated with user-selected information from the computer touch screen and to display a zoomed view of the user-selected information on the computer touch screen. Further, the vehicle-mount computer's central processing unit is configured to override screen-blanking when user-selected information is displayed.

Owner:HAND HELD PRODS

Computer system for automatic organization, indexing and viewing of information from multiple sources

ActiveUS7275063B2Facilitate communicationMultimedia data indexingFile access structuresPathPingSoftware system

Owner:EHIERARCHY LLC

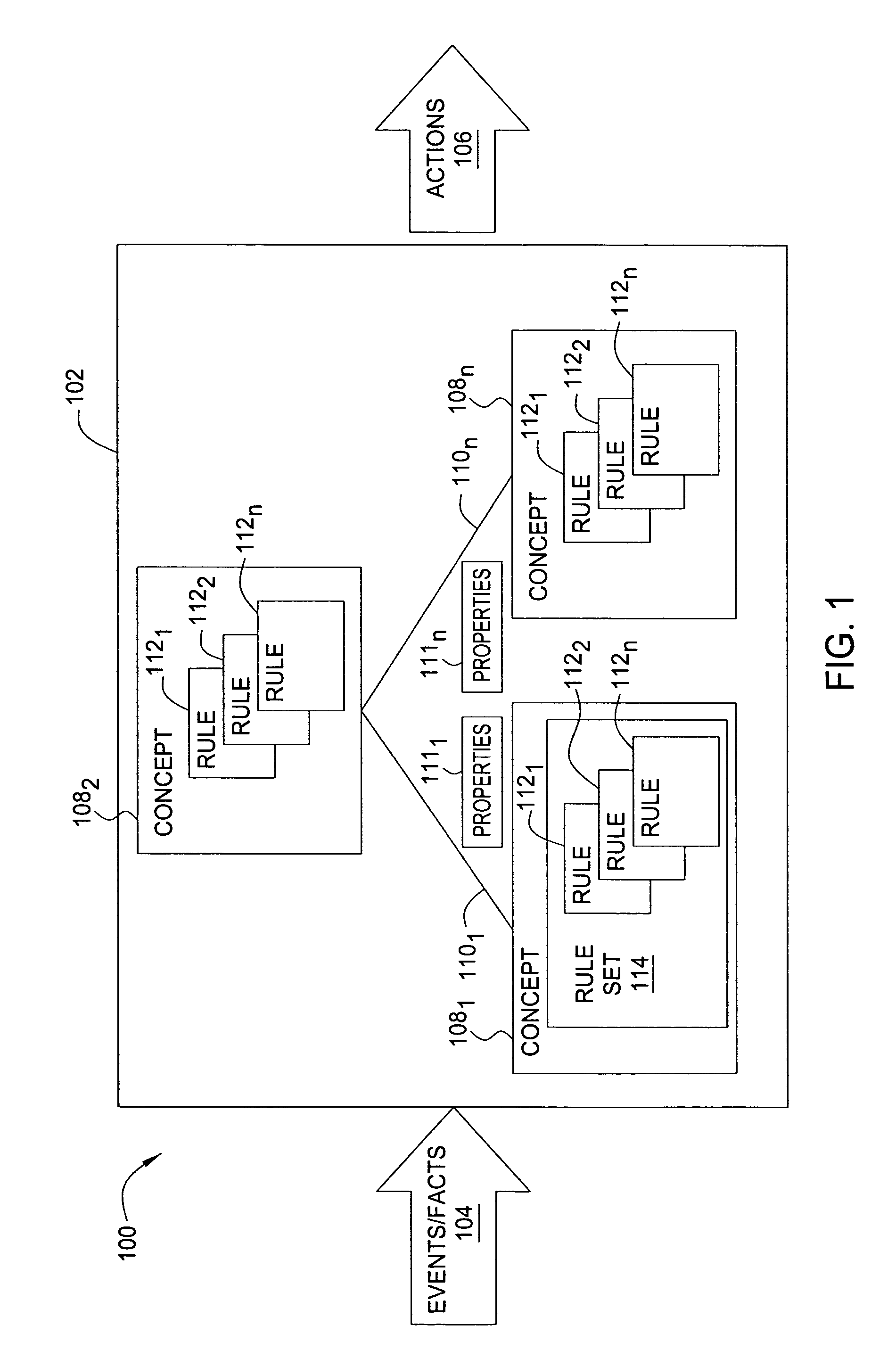

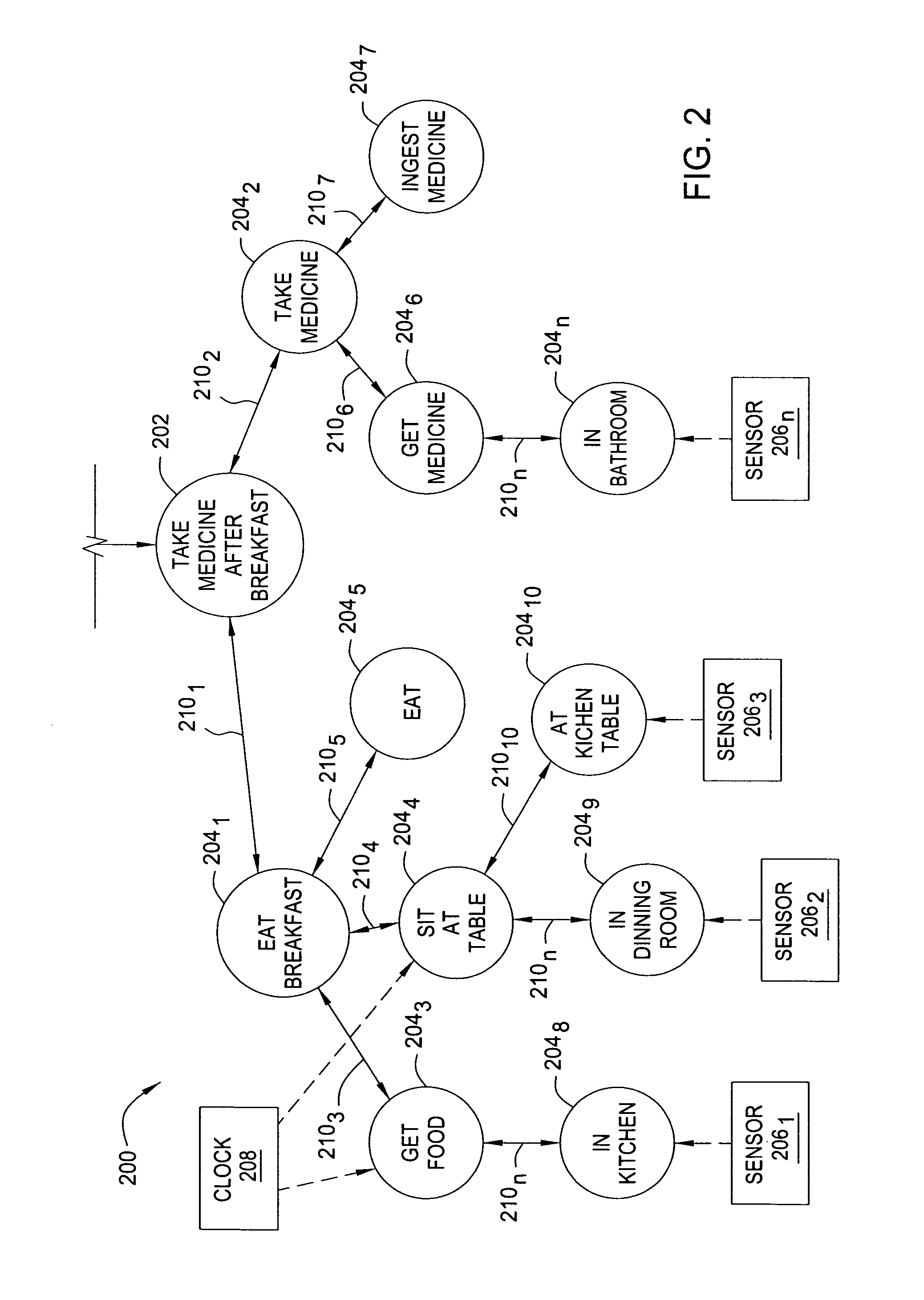

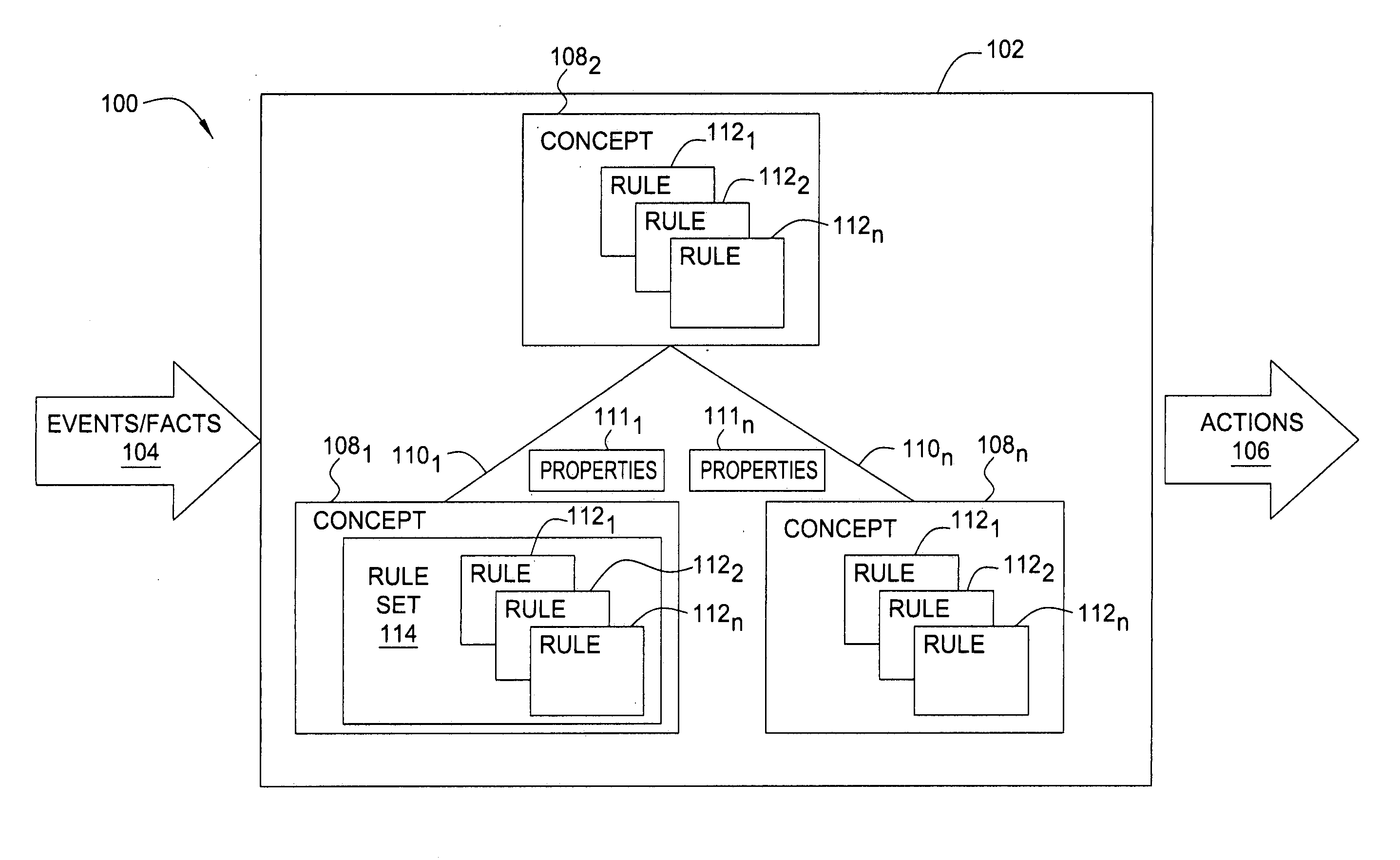

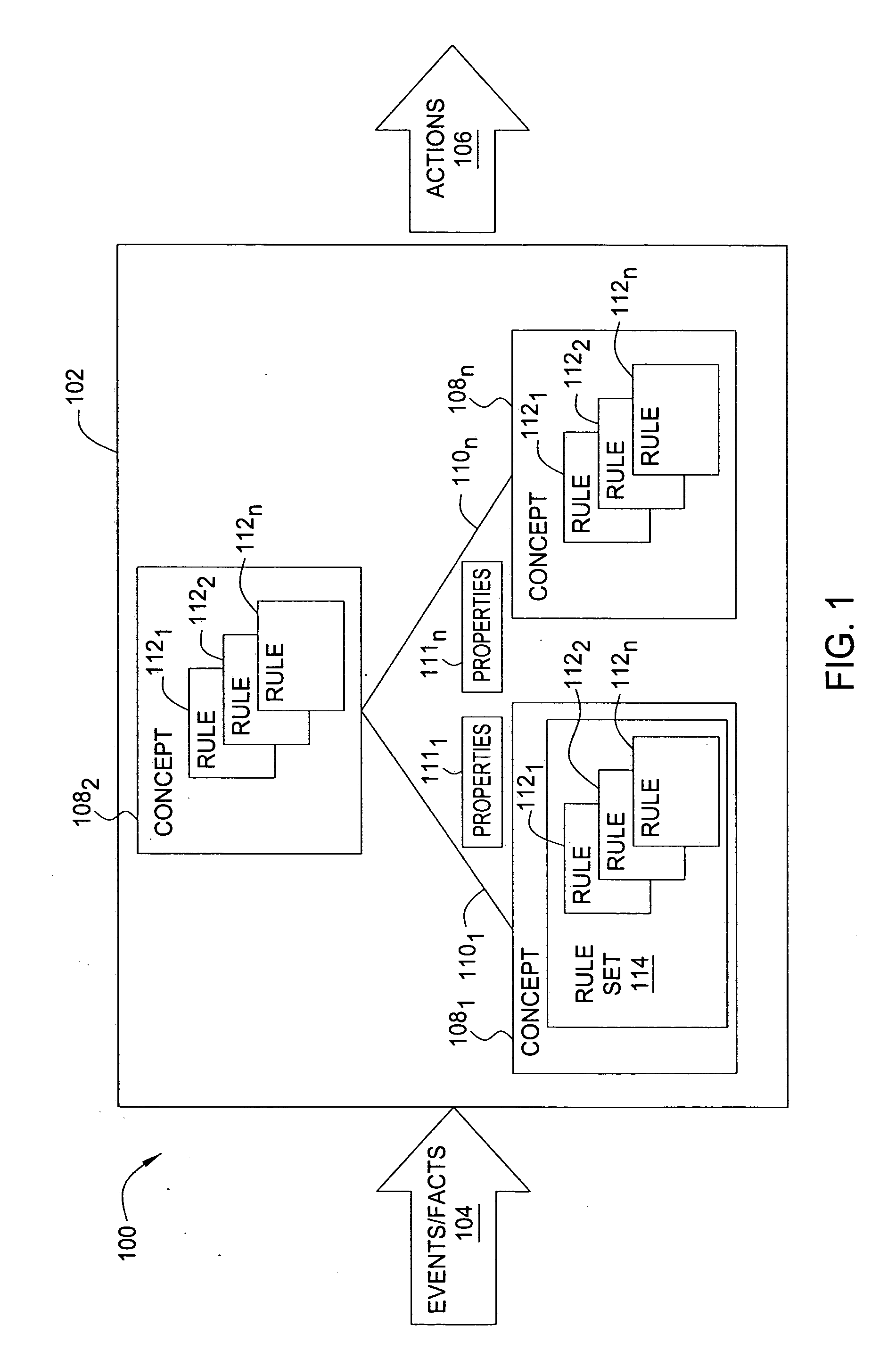

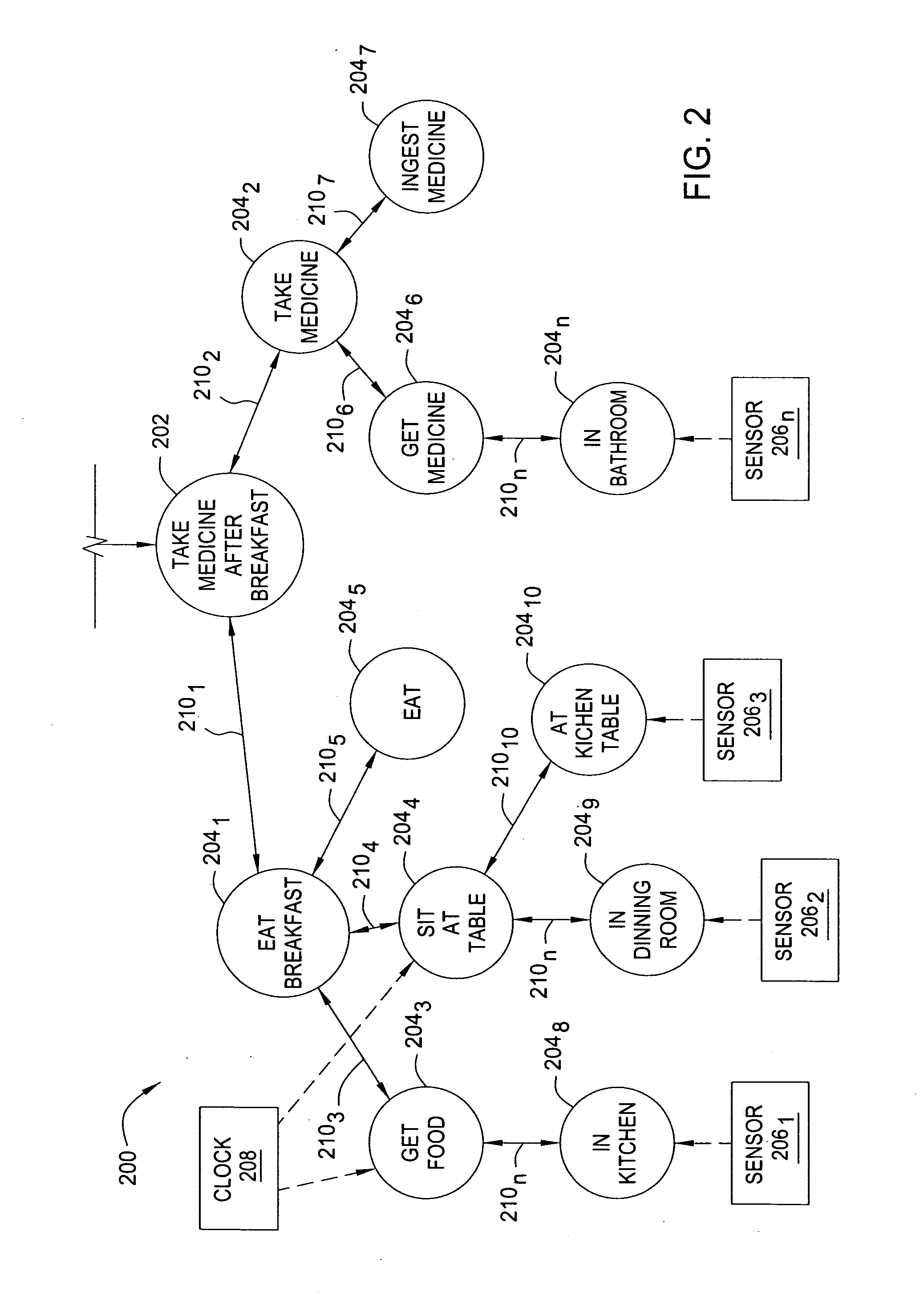

Method and apparatus for building an intelligent automated assistant

A method and apparatus are provided for building an intelligent automated assistant. Embodiments of the present invention rely on the concept of “active ontologies” (e.g., execution environments constructed in an ontology-like manner) to build and run applications for use by intelligent automated assistants. In one specific embodiment, a method for building an automated assistant includes interfacing a service-oriented architecture that includes a plurality of remote services to an active ontology, where the active ontology includes at least one active processing element that models a domain. At least one of the remote services is then registered for use in the domain.

Owner:APPLE INC

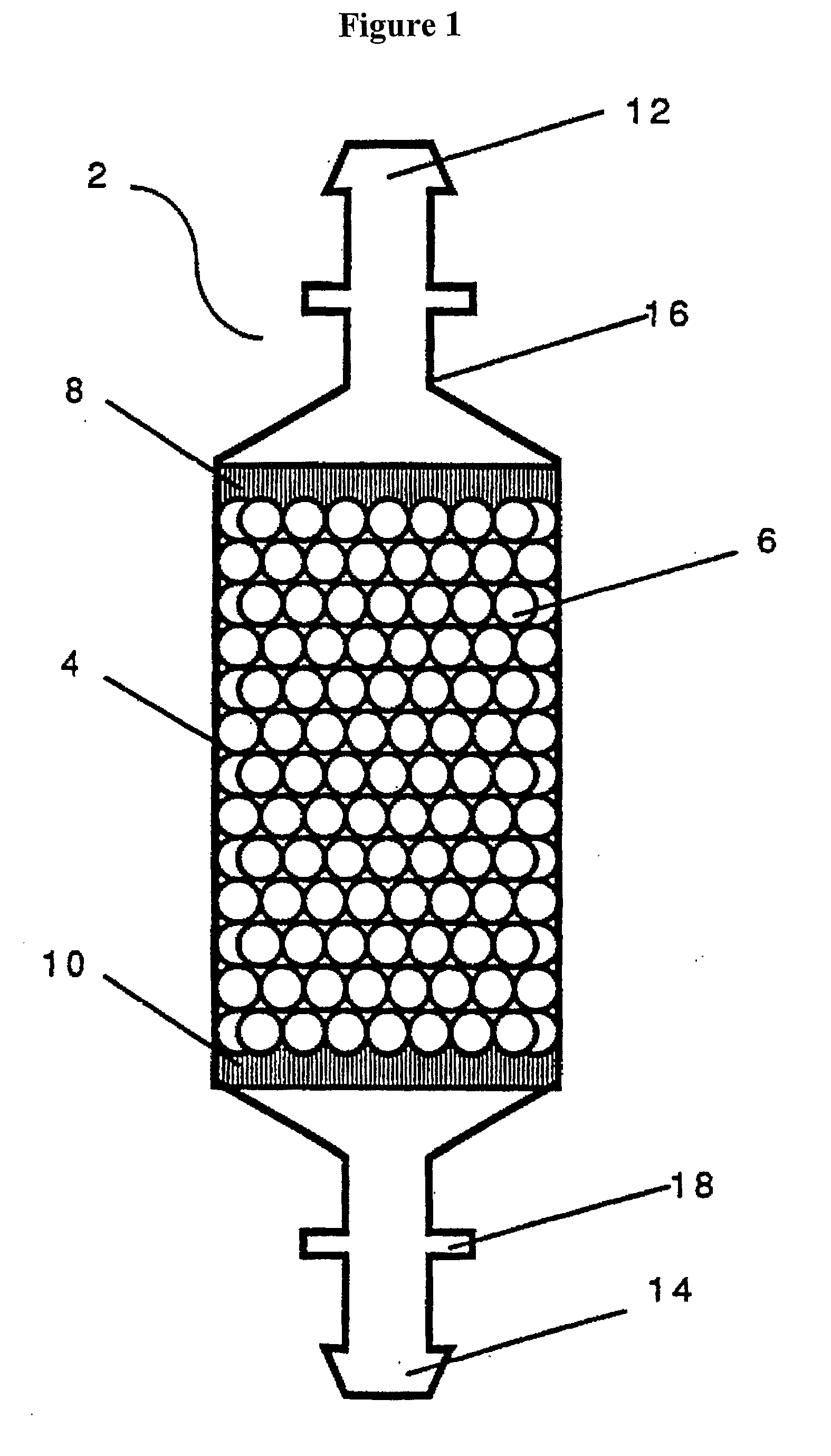

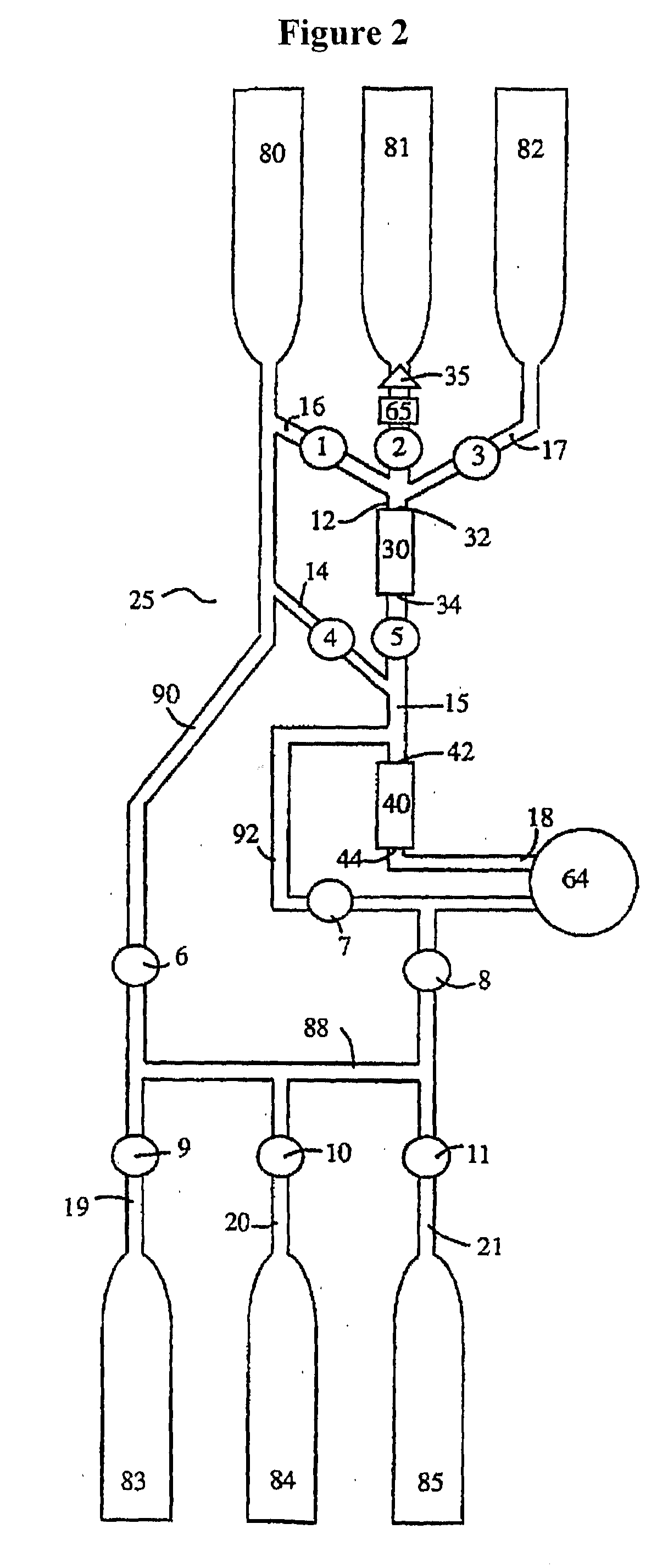

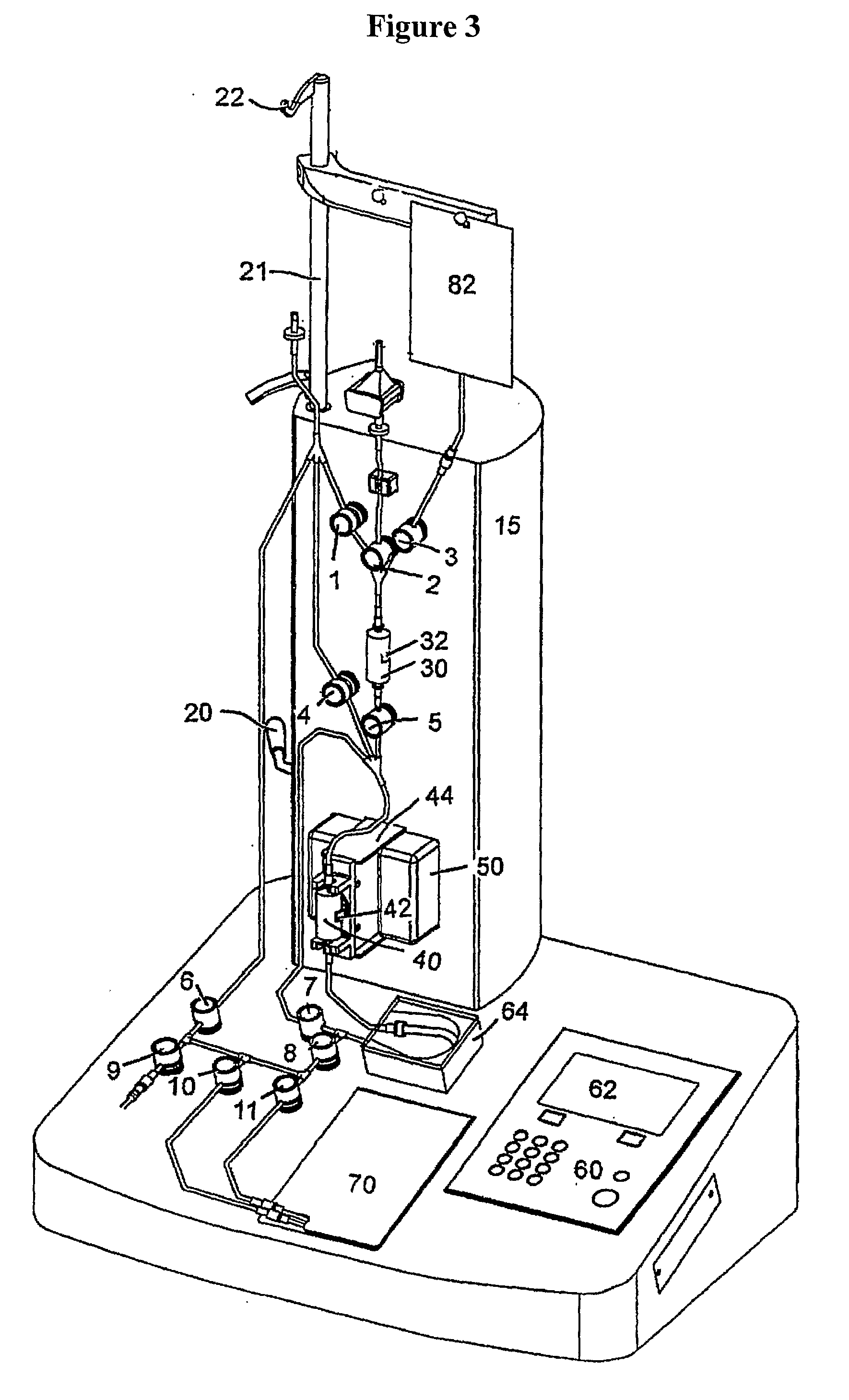

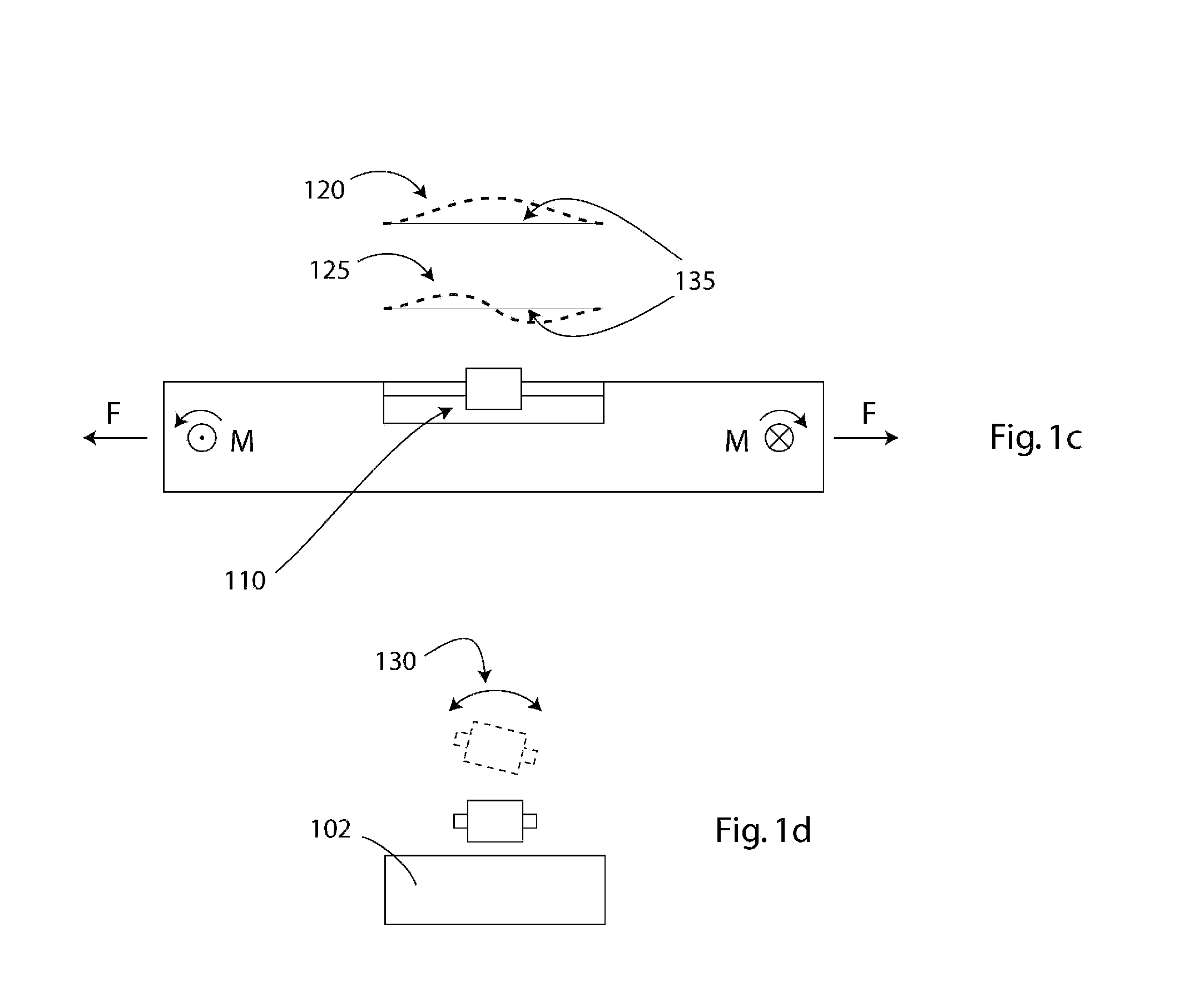

Sample Processing System and Methods

ActiveUS20110003380A1High magnetic separationImprove efficiencyBioreactor/fermenter combinationsElectrostatic separationEngineeringCell separation

The invention relates to a system, comprising: a) a sample processing unit, comprising an input port and an output port coupled to a rotating container having at least one sample chamber, the sample processing unit configured provide a first processing step to a sample or to rotate the container so as to apply a centrifugal force to a sample deposited in the chamber and separate at least a first component and a second component of the deposited sample; and b) a sample separation unit coupled to the output port of the sample processing unit, the cell separation unit comprising separation column holder (42), a pump (64) and a plurality of valves (1-11) configured to at least partially control fluid flow through a fluid circuitry and a separation column (40) positioned in the holder, the separation column configured to separate labeled and unlabeled components of sample flowed through the column.

Owner:MILTENYI BIOTEC B V & CO KG

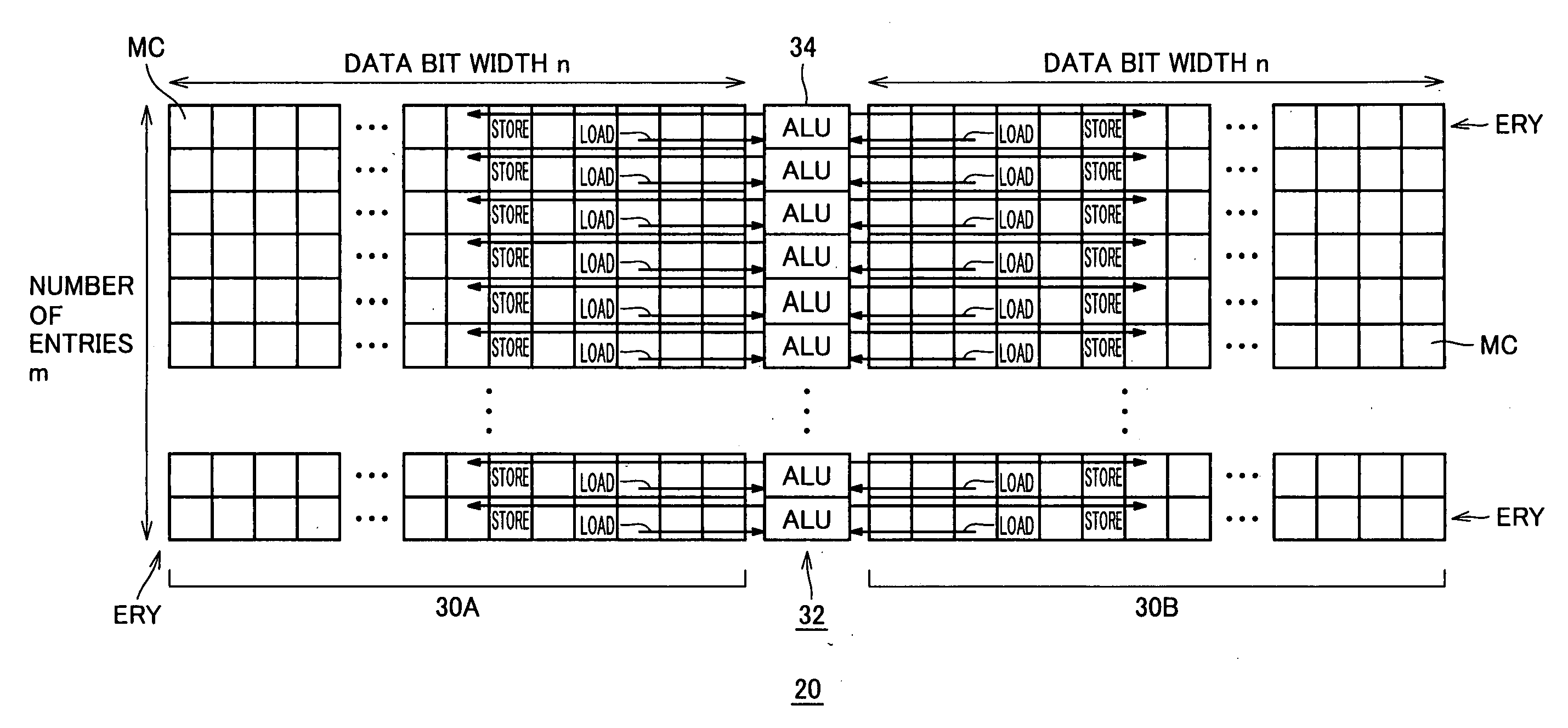

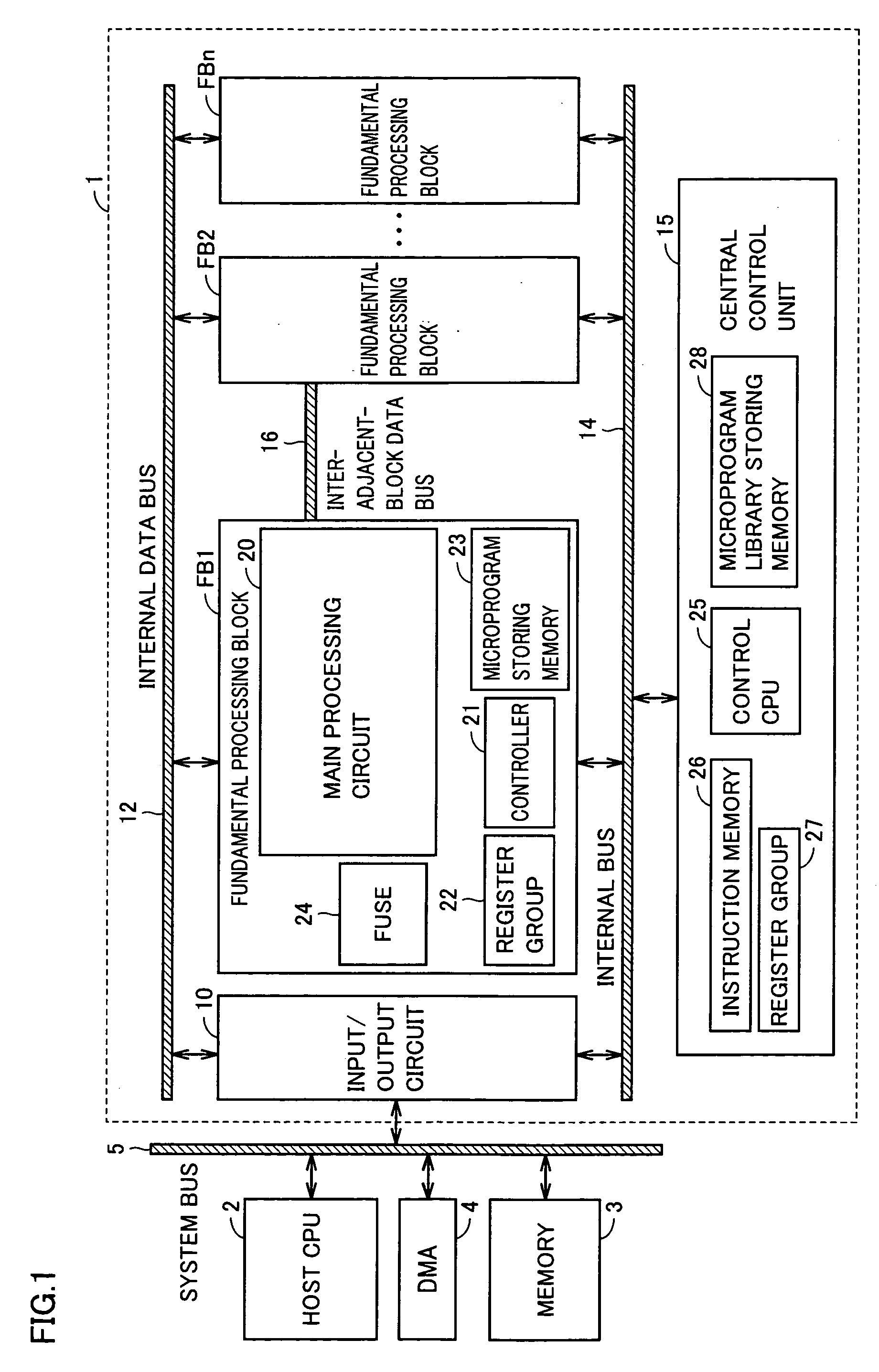

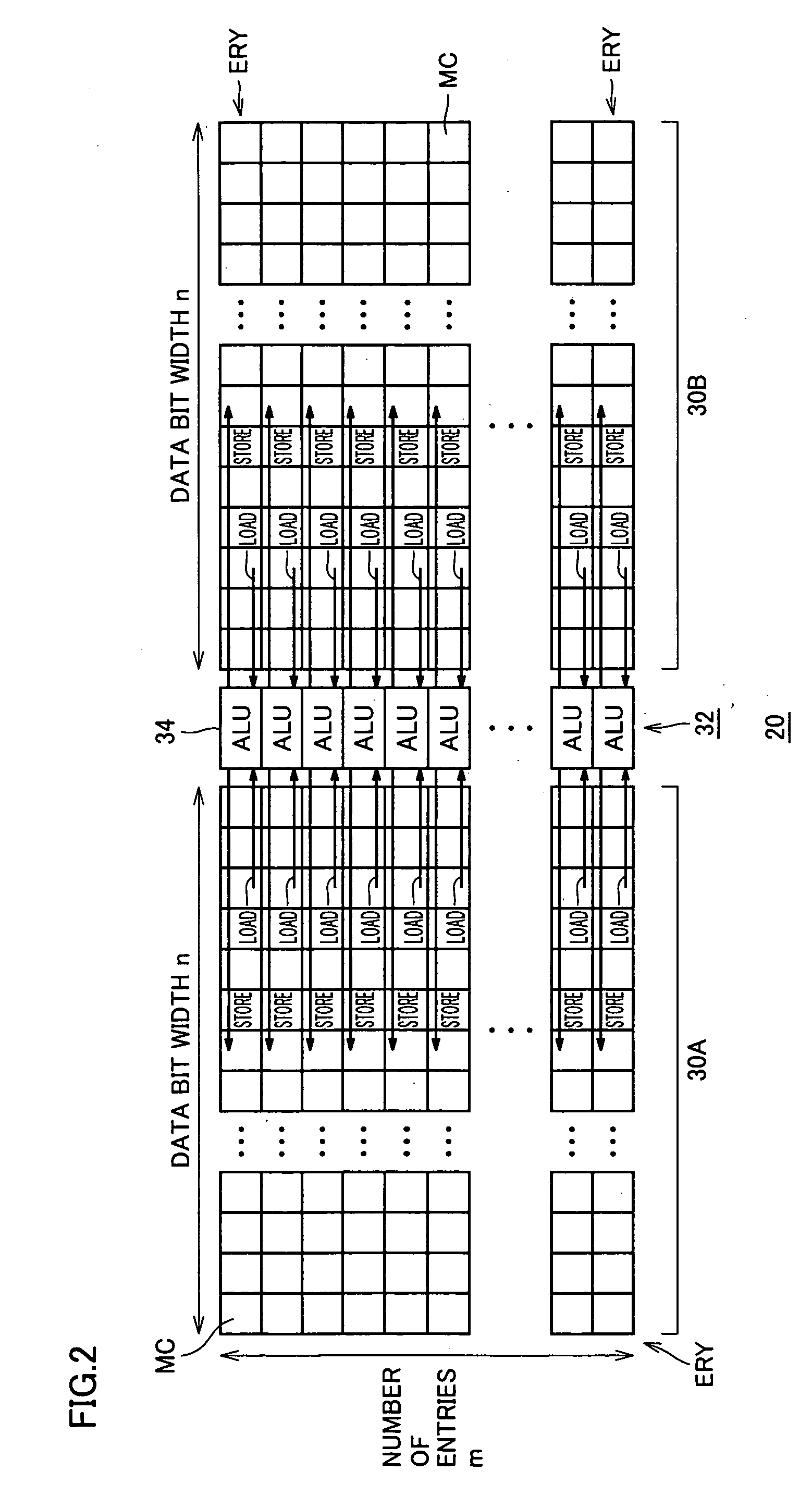

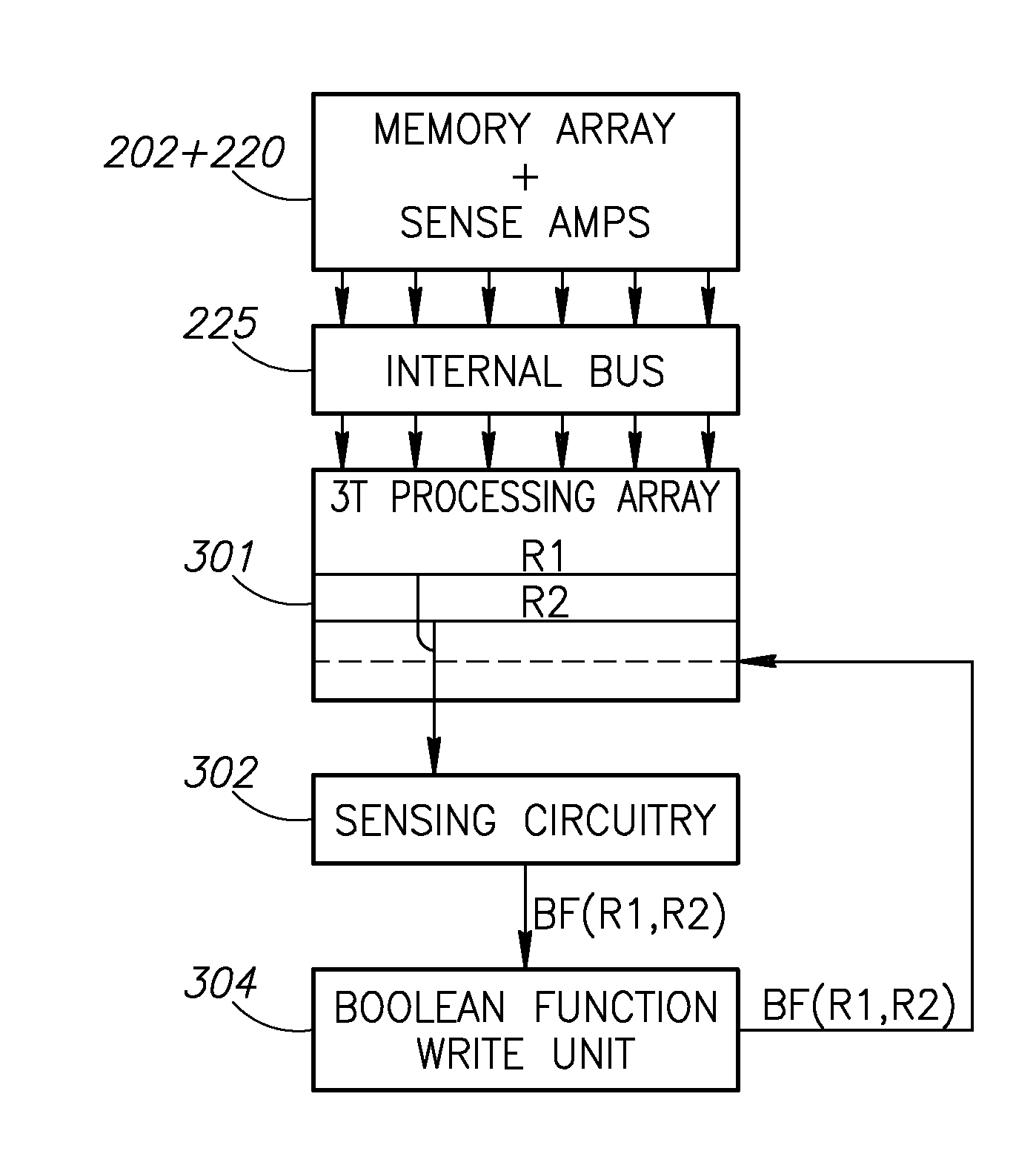

Parallel operational processing device

InactiveUS20070180006A1Easy to operateReduce power consumptionEnergy efficient ICTDigital data processing detailsAudio power amplifierParallel computing

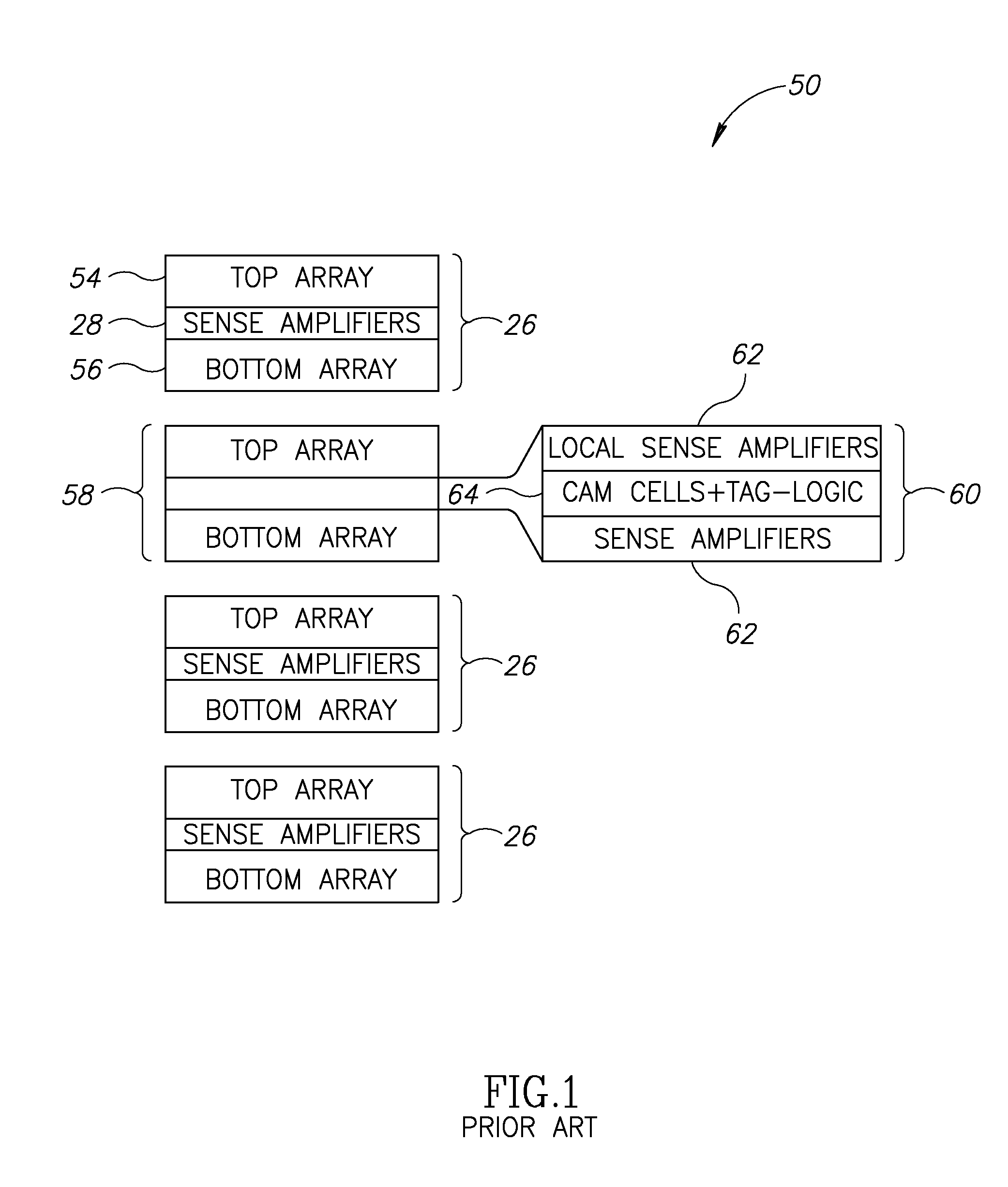

In a parallel operational processing device having an operational processing unit arranged between memory blocks each having a plurality of memory cells arranged in rows and columns, the respective columns of each memory block are alternately connected to the operational processing units on the opposite sides of the memory block. By selecting one word line in one memory block, data can be transferred to two operational processing units. The number of the word lines selected per one operational processing unit is reduced, and power consumption is reduced. The bit operation units and sense amplifiers / write drivers of the operational processing units have arrangement pitch conditions mitigated and are reduced in number, and an isolation region between the memory blocks is not required and the layout area is reduced. Thus, the parallel operational processing device with a layout area and the power consumption reduced, can achieve a fast operation.

Owner:RENESAS ELECTRONICS CORP

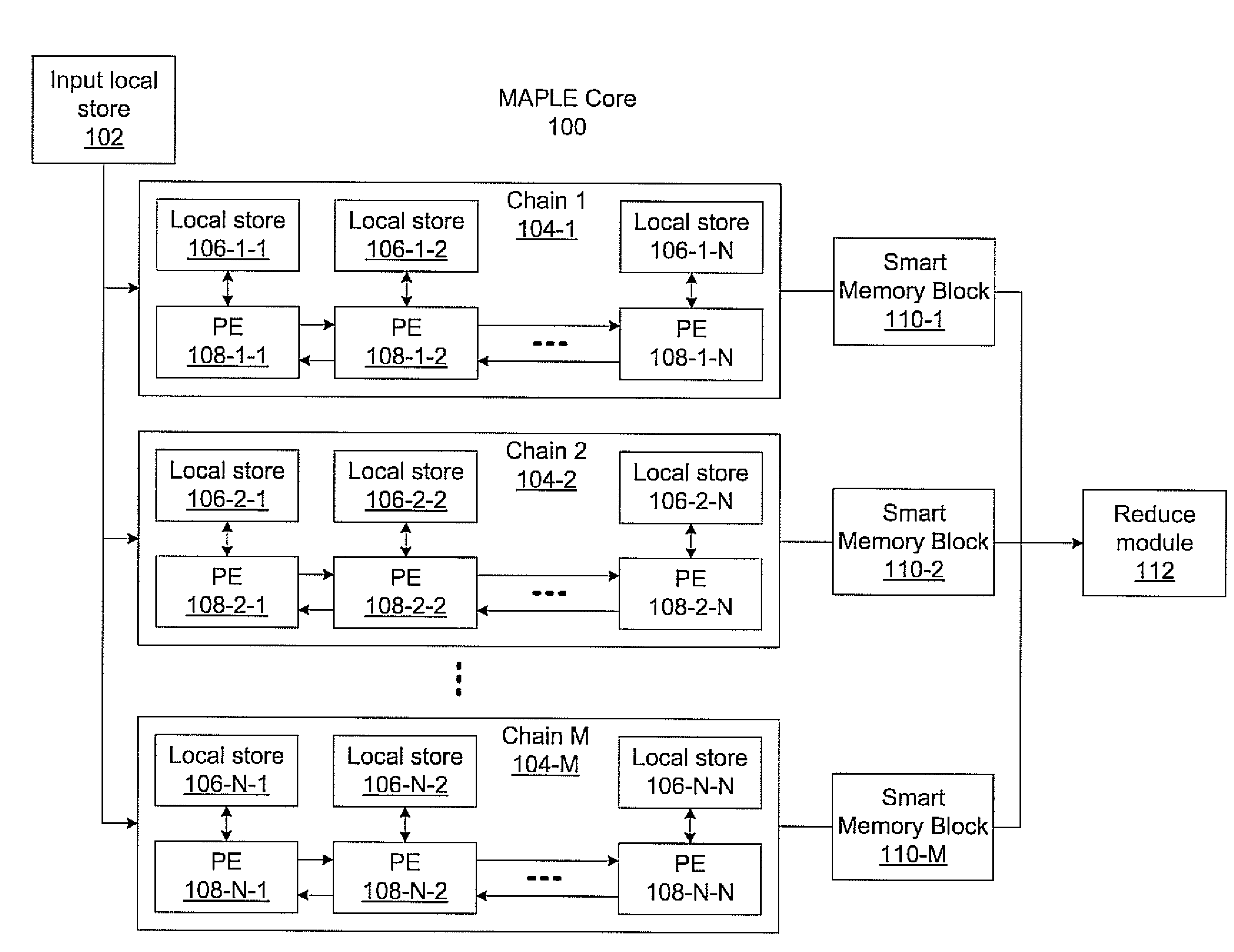

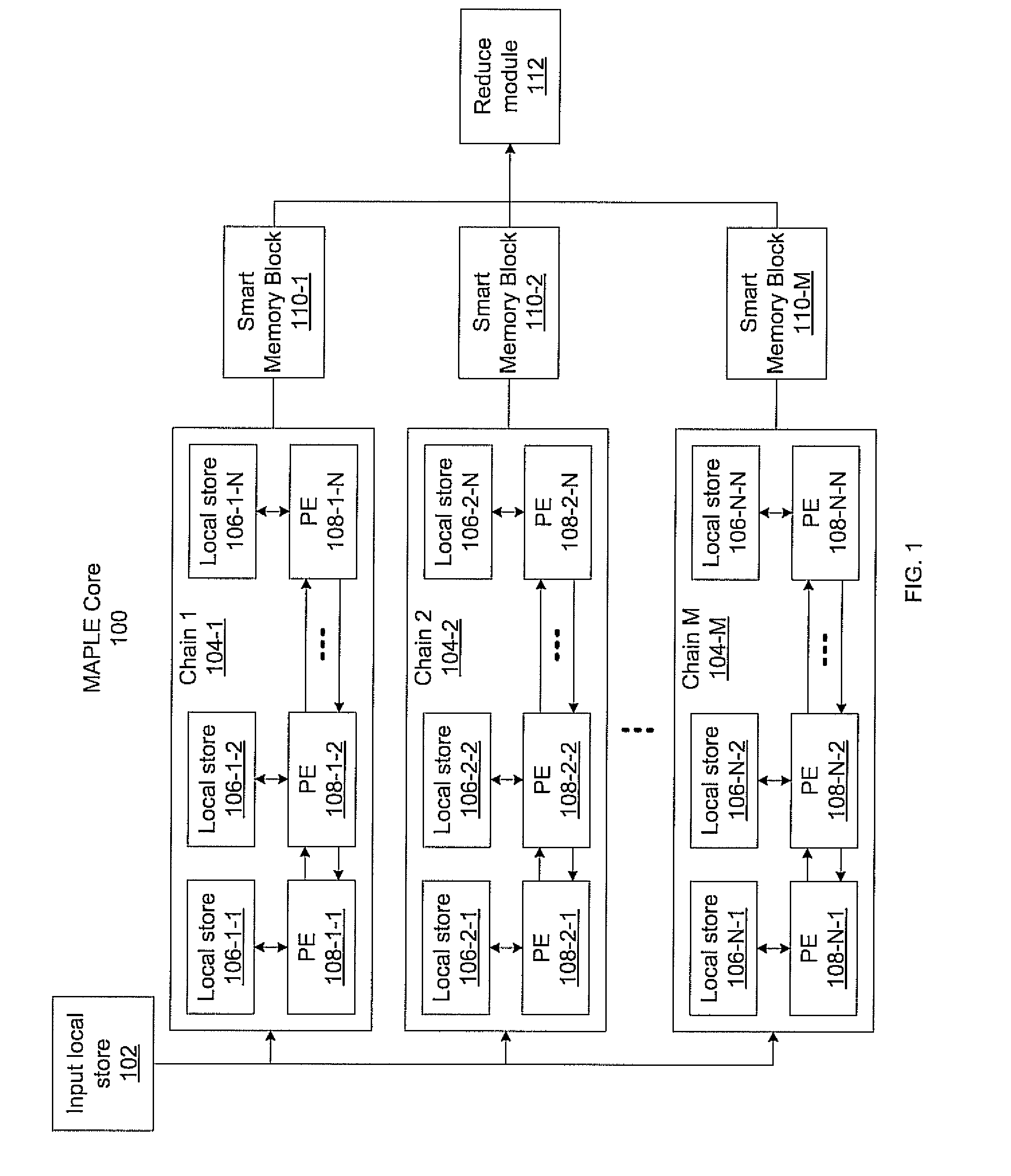

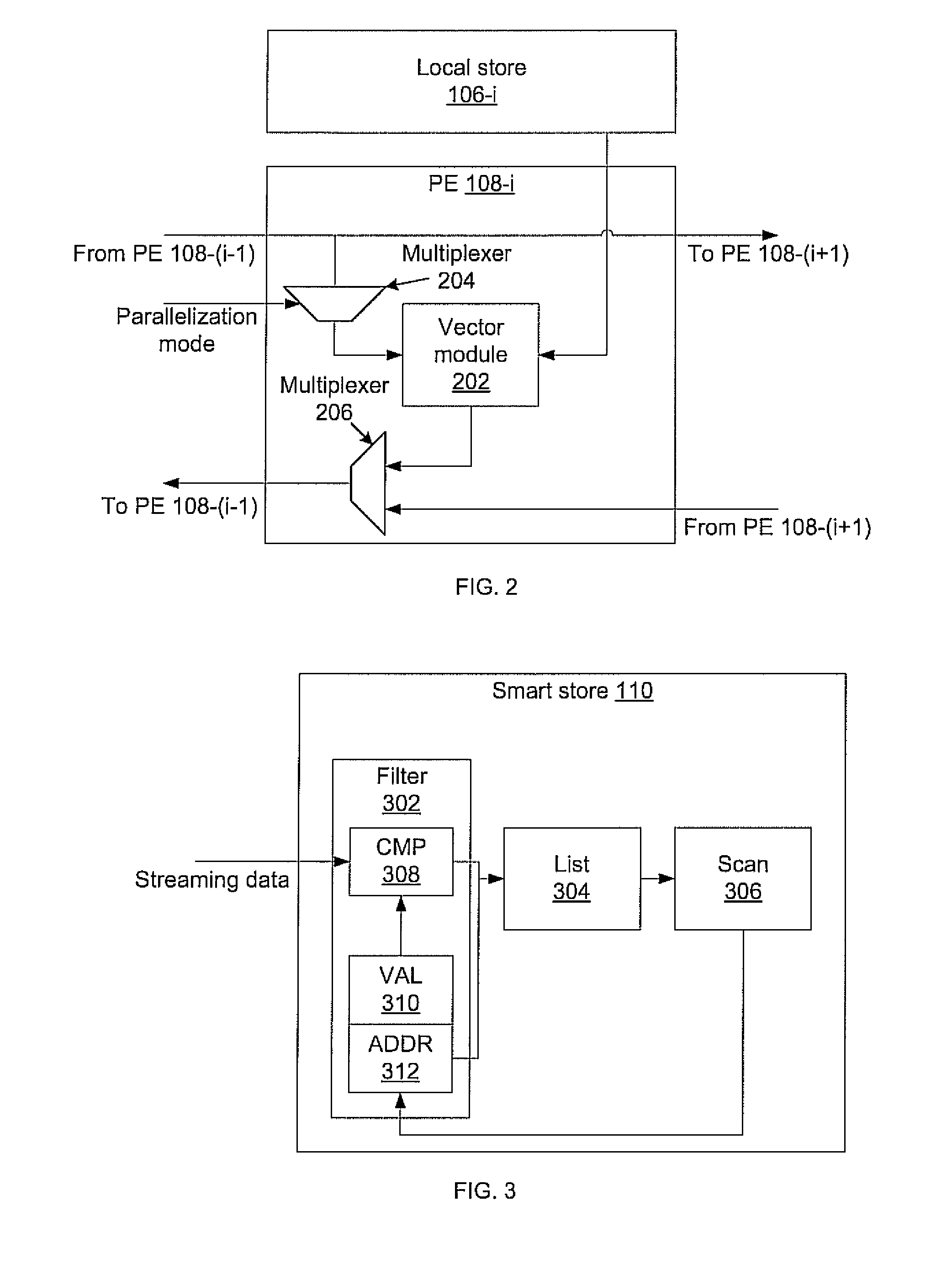

Massively parallel, smart memory based accelerator

Systems and methods for massively parallel processing on an accelerator that includes a plurality of processing cores. Each processing core includes multiple processing chains configured to perform parallel computations, each of which includes a plurality of interconnected processing elements. The cores further include multiple of smart memory blocks configured to store and process data, each memory block accepting the output of one of the plurality of processing chains. The cores communicate with at least one off-chip memory bank.

Owner:NEC CORP

Neighborhood operations for parallel processing

InactiveUS20120246380A1Memory adressing/allocation/relocationDigital storageProcessing elementParallel processing

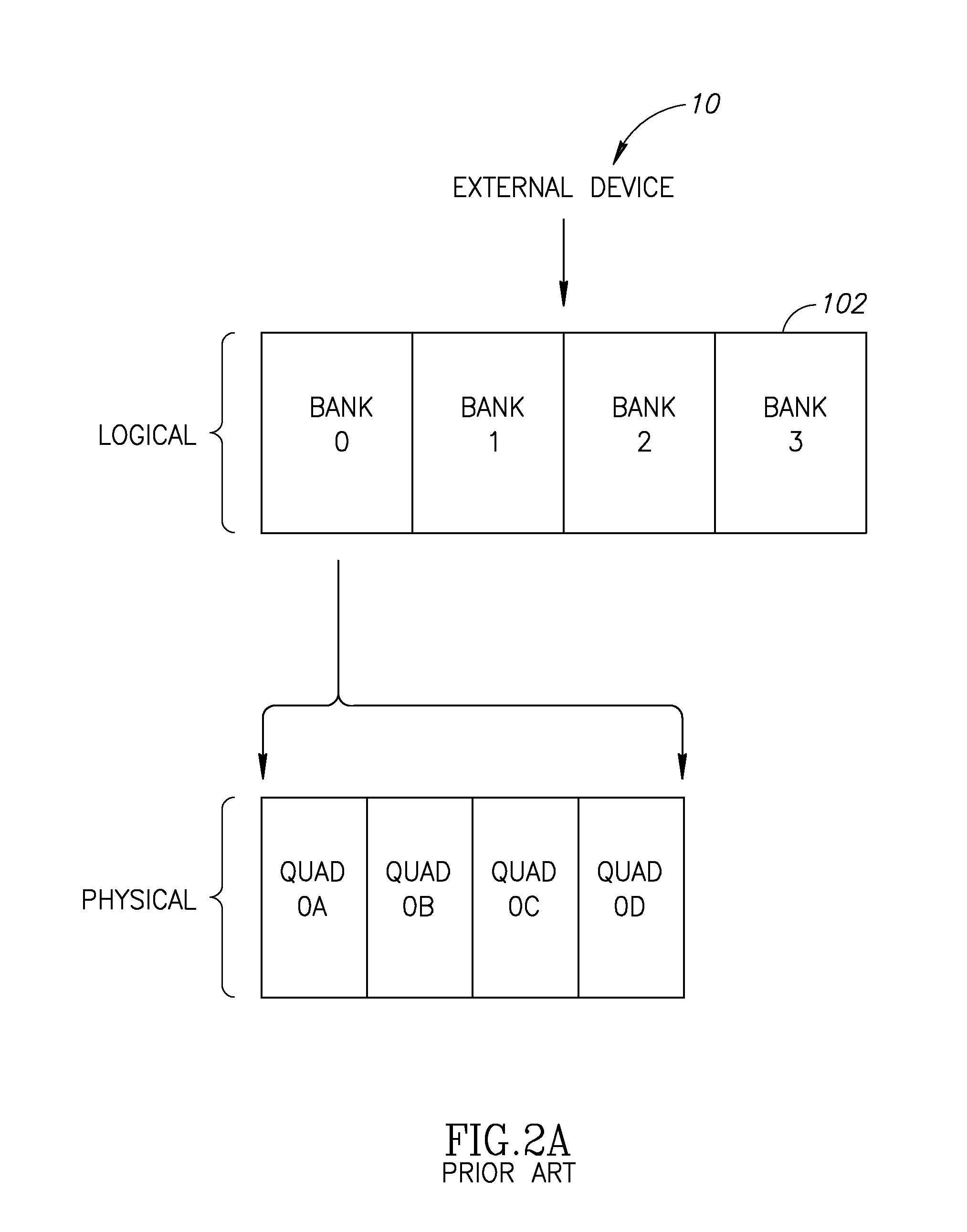

A memory device includes a plurality of storage units in which to store data of a bank, wherein the data has a logical order prior to storage and a physical order different than the logical order within the plurality of storage units and a within-device reordering unit to reorder the data of a bank into the logical order prior to performing on-chip processing. In another embodiment, the memory device includes an external device interface connectable to an external device communicating with the memory device, an internal processing element to process data stored on the device and multiple banks of storage. Each bank includes a plurality of storage units and each storage unit has two ports, an external port connectable to the external device interface and an internal port connected to the internal processing element.

Owner:GSI TECH

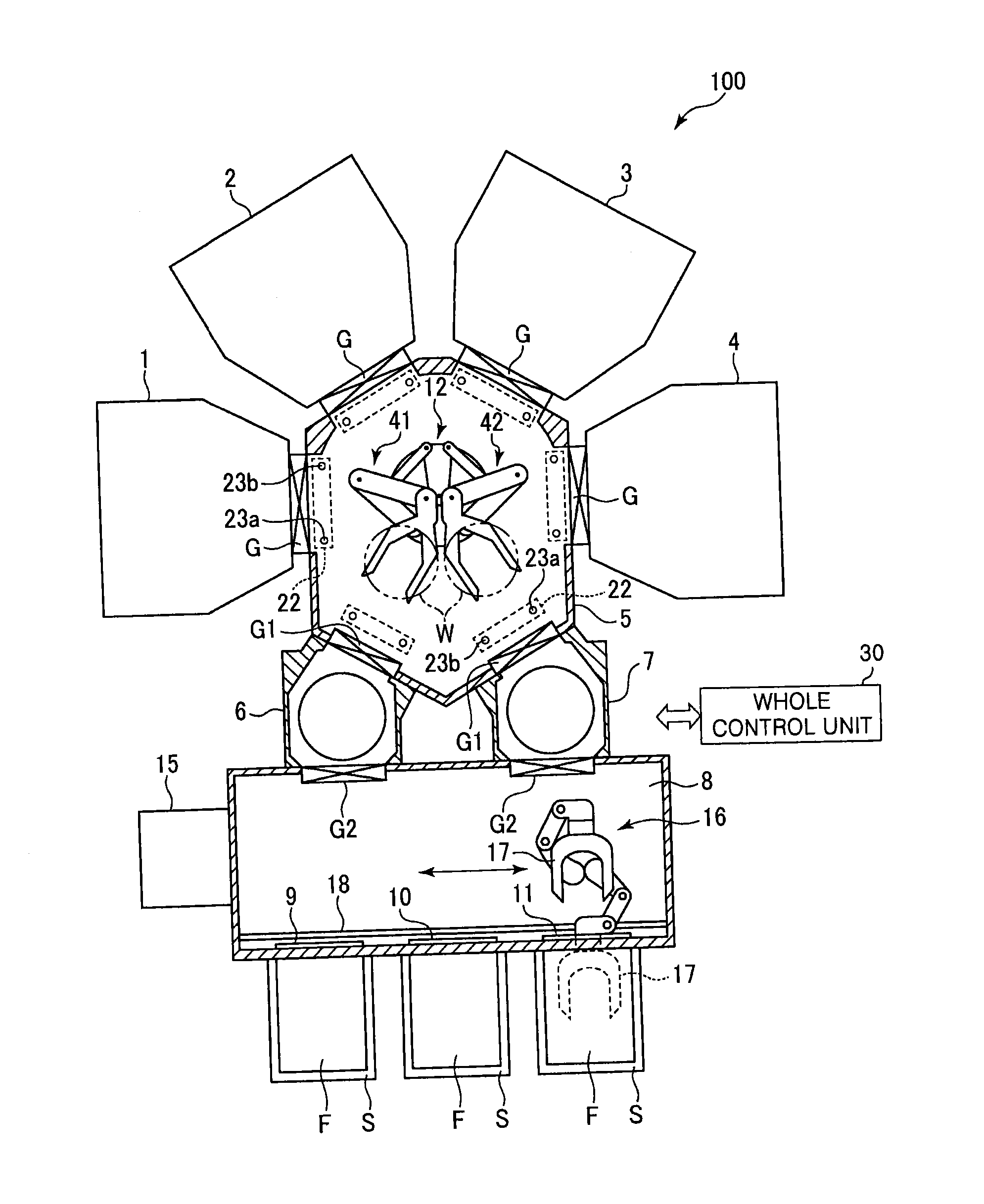

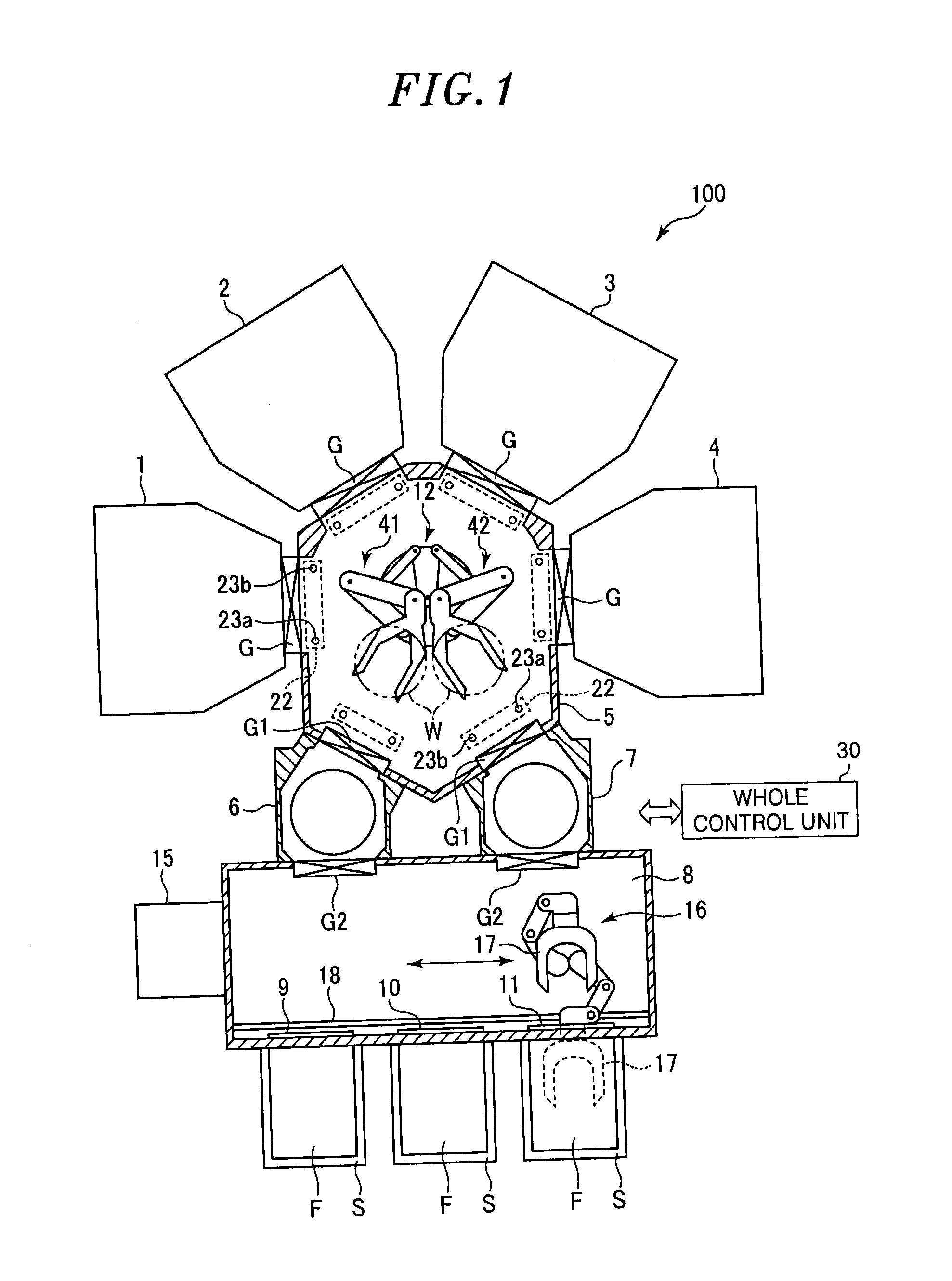

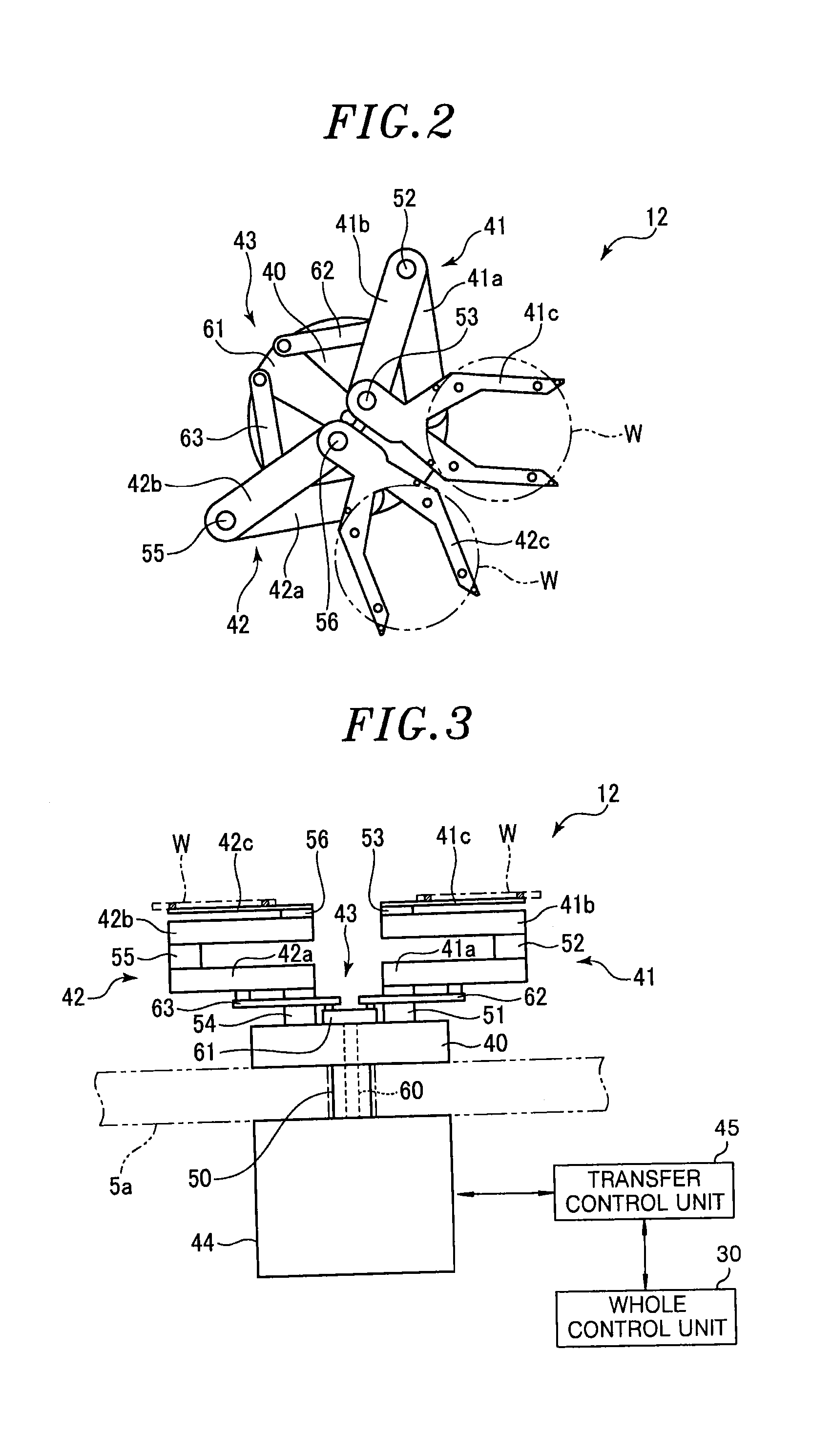

Substrate transfer device and substrate processing system

InactiveUS20130180448A1Suppress position deviationHigh positioning accuracyLiquid surface applicatorsSemiconductor/solid-state device manufacturingRoom temperatureProcessing element

A substrate transfer device includes a pick which has positioning pins to position a substrate and holds a positioned substrate; a drive unit which drives the pick such that the substrate is loaded / unloaded to / from a vacuum processing unit by using a pick; and a transfer control unit which controls a transfer operation of the substrate using the pick. The transfer control unit obtains in advance information on a reference position of the substrate at room temperature when the substrate is loaded into the vacuum processing unit, calculates a positional deviation from the reference position of the substrate when the substrate is loaded into the vacuum processing unit in actual processing, and controls a drive unit such that the substrate is loaded into the vacuum processing unit by correcting the positional deviation.

Owner:TOKYO ELECTRON LTD

Method and apparatus for building an intelligent automated assistant

A method and apparatus are provided for building an intelligent automated assistant. Embodiments of the present invention rely on the concept of “active ontologies” (e.g., execution environments constructed in an ontology-like manner) to build and run applications for use by intelligent automated assistants. In one specific embodiment, a method for building an automated assistant includes interfacing a service-oriented architecture that includes a plurality of remote services to an active ontology, where the active ontology includes at least one active processing element that models a domain. At least one of the remote services is then registered for use in the domain.

Owner:APPLE INC

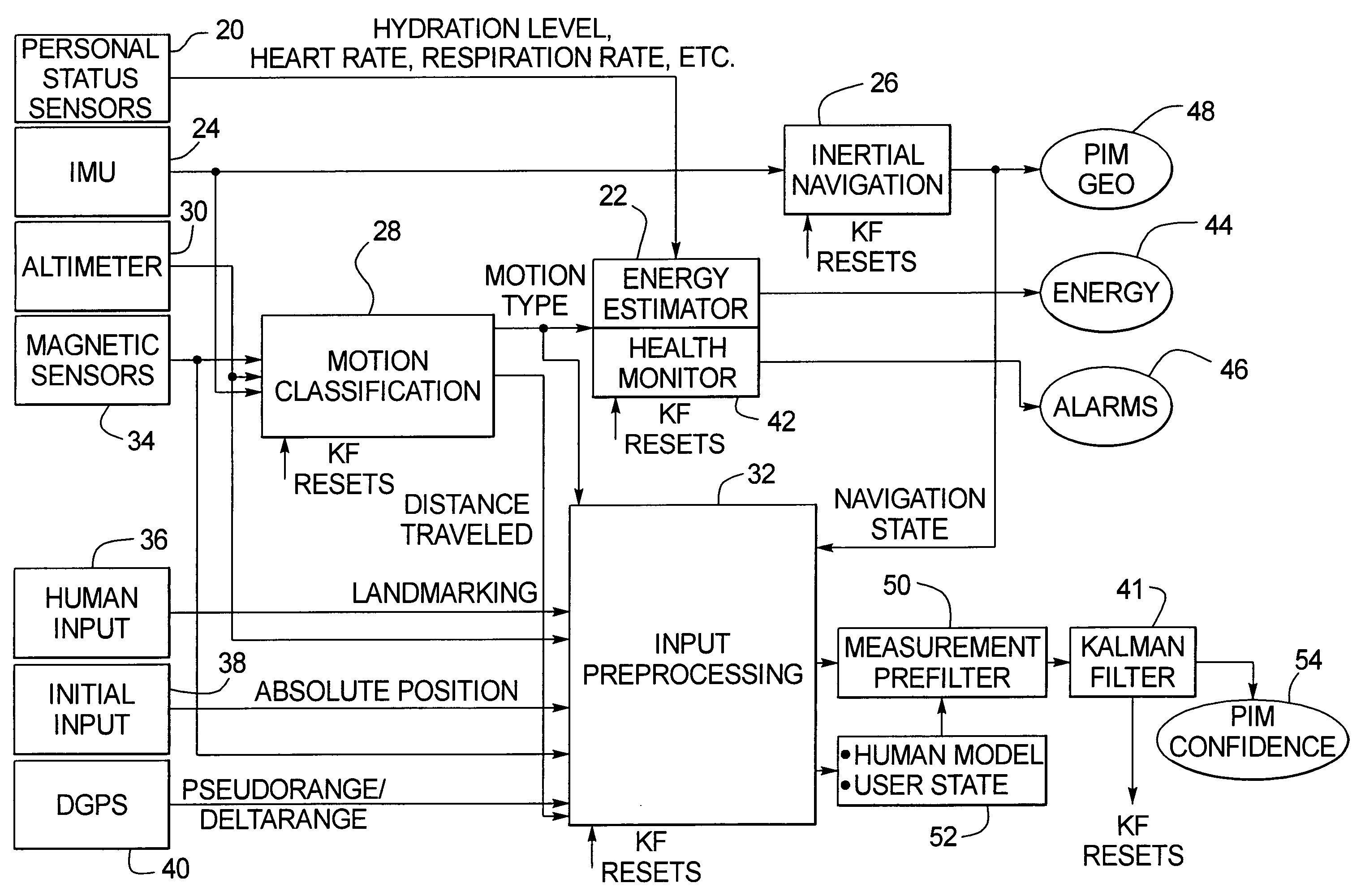

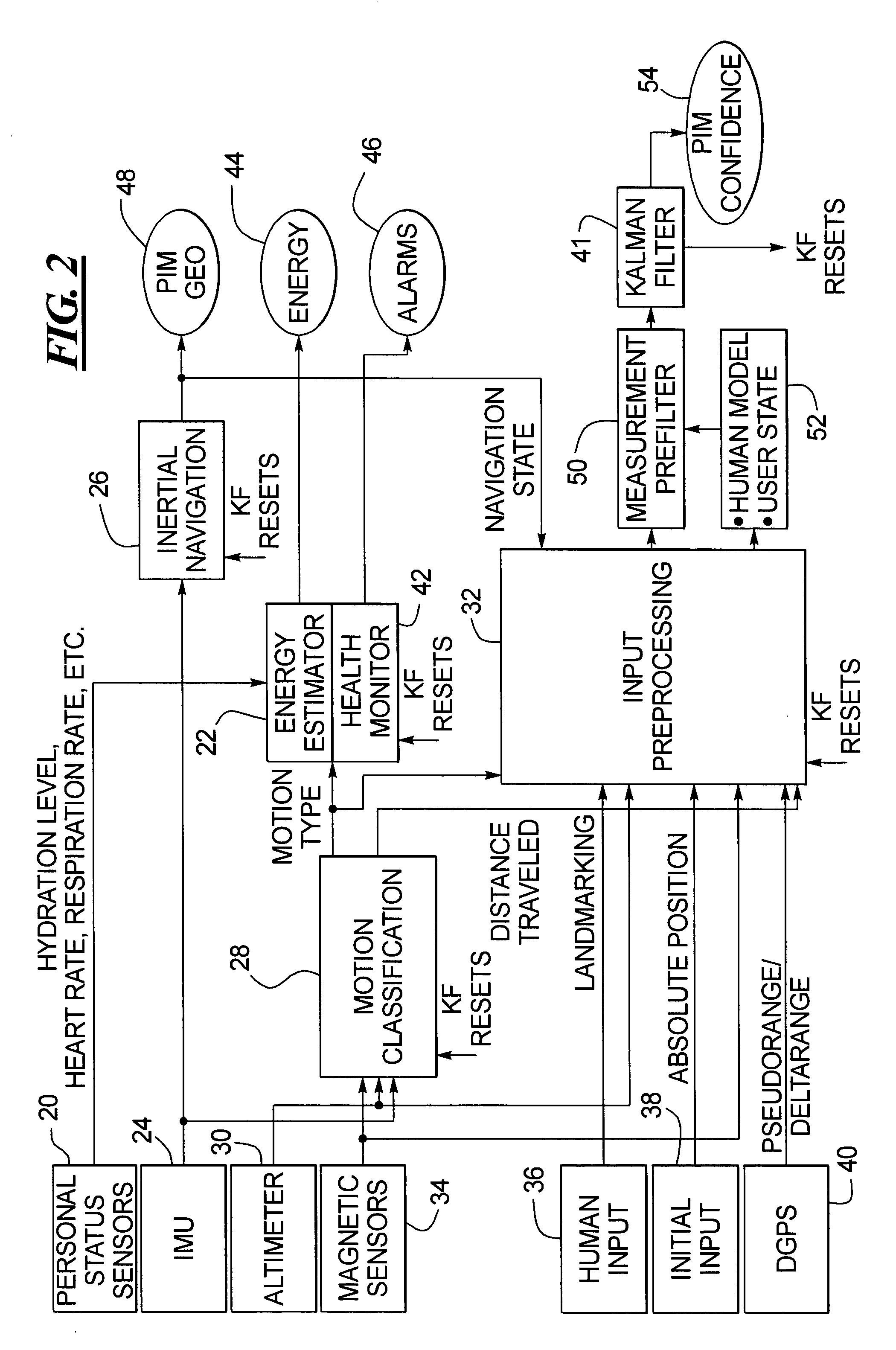

Human motion identification and measurement system and method

A system and method for classifying and measuring human motion senses the motion of the human and the metabolism of the human. A motion classification unit determines the motion type being carried out by the human and provides the motion classification information to an energy estimator and a health monitor. The energy estimator also receives the metabolism information and therefrom provides an estimate of energy expended by the human. The health monitor triggers an alarm if health related thresholds are traversed. The motion classification is also provided to a processing unit that in turn provides the data to a Kalman filter, which has an output that is provided as feedback to the motion classification unit, the energy estimator and health monitor. Altimeter, GPS and magnetic sensors may also be provided for monitoring the human motion, and initial input and landmark input data inputs are provided to the system.

Owner:HONEYWELL INT INC

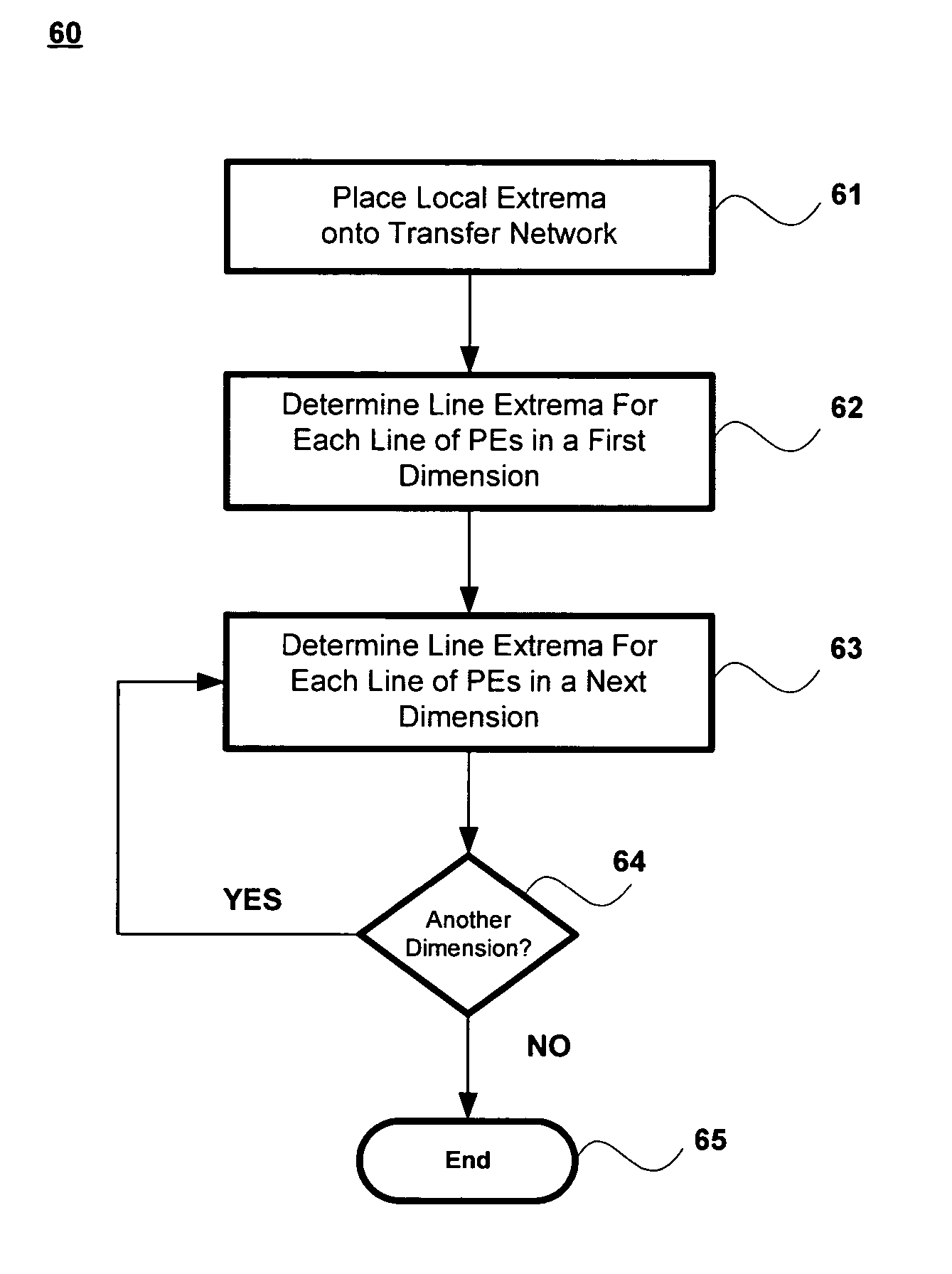

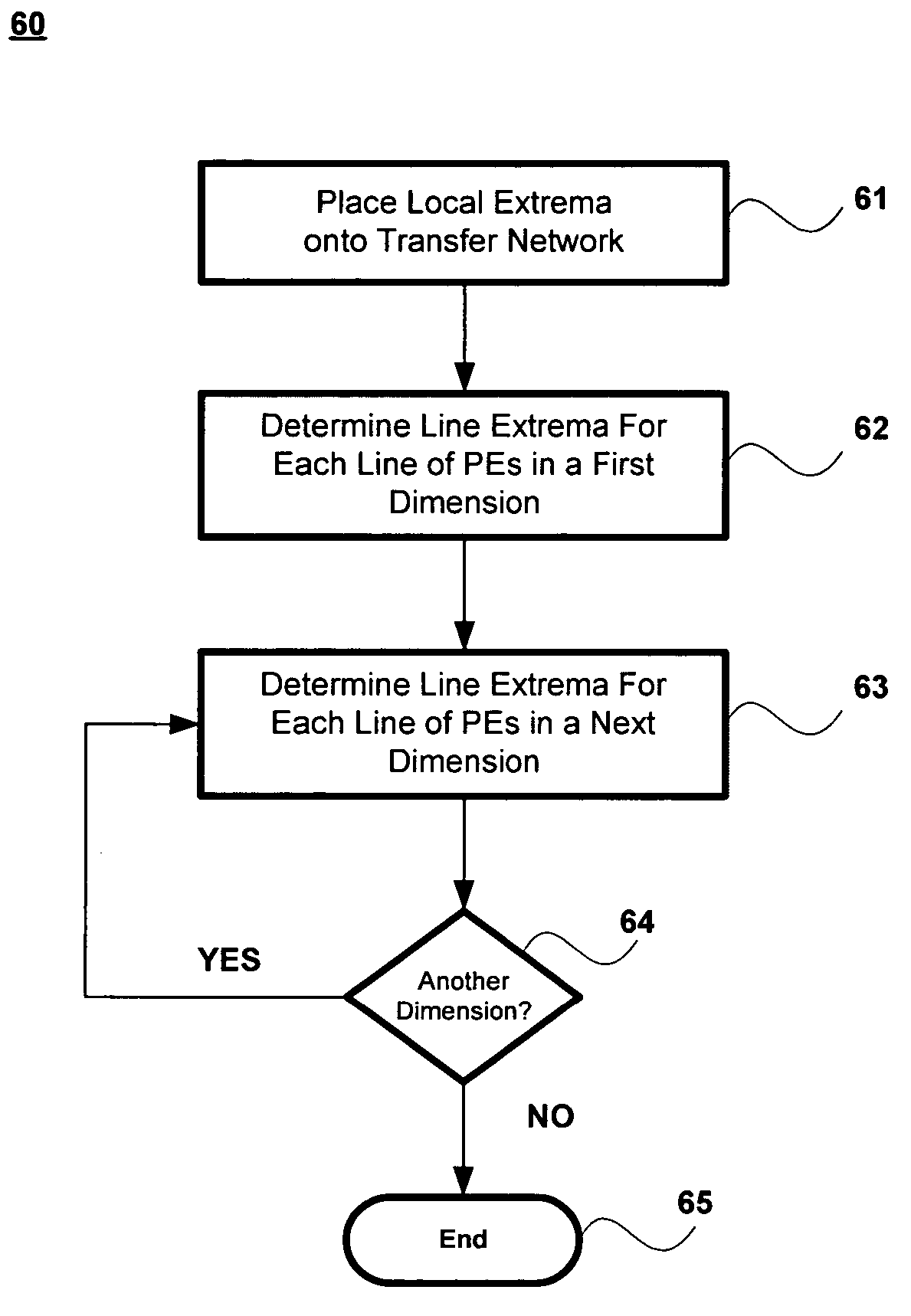

Method for finding global extrema of a set of shorts distributed across an array of parallel processing elements

ActiveUS7574466B2Single instruction multiple data multiprocessorsDigital data processing detailsProcessing elementParallel processing

A method for finding an extrema for an n-dimensional array having a plurality of processing elements, the method includes determining within each processing element a first dimensional extrema for a first dimension, wherein the first dimensional extrema is related to the local extrema of the processing elements in the first dimension and wherein the first dimensional extrema has a most significant byte and a least significant byte, determining within each processing element a next dimensional extrema for a next dimension of the n-dimensional array, wherein the next dimensional extrema is related to the first dimensional extrema and wherein the next dimensional extrema has a most significant byte and a least significant byte; and repeating the determining within each processing element a next dimensional extrema for each of the n-dimensions, wherein each of the next dimensional extrema is related to a dimensional extrema from a previously selected dimension.

Owner:MICRON TECH INC

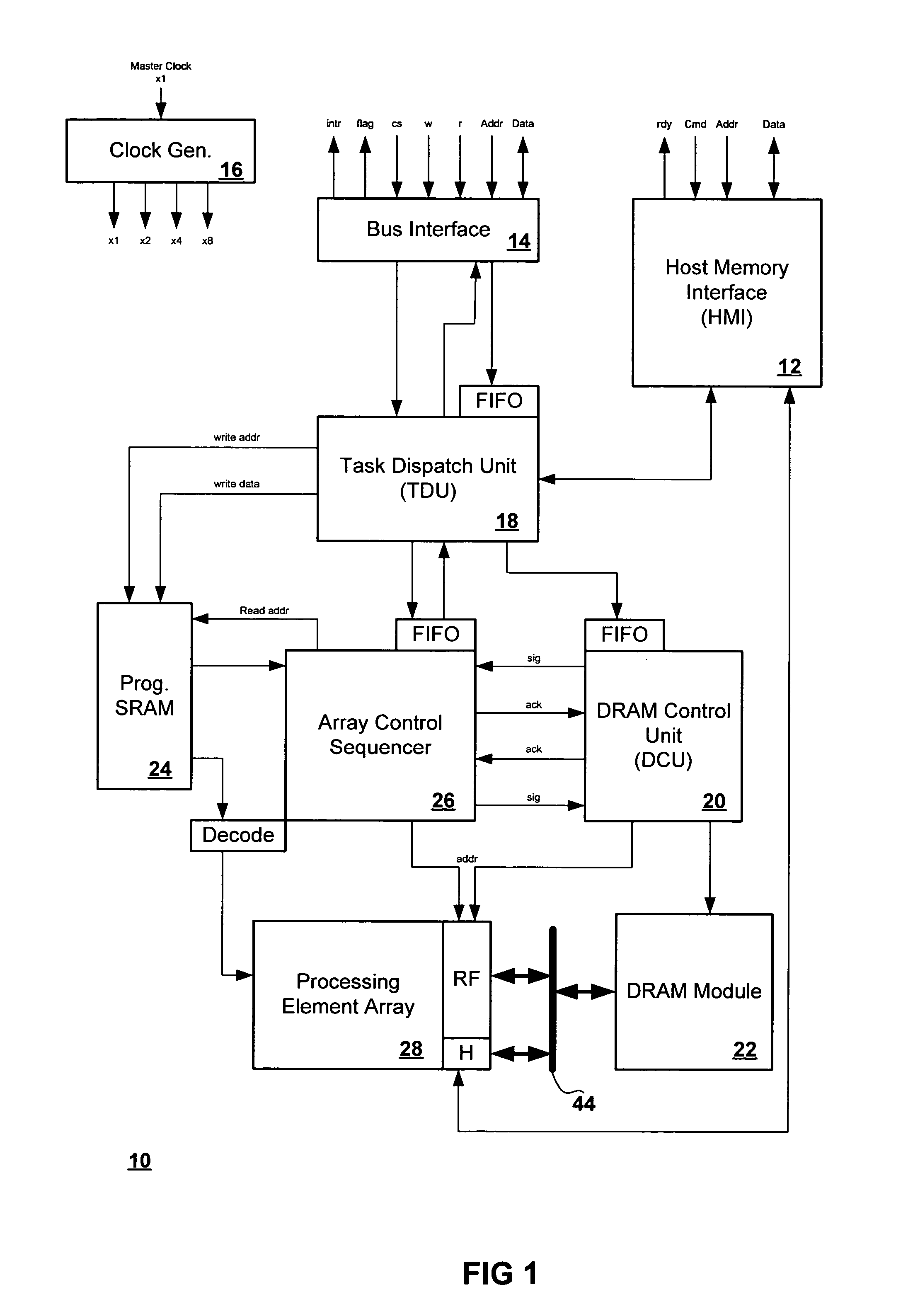

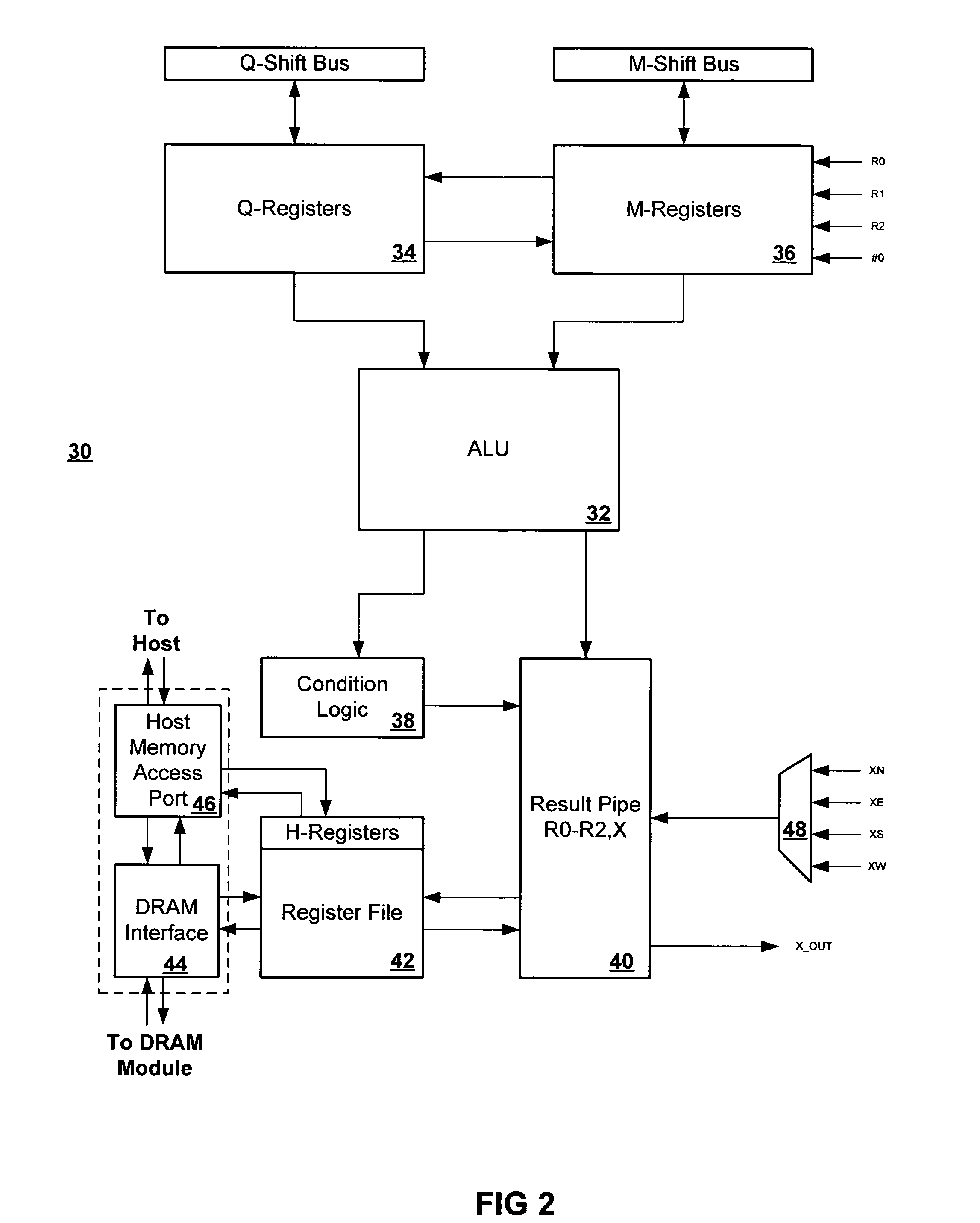

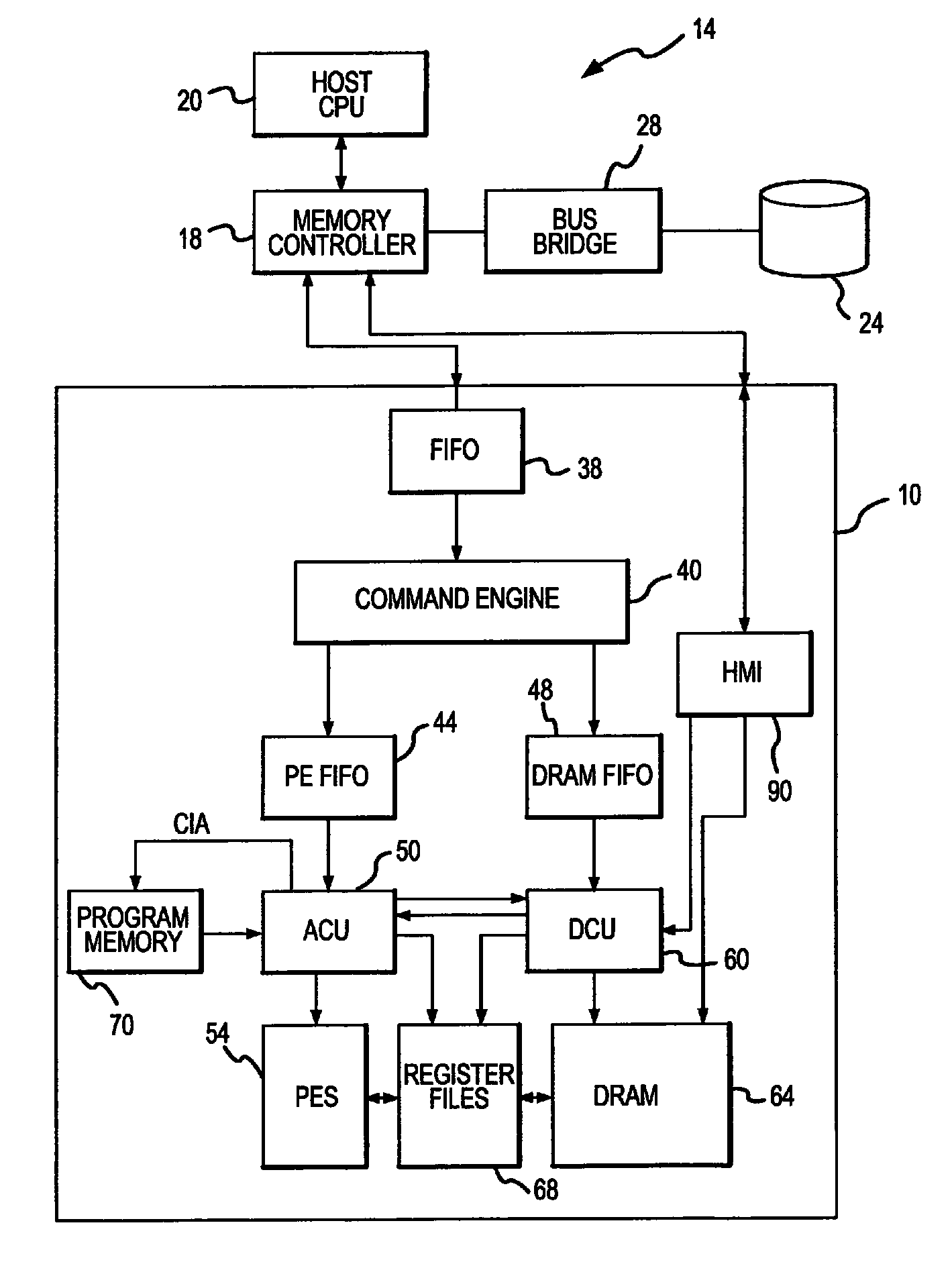

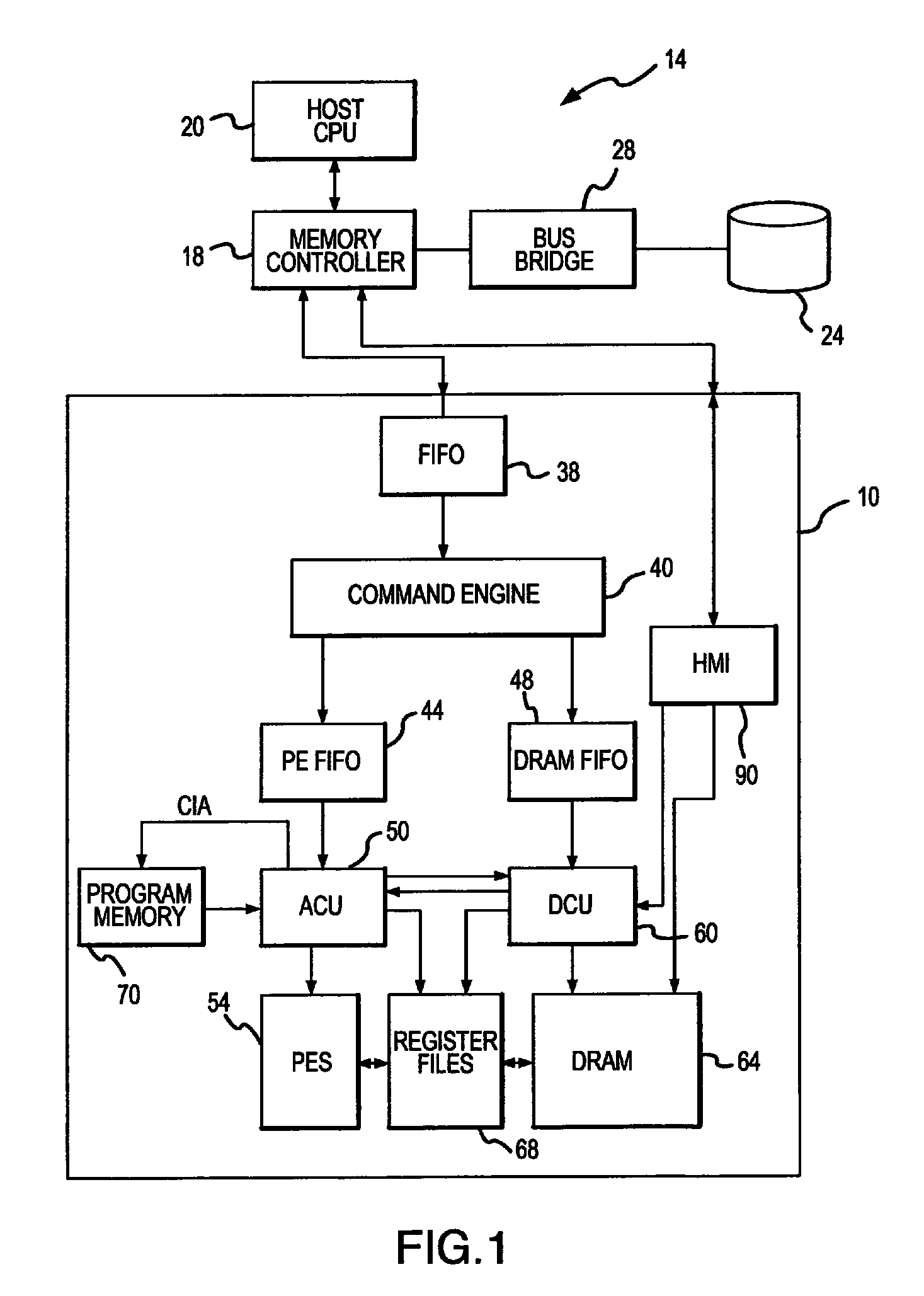

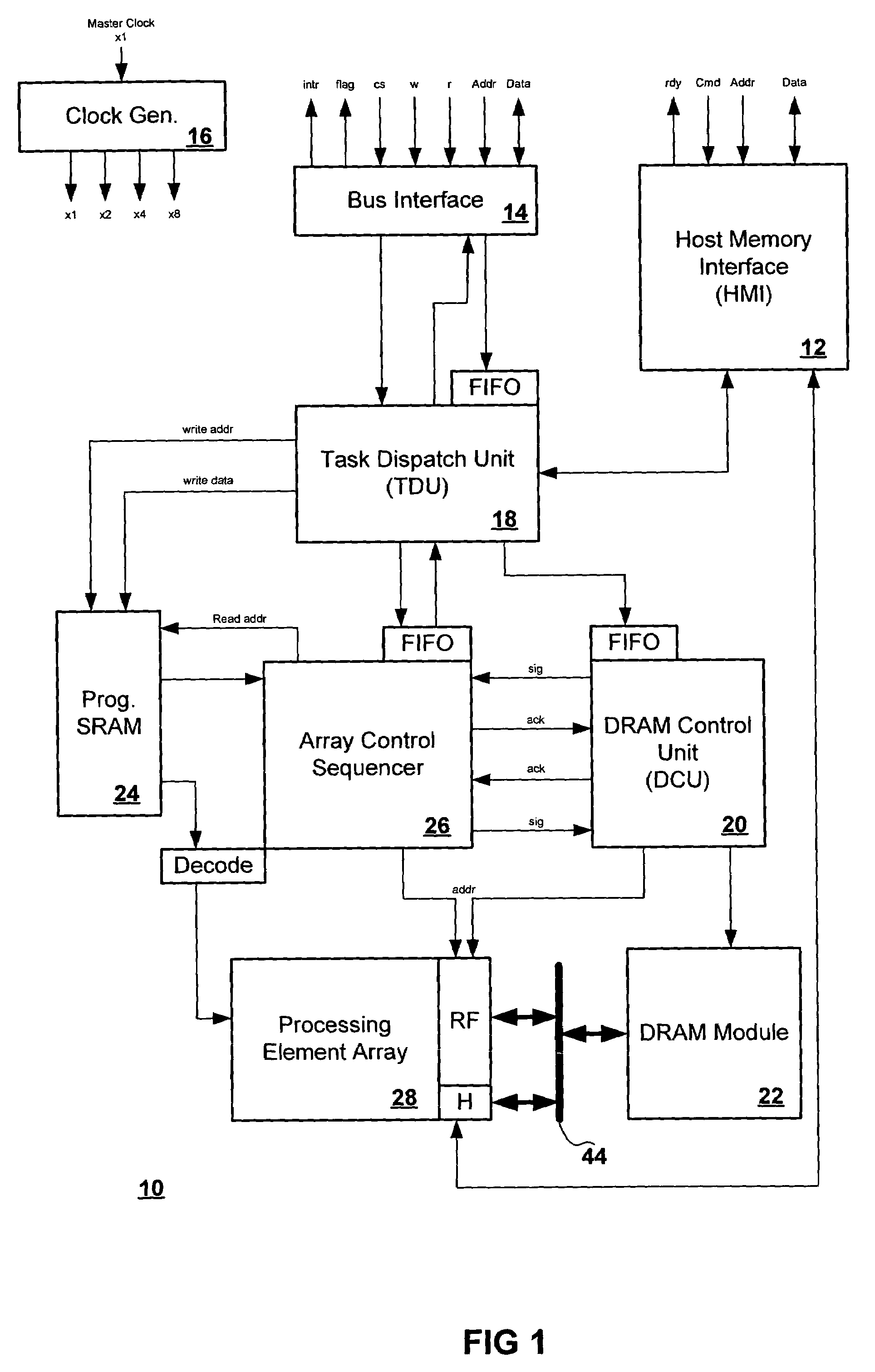

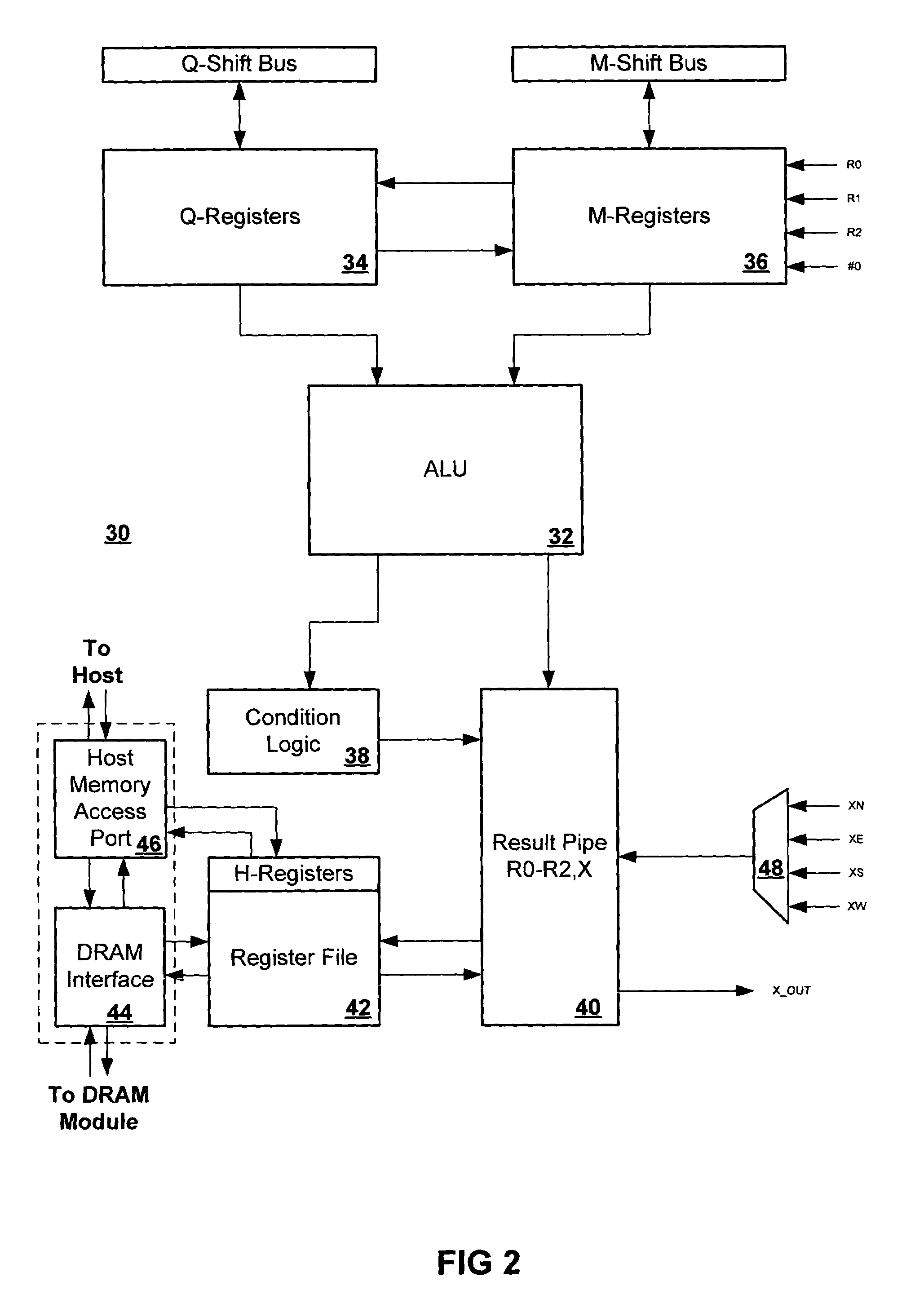

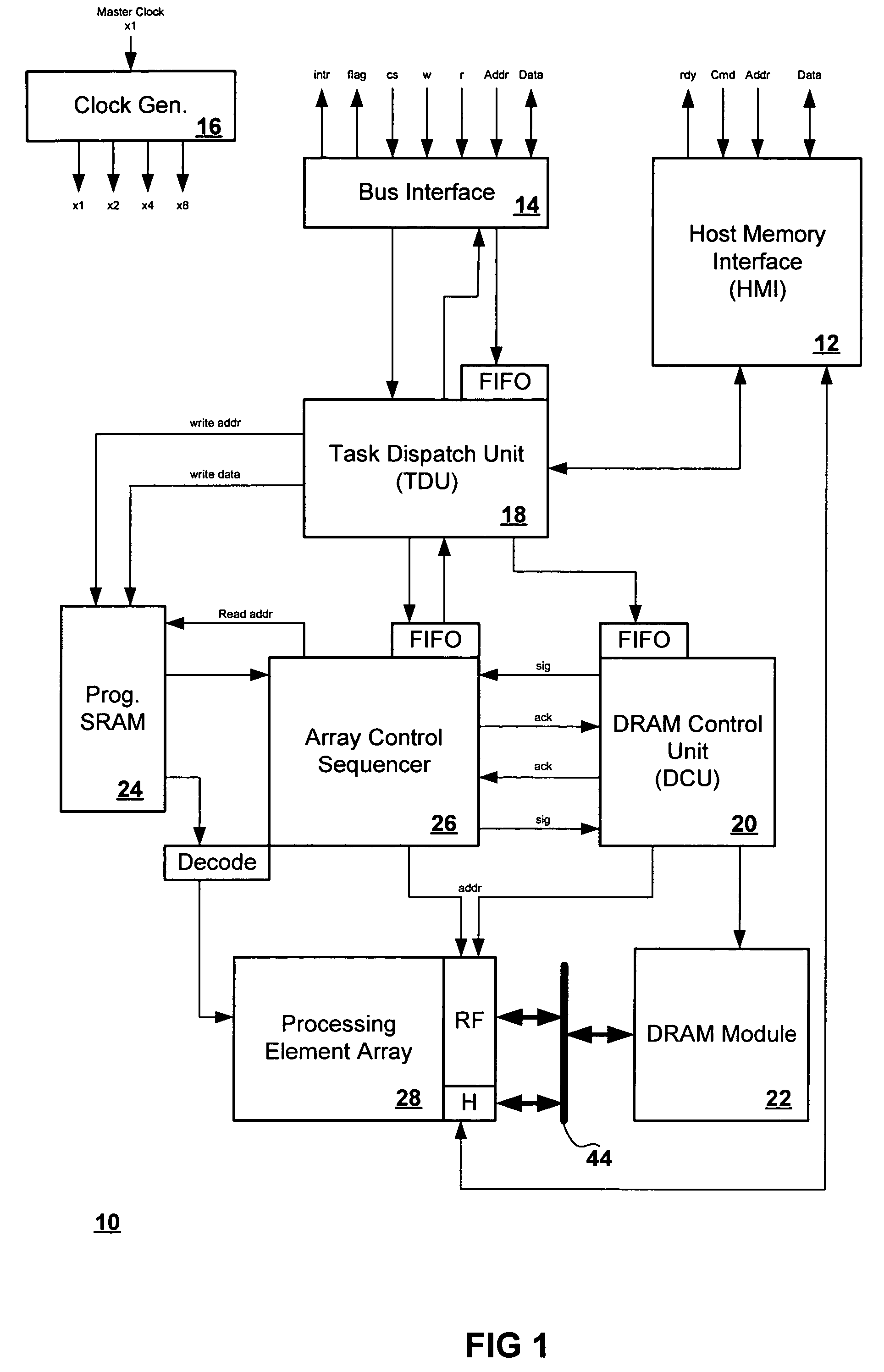

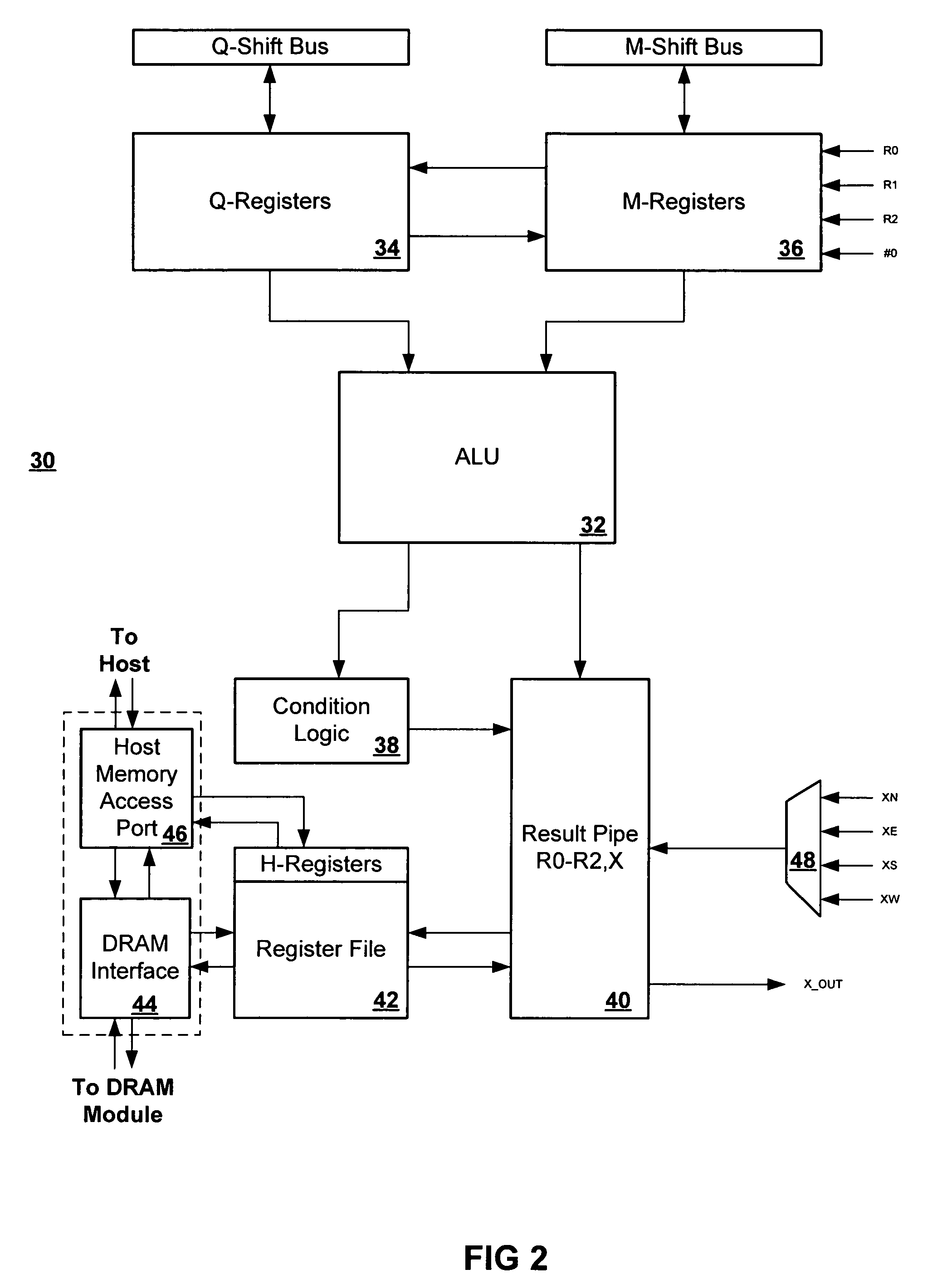

Active memory data compression system and method

ActiveUS9015390B2Concurrent instruction executionArchitecture with single central processing unitMass storageData compression

An integrated circuit active memory device receives task commands from a component in a host computer system that may include the active memory device. The host system includes a memory controller coupling the active memory device to a host CPU and a mass storage device. The active memory device includes a command engine issuing instructions responsive to the task commands to either an array control unit or a DRAM control unit. The instructions provided to the DRAM control unit cause data to be written to or read from a DRAM and coupled to or from either the processing elements or a host / memory interface. The processing elements execute instructions provided by the array control unit to decompress data written to the DRAM through the host / memory interface and compress data read from the DRAM through the host / memory interface.

Owner:MICRON TECH INC

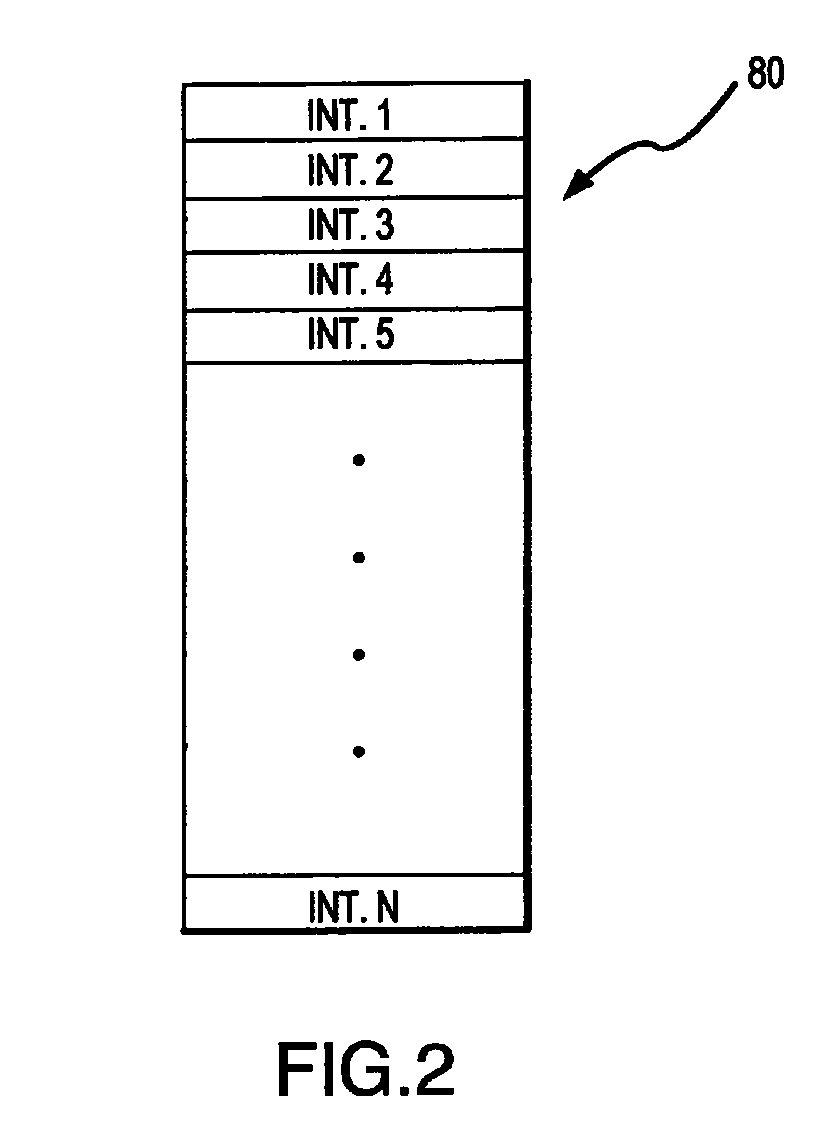

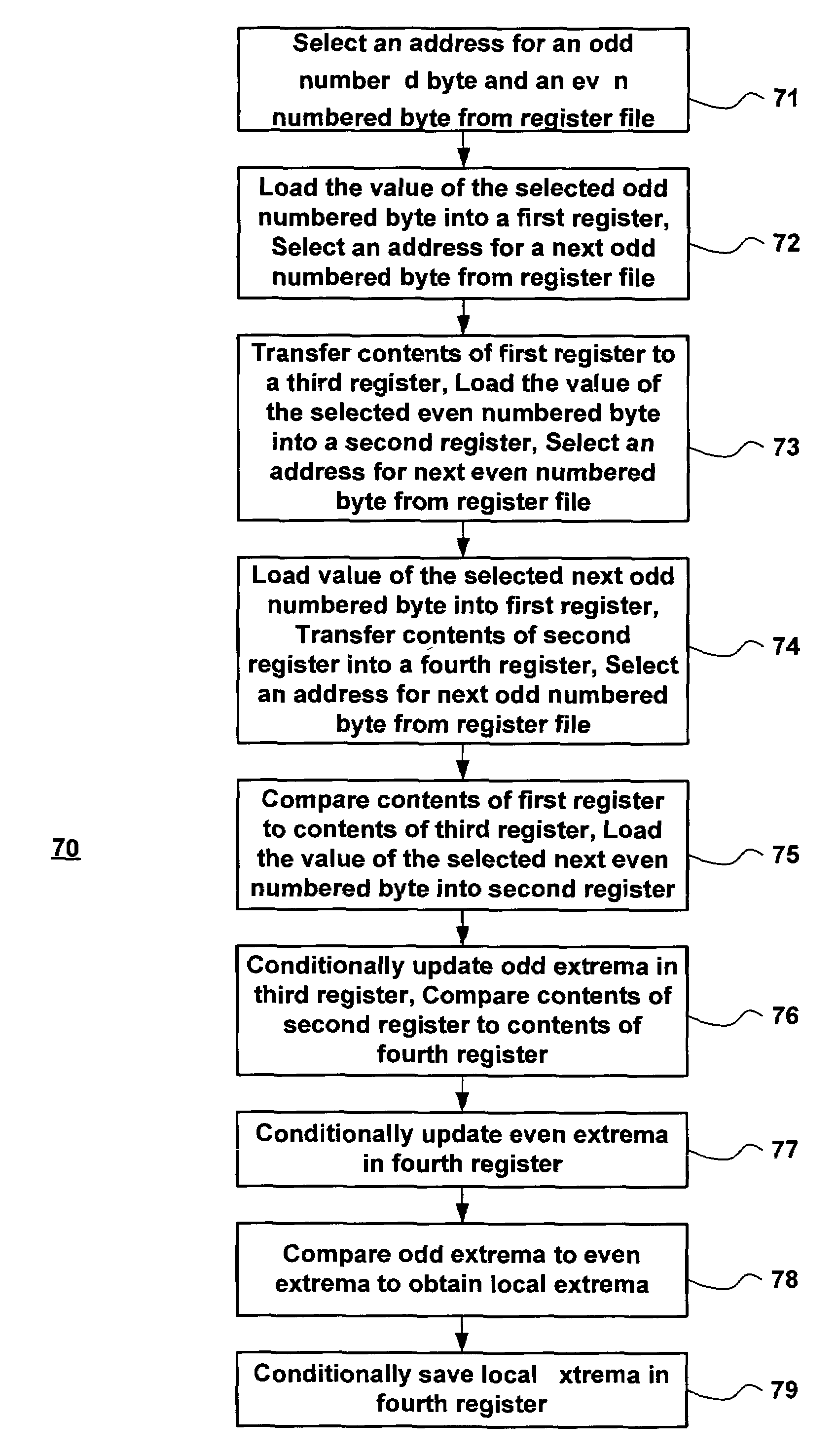

Method for finding local extrema of a set of values for a parallel processing element

ActiveUS7454451B2Digital data processing detailsDigital computer detailsTheoretical computer scienceProcessing element

A method for finding a local extrema for a single processing element having a set of values associated therewith includes separating the set of values into an odd set of values and an even set of values, determining a first extrema from the odd set of values, determining a second extrema from the even set of values, and determining the local extrema from the first extrema and the second extrema. The first extrema is found by comparing each odd-numbered value in the set to each other odd-numbered value in the set and the second extrema is found by comparing each even-numbered value in the set to each other even-numbered value in the set.

Owner:MICRON TECH INC

Method for finding global extrema of a set of bytes distributed across an array of parallel processing elements

ActiveUS7447720B2Digital data processing detailsDigital computer detailsProcessing elementParallel processing

A method for finding an extrema for an n-dimensional array having a plurality of processing elements, the method includes determining within each of the processing elements a dimensional extrema for a first dimension of the n-dimensional array, wherein the dimensional extrema is related to one or more local extrema of the processing elements in the first dimension, determining within each of the processing elements a next dimensional extrema for a next dimension of the n-dimensional array, wherein the next dimensional extrema is related to one or more of the first dimensional extrema, and repeating the determining within each of the processing elements a next dimensional extrema for each of the n-dimensions, wherein each of the next dimensional extrema is related to a dimensional extrema from a previously selected dimension.

Owner:MICRON TECH INC

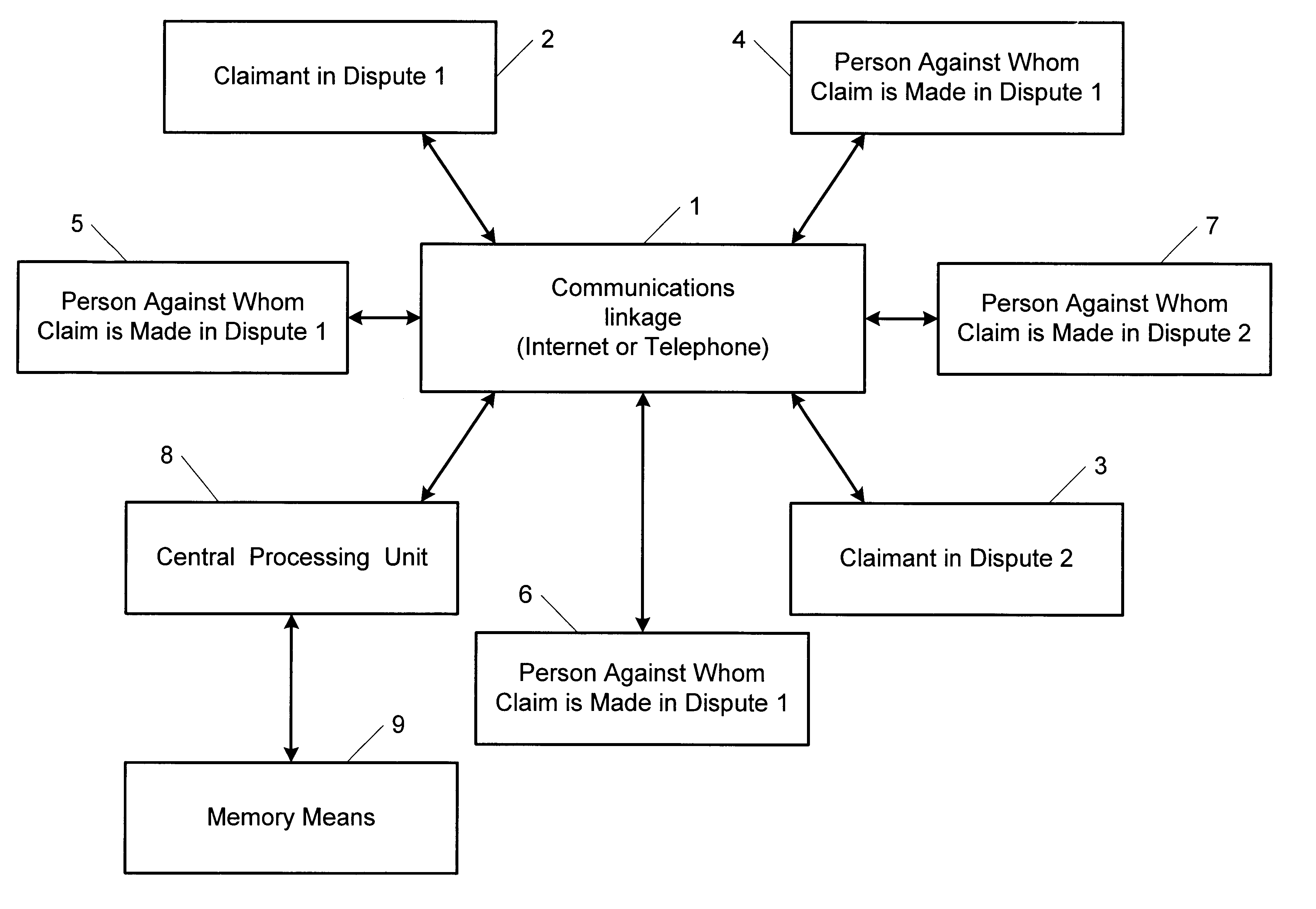

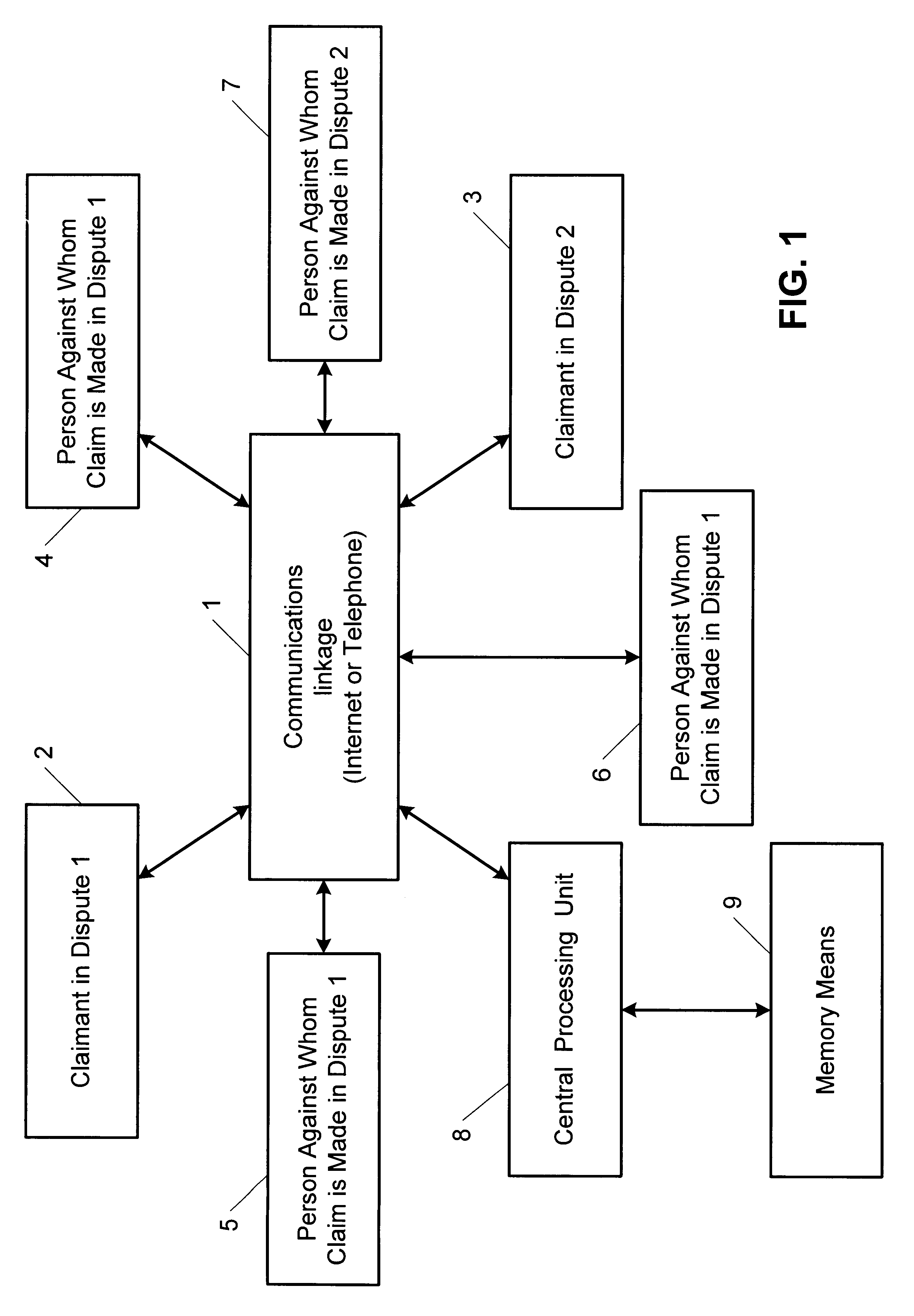

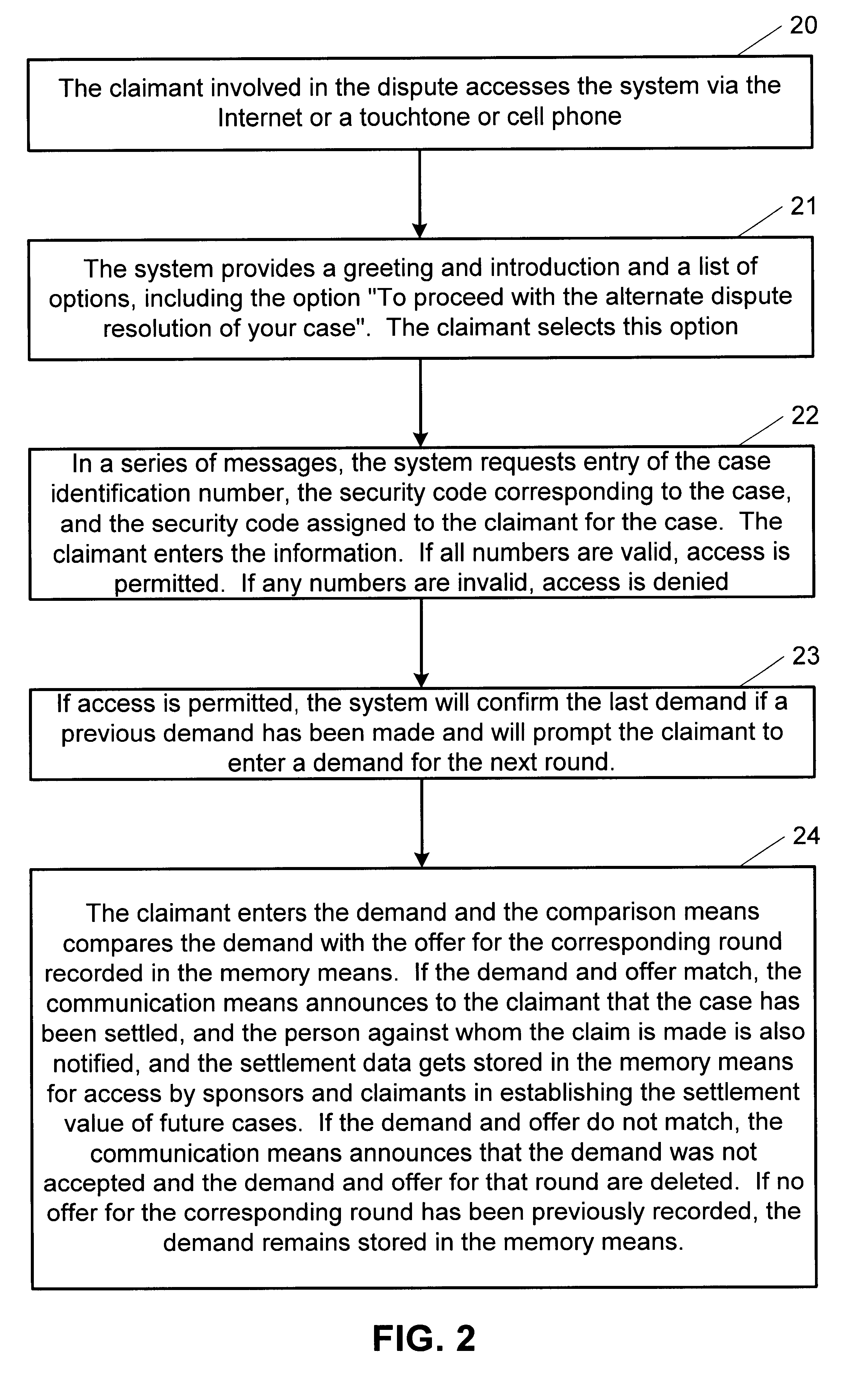

Computerized dispute resolution system and method

A computerized system for automated dispute resolution through an Intranet website via the Internet or other communications linkage for communicating and processing a series of demands to satisfy a claim made by or on behalf of a claimant or other person involved in a dispute with at least one other person, such as a defendant, his or her insurer, or other sponsor, and a series of offers to settle the claim through at least one central processing unit including operation system software for controlling the central processing unit is disclosed. Preferably the system also allows for the collection, processing and dissemination of settlement data generated from the settlement through the operation of the system for use by sponsors and claimants in establishing the settlement value of future cases. Also disclosed is a method for communicating and processing a series of demands and a series of offers through the system.

Owner:CYBERSETTLE HLDG INC

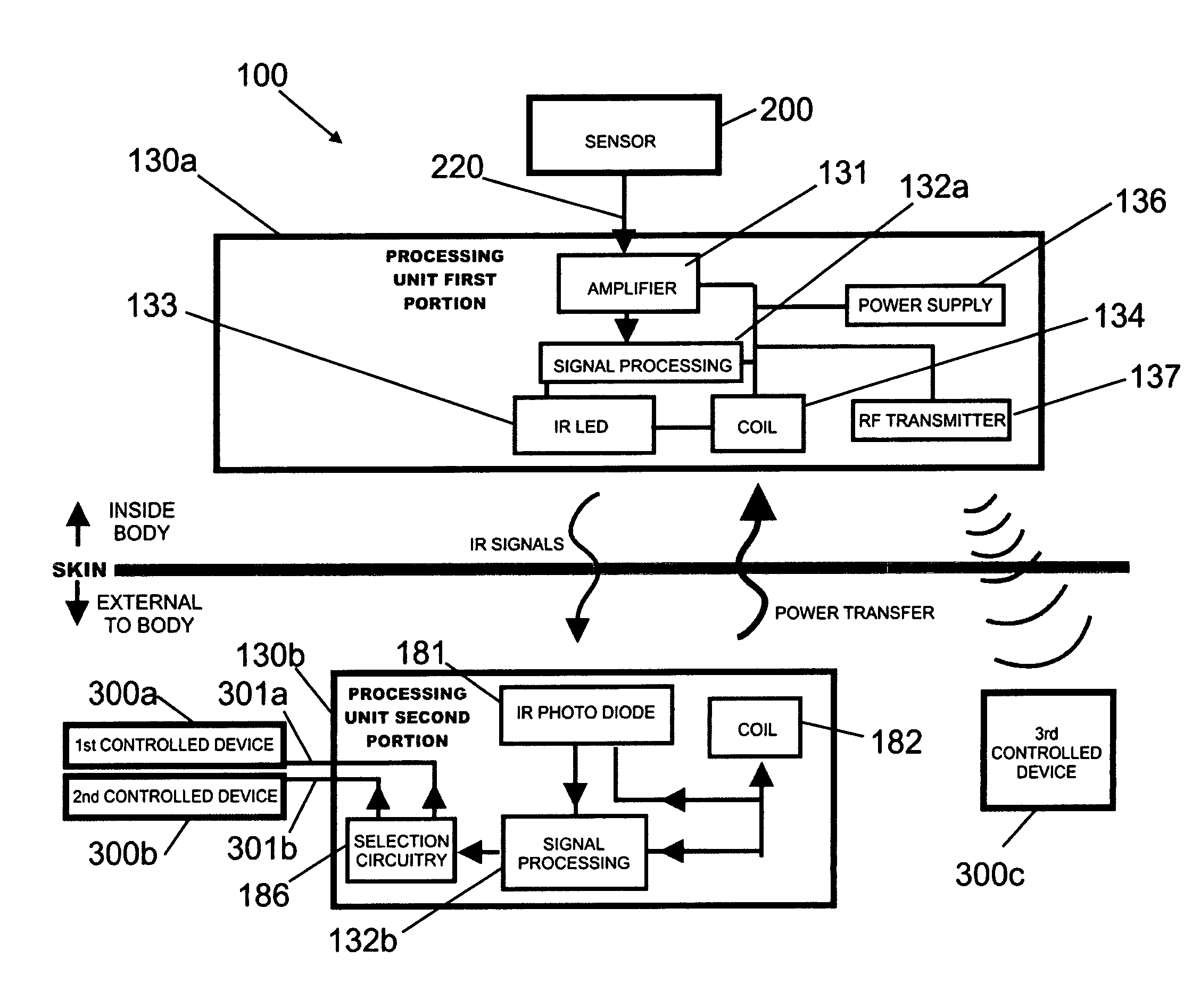

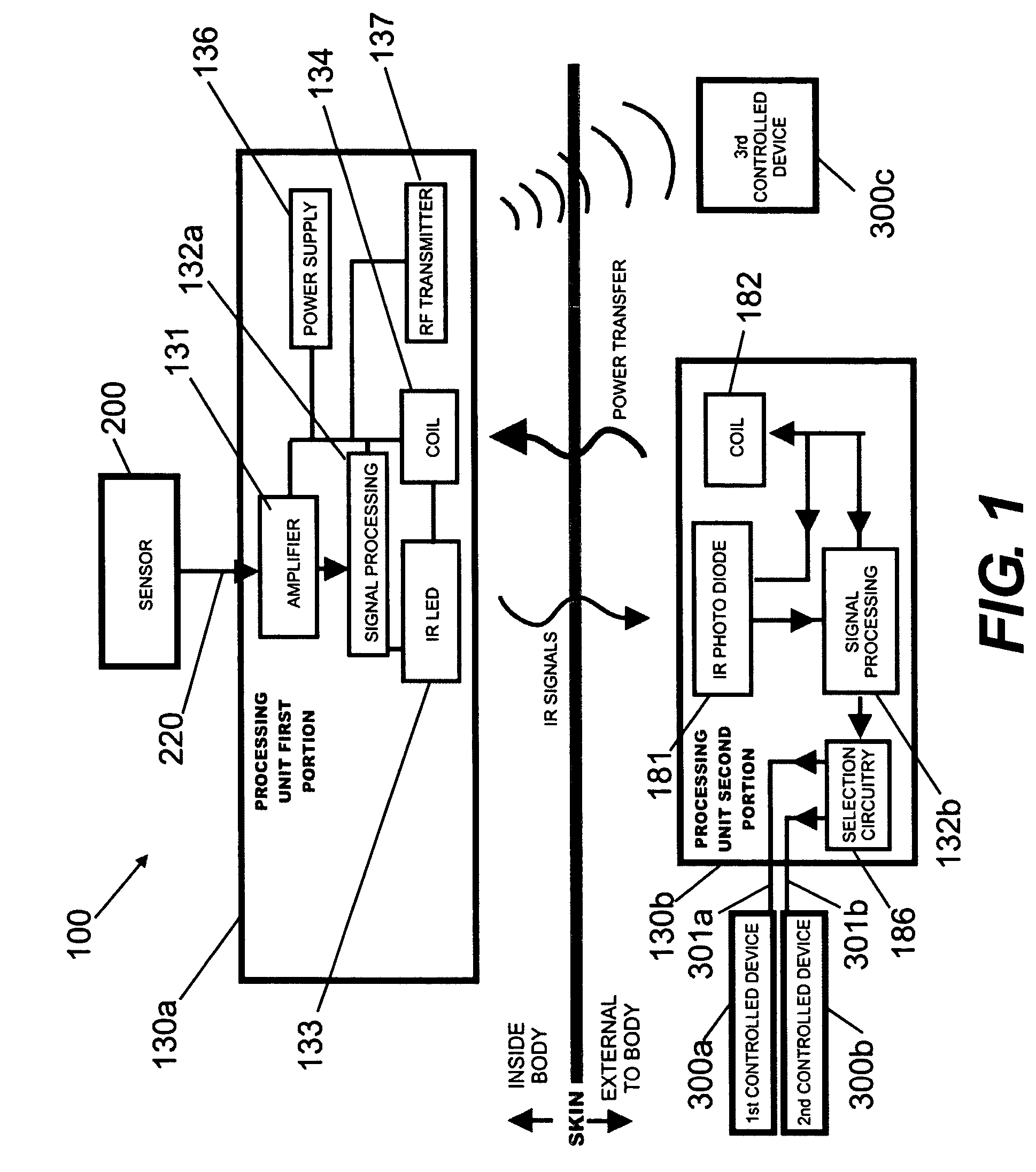

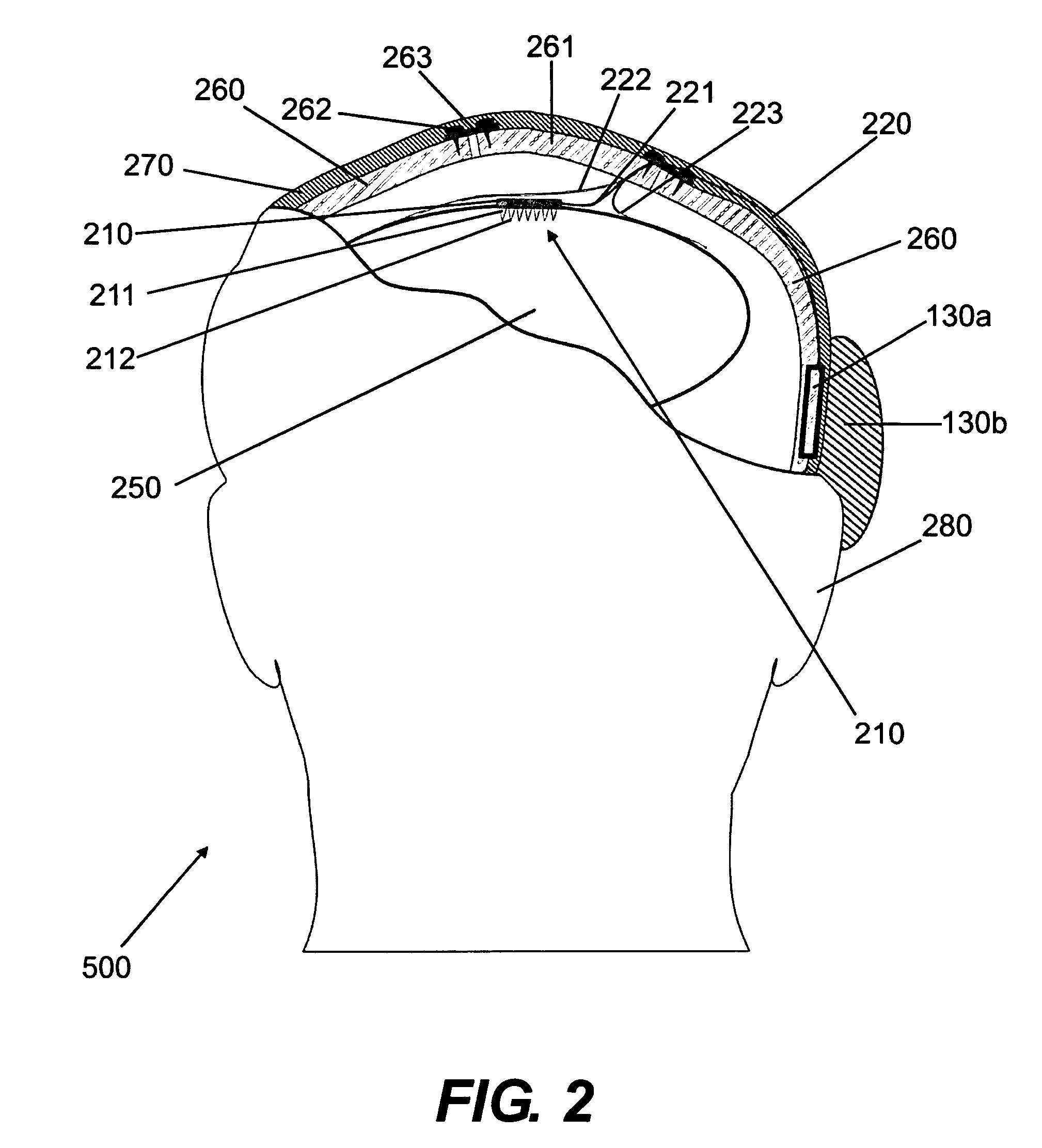

Biological interface system

A system and method for an improved biological interface system that processes multicellular signals of a patient and controls one or more devices is disclosed. The system includes a sensor that detects the multicellular signals and a processing unit for producing the control signal based on the multicellular signals. The system may include improved communication, self-diagnostics, and surgical insertion tools.

Owner:BRAINSGATE LTD +1

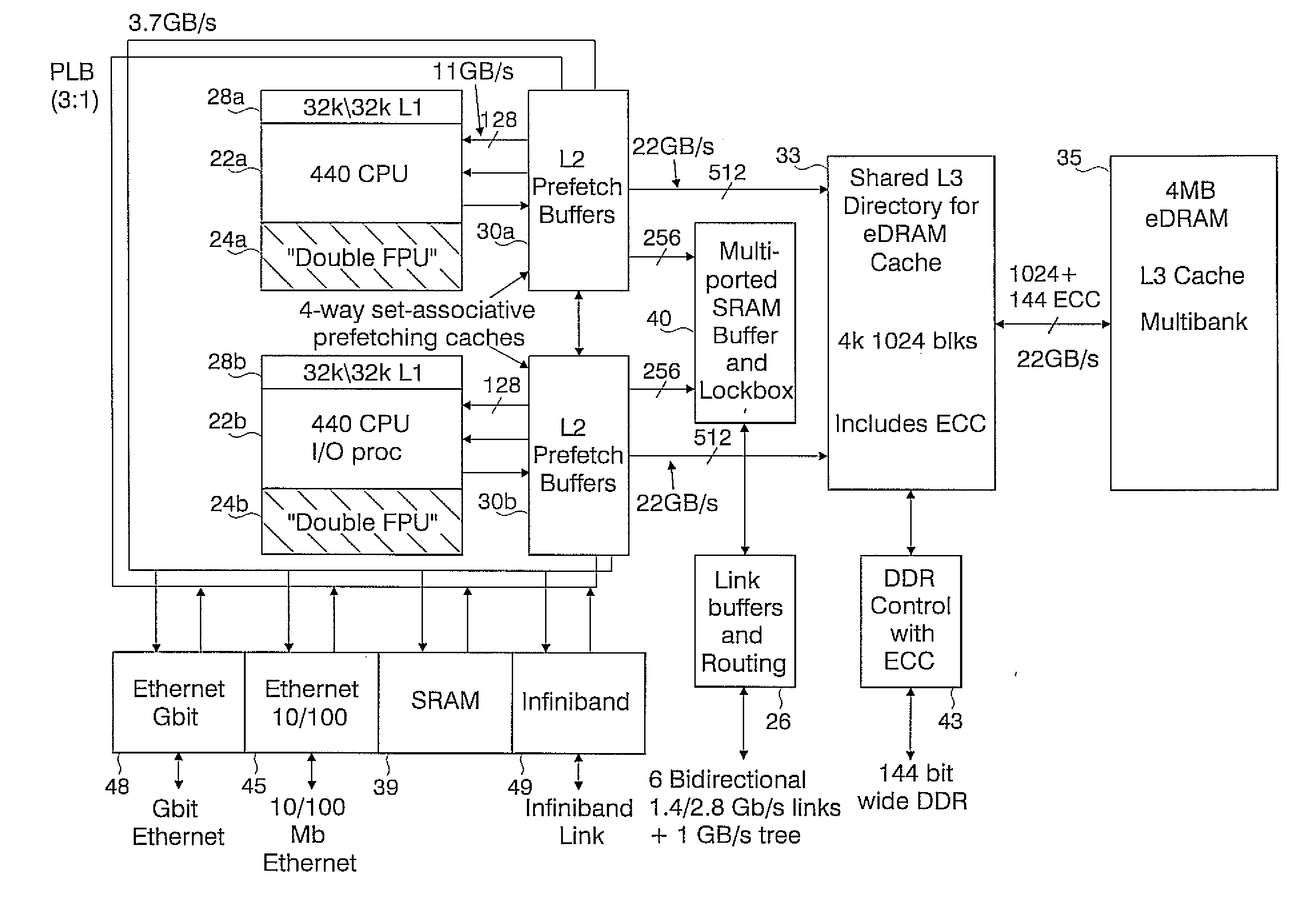

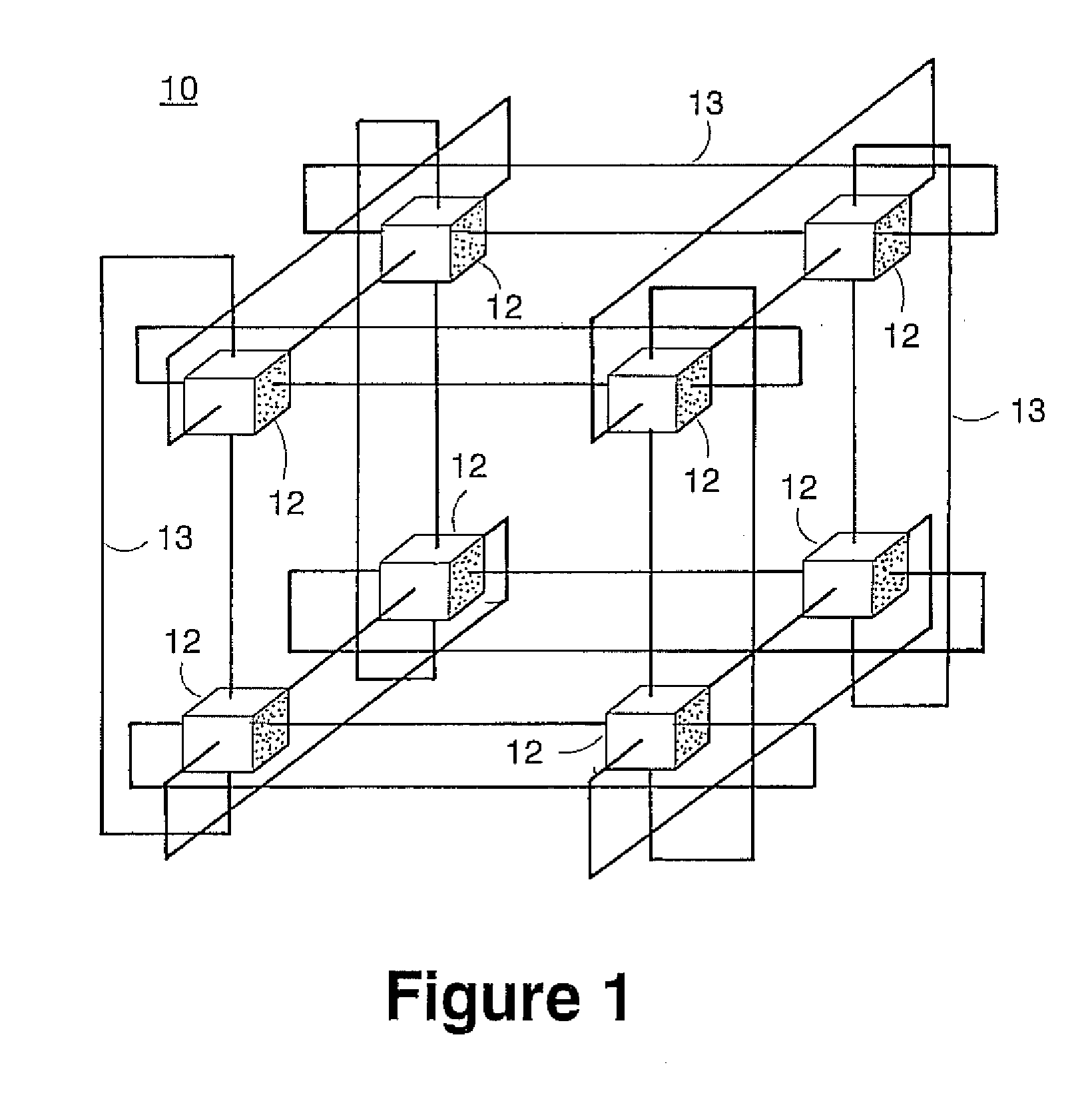

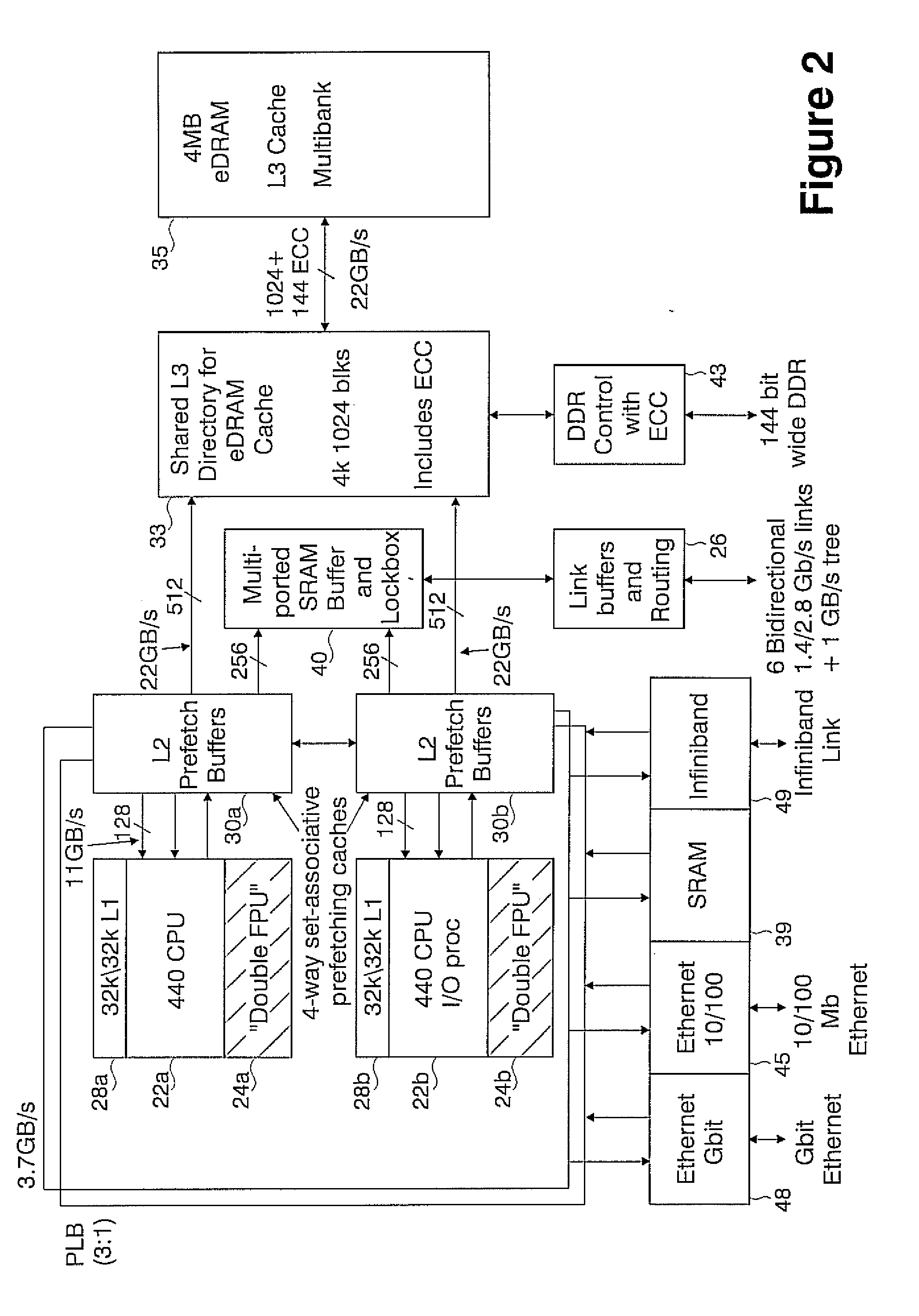

Novel massively parallel supercomputer

InactiveUS20090259713A1Low costReduced footprintError preventionProgram synchronisationSupercomputerPacket communication

Owner:INT BUSINESS MASCH CORP

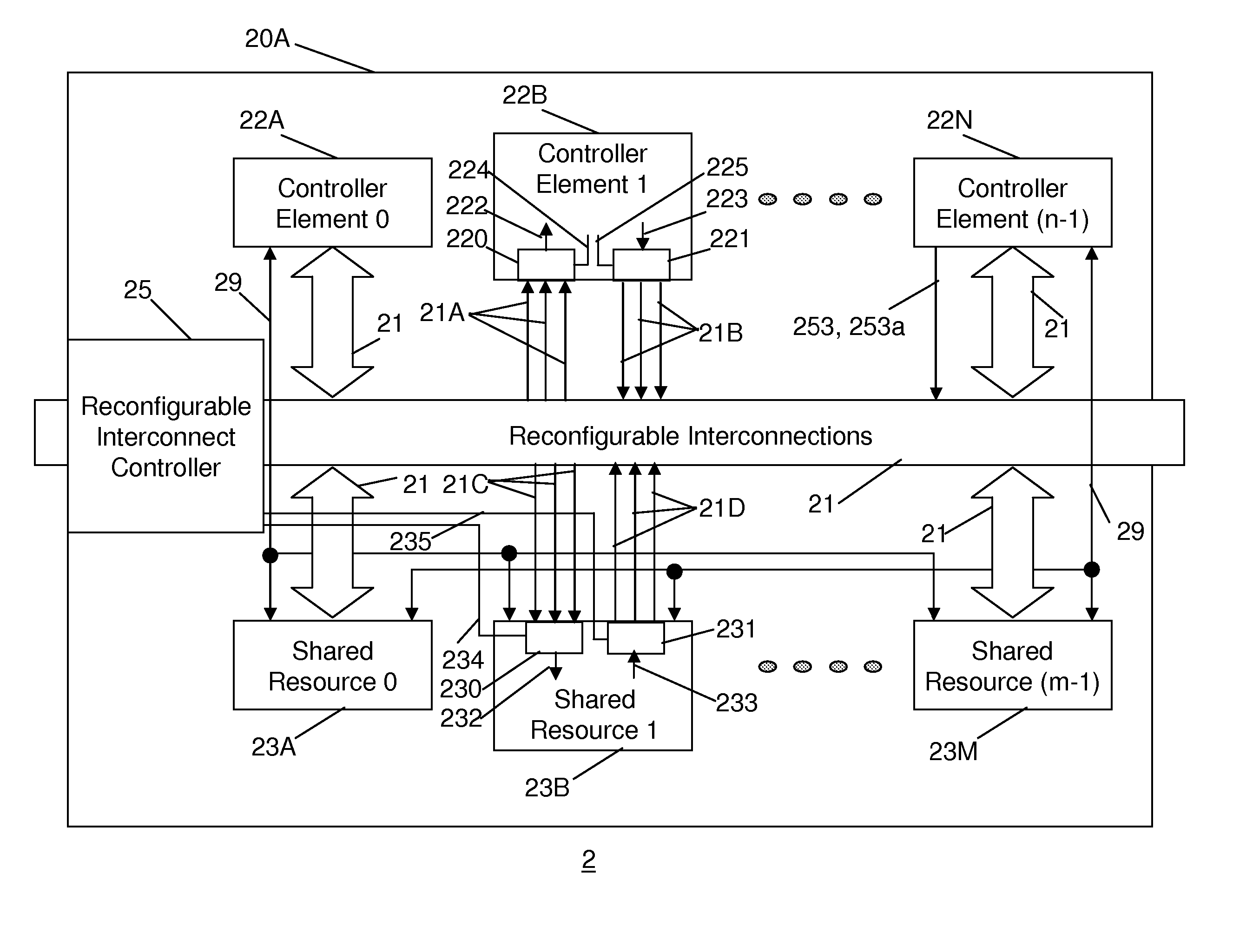

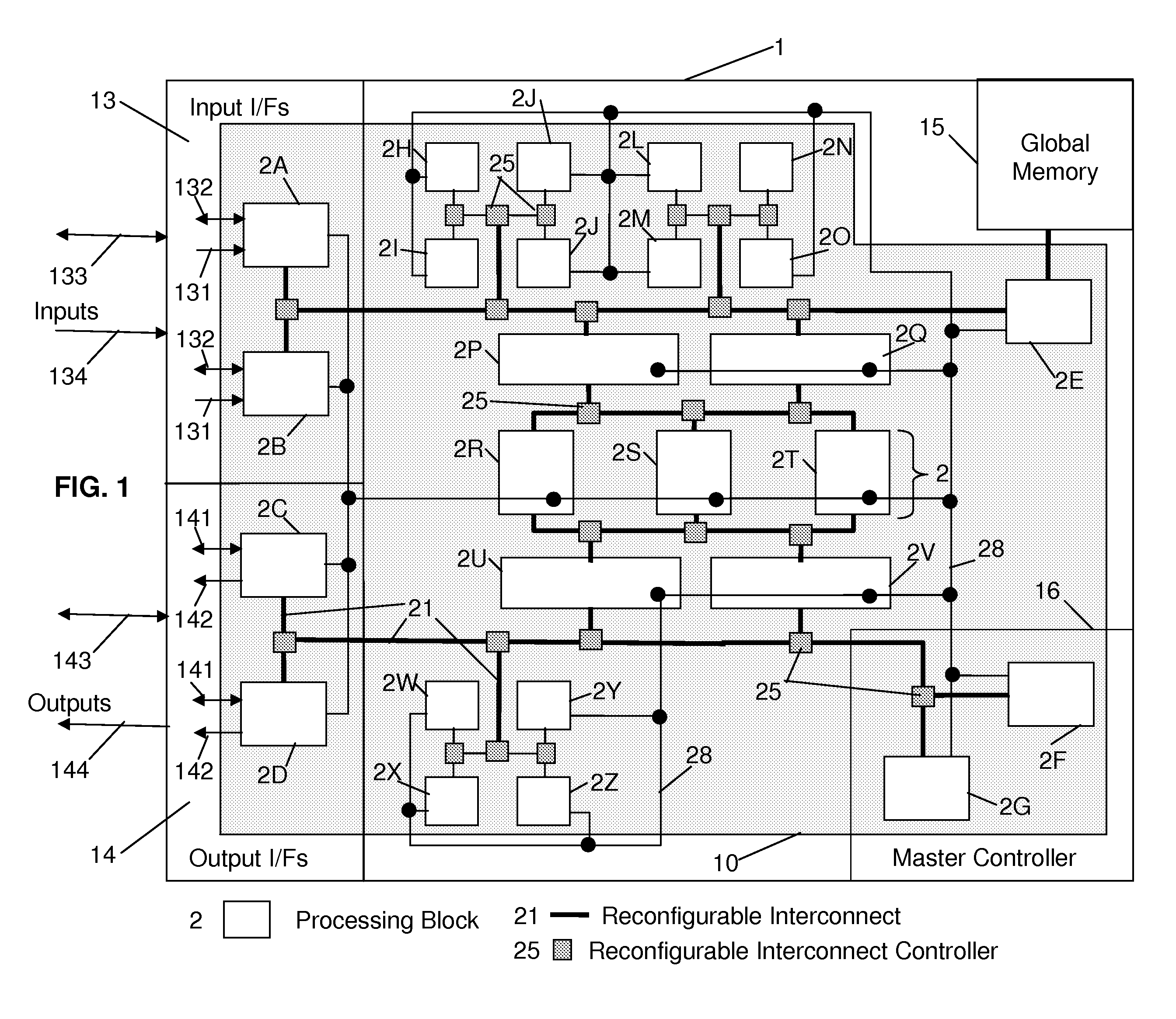

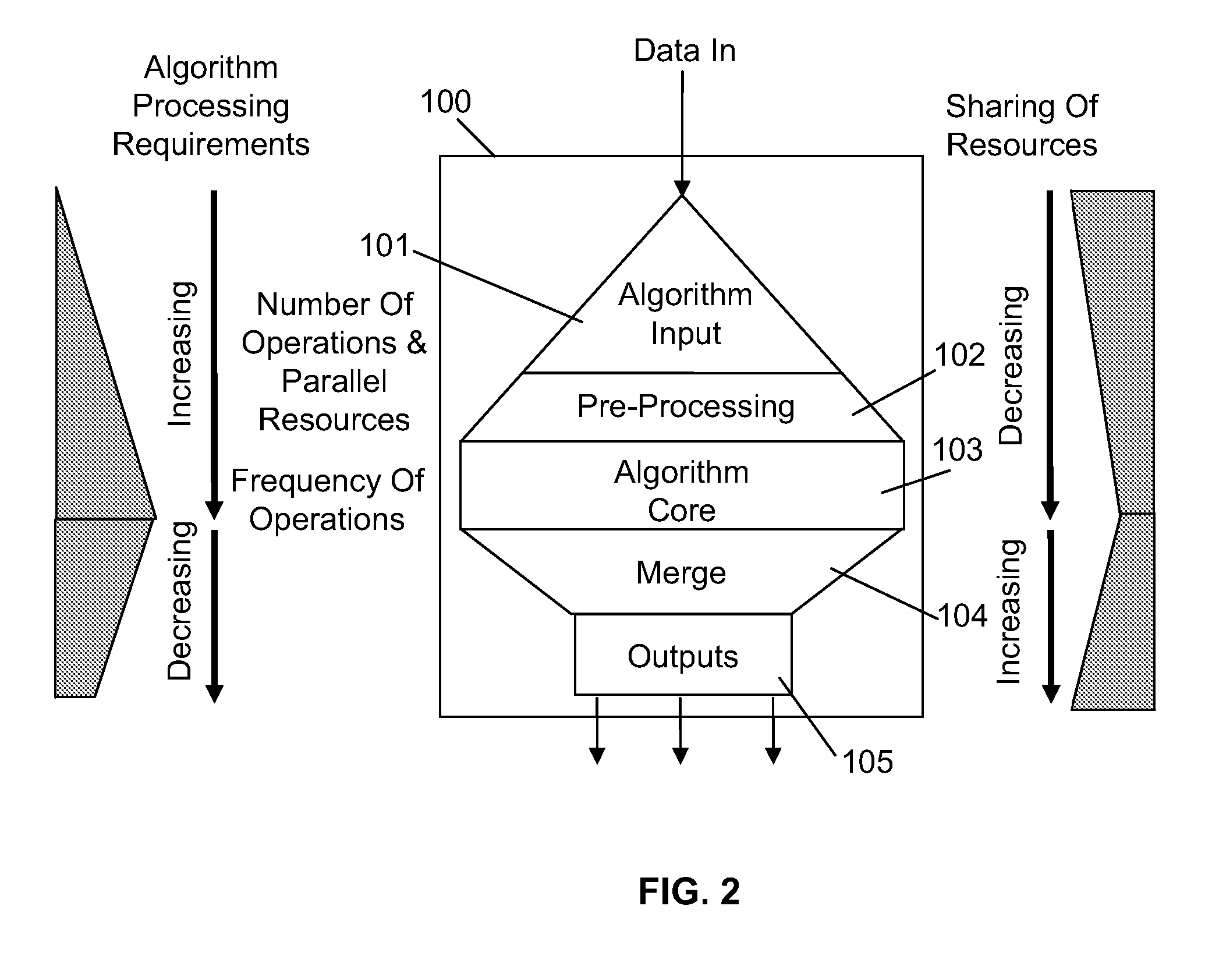

Reconfigurable integrated circuit

InactiveUS20070143577A1Energy efficient ICTArchitecture with single central processing unitNon real timeResource block

A reconfigurable integrated circuit is provided wherein the available hardware resources can be optimised for a particular application. Dynamically reconfiguring (in both real-time and non real-time) the available resources and sharing a plurality of processing elements with a plurality of controller elements achieve this. In a preferred embodiment the integrated circuit includes a plurality of processing blocks, which interface to a reconfigurable interconnection means. A processing block has two forms, namely a shared resource block and a dedicated resource block. Each processing block consists of one or a plurality of controller elements and a plurality of processing elements. The controller element and processing element generally comprise diverse rigid coarse and fine grained circuits and are interconnected through dedicated and reconfigurable interconnect. The processing blocks can be configured as a hierarchy of blocks and or fractal architecture.

Owner:AKYA HLDG

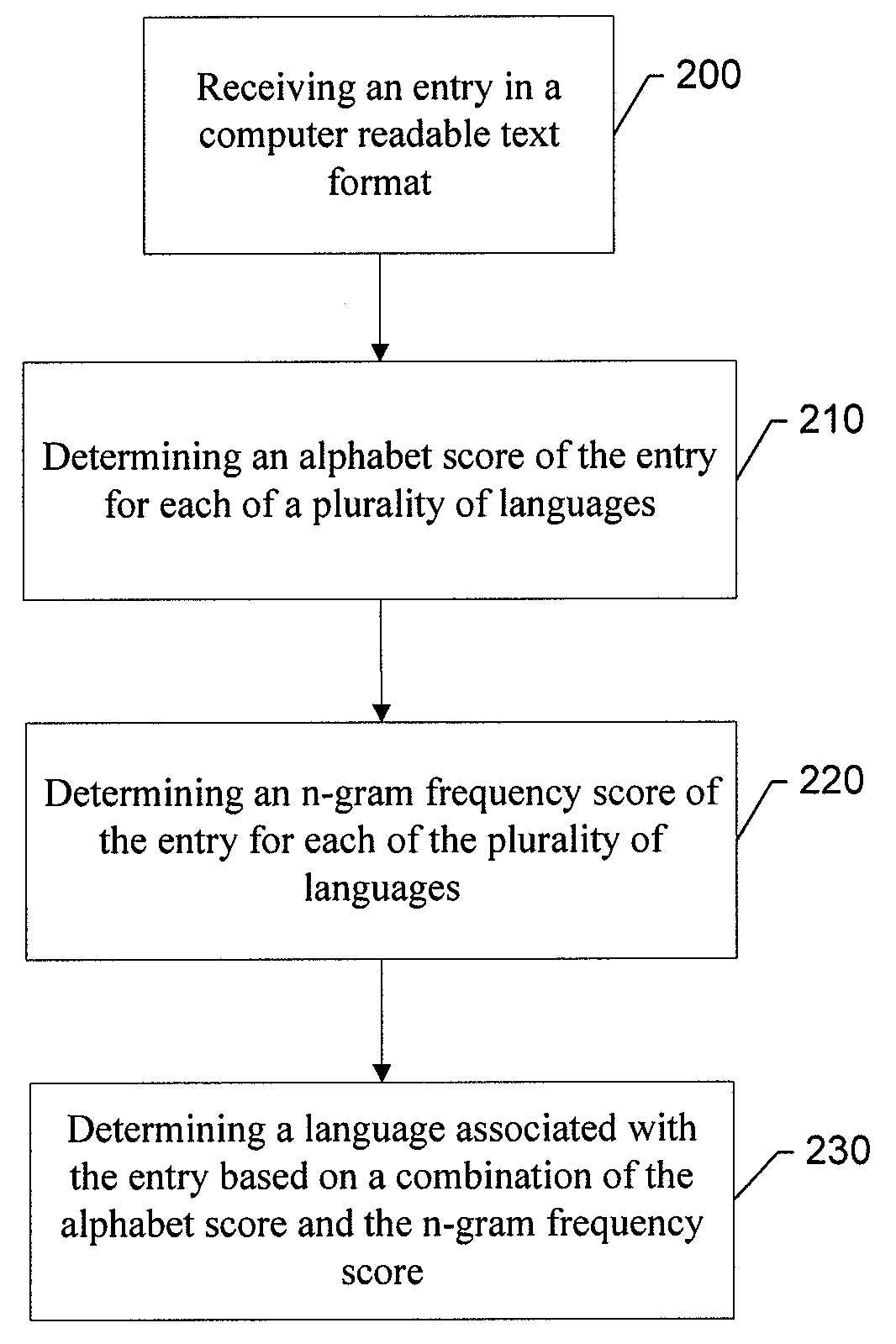

Method, apparatus and computer program product for providing flexible text based language identification

ActiveUS7552045B2Accurate analysisHighly configurable multilingualSpeech analysisNatural language data processingProcessing elementHuman language

An apparatus for providing flexible text based language identification includes an alphabet scoring element, an n-gram frequency element and a processing element. The alphabet scoring element may be configured to receive an entry in a computer readable text format and to calculate an alphabet score of the entry for each of a plurality of languages. The n-gram frequency element may be configured to calculate an n-gram frequency score of the entry for each of the plurality of languages. The processing element may be in communication with the n-gram frequency element and the alphabet scoring element. The processing element may also be configured to determine a language associated with the entry based on a combination of the alphabet score and the n-gram frequency score.

Owner:NOKIA TECH OY

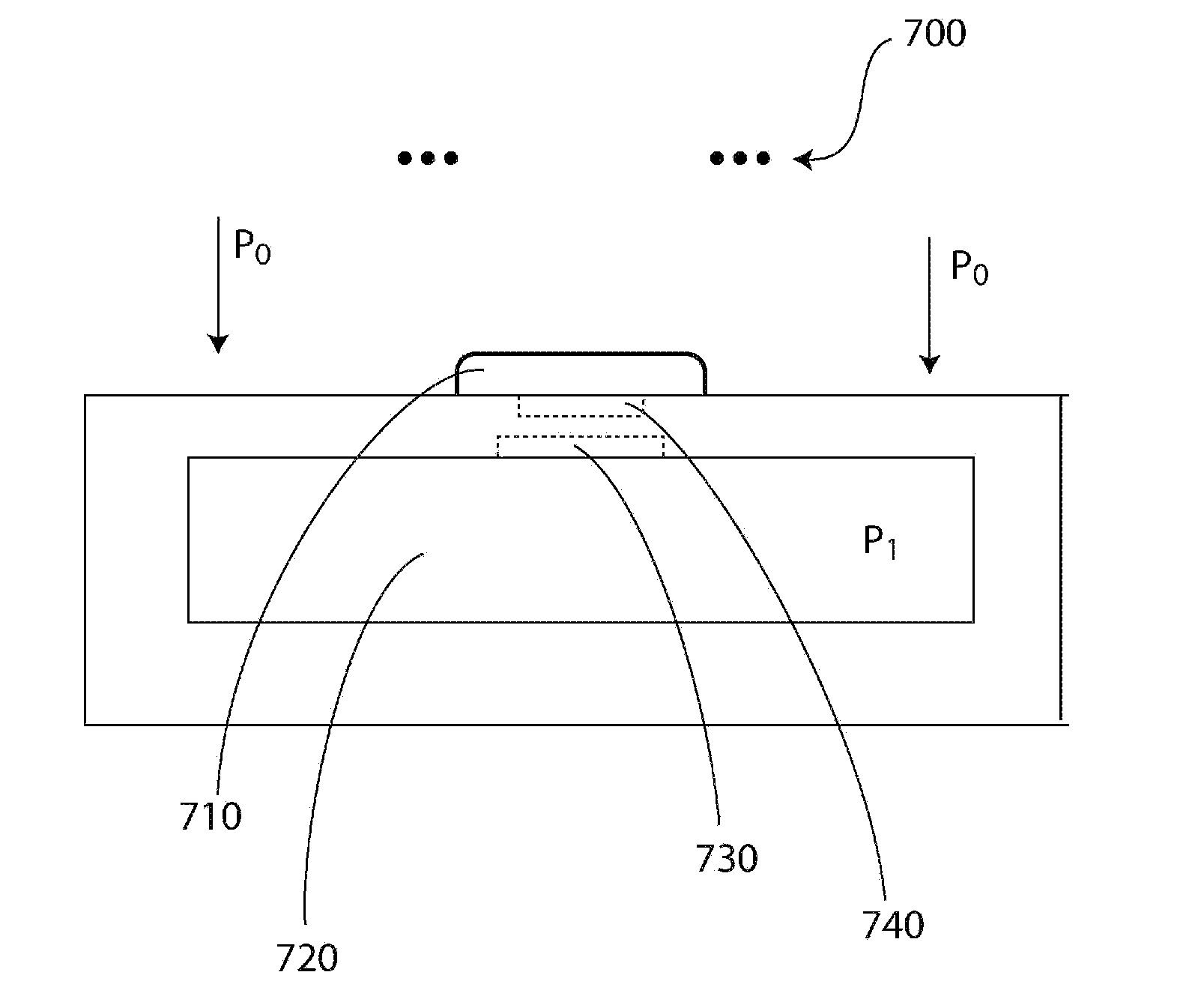

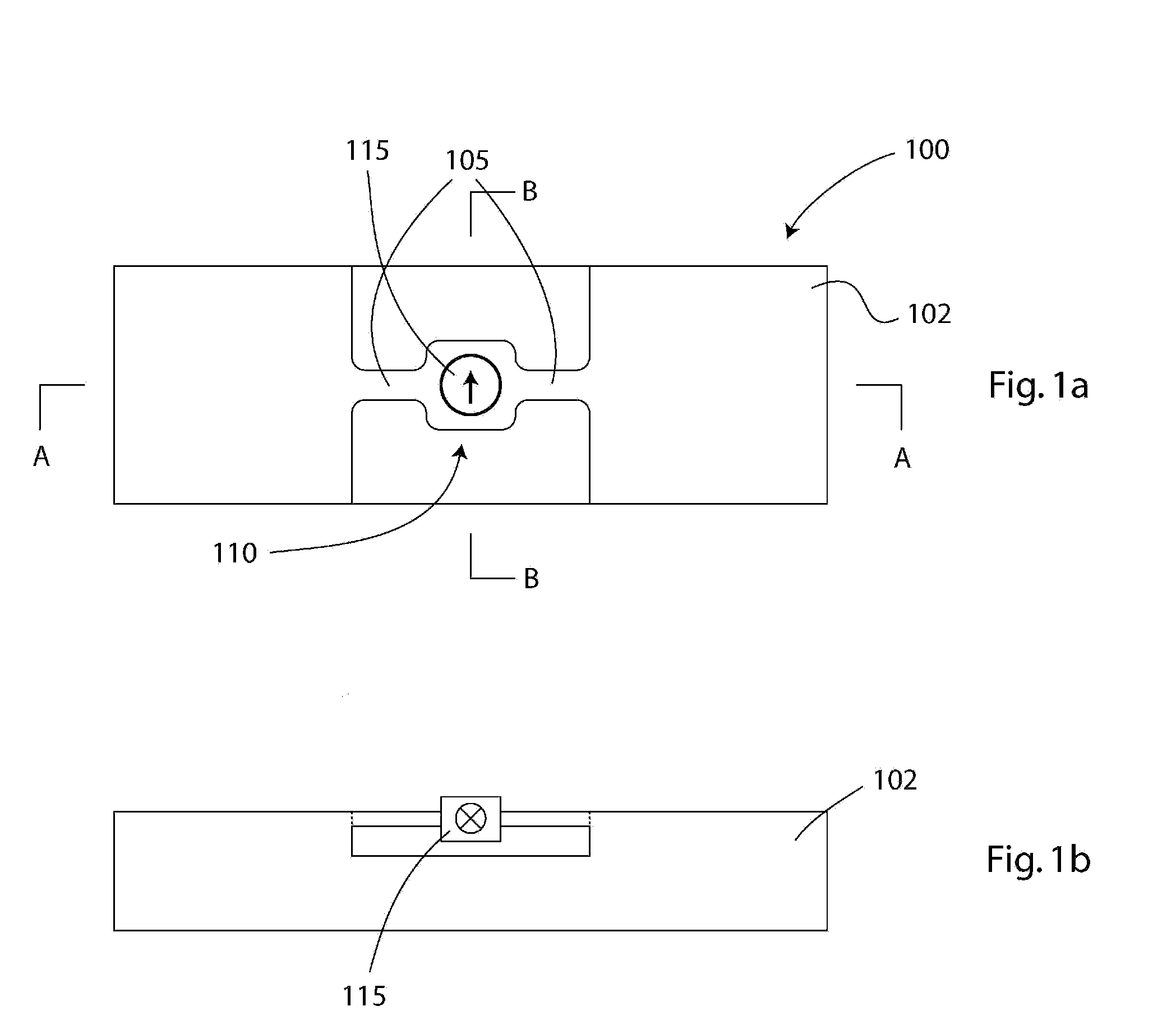

Telemetry method and apparatus using magnetically-driven MEMS resonant structure

InactiveUS20070236213A1High quality factorImprove reliabilityMagnetic property measurementsDiagnostic recording/measuringIntraocular pressurePressure sense

A telemetry method and apparatus using pressure sensing elements remotely located from associated pick-up, and processing units for the sensing and monitoring of pressure within an environment. This includes remote pressure sensing apparatus incorporating a magnetically-driven resonator being hermetically-sealed within an encapsulating shell or diaphragm and associated new method of sensing pressure. The resonant structure of the magnetically-driven resonator is suitable for measuring quantities convertible to changes in mechanical stress or mass. The resonant structure can be integrated into pressure sensors, adsorbed mass sensors, strain sensors, and the like. The apparatus and method provide information by utilizing, or listening for, the residence frequency of the oscillating resonator. The resonant structure listening frequencies of greatest interest are those at the mechanical structure's fundamental or harmonic resonant frequency. The apparatus is operable within a wide range of environments for remote one-time, random, periodic, or continuous / on-going monitoring of a particular fluid environment. Applications include biomedical applications such as measuring intraocular pressure, blood pressure, and intracranial pressure sensing.

Owner:LAUNCHPOINT TECH

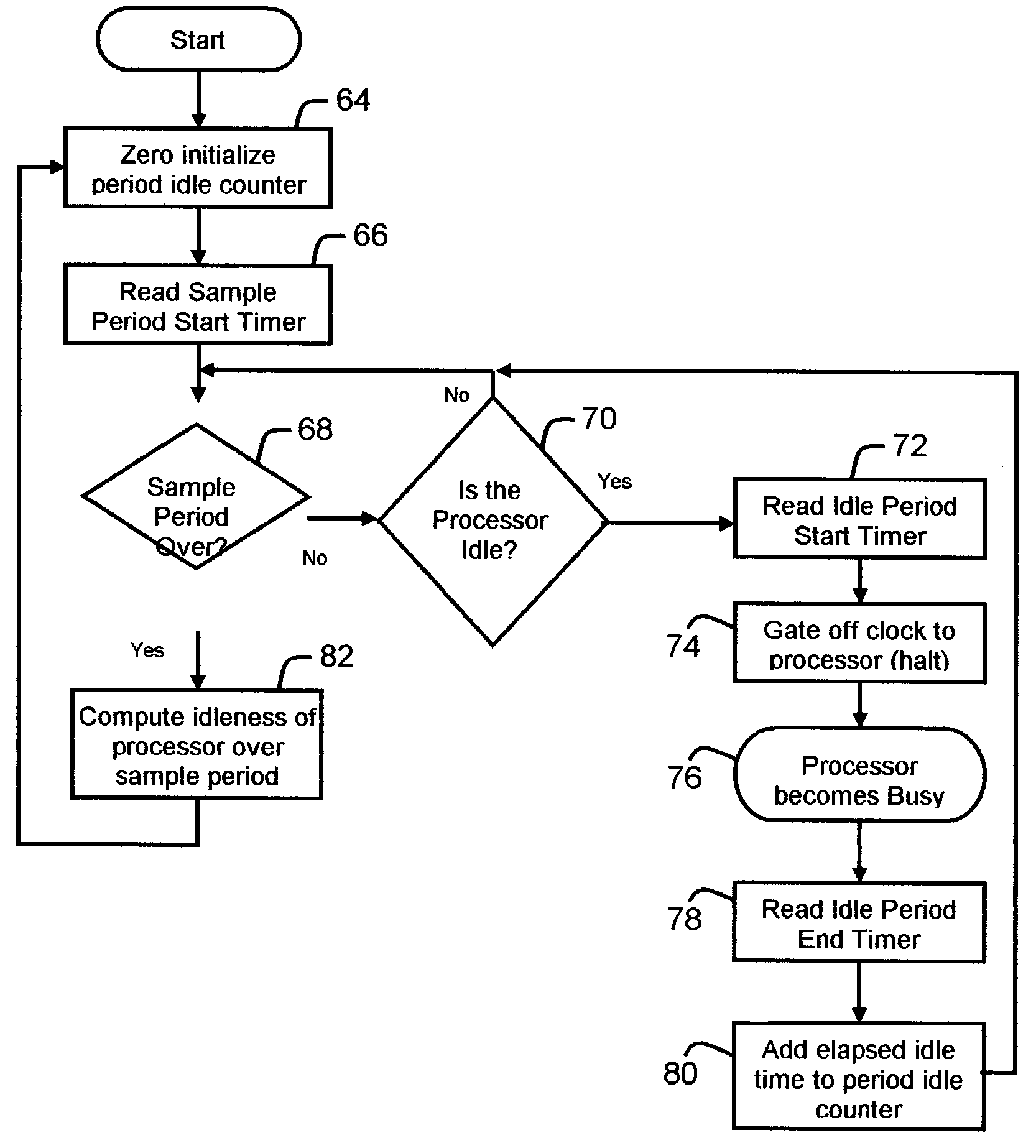

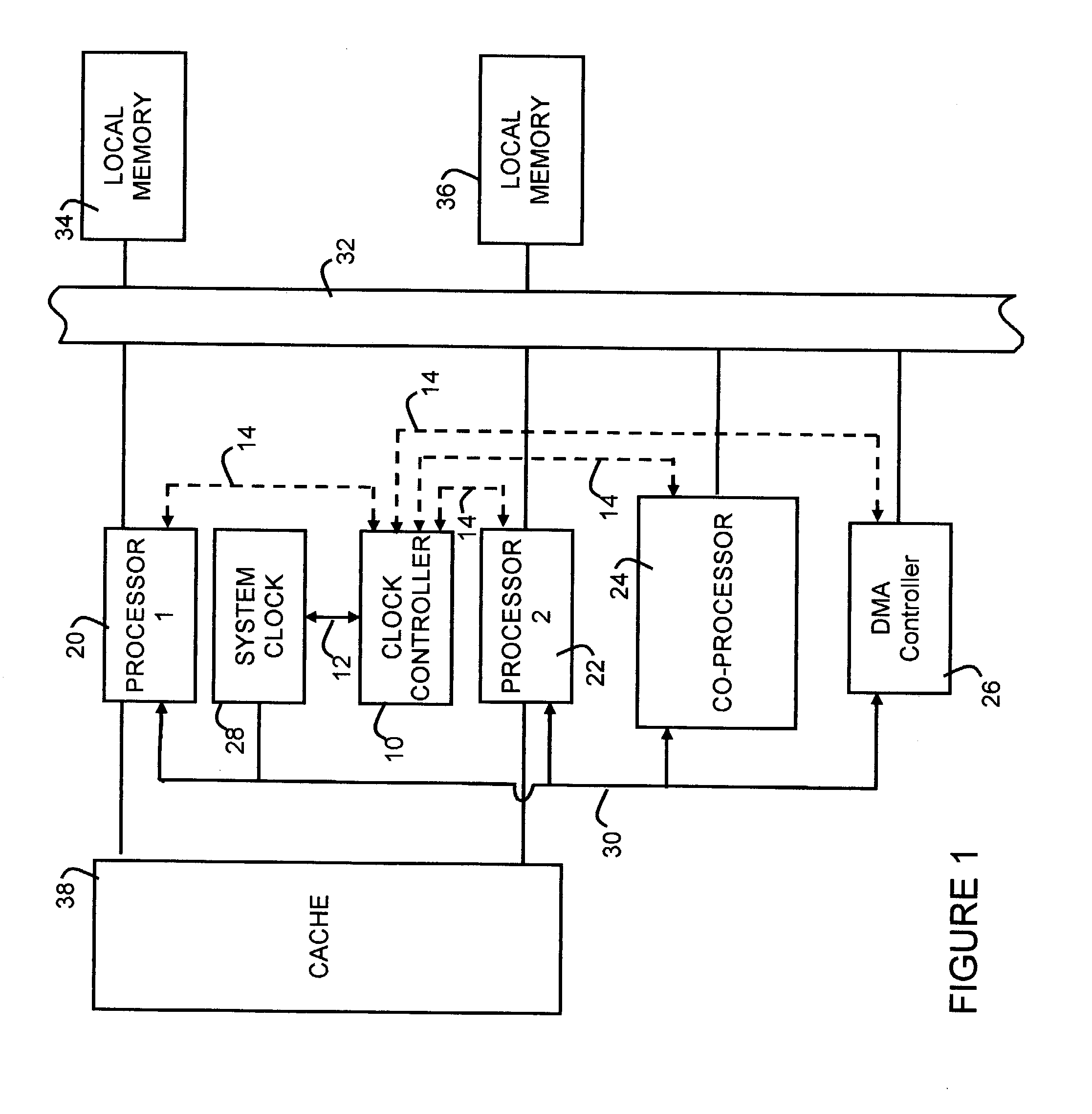

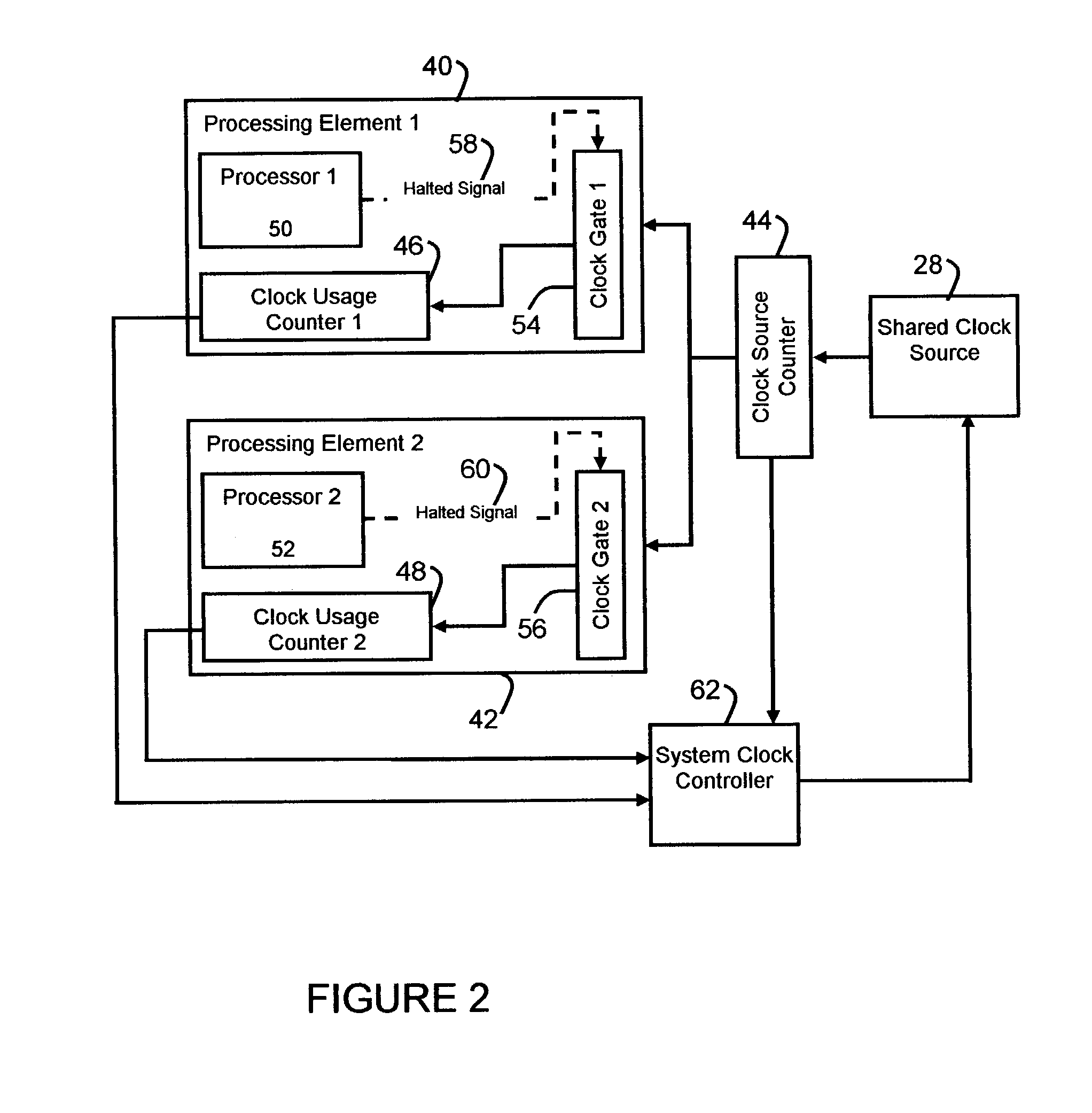

System clock power management for chips with multiple processing modules

ActiveUS7043649B2Reduce power consumptionEasy to operateEnergy efficient ICTPower supply for data processingProcessing elementComputer science

A system and method are disclosed for controlling the frequency of a common clock which is shared by a plurality of processing elements. The usage of the common clock by each of the plurality of processing elements is measured, and the common clock is controlled to have a frequency determined as a function of the measured common clock usage by the plurality of processing elements.

Owner:NVIDIA CORP

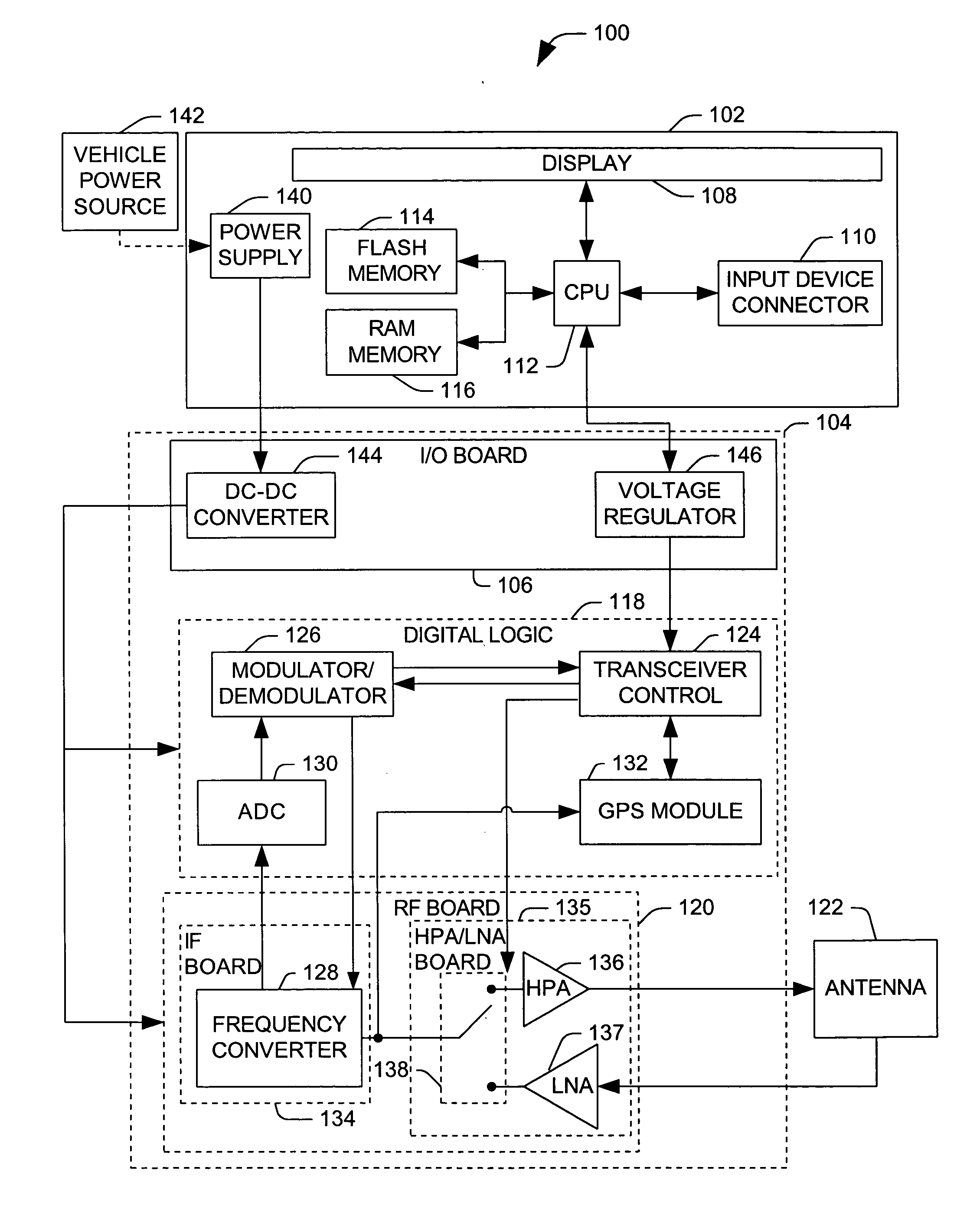

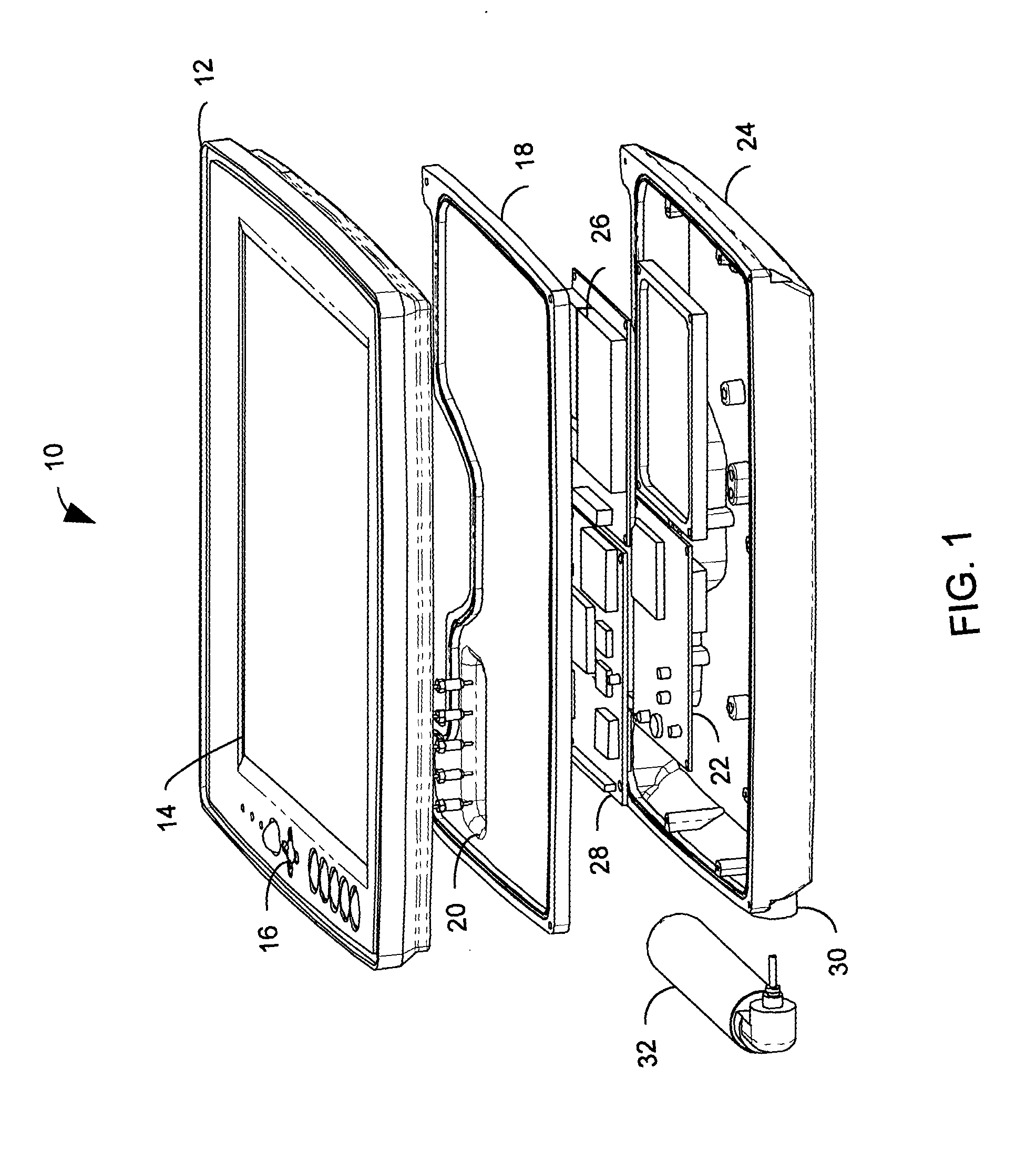

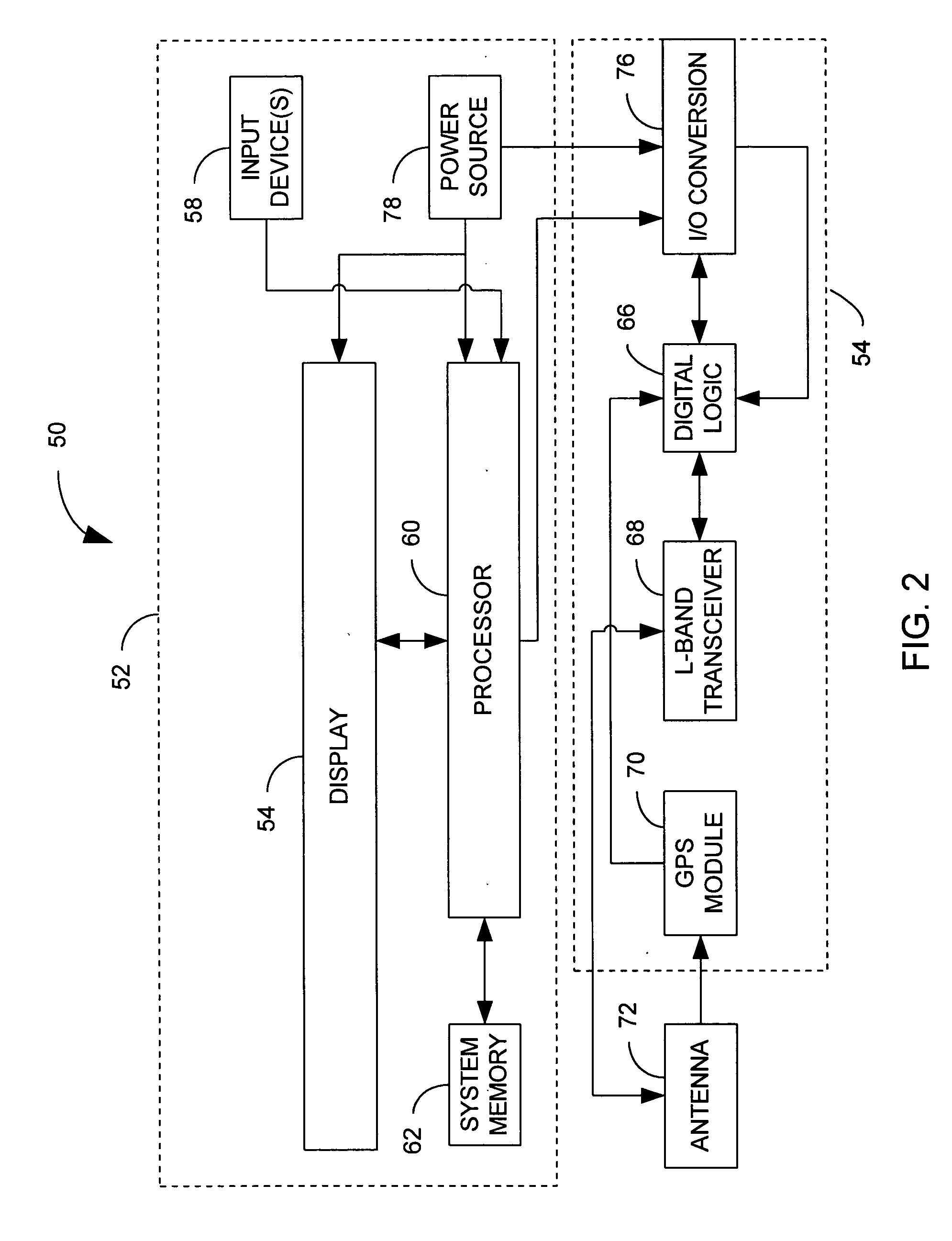

Dismount tablet computer assembly for wireless communication applications

InactiveUS20050033513A1Instruments for road network navigationRoad vehicles traffic controlInformation processingTablet computer

Systems and methods are disclosed for utilizing one or more tablet computer assemblies in a portable communications system. A tablet computer assembly includes a global positioning system module, an L-band transceiver, and a processing system. The global positioning system module that produces location information associated with the position of the tablet computer assembly. The L-band transceiver broadcasts the location information to at least one portable communication device through a relay network and receives location information from the at least one portable communications device via the relay network. The processing unit provides messages to the L-band transceiver and updates a display associated with the tablet computer assembly according the received location information and the location information produced at the global positioning system module.

Owner:NORTHROP GRUMMAN SYST CORP

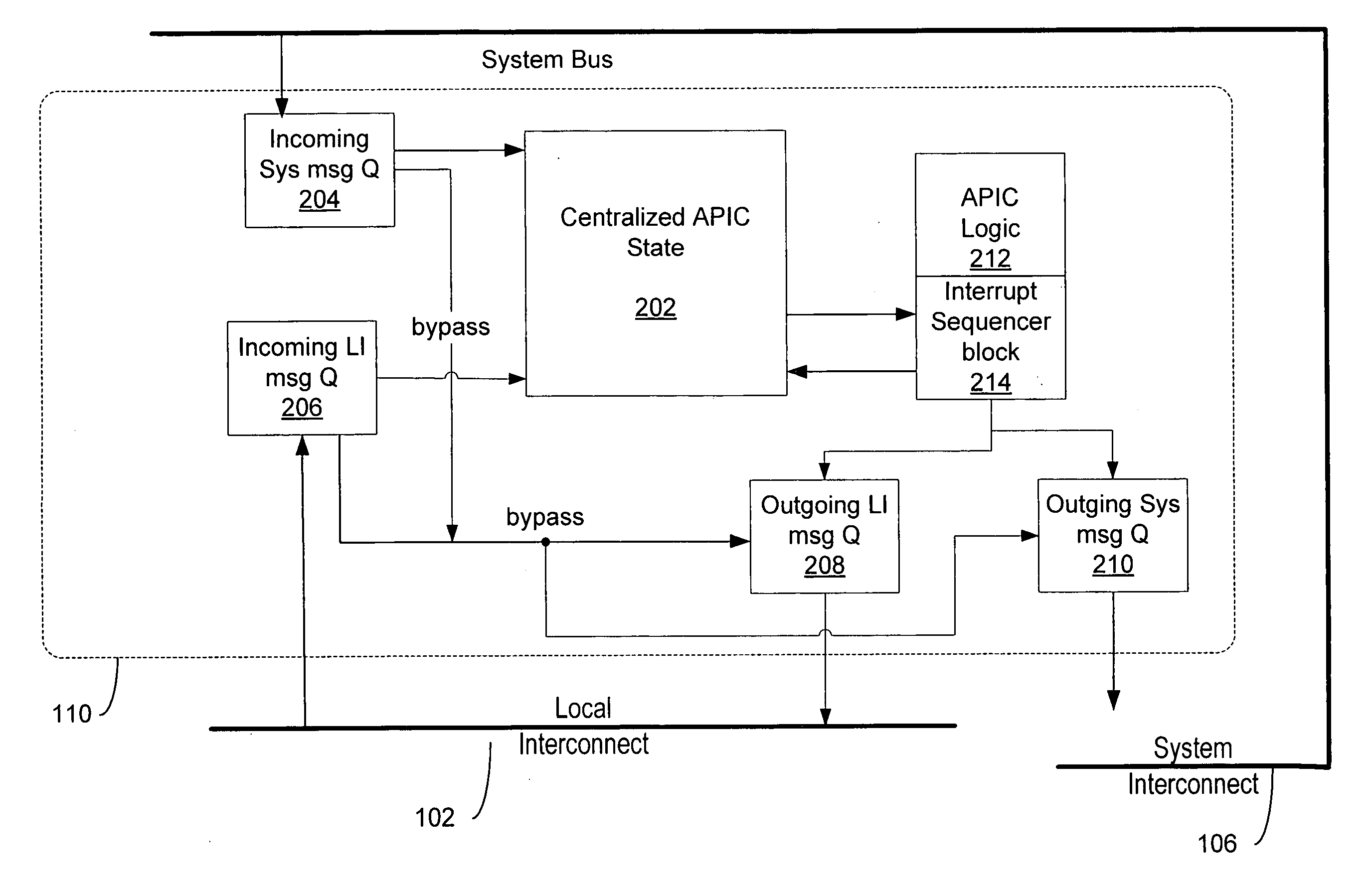

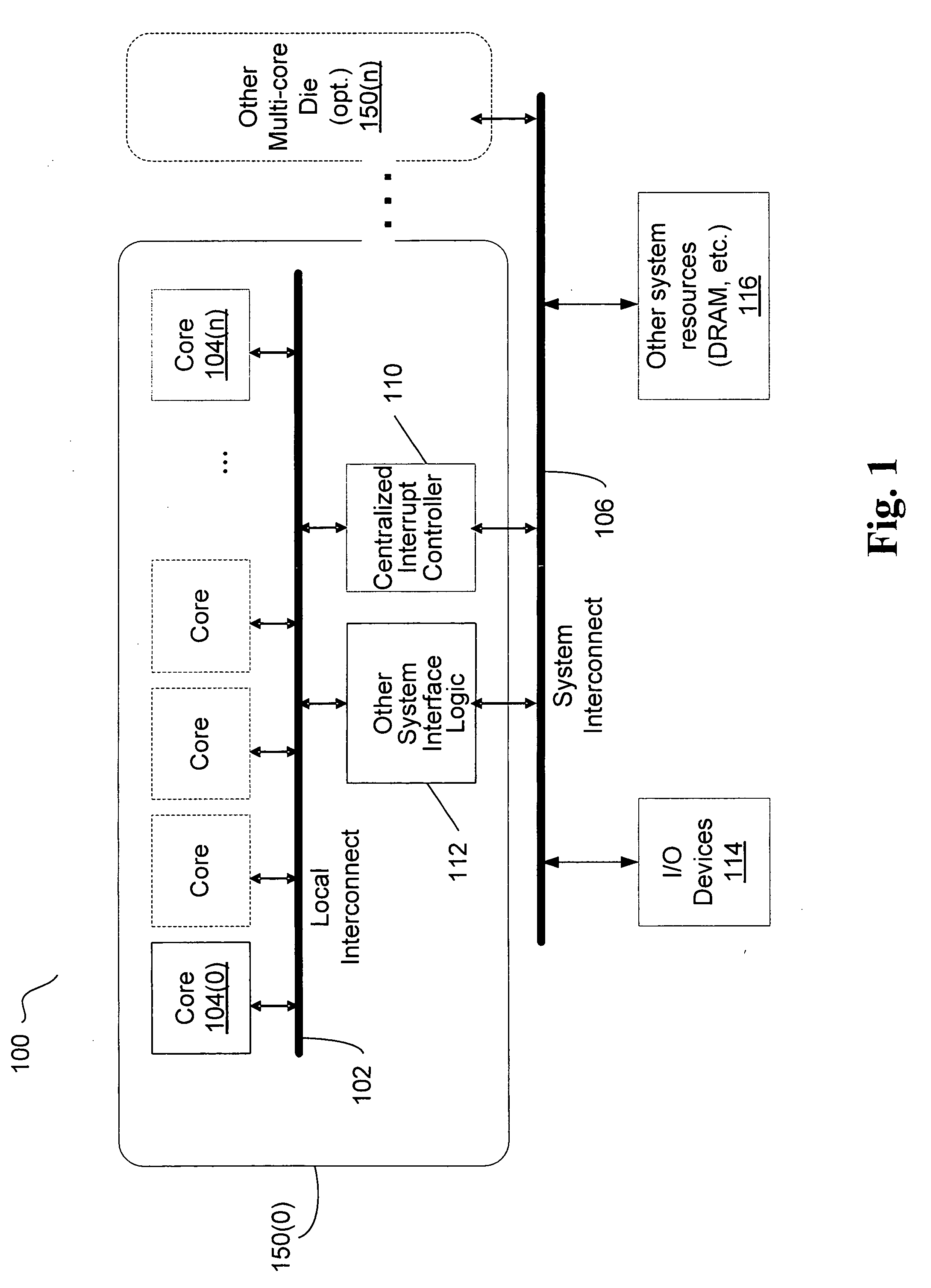

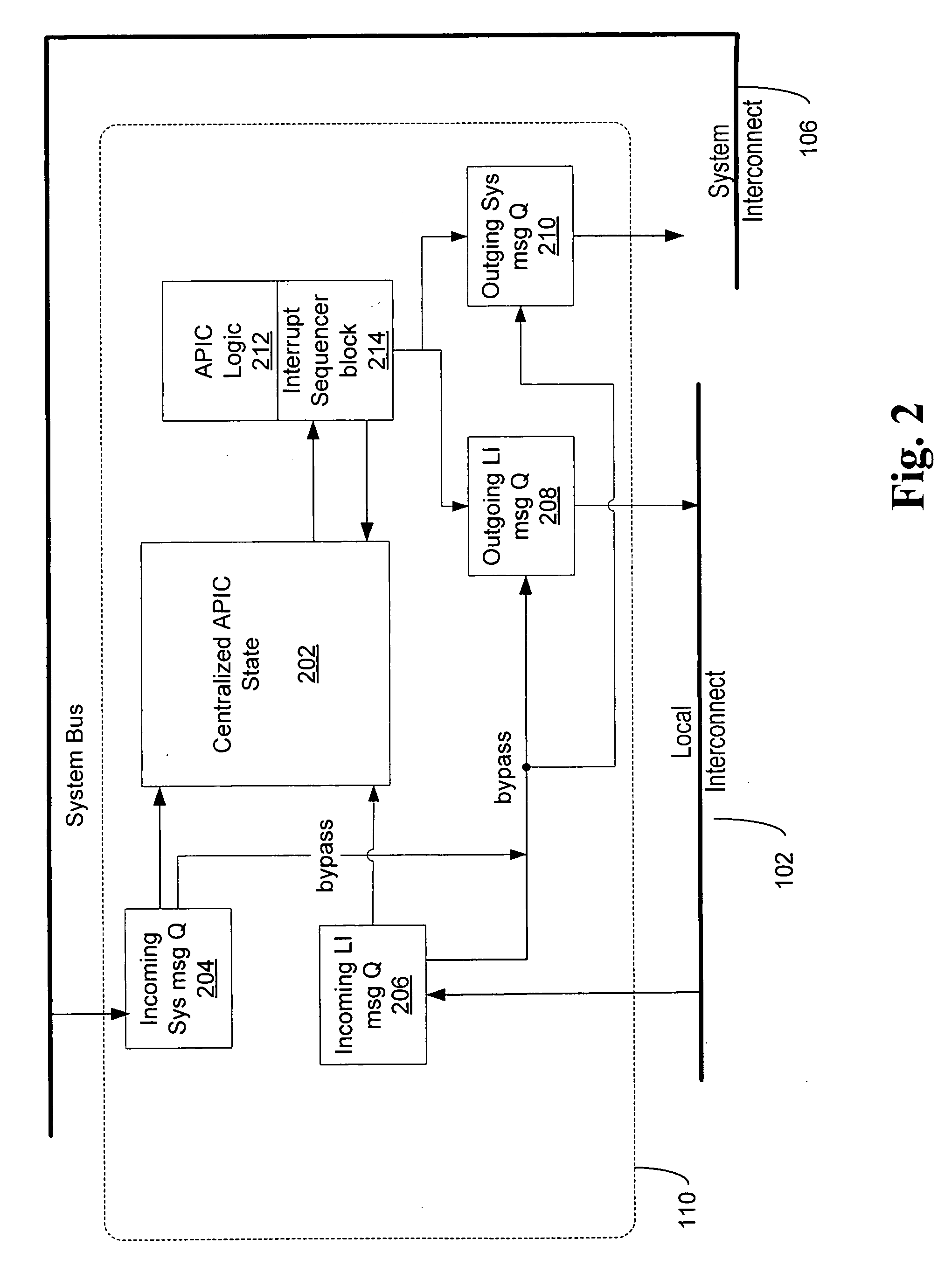

Centralized interrupt controller

InactiveUS20070106827A1Energy efficient ICTEnergy efficient computingProcessing elementEmbedded system

A centralized interrupt controller with a single copy of APIC logic provides APIC interrupt delivery services for all processing units of a multi-sequencer chip or system. An interrupt sequencer block of the centralized interrupt controller schedules the interrupt services according to a fairness scheme. At least one embodiment of the centralized interrupt controller also includes firewall logic to filter out transmission of selected interrupt messages. Other embodiments are also described and claimed.

Owner:INTEL CORP

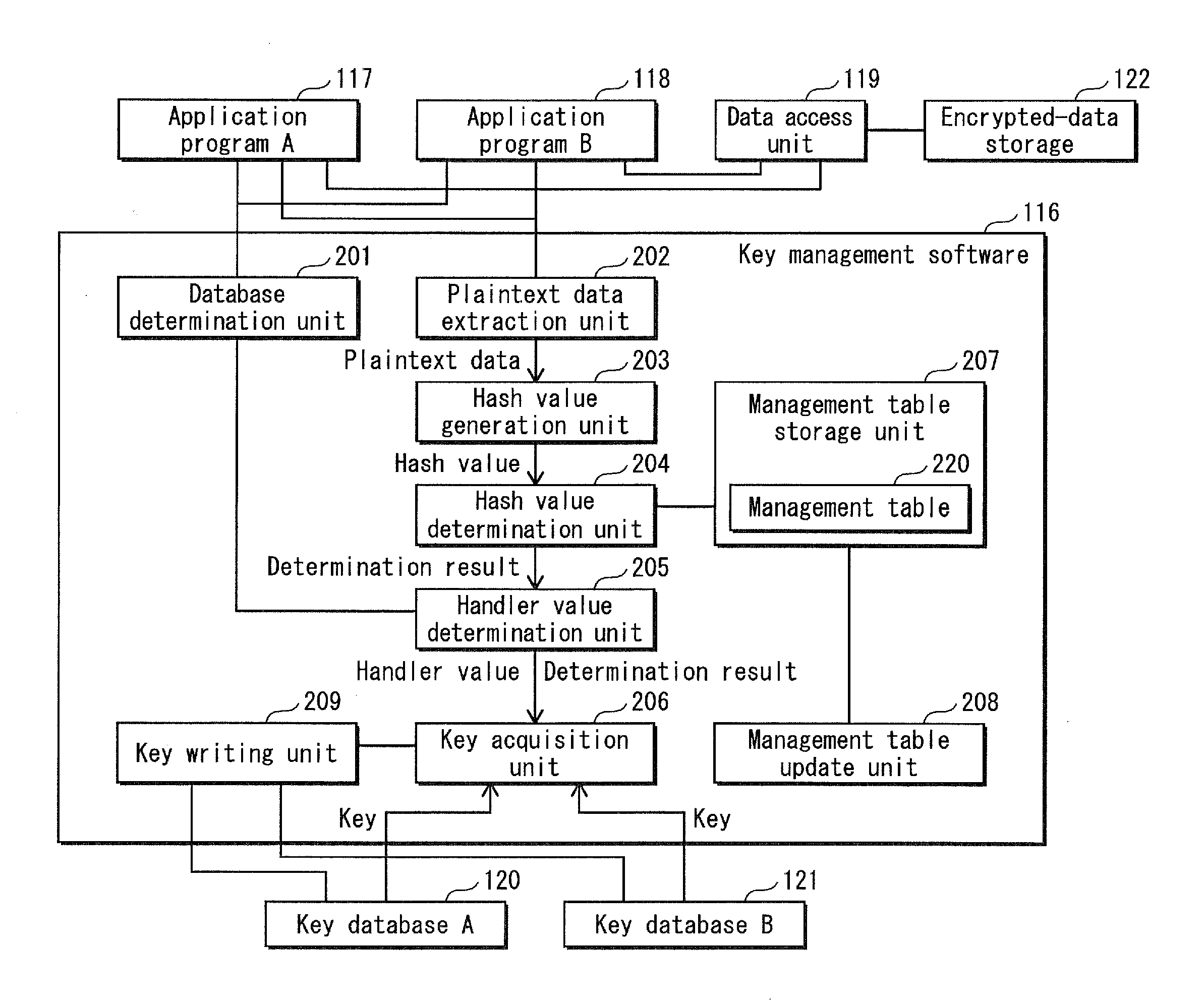

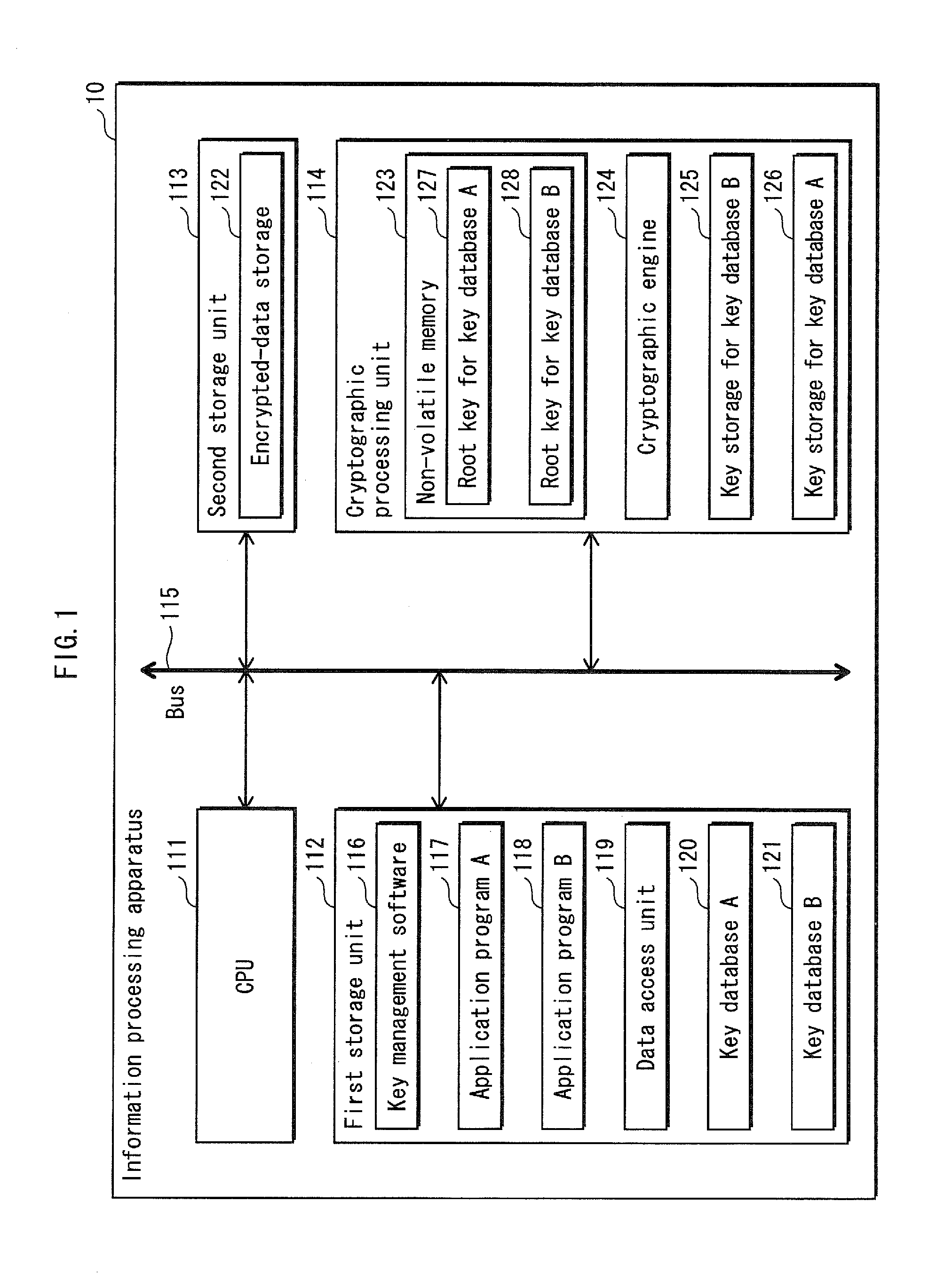

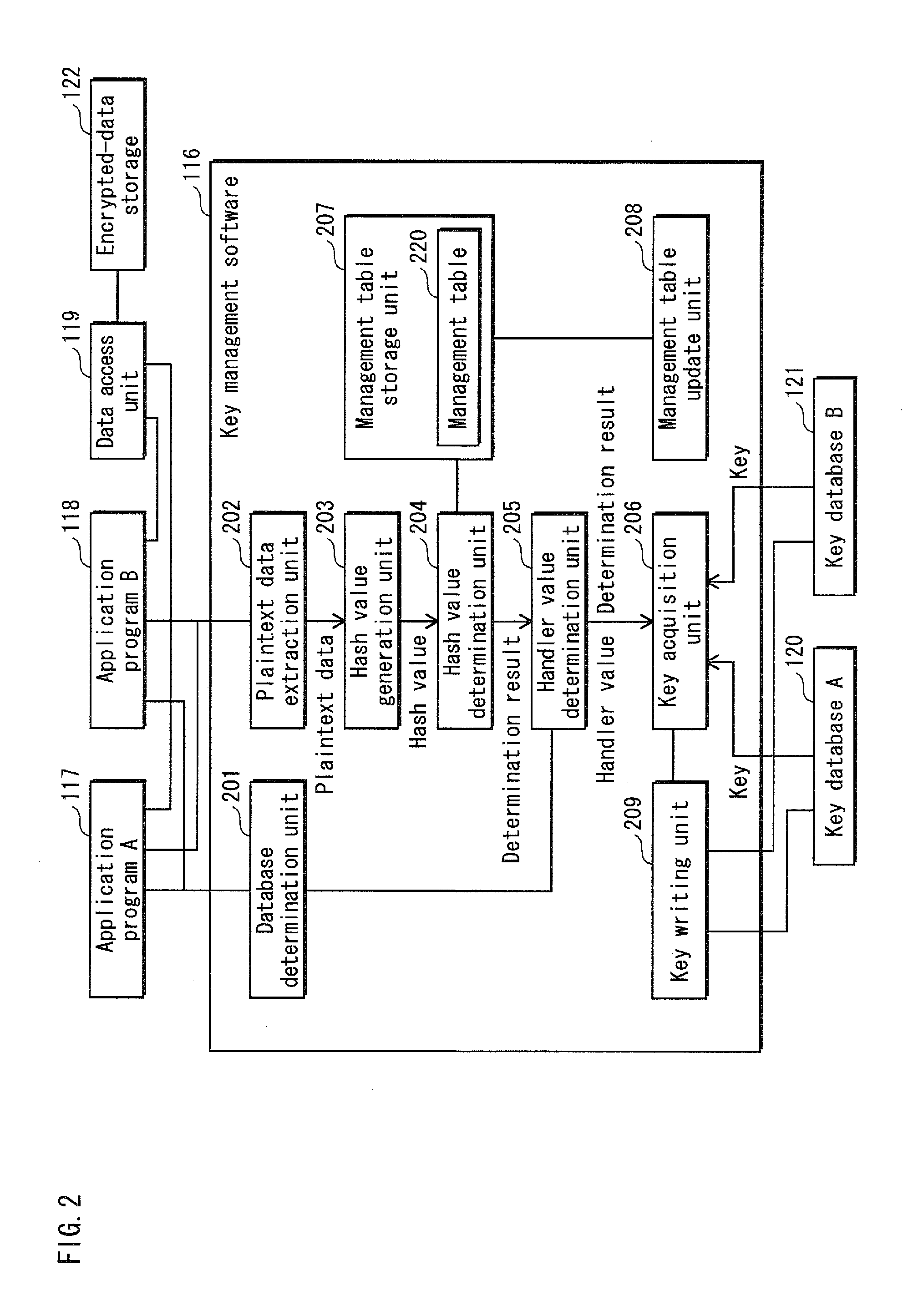

Information processing device, method, program, and integrated circuit

InactiveUS20110173460A1Save stepGood synchronizationUnauthorized memory use protectionHardware monitoringTree structureSoftware

The aim is to provide high-speed data synchronization. To achieve the aim, in data synchronization using a plurality of key databases with respect to same data pieces, a key for one key database, which has been determined in advance, is used for updating the data piece managed under the other key database. This reduces the number of key decryption operations. A key management software 116, which manages a key database A120 and a key database B121 each having a tree structure, determines whether to perform data synchronization when requested by an upper-level application to perform data encryption, and performs synchronization of encrypted data by using a key of the other database which has been determined in advance. This reduces the number of times the encrypted key is loaded onto a cryptographic processing unit 114, and realizes high-speed cryptographic processing on data.

Owner:PANASONIC CORP

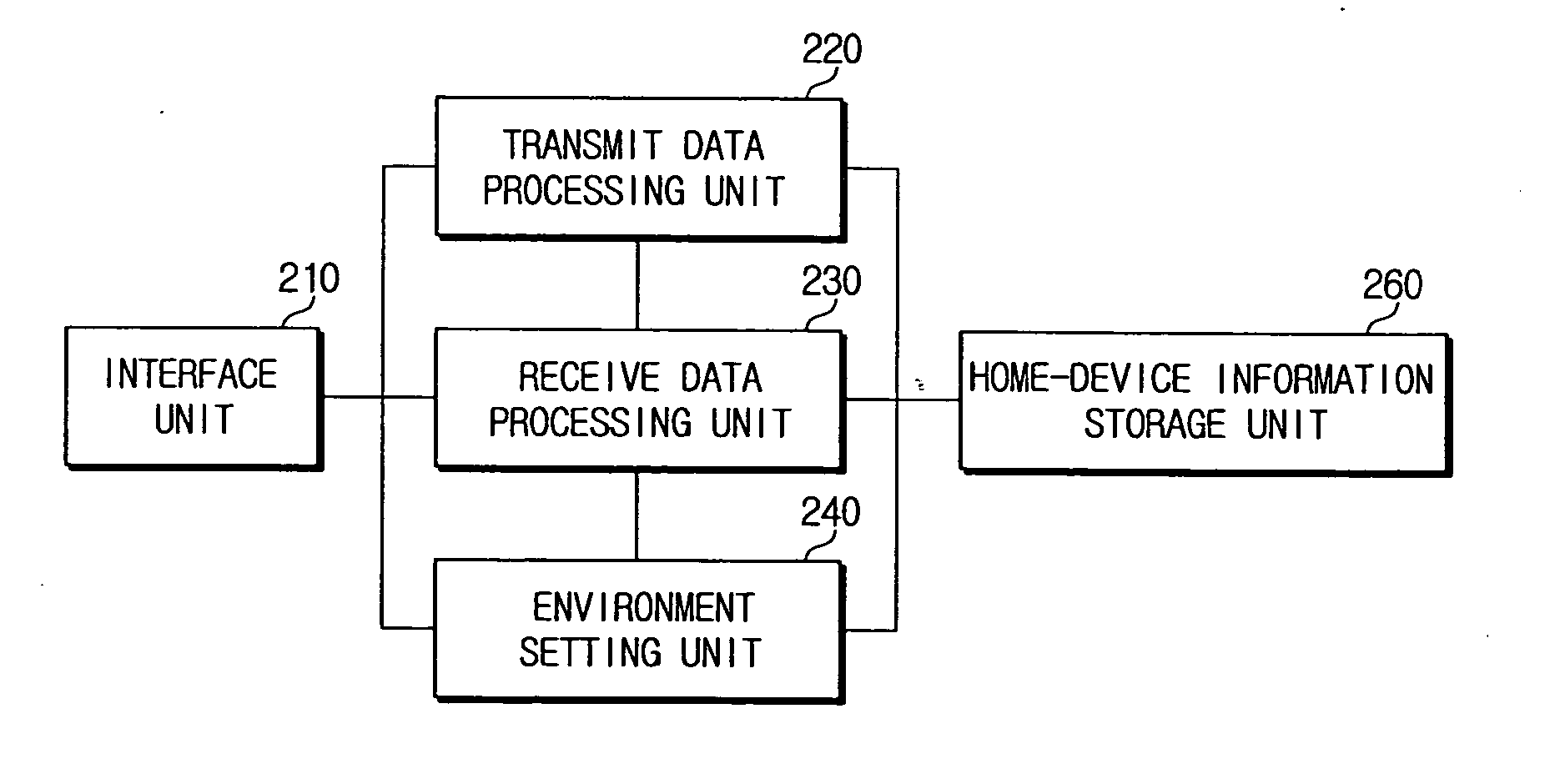

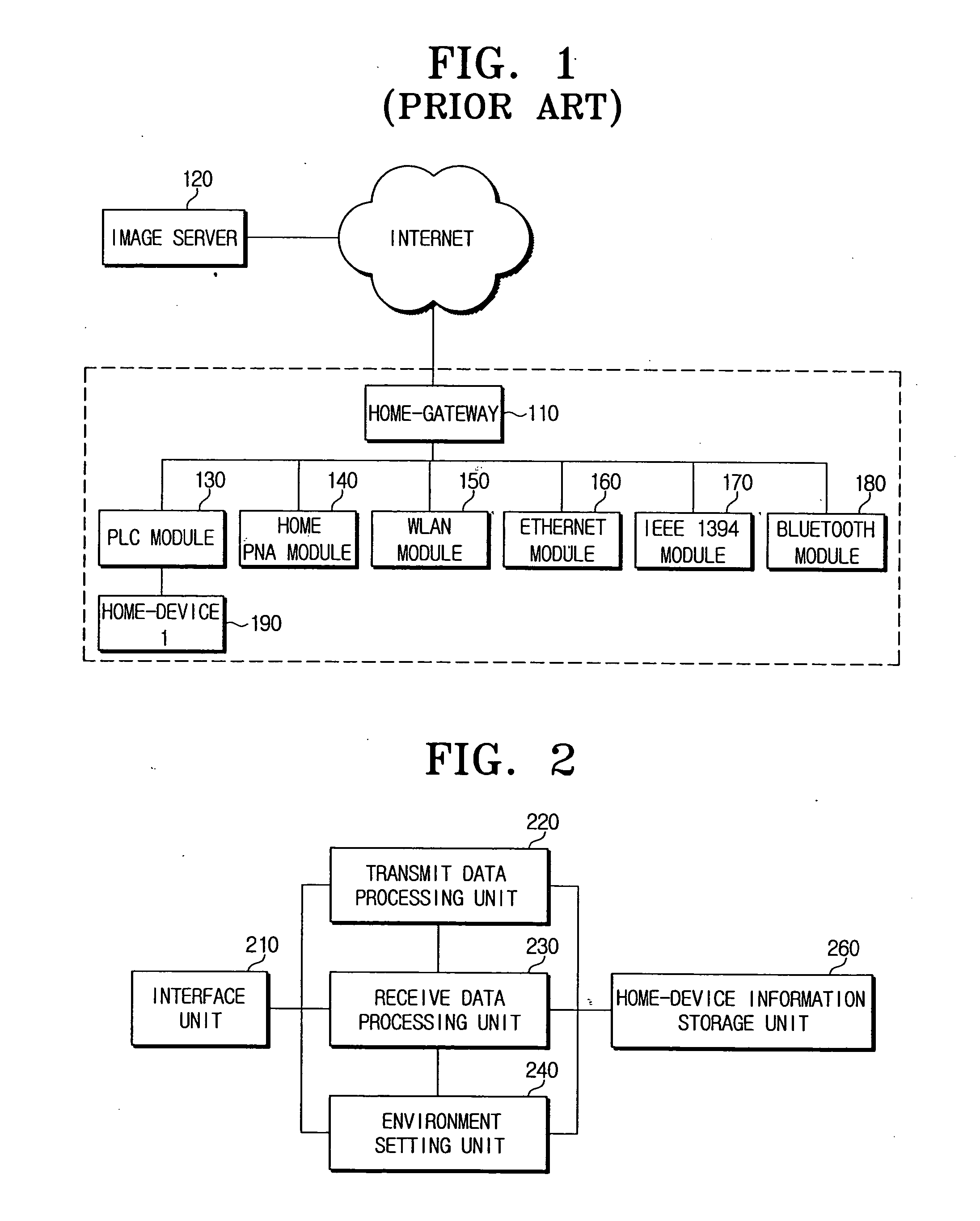

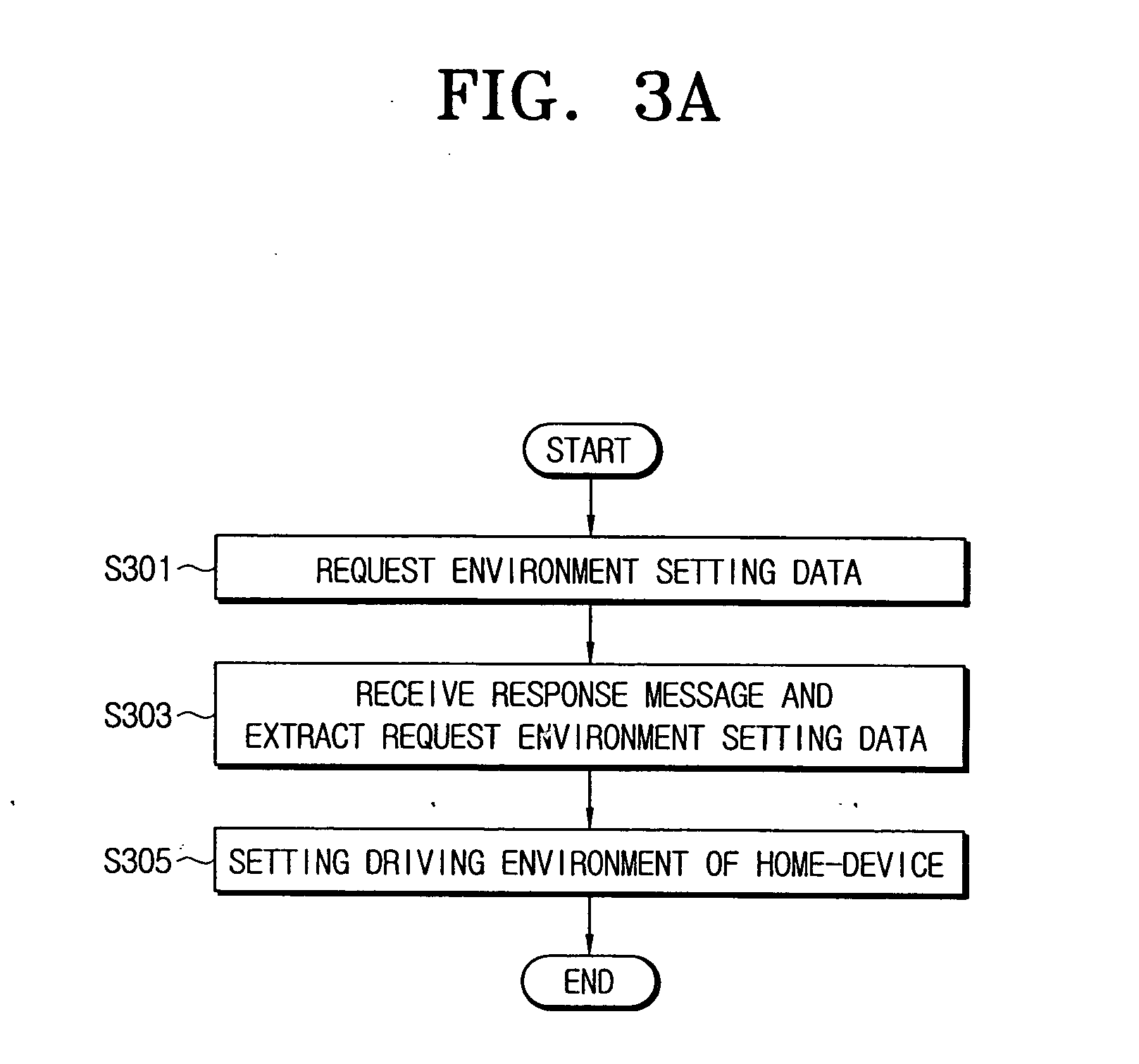

Apparatus for managing home-devices remotely in home-network and method thereof

An apparatus for providing an interface between a home-network and a external network and remotely managing the home-device connected to the home-network. The apparatus includes a transmit data processing unit for transmitting information on the home-device to a provider server connected to the external network, and requesting environment setting data for setting a driving environment of the home-device; a receive data processing unit for receiving a response message based on the request, from the provider server, and extracting the environment setting data included in the response message; and an environment setting unit for setting the driving environment for the operation of the home-device, based on the environment setting data.

Owner:SAMSUNG ELECTRONICS CO LTD

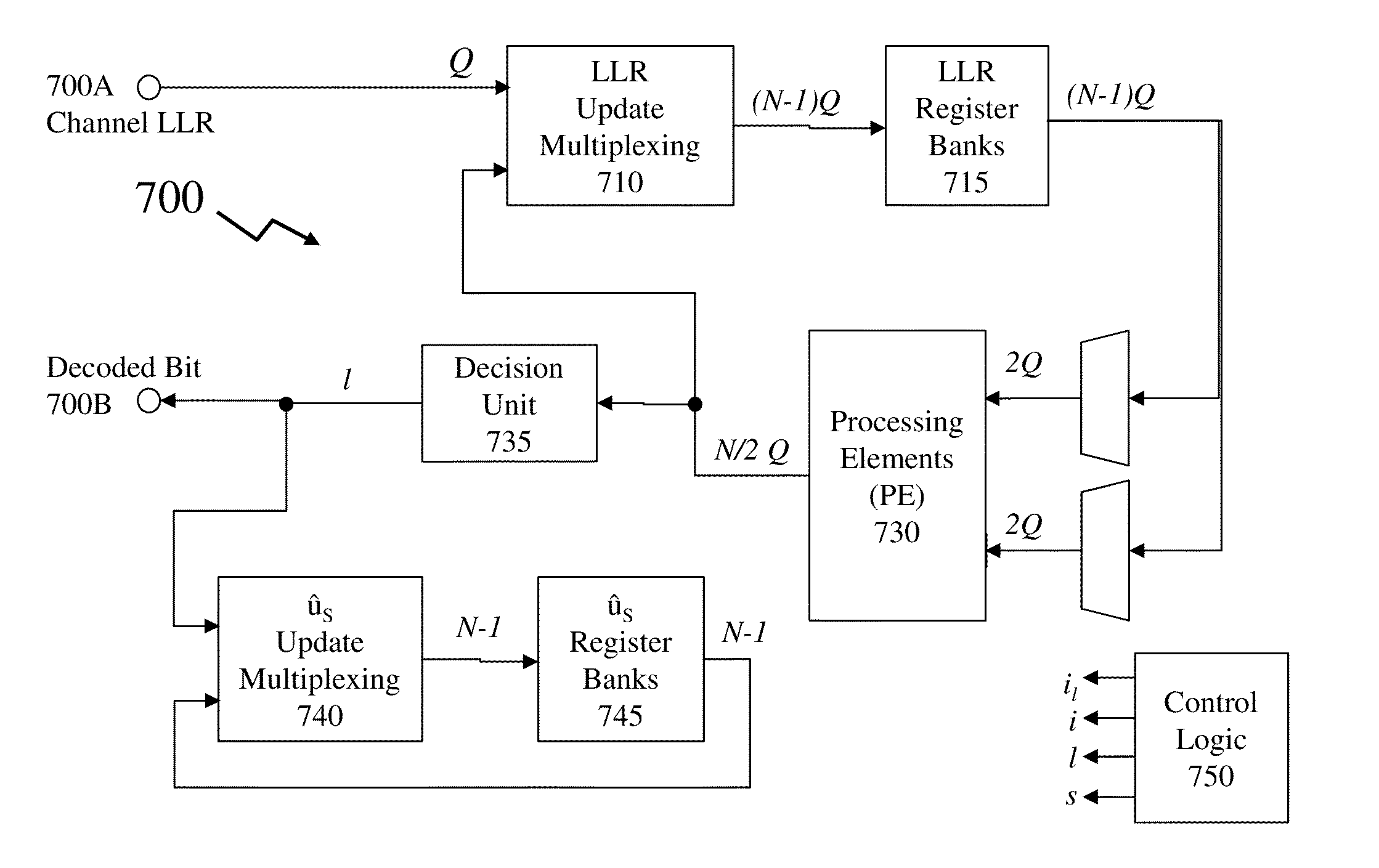

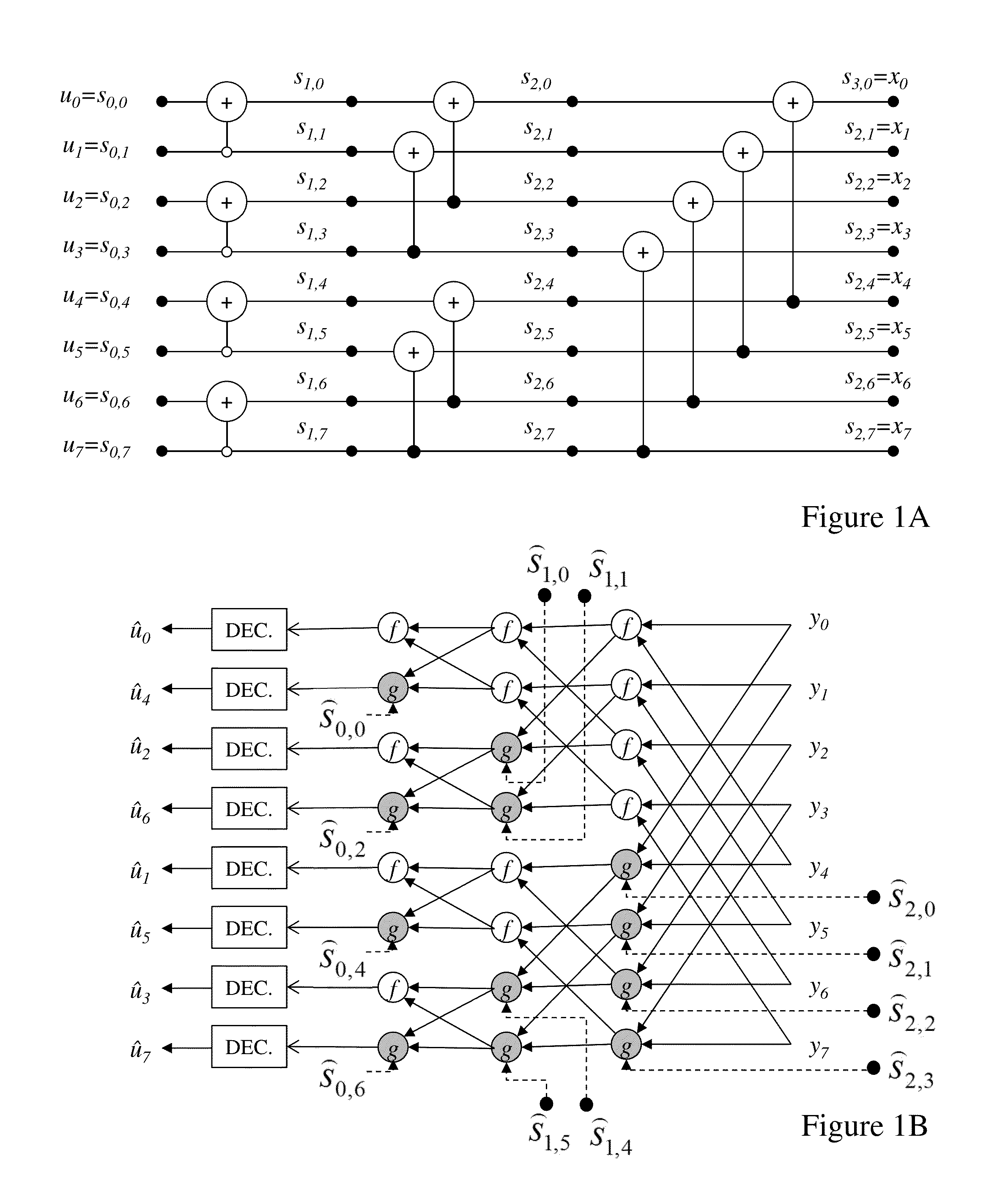

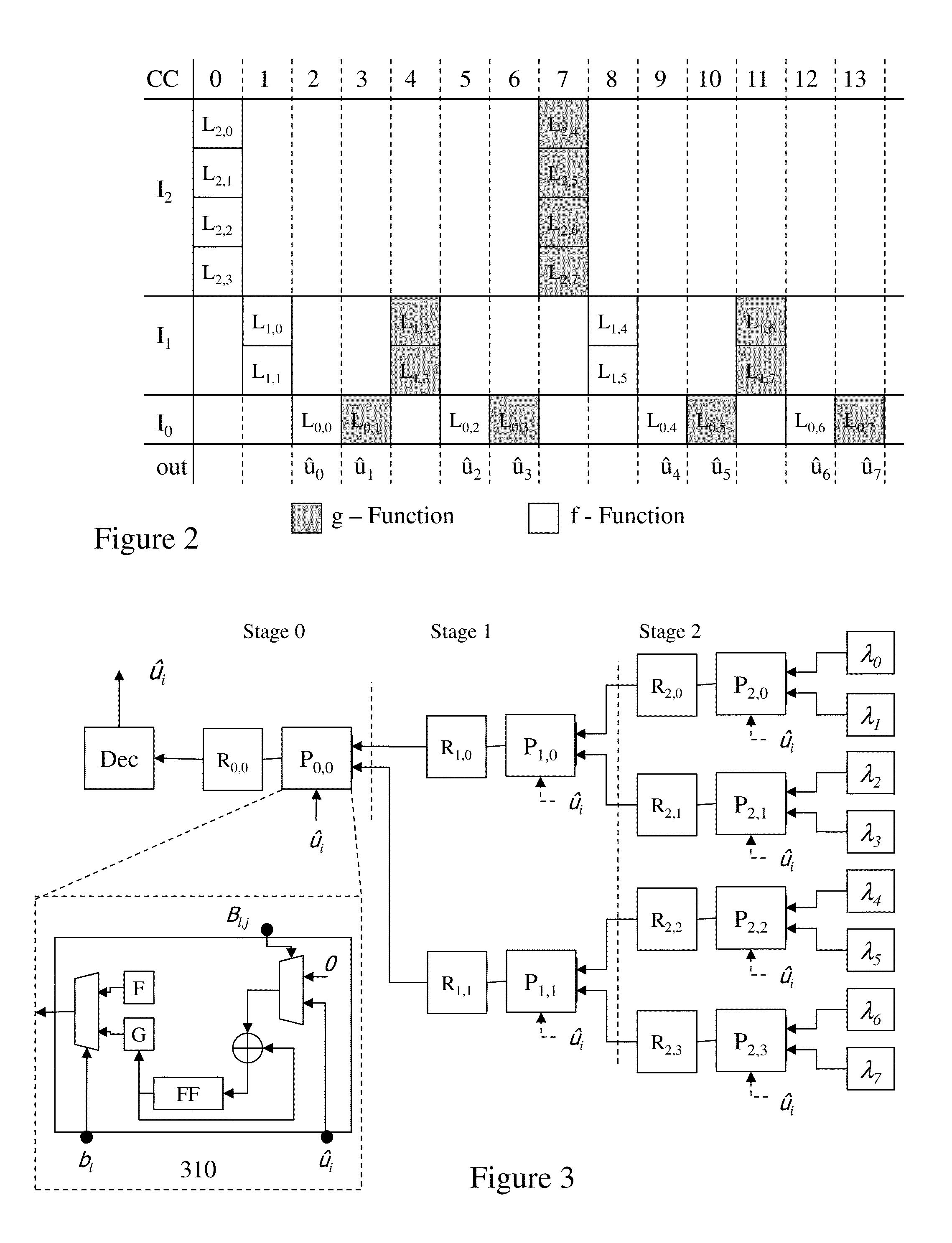

Methods and Systems for Decoding Polar Codes

ActiveUS20130117344A1Improve performanceMitigate such drawbackCode conversionError correction/detection using linear codesProcessing elementHardware implementations

Coding within noisy communications channels is essential but a theoretical maximum rate defines the rate at which information can be reliably transmitted on this noisy channel. Capacity-achieving codes with an explicit construction eluded researchers until polar codes were proposed. However, whilst asymptotically reaching channel capacity these require increasing code lengths, and hence increasingly complex hardware implementations. It would be beneficial to address architectures and decoding processes to reduce polar code decoder complexity both in terms of the number of processing elements required, but also the number of memory elements and the number of steps required to decode a codeword. Beneficially architectures and design methodologies established by the inventors address such issues whilst reducing overall complexity as well as providing methodologies for adjusting decoder design based upon requirements including, but not limited to, cost (e.g. through die area) and speed (e.g. through latency, number of cycles, number of elements etc).

Owner:THE ROYAL INSTITUTION FOR THE ADVANCEMENT OF TECH MCGILL UNIV +1

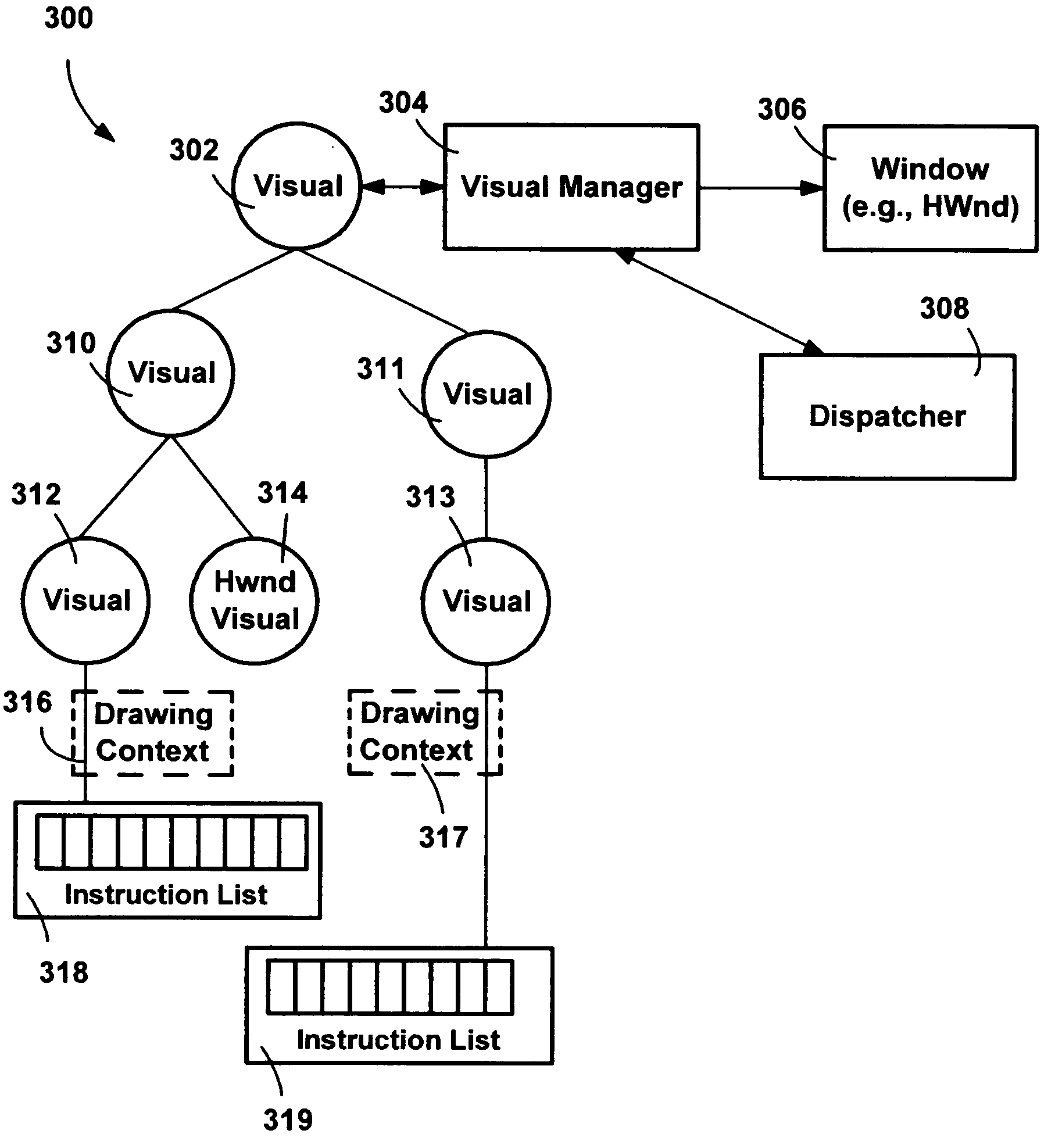

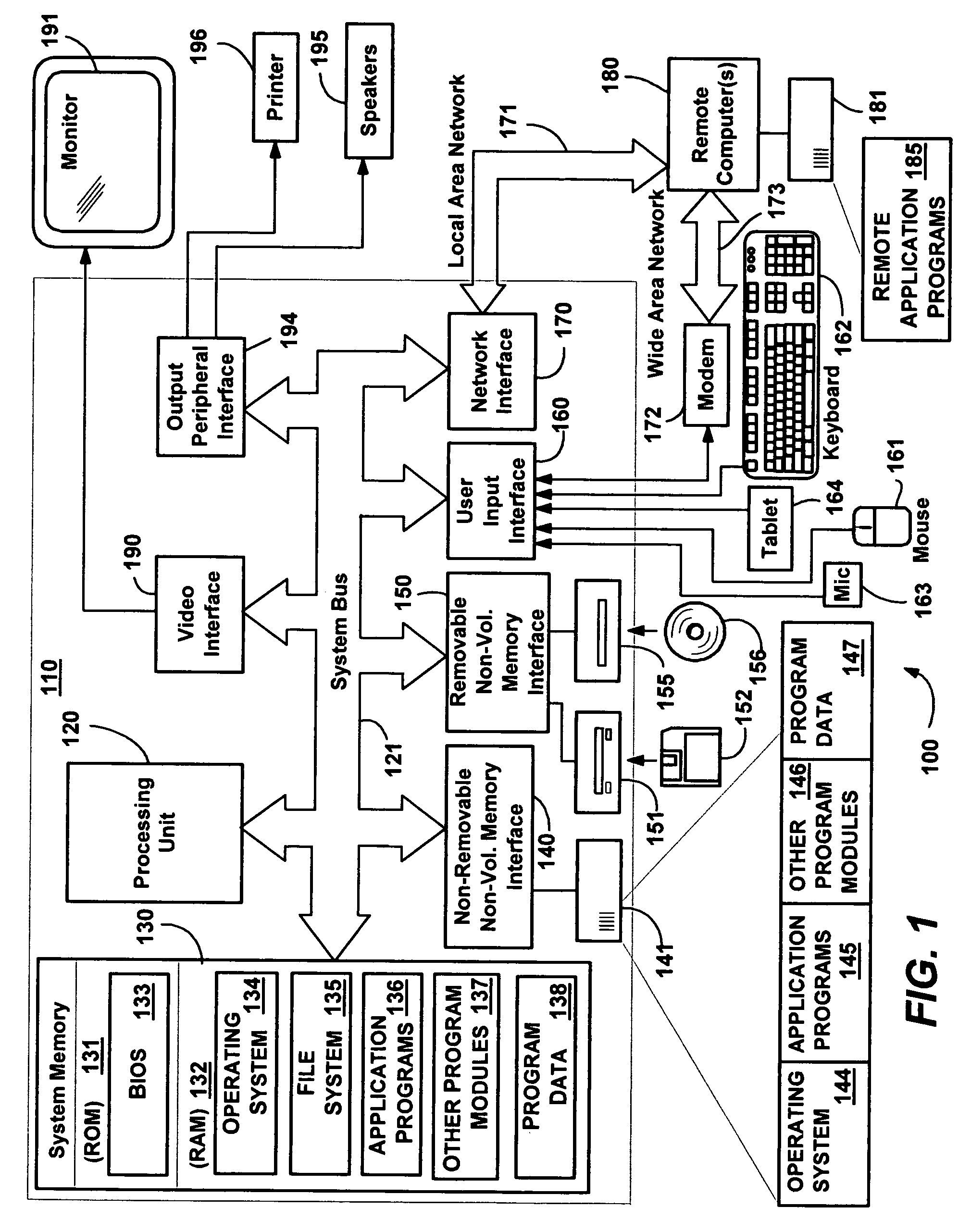

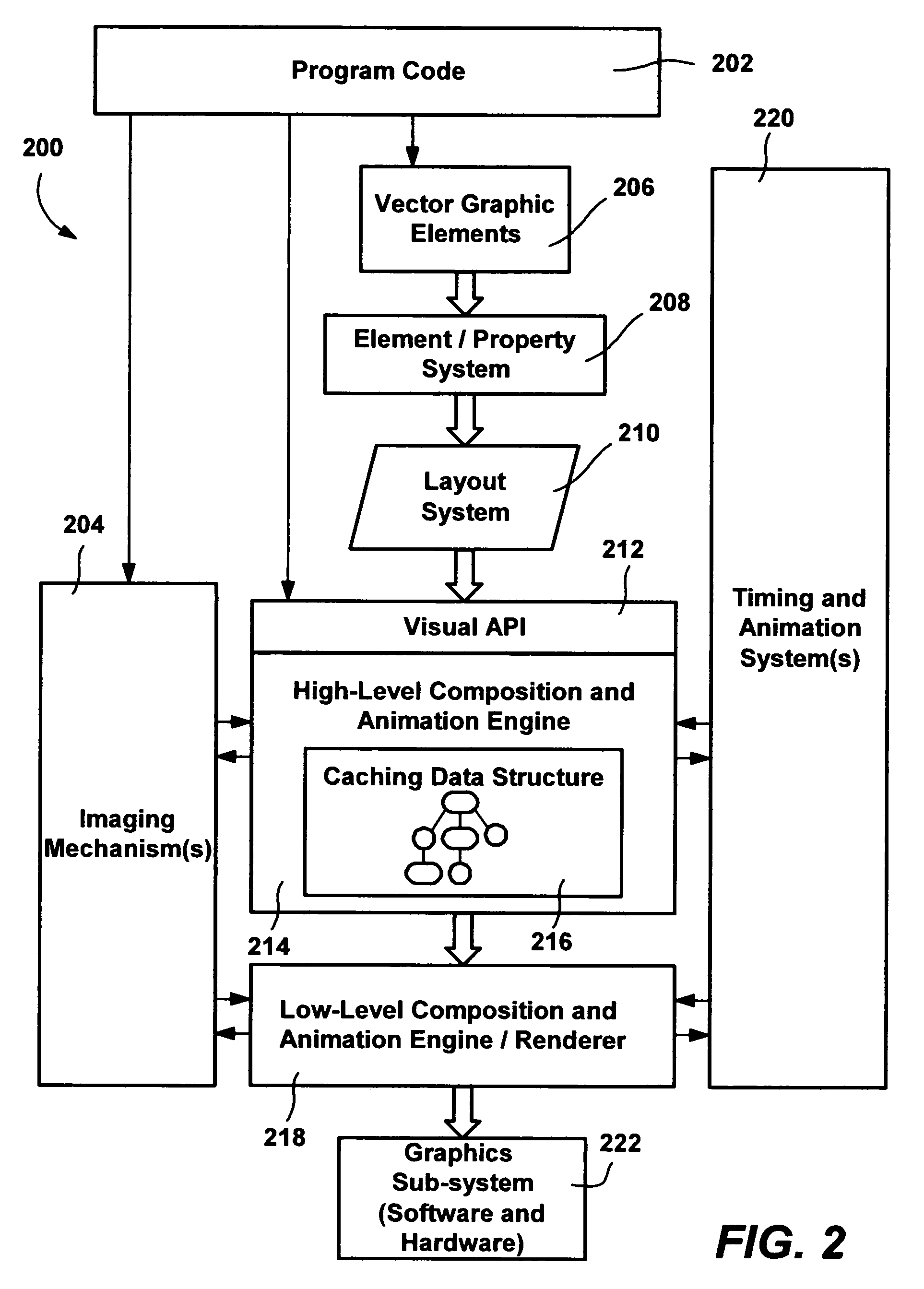

Media Integration Layer

InactiveUS20050140694A1Effect is complexNot adversely impact normal application performanceCathode-ray tube indicatorsAnimationMedia typeMedia integration

A media integration layer including an application programming interface (API) and an object model allows program code developers to interface in a consistent manner with a scene graph data structure in order to output graphics. Via the interfaces, program code adds child visuals to other visuals to build up a hierarchical scene graph, writes Instruction Lists such as geometry data, image data, animation data and other data for output, and may specify transform, clipping and opacity properties on visuals. The media integration layer and API enable programmers to accomplish composition effects within their applications in a straightforward manner, while leveraging the graphics processing unit in a manner that does not adversely impact normal application performance. A multiple-level system includes the ability to combine different media types (such as 2D, 3D, Video, Audio, text and imaging) and animate them smoothly and seamlessly.

Owner:MICROSOFT TECH LICENSING LLC