Patents

Literature

4633 results about "Memory block" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

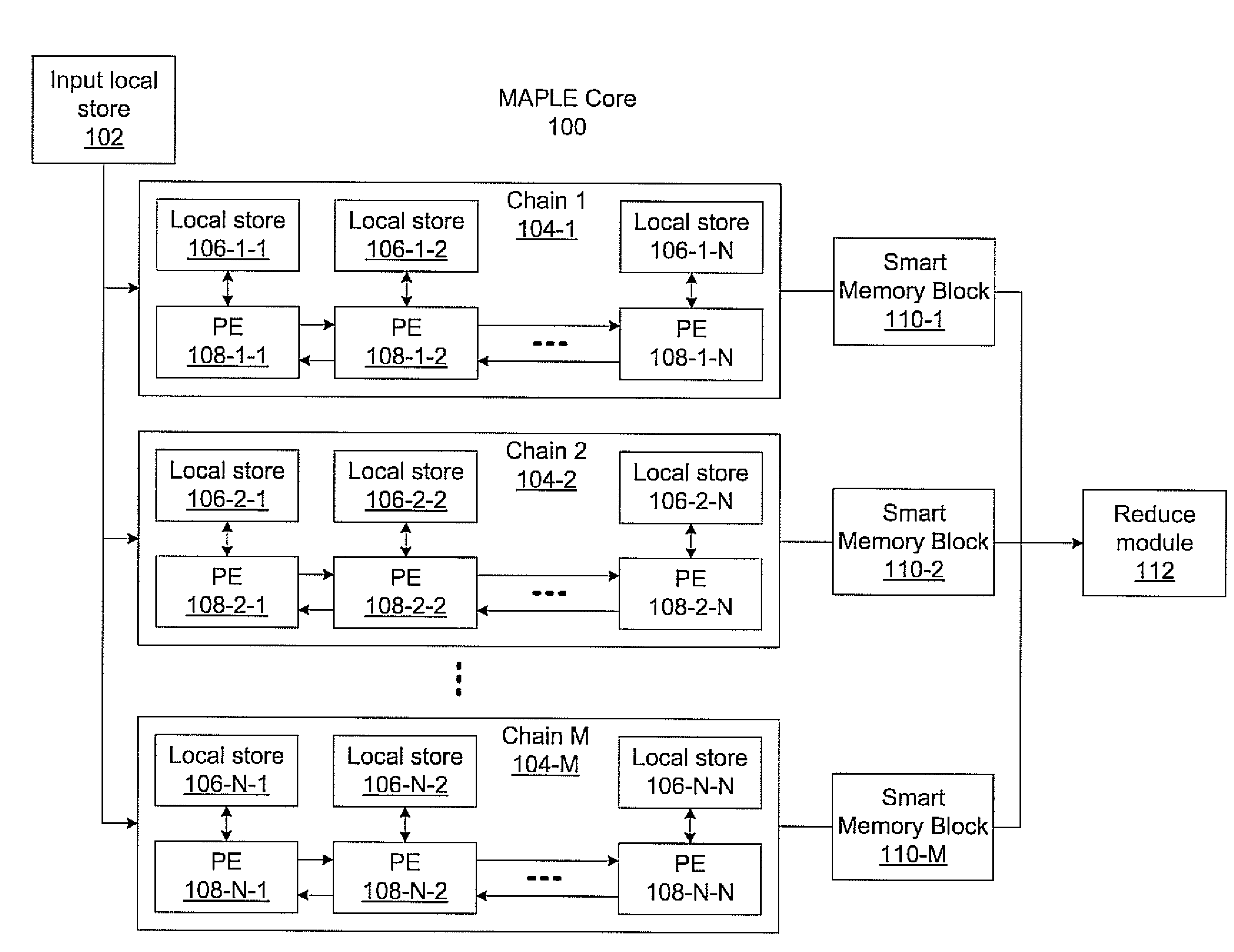

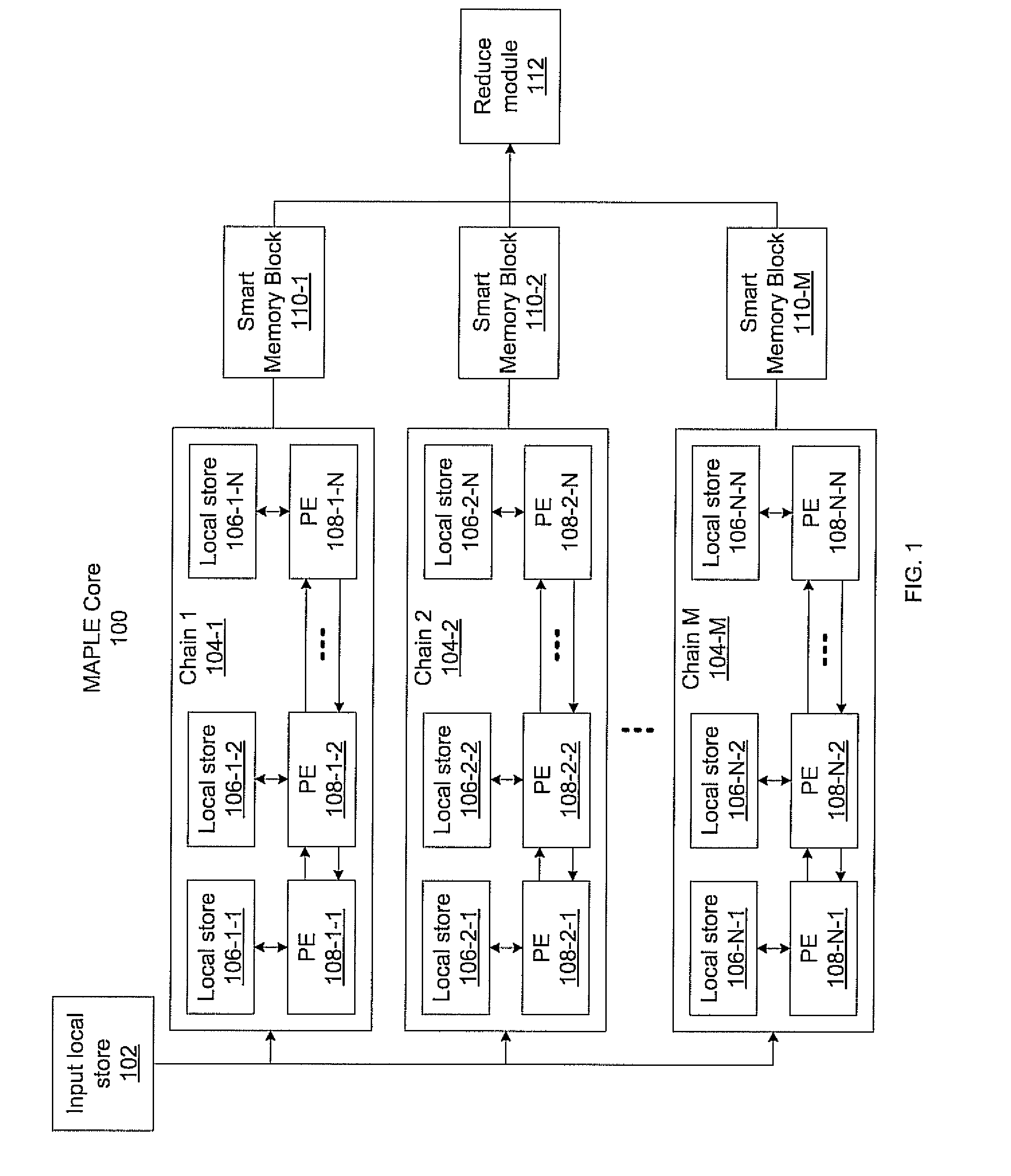

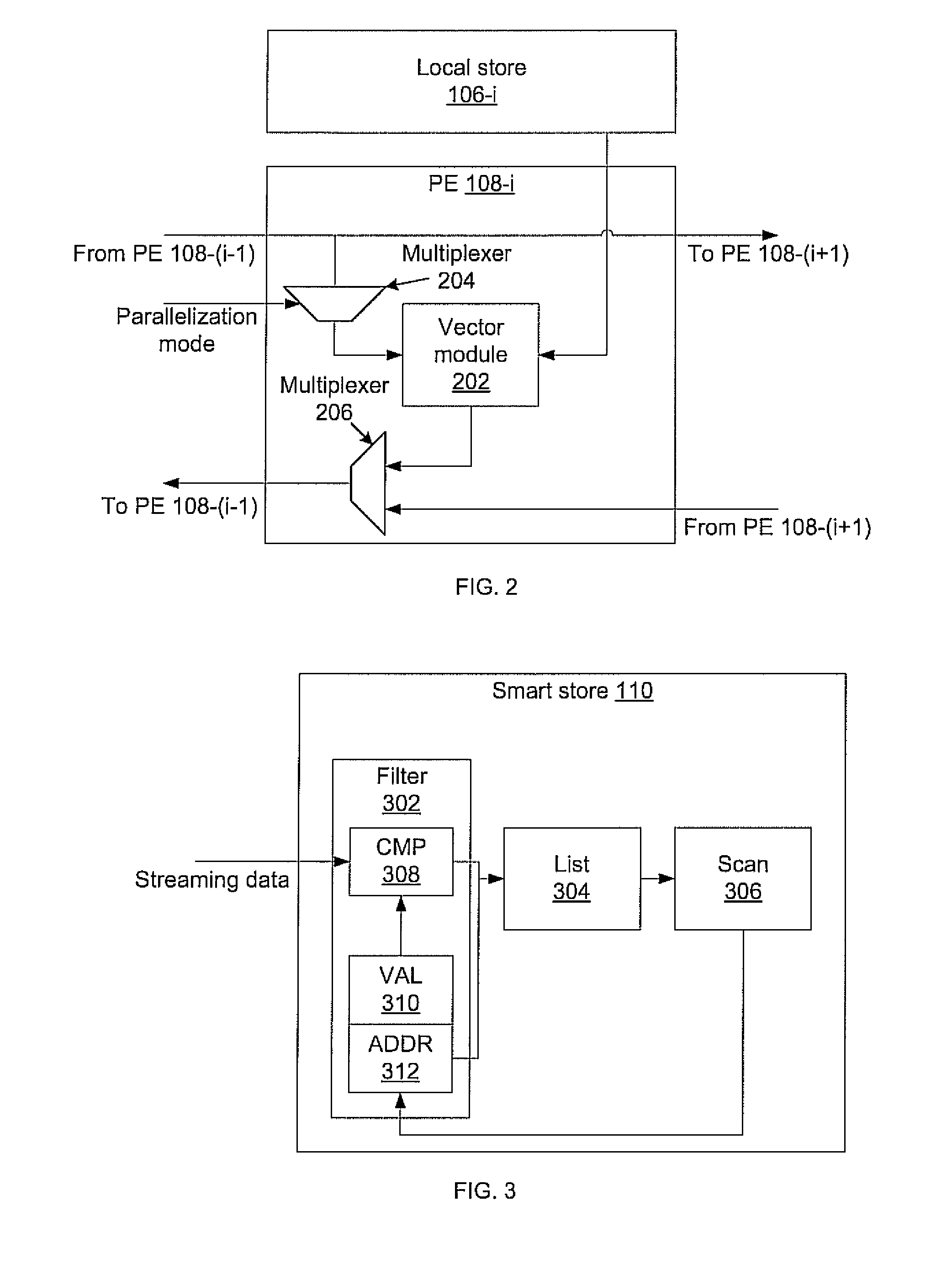

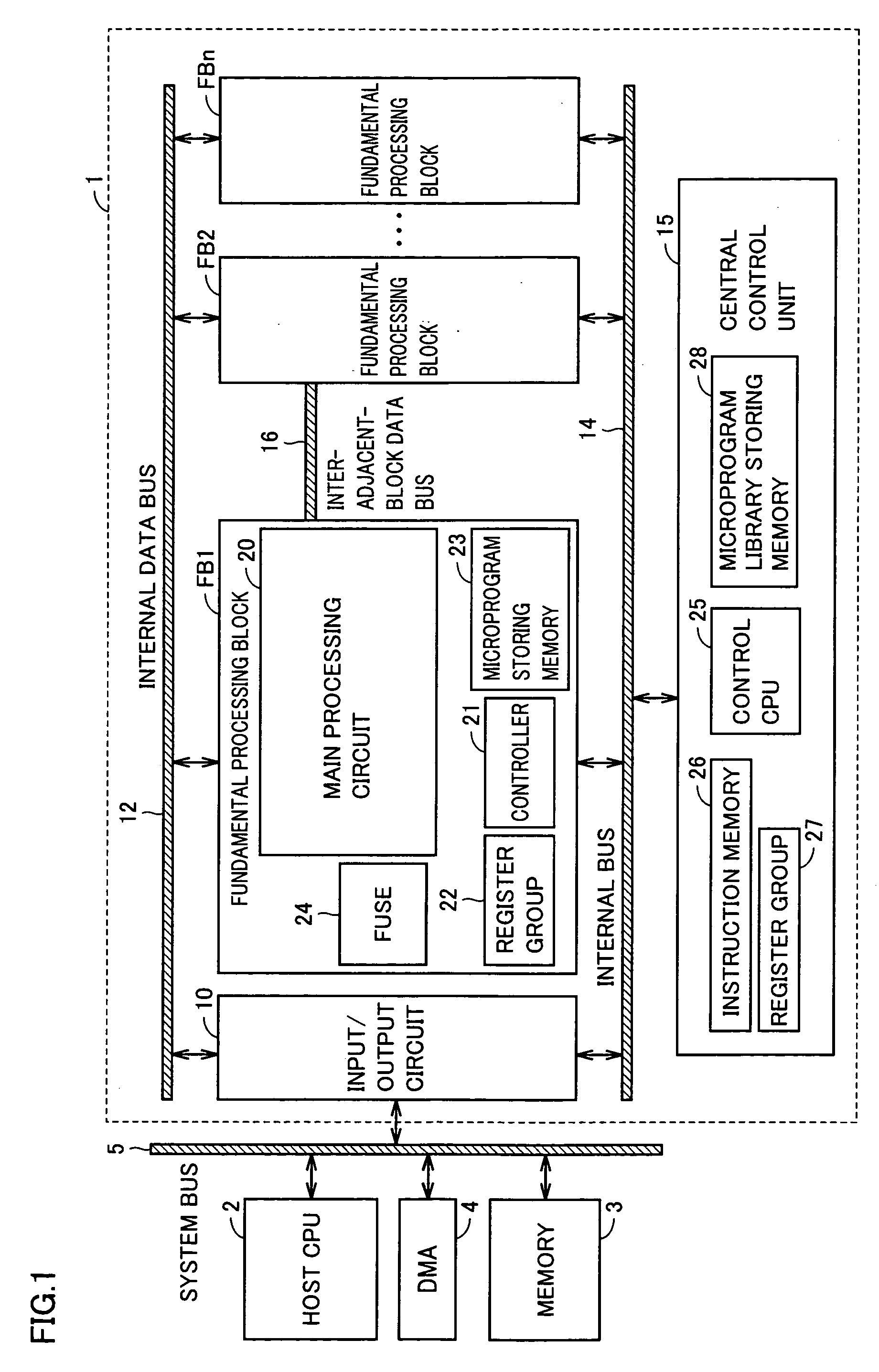

Massively parallel, smart memory based accelerator

Systems and methods for massively parallel processing on an accelerator that includes a plurality of processing cores. Each processing core includes multiple processing chains configured to perform parallel computations, each of which includes a plurality of interconnected processing elements. The cores further include multiple of smart memory blocks configured to store and process data, each memory block accepting the output of one of the plurality of processing chains. The cores communicate with at least one off-chip memory bank.

Owner:NEC CORP

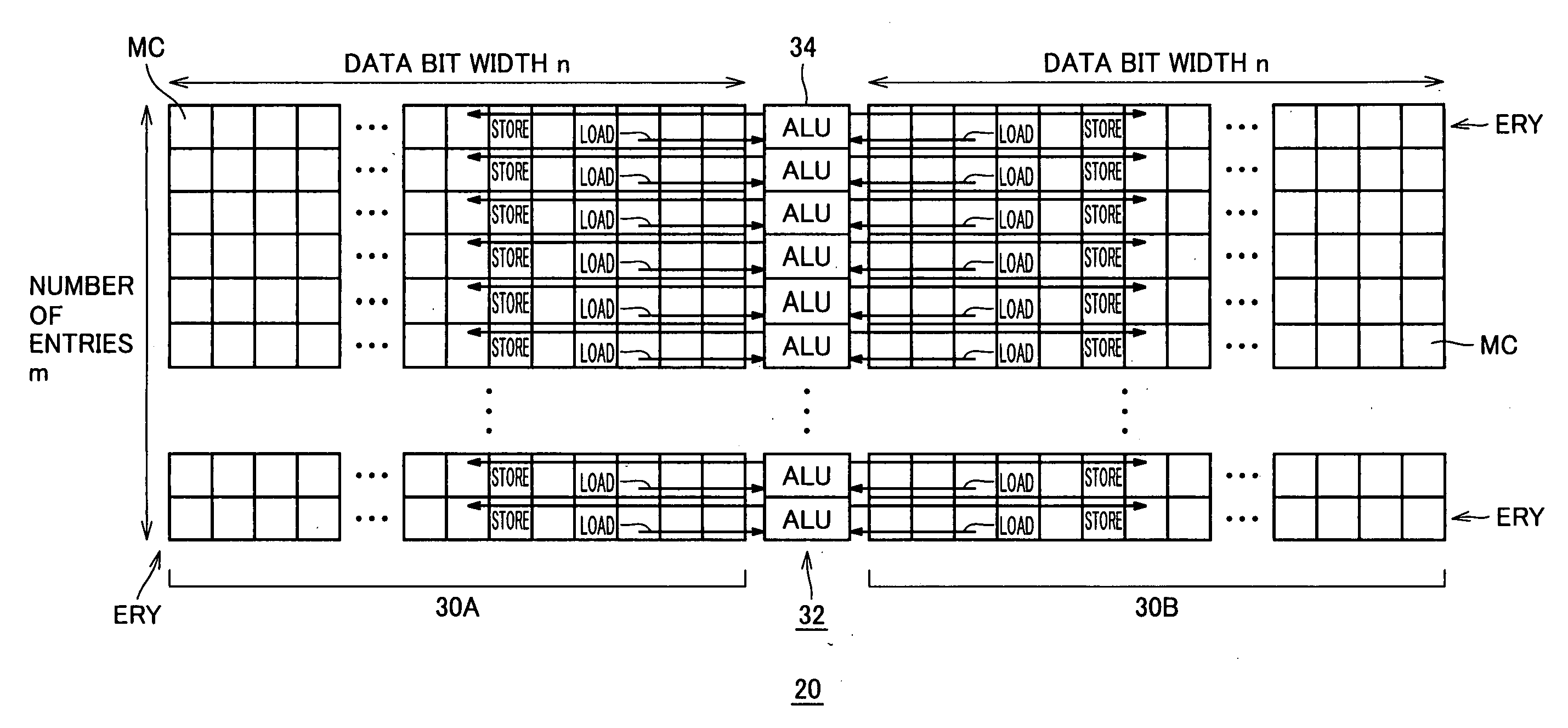

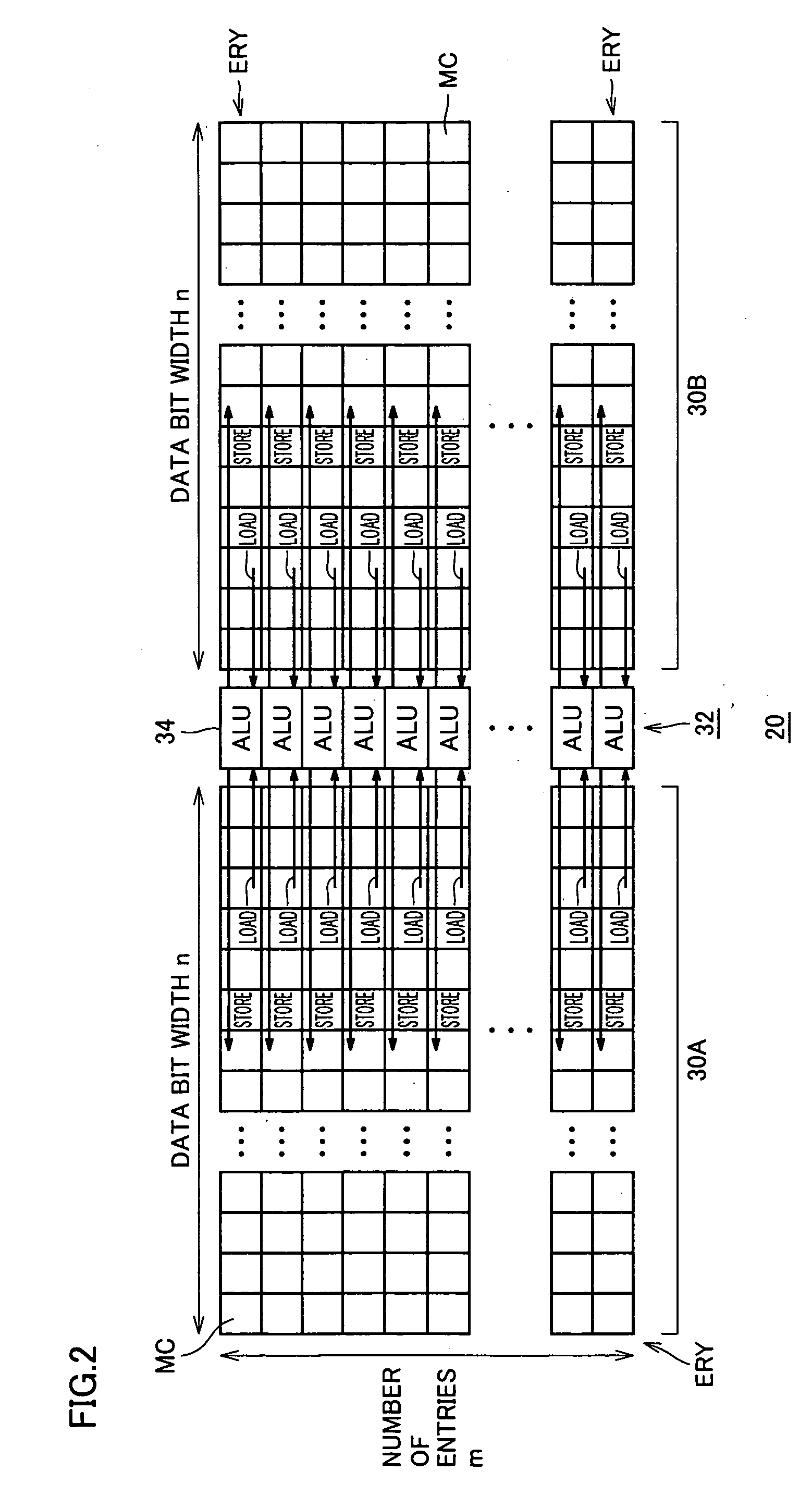

Parallel operational processing device

InactiveUS20070180006A1Easy to operateReduce power consumptionEnergy efficient ICTDigital data processing detailsAudio power amplifierParallel computing

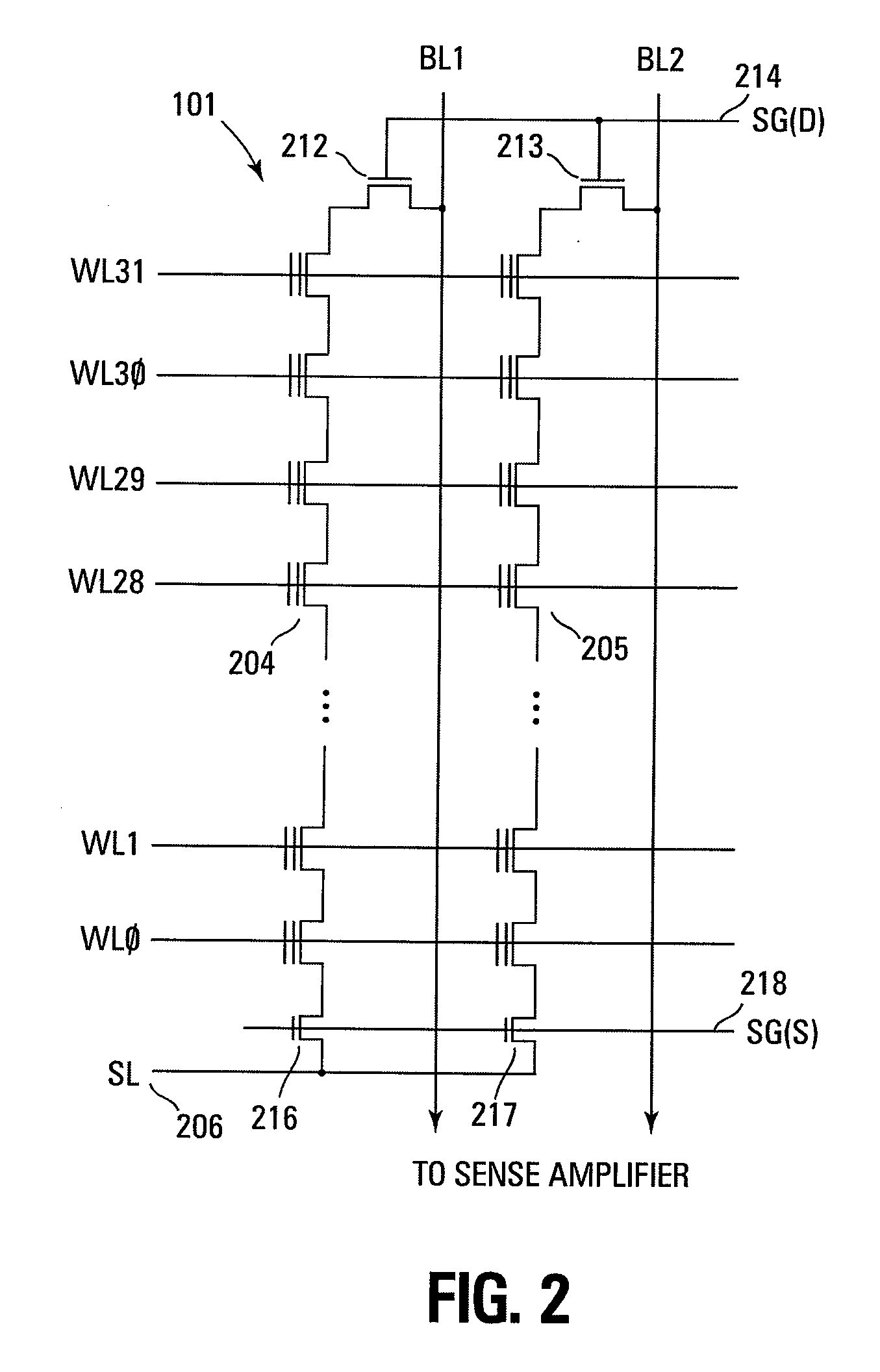

In a parallel operational processing device having an operational processing unit arranged between memory blocks each having a plurality of memory cells arranged in rows and columns, the respective columns of each memory block are alternately connected to the operational processing units on the opposite sides of the memory block. By selecting one word line in one memory block, data can be transferred to two operational processing units. The number of the word lines selected per one operational processing unit is reduced, and power consumption is reduced. The bit operation units and sense amplifiers / write drivers of the operational processing units have arrangement pitch conditions mitigated and are reduced in number, and an isolation region between the memory blocks is not required and the layout area is reduced. Thus, the parallel operational processing device with a layout area and the power consumption reduced, can achieve a fast operation.

Owner:RENESAS ELECTRONICS CORP

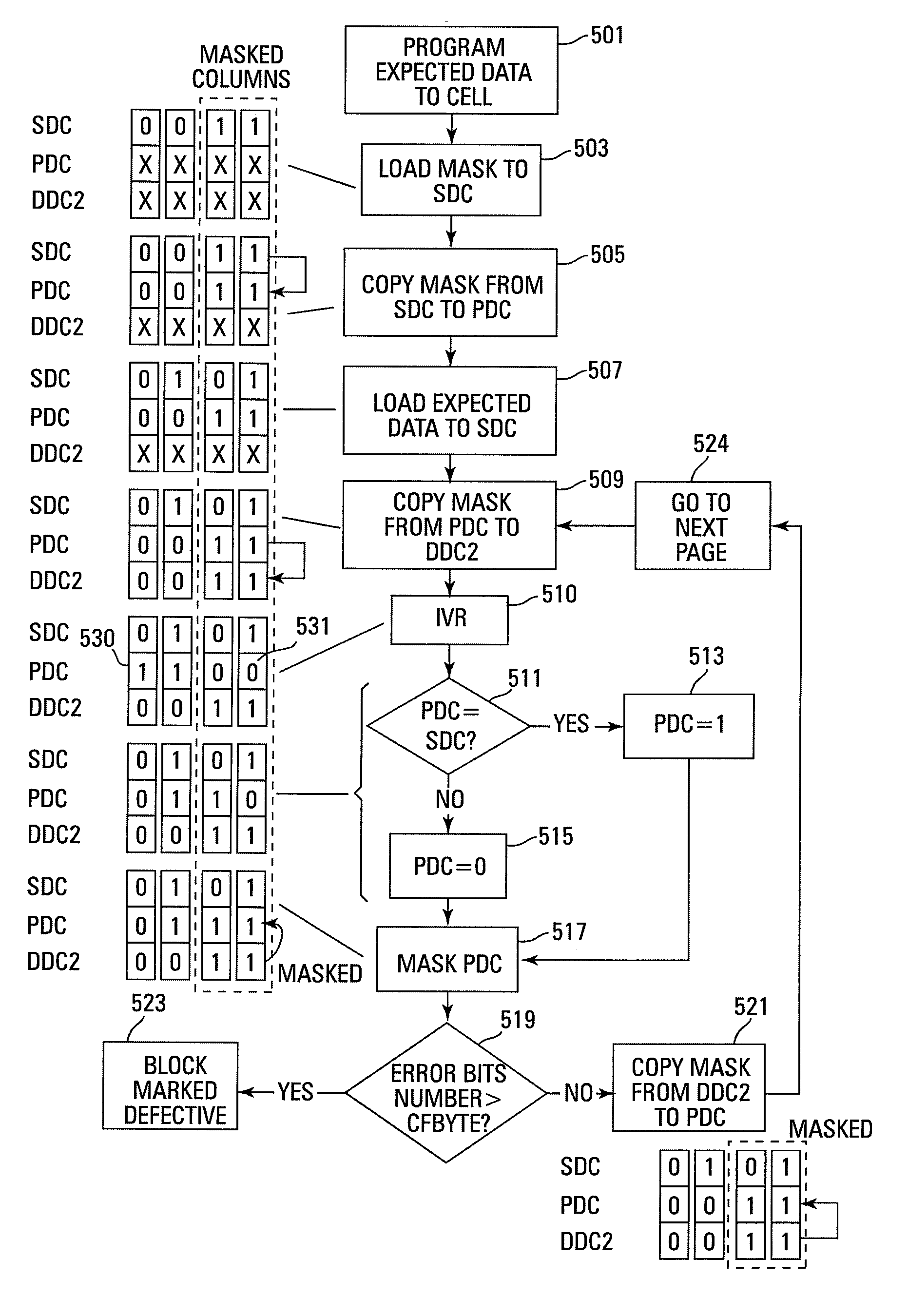

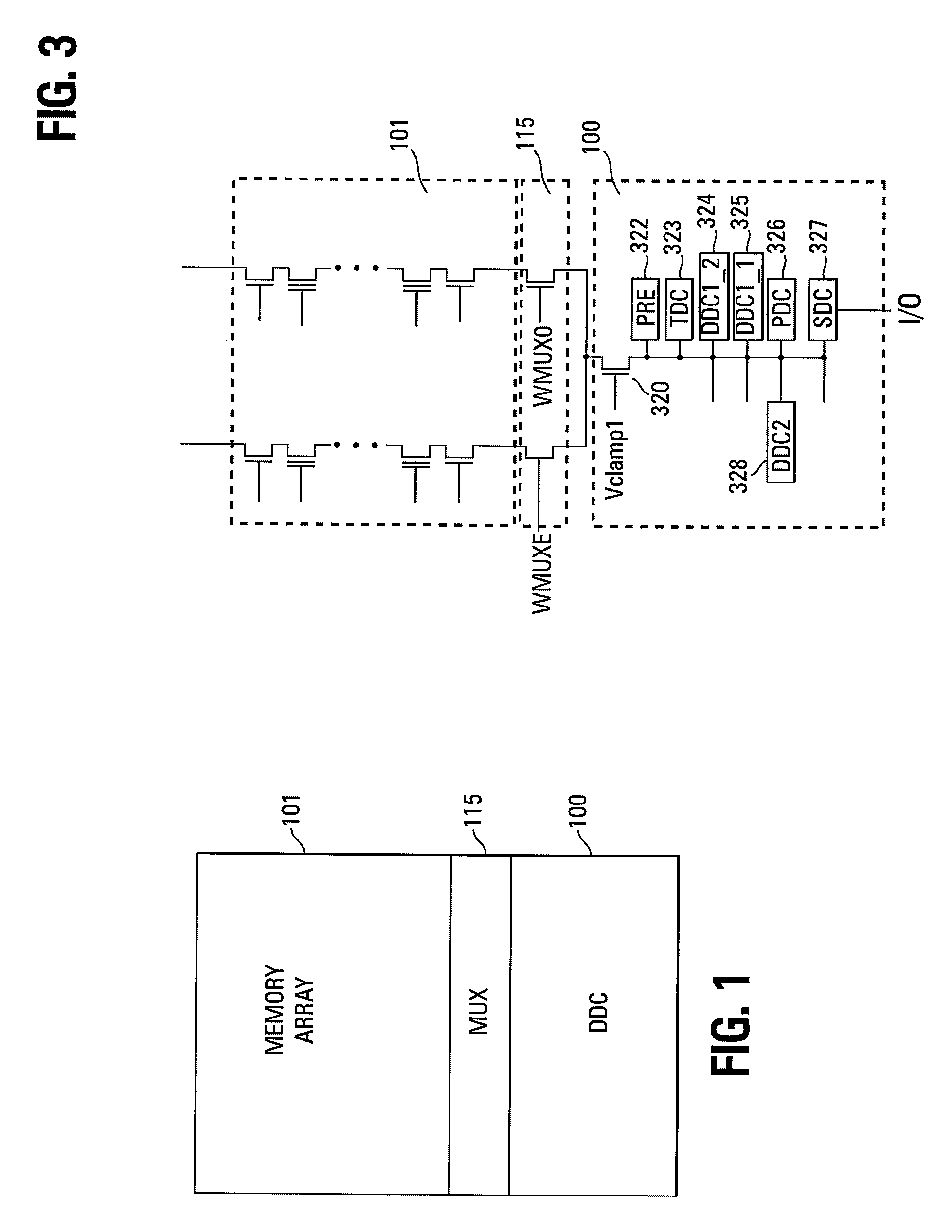

Small unit internal verify read in a memory device

Methods for small unit internal verify read operation and a memory device are disclosed. In one such method, expected data is programmed into a grouping of columns of memory cells (e.g., memory block). Mask data is loaded into a third dynamic data cache of three dynamic data caches. The expected data is loaded into a second data cache. After a read operation of programmed columns of memory cells, the read data is compared to the expected data and error bit indicators are stored in the second data cache in the error bit locations. The second data cache is masked with the mask data so that only those error bits that are unmasked are counted. If the number of unmasked error bit indicators is greater than a threshold, the memory block is marked as unusable.

Owner:MICRON TECH INC

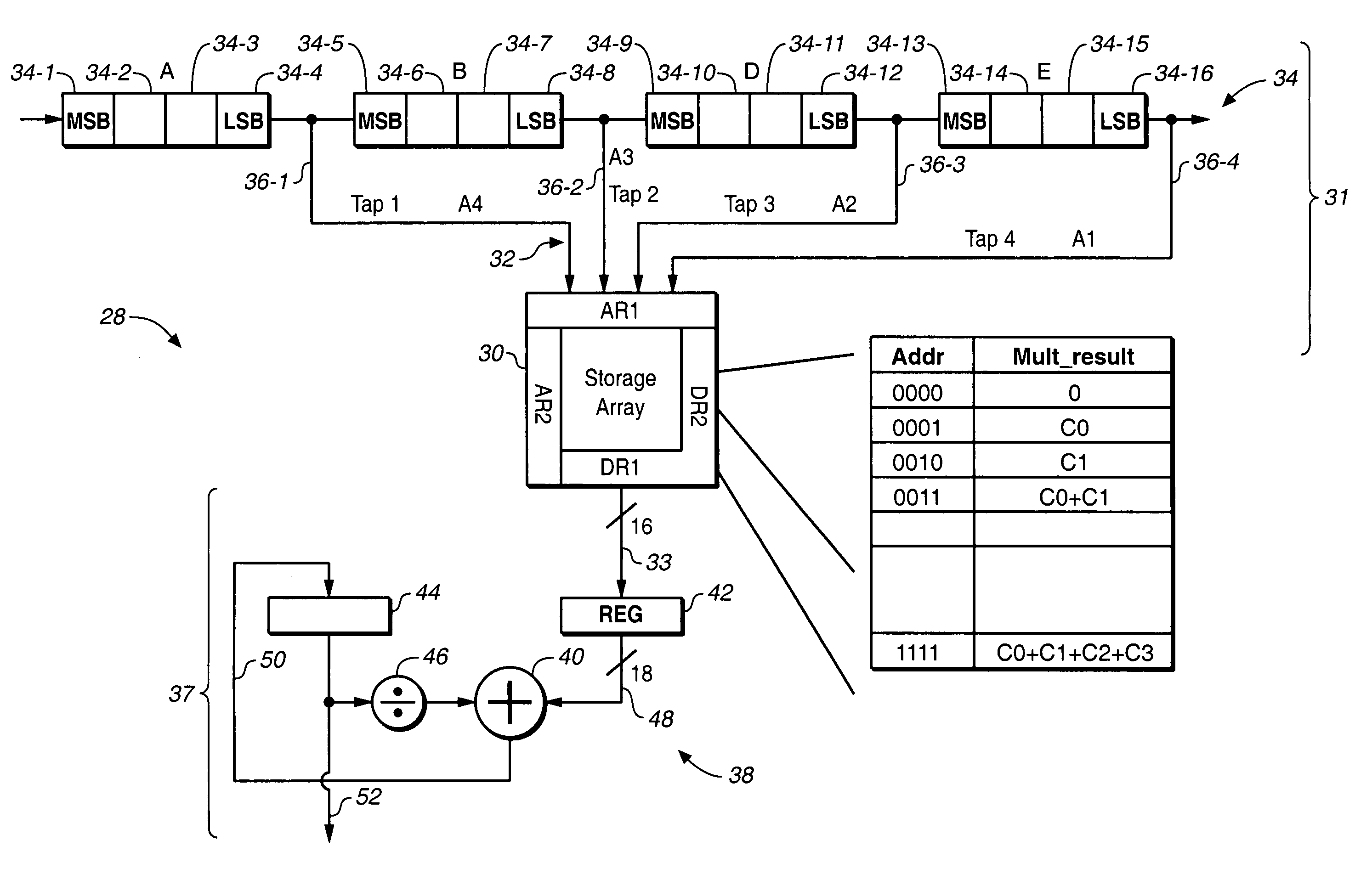

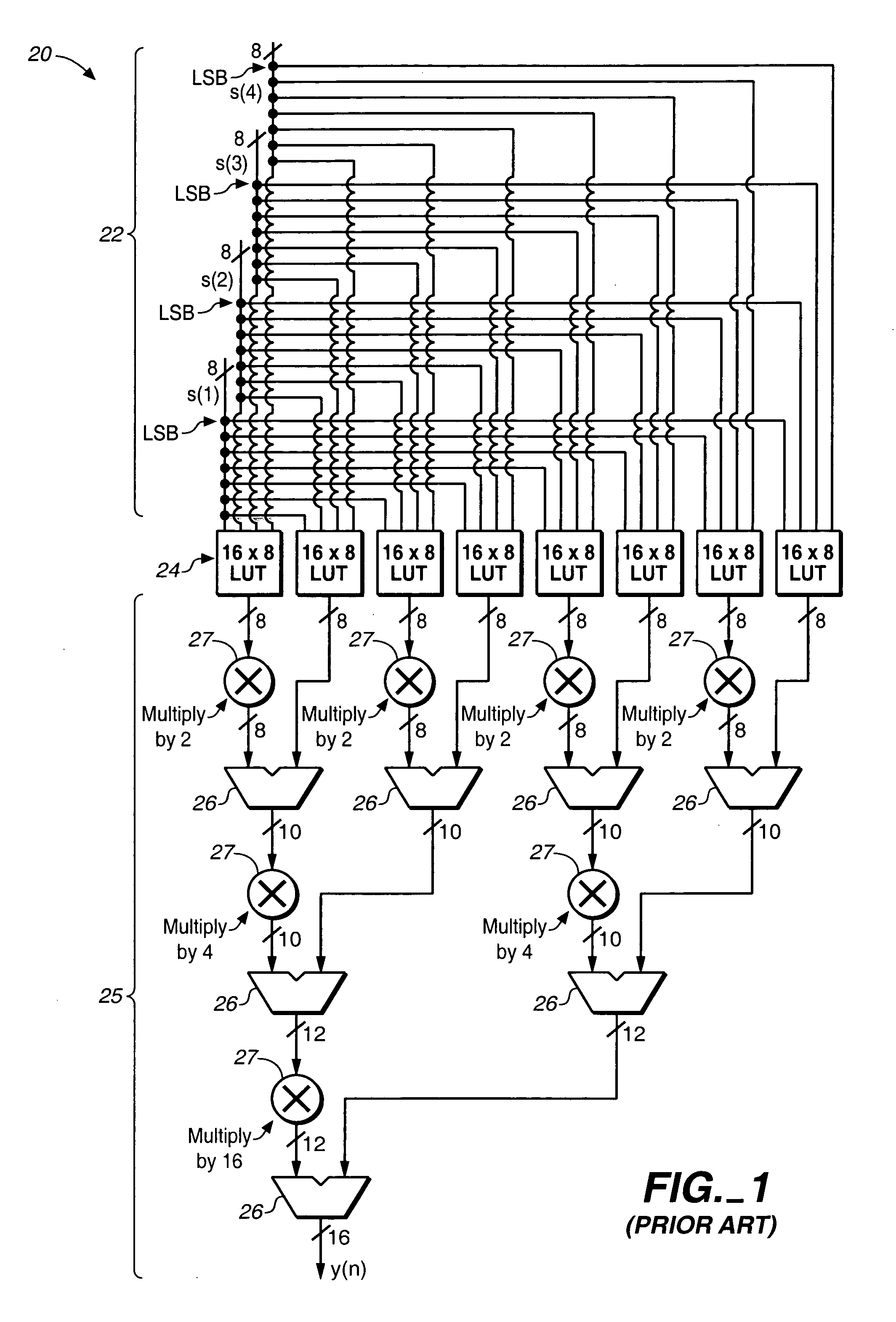

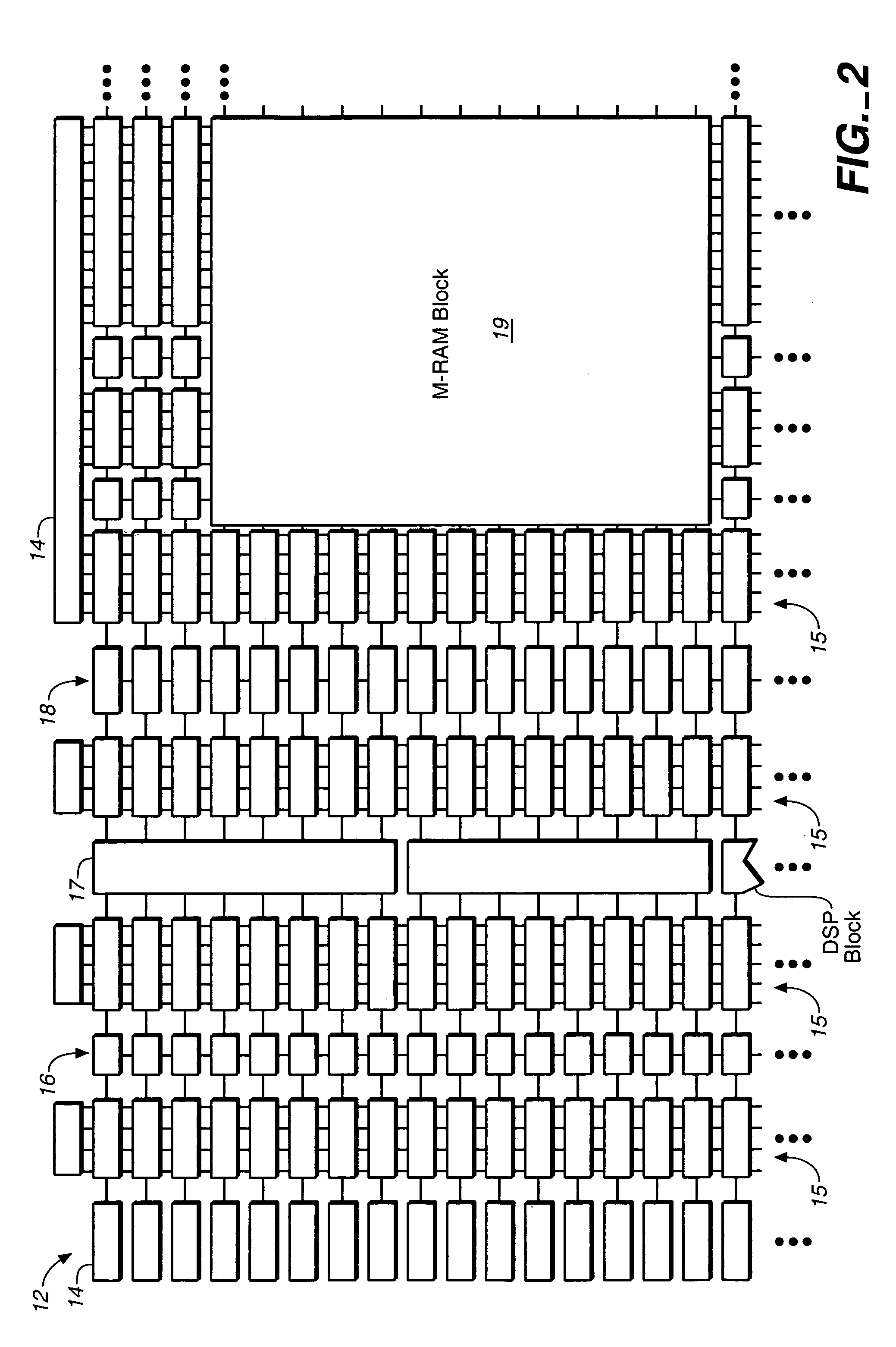

Variable fixed multipliers using memory blocks

InactiveUS6943579B1Computations using contact-making devicesComputation using non-contact making devicesProgrammable logic deviceOperand

A programmable logic device includes at least one RAM block generating a first multi-bit calculation result which may, but does not necessarily, involve a multiplication of two operands. A shift operation is driven by a second multi-bit calculation result shifts the second multi-bit calculation result by at least one bit to generate a shifted second multi-bit calculation result. A multi-bit adder coupled to the at least one RAM block adds the shifted second multi-bit calculation result to the first multi-bit calculation result.

Owner:ALTERA CORP

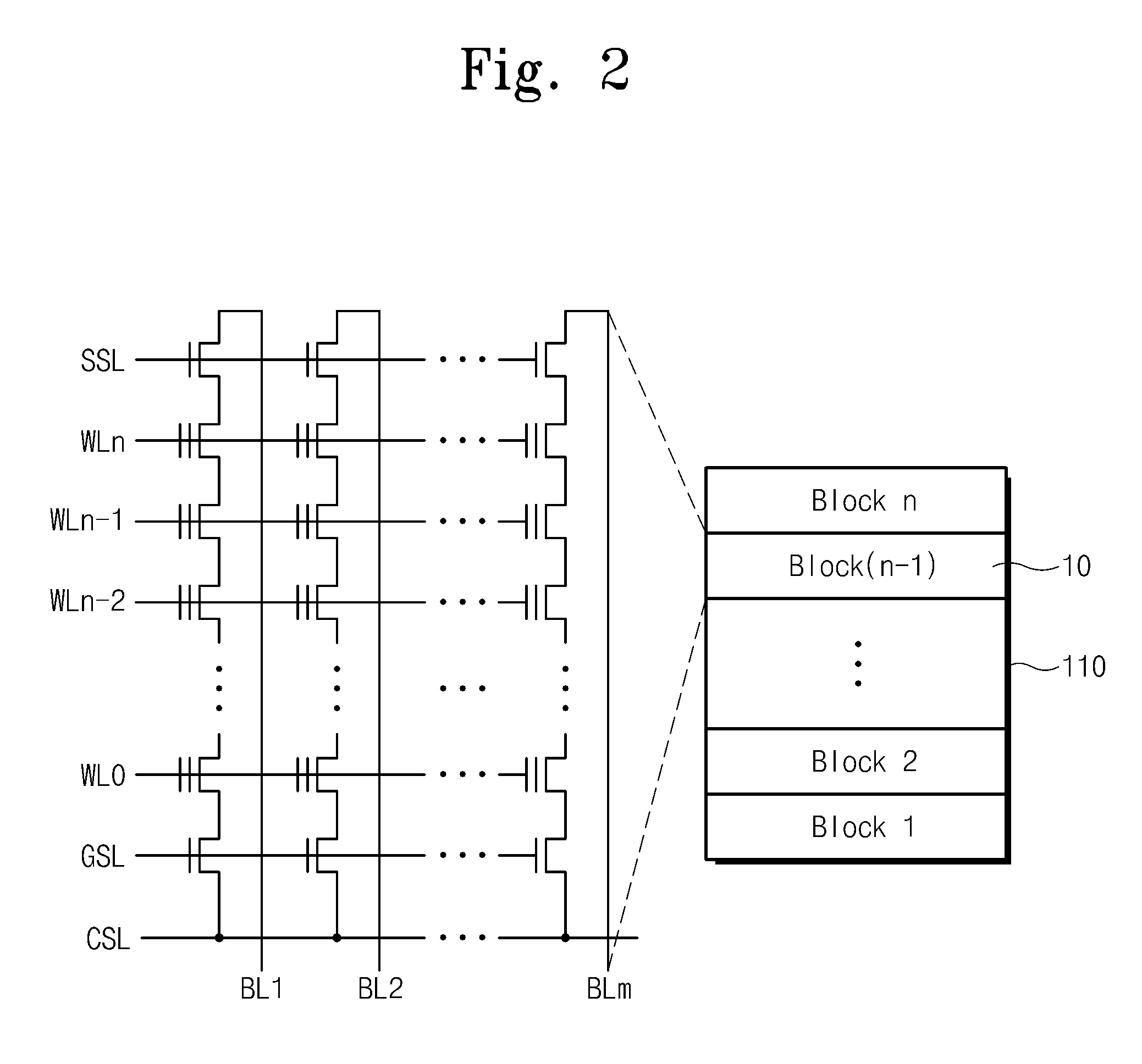

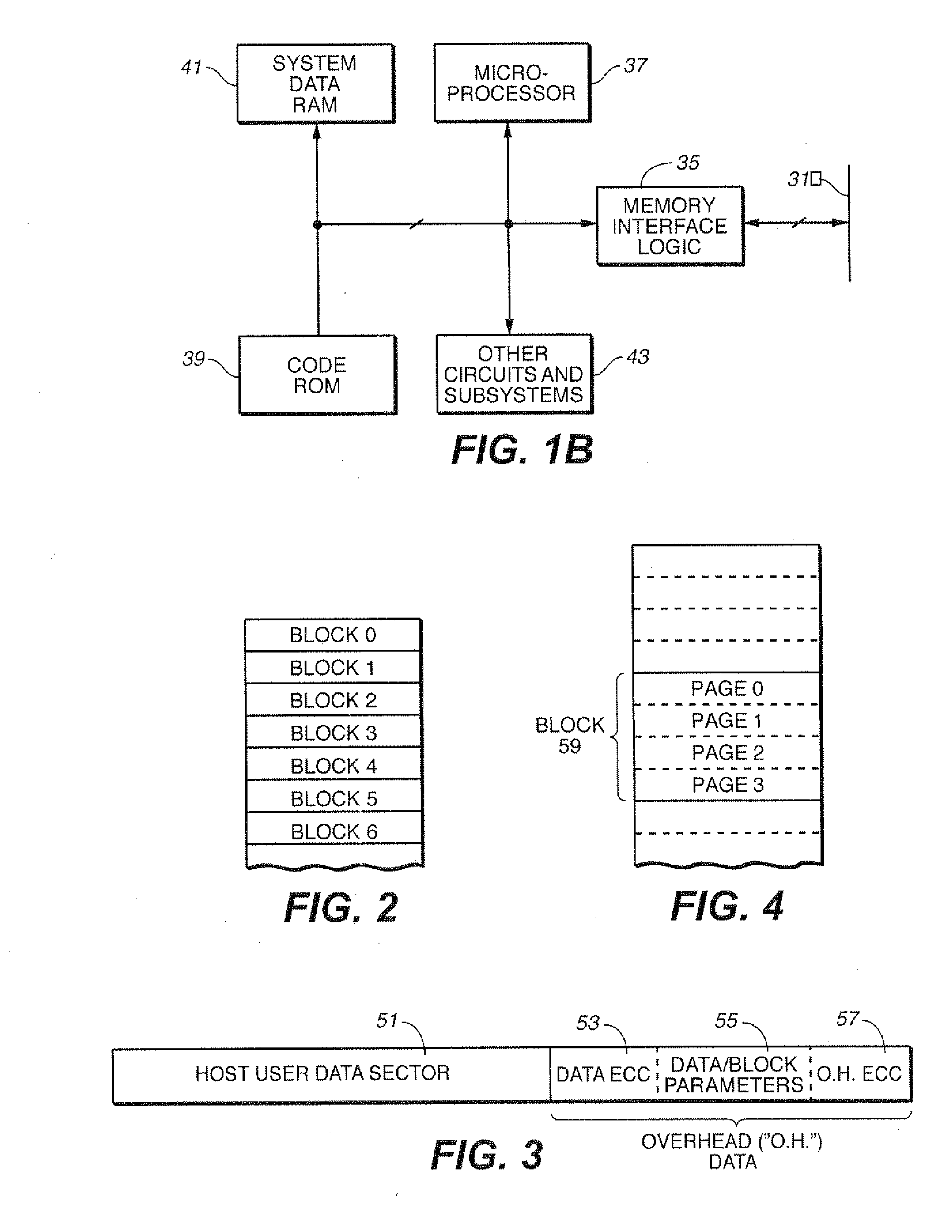

Methods of copying a page in a memory device and methods of managing pages in a memory system

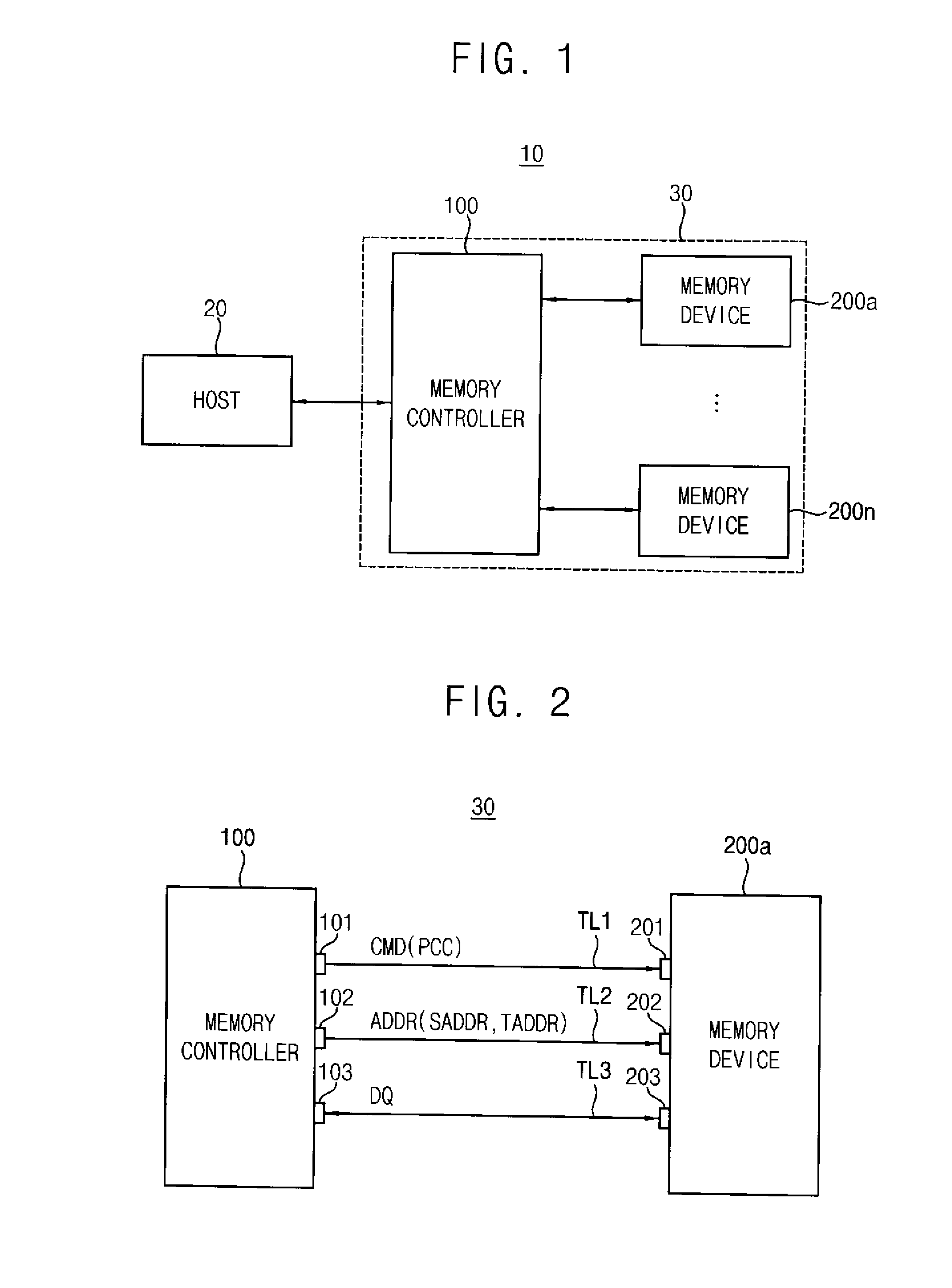

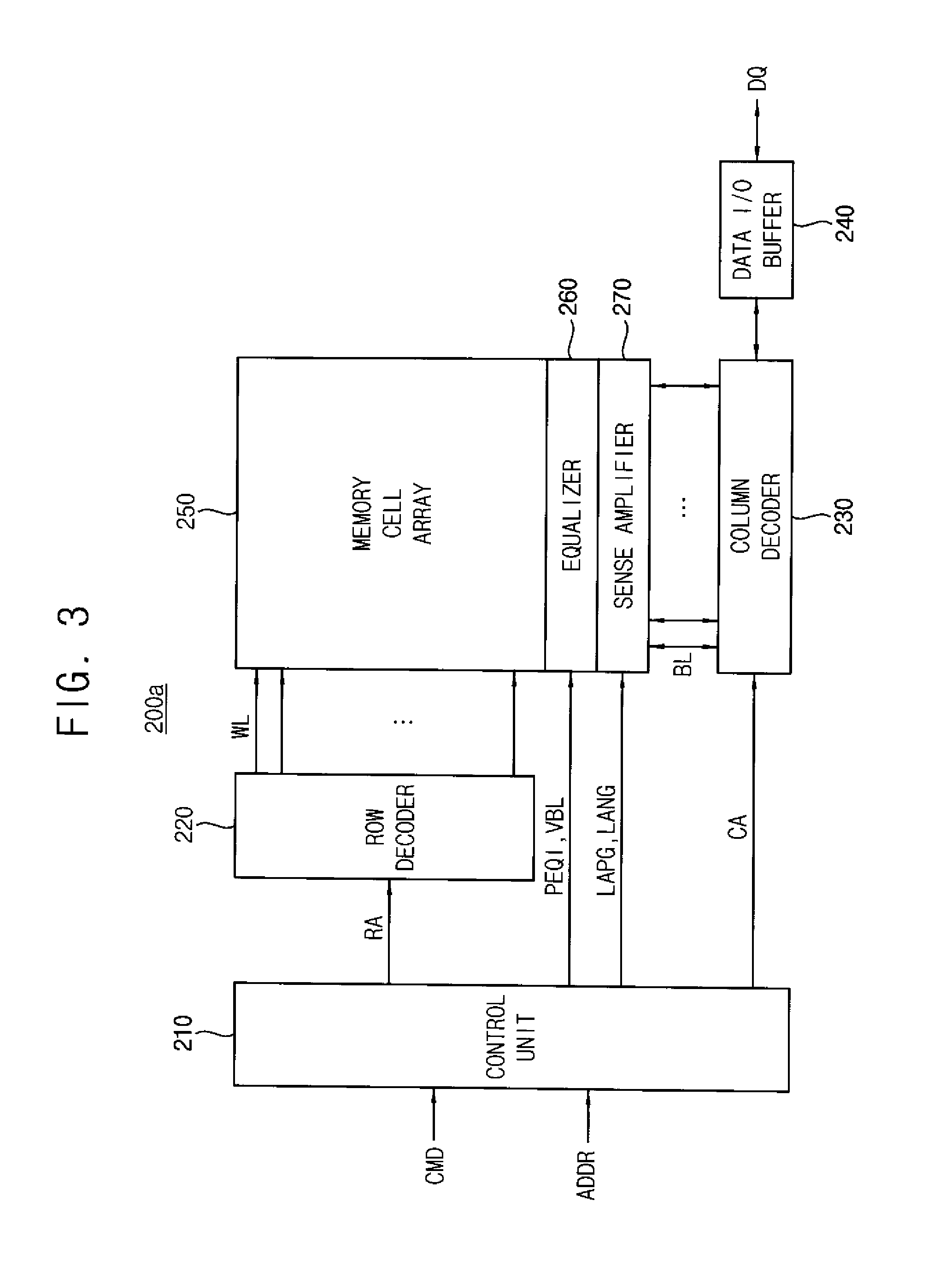

A method of copying a page in a memory device having a plurality of memory blocks and a plurality of sets of bit lines is disclosed, wherein each of the plurality of memory blocks includes a plurality of pages, and each set of bit lines corresponds to a respective memory block, wherein first bit lines of a source memory block that includes a source page are respectively coupled to second bit lines of a target memory block that includes a target page. The method includes disconnecting between the first bit lines of thea source memory block including a source page and from the second bit lines of a the target memory block including a target page; transferring data stored in the source page to the first bit lines of the source memory block; transferring the data from the first bit lines of the source memory block to the second bit lines of the target memory block; and writing the data transferred to the second bit lines of the target memory block into the target page.

Owner:SAMSUNG ELECTRONICS CO LTD

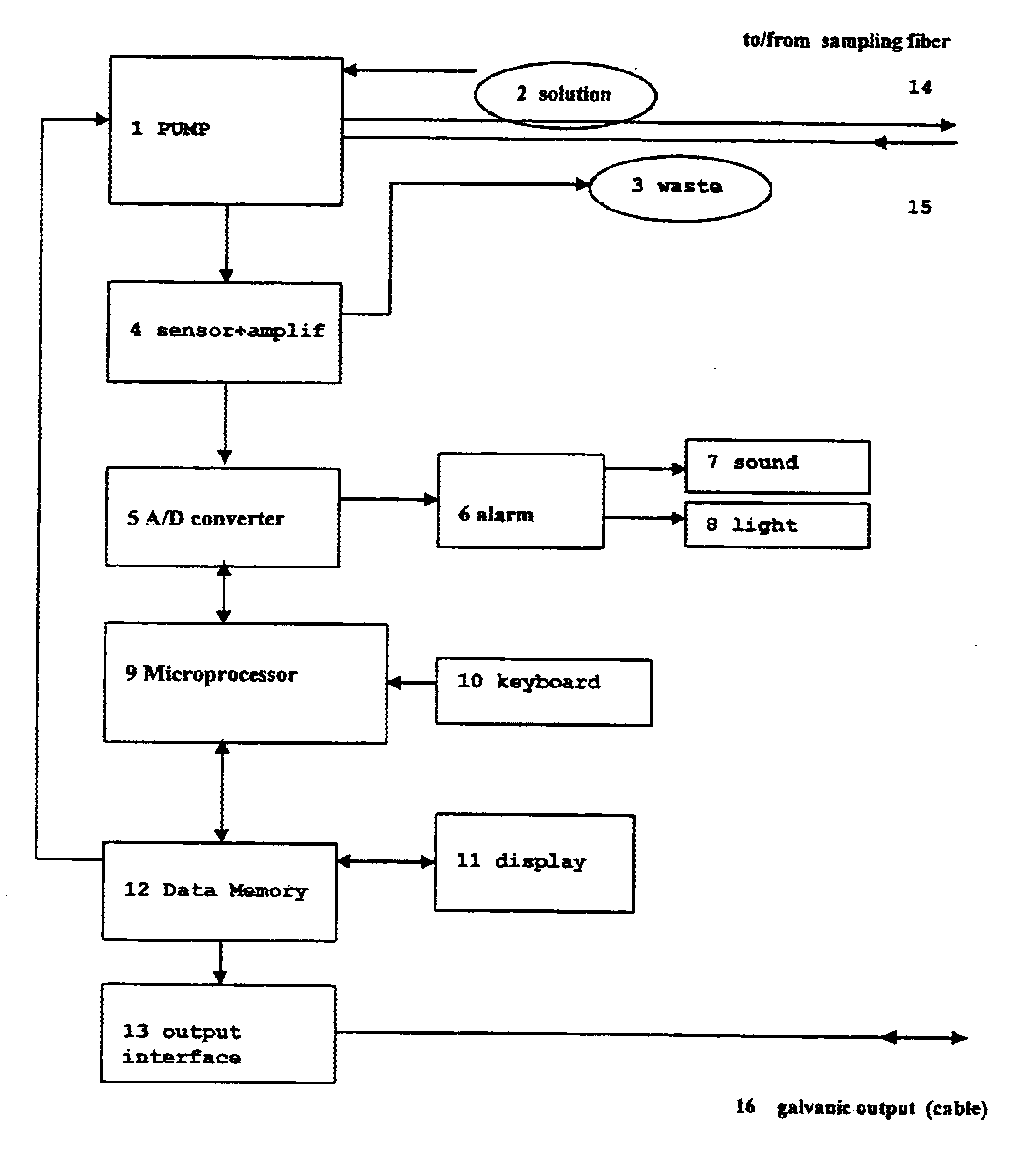

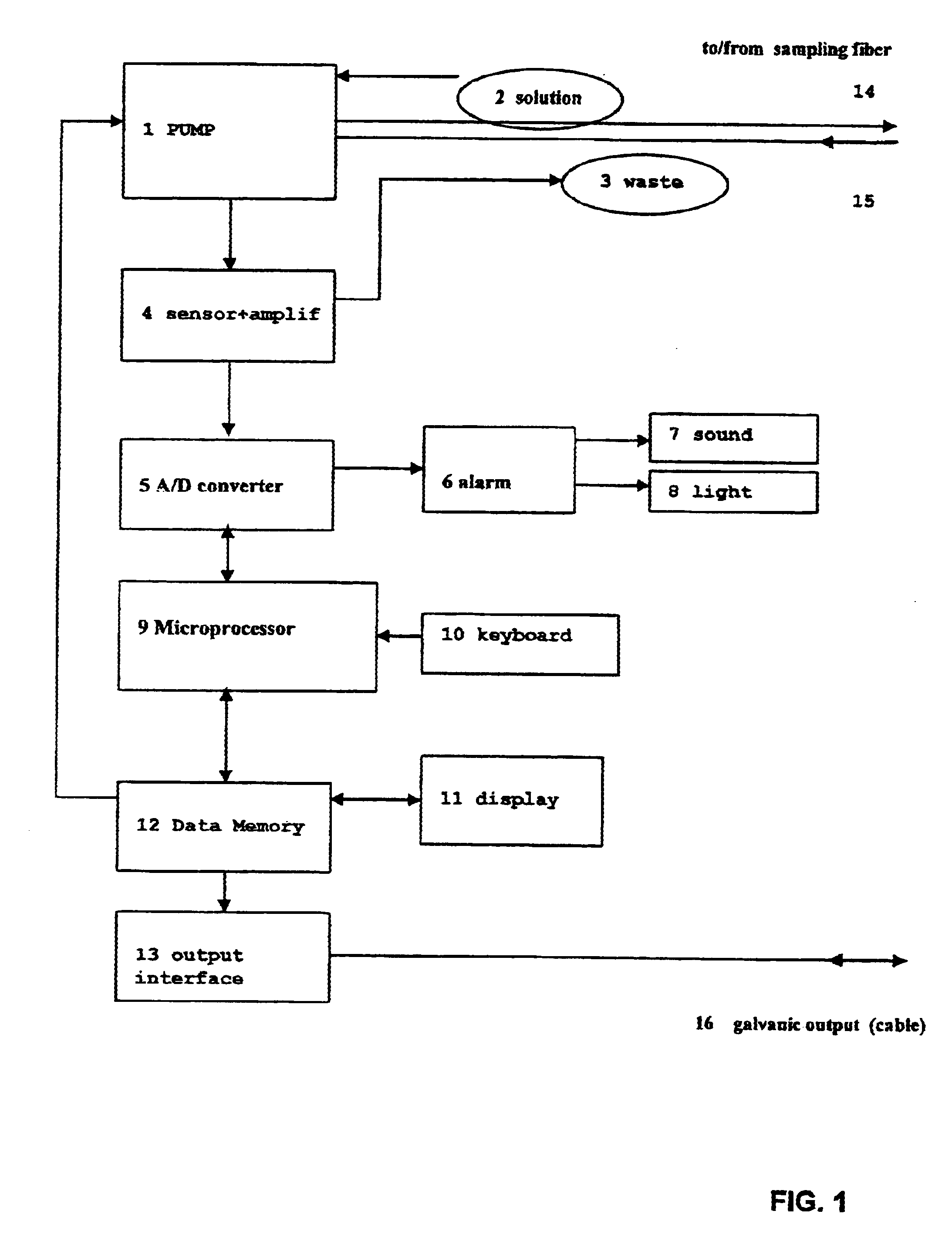

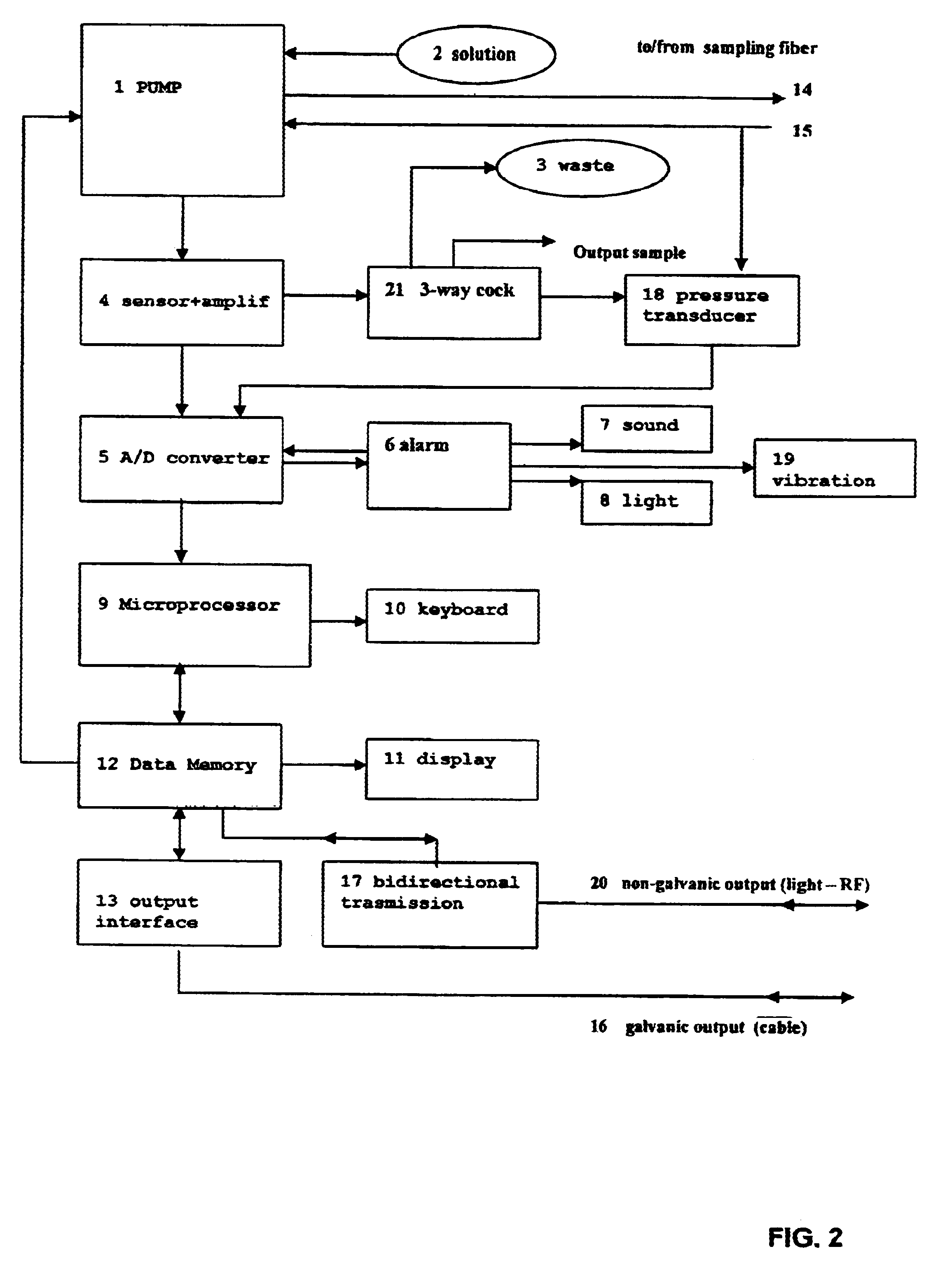

Apparatus for measurement and control of the content of glucose, lactate or other metabolites in biological fluids

InactiveUS6618603B2Immobilised enzymesBioreactor/fermenter combinationsMetaboliteGlucose Measurement

An apparatus for the continuous measurement of glucose and lactate in interstitial fluids including a glucose measurement cell, an A / D conversion block, a memory block and a bi-directional communication between the interface block and an external calculation unit.

Owner:A MENARINI IND FARM RIUNITE SRL

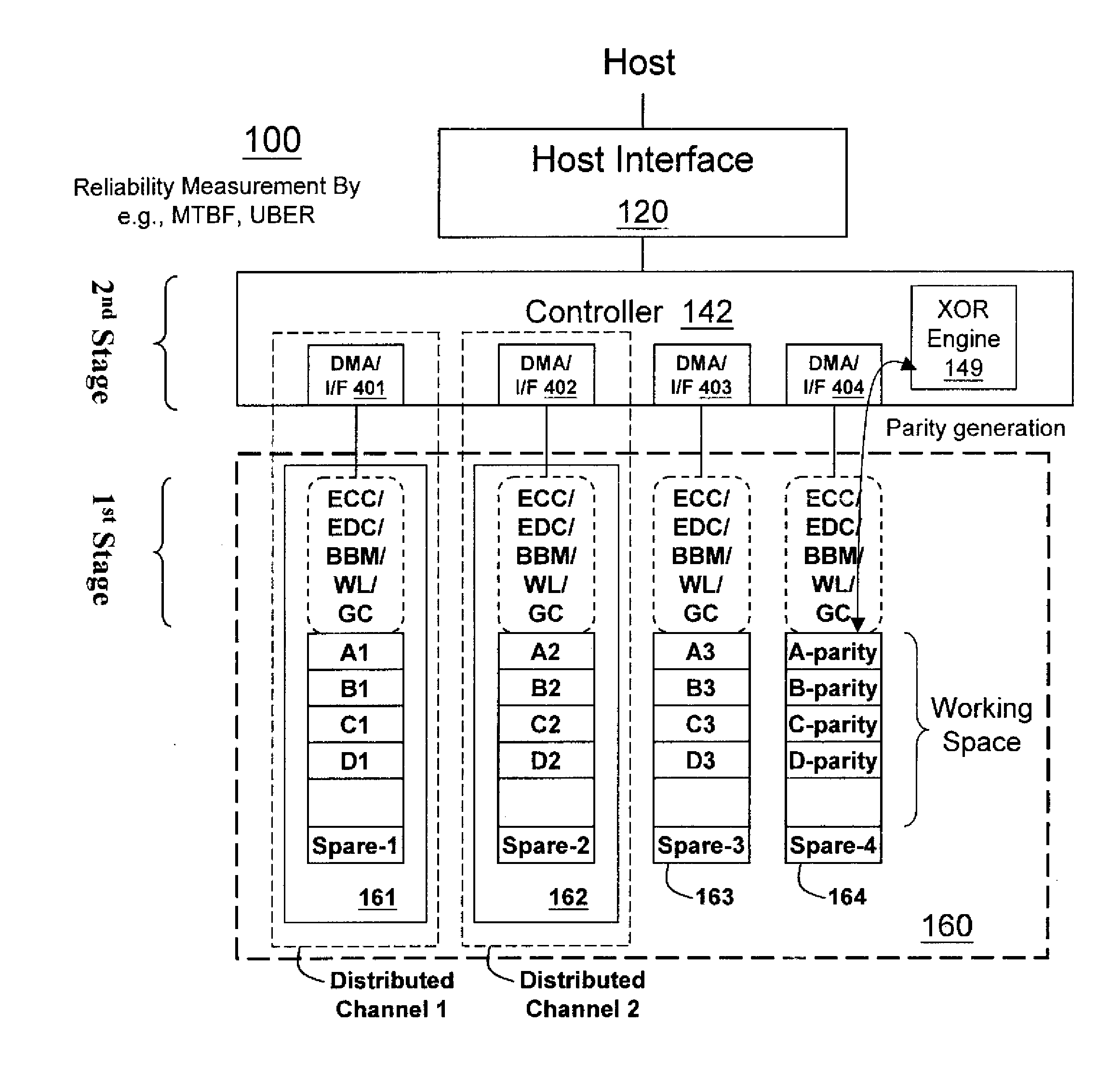

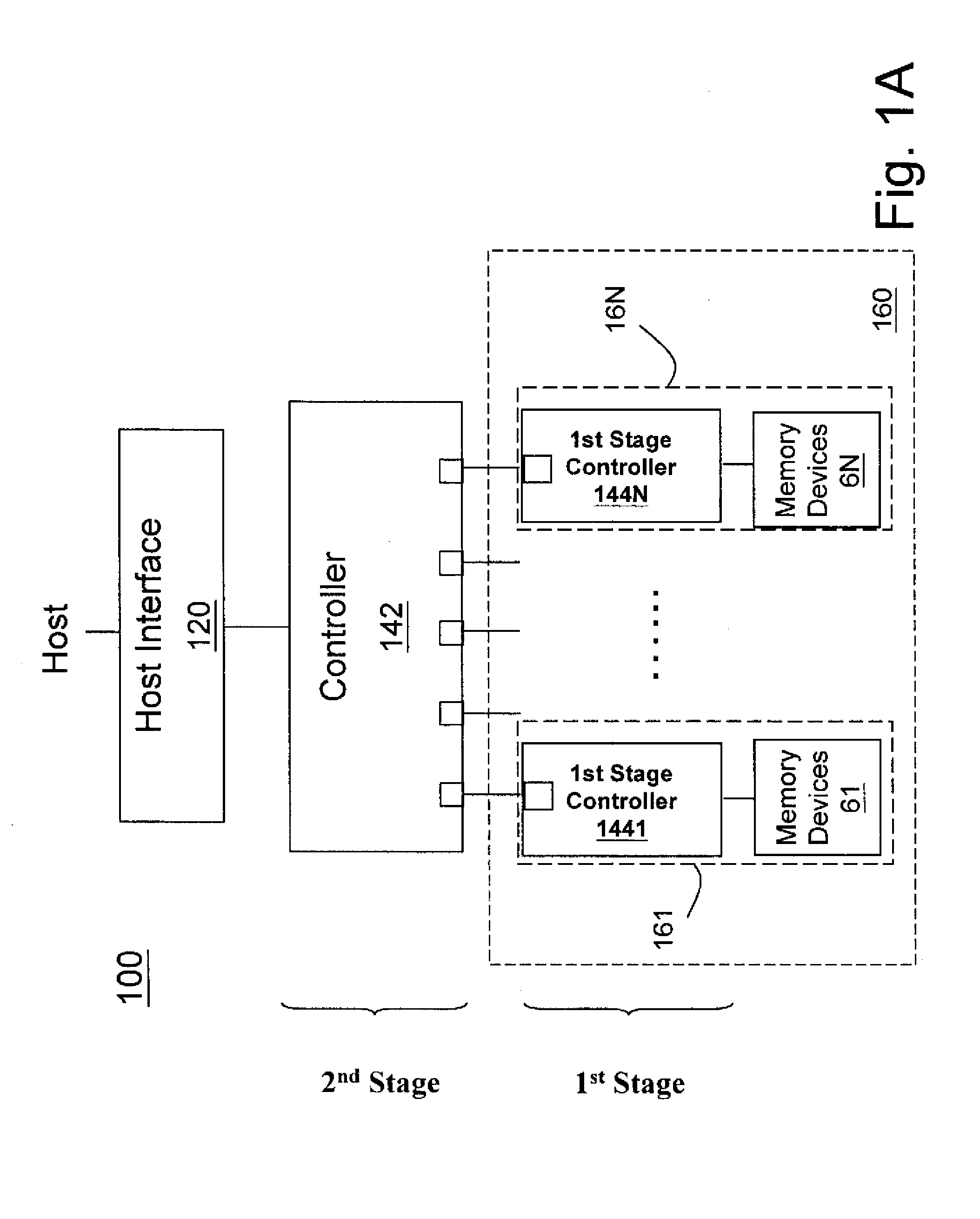

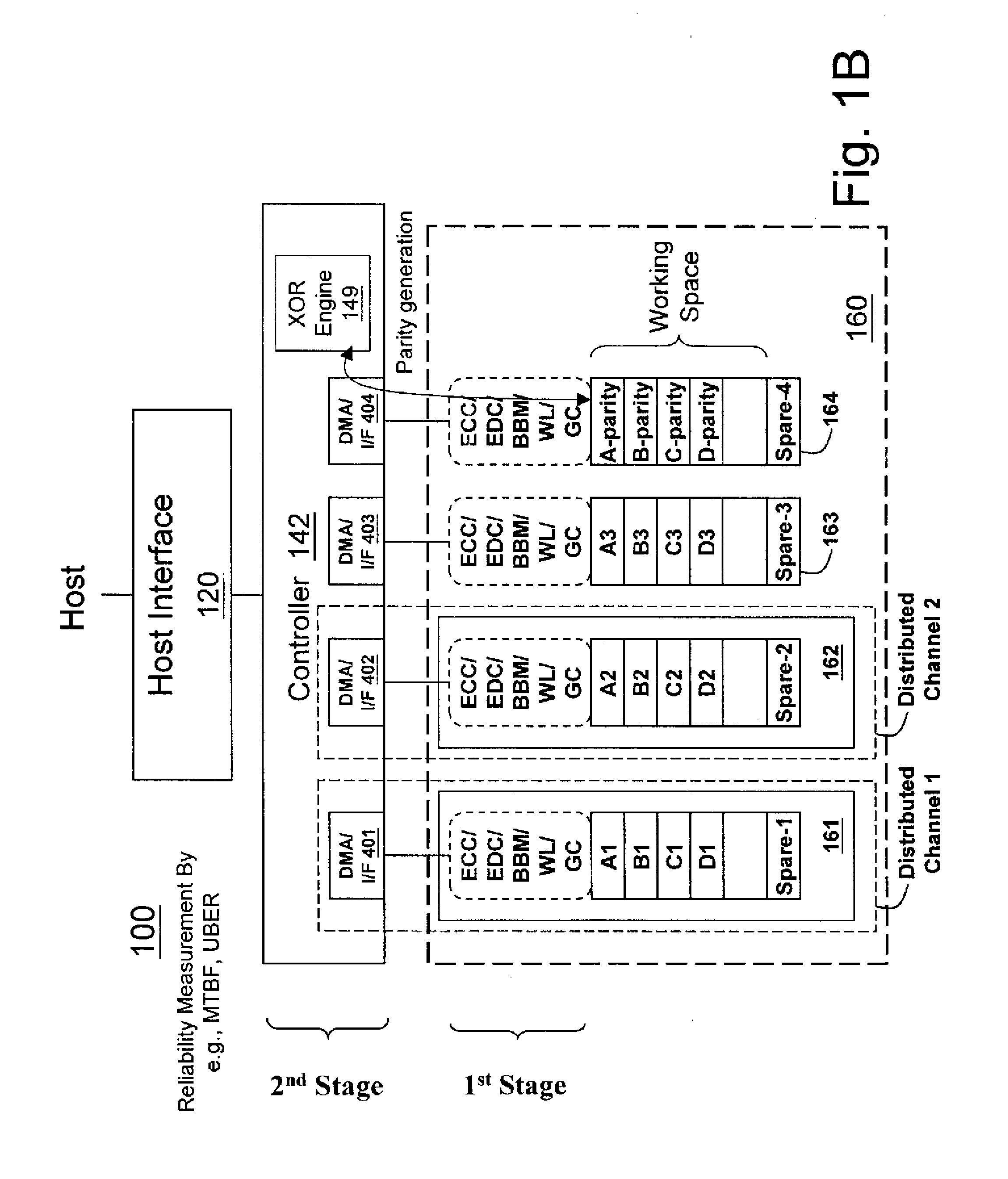

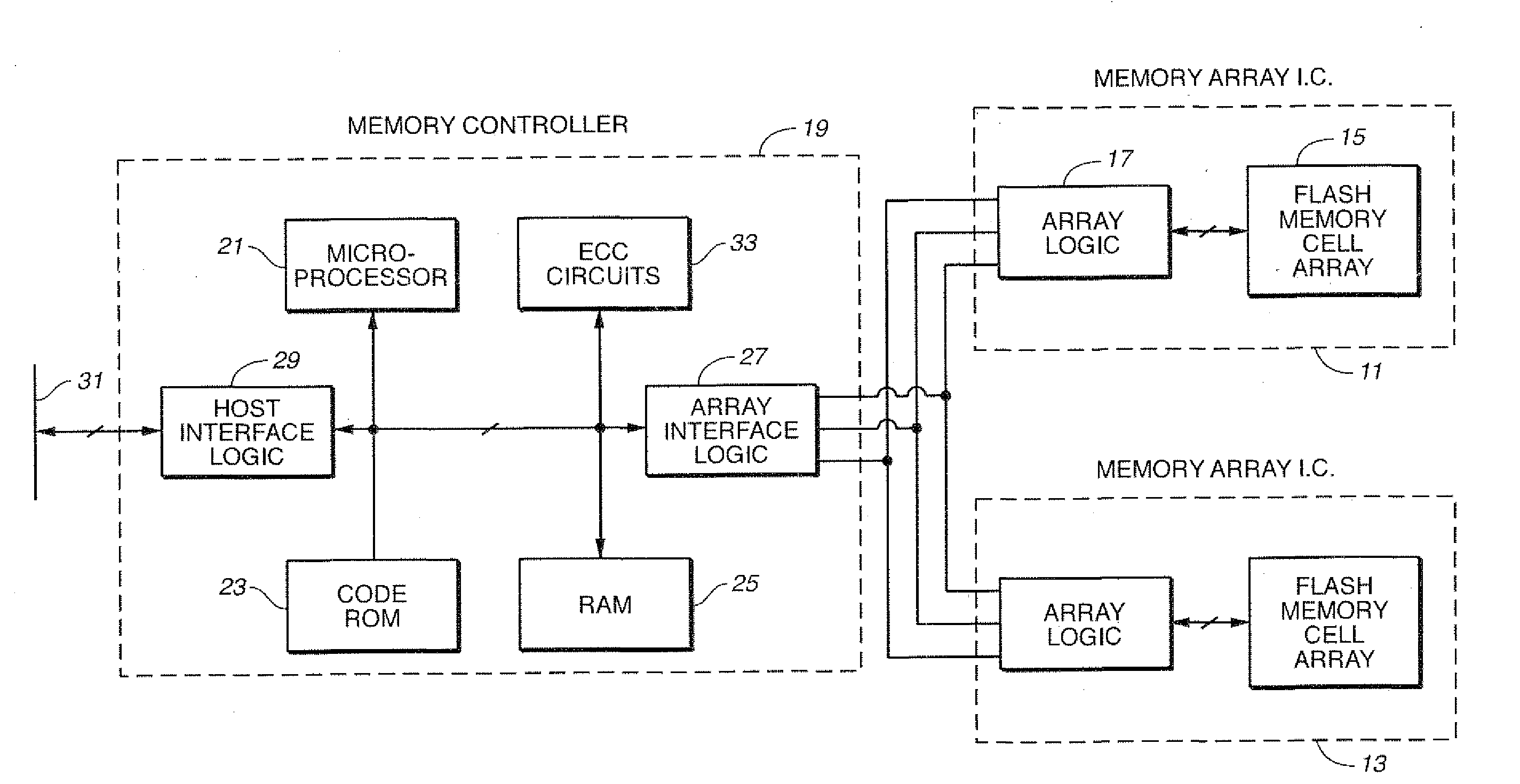

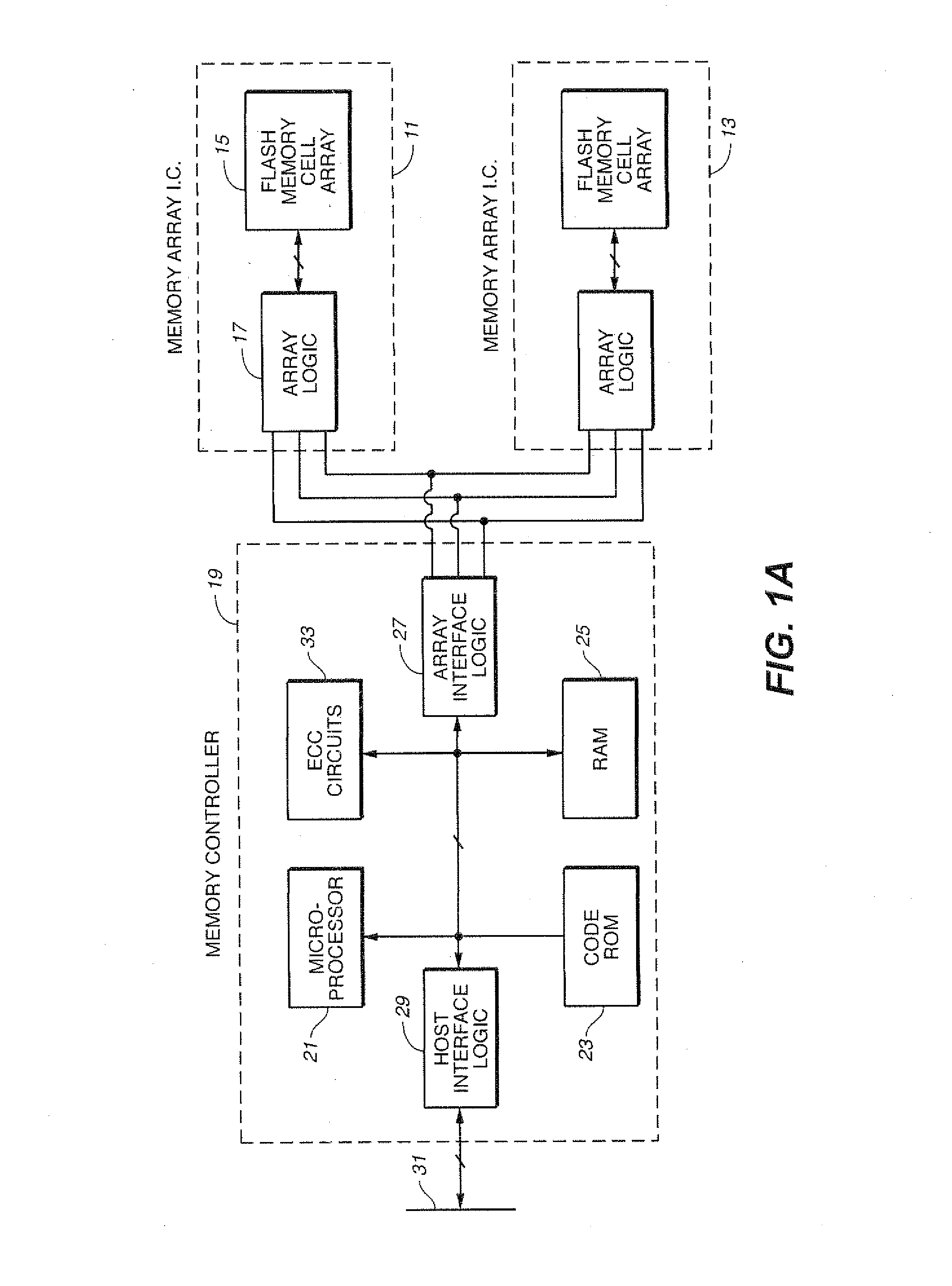

Non-volatile memory data storage system with reliability management

InactiveUS20100017650A1Improve reliabilityReliable managementMemory loss protectionMemory adressing/allocation/relocationRAIDData recovery

A non-volatile memory data storage system, comprising: a host interface for communicating with an external host; a main storage including a first plurality of flash memory devices, wherein each memory device includes a second plurality of memory blocks, and a third plurality of first stage controllers coupled to the first plurality of flash memory devices; and a second stage controller coupled to the host interface and the third plurality of first stage controller through an internal interface, the second stage controller being configured to perform RAID operation for data recovery according to at least one parity.

Owner:NANOSTAR CORP

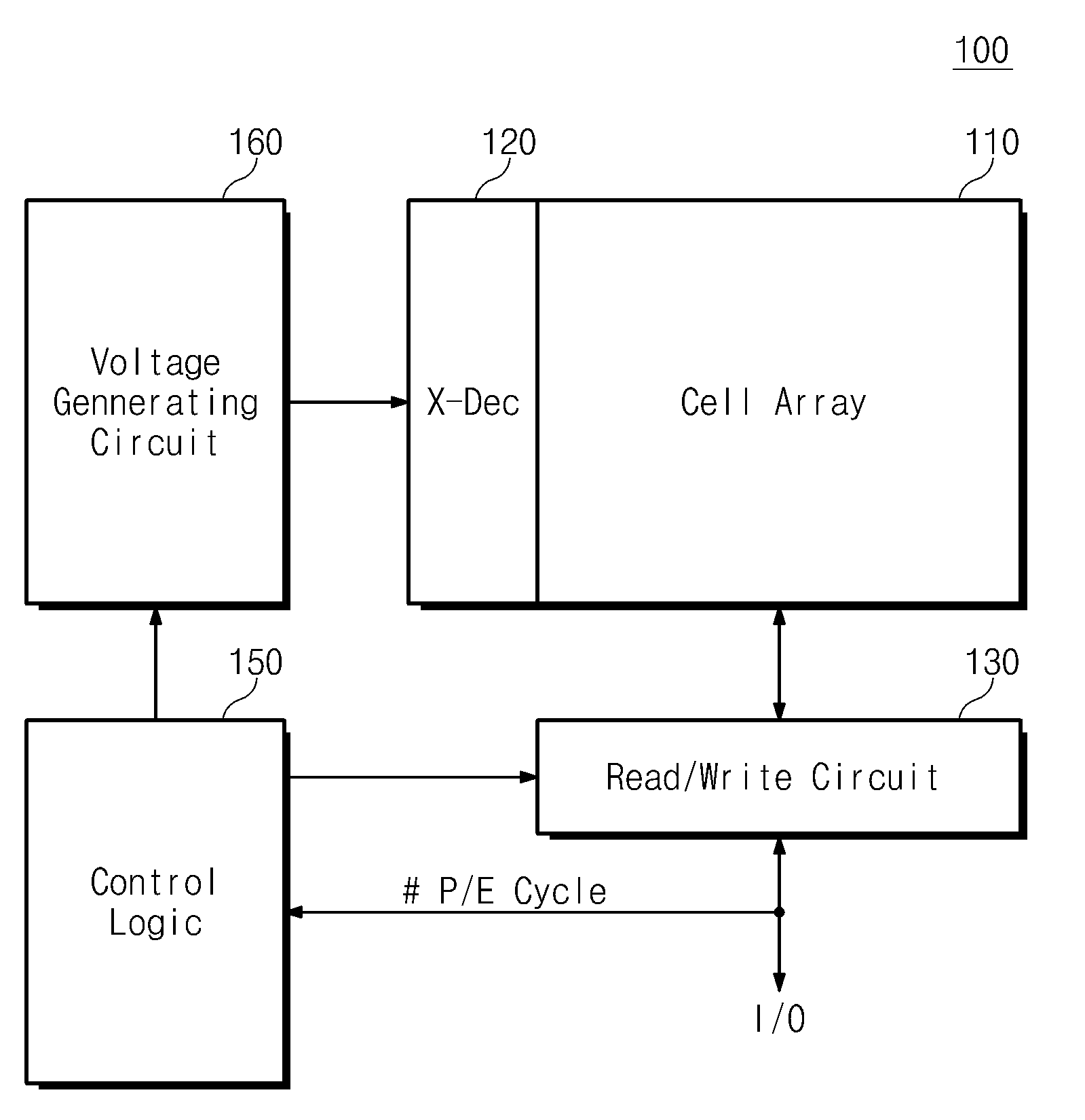

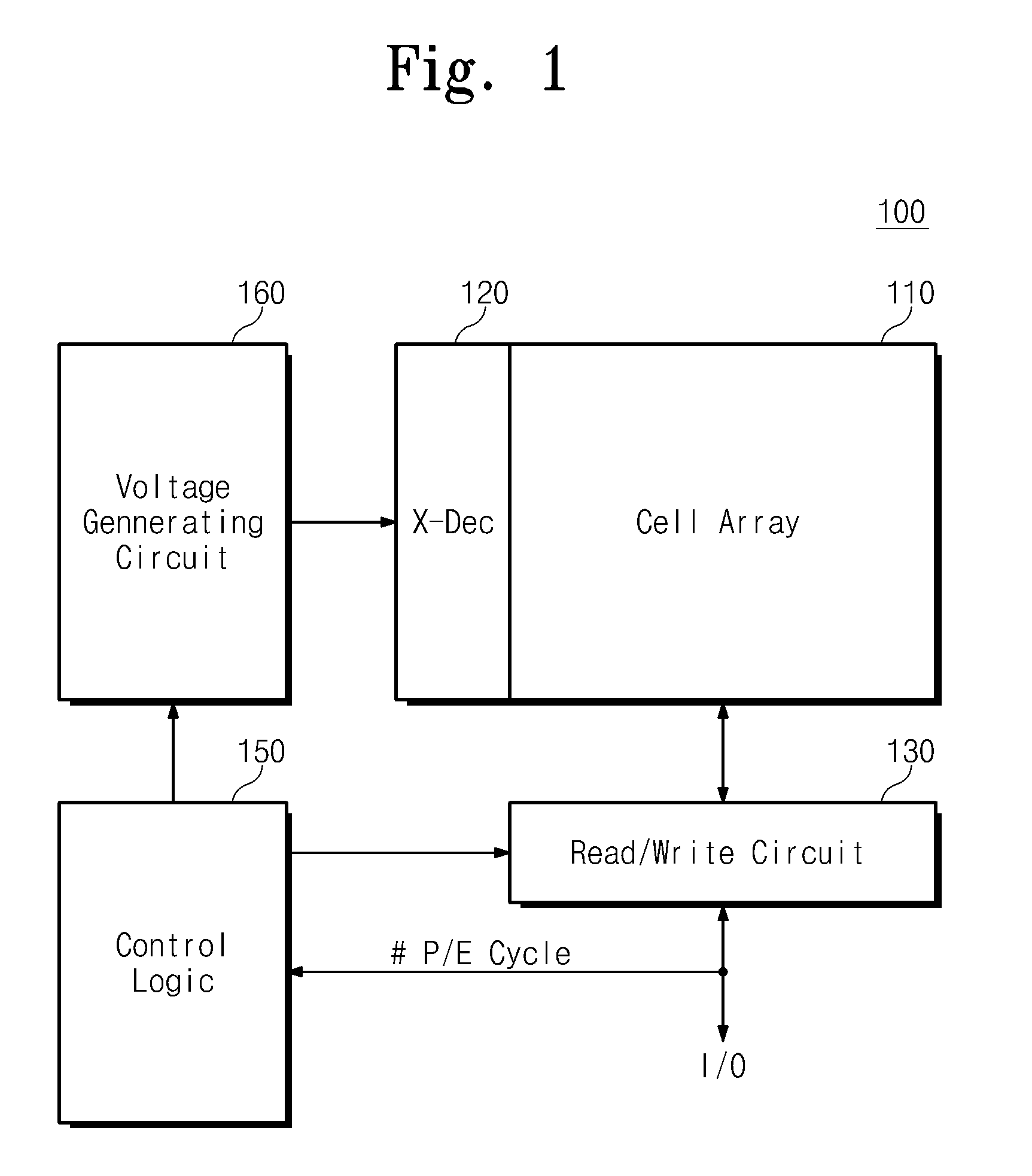

Nonvolatile memory device and related programming method

A nonvolatile memory device comprises a memory cell array comprising a plurality of memory blocks each divided into a plurality of regions, and a control logic component. The control logic component selects a memory block to be programmed based on program / erase cycles of the memory blocks, and selects a program rule used to program the regions of the selected memory block.

Owner:SAMSUNG ELECTRONICS CO LTD

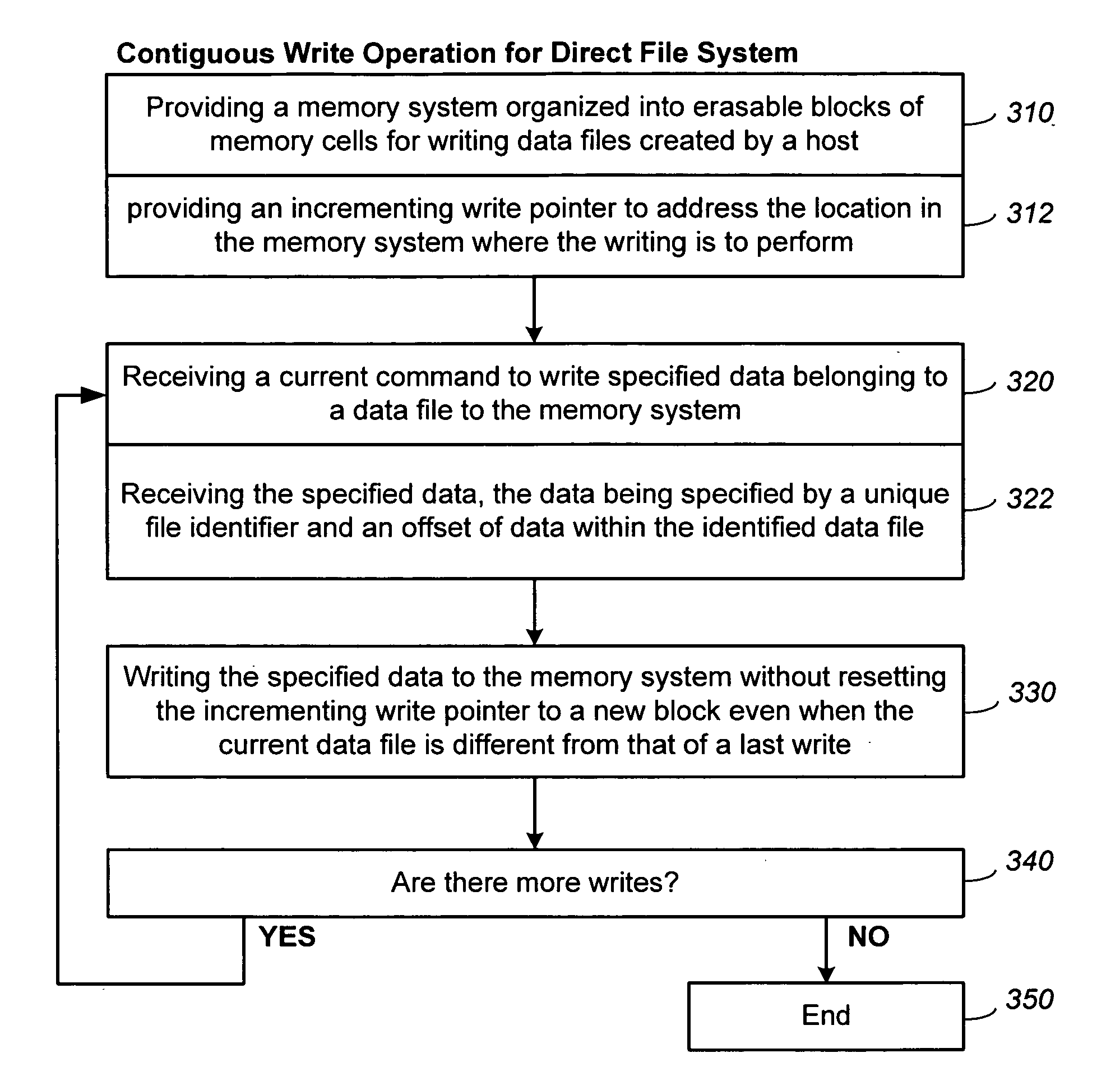

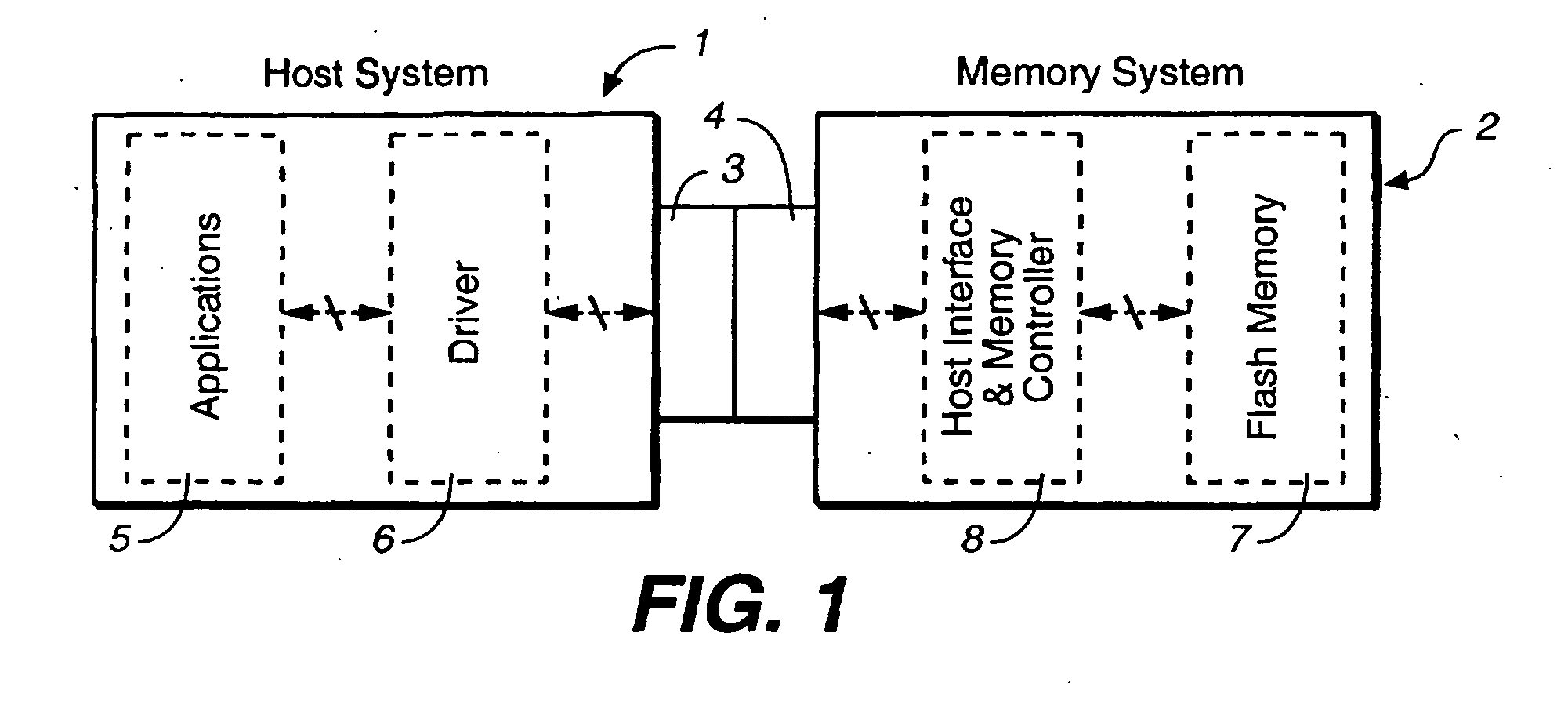

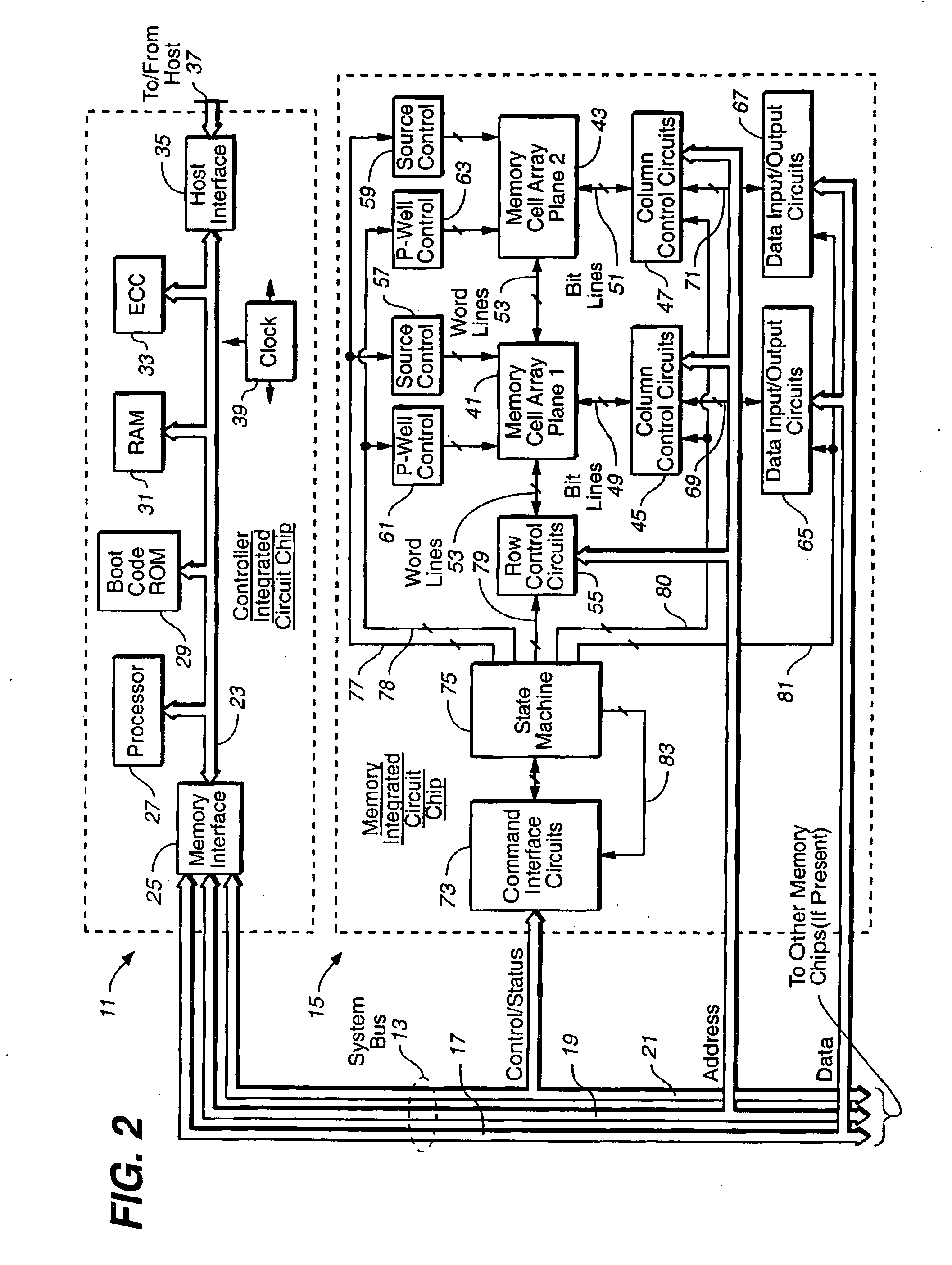

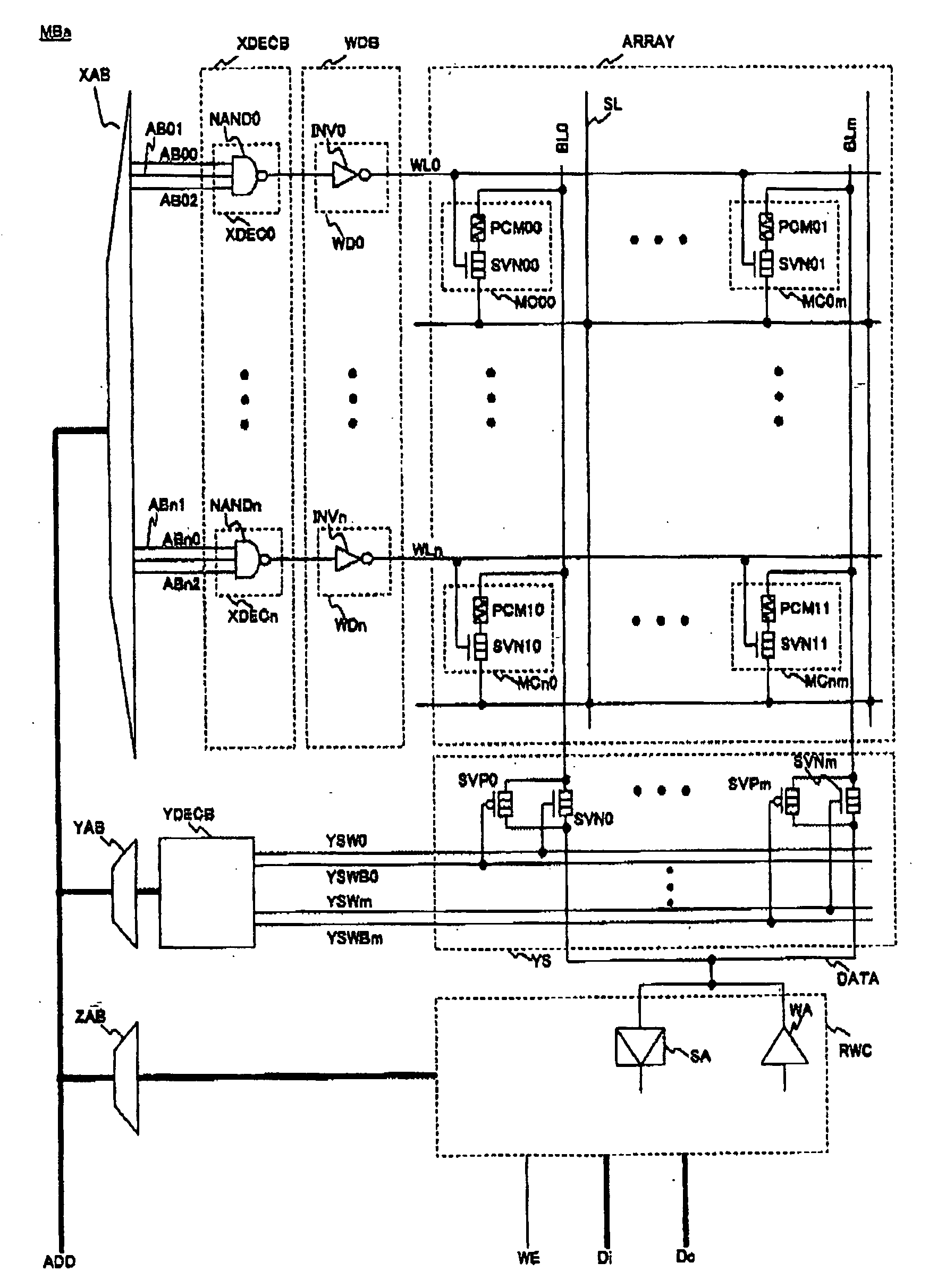

Methods for memory allocation in non-volatile memories with a directly mapped file storage system

InactiveUS20070156998A1Improve performanceEfficient packagingMemory architecture accessing/allocationMemory systemsData compressionWrite pointer

In a memory system with a file storage system, a scheme for allocating memory locations for a write operation is to write the files substantially contiguously in a memory block one after another rather than to start a new file in a new block. In this way, they are more efficiently packed into the blocks by being written contiguously one after another. In a preferred embodiment, an incrementing write pointer points to the write location in memory for the next data for a file, which is independent of the offset address of the data within the file. When a current write block becomes filled with file data, an erased block is allocated, and the write pointer is moved to this block. Similarly a relocation pointer is used for data relocation during garbage collection or data compaction operations.

Owner:SANDISK TECH LLC

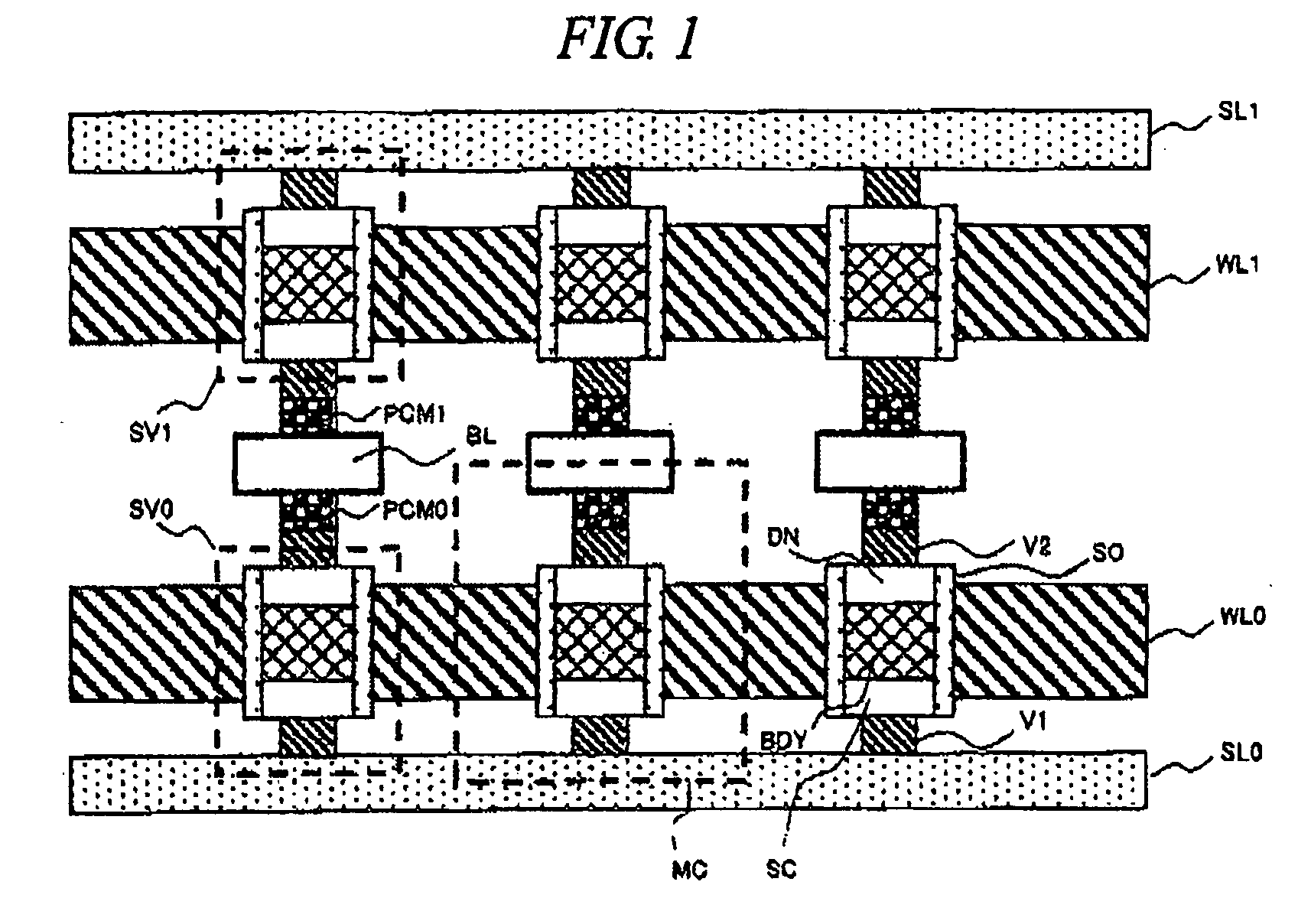

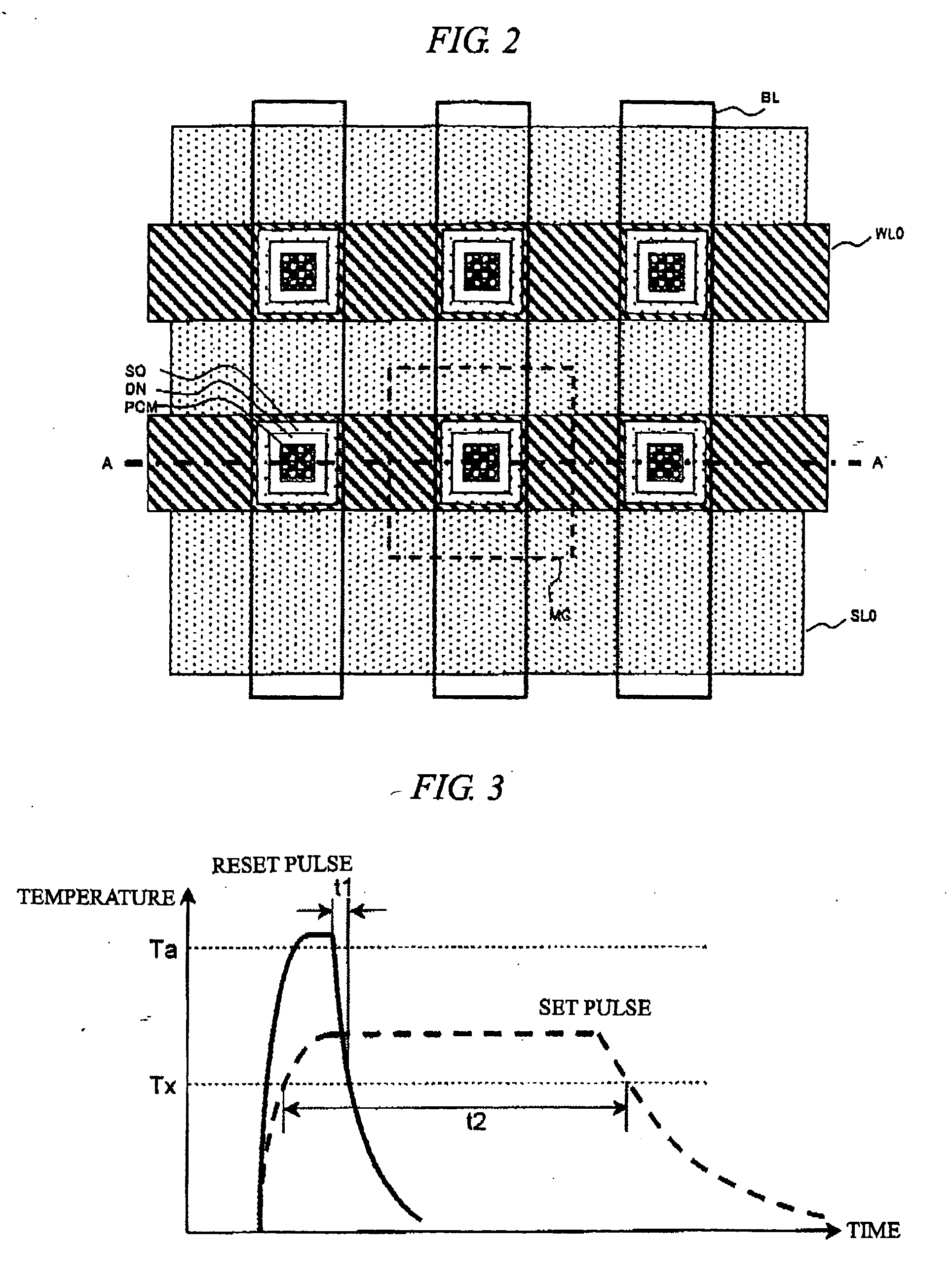

Semiconductor device

InactiveUS20050201182A1Reduce cost per bitSimple processSolid-state devicesSemiconductor/solid-state device manufacturingElectrical resistance and conductanceDevice material

Memory blocks having memory cells which are comprised of vertical transistors and memory elements in which the resistance value is varied depending on the temperature imposed on the upper side thereof, are laminated to realize a highly-integrated non-volatile memory.

Owner:HITACHI LTD

Scrub Techniques for Use with Dynamic Read

The decision on whether to refresh or retire a memory block is based on the set of dynamic read values being used. In a memory system using a table of dynamic read values, the table is configured to include how to handle read error (retire, refresh) in addition to the read parameters for the different dynamic read cases. In a refinement, the read case number can used to prioritize blocks selected for refresh or retire. In cases where the read scrub is to be made more precise, multiple dynamic read cases can be applied. Further, which cases are applied can be intelligently selected.

Owner:SANDISK TECH LLC

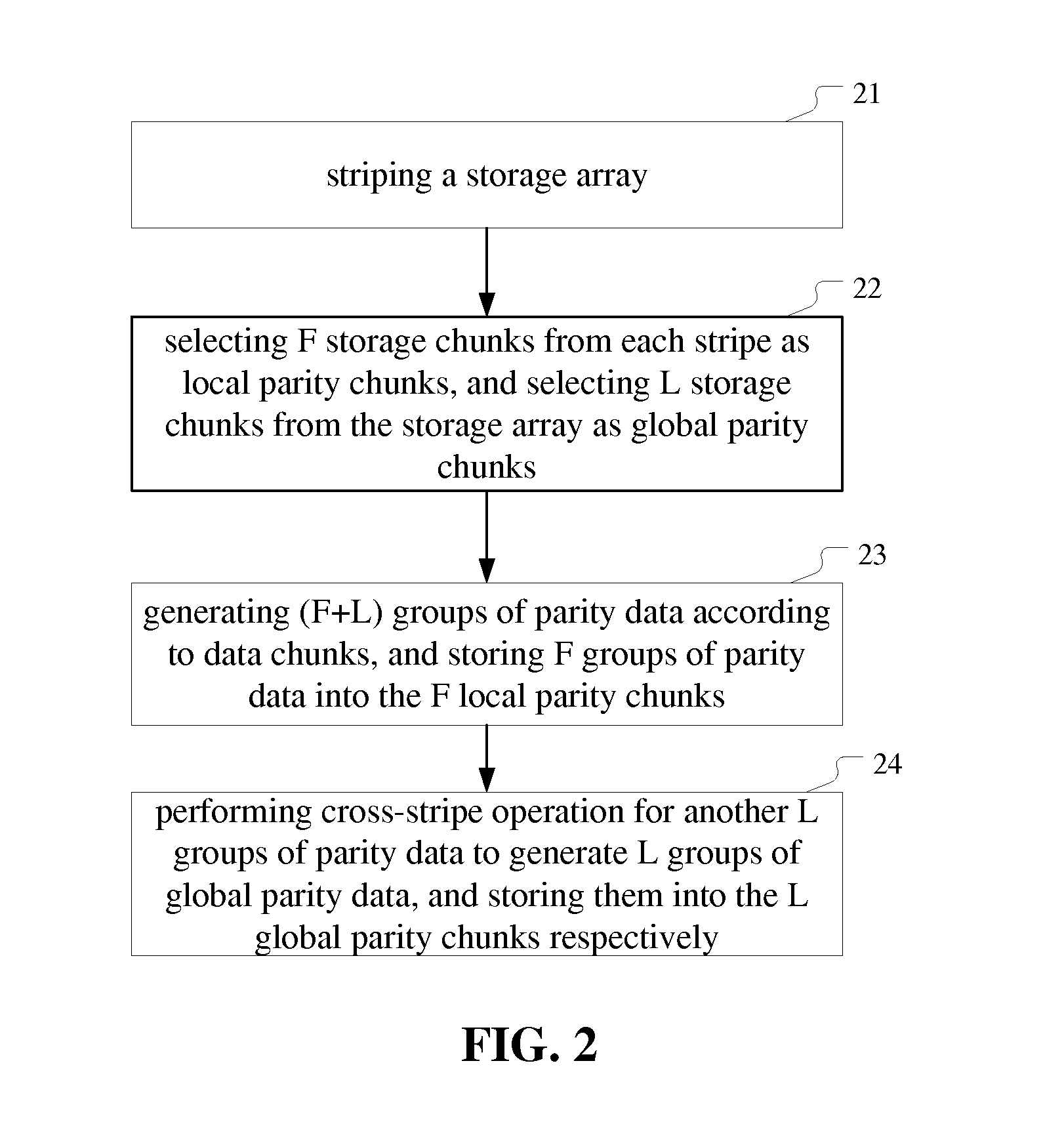

Managing a storage array

ActiveUS20140040702A1Easy to manageError capabilityCode conversionError correction/detection using interleaving techniquesFault toleranceErasure code

The present invention provides a method and apparatus of managing a storage array. The method comprises: striping the storage array to form a plurality of stripes; selecting F storage chunks from each stripe as local parity chunks, and selecting another L storage chunks from the storage array as global parity chunks; performing (F+L) fault tolerant erasure coding on all data chunks in a stripe to generate (F+L) groups of parity data, and storing F groups of parity data therein into the F local parity chunks; performing cross-stripe operation on another L groups of parity data to generate L groups of global parity data, and storing them into the L global parity chunks, respectively. The apparatus corresponds to the method. With the invention, a plurality of errors in the storage array can be detected and / or recovered to improve fault tolerance and space utilization of the storage array.

Owner:IBM CORP

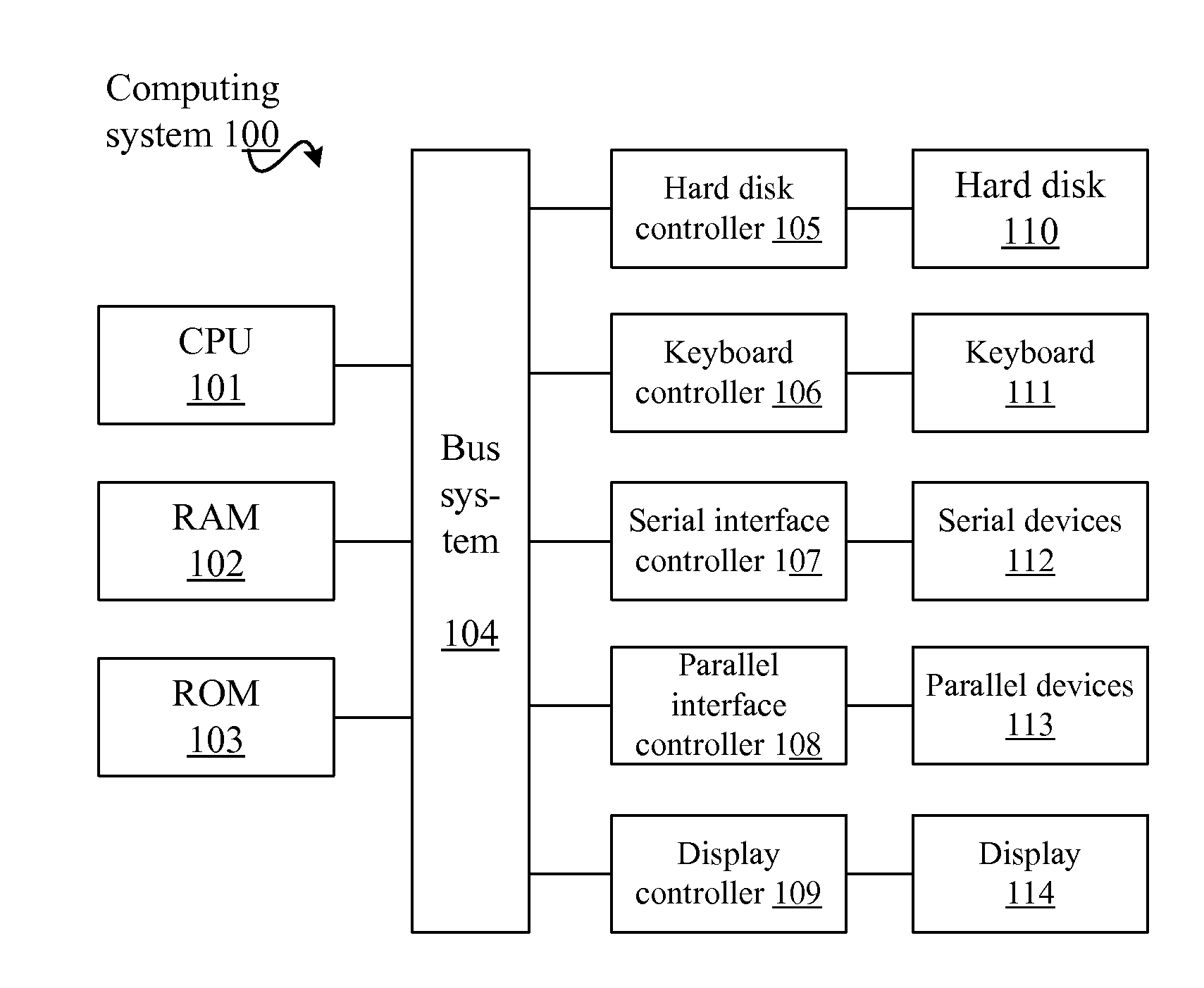

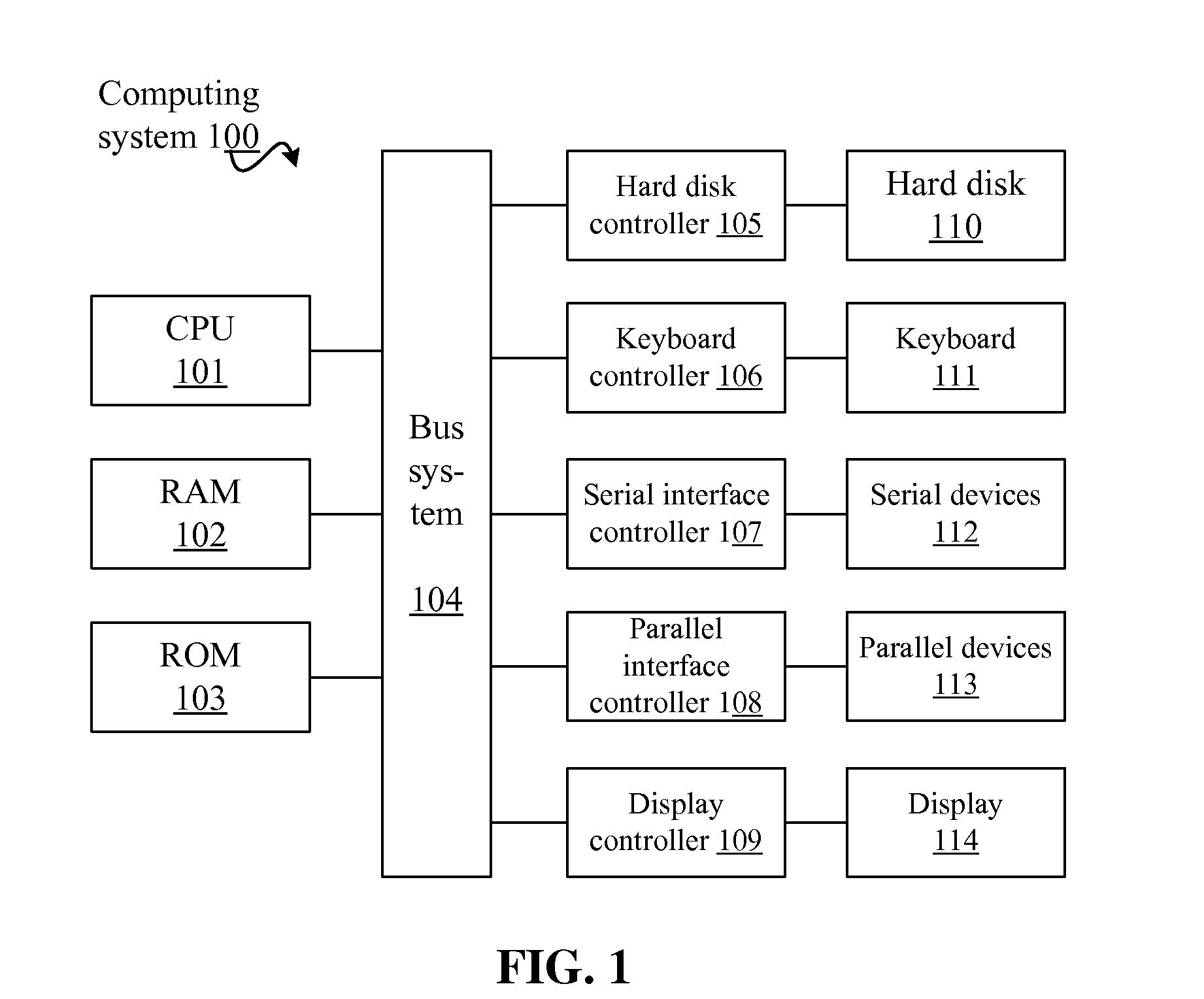

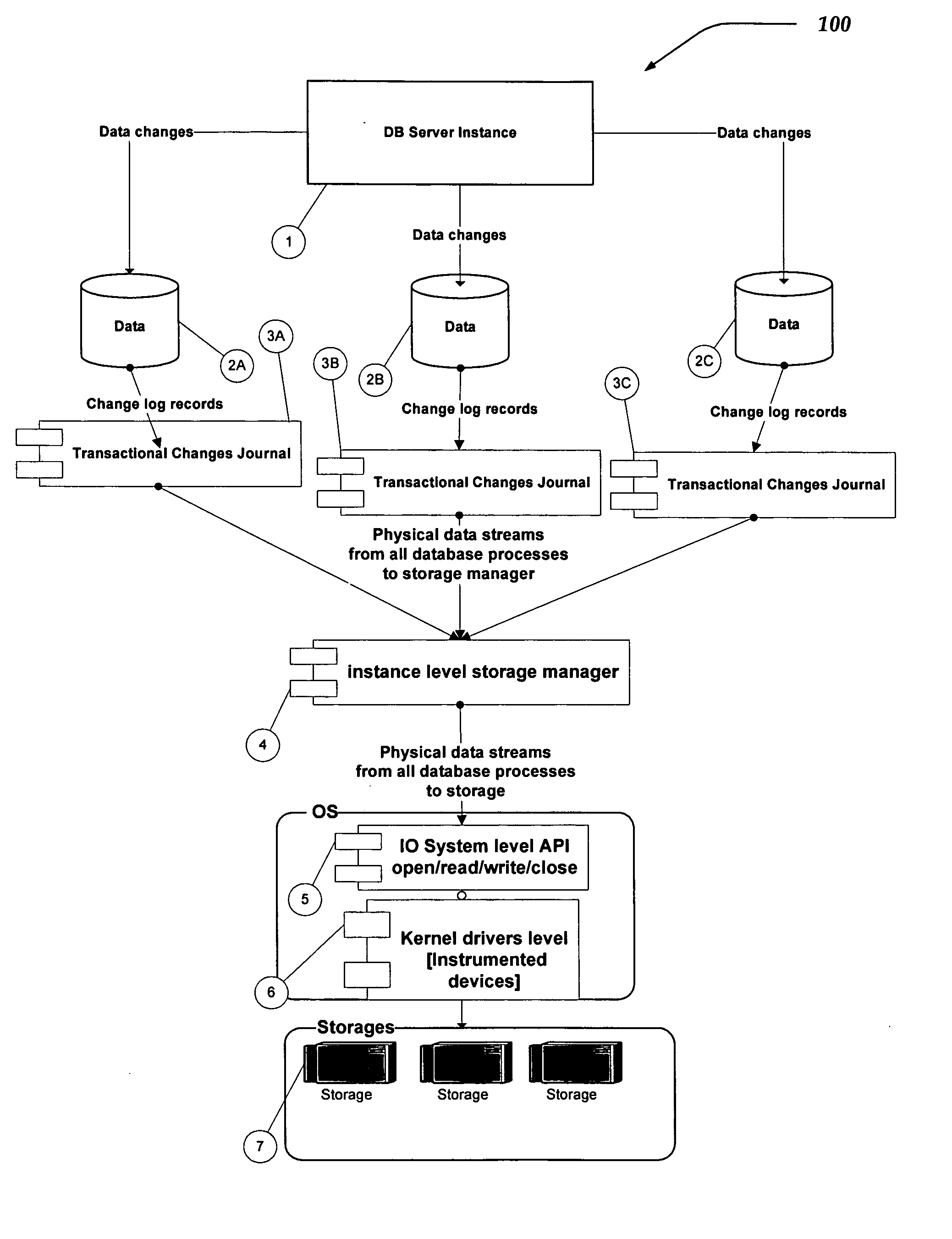

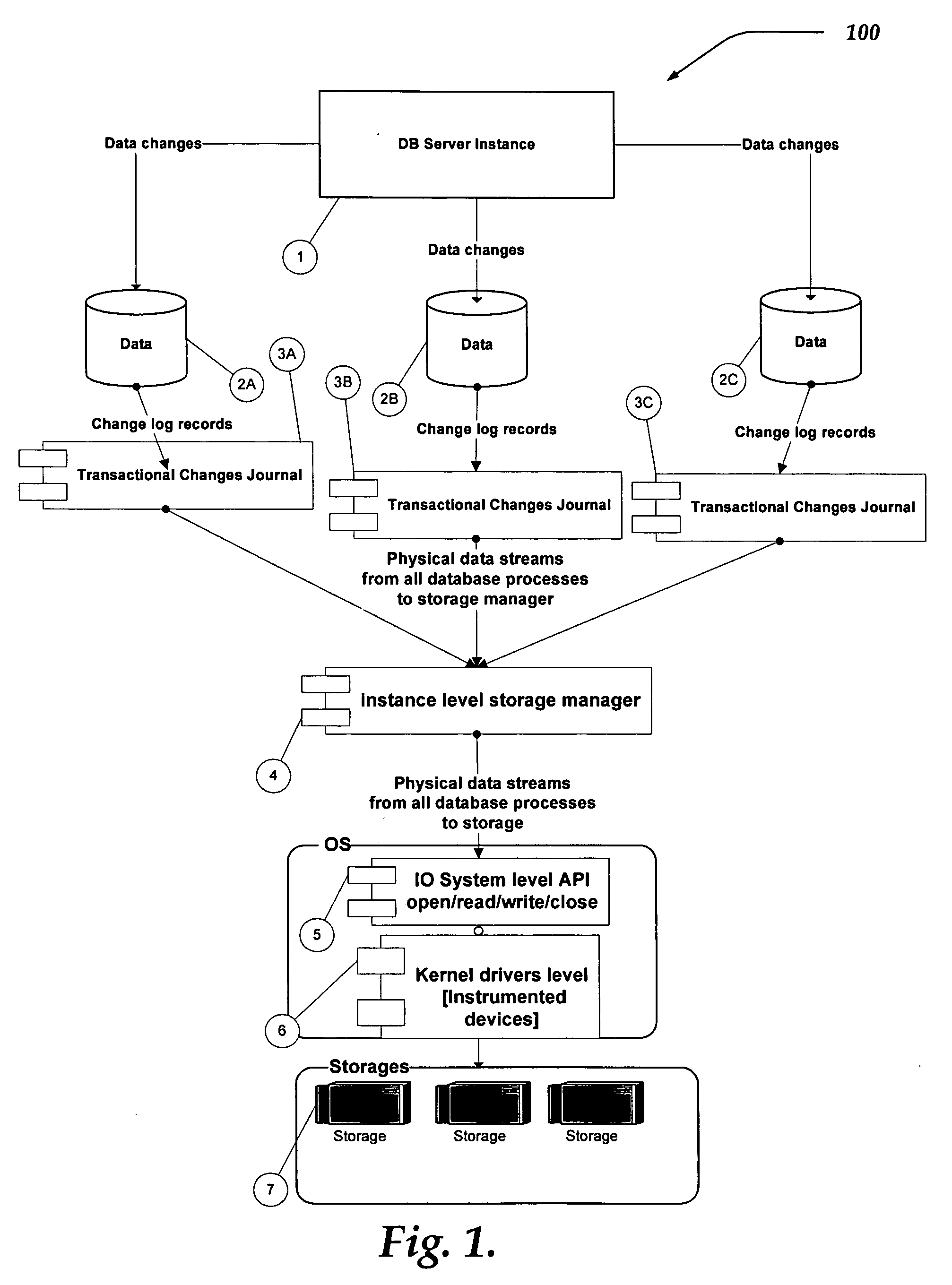

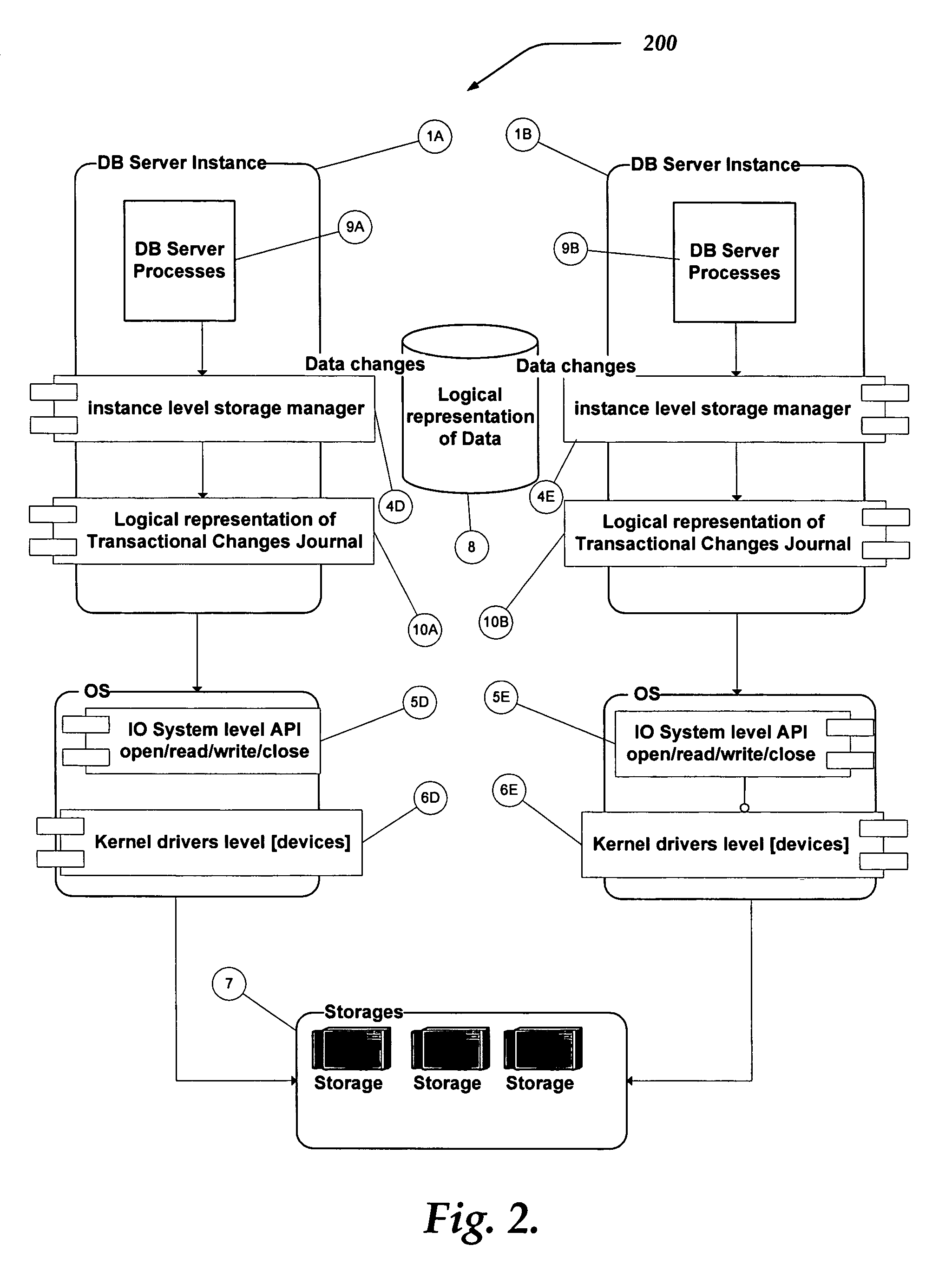

System and method for database replication by interception of in memory transactional change records

InactiveUS20060047713A1Database distribution/replicationSpecial data processing applicationsTerm memorySource level

A system and method are directed towards providing a database replication technique using interception in memory of the transaction change data records. The invention employs Input / Output instrumentation to capture and split out the in memory transaction change journal records. Captured memory blocks are sent to a parser, which concatenates the records into a single record, and creates a redo / undo vector that can be converted to original DML / DDL statements. Source level transformations can be applied to the vectors, which are then sent to a post agent on the same or a different computing device. The post agents may perform destination level transformations, and generate DML / DDL statements to be executed by the corresponding destination RDBMS instance. Post agents may also perform conflict detection and resolution during DML / DDL statement executions. Transaction consistency is supported by performing commits / rollback on the destination after receiving the redo / undo vector representing a commit / rollback on the source.

Owner:WISDOMFORCE TECH

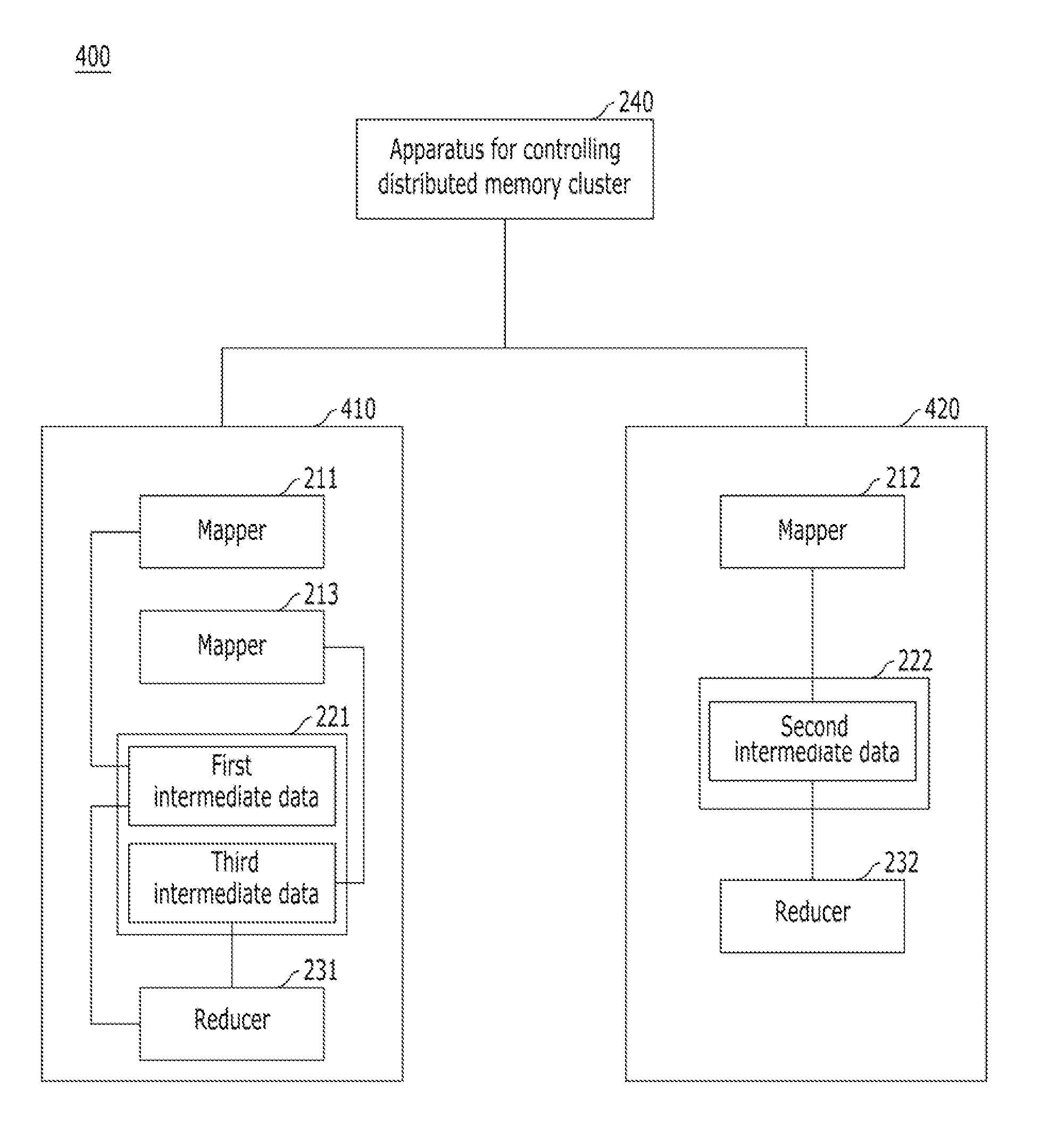

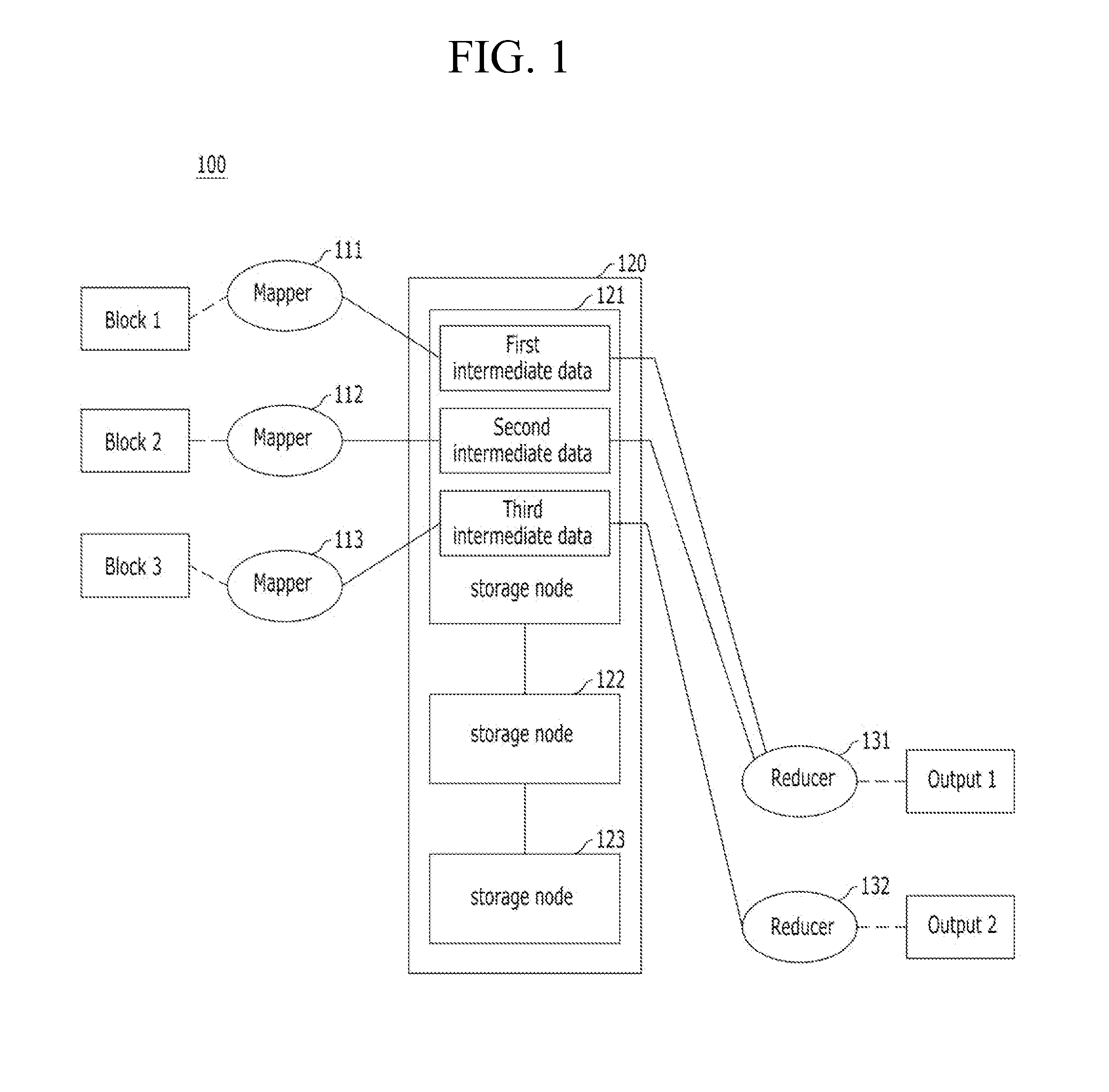

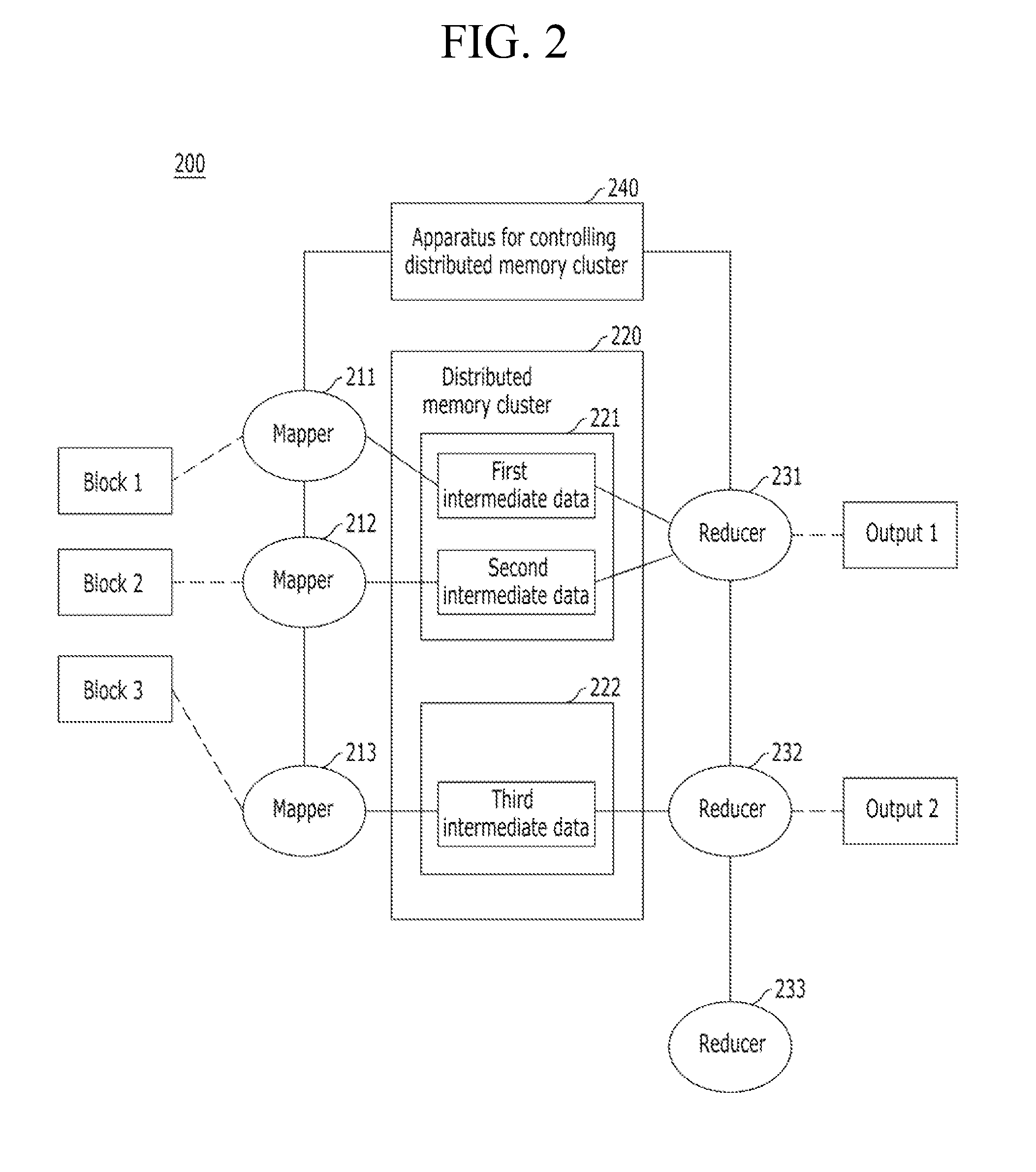

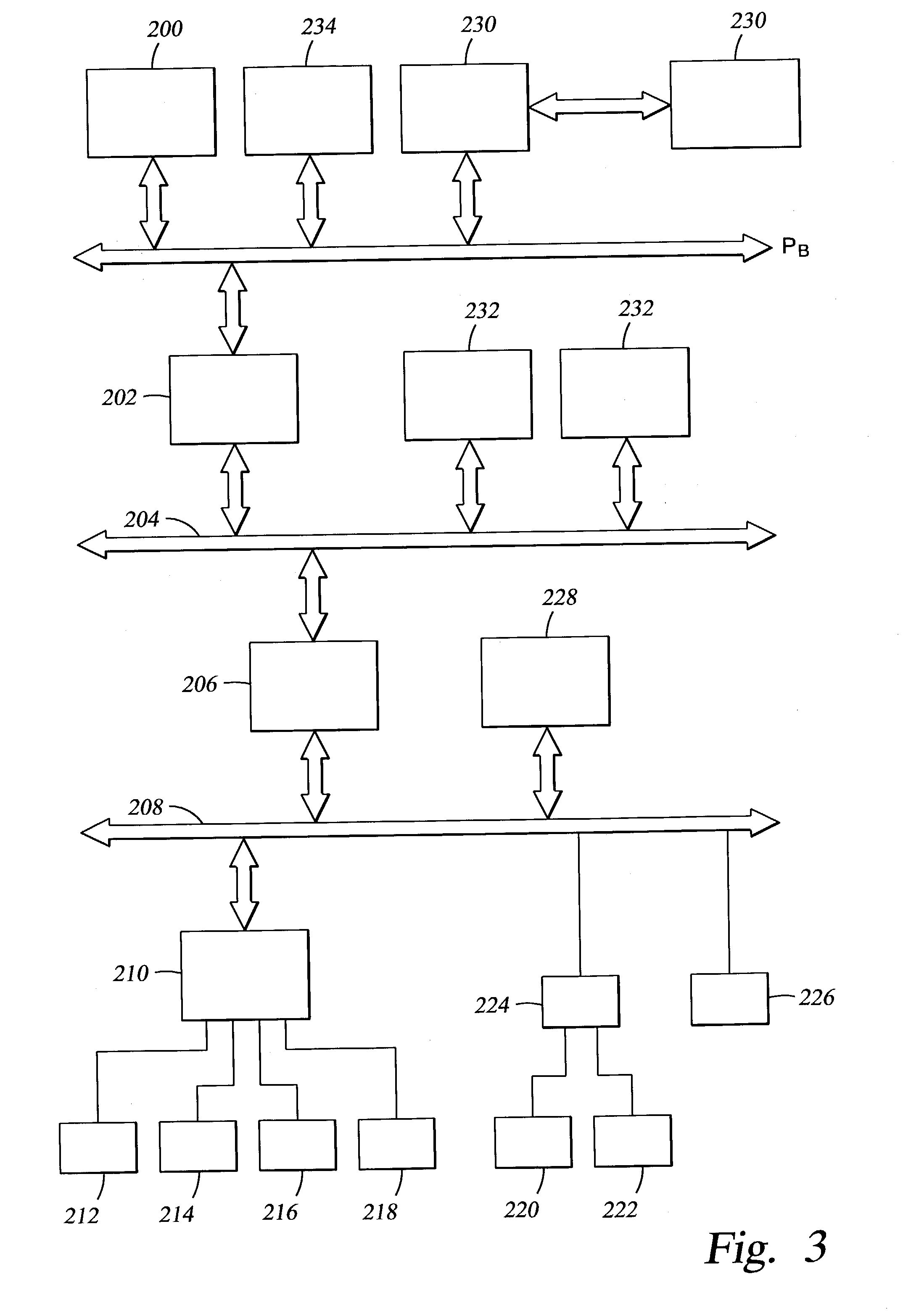

Apparatus and method for controlling distributed memory cluster

ActiveUS20120209943A1Valid choiceMemory adressing/allocation/relocationDigital computer detailsNode clusteringDistributed memory

Provided are an apparatus and method for controlling a distributed memory cluster. A distributed computing system may include a computing node cluster, a distributed memory cluster, and a controlling node. The computing node cluster may include a plurality of computing nodes including first computing nodes that each generates associated data. The distributed memory cluster may be configured to store the associated data of the first computing nodes. The controlling node may be configured to select memory blocks of the associated data for distribution on the distributed memory cluster based on a node selection rule and memory cluster structure information, and to select second computing nodes from the computing node cluster based on a location selection rule and the memory cluster structure information.

Owner:KT CORP

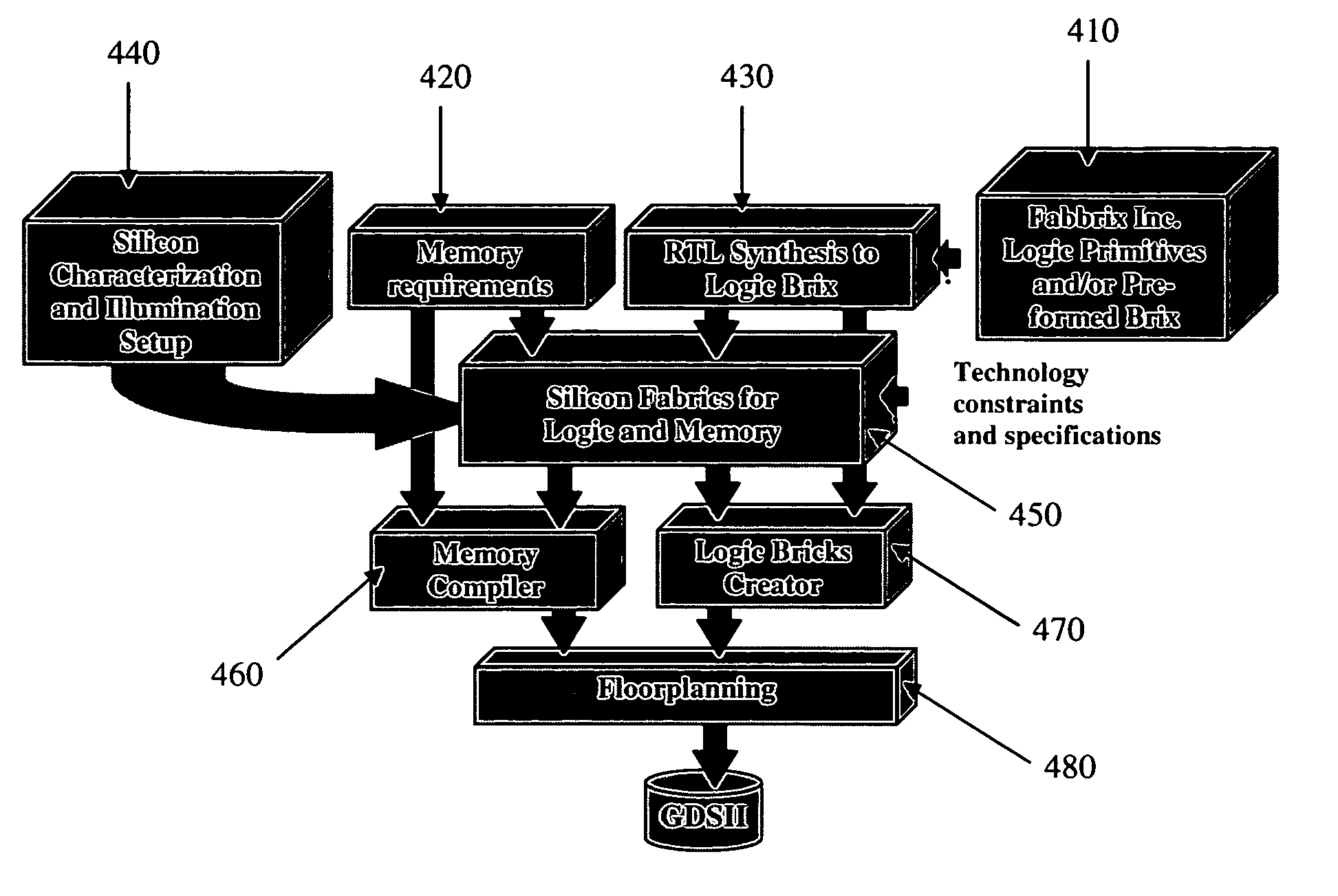

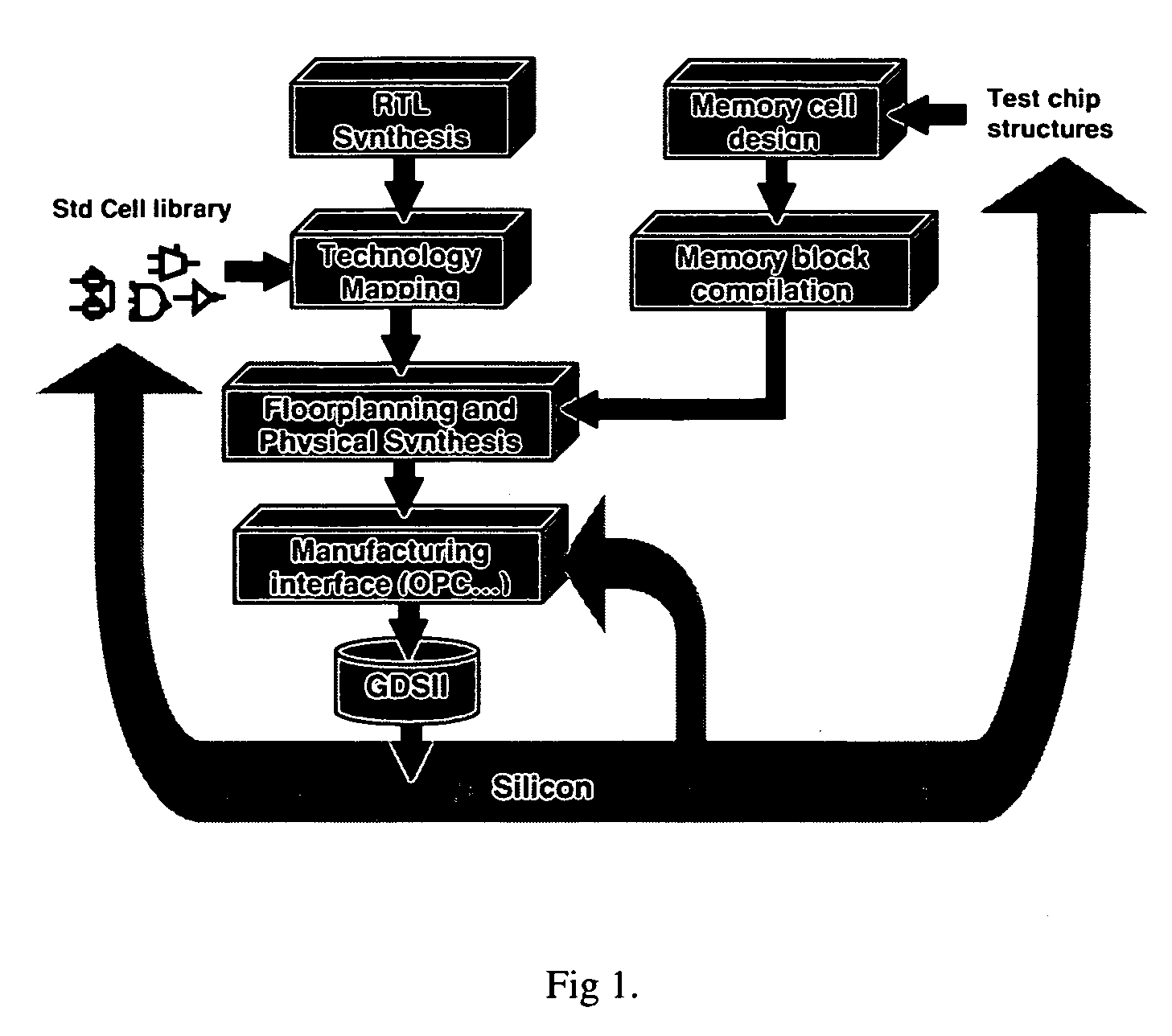

Method and process for design of integrated circuits using regular geometry patterns to obtain geometrically consistent component features

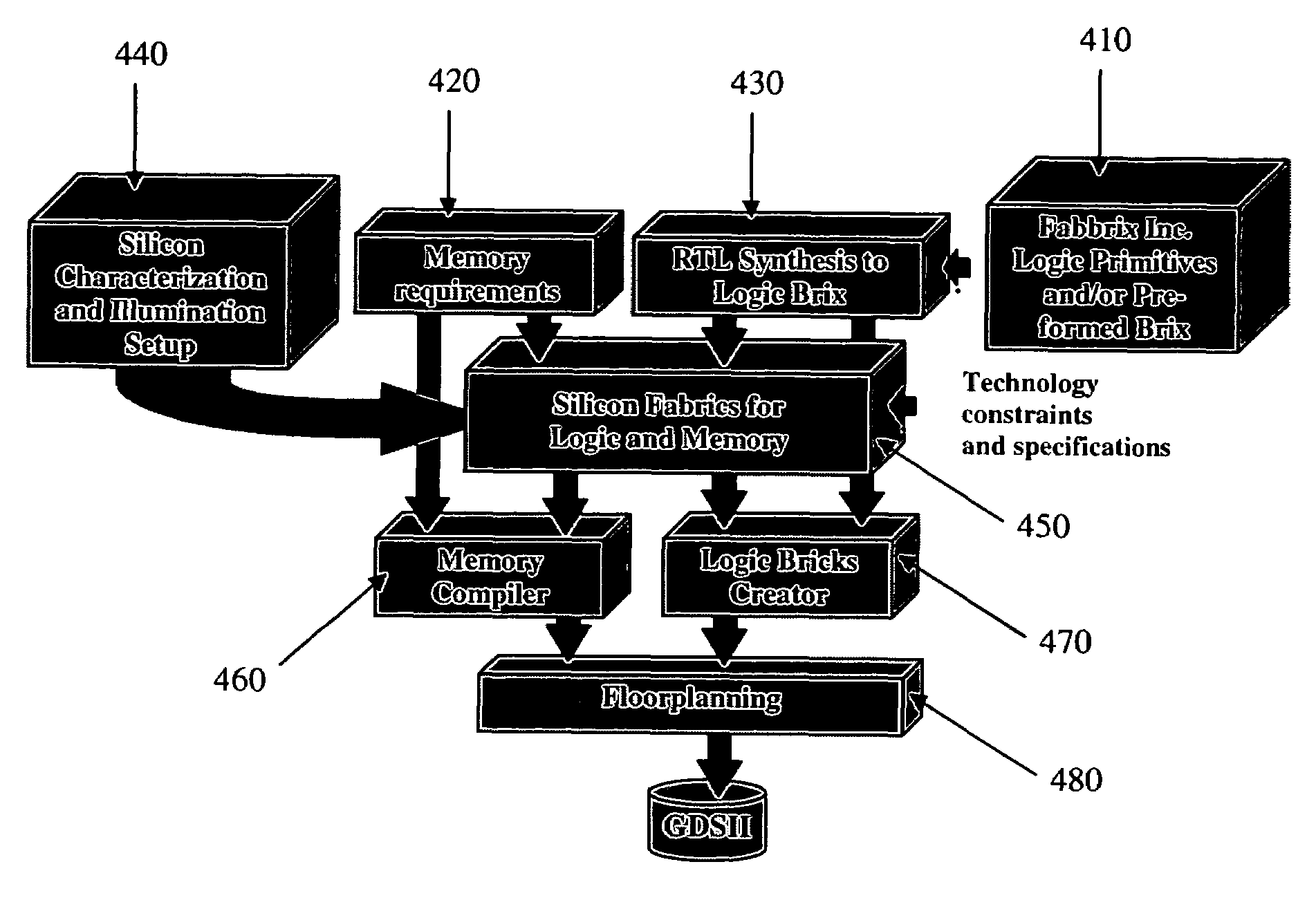

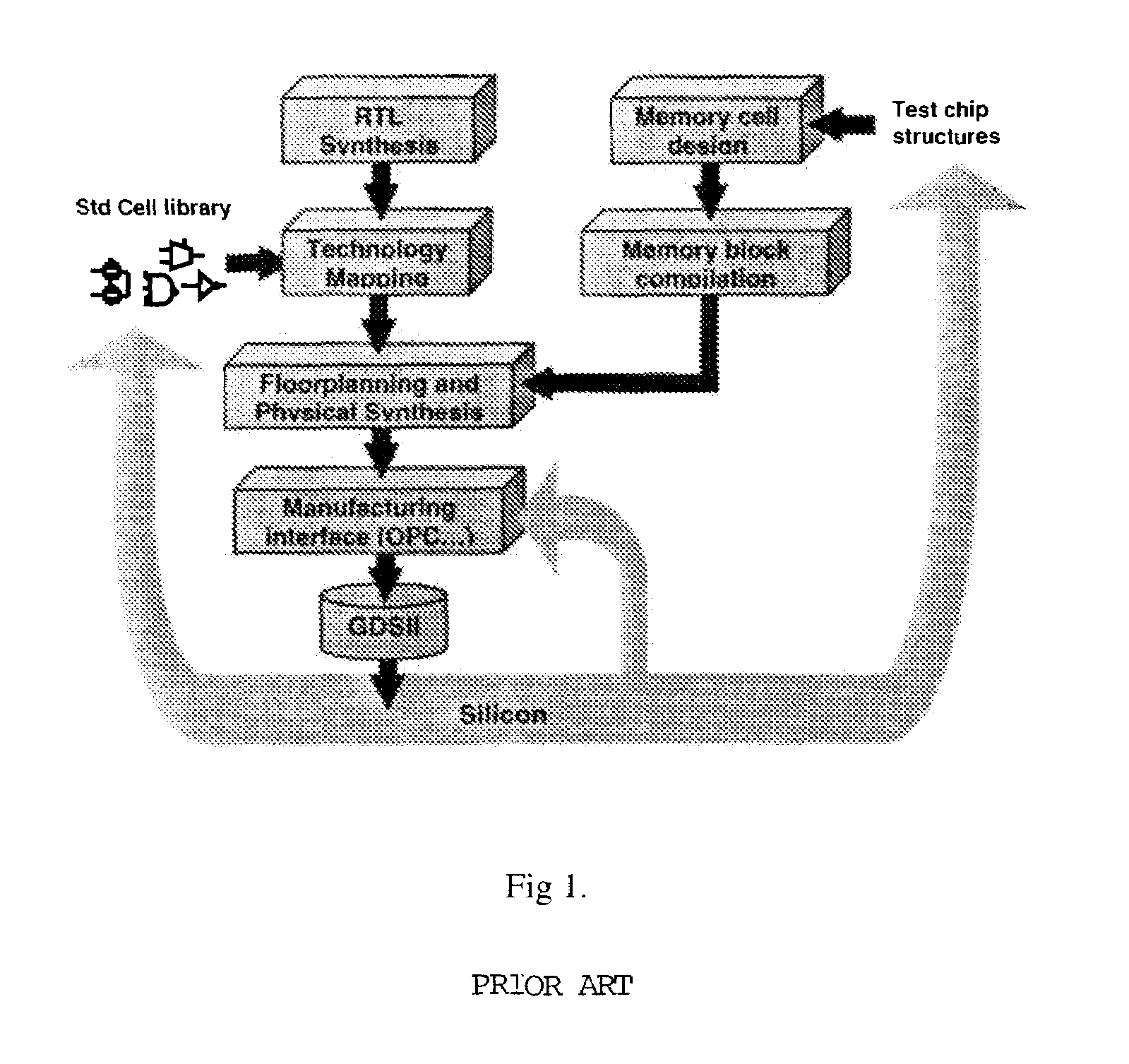

ActiveUS20060112355A1CAD circuit designSpecial data processing applicationsComputer architectureBrick

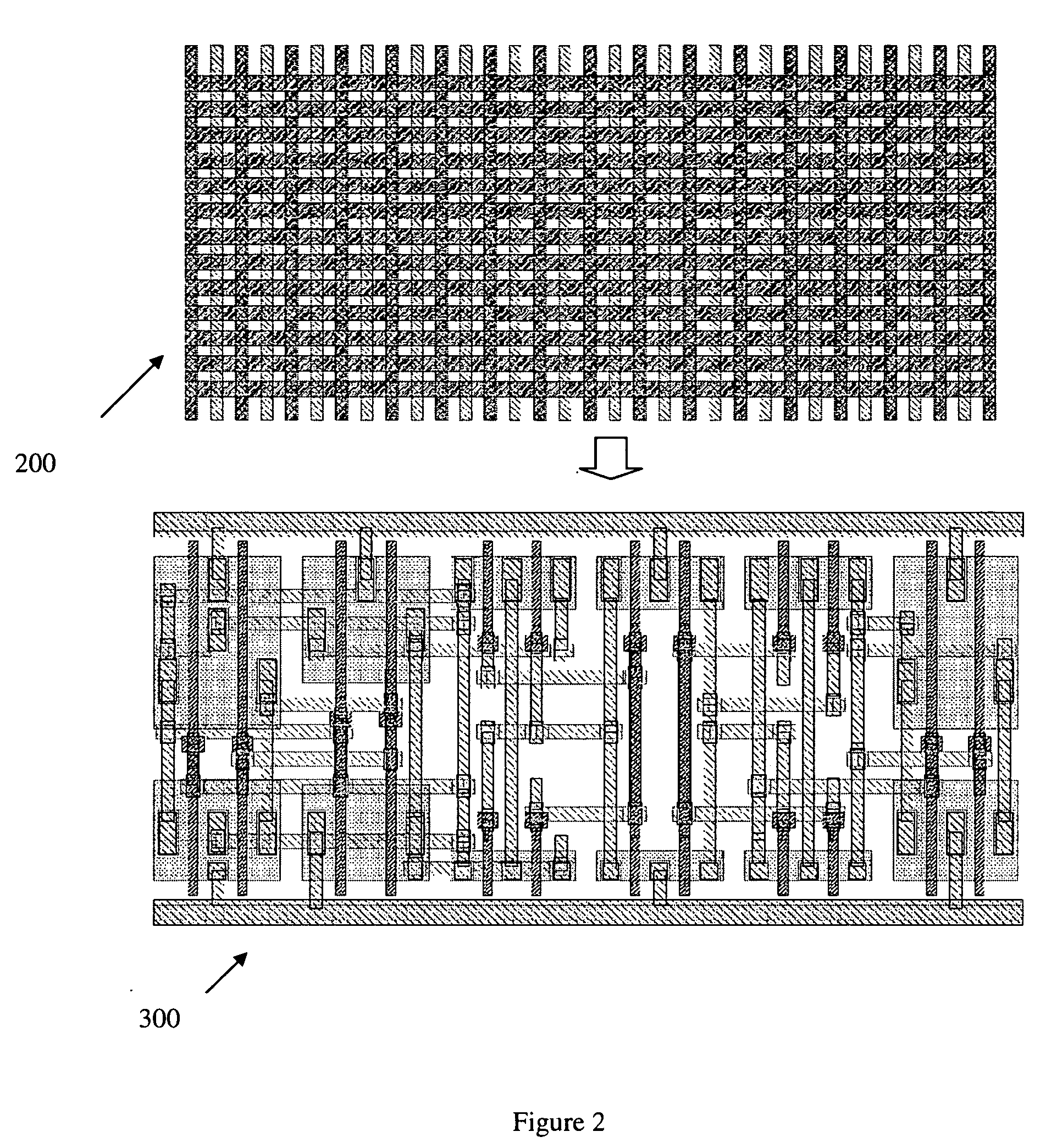

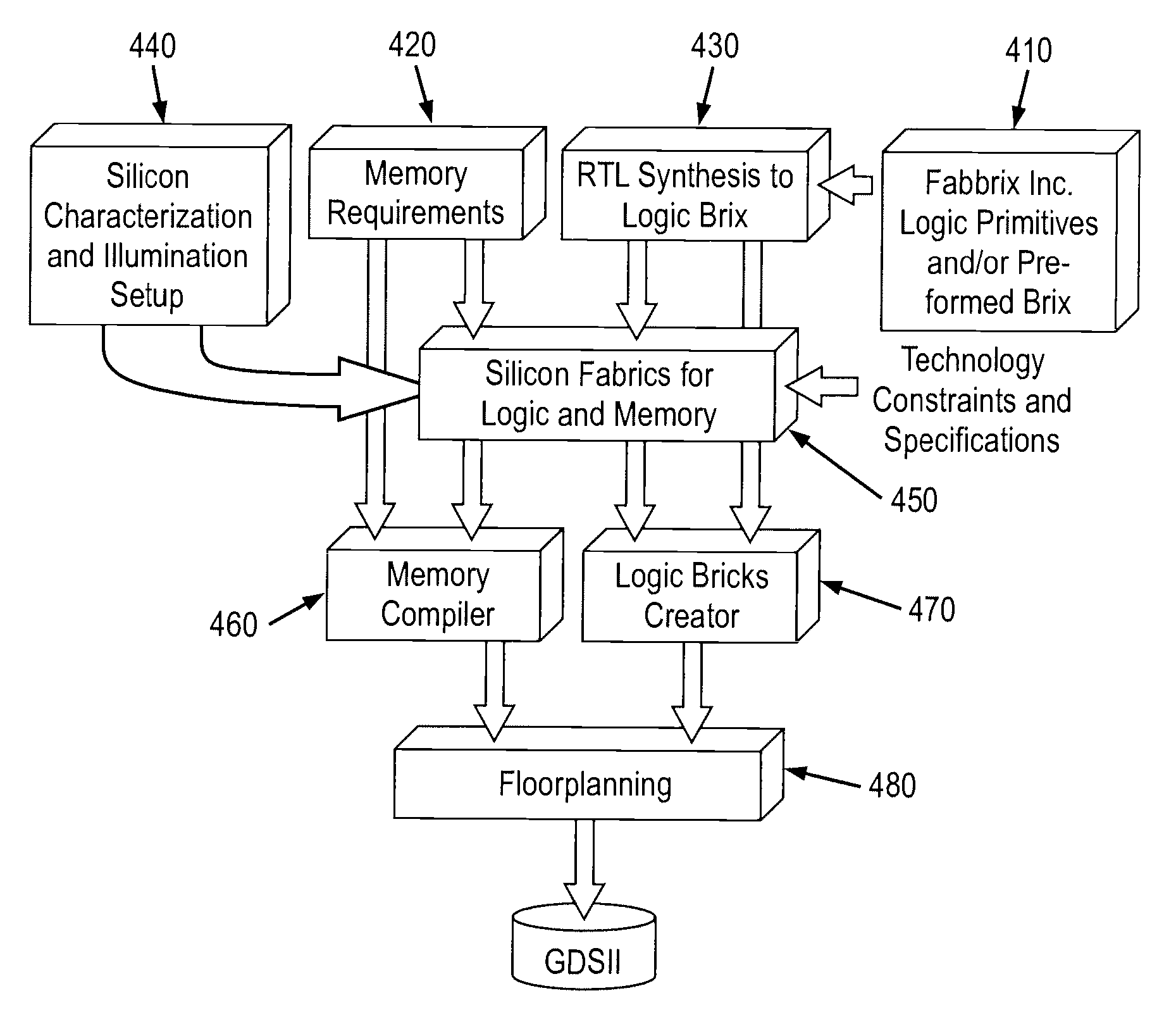

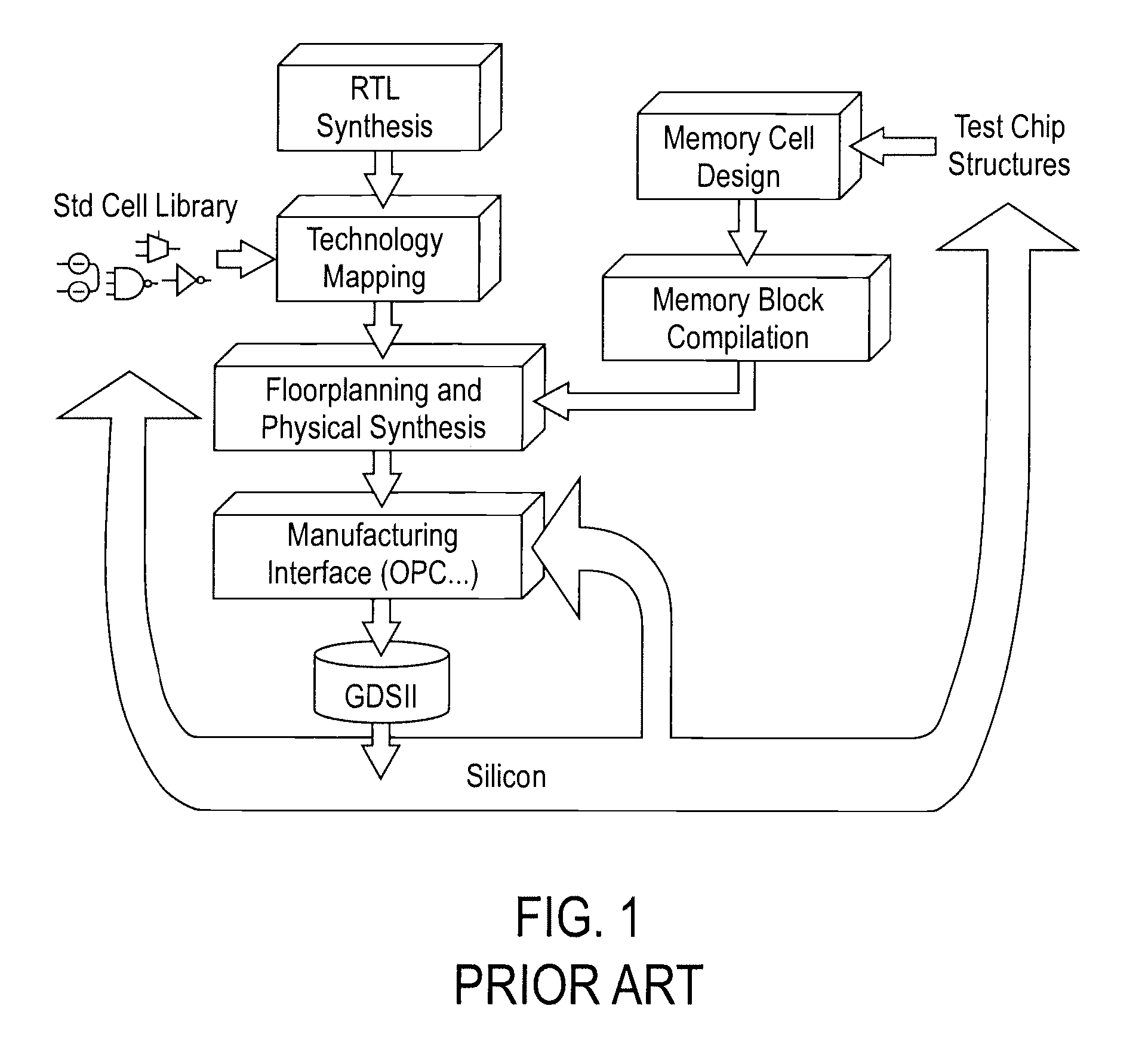

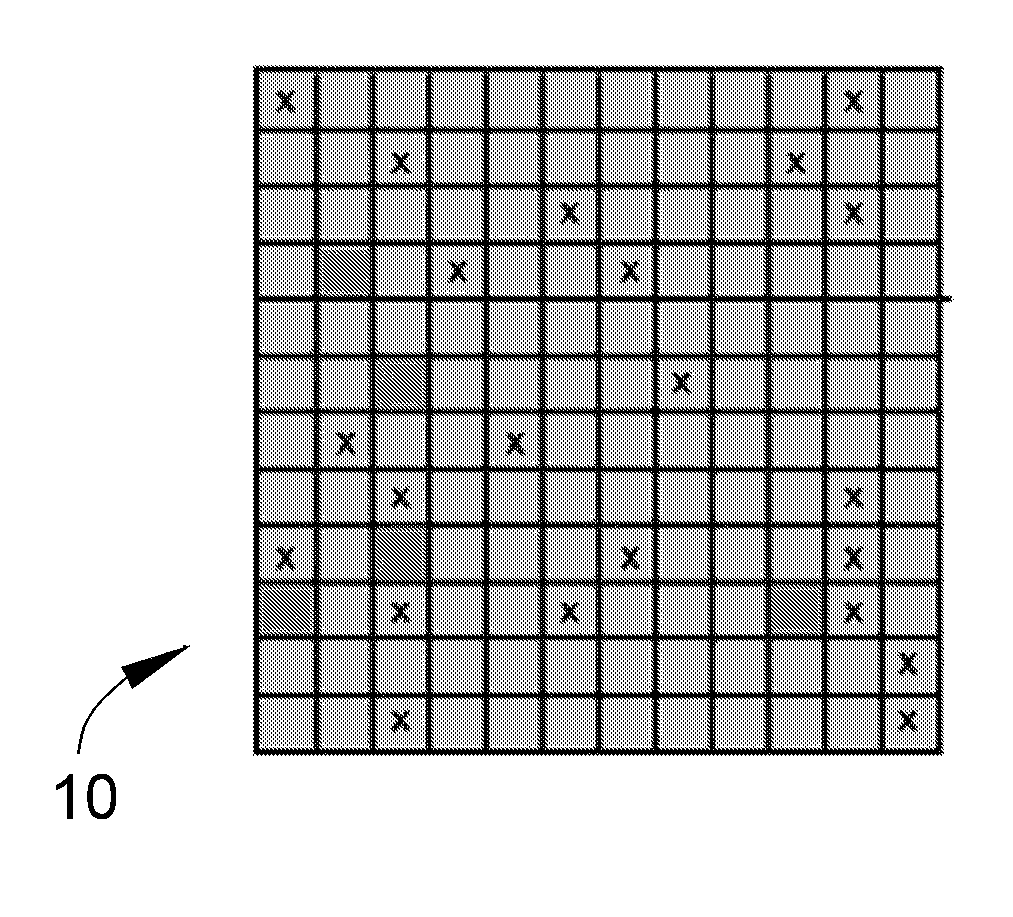

The invention provides a method and process for designing an integrated circuit based on using the results from both 1) a specific set of silicon test structure characterizations and 2) the decomposition of logic into combinations of simple logic primitives, from which a set of logic bricks are derived that can be assembled for a manufacturable-by-construction design. This implementation of logic is compatible with the lithography settings that are used for implementation of the memory blocks and other components on the integrated circuit, particularly by implementing geometrically consistent component features. The invention provides the ability to recompile a design comprised of logic and memory blocks onto a new geometry fabric to implement a set of technology-specific design changes, without requiring a complete redesign of the entire integrated circuit.

Owner:PDF SOLUTIONS INC

Method and process for design of integrated circuits using regular geometry patterns to obtain geometrically consistent component features

InactiveUS20080098334A1CAD circuit designOriginals for photomechanical treatmentComputer architectureBrick

The invention provides a method and process for designing an integrated circuit based on using the results from both 1) a specific set of silicon test structure characterizations and 2) the decomposition of logic into combinations of simple logic primitives, from which a set of logic bricks are derived that can be assembled for a manufacturable-by-construction design. This implementation of logic is compatible with the lithography settings that are used for implementation of the memory blocks and other components on the integrated circuit, particularly by implementing geometrically consistent component features. The invention provides the ability to recompile a design comprised of logic and memory blocks onto a new geometry fabric to implement a set of technology-specific design changes, without requiring a complete redesign of the entire integrated circuit.

Owner:PDF SOLUTIONS INC

Method for restoring and maintaining solid-state drive performance

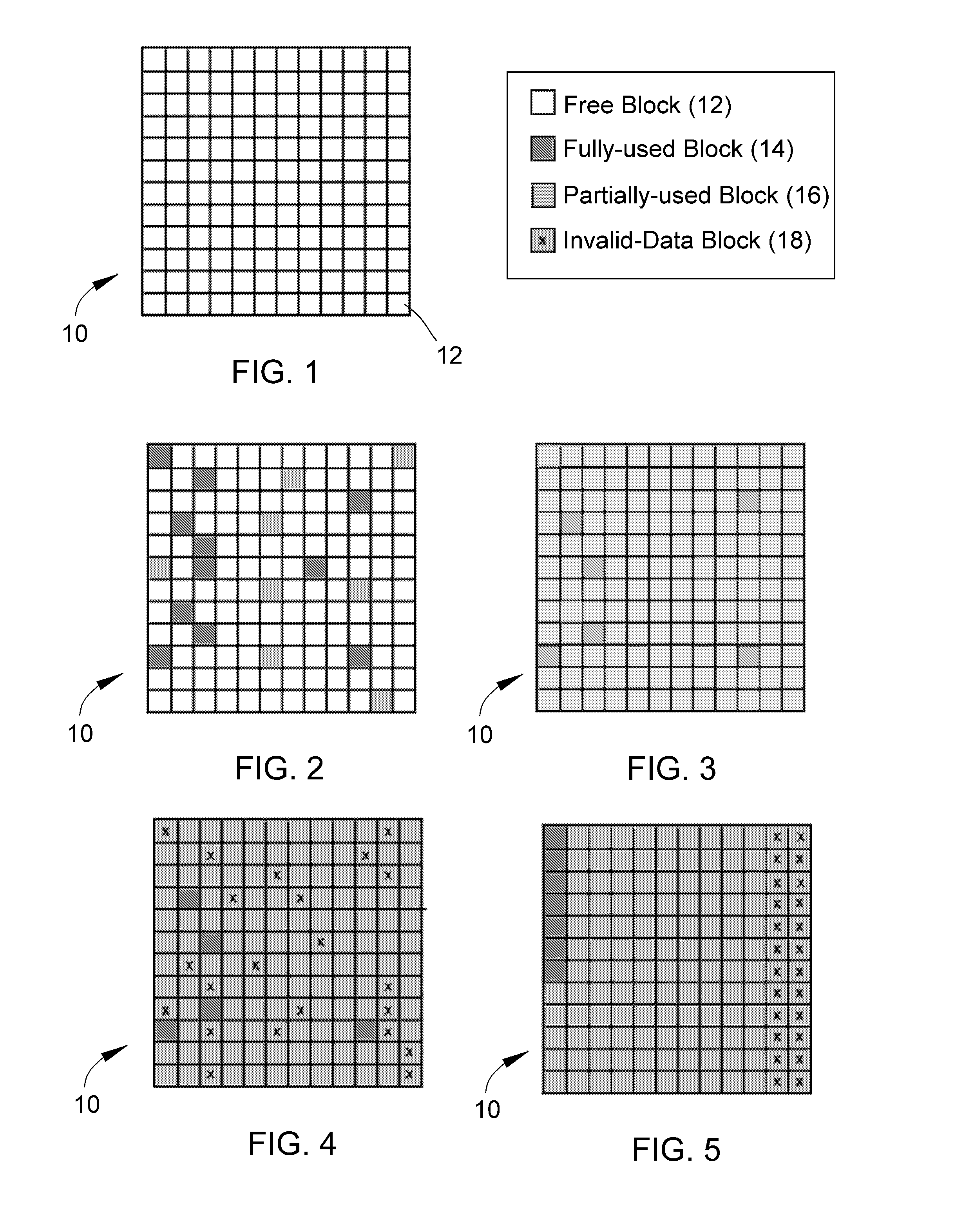

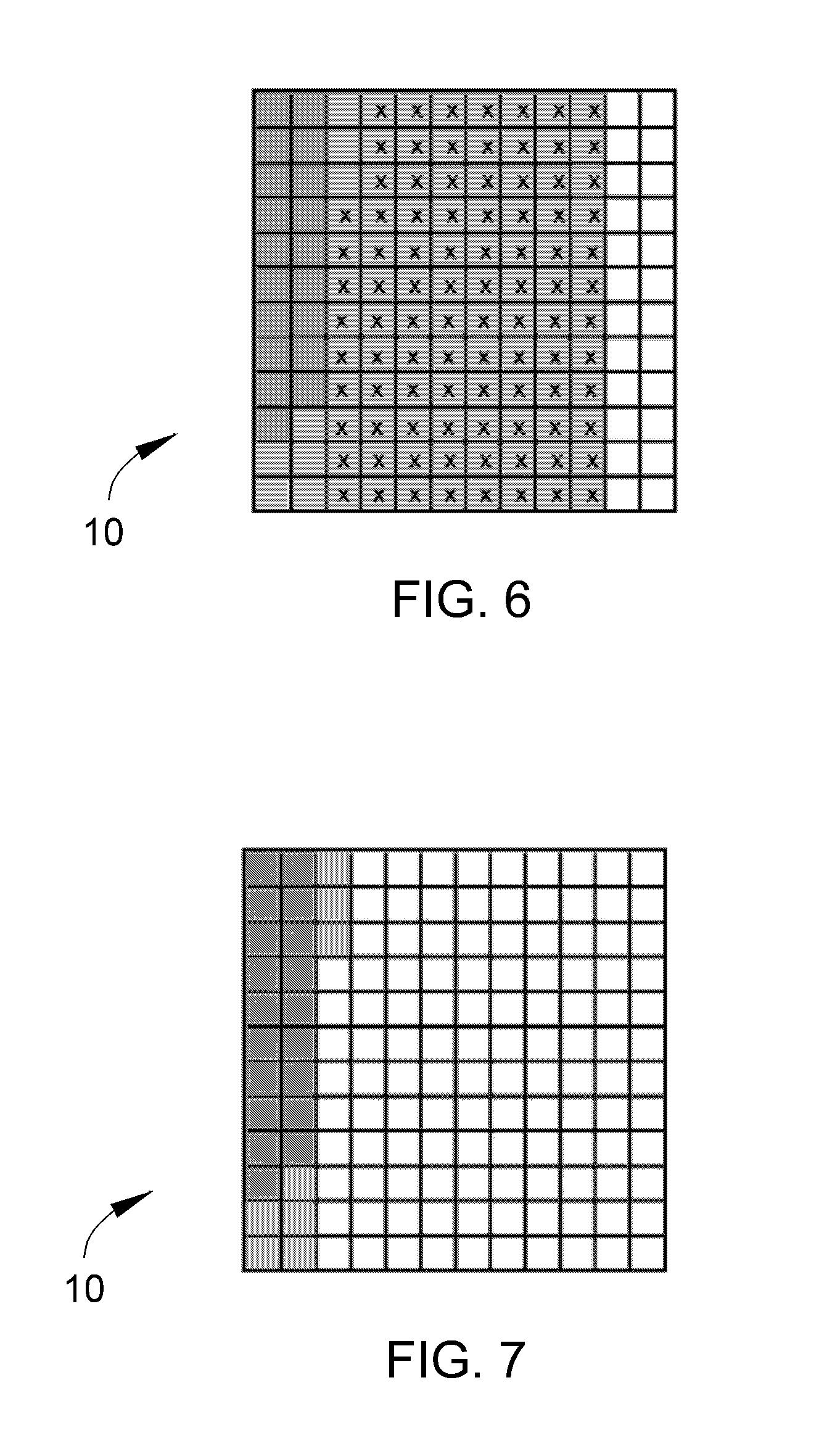

InactiveUS20110119462A1Memory architecture accessing/allocationMemory adressing/allocation/relocationInvalid DataTerm memory

A method of maintaining a solid-state drive so that free space within memory blocks of the drive becomes free usable space to the drive. The drive comprises cells organized in pages that are organized in memory blocks in which at least user files are stored. A defragmentation utility is executed to cause at least some of the memory blocks that are partially filled with data and contain file fragments to be combined or aligned and to cause at least some of the memory blocks that contain only invalid data to be combined or aligned. A block consolidation utility is then executed to eliminate at least some of the partially-filled blocks by consolidating the file fragments into a fewer number of the memory blocks. The consolidation utility also increases the number of memory blocks that contain only invalid memory. All of the memory blocks containing only invalid data are then erased.

Owner:OCZ STORAGE SOLUTIONS

Method and process for design of integrated circuits using regular geometry patterns to obtain geometrically consistent component features

The invention provides a method and process for designing an integrated circuit based on using the results from both 1) a specific set of silicon test structure characterizations and 2) the decomposition of logic into combinations of simple logic primitives, from which a set of logic bricks are derived that can be assembled for a manufacturable-by-construction design. This implementation of logic is compatible with the lithography settings that are used for implementation of the memory blocks and other components on the integrated circuit, particularly by implementing geometrically consistent component features. The invention provides the ability to recompile a design comprised of logic and memory blocks onto a new geometry fabric to implement a set of technology-specific design changes, without requiring a complete redesign of the entire integrated circuit.

Owner:PDF SOLUTIONS INC

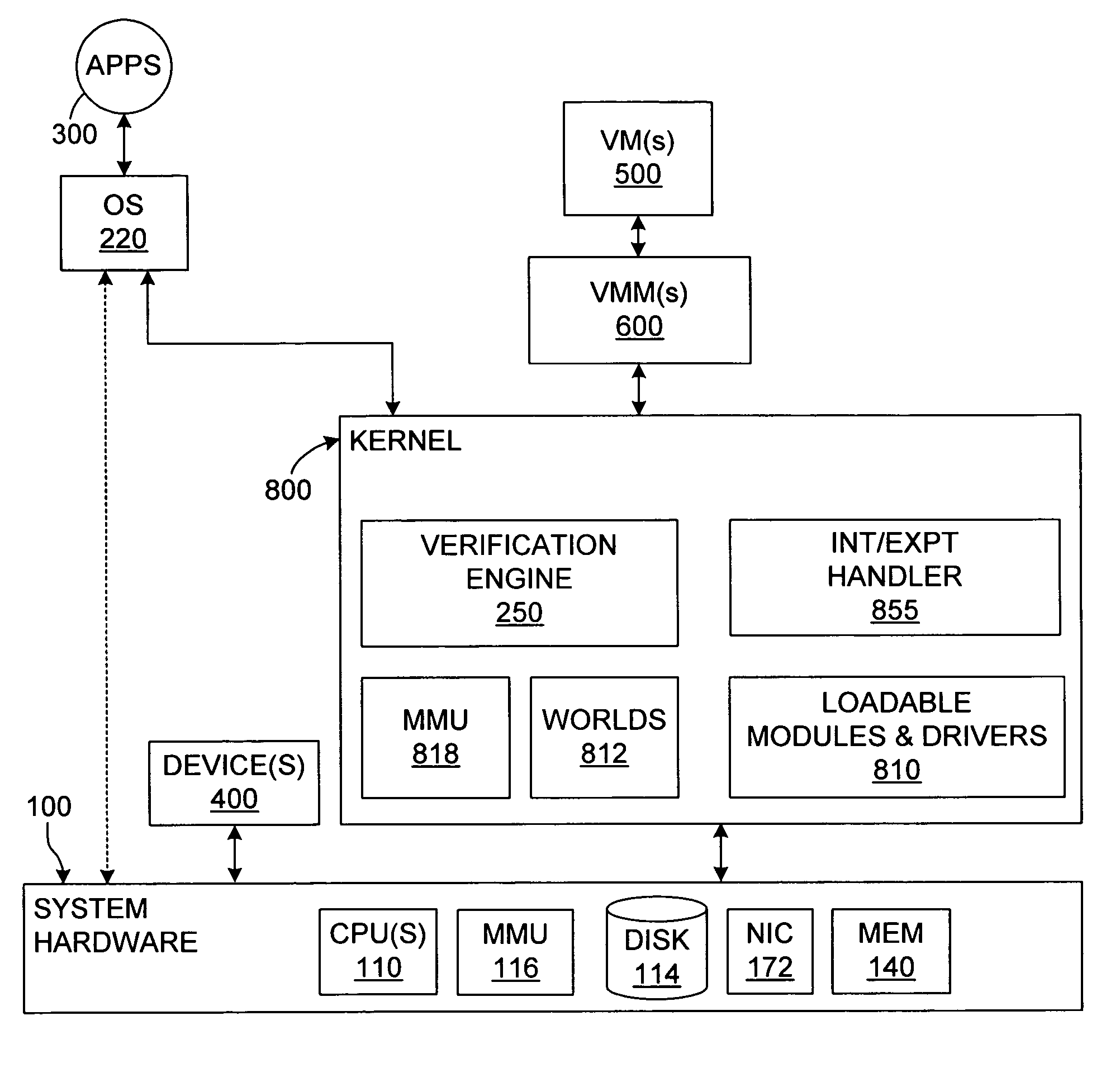

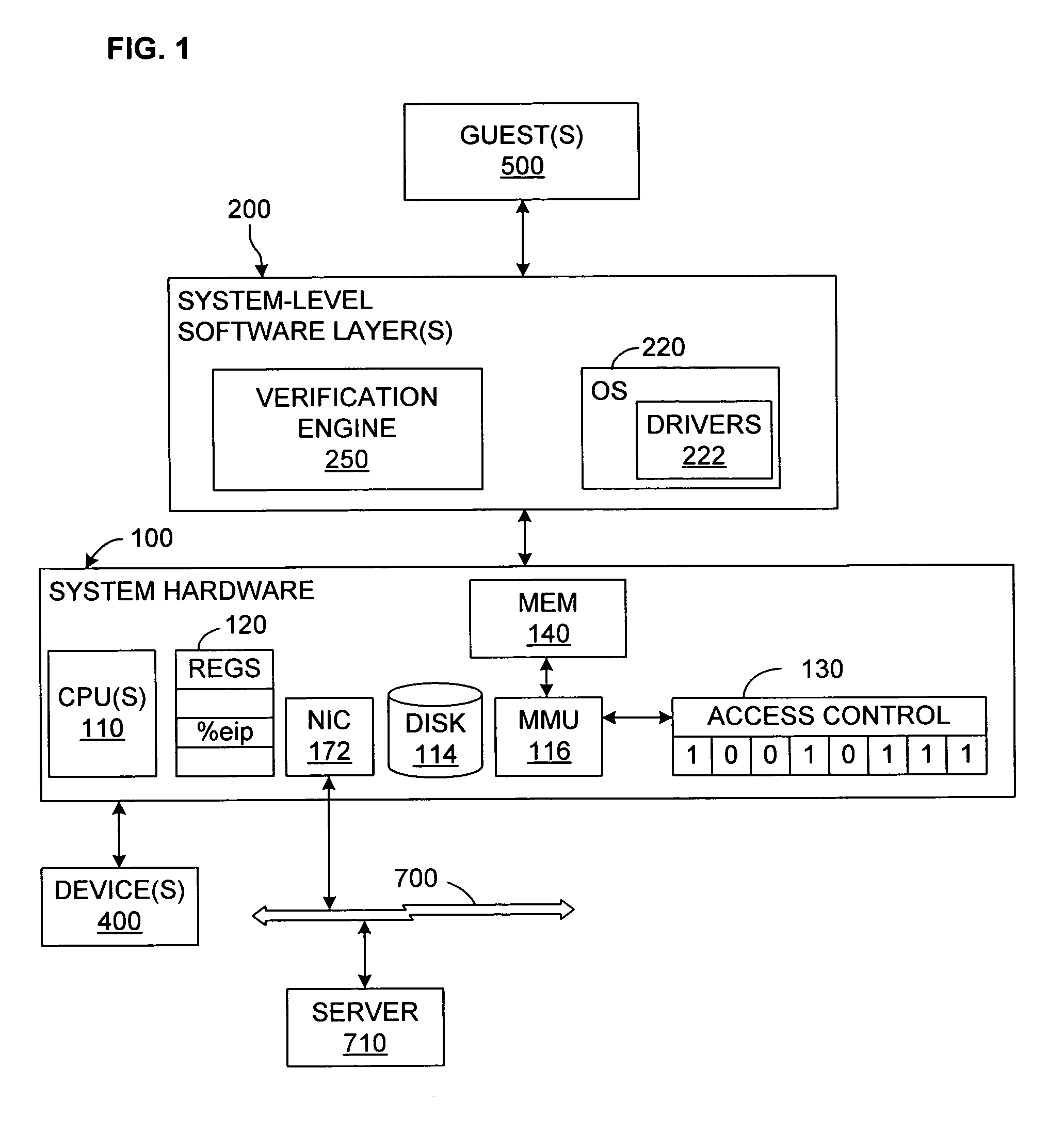

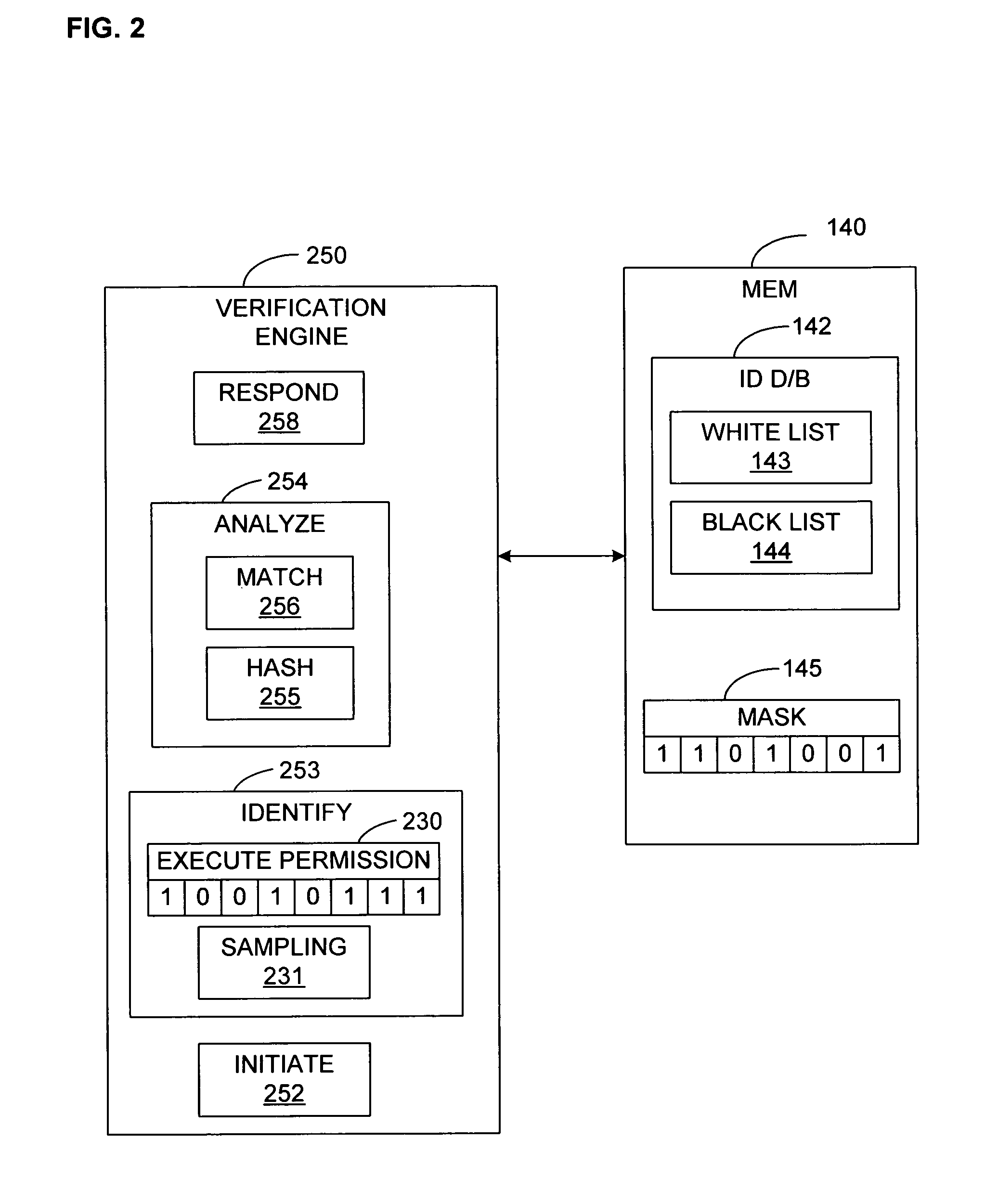

Dynamic verification of validity of executable code

ActiveUS7984304B1Memory loss protectionUnauthorized memory use protectionOperating systemMemory block

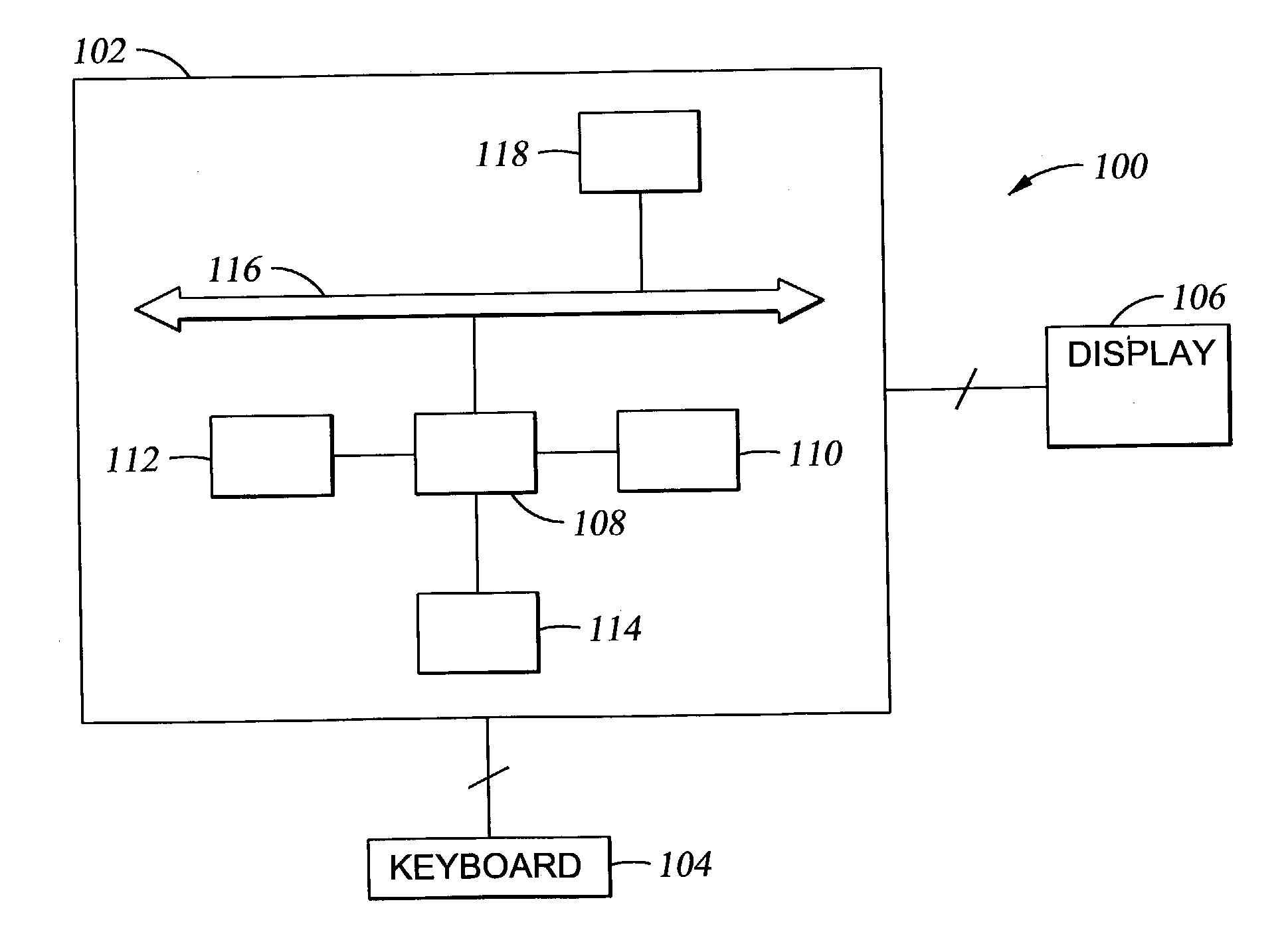

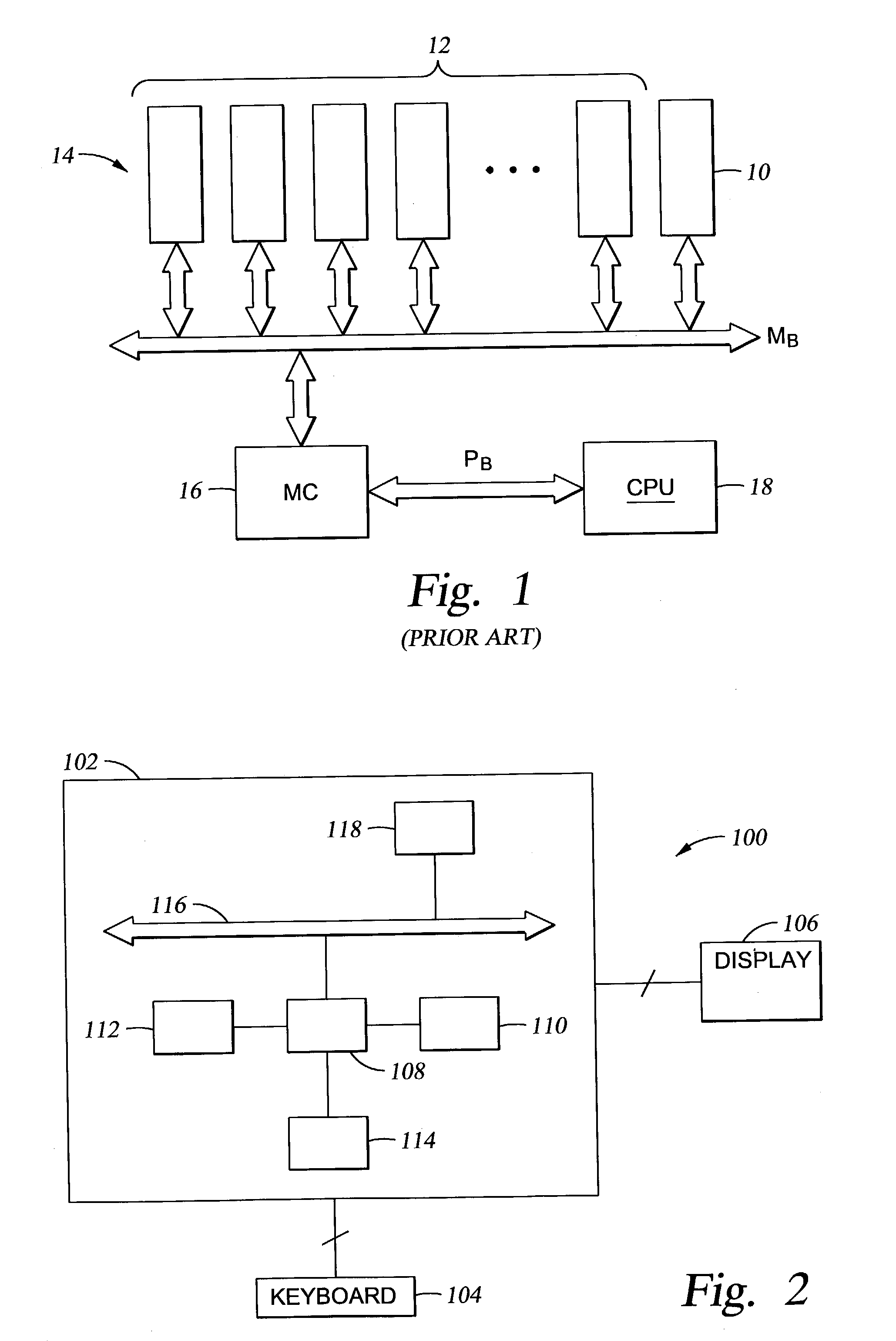

Computer-executable instructions in a computer are verified dynamically, after they have been identified for submission for execution, but before they are actually executed. In particular, for at least one current instruction that has been identified for submission to the processor for execution, an identifying value, for example, a hash value, is determined for a current memory block that contains the current instruction. The identifying value of the current memory block is then compared with a set of reference values. If the identifying value satisfies a validation condition, then execution of the current instruction by the processor is allowed. If the validation condition is not satisfied, then a response is generated: In the common case, execution of the current instruction is not allowed, or some other predetermined measure is taken.

Owner:VMWARE INC

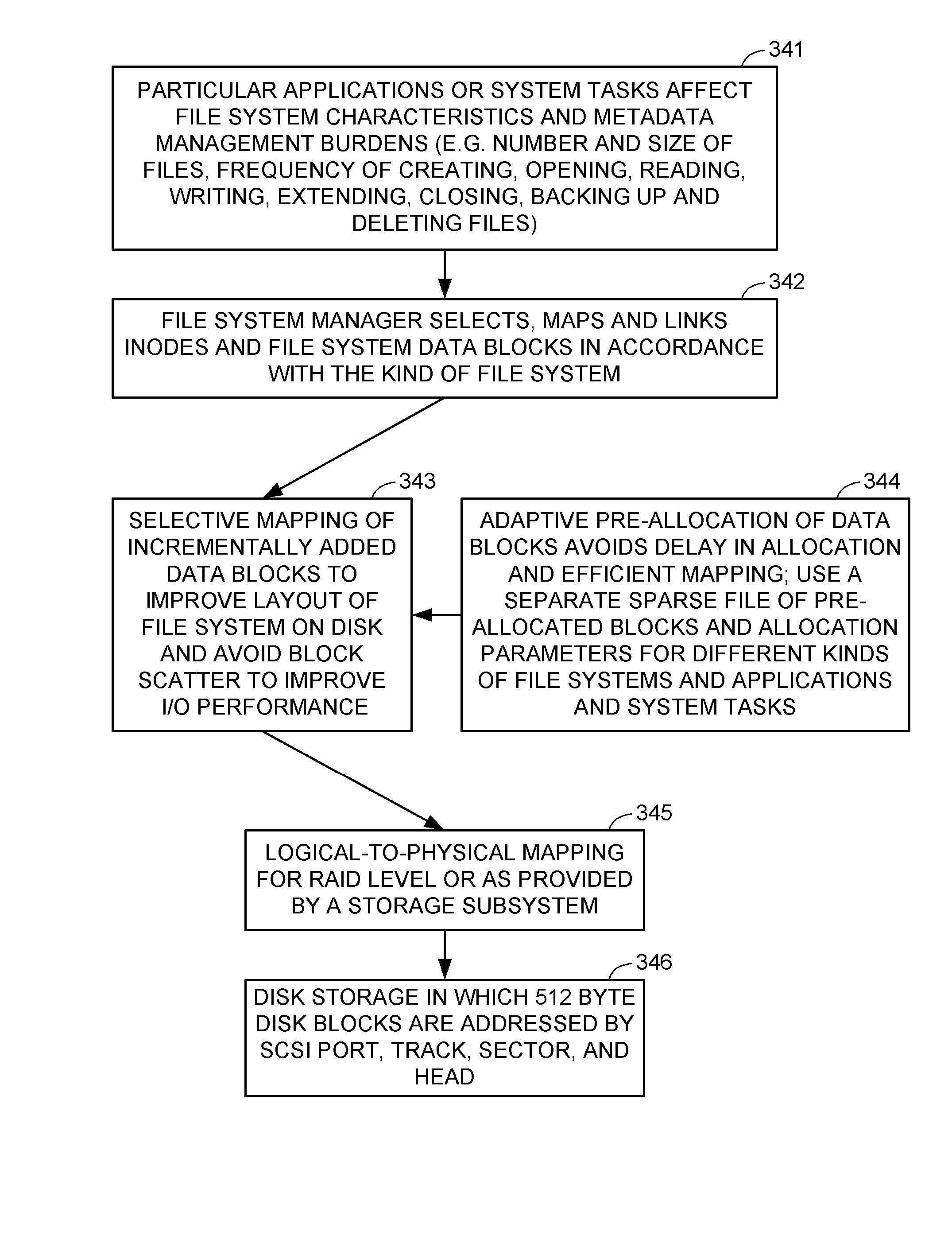

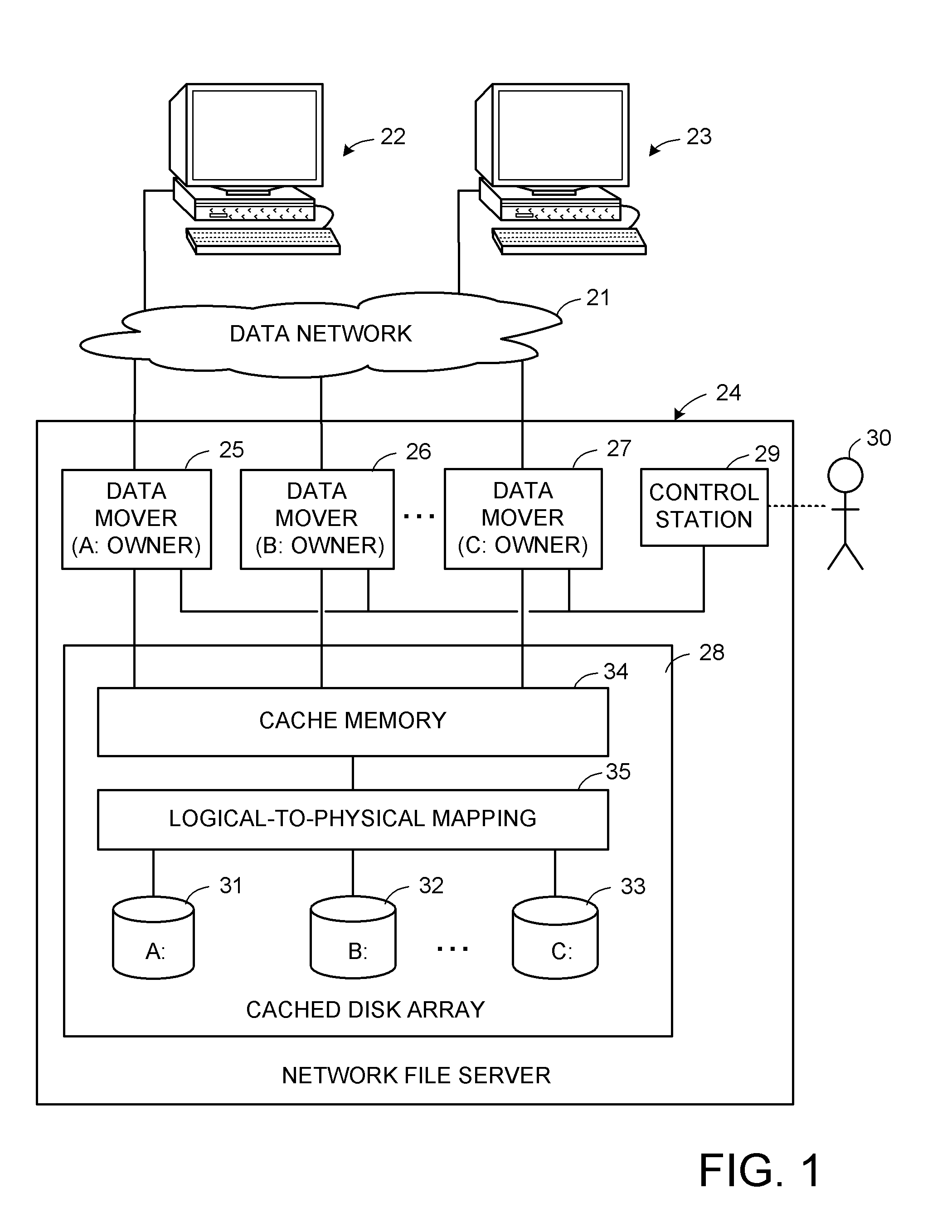

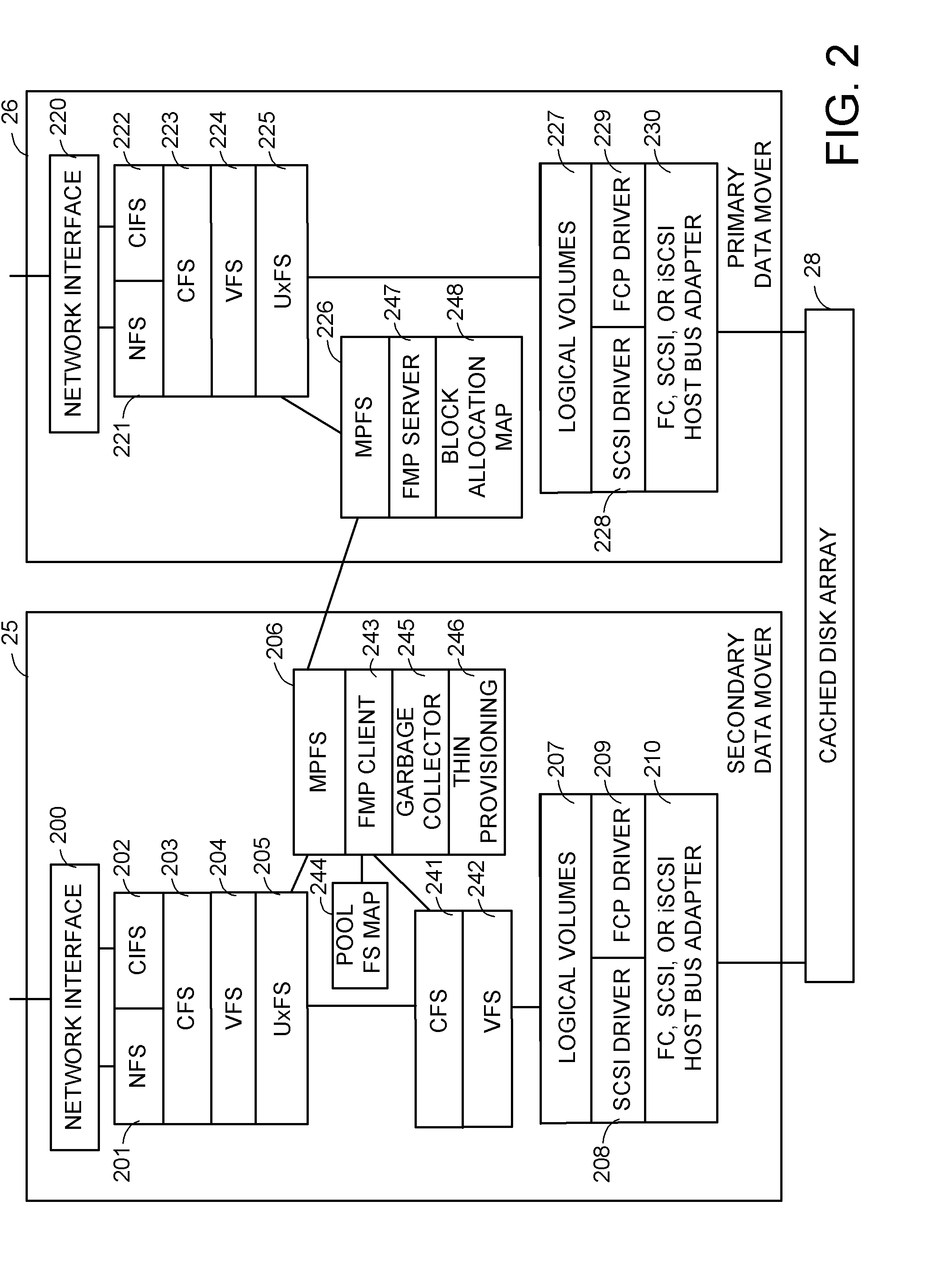

Storage array virtualization using a storage block mapping protocol client and server

A cached disk array includes a disk storage array, a global cache memory, disk directors coupling the cache memory to the disk storage array, and front-end directors for linking host computers to the cache memory. The front-end directors service storage access requests from the host computers, and the disk directors stage requested data from the disk storage array to the cache memory and write new data to the disk storage. At least one of the front-end directors or disk directors is programmed for block resolution of virtual logical units of the disk storage, and for obtaining, from a storage allocation server, space allocation and mapping information for pre-allocated blocks of the disk storage, and for returning to the storage allocation server requests to commit the pre-allocated blocks of storage once data is first written to the pre-allocated blocks of storage.

Owner:EMC IP HLDG CO LLC

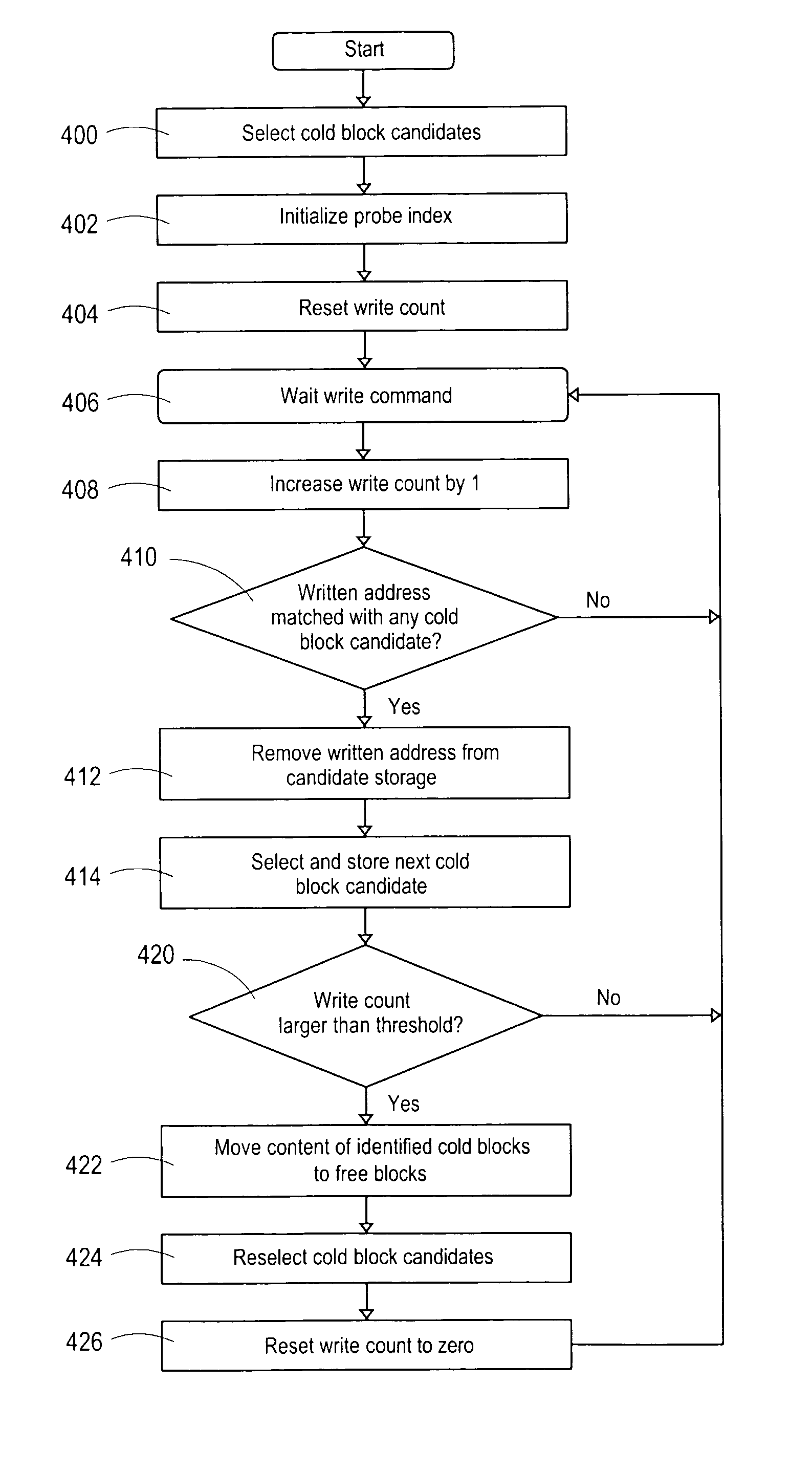

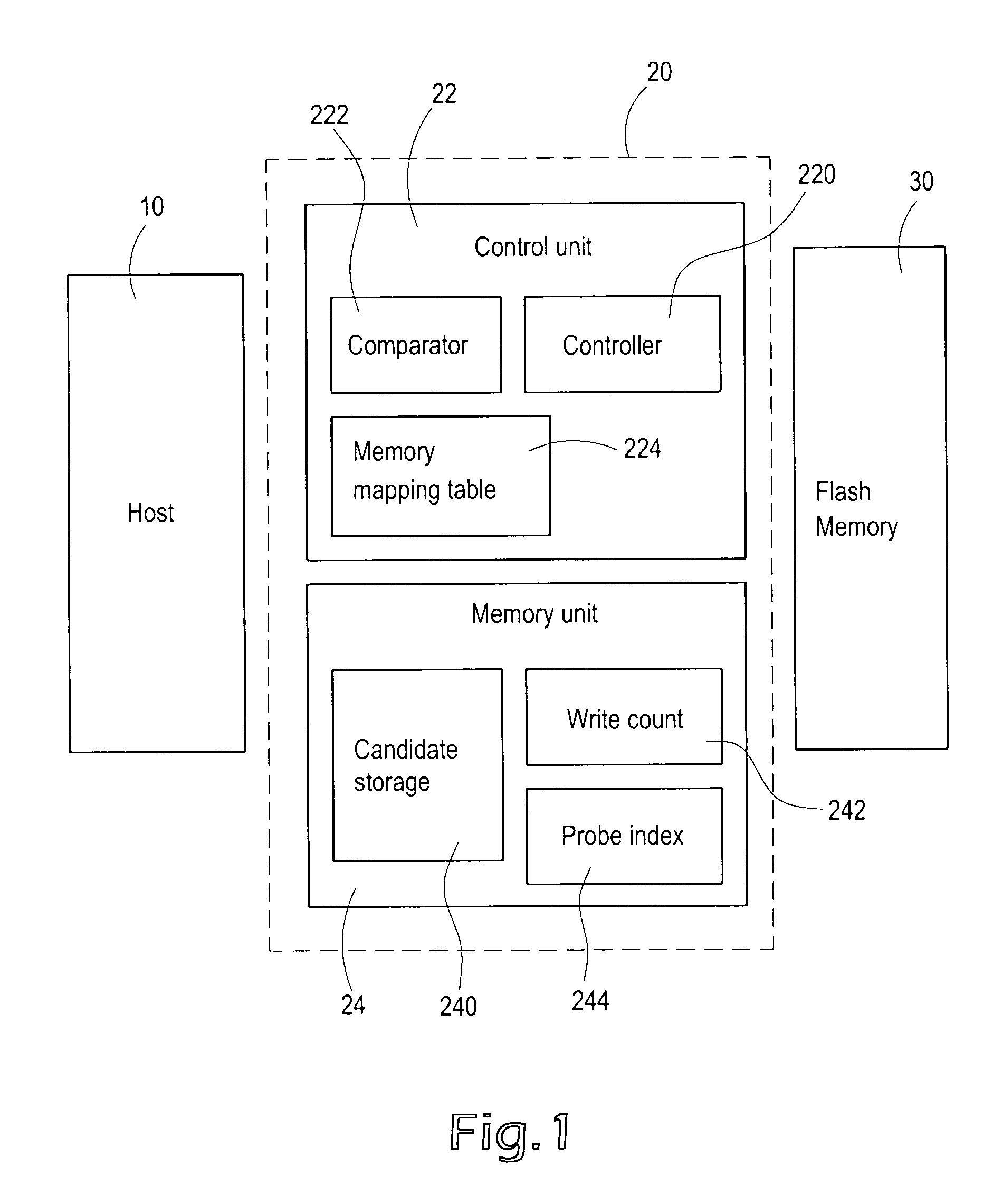

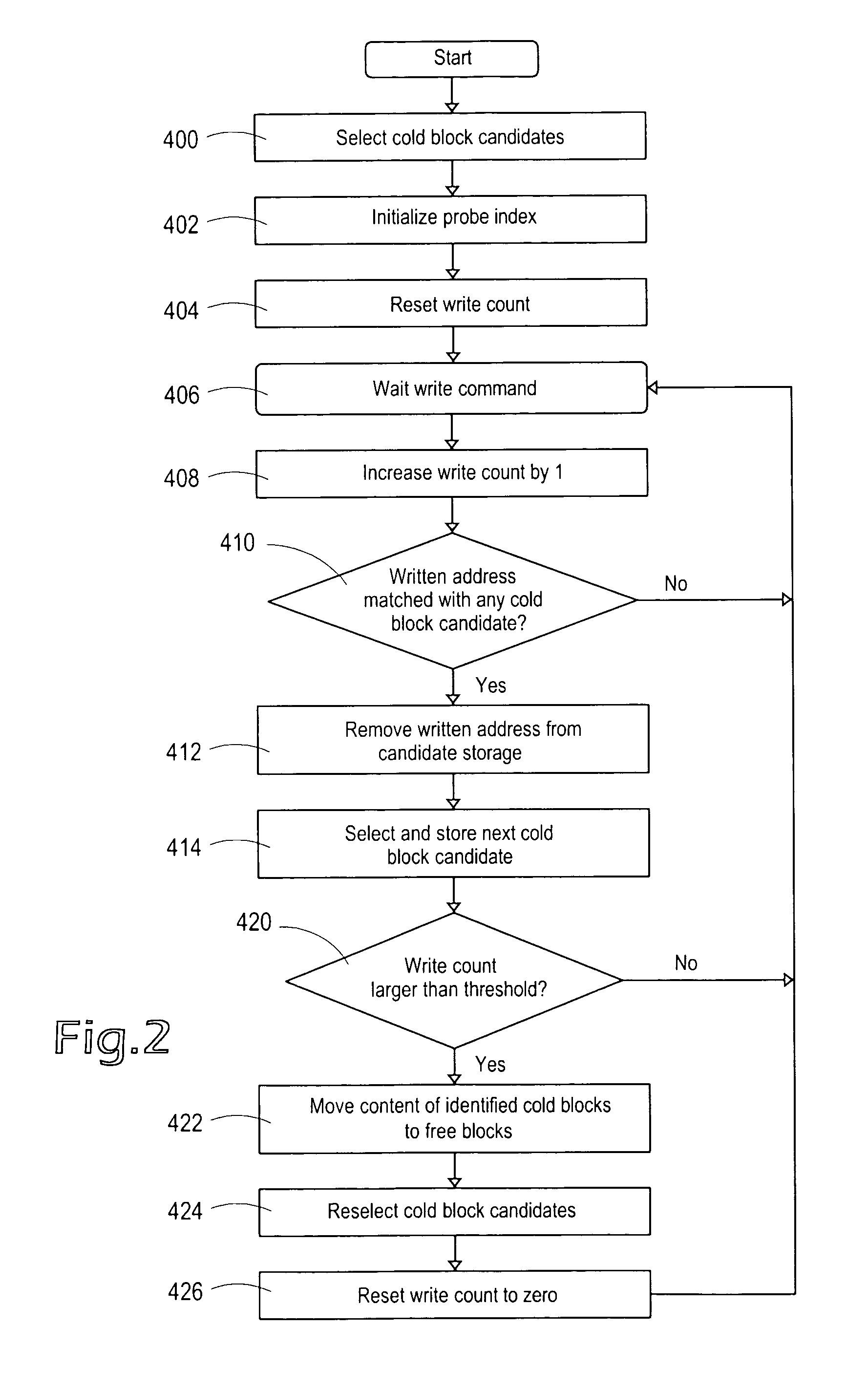

Wear leveling method and apparatus for nonvolatile memory

PendingUS20070208904A1Uniform wearImprove efficiencyMemory architecture accessing/allocationRead-only memoriesStorage cellControl unit

A wear leveling apparatus uniformly distributes wear over a nonvolatile memory containing a plurality of memory blocks. The wear leveling apparatus includes a memory unit for storing a record of cold block candidates in the nonvolatile memory and a control unit configured to update the memory unit and release the cold block candidates under a threshold condition. The control unit selects a new memory block to replace one cold block candidate in the memory unit when the cold block candidate is matched with a written address in a write command for the nonvolatile memory. The cold block candidates remained in the memory unit are identified as cold blocks when the nonvolatile memory has been written more than a predetermined write count threshold. The memory blocks with infrequent erasure can be identified and released to uniformly distribute wear over the nonvolatile memory.

Owner:SUNPLUS TECH CO LTD

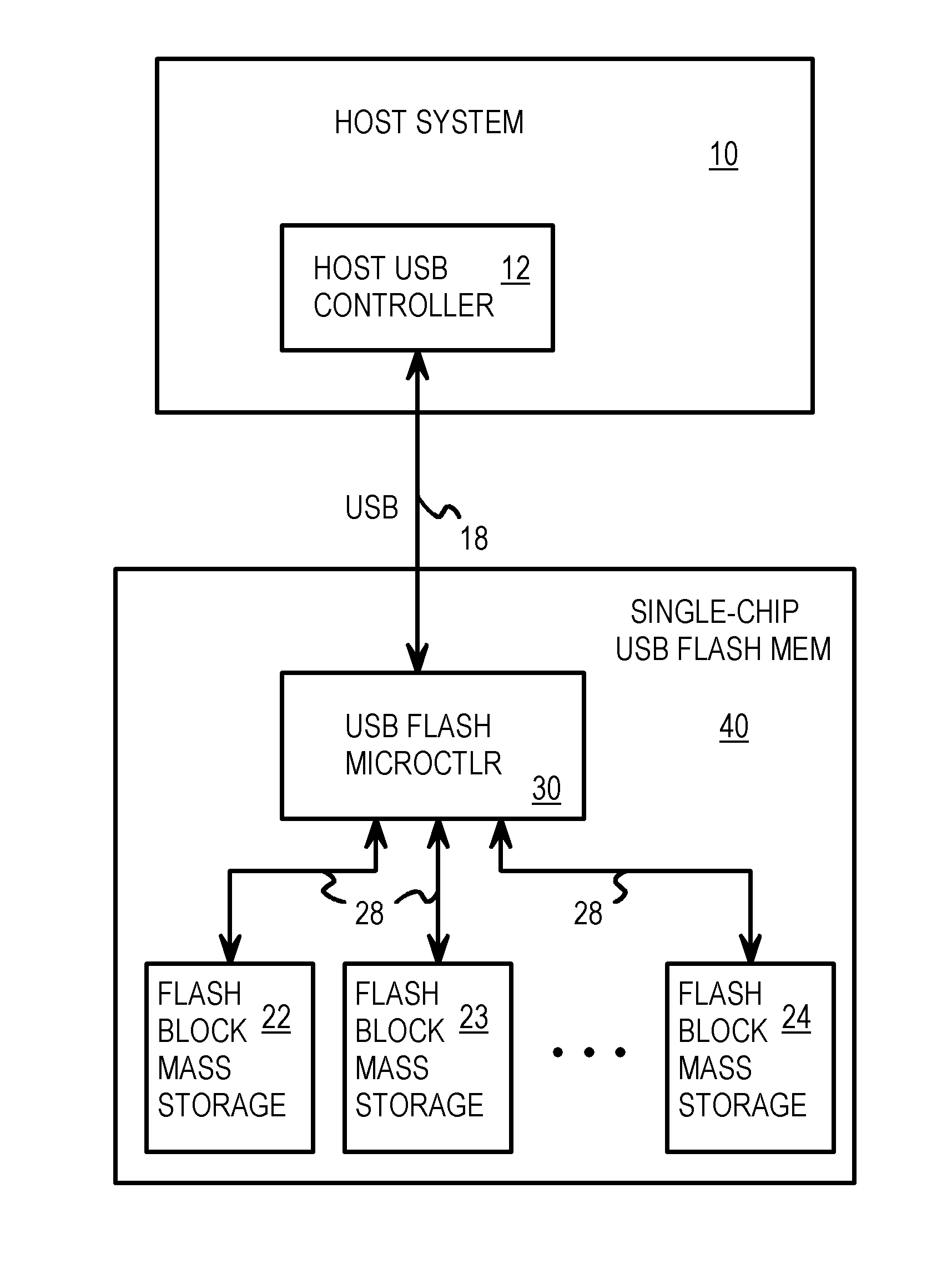

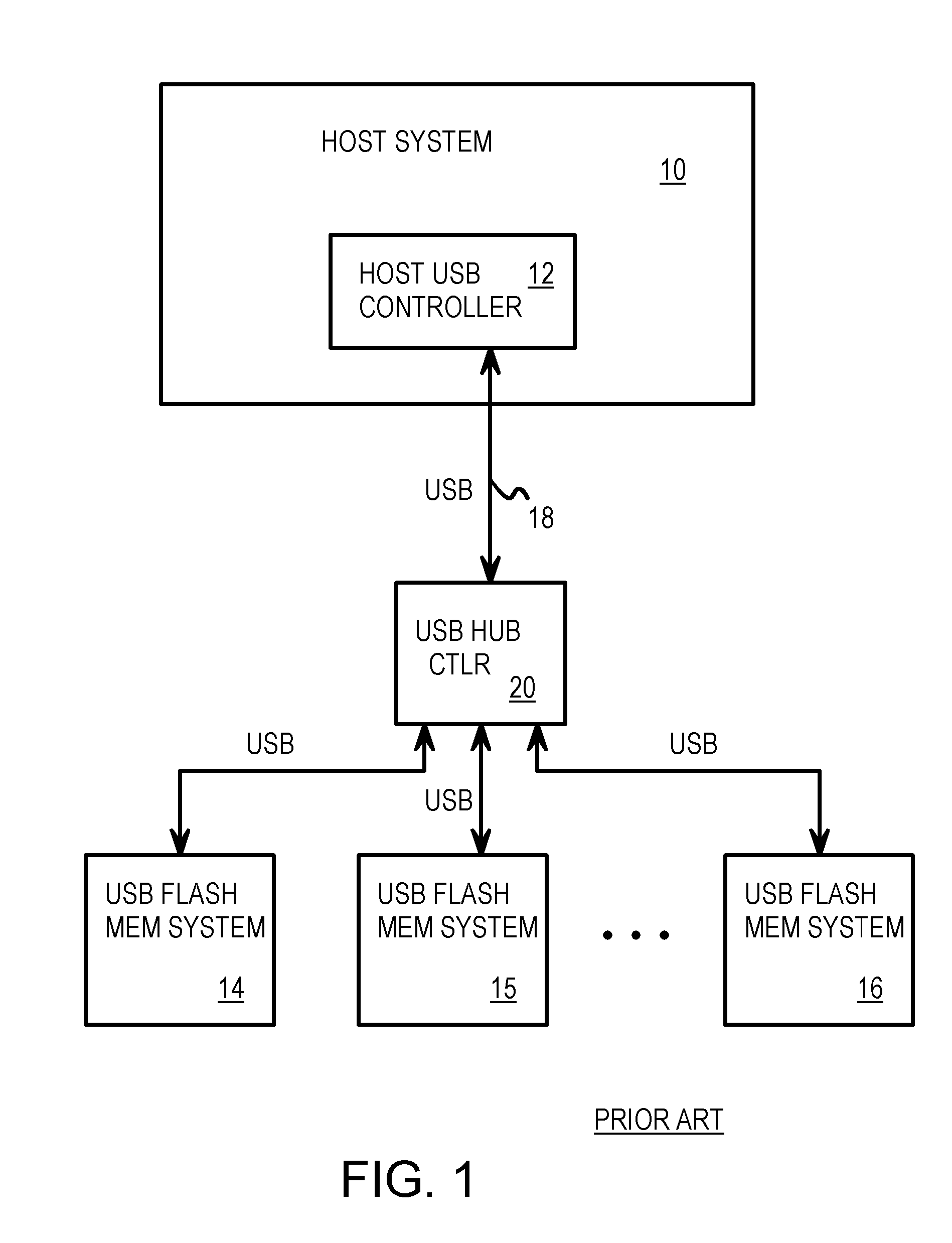

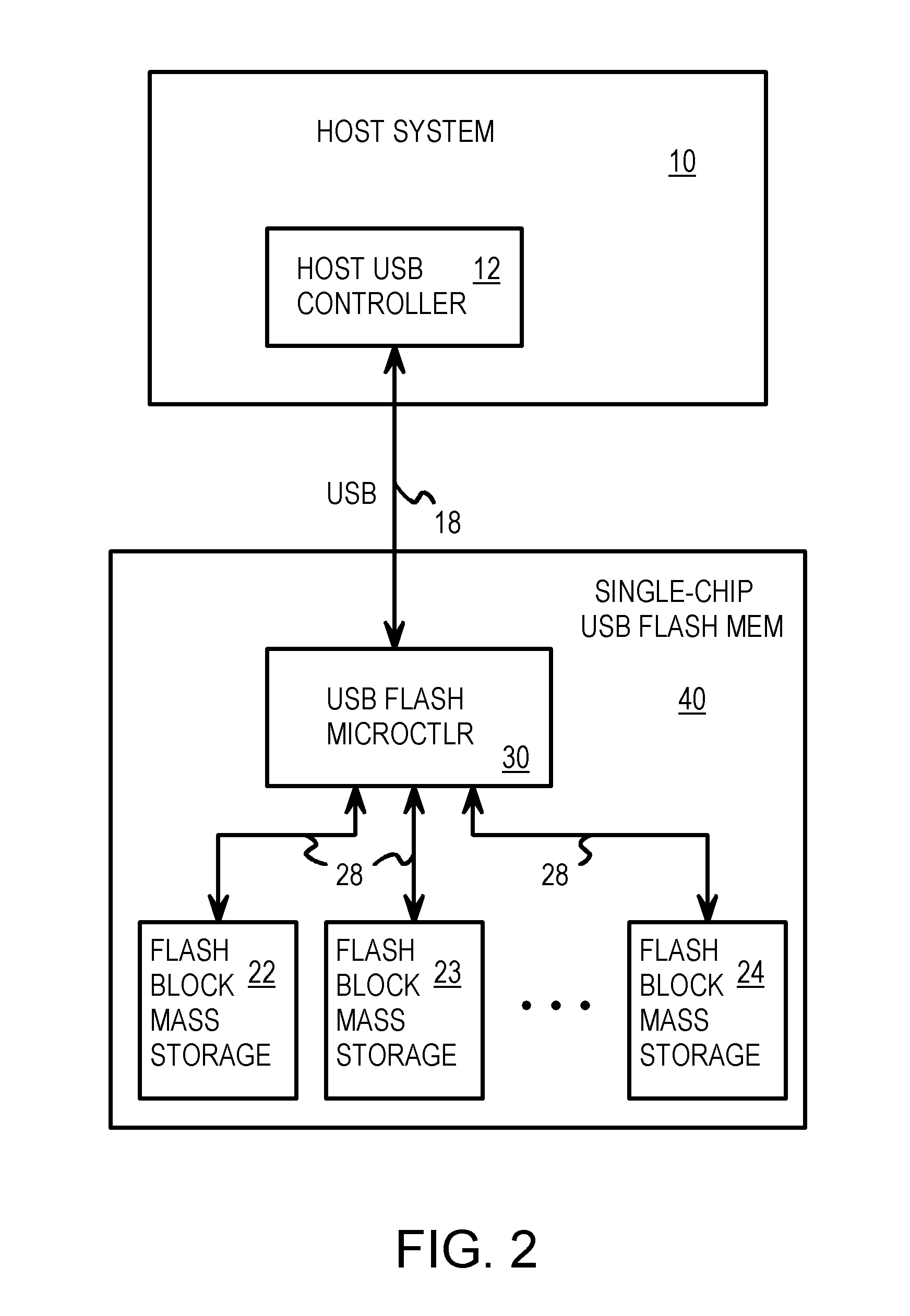

Single-Chip USB Controller Reading Power-On Boot Code from Integrated Flash Memory for User Storage

A Universal-Serial-Bus (USB) single-chip flash device contains a USB flash microcontroller and flash mass storage blocks containing flash memory arrays that are block-addressable rather than randomly-addressable. USB packets from a host USB bus are read by a serial engine on the USB flash microcontroller. Various routines that execute on a CPU in the USB flash microcontroller are activated in response to commands in the USB packets. A flash-memory controller in the USB flash microcontroller transfers data from the serial engine to the flash mass storage blocks for storage. Rather than boot from an internal ROM coupled to the CPU, a boot loader is transferred by DMA from the first page of the flash mass storage block to an internal RAM. The flash memory is automatically read from the first page at power-on. The CPU then executes the boot loader from the internal RAM to load the control program.

Owner:SUPER TALENT TECH CORP

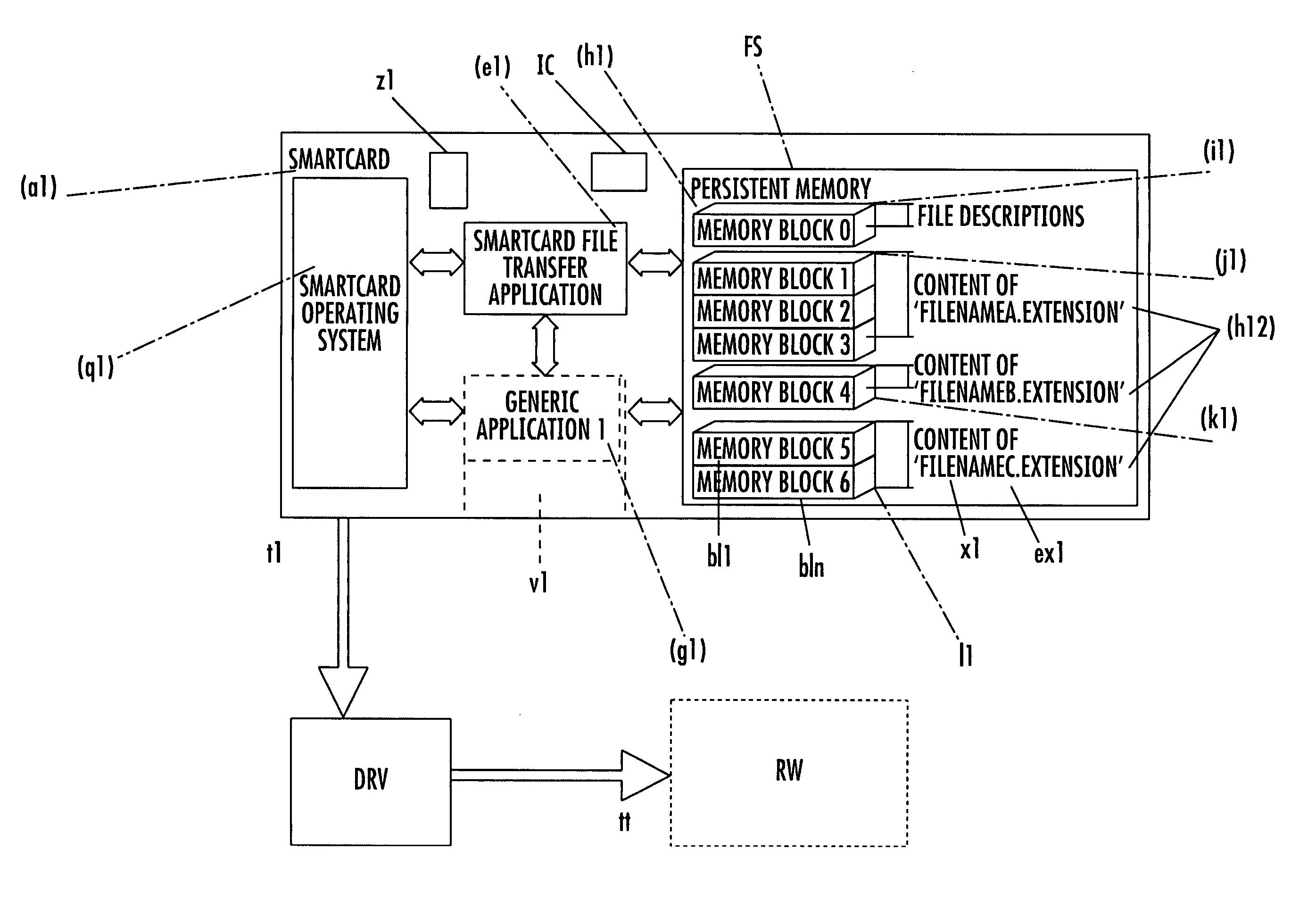

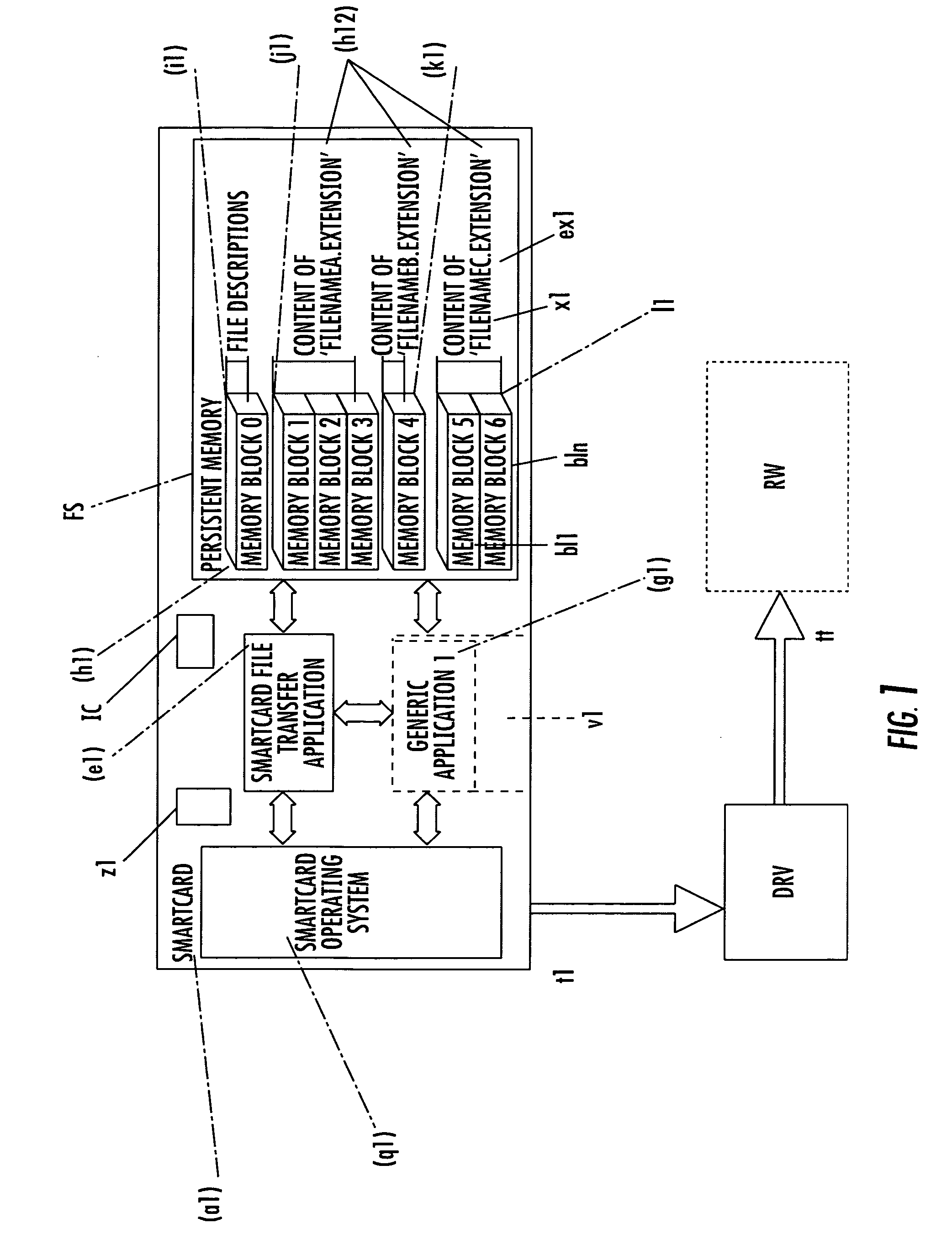

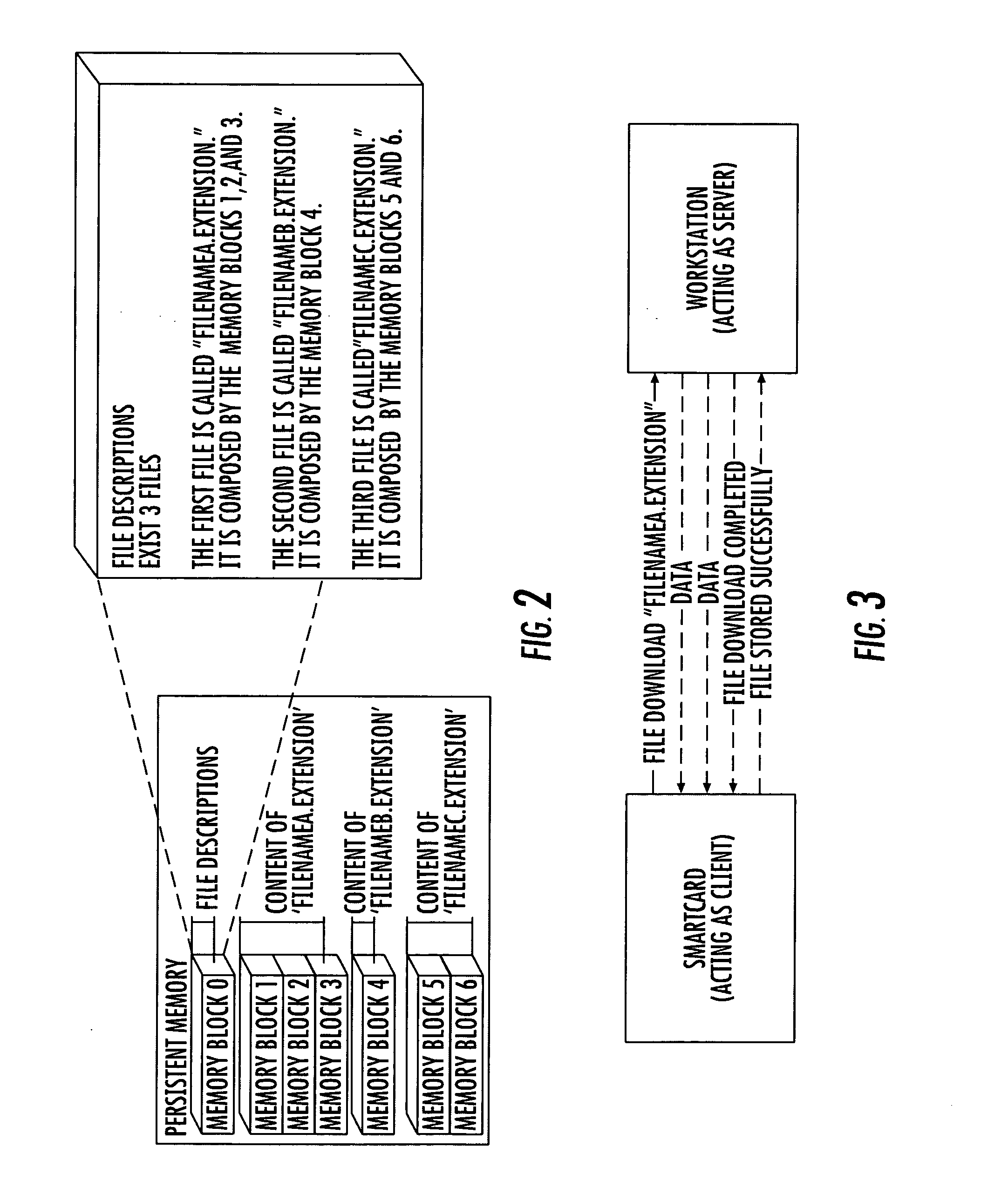

IC card file system

InactiveUS20070152070A1AccessibilityAcutation objectsDigital data information retrievalIntel HEXApplication software

File system for IC CARD comprising an integrated circuit IC, non volatile memories ROM and / or E2PROM and at least a volatile memory RAM, for organizing files storage inside the non volatile memories and defining, through a logical structure, their accessibility by an IC Card application, stored inside one of said non volatile memories or IC or loaded in the volatile memory and in communication with an external read-write device; an interchange application, stored inside one of said non volatile memories, drives the organization of files in an additional tag-length logic structures of arbitrary length, allowing the identification of files through alphanumeric identifiers of arbitrary length and extension, and their accessibility by an external read-write device, eventually non IC card purpose, like a workstation a personal computer or a PDA interconnected to the IC Card by means of standard communication interface. The file system organizes said tag-length logic structure as individually memory blocks, each identified by an hexadecimal identification number and a block size and one of these memory blocks, more particularly one per non volatile memory, describes the content of the non volatile memory, comprising the number of files stored, their file name and extension and, for each file, the location of memory blocks composing its content.

Owner:STMICROELECTRONICS INT NV

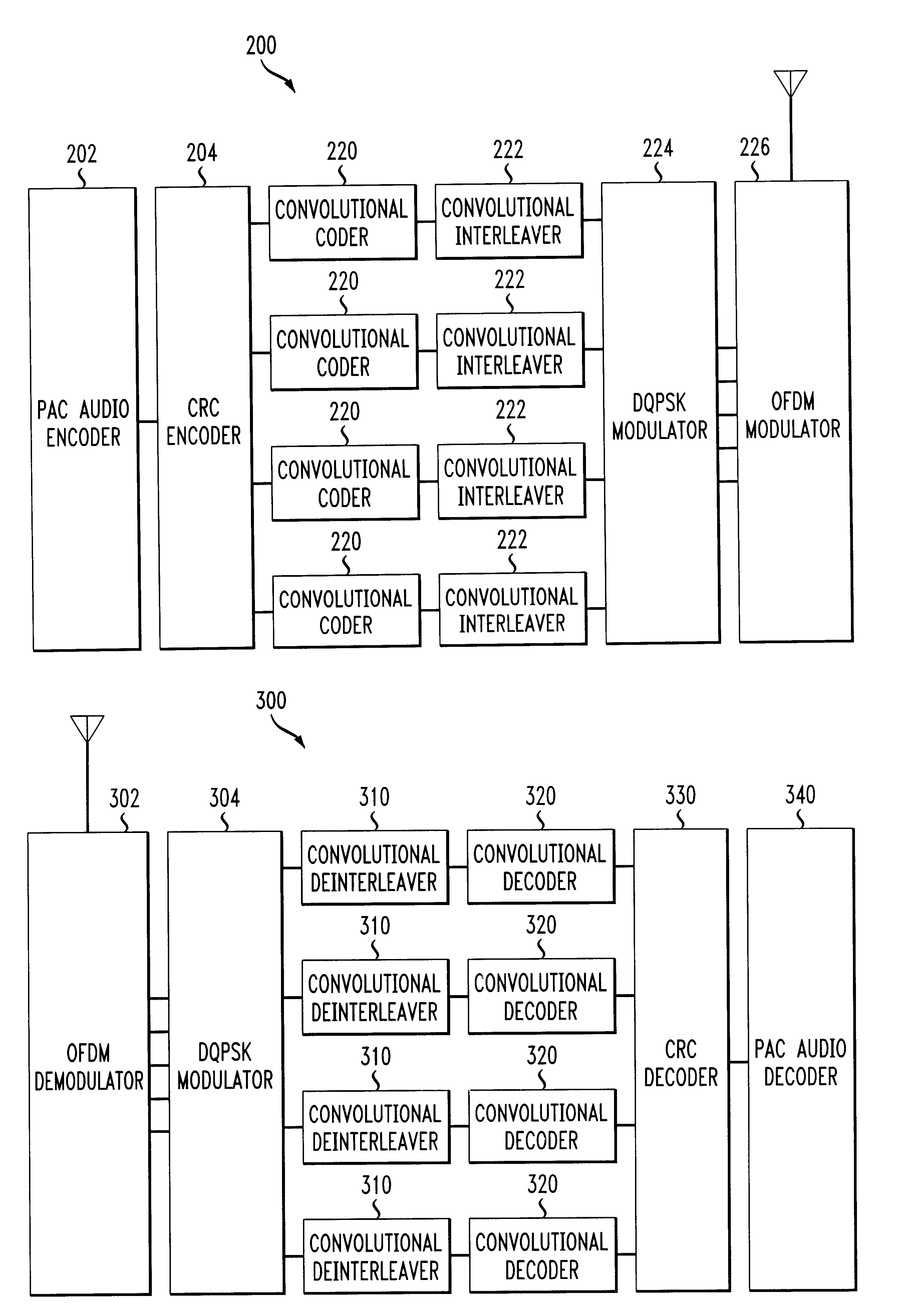

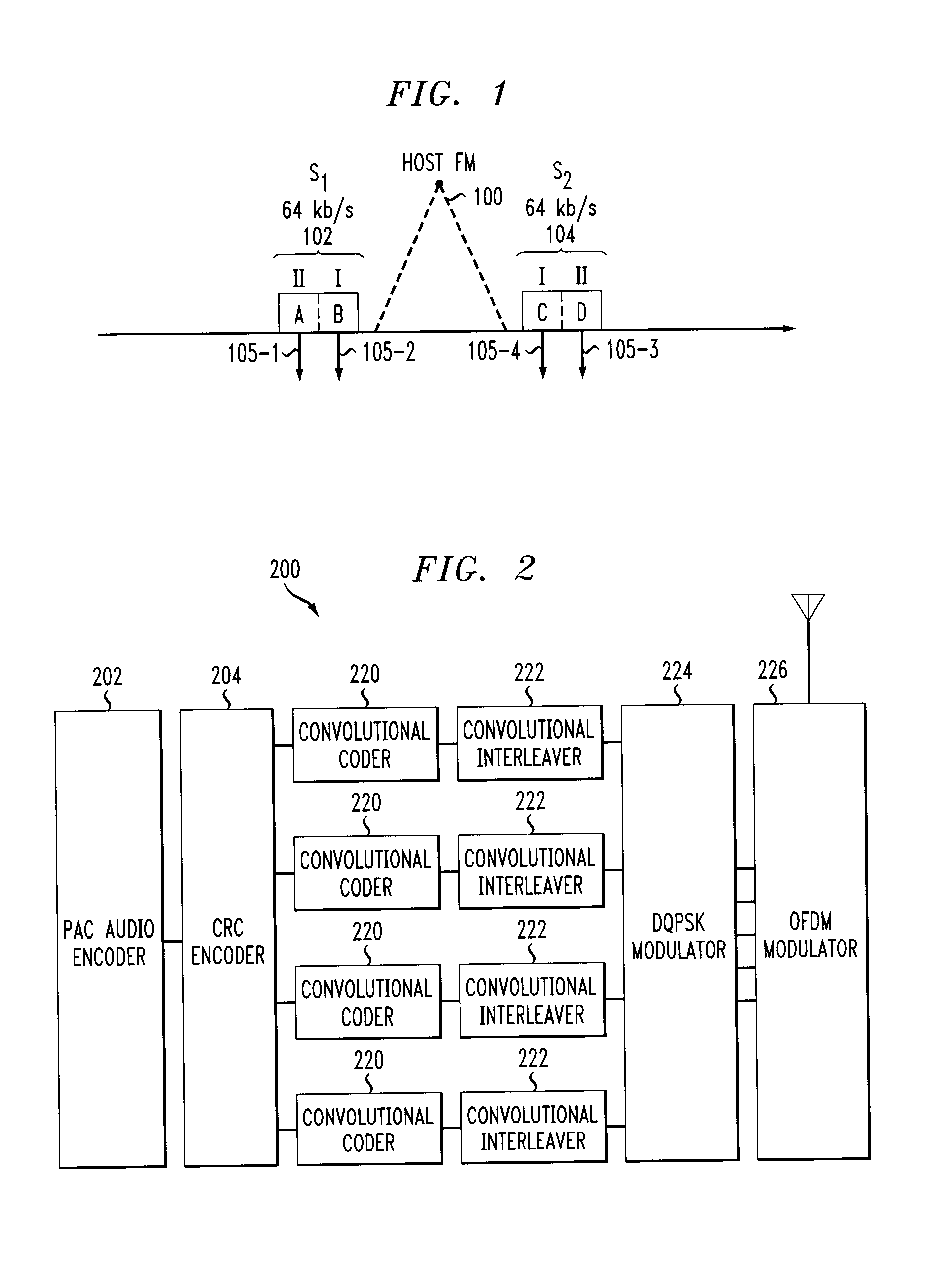

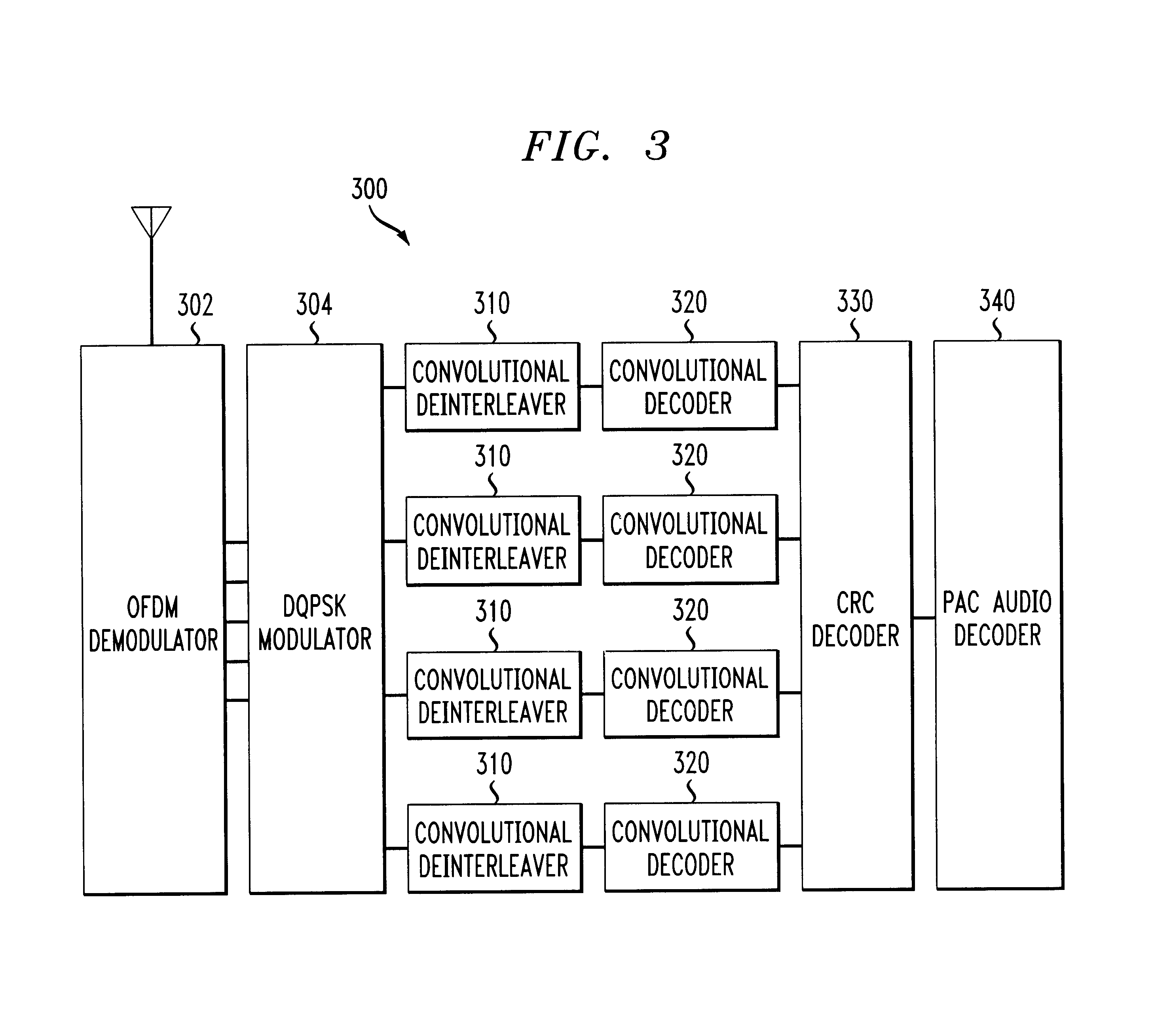

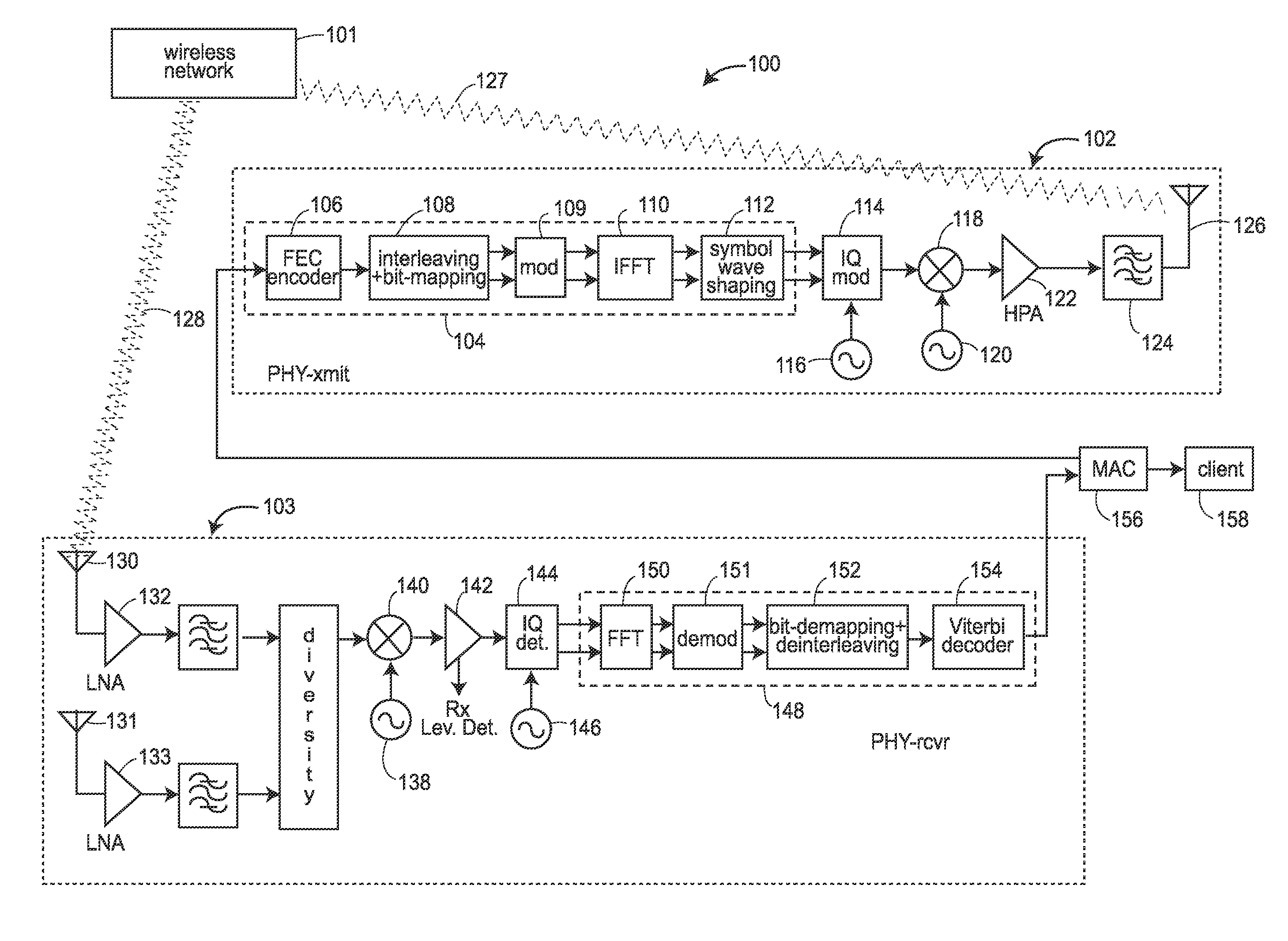

Symbol self synchronous interleaving method and apparatus for OFDM-based communication system

InactiveUS6985537B1Reduce delaysBroadcast with distributionRadio transmissionIn-band on-channelCommunications system

An interleaving method and apparatus is disclosed for an in-band on-channel (IBOC) digital audio broadcasting (DAB) system. The disclosed interleaver method and apparatus utilize a convolutional interleaver having a row size equal to one OFDM symbol and a time span of arbitrary size. A structured memory block is utilized in the de-interleaver at the receiver having a row size of one OFDM symbol (the number of active sub-carriers in the applicable sub-band of the IBOC system). The self-synchronizing nature of the present invention permits a receiver in an OFDM-based IBOC system to sort the scrambled blocks and descramble the received symbols according to its own frame count, without regard to the frame count of the transmitter. The disclosed interleaver method and apparatus does not require interleaver synchronization between the transmitter and receiver. In one implementation, separate convolutional encoders and convolutional interleavers are applied to each sub-band in a multi-stream structure to provide independent error spreading for each sub-band.

Owner:LUCENT TECH INC

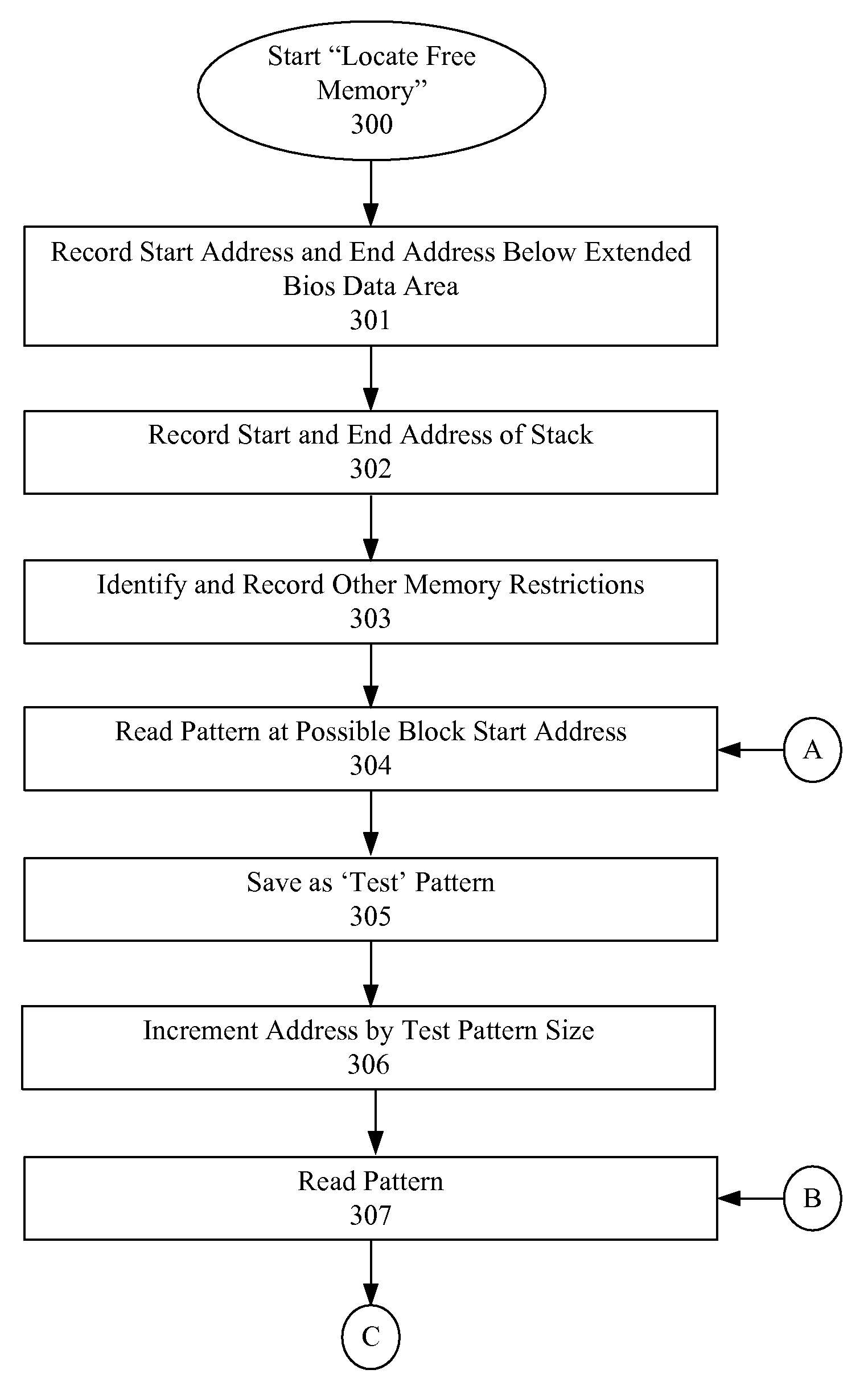

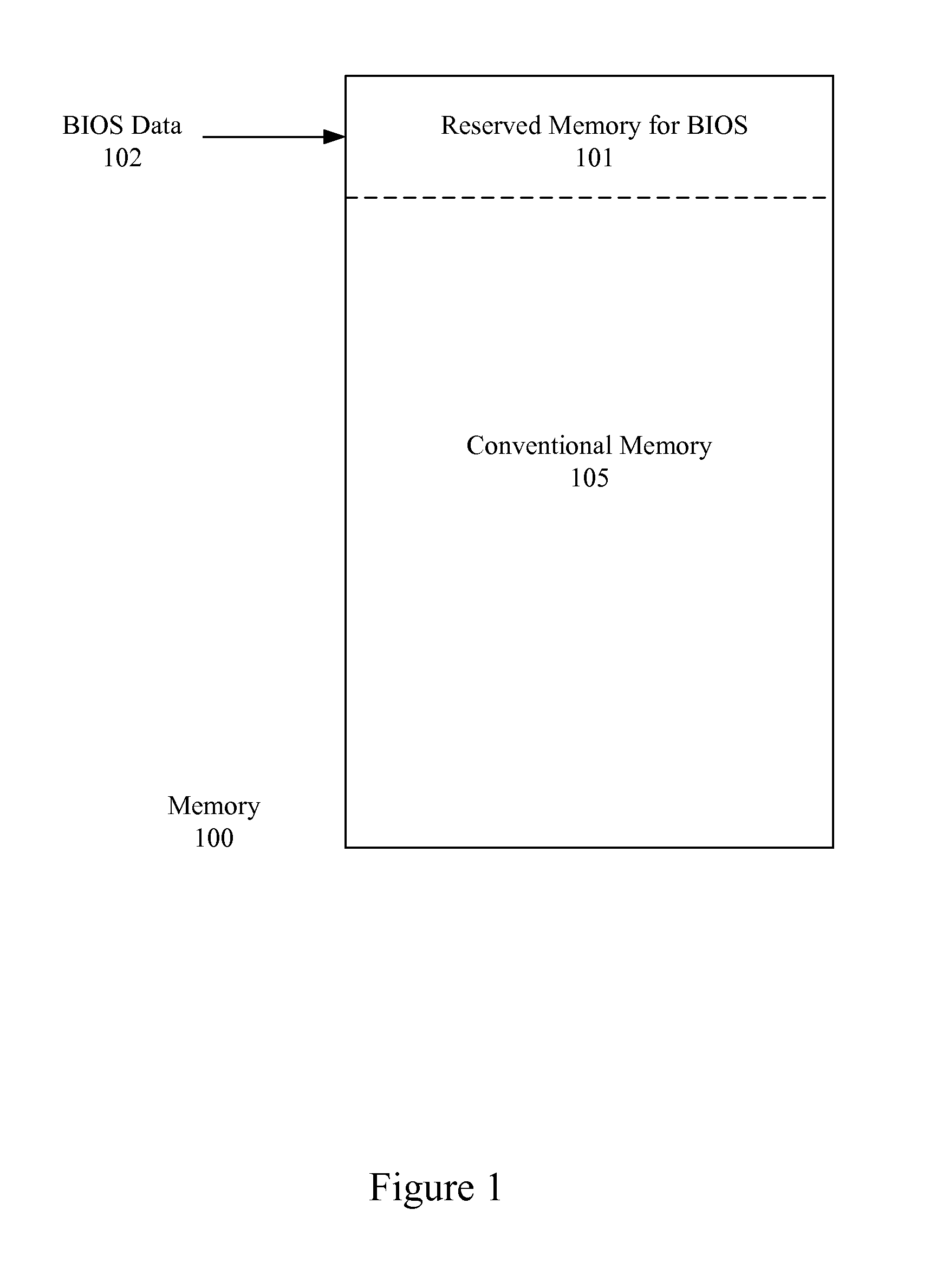

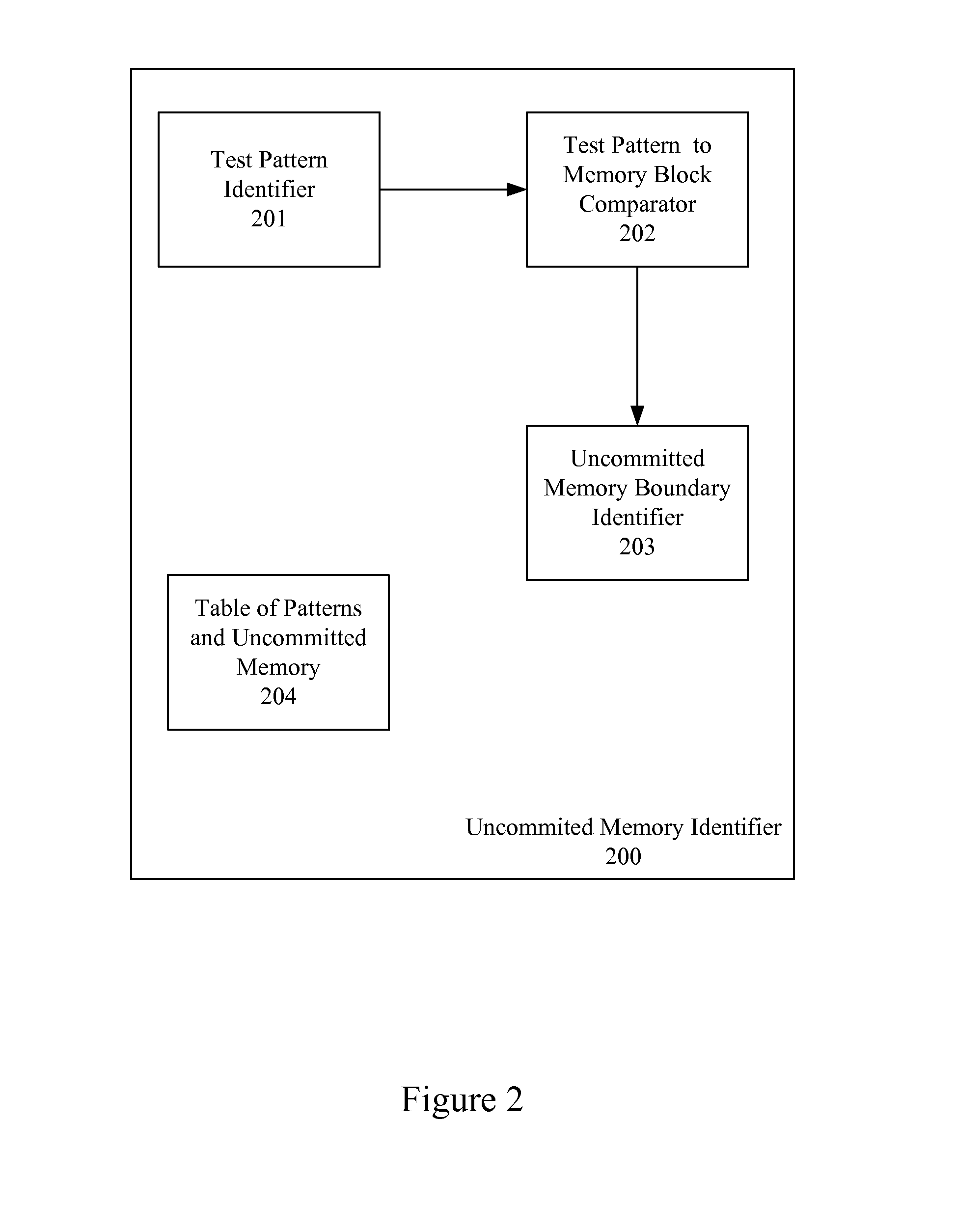

Identification of Uncommitted Memory Blocks During an Initialization Procedure

InactiveUS20080065852A1Easy to useDigital computer detailsProgram controlConventional memoryOption ROM

An apparatus and method are described for identifying uncommitted memory in a system RAM during an initialization process of a computer system, such as a boot procedure or power-on self test, during which memory management is uncontrolled. In various embodiments of the invention, repeating patterns that are indicative of uncommitted memory blocks are identified within a conventional memory area of the system RAM. At least some of the uncommitted memory blocks are allocated for use by an option ROM or other BIOS data and a table is created identifying these uncommitted memory blocks. After the BIOS code exits the system RAM, the table is used to restore the uncommitted memory blocks into their previous data states.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

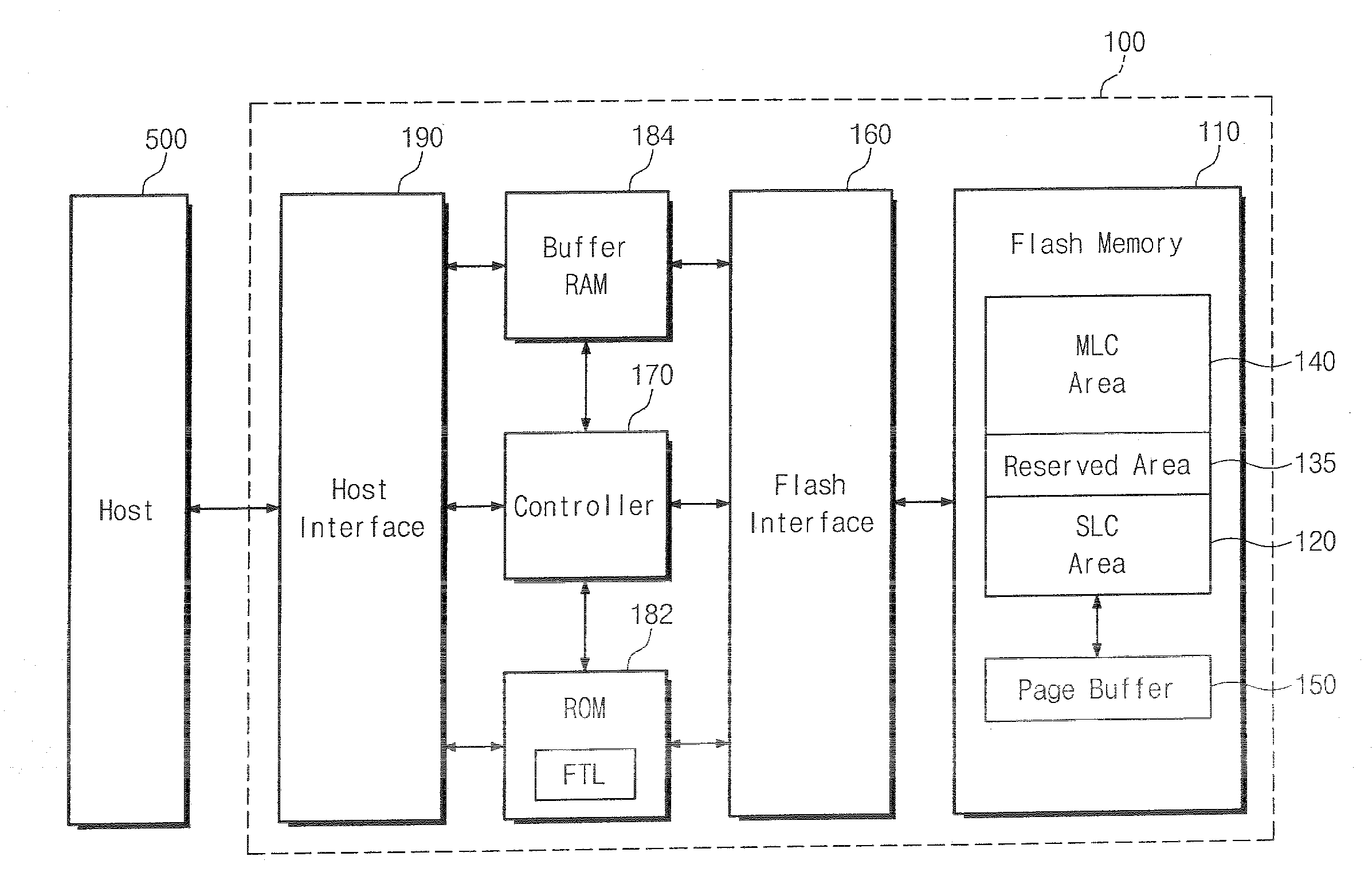

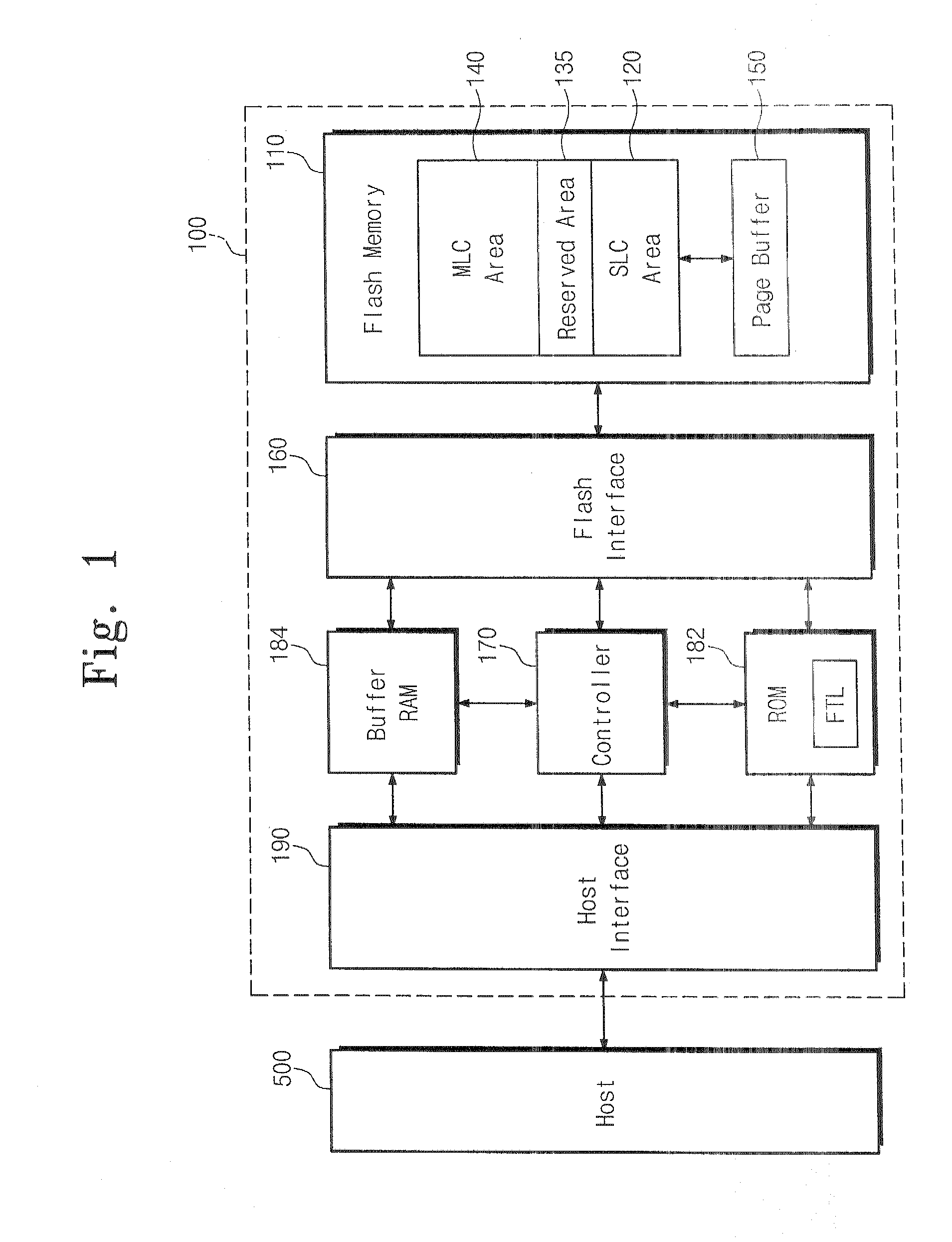

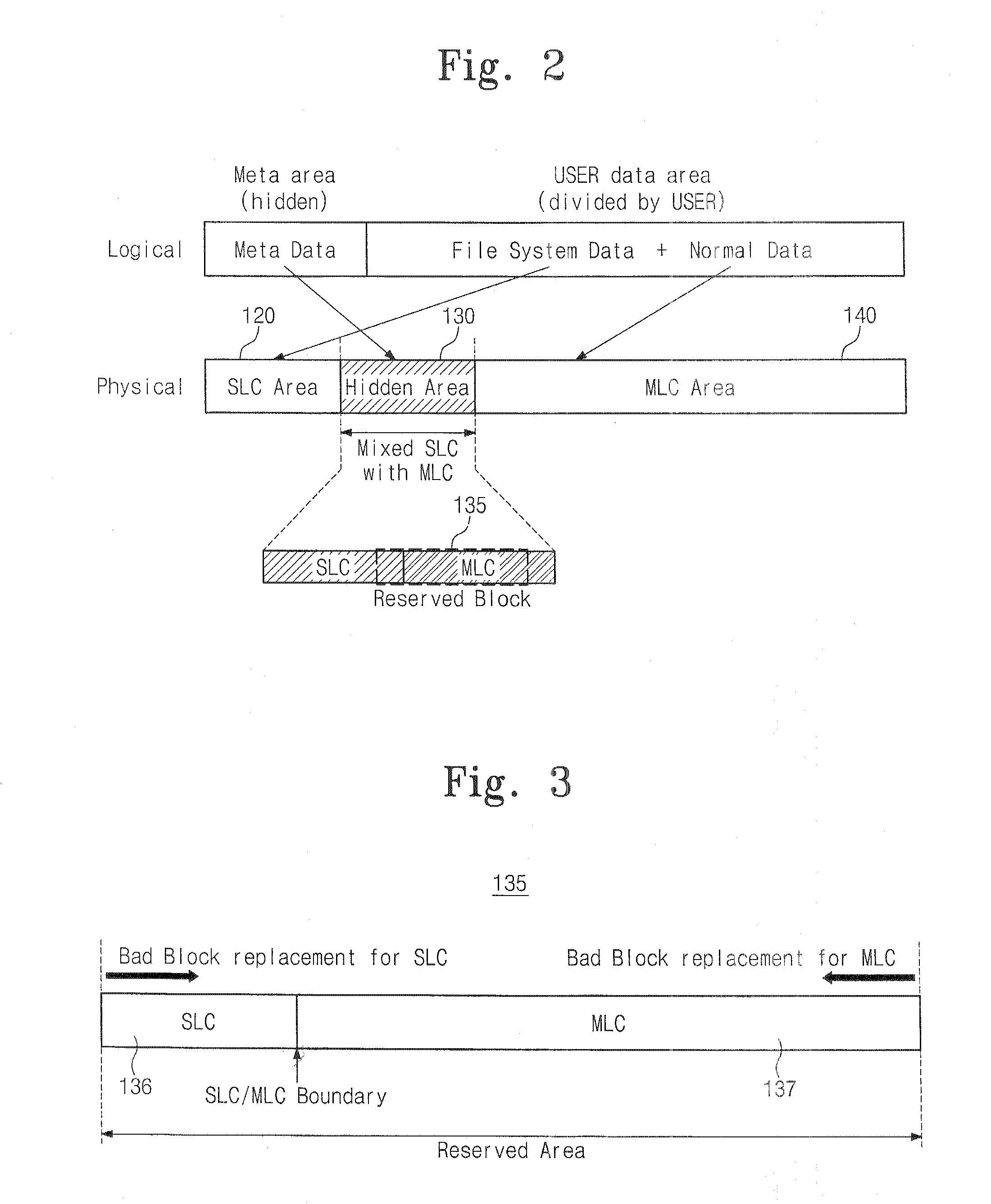

Hybrid flash memory device and method for assigning reserved blocks thereof

ActiveUS20080112238A1Memory adressing/allocation/relocationRead-only memoriesDistribution functionMemory block

A hybrid flash memory device includes an array including a first area and a second area having a larger number of stored bits per cell than the first area The device includes a hidden area including a first reserved block area and a second reserved block area, wherein the first reserved block area includes a plurality of first memory blocks having the same number of stored bits per cell as the first area, the second reserved block area includes a plurality of second memory blocks having the same number of stored bits per cell as the second area, and a flash translation layer configured to replace a bad block generated in the first main area with the first memory block and replace a bad block generated in the second main area with the second memory block, wherein the flash translation layer flexibly assigns functions of the first memory blocks or the second memory blocks depending on whether the first and second memory blocks are all used.

Owner:SAMSUNG ELECTRONICS CO LTD

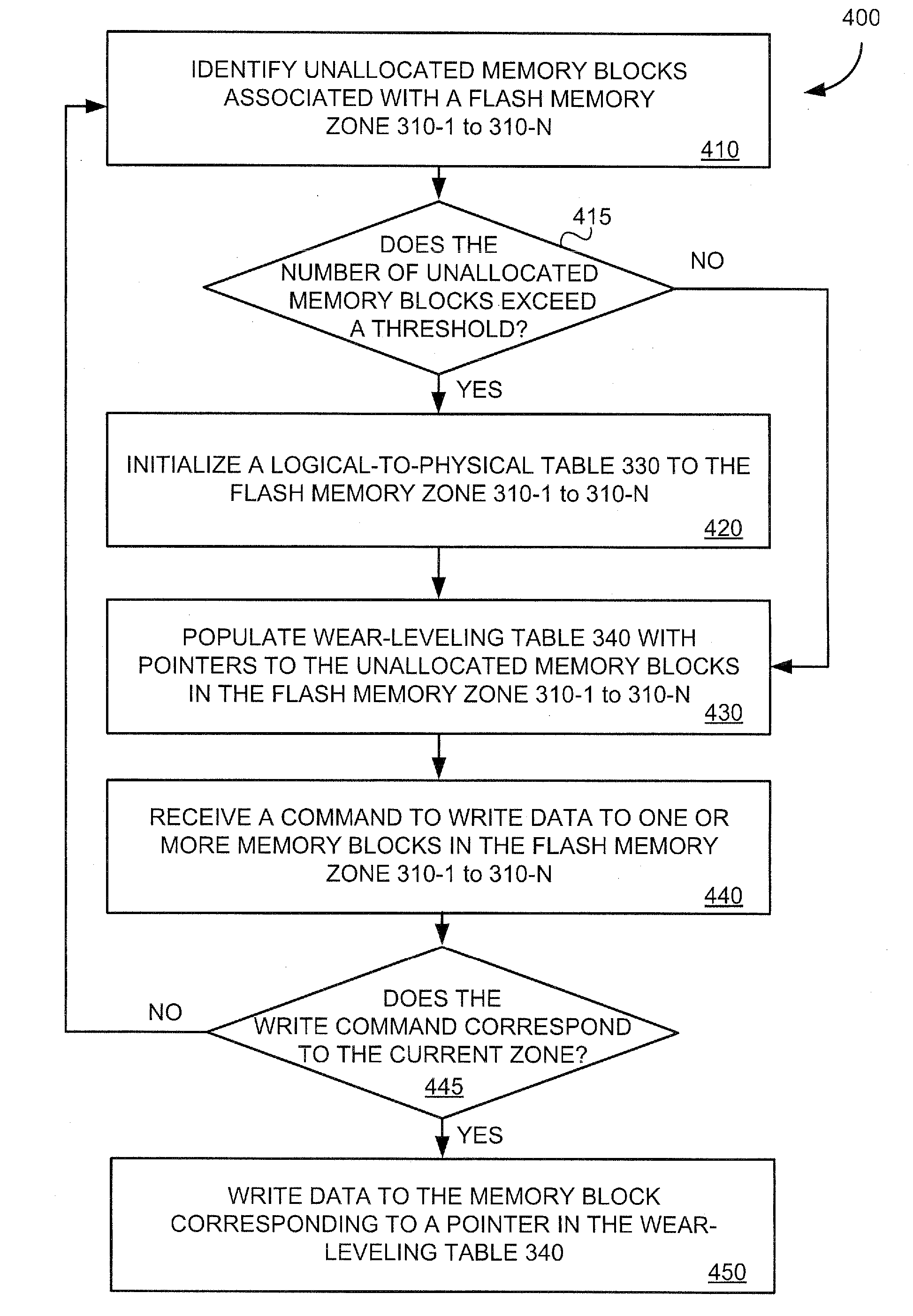

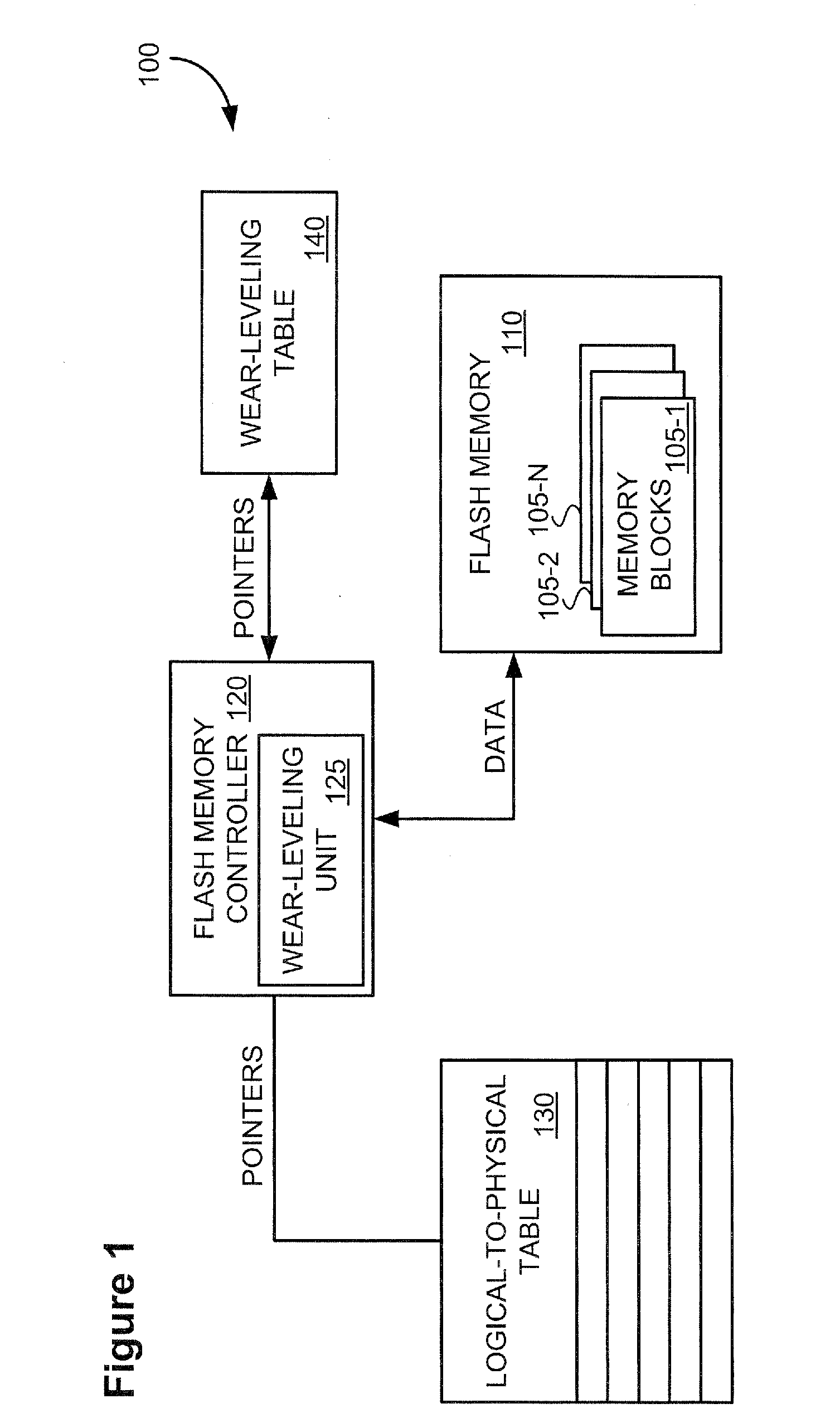

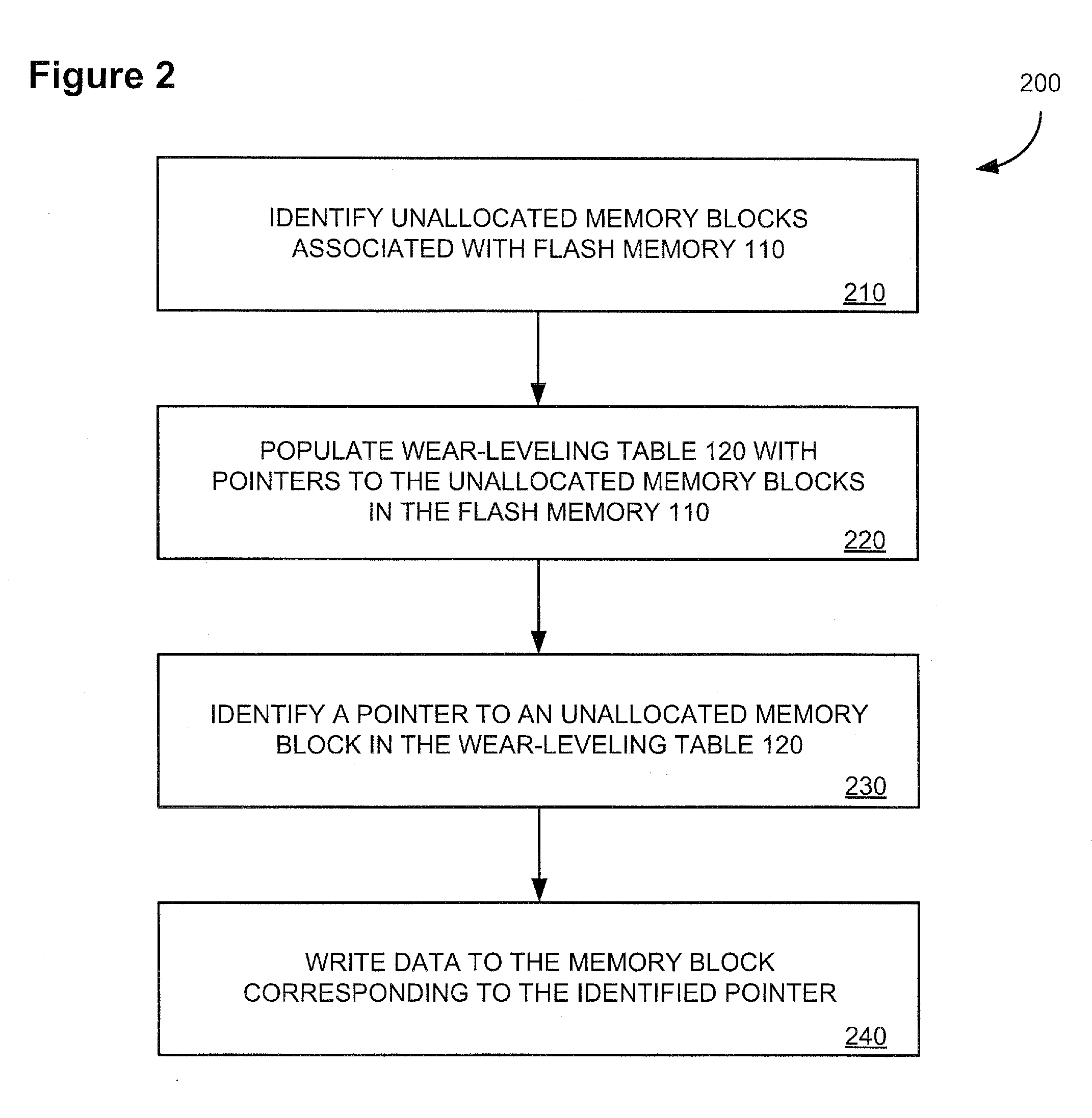

Flash drive fast wear leveling

ActiveUS20070050536A1Memory architecture accessing/allocationMemory adressing/allocation/relocationComputer scienceNon-volatile memory

A system and method comprising a non-volatile memory including one or more memory blocks to store data, a controller to allocate one or more of the memory blocks to store data, and a wear-leveling table populated with pointers to unallocated memory blocks in the non-volatile memory, the controller to identify one or more pointers in the wear-leveling table and to allocate the unallocated memory blocks associated with the identified pointers for the storage of data.

Owner:MONTEREY RES LLC

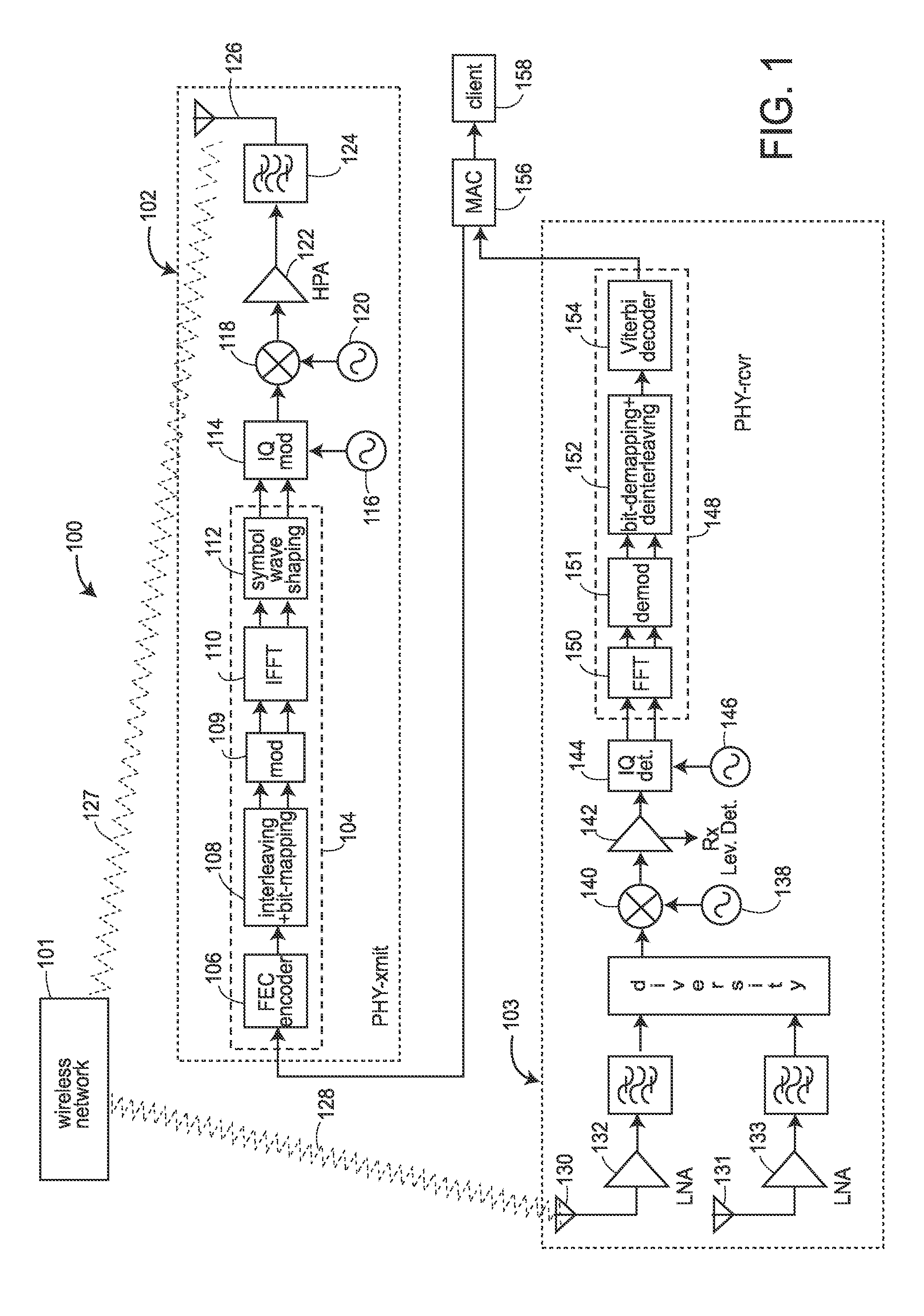

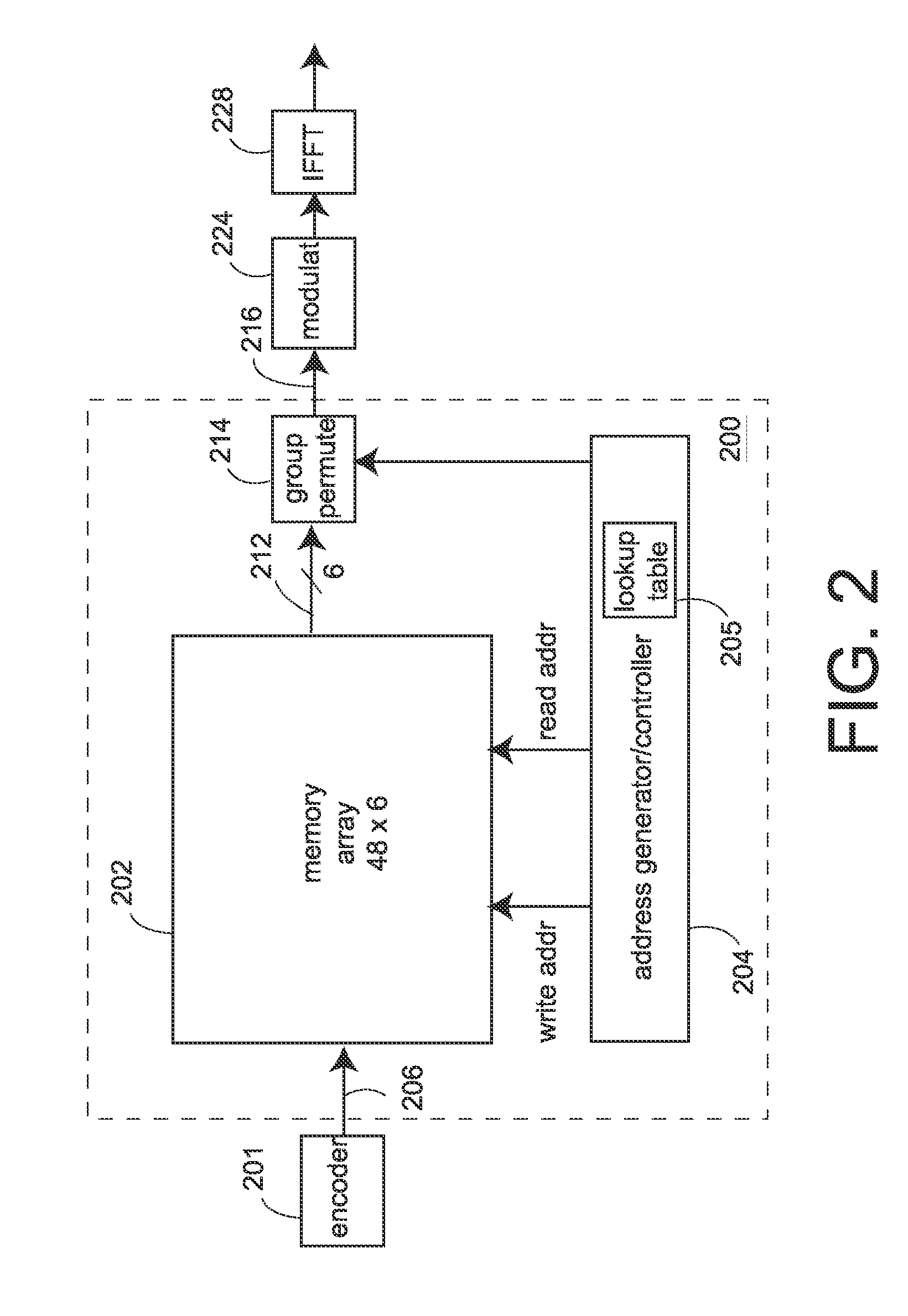

Interleaver, deinterleaver, interleaving method, and deinterleaving method for OFDM data

ActiveUS7170849B1Saving in latencySave powerCode conversionCoding detailsParallel computingMemory block

An interleaver and interleaving method each includes two stages, and is useful in coded orthogonal frequency division multiplexed (COFDM) wireless local area networks. A first stage performs a first block permutation and a second stage performs bit order permutation to effectuate a second group permutation. A corresponding de-interleaver does just the opposite at the receiver. A double-buffer version includes writing data into one memory block in a first order while reading data from the second block in a second order, with the first and second orders selected to effectuate the first block permutation.

Owner:CISCO TECH INC

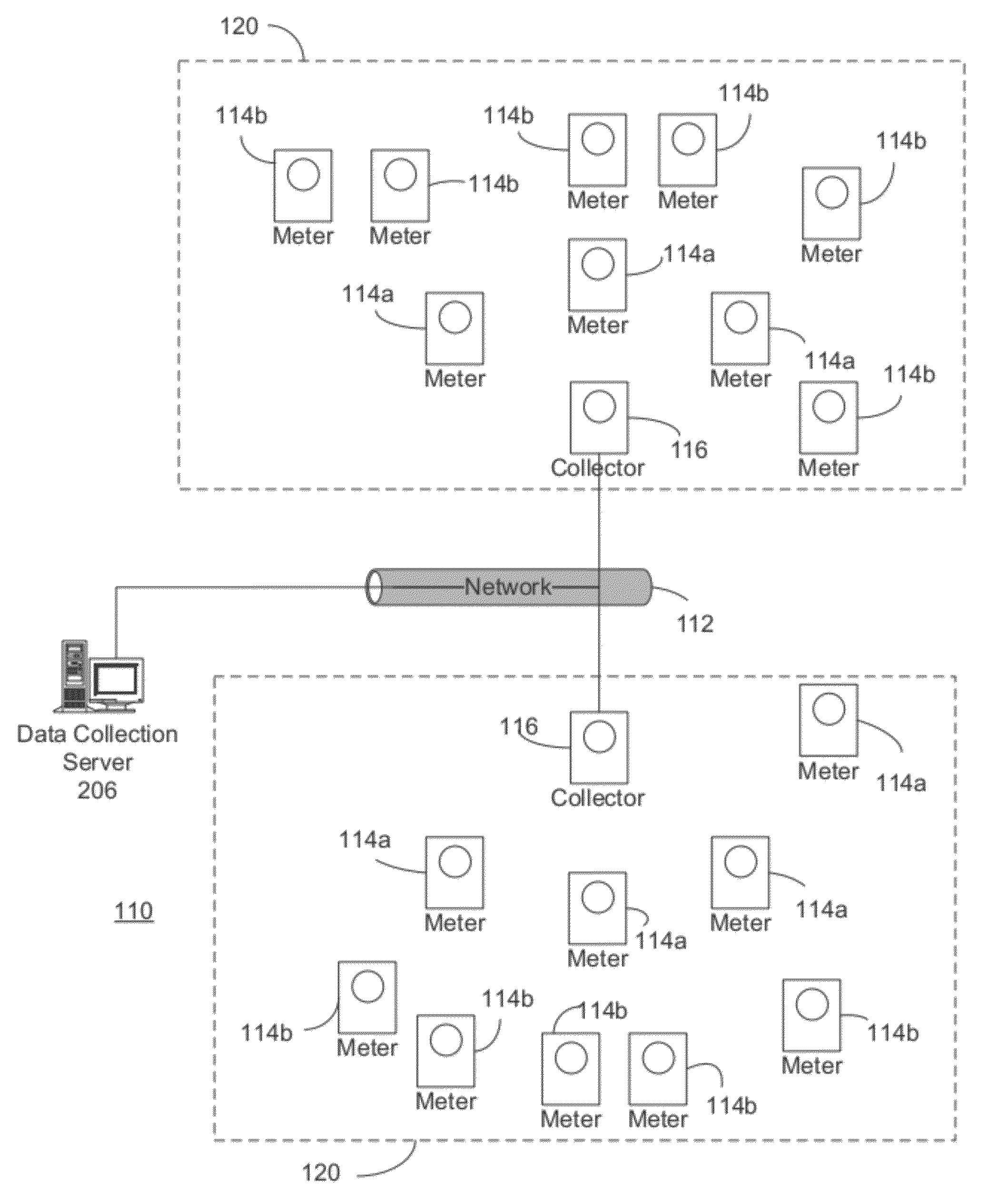

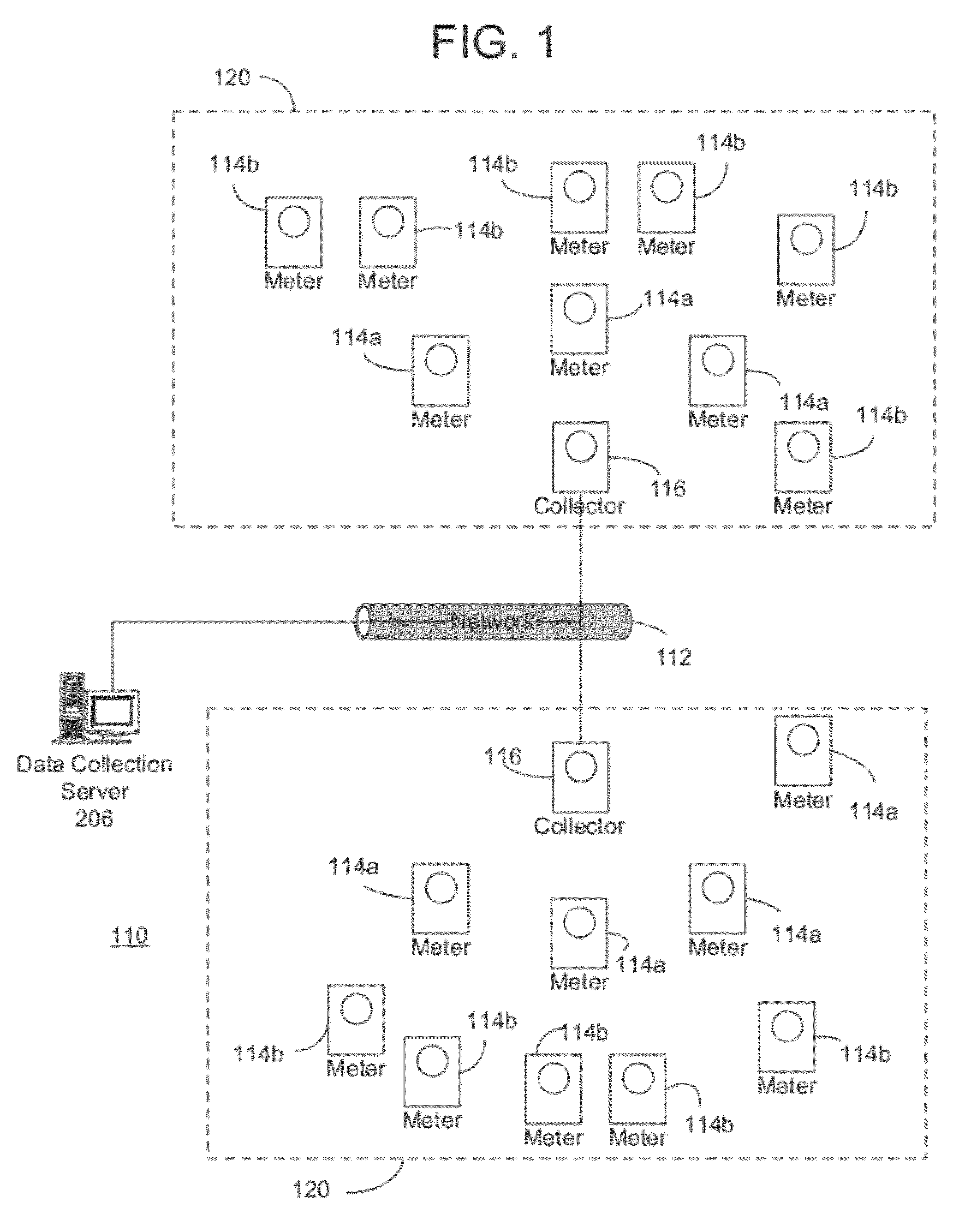

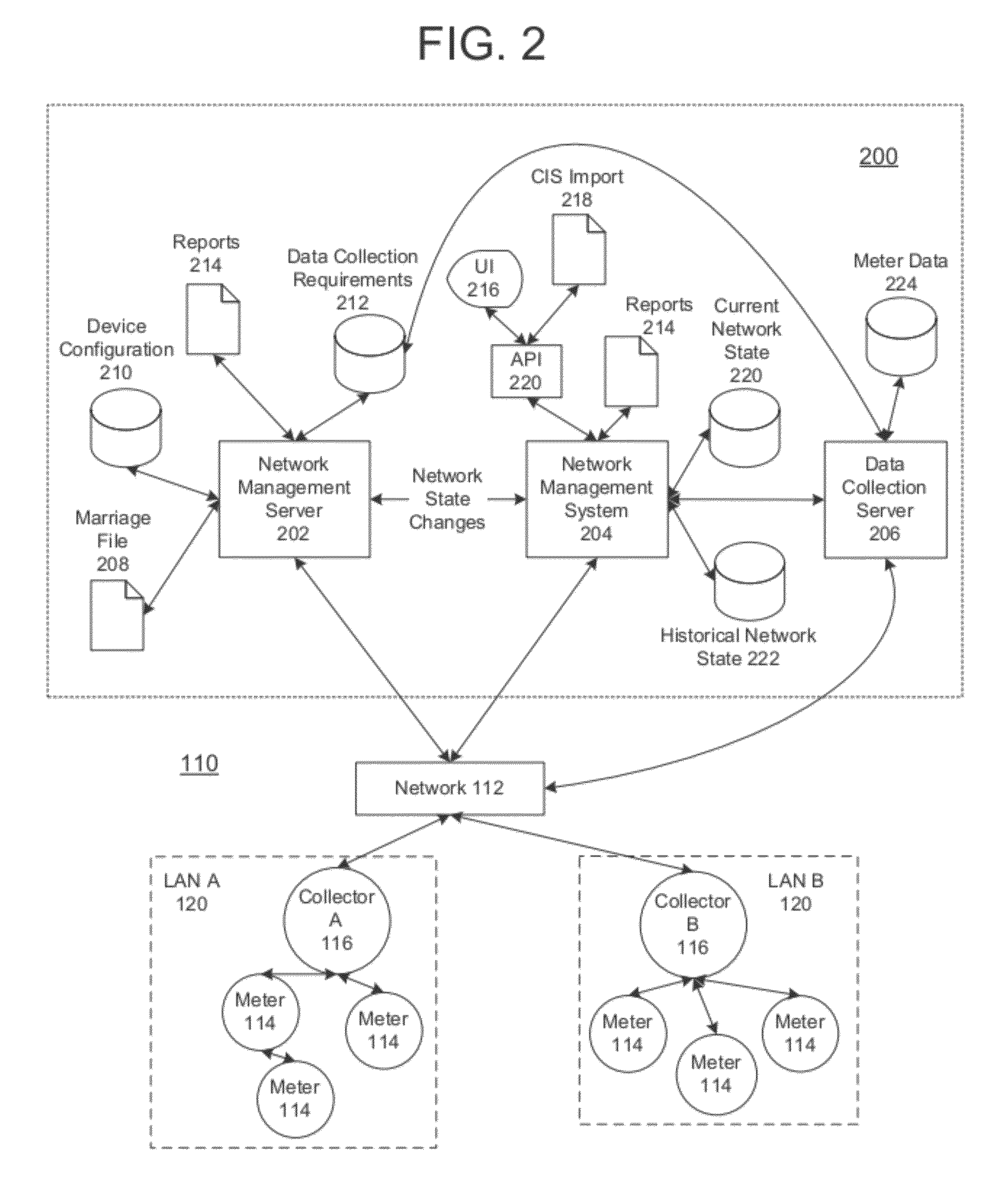

Virtual option board for use in performing metering operations

Methods, systems, and apparatus are provided for adding functionality to a metering device. A metering device may include a microcontroller (MCU) having separate blocks of memory for storing different types of data. The MCU may store main program code as firmware in one block of the flash memory, while also storing a virtual option board as firmware in a separate block of flash memory. The main program code may be used by the metering device to implement a base level of functionality in the metering device. The virtual option board may be used by the metering device to implement additional functionality. The functionality added by the virtual option board may include customer-specific metering operations and / or market-specific metering operations.

Owner:ELSTER SOLUTIONS

Fail-over of multiple memory blocks in multiple memory modules in computer system

InactiveUS20040073829A1Error detection/correctionEmergency protective arrangements for automatic disconnectionFailoverMemory address

A computer system has a memory controller for controlling accesses to multiple memory modules, each having multiple memory blocks, and a fail-over circuit for failing-over individual memory blocks from multiple memory modules. The digital information stored in an individual memory block that has experienced memory errors in excess of a permissible threshold is copied to an auxiliary memory location. The memory accesses directed to the failed-over memory block are intercepted and redirected to the auxiliary memory location. Tags are stored to identify failed-over memory modules and corresponding auxiliary memory modules, so a tag look-up for an accessed memory address can generate a hit signal when the memory access is to a failed-over memory module and cause the auxiliary memory module to respond to the memory access.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP