Patents

Literature

117 results about "Internal RAM" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Internal RAM, or IRAM, is the address range of RAM that is internal to the CPU. Some object files contain an .iram section. Generally, IRAM is composed of very high speed SRAM located alongside of the CPU. It acts similar to a CPU cache, but is software addressable. This saves transistors and power, and is potentially much faster, but forces programmers to specifically allocate it in order to benefit. In contrast, cache is invisible to the programmer.

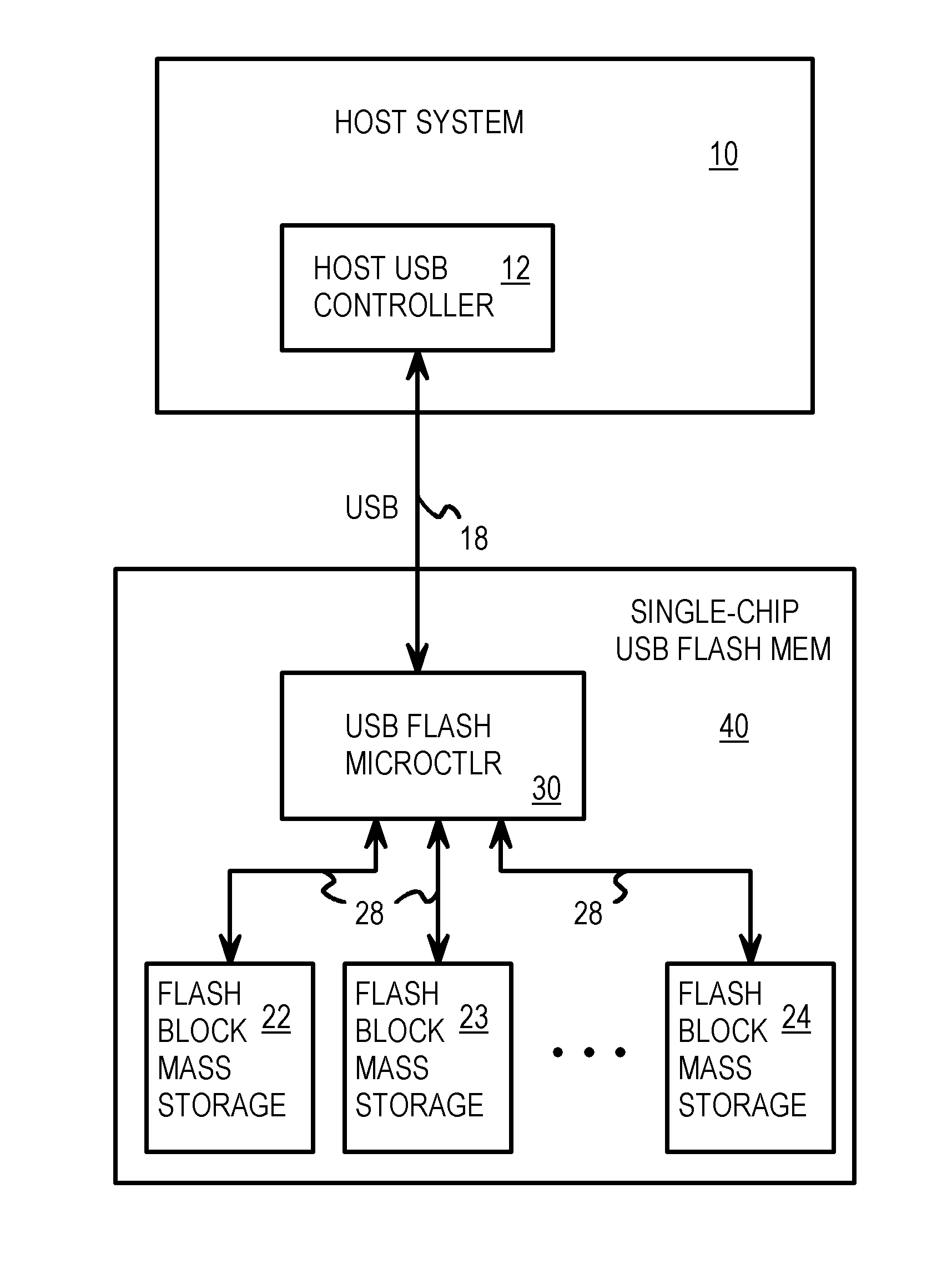

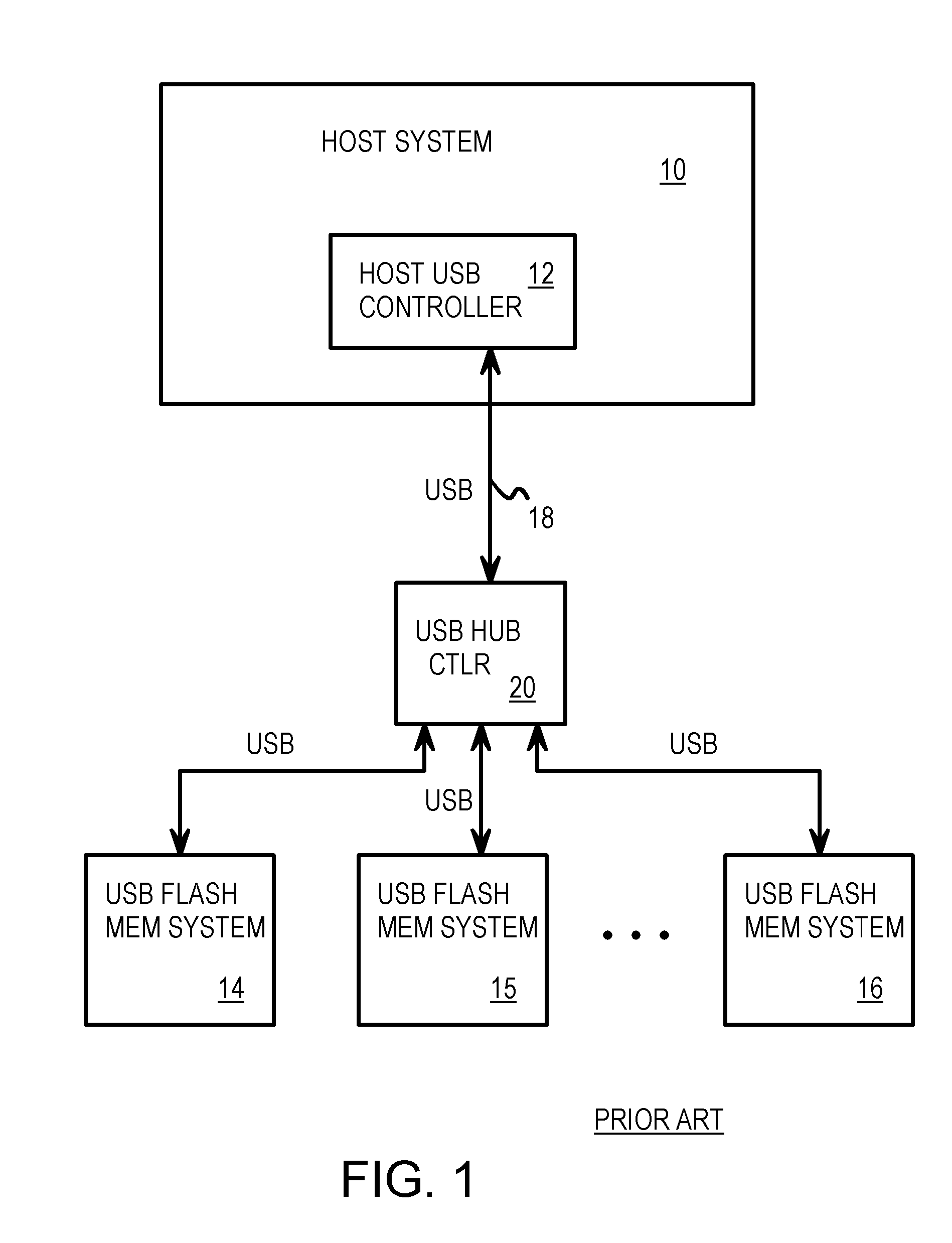

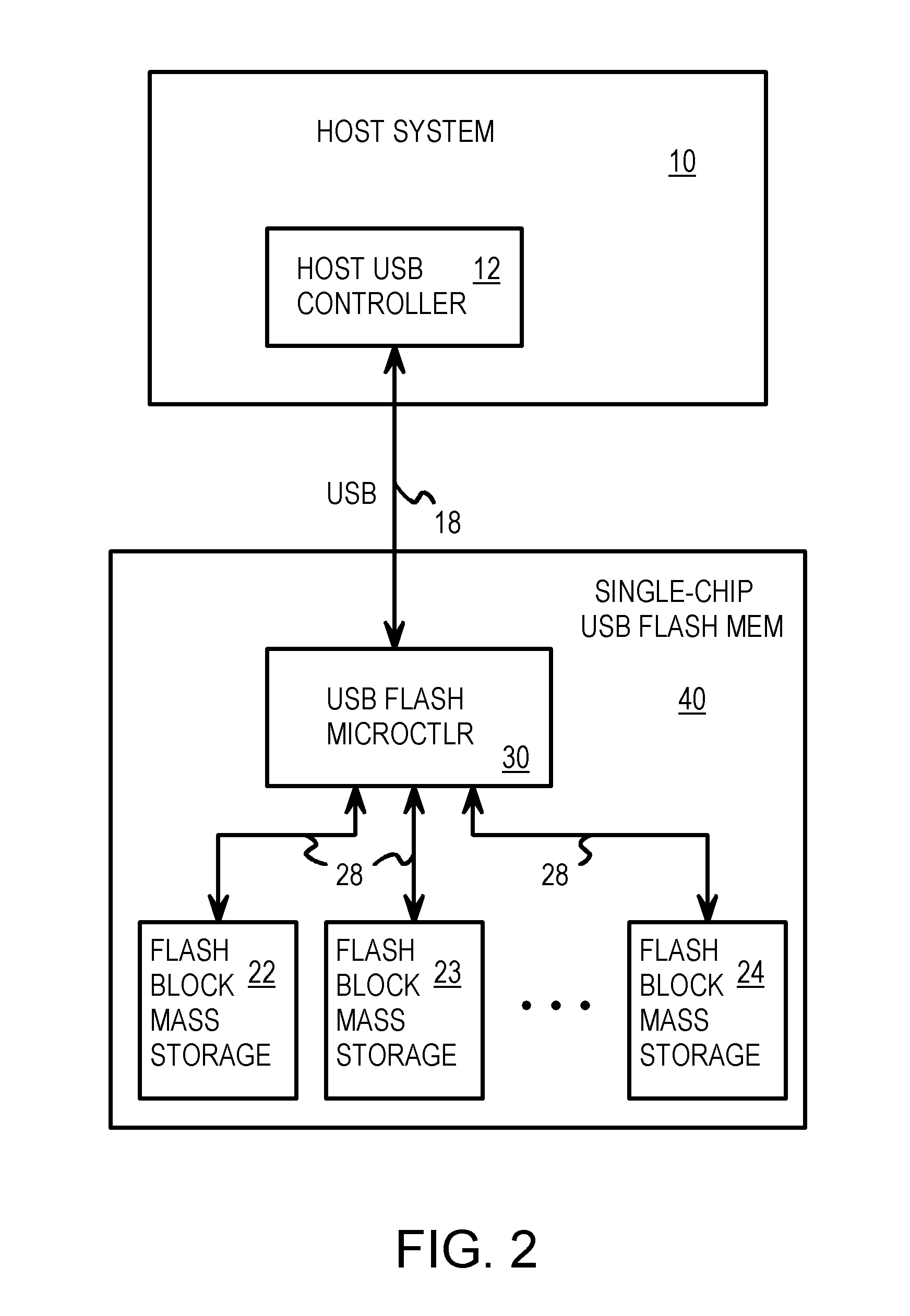

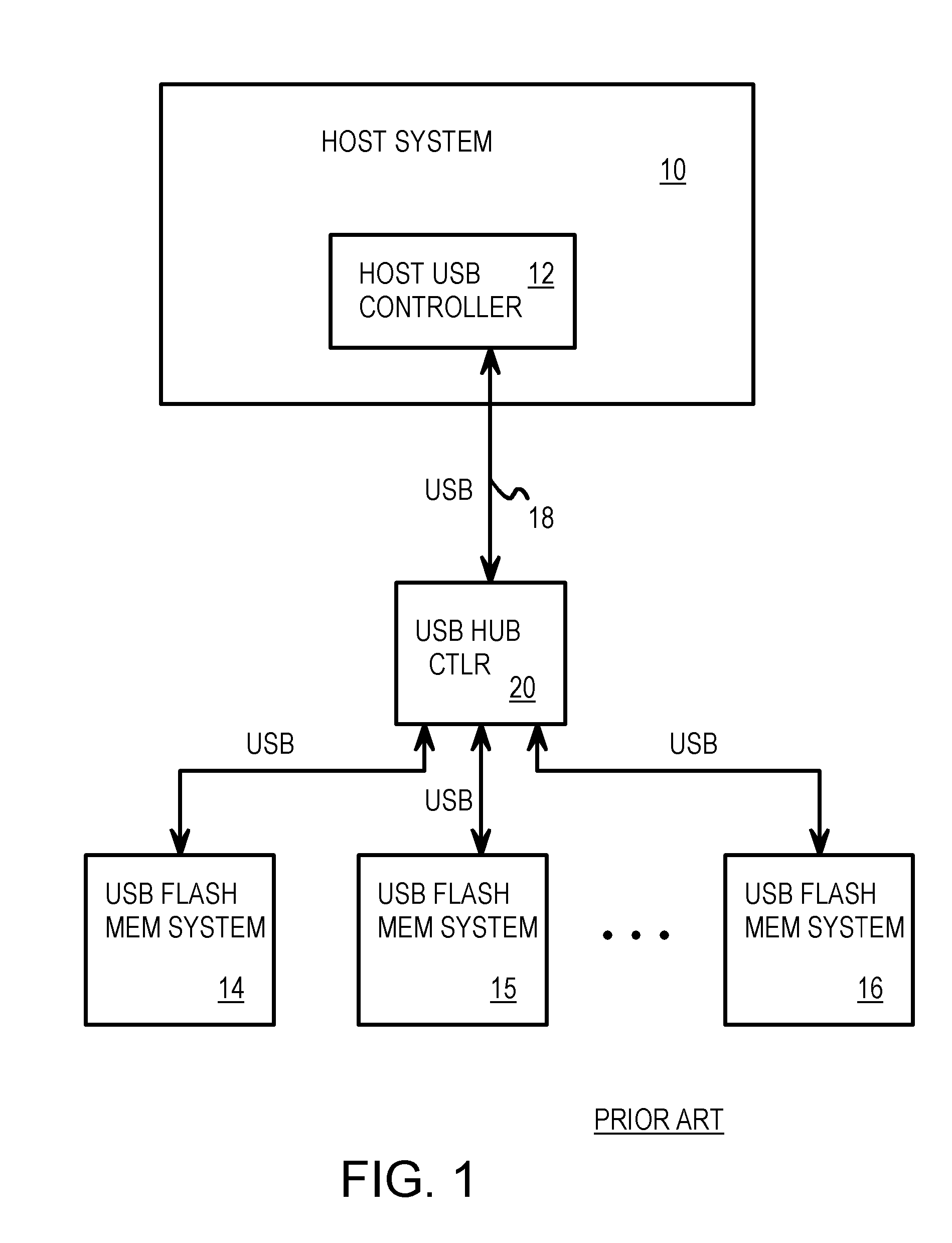

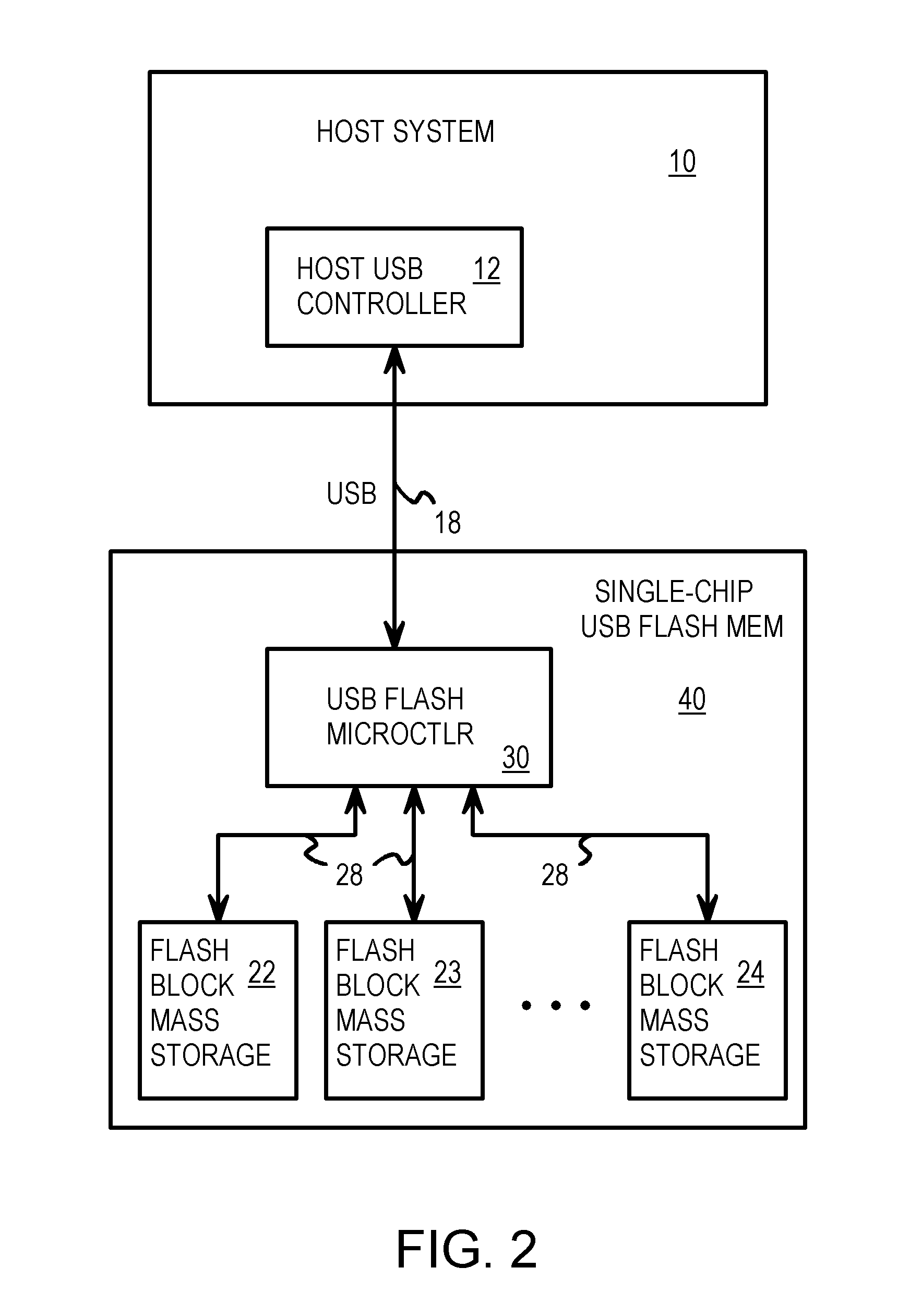

Single-Chip USB Controller Reading Power-On Boot Code from Integrated Flash Memory for User Storage

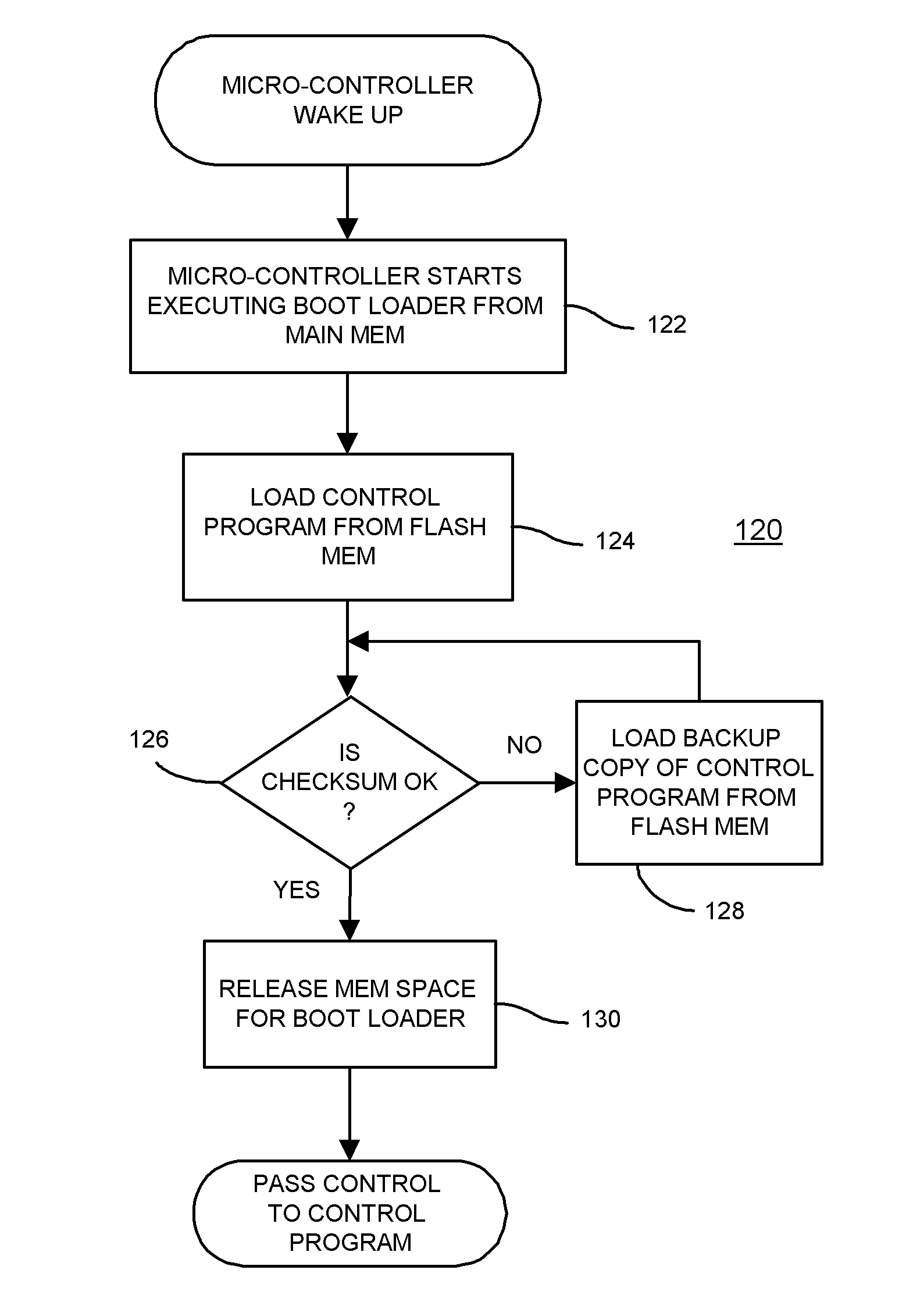

A Universal-Serial-Bus (USB) single-chip flash device contains a USB flash microcontroller and flash mass storage blocks containing flash memory arrays that are block-addressable rather than randomly-addressable. USB packets from a host USB bus are read by a serial engine on the USB flash microcontroller. Various routines that execute on a CPU in the USB flash microcontroller are activated in response to commands in the USB packets. A flash-memory controller in the USB flash microcontroller transfers data from the serial engine to the flash mass storage blocks for storage. Rather than boot from an internal ROM coupled to the CPU, a boot loader is transferred by DMA from the first page of the flash mass storage block to an internal RAM. The flash memory is automatically read from the first page at power-on. The CPU then executes the boot loader from the internal RAM to load the control program.

Owner:SUPER TALENT TECH CORP

Single-chip USB controller reading power-on boot code from integrated flash memory for user storage

A Universal-Serial-Bus (USB) single-chip flash device contains a USB flash microcontroller and flash mass storage blocks containing flash memory arrays that are block-addressable rather than randomly-addressable. USB packets from a host USB bus are read by a serial engine on the USB flash microcontroller. Various routines that execute on a CPU in the USB flash microcontroller are activated in response to commands in the USB packets. A flash-memory controller in the USB flash microcontroller transfers data from the serial engine to the flash mass storage blocks for storage. Rather than boot from an internal ROM coupled to the CPU, a boot loader is transferred by DMA from the first page of the flash mass storage block to an internal RAM. The flash memory is automatically read from the first page at power-on. The CPU then executes the boot loader from the internal RAM to load the control program.

Owner:SUPER TALENT TECH CORP

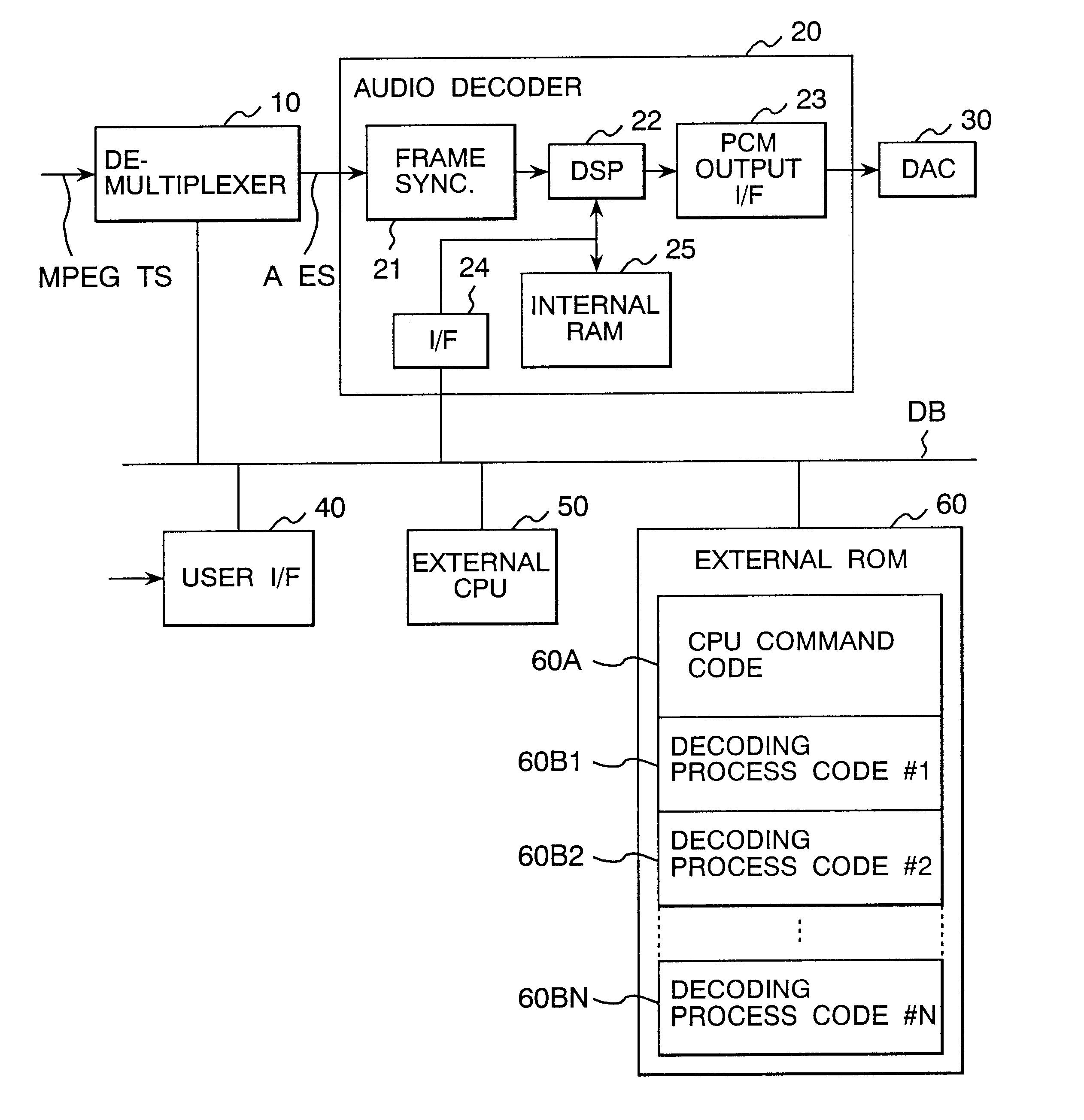

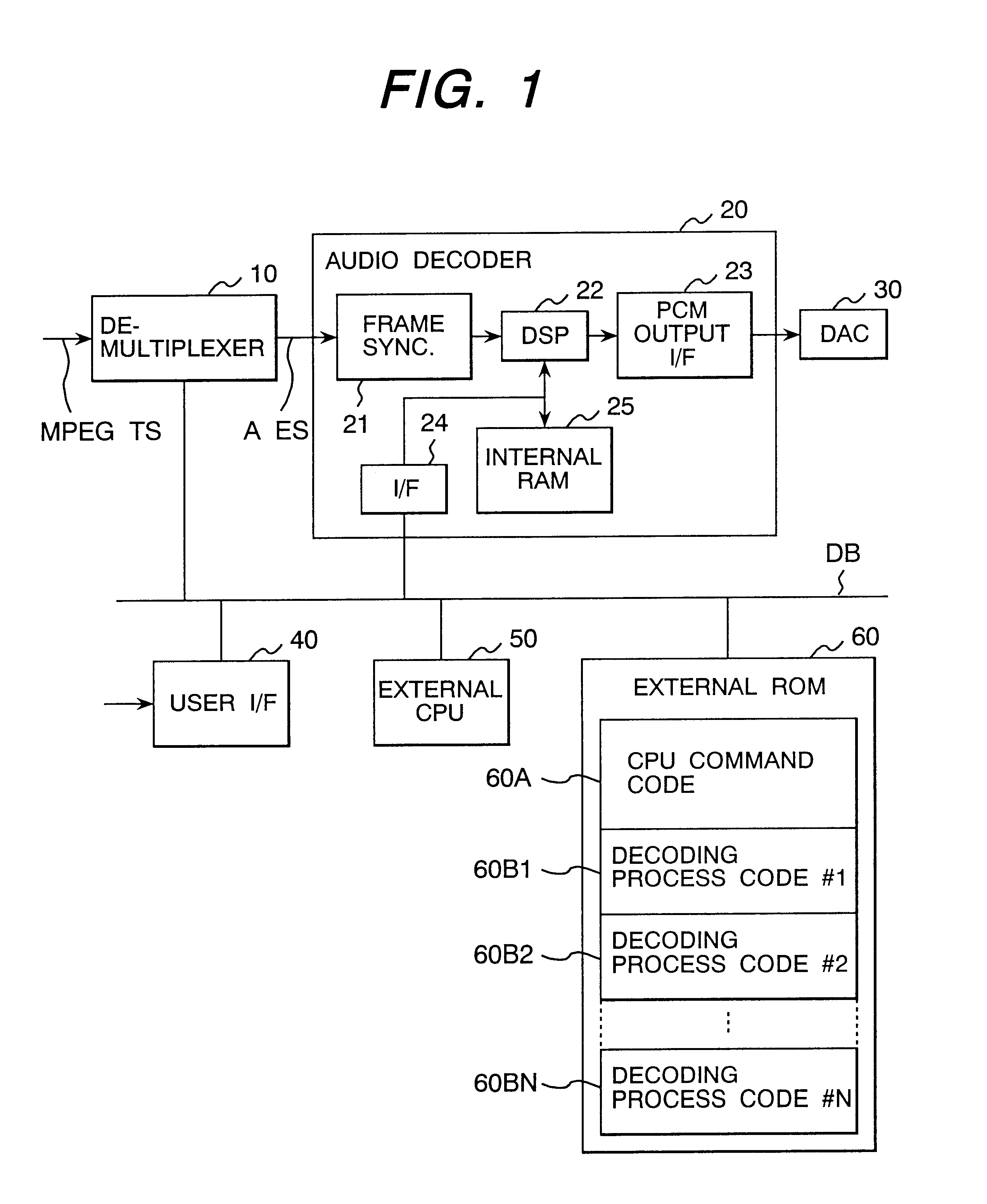

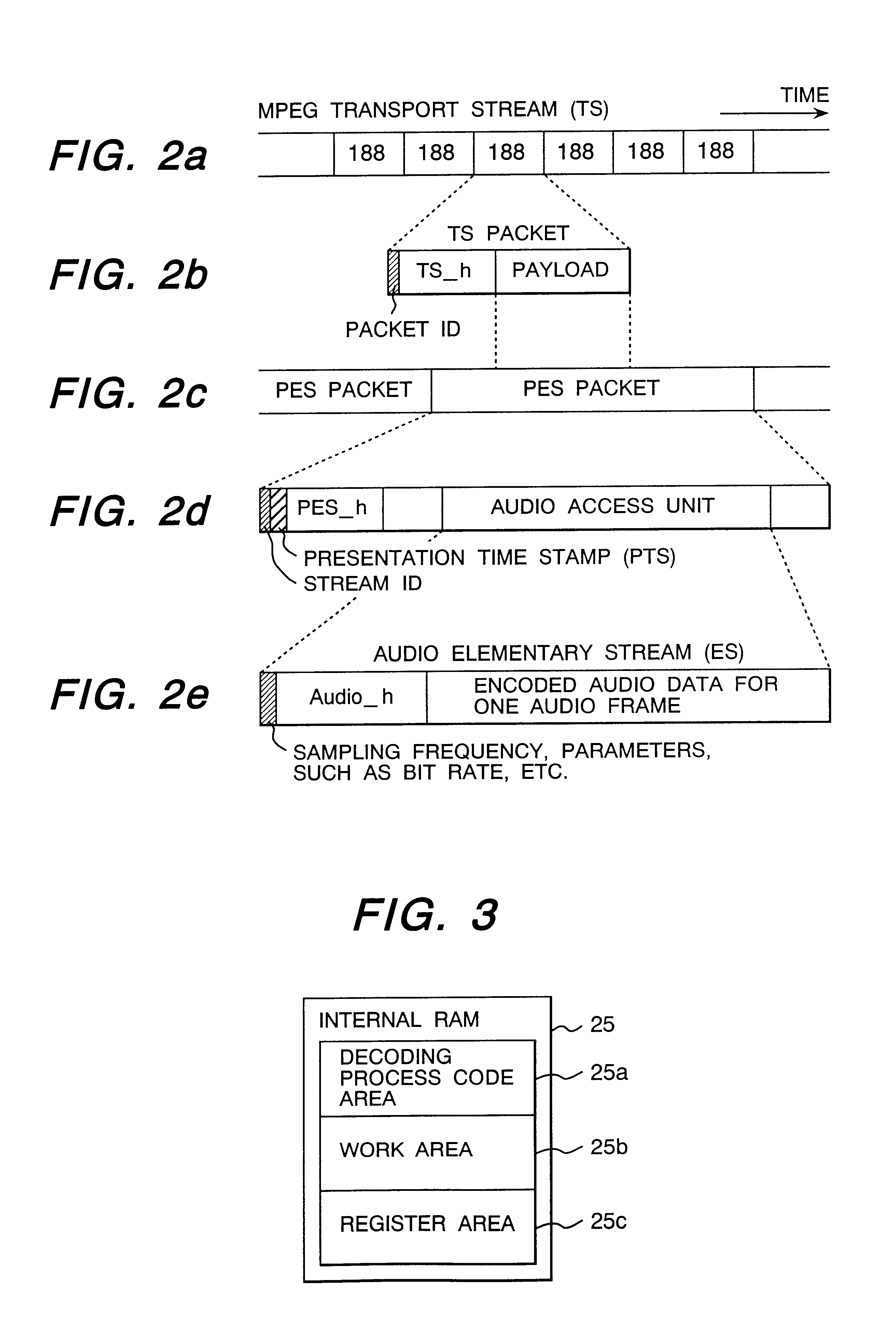

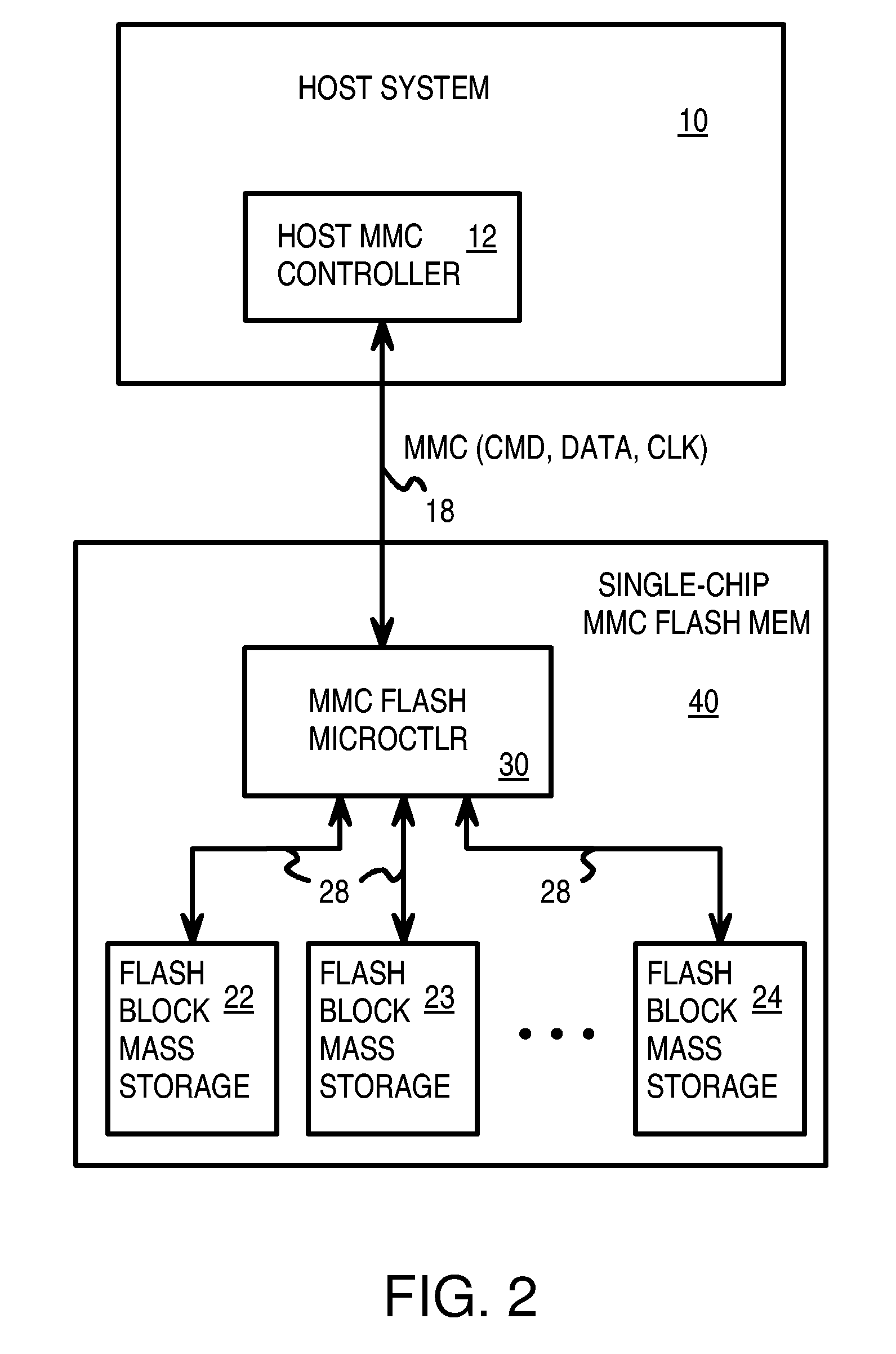

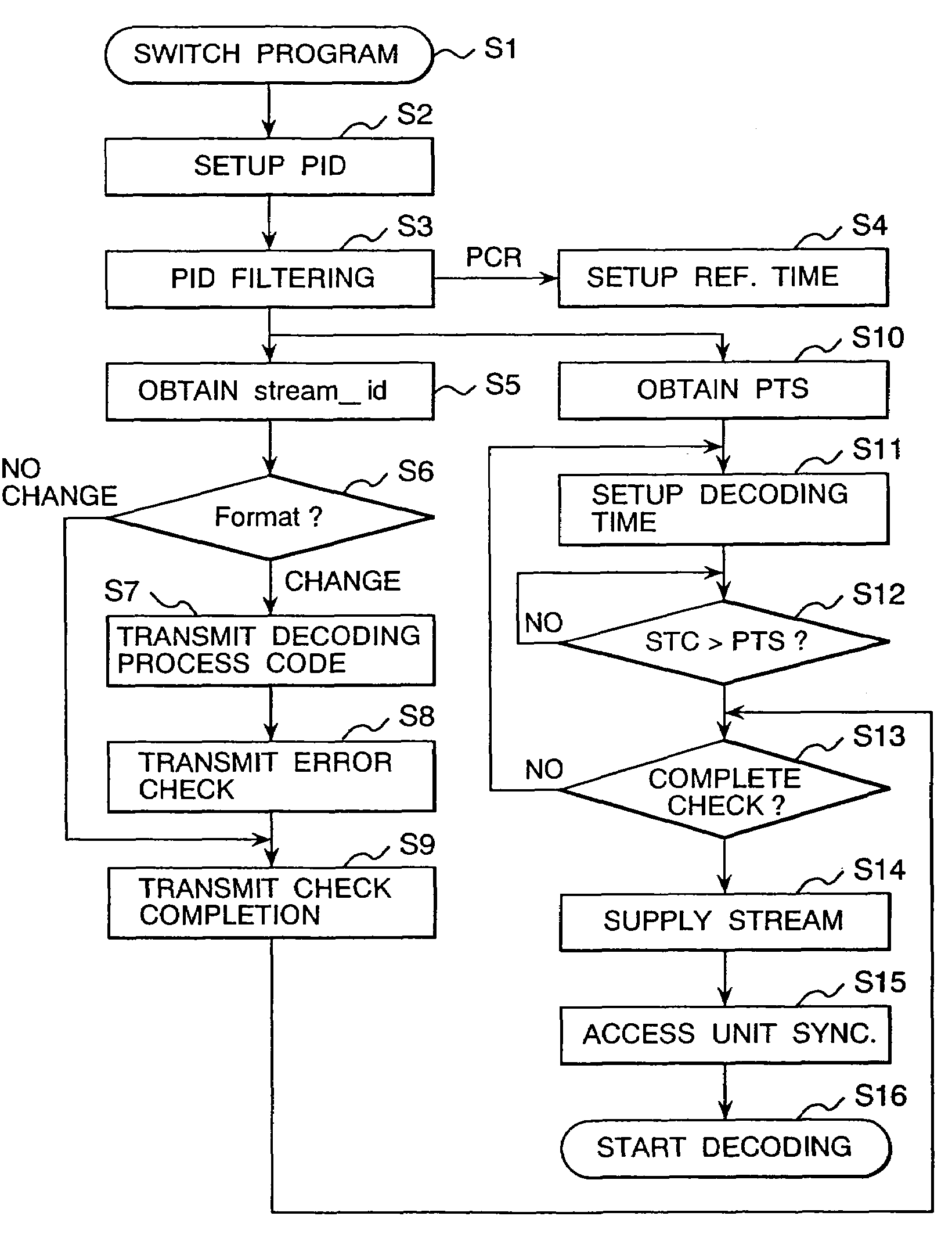

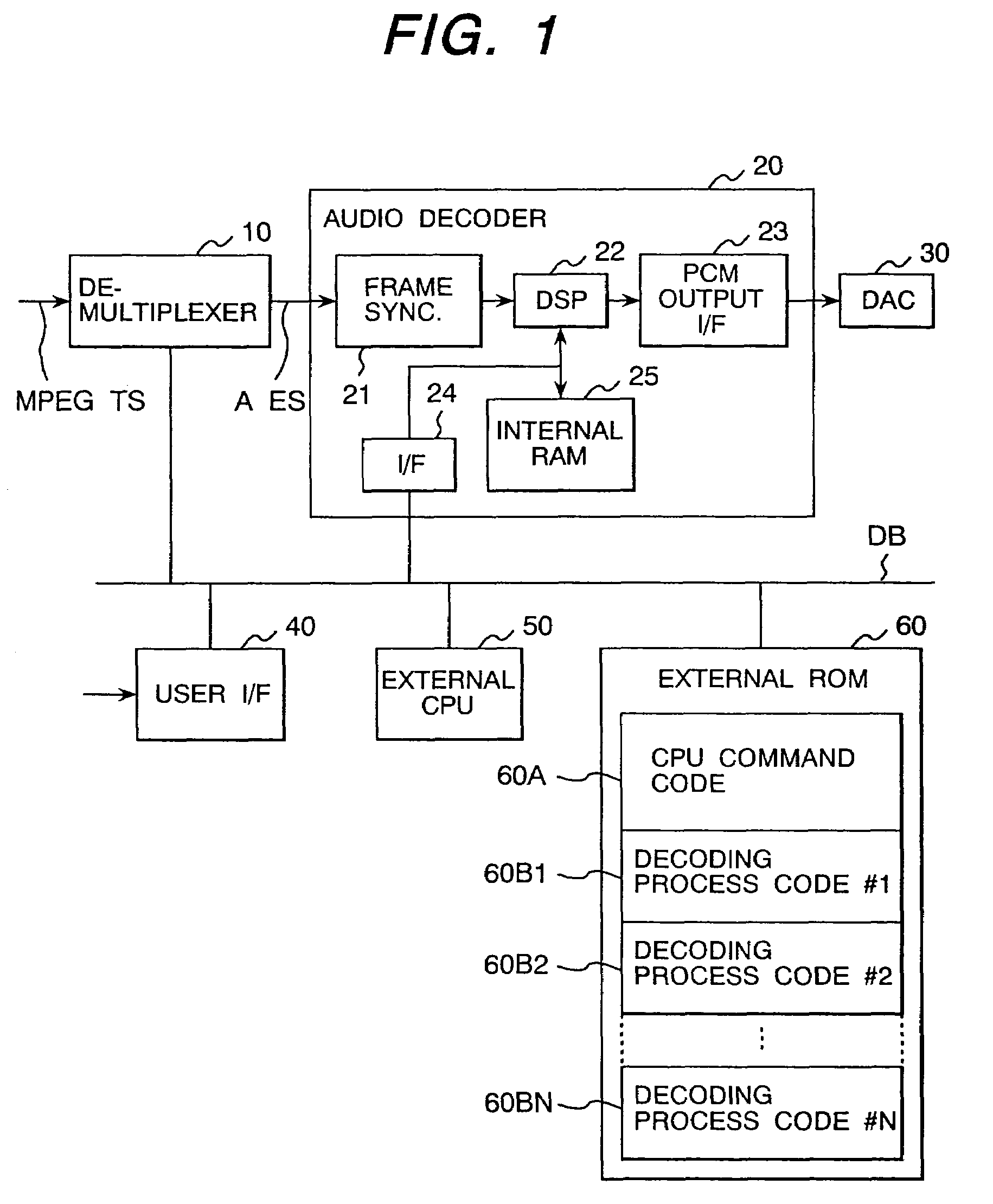

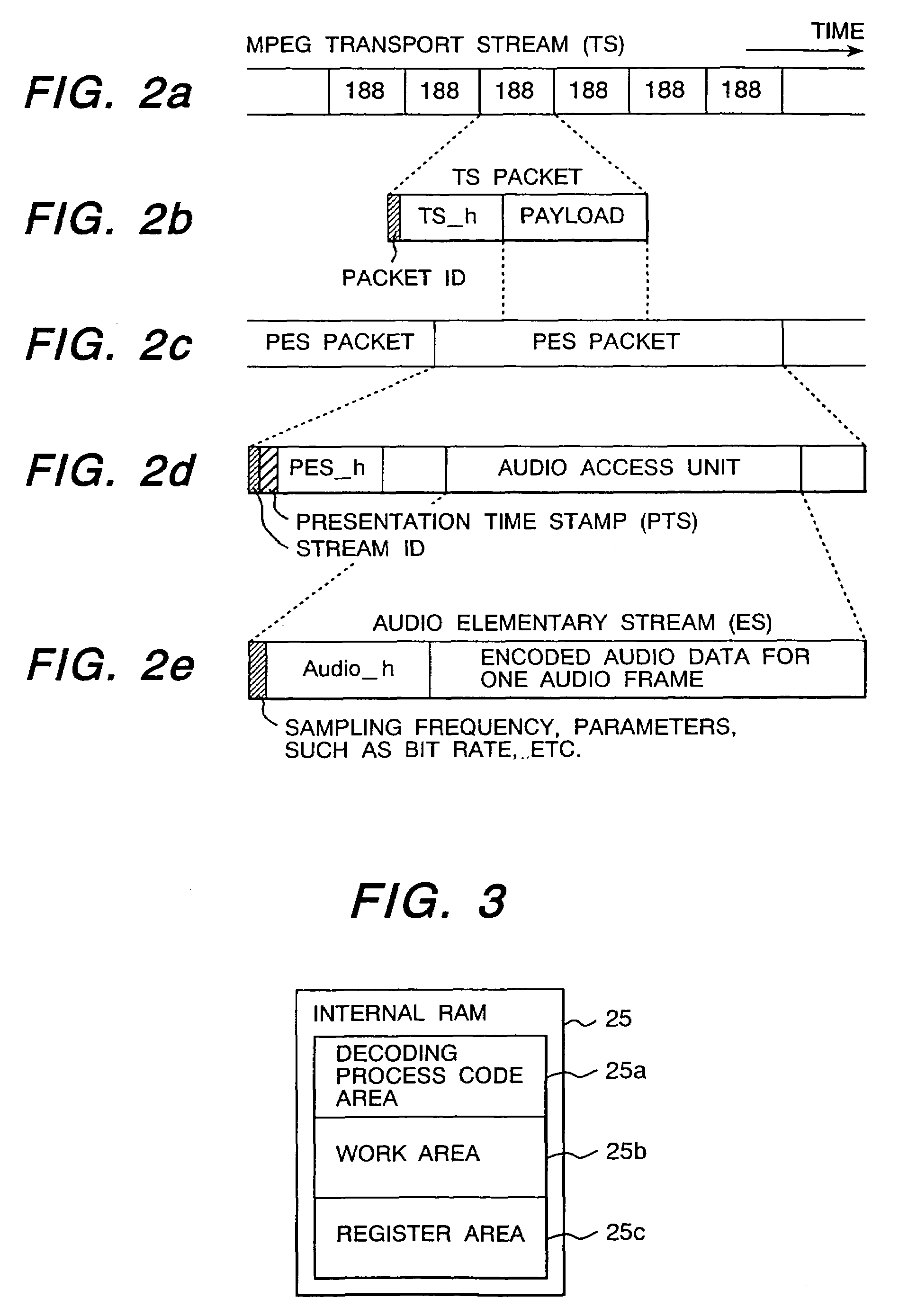

Multiplexed audio data decoding apparatus and receiver apparatus

InactiveUS6816491B1Interchange of the read-only memoryIncrease flexibilityTelevision system detailsPulse modulation television signal transmissionMultiplexingAudio frequency

A multiplexed audio data decoder apparatus is provided in which integration of an audio decoder is easy, and has a high flexibility when the number of the formats to be processed is increased or when the specification is changed. In an external ROM 60 there are accumulated a plurality of decoding program codes corresponding to respective plural methods for compressing and encoding. A controller means 50 transfers the decoding program code corresponding to the method for compressing and encoding after changing thereof, from the external ROM 60 to an internal RAM 25. A DSP 22 starts decoding processing by using the decoding program code which is transmitted into the internal RAM 25.

Owner:MAXELL HLDG LTD

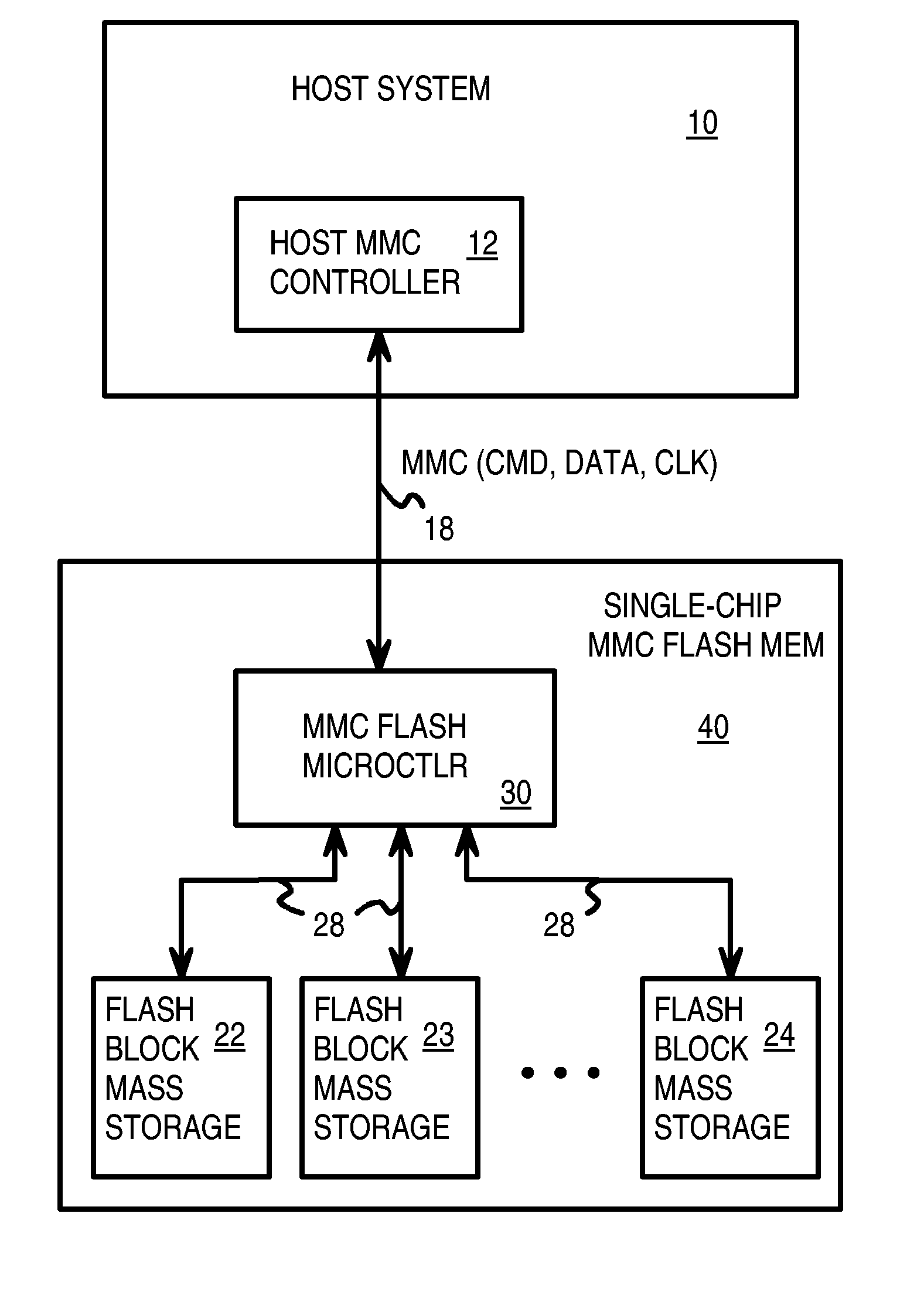

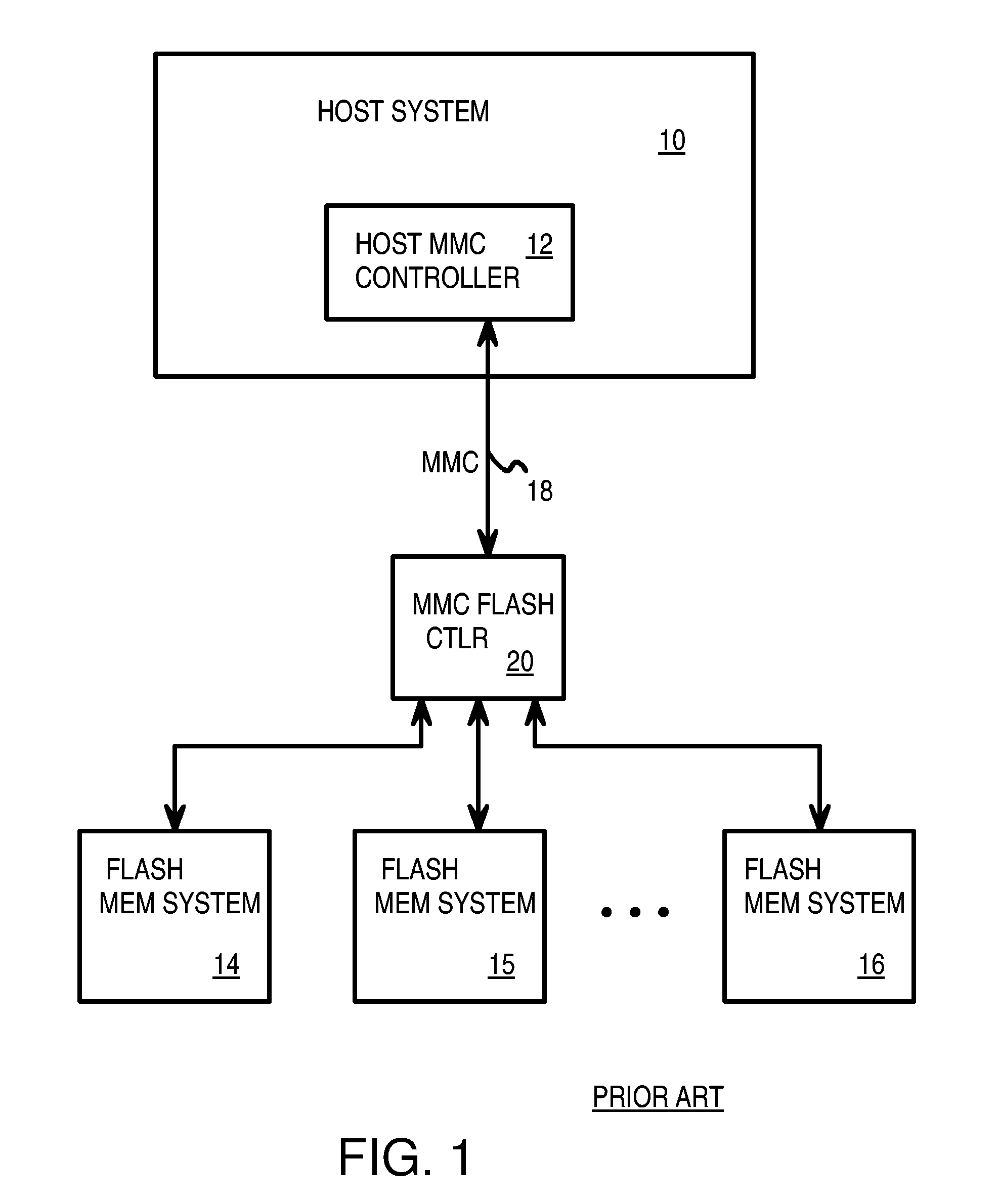

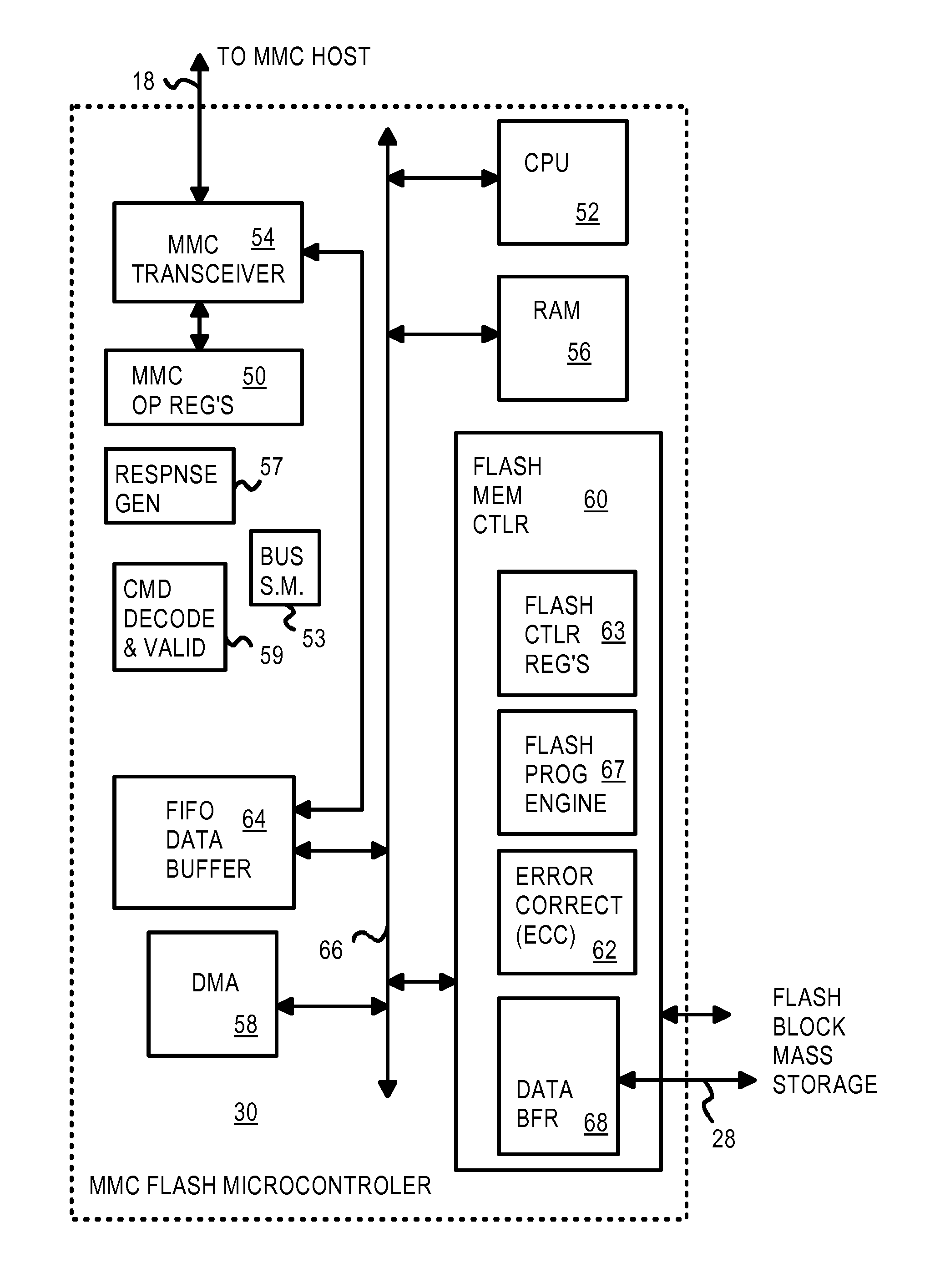

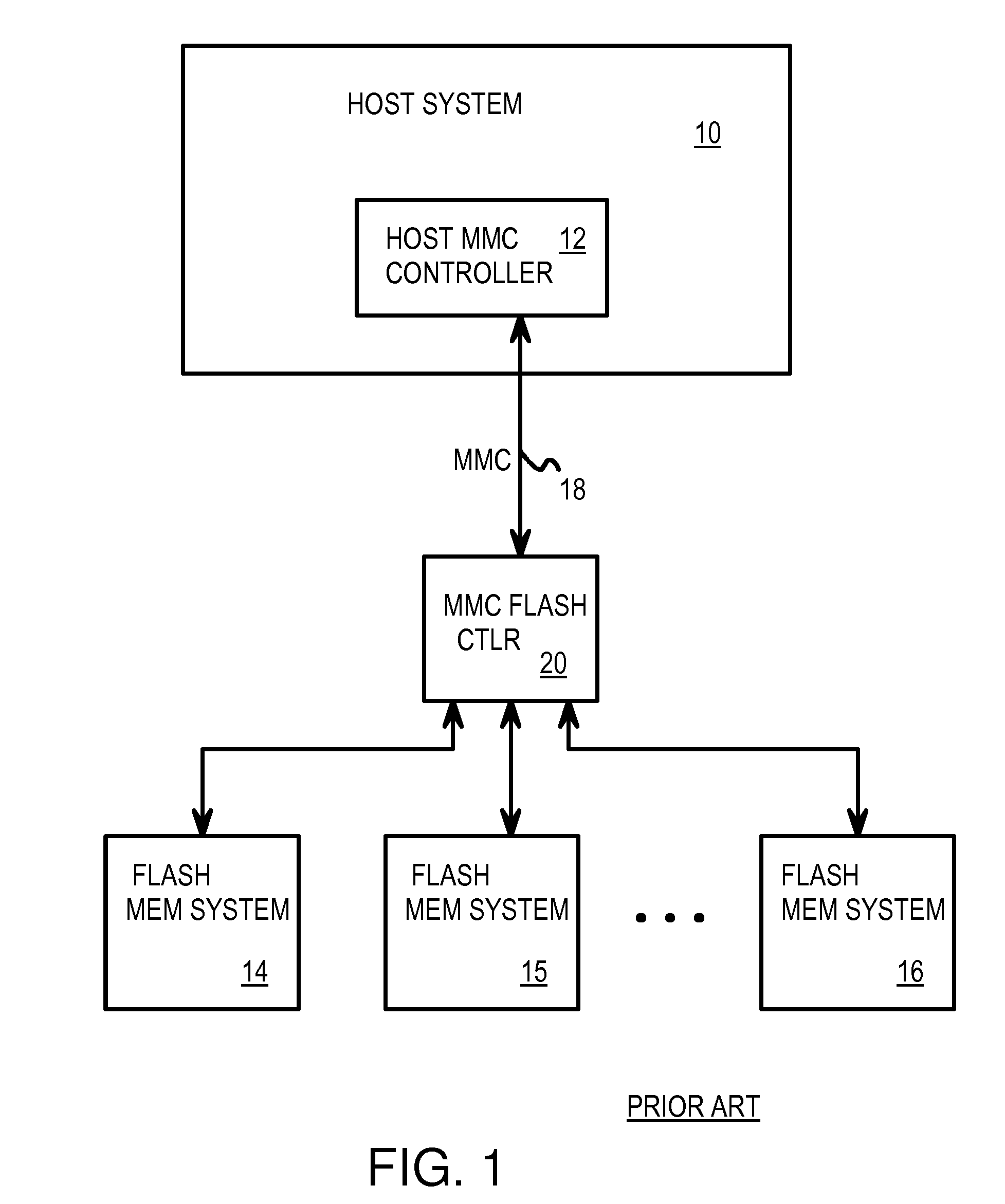

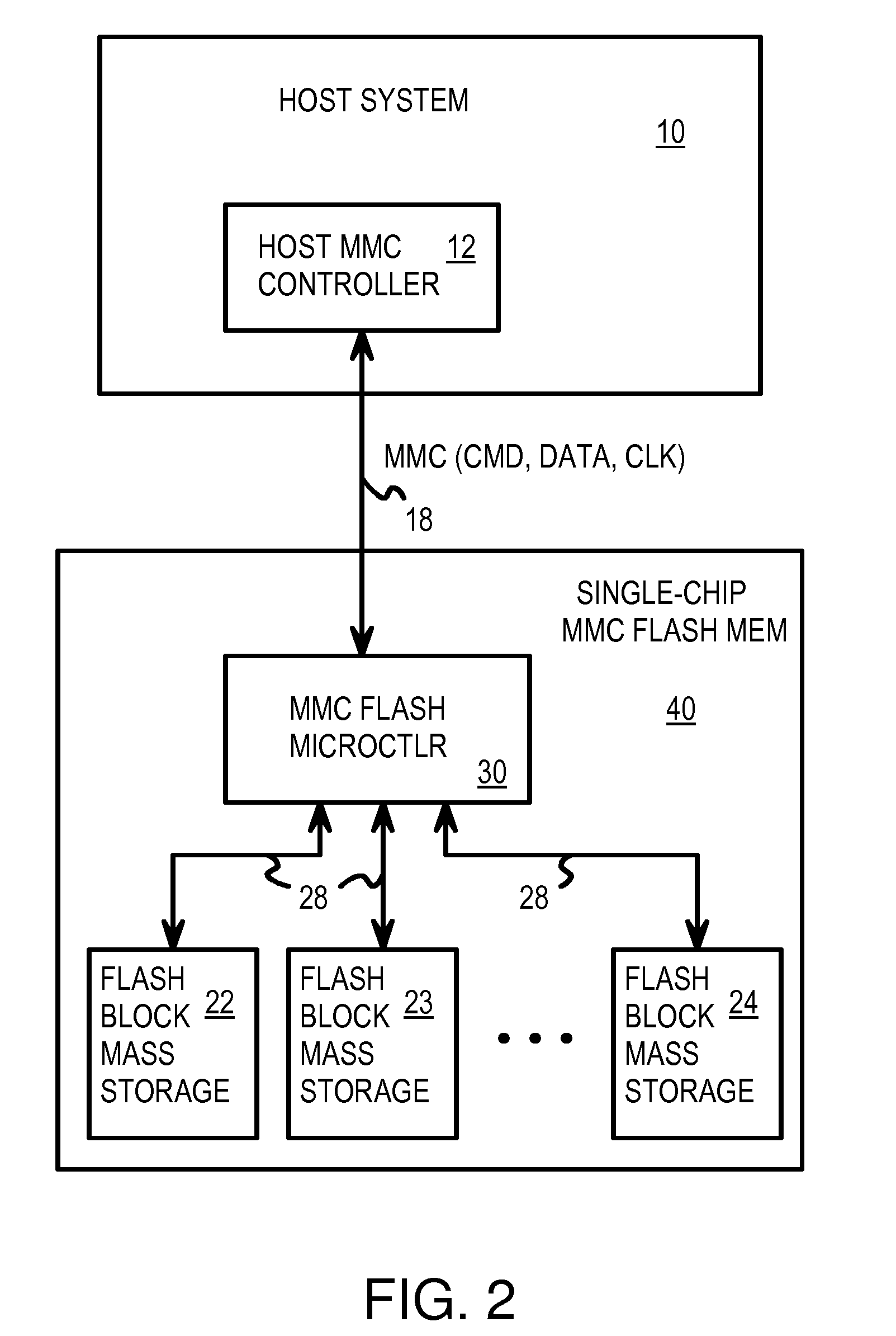

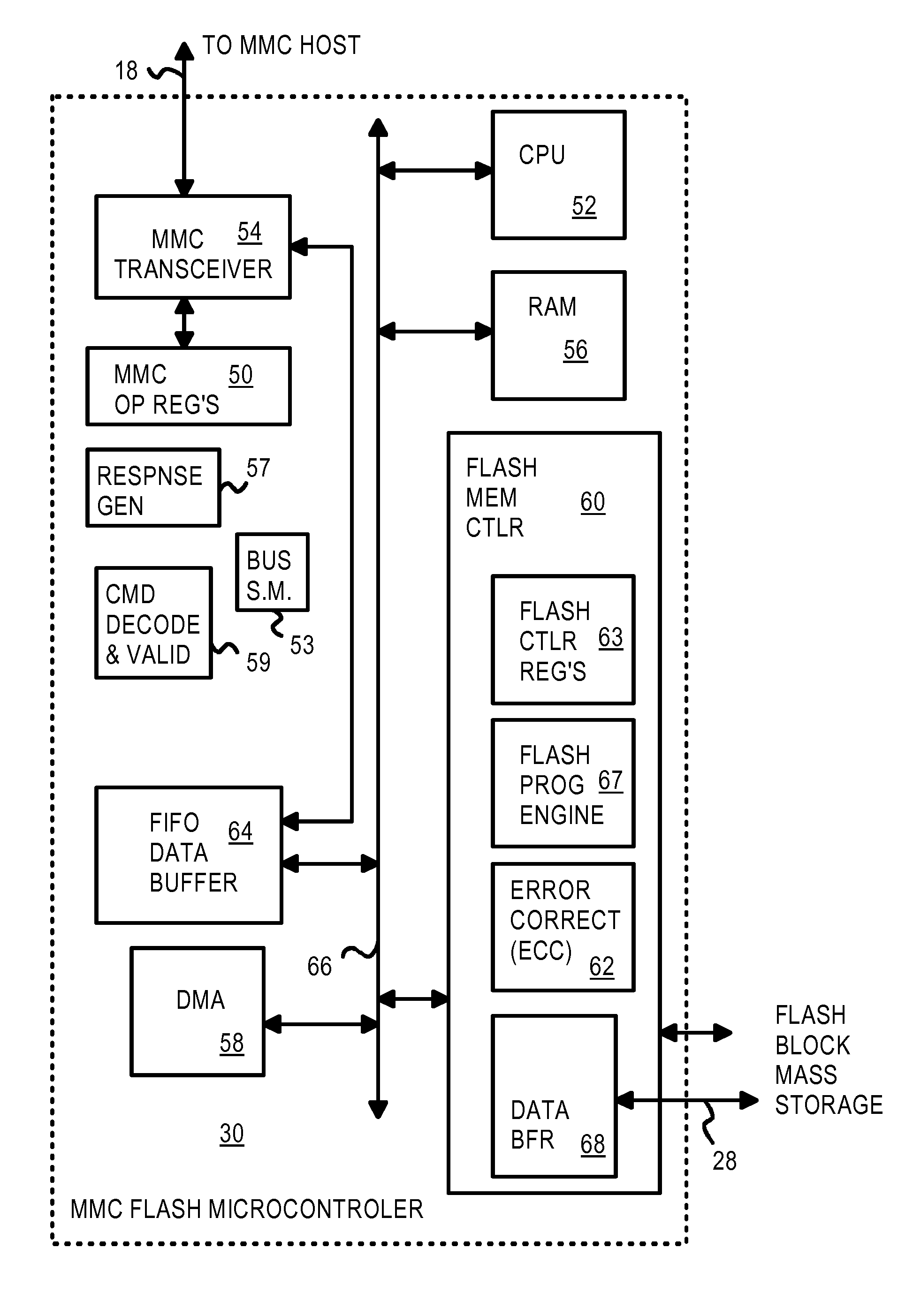

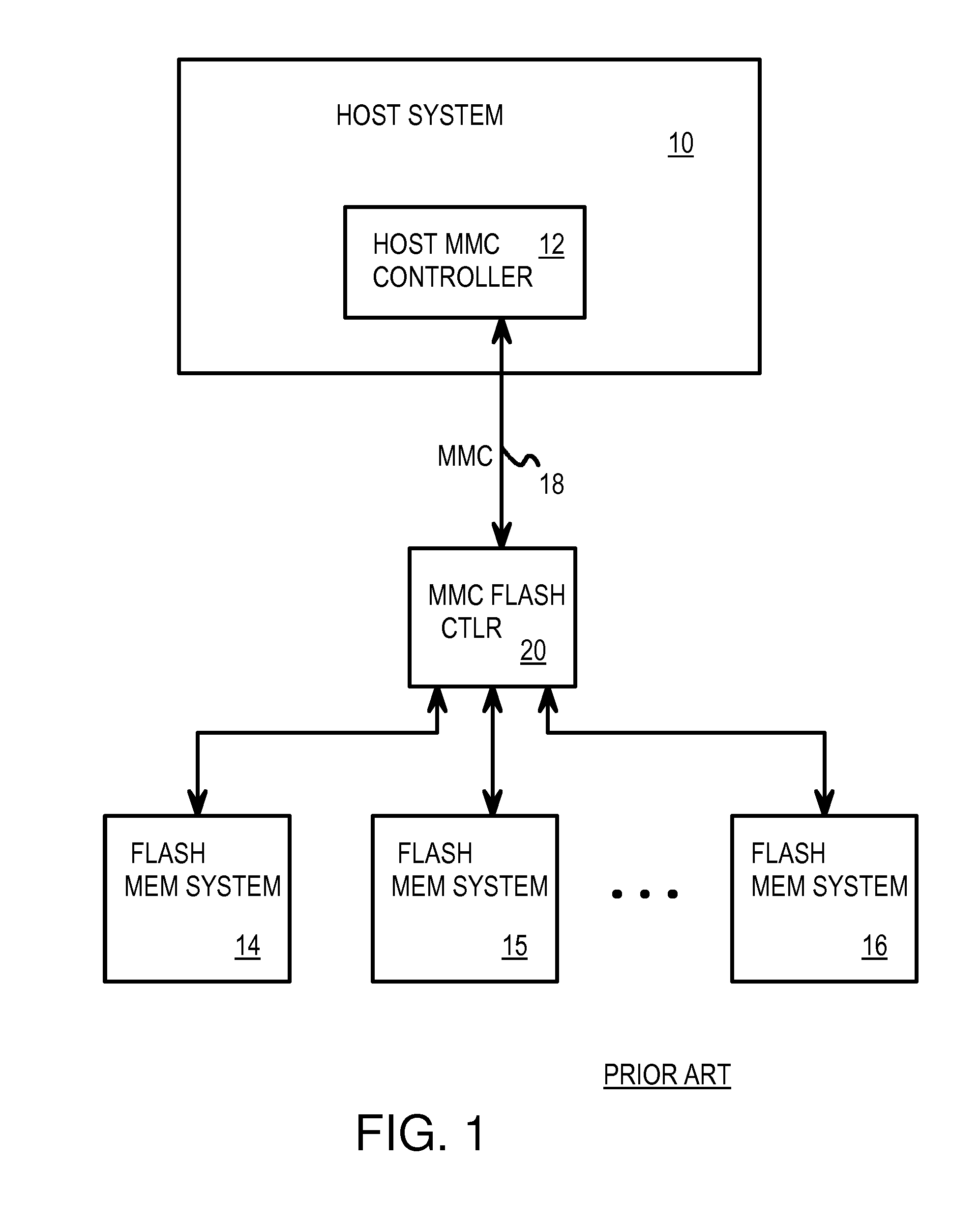

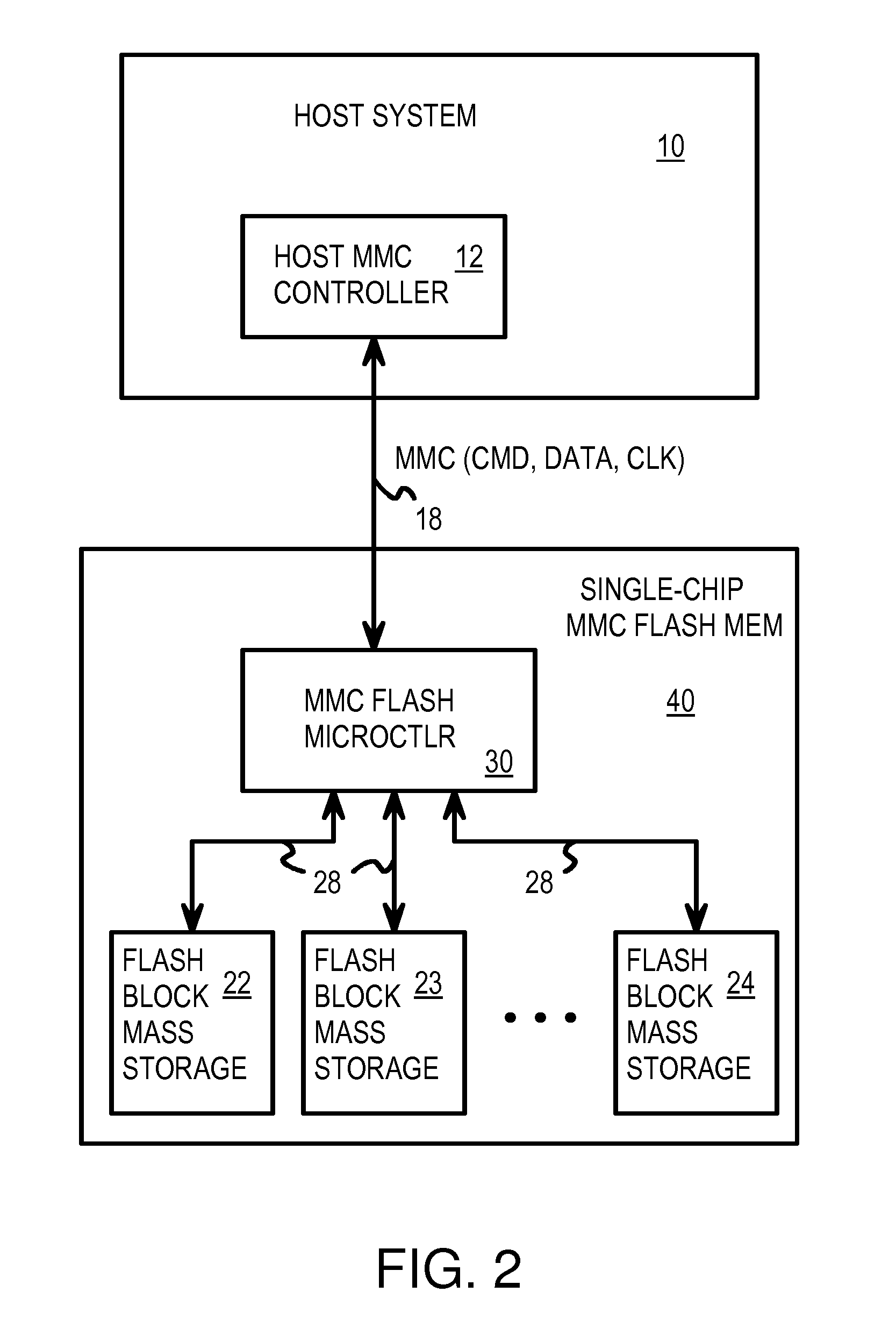

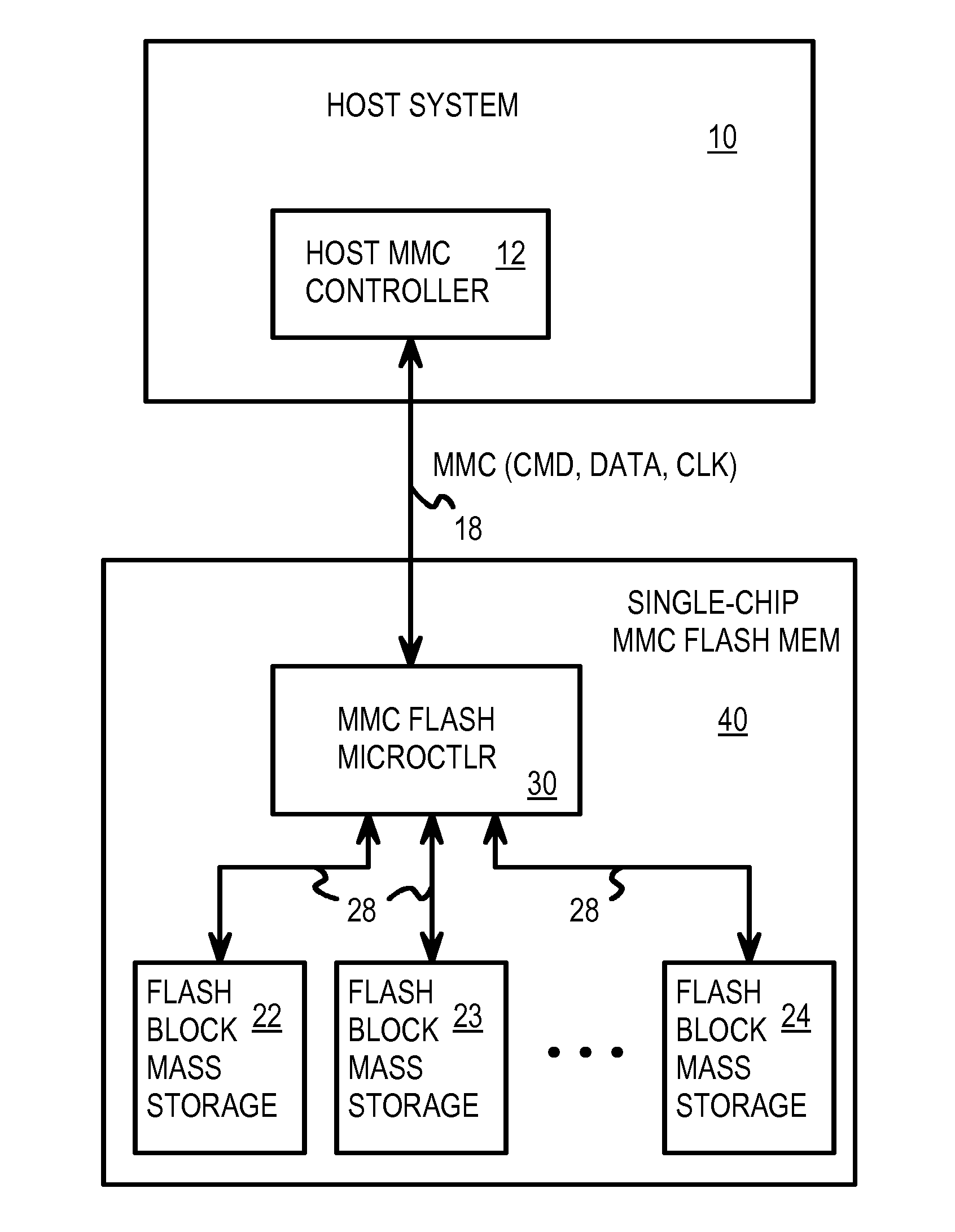

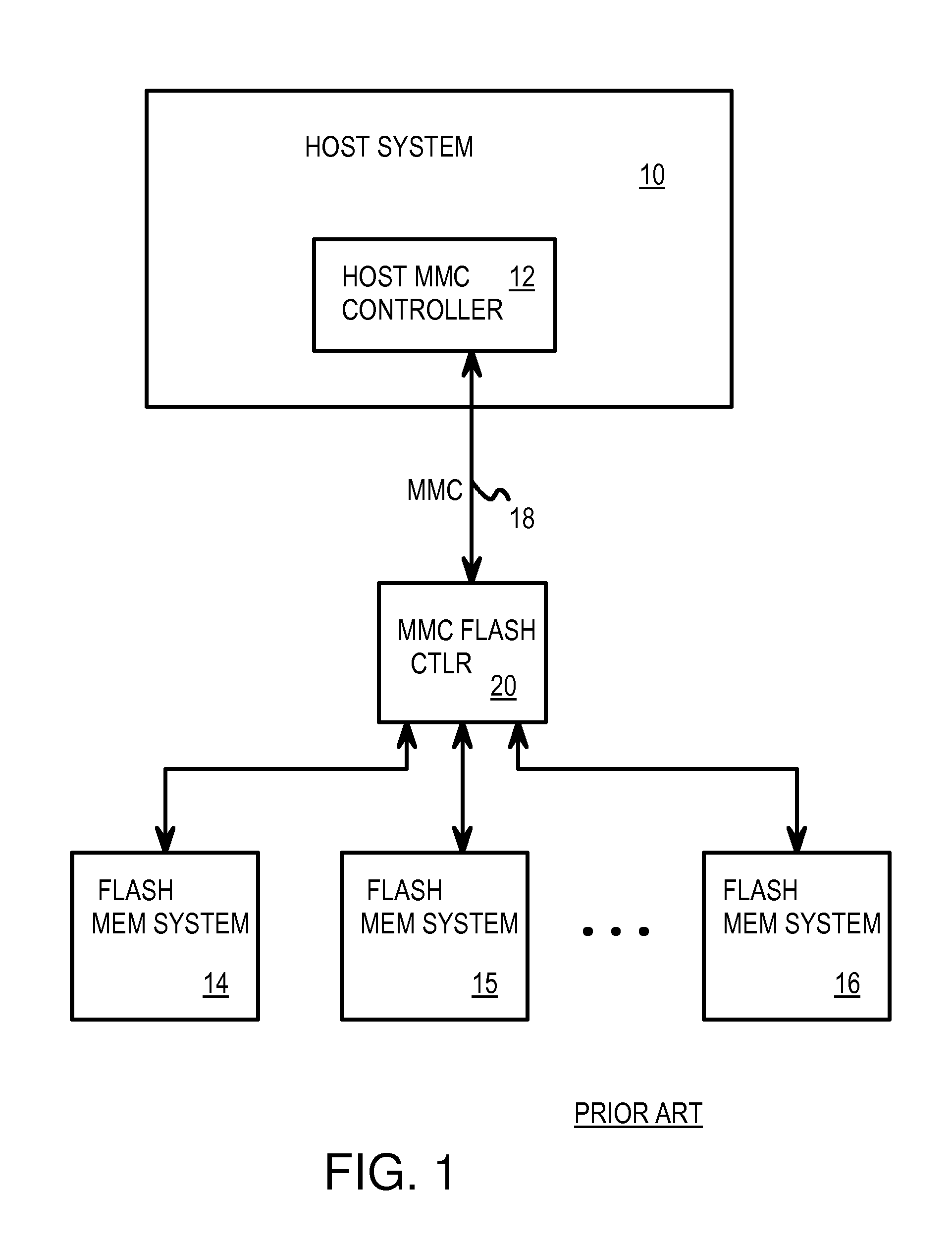

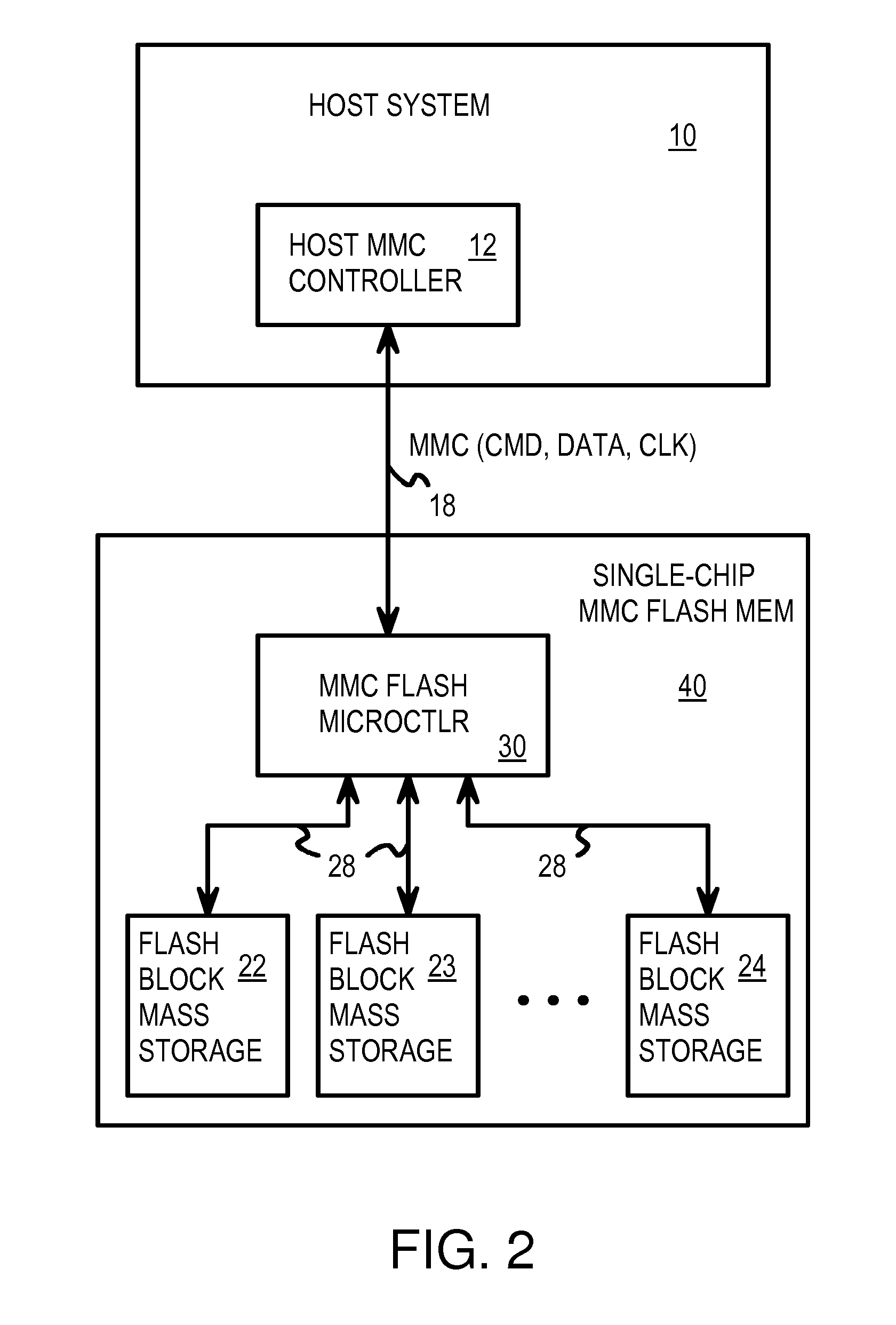

Single-Chip Multi-Media Card/Secure Digital (MMC/SD) Controller Reading Power-On Boot Code from Integrated Flash Memory for User Storage

A Multi-Media Card / Secure Digital (MMC / SD) single-chip flash device contains a MMC / SD flash microcontroller and flash mass storage blocks containing flash memory arrays that are block-addressable rather than randomly-addressable. MMC / SD transactions from a host MMC / SD bus are read by a bus transceiver on the MMC / SD flash microcontroller. Various routines that execute on a CPU in the MMC / SD flash microcontroller are activated in response to commands in the MMC / SD transactions. A flash-memory controller in the MMC / SD flash microcontroller transfers data from the bus transceiver to the flash mass storage blocks for storage. Rather than boot from an internal ROM coupled to the CPU, a boot loader is transferred by DMA from the first page of the flash mass storage block to an internal RAM. The flash memory is automatically read from the first page at power-on. The CPU then executes the boot loader from the internal RAM to load the control program.

Owner:SUPER TALENT TECH CORP

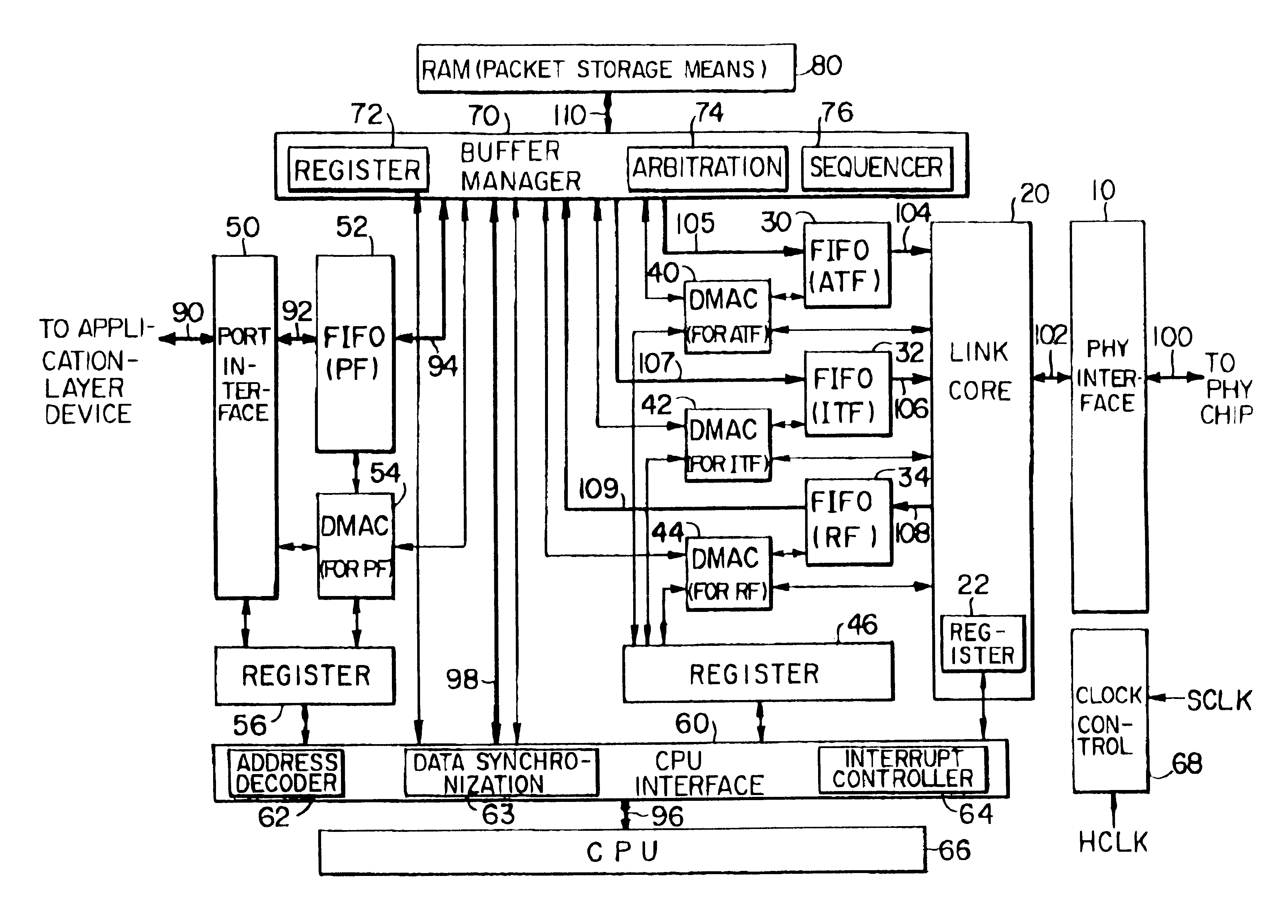

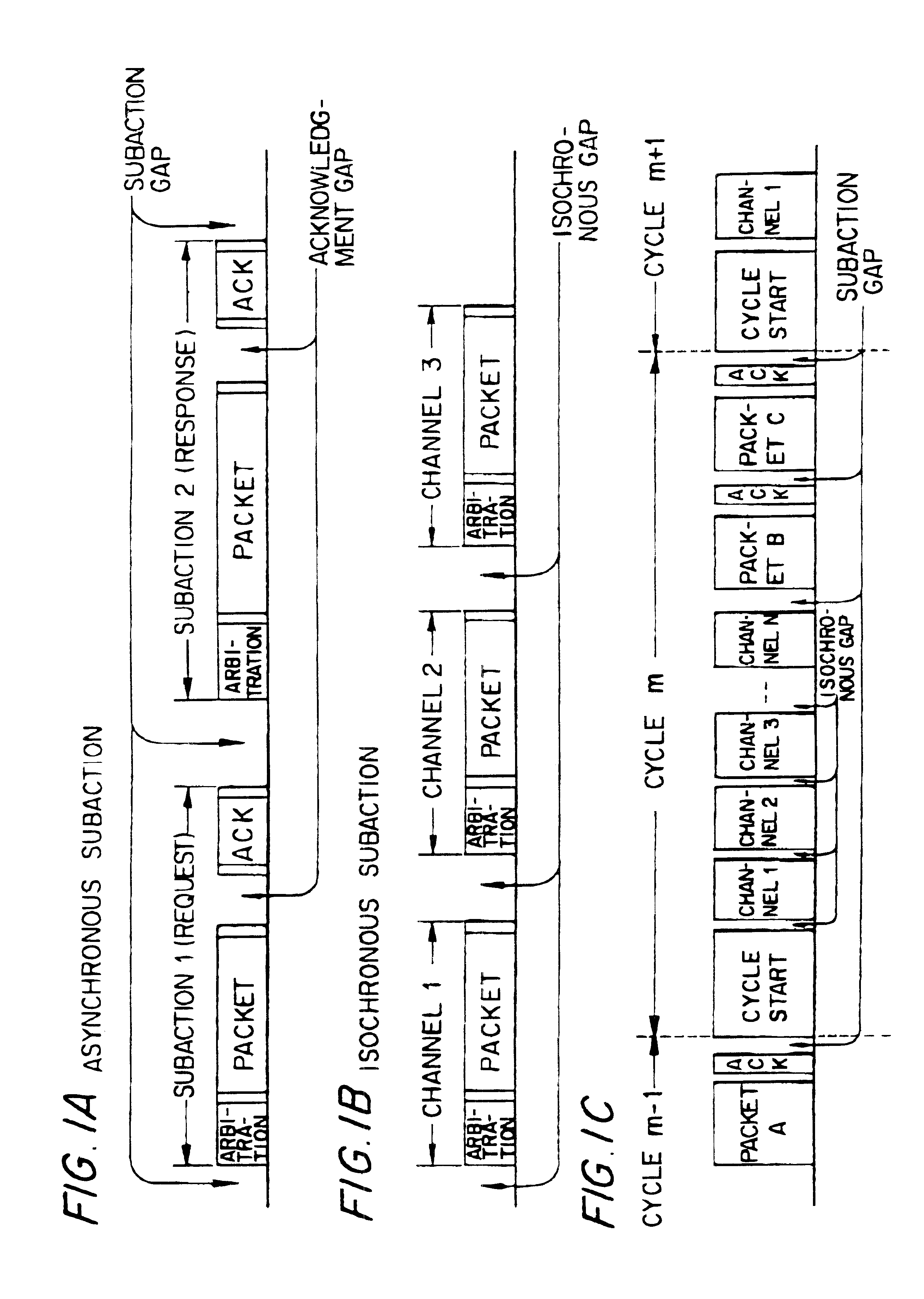

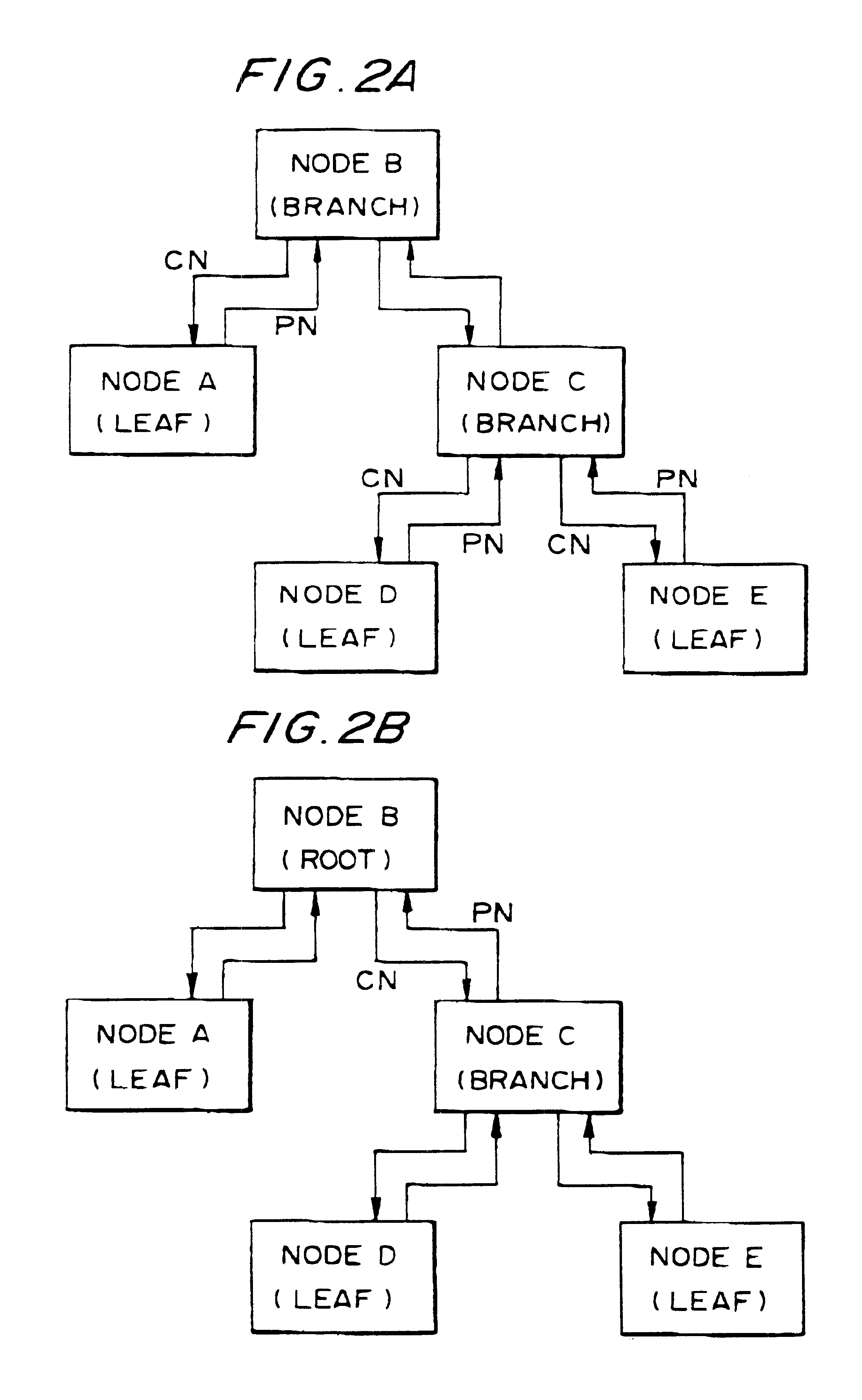

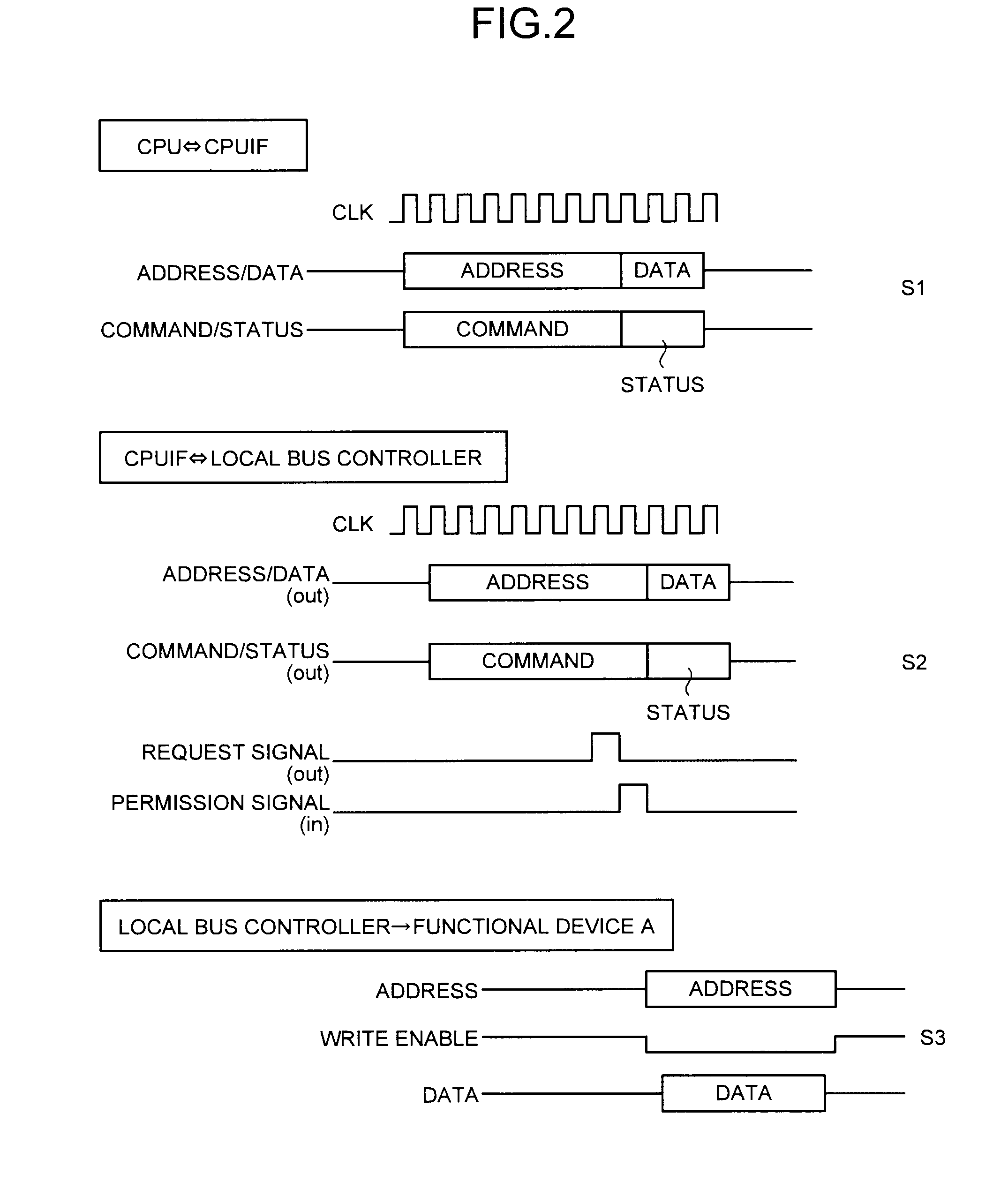

Data transfer control device and electronic equipment

InactiveUS6775245B1Reduce processing loadImprovement in actual transfer speedHome automation networksBus networksStructure of Management InformationData transmission

The objective is to provide a data transfer control device and electronic equipment that are capable of reducing processing overheads, thus enabling high-speed data transfer within a compact hardware configuration. In addition to a FIFO, an internal RAM capable of storing packets in a randomly accessible manner is provided between a link core and a CPU in a data transfer control device conforming to the IEEE 1394 standard. The RAM storage area is divided into a header area, a data area, and a CPU work area, and the header and data areas are divided into areas for reception and transmission. Tags are used to write the header of a receive packet to the header area and the data thereof to the data area. The data area is divided into areas for isochronous transfer and asynchronous transfer. Pointers are provided for controlling the size of each area in RAM variably, and the size of each area can be varied dynamically after power is switched on. Each area has a ring buffer structure. The size of area storing the header or data of one packet is fixed.

Owner:SEIKO EPSON CORP

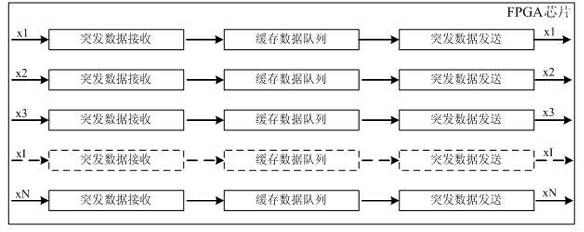

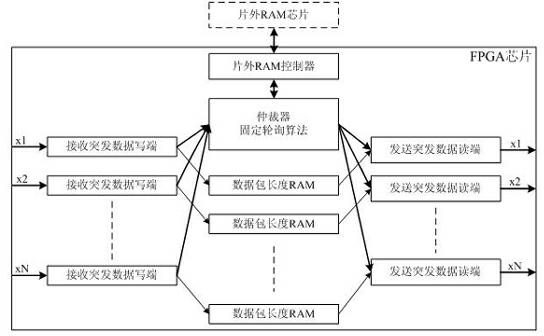

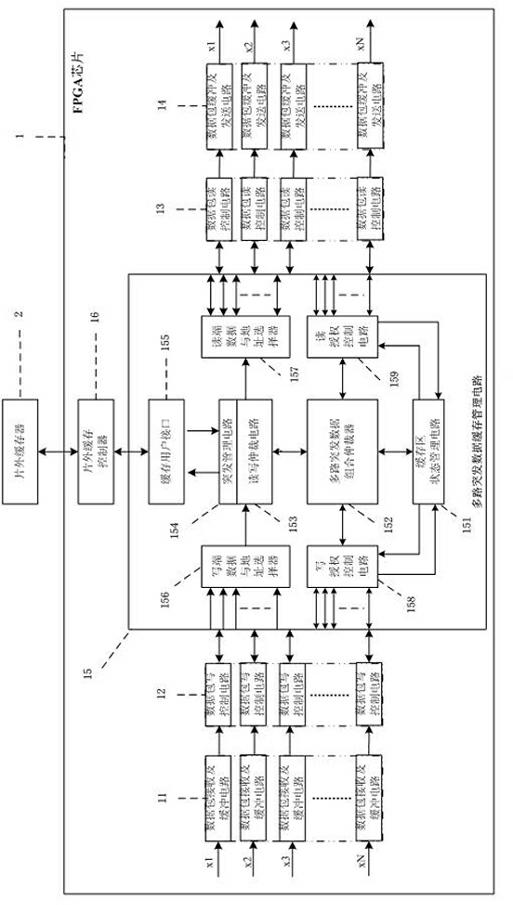

System and method for realizing multipath burst data business caching based on FPGA (Field Programmable Gate Array)

The invention discloses a system and method for realizing multipath burst data business caching based on an FPGA (Field Programmable Gate Array), wherein the system comprises an off-chip cache and an FPGA chip, wherein the off-chip cache is used for caching multipath burst data, and the FPGA chip is used for providing an RAM (Random Access Memory) resource; the FPGA chip also comprises an off-chip cache controller, a multipath burst data caching management circuit, packet receiving and buffering circuits with the same number as that of data channels, a packet write control circuit, a packet read control circuit and a packet buffering and transmitting circuit, wherein the multipath burst data caching management circuit is used for processing request arbitration and channel authorization ofthe multipath burst data, generating line address information of current read / write operation and writing a packet into the off-chip cache or reading the packet from the off-chip cache. By adopting the invention, the number of the channels can be simply increased or reduced, and each path of burst data business can be relatively and evenly cached so that bottleneck caused by internal RAM shortageof an FPGA chip can be avoided.

Owner:SHENZHEN ZTE NETVIEW TECH

Single-Chip Multi-Media Card/Secure Digital (MMC/SD) Controller Reading Power-On Boot Code from Integrated Flash Memory for User Storage

A Multi-Media Card / Secure Digital (MMC / SD) single-chip flash device contains a MMC / SD flash microcontroller and flash mass storage blocks containing flash memory arrays that are block-addressable rather than randomly-addressable. MMC / SD transactions from a host MMC / SD bus are read by a bus transceiver on the MMC / SD flash microcontroller. Various routines that execute on a CPU in the MMC / SD flash microcontroller are activated in response to commands in the MMC / SD transactions. A flash-memory controller in the MMC / SD flash microcontroller transfers data from the bus transceiver to the flash mass storage blocks for storage. Rather than boot from an internal ROM coupled to the CPU, a boot loader is transferred by DMA from the first page of the flash mass storage block to an internal RAM. The flash memory is automatically read from the first page at power-on. The CPU then executes the boot loader from the internal RAM to load the control program.

Owner:SUPER TALENT TECH CORP

Single-chip multi-media card/secure digital (MMC/SD) controller reading power-on boot code from integrated flash memory for user storage

Owner:SUPER TALENT TECH CORP

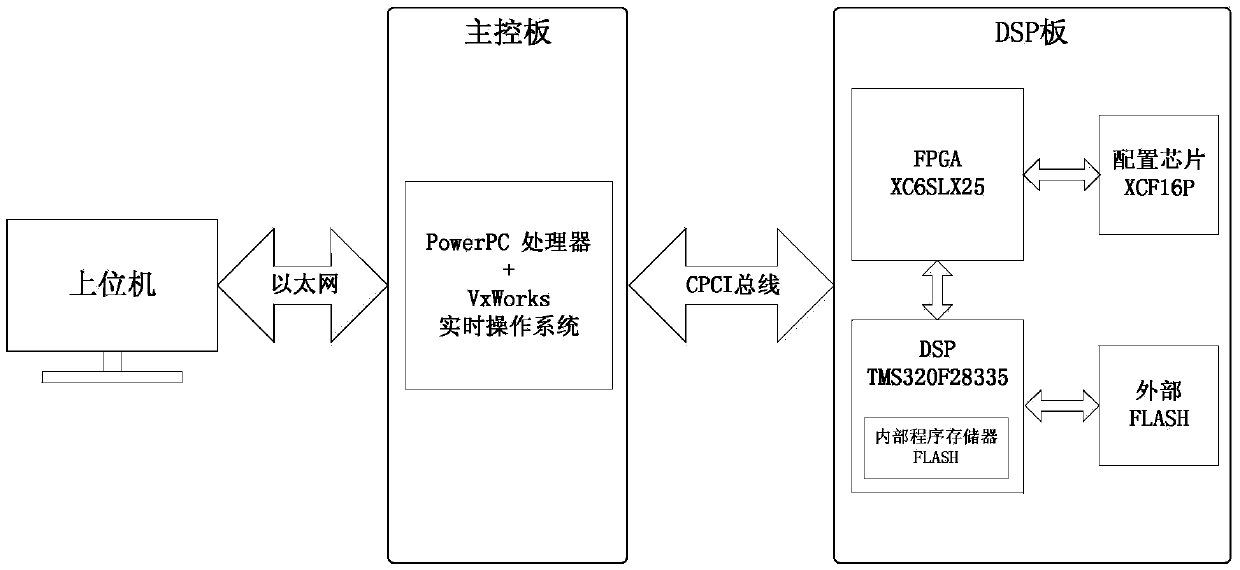

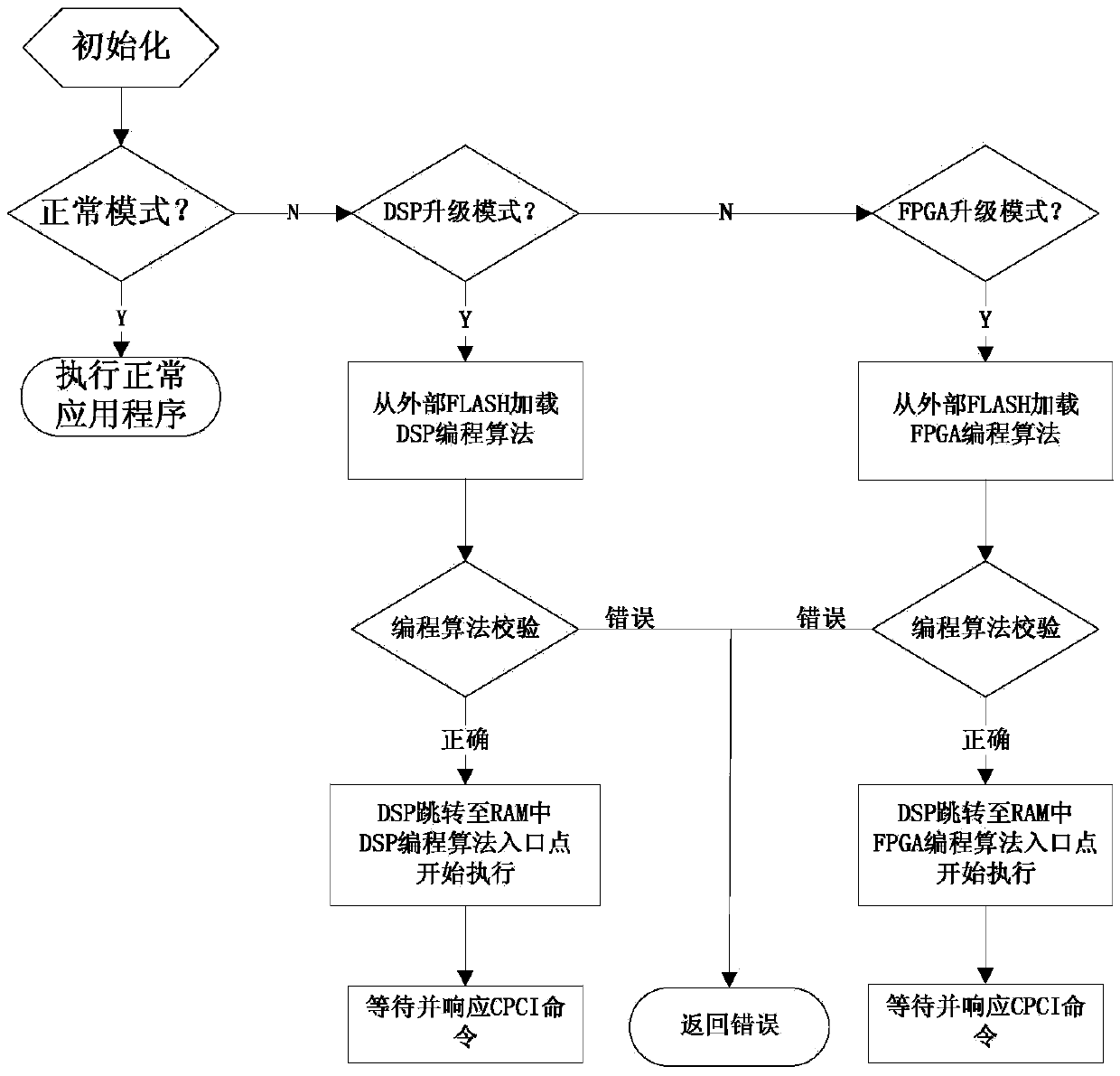

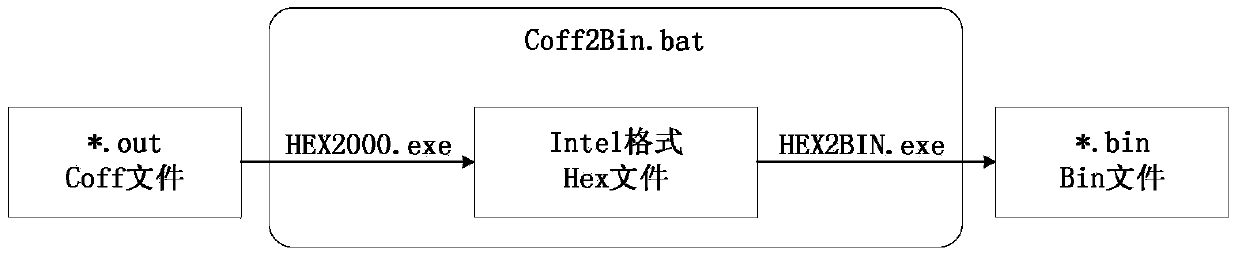

DSP and FPGA online upgrading method for embedded system

InactiveCN105373407ASolve online upgrade problemsReduce complexityProgram loading/initiatingEntry pointApplication software

The invention discloses a DSP and FPGA online upgrading method for an embedded system, which is used for solving the technical problem of complex program of an existing online upgrading method. The technical scheme is that DSP or FPGA firmware required to be upgraded is uploaded to a main control board by an upper computer; the main control board executes a corresponding DSP or FPGA online upgrading function; a DSP board is reset after being upgraded online; and a new user program is reloaded and executed. Two programming algorithms are stored in an extended FLASH of a DSP, so that the DSP directly loads the corresponding programming algorithm to an internal RAM from the extended FLASH by utilizing a working mode detection function, and the programming algorithm skips to a program entry point to be executed; meanwhile, the online upgrading problem of the DSP and FPGA firmware of the embedded system is solved; and the programming algorithm is separated from an application, so that the complexity of user application design is lowered, and the space of a program memory in the DSP is not occupied.

Owner:中国船舶重工集团公司第七〇五研究所

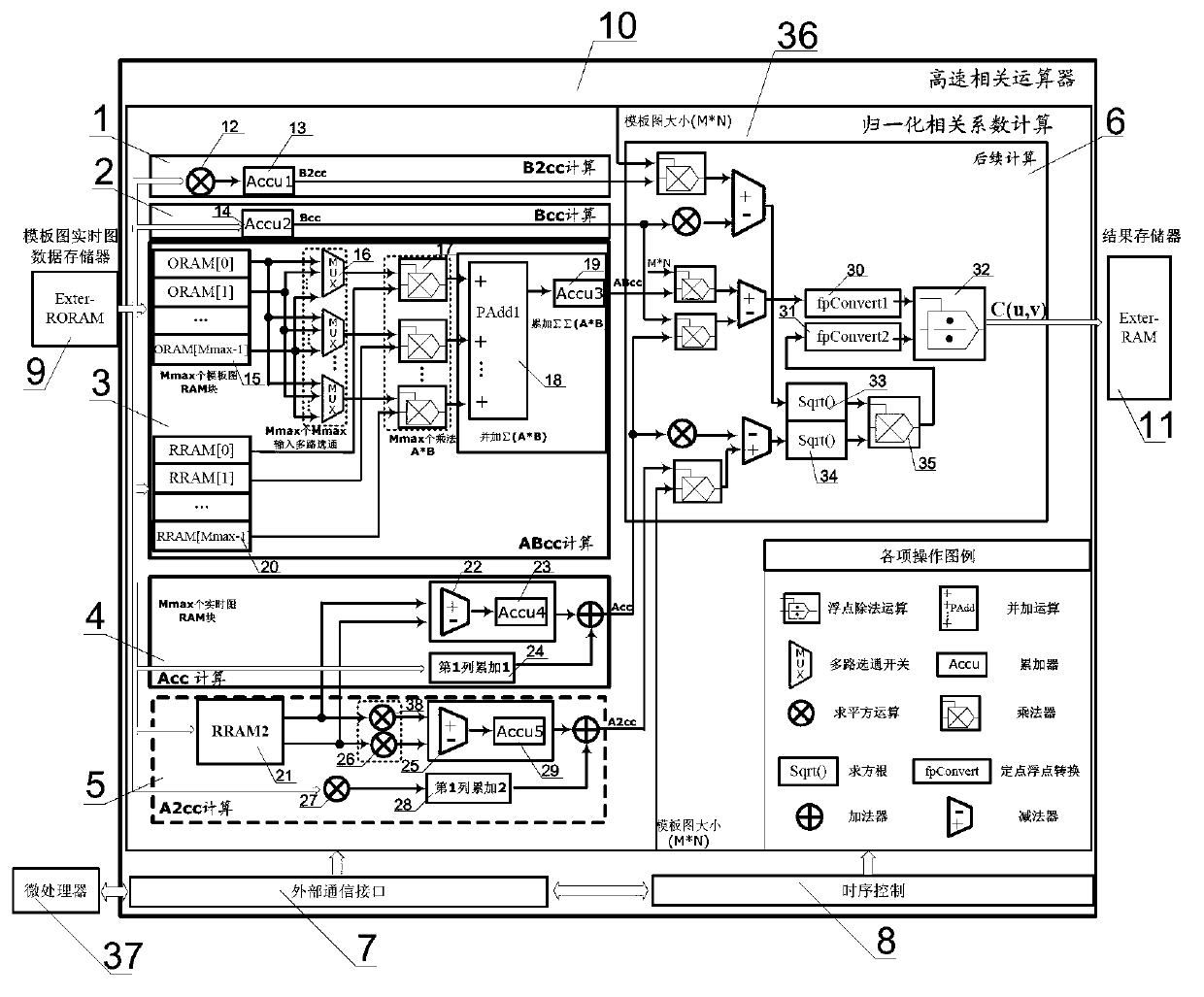

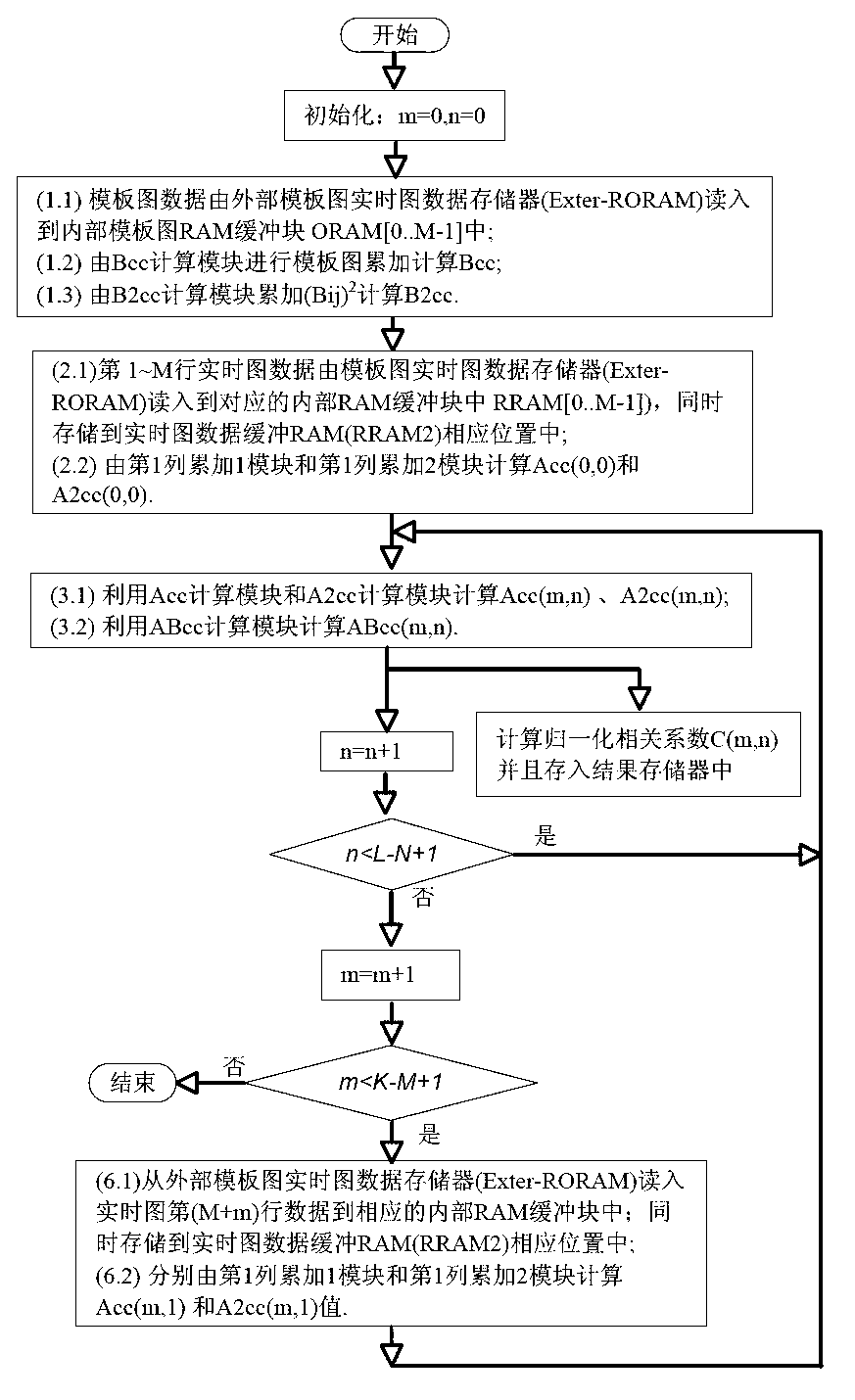

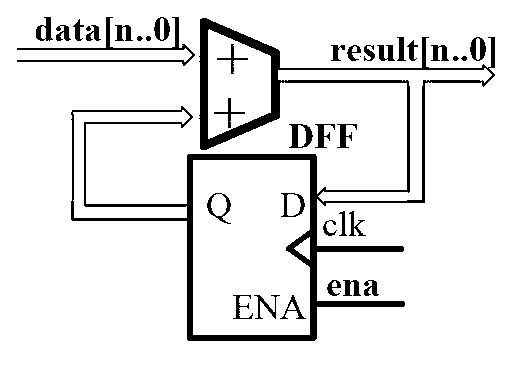

High-speed parallel implementation method and device for template matching based on normalized correlation coefficient

ActiveCN103310228AReduce logic resource consumptionRun fastCharacter and pattern recognitionTotal sum of squaresTemplate matching

The invention discloses a high-speed parallel implementation method and device for template matching based on a normalized correlation coefficient. The method comprises the following steps of reading a real-time graph and template graph data in a corresponding internal RAM (random access memory) buffer block and a real-time graph data buffer RAM, and meanwhile calculating the sum of a template graph gray value and the squared sum of the template graph gray value, and calculating the sum of a real-time graph gray value and the squared sum of the real-time graph gray value at a search position (0, 0); then calculating the sum of the product of the real-time graph gray values of various columns in the first row of the search position of the following columns of the first row in the search position, and the normalized correlation coefficient; and meanwhile, further reading the real-time graph data of a new row in the corresponding internal RAM buffer block and the real-time graph data buffer RAM corresponding position, and calculating the value of the first column in the current row at the same time, and calculating the normalized correlation coefficients of following rows in sequence. The device is composed of a high-speed correlation operator, an external data result memory and a microprocessor.

Owner:NANJING UNIV OF POSTS & TELECOMM

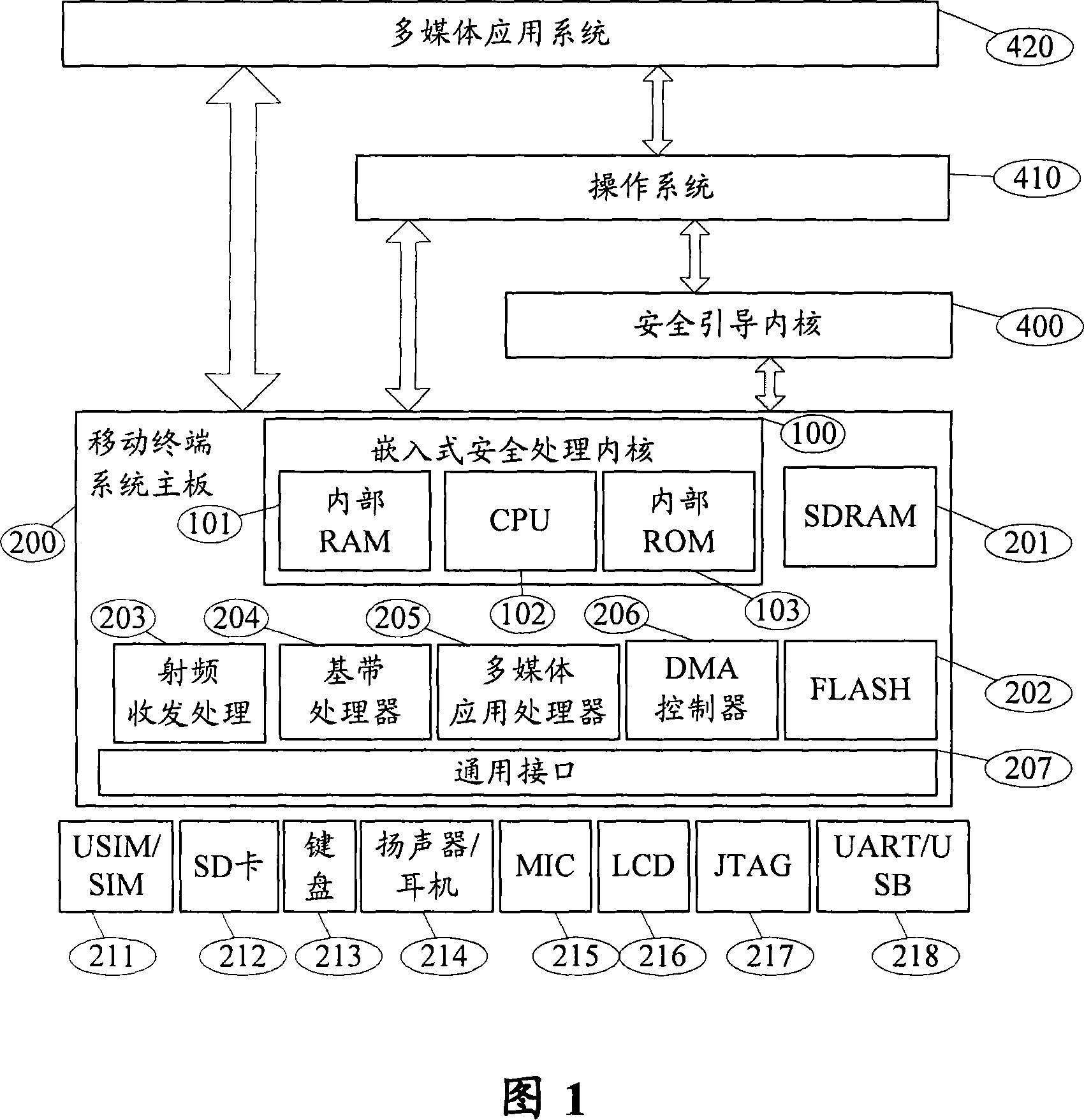

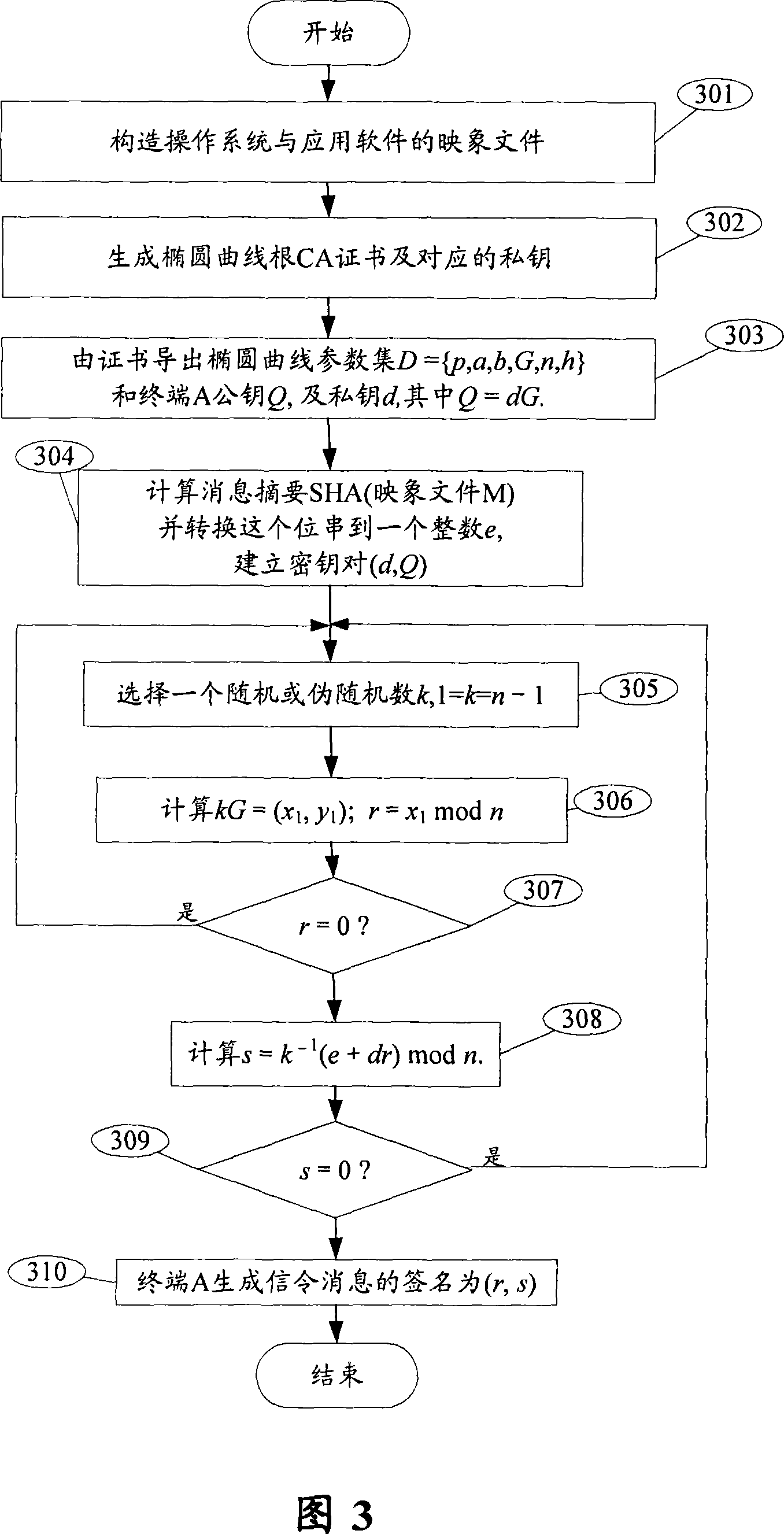

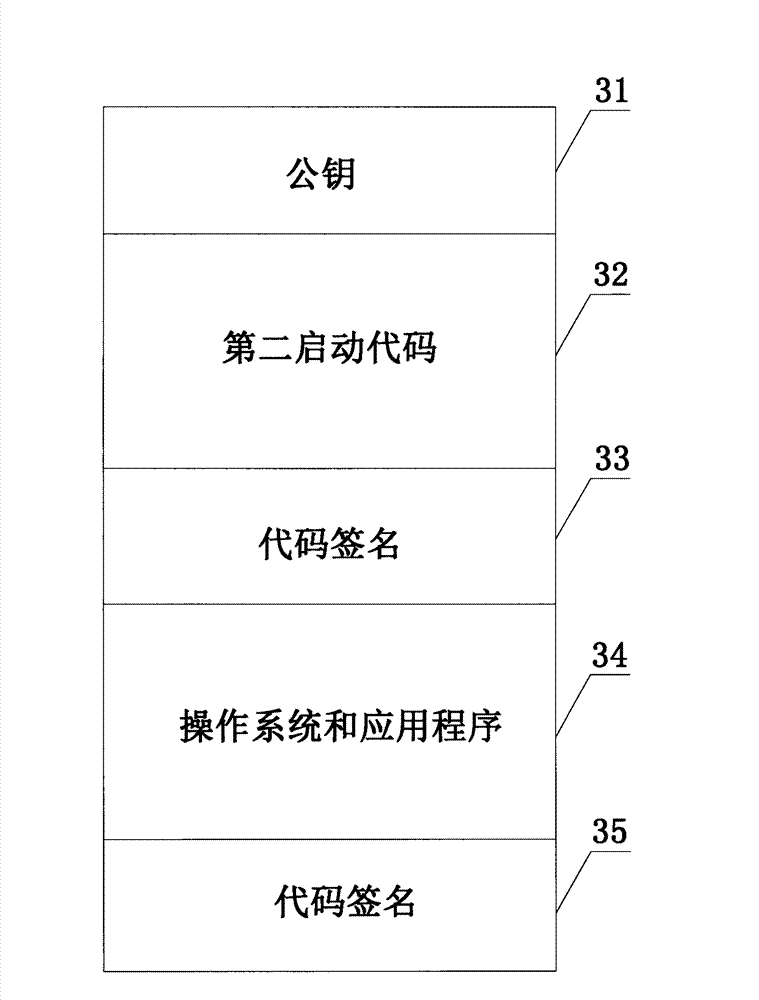

Secure guiding system, method, code signature construction method and authentication method

ActiveCN101034991AEnsure safetyAvoid churnPublic key for secure communicationUser identity/authority verificationOperational systemCode signing

The invention is a mobile terminal safe booting method, comprising the steps of: 1. safe booting program builds an interrupt vector list in the internal RAM of a safe processing kernel; 2. initializing the internal RAM; 3. the safe processing kernel boots program to build access to the internal RAM and makes hardware initialization, where the hardware comprises flash memory out of safe processing kernel chip; 4. loading and processing configuration data in the flash memory; 5. loading operating system software mapping file and completing authentication on the operating system software mapping file based on ECC (Elliptic Curve Cryptography); 6. loading application system software mapping file and completing authentication on the application system software mapping file based on ECC; and 7. after the application system software mapping file passes the authentication, transmitting the control to the application system. And the invention also discloses a mobile terminal safe booting system, and a code signing constructing method and a code signing authentication method.

Owner:BEIJING SHENZHOU ANFU TECH CO LTD

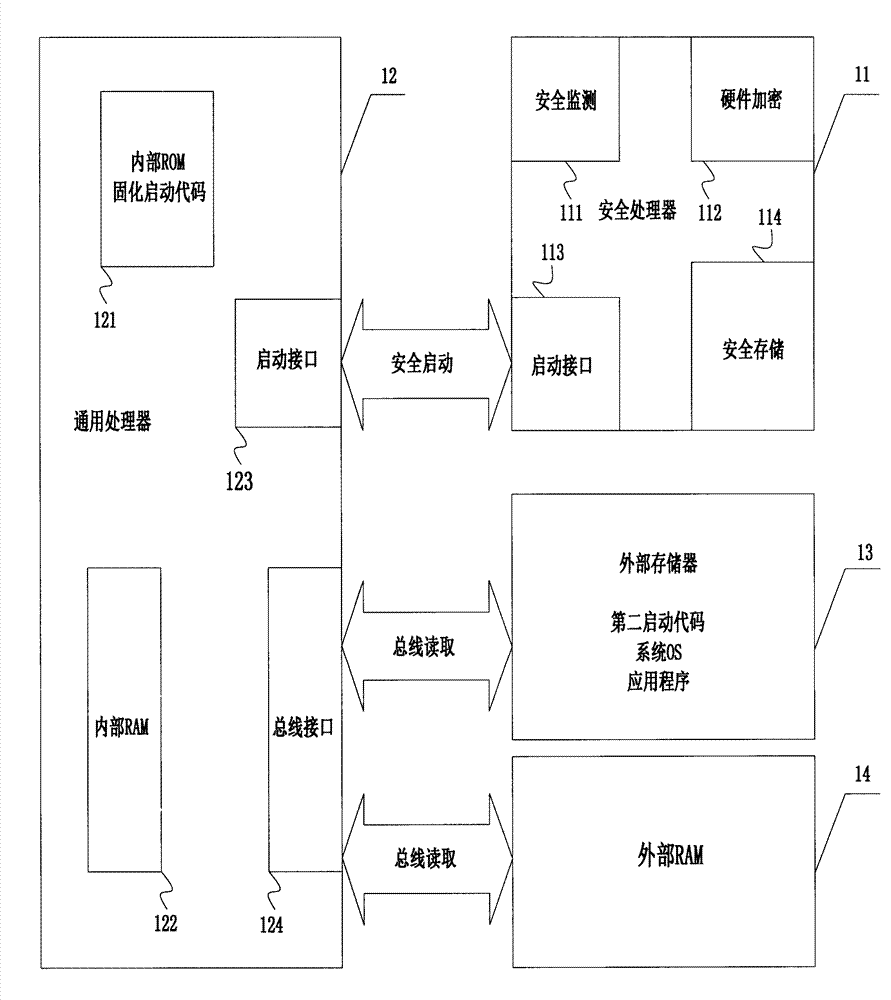

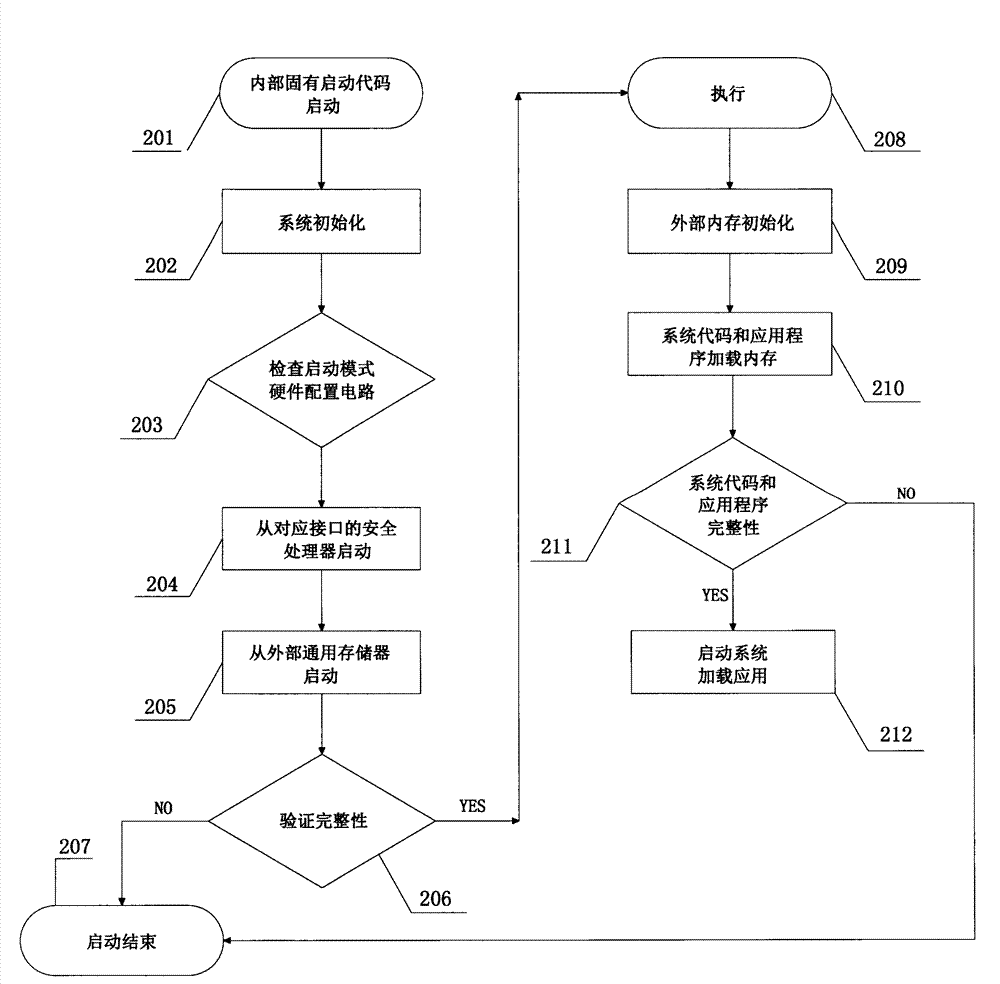

Core safety architecture implementation method of intelligent financial transaction terminal

InactiveCN103049694AReduce complexityImprove reliabilityPlatform integrity maintainanceRandom access memoryFinancial transaction

A first system startup code, a second startup code, a verification key and a transaction key are saved in a safety processor, wherein the verification key is used for verifying the integrity of the second startup code which is an inherent part of a common processor, and the transaction key is used for verifying the integrity of transaction information. The verification key verifying the system integrity of the second startup code of the common processor after a read-in and an execution of the first startup code in a RAM (Random Access Memory) inside the common processor and a read-in and an execution of the second startup code in the RAM inside the common processor; a startup program is stopped if the verification cannot pass; a system code and an application program code are loaded if the verification passes and the integrity of the system code and an application program are verified through the verification code; and the startup program is stopped if the verification result is negative and the startup program is started if the verification result is positive.

Owner:上海慧银信息科技有限公司

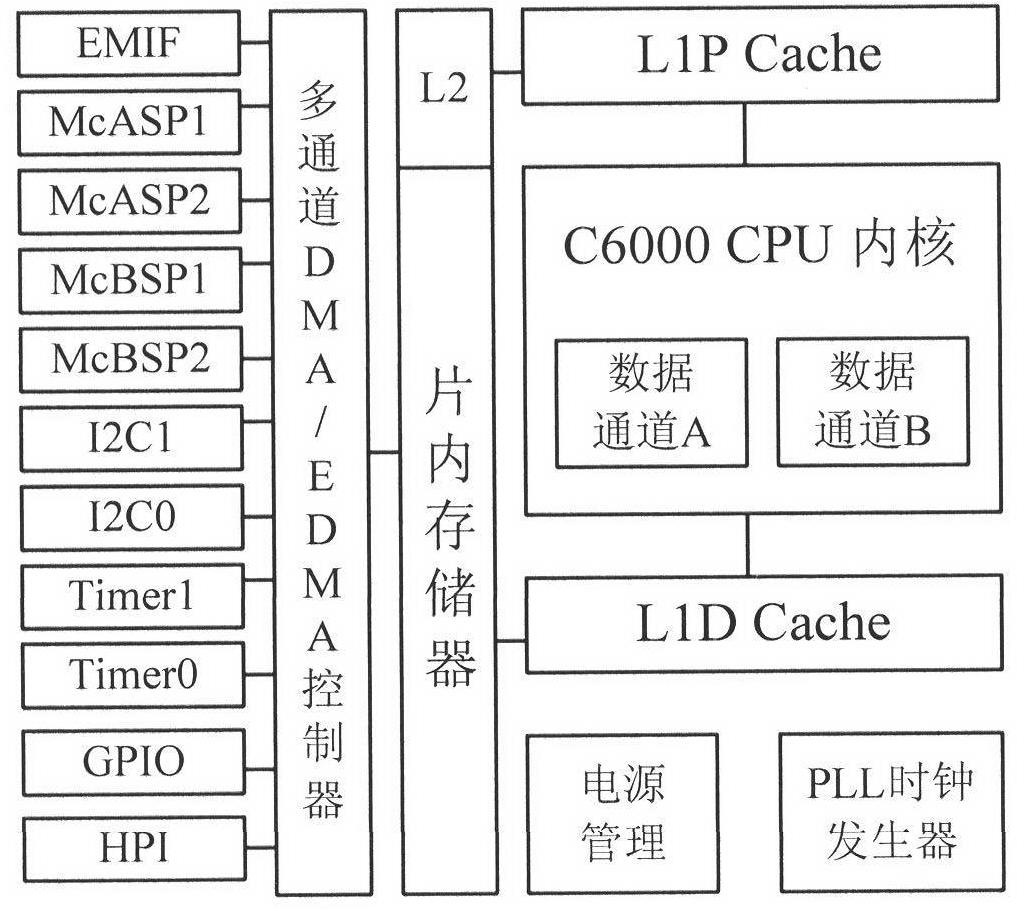

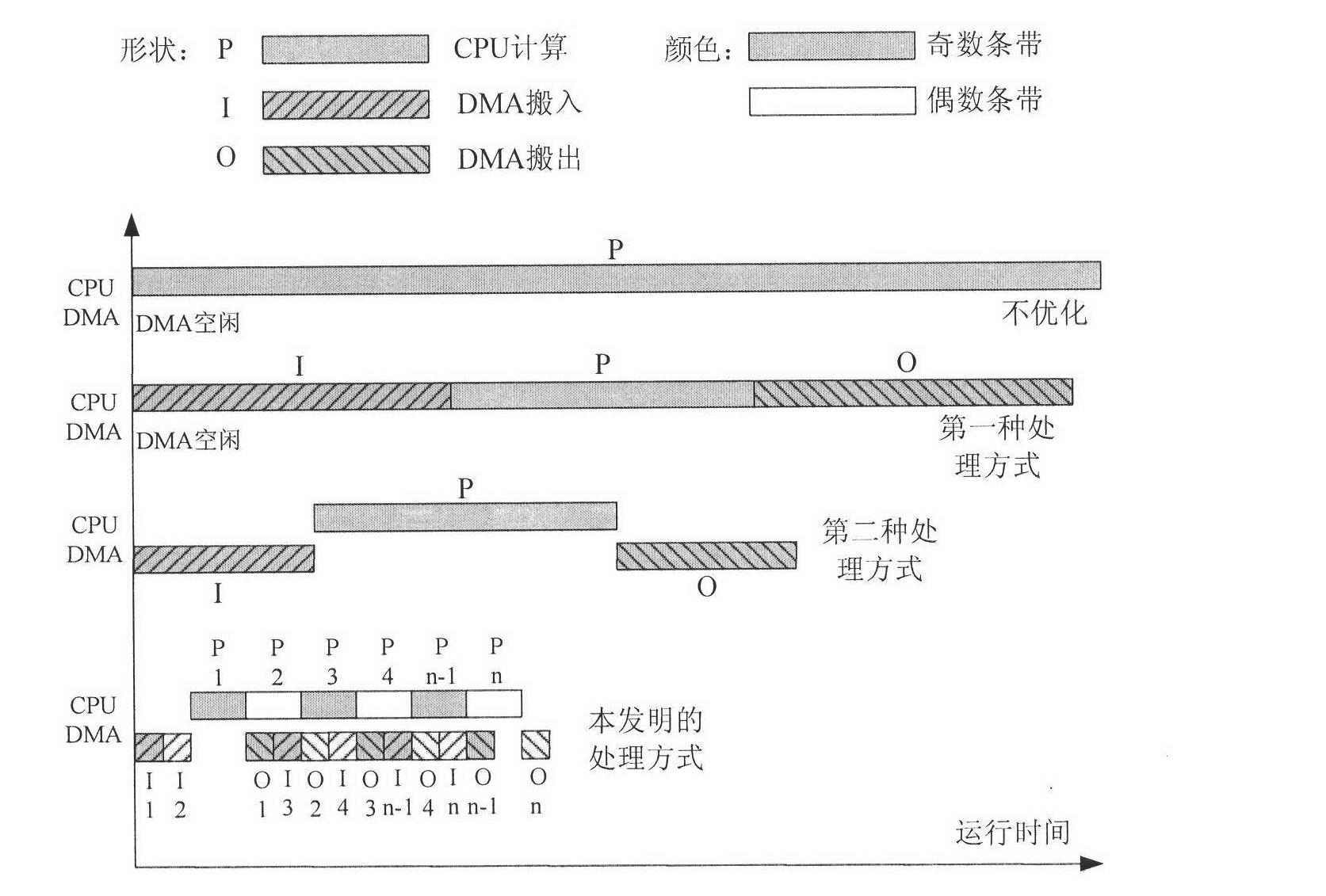

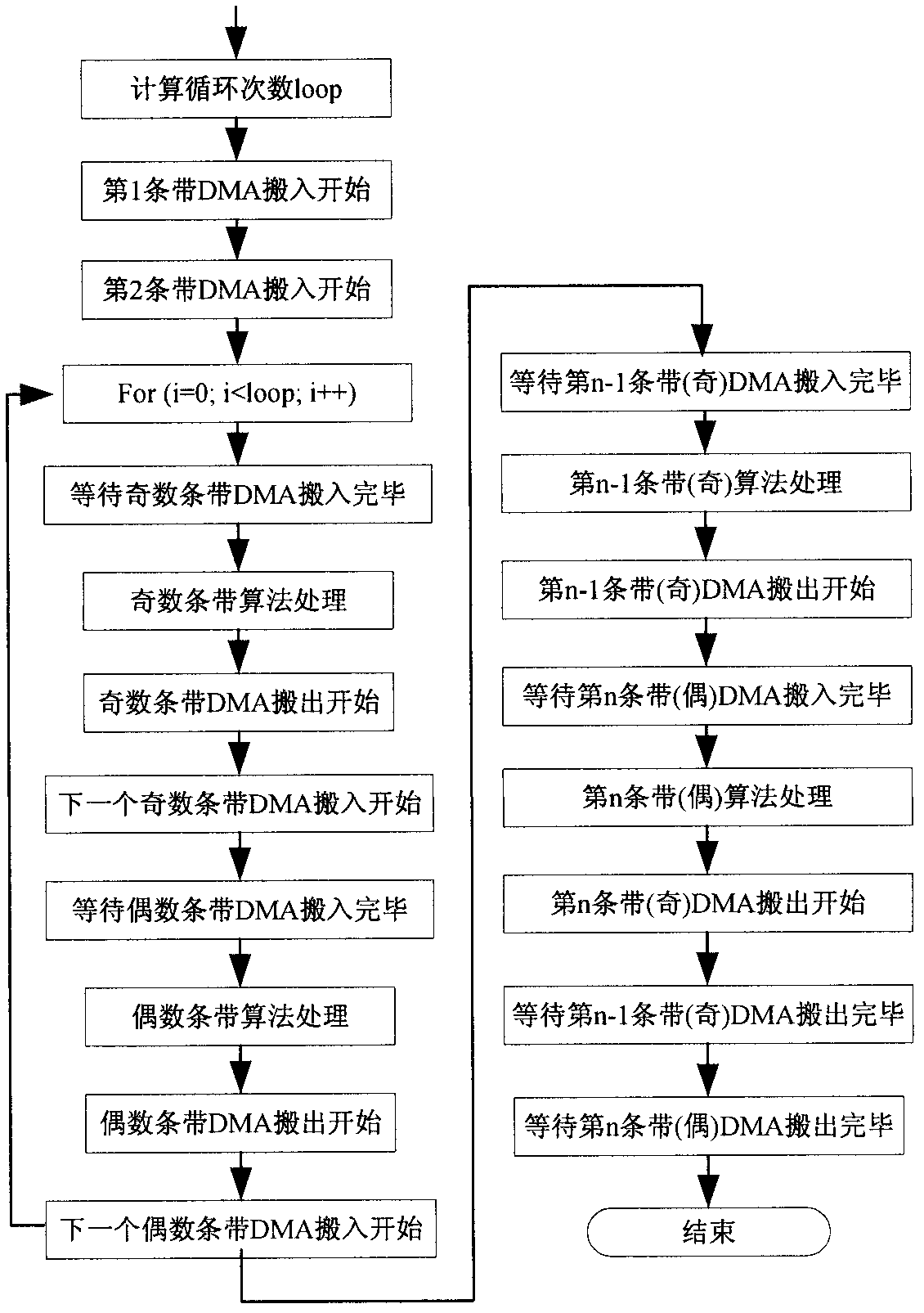

Double-buffer ping-bang parallel-structure image processing optimization method based on DMA (direct memory access)

InactiveCN102222316AImproved performance in real-time image processingIncrease profitImage memory managementProcessor architectures/configurationDirect memory accessImaging processing

The invention relates to a double-buffer ping-bang parallel-structure image processing optimization method based on DMA (direct memory access). The method comprises the following steps: a DSP (digital signal processor) is externally connected with an SDRAM (synchronous dynamic random access memory), images to be processed are stored in the SDRAM, dividing the image data in the SDRAM into 2N image bands, opening up odd-even buffer areas for storing odd-even image band data in the DSP, then utilizing fast data transmission capability of the DSP and a parallel working mode of a DMA controller and a CPU (central processing unit) to realize optimization processing for the images stored in the SDRAM. In the double-buffer ping-bang parallel-structure image processing optimization method, the utilization ratio of the CPU and the DMA controller is effectively improved, the operation speed of image processing algorithm is accelerated, the performance of the DSP in the aspect of real-time image processing is improved, and the method can be widely applied in the fields of real-time image processing, such as scene matching, image fusion and target tracking and the like, and also can be used for the field of military.

Owner:BEIJING AEROSPACE AUTOMATIC CONTROL RES INST

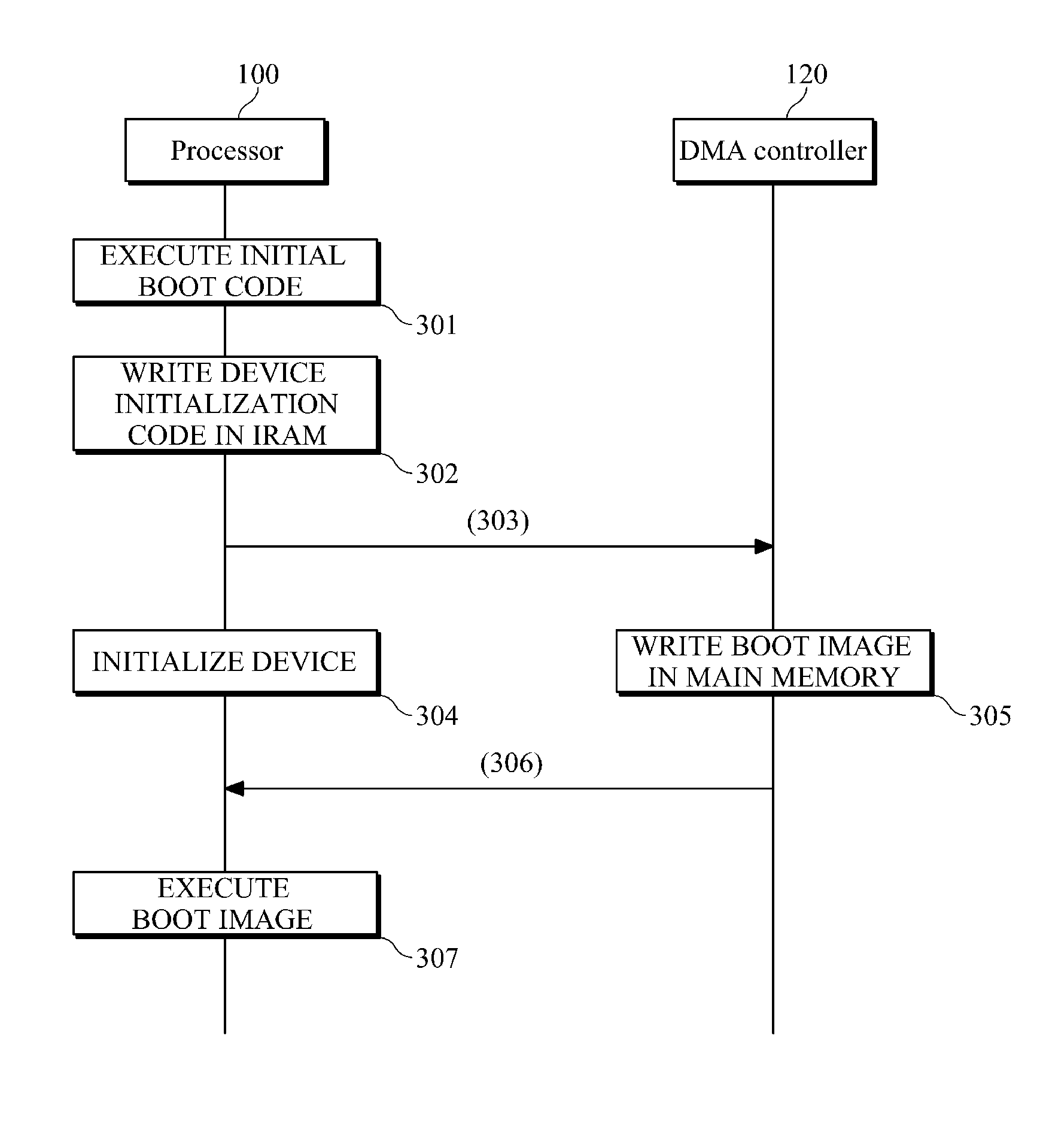

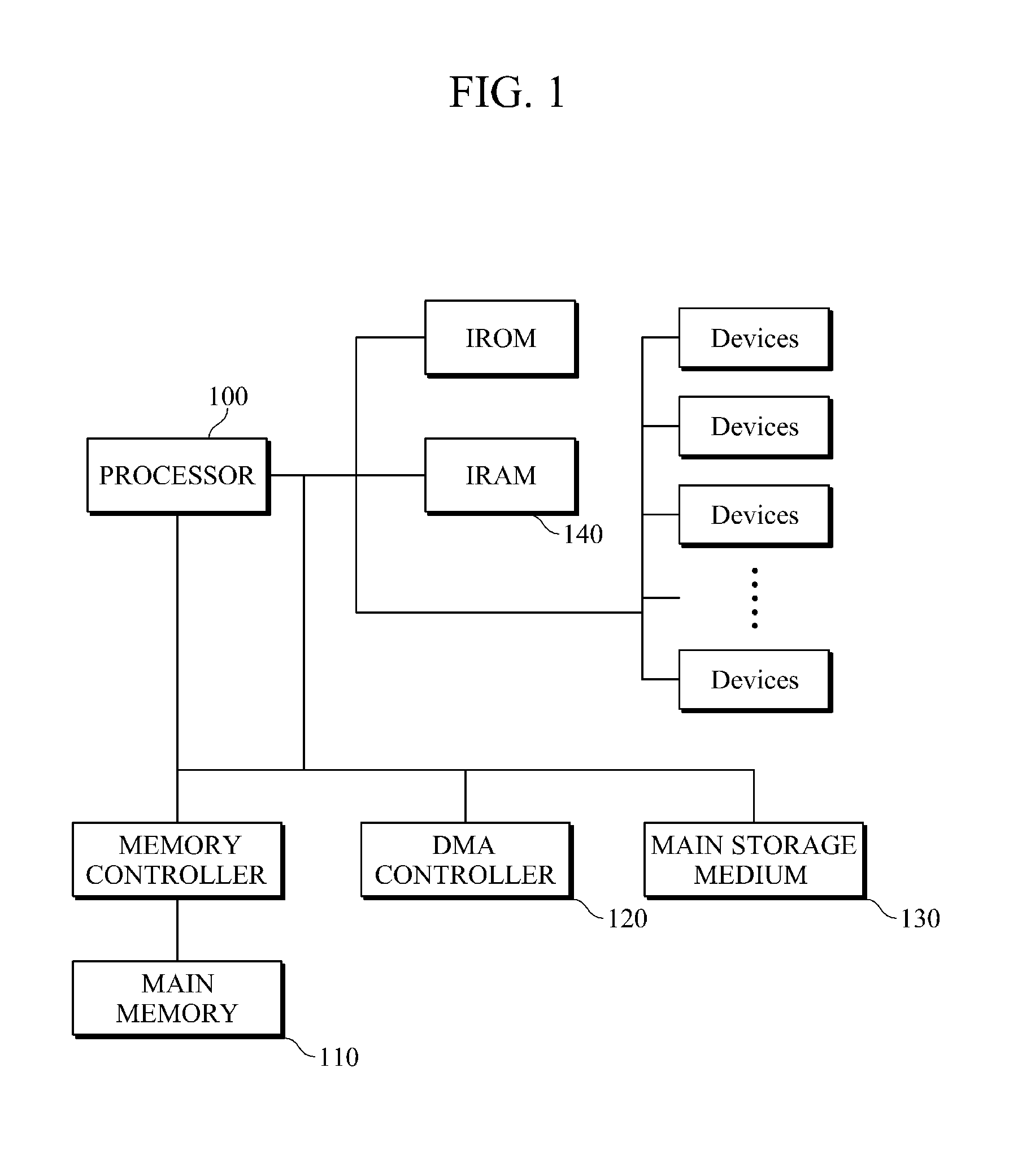

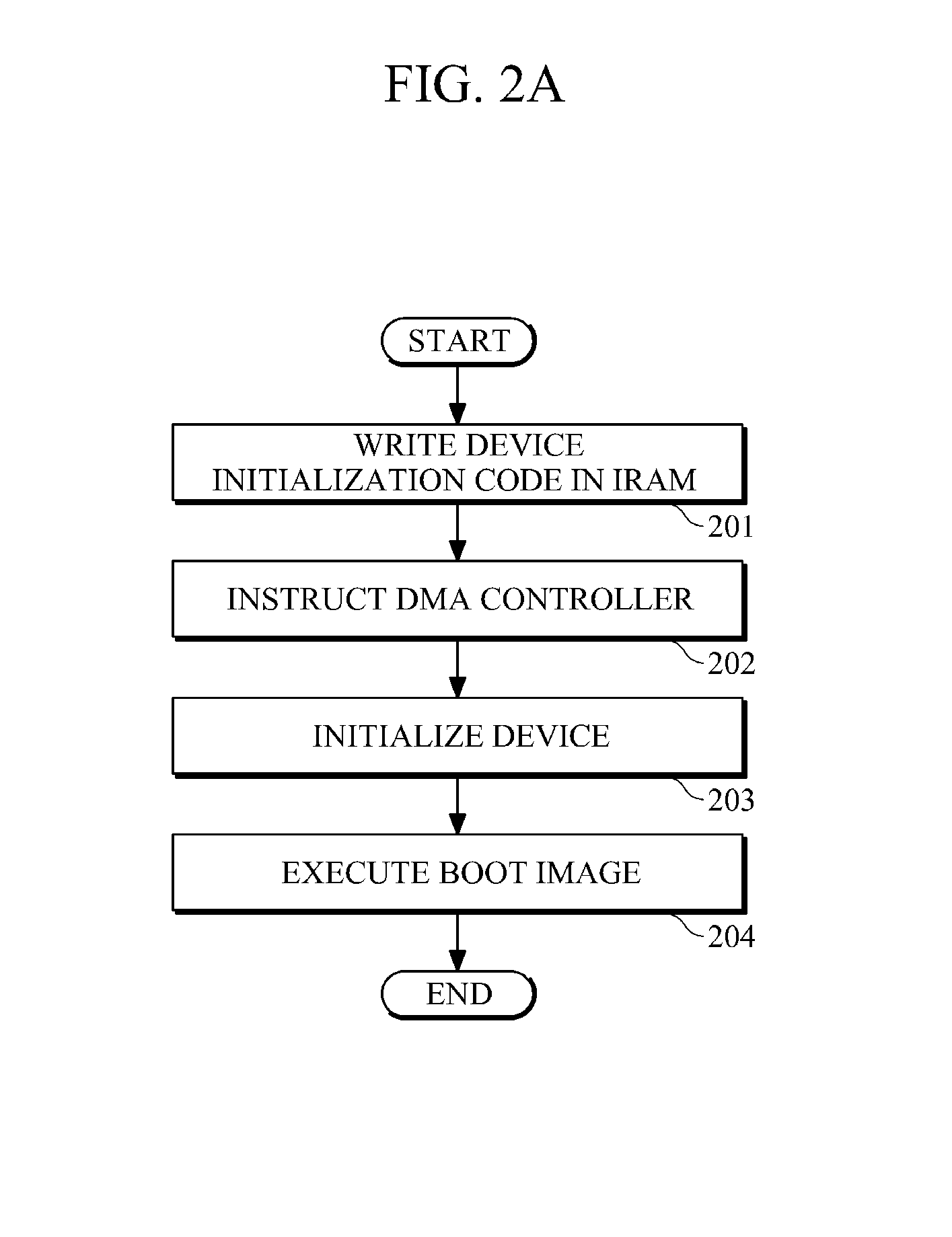

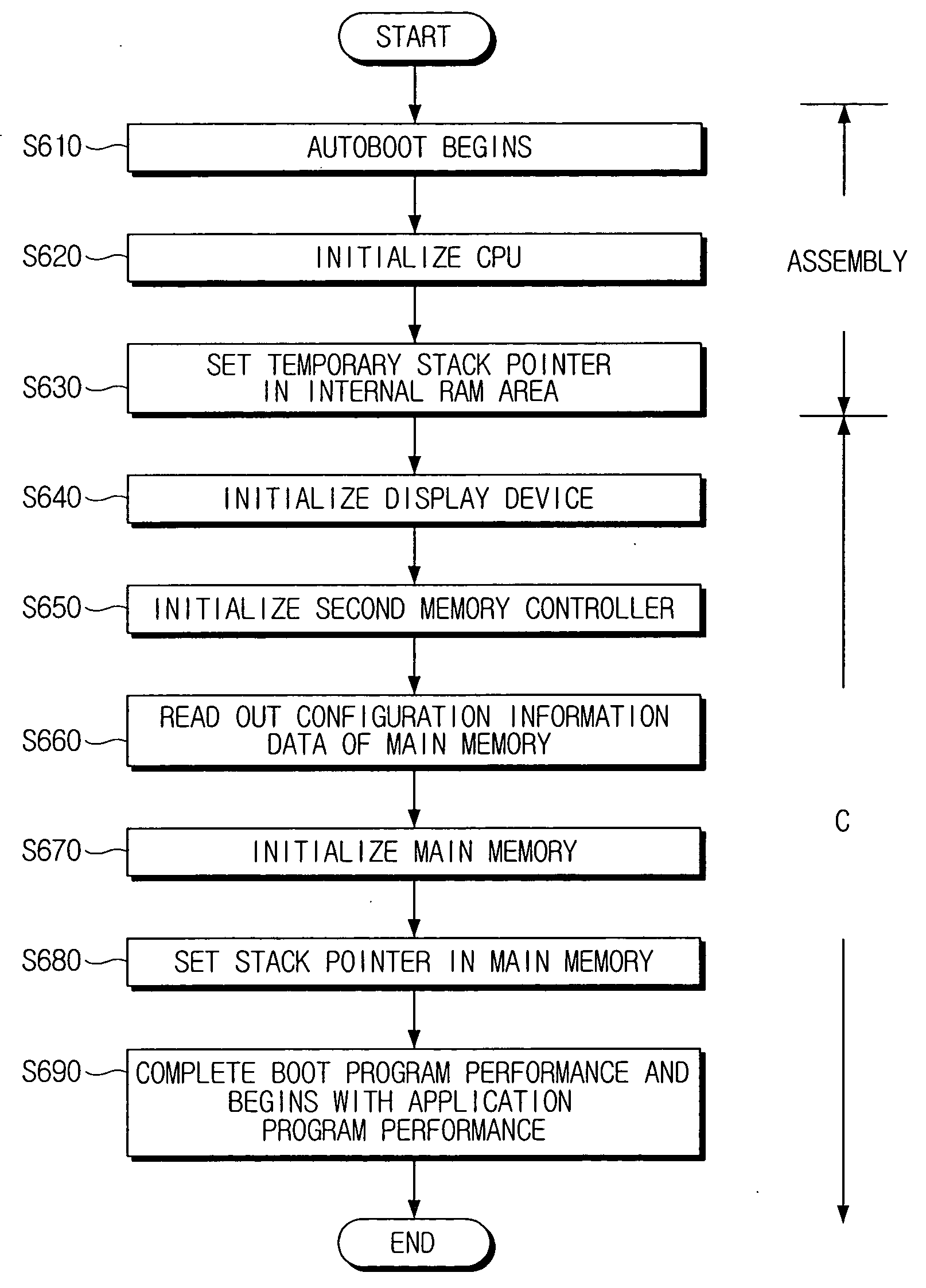

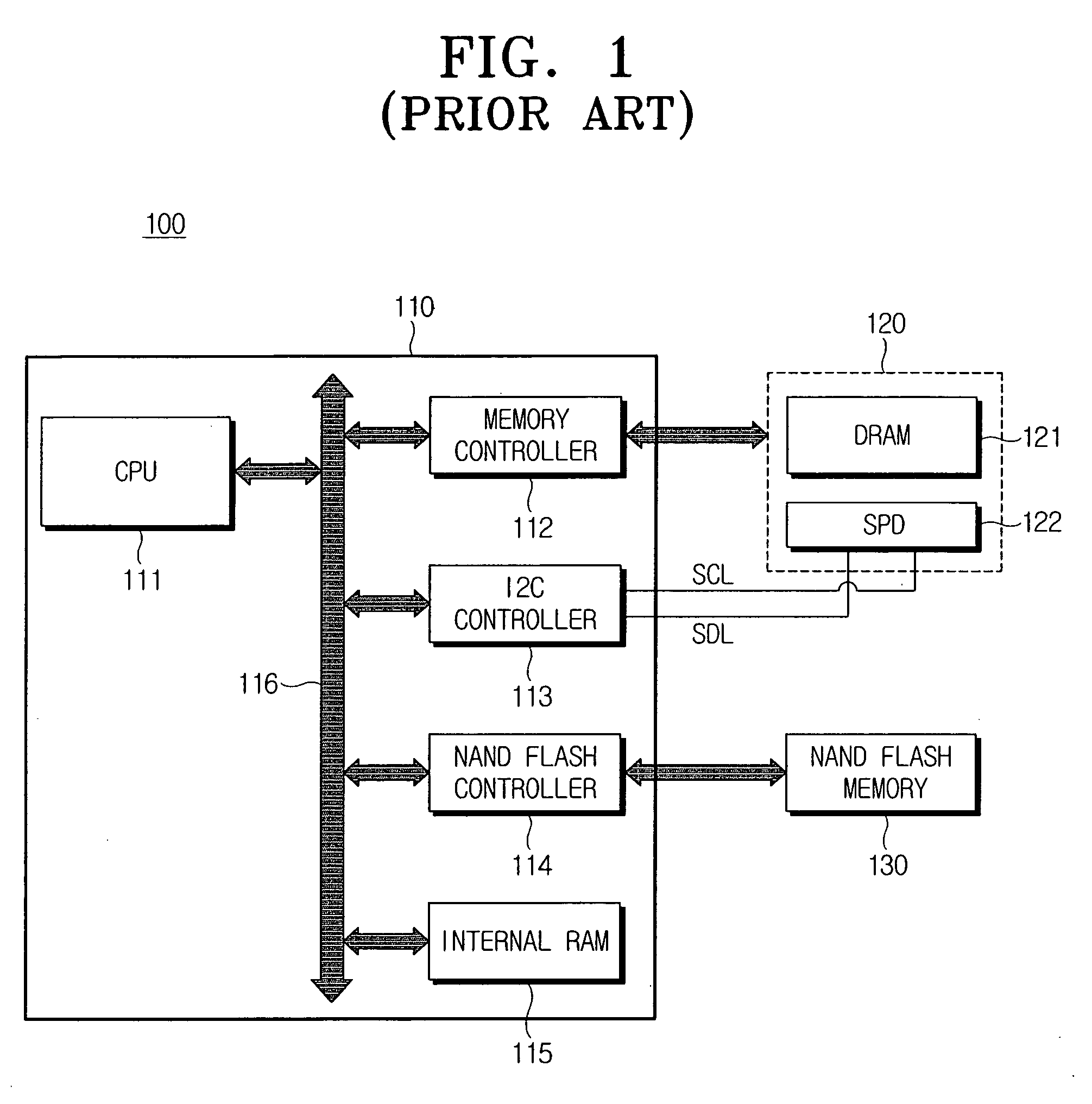

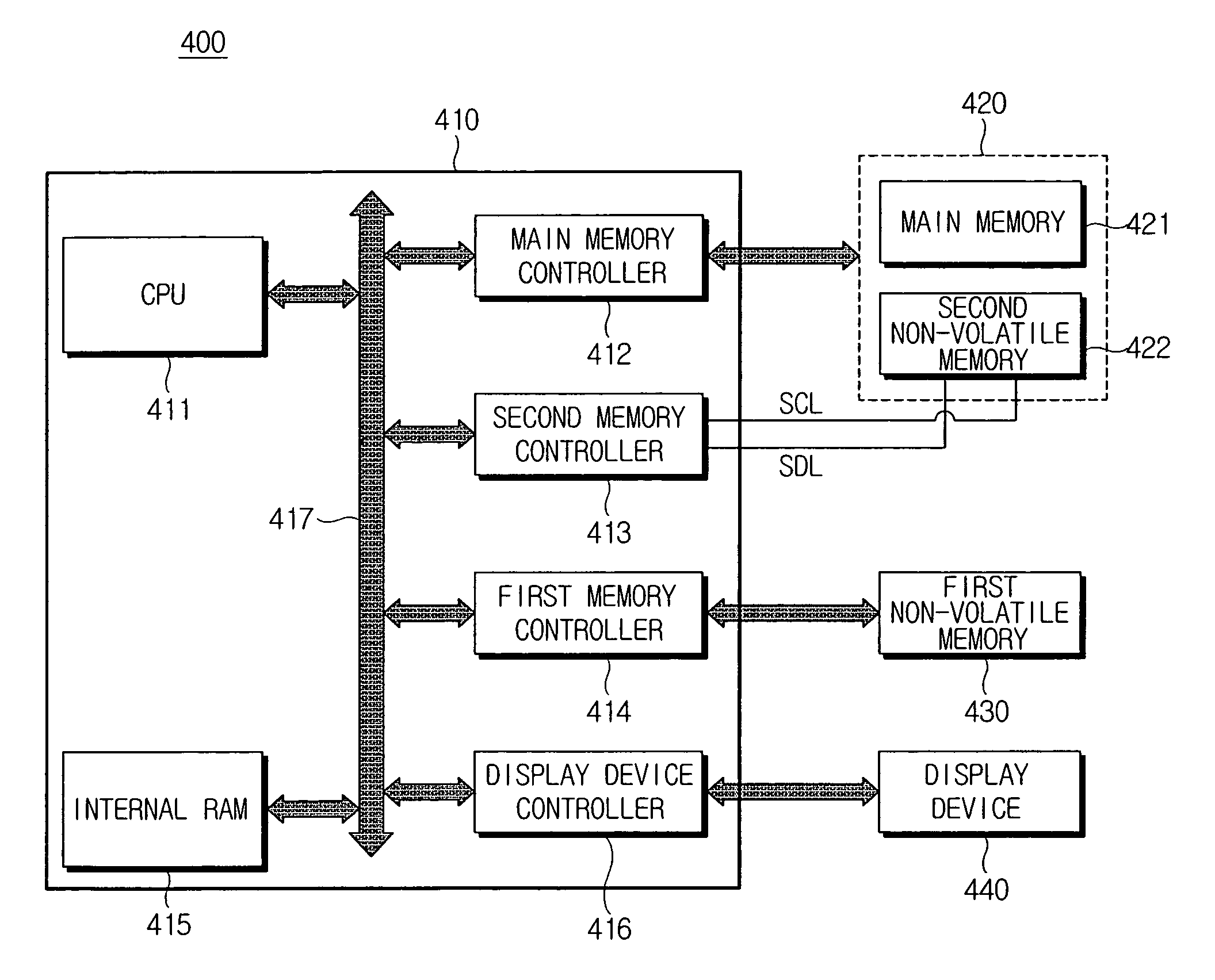

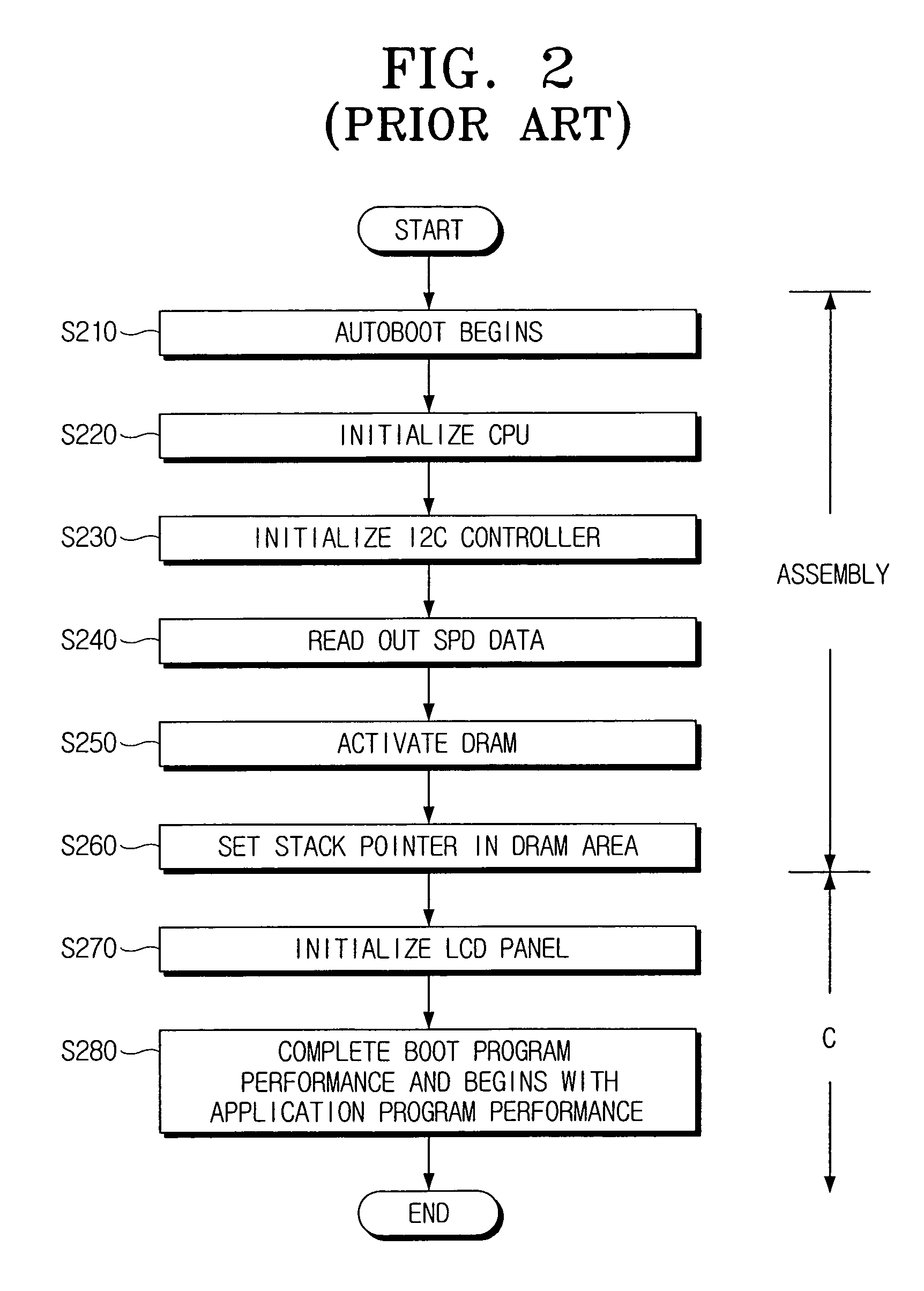

Method and terminal of booting a computing system

Provided is a method of booting a computing system which performs boot image transmission and device initialization in parallel. For example, using an Internal RAM and direct memory access (DMA), hardware initialization and loading of boot image from a main storage medium to a main memory are performed in parallel, thereby reducing time spent on booting.

Owner:SAMSUNG ELECTRONICS CO LTD

Single-Chip Multi-Media Card/Secure Digital (MMC/SD) Controller Reading Power-On Boot Code from Integrated Flash Memory for User Storage

InactiveUS20110066920A1Energy efficient ICTMemory adressing/allocation/relocationMass storageMicrocontroller

A Multi-Media Card / Secure Digital (MMC / SD) single-chip flash device contains a MMC / SD flash microcontroller and flash mass storage blocks containing flash memory arrays that are block-addressable rather than randomly-addressable. MMC / SD transactions from a host MMC / SD bus are read by a bus transceiver on the MMC / SD flash microcontroller. Various routines that execute on a CPU in the MMC / SD flash microcontroller are activated in response to commands in the MMC / SD transactions. A flash-memory controller in the MMC / SD flash microcontroller transfers data from the bus transceiver to the flash mass storage blocks for storage. Rather than boot from an internal ROM coupled to the CPU, a boot loader is transferred by DMA from the first page of the flash mass storage block to an internal RAM. The flash memory is automatically read from the first page at power-on. The CPU then executes the boot loader from the internal RAM to load the control program.

Owner:SUPER TALENT ELECTRONICS

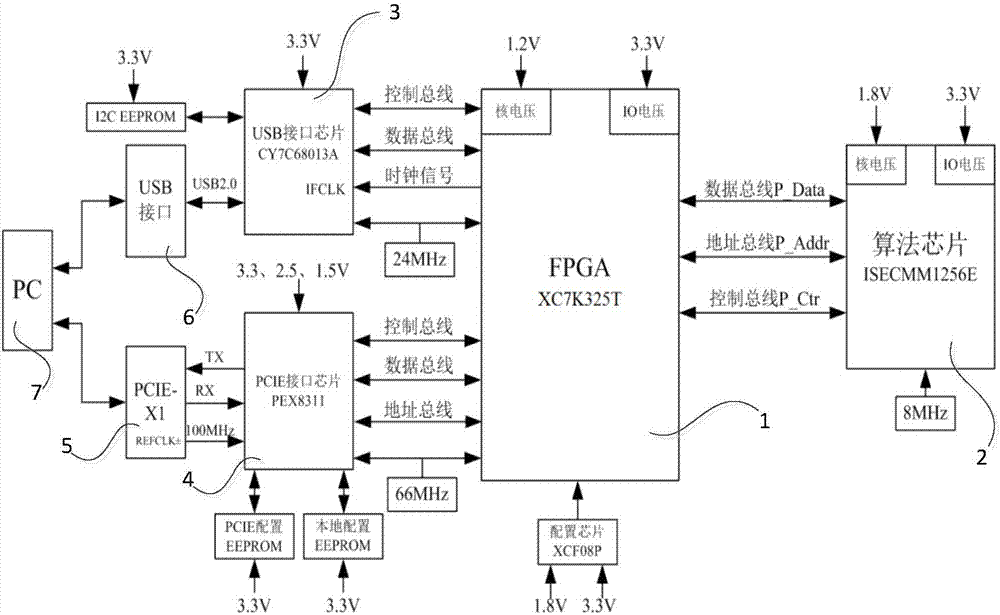

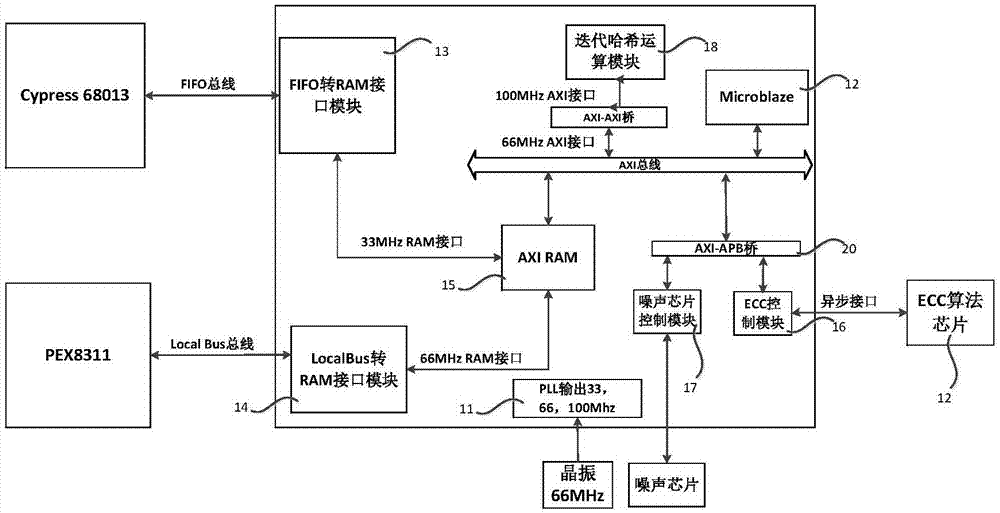

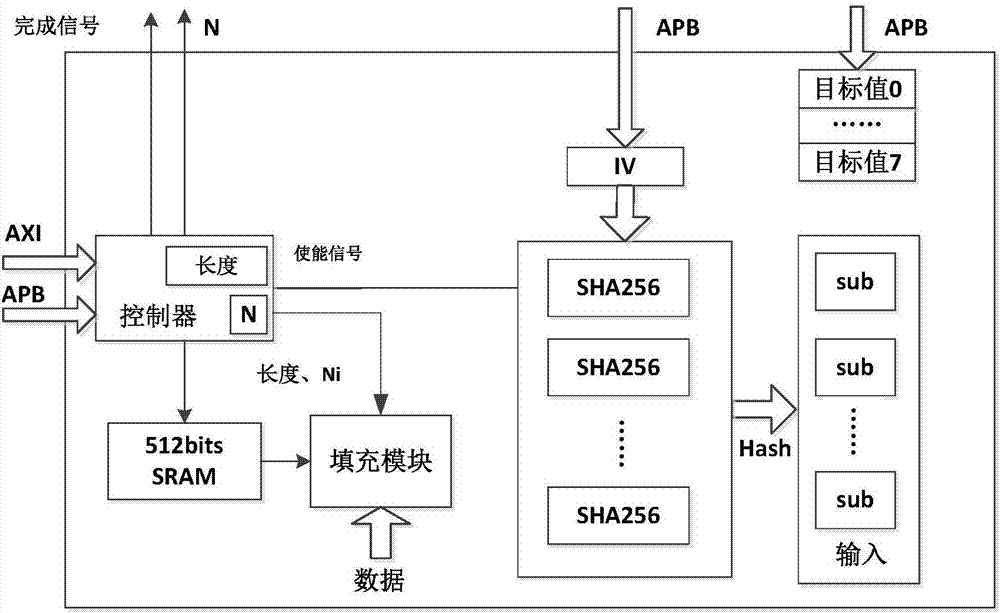

Algorithm processing module for block chain

The invention discloses an algorithm processing module for a block chain, and the module comprises a PCIE interface chip which is used for communication with a PCIE interface of an outer main unit; a USB control chip which is used for communication with a USB interface of the outer main unit; an algorithm chip which is used for cooperating with an FPGA for ECC calculation, wherein the FPGA comprises a Microblaze module which is used for controlling the operation of each submodule of the FPGA; an FIFO-RAM interface module which is used for achieving the transformation from the USB interface to an internal RAM interface, reading data from the USB chip and storing the data in the RAM module; a Local Bus-RAM interface module which is used for the transformation from the Local Bus interface to the internal RAM module interface; the internal RAM module which is used for storing the downloaded data of a user and the data to be uploaded to the user; an ECC control module which is used for carrying out the transformation from an APB bus to an ECC chip asynchronous interface, and carrying out the call of the algorithm chip to carry out the dot multiplying and modular multiplication calculation; a noise chip control module which is used for the transformation from the ABP bus to the noise chip interface; and an iterative Hash calculation module which is used for carrying out the iterative Hash calculation and carrying out the parallel processing of the algorithm module.

Owner:BEIJING INST OF COMP TECH & APPL

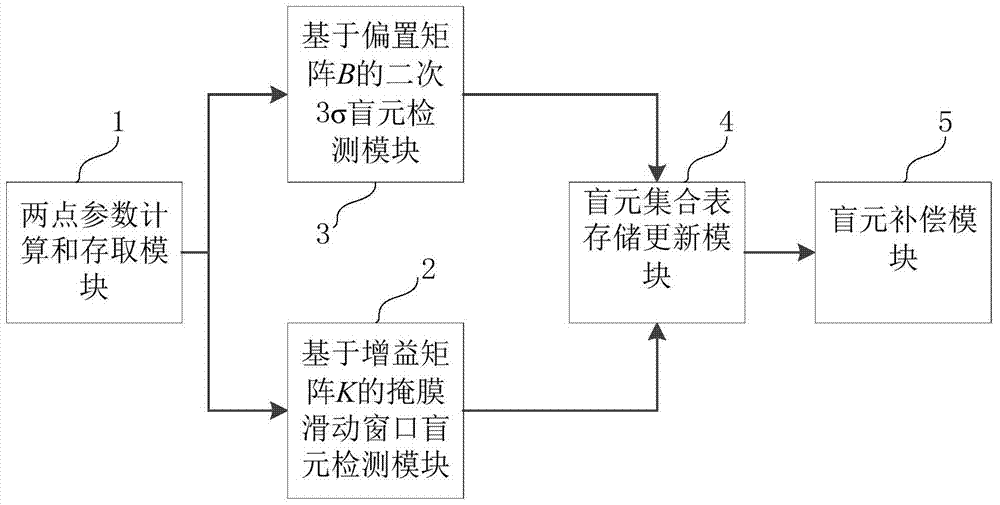

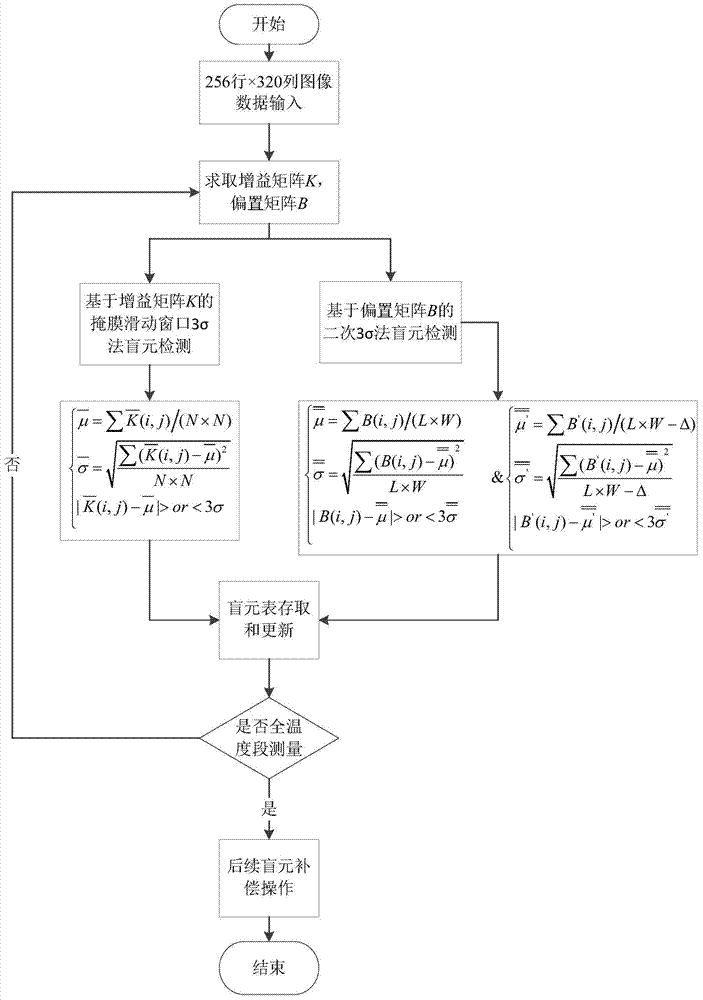

FPGA-based infrared focal plane array blind pixel detection system and FPGA-based infrared focal plane array blind pixel detection method

InactiveCN104515599AAccurate collectionImprove real-time performancePyrometry using electric radation detectorsSlide windowComputer vision

The invention discloses an FPGA-based infrared focal plane array blind pixel detection system and an FPGA-based infrared focal plane array blind pixel detection method. The system comprises a two-point parameter calculation and storage module, a mask slide window blind pixel detection module based on a gain matrix K, a secondary 3Sigma blind pixel detection module based on a bias matrix B, a blind pixel set table storage and update module, and a blind pixel compensation module. The detection method comprises the following steps: performing two-point parameter calculation on an original digital image signal to obtain a two-point parameter matrix and storing the two-point parameter matrix in an internal RAM of an FPGA; carrying out mask slide window blind pixel detection based on the gain matrix K and secondary 3Sigma blind pixel detection based on the bias matrix B on the two-point parameter matrix and combining the results of two times of blind pixel detection to obtain a blind pixel set table; and adjusting the detection temperature and repeating the above steps to obtain blind pixel set tables corresponding to different temperatures, and sorting and merging the blind pixel set tables corresponding to different temperatures for subsequent compensation. The system and the method of the invention have the advantages of high detection efficiency and good quality, and missing pixels can be reduced in detection.

Owner:NANJING UNIV OF SCI & TECH

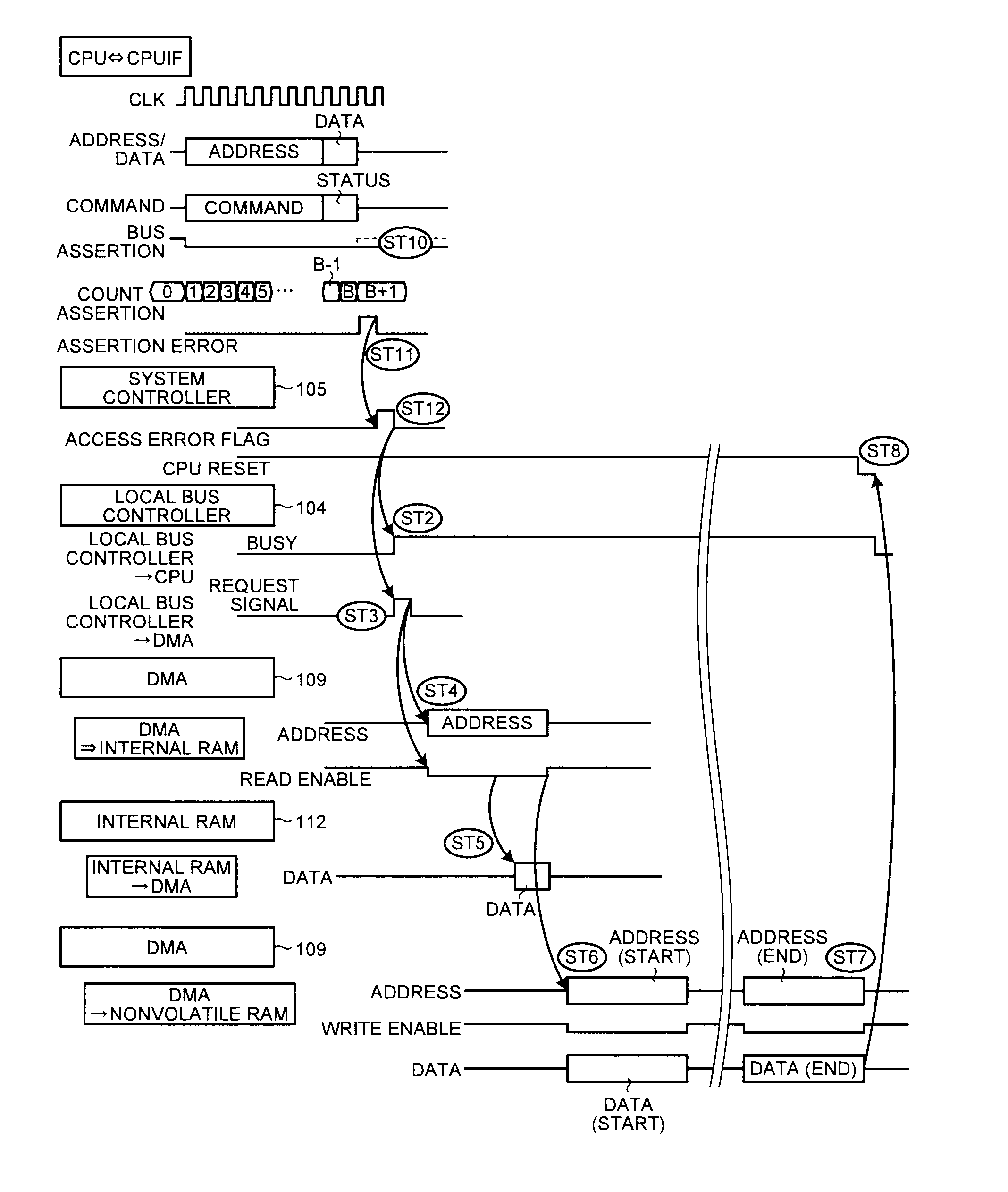

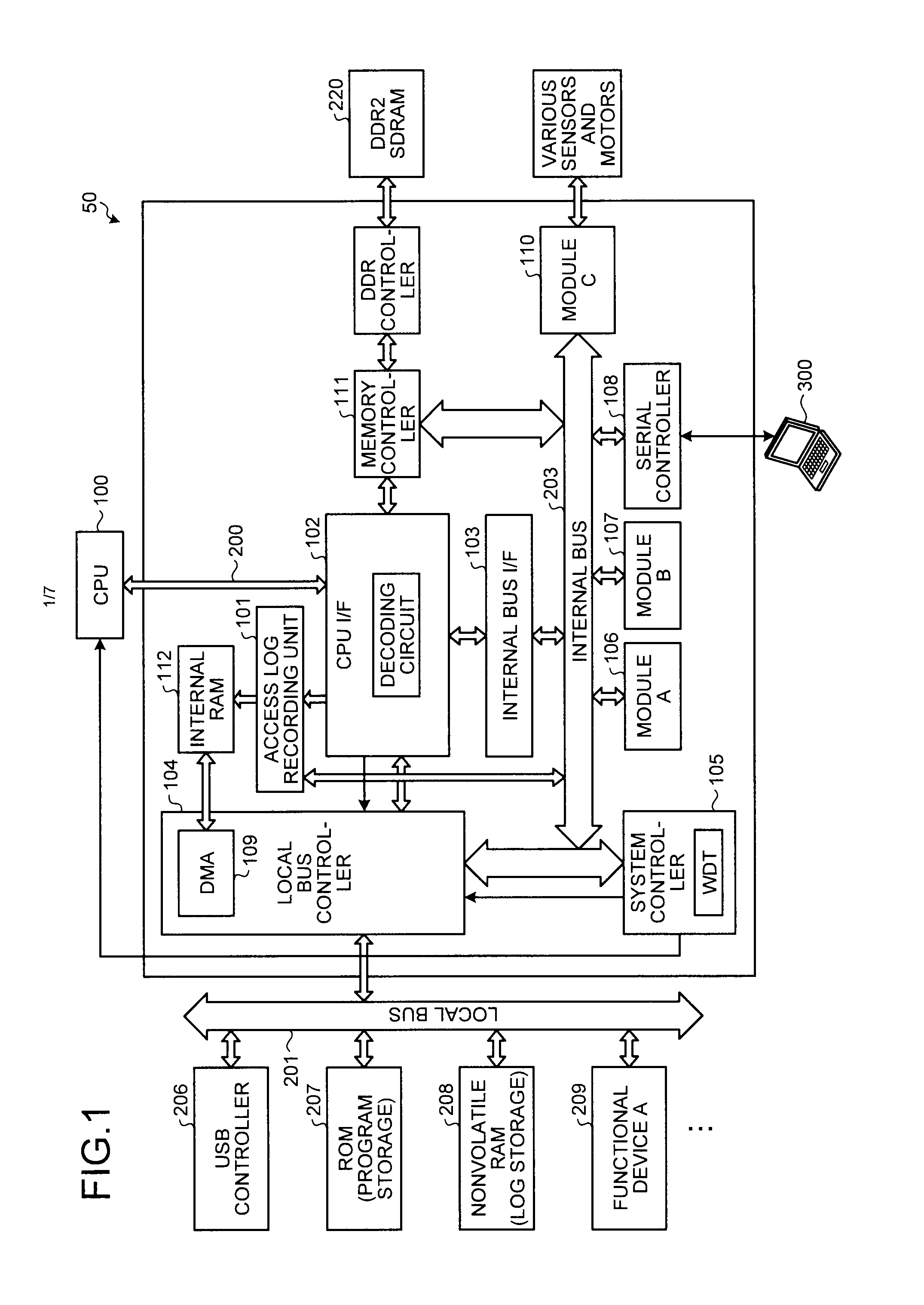

Information processing apparatus, image forming apparatus, and information processing program

A CPU I / F decodes a signal transmitted from a CPU to a target location, and transmits the decoded signal to a mediating module mediating with the target location and to an access log recording unit. The access log recording unit generates an access log using the signal received from the CPU I / F, and stores the access log in an internal RAM. A DMA stores the access log stored in the internal RAM in a nonvolatile RAM when a system controller detects any occurrence of an error in the CPU.

Owner:RICOH KK

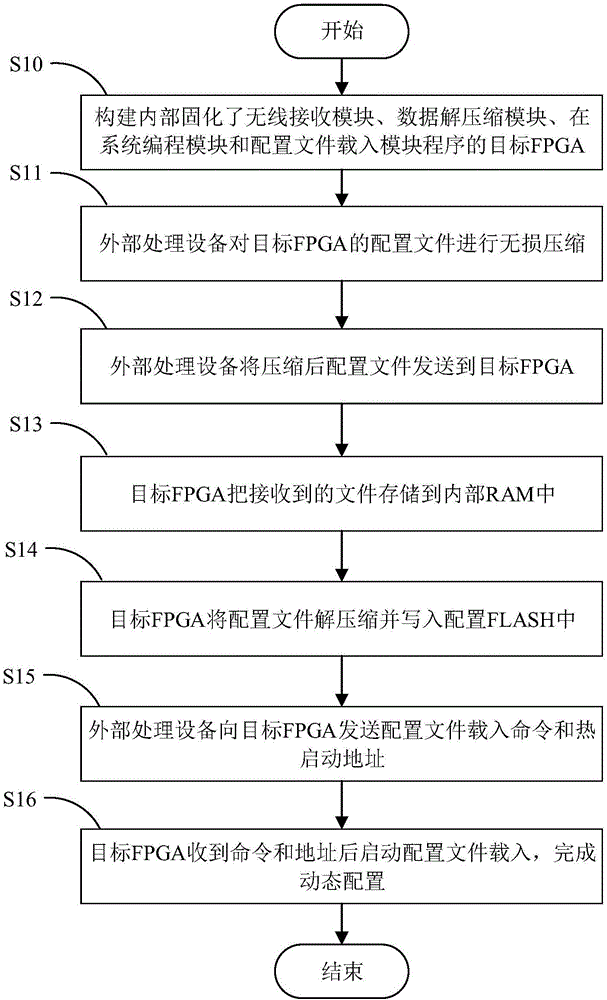

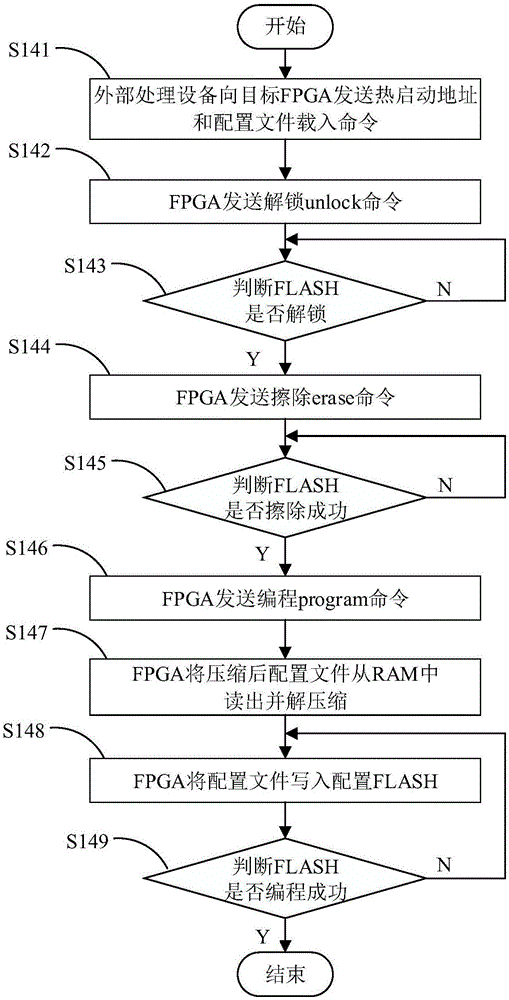

Method for dynamically configuring FPGA (field programmable gate arrays) on basis of file compression and non-contact modes

InactiveCN106843955AReduce sizeReduce transfer timeProgram loading/initiatingIn-system programmingRandom access memory

The invention provides a method for dynamically configuring FPGA (field programmable gate arrays) on the basis of file compression and non-contact modes. By the aid of the method, the technical problems of high hardware complexity, low configuration speeds and poor flexibility of existing dynamic configuration can be solved. The method includes implementation steps of constructing the target FPGA; carrying out lossless compression on configuration files of the target FPGA by the aid of external processing equipment; transmitting compressed configuration files to the target FPGA in wireless modes; storing the received compressed configuration files in internal RAM (random access memories) by the aid of wireless receiving modules; reading the compressed configuration files from the RAM by the aid of data decompression modules, decompressing the compressed configuration files and then writing the configuration files into configuration FLASH; transmitting configuration file loading commands and hot start addresses by the aid of the external processing equipment; starting to load the configuration files from the hot start addresses of the configuration FLASH by the aid of configuration file loading modules so as to completely dynamically configure the FPGA. Programs of the wireless receiving modules, the data decompression modules, in-system programming modules and the configuration file loading modules are solidified inside the target FPGA.

Owner:XIDIAN UNIV

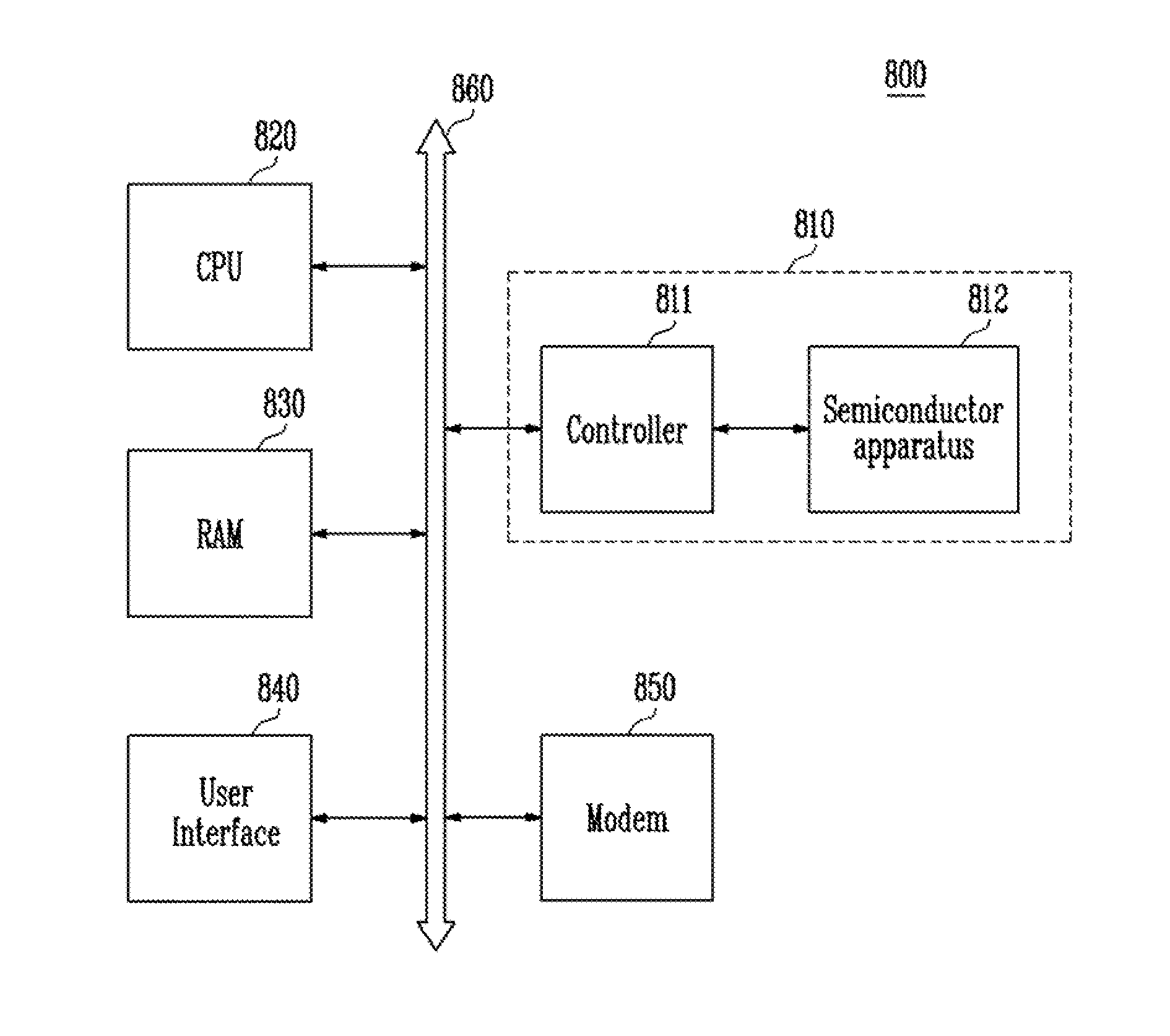

Memory system and operating method thereof

ActiveUS20160357472A1Shorten speedDecrease in speed can be minimizedInput/output to record carriersRead-only memoriesRandom access memorySemiconductor

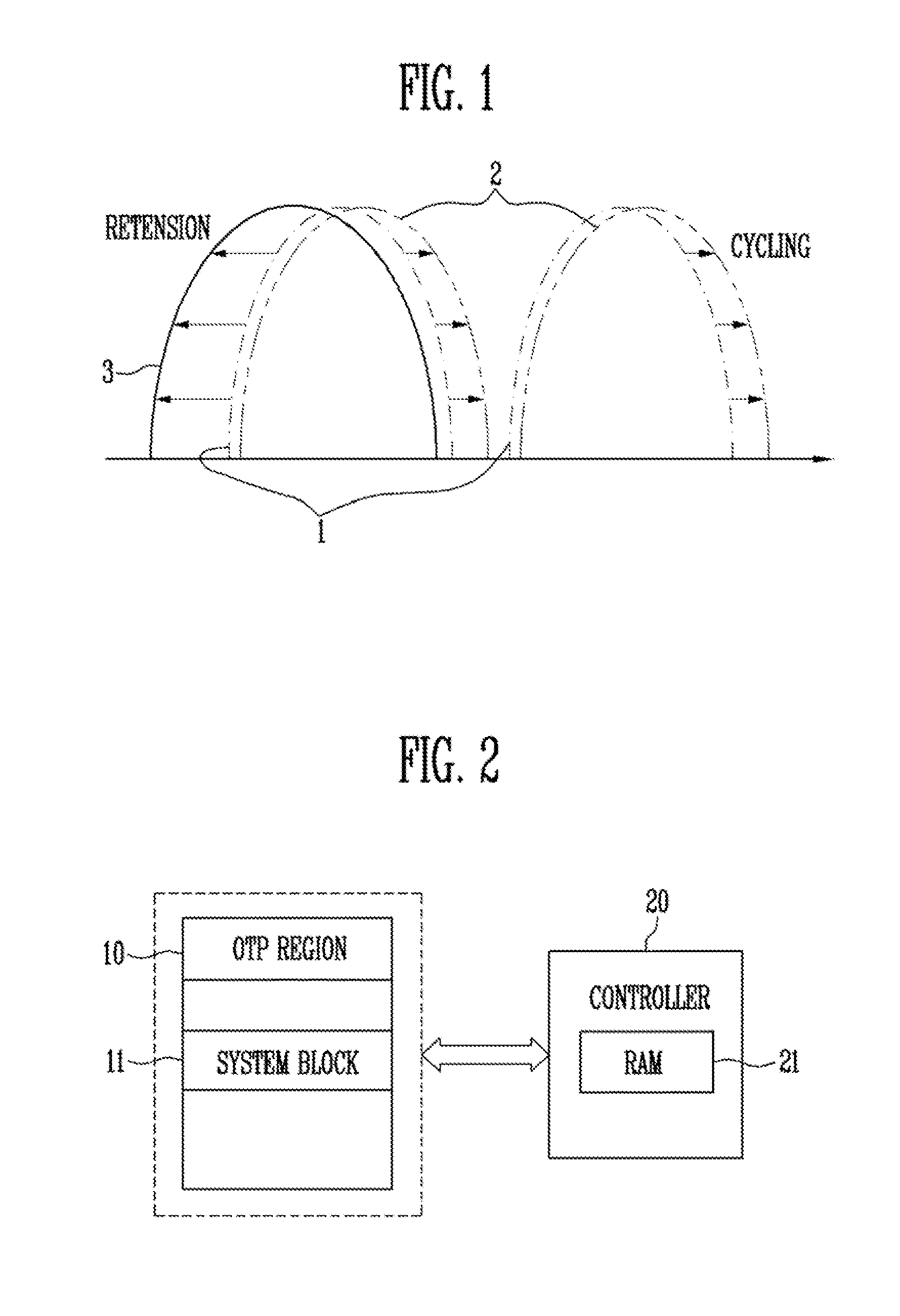

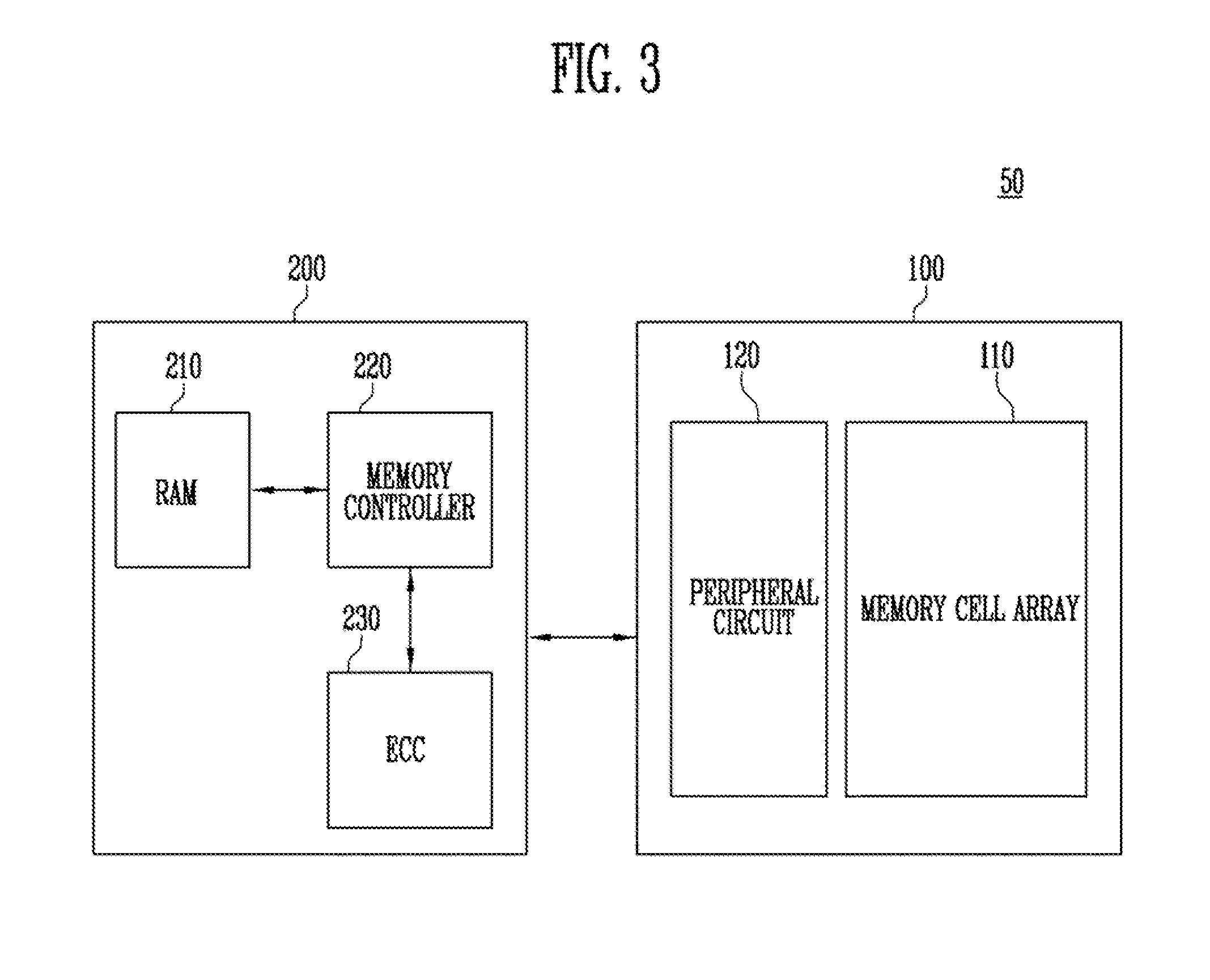

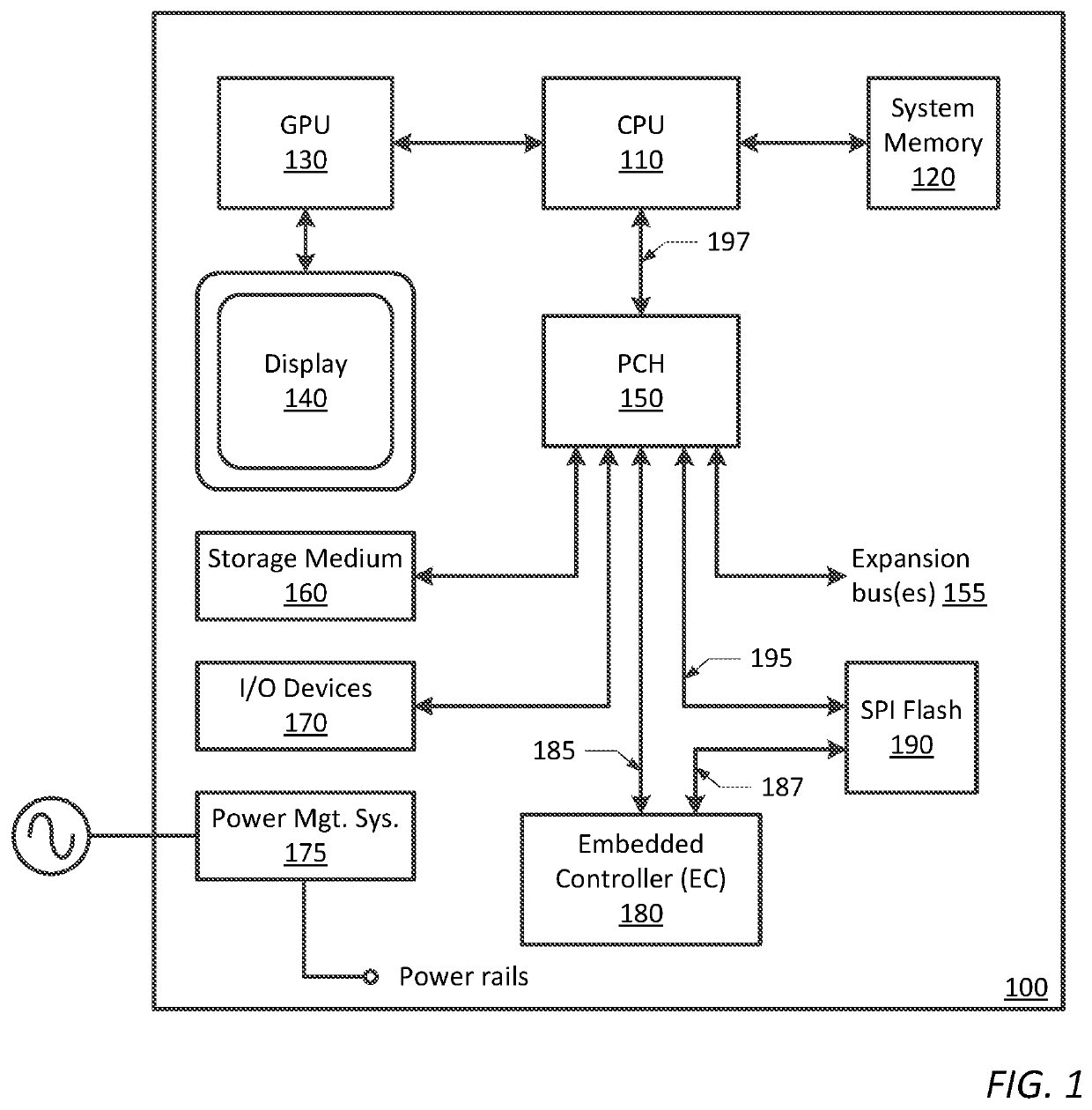

A memory system includes a semiconductor memory device including memory cells and an internal Random Access Memory (RAM); and a controller suitable for transmitting read retry table information to the semiconductor memory device when a read operation for the memory cells fails, wherein the internal RAM stores a read retry table during operation of the memory system, and wherein the semiconductor memory device performs a read retry operation with a read retry voltage determined based on the read retry table and the read retry table information.

Owner:SK HYNIX INC

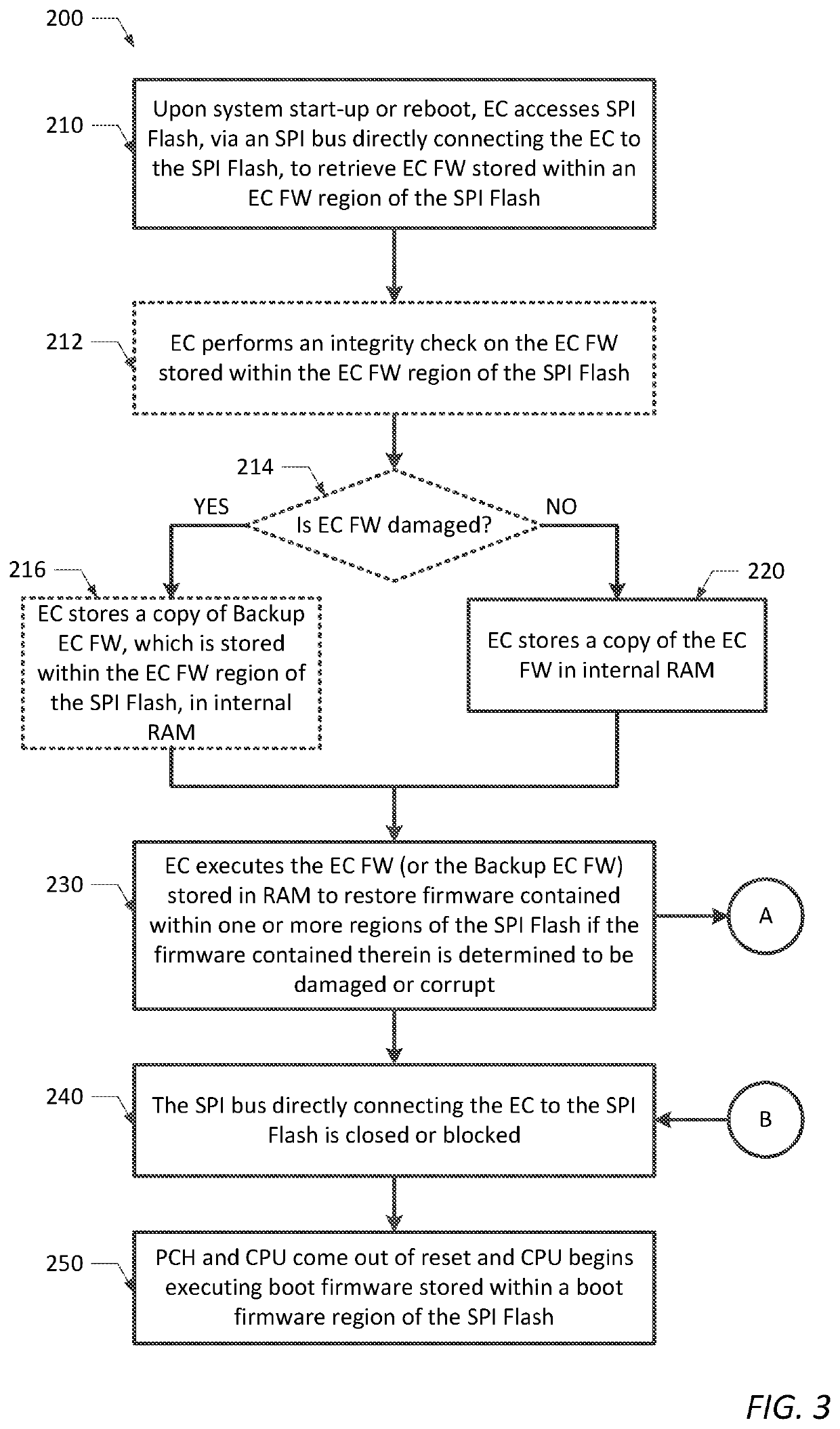

Information Handling System And Method For Restoring Firmware In One Or More Regions Of A Flash Memory Device

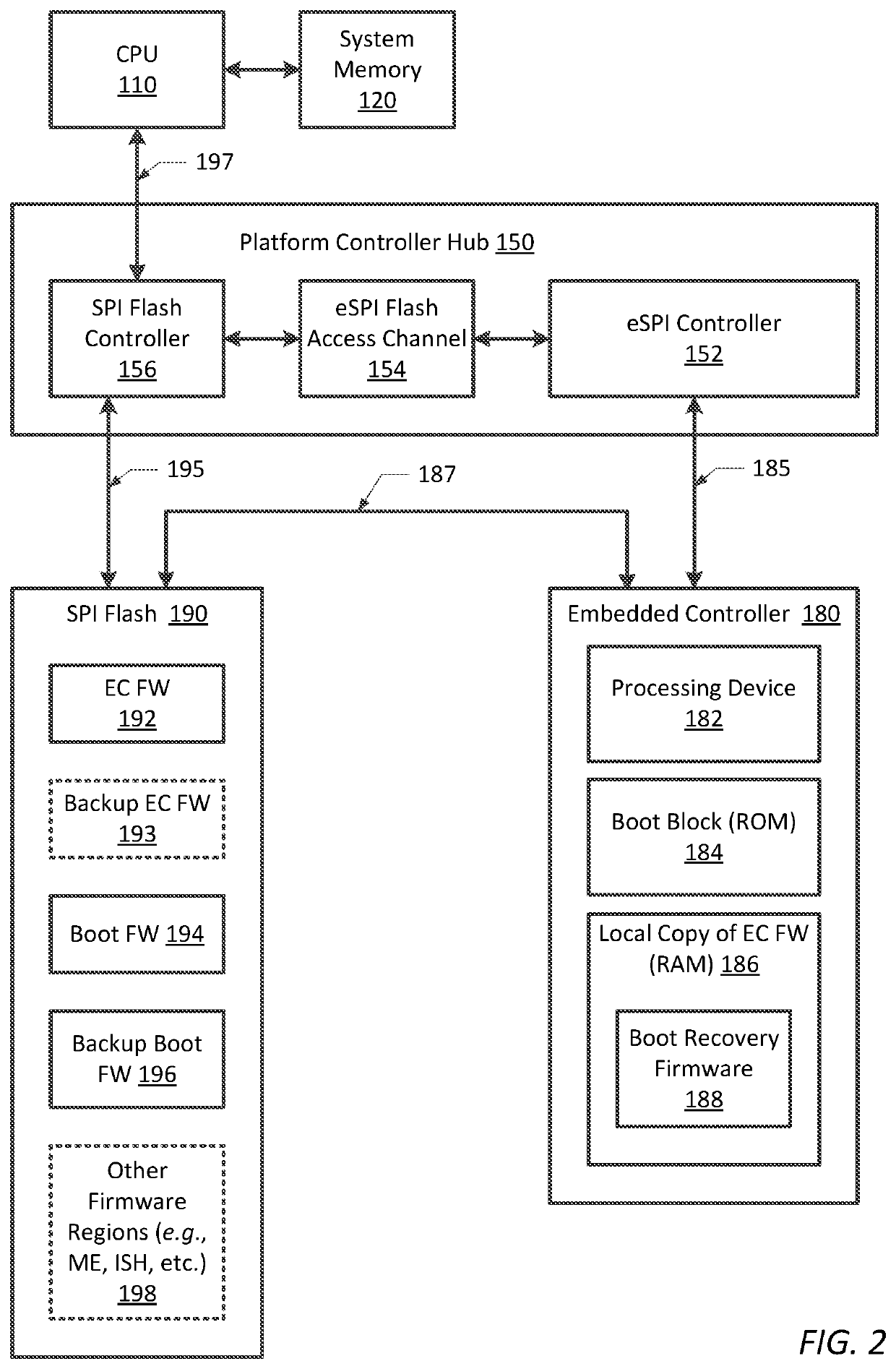

ActiveUS20200201714A1Detecting faulty hardware by power-on testEncryption apparatus with shift registers/memoriesPlatform Controller HubHandling system

An information handling system (IHS) may include a platform controller hub (PCH), an embedded controller (EC) configured to execute a boot block stored in ROM to initiate a boot process for the IHS, a Flash memory device configured to store EC application firmware, boot firmware and backup boot firmware, which is substantially identical to the boot firmware, and an SPI bus that directly connects the EC to the Flash memory device during a portion of the boot process when the PCH is in reset. The EC uses the SPI bus to access the Flash memory device, retrieve the EC application firmware stored therein, store a local copy of the EC application firmware in internal RAM and execute the local copy of the EC application firmware while the PCH is in reset. The EC application firmware stored in RAM includes boot recovery firmware, which may be executed by the EC to restore the boot firmware if the boot firmware is damaged or corrupt.

Owner:DELL PROD LP

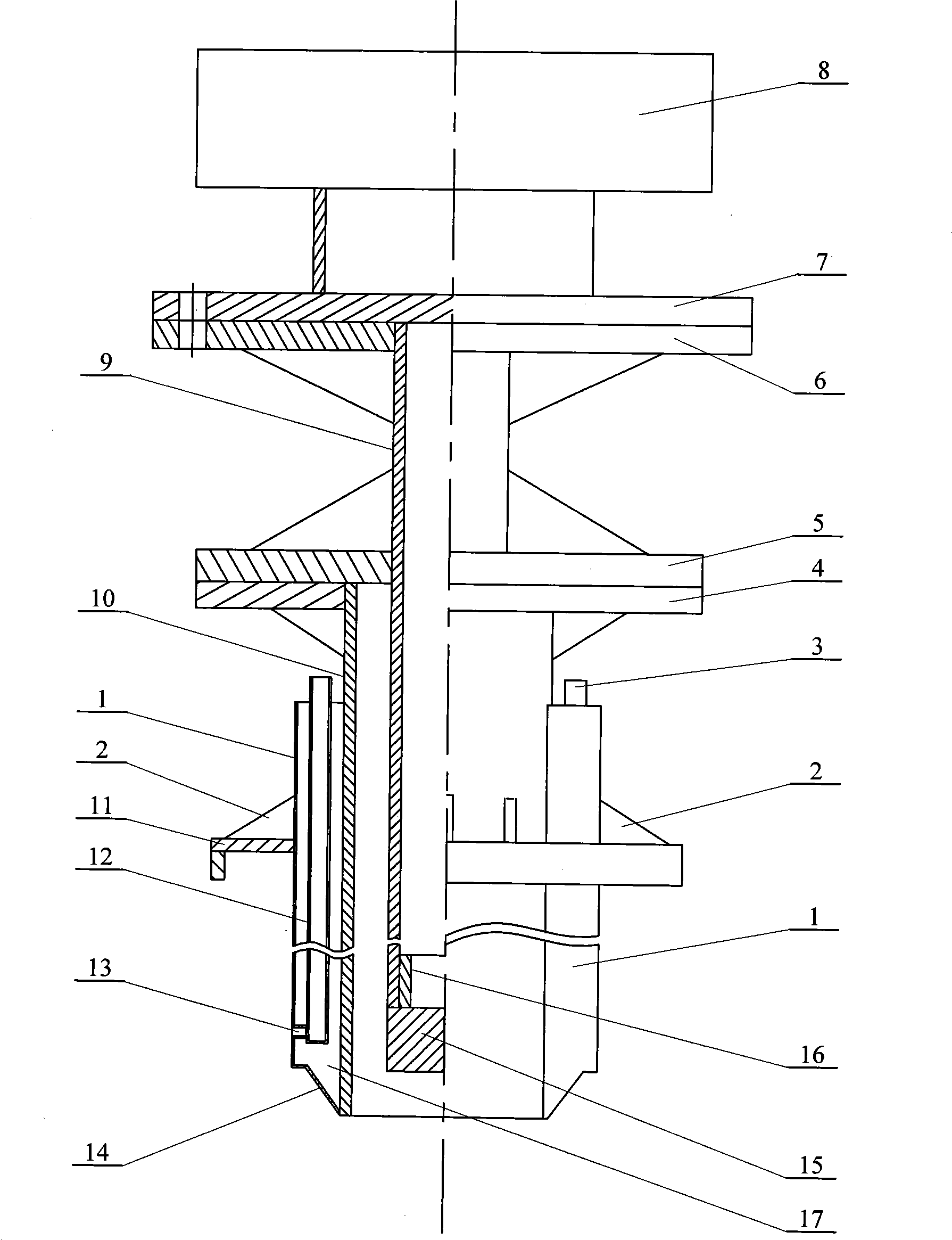

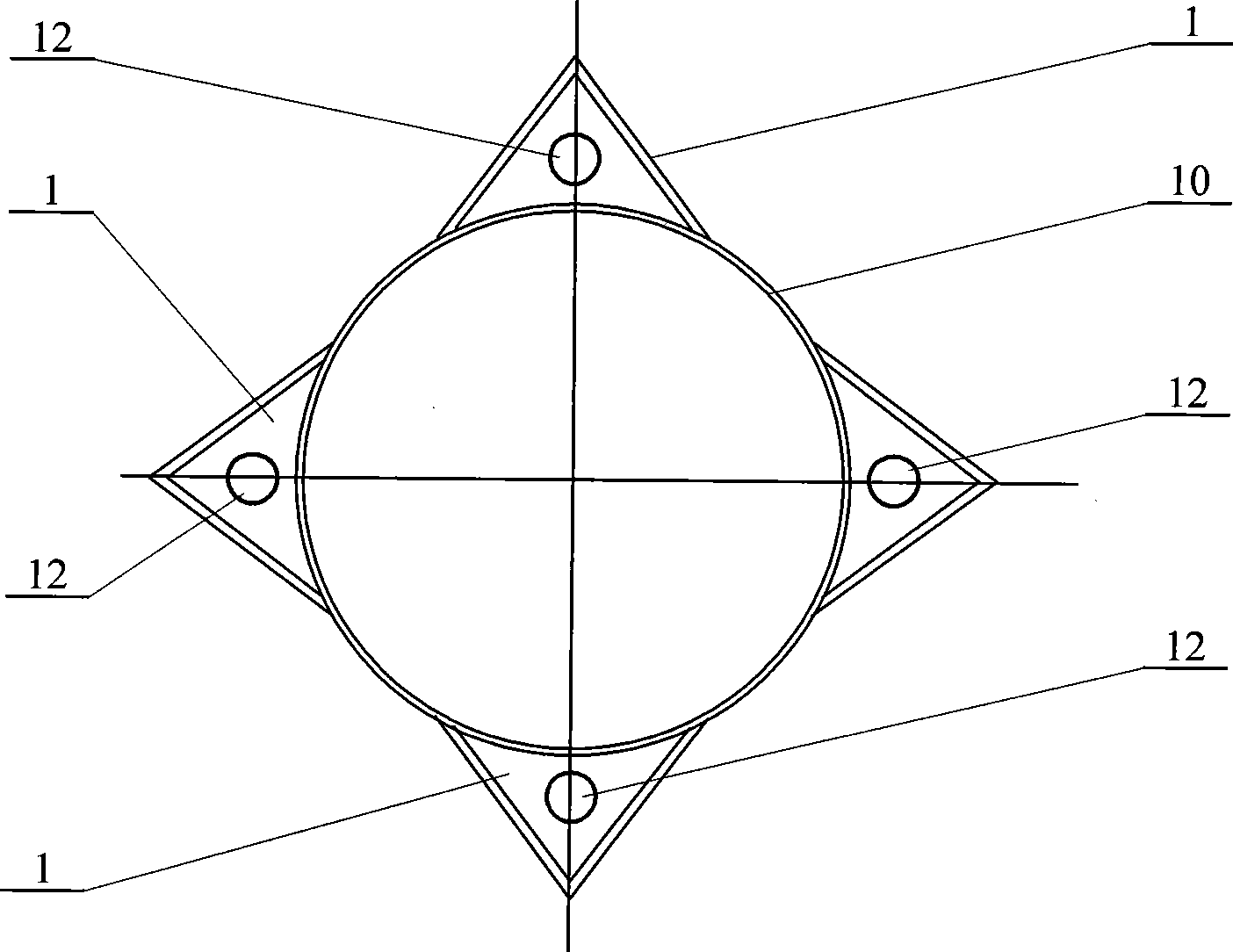

Pile forming apparatus and method for mud-jacking inner-ramming pedestal pile

The invention provides a pile-forming device for a grouting internal-ramming pedestal pile and a pile-forming method thereof, relating to a pile-forming device and a method. The device and the method aim at solving the problems that the existing internal-ramming pile has bad side friction and anti-pulling capability, is easy to generate the necking and breaking problem and has low construction efficiency. The injection pipe of the device is fixed in an external steel plate with a sealed cavity; the bottom end of the external steel plate with the sealed cavity is fixedly provided with a lower sealing plate with a sealed cavity; the invention is provided with four methods as follows: method one: an external pipe is impacted by a hammer, meanwhile, the grout is injected into the injection pipe by a pump, with the injection pressure of 0.3-10MPa; method two: an internal pipe is impacted by a diesel hammer, a hydraulic hammer or a vibration hammer and the filling material is impacted; method three: the external pipe and a pre-fabricated pile are impacted to a design depth by the diesel hammer, the hydraulic hammer or the vibration hammer; method four: the pre-fabricated pile is impacted into the pile hole, wherein, the diameter of the external pipe is less than or equal to the maximum internal tangent round of the pre-fabricating pile. The device has high construction efficiency and is suitable for various soil qualities. The method reduces the generation of necking and breaking, and improves the bearing capability by more than 30%.

Owner:李永刚

Multiplexed audio data decoding apparatus and receiver apparatus

InactiveUS7447241B2Avoid lostIncrease flexibilityTelevision system detailsPulse modulation television signal transmissionMultiplexingAudio frequency

A multiplexed audio data decoder apparatus is provided in which integration of an audio decoder is easy, and has a high flexibility when the number of the formats to be processed is increased or when the specification is changed. In an external ROM 60 there are accumulated a plurality of decoding program codes corresponding to respective plural methods for compressing and encoding. A controller means 50 transfers the decoding program code corresponding to the method for compressing and encoding after changing thereof, from the external ROM 60 to an internal RAM 25. A DSP 22 starts decoding processing by using the decoding program code which is transmitted into the internal RAM 25.

Owner:MAXELL HLDG LTD

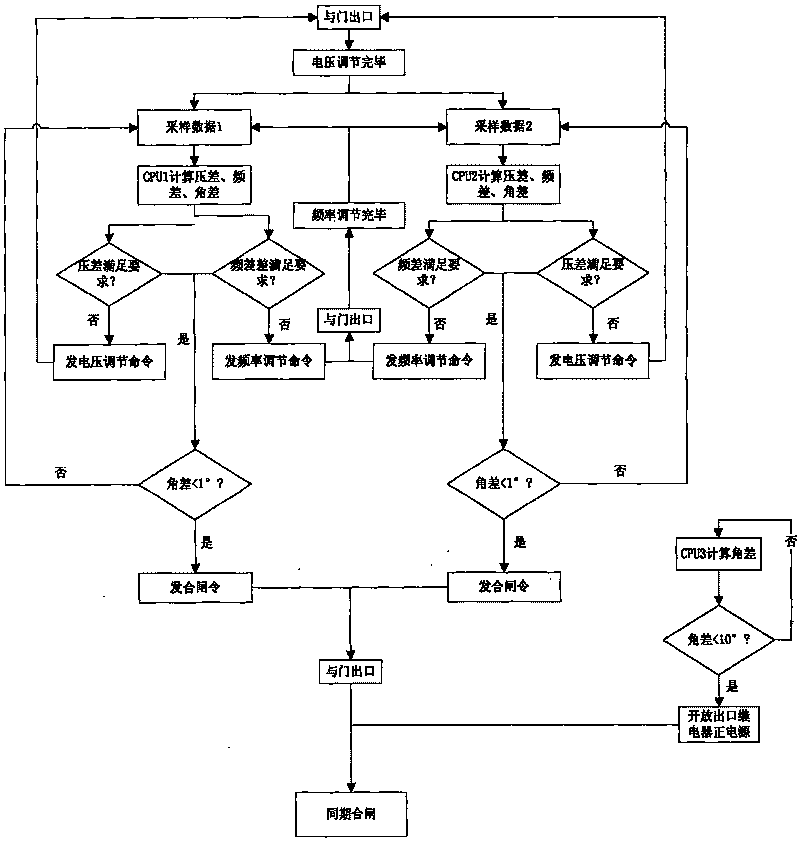

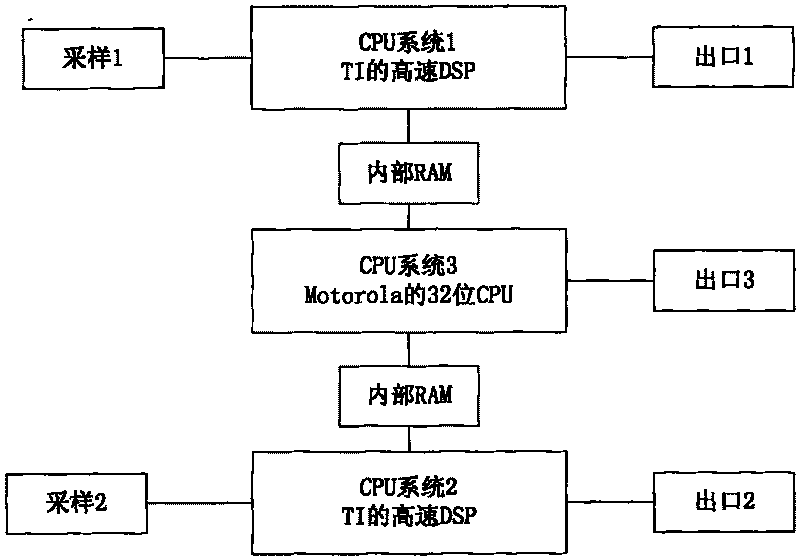

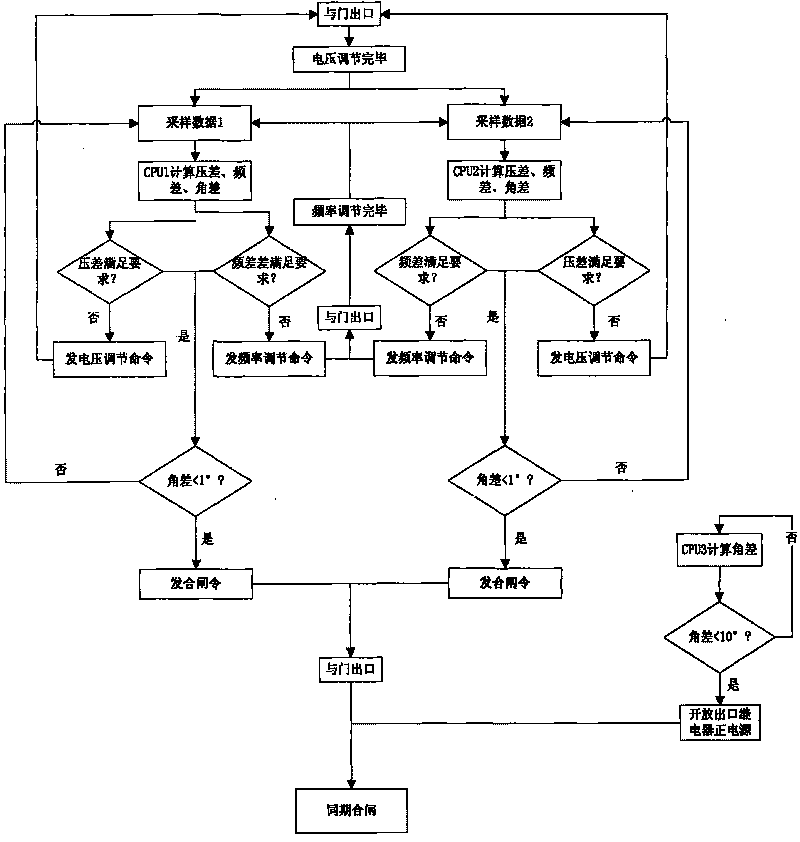

Synchronously-closed multi-CPU coprocessing method

ActiveCN101764415AEliminate the possibility of non-synchronous closingSingle network parallel feeding arrangementsRandom access memoryFrequency regulation

The invention discloses a synchronously-closed multi-CPU (Central Processing Unit) coprocessing method, which comprises the following steps: (1) acquiring voltage signals of two sides of synchronous points through independent AD sampling by first and second CPU systems; (2) respectively calculating the voltage difference, the frequency difference and the angle difference of two sides of the synchronous points by the first and second CPU systems; (3) when the voltage difference of two sides of the synchronous points calculated by the first and second CPU systems does not meet the synchronous requirements, respectively transmitting a voltage regulating signal which passes through an AND gate outlet until the voltage difference meets the synchronous conditions; (4) when the frequency difference of two sides of the synchronous points calculated by the first and second CPU systems does not meet the synchronous requirements, respectively transmitting a frequency regulating signal which passes through an AND gate outlet until the frequency difference meets the synchronous conditions; (5) simultaneously operating the step (3) and the step (4), stopping regulating when the voltage difference and the frequency difference simultaneously meet the requirements; (6) sharing sample data among a third CPU system, the first CPU system and the second CPU system through an internal RAM (Random Access Memory); and (7) turning on a positive power supply of an outlet relay when the angle difference of two sides of the synchronous points is detected within 10 degrees by the third CPU system.

Owner:南京弘毅电气自动化有限公司

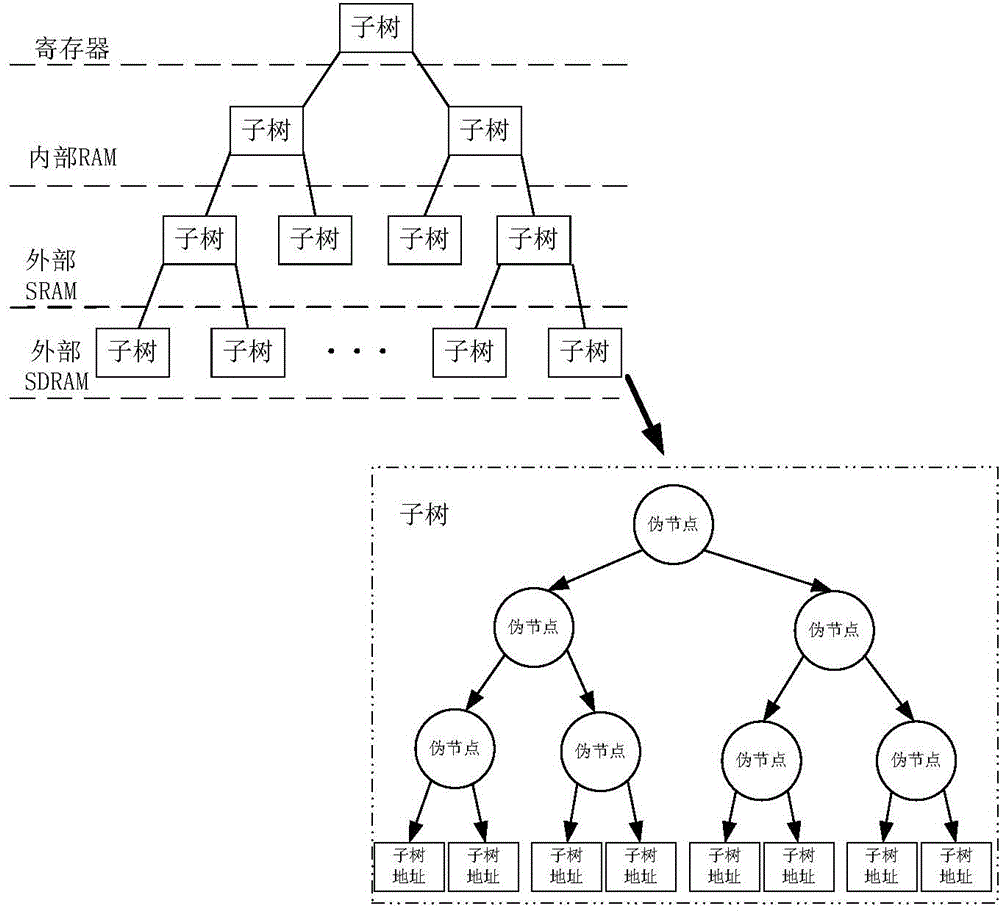

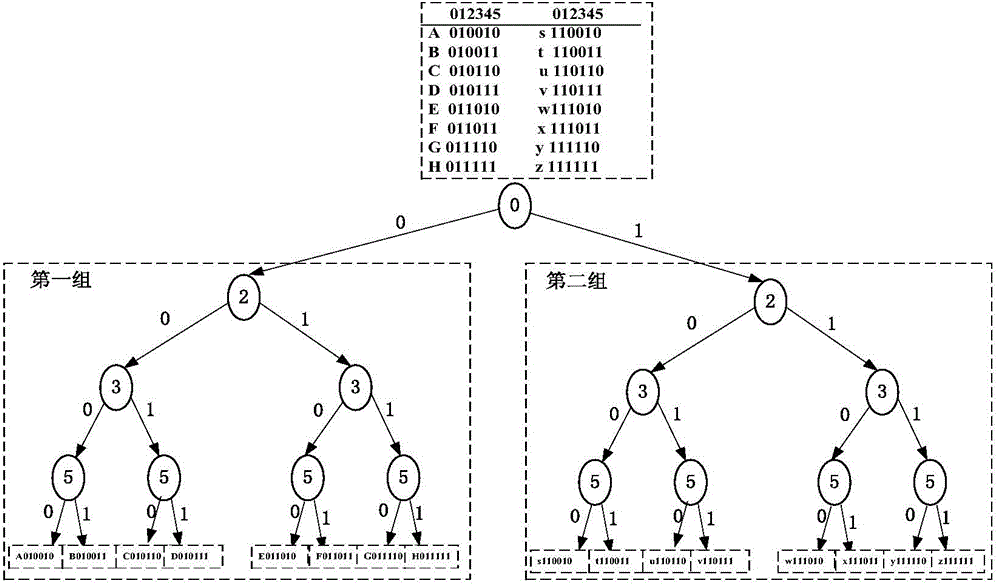

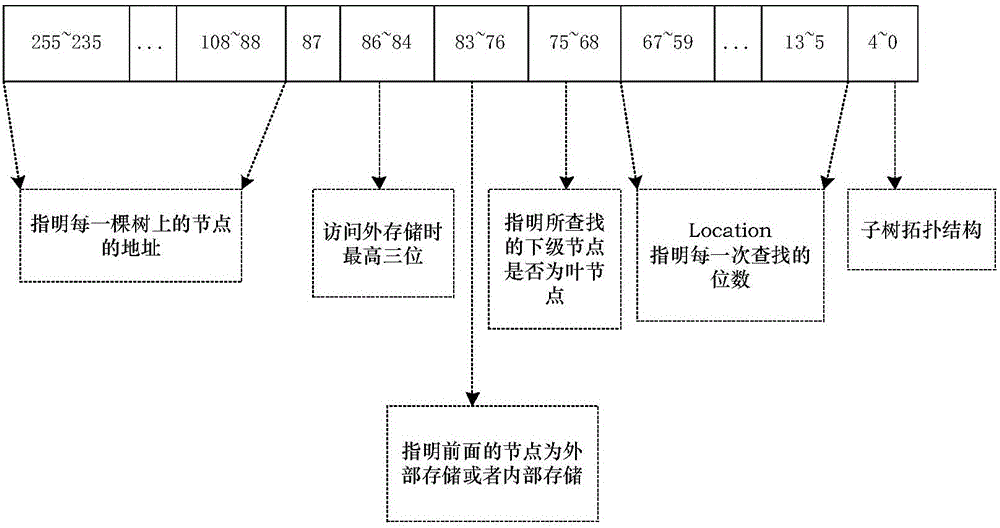

Trie searching method and device applied to network processor

InactiveCN104090942AFast searchReduce the number of memory accessesSpecial data processing applicationsExternal storageRouting table

The invention provides a Trie searching method applied to a network processor. The Trie searching method applied to the network processor is characterized by comprising the following steps that firstly, a multi-level storage structure is established, wherein the storage structure comprises a register file, an internal RAM, an external SRAM and an external SDRAM, and the priority of the register file, the priority of the internal RAM, the priority of the external SRAM and the priority of the external SDRAM are gradually reduced; secondly, a balance tree is established, wherein each bit of all routing tables is traversed, the bit of which the number of values 0 and the number of values 1 are roughly equal is found, set as a current root node and marked as a used bit, the process is repeated, and the relative balance tree is established; thirdly, data storage is conducted, wherein every time data storage is conducted, a plurality of adjacent bits of data are organized into a sub-tree structure to conduct data storage. The hierarchical storage structure is adopted for the Trie structure, the time for a key to have access to the external memories is shortened, and high searching speed is obtained at low memory cost.

Owner:NO 32 RES INST OF CHINA ELECTRONICS TECH GRP

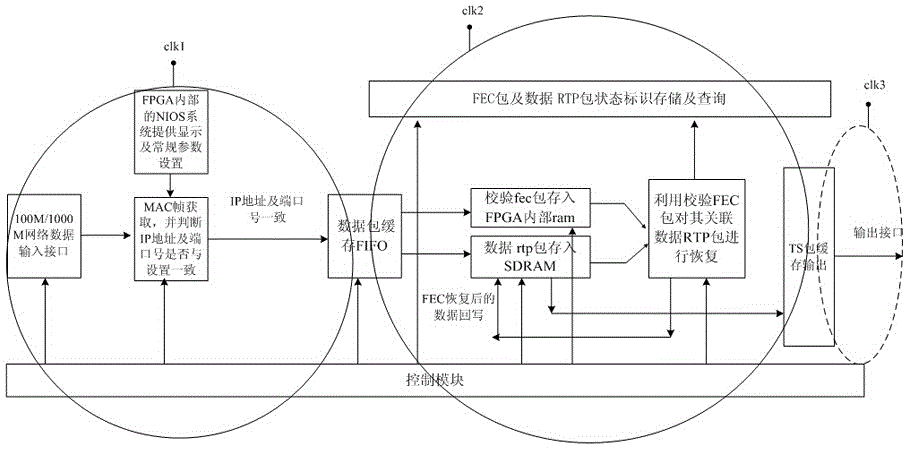

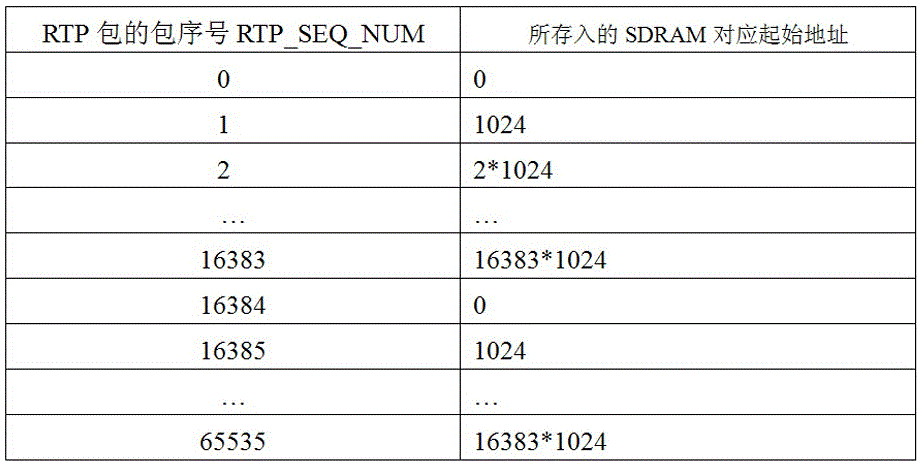

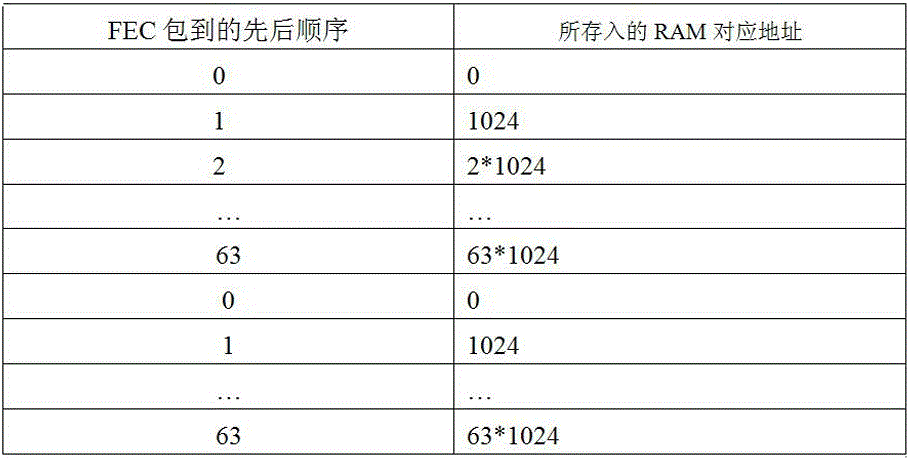

Network transmission real-time audio-video error correction method and system based on FPGA

ActiveCN105872849AImprove error correction processing capabilitiesImprove computing efficiencySelective content distributionComplete dataNetworked Transport of RTCM via Internet Protocol

The invention discloses a network transmission real-time audio-video error correction method and a network transmission real-time audio-video error correction system based on an FPGA, and relates to the field of digital video broadcasting technologies. The technical points of the method provided by the invention comprise analyzing data packets remotely transmitted via a network, processing the data packets matched with a local IP address and a local port number, and judging a check FEC packet and a data RTP packet and respectively storing into the internal RAM and external SDRAM of the FPGA. The check FEC packet is used for recovering the related data RTP packet, the recovered data RTP packet is written back into the SDRAM, a control module reads the complete data packet in the SDRAM for outputting, and thus the loss packet recovery of network remote transmission is achieved.

Owner:CHENGDU KAITENG SIFANG DIGITAL RADIO & TELEVISION EQUIP CO LTD

Electronic device and booting method thereof

An electronic device and a booting method thereof are provided, wherein the method includes the steps of copying the boot image from the first non-volatile memory to the internal RAM when an booting operation of the electronic device begins, setting a stack pointer in the internal RAM by executing a control code to set the stack pointer among control codes of the boot image, and activating the main memory by executing a control code to initialize the main memory controller and activate the main memory among the control codes of the boot image, the control code to initialize the main memory controller and activate the main memory using the stack pointer. Accordingly, since the control code to initialize the main memory controller to activate the main memory is written in a high-level programming language instead of assembly language, the display device can be driven before the main memory is activated.

Owner:HEWLETT PACKARD DEV CO LP

Electronic device and booting method thereof

ActiveUS7694122B2Digital computer detailsData resettingDisplay deviceHigh-level programming language

An electronic device and a booting method thereof are provided, wherein the method includes the steps of copying the boot image from the first non-volatile memory to the internal RAM when a booting operation of the electronic device begins, setting a stack pointer in the internal RAM by executing a control code to set the stack pointer among control codes of the boot image, and activating the main memory by executing a control code to initialize the main memory controller and activate the main memory among the control codes of the boot image, the control code to initialize the main memory controller and activate the main memory using the stack pointer. Accordingly, since the control code to initialize the main memory controller to activate the main memory is written in a high-level programming language instead of assembly language, the display device can be driven before the main memory is activated.

Owner:HEWLETT PACKARD DEV CO LP

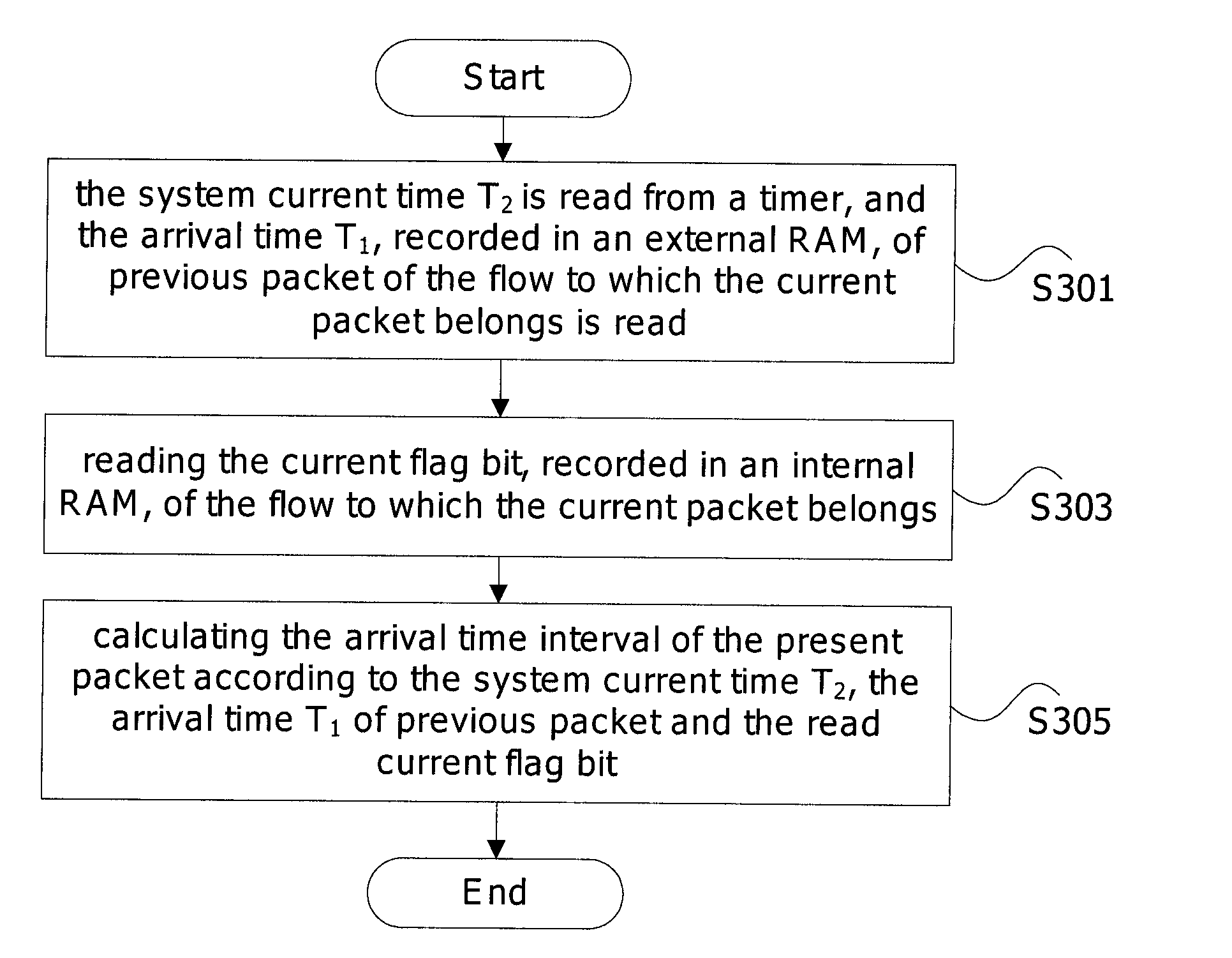

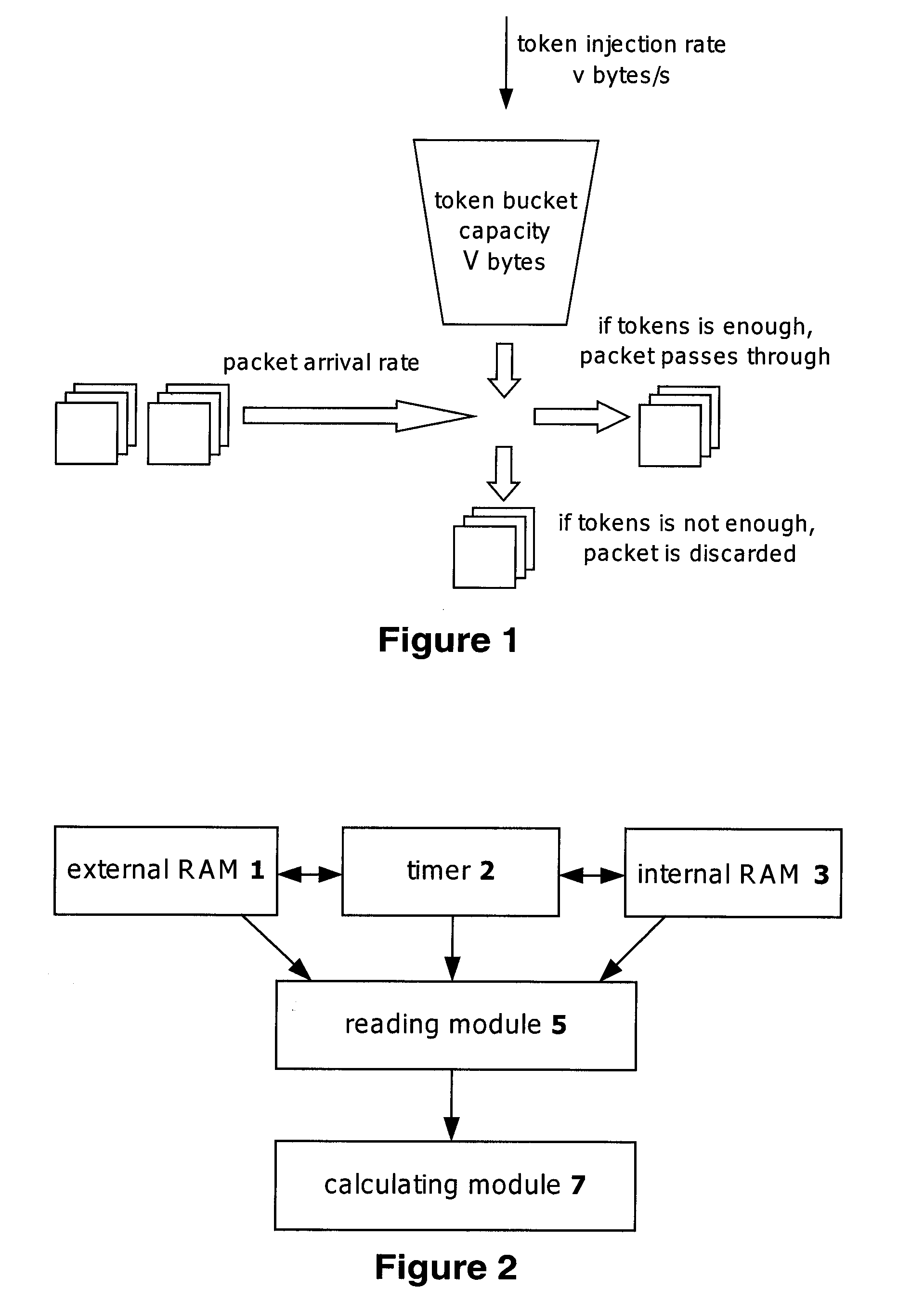

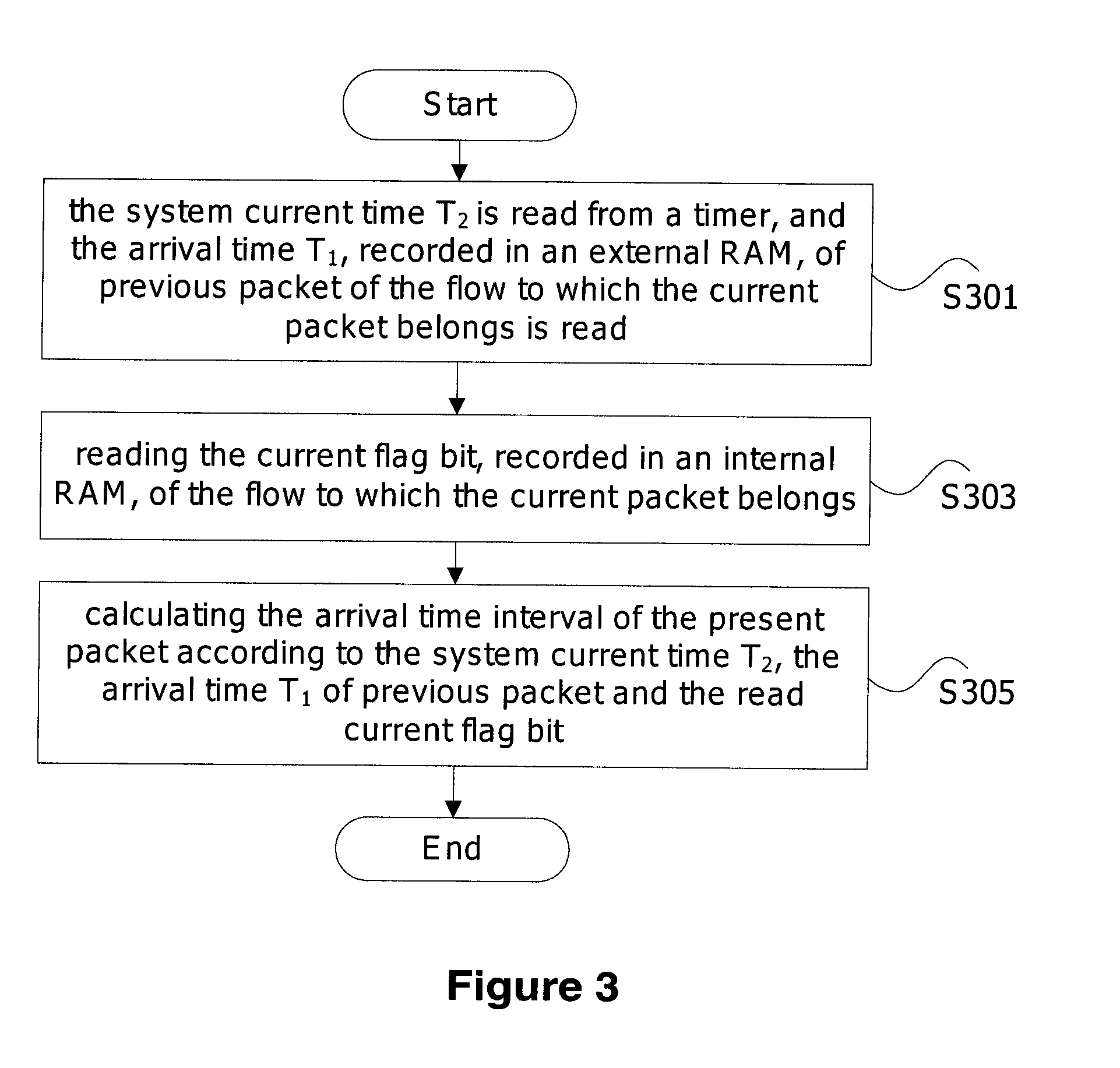

Method and apparatus for calculating packet arrival time interval

ActiveUS20120140668A1Large storage spaceEasy to solveSynchronisation arrangementReceivers monitoringPacket arrivalMaximum depth

A method and an apparatus for calculating packet arrival time interval are provided by the present invention. In the above-mentioned method, when the current packet arrives, system current time T2 is read from a timer, and the arrival time T1, recorded in an external RAM, of previous packet of the flow to which the current packet belongs is read (301), wherein the timer implements a cycle timing with a period of preset time period Tmax, the preset time period Tmax is larger than or equal to the time for filling the maximum depth of the token bucket of the flow at the minimum token injection rate; a current flag bit, recorded in an internal RAM, of the flow to which the current packet belongs is read (303), wherein the current flag bit is used for indicating the number of cycles of the timer between the system current time T2 and the arrival time T1 of previous packet; and the arrival time interval of the present packet is calculated according to the system current time T2, the arrival time T1 of previous packet and the current flag bit (305). Application of the present invention can reduce the consumption of the internal RAM and improve the operability for realizing by the hardware chips.

Owner:ZTE CORP

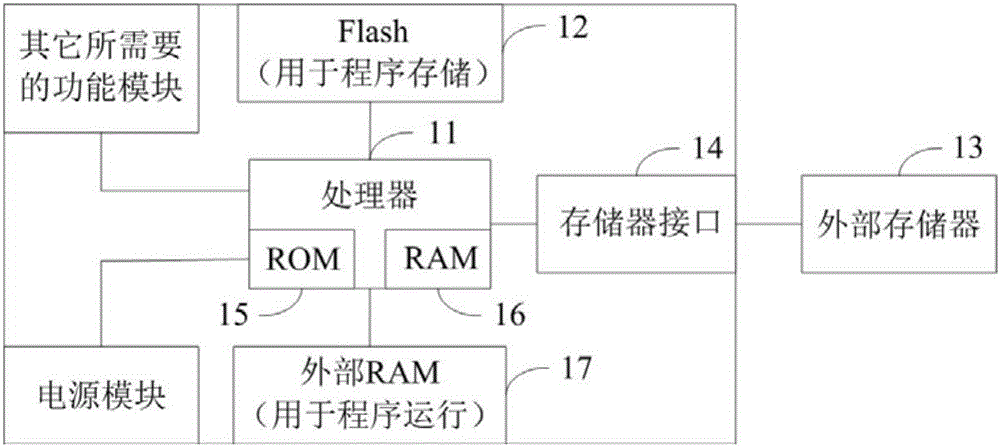

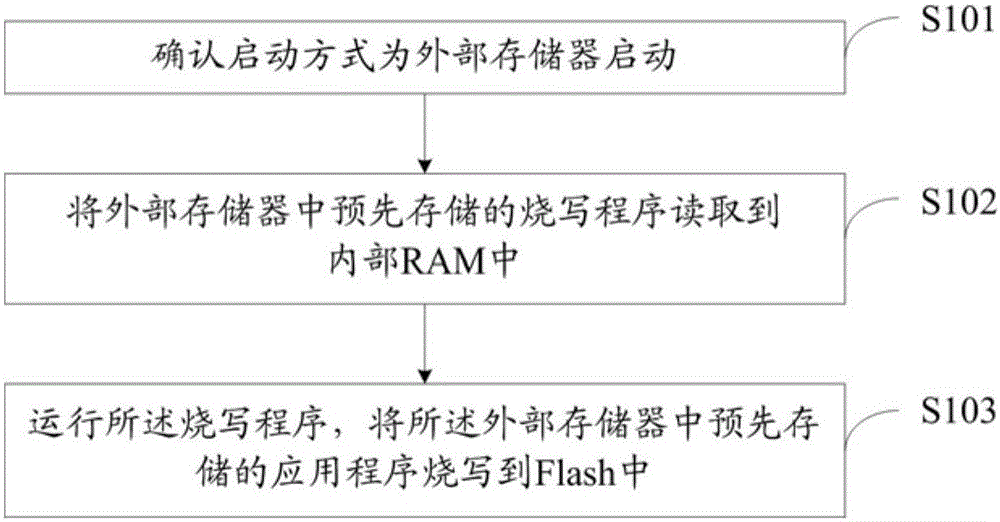

Program burning method, processor and electronic circuit

InactiveCN105677429AEasy to writeFast and simple programming methodSoftware engineeringProgram loading/initiatingElectricityExternal storage

The invention discloses a program burning method, a processor and an electronic circuit and belongs to the technical field of electronics. The program burning method comprises the steps that a starting mode is confirmed to be external storage starting; a burning program which is stored in an external storage in advance is read to an internal RAM; the burning program is operated, and an application program which is stored in the external storage in advance is burnt to Flash. According to the program burning method, the processor and the electronic circuit, the working process of operating the burning program is added, the burning program is stored in the external storage firstly so that the processor can read the burning program while power is on, and the application program is burnt to the Flash after the burning process is started and stored permanently. Compared with the prior art, the program burning method has the advantages that the program burning method can be independent from a PC and is wide in application prospect, convenient, rapid and simple.

Owner:BEIJING TECHSHINO TECH