System and method for realizing multipath burst data business caching based on FPGA (Field Programmable Gate Array)

A burst data and cache technology, applied in the field of communication, can solve the problems of inability to achieve more channels, limited number of channels, and high hardware cost, and achieve the effect of flexibility, reducing the number of channels, and balancing the cache.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0051] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

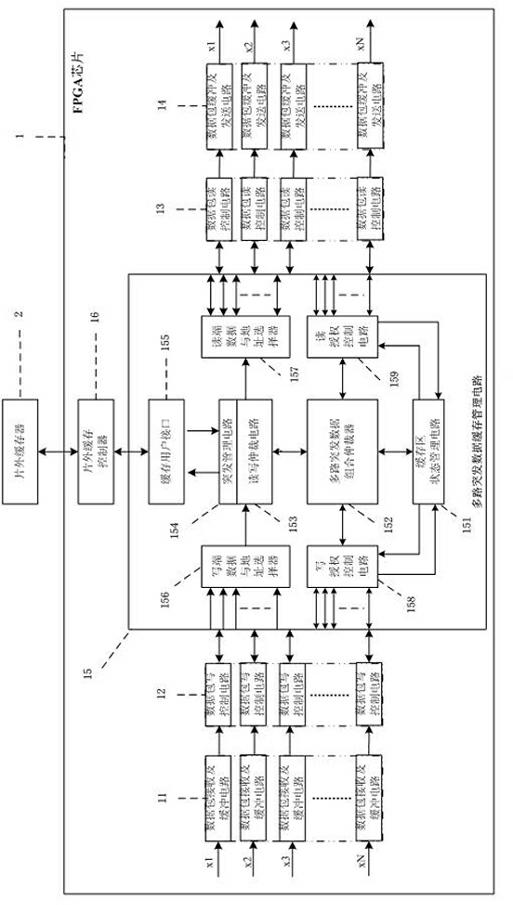

[0052] (1), if image 3 As shown, in this embodiment, the system using FPGA to implement buffering of multi-channel burst data services includes: an FPGA chip 1 and an off-chip buffer 2 that provide block RAM resources.

[0053] Wherein the FPGA chip further includes: a data packet receiving and buffering circuit 11 consistent with the number of data channels, a data packet writing control circuit 12, a data packet reading control circuit 13, a data packet buffering and sending circuit 14, and a multi-channel burst data buffer A management circuit 15 and an off-chip cache controller 16 .

[0054]...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More