Patents

Literature

367 results about "Arbiter" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Arbiters are electronic devices that allocate access to shared resources.

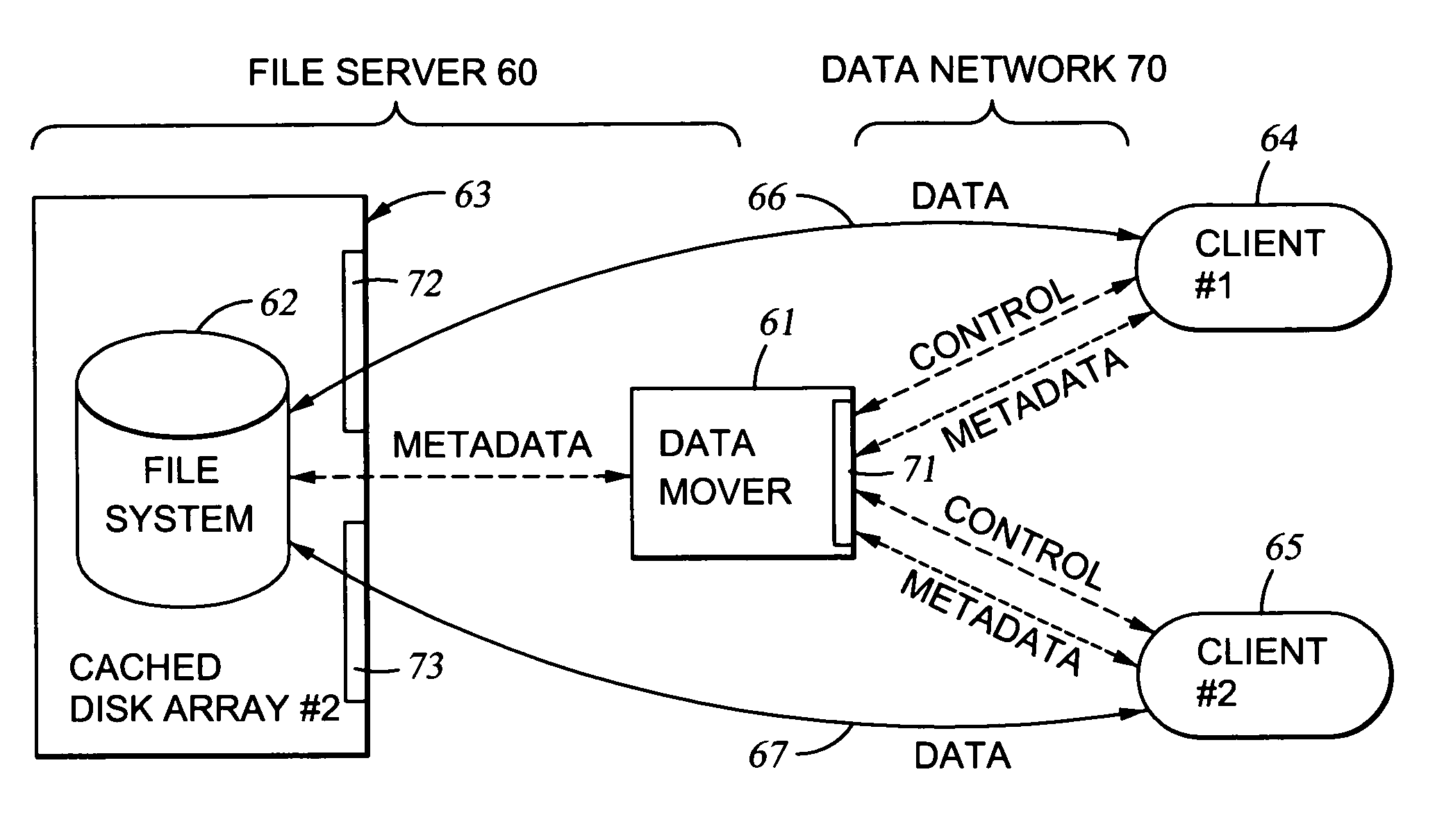

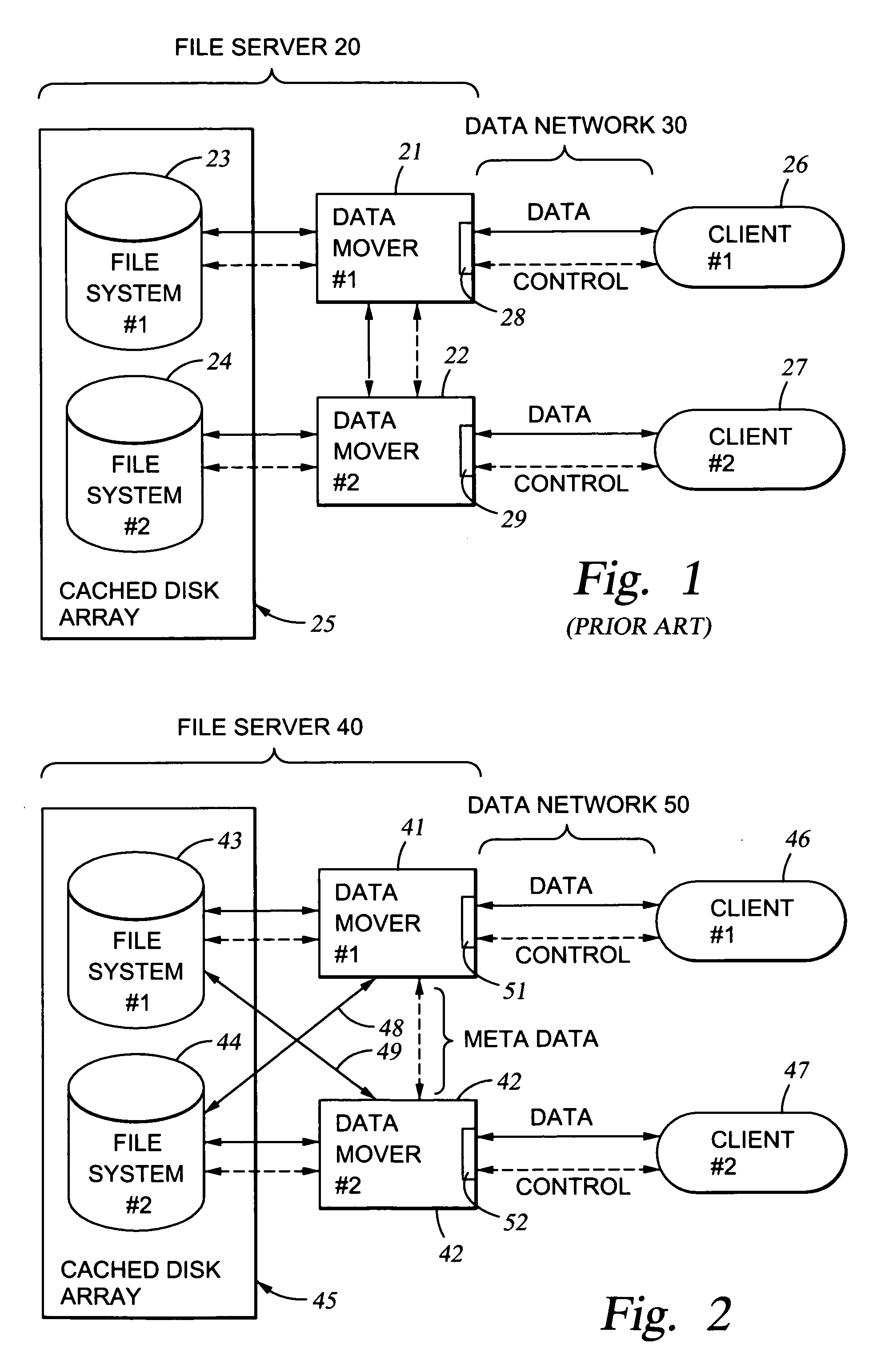

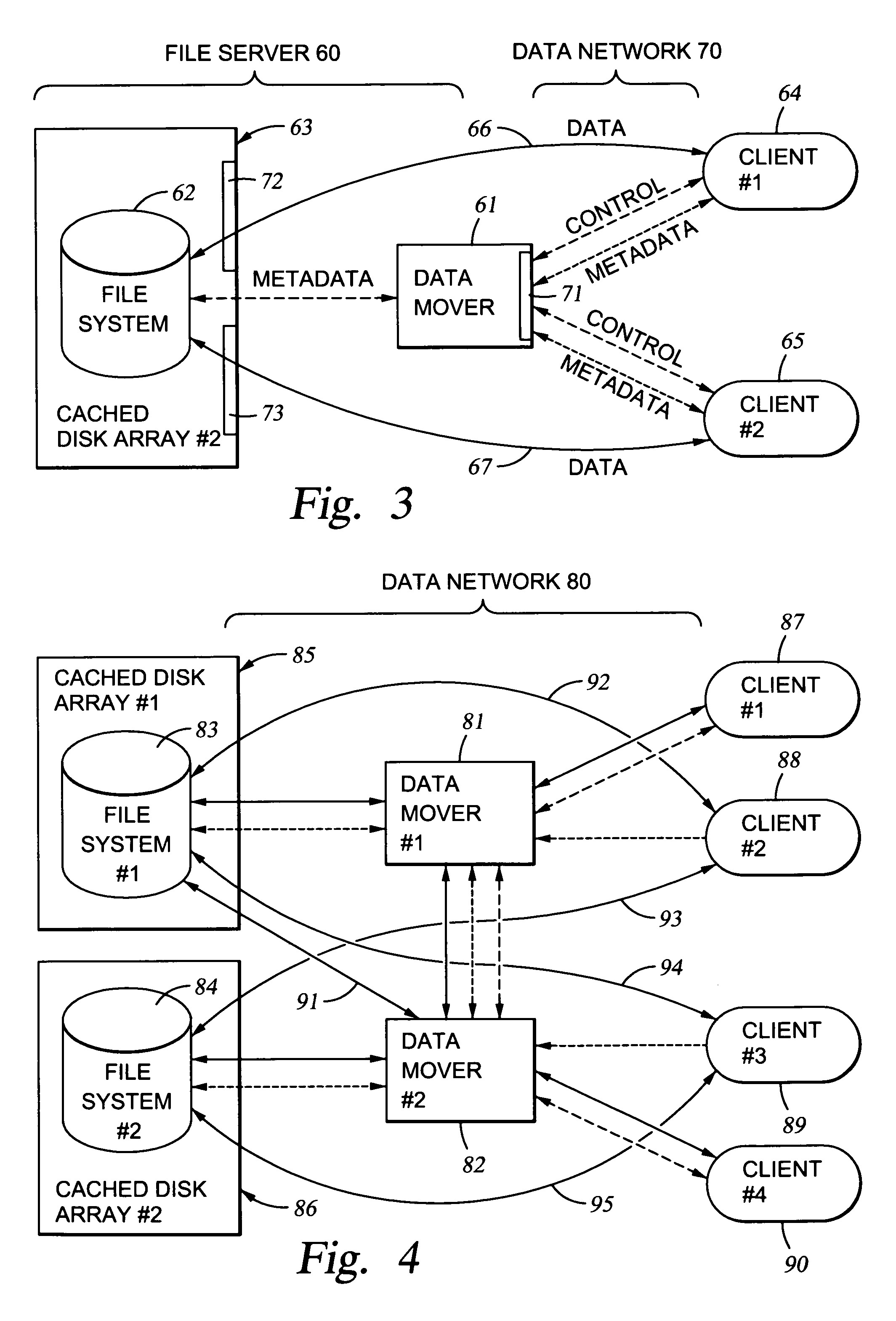

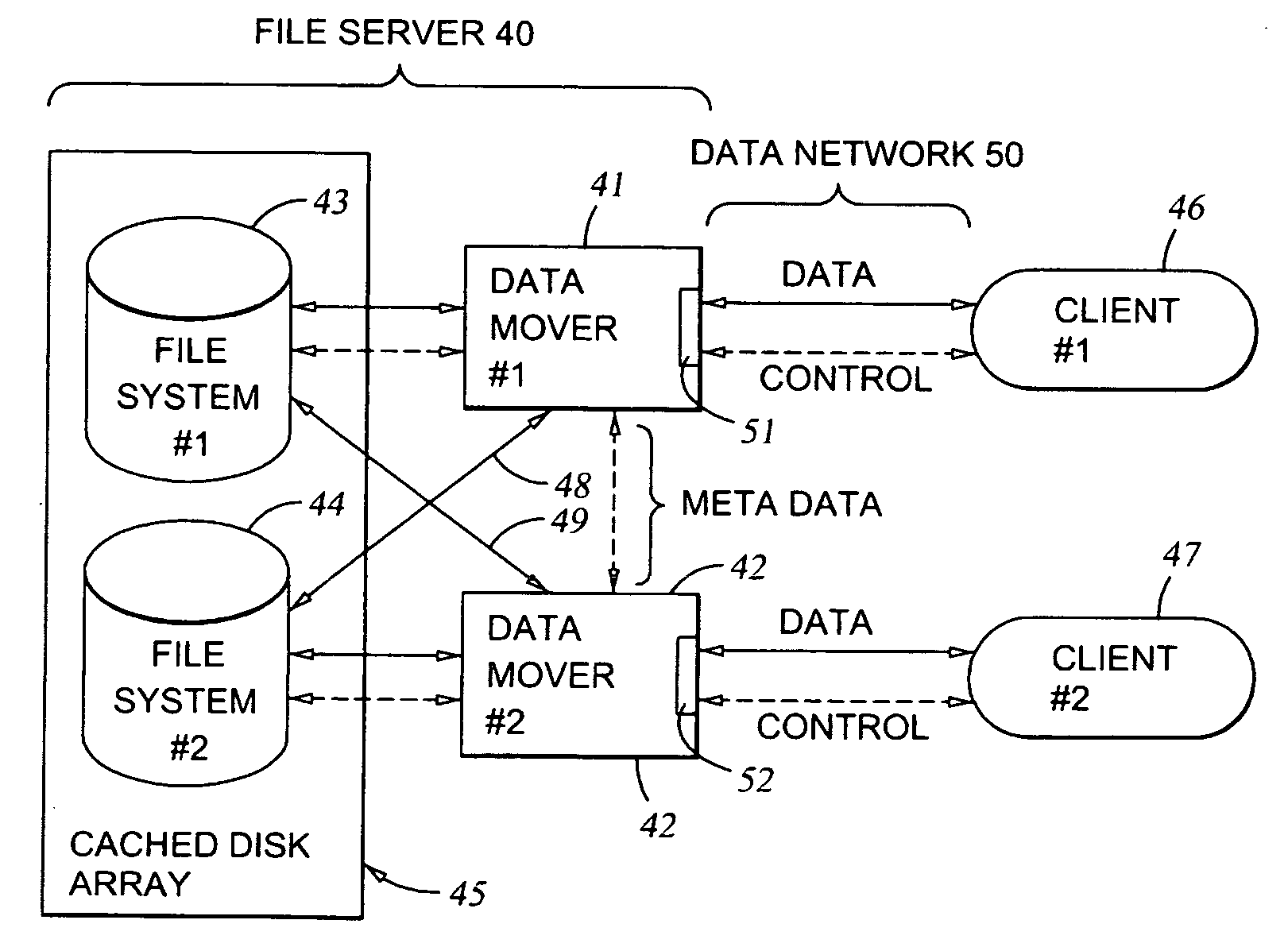

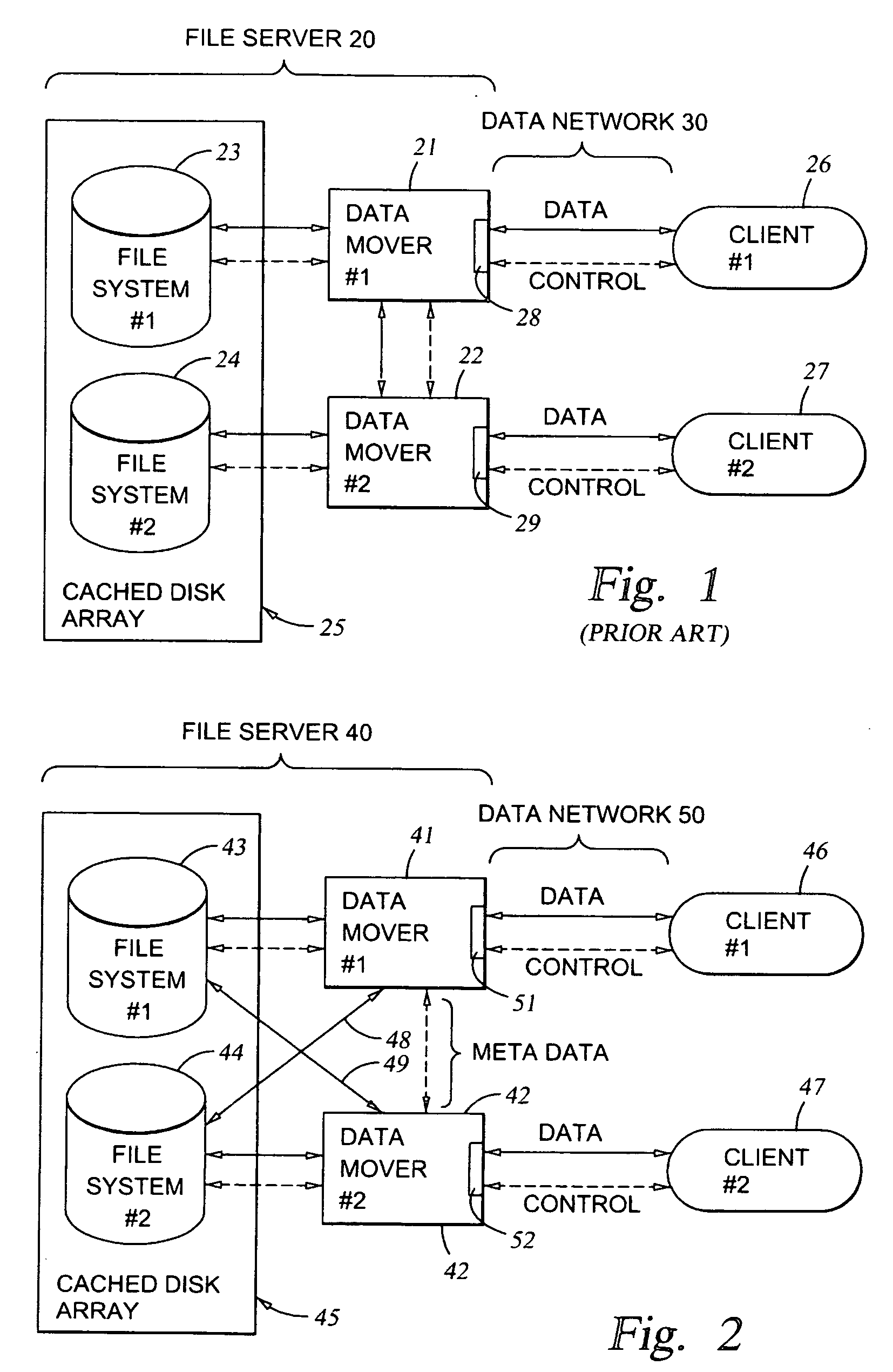

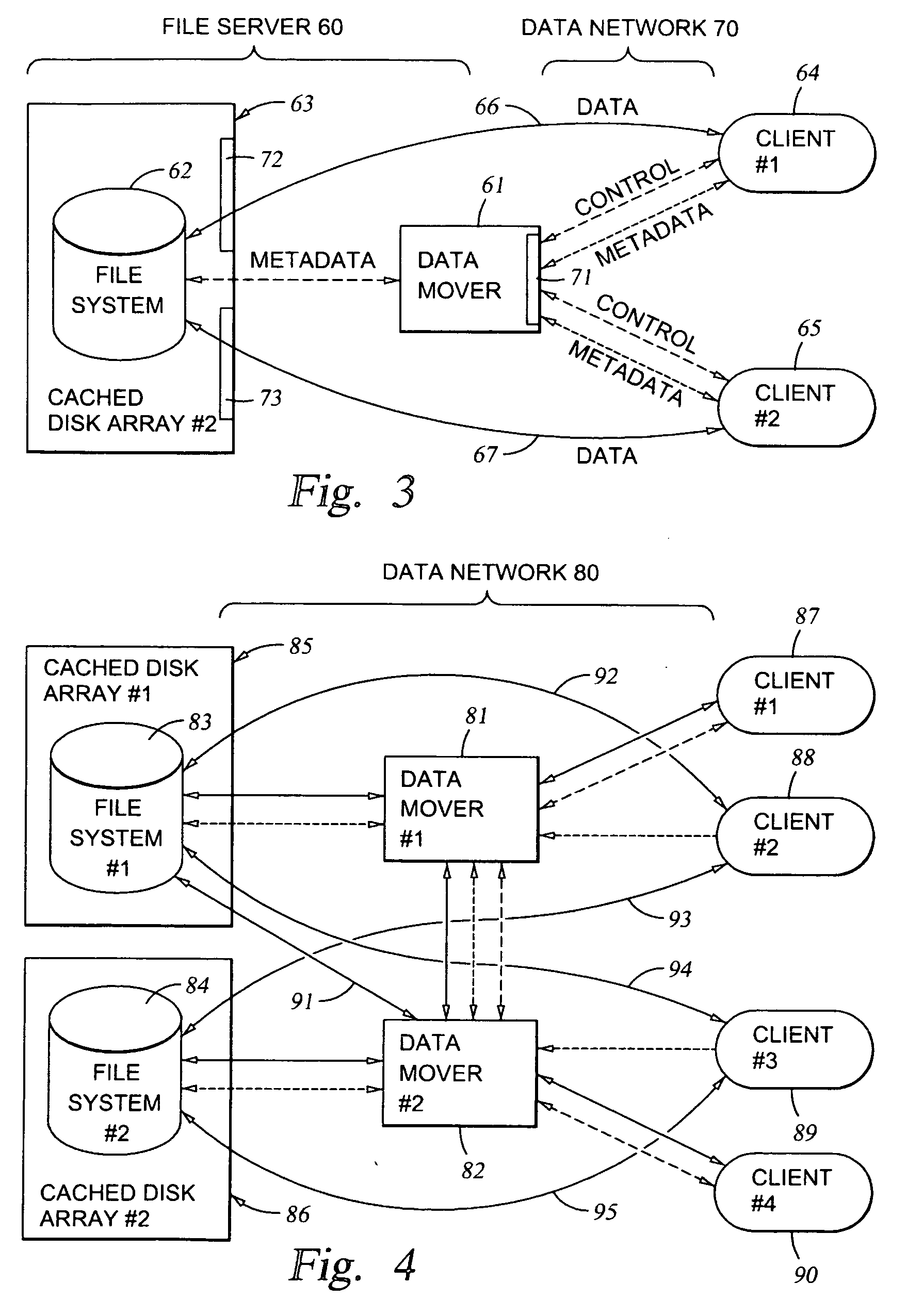

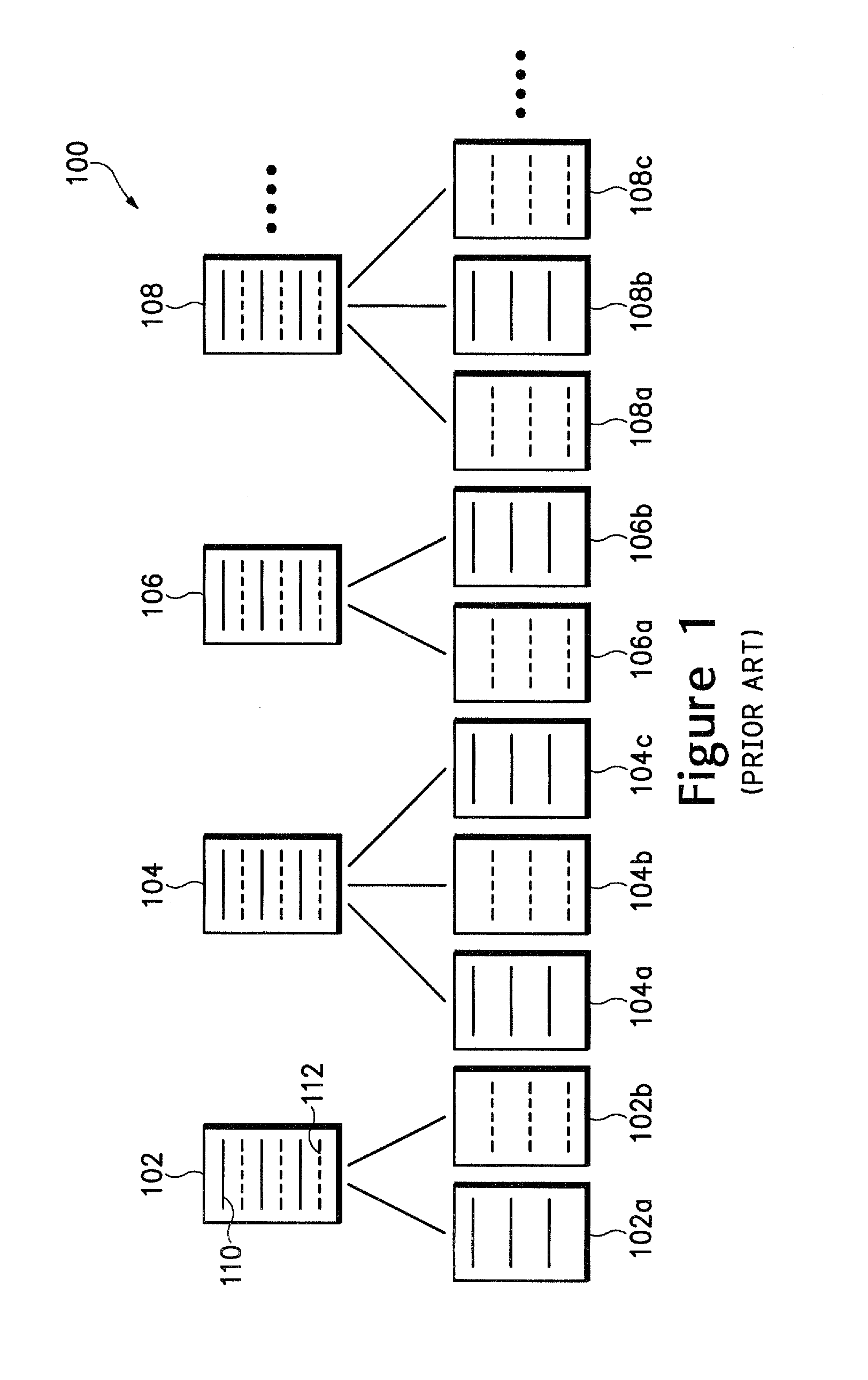

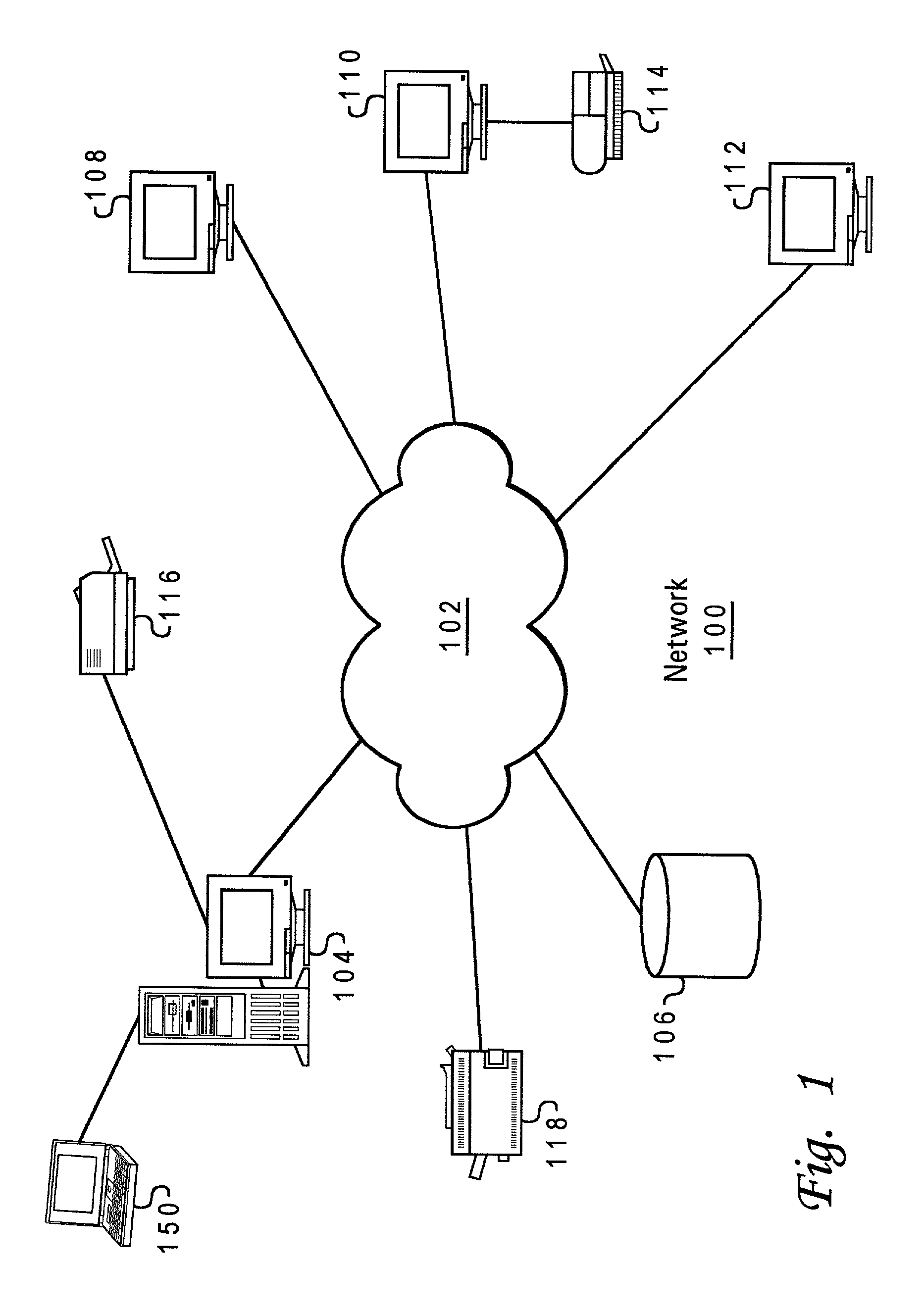

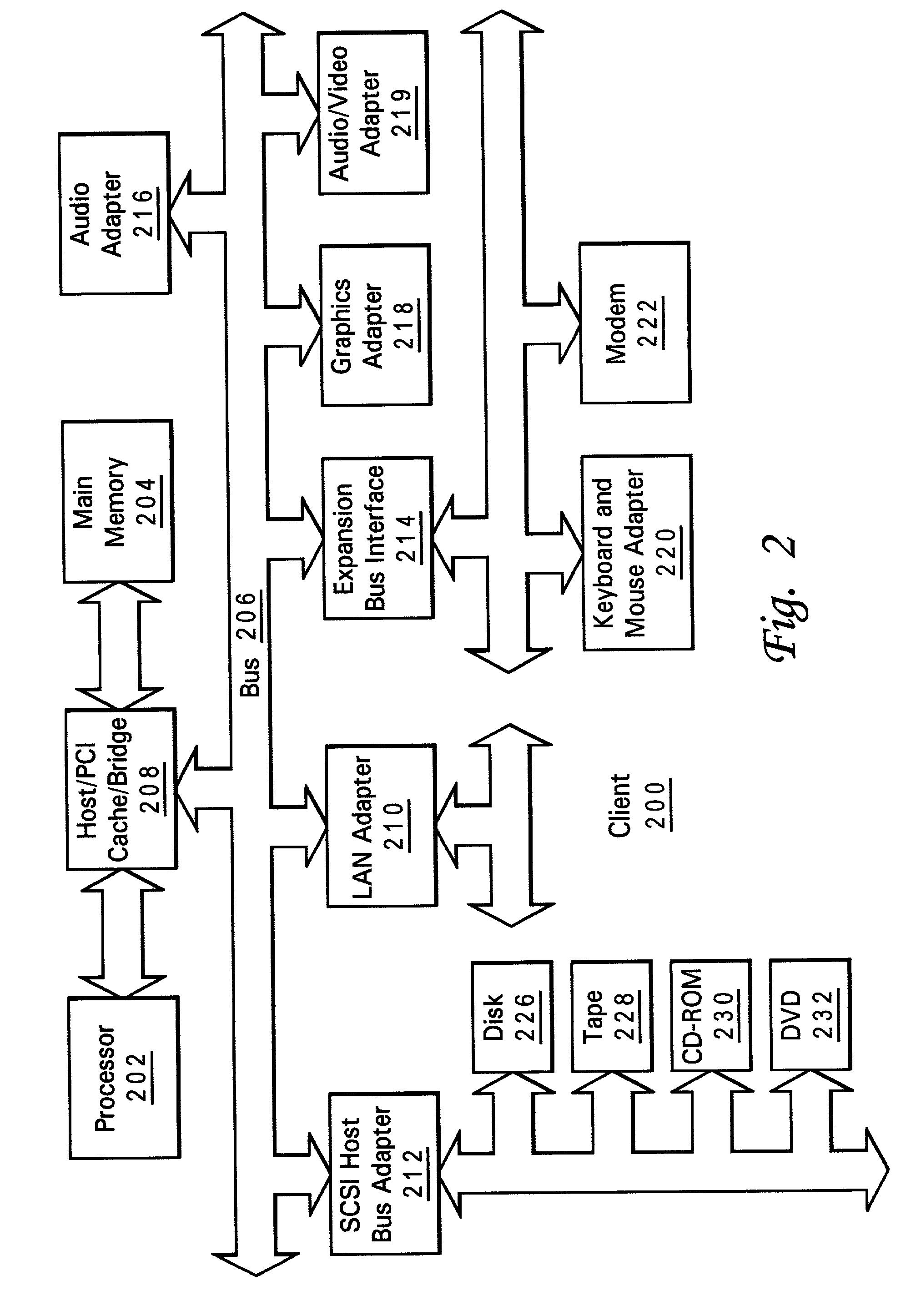

File server system providing direct data sharing between clients with a server acting as an arbiter and coordinator

InactiveUS6973455B1Digital data information retrievalData processing applicationsData accessNetwork data

A client is permitted to send data access commands directly to network data storage of a network file server after obtaining a lock on at least a portion of the file and obtaining metadata indicating storage locations for the data in the data storage. For example, the client sends to the file server at least one request for access to a file. In response, the file server grants a lock to the client, and returns to the client metadata of the file including information specifying data storage locations in the network data storage for storing data of the file. The client receives the metadata, and uses the metadata to produce at least one data access command for accessing the data storage locations in the network storage. The client sends the data access command to the network data storage to read or write data to the file. For a write operation, the client may modify the metadata. When the client is finished writing to the file, the client returns any modified metadata to the file server.

Owner:EMC IP HLDG CO LLC

File server system providing direct data sharing between clients with a server acting as an arbiter and coordinator

InactiveUS20050251500A1Data processing applicationsDigital data information retrievalData accessNetwork data

A client is permitted to send data access commands directly to network data storage of a network file server after obtaining a lock on at least a portion of the file and obtaining metadata indicating storage locations for the data in the data storage. For example, the client sends to the file server at least one request for access to a file. In response, the file server grants a lock to the client, and returns to the client metadata of the file including information specifying data storage locations in the network data storage for storing data of the file. The client receives the metadata, and uses the metadata to produce at least one data access command for accessing the data storage locations in the network storage. The client sends the data access command to the network data storage to read or write data to the file. For a write operation, the client may modify the metadata. When the client is finished writing to the file, the client returns any modified metadata to the file server.

Owner:EMC CORP

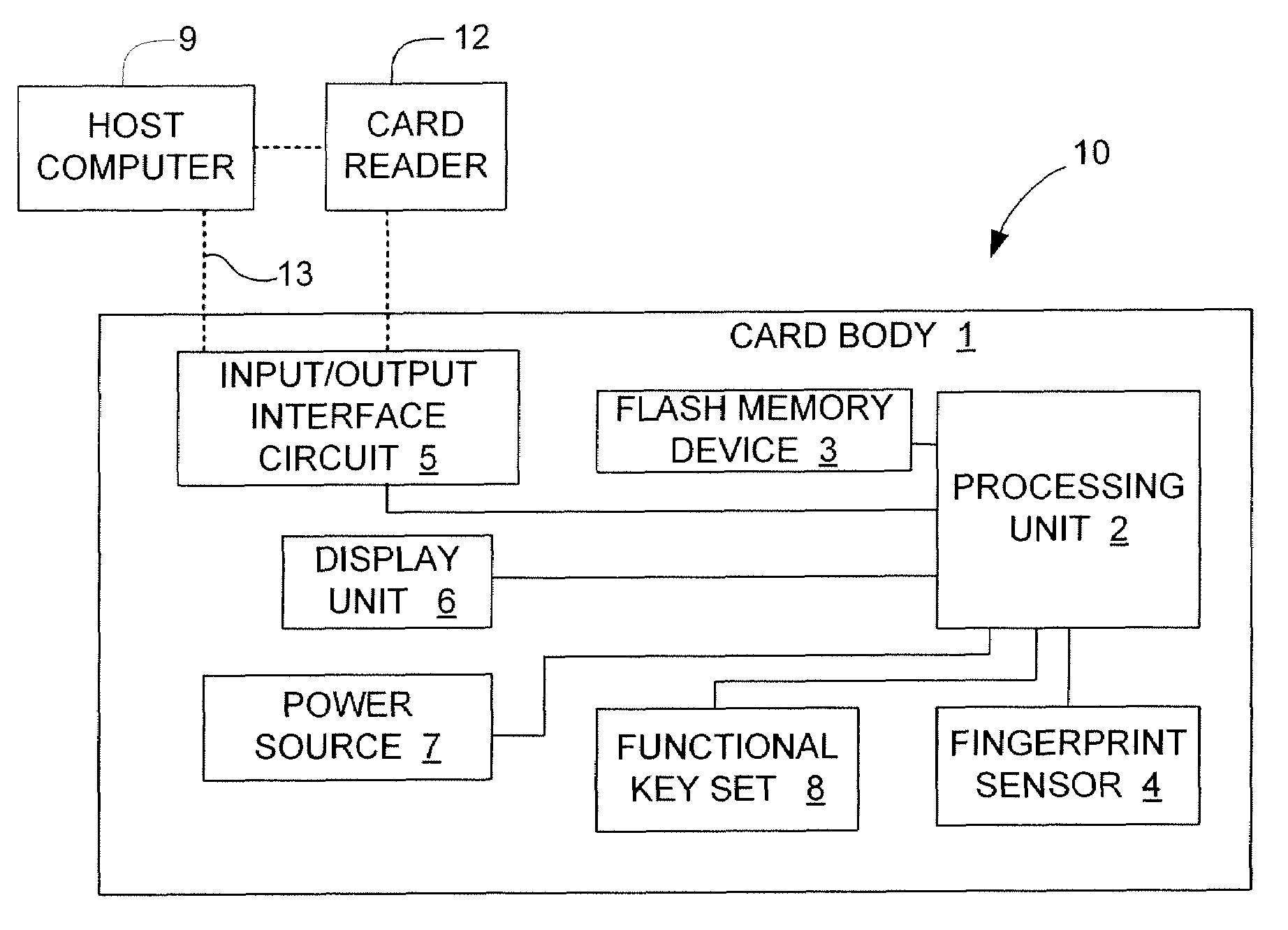

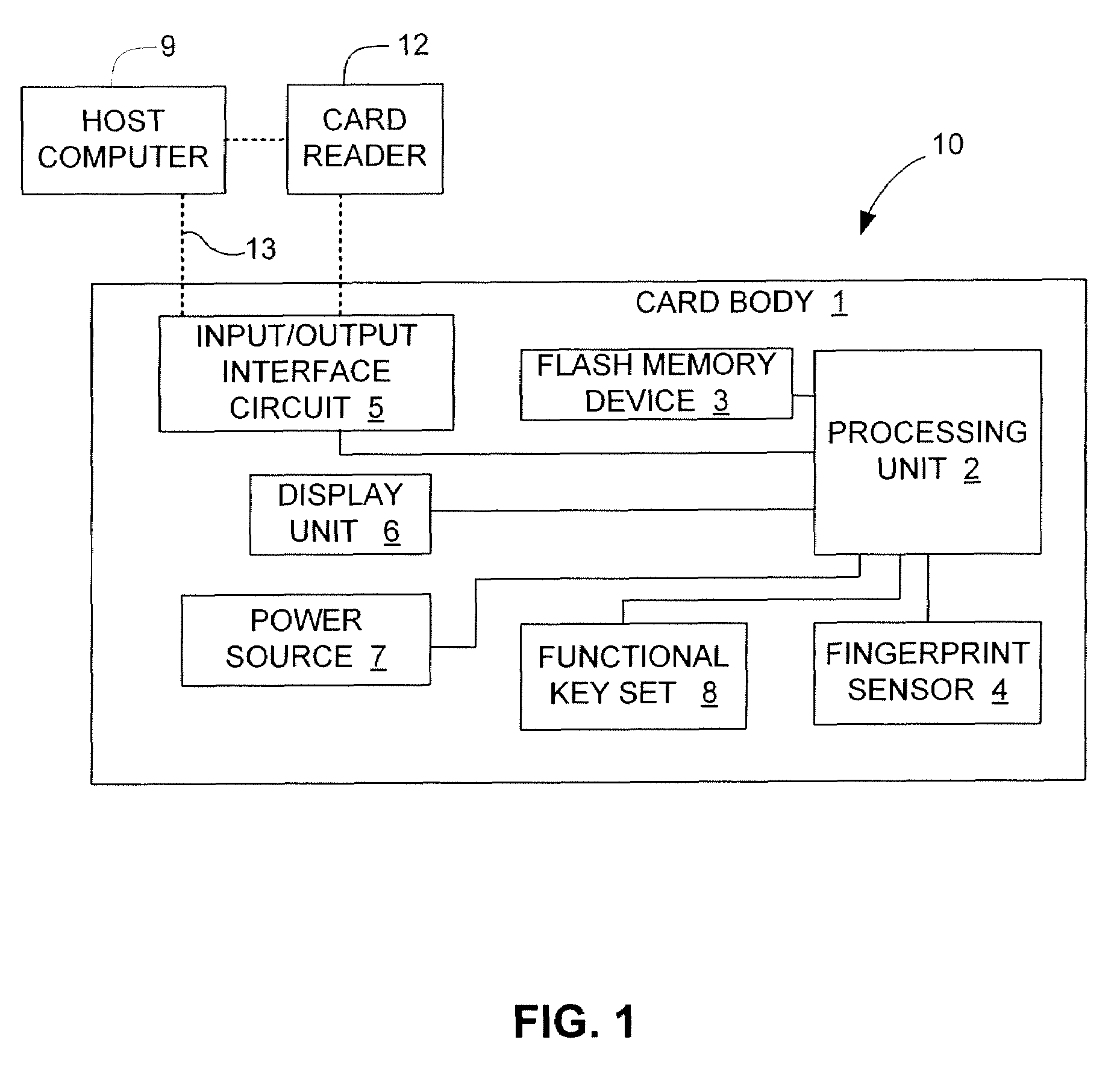

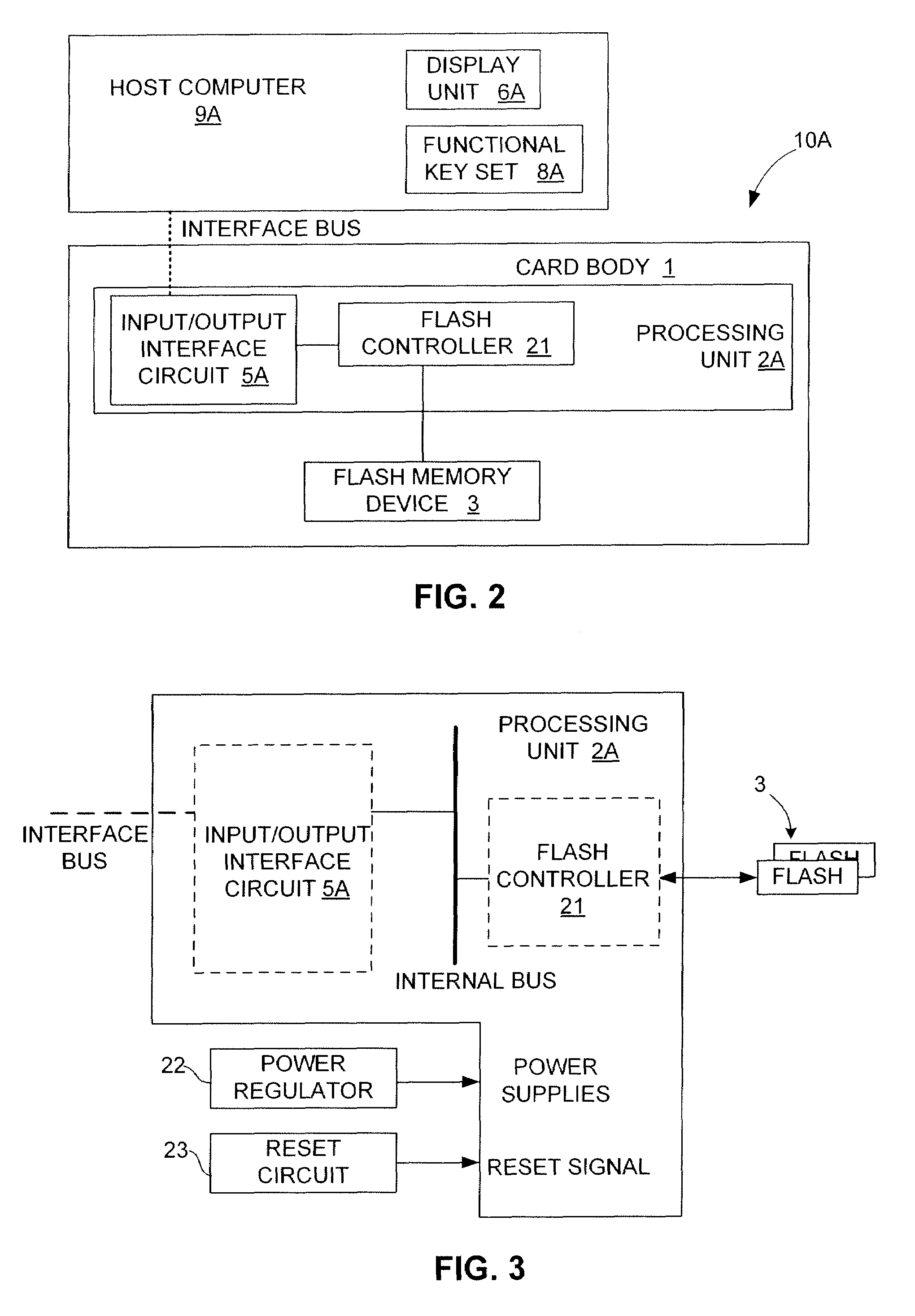

Managing Bad Blocks In Flash Memory For Electronic Data Flash Card

InactiveUS20070283428A1Reduce search timeAvoid congestionDigital data processing detailsUser identity/authority verificationLogical block addressingComputer access

An electronic data flash card accessible by a host computer, includes a flash memory controller connected to a flash memory device, and an input-output interface circuit activated to establish a communication with the host. In an embodiment, the flash card uses a USB interface circuit for communication with the host. A flash memory controller includes an arbitrator for mapping logical addresses with physical block addresses, and for performing block management operations including: storing reassigned data to available blocks, relocating valid data in obsolete blocks to said available blocks and reassigning logical block addresses to physical block addresses of said available blocks, finding bad blocks of the flash memory device and replacing with reserve blocks, erasing obsolete blocks for recycling after relocating valid data to available blocks, and erase count wear leveling of blocks, etc. Furthermore, each flash memory device includes an internal buffer for accelerating the block management operations.

Owner:SUPER TALENT TECH CORP

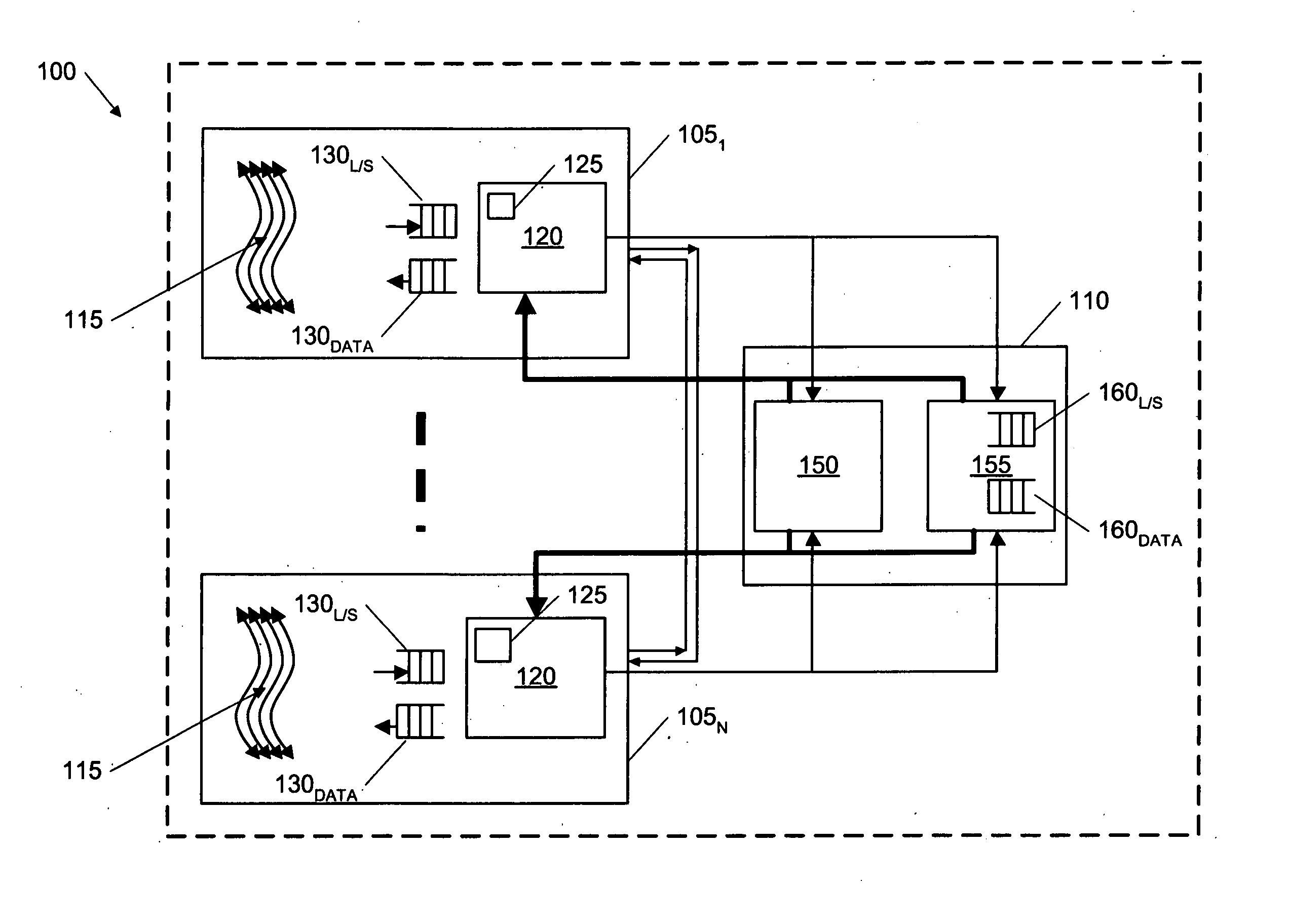

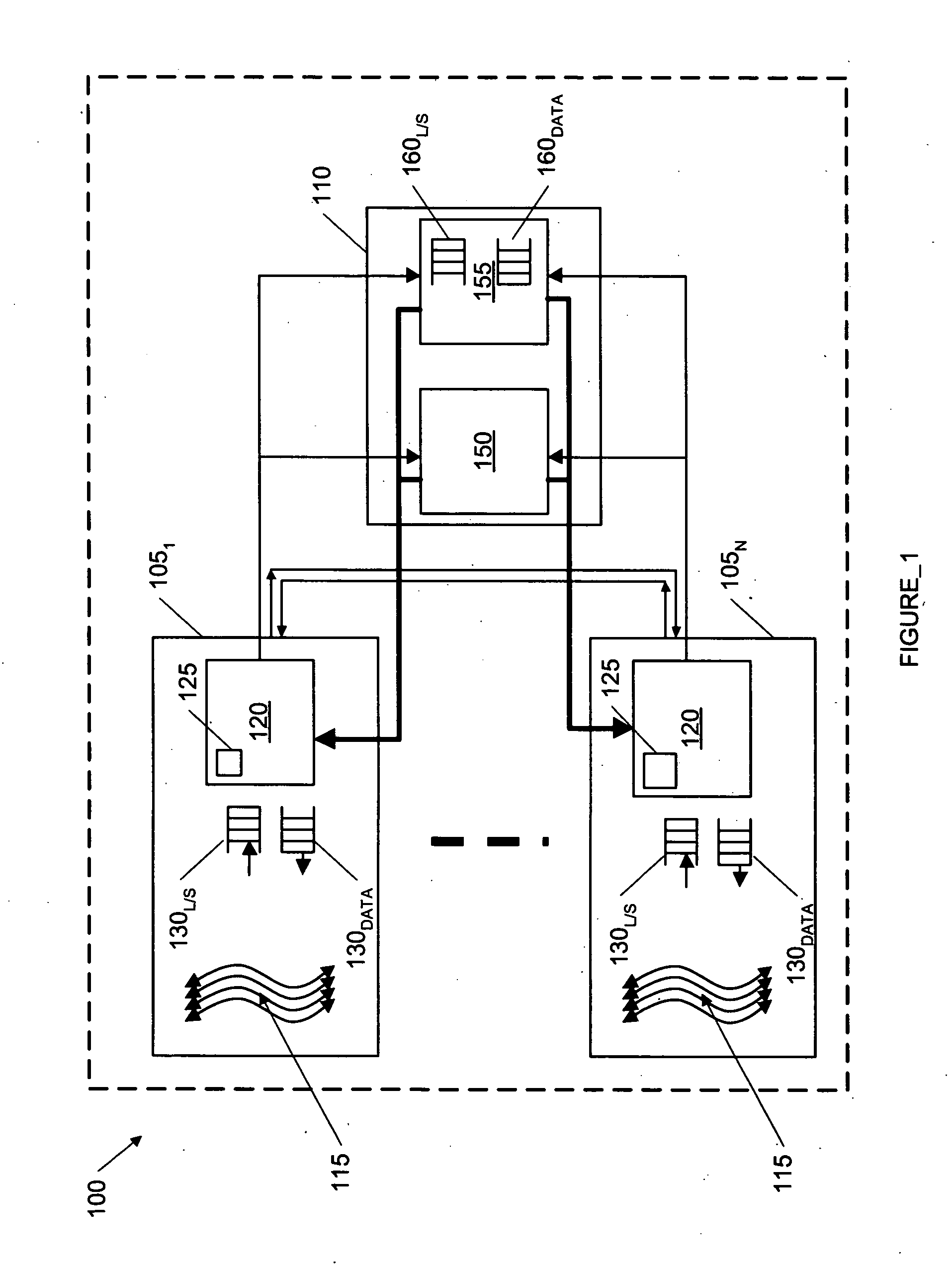

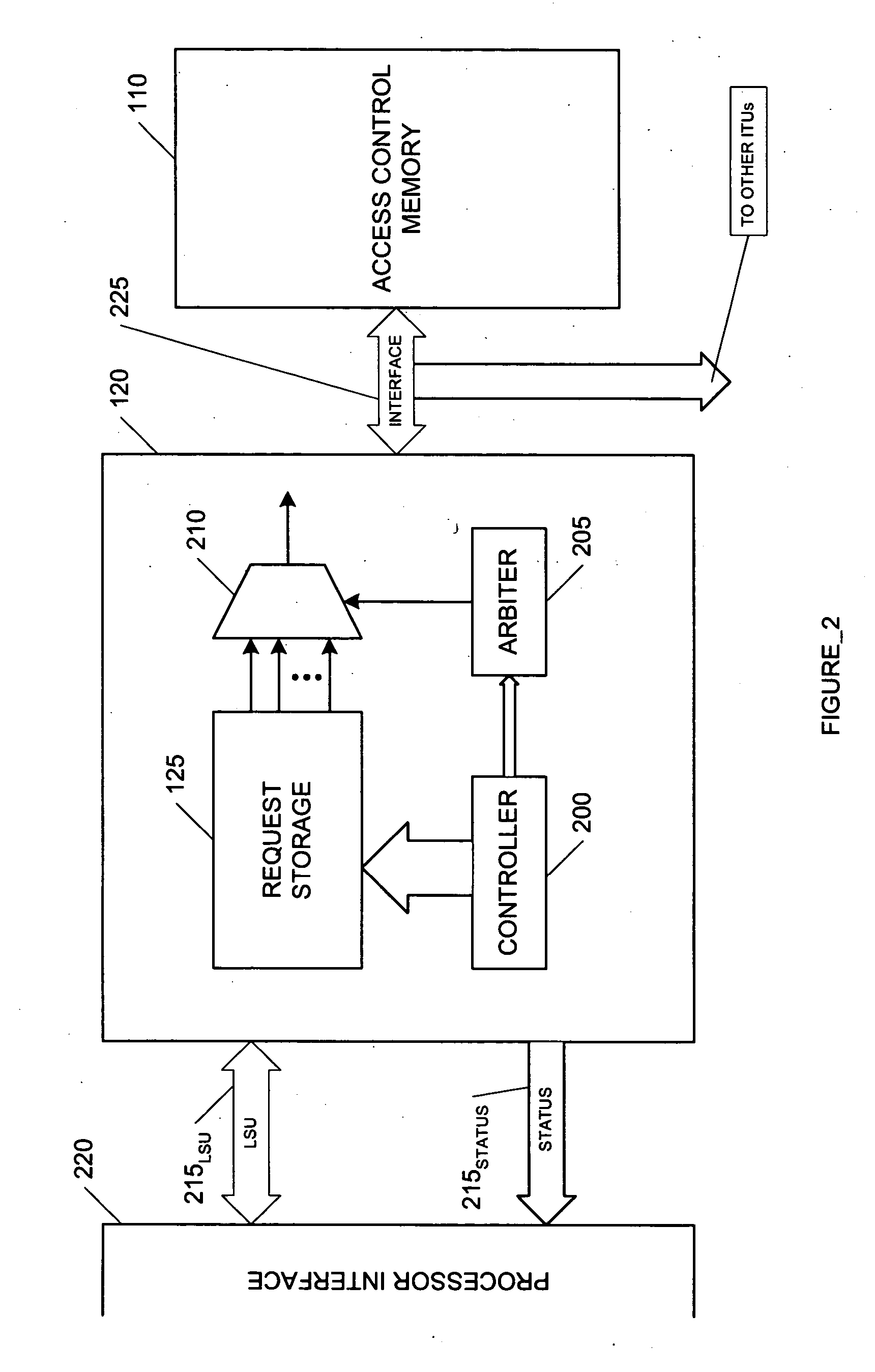

Smart memory based synchronization controller for a multi-threaded multiprocessor SoC

A memory interface for use with a multiprocess memory system having a gating memory, the gating memory associating one or more memory access methods with each of a plurality of memory locations of the memory system wherein the gating memory returns a particular one access method for a particular one memory location responsive to a memory access instruction relating to the particular one memory location, the interface including: a request storage for storing a plurality of concurrent memory access instructions for one or more of the particular memory locations, each the memory access instruction issued from an associated independent thread context; an arbiter, coupled to the request storage, for selecting a particular one of the memory access instructions to apply to the gating memory; and a controller, coupled to the request storage and to the arbiter, for: storing the plurality of memory access instructions in the request storage; initiating application of the particular one memory access instruction selected by the arbiter to the gating memory; receiving the particular one access method associated with the particular one memory access method from the gating memory; and initiating a communication of the particular access method to the thread context associated with the particular one access instruction.

Owner:MIPS TECH INC

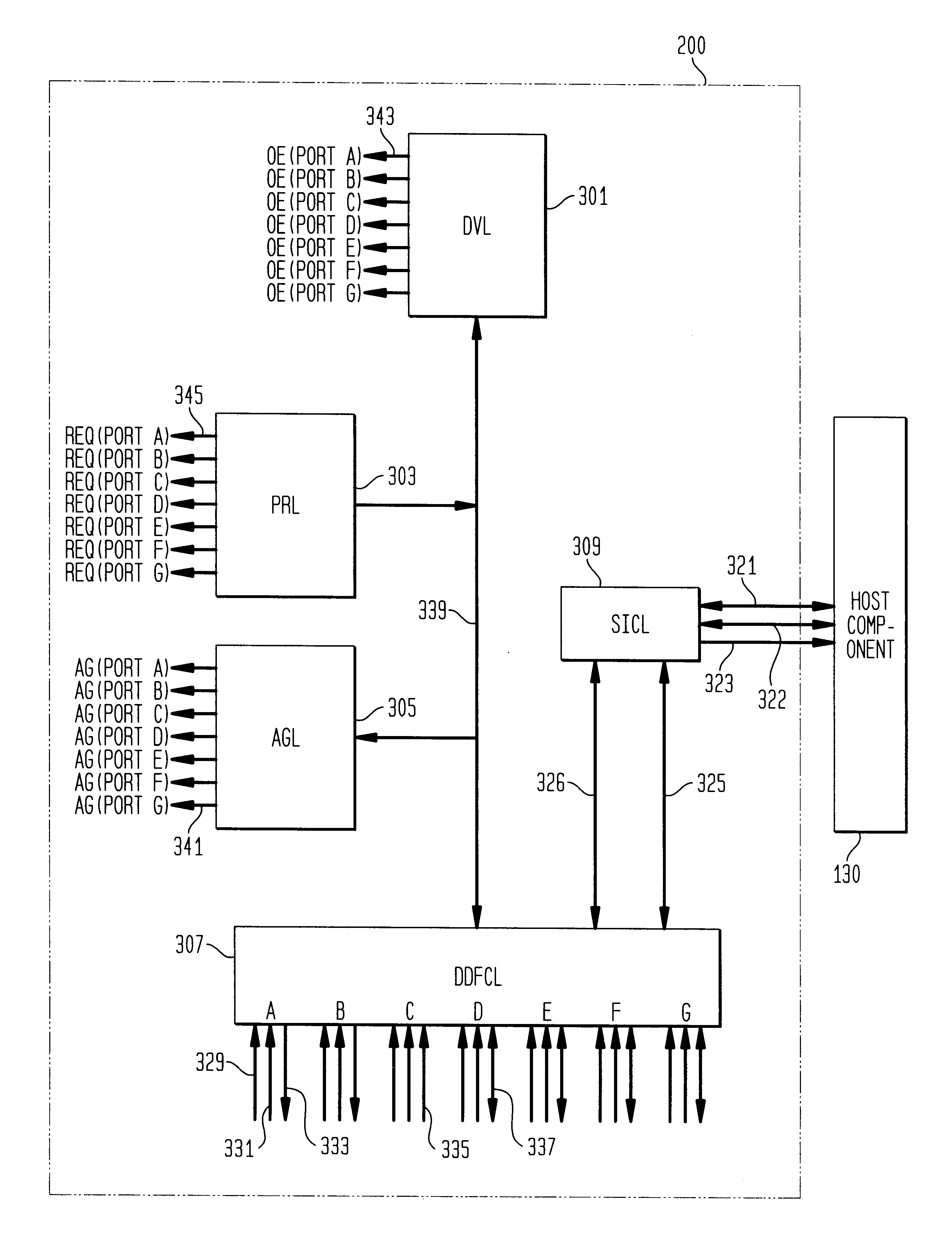

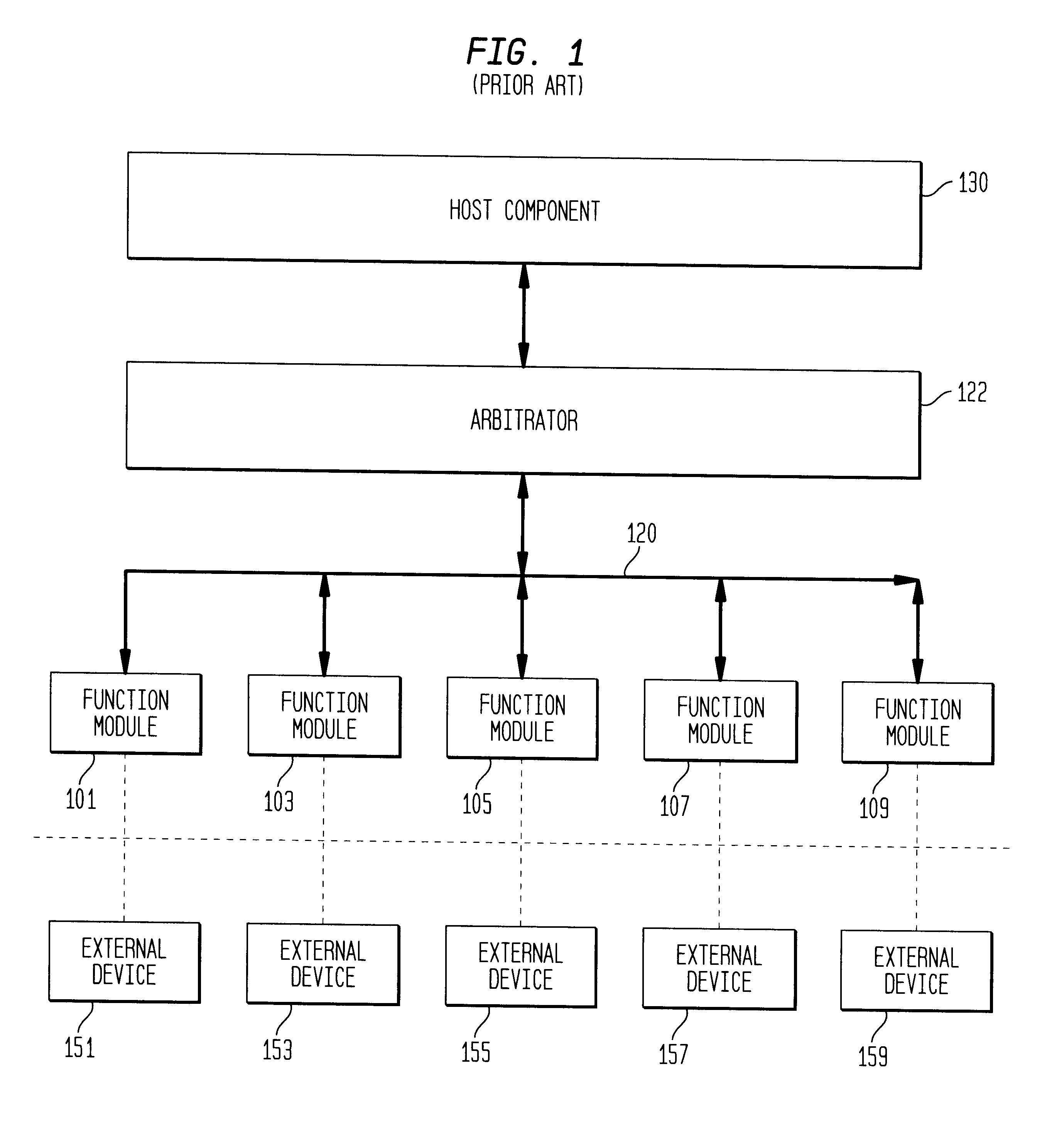

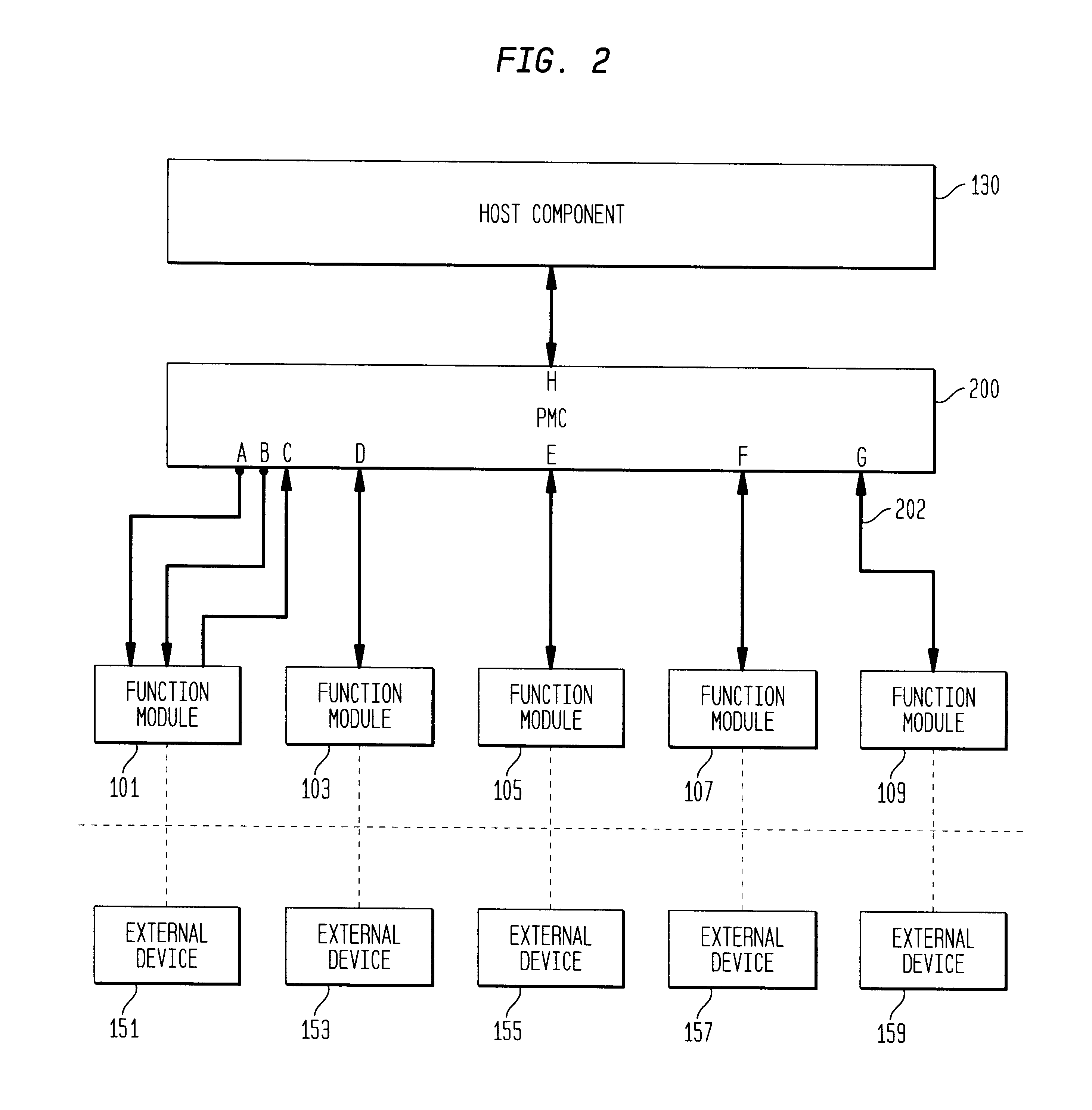

Port manager controller for connecting various function modules

An improved method and apparatus for connecting various function modules located within a computer or communications system are proposed. In accordance with the principles of the present invention, a port manager controller (PMC) has a direct interface to each of the function modules and to a host component such as a system memory or a CPU. The PMC replaces both the local bus and the arbitrator of prior art systems. All the requests by function modules to access the host component are first processed by the PMC. The PMC schedules the incoming requests in accordance with predefined parameters, such as priority, efficiency, and / or timing. The PMC is capable of handling more than one request at a time. The PMC is also capable of dynamically adapting to load conditions and rearranging the incoming requests to efficiently utilize the available bandwidth. Thus, the PMC reduces latency and improves the performance of the computer or communications system. The PMC also eliminates the need for changes in bus architecture when new function modules are added or old function modules are removed and permits the reuse of old function modules. The PMC also reduces the need for internal buffers and thereby reduces manufacturing costs.

Owner:LUCENT TECH INC +1

Memory latency and bandwidth optimizations

InactiveUS20040073767A1Memory adressing/allocation/relocationMicro-instruction address formationRAIDComputer architecture

Owner:HEWLETT PACKARD DEV CO LP

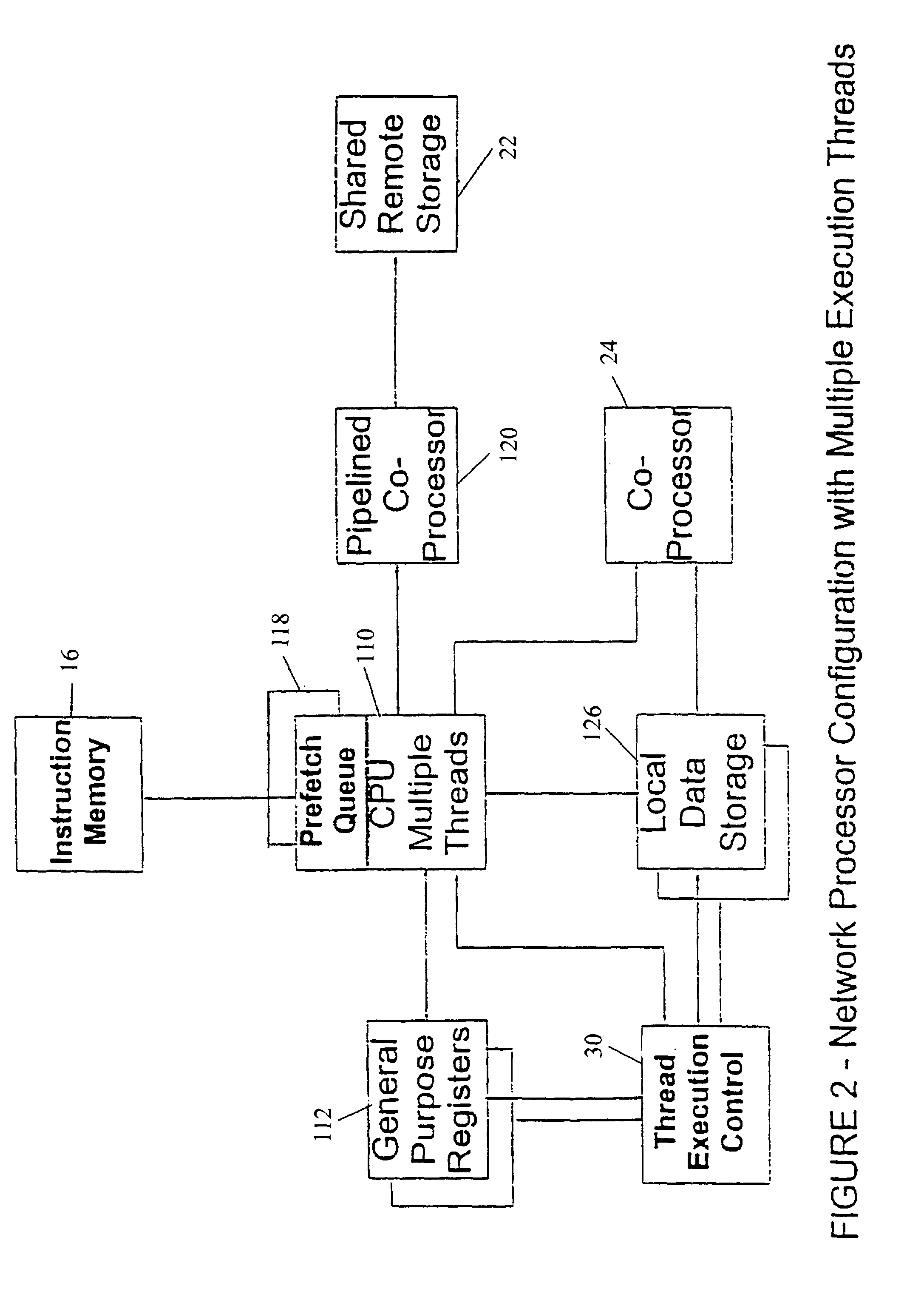

Network processor which makes thread execution control decisions based on latency event lengths

InactiveUS7093109B1Easy to useZero overheadDigital computer detailsMultiprogramming arrangementsLong latencyCoprocessor

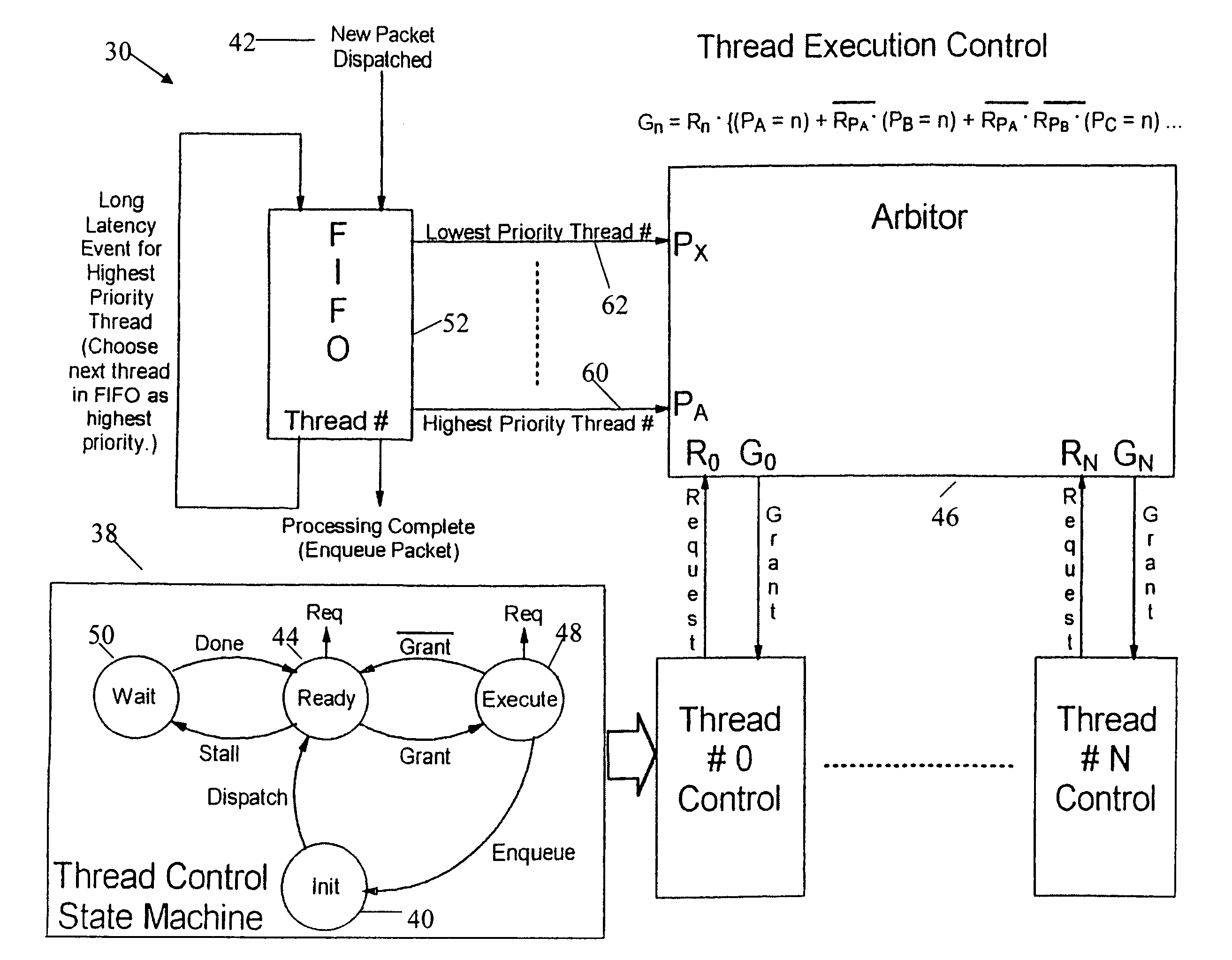

A control mechanism is established between a network processor and a tree search coprocessor to deal with latencies in accessing the data such as information formatted in a tree structure. A plurality of independent instruction execution threads are queued to enable them to have rapid access to the shared memory. If execution of a thread becomes stalled due to a latency event, full control is granted to the next thread in the queue. The grant of control is temporary when a short latency event occurs or full when a long latency event occurs. Control is returned to the original thread when a short latency event is completed. Each execution thread utilizes an instruction prefetch buffer that collects instructions for idle execution threads when the instruction bandwidth is not fully utilized by an active execution thread. The thread execution control is governed by the collective functioning of a FIFO, an arbiter and a thread control state machine.

Owner:INTEL CORP

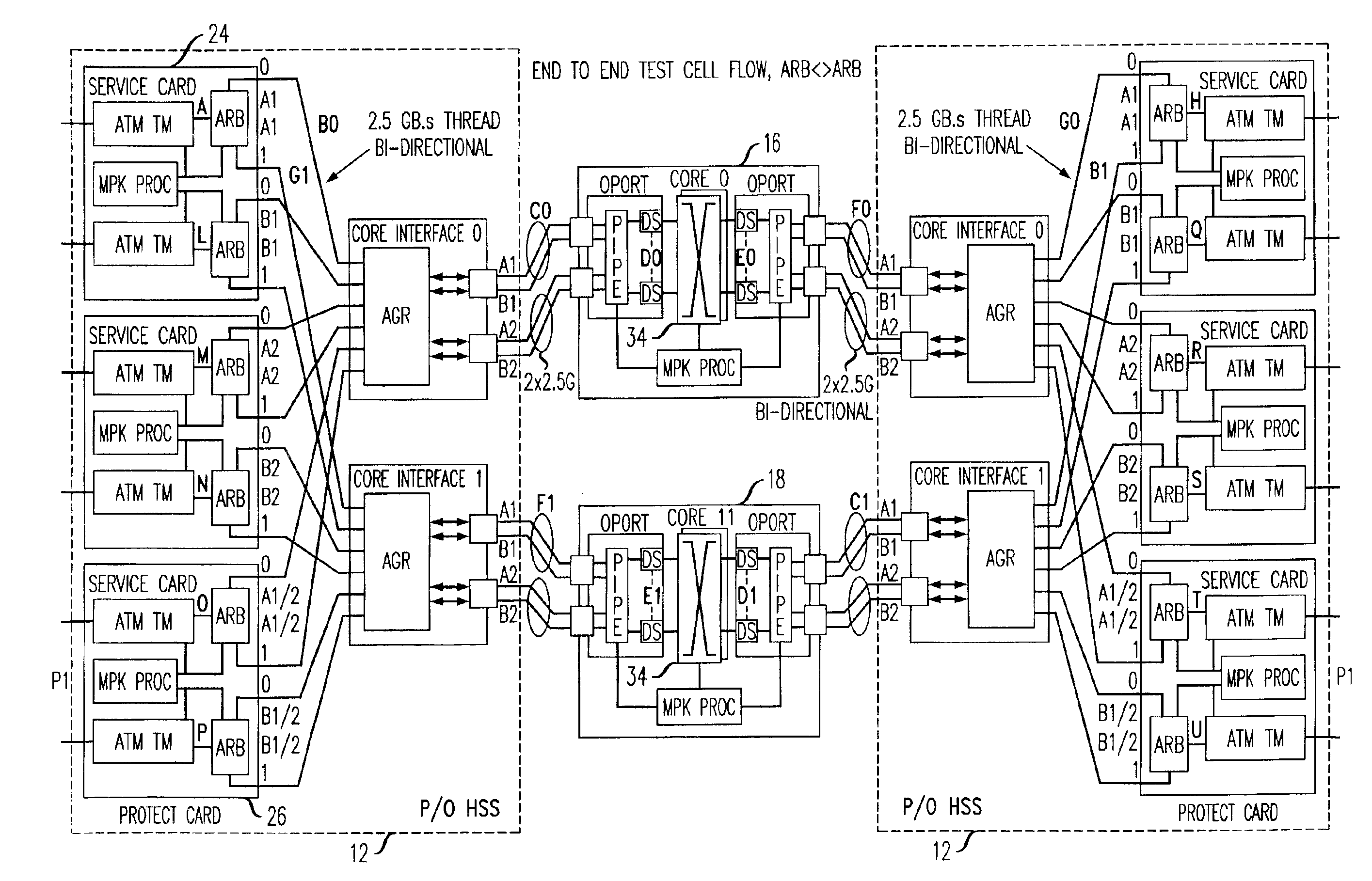

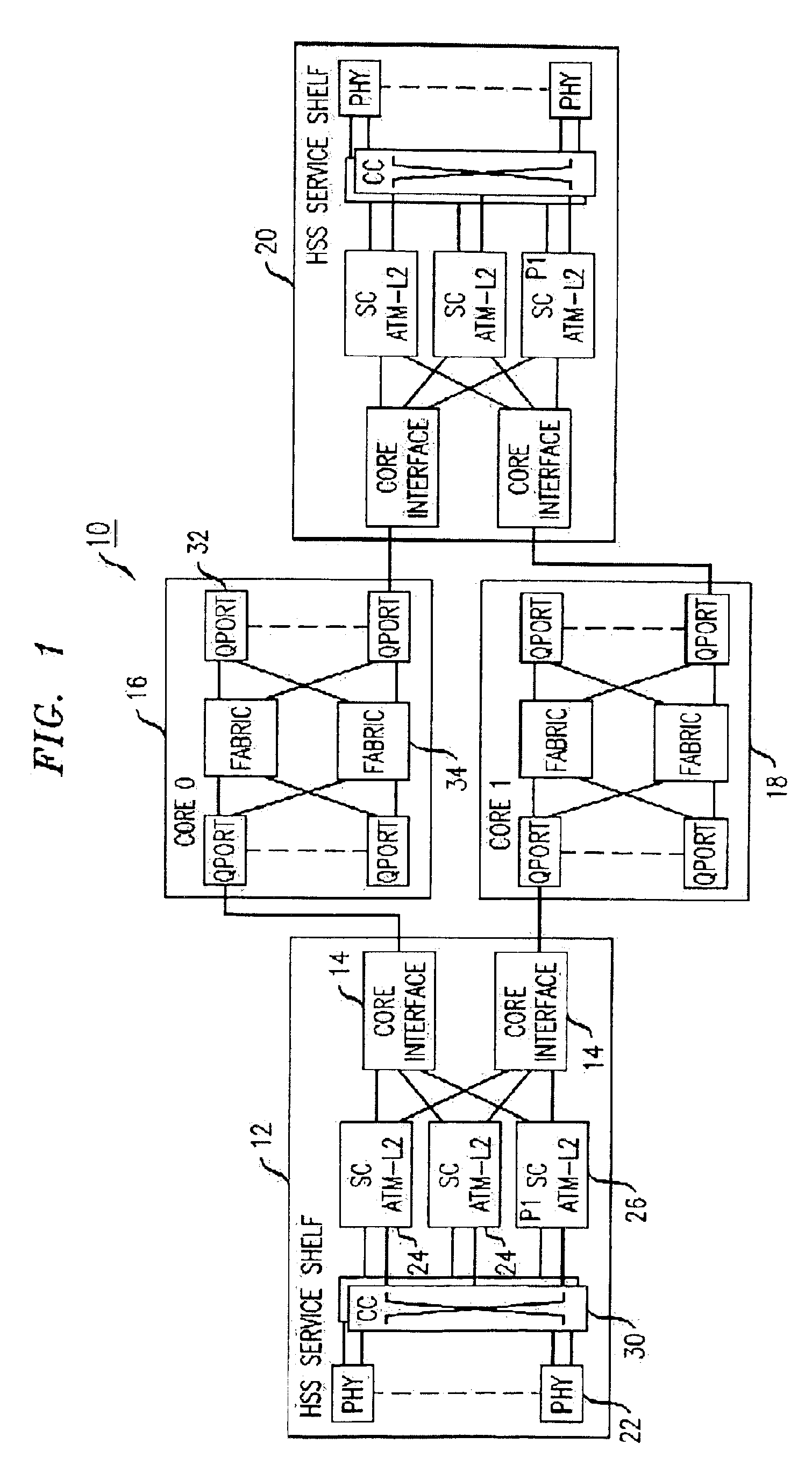

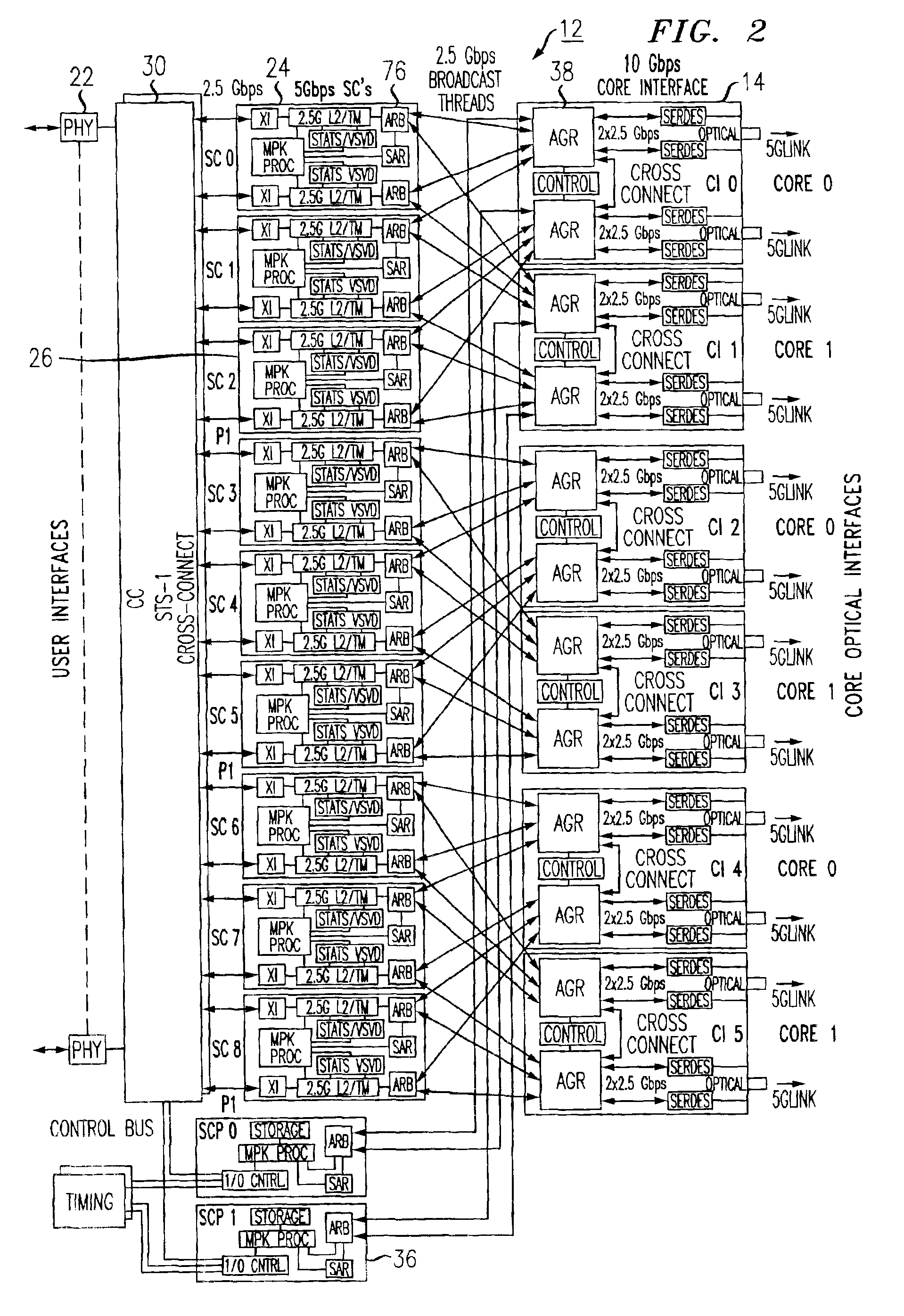

Controlled switchover of unicast and multicast data flows in a packet based switching system

ActiveUS7058010B2Special service provision for substationError preventionTraffic capacityData stream

The present invention is a methodology for controlled switchover of unicast and multicast data flows in packet based switching system. In some cases it is advantageous to purposefully support switchover of flows from one path to the other without causing loss of data. This is termed a “controlled” or “hitless” switchover. In accordance with the present invention switchover methodology, given that an ingress arbiter device is transmitting to both cores simultaneously, it is required that the flows to both switching cores be synchronized at an aggregator level and that an egress arbiter be given time to cease receiving packets from one Core then switch over to the other Core, and continue receiving packets.

Owner:LUCENT TECH INC

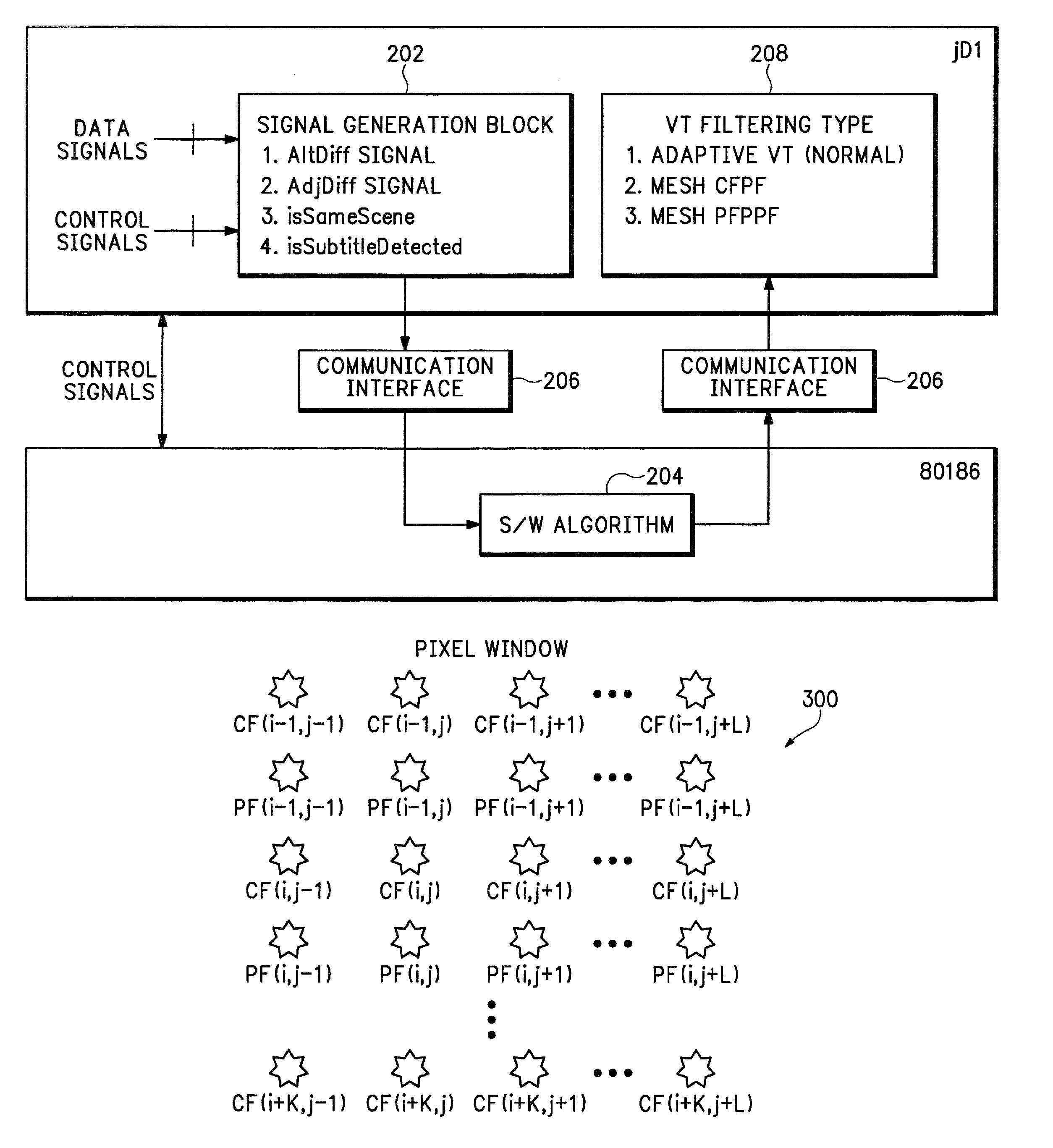

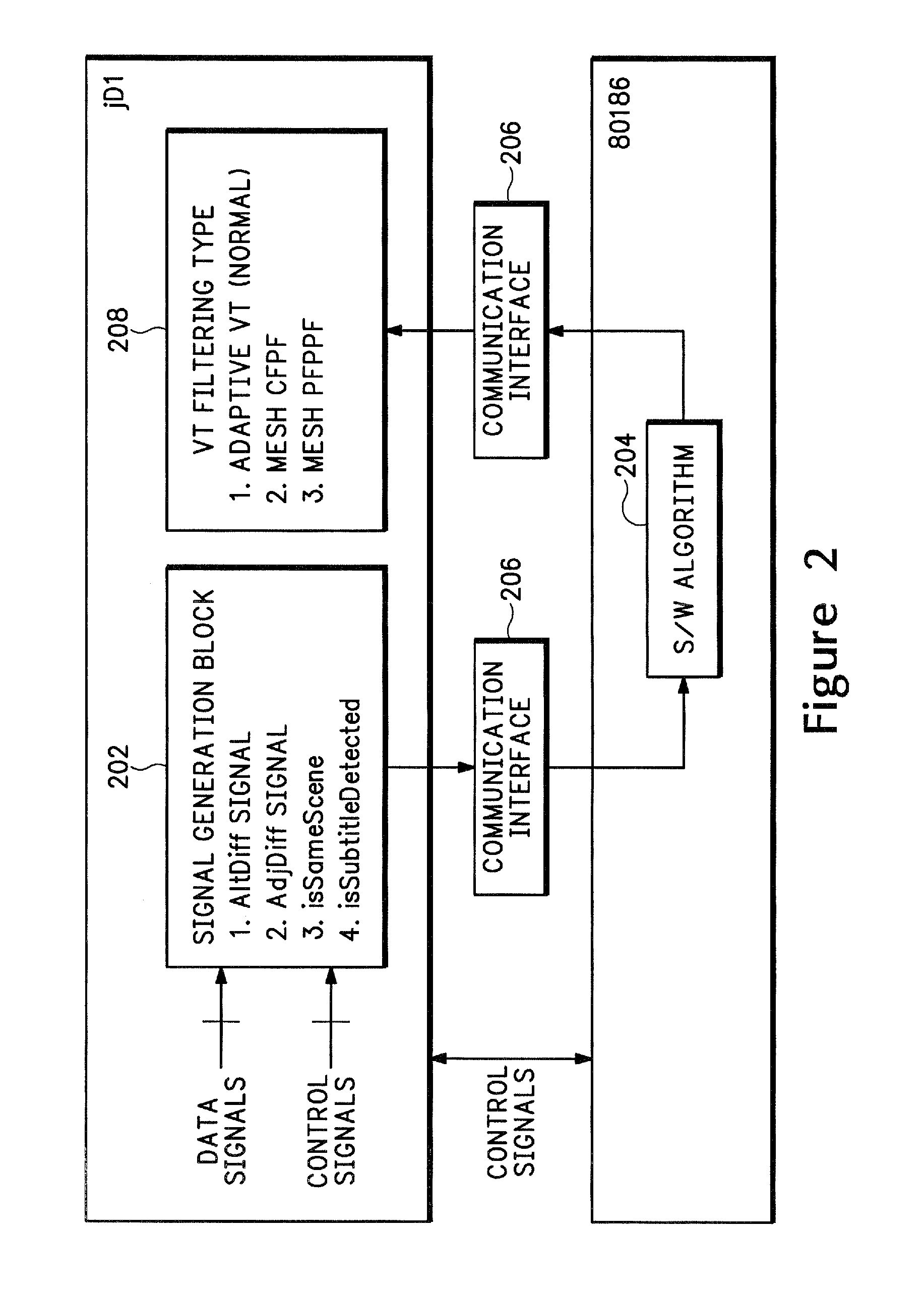

System and method for detecting a non-video source in video signals

InactiveUS7129990B2Television system detailsColor signal processing circuitsPattern recognitionPattern detection

A system detects a non-video source embedded in a video sequence and provides direction to a deinterlacing algorithm accordingly. The system comprises a signal generator for generating a plurality of signals. The signals are generated in accordance with pixels input from the video sequence. The system further comprises a plurality of pattern detection state machines, each for receiving the signals and for detecting a pattern in the video sequence. The pattern is detected in accordance with a preset threshold, wherein the pattern detection state machine varies the preset threshold in accordance with the received signals. The system further comprises an arbiter state machine coupled with the plurality of pattern detection state machines for governing the pattern detection state machines and for determining whether or not a non-video source is embedded in the video sequence.

Owner:PIXELWORKS SEMICON TECH SHANGHAI CO LTD

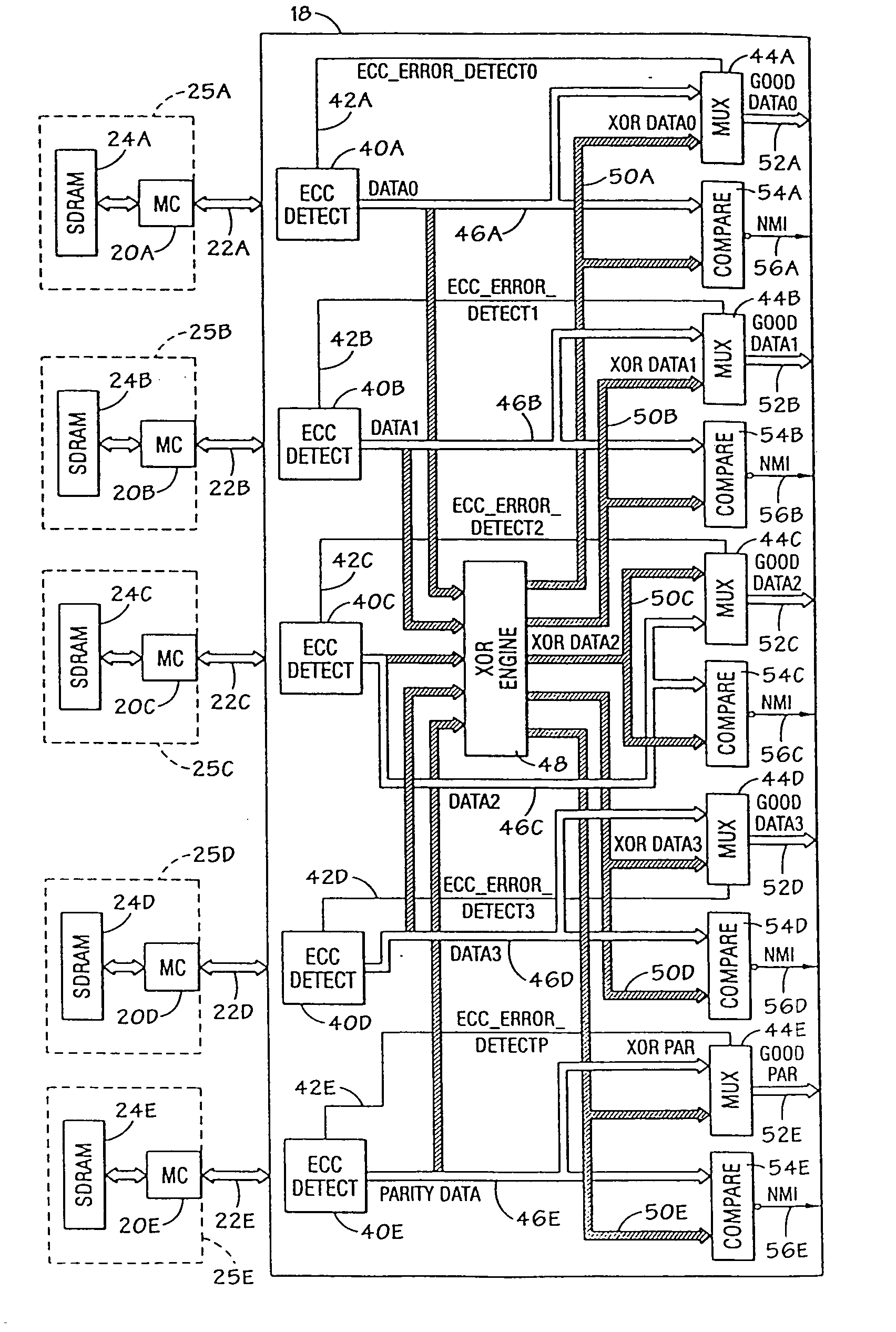

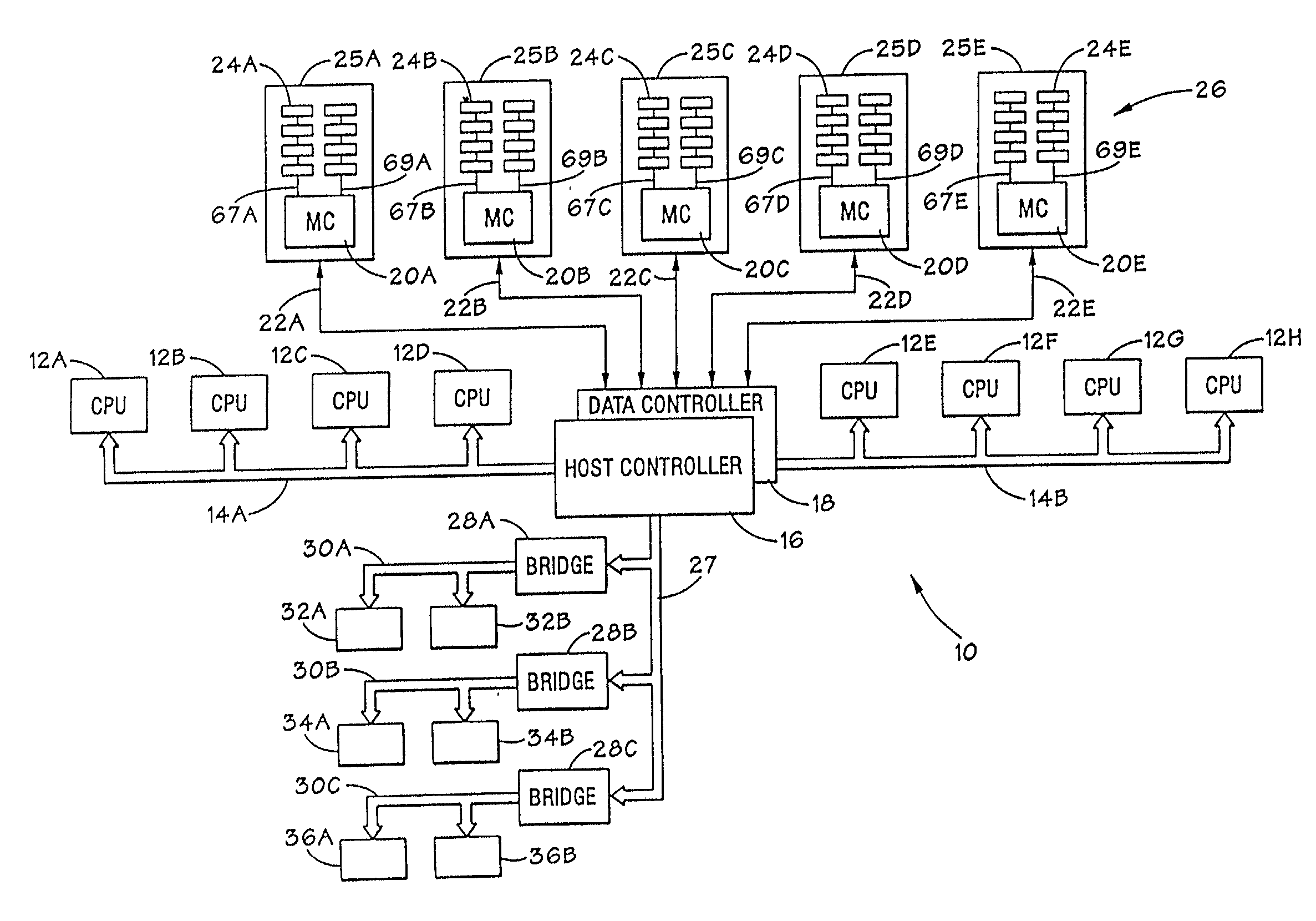

Memory latency and bandwidth optimizations

InactiveUS20030070055A1Memory systemsMicro-instruction address formationMemory moduleSemiconductor memory

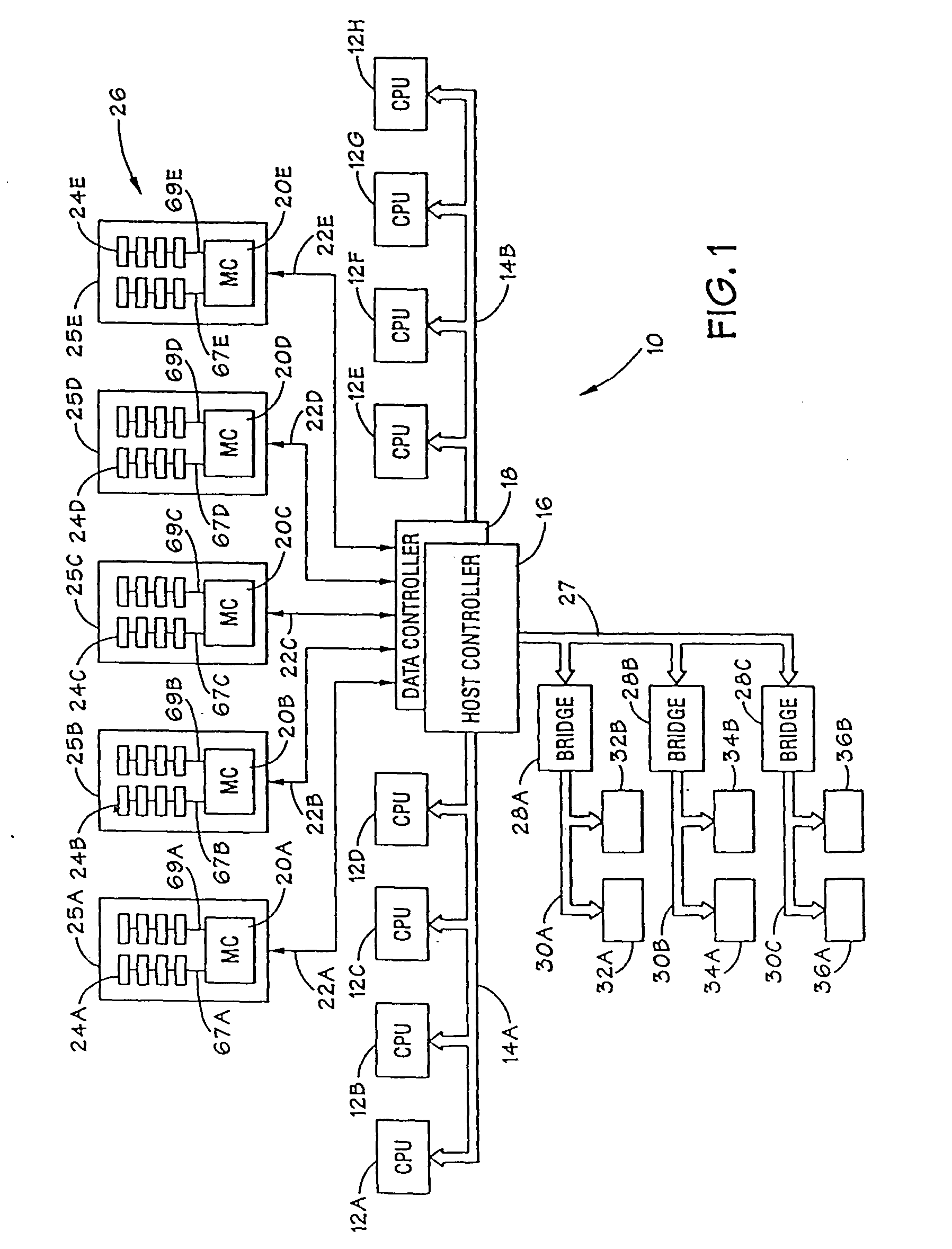

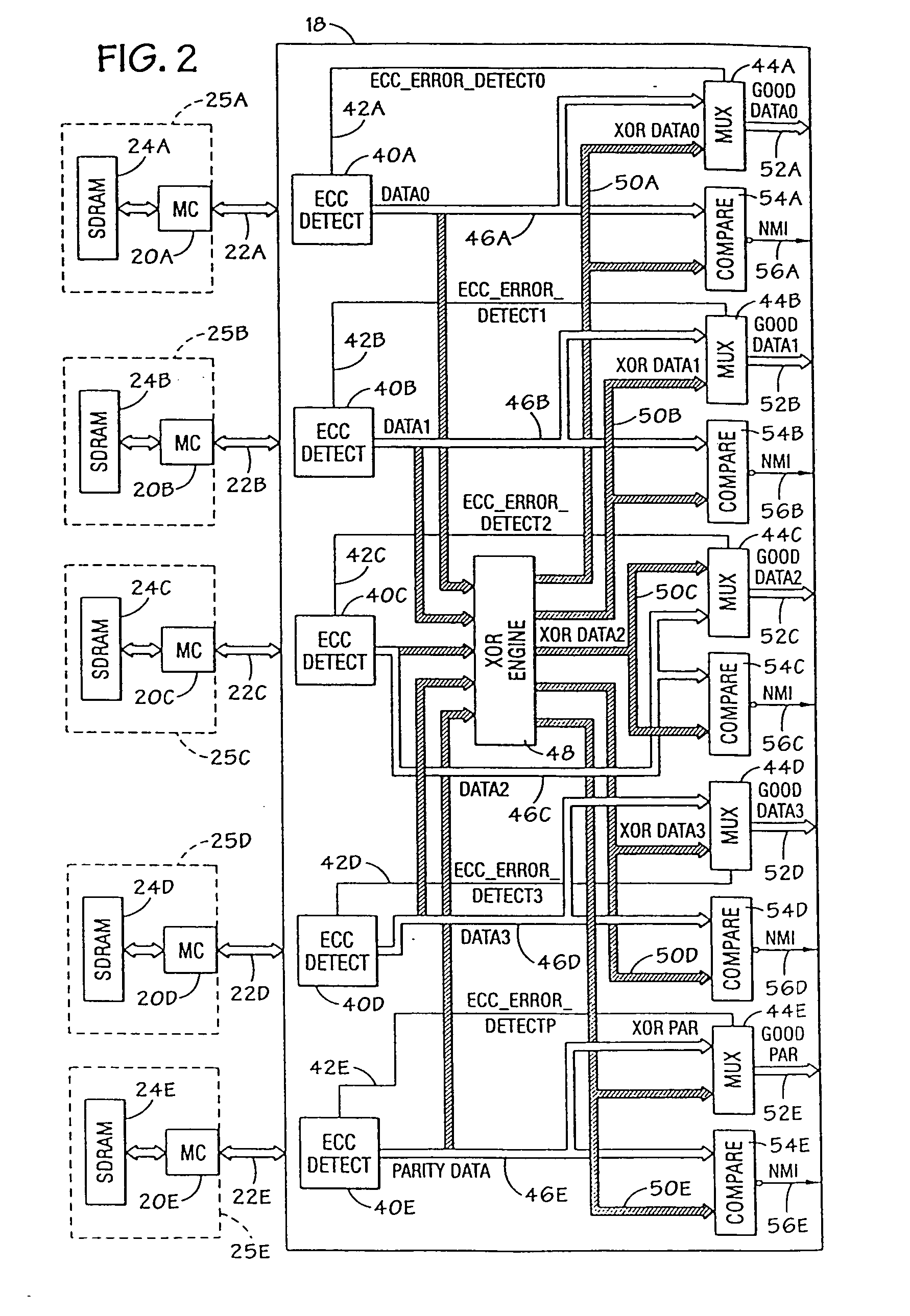

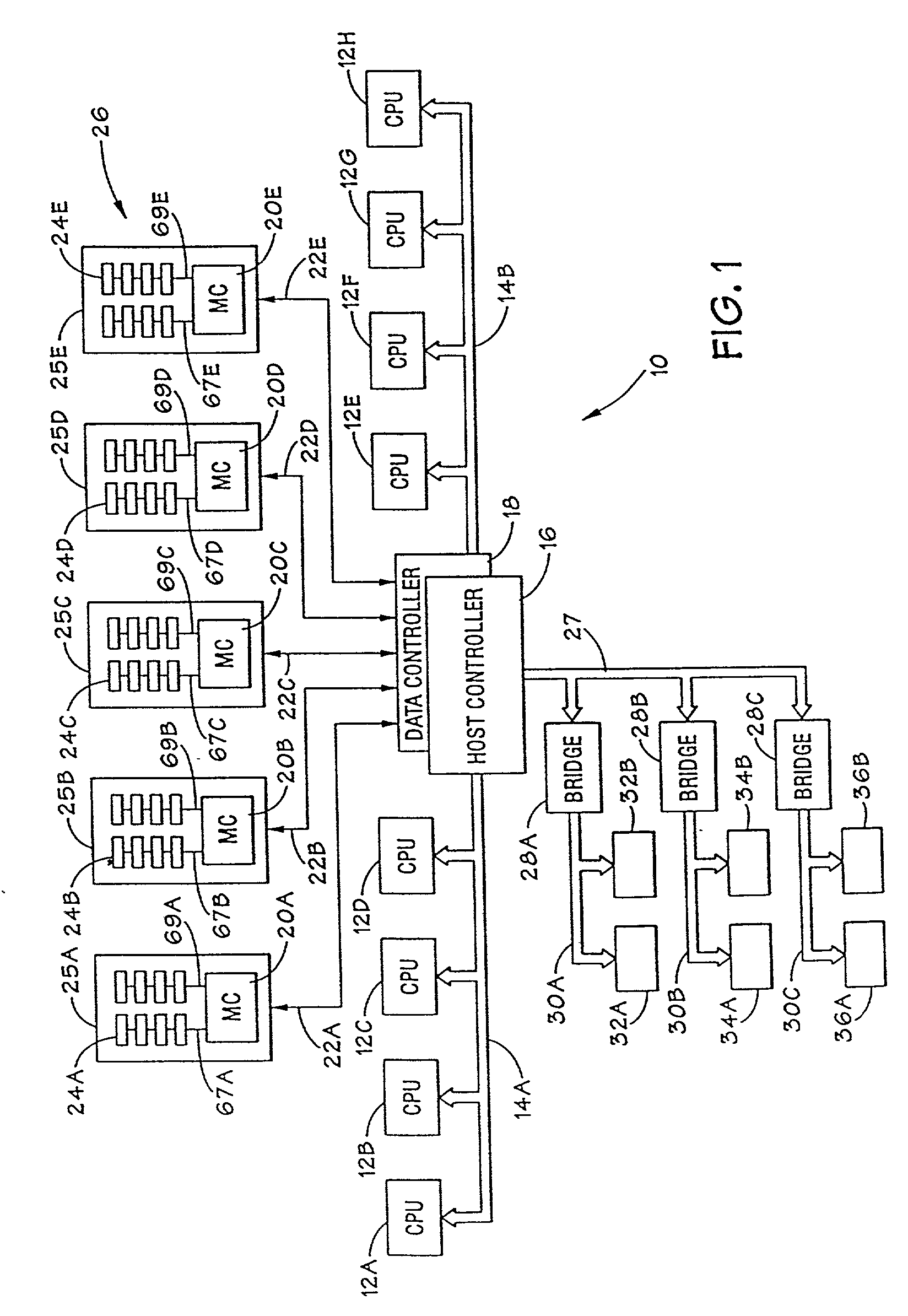

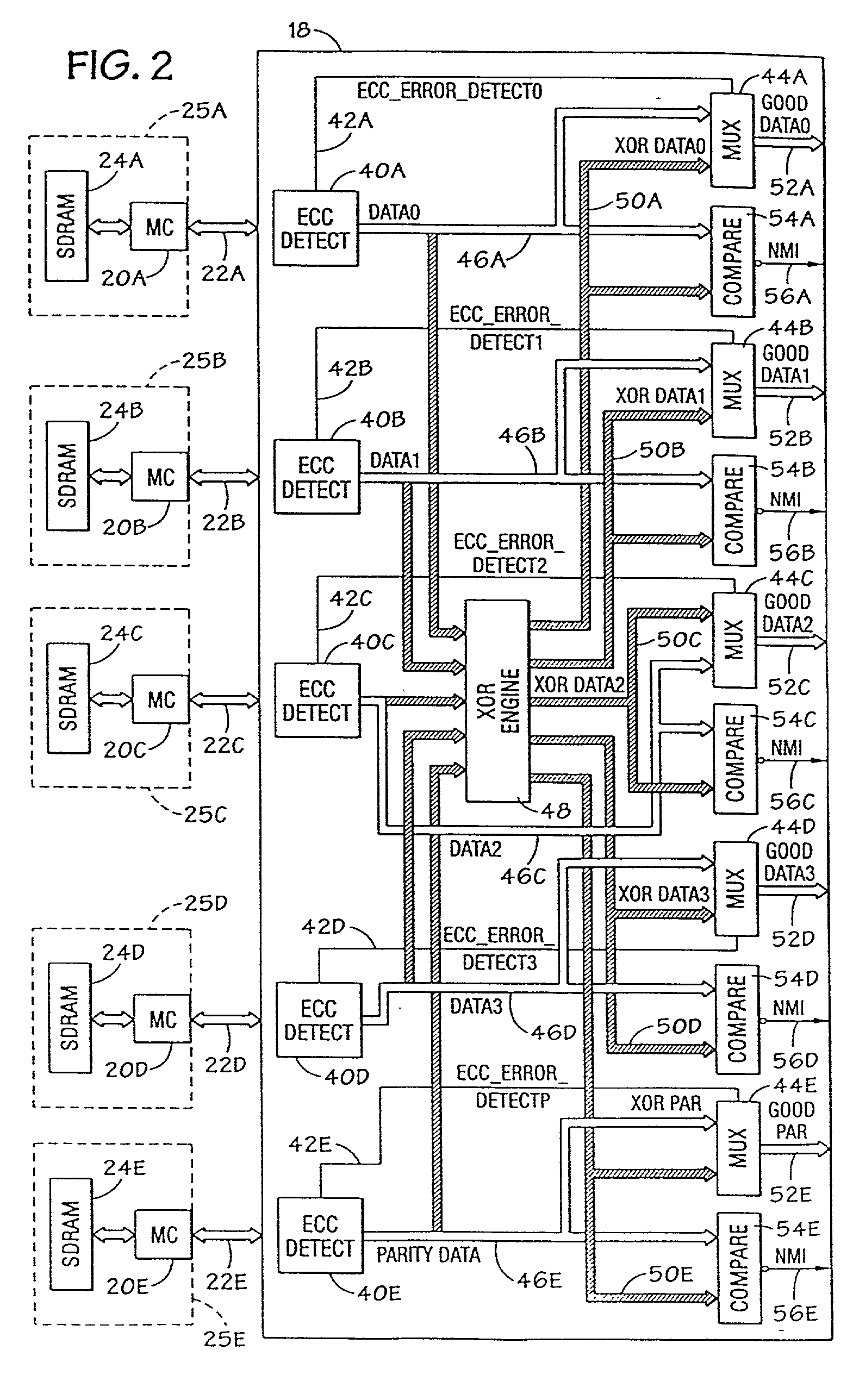

A computer system includes a plurality of memory modules that contain semiconductor memory, such as DIMMs. The system includes a host / data controller that utilizes an XOR engine to store data and parity information in a striped fashion on the plurality of memory modules to create a redundant array of industry standard DIMMs (RAID). The host / data controller also interleaves data on a plurality of channels associated with each of the plurality of memory modules. To optimize memory bandwidth and reduce memory latency, various techniques are implemented in the present RAID system. Present techniques include providing dual memory arbiters, sorting read cycles by chip select or bank address, providing programmable upper and lower boundary registers to facilitate programmable memory mapping, and striping and interleaving memory data to provide a burst length of one.

Owner:HEWLETT PACKARD DEV CO LP

Tamper-resistant memory integrated circuit and encryption circuit using same

InactiveUS20130129083A1Improve reliabilityEliminate needRandom number generatorsDigital storageBit lineComputer architecture

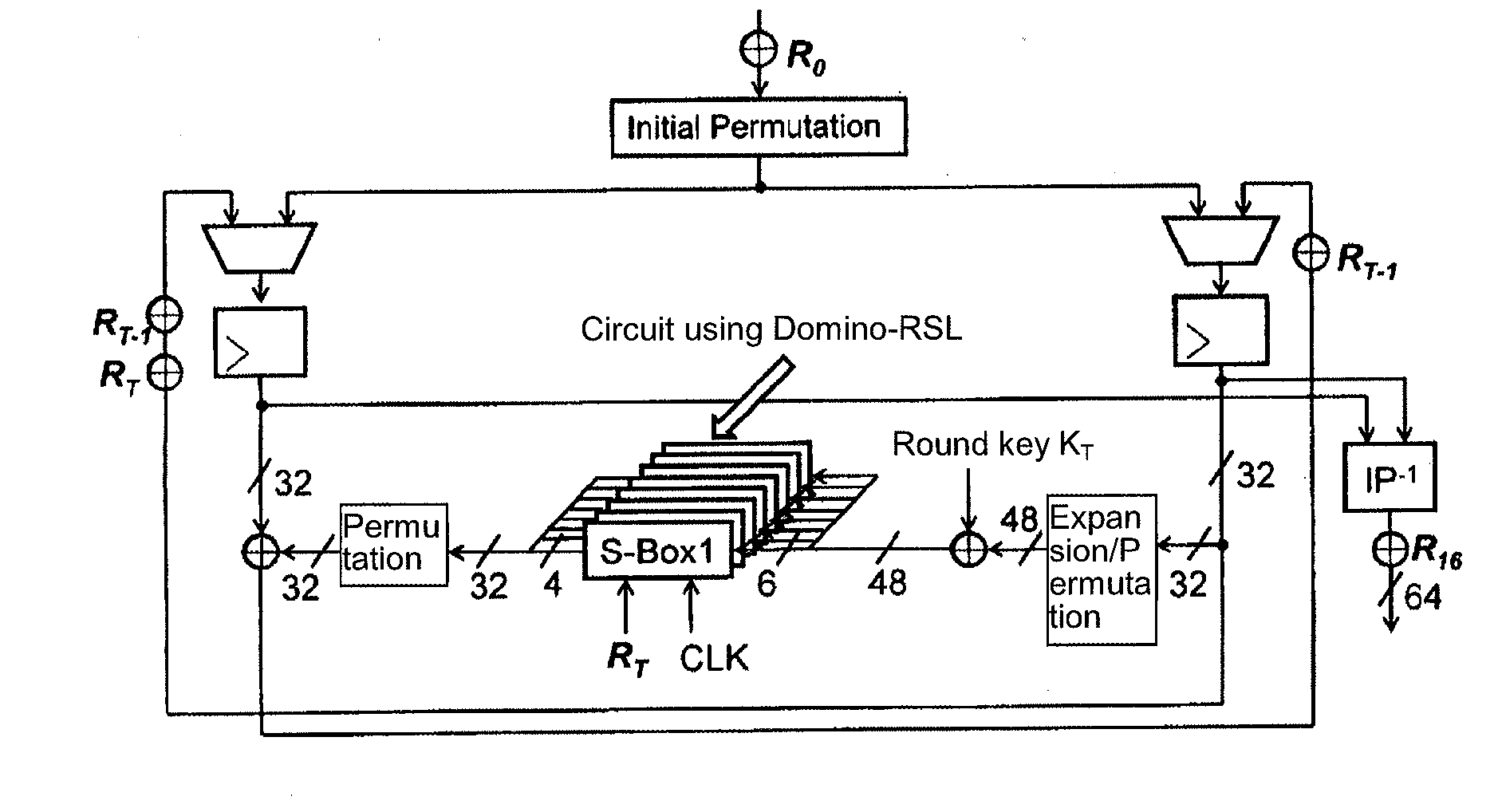

The present invention provides an integrated memory circuit applicable to an S-box of a cryptographic circuit, the integrated memory circuit having a row decoder, a column decoder, and a sense amplifier composed of a domino-RSL circuit, wherein data reading and data writing from / to memory cells of a memory cell array are performed via two complementary bit lines, and the transition probability of a signal line is equalized by input of random-number data supplied from a random-number generating circuit using an arbiter circuit.

Owner:THE RITSUMEIKAN TRUST

Control mechanism for fine-tuned cache to backing-store synchronization

ActiveUS20140122809A1Decreased write bandwidthAttenuation bandwidthMemory adressing/allocation/relocationMemory addressDirty data

One embodiment of the present invention sets forth a technique for processing commands received by an intermediary cache from one or more clients. The technique involves receiving a first write command from an arbiter unit, where the first write command specifies a first memory address, determining that a first cache line related to a set of cache lines included in the intermediary cache is associated with the first memory address, causing data associated with the first write command to be written into the first cache line, and marking the first cache line as dirty. The technique further involves determining whether a total number of cache lines marked as dirty in the set of cache lines is less than, equal to, or greater than a first threshold value, and: not transmitting a dirty data notification to the frame buffer logic when the total number is less than the threshold value, or transmitting a dirty data notification to the frame buffer logic when the total number is equal to or greater than the first threshold value.

Owner:NVIDIA CORP

System and method for providing multi-initiator capability to an ATA drive

InactiveUS6961813B2Reduce necessityInput/output to record carriersError detection/correctionMulti portSerial ATA

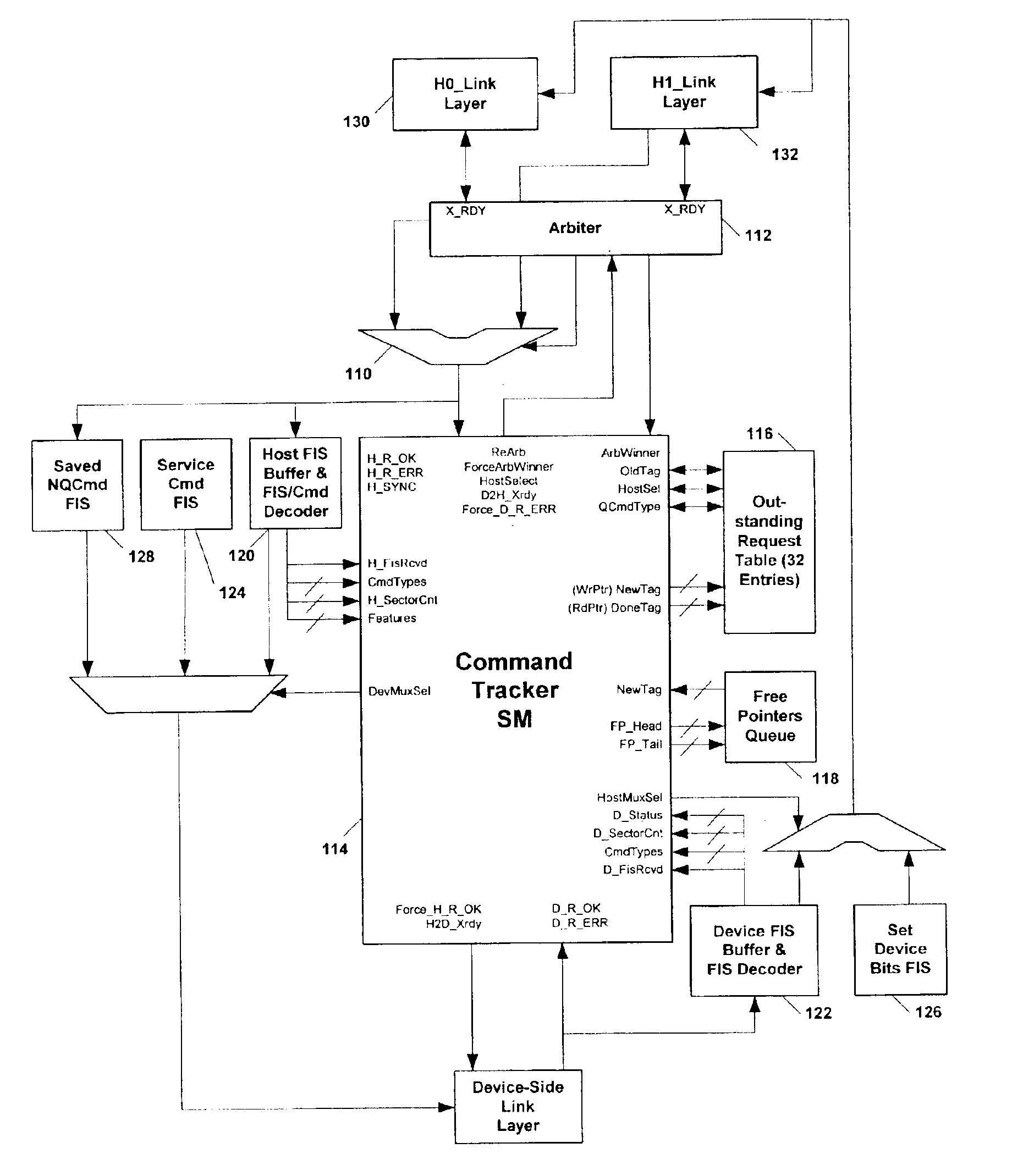

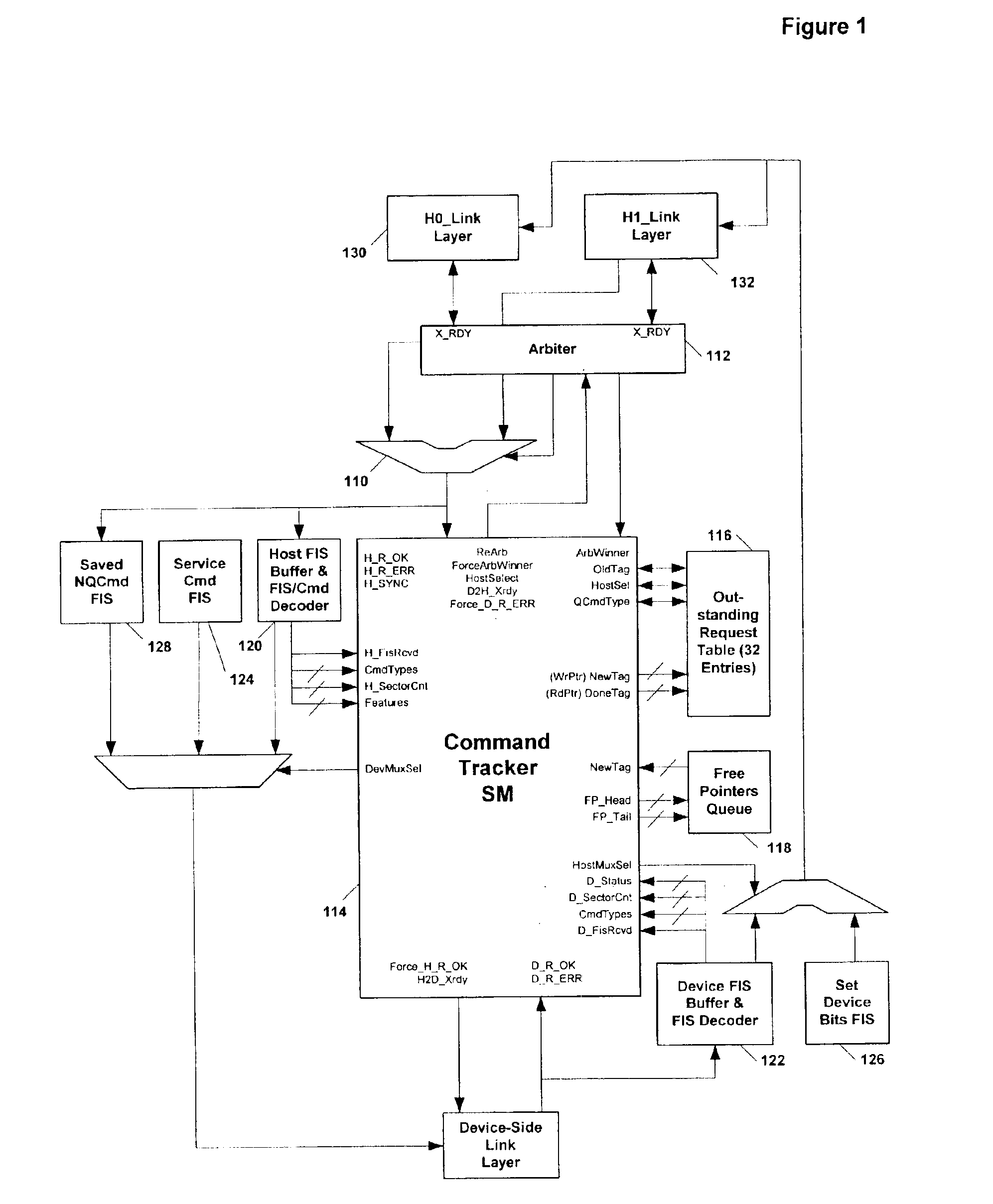

A multi-port adapter and method of operation suitable for use with serial ATA devices is disclosed. An adapter includes a switch that receives input from multiple host devices and an arbiter module for assigning a priority scheme to received commands. An outstanding request table is implemented as a memory module for storing identifying information associated with commands received from multiple host devices, and a free pointers queue is maintained to track slots available in the outstanding request table. A command tracker state machine decodes incoming requests from hosts, monitors the execution by these commands by the ATA device, and updates the memory module to reflect completion of commands. Also disclosed is a storage system including an adapter of the present invention and ATA storage devices.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

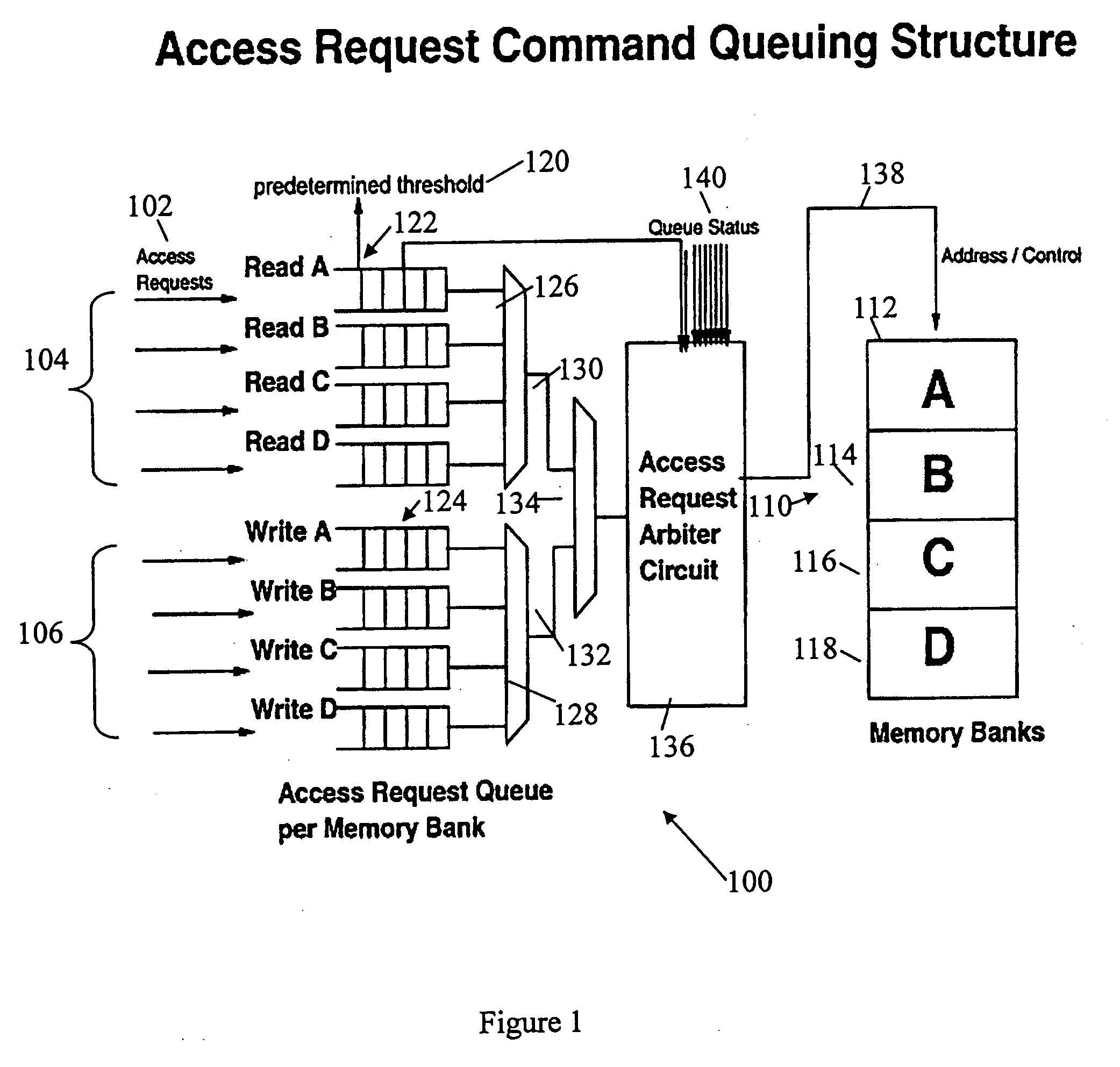

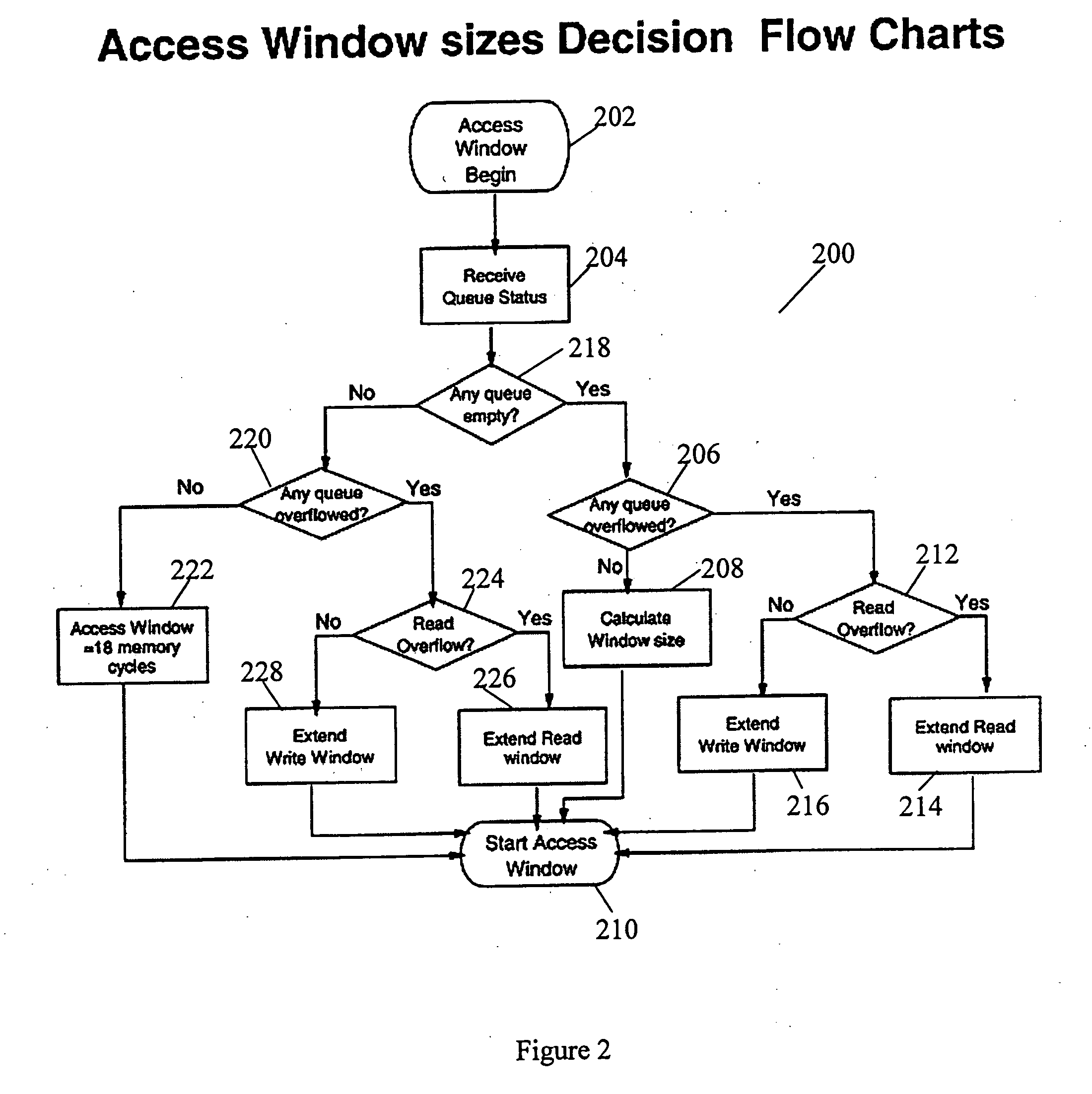

DRAM access command queuing structure

ActiveUS20060026342A1Solve insufficient bandwidthAvoid bottleneck and conflictMemory adressing/allocation/relocationMemory systemsMemory bankDram memory

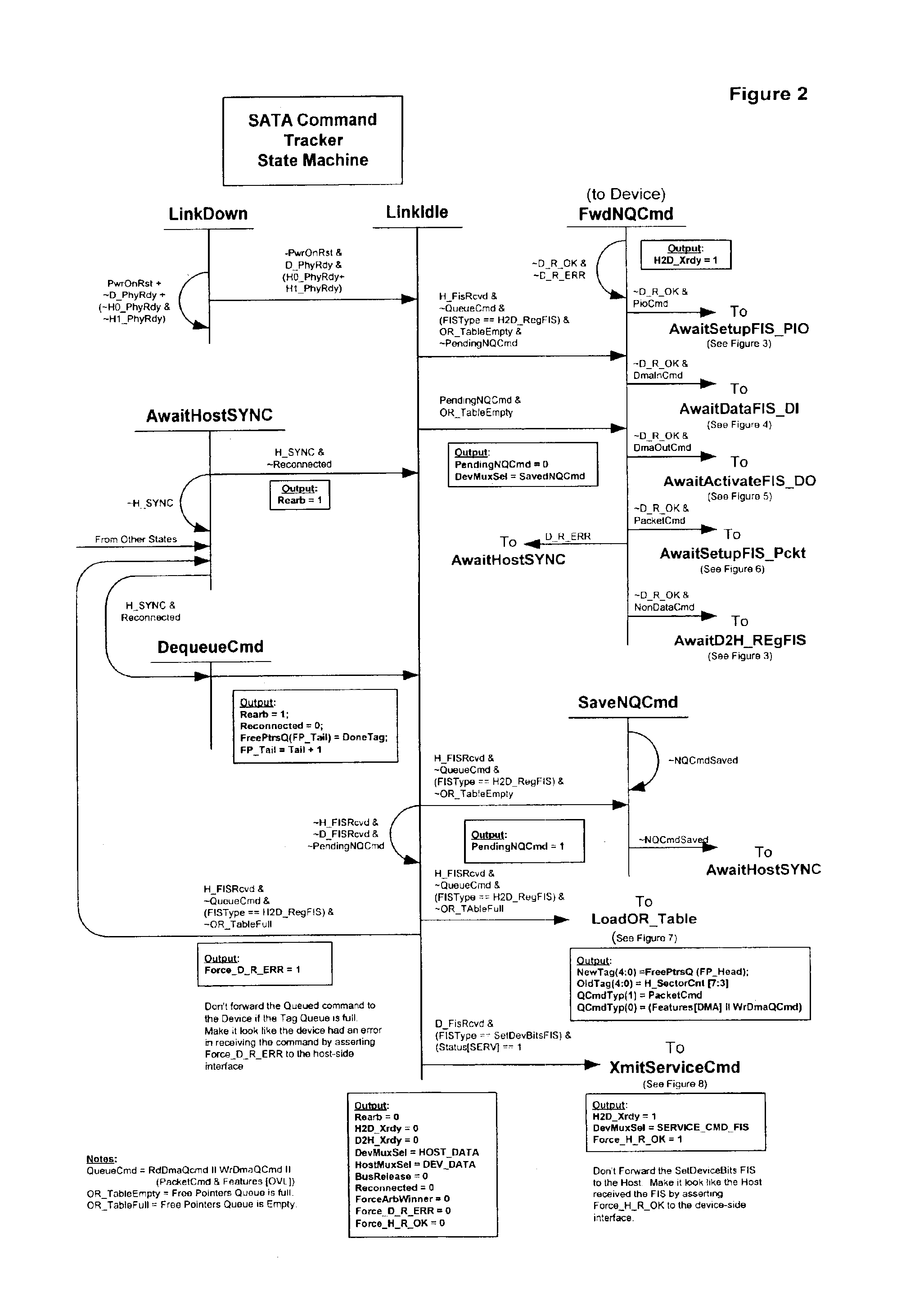

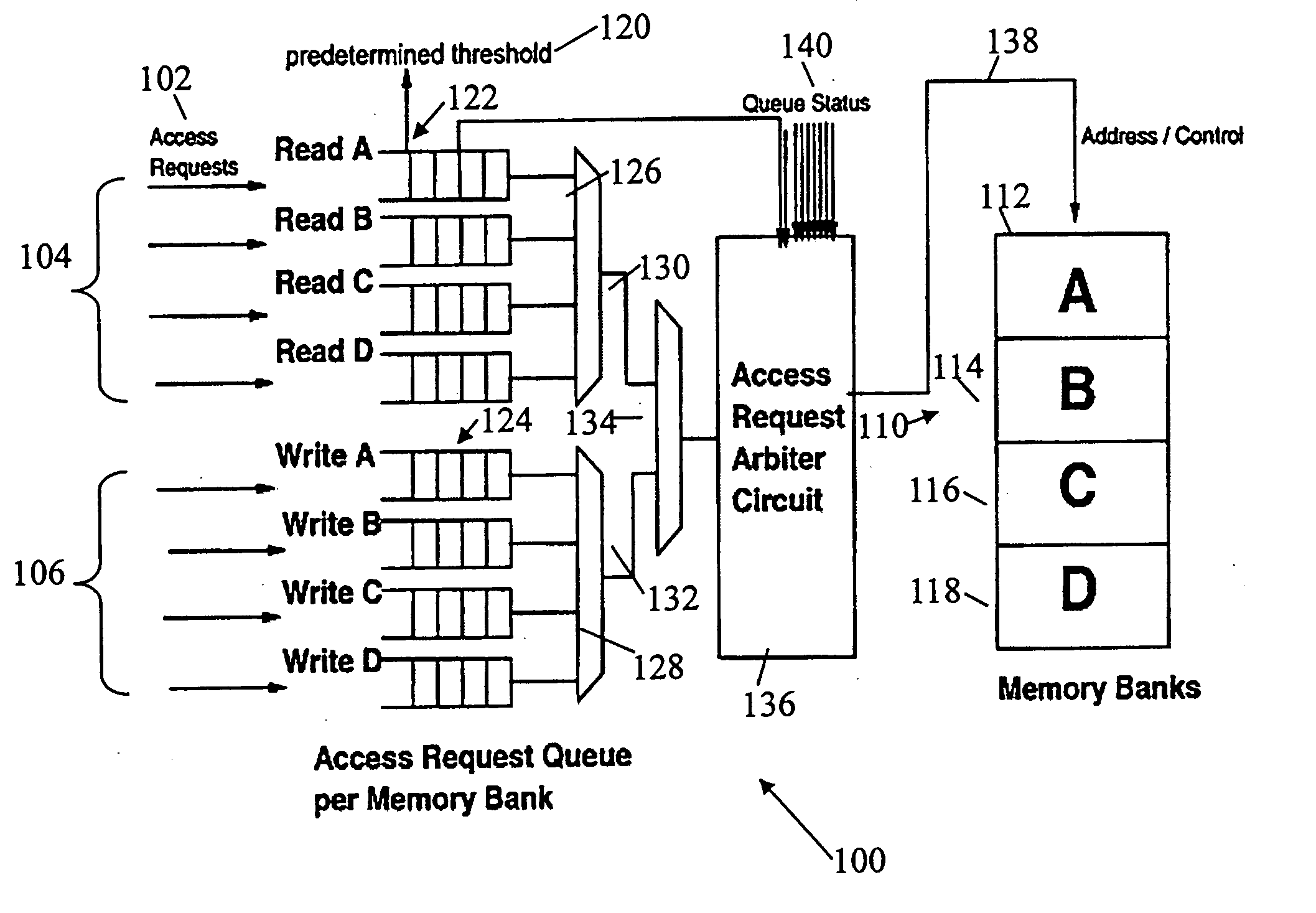

Access arbiters are used to prioritize read and write access requests to individual memory banks in DRAM memory devices, particularly fast cycle DRAMs. This serves to optimize the memory bandwidth available for the read and the write operations by avoiding consecutive accesses to the same memory bank and by minimizing dead cycles. The arbiter first divides DRAM accesses into write accesses and read accesses. The access requests are divided into accesses per memory bank with a threshold limit imposed on the number of accesses to each memory bank. The write receive packets are rotated among the banks based on the write queue status. The status of the write queue for each memory bank may also be used for system flow control. The arbiter also typically includes the ability to determine access windows based on the status of the command queues, and to perform arbitration on each access window.

Owner:GLOBALFOUNDRIES US INC

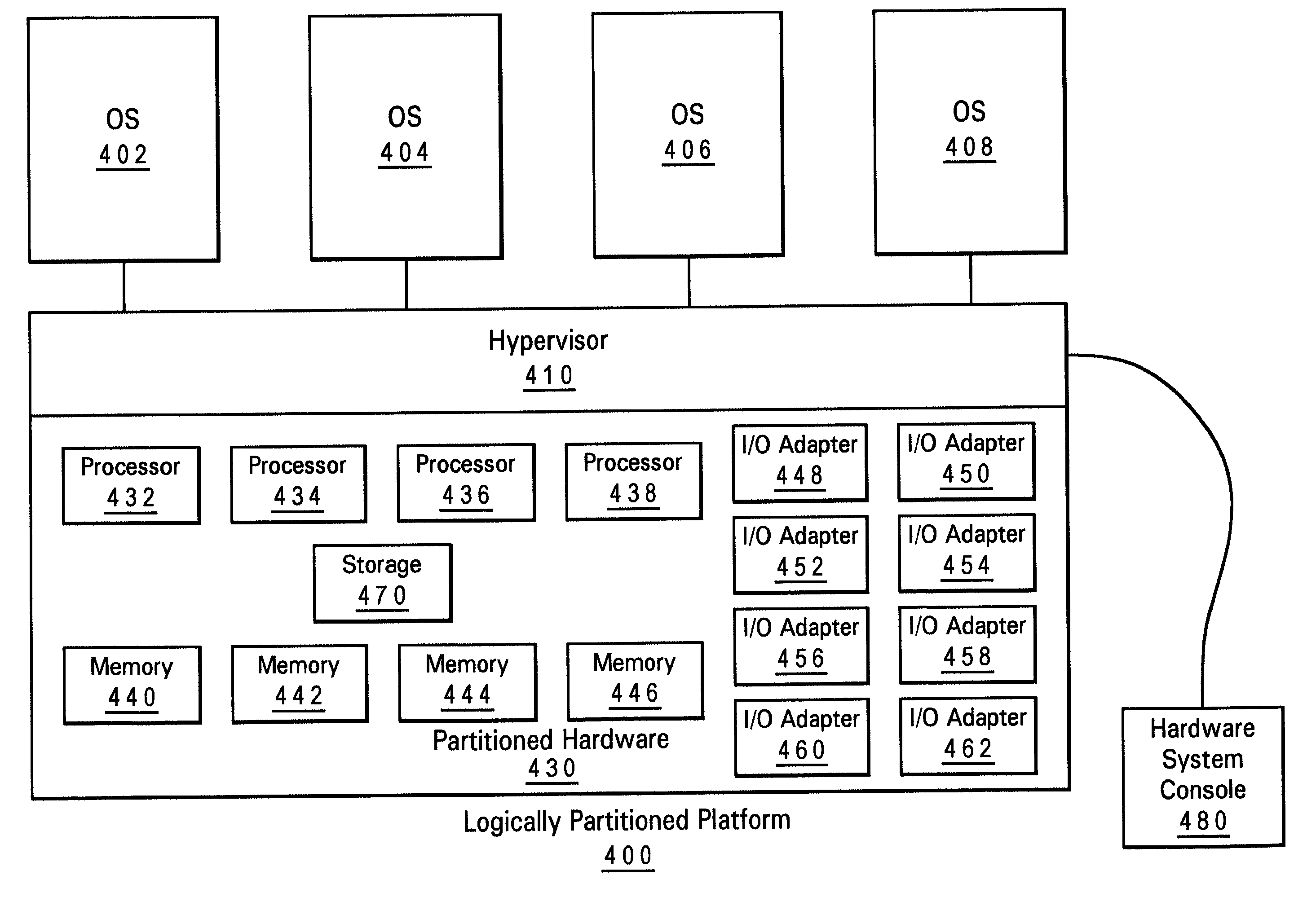

DMA windowing in an LPAR environment using device arbitration level to allow multiple IOAs per terminal bridge

InactiveUS20020010811A1Input/output processes for data processingData conversionData processing systemDirect memory access

A method, system, and apparatus for preventing input / output (I / O) adapters used by an operating system (OS) image, in a logically partitioned data processing system, from fetching or corrupting data from a memory location allocated to another OS image within the data processing system is provided. A hypervisor prevents transmission of data between an input / output adapter in one of the logical partitions and memory locations assigned to other logical partitions during a direct memory access (DMA) operation by assigning each of the input / output adapters a range of I / O bus DMA addresses. The I / O adapters (IOAs) are connected to PCI host bridges via terminal bridges. A single terminal bridge may support multiple IOAs, in which case every terminal bridge has a plurality of sets of range registers, each associated with a respective one of the IOAs to which it is connected. An arbiter is provided which selects one of the input / output adapters to use the PCI bus. The terminal bridge can examine the grant signals from the arbiter to the IOAs, to determine which set of range registers is to be used.

Owner:IBM CORP

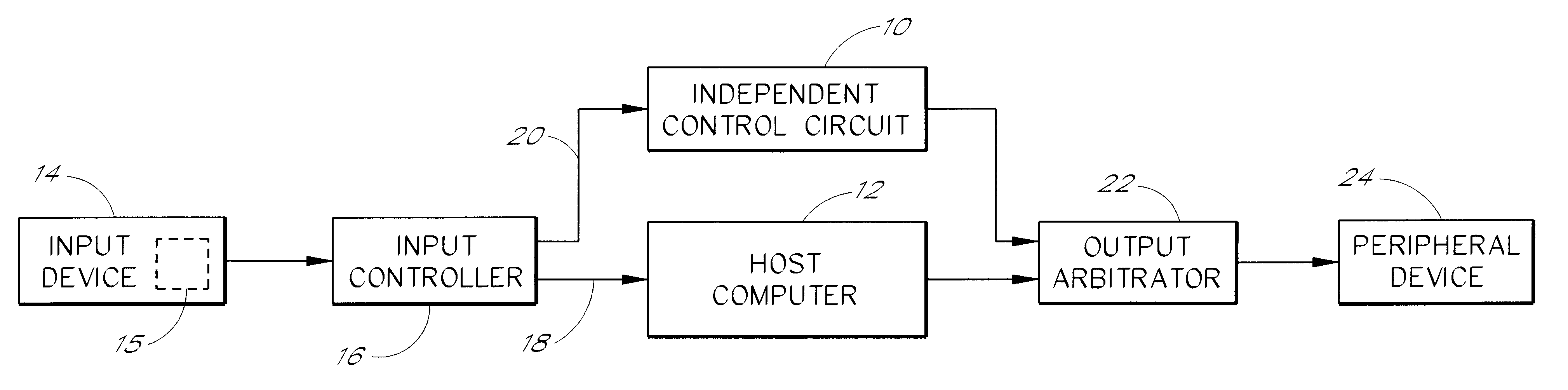

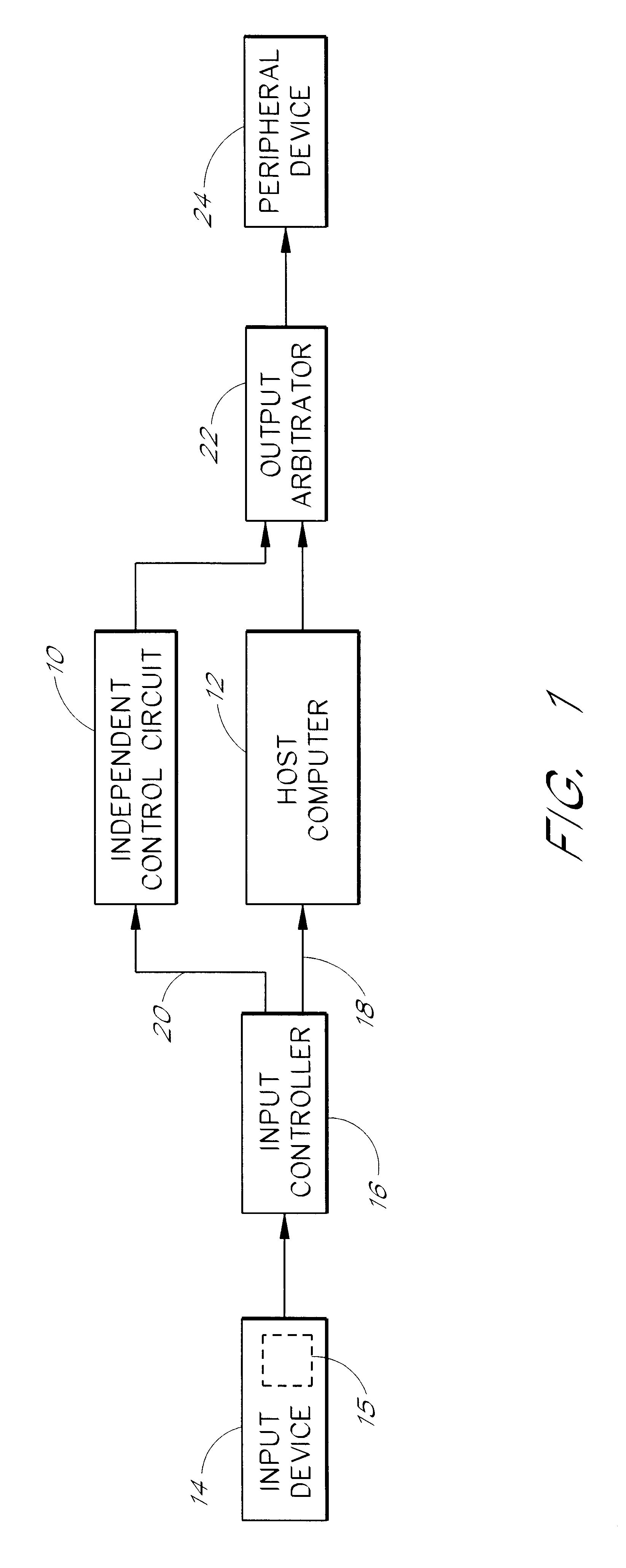

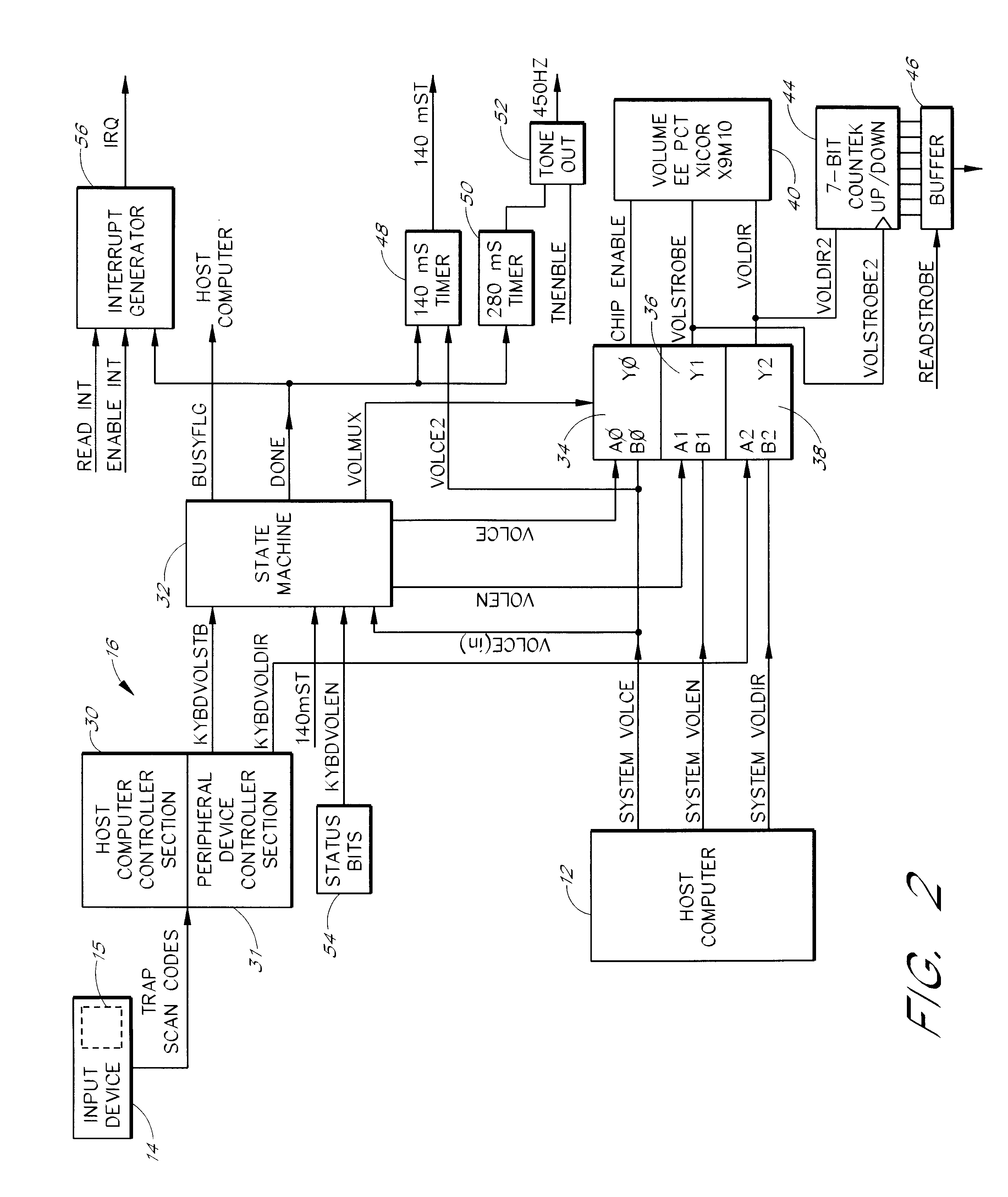

Adjusting the volume by a keyboard via an independent control circuit, independent of a host computer

A computer system having dual paths for controlling a peripheral device electrically associated with a host computer. The peripheral device is electrically connected to the host computer and to an independent control circuit. Control inputs for the peripheral device and data and / or control inputs for the host computer are generated by a keyboard or other input device and transmitted to an input controller which directs certain data and / or control inputs to the host computer for processing and directs certain peripheral device control inputs to a state machine for the generation of peripheral device control signals. In such a manner, the independent control circuit provides for the control of the peripheral device while the host computer may process data unrelated to the control of the peripheral device. In one aspect, control of the peripheral device may be effected by both the host computer and the independent control circuit. Accordingly, in this aspect, the independent control circuit further comprises an arbitrator which resolves any control conflicts that arise between the host computer and the independent control circuit.

Owner:SAMSUNG ELECTRONICS CO LTD

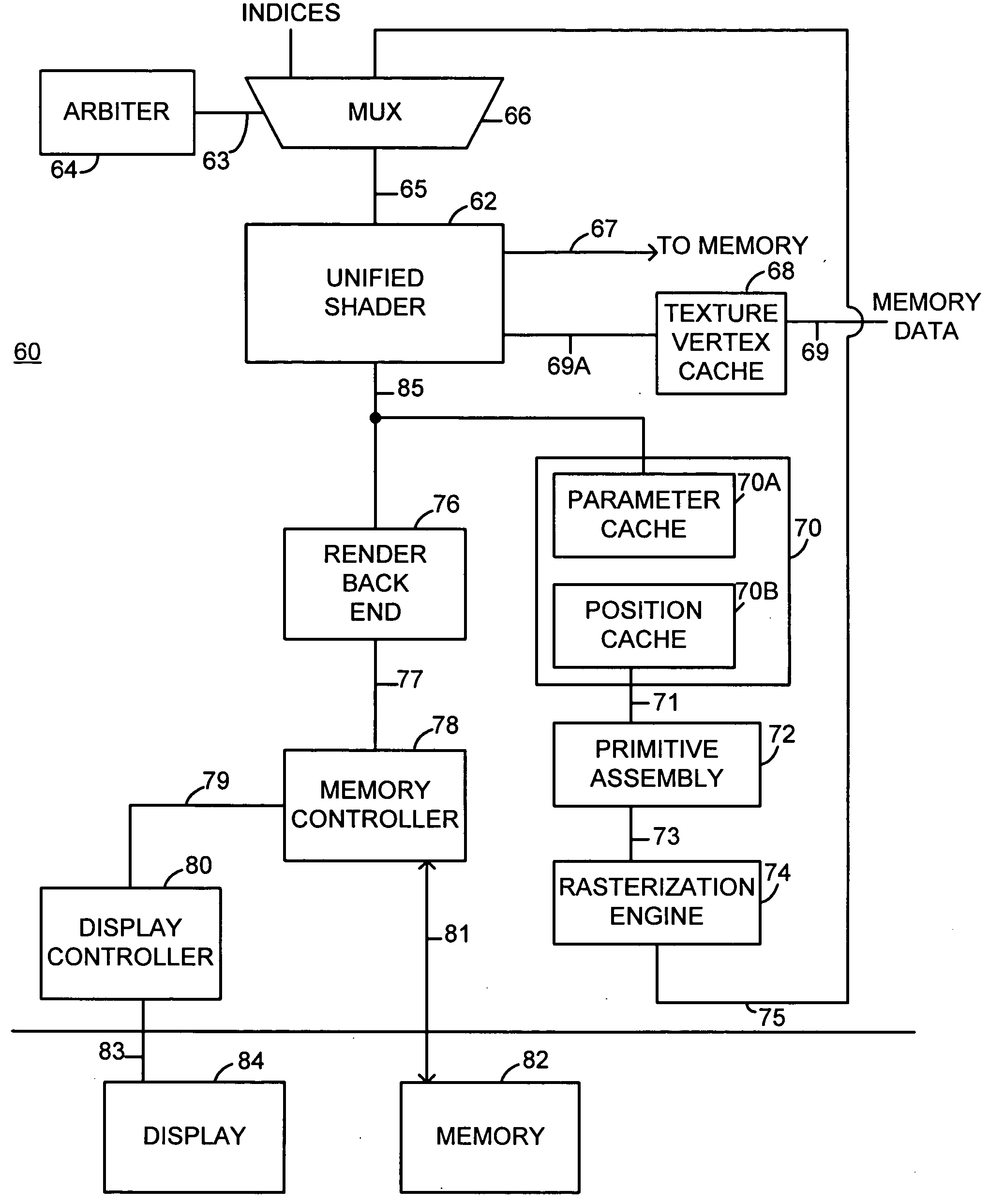

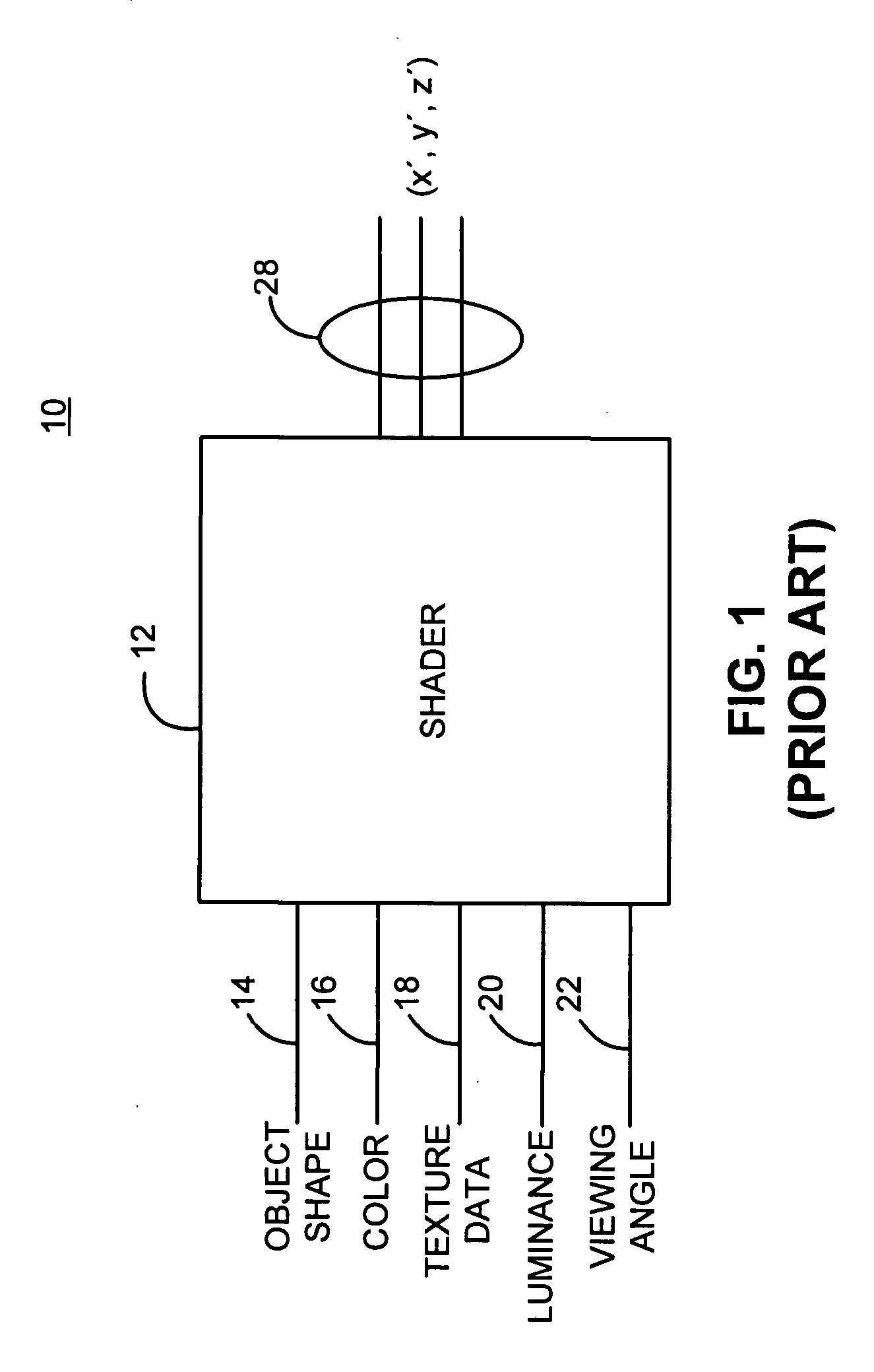

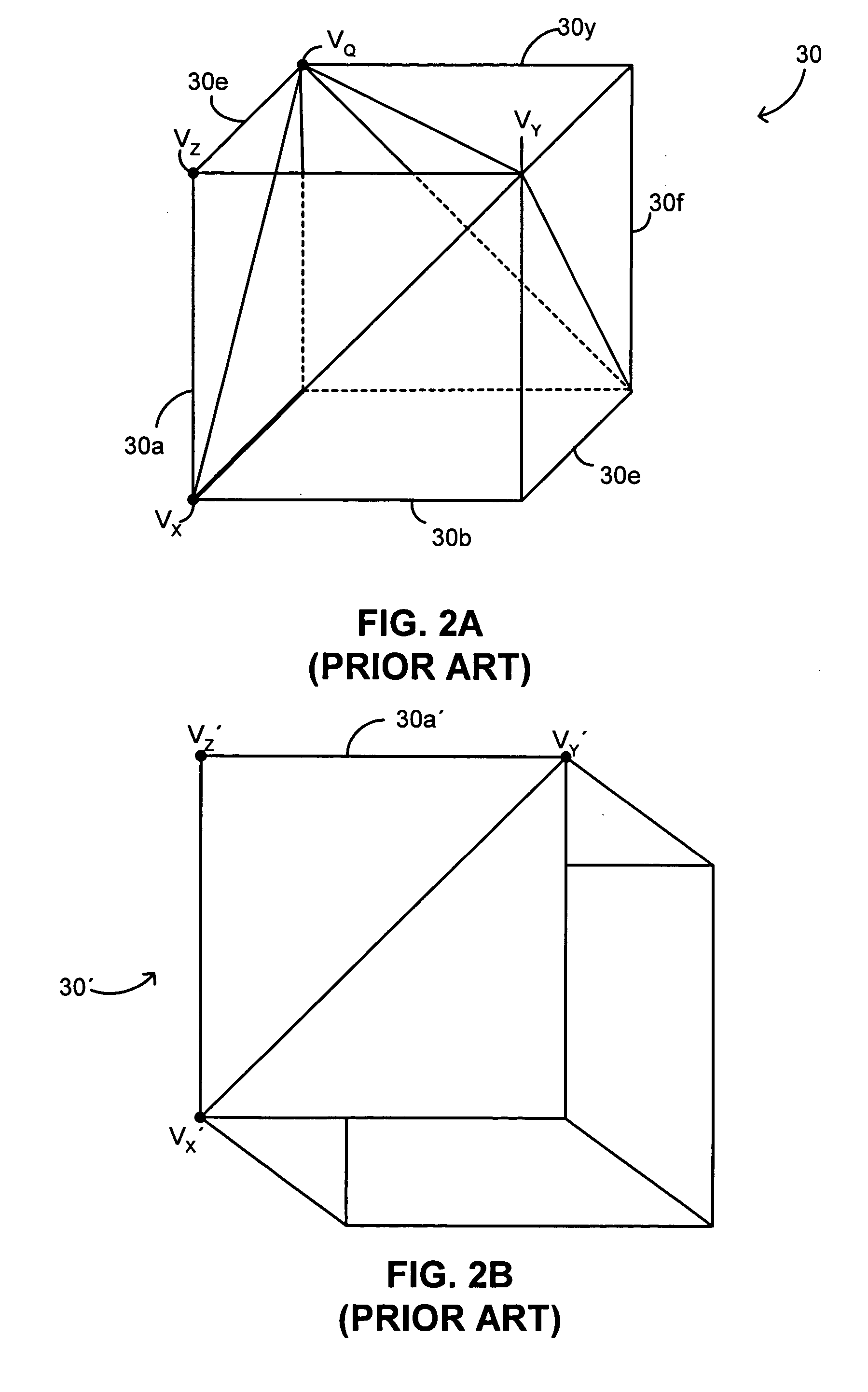

Graphics processing architecture employing a unified shader

InactiveUS20050110792A1More computationally efficientFlexiblyDigital computer detailsProcessor architectures/configurationComputer architectureControl signal

Owner:ATI TECH INC

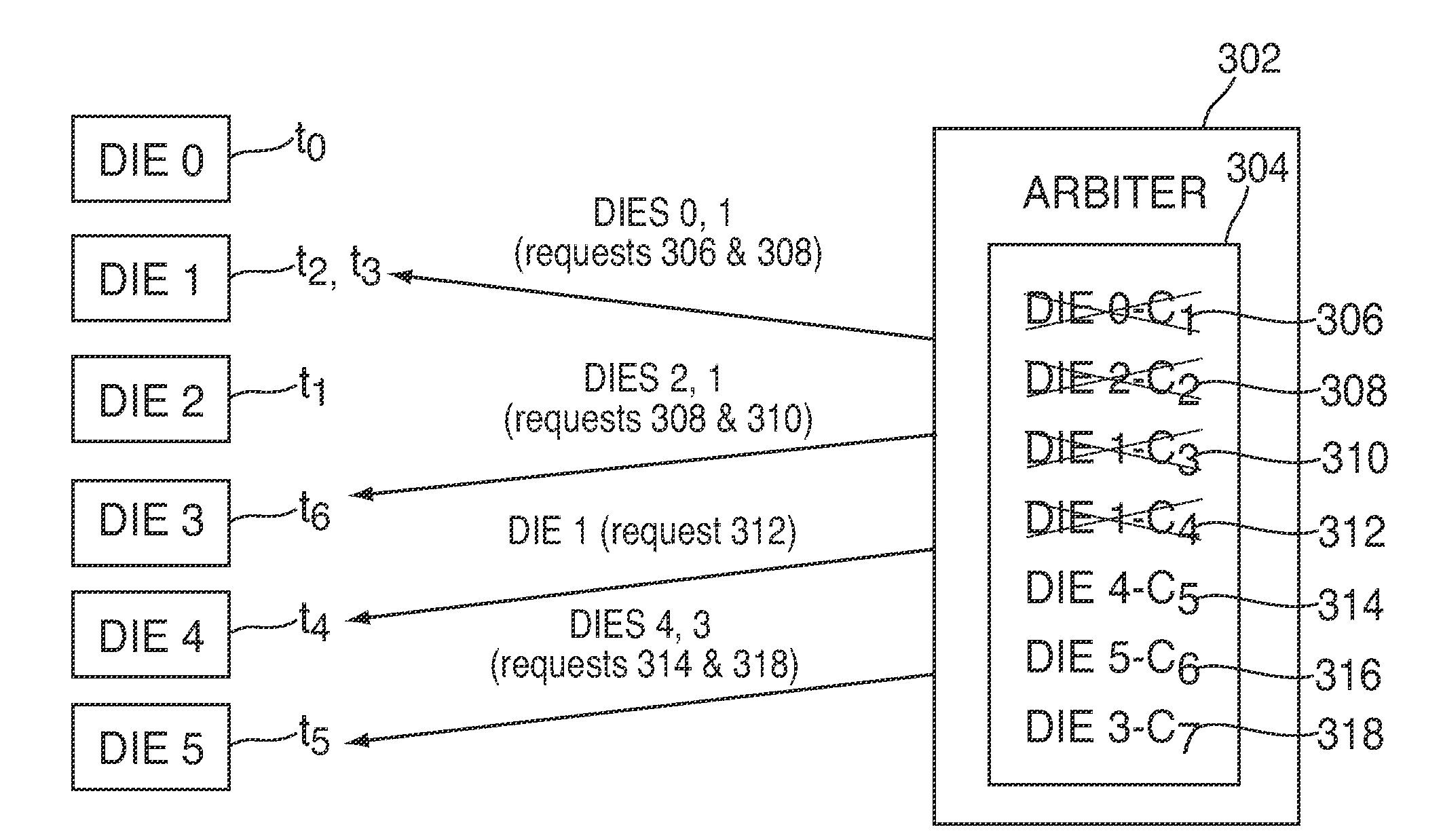

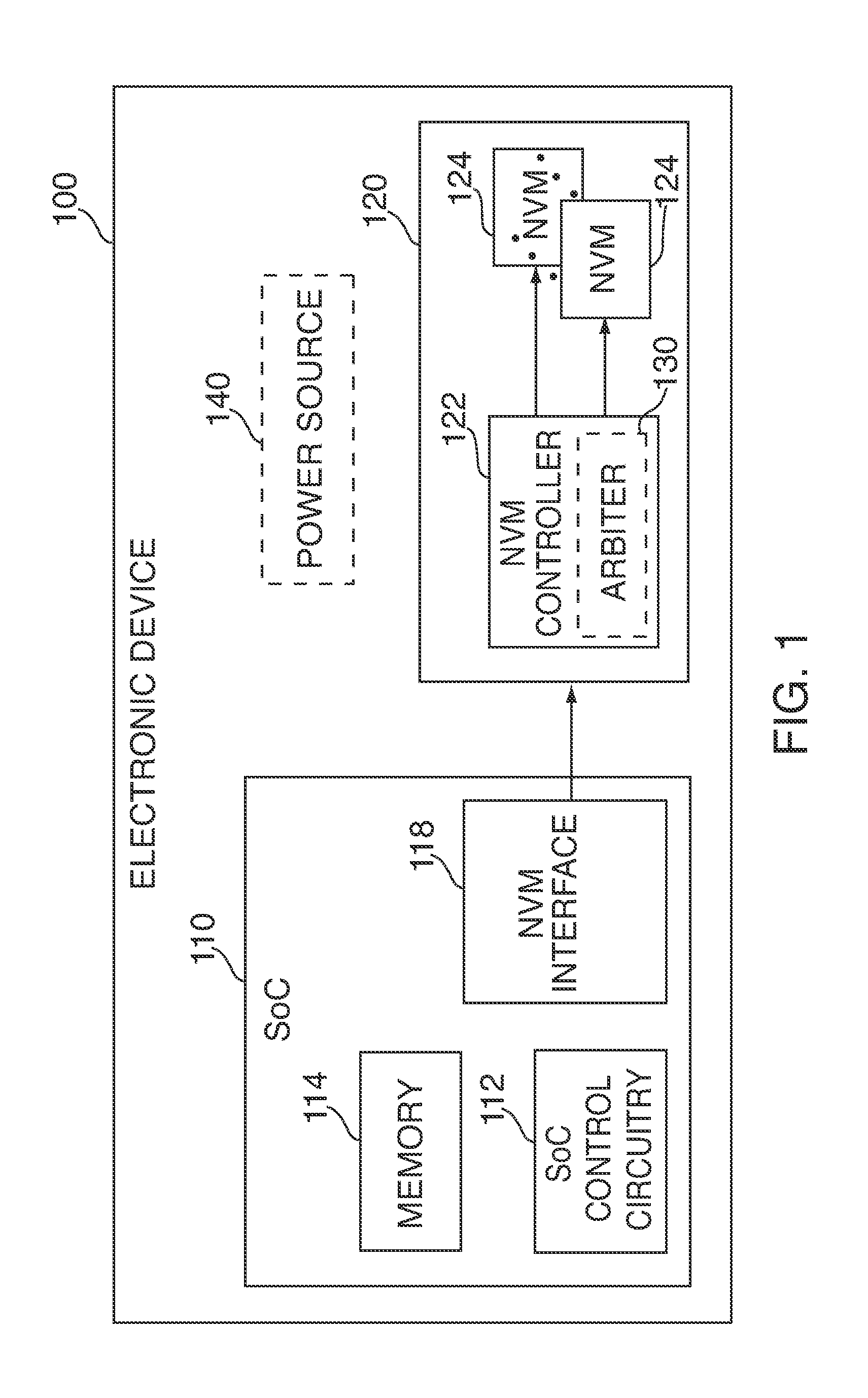

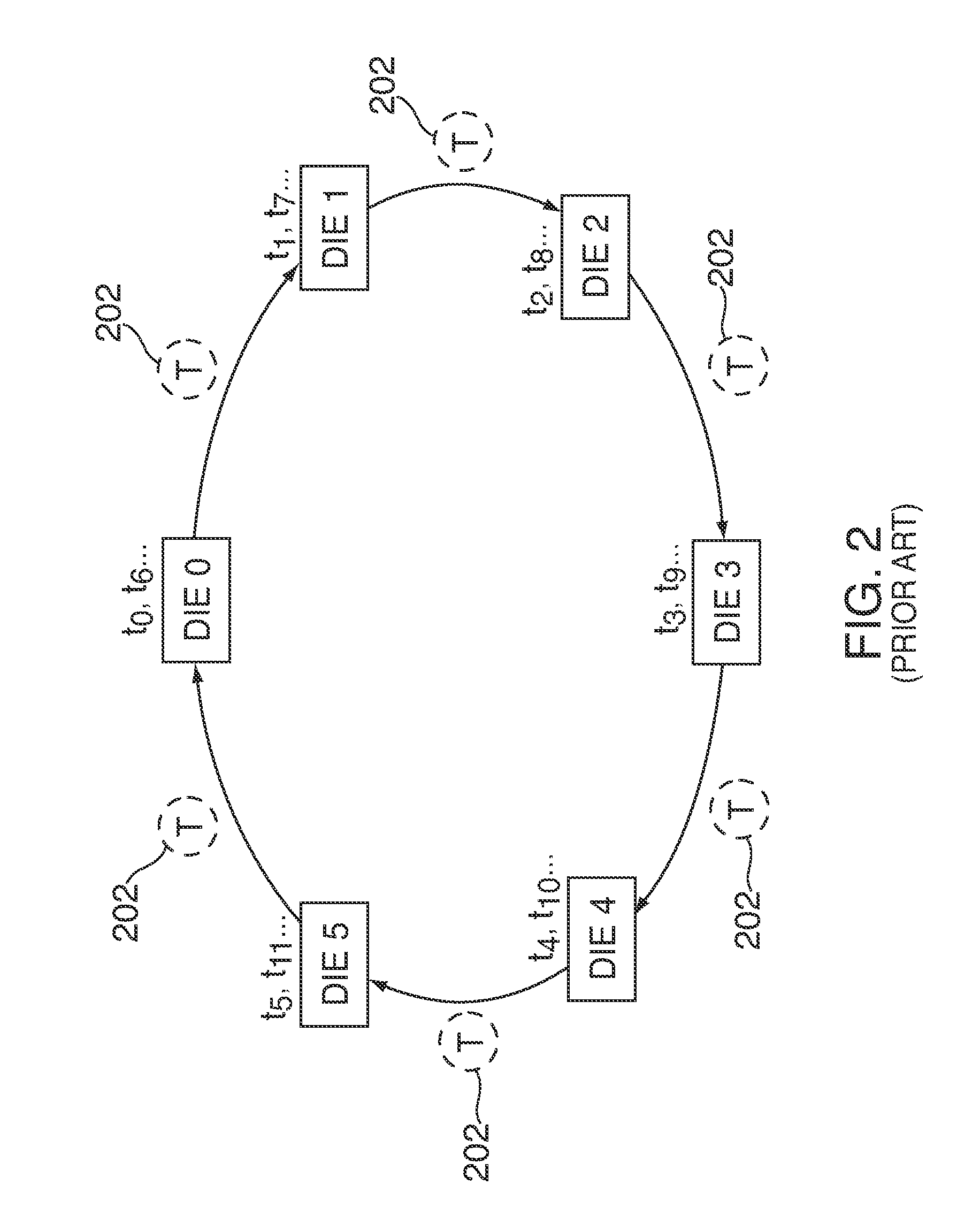

Asynchronous management of access requests to control power consumption

ActiveUS20120290864A1Minimum latencyMinimum power consumptionHardware monitoringPower supply for data processingControl powerArbiter

Systems and methods are disclosed for asynchronous management of access requests to control power consumption. In some cases, by asynchronously managing power within a system, multiple dies of a NVM can simultaneously draw current in order to match the power demand. In particular, an arbiter of the system can receive multiple requests to draw current, where each request may be associated with a different die of the NVM. In some embodiments, the arbiter can determine the servicing order using the time of arrival of the request (e.g., a first-in, first-out scheme). In other embodiments, the arbiter can simultaneously service multiple requests so long as the servicing of the multiple requests does not exceed a power budget.

Owner:APPLE INC

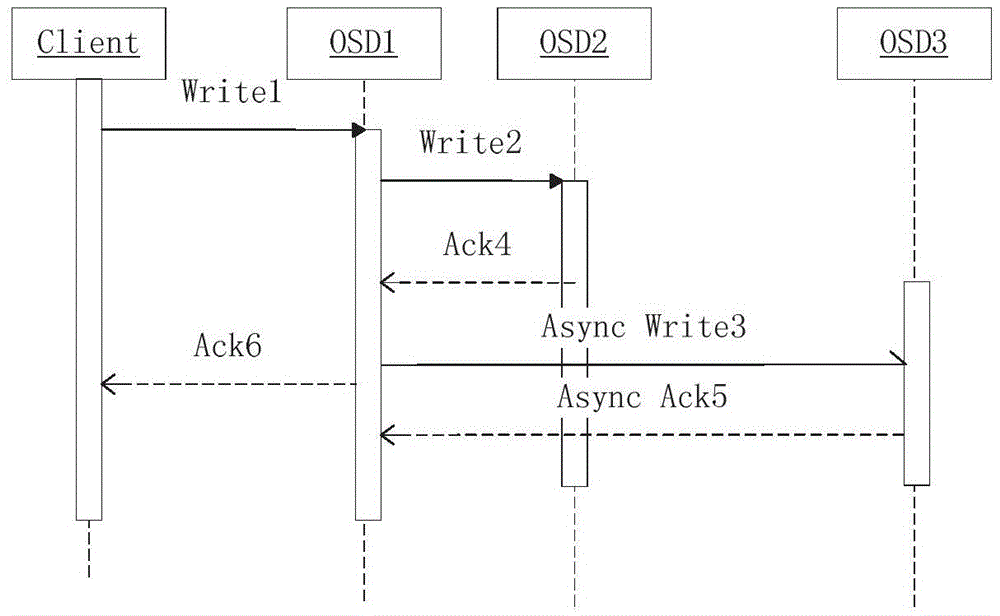

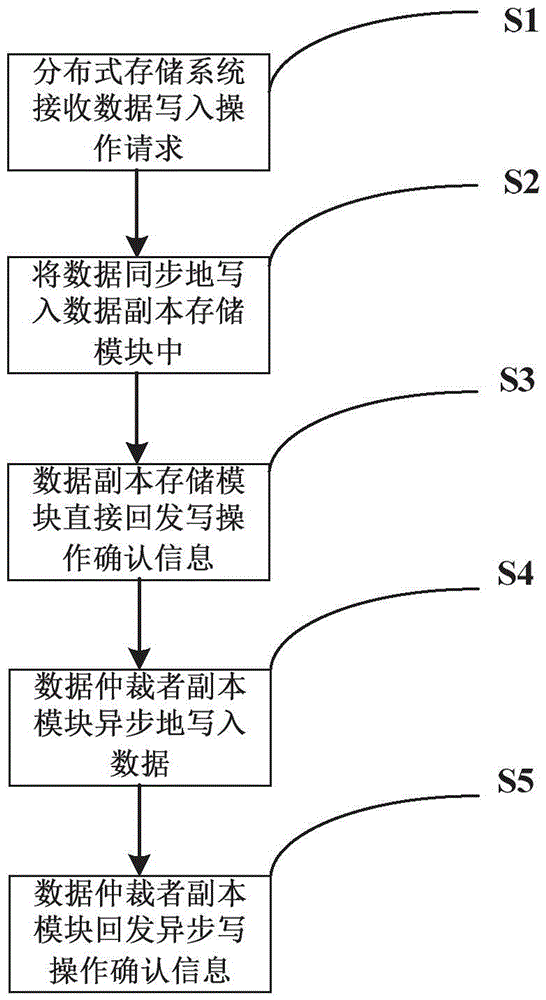

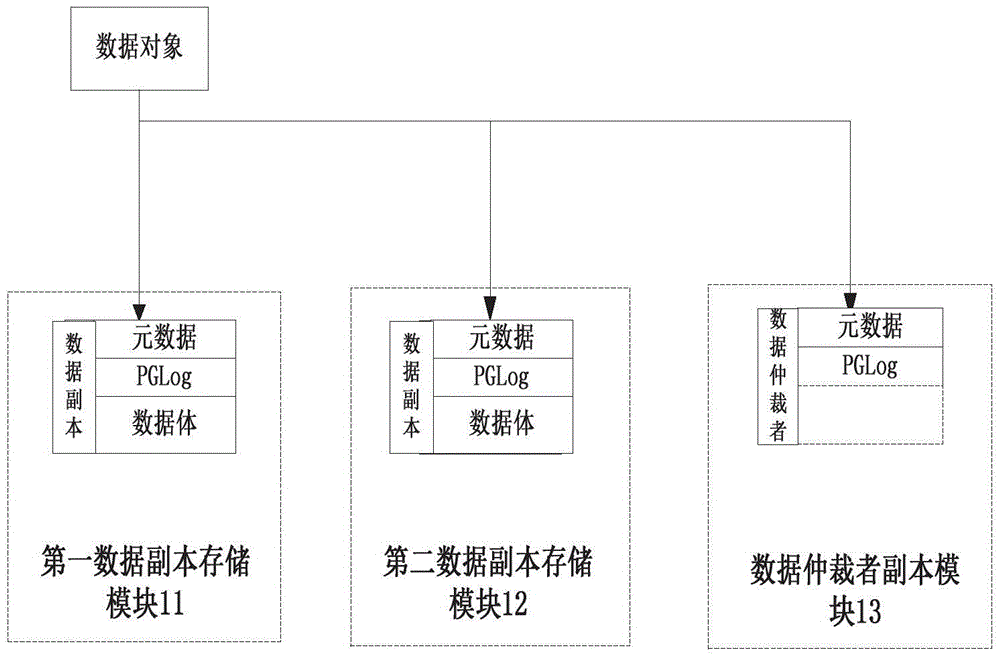

Distributed storage system and method based on data arbiter copy

The invention provides a distributed storage system and method based on a data arbiter copy and used for online distributed data storage. The method comprises the following steps that: S1, the distributed storage system receives a data write-in operation request; S2, the distributed storage system starts data write-in operation after receiving the data write-in operation request and synchronously writes the written data into a data copy storage module; S3, the data write-in operation of the data copy storage module is completed, and the data copy storage module directly returns writing operation confirmation information; S4, a data arbiter copy module continuously and asynchronously write in data from the data copy storage module, and a complete data arbitration information backup used for data migration and restoration is carried out; and S5, the write-in operation of the data arbiter copy module is completed, and asynchronous writing operation confirmation information is returned. The distributed storage system and method solve the problems in the prior art that an existing distributed storage system has a relatively small effectively storage space, is low in reading and writing efficiency and has difficulty in data restoration, and a conventional double-copy storage method leads to a brain-split phenomenon.

Owner:EISOO SOFTWARE

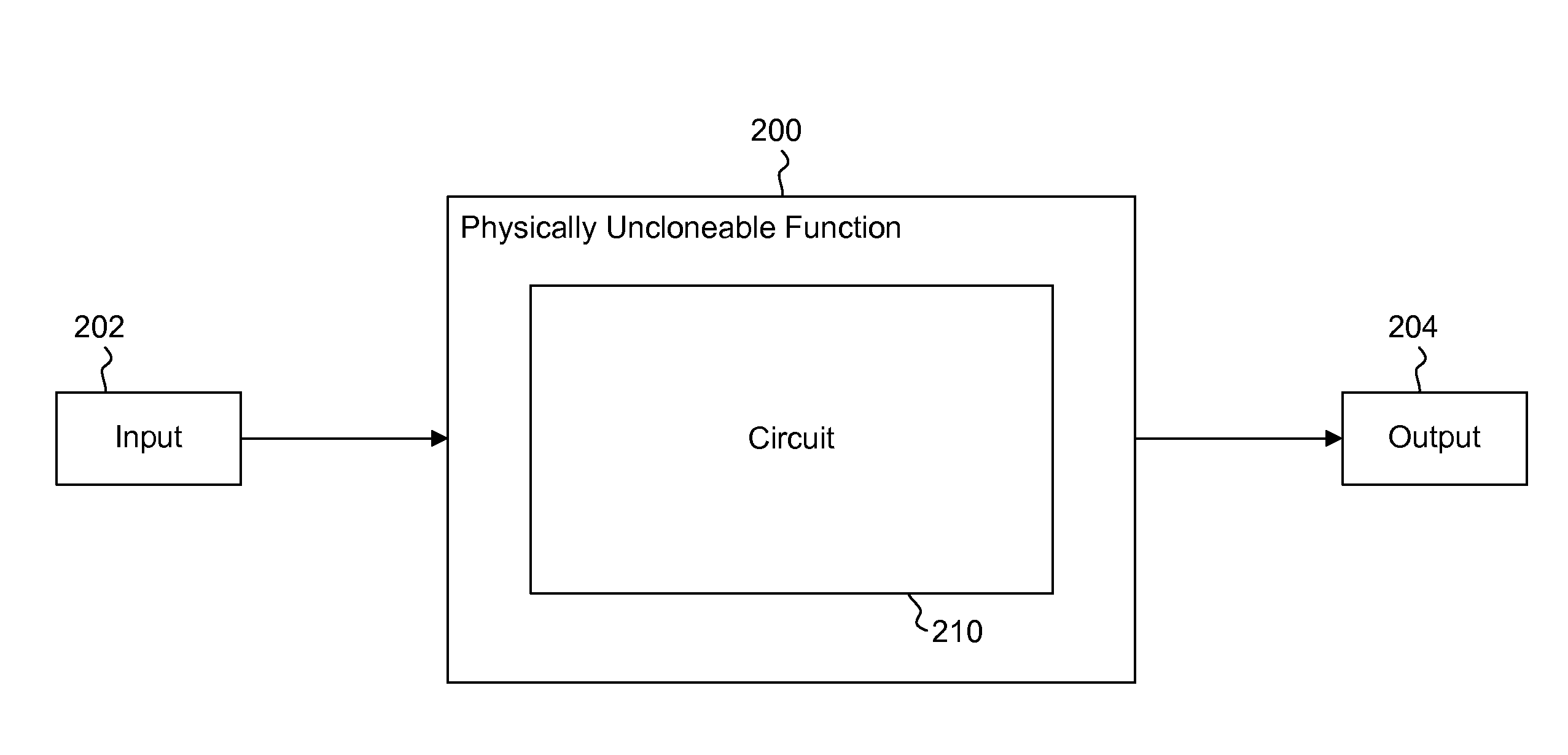

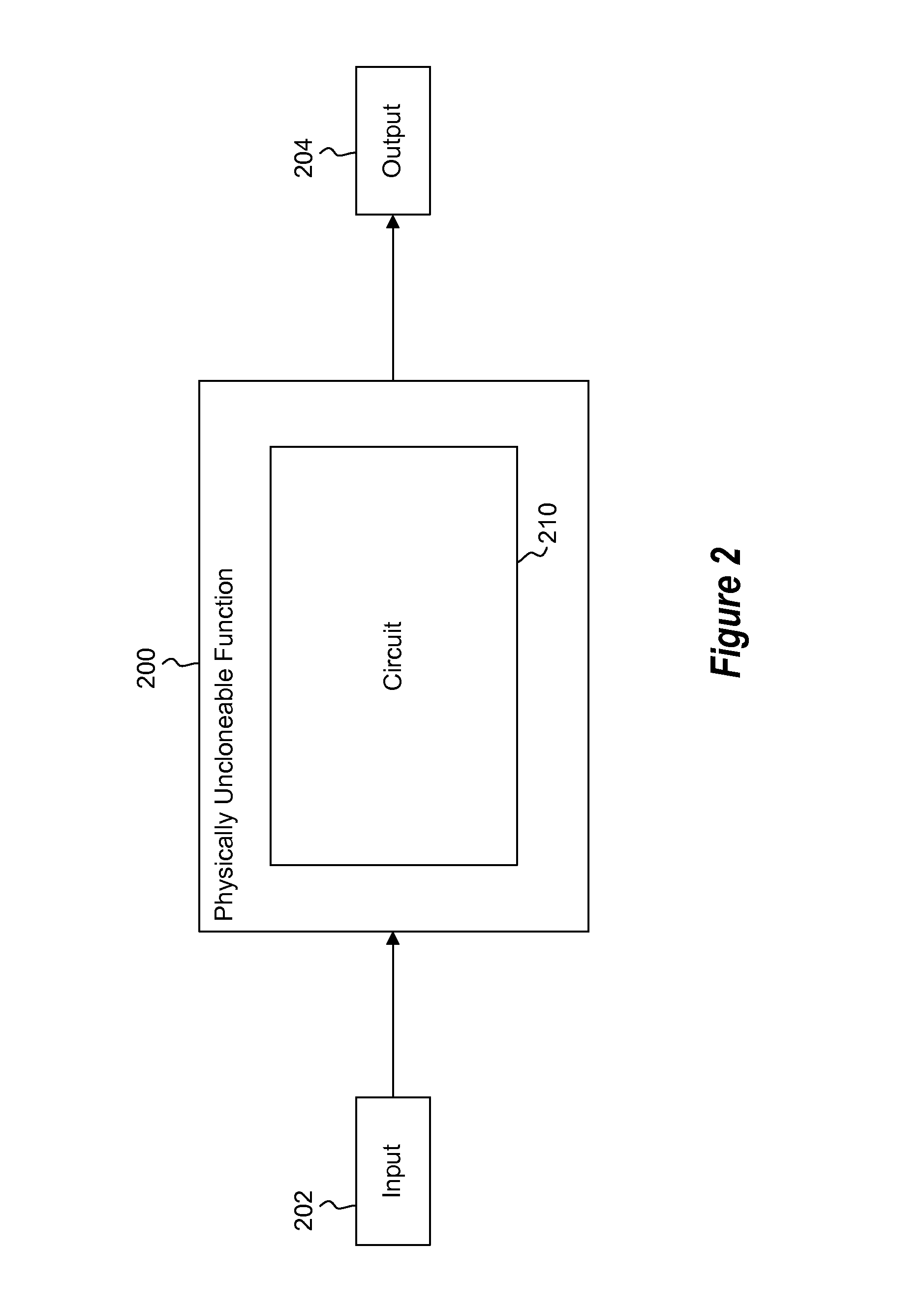

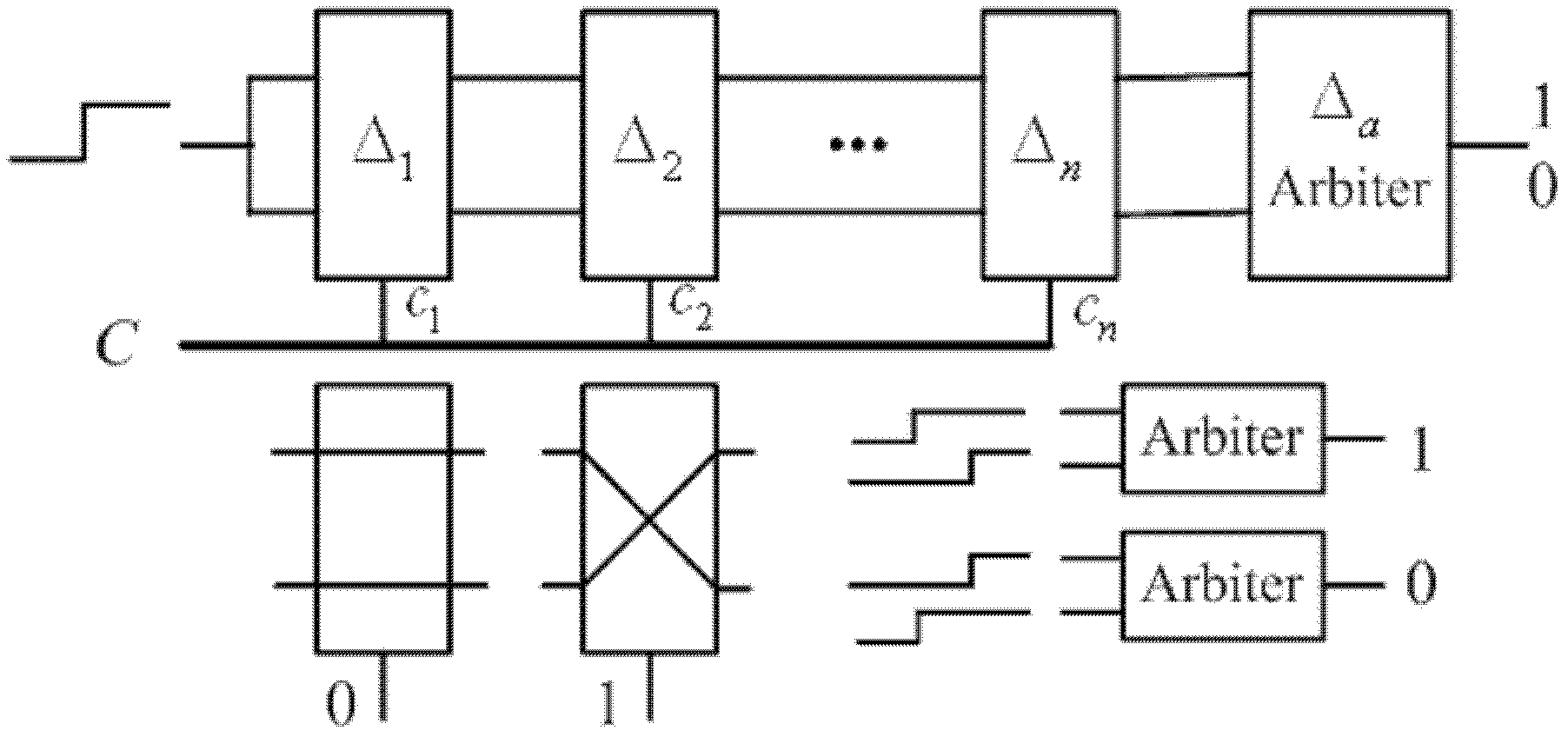

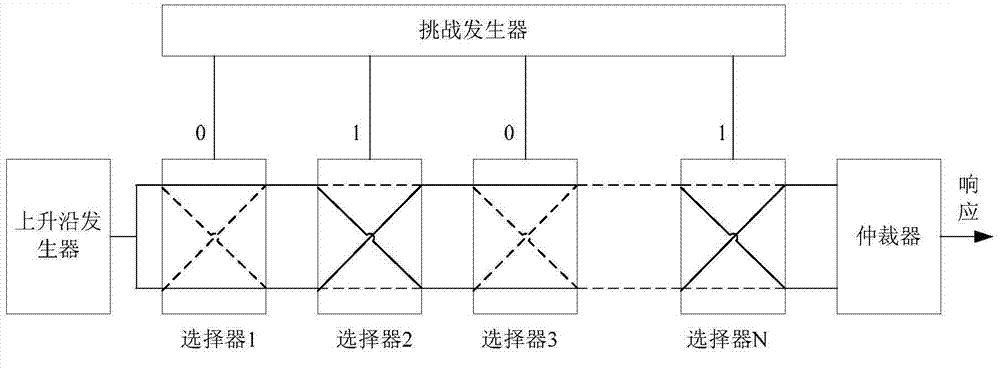

Differential uncloneable variability-based cryptography

InactiveUS20110239002A1Unauthorized memory use protectionHardware monitoringKey (cryptography)Physical unclonable function

Differential uncloneable variability-based cryptography techniques are provided. The differential cryptography includes a hardware based public physically uncloneable function (PPUF) to perform the cryptography. The PPUF includes a first physically uncloneable function (PUF) and a second physically uncloneable function. An arbiter determines the output of the circuit using the outputs of the first and second PUFs. Cryptography can be performed by simulating the PPUF with selected input. The output of the simulation, along with timing information about a set of inputs from where the corresponding input is randomly selected for simulation, is used by the communicating party that has the integrated circuit with the PPUF to search for an input that produces the output. The input can be configured to be the secret key or a part of the secret key.

Owner:EMPIRE TECH DEV LLC

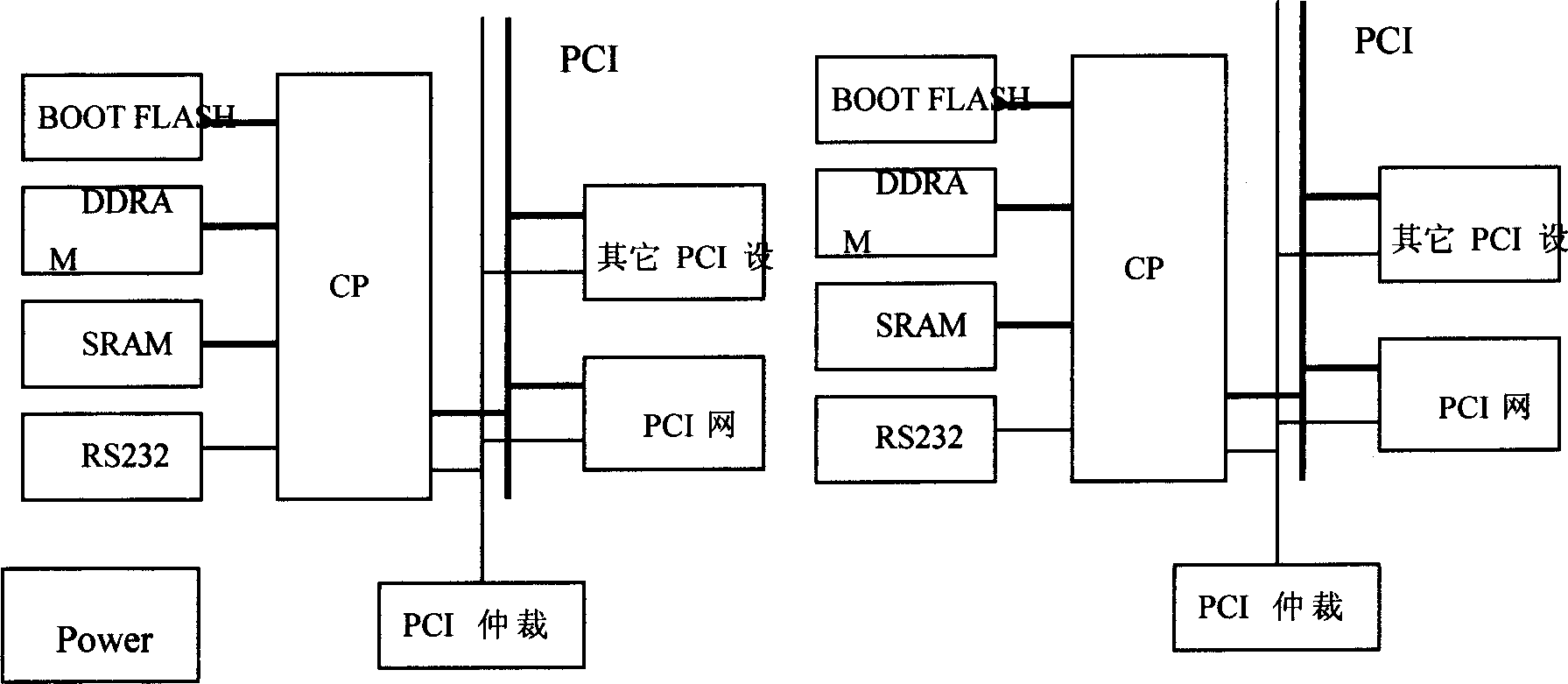

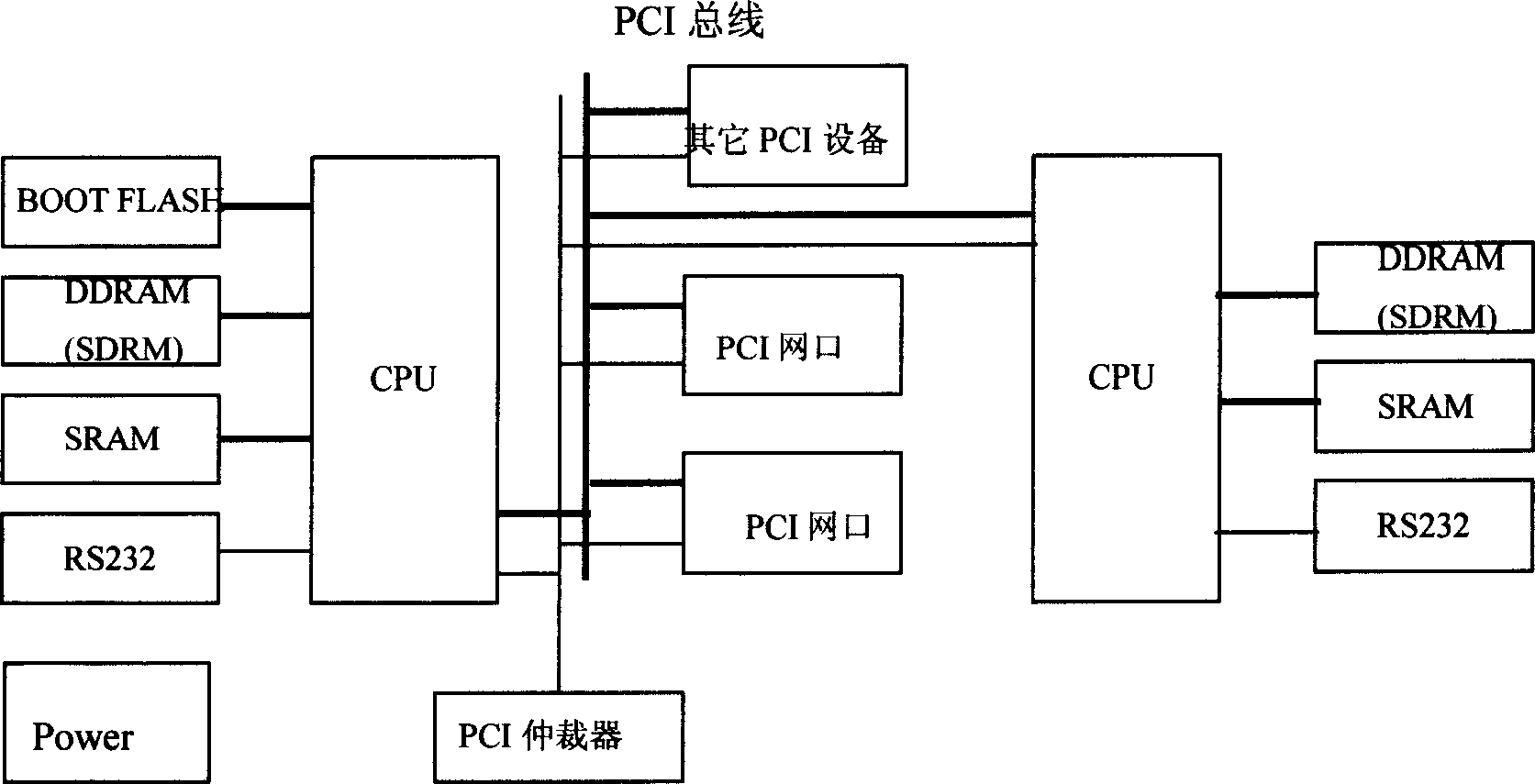

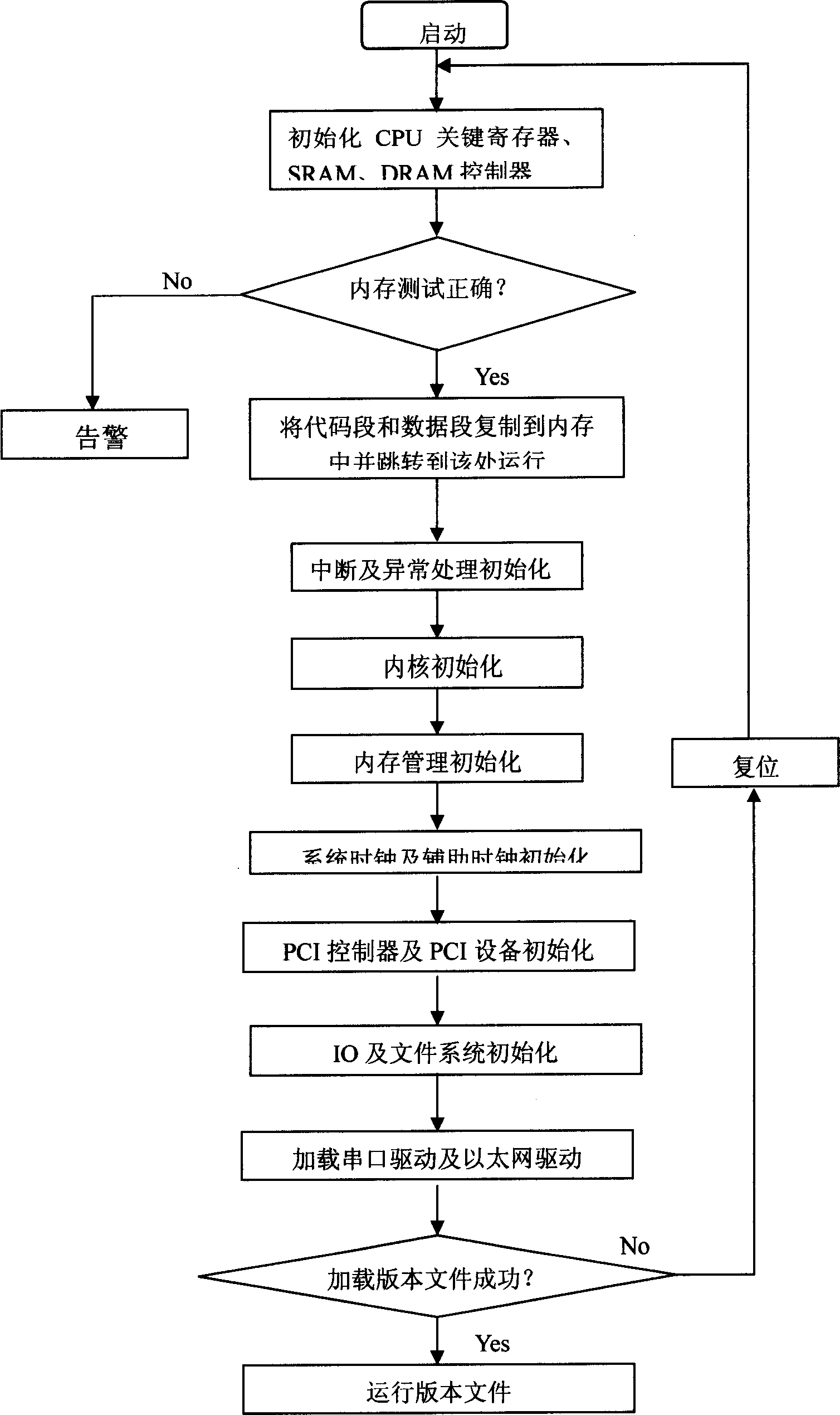

Multiprocessor system and method for sharing bootstrap module thereof

InactiveCN1525353ASimple methodSave controllerMultiple digital computer combinationsElectric digital data processingMulti processorMatched control

The invention is a kind of multi-processor system and the method for sharing guiding model, which refers to multi-CPU system with PCI controller in communication field. The system includes several processors, each processor has matched control state register, dynamic RAM, static RAM, series port, the processors are connected together through PCI bus, and uses a PCI arbiter, one processor with the guiding model is uses as the primary processor, the other processors are used as slave processors. When powdered on, the primary CPU takes instruction form itself guiding model, and the slave processor acquires instruction from RAM, the primary CPU resets the slave CPUs after initializing them, now, it can run. The invention is simple; it can save the guiding model, and the Ethernet controller.

Owner:ZTE CORP

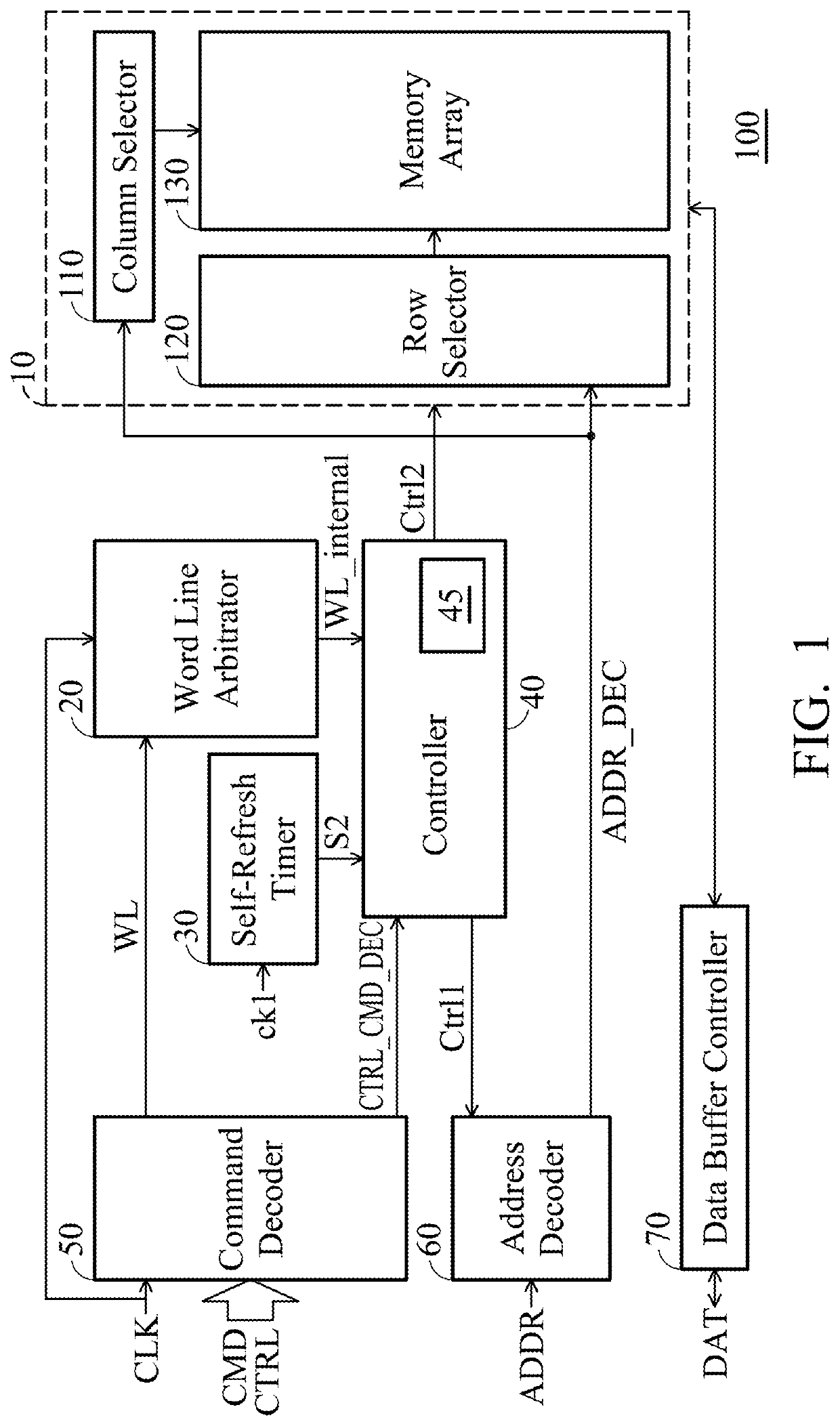

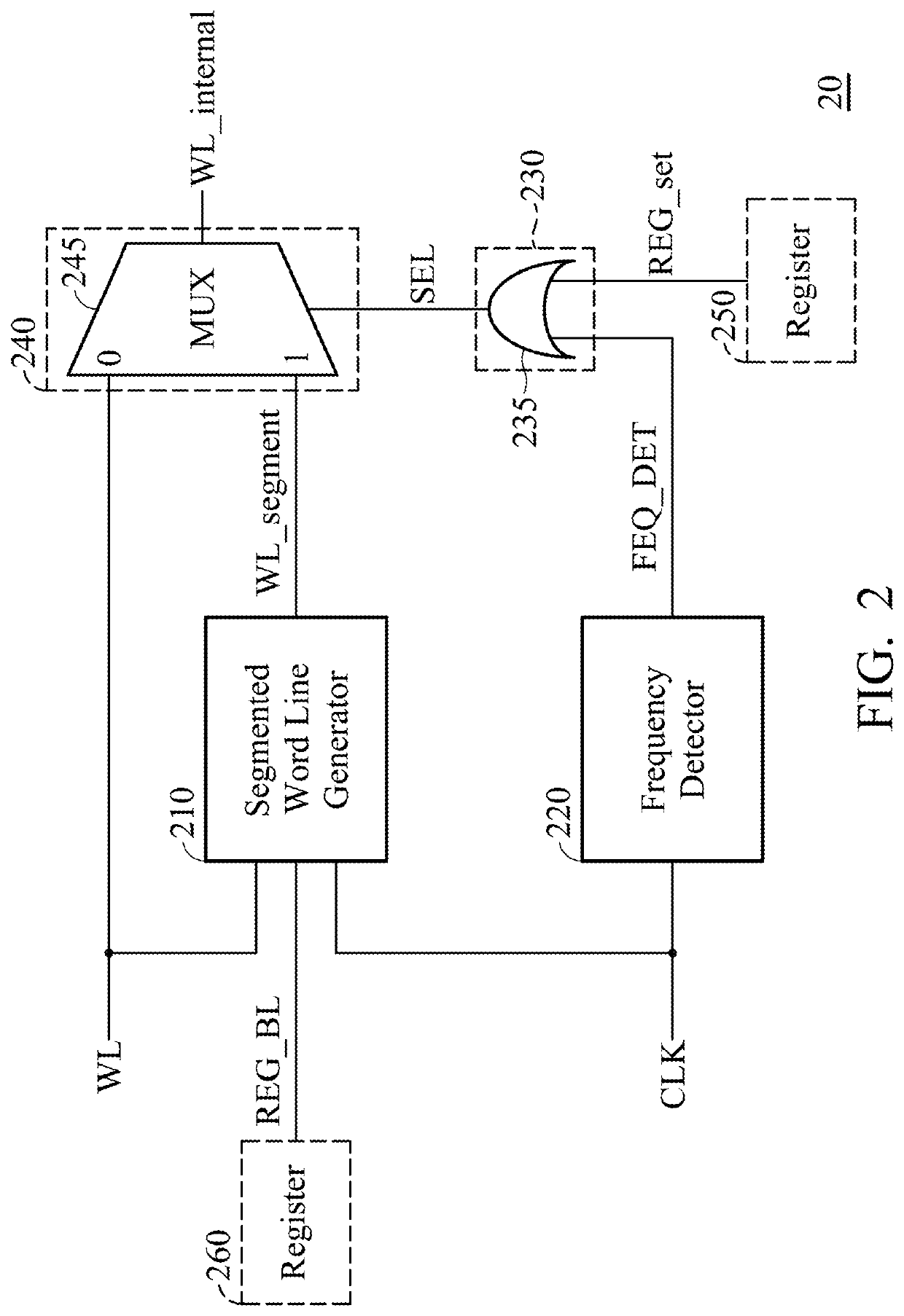

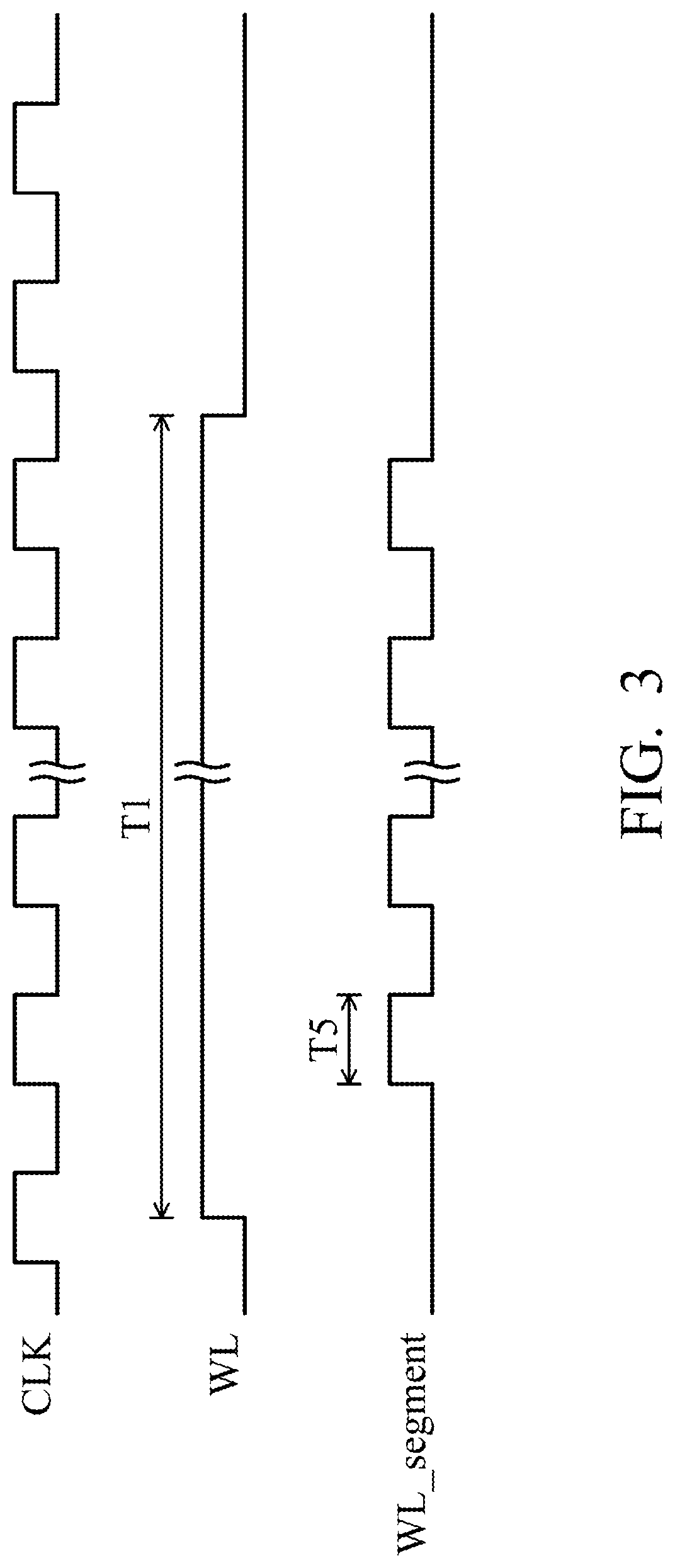

Memory device and refresh method for psram

A memory device is provided. The memory device includes a pseudo static random access memory (PSRAM), a word line (WL) arbitrator and a refresh controller. The WL arbitrator receives a WL signal and segments the WL signal according to a burst length setting value, to obtain a segmented WL signal. In a synchronous mode, the refresh controller provides a first refresh trigger signal corresponding to the WL signal to refresh the PSRAM. In a smart refresh mode, the refresh controller provides a second refresh trigger signal corresponding to the segmented WL signal to refresh the PSRAM.

Owner:WINBOND ELECTRONICS CORP

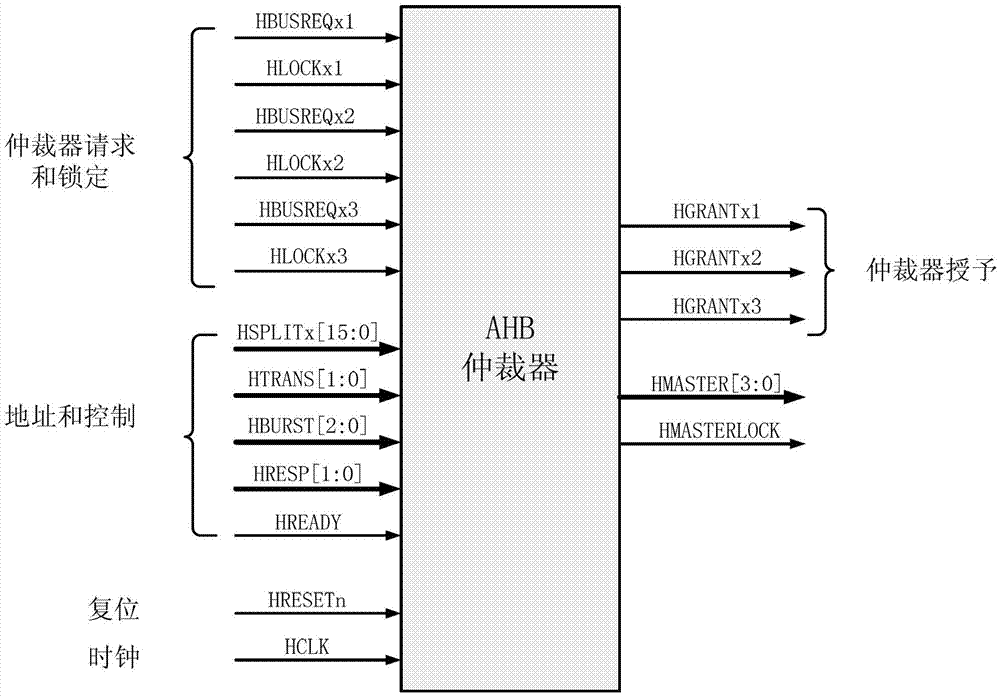

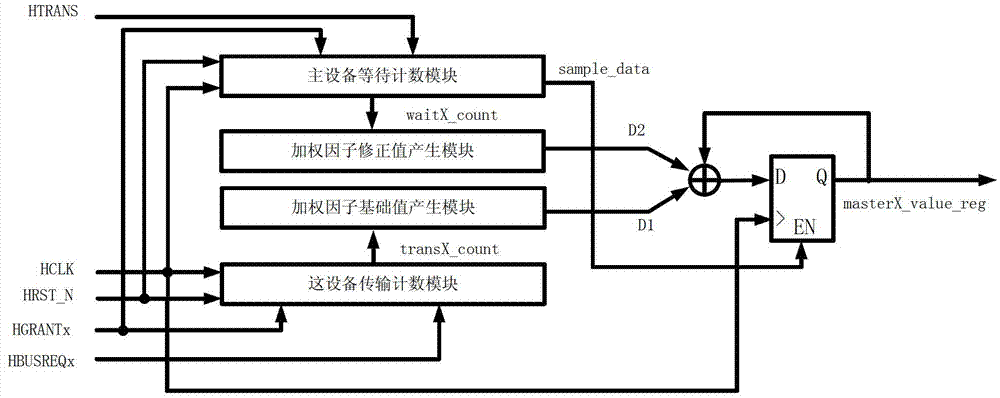

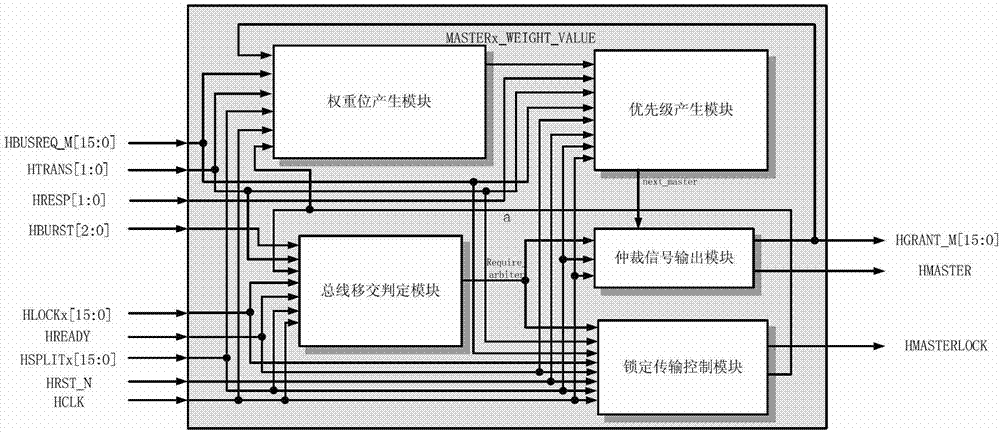

AMBA (Advanced Microcontroller Bus Architecture) bus based self-adaption real-time weighting prior arbitration method and arbitrator

InactiveCN103077141AReduce waiting timeMinimize the difference in latencyElectric digital data processingAdvanced Microcontroller Bus ArchitectureArbiter

The invention discloses an AMBA (Advanced Microcontroller Bus Architecture) bus based self-adaption real-time weighting prior arbitration method and an arbitrator. In once circulation, the priority levels of all main equipment are determined by a weighting factor; the greater the weighting factor is, the higher the priority level of the main equipment is; the priority levels of all the main equipment are re-sequenced after the bus arbitration at each time; after one of the main equipment obtains once bus authority, the corresponding weighting factor of the main equipment is progressively reduced by 1; along with the reduction of the weighting factor, the priority levels of all the main equipment are changed in real time; a new priority level sequence is taken as a basis for the next arbitration; and after the weighting factor of one of the main equipment is reduced to 0, the priority levels of all the main equipment are reset again and the next circulation is started. The defect of a weighting prior round-robin algorithm that the waiting time of the main equipment with low priority level in once circulation is over long is overcome, and meanwhile, the problem that the bus bandwidth distributed by each main equipment cannot change in real time according to the change in system function because the weighting factor is fixed is solved.

Owner:XI AN JIAOTONG UNIV

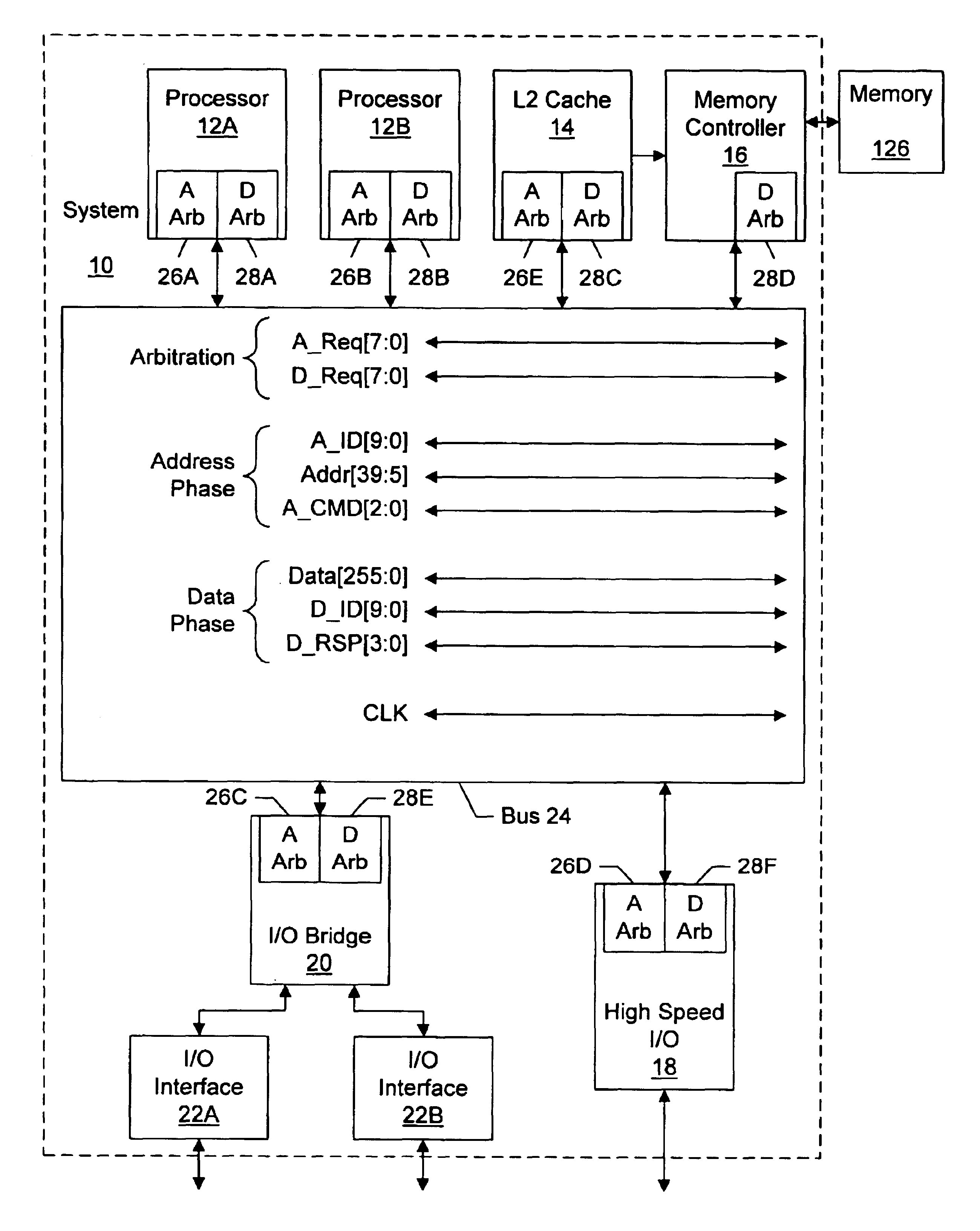

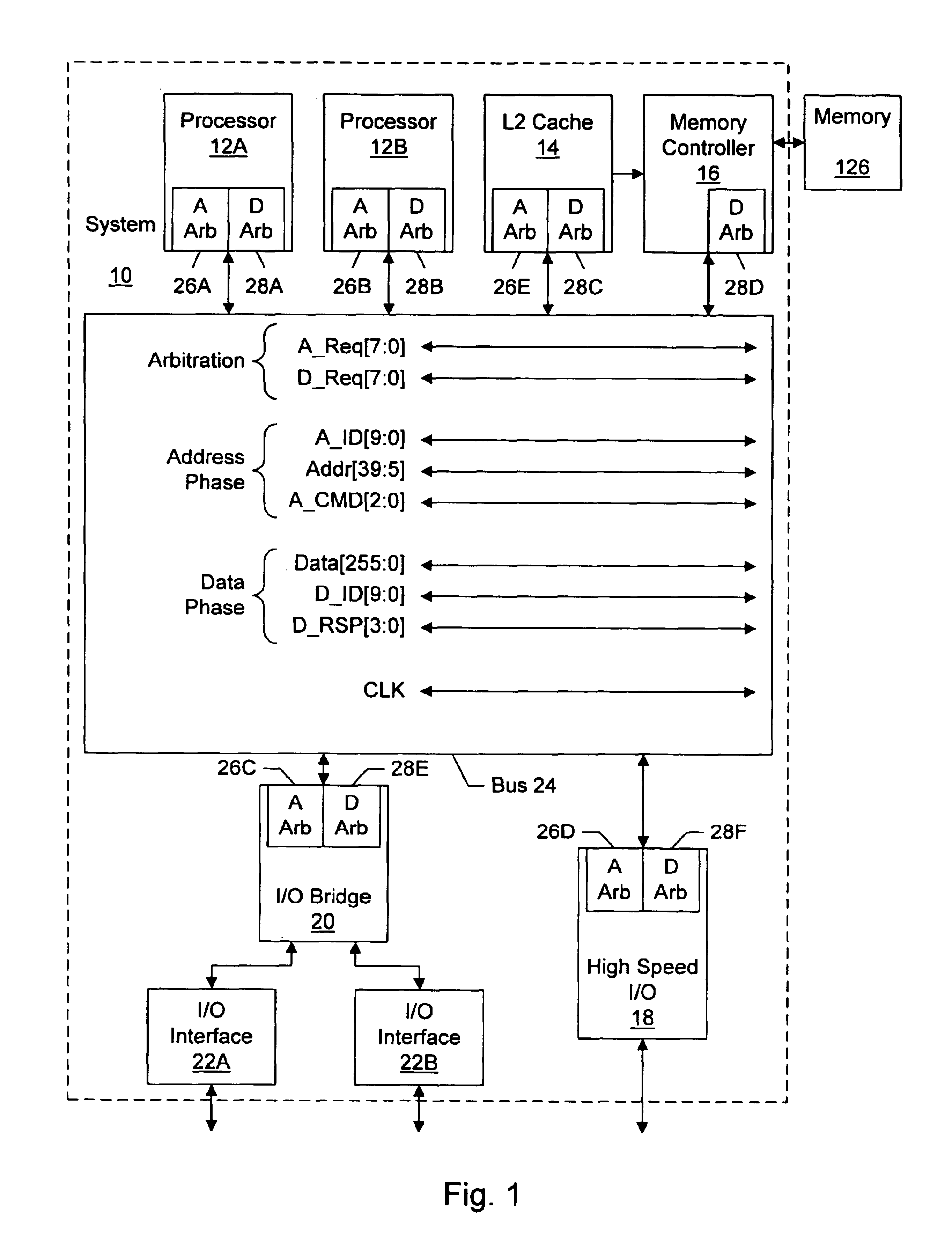

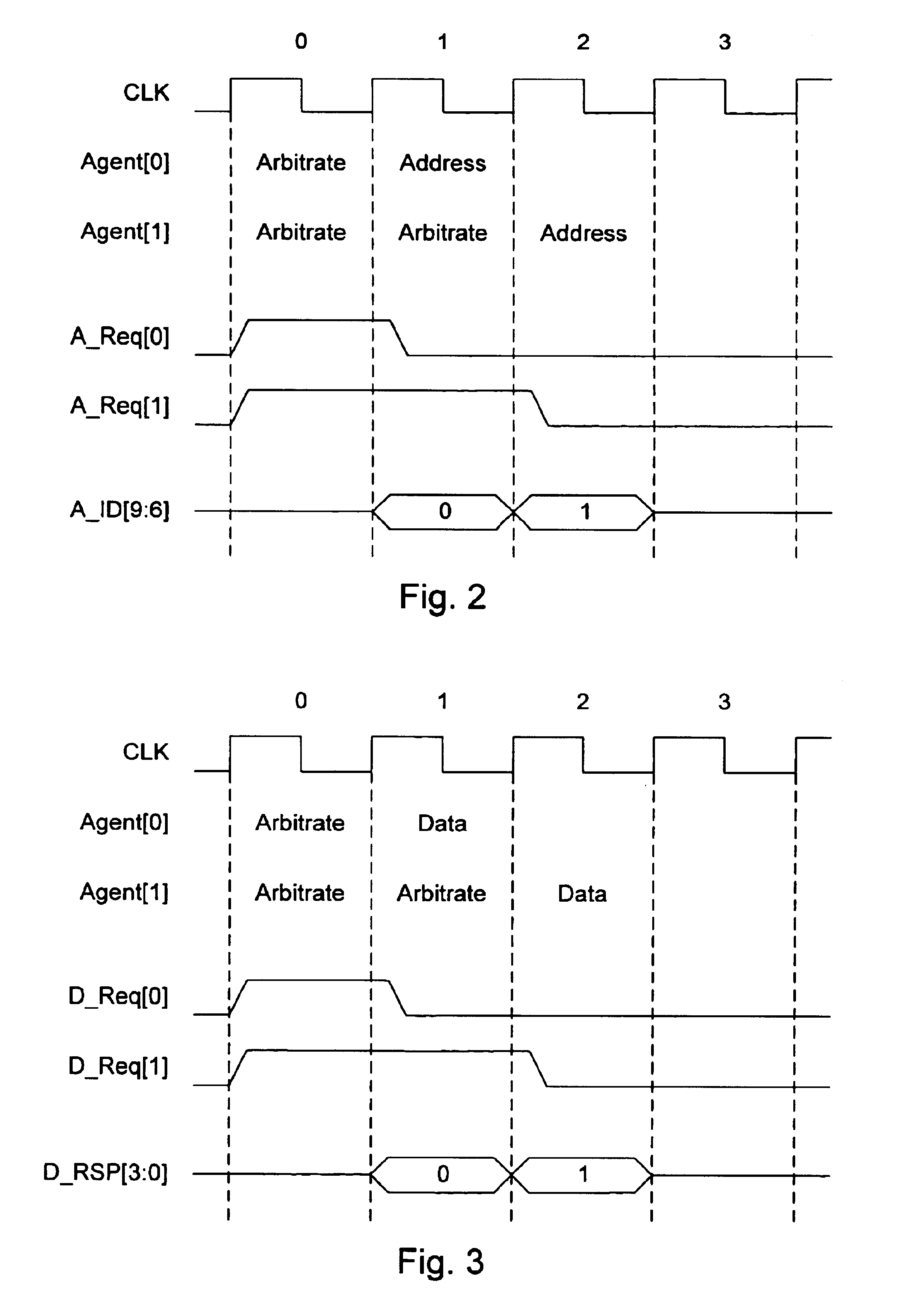

Fast arbitration scheme for a bus

A distributed arbitration scheme includes arbiters with each agent. The arbiters receive request signals indicating which agents are arbitrating for the bus. Additionally, the agent currently using the bus broadcasts an agent identifier assigned to that agent. The arbiters receive the agent identifier and use the agent identifier as an indication of the winner of the preceding arbitration. Accordingly, the arbiters determine if the corresponding agent wins the arbitration, but may not attempt to calculate which other agent wins the arbitration. In one embodiment, the arbiter maintains a priority state indicative of which of the other agents are higher priority than the corresponding agent and which of the other agents are lower priority. In one implementation, the bus may be a split transaction bus and thus each requesting agent may include an address arbiter and each responding agent may include a data arbiter.

Owner:AVAGO TECH INT SALES PTE LTD

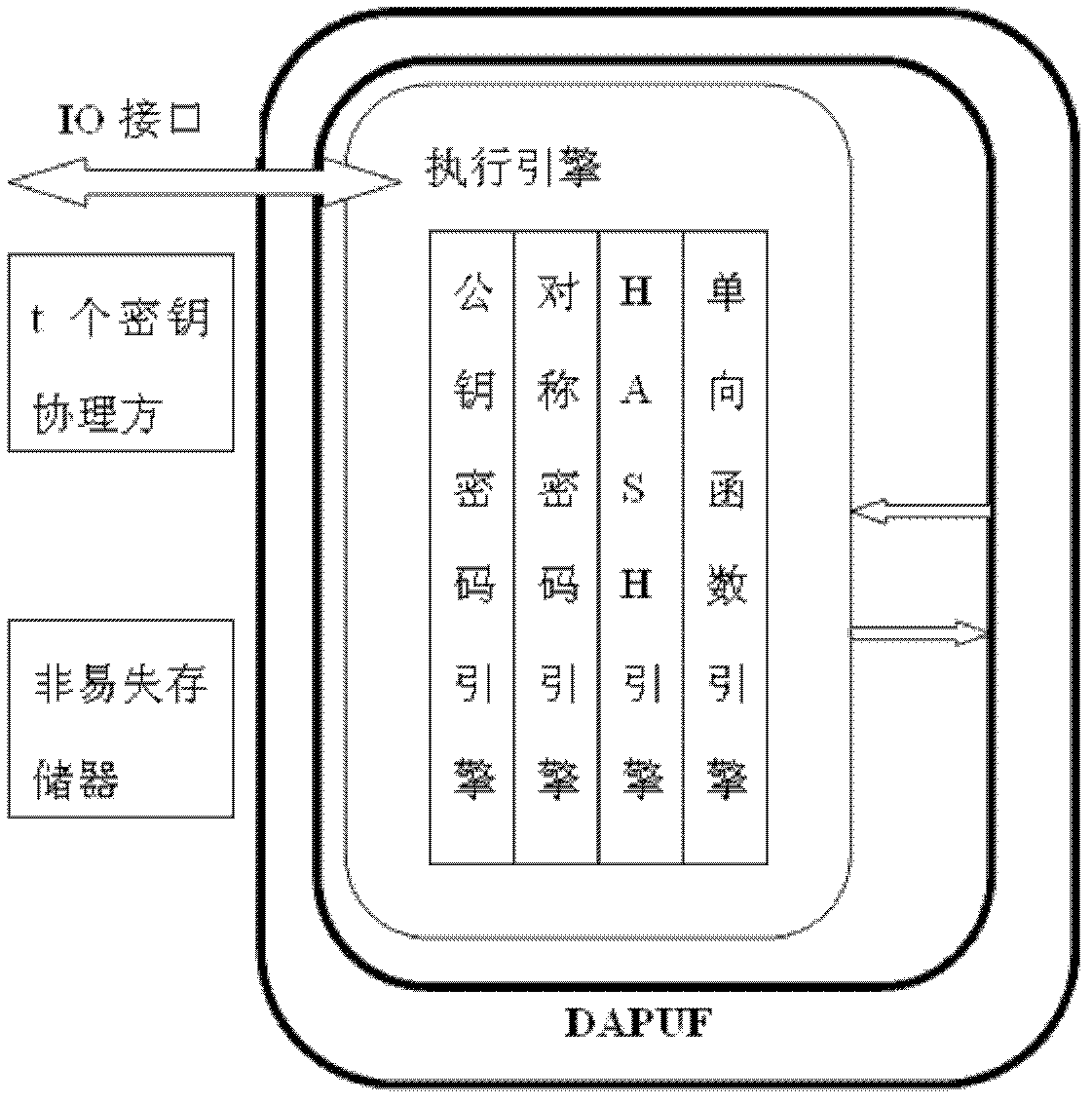

Crypto chip system and secret key extraction method

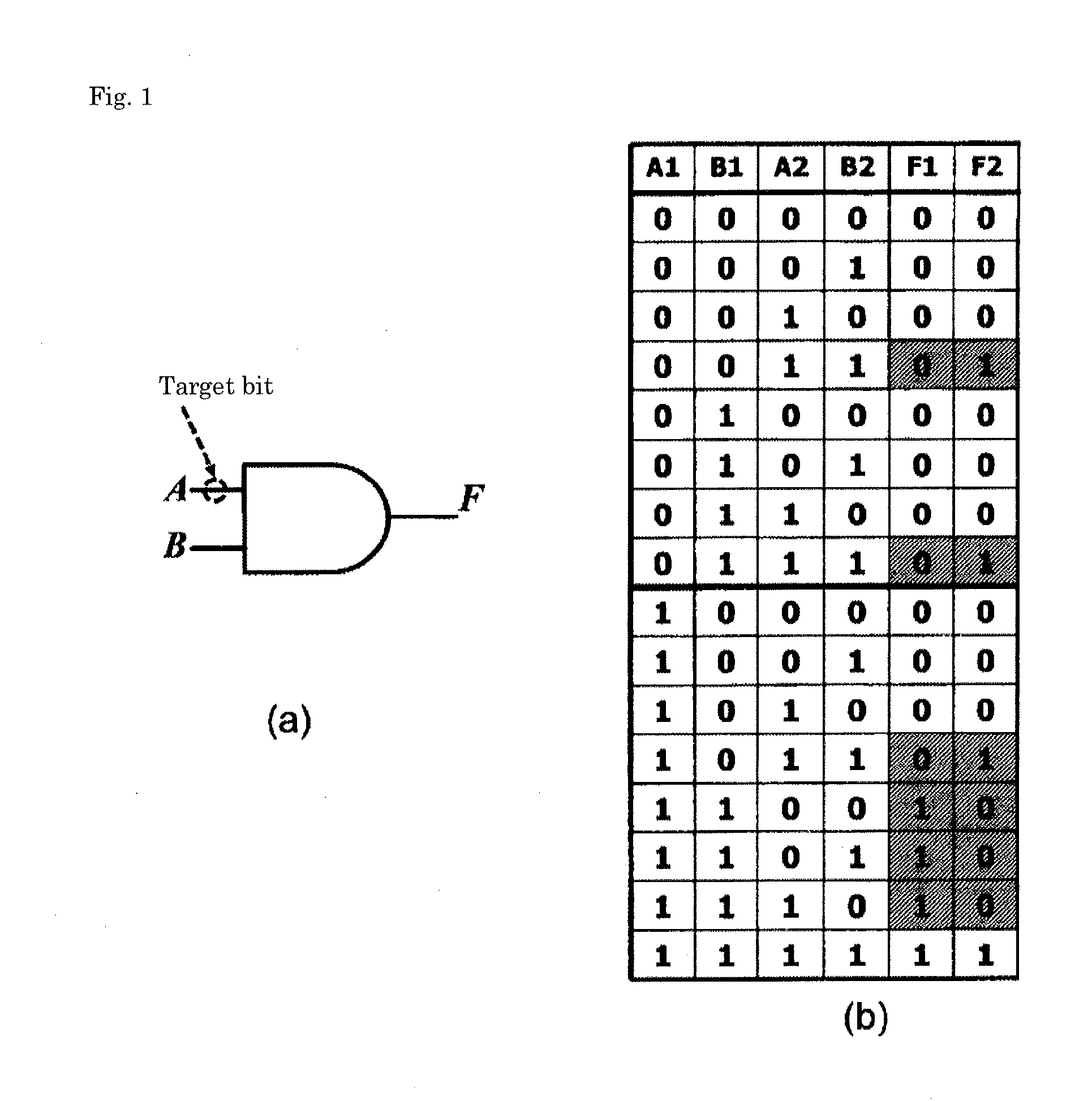

InactiveCN102546149AIncrease randomnessSmall output deviationEncryption apparatus with shift registers/memoriesComputer hardwareExclusive or

The invention discloses a crypto chip system and a secret key extraction method. The system comprises a public key crypto engine, a symmetry crypto engine, a HASH engine, a one-way function engine, a nonvolatile memory, an execution engine, t secret key assistant management parties and a double-arbiter physical unclonable function module DAPUF. The other purpose of the invention aims at providing a secret key extraction method of the crypto chip system. The method comprises the steps of (1) a secret key generation stage, and (2) a secret key reconstruction stage. According to the invention, an effective bit is selected by an exclusive-or result of the DAPUF, and in combination with the steps and under a condition that multiple challenge / response characteristics are provided, the system and the method enable the obtained response to have the characteristics of no 01 deviation on probability, reliable reconstruction certainty, low average time complexity, small challenge and response redundancy, physical invasion attack sensation and the like.

Owner:SOUTH CHINA UNIV OF TECH +1

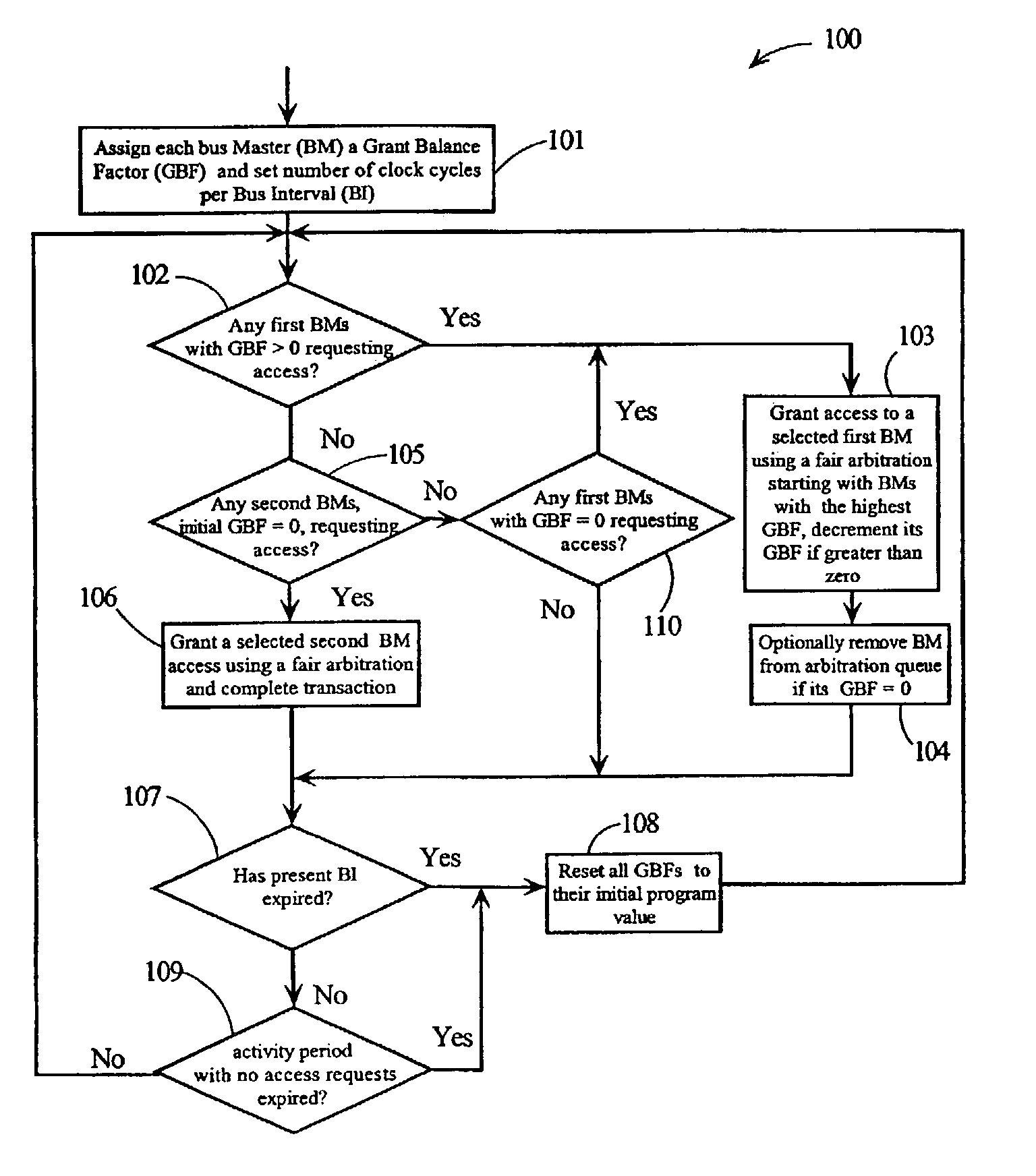

Method and apparatus for bus access allocation

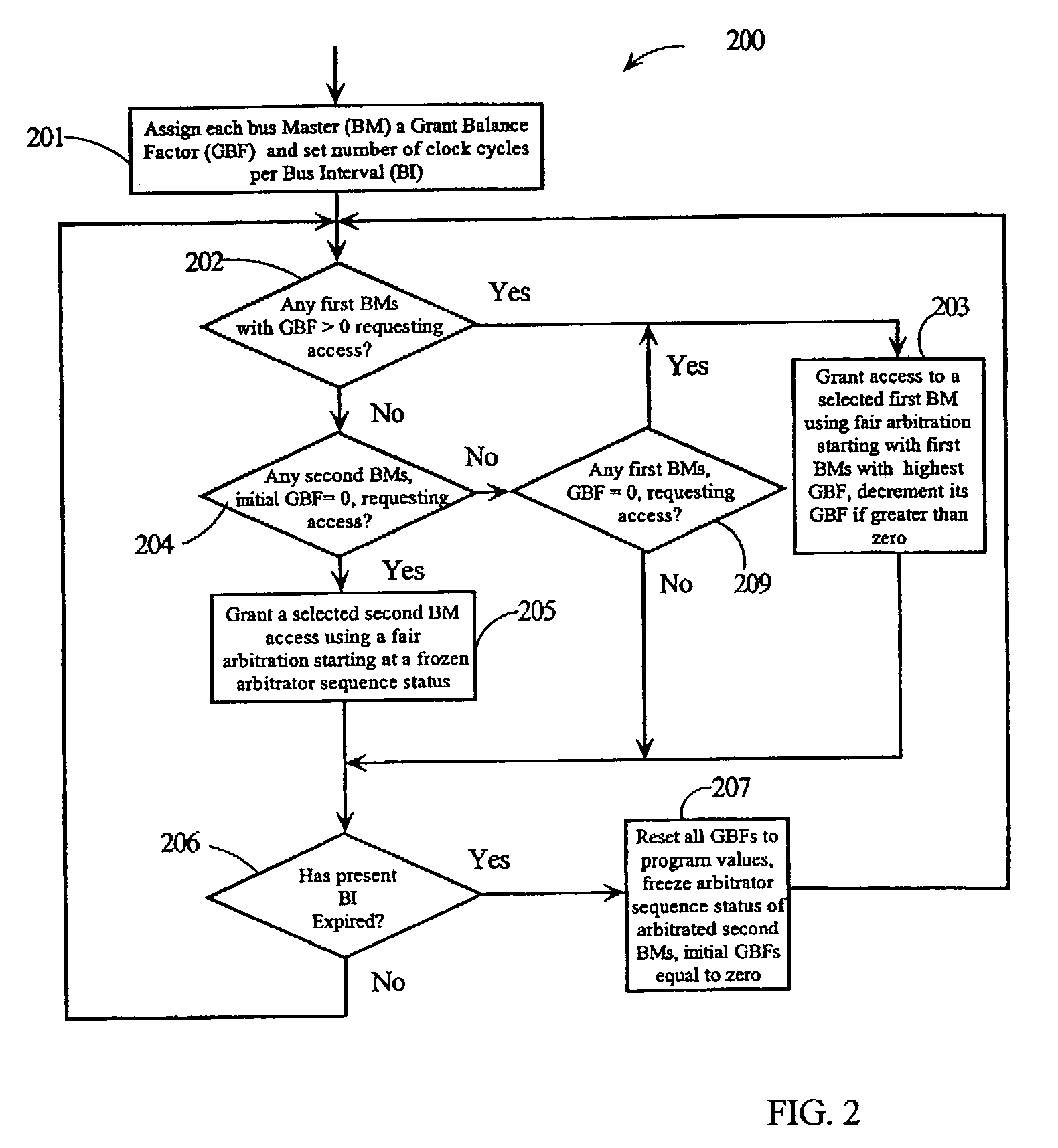

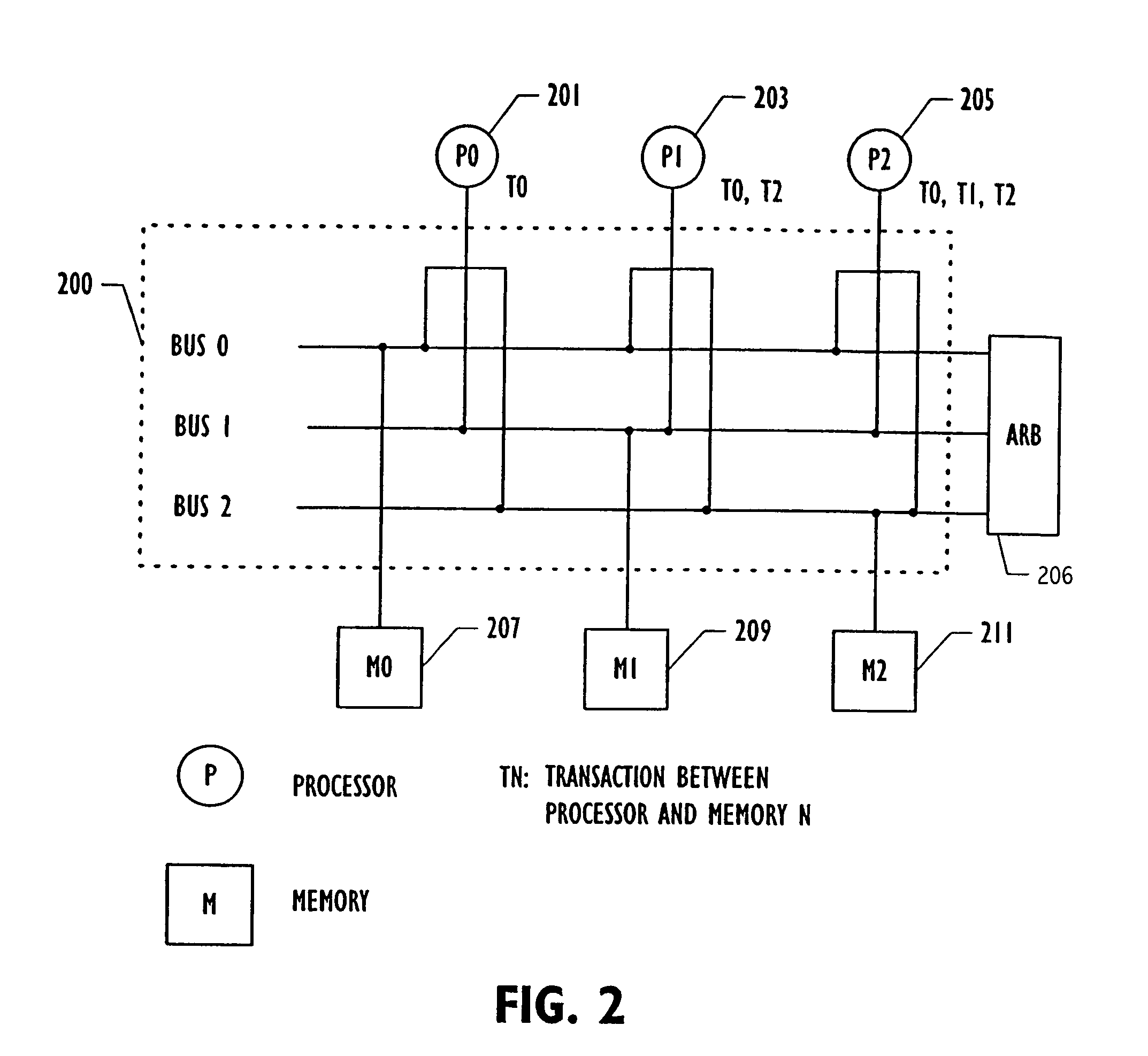

A method for granting access to a bus is disclosed where a fair arbitration is modified to account for varying conditions. Each bus master (BM) is assigned a Grant Balance Factor value (hereafter GBF) that corresponds to a desired bandwidth from the bus. Arbitration gives priority BMs with a GBF greater than zero in a stratified protocol where requesting BMs with the same highest priority are granted access first. The GBF of a BM is decremented each time an access is granted. Requesting BMs with a GBF equal to zero are fairly arbitrated when there are no requesting BMs with GBFs greater than zero wherein they receive equal access using a frozen arbiter status. The bus access time may be partitioned into bus intervals (BIs) each comprising N clock cycles. BIs and GBFs may be modified to guarantee balanced access over multiple BIs in response to error conditions or interrupts.

Owner:IBM CORP

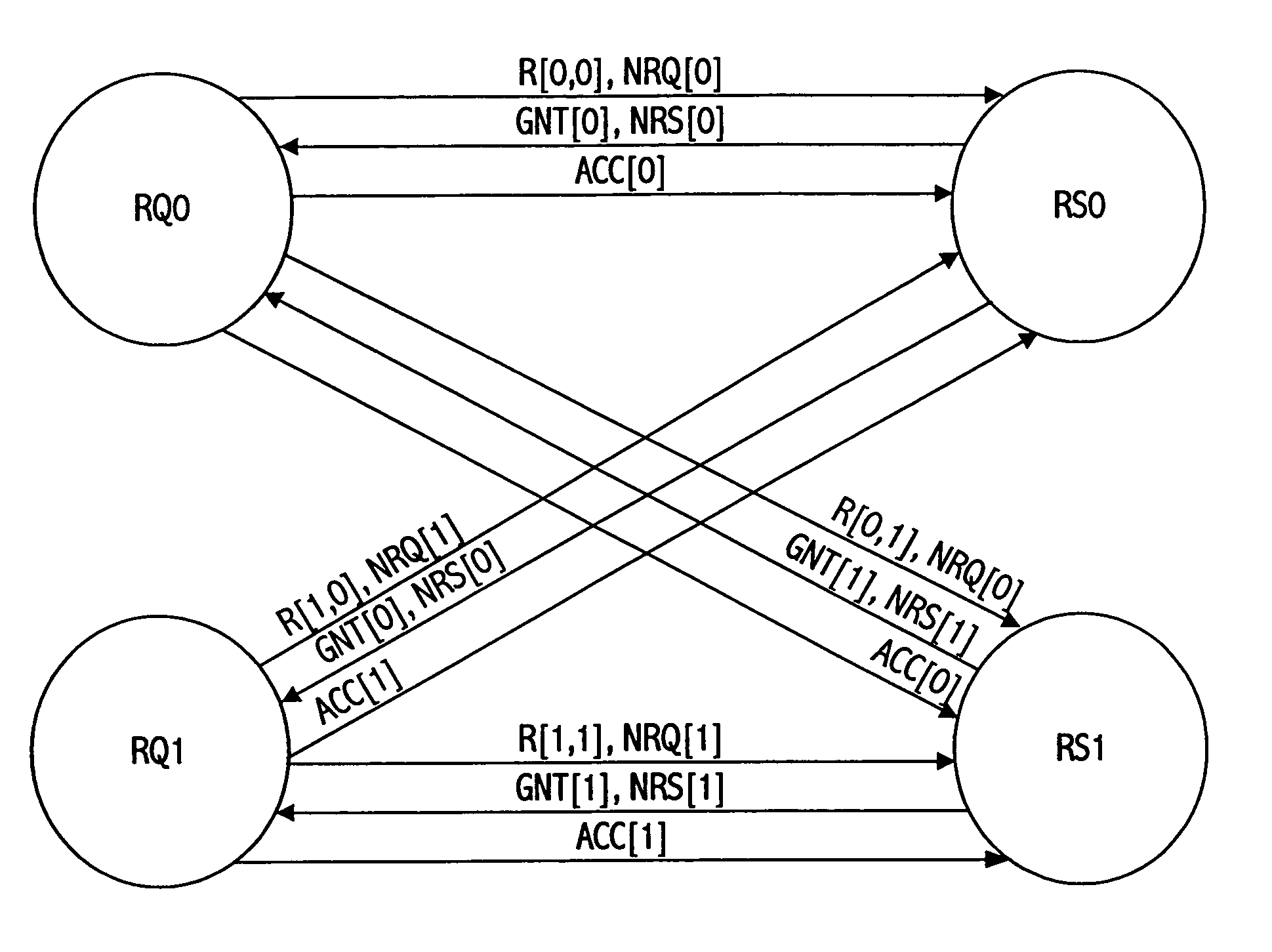

Distributed least choice first arbiter

InactiveUS7006501B1Increase the number ofImprove resource usageTime-division multiplexData switching by path configurationResource basedResource allocation

A distributed arbiter prioritizes requests for resources based on the number of requests made by each requester. Each resource gives the highest priority to servicing requests made by the requester that has made the fewest number of requests. That is, the requester with the fewest requests (least number of choices) is chosen first. Resources may be scheduled sequentially or in parallel. If a requester receives multiple grants from resources, the requester may select a grant based on resource priority, which is inversely related to the number of requests received by a granting resource. In order to prevent starvation, a round robin scheme may be used to allocate a resource to a requester, prior to issuing grants based on requester priority.

Owner:ORACLE INT CORP

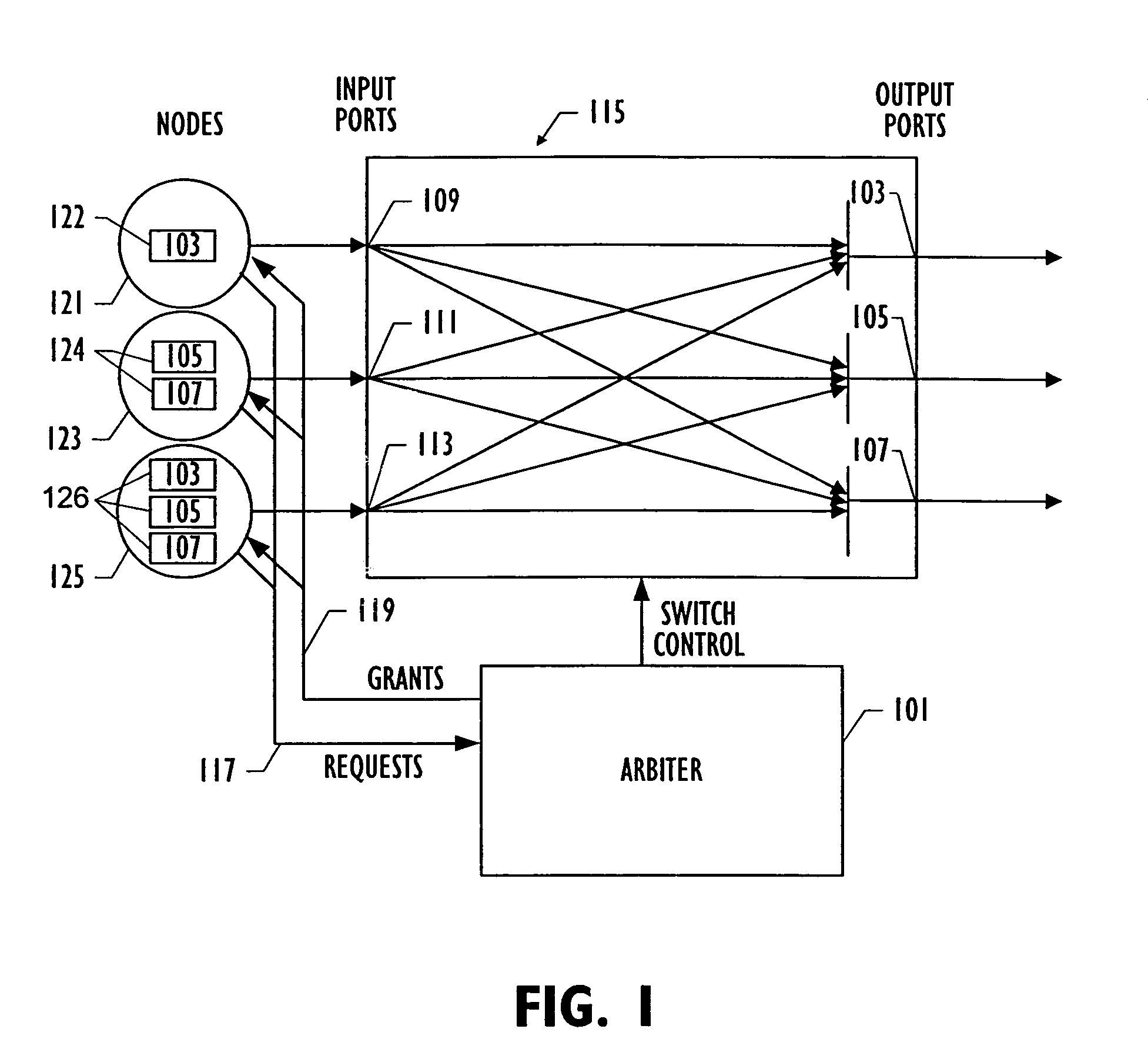

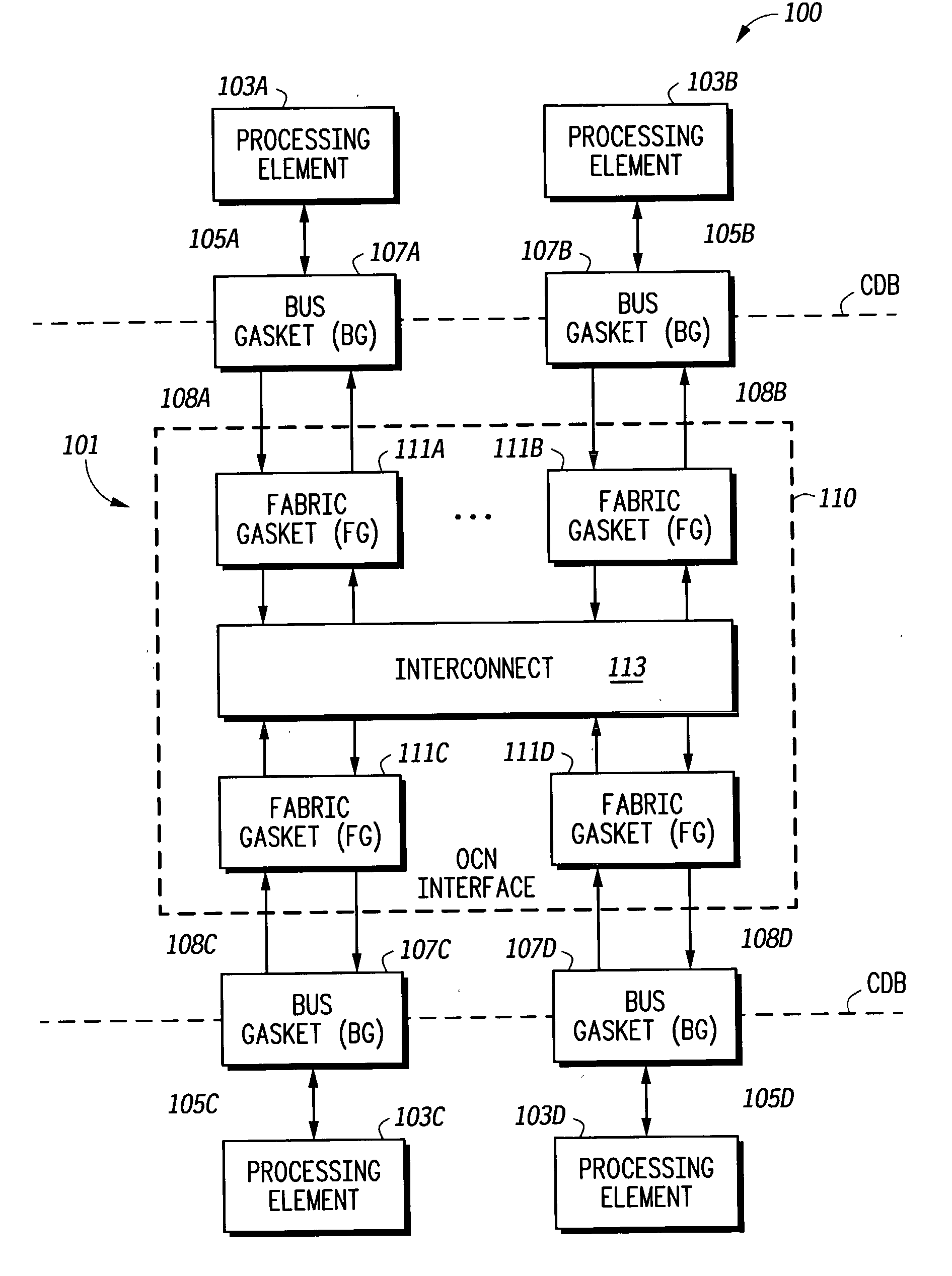

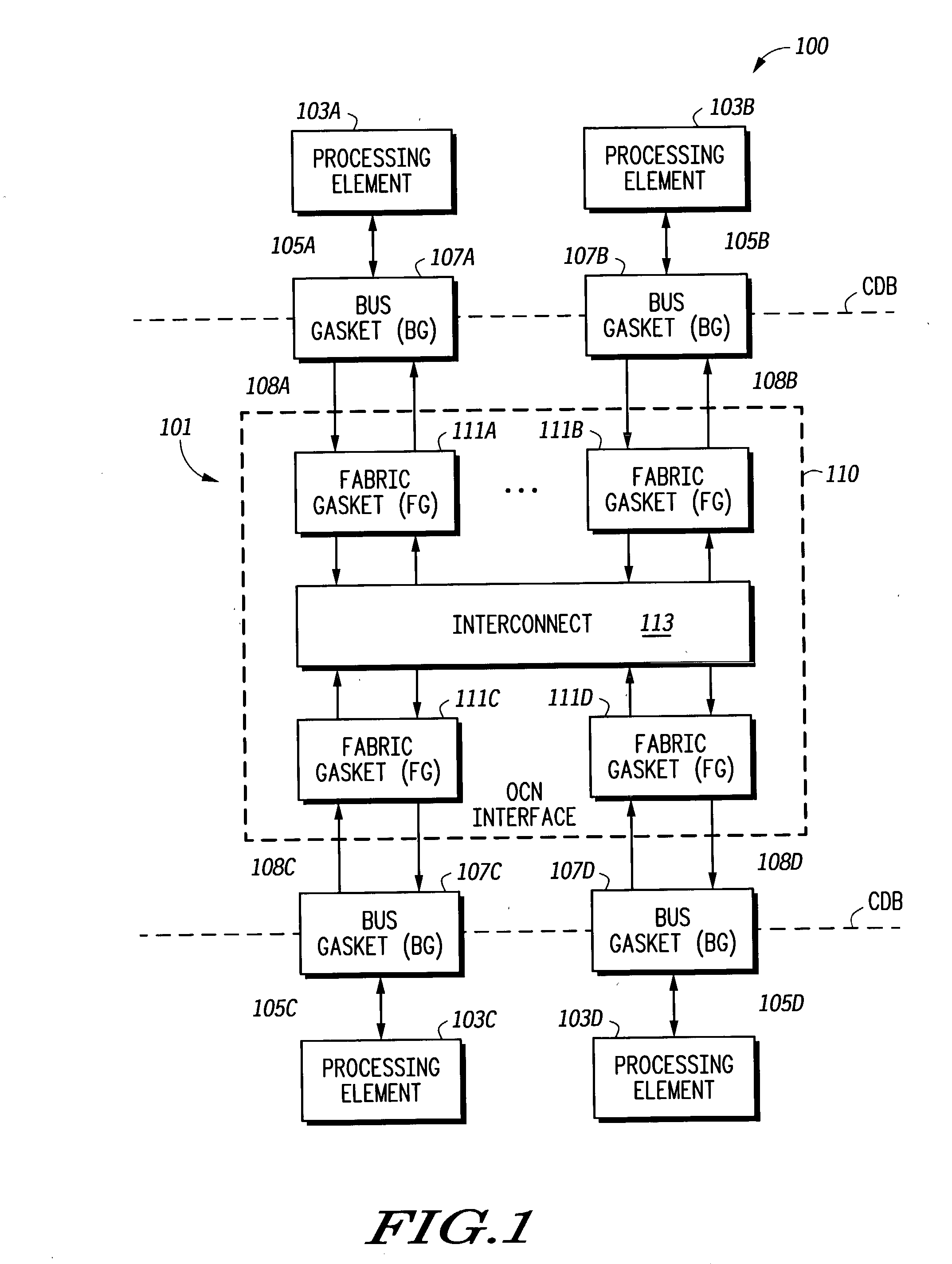

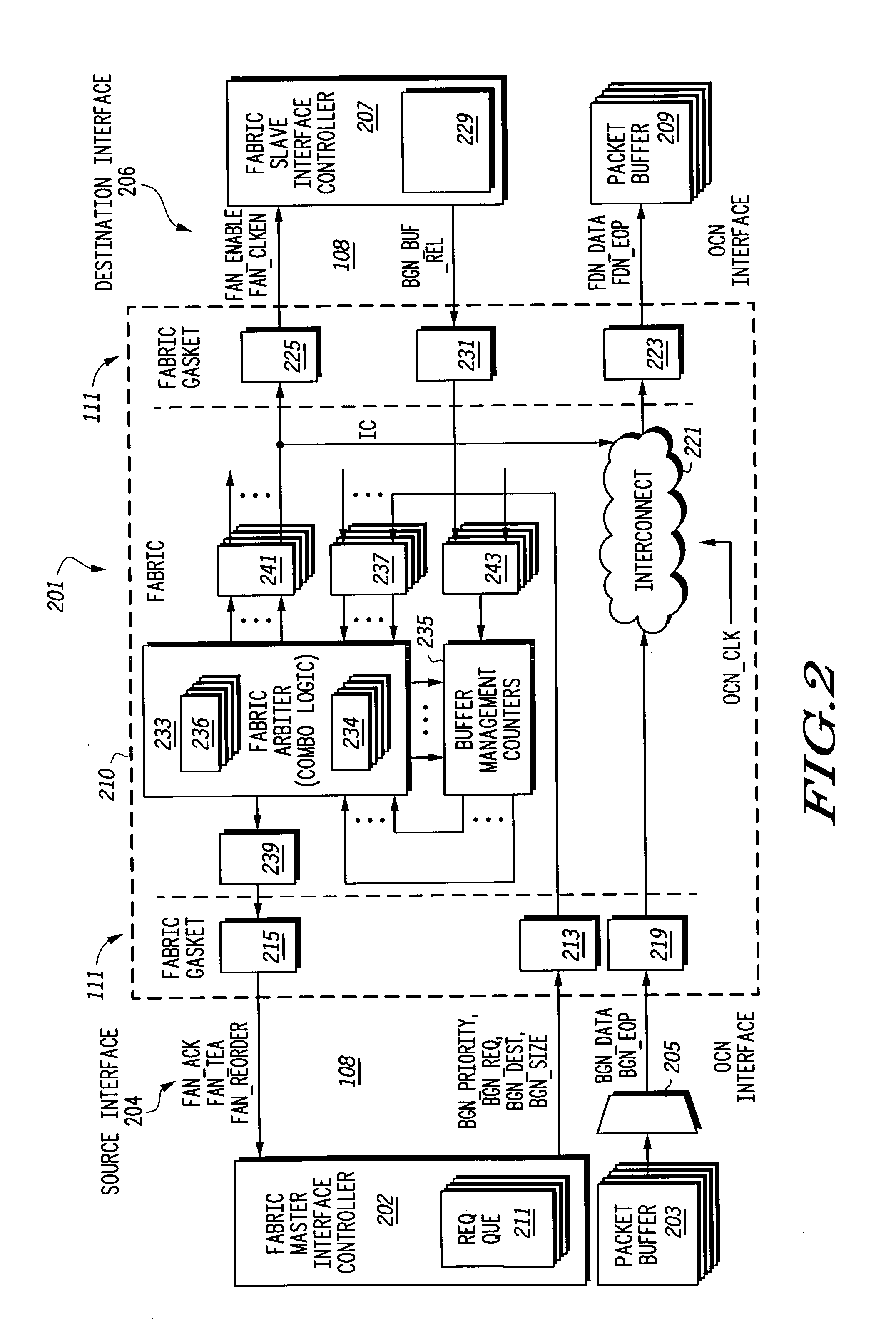

Scalable on chip network

ActiveUS20040024946A1Architecture with single central processing unitInput/output processes for data processingNetwork packetClock rate

A scalable OCN for supporting an application using processing elements integrated in an IC including ports, an interconnect, port interfaces, and an arbiter. Each port conforms to a consistent port interface protocol regardless of number of ports, frequency of operation, maximum datum width or data path concurrency. The interconnect has a scalable maximum datum width and a scalable data path concurrency, and includes selectable data paths between any two ports to enable transfer of datums between the ports. Each port interface formulates packets for transmission and receives packets via the corresponding port and the interconnect, where each packet comprising one or more datums. The arbiter controls packet transfer via the interconnect between source and destination ports. The interconnect has a scalable data path concurrency. Pipeline stages may be added to support a selected clock frequency. The OCN may be a component library including bus gasket, interconnect and arbiter components.

Owner:NORTH STAR INNOVATIONS +1

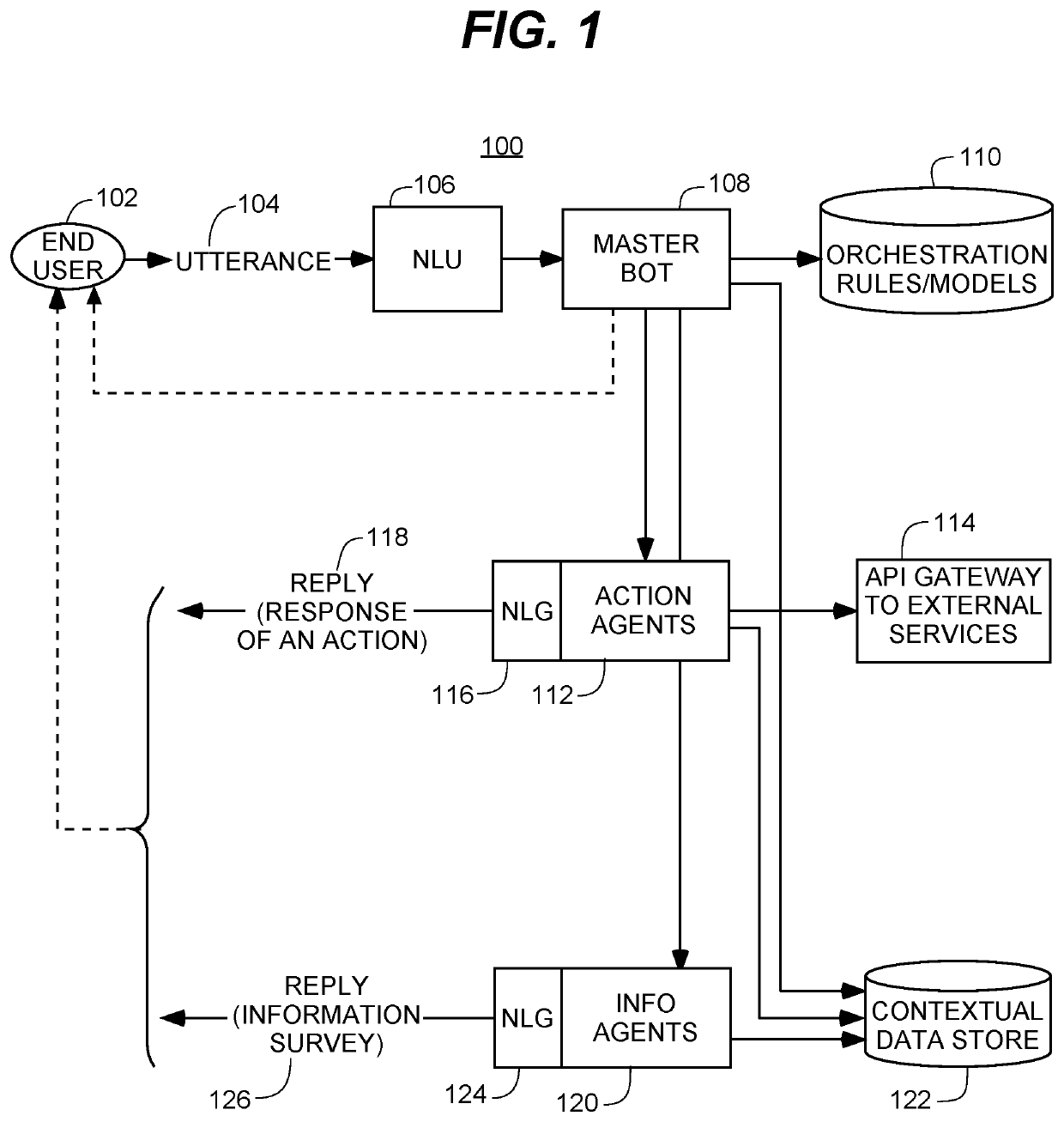

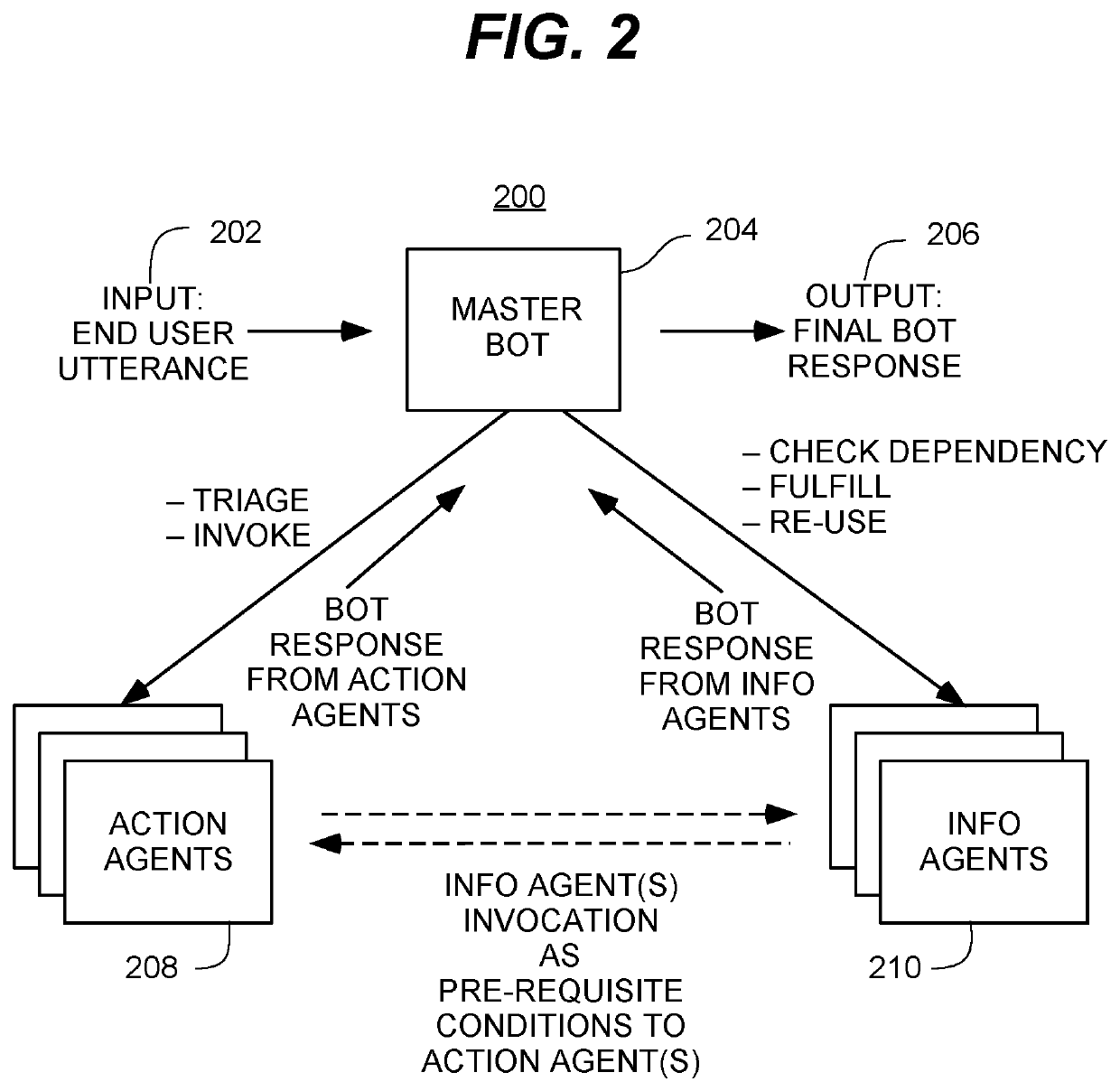

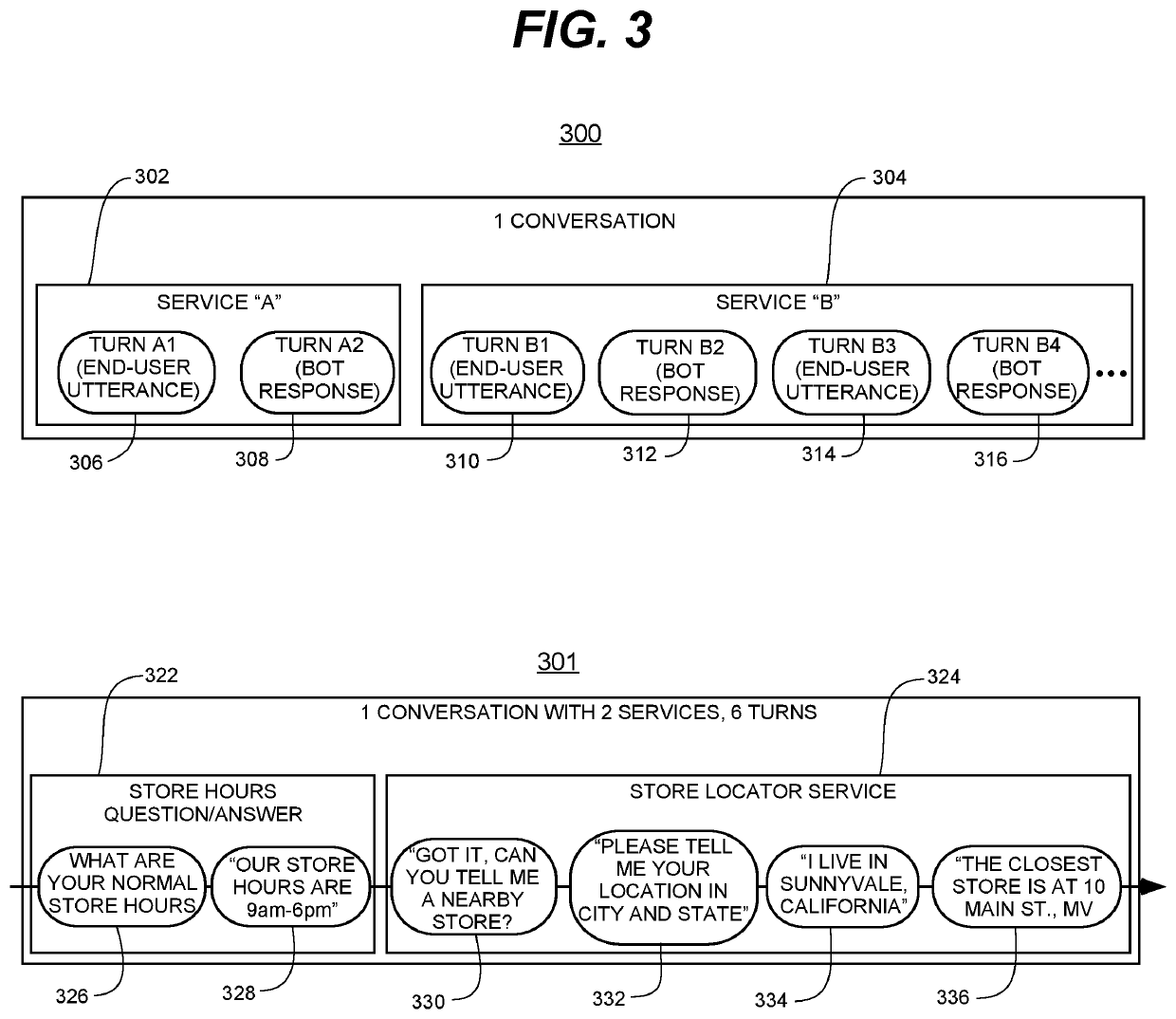

Methods and systems for deploying and managing scalable multi-service virtual assistant platform

The present invention is a scalable multi-service virtual assistant platform that can construct a fluid and dynamic dialogue by assembling responses to end user utterances from two kinds of agents, information agents and action agents. The information agents and action agents are managed by a masterbot or arbiter. The virtual assistant can gain new skills by getting instructions about a new service expressed in a form of pre-requisites and action combinations; the virtual assistant platform automatically handles dialogue generation, arbitration and optimization to survey prerequisites from the end user, and eventually to take action. The present invention allows a large number of services to implemented using a small number of building blocks. These building blocks can be used to assemble a much larger number of services. In turn, each service can be delivered through a large variety of conversations with end users, enabling a fluid and dynamic dialogue to be seamlessly implemented.

Owner:LINC GLOBAL INC

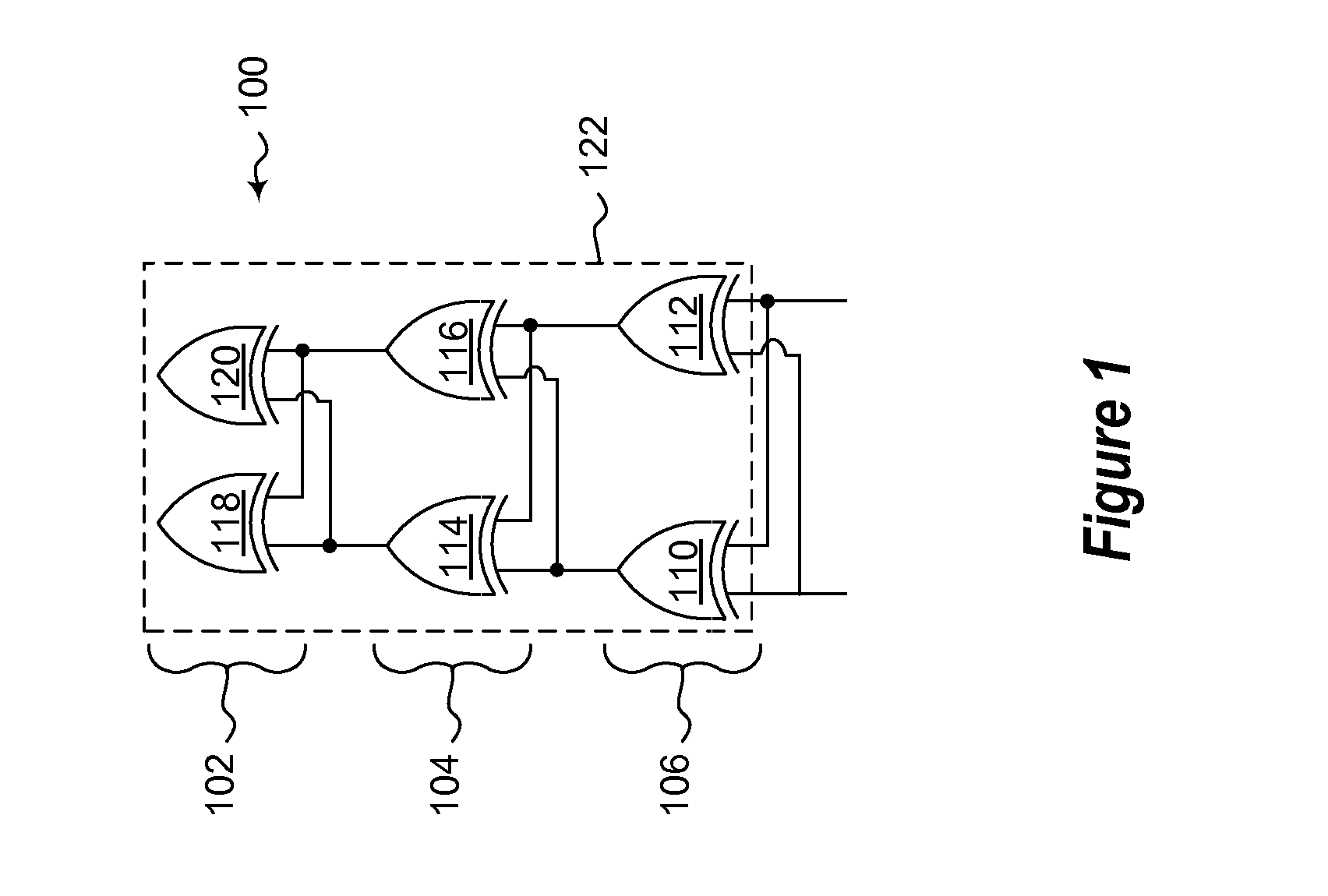

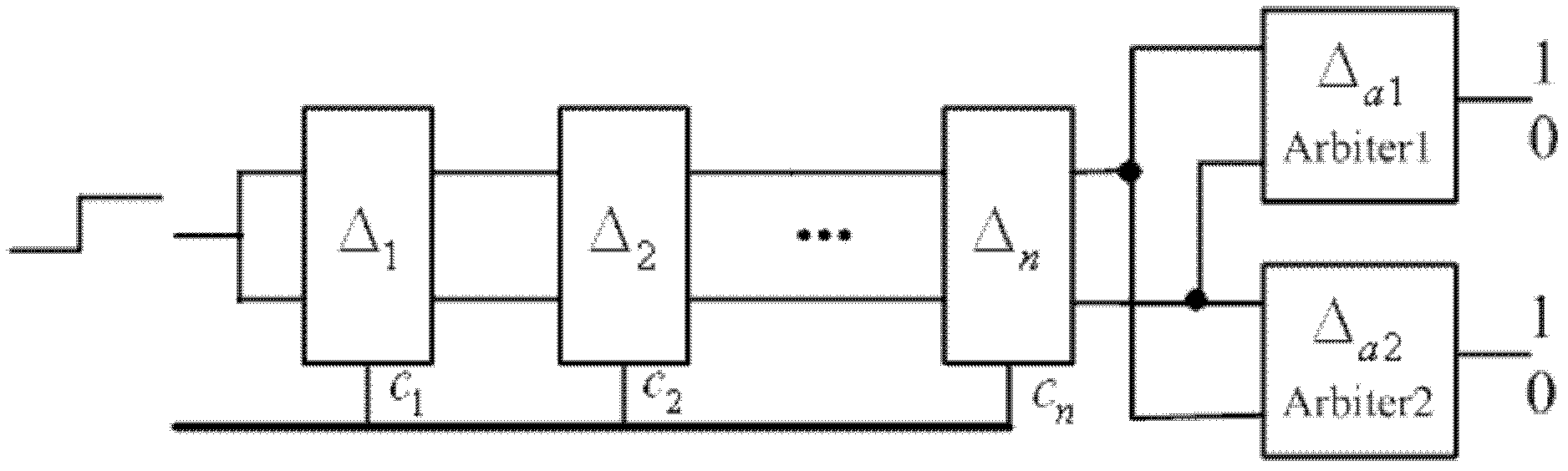

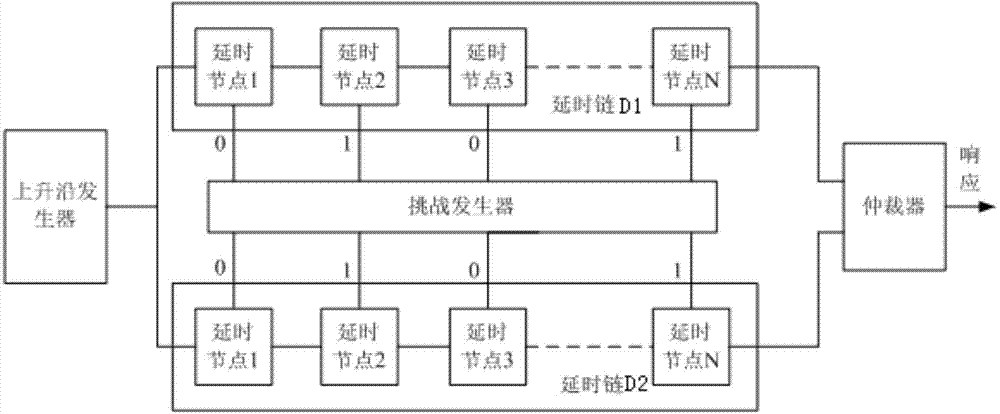

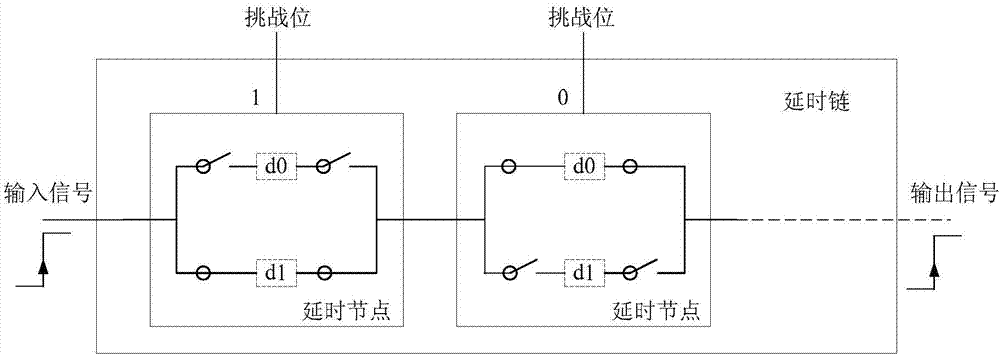

Physical unclonable function circuit structure based on double delay chains

ActiveCN103902929ABalance of challengeDelay Difference EqualizationInternal/peripheral component protectionControl engineeringHemt circuits

The invention discloses a physical unclonable function circuit structure based on double delay chains. The physical unclonable function circuit structure comprises a rising edge generator, challenge generators, a delay chain D1, a delay chain D2 and an arbiter. The signal output end of the rising edge generator is respectively connected with the signal input end of the delay chain D1 and the signal input end of the delay chain D2, the signal output end of the delay chain D1 and the signal output end of the delay chain D2 are connected with the signal input end of the arbiter, the delay chain D1and the delay chain D2 are respectively formed by connecting N delay nodes, each delay node is provided with a challenge position used for adjusting delay time of input signals, and each challenge position is connected with the corresponding challenge generator which generates a random challenge value for the challenge position. The physical unclonable function circuit structure has the advantages that the same circuit structure is adopted for the delay chain D1and the delay chain D2, the same transmission signals and challenge values are input, but the two delay chains are isolated from each other without any intersection or connection, and if large fixed delay difference exists between the two delay chains, the delay difference can be balanced by setting the challenge values of all the delay nodes.

Owner:HANGZHOU SYNOCHIP DATA SECURITY TECH CO LTD