Patents

Literature

11299 results about "Bit line" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

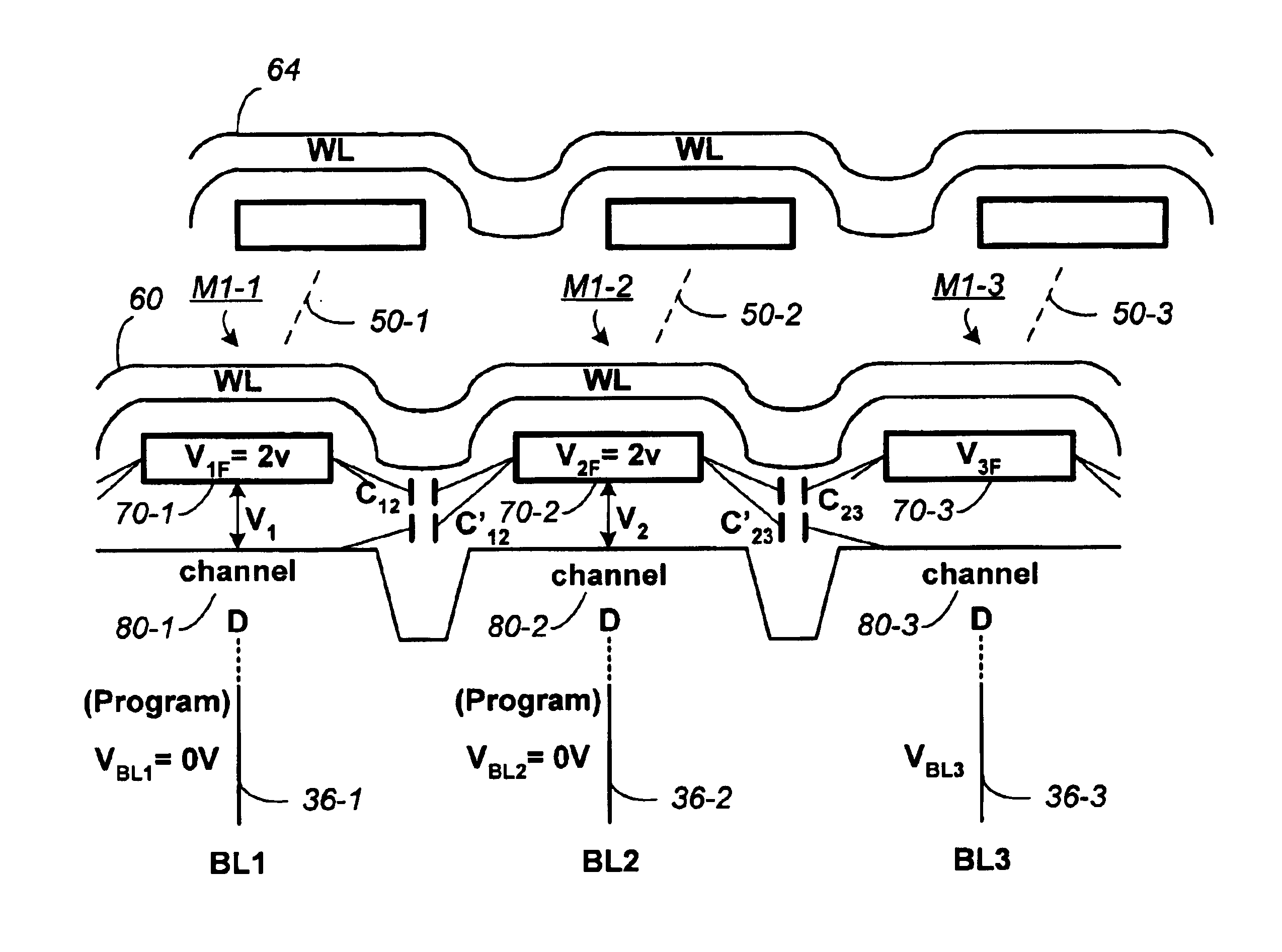

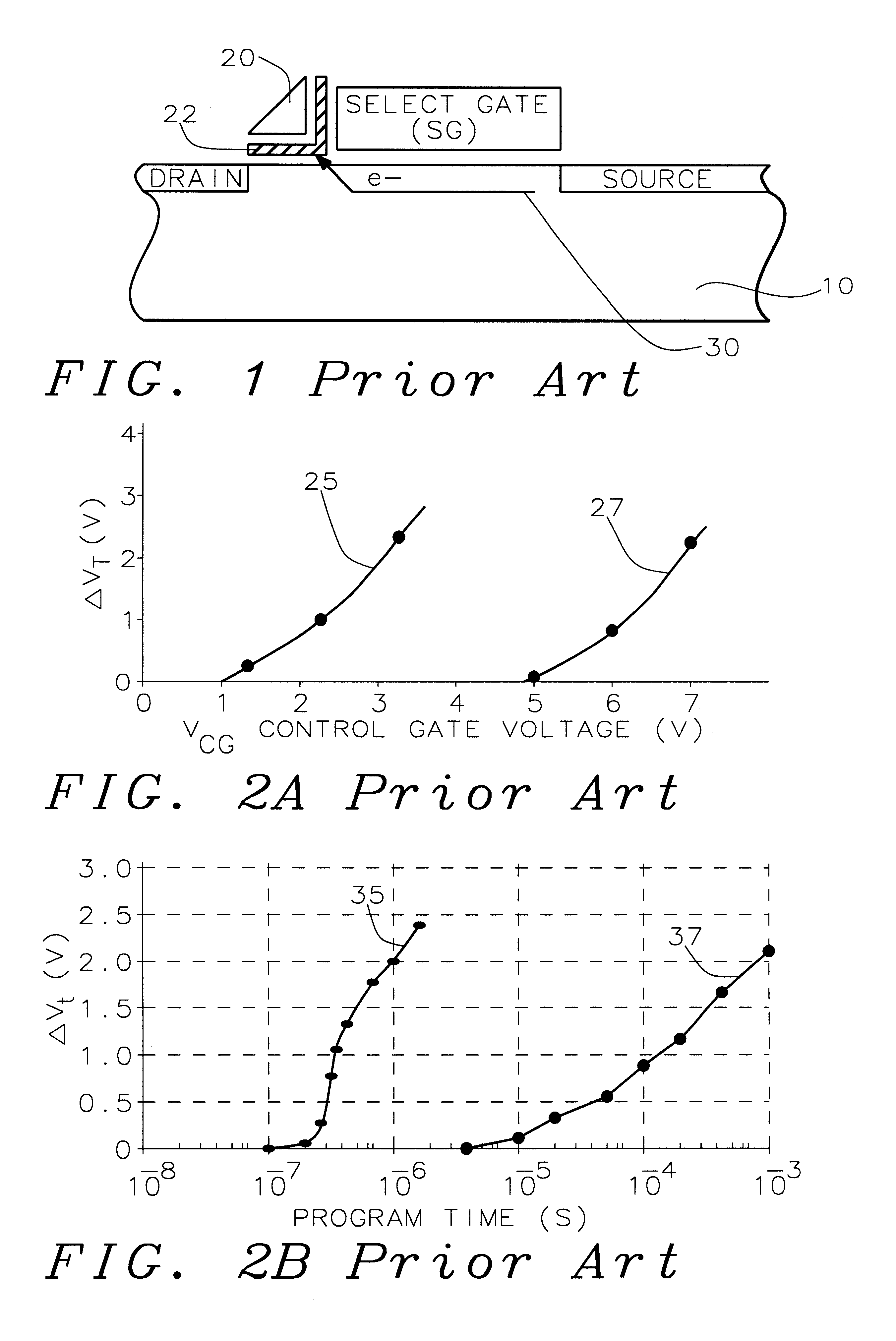

Non-volatile memory and method with bit line compensation dependent on neighboring operating modes

ActiveUS6956770B2Large capacityImprove performanceRead-only memoriesDigital storageBit lineHigh density

When programming a contiguous page of memory storage units, every time a memory storage unit has reached its targeted state and is program-inhibited or locked out from further programming, it creates a perturbation on an adjacent memory storage unit still under programming. The present invention provides as part of a programming circuit and method in which an offset to the perturbation is added to the adjacent memory storage unit still under programming. The offset is added as voltage offset to a bit line of a storage unit under programming. The voltage offset is a predetermined function of whether none or one or both of its neighbors are in a mode that creates perturbation, such as in a program inhibit mode. In this way, an error inherent in programming in parallel high-density memory storage units is eliminated or minimized.

Owner:SANDISK TECH LLC

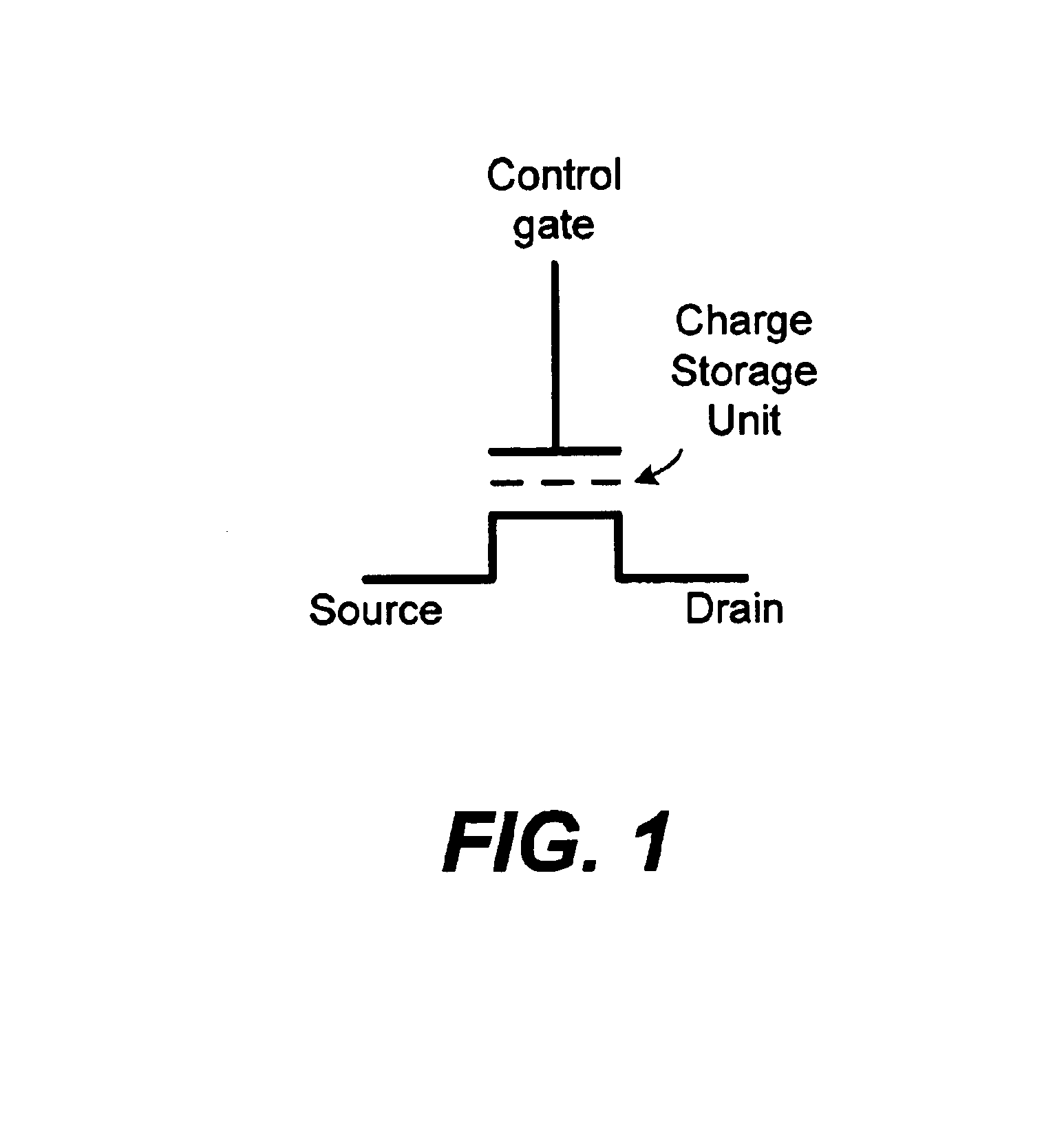

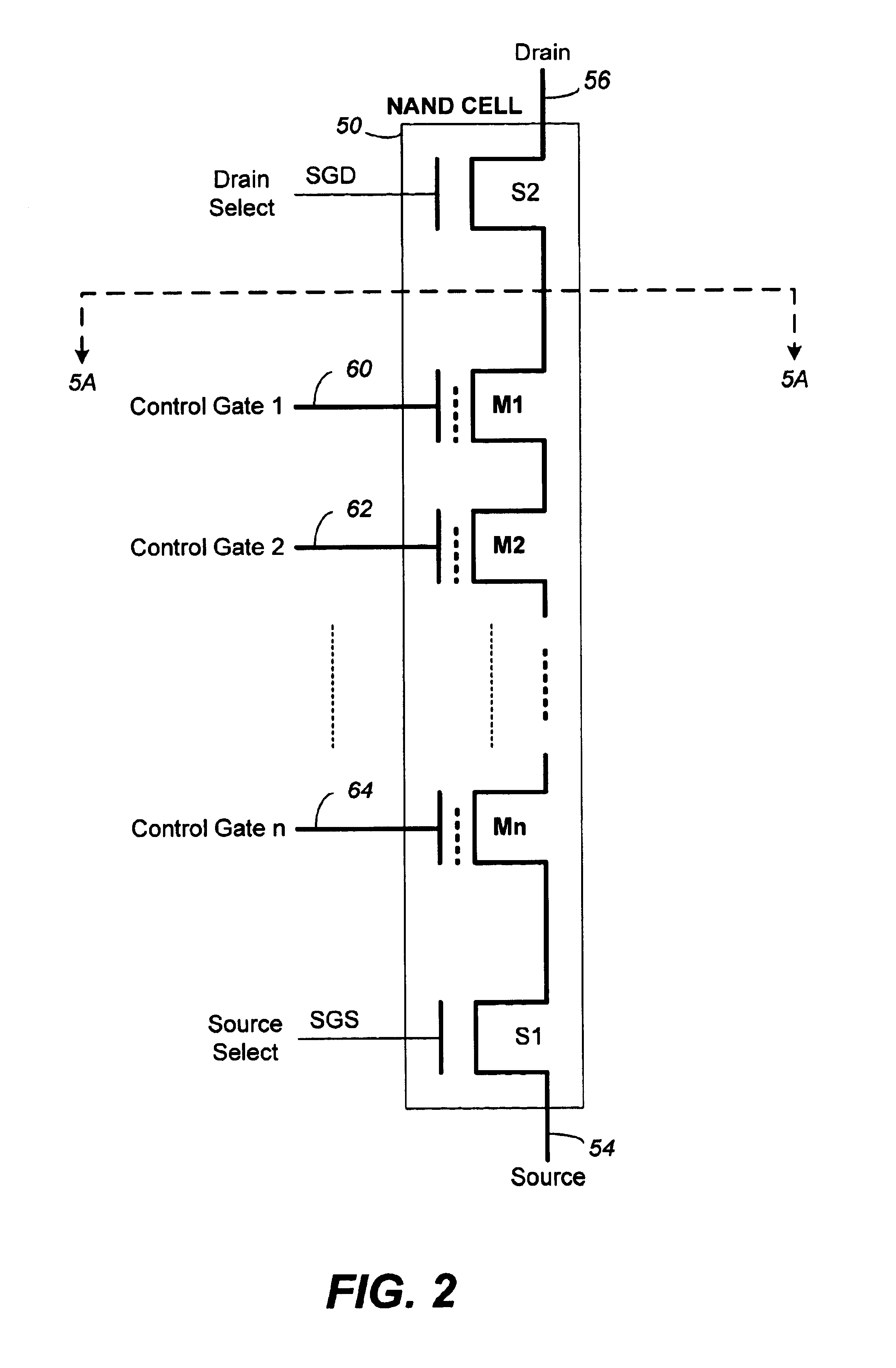

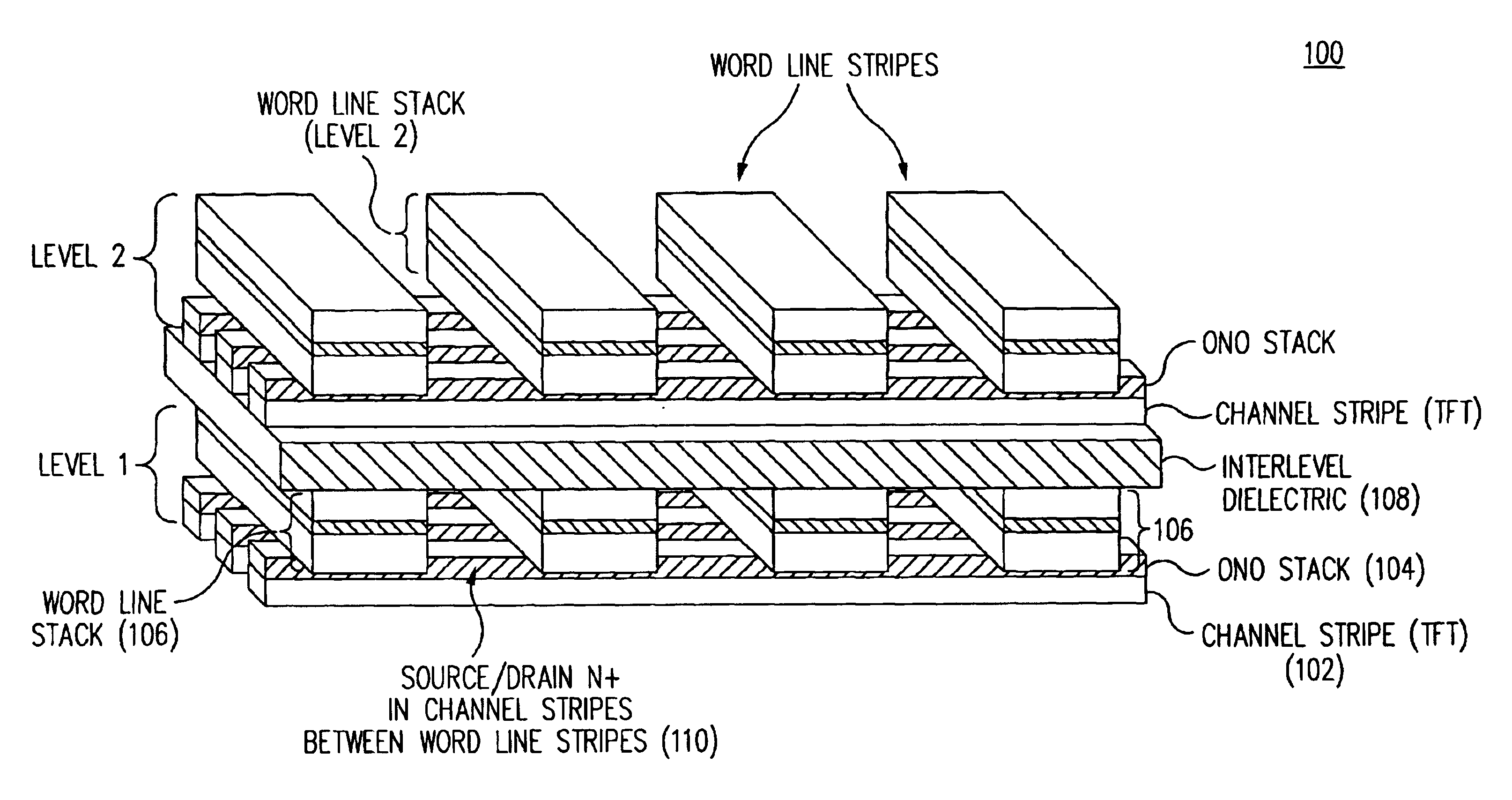

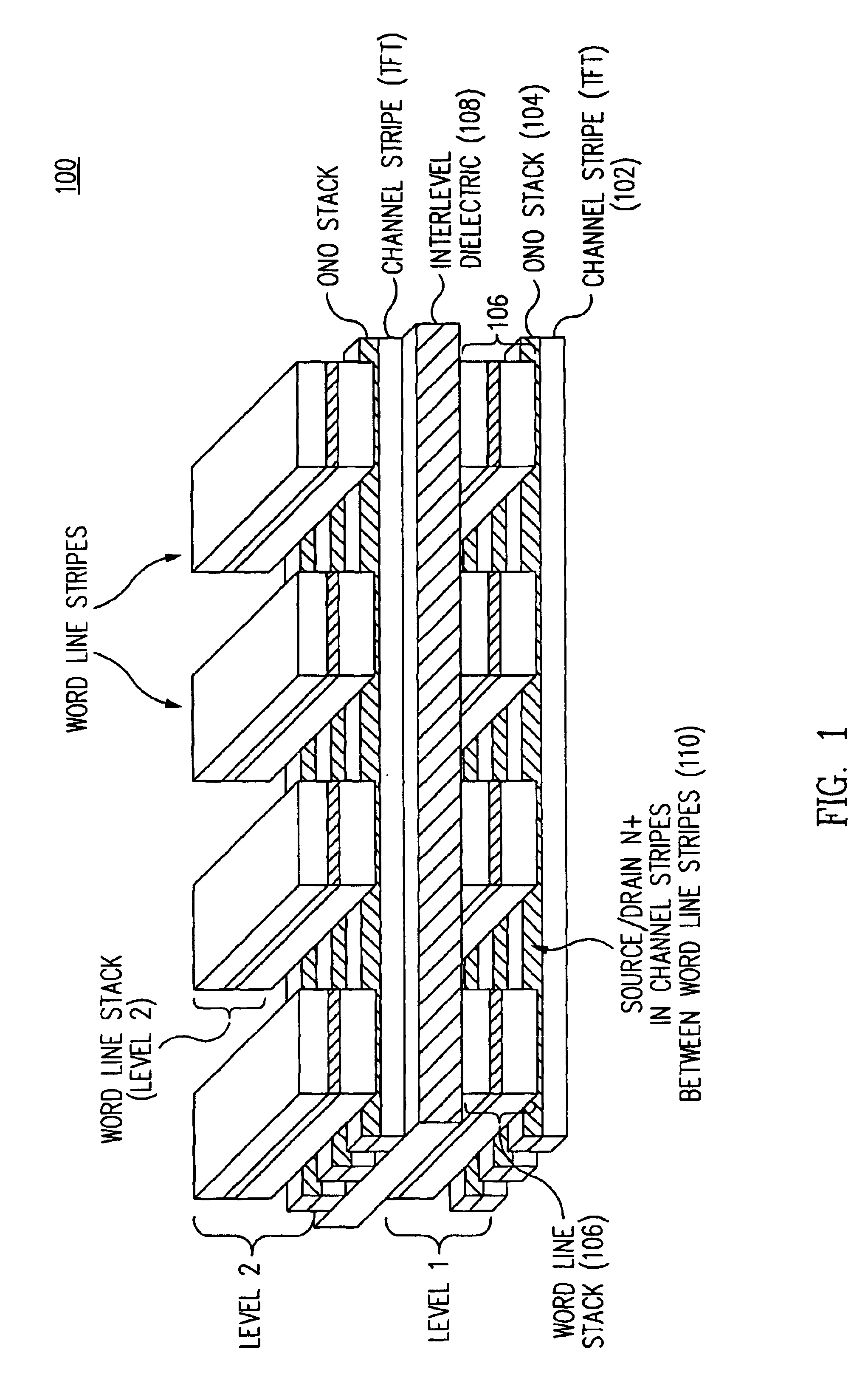

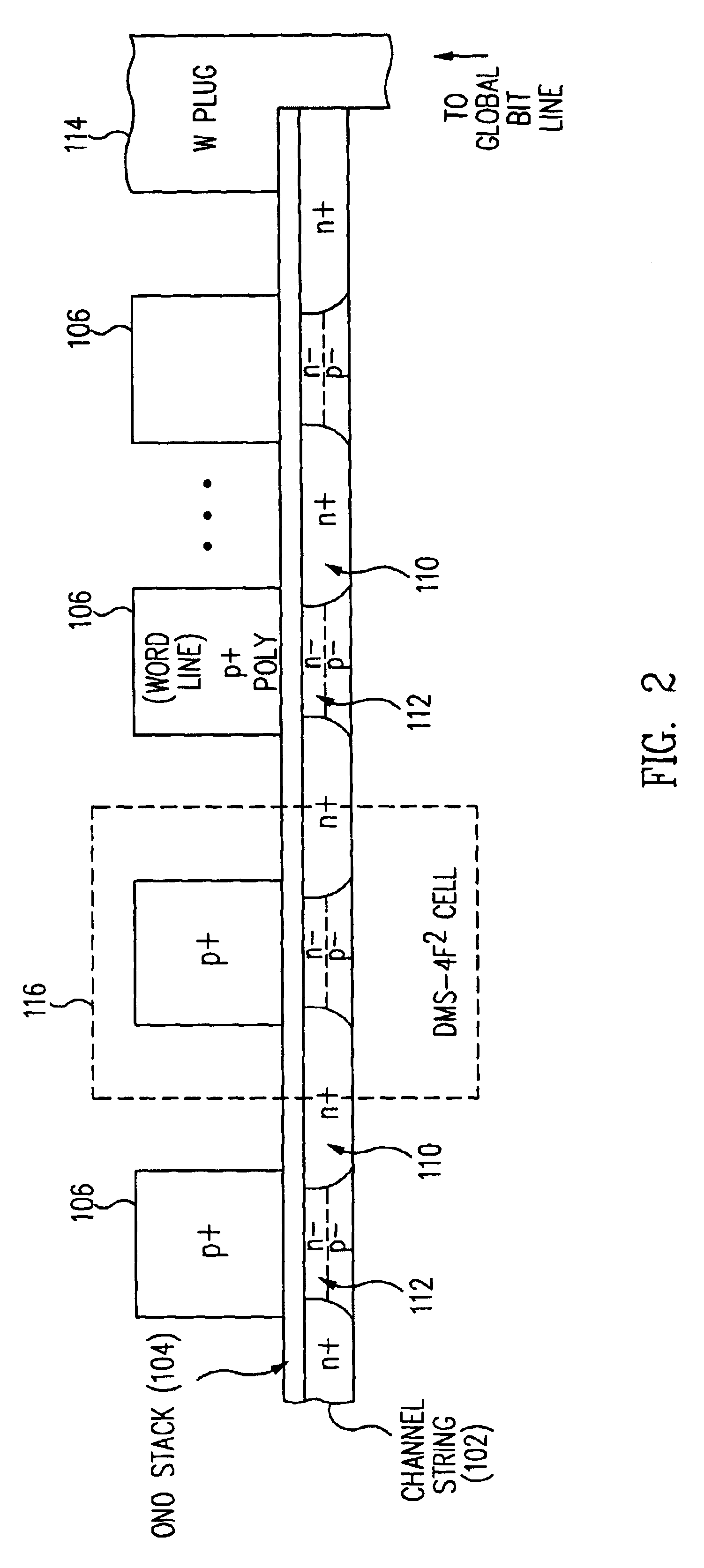

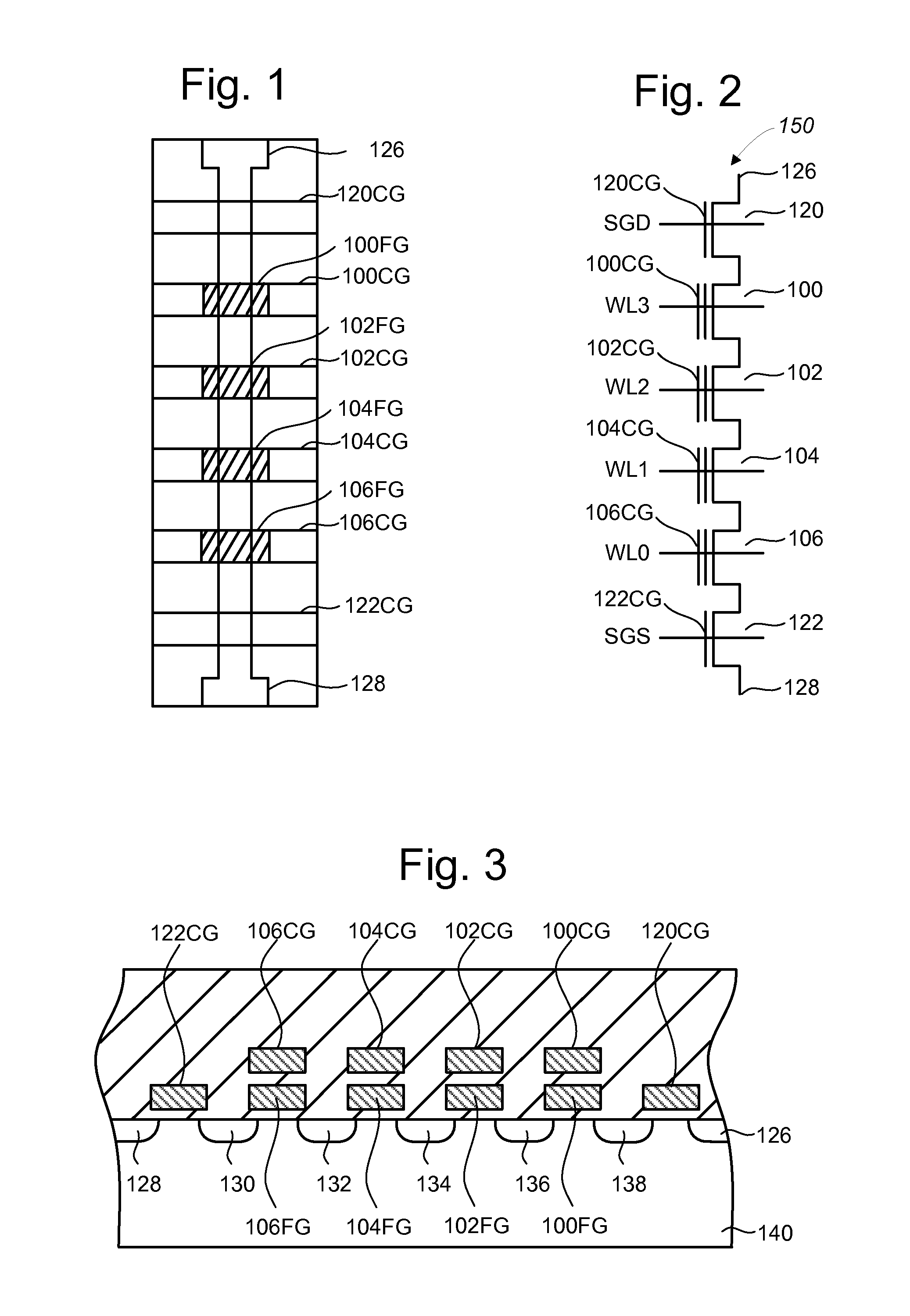

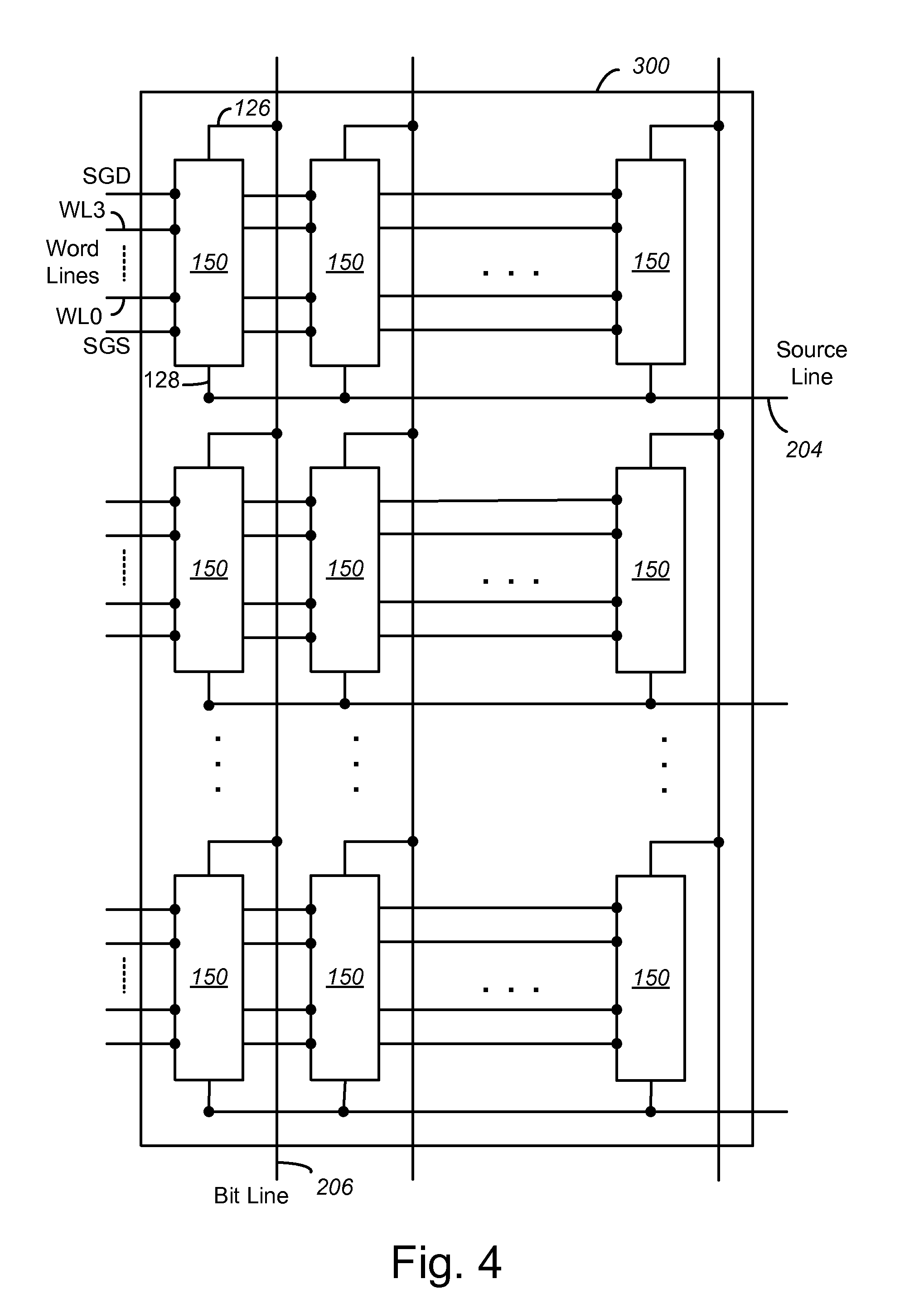

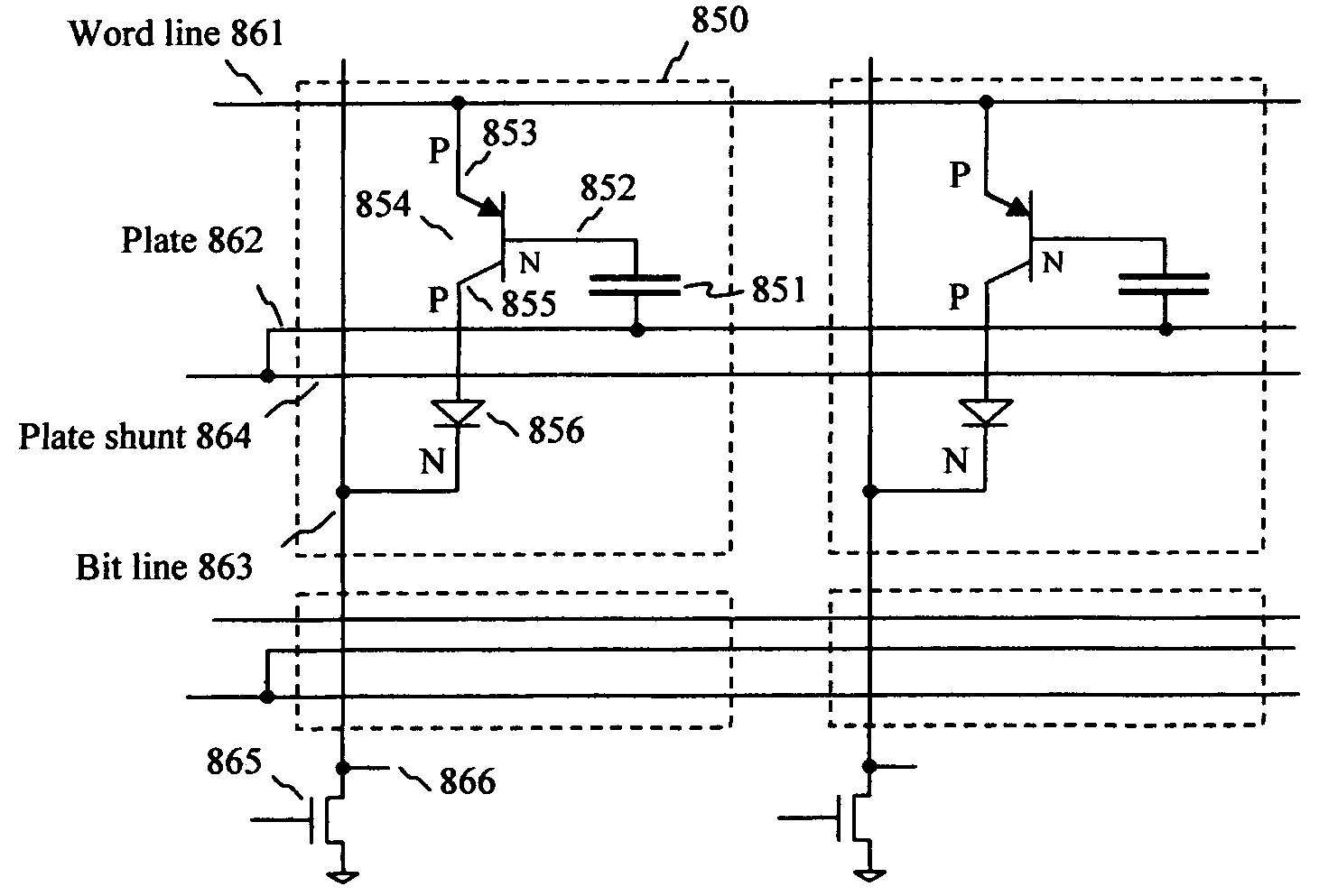

Method for fabricating programmable memory array structures incorporating series-connected transistor strings

InactiveUS7005350B2Reduce in quantityDense memory arraySolid-state devicesRead-only memoriesBit lineComputer architecture

A three-dimensional flash memory array incorporates thin film transistors having a charge storage dielectric arranged in series-connected NAND strings to achieve a 4F2 memory cell layout. The memory array may be programmed and erased using only tunneling currents, and no leakage paths are formed through non-selected memory cells. Each NAND string includes two block select devices for respectively coupling one end of the NAND string to a global bit line, and the other end to a shared bias node. Pairs of NAND strings within a block share the same global bit line. The memory cells are preferably depletion mode SONOS devices, as are the block select devices. The memory cells may be programmed to a near depletion threshold voltage, and the block select devices are maintained in a programmed state having a near depletion mode threshold voltage. NAND strings on more than one layer may be connected to global bit lines on a single layer. By interleaving the NAND strings on each memory level and using two shared bias nodes per block, very little additional overhead is required for the switch devices at each end of the NAND strings. The NAND strings on different memory levels are preferably connected together by way of vertical stacked vias, each preferably connecting to more than one memory level. Each memory level may be produced with less than three masks per level.

Owner:SANDISK TECH LLC

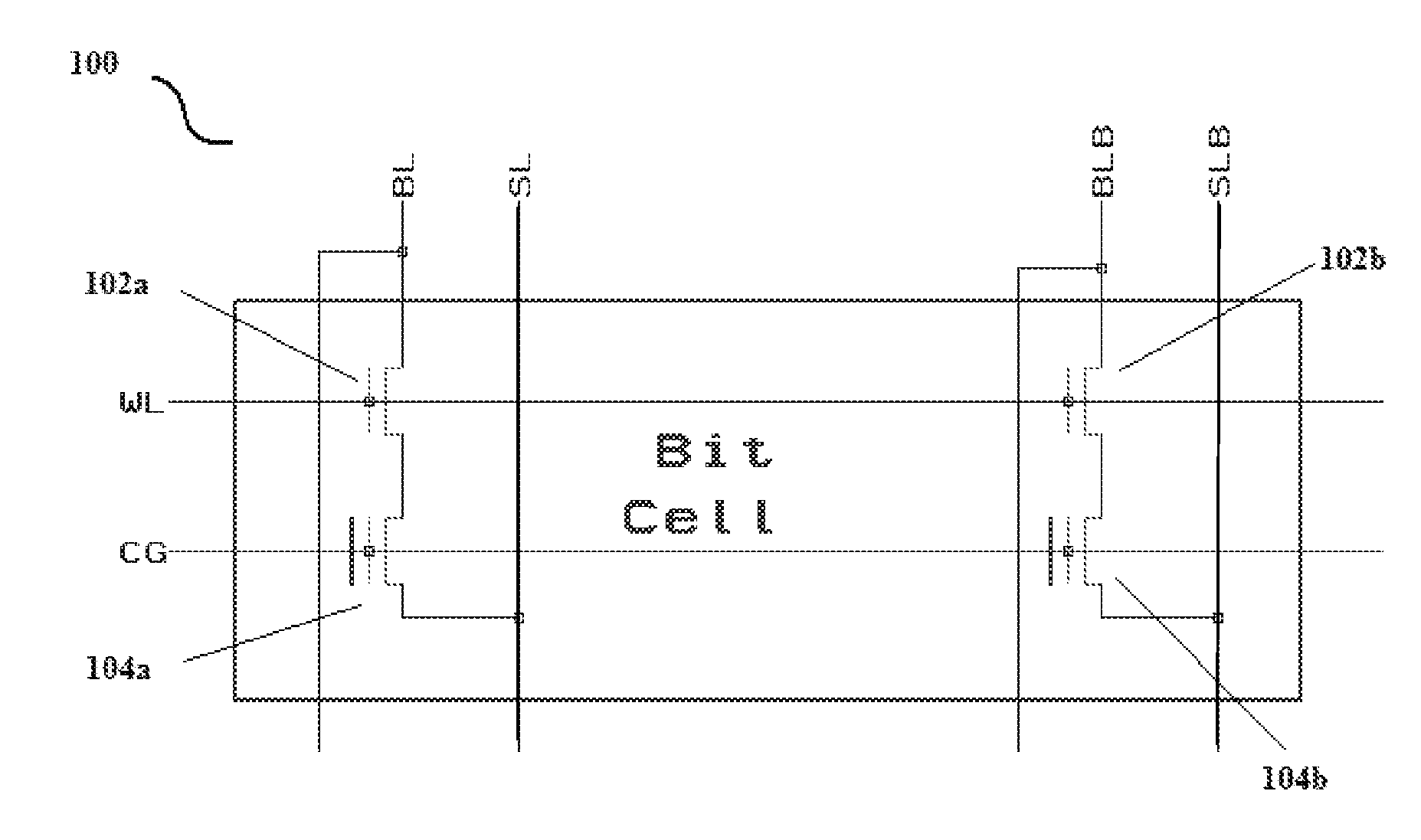

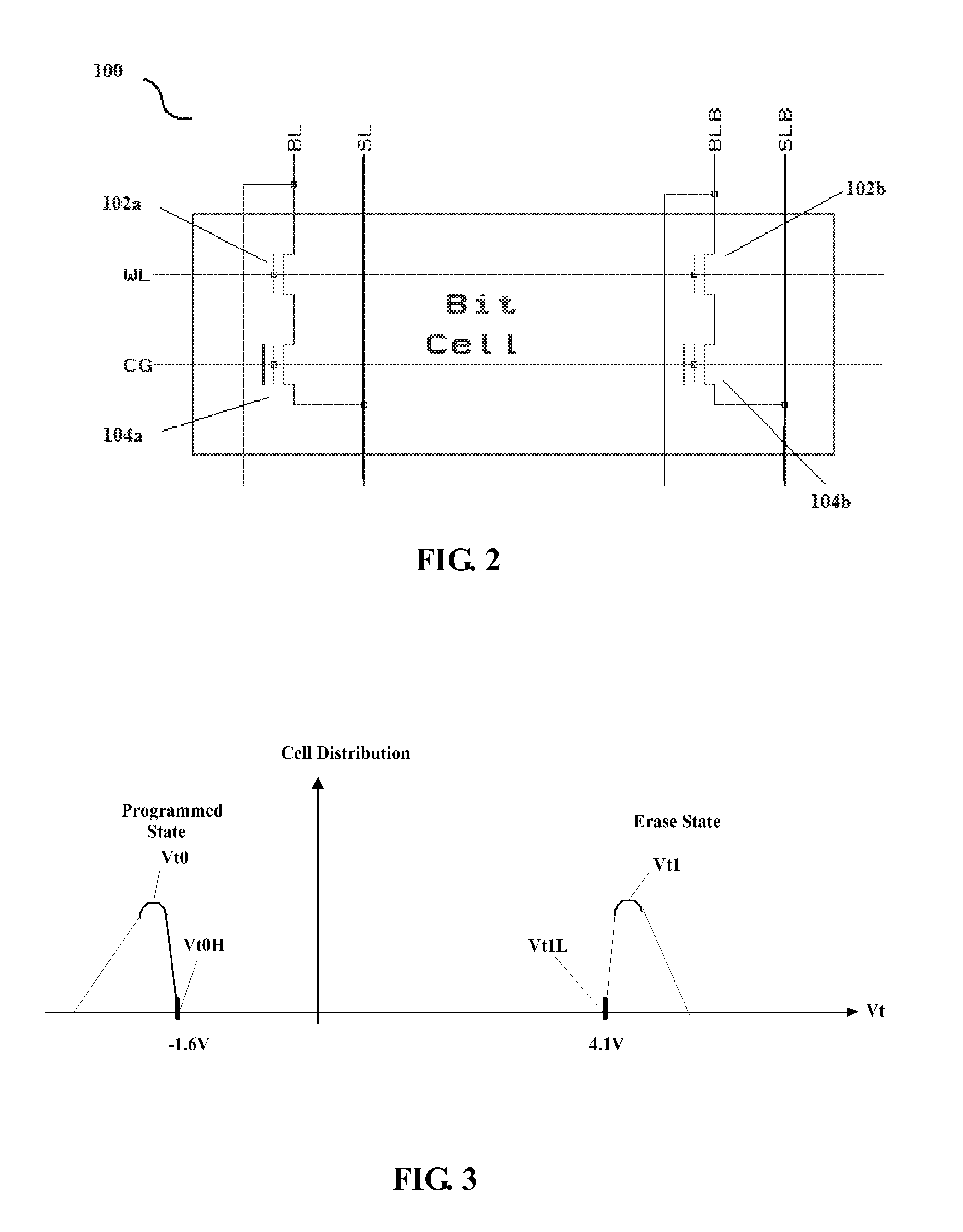

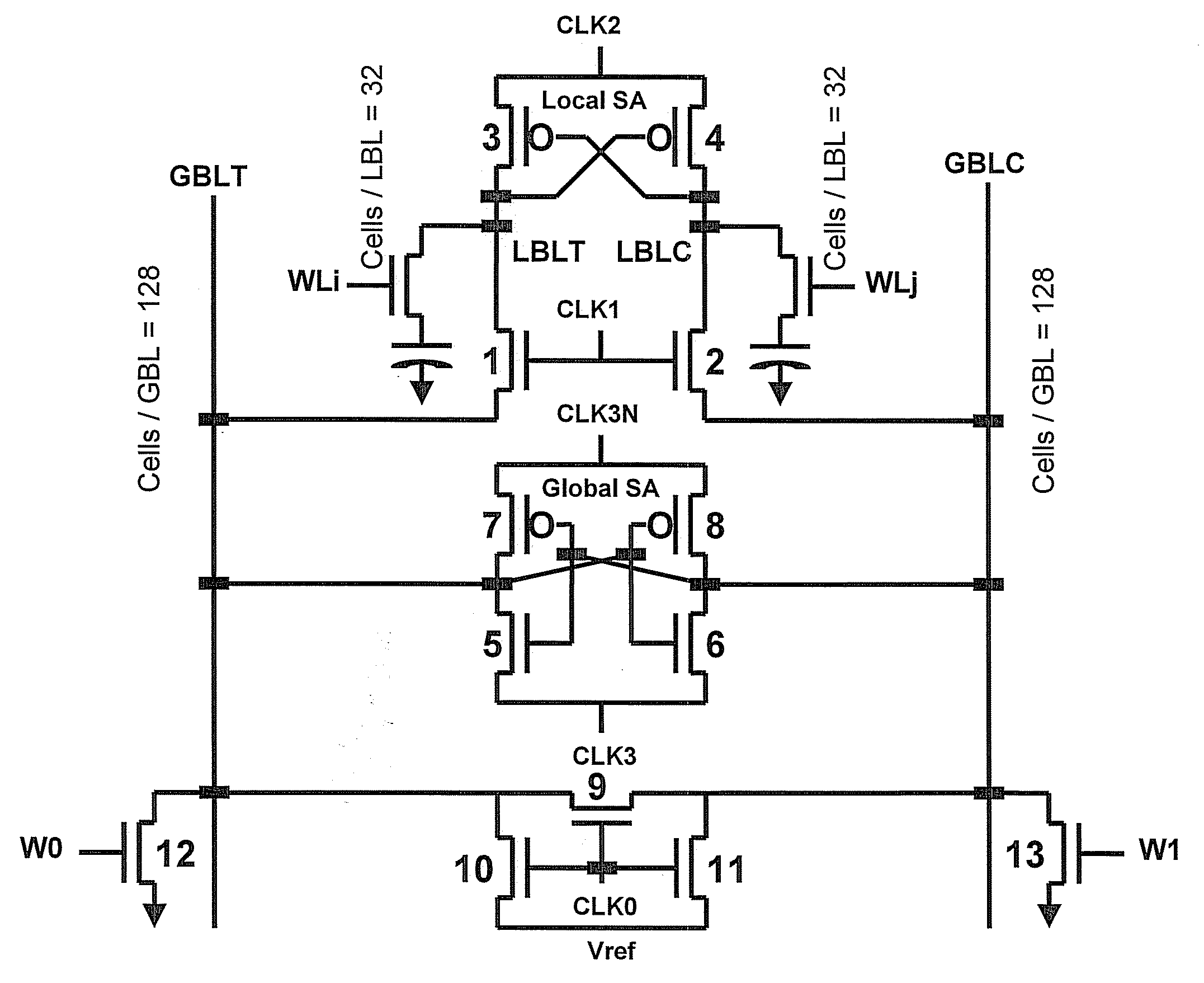

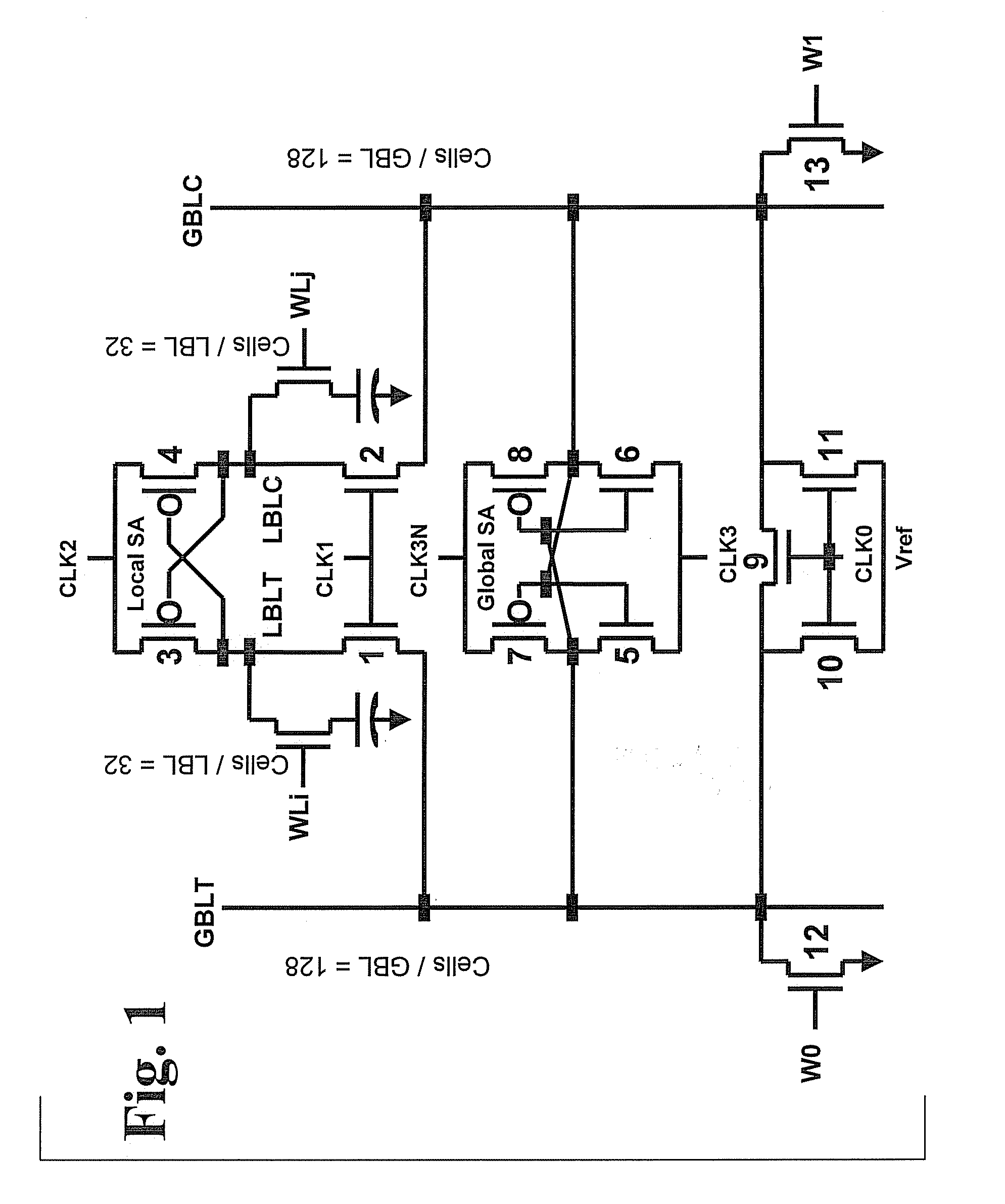

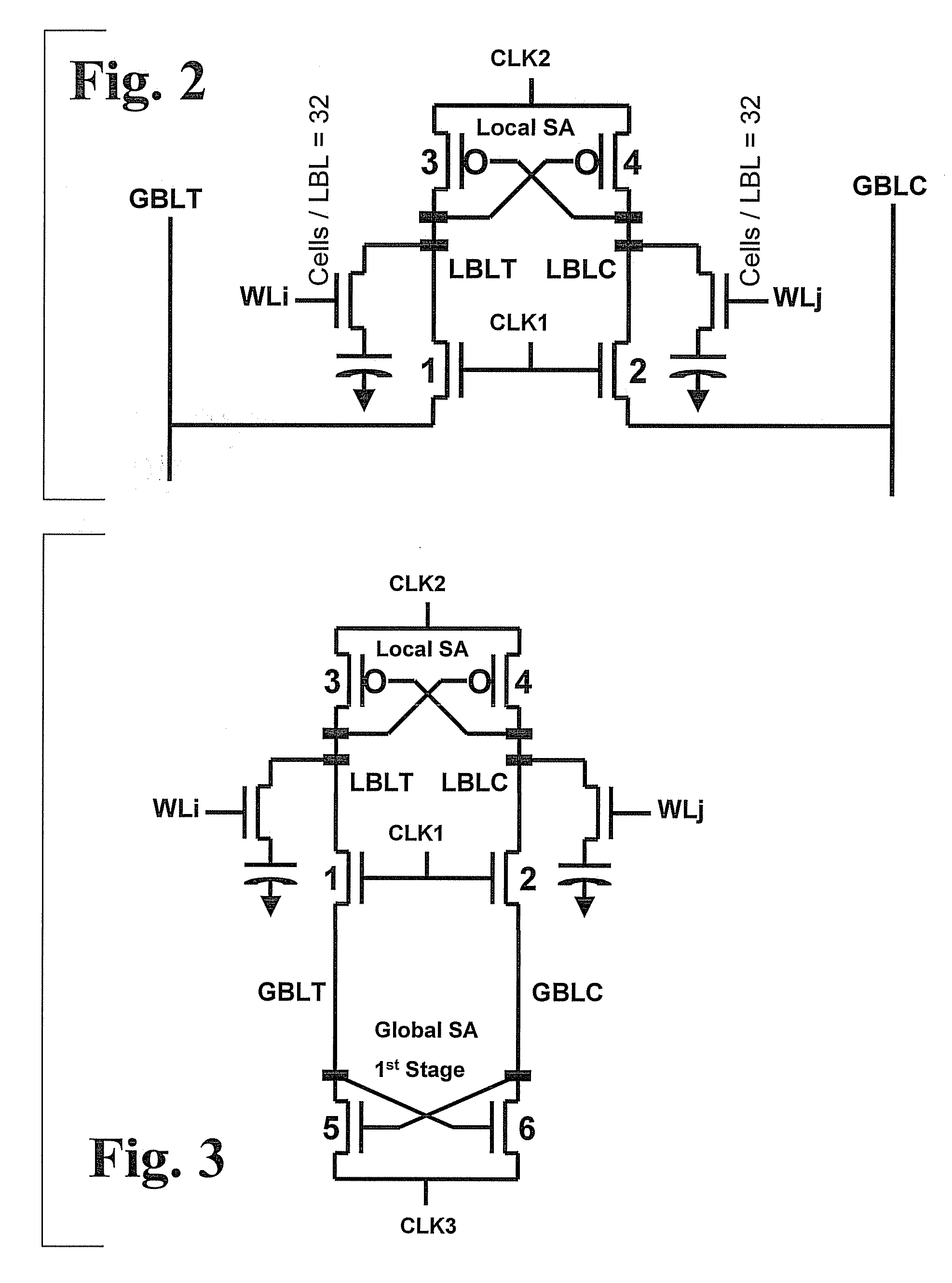

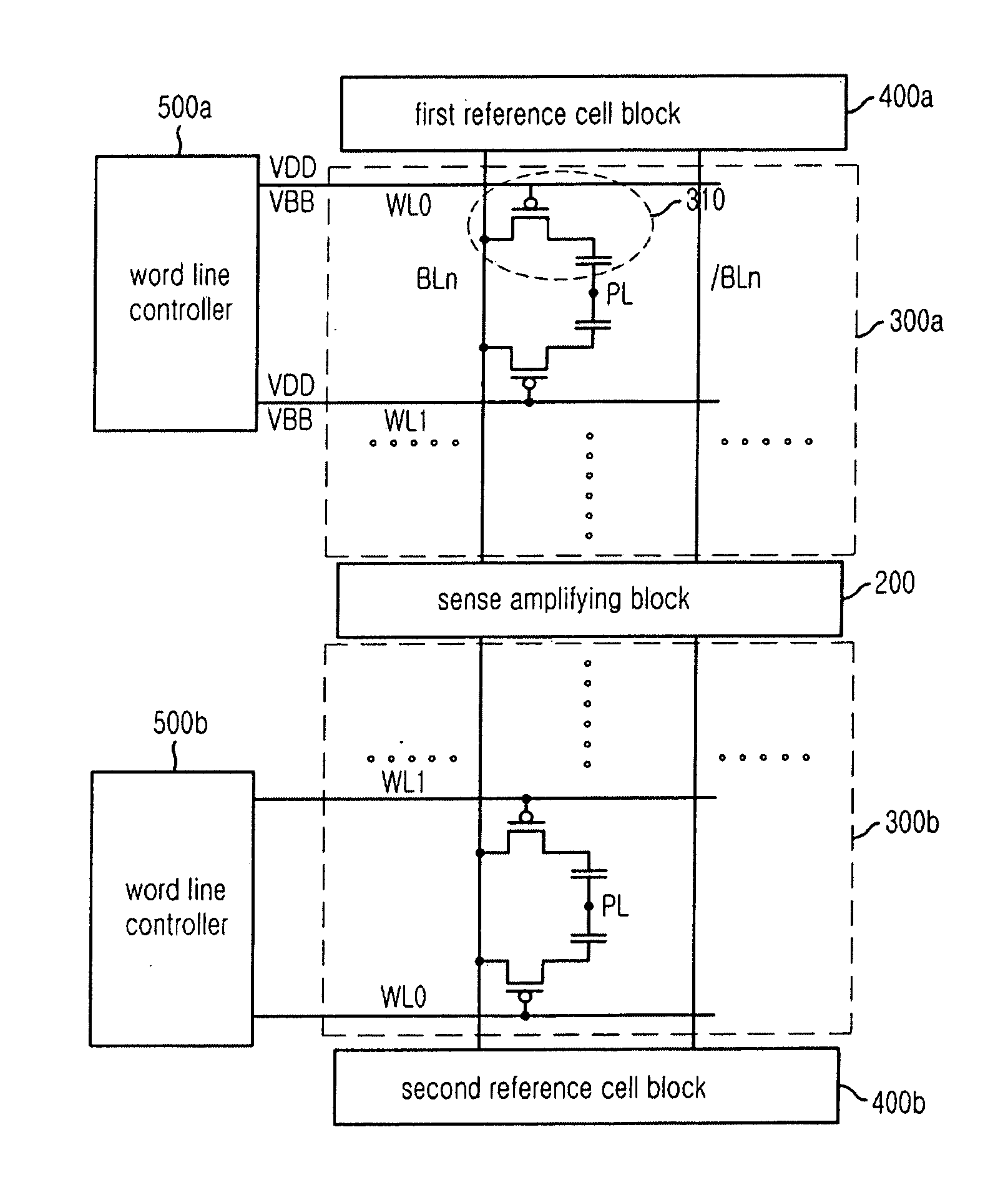

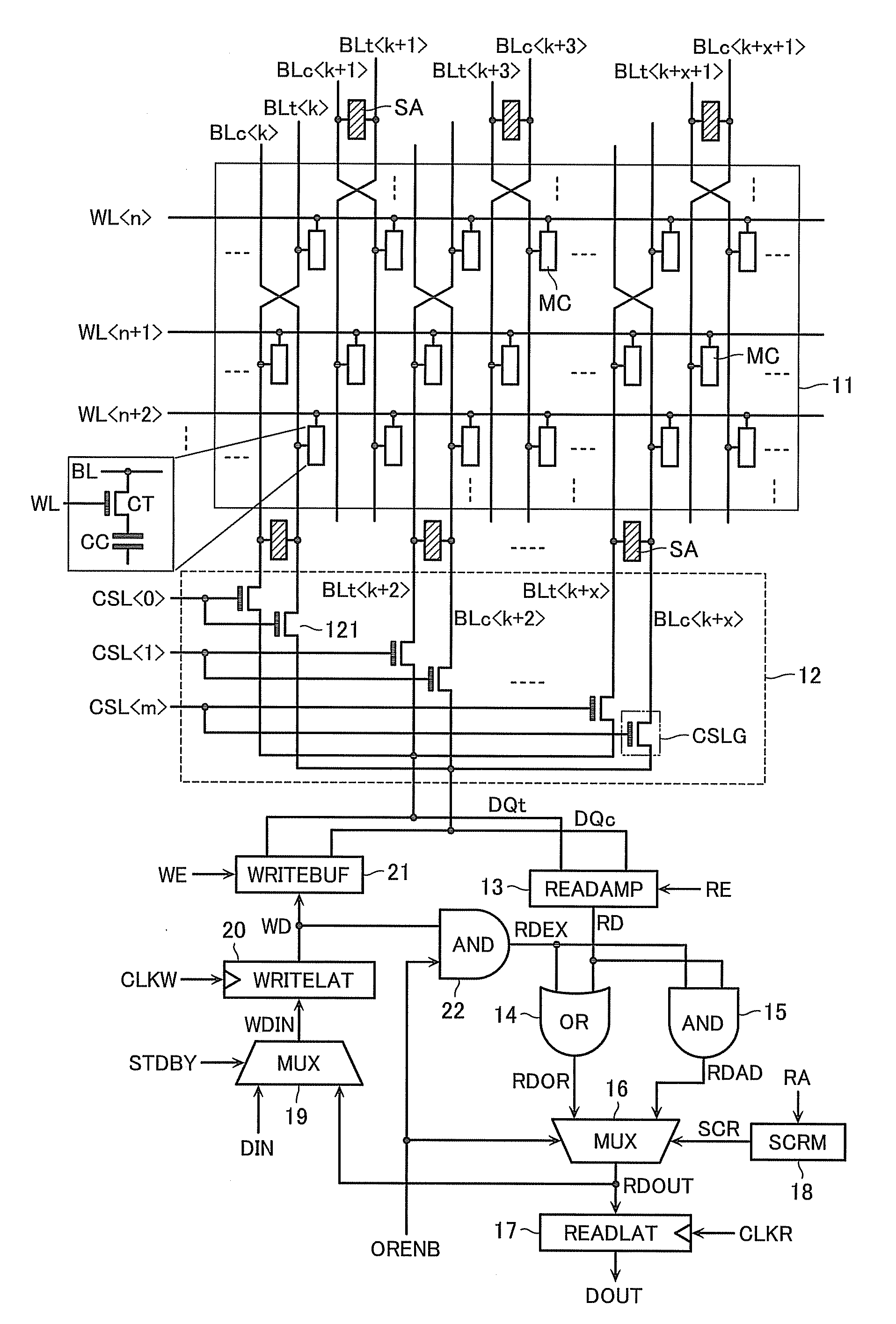

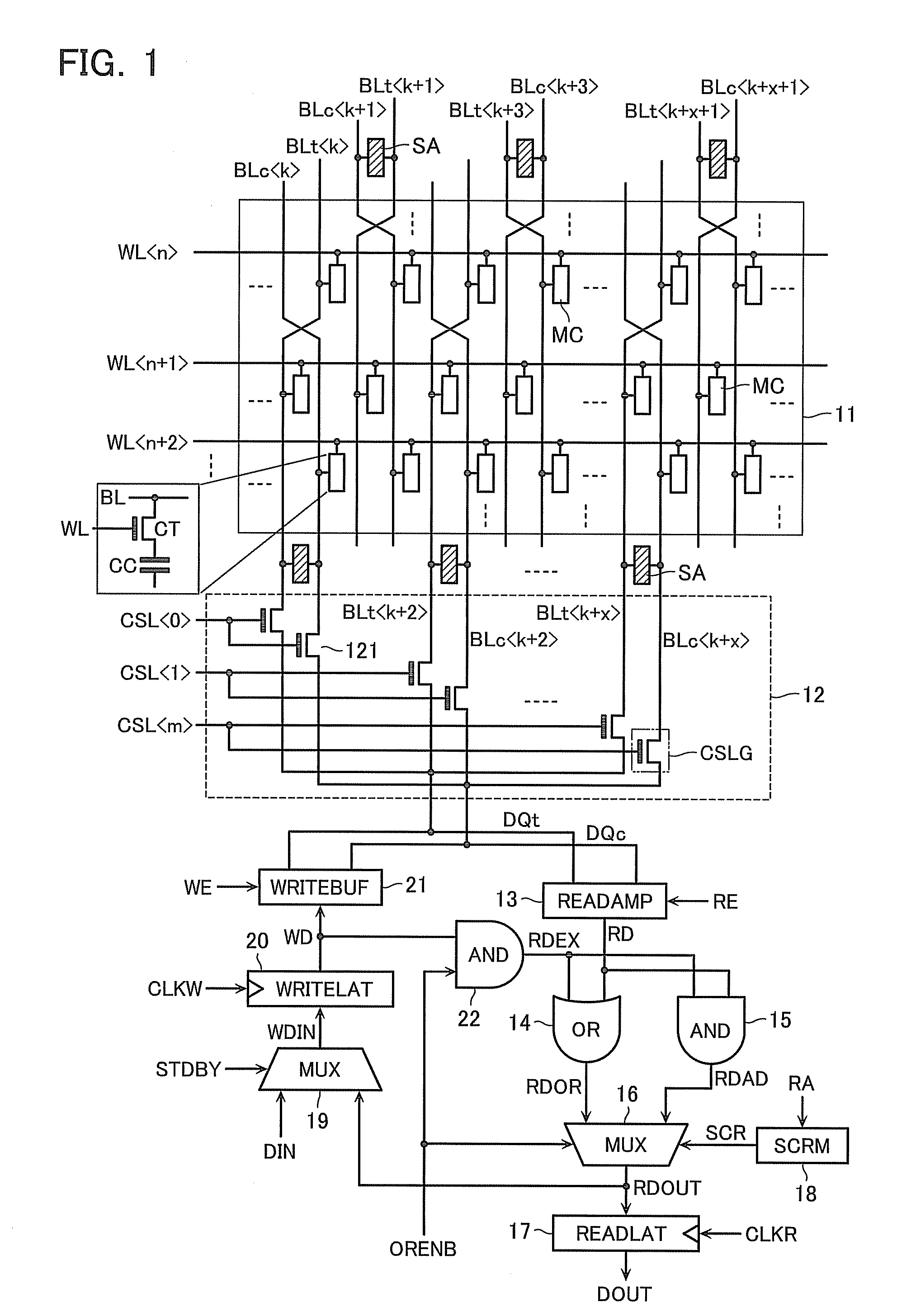

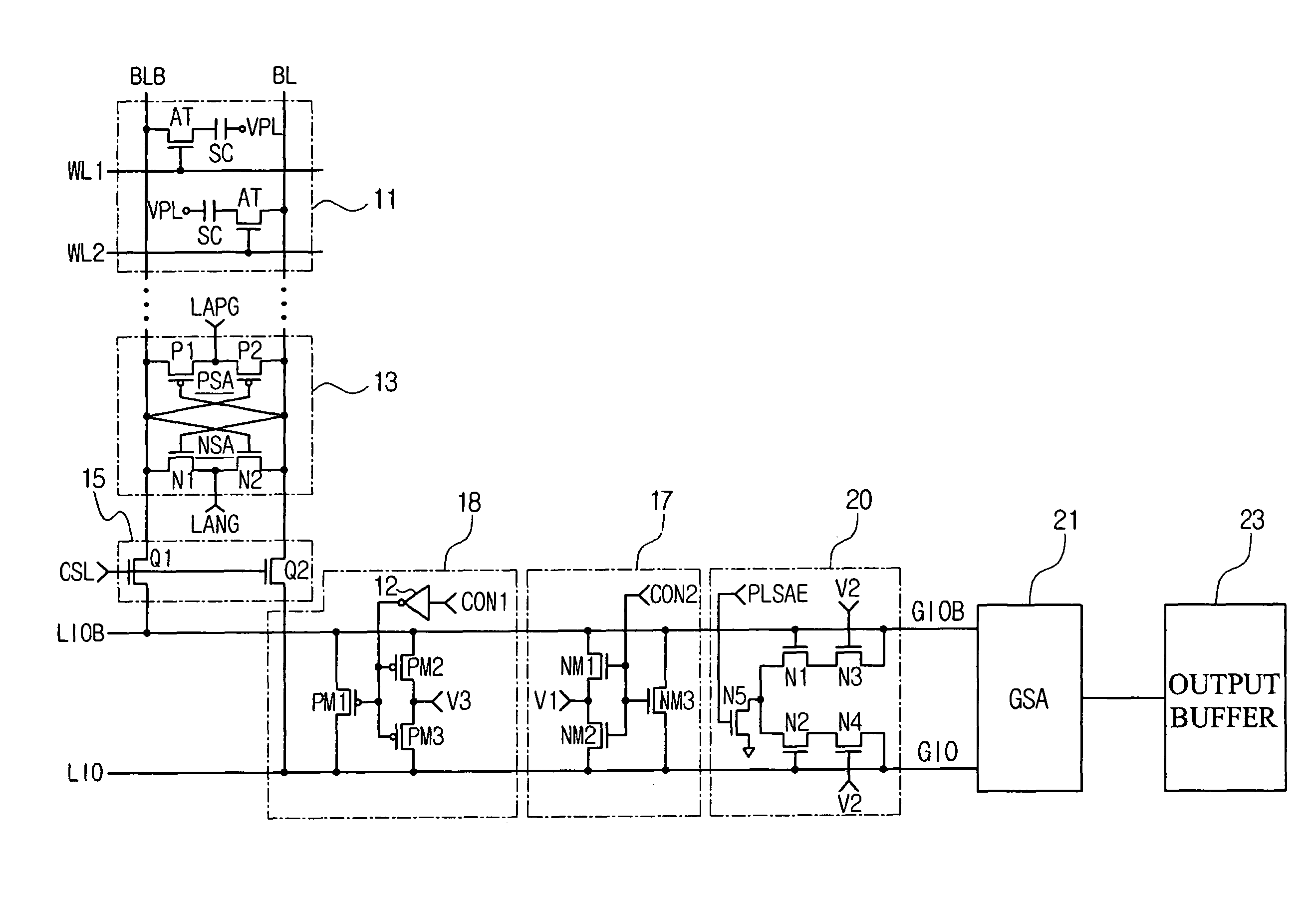

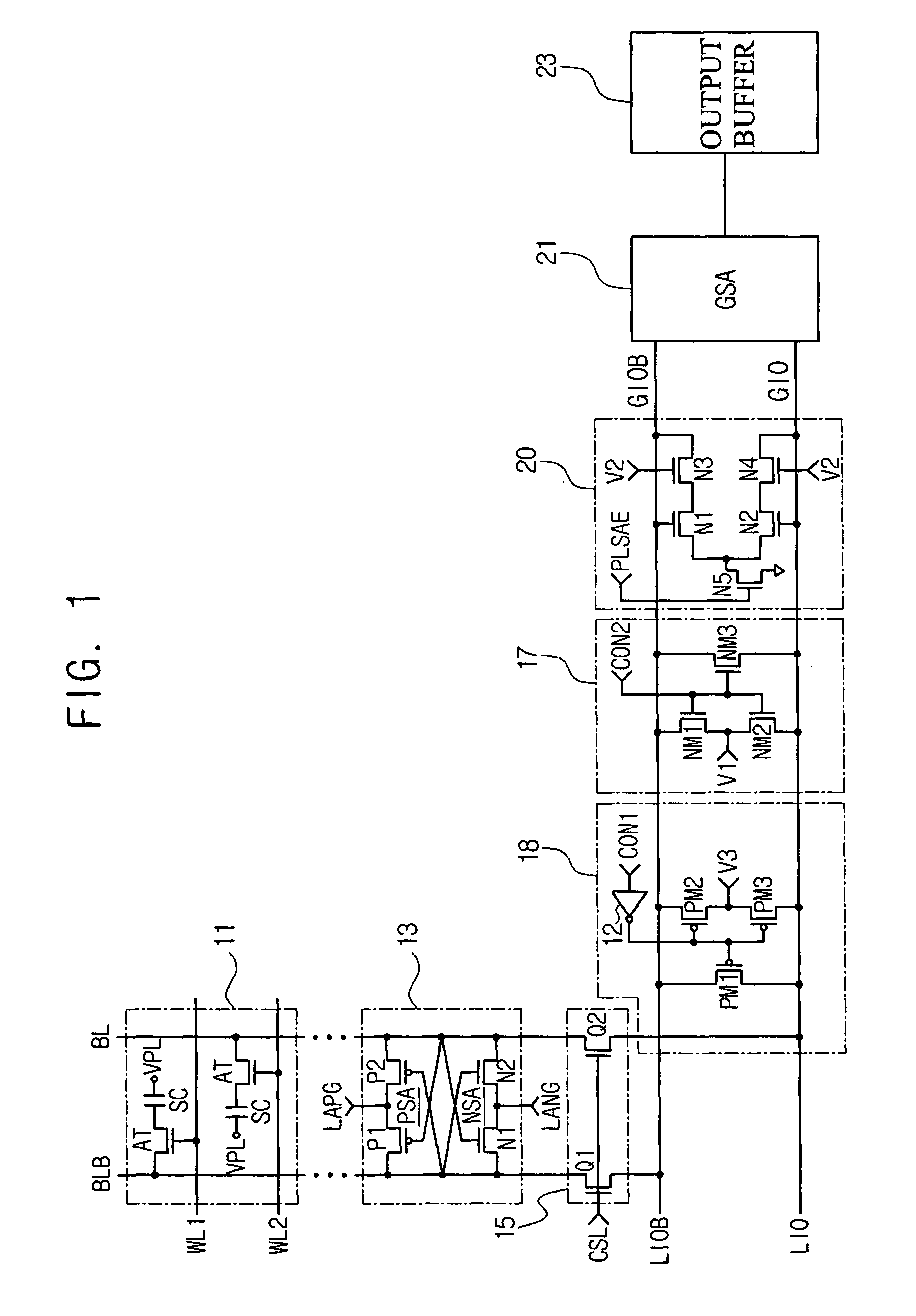

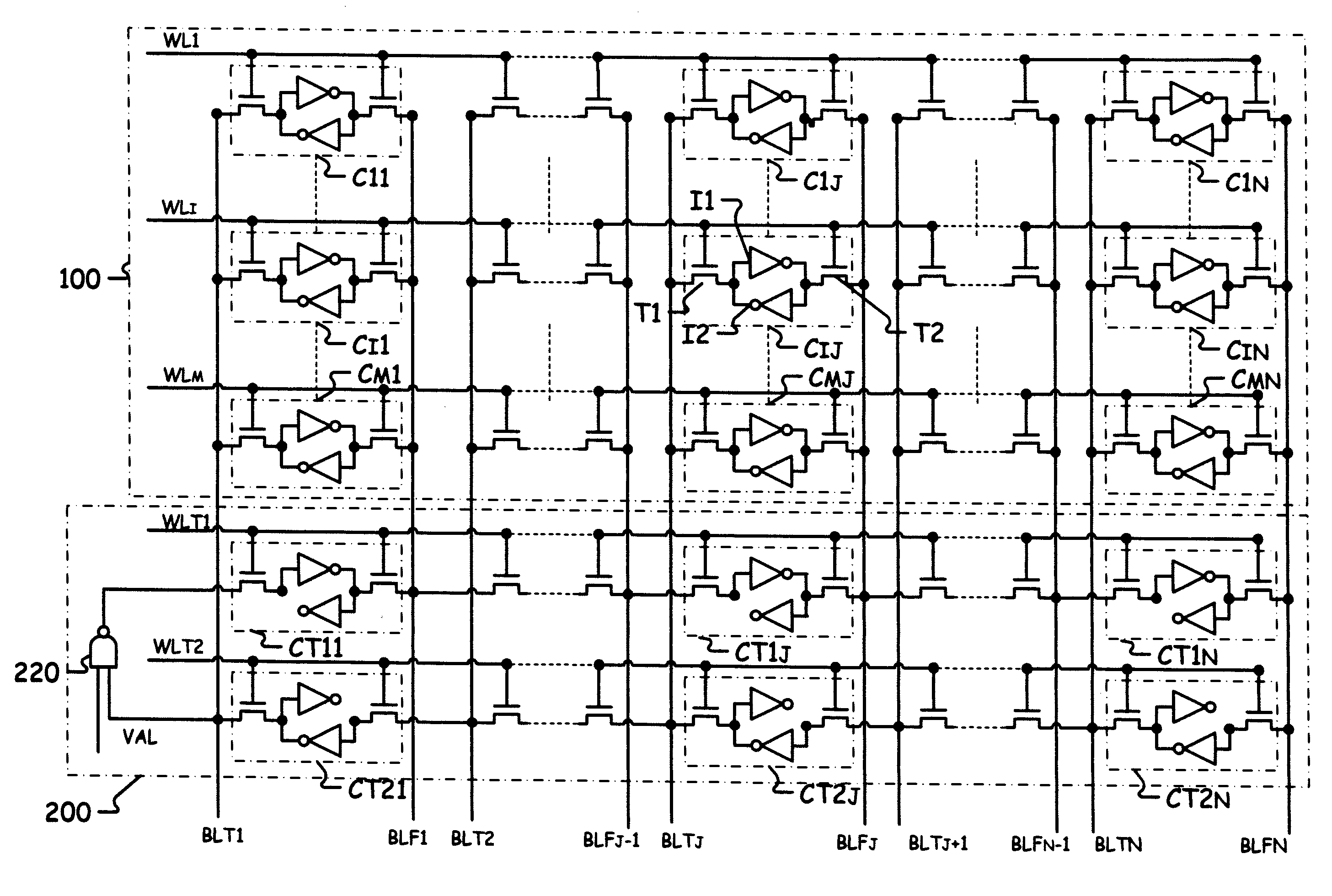

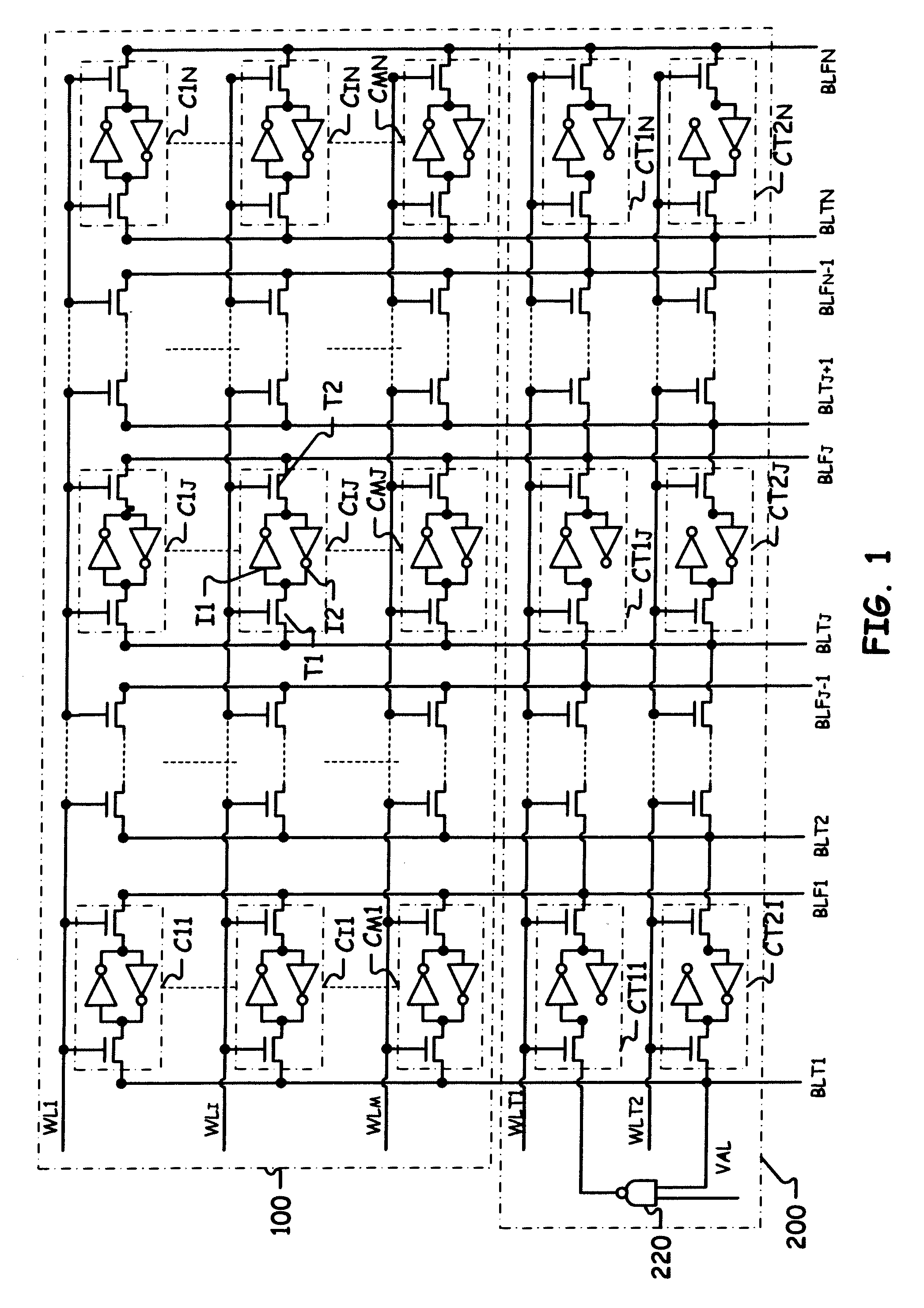

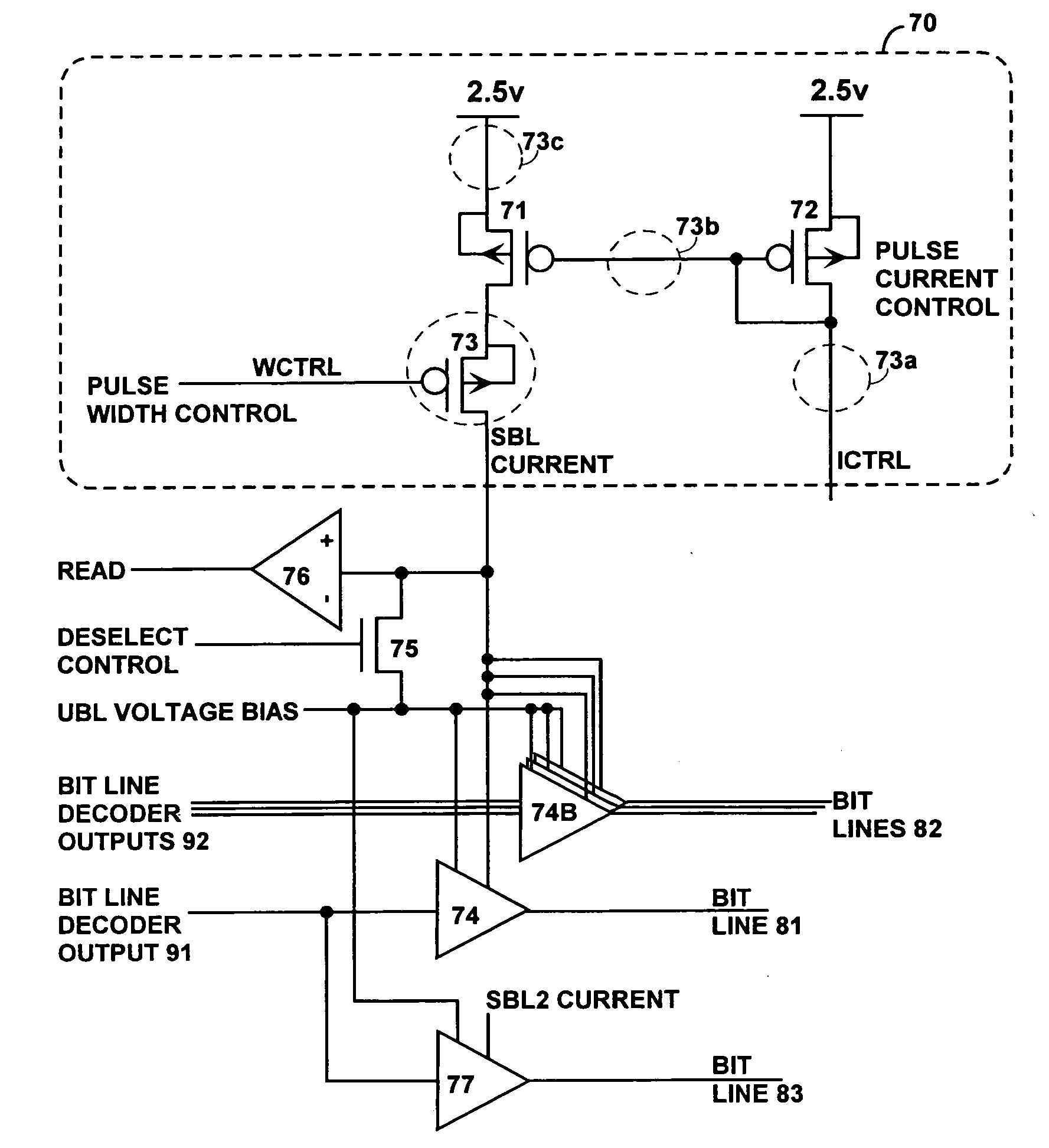

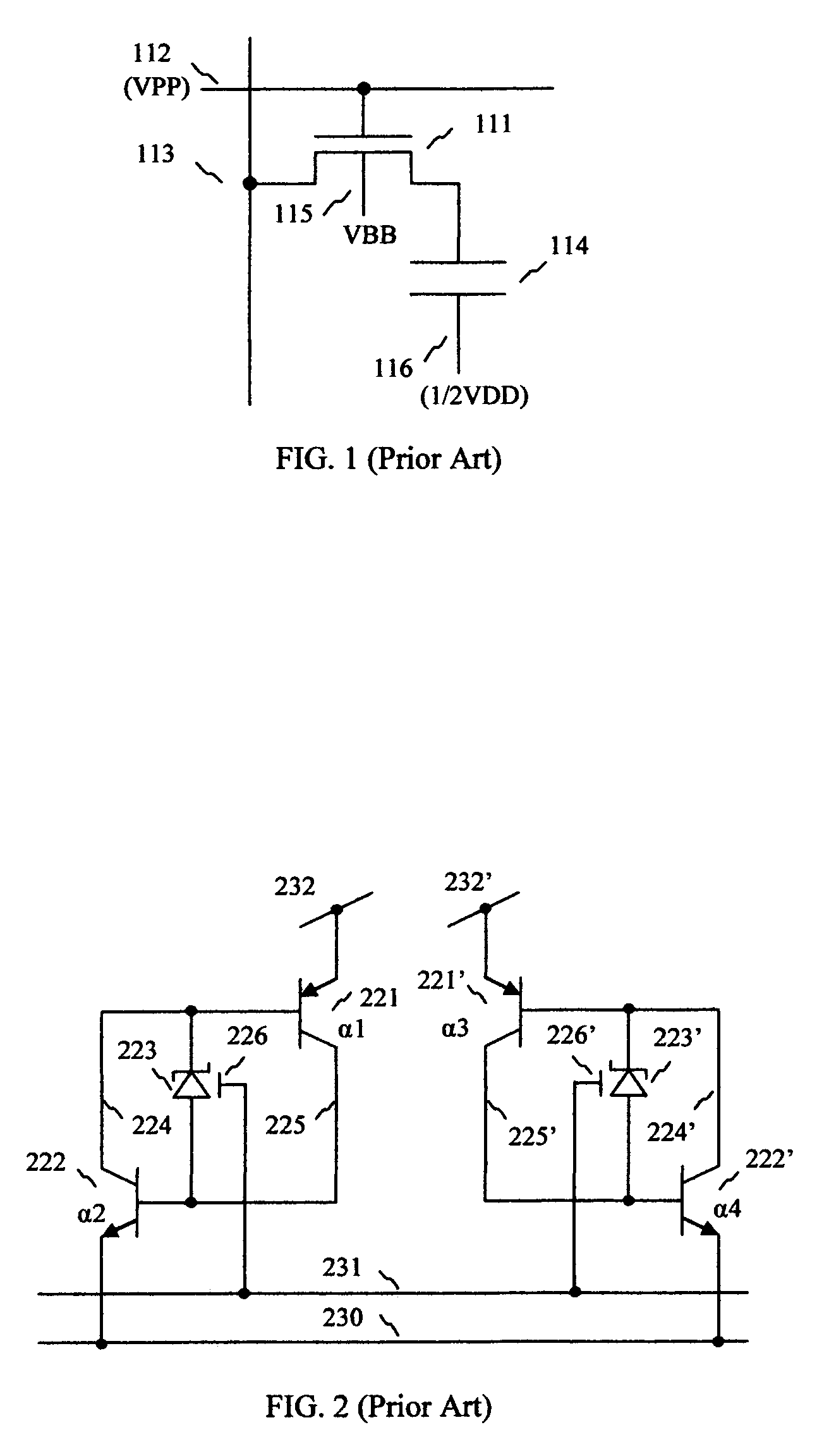

Dram-like nvm memory array and sense amplifier design for high temperature and high endurance operation

InactiveUS20110267883A1Improve threshold voltage sensing marginLarge silicon areaRead-only memoriesDigital storageBit lineAudio power amplifier

A DRAM-like non-volatile memory array includes a cell array of non-volatile cell units with a DRAM-like cross-coupled latch-type sense amplifier. Each non-volatile cell unit has two non-volatile cell devices with respective bit lines and source lines running in parallel and laid out perpendicular to the word line associated with the non-volatile cell unit. The two non-volatile cell devices are programmed with erased and programmed threshold voltages as a pair for storing a single bit of binary data. The two bit lines of each non-volatile cell unit are coupled through a Y-decoder and a latch device to the two respective inputs of the latch-type sense amplifier which provides a large sensing margin for the cell array to operate properly even with a narrowed threshold voltage gap. Each non-volatile cell device may be a 2 T FLOTOX-based EEPROM cell, a 2 T flash cell, 11 T flash cell or a 1.5 T split-gate flash cell.

Owner:APLUS FLASH TECH

eDRAM HIERARCHICAL DIFFERENTIAL SENSE AMP

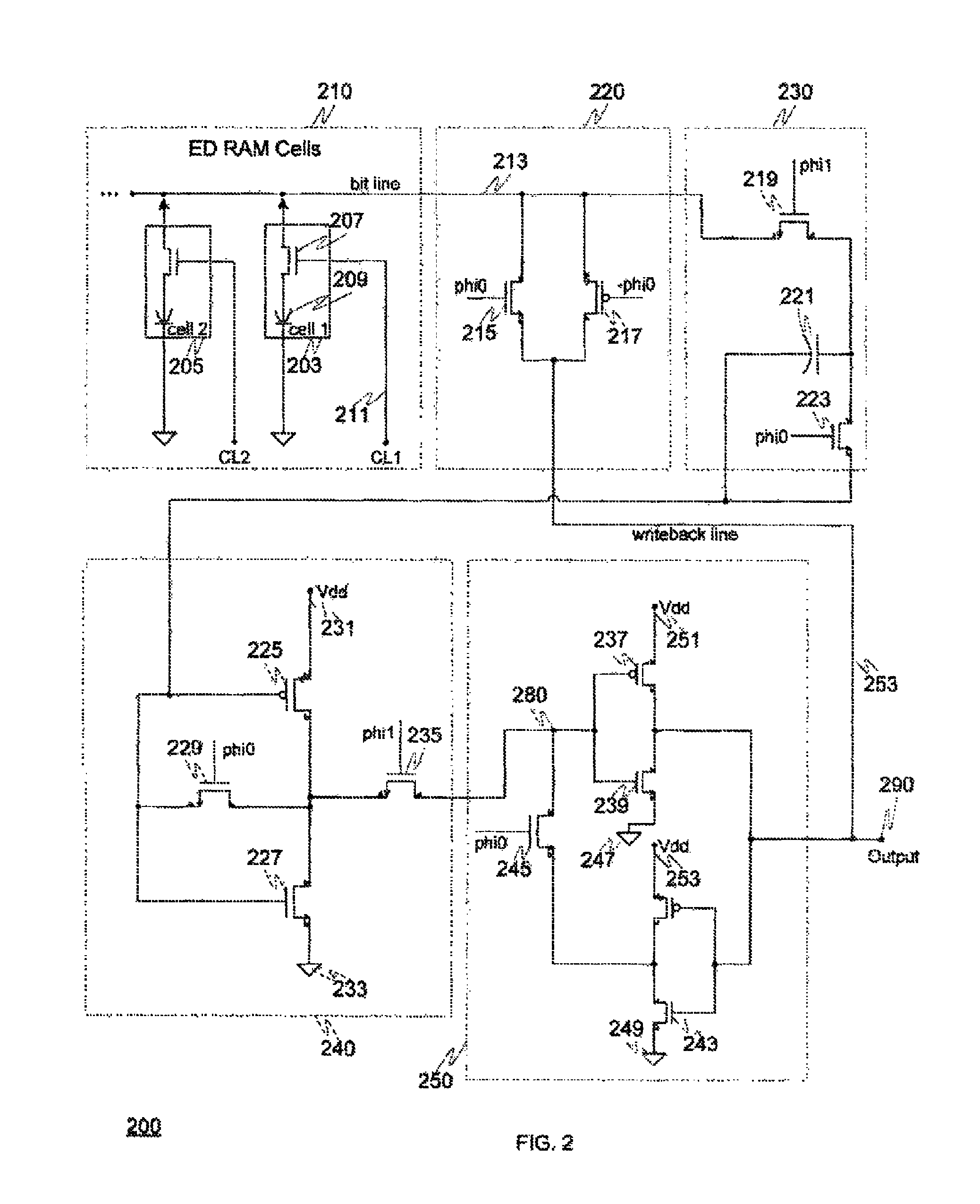

In an embodiment of the present invention, a hierarchical differential sensing approach is effectuated wherein an array of 1T DRAM cells are organized in rows and columns in which the rows represent words and the columns represent bits of the word, each bit column having more than one pair of balanced, true and complement local bit lines, the local bit lines being connected to a pair of balanced, true and complement global bit lines by way of CMOS transistor switches.

Owner:GLOBALFOUNDRIES INC

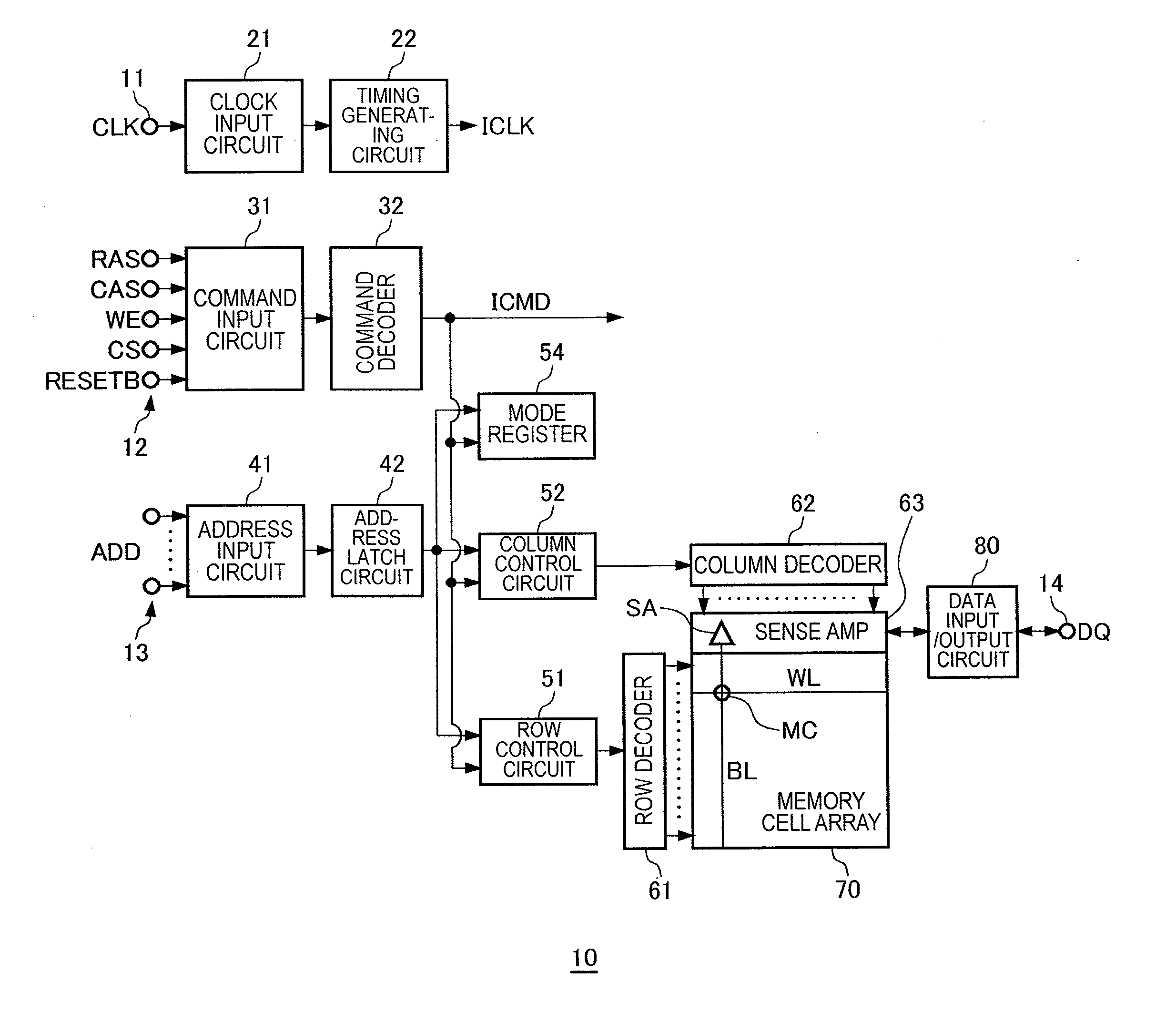

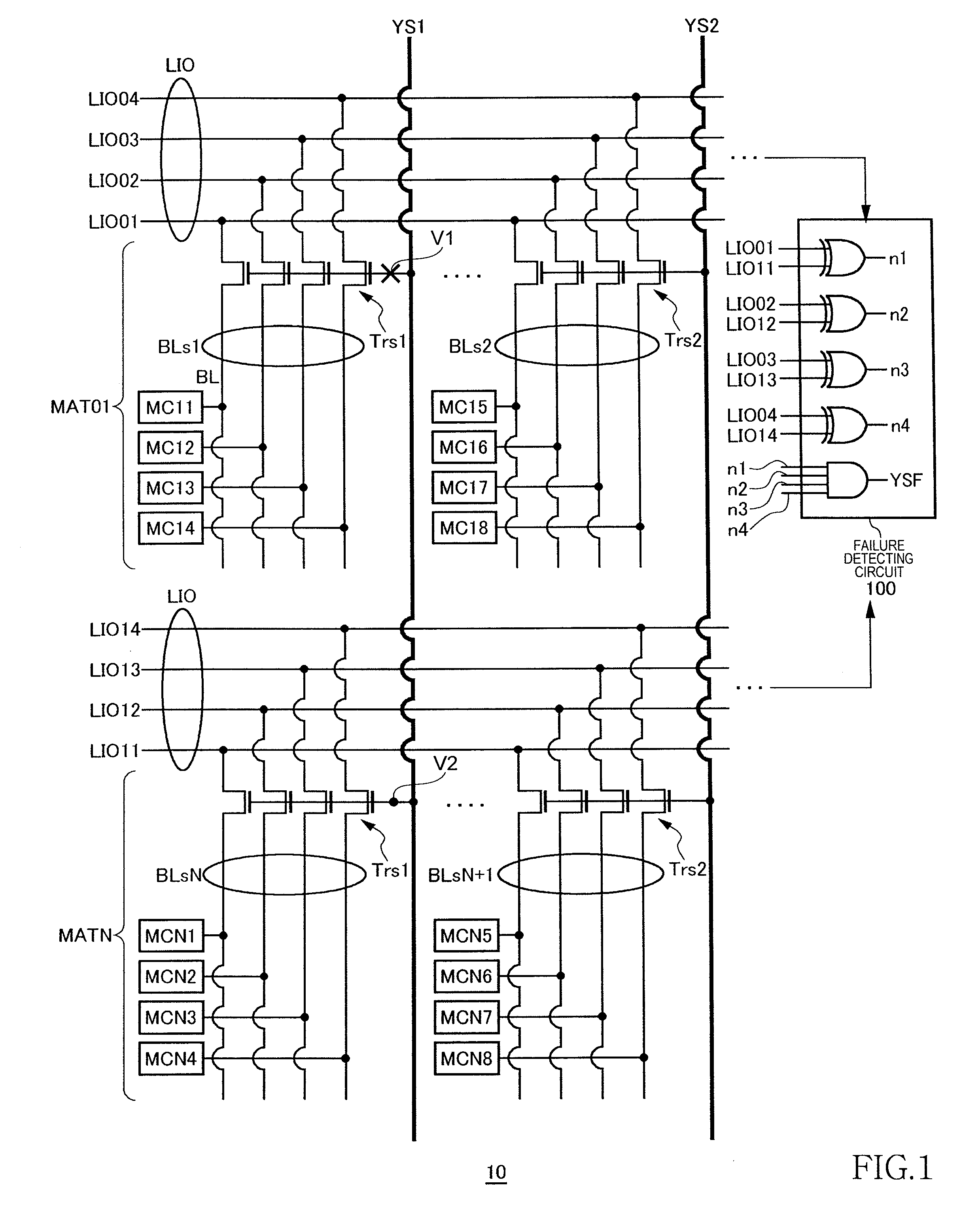

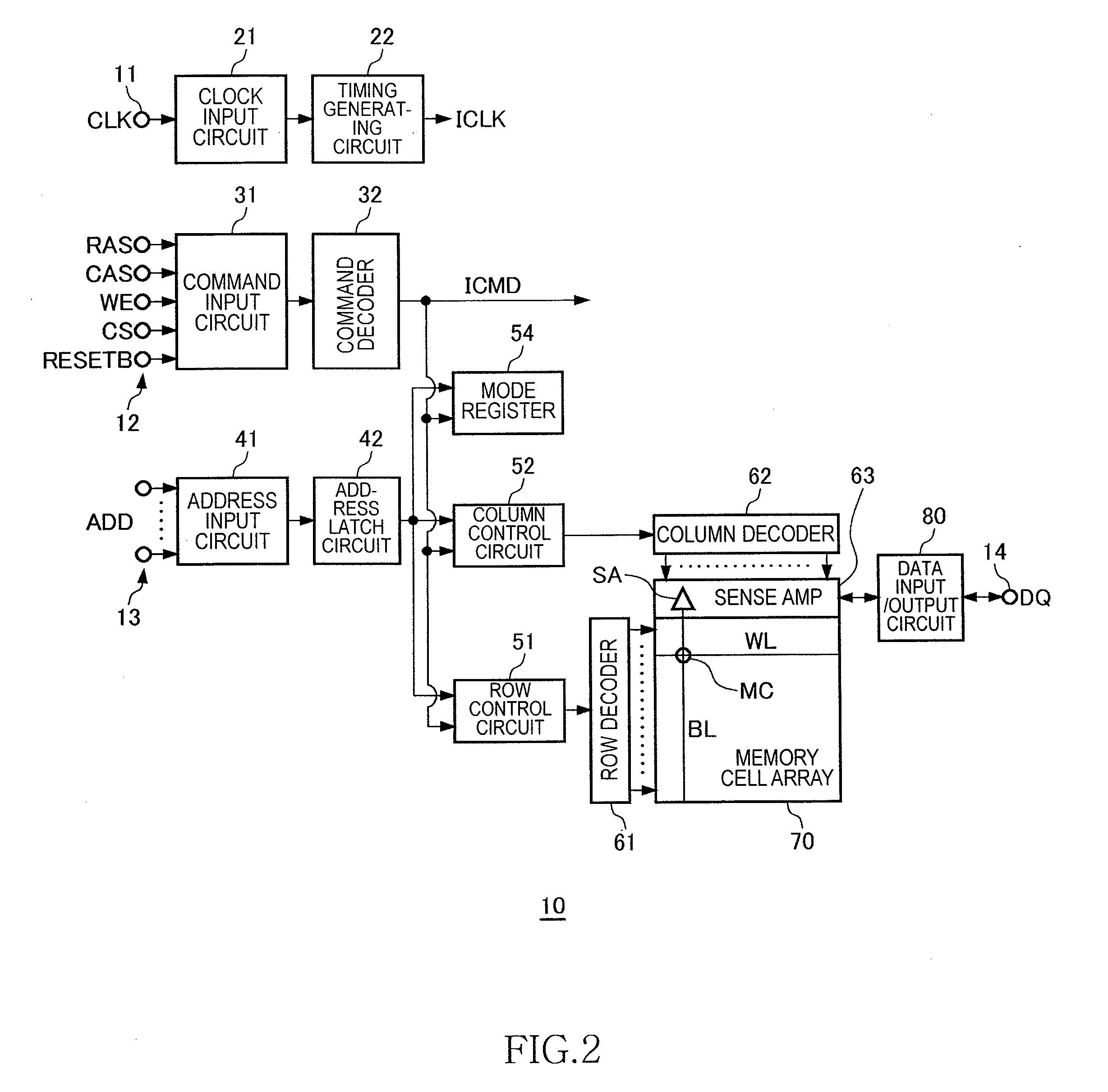

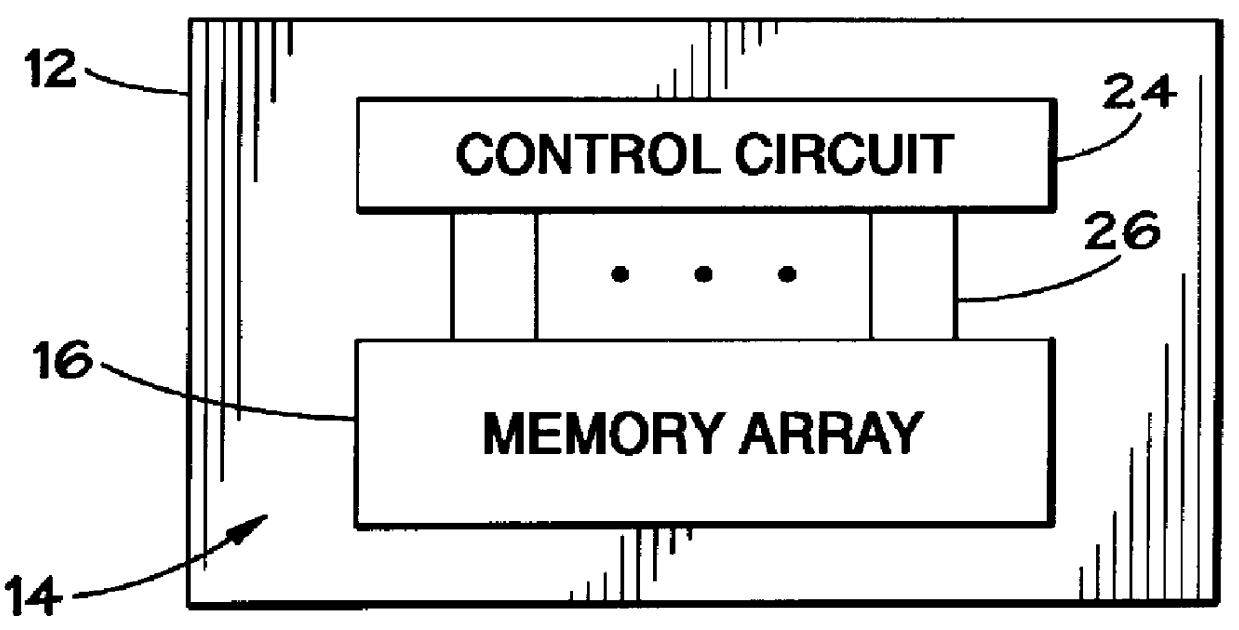

Semiconductor device having bit lines and local I/O lines

InactiveUS20120120705A1Facilitates discrimination of failureFacilitates efficient discriminationDigital storageBit lineContact failure

The present invention efficiently decides line failure and contact failure in a semiconductor device. The semiconductor device has a plurality of bit line groups in which connection with local I / O lines is controlled by the same column selection signal line. A failure detecting circuit compares a first data group read from a first bit line group and a second data group read from a second bit line group to detect whether or not connection failure (contact failure) with the column selection signal line occurs in one of the first and second bit line groups.

Owner:LONGITUDE SEMICON S A R L

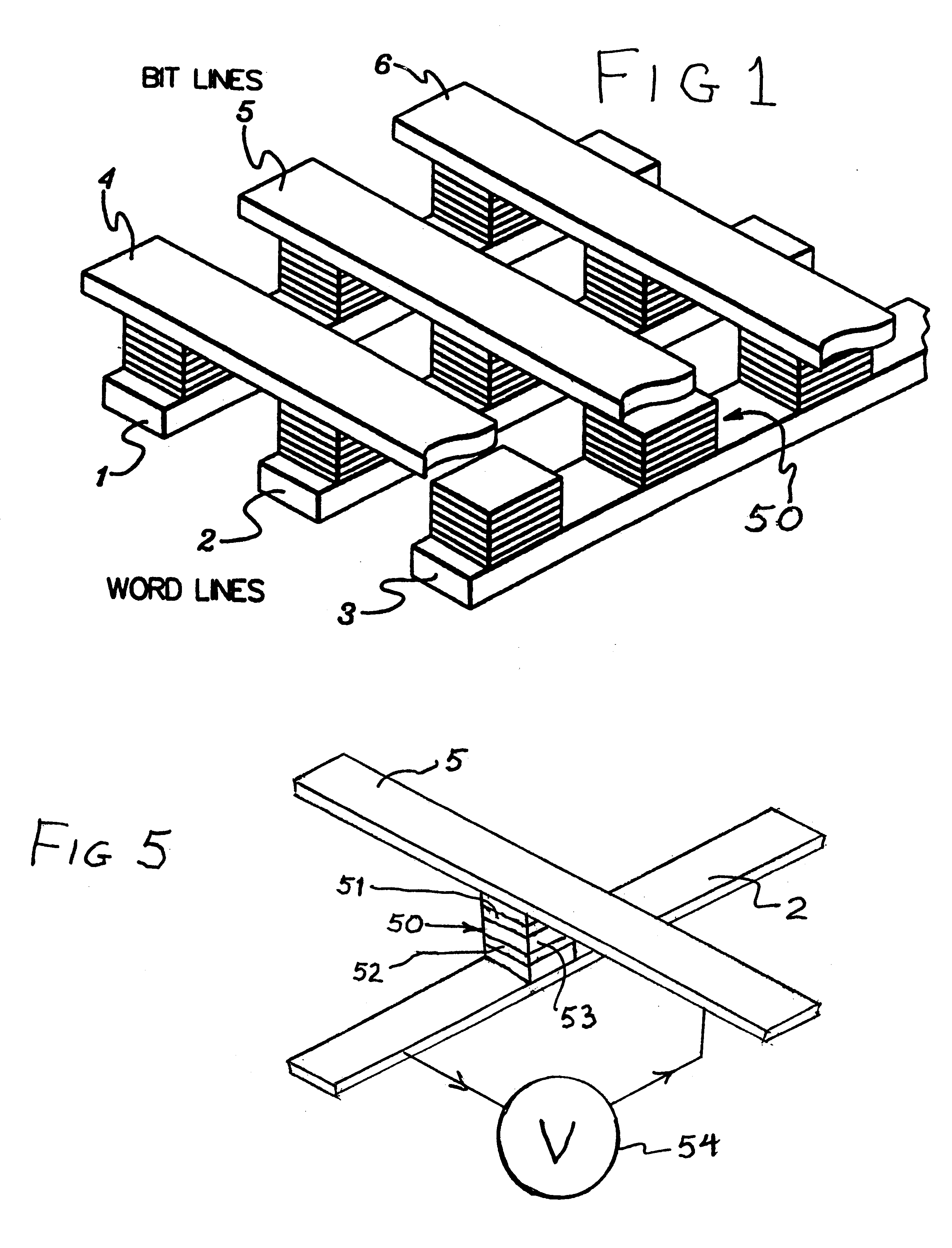

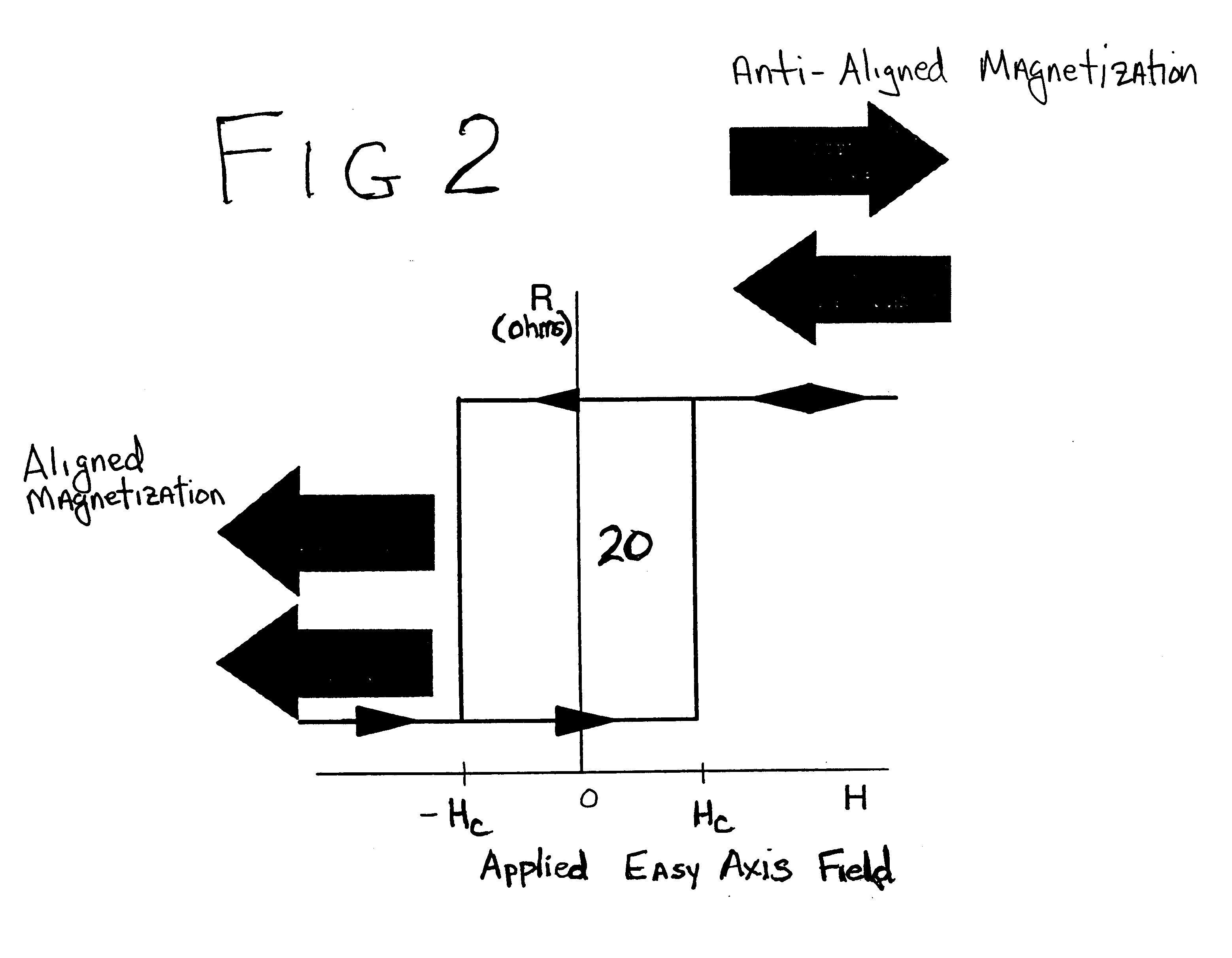

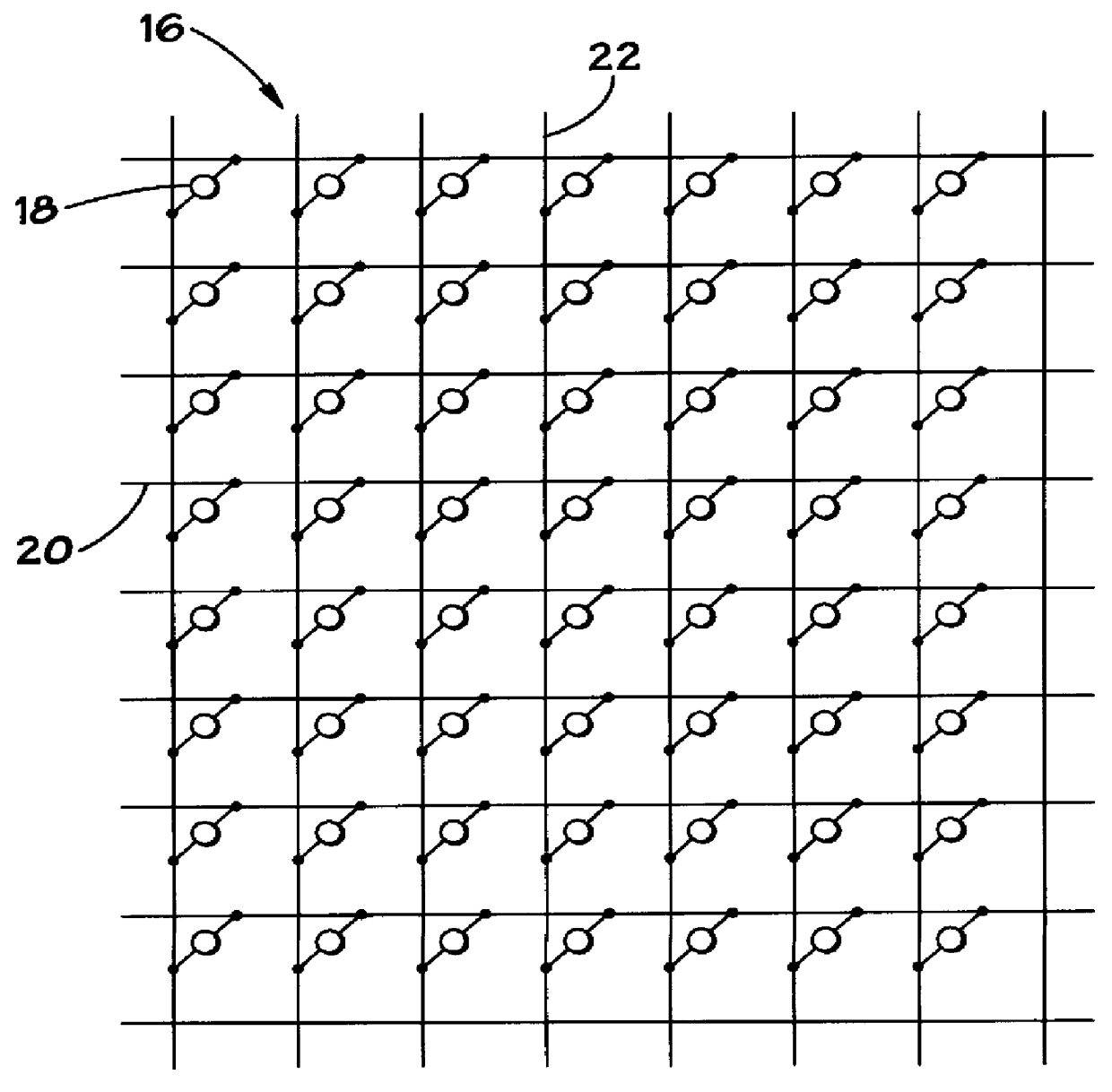

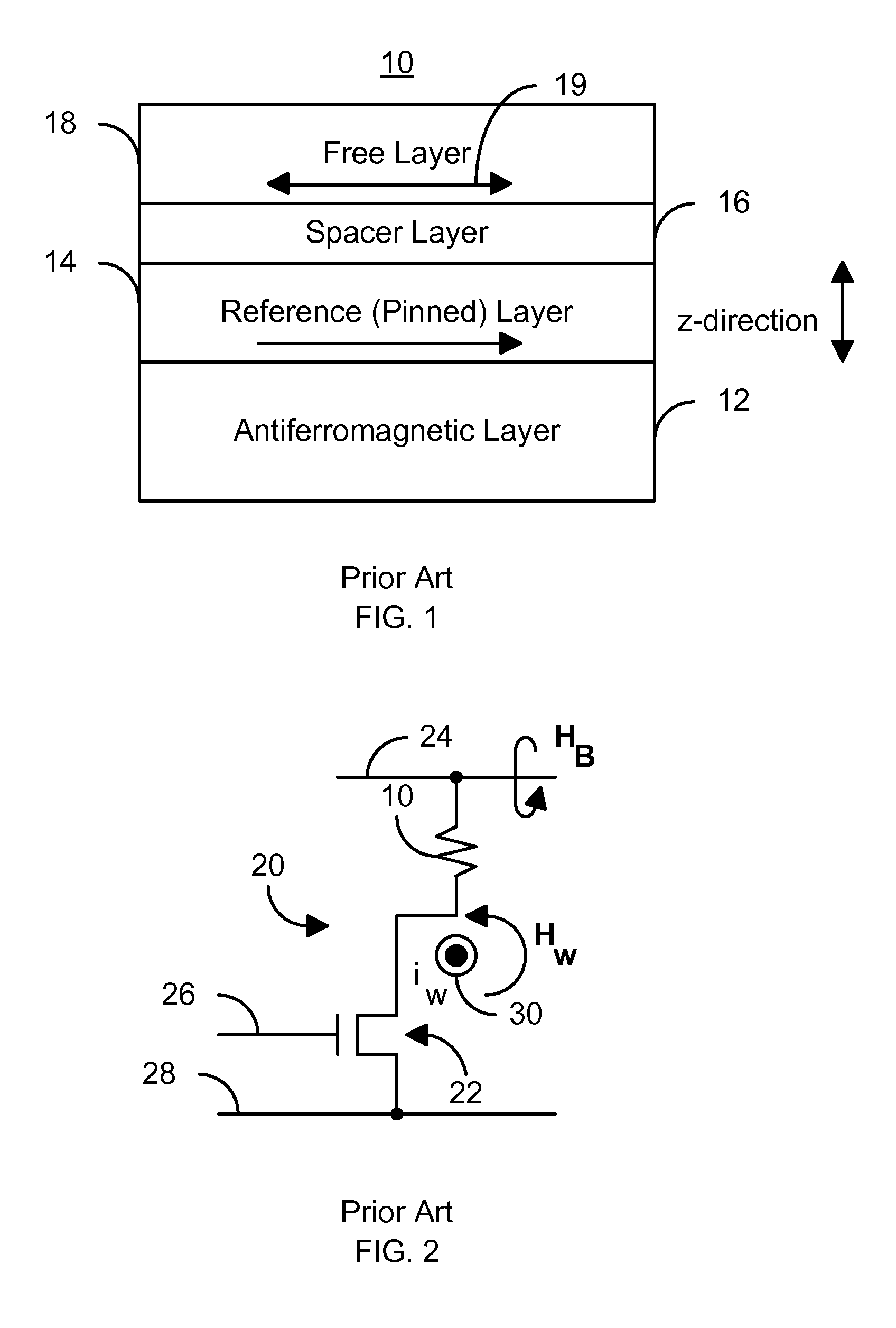

Thermally-assisted magnetic random access memory (MRAM)

It is important to ensure good selectivity of a single magnetic tunnel junction storage cell within a memory array without affecting nearby storage cells. For this purpose, this memory array of storage cells preferably comprises a) an array of electrically conducting bit lines and electrically conducting word lines which form intersections therebetween, b) a storage cell disposed at each of said intersections, each storage cell comprising at least one reversible magnetic region or layer characterized by a magnetization state which can be reversed by applying thereto a selected external magnetic field, said reversible magnetic layer comprising a material whose magnetization state is more easily reversed upon a change in the temperature thereof, and c) a temperature change generator for changing the temperature of said reversible magnetic layer of only a selected one of said array of storage cells at any moment. To select a cell, it is preferable to select a cell by using a brief pulse of tunnelling current between the intersecting bit and word lines at that cell in order to provide sufficient Joule heating to facilitate a change in the magnetization state of its reversible magnetic layer, which preferably comprises a ferrimagnetic material.

Owner:IBM CORP

Semiconductor memory device for low voltage

A semiconductor memory device includes a first cell array including a plurality of unit cells and a bit line sense amplifying unit for sensing and amplifying data signals stored in the unit cells. Each unit cell is provided with a PMOS transistor and a capacitor. Therefore, the semiconductor memory device efficiently operates with low voltage without any degradation of operation speed.

Owner:SK HYNIX INC

Compensating for coupling during programming

Shifts in the apparent charge stored on a floating gate (or other charge storing element) of a non-volatile memory cell can occur because of the coupling of an electric field based on the charge stored in adjacent floating gates (or other adjacent charge storing elements). To compensate for this coupling, the read or programming process for a given memory cell can take into account the programmed state of an adjacent memory cell. To determine whether compensation is needed, a process can be performed that includes sensing information about the programmed state of an adjacent memory cell (e.g., on an adjacent bit line or other location).

Owner:SANDISK TECH LLC

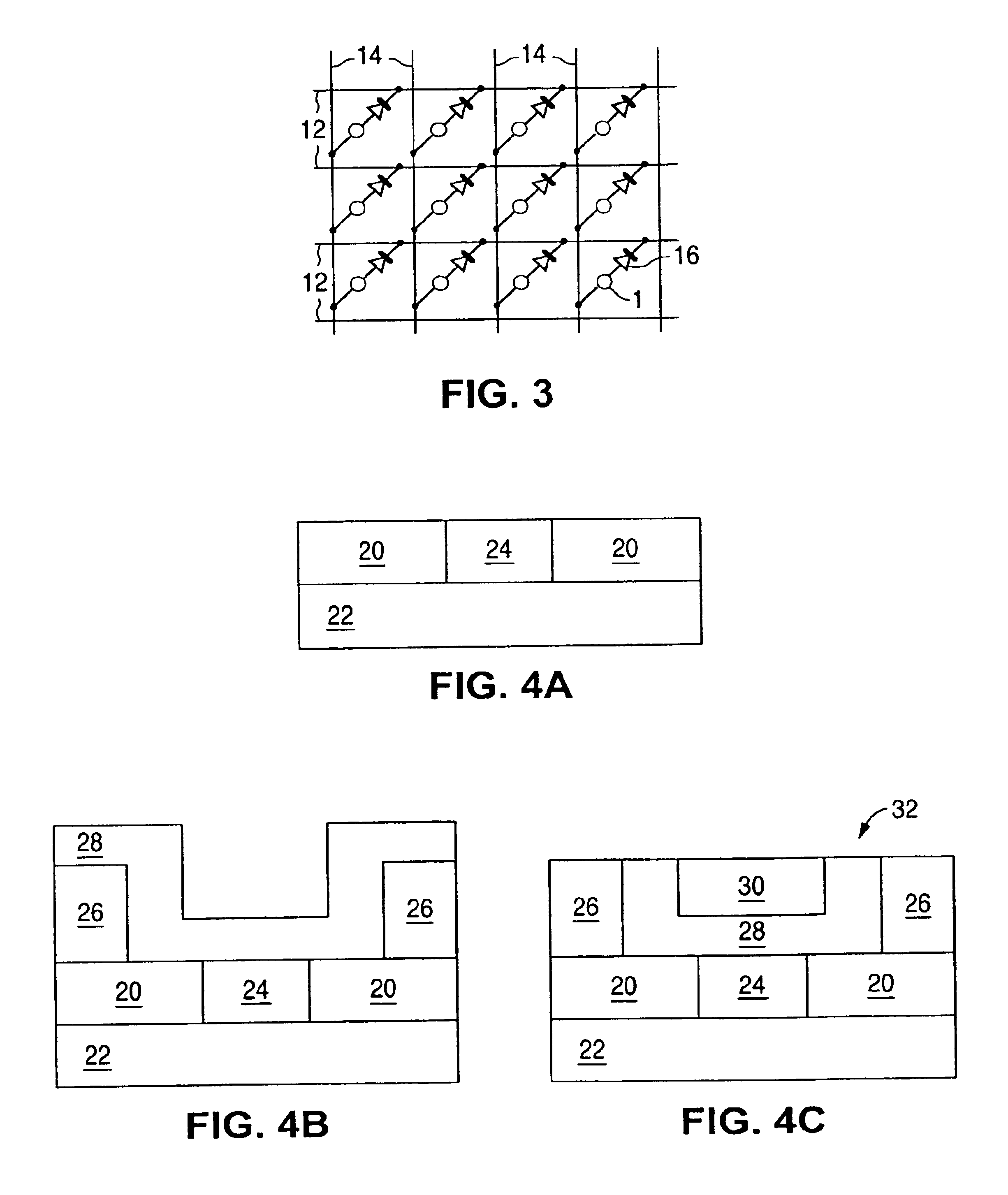

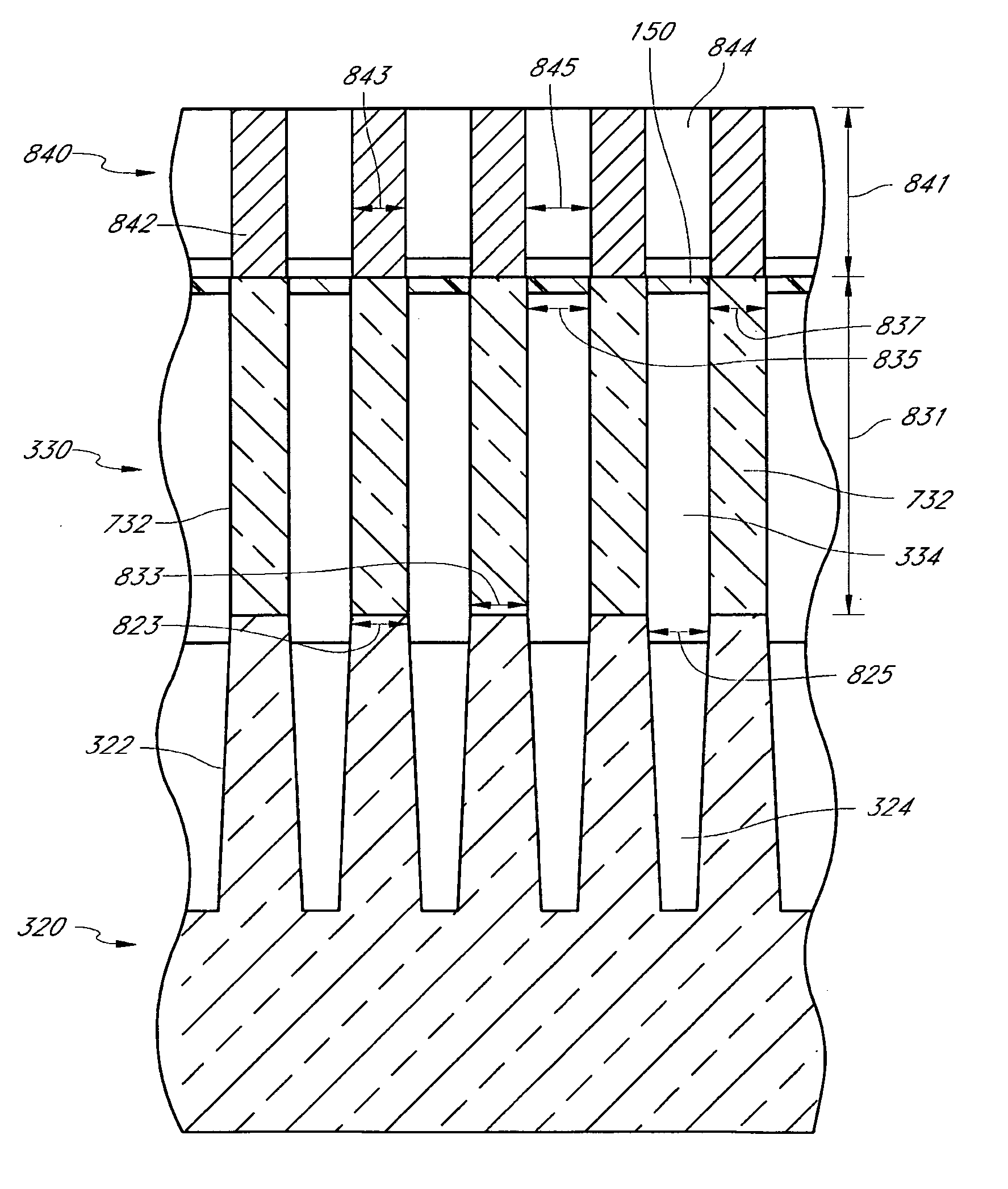

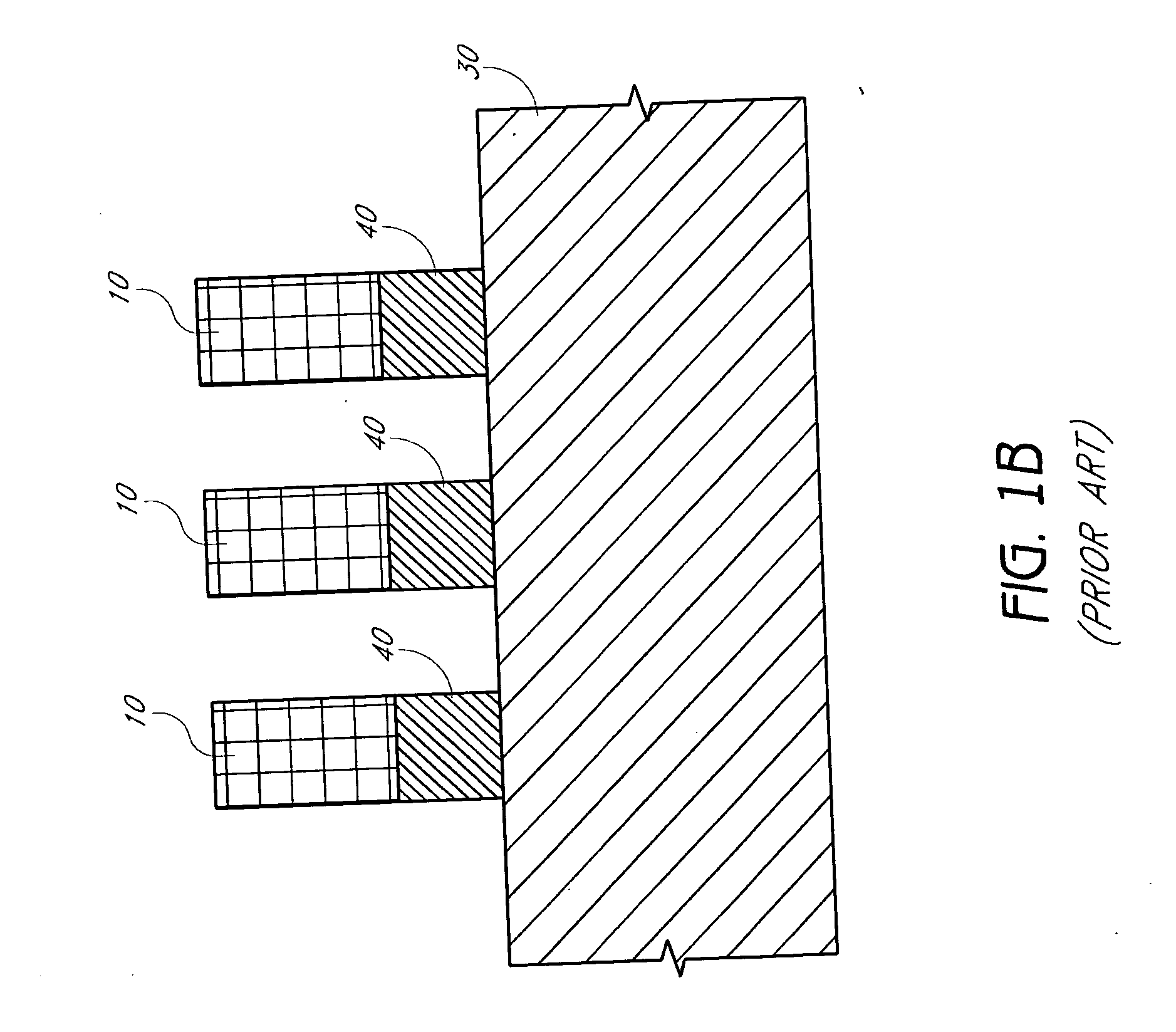

Integrated circuit memory cell having a small active area and method of forming same

InactiveUS6114713ASemiconductor/solid-state device detailsSolid-state devicesBit lineElectrical conductor

A method for manufacturing a memory device having a plurality of memory cells. Each memory cell has a non-volatile resistive memory element with a small active area. A plurality of memory cells are formed at selected locations of at least a portion of a semiconductor wafer. To form the memory cells, a lower electrode layer and a memory material layer are deposited over at least a portion of the wafer. Patterns are formed over desired contact locations of the memory material layer and etching is used to remove portions of the memory material layer. The etching step undercuts the patterns and forms memory elements having a protruding contact portion with an apex contact area. The pattern is removed, and an upper electrode is formed and electrically coupled to the contact area. Corresponding access devices and word / bit line conductor grids are provided and coupled to the memory cells.

Owner:ROUND ROCK RES LLC

Semiconductor memory device

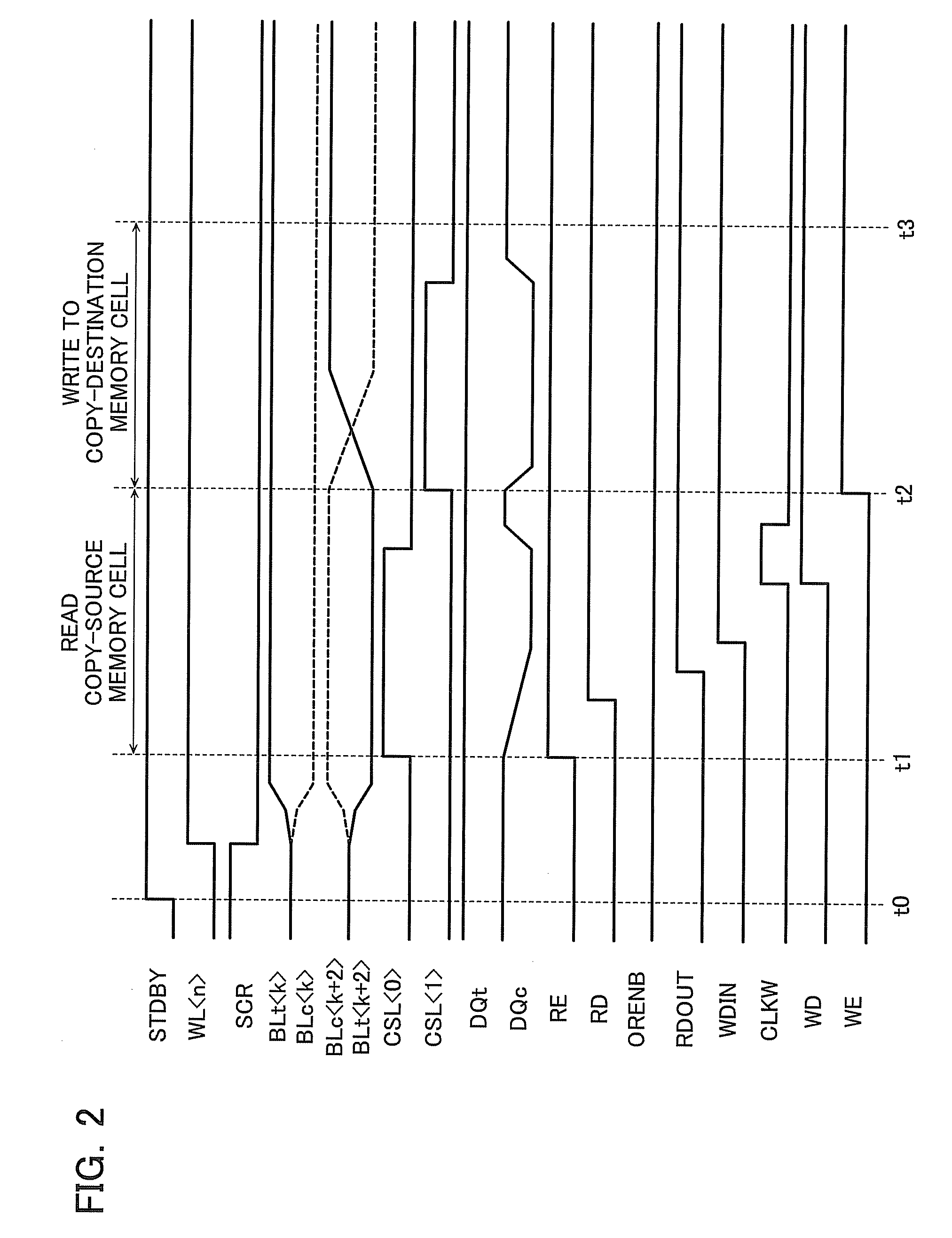

A sense amplifier circuit senses and amplifies a signal read from memory cells arranged at intersections of word-lines and bit-lines. A write circuit reads first data held in a first memory cell of the memory cells, and writes second data corresponding to the first data in a second memory cell different from the first memory cell. A data latch circuit holds data read from the first memory cell. A logic operation circuit performs a logic operation using data read from the second memory cell and data held in the data latch circuit as input values and outputs third data as an operation value. A write-back circuit writes the third data back to the first memory cell.

Owner:KIOXIA CORP

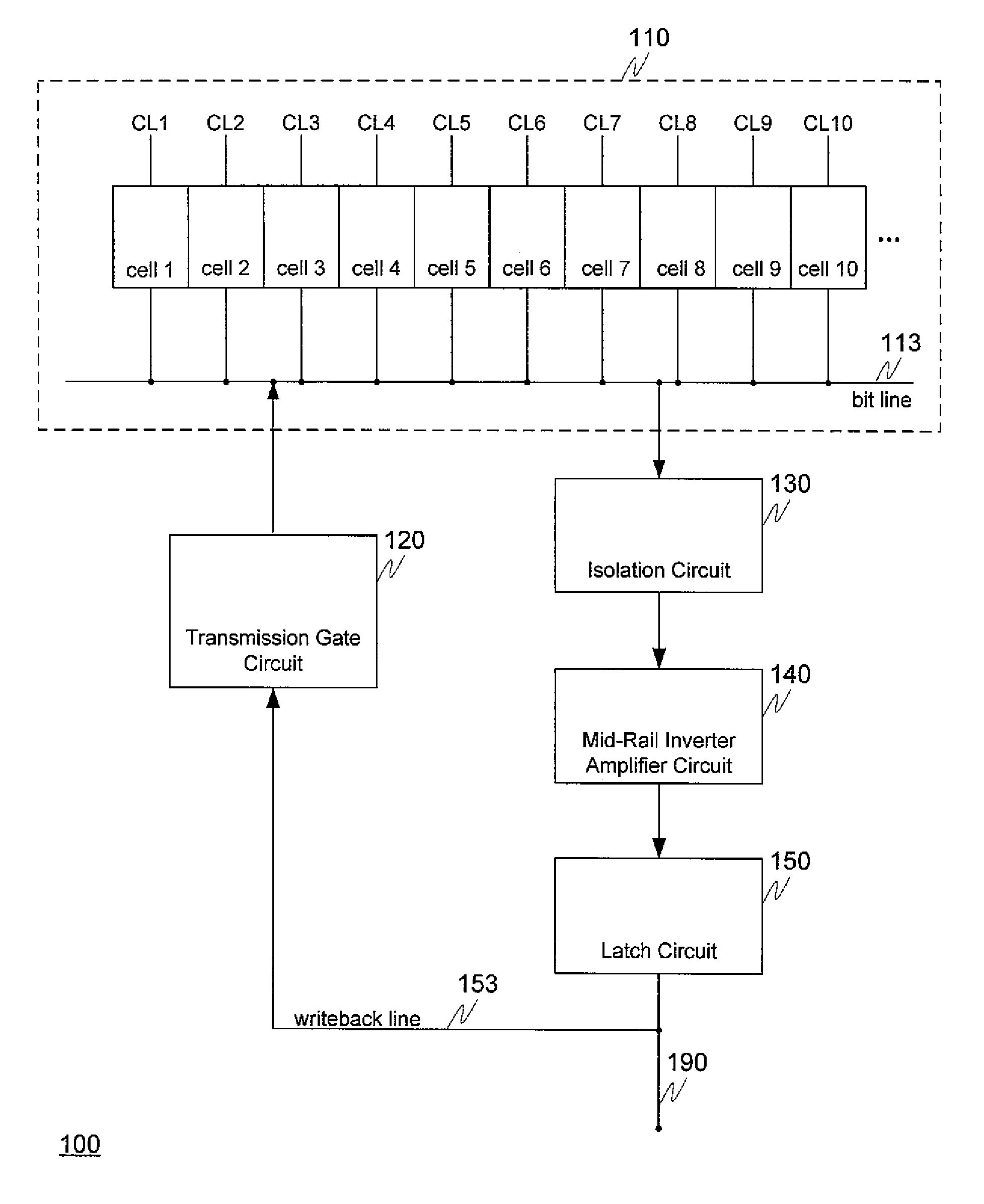

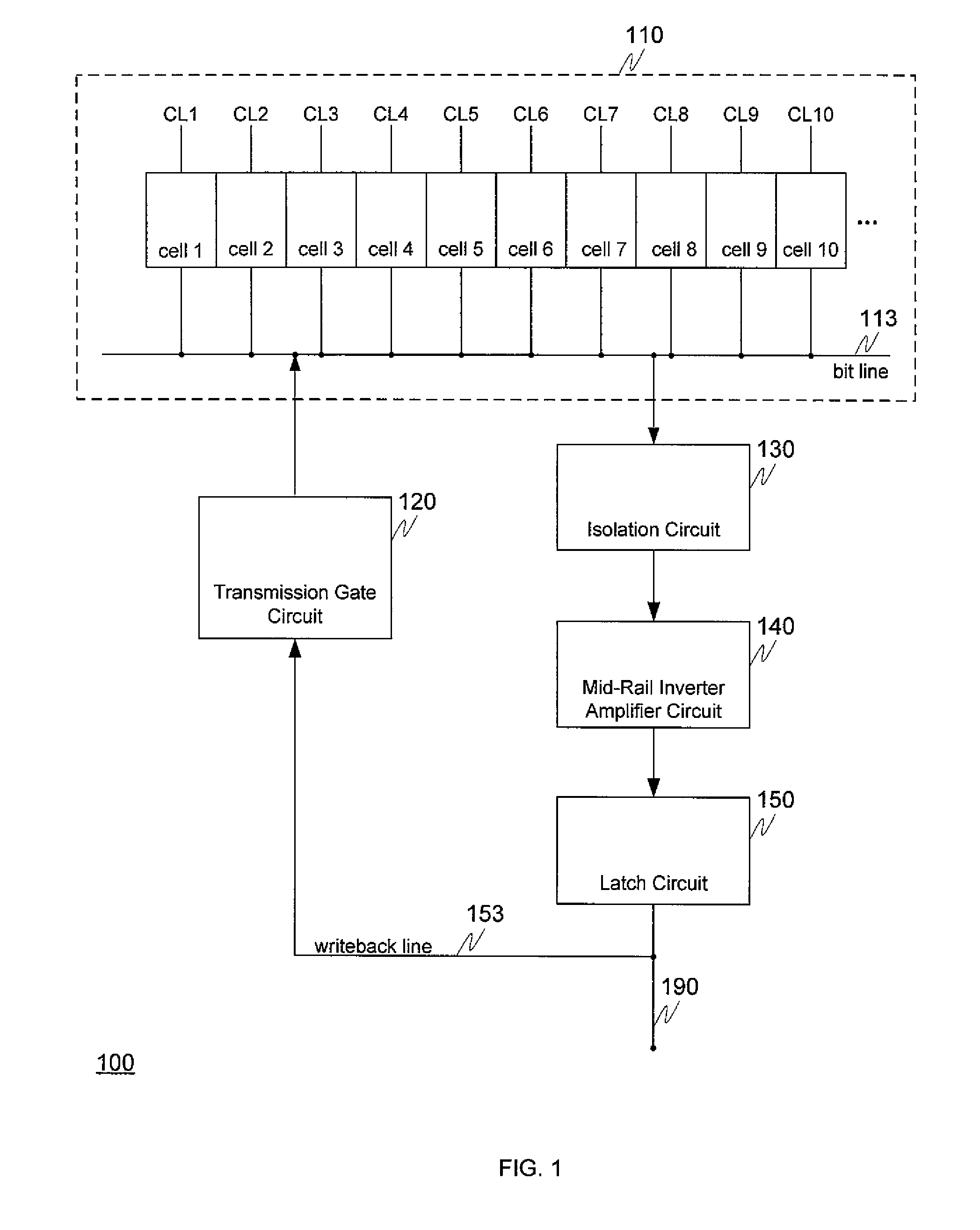

High performance eDRAM sense amplifier

Embedded dynamic random access memory (eDRAM) sense amplifier circuitry in which a bit line connected to each of a first plurality of eDRAM cells is controlled by cell control lines tied to each of the cells. During a READ operation the eDRAM cell releases its charge indicating its digital state. The digital charge propagates through the eDRAM sense amplifier circuitry to a mid-rail amplifier inverter circuit which amplifies the charge and provides it to a latch circuit. The latch circuit, in turn, inverts the charge to correctly represent at its output the logical value stored in the eDRAM cell being read, and returns the charge through the eDRAM sense amplifier circuitry to replenish the eDRAM cell.

Owner:INT BUSINESS MASCH CORP

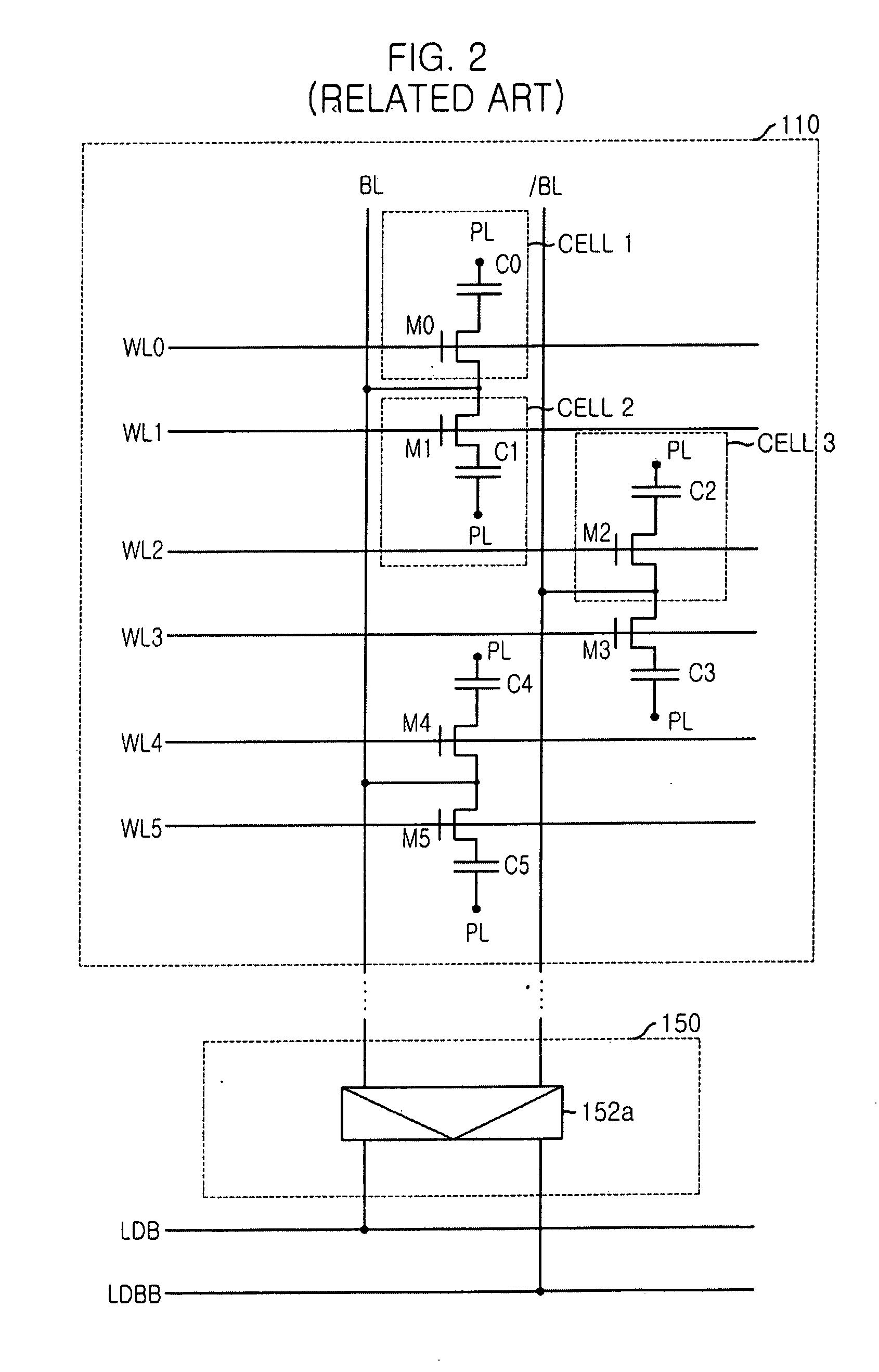

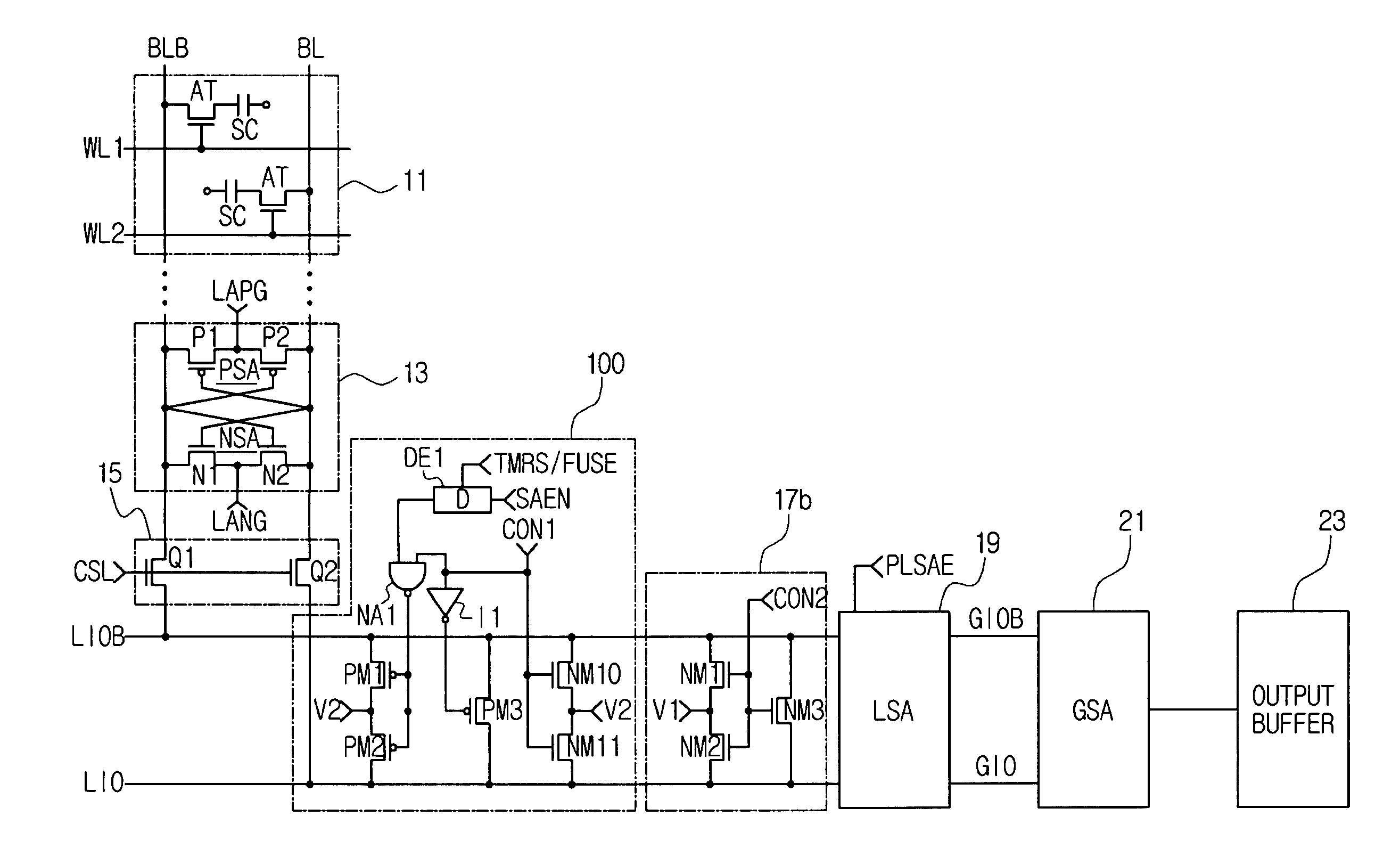

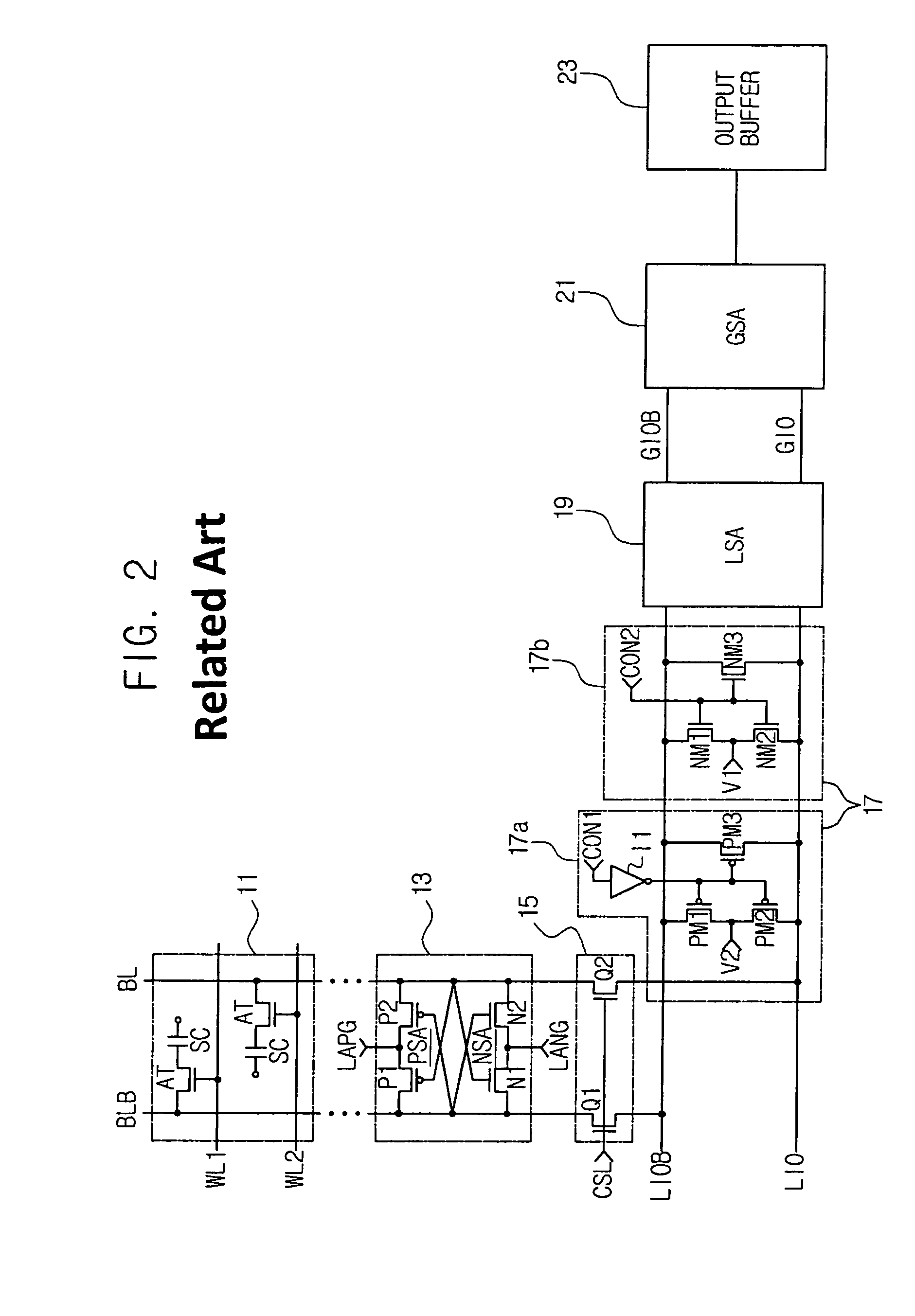

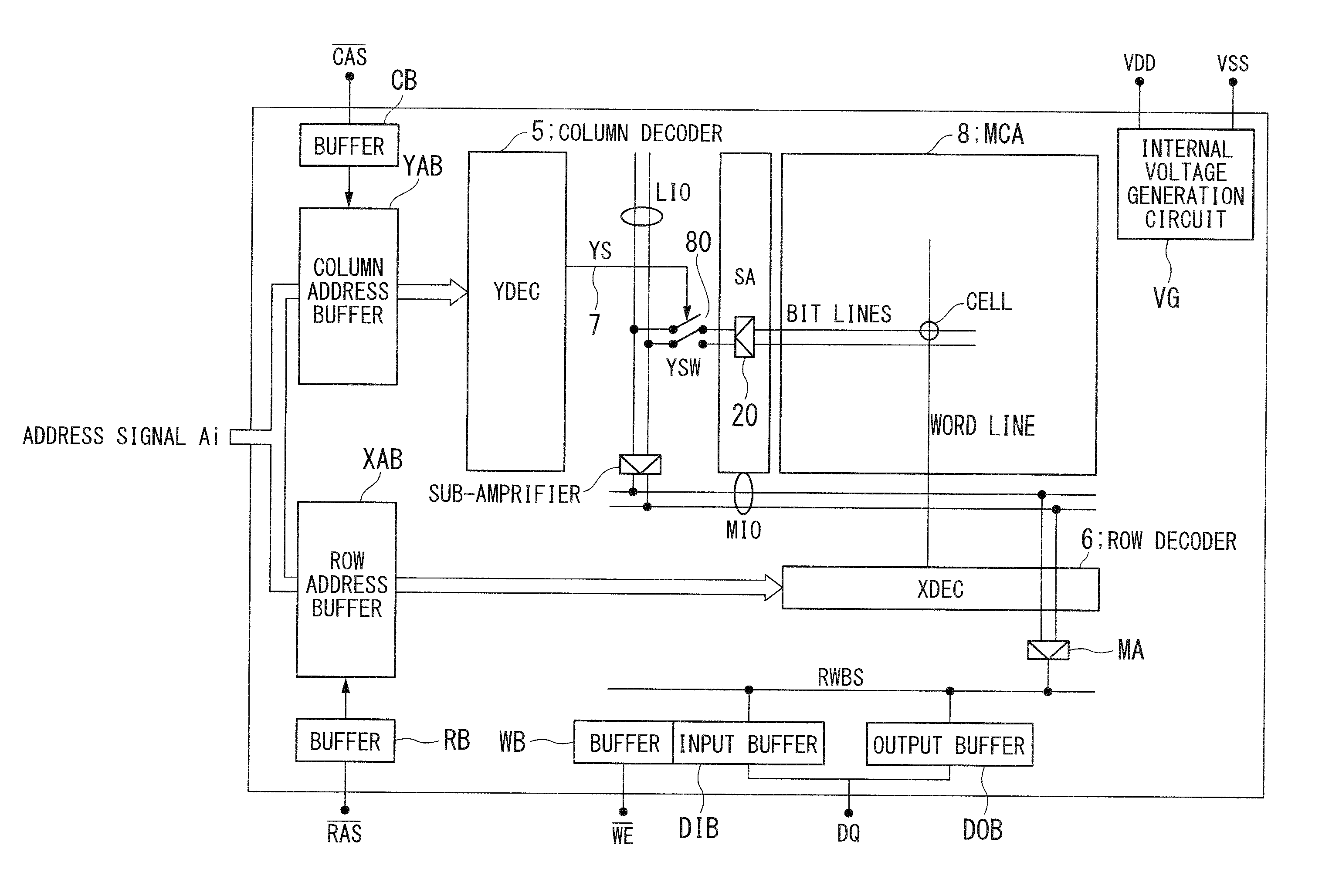

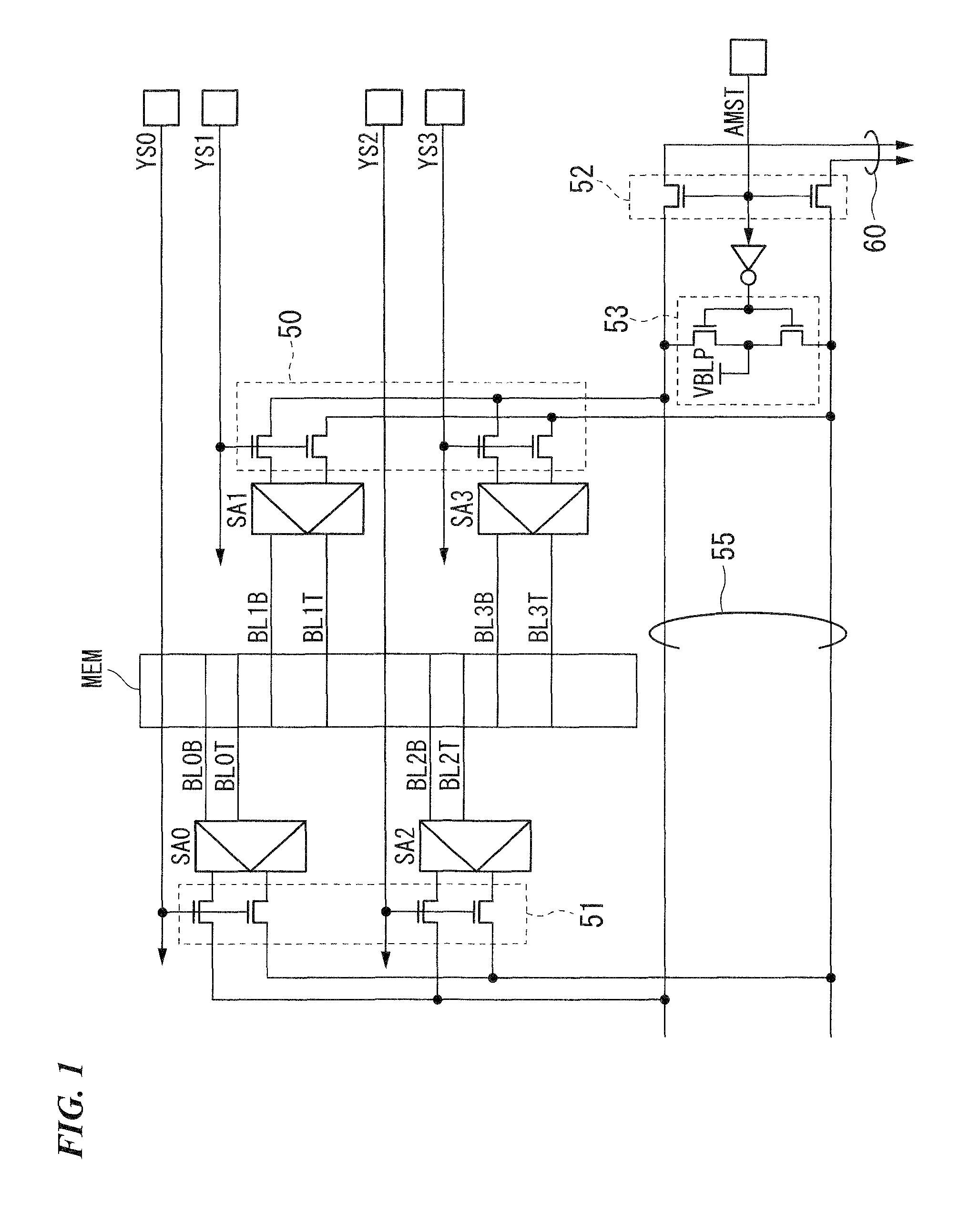

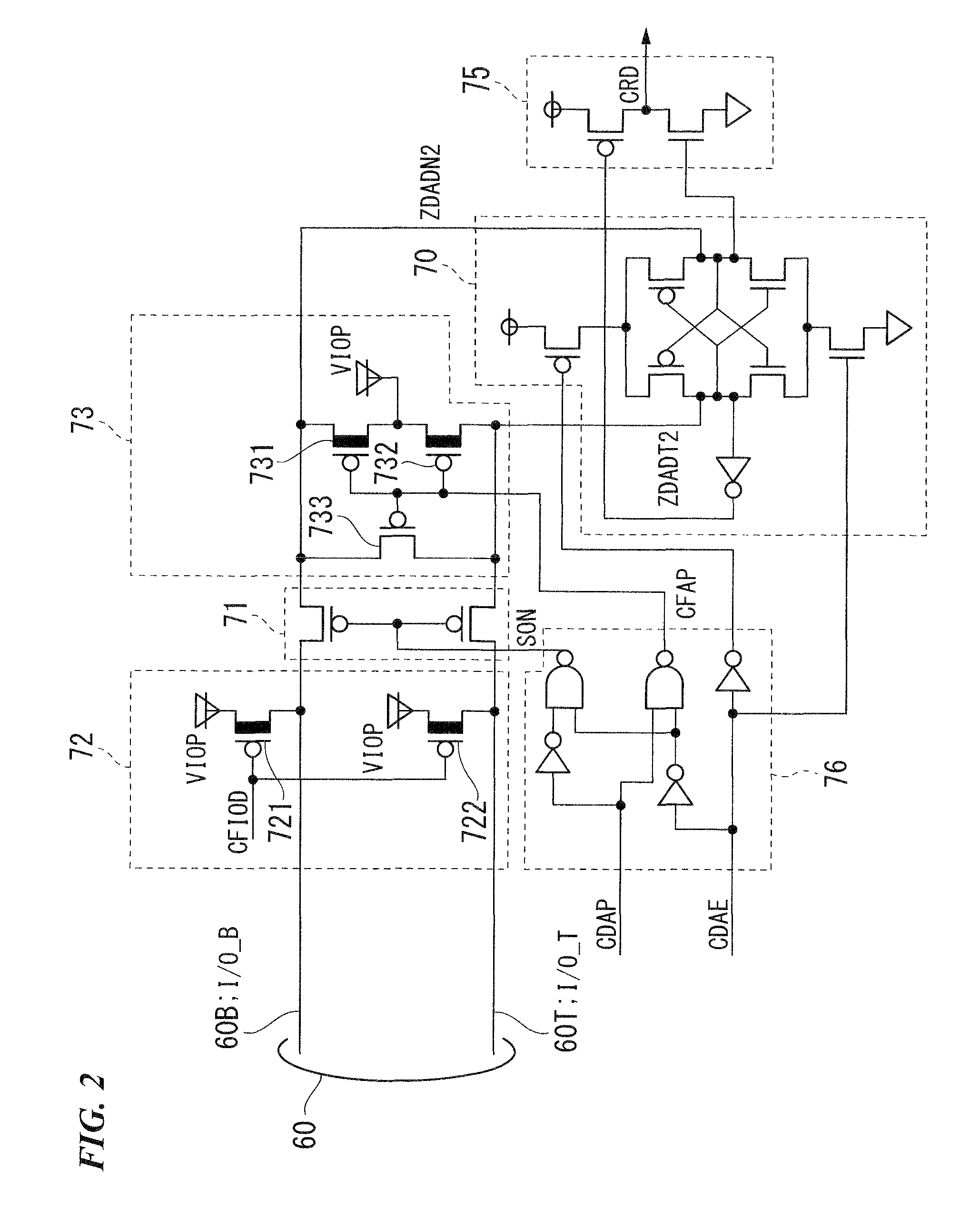

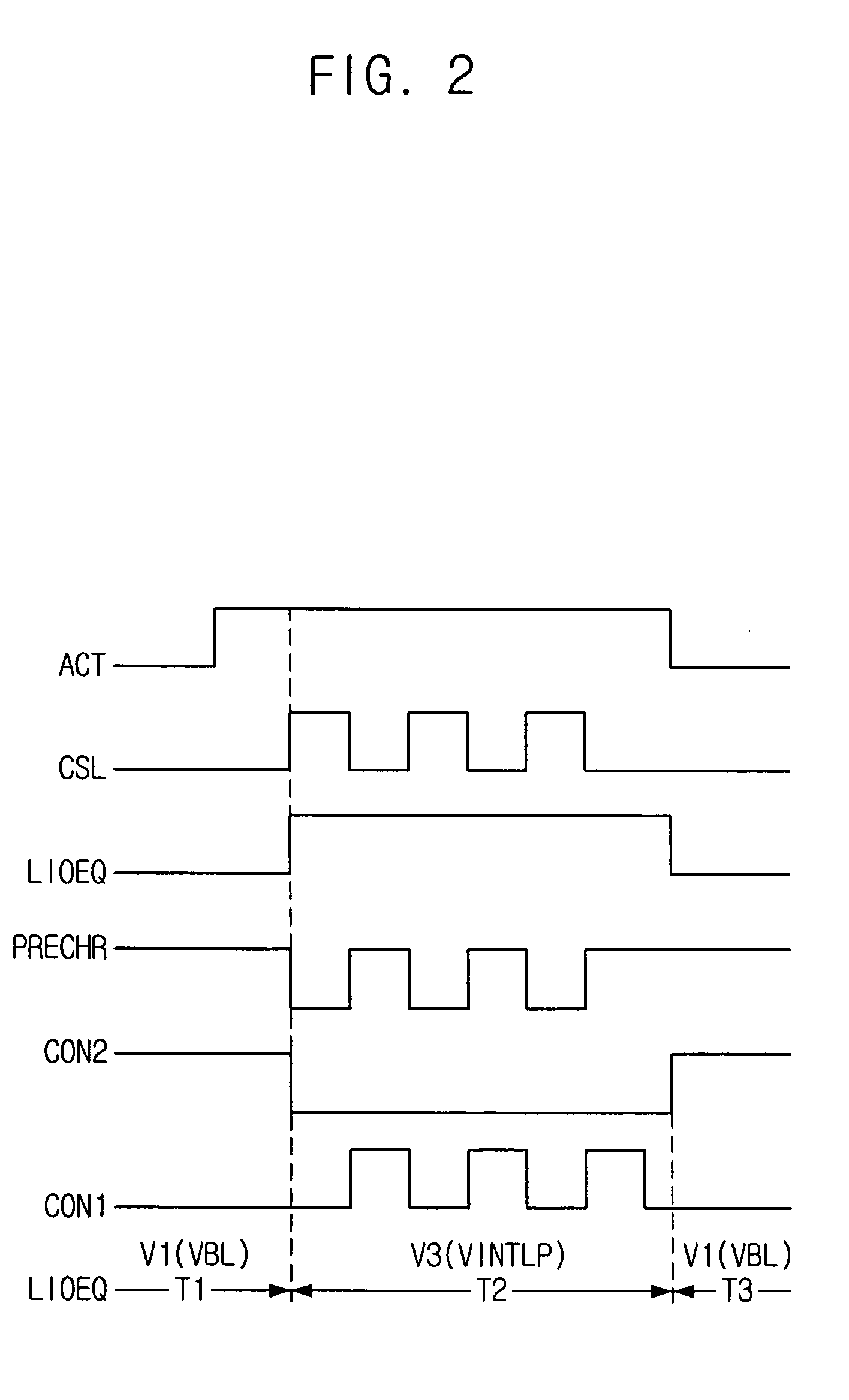

Semiconductor memory device adopting improved local input/output line precharging scheme

A semiconductor memory device capable of preventing or minimizing bit line disturbance and performing a low-voltage high-speed operation includes a read data path circuit including a bit line sense amplifier, a local input / output line sense amplifier, a column selecting unit to operationally connect bit lines connected to the bit line sense amplifier to local input / output lines connected to the local input / output line sense amplifier in response to a column selection signal, and a local input / output line precharging unit to precharge the pair of local input / output lines by a first precharging unit, equalizing the pair of local input / output lines by an equalizing unit, and to precharge the local input / output lines by a second precharging unit following an elapsed time after the bit line sense amplifier is activated, while the column selection is deactivated.

Owner:SAMSUNG ELECTRONICS CO LTD

Semiconductor device

A semiconductor device includes a column decoder that generates a column selecting signal that selects any of a plurality of bit line pairs to which memory cells are connected according to a column address that is input; a bit line selecting switch that connects by the column selecting signal any of a plurality of bit line pairs and a data I / O line pair that outputs data that has been read from a memory cell to the outside; a data amplifier that amplifies a voltage differential of a data I / O line pair and outputs data that has been read to an output buffer; a data I / O line switch that is provided in the data I / O lines; an I / O line precharge circuit that precharges a data I / O line pair that is not on the side of the data amplifier; and an amplifier precharge circuit that precharges a data I / O line pair that is on the side of the data amplifier.

Owner:LONGITUDE LICENSING LTD

Semiconductor memory device having improved local input/output line precharge scheme

ActiveUS8213248B2Preventing bit line disturbanceRun at high speedDigital storageBit lineDatapath circuits

A data path circuit of a semiconductor memory device includes: a bit line sense amplifier driven by a first power supply voltage; a local input / output line sense amplifier; a column selecting unit operatively connecting a pair of bit lines connected to the bit line sense amplifier and a pair of local input / output lines connected to the local input / output line sense amplifier in response to a column selection signal; and a local input / output line precharge unit precharging the pair of local input / output lines with a second power supply voltage different from the first power supply voltage during a period for which the column selection signal is in an inactive state.

Owner:SAMSUNG ELECTRONICS CO LTD

Memory including a performance test circuit

ActiveUS20090154273A1Easy to manufactureLimit memory consumptionElectronic circuit testingError detection/correctionBit lineTerm memory

A memory includes a plurality of memory cells each including a true data input connected to a true bit line and complementary data input connected to a complementary bit line, and two inverters connected head-to-tail firstly to the true data input and secondly to the complementary data input. The memory also includes a test circuit includes a plurality of test cells, each test cell includes a true data input connected to a complementary data input of the preceding test cell and a complementary data input connected to the true data input of the following test cell, the complementary data input of the last test cell being connected to the true data input of the first test cell, each test cell comprising a first inverter connected between the true data input and the complementary data input. The looped chain thus formed propagates a signal whose period is a function of the performance of the storage cells.

Owner:STMICROELECTRONICS SRL

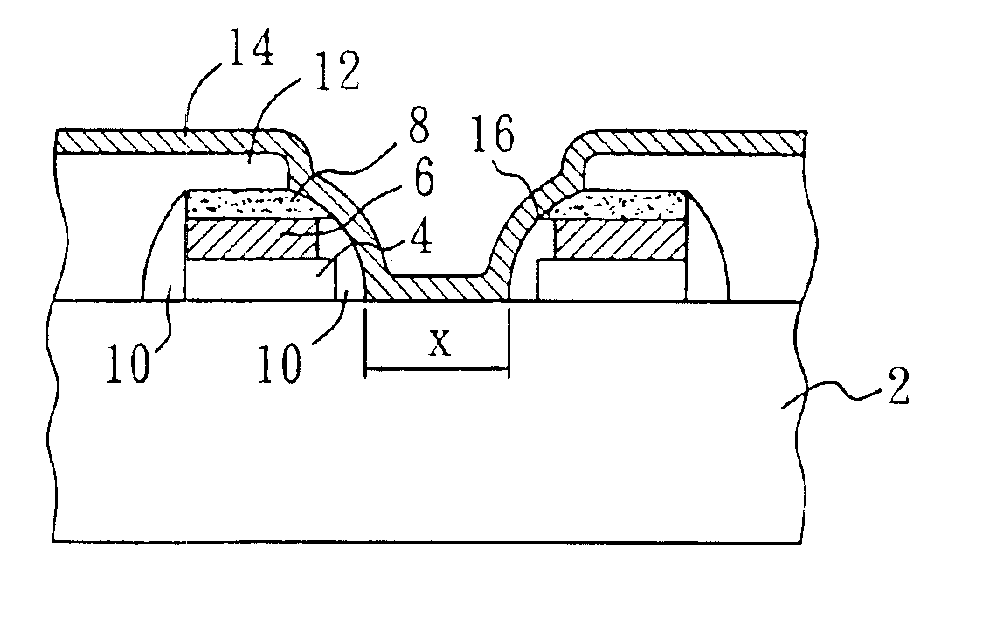

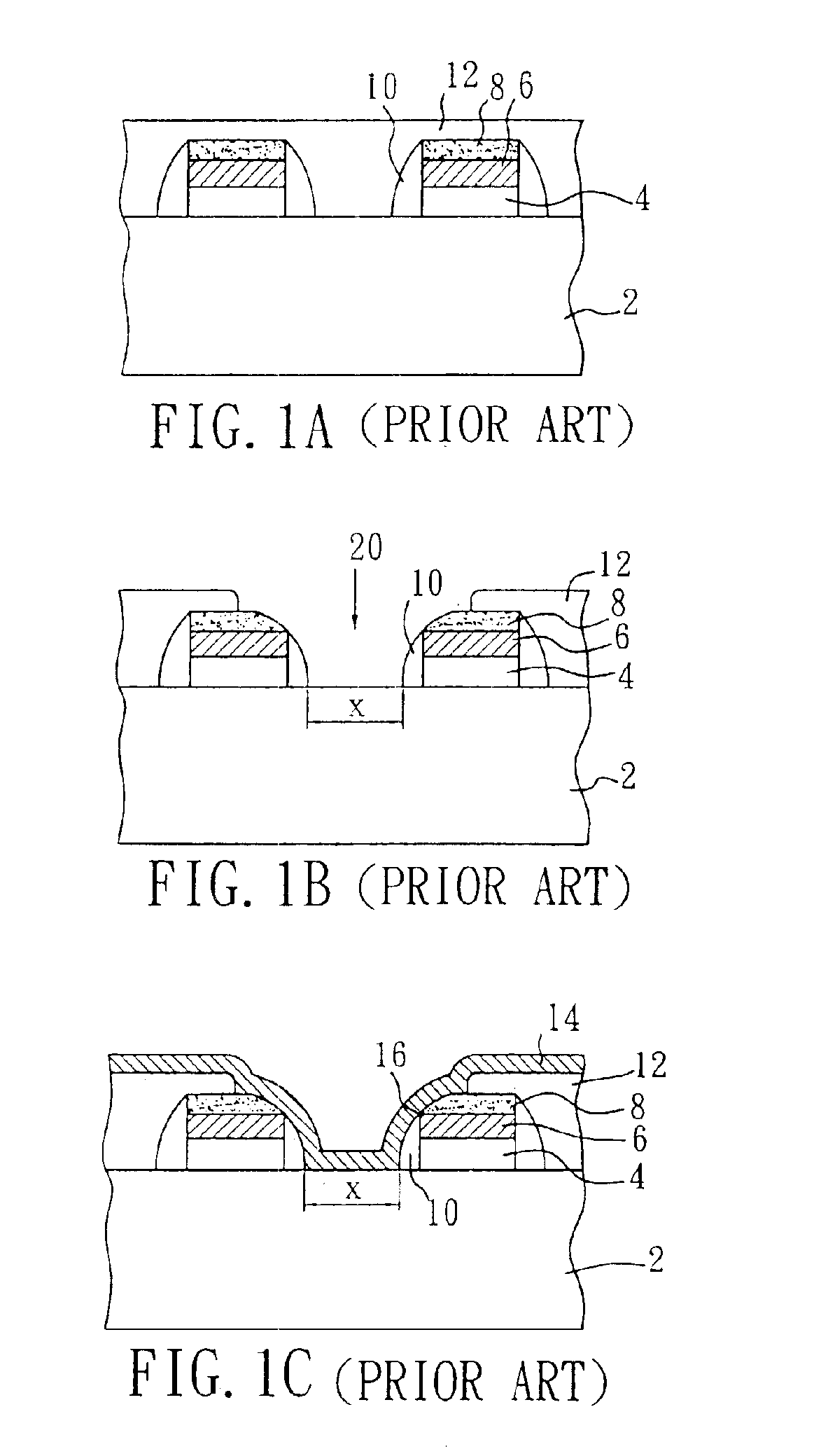

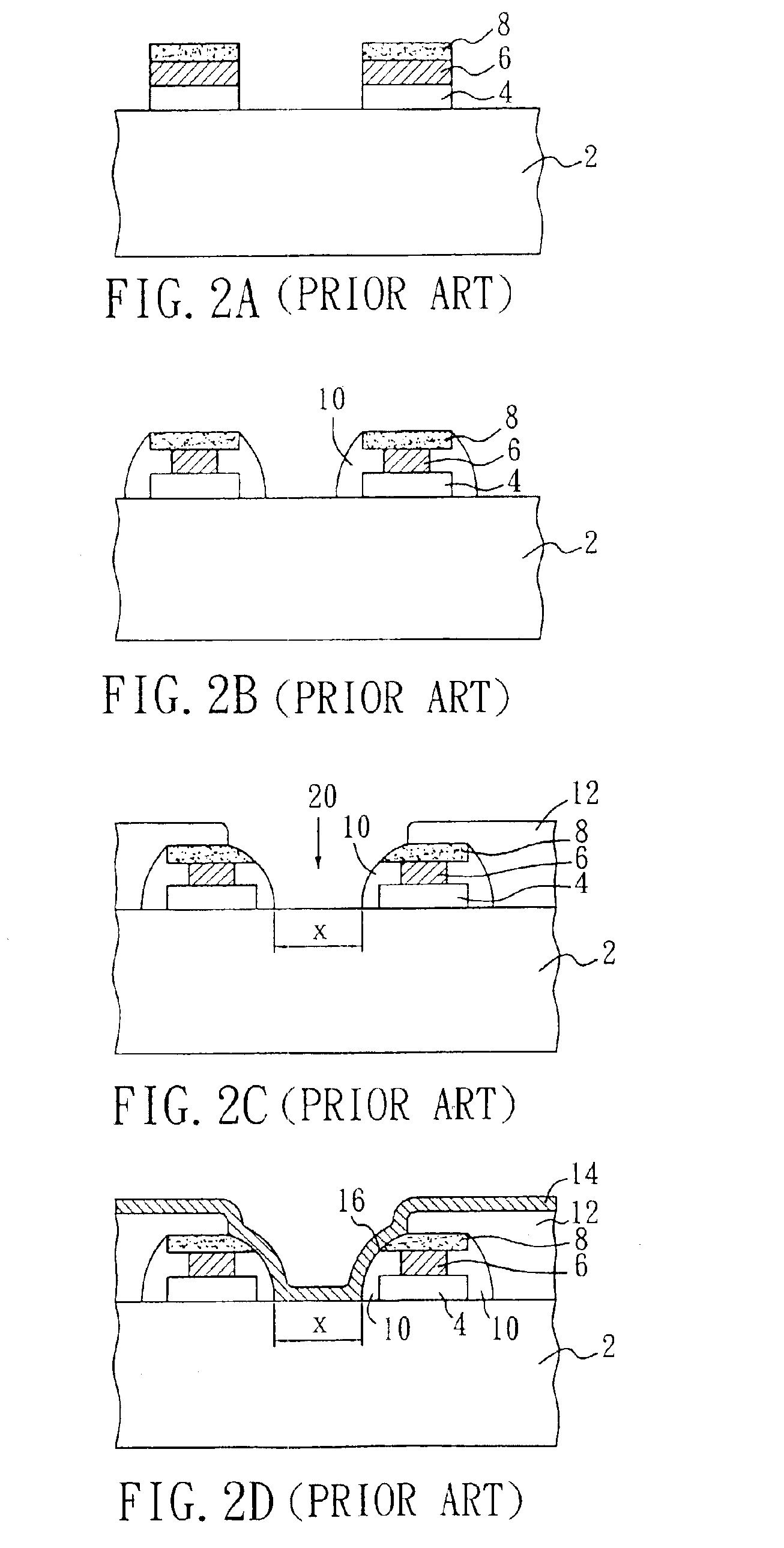

Method of forming self-aligned contact structure with locally etched gate conductive layer

InactiveUS6855610B2Reduce resistanceLarge processing windowSemiconductor/solid-state device detailsSolid-state devicesBit lineDielectric layer

A method of forming a self-aligned contact structure with a locally etched conductive layer comprises the steps of: preparing a substrate formed with gate structures comprising a first conductive layer, a second conductive layer, and an insulating layer; depositing a photoresist material layer on the substrate; performing a lithographic step with a bit-line contact node photomask or a bit-line contact photomask to expose a portion of the surface of the substrate; etching the exposed second conductive layer with an etchant; removing the remaining photoresist material layer; forming a sidewall spacer on the sidewalls of each gate structure; forming a dielectric layer to cover the substrate; and performing lithographic and etching steps to remove the dielectric layer and to form self-aligned contact structure.

Owner:PROMOS TECH INC

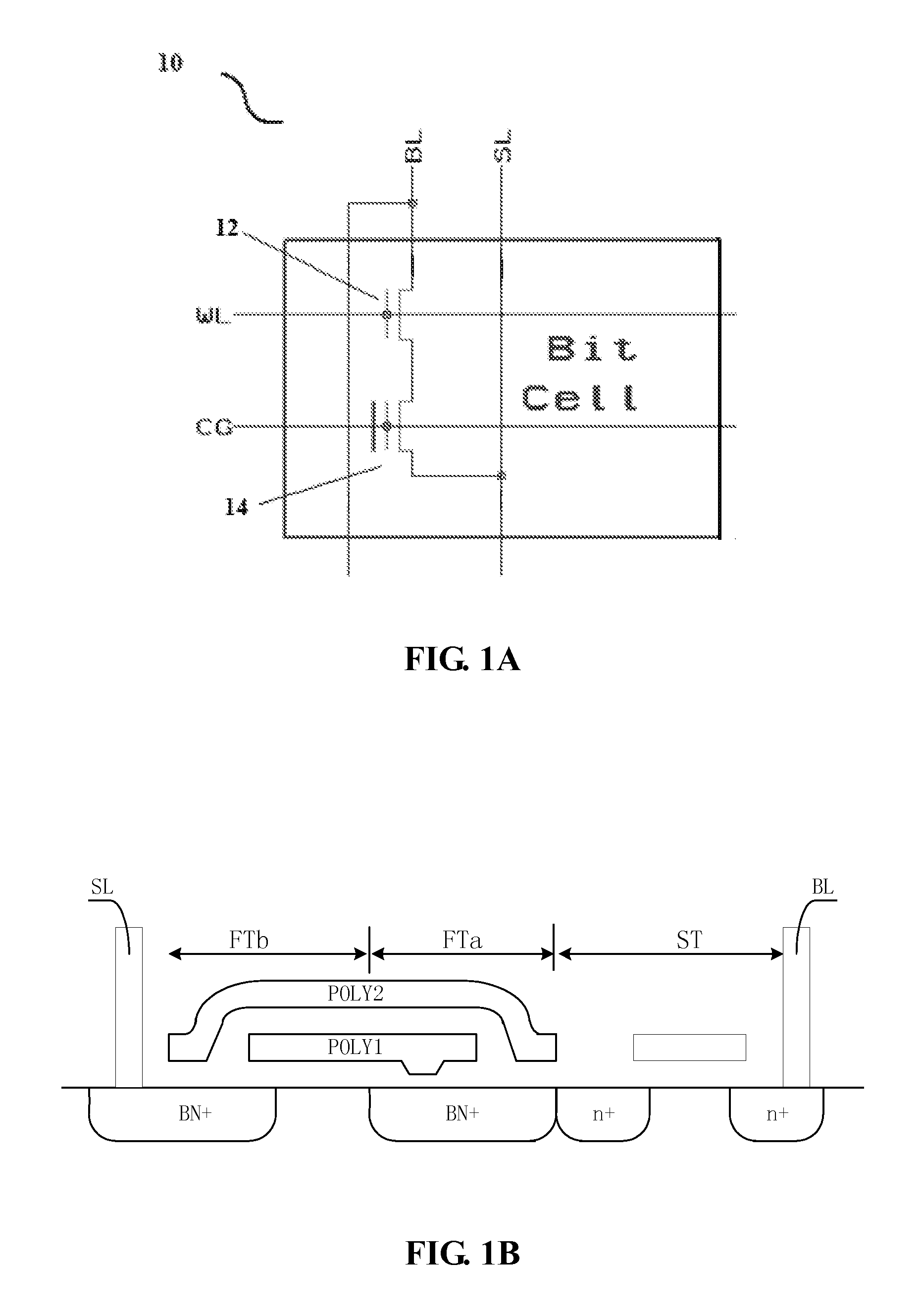

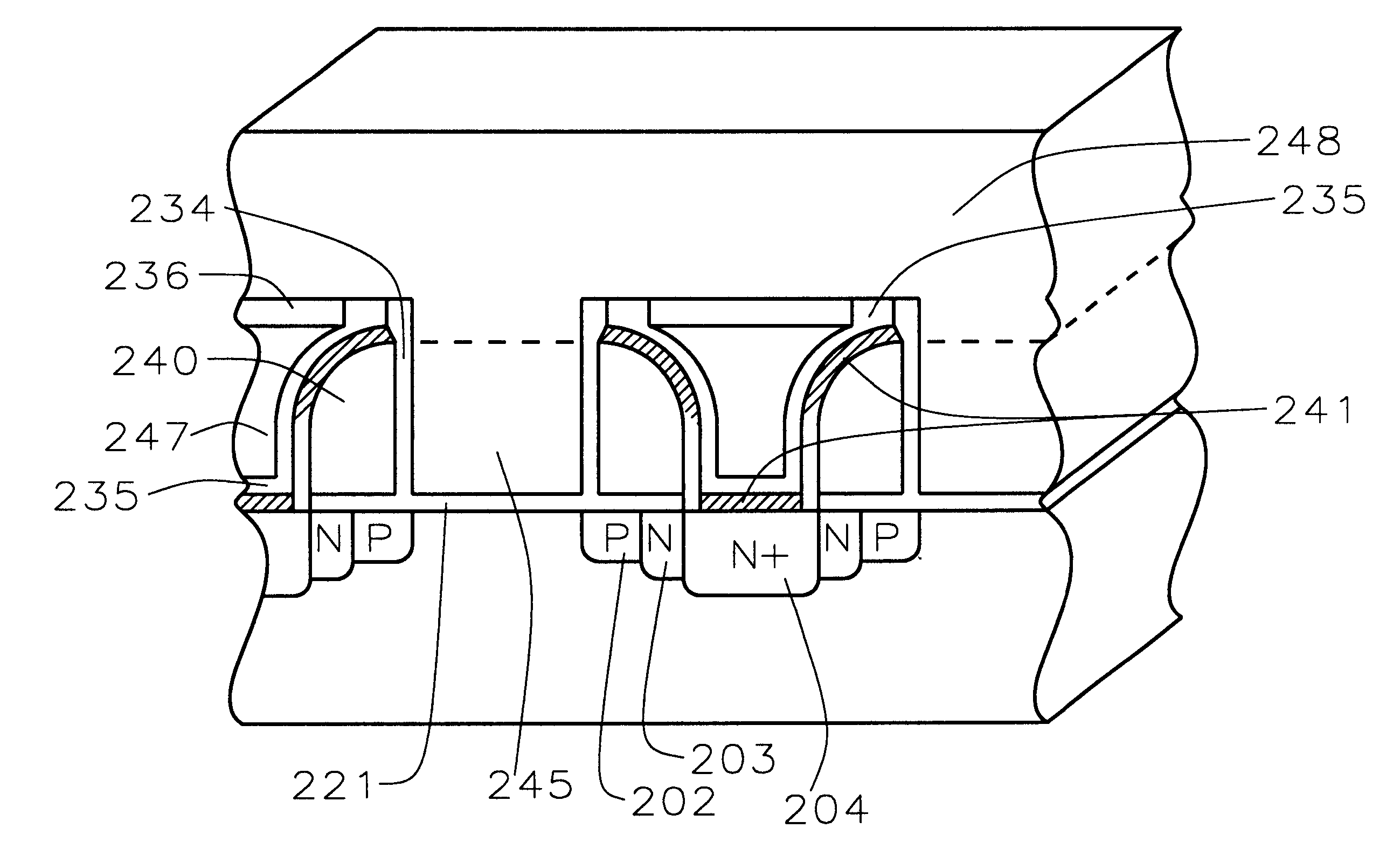

Process for making and programming and operating a dual-bit multi-level ballistic MONOS memory

A fast low voltage ballistic program, ultra-short channel, ultra-high density, dual-bit multi-level flash memory is described with a two or three polysilicon split gate side wall process. The structure and operation of this invention is enabled by a twin MONOS cell structure having an ultra-short control gate channel of less than 40nm, with ballistic injection which provides high electron injection efficiency and very fast program at low program voltages of 3~5V. The cell structure is realized by (i) placing side wall control gates over a composite of Oxide-Nitride-Oxide (ONO) on both sides of the word gate, and (ii) forming the control gates and bit diffusion by self-alignment and sharing the control gates and bit diffusions between memory cells for high density. Key elements used in this process are: 1) Disposable side wall process to fabricate the ultra short channel and the side wall control gate with or without a step structure, and 2) Self-aligned definition of the control gate over the storage nitride and the bit line diffusion, which also runs in the same direction as the control gate. The features of fast program, low voltage, ultra-high density, dual-bit, multi-level MONOS NVRAM of the present invention include: 1) Electron memory storage in nitride regions within an ONO layer underlying the control gates, 2) high density dual-bit cell in which there are two nitride memory storage elements per cell, 3) high density dual-bit cell can store multi-levels in each of the nitride regions, 4) low current program controlled by the word gate and control gate, 5) fast, low voltage program by ballistic injection utilizing the controllable ultra-short channel MONOS, and 6) side wall control poly gates to program and read multi-levels while masking out memory storage state effects of the unselected adjacent nitride regions and memory cells. The ballistic MONOS memory cell is arranged in the following array: each memory cell contains two nitride regions for one word gate, and ½ a source diffusion and ½ a bit diffusion. Control gates can be defined separately or shared together over the same diffusion. Diffusions are shared between cells and run in parallel to the side wall control gates, and perpendicular to the word line.

Owner:HALO LSI INC

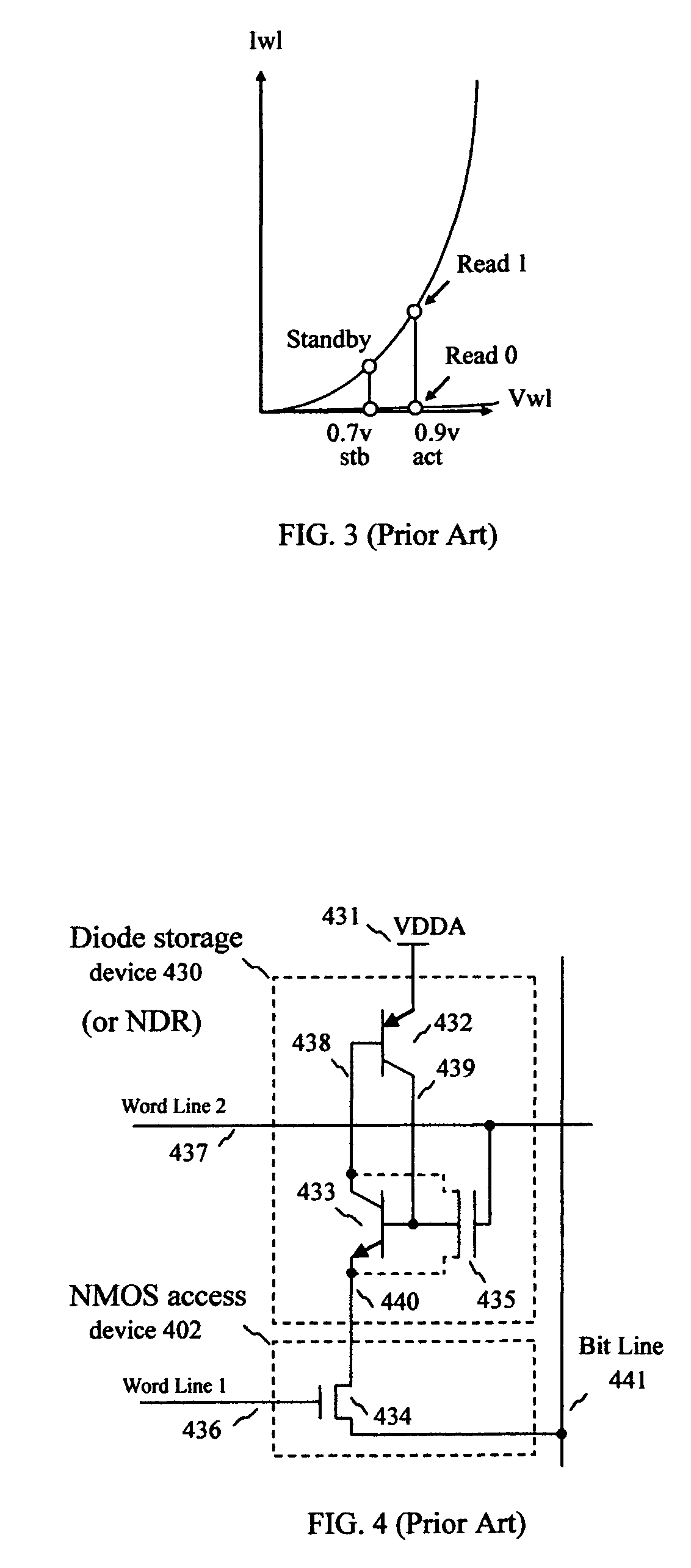

Memory sensing circuit and method for low voltage operation

InactiveUS7046568B2Large capacityImprove performanceRead-only memoriesDigital storageBit lineAudio power amplifier

A sensing module operates with a sense amplifier sensing a conduction current of a memory cell via a coupled bit line under constant voltage condition in order to minimize bit-line to bit-line coupling. The rate of discharge of a dedicated capacitor as measured by a change in the voltage drop there across in a predetermined period is used to indicate the magnitude of the conduction current. The voltage cannot drop below a minimum level imposed by a circuit for maintaining the constant voltage condition on the bit line. A voltage shifter is used to boost the voltage during the discharge and to unboost the voltage after the discharge, so that the change in voltage drop properly reflects the rate of discharge without running into the minimum level.

Owner:SANDISK TECH LLC

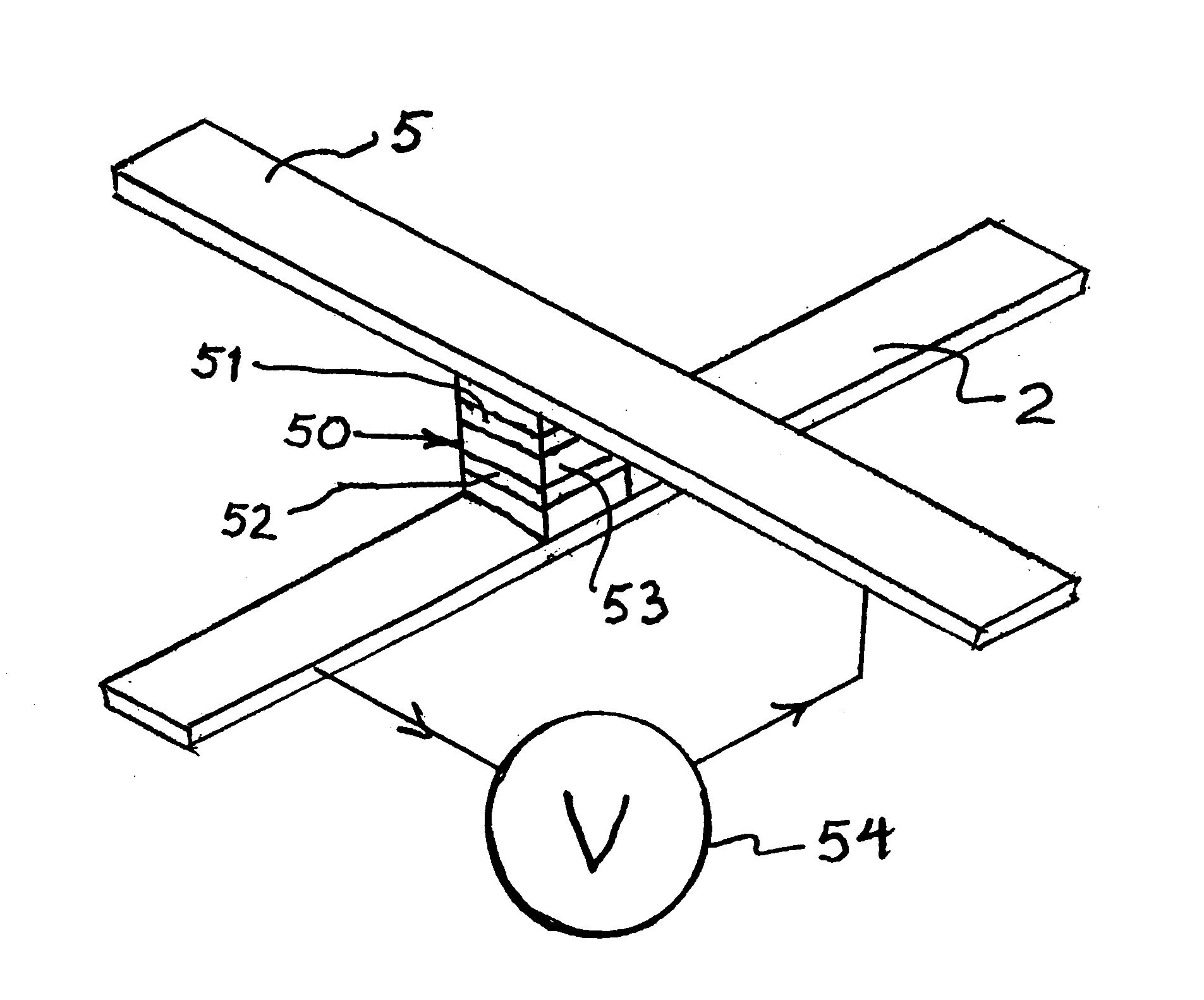

Memory device and method of operating same

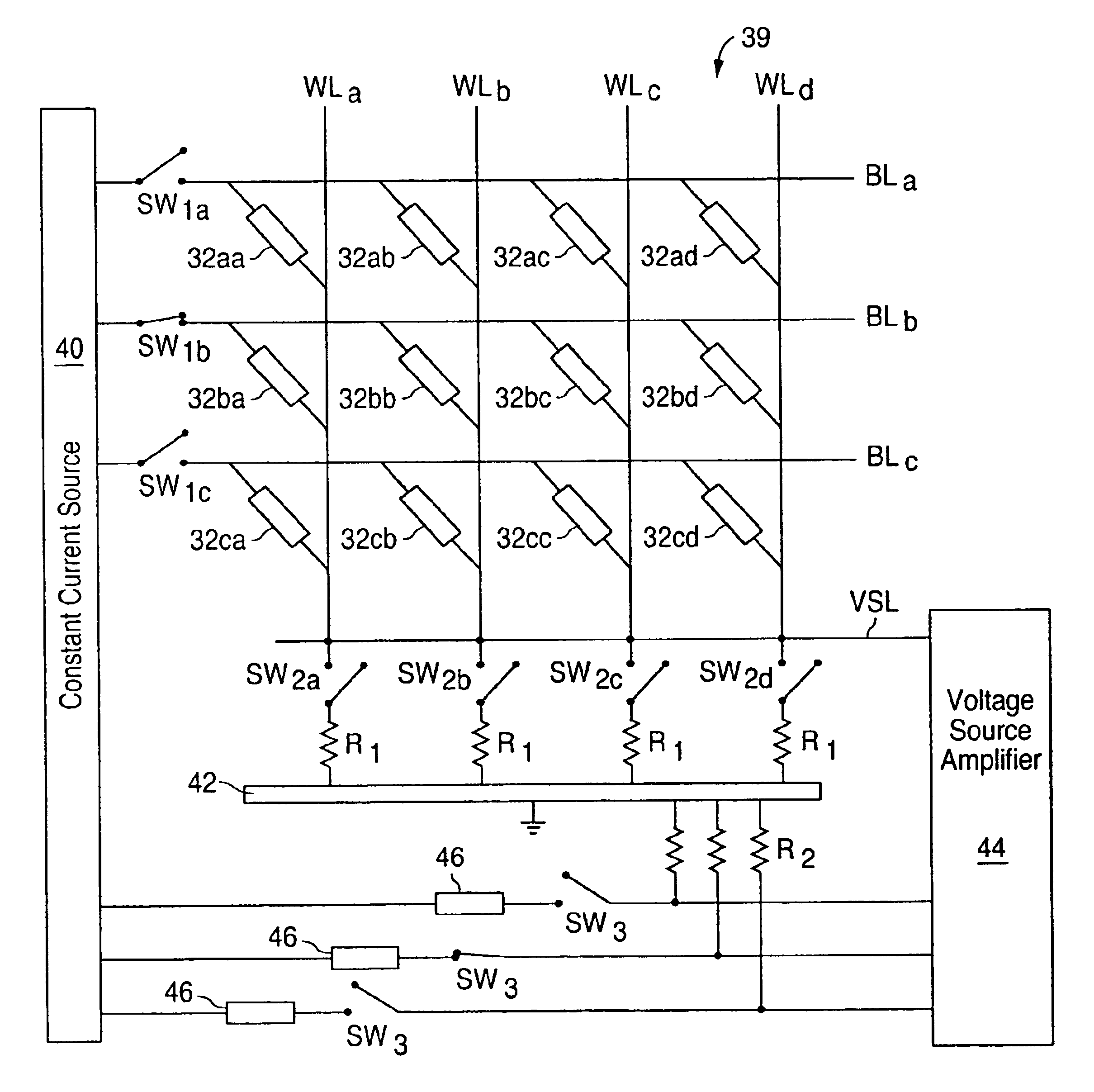

An array of phase changing memory cells that includes a current source, a voltage sensor, a plurality of conductive bit lines electrically connected to the current source, a plurality of conductive word lines each electrically connected to a ground plane via a first resistor and to the voltage sensor, and a plurality of memory cells. Each memory cell is connected between one of the bit lines and one of the word lines and includes phase change memory material. One of the memory cells is selected by turning on switches just on the bit line and word line connected thereto, or by turning a switch connected in series between the corresponding bit and word lines, where the read current flows through the selected memory cell and the voltage sensor measures a voltage drop across the selected memory cell.

Owner:SILICON STORAGE TECHNOLOGY

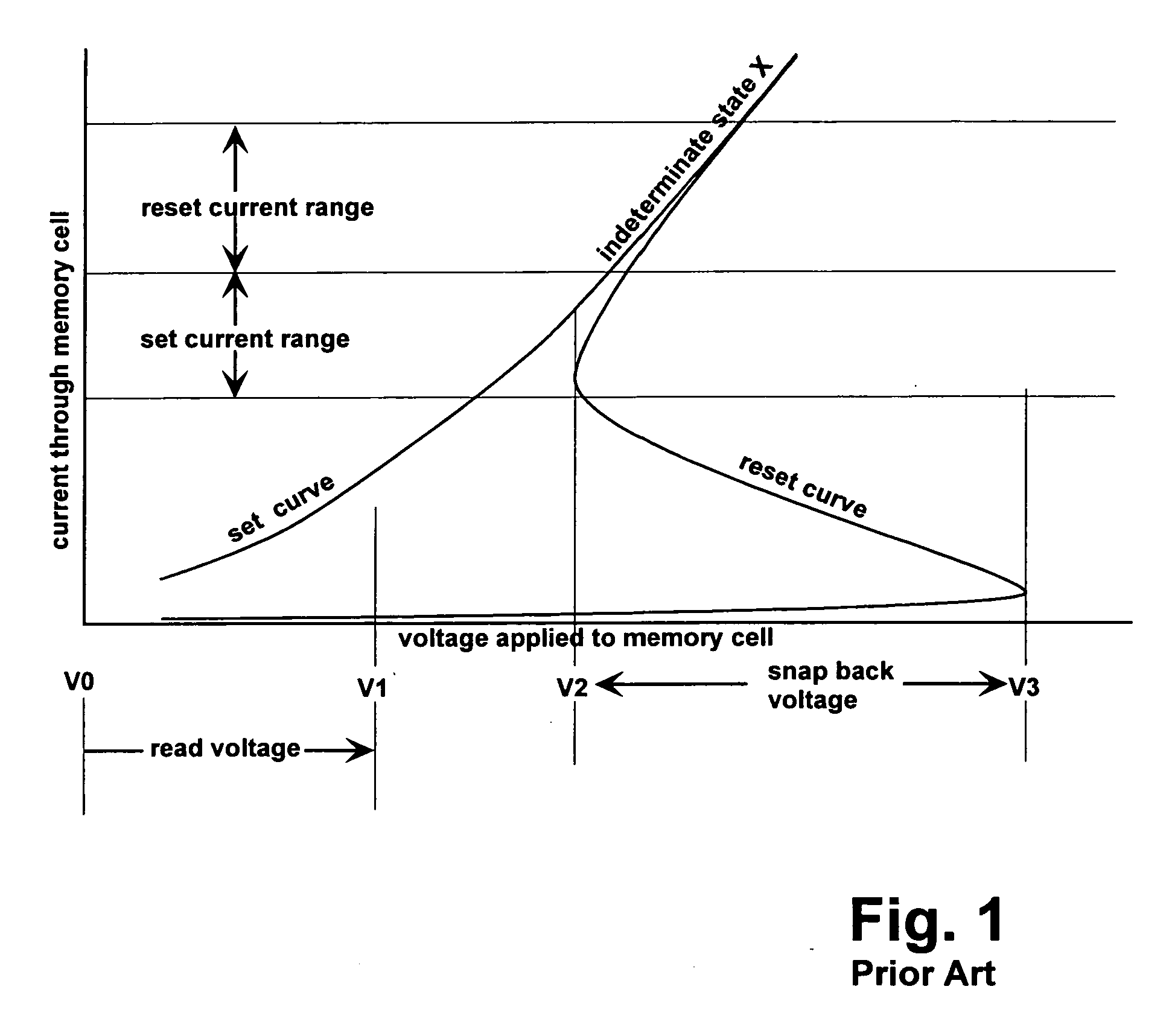

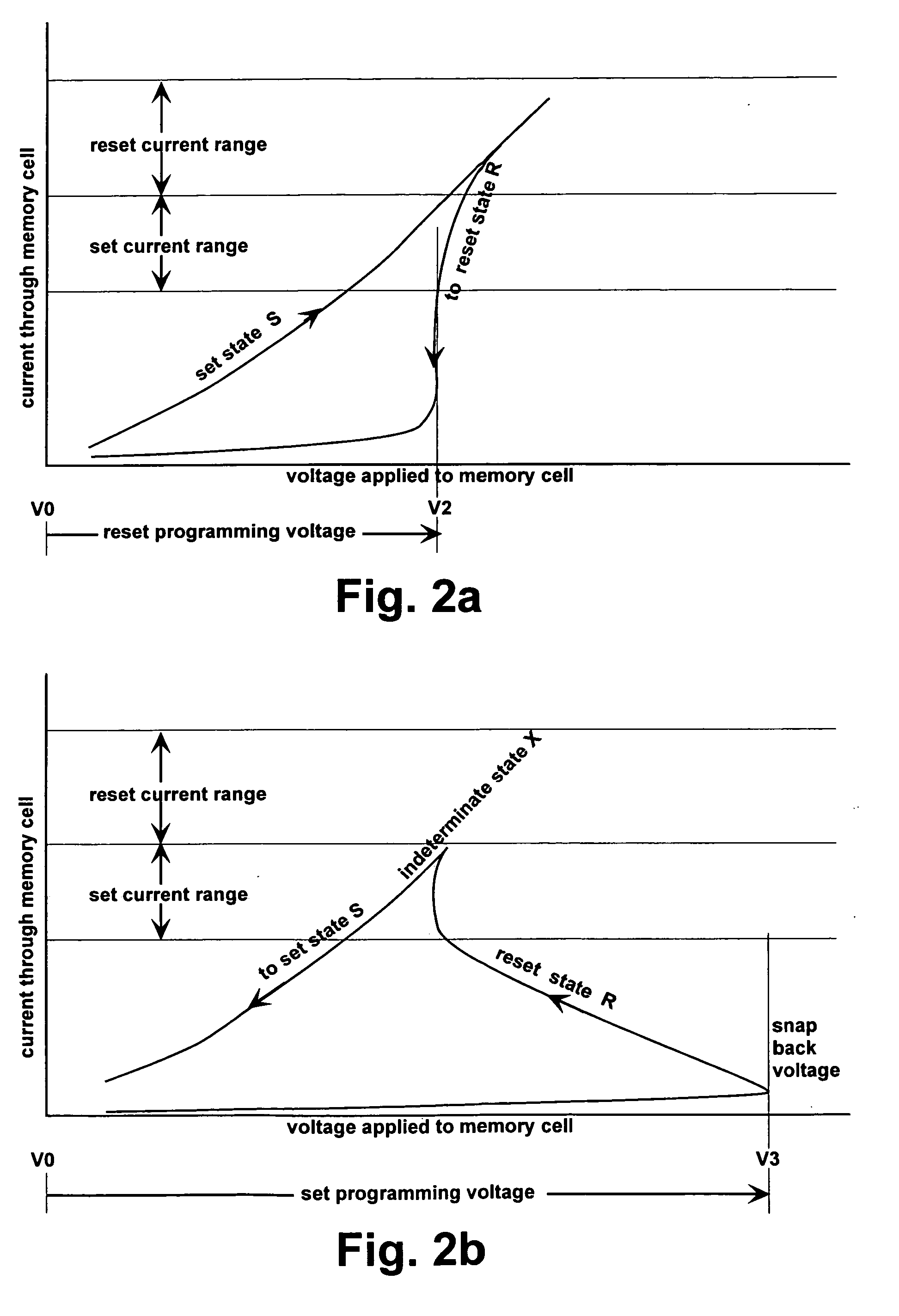

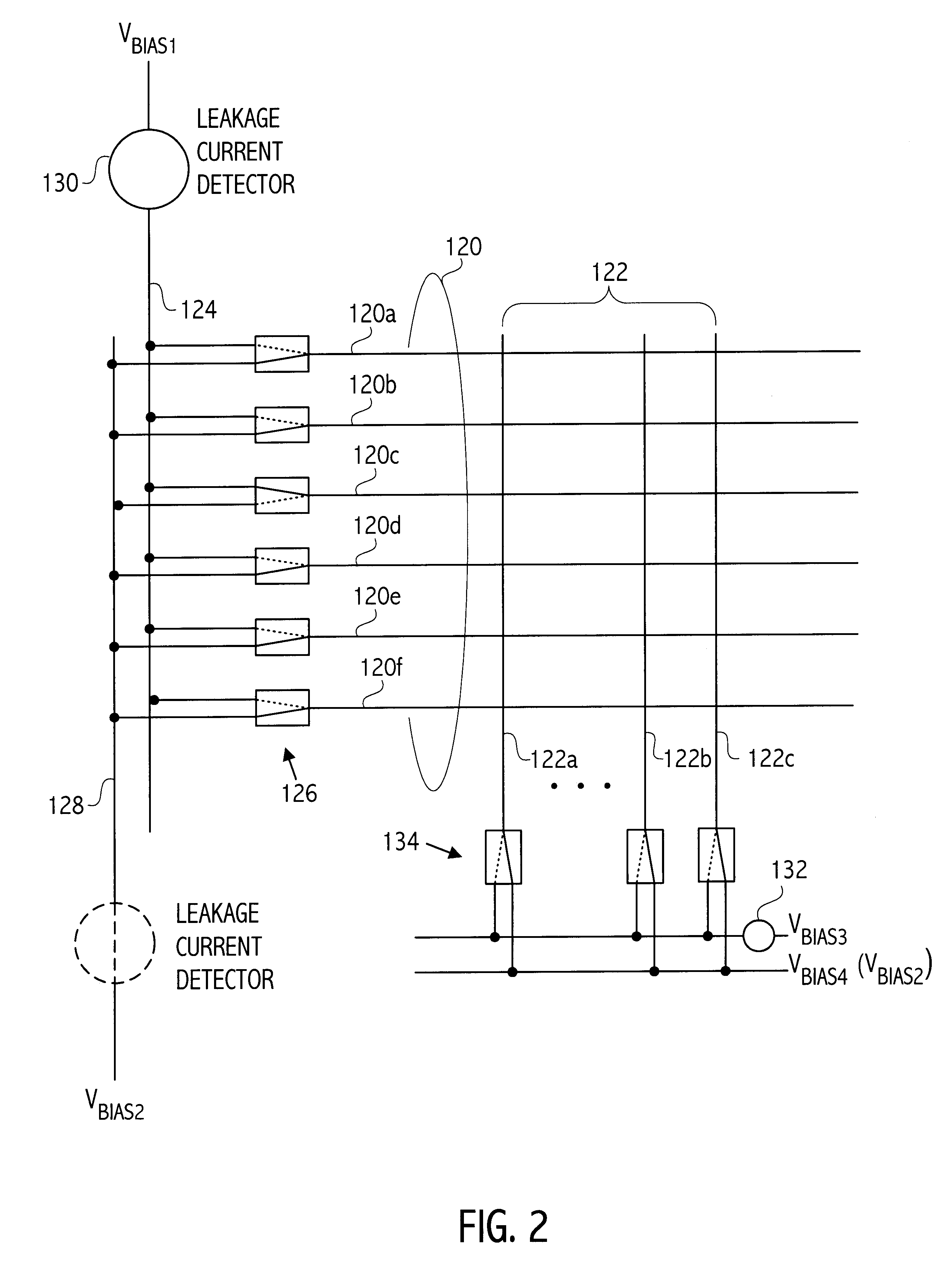

Structure and method for biasing phase change memory array for reliable writing

ActiveUS20060157679A1Minimize leakage currentReduce the possibilitySolid-state devicesDigital storageBit linePhase-change memory

A memory array having memory cells comprising a diode and a phase change material is reliably programmed by maintaining all unselected memory cells in a reverse biased state. Thus leakage is low and assurance is high that no unselected memory cells are disturbed. In order to avoid disturbing unselected memory cells during sequential writing, previously selected word and bit lines are brought to their unselected voltages before new bit lines and word lines are selected. A modified current mirror structure controls state switching of the phase change material.

Owner:SANDISK TECH LLC

Method of forming pitch multipled contacts

ActiveUS20070049035A1Solid-state devicesSemiconductor/solid-state device manufacturingBit lineLithographic artist

Methods of forming electrically conductive and / or semiconductive features for use in integrated circuits are disclosed. Various pattern transfer and etching steps can be used, in combination with pitch-reduction techniques, to create densely-packed features. The features can have a reduced pitch in one direction and a wider pitch in another direction. Conventional photo-lithography steps can be used in combination with pitch-reduction techniques to form elongate, pitch-reduced features such as bit-line contacts, for example.

Owner:MICRON TECH INC

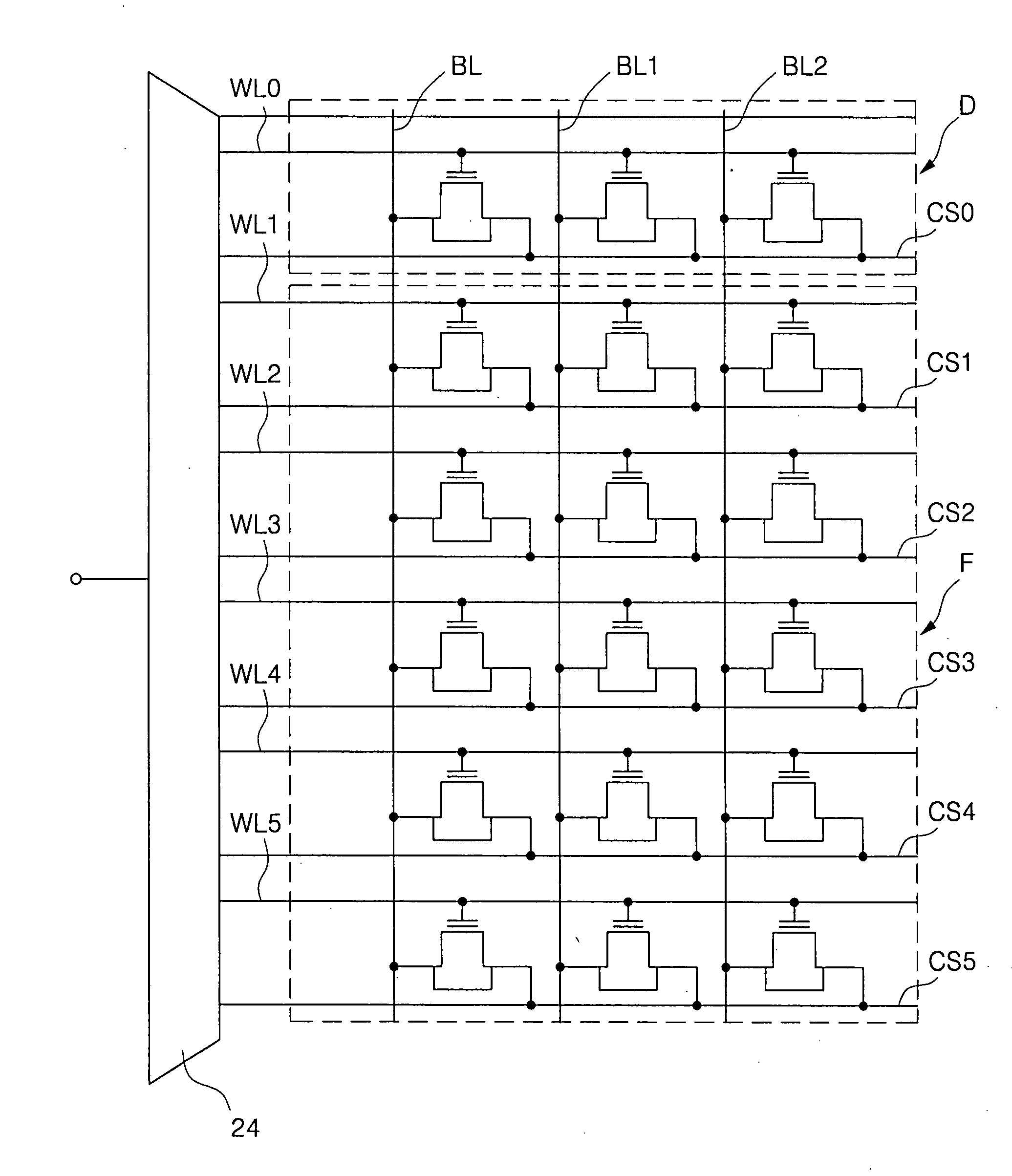

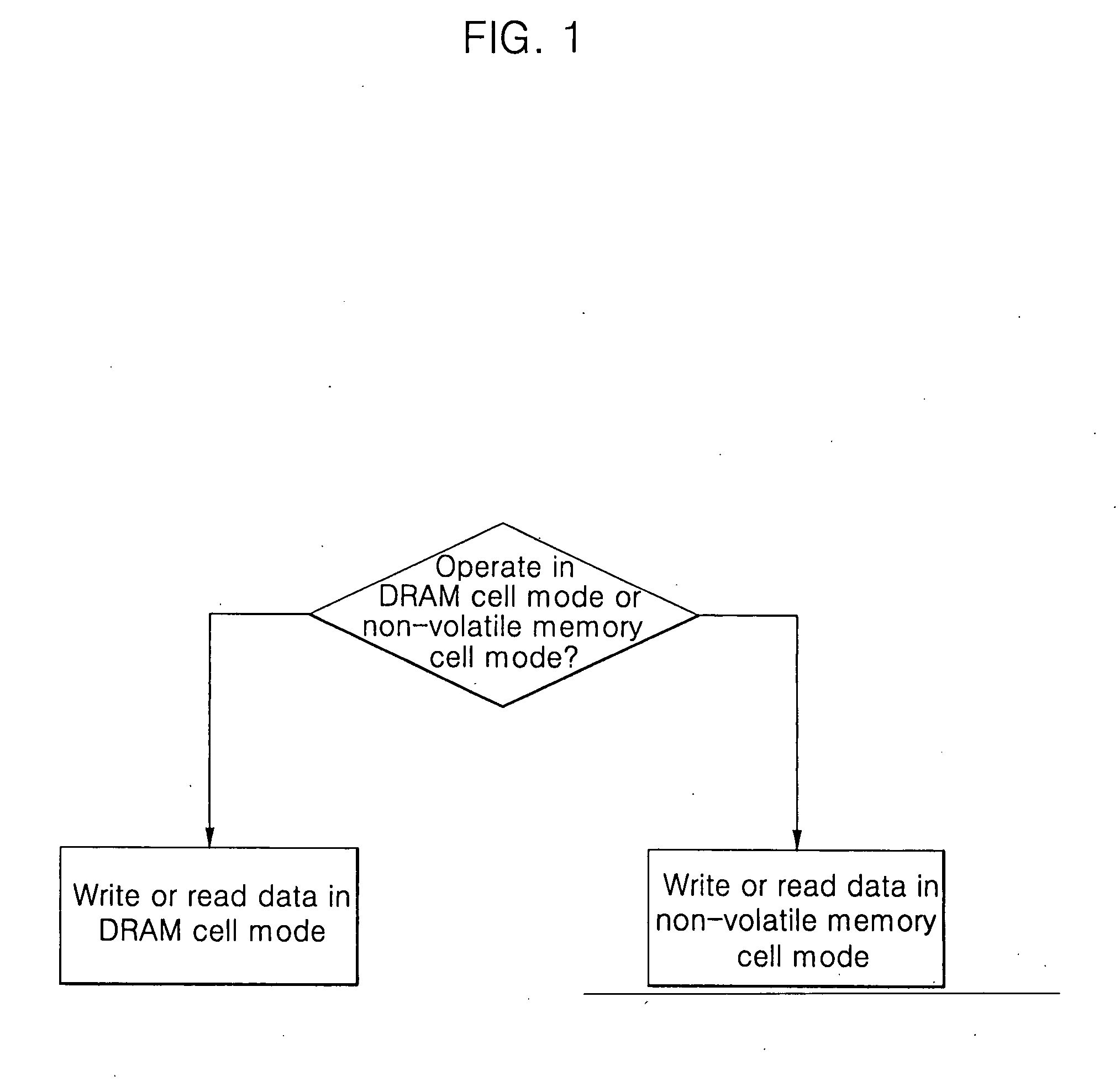

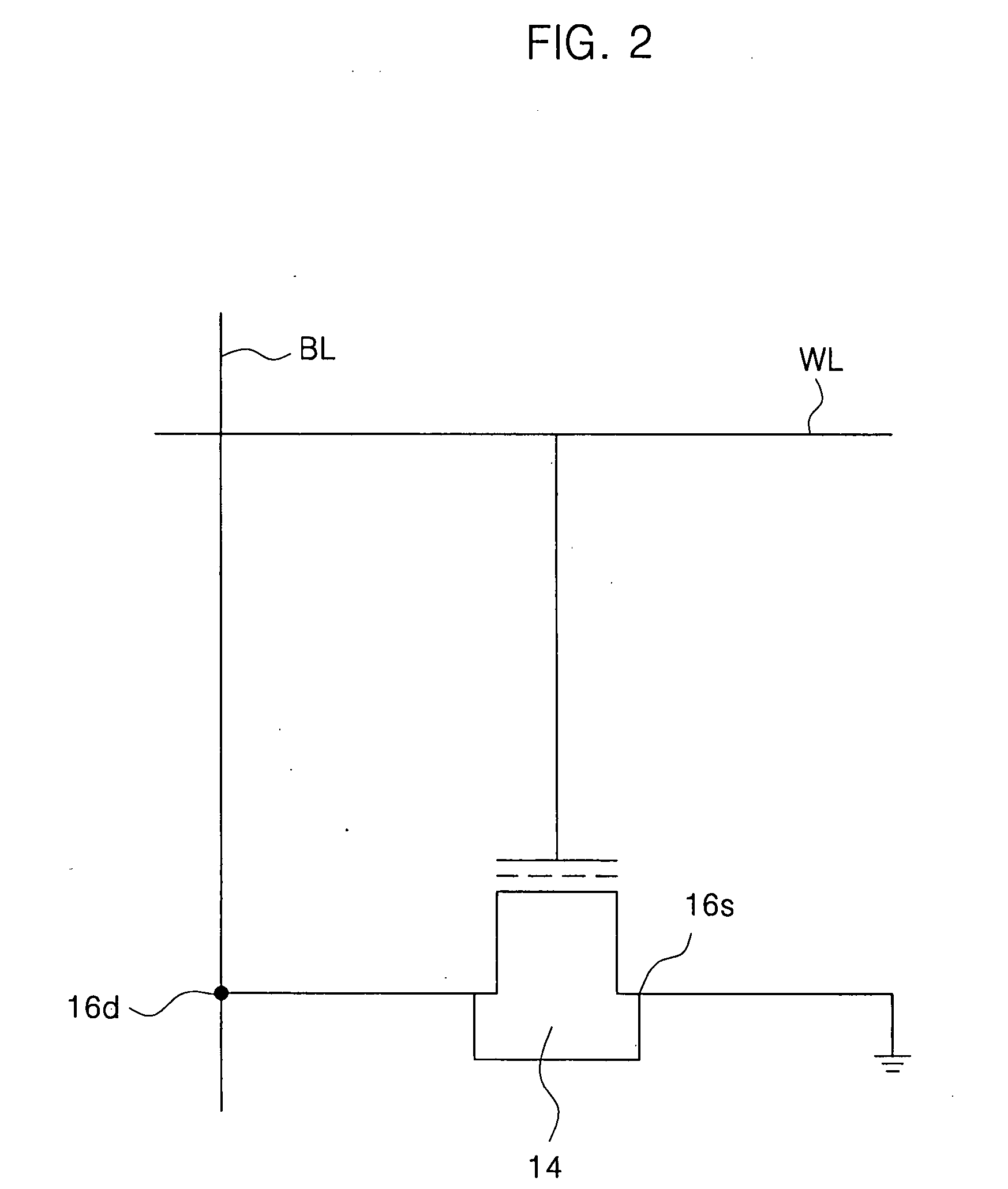

Semiconductor memory device having DRAM cell mode and non-volatile memory cell mode and operation method thereof

A semiconductor memory device may have a DRAM cell mode and a non-volatile memory cell mode without a capacitor, including multiple transistors arranged in an array and having floating bodies, word lines connected to gate electrodes of the transistors, bit lines at a first side of the gate electrodes connected to drains of the transistors, source lines at a second side of the gate electrodes, different from the first side, and connected to sources of the transistors on the semiconductor substrate, and charge storage regions between the gate electrodes and the floating bodies.

Owner:SAMSUNG ELECTRONICS CO LTD

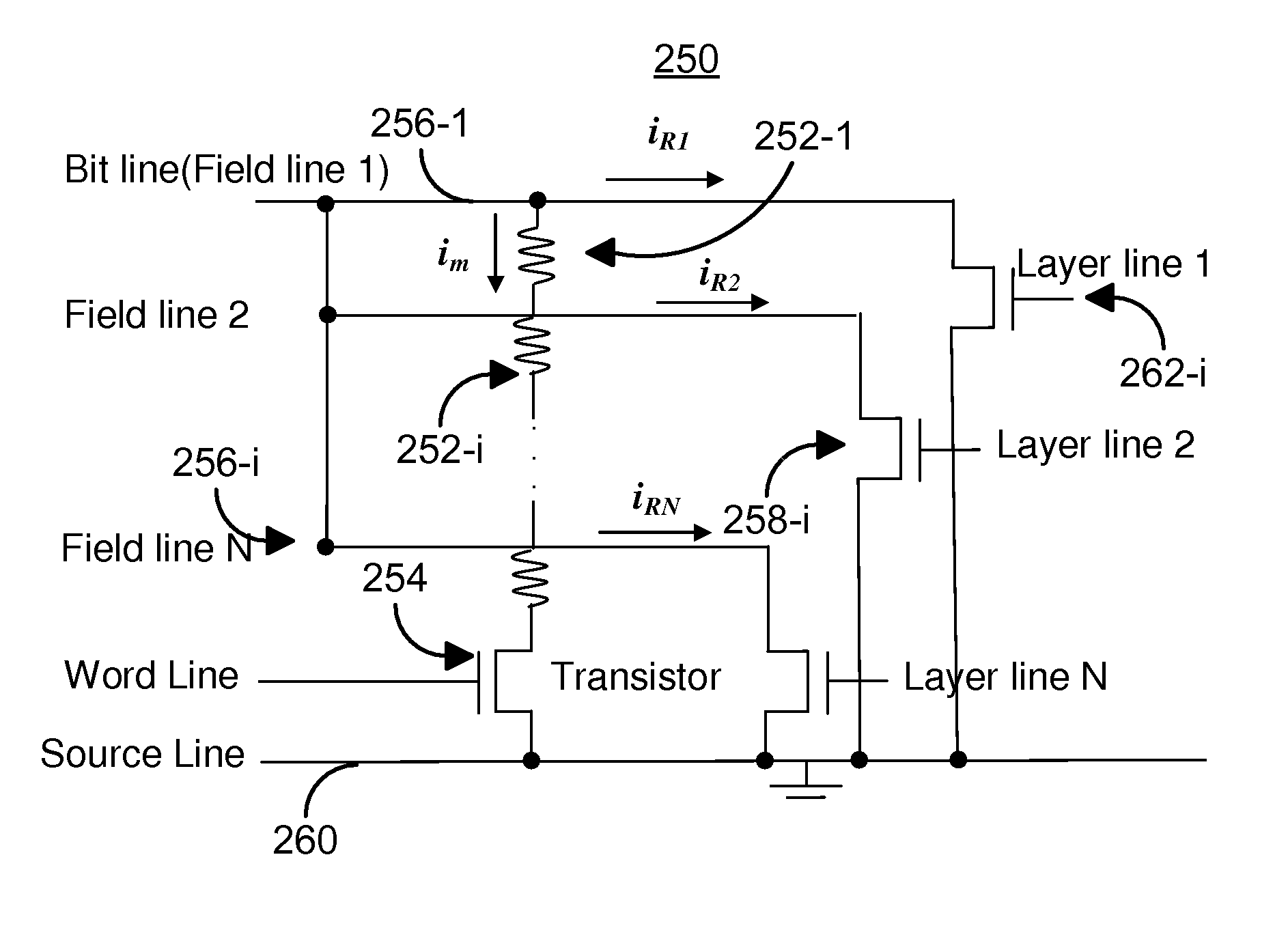

Method and system for using a pulsed field to assist spin transfer induced switching of magnetic memory elements

A method and system for providing and utilizing a magnetic memory are described. The magnetic memory includes a plurality of magnetic storage cells. Each magnetic storage cell includes magnetic element(s) programmable due to spin transfer when a write current is passed through the magnetic element(s) and selection device(s). The method and system include driving a first current in proximity to but not through the magnetic element(s) of a portion of the magnetic storage cells. The first current generates a magnetic field. The method and system also include driving a second current through the magnetic element(s) of the portion of the magnetic storage cells. The first and second currents are preferably both driven through bit line(s) coupled with the magnetic element(s). The first and second currents are turned on at a start time. The second current and the magnetic field are sufficient to program the magnetic element(s).

Owner:RENESAS ELECTRONICS CORP +1

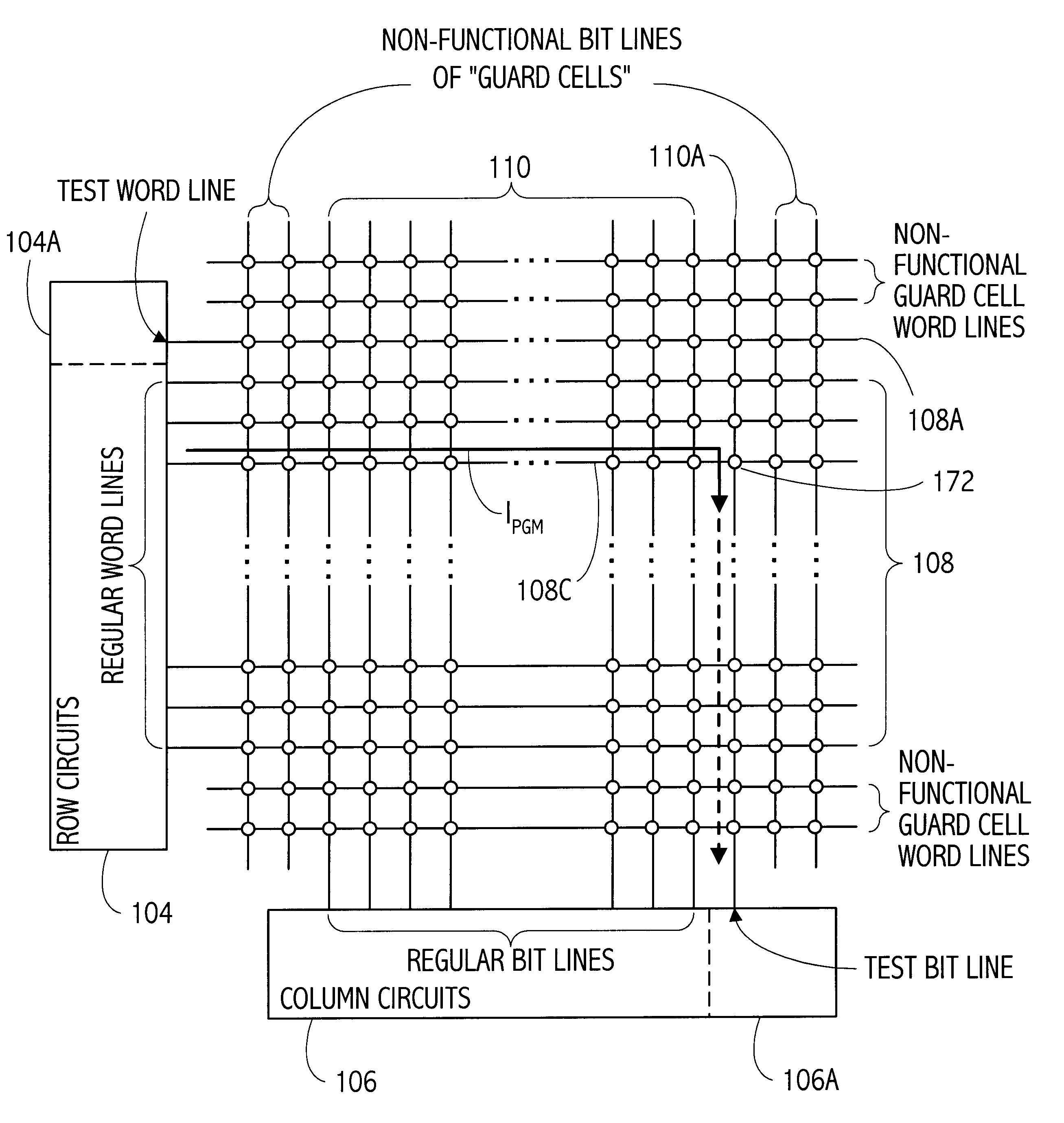

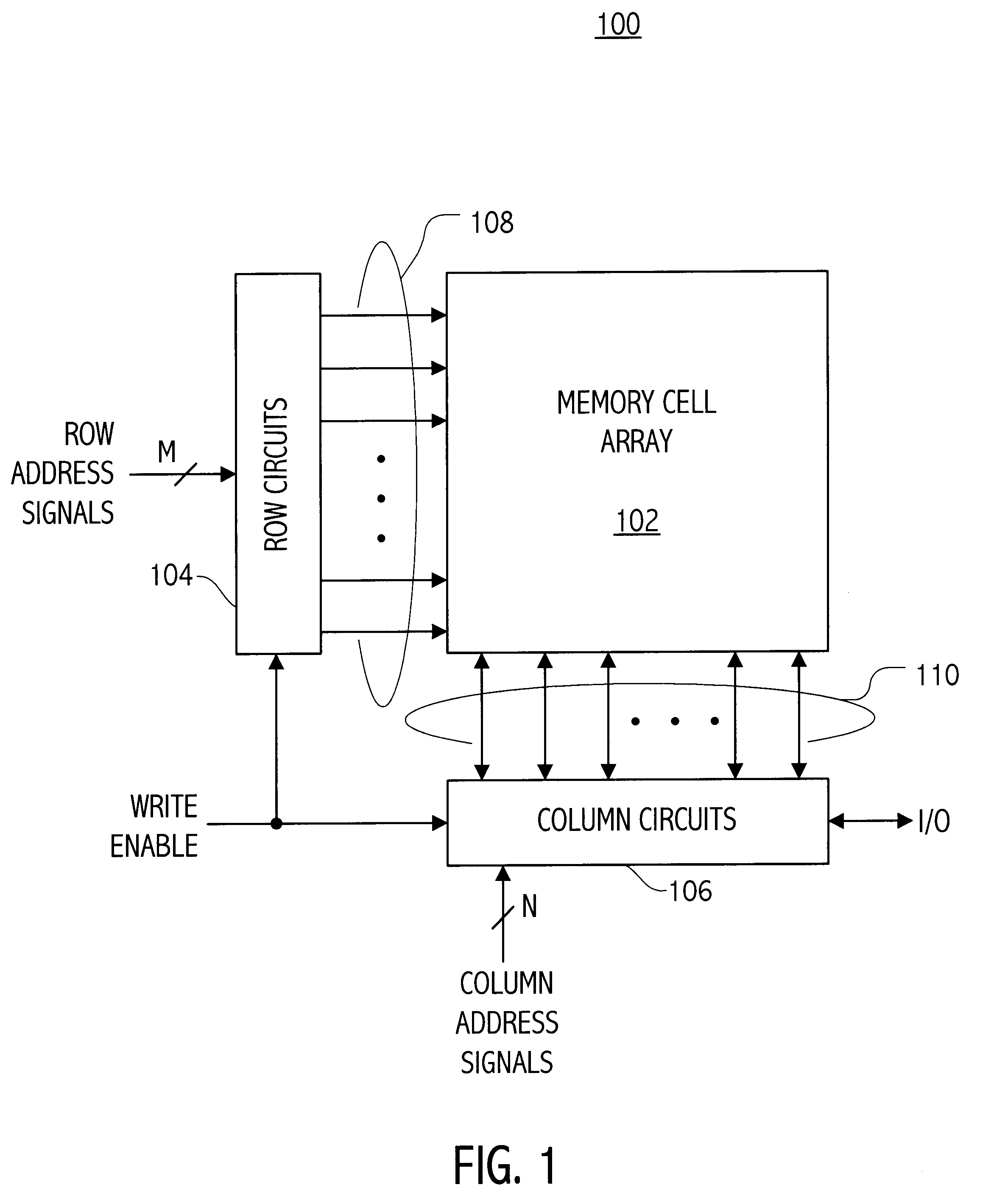

Memory array organization and related test method particularly well suited for integrated circuits having write-once memory arrays

In a preferred integrated circuit embodiment, a write-once memory array includes at least one test bit line which provides a respective test memory cell at the far end of each respective word line relative to its word line driver, and further includes at least one test word line which provides a respective test memory cell at the far end of each respective bit line relative to its bit line driver. An intra-layer short between word lines may be detected, such as during manufacturing testing, by biasing adjacent word lines to different voltages and detecting whether any leakage current flowing from one to another exceeds that normally accounted for by the memory cells and other known circuits. Intra-layer bit line shorts and inter-layer word line and bit line shorts may also be similarly detected. An "open" in a word line or bit line may be detected by trying to program the test memory cell at the far end of each such word line or bit line. If successfully programmed, the continuity of each word line and bit line is assured, and the programming circuitry for each word line and bit line is also known to be functional.

Owner:SANDISK TECH LLC

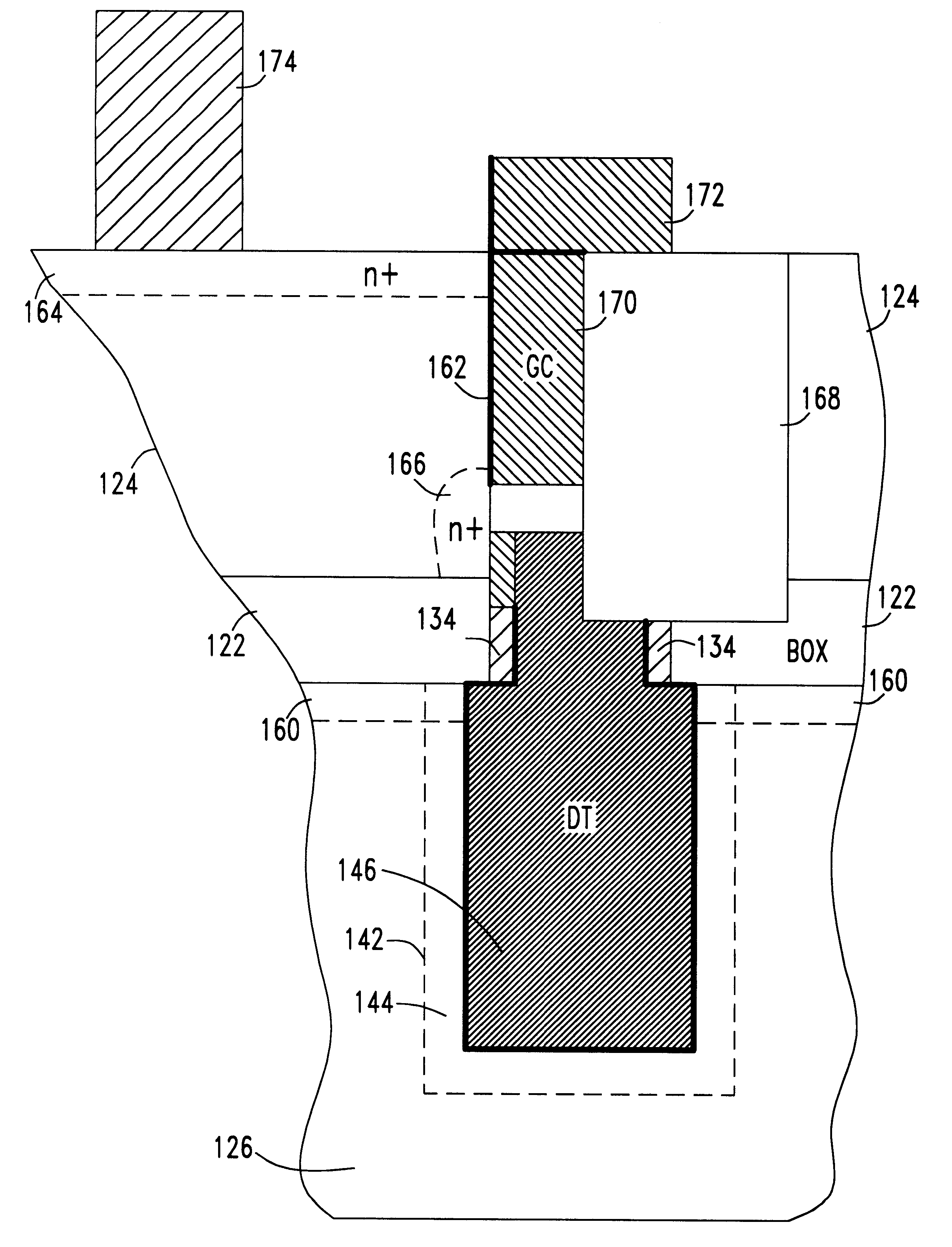

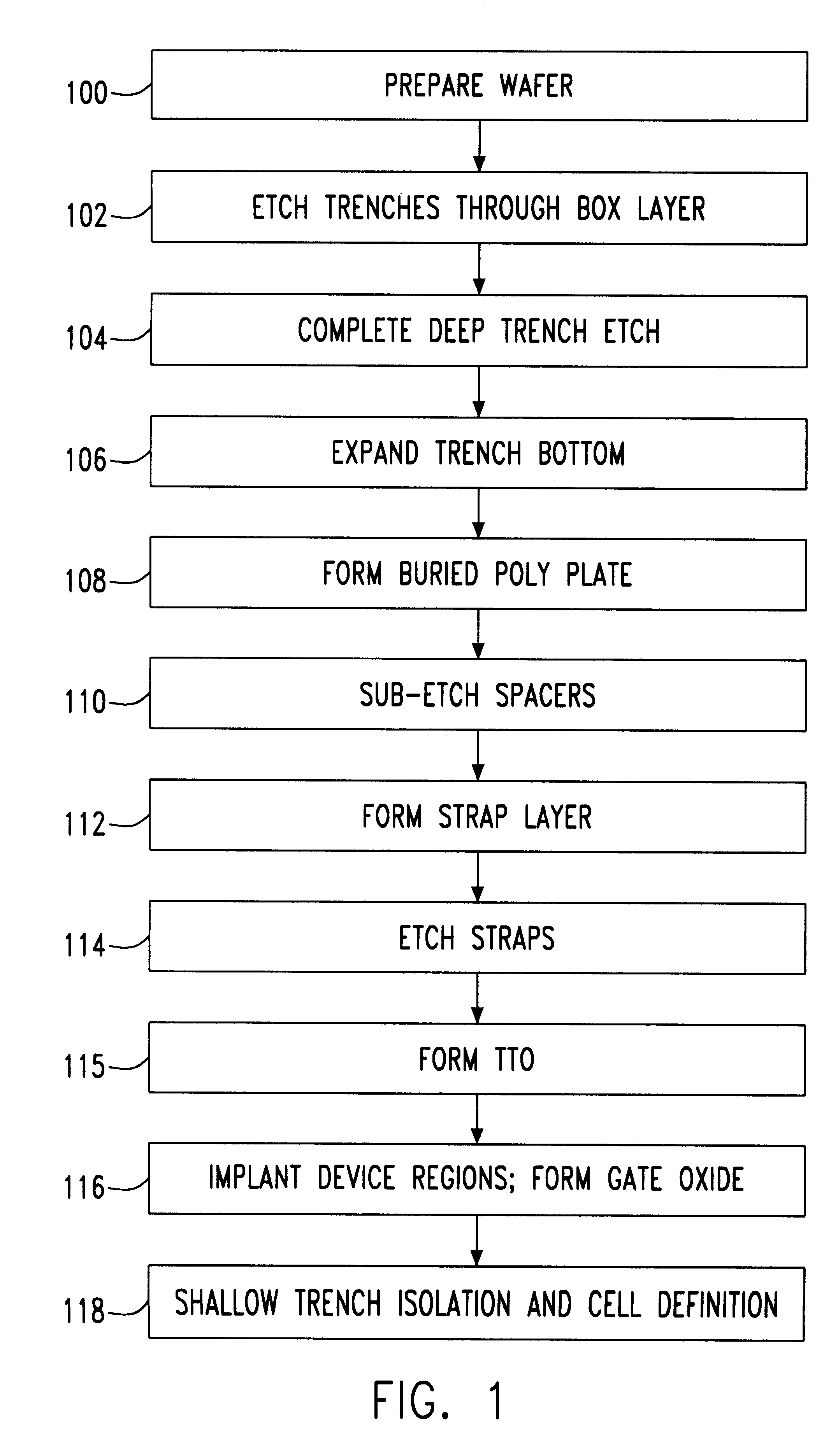

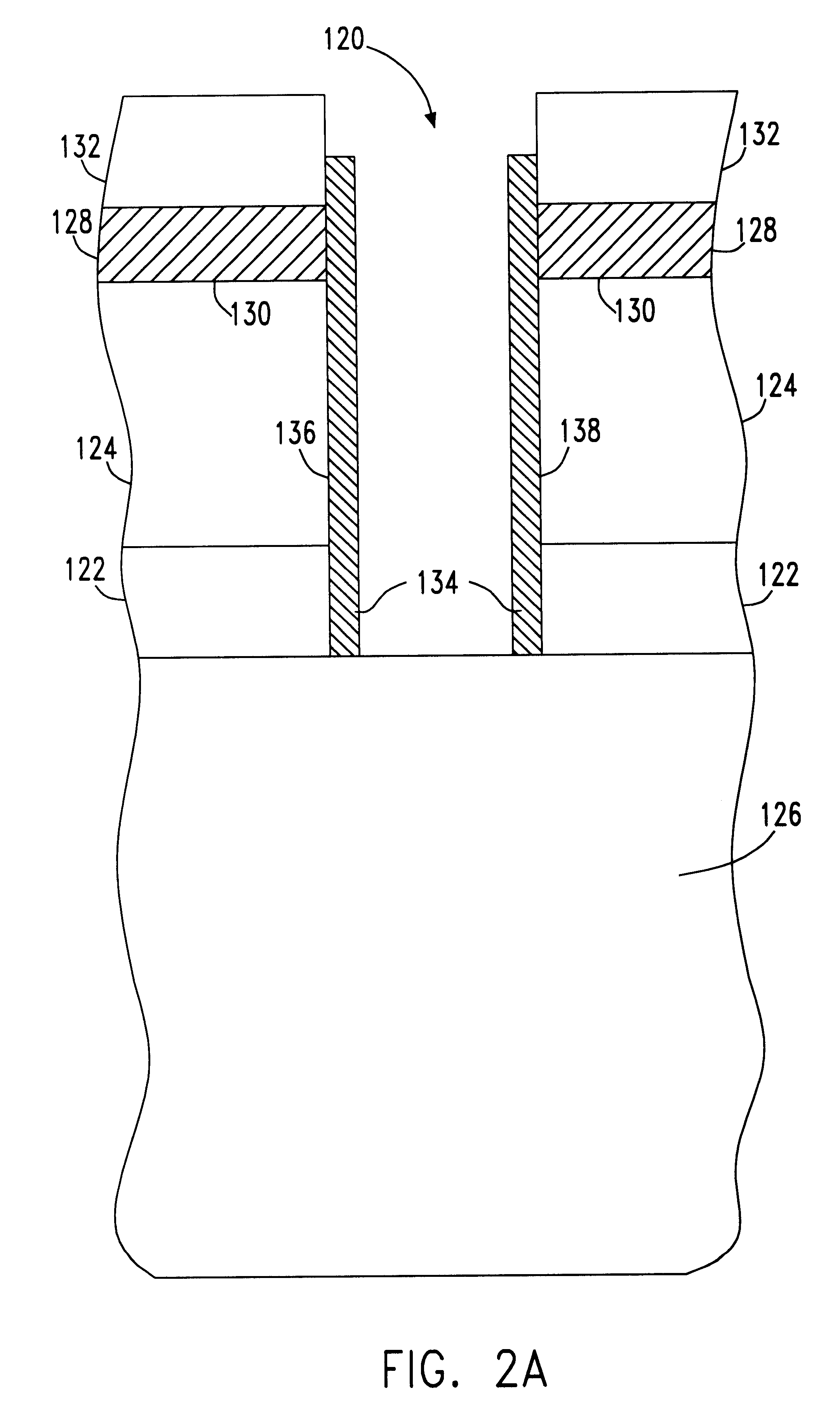

Silicon-on-insulator vertical array device trench capacitor DRAM

InactiveUS6566177B1Solid-state devicesSemiconductor/solid-state device manufacturingEngineeringBottle

A silicon on insulator (SOI) dynamic random access memory (DRAM) cell and array and method of manufacture. The memory cell includes a trench storage capacitor connected by a self aligned buried strap to a vertical access transistor. A buried oxide layer isolates an SOI layer from a silicon substrate. The trench capacitor is formed in the substrate and the access transistor is formed on a sidewall of the SOI layer. A polysilicon strap connected to the polysilicon plate of the storage capacitor provides a self-aligned contact to the source of the access transistor. Initially, the buried oxide layer is formed in the wafer. Deep trenches are etched, initially just through the SOI layer and the BOX layer. Protective sidewalls are formed in the trenches. Then, the deep trenches are etched into the substrate. The volume in the substrate is expanded to form a bottle shaped trench. A polysilicon capacitor plate is formed in the deep trenches and conductive polysilicon straps are formed in the trenches between the capacitor plates and the SOI sidewalls. Device regions are defined in the wafer and a sidewall gate is formed in the deep trenches. Shallow trenches isolation (STI) is used to isolate and define cells. Bitlines and wordlines are formed on the wafer.

Owner:GOOGLE LLC

Semiconductor device and operating method thereof

InactiveUS20070123189A1Lower unit costReduce memory areaNanoinformaticsSolid-state devicesOrganic memoryBit line

In an organic memory which is included in a radio chip formed from a thin film, data are written to the organic memory by a signal inputted with a wired connection, and the data is read with a signal by radio transmission. A bit line and a word line which form the organic memory are each selected by a signal which specifies an address generated based on the signal inputted with a wired connection. A voltage is applied to a selected memory element. Thus writing is performed. Reading is performed by a clock signal or the like which are generated from a radio signal.

Owner:SEMICON ENERGY LAB CO LTD

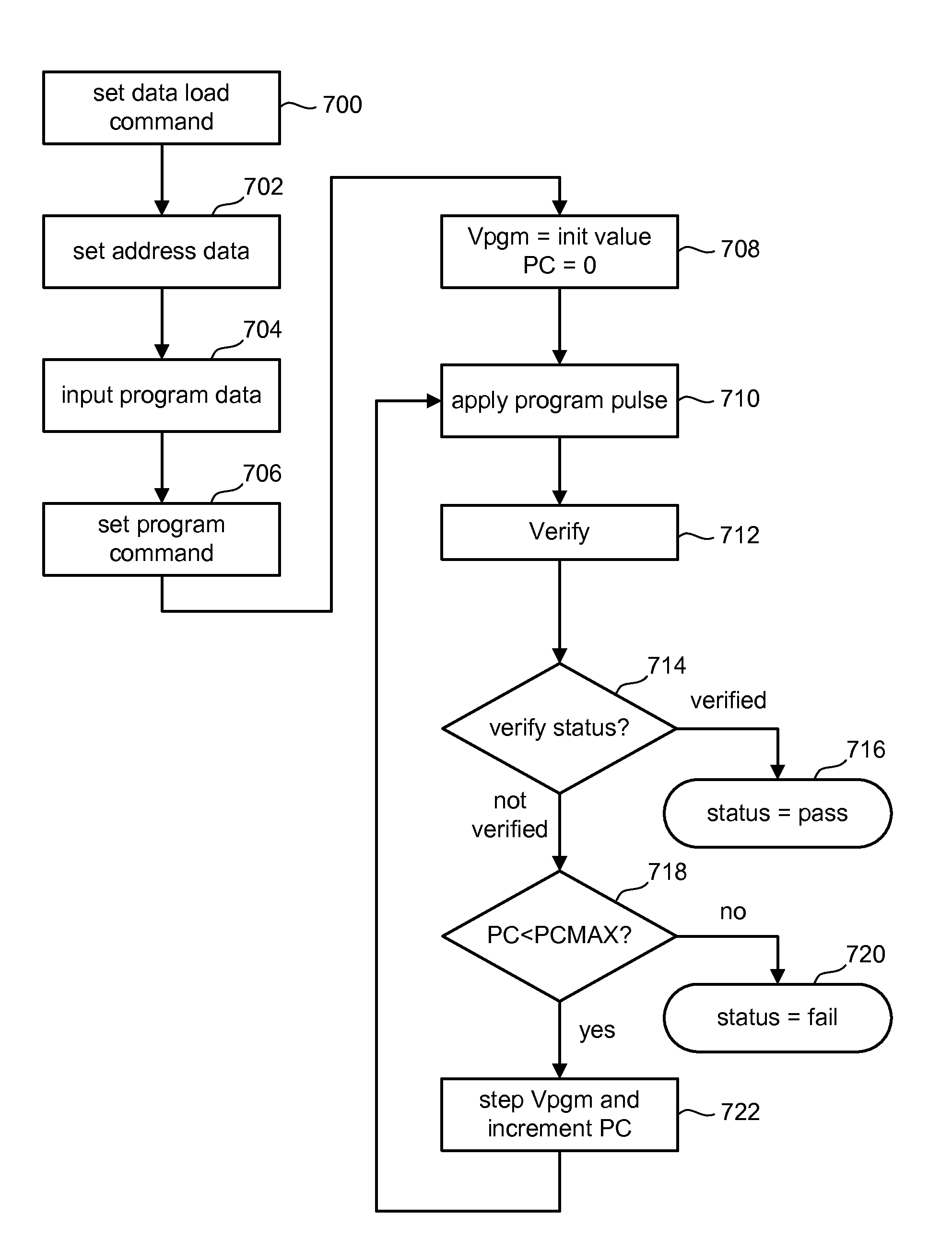

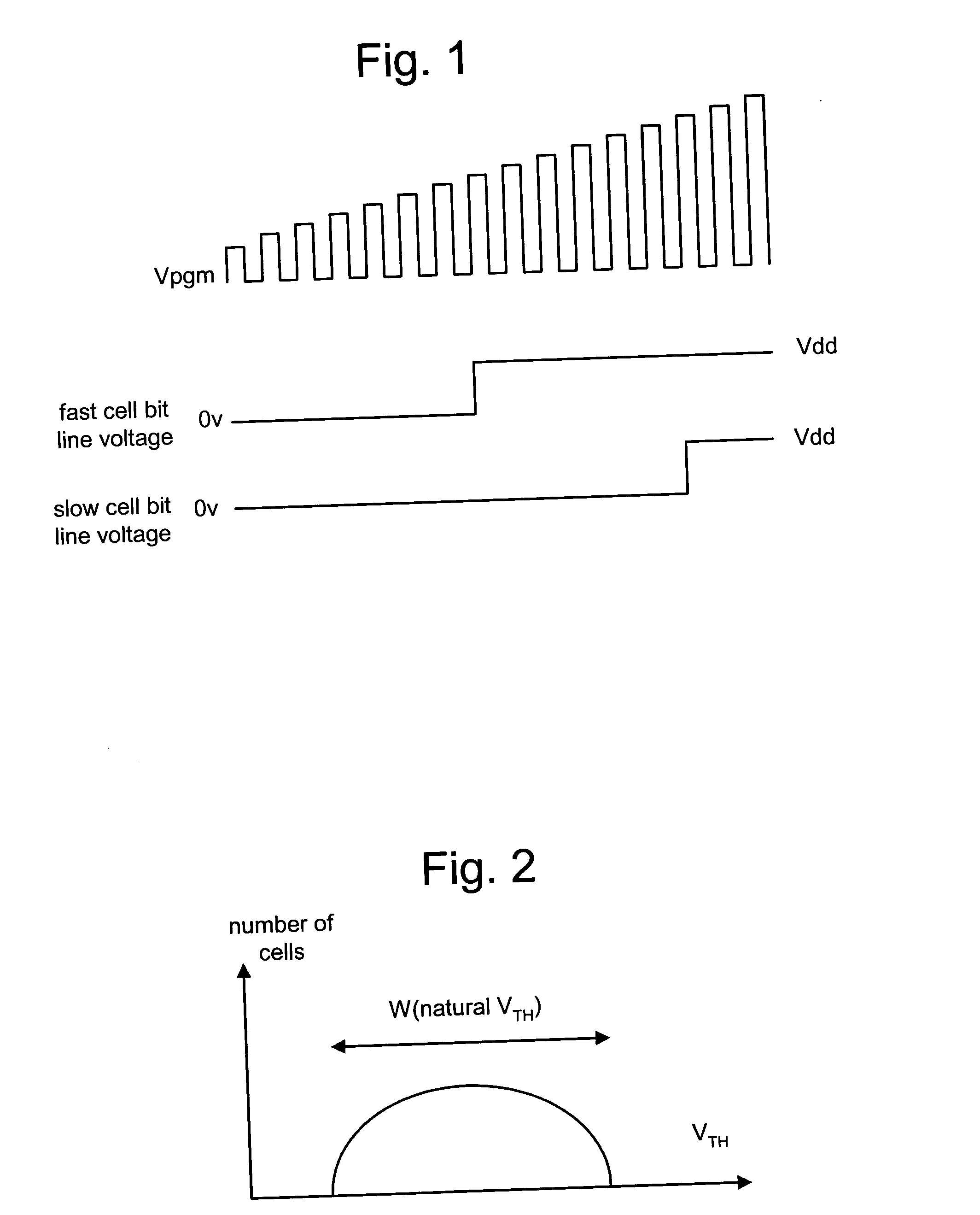

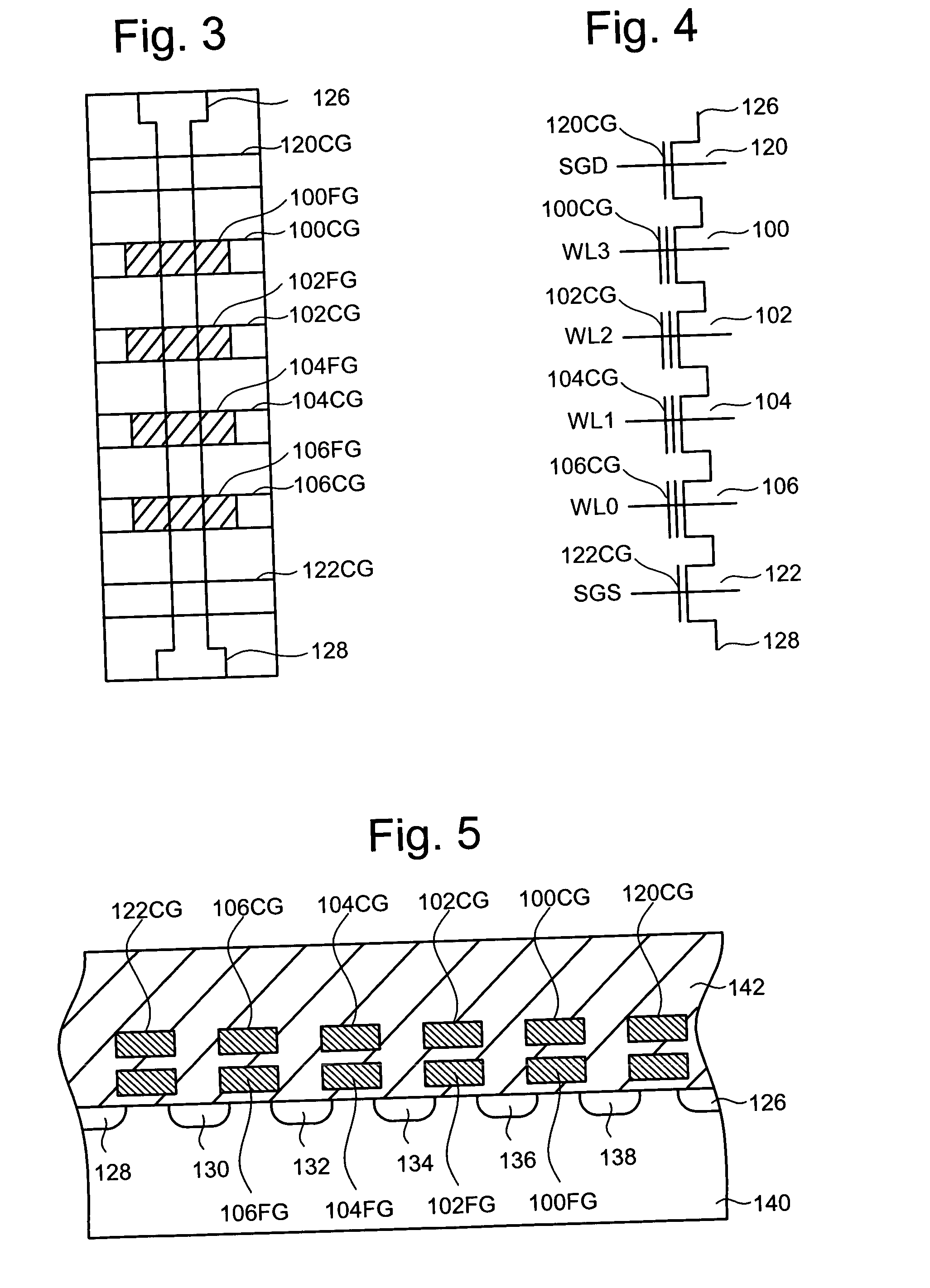

Behavior based programming of non-volatile memory

ActiveUS20050083735A1Speed up the processTransistorSolid-state devicesBit lineComputer architecture

The process for programming a set of memory cells is improved by adapting the programming process based on behavior of the memory cells. For example, a set of program pulses is applied to the word line for a set of flash memory cells. A determination is made as to which memory cells are easier to program and which memory cells are harder to program. Bit line voltages (or other parameters) can be adjusted based on the determination of which memory cells are easier to program and which memory cells are harder to program. The programming process will then continue with the adjusted bit line voltages (or other parameters).

Owner:KIOXIA CORP +1

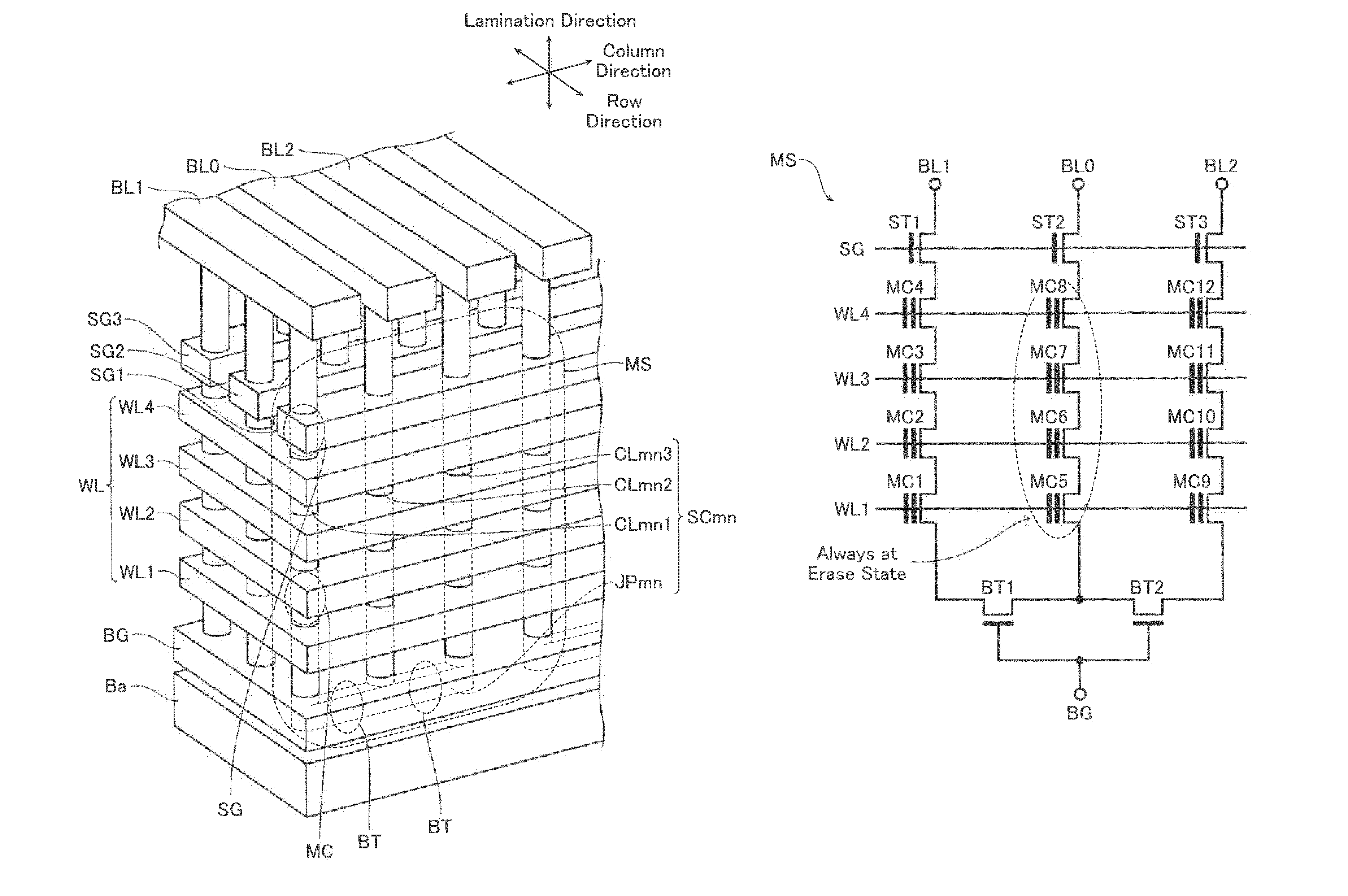

Planar capacitor memory cell and its applications

InactiveUS7209384B1Less complicated to fabricateImprove performanceTransistorSolid-state devicesHemt circuitsEngineering

A capacitor memory is realized, wherein a capacitor stores data and a diode controls to store data “1” or “0”. Diode has four terminals wherein first terminal serves as word line, second terminal serves as storage node, third terminal is floating, and fourth terminal serves as bit line, wherein back channel effect is suppressed adding additional ions in the bottom side of third terminal or applying negative voltage in the well or substrate. A capacitor plate couples to second terminal, which plate has no coupling region to first, third and fourth terminal. With no coupling, the inversion layer of plate in the storage node is isolated from the adjacent nodes. In doing so, the plate can swing ground level to positive supply level to write. As a result, no negative generator is required for controlling plate. Word line and bit line keep ground level during standby, and rise to supply level for read or write operation. In this manner, no holding current is required during standby, and operating current is dramatically reduced with no negative generator. Write has a sequence to clear the state of cell before writing to store data regardless of previous state. Refresh cycle is periodically asserted to sustain data. The present invention can be applied for destructive read, or for nondestructive read adding pull-down device to bit line. The height of cell is almost same as control circuit on the bulk or SOI wafer.

Owner:KIM JUHAN

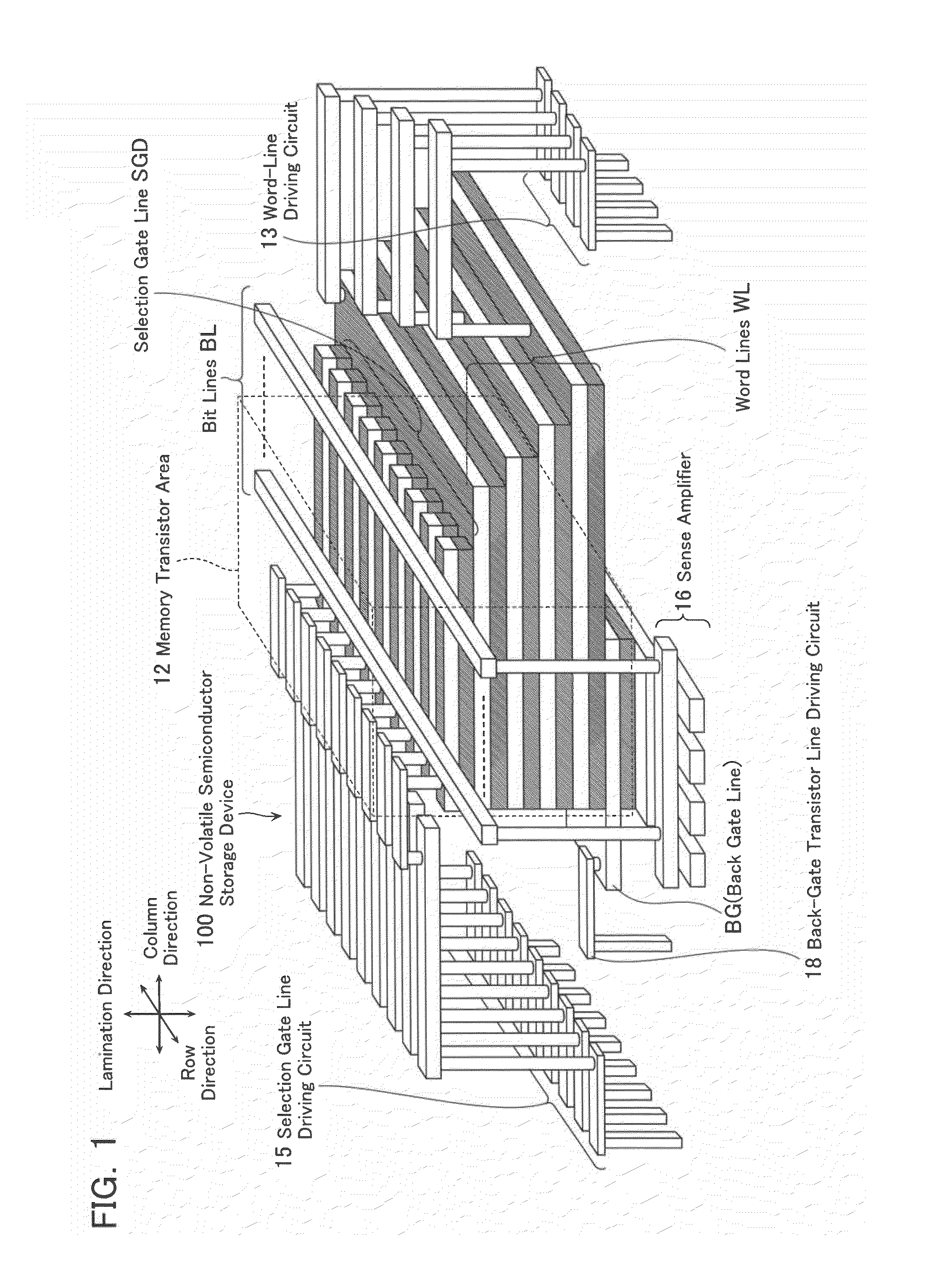

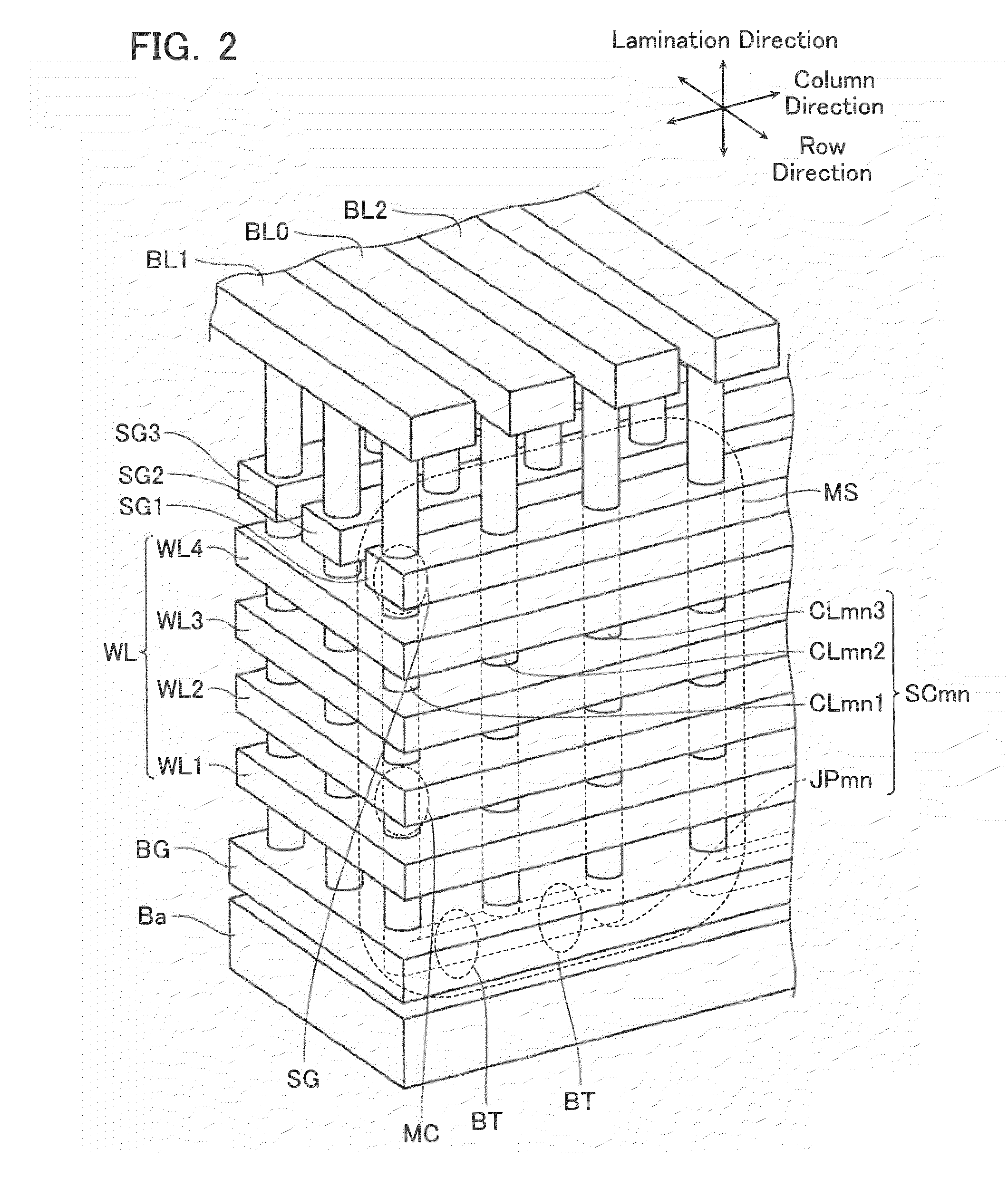

Non-volatile semiconductor storage device

Owner:KIOXIA CORP

Process for making and programming and operating a dual-bit multi-level ballistic flash memory

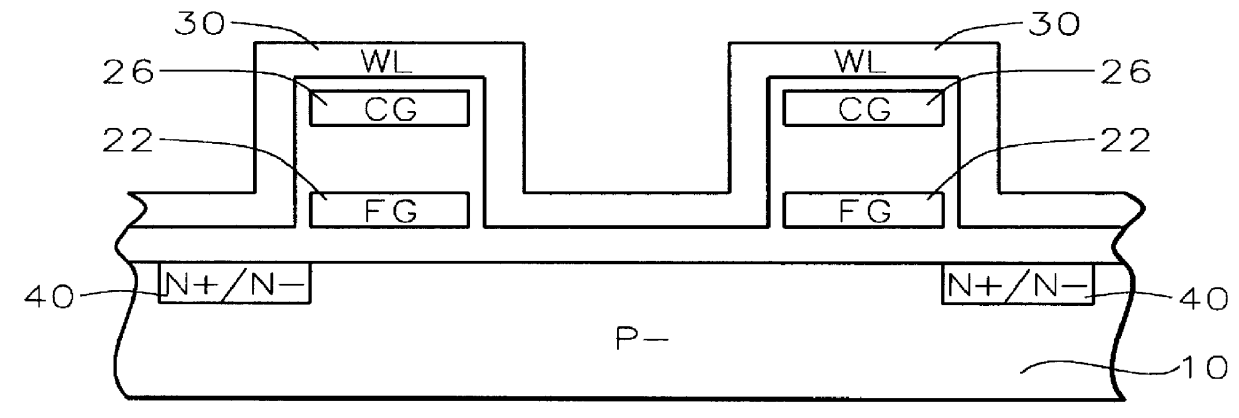

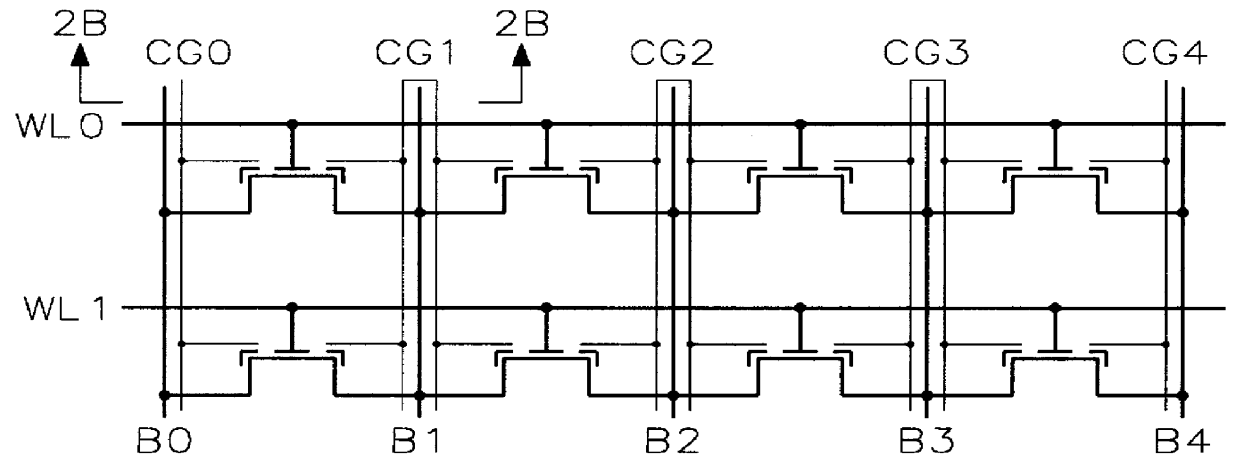

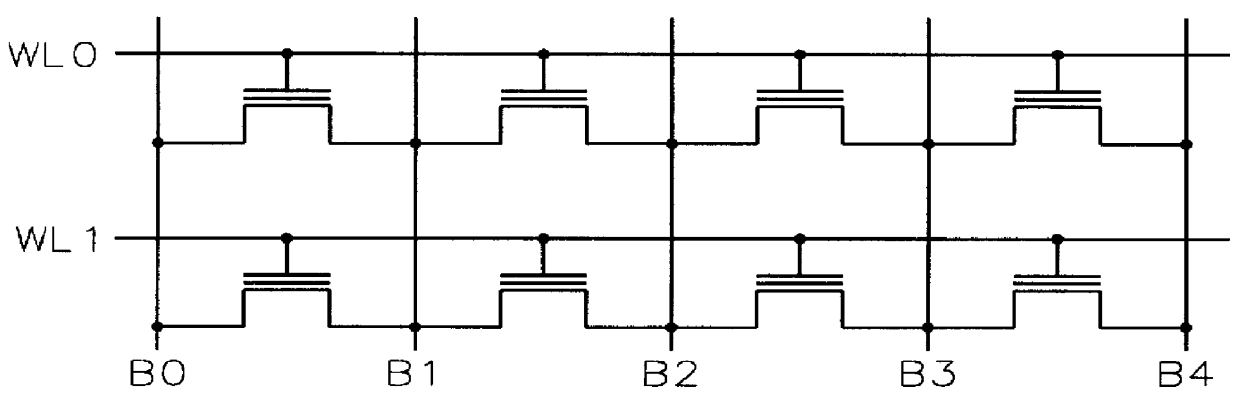

An fast program, ultra-high density, dual-bit, multi-level flash memory process, which can be applied to a ballistic step split gate side wall transistor, or to a ballistic planar split gate side wall transistor, which enables program operation by low voltage requirement on the floating gate during program is described. Two side wall floating gates are paired with a single word line select gate, and word lines are arranged to be perpendicular both the bit lines and control gate lines. Two adjacent memory cells on the same word line do not require an isolation region. Also, the isolation region between adjacent memory cells sharing the same bitline is defined by the minimum lithography feature, utilizing a self align fill technique. Adjacent memory cells on the same word line share bitline diffusion as well as a third poly control gate. Control gates allow program and read access to the individual floating gate. In addition to the dual-bit nature of the cell, density can be even further improved by multi-level storage. In one embodiment, the dual multi-level structure is applied to the ballistic step split gate side wall transistor. In a second embodiment, the dual multi-level structure is applied to the ballistic planar split gate side wall transistor. Both types of ballistic transistors provide fast, low voltage programming. The control gates are used to override or suppress the various threshold voltages on associated floating gates, in order to program to and read from individual floating gates. The targets for this non-volatile memory array are to provide the capabilities of high speed, low voltage programming (band width) and high density storage.

Owner:HALO LSI DESIGN & DEVICE TECH