Patents

Literature

1499results about How to "Run at high speed" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

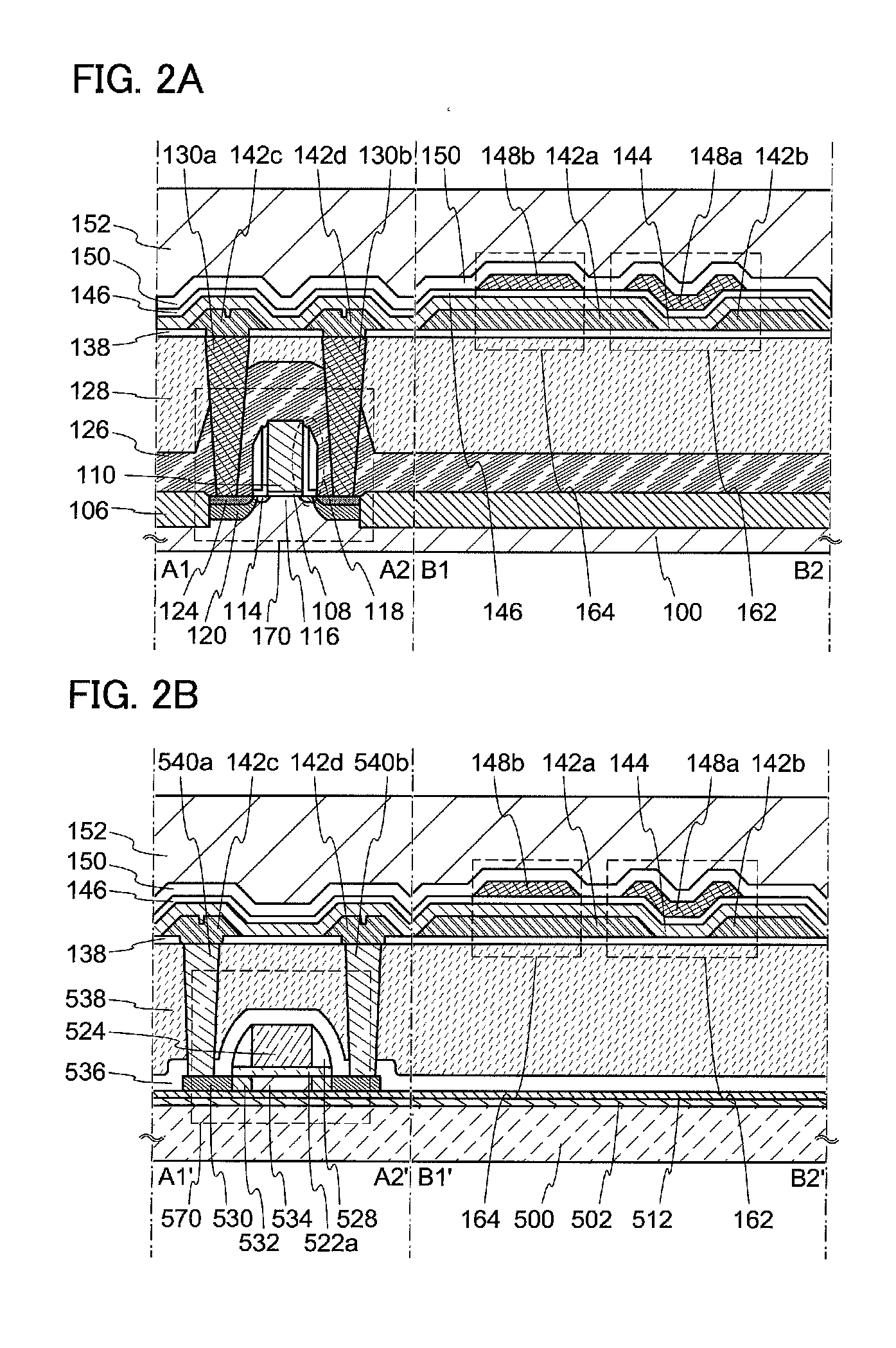

Semiconductor device and method for manufacturing the same

ActiveUS20100025678A1Comparatively-easy manufacturing processRun at high speedTransistorSolid-state devicesProduction rateOhmic contact

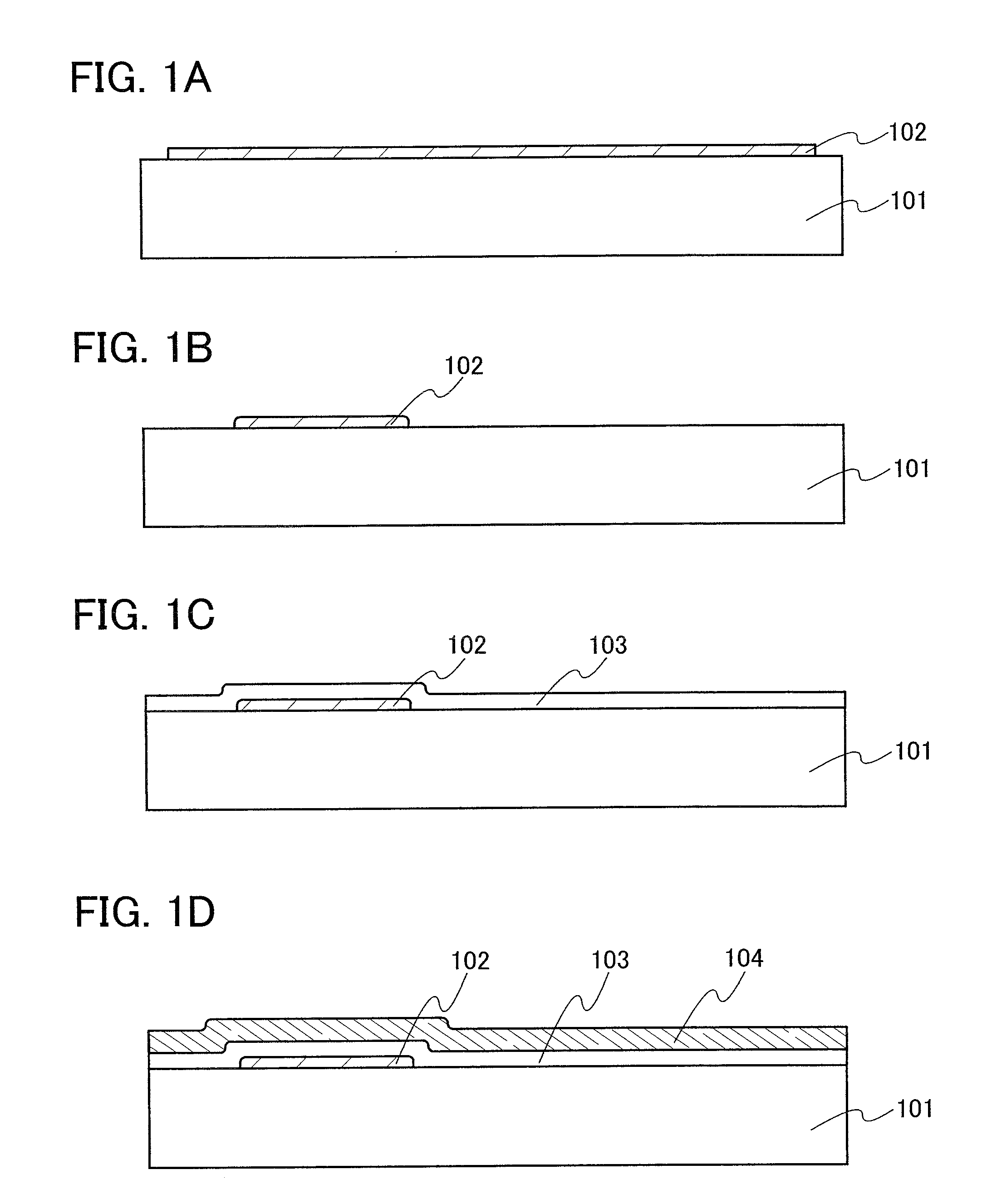

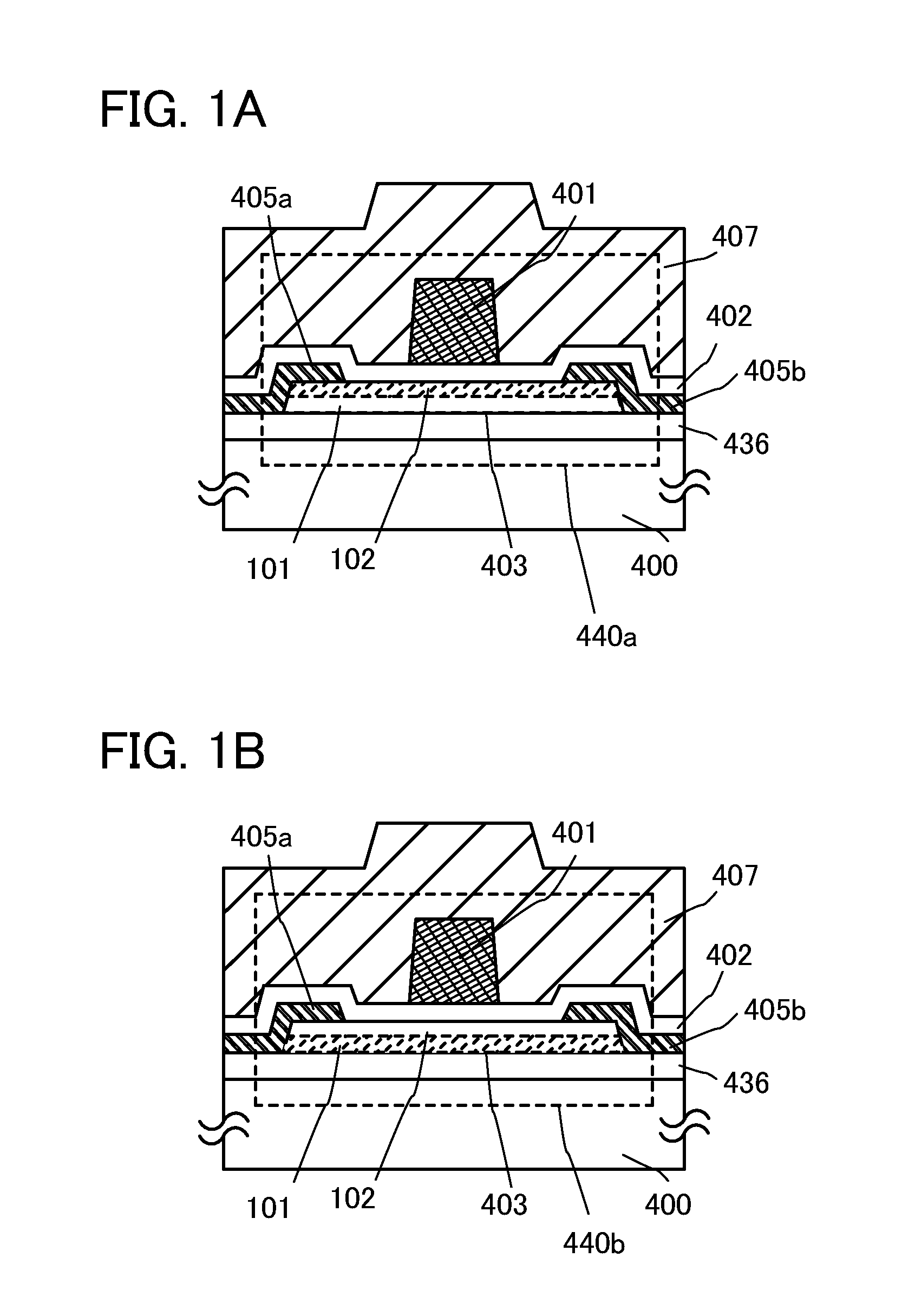

It is an object to provide a semiconductor device including a thin film transistor with favorable electric properties and high reliability, and a method for manufacturing the semiconductor device with high productivity. In an inverted staggered (bottom gate) thin film transistor, an oxide semiconductor film containing In, Ga, and Zn is used as a semiconductor layer, and a buffer layer formed using a metal oxide layer is provided between the semiconductor layer and a source and drain electrode layers. The metal oxide layer is intentionally provided as the buffer layer between the semiconductor layer and the source and drain electrode layers, whereby ohmic contact is obtained.

Owner:SEMICON ENERGY LAB CO LTD

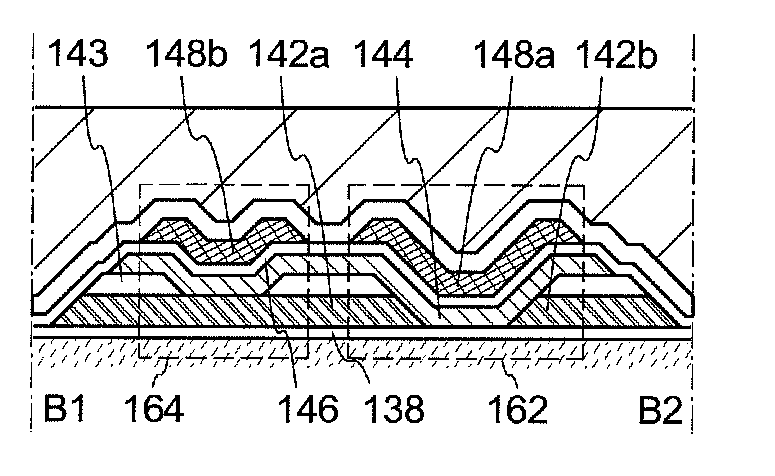

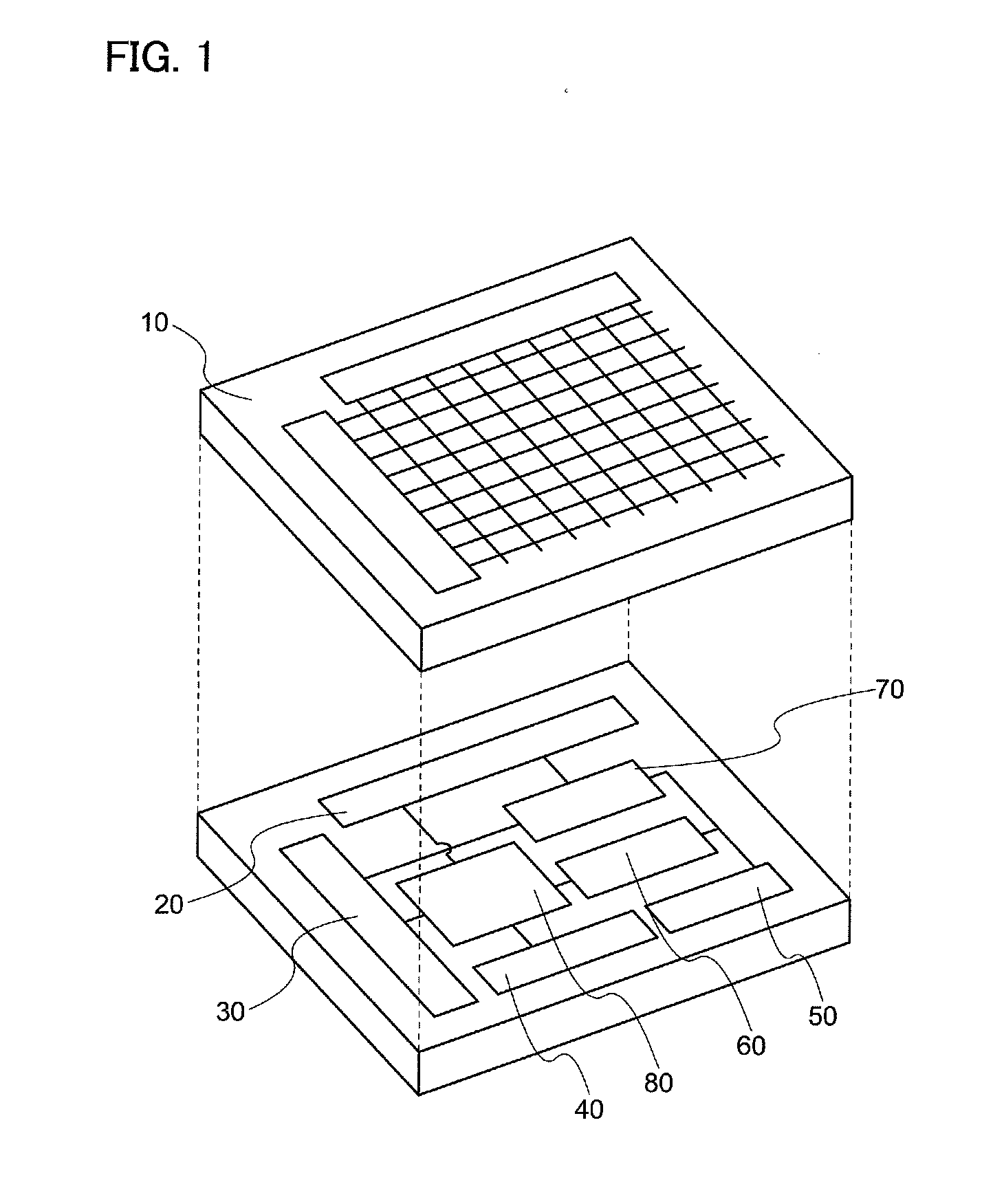

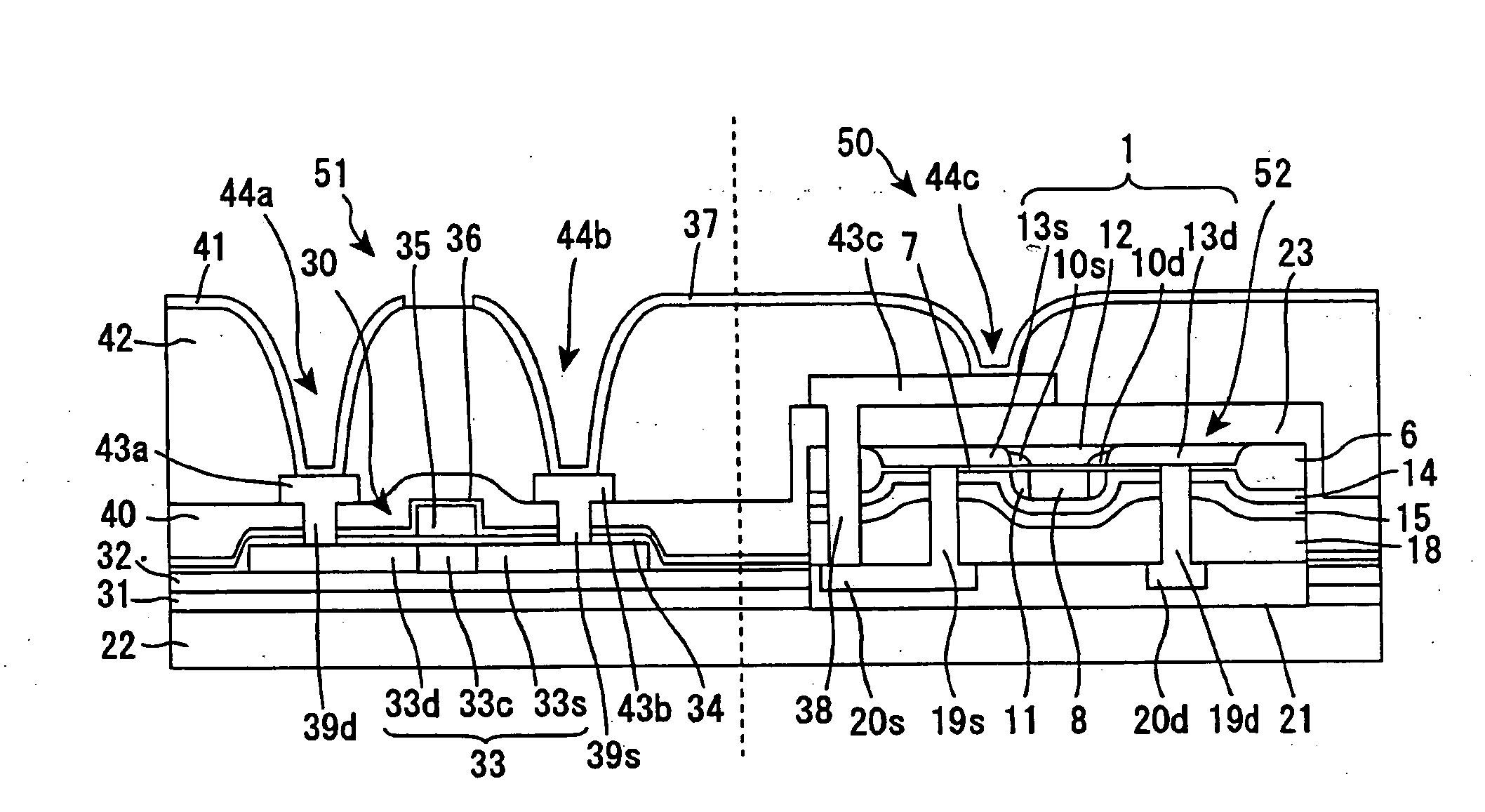

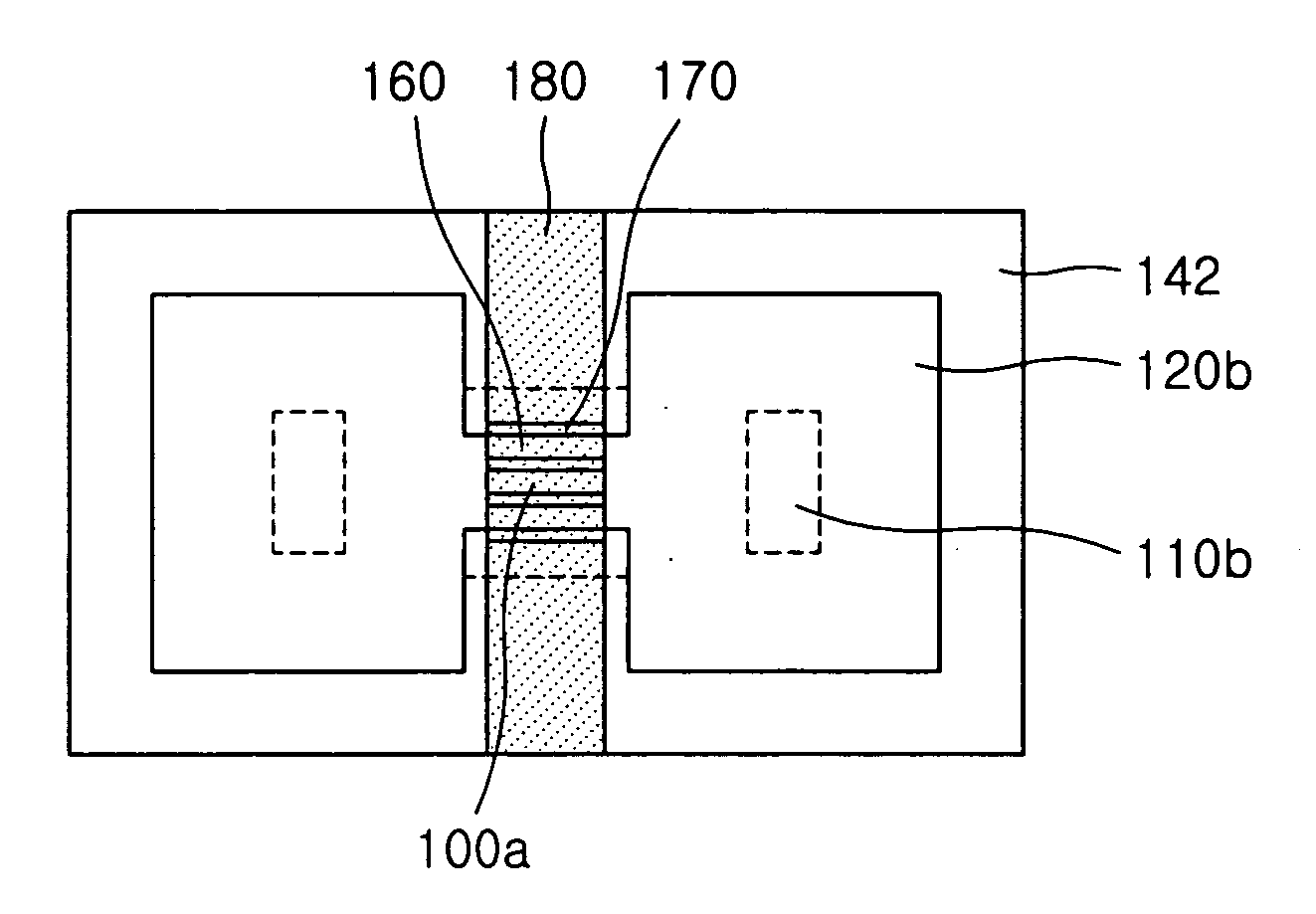

Semiconductor device

ActiveUS20090002590A1Low costIncrease speedSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringSingle crystal

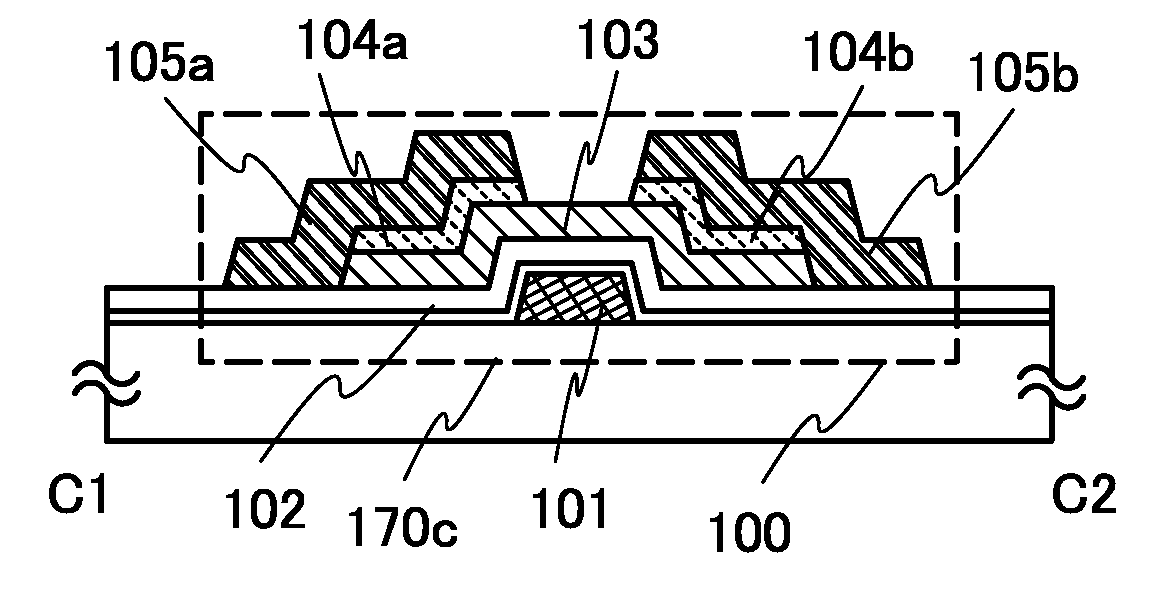

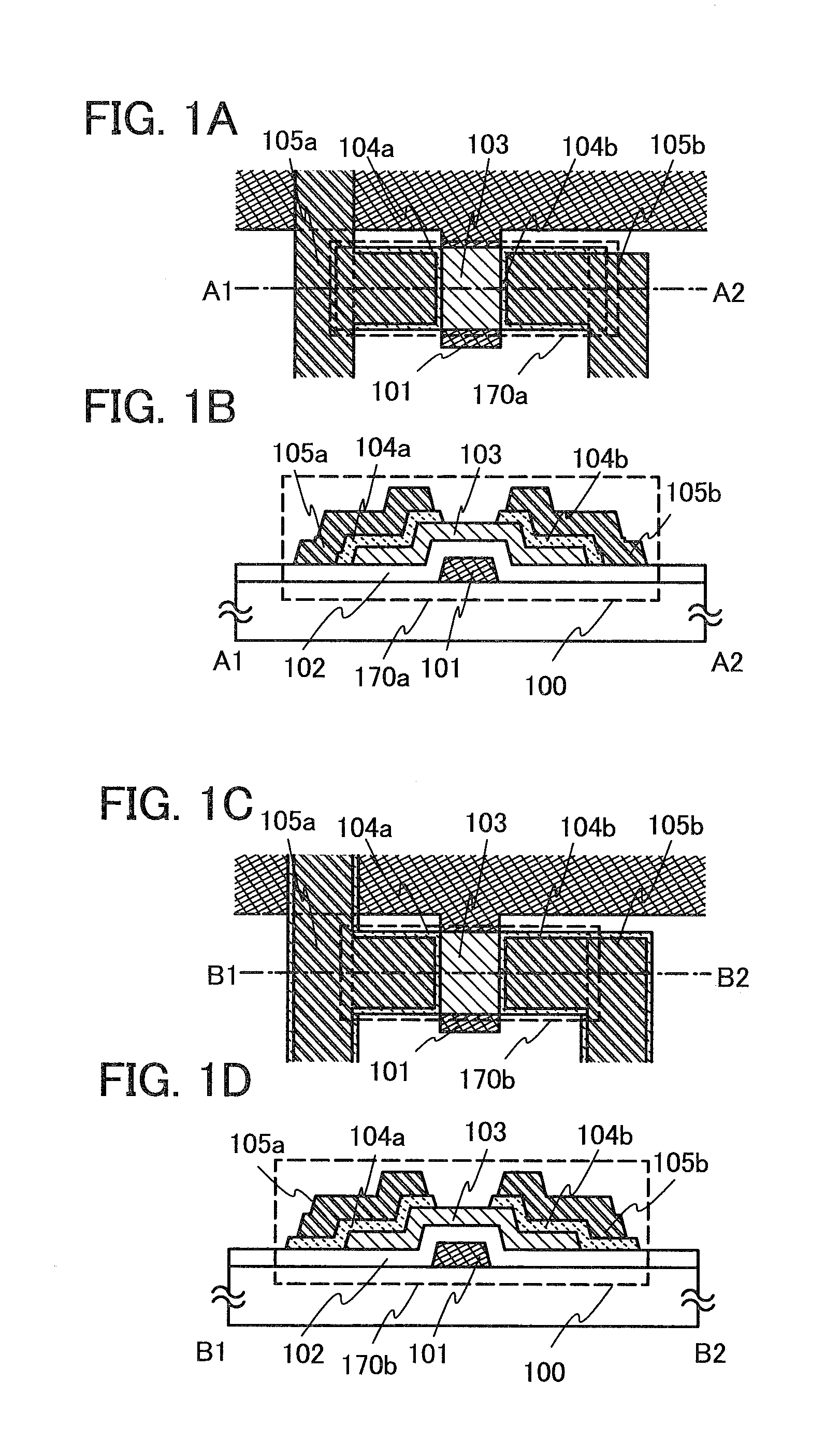

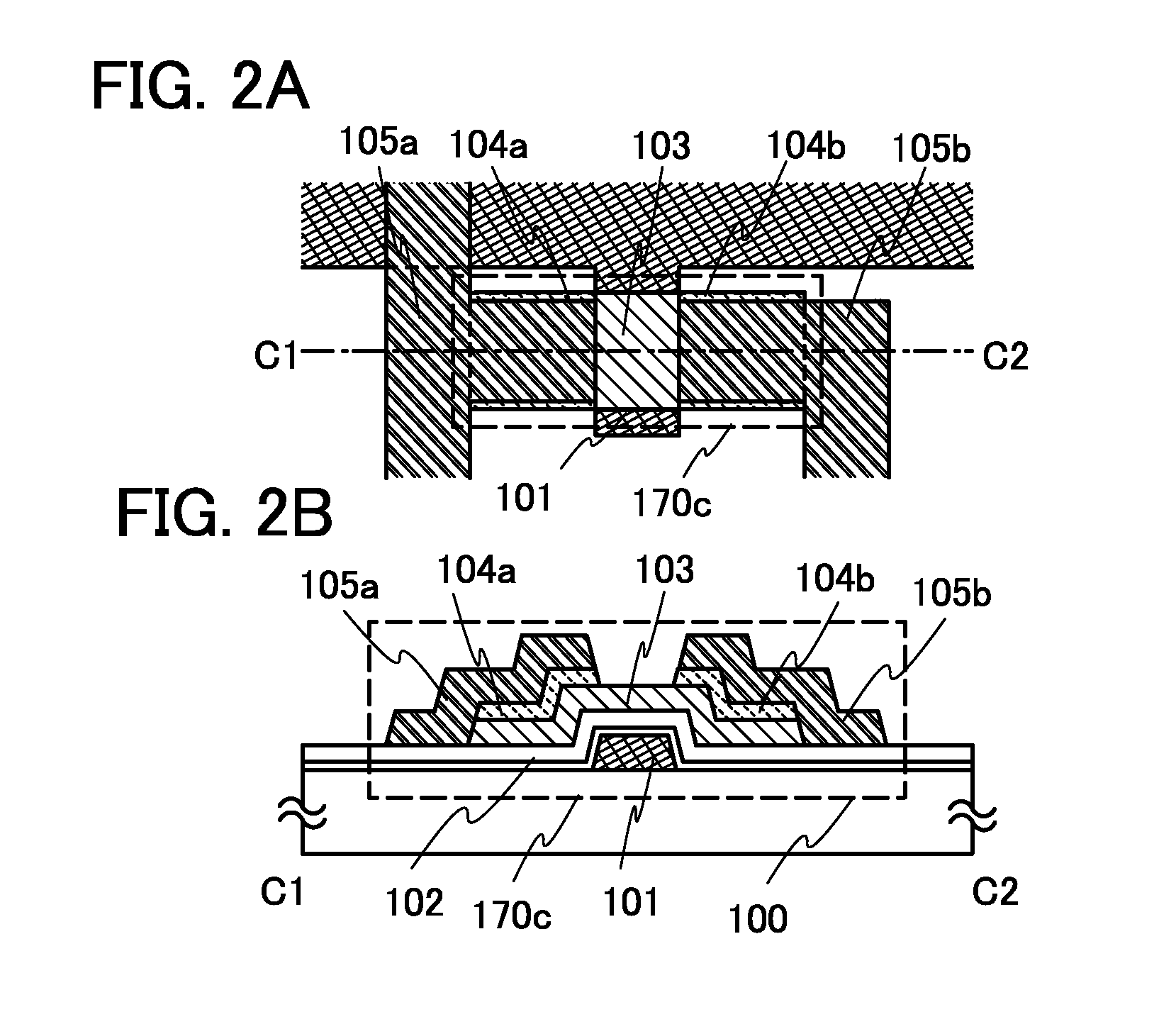

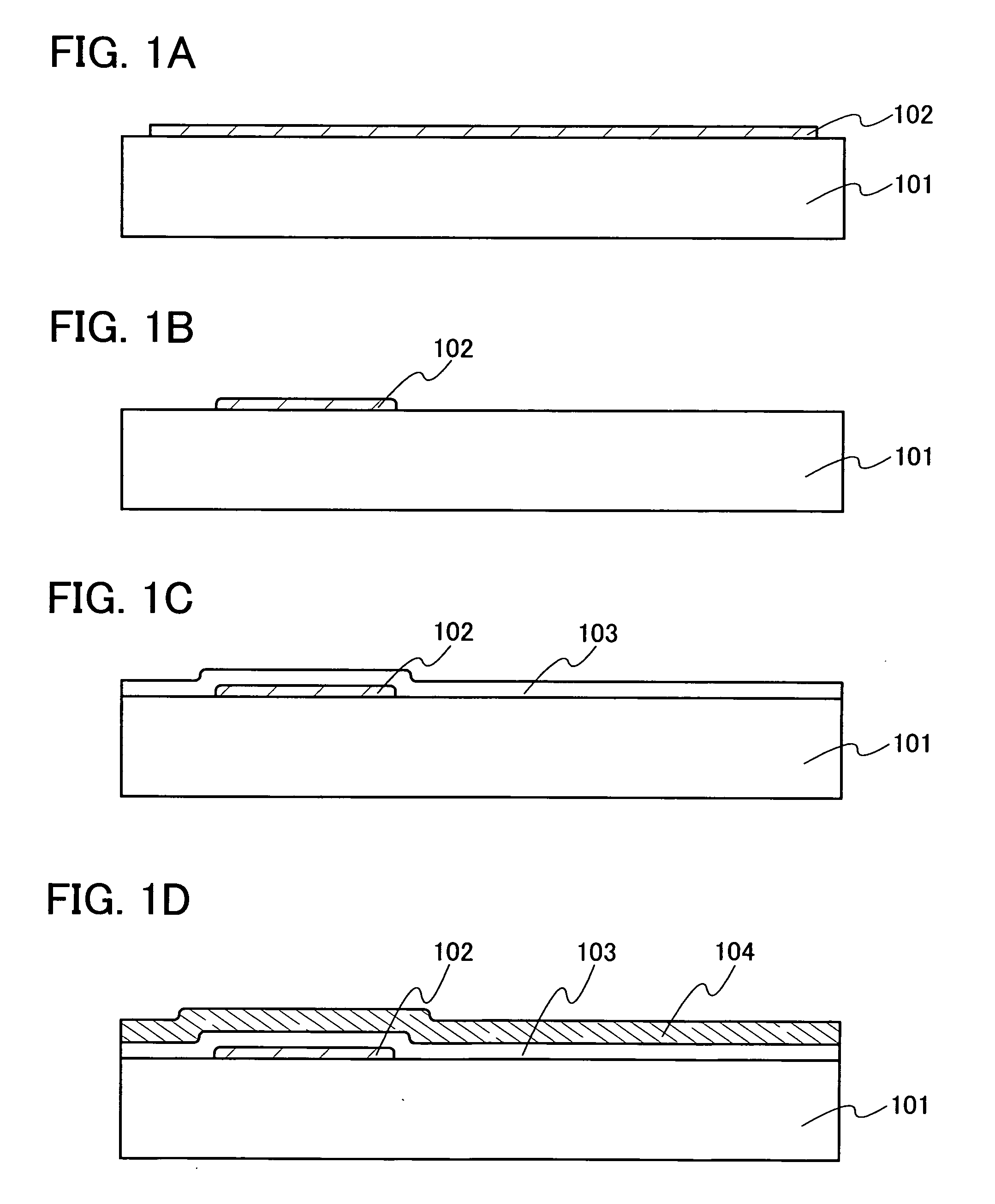

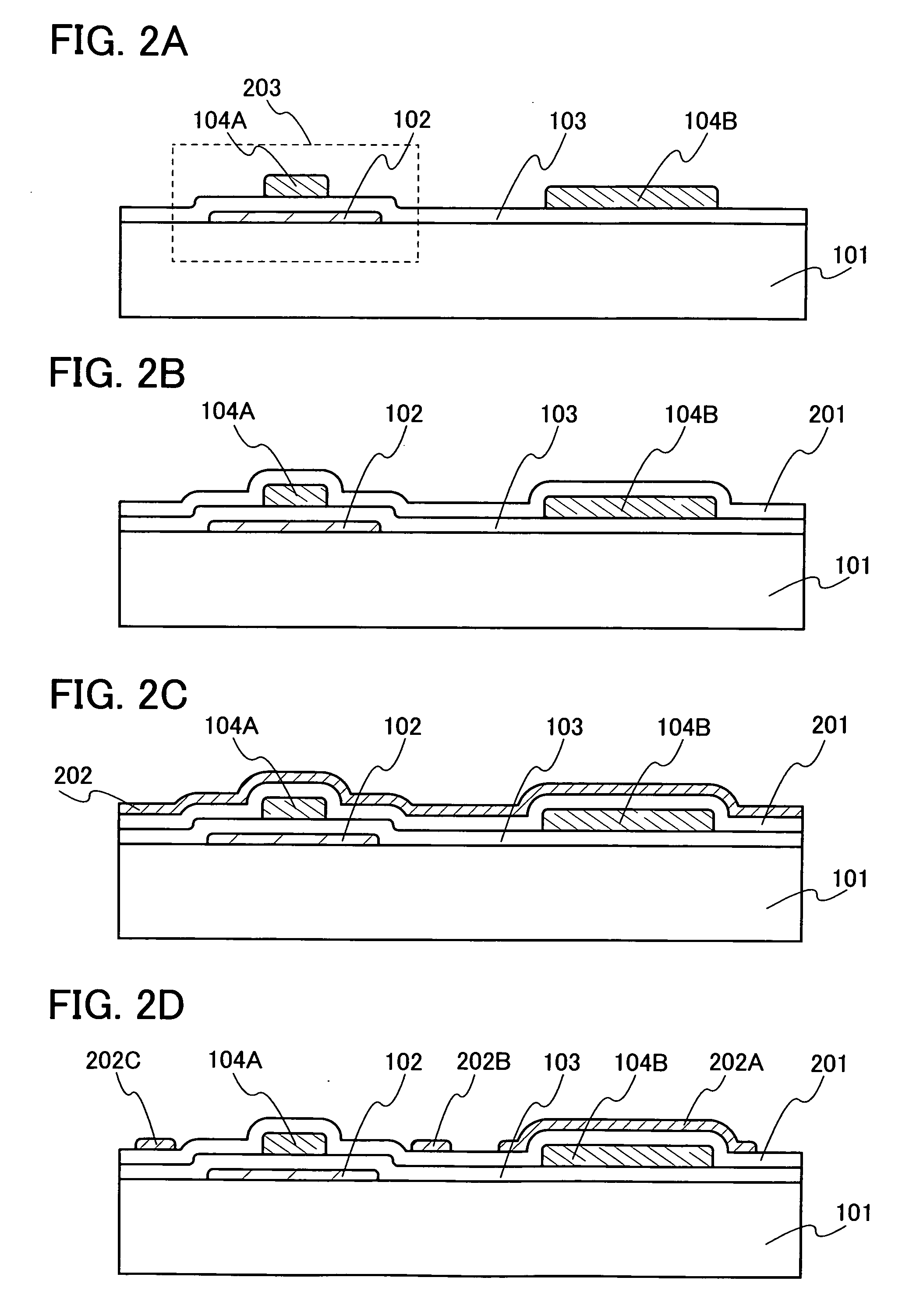

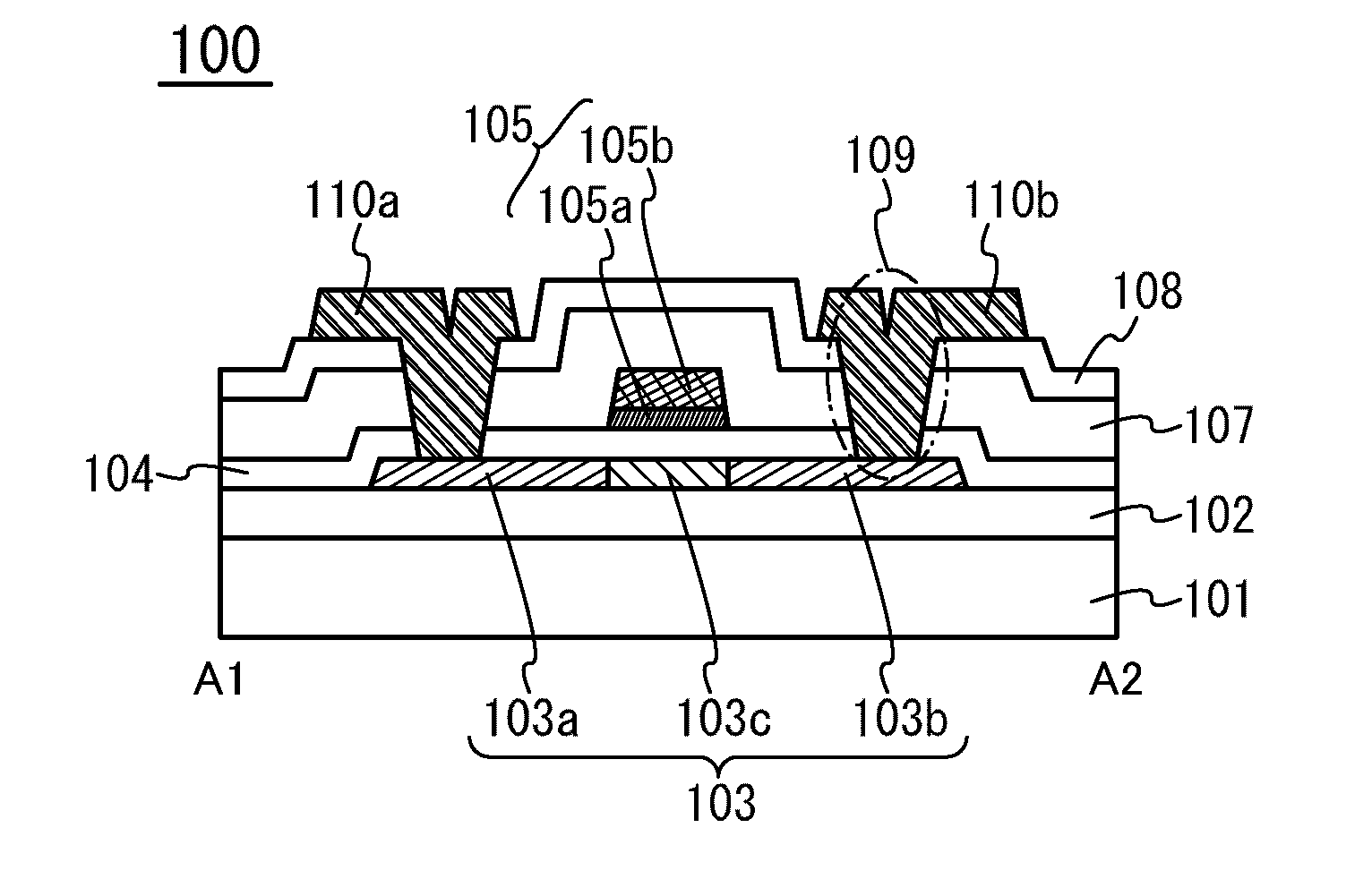

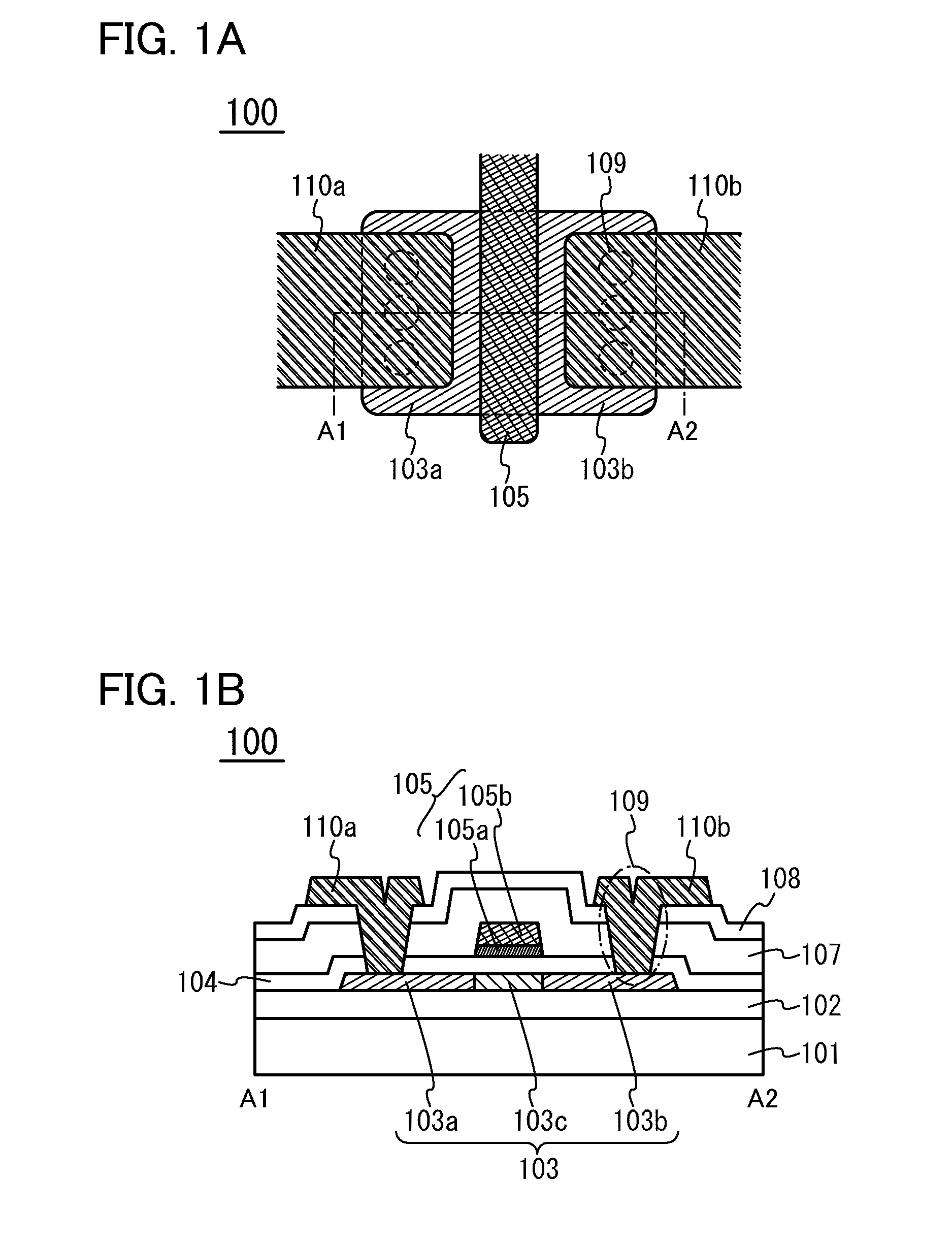

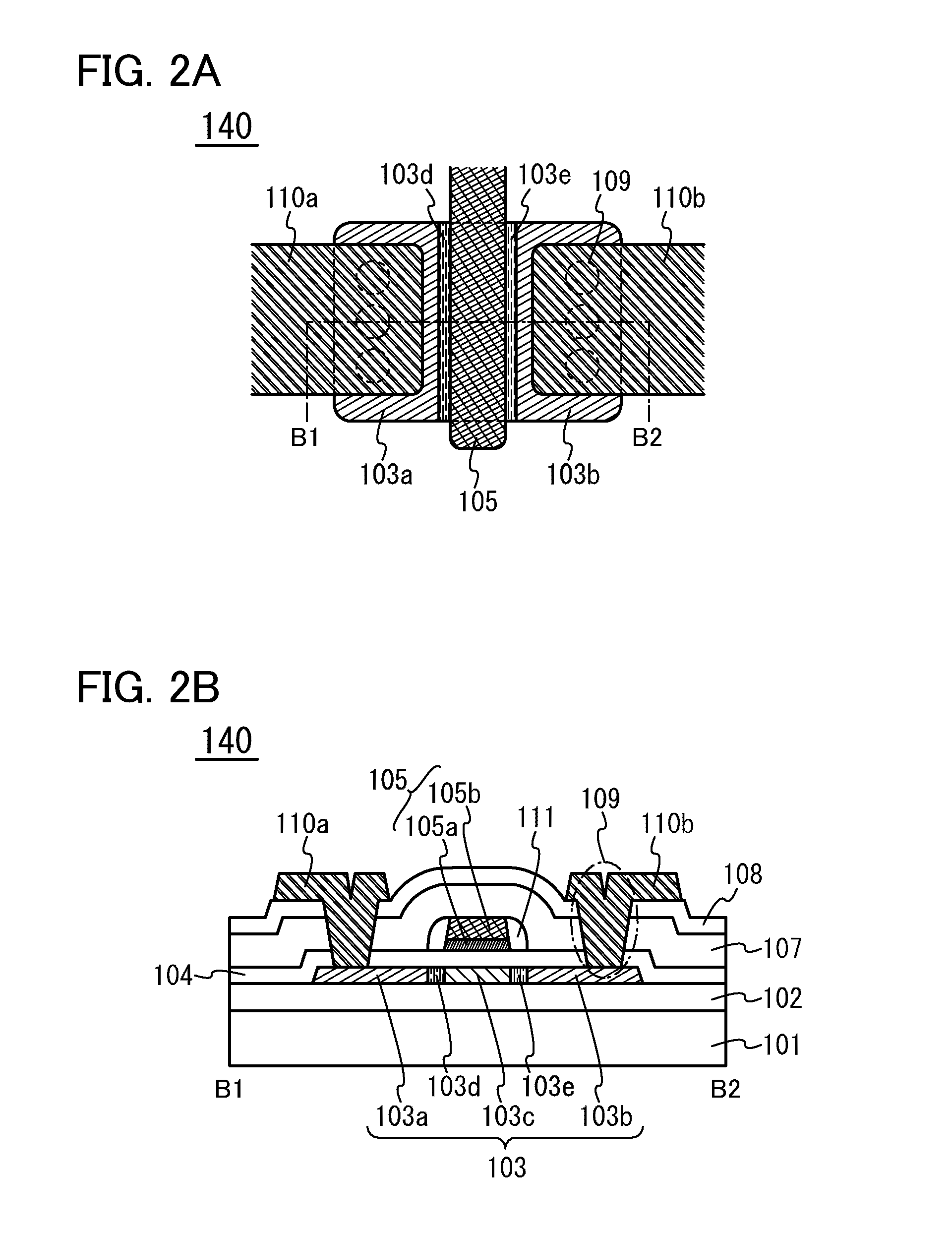

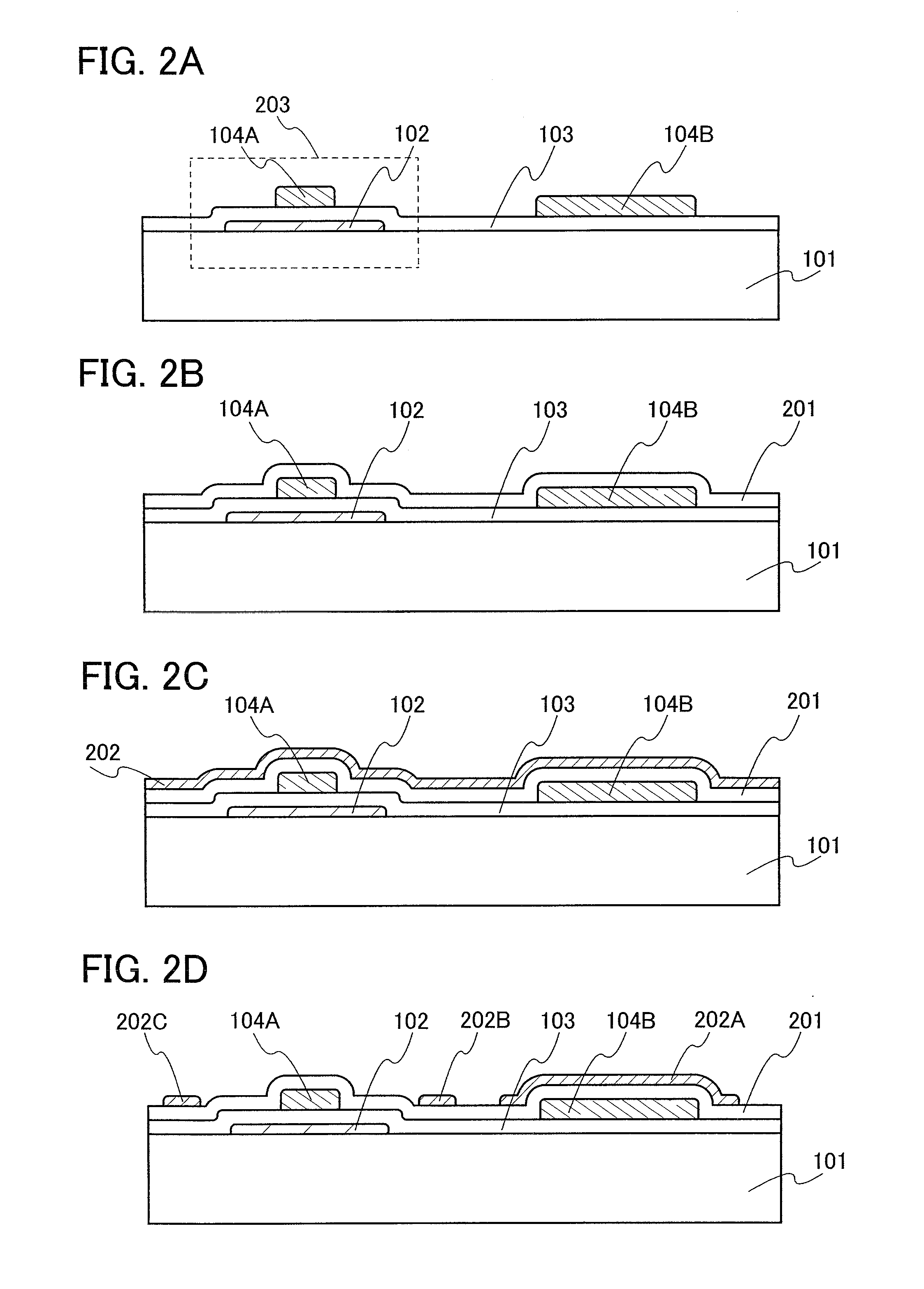

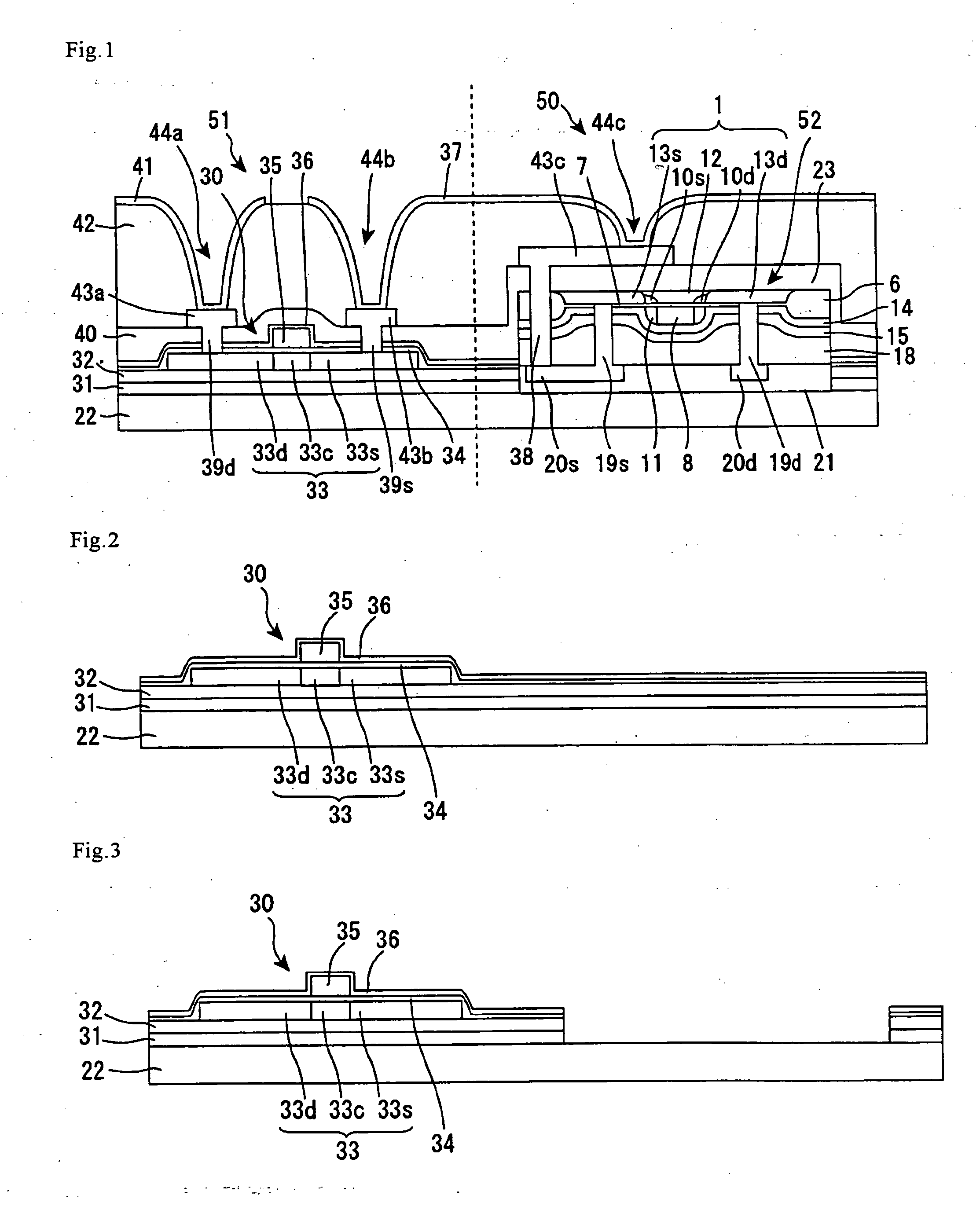

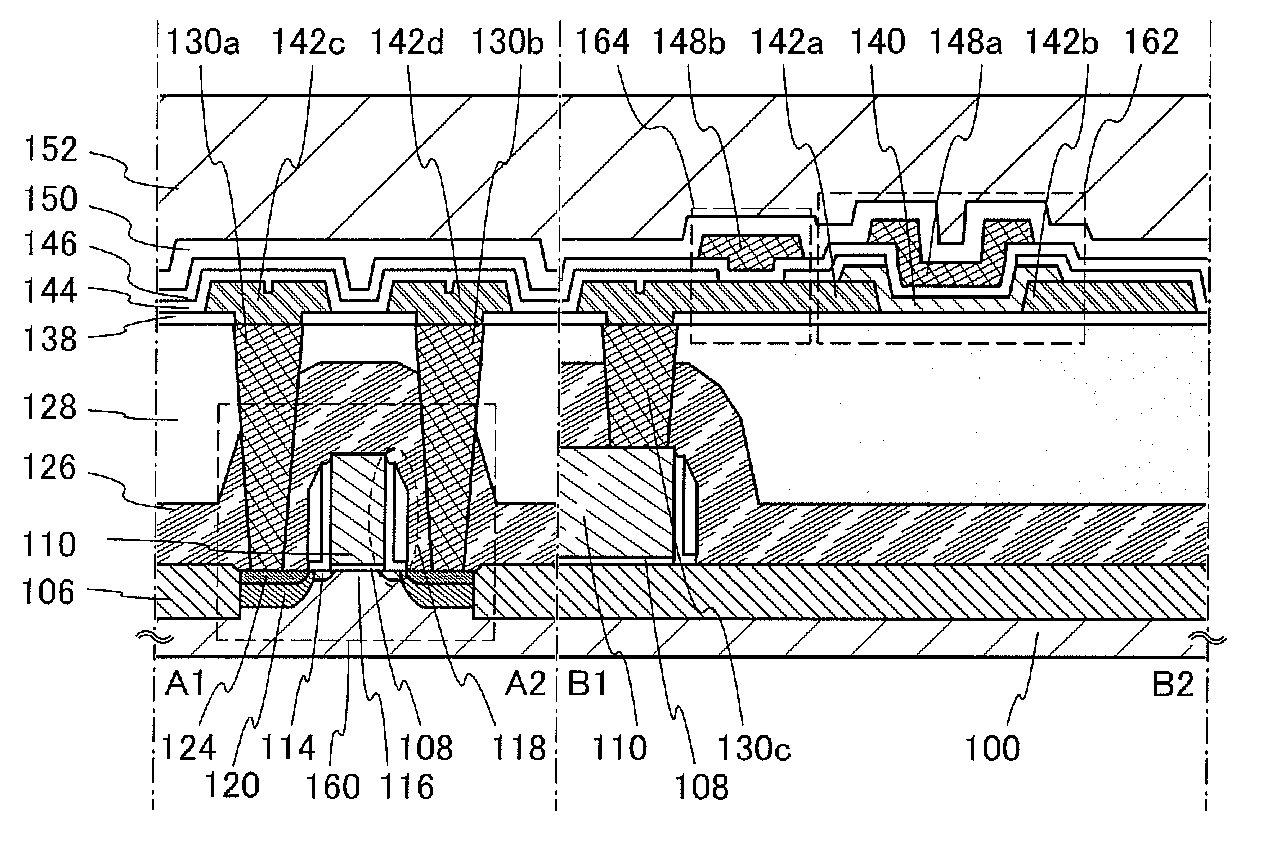

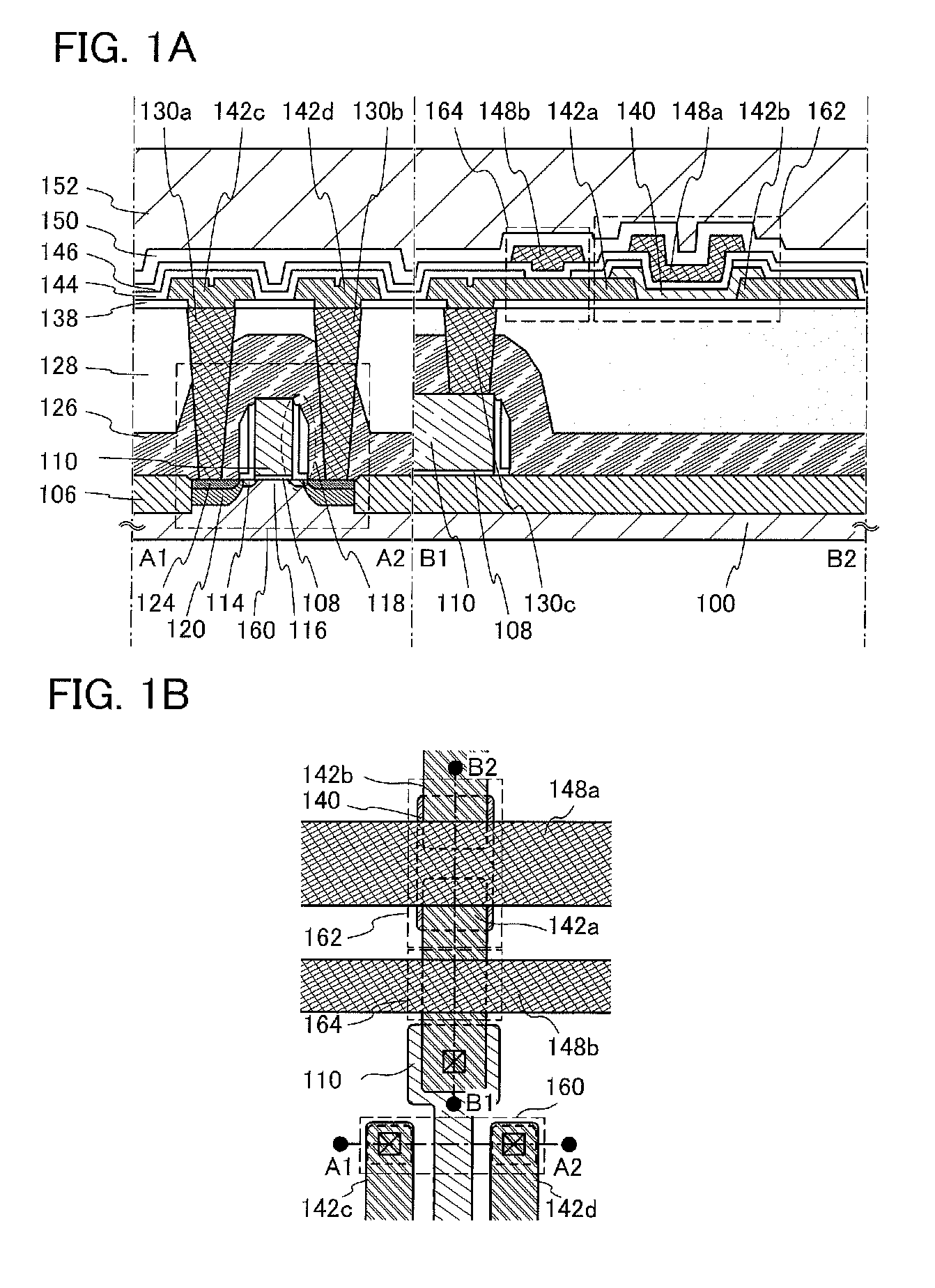

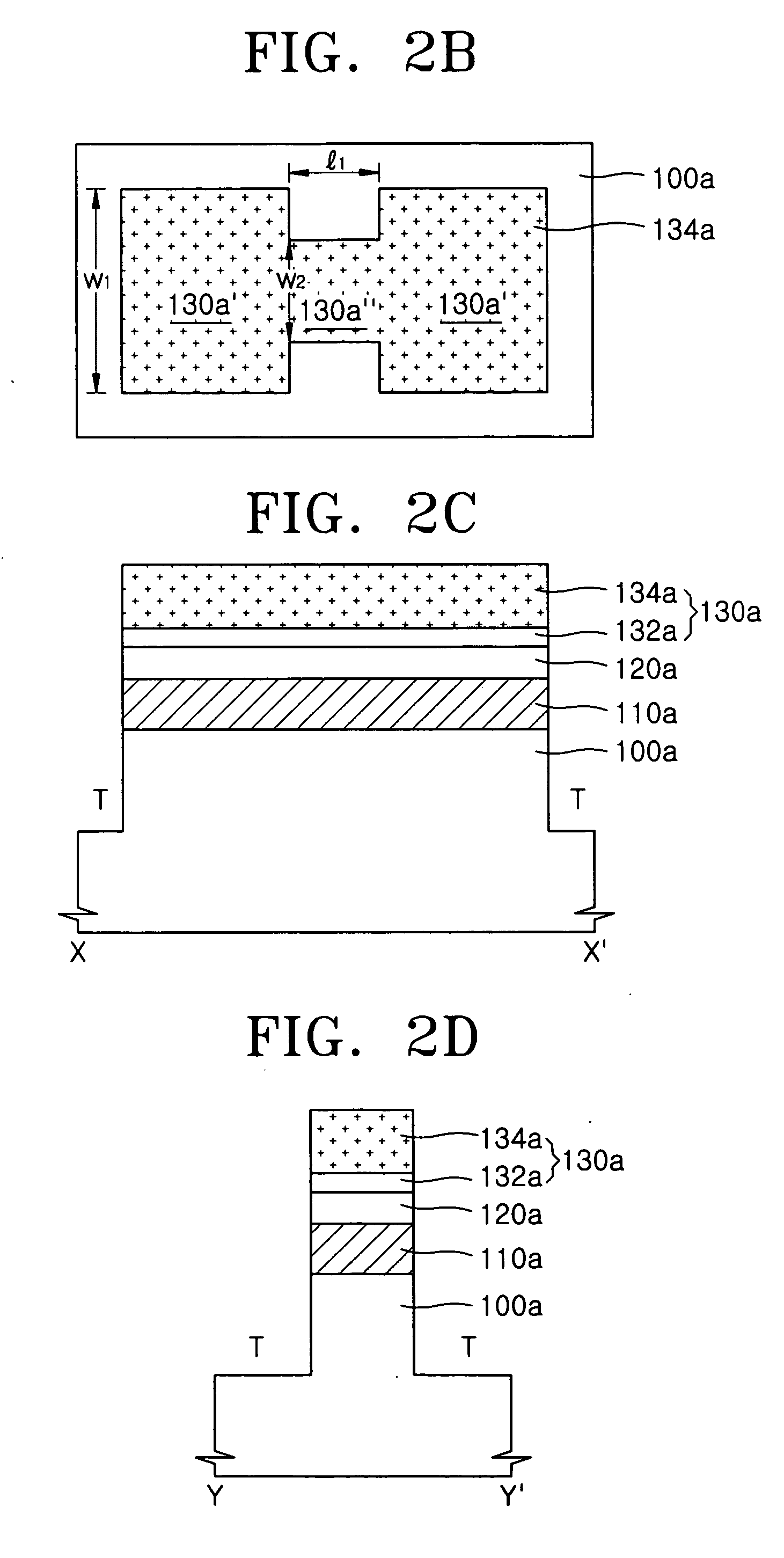

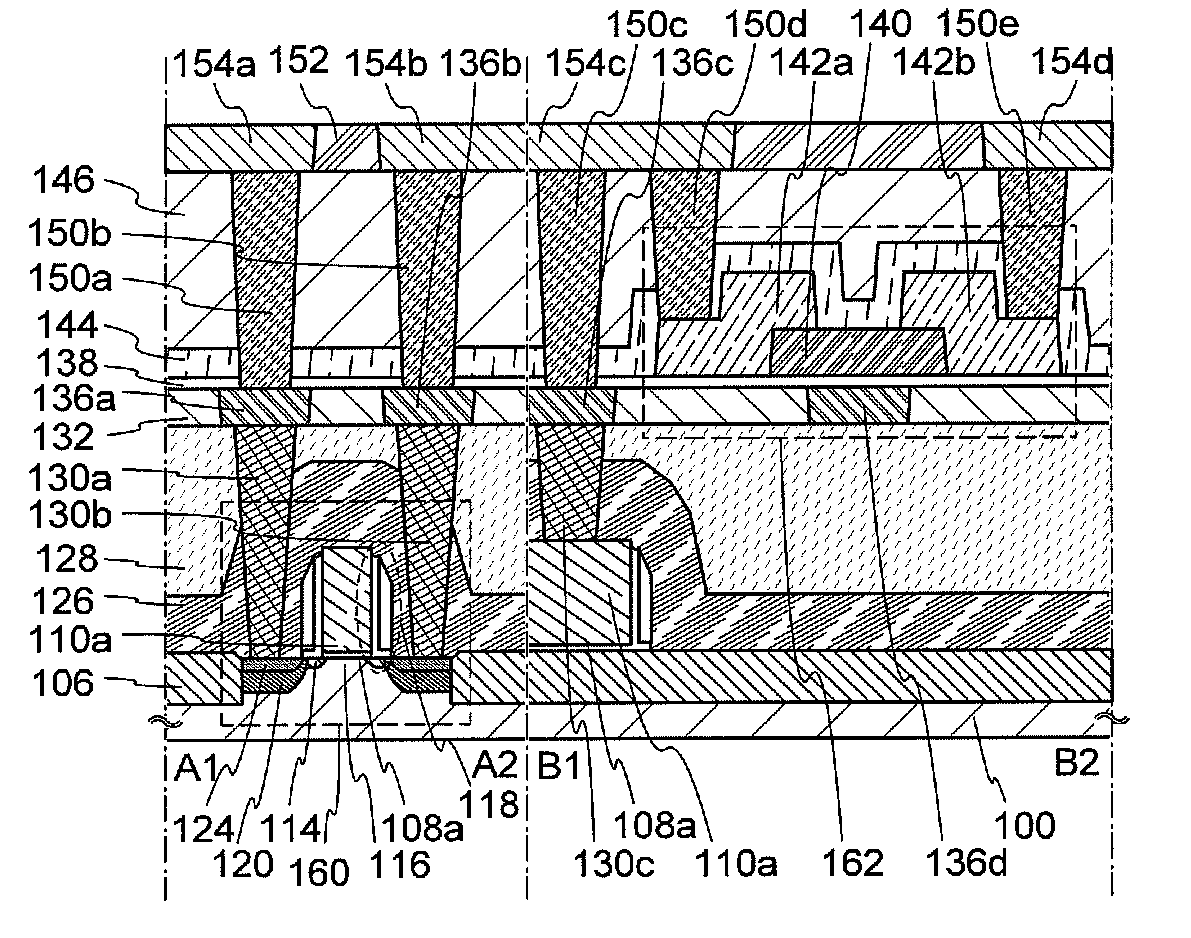

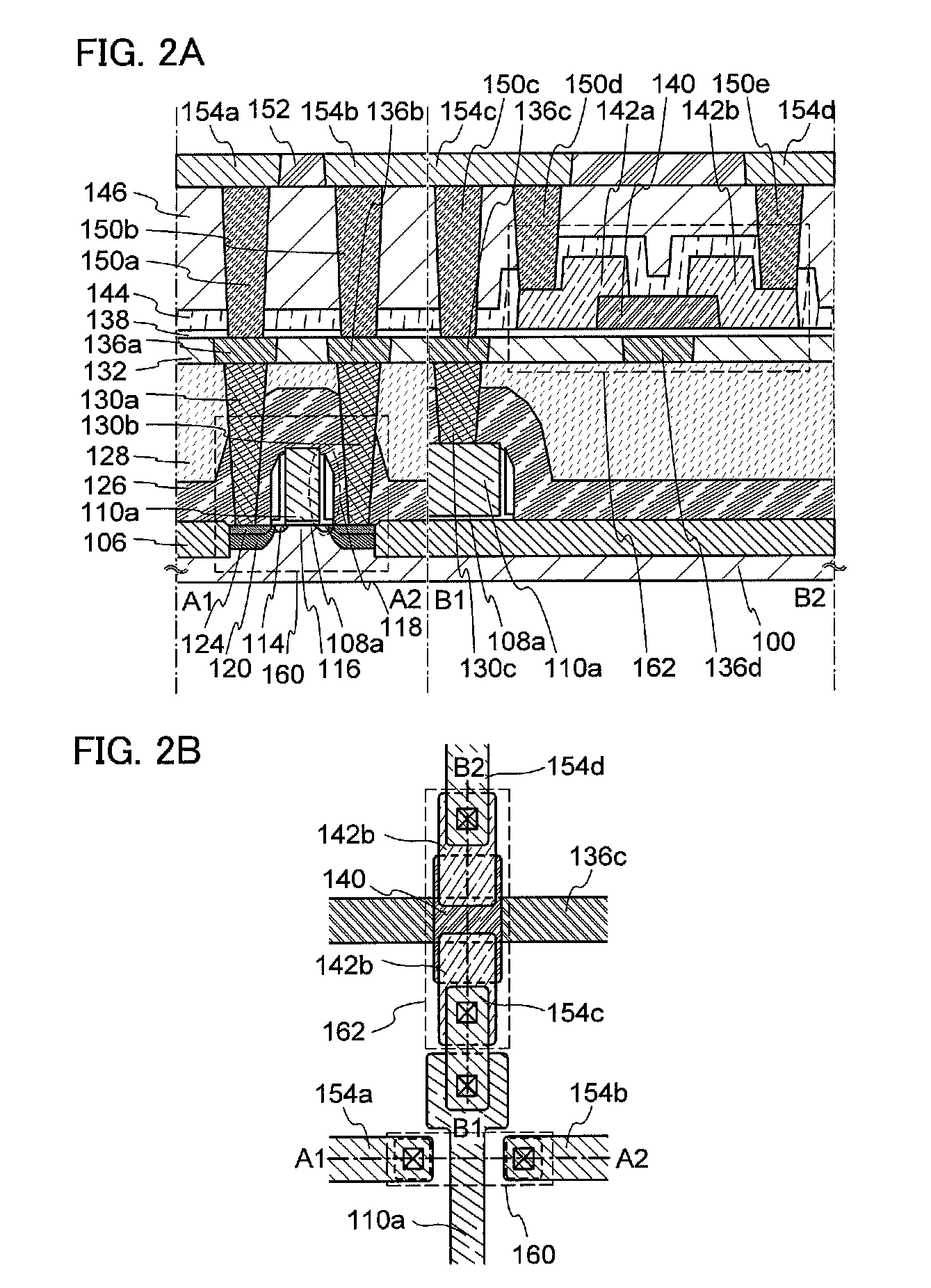

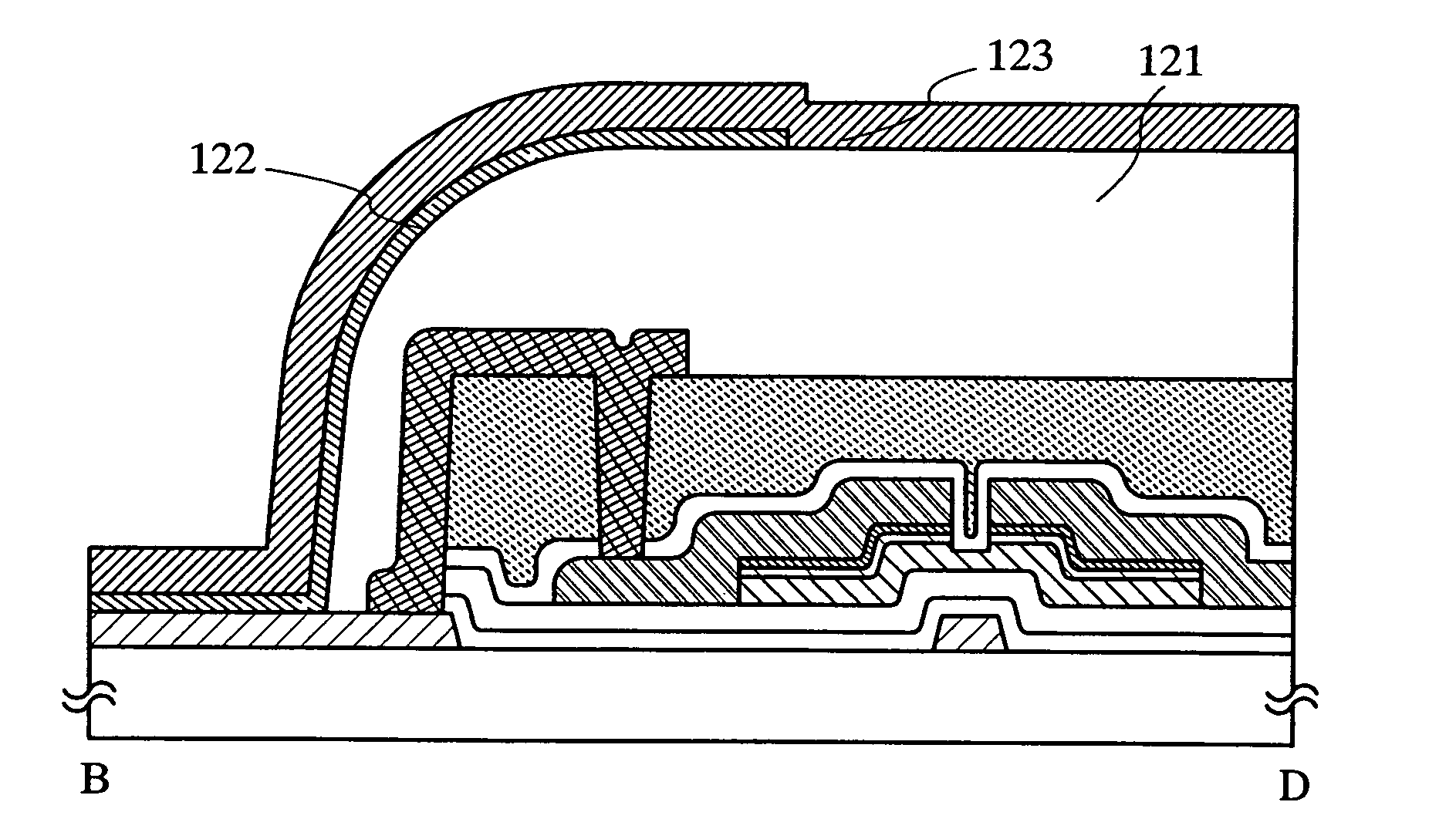

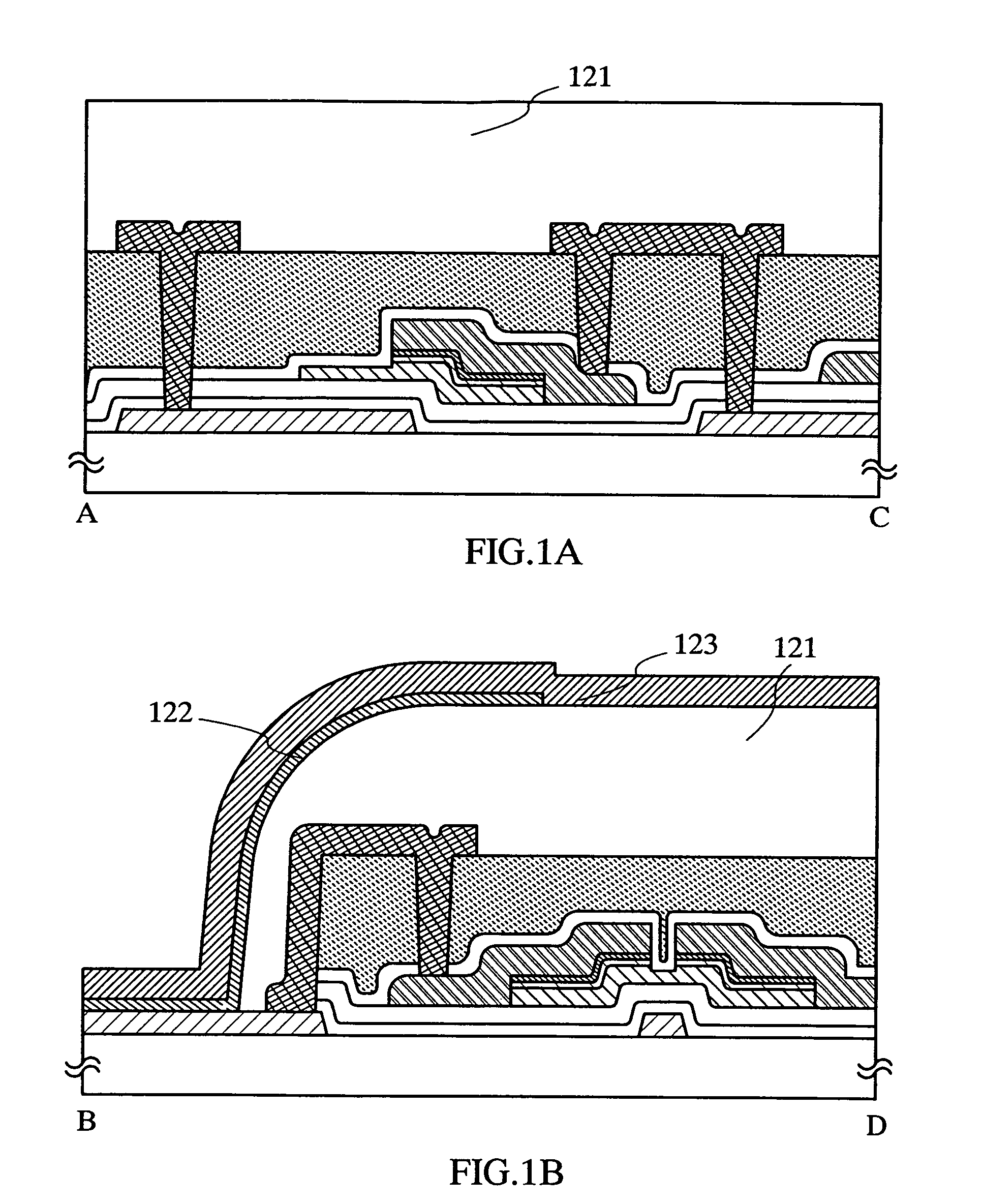

It is an object to provide a semiconductor device which has a large size and operates at high speed. A top gate transistor which includes a semiconductor layer of single-crystal and a bottom gate transistor which includes a semiconductor layer of amorphous silicon (microcrystalline silicon) are formed over the same substrate. Then, gate electrodes of each transistor are formed with the same layer, and source and drain electrodes are also formed with the same layer. Thus, manufacturing steps are reduced. In other words, two types of transistors can be manufactured by adding only a few steps to the manufacturing process of a bottom gate transistor.

Owner:SEMICON ENERGY LAB CO LTD

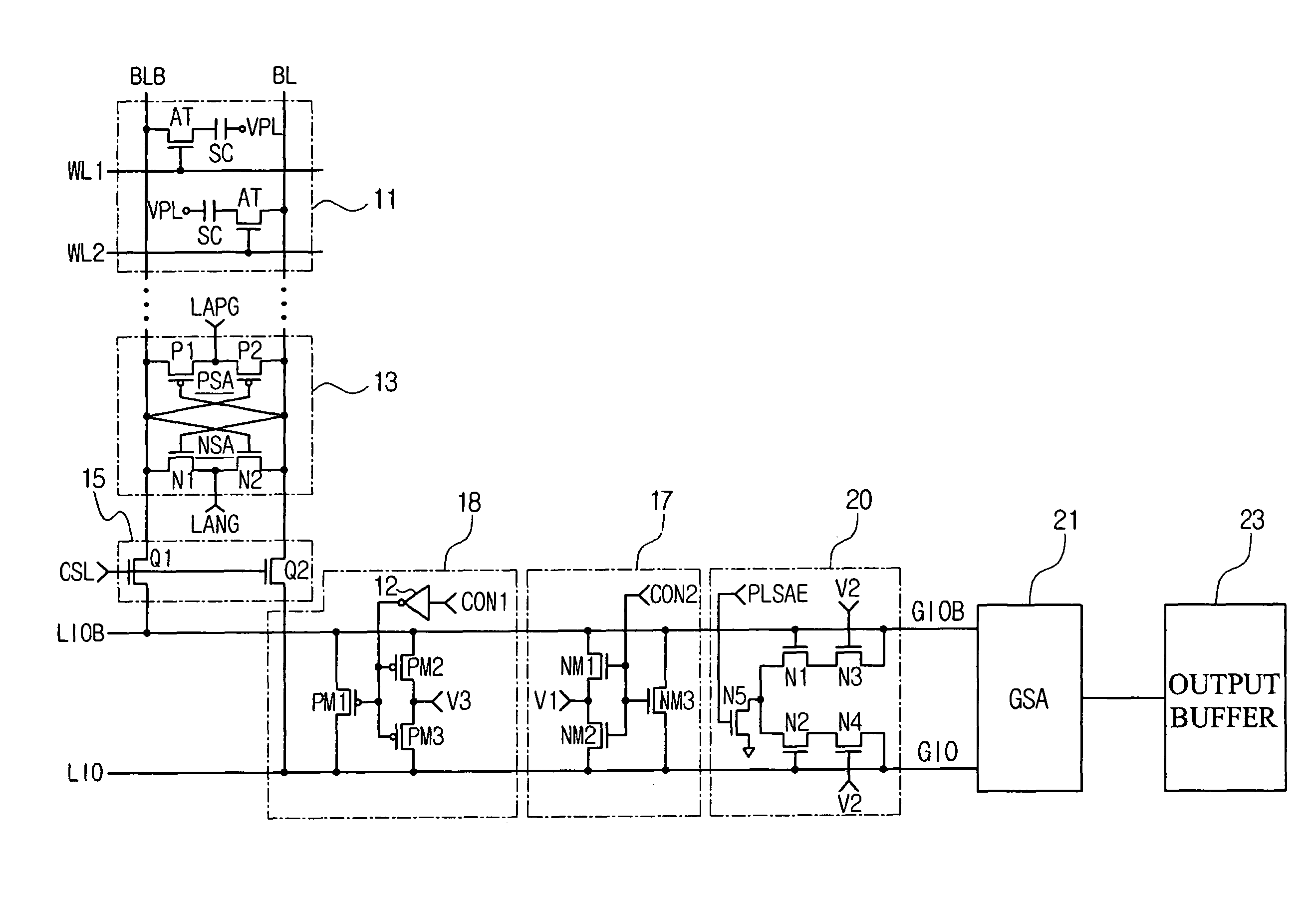

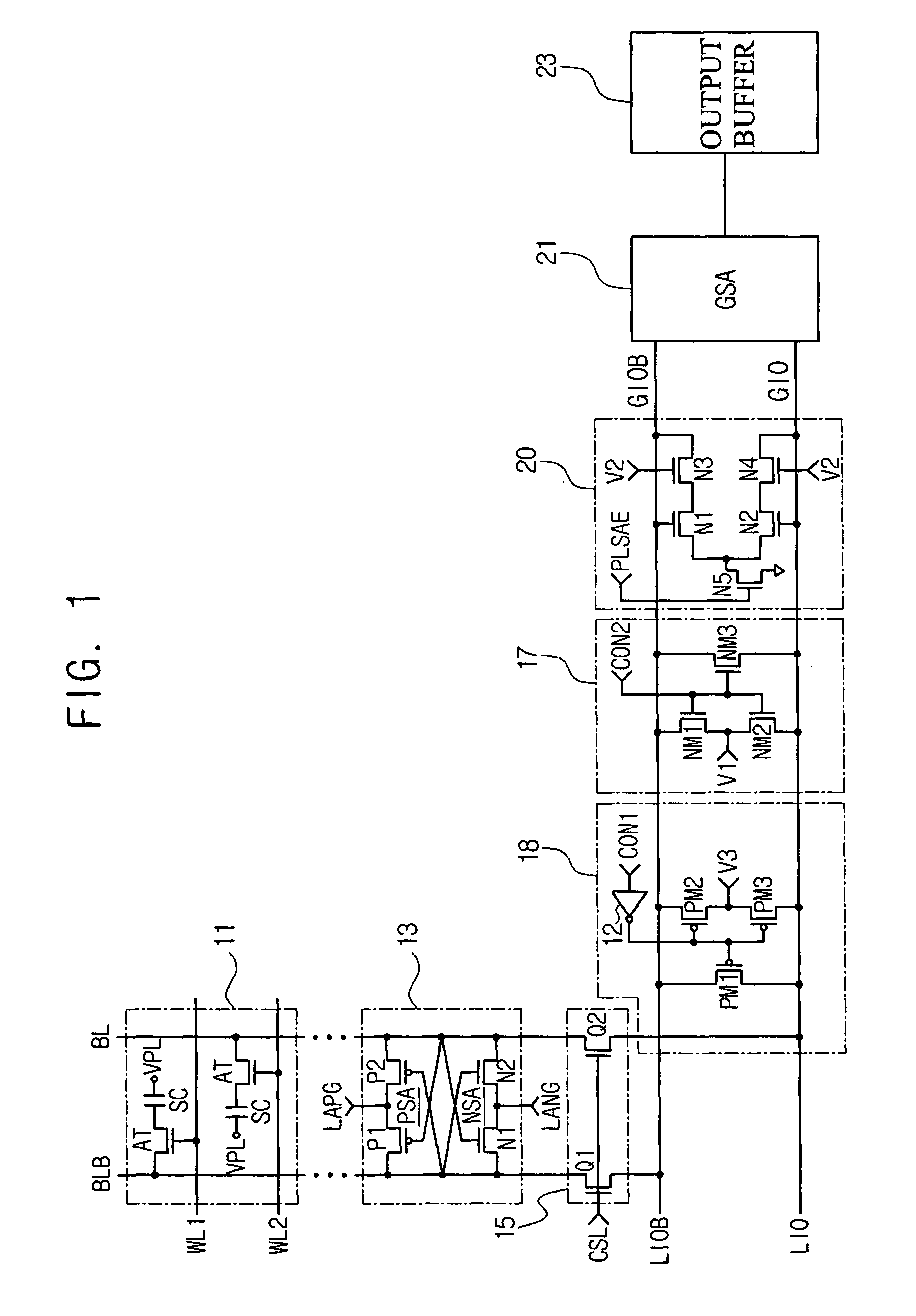

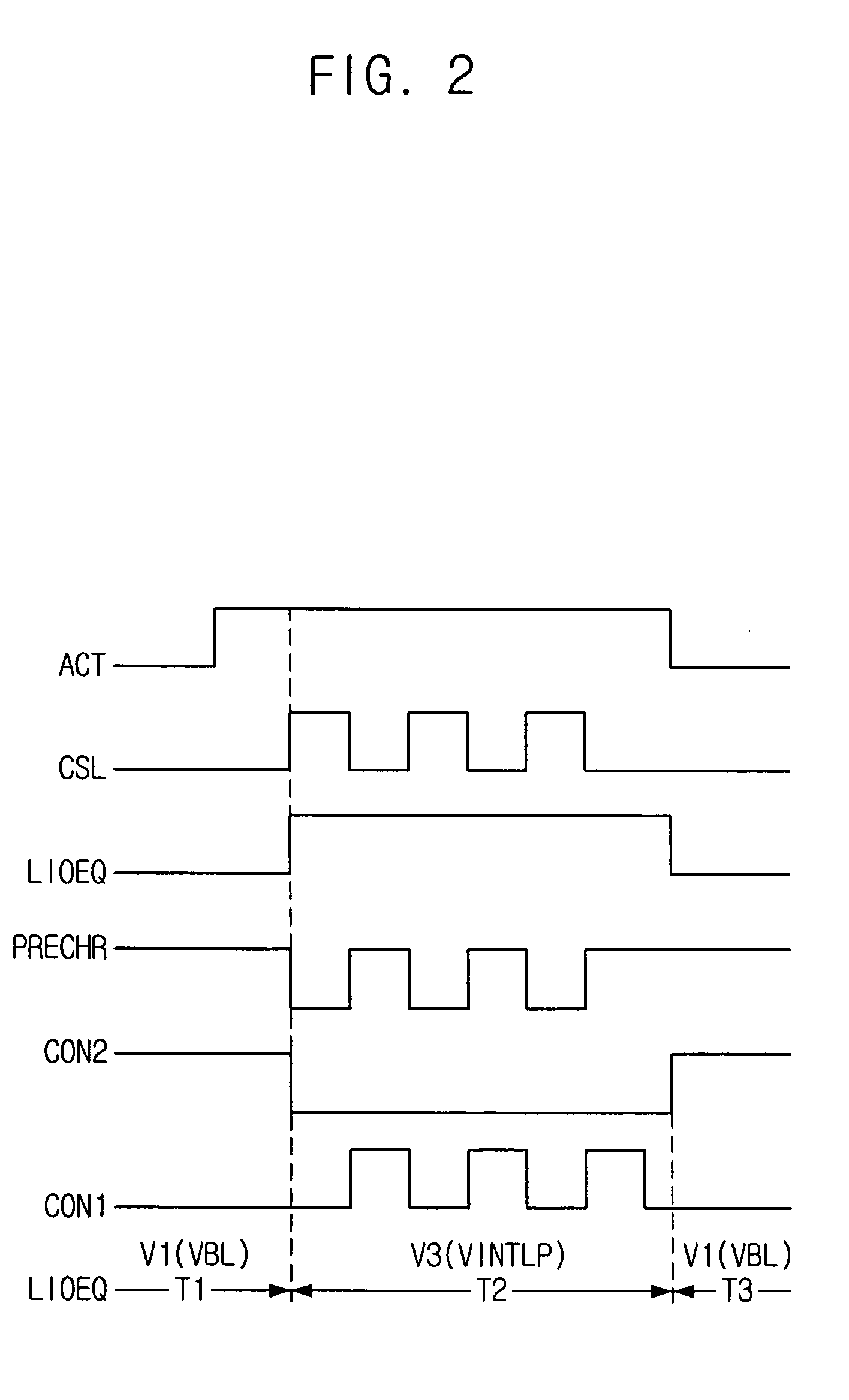

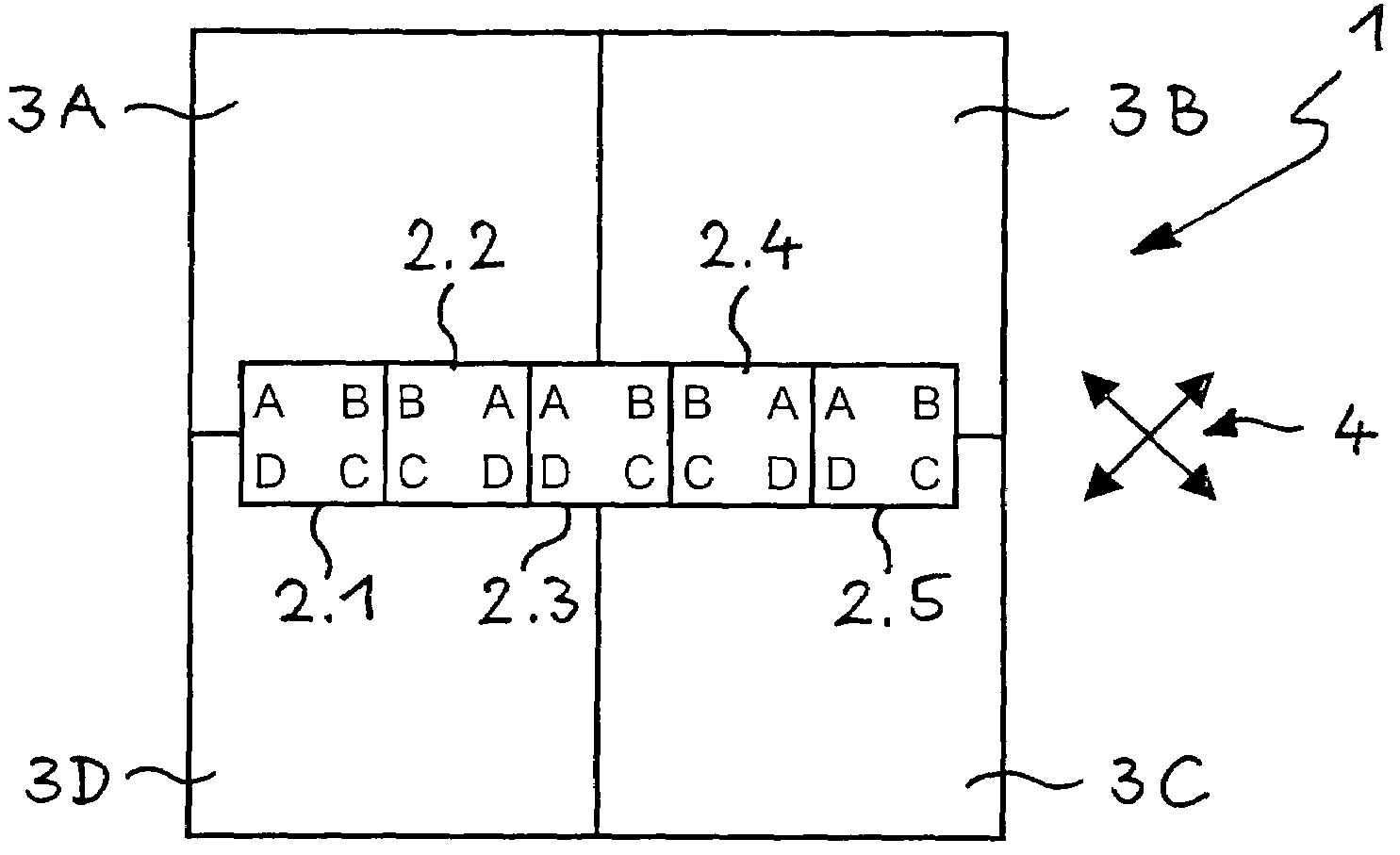

Semiconductor memory device having improved local input/output line precharge scheme

ActiveUS8213248B2Preventing bit line disturbanceRun at high speedDigital storageBit lineDatapath circuits

A data path circuit of a semiconductor memory device includes: a bit line sense amplifier driven by a first power supply voltage; a local input / output line sense amplifier; a column selecting unit operatively connecting a pair of bit lines connected to the bit line sense amplifier and a pair of local input / output lines connected to the local input / output line sense amplifier in response to a column selection signal; and a local input / output line precharge unit precharging the pair of local input / output lines with a second power supply voltage different from the first power supply voltage during a period for which the column selection signal is in an inactive state.

Owner:SAMSUNG ELECTRONICS CO LTD

Highly sensitive, fast pixel for use in an image sensor

ActiveUS7560701B2Overcomes speed limitationReasonable sensitivitySolid-state devicesMaterial analysis by optical meansElectric signalDemodulation

Owner:AMS SENSORS SINGAPORE PTE LTD

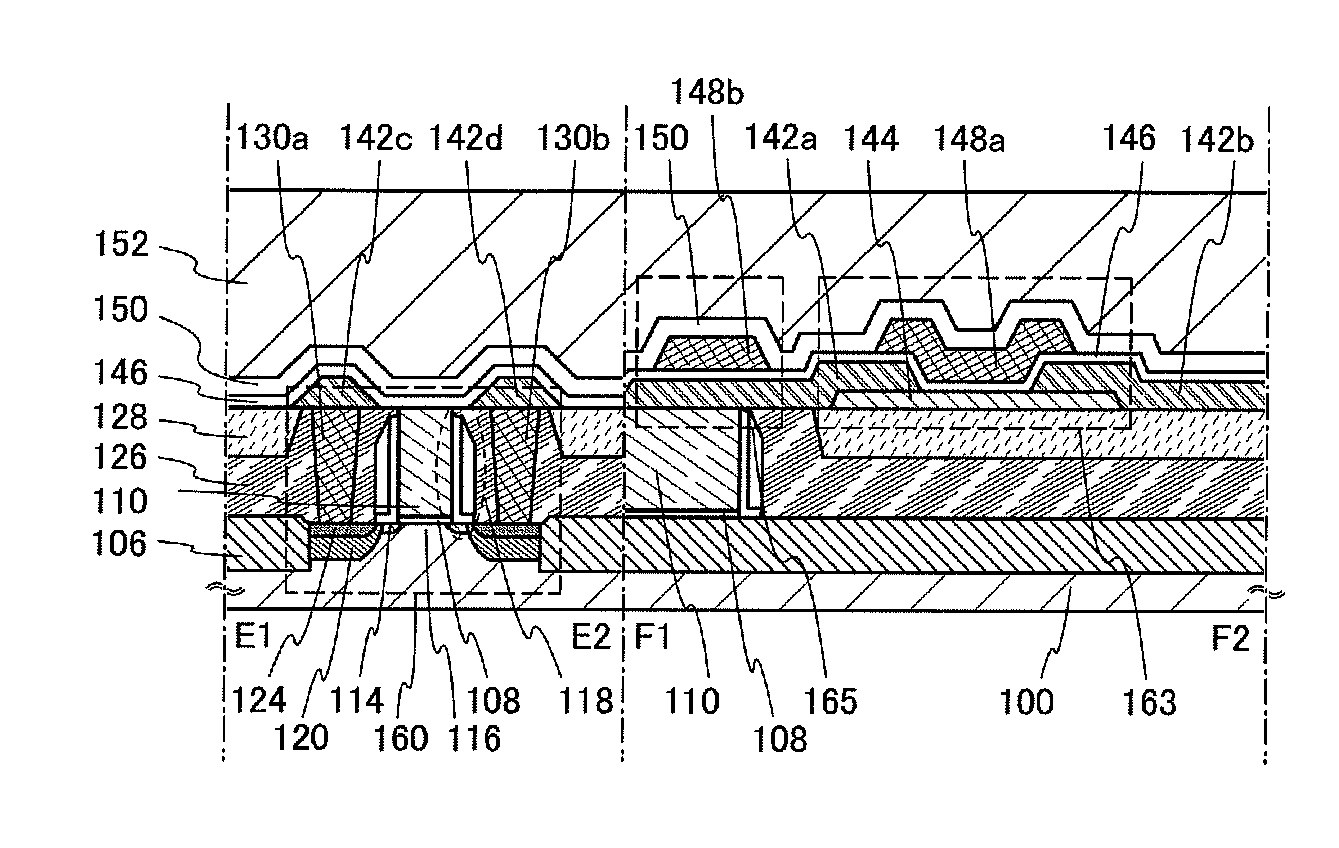

Semiconductor device and manufacturing method thereof

ActiveUS20120161126A1Reduce parasitic capacitanceIncrease speedTransistorSolid-state devicesDevice materialWurtzite crystal structure

A semiconductor device capable of high speed operation is provided. Further, a semiconductor device in which change in electric characteristics due to a short channel effect is hardly caused is provided. An oxide semiconductor having crystallinity is used for a semiconductor layer of a transistor. A channel formation region, a source region, and a drain region are formed in the semiconductor layer. The source region and the drain region are formed by self-aligned process in which one or more elements selected from Group 15 elements are added to the semiconductor layer with the use of a gate electrode as a mask. The source region and the drain region can have a wurtzite crystal structure.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device

InactiveUS20100193785A1Low costReduce power consumptionTransistorSolid-state devicesSemiconductor packageSingle crystal

It is an object to provide a semiconductor device which has a large size and operates at high speed. A top gate transistor which includes a semiconductor layer of single-crystal and a bottom gate transistor which includes a semiconductor layer of amorphous silicon (microcrystalline silicon) are formed over the same substrate. Then, gate electrodes of each transistor are formed with the same layer, and source and drain electrodes are also formed with the same layer. Thus, manufacturing steps are reduced. In other words, two types of transistors can be manufactured by adding only a few steps to the manufacturing process of a bottom gate transistor.

Owner:SEMICON ENERGY LAB CO LTD

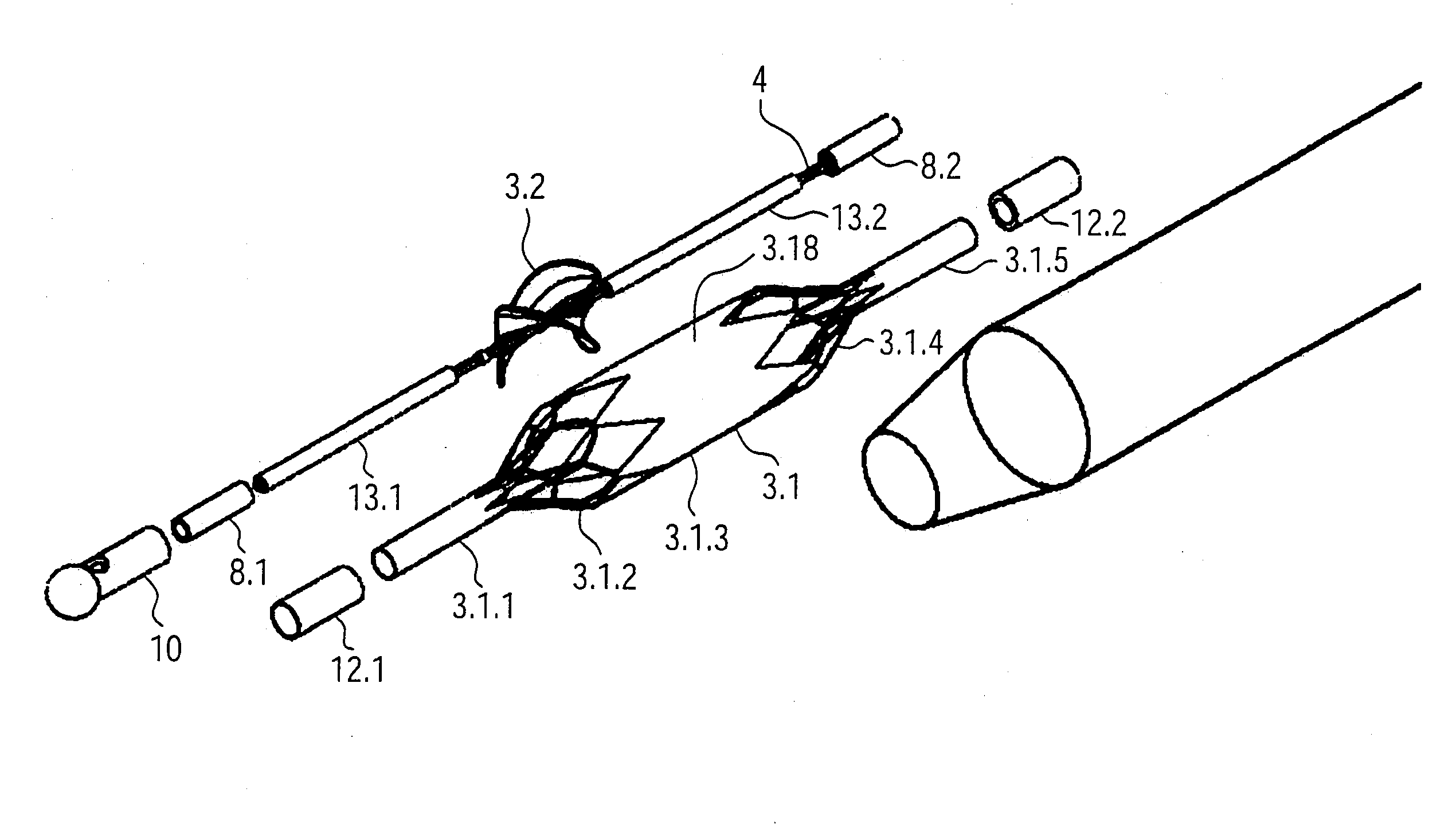

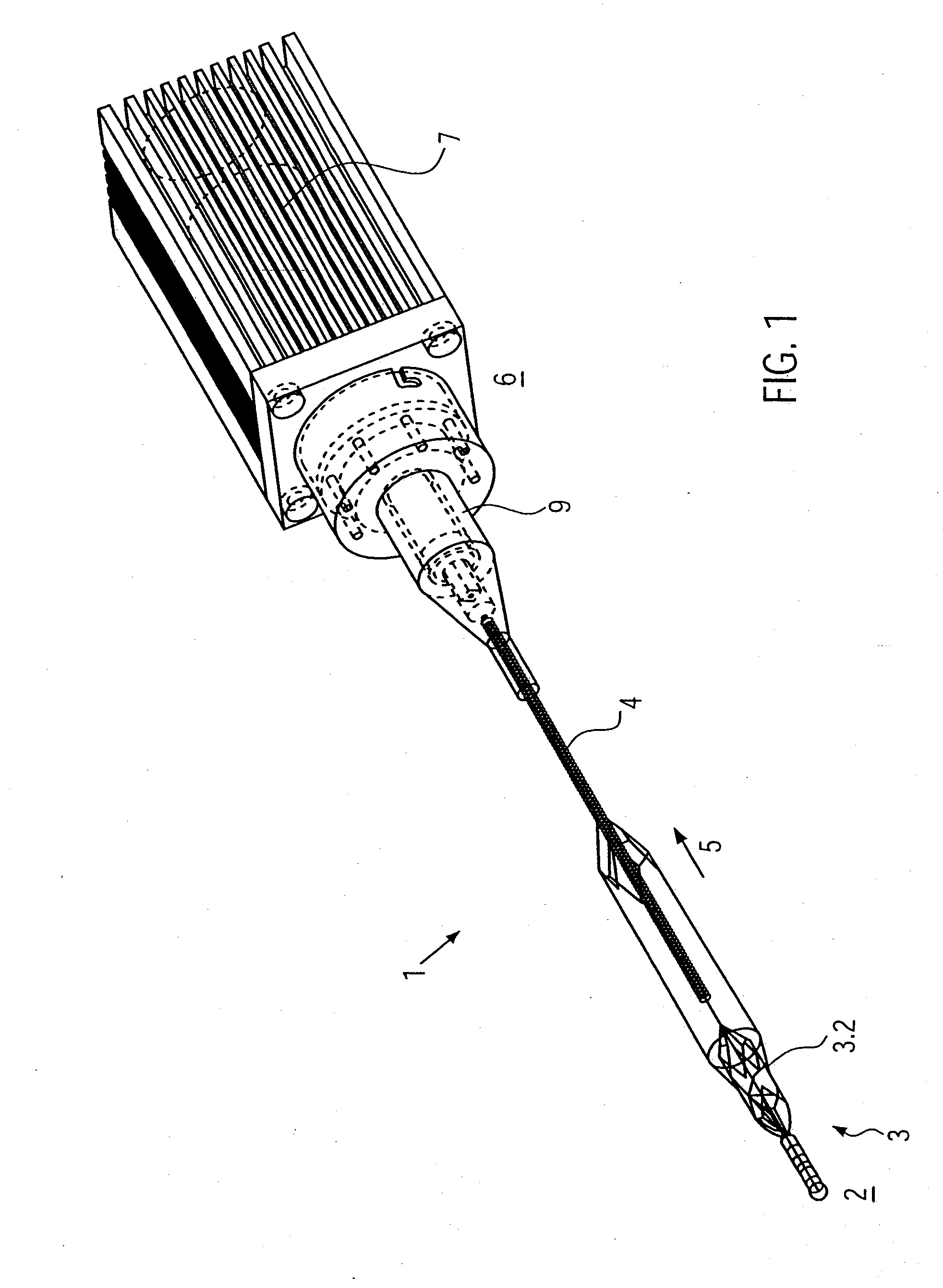

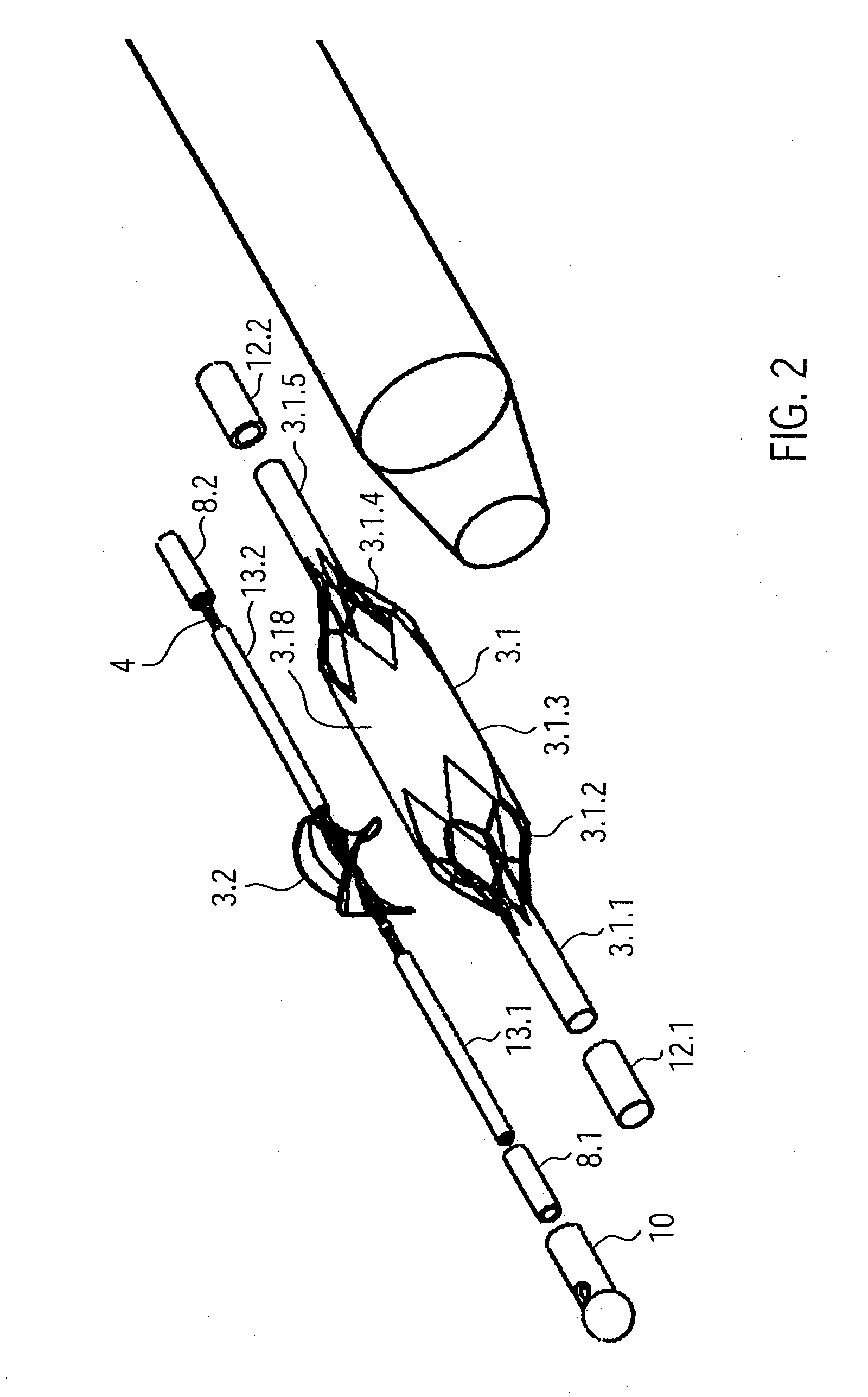

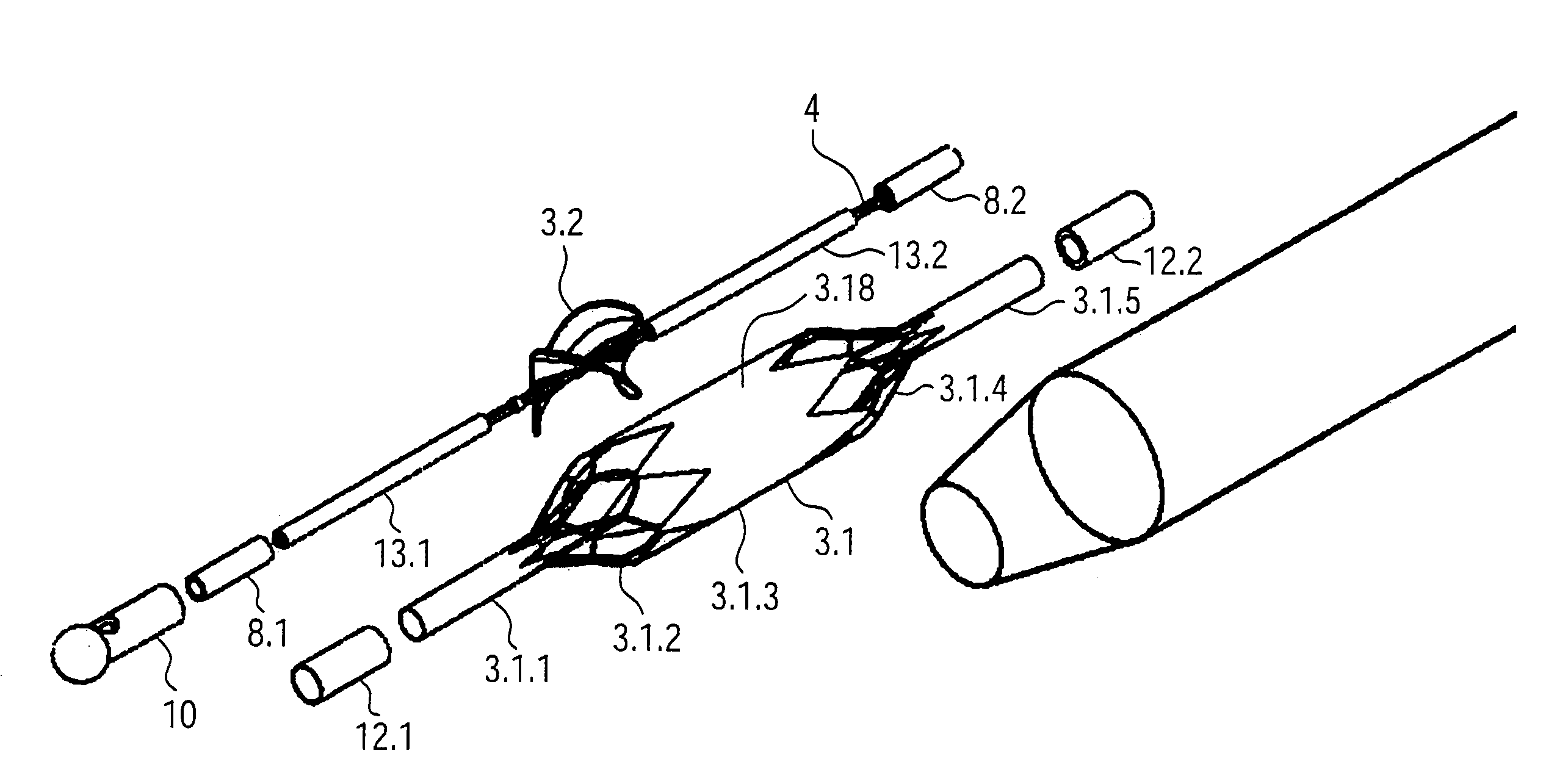

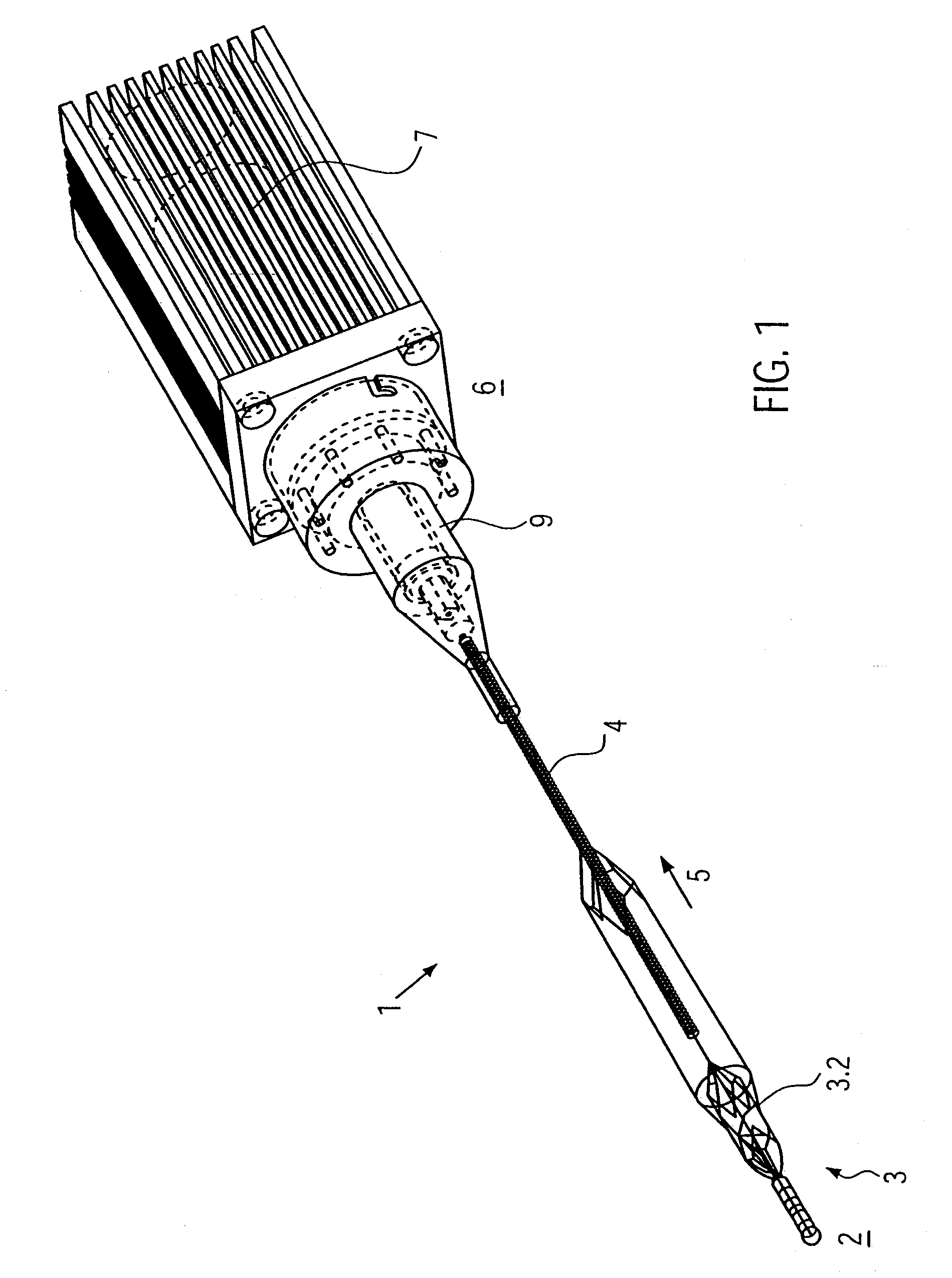

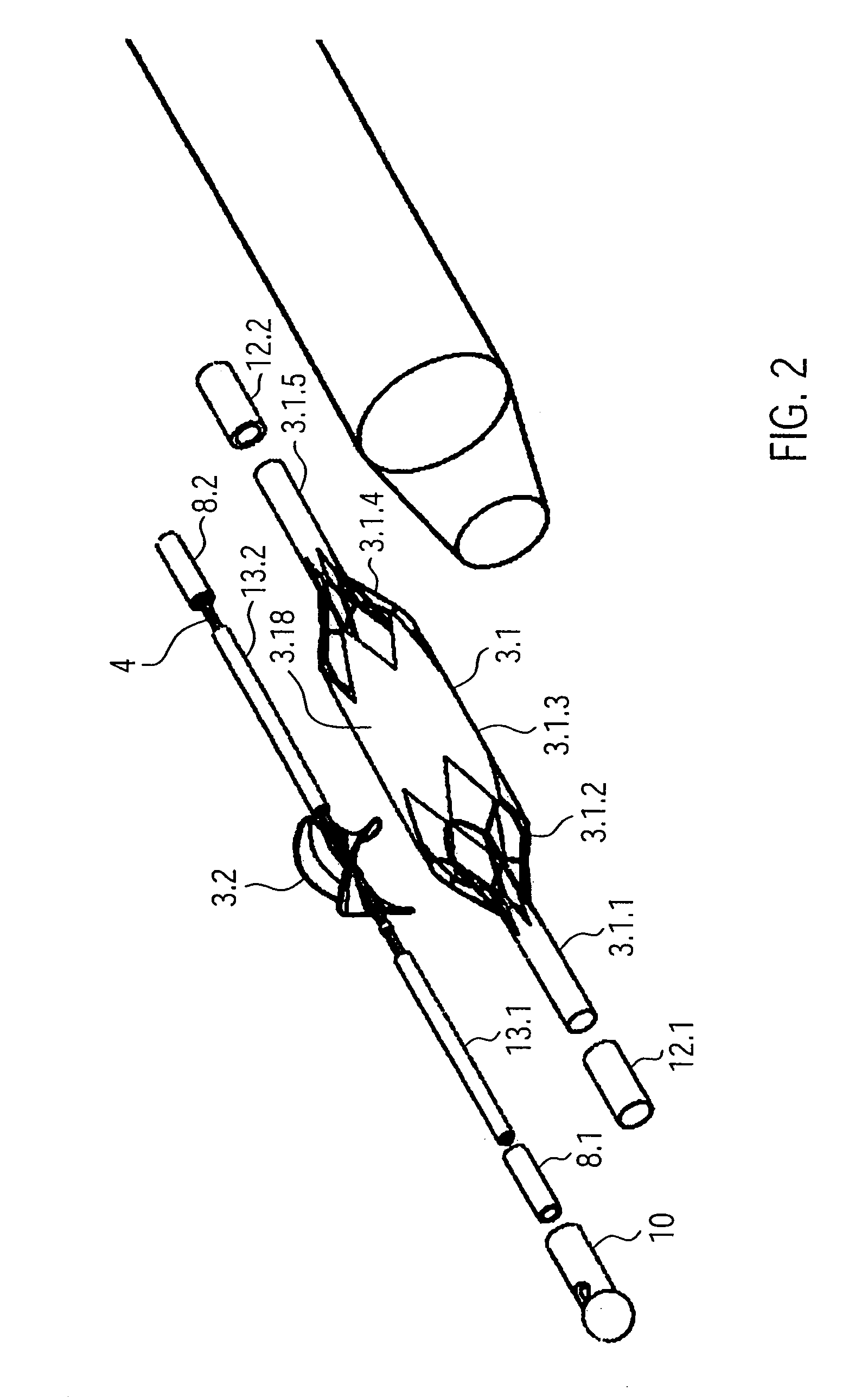

Catheter device

ActiveUS20090093796A1Maximum pump performanceImprove performancePump componentsSurgeryDrive shaftMechanical engineering

The catheter device comprises a drive shaft connected to a motor, and a rotor mounted on the drive shaft at the distal end section. The rotor has a frame structure which is formed by a screw-like boundary frame and rotor struts extending radially inwards from the boundary frame. The rotor struts are fastened to the drive shaft by their ends opposite the boundary frame. Between the boundary frame and the drive shaft extends an elastic covering. The frame structure is made of an elastic material such that, after forced compression, the rotor unfolds automatically.

Owner:AIS AACHEN INNOVATIVE SOLUTIONS

Semiconductor device

ActiveUS20110156027A1Long storageReduce power consumptionTransistorSolid-state devicesSemiconductor materialsEngineering

An object of one embodiment of the present invention is to provide a semiconductor device with a novel structure in which stored data can be stored even when power is not supplied in a data storing time and there is no limitation on the number of times of writing. The semiconductor device includes a first transistor which includes a first channel formation region using a semiconductor material other than an oxide semiconductor, a second transistor which includes a second channel formation region using an oxide semiconductor material, and a capacitor. One of a second source electrode and a second drain electrode of the second transistor is electrically connected to one electrode of the capacitor.

Owner:SEMICON ENERGY LAB CO LTD

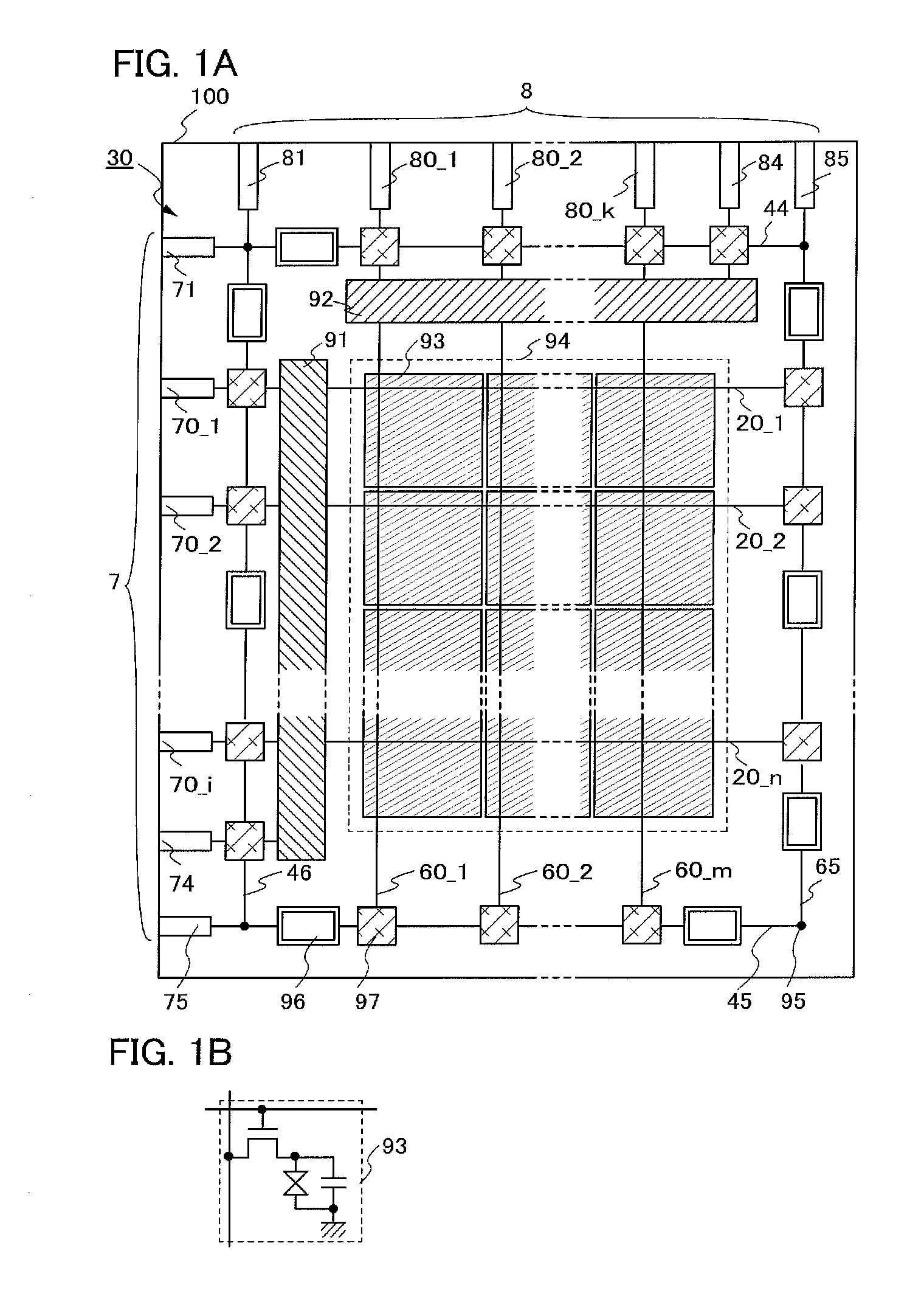

Display device and electronic device

InactiveUS7978274B2Prevent charge leakageShorten the timeStatic indicating devicesSolid-state devicesDisplay deviceHigh definition

An object of the invention is to provide a circuit technique which enables reduction in power consumption and high definition of a display device. A switch controlled by a start signal is provided to a gate electrode of a transistor, which is connected to a gate electrode of a bootstrap transistor. When the start signal is input, a potential is supplied to the gate electrode of the transistor through the switch, and the transistor is turned off. The transistor is turned off, so that leakage of a charge from the gate electrode of the bootstrap transistor can be prevented. Accordingly, time for storing a charge in the gate electrode of the bootstrap transistor can be shortened, and high-speed operation can be performed.

Owner:SEMICON ENERGY LAB CO LTD

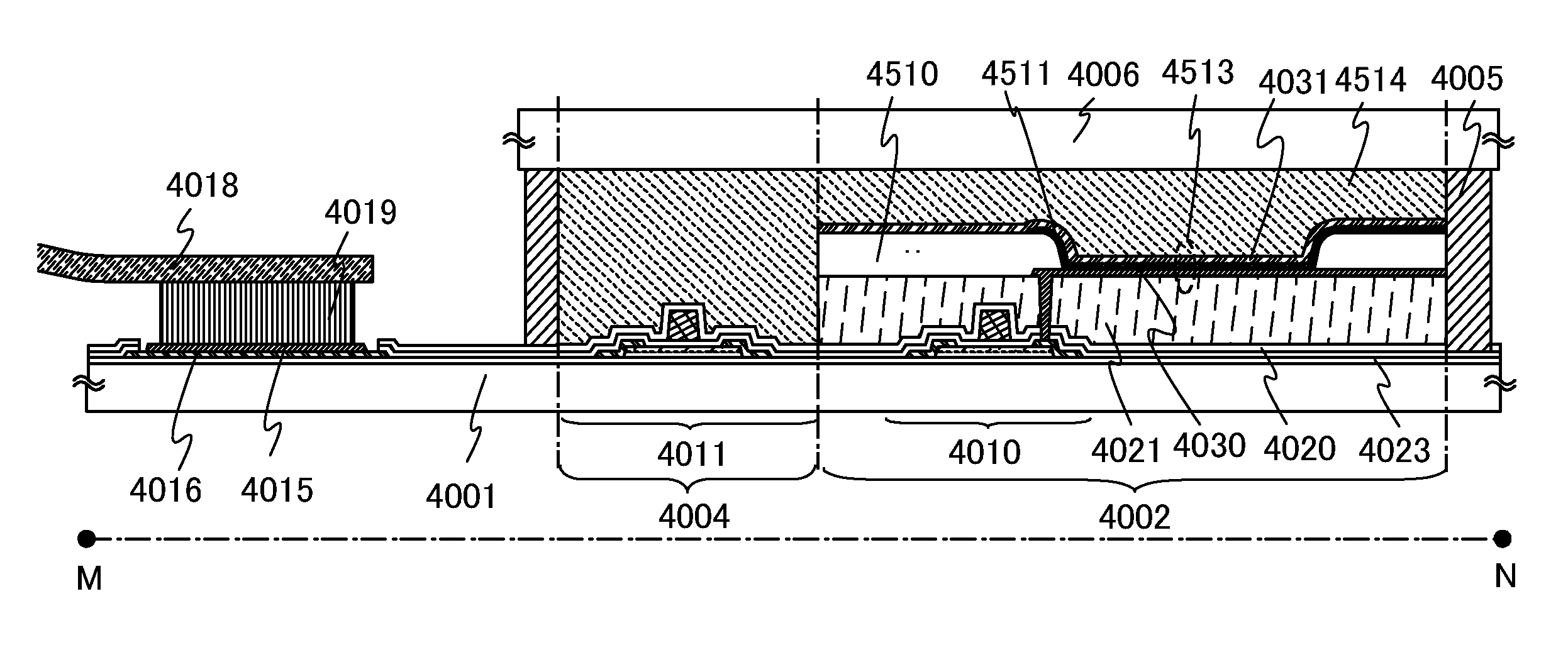

Semiconductor device, production method thereof, and display device

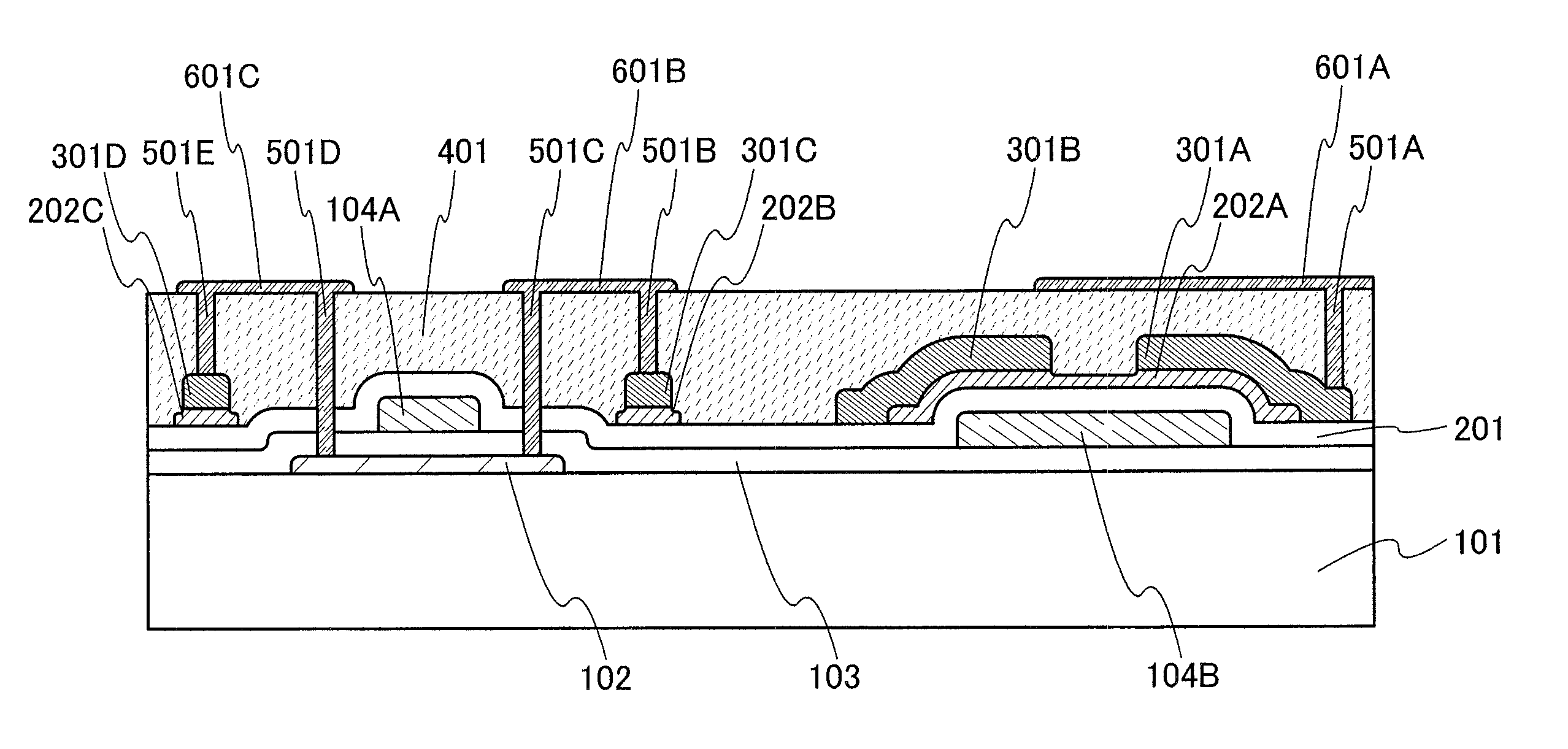

InactiveUS20090242893A1Reduce parasitic capacitanceReduce power consumptionSolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceEngineering

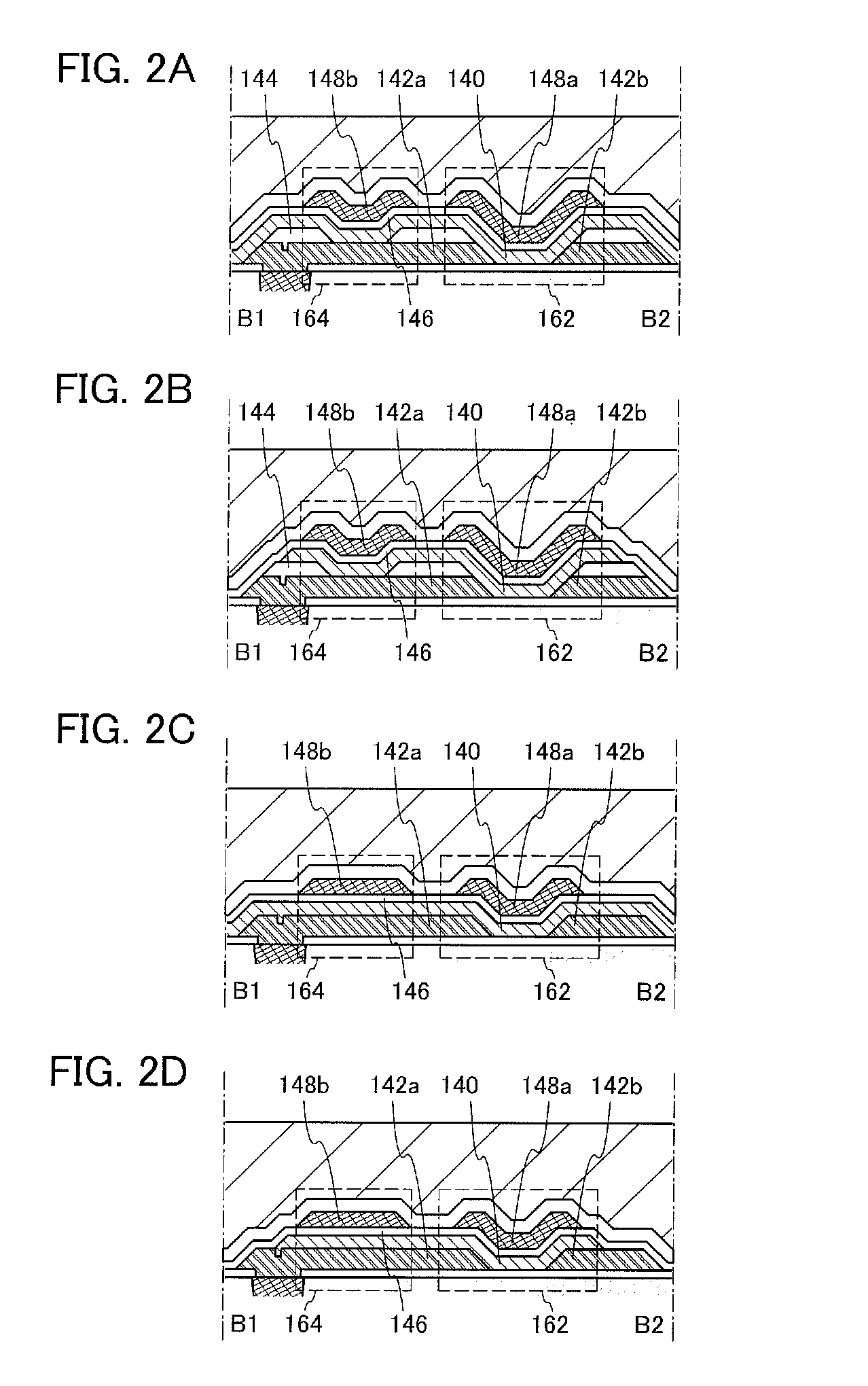

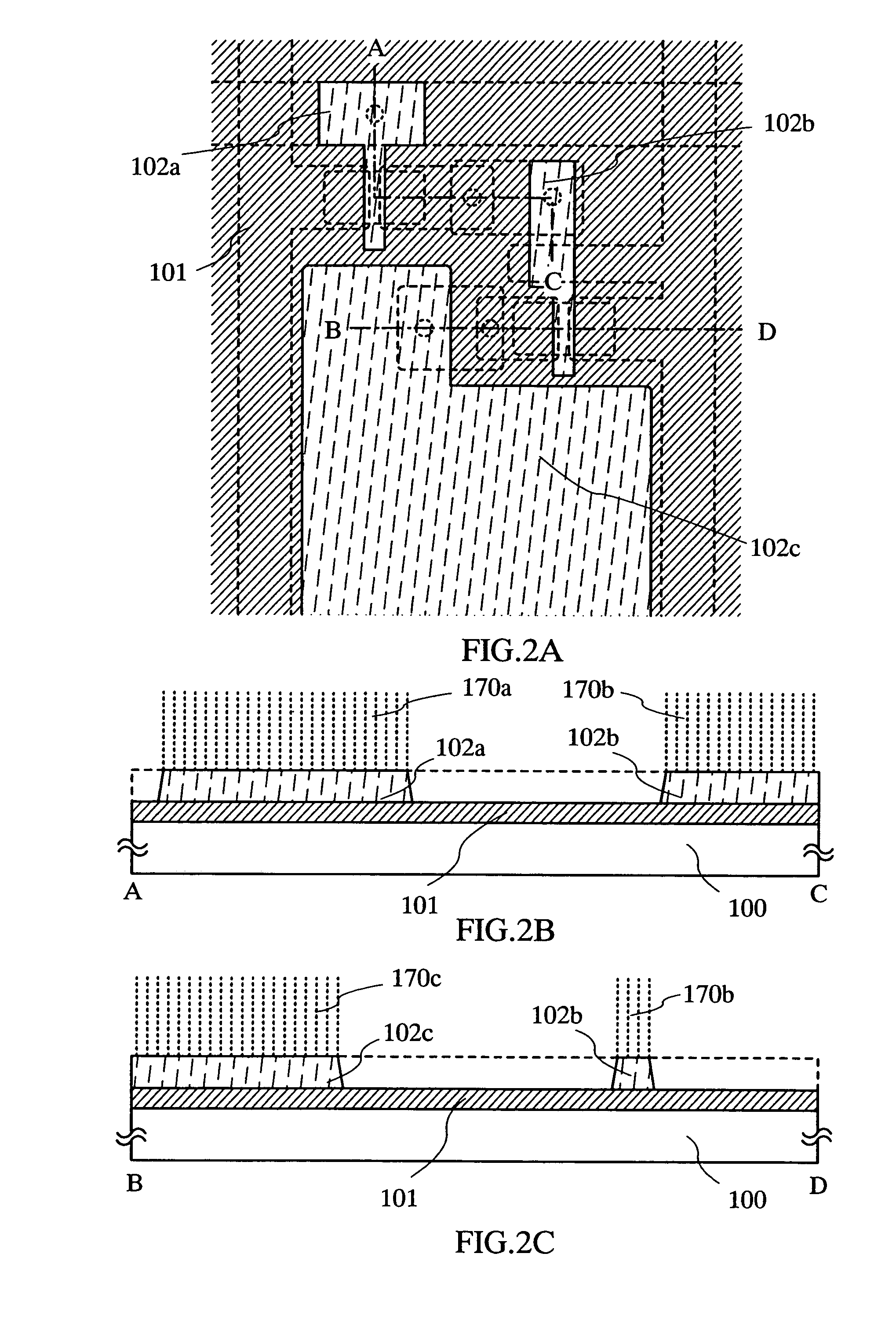

The present invention provides a semiconductor device which can be produced by simple and cheap processes and effectively achieve improved performances and a reduced electric power consumption. Further, the present invention provides a production method thereof and a display device including the semiconductor device or a semiconductor device produced by the production method. The present invention is a semiconductor device including a pixel part and an integrated circuit part on a substrate, the pixel part including a switching element having a gate electrode formed on a semiconductor thin film, the integrated circuit part including a semiconductor layer on a gate electrode, wherein a passivation film is formed on the gate electrode in the pixel part.

Owner:SHARP KK

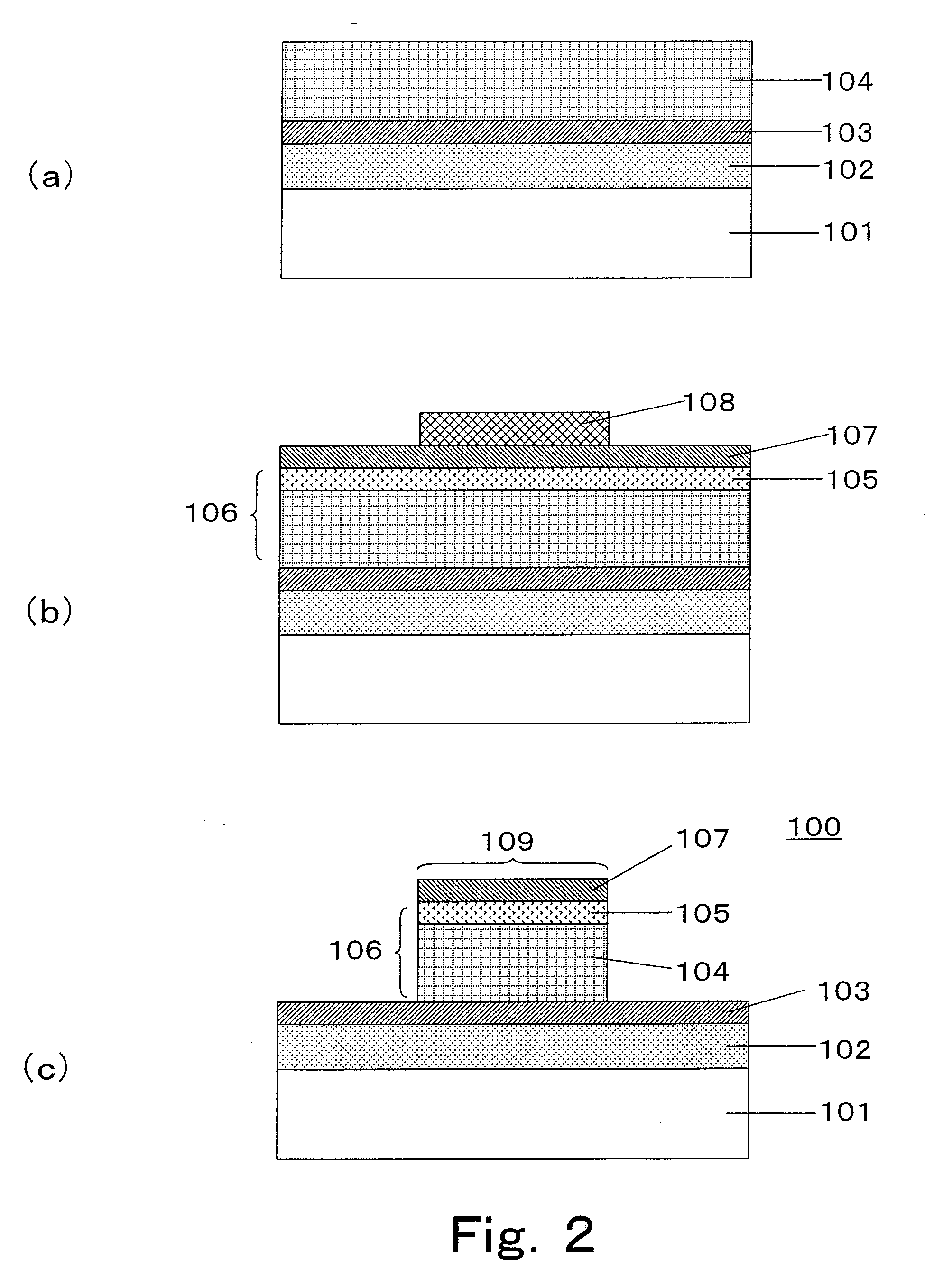

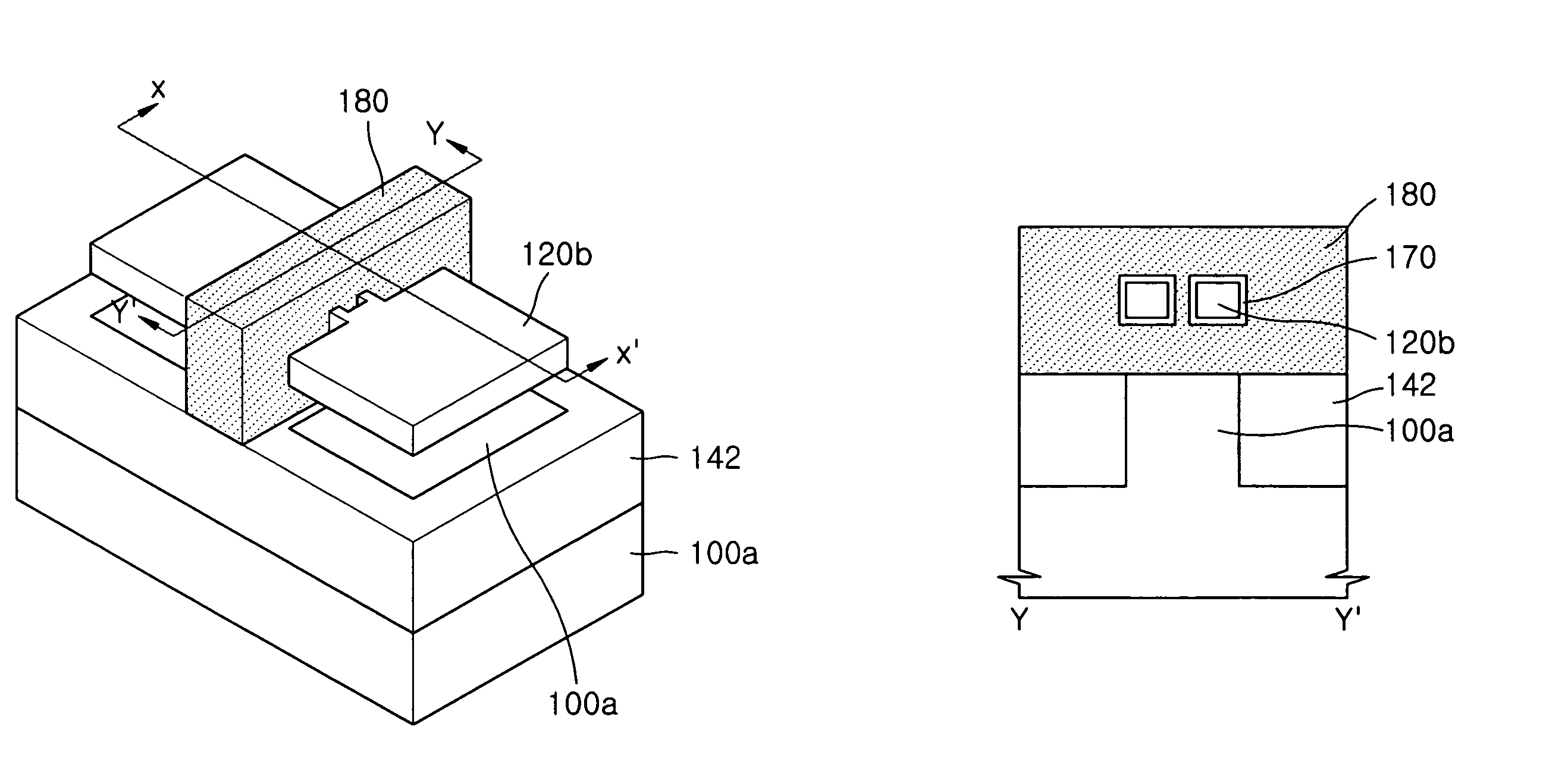

Nonvolatile memory element, manufacturing method thereof, and nonvolatile semiconductor apparatus using the nonvolatile memory element

ActiveUS20090283736A1Reversibly-stable rewrite characteristicHigh affinitySolid-state devicesSemiconductor/solid-state device manufacturingOxygen deficientElectric signal

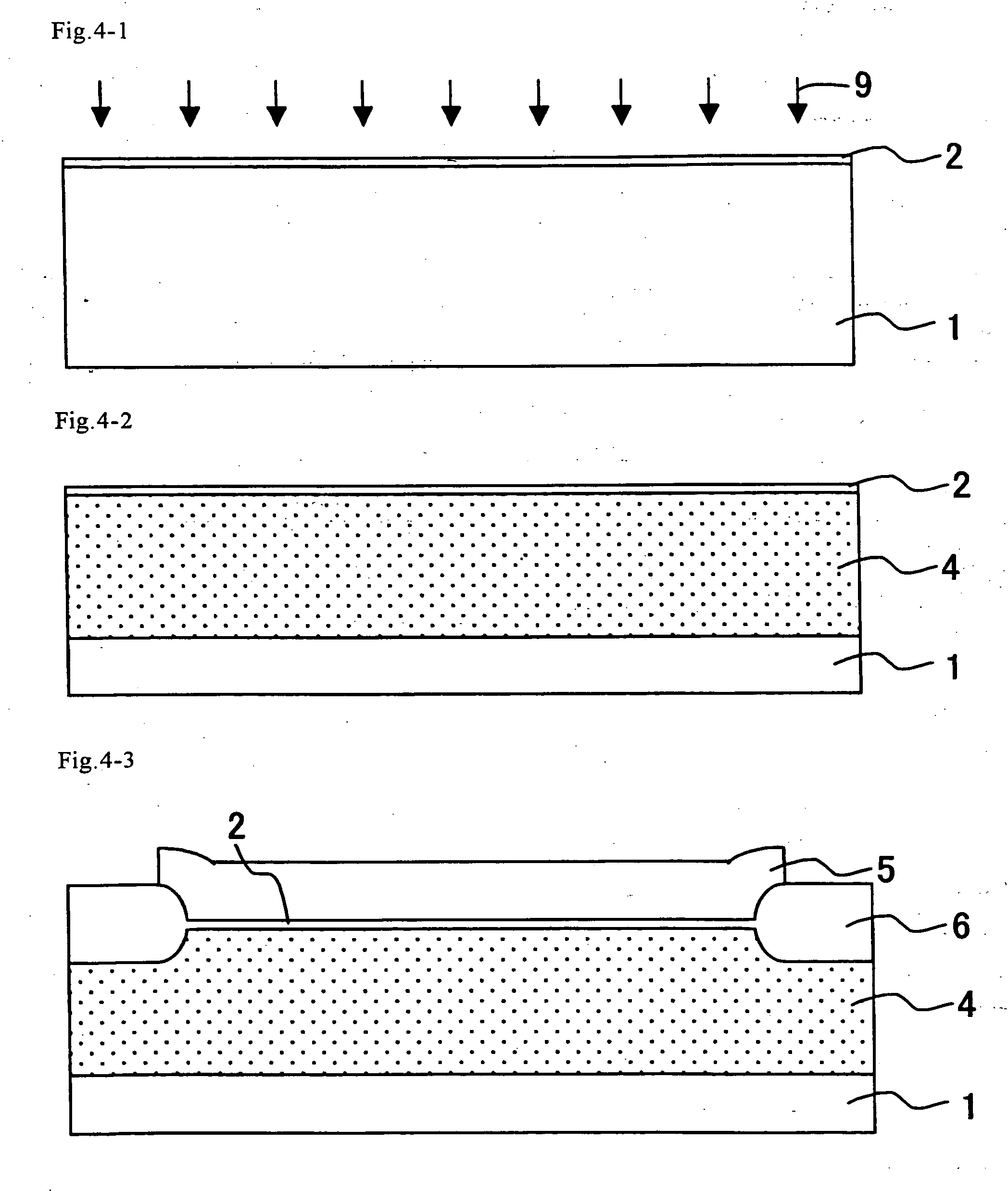

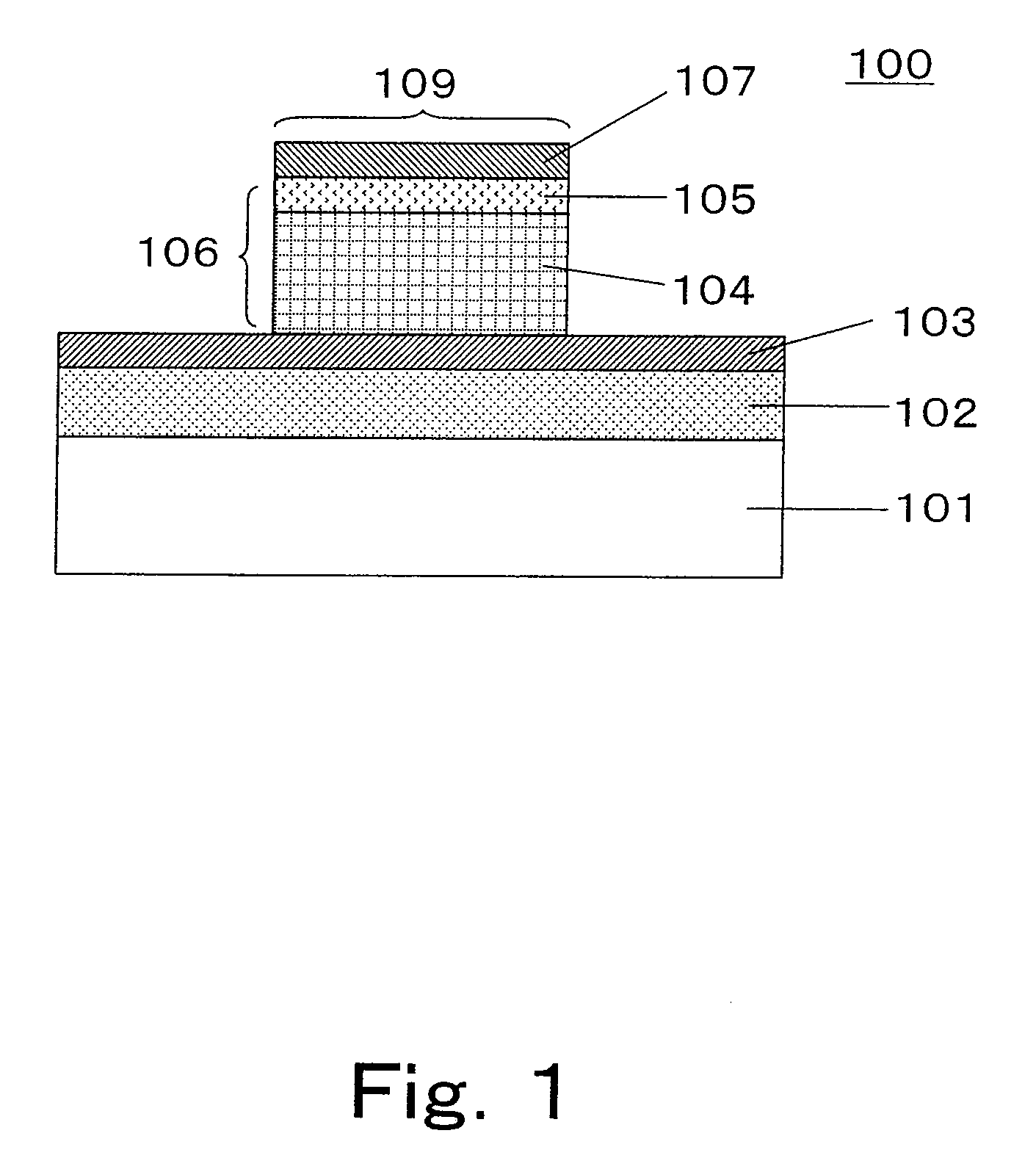

A nonvolatile memory element comprises a first electrode layer (103), a second electrode (107), and a resistance variable layer (106) which is disposed between the first electrode layer (103) and the second electrode layer (107), a resistance value of the resistance variable layer varying reversibly according to electric signals having different polarities which are applied between the electrodes (103), (107), wherein the resistance variable layer (106) has a first region comprising a first oxygen-deficient tantalum oxide having a composition represented by TaOx (0<x<2.5) and a second region comprising a second oxygen-deficient tantalum oxide having a composition represented by TaOy (x<y<2.5), the first region and the second region being arranged in a thickness direction of the resistance variable layer.

Owner:PANASONIC SEMICON SOLUTIONS CO LTD

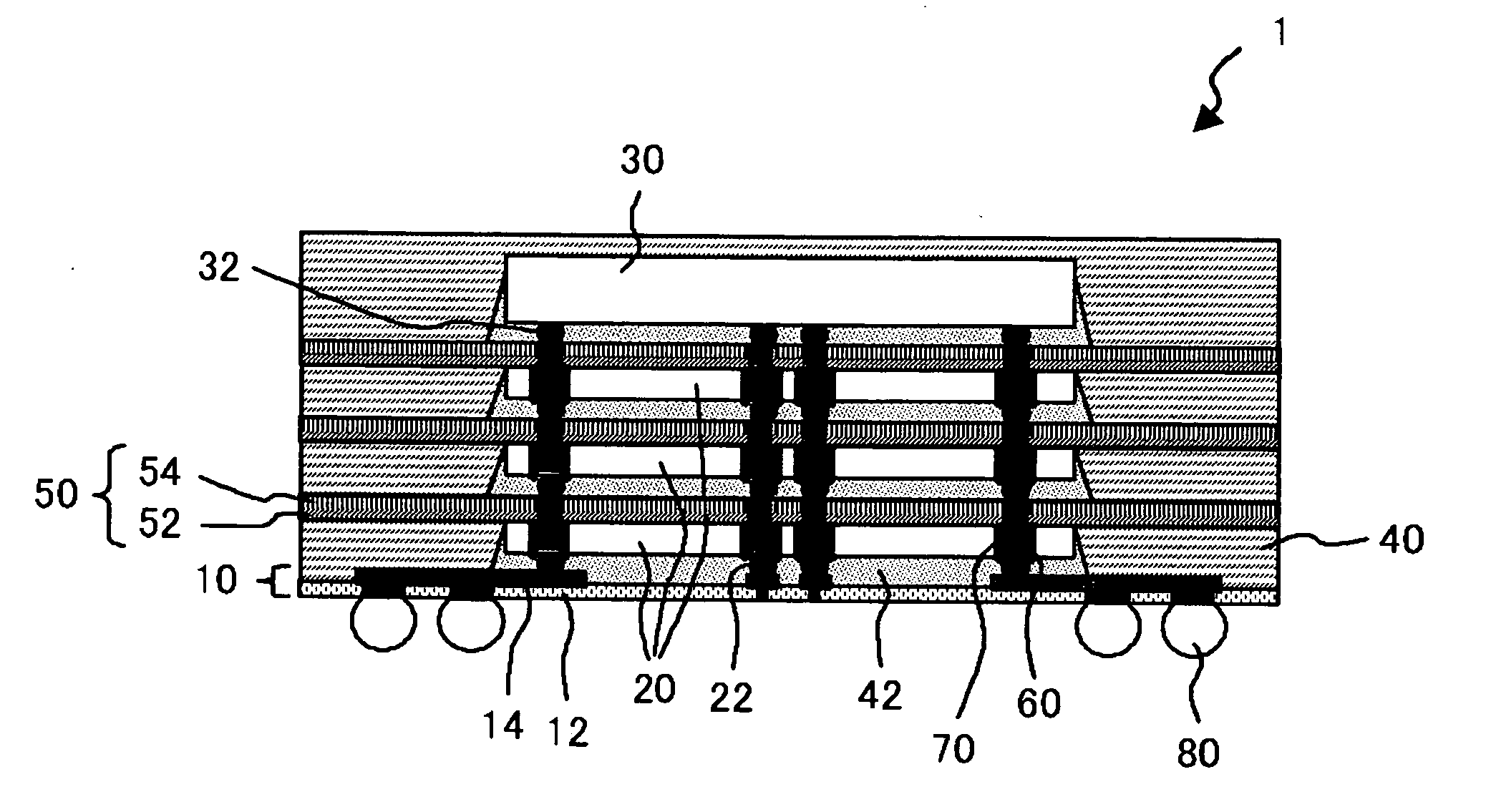

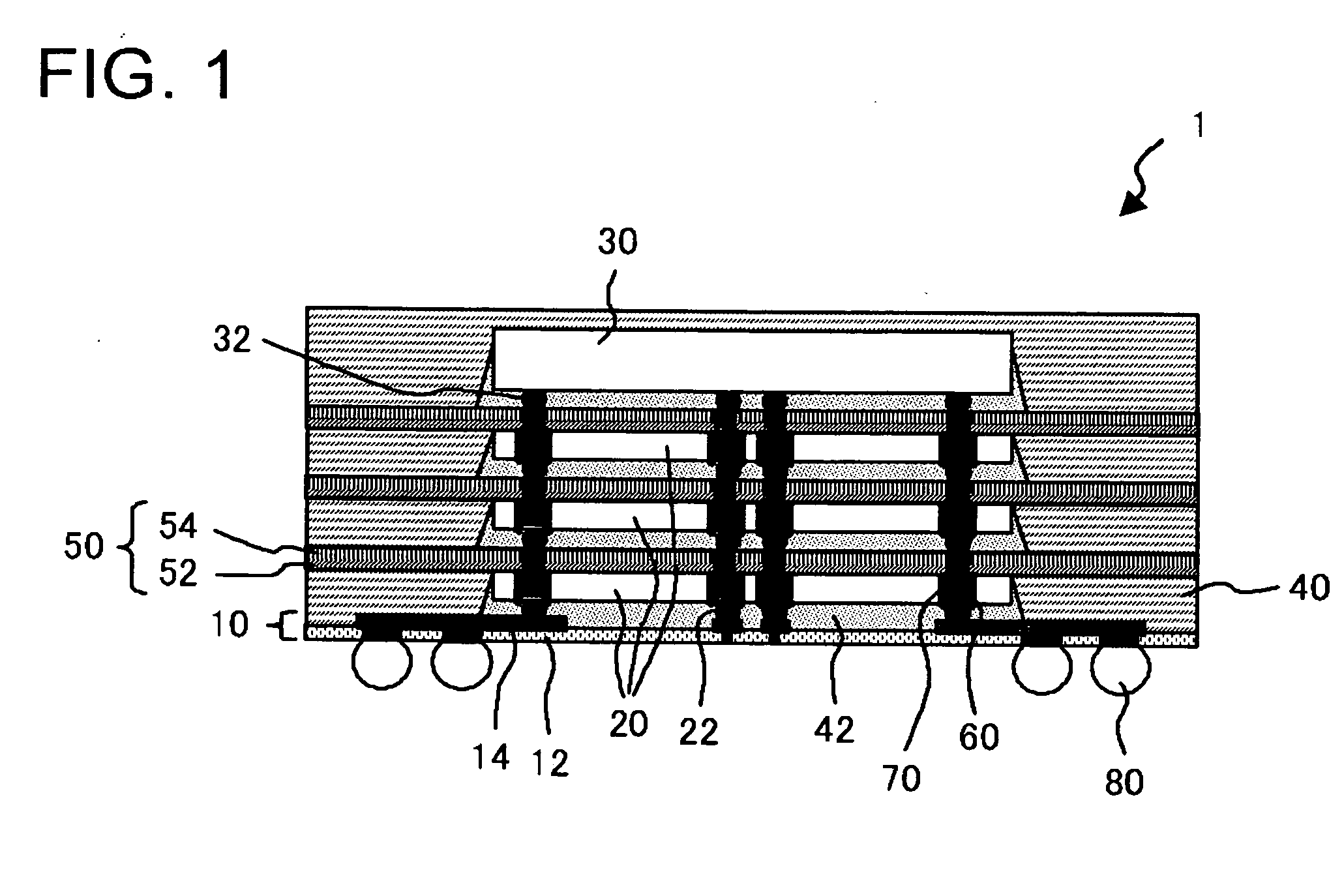

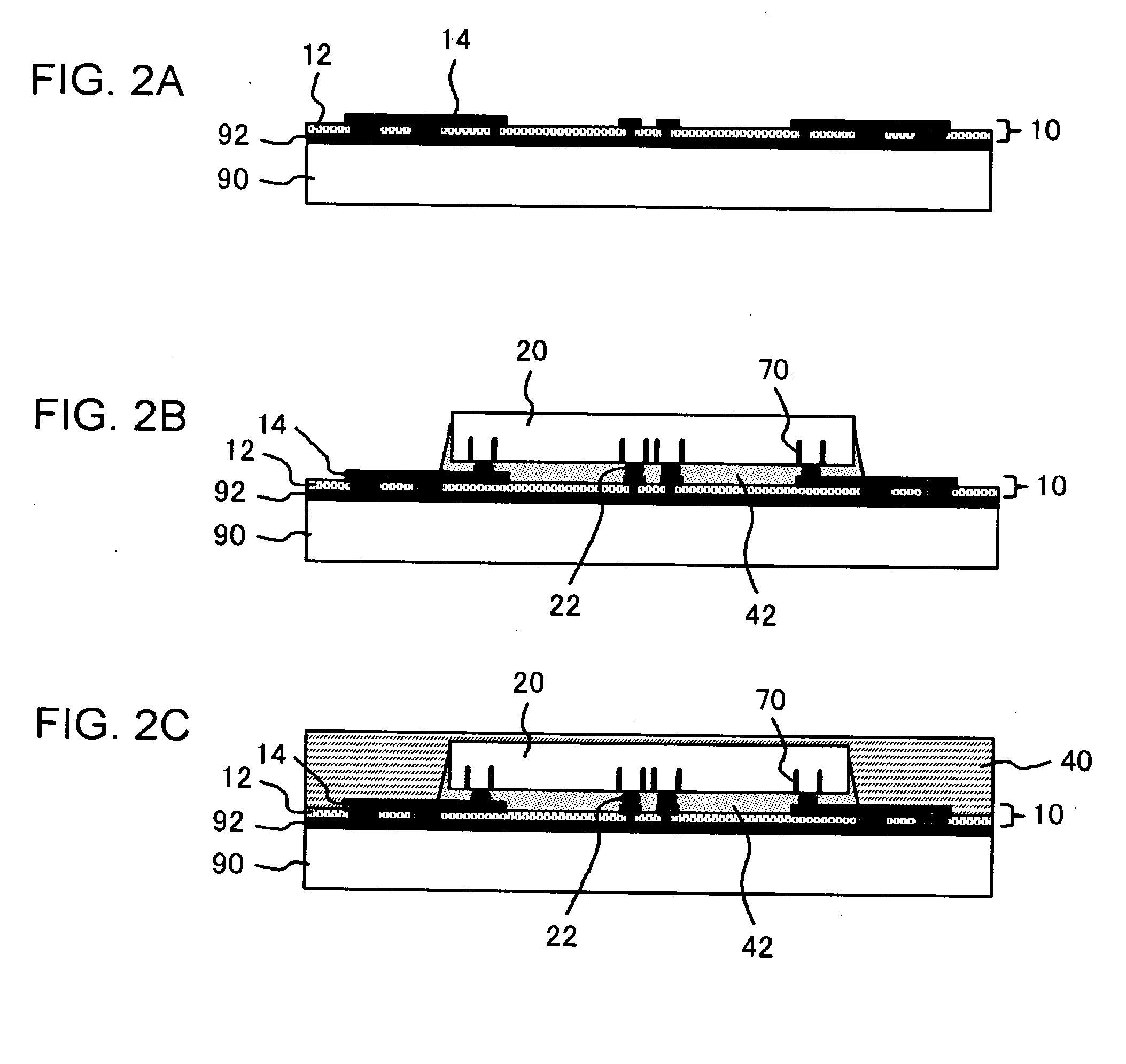

Semiconductor device and method of manufacturing the same

InactiveUS20070126085A1Reduce path lengthRun at high speedSemiconductor/solid-state device detailsSolid-state devicesDevice materialSemiconductor chip

A semiconductor device includes an interconnect member, a first semiconductor chip, a second semiconductor chip, a resin layer, an inorganic insulating layer, and a through electrode. The first semiconductor chip is mounted in a face-down manner on the interconnect member. The resin layer covers the side surface of the first semiconductor chip. This inorganic insulating layer is in contact with the back surface of the first semiconductor chip, and directly covers the back surface. Also, the inorganic insulating layer extends over the resin layer. The through electrode penetrates the inorganic insulating layer and the semiconductor substrate of the first semiconductor chip. The second semiconductor chip is mounted in a face-down manner on the inorganic insulating layer that covers the back surface of the first semiconductor chip in the uppermost layer.

Owner:NEC ELECTRONICS CORP

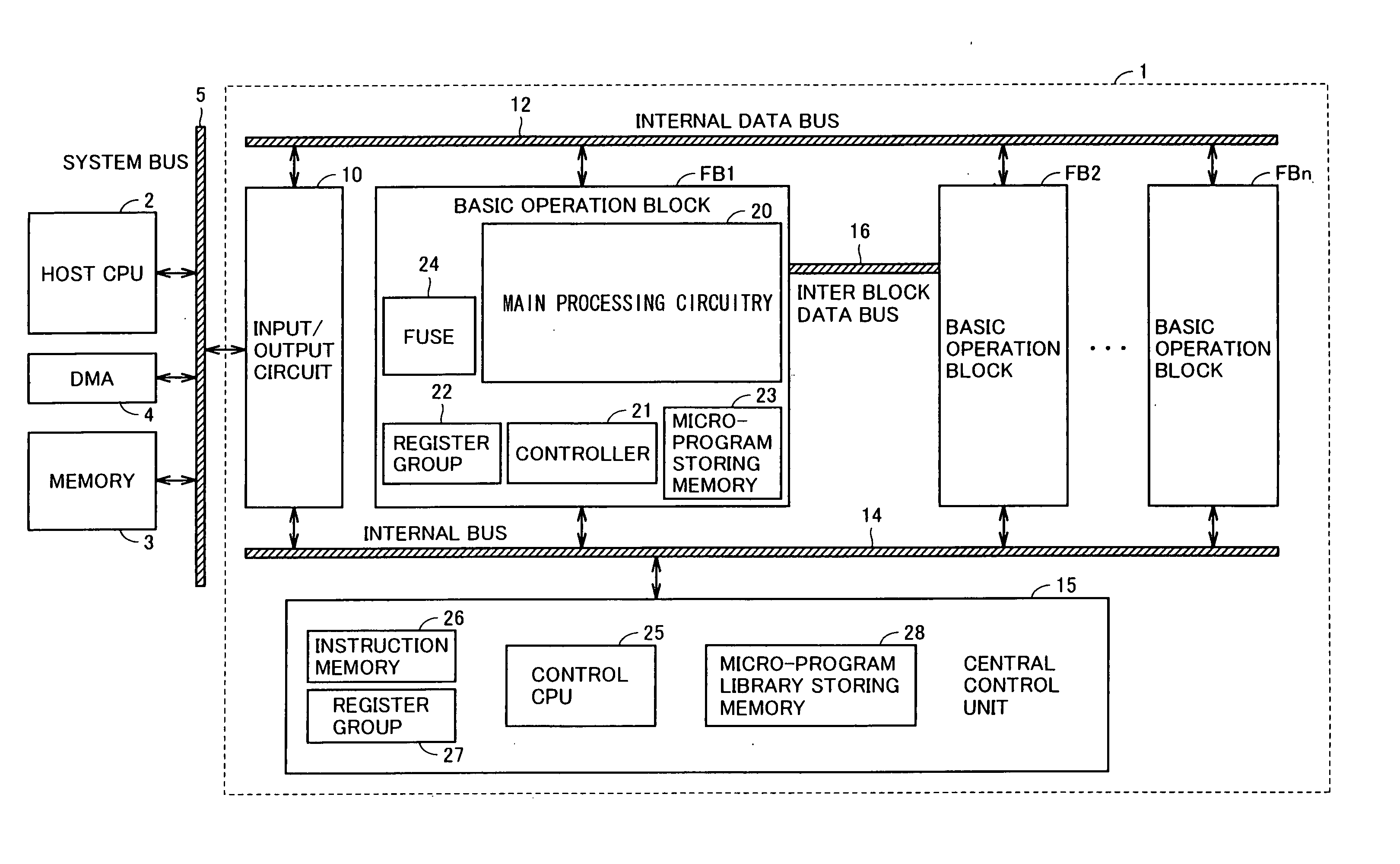

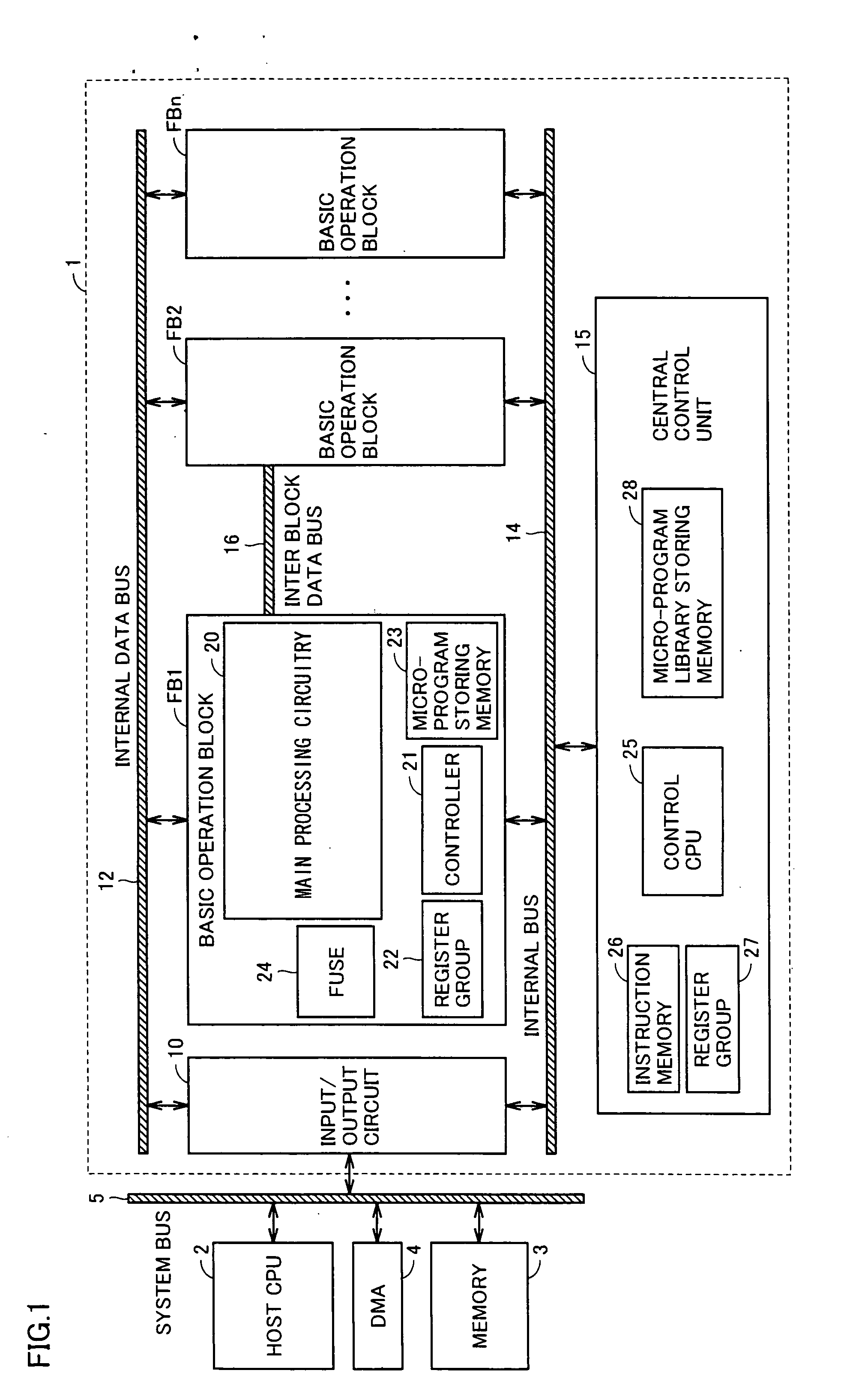

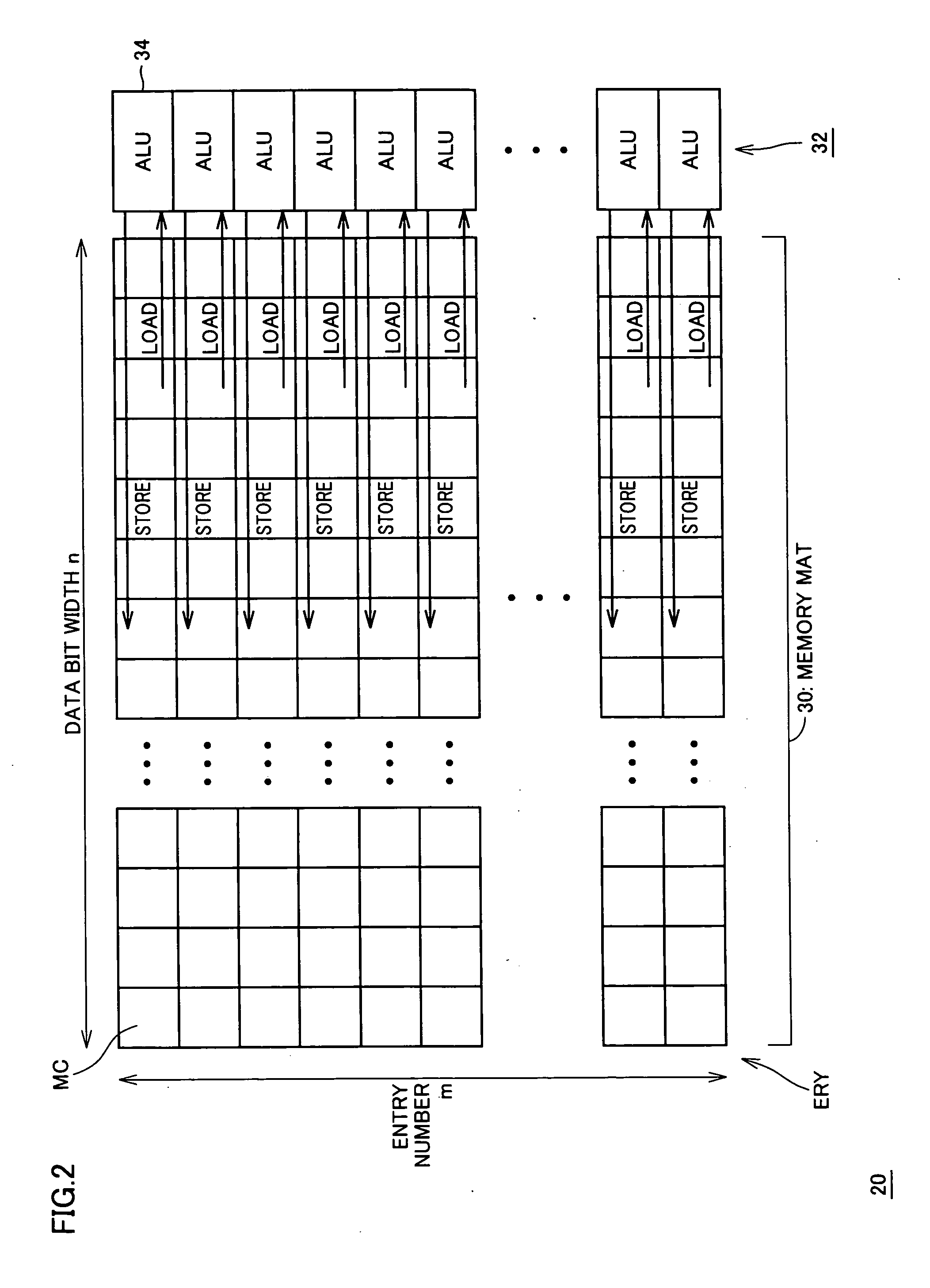

Semiconductor device and semiconductor signal processing apparatus

InactiveUS20050285862A1Operation control becomes easyEasy to processImage memory managementMultiple digital computer combinationsArithmetic logic unitDevice material

A memory cell mat is divided into a plurality of entries, and an arithmetic logic unit is arranged corresponding to each entry. Between the entries and the corresponding arithmetic logic units, arithmetic / logic operation is executed in bit-serial and entry-parallel manner. Where parallel operation is not very effective, data is transferred in entry-serial and bit-parallel manner to a group of processors provided at a lower portion of the memory mat. In this manner, a large amount of data can be processed at high speed regardless of the contents of operation or data bit width.

Owner:RENESAS ELECTRONICS CORP

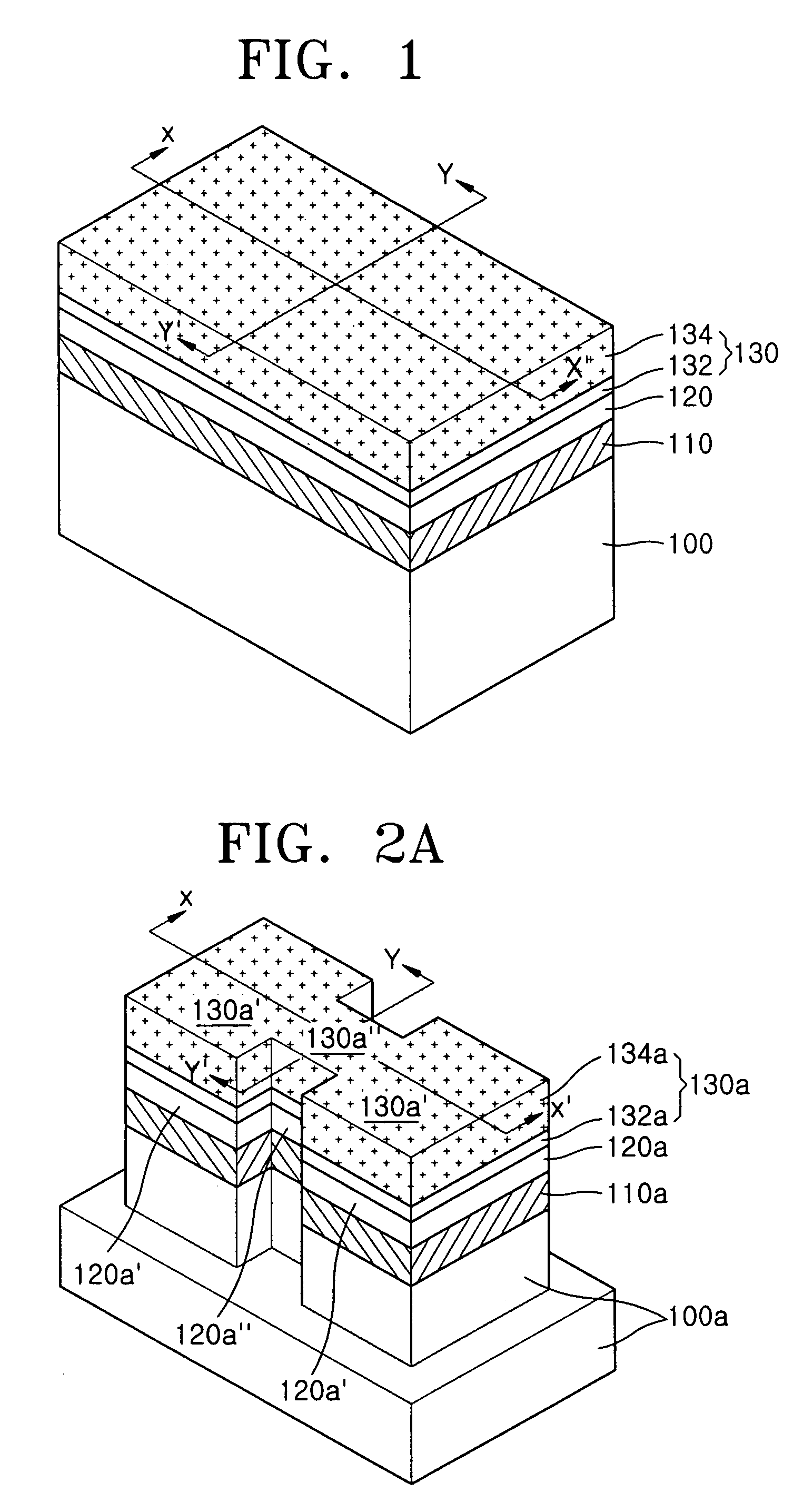

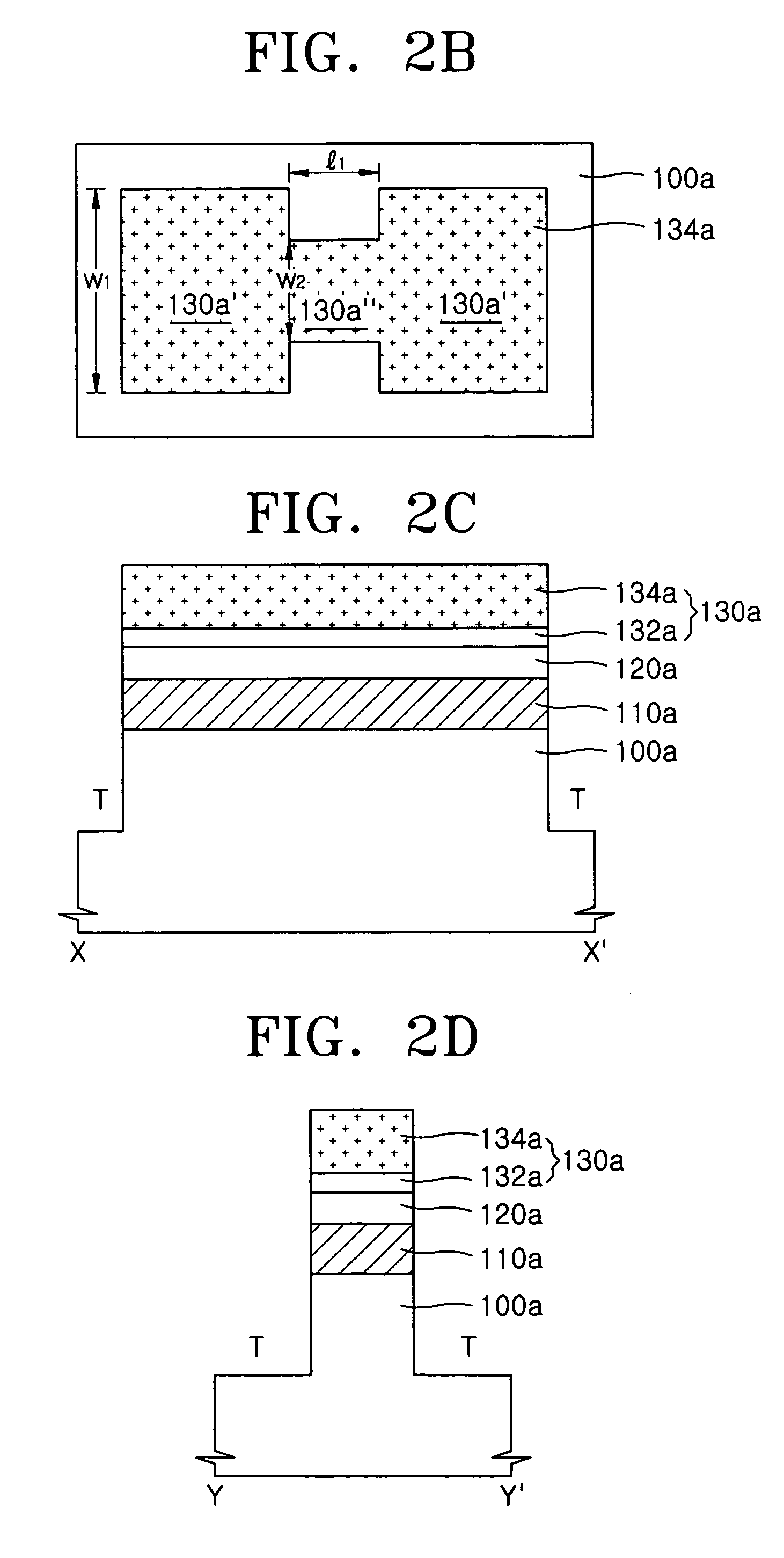

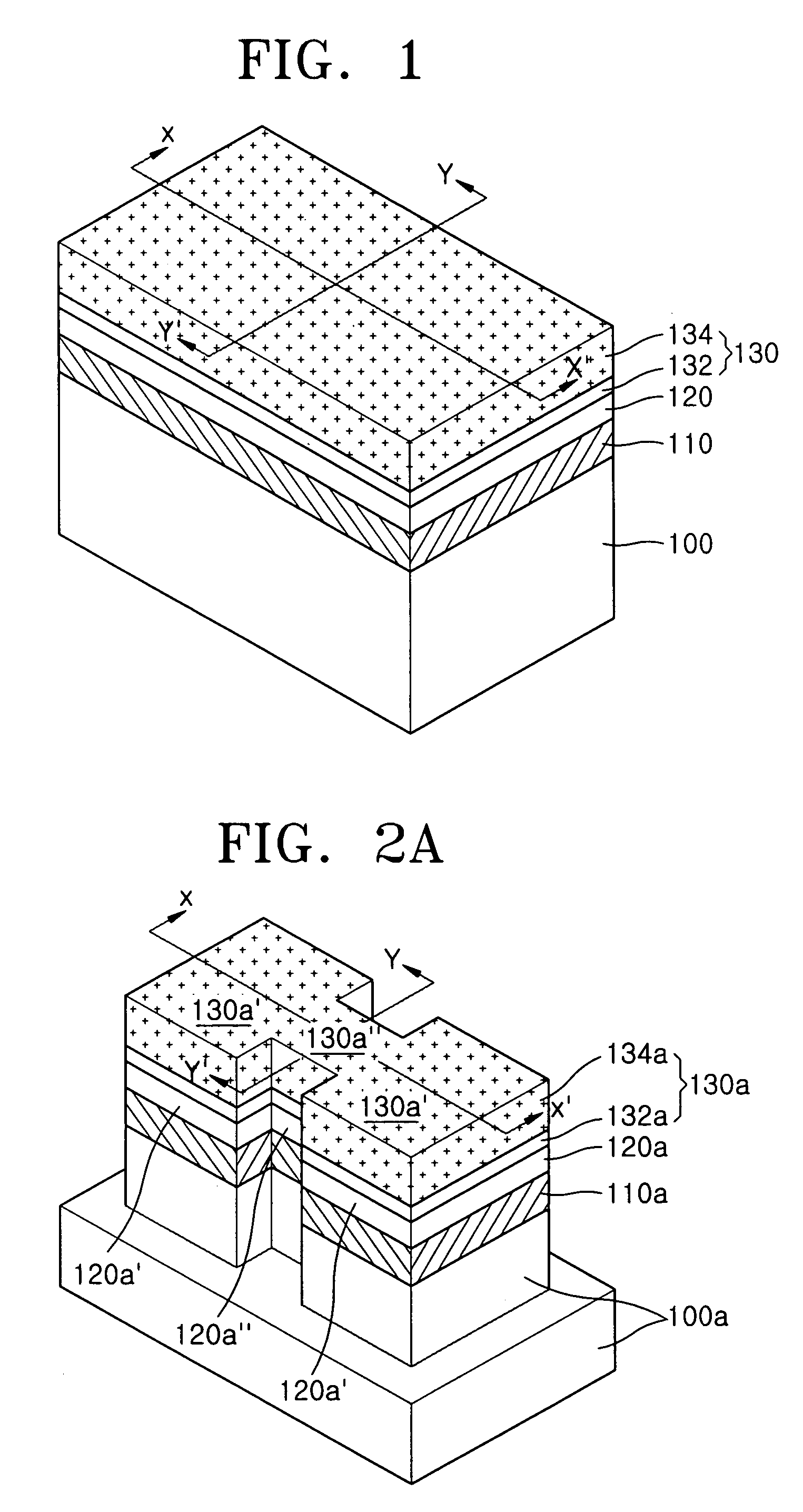

Multi bridge channel field effect transistors with nano-wire channels and methods of manufacturing the same

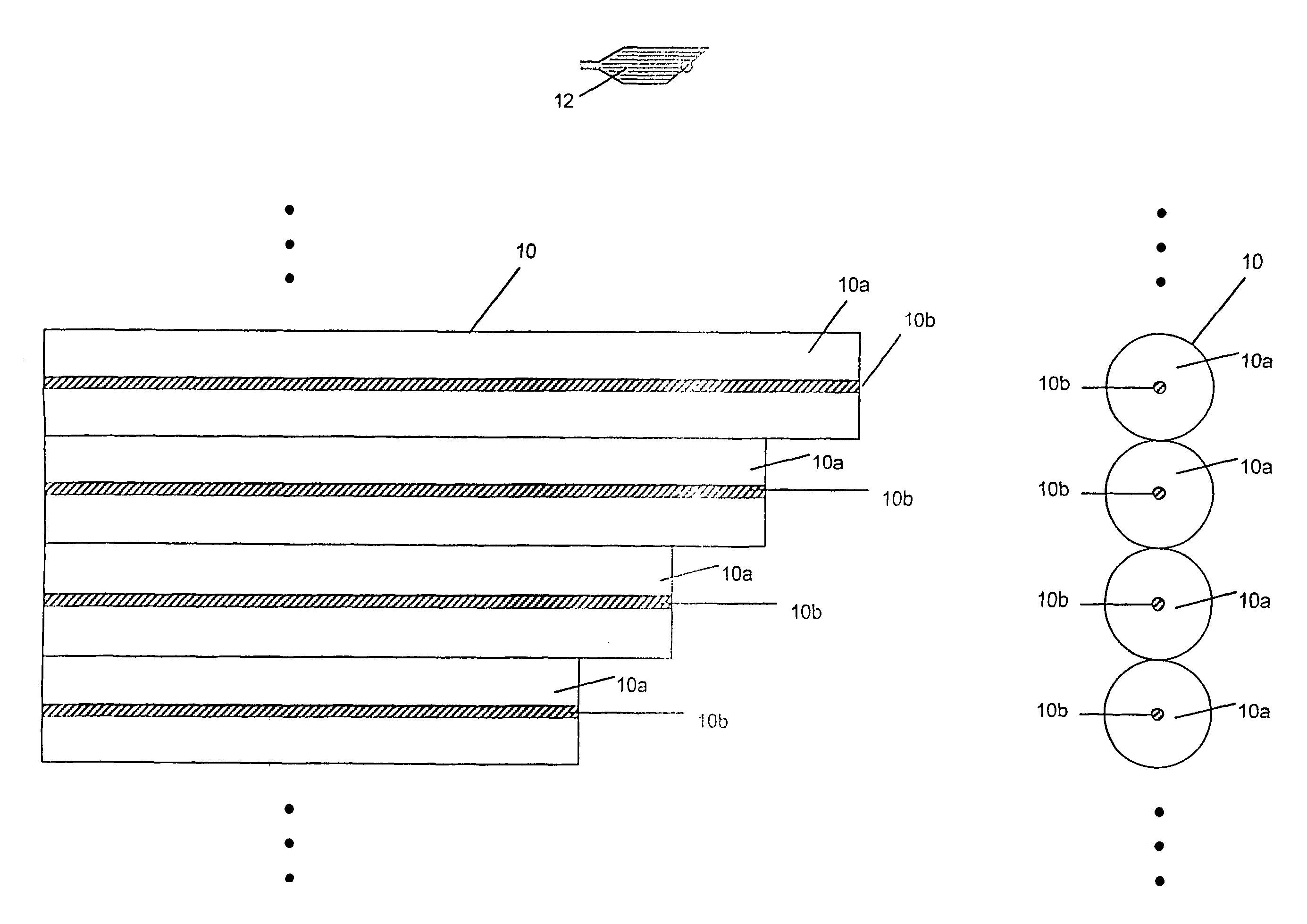

A field effect transistor (FET) includes spaced apart source and drain regions disposed on a substrate and at least one pair of elongate channel regions disposed on the substrate and extending in parallel between the source and drain regions. A gate insulating region surrounds the at least one pair of elongate channel regions, and a gate electrode surrounds the gate insulating region and the at least one pair of elongate channel regions. Support patterns may be interposed between the semiconductor substrate and the source and drain regions. The elongate channel regions may have sufficiently small cross-section to enable complete depletion thereof. For example, a width and a thickness of the elongate channel regions may be in a range from about 10 nanometers to about 20 nanometers. The elongate channel regions may have rounded cross-sections, e.g., each of the elongate channel regions may have an elliptical cross-section. The at least one pair of elongate channel regions may include a plurality of stacked pairs of elongate channel regions.

Owner:SAMSUNG ELECTRONICS CO LTD

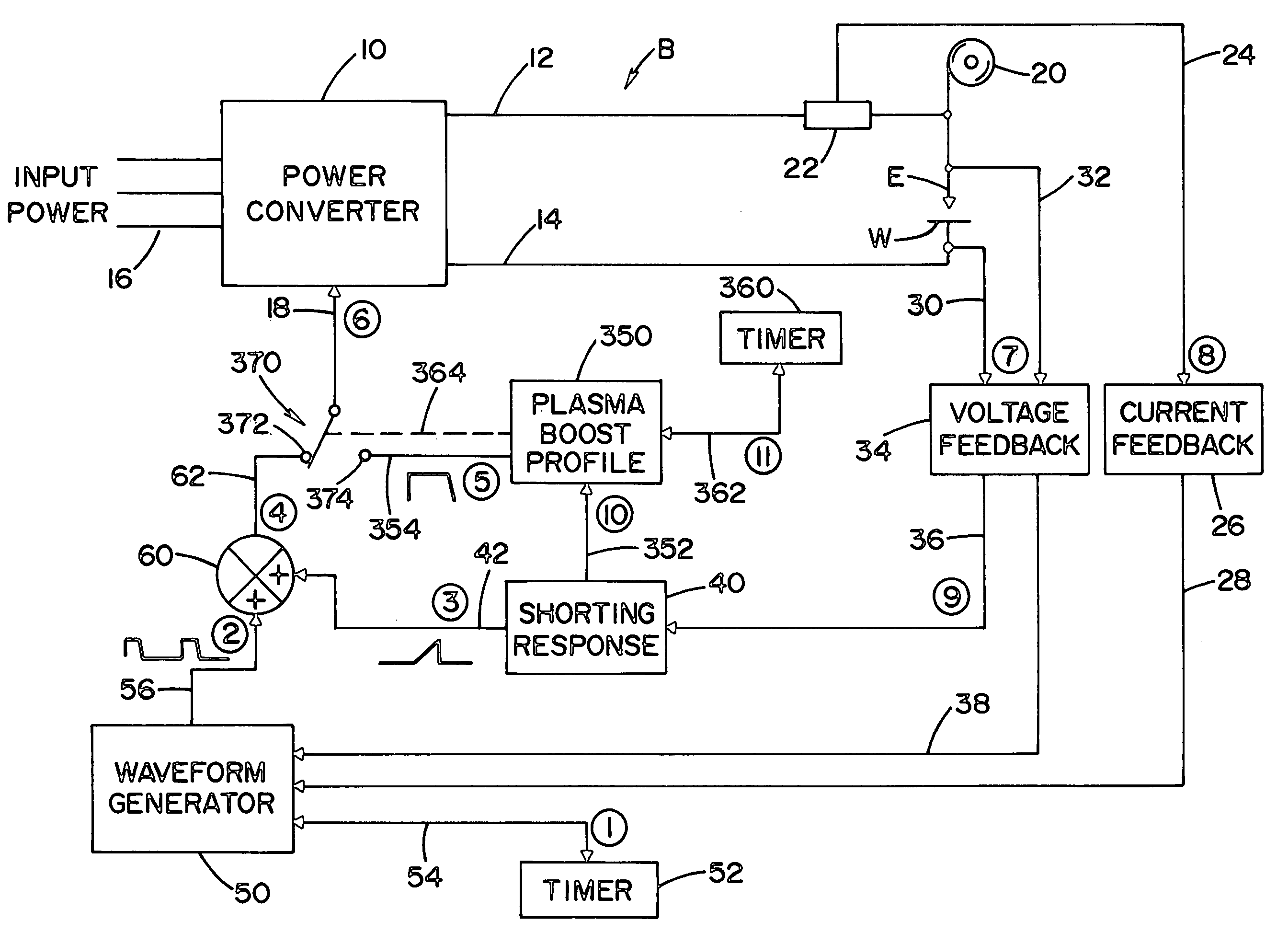

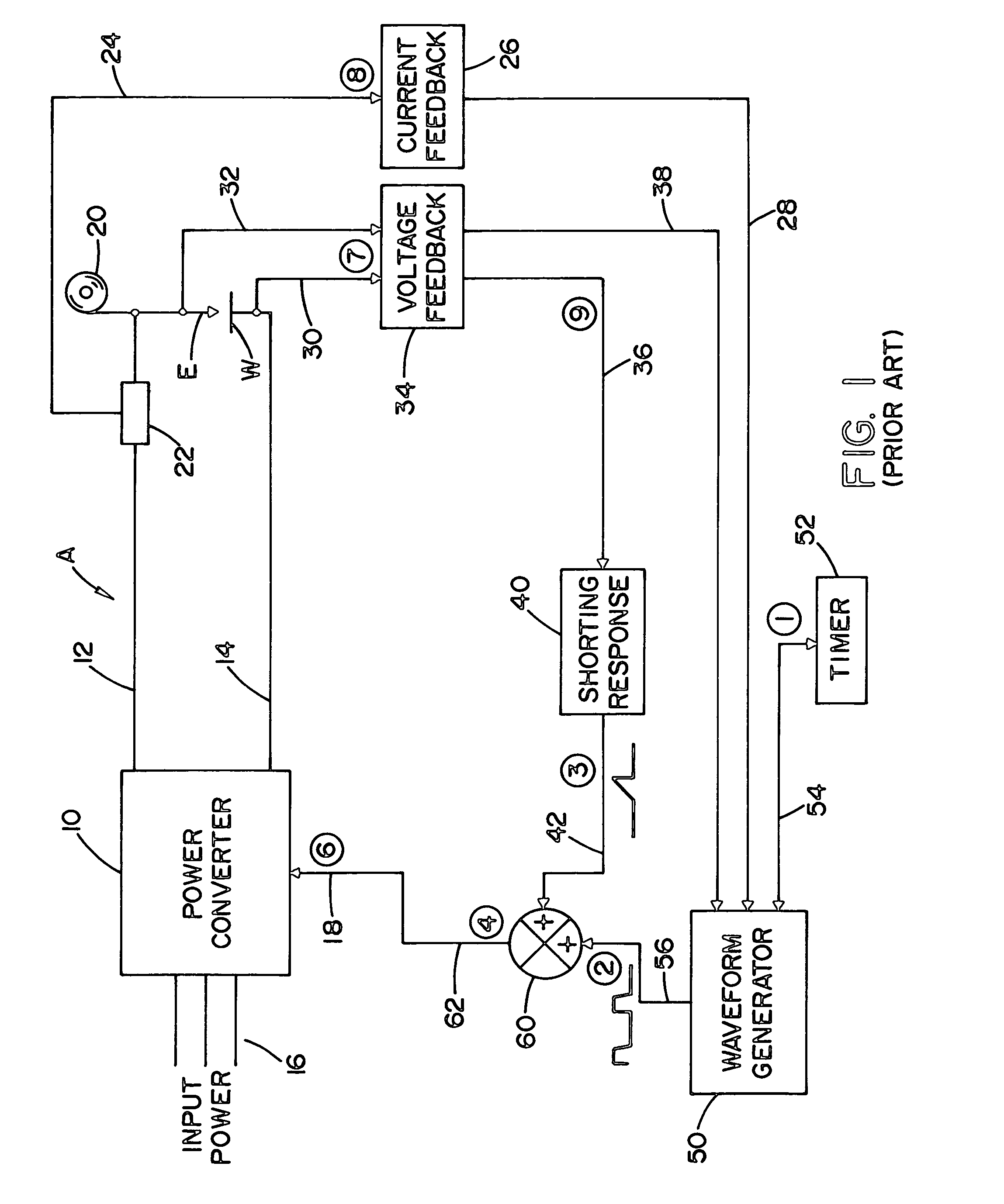

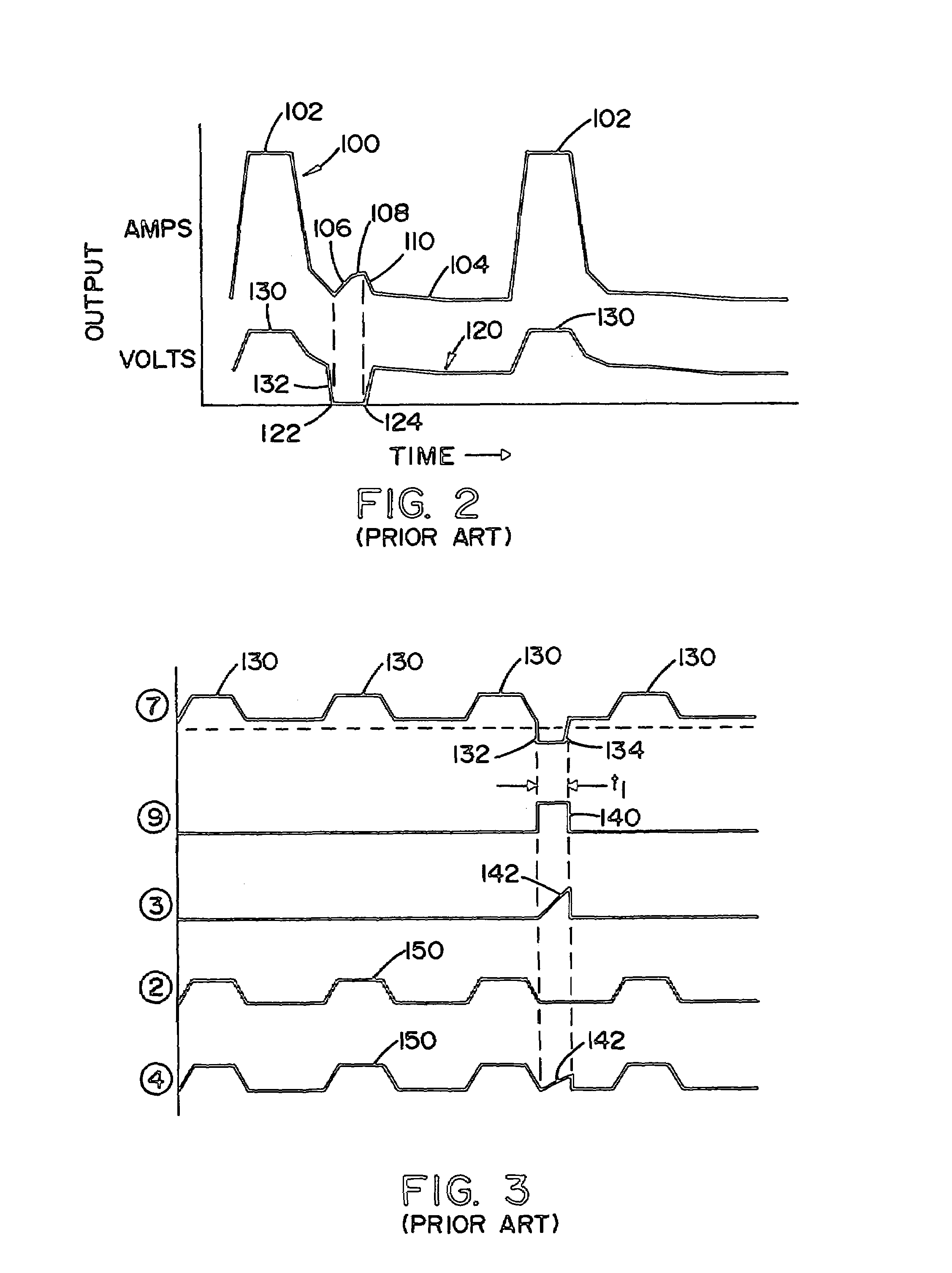

Pulse welder and method of using same

ActiveUS7304269B2Reduce arc forcePromote shorting eventsCoin-freed apparatus detailsArc welding apparatusPower flowEngineering

An electric arc welder for performing a pulse welding process by a current between an advancing electrode and workpiece where the welder comprises a short detecting circuit for creating a short signal upon occurrence of a short circuit between the advancing electrode and the workpiece and a boost circuit to create a plasma boost pulse after the short circuit is cleared during the time period when the welder is not outputting the peak pulse current.

Owner:LINCOLN GLOBAL INC

Catheter device

ActiveUS8439859B2Maximum pump performanceImprove performanceStarters with fluid-driven auxillary enginesHeart stimulatorsDrive shaftCatheter device

The catheter device comprises a drive shaft connected to a motor, and a rotor mounted on the drive shaft at the distal end section. The rotor has a frame structure which is formed by a screw-like boundary frame and rotor struts extending radially inwards from the boundary frame. The rotor struts are fastened to the drive shaft by their ends opposite the boundary frame. Between the boundary frame and the drive shaft extends an elastic covering. The frame structure is made of an elastic material such that, after forced compression, the rotor unfolds automatically.

Owner:AIS AACHEN INNOVATIVE SOLUTIONS

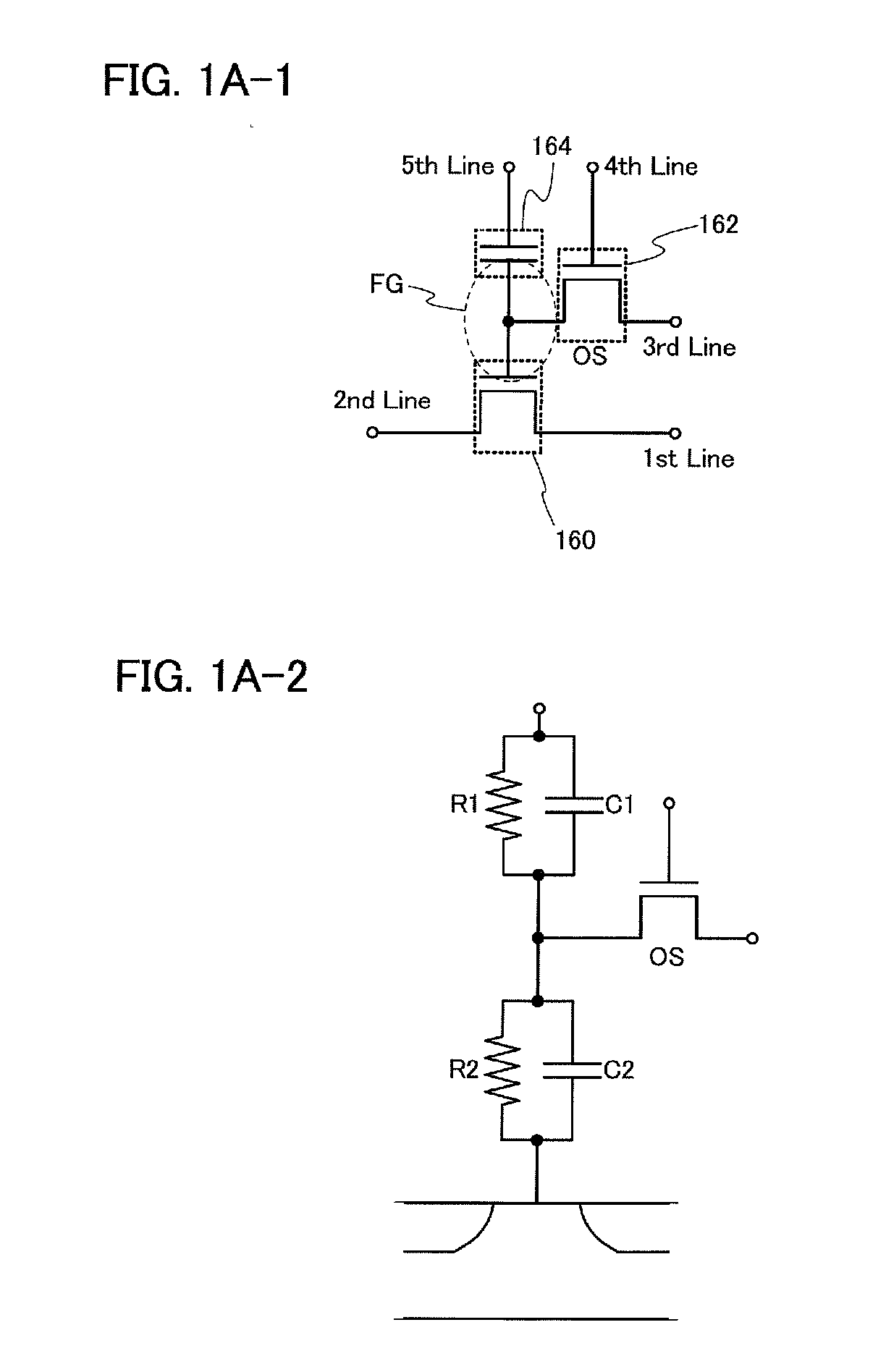

Semiconductor device

InactiveUS20110147737A1Reduce power consumptionFrequency of refresh can be lowTransistorSemiconductor/solid-state device detailsEngineeringSemiconductor

A first transistor including a channel formation region, a first gate insulating layer, a first gate electrode, and a first source electrode and a first drain electrode; a second transistor including an oxide semiconductor layer, a second source electrode and a second drain electrode, a second gate insulating layer, and a second gate electrode; and a capacitor including one of the second source electrode and the second drain electrode, the second gate insulating layer, and an electrode provided to overlap with one of the second source electrode and the second drain electrode over the second gate insulating layer are provided. The first gate electrode and one of the second source electrode and the second drain electrode are electrically connected to each other.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device

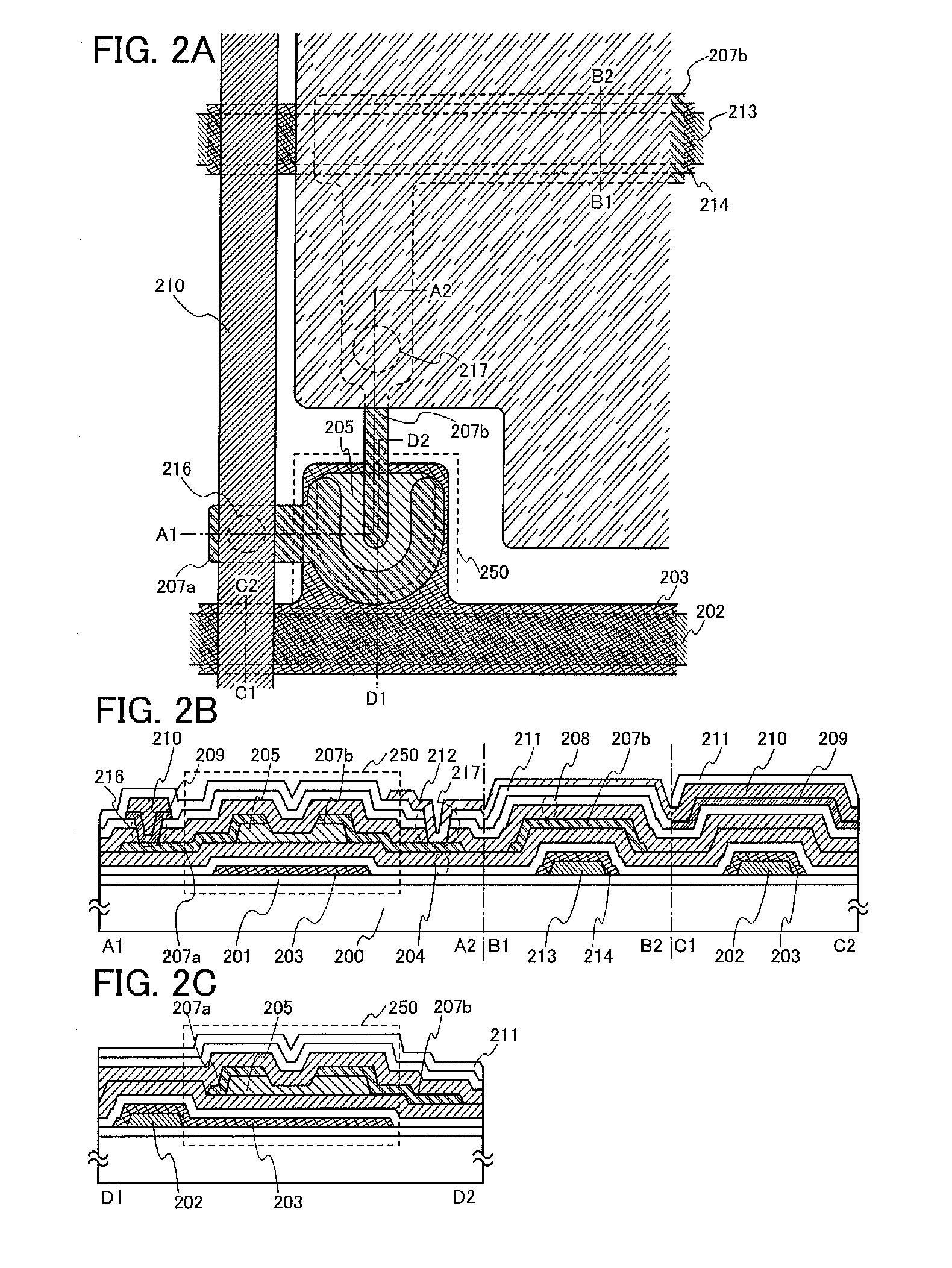

ActiveUS20110084268A1Guaranteed high speed operationReduce power consumptionElectroluminescent light sourcesSolid-state devicesDisplay deviceEngineering

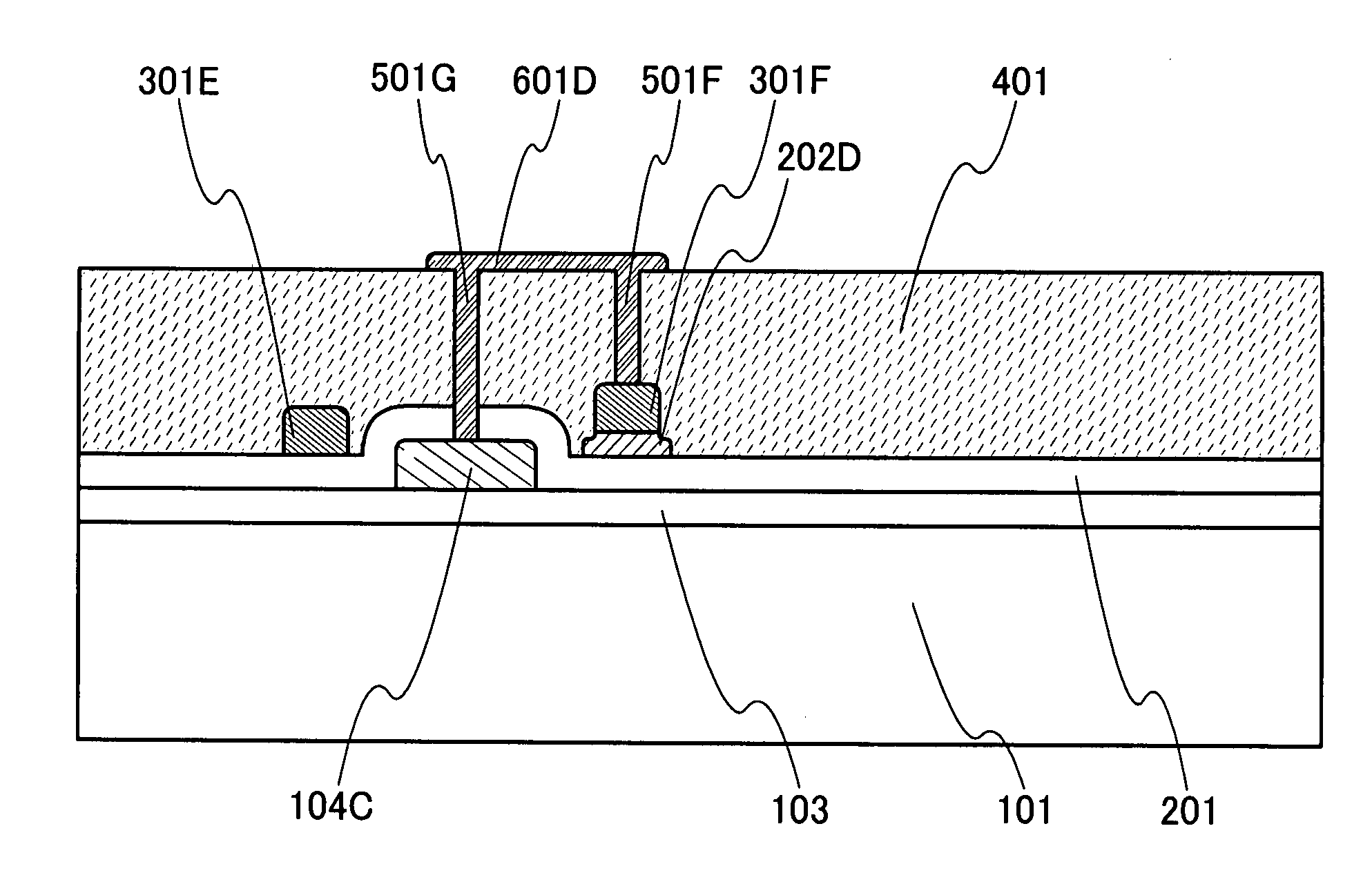

It is an object to provide a semiconductor device typified by a display device having a favorable display quality, in which parasitic resistance generated in a connection portion between a semiconductor layer and an electrode is suppressed and an adverse effect such as voltage drop, a defect in signal wiring to a pixel, a defect in grayscale, and the like due to wiring resistance are prevented. In order to achieve the above object, a semiconductor device according to the present invention may have a structure where a wiring with low resistance is connected to a thin film transistor in which a source electrode and a drain electrode that include metal with high oxygen affinity are connected to an oxide semiconductor layer with a suppressed impurity concentration. In addition, the thin film transistor including the oxide semiconductor may be surrounded by insulating films to be sealed.

Owner:SEMICON ENERGY LAB CO LTD

Multi bridge channel field effect transistors with nano-wire channels and methods of manufacturing the same

A field effect transistor (FET) includes spaced apart source and drain regions disposed on a substrate and at least one pair of elongate channel regions disposed on the substrate and extending in parallel between the source and drain regions. A gate insulating region surrounds the at least one pair of elongate channel regions, and a gate electrode surrounds the gate insulating region and the at least one pair of elongate channel regions. Support patterns may be interposed between the semiconductor substrate and the source and drain regions. The elongate channel regions may have sufficiently small cross-section to enable complete depletion thereof. For example, a width and a thickness of the elongate channel regions may be in a range from about 10 nanometers to about 20 nanometers. The elongate channel regions may have rounded cross-sections, e.g., each of the elongate channel regions may have an elliptical cross-section. The at least one pair of elongate channel regions may include a plurality of stacked pairs of elongate channel regions.

Owner:SAMSUNG ELECTRONICS CO LTD

Semiconductor device

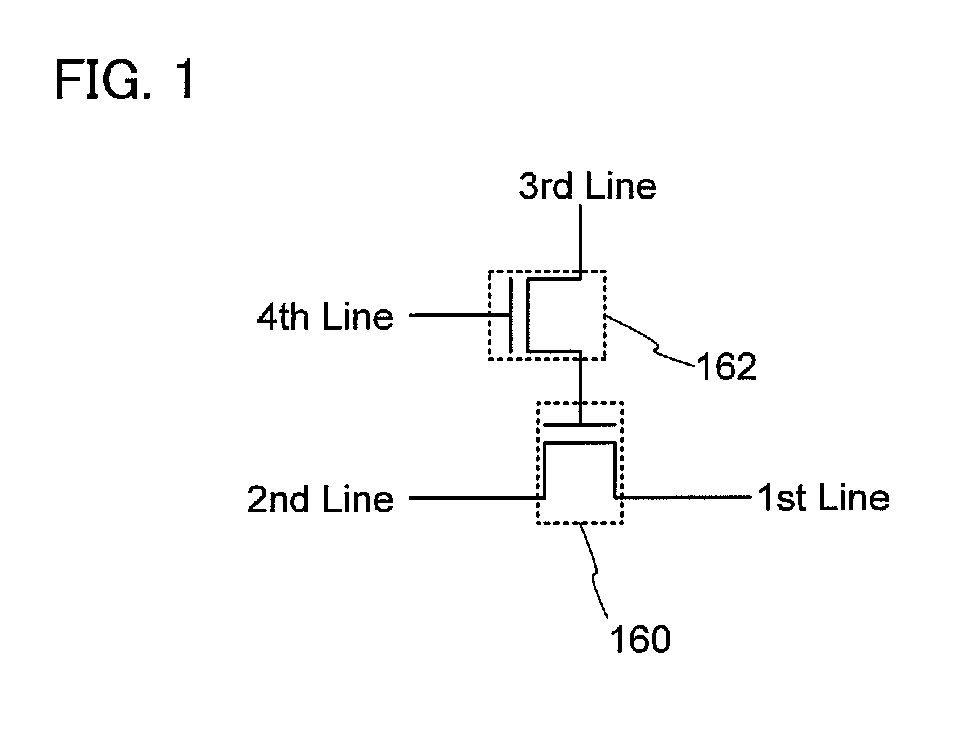

ActiveUS20110101339A1Reduce power consumptionFrequency of refresh can be lowTransistorSolid-state devicesSemiconductor materialsDevice material

An object is to provide a semiconductor device with a novel structure. The semiconductor device includes a first wiring; a second wiring; a third wiring; a fourth wiring; a first transistor having a first gate electrode, a first source electrode, and a first drain electrode; and a second transistor having a second gate electrode, a second source electrode, and a second drain electrode. The first transistor is provided in a substrate including a semiconductor material. The second transistor includes an oxide semiconductor layer.

Owner:SEMICON ENERGY LAB CO LTD

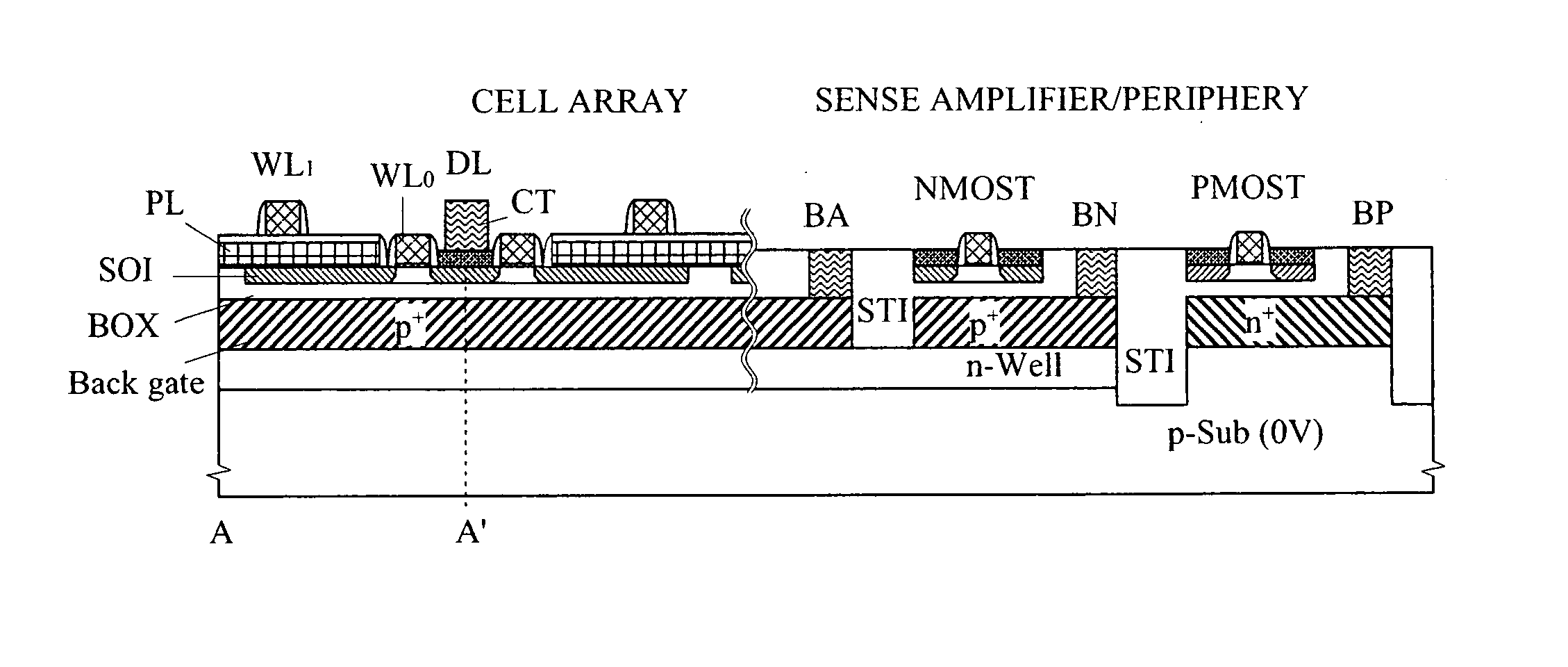

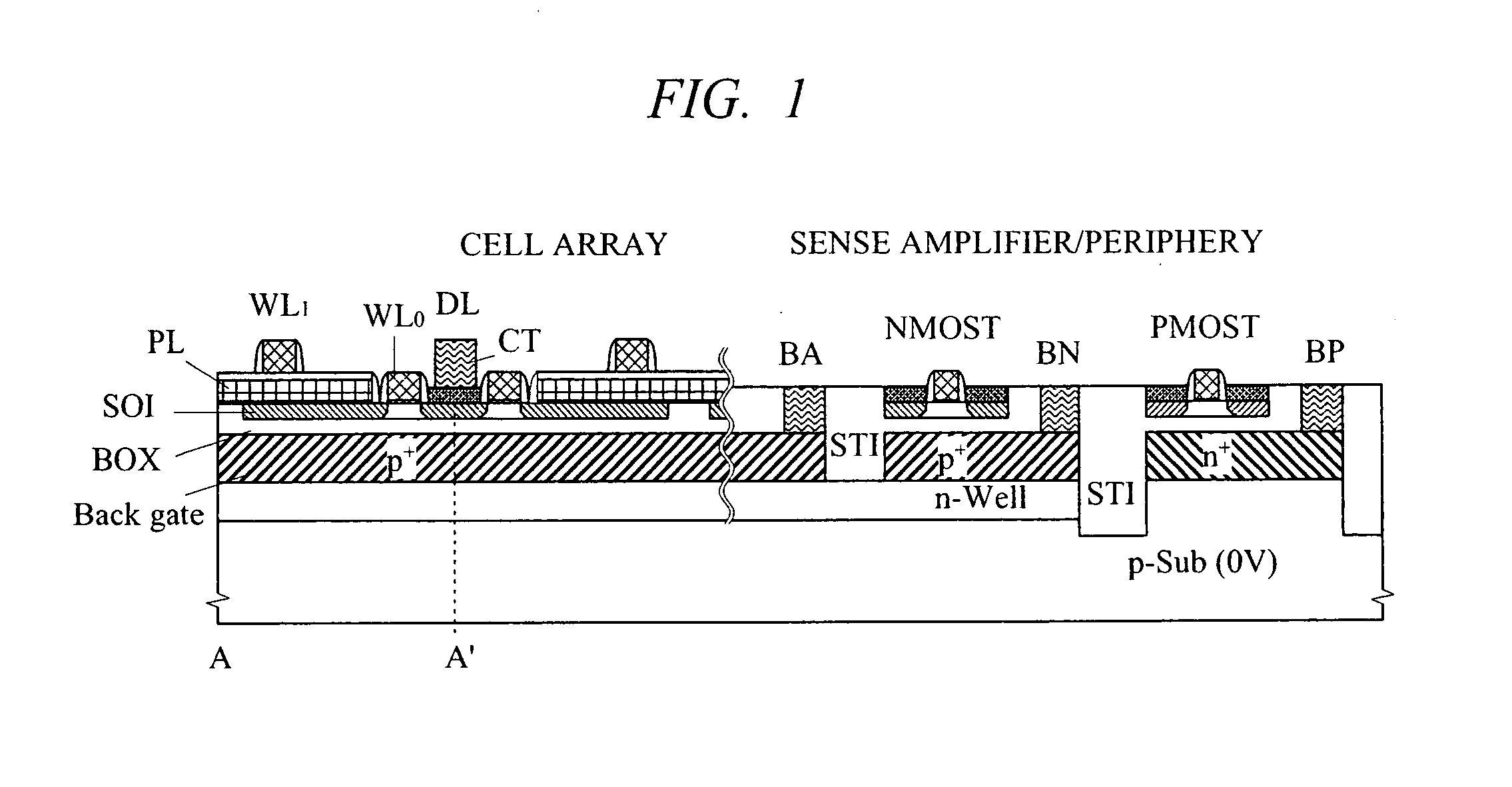

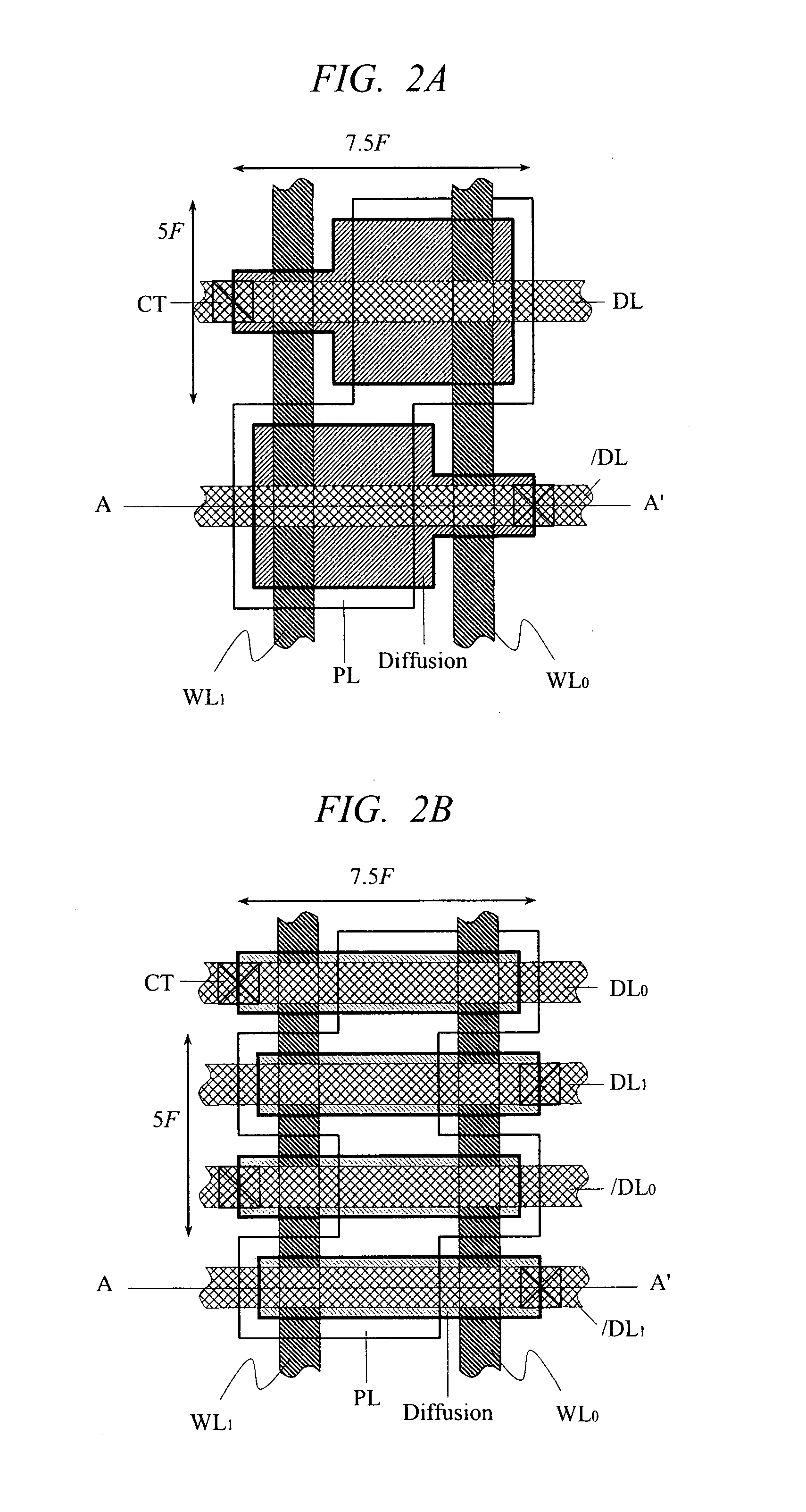

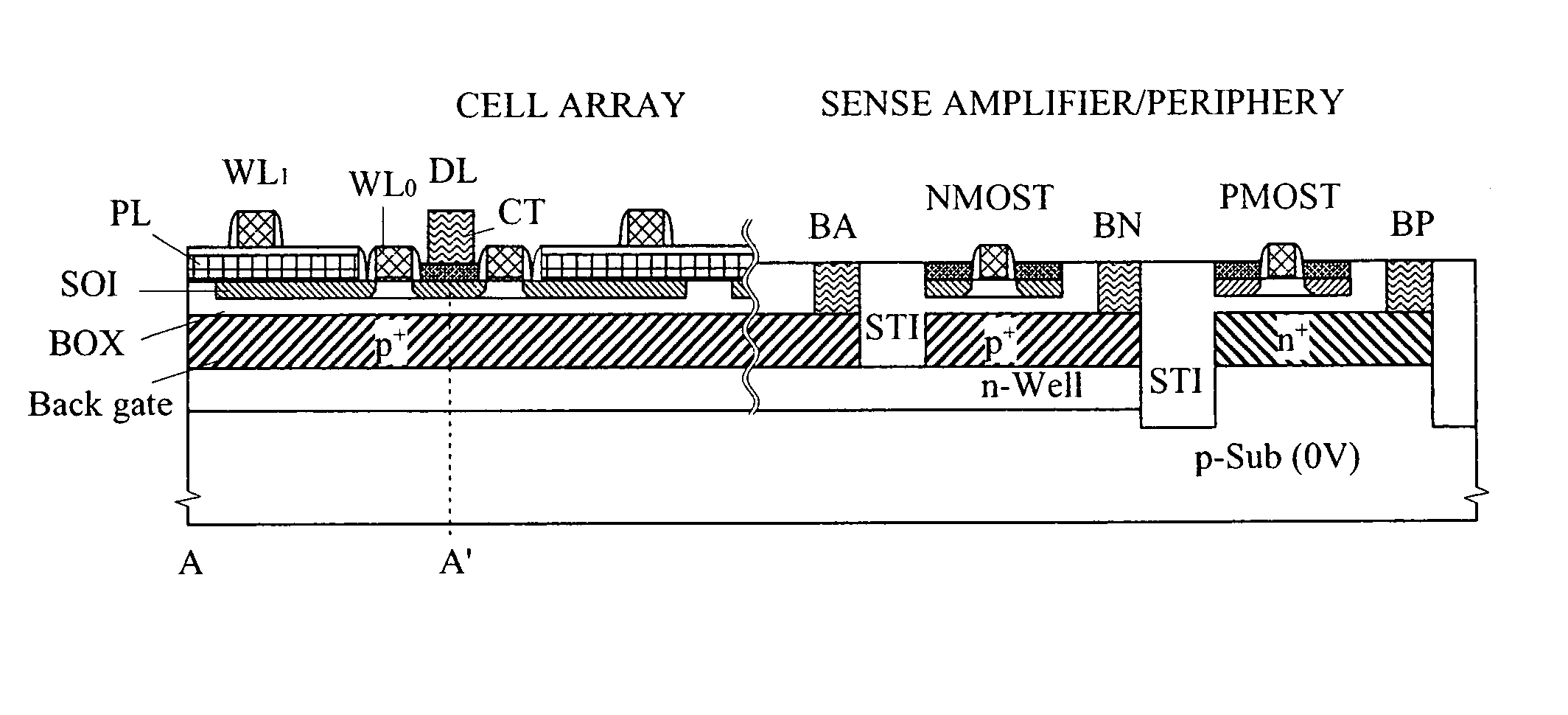

Semiconductor device

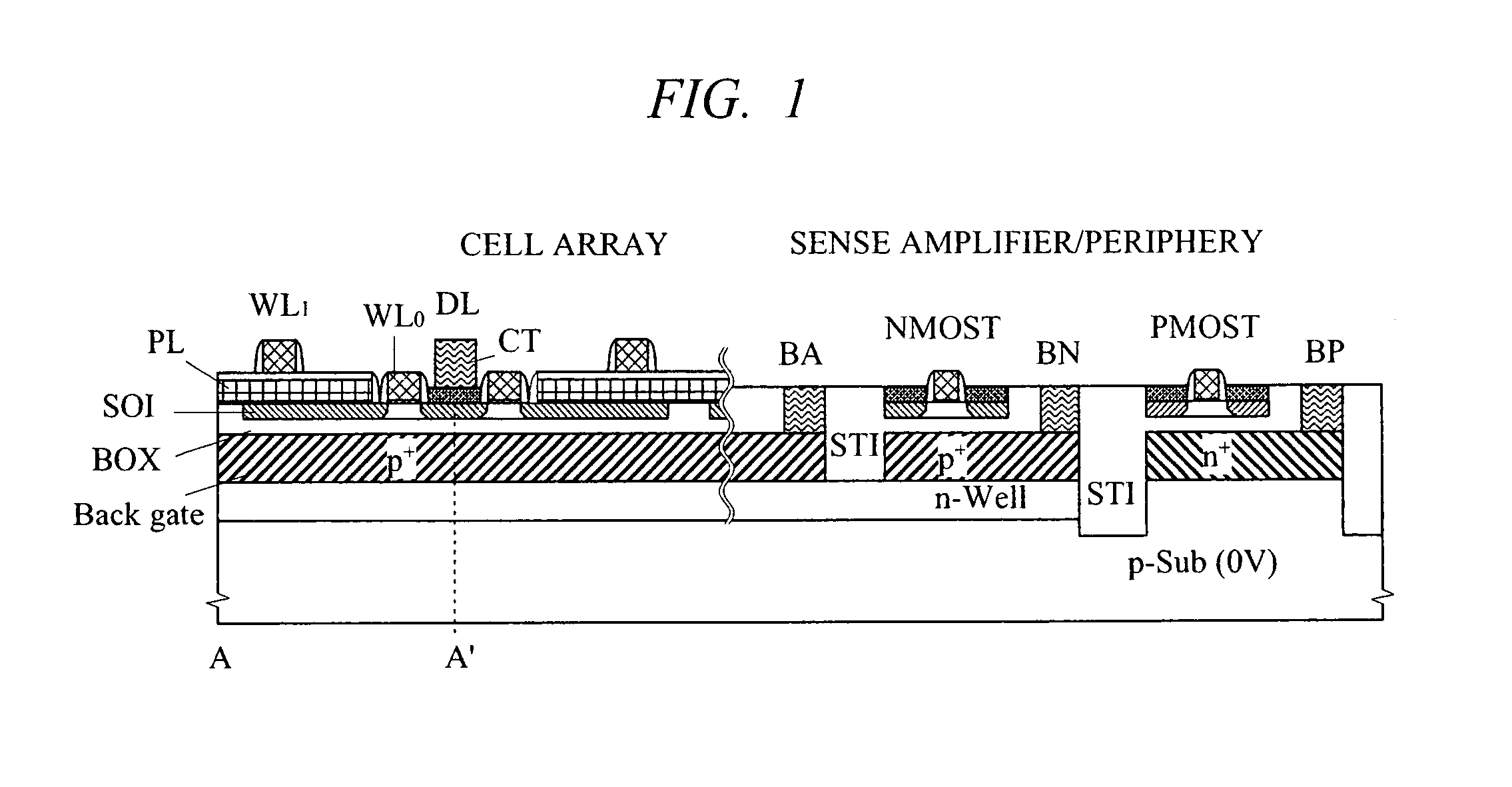

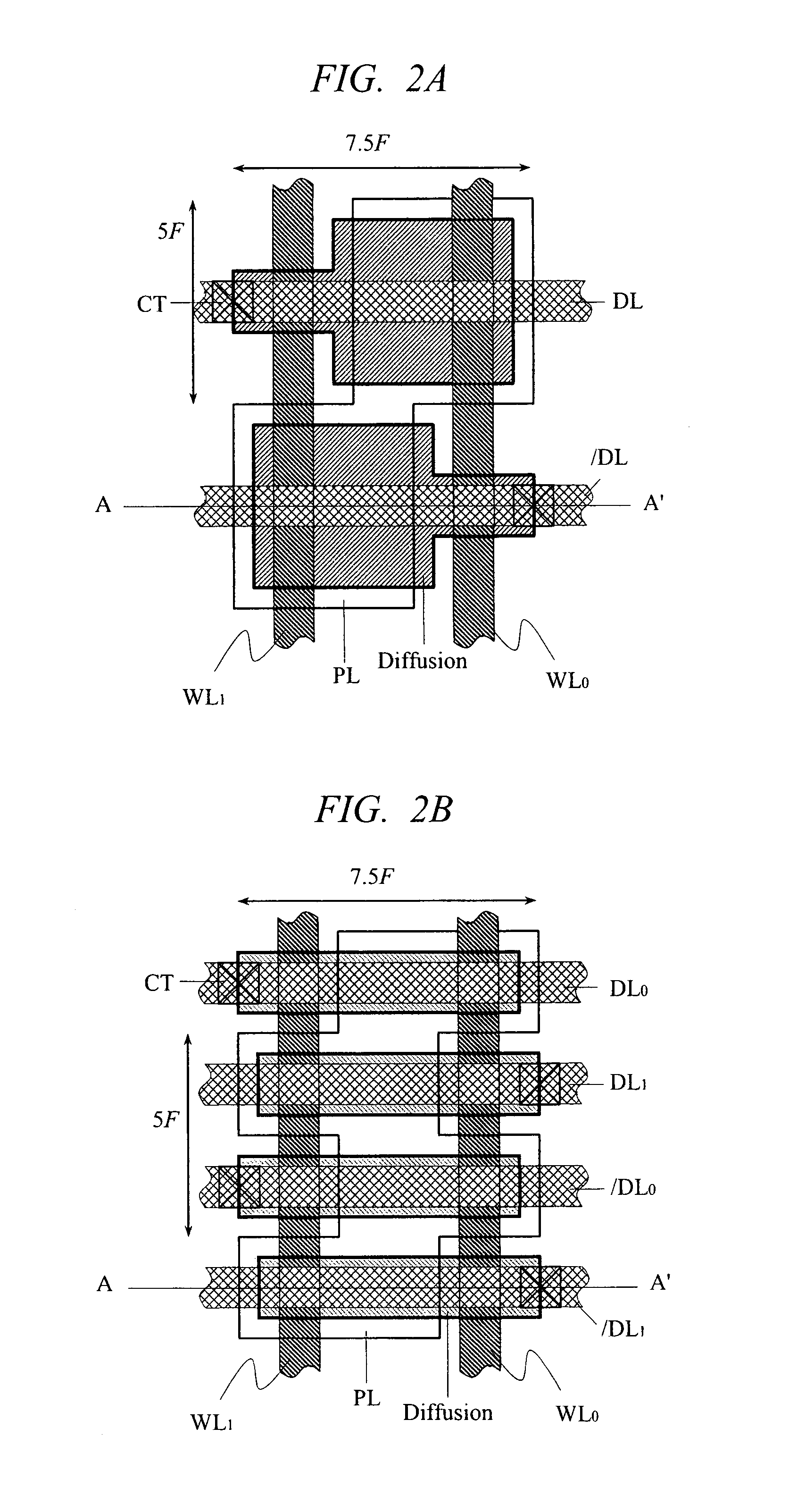

InactiveUS20090003105A1Run at high speedSmall sizeTransistorSolid-state devicesJunction leakageAudio power amplifier

A high-speed and low-voltage DRAM memory cell capable of operating at 1 V or less and an array peripheral circuit are provided. A DRAM cell is comprised of a memory cell transistor and planar capacitor which utilize a FD-SOI MOST structure. Since there is no junction leakage current, loss of stored charge is eliminated, and the low-voltage operation can be realized. Further, a gate and a well in a cross-coupled type sense amplifier using FD-SOI MOSTs are connected. By this means, a threshold value dynamically changes and high-speed sensing operation can be realized.

Owner:HITACHI LTD

Semiconductor device

A high-speed and low-voltage DRAM memory cell capable of operating at 1 V or less and an array peripheral circuit are provided. A DRAM cell is comprised of a memory cell transistor and planar capacitor which utilize a FD-SOI MOST structure. Since there is no junction leakage current, loss of stored charge is eliminated, and the low-voltage operation can be realized. Further, a gate and a well in a cross-coupled type sense amplifier using FD-SOI MOSTs are connected. By this means, a threshold value dynamically changes and high-speed sensing operation can be realized.

Owner:HITACHI LTD

Semiconductor device and method for manufacturing the same

ActiveUS20120319114A1Improve conduction characteristicsRapid responseTransistorSemiconductor/solid-state device manufacturingDopantPower semiconductor device

A transistor including an oxide semiconductor layer and having electric characteristics required depending on an intended use, and a semiconductor device including the transistor are provided. In a transistor in which a semiconductor layer, a source electrode layer and a drain electrode layer, a gate insulating film, and a gate electrode layer are stacked in this order over an oxide insulating film, an oxide semiconductor stack composed of at least two oxide semiconductor layers having different energy gaps is used as the semiconductor layer. Oxygen and / or a dopant may be introduced into the oxide semiconductor stack.

Owner:SEMICON ENERGY LAB CO LTD

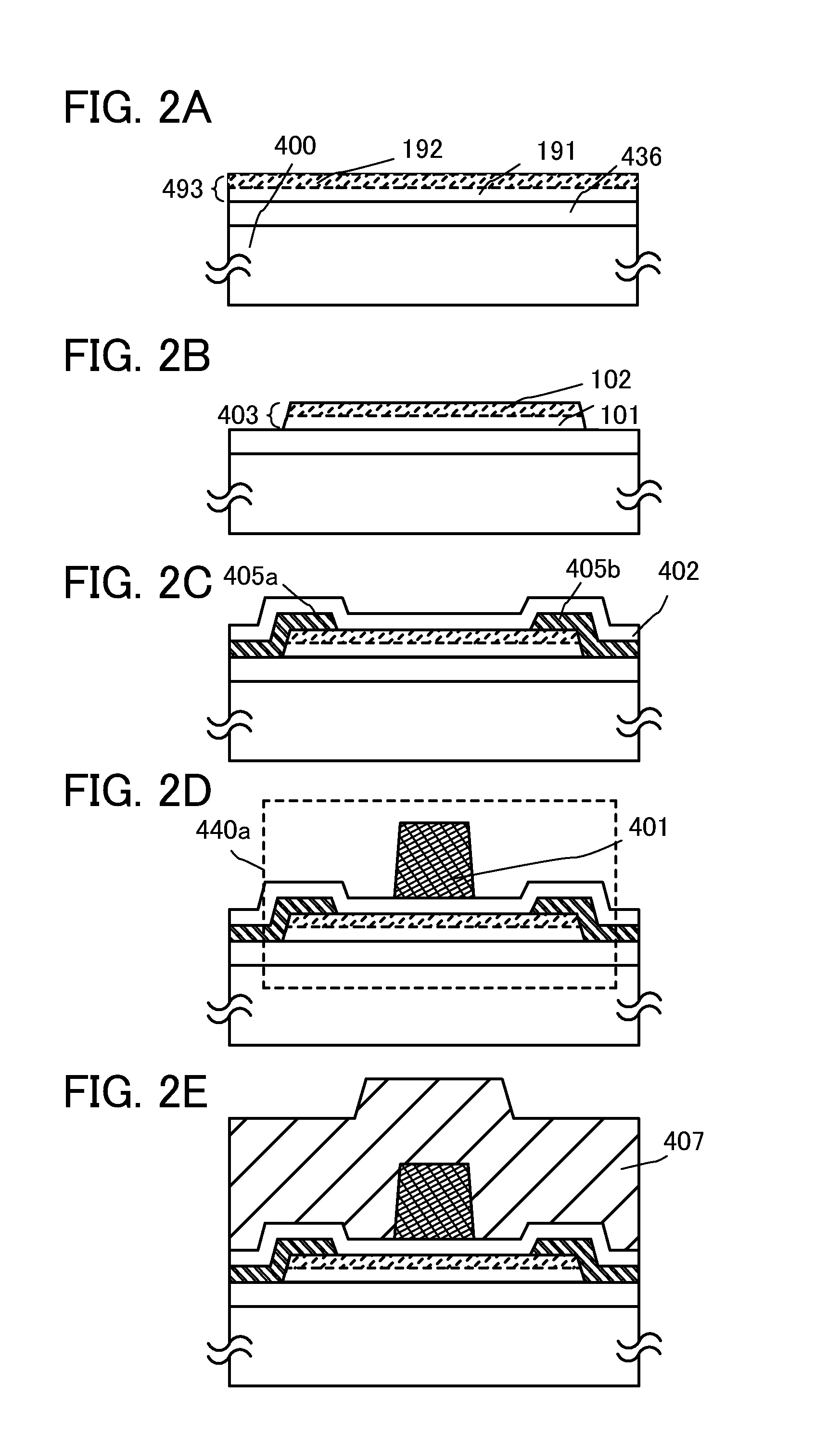

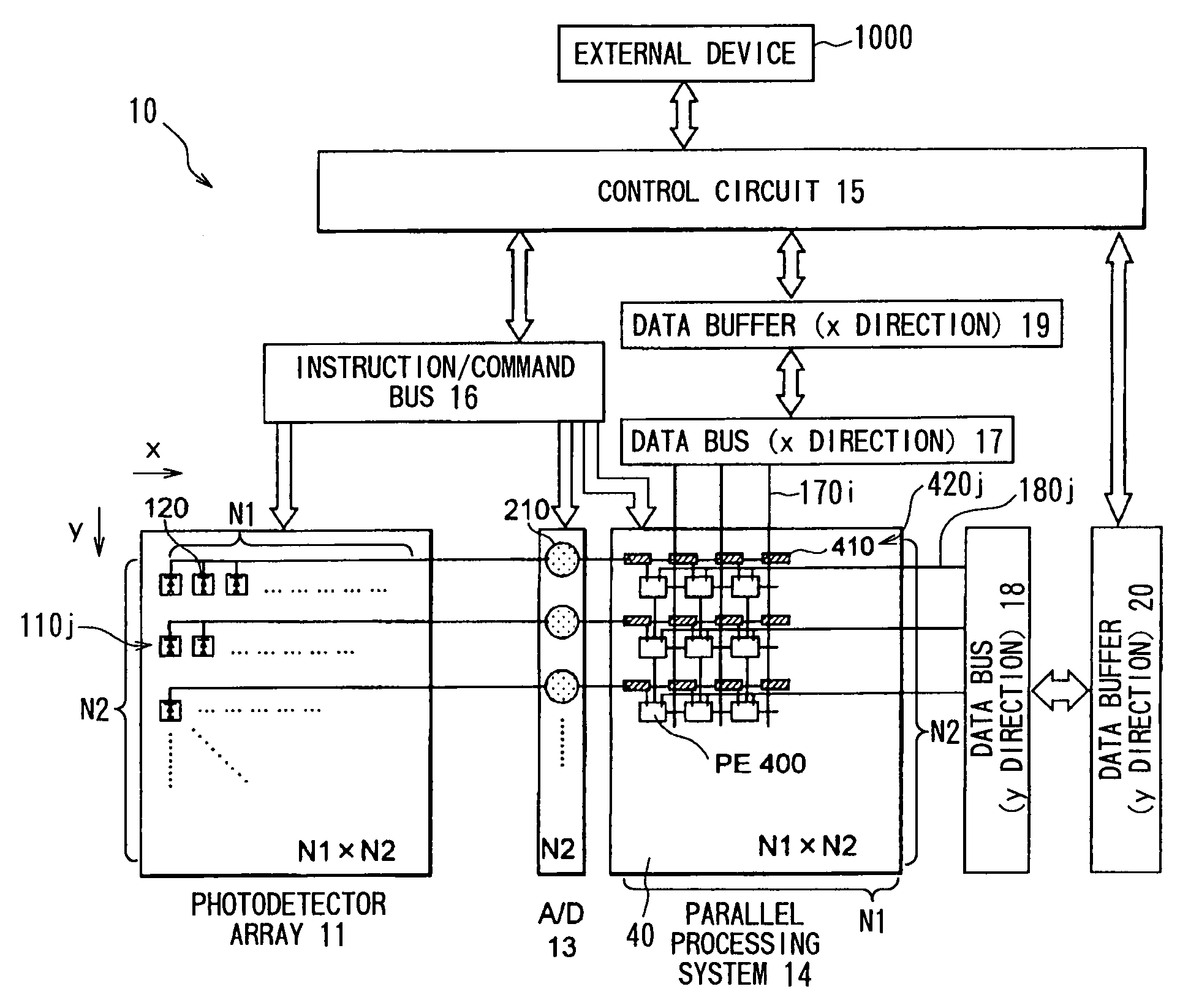

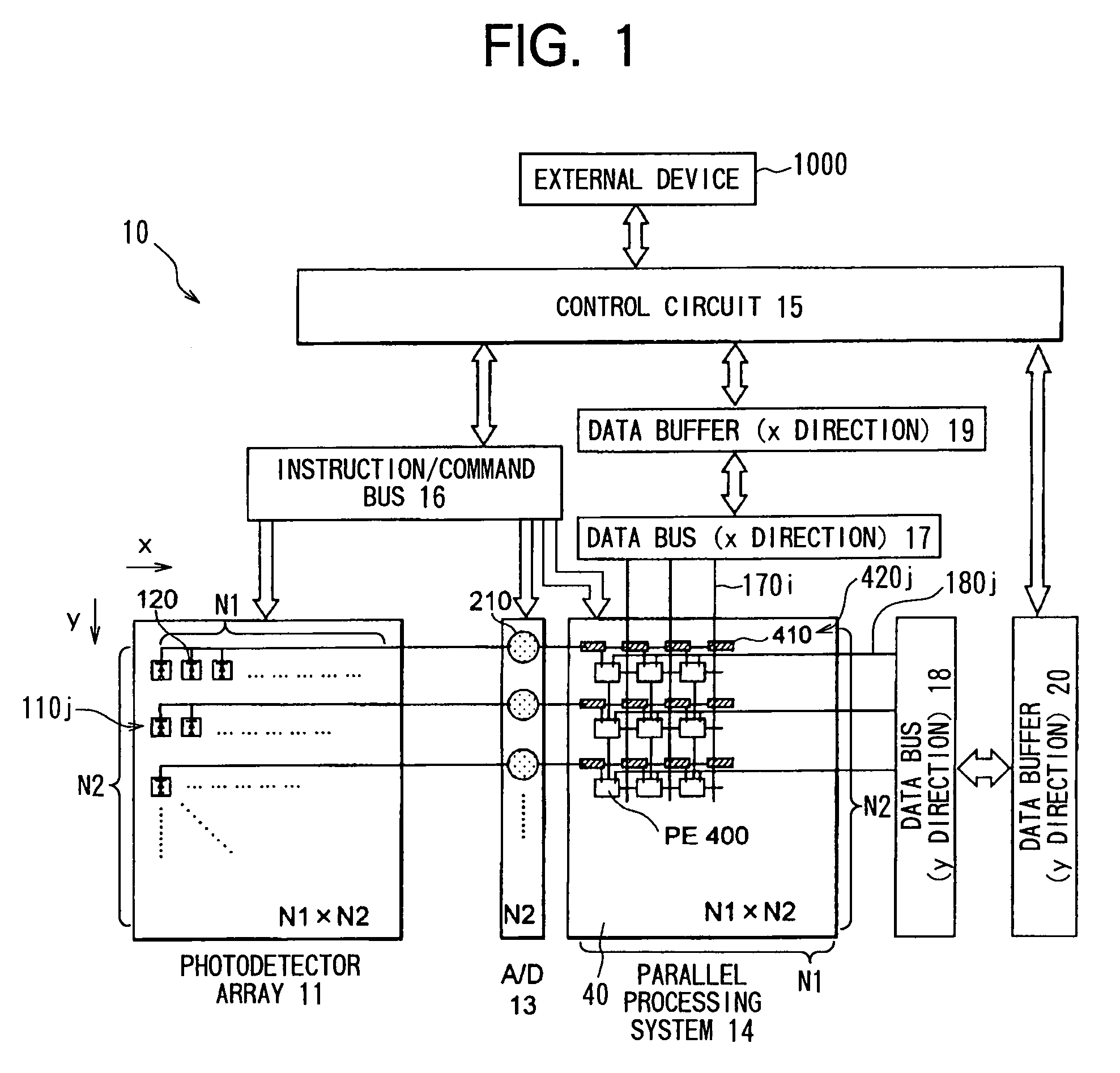

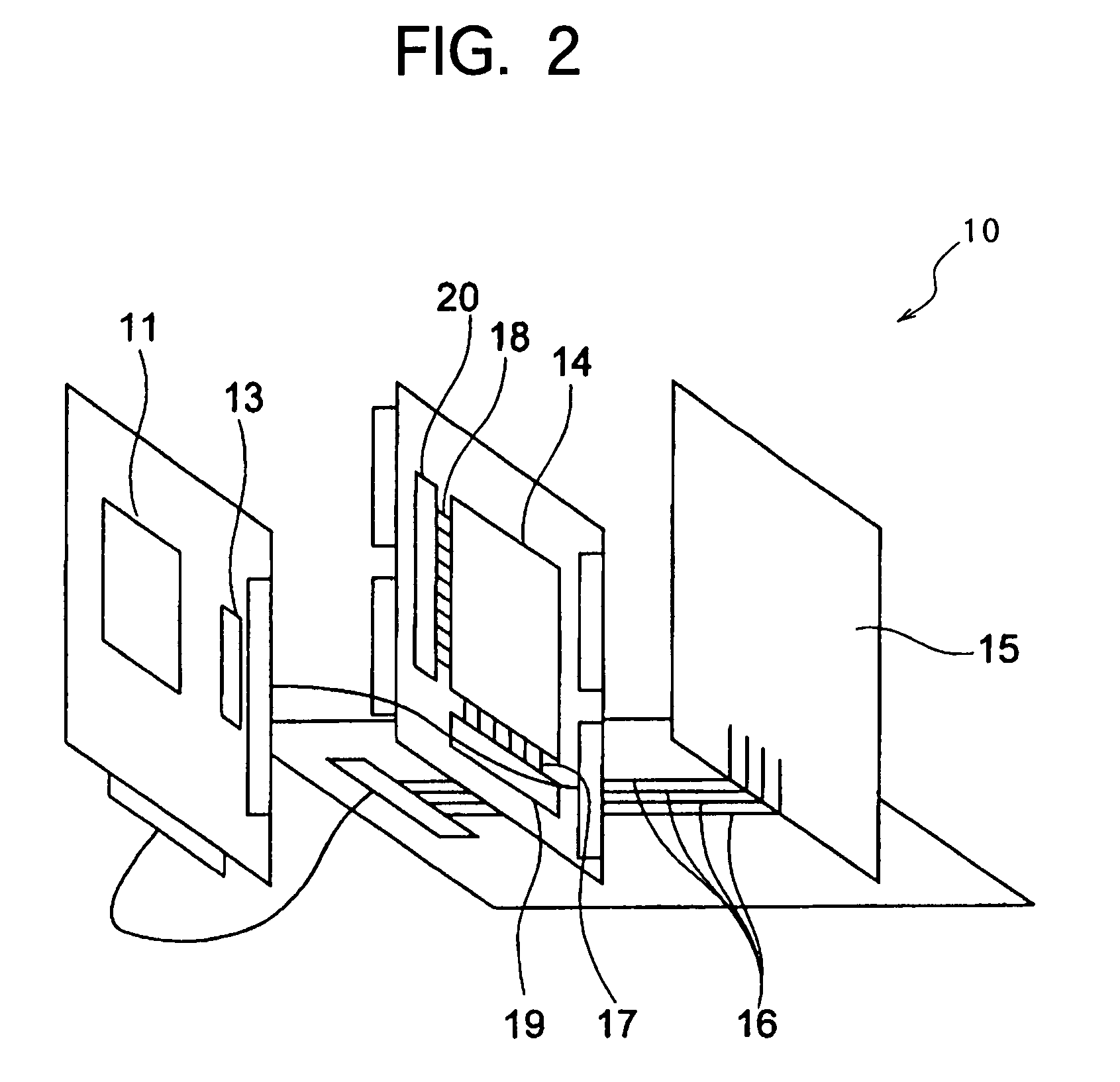

High-speed vision sensor with image processing function

InactiveUS6970196B1Simple circuit structureIncrease speedProgramme controlTelevision system detailsShift registerHigh rate

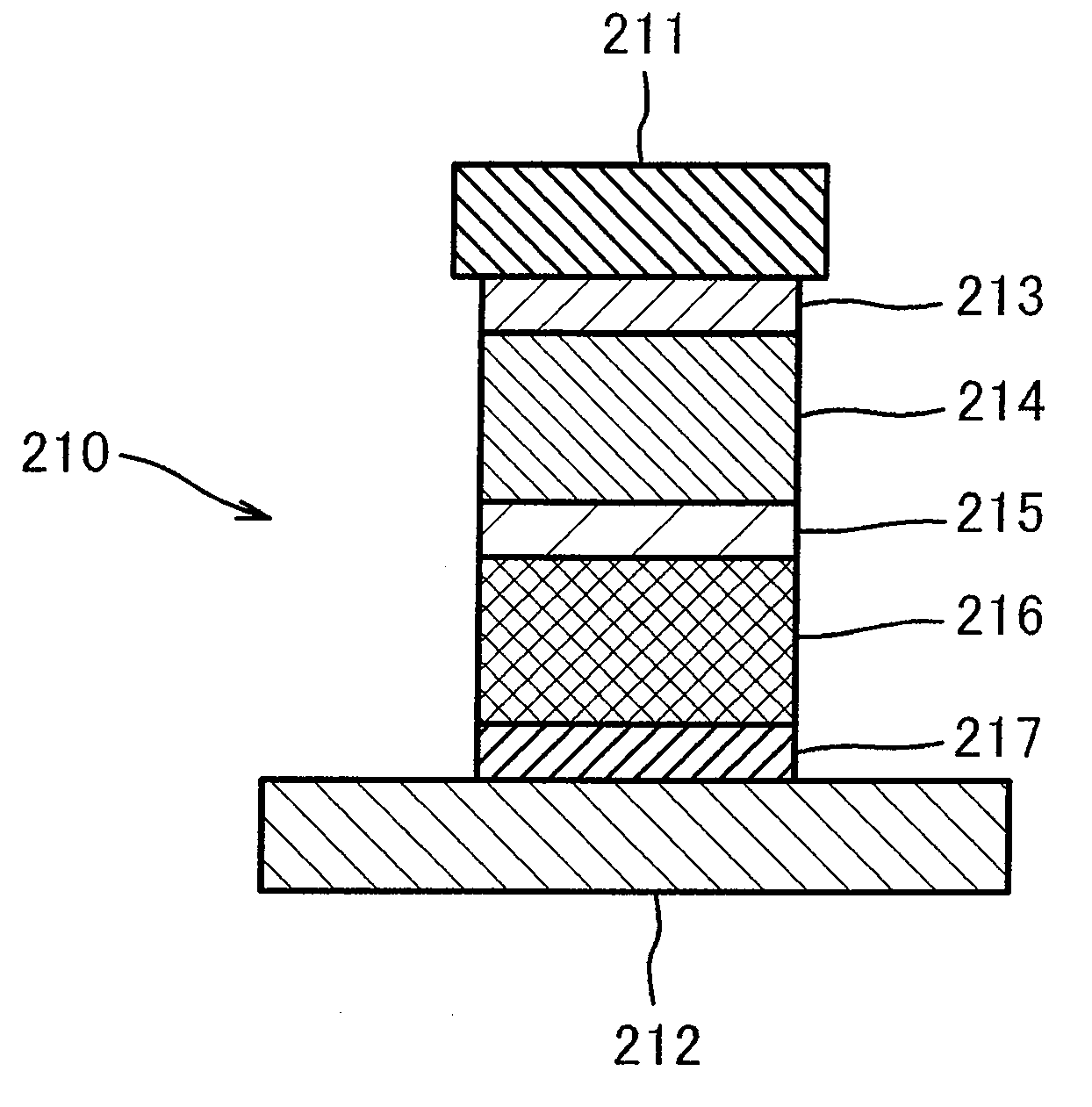

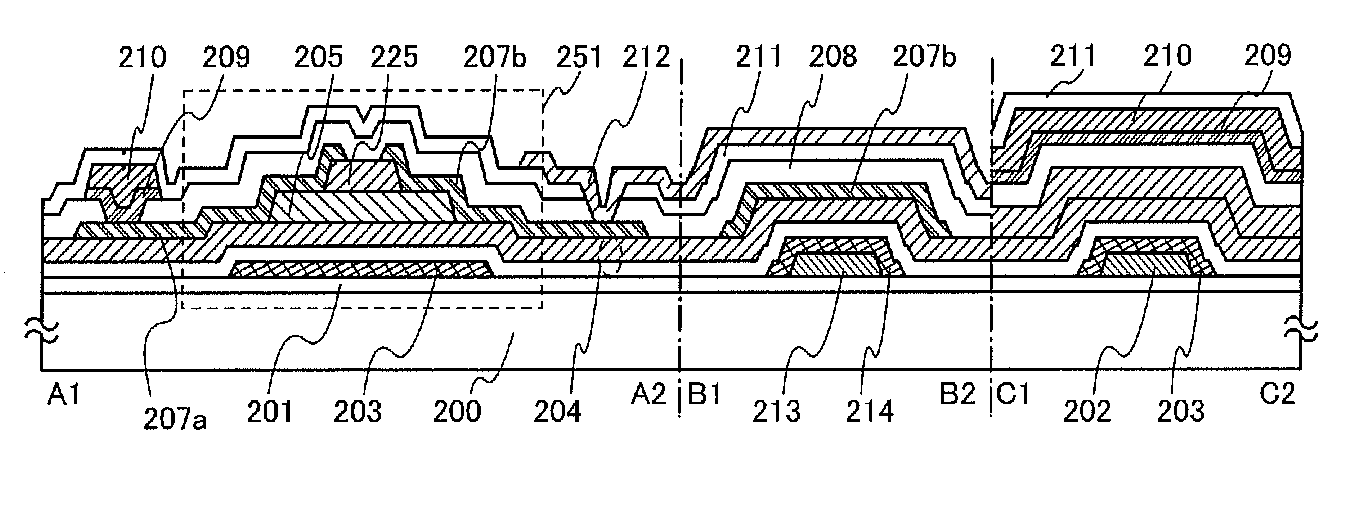

A high-speed vision sensor includes: an analog-to-digital converter array 13, in which one analog-to-digital converter 210 is provided in correspondence with all the photodetector elements 120 that are located on each row in a photodetector array 11; a parallel processing system 14 that includes processor elements 400 and shift registers 410, both of which form a one-to-one correspondence with the photodetector elements 120; and data buses 17, 18 and data buffers 19 and 20 for data transfer to processing elements 400. The processing elements 400 perform high-speed image processing between adjacent pixels by parallel processings. By using the data buses 17, 18, it is possible to attain, at a high rate of speed, such calculation processing that requires data supplied from outside.

Owner:HAMAMATSU PHOTONICS KK

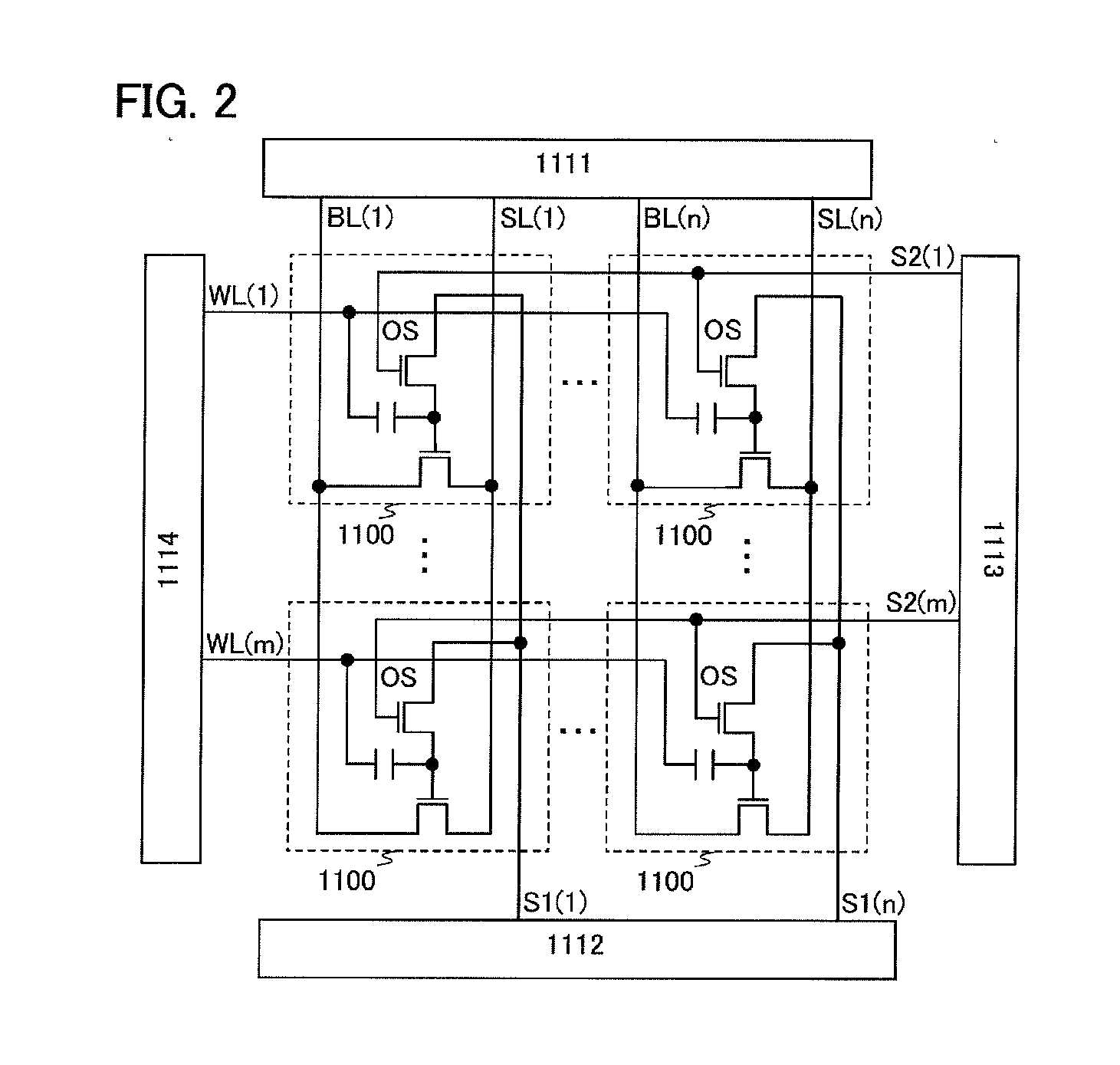

Semiconductor device

ActiveUS20110157961A1Reduce power consumptionFrequency of refresh can be lowTransistorSolid-state devicesPower semiconductor deviceDriver circuit

The semiconductor device includes a source line, a bit line, a first signal line, a second signal line, a word line, memory cells connected in parallel between the source line and the bit line, a first driver circuit electrically connected to the source line and the bit line, a second driver circuit electrically connected to the first signal line, a third driver circuit electrically connected to the second signal line, and a fourth driver circuit electrically connected to the word line. The memory cell includes a first transistor including a first gate electrode, a first source electrode, and a first drain electrode, a second transistor including a second gate electrode, a second source electrode, and a second drain electrode, and a capacitor. The second transistor includes an oxide semiconductor material.

Owner:SEMICON ENERGY LAB CO LTD

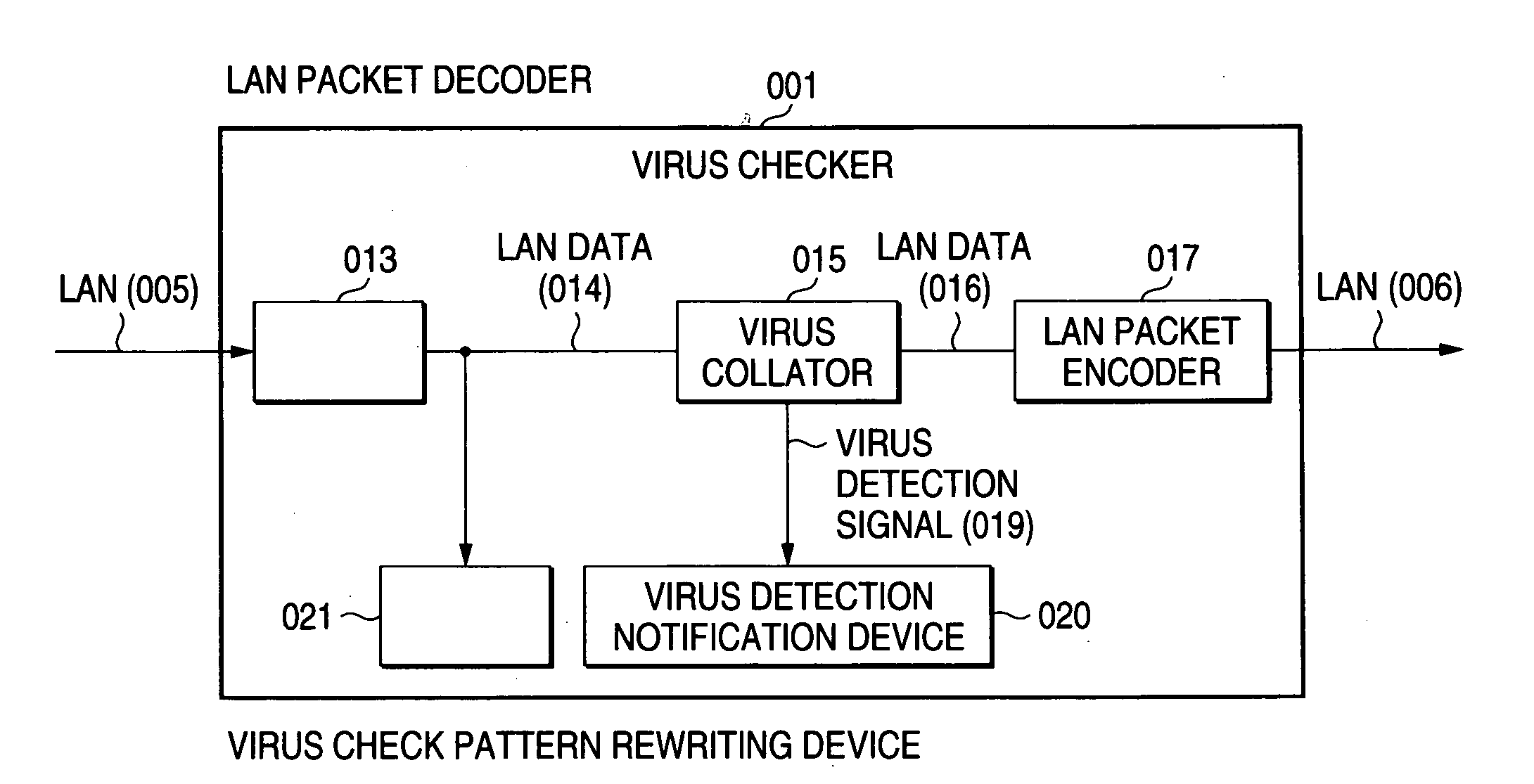

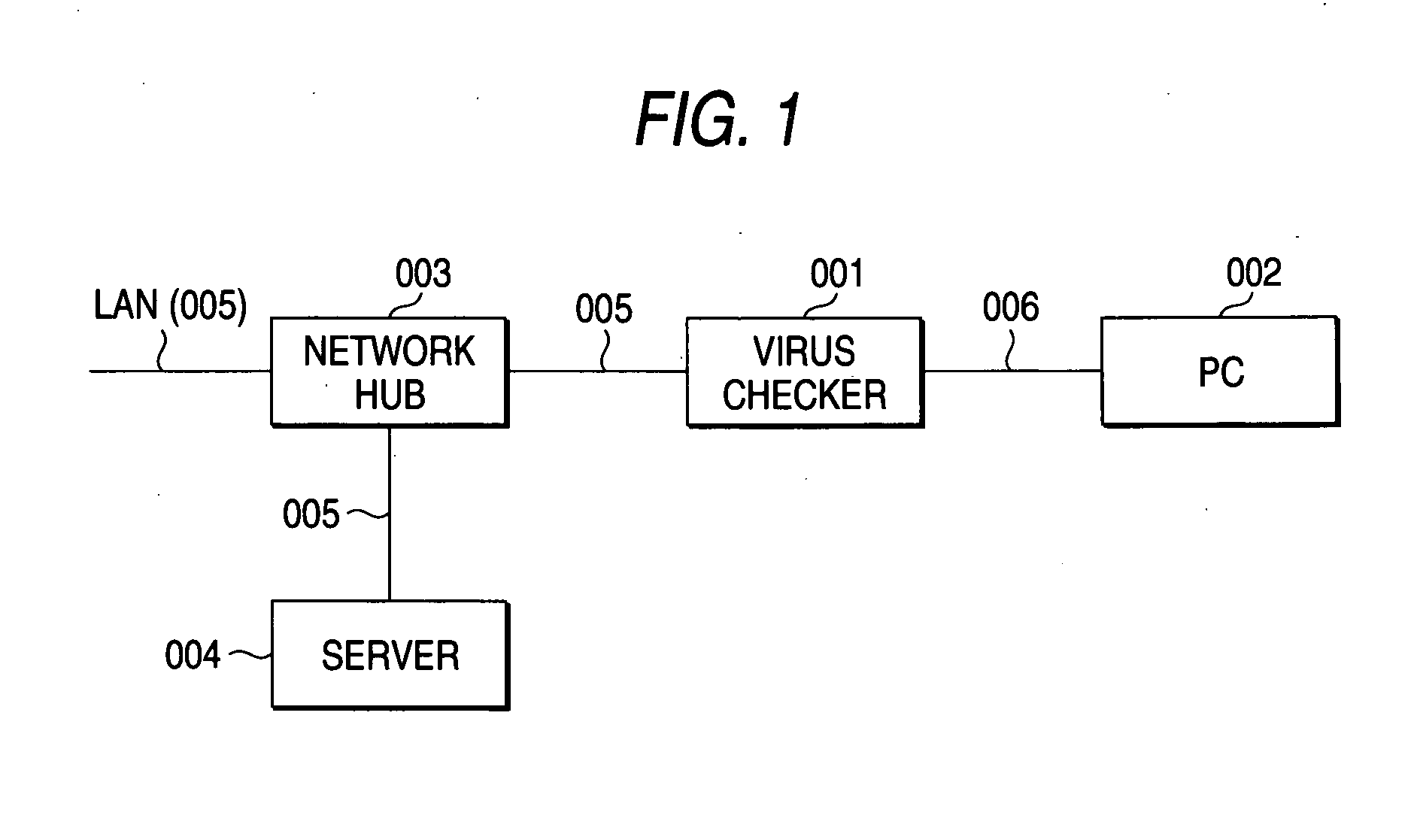

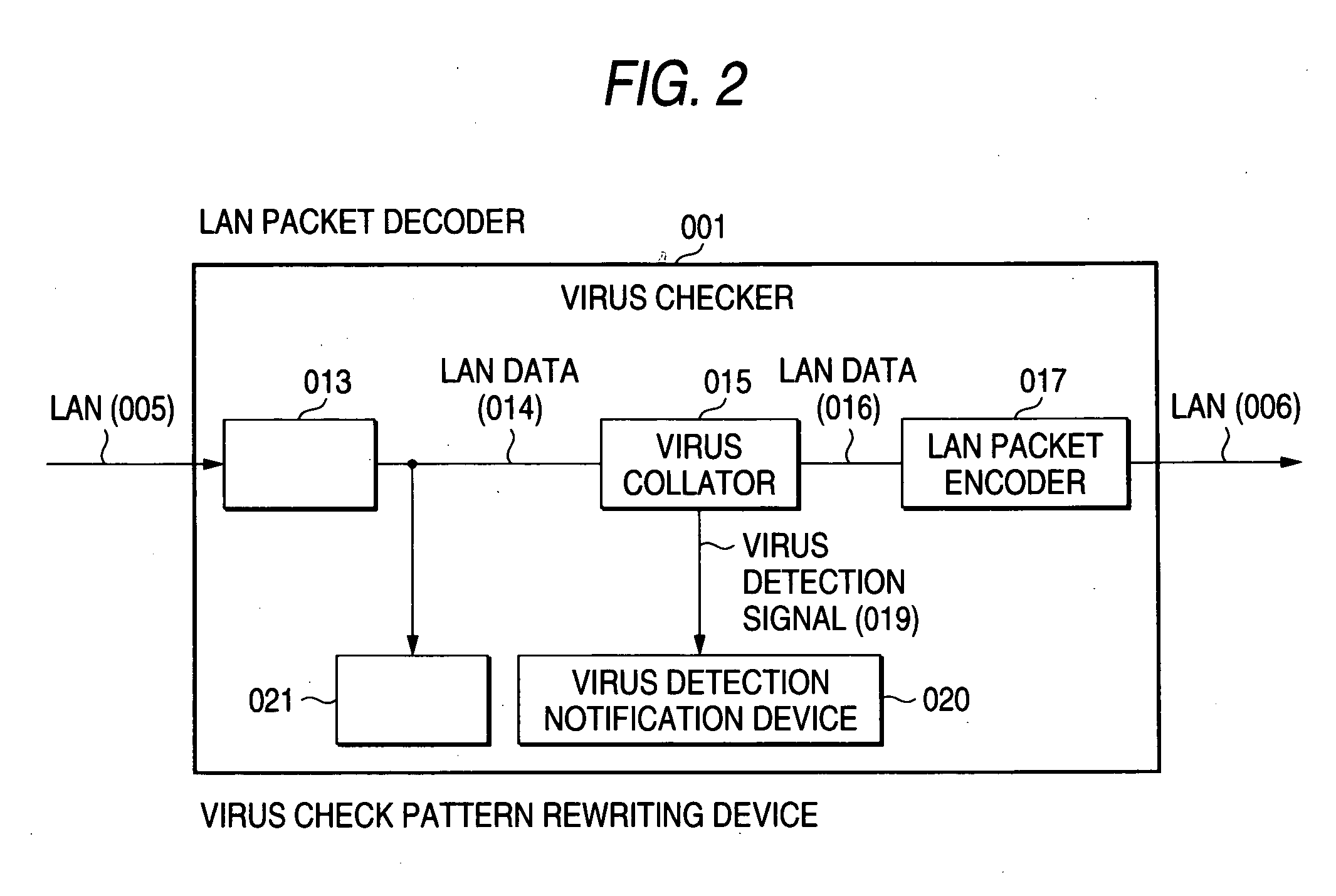

Virus check device and system

InactiveUS20060242686A1High speed machiningSimple processDigital data processing detailsError detection/correctionDigital dataInformation processing

The present invention detects a computer virus at high speed from digital data acquired through a network using hardware in virus monitoring. With the invention, in an information processing terminal 002 capable of communicating with other information processing apparatus through a communication network 005, a virus checking apparatus 001 constructed of a hardware circuit is disposed in the side of an input channel of the network 005 and a virus is checked from input data from the network 005 by the virus checking apparatus 001. In order to change a virus pattern collated with the input data by hardware, the hardware circuit is detachably mounted or a rewritable logic device is used in the hardware circuit. The virus pattern of the logic device can be rewritten by sending virus definition information of a server 004 or control data generated based on this information to the virus checking apparatus 001.

Owner:NAT INST OF ADVANCED IND SCI & TECH

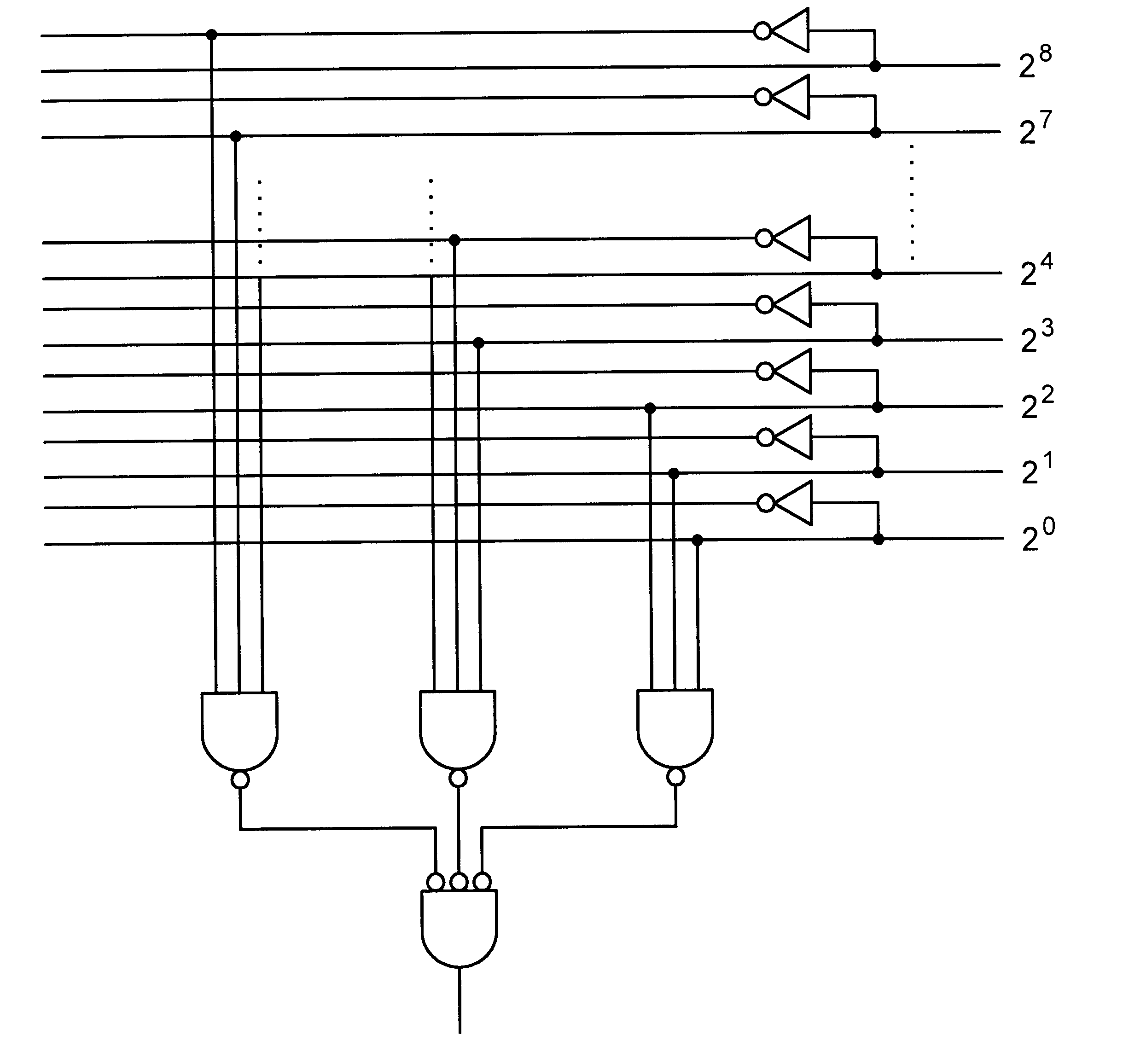

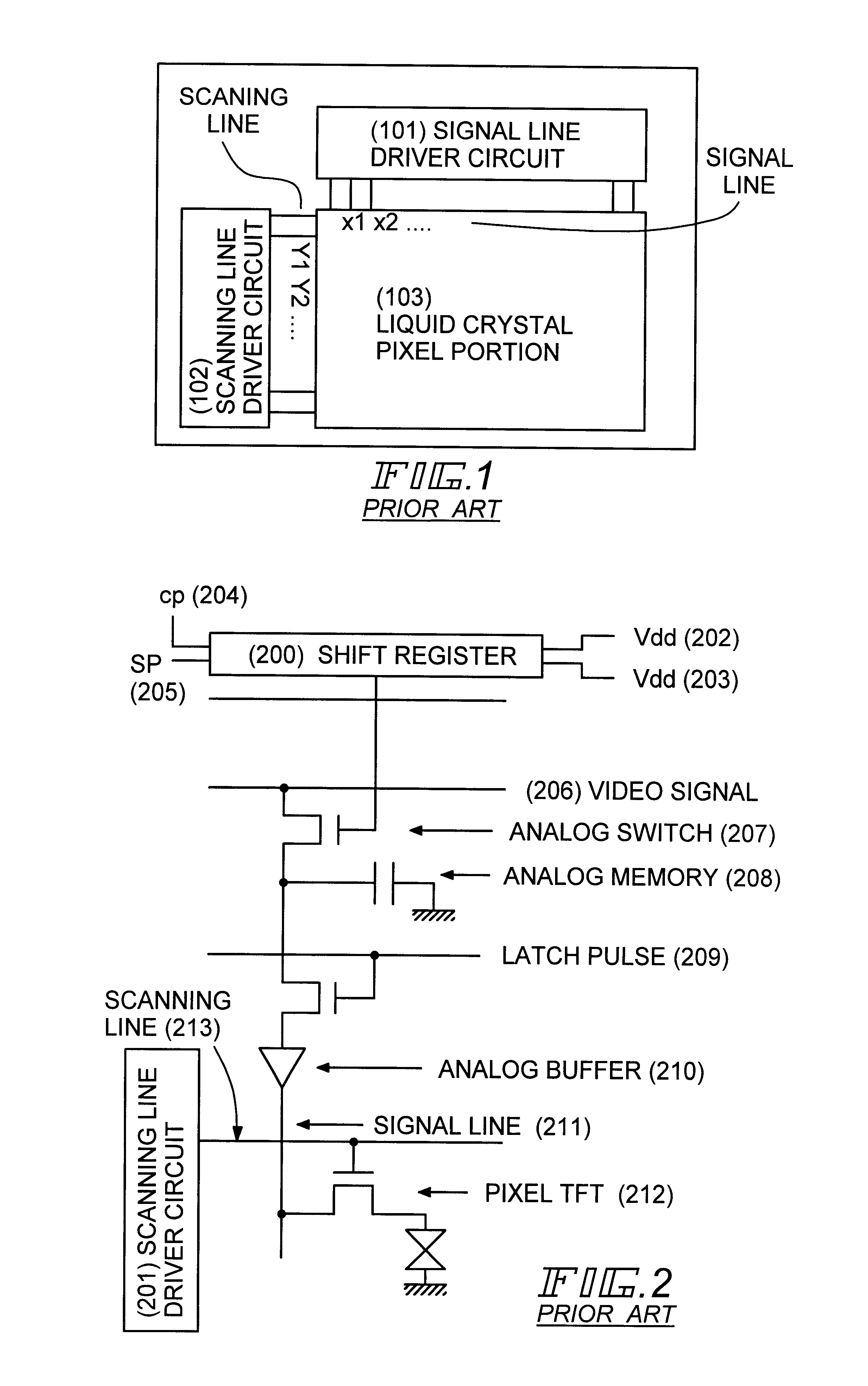

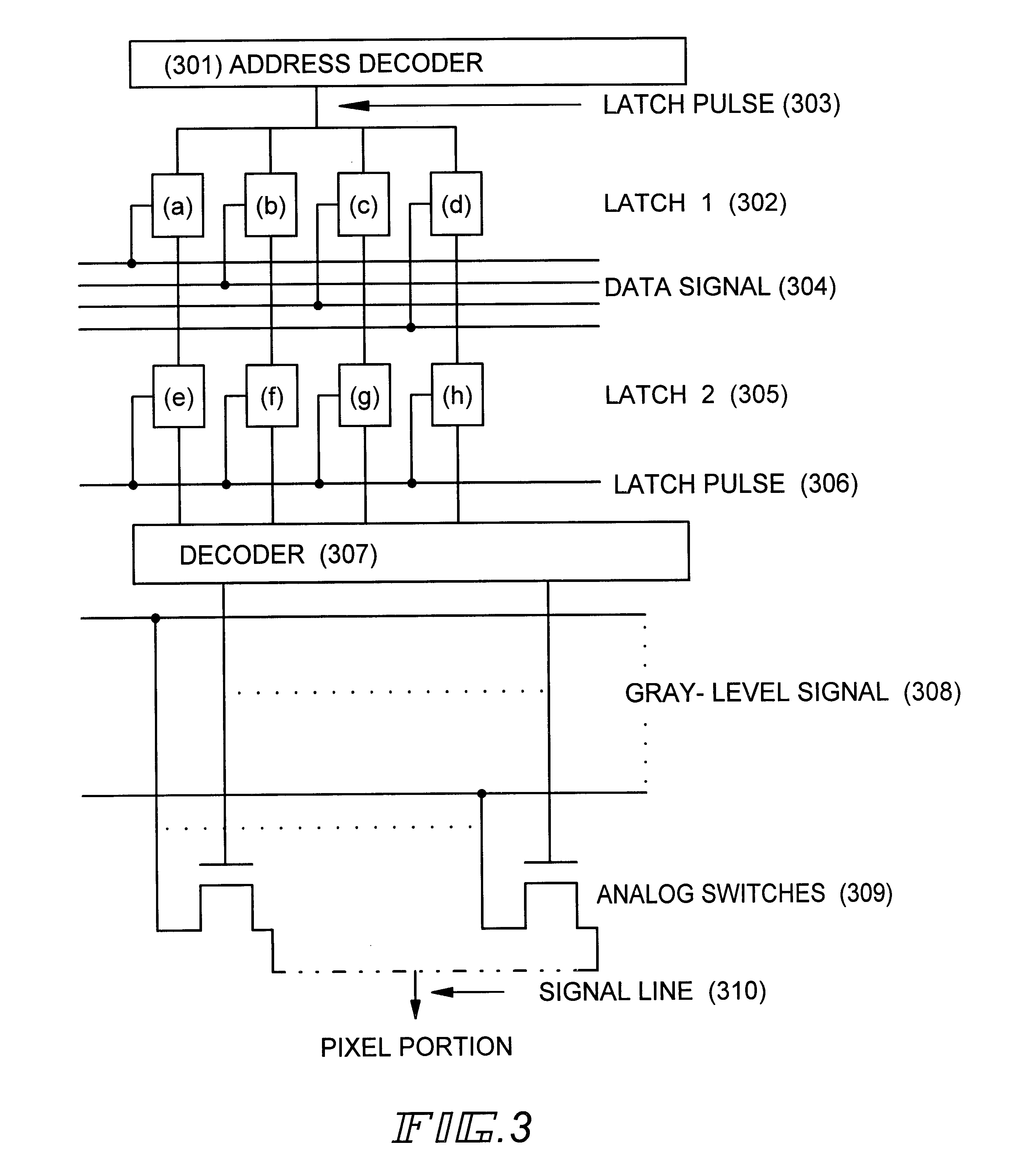

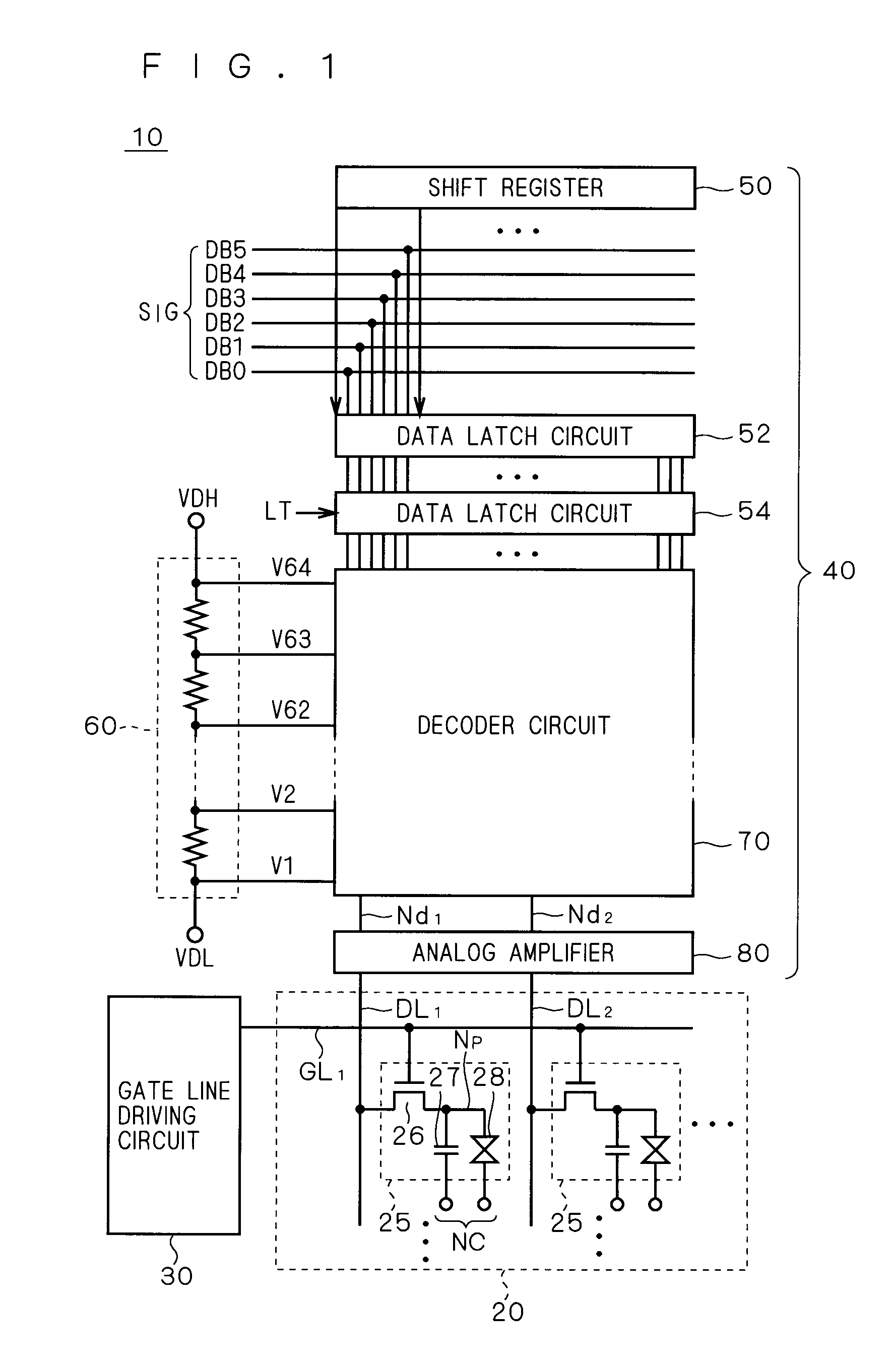

Drive circuit for display device

InactiveUS6344843B1Reduce scan timeRun at high speedCathode-ray tube indicatorsInput/output processes for data processingAddress decoderGray level

A driver circuit for use in an active matrix display having switching devices at pixels. The driver circuit uses no shift registers. Random access to signal lines or scanning lines can be obtained. The display quality is improved. The production yield is improved. Also, lower electric power consumption and higher-speed operation can be accomplished. Data about gray levels assumes the form of digital values and is supplied to the driver circuit. The signal lines or scanning lines are selected by an address decoder circuit.

Owner:SEMICON ENERGY LAB CO LTD

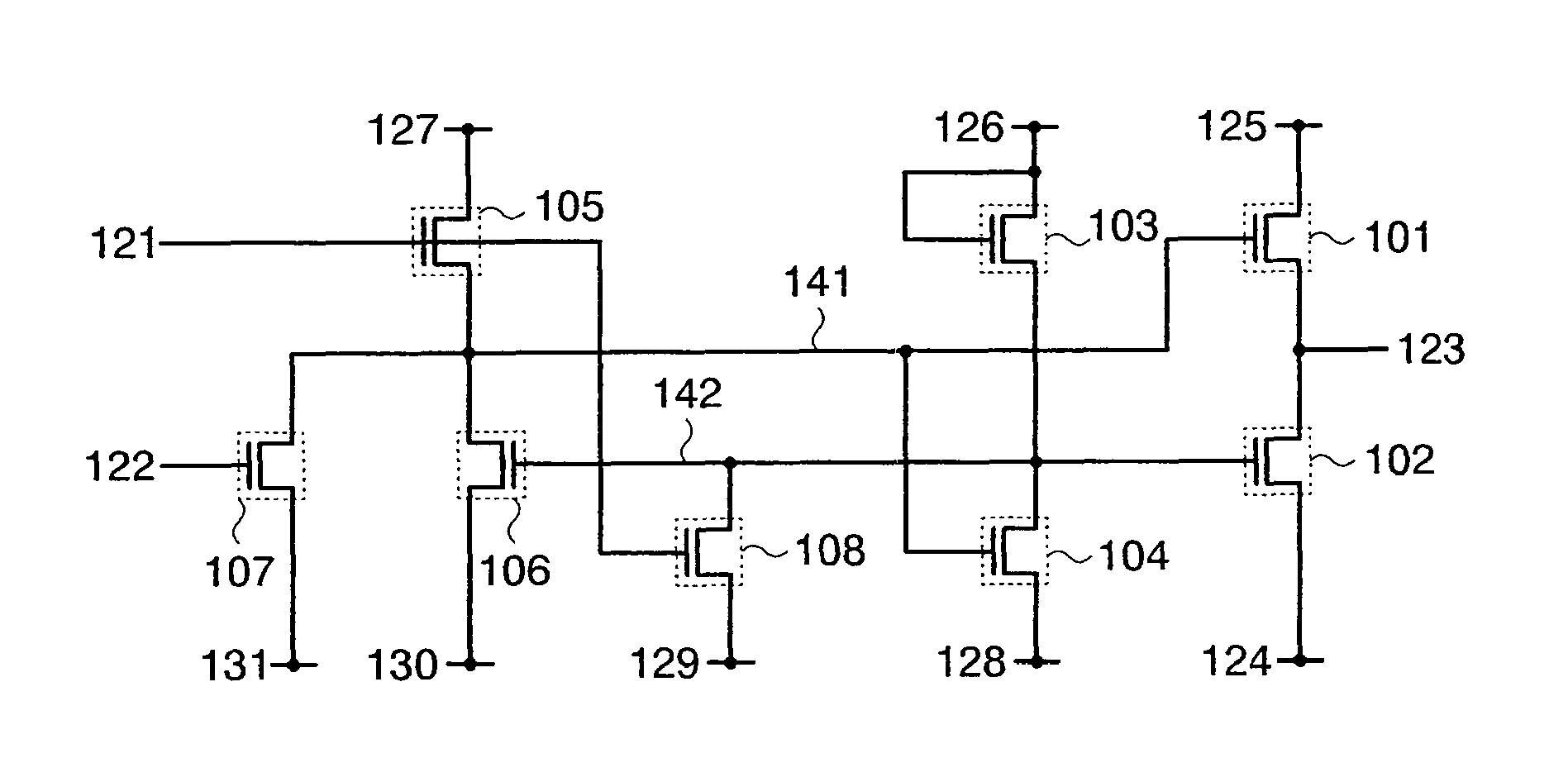

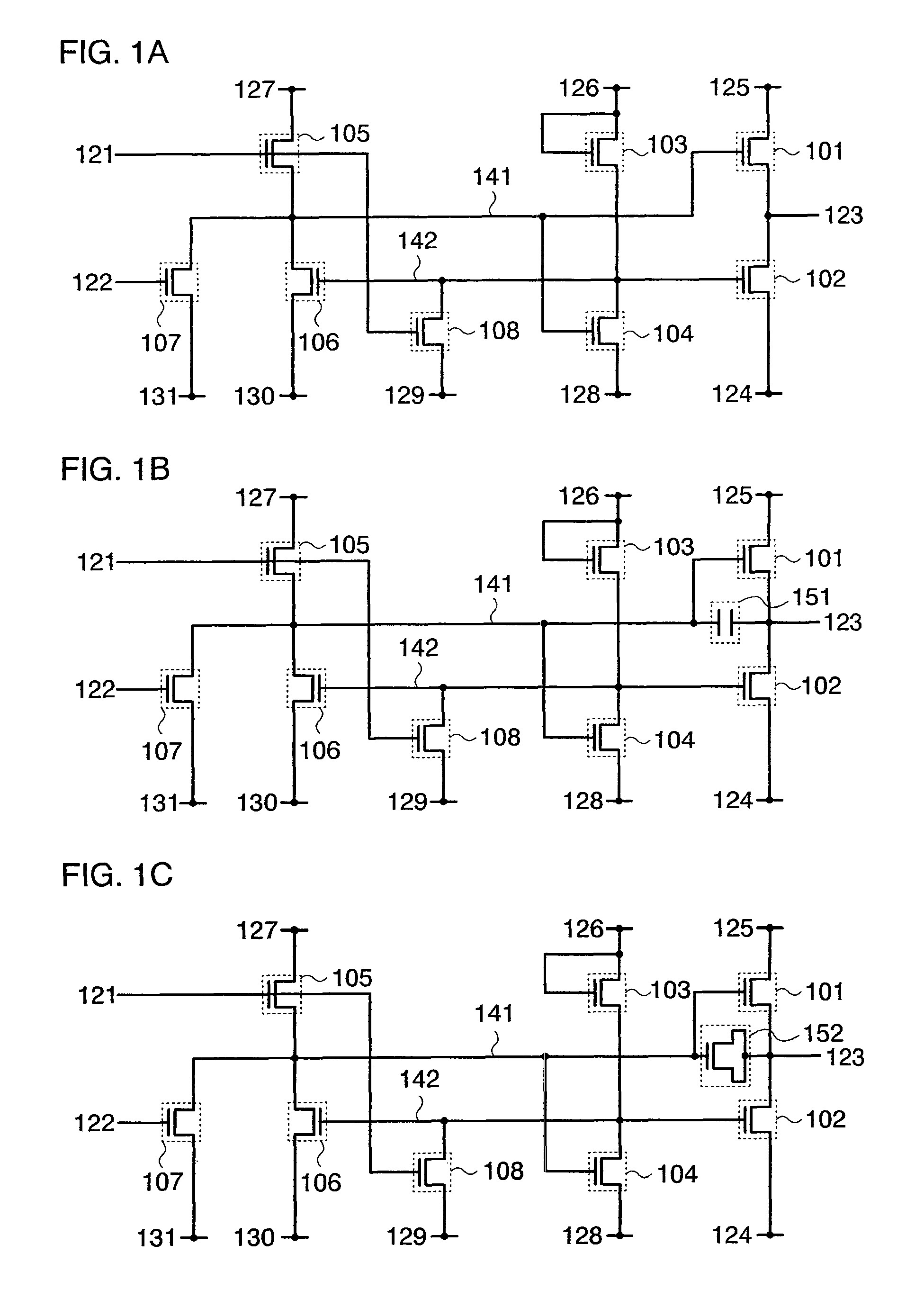

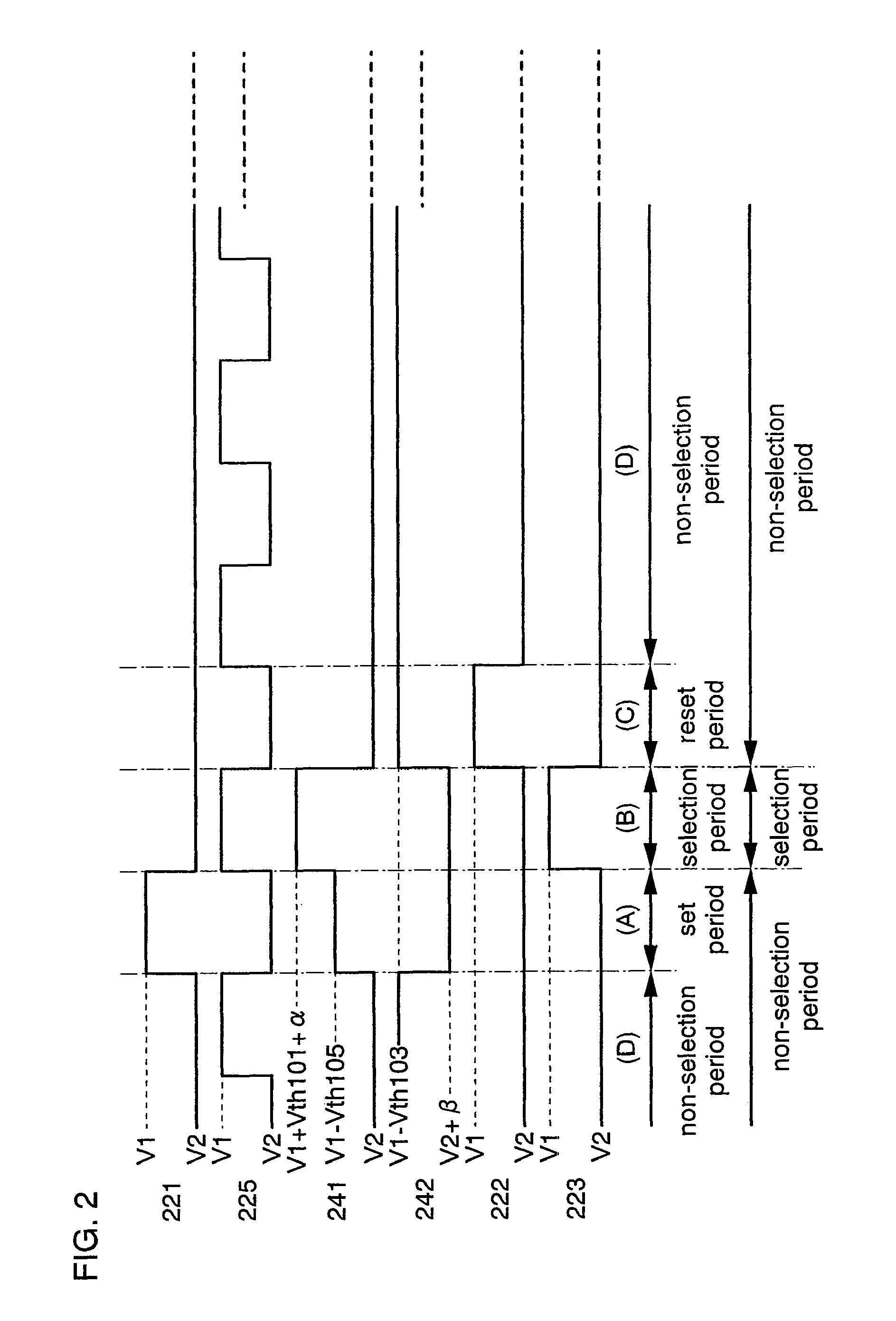

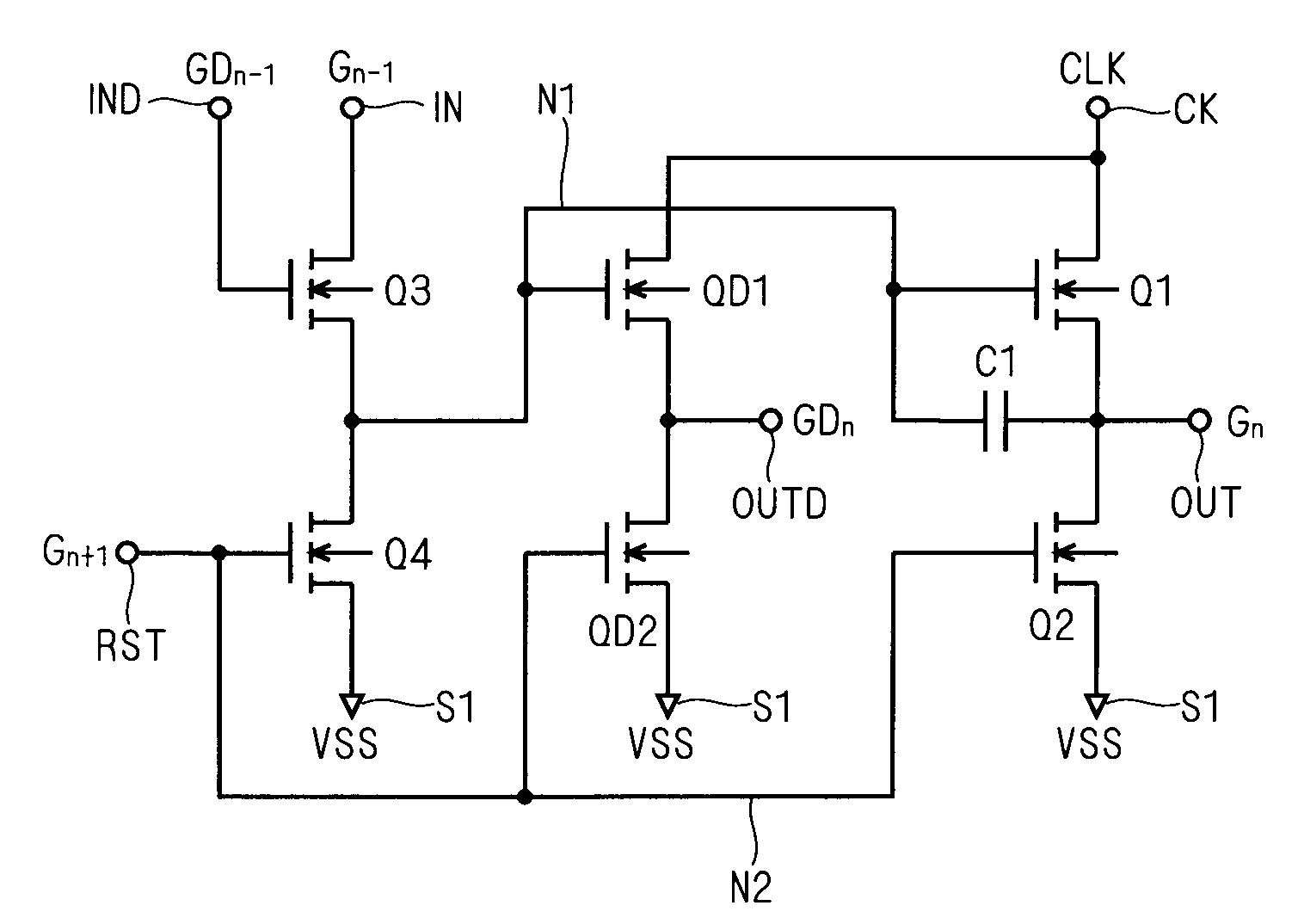

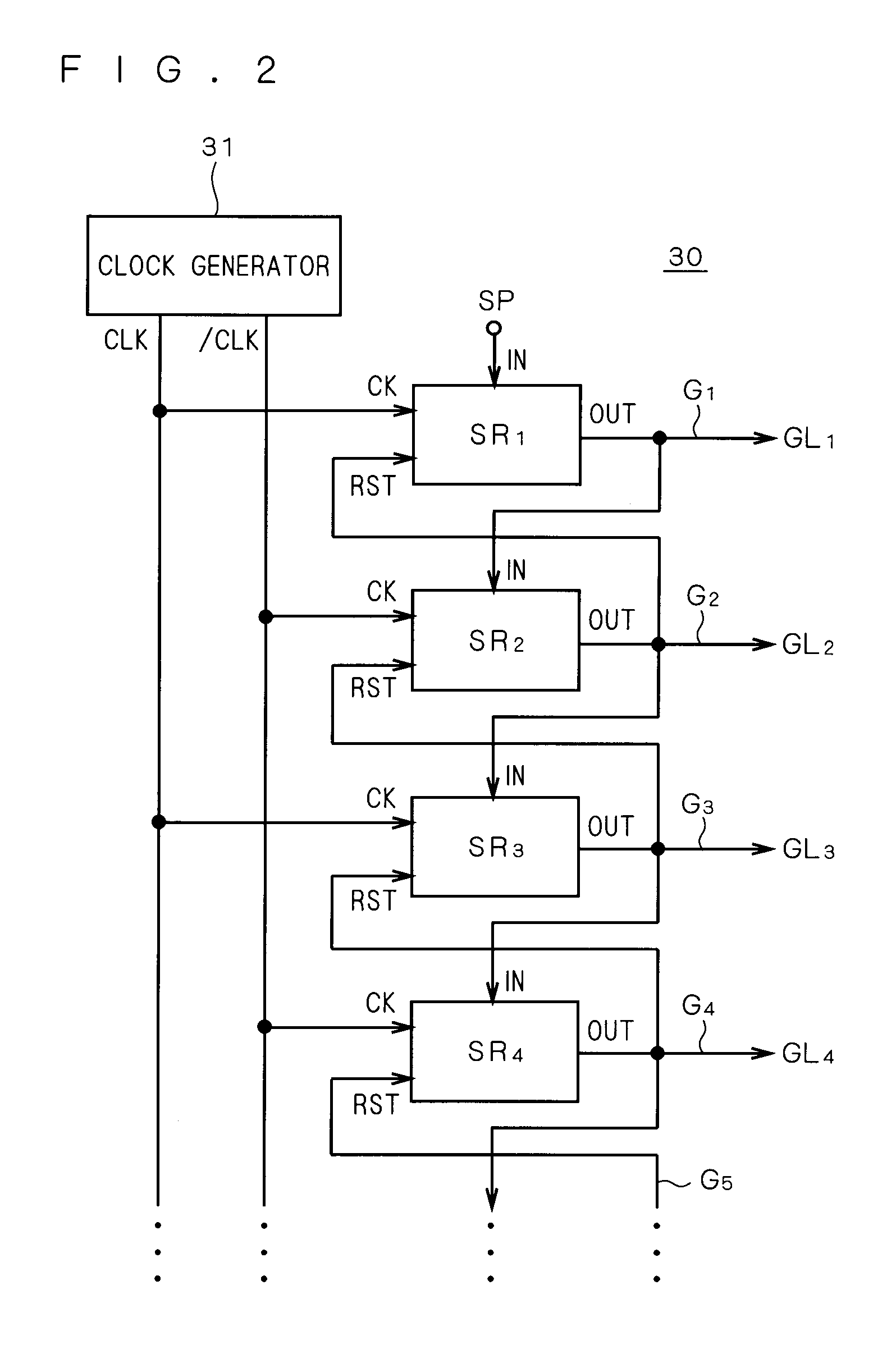

Shift register circuit and image display apparatus containing the same

ActiveUS20080080661A1Speed up the charging processRun at high speedStatic indicating devicesDigital storageShift registerHemt circuits

A high-speed shift register circuit is provided. The shift register circuit includes a first transistor supplying a clock signal to a first output terminal, a second transistor discharging the first output terminal, a third transistor supplying the above clock signal to a second output terminal, and a fourth transistor discharging the second output terminal. The gates of the first and third transistors are both connected to a first node, and the gates of the second and fourth transistors are both connected to a second node. The first node is charged by a fifth transistor which is connected between the first node and a first input terminal and which has a gate connected to a second input end.

Owner:TRIVALE TECH LLC

Display device, manufacturing method thereof, and television set

InactiveUS7564058B2Improve switching characteristicsImprove image contrastSolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceEngineering

A manufacturing method of a display device having TFTs capable of high-speed operation with few variations of threshold voltage is provided, in which materials are used with high efficiency and a small number of photomasks is required. The display device of the invention comprises a gate electrode layer and a pixel electrode layer formed over an insulating surface, a gate insulating layer formed over the gate electrode layer, a crystalline semiconductor layer formed over the gate insulating layer, a semiconductor layer having one conductivity type formed in contact with the crystalline semiconductor layer, a source electrode layer and a drain electrode layer formed in contact with the semiconductor layer having one conductivity type, an insulating later formed over the source electrode layer, the drain electrode layer, and the pixel electrode layer, a first opening formed in the insulating layer to reach the source electrode layer or the drain electrode layer, a second opening formed in the gate insulating layer and the insulating layer to reach the pixel electrode layer, and a wiring layer formed in the first opening and the second opening to electrically connect the source electrode layer or the drain electrode layer to the pixel electrode layer.

Owner:SEMICON ENERGY LAB CO LTD

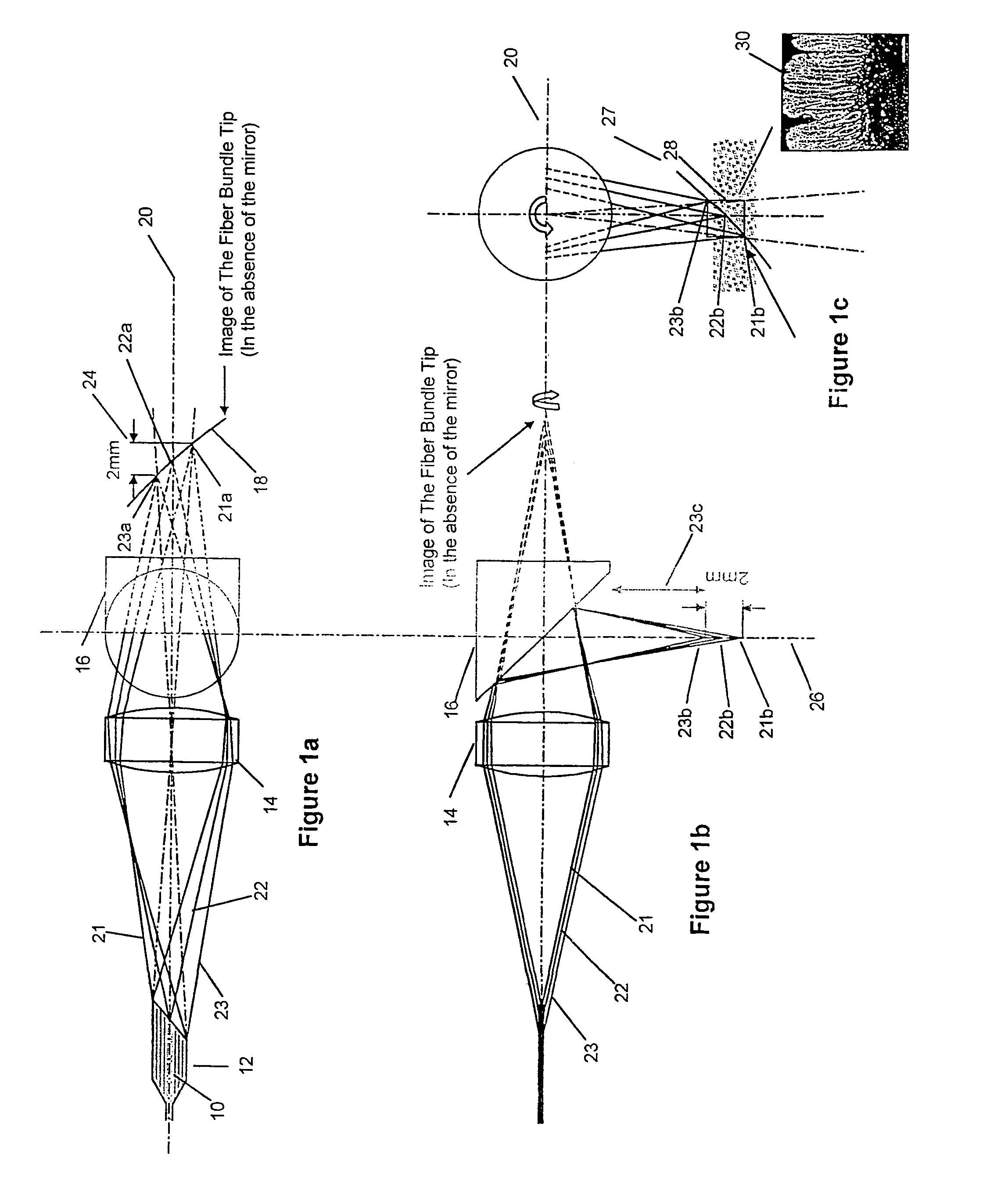

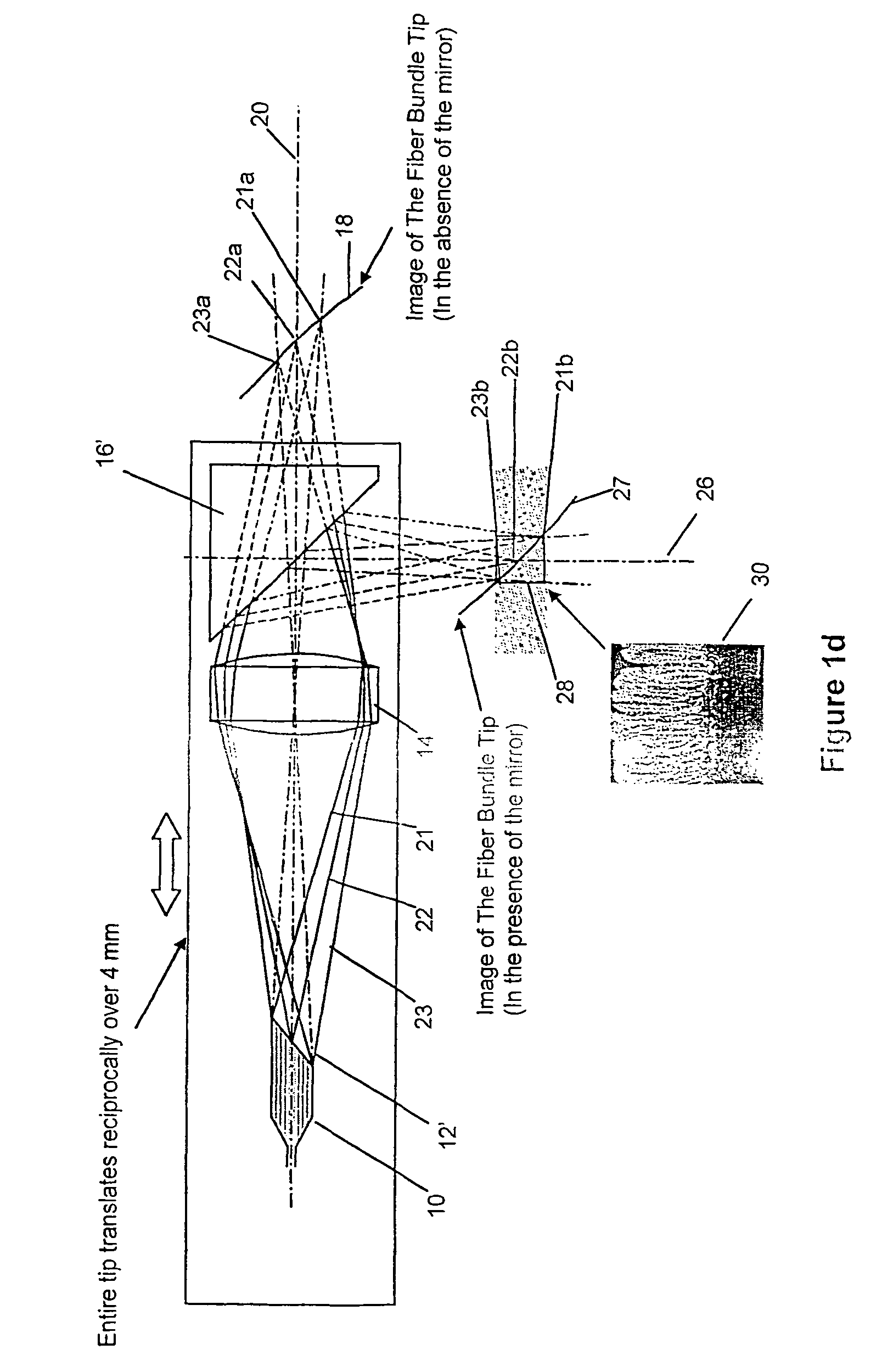

Method and apparatus for high resolution coherent optical imaging

InactiveUS7242833B2Simple device designGood for high speed operationSurgeryScattering properties measurementsOptical radiationOptical depth

A method and an apparatus for examining the subsurface microstructure of a sample are provided. Radiation from a plurality of optical radiation sources travels along a first optical path. In the first optical path, a device focuses the optical radiati n from each of the optical sources into a plurality of respective focal points along the first optical path to provide substantially continuous coverage of a selected portion of the first optical path. Then, a sample on the first optical path within the selected length extending into the sample is scanned along said selected portion of the first optical path.

Owner:UNIV HEALTH NETWORK