Patents

Literature

106848 results about "Semiconductor device" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A semiconductor device is an electronic component that exploits the electronic properties of semiconductor material, principally silicon, germanium, and gallium arsenide, as well as organic semiconductors. Semiconductor devices have replaced vacuum tubes in most applications. They use electrical conduction in the solid state rather than the gaseous state or thermionic emission in a vacuum.

Semiconductor device, manufacturing method, and electronic device

ActiveUS20060244107A1Stabilize element propertyEasy to manufactureTransistorSemiconductor/solid-state device detailsSurface levelIntrinsic resistance

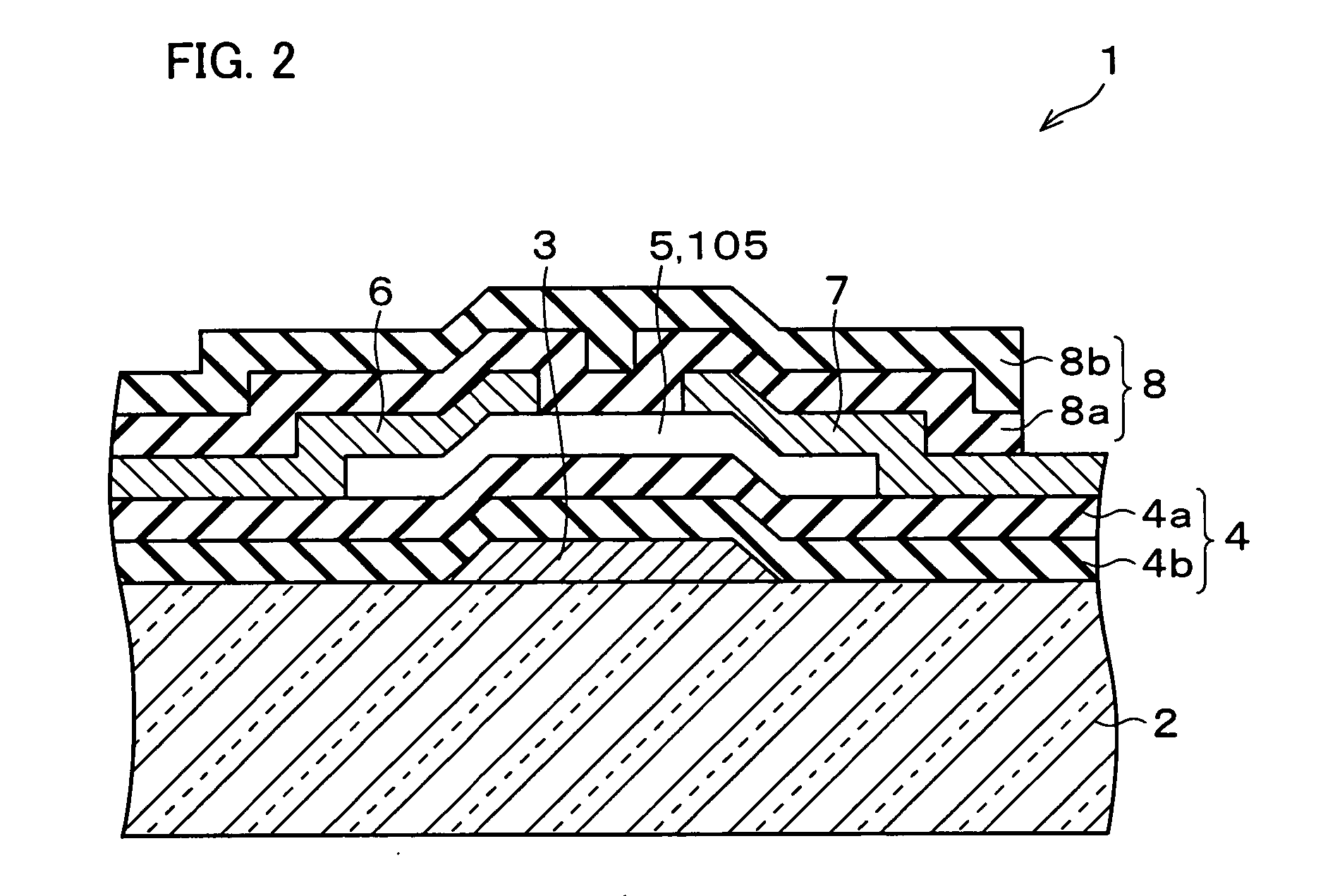

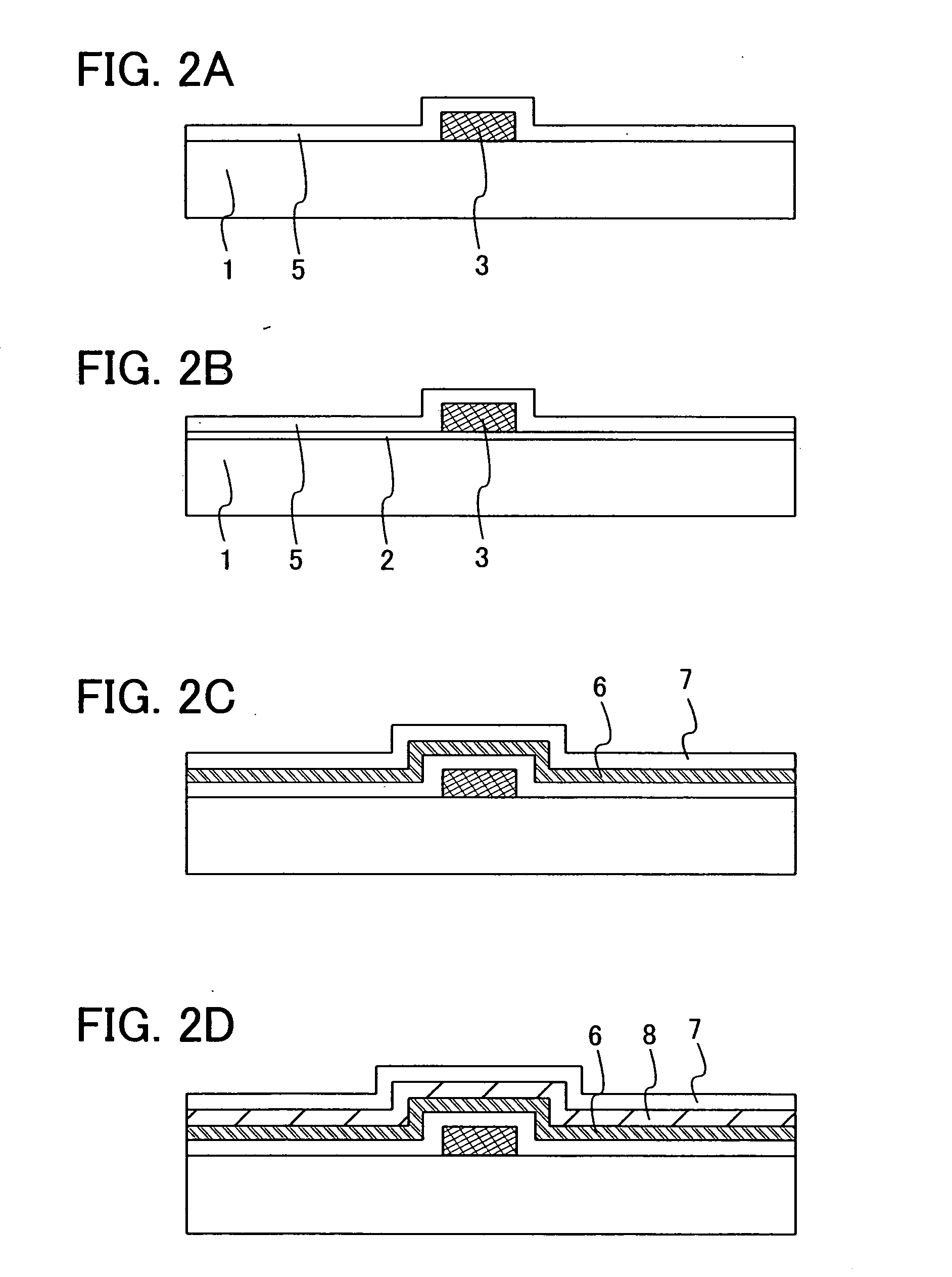

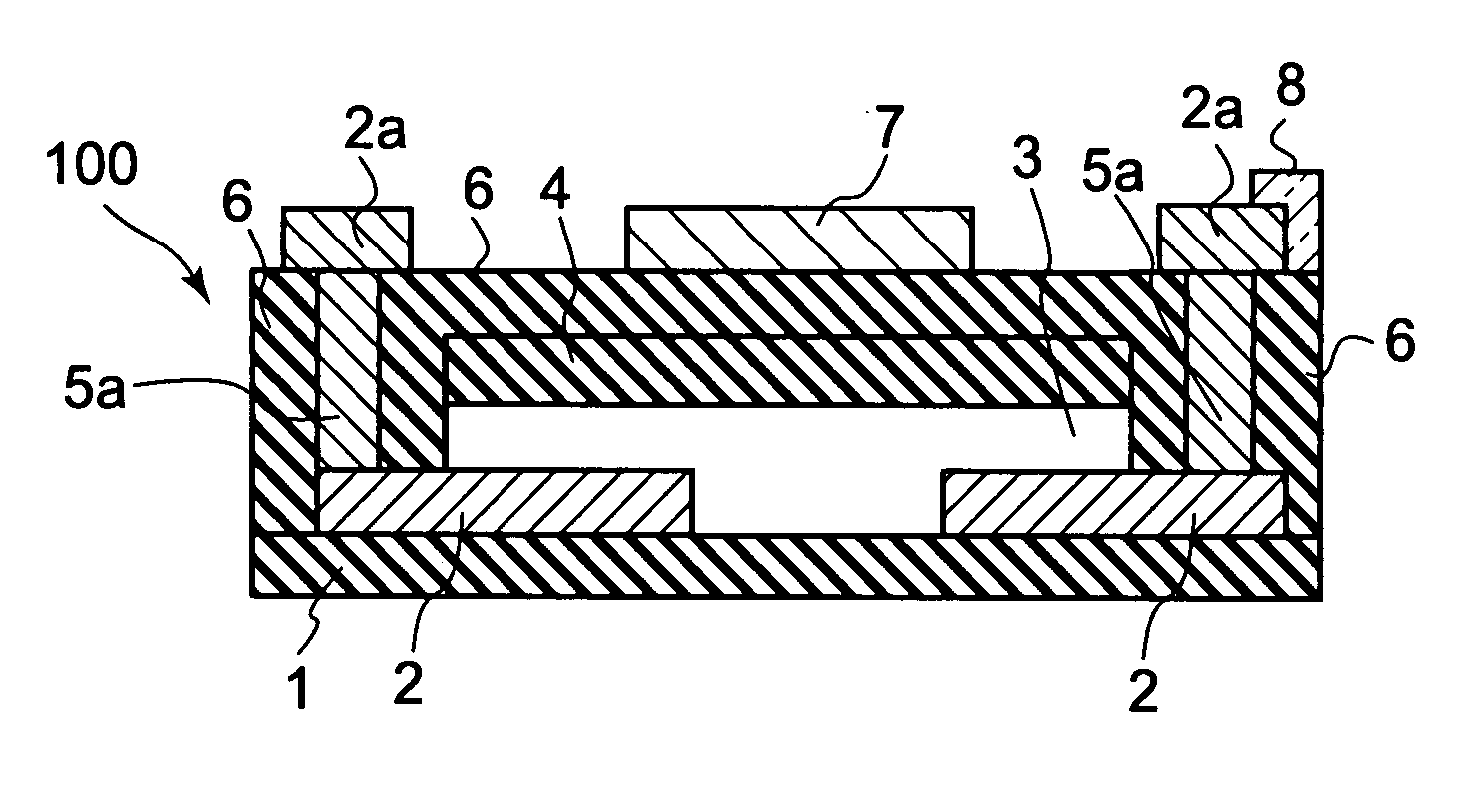

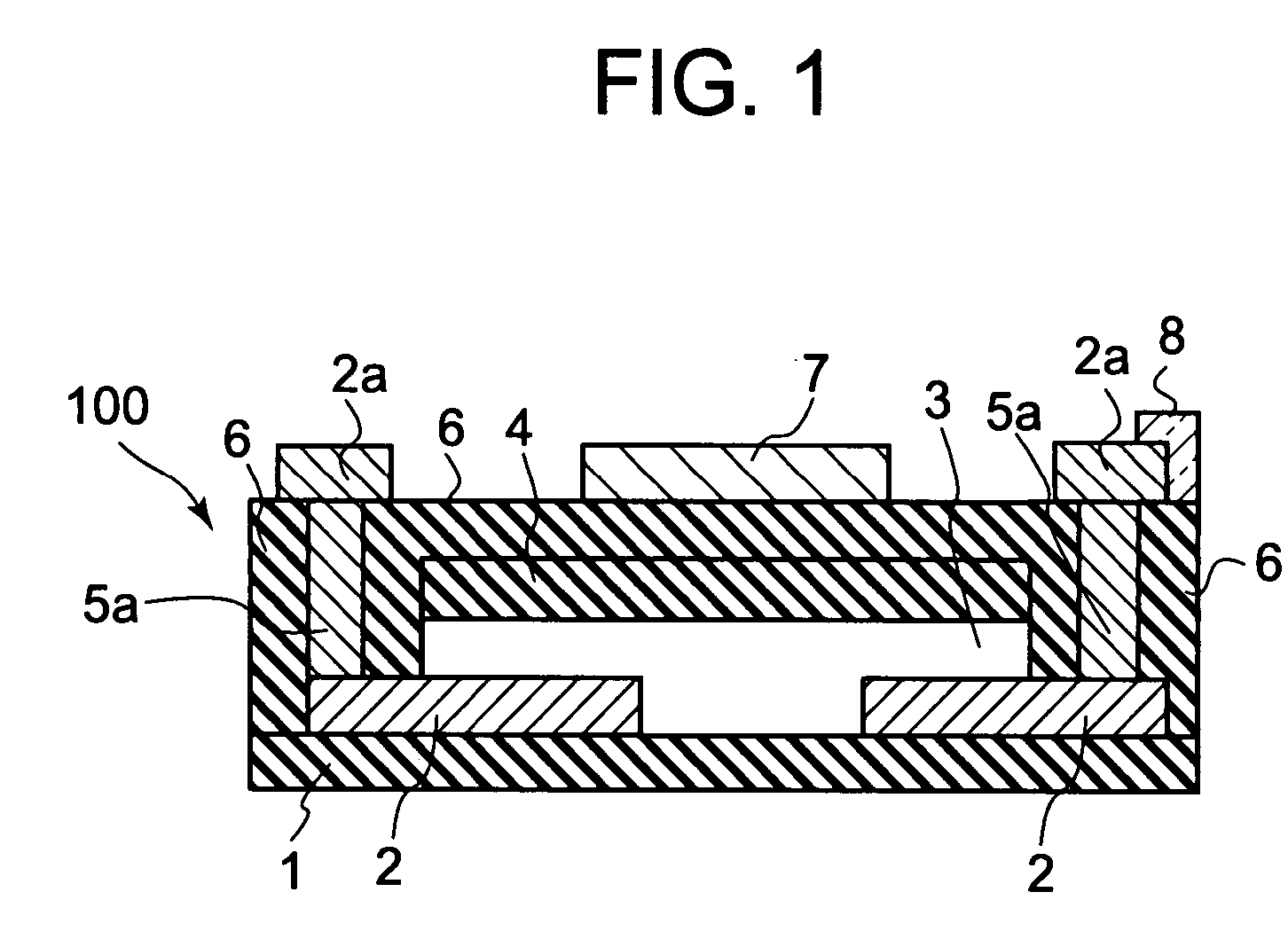

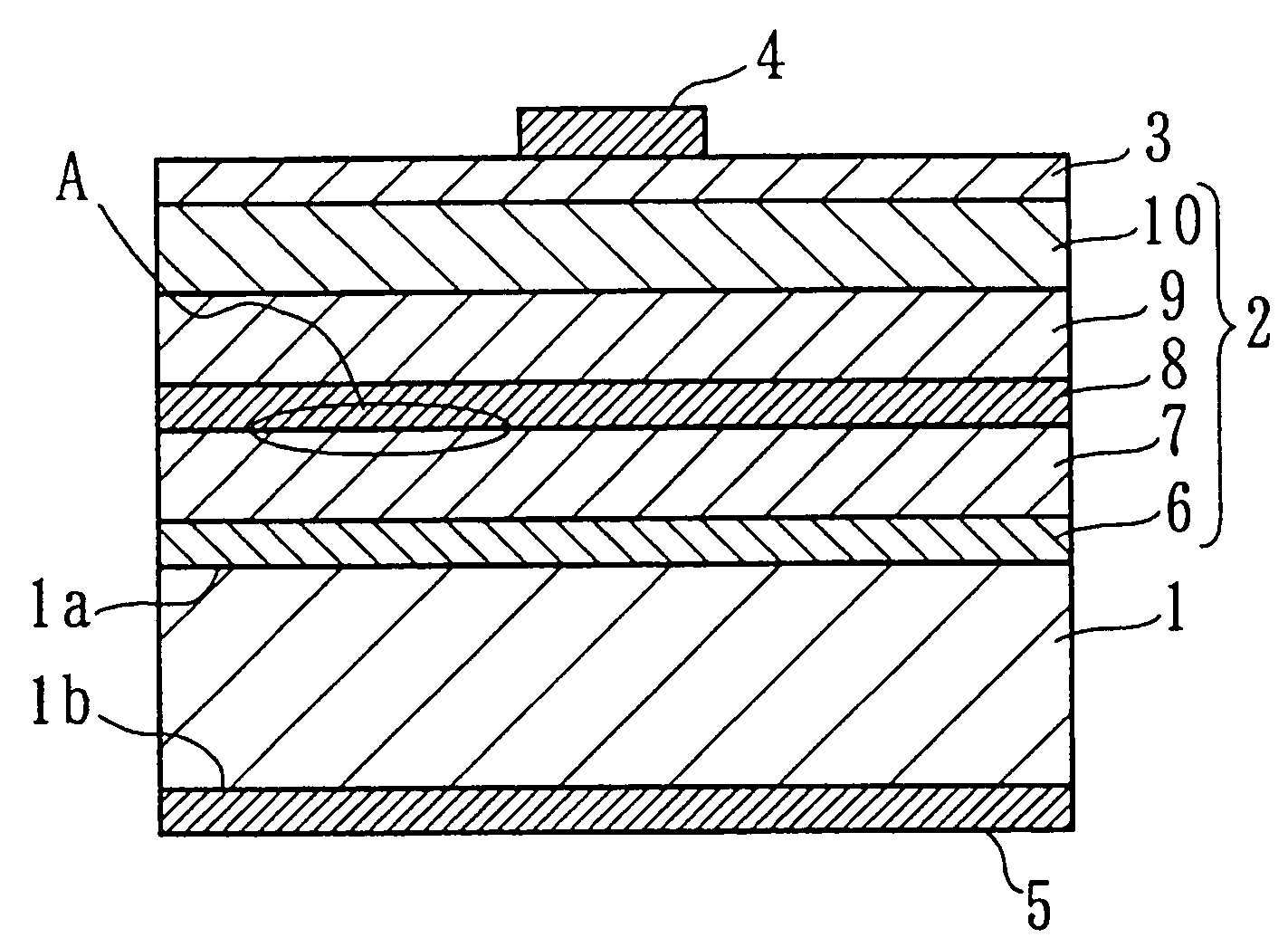

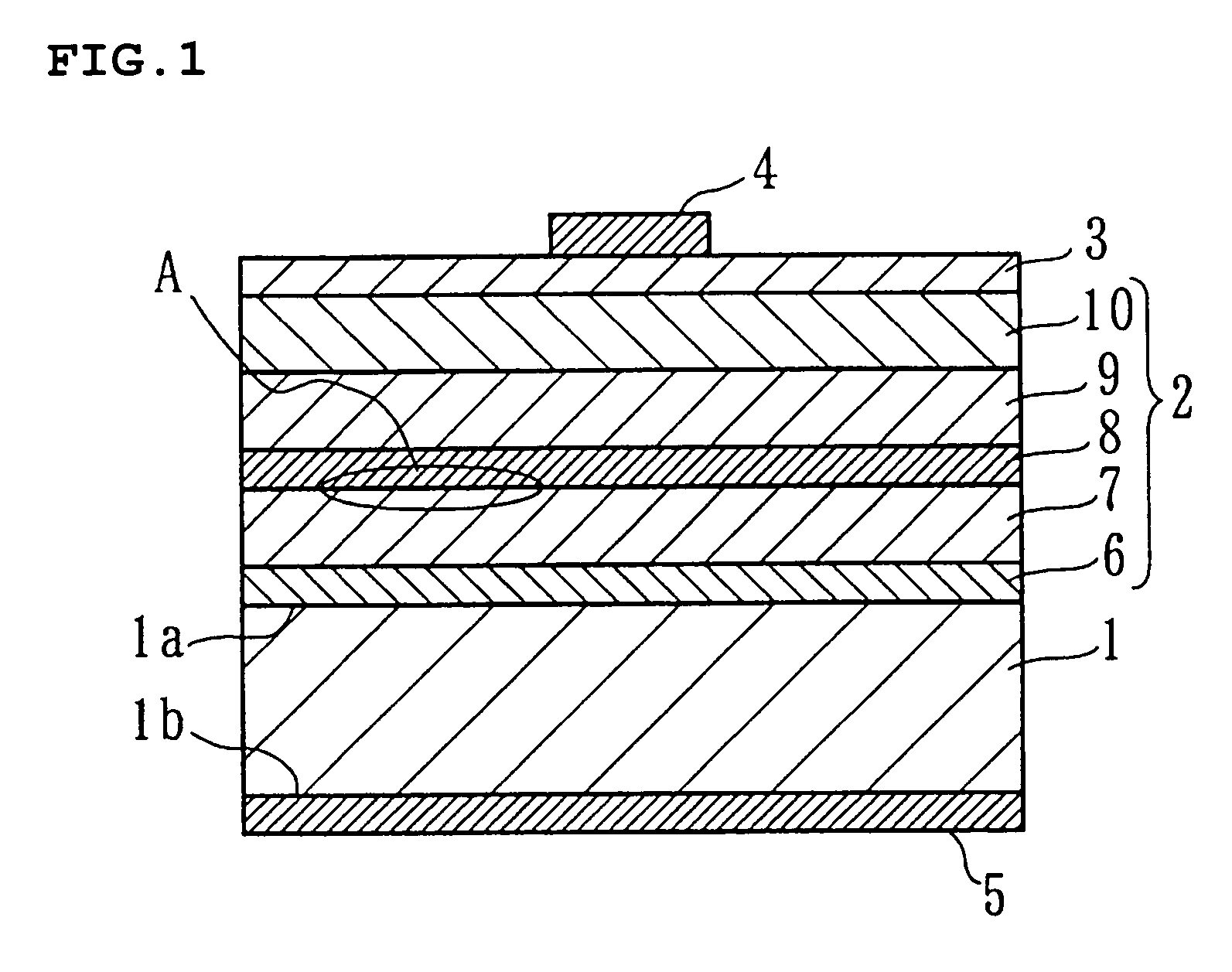

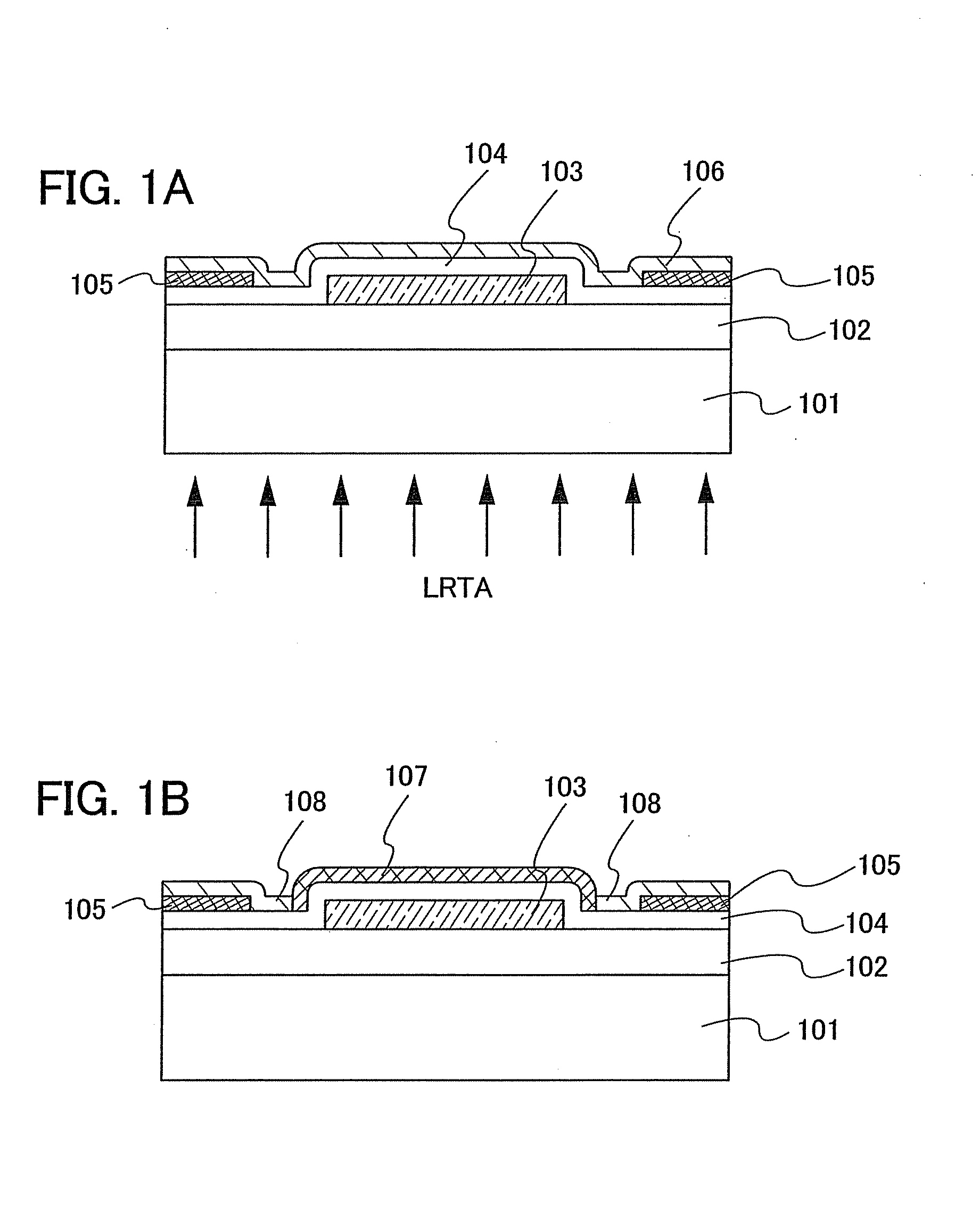

In a thin film transistor (1), a gate insulating layer (4) is formed on a gate electrode (3) formed on an insulating substrate (2). Formed on the gate insulating layer (4) is a semiconductor layer (5). Formed on the semiconductor layer (5) are a source electrode (6) and a drain electrode (7). A protective layer (8) covers them, so that the semiconductor layer (5) is blocked from an atmosphere. The semiconductor layer (5) (active layer) is made of, e.g., a semiconductor containing polycrystalline ZnO to which, e.g., a group V element is added. The protective layer (8) thus formed causes decrease of a surface level of the semiconductor layer (5). This eliminates a depletion layer spreading therewithin. Accordingly, the ZnO becomes an n-type semiconductor indicating an intrinsic resistance, with the result that too many free electrons are generated. However, the added element works on the ZnO as an accepter impurity, so that the free electrons are reduced. This decreases a gate voltage required for removal of the free electrons, so that the threshold voltage of the thin film transistor (1) becomes on the order of 0V. This allows practical use of a semiconductor device which has an active layer made of zinc oxide and which includes an protective layer for blocking the active layer from an atmosphere.

Owner:SHARP KK +2

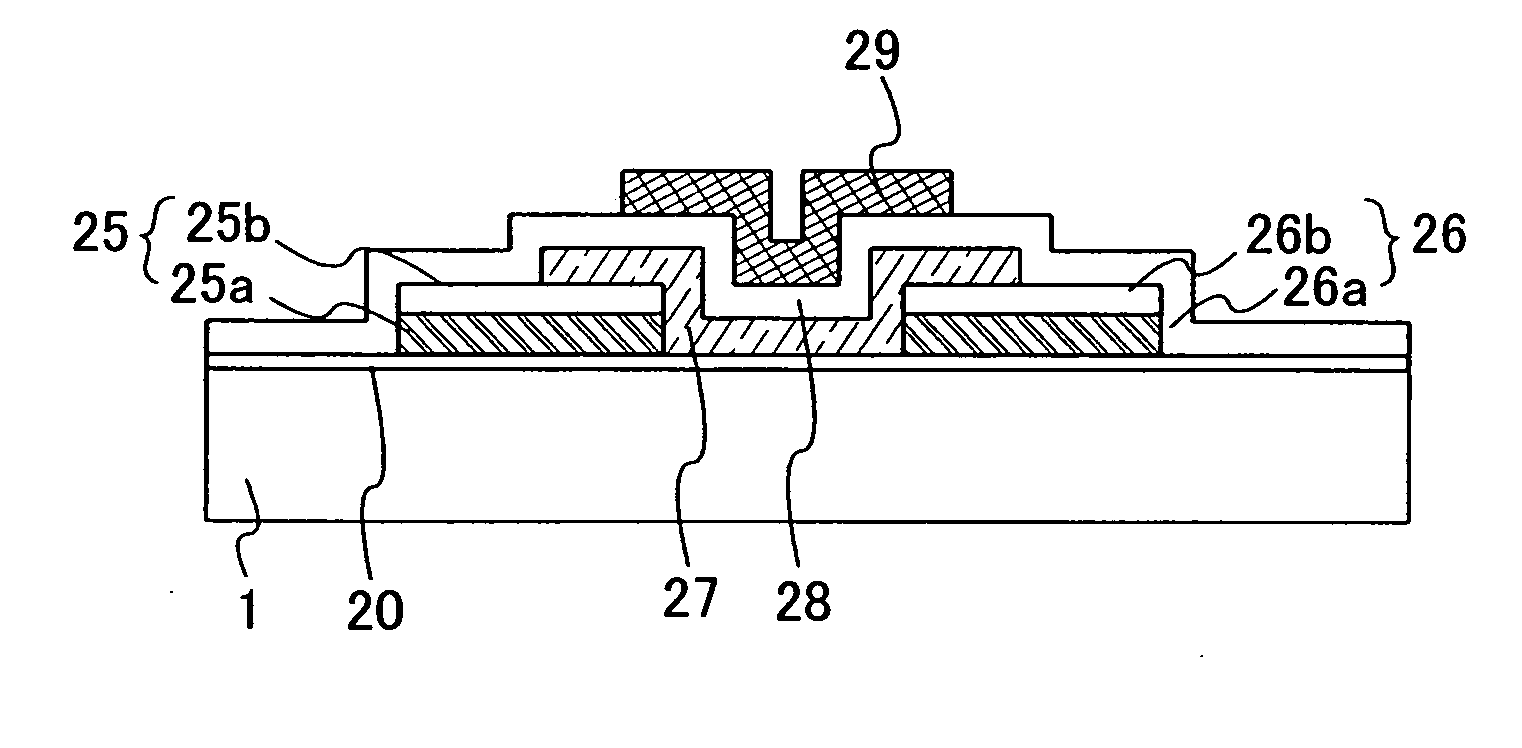

Semiconductor device and manufacturing method thereof

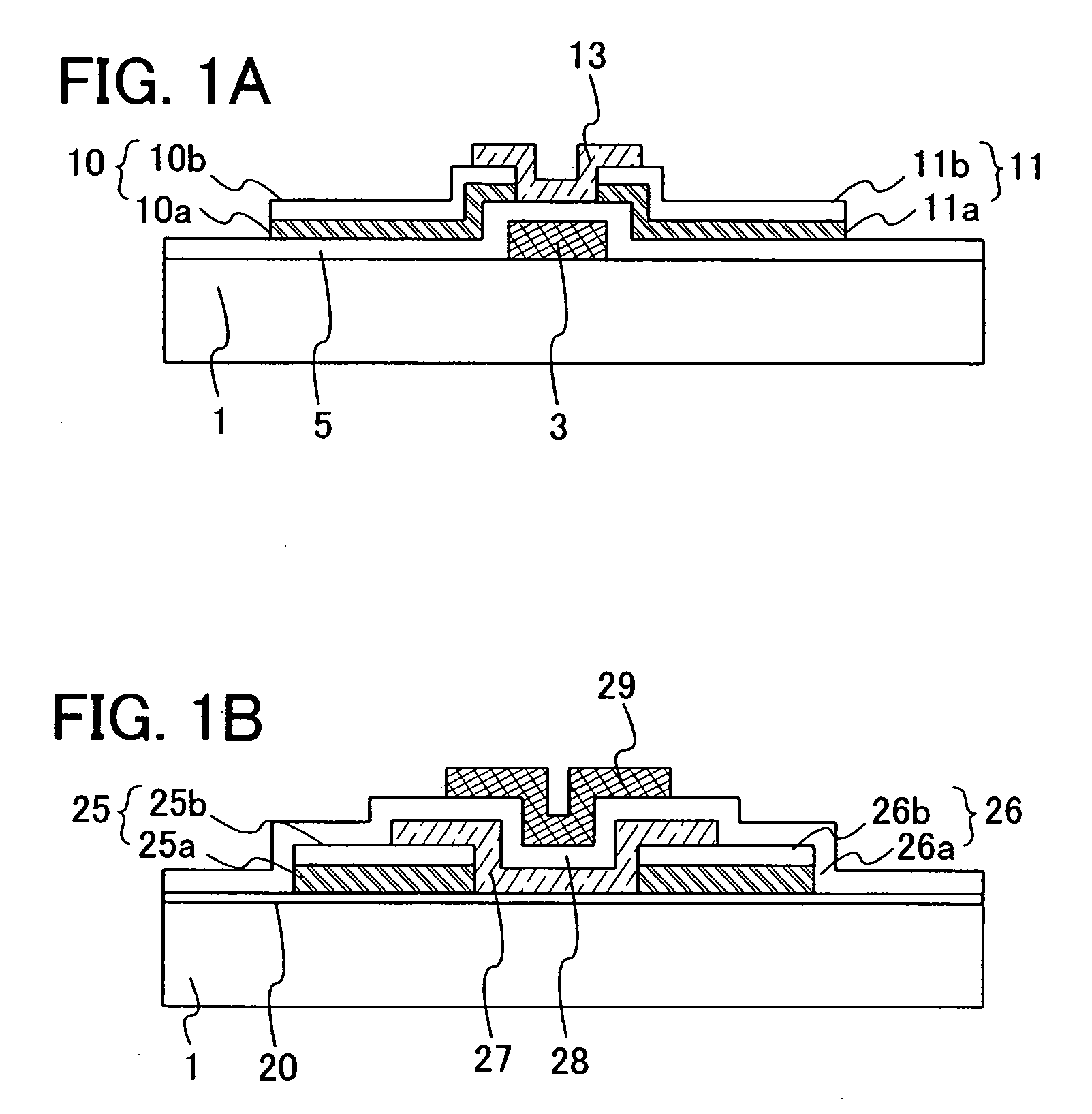

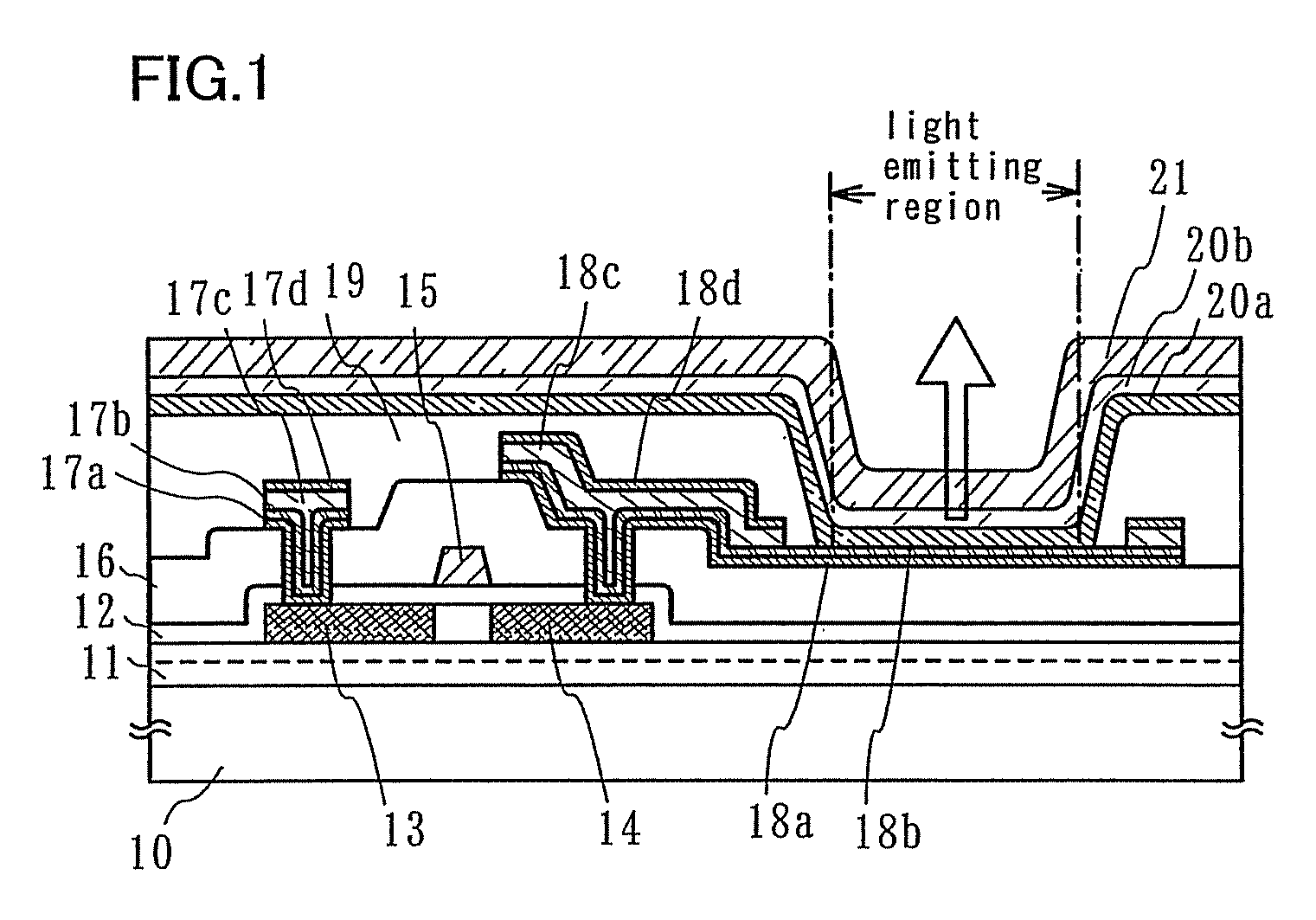

ActiveUS20070108446A1Low resistance of wireLower resistanceTransistorElectroluminescent light sourcesAlloySilicon oxide

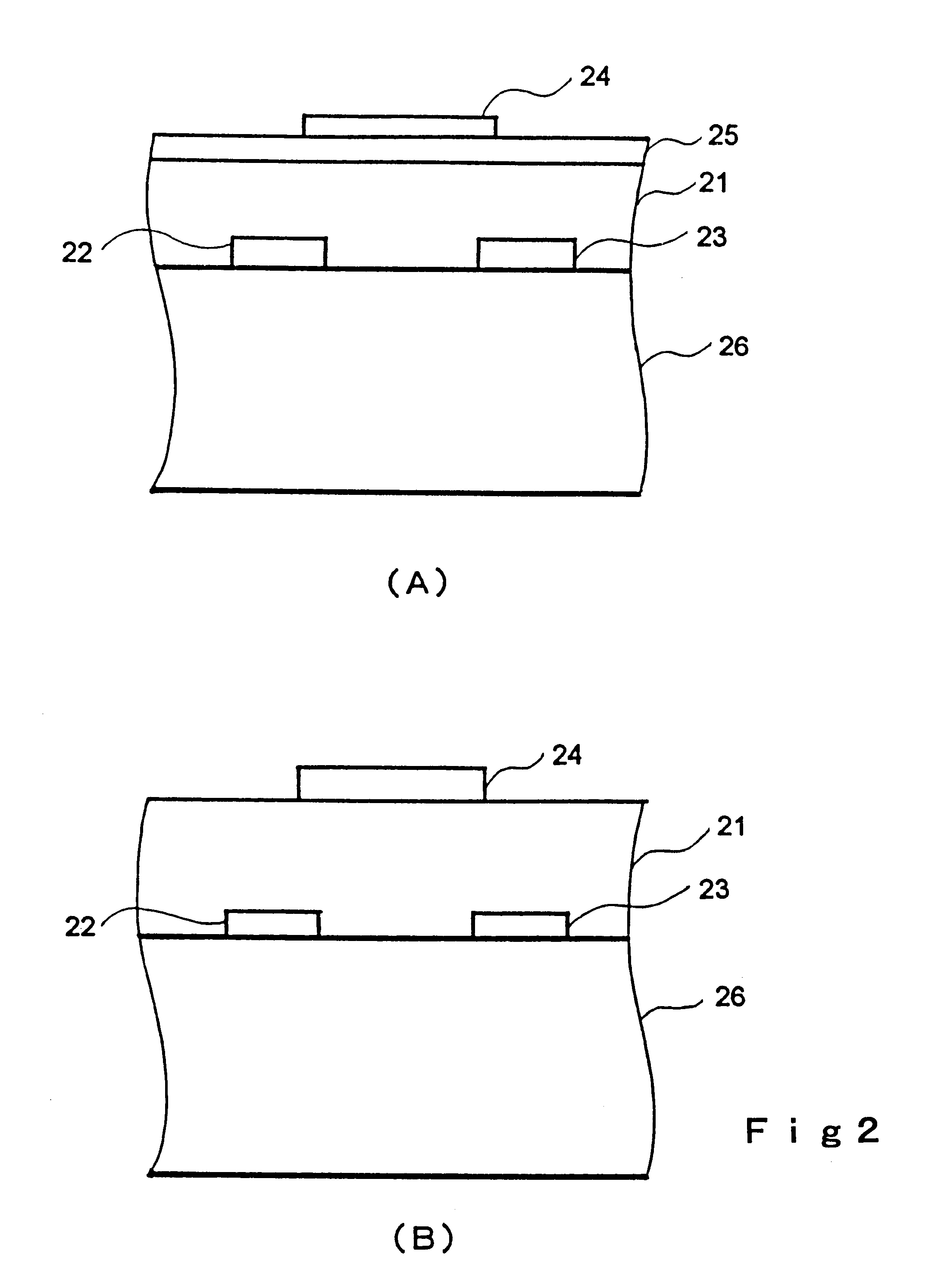

To provide a semiconductor device in which a defect or fault is not generated and a manufacturing method thereof even if a ZnO semiconductor film is used and a ZnO film to which an n-type or p-type impurity is added is used for a source electrode and a drain electrode. The semiconductor device includes a gate insulating film formed by using a silicon oxide film or a silicon oxynitride film over a gate electrode, an Al film or an Al alloy film over the gate insulating film, a ZnO film to which an n-type or p-type impurity is added over the Al film or the Al alloy film, and a ZnO semiconductor film over the ZnO film to which an n-type or p-type impurity is added and the gate insulating film.

Owner:SEMICON ENERGY LAB CO LTD

Transistor and semiconductor device

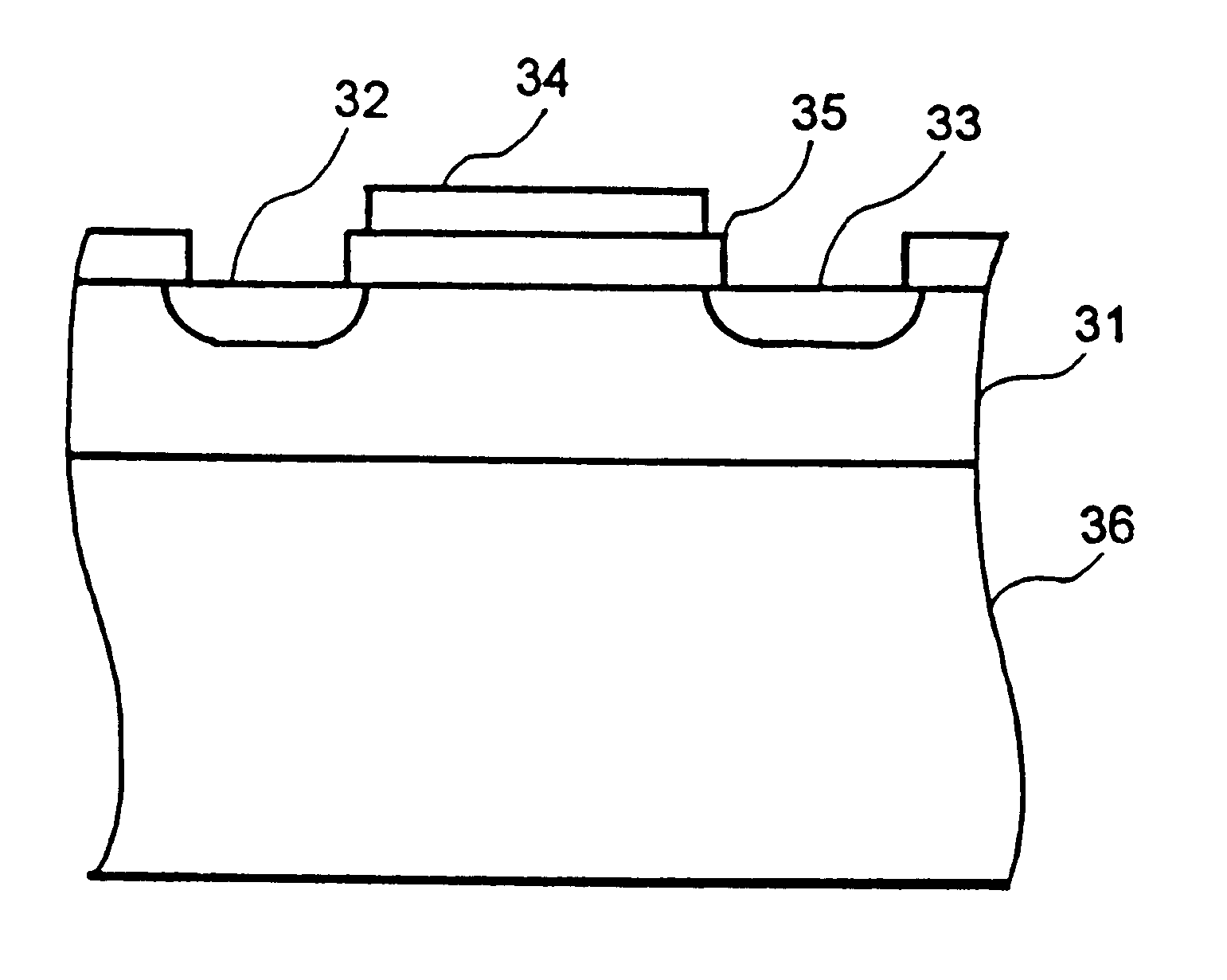

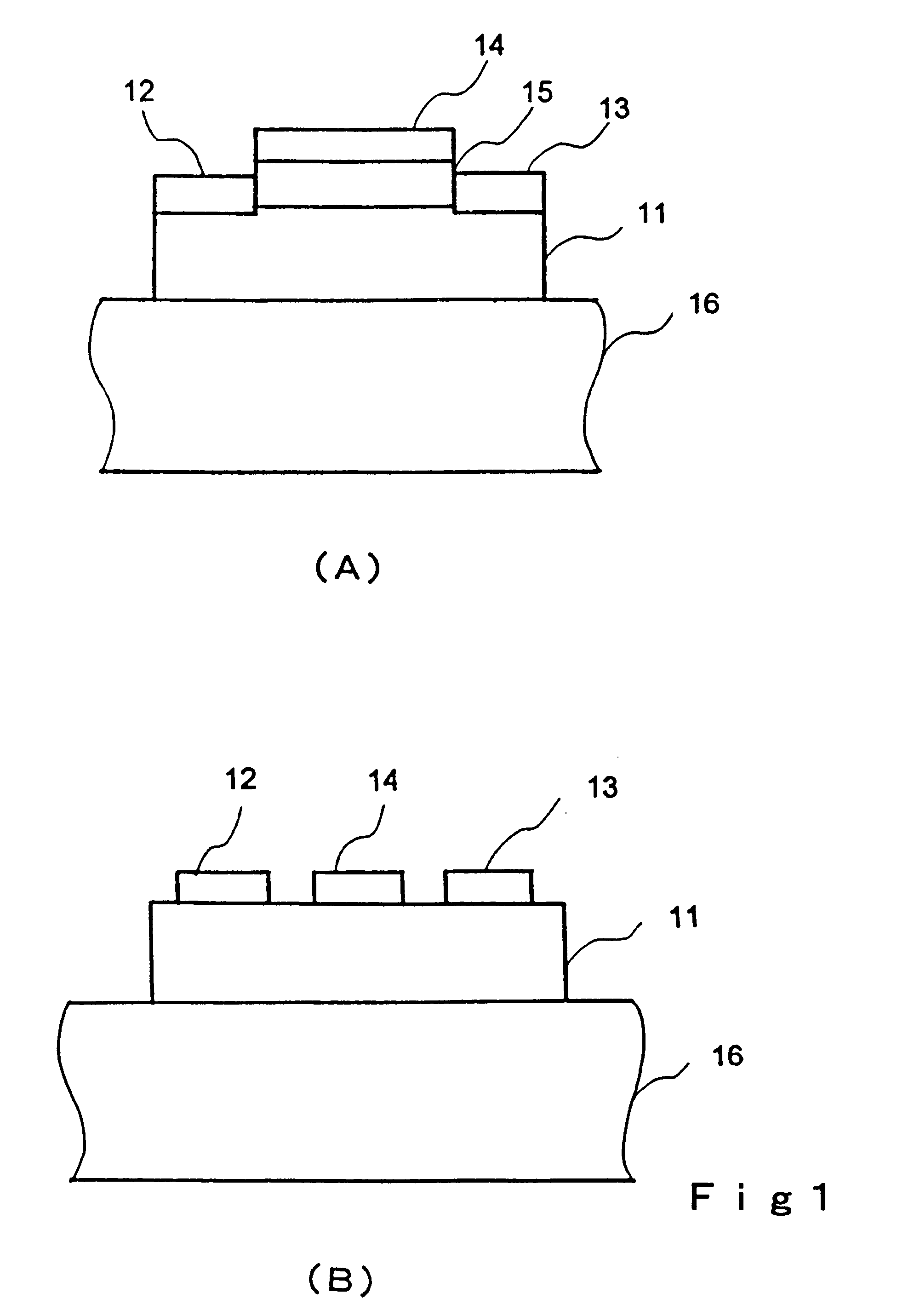

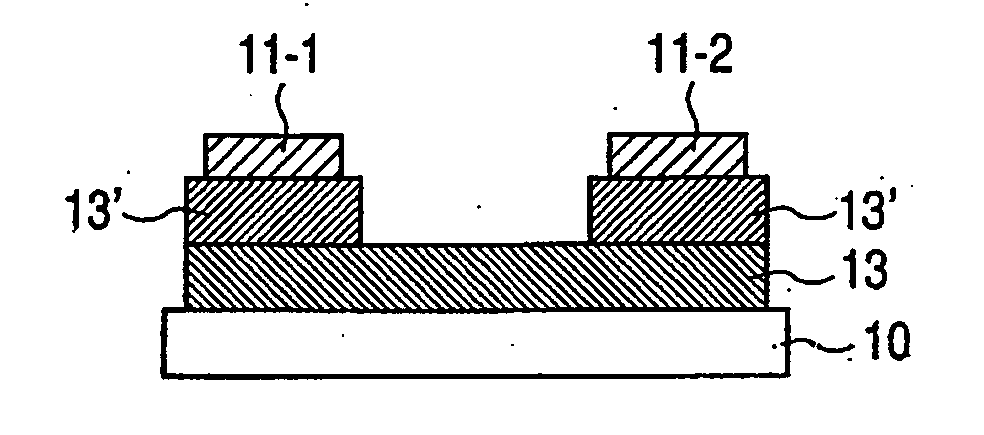

A transistor is provided, which is entirely and partially transparent by the use of a transparent channel layer made of zinc oxide or the like. A channel layer 11 formed of a transparent semiconductor such as zinc oxide ZnO. A transparent electrode is used for all of a source 12, a drain 13 and a gate 14, or a part of them. As the transparent electrode, a transparent conductive material such as conductive ZnO doped with, for example, group III elements is used. As a gate insulating layer 15, a transparent insulative material such as insulative ZnO doped with elements capable of taking a valence of one as a valence number or group V elements is used. If a substrate 16 must be transparent, for example, glass, sapphire, plastic or the like can be used as a transparent material.

Owner:JAPAN SCI & TECH CORP

Electric elements and circuits utilizing amorphous oxides

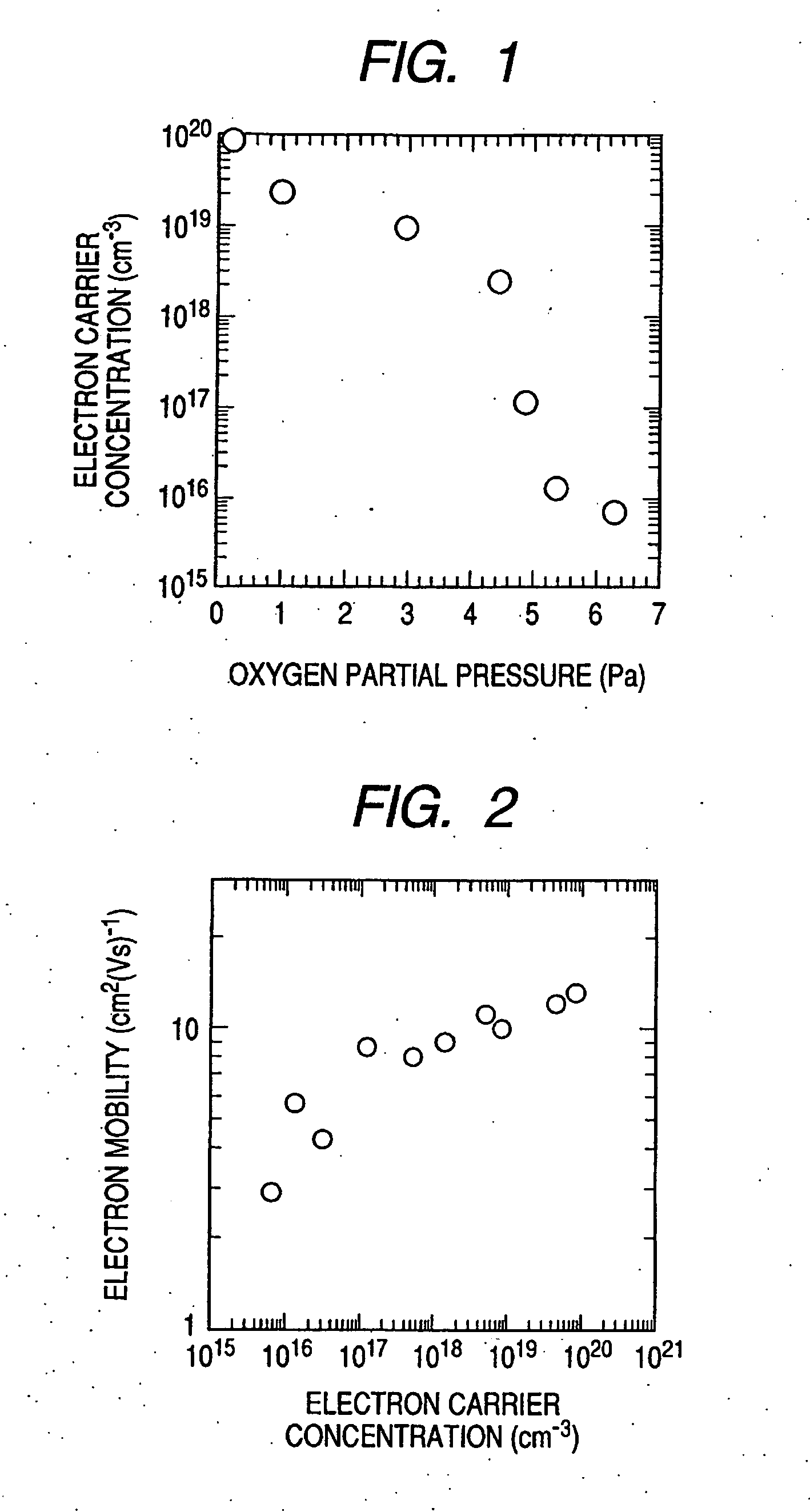

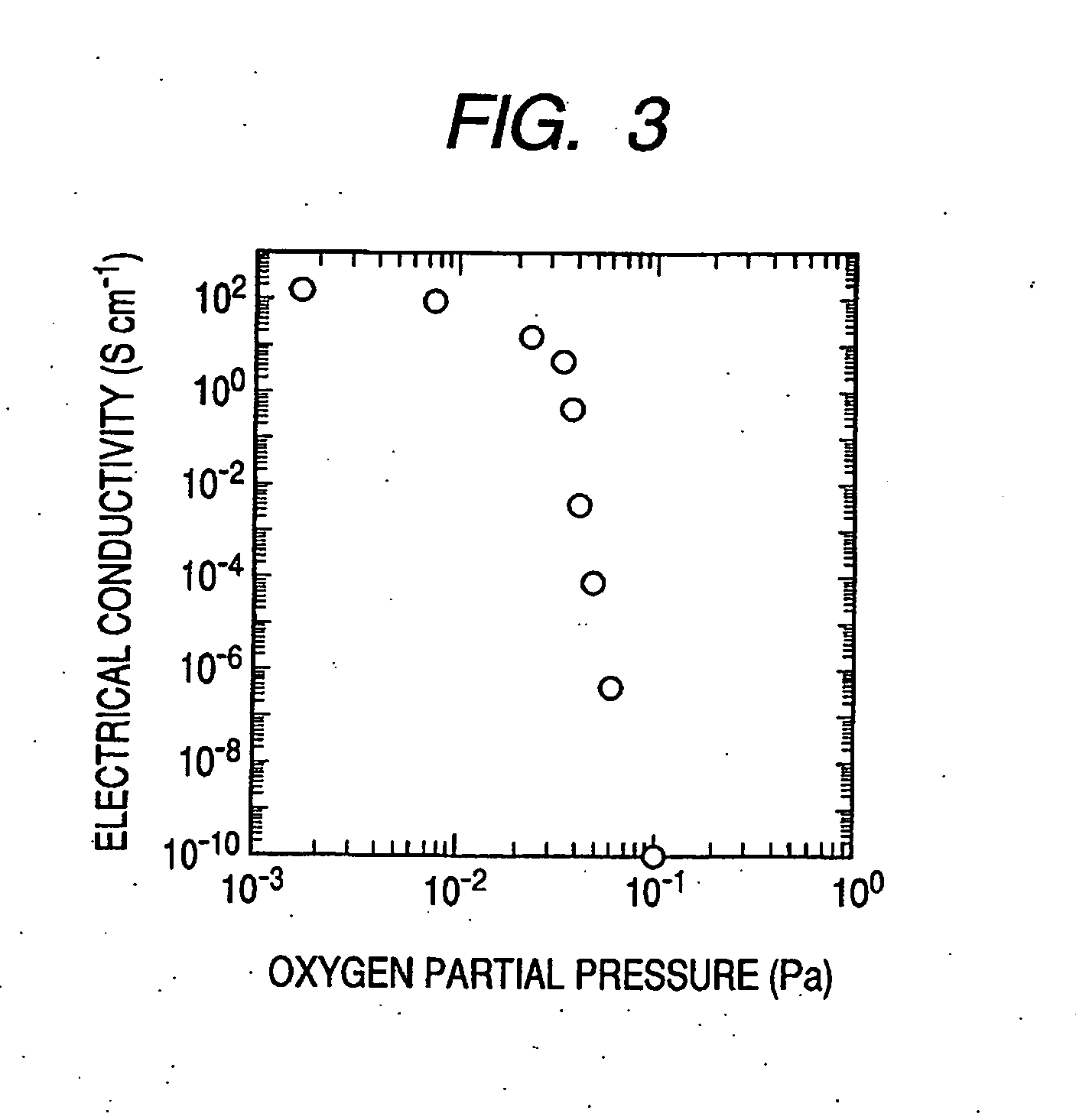

Semiconductor devices and circuits with use of transparent oxide film are provided. The semiconductor device having a P-type region and an N-type region, wherein amorphous oxides with electron carrier concentration less than 1018 / cm3 is used for the N-type region.

Owner:CANON KK +2

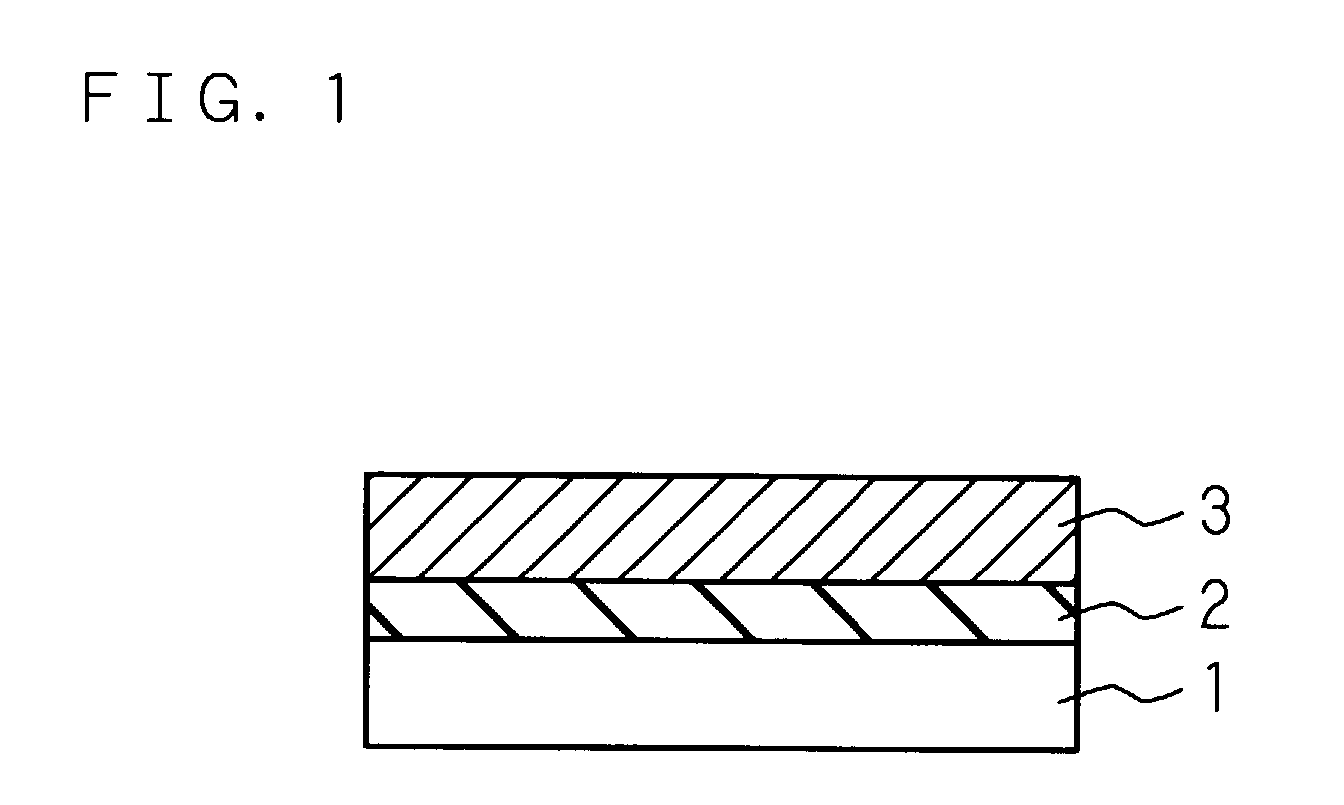

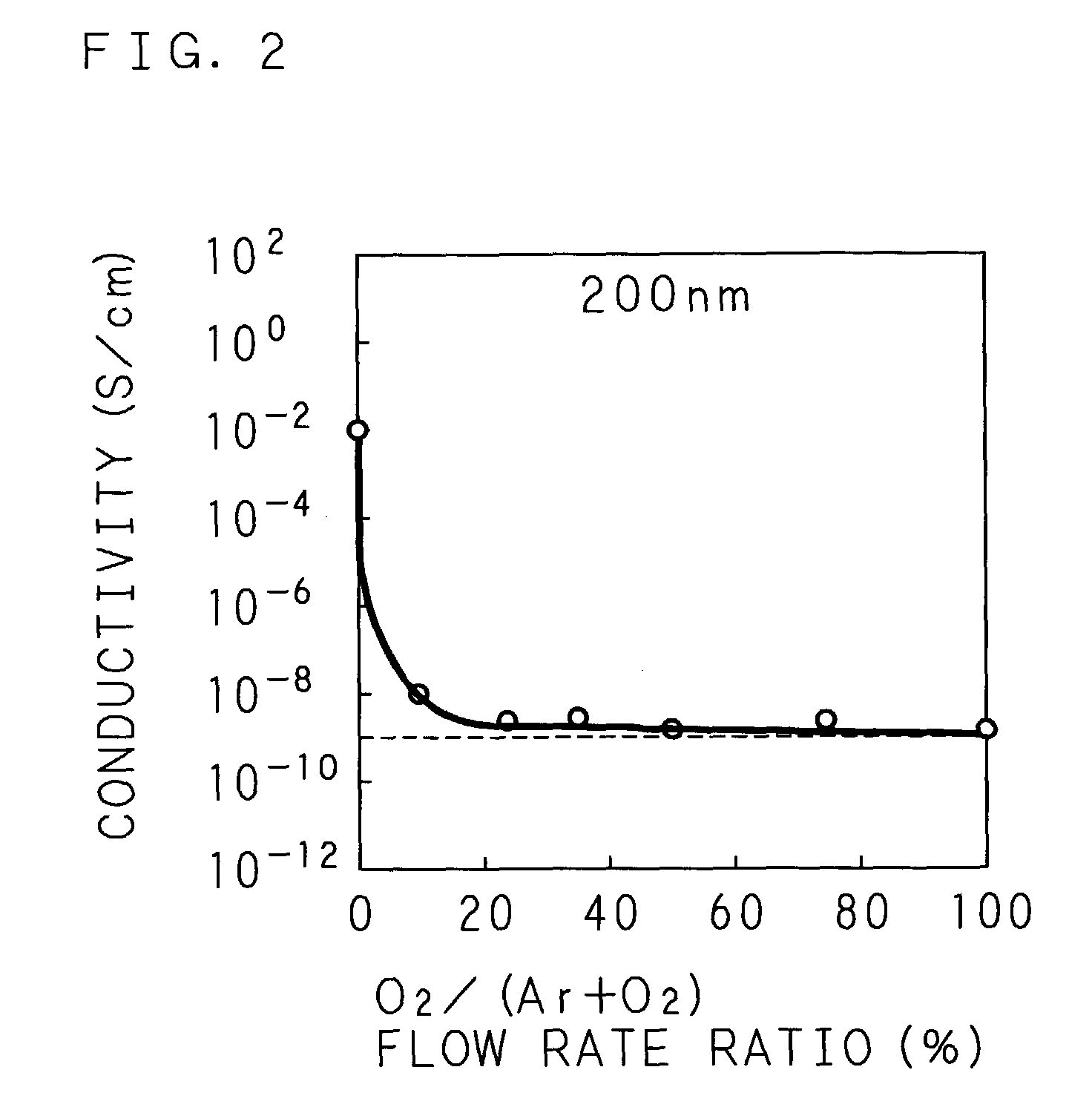

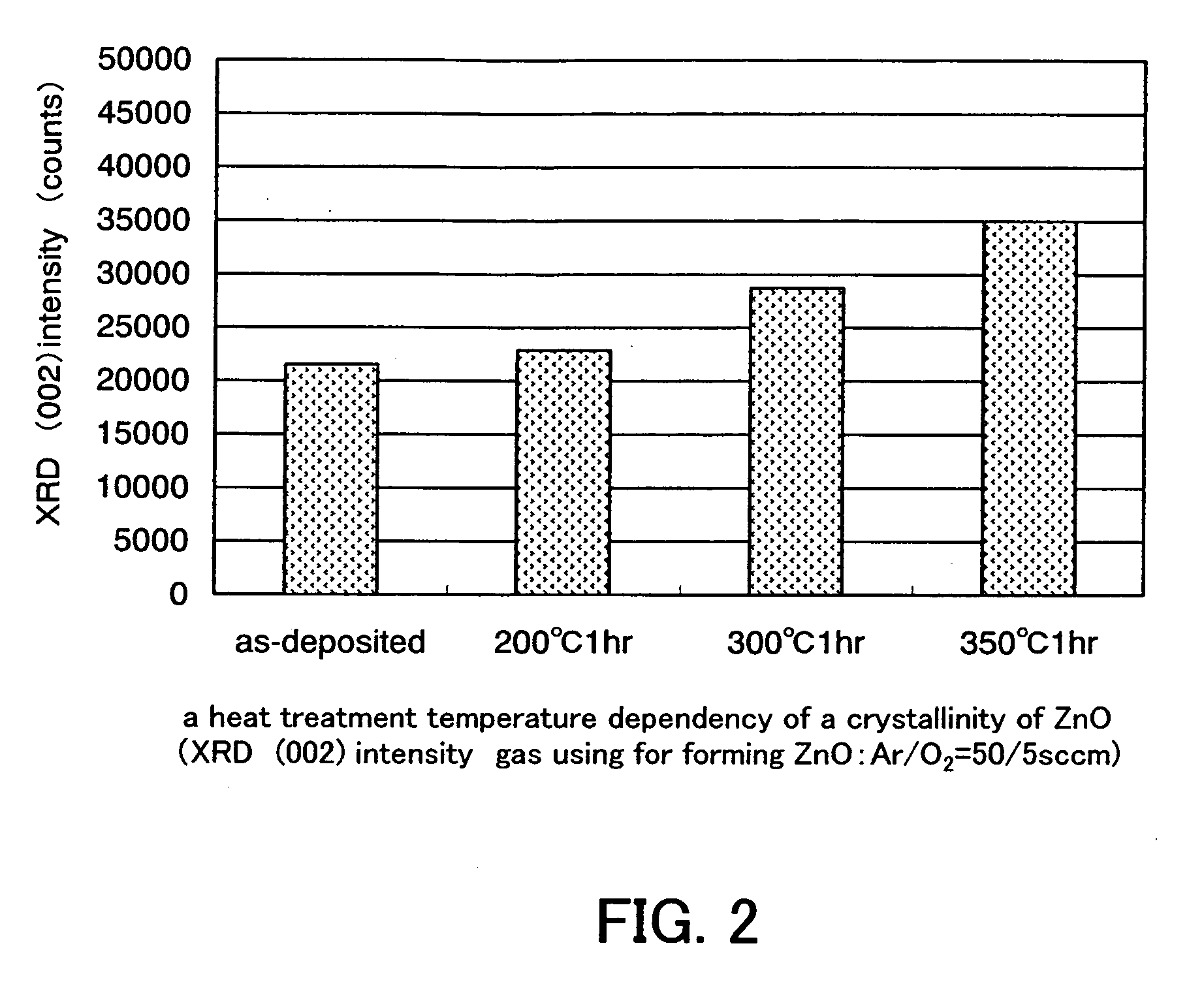

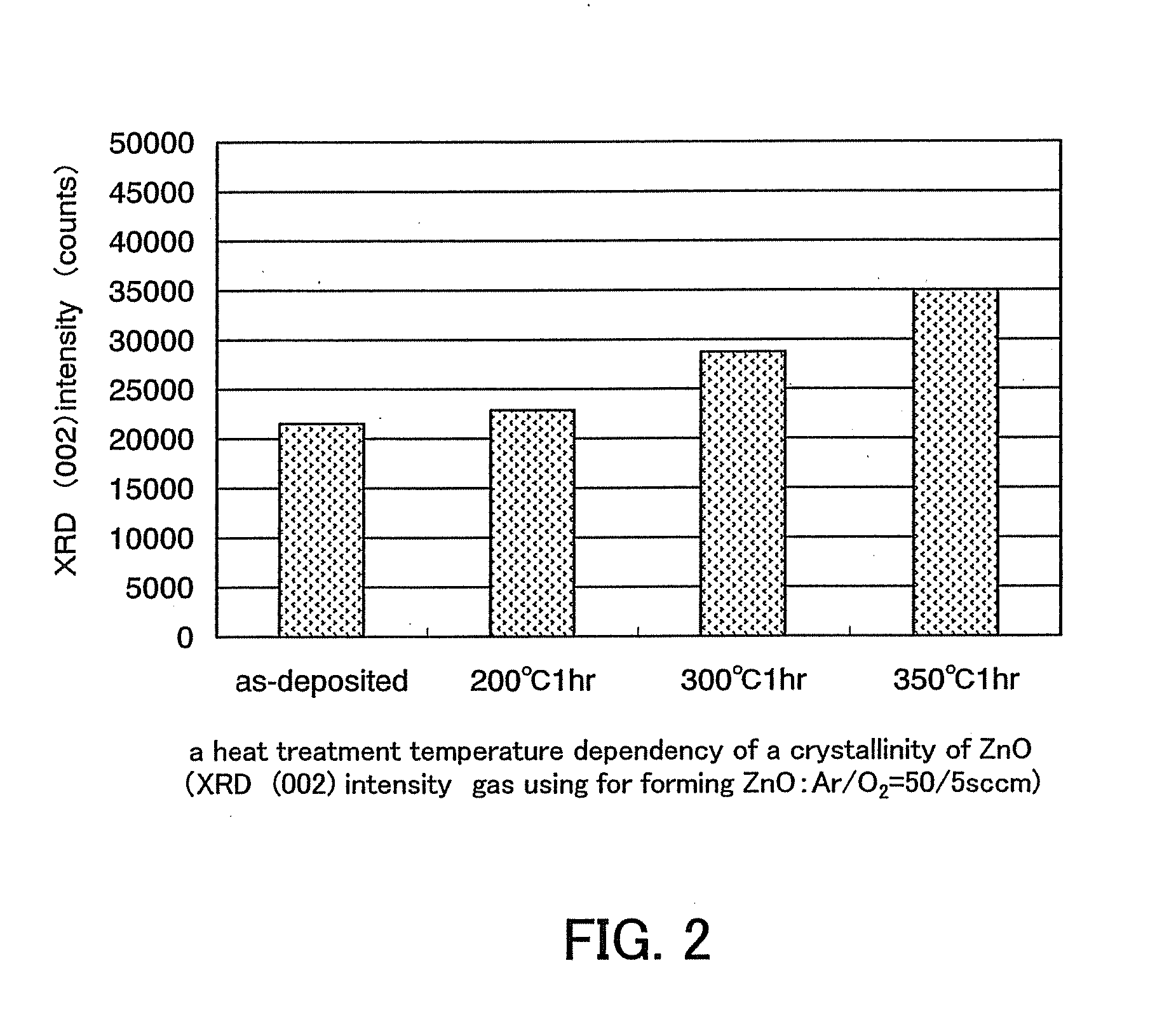

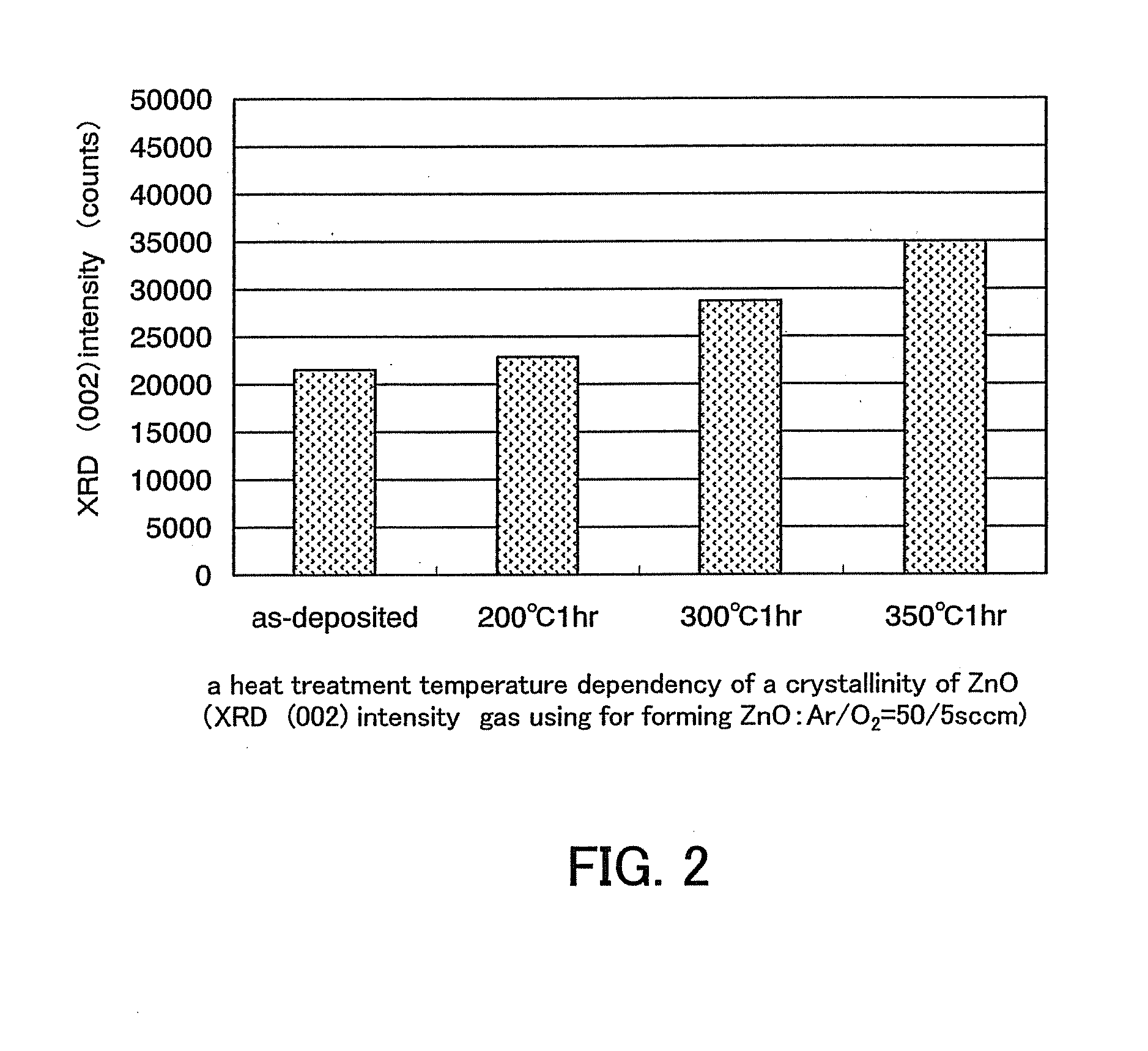

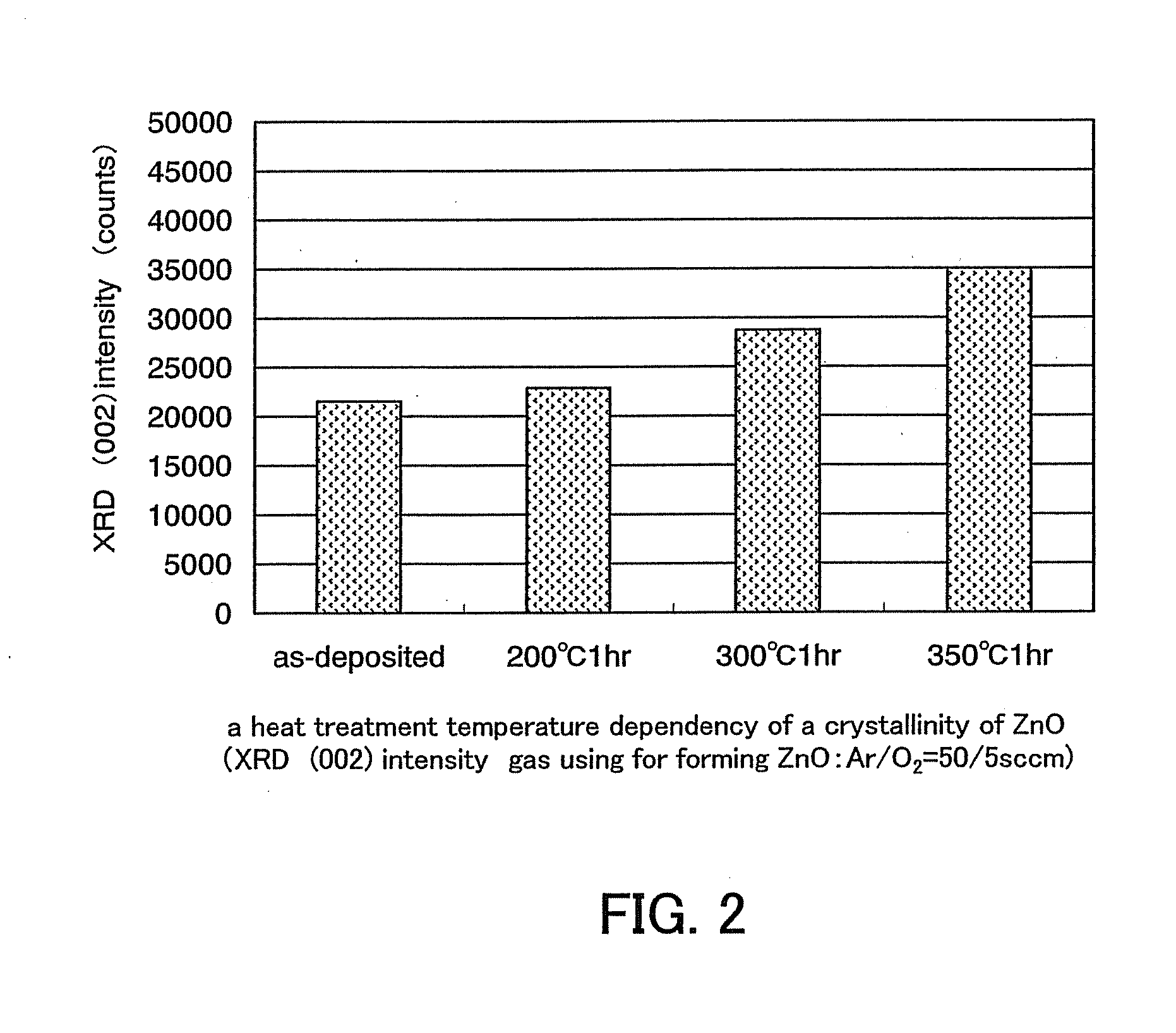

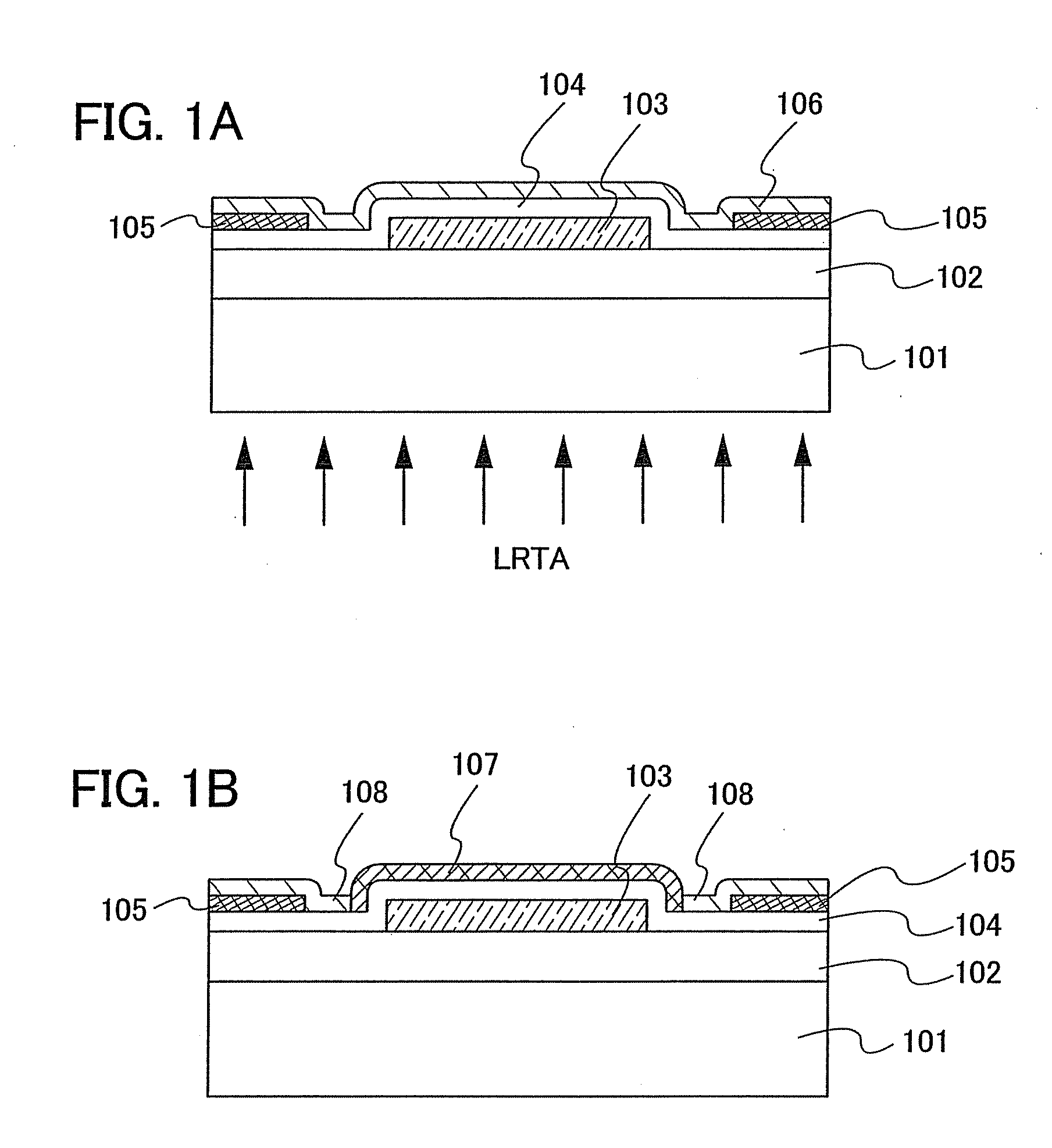

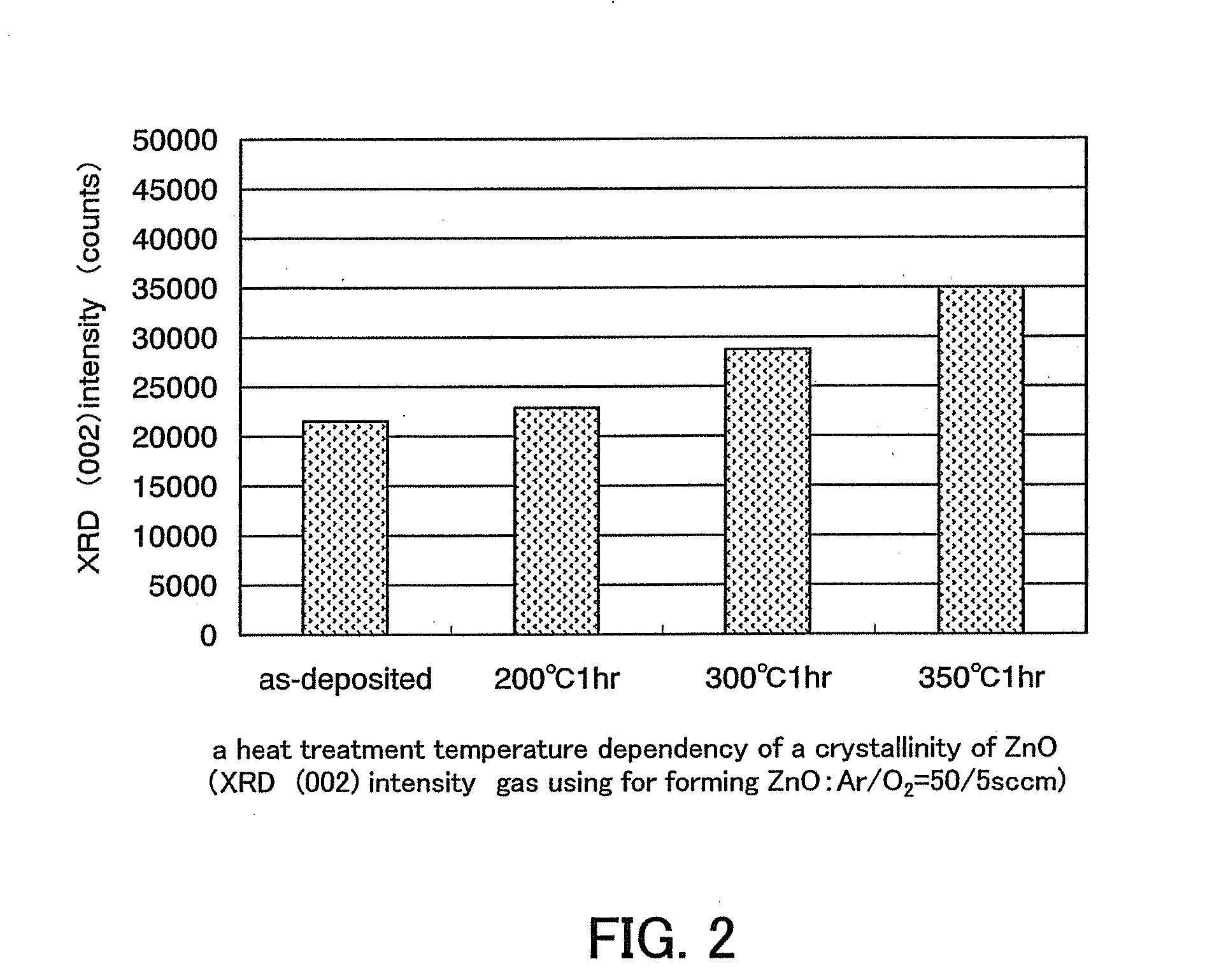

Method for forming ZnO film, method for forming ZnO semiconductor layer, method for fabricating semiconductor device, and semiconductor device

InactiveUS7049190B2High crystallinityLow costTransistorPolycrystalline material growthX-rayElectrical resistivity and conductivity

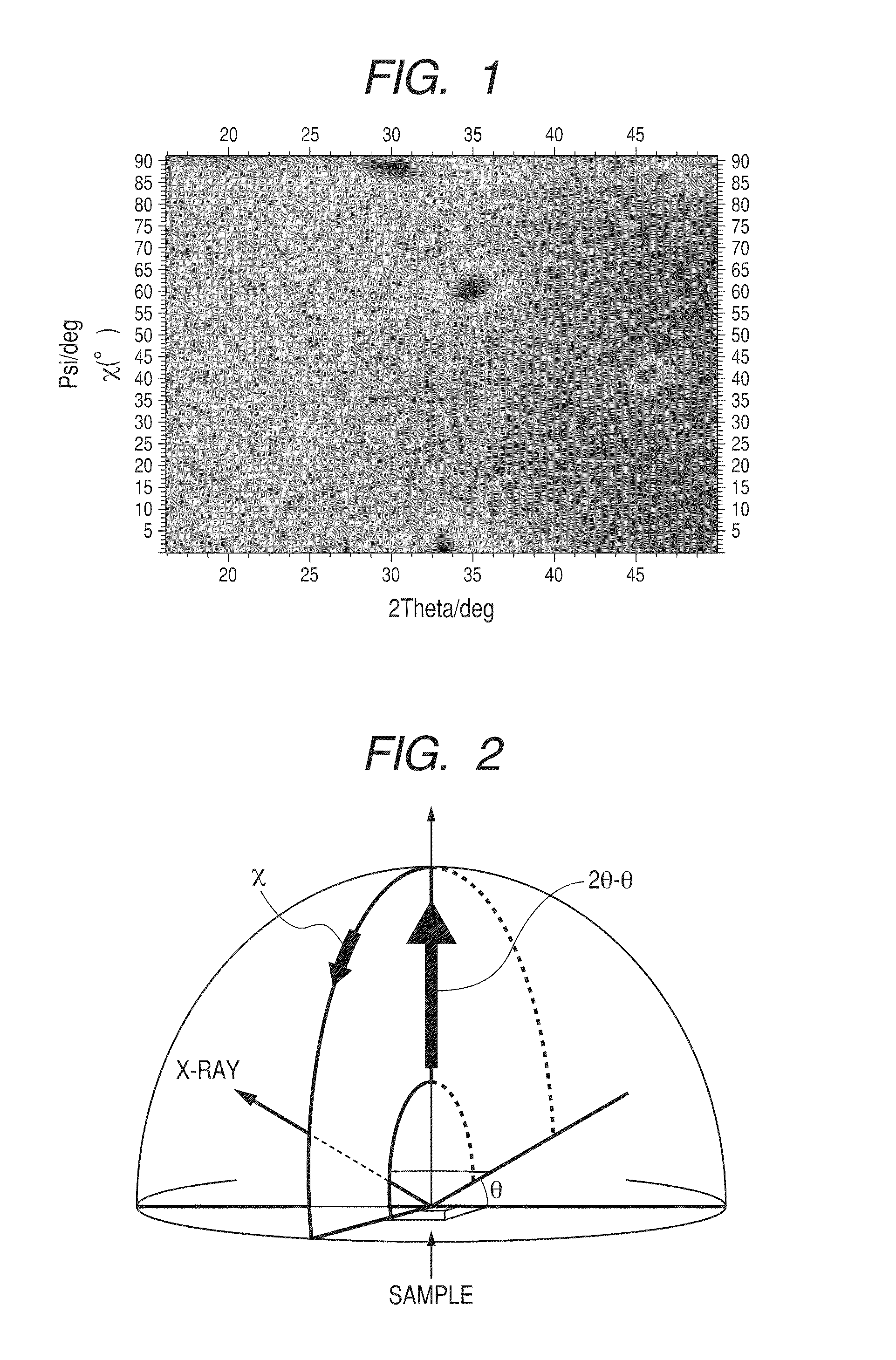

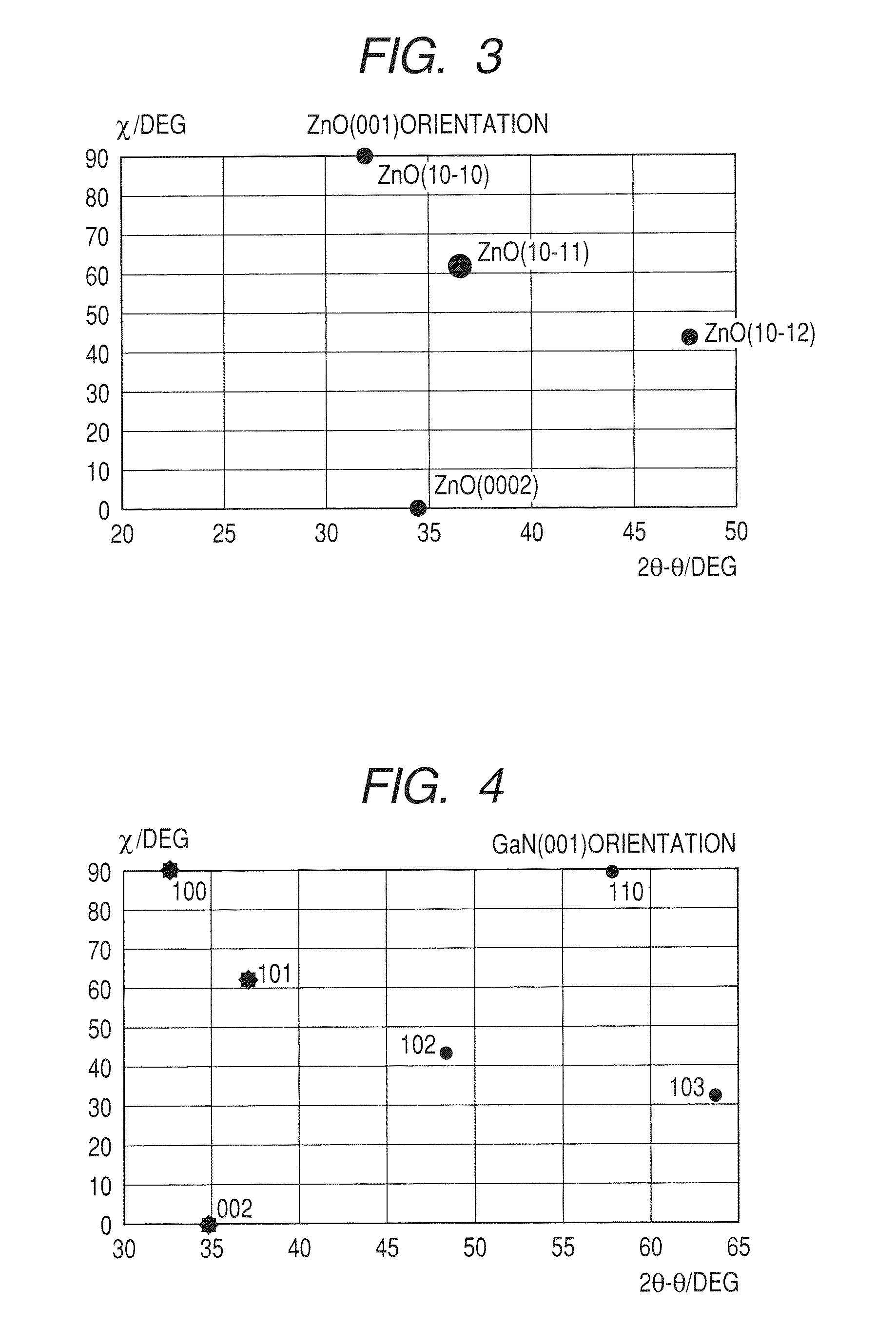

A ZnO buffer layer having an electric conductivity of 1×10−9 S / cm or lower or alternatively a ZnO buffer layer having a diffraction peak of a crystal face other than (002) and (004) in X-ray diffraction is formed on a substrate by sputtering. A ZnO semiconductor layer is formed on the ZnO buffer layer. The ZnO semiconductor layer is formed under the condition that the flow rate ratio of an oxygen gas in a sputtering gas is lower than that in the formation of the ZnO buffer layer.

Owner:SANYO ELECTRIC CO LTD

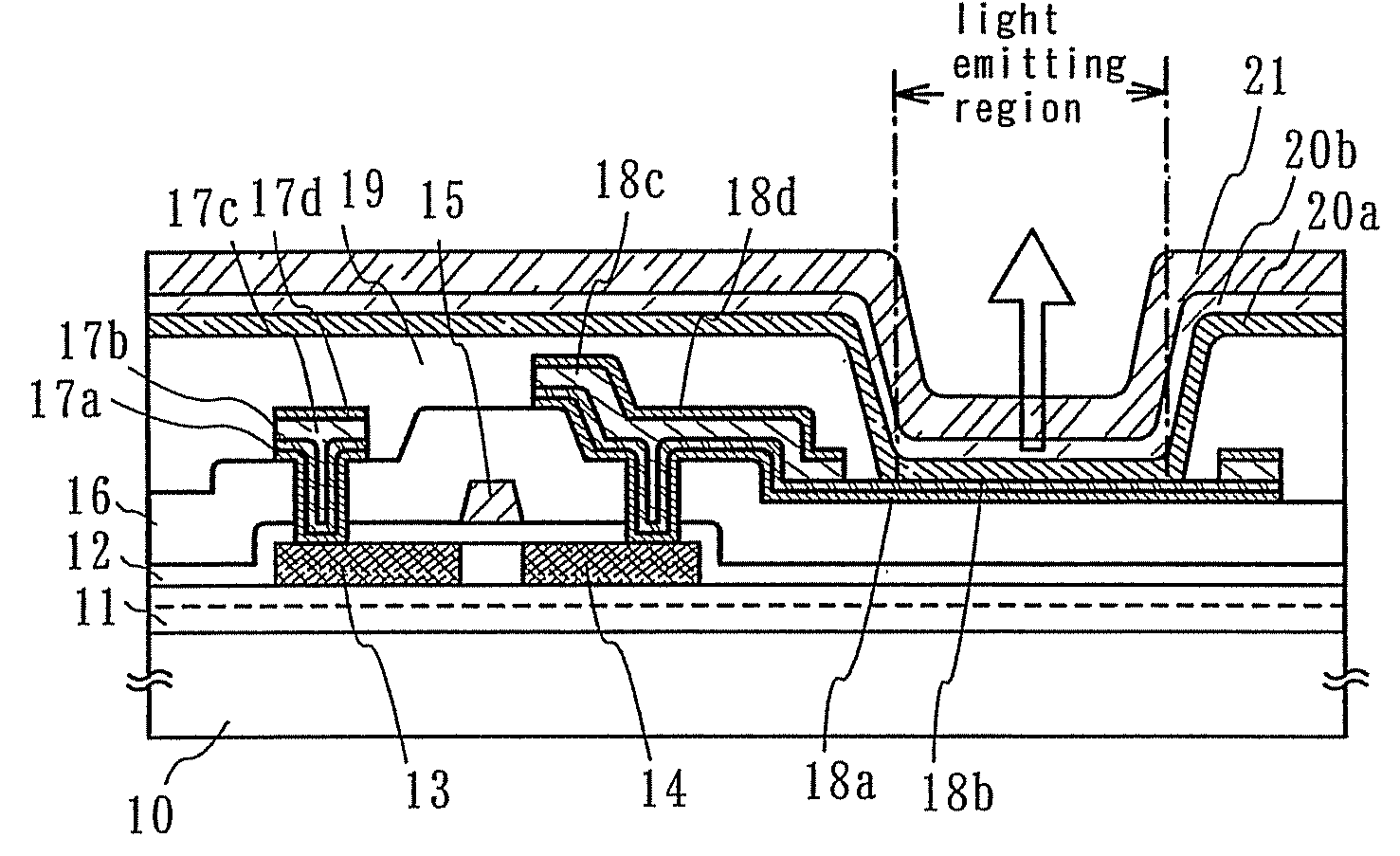

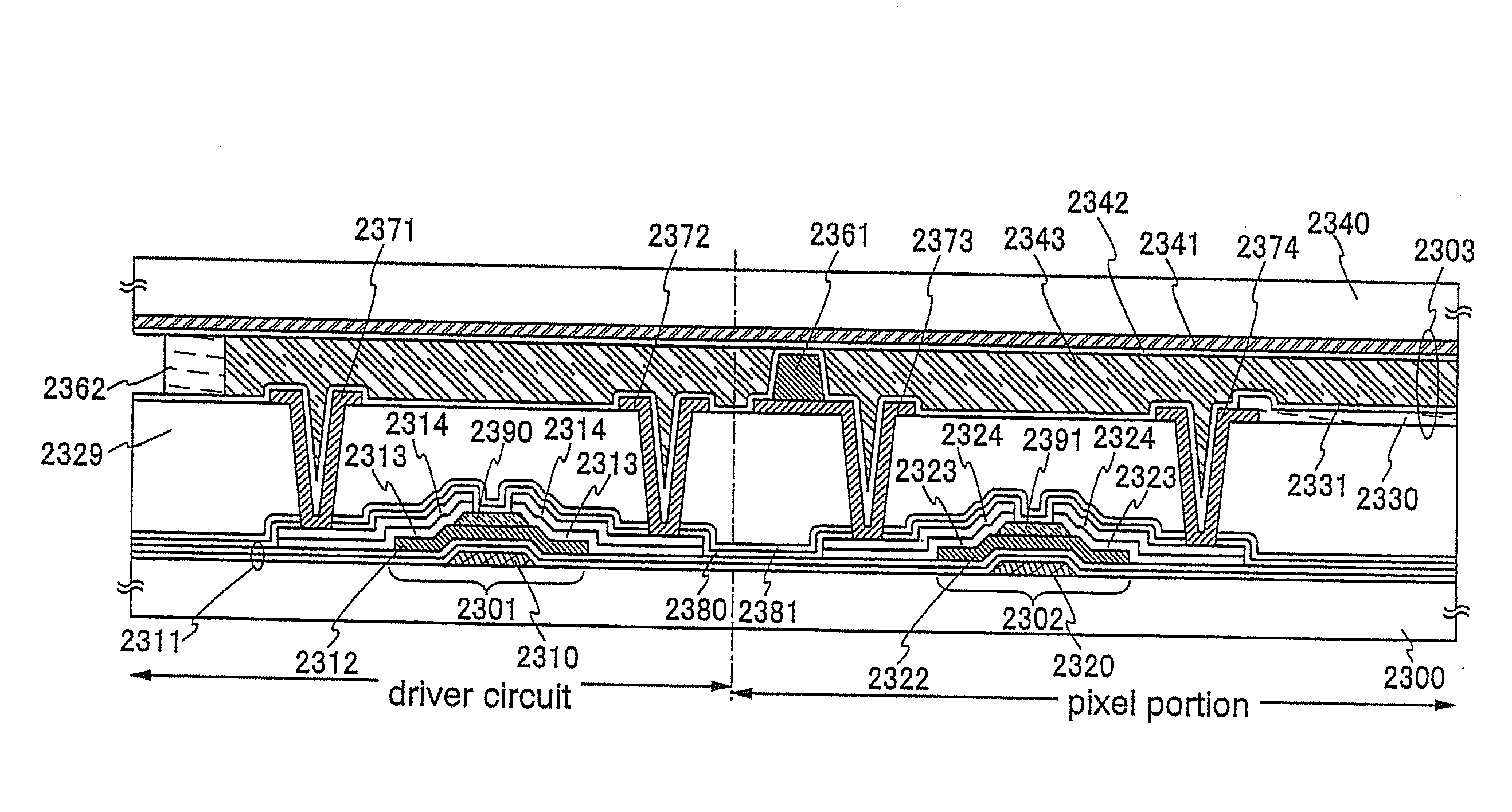

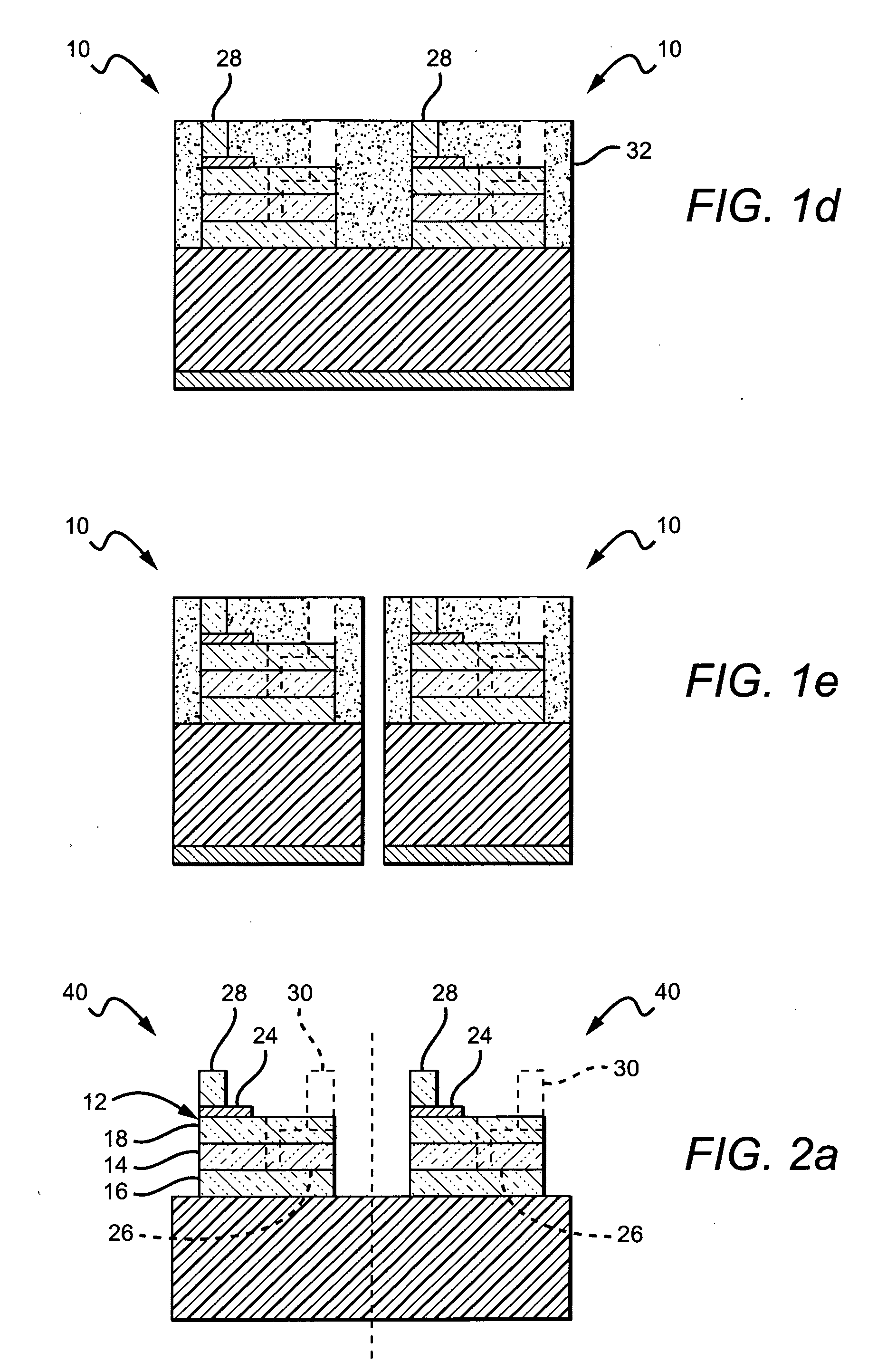

Semiconductor Device and Method for Manufacturing the Same

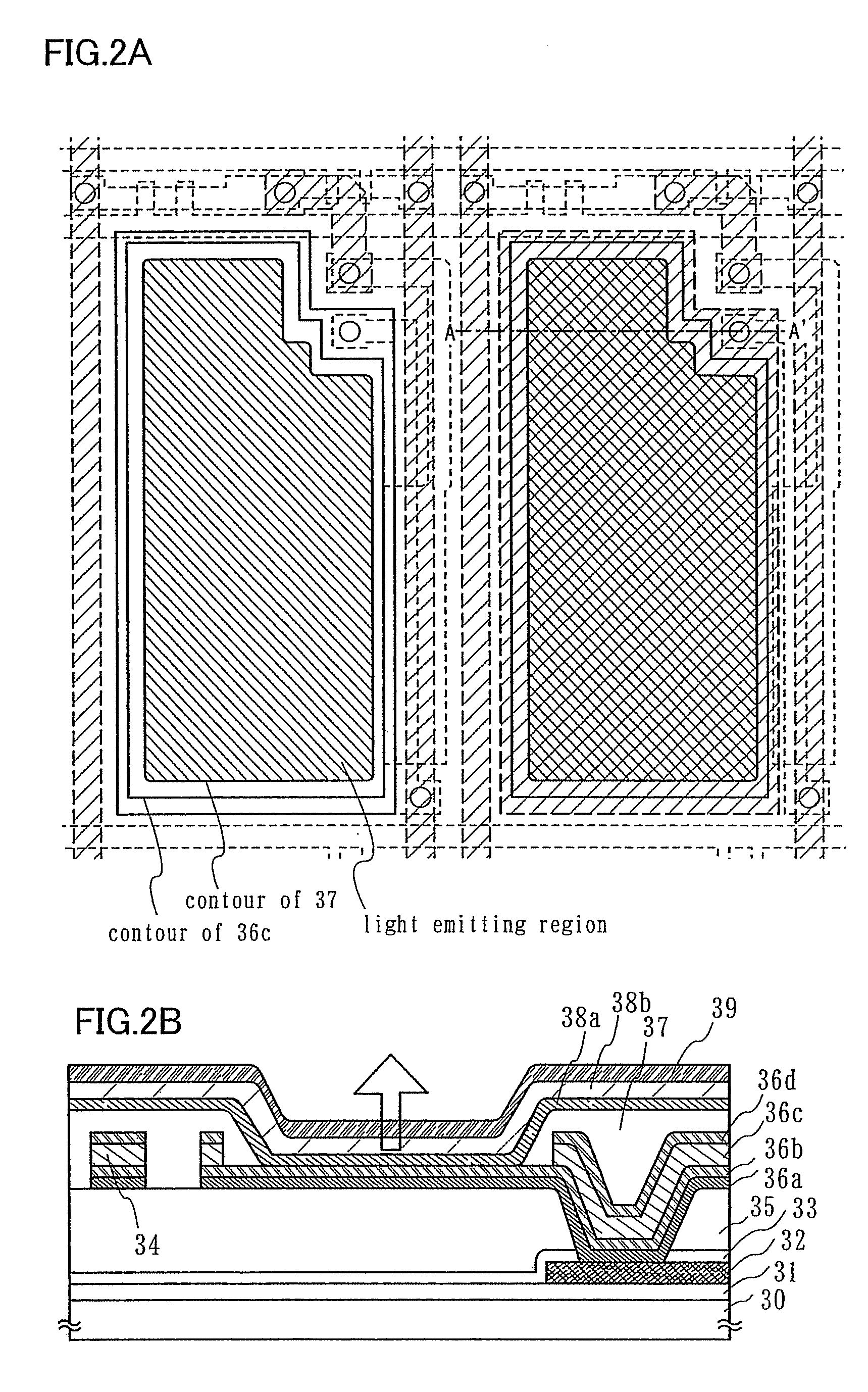

ActiveUS20090134399A1Good step coverageThin thicknessDischarge tube luminescnet screensElectroluminescent light sourcesActive matrixMetal electrodes

A manufacturing method of an active matrix light emitting device in which the active matrix light emitting device can be manufactured in a shorter time with high yield at low cost compared with conventional ones will be provided. It is a feature of the present invention that a layered structure is employed for a metal electrode which is formed in contact with or is electrically connected to a semiconductor layer of each TFT arranged in a pixel area of an active matrix light emitting device. Further, the metal electrode is partially etched and used as a first electrode of a light emitting element. A buffer layer, a layer containing an organic compound, and a second electrode layer are stacked over the first electrode.

Owner:SEMICON ENERGY LAB CO LTD

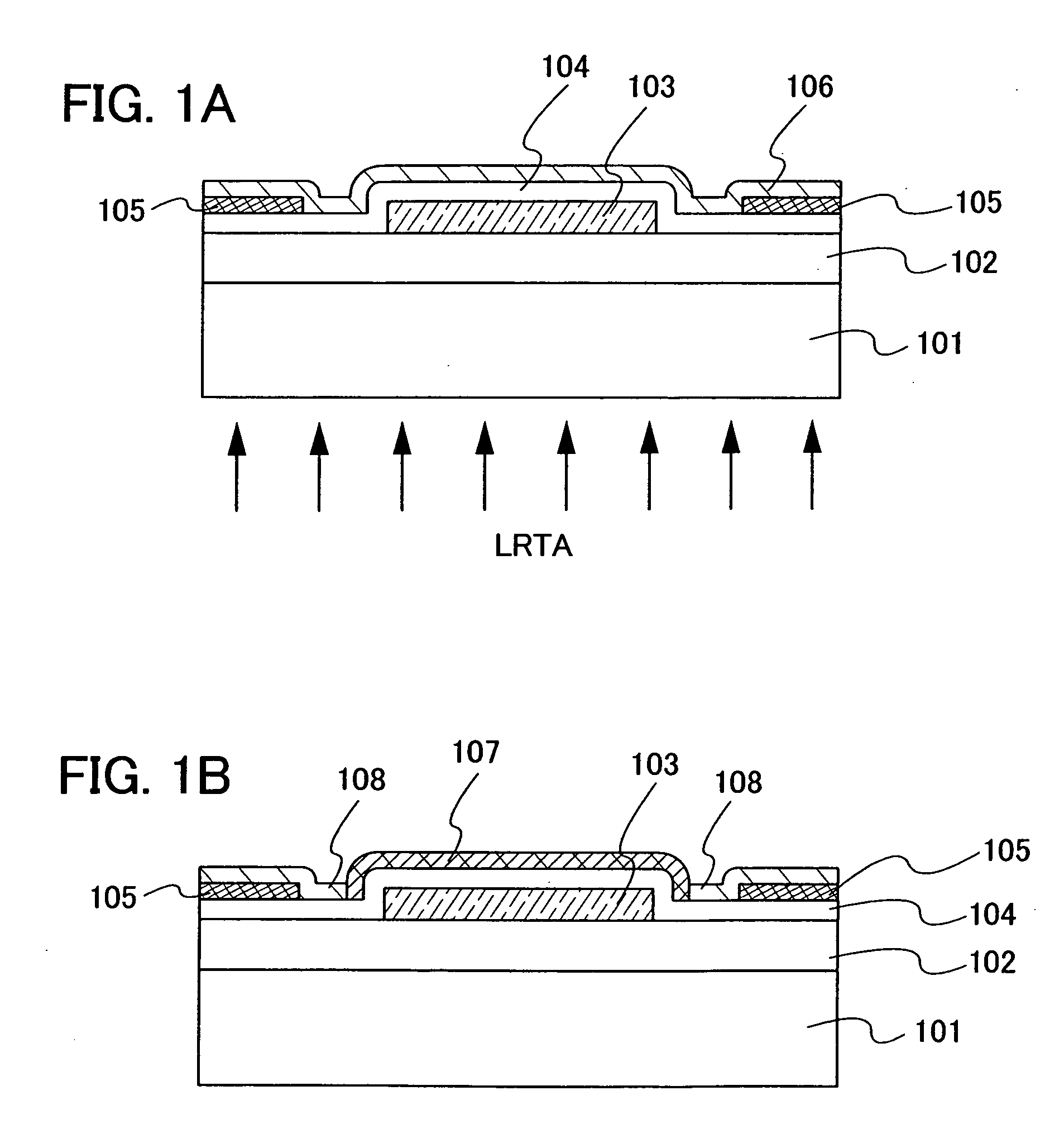

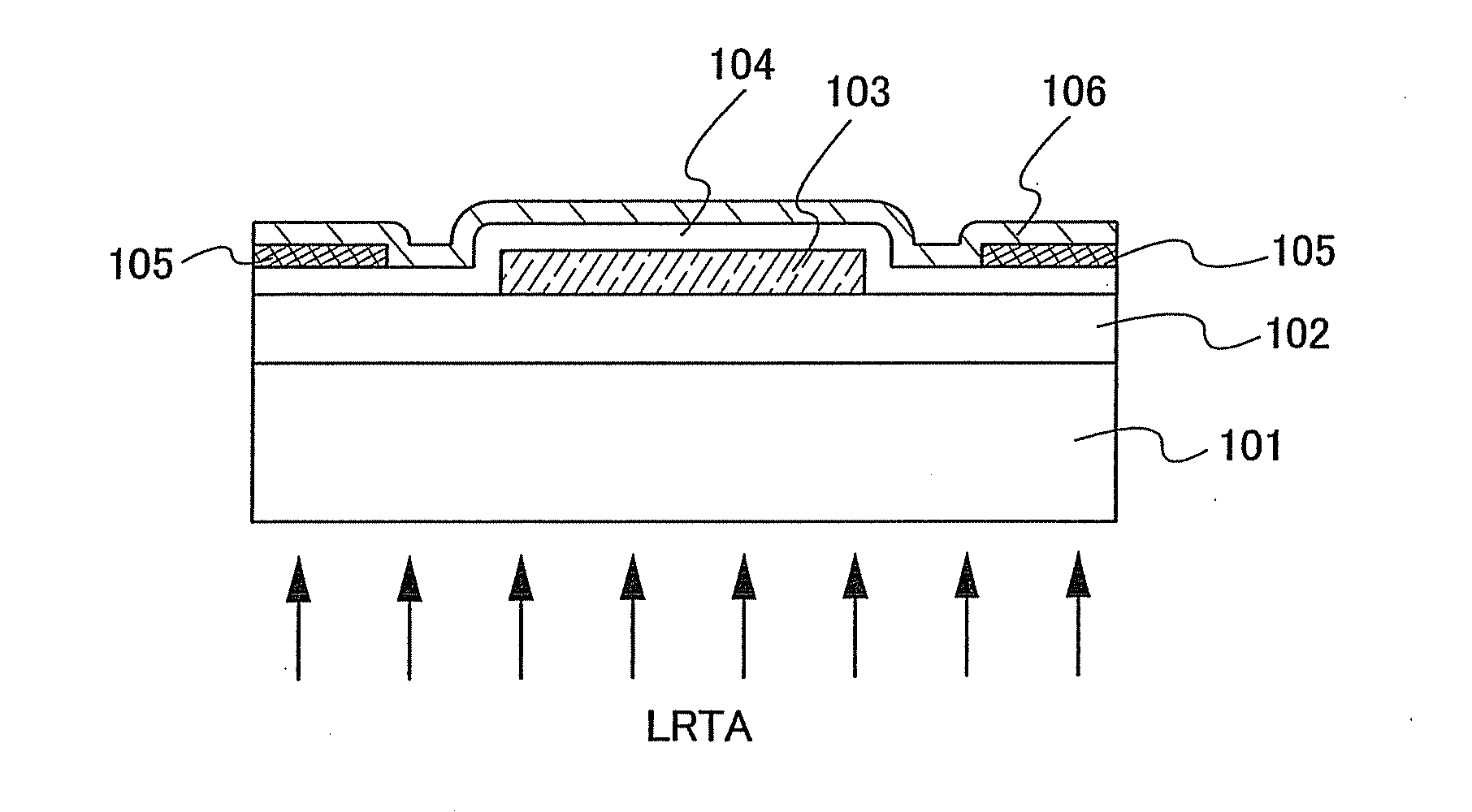

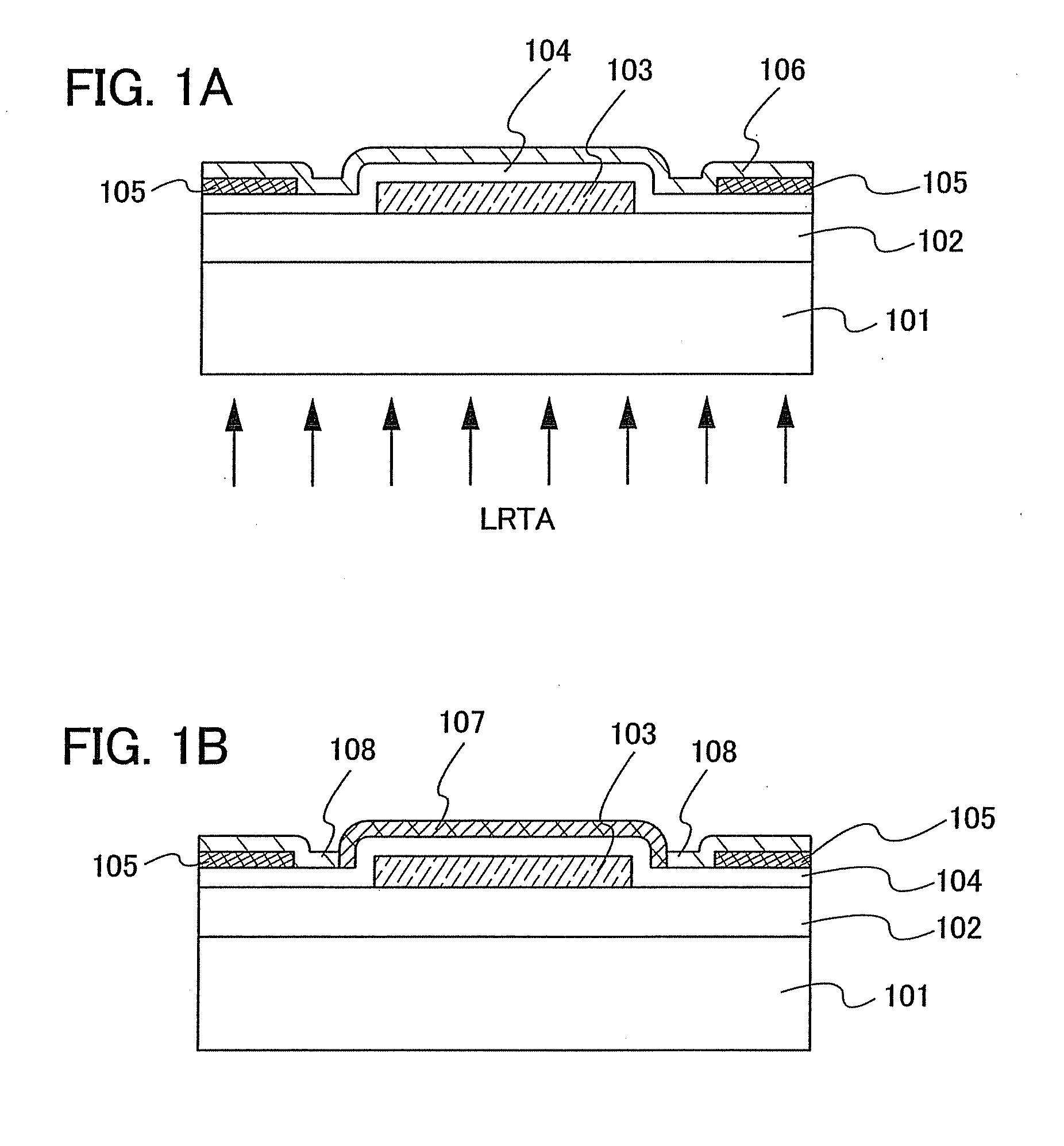

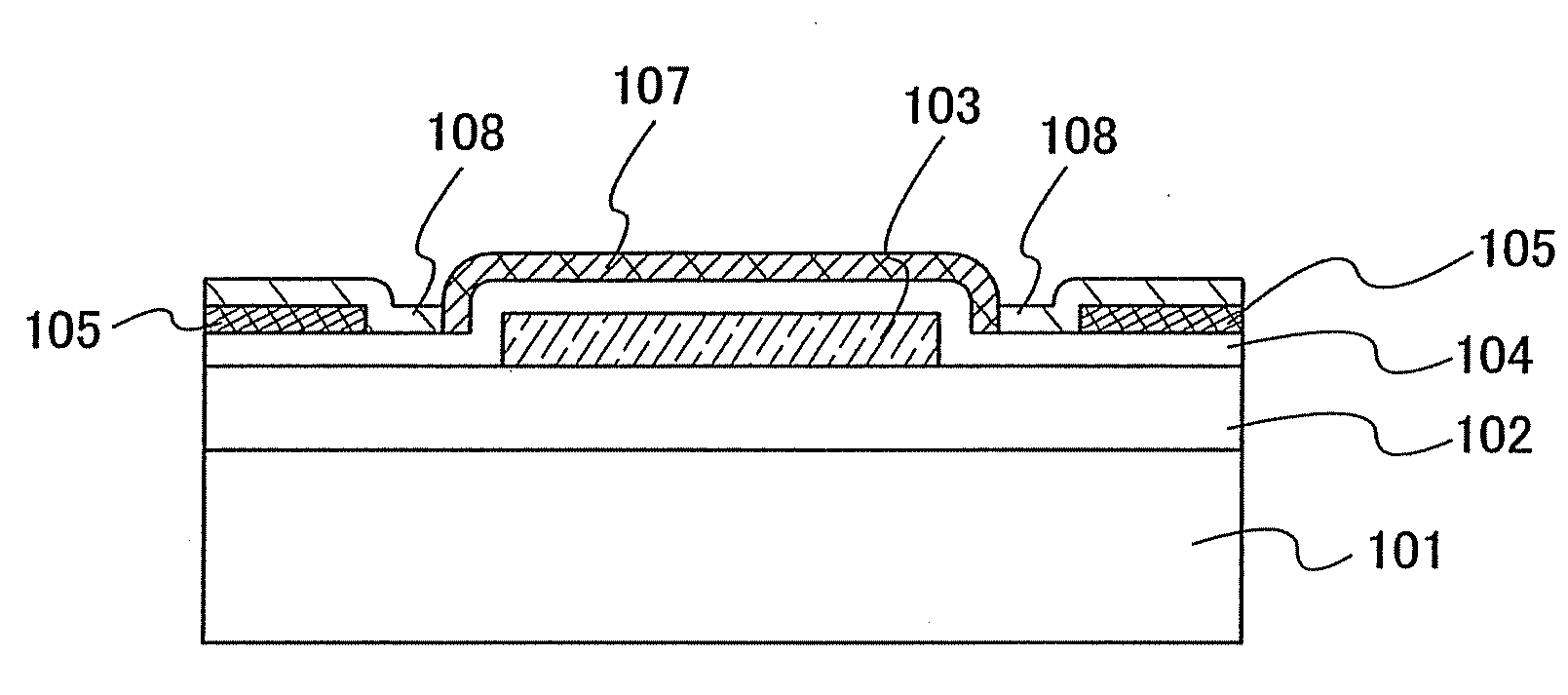

Semiconductor device including active layer made of zinc oxide with controlled orientations and manufacturing method thereof

InactiveUS20070187678A1Improve heat resistanceImprove propertiesSemiconductor/solid-state device manufacturingSemiconductor devicesZincActive layer

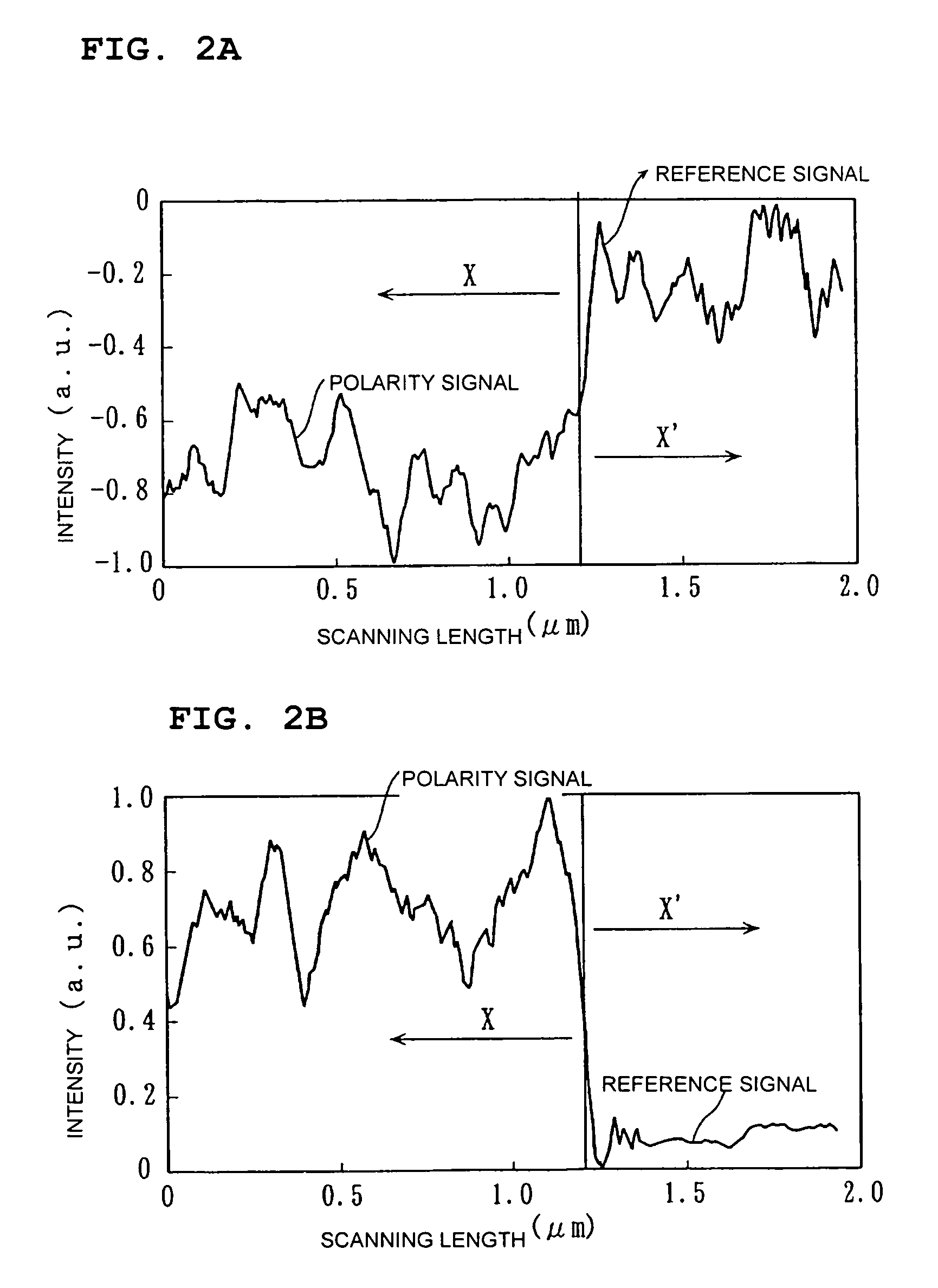

A semiconductor device includes an oxide semiconductor thin film layer primarily including zinc oxide having at least one orientation other than (002) orientation. The zinc oxide may have a mixed orientation including (002) orientation and (101) orientation. Alternatively, the zinc oxide may have a mixed orientation including (100) orientation and (101) orientation.

Owner:KOICHI IND PROMOTION CENT +1

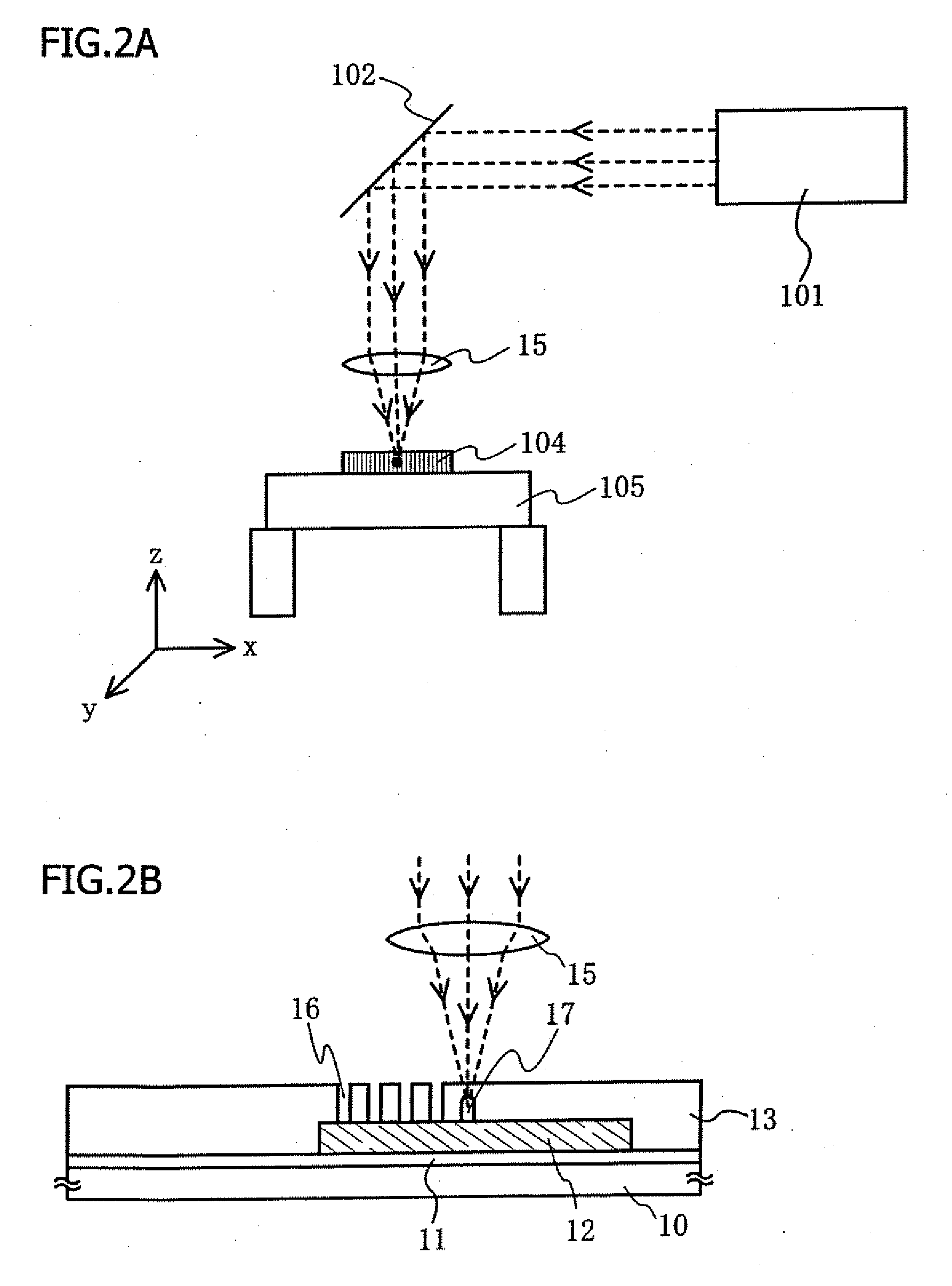

Semiconductor device and method for manufacturing the same, and electric device

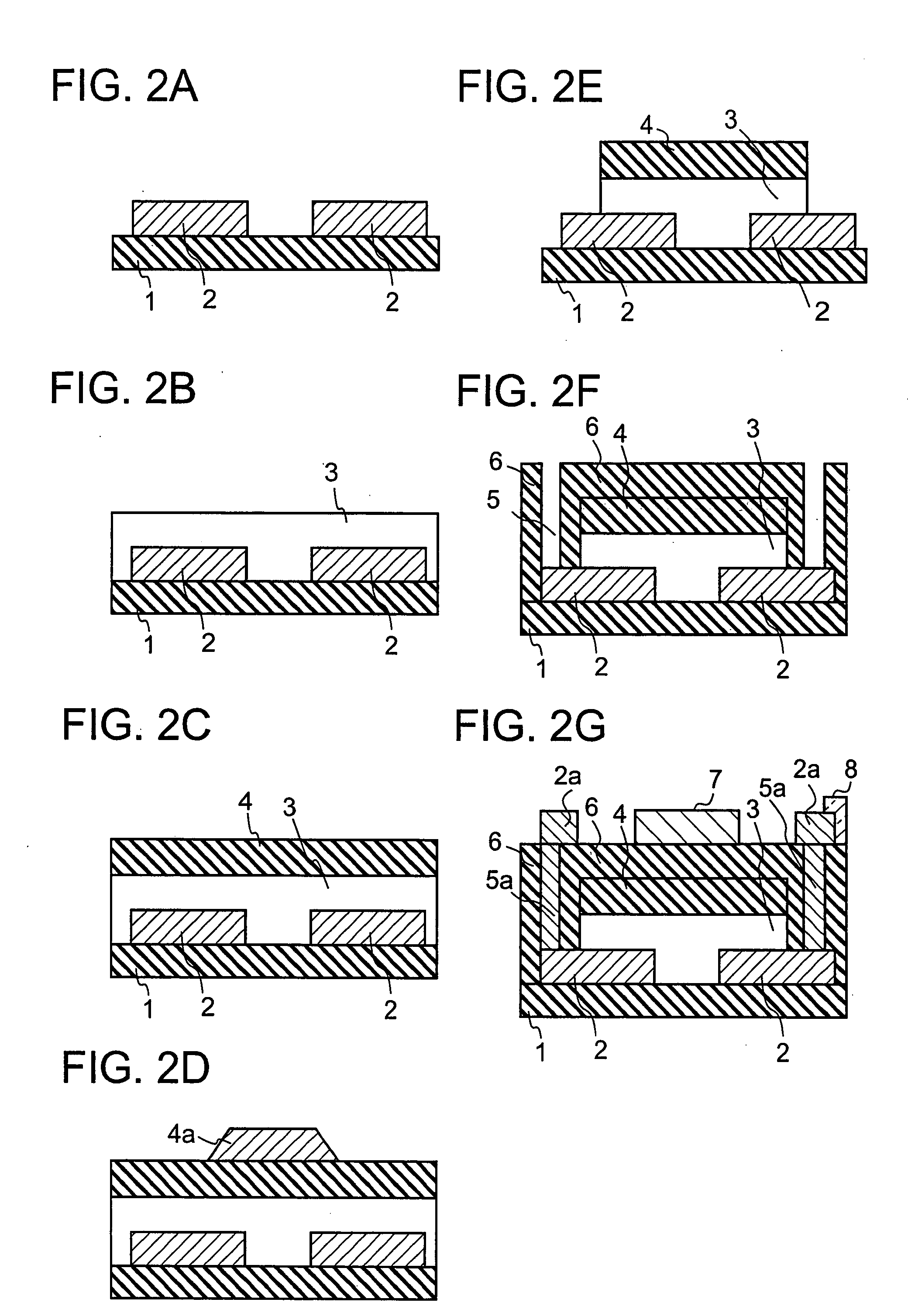

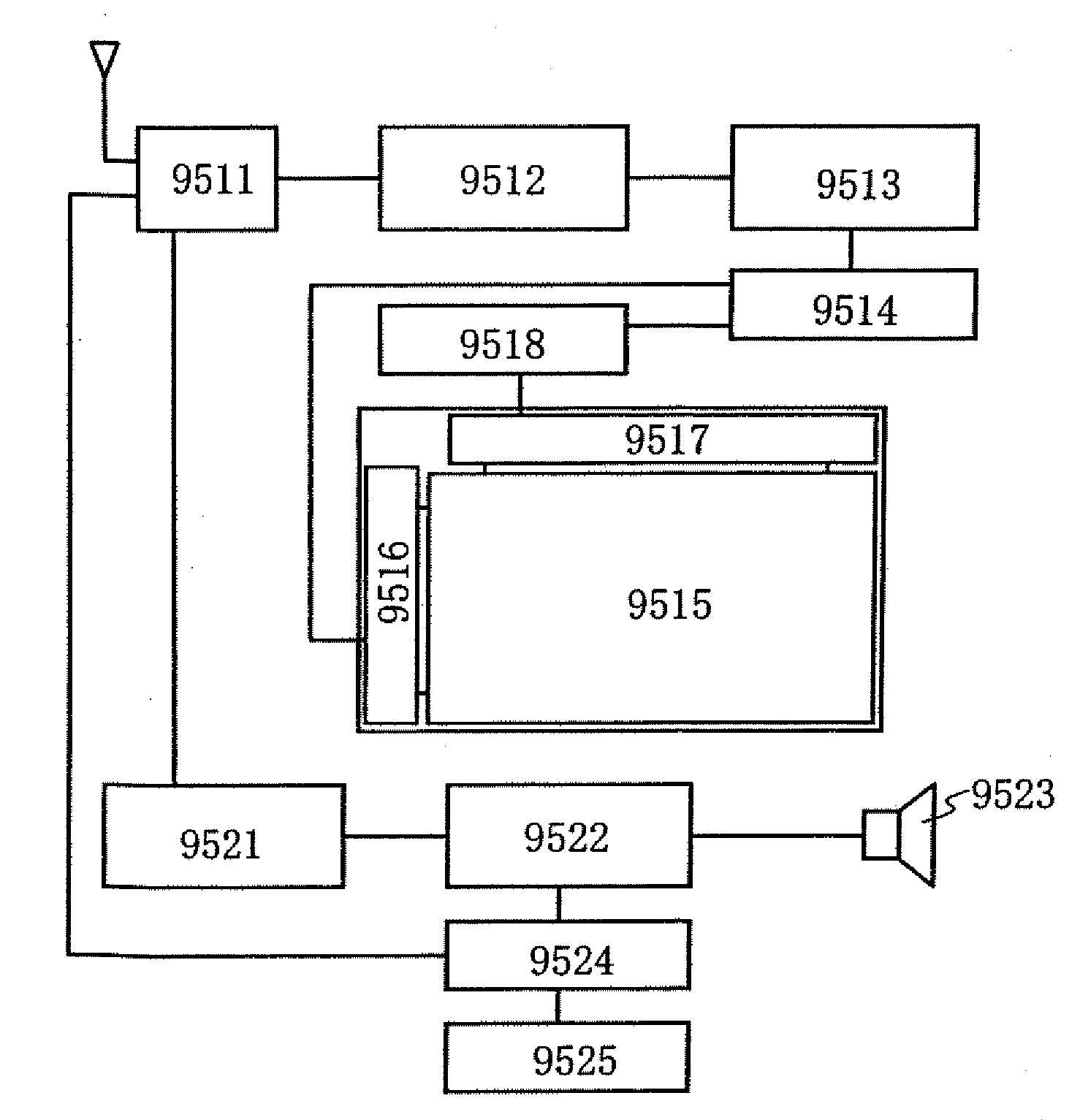

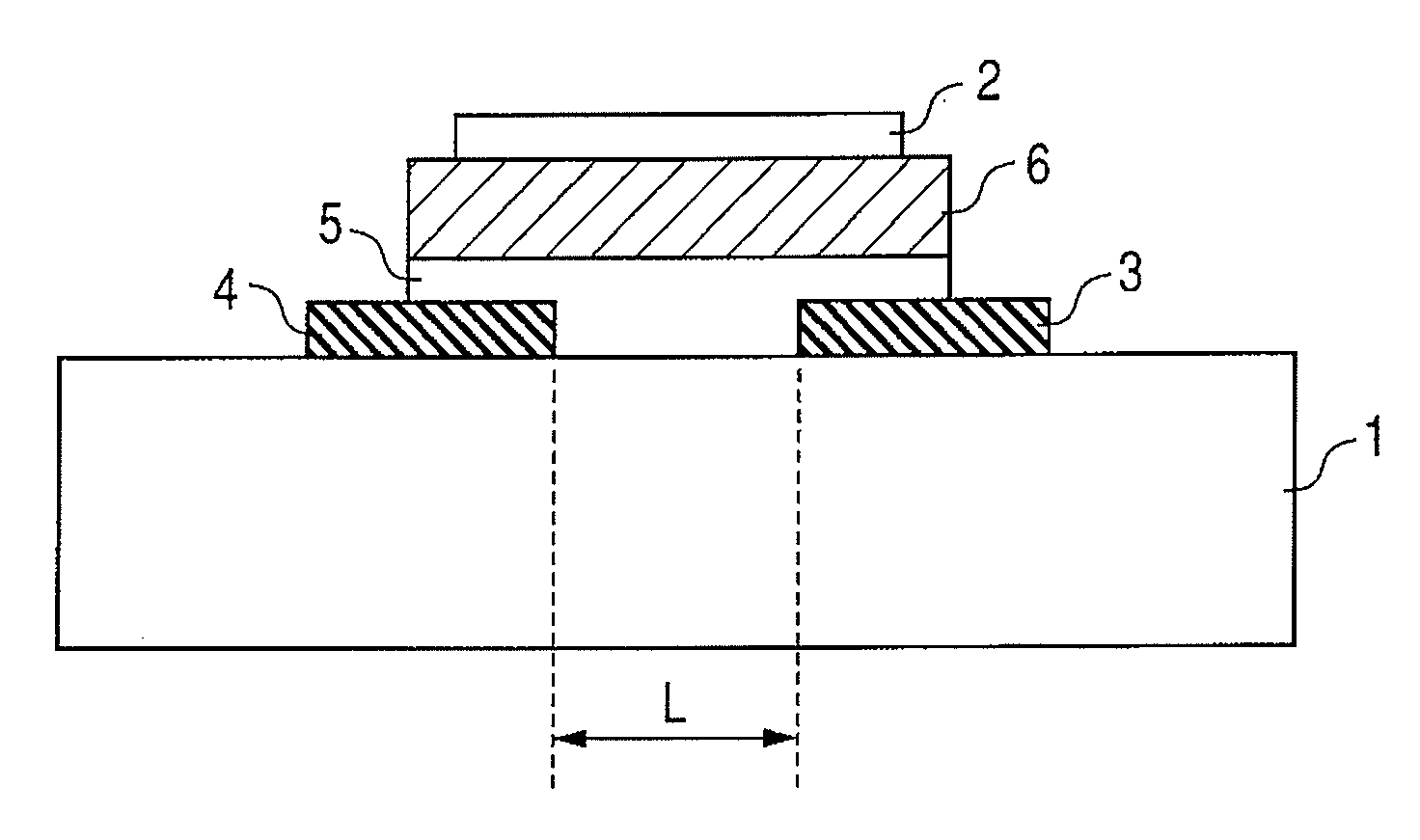

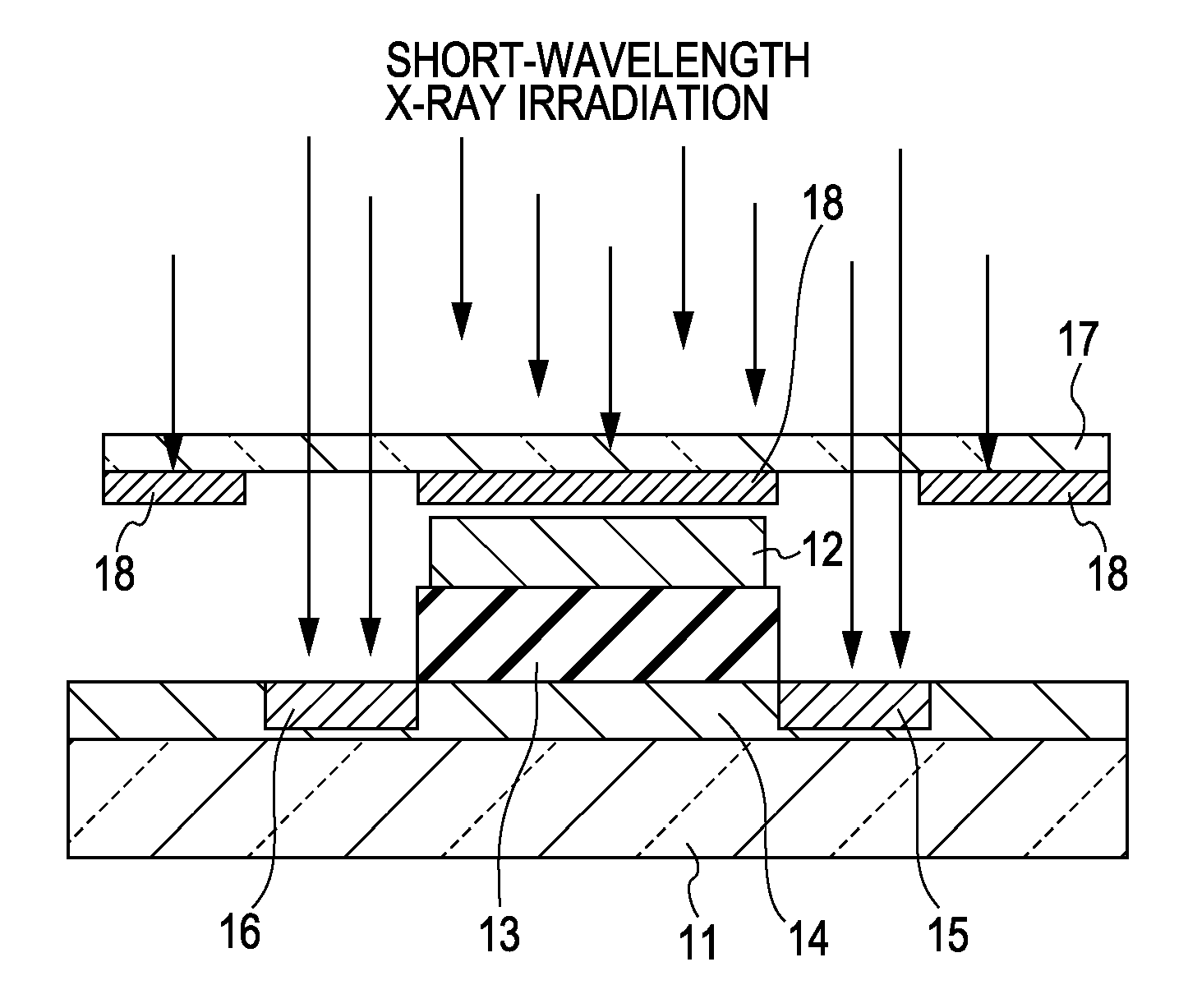

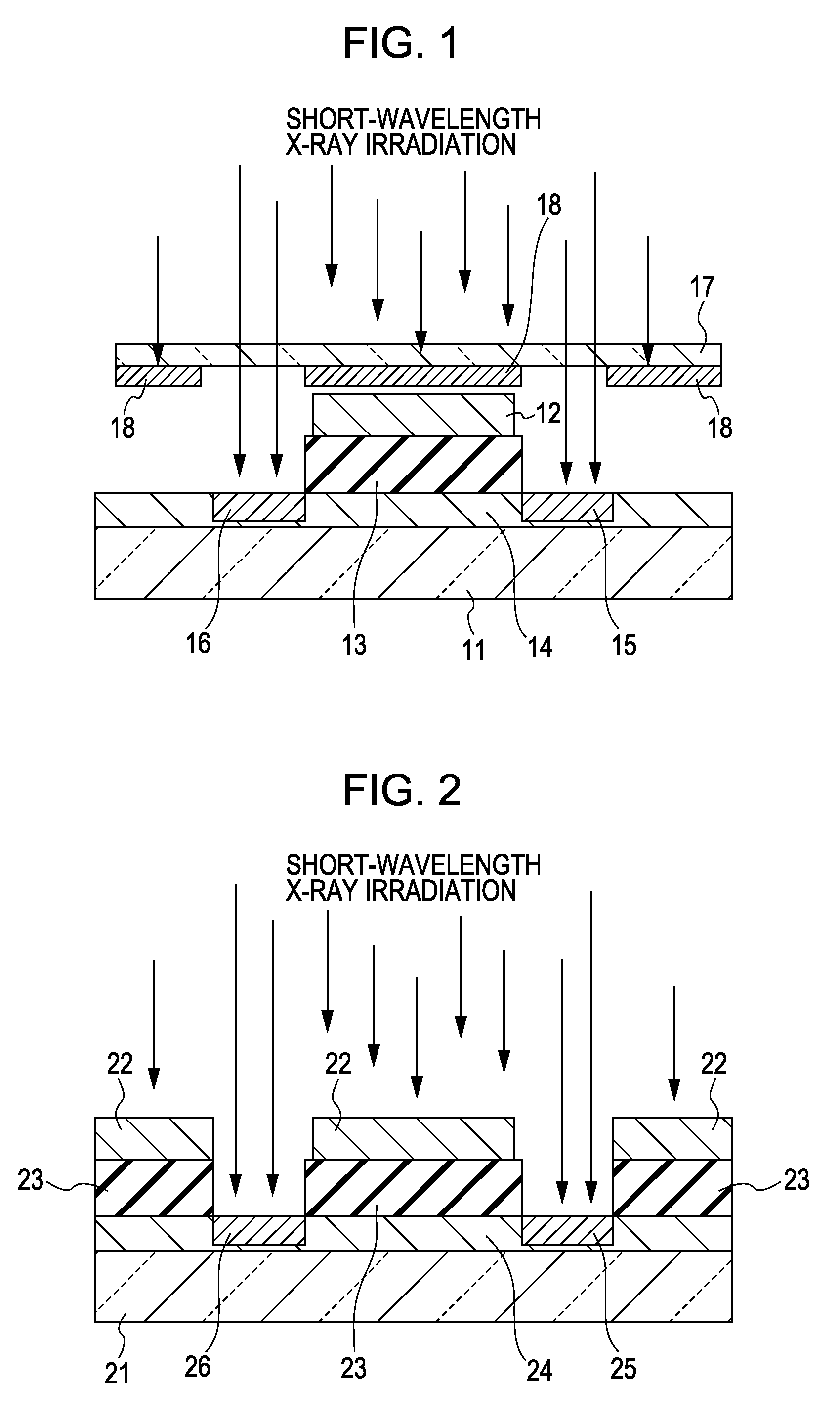

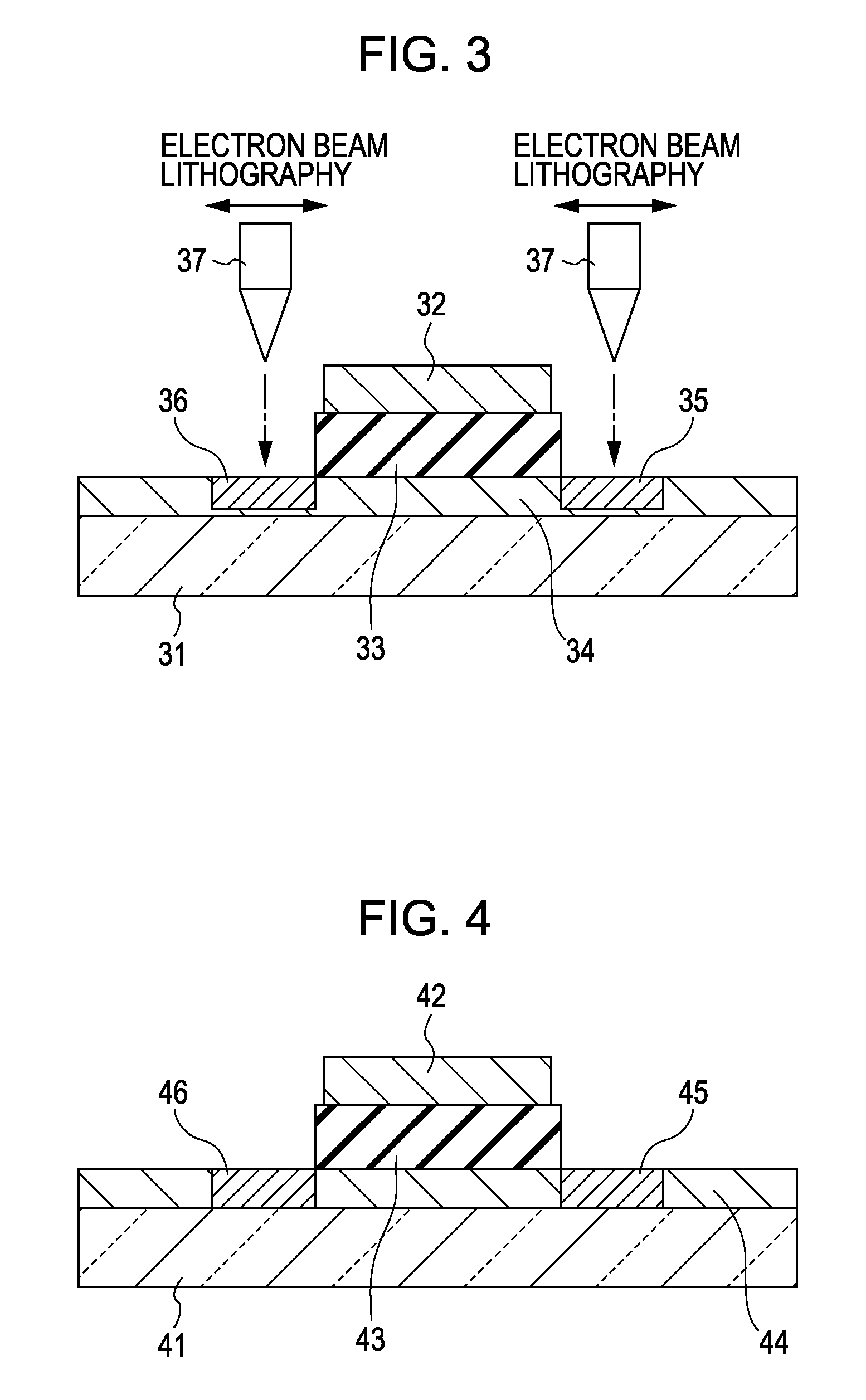

InactiveUS20090073325A1Simple stepsHighly integratedTransistorTelevision system detailsElectrical resistance and conductanceLongest Diameter

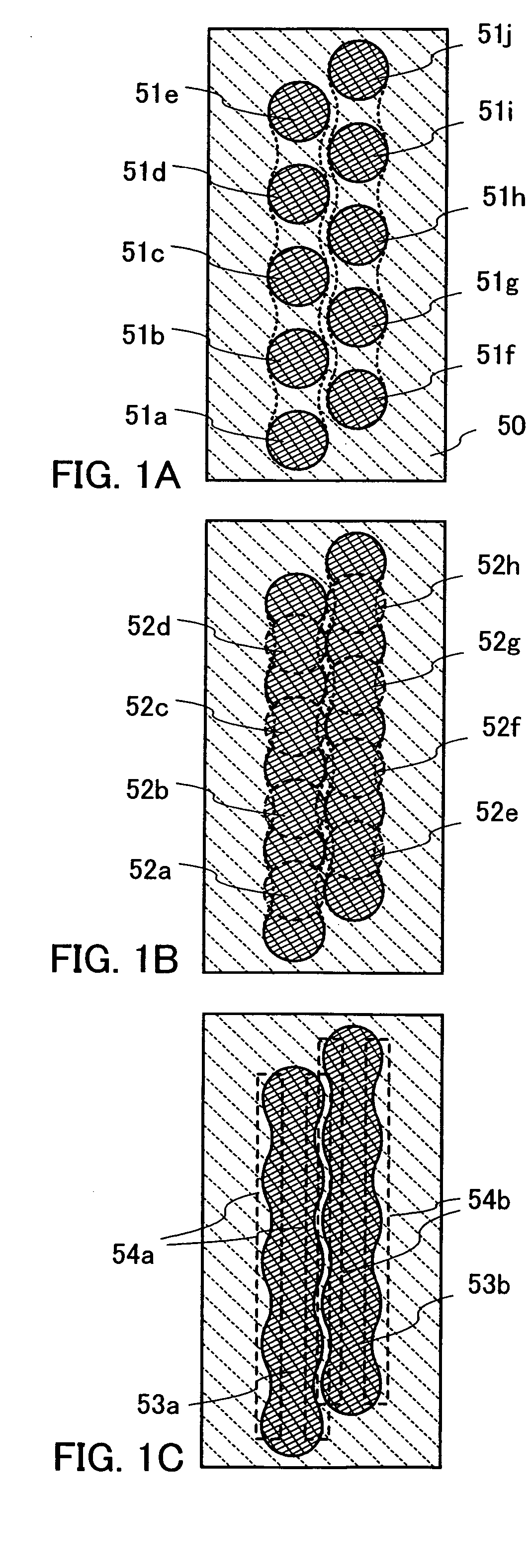

It is an object of the present invention to simplify steps needed to process a wiring in forming a multilayer wiring. In addition, when a droplet discharging technique or a nanoimprint technique is used to form a wiring in a contact hole having a comparatively long diameter, the wiring in accordance with the shape of the contact hole is formed, and the wiring portion of the contact hole is likely to have a depression compared with other portions. A penetrating opening is formed by irradiating a light-transmitting insulating film with laser light having high intensity and a pulse high in repetition frequency. A plurality of openings having a minute contact area is provided instead of forming one penetrating opening having a large contact area to have an even thickness of a wiring by reducing a partial depression and also to ensure contact resistance.

Owner:SEMICON ENERGY LAB CO LTD

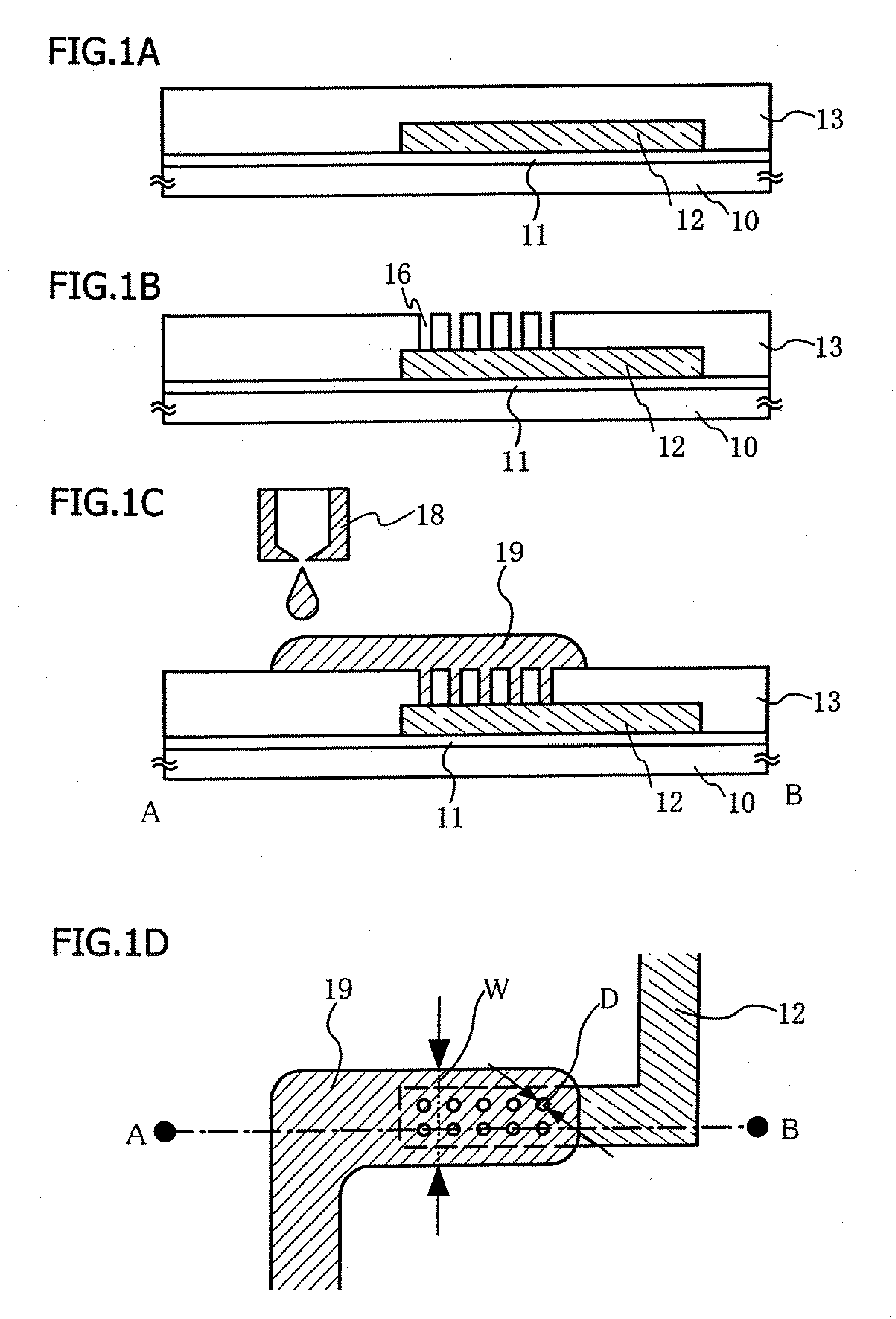

Semiconductor device, electronic device, and method of manufacturing semiconductor device

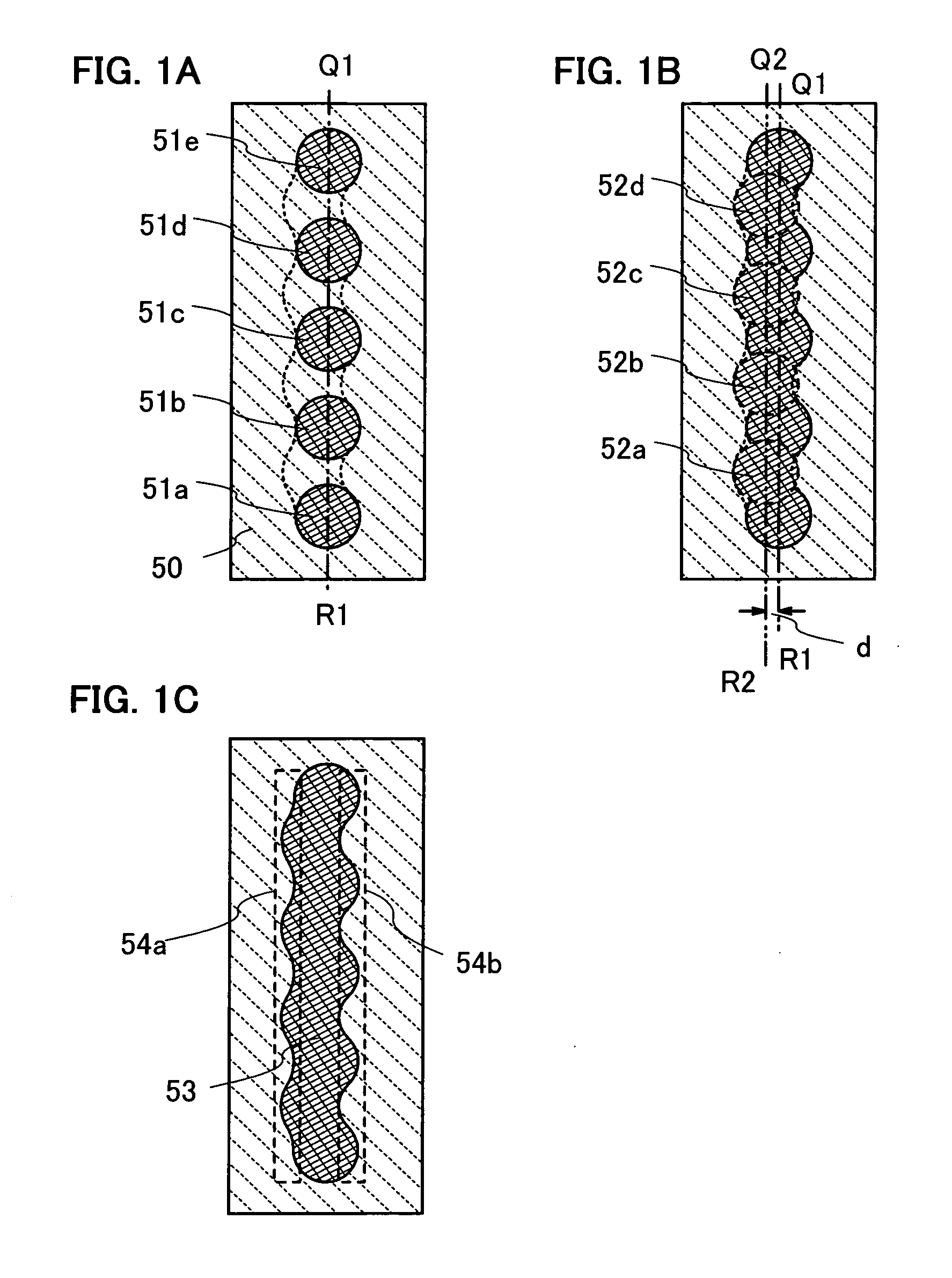

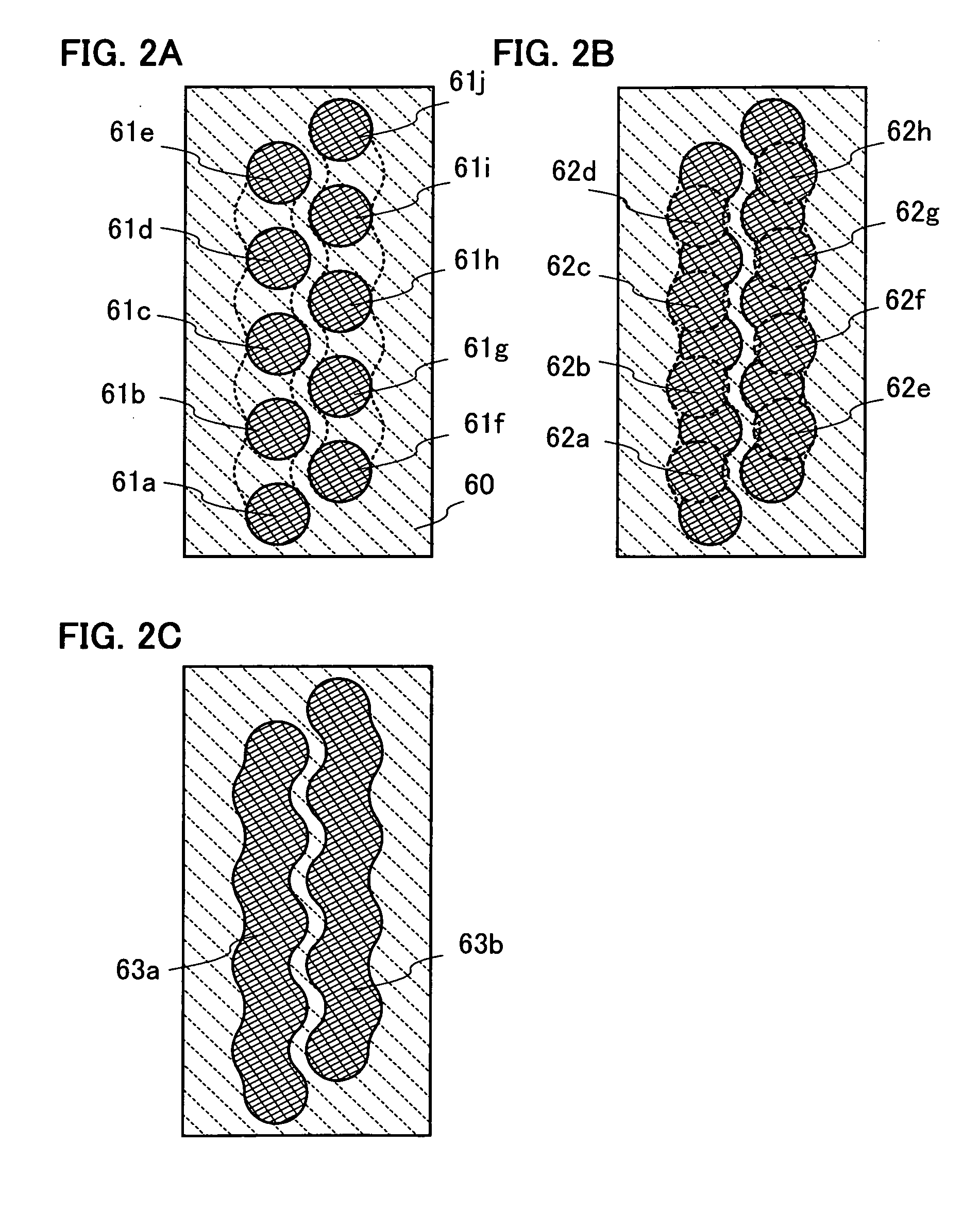

InactiveUS20060170111A1Stable formationImprove performanceSemiconductor/solid-state device detailsSolid-state devicesDevice materialShortest distance

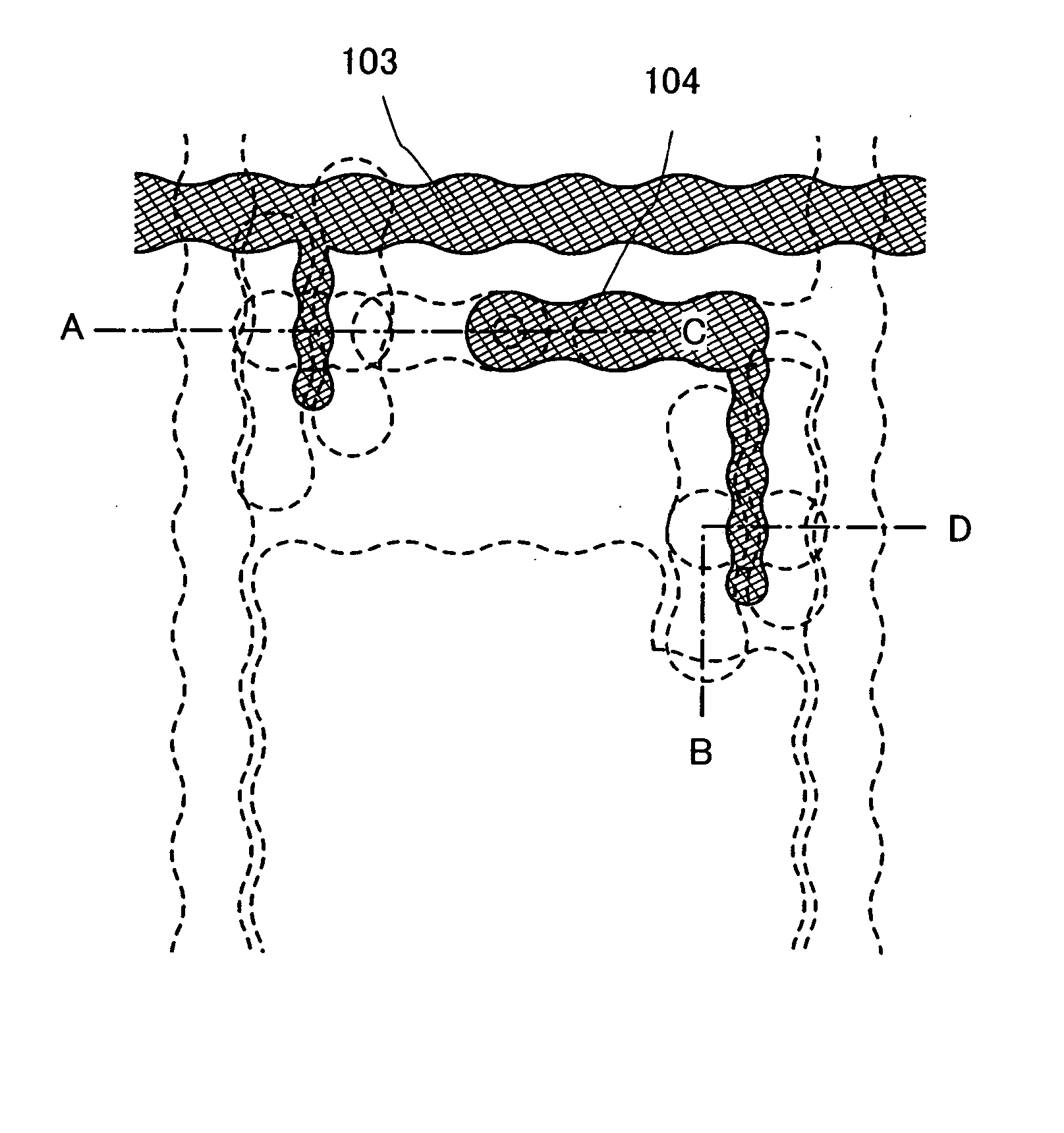

Conductive layers having knots are adjacently formed with uniform distance therebetween. Droplets of the conductive layers are discharged to stagger centers of the droplets in a length direction of wirings so that the centers of the discharged droplets are not on the same line in a line width direction between the adjacent conductive layers. Since the centers of the droplets are staggered, parts of the conductive layers each having a widest line width (the widest width of knot) are not connected to each other, and the conductive layers can be formed adjacently with a shorter distance therebetween.

Owner:SEMICON ENERGY LAB CO LTD

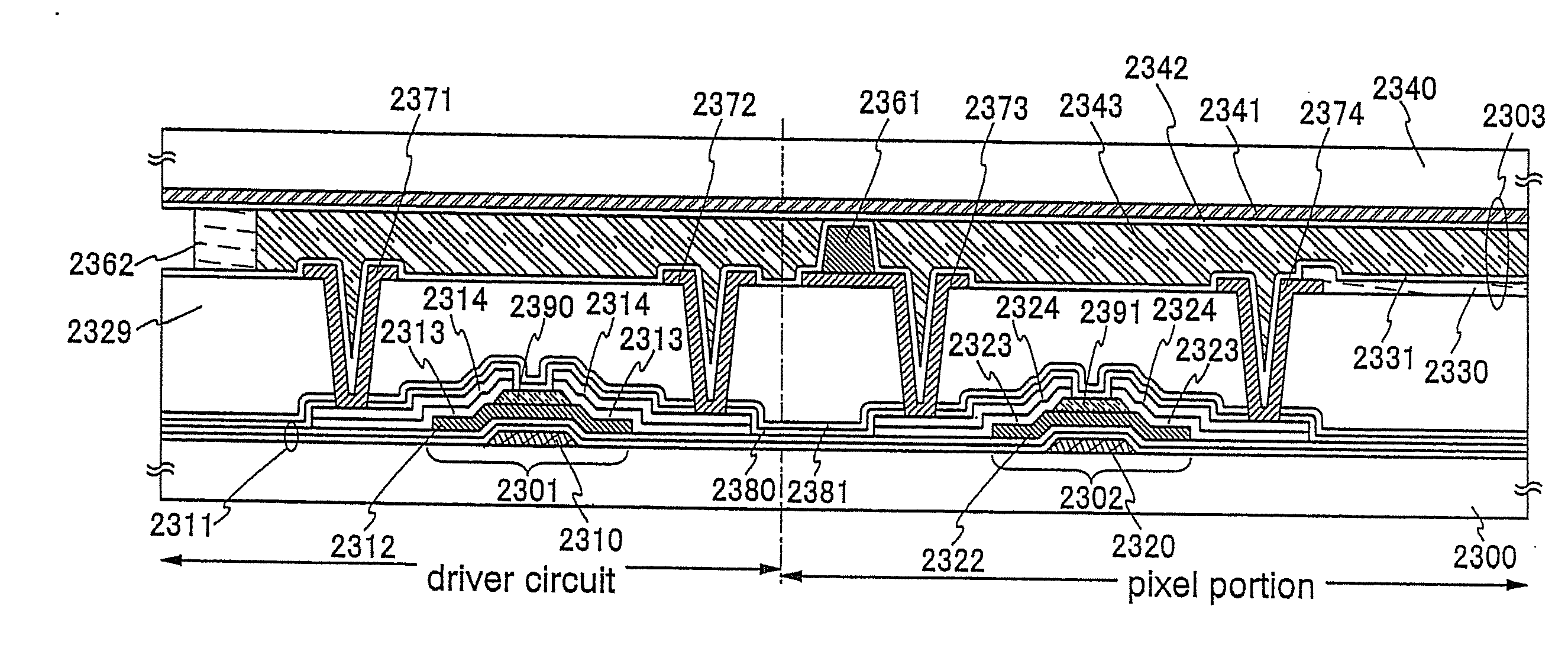

Semiconductor device in which zinc oxide is used as a semiconductor material and method for manufacturing the semiconductor device

ActiveUS7501293B2Improve surface smoothnessHigh crystallinityTransistorLaser detailsSemiconductor materialsDevice material

A semiconductor device having excellent crystallinity and excellent electric characteristics includes a ZnO thin film having excellent surface smoothness. ZnO-based thin films (an n-type contact layer, an n-type clad layer, an active layer, a p-type clad layer, and a p-type contact layer) primarily including ZnO are formed sequentially by an ECR sputtering method or other suitable method on a zinc-polar surface of a ZnO substrate. A transparent electrode and a p-side electrode are formed by an evaporation method or other suitable method on a surface of the p-type contact layer, and an n-side electrode is formed on an oxygen-polar surface of the ZnO substrate.

Owner:MURATA MFG CO LTD

Semiconductor device and display device

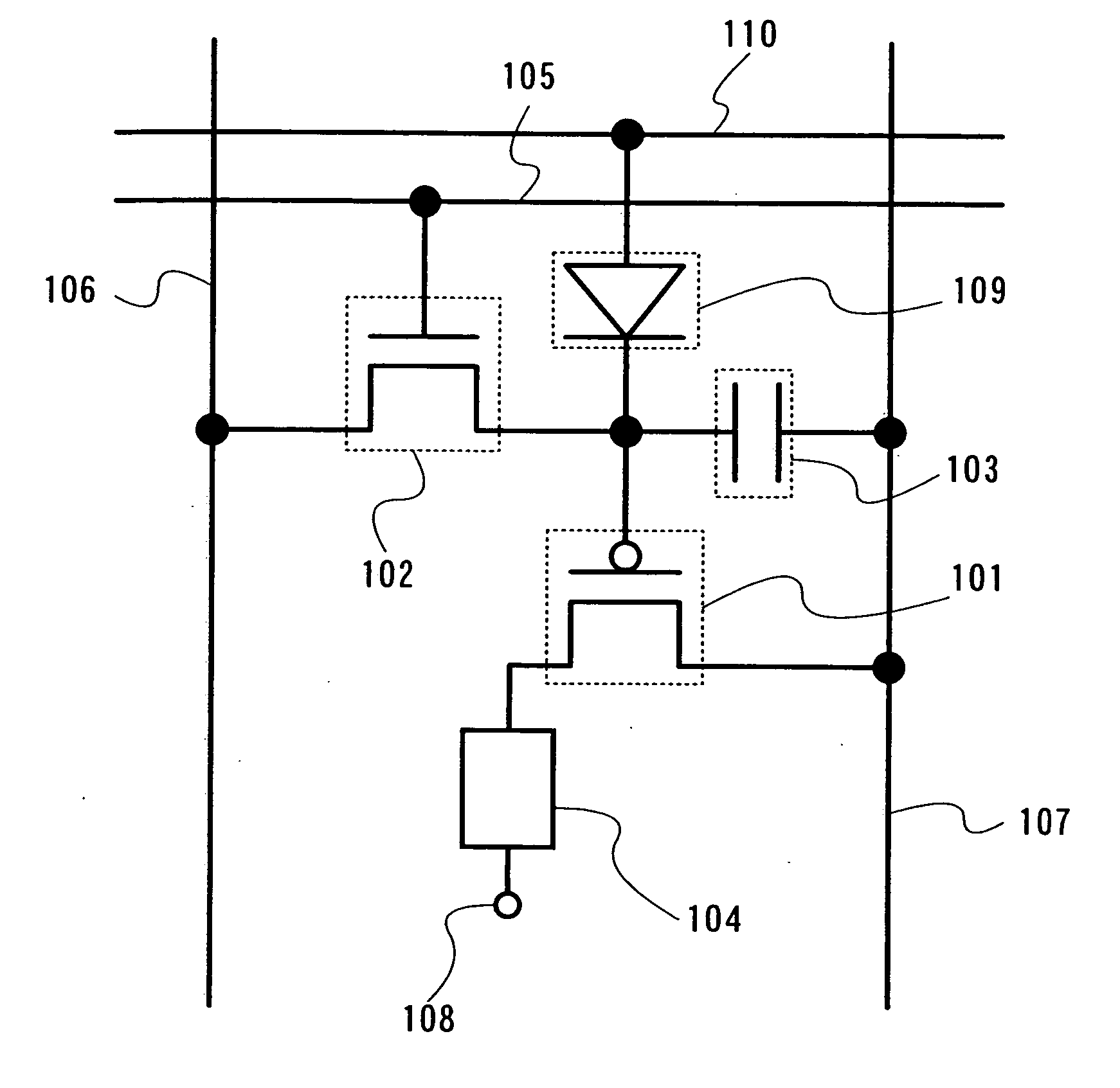

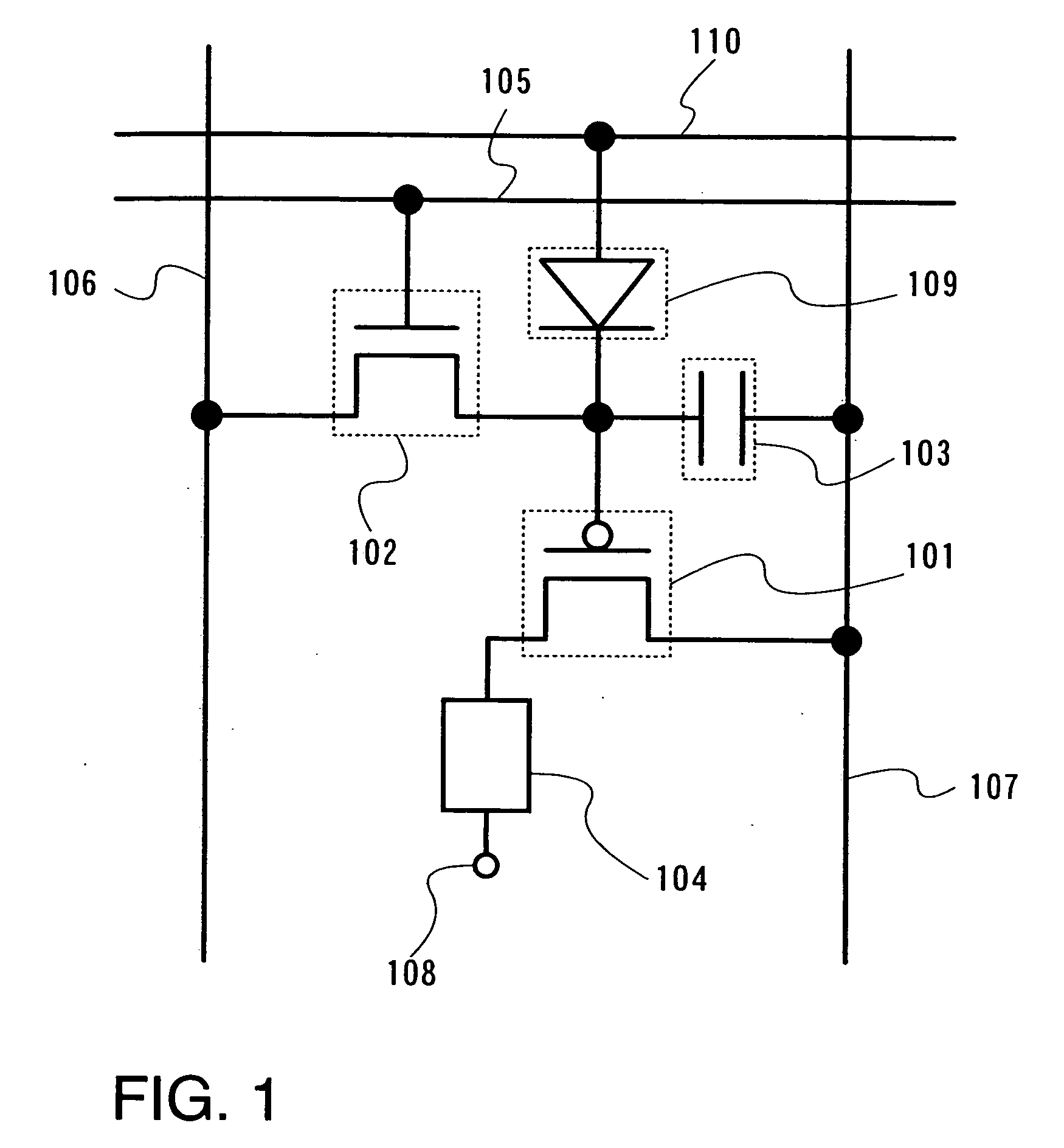

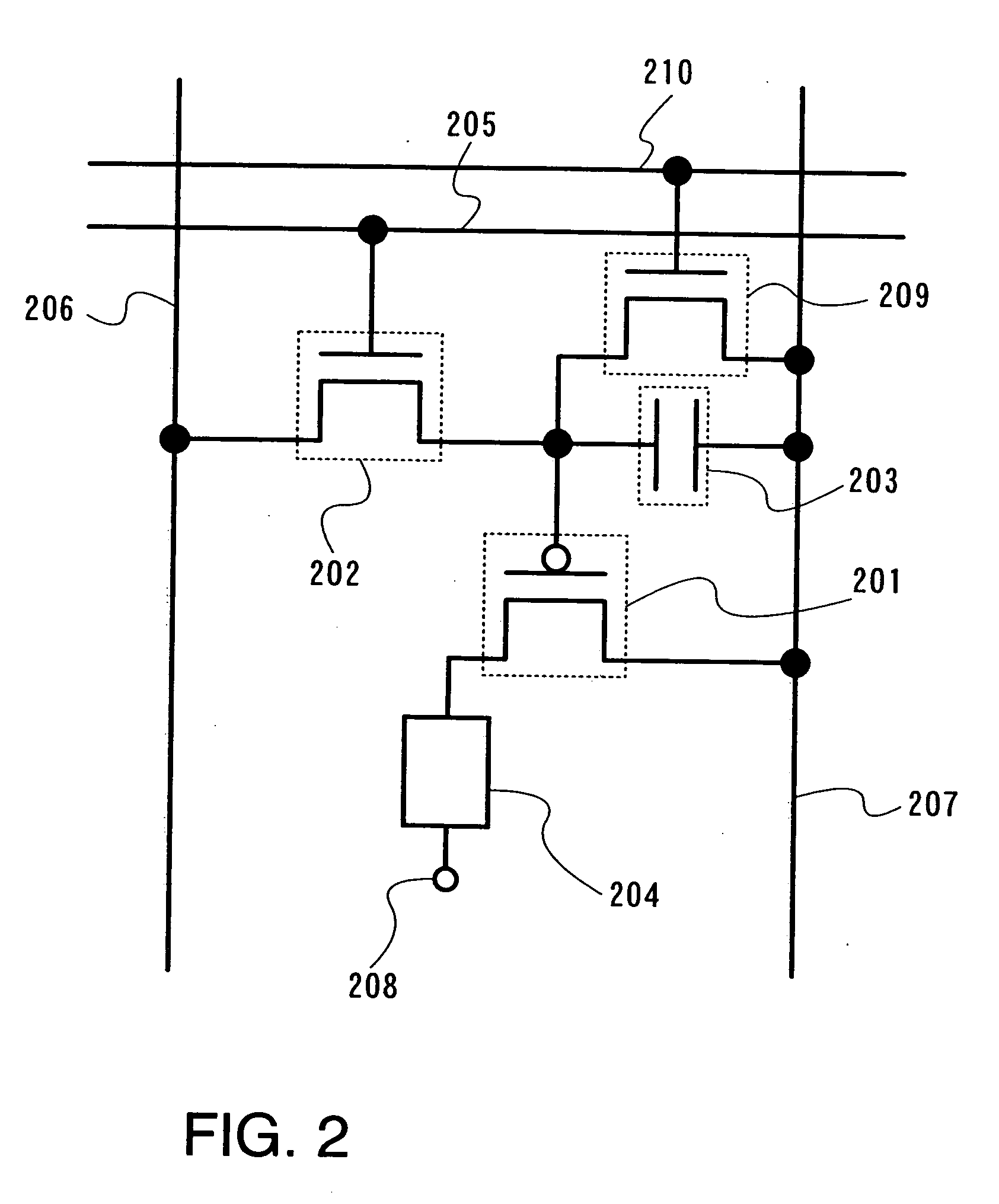

InactiveUS20060238135A1Total current dropReduce trafficElectrical apparatusElectroluminescent light sourcesDevice materialScan line

When a signal inputted to a pixel is erased by setting potentials of a gate terminal and a source terminal of a driving transistor to be equal, a current slightly flows through the driving transistor in some cases, which leads to occur a display defect. The invention provides a display device which improves the yield while suppressing the increase in manufacturing cost. When a potential of a scan line for erasure is raised, a potential of the gate terminal of the driving transistor is raised accordingly. For example, the scan line and the gate terminal of the driving transistor are connected through a rectifying element.

Owner:SEMICON ENERGY LAB CO LTD

Process for producing oriented inorganic crystalline film, and semiconductor device using the oriented inorganic crystalline film

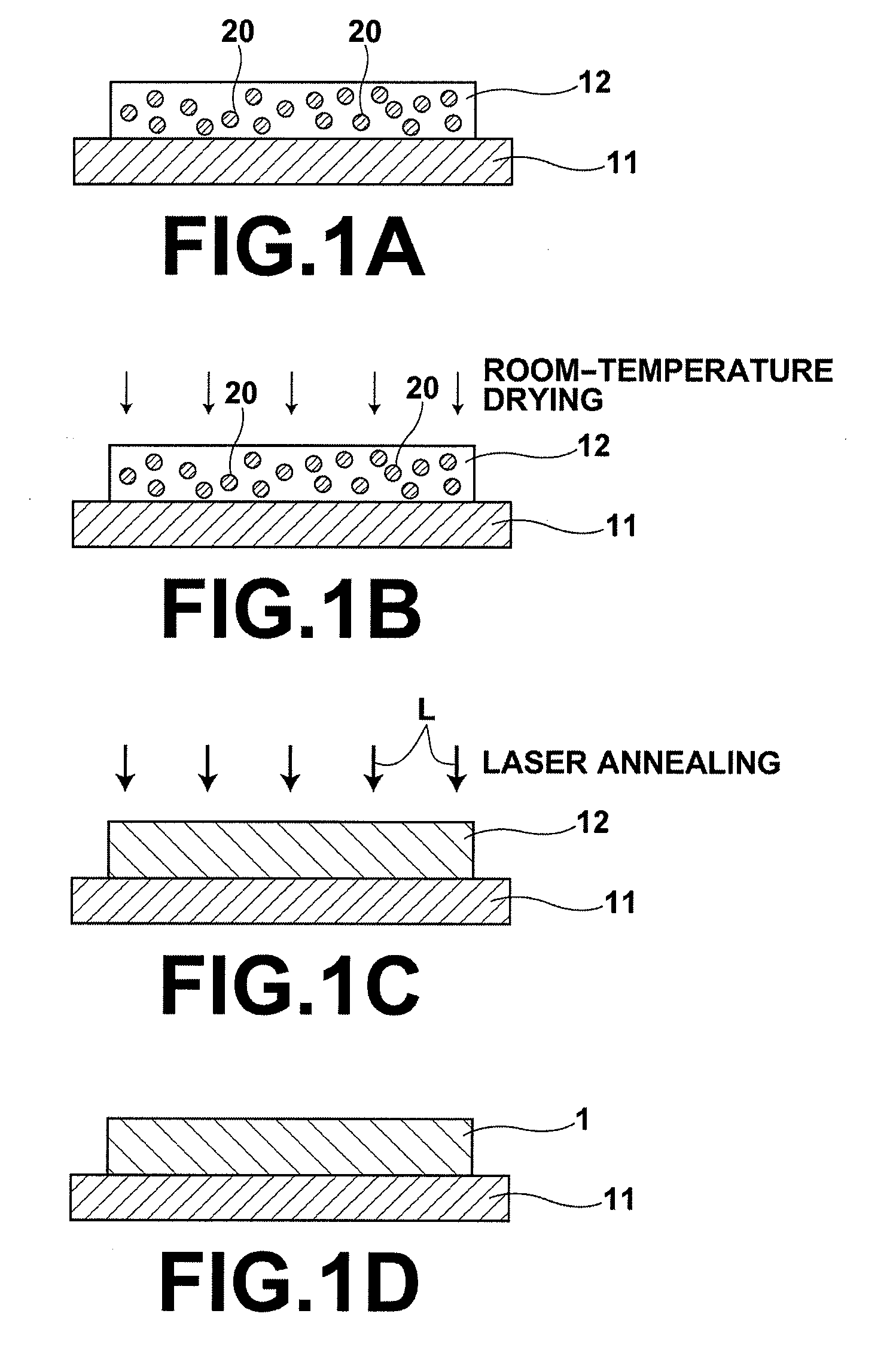

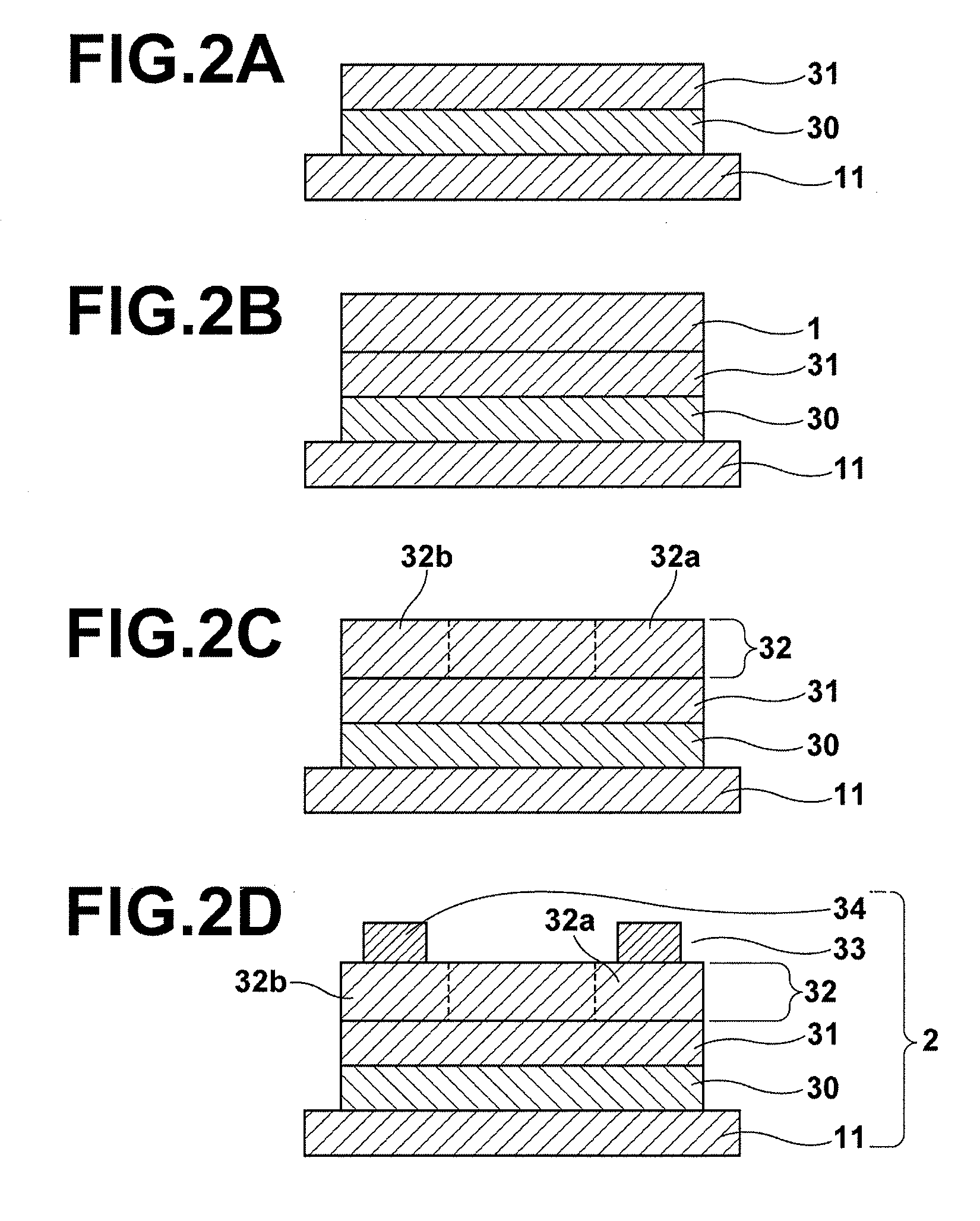

ActiveUS20090152506A1Orientation can be controlledLow costFrom gel stateFrom solid stateOrganic solventDevice material

In a process for producing an oriented inorganic crystalline film, a non-monocrystalline film containing inorganic crystalline particles is formed on a substrate by a liquid phase technique using a raw-material solution which contains a raw material and an organic solvent, where the inorganic crystalline particles have a layered crystal structure and are contained in the raw material. Then, the non-monocrystalline film is crystallized by heating the non-monocrystalline film to a temperature equal to or higher than the crystallization temperature of the non-monocrystalline film so that part of the inorganic crystalline particles act as crystal nuclei.

Owner:FUJIFILM CORP

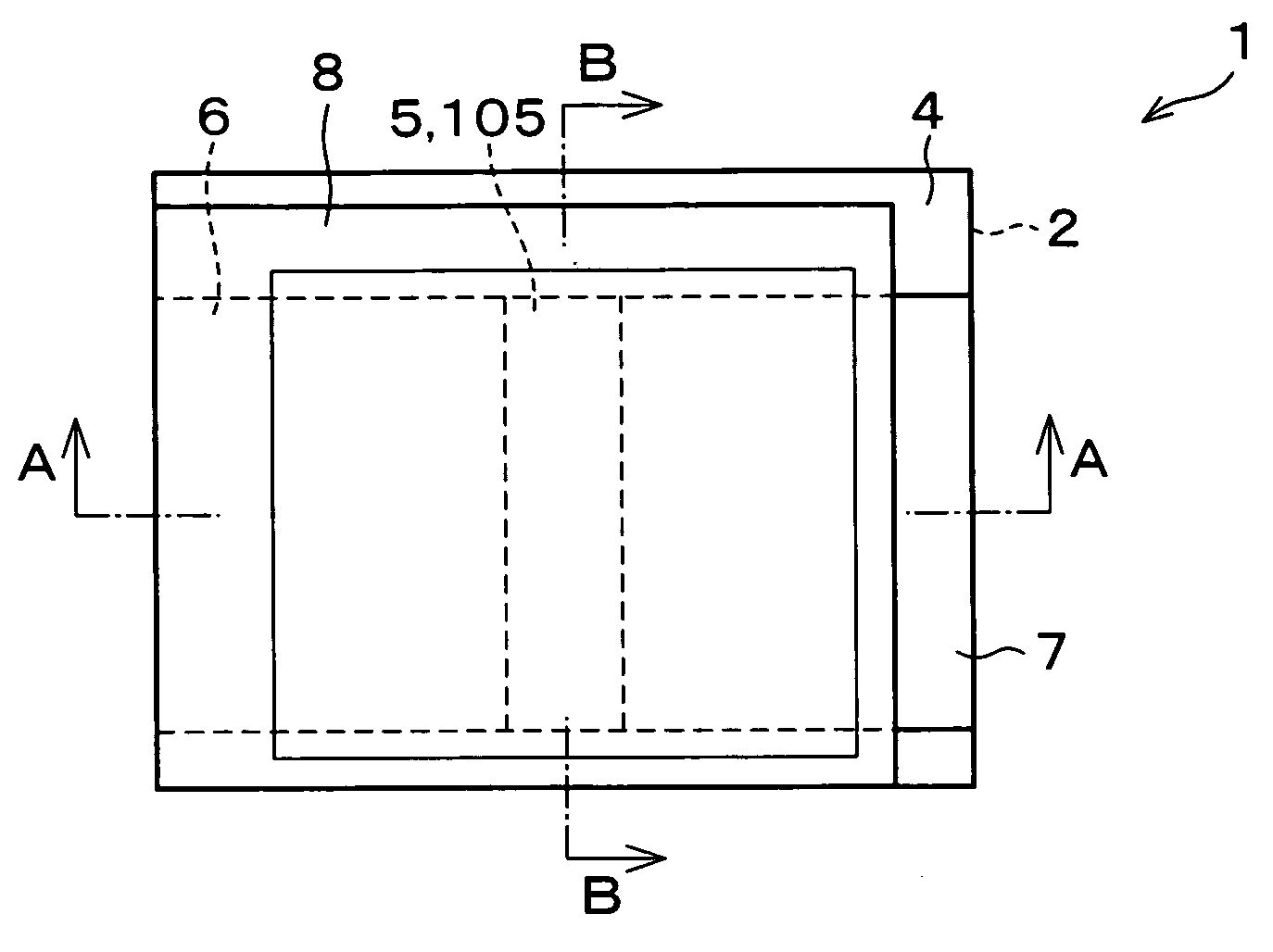

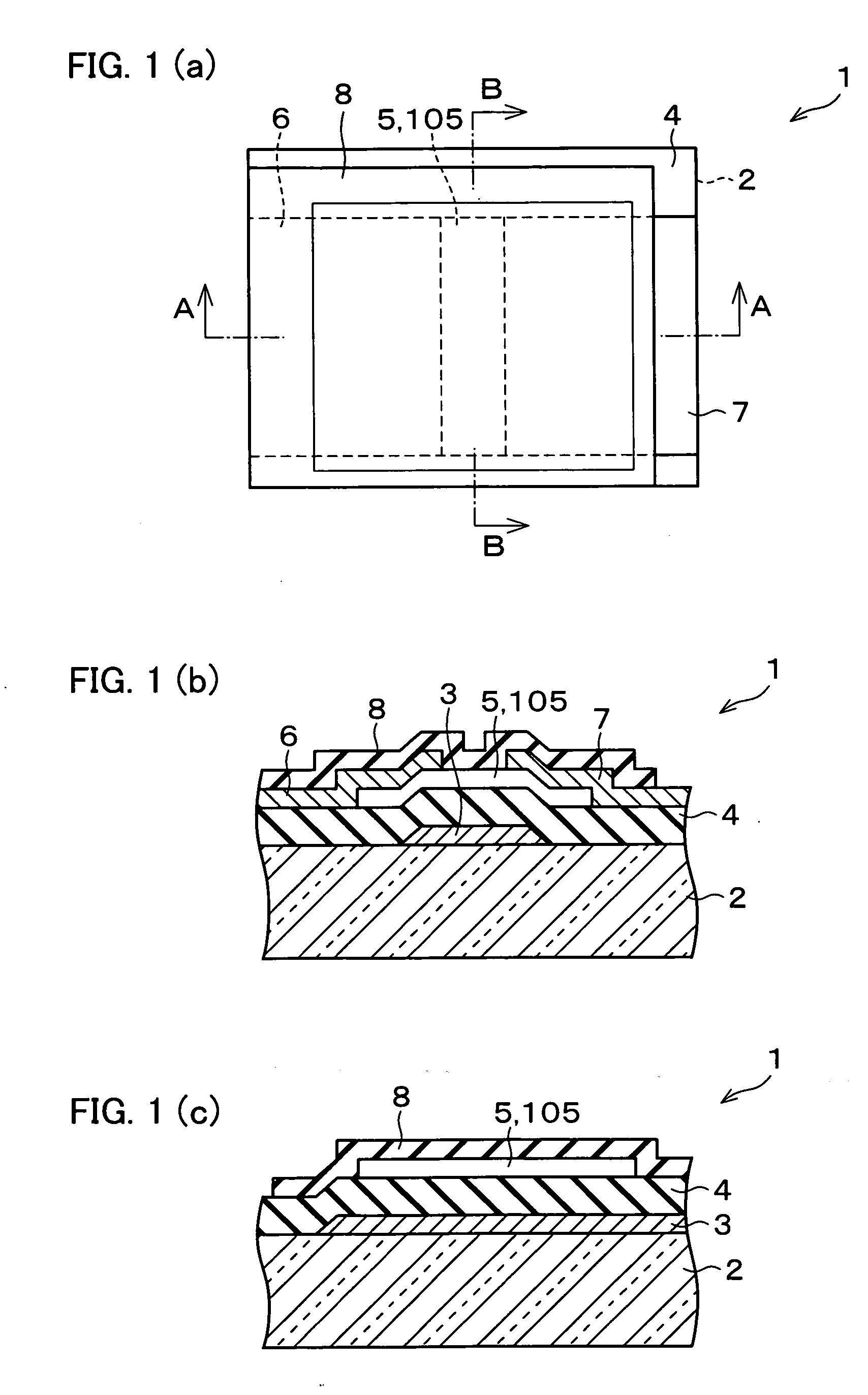

Semiconductor device

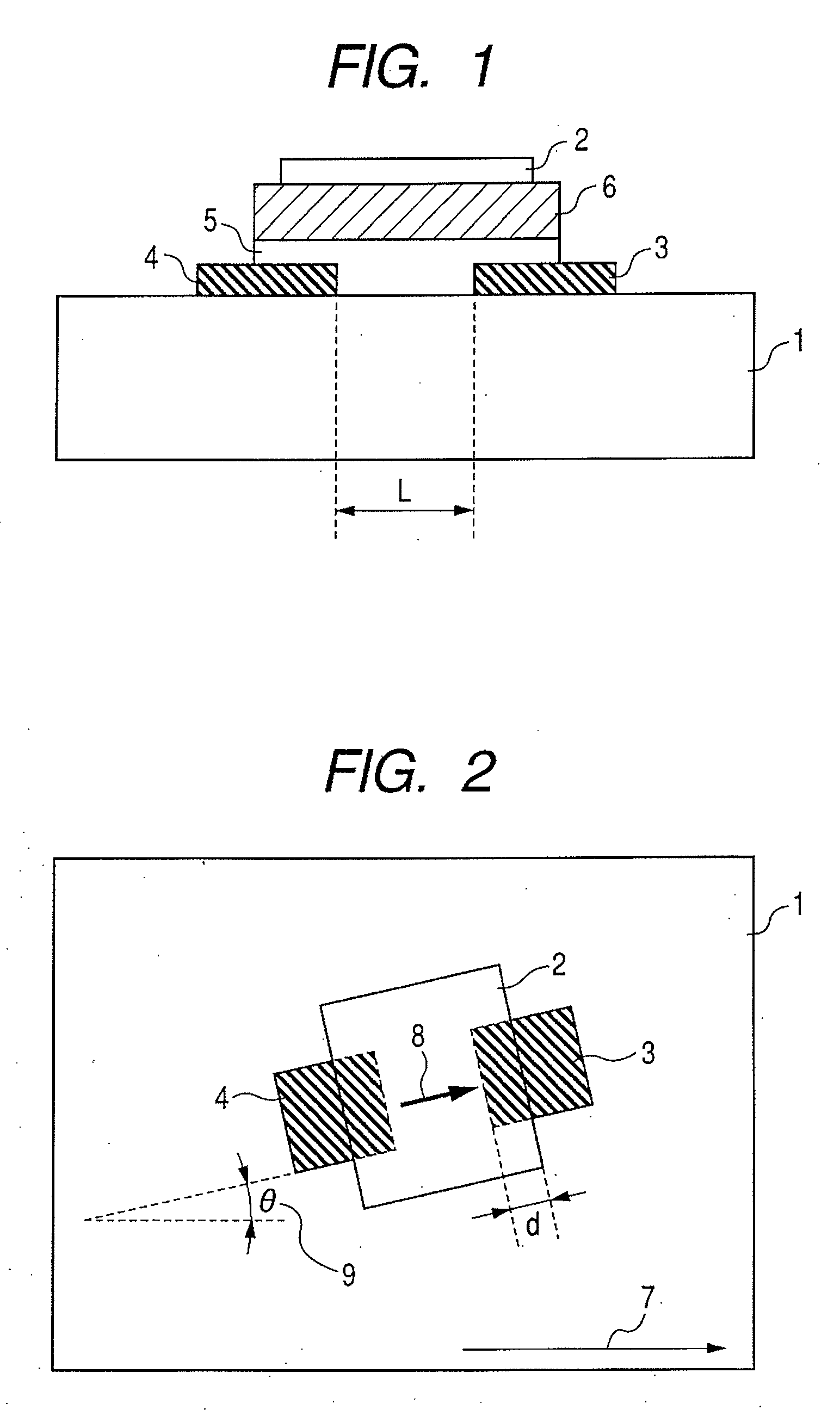

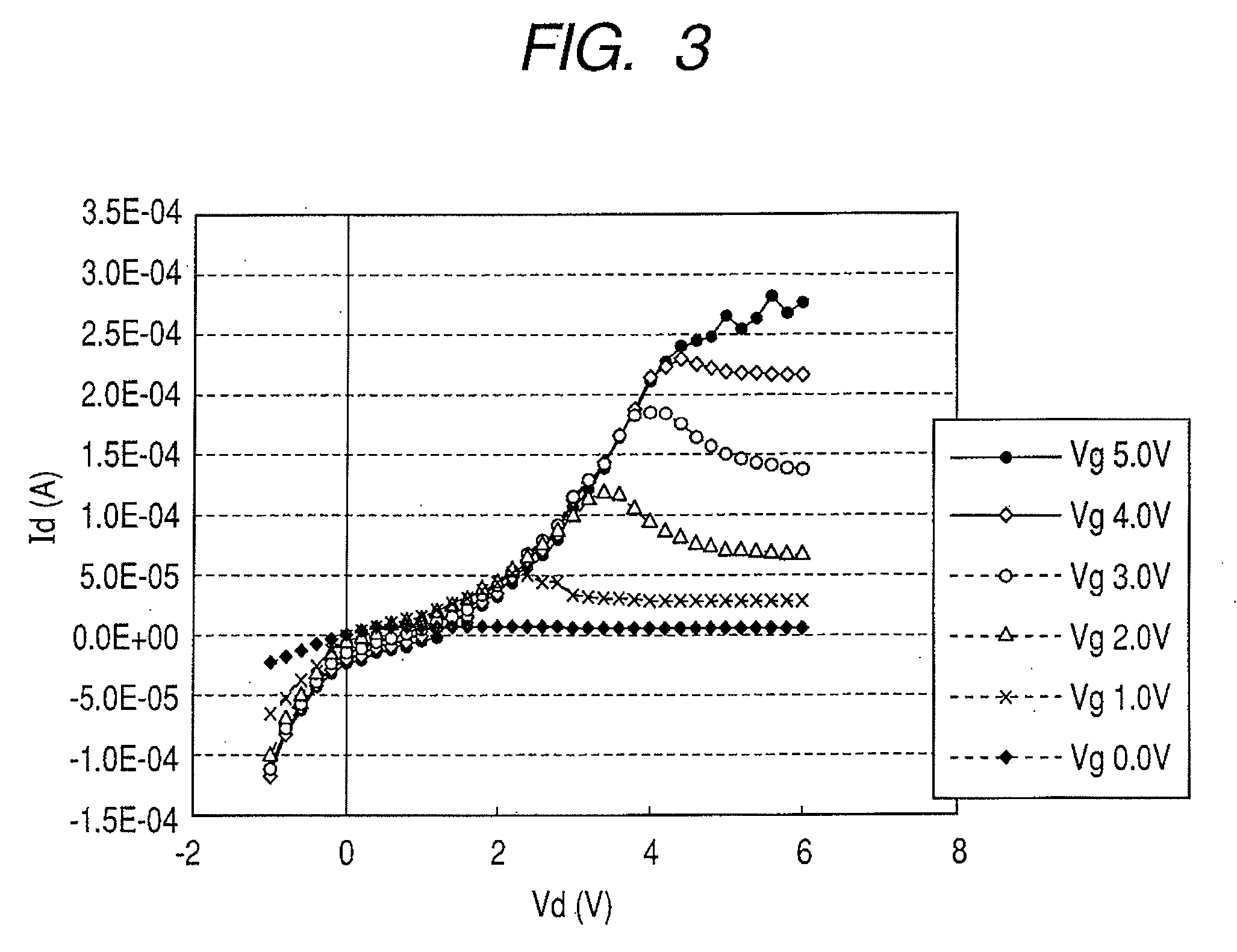

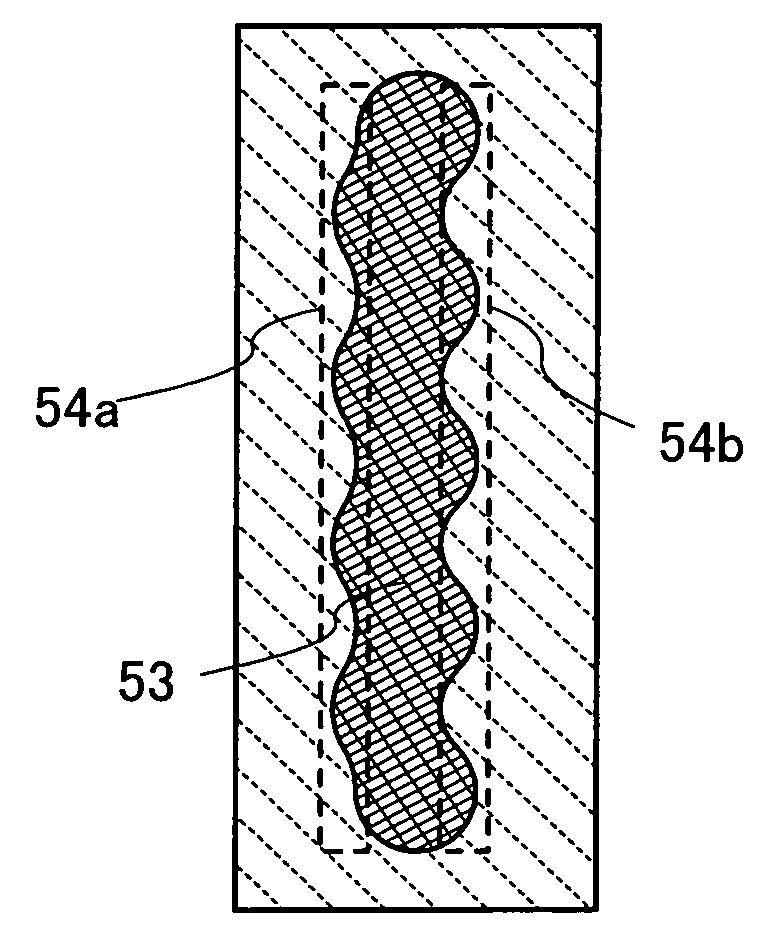

InactiveUS20090114910A1Uniform and high stabilityIncrease productionTransistorSolid-state devicesIn planeDevice material

In the present invention, a thin film transistor is formed on a plastic film substrate (1) having anisotropy of thermal shrinkage rate or coefficient of thermal expansion in in-plane directions of the substrate. A channel is formed such thatthe direction (7) in which the thermal shrinkage rate or the coefficient of thermal expansion of the substrate is largest is nonparallel tothe direction (8) of a current flowing through the channel of the thin film transistor. Then, a thin film transistor having stable and uniform electrical characteristics, which is formed on the plastic film substrate, is provided.

Owner:CANON KK

Semiconductor device, electronic device, and method of manufacturing semiconductor device

InactiveUS20060169973A1Stable formationImprove performanceSolid-state devicesSemiconductor/solid-state device manufacturingDevice materialDisplay device

To provide a semiconductor device and a display device which can be manufactured through a simplified process and the manufacturing technique. Another object is to provide a technique by which a pattern of wirings or the like which is partially constitutes a semiconductor device or a display device can be formed with a desired shape with controllability.

Owner:SEMICON ENERGY LAB CO LTD

Method of fabricating oxide semiconductor device

InactiveUS20070054507A1Efficient solutionReduce conductivitySemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductorMaterials science

A method for fabricating a device using an oxide semiconductor, including a process of forming the oxide semiconductor on a substrate and a process of changing the conductivity of the oxide semiconductor by irradiating a predetermined region thereof with an energy ray.

Owner:CANON KK

Substrate for growing wurtzite type crystal and method for manufacturing the same and semiconductor device

ActiveUS20100092800A1Low costHigh crystallinityPolycrystalline material growthVacuum evaporation coatingNitrideSemiconductor

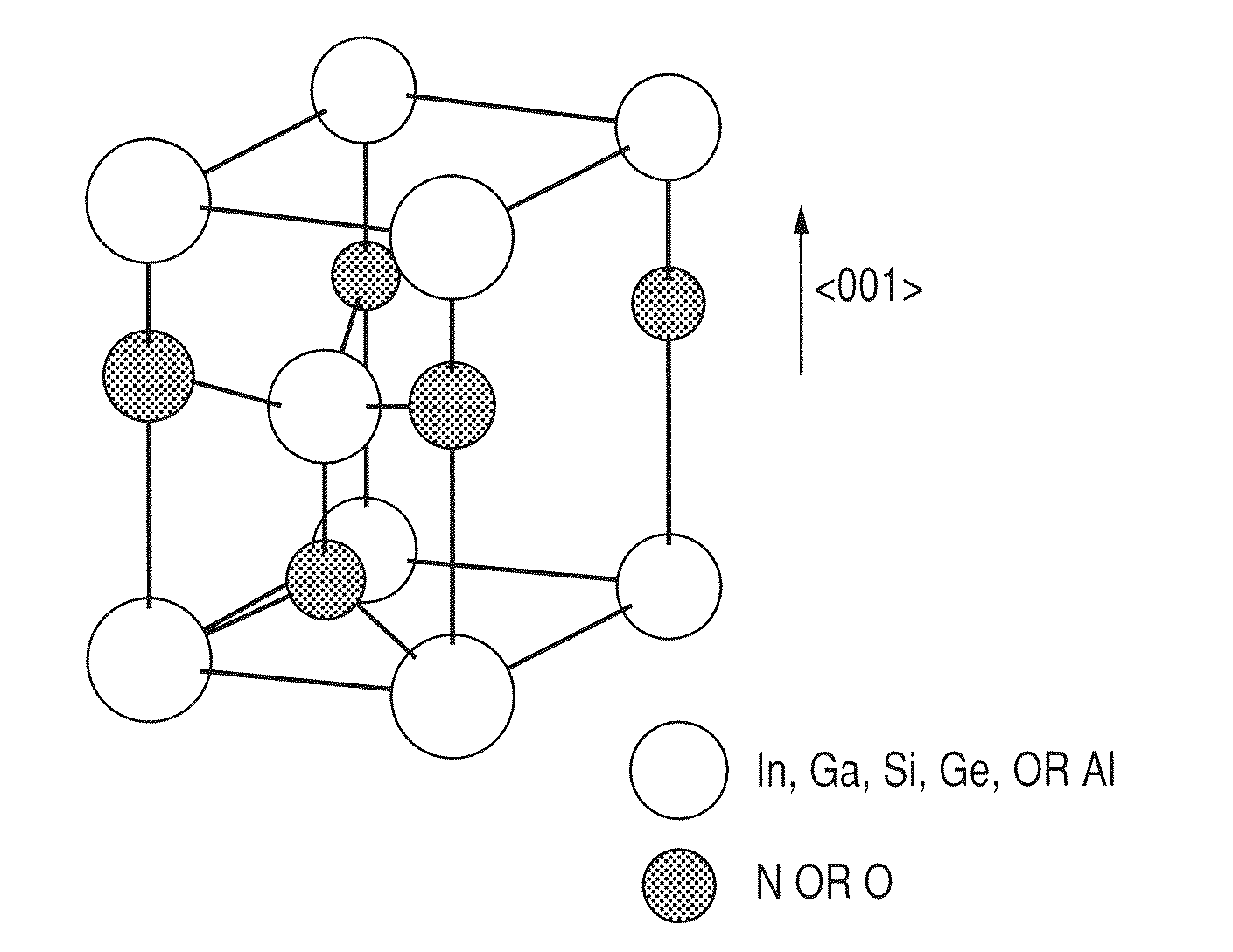

A laminated structure comprises a first layer comprising a crystal with six-fold symmetry, and a second layer comprising a metal oxynitride crystal formed on the first layer, wherein the second layer comprises at least one element selected from the group consisting of In, Ga, Si, Ge and Al, N, O and Zn, as main elements, and wherein the second layer has in-plane orientation.

Owner:CANON KK

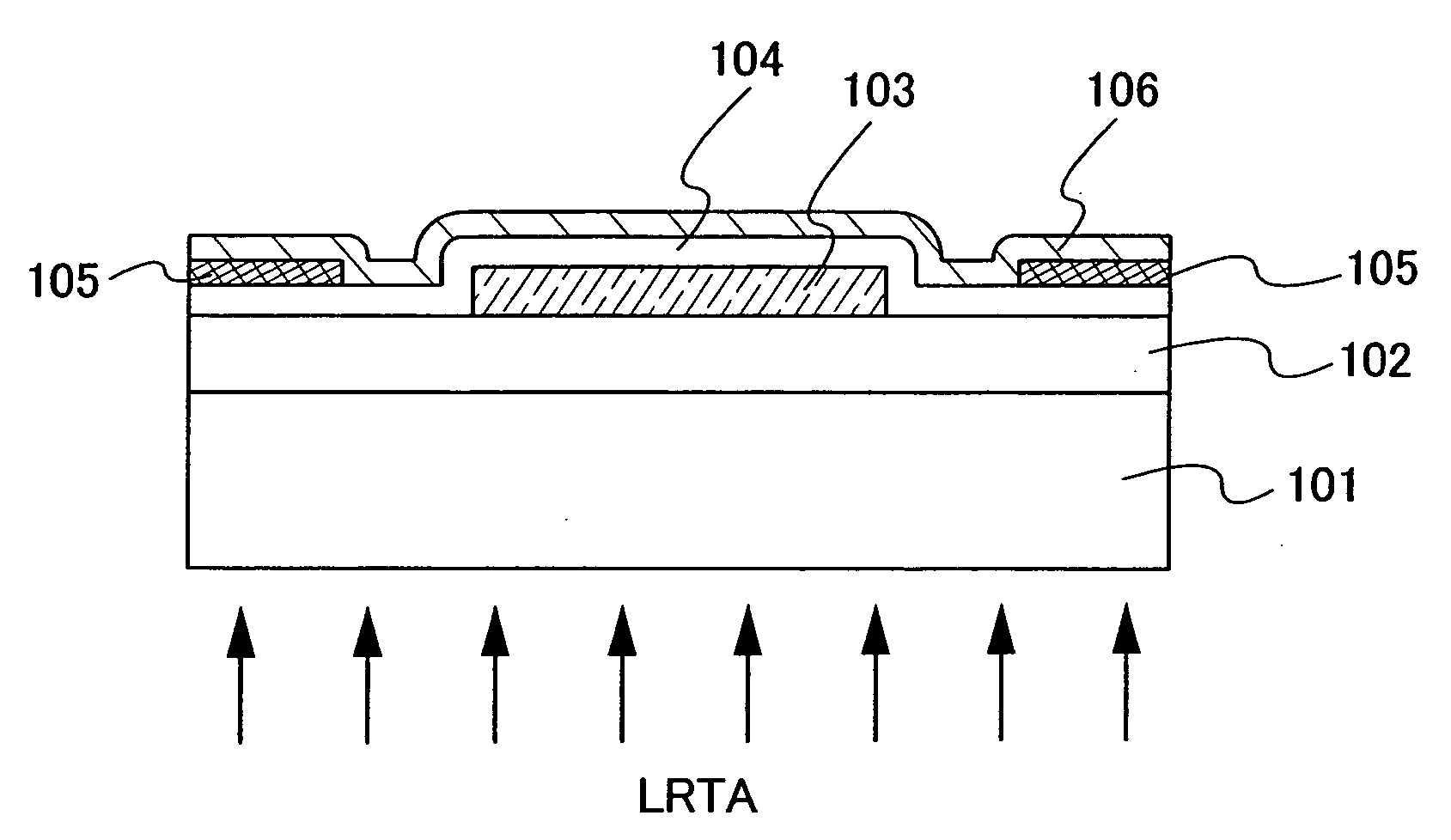

Semiconductor device and manufacturing method thereof

An object is to provide a semiconductor device of which a manufacturing process is not complicated and by which cost can be suppressed, by forming a thin film transistor using an oxide semiconductor film typified by zinc oxide, and a manufacturing method thereof. For the semiconductor device, a gate electrode is formed over a substrate; a gate insulating film is formed covering the gate electrode; an oxide semiconductor film is formed over the gate insulating film; and a first conductive film and a second conductive film are formed over the oxide semiconductor film. The oxide semiconductor film has at least a crystallized region in a channel region.

Owner:SEMICON ENERGY LAB CO LTD

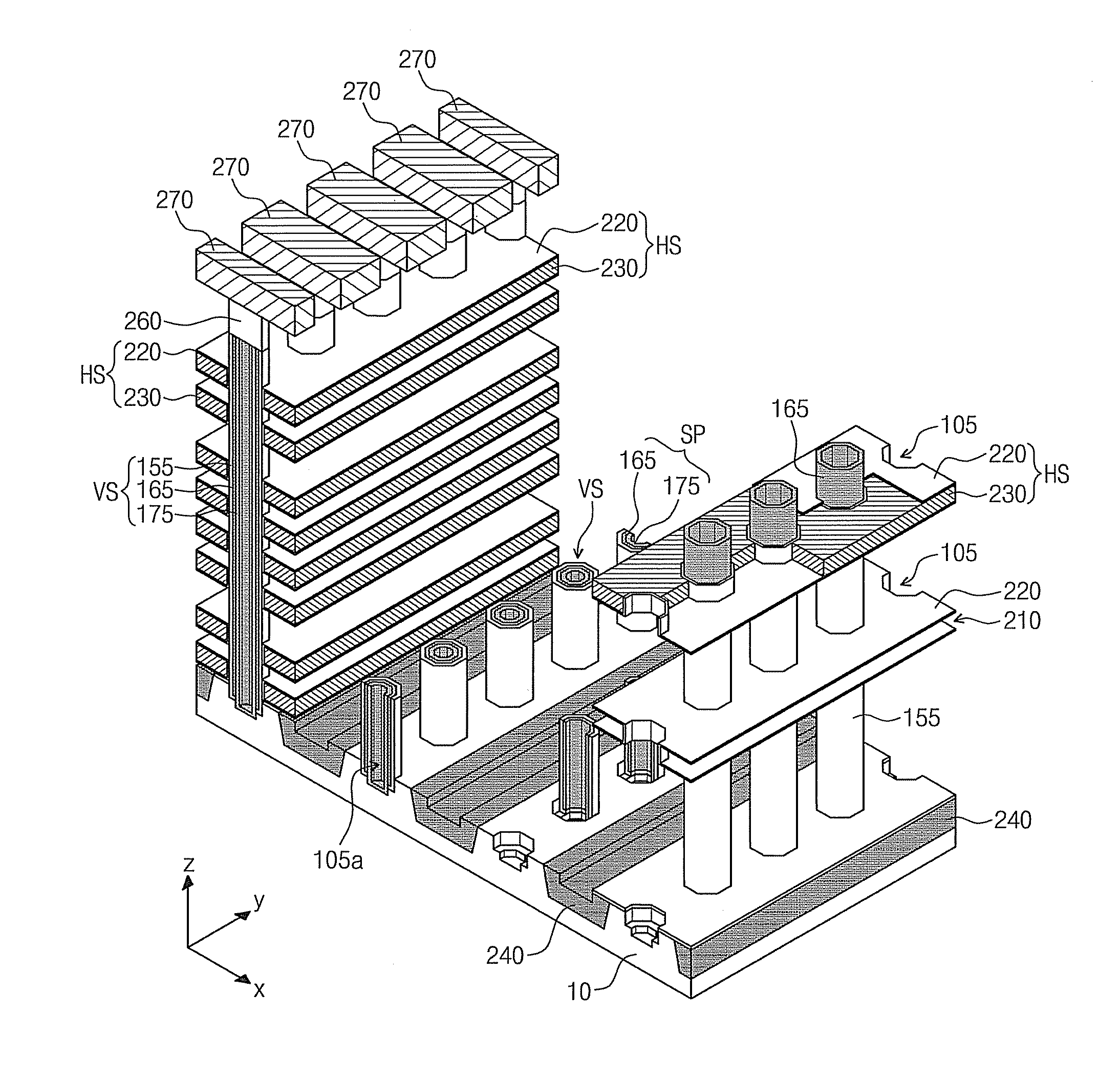

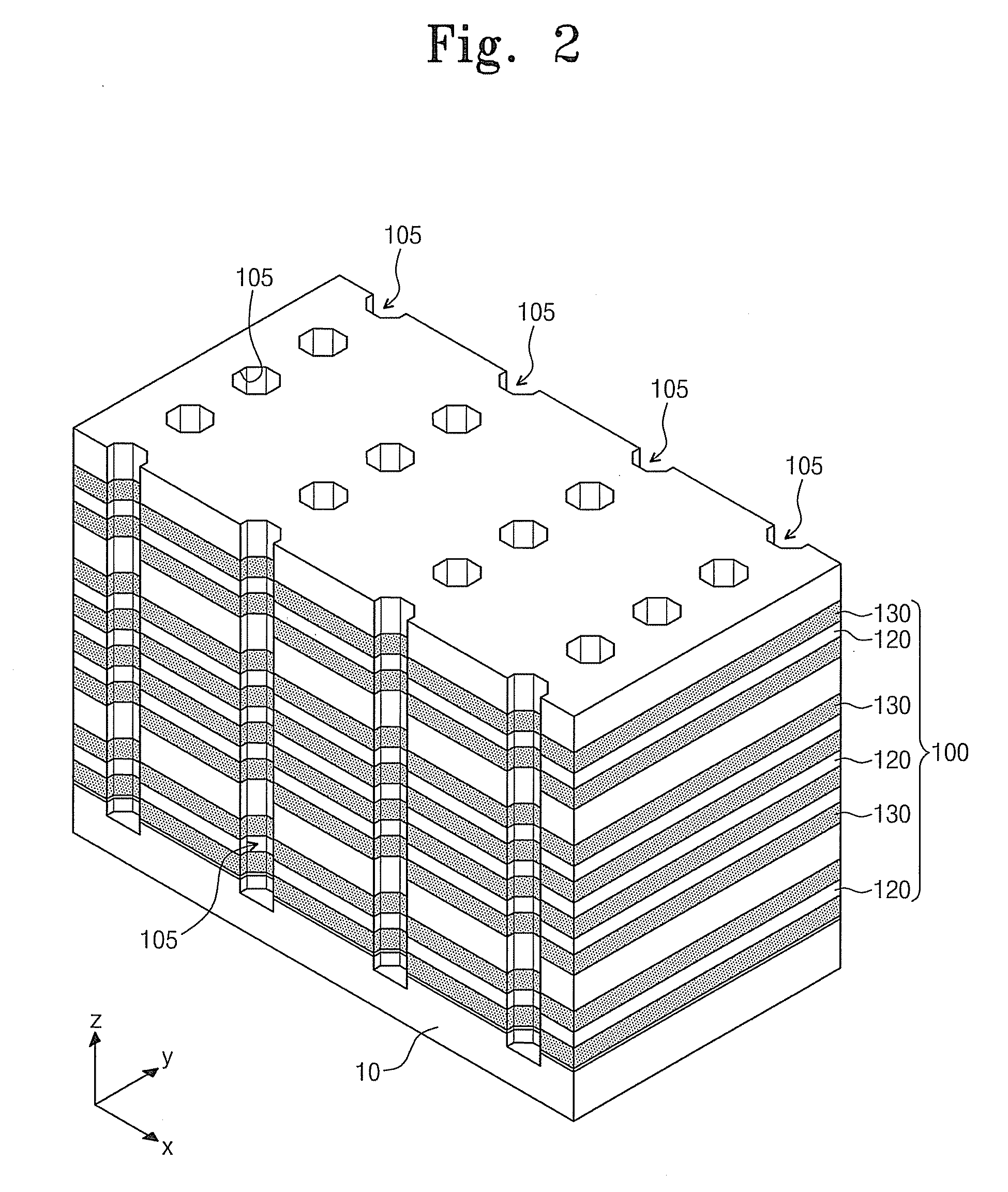

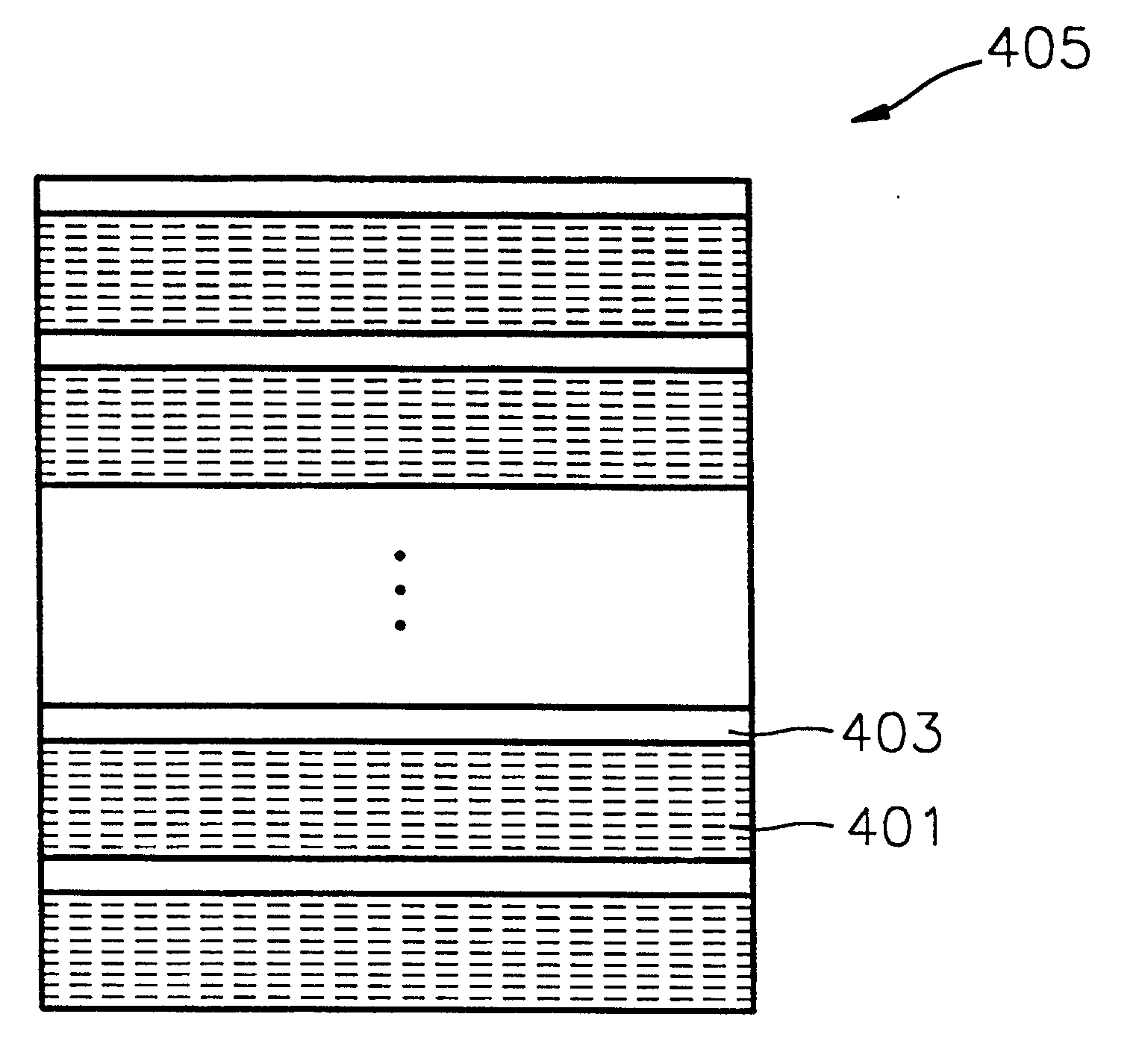

Three-Dimensional Semiconductor Memory Devices And Methods Of Fabricating The Same

ActiveUS20110233648A1Increasing the thicknessReduce resistanceSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringSemiconductor

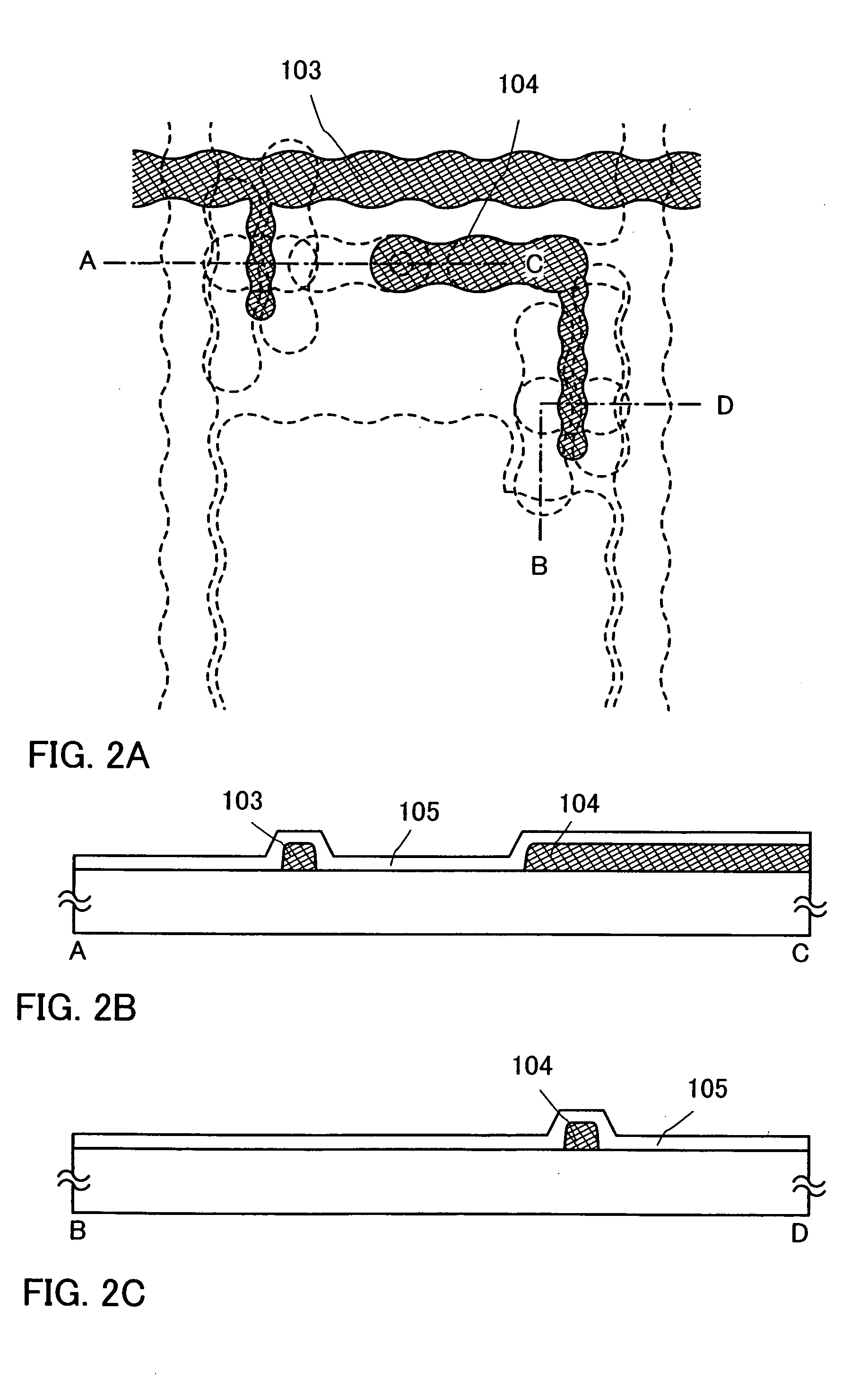

Three-dimensional semiconductor memory devices and methods of fabricating the same. The three-dimensional semiconductor devices include an electrode structure with sequentially-stacked electrodes disposed on a substrate, semiconductor patterns penetrating the electrode structure, and memory elements including a first pattern and a second pattern interposed between the semiconductor patterns and the electrode structure, the first pattern vertically extending to cross the electrodes and the second pattern horizontally extending to cross the semiconductor patterns.

Owner:SAMSUNG ELECTRONICS CO LTD

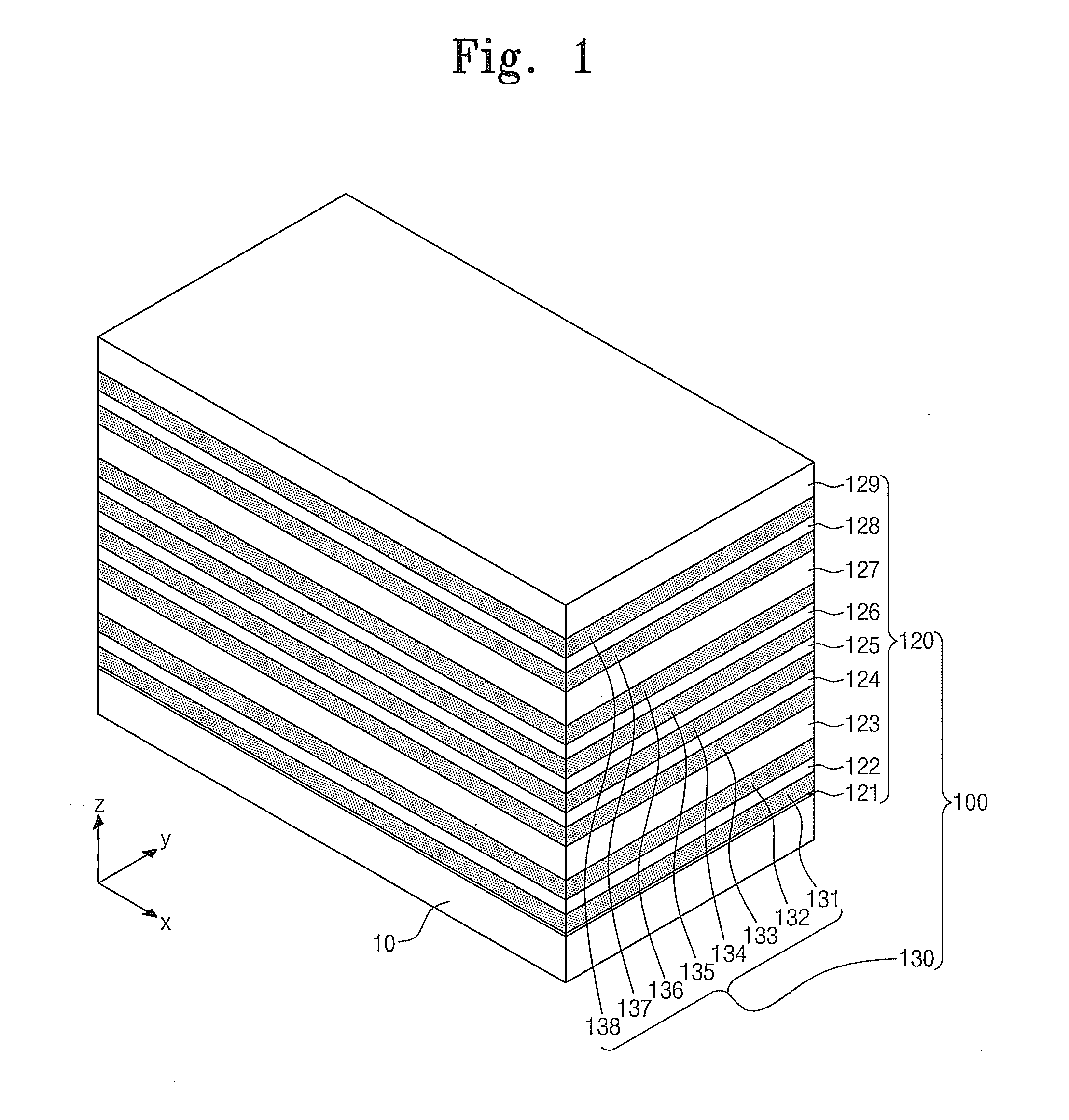

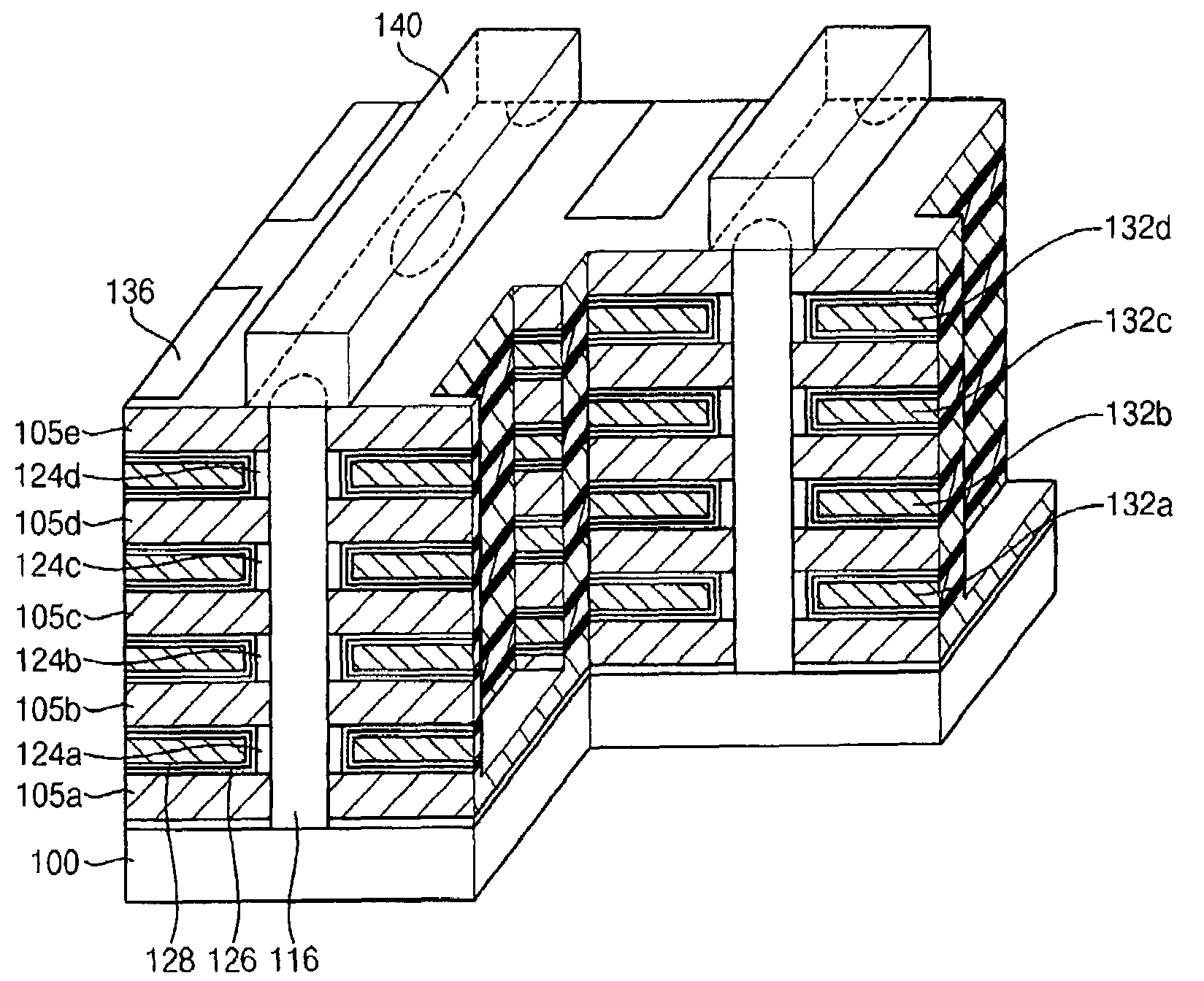

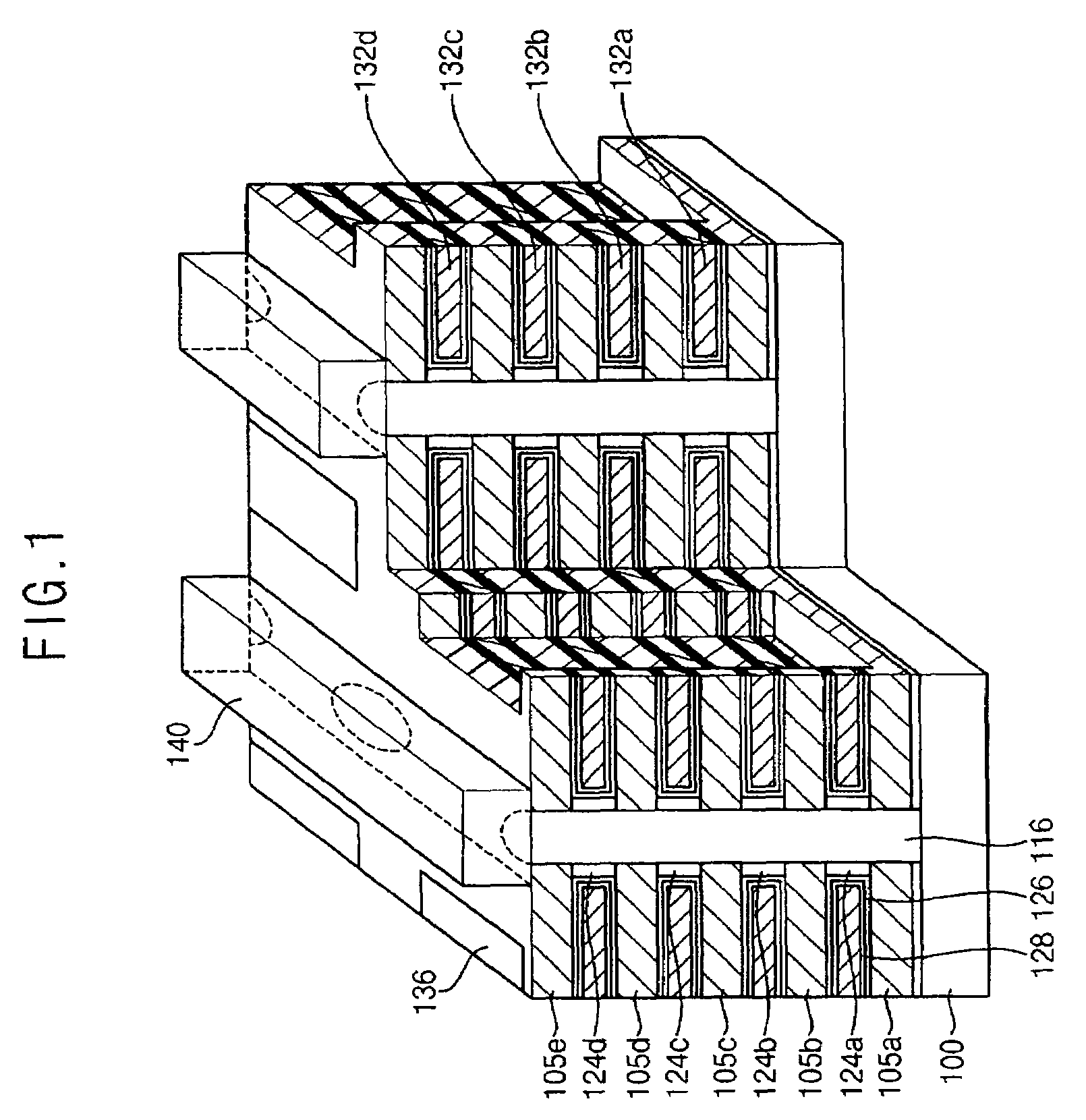

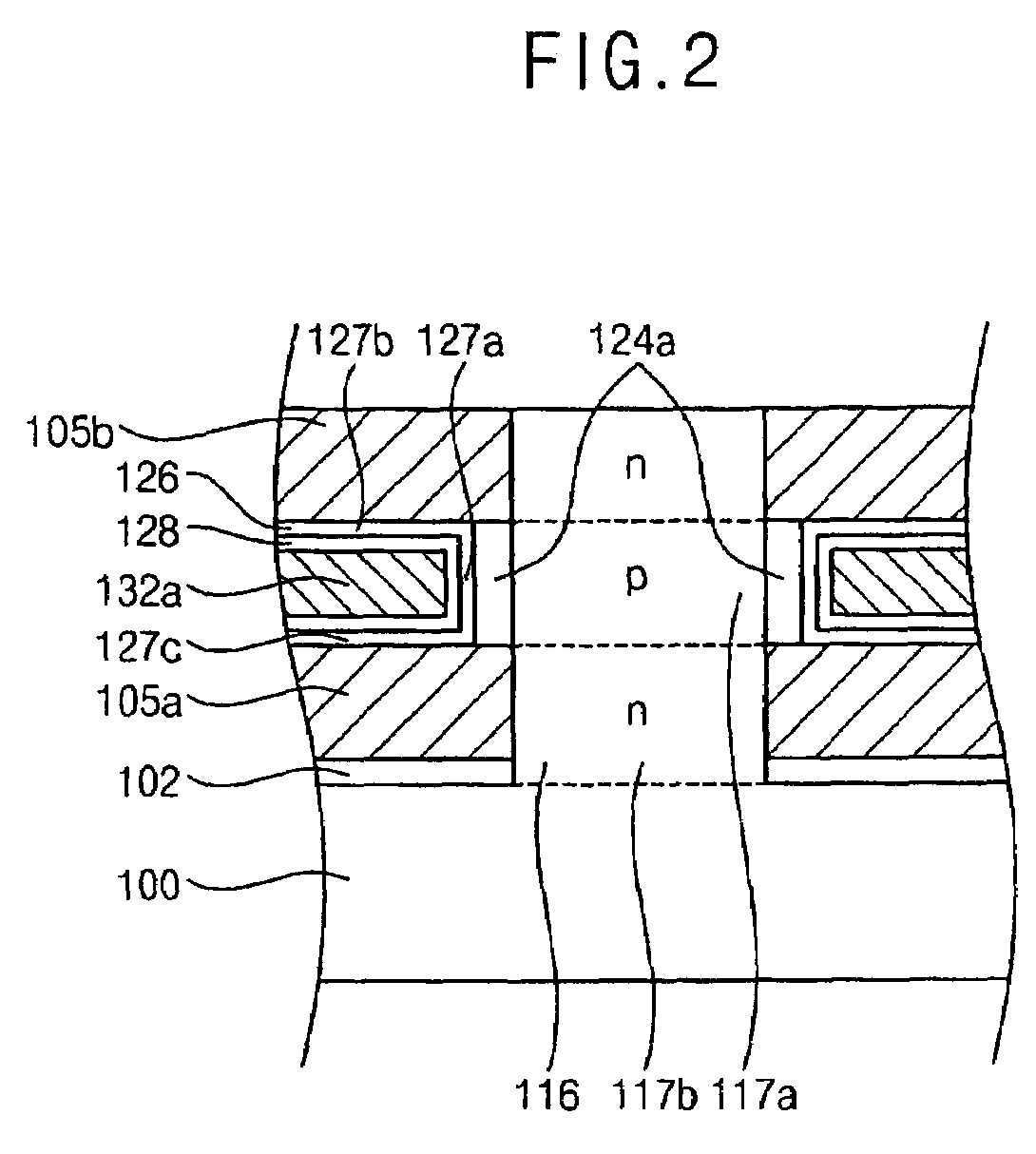

Vertical-type non-volatile memory devices

ActiveUS7679133B2Reduce the possibilityReduce in quantityTransistorSolid-state devicesSemiconductor materialsDevice material

In a semiconductor device, and a method of manufacturing thereof, the device includes a substrate of single-crystal semiconductor material extending in a horizontal direction and a plurality of interlayer dielectric layers on the substrate. A plurality of gate patterns are provided, each gate pattern being between a neighboring lower interlayer dielectric layer and a neighboring upper interlayer dielectric layer. A vertical channel of single-crystal semiconductor material extends in a vertical direction through the plurality of interlayer dielectric layers and the plurality of gate patterns, a gate insulating layer being between each gate pattern and the vertical channel that insulates the gate pattern from the vertical channel.

Owner:SAMSUNG ELECTRONICS CO LTD

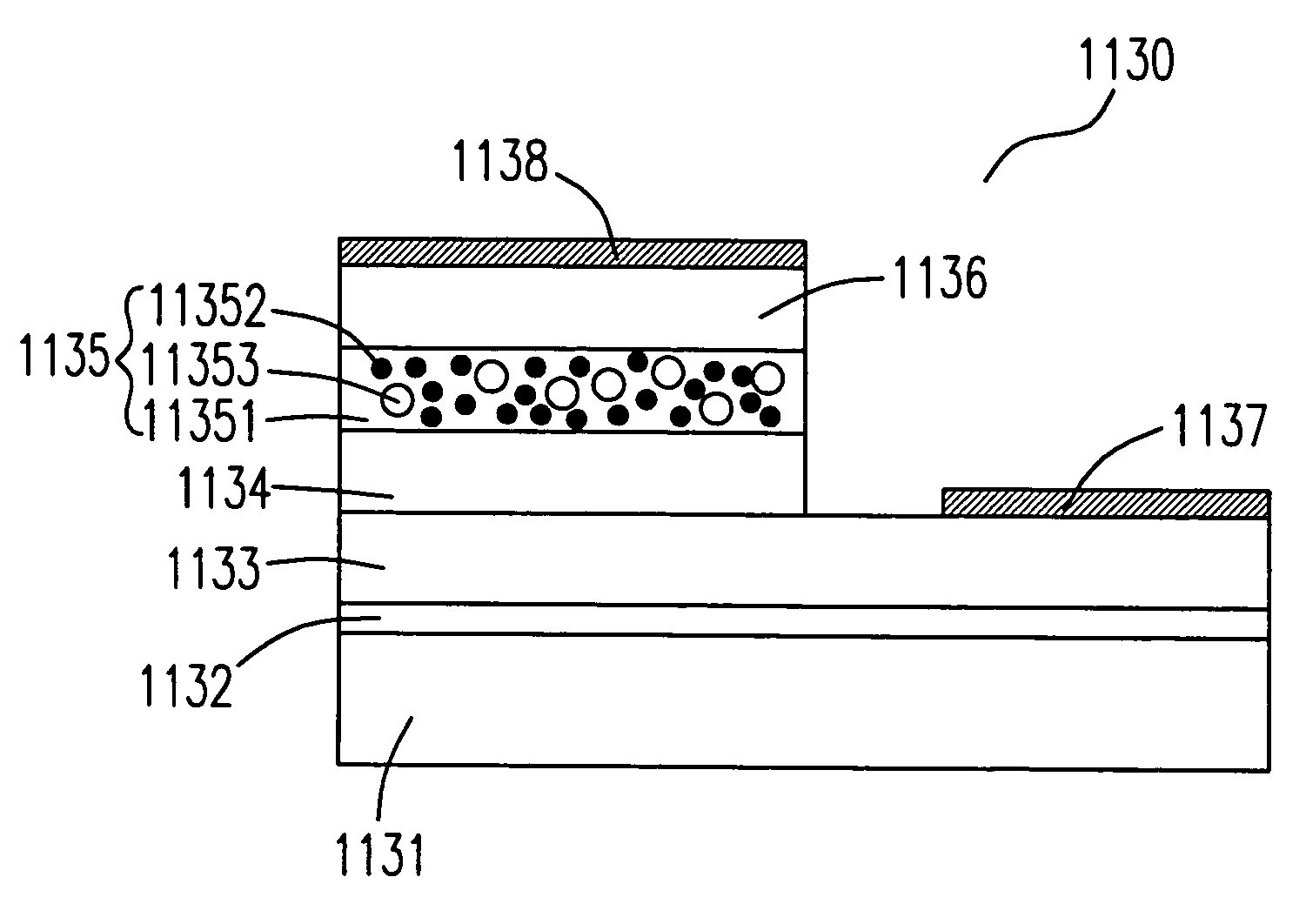

Light emitting semiconductor device

A novel NPBL and ANPL light emitting semiconductor device and a method for fabricating the same are provided. In the present invention, plural nano-particles are applied in the active layer of the light emitting semiconductor device, so that the leakage current thereof is reduced. In addition, the provided light emitting semiconductor device fabricated via a planar technology process is microscopically planar, but not planar at micro- and nano-scale. Hence the parasitic wave guiding effect, which suppresses the light extraction efficiency of the light emitting semiconductor device, is destroyed thereby.

Owner:ARIMA COMP

Semiconductor Device and Manufacturing Method Thereof

Owner:SEMICON ENERGY LAB CO LTD

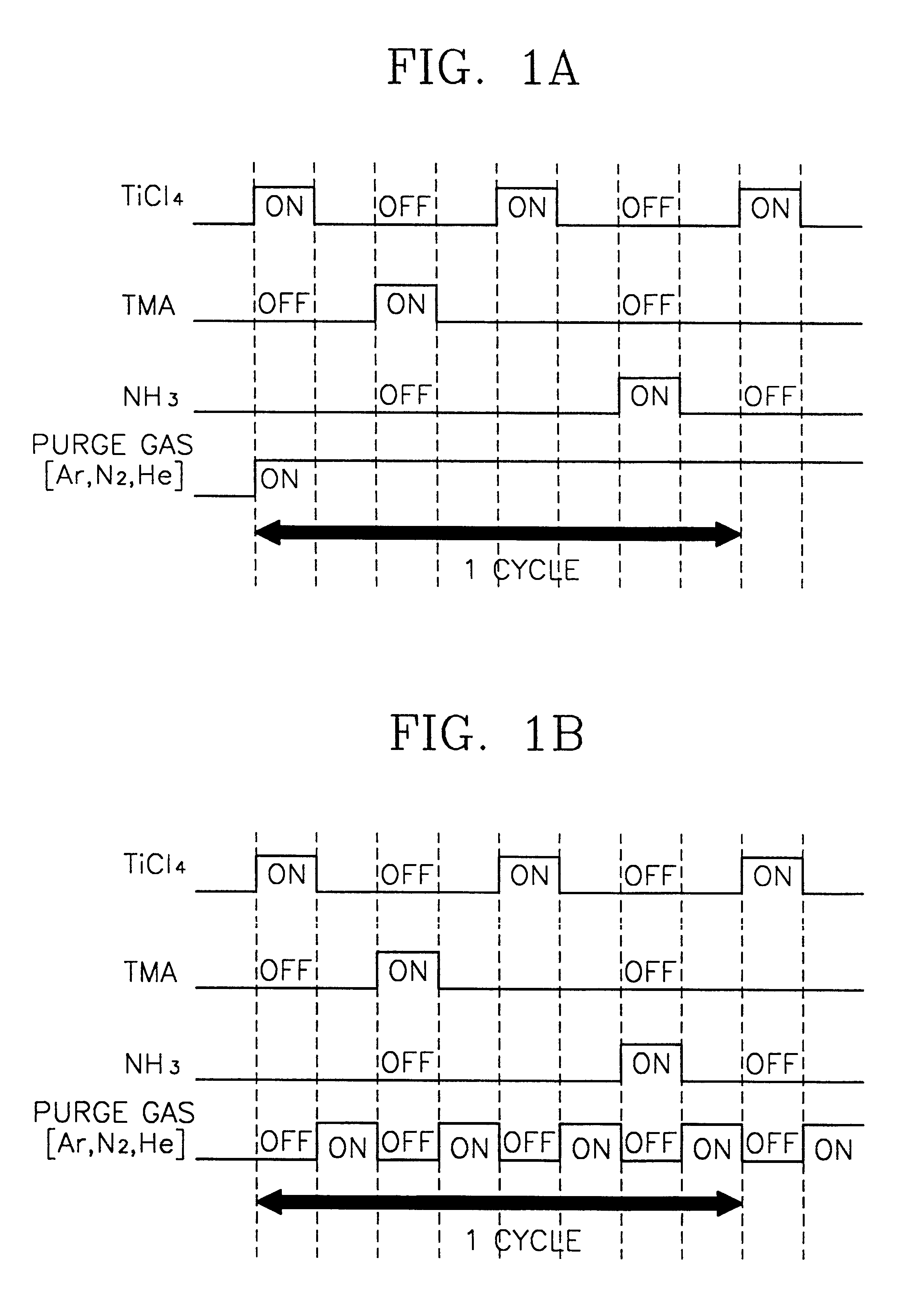

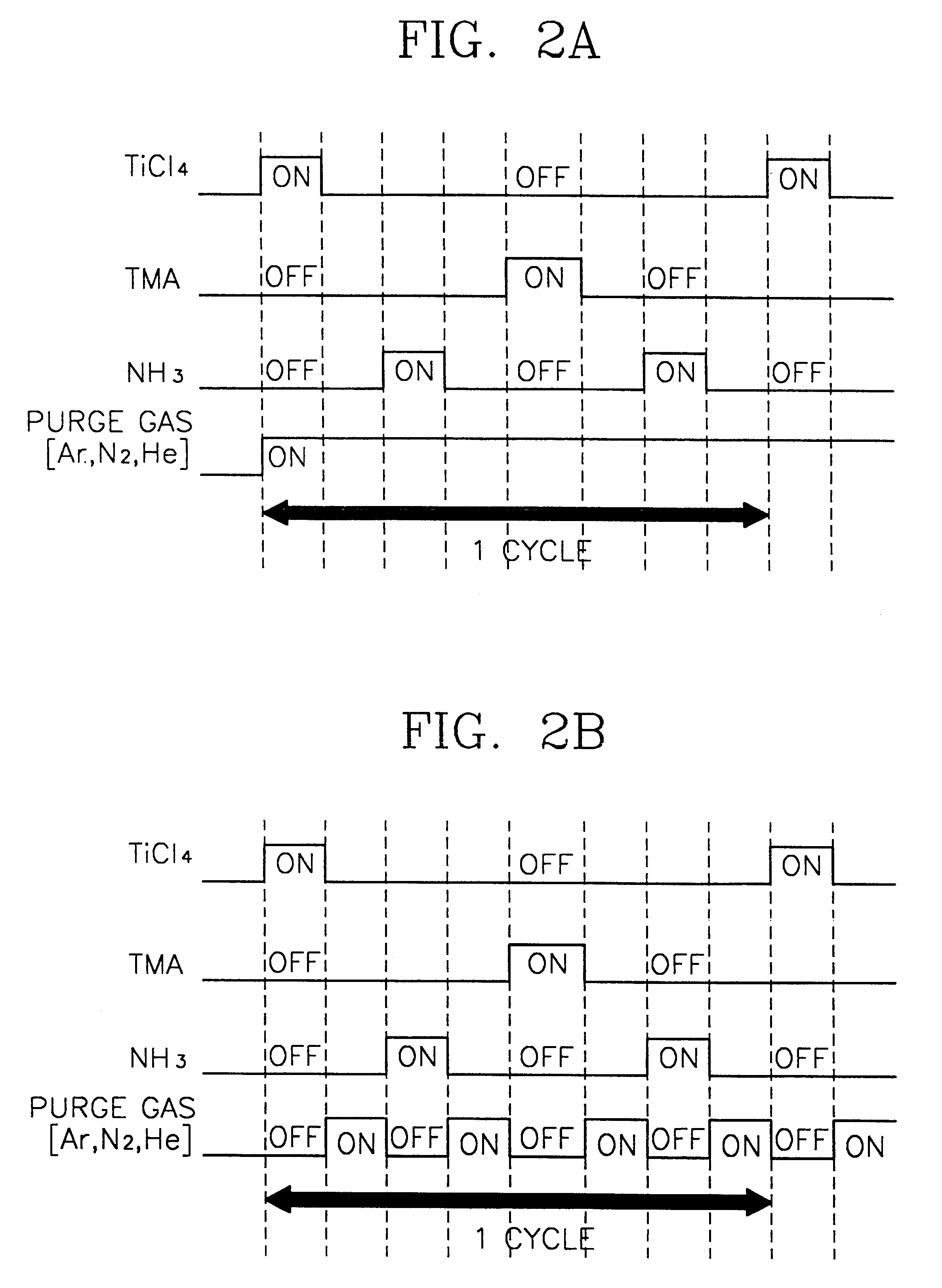

Method of forming metal layer using atomic layer deposition and semiconductor device having the metal layer as barrier metal layer or upper or lower electrode of capacitor

InactiveUS6287965B1High thermal resistantEasy to adjustSemiconductor/solid-state device manufacturingCapacitorsNiobiumDevice material

A method of forming a metal layer having excellent thermal and oxidation resistant characteristics using atomic layer deposition is provided. The metal layer includes a reactive metal (A), an element (B) for the amorphous combination between the reactive metal (A) and nitrogen (N), and nitrogen (N). The reactive metal (A) may be titanium (Ti), tantalum (Ta), tungsten (W), zirconium (Zr), hafnium (Hf), molybdenum (Mo) or niobium (Nb). The amorphous combination element (B) may be aluminum (Al), silicon (Si) or boron (B). The metal layer is formed by alternately injecting pulsed source gases for the elements (A, B and N) into a chamber according to atomic layer deposition to thereby alternately stack atomic layers. Accordingly, the composition ratio of a nitrogen compound (A-B-N) of the metal layer can be desirably adjusted just by appropriately determining the number of injection pulses of each source gas. According to the composition ratio, a desirable electrical conductivity and resistance of the metal layer can be accurately obtained. The atomic layers are individually deposited, thereby realizing excellent step coverage even in a complex and compact region. A metal layer formed by atomic layer deposition can be employed as a barrier metal layer, a lower electrode or an upper electrode in a semiconductor device.

Owner:SAMSUNG ELECTRONICS CO LTD

Semiconductor Device and Manufacturing Method Thereof

An object is to provide a semiconductor device of which a manufacturing process is not complicated and by which cost can be suppressed, by forming a thin film transistor using an oxide semiconductor film typified by zinc oxide, and a manufacturing method thereof. For the semiconductor device, a gate electrode is formed over a substrate; a gate insulating film is formed covering the gate electrode; an oxide semiconductor film is formed over the gate insulating film; and a first conductive film and a second conductive film are formed over the oxide semiconductor film. The oxide semiconductor film has at least a crystallized region in a channel region.

Owner:SEMICON ENERGY LAB CO LTD

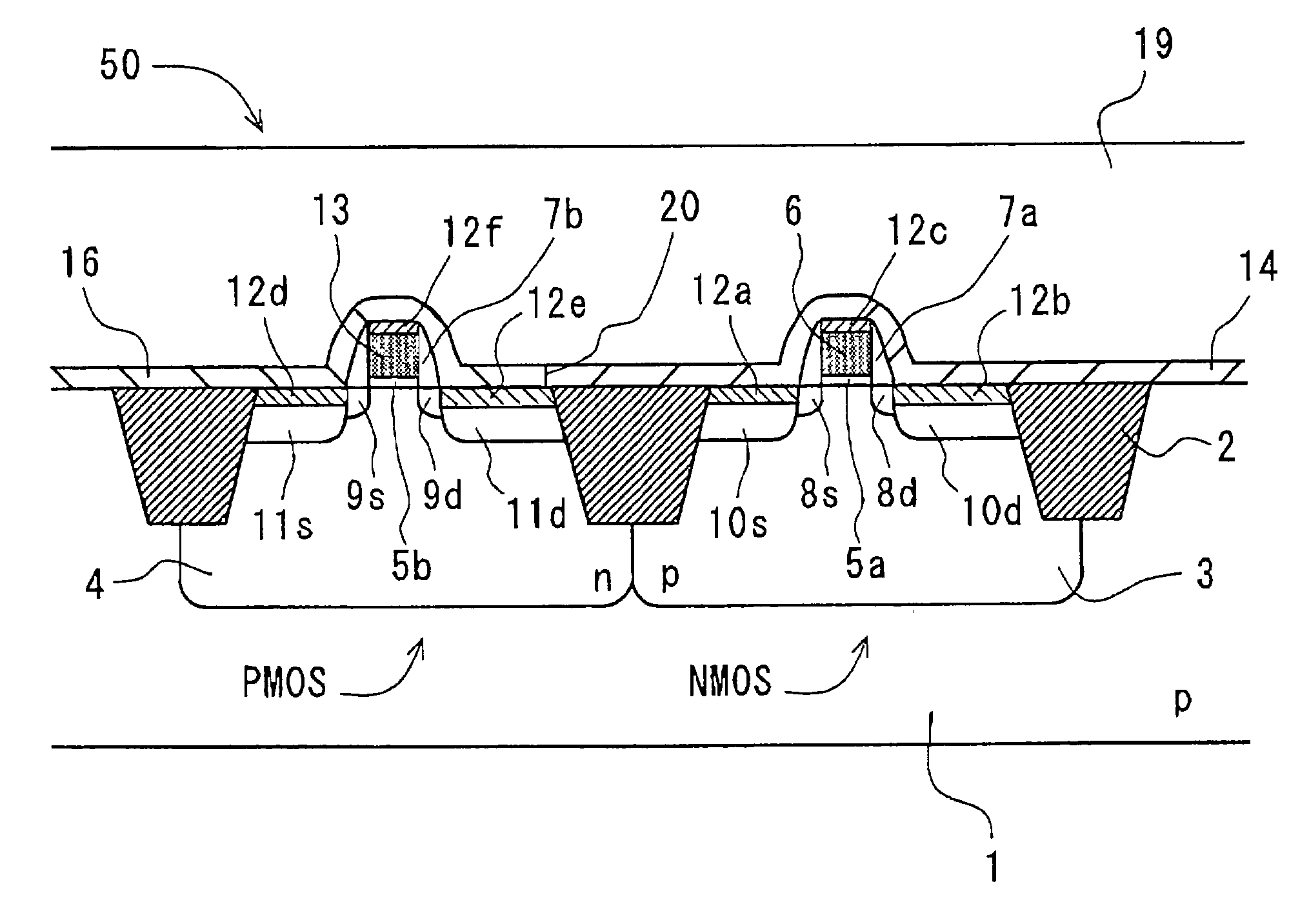

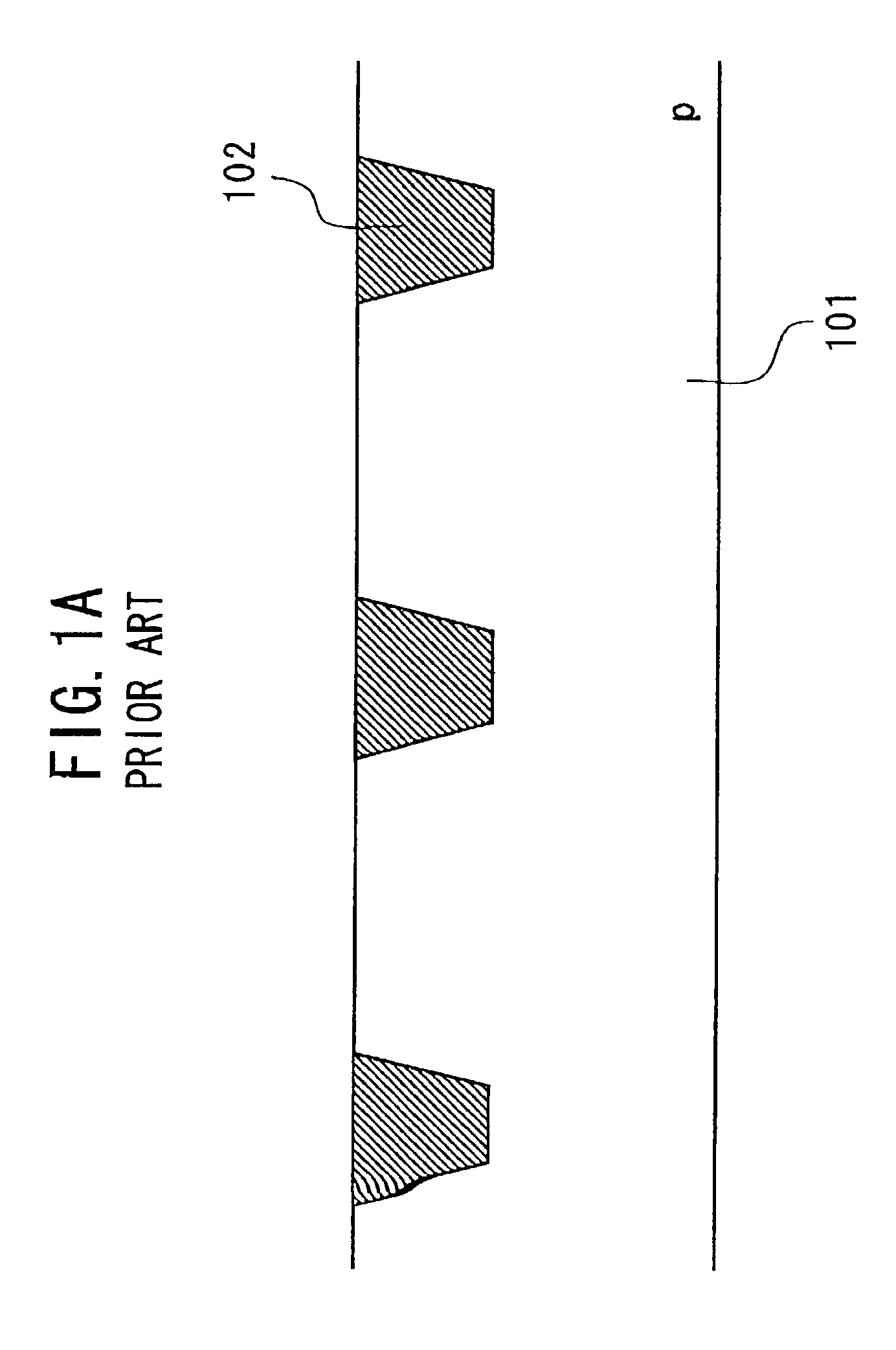

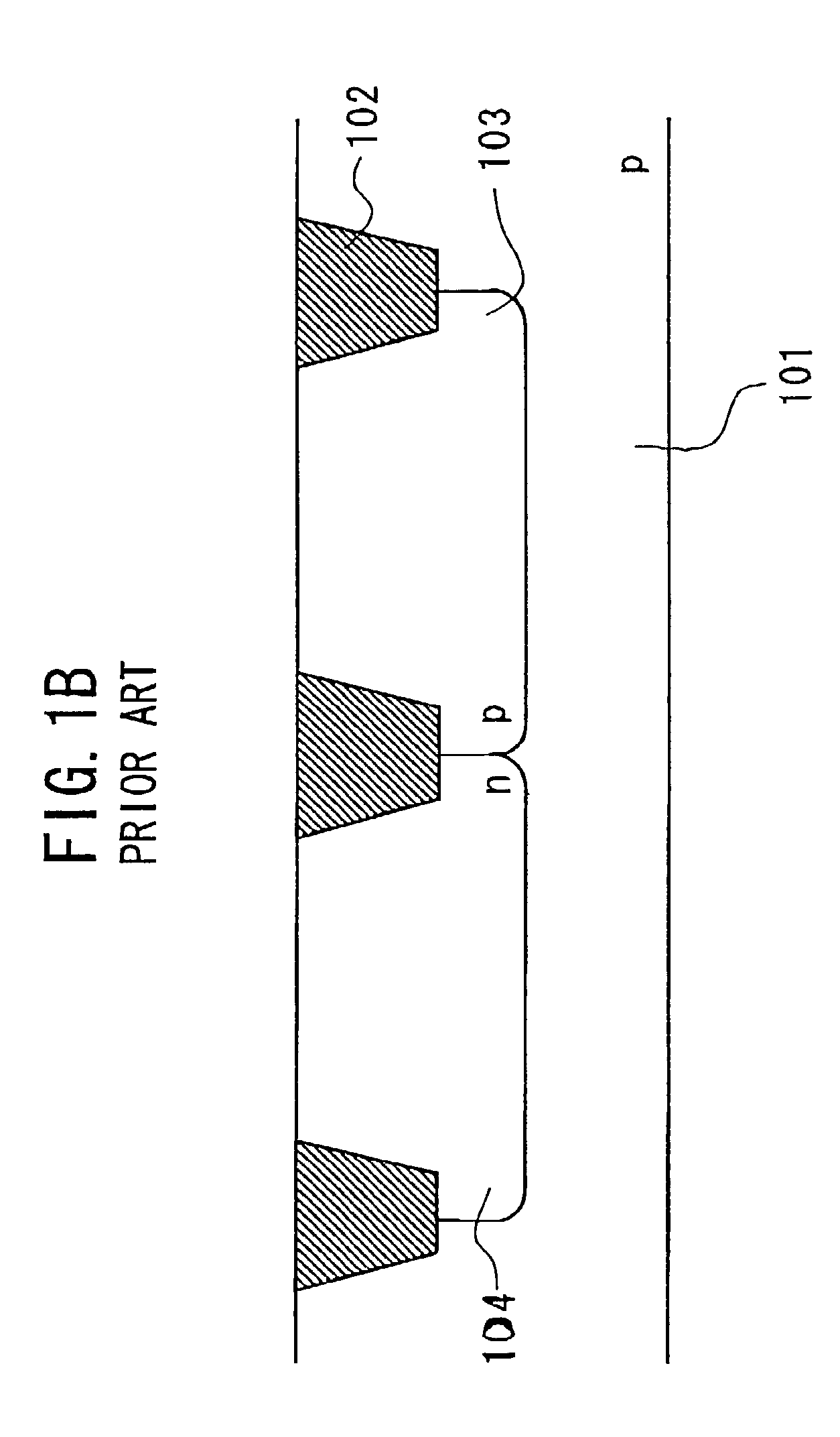

Semiconductor device and method of fabricating the same

InactiveUS20030040158A1TransistorSemiconductor/solid-state device manufacturingMOSFETElectron mobility

A semiconductor device improves the electron mobility in the n-channel MOSFET and reduces the bend or warp of the semiconductor substrate or wafer. The fist nitride layer having a tensile stress is formed on the substrate to cover the n-channel MOSFET. The tensile stress of the first nitride layer serves to relax a compressive stress existing in the channel region. The second nitride layer having an actual compressive stress is formed on the substrate to cover the p-channel MOSFET. The first and second nitride layers serve to decrease bend or warp of the substrate. Preferably, the first nitride layer is a nitride layer of Si formed by a LPCVD process, and the second nitride layer is a nitride layer of Si formed by a PECVD process.

Owner:NEC ELECTRONICS CORP

Method of growing nitride semiconductors, nitride semiconductor substrate and nitride semiconductor device

InactiveUS6153010APolycrystalline material growthLaser detailsNitrogen sourceCrystallographic defect

PCT No. PCT / JP98 / 01640 Sec. 371 Date Dec. 9, 1998 Sec. 102(e) Date Dec. 9, 1998 PCT Filed Apr. 9, 1998 PCT Pub. No. WO98 / 47170 PCT Pub. Date Oct. 22, 1998A method of growing a nitride semiconductor crystal which has very few crystal defects and can be used as a substrate is disclosed. This invention includes the step of forming a first selective growth mask on a support member including a dissimilar substrate having a major surface and made of a material different from a nitride semiconductor, the first selective growth mask having a plurality of first windows for selectively exposing the upper surface of the support member, and the step of growing nitride semiconductor portions from the upper surface, of the support member, which is exposed from the windows, by using a gaseous Group 3 element source and a gaseous nitrogen source, until the nitride semiconductor portions grown in the adjacent windows combine with each other on the upper surface of the selective growth mask.

Owner:NICHIA CORP

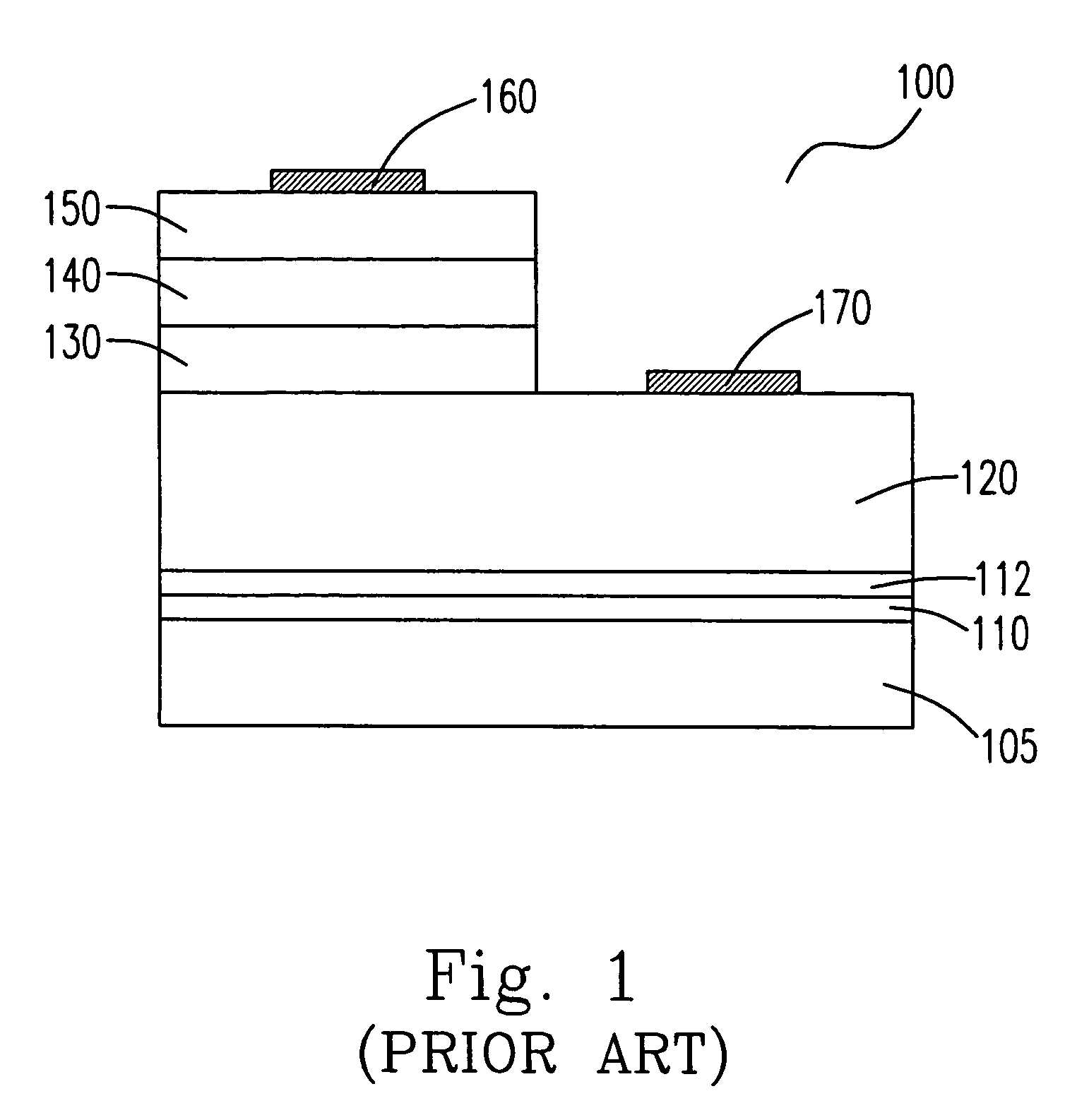

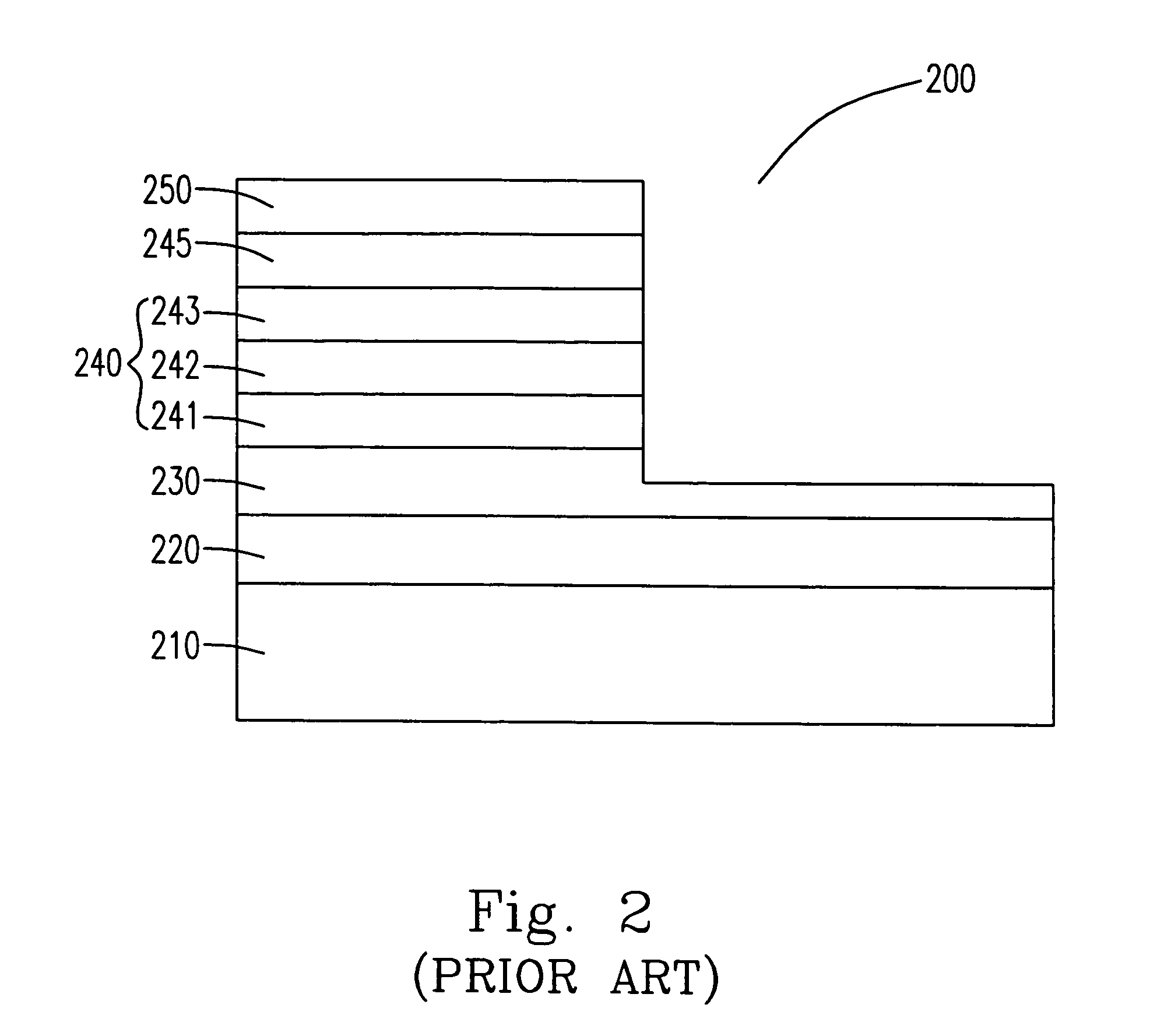

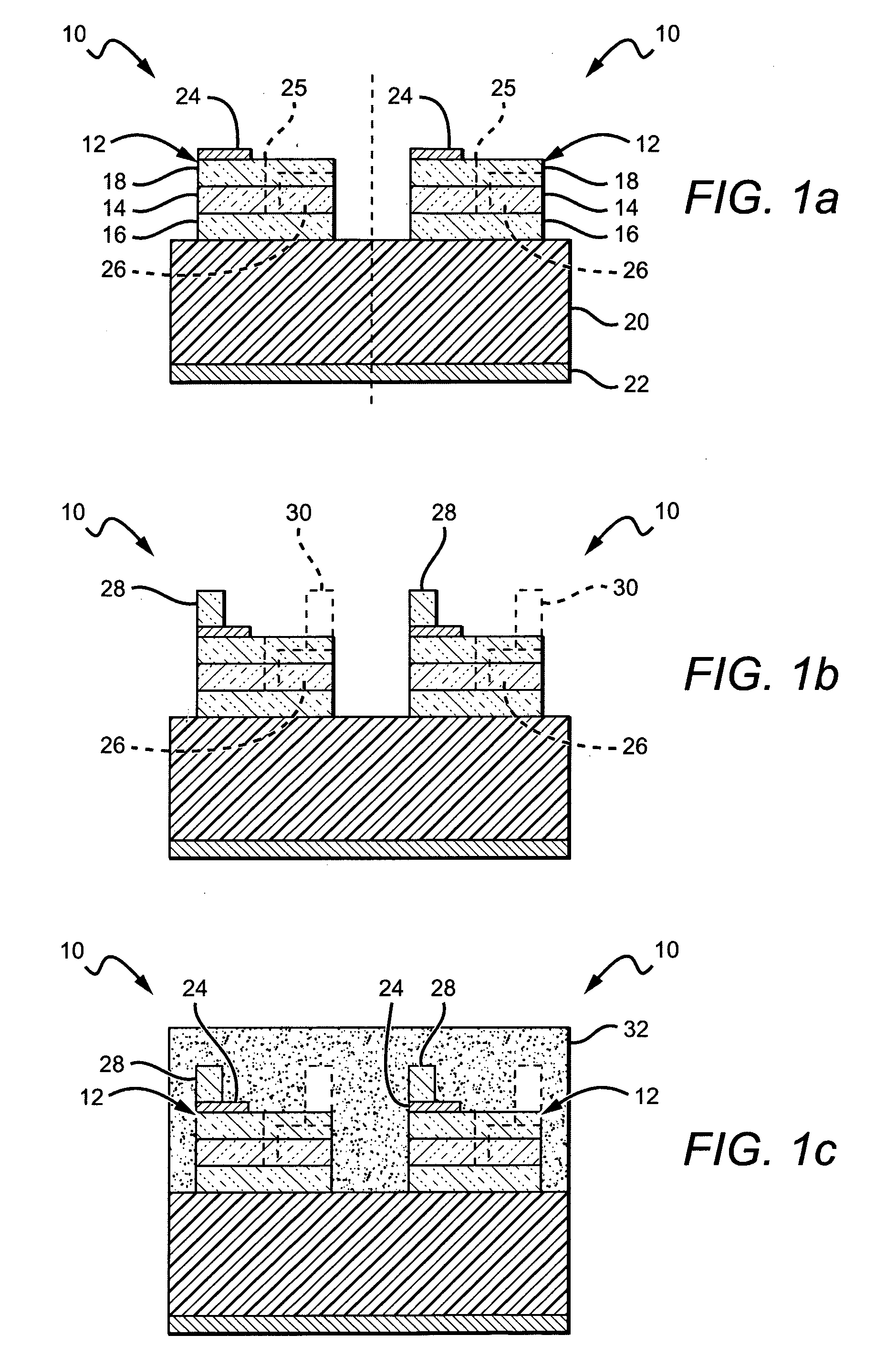

Wafer level phosphor coating method and devices fabricated utilizing method

ActiveUS20080179611A1Solid-state devicesSemiconductor/solid-state device manufacturingPhosphorLight-emitting diode

Methods for fabricating light emitting diode (LED) chips comprising providing a plurality of LEDs typically on a substrate. Pedestals are deposited on the LEDs with each of the pedestals in electrical contact with one of the LEDs. A coating is formed over the LEDs with the coating burying at least some of the pedestals. The coating is then planarized to expose at least some of the buried pedestals while leaving at least some of said coating on said LEDs. The exposed pedestals can then be contacted such as by wire bonds. The present invention discloses similar methods used for fabricating LED chips having LEDs that are flip-chip bonded on a carrier substrate and for fabricating other semiconductor devices. LED chip wafers and LED chips are also disclosed that are fabricated using the disclosed methods.

Owner:CREELED INC

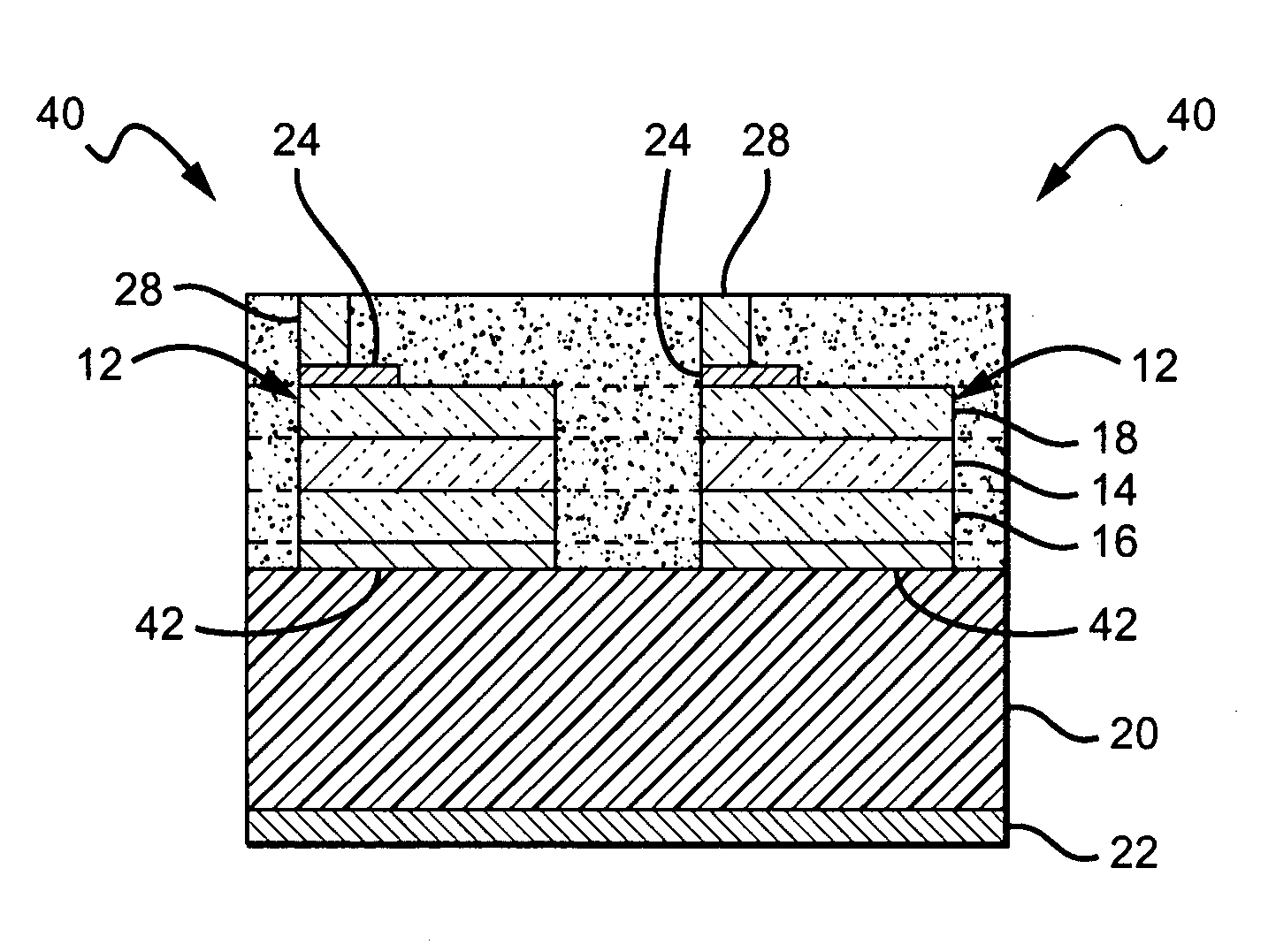

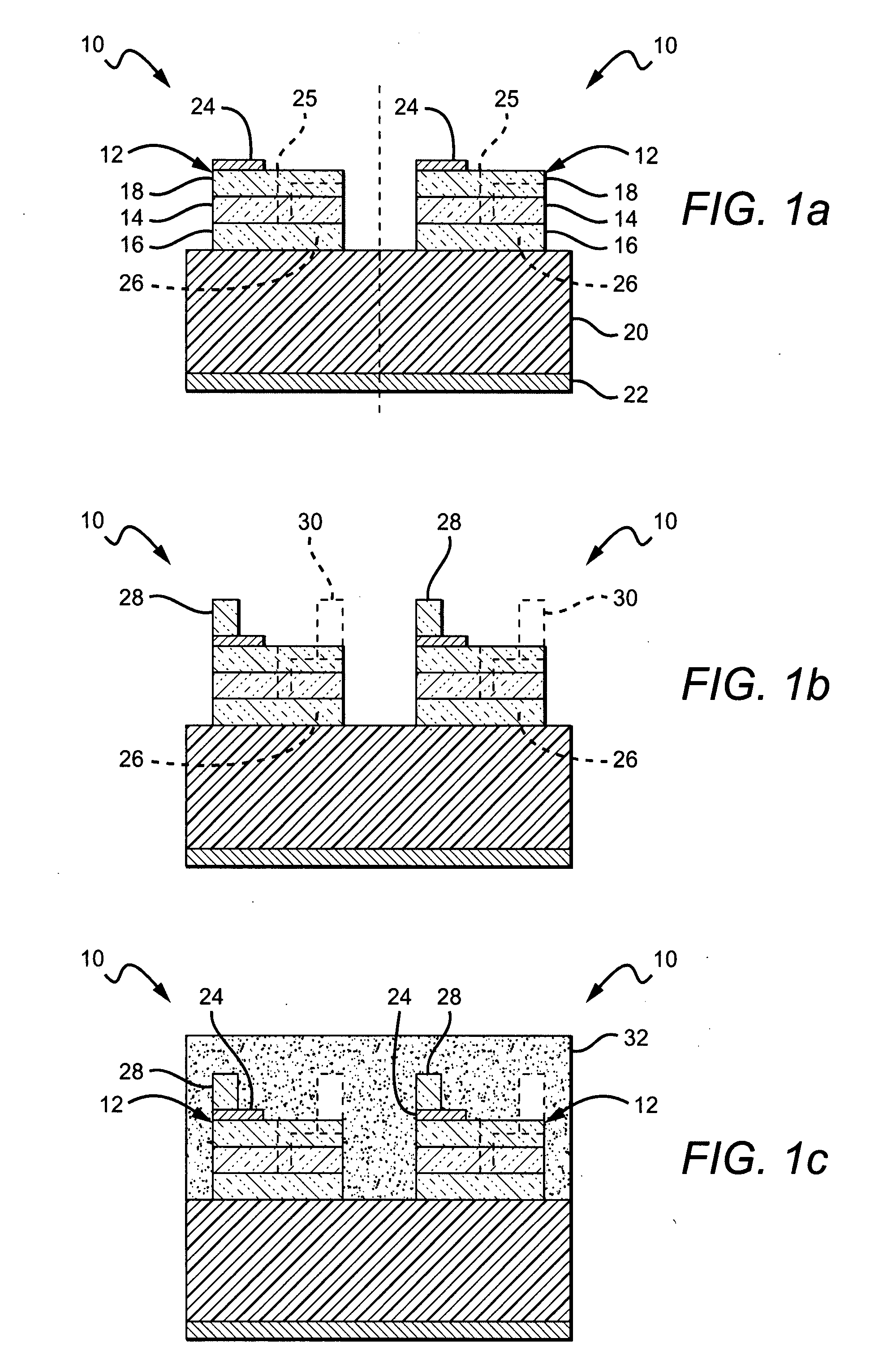

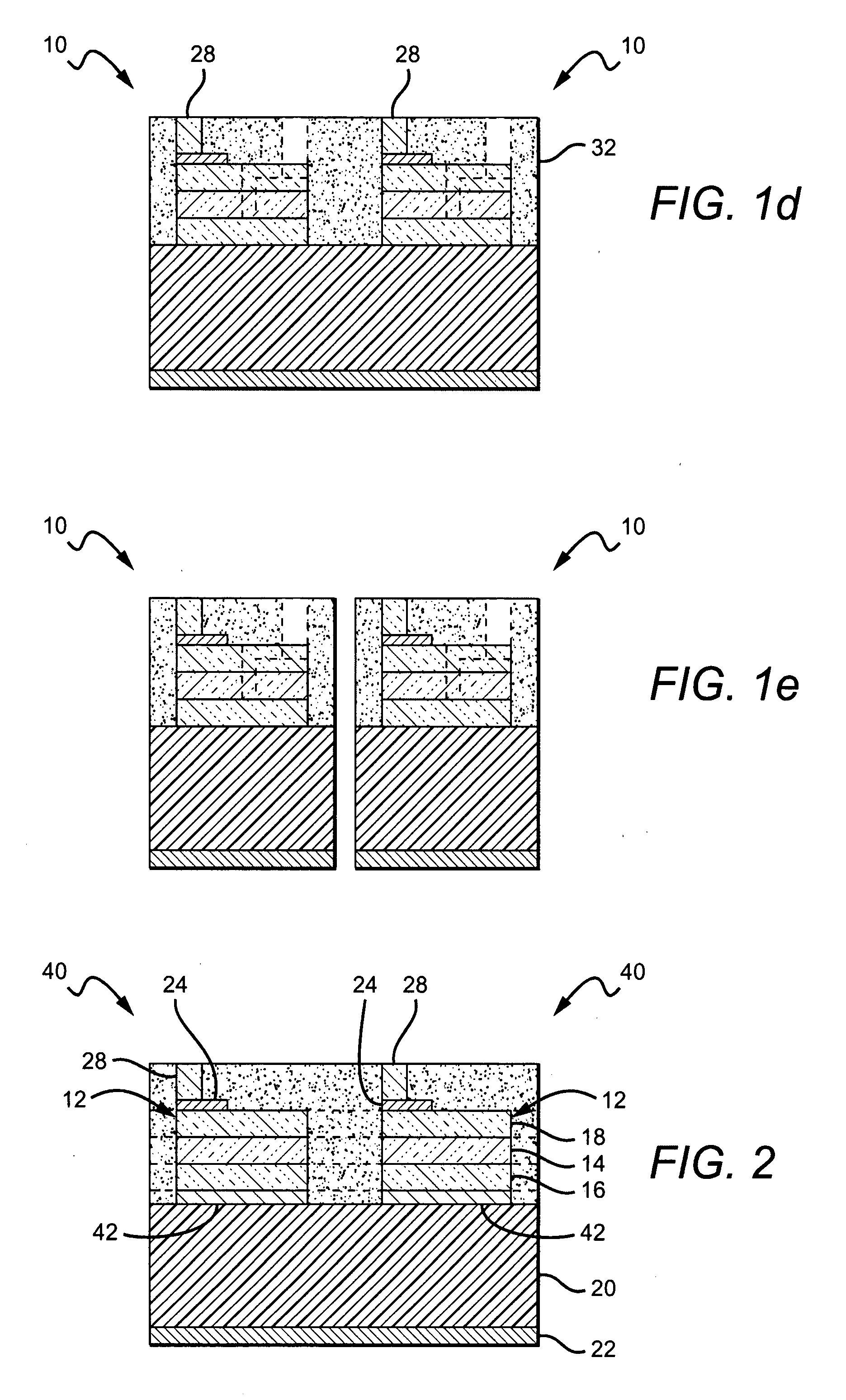

Semiconductor Device and Manufacturing Method Thereof

An object is to provide a semiconductor device of which a manufacturing process is not complicated and by which cost can be suppressed, by forming a thin film transistor using an oxide semiconductor film typified by zinc oxide, and a manufacturing method thereof. For the semiconductor device, a gate electrode is formed over a substrate; a gate insulating film is formed covering the gate electrode; an oxide semiconductor film is formed over the gate insulating film; and a first conductive film and a second conductive film are formed over the oxide semiconductor film. The oxide semiconductor film has at least a crystallized region in a channel region.

Owner:SEMICON ENERGY LAB CO LTD

Wafer level phosphor coating method and devices fabricated utilizing method

ActiveUS20080173884A1Semiconductor/solid-state device detailsSolid-state devicesPhosphorLight-emitting diode

Methods for fabricating light emitting diode (LED) chips comprising providing a plurality of LEDs typically on a substrate. Pedestals are deposited on the LEDs with each of the pedestals in electrical contact with one of the LEDs. A coating is formed over the LEDs with the coating burying at least some of the pedestals. The coating is then planarized to expose at least some of the buried pedestals while leaving at least some of said coating on said LEDs. The exposed pedestals can then be contacted such as by wire bonds. The present invention discloses similar methods used for fabricating LED chips having LEDs that are flip-chip bonded on a carrier substrate and for fabricating other semiconductor devices. LED chip wafers and LED chips are also disclosed that are fabricated using the disclosed methods.

Owner:CREELED INC

Semiconductor Device and Manufacturing Method Thereof

ActiveUS20080308797A1High yieldReduce the ratioTransistorDischarge tube luminescnet screensEngineeringZinc

An object is to provide a semiconductor device of which a manufacturing process is not complicated and by which cost can be suppressed, by forming a thin film transistor using an oxide semiconductor film typified by zinc oxide, and a manufacturing method thereof. For the semiconductor device, a gate electrode is formed over a substrate; a gate insulating film is formed covering the gate electrode; an oxide semiconductor film is formed over the gate insulating film; and a first conductive film and a second conductive film are formed over the oxide semiconductor film. The oxide semiconductor film has at least a crystallized region in a channel region.

Owner:SEMICON ENERGY LAB CO LTD

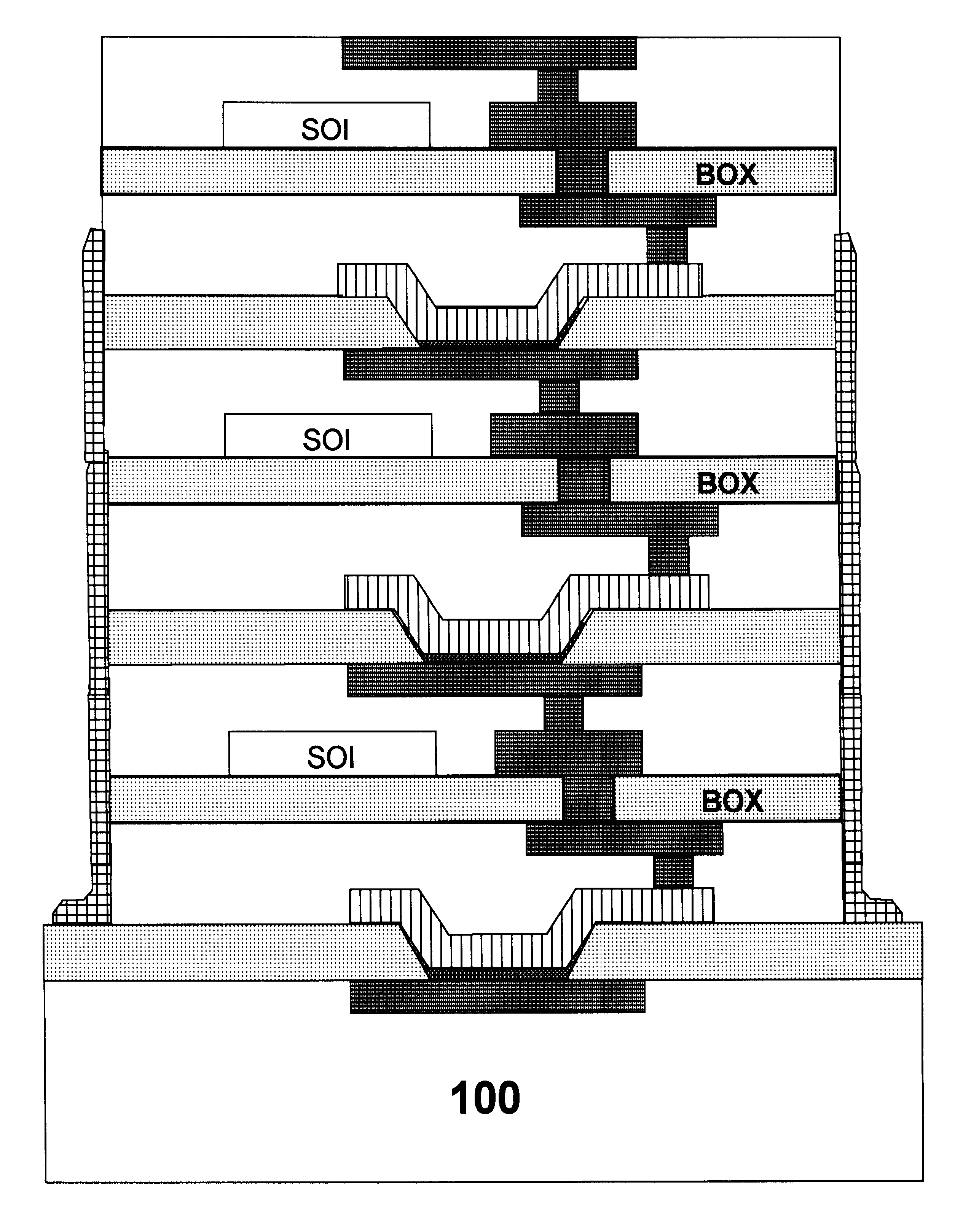

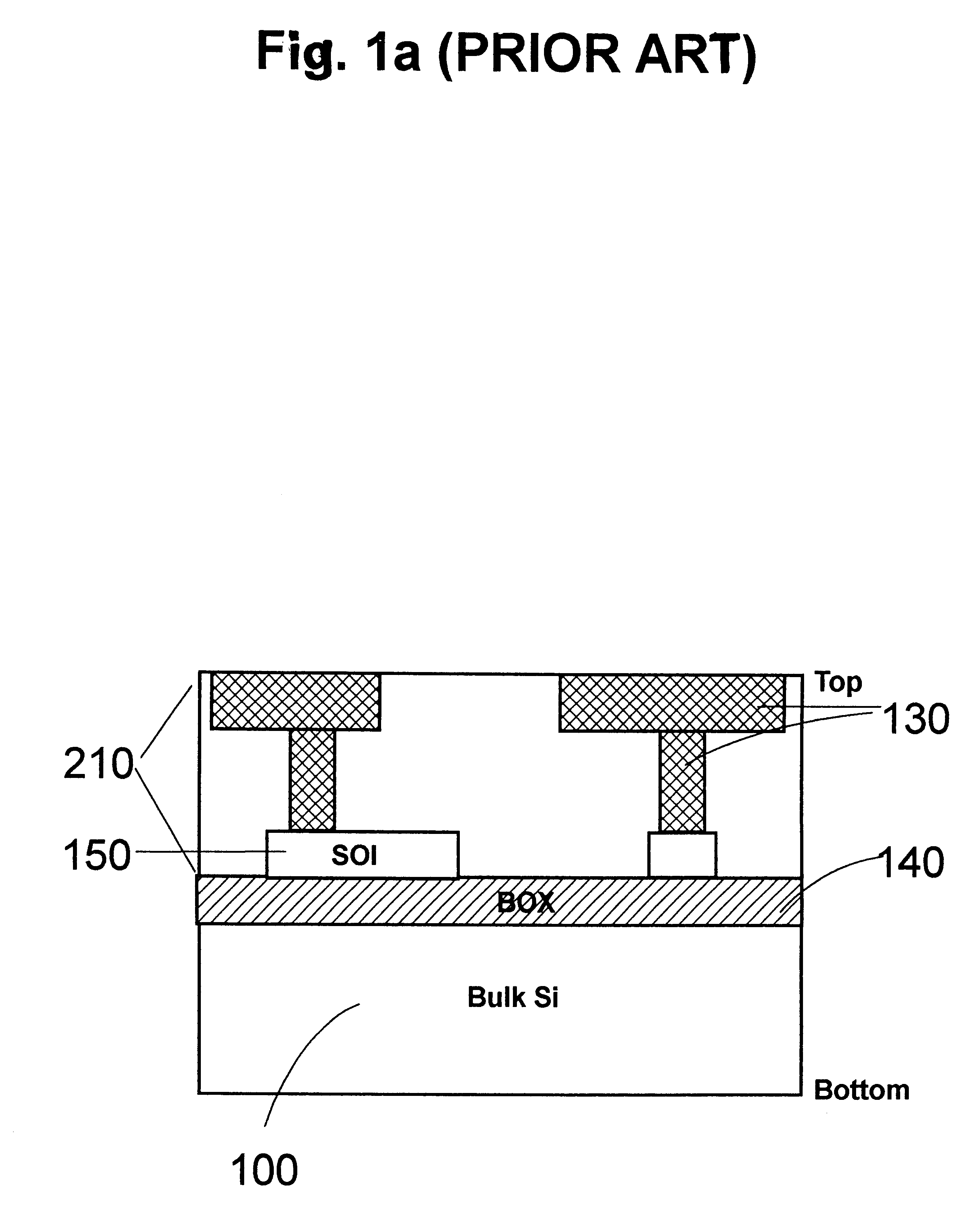

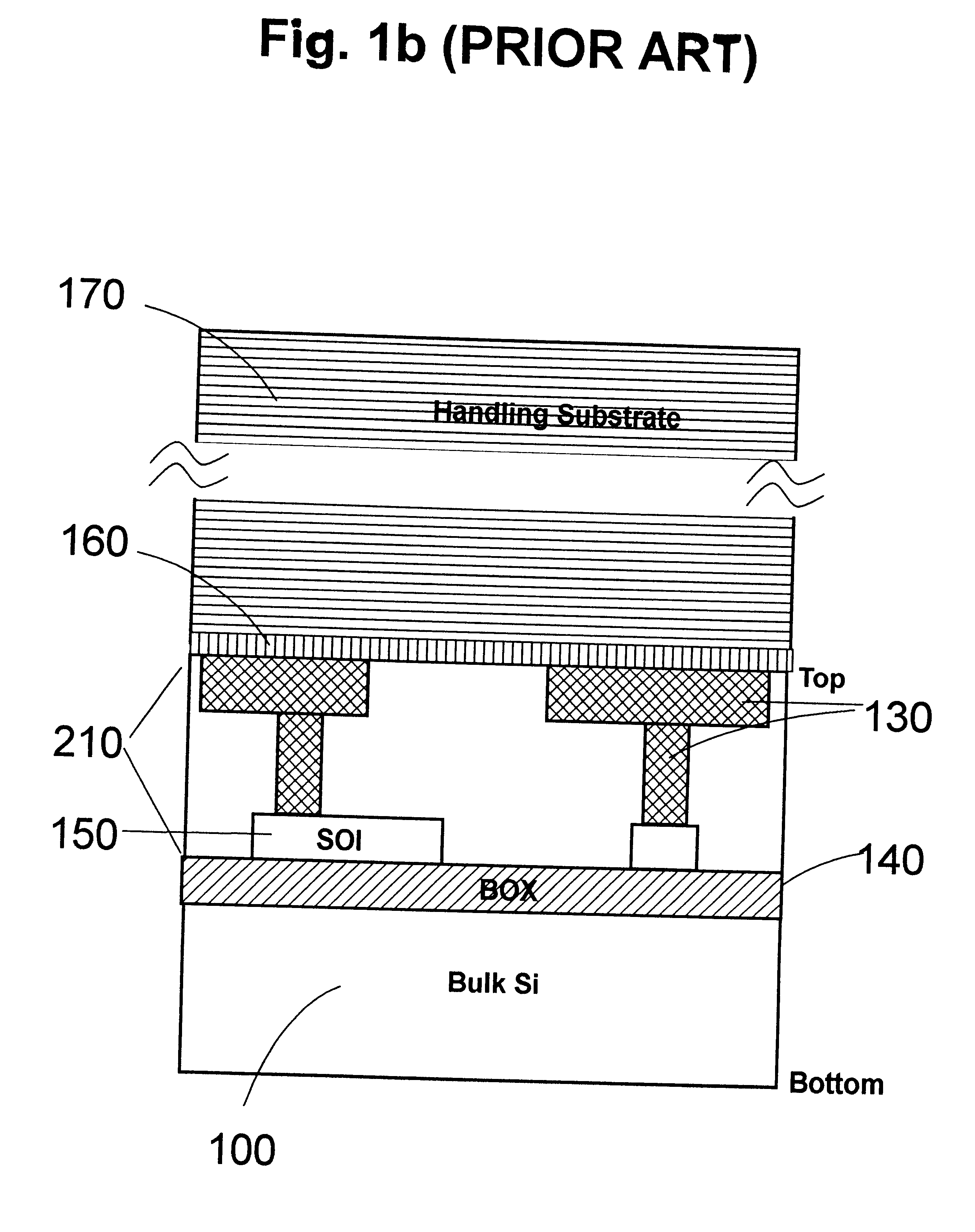

Three-dimensional chip stacking assembly

InactiveUS6355501B1Precise alignmentGood mechanical integritySolid-state devicesSemiconductor/solid-state device manufacturingEngineeringThree-dimensional integrated circuit

An assembly consisting of three dimensional stacked SOI chips, and a method of forming such integrated circuit assembly, each of the SOI chips including a handler making mechanical contact to a first metallization pattern making electrical contact to a semiconductor device. The metalized pattern, in turn, contacts a second metallization pattern positioned on an opposite surface of the semiconductor device. The method of fabricating the three-dimensional IC assembly includes the steps of: a) providing a substrate having a third metalized pattern on a first surface of the substrate; b) aligning one of the SOI chips on the first surface of the substrate, by having the second metallization pattern of the SOI chip make electrical contact with the third metalized pattern of the substrate; c) removing the handler from the SOI chip, exposing the first metallization pattern of the SOI chip; d) aligning a second one of the SOI chips with the first SOI chip, having the second metallization pattern of the second SOI chip make electrical contact to the exposed first metallization pattern of the first SOI chip; and e) repeating steps c) and d) for mounting subsequent SOI chips one on top of the other.

Owner:IBM CORP