Patents

Literature

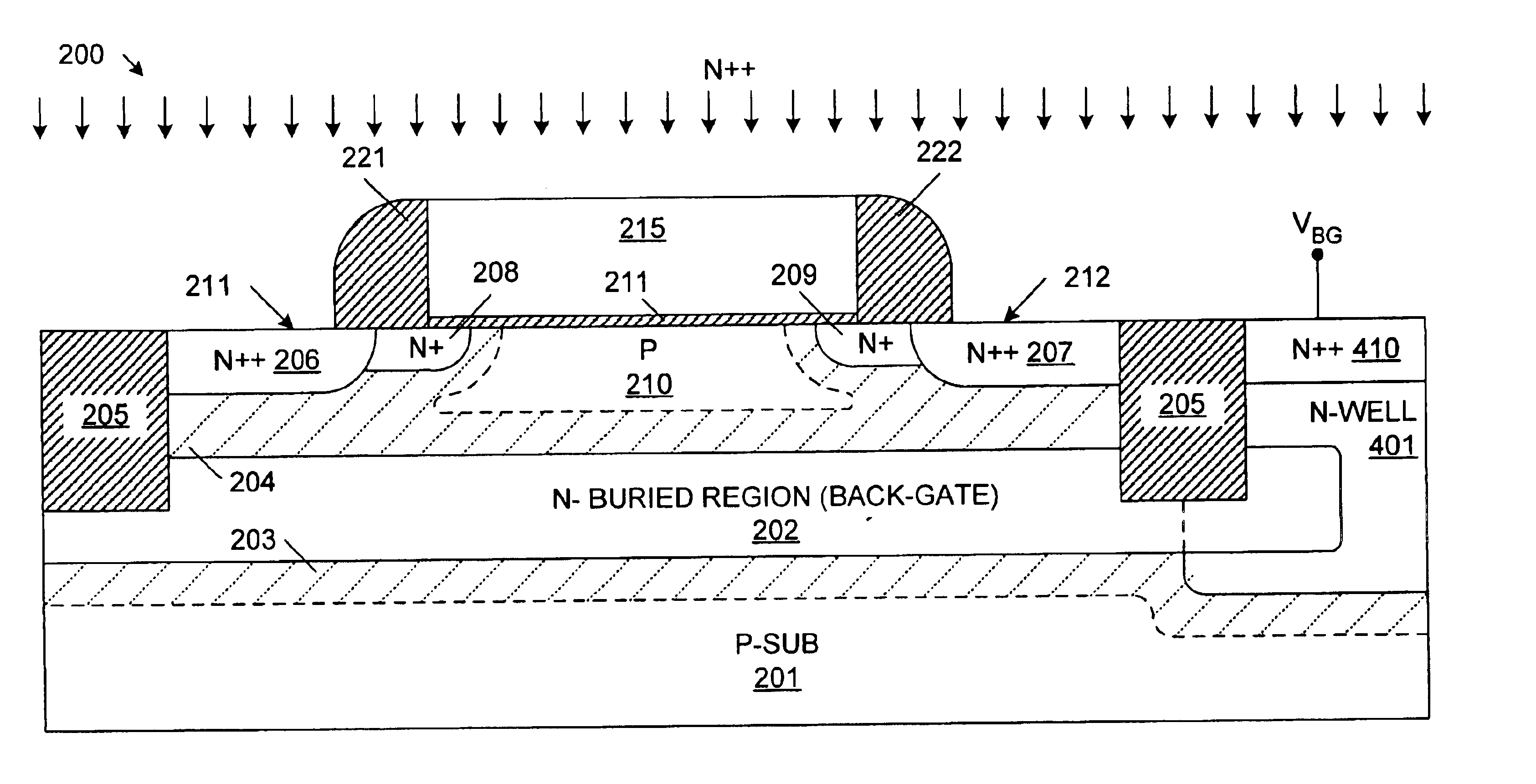

1024 results about "Depletion region" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In semiconductor physics, the depletion region, also called depletion layer, depletion zone, junction region, space charge region or space charge layer, is an insulating region within a conductive, doped semiconductor material where the mobile charge carriers have been diffused away, or have been forced away by an electric field. The only elements left in the depletion region are ionized donor or acceptor impurities.

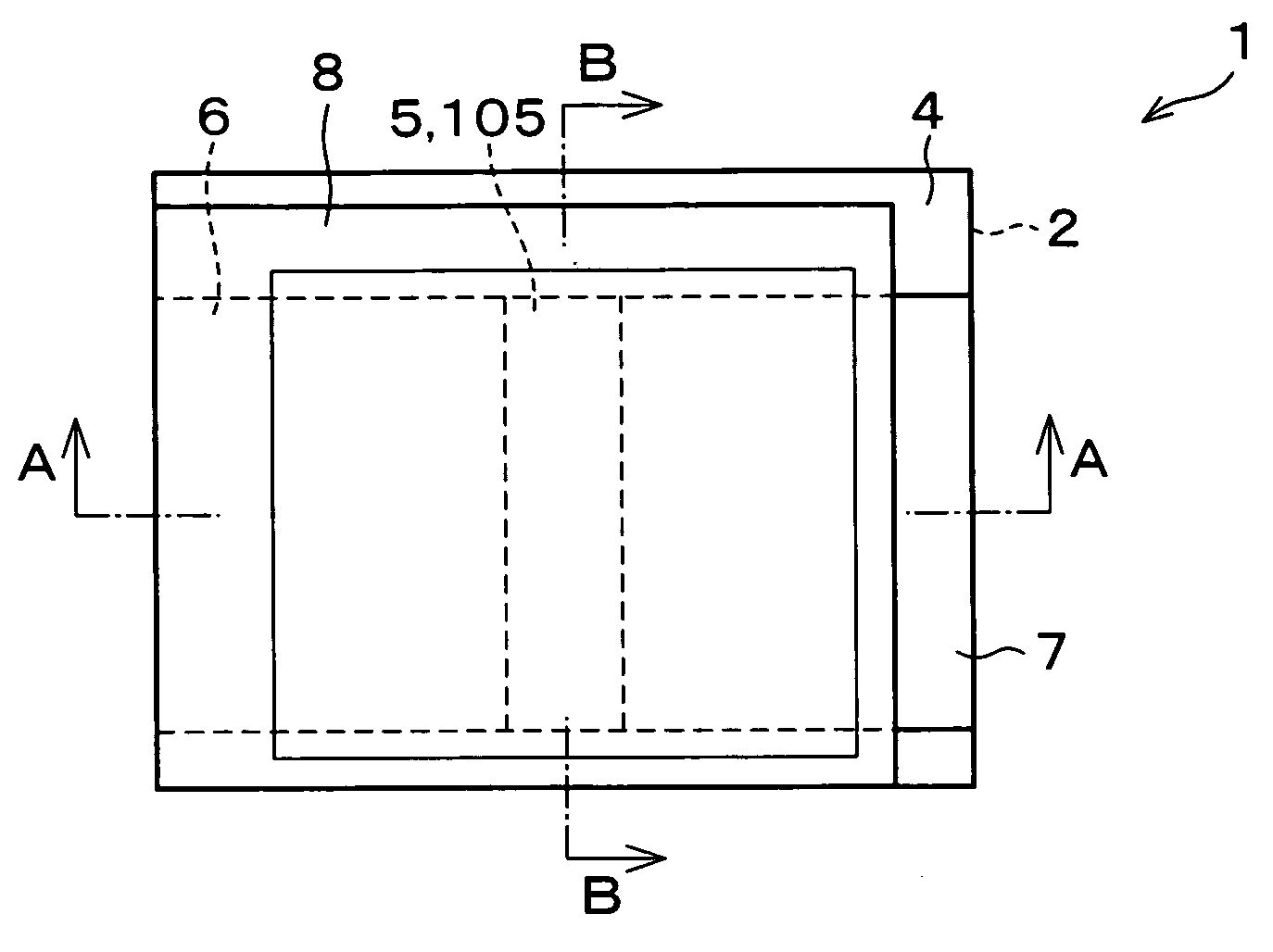

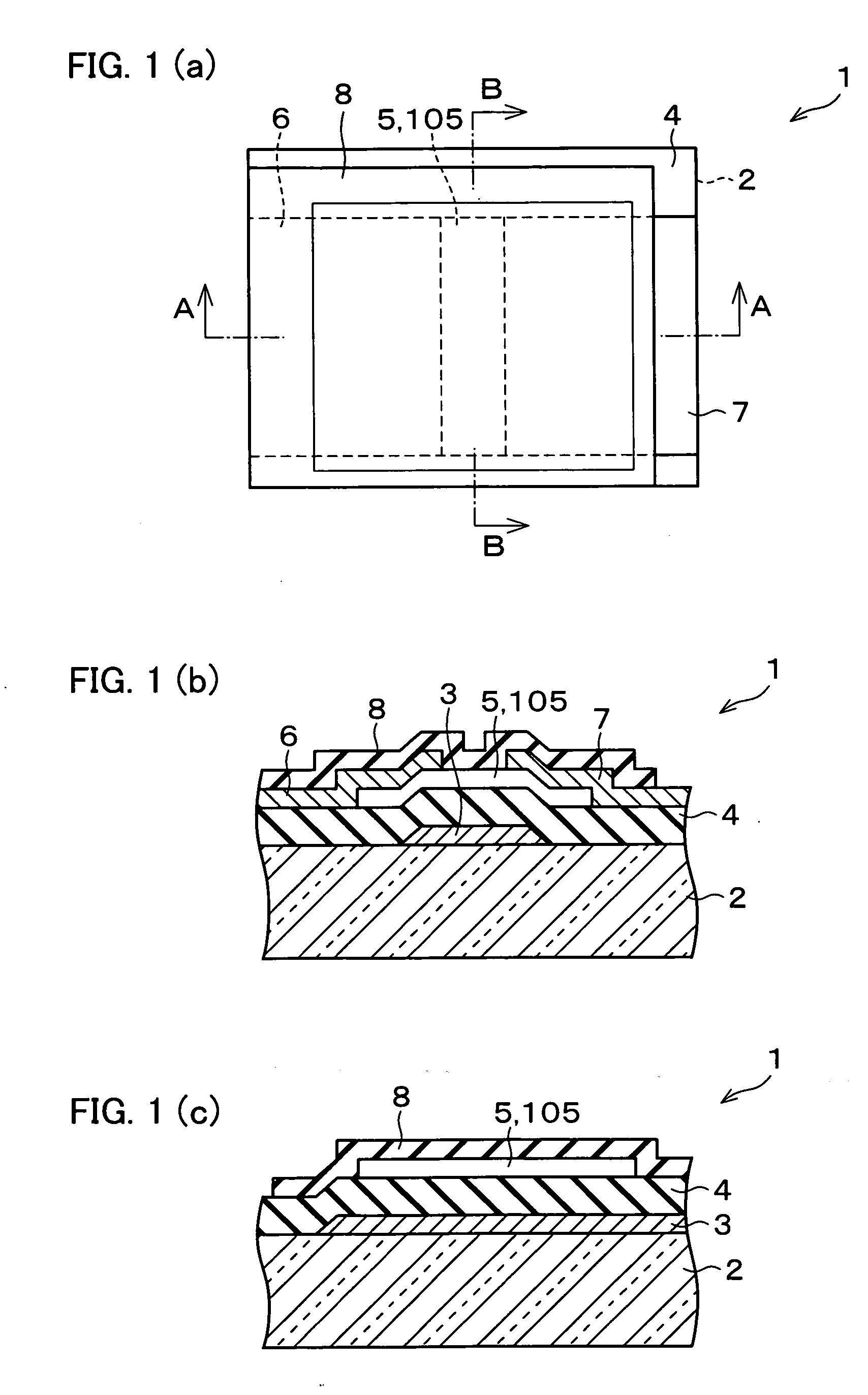

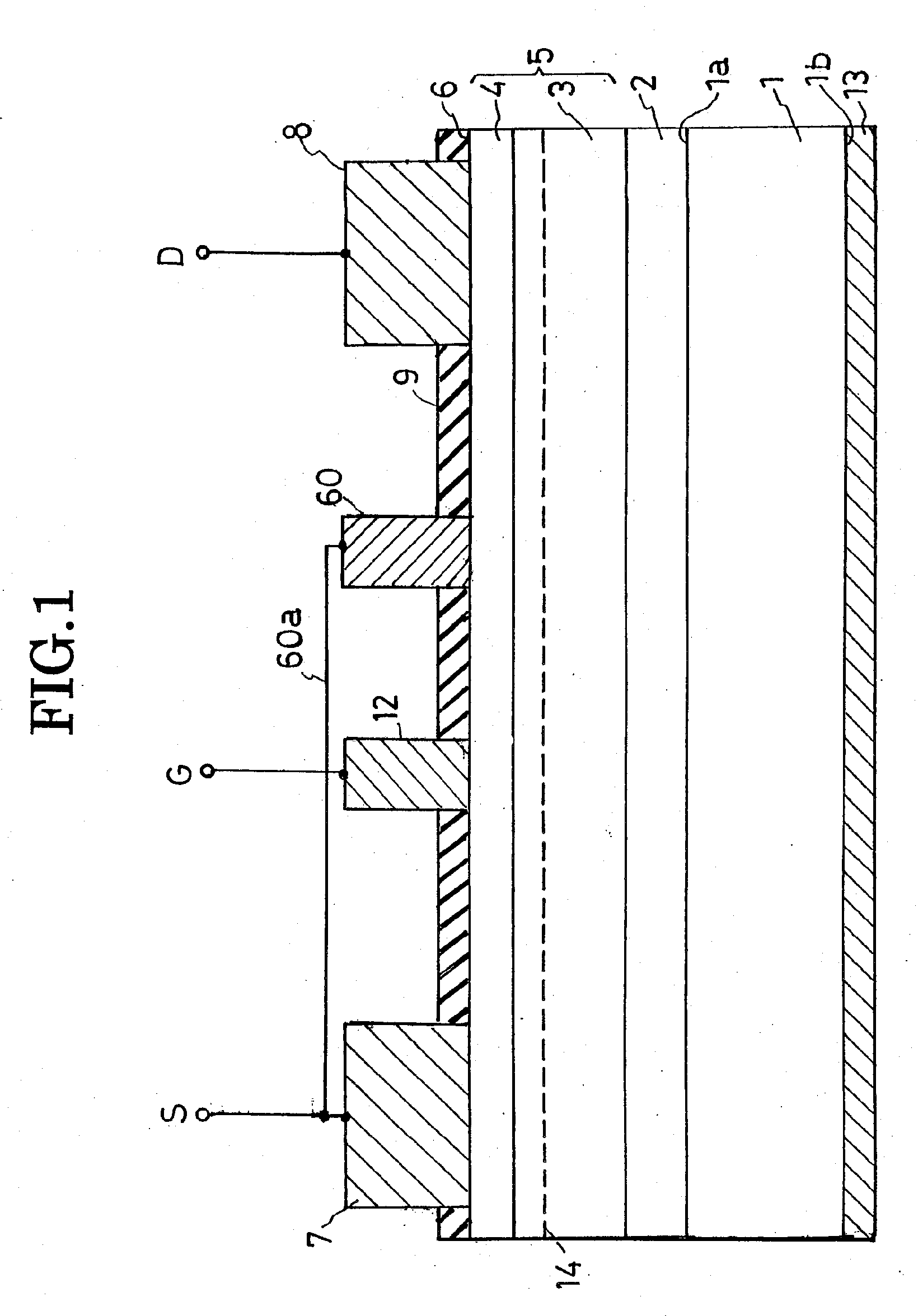

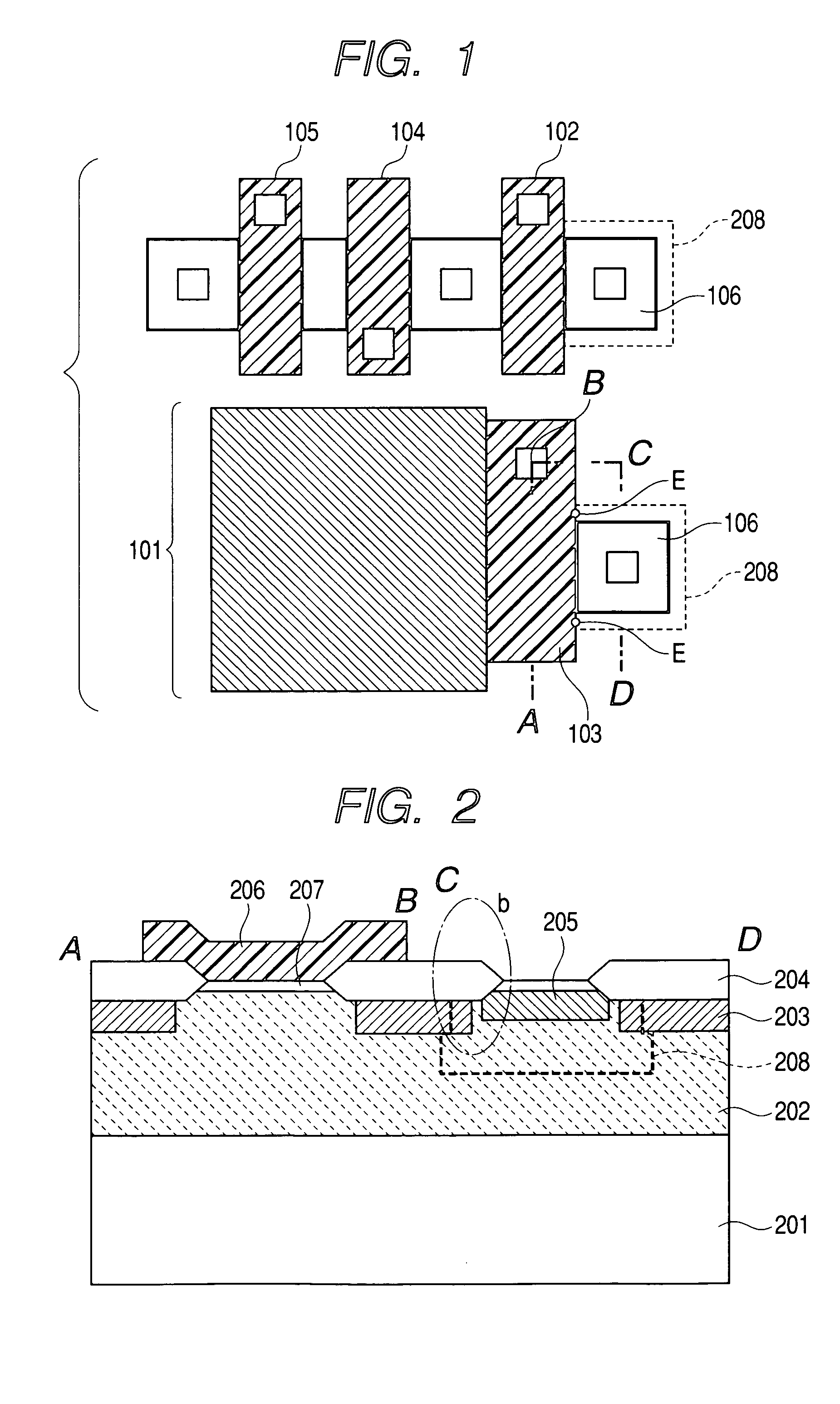

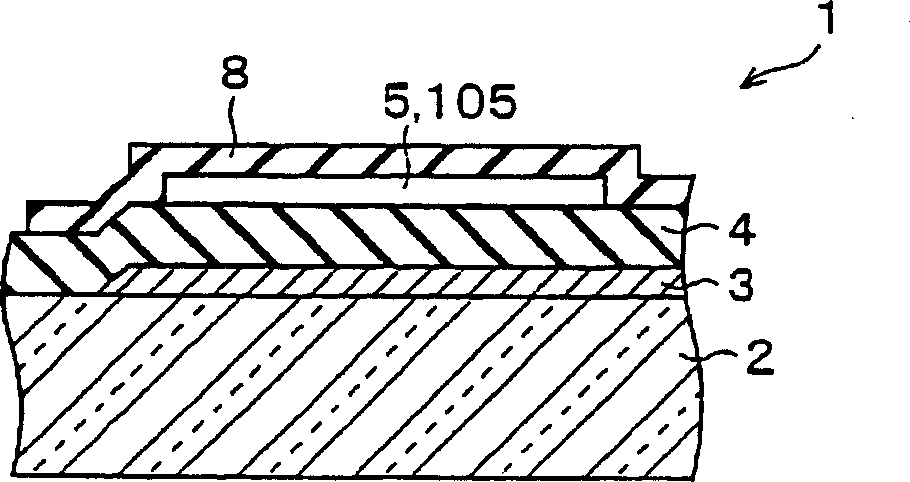

Semiconductor device, manufacturing method, and electronic device

ActiveUS20060244107A1Stabilize element propertyEasy to manufactureTransistorSemiconductor/solid-state device detailsSurface levelIntrinsic resistance

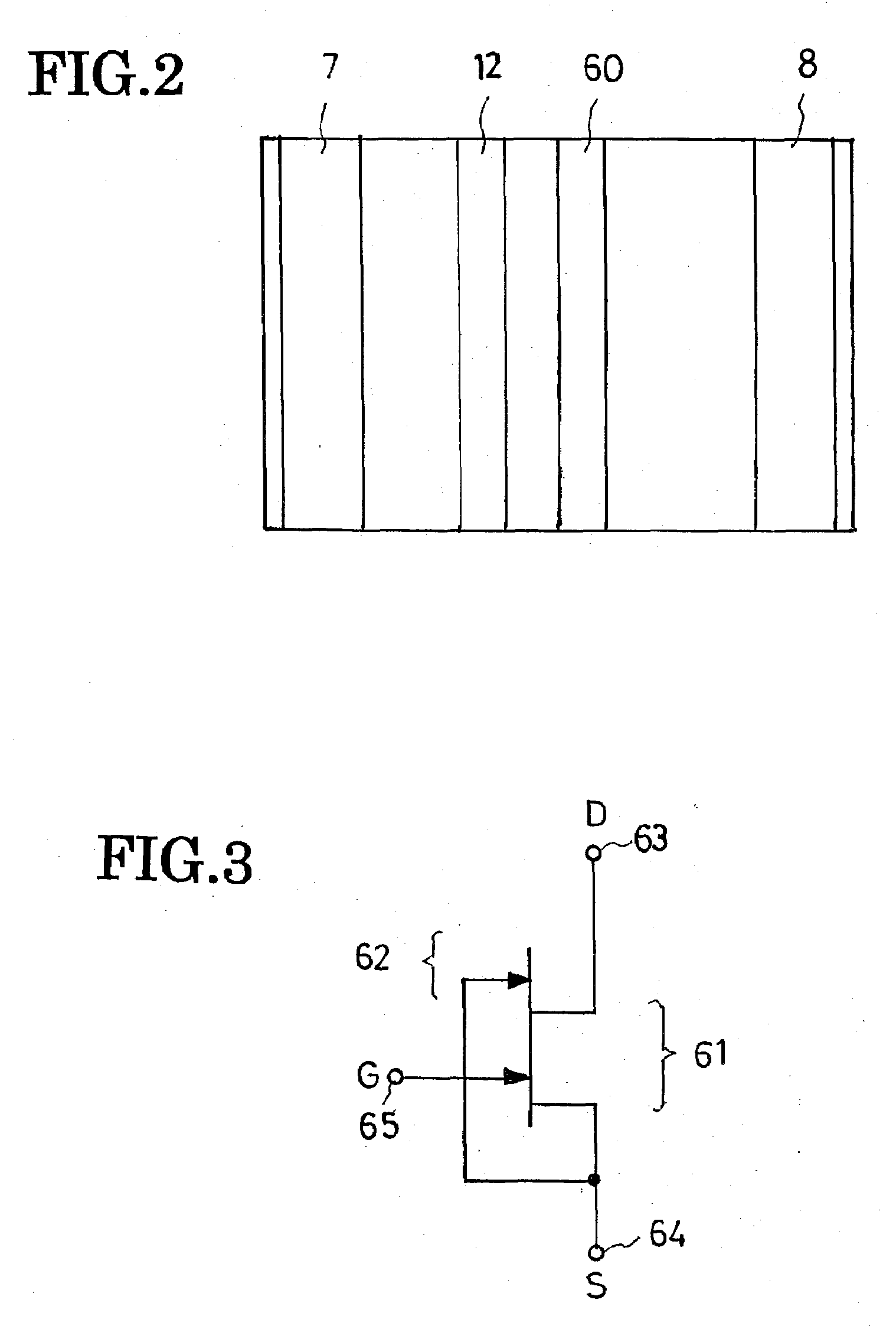

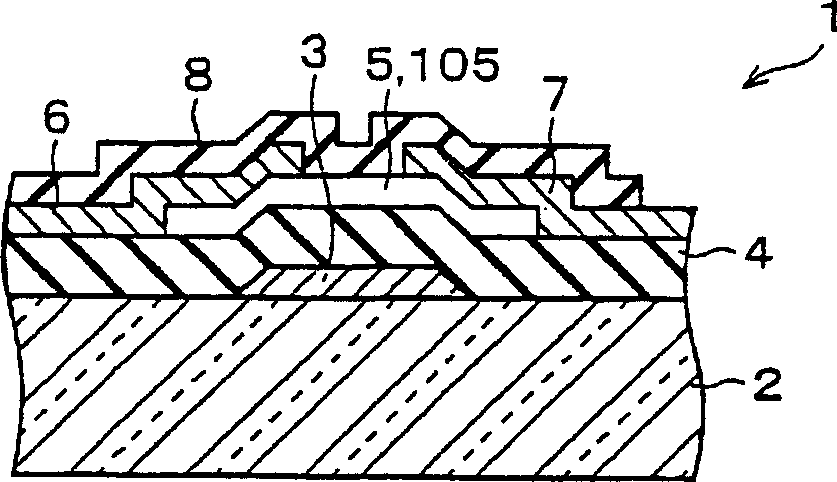

In a thin film transistor (1), a gate insulating layer (4) is formed on a gate electrode (3) formed on an insulating substrate (2). Formed on the gate insulating layer (4) is a semiconductor layer (5). Formed on the semiconductor layer (5) are a source electrode (6) and a drain electrode (7). A protective layer (8) covers them, so that the semiconductor layer (5) is blocked from an atmosphere. The semiconductor layer (5) (active layer) is made of, e.g., a semiconductor containing polycrystalline ZnO to which, e.g., a group V element is added. The protective layer (8) thus formed causes decrease of a surface level of the semiconductor layer (5). This eliminates a depletion layer spreading therewithin. Accordingly, the ZnO becomes an n-type semiconductor indicating an intrinsic resistance, with the result that too many free electrons are generated. However, the added element works on the ZnO as an accepter impurity, so that the free electrons are reduced. This decreases a gate voltage required for removal of the free electrons, so that the threshold voltage of the thin film transistor (1) becomes on the order of 0V. This allows practical use of a semiconductor device which has an active layer made of zinc oxide and which includes an protective layer for blocking the active layer from an atmosphere.

Owner:SHARP KK +2

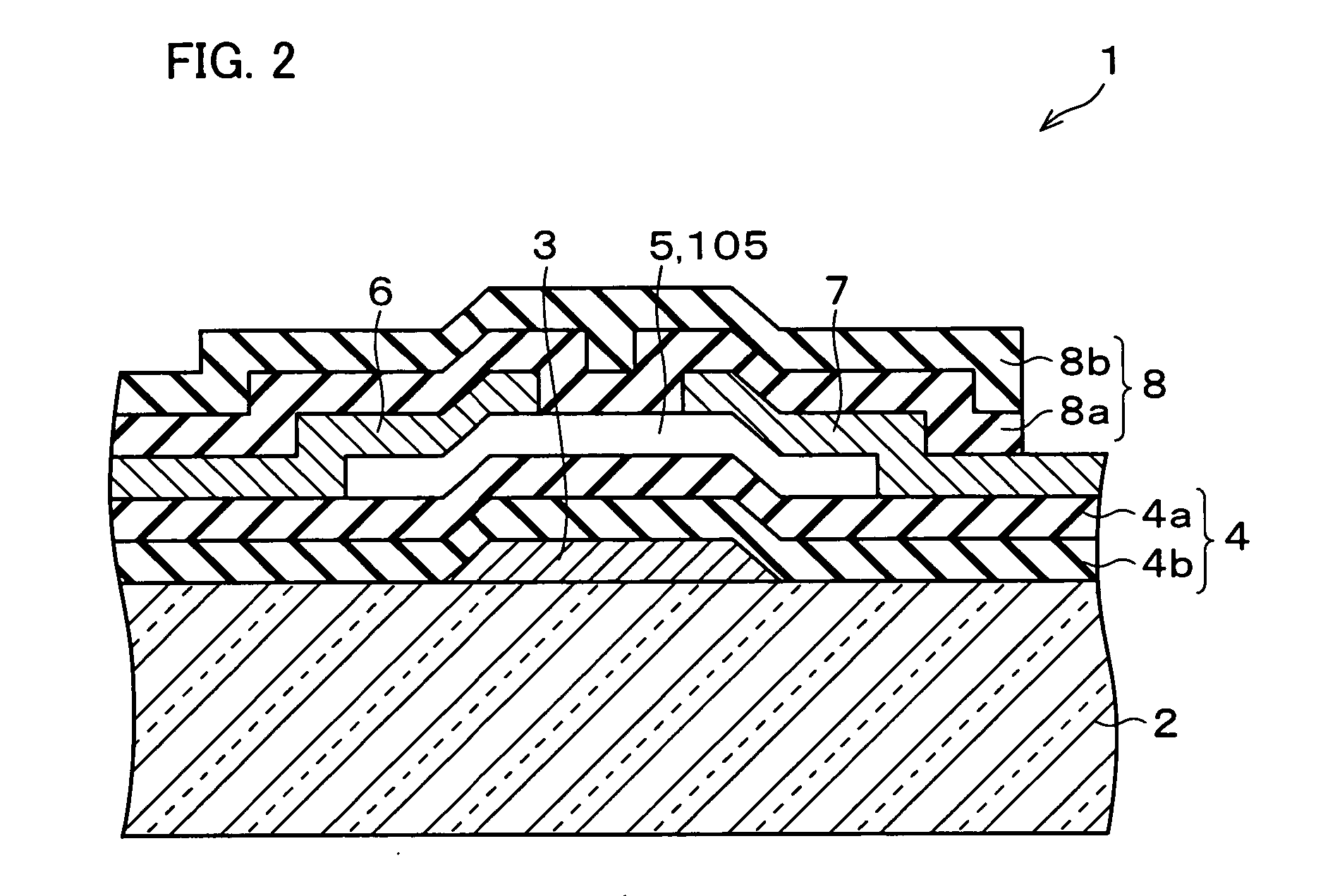

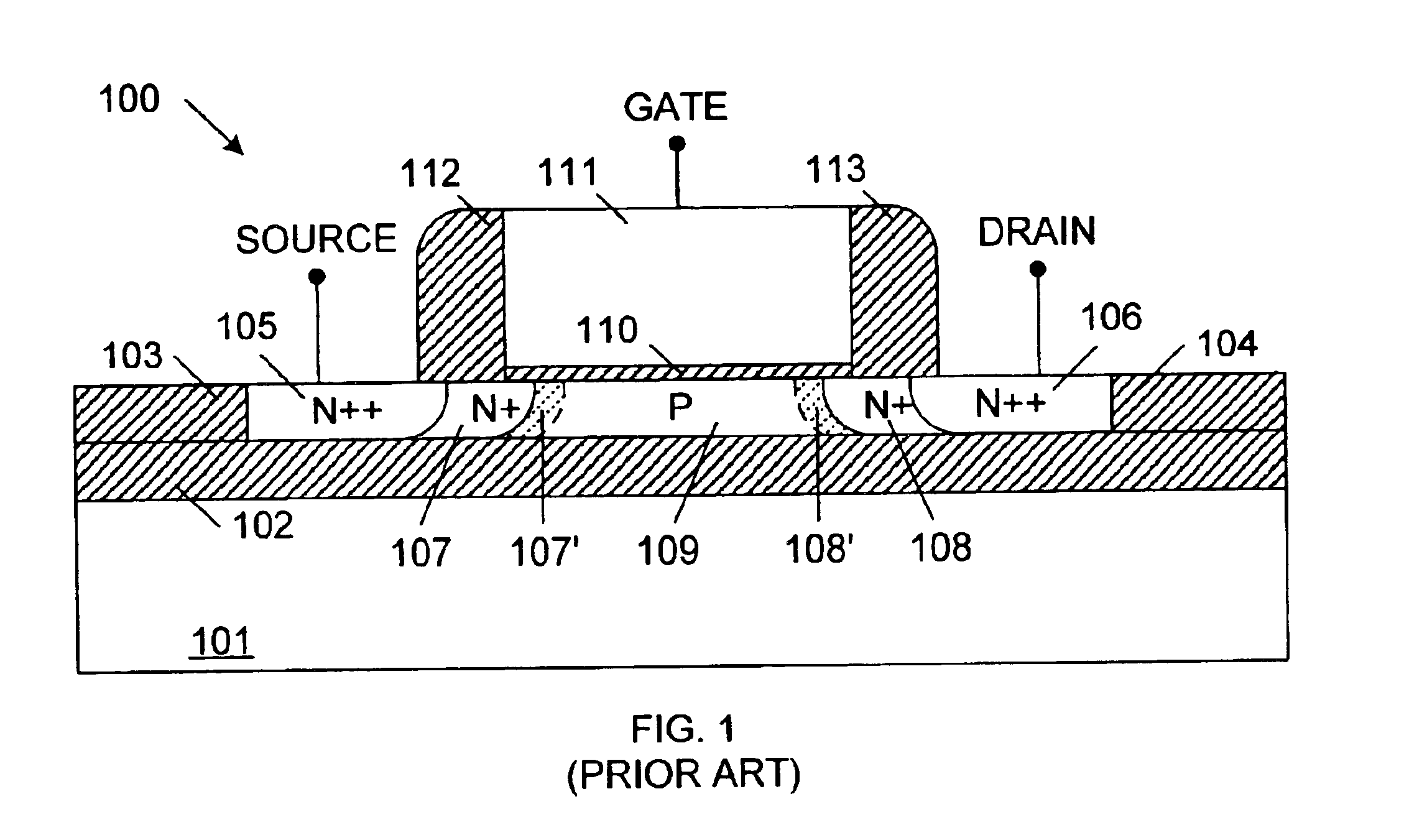

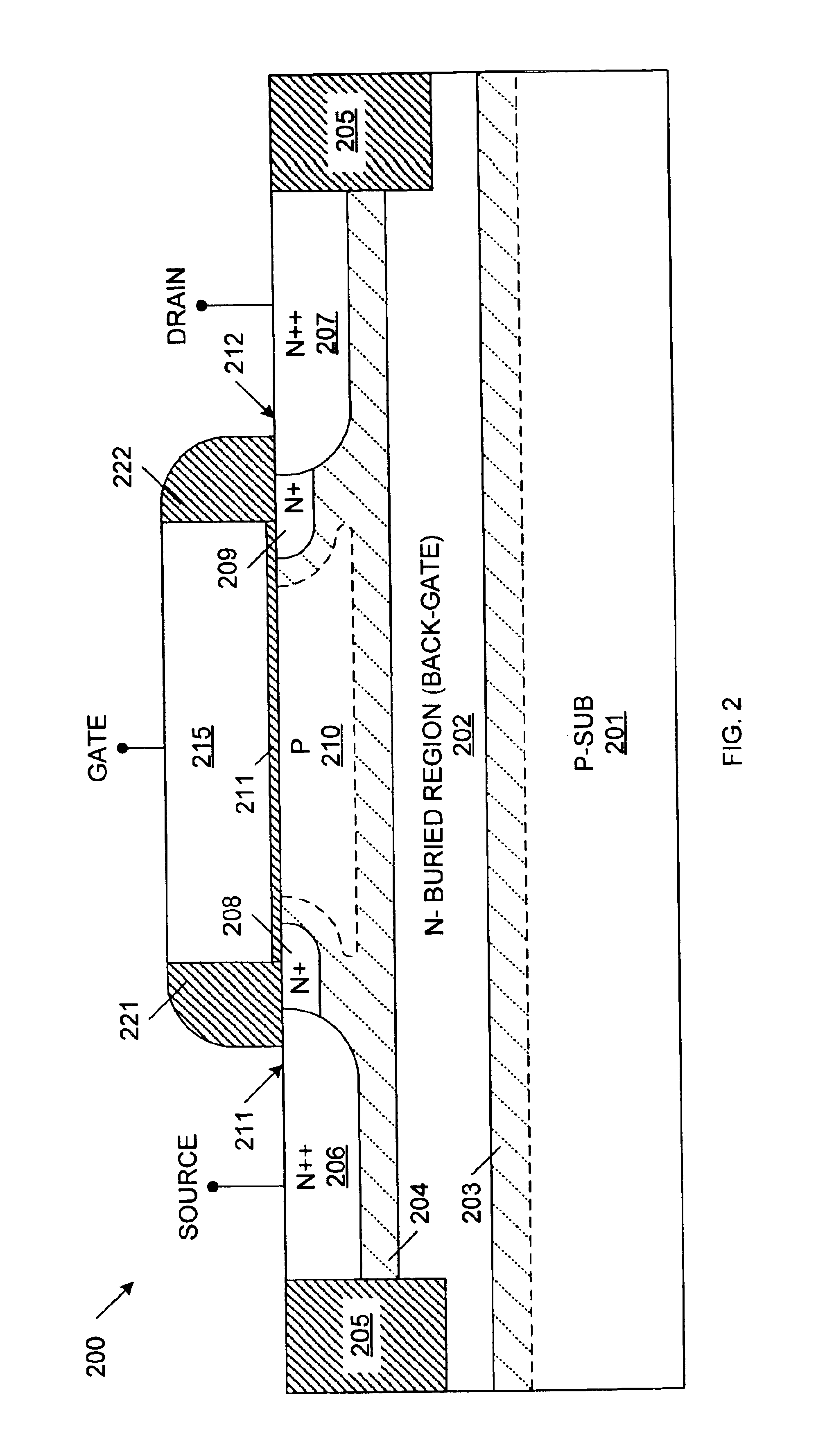

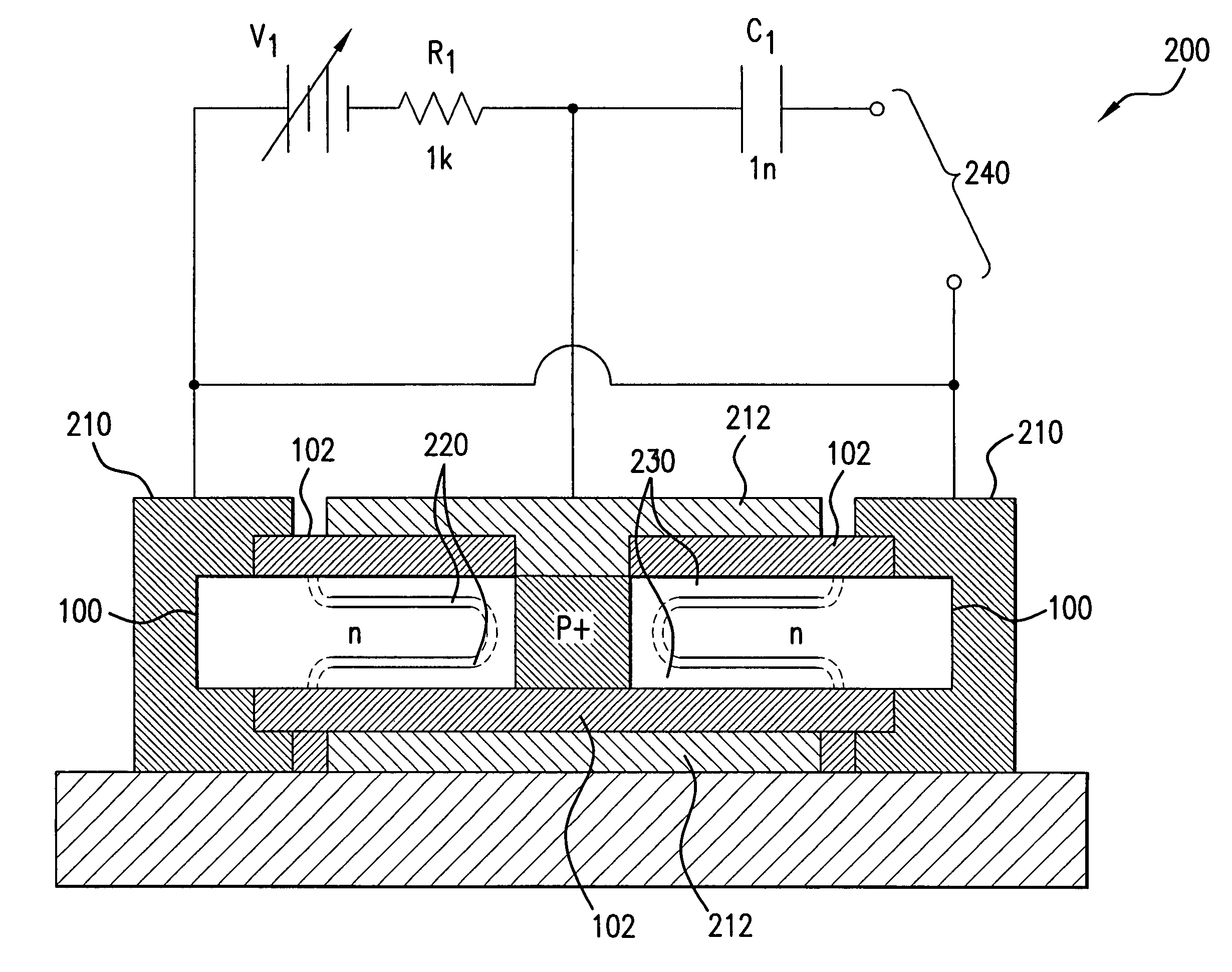

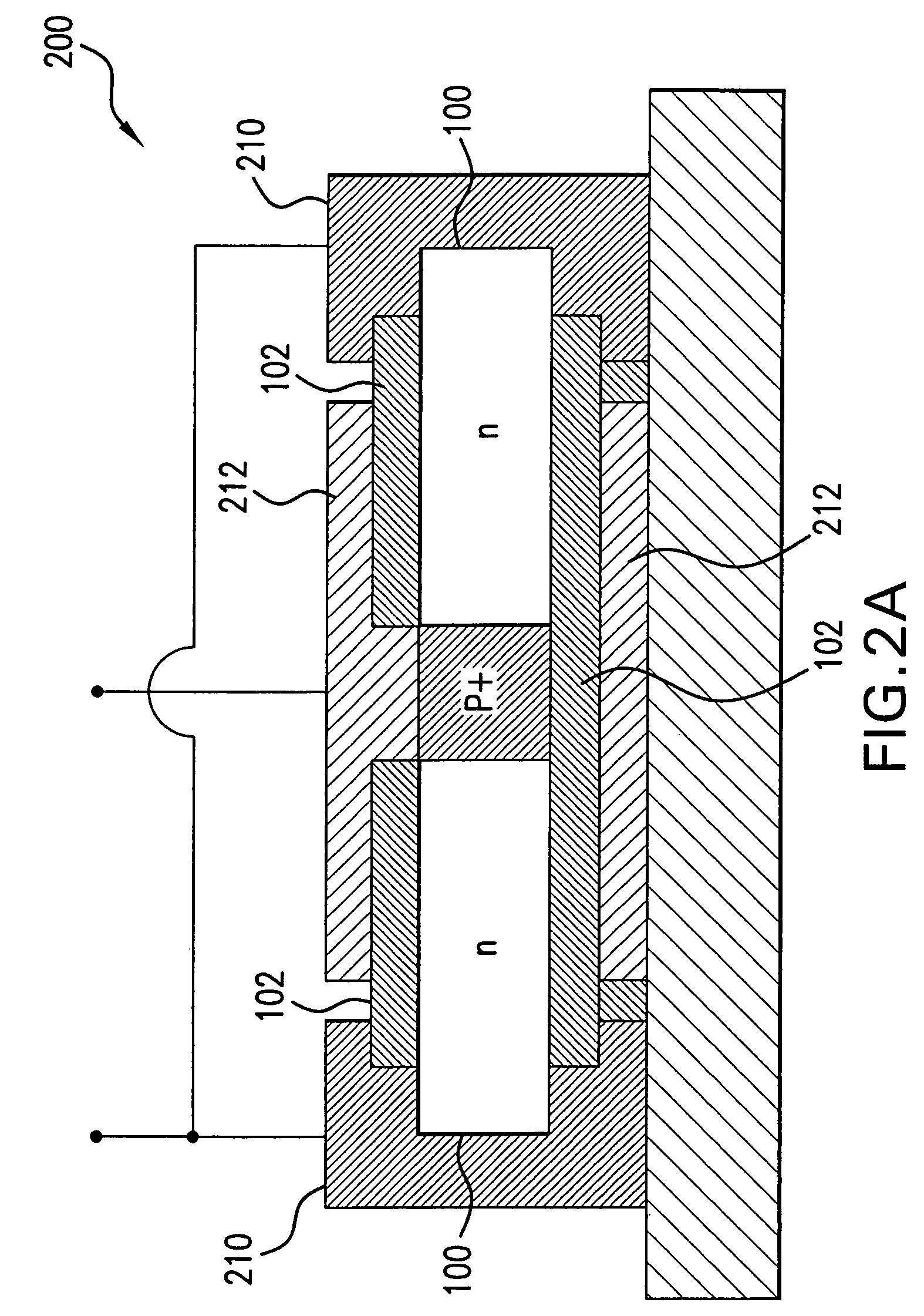

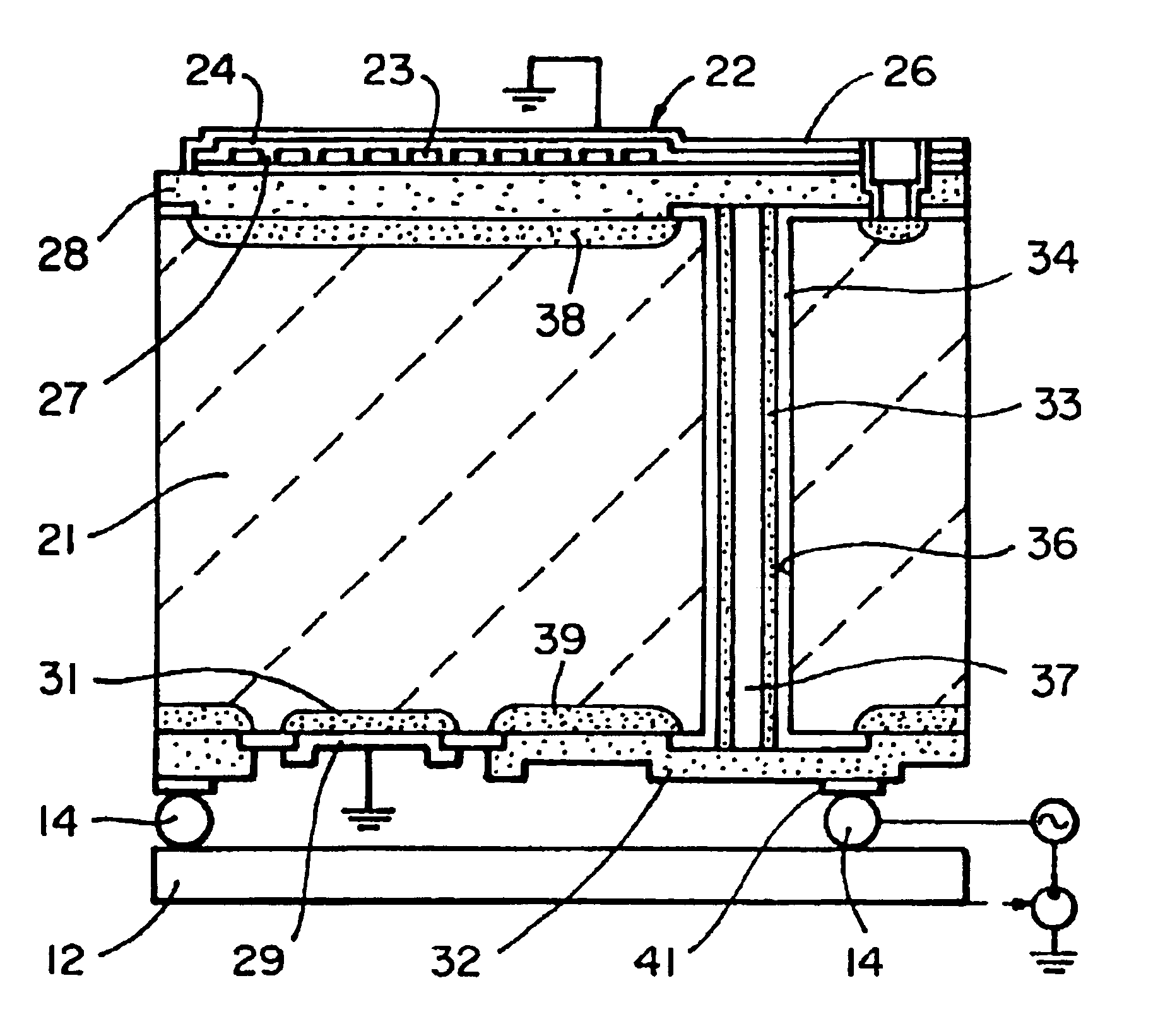

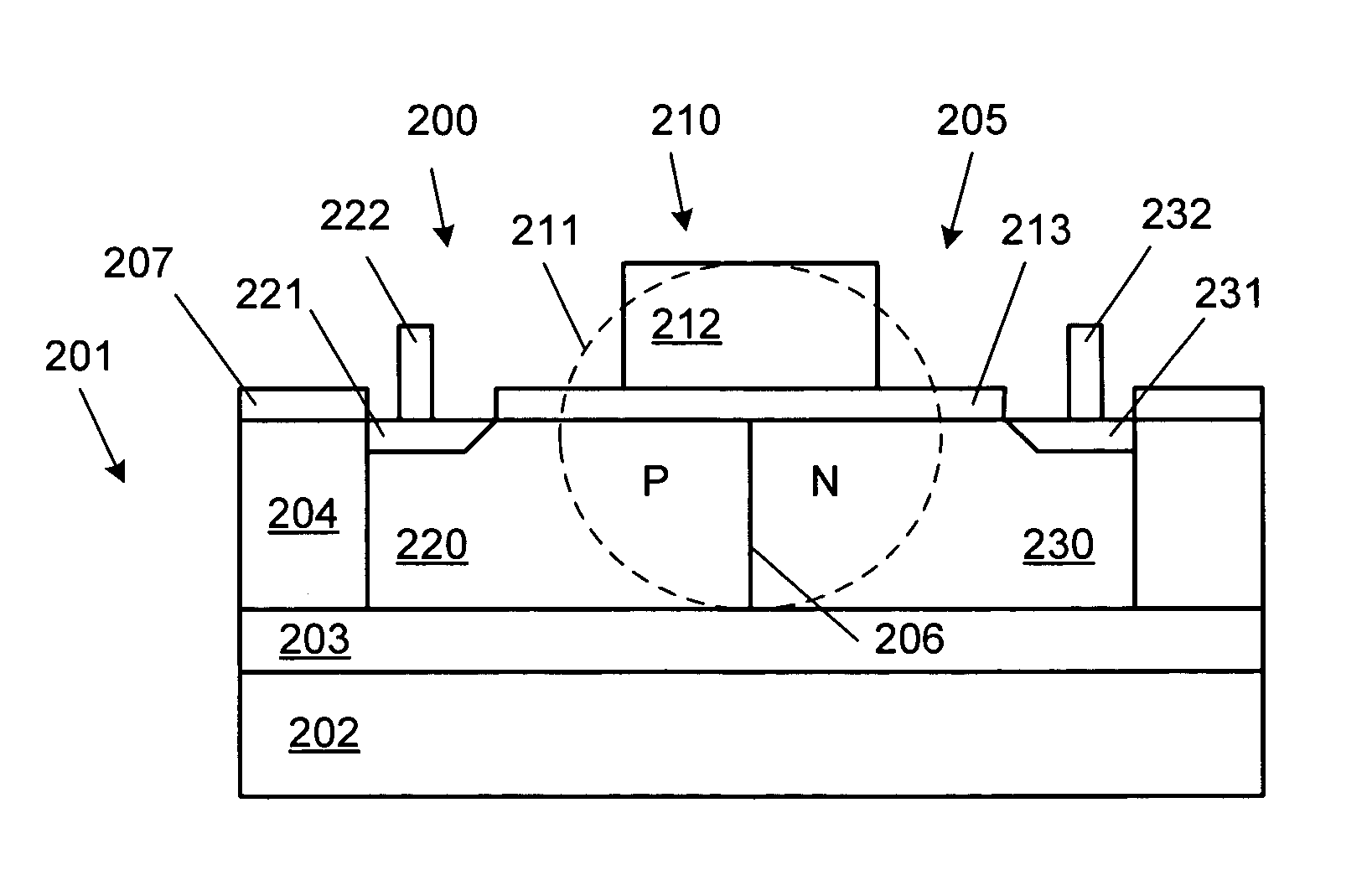

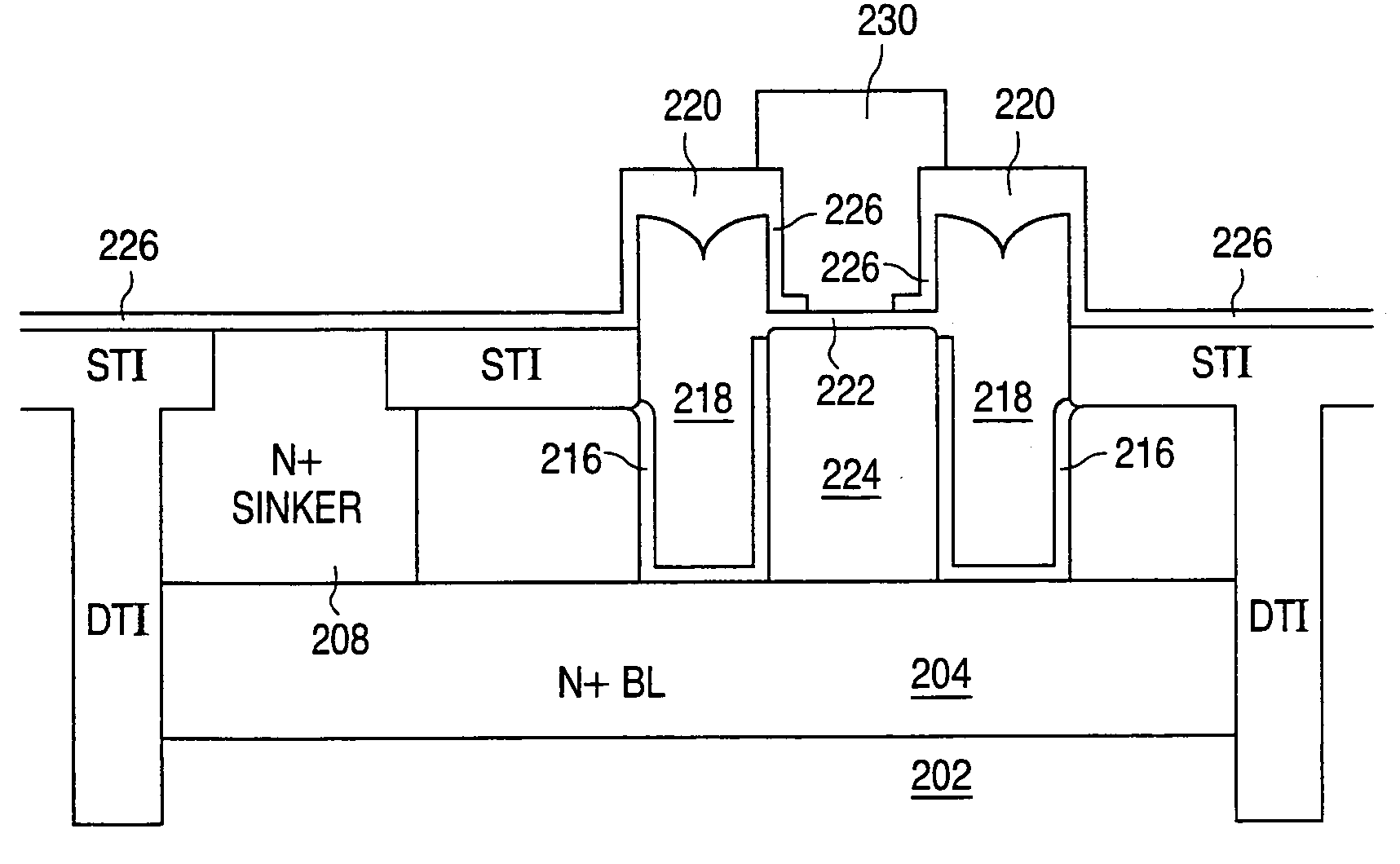

Method of fabricating a one transistor floating-body DRAM cell in bulk CMOS process with electrically isolated charge storage region

InactiveUS6913964B2Limiting leakage currentEnsure adequate isolationTransistorSolid-state devicesEngineeringField-effect transistor

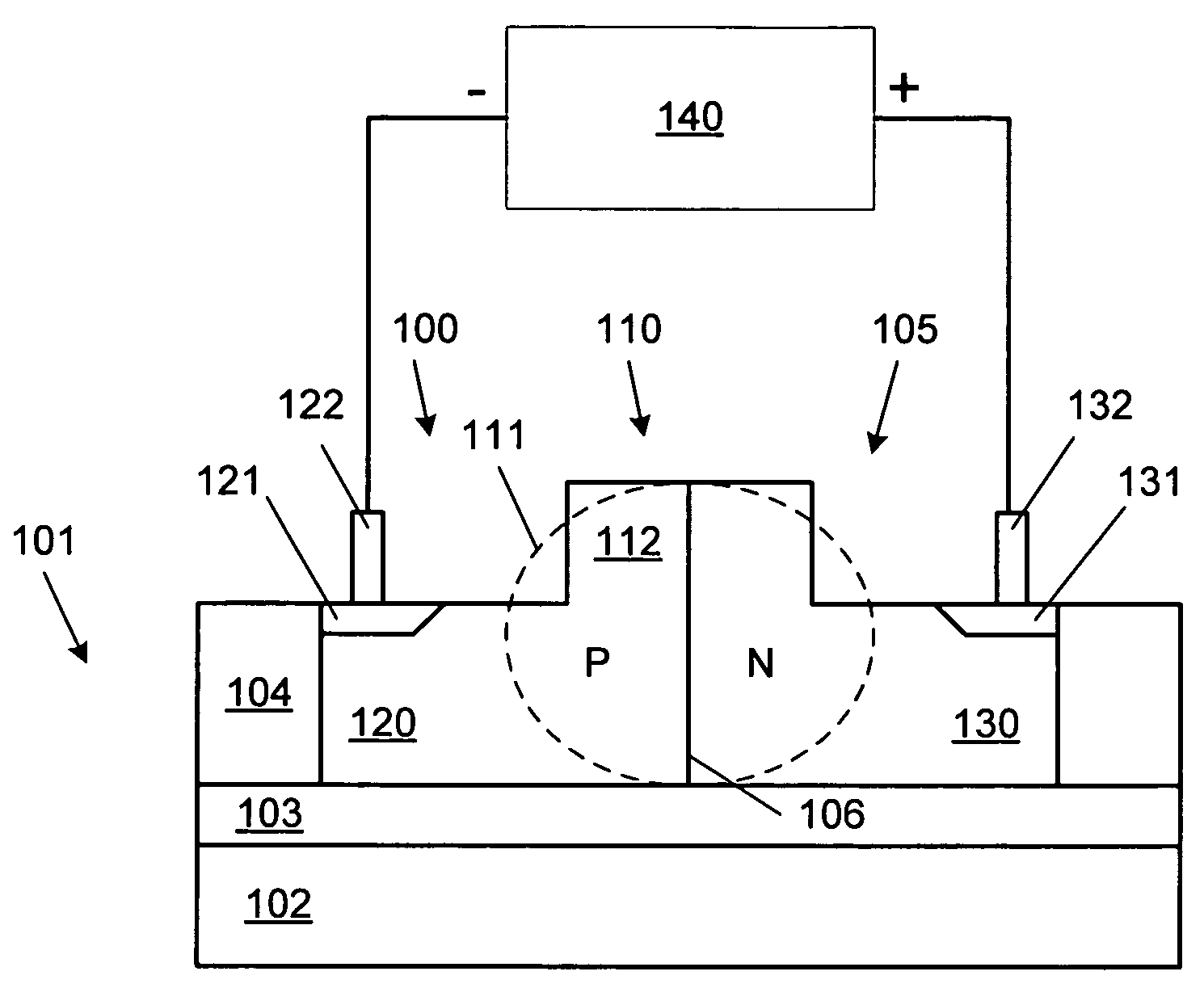

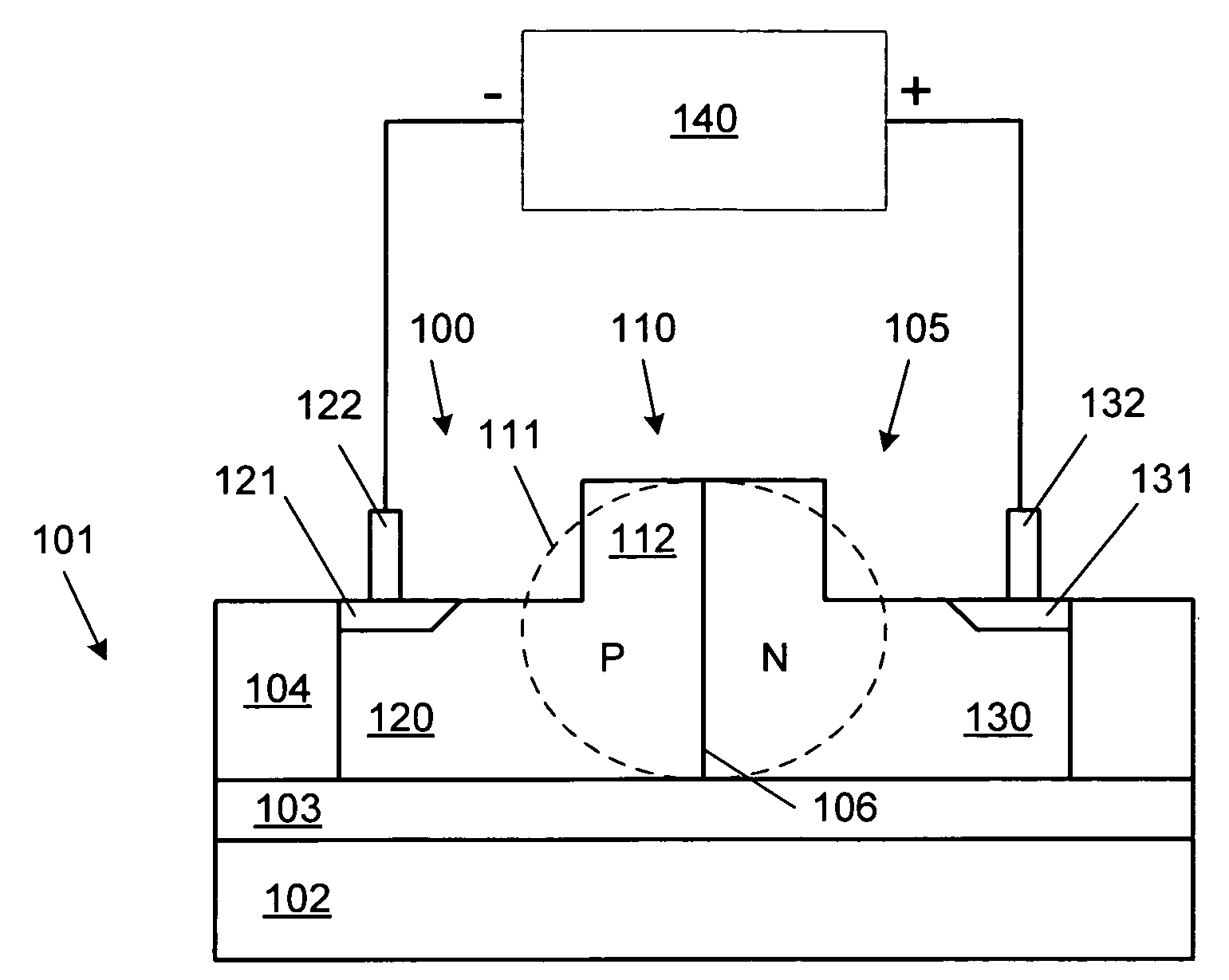

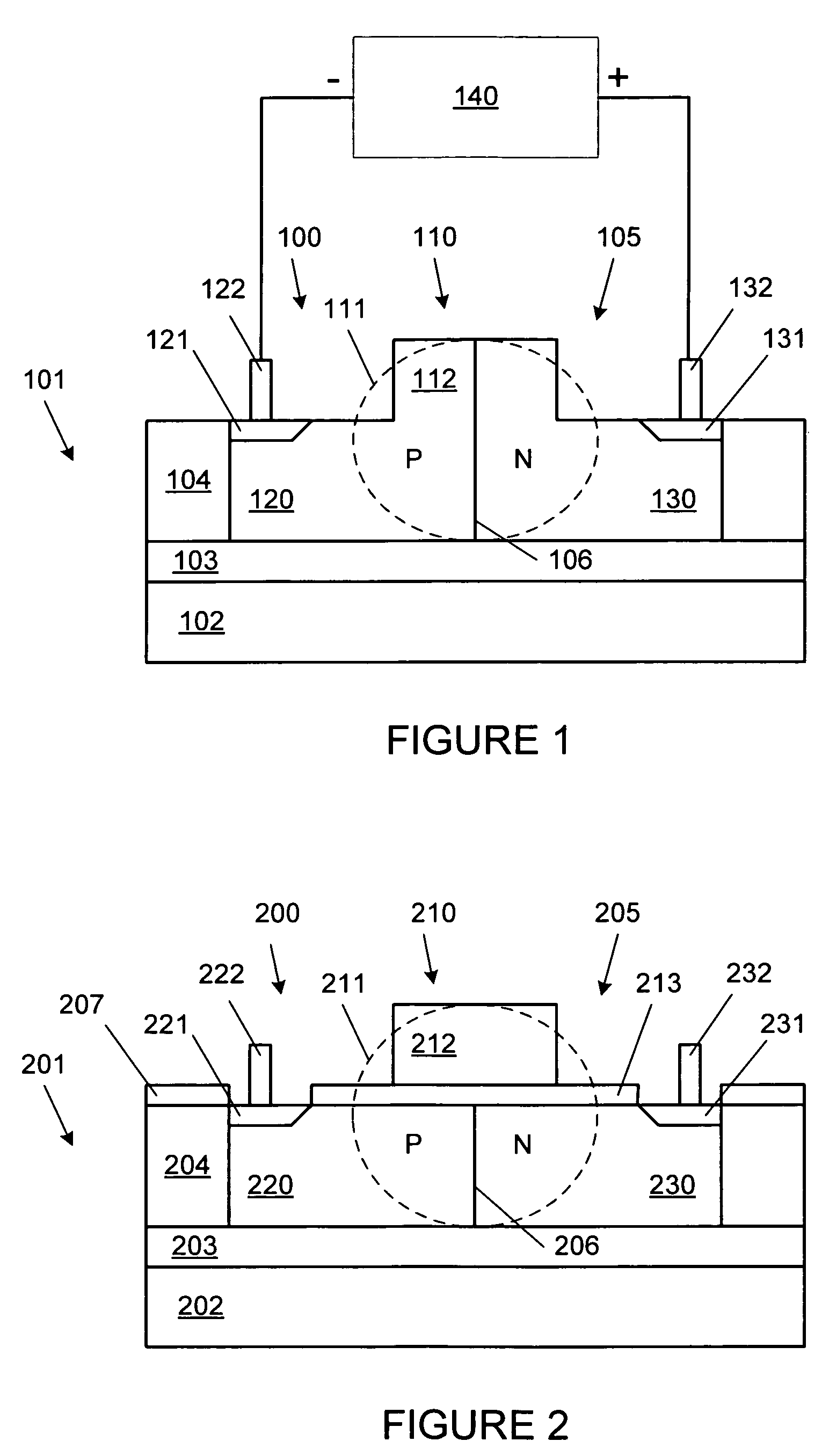

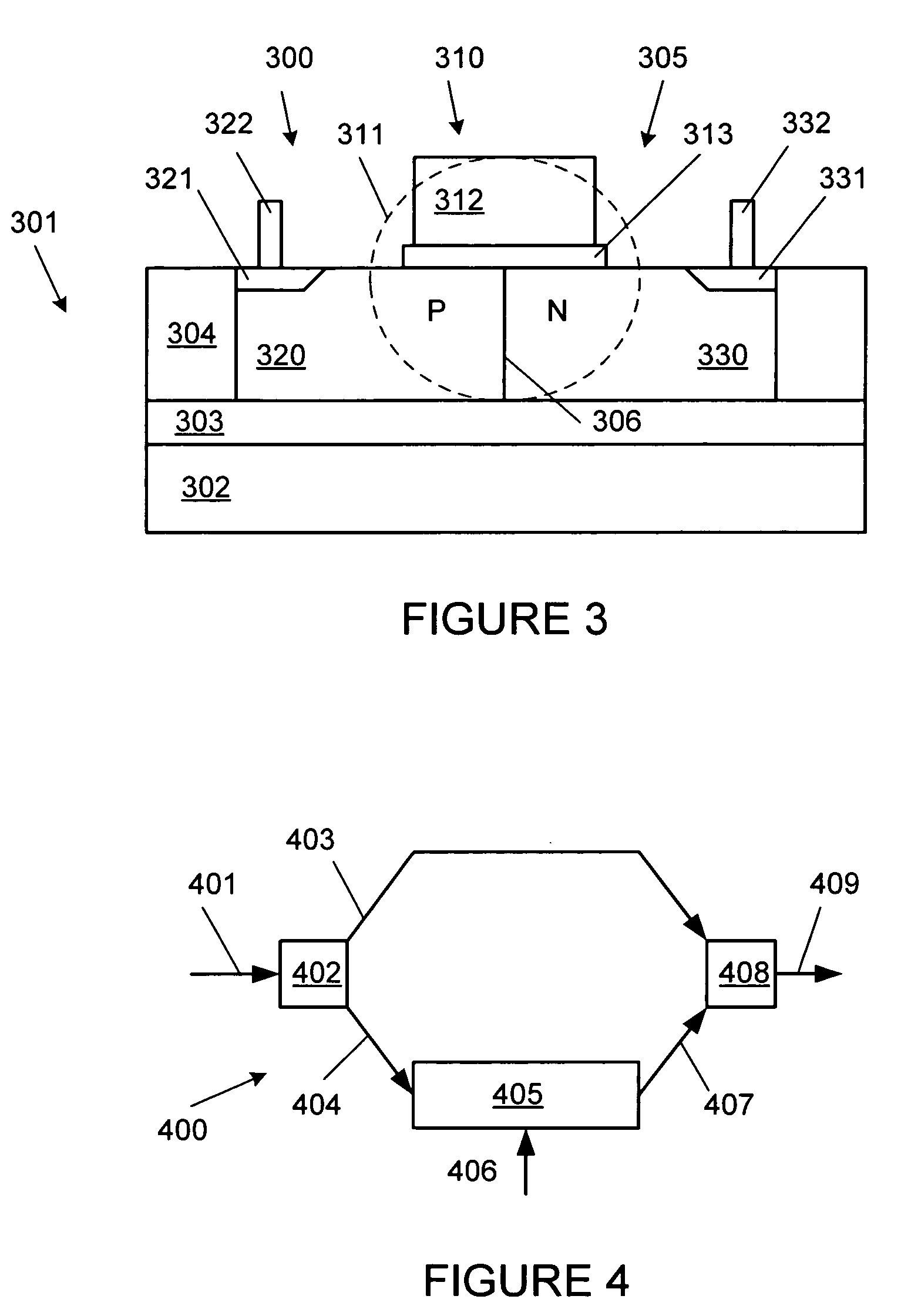

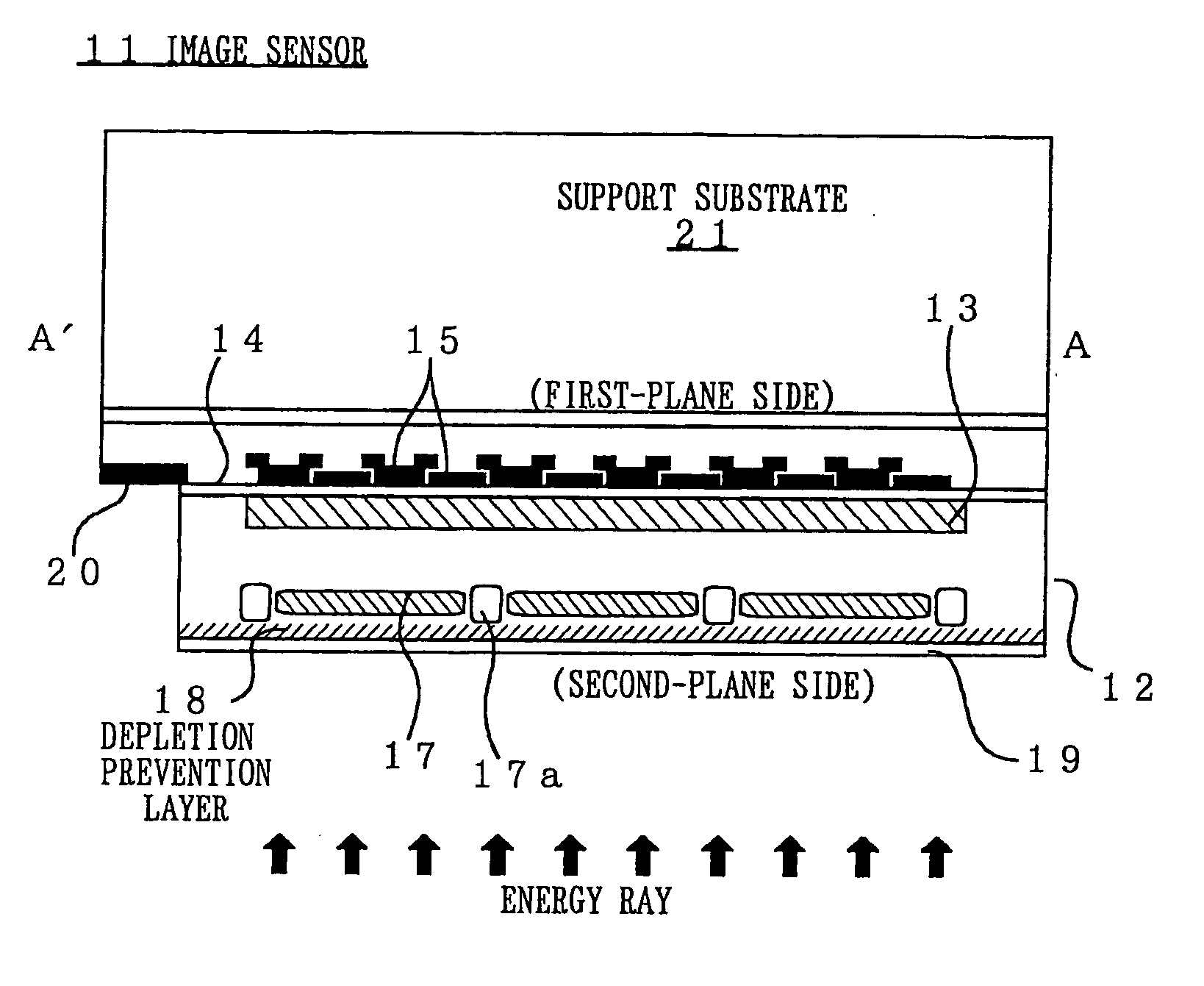

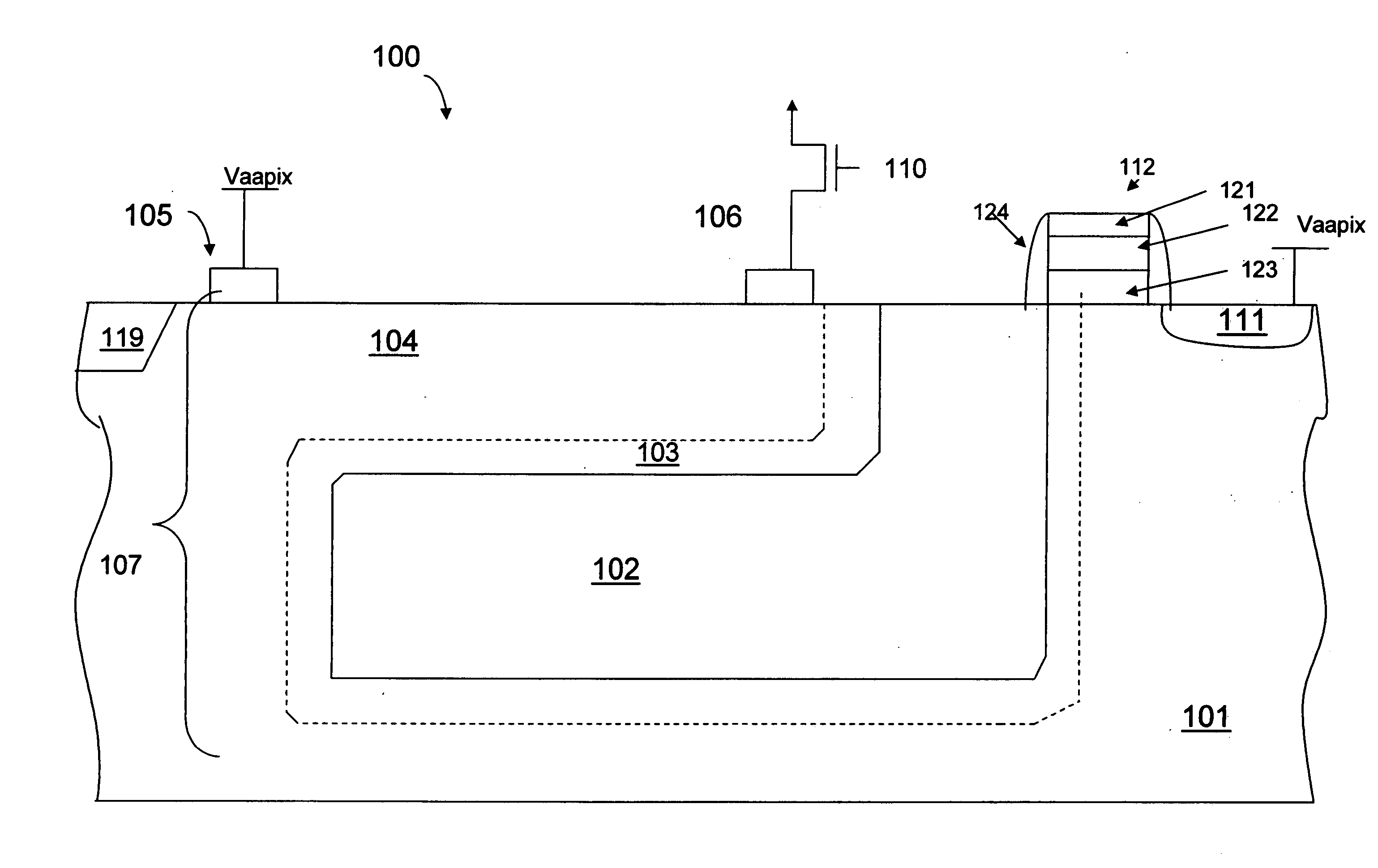

A one-transistor, floating-body (1T / FB) dynamic random access memory (DRAM) cell is provided that includes a field-effect transistor fabricated using a process compatible with a standard CMOS process. The field-effect transistor includes a source region and a drain region of a first conductivity type and a floating body region of a second conductivity type, opposite the first conductivity type, located between the source region and the drain region. A buried region of the first conductivity type is located under the source region, drain region and floating body region. The buried region helps to form a depletion region, which is located between the buried region and the source region, the drain region and the floating body region. The floating body region is thereby isolated by the depletion region. A bias voltage can be applied to the buried region, thereby controlling leakage currents in the 1T / FB DRAM cell.

Owner:MOSYS INC

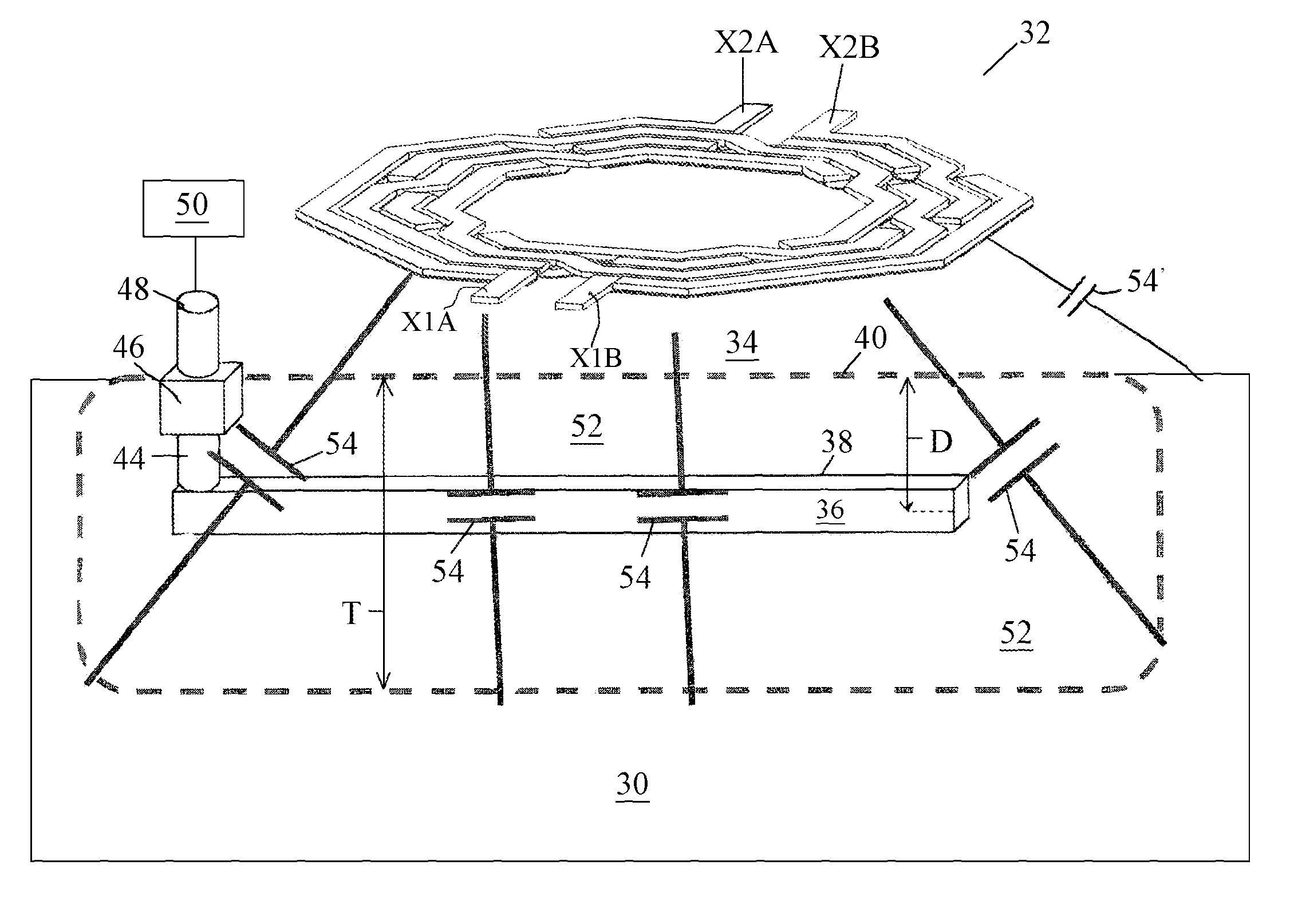

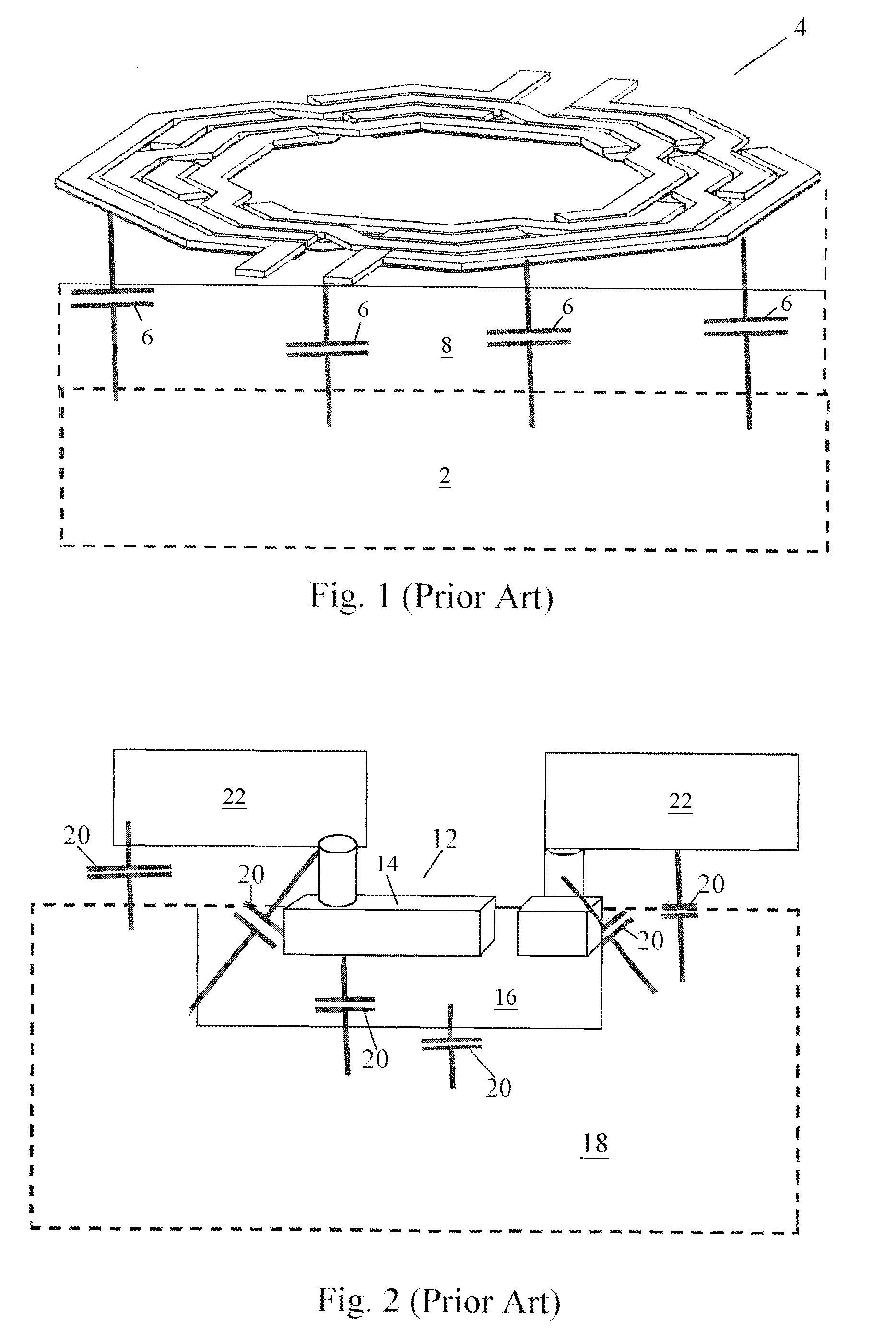

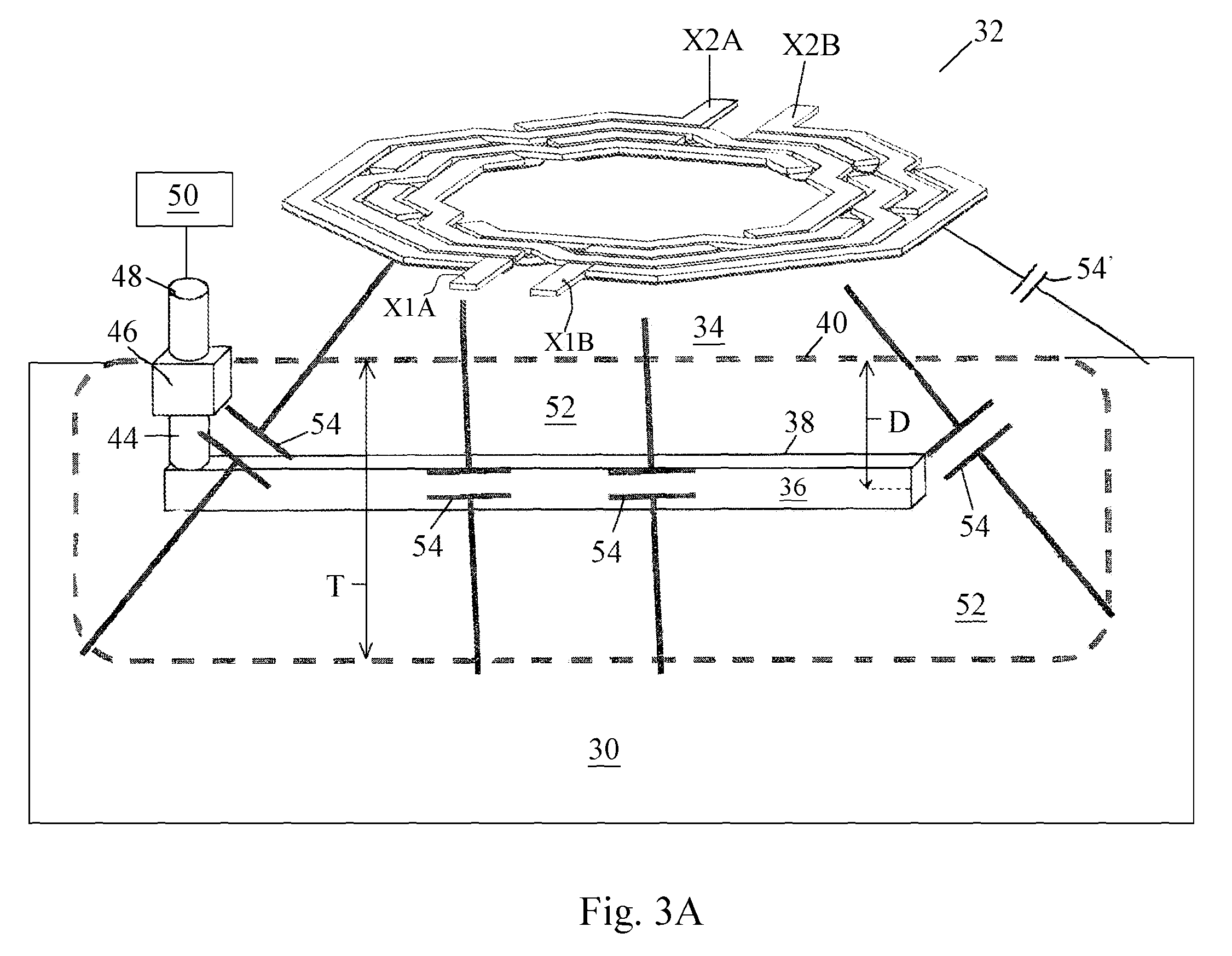

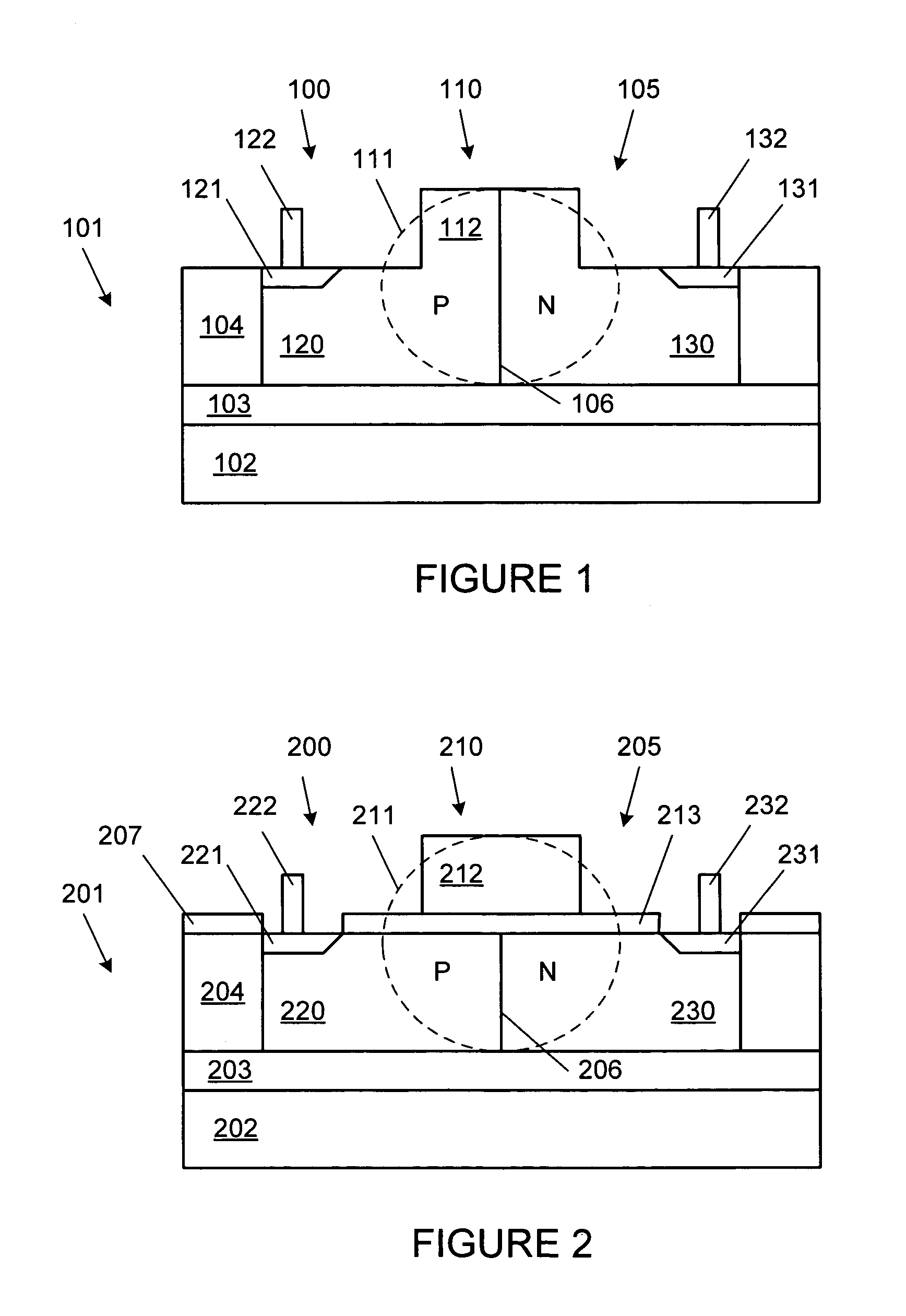

Reducing high-frequency signal loss in substrates

ActiveUS8129817B2Reduce signal lossSemiconductor/solid-state device detailsSolid-state devicesIntegrated circuitDepletion region

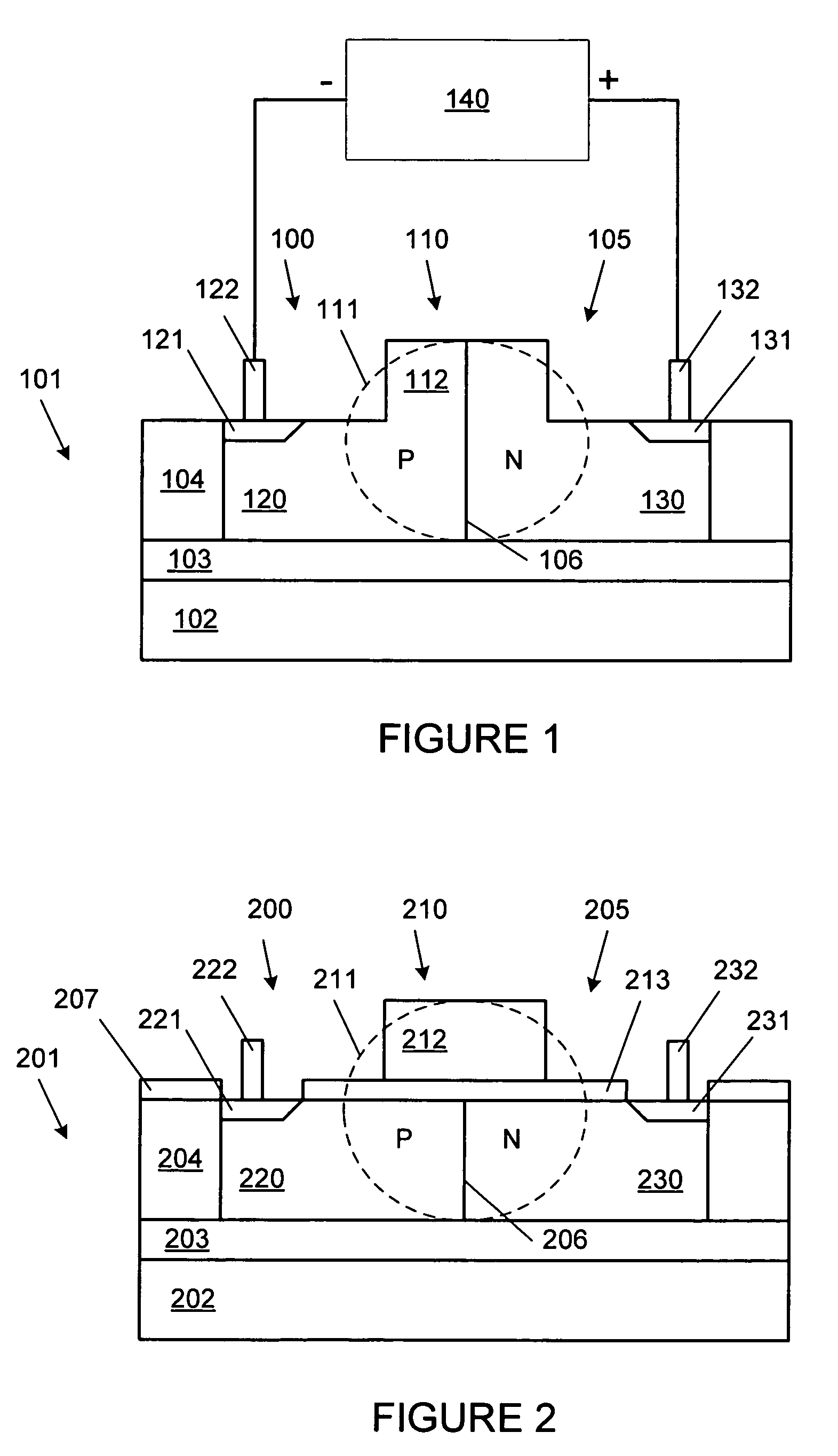

An integrated circuit structure includes a semiconductor substrate of a first conductivity type; and a depletion region in the semiconductor substrate. A deep well region is substantially enclosed by the depletion region, wherein the deep well region is of a second conductivity type opposite the first conductivity type. The depletion region includes a first portion directly over the deep well region and a second portion directly under the deep well region. An integrated circuit device is directly over the depletion region.

Owner:TAIWAN SEMICON MFG CO LTD

PN diode optical modulators fabricated in rib waveguides

ActiveUS20060008223A1Reduce speedSemiconductor/solid-state device manufacturingOptical waveguide light guideLow speedPhase shifted

Owner:CISCO TECH INC

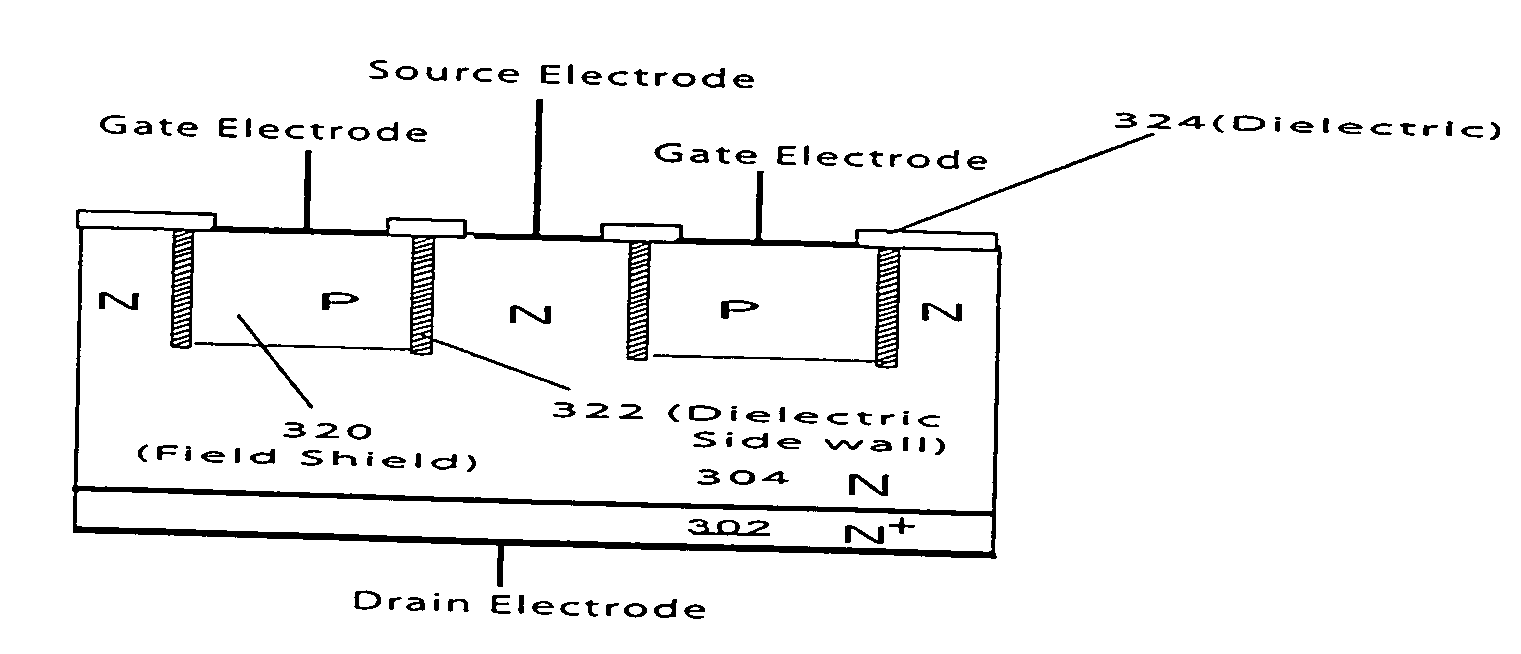

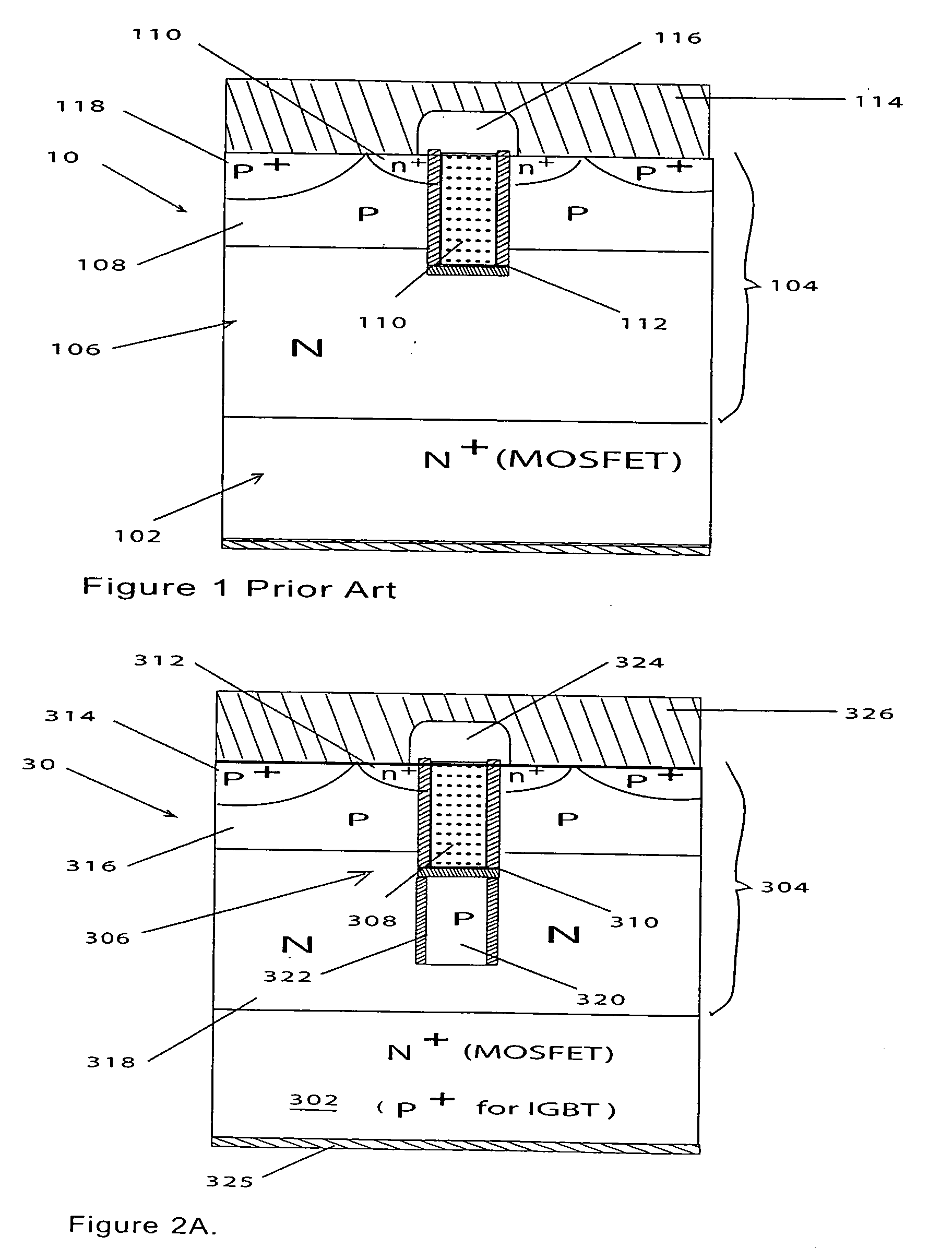

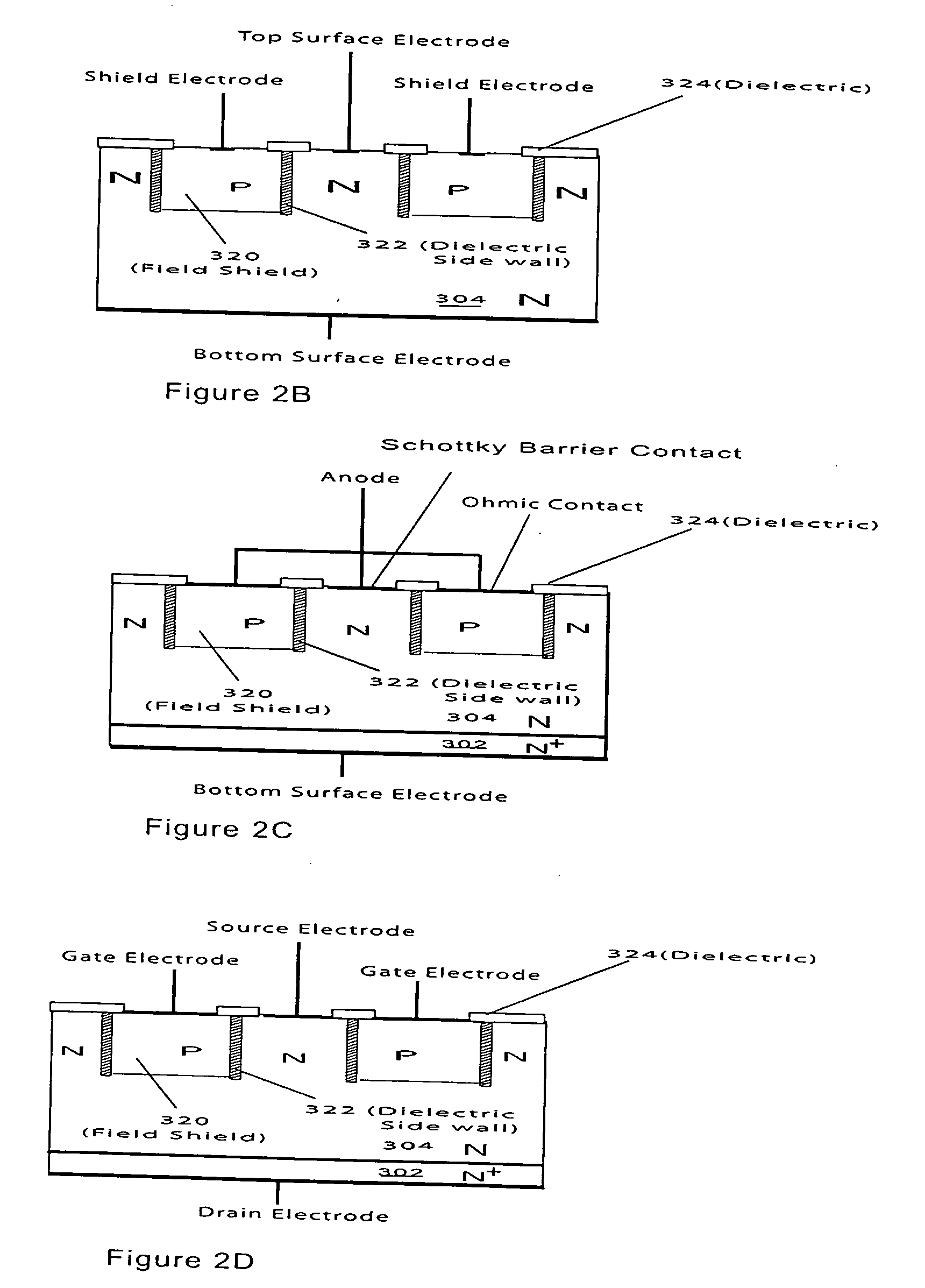

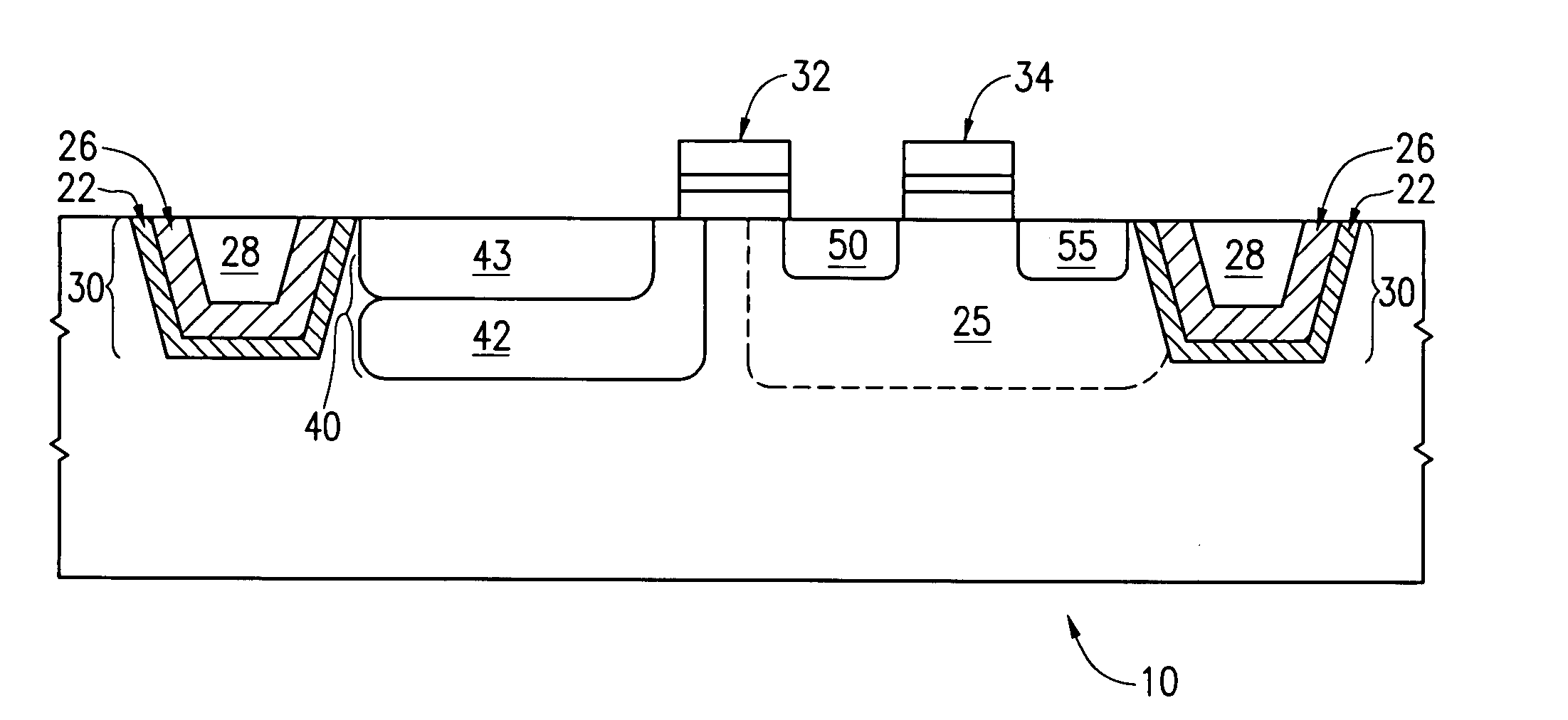

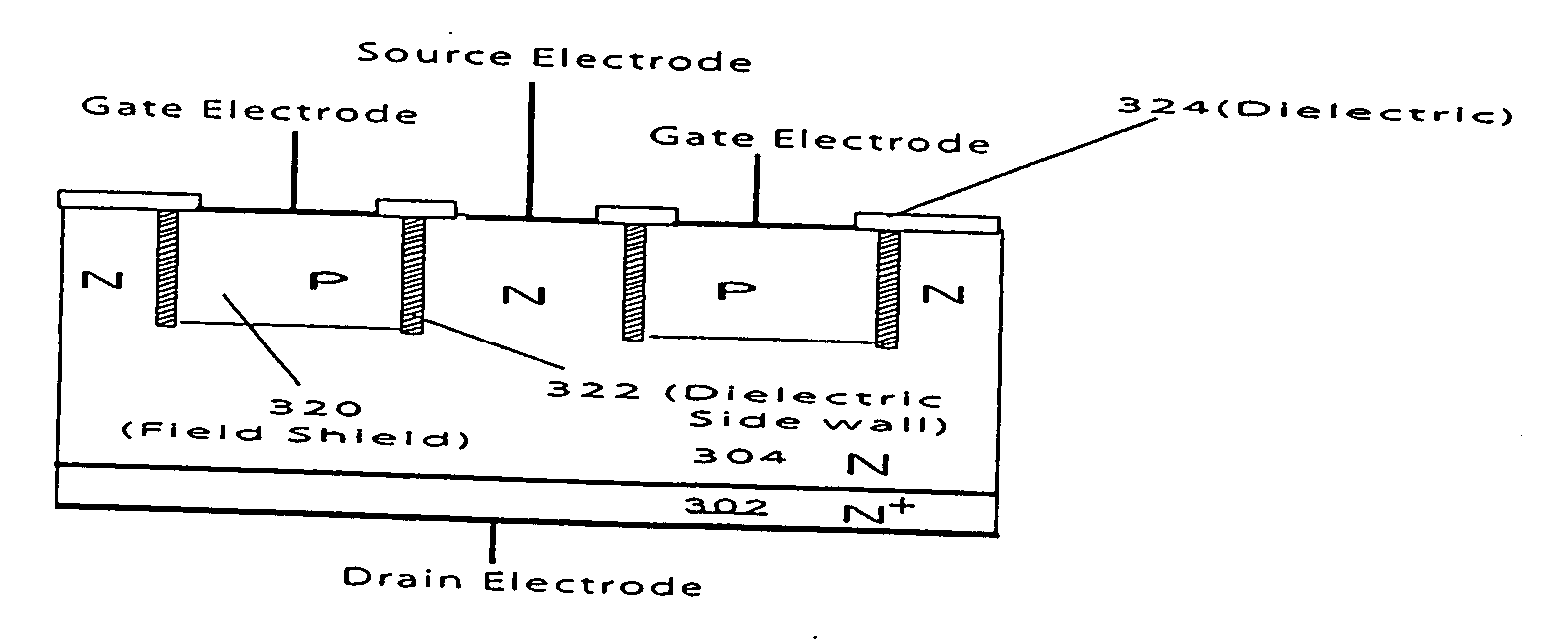

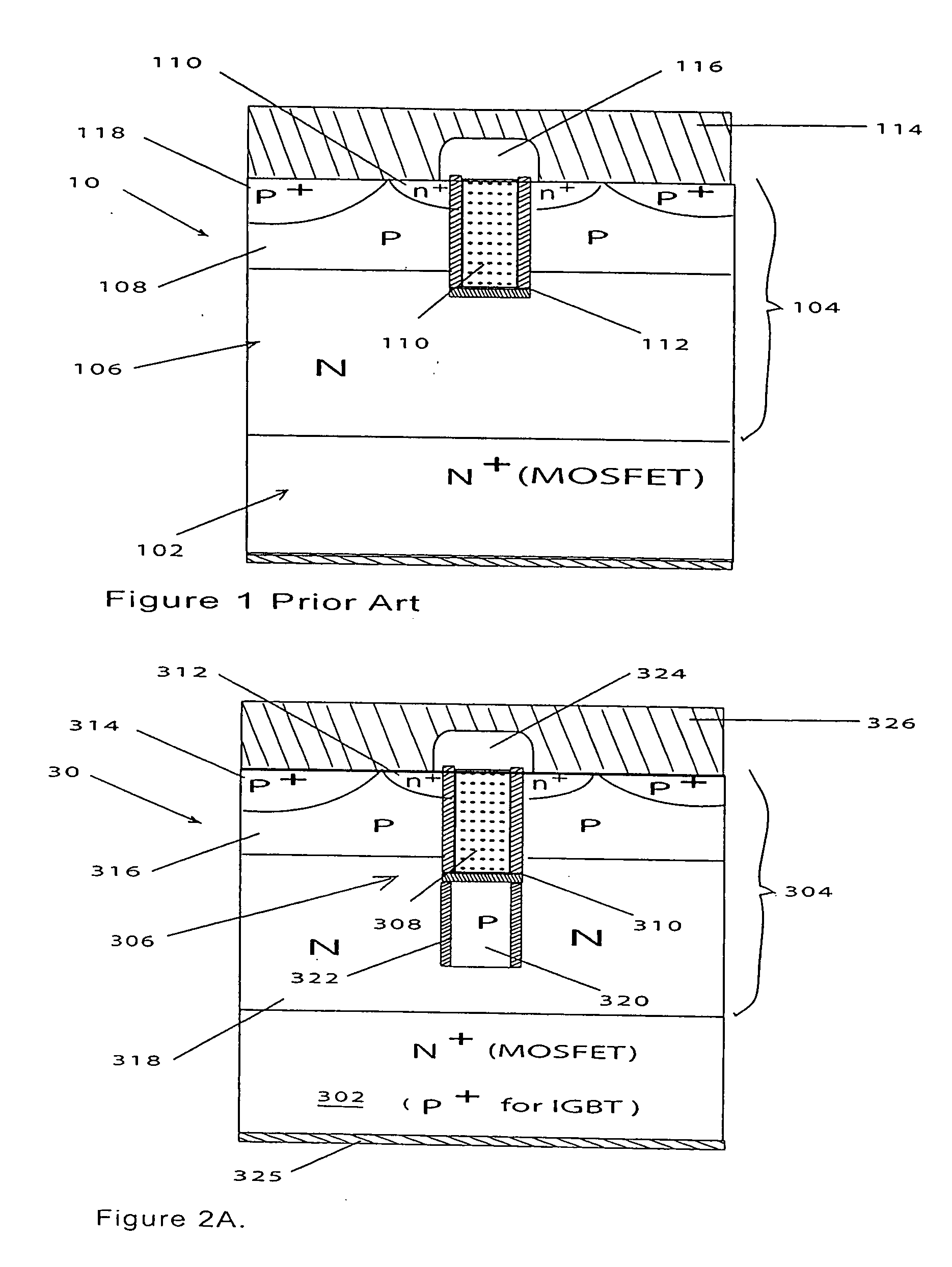

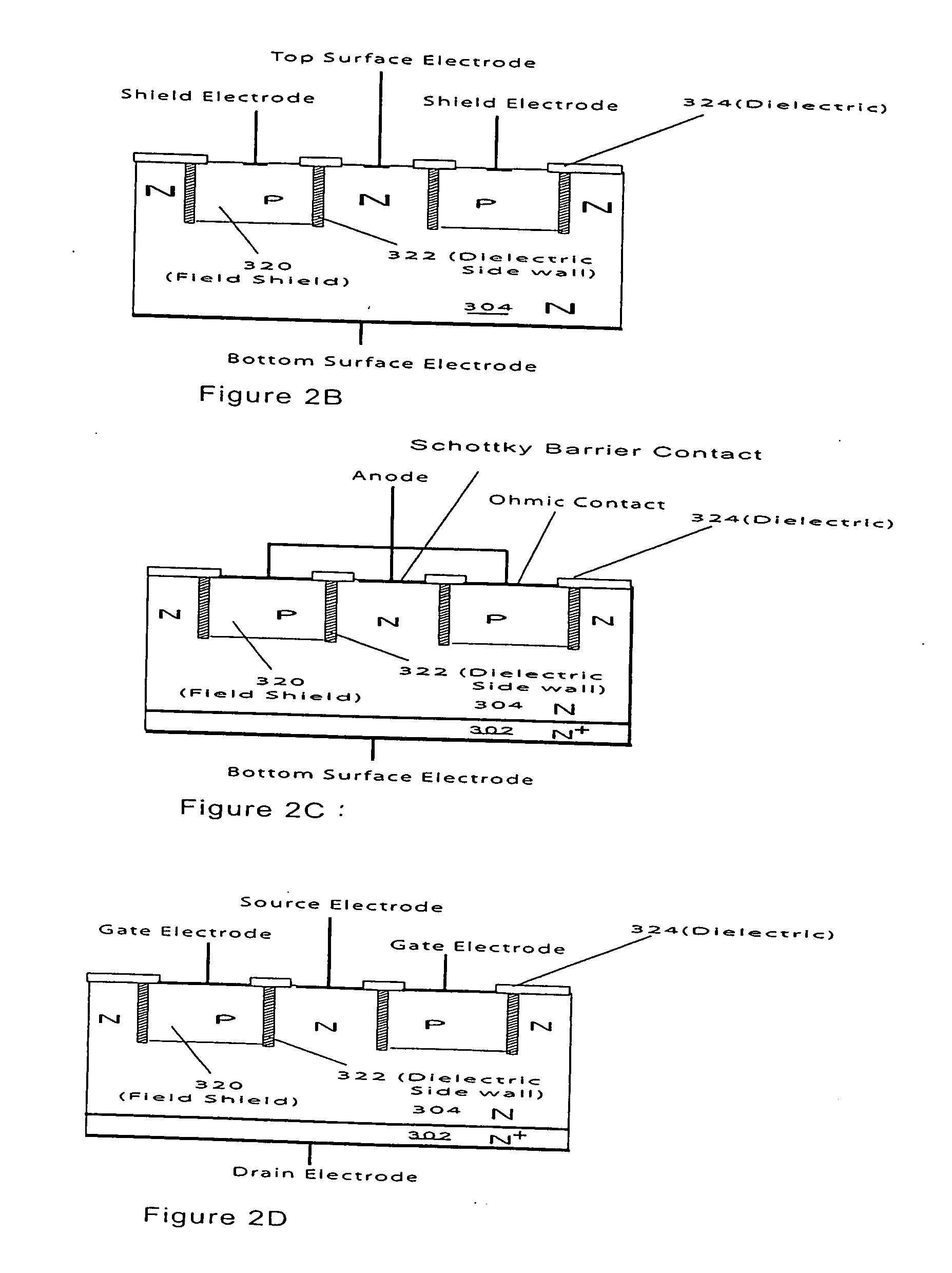

Semiconductor device containing dielectrically isolated pn junction for enhanced breakdown characteristics

InactiveUS20050167695A1Increased avalanche breakdown voltageLower on-resistanceThyristorSemiconductor/solid-state device manufacturingDevice materialPower MOSFET

A semiconductor device includes a field shield region that is doped opposite to the conductivity of the substrate and is bounded laterally by dielectric sidewall spacers and from below by a PN junction. For example, in a trench-gated MOSFET the field shield region may be located beneath the trench and may be electrically connected to the source region. When the MOSFET is reverse-biased, depletion regions extend from the dielectric sidewall spacers into the “drift” region, shielding the gate oxide from high electric fields and increasing the avalanche breakdown voltage of the device. This permits the drift region to be more heavily doped and reduces the on-resistance of the device. It also allows the use of a thin, 20 Å gate oxide for a power MOSFET that is to be switched with a 1V signal applied to its gate while being able to block over 30V applied across its drain and source electrodes, for example.

Owner:ALPHA & OMEGA SEMICON INC

Dynamic deep depletion field effect transistor

Owner:INFINEON TECH AMERICAS CORP

Monolithic integrated circuit of a field-effect semiconductor device and a diode

InactiveUS20070228477A1Flow assuranceEasy to FeedbackTransistorSolid-state devicesMESFETField effect

A field-effect semiconductor device such as a HEMT or MESFET is monolithically integrated with a Schottky diode for feedback, regeneration, or protection purposes. The field-effect semiconductor device includes a main semiconductor region having formed thereon a source, a drain, and a gate between the source and the drain. Also formed on the main semiconductor region, preferably between gate and drain, is a Schottky electrode electrically coupled to the source. The Schottky electrode provides a Schottky diode in combination with the main semiconductor region. A current flow is assured from Schottky electrode to drain without interruption by a depletion region expanding from the gate.

Owner:SANKEN ELECTRIC CO LTD

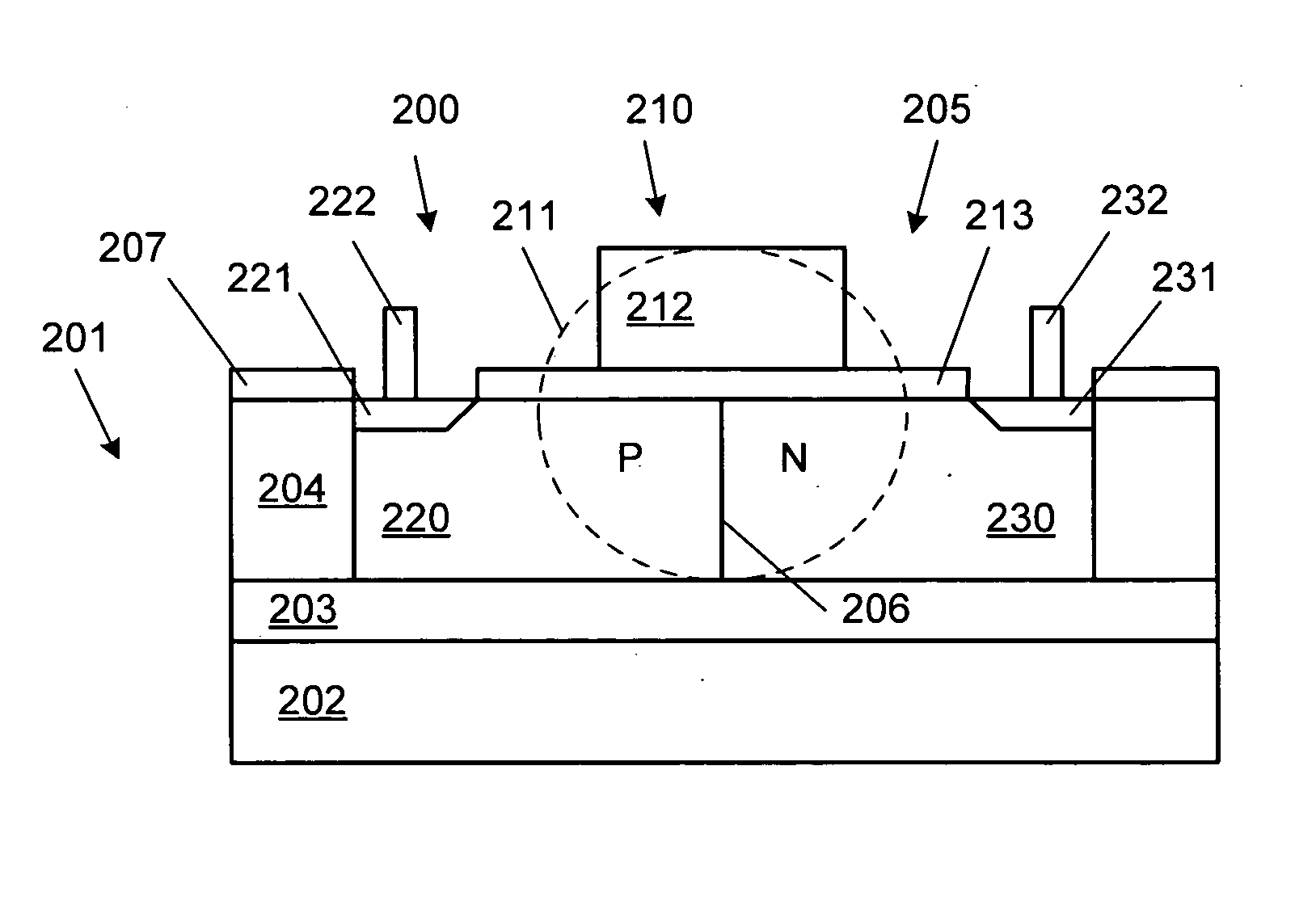

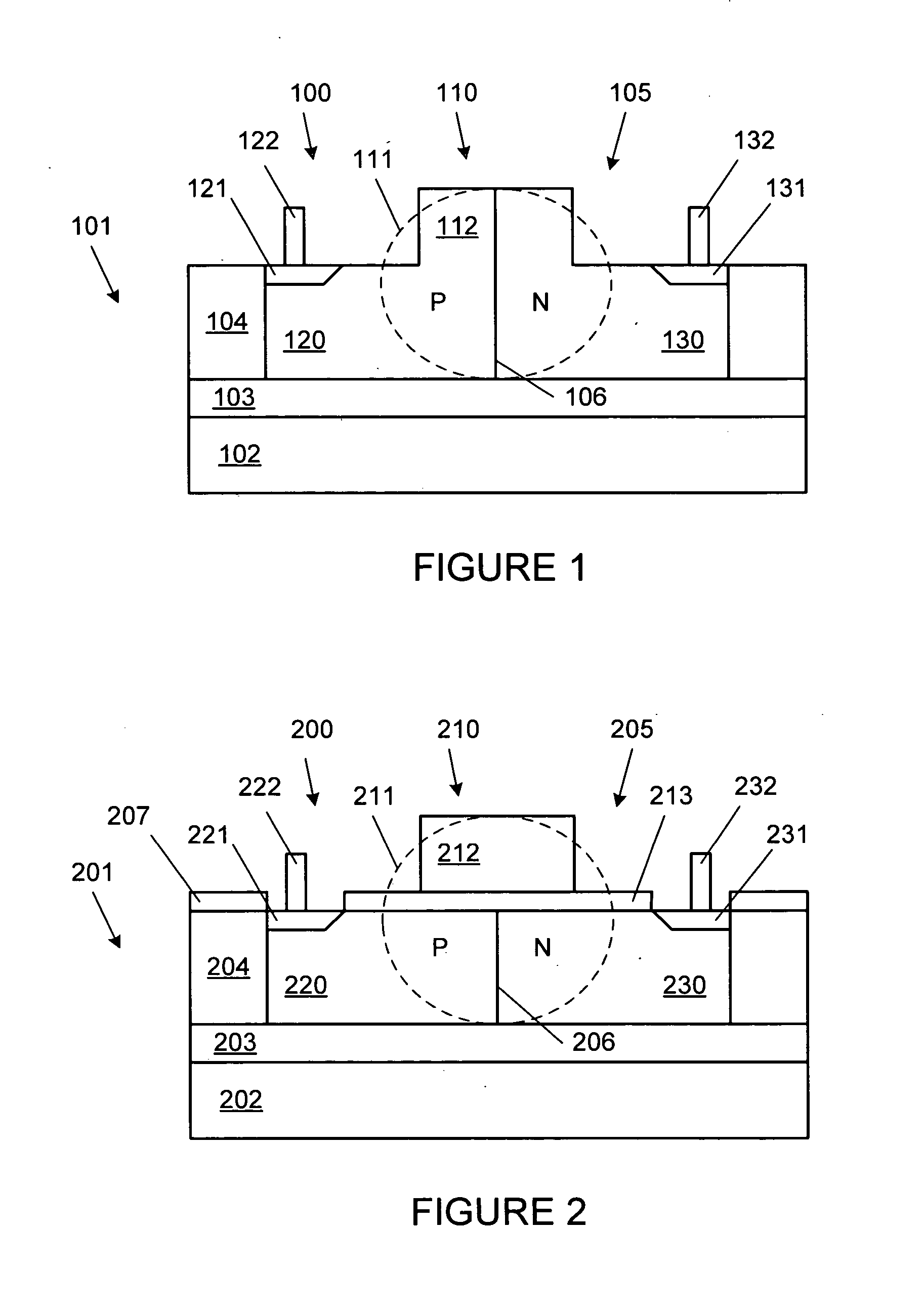

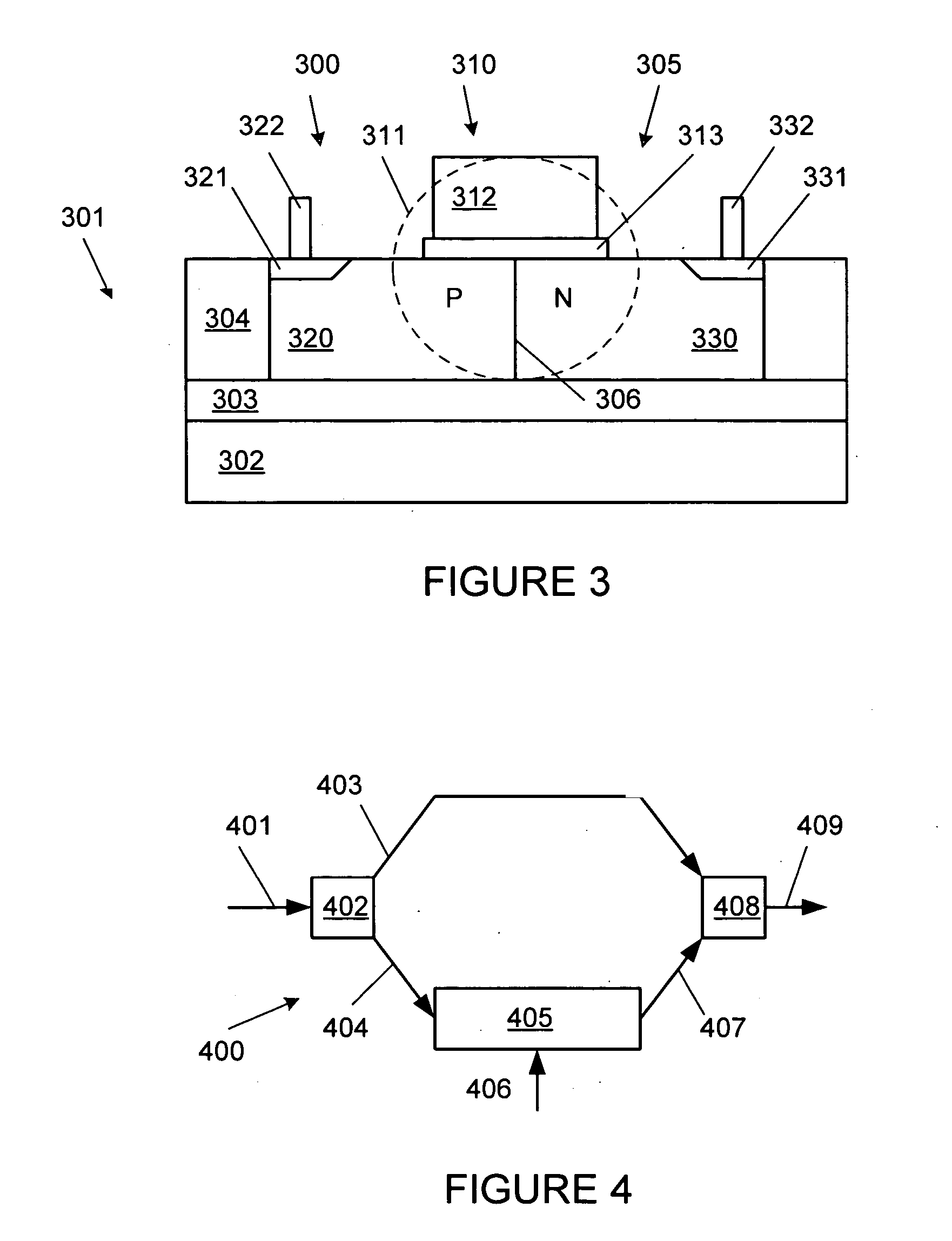

Doping profiles in PN diode optical modulators

ActiveUS7085443B1Coupling light guidesOptical waveguide light guideElectrical resistance and conductanceDopant

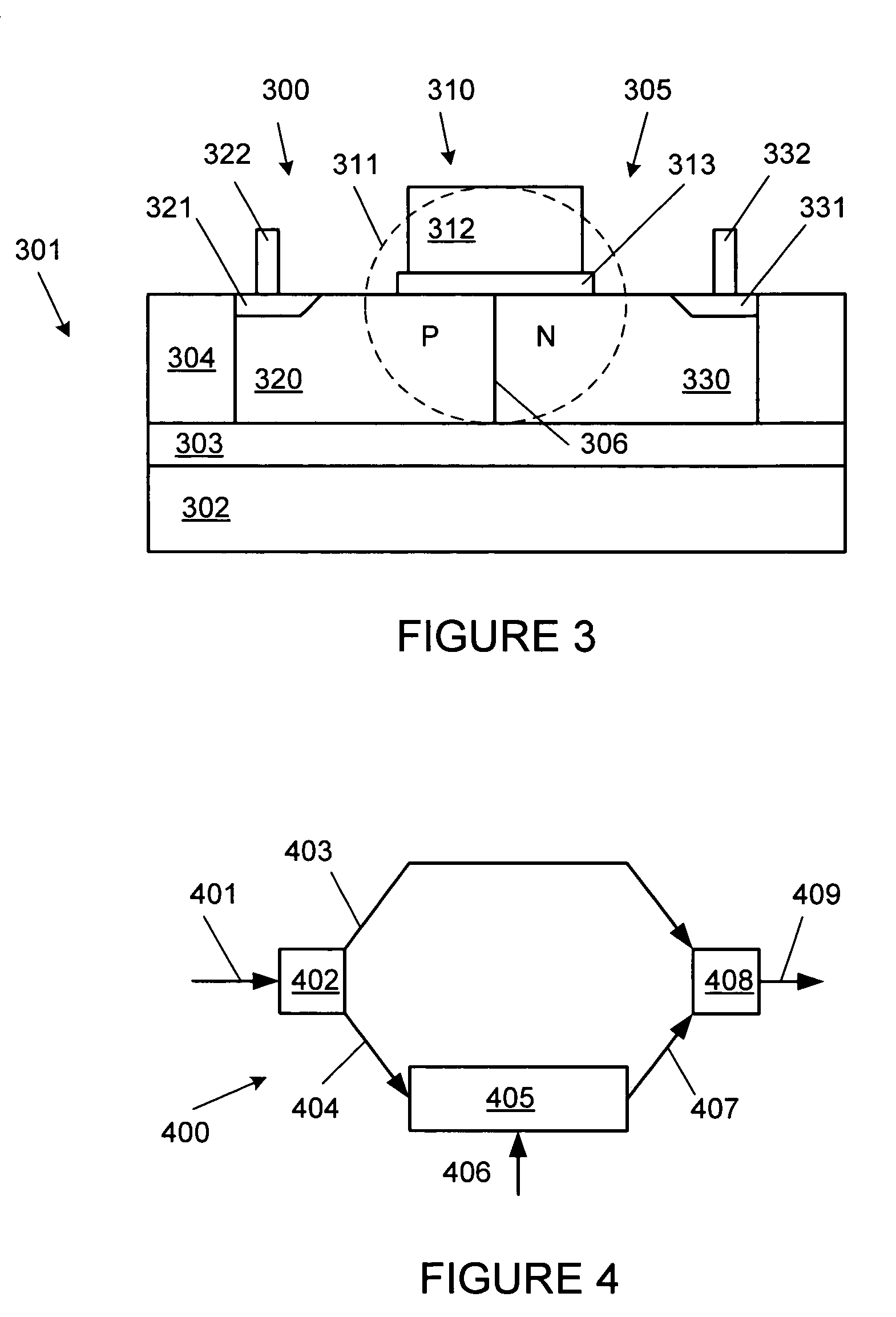

High speed optical modulators can be made of a lateral PN diode formed in a silicon optical waveguide, disposed on a SOI or other silicon based substrate. A PN junction is formed at the boundary of the P and N doped regions. The depletion region at the PN junction overlaps with the center of a guided optical mode propagating through the waveguide. Electrically modulating a lateral PN diode causes a phase shift in an optical wave propagating through the waveguide. Each of the doped regions can have a stepped or gradient doping profile within it or several doped sections with different doping concentrations. Forming the doped regions of a PN diode modulator with stepped or gradient doping profiles can optimize the trade off between the series resistance of the PN diode and the optical loss in the center of the waveguide due to the presence of dopants.

Owner:CISCO TECH INC

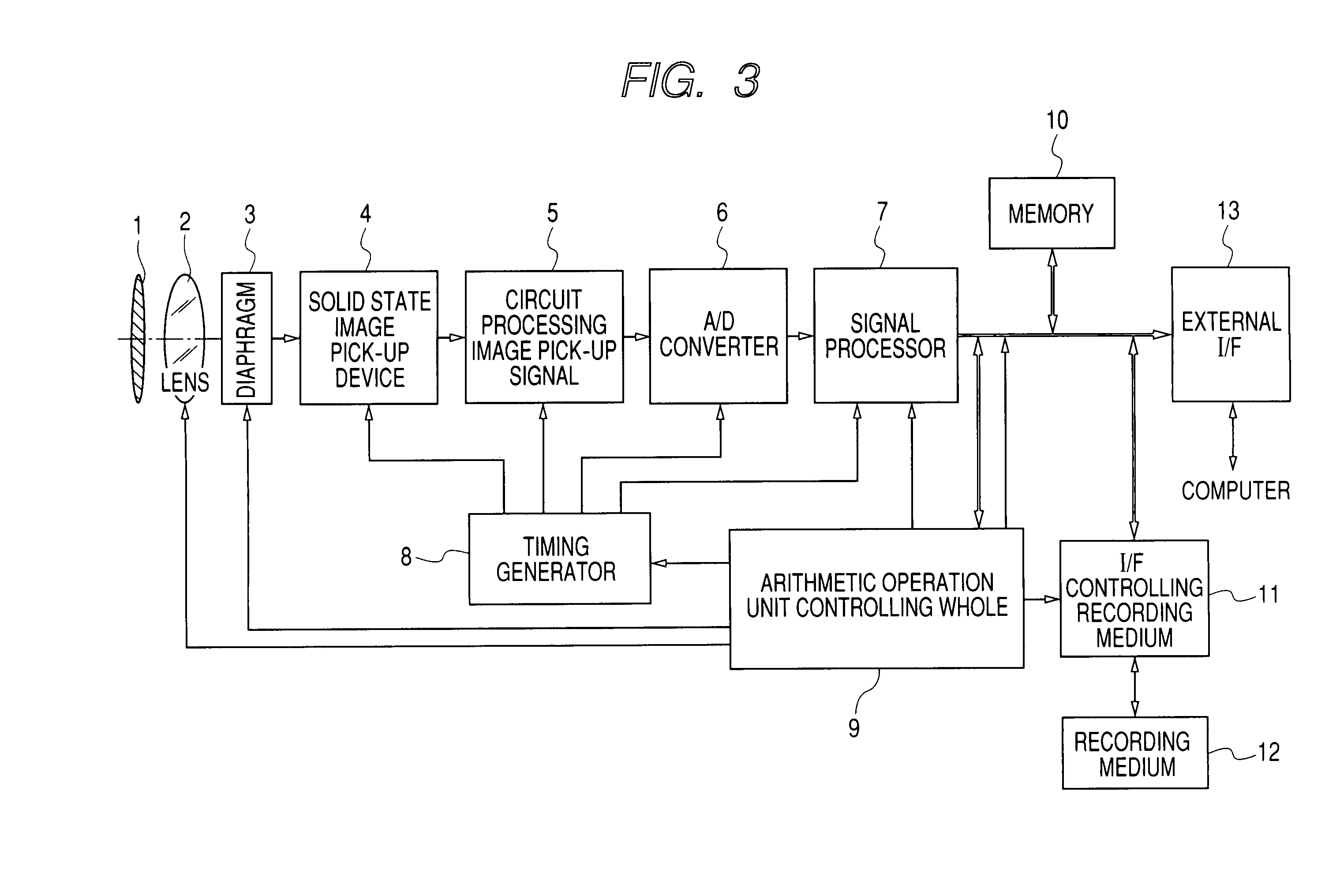

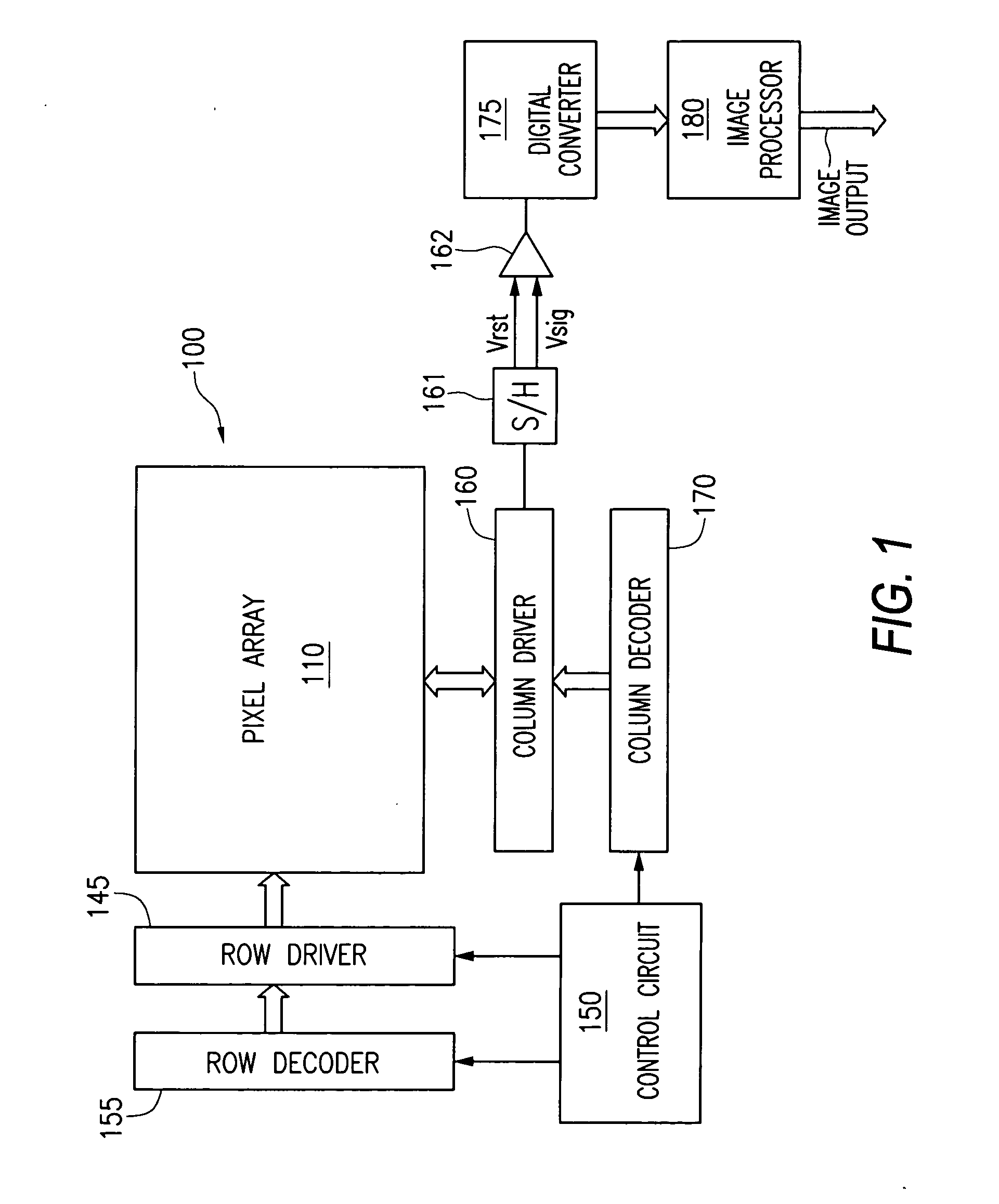

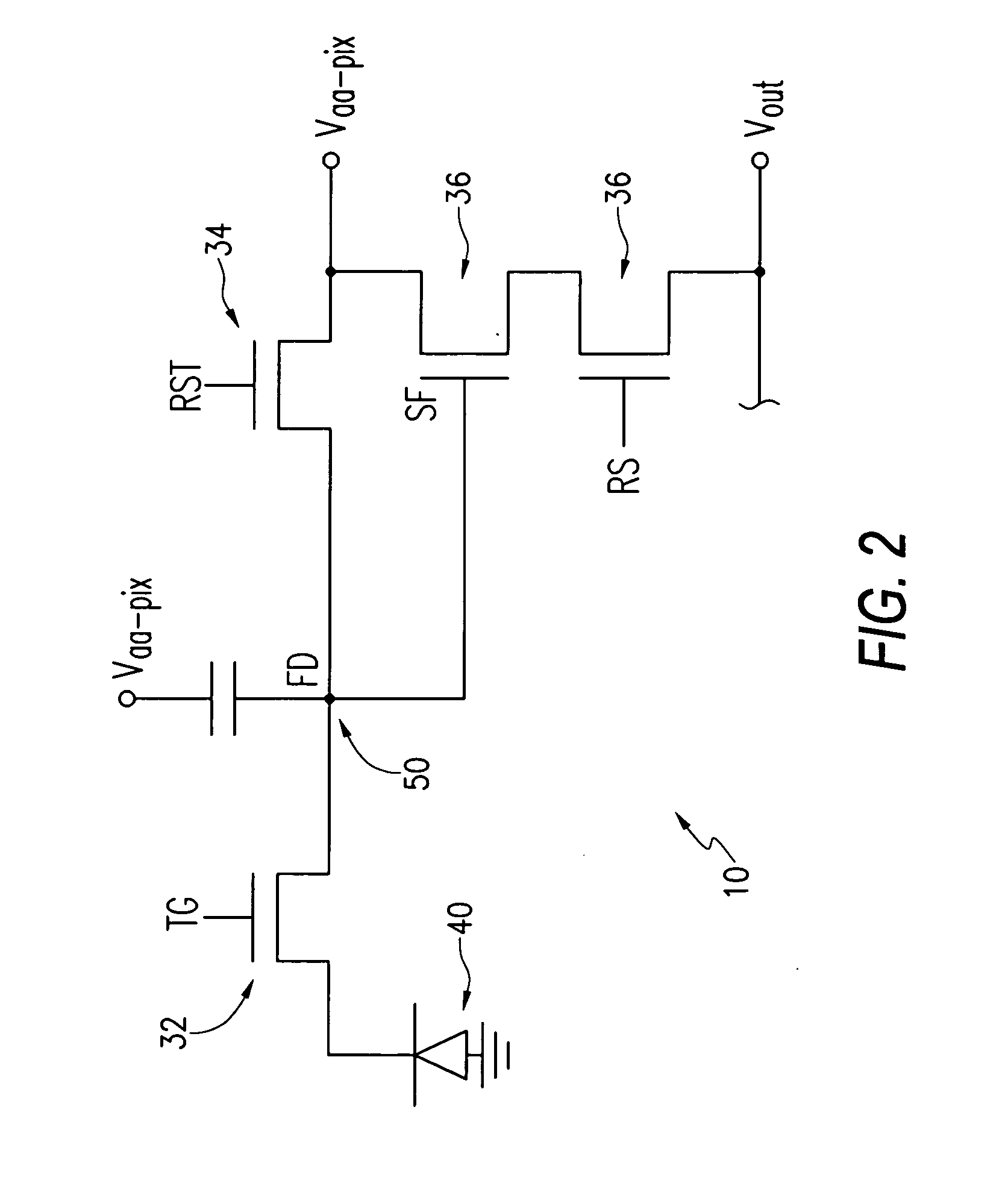

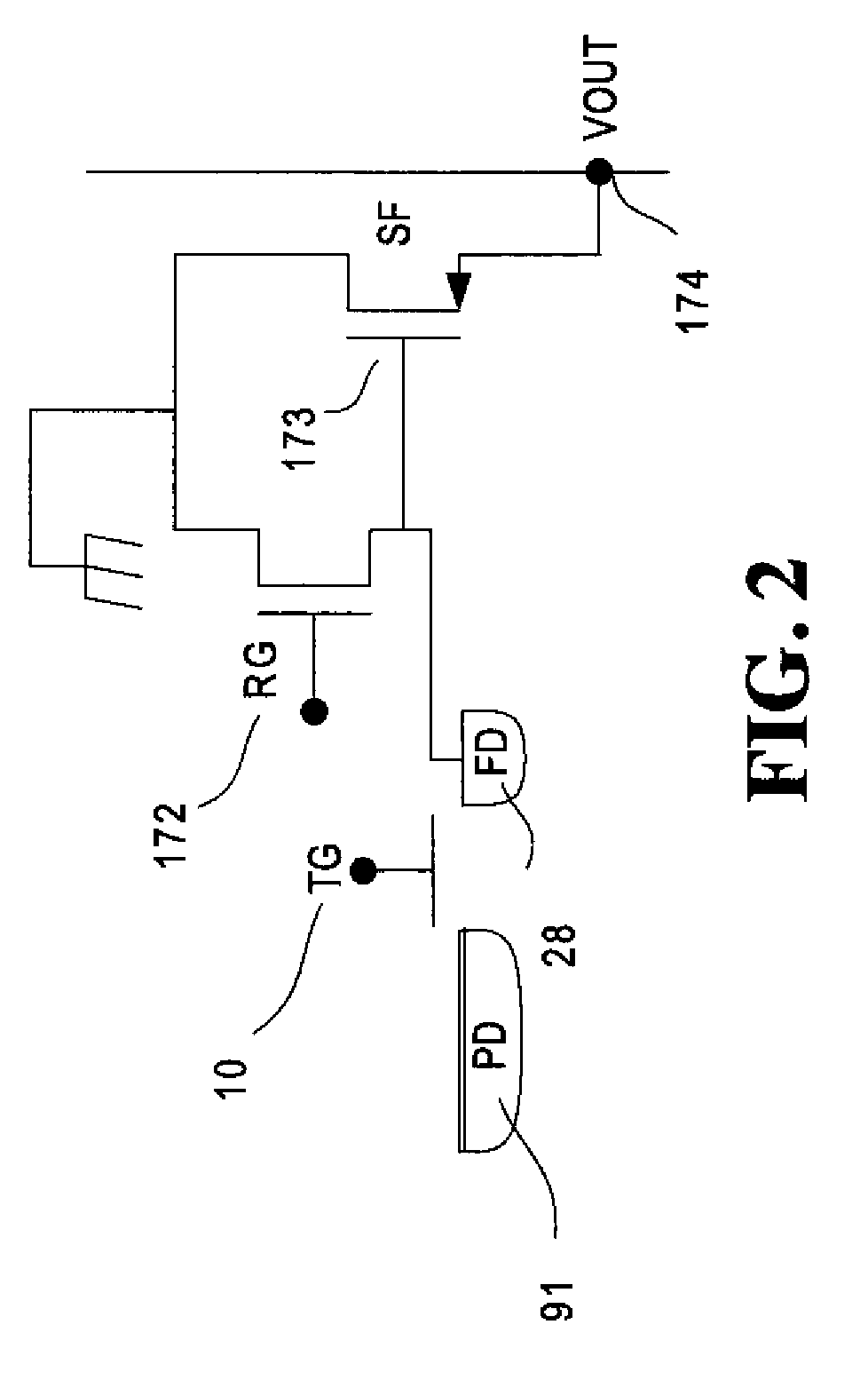

Photoelectric conversion apparatus and image pick-up system using the photoelectric conversion apparatus

InactiveUS7187052B2Total current dropImprove signal-to-noise ratioTransistorTelevision system detailsPhotoelectric conversionFloating diffusion

A primary object of the present invention is to provide a photoelectric conversion apparatus with less leak current in a floating diffusion region. In order to obtain the above object, a photoelectric conversion apparatus according to the present invention includes a photodiode for converting light into a signal charge, a first semiconductor region having a first conductivity type, a floating diffusion region formed from a second semiconductor region having a second conductivity type for converting the signal charge generated by the photodiode into a signal voltage, the second semiconductor region being formed in the first semiconductor region, and an electrode formed above the first semiconductor region through an insulating film and having an effect of increasing a concentration of majority carriers in the first semiconductor region, in which the electrode is not formed above a depletion region formed from the second semiconductor region.

Owner:CANON KK

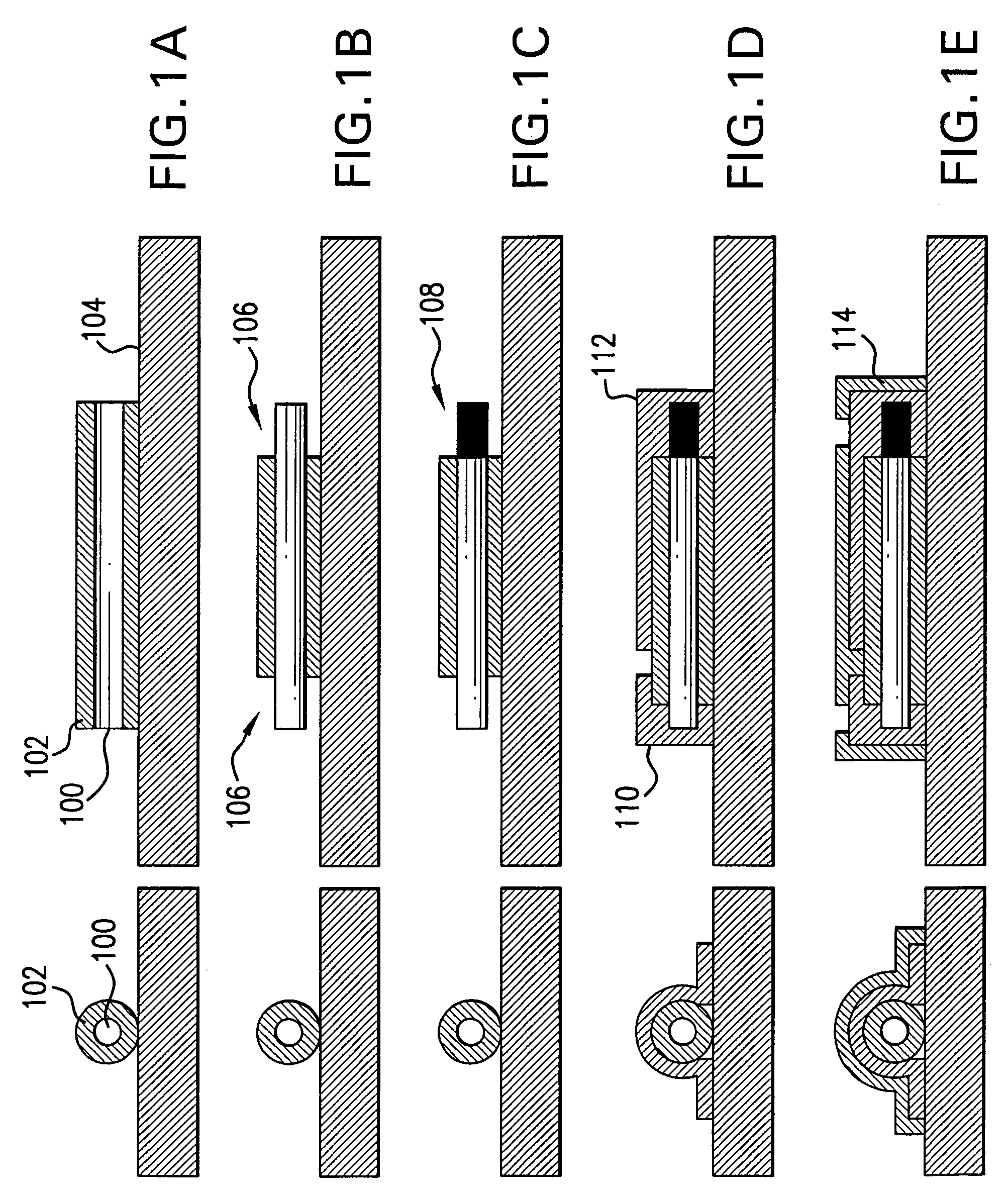

Using high-k dielectrics in isolation structures method, pixel and imager device

ActiveUS20050151218A1Maintain pinned photodiode characteristicsImprove the level ofSolid-state devicesSemiconductor/solid-state device manufacturingDielectricPhotodiode

An imager device that has an isolation structure such that pinned photodiode characteristics are maintained without increasing doping levels. The invention provides an isolation structure to maintain pinned photodiode characteristics without increasing doping levels around the photodiode. By creating a substrate region surrounding the charge-collection region of the photodiode, the photodiode may be electrically isolated from the bulk substrate. This region fixes the depletion region so that it does not migrate toward the surface of the substrate or the STI region. By doing so, the region prevents charge from being depleted from the substrate and the accumulation region, reducing dark current.

Owner:SAMSUNG ELECTRONICS CO LTD

Nanowire varactor diode and methods of making same

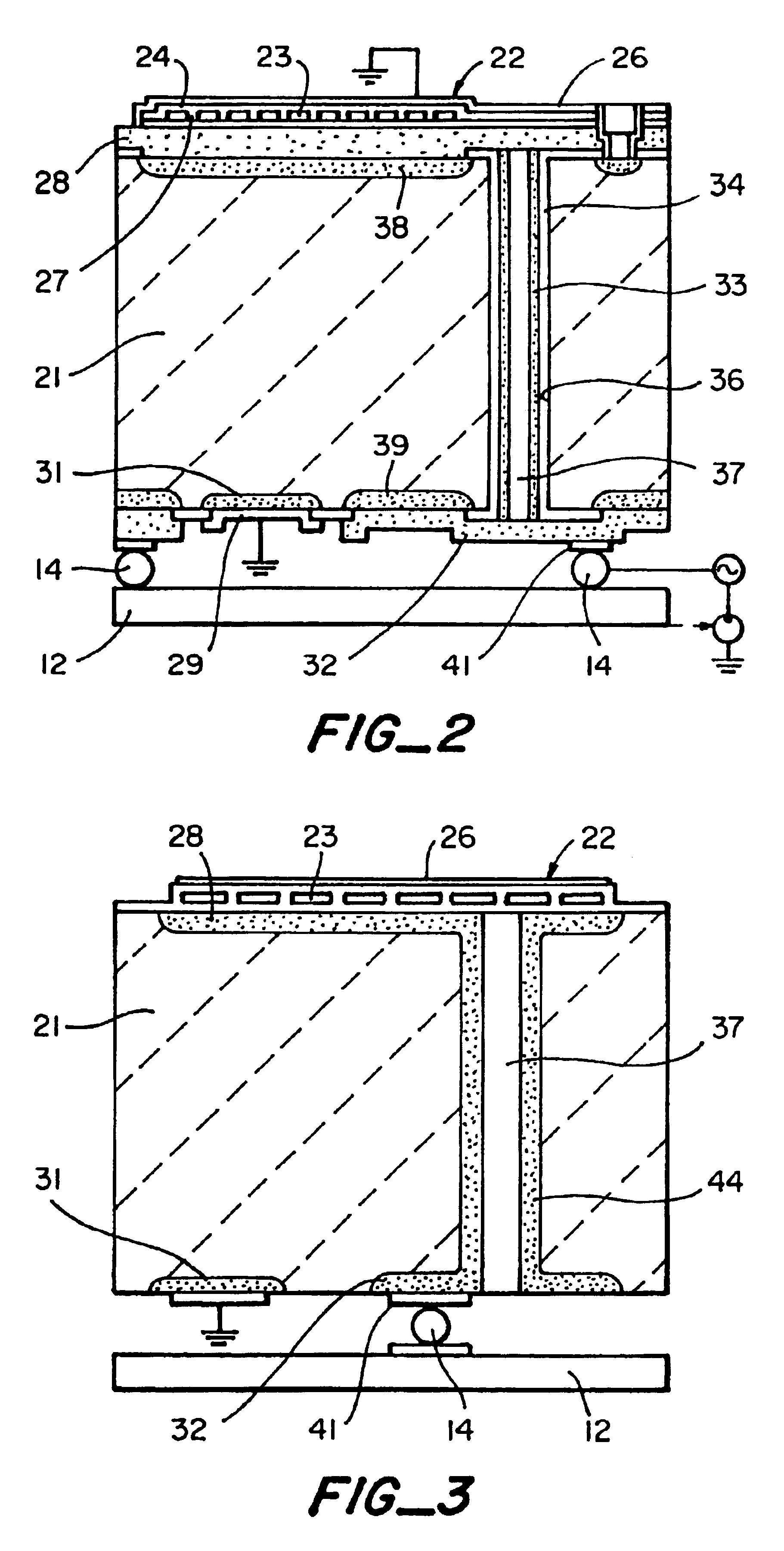

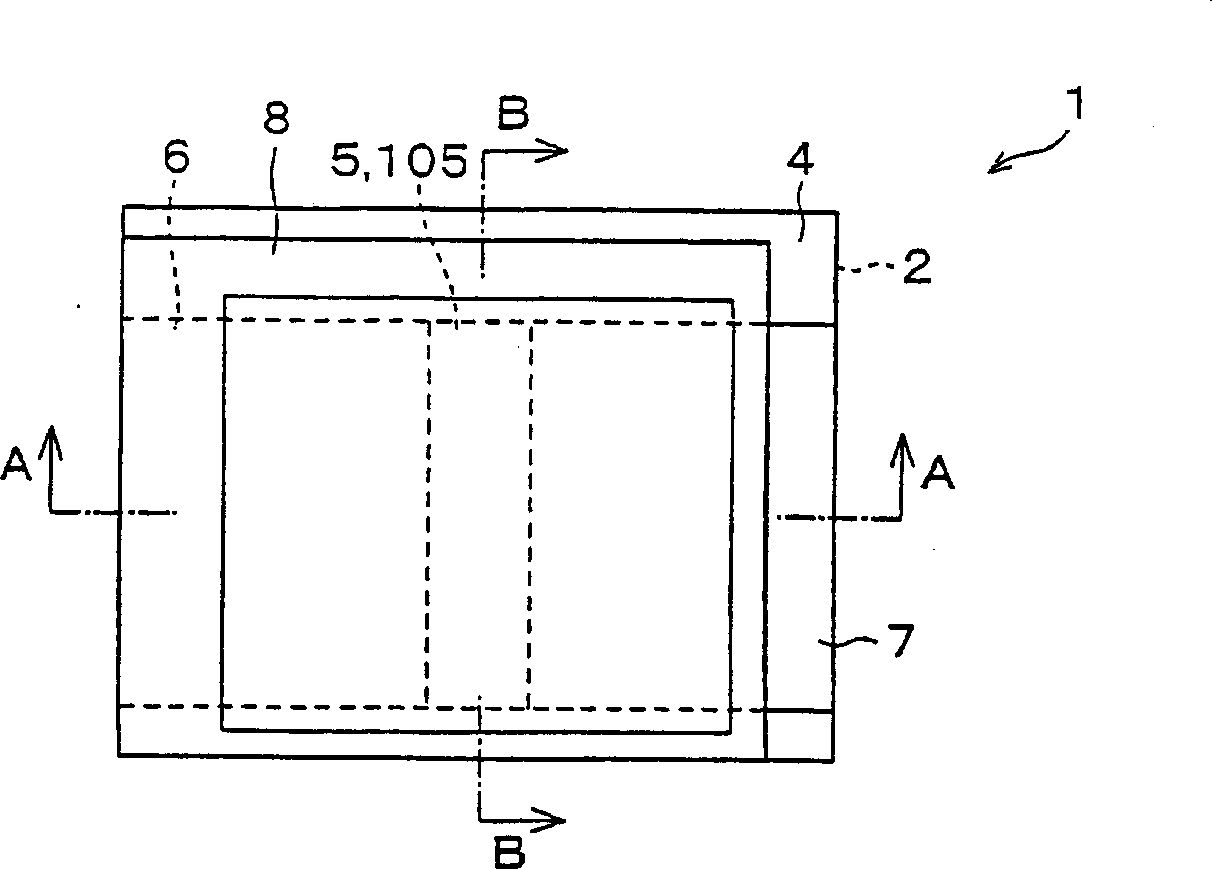

InactiveUS7115971B2Facilitate conductionNanoinformaticsSemiconductor/solid-state device manufacturingNanowireNon doped

A nanowire varactor diode and methods of making the same are disclosed. The structure comprises a coaxial capacitor running the length of the semiconductor nanowire. In one embodiment, a semiconductor nanowire of a first conductivity type is deposited on a substrate. An insulator is formed on at least a portion of the nanowire's surface. A region of the nanowire is doped with a second conductivity type material. A first electrical contact is formed on at least part of the insulator and the doped region. A second electrical contact is formed on a non-doped potion of the nanowire. During operation, the conductivity type at the surface of the nanowire inverts and a depletion region is formed upon application of a voltage to the first and second electrical contacts. The varactor diode thereby exhibits variable capacitance as a function of the applied voltage.

Owner:NANOSYS INC

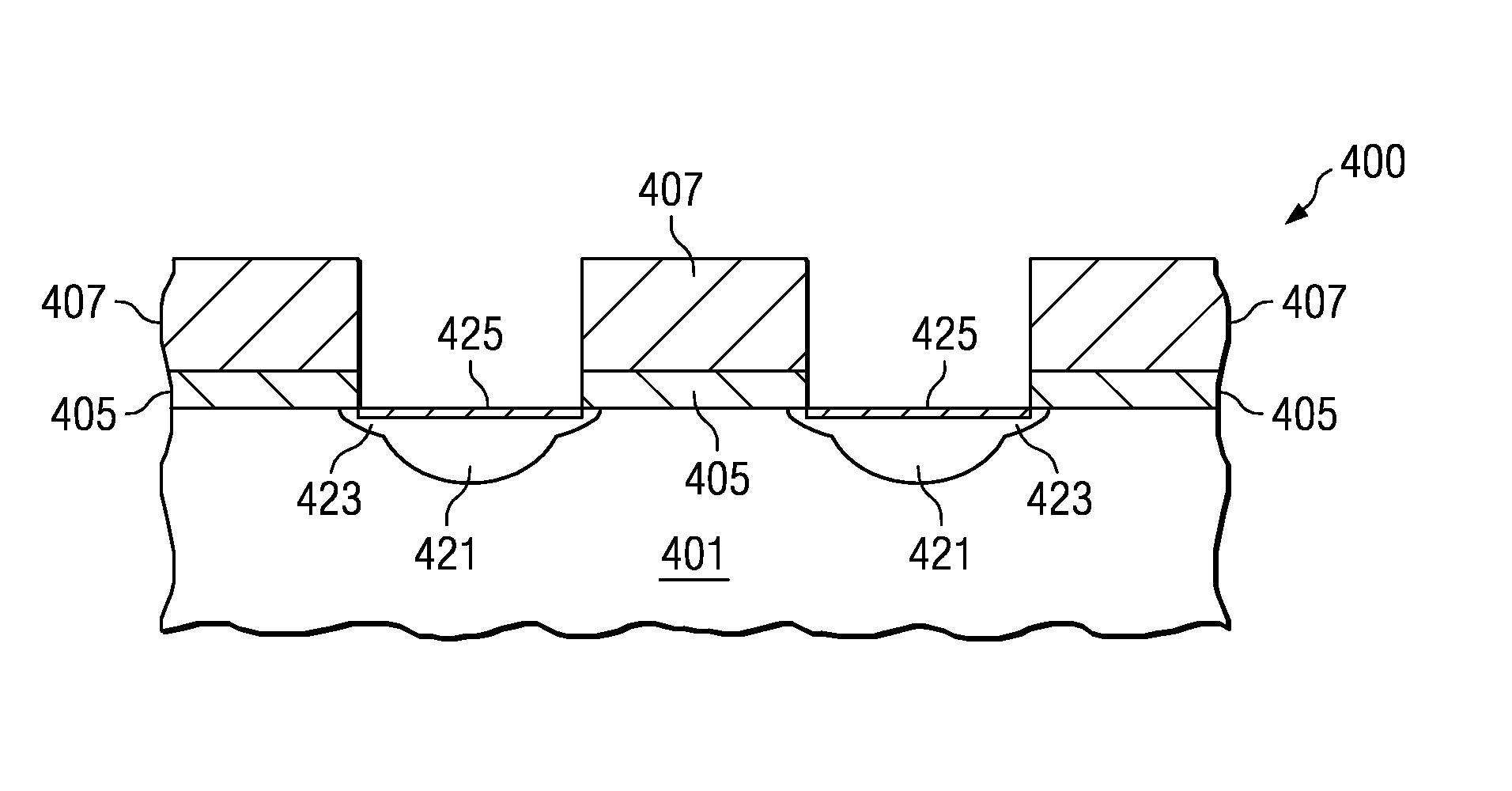

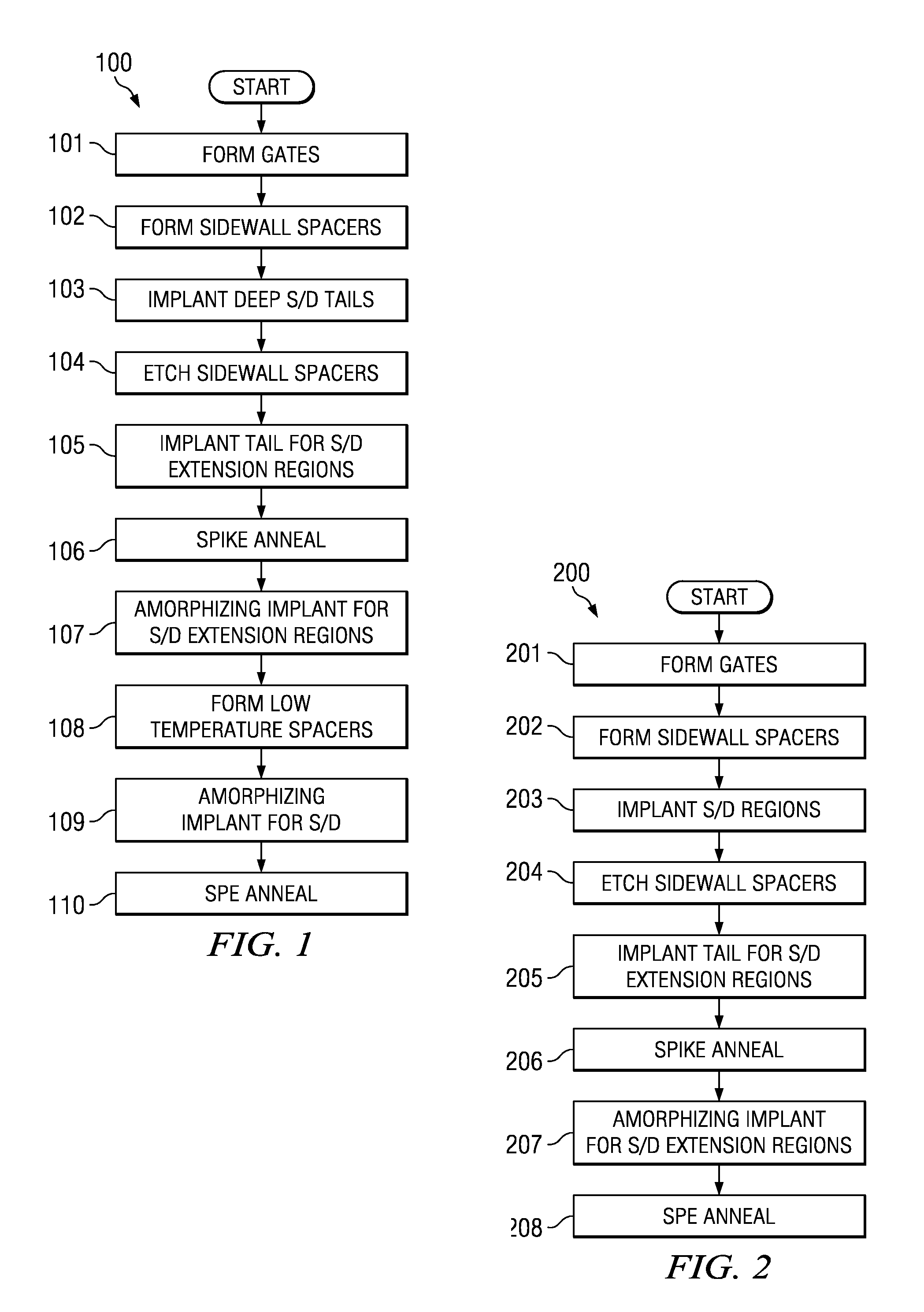

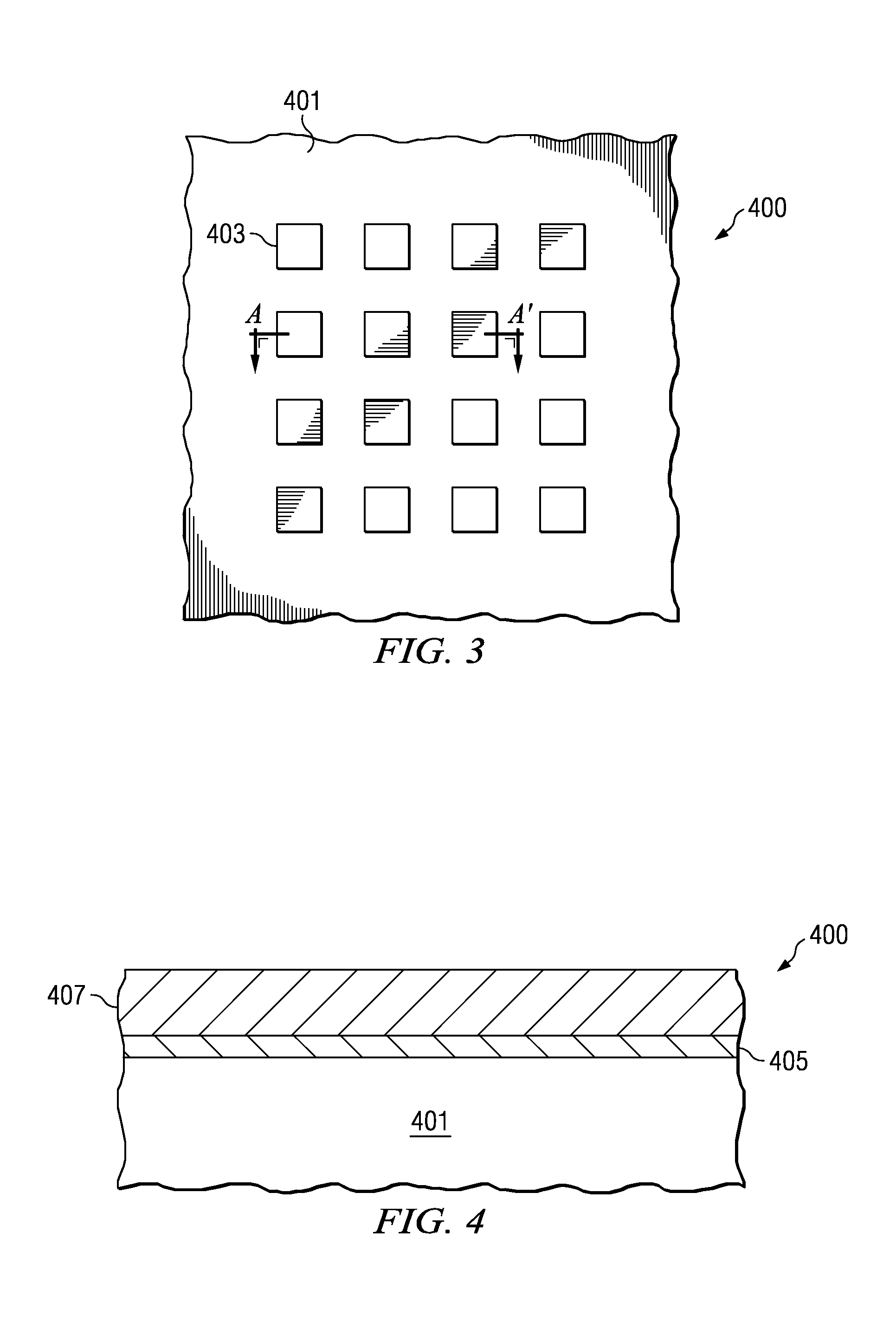

Highly Conductive Shallow Junction Formation

InactiveUS20090224319A1TransistorSemiconductor/solid-state device manufacturingJunction formationPhysical chemistry

The invention relates to a method of forming a shallow junction. The method (100) comprises forming source / drain extension regions with a non-amorphizing tail implant (105) which is annealed conventionally (spike / RTP) and amorphizing implant which is re-grown epitaxially(SPER) (110). The non-amorphizing tail implant is generally annealed (106) before a doped amorphous layer for SPE is formed (107). SPE provides a high active dopant concentration in a shallow layer. The non-amorphizing tail implant (105) expands the source / drain extension region beyond the range dictated by the SPE-formed layer and keeps the depletion region of the P-N junction away from where end-of-range defects form during the SPE process. Thus, the SPE-formed layer primarily determines the conductivity of the junction while the tail implant determines the location of the depletion region. End-of-range defects form, but are not in a position to cause significant reverse bias leakage.

Owner:TEXAS INSTR INC

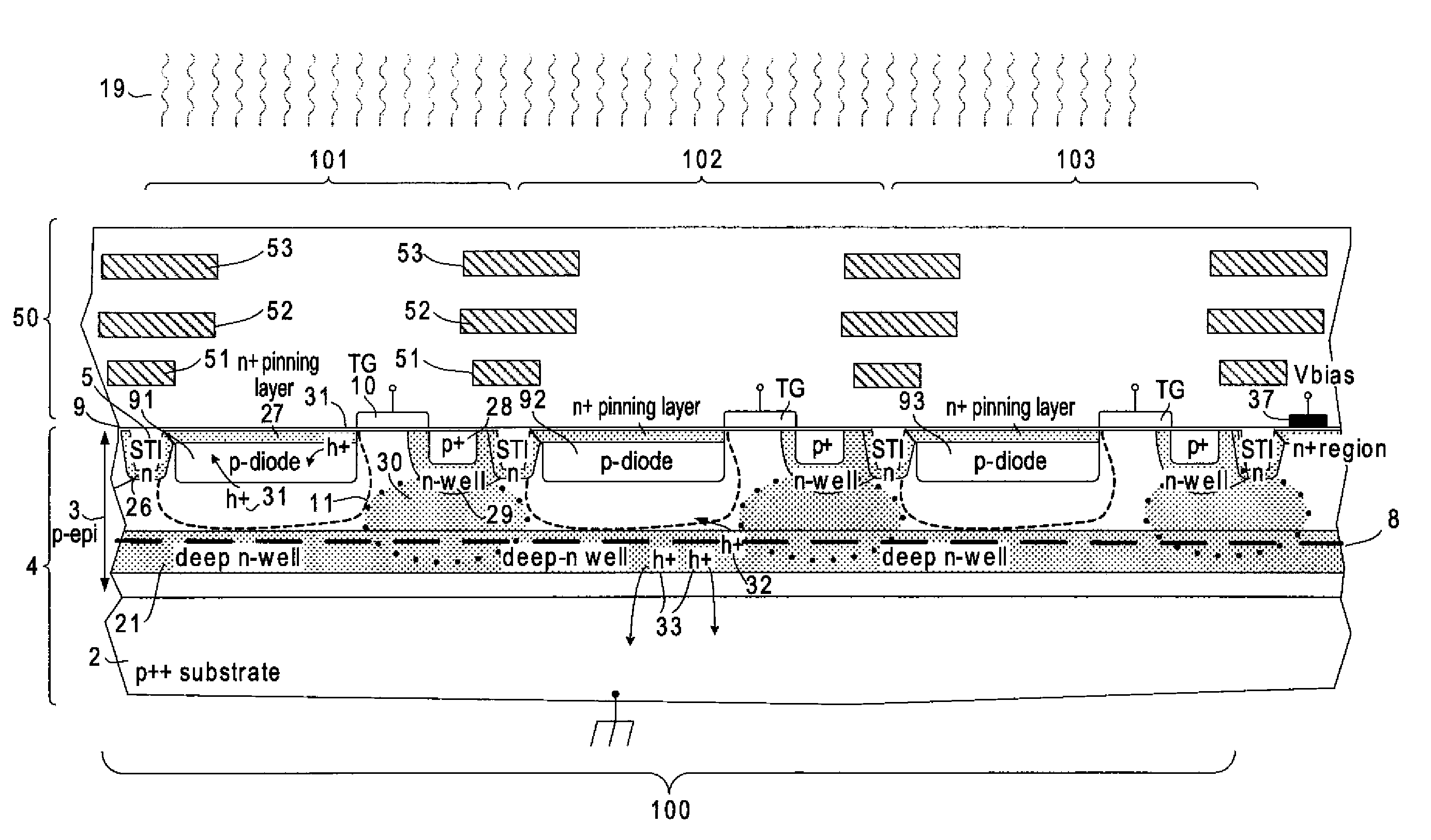

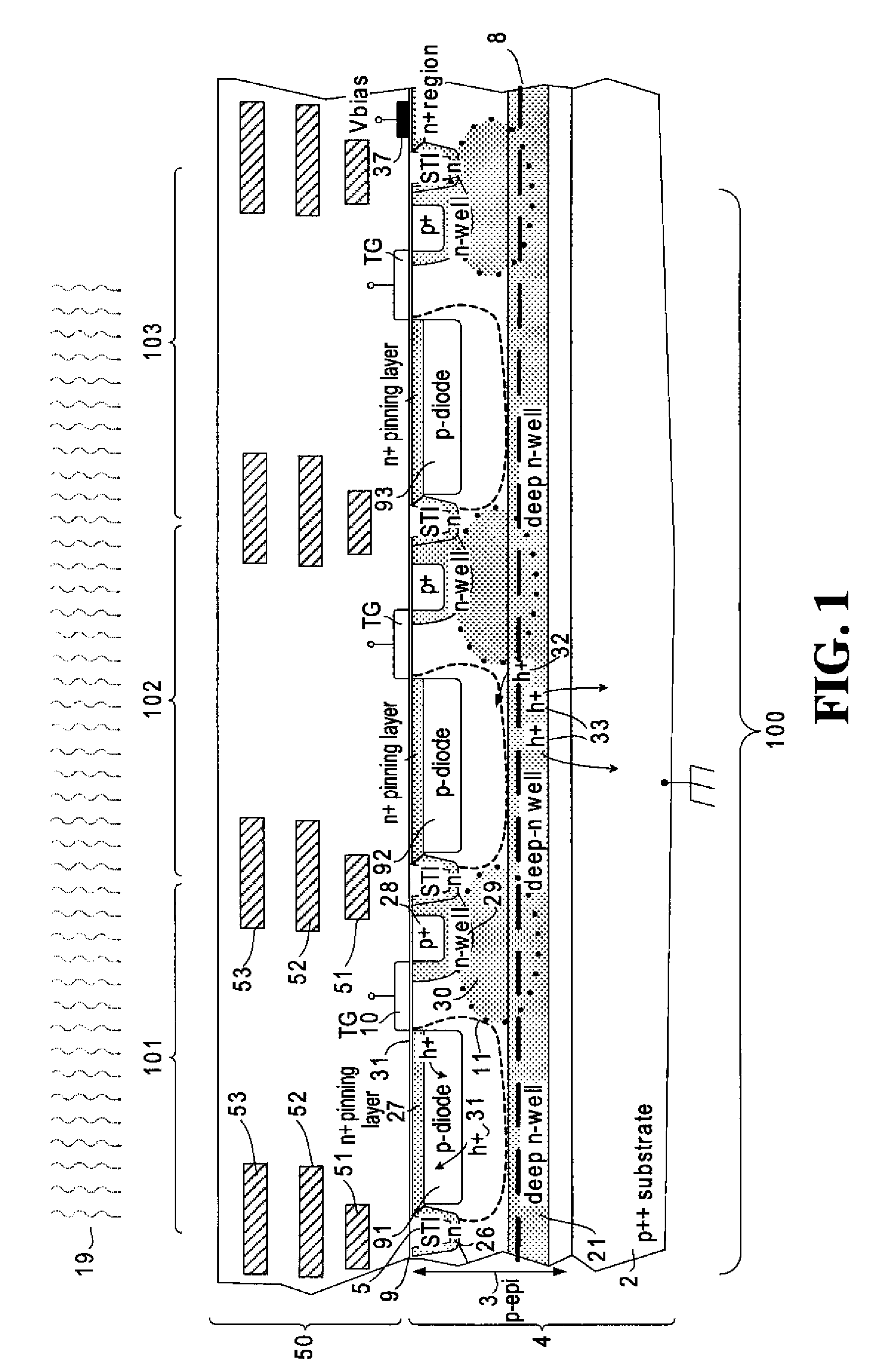

Back illuminated sensor with low crosstalk

ActiveUS20100148289A1Improved crosstalk performanceSolid-state devicesSemiconductor/solid-state device manufacturingPhotovoltaic detectorsPhotodetector

A back-illuminated image sensor includes a sensor layer having a frontside and a backside opposite the frontside. An insulating layer is situated adjacent the backside and a circuit layer is adjacent the frontside. A plurality of photodetectors of a first type conductivity convert light incident on the backside into photo-generated charges. The photodetectors are disposed in the sensor layer adjacent the frontside. A region of a second type conductivity is formed in at least a portion of the sensor layer adjacent the frontside and is connected to a voltage terminal for biasing the second type conductivity region at a predetermined voltage. A well of the second type conductivity is formed in the sensor layer adjacent the backside. Trench isolations in the sensor layer start at the frontside and extend beyond the depletion region of the photodiodes.

Owner:OMNIVISION TECH INC

Electrical through wafer interconnects

InactiveUS6836020B2Reduce capacitanceLower resistanceSemiconductor/solid-state device detailsSolid-state devicesElectrical conductorDepletion region

A wafer with through wafer interconnects. The wafer includes spaced through wafer vias which extend between the back side and front side of the wafer. A conductor within each of said vias connects to front and back side pads. Functions associated with said conductor and said pads provide a depletion region in the wafer between the pads and wafer or pads and conductor and the wafer.

Owner:THE BOARD OF TRUSTEES OF THE LELAND STANFORD JUNIOR UNIV

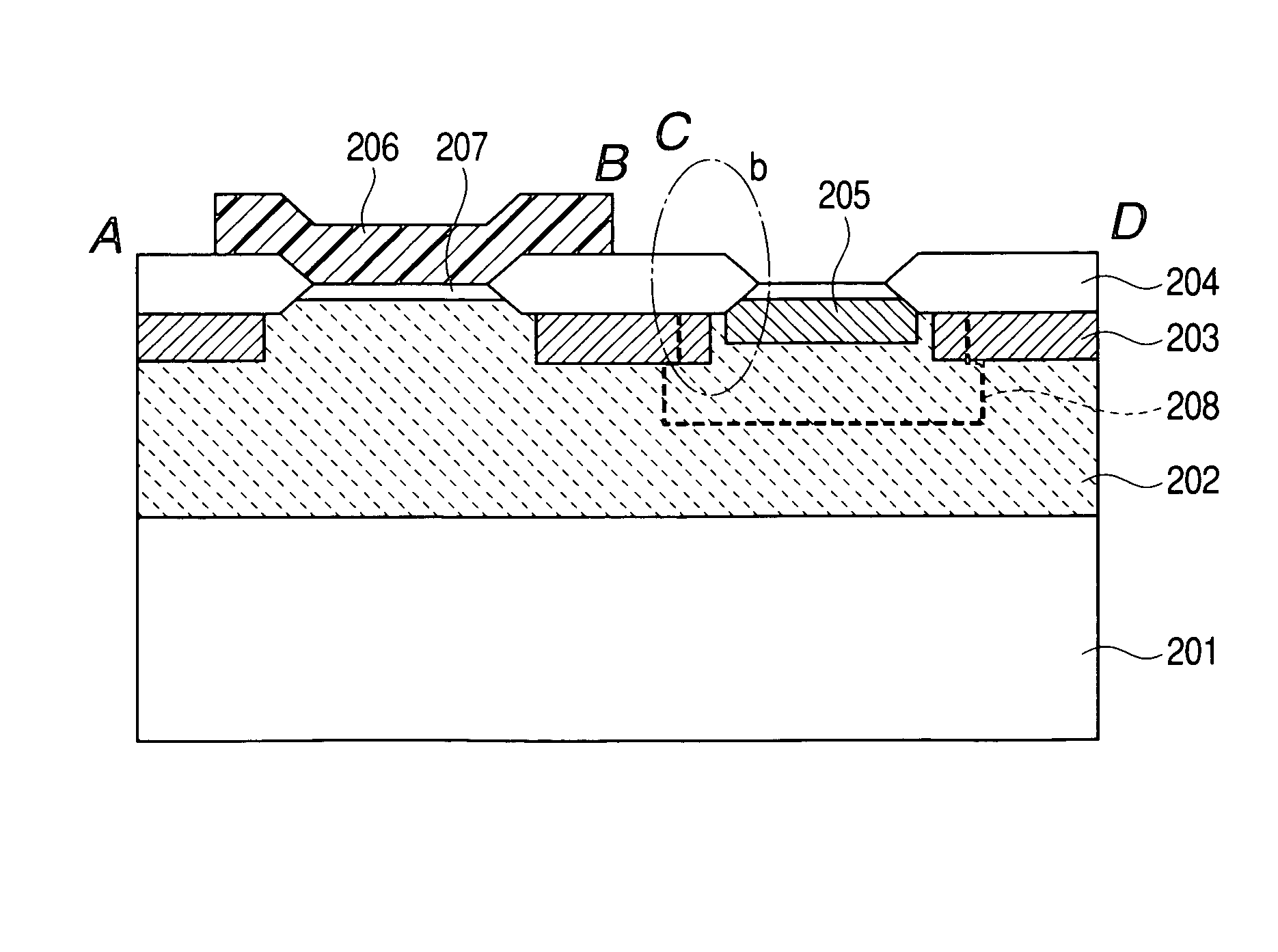

Semiconductor device, its manufacturing method, and electronic device

InactiveCN1806322ATransistorSemiconductor/solid-state device manufacturingIntrinsic resistanceGate voltage

A thin film transistor (1) wherein a gate electrode (3) is formed on an insulative substrate (2), a gate insulating layer (4) is formed on the gate electrode (3), a semiconductor layer (5) is formed on the gate insulating layer (4), a source electrode (6) and a drain electrode (7) are formed on the semiconductor layer (5), and a protective layer (8) covering them are formed. The semiconductor layer (5) is isolated from the atmosphere. The semiconductor layer (5) (active layer) is formed of a ZnO polycrystalline semiconductor doped with, for example, a group V element. Since the surface state of the ZnO semiconductor is reduced thanks to the protective layer (8) and inward expansion of the depletion layer is prevented, the ZnO semiconductor is of an n-type showing its intrinsic resistance value and contains excessive free electrons. The added element acts as acceptor impurities in the ZnO semiconductor, decreasing the excessive electrons. Thus the gate voltage to eliminate the excessive free electrons lowers, thereby making the threshold voltage around 0 V. A semiconductor device using a zinc oxide for an active layer and having a protective layer for isolating the active layer from the atmosphere can be actually used.

Owner:SHARP KK +2

PN diode optical modulators fabricated in strip loaded waveguides

ActiveUS7136544B1Minimal impactDifficult to controlOptical waveguide light guideNon-linear opticsPhase shiftedWaveguide

High speed optical modulators can be made of a lateral PN diode formed in a strip loaded optical waveguide on a SOI or other silicon based substrate. A PN junction is formed at the boundary of the P and N doped regions. The depletion region at the PN junction overlaps with the center of a guided optical mode propagating through the waveguide. Electrically modulating a lateral PN diode causes a phase shift in an optical wave propagating through the waveguide. Due to differences in fabrication methods, forming strip loaded waveguides with consistent properties for use in PN diode optical modulators is much easier than fabricating similar rib waveguides.

Owner:CISCO TECH INC

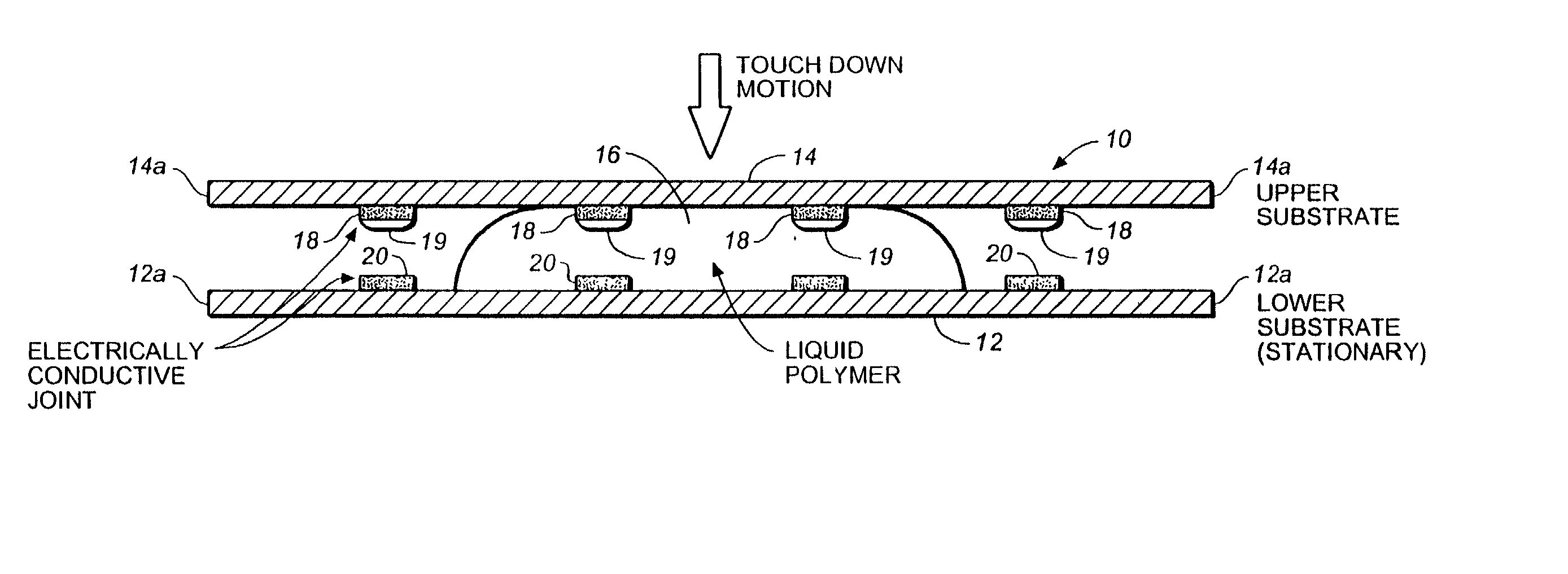

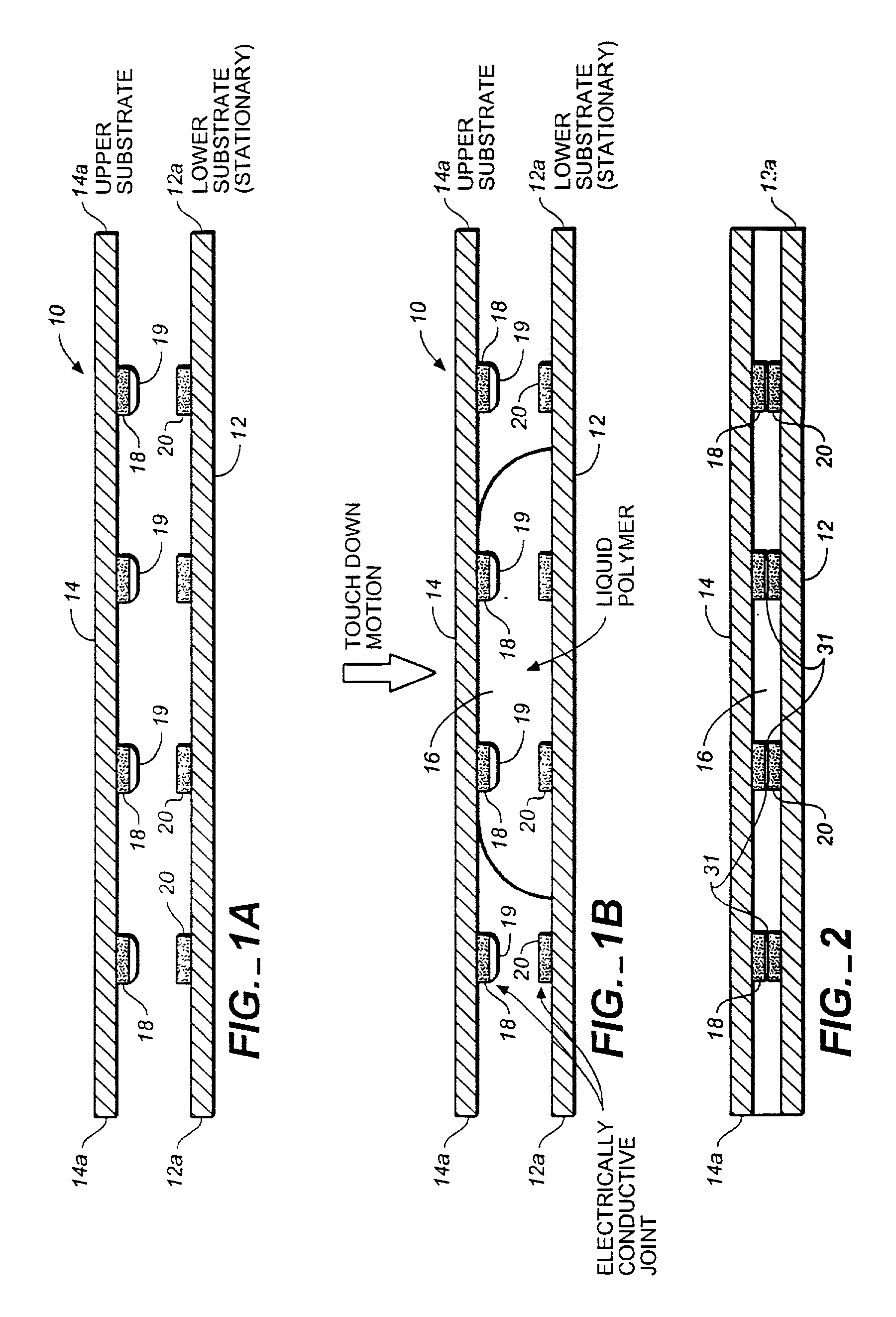

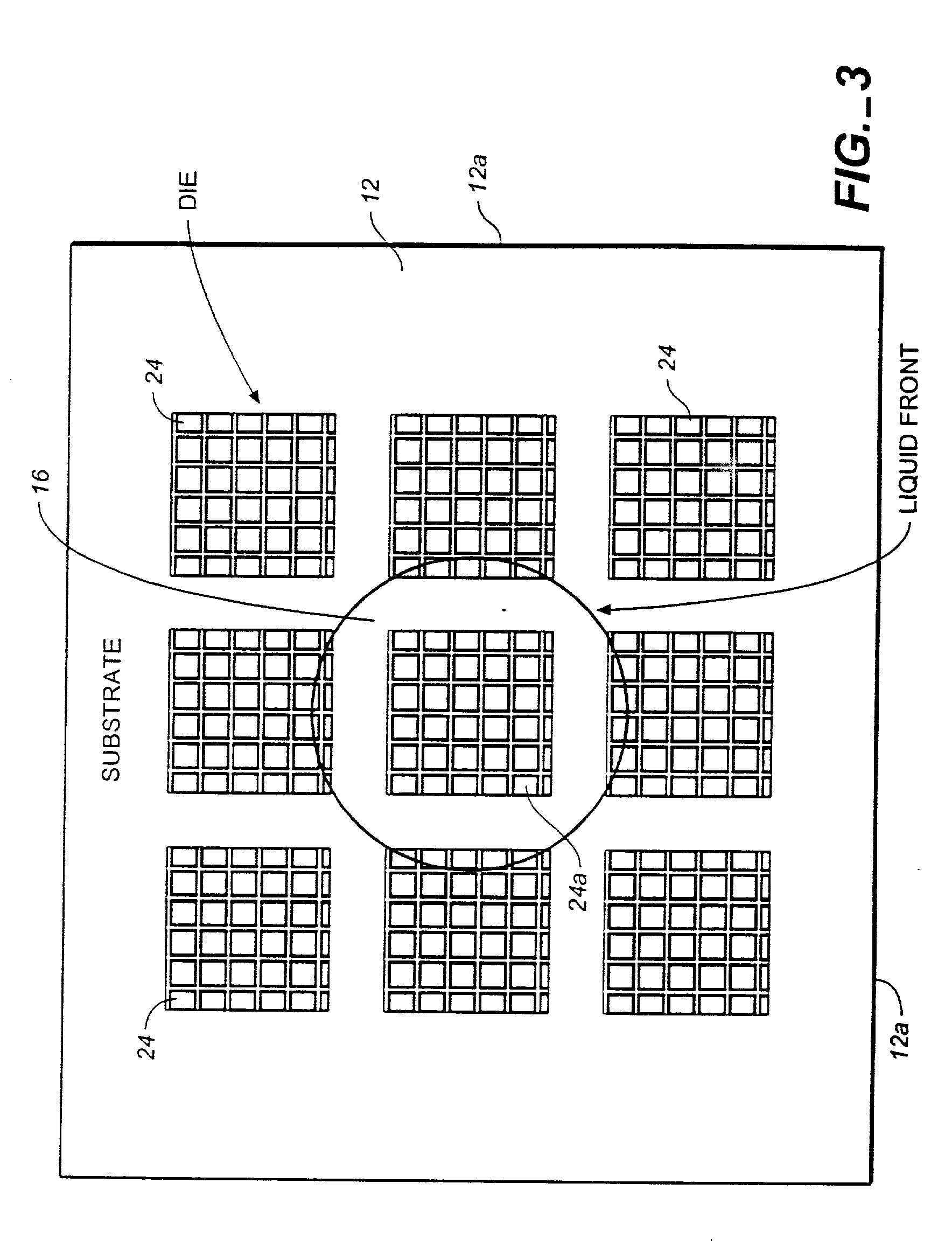

Method for joining and an ultra-high density interconnect

Embodiments of the invention are directed to a method comprising depositing a dielectric layer on a circuitized layer having a conductive region. The dielectric layer is preferably a bonding sheet. An aperture is formed in the dielectric layer over the conductive region. A conductive body, disposed on another circuitized substrate, is inserted into the aperture. The conductive body comprises a main region (e.g., a conductive post) and a depletion region (e.g., a thin layer of metal or transient liquid alloy bonding material). The depletion region contacts the conductive region on the circuitized layer, and the circuitized layers are laminated together. Heat and pressure can be applied to the combination in order to form an intermetallic region from the depletion region.

Owner:FUJITSU LTD

Doping profiles in PN diode optical modulators

ActiveUS7251408B1Coupling light guidesOptical waveguide light guideDopantElectrical resistance and conductance

High speed optical modulators can be made of a lateral PN diode formed in a silicon optical rib waveguide, disposed on a SOI or other silicon based substrate. A PN junction is formed at the boundary of the P and N doped regions. The depletion region at the PN junction overlaps with the center of a guided optical mode propagating through the waveguide. Electrically modulating a lateral PN diode causes a phase shift in an optical wave propagating through the waveguide. Each of the doped regions can have a stepped or gradient doping profile within it or several doped sections with different doping concentrations. Forming the doped regions of a PN diode modulator with stepped or gradient doping profiles can optimize the trade off between the series resistance of the PN diode and the optical loss in the center of the waveguide due to the presence of dopants.

Owner:CISCO TECH INC

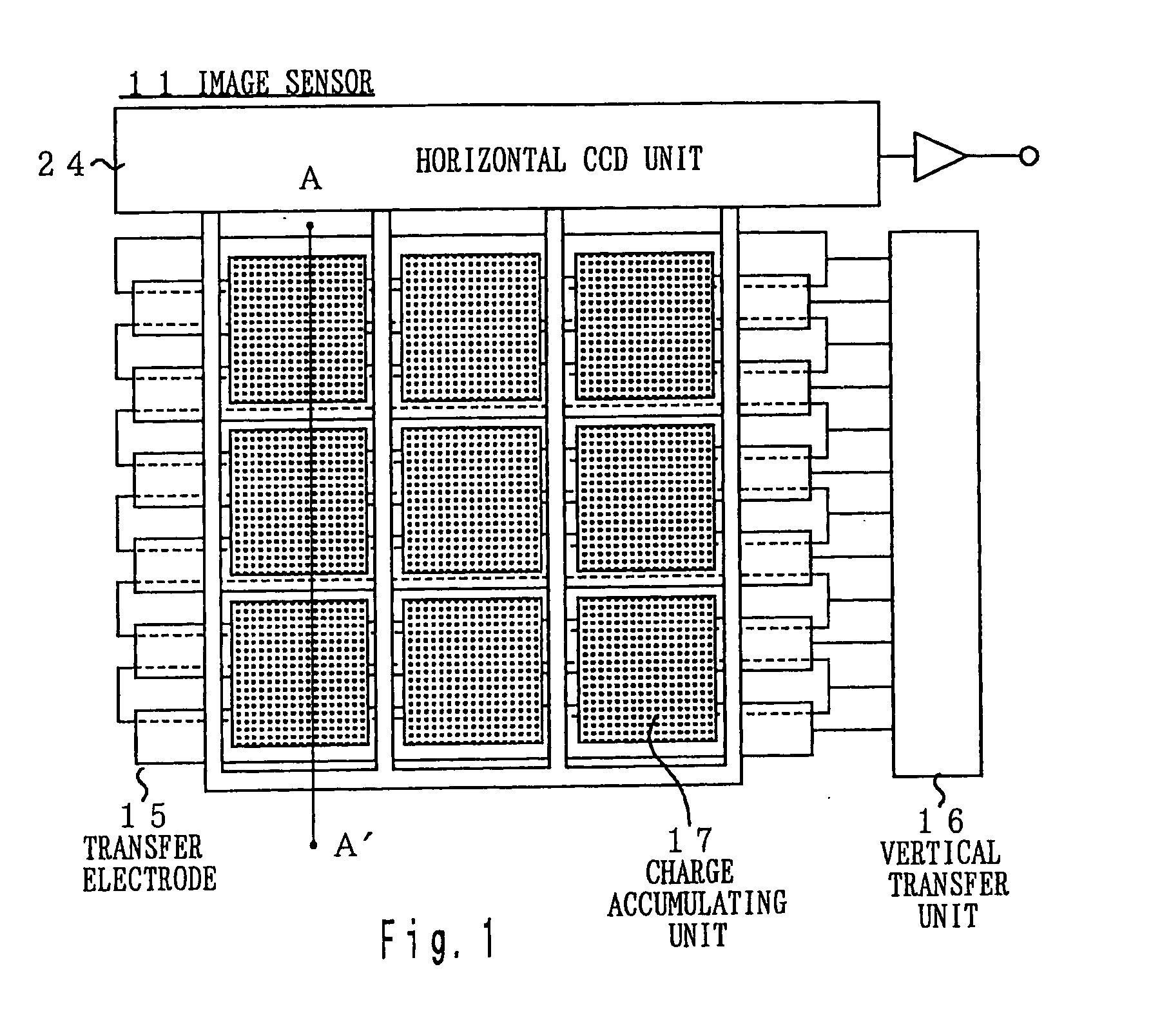

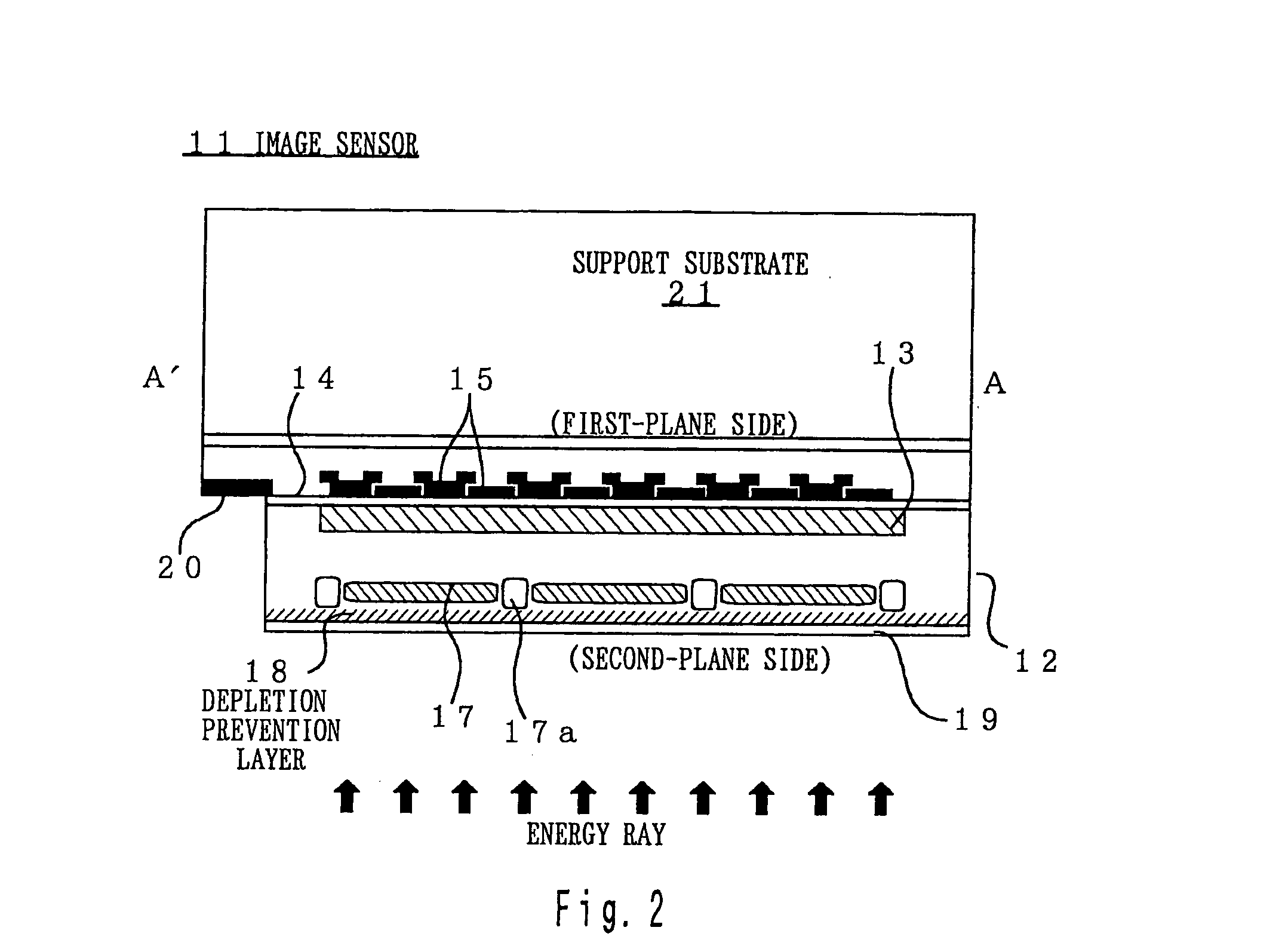

Image sensor, method of fabricating the same, and exposure apparatus, measuring device, alignment device, and aberration measuring device using the image sensor

InactiveUS20040007722A1Suppress dark currentReliable transmissionSolid-state devicesDiodeMeasurement deviceImage signal

In the present invention, a charge transfer unit is arranged on a first-plane side of a thinly-formed semiconductor base. Charge accumulating units are arranged on a second-plane side, the opposite side. A depletion prevention layer is arranged closer to the second-plane side than the charge accumulating units. The depletion prevention layer prevents a depletion region around the charge accumulating units from reaching the second plane of the semiconductor base. The depletion prevention layer can suppress surface dark current going into the charge accumulating units. Meanwhile, an energy ray incident from the second-plane side pass through the depletion prevention layer to generate signal charges in the charge accumulating units (depletion regions). The charge accumulating units collect, on a pixel-by-pixel basis, the signal charges which are to be transported to the charge transfer unit under voltage control or the like, and then are read to exterior as image signals.

Owner:NIKON CORP

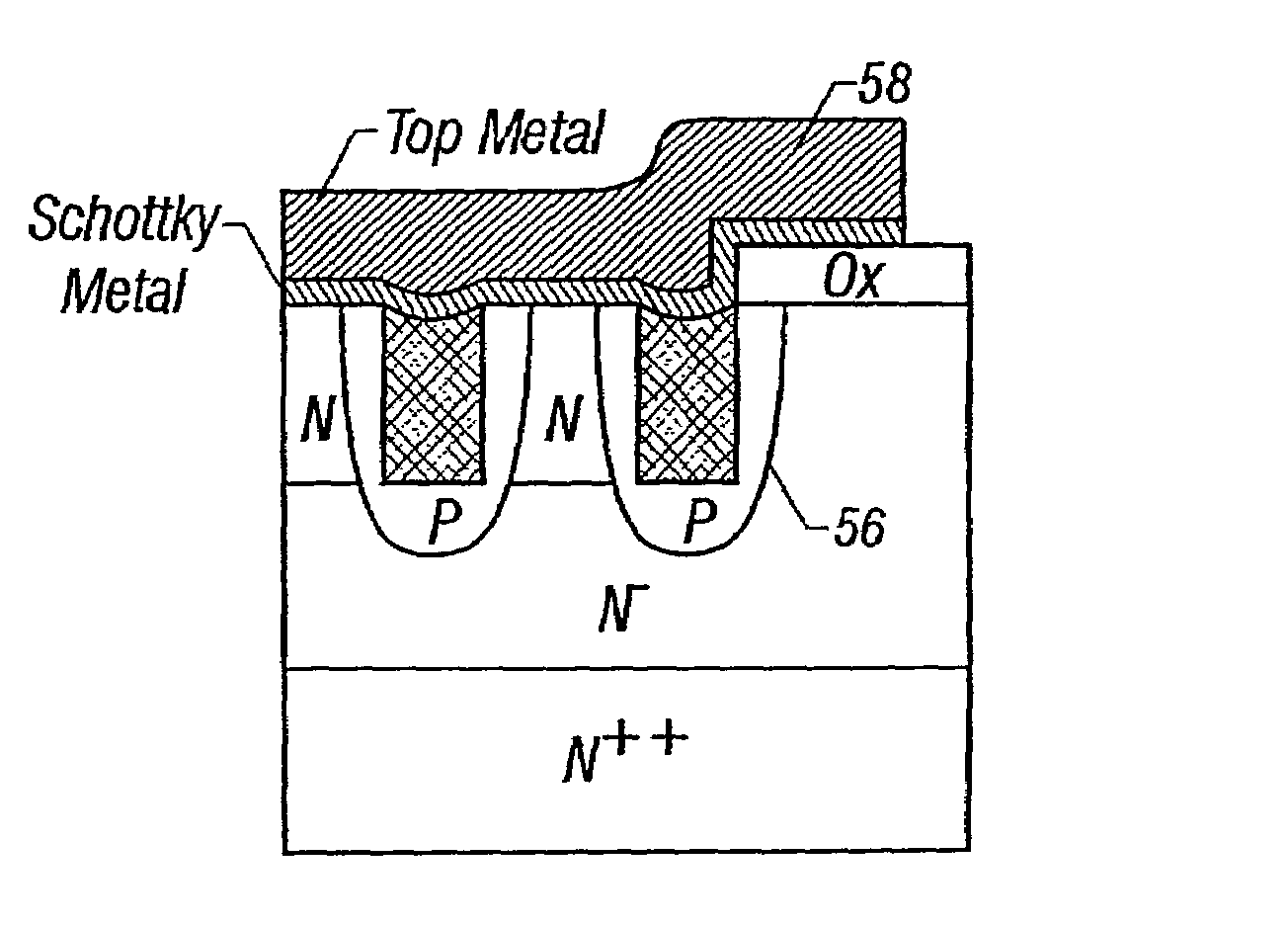

Method of fabricating trench junction barrier rectifier

InactiveUS7186609B2Improve electrical performanceMinimize diffusion of boronThyristorSolid-state devicesDopantDepletion region

A Schottky rectifier includes a rectifying interface between a semiconductor body and a metal layer. Trenches are formed in the surface of the semiconductor body and regions of a conductivity type opposite to the conductivity type of the body are formed along the sidewalls and bottoms of the trenches, the regions forming PN junctions with the rest of the body. When the rectifier is reverse-biased, the depletion regions along the PN junctions merge to occupy the entire width of the mesas. The device is fabricated by implanting dopant directly through the sidewalls and bottoms of the trenches, by filling the trenches with a material containing dopant and causing the dopant to diffuse through the sidewalls and bottoms of the trenches, or by implanting and diffusing the dopant into a gate filling material.

Owner:SILICONIX

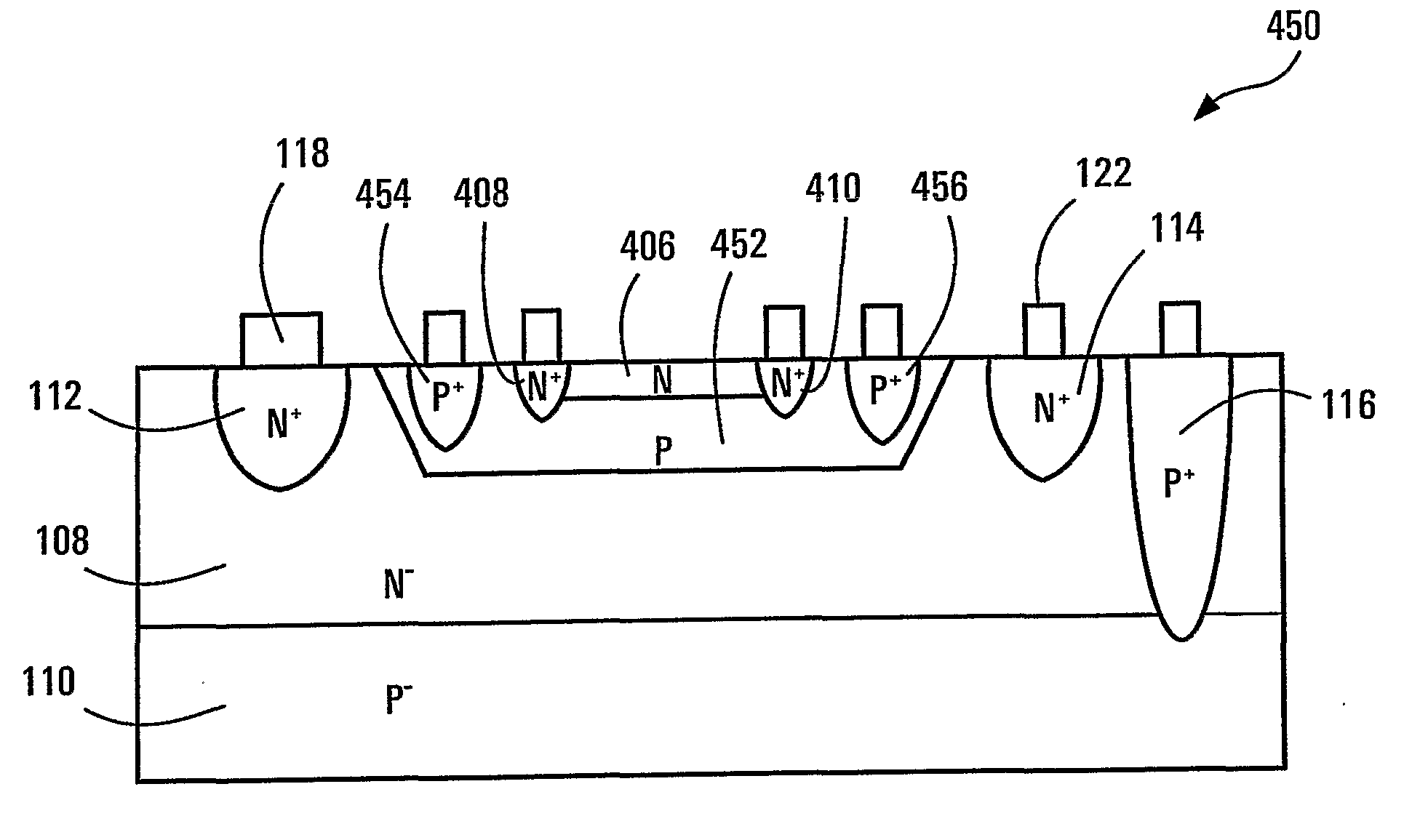

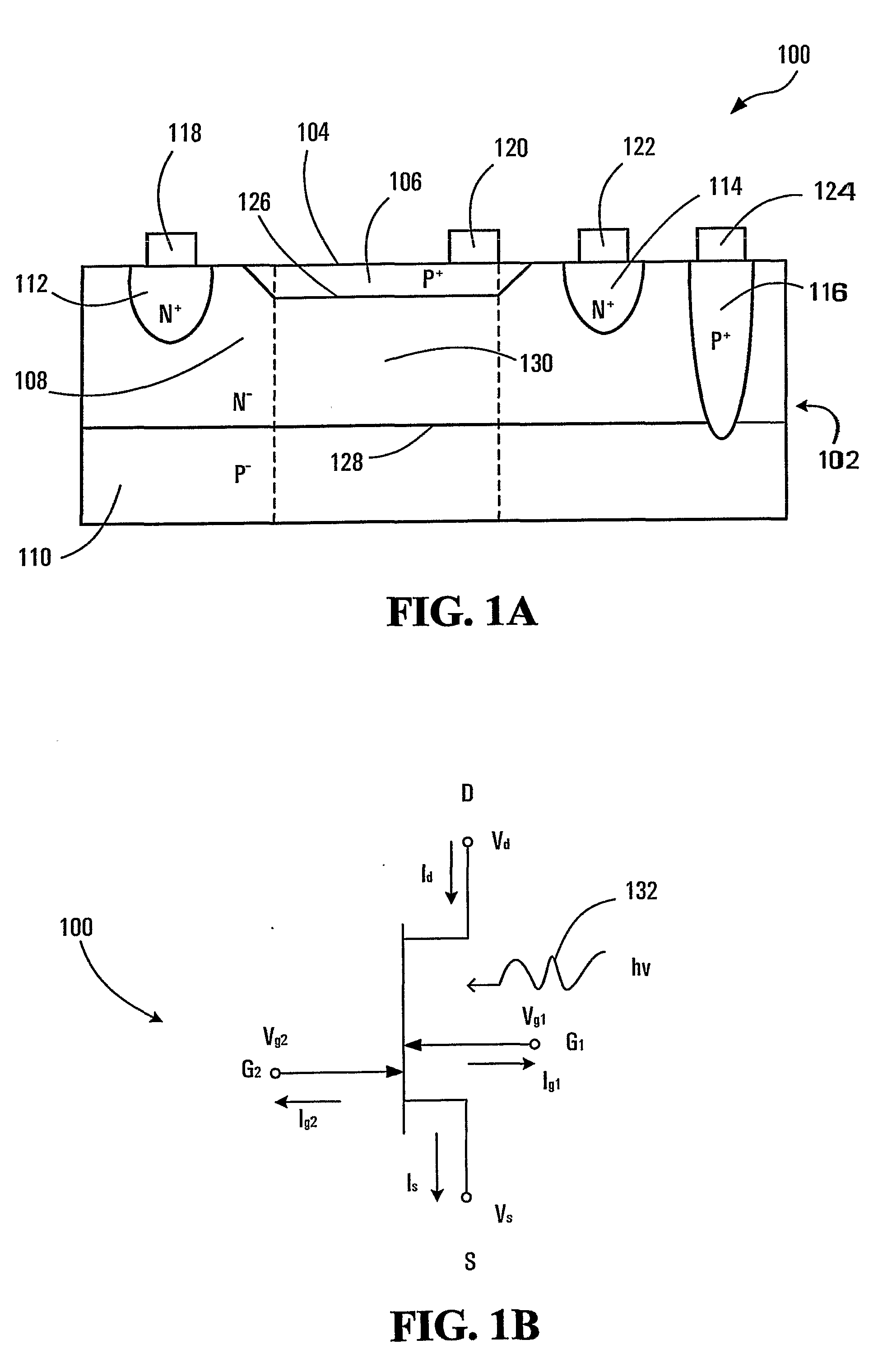

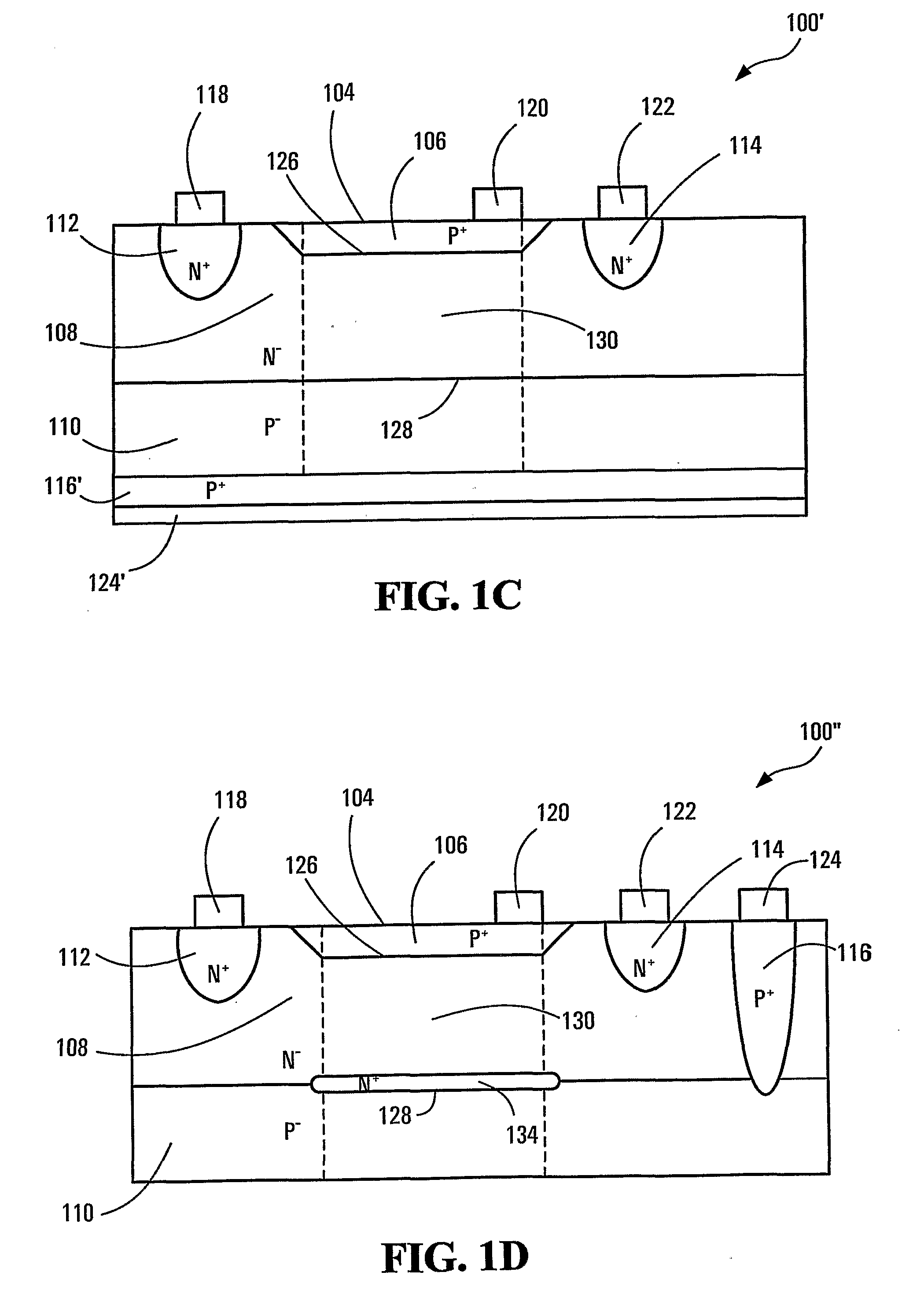

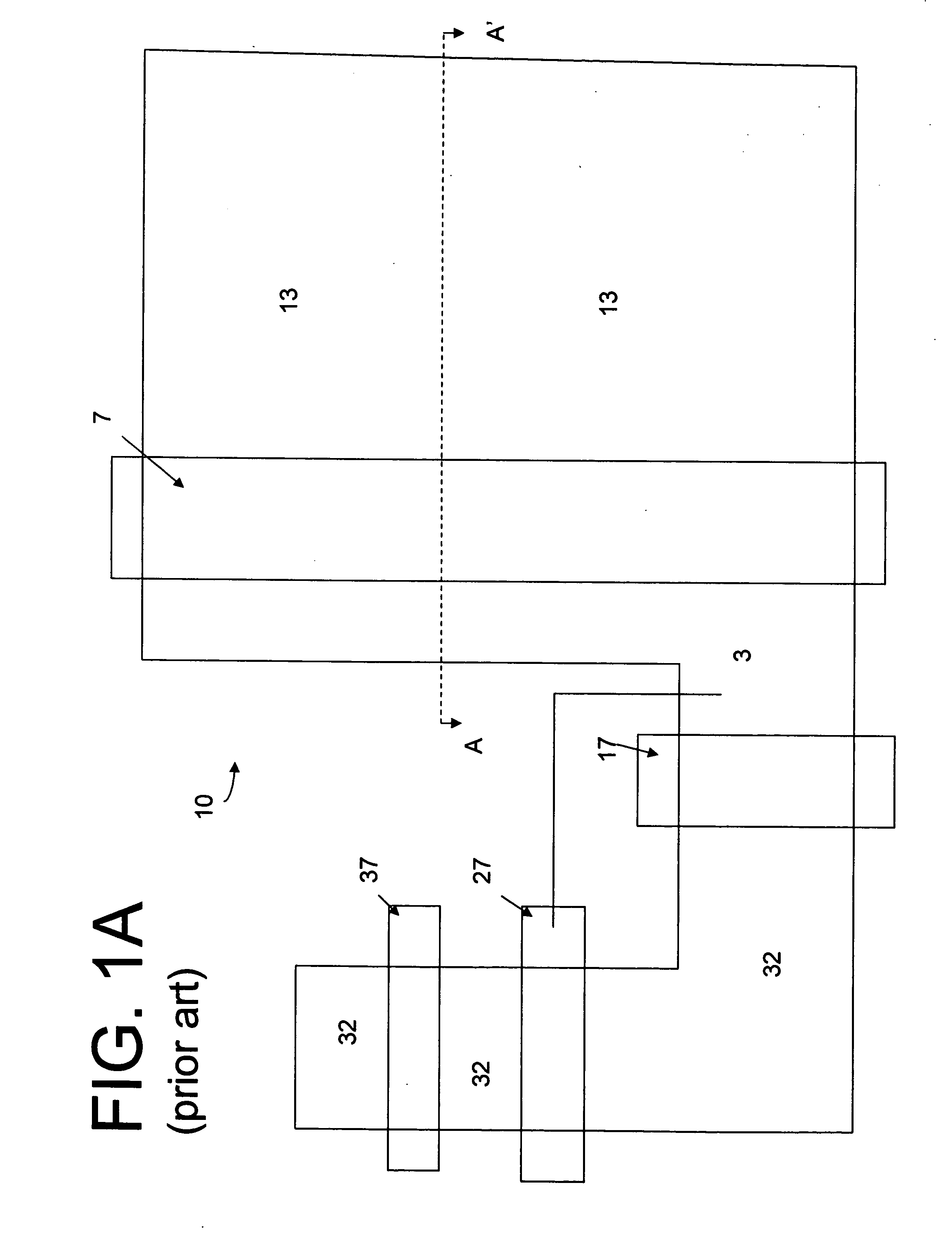

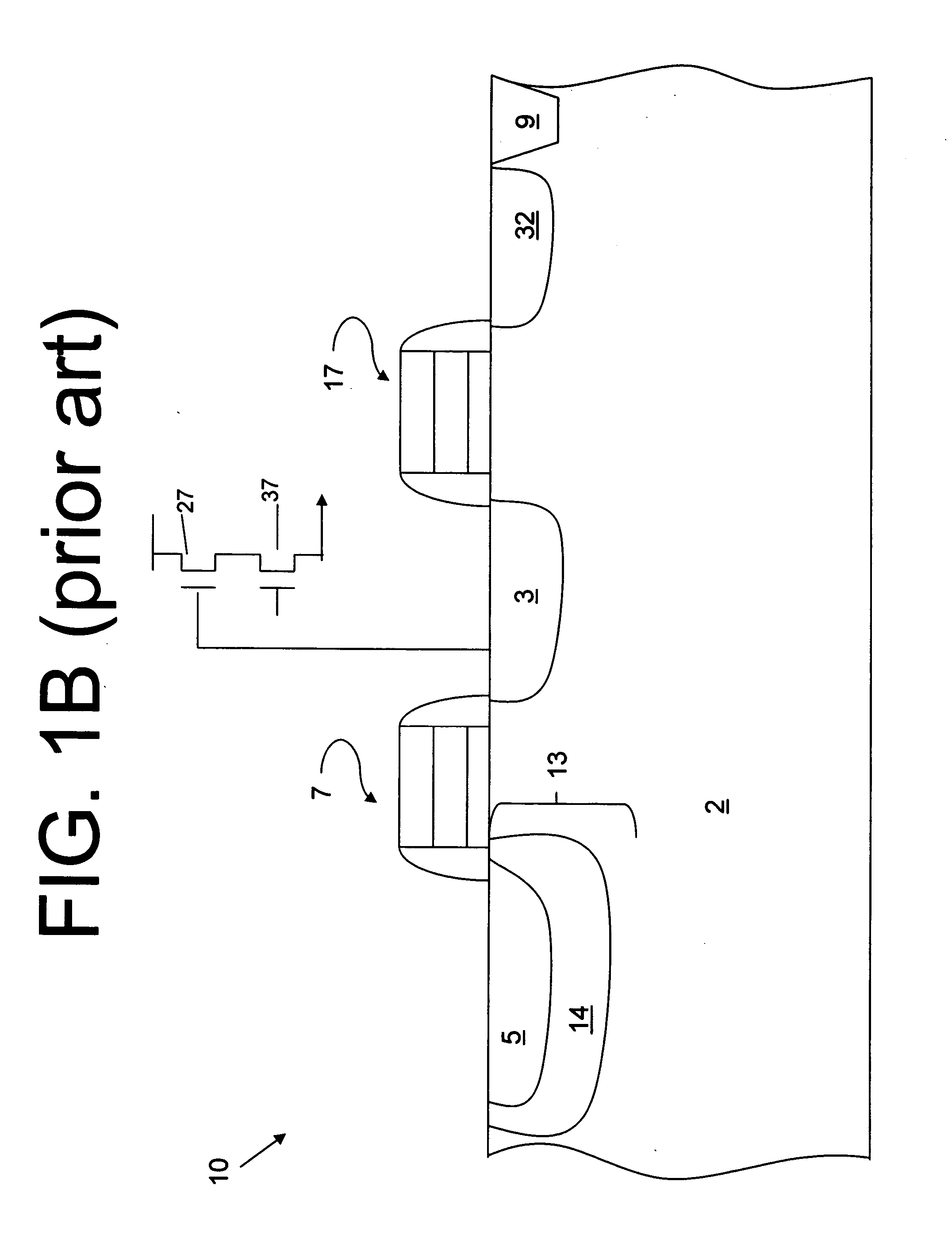

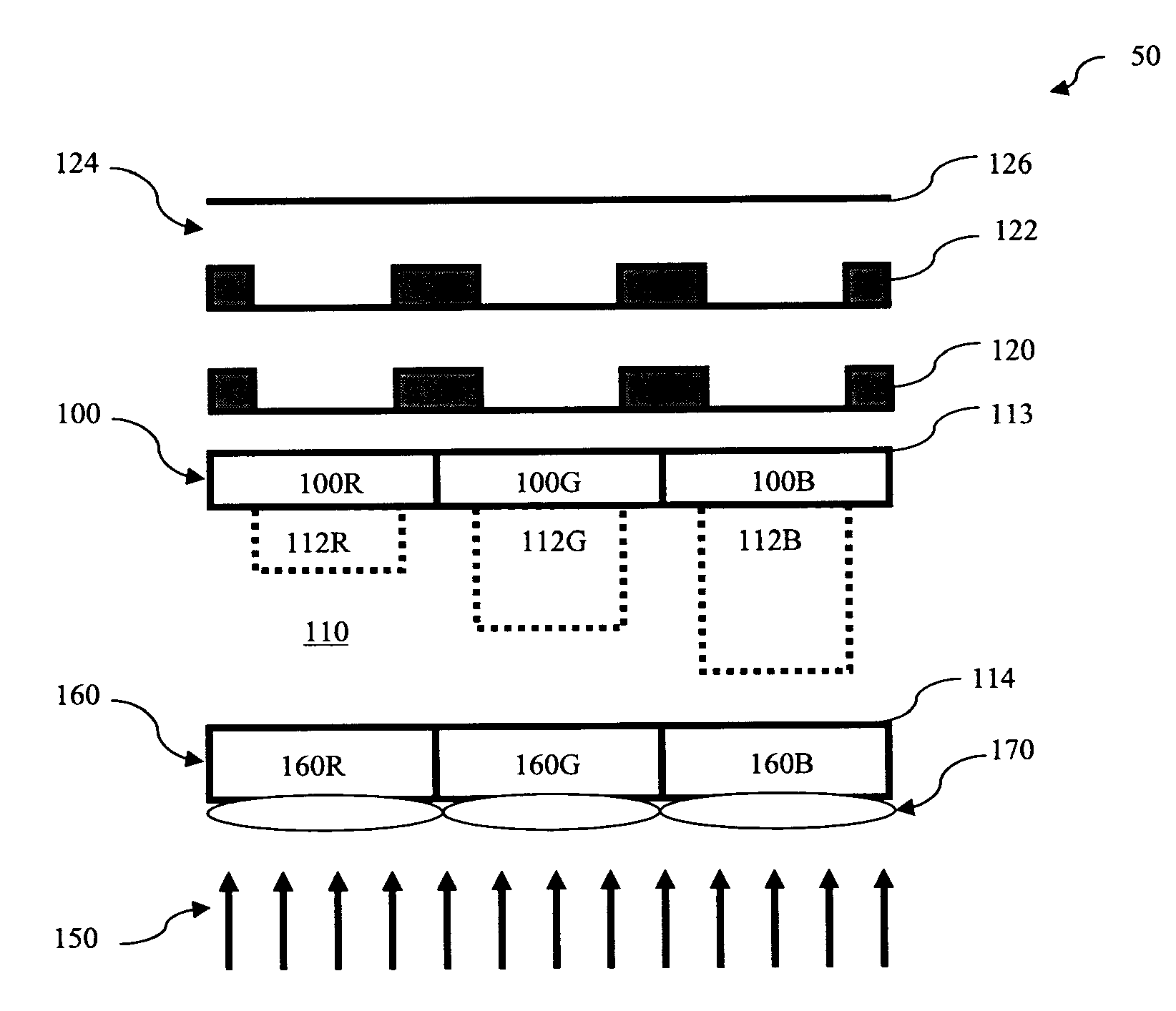

Method and device for wavelength-sensitive photo-sensing

A semiconductor device includes a conducting channel (130) formed beneath a substrate surface with a pre-determined photo-conductivity spectral response. The channel is formed between two pn-junctions (126, 128) defining first and third photo-electric depletion regions at respective depths relative to the surface corresponding to penetration depths of light of different wavelengths. The first region (106) which has the light absorbing surface (104) above the first pn-junction (126) is specific to a first colour. The channel region (130) between the two pn-junctions (126, 128) is photo-conductive to a second colour. The third region below the second pn-junction (128) is sensitive to a third colour. Electrical contacts (118, 120, 122, 124) are disposed on the source (112), the top gate (106), the drain (114) and the bottom gate (116) for receiving the electrical currents induced by the presence of the absorbed wavelengths.

Owner:NANYANG TECH UNIV

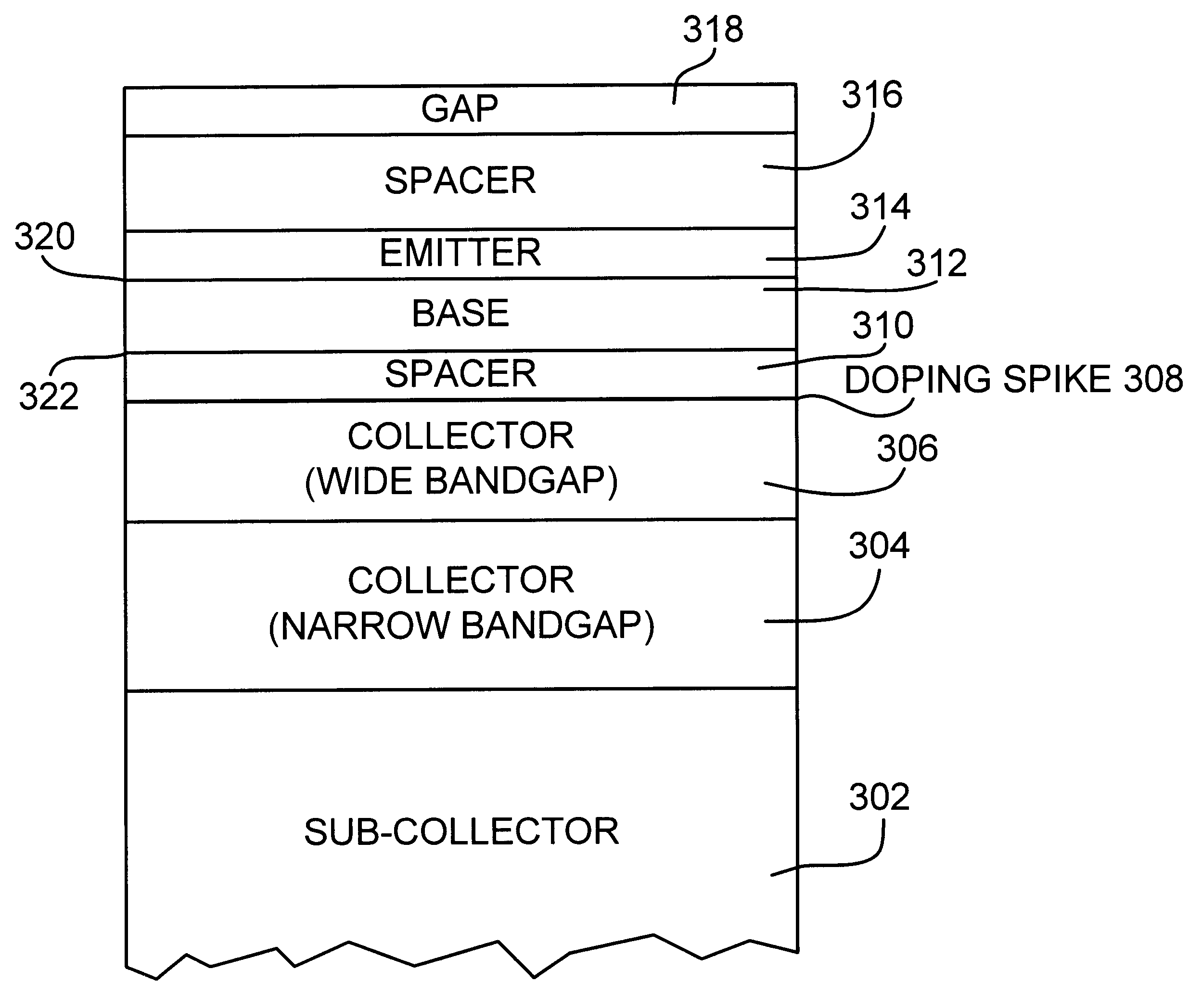

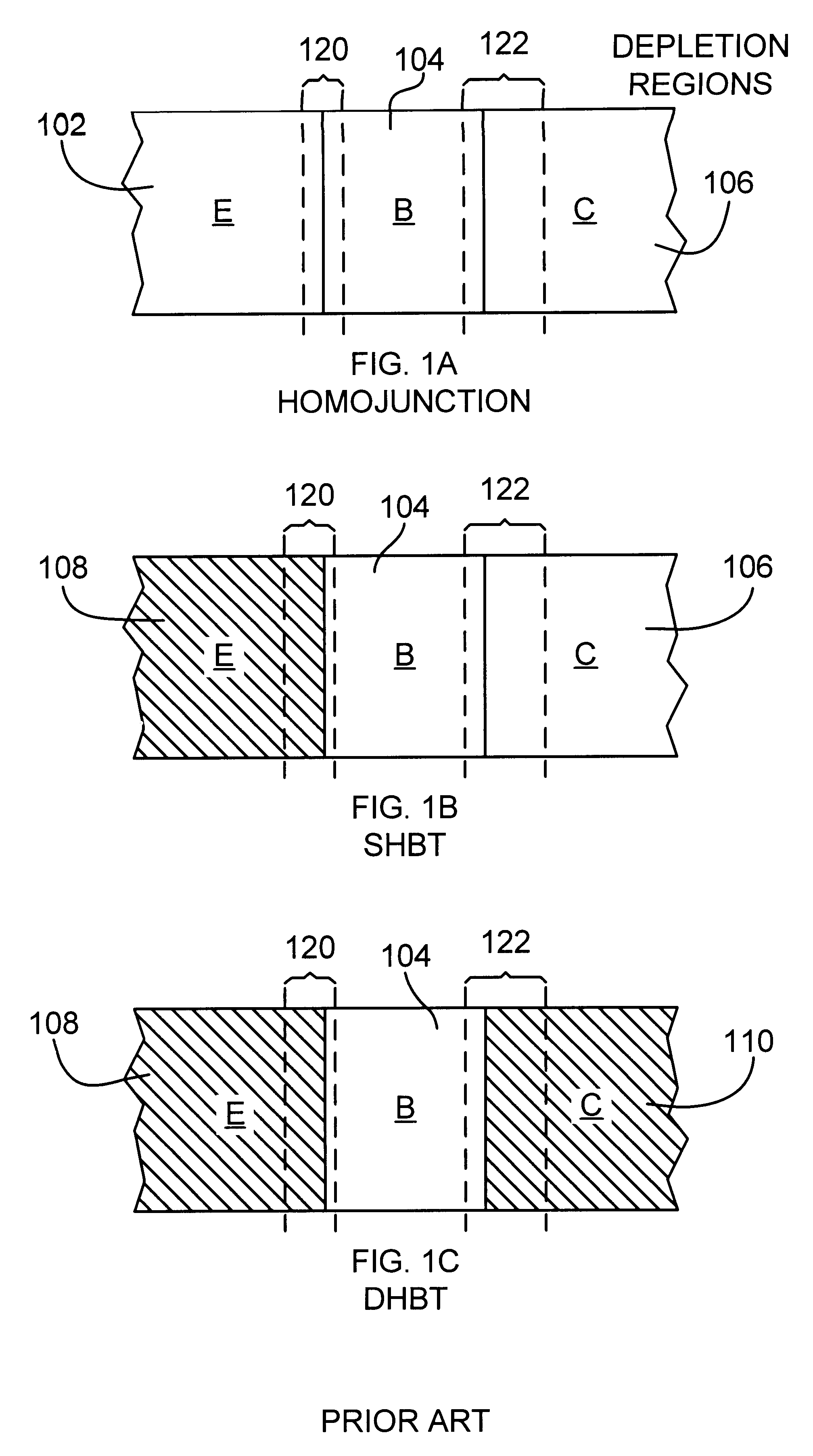

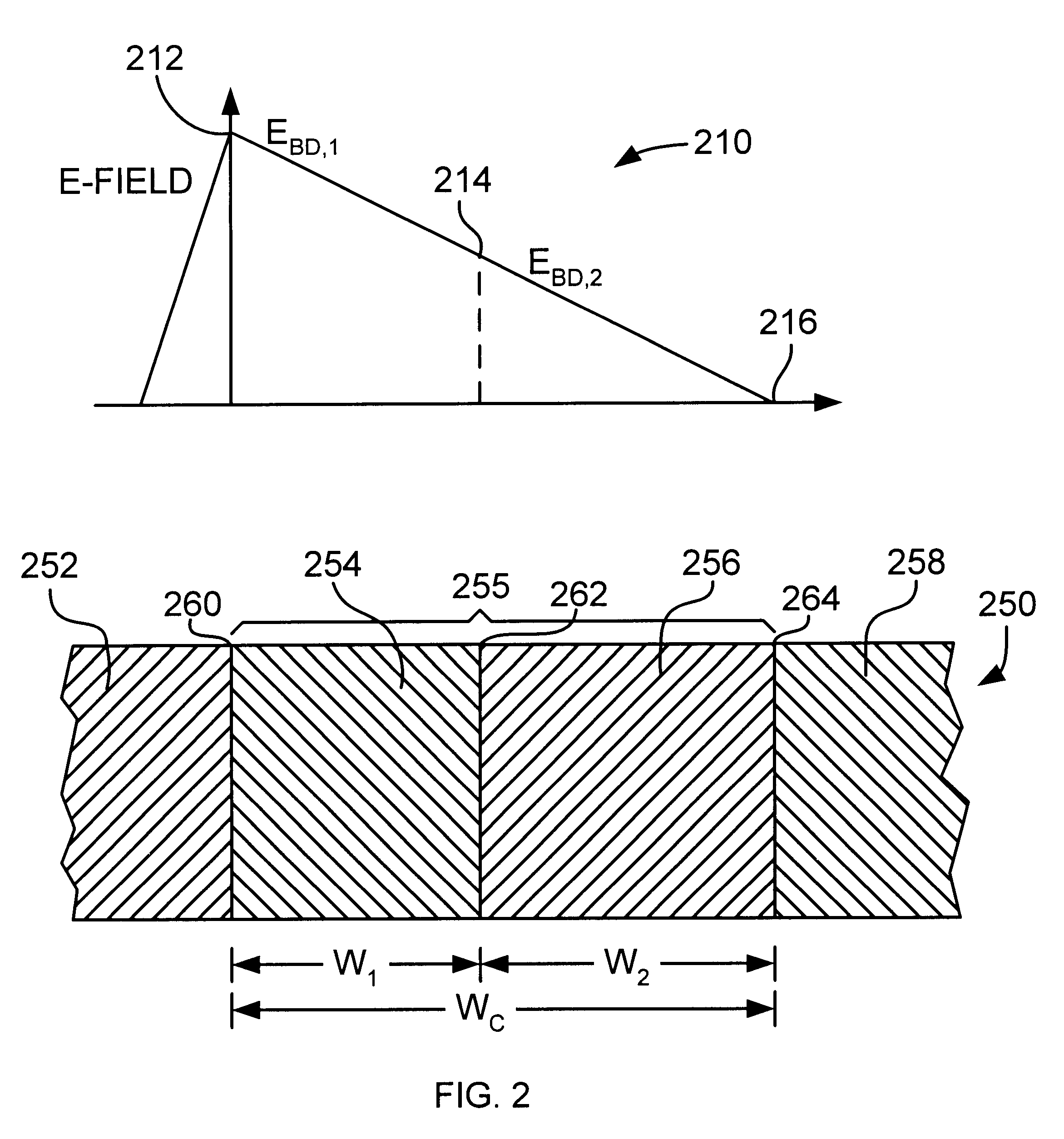

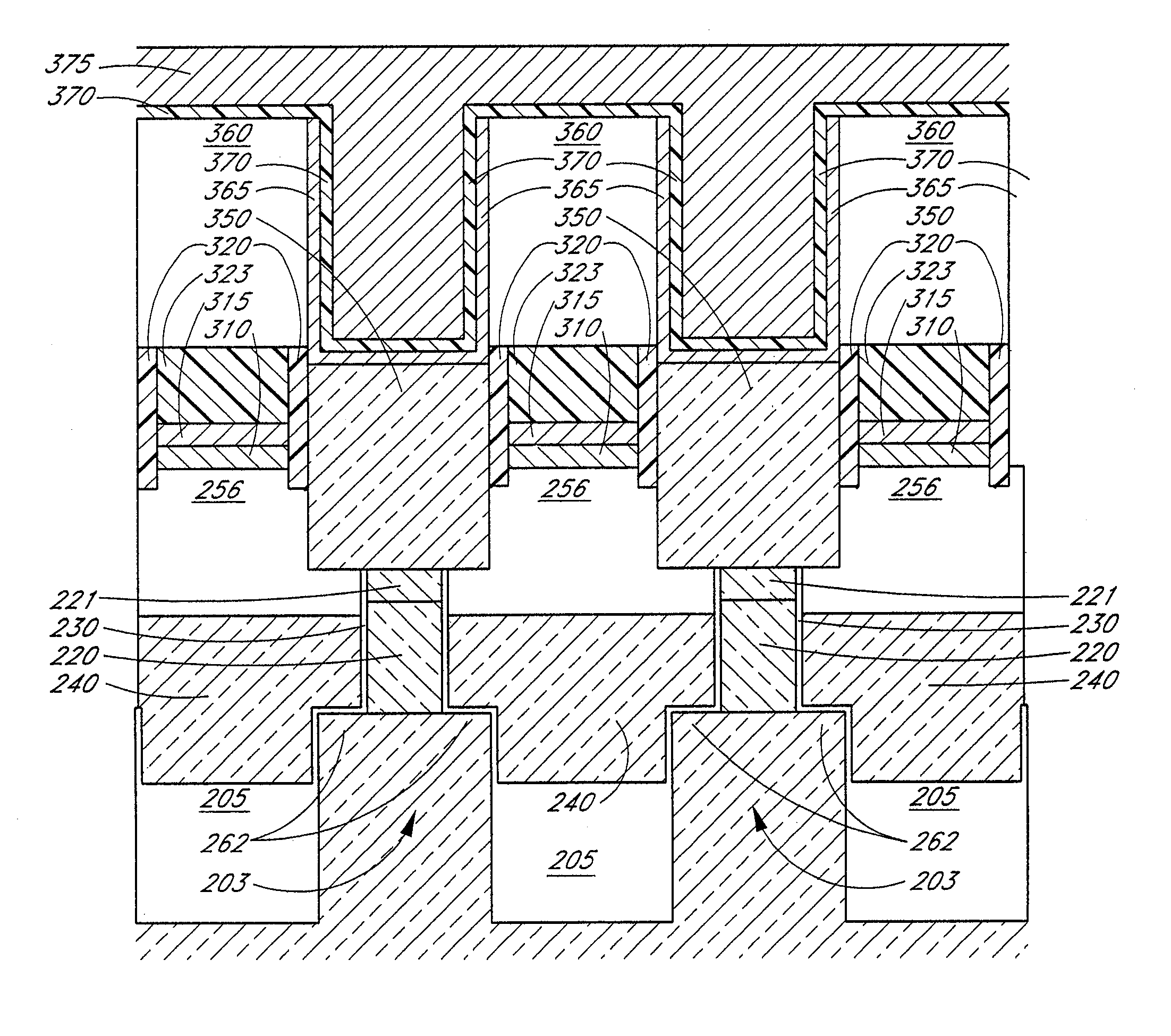

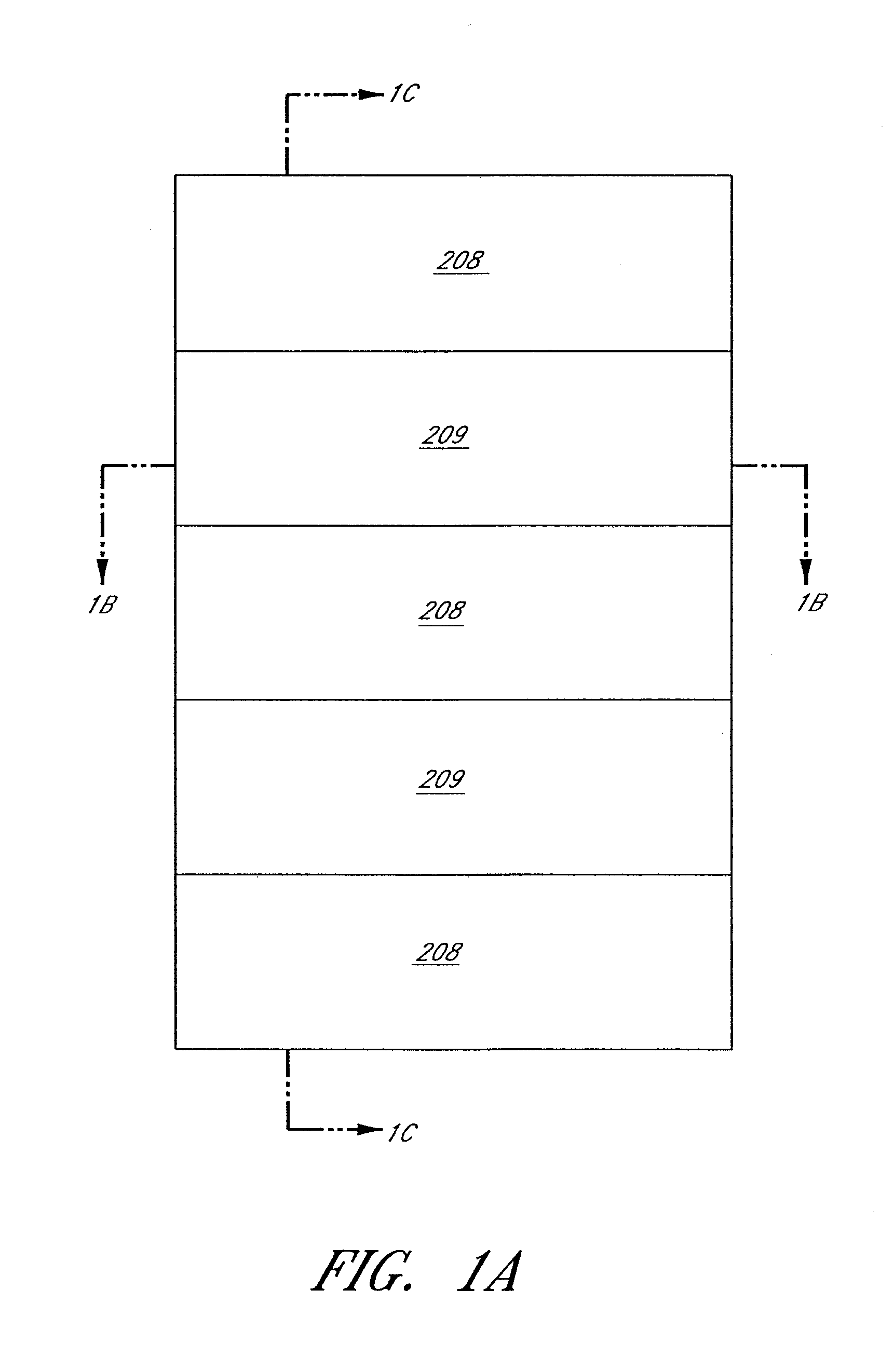

Methods and apparatus for a composite collector double heterojunction bipolar transistor

InactiveUS6563145B1Semiconductor/solid-state device manufacturingSemiconductor devicesEngineeringWideband

A compound collector double heterojunction bipolar transistor (CCHBT) incorporates a collector comprising two layers: a wide bandgap collector region (e.g., GaAs), and a narrow bandgap collector region (e.g., InGaP). The higher electric field is supported in the wide bandgap region, thereby increasing breakdown voltage and reducing offset voltage. At the same time, the use of wide bandgap material in the depleted portion of the collector, and a higher mobility material toward the end and outside of the depletion region, reduces series resistance as well as knee voltage.

Owner:SKYWORKS SOLUTIONS INC

Methods of reducing floating body effect

Methods of reducing the floating body effect in vertical transistors are disclosed. The floating body effect occurs when an active region in a pillar is cut off from the substrate by a depletion region and the accompanying electrostatic potential created. In a preferred embodiment, a word line is recessed into the substrate to tie the upper active region to the substrate. The resulting memory cells are preferably used in dynamic random access memory (DRAM) devices.

Owner:MICRON TECH INC

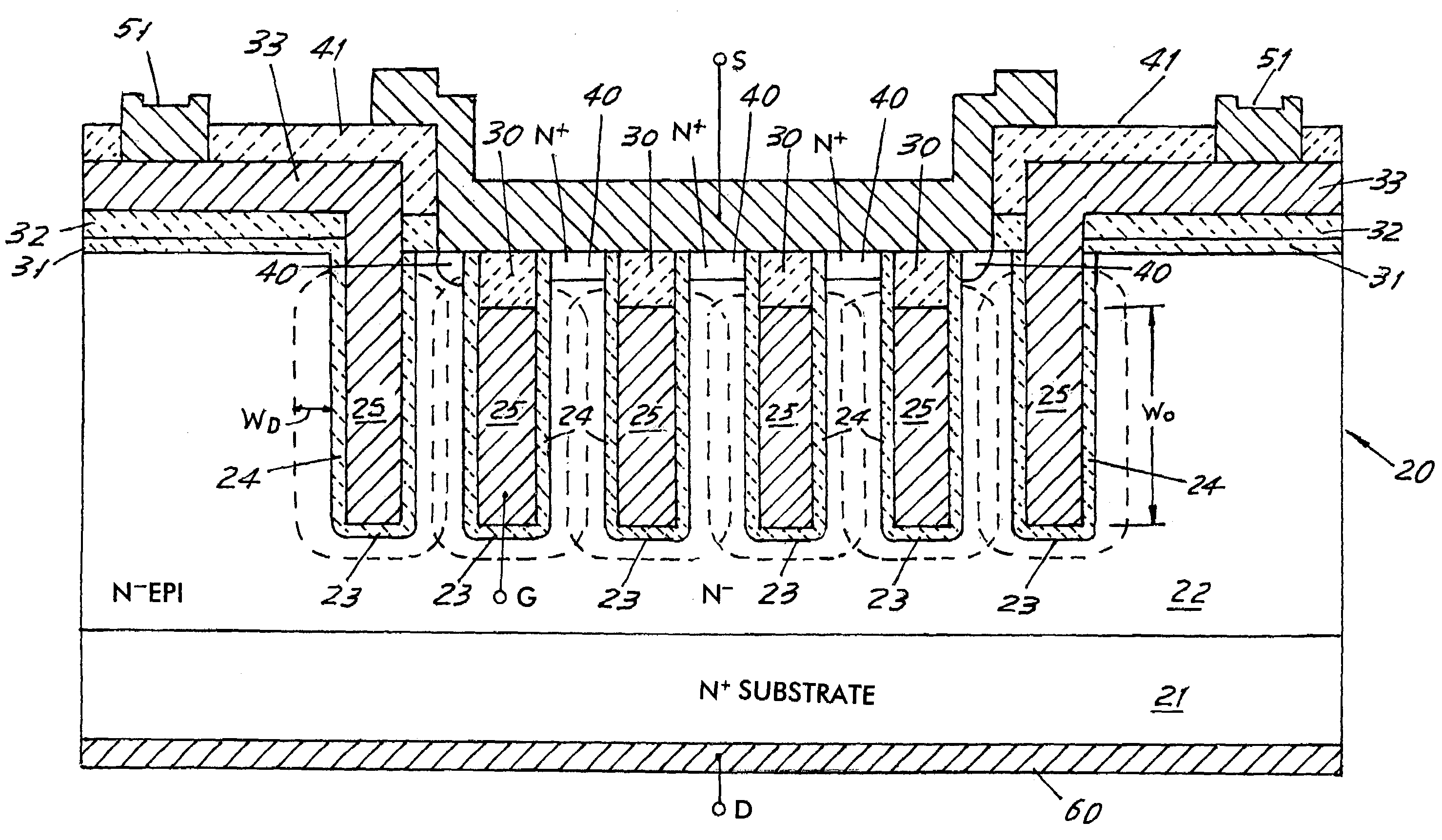

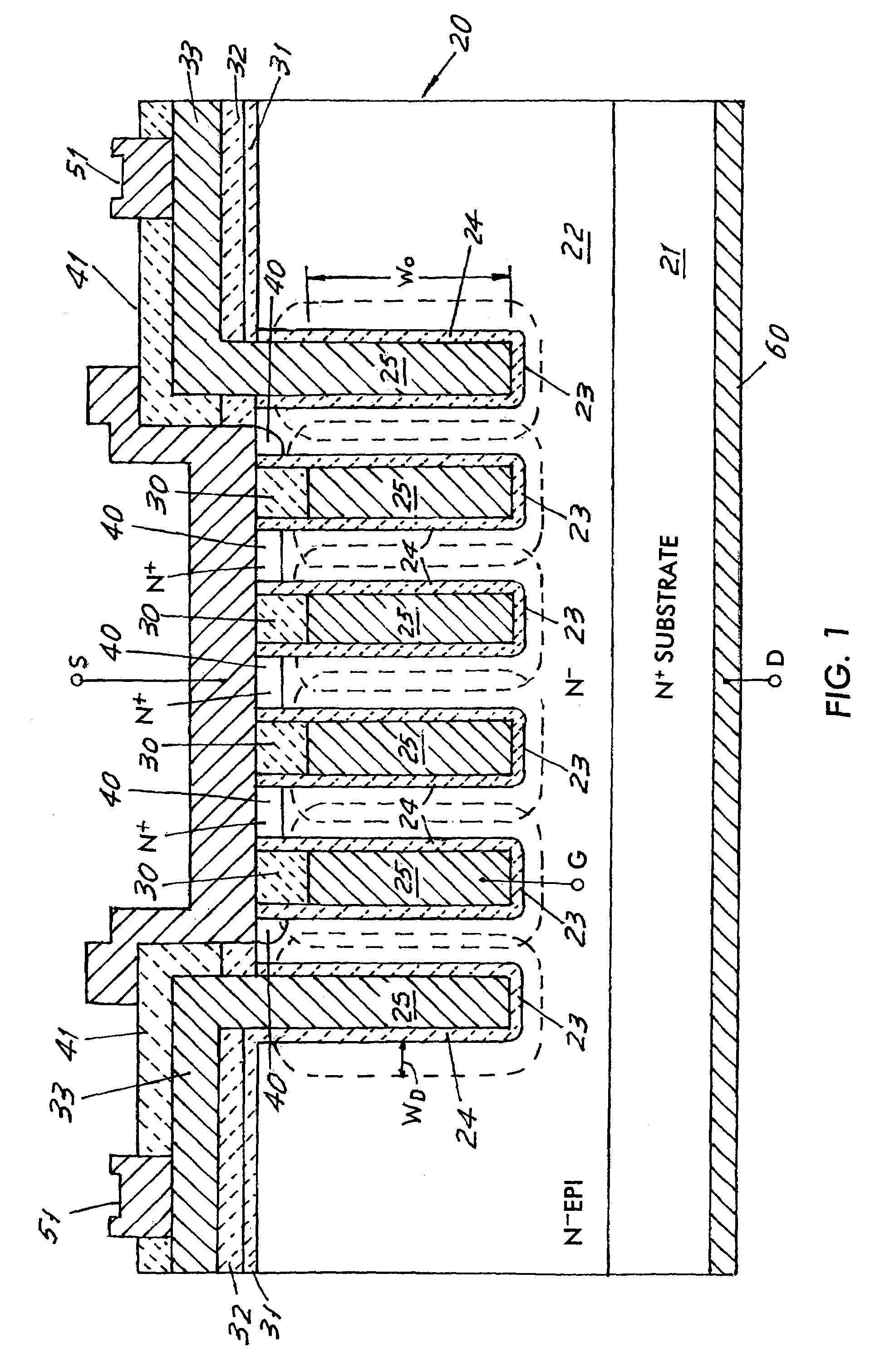

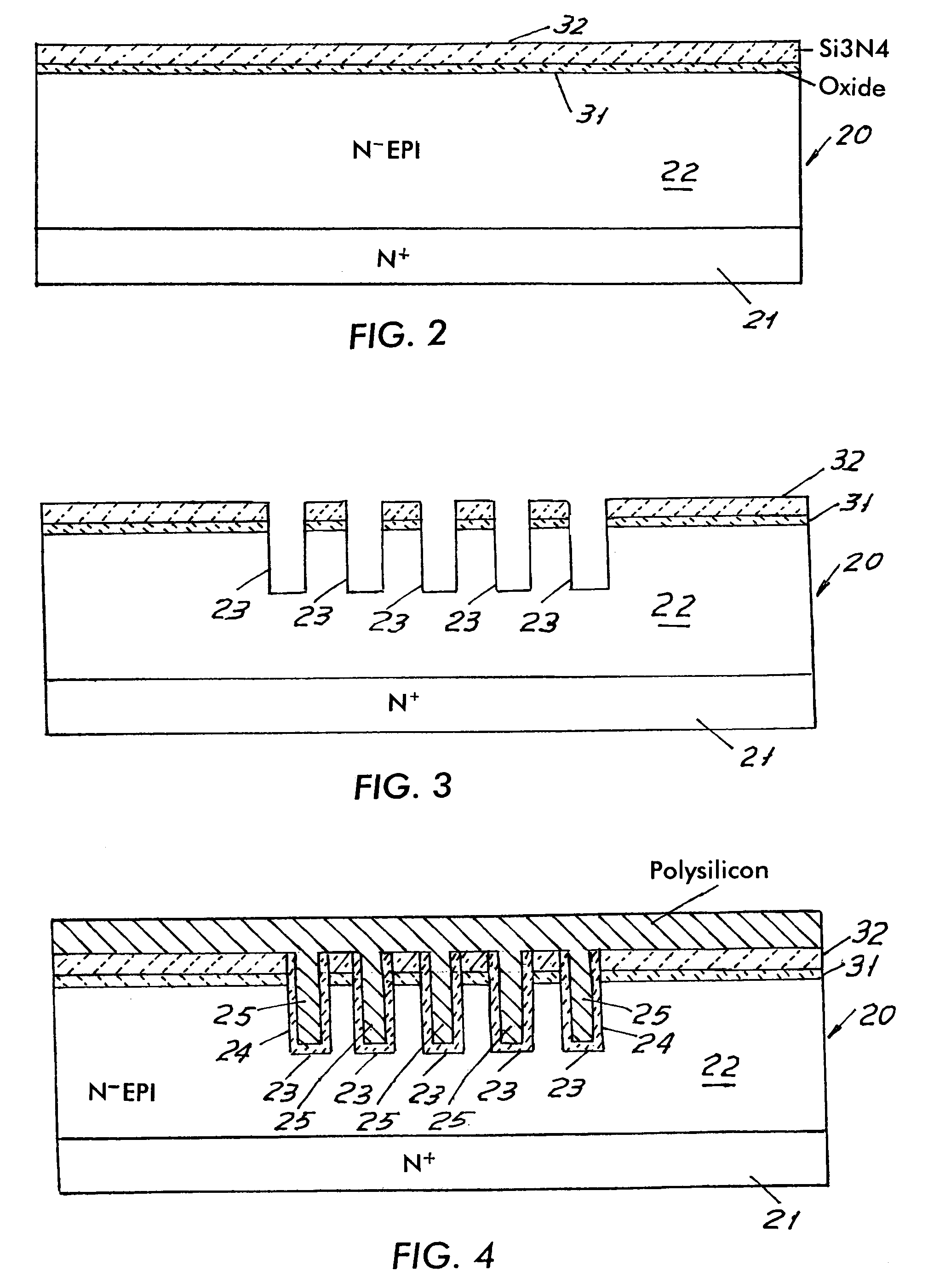

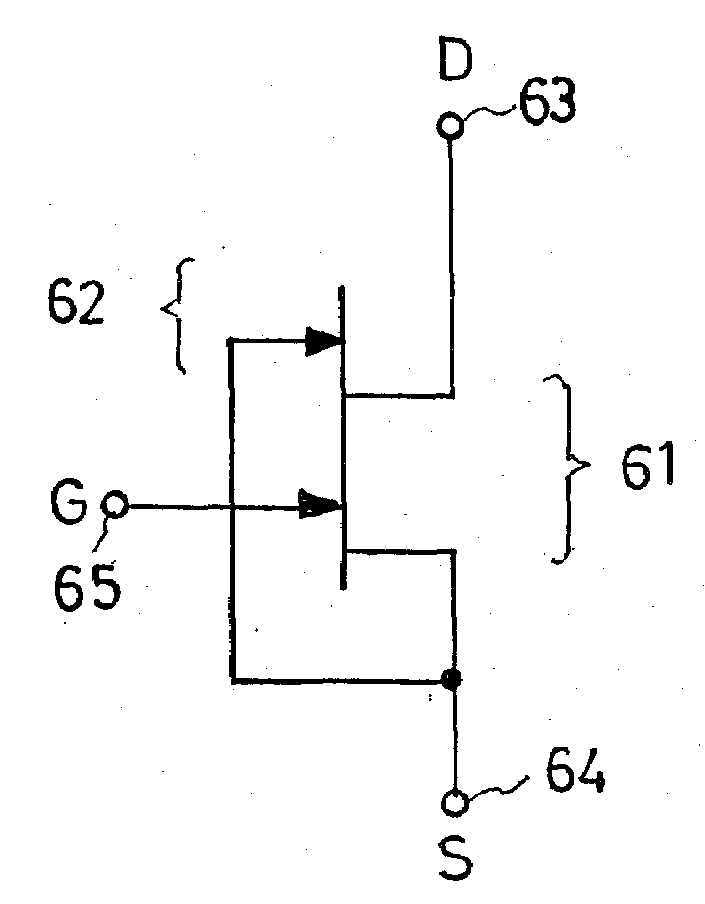

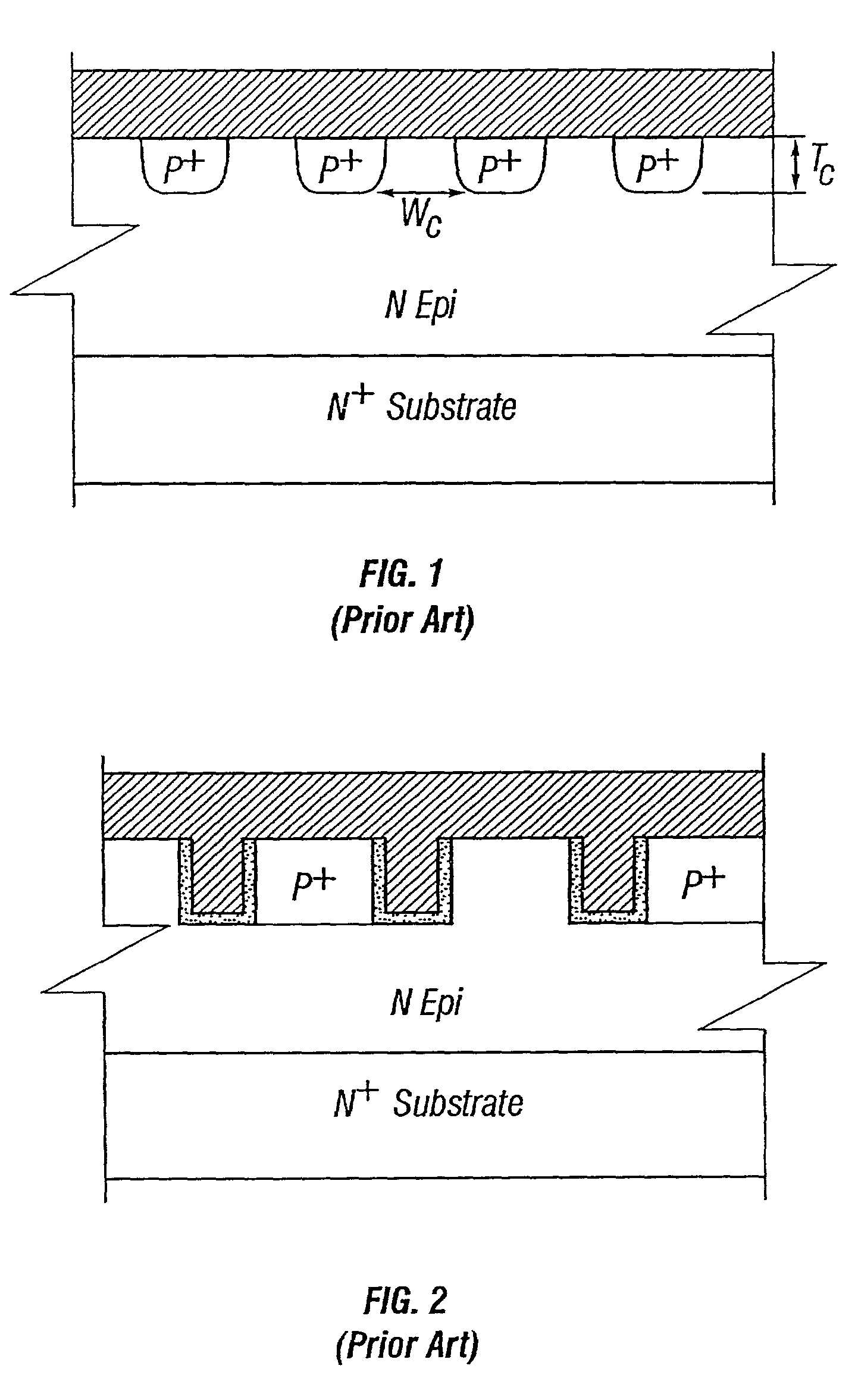

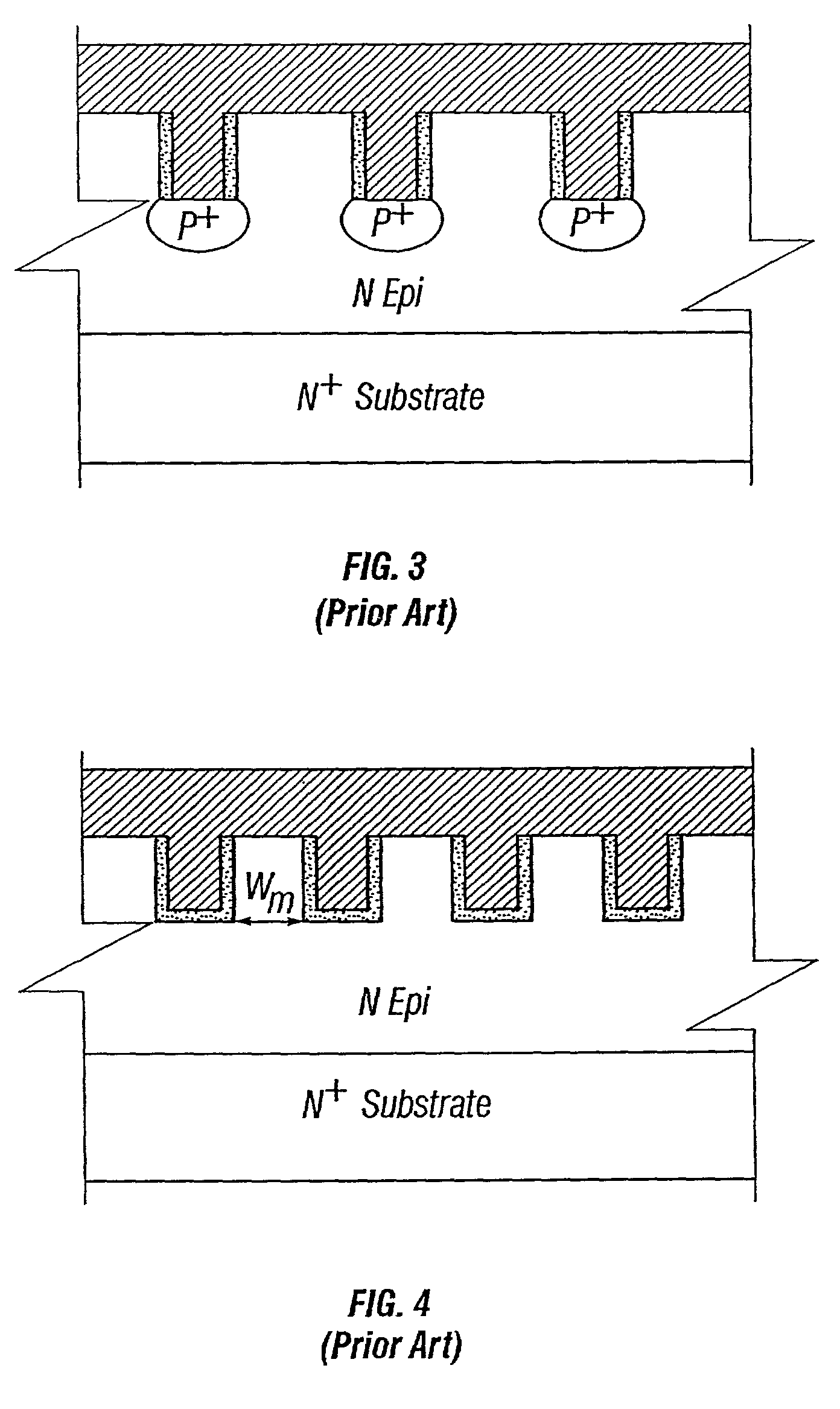

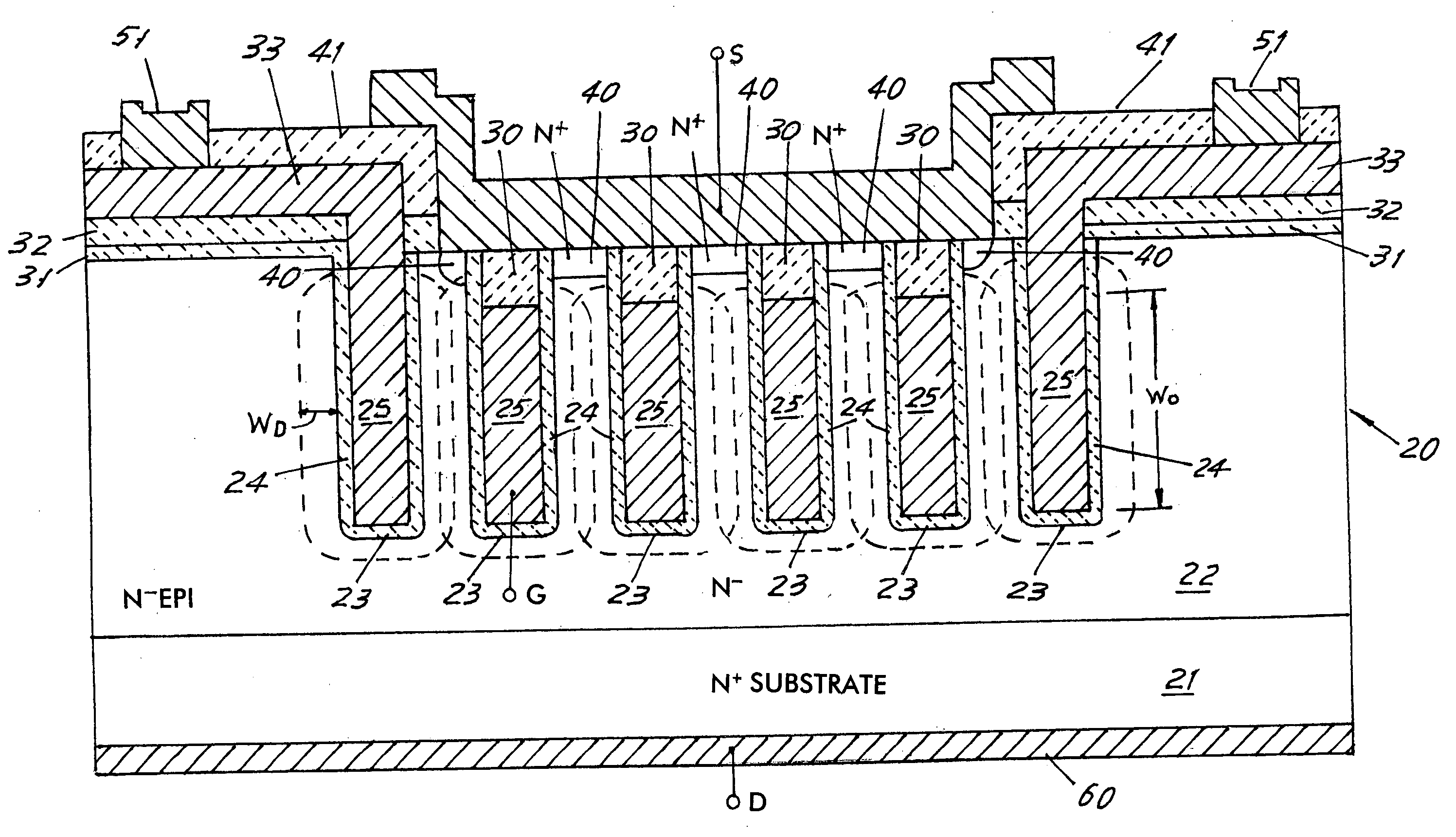

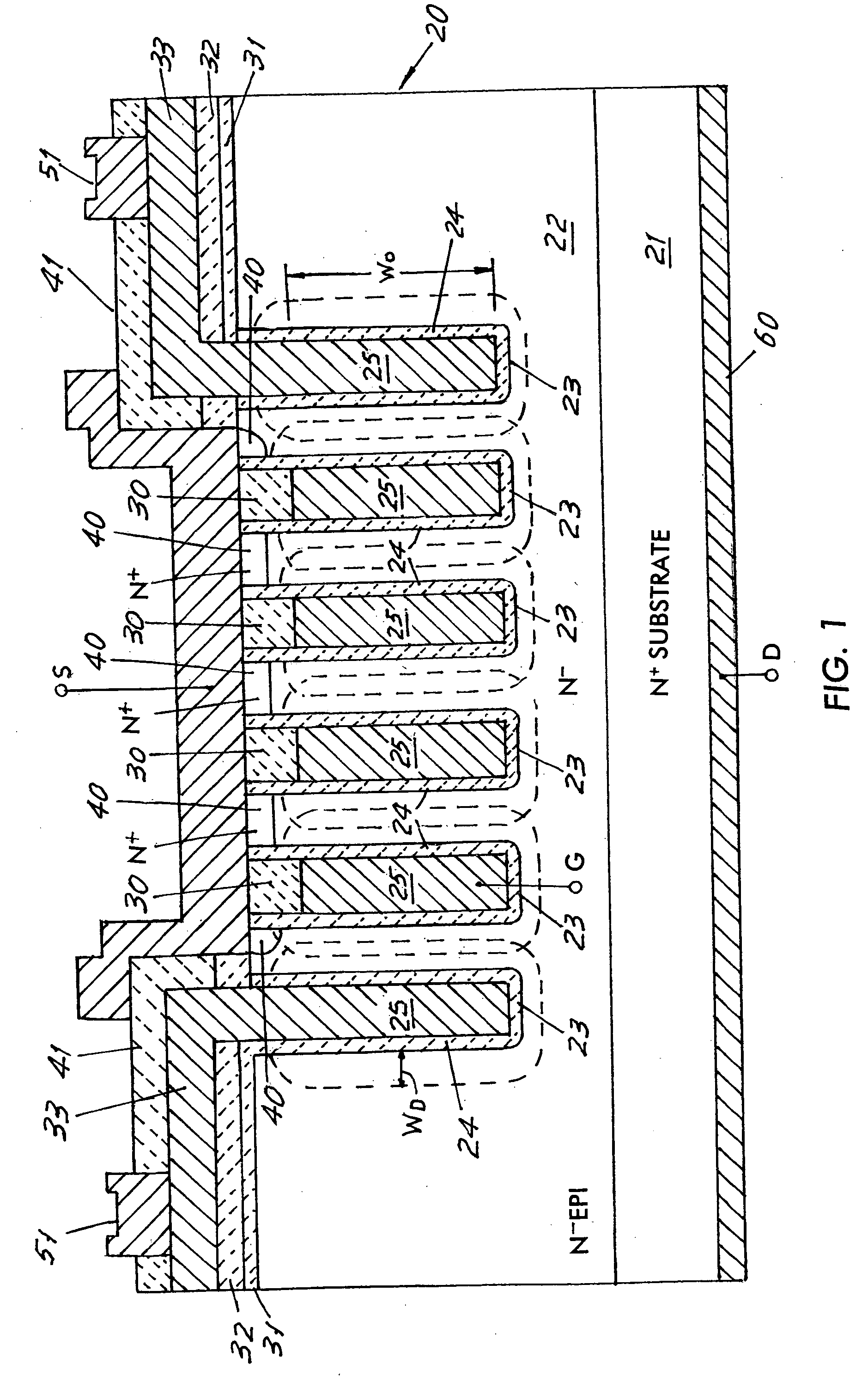

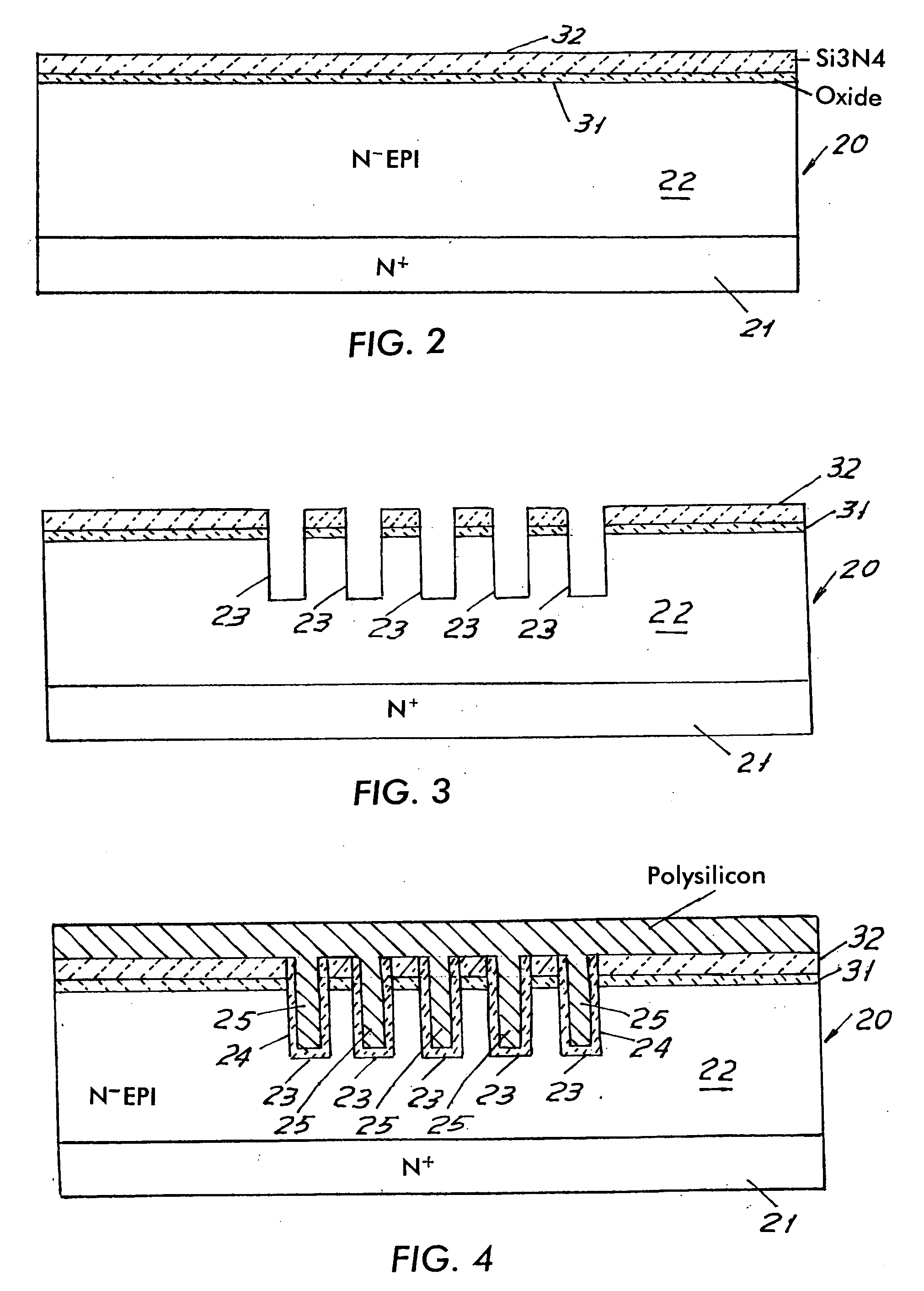

Dynamic deep depletion field effect transistor

A vertical conduction trench FET has a plurality of trenches containing conductive polysilicon gates. The mesas between the trenches have a source diffusion region connected to a common source electrode. The trenches are spaced so that the depletion regions induced by the trench gate will overlap to pinch off conduction through the mesa to turn off the device. The gate potential is pulsed. The polysilicon in the trenches may be separated into two insulated portions. The pulses may be applied simultaneously or sequentially to the polysilicon gates.

Owner:INFINEON TECH AMERICAS CORP

Active photosensitive structure with buried depletion layer

An imager pixel has a photosensitive JFET structure having a channel region located above a buried charge accumulation region. The channel region has a resistance characteristic that changes depending on the level of accumulated charge in the accumulation region. During an integration period, incident light causes electrons to be accumulated inside the buried accumulation region. The resistance characteristic of the channel region changes in response to a field created by the charges accumulated in the accumulation region. Thus, when a voltage is applied to one side of the channel, the current read out from the other side is characteristic of the amount of stored charges.

Owner:MICRON TECH INC

Semiconductor device and method

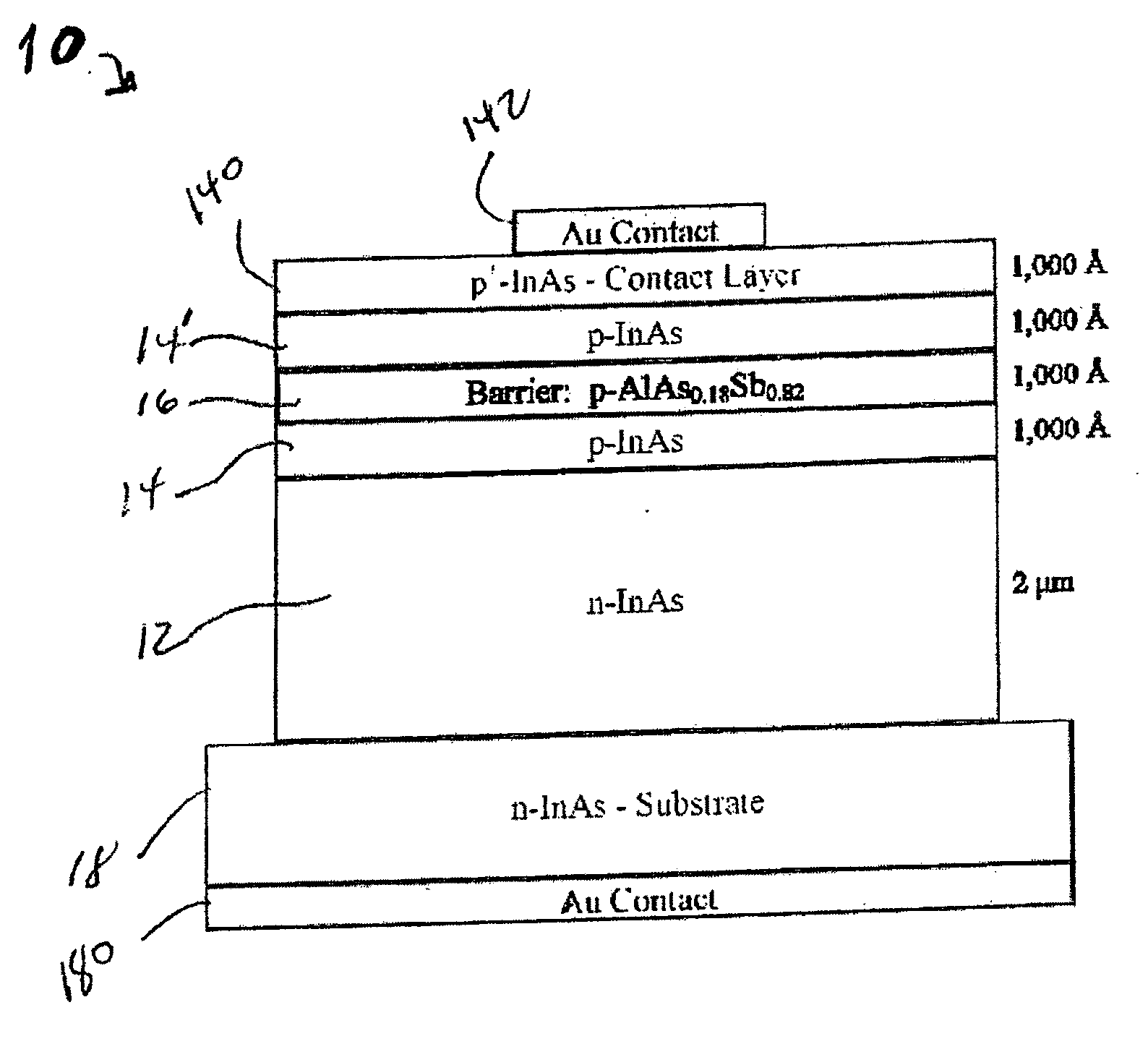

ActiveUS20100230720A1Eliminate surface leakage currentReduce surface currentSemiconductor/solid-state device manufacturingNanoopticsValence bandConduction band

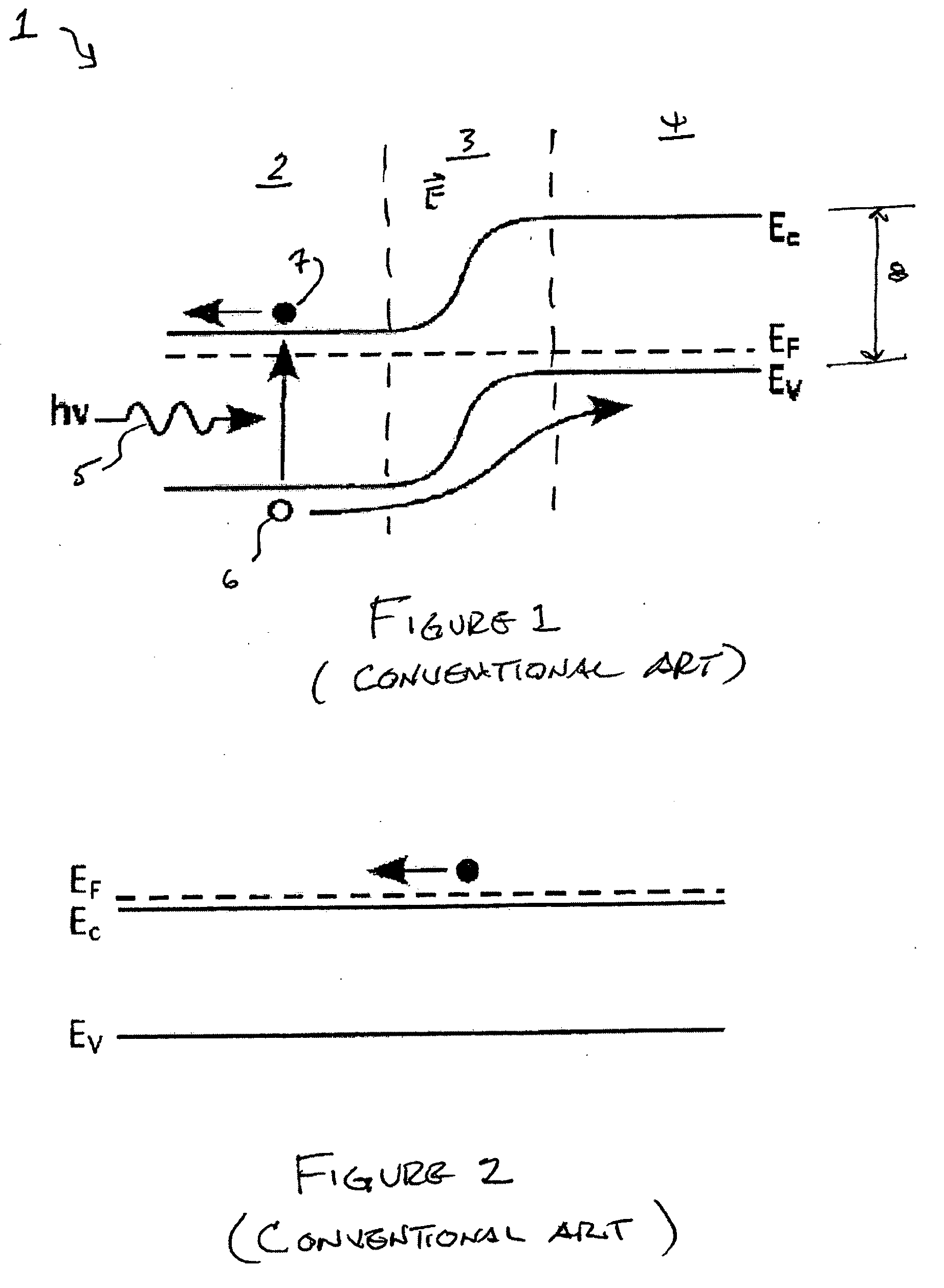

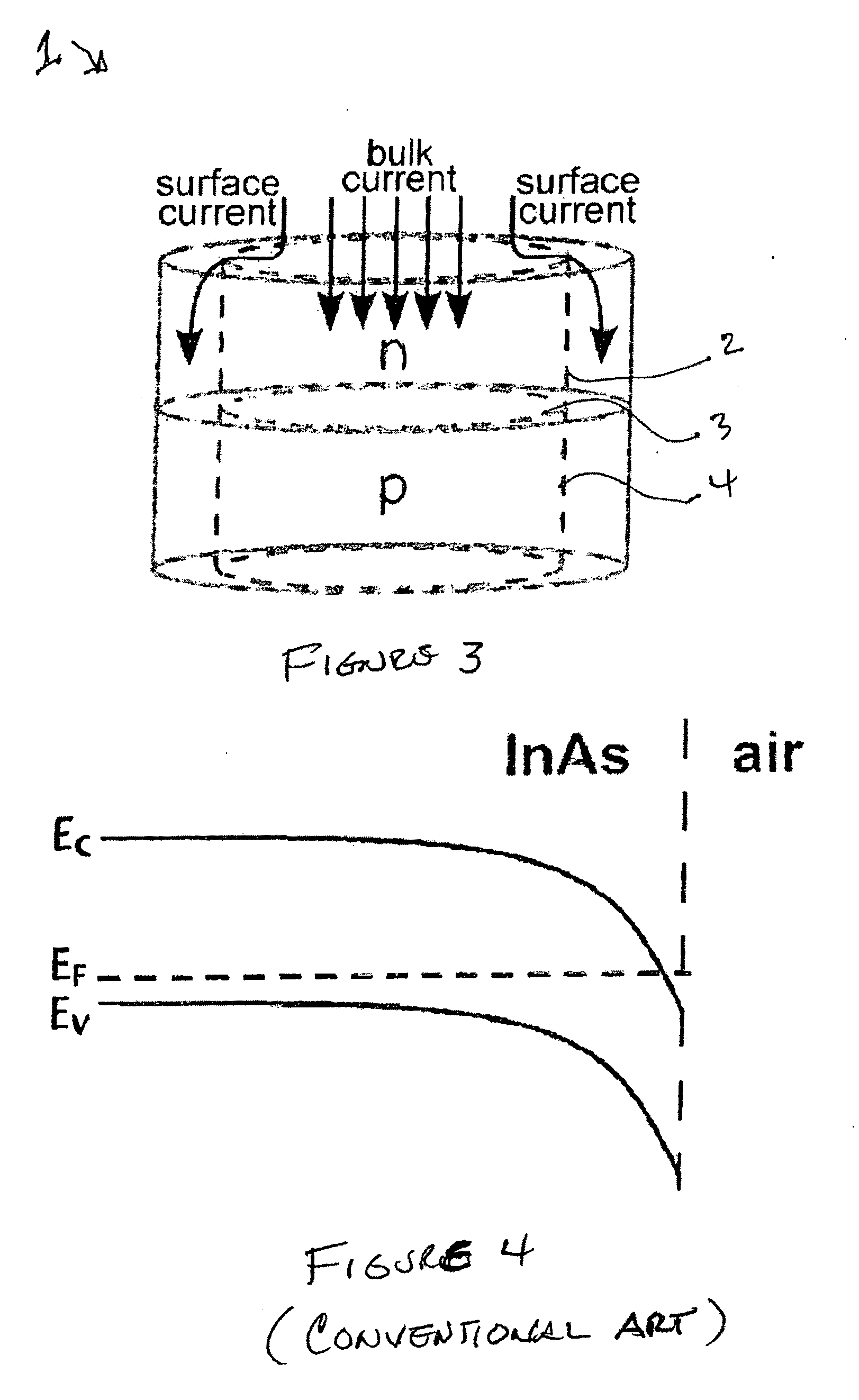

The present invention is directed to a semiconductor device that includes at least one p-n junction including a p-type material, an n-type material, and a depletion region. The at least one p-n junction is configured to generate bulk photocurrent in response to incident light. The at least one p-n junction is characterized by a conduction band energy level, a valence band energy level and a surface Fermi energy level. The surface Fermi energy level is pinned either near or above the conduction band energy level or near or below the valence band energy level. A unipolar barrier structure is disposed in a predetermined region within the at least one p-n junction. The unipolar barrier is configured to raise the conduction band energy level if the surface Fermi energy level is pinned near or above the conduction band energy level or lower the valence band energy level if the surface Fermi energy level is pinned near or below the valence band energy level such that the unipolar barrier is configured to propagate the bulk photocurrent and substantially block surface leakage current. The at least one p-n junction and the unipolar barrier are integrally formed.

Owner:UNIVERSITY OF ROCHESTER

Backside depletion for backside illuminated image sensors

ActiveUS20080224247A1Solid-state devicesSemiconductor/solid-state device manufacturingPhotodiodeDepletion region

A backside illuminated image sensor is provided which includes a substrate having a front side and a backside, a sensor formed in the substrate at the front side, the sensor including at least a photodiode, and a depletion region formed in the substrate at the backside, a depth of the depletion region is less than 20% of a thickness of the substrate.

Owner:TAIWAN SEMICON MFG CO LTD

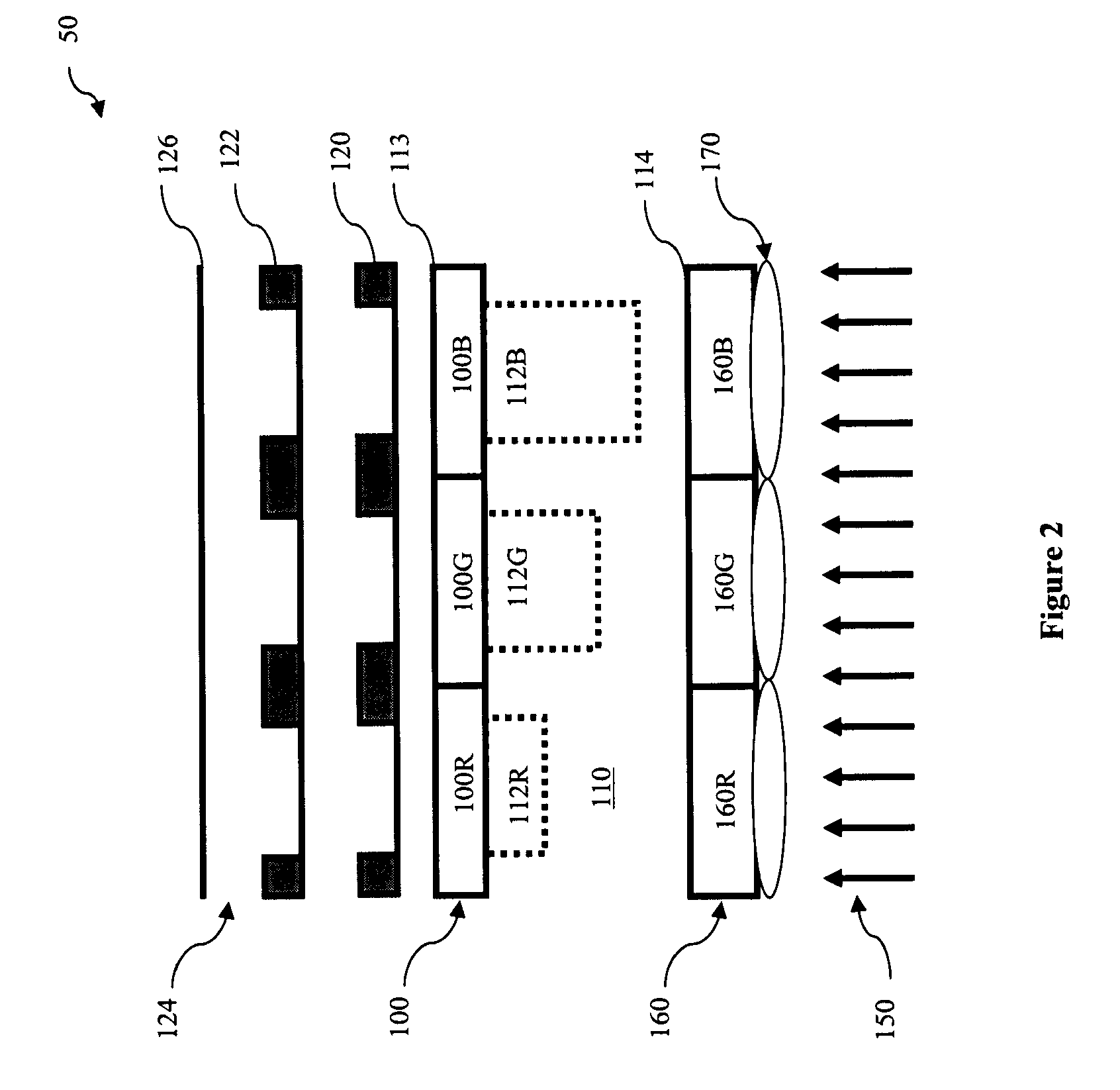

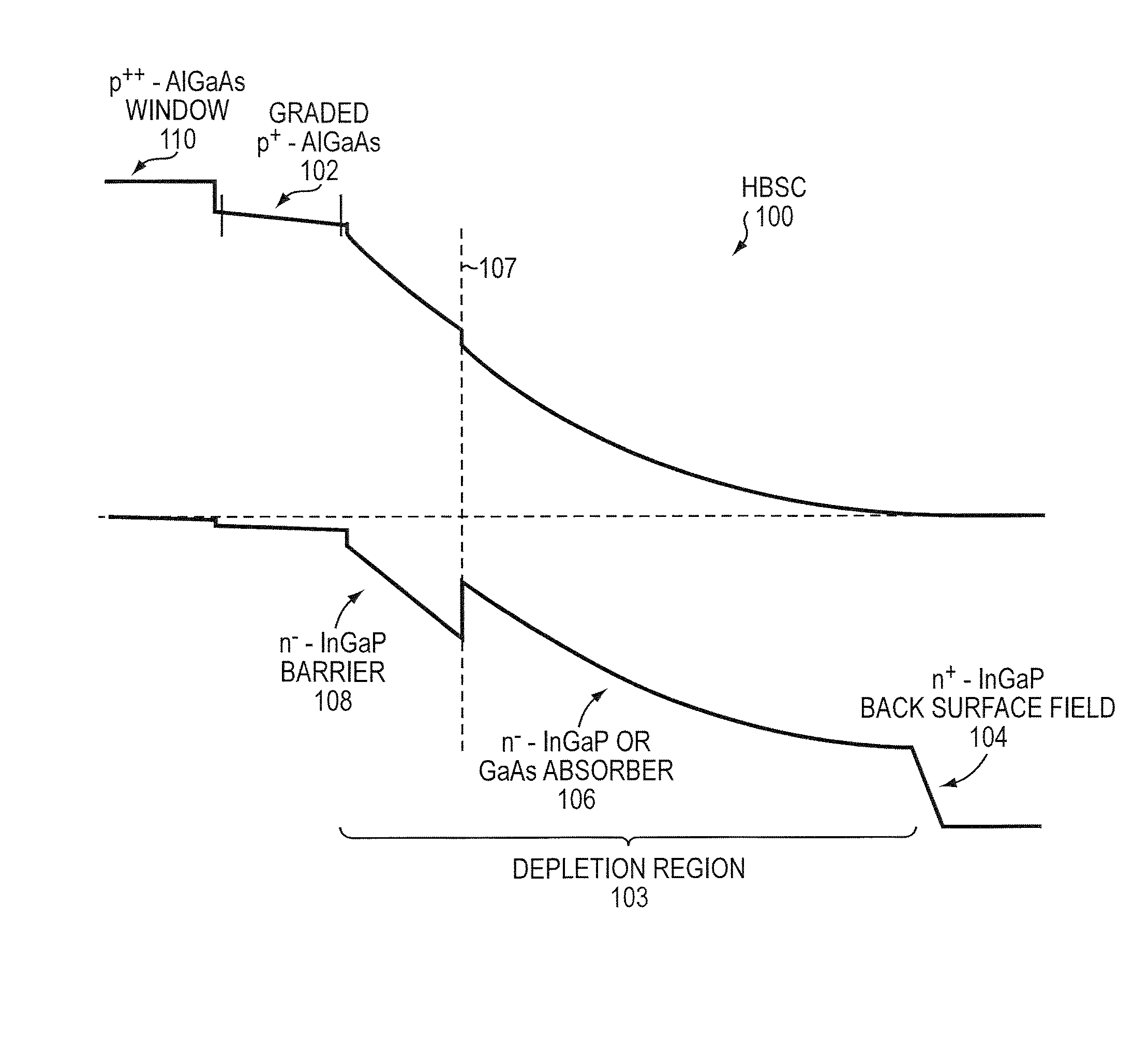

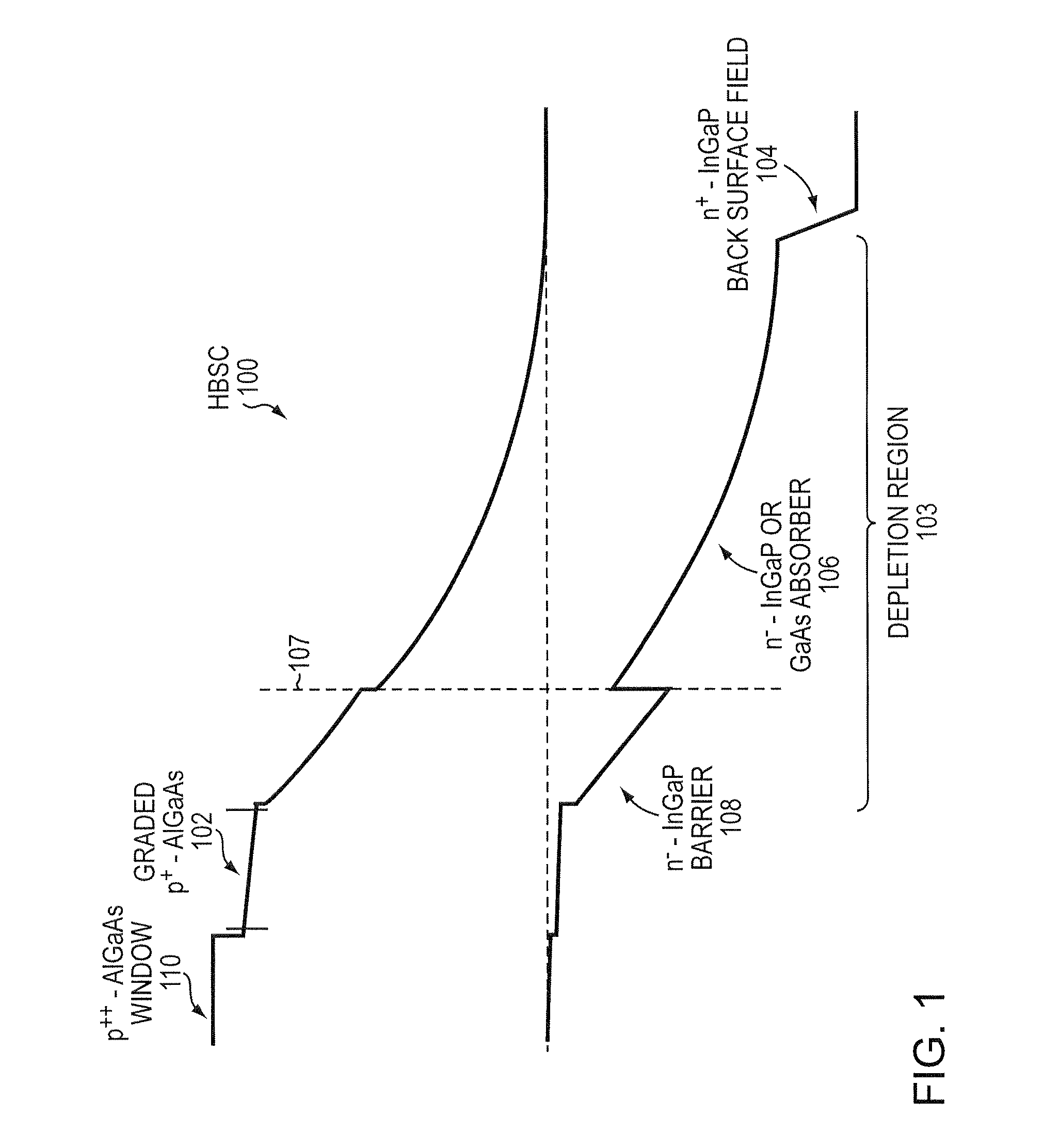

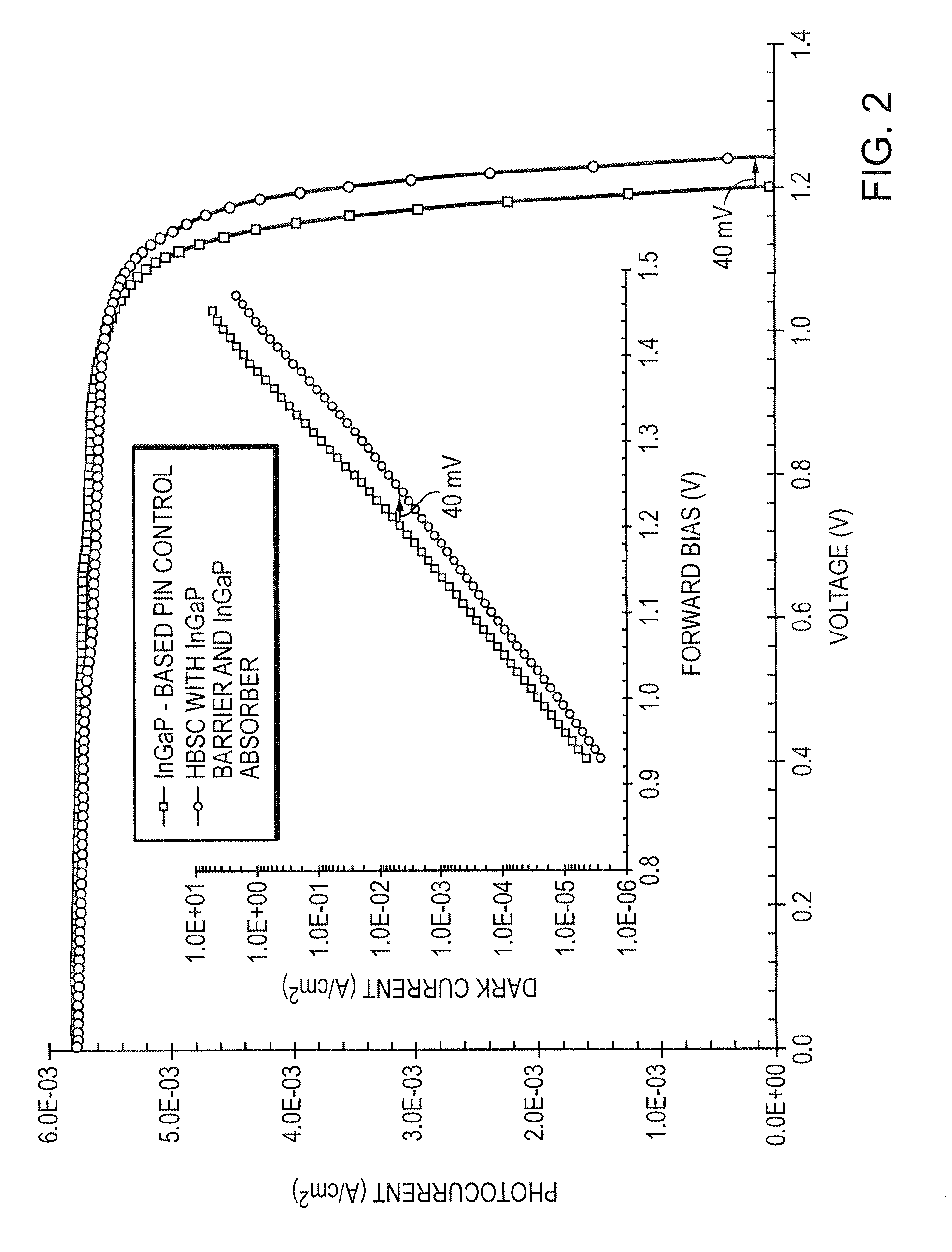

Ingap heterojunction barrier solar cells

ActiveUS20100096010A1Improve photovoltaic conversion efficiencyMaximize photocurrentNanotechSemiconductor/solid-state device manufacturingHeterojunctionIndium

A new solar cell structure called a heterojunction barrier solar cell is described. As with previously reported quantum-well and quantum-dot solar cell structures, a layer of narrow band-gap material, such as GaAs or indium-rich InGaP, is inserted into the depletion region of a wide band-gap PN junction. Rather than being thin, however, the layer of narrow band-gap material is about 400-430 nm wide and forms a single, ultrawide well in the depletion region. Thin (e.g., 20-50 nm), wide band-gap InGaP barrier layers in the depletion region reduce the diode dark current. Engineering the electric field and barrier profile of the absorber layer, barrier layer, and p-type layer of the PN junction maximizes photogenerated carrier escape. This new twist on nanostructured solar cell design allows the separate optimization of current and voltage to maximize conversion efficiency.

Owner:KOPIN CORPORATION

Semiconductor device containing dielectrically isolated PN junction for enhanced breakdown characteristics

InactiveUS20050167744A1Increased avalanche breakdown voltageLower on-resistanceSemiconductor/solid-state device manufacturingDiodePower MOSFETGate oxide

A semiconductor device includes a field shield region that is doped opposite to the conductivity of the substrate and is bounded laterally by dielectric sidewall spacers and from below by a PN junction. For example, in a trench-gated MOSFET the field shield region may be located beneath the trench and may be electrically connected to the source region. When the MOSFET is reverse-biased, depletion regions extend from the dielectric sidewall spacers into the “drift” region, shielding the gate oxide from high electric fields and increasing the avalanche breakdown voltage of the device. This permits the drift region to be more heavily doped and reduces the on-resistance of the device. It also allows the use of a thin, 20 Å gate oxide for a power MOSFET that is to be switched with a 1V signal applied to its gate while being able to block over 30V applied across its drain and source electrodes, for example.

Owner:ALPHA & OMEGA SEMICON INC

Super self-aligned BJT with base shorted field plate and method of fabricating

ActiveUS7132344B1Raise the ratioSemiconductor/solid-state device manufacturingSemiconductor devicesVertical fieldSubstrate surface

A bipolar junction transistor (BJT) structure and fabrication method are provided in which a doped polysilicon filled trench is utilized to form both the extrinsic base contact region and a vertical field plate. A sacrificial mandrel of dielectric material is formed over regions that will become the BJT active area. This allows the polysilicon filled trench to be extended above the original semiconductor substrate surface. In this way, the base-collector and emitter-base junctions are both self-aligned to the field plate trench. The field plate is utilized to control and shape the electric field in the base-collector depletion region, allowing heavier collector well doping for the same breakdown voltage. This results in improvement in both the breakdown / Ron ratio and the fT*BVcbo product.

Owner:NAT SEMICON CORP