Patents

Literature

440 results about "Shallow junction" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

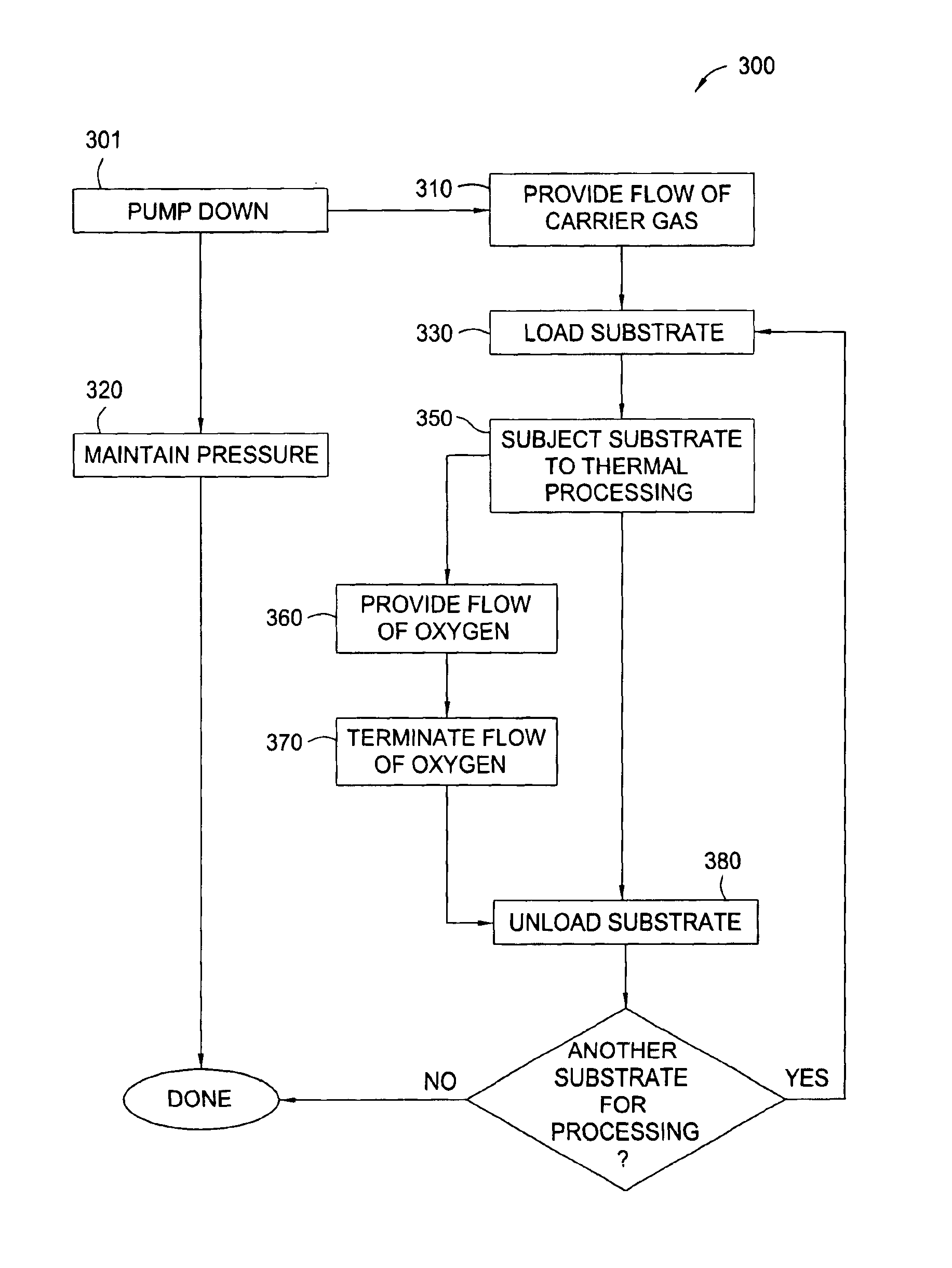

Method for forming film having low resistance and shallow junction depth

ActiveUS9478415B2Semiconductor/solid-state device manufacturingChemical vapor deposition coatingSilicon oxideLow resistance

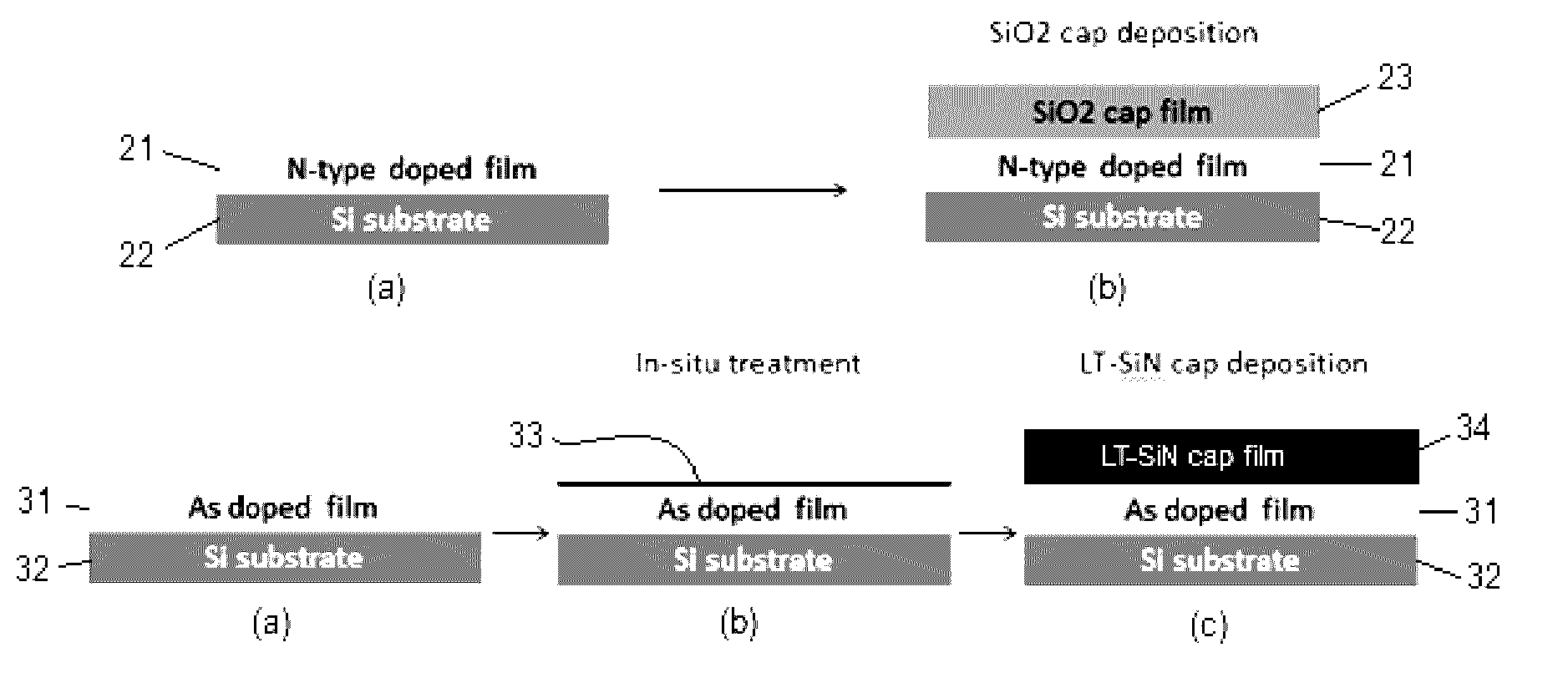

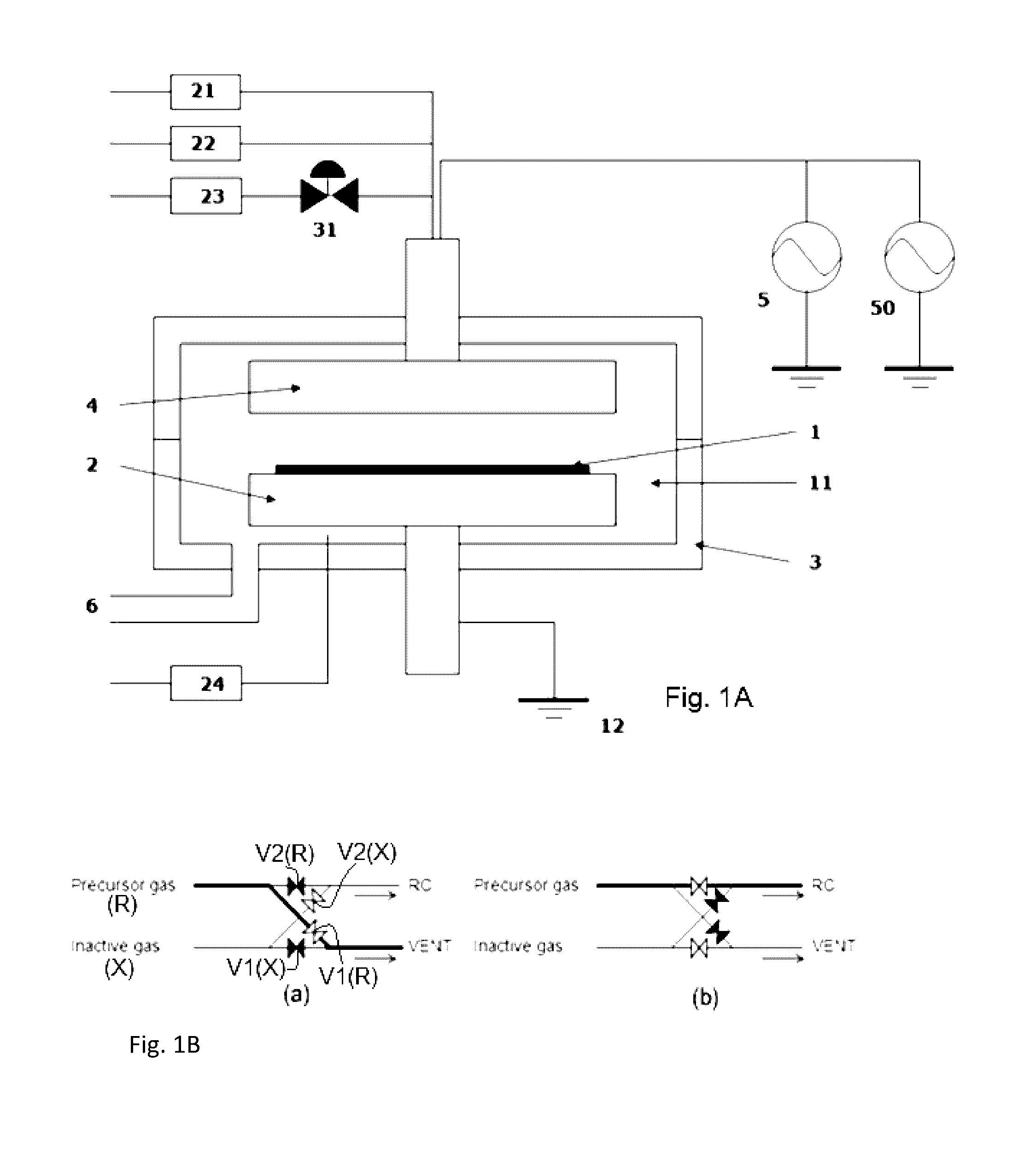

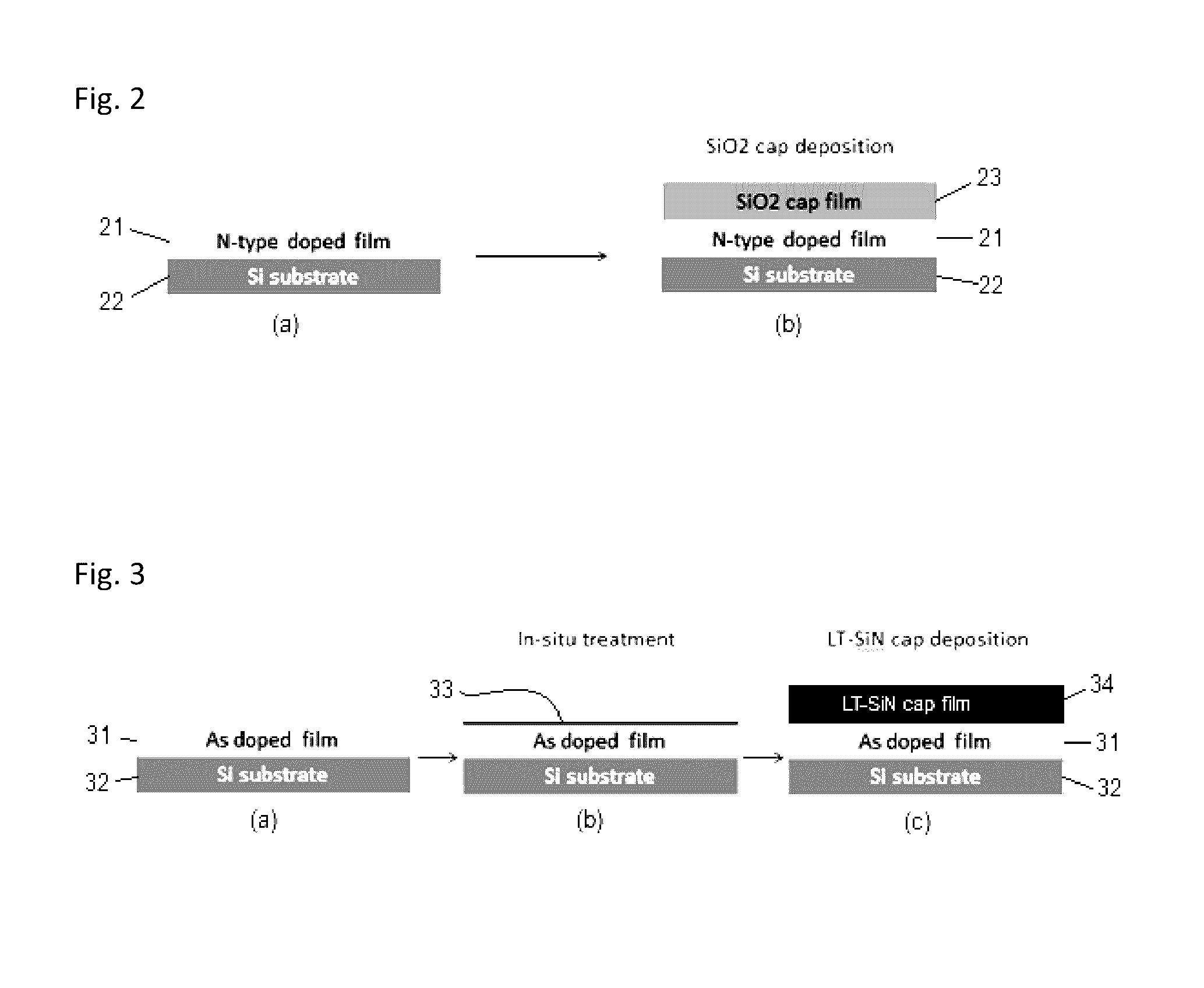

A method for forming on a substrate a doped silicon oxide film with a cap film, includes: forming an arsenosilicate glass (ASG) film as an arsenic (As)-doped silicon oxide film on a substrate; continuously treating a surface of the ASG film with a treating gas constituted by Si, N, and H without excitation; and continuously forming a silicon nitride (SiN) film as a cap film on the treated surface of the ASG film.

Owner:ASM IP HLDG BV

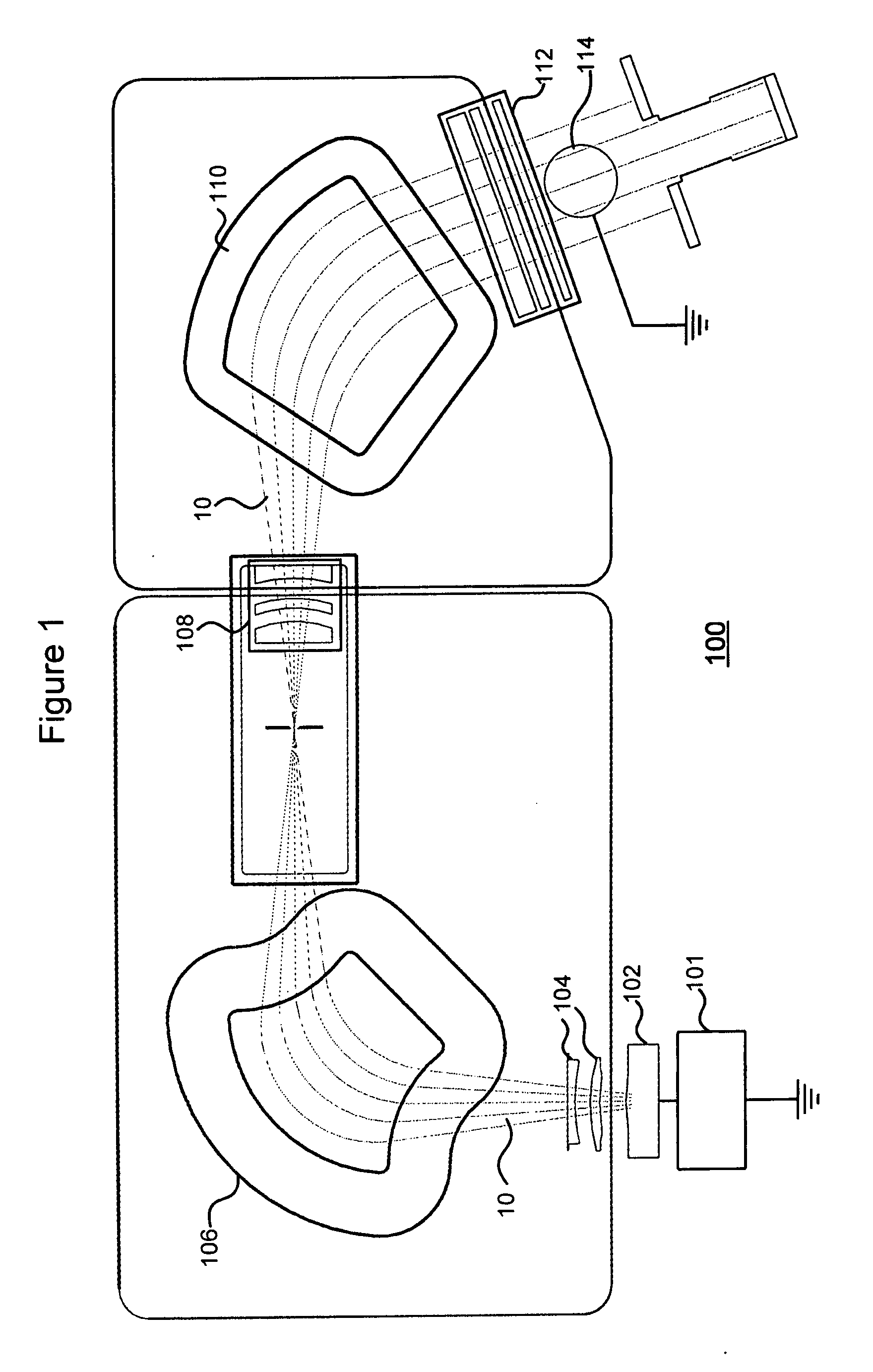

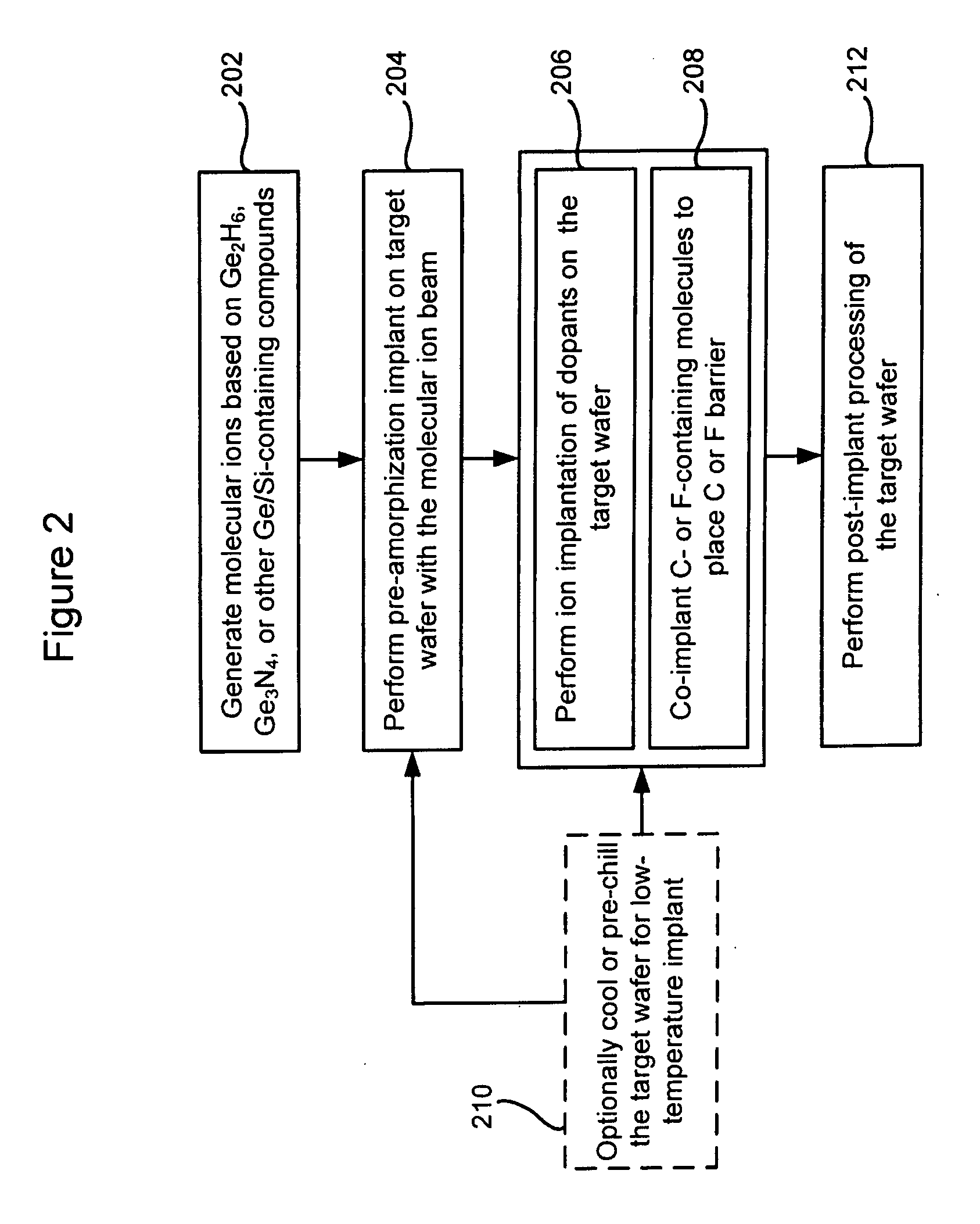

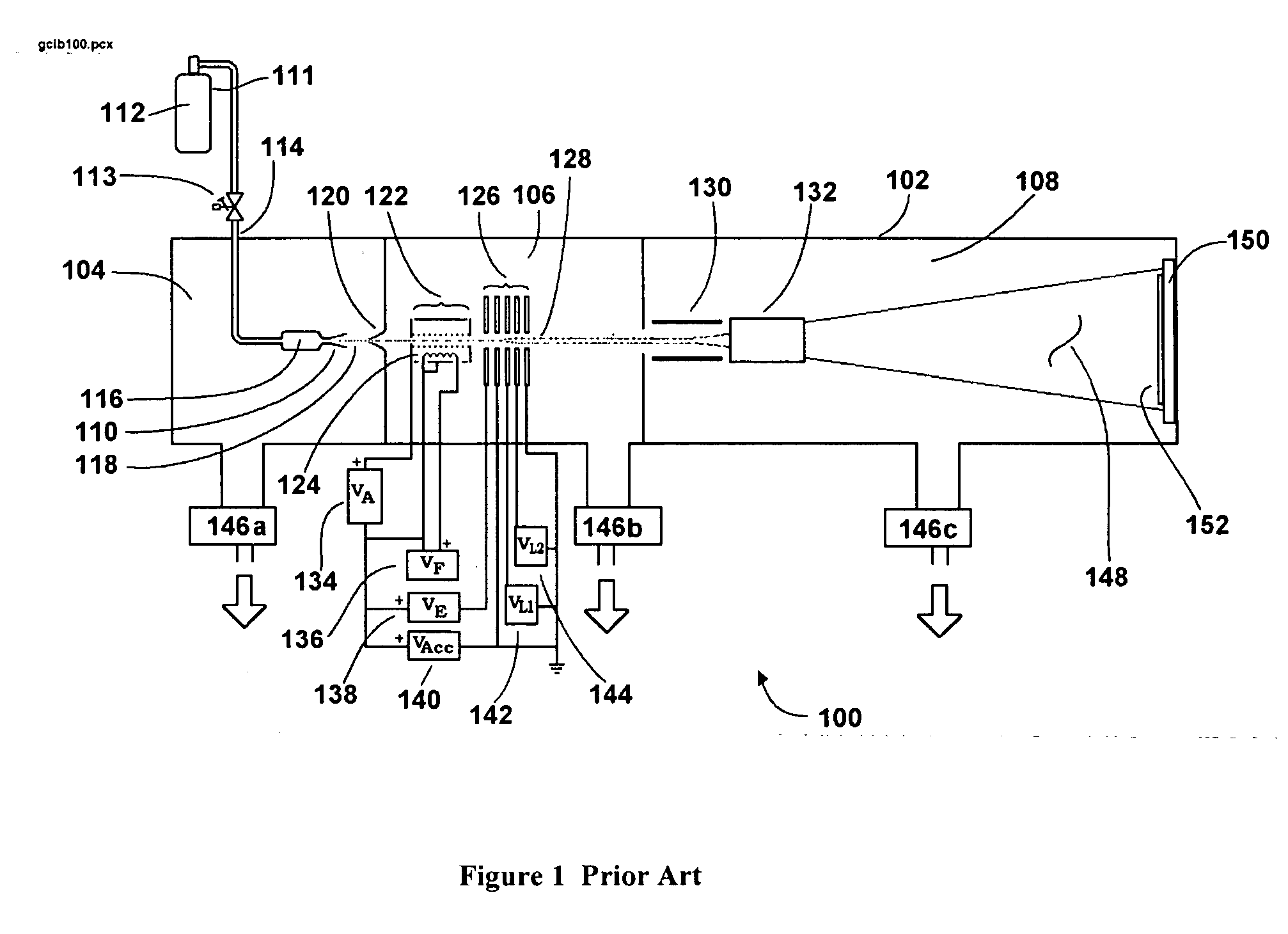

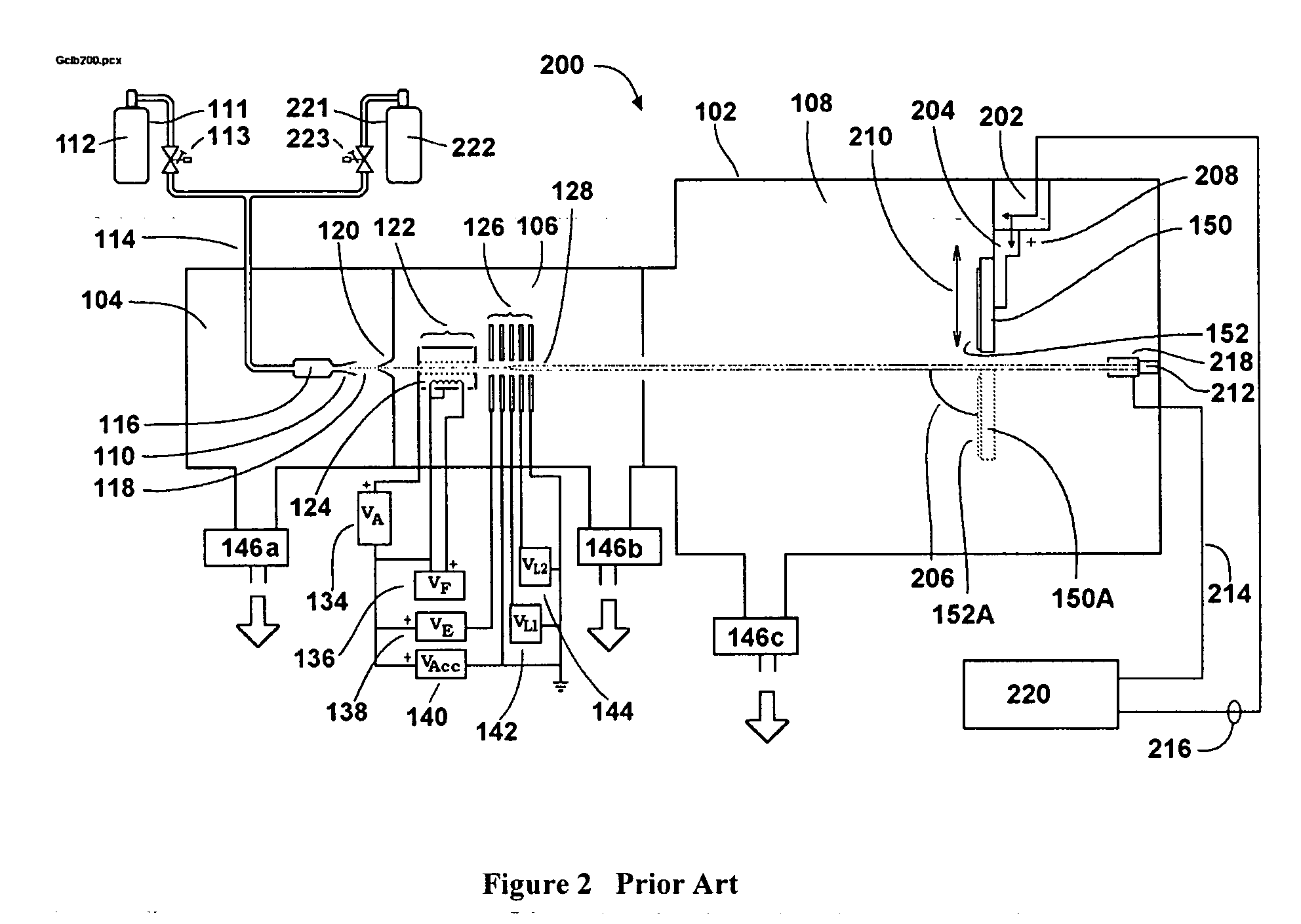

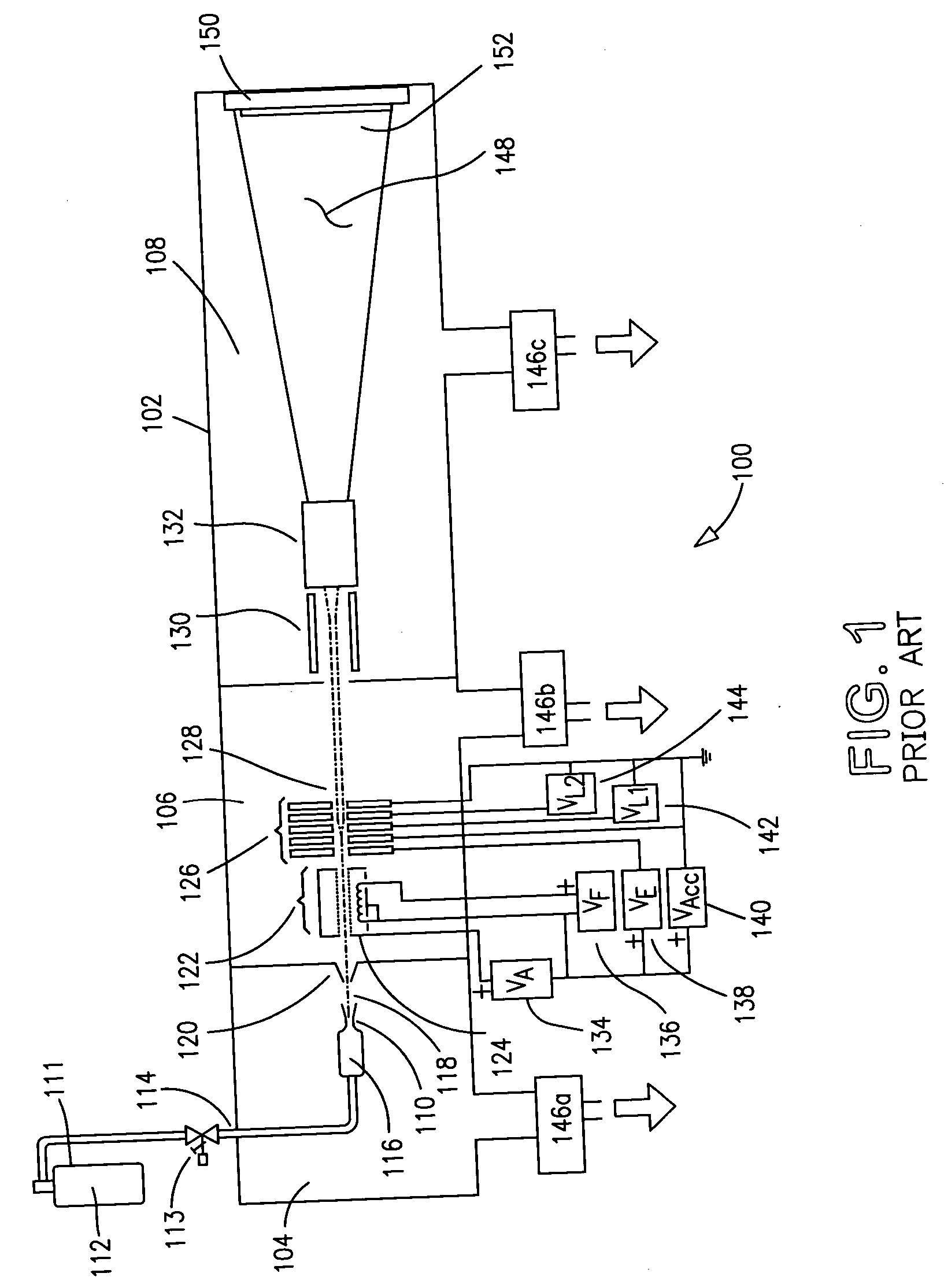

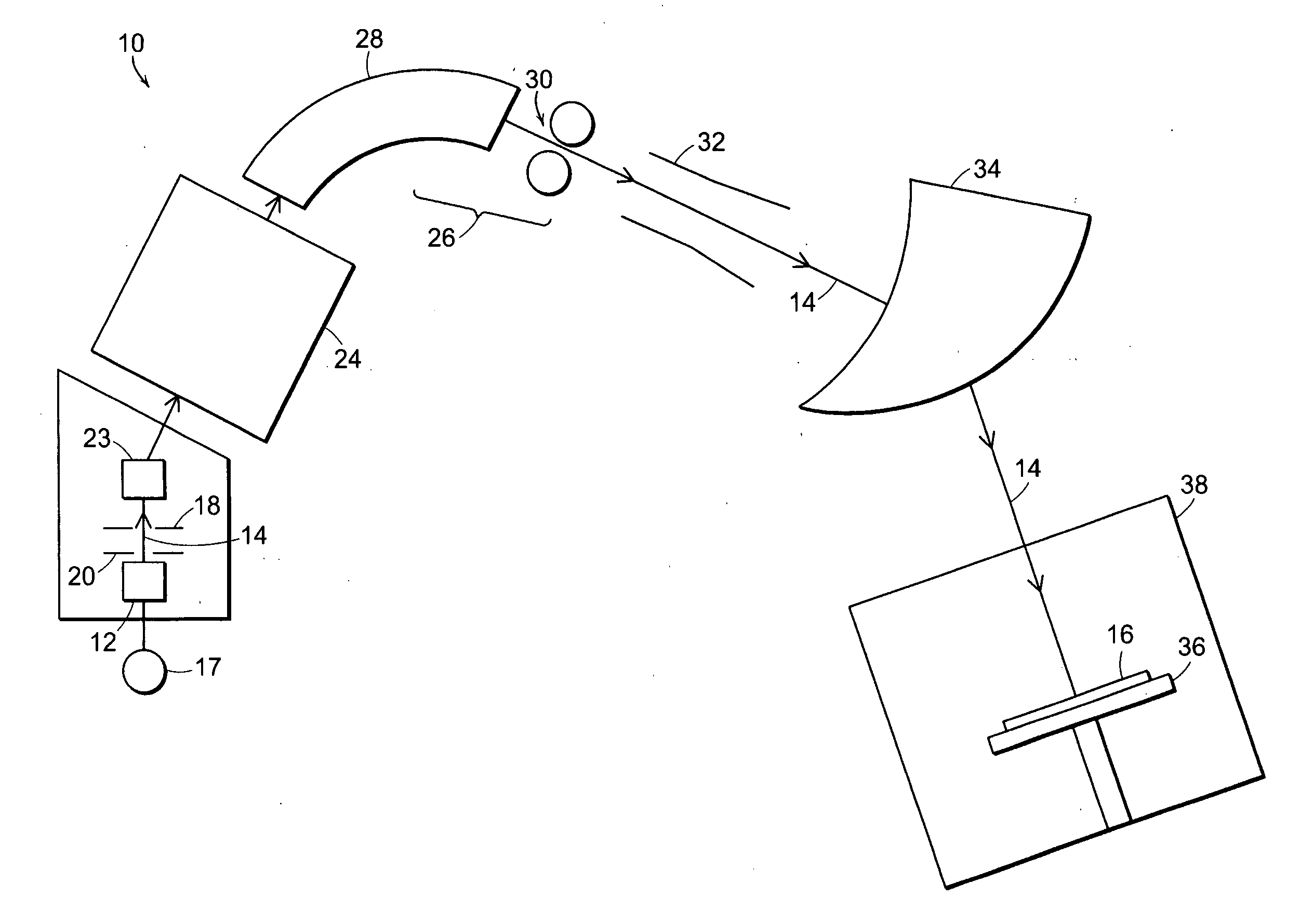

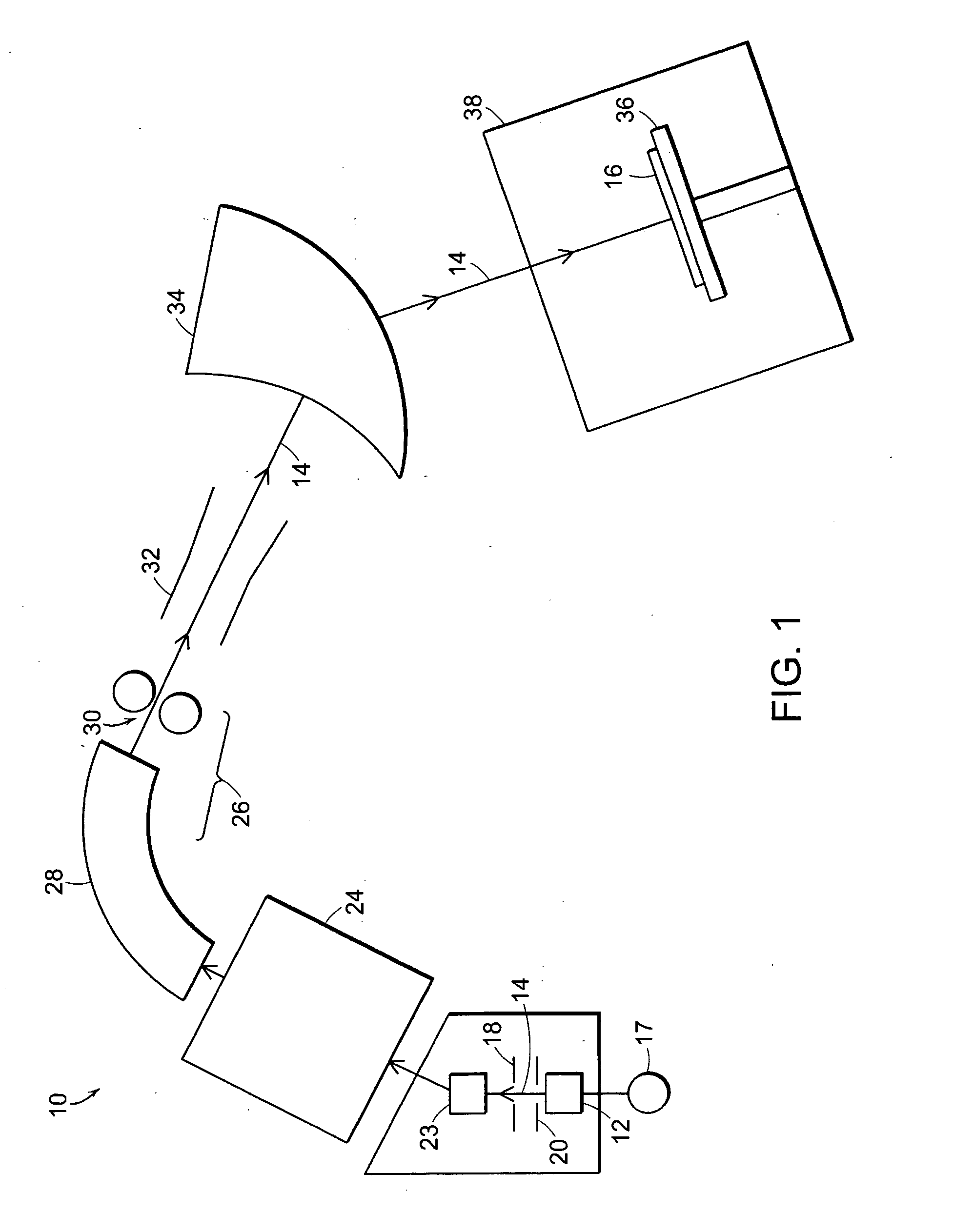

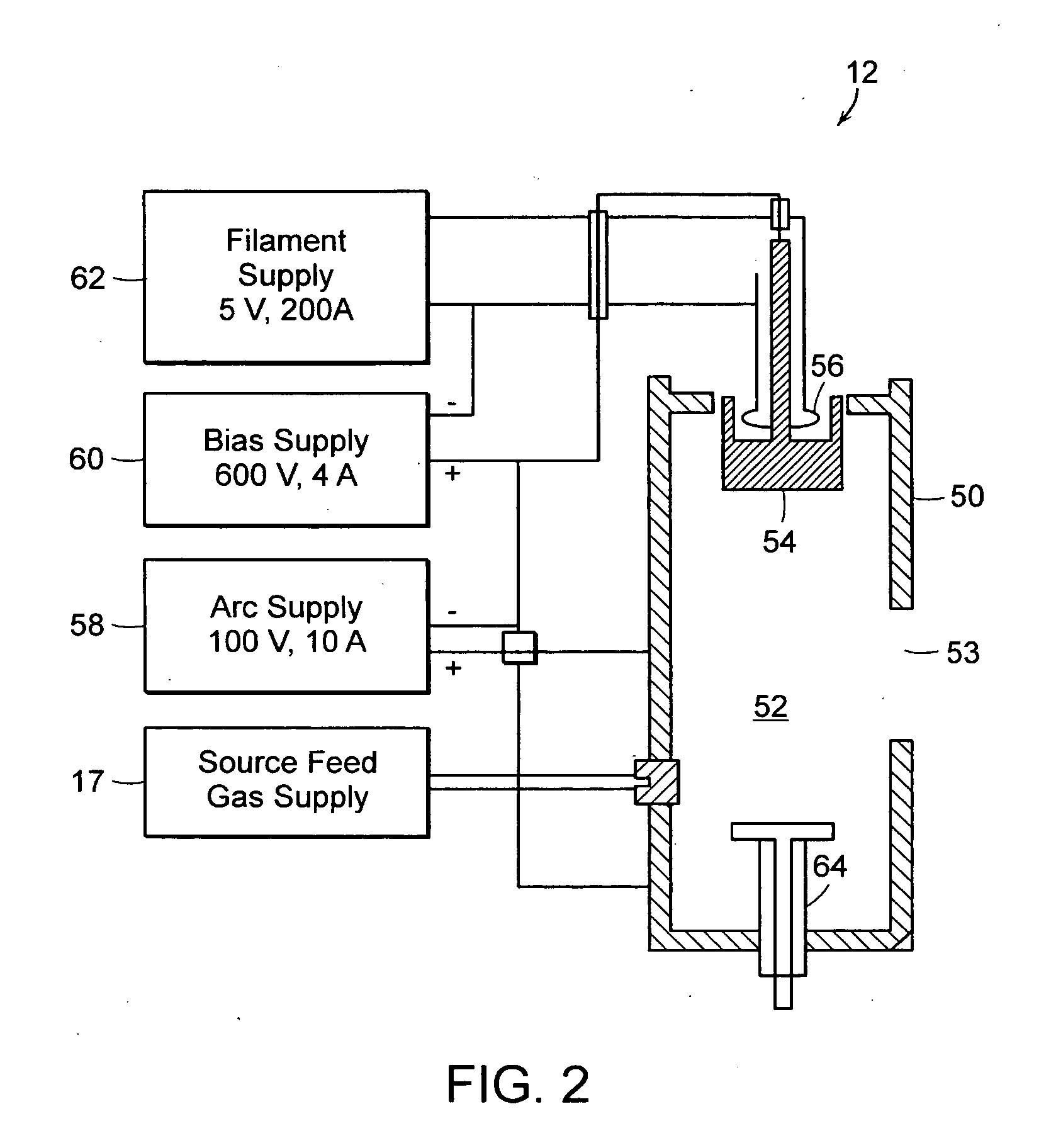

Techniques for forming shallow junctions

ActiveUS20080108208A1Electric discharge tubesSemiconductor/solid-state device manufacturingIon beamInorganic fluorine compounds

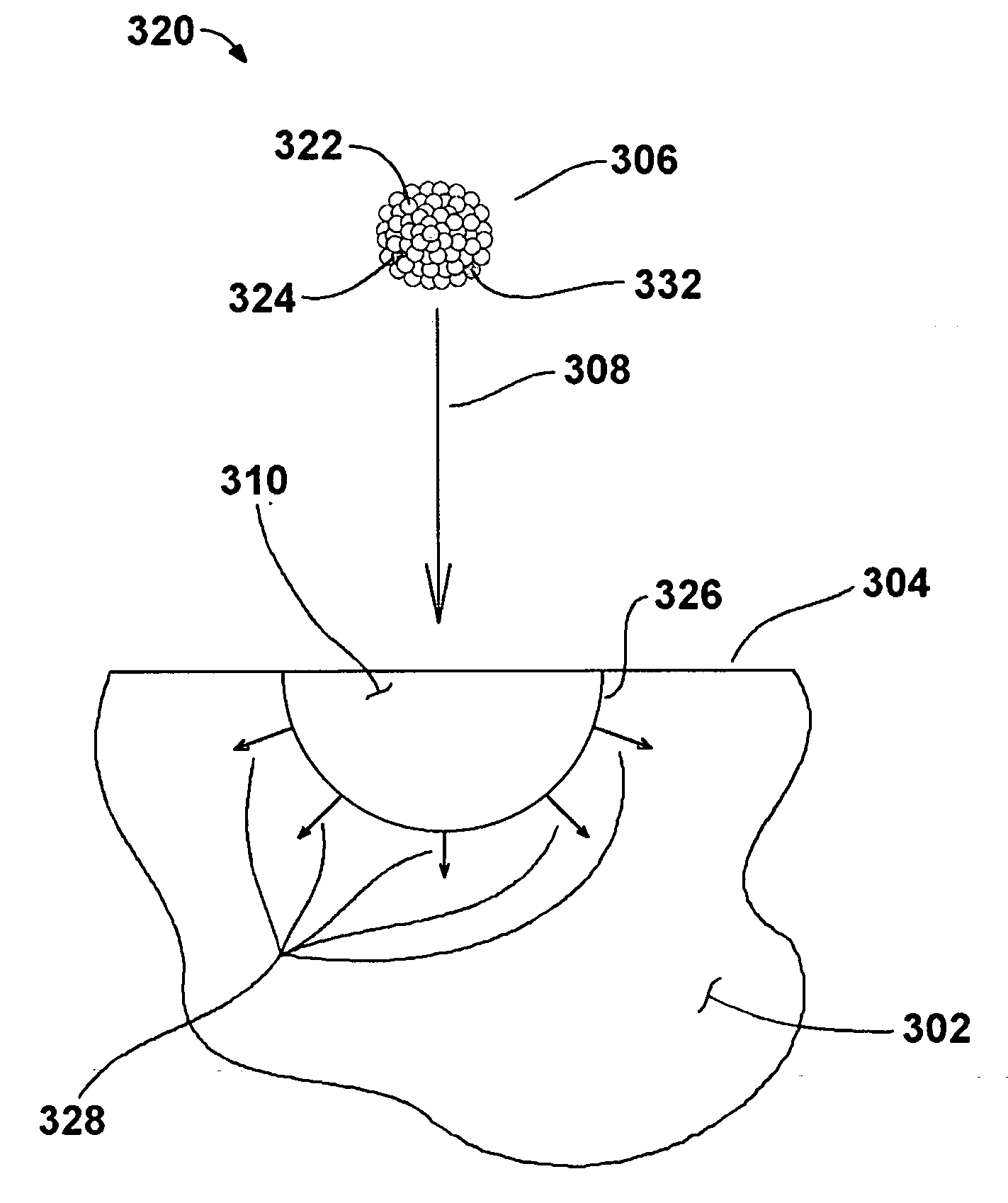

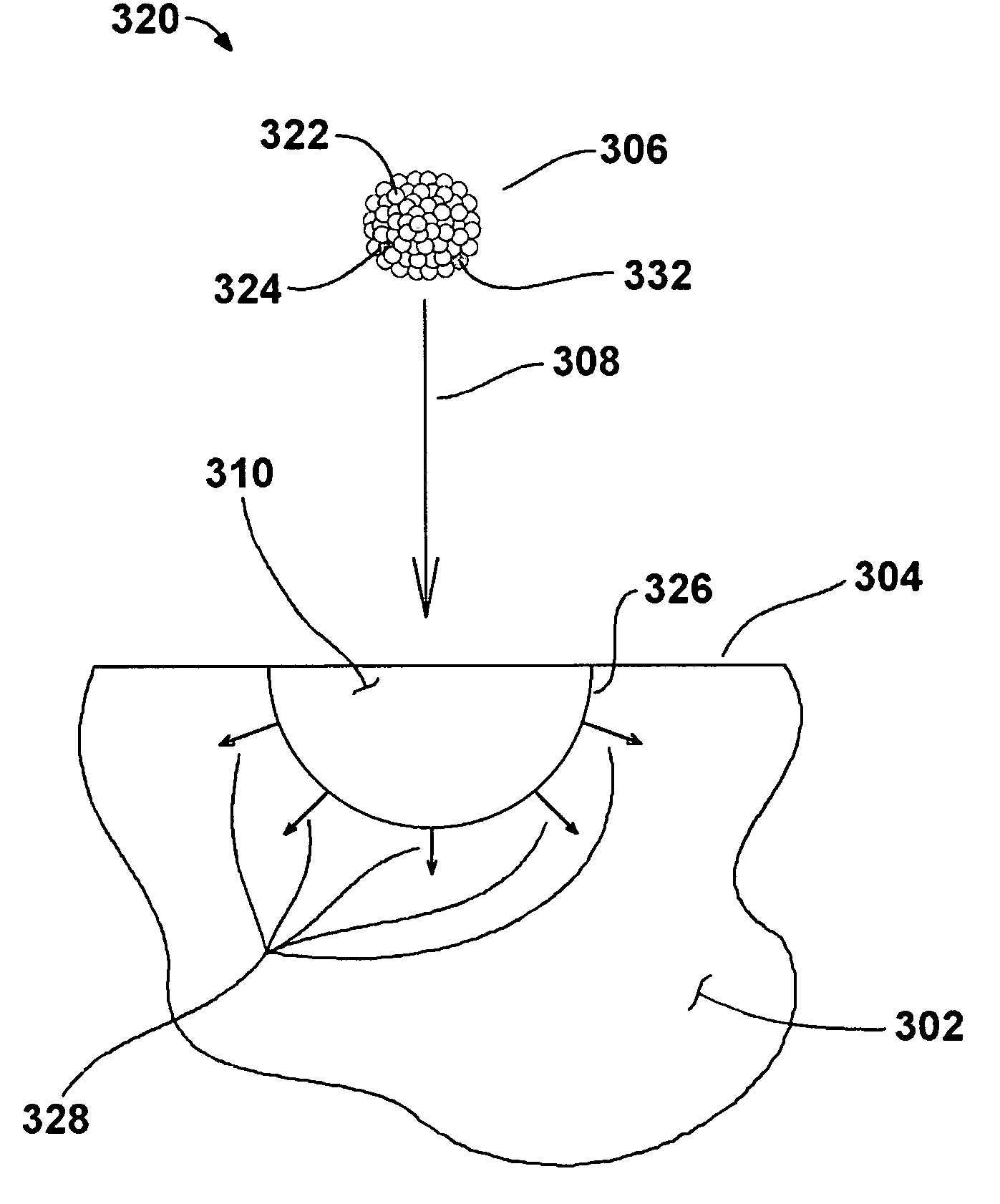

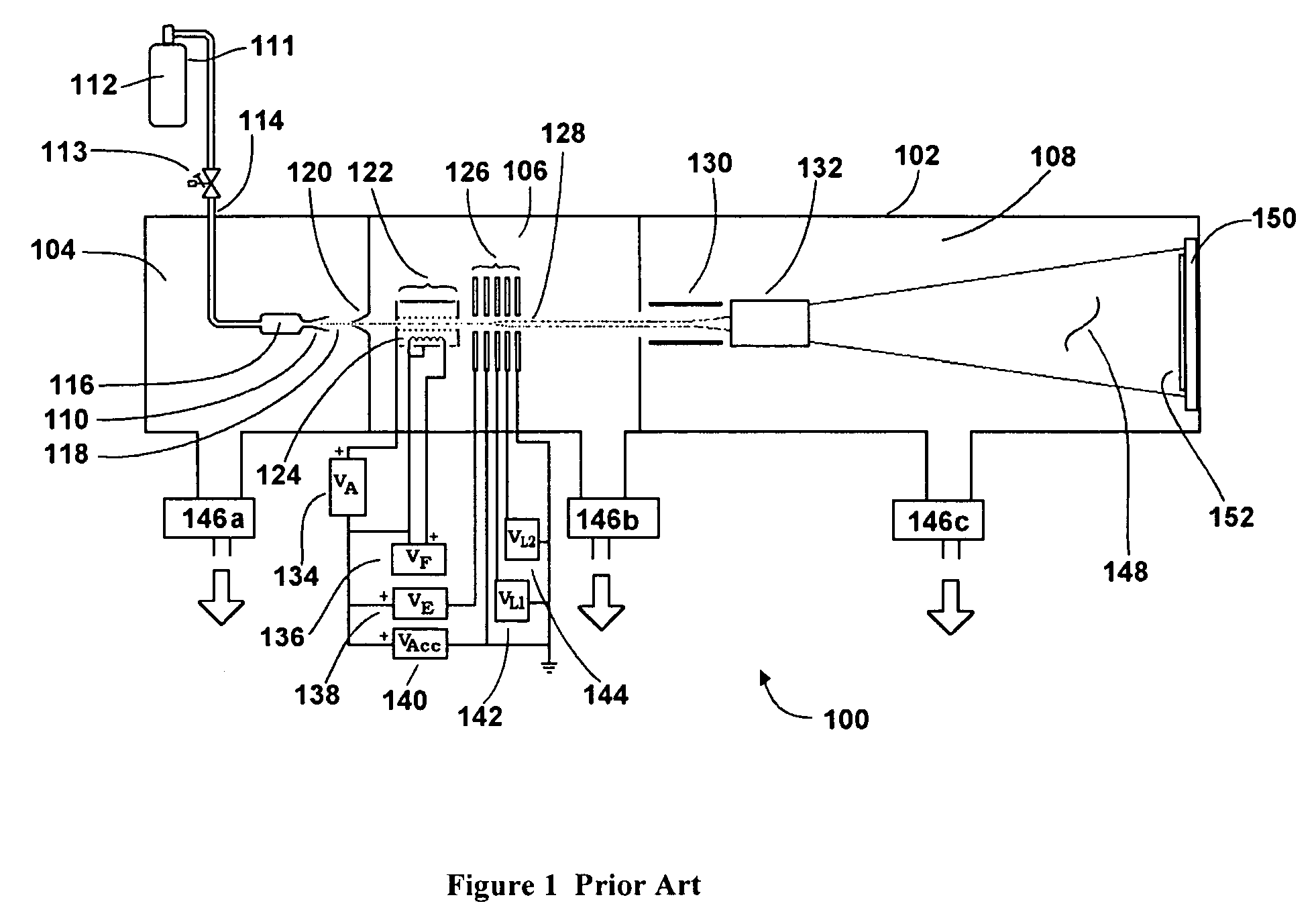

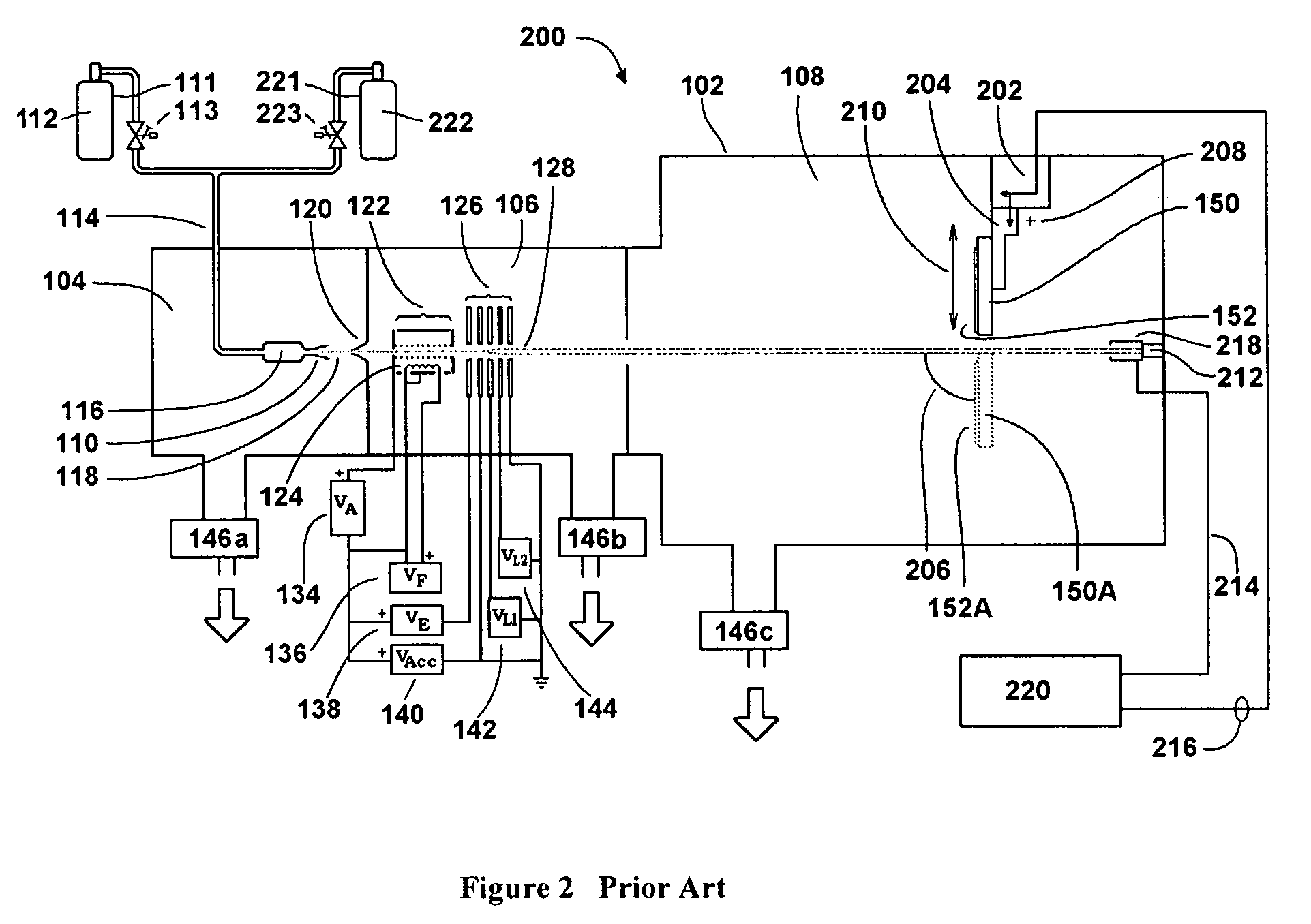

Techniques for forming shallow junctions are disclosed. In one particular exemplary embodiment, the techniques may be realized as a method for forming shallow junctions. The method may comprise generating an ion beam comprising molecular ions based on one or more materials selected from a group consisting of: digermane (Ge2H6), germanium nitride (Ge3N4), germanium-fluorine compounds (GFn, wherein n=1, 2, or 3), and other germanium-containing compounds. The method may also comprise causing the ion beam to impact a semiconductor wafer.

Owner:VARIAN SEMICON EQUIP ASSOC INC

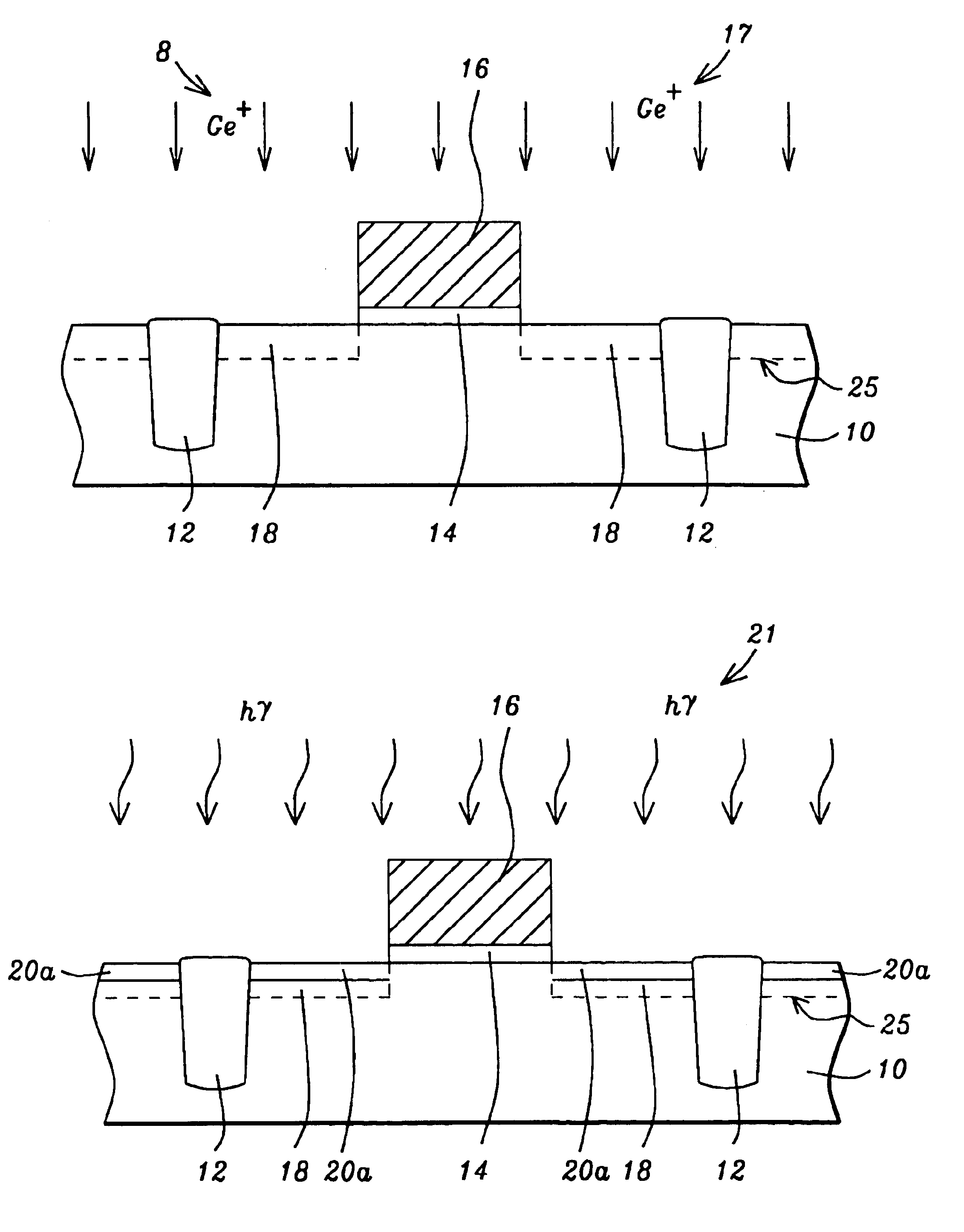

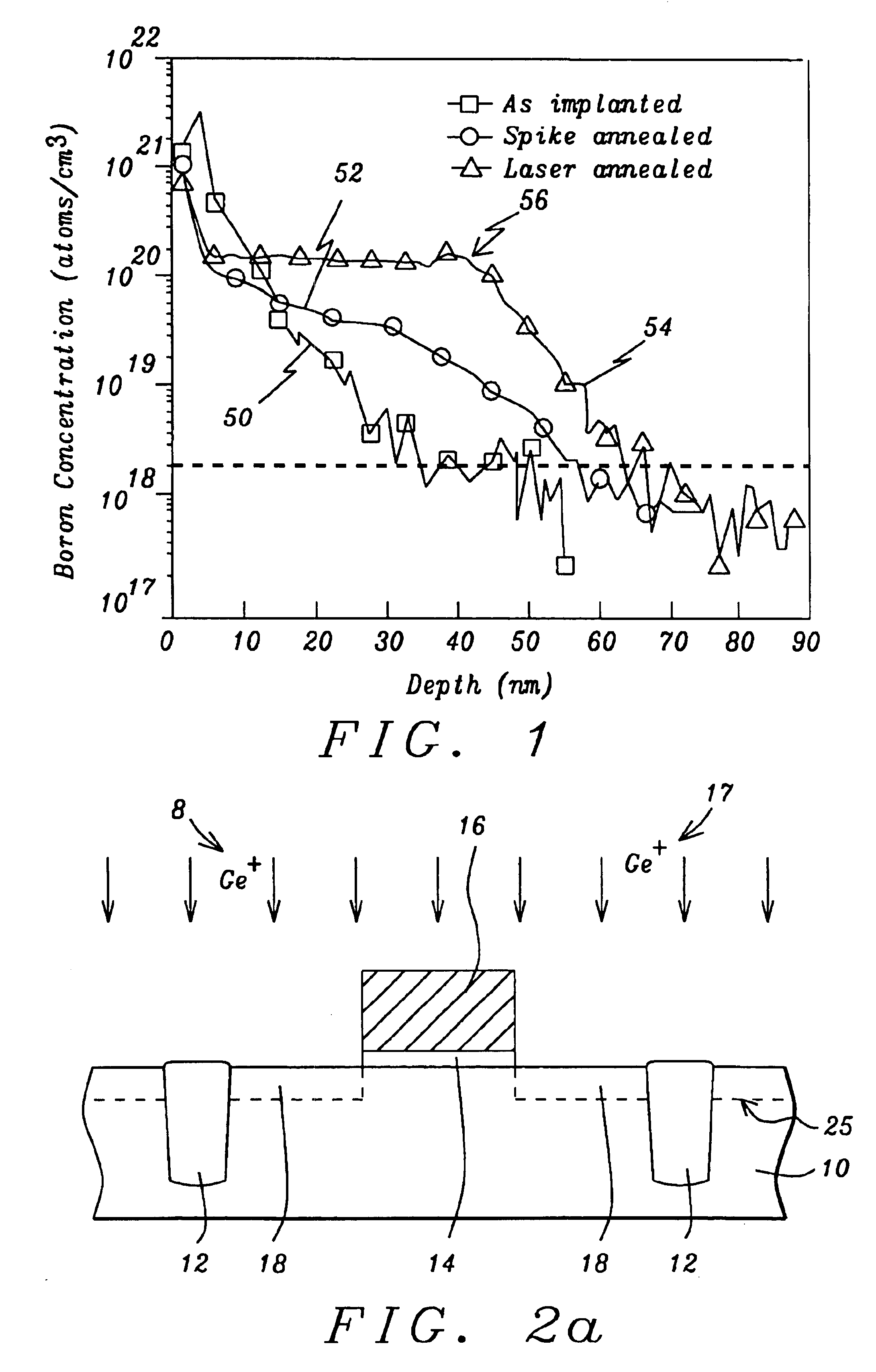

Method of multiple pulse laser annealing to activate ultra-shallow junctions

A method for forming a highly activated ultra shallow ion implanted semiconductive elements for use in sub-tenth micron MOSFET technology is described. A key feature of the method is the ability to activate the implanted impurity to a highly active state without permitting the dopant to diffuse further to deepen the junction. A selected single crystalline silicon active region is first amorphized by implanting a heavy ion such as silicon or germanium. A semiconductive impurity for example boron is then implanted and activated by pulsed laser annealing whereby the pulse fluence, frequency, and duration are chosen to maintain the amorphized region just below it's melting temperature. It is found that just below the melting temperature there is sufficient local ion mobility to secure the dopant into active positions within the silicon matrix to achieve a high degree of activation with essentially no change in concentration profile. The selection of the proper laser annealing parameters is optimized by observation of the reduction of sheet resistance and concentration profile as measured on a test site. Application of the method is applied to forming a MOS FET and a CMOS device. The additional processing steps required by the invention are applied simultaneously to both n-channel and p-channel devices of the CMOS device pair.

Owner:CHARTERED SEMICONDUCTOR MANUFACTURING

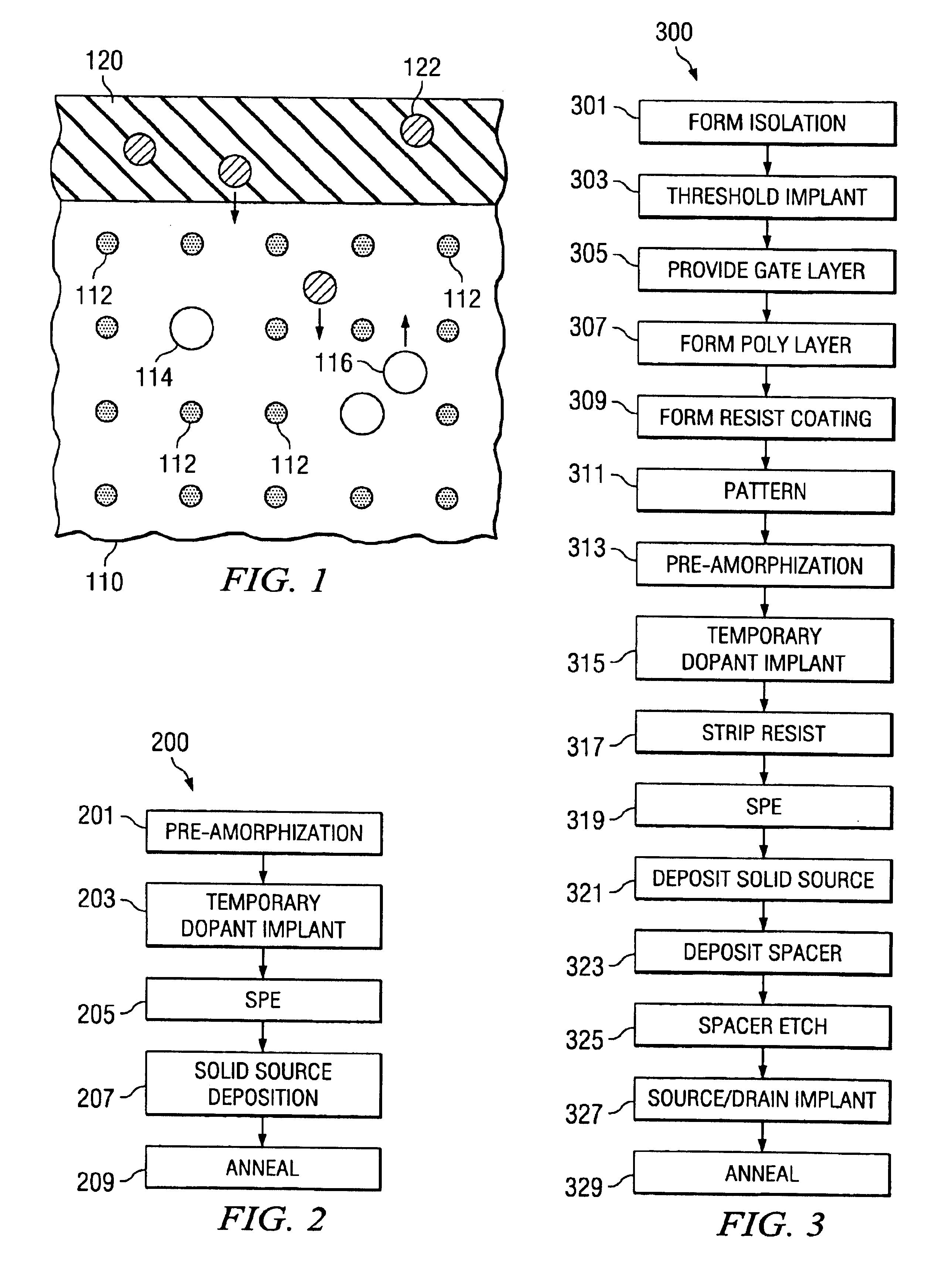

Fabrication of abrupt ultra-shallow junctions

InactiveUS6852603B2Promote formationFaster diffusing speciesSemiconductor/solid-state device manufacturingDiffusionDopant

One aspect of the invention relates to a method of forming P-N junctions within a semiconductor substrate. The method involves providing a temporary impurity species, such as fluorine, within the semiconductor crystal matrix prior to solid source in-diffusion of the primary dopant, such as boron. The impurity atom is a faster diffusing species relative to silicon atoms. During in-diffusion, the temporary impurity species acts to reduce the depth to which the primary dopant diffuses and thereby facilitates the formation of very shallow junctions.

Owner:TEXAS INSTR INC

Highly Conductive Shallow Junction Formation

InactiveUS20090224319A1TransistorSemiconductor/solid-state device manufacturingJunction formationPhysical chemistry

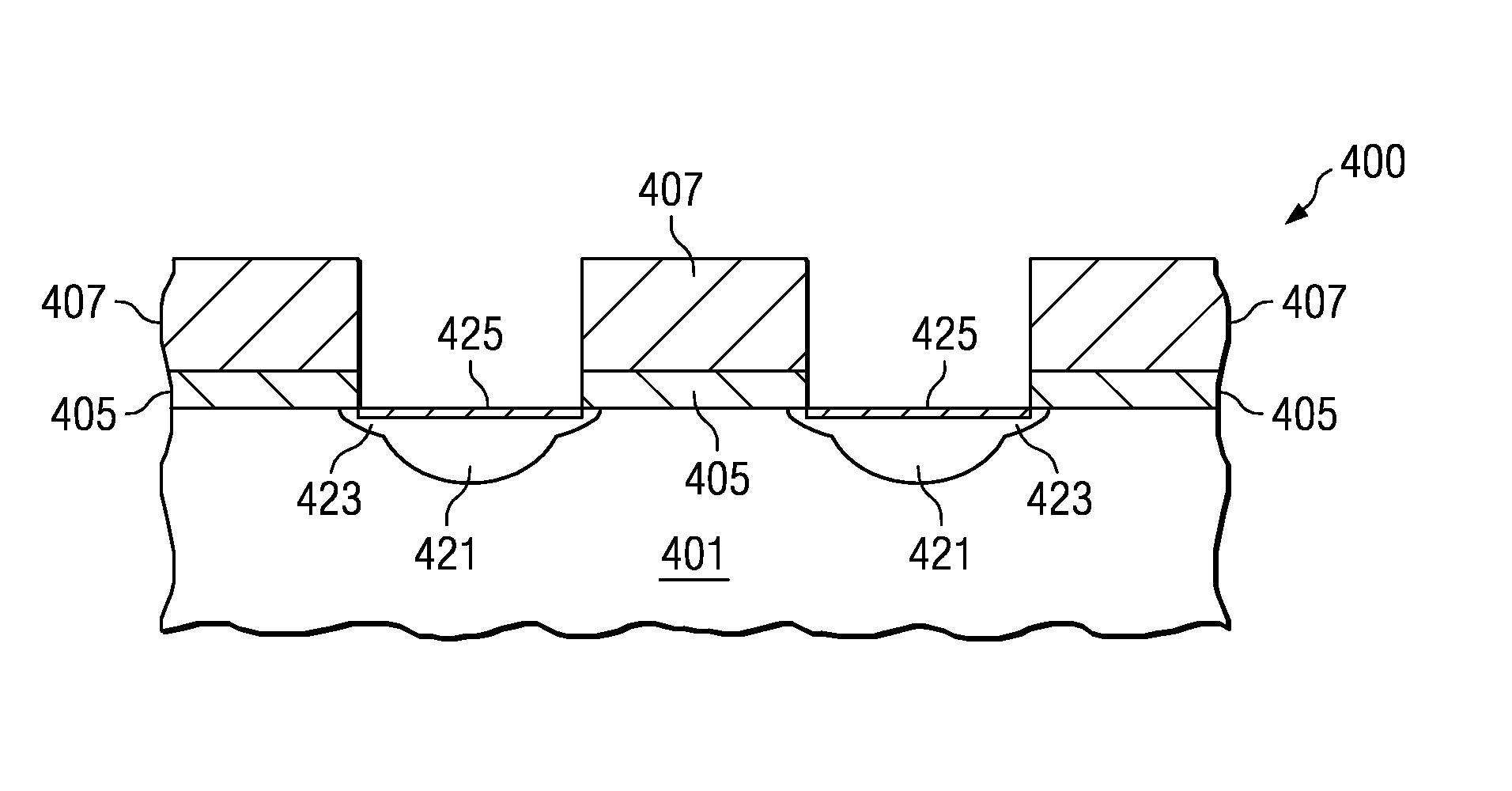

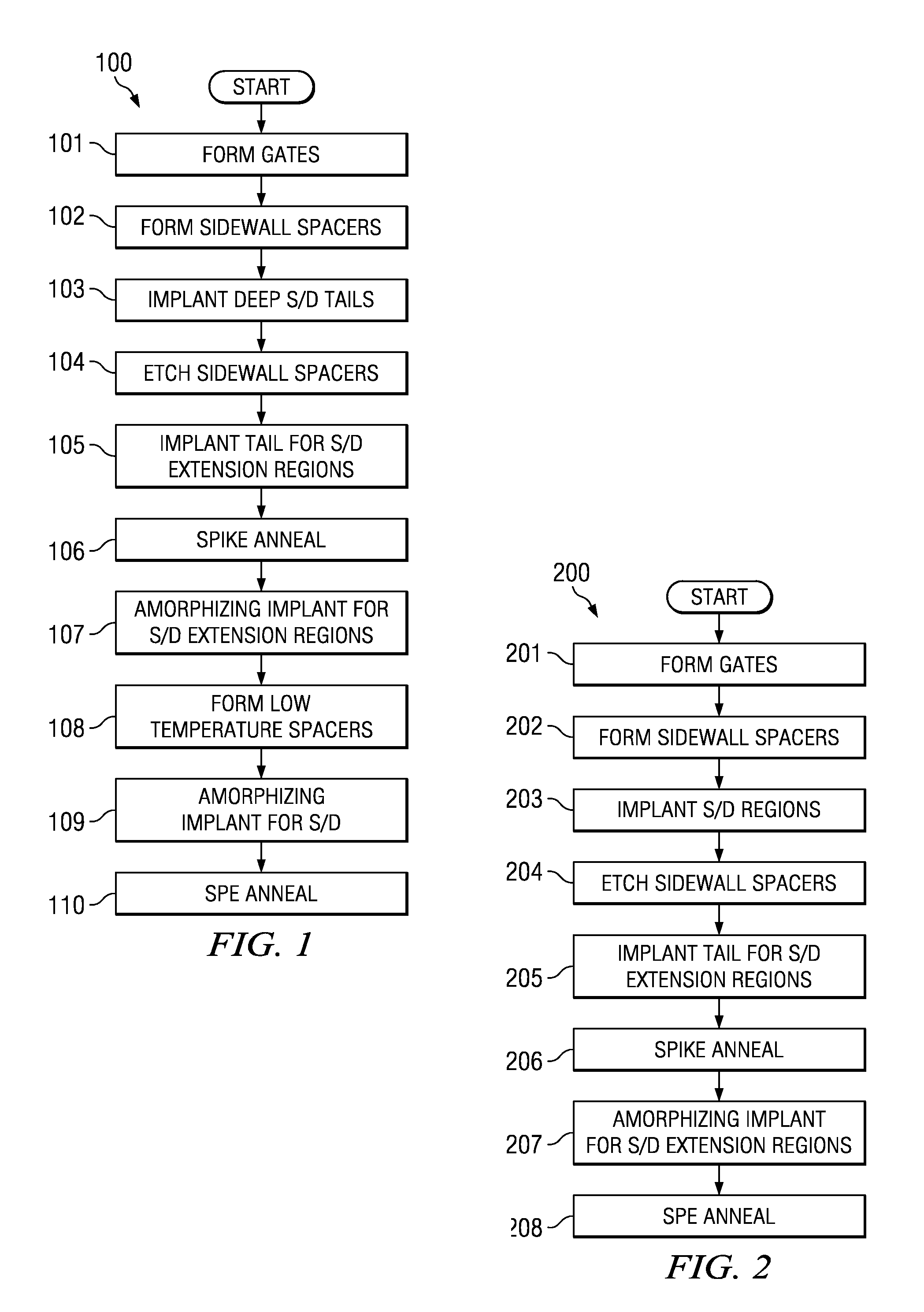

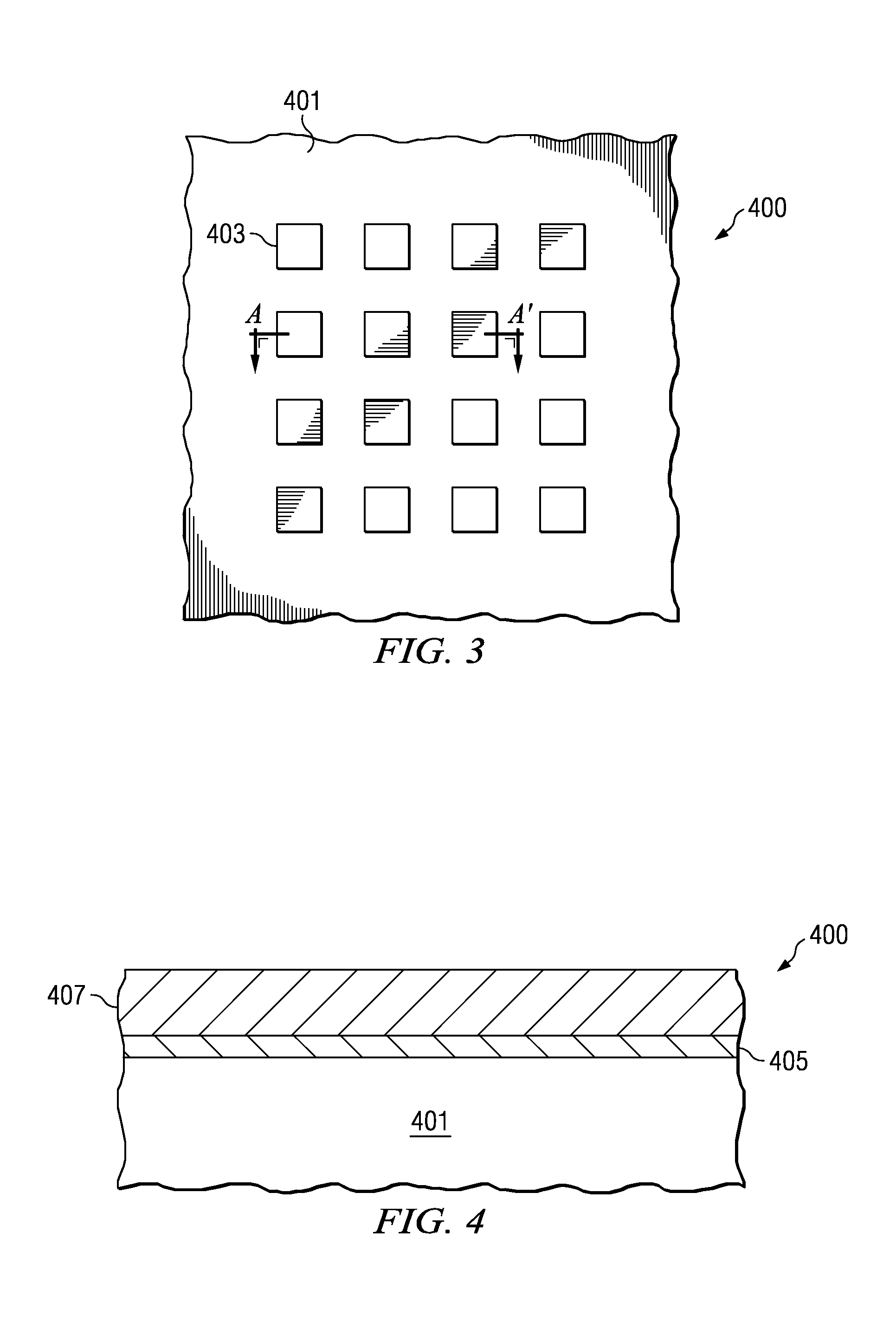

The invention relates to a method of forming a shallow junction. The method (100) comprises forming source / drain extension regions with a non-amorphizing tail implant (105) which is annealed conventionally (spike / RTP) and amorphizing implant which is re-grown epitaxially(SPER) (110). The non-amorphizing tail implant is generally annealed (106) before a doped amorphous layer for SPE is formed (107). SPE provides a high active dopant concentration in a shallow layer. The non-amorphizing tail implant (105) expands the source / drain extension region beyond the range dictated by the SPE-formed layer and keeps the depletion region of the P-N junction away from where end-of-range defects form during the SPE process. Thus, the SPE-formed layer primarily determines the conductivity of the junction while the tail implant determines the location of the depletion region. End-of-range defects form, but are not in a position to cause significant reverse bias leakage.

Owner:TEXAS INSTR INC

Formation of doped regions and/or ultra-shallow junctions in semiconductor materials by gas-cluster ion irradiation

ActiveUS20050277246A1Improve solid solubilityImprove efficiencyElectric discharge tubesVacuum evaporation coatingSemiconductor materialsGas cluster ion beam

Method of forming one or more doped regions in a semiconductor substrate and semiconductor junctions formed thereby, using gas cluster ion beams.

Owner:TEL EPION

Semiconductor device fabricating method

ActiveUS20050266631A1High speedImprove channel mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialSemiconductor

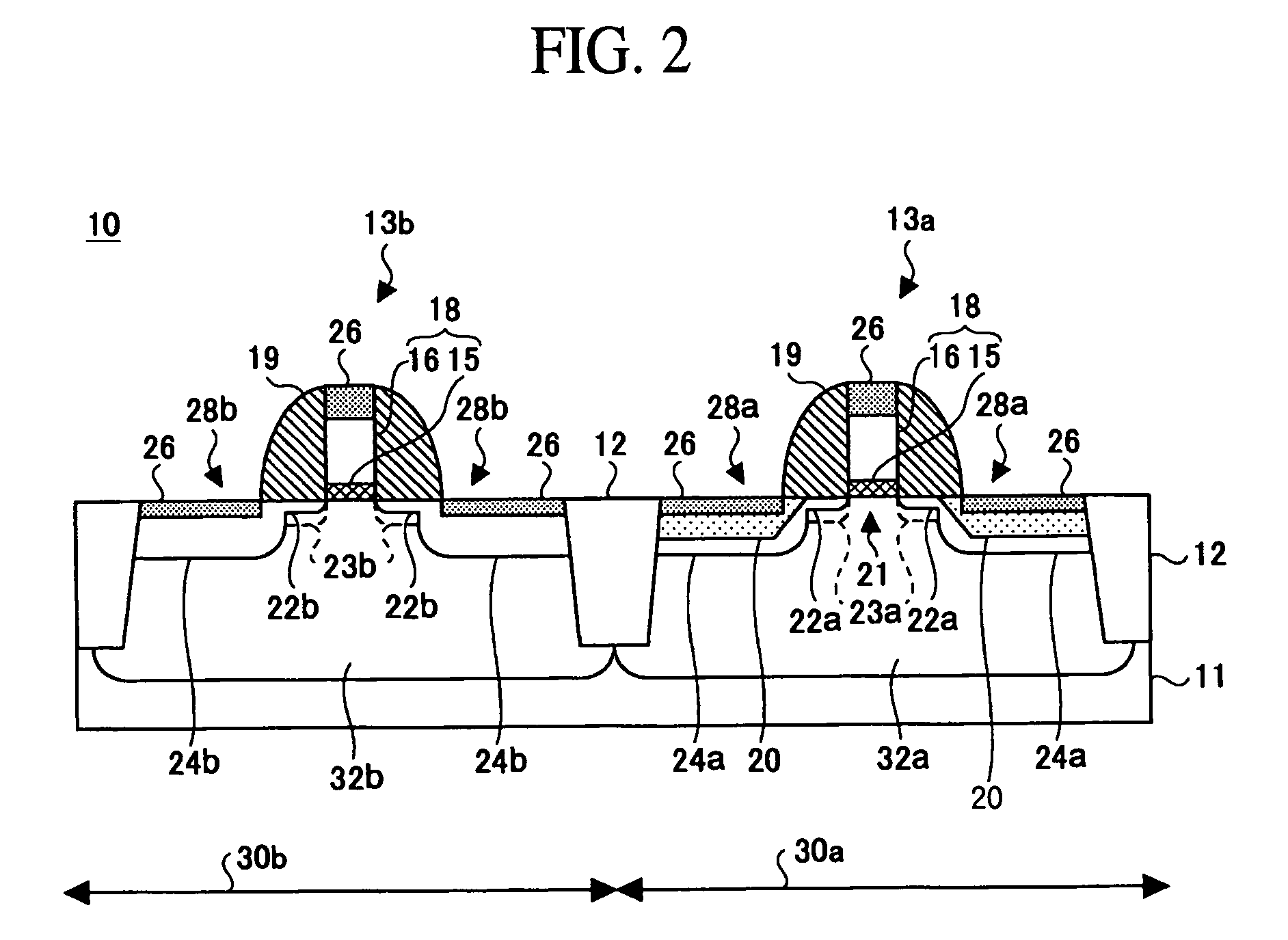

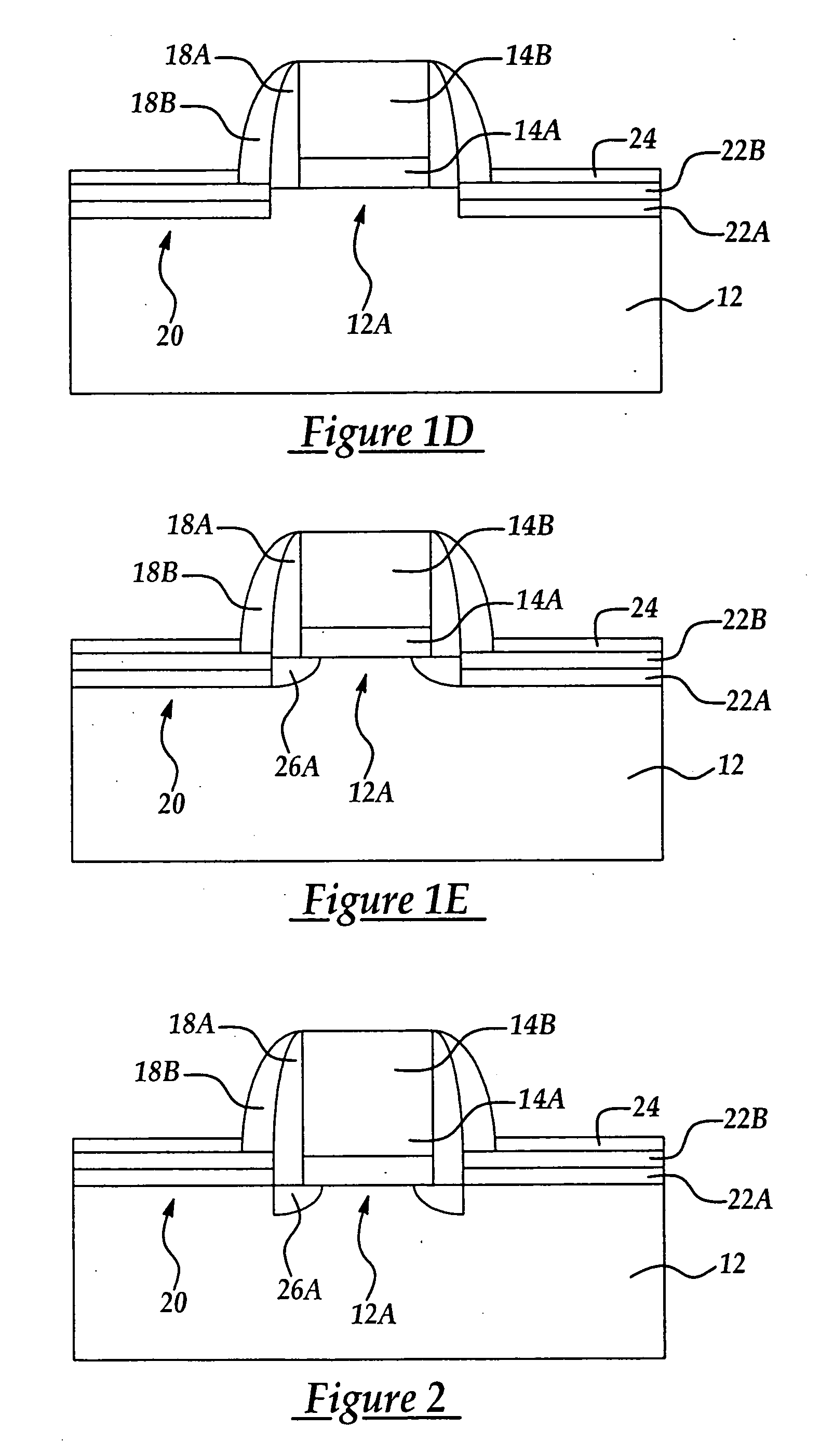

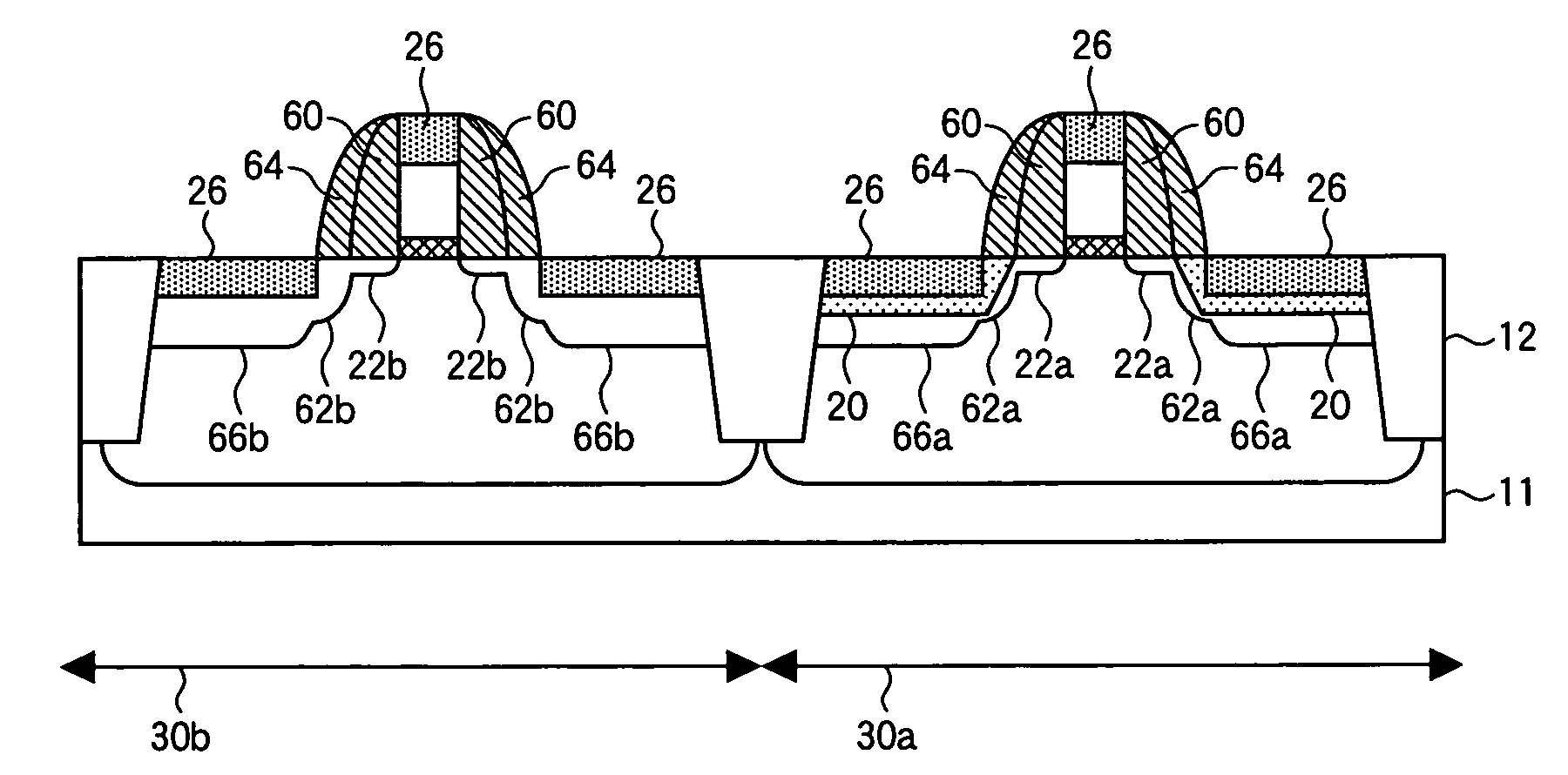

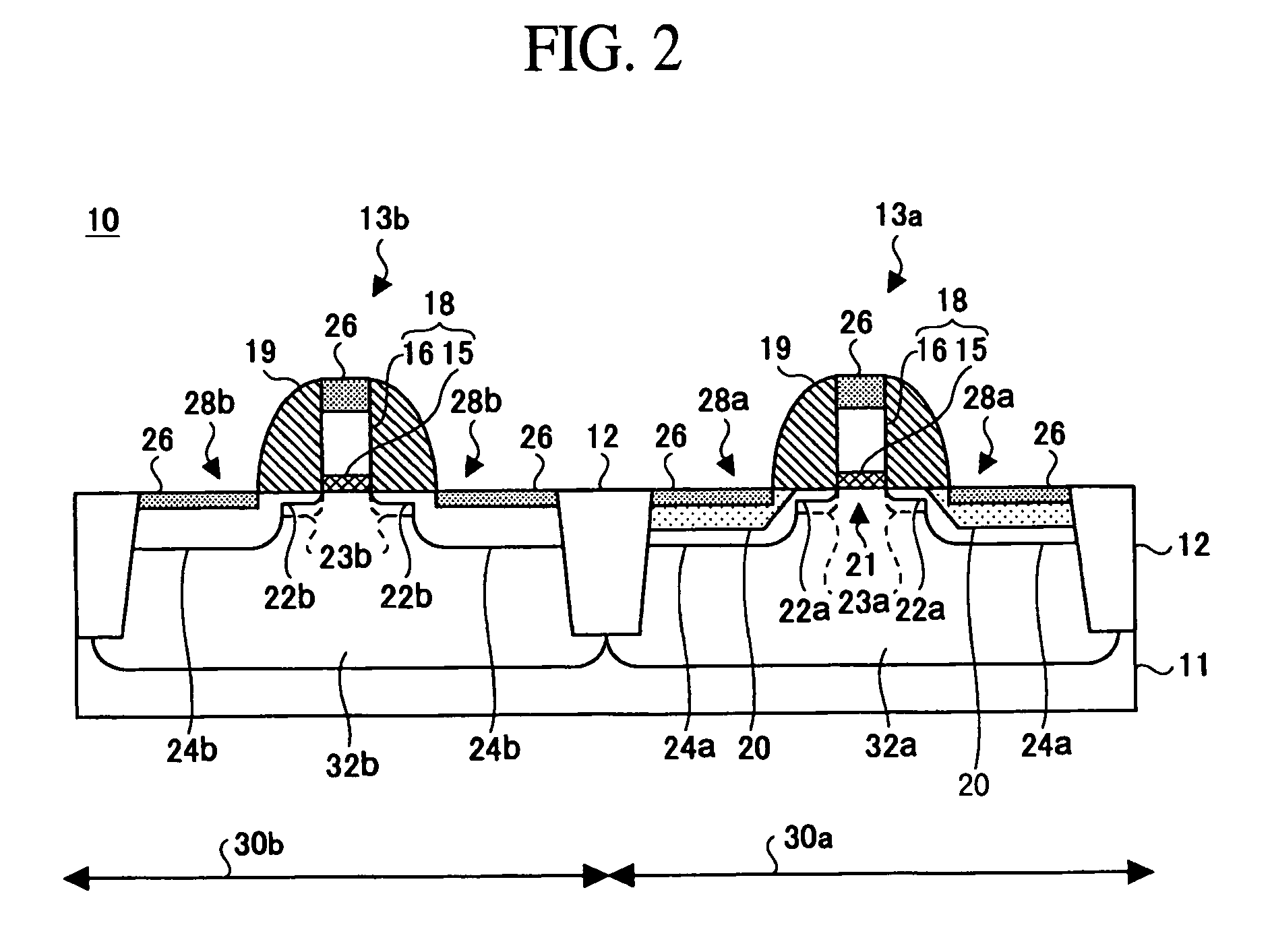

Compression stress applying portions 20 of SiGe film are formed in the source / drain regions of the p-MOSA region 30a. Then, impurities are implanted in the p-MOS region 30a and the n-MOS region 30b to form shallow junction regions 22a, 22b and deep junction regions 23a, 23b. The impurity in the shallow junction regions 22a, 22b is prevented from being diffused immediately below the gate insulation film 15 by the thermal processing in forming the SiGe film, the short channel effect is prevented, and the hole mobility of the channel region of the p-MOS transistor 14a. The operation speed of the p-MOS transistor 13a is balanced with that of the n-MOS transistor, whereby the operation speed of the complementary semiconductor device 10 can be increased. The semiconductor device fabricating method can increase and balance the operation speed of a p-transistor with that of an n-transistor.

Owner:FUJITSU SEMICON LTD

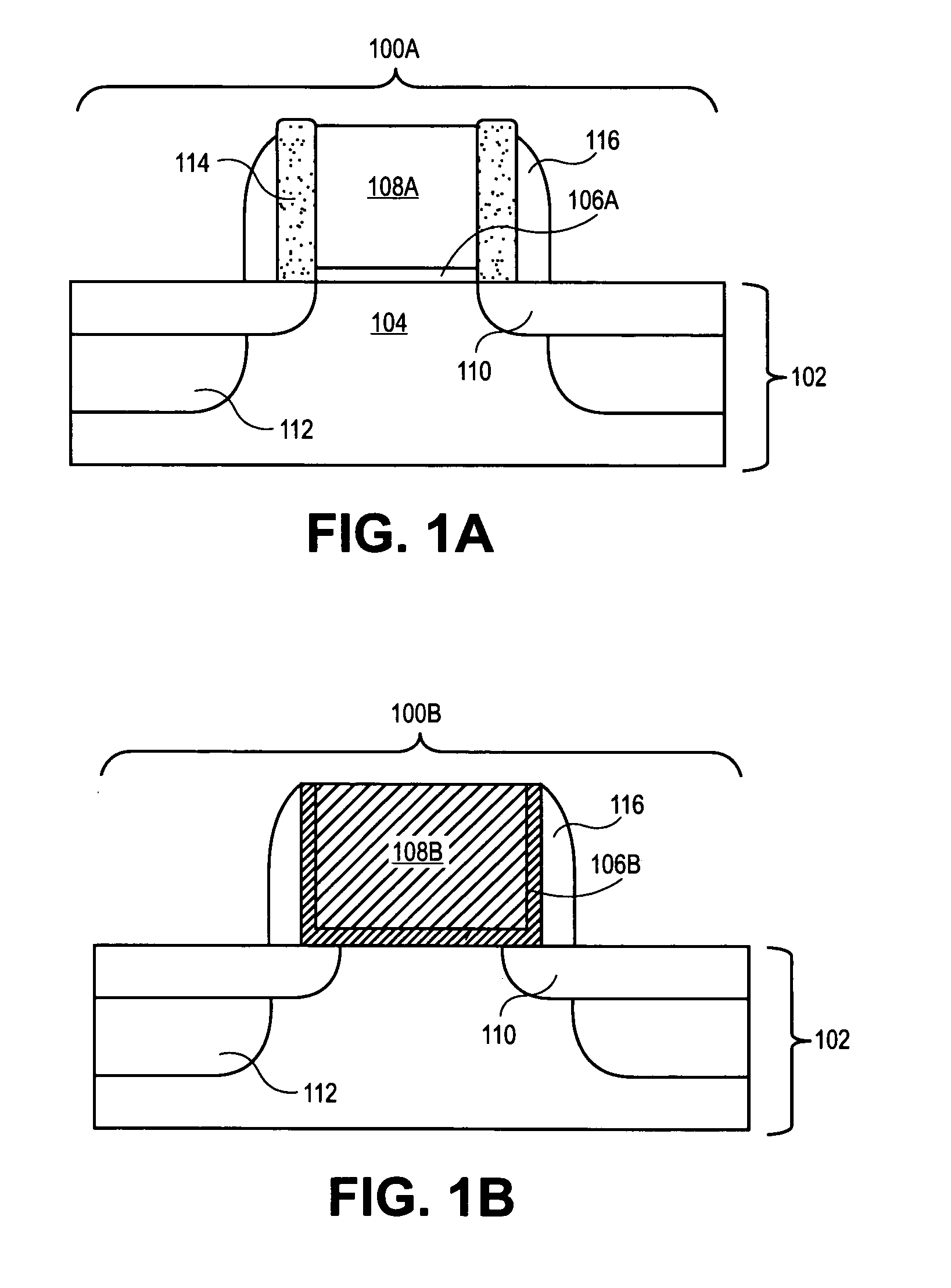

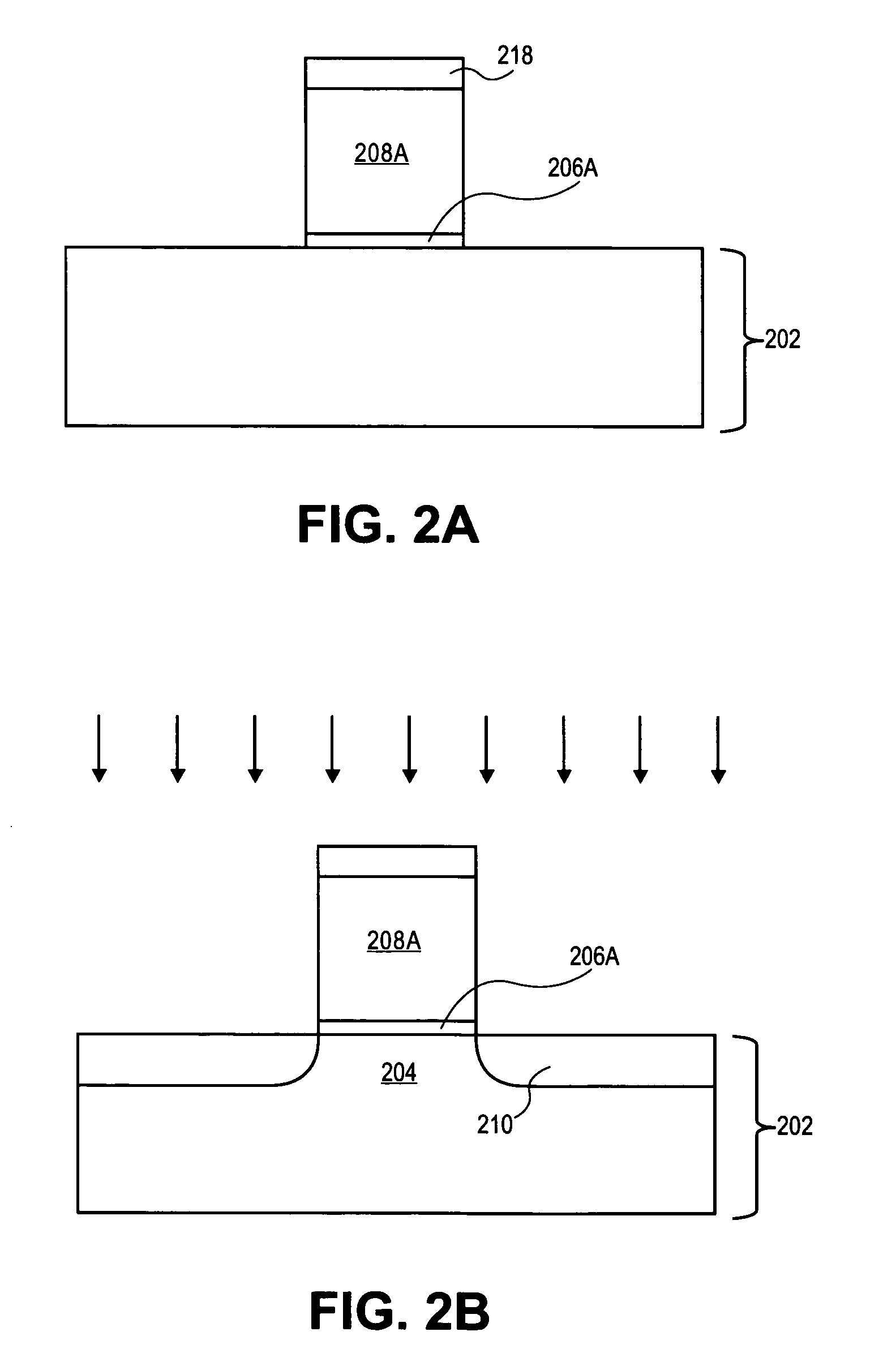

Forming ultra-shallow junctions

InactiveUS7456068B2Semiconductor/solid-state device manufacturingSemiconductor devicesEngineeringSemiconductor

A method to form an ultra-shallow junction is described. In one embodiment, a replacement gate process is utilized to enable the overlap of a gate electrode over the regions of a semiconductor substrate where tip extensions reside. In another embodiment, a sacrificial spacer is utilized in conjunction with the replacement gate process. In one embodiment, an initial gate electrode is formed with a gate length smaller than the desired final gate length and is subsequently replaced with an expanded gate electrode having the desired gate length.

Owner:INTEL CORP

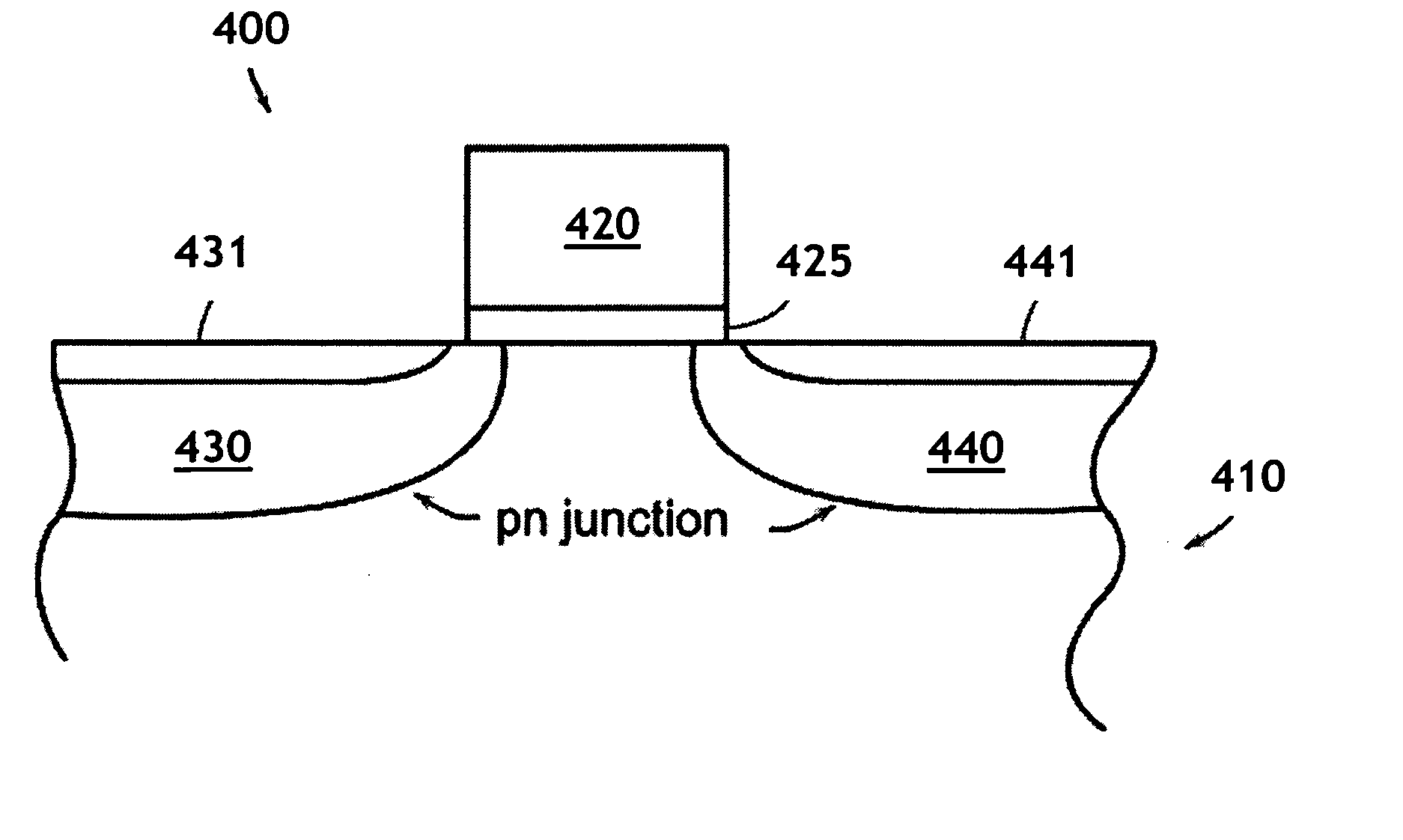

Ultra-shallow junction MOSFET having a high-k gate dielectric and in-situ doped selective epitaxy source/drain extensions and a method of making same

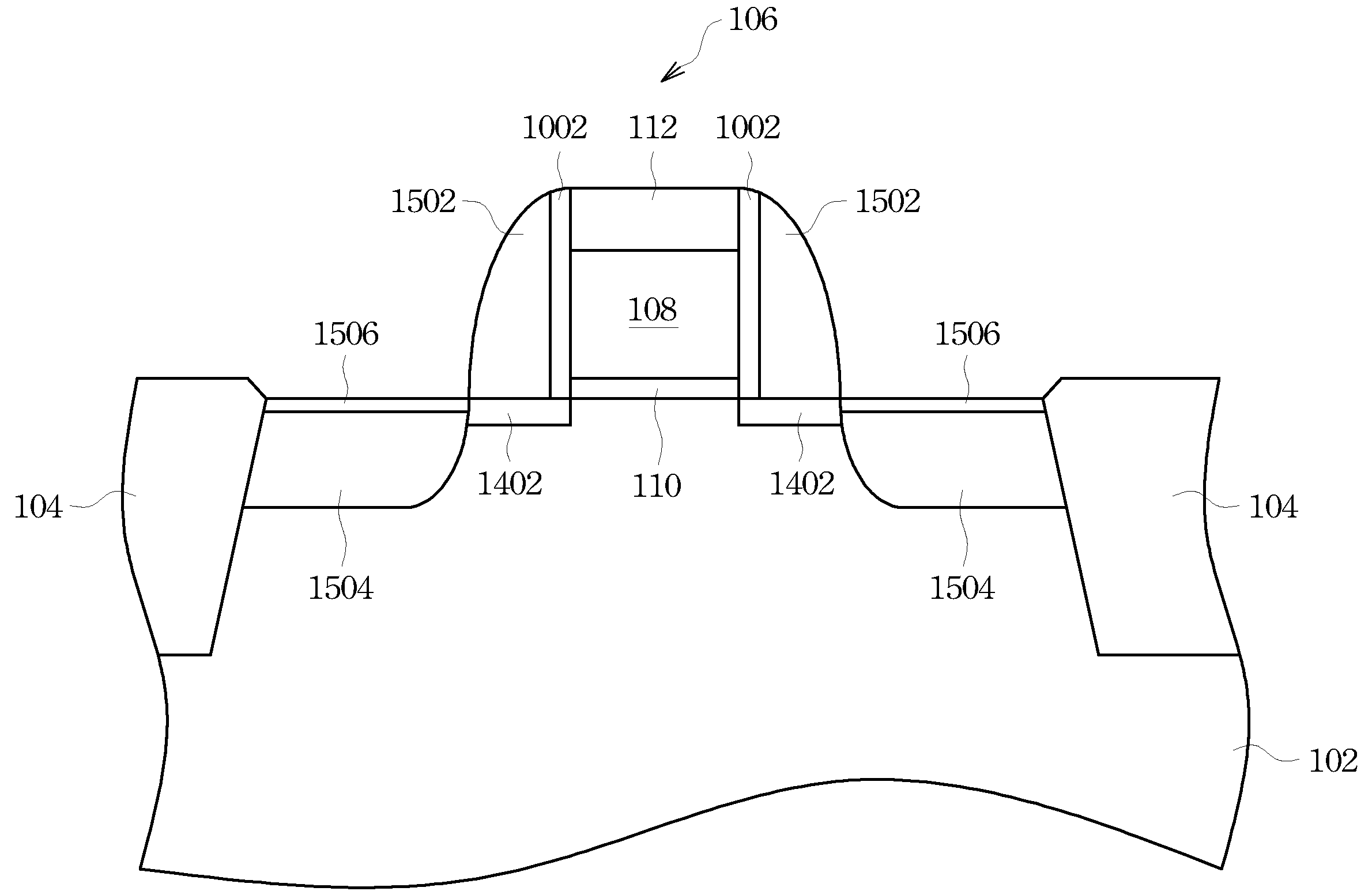

ActiveUS20050093084A1Eliminates and ameliorates leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETGate dielectric

A MOSFET includes a gate having a high-k gate dielectric on a substrate and a gate electrode on the gate dielectric. The gate dielectric protrudes beyond the gate electrode. A deep source and drain having shallow extensions are formed on either side of the gate. The deep source and drain are formed by selective in-situ doped epitaxy or by ion implantation and the extensions are formed by selective, in-situ doped epitaxy. The extensions lie beneath the gate in contact with the gate dielectric. The material of the gate dielectric and the amount of its protrusion beyond the gate electrode are selected so that epitaxial procedures and related procedures do not cause bridging between the gate electrode and the source / drain extensions. Methods of fabricating the MOSFET are described.

Owner:TAIWAN SEMICON MFG CO LTD

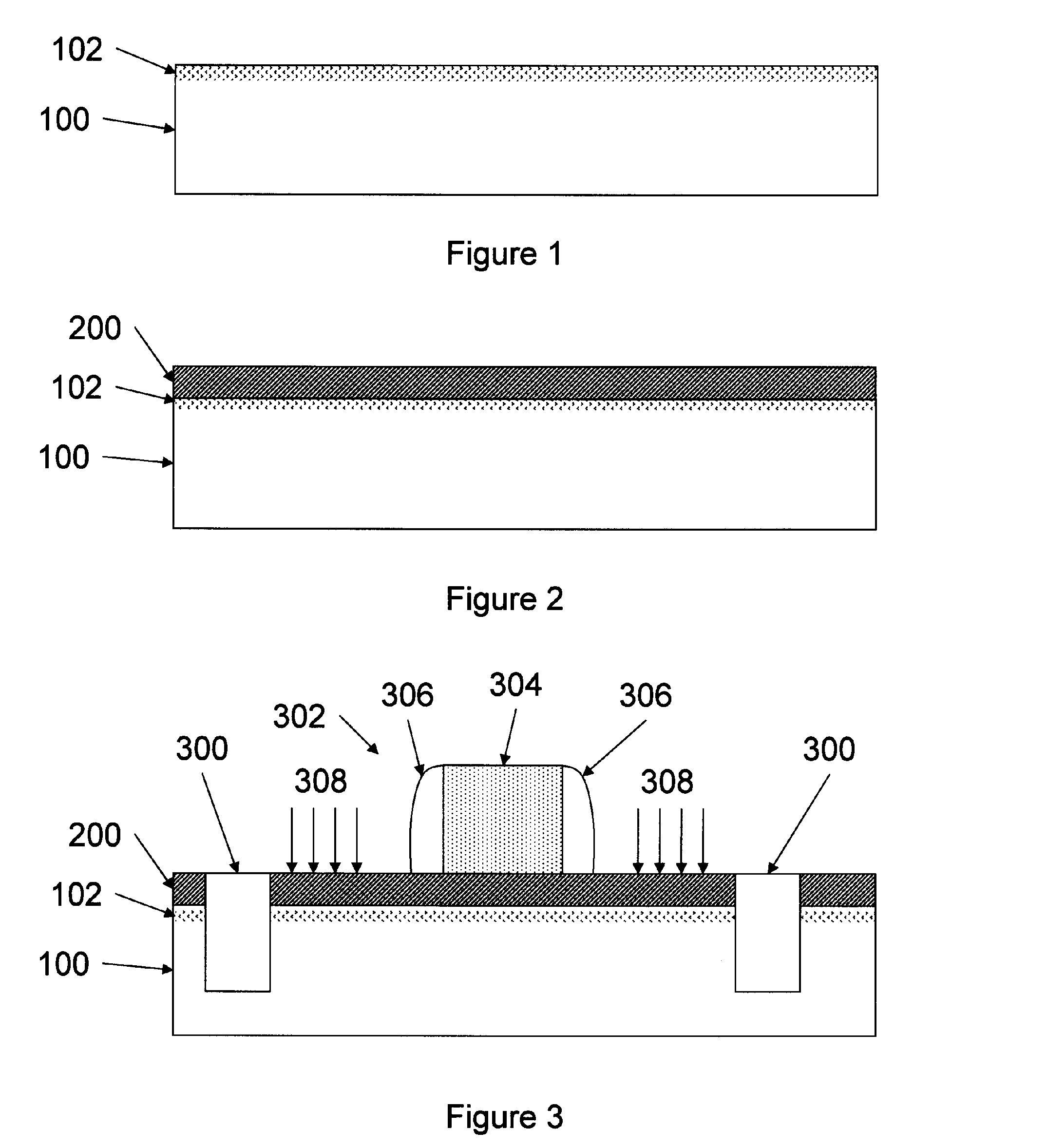

Formation of shallow junctions by diffusion from a dielectric doped by cluster or molecular ion beams

ActiveUS20090047768A1TransistorSemiconductor/solid-state device manufacturingDopantGas cluster ion beam

A process for forming diffused region less than 20 nanometers deep with an average doping dose above 1014 cm−2 in an IC substrate, particularly LDD region in an MOS transistor, is disclosed. Dopants are implanted into a source dielectric layer using gas cluster ion beam (GCIB) implantation, molecular ion implantation or atomic ion implantation resulting in negligible damage in the IC substrate. A spike anneal or a laser anneal diffuses the implanted dopants into the IC substrate. The inventive process may also be applied to forming source and drain (S / D) regions. One source dielectric layer may be used for forming both NLDD and PLDD regions.

Owner:TEXAS INSTR INC

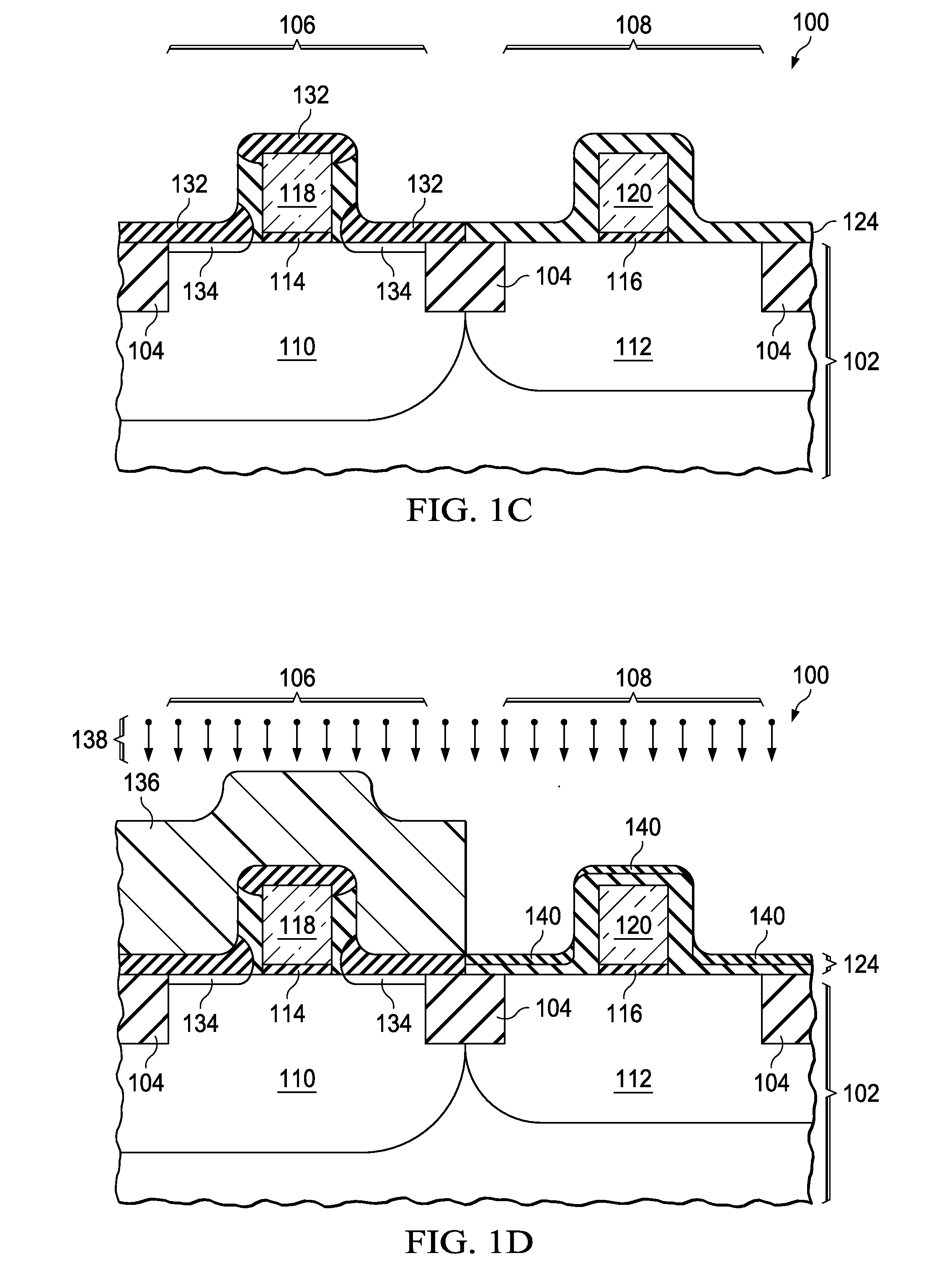

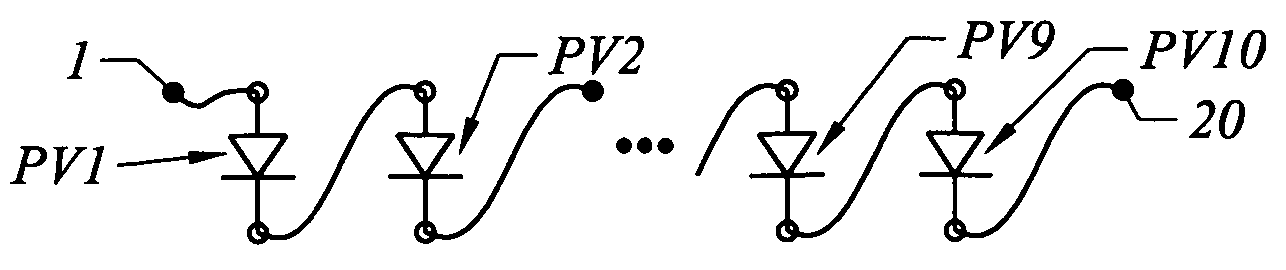

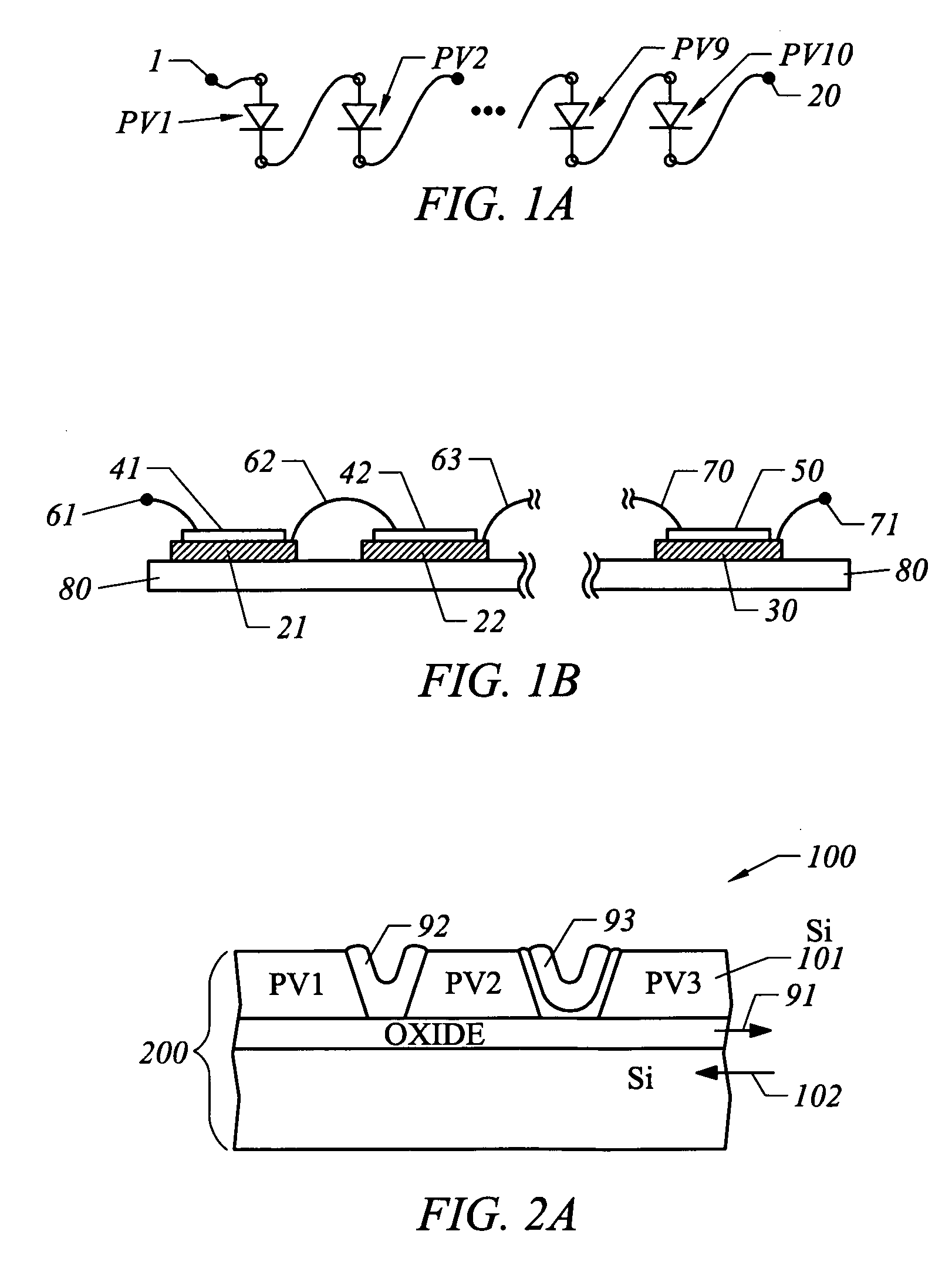

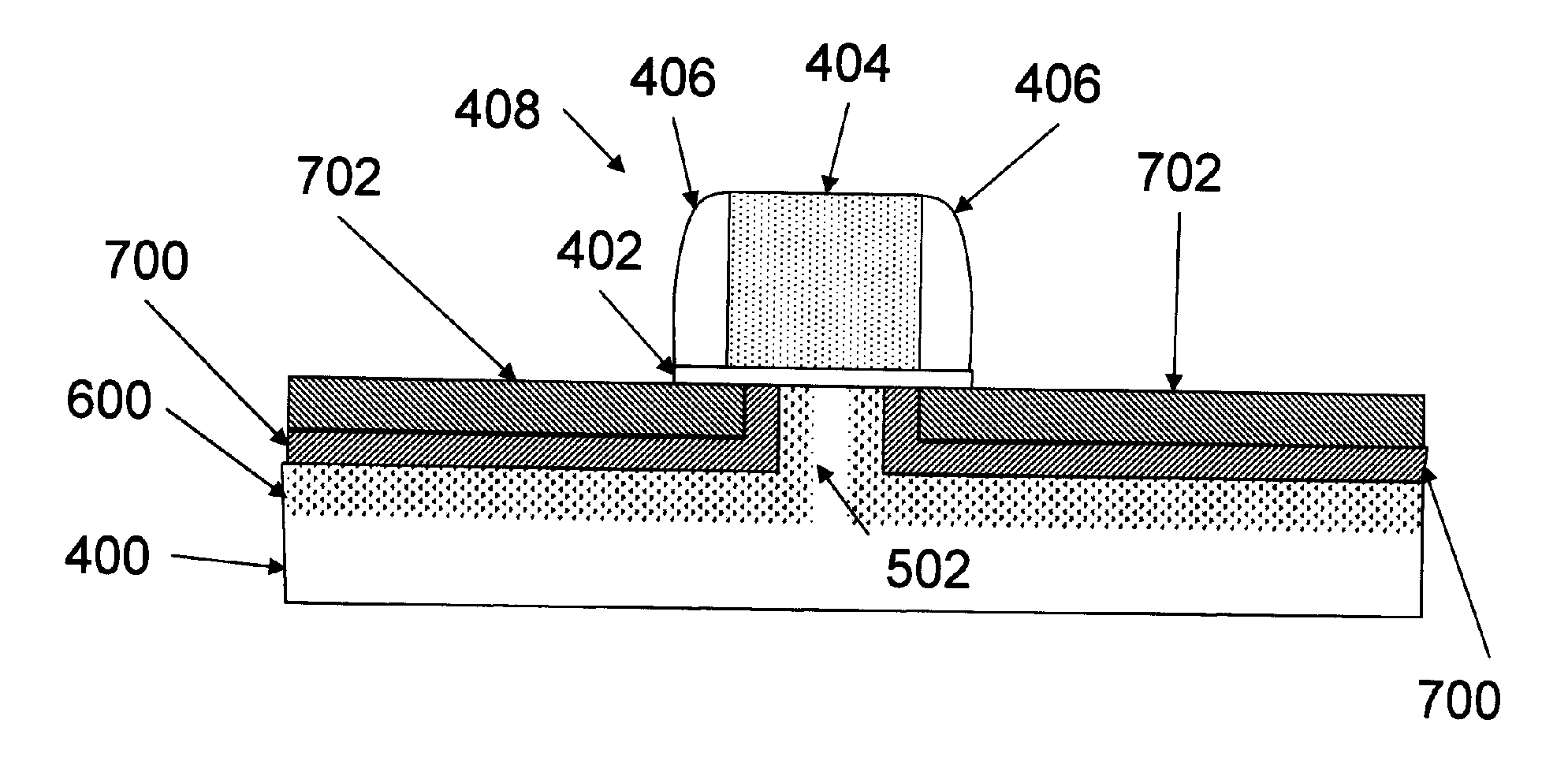

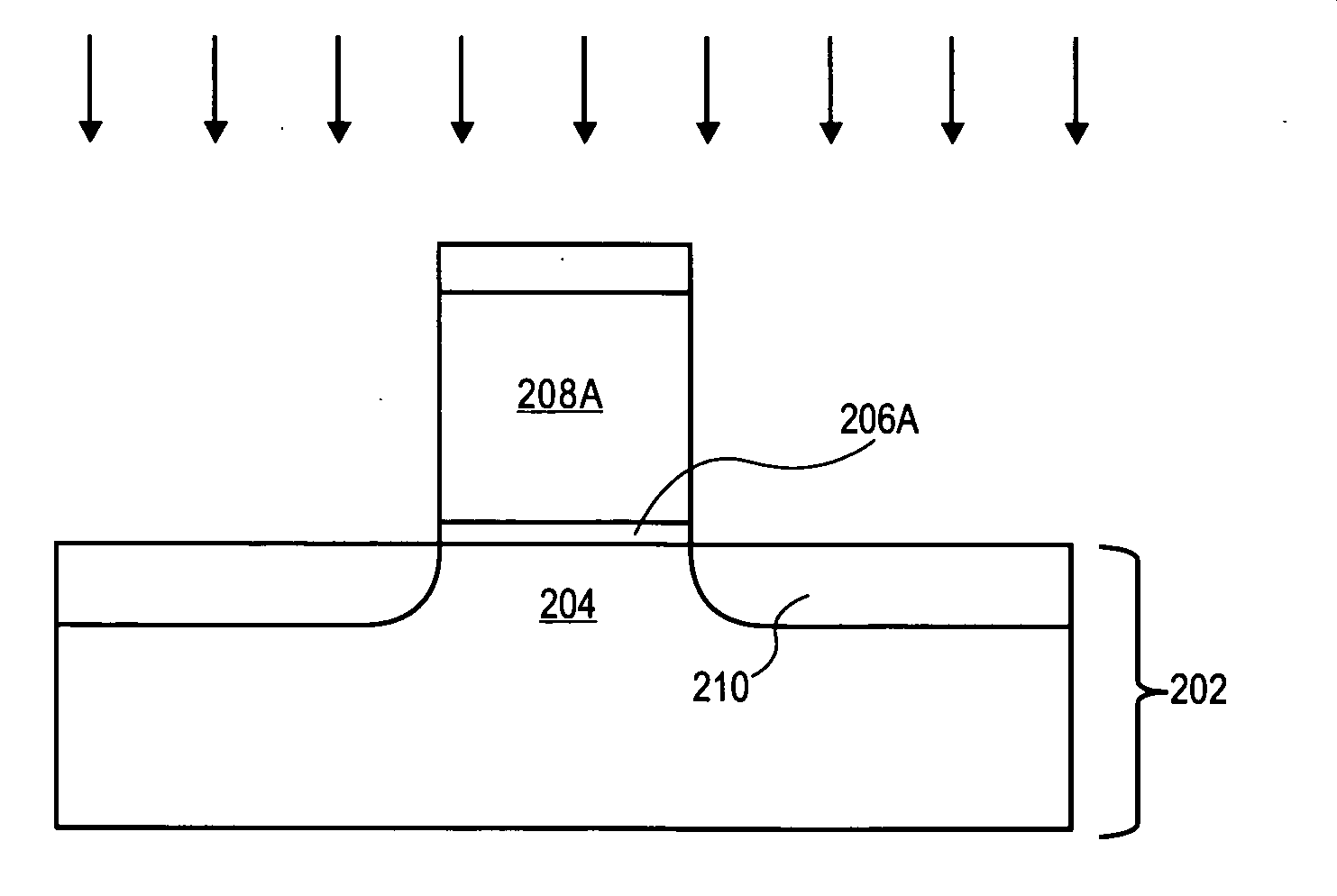

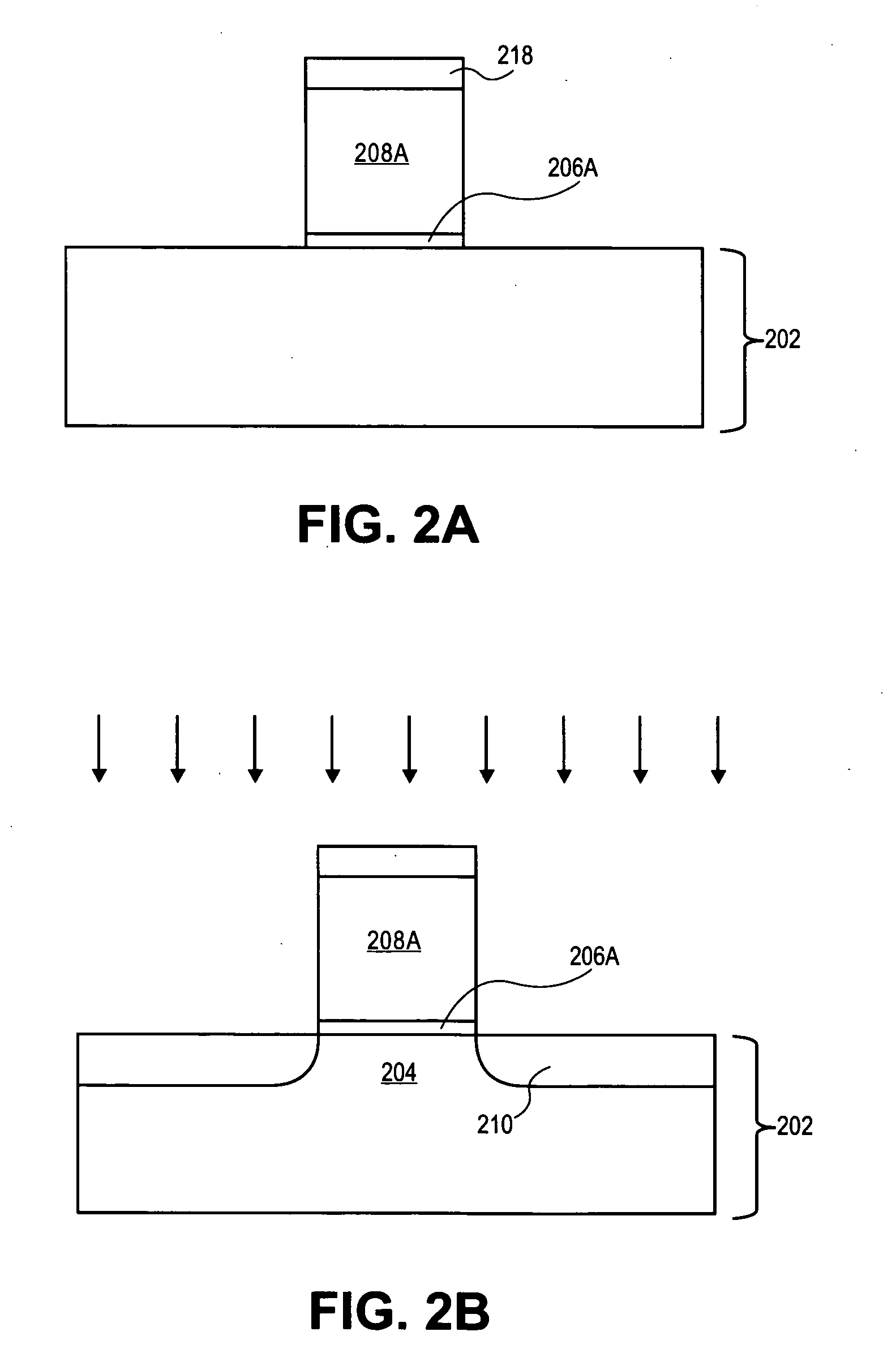

Discrete and integrated photo voltaic solar cells

ActiveUS20050145274A1Improve efficiencyPV power plantsSemiconductor/solid-state device manufacturingIsolation layerEngineering

A photovoltaic (PV) cell device comprises a first semiconductor substrate; a second semiconductor substrate bonded to the first semiconductor substrate; an insulating layer provided between the first and second substrates to electrically isolate the first substrate from the second substrate; a plurality of PV cells defined on the first substrate, each PV cell including a n-type region and a p-type region; a plurality of vertical trenches provided in the first substrate to separated the PV cells, the vertical trenches terminating at the insulating layer; a plurality of isolation structures provided within the vertical trenches, each isolation structure including a first isolation layer including oxide and a second isolation layer including polysilicon; and an interconnect layer patterned to connect the PV cells to provide X number of PV cells in series and Y number of PV cells in parallel. The n-type regions are formed by performing ion implantation of arsenic to provide shallow junction depths for the n-type regions, so that PV cell device is optimized for sunlight.

Owner:LITTELFUSE INC

Formation of ultra-shallow junctions by gas-cluster ion irradiation

ActiveUS20050202657A1Improve solid solubilityImprove efficiencyElectric discharge tubesSemiconductor/solid-state device manufacturingGas cluster ion beamIrradiation

Method of forming one or more doped regions in a semiconductor substrate and semiconductor junctions formed thereby, using gas cluster ion beams.

Owner:TEL EPION

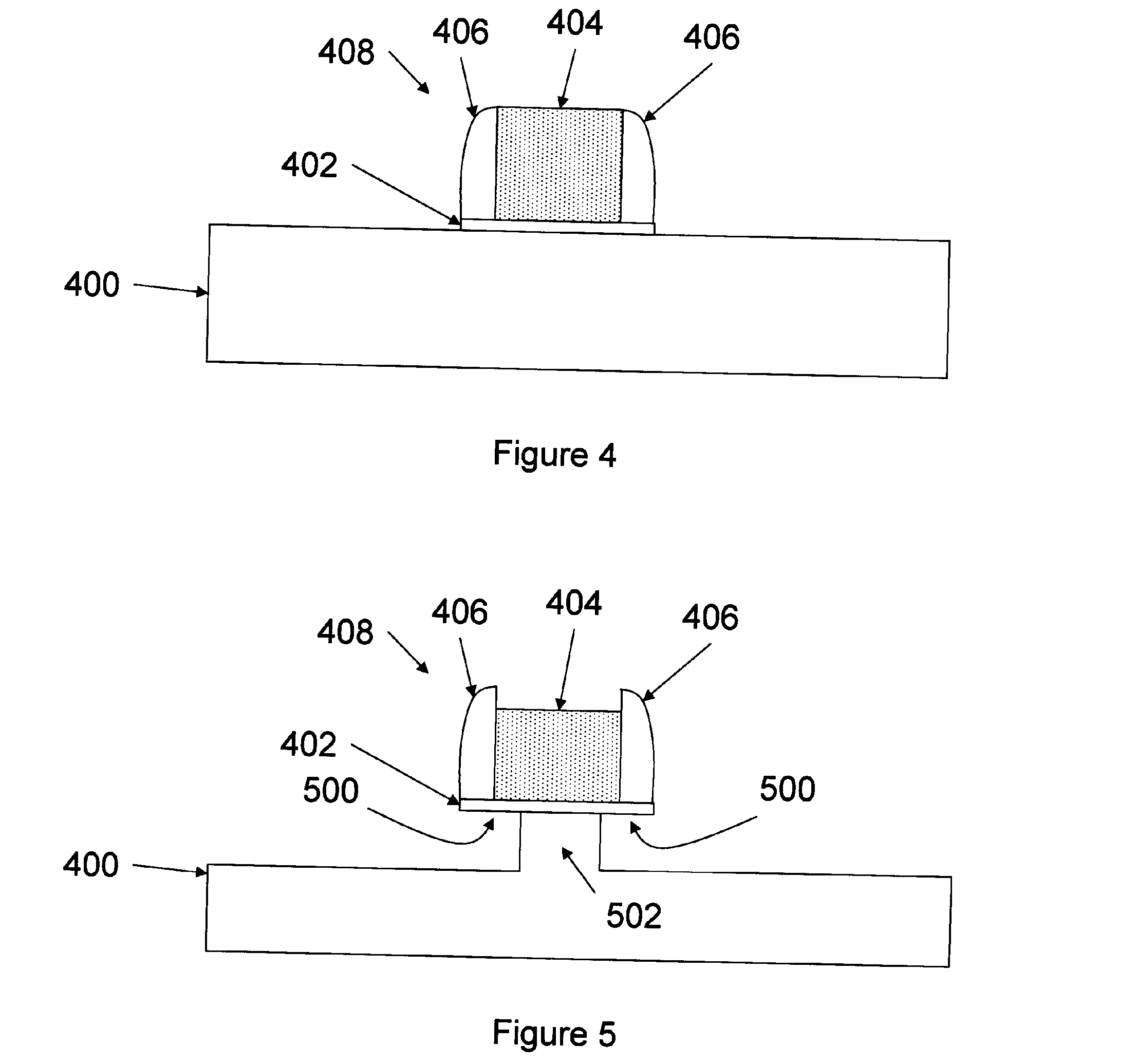

Ultra shallow junction formation by epitaxial interface limited diffusion

ActiveUS20060076627A1Maximizing dopant activationIncrease oxygen contentSemiconductor/solid-state device manufacturingSemiconductor devicesField-effect transistorOxygen content

A method of forming a field effect transistor creates shallower and sharper junctions, while maximizing dopant activation in processes that are consistent with current manufacturing techniques. More specifically, the invention increases the oxygen content of the top surface of a silicon substrate. The top surface of the silicon substrate is preferably cleaned before increasing the oxygen content of the top surface of the silicon substrate. The oxygen content of the top surface of the silicon substrate is higher than other portions of the silicon substrate, but below an amount that would prevent epitaxial growth. This allows the invention to epitaxially grow a silicon layer on the top surface of the silicon substrate. Further, the increased oxygen content substantially limits dopants within the epitaxial silicon layer from moving into the silicon substrate.

Owner:GLOBALFOUNDRIES US INC

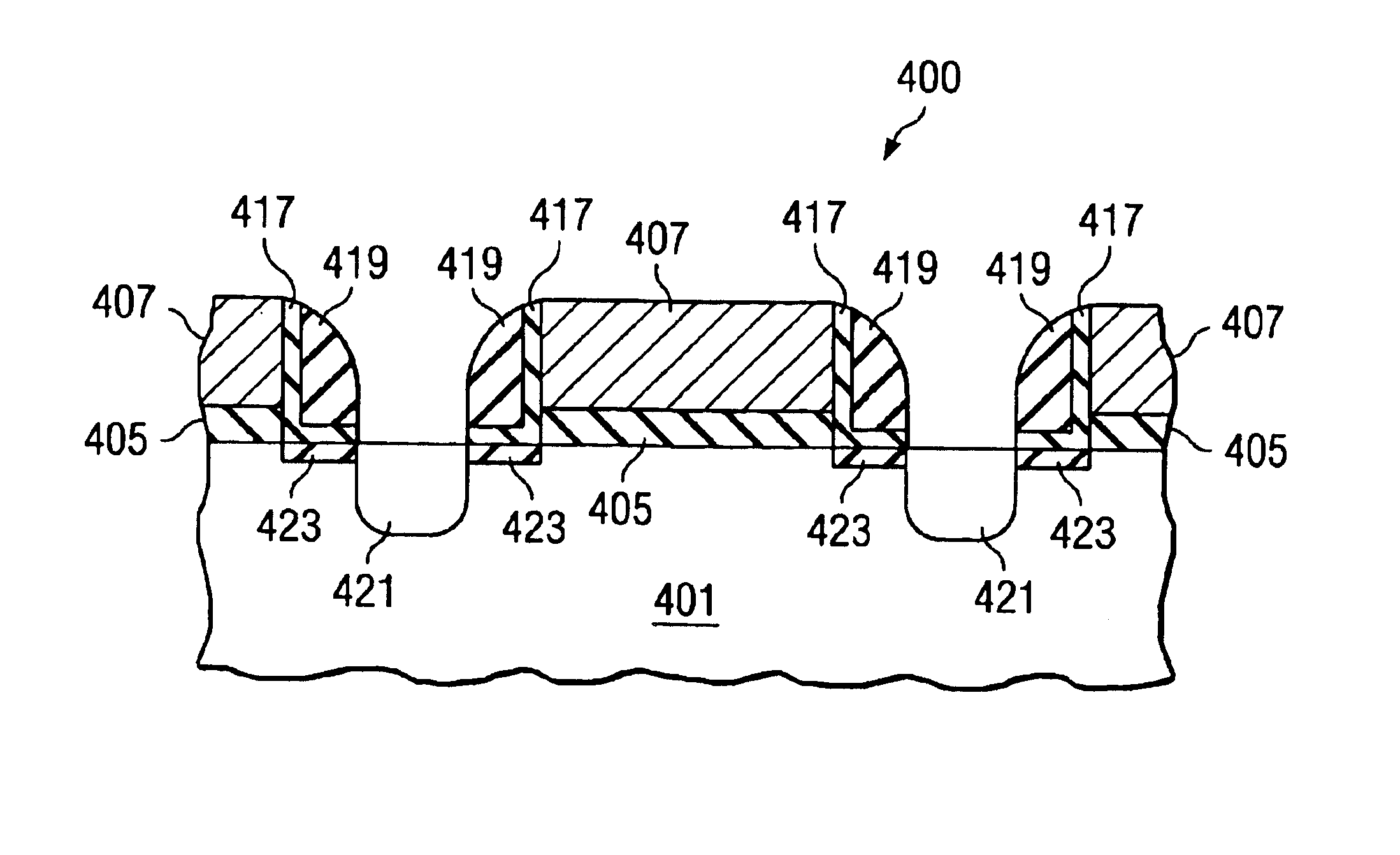

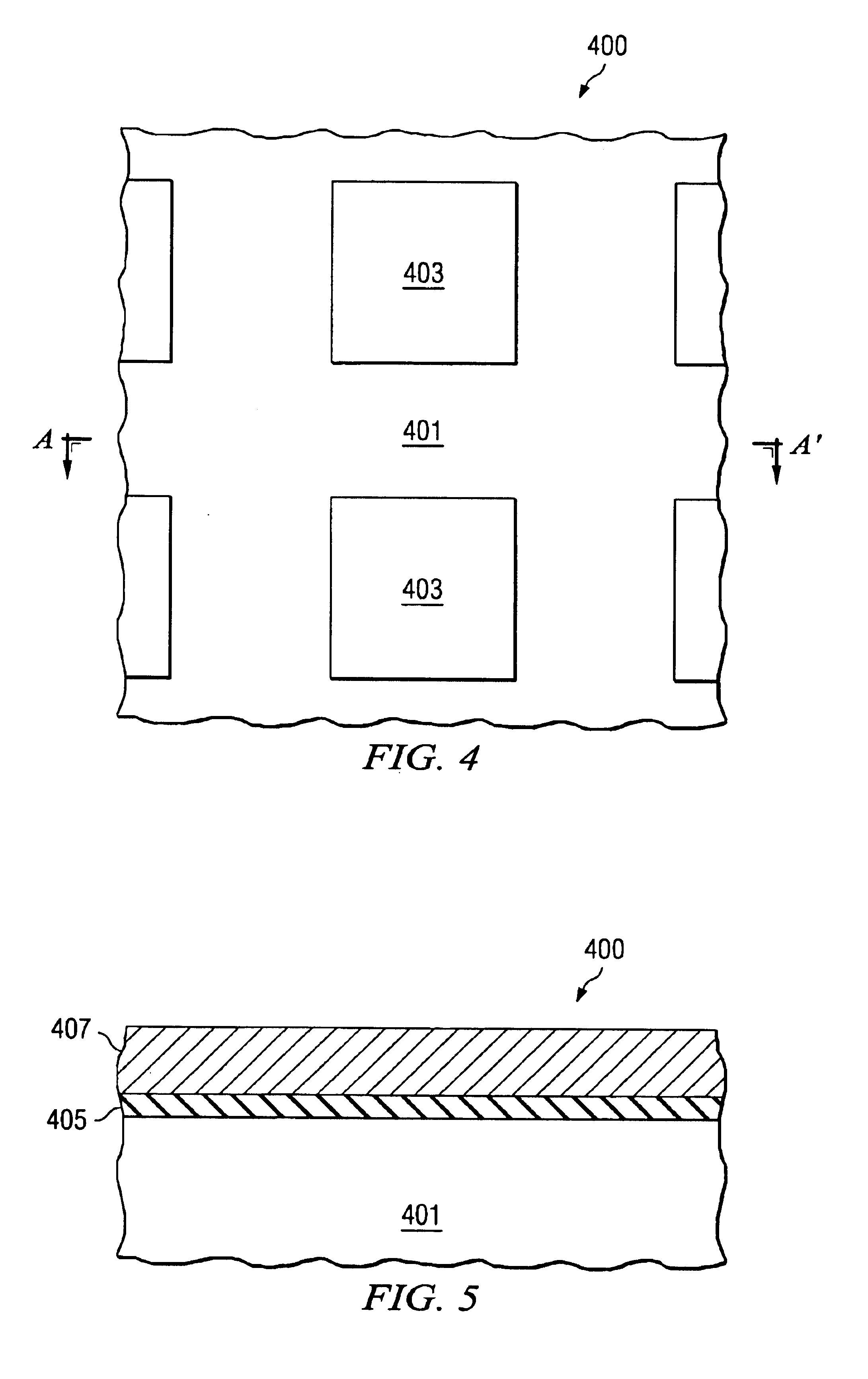

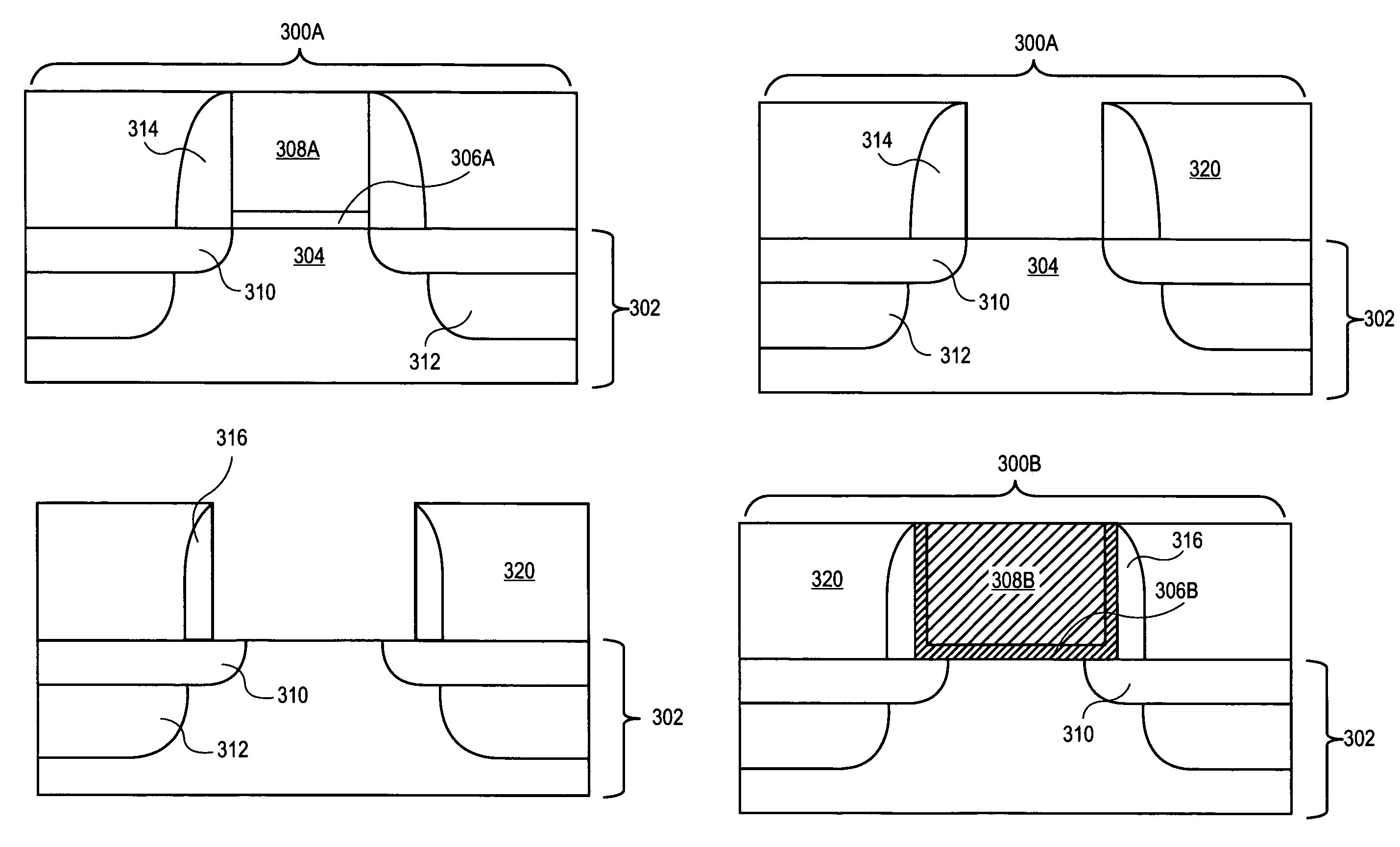

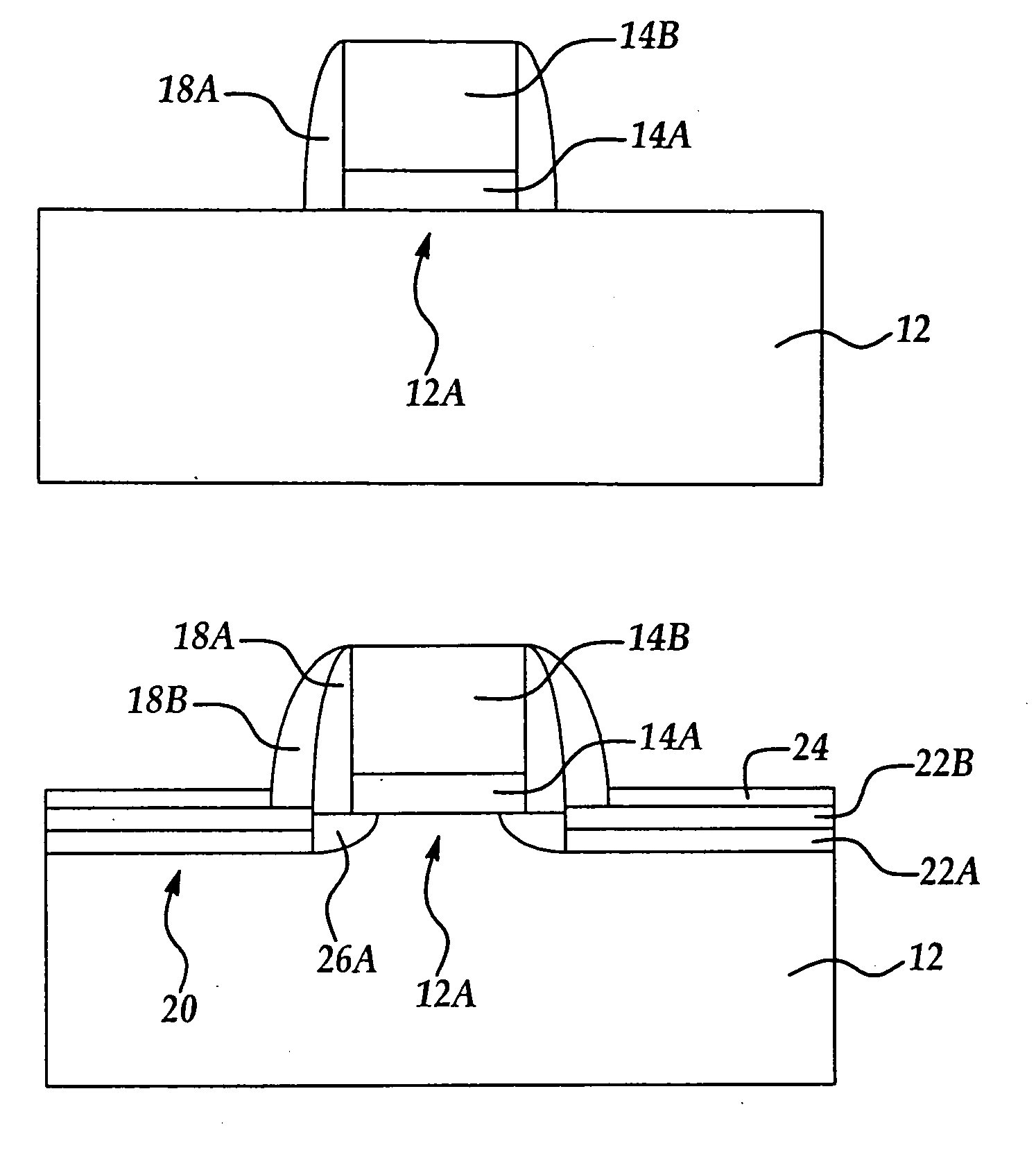

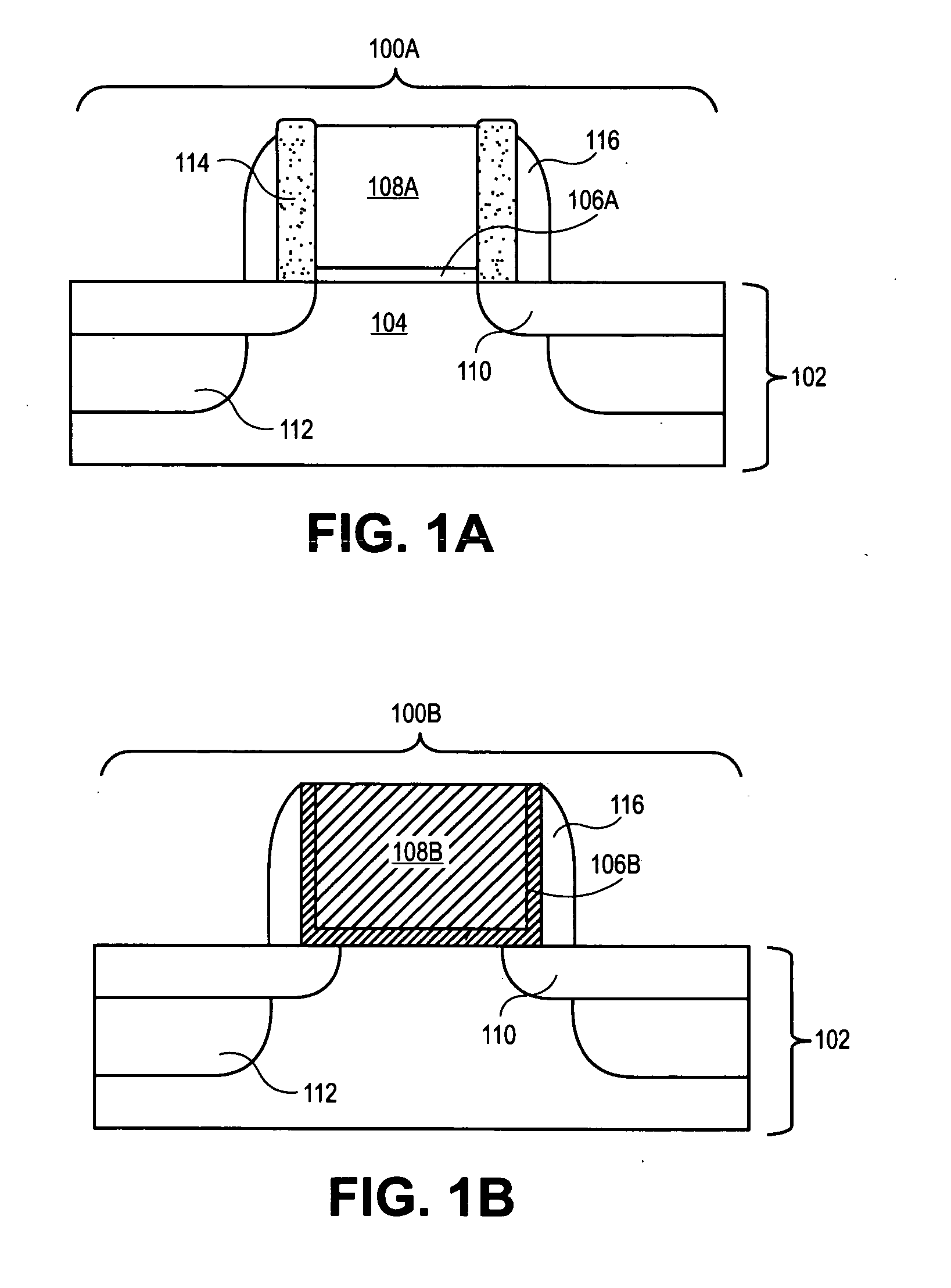

Ultra shallow junction formation by solid phase diffusion

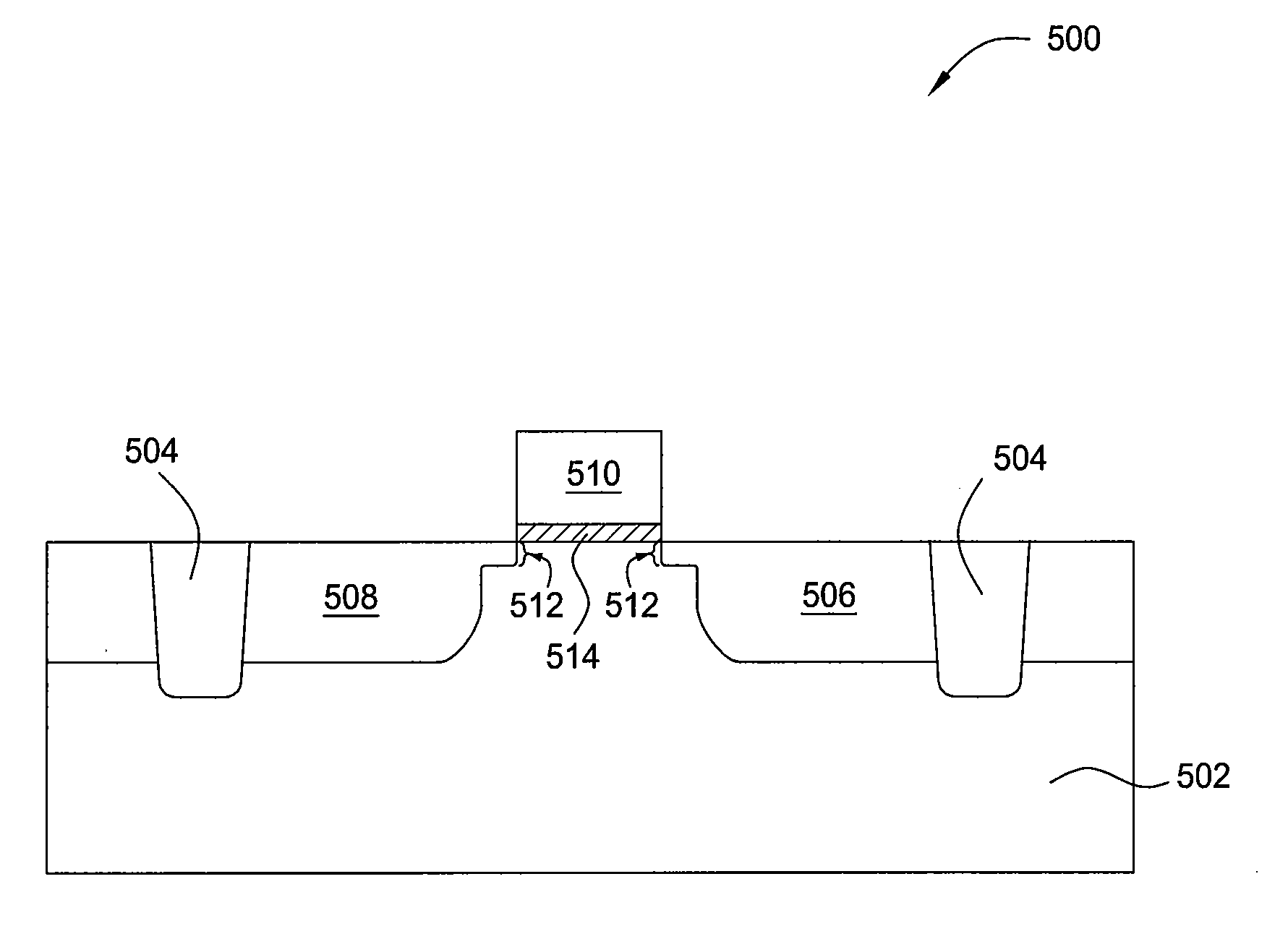

ActiveUS20070093033A1Improve device performanceImprove reliabilityTransistorSemiconductor/solid-state device manufacturingDopantGate dielectric

An ultra shallow junction (USJ) FET device and method for forming the same with improved control over SDE or LDD doped region interfaces to improve device performance and reliability is provided, the method including providing a semiconductor substrate; forming a gate structure comprising a gate dielectric, an overlying gate electrode, and first offset spacers adjacent either side of the gate electrode; forming at least one doped semiconductor layer comprising dopants over a respective source and drain region adjacent the respective first offset spacers; forming second offset spacers adjacent the respective first offset spacers; and, thermally treating the at least one semiconductor layer to cause out-diffusion of the dopants to form doped regions in the semiconductor substrate.

Owner:TAIWAN SEMICON MFG CO LTD

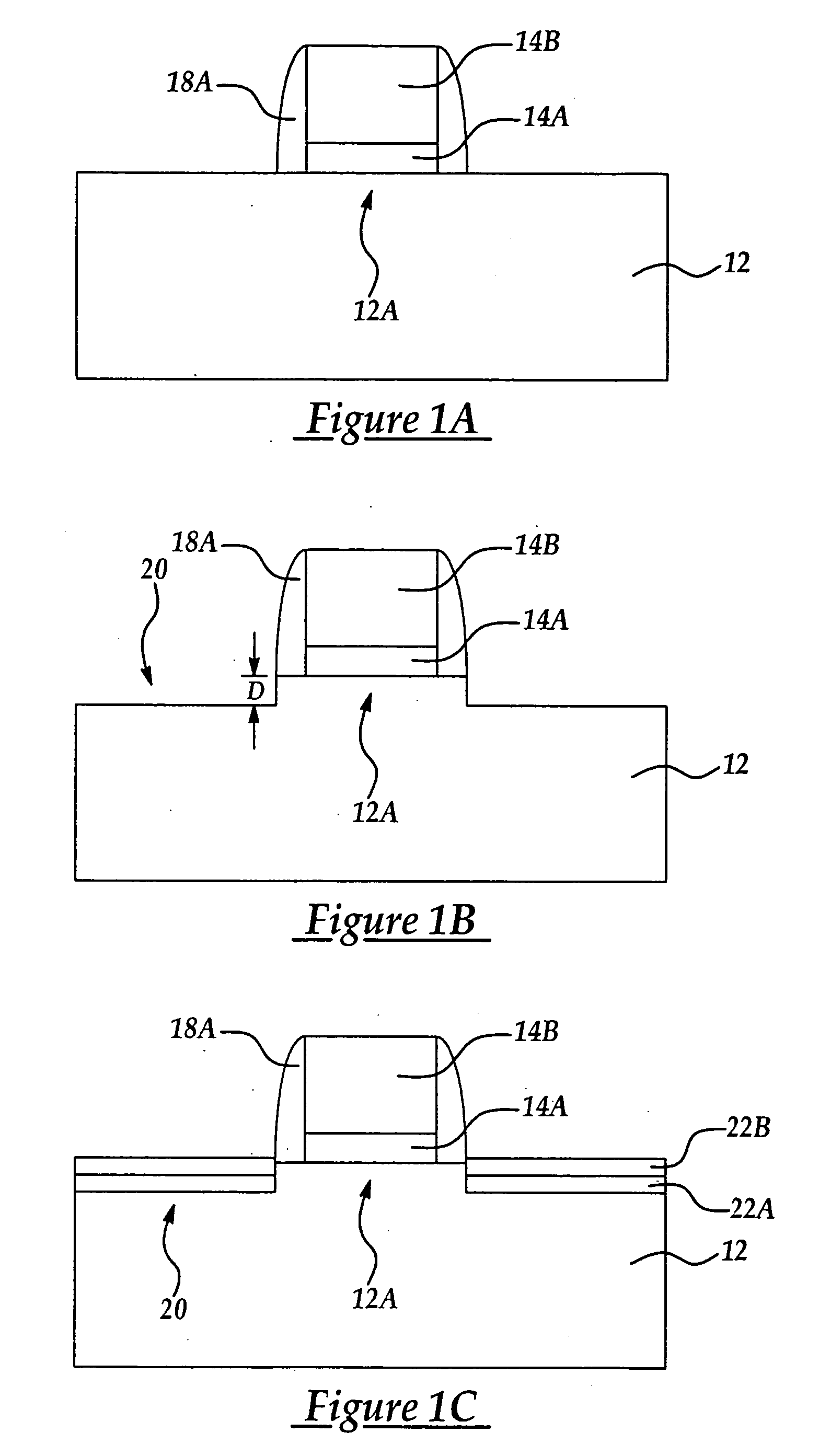

Forming ultra-shallow junctions

InactiveUS20070287259A1Semiconductor/solid-state device manufacturingSemiconductor devicesSemiconductorGate length

A method to form an ultra-shallow junction is described. In one embodiment, a replacement gate process is utilized to enable the overlap of a gate electrode over the regions of a semiconductor substrate where tip extensions reside. In another embodiment, a sacrificial spacer is utilized in conjunction with the replacement gate process. In one embodiment, an initial gate electrode is formed with a gate length smaller than the desired final gate length and is subsequently replaced with an expanded gate electrode having the desired gate length.

Owner:INTEL CORP

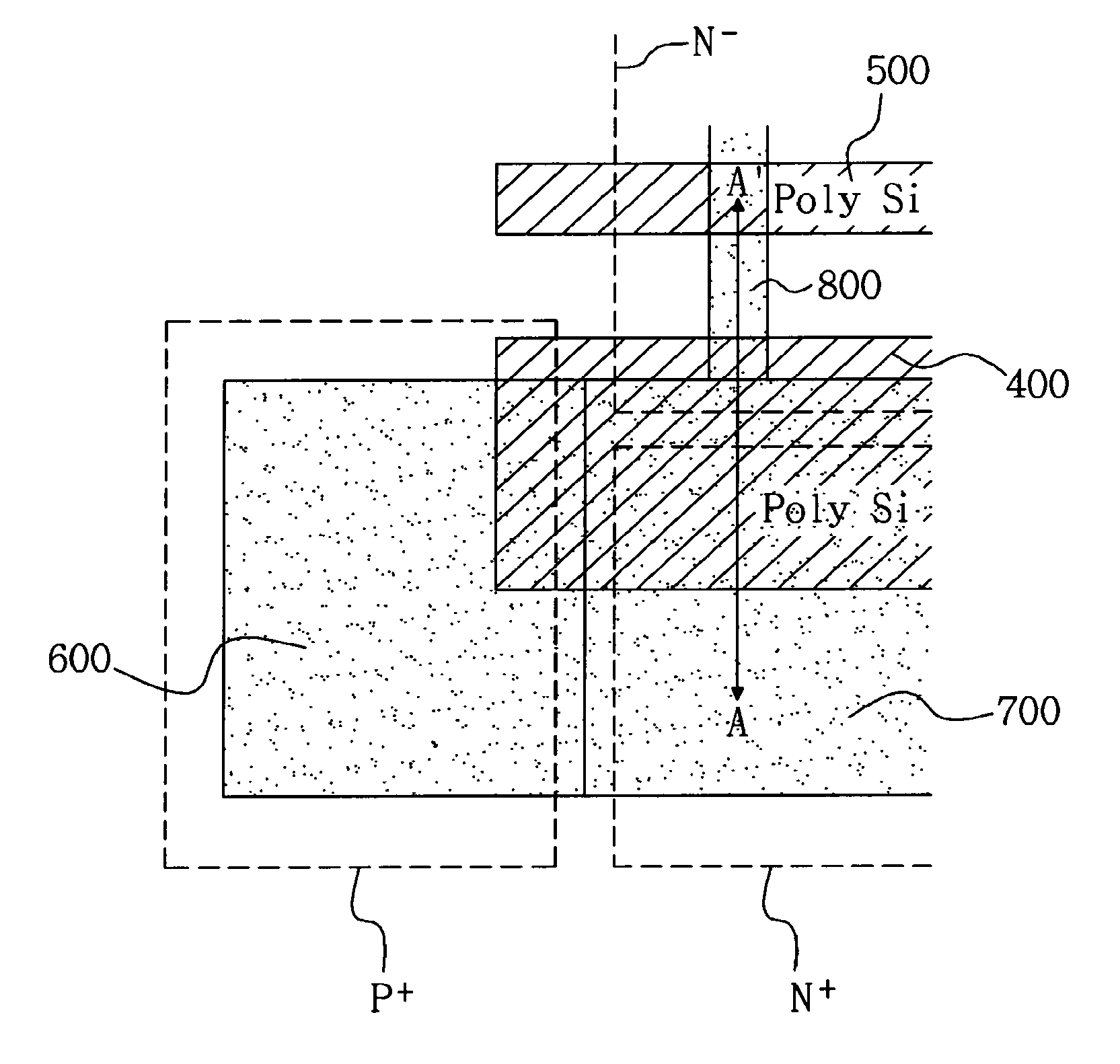

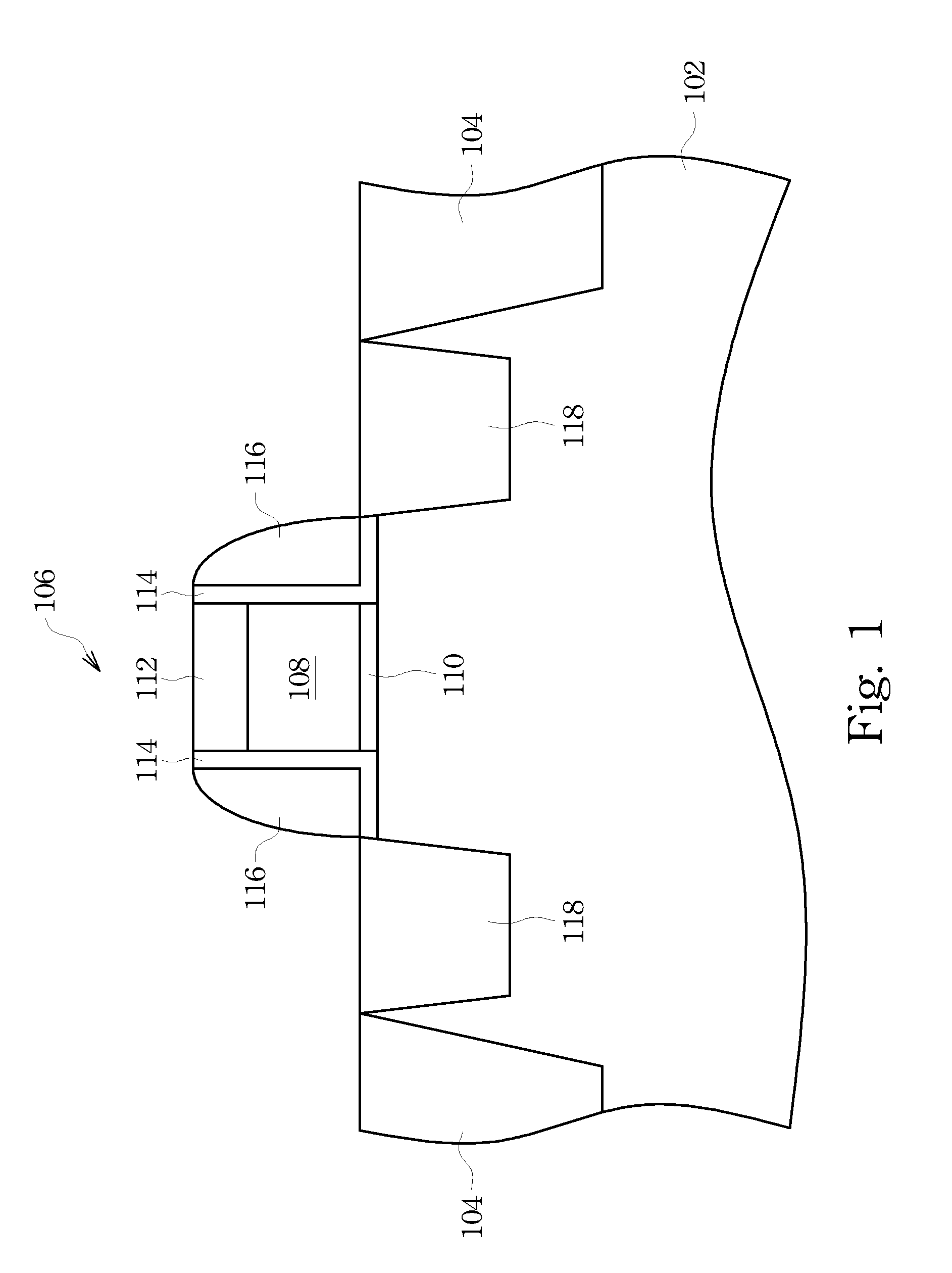

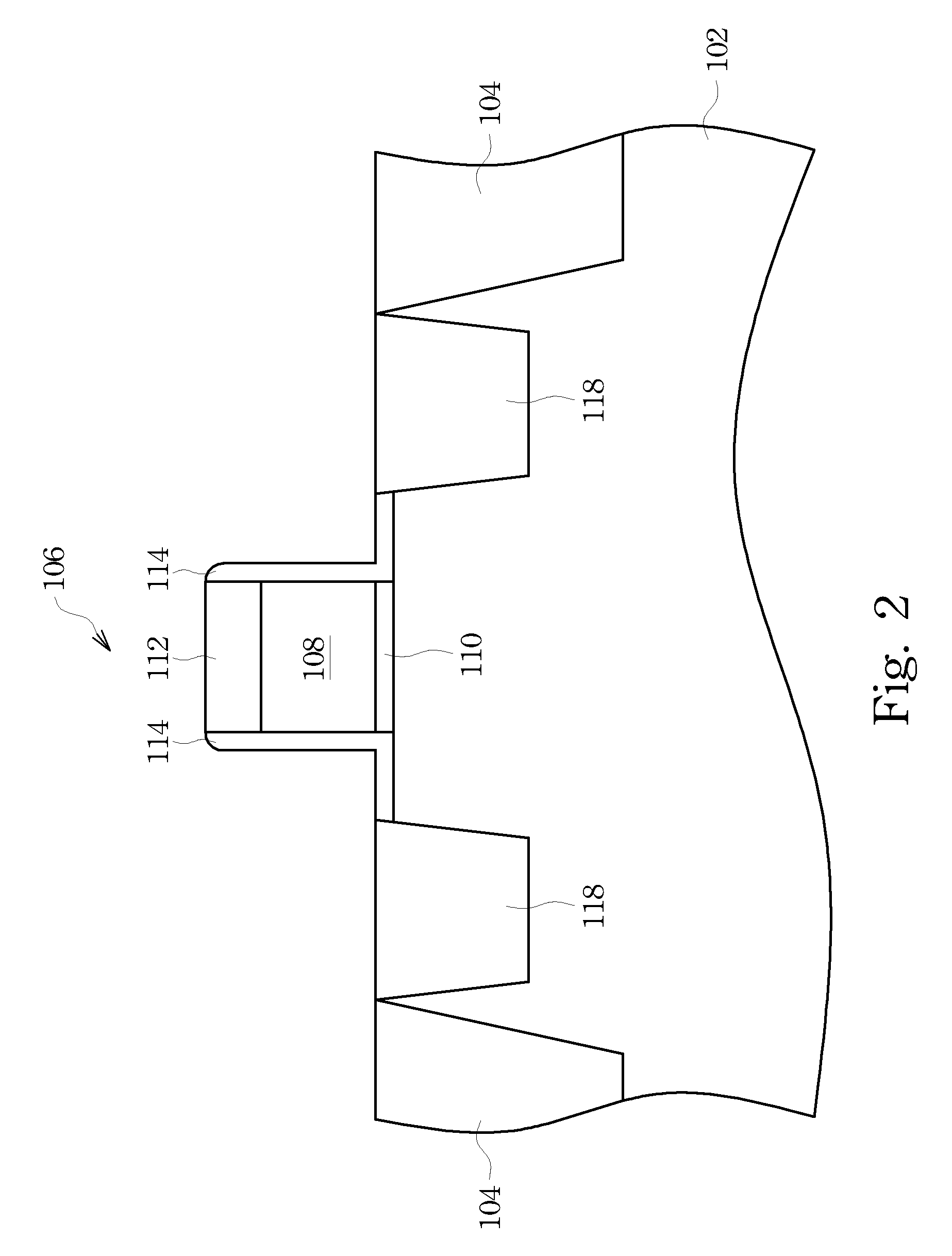

Body biasing structure of SOI

ActiveUS7432552B2Suppression of floating body effectTransistorSolid-state devicesMOSFETFloating body effect

Owner:SEOUL NAT UNIV R&DB FOUND +1

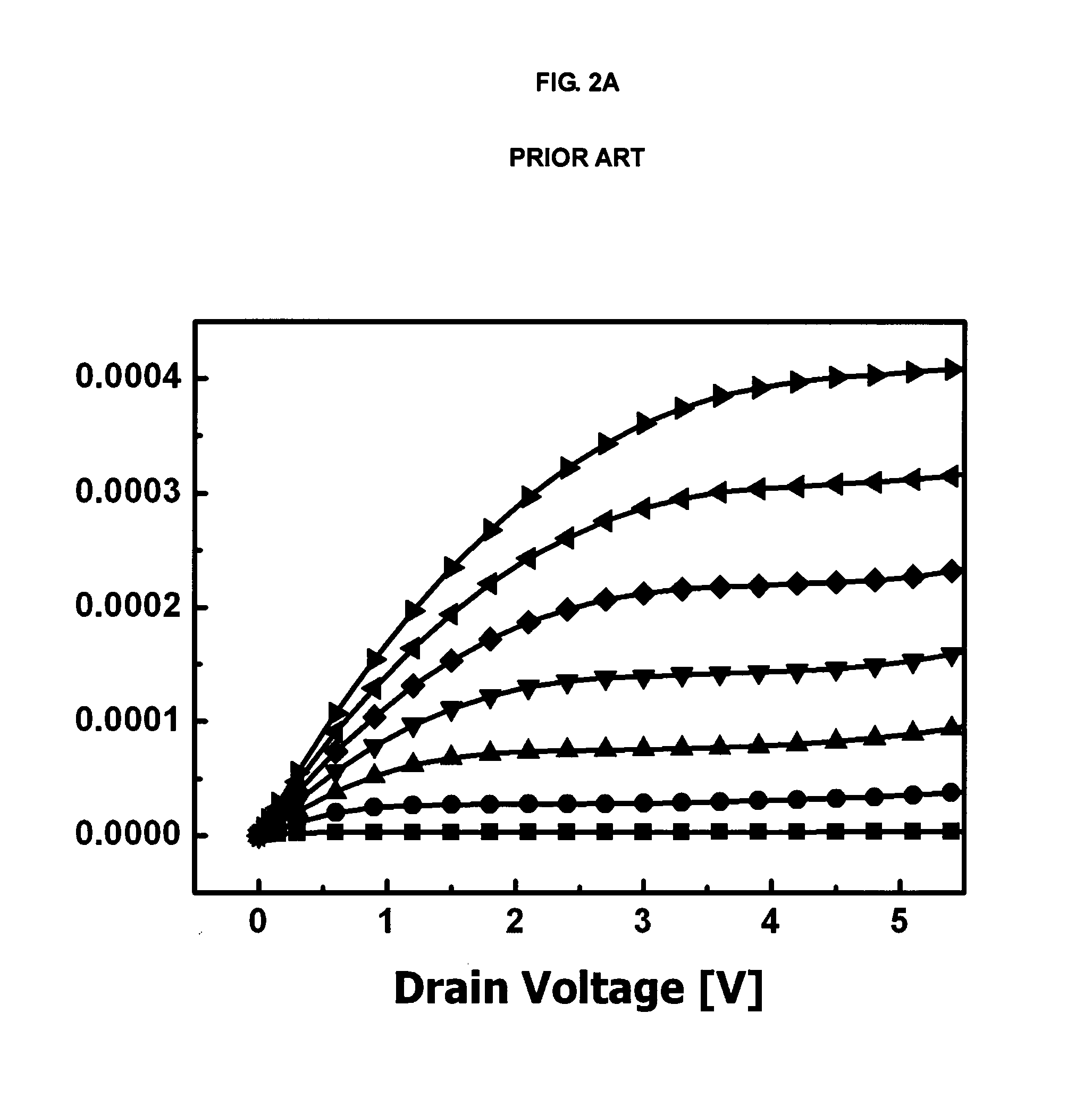

Advances in spike anneal processes for ultra shallow junctions

InactiveUS6897131B2Mitigating dopant diffusionHigh dopant activationSemiconductor/solid-state device manufacturingElectrical resistance and conductanceCooling down

Lamp based spike annealing was improved to address the aggressive requirements of <100 nm Ultra Shallow Junction (USJ) technologies. Improvements focused on enhancing cool down rates, and thereby improving spike sharpness. Boron ion implanted substrates with varying ion-implanted energy and dose were then annealed to characterize the improvements in spike annealing. A greater than 10% improvement in sheet resistance and junction depth was realized on substrates that were annealed with the improved spike profile. The improved spike anneal had the same comparable uniformity to the standard spike anneal.

Owner:APPLIED MATERIALS INC

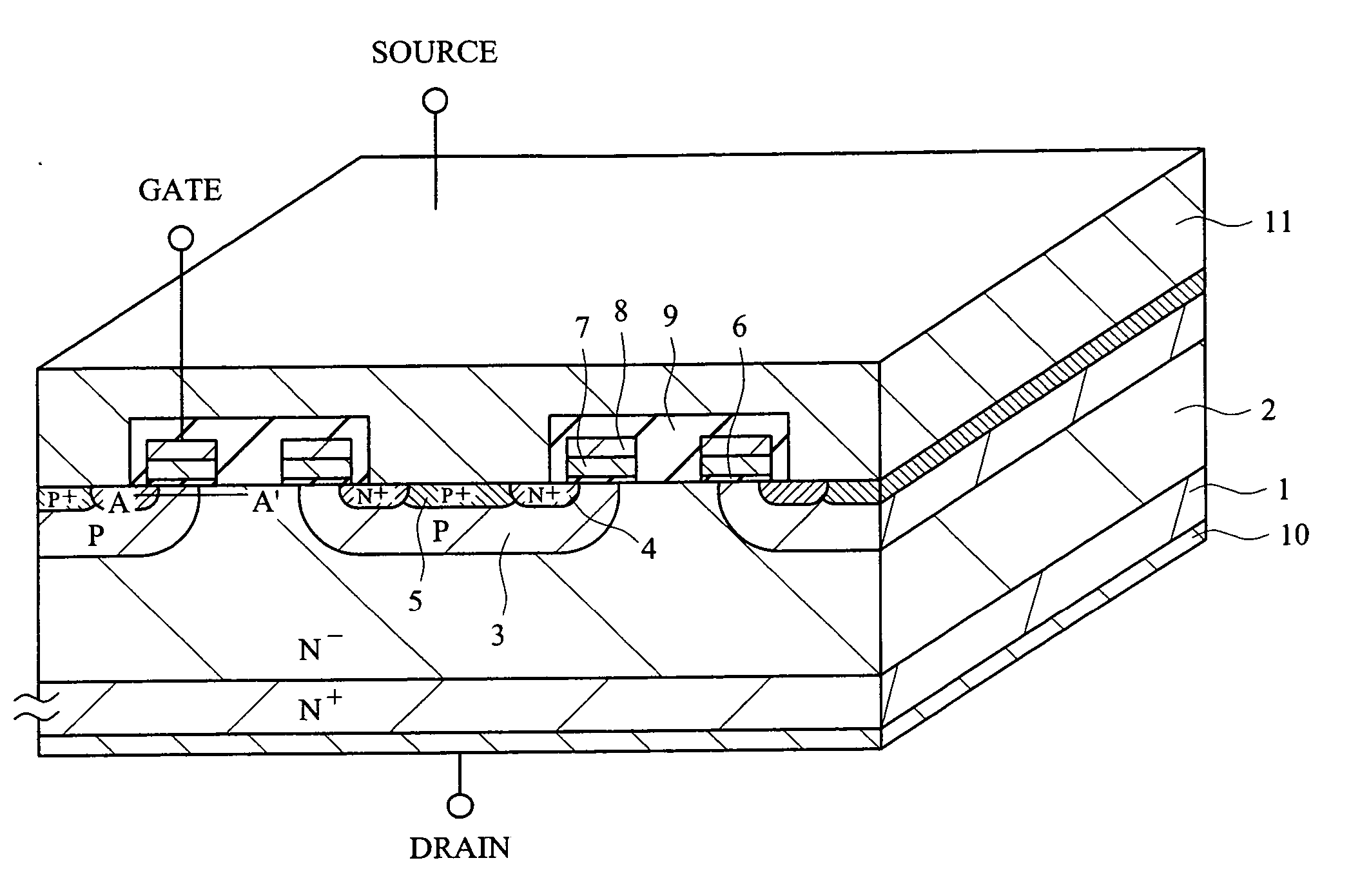

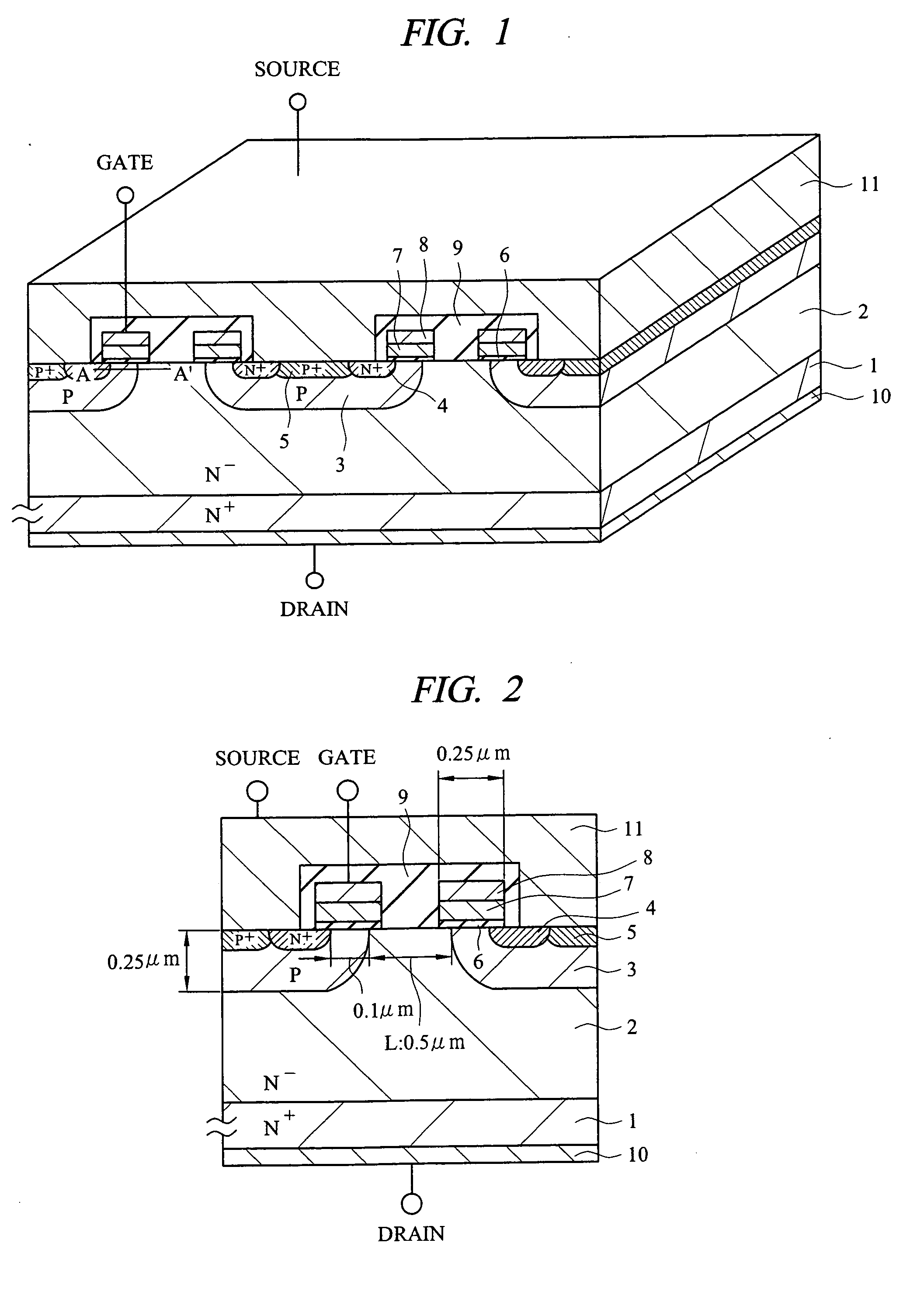

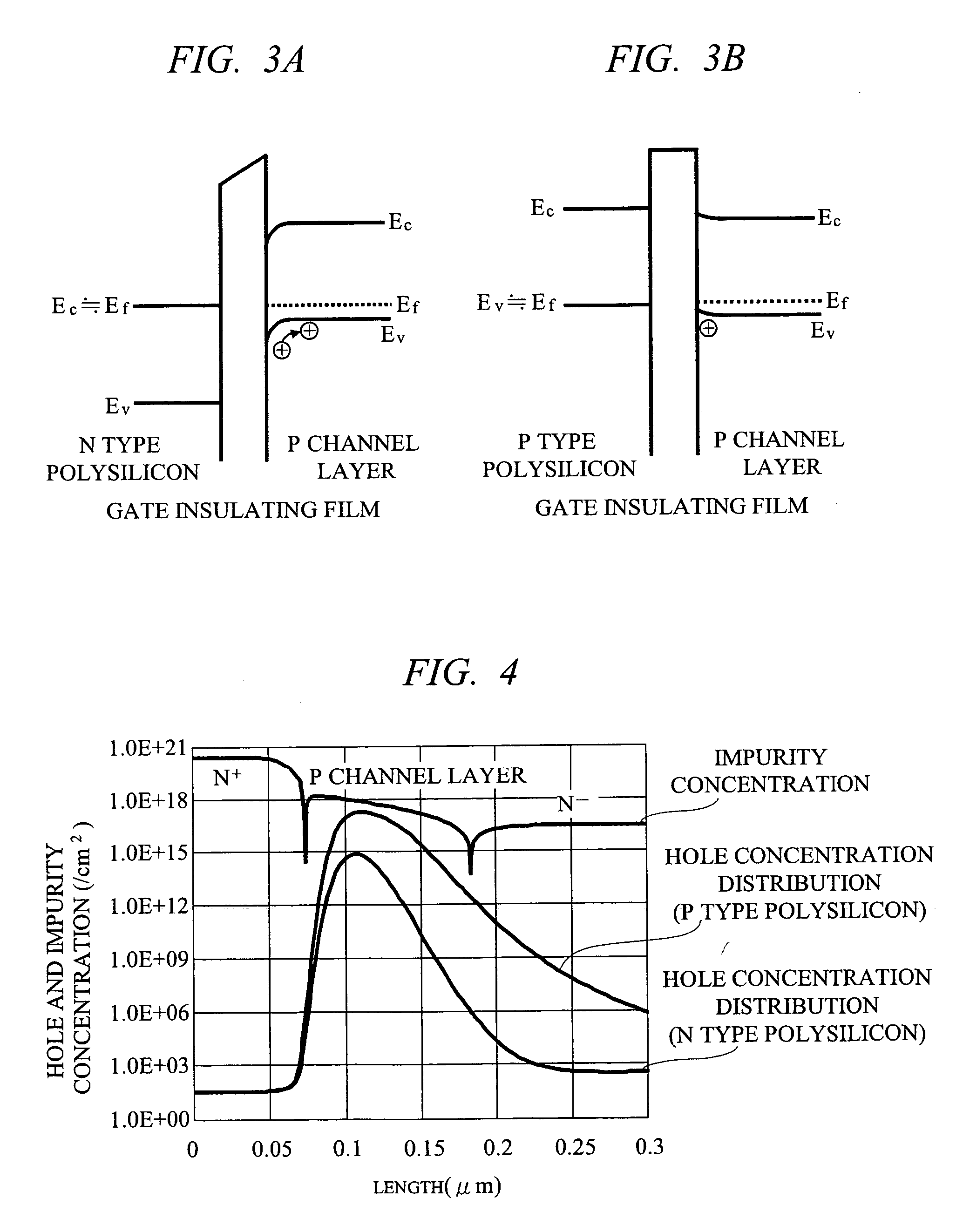

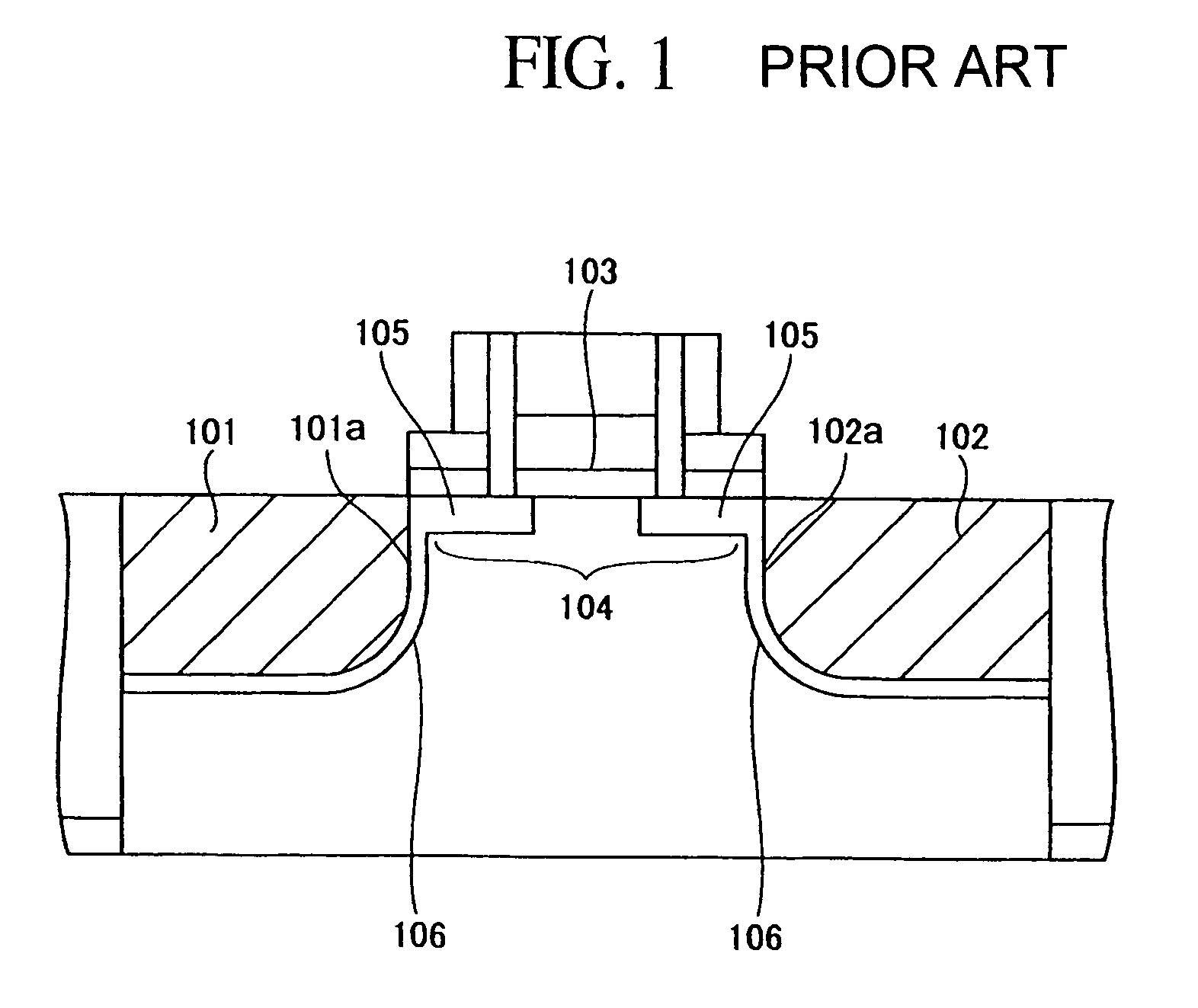

DMOSFET and planar type MOSFET

A technology capable of realizing a MOSFET with low ON-resistance and low feedback capacitance, in which the punch through of a channel layer can be prevented even when the shallow junction of the channel layer is formed in a planar type MOSFET is provided. A P type polysilicon is used for a gate electrode in a planar type MOSFET, in particular, in an N channel DMOSFET.

Owner:RENESAS TECH CORP

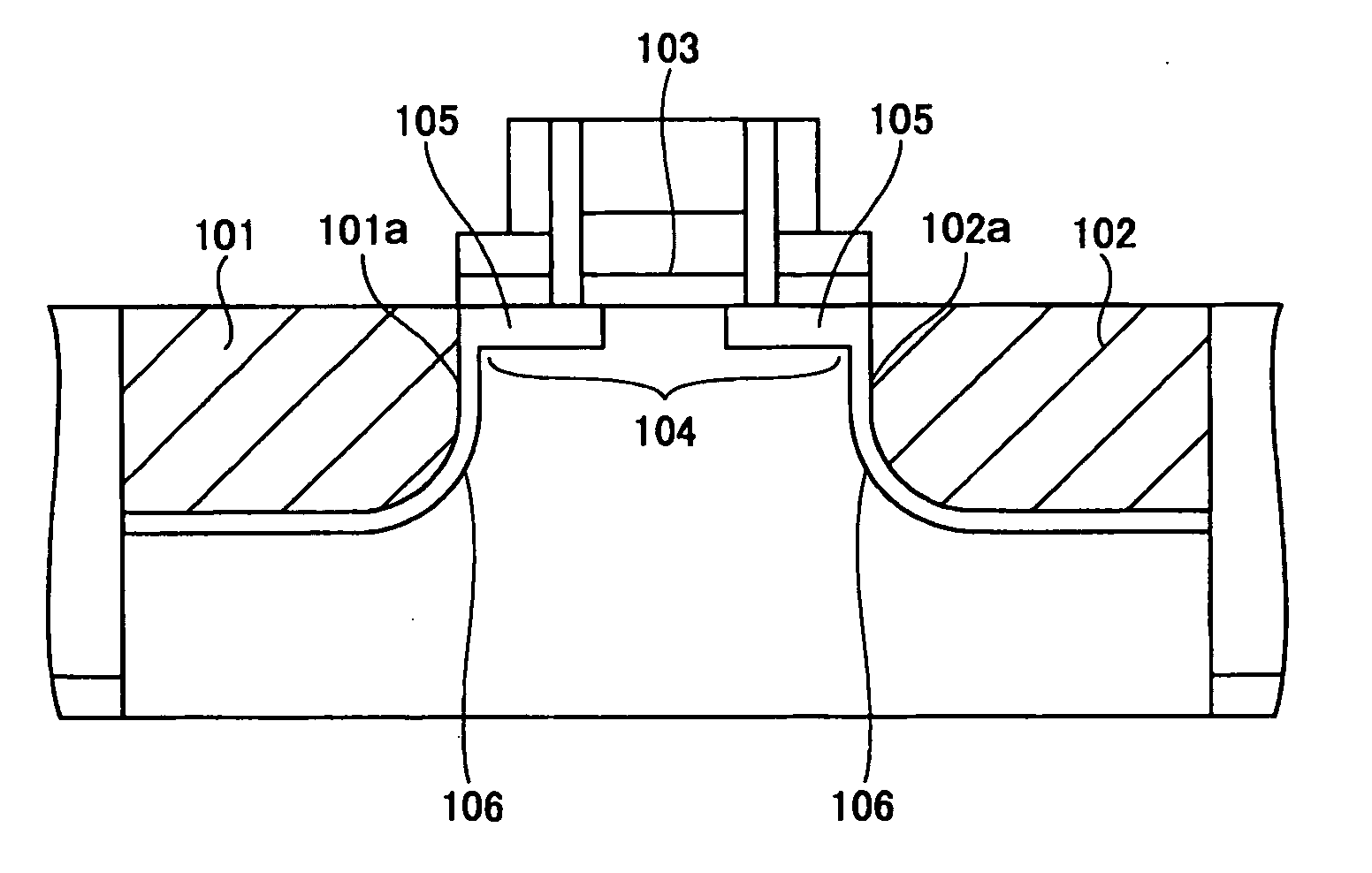

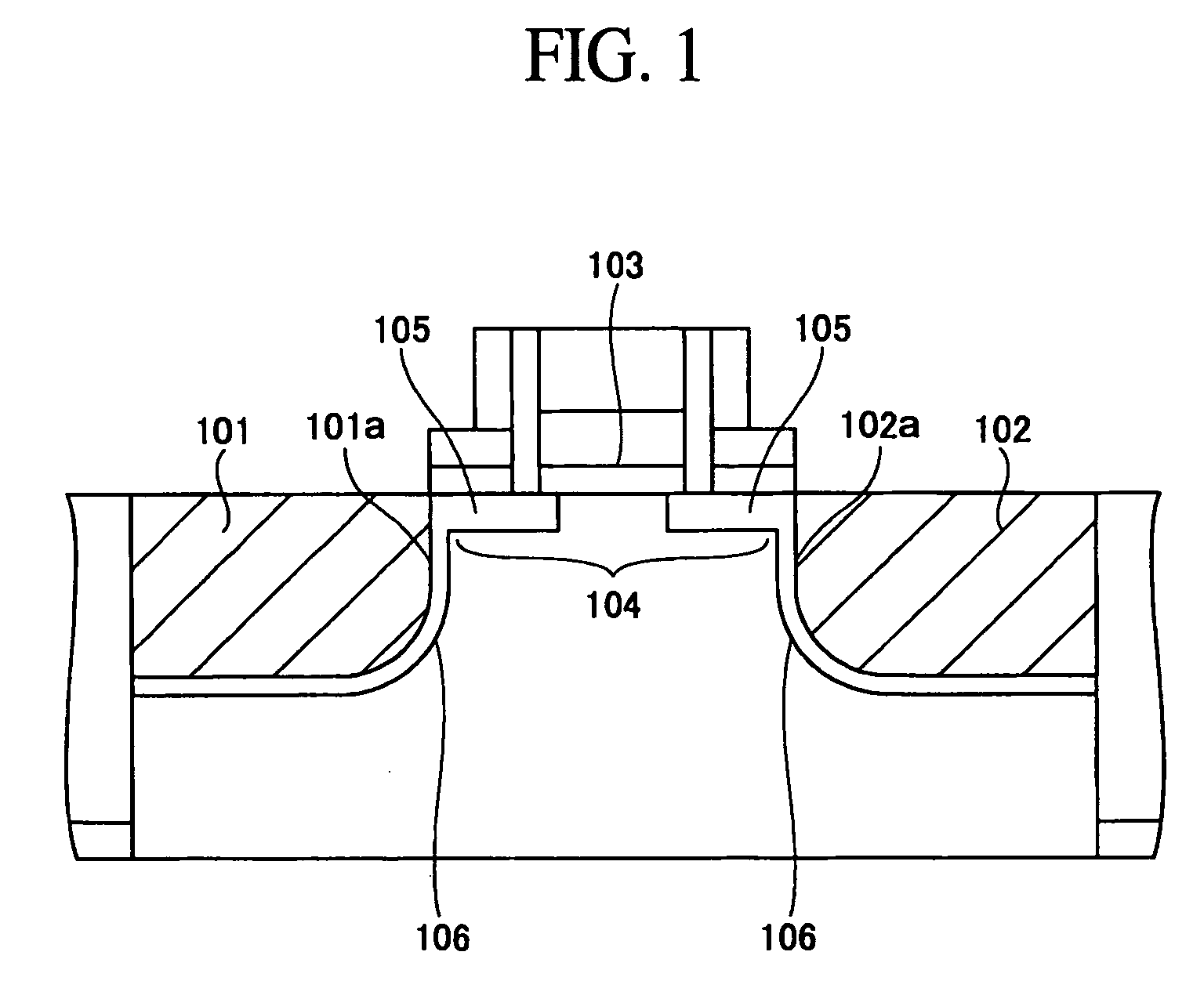

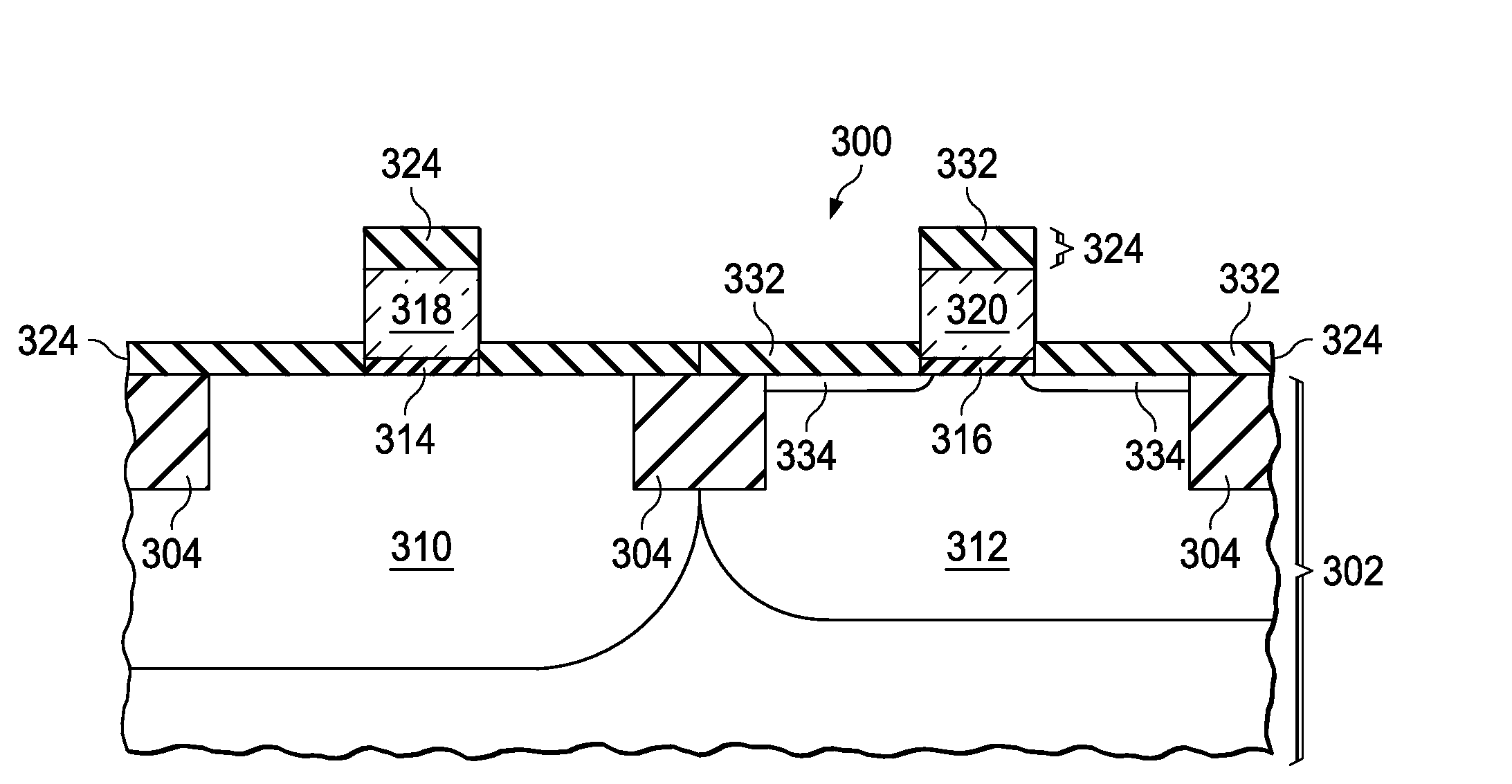

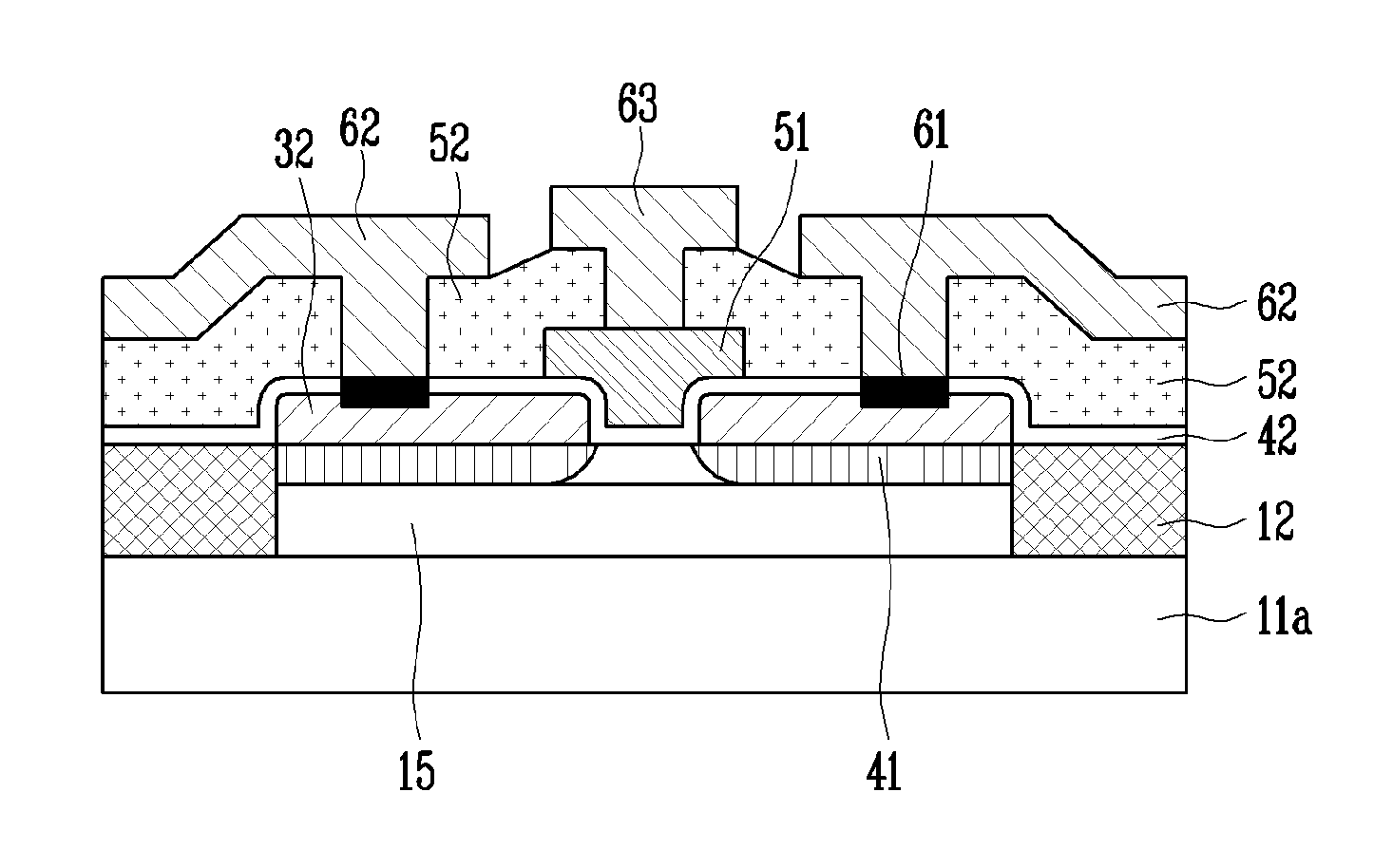

Method of fabricating a complementary semiconductor device having a strained channel p-transistor

ActiveUS7407860B2High speedImprove channel mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductorImpurity

Compression stress applying portions 20 of SiGe film are formed in the source / drain regions of the p-MOSA region 30a. Then, impurities are implanted in the p-MOS region 30a and the n-MOS region 30b to form shallow junction regions 22a, 22b and deep junction regions 23a, 23b. The impurity in the shallow junction regions 22a, 22b is prevented from being diffused immediately below the gate insulation film 15 by the thermal processing in forming the SiGe film, the short channel effect is prevented, and the hole mobility of the channel region of the p-MOS transistor 14a. The operation speed of the p-MOS transistor 13a is balanced with that of the n-MOS transistor, whereby the operation speed of the complementary semiconductor device 10 can be increased. The semiconductor device fabricating method can increase and balance the operation speed of a p-transistor with that of an n-transistor.

Owner:FUJITSU SEMICON LTD

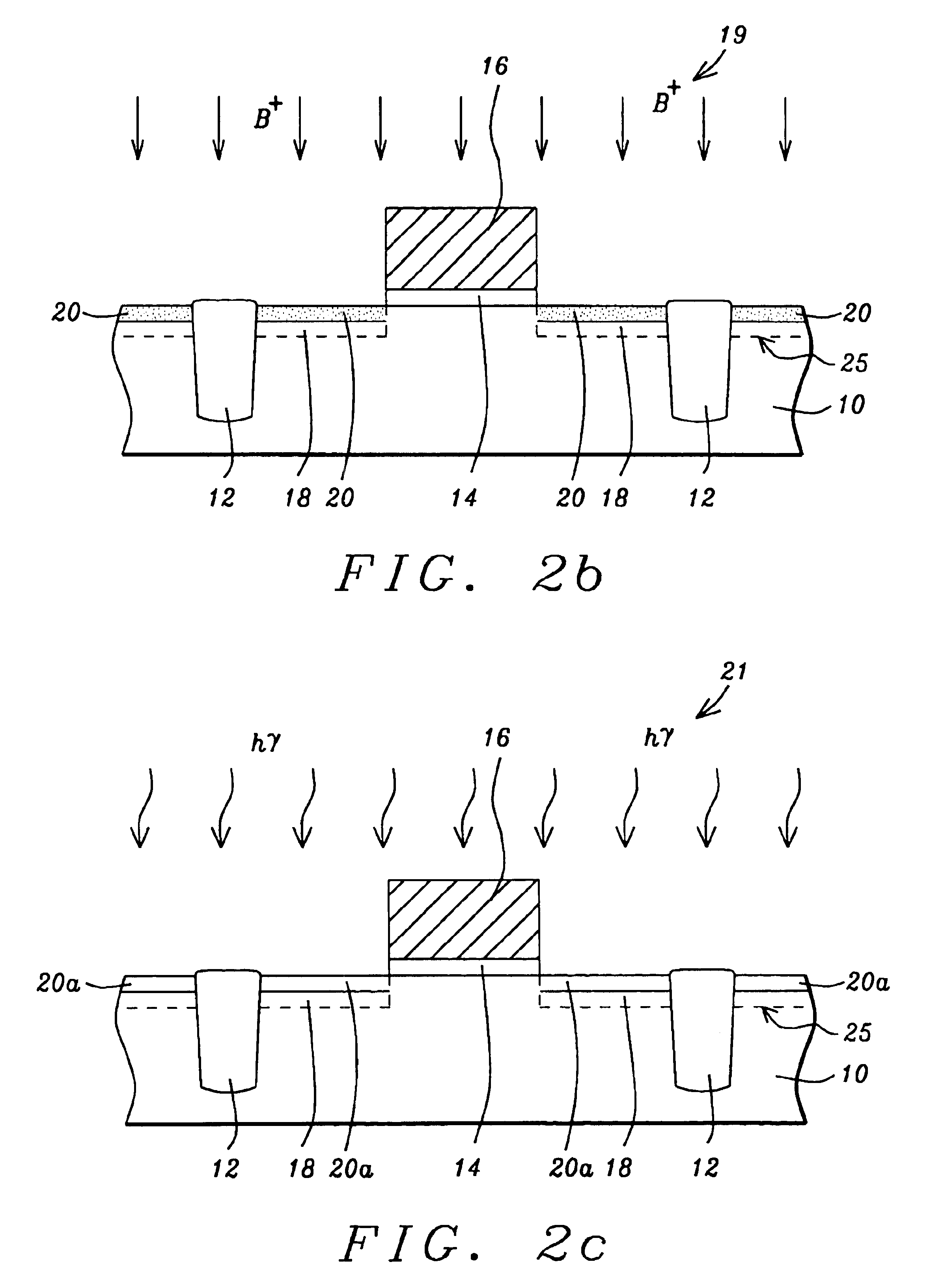

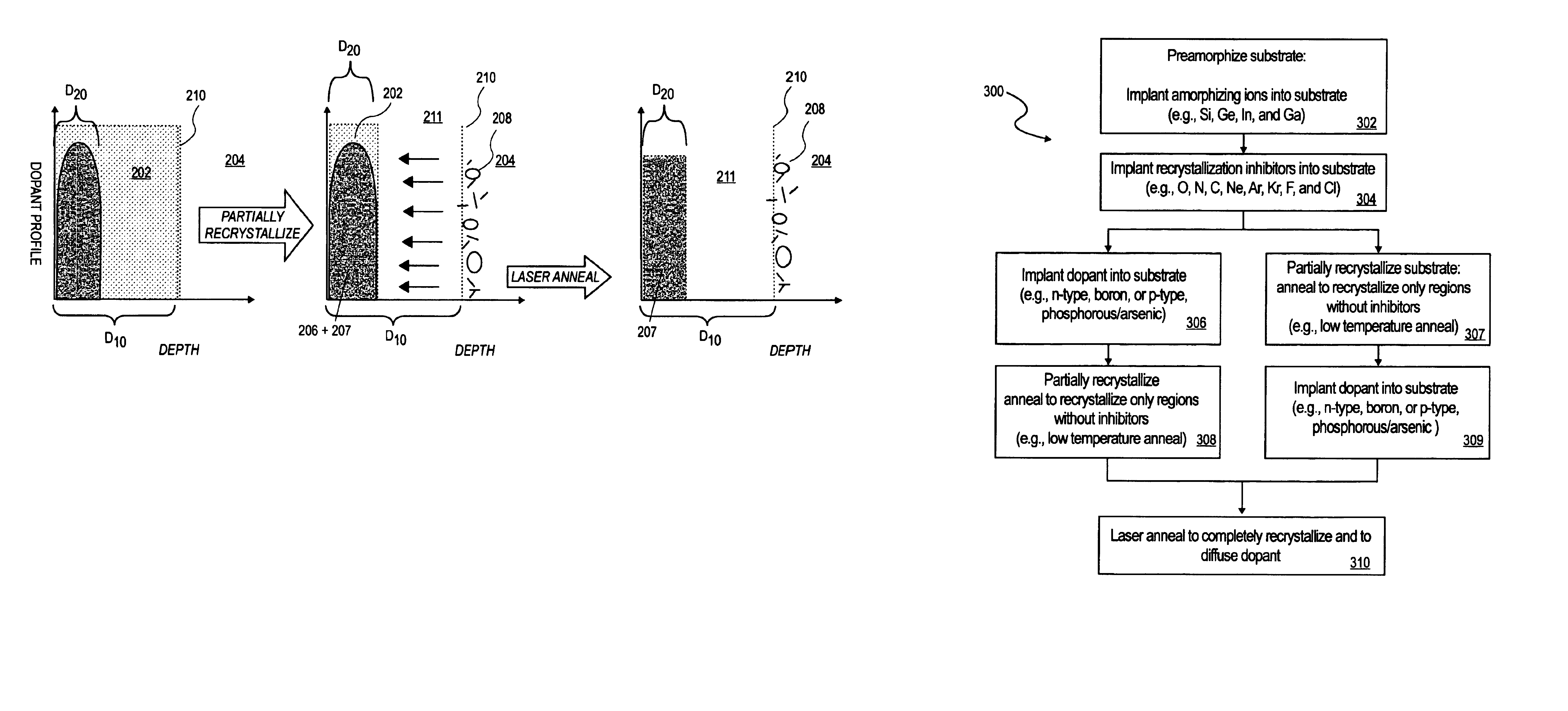

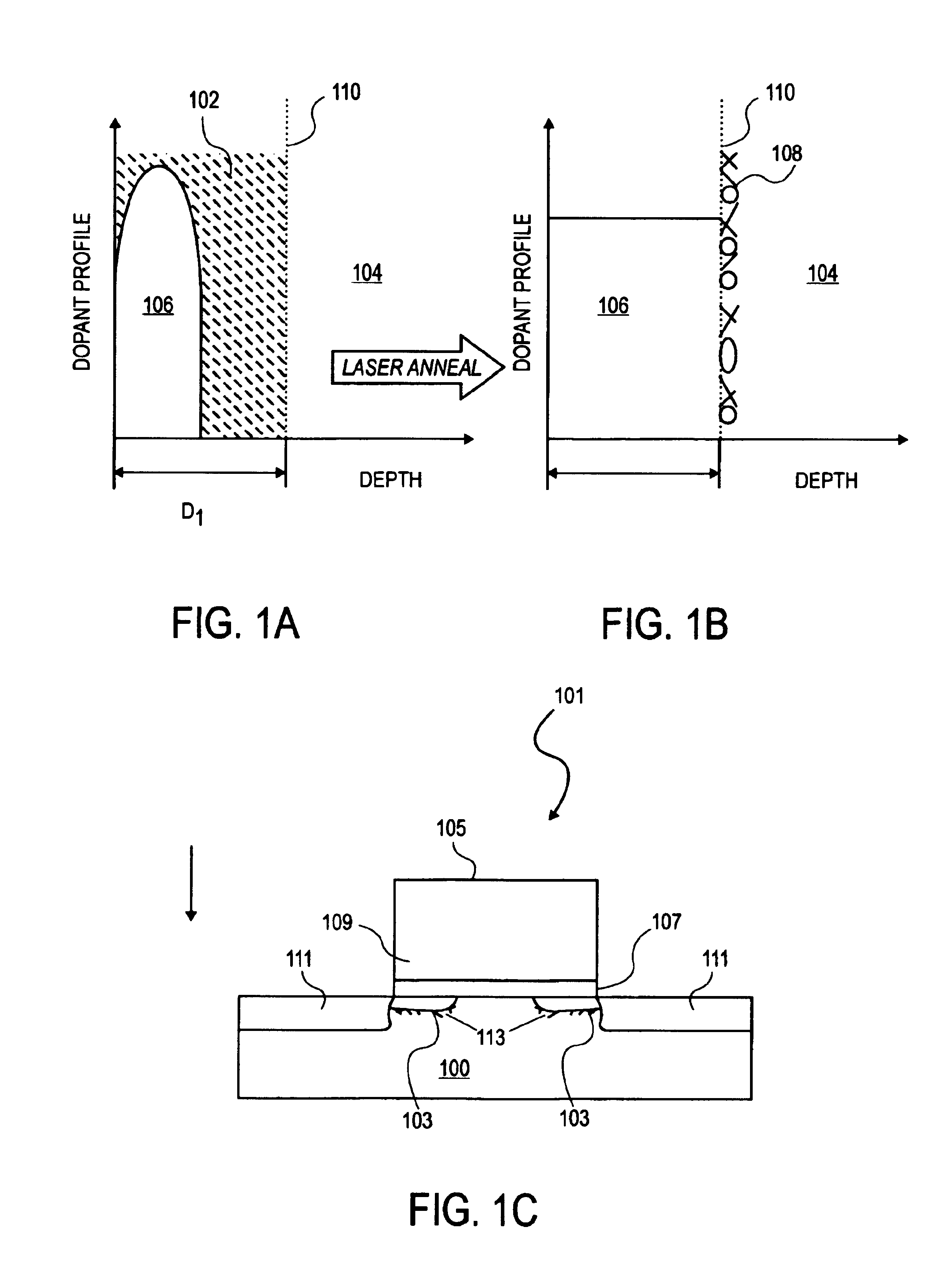

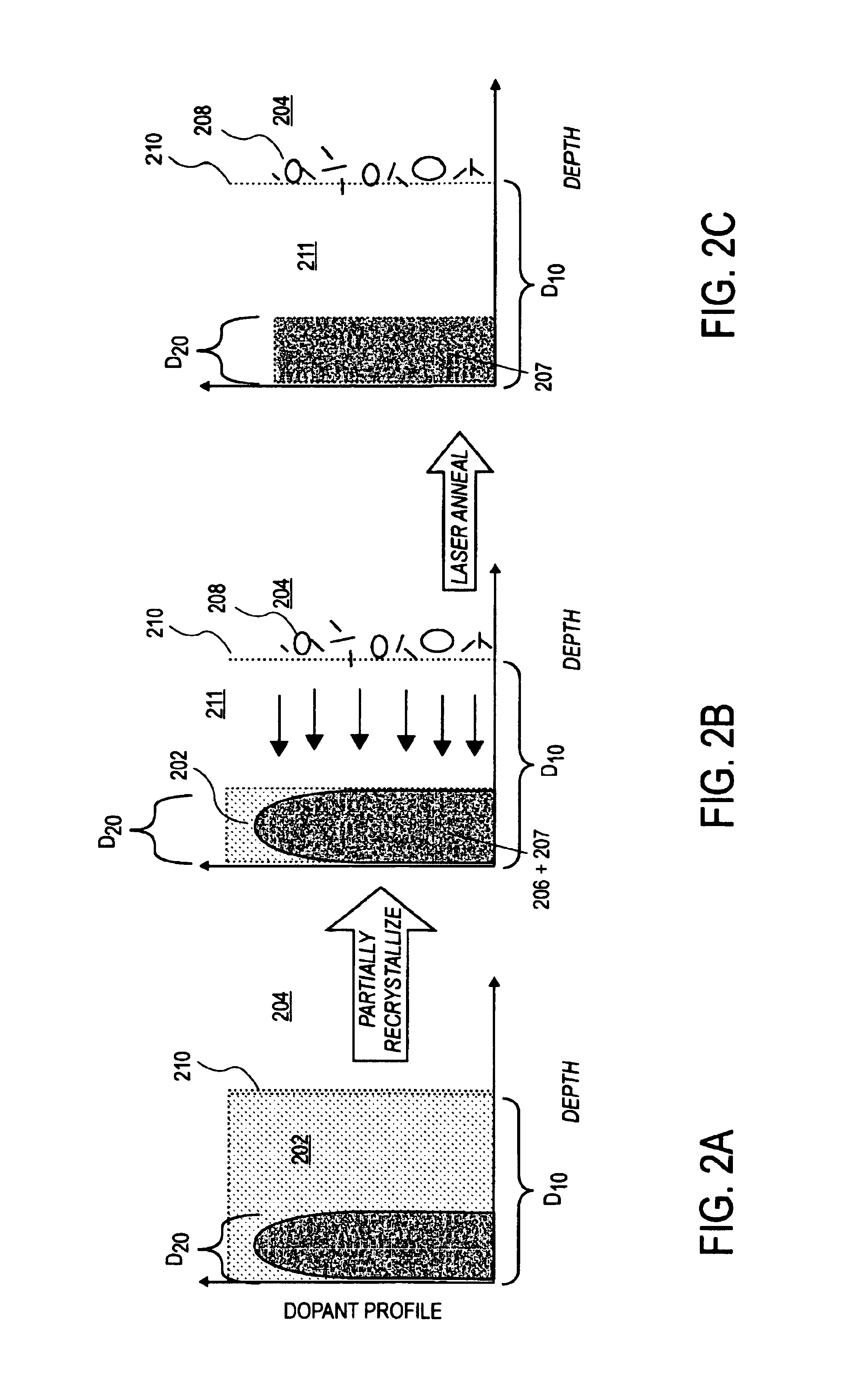

Method of forming a shallow junction

A method of forming a shallow junction in a semiconductor substrate is disclosed. The method of one embodiment comprises preamorphizing a first region of a semiconductor substrate to a first depth and implanting recrystallization inhibitors into a second region of the semiconductor substrate. The second region is a part of the first region and has a second depth. Next, a dopant is implanted into a third region of the semiconductor substrate with the third region being a part of the second region and a first annealing is performed to selectively recrystallize the first region that has no recrystallization inhibitors. Next, a second annealing is performed to recrystallize the second region and diffuse the dopant within the second region.

Owner:INTEL CORP

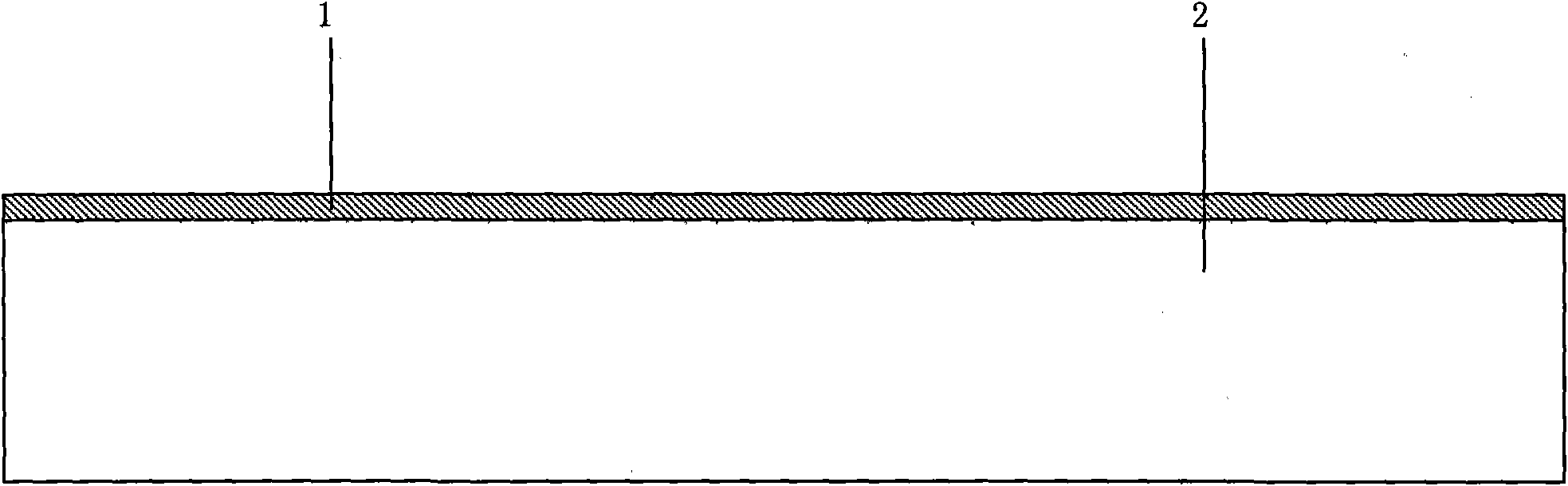

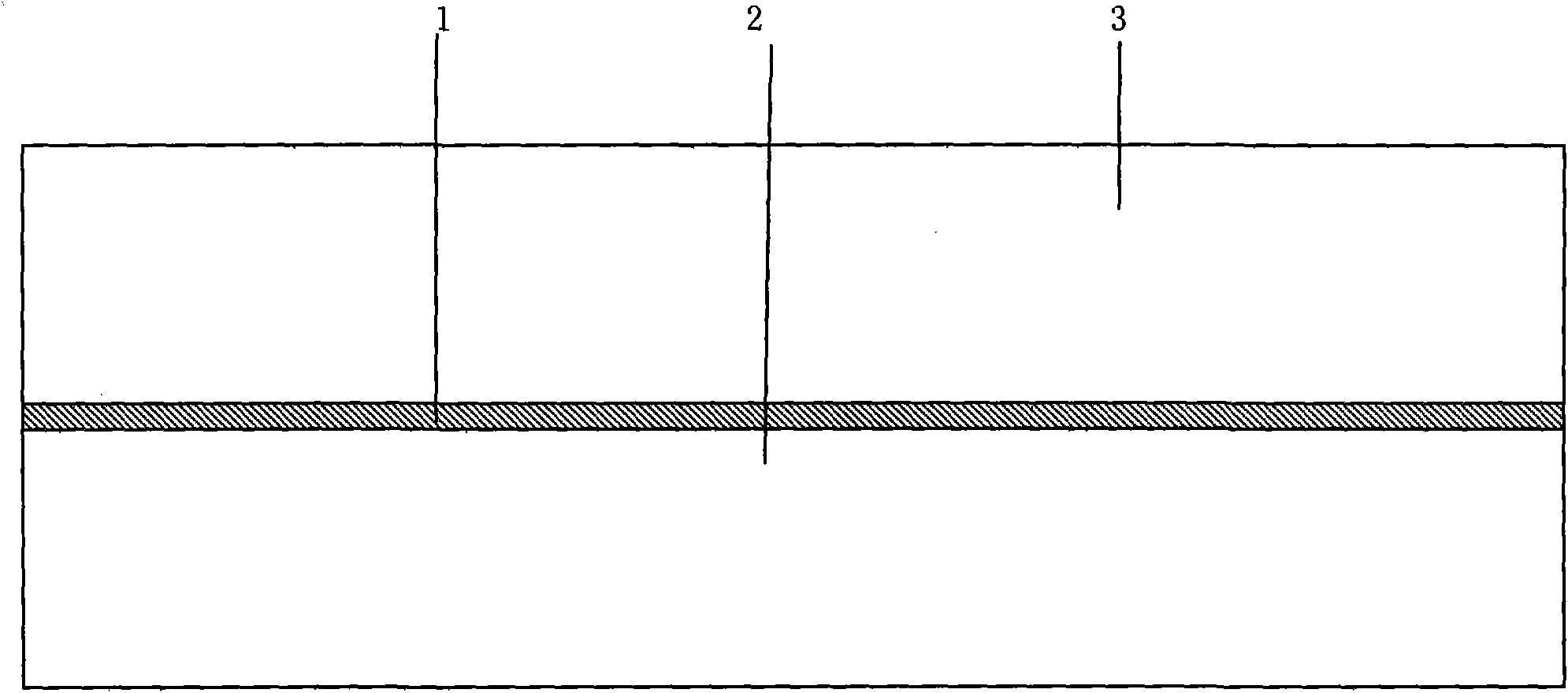

Germanium semiconductor device and method of manufacturing the same

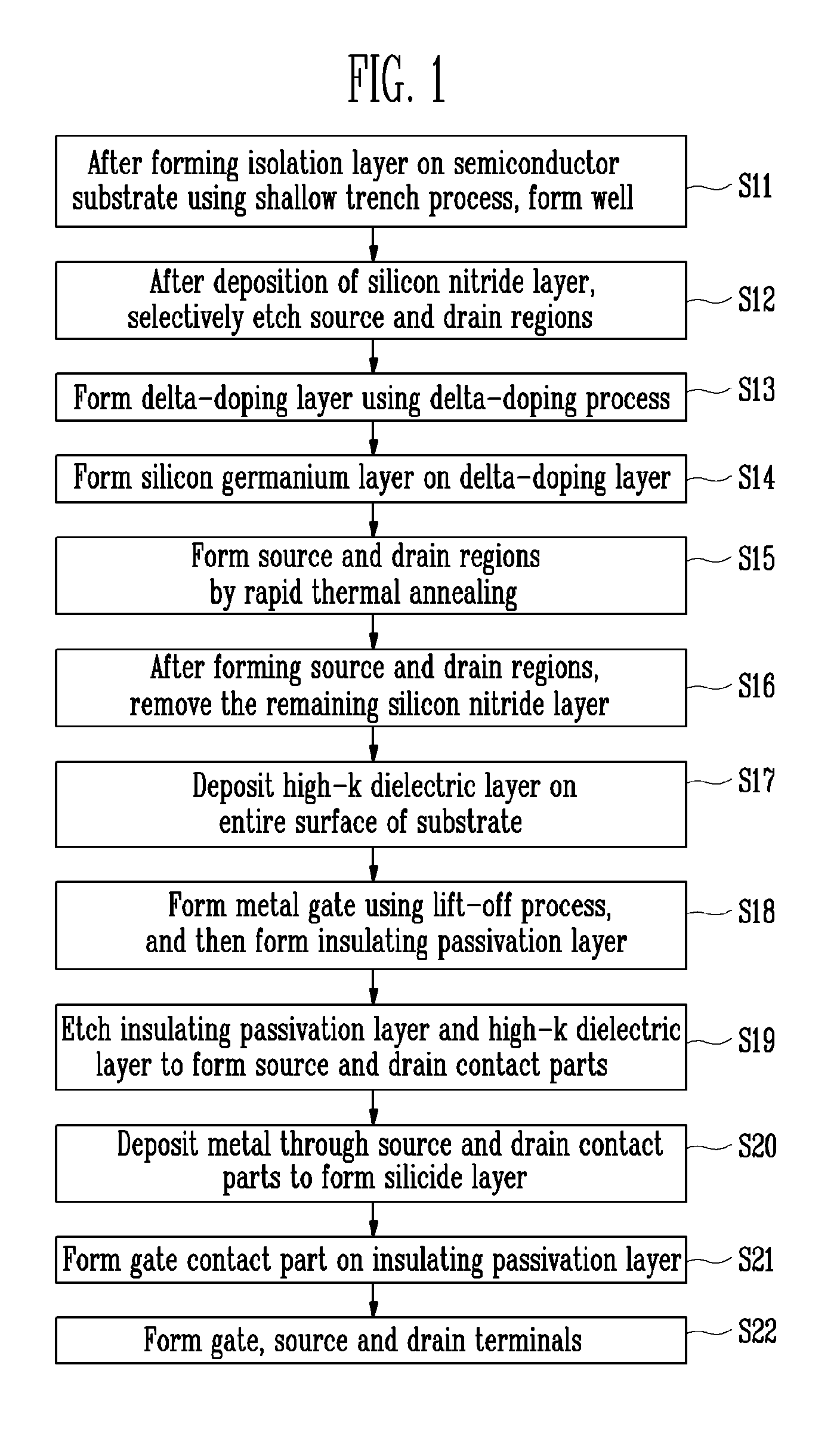

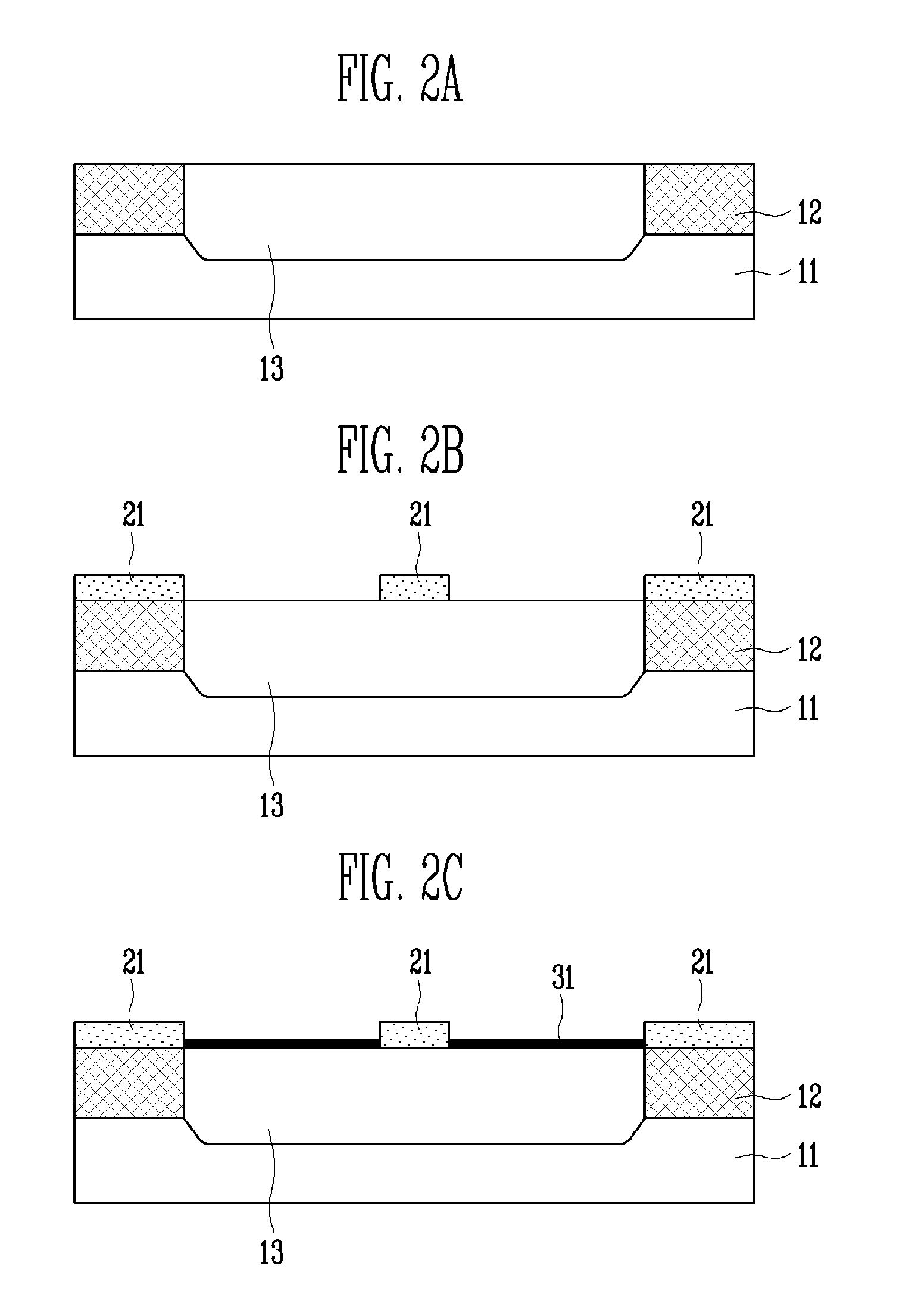

InactiveUS20080135878A1Reduce contact resistanceIncrease currentTransistorSolid-state devicesHigh concentrationDevice material

A germanium semiconductor device and a method of manufacturing the same are provided. The method includes the steps of: forming an isolation layer on a substrate using a shallow trench; forming a silicon-nitride layer on the substrate, and selectively etching the silicon nitride layer to expose source and drain regions; injecting impurities onto a surface of the substrate over the exposed source and drain regions using delta-doping to form a delta-doping layer; selectively growing a silicon germanium layer containing impurities on the delta-doping layer; rapidly annealing the substrate and forming source and drain regions by diffusion of the impurities; depositing an insulating layer on the entire surface of the substrate; etching the insulating layer and forming source and drain contact parts to be in contact with source and drain terminals; depositing metal over the insulating layer having the source and drain contact parts thereon and forming a metal silicide layer; and after forming the silicide layer, forming the source and drain terminals to be in contact with the silicide layer. Accordingly, the source and drain regions having a shallow junction depth may be ensured by forming the source and drain regions through annealing after delta-doping and selectively growing the silicon germanium layer containing high-concentration impurities. Also, the germanium silicide layer is stably formed by the silicon germanium layer grown in the source and drain regions, and thus contact resistance is lowered and driving current of the device is improved.

Owner:ELECTRONICS & TELECOMM RES INST +1

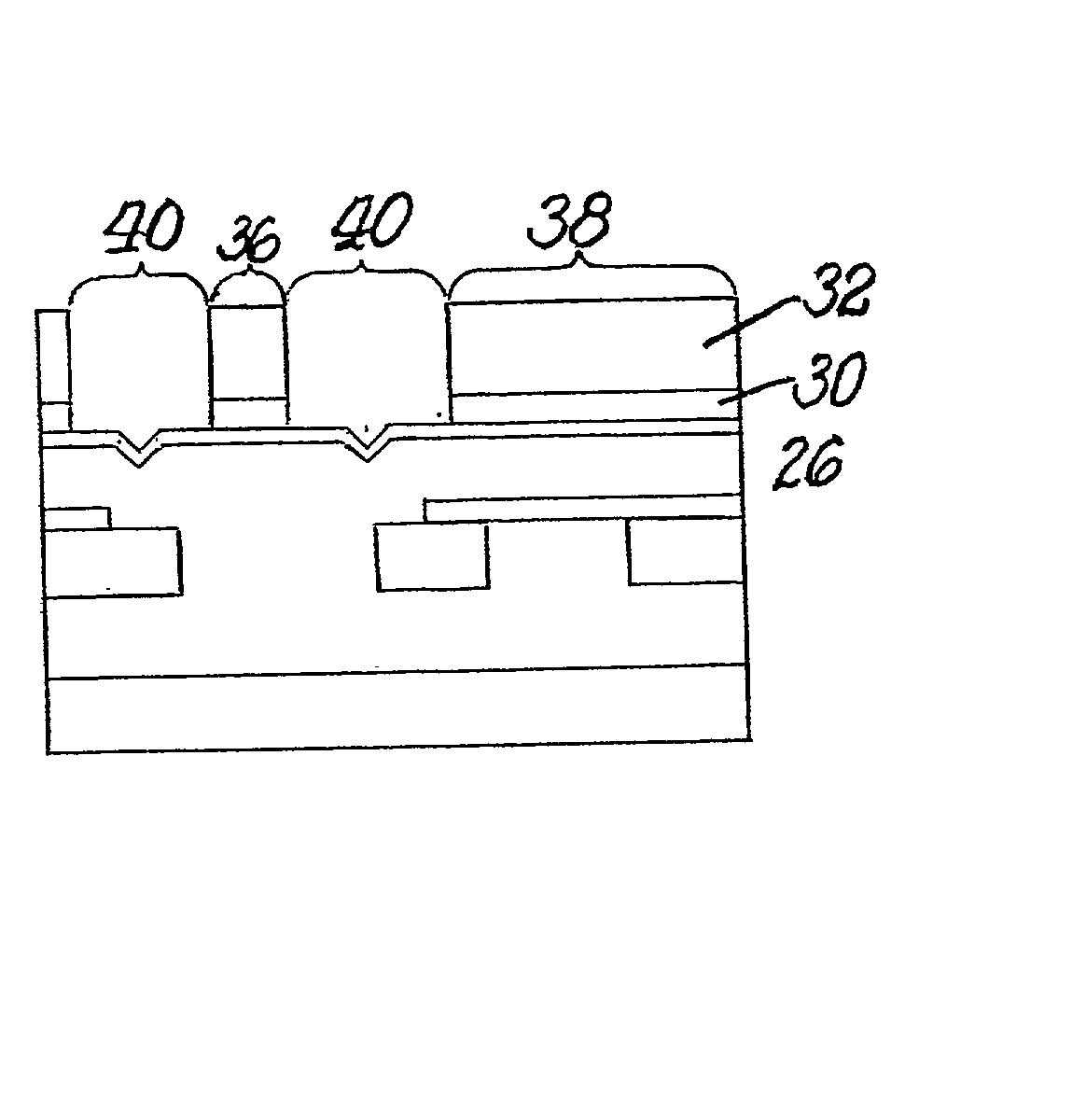

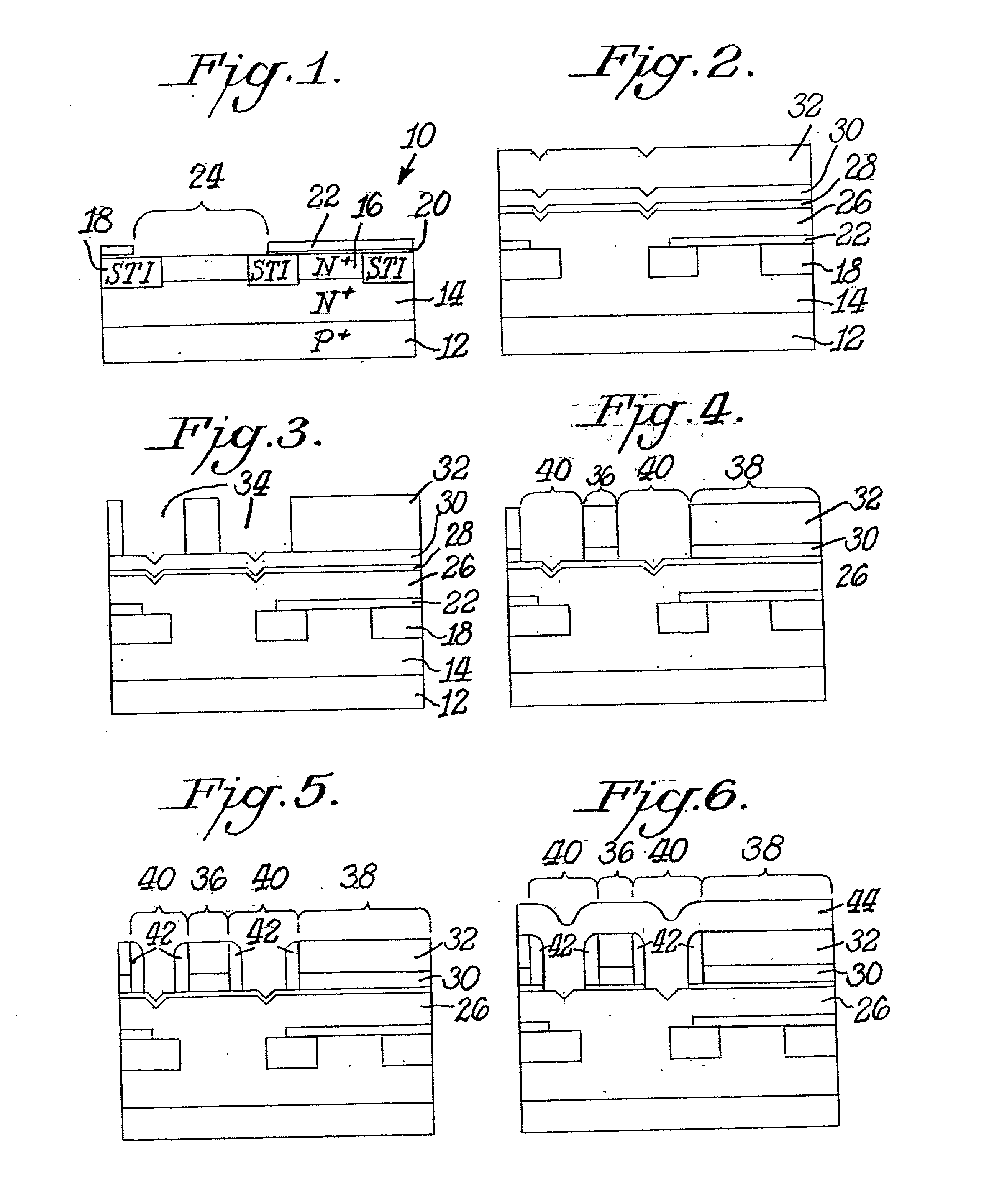

Bipolar device having shallow junction raised extrinsic base and method for making the same

A raised extrinsic base, silicon germanium (SiGe) heterojunction bipolar transistor (HBT), and a method of making the same is disclosed herein. The heterojunction bipolar transistor includes a substrate, a silicon germanium layer formed on the substrate, a collector layer formed on the substrate, a raised extrinsic base layer formed on the silicon germanium layer, and an emitter layer formed on the silicon germanium layer. The silicon germanium layer forms a heterojunction between the emitter layer and the raised extrinsic base layer. The bipolar transistor further includes a base electrode formed on a portion of the raised extrinsic base layer, a collector electrode formed on a portion of the collector layer, and an emitter electrode formed on a portion of the emitter layer. Thus, the heterojunction bipolar transistor includes a self-aligned raised extrinsic base, a minimal junction depth, and minimal interstitial defects influencing the base width, all being formed with minimal thermal processing. The heterojunction bipolar transistor simultaneously improves three factors that affect the speed and performance of bipolar transistors: base width, base resistance, and base-collector capacitance.

Owner:INTELLECTUAL DISCOVERY INC

Methods of implanting ions and ion sources used for same

Methods of ion implantation and ion sources used for the same are provided. The methods involve generating ions from a source feed gas that comprises multiple elements. For example, the source feed gas may comprise boron and at least two other elements (e.g., XaBbYc). The use of such source feed gases can lead to a number of advantages over certain conventional processes including enabling use of higher implant energies and beam currents when forming implanted regions having ultra-shallow junction depths. Also, in certain embodiments, the composition of the source feed gas may be selected to be thermally stable at relatively high temperatures (e.g., greater than 350° C.) which allows use of such gases in many conventional ion sources (e.g., indirectly heated cathode (IHC), Bernas) which generate such temperatures during use.

Owner:VARIAN SEMICON EQUIP ASSOC INC

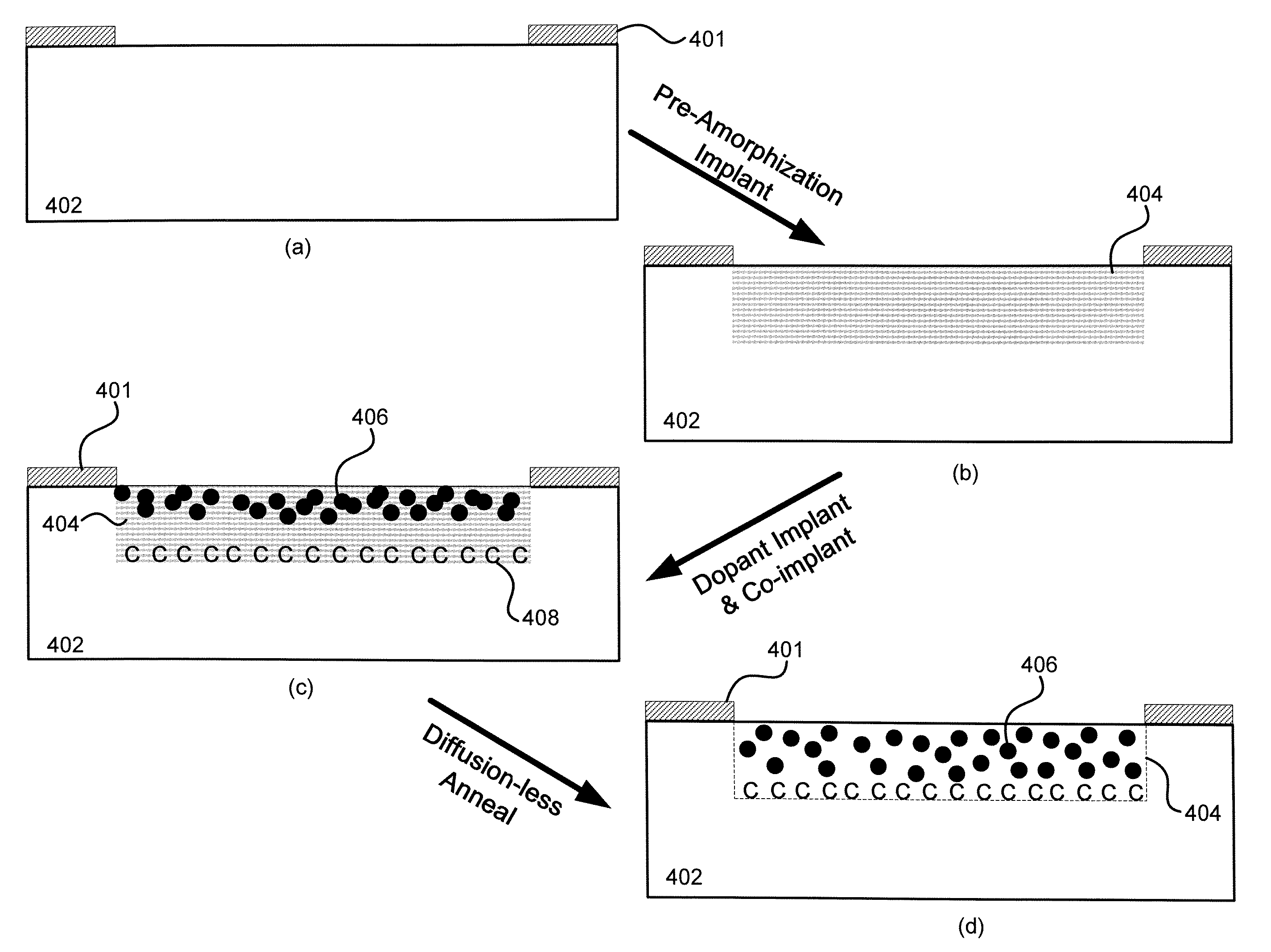

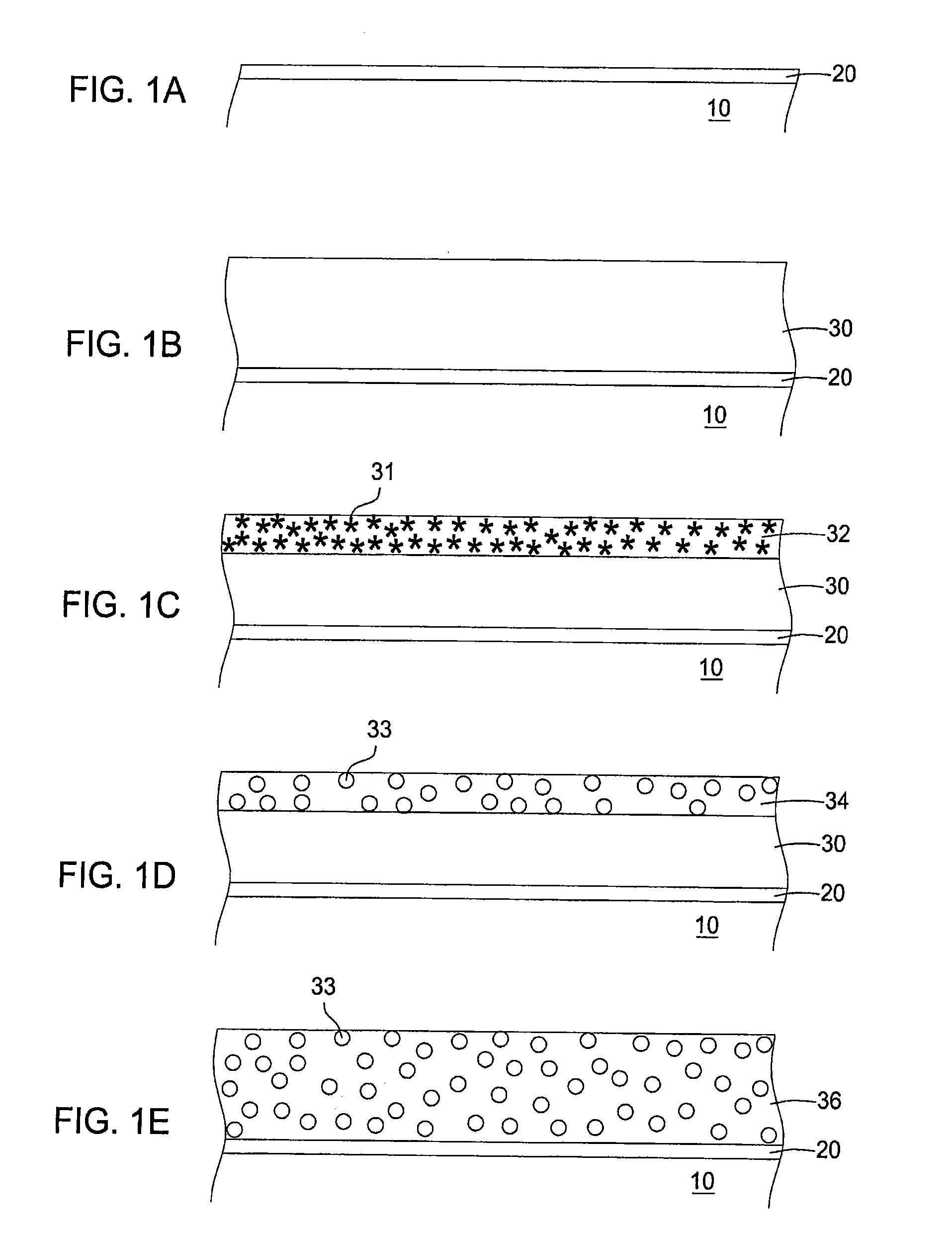

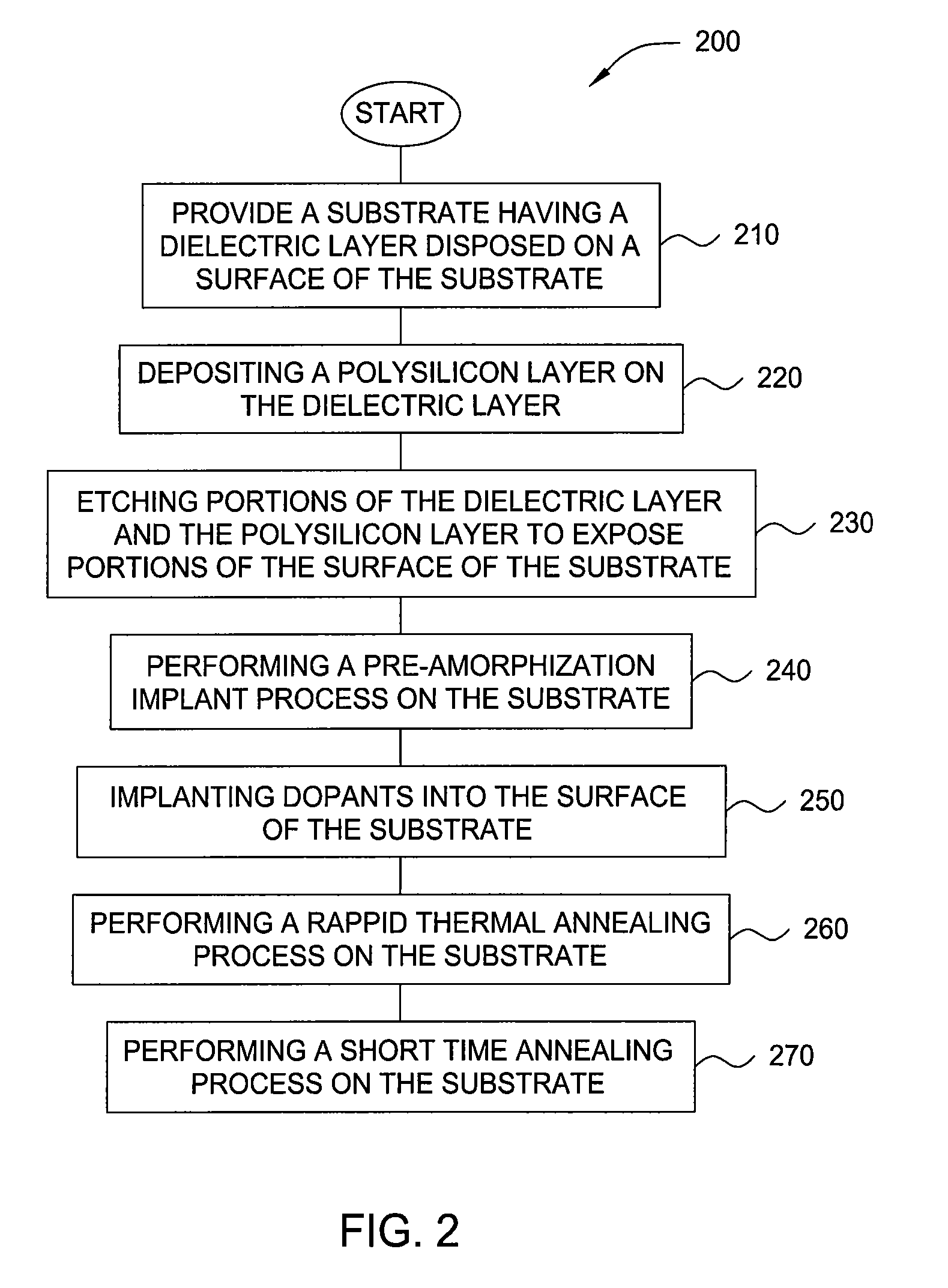

Use of carbon co-implantation with millisecond anneal to produce ultra-shallow junctions

InactiveUS20080023732A1Short timeShort time thermal annealTransistorSemiconductor/solid-state device manufacturingDopantRapid thermal annealing

Embodiments of the present invention include methods for forming an ultra-shallow junction in a substrate. In one embodiment, the method includes providing a silicon substrate, co-implanting the silicon substrate with carbon and a dopant to form a doped silicon substrate, and exposing the silicon substrate to a short time thermal anneal. In certain embodiments, the silicon substrate is exposed to a rapid thermal anneal after co-implanting the silicon substrate but prior to exposing the silicon substrate to a short time thermal anneal. In certain embodiments, the pre-amorphization implant is performed on the silicon substrate prior to implanting the silicon substrate with carbon and a dopant. In certain embodiments, the silicon substrate is a monocrystalline silicon substrate.

Owner:APPLIED MATERIALS INC

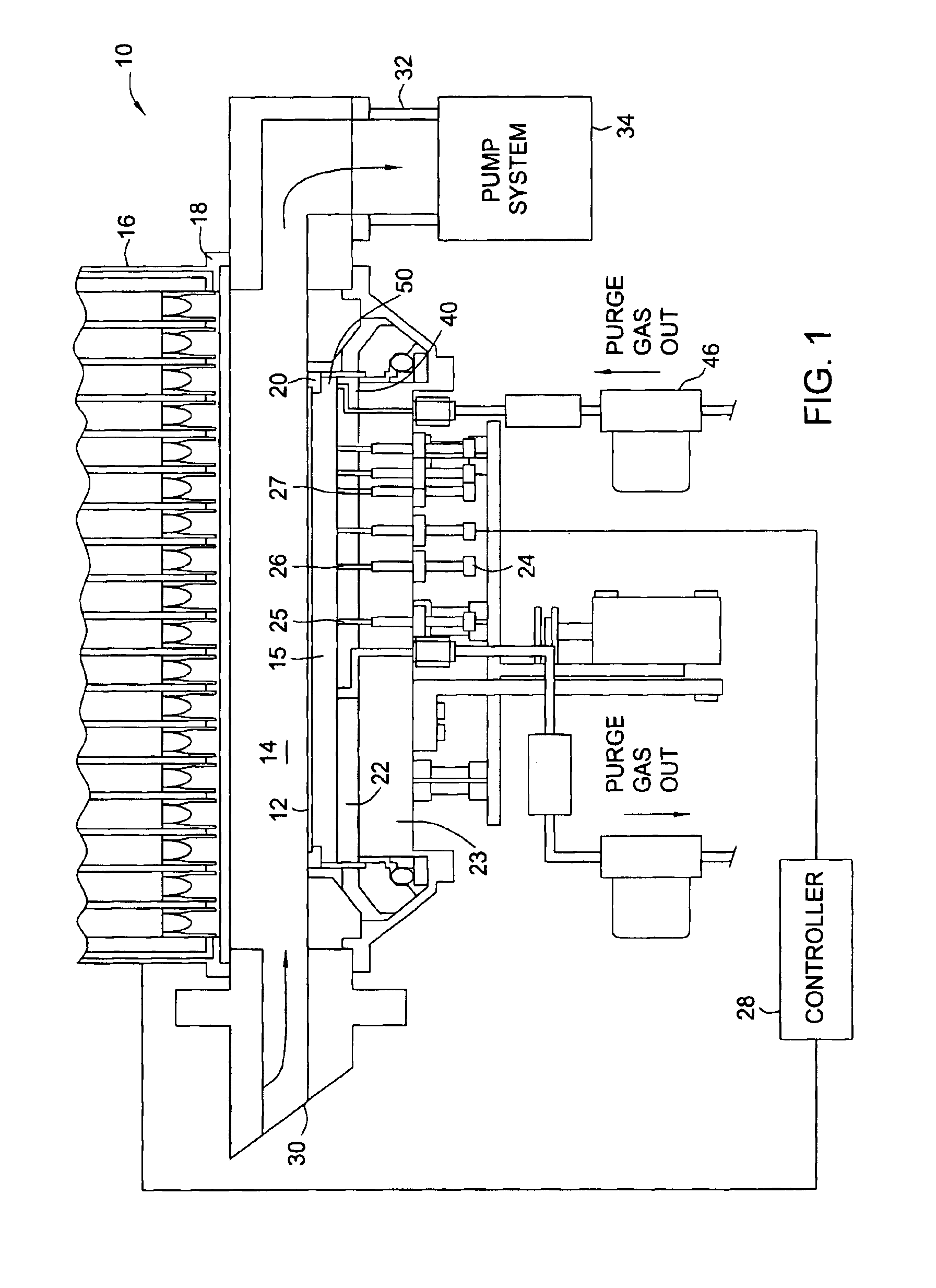

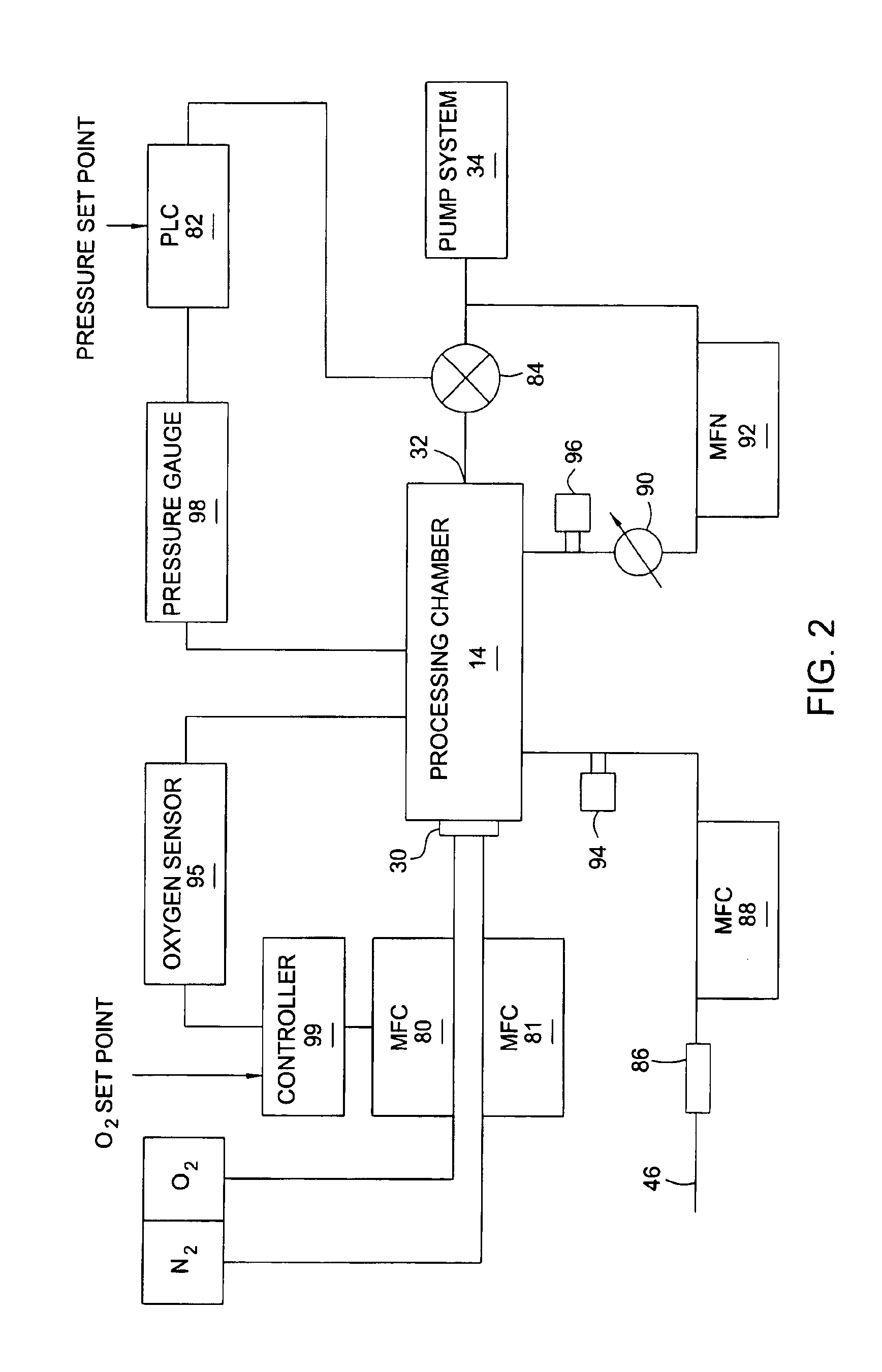

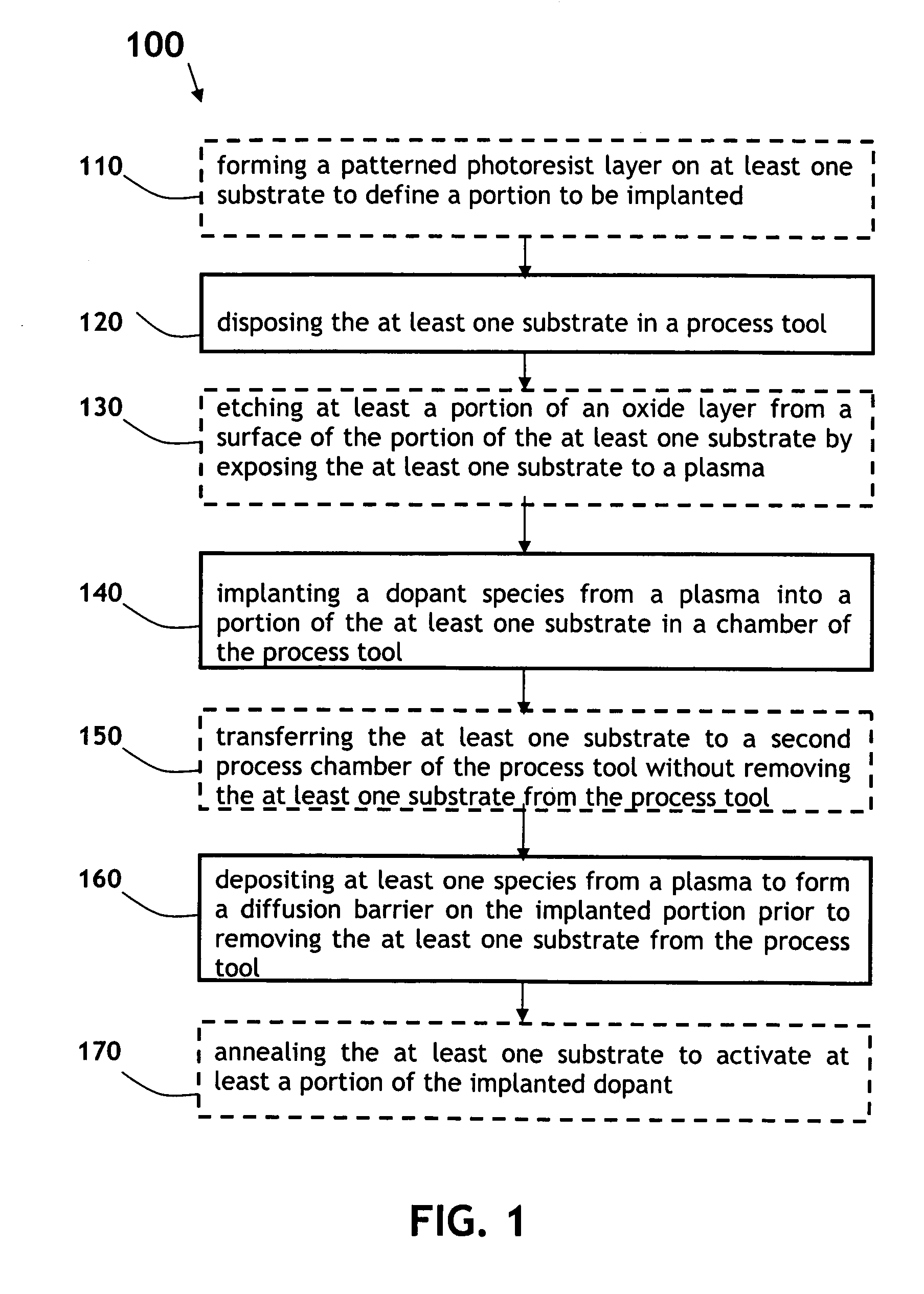

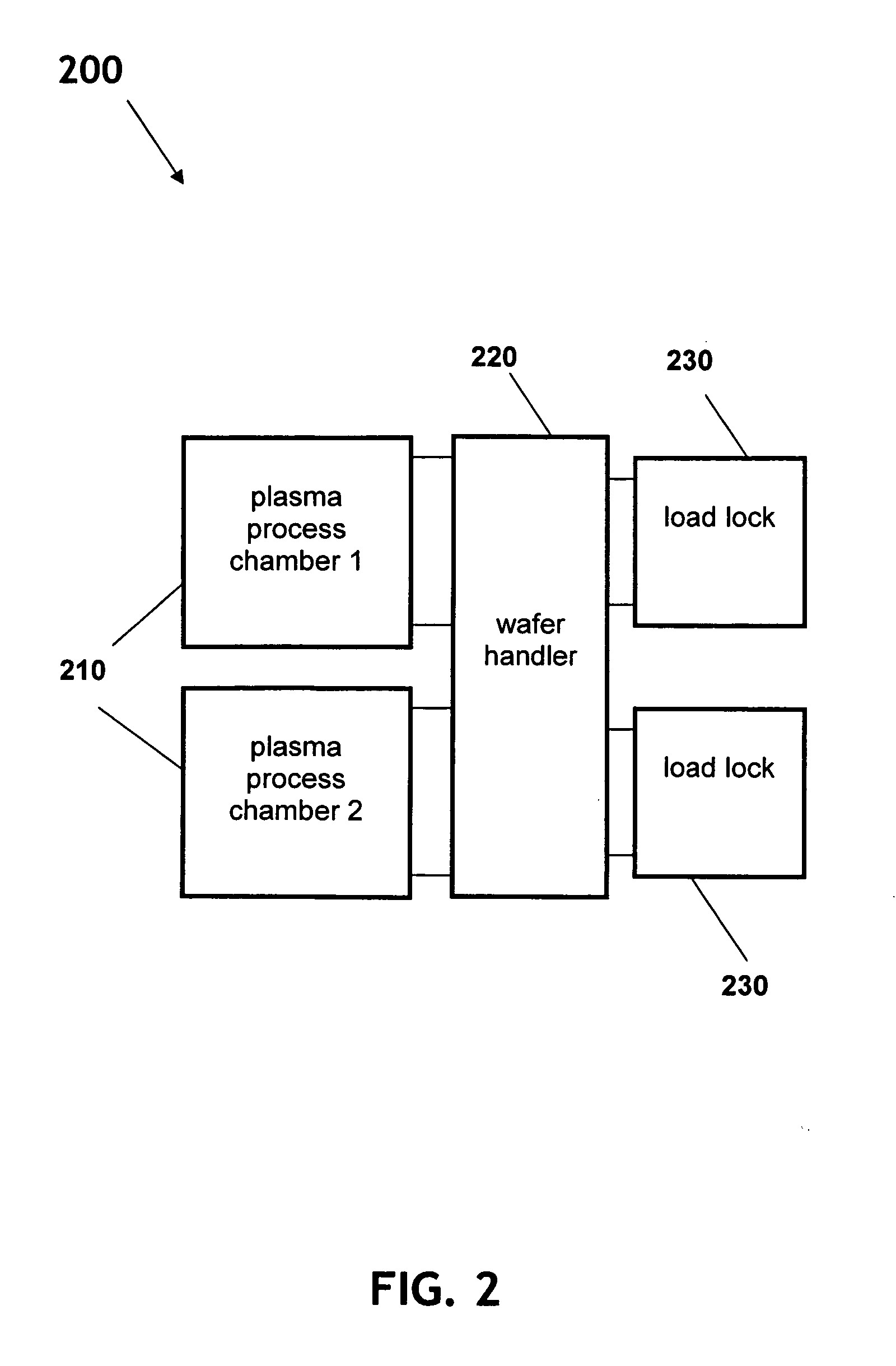

Shallow-junction fabrication in semiconductor devices via plasma implantation and deposition

InactiveUS20060205192A1Reduce lossesInhibition formationTransistorSemiconductor/solid-state device manufacturingDopantDevice material

A method for fabricating a semiconductor-based device includes disposing a substrate in a process chamber of a process tool, plasma implanting a dopant species from a plasma into a portion of the substrate in the process chamber, and plasma depositing a diffusion barrier on the implanted portion of the substrate prior to removing the at least one substrate from the process tool. The diffusion barrier can be deposited in the same chamber as that used for dopant implantation or a different chamber of the process tool.

Owner:VARIAN SEMICON EQUIP ASSOC INC

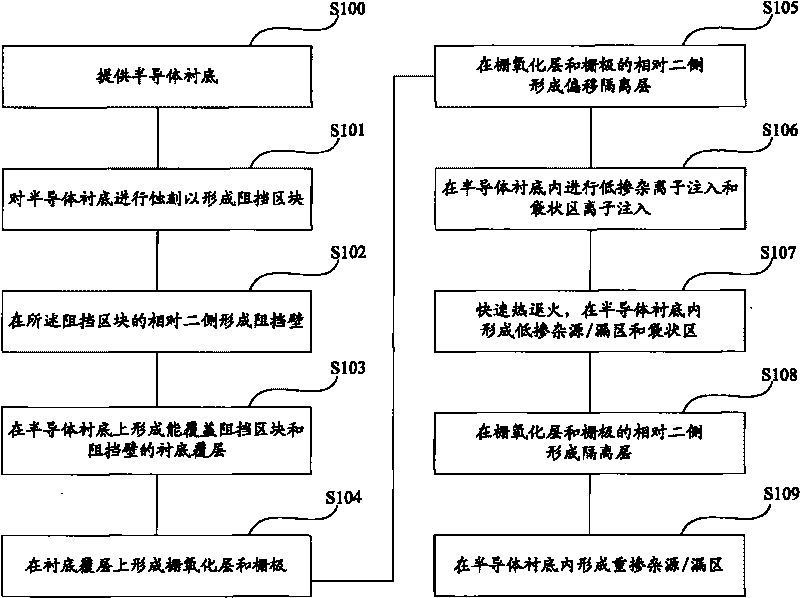

Semiconductor device and manufacture method thereof

InactiveCN101740393AInterpenetration barrierImprove short channel effectSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceRapid thermal annealing

The invention relates to a semiconductor device and a manufacture method thereof, wherein the manufacture method comprises the following steps of: providing a semiconductor underlay; etching the semiconductor underlay so as to form a barrier region block; forming barrier walls at both sides of the barrier region block; forming an underlay coating on the semiconductor underlay, wherein the barrier walls and the surface of the underlay coating have fall; forming a gate oxide and a grid electrode on the underlay coating and the semiconductor underlay; carrying out low-doping ion implantation in the semiconductor underlay; carrying out rapid thermal annealing to form a low-doping source / drain region in the semiconductor underlay; forming isolation layers at opposite sides of the gate oxide and the grid electrode; and forming a heavy-doping source / drain region in the semiconductor underlay. The invention has technical scheme that the barrier walls are formed in the semiconductor underlay, thereby effectively separating the interpenetration between the source region and the drain region, obviously improving the short channel effect of the semiconductor device, avoiding the generation of a punch-through effect between the source region and the drain region and improving the electrical behaviour of the semiconductor device. Meanwhile, a bigger process regulating space is provided for the reduction of junction capacitance and the enlargement of process window in the ultra shallow junction process.

Owner:SEMICON MFG INT (SHANGHAI) CORP

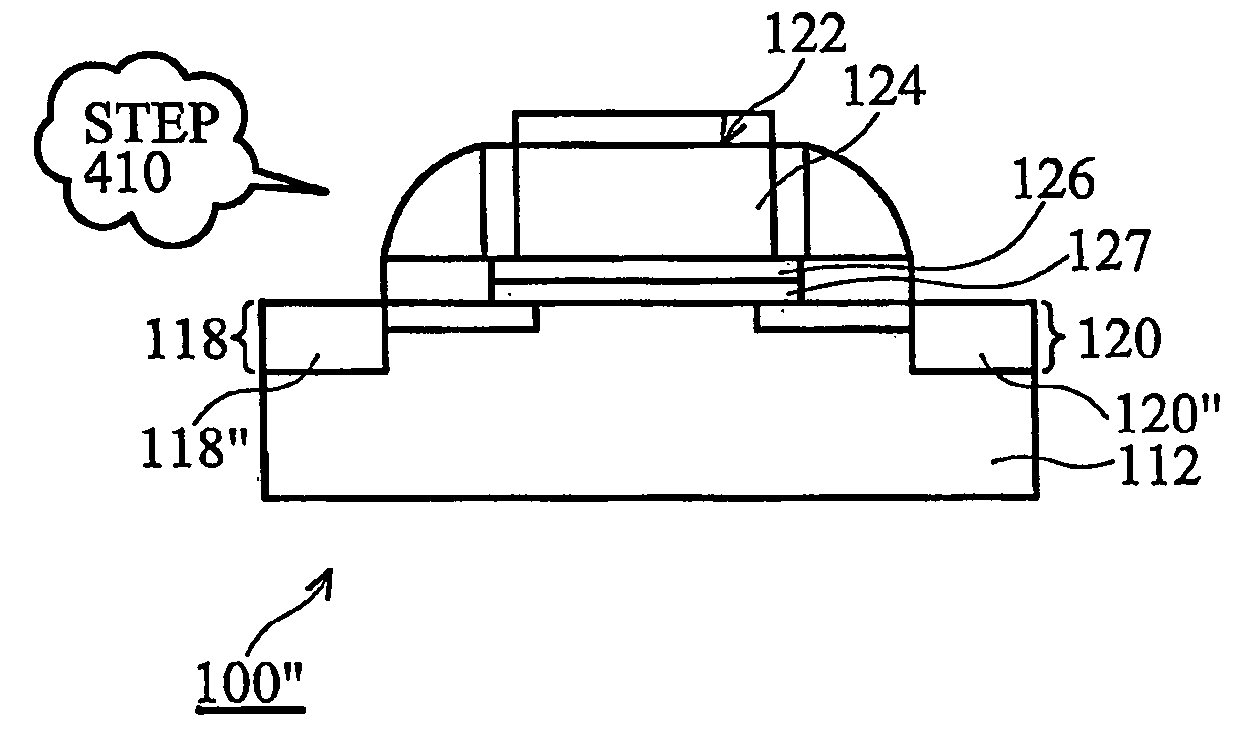

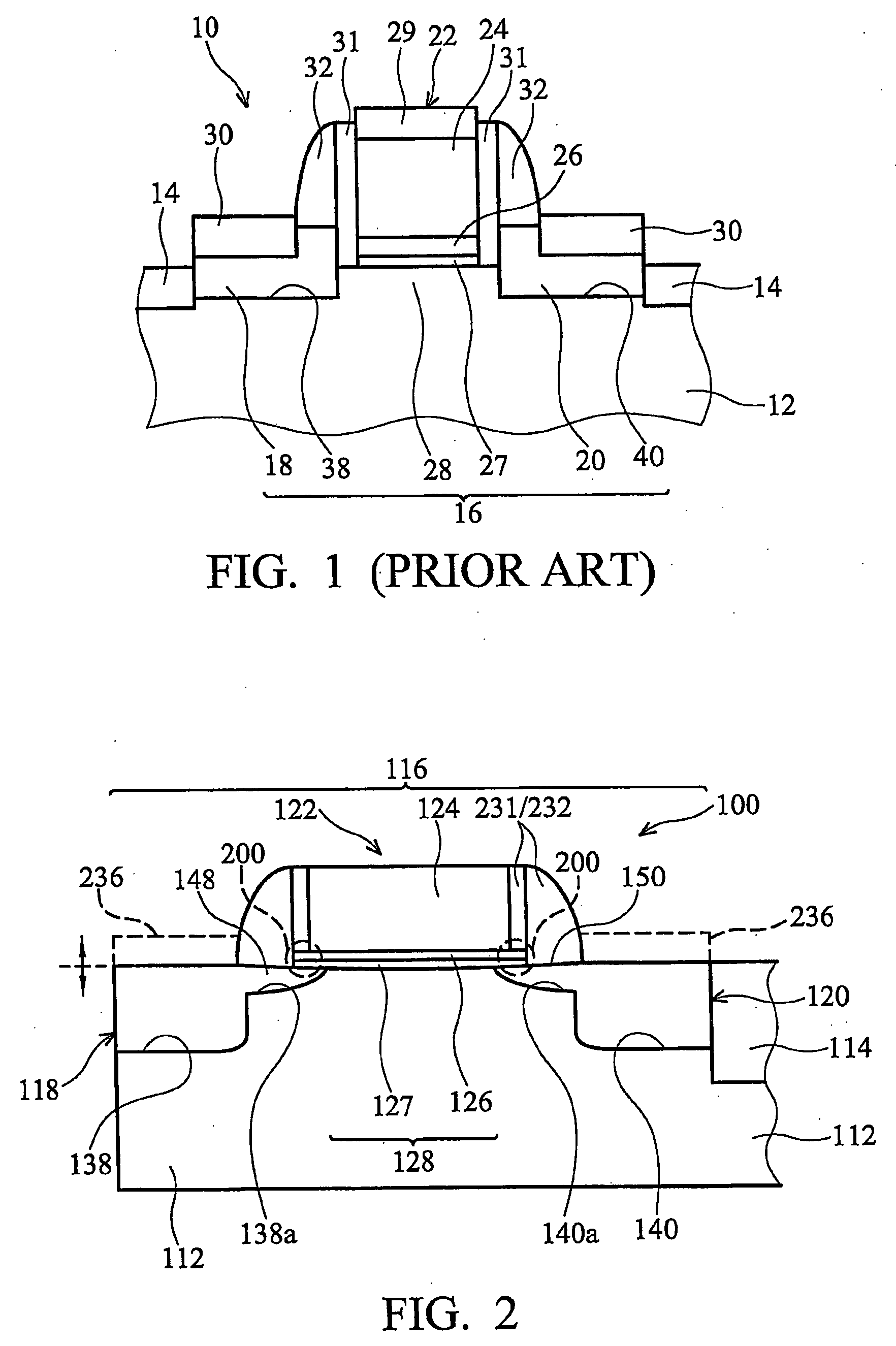

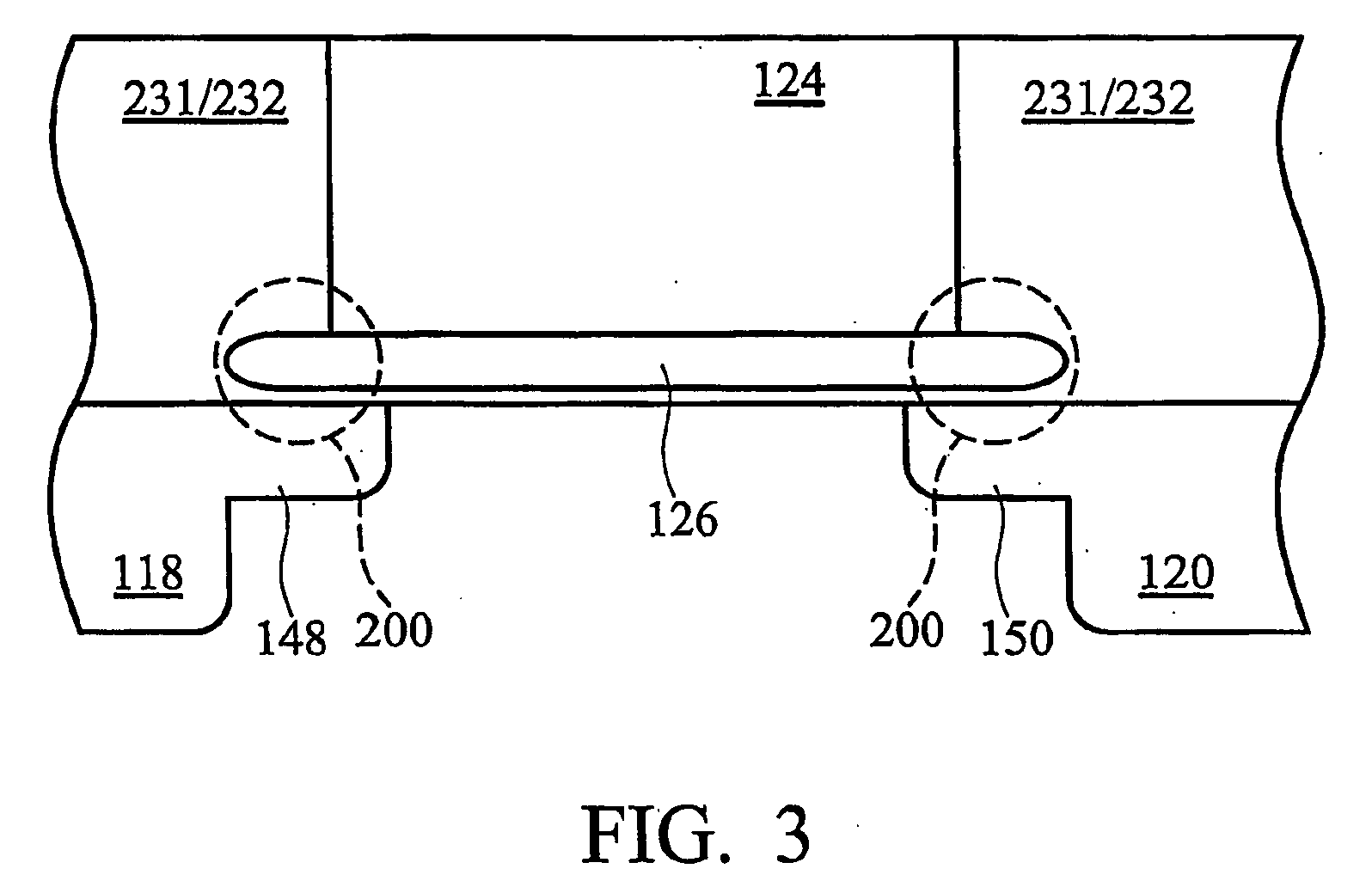

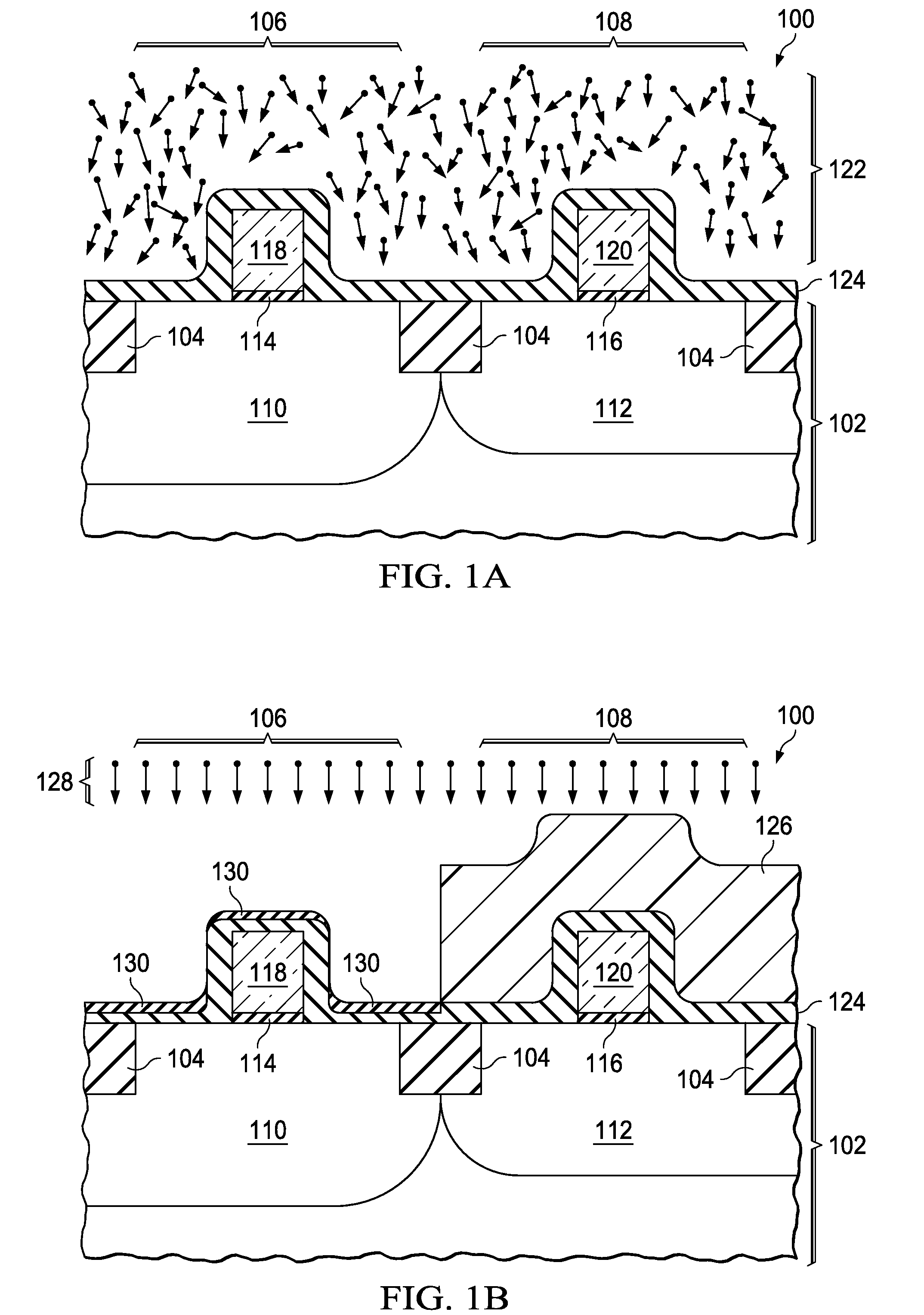

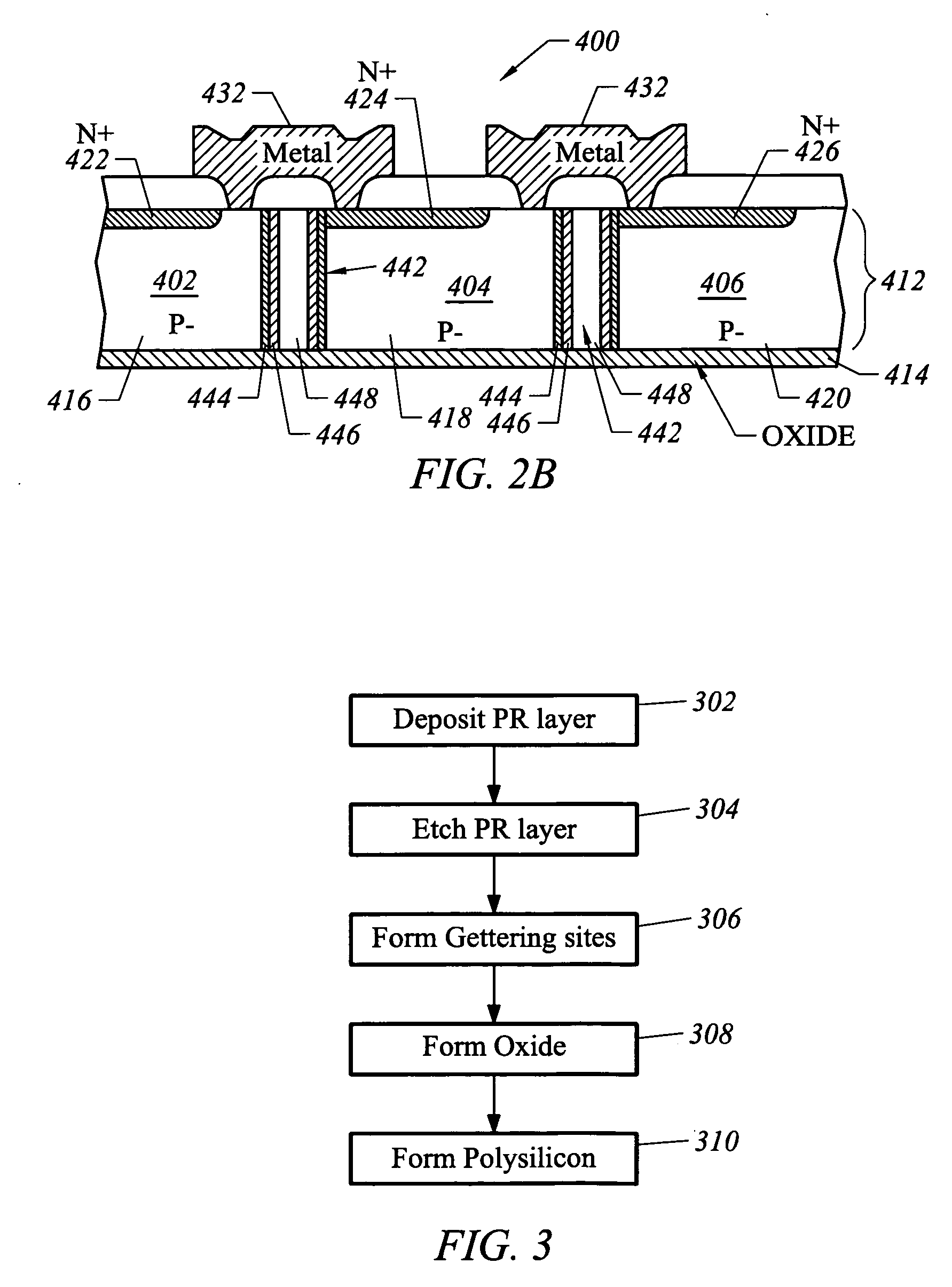

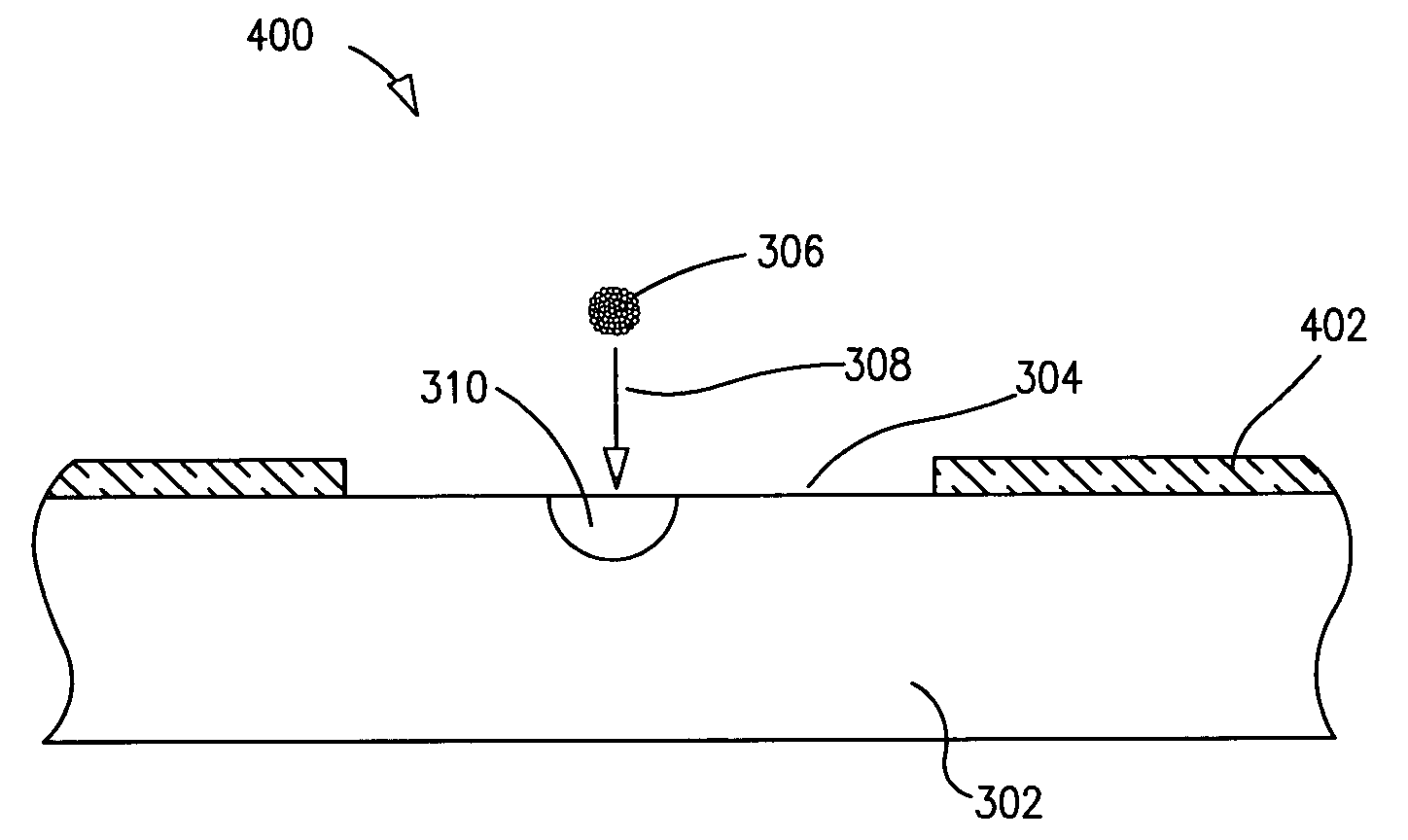

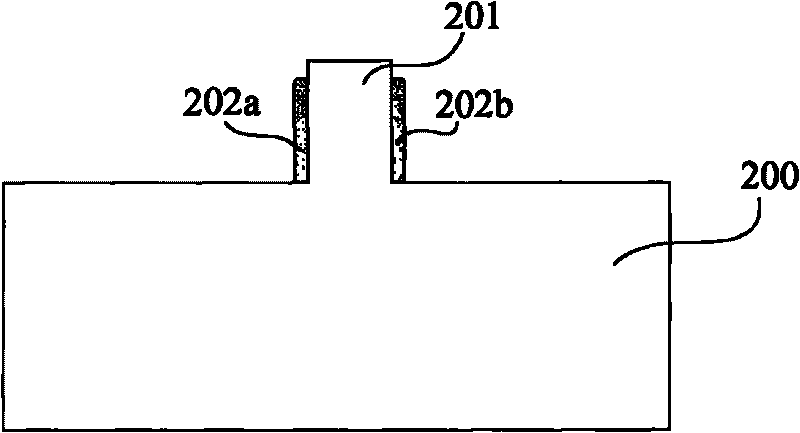

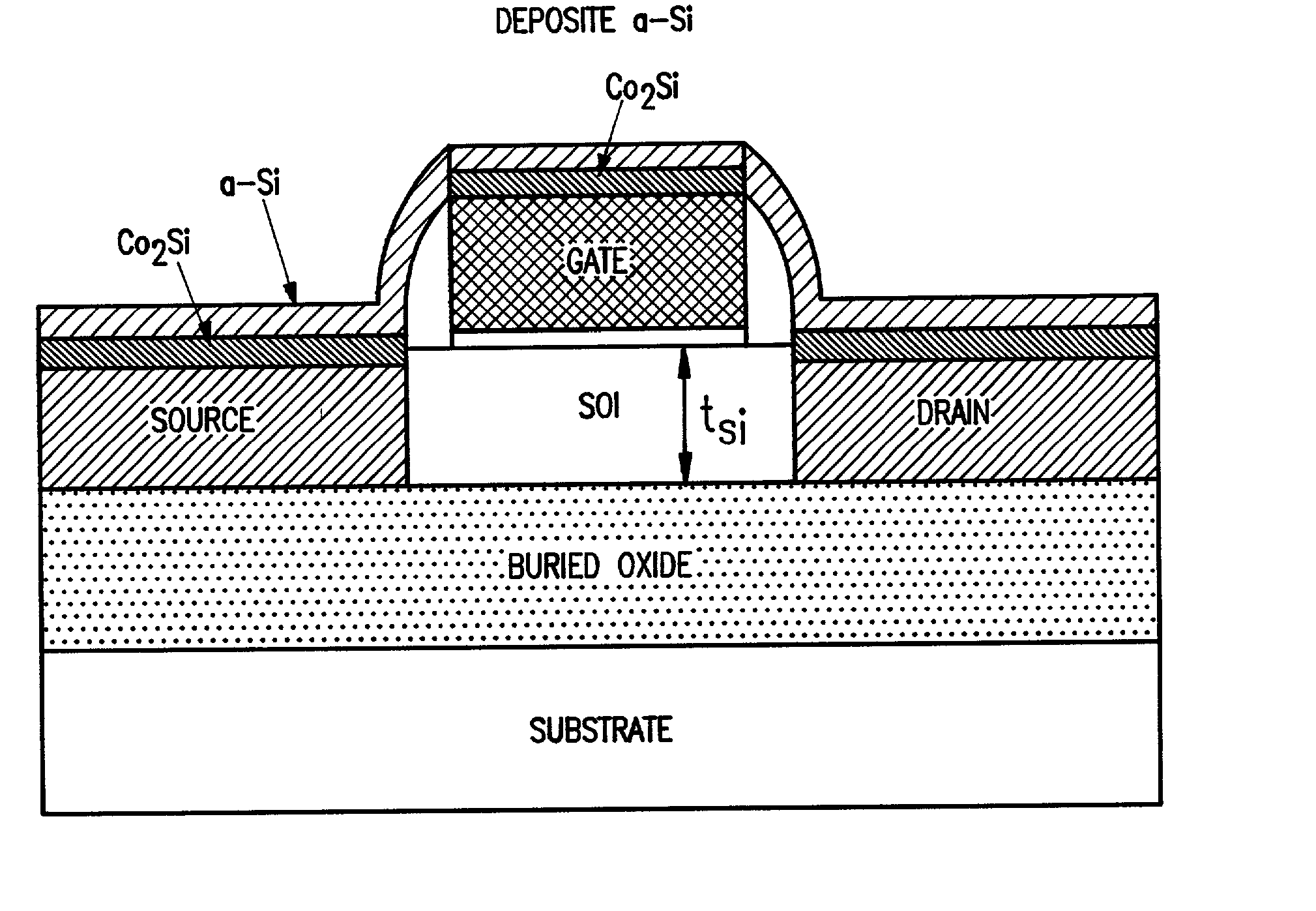

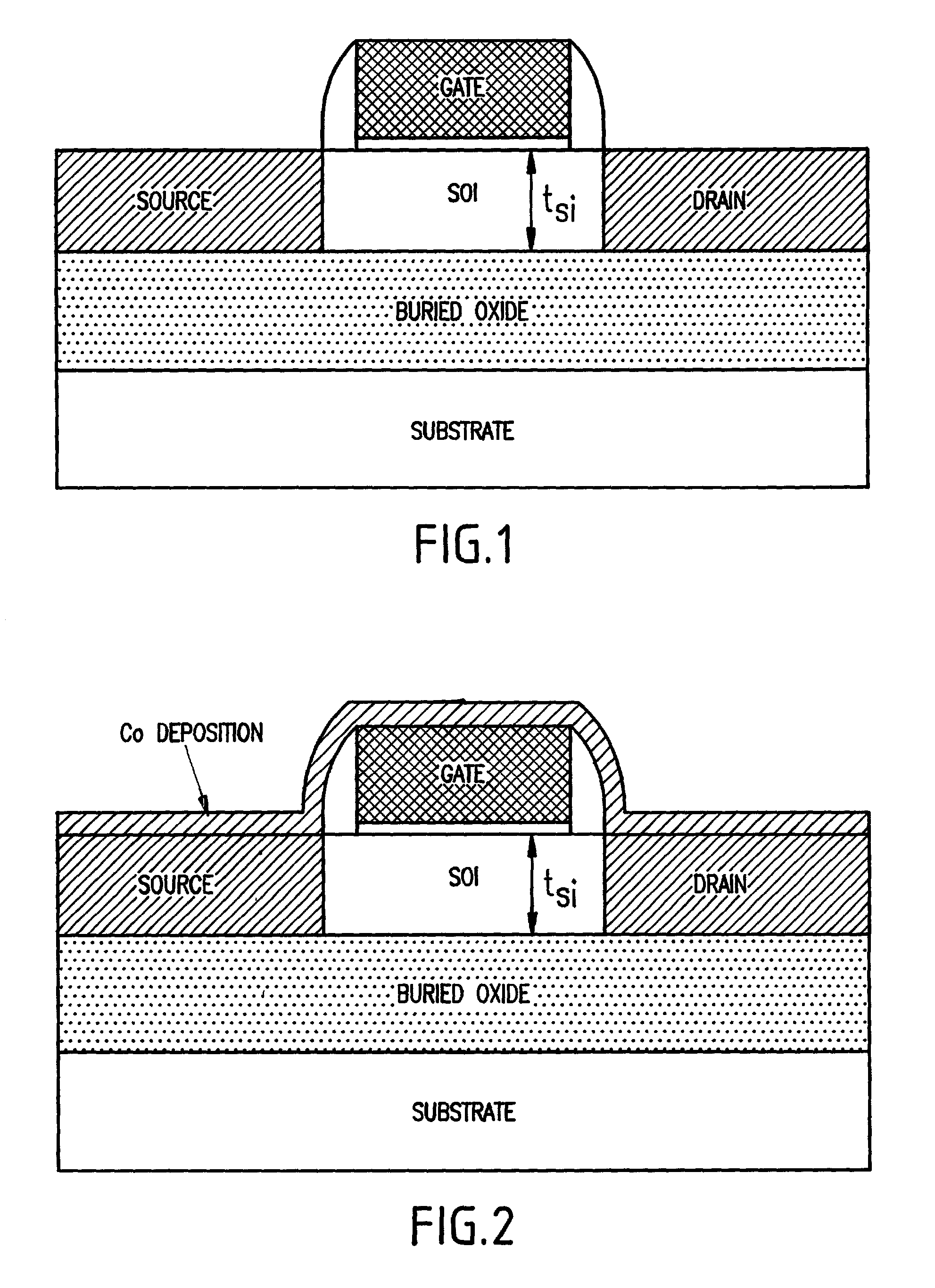

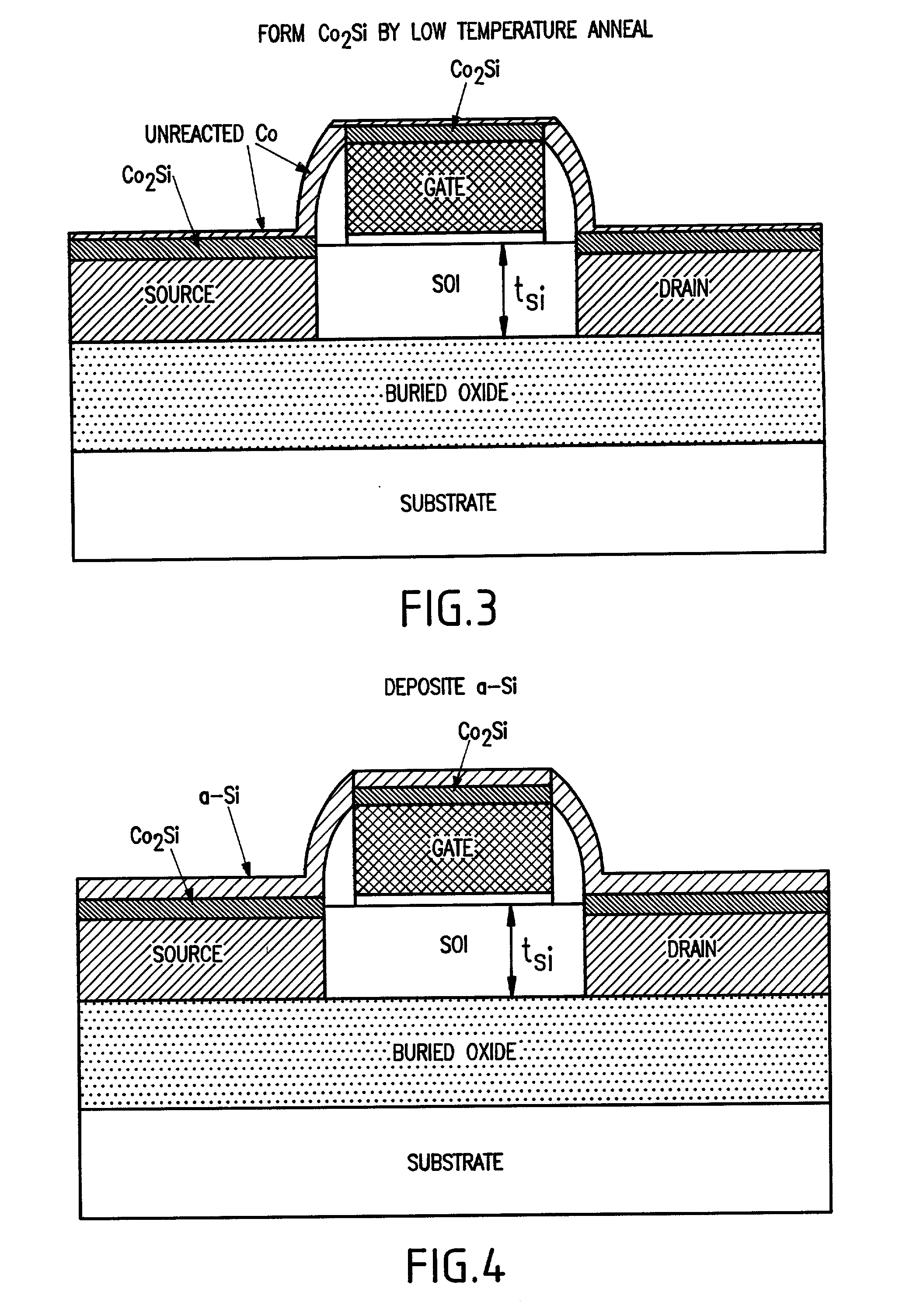

Self-aligned silicide (salicide) process for low resistivity contacts to thin film silicon-on-insulator and bulk MOSFETS and for shallow Junctions

A method (and resulting structure) for fabricating a silicide for a semiconductor device, includes depositing a metal or an alloy thereof on a silicon substrate, reacting the metal or the alloy to form a first silicide phase, etching any unreacted metal, depositing a silicon cap layer over the first silicide phase, reacting the silicon cap layer to form a second silicide phase, for the semiconductor device, and etching any unreacted silicon. The substrate can be either a silicon-on-insulator (SOI) substrate or a bulk silicon substrate.

Owner:IBM CORP

Formation of doped regions and/or ultra-shallow junctions in semiconductor materials by gas-cluster ion irradiation

ActiveUS7410890B2Electric discharge tubesVacuum evaporation coatingSemiconductor materialsGas cluster ion beam

Owner:TEL EPION

Ultra-Shallow Junctions using Atomic-Layer Doping

A semiconductor device and a method of manufacturing are provided. A substrate has a gate stack formed thereon. Ultra-shallow junctions are formed by depositing an atomic layer of a dopant and performing an anneal to diffuse the dopant into the substrate on opposing sides of the gate stack. The substrate may be recessed prior to forming the atomic layer and the recess may be filled by an epitaxial process. The depositing, annealing, and, if used, epitaxial growth may be repeated a plurality of times to achieve the desired junctions. Source / drain regions are also provided on opposing sides of the gate stack.

Owner:TAIWAN SEMICON MFG CO LTD

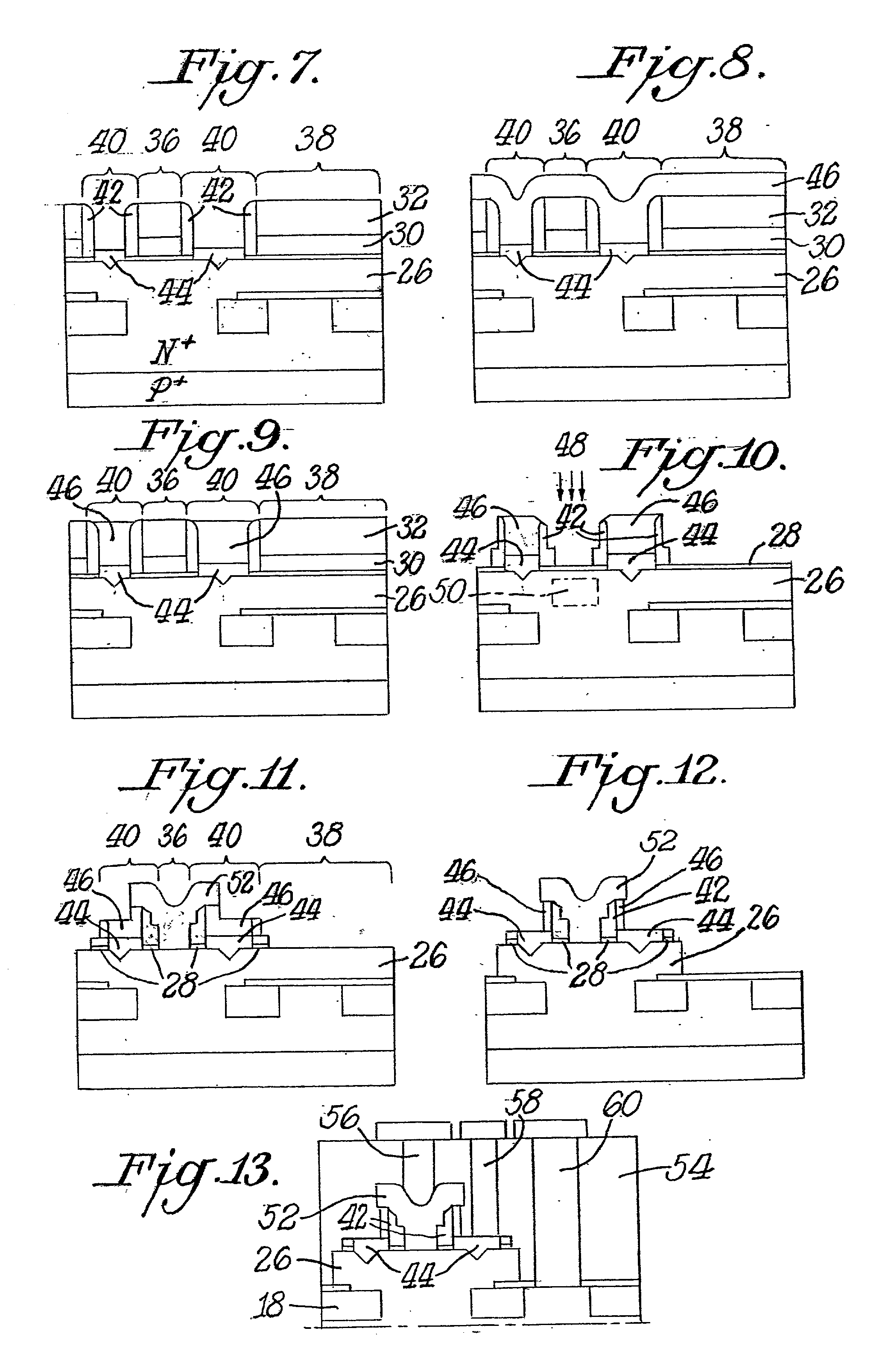

Method for manufacturing shallow junction complementary bipolar transistor

InactiveCN101673715AImprove pressure resistanceAchieve physical isolationSemiconductor/solid-state device manufacturingEtchingEngineering

The invention discloses a method for manufacturing a shallow junction complementary bipolar transistor. The main technological steps of the method are as follows: 1) forming an SOI material chip by the methods of silicon / silicon bonding, thinning and polishing; and 2) manufacturing the shallow junction complementary bipolar transistor by using the methods of deep-trench etching, deep trench isolation with polysilicon backfilling and a shallow isolation wall and combining with a longitudinal NPN pipe with a shallow junction polysilicon emitter and the complementary bipolar technology which is compatible with the longitudinal PNP pipe. The method improves the pressure resistance (BVCEO is greater than 5.0V) and the Early voltage of the complementary bipolar transistor and simultaneously takes into consideration of the characteristic frequency. The method greatly reduces the drain current of an isolation junction, and the drain current of the shallow junction complementary bipolar transistor is smaller than 10<minus 12>A. The method can be widely applied in the field of manufacture of high-speed complementary bipolar technologies.

Owner:NO 24 RES INST OF CETC