Patents

Literature

6981results about How to "Improve pressure resistance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

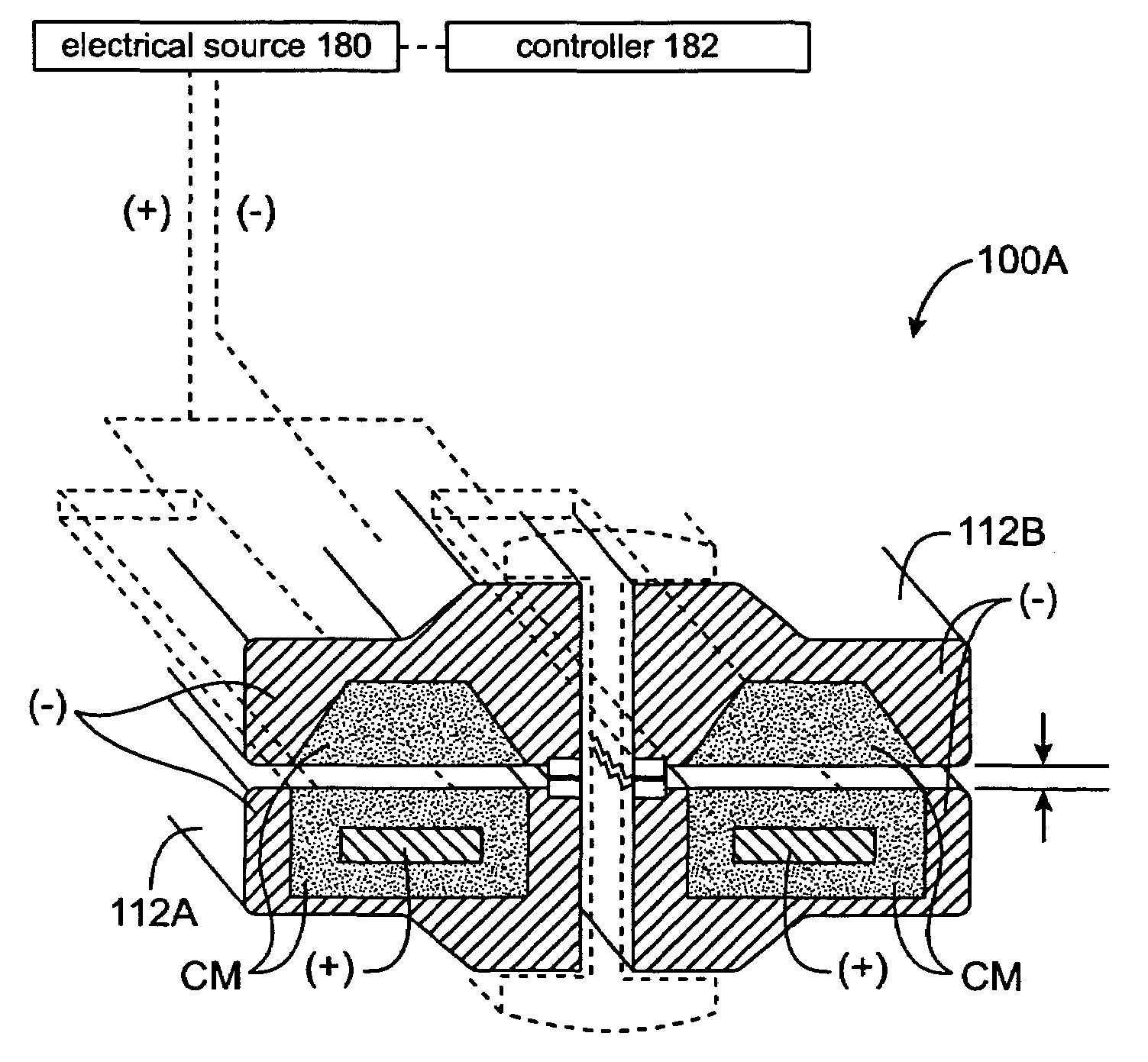

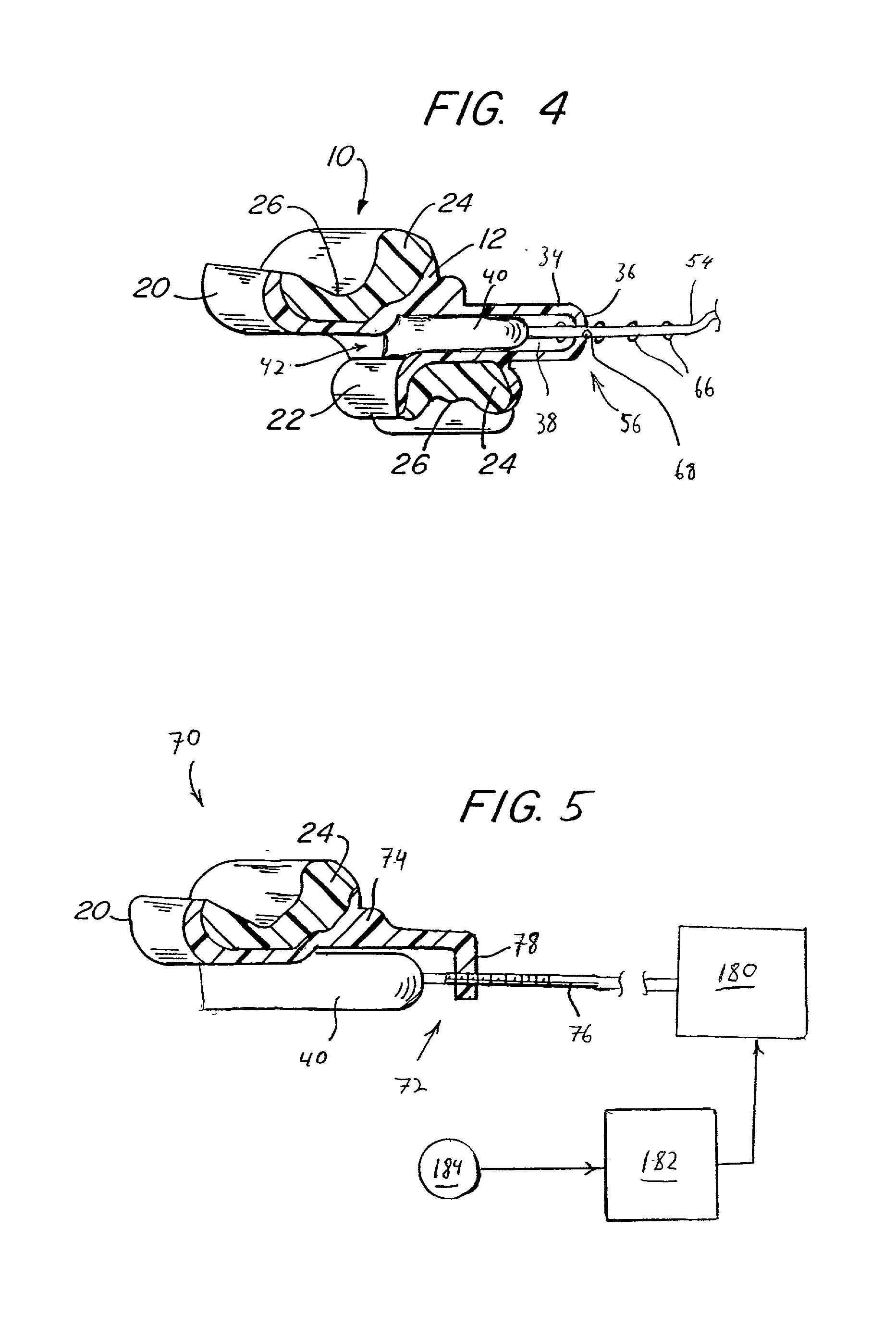

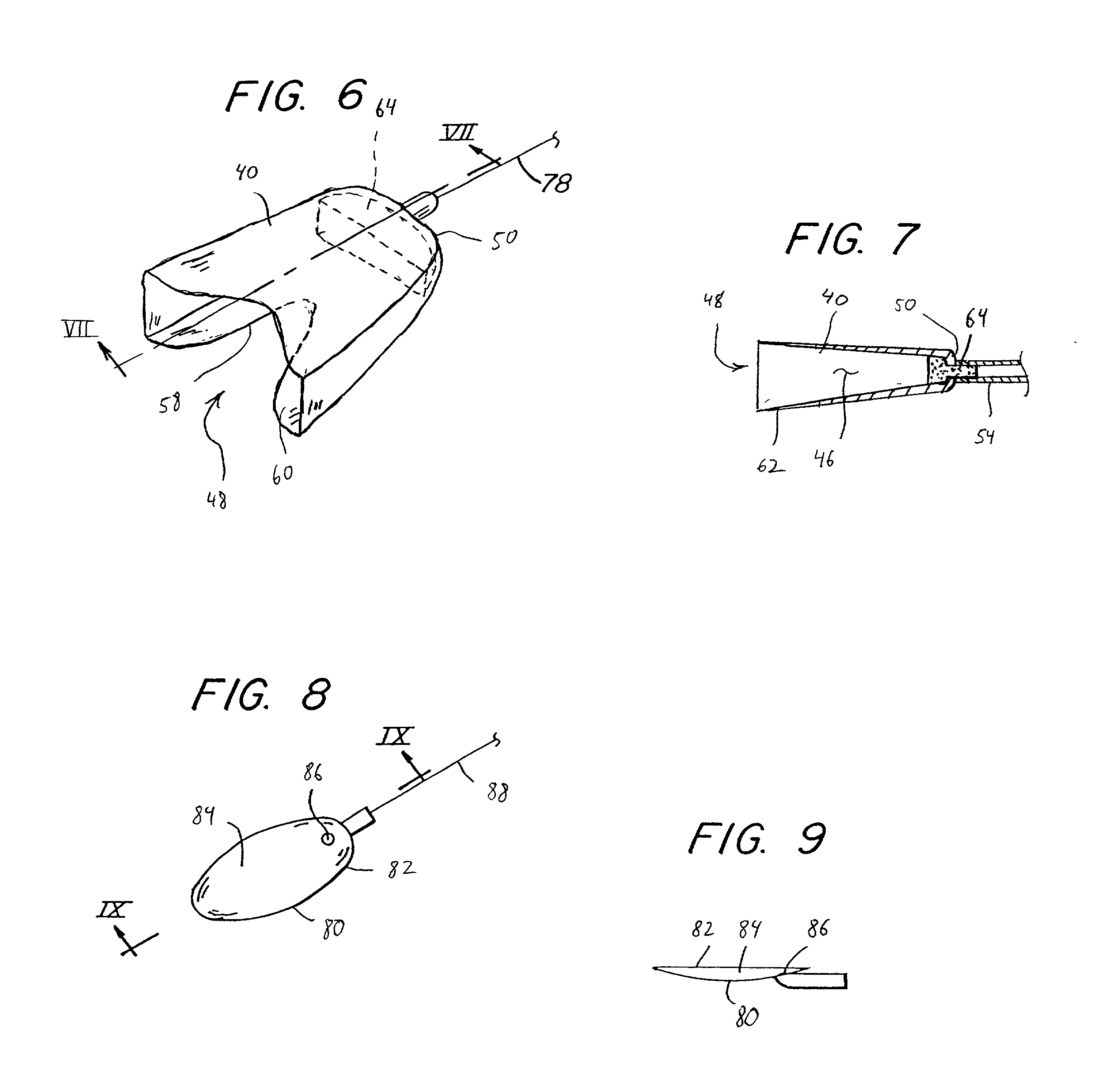

Electrosurgical instrument and method of use

ActiveUS7087054B2Reduce conductancePrevent any substantial dehydrationElectrotherapySurgical instruments for heatingEngineeringMedical device

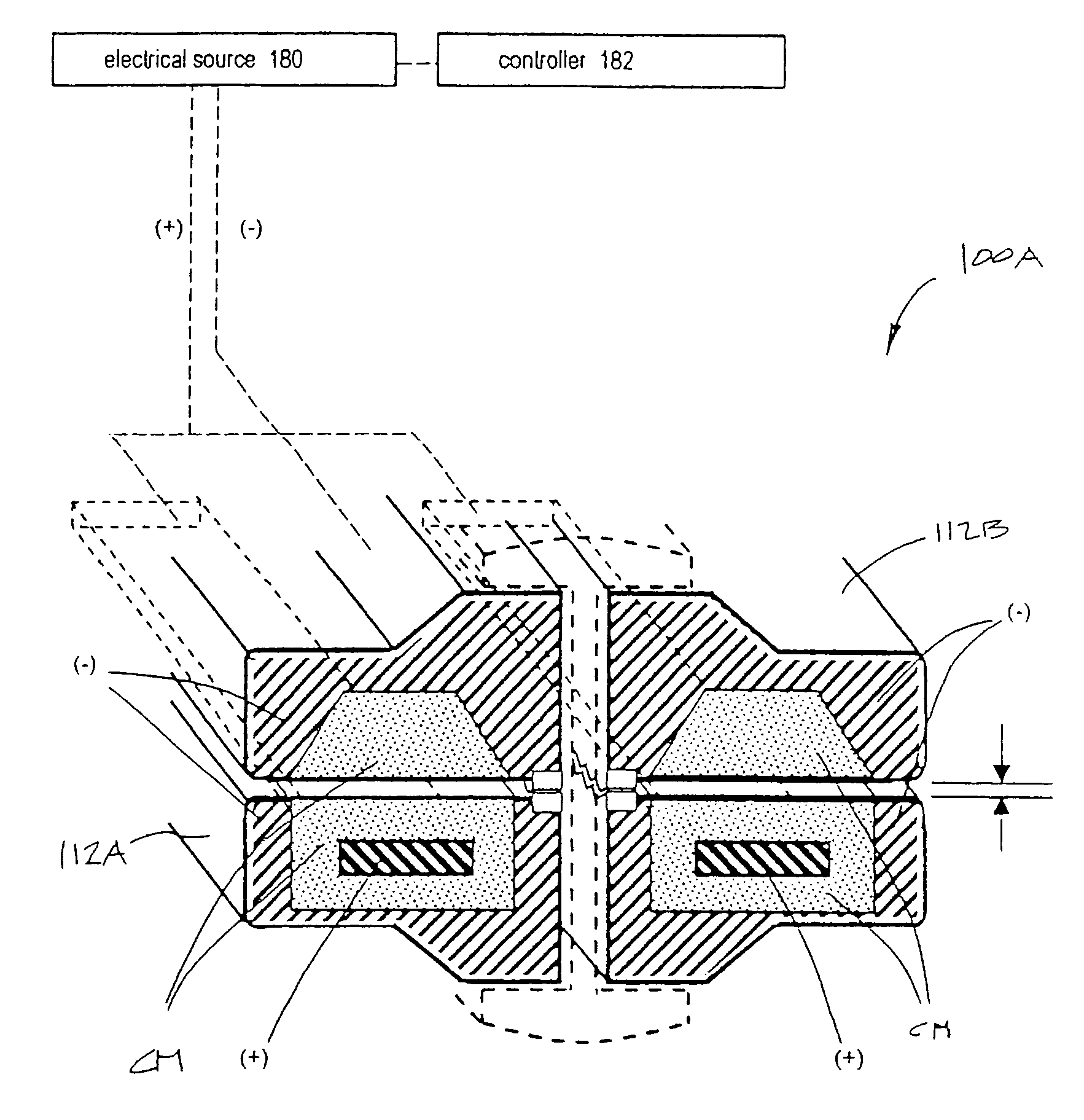

An electrosurgical medical device and method for creating thermal welds in engaged tissue. In one embodiment, at least one jaw of the instrument defines a tissue engagement plane that carries a recessed central portion. In another embodiment, the controller coupled to the Rf source is adapted to switch from a power control operational mode to a voltage controlled operational mode at a selected transition impedance level.

Owner:ETHICON ENDO SURGERY INC

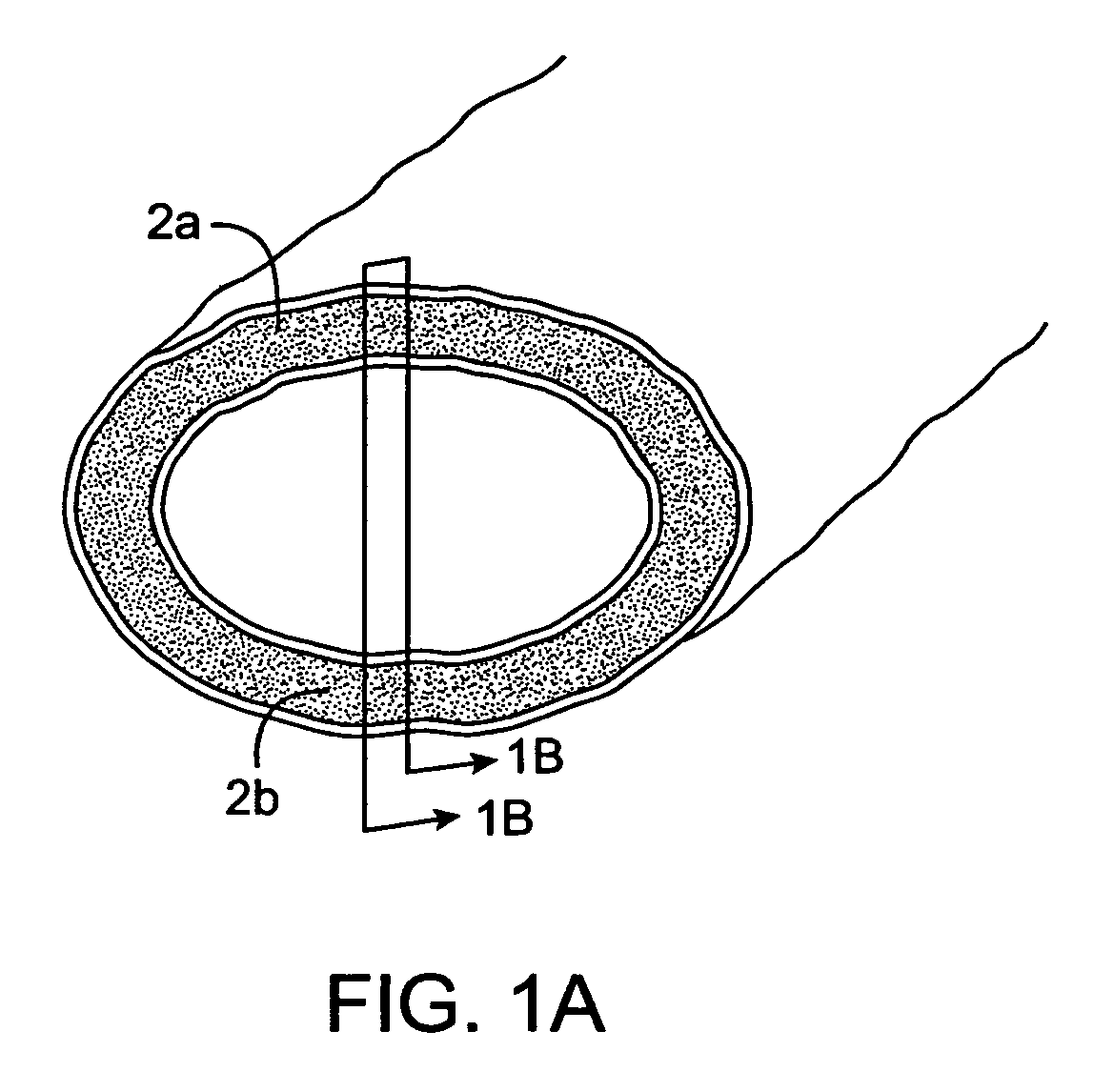

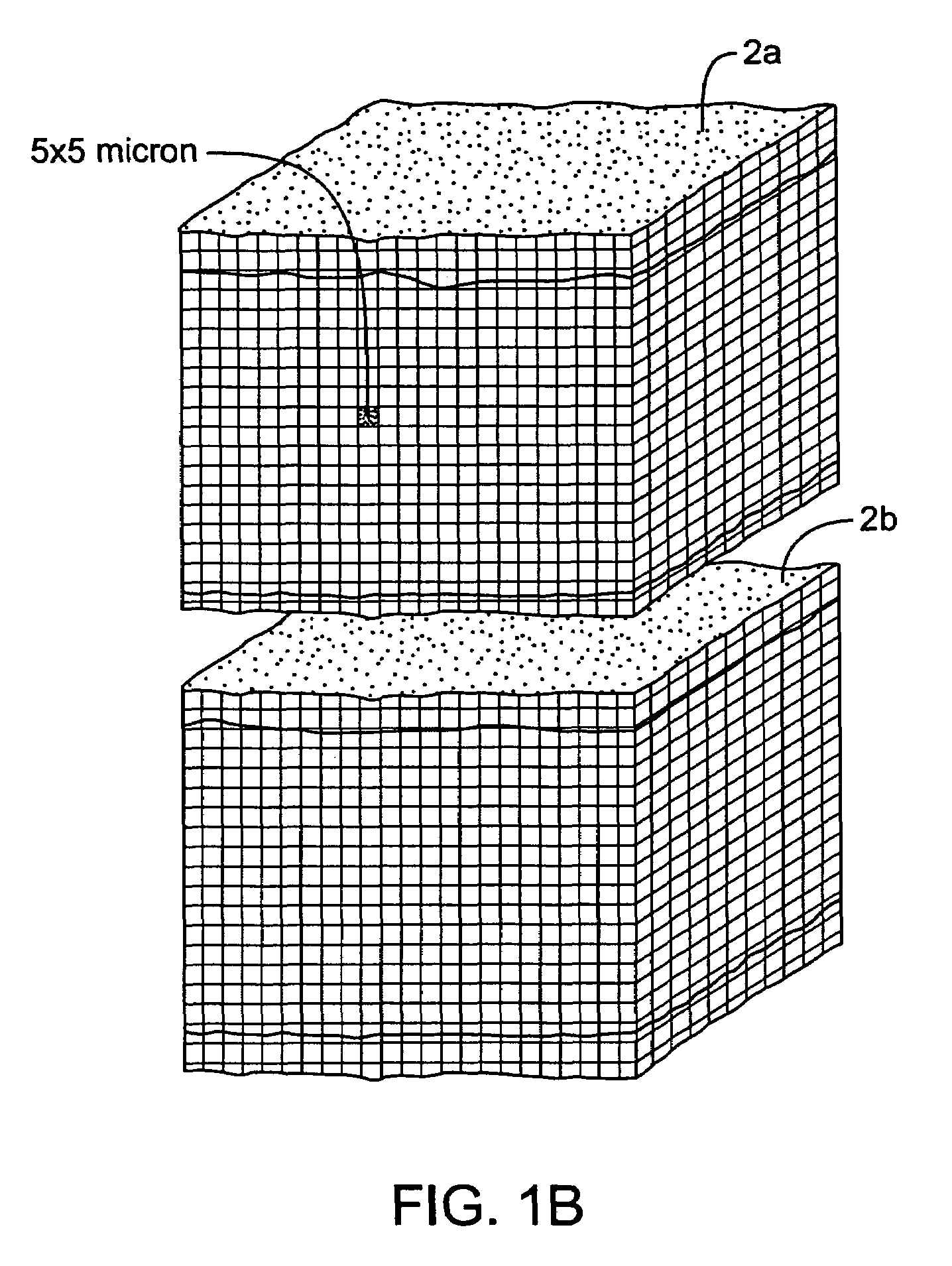

Electrosurgical instrument and method of use

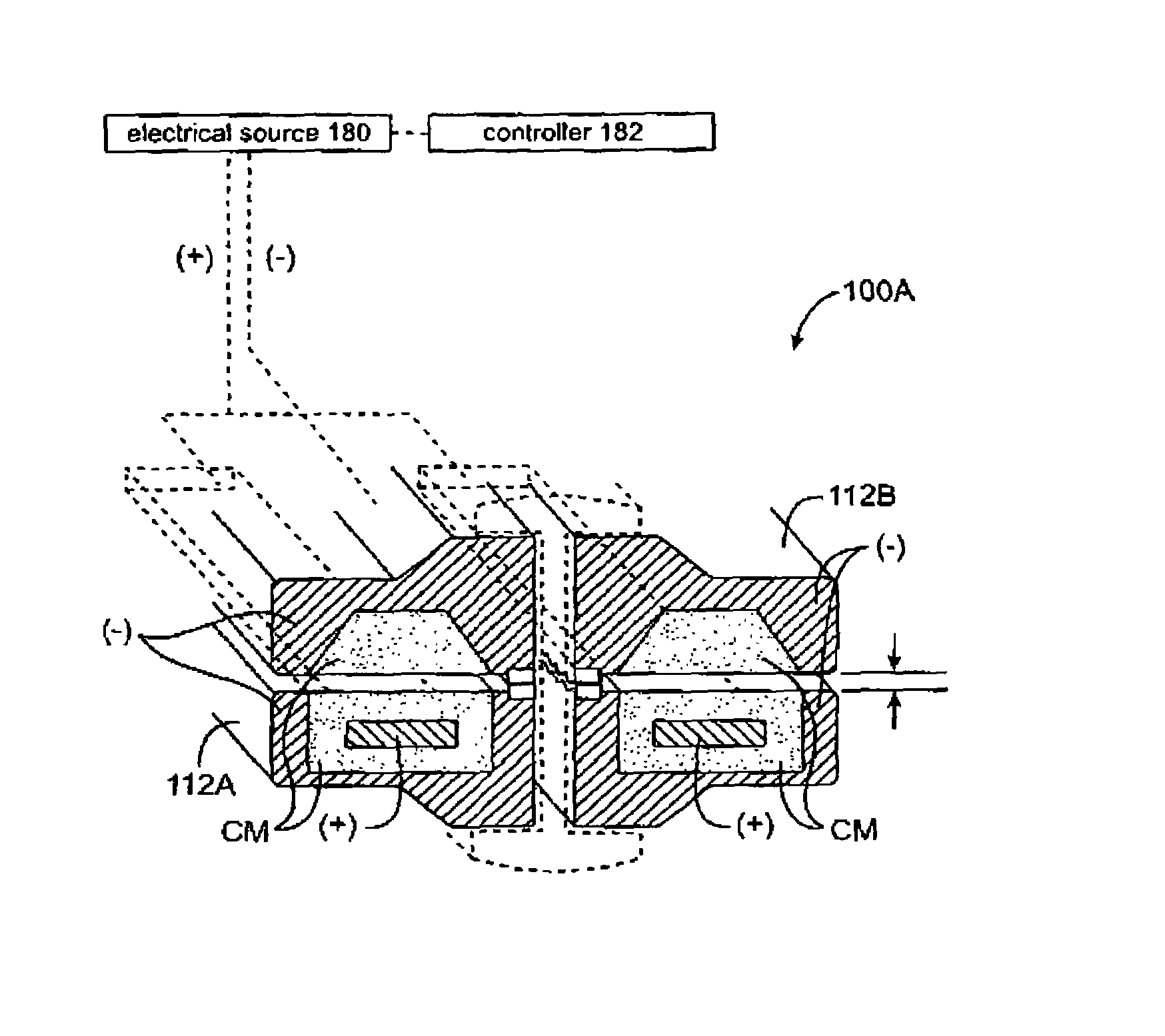

InactiveUS7083619B2Reduce conductancePrevent any substantial dehydrationSurgical instruments for heatingCoatingsMicron scaleElastomer

An electrosurgical medical device and method for creating thermal welds in engaged tissue. In one embodiment, at least one jaw of the instrument defines a tissue engagement plane carrying a conductive-resistive matrix of a conductively-doped non-conductive elastomer. The engagement surface portions thus can be described as a positive temperature coefficient material that has a unique selected decreased electrical conductance at each selected increased temperature thereof over a targeted treatment range. The conductive-resistive matrix can be engineered to bracket a targeted thermal treatment range, for example about 60° C. to 80° C., at which tissue welding can be accomplished. In one mode of operation, the engagement plane will automatically modulate and spatially localize ohmic heating within the engaged tissue from Rf energy application—across micron-scale portions of the engagement surface.

Owner:ETHICON ENDO SURGERY INC

Electrosurgical instrument and method of use

InactiveUS7311709B2Reduce conductancePrevent any substantial dehydrationSurgical instruments for heatingCoatingsMicron scaleSpatial positioning

An electrosurgical medical device and method for creating thermal welds in engaged tissue. In one embodiment, at least one jaw of the instrument defines a tissue engagement plane carrying a variable resistive body of a positive temperature coefficient material that has a selected decreased electrical conductance at each selected increased temperature thereof over a targeted treatment range. The variable resistive body can be engineered to bracket a targeted thermal treatment range, for example about 60° C. to 80° C., at which tissue welding can be accomplished. In one mode of operation, the engagement plane will automatically modulate and spatially localize ohmic heating within the engaged tissue from Rf energy application across micron-scale portions of the engagement surface. In another mode of operation, a variable resistive body will focus conductive heating in a selected portion of the engagement surface.

Owner:ETHICON ENDO SURGERY INC

Electrosurgical instrument and method of use

InactiveUS7112201B2Reduce conductancePrevent any substantial dehydrationSurgical instruments for heatingCoatingsMicron scaleElastomer

An electrosurgical medical device and method for creating thermal welds in engaged tissue. In one embodiment, at least one jaw of the instrument defines a tissue engagement plane carrying a conductive-resistive matrix of a conductively-doped non-conductive elastomer. The engagement surface portions thus can be described as a positive temperature coefficient material that has a unique selected decreased electrical conductance at each selected increased temperature thereof over a targeted treatment range. The conductive-resistive matrix can be engineered to bracket a targeted thermal treatment range, for example about 60° C. to 80° C., at which tissue welding can be accomplished. In one mode of operation, the engagement plane will automatically modulate and spatially localize ohmic heating within the engaged tissue from Rf energy application—across micron-scale portions of the engagement surface. In another mode of operation, a conductive-resistive matrix can induce a “wave” of Rf energy density to sweep across the tissue to thereby weld tissue.

Owner:ETHICON ENDO SURGERY INC

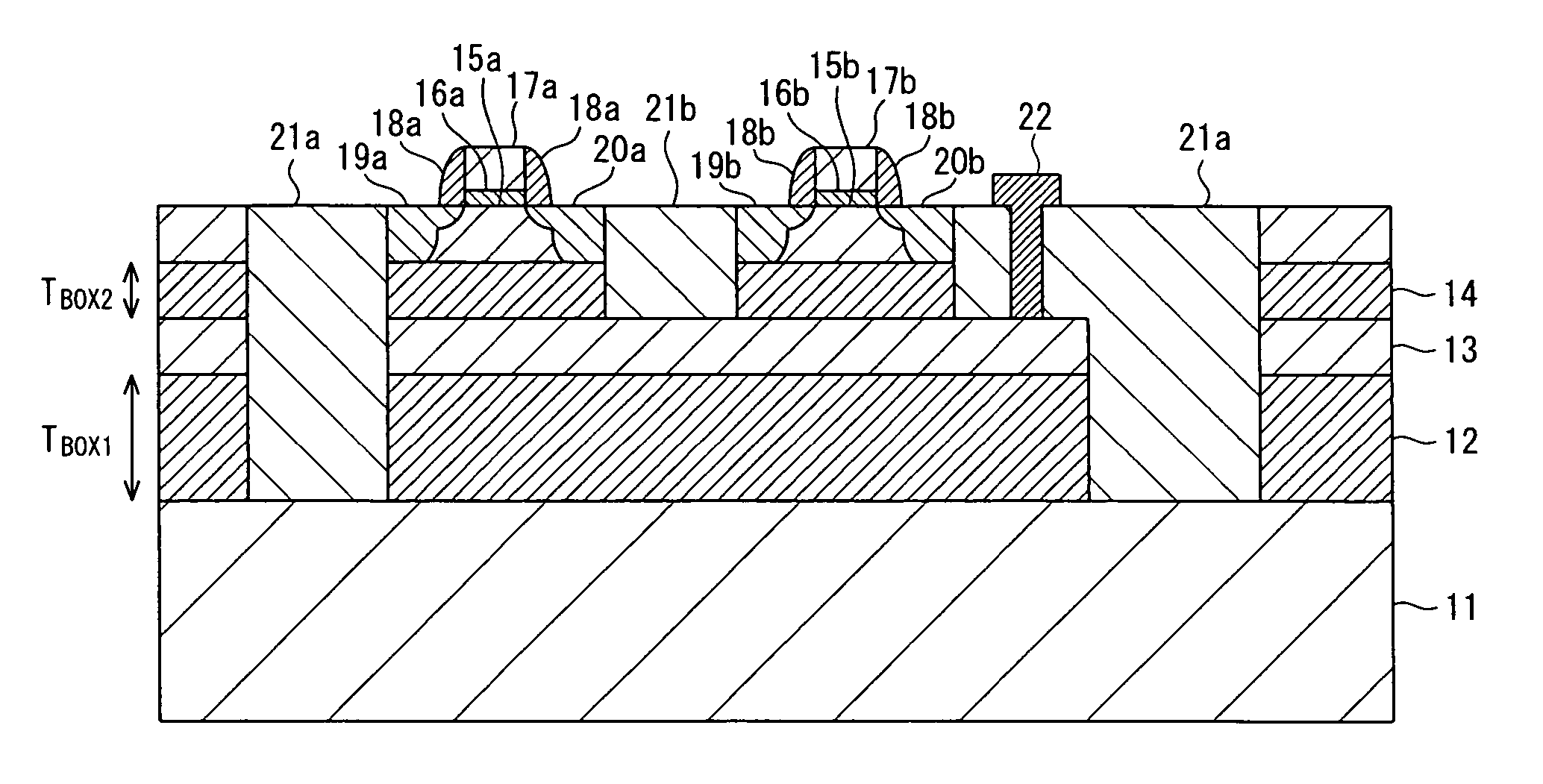

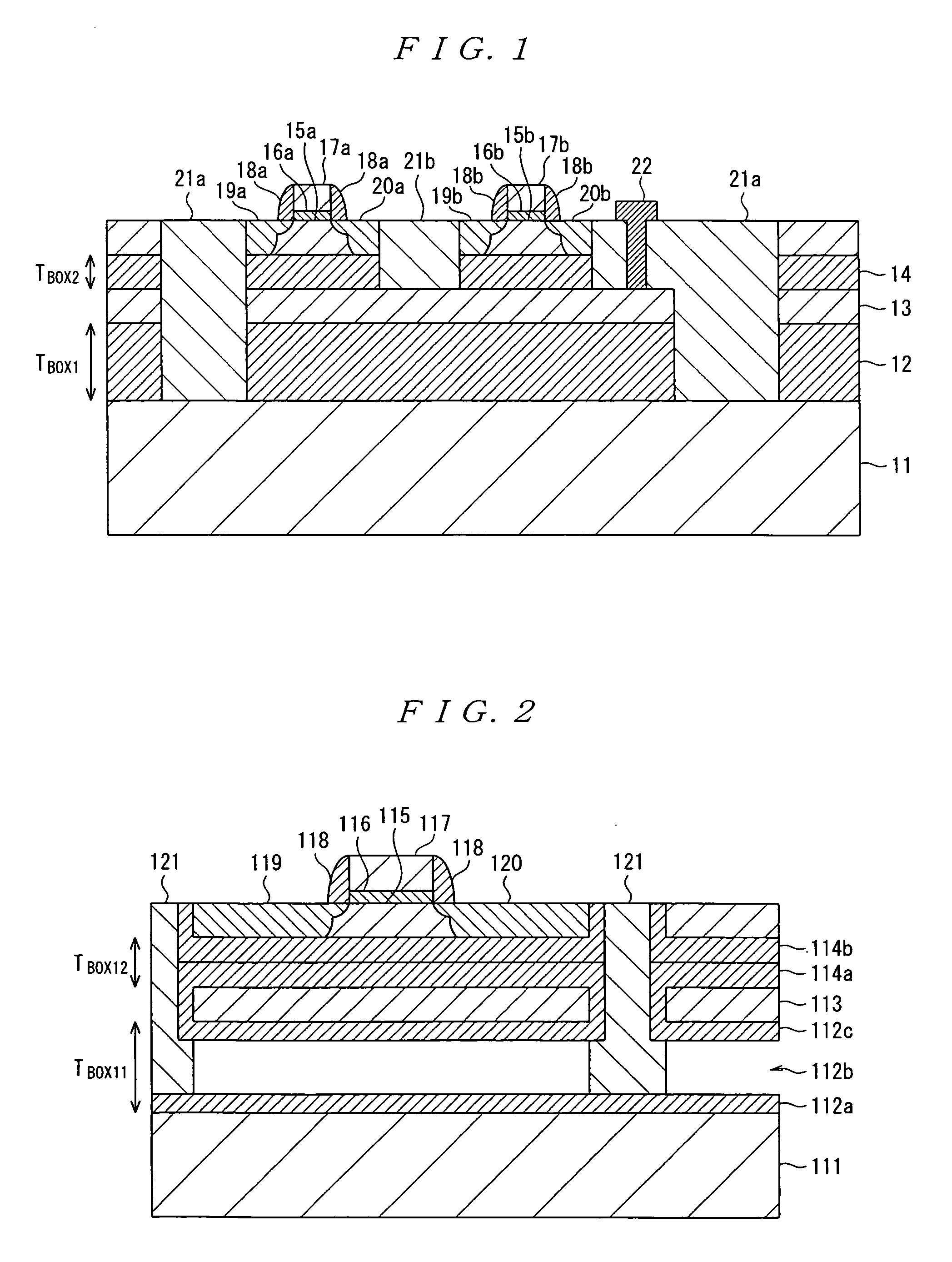

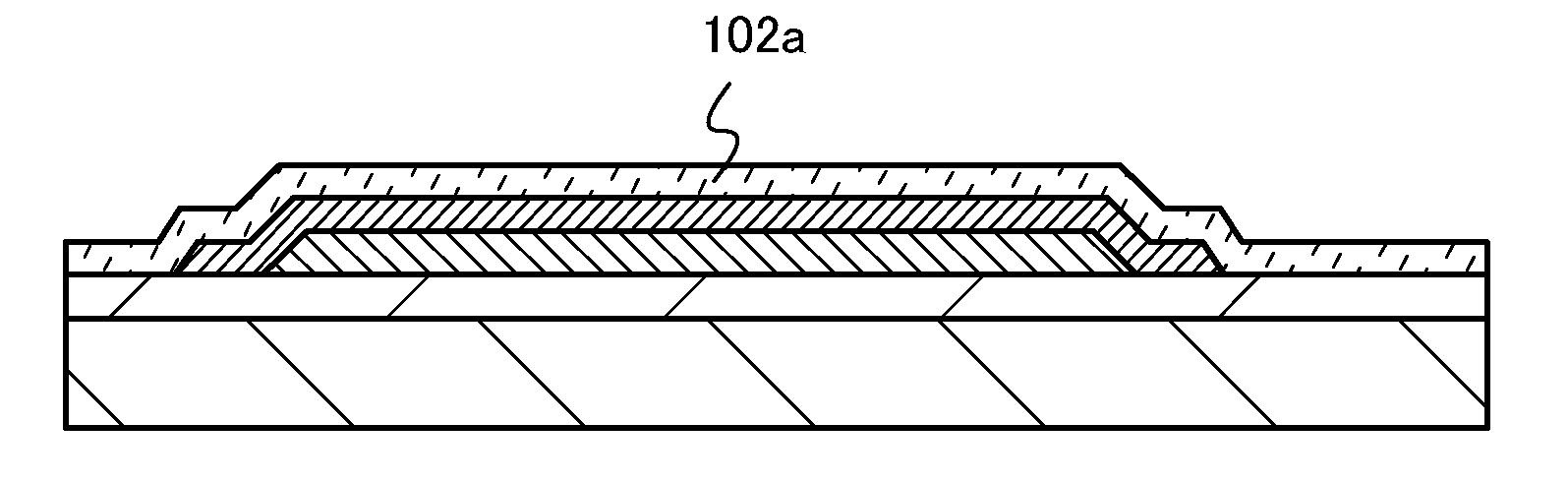

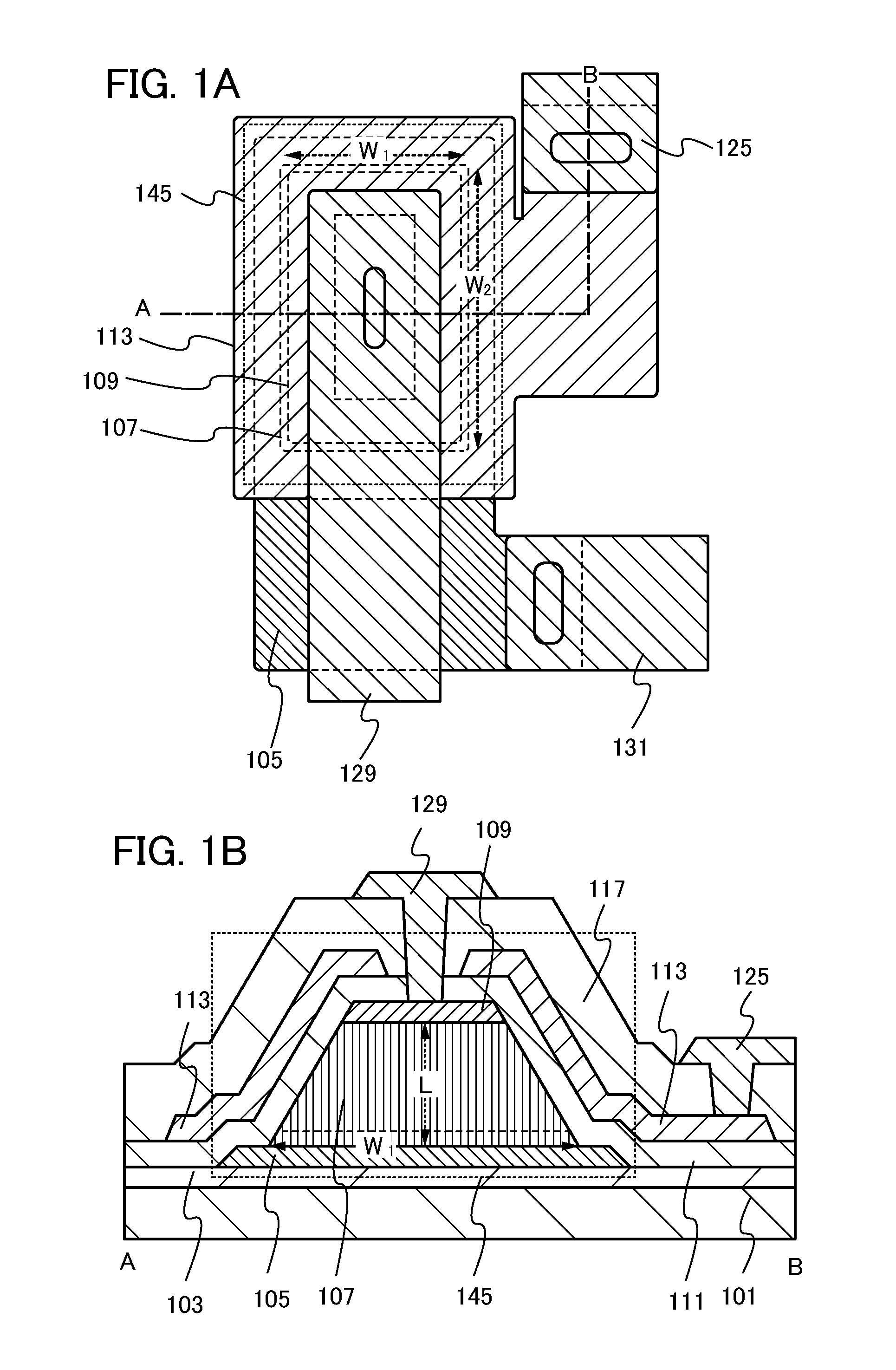

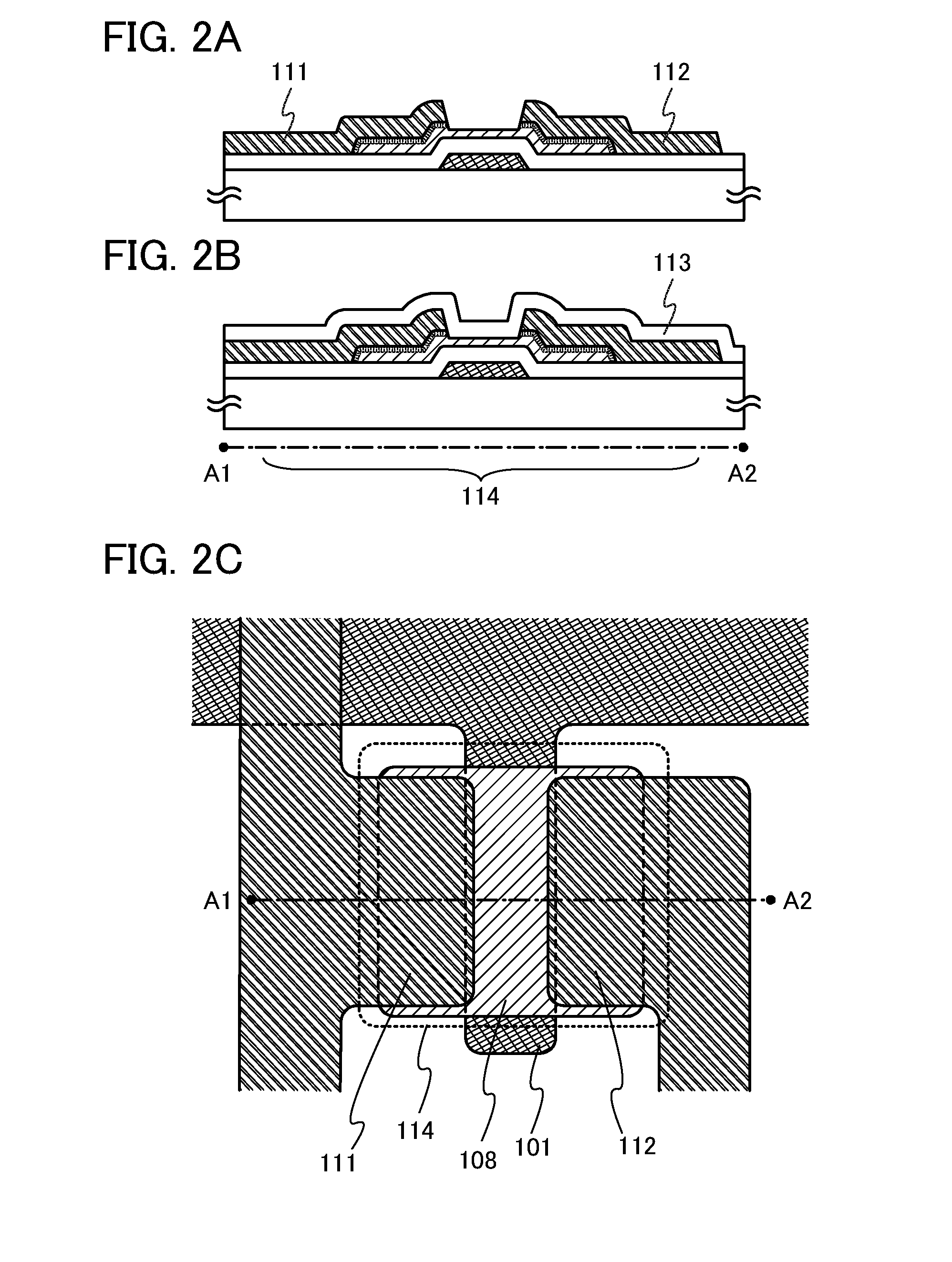

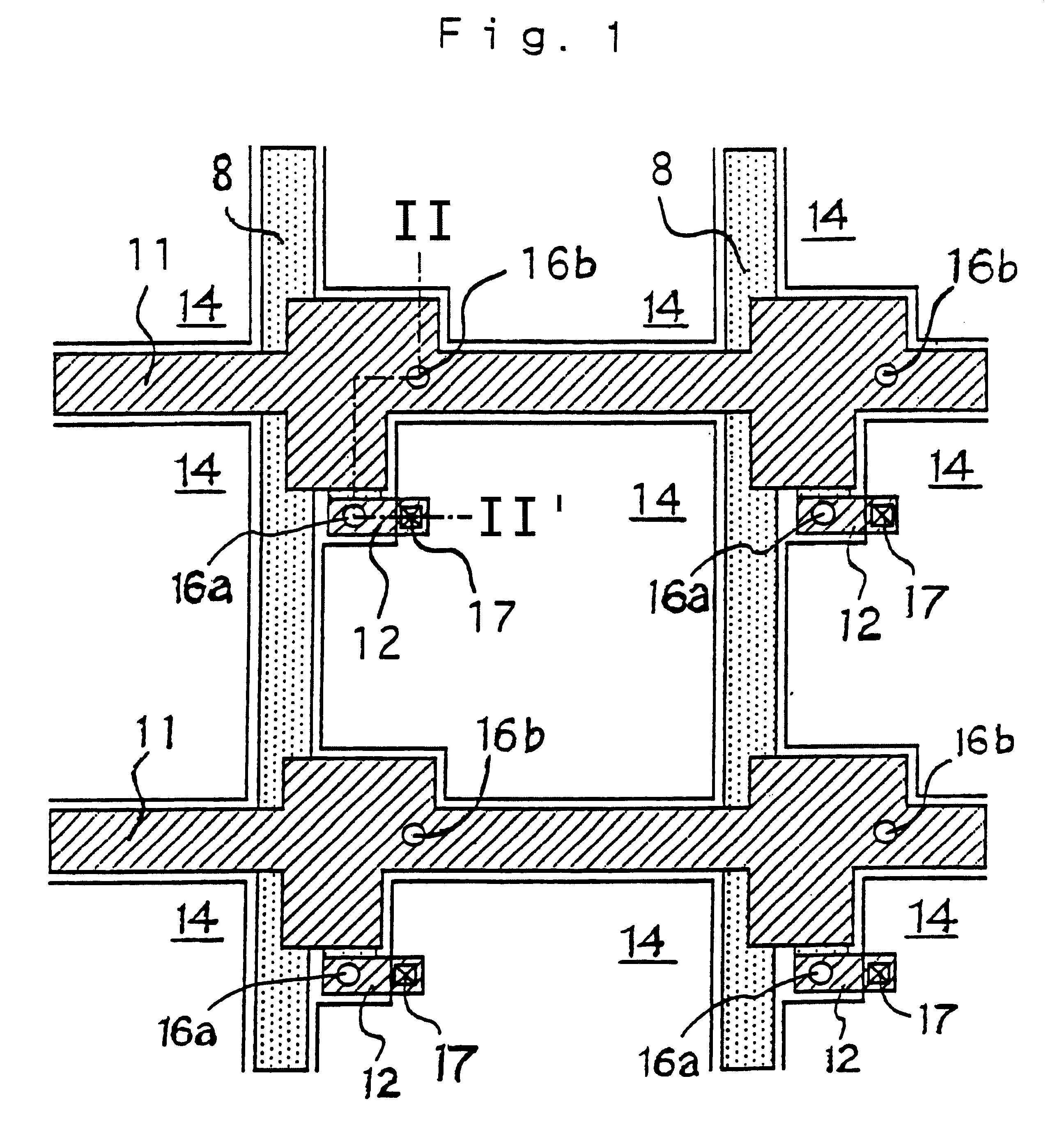

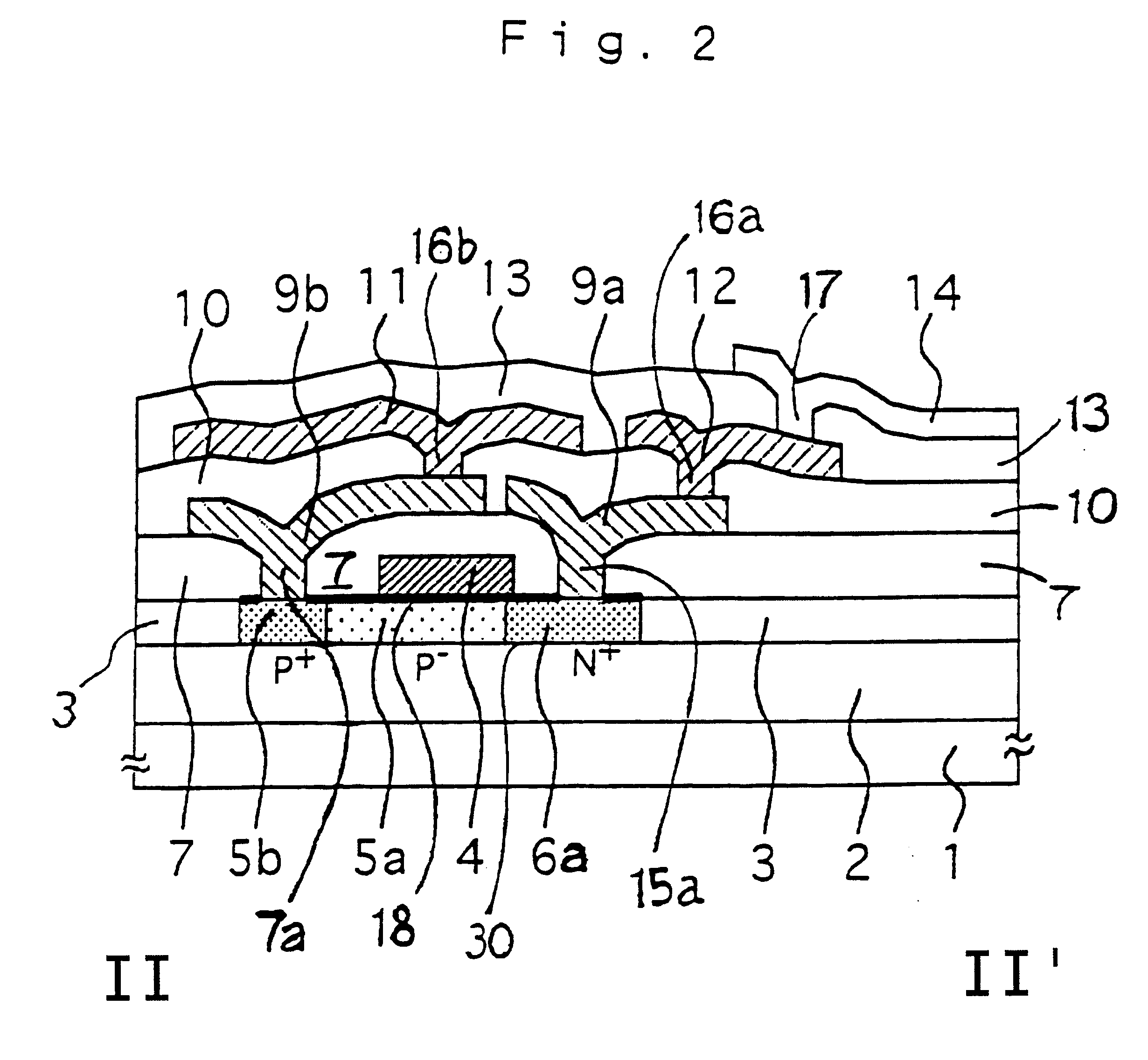

Semiconductor device and semiconductor device manufacturing method

InactiveUS20070075317A1Increase flexibilityImprove pressure resistanceSolid-state devicesSemiconductor/solid-state device manufacturingDevice materialEngineering

A semiconductor device includes a back gate electrode composed of a first single-crystal semiconductor layer formed on a first insulating layer; a second insulating layer formed on the first single-crystal semiconductor layer and having a film thickness smaller than a film thickness of the first insulating layer; a second single-crystal semiconductor layer formed on the second insulating layer; a gate electrode formed on the second single-crystal semiconductor layer; and source and drain layers that are formed on the second single-crystal semiconductor layer and arranged on respective sides of the gate electrode.

Owner:SEIKO EPSON CORP +1

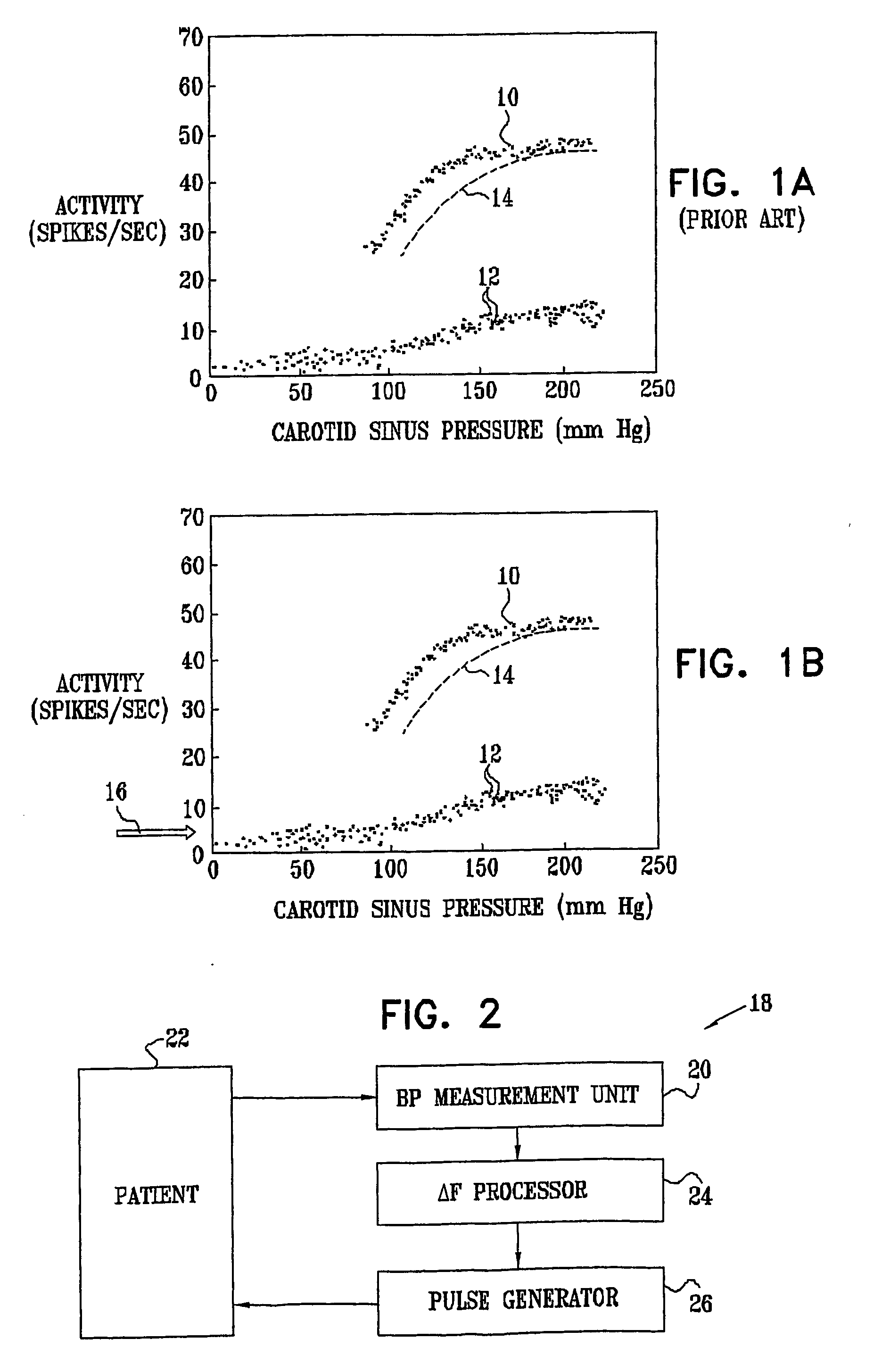

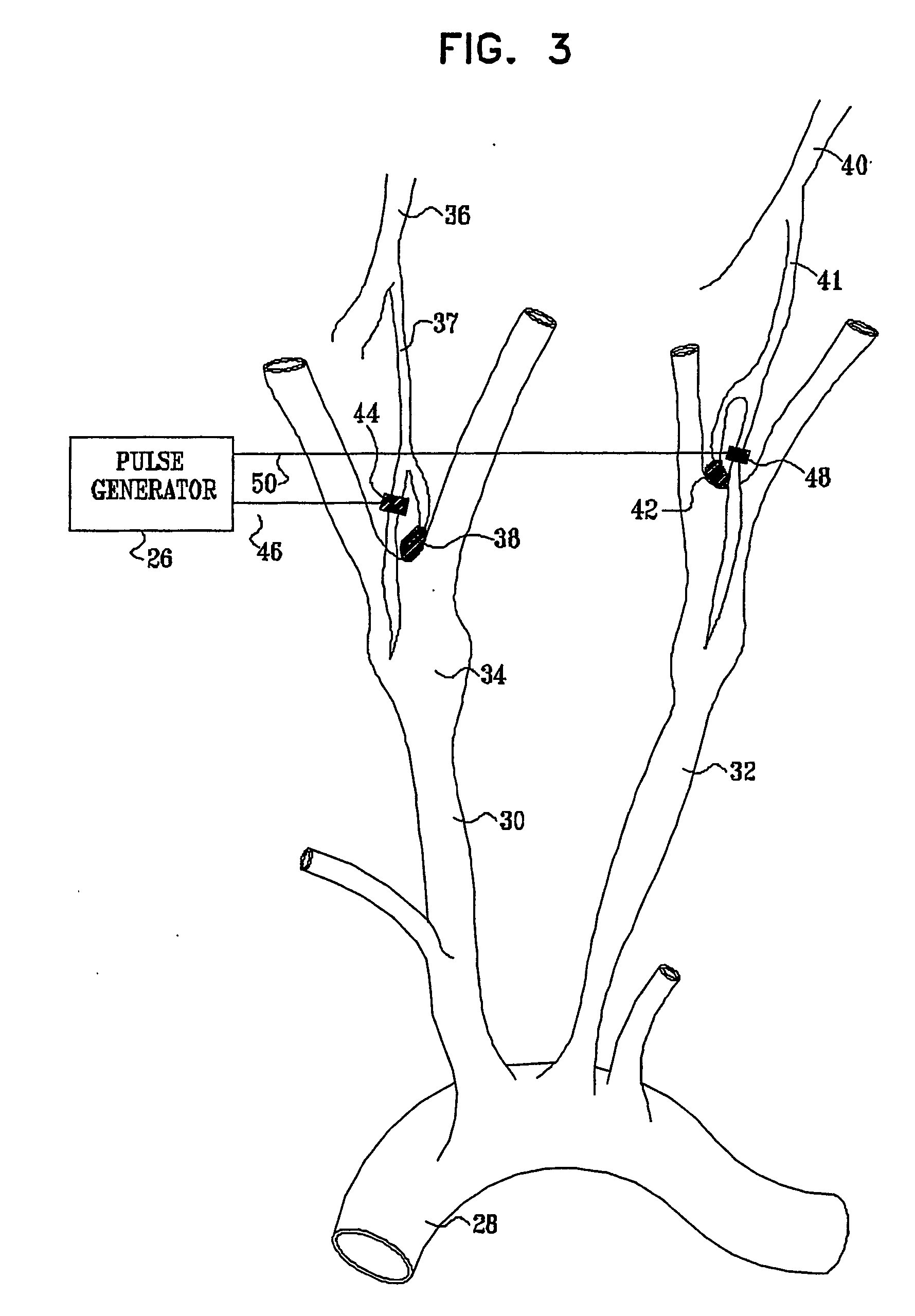

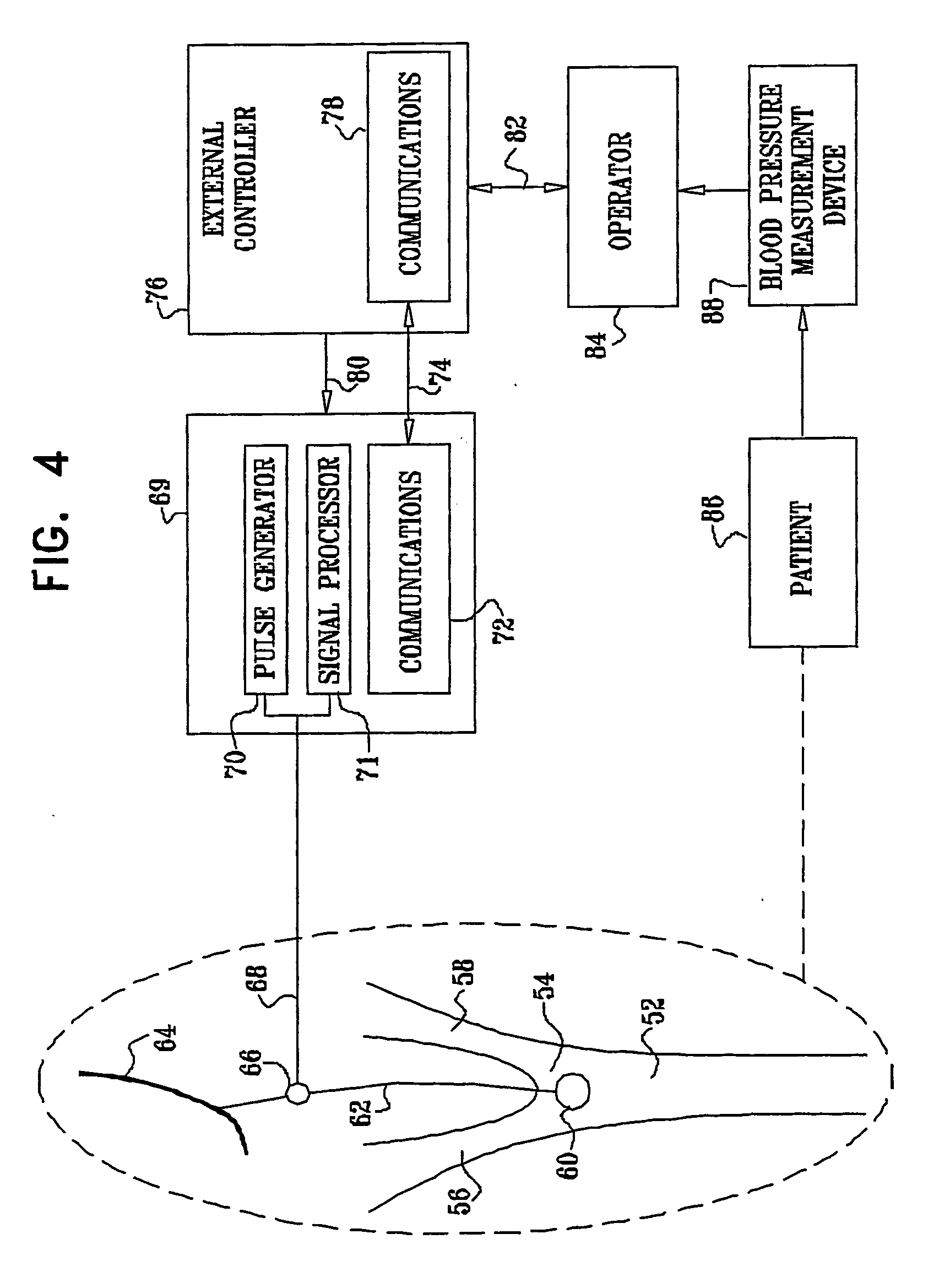

Technique for blood pressure regulation

InactiveUS20060089678A1High baroreceptor discharge rateHigh activityInternal electrodesEvaluation of blood vesselsWhole bodyBaroreceptor function

An implantable device (20) uses the carotid baroreflex in order to control systemic blood pressure. The implant includes sampling and pulse stimulation electrodes (44) preferably located on the carotid sinus nerve branch of the glossopharyngeal nerve, adjacent and distal to the carotid sinus baroreceptors. The stimulators have an external control unit, which communicates with the implant for determining appropriate operational parameters, and for retrieving telemetry information from the device's data bank. Typically two internal devices are implanted, one at each side of the patient's neck.

Owner:BRAINSGATE LTD

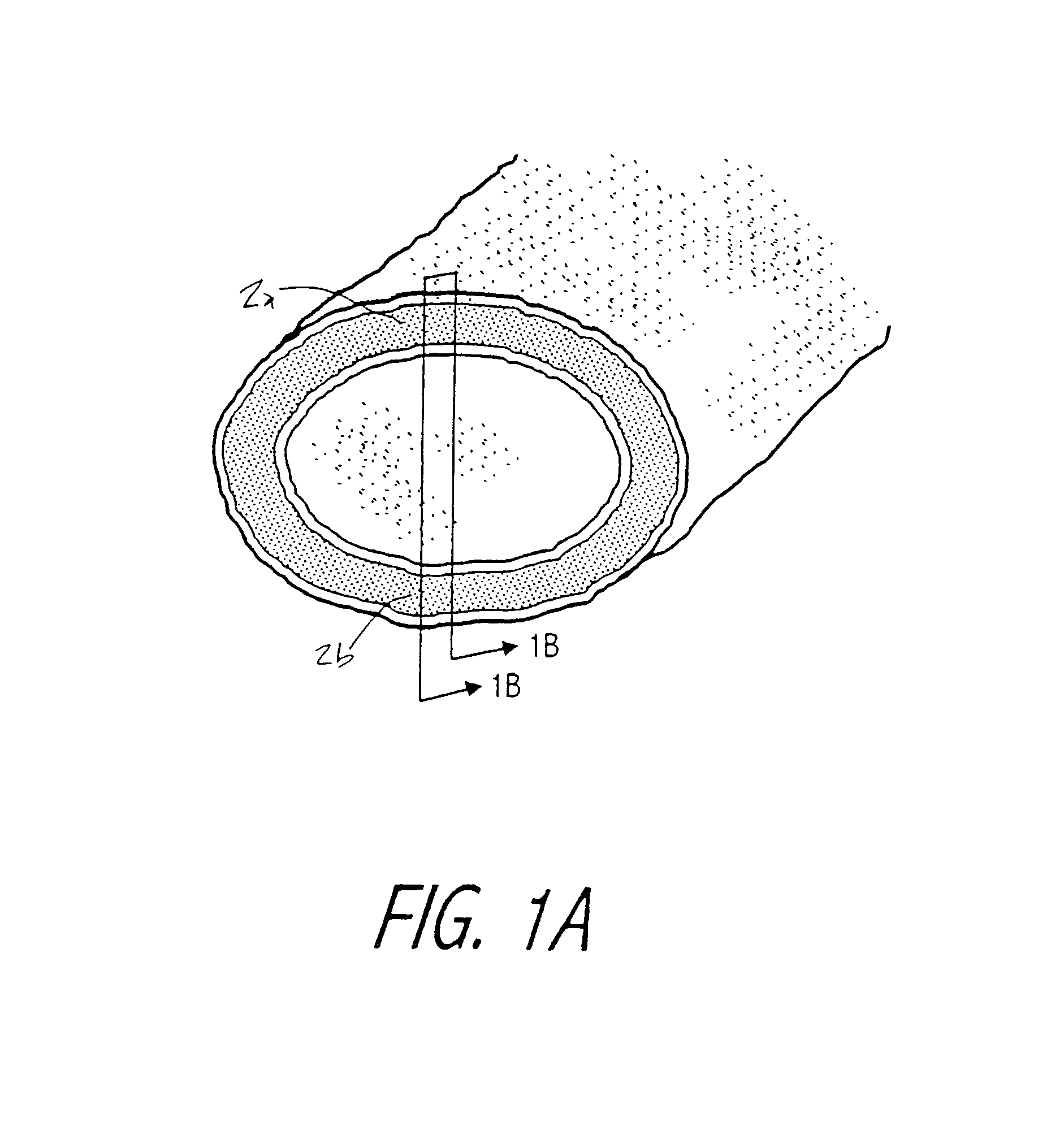

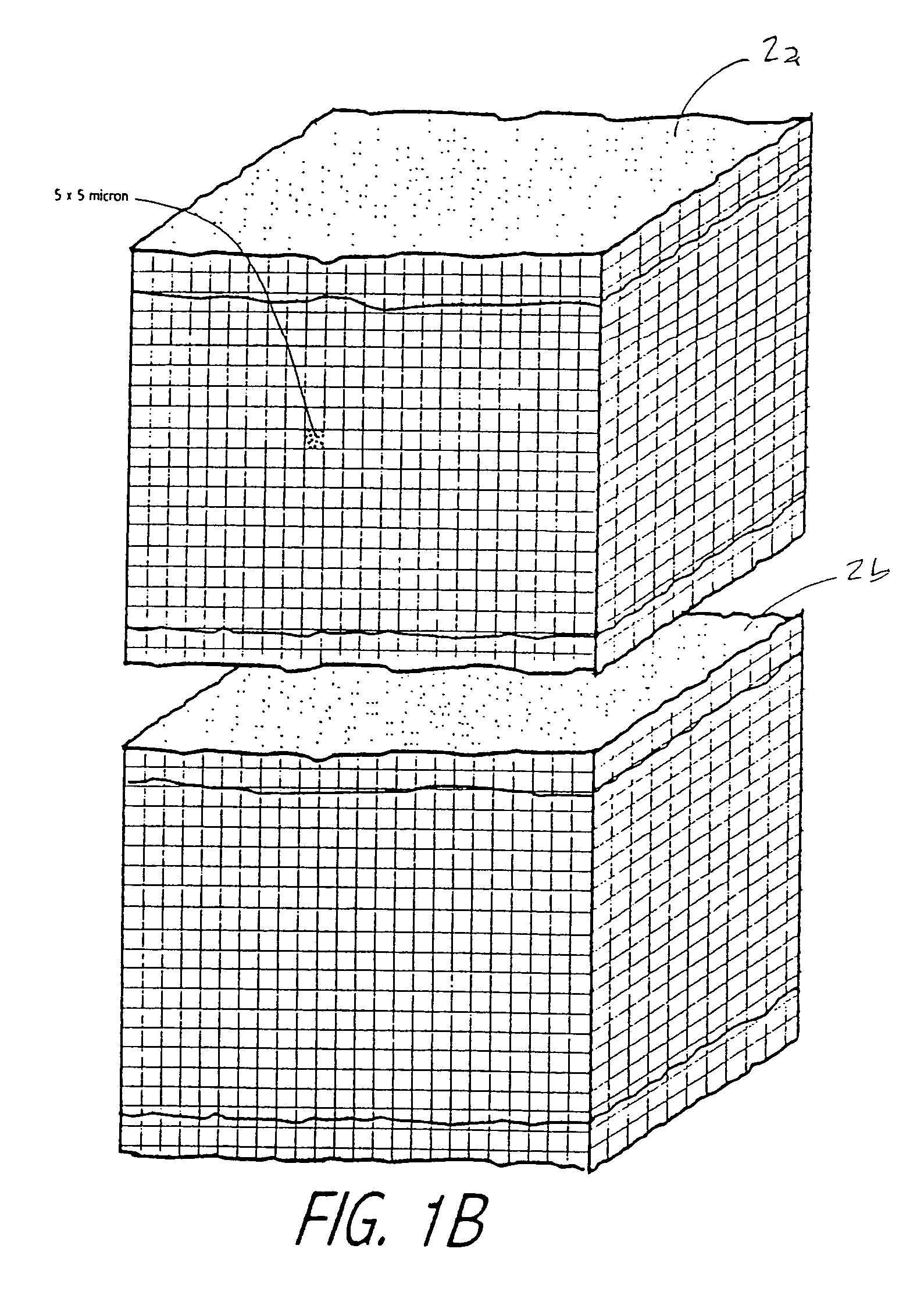

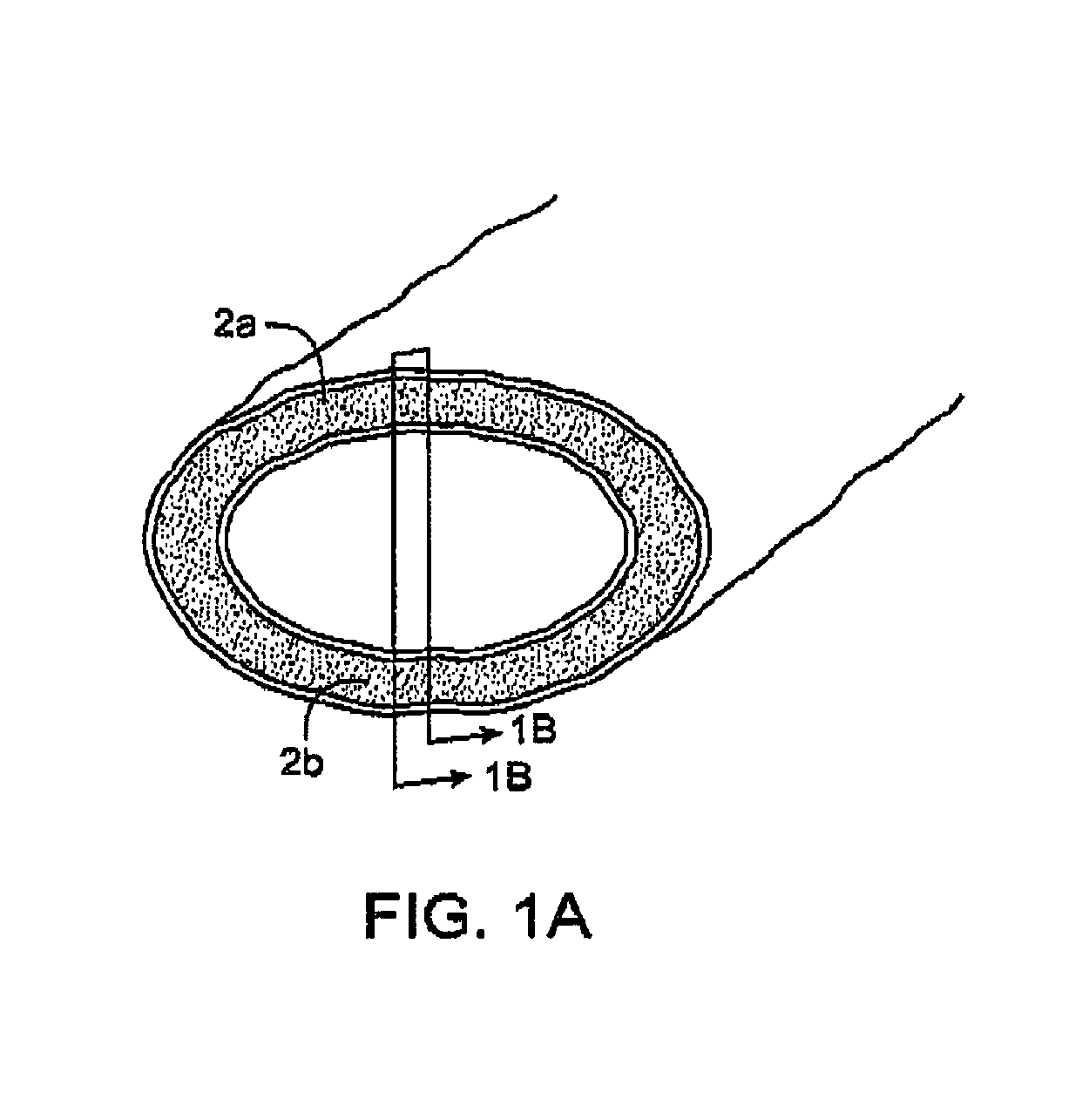

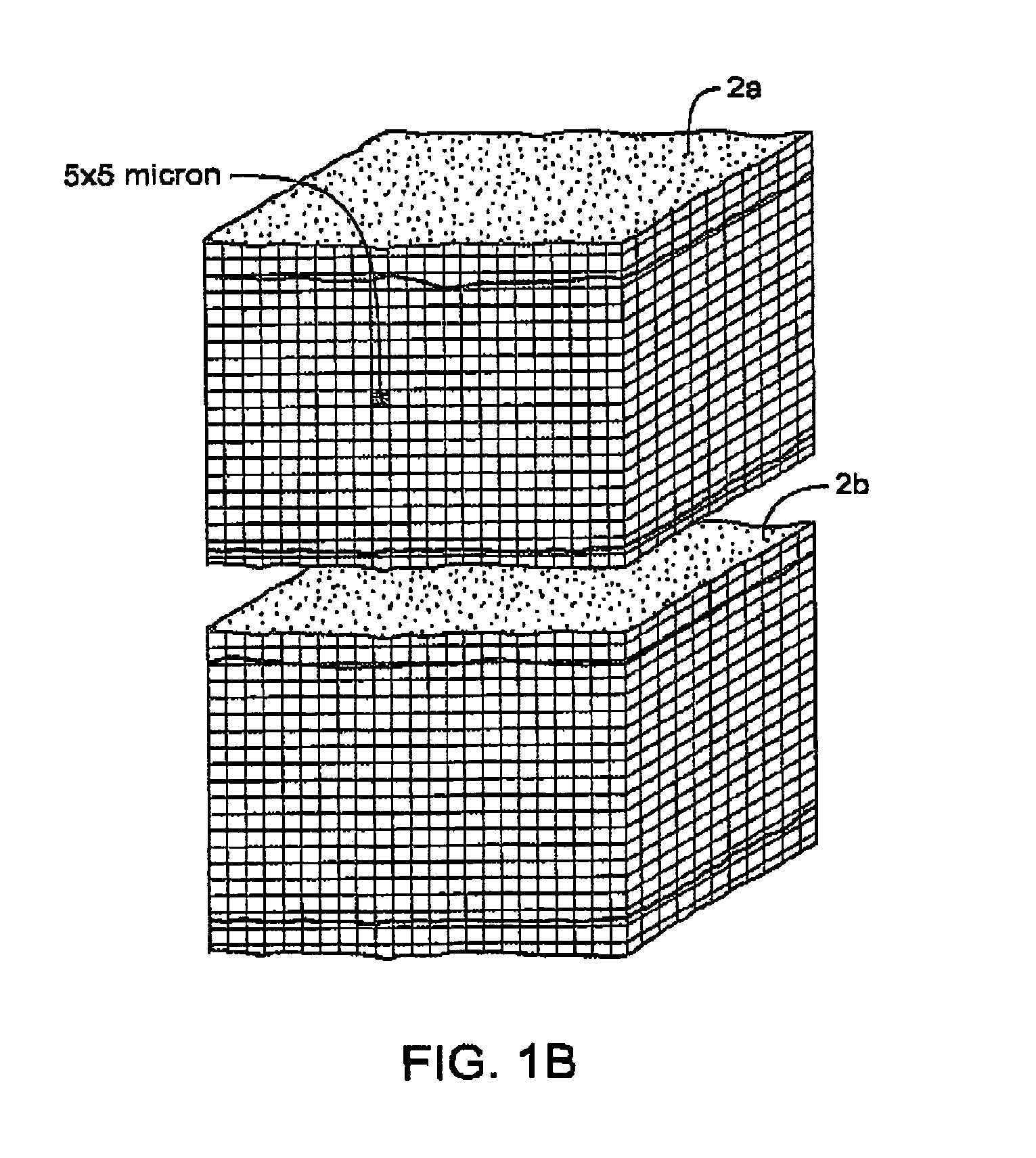

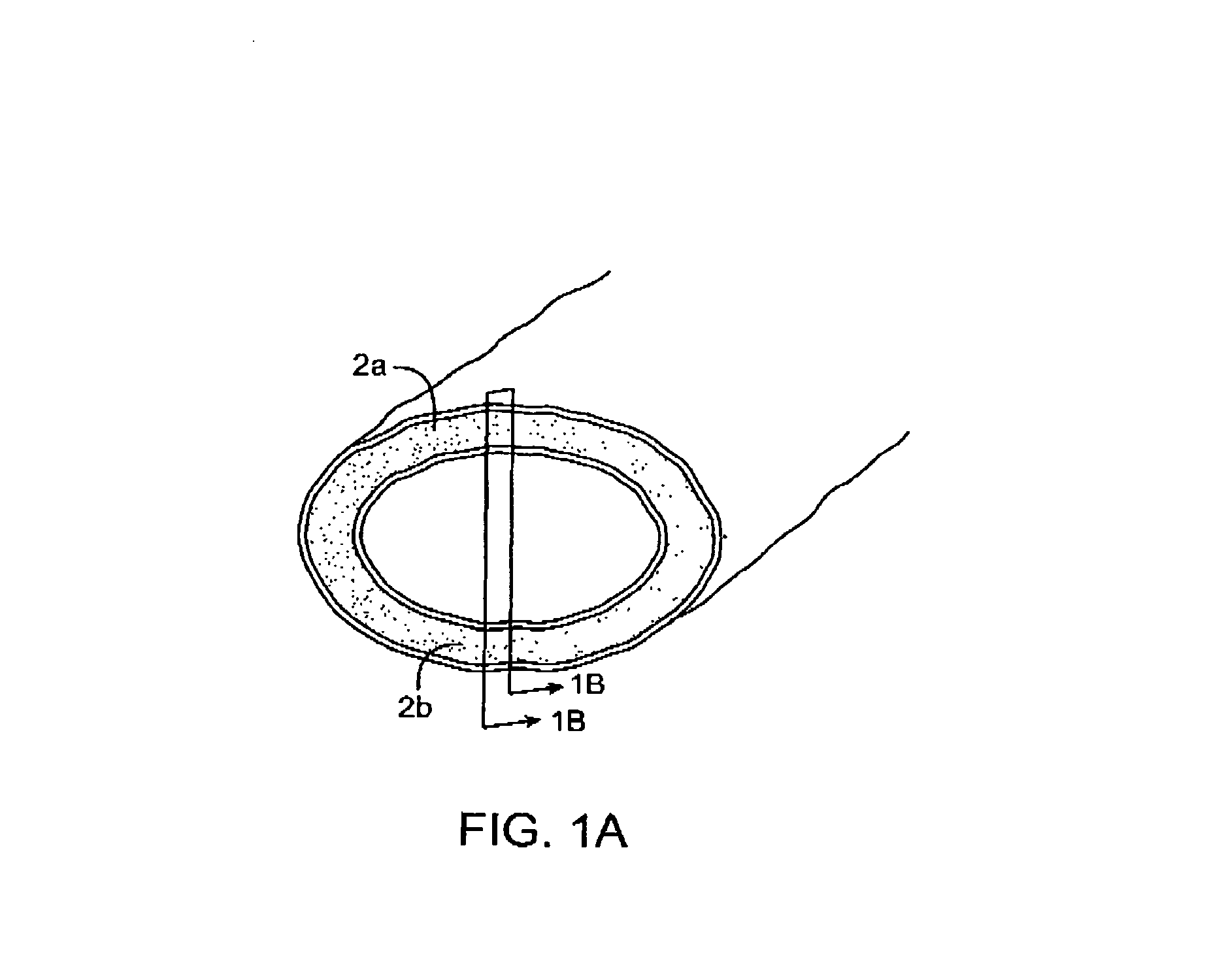

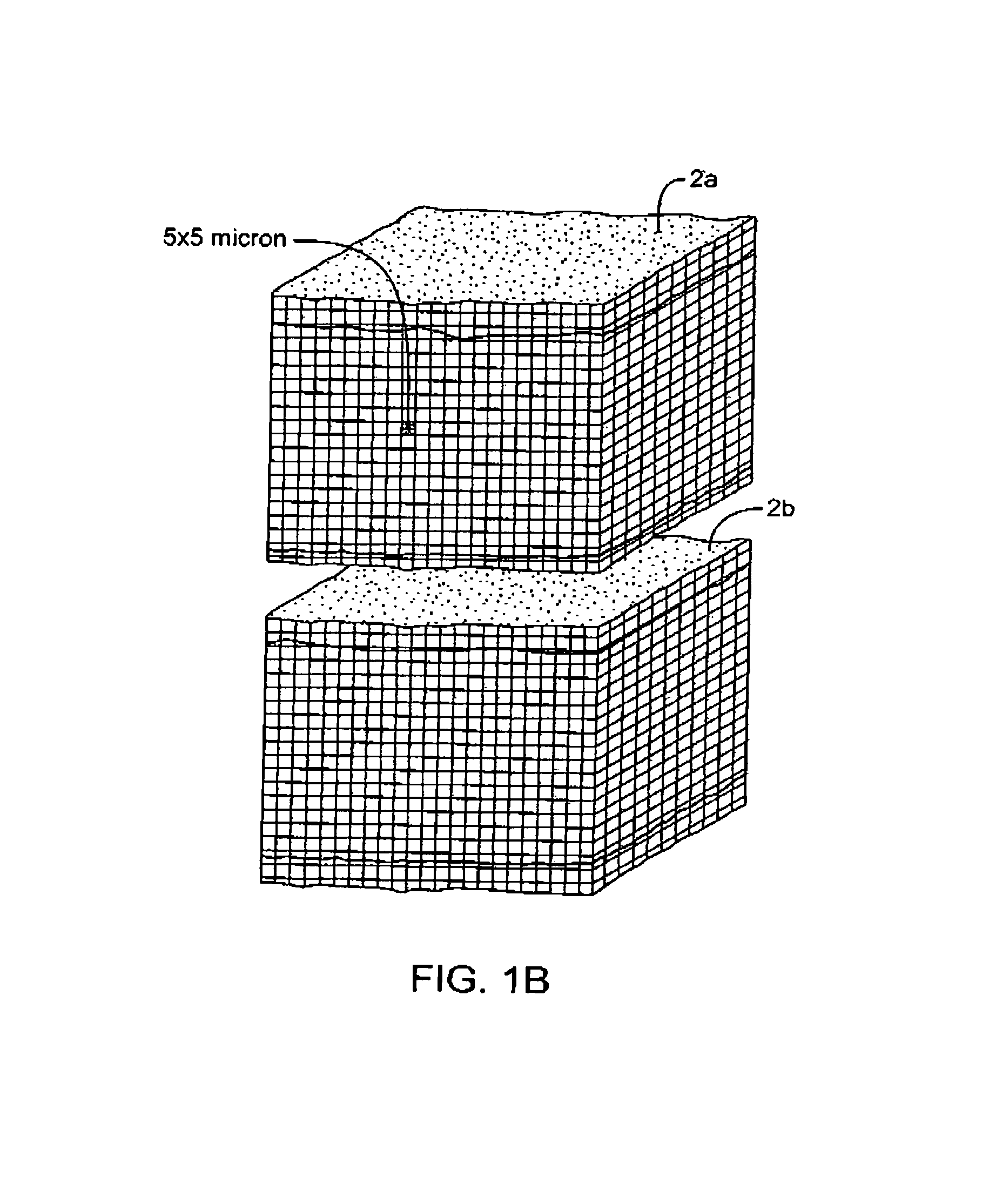

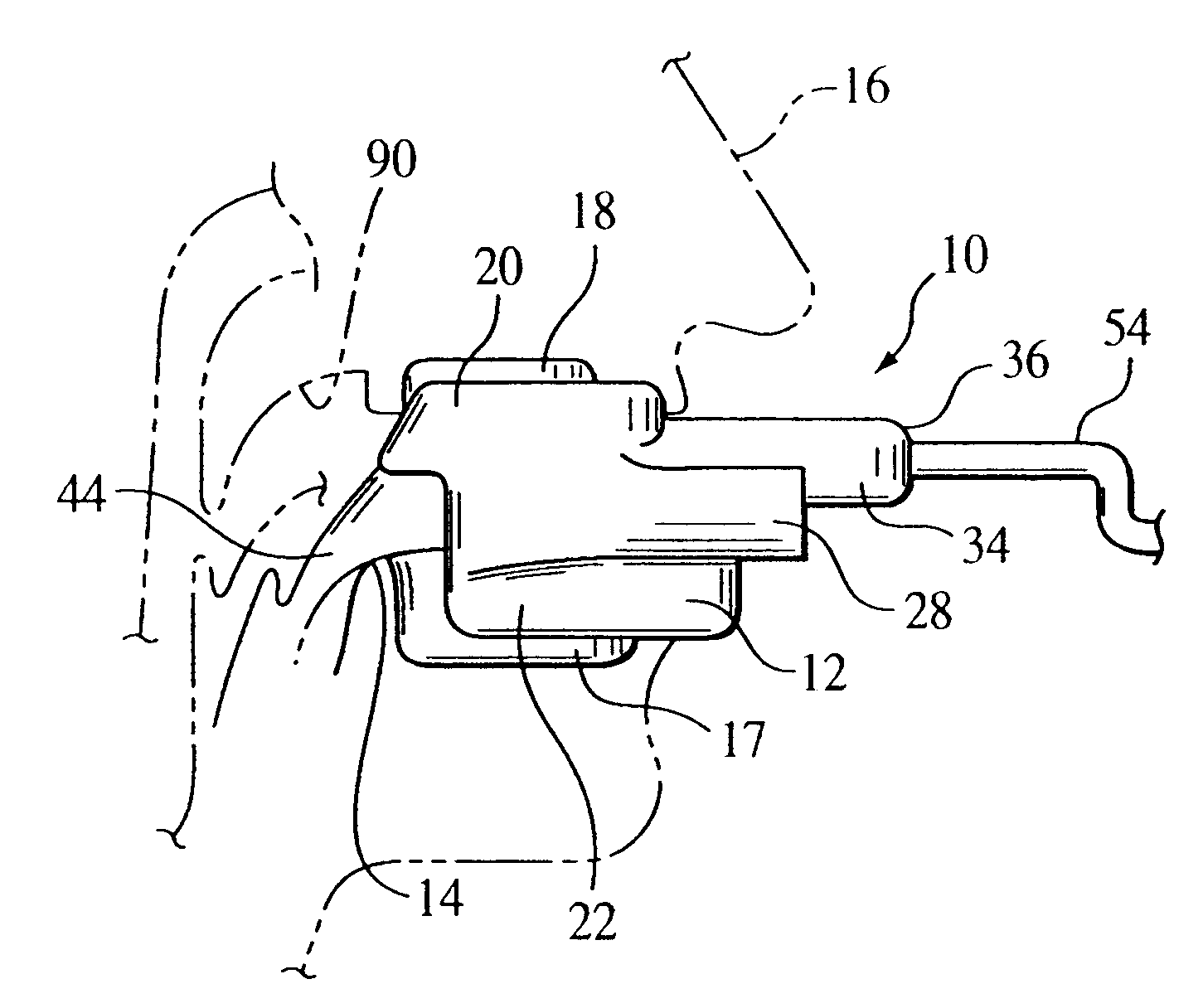

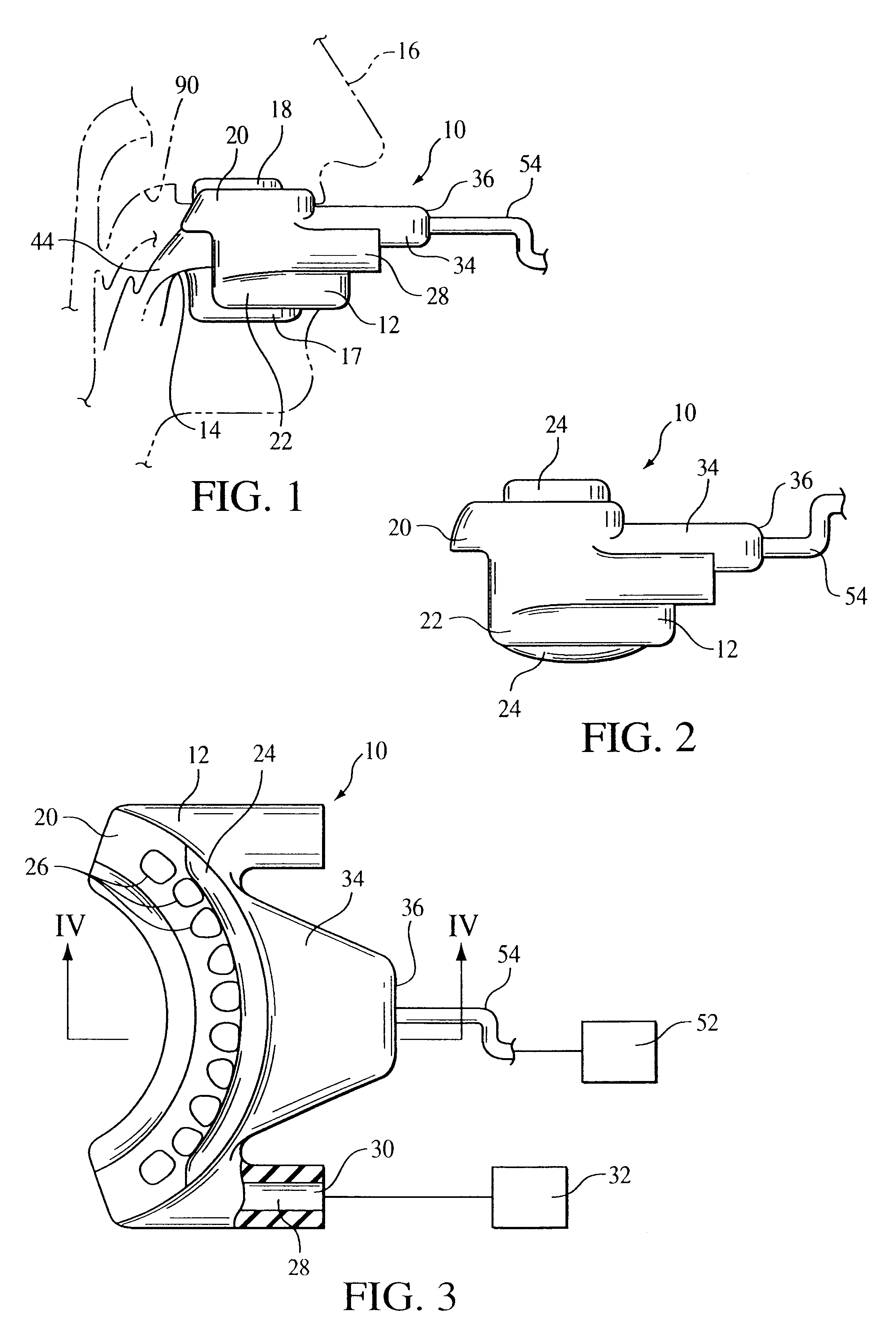

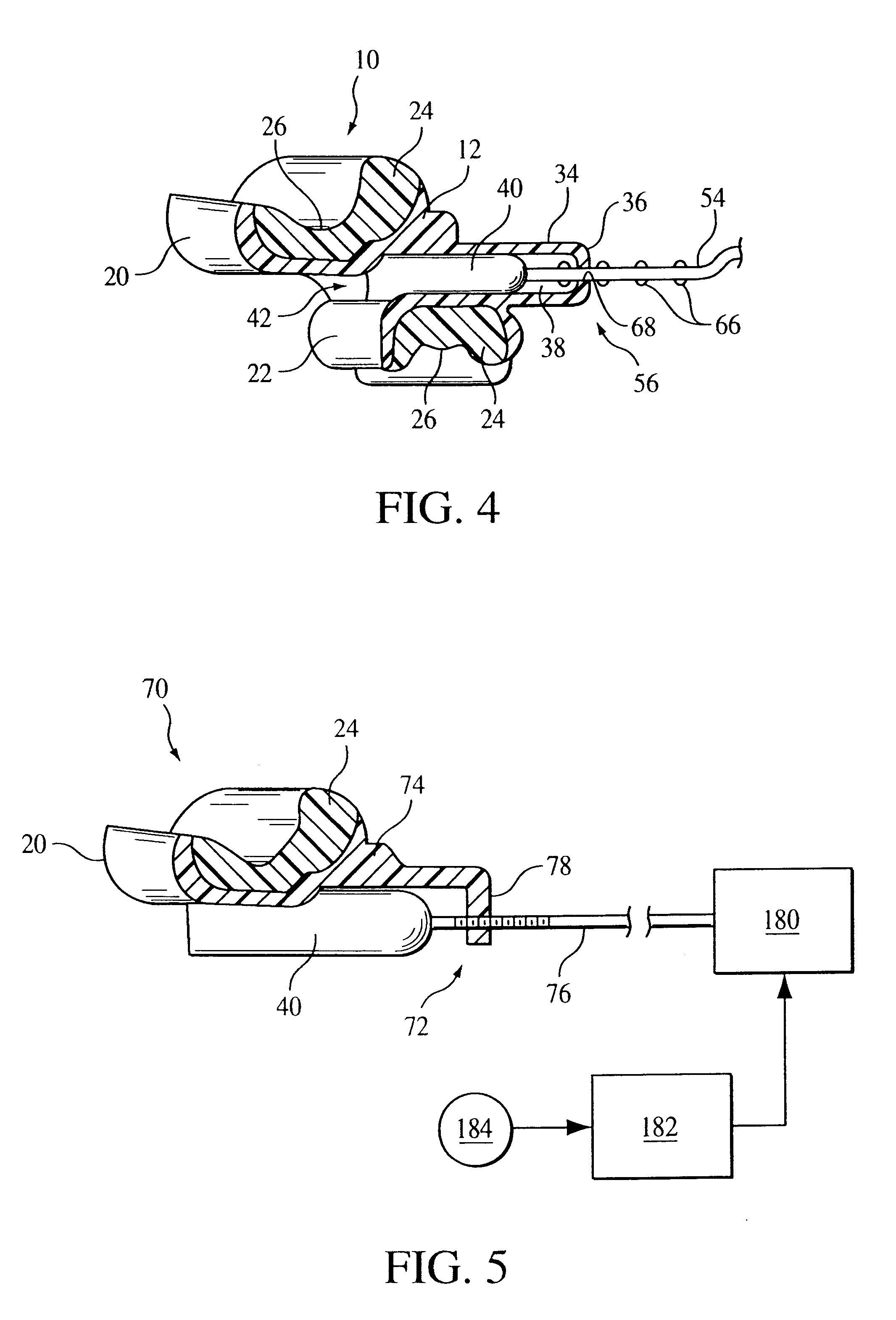

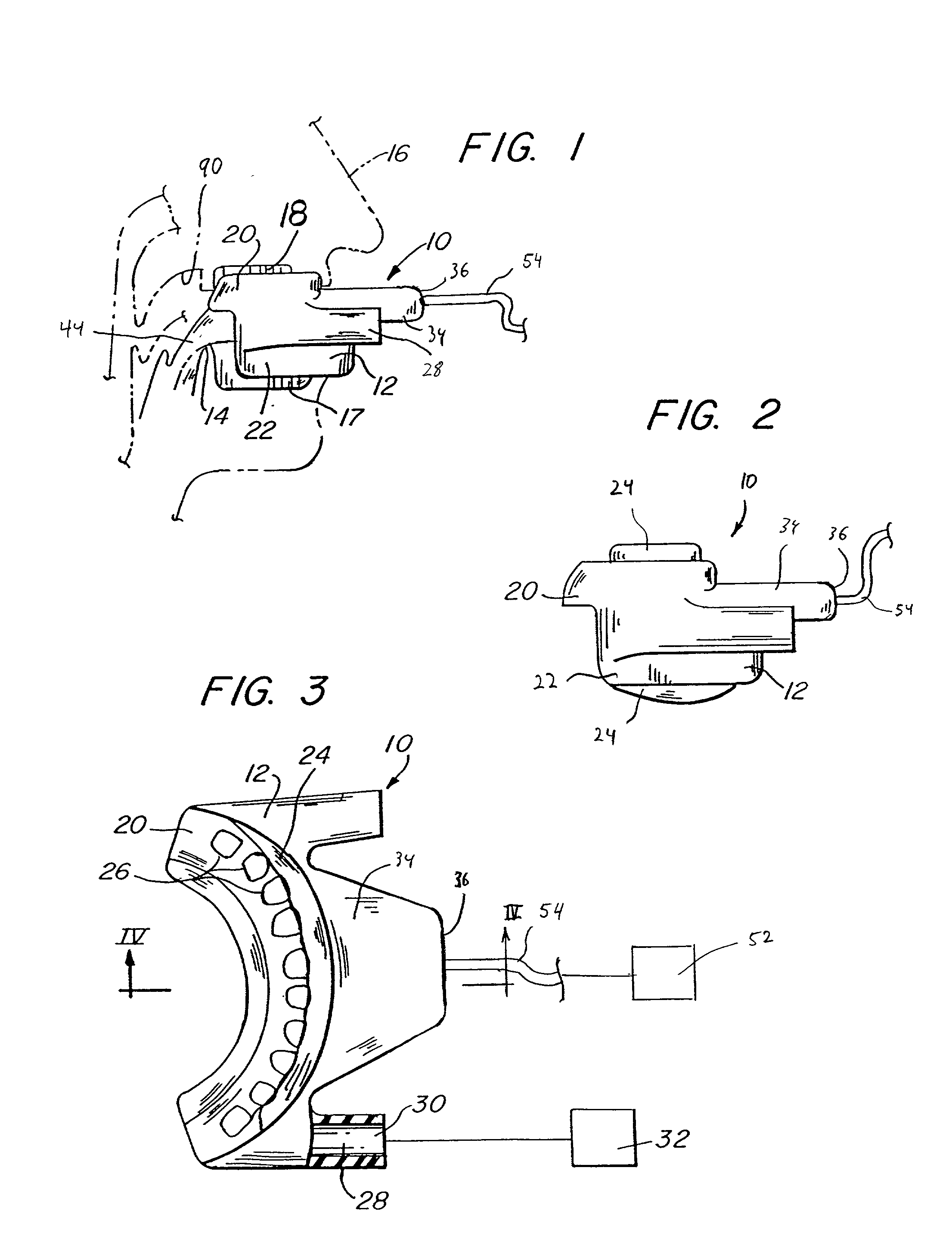

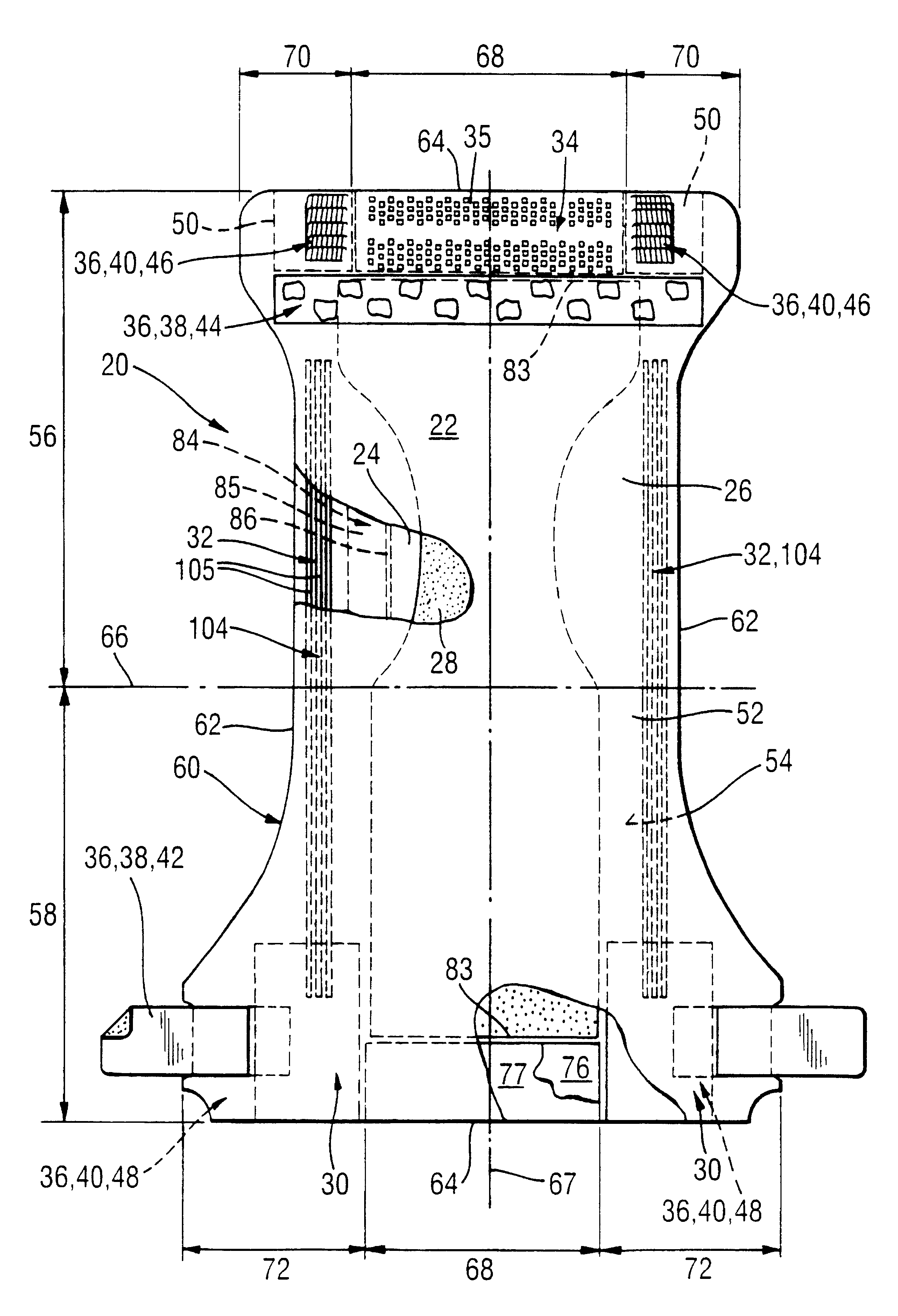

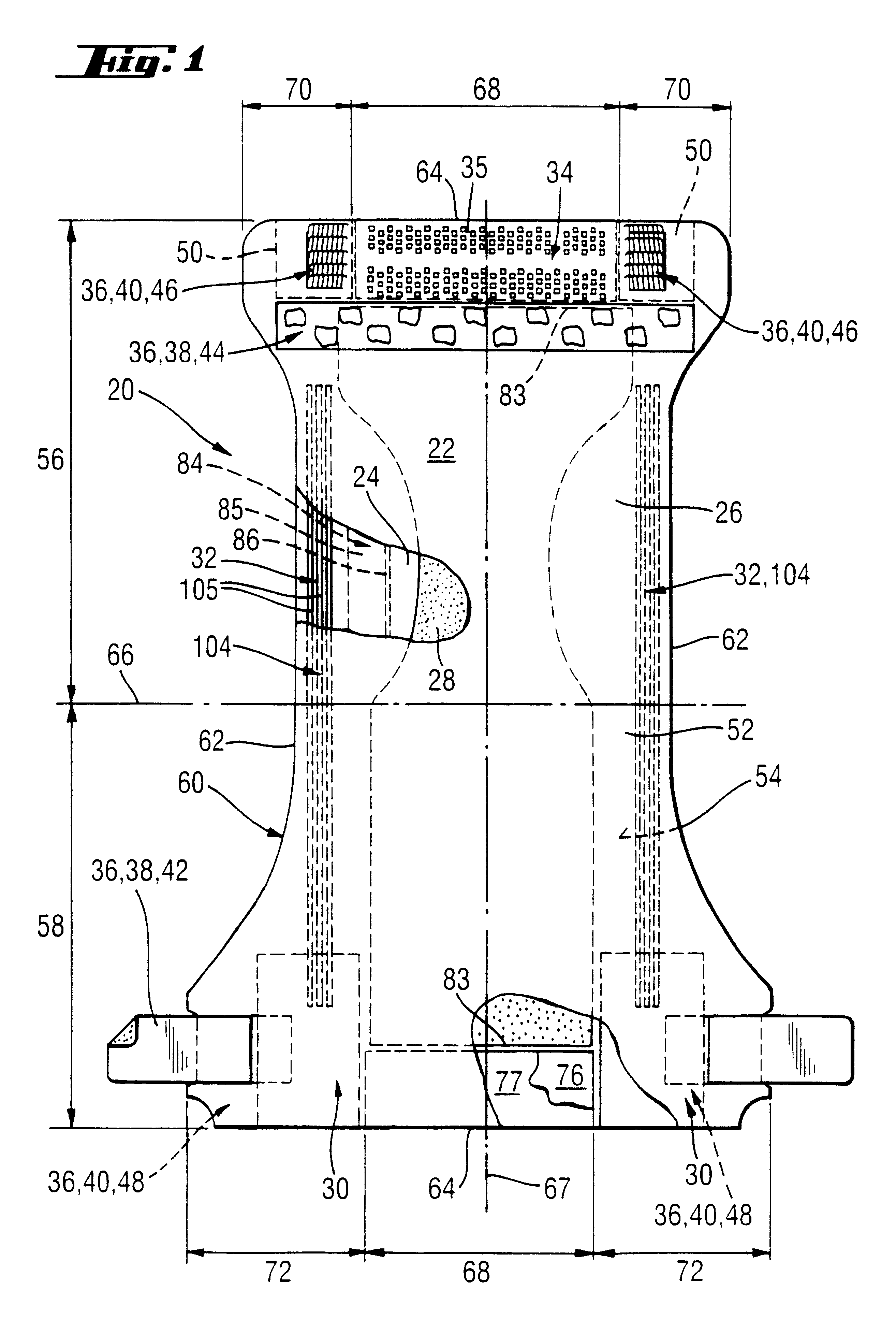

Intraoral apparatus for enhancing airway patency

InactiveUS6877513B2Enhancing upper airway stabilityEnhanced upper airway patencyTracheal tubesOperating means/releasing devices for valvesPositive airway pressureInstability

An apparatus for selectively positioning intraoral anatomic features of a human patient to enhance upper airway stability for use alone or in combination with positive airway pressure as therapeutic treatment for obstructive sleep apnea and other conditions, such as snoring, which are symptomatic of upper airway instability.

Owner:RIC INVESTMENTS LLC

Intraoral apparatus for enhancing airway patency

InactiveUS20010047805A1Eliminate the obstructive/restrictive episodesImprove pressure resistanceTracheal tubesOperating means/releasing devices for valvesPositive airway pressureInstability

An apparatus for selectively positioning intraoral anatomic features of a human patient to enhance upper airway stability for use alone or in combination with positive airway pressure as therapeutic treatment for obstructive sleep apnea and other conditions, such as snoring, which are symptomatic of upper airway instability.

Owner:RIC INVESTMENTS LLC

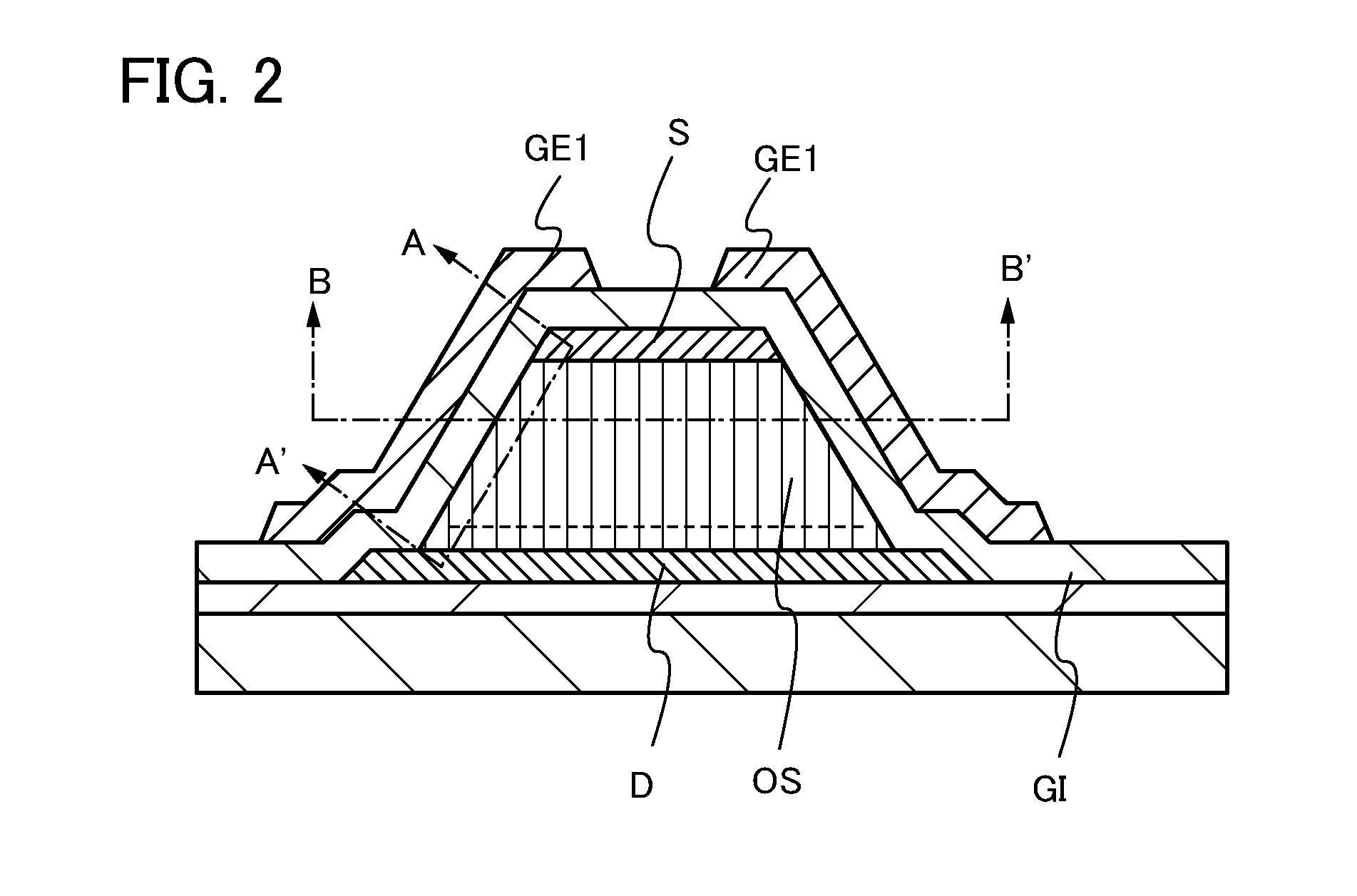

Semiconductor device and method for manufacturing the same

ActiveUS20110127522A1High on-off ratioHigh puritySolid-state devicesSemiconductor/solid-state device manufacturingSemiconductor materialsElectron donor

Objects are to provide a semiconductor device for high power application in which a novel semiconductor material having high productivity is used and to provide a semiconductor device having a novel structure in which a novel semiconductor material is used. The present invention is a vertical transistor and a vertical diode each of which has a stacked body of an oxide semiconductor in which a first oxide semiconductor film having crystallinity and a second oxide semiconductor film having crystallinity are stacked. An impurity serving as an electron donor (donor) which is contained in the stacked body of an oxide semiconductor is removed in a step of crystal growth; therefore, the stacked body of an oxide semiconductor is highly purified and is an intrinsic semiconductor or a substantially intrinsic semiconductor whose carrier density is low. The stacked body of an oxide semiconductor has a wider band gap than a silicon semiconductor.

Owner:SEMICON ENERGY LAB CO LTD

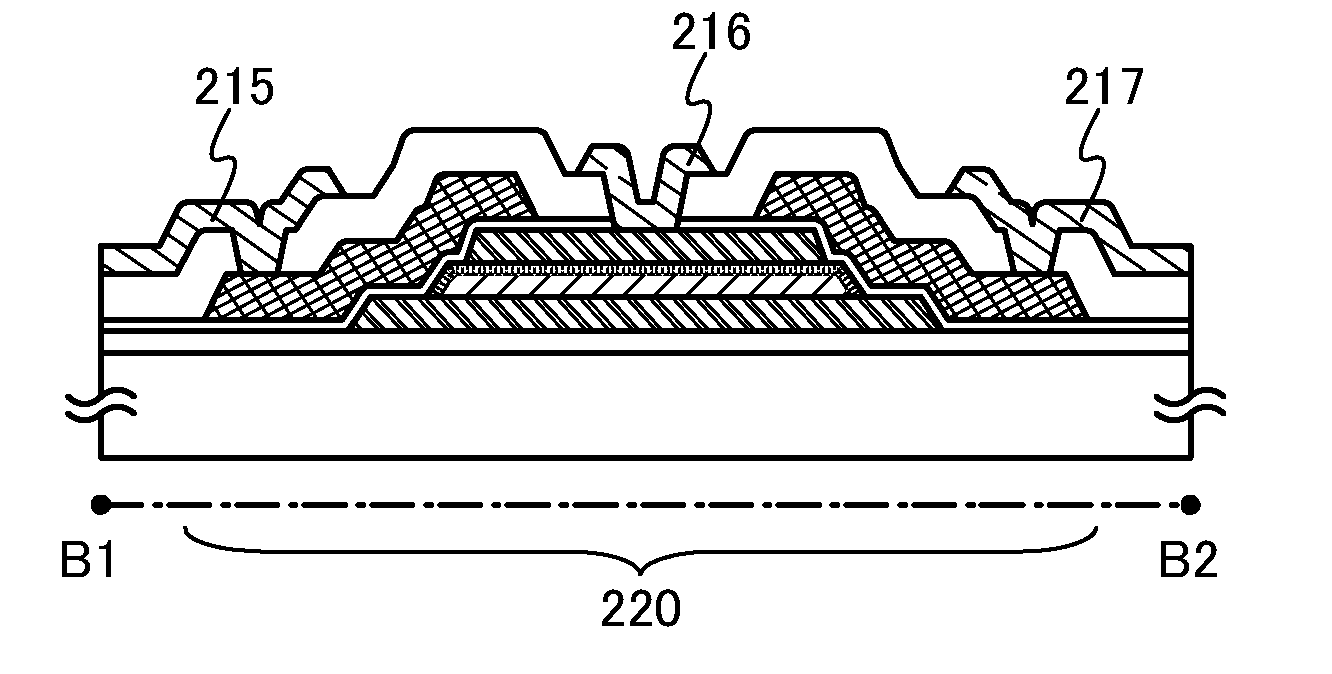

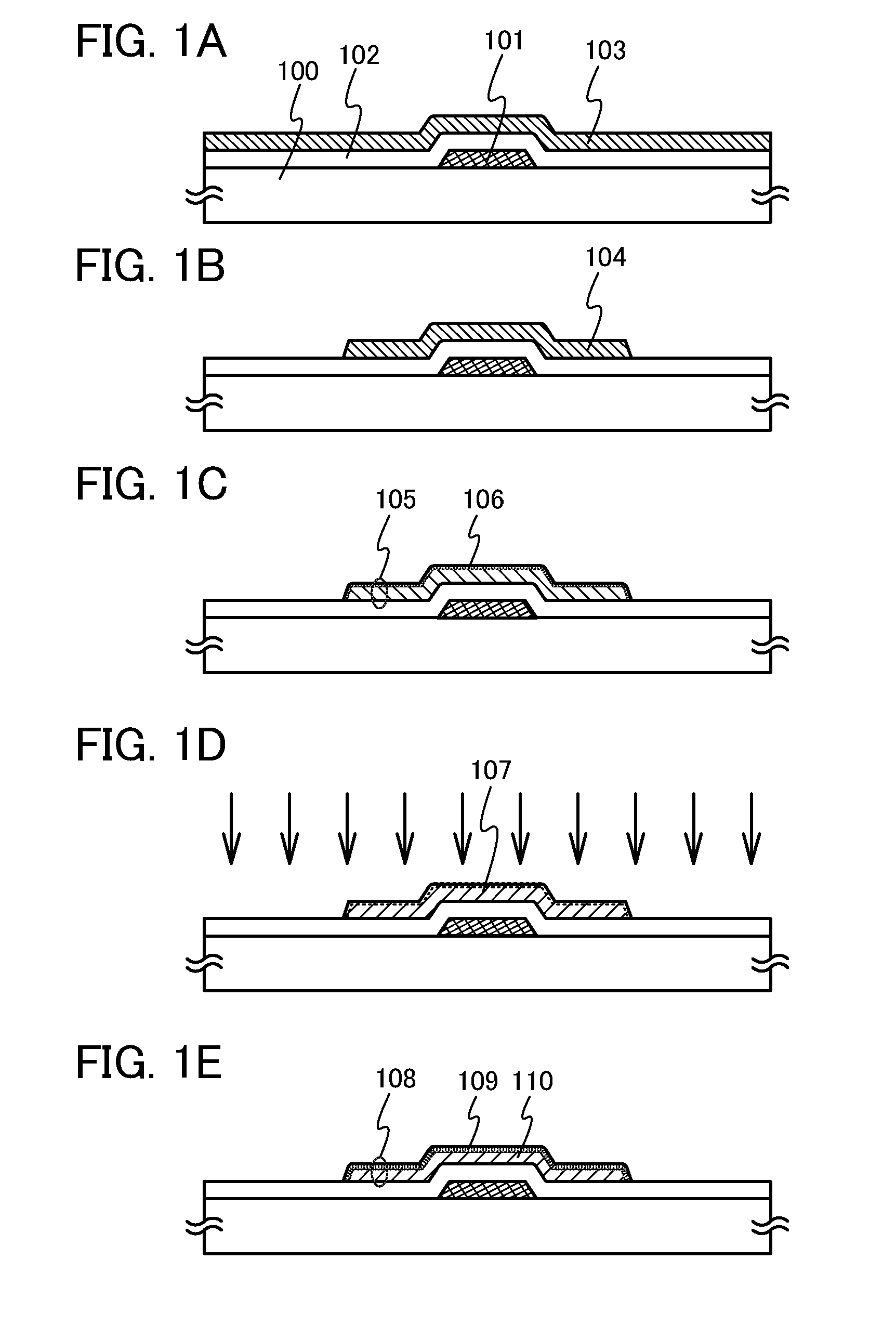

Semiconductor device and manufacturing method thereof

ActiveUS20110136301A1Improve barrier propertiesPromote absorptionElectroluminescent light sourcesSemiconductor/solid-state device manufacturingOxide semiconductorOxide

A semiconductor device for high power application in which a novel semiconductor material having high mass productivity is provided. An oxide semiconductor film is formed, and then, first heat treatment is performed on the exposed oxide semiconductor film in order to reduce impurities such as moisture or hydrogen in the oxide semiconductor film. Next, in order to further reduce impurities such as moisture or hydrogen in the oxide semiconductor film, oxygen is added to the oxide semiconductor film by an ion implantation method, an ion doping method, or the like, and after that, second heat treatment is performed on the exposed oxide semiconductor film.

Owner:SEMICON ENERGY LAB CO LTD

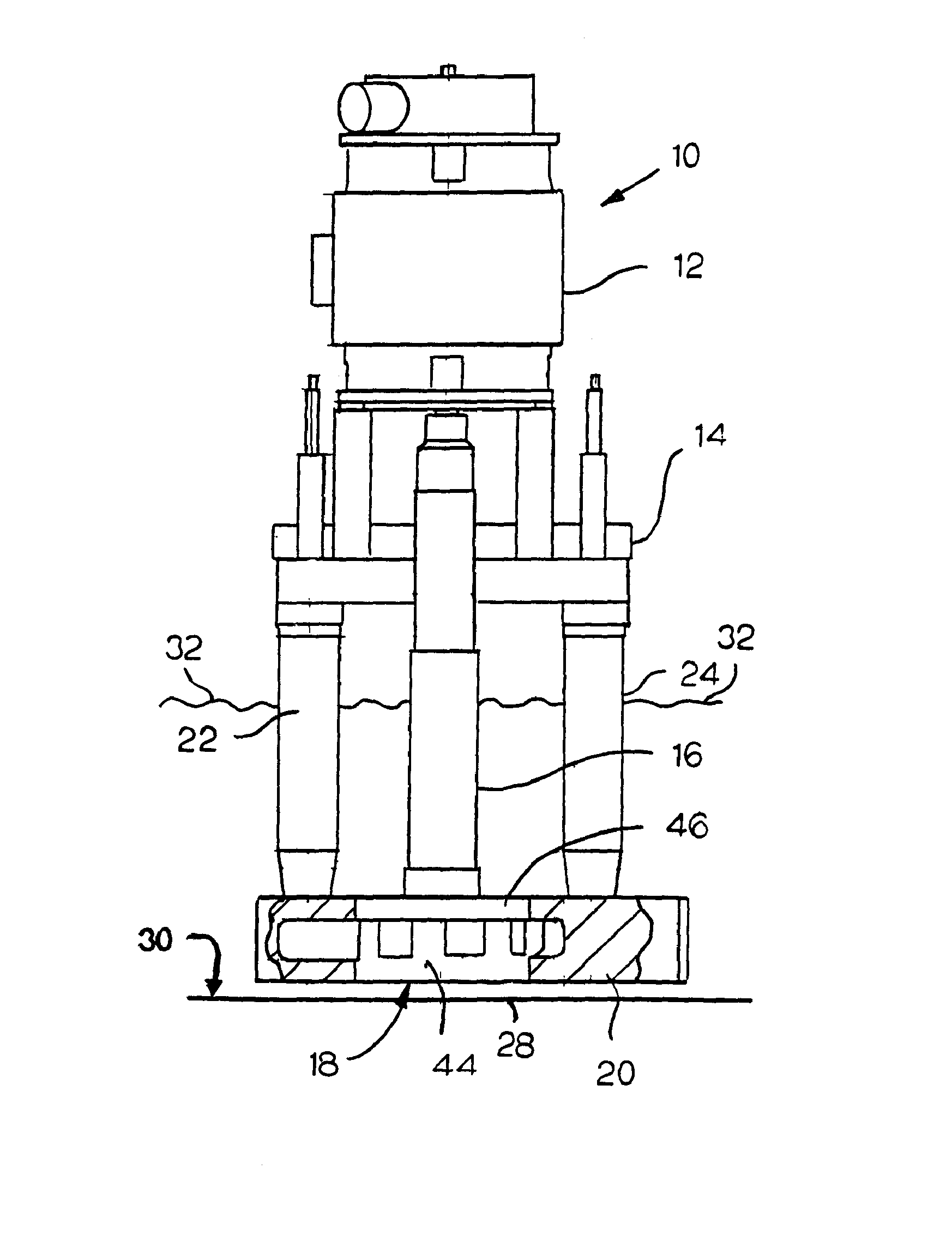

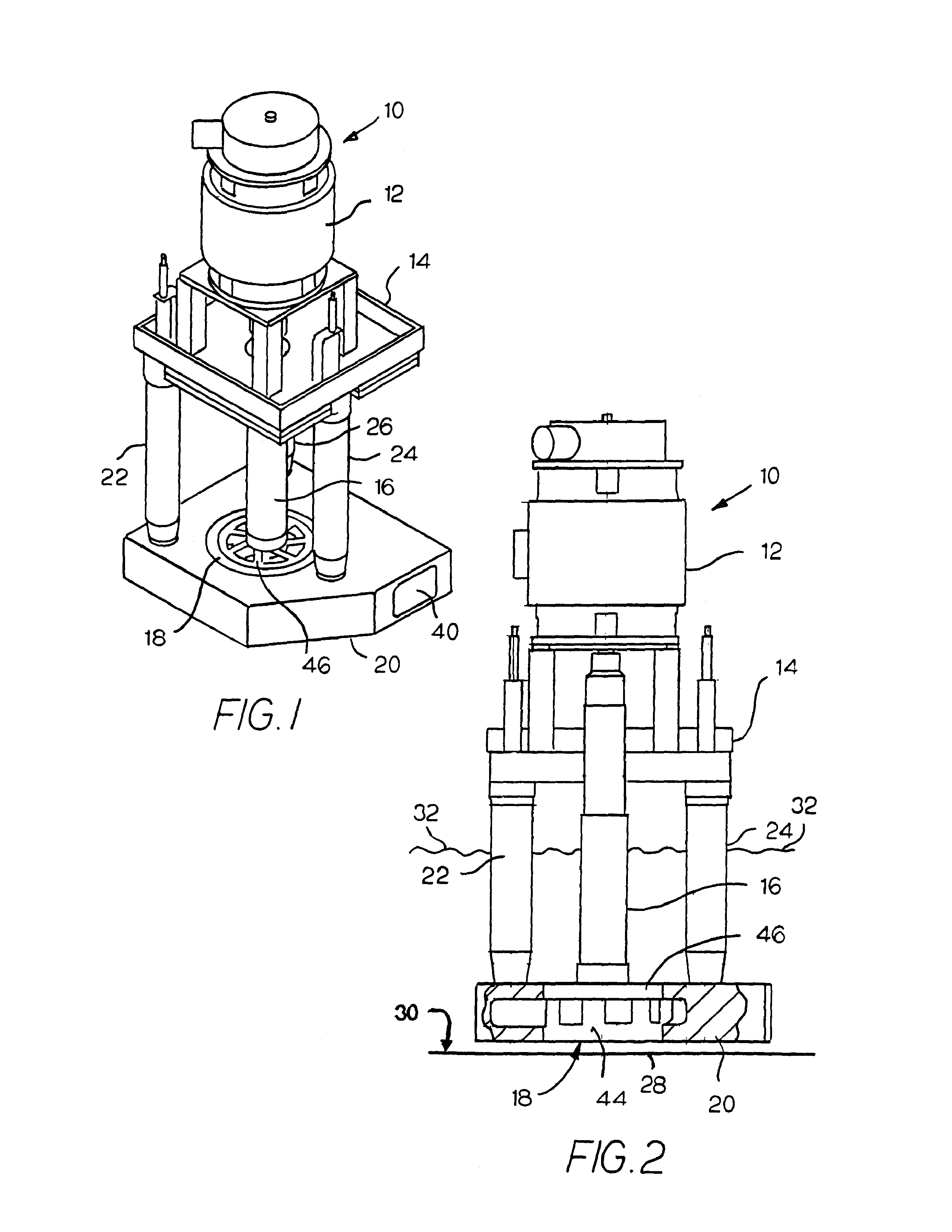

High flow/dual inducer/high efficiency impeller for liquid applications including molten metal

A centrifugal pump has a pump base with inlet inducer openings that receive molten metal into an impeller chamber. An impeller structure in the impeller chamber passes the metal in a radial direction through an outlet inducer opening into a volute passage for discharge into the pool of metal in which the pump is located.

Owner:MORANDO JORGE A

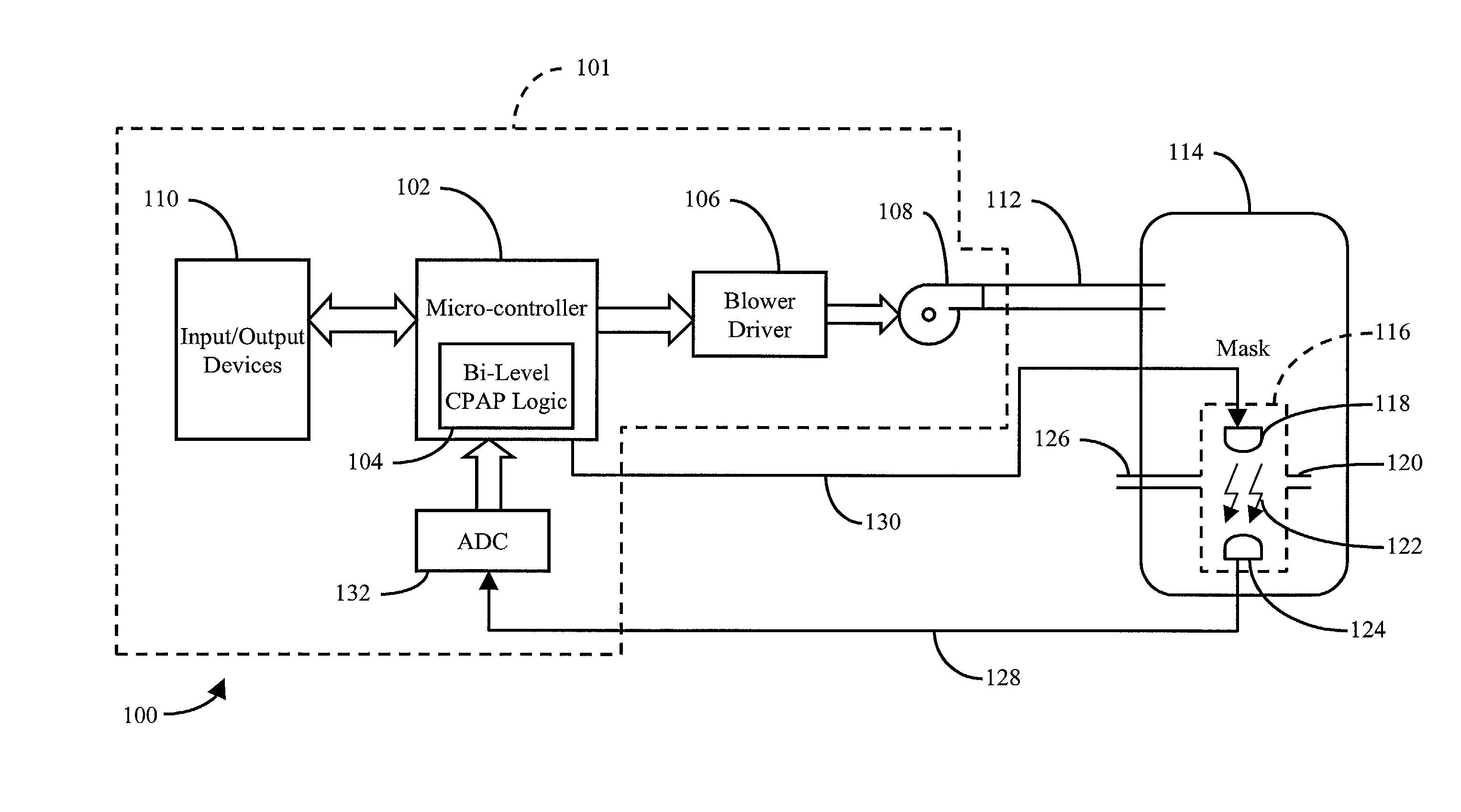

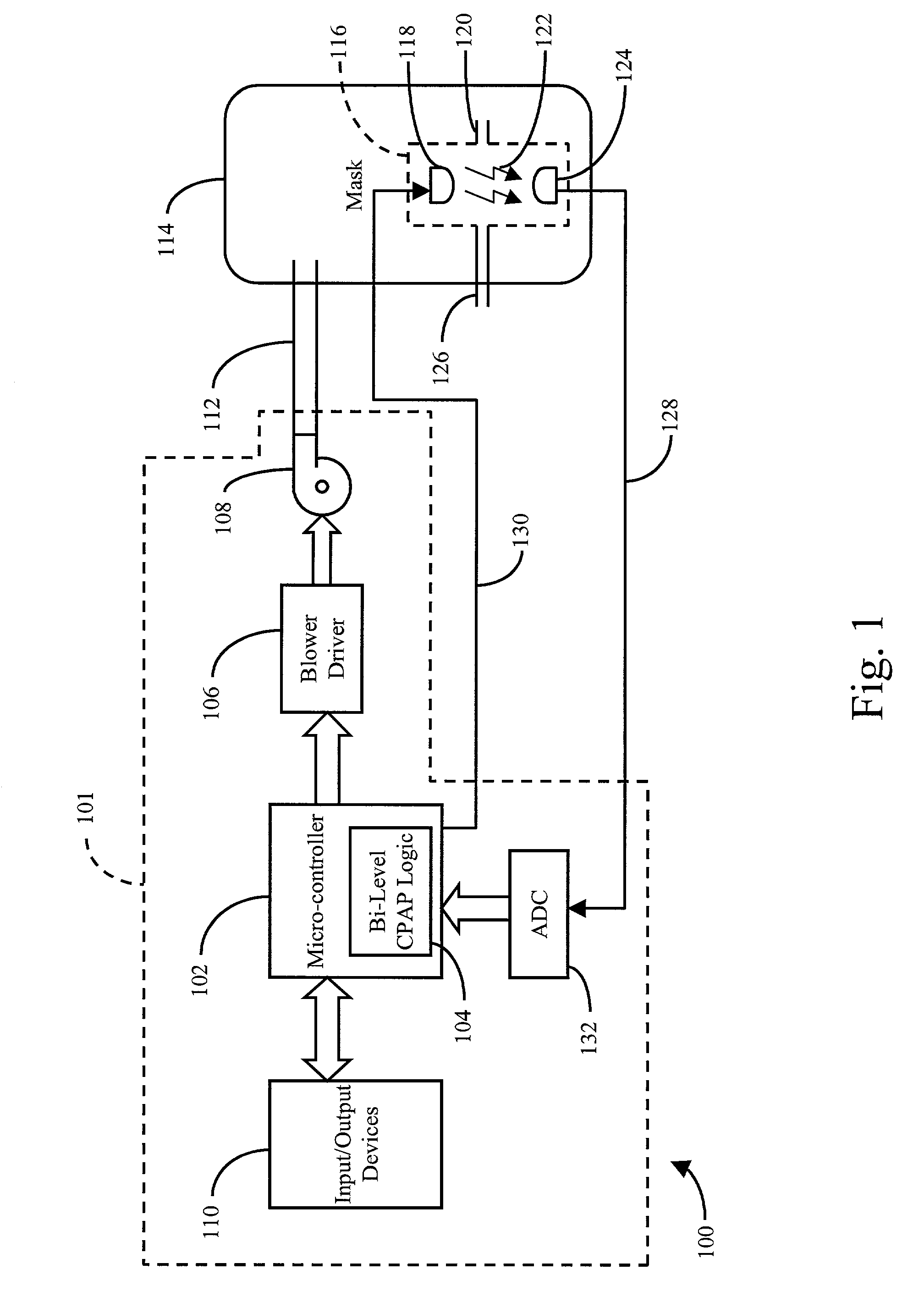

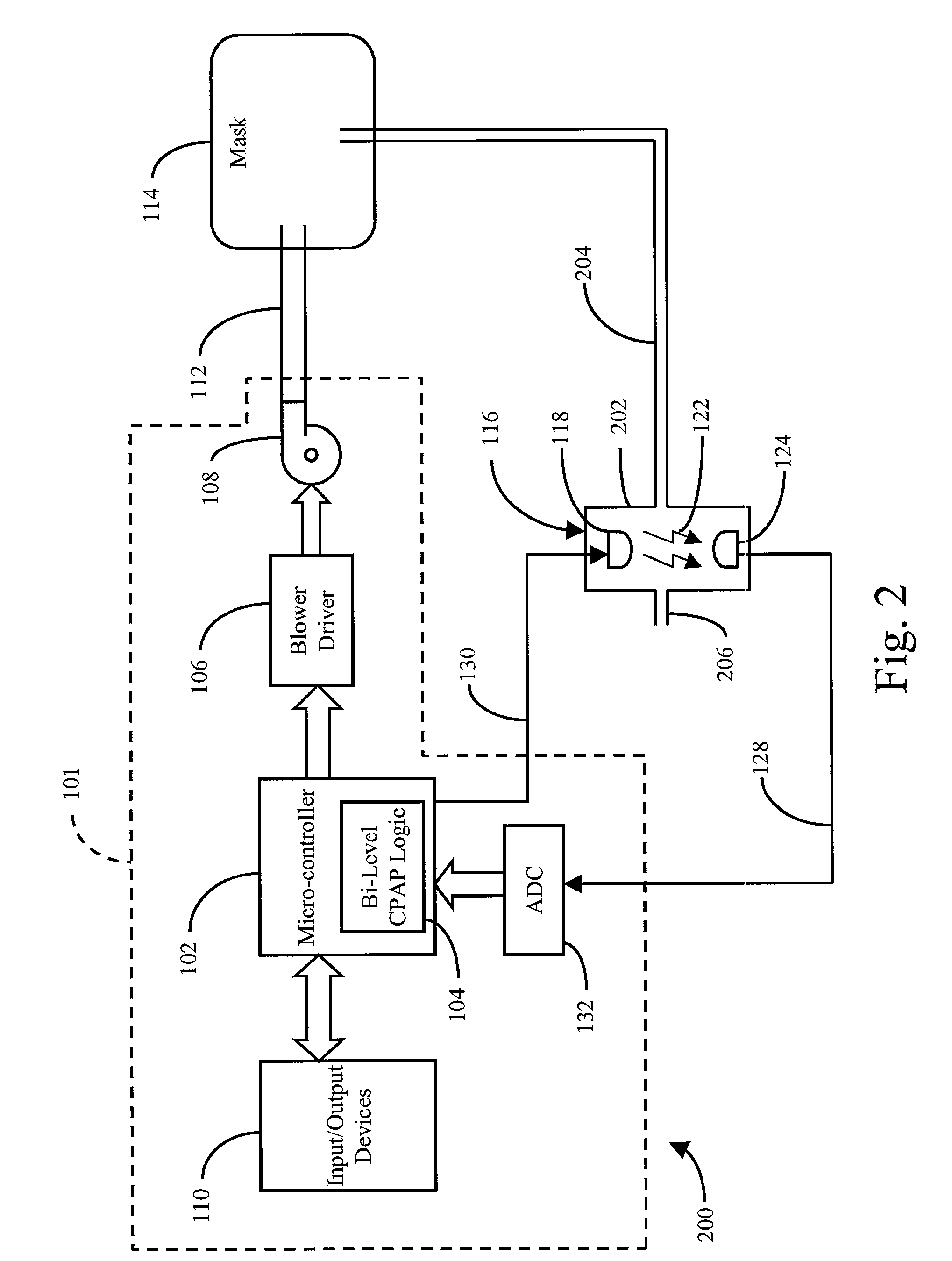

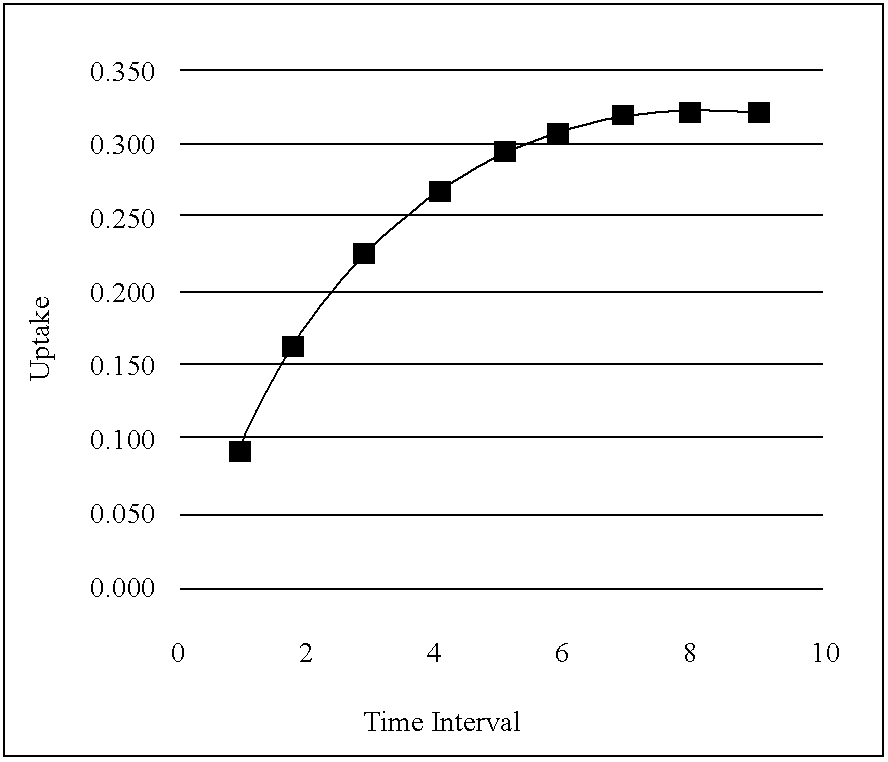

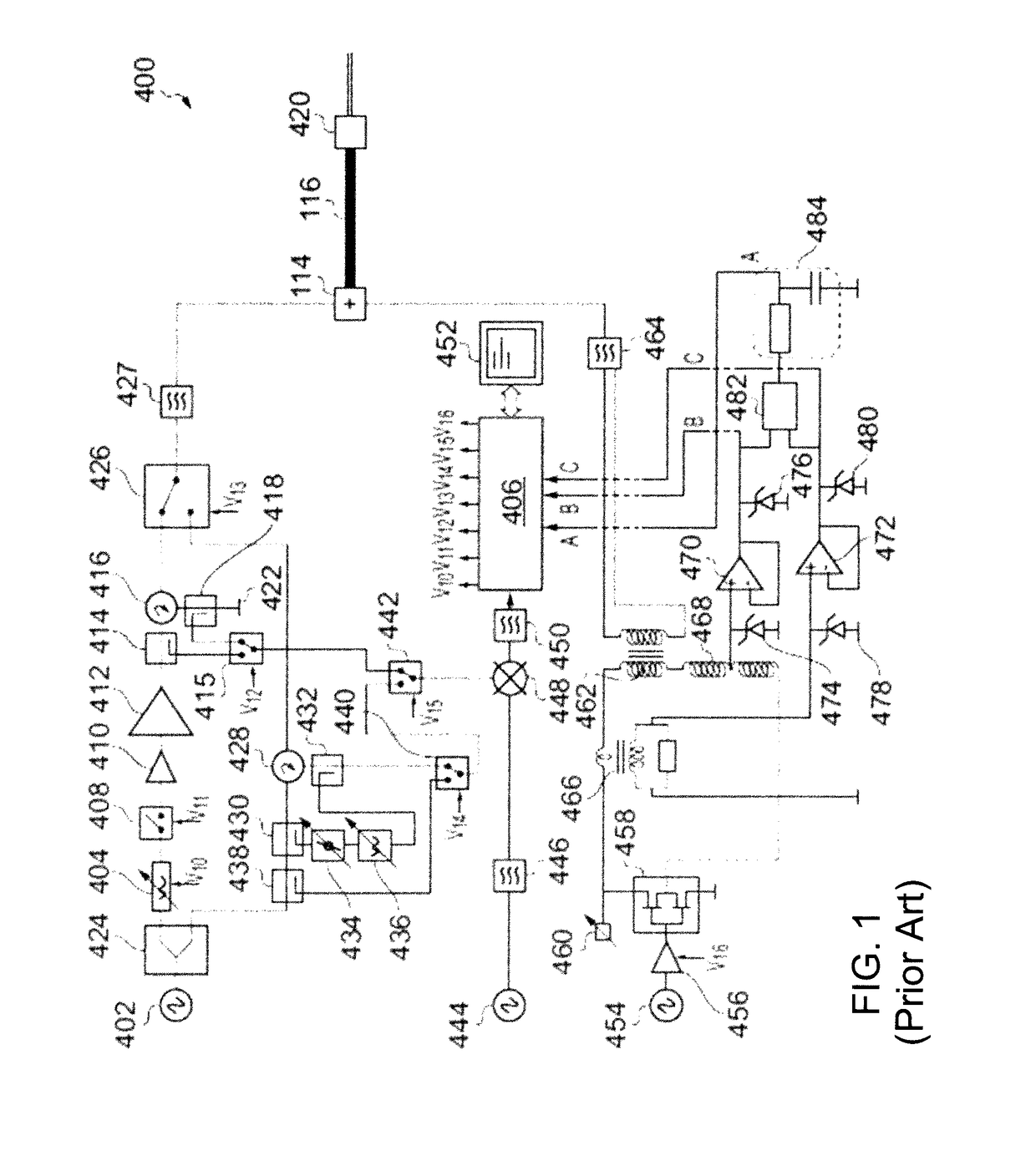

Carbon dioxide-based Bi-level CPAP control

InactiveUS6990980B2Few transmissionImprove pressure resistanceRespiratorsOperating means/releasing devices for valvesInhalationIntensive care medicine

A system and method of providing bi-level CPAP therapy is provided that incorporates an infrared carbon-dioxide sensor to determine whether a patient is inhaling or exhaling. Patient exhalation causes the infrared light to be absorbed, while patient inhalation reduces the presence of carbon-dioxide causes little or no absorption of carbon-dioxide. The level of carbon-dioxide in an associated patient breathing interface is monitored for thresholds that trigger higher CPAP pressure upon inhalation and lower CPAP pressure upon exhalation.

Owner:INVACARE CORP

Absorbent structures comprising fluid storage members with improved ability to dewater acquisition/distribution members

InactiveUS6551295B1Effectively and efficiently dewateredImprove distributionOther chemical processesBaby linensAbsorption capacityDesorption

The present invention is an absorbent structure to be used in absorbent articles, having at least a first region for acquisition / distribution of fluid and a second region for storage of fluid. The first region can contain materials which have a relatively high capillary desorption pressure, as the materials in the second region exhibit a sufficiently high capillary absorption pressure so as to still efficiently drain the first region.The first region material has a Capillary Sorption Desorption Height (CSDH 90) of more than 40 cm and the second region material satisfies at least one of following requirements:(a) an absorption capacity of at least 15 g / g at 35 cm in the capsorption test;(b) an absorption capacity of at least 15 g / g at 0 cm in the capsorption test and an absorption efficiency of at least 55% at 40 cm;(c) a Capillary Sorption Absorption height at 50% of its capacity at 0 cm absorption height (CSAH 50) of at least 35 cm in the capsorption test.

Owner:THE PROCTER & GAMBLE COMPANY

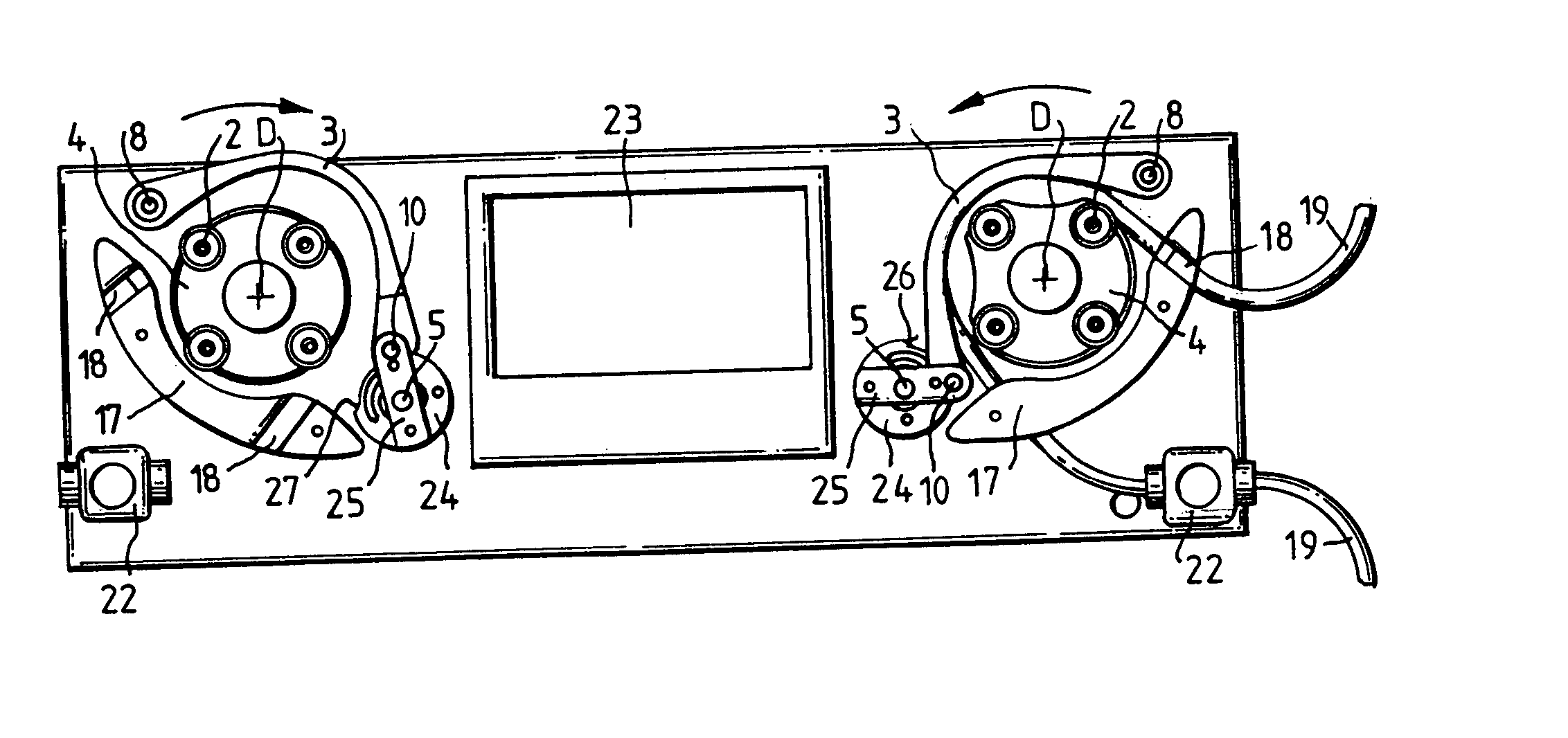

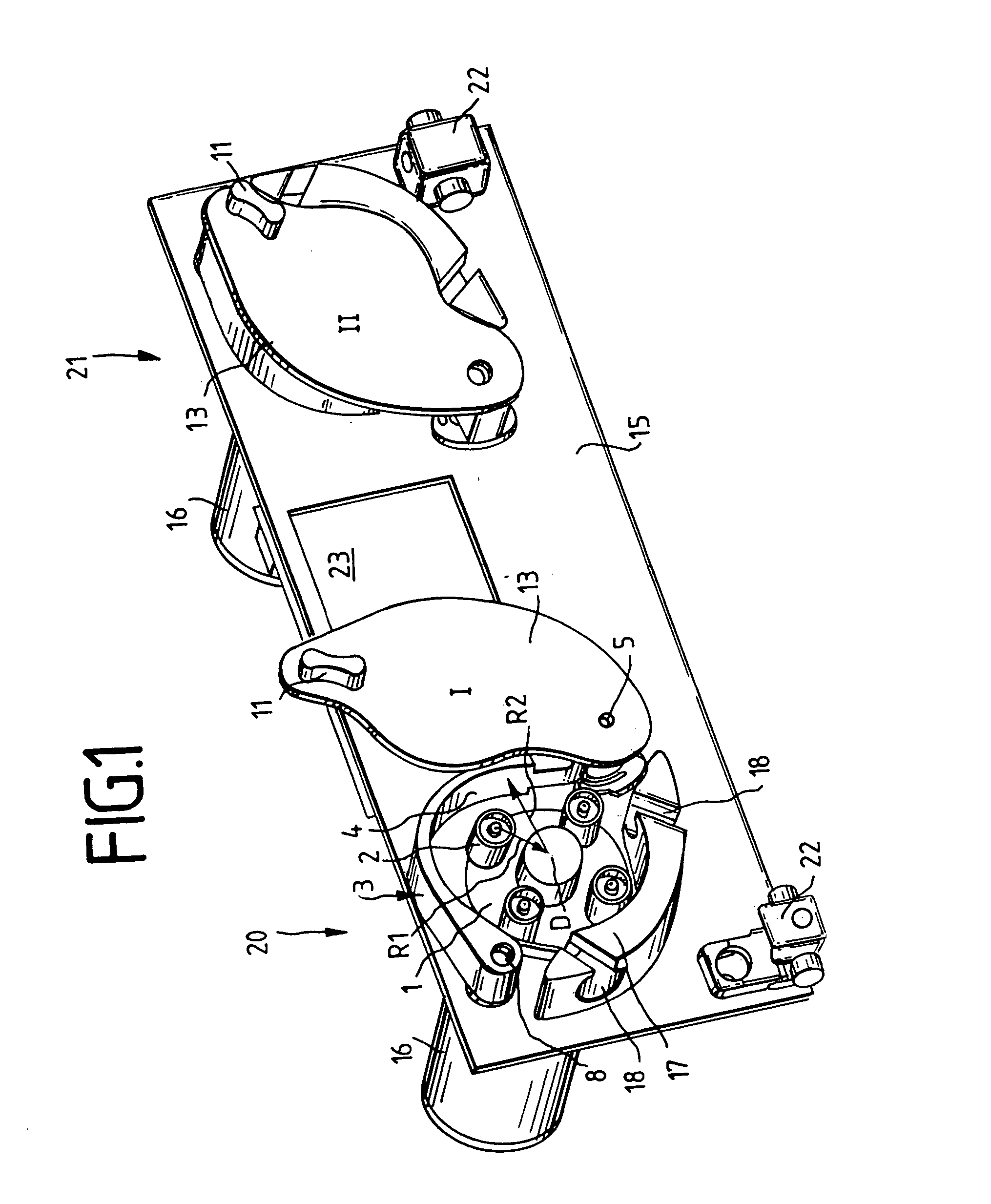

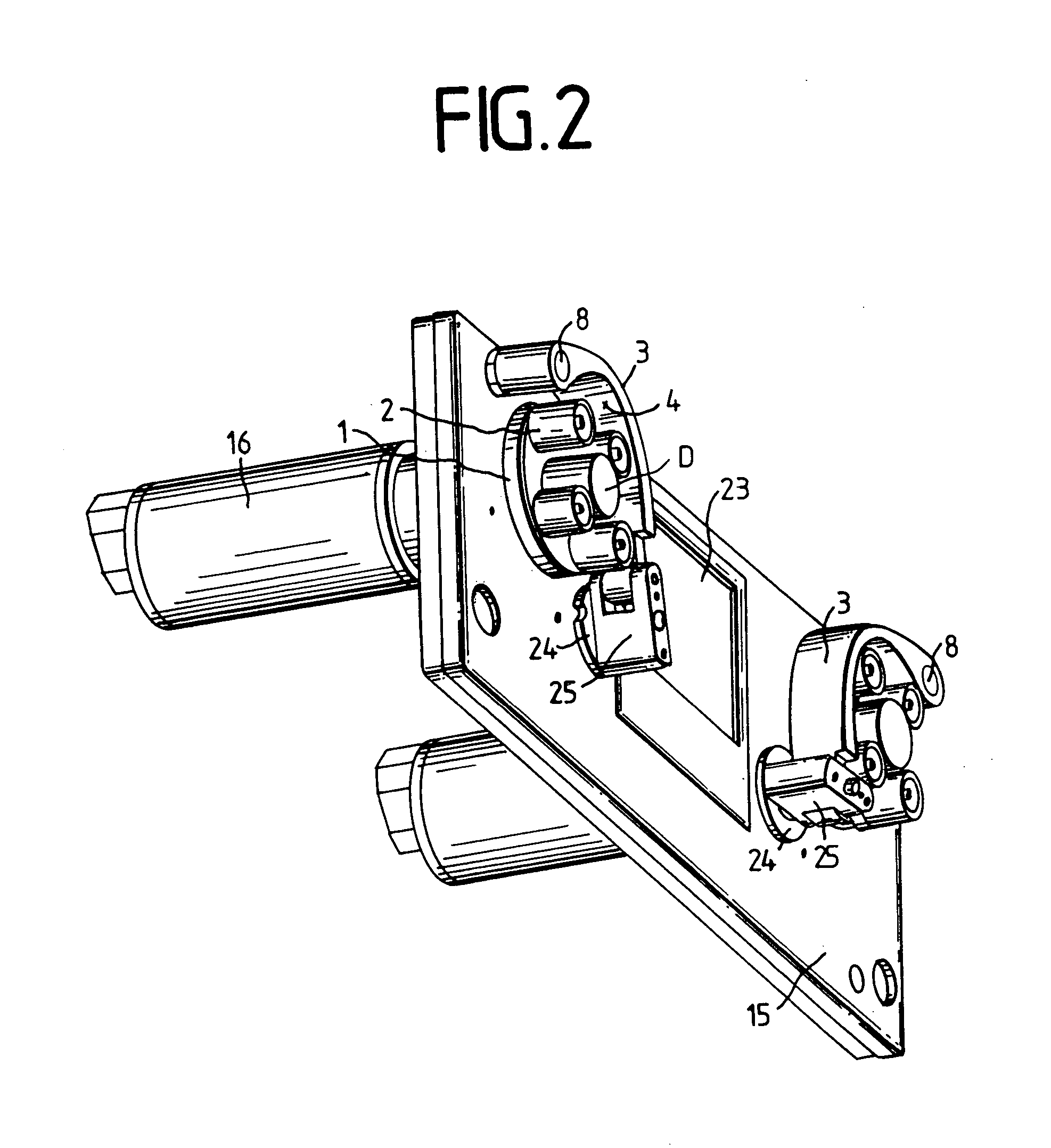

Peristaltic hose pump

InactiveUS20040037724A1Increase delivery pressureIncrease delivery rateFlexible member pumpsEngine componentsSynthetic materialsEngineering

The invention relates to a peristaltic hose pump comprising a roller wheel (1), which can rotate about a roller wheel axis D and which has rollers (2) that are mounted on the roller wheel (1). The rollers (2) roll away on a circular path having a radius R1 with regard to the roller wheel rotation axis D. The peristaltic hose pump also comprises a pressure arched element (3) with a supporting surface (4), whereby the supporting surface (4) extends along a circular path having a radius R2 around the rotation axis D of the roller wheel (1). In addition, a flexible hose (19) can be placed between the supporting surface (4) and the rollers (2) of the roller wheel (1). According to the invention, the supporting surface (4) is formed out of an elastically deformable synthetic material, and the pressure arched element (3) is pre-shaped with the provision that the extension of the supporting surface (4), when the pressure arched element (3) is not under tension, essentially corresponds to the extension of the supporting surface (4) when under tension.

Owner:W O M WORLD OF MEDICINE GMBH

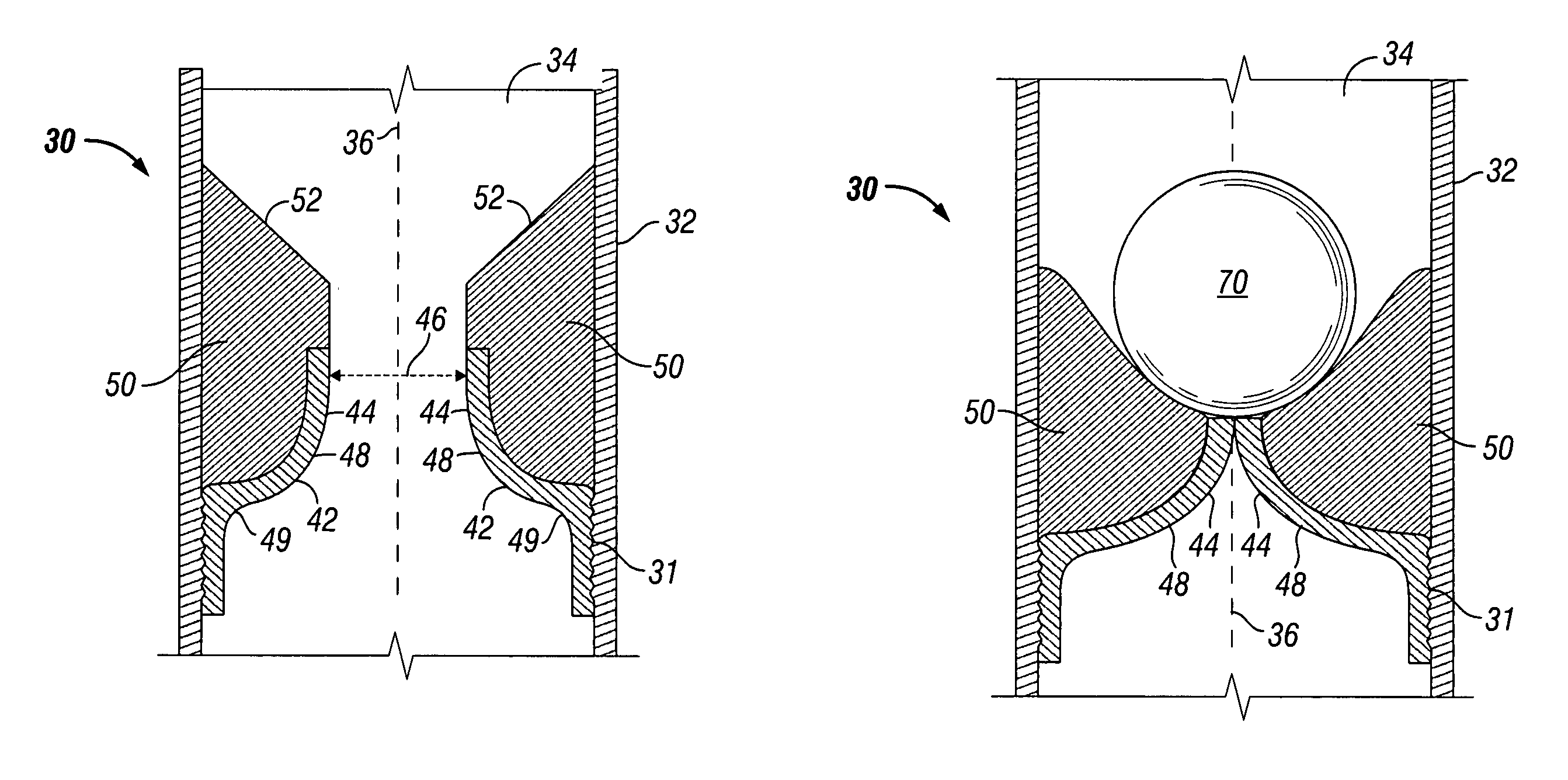

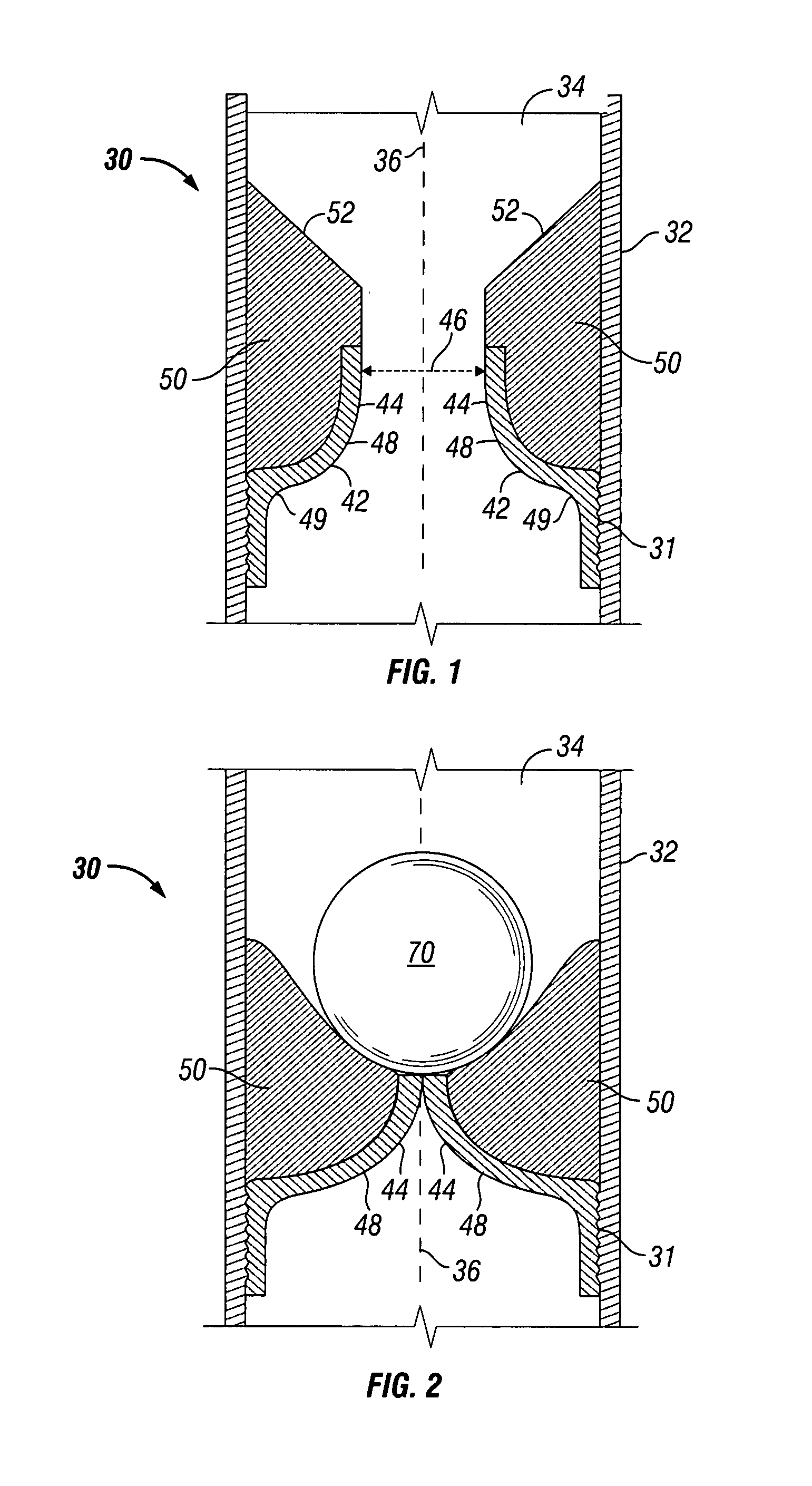

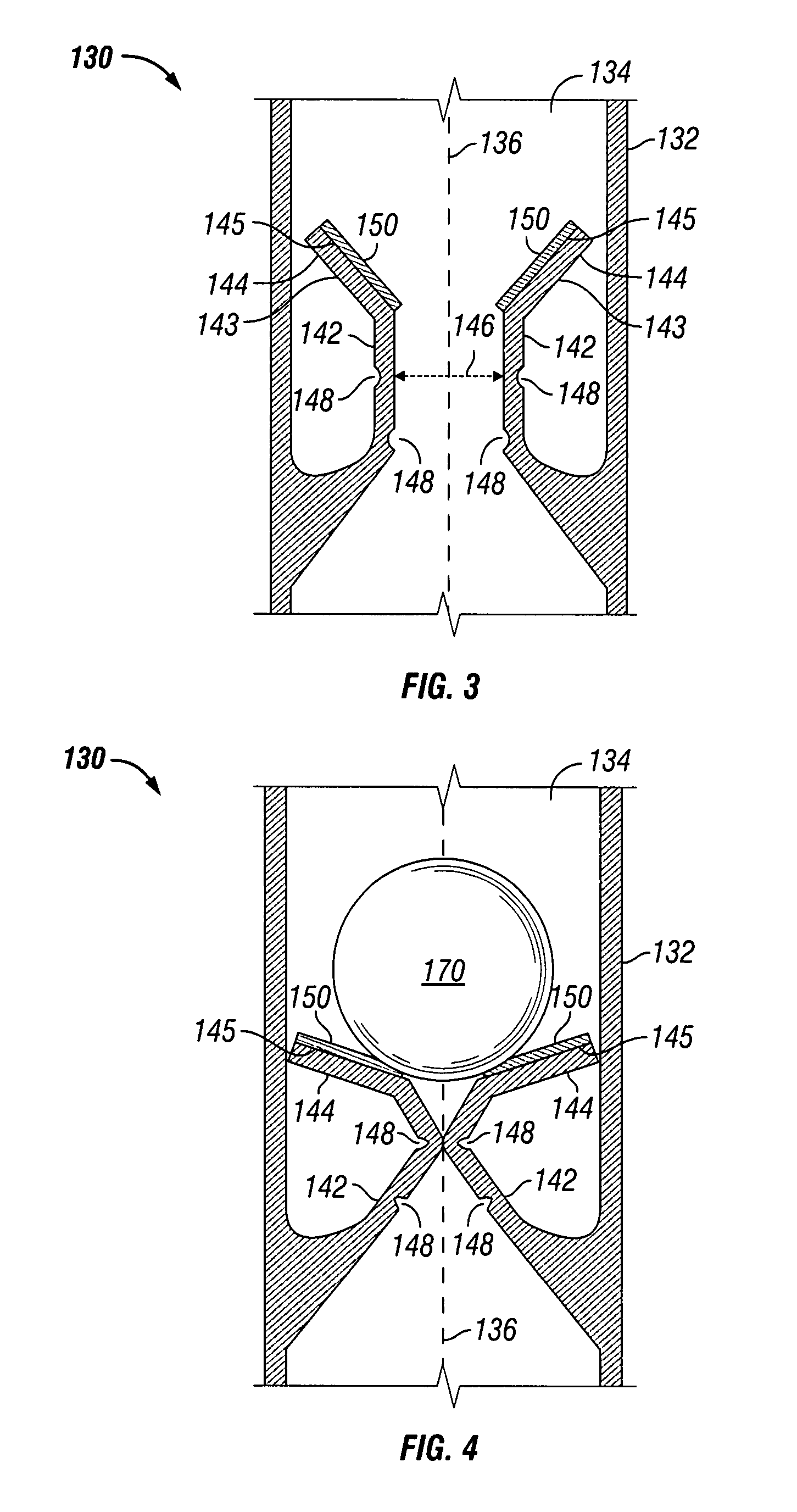

Deformable ball seat

ActiveUS7503392B2Increase surface areaReduce the possibilityCheck valvesFluid removalEngineeringMechanical engineering

Apparatuses for restricting fluid flow through a well conduit comprise a housing having a longitudinal bore and a collapsible seat disposed within the bore. The seat has a first position defining a first seat inner diameter when the apparatus is in the run-in position and a second position defining a second seat inner diameter when the apparatus is in the set position. The first seat inner diameter is greater than the second seat inner diameter. A plug element is adapted to be disposed into the bore and landed on the seat to move the seat from the first position to the second position. While in the second position, the seat restricts fluid flow through the bore and provides additional support to the plug member landed on the seat.

Owner:BAKER HUGHES HLDG LLC

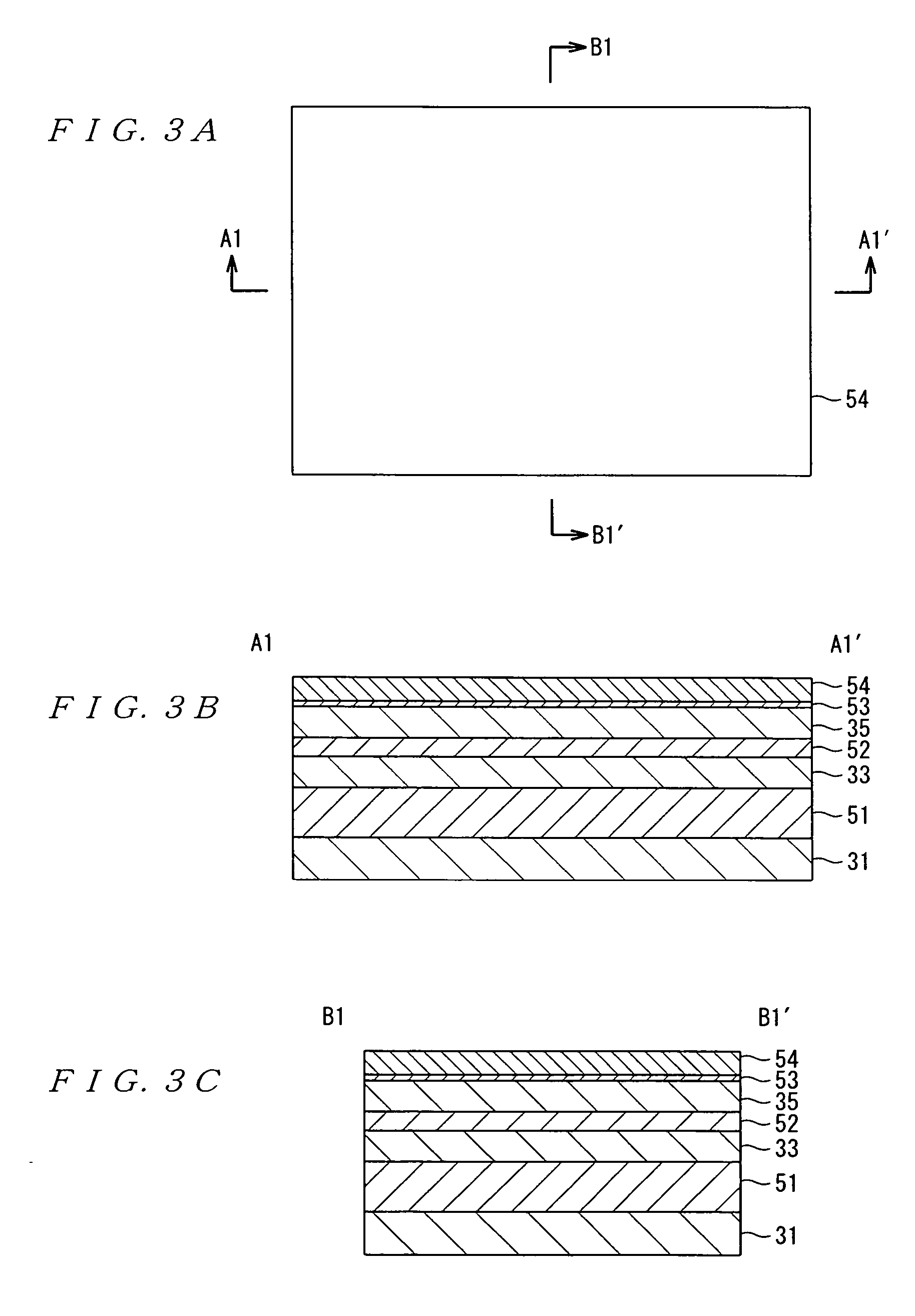

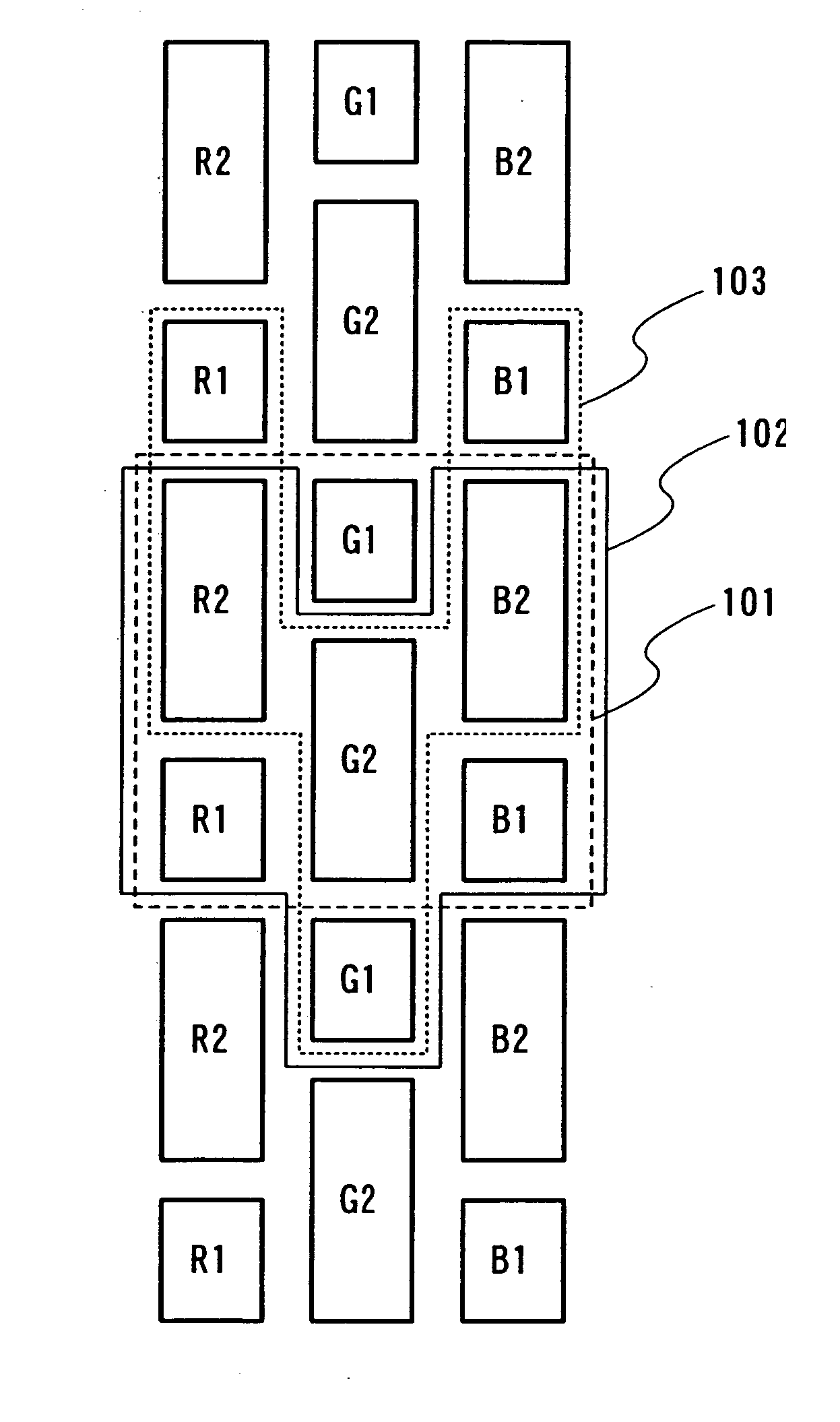

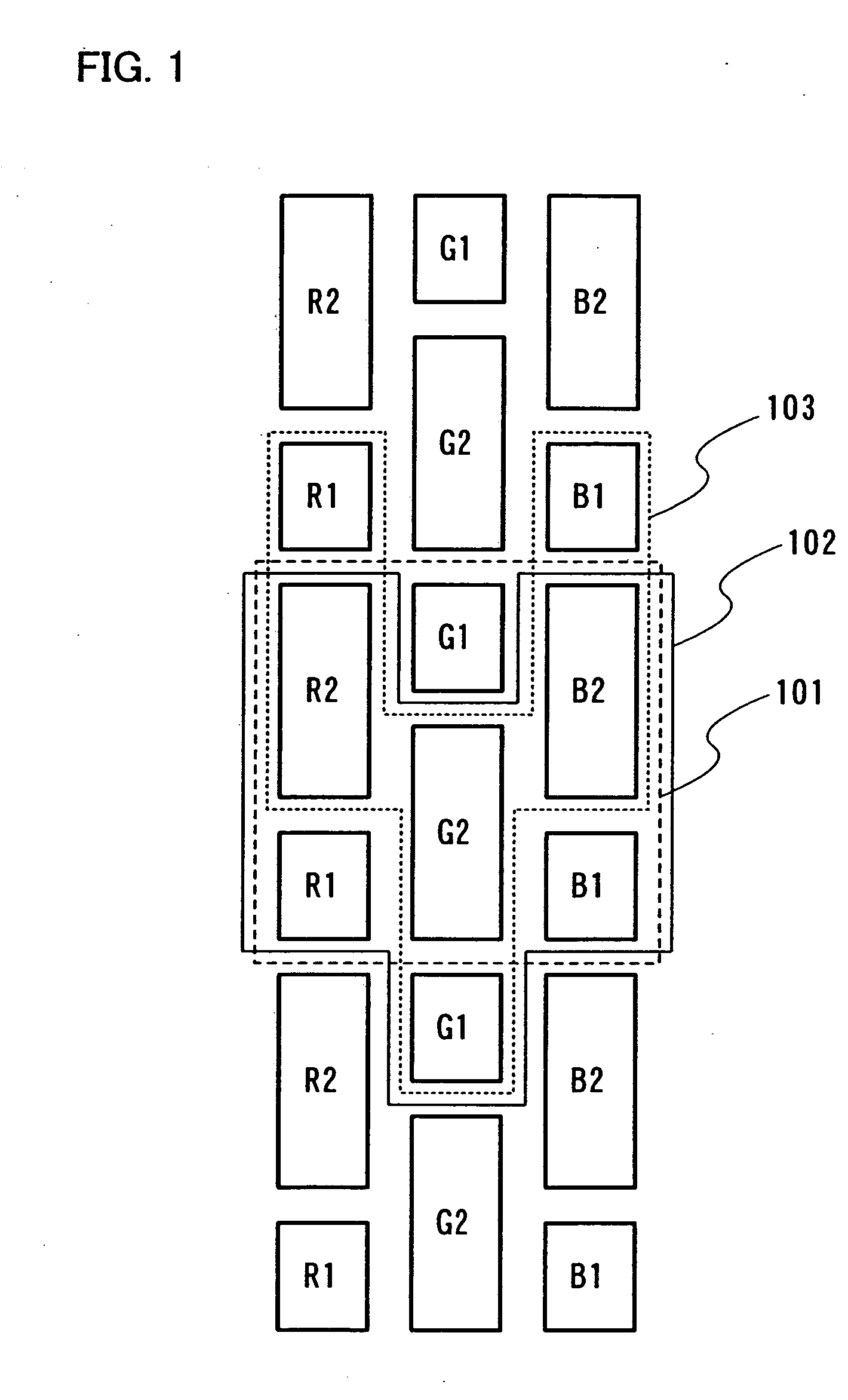

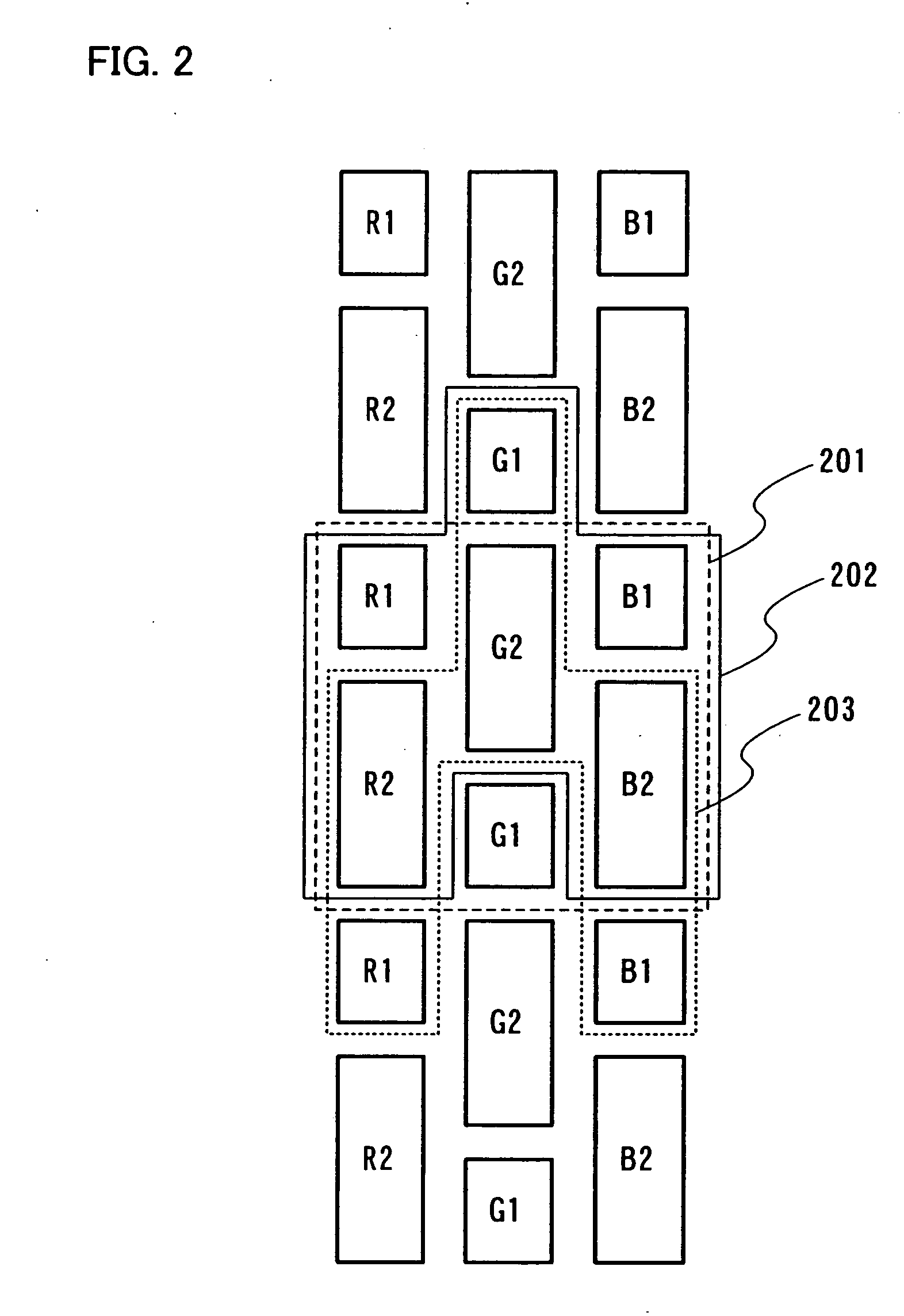

Display device, electronic device and method of driving display device

InactiveUS20070002084A1Display clearSmooth displayElectroluminescent light sourcesSolid-state devicesDisplay deviceComputer science

The present invention provides a display device which can display characters clearly and display images smoothly. An area gray scale method is adopted and a configuration of one pixel is changed depending on a mode, by selecting one or more display regions in each pixel. When characters are needed to be displayed clearly, one pixel is configured by selecting a stripe arrangement. Thus, clear display can be conducted. When images are needed to be displayed, one pixel is configured by selecting an indented state. Thus, smooth display can be conducted.

Owner:SEMICON ENERGY LAB CO LTD

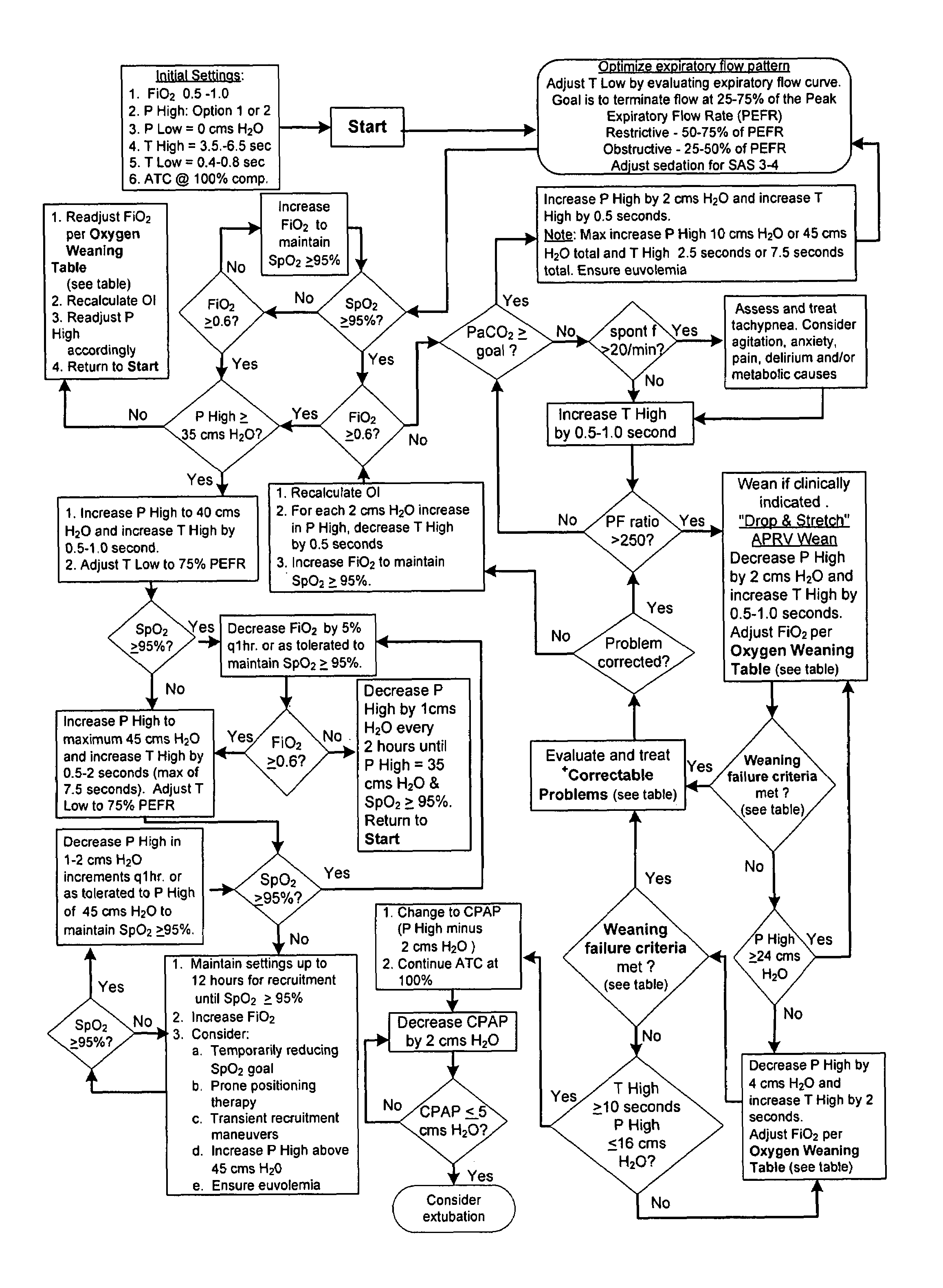

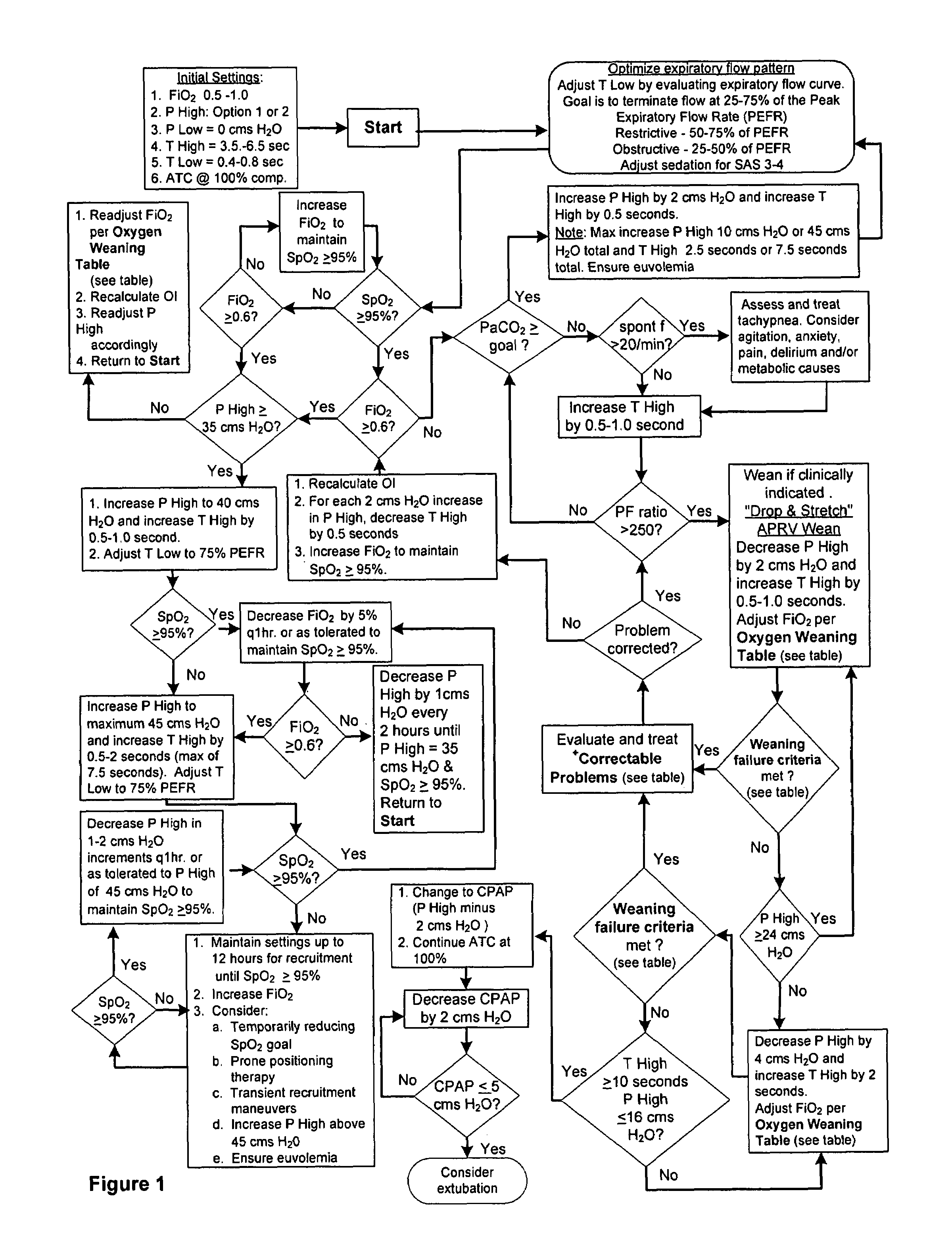

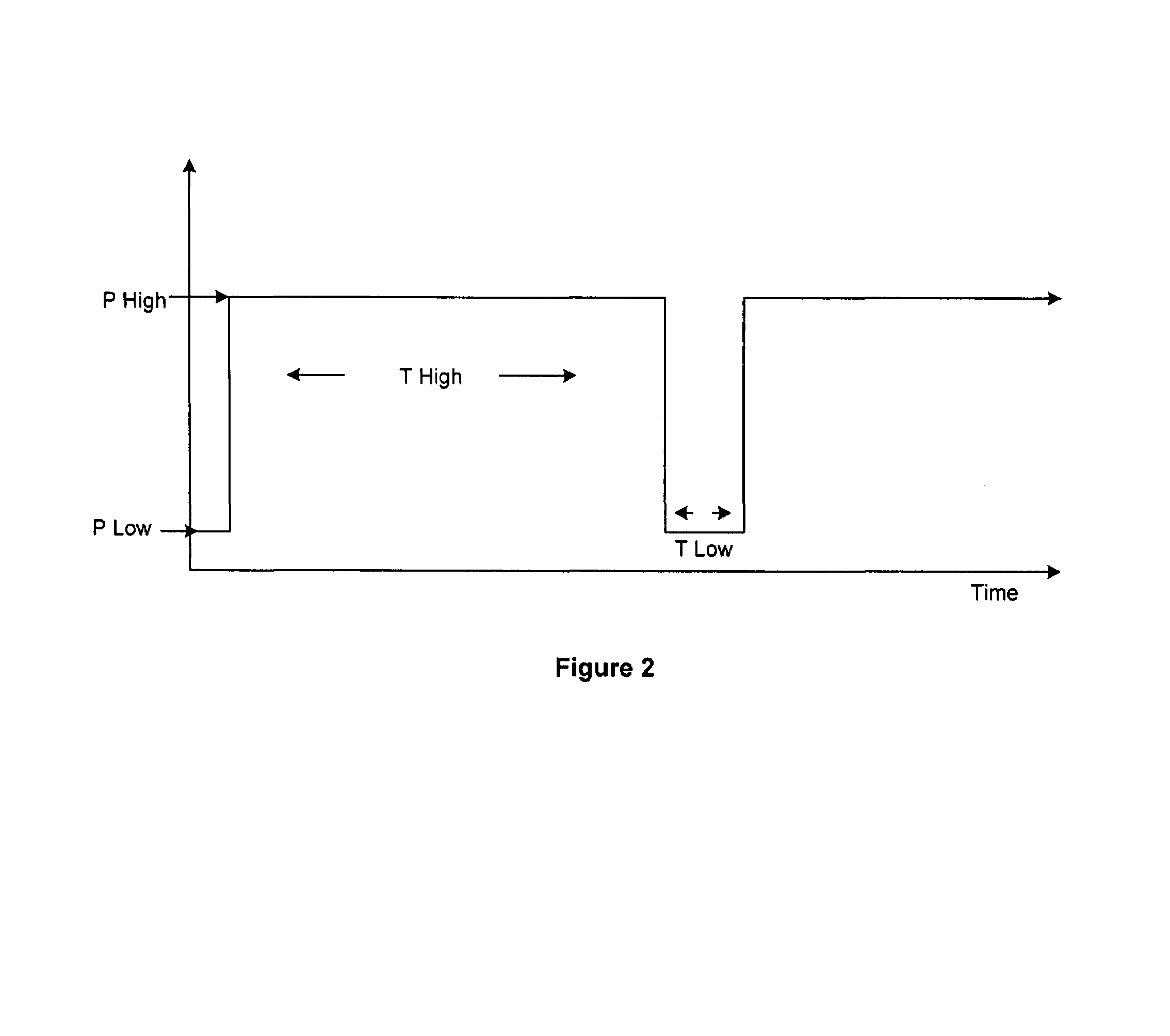

Ventilation method and control of a ventilator based on same

InactiveUS7246618B2Prevents de-recruitmentLower Level RequirementsRespiratorsOperating means/releasing devices for valvesAirway pressuresIntensive care medicine

The invention provides an improved ventilation method and method for controlling a ventilator apparatus in accordance with same. More specifically, the present invention relates to a method of controlling a ventilator apparatus comprising the steps of placing a ventilator in a mode capable of adjusting airway pressure (P) and time (T), monitoring expiratory gas flow, analyzing the expiratory gas flow over time (T) to establish an expiratory gas flow pattern, and setting and / or adjusting a low time (T2) based on the expiratory gas flow pattern. Alternatively, the present invention relates to a method of controlling a ventilator apparatus comprising the steps of placing a ventilator in a mode capable of adjusting airway pressure (P) and time (T), and setting a low airway pressure (P2) of substantially zero cmH2O.

Owner:HABASHI NADER M

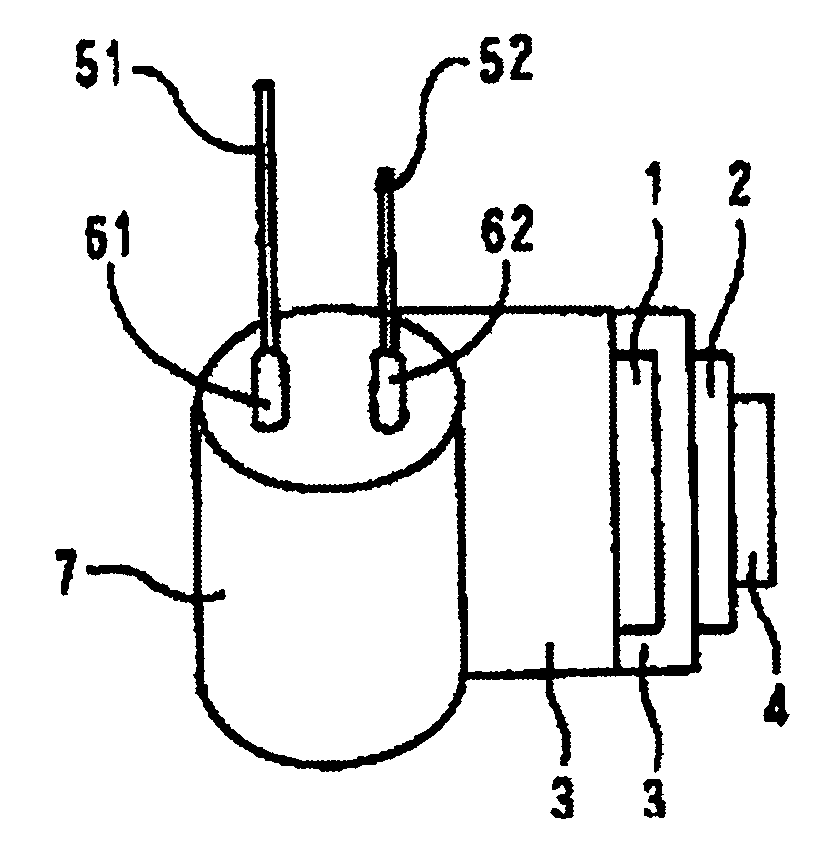

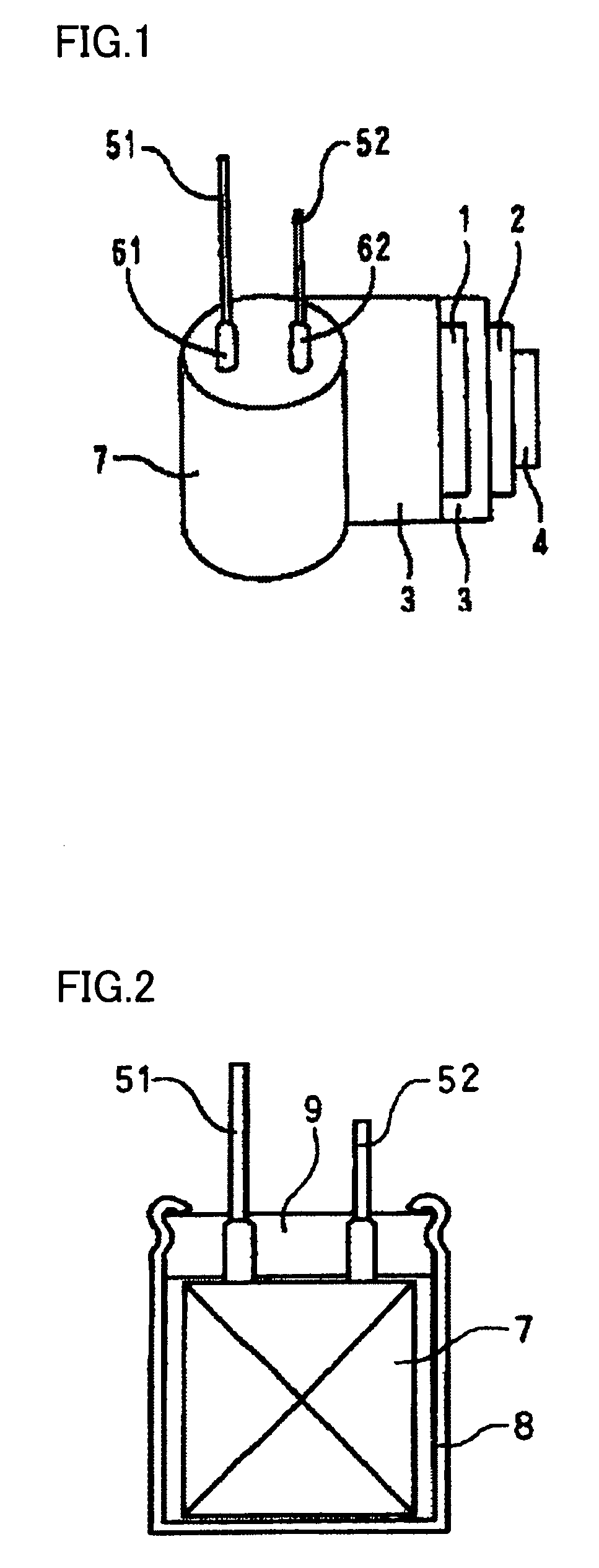

Method of manufacturing electrolytic capacitor and electrolytic capacitor

ActiveUS7497879B2Improve pressure resistanceSmall currentHybrid capacitor electrolytesSolid electrolytic capacitorsDielectricElectrolysis

A method of manufacturing an electrolytic capacitor including the following steps as well as an electrolytic capacitor manufactured by the method are provided. The method includes: a dispersion impregnation step of impregnating, with a dispersion containing electrically conductive solid particles or powder and a solvent, a capacitor element having an anode foil with a dielectric coating film formed thereon and an opposite cathode foil that are wound with a separator interposed therebetween; a dry step of evaporating the solvent after the dispersion impregnation step to form an electrically conductive solid layer on a surface of the dielectric coating film; and an electrolytic solution impregnation step of impregnating a gap in the electrically conductive solid layer with an electrolytic solution. Accordingly, an electrolytic capacitor that can be manufactured more easily that is excellent in voltage proofing property and that has a lower ESR and a lower leakage current is provided.

Owner:SANYO ELECTRIC CO LTD +1

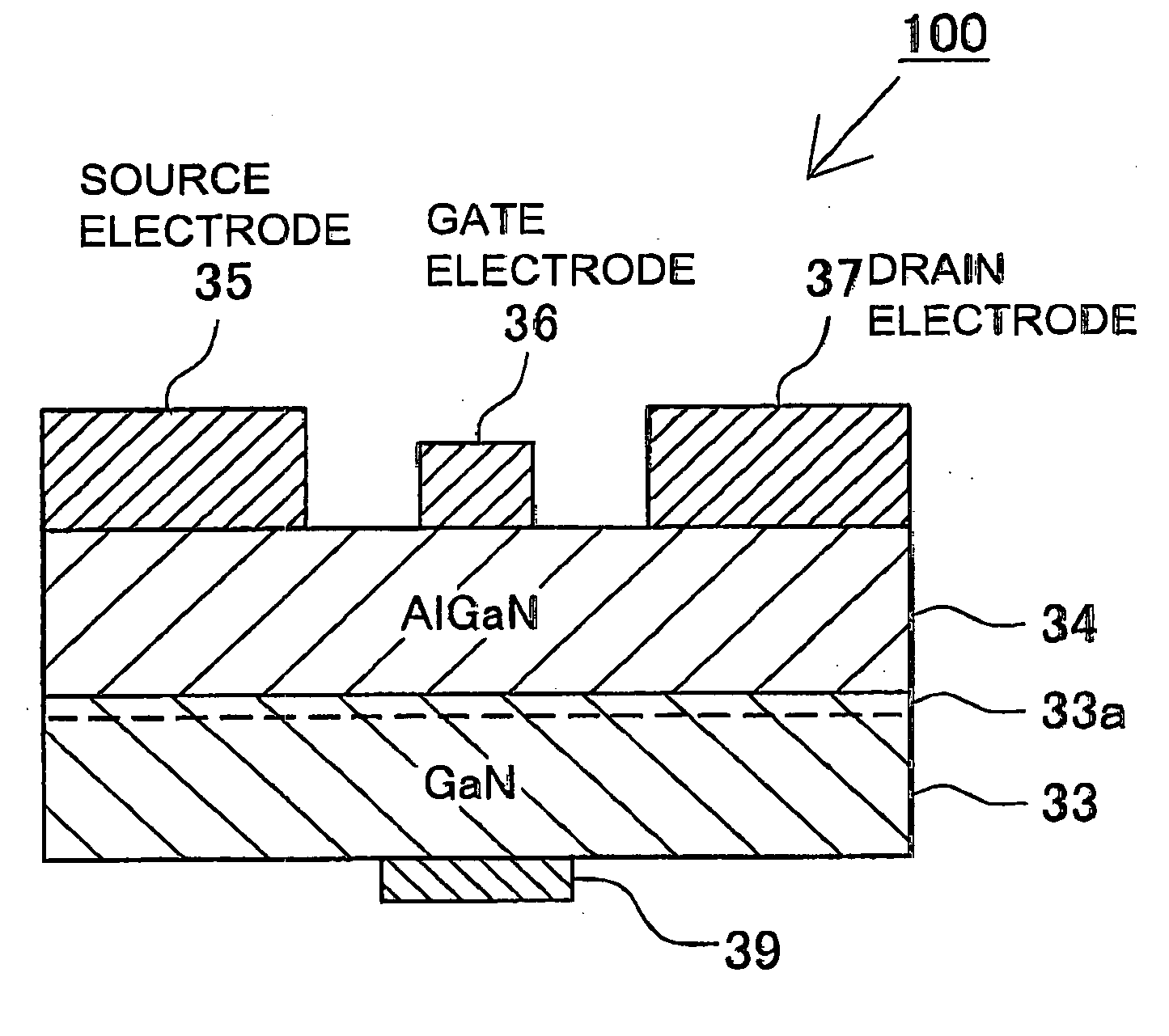

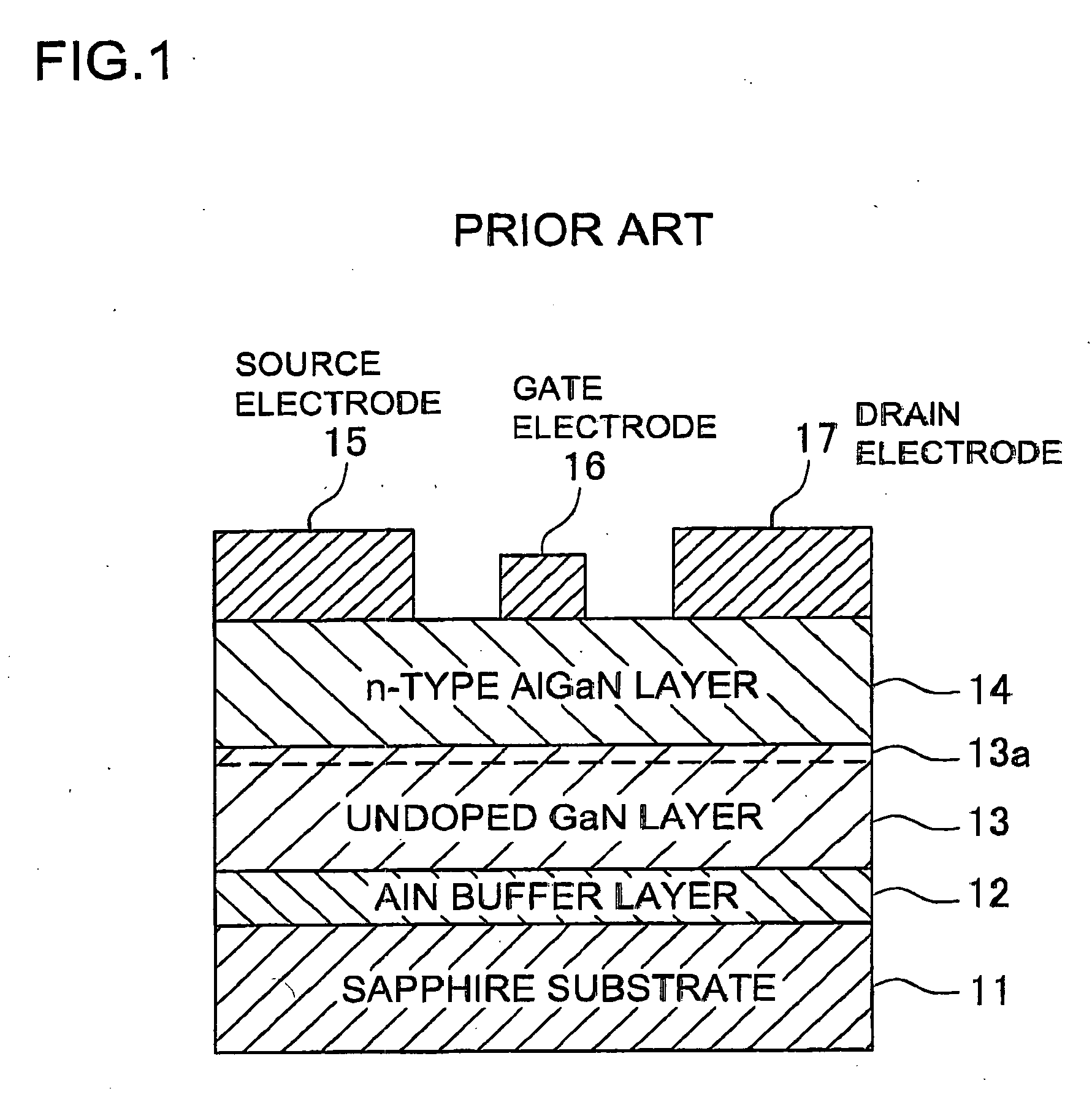

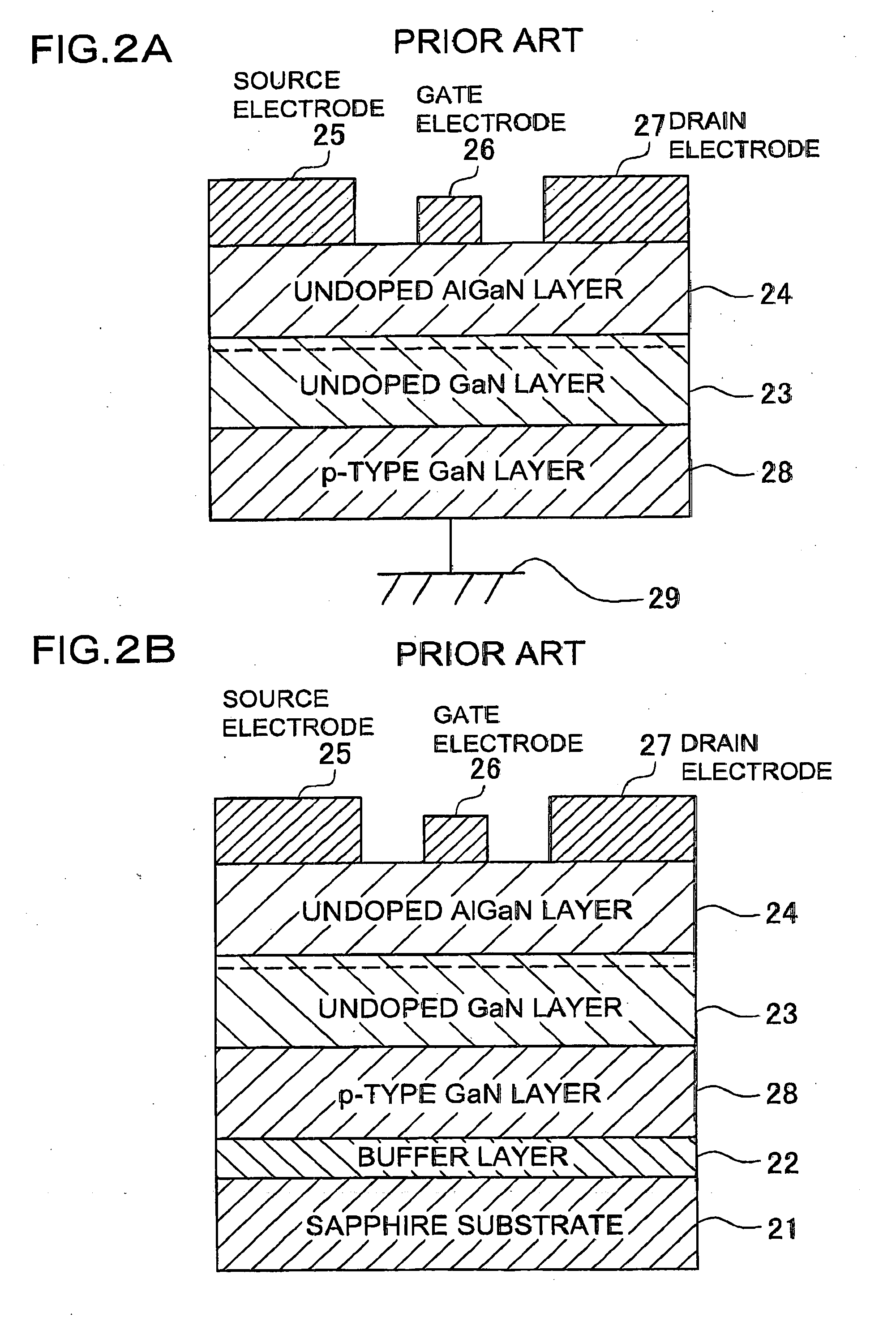

Field effect transistor and method of manufacturing the same

ActiveUS20060108602A1Improve pressure resistanceImprove efficiencyTransistorSolid-state devicesElectrical conductorGallium nitride

A field effect transistor includes an i-type first semiconductor layer and a second semiconductor layer that is formed on the first semiconductor layer and the band gap energy of that is higher in magnitude than that of the first semiconductor layer. The first semiconductor layer and second semiconductor layer are each made of a gallium nitride-based compound semiconductor layer. A gate electrode 36 is formed on the second semiconductor layer; and a second electrode 39 is formed on the first semiconductor layer. Thus, the field effect transistor is constructed in such a manner as the first semiconductor layer and second semiconductor layer are interposed between the gate electrode 36 and the second electrode 39. By constructing like this, it is possible to discharge the holes that are accumulated in the channel from the elemental structure and to improve the withstand voltage of the field effect transistor.

Owner:NICHIA CORP

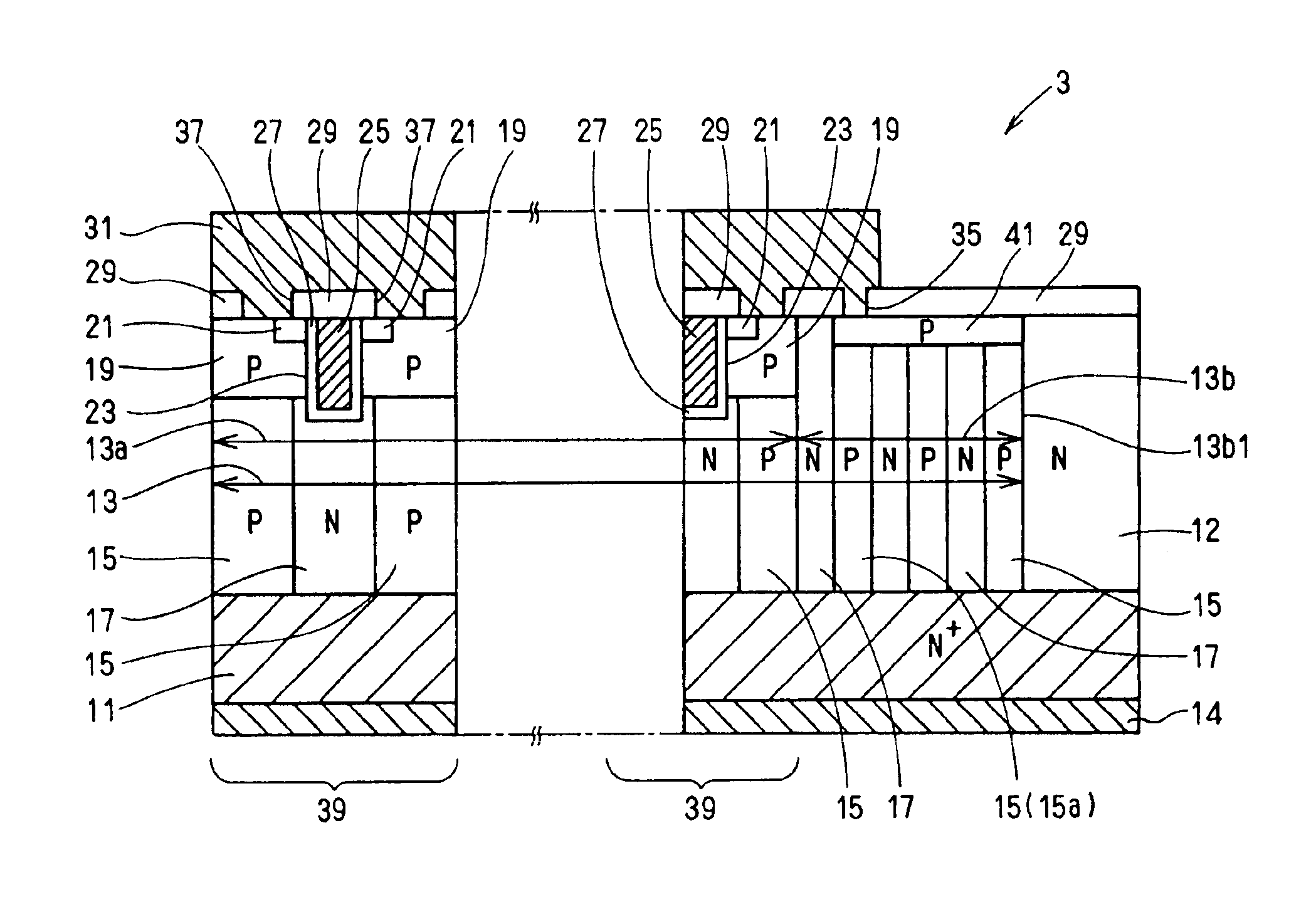

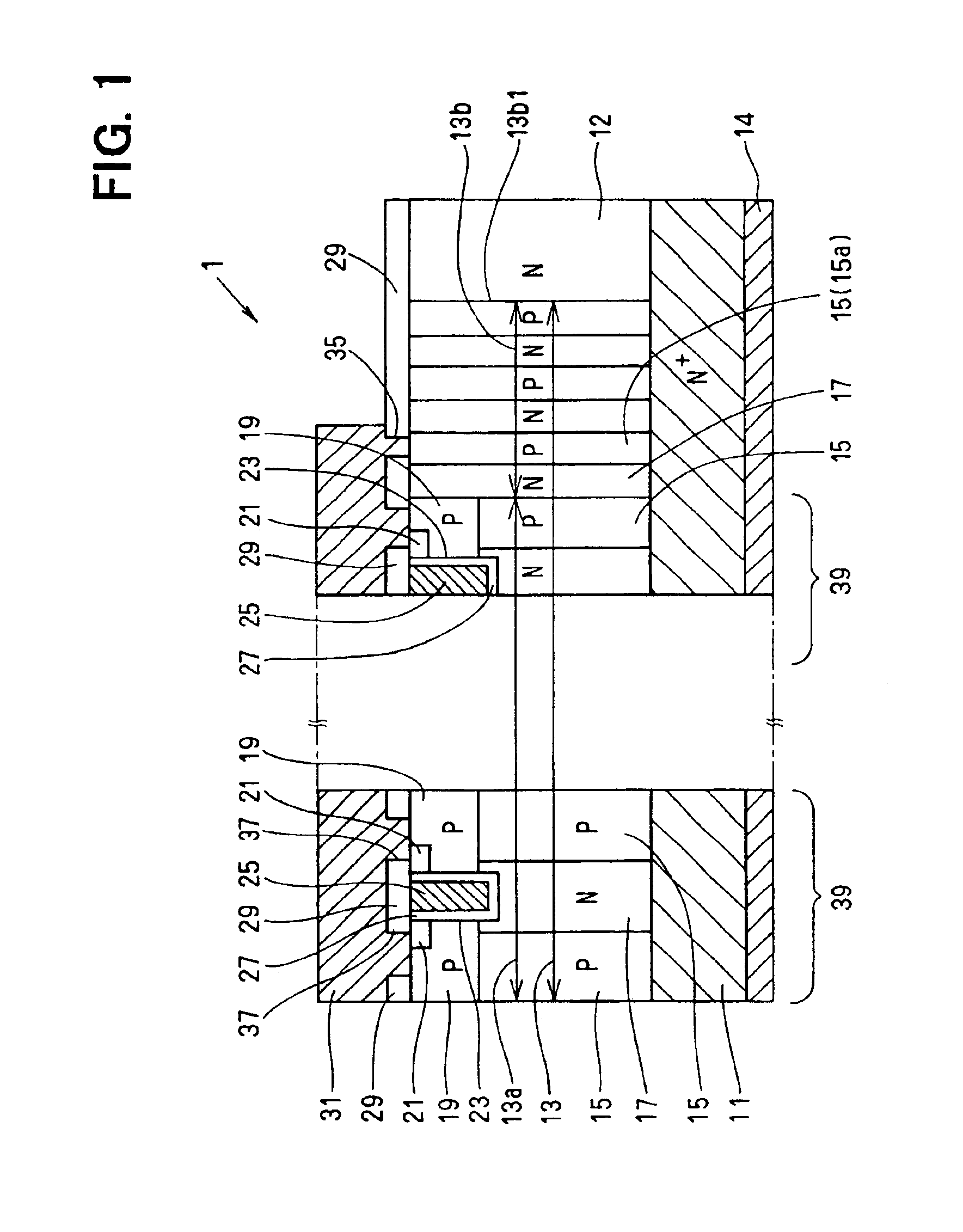

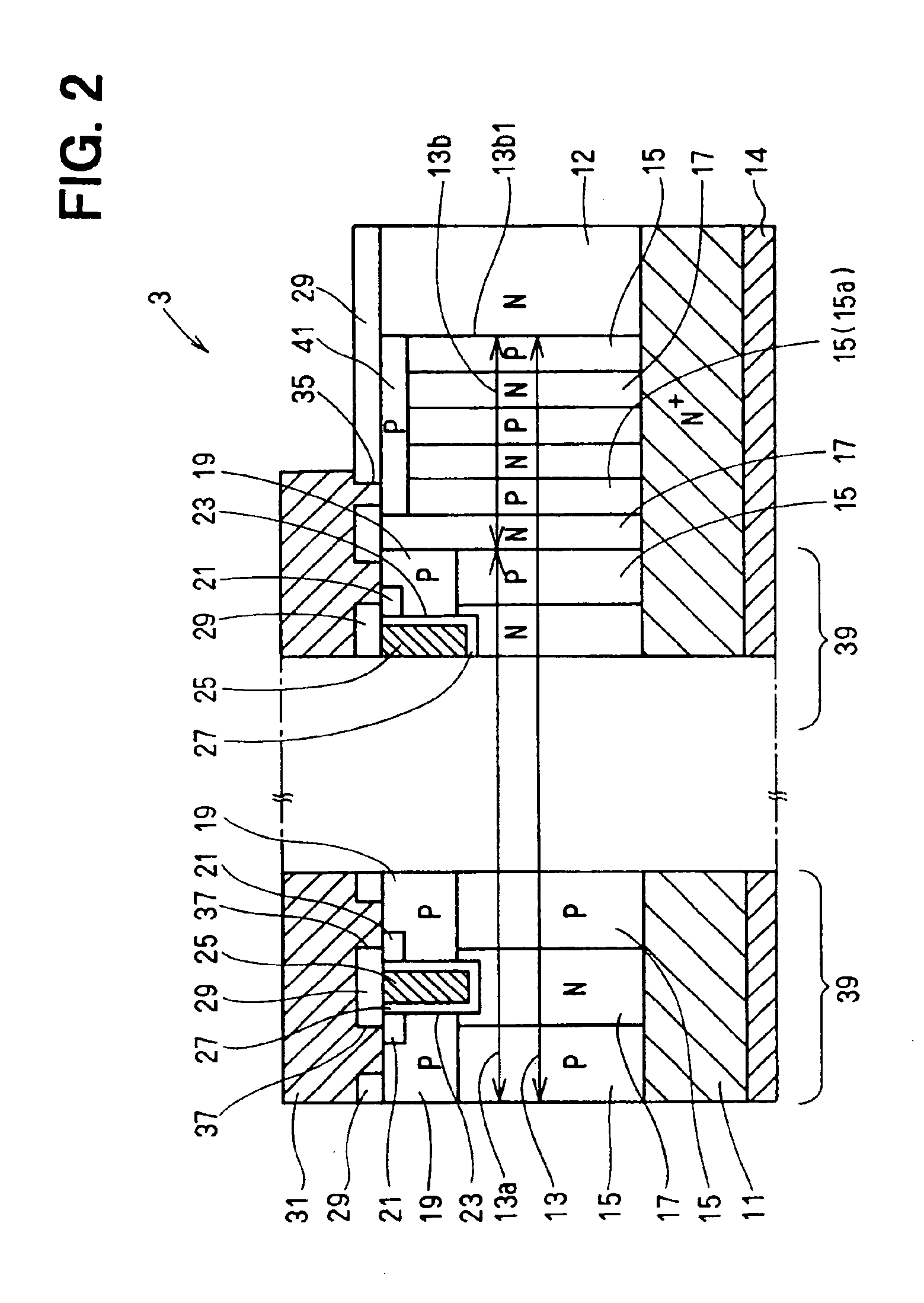

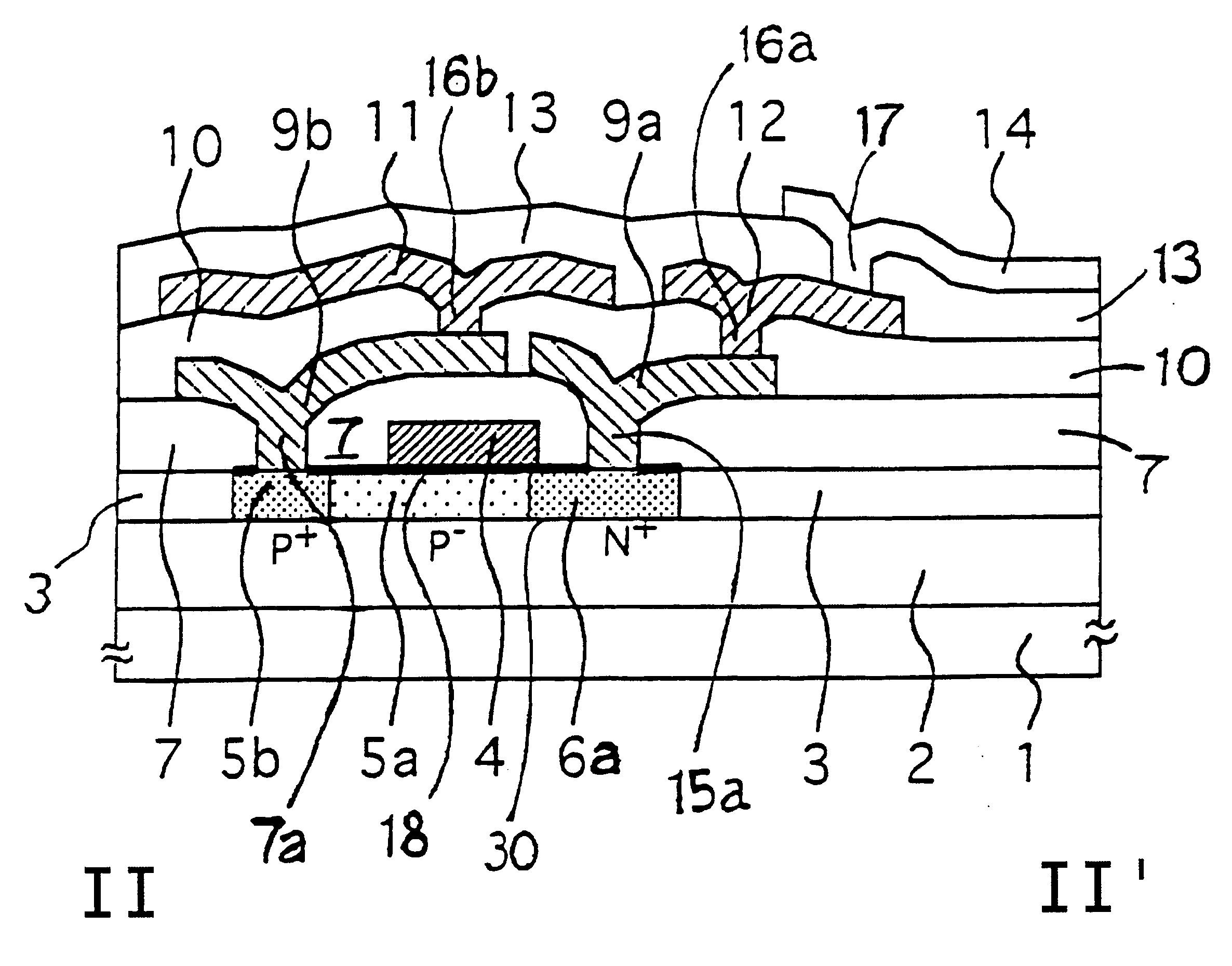

Semiconductor device having a vertical type semiconductor element

InactiveUS6982459B2Improve pressure resistanceElectric field is decreasedSemiconductor/solid-state device manufacturingSemiconductor devicesElectrode ContactField-effect transistor

A vertical type MOS field effect transistor has a super junction structure between a source electrode and an N+-type drain region. The super junction structure is constituted by a plurality of P-type single crystal silicon regions and a plurality of N-type single crystal silicon regions. Each of the plurality of P-type single crystal silicon regions and each of the plurality of N-type single crystal silicon regions are arrayed alternately. The super junction has two parts, that is, a cell forming region where a MOS structure is disposed and a peripheral region located at a periphery of the cell forming region. The source electrode contacts one of the P-type single crystal silicon regions in the peripheral region while disposed away from an end portion of the peripheral region that is located at an outermost in the peripheral region.

Owner:DENSO CORP

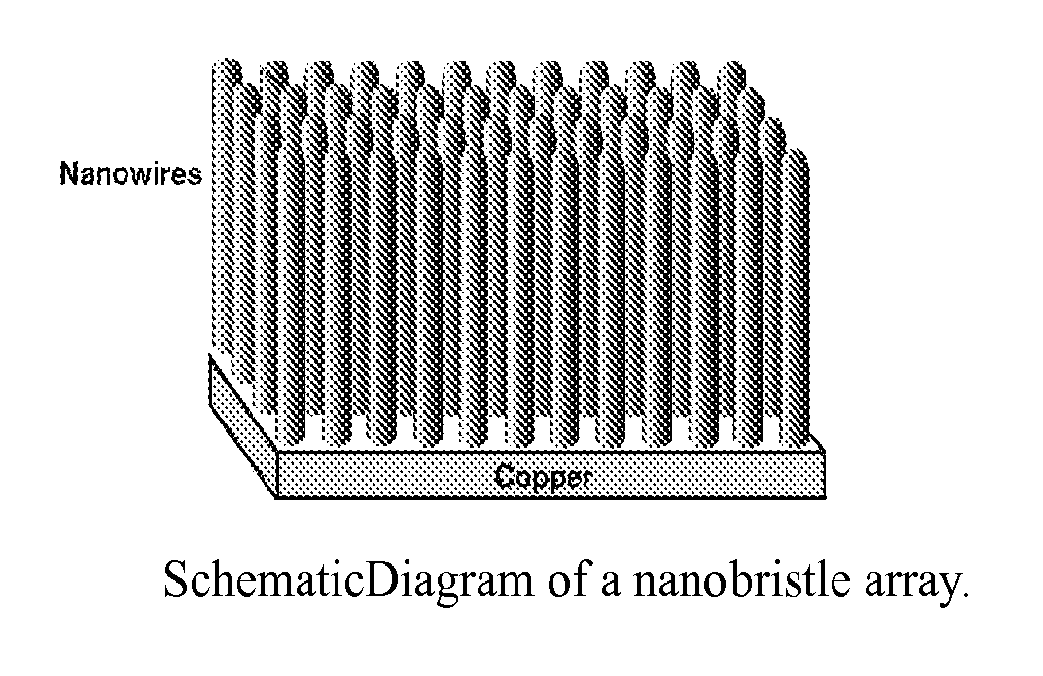

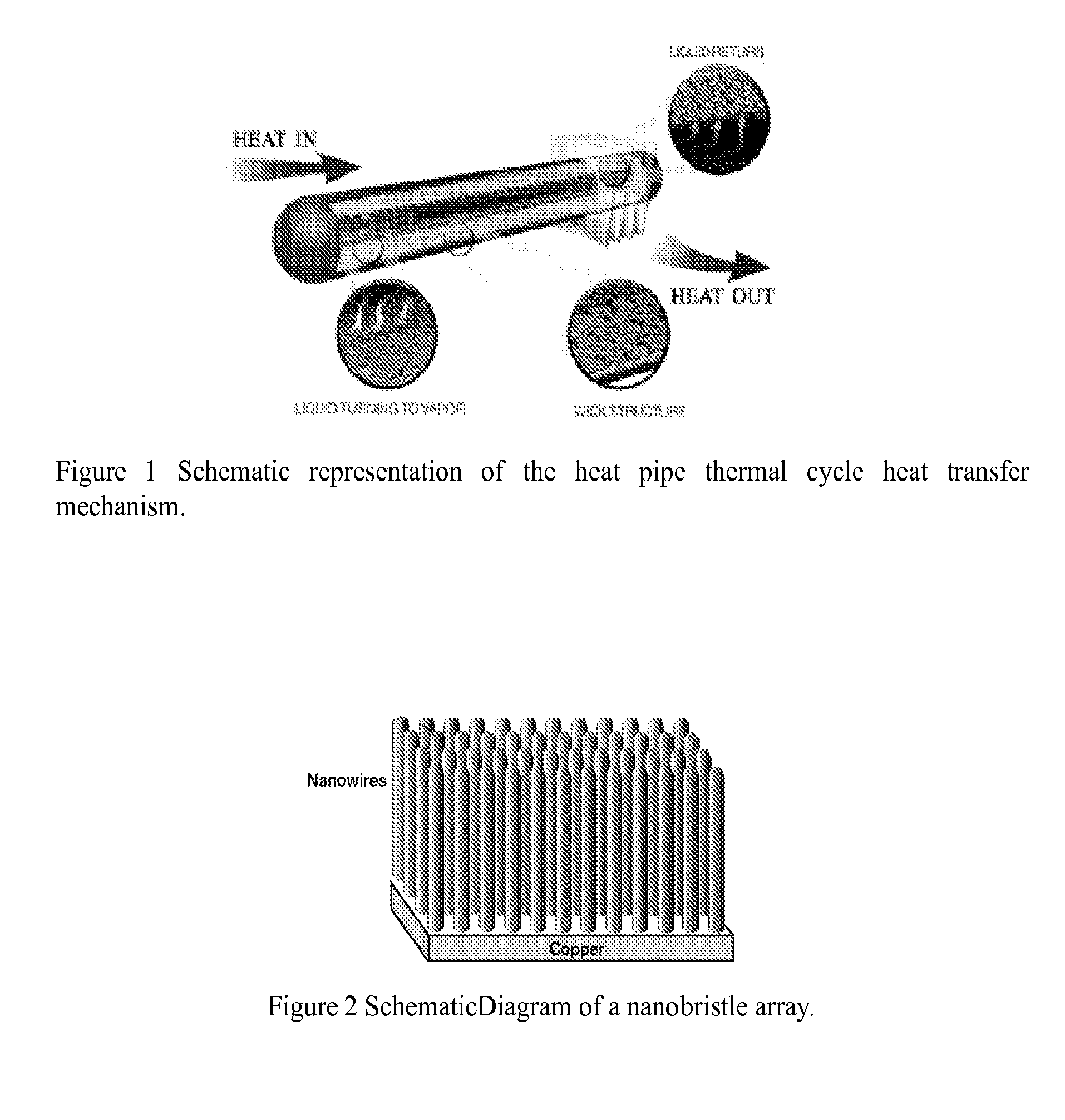

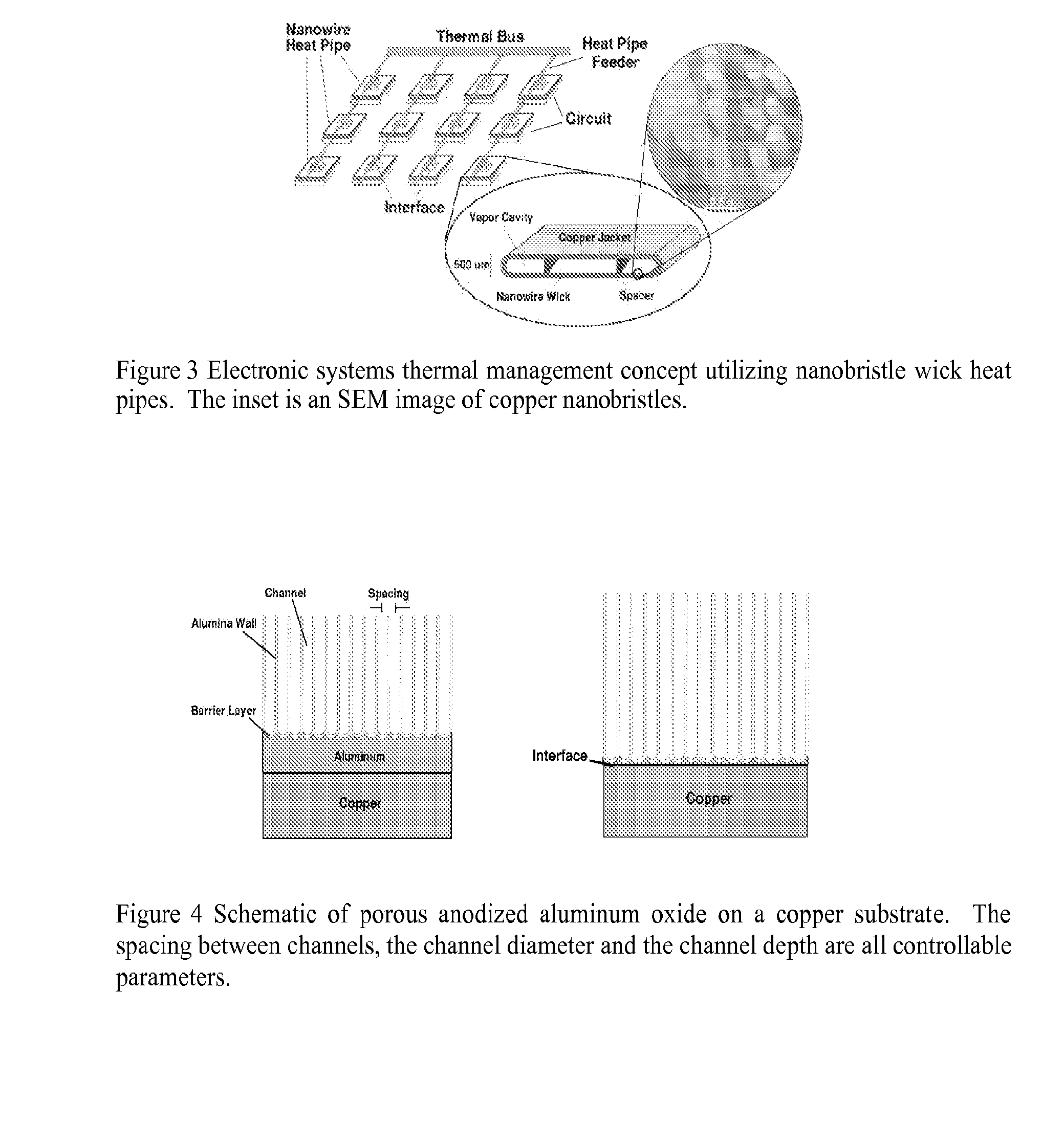

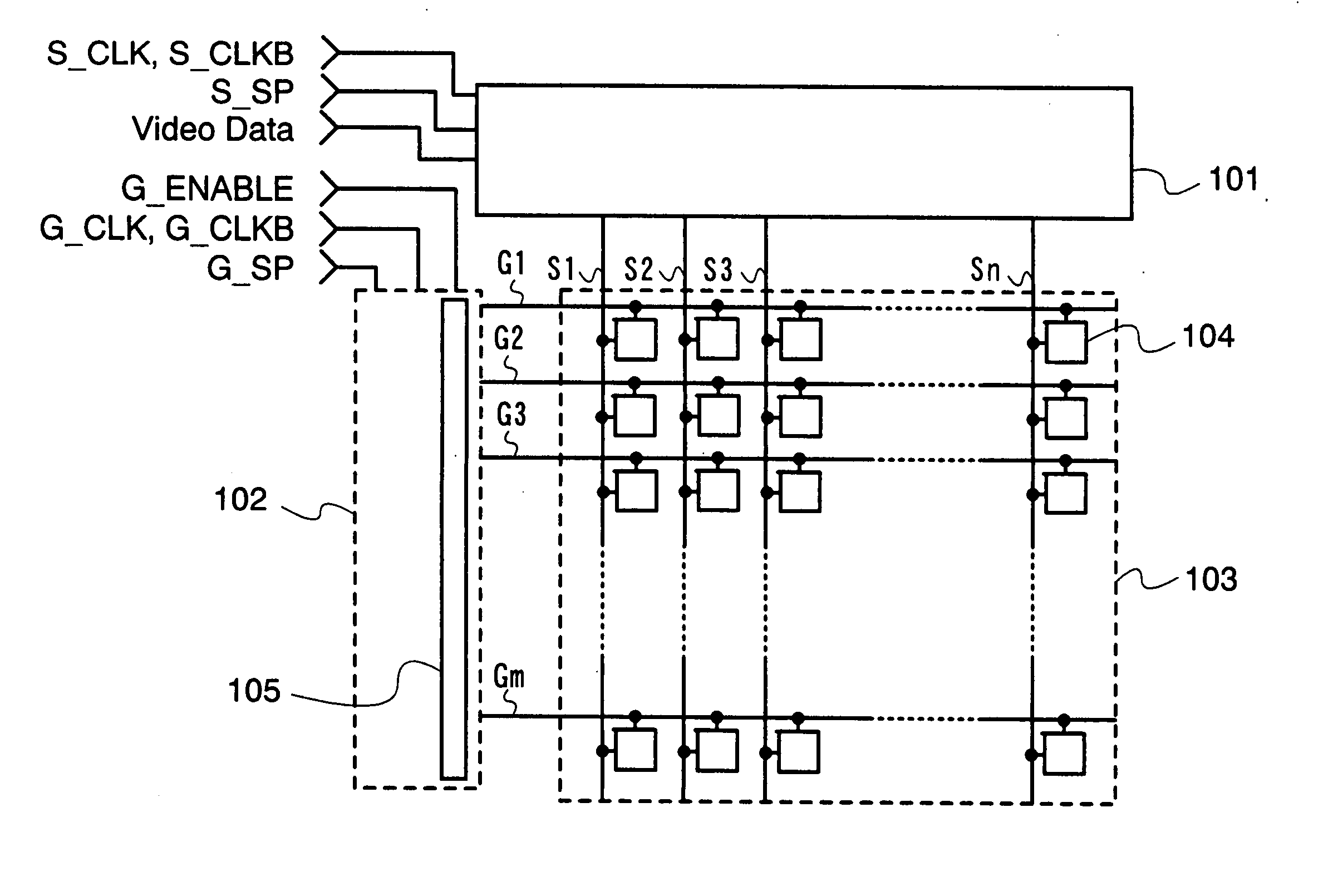

Heat Pipe with Nanostructured Wick

InactiveUS20100200199A1Improve efficiencyPerformance advantageMaterial nanotechnologyAnodisationNanowireBristle

A heat pipe with a nanostructured wick is disclosed, with the method of forming the nanostructured wick on a metal substrate. The wicking material is a pattern of metallic nanostructures in the form of bristles or nanowires attached to a substrate, where the bristles are substantially freestanding.

Owner:ILLUMINEX CORP

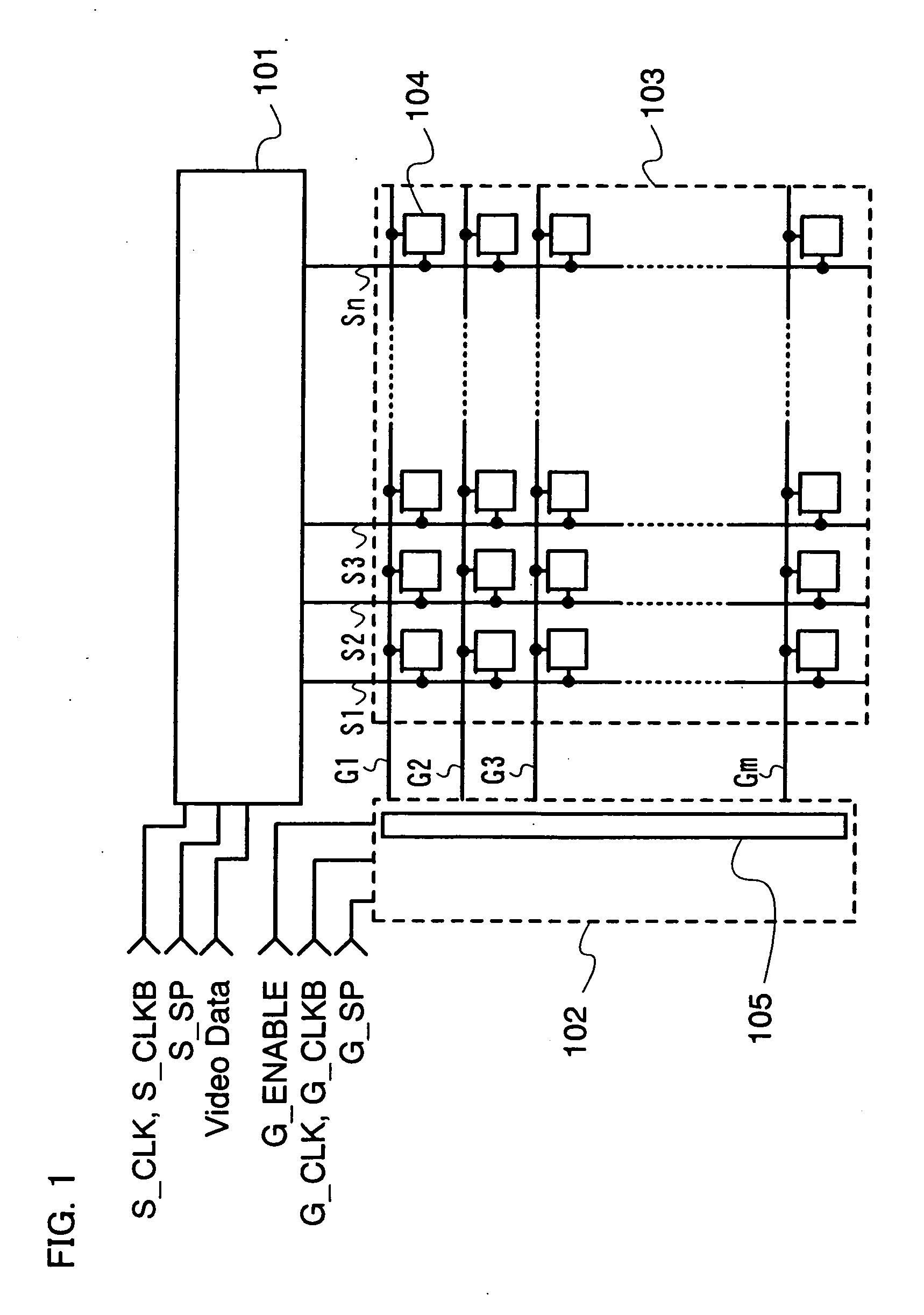

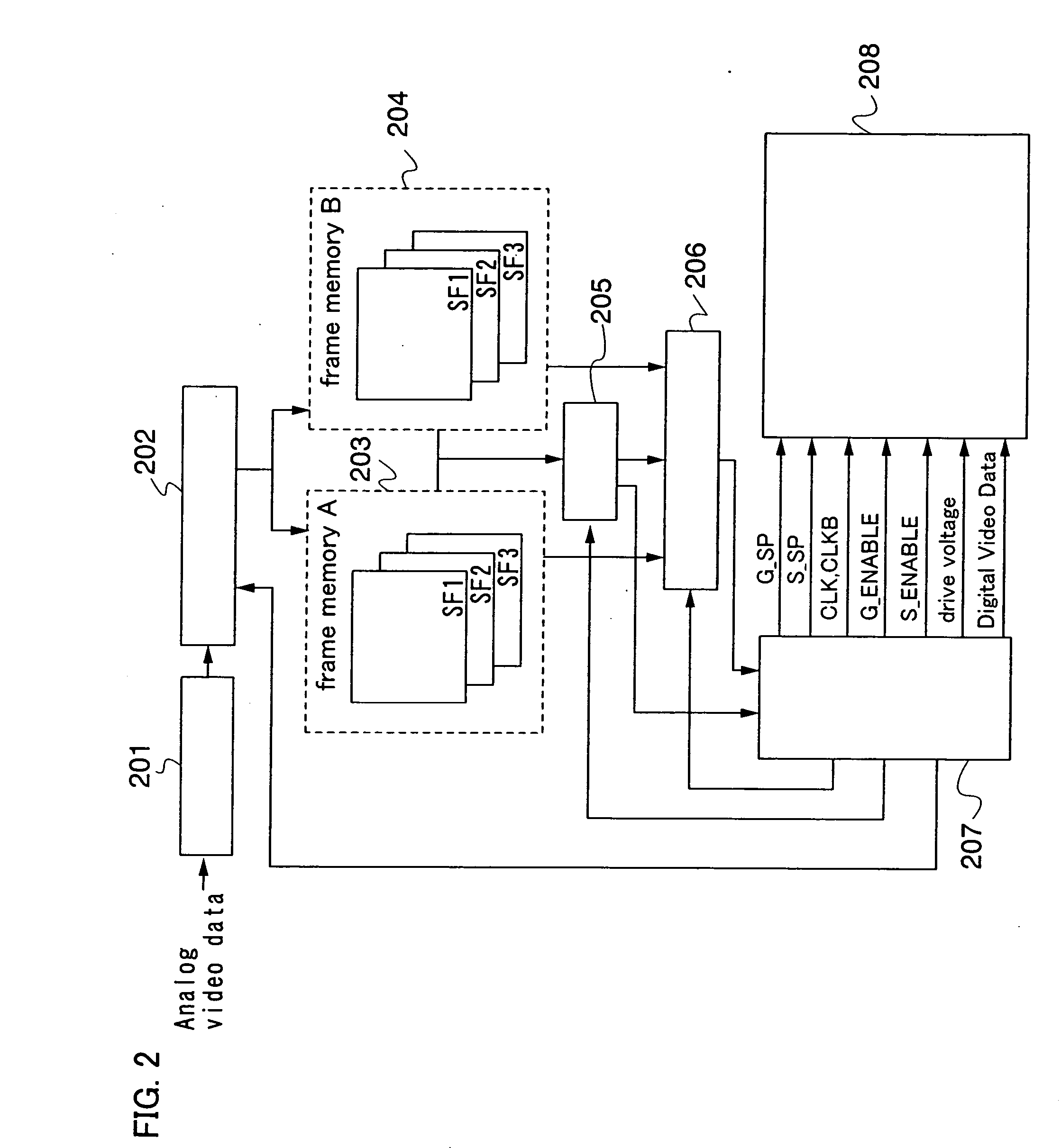

Active matrix display device, method for driving the same, and electronic device

InactiveUS20060267889A1Reduce the number of timesPower consumption can be providedElectrical apparatusElectroluminescent light sourcesDriver circuitScan line

An object of the invention is to provide a display device which can reduce the number of times signal writing to a pixel is carried out and power consumption. A display device which can reduce the number of times signal writing to a pixel is carried out and power consumption can be provided. According to an active matrix display device of the invention, in the case a signal to be written to a pixel row is identical with a signal stored in the pixel row, the scan line driver circuit does not output a selecting pulse to a scan line corresponding to the pixel row, and the signal line driver circuit makes the signal lines in a floating state or keeps without changing the state of the signal line from the previous state.

Owner:SEMICON ENERGY LAB CO LTD

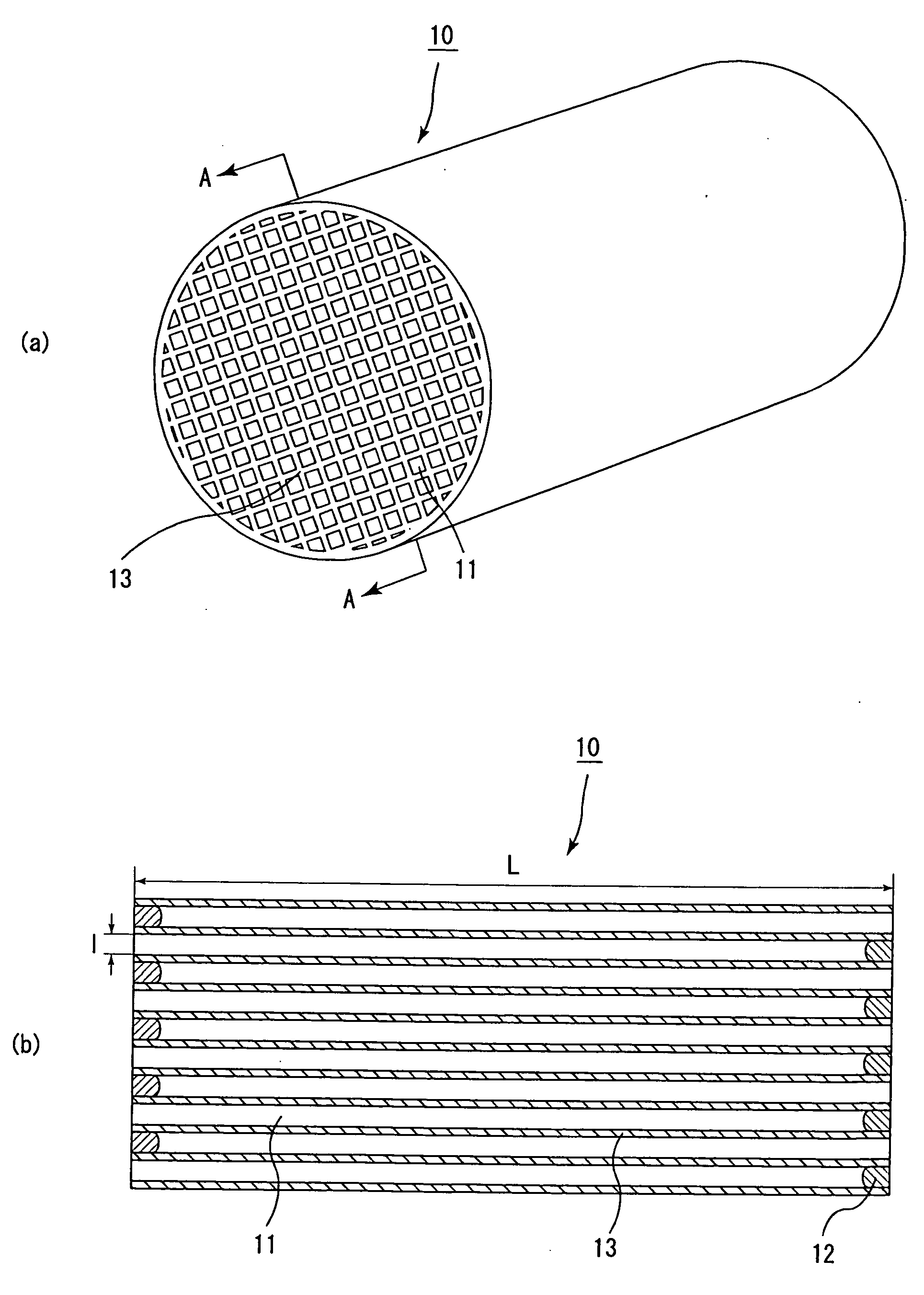

Honeycomb filter for exhaust gas decontamination and exhaust gas decontamination apparatus

ActiveUS20050160710A1Less susceptible to high initial pressure lossGuaranteed continuous useCombination devicesPhysical/chemical process catalystsParticulatesHoneycomb

A honeycomb filter for purifying exhaust gases that can almost completely burn and remove particulates accumulated on a wall portion by a regenerating process allowing residual ashes on the wall portion to easily move inside a through hole because the ashes are easily separated from the wall portion. In the honeycomb filter a columnar body made of porous ceramics, having parallel through holes in the length direction with a wall portion interposed therebetween, is designed so that part or all of the wall portion that separates the through holes from each other functions as a filter collecting particulates, wherein a length l of the longest side in a cross section perpendicular to the length direction of the through hole and a length L in the length direction of the columnar body satisfy: 60≦L / l≦500, and a surface roughness Ra (according to JIS B 0601) of the through hole inner wall satisfies: Ra≦100 μm.

Owner:IBIDEN CO LTD

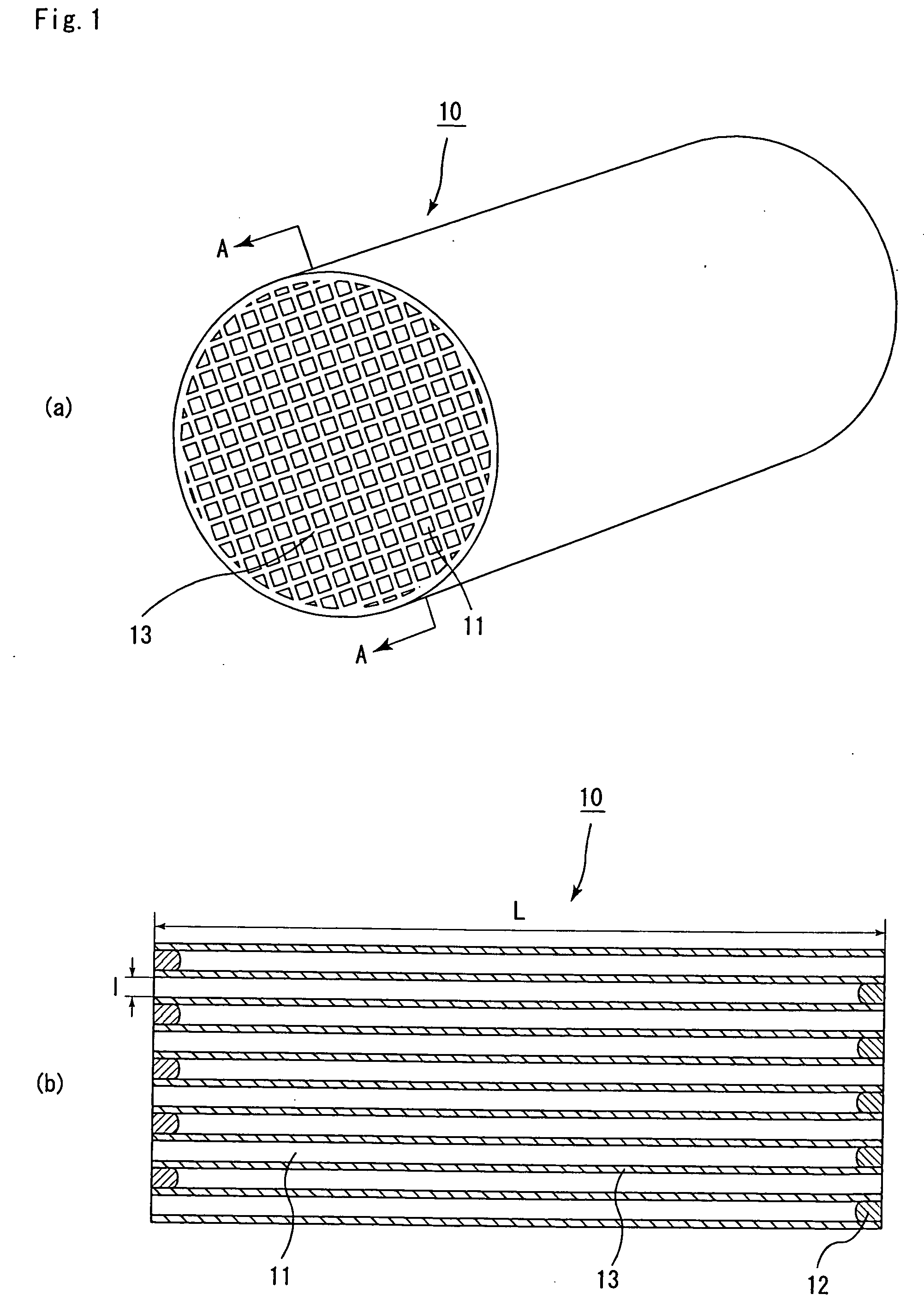

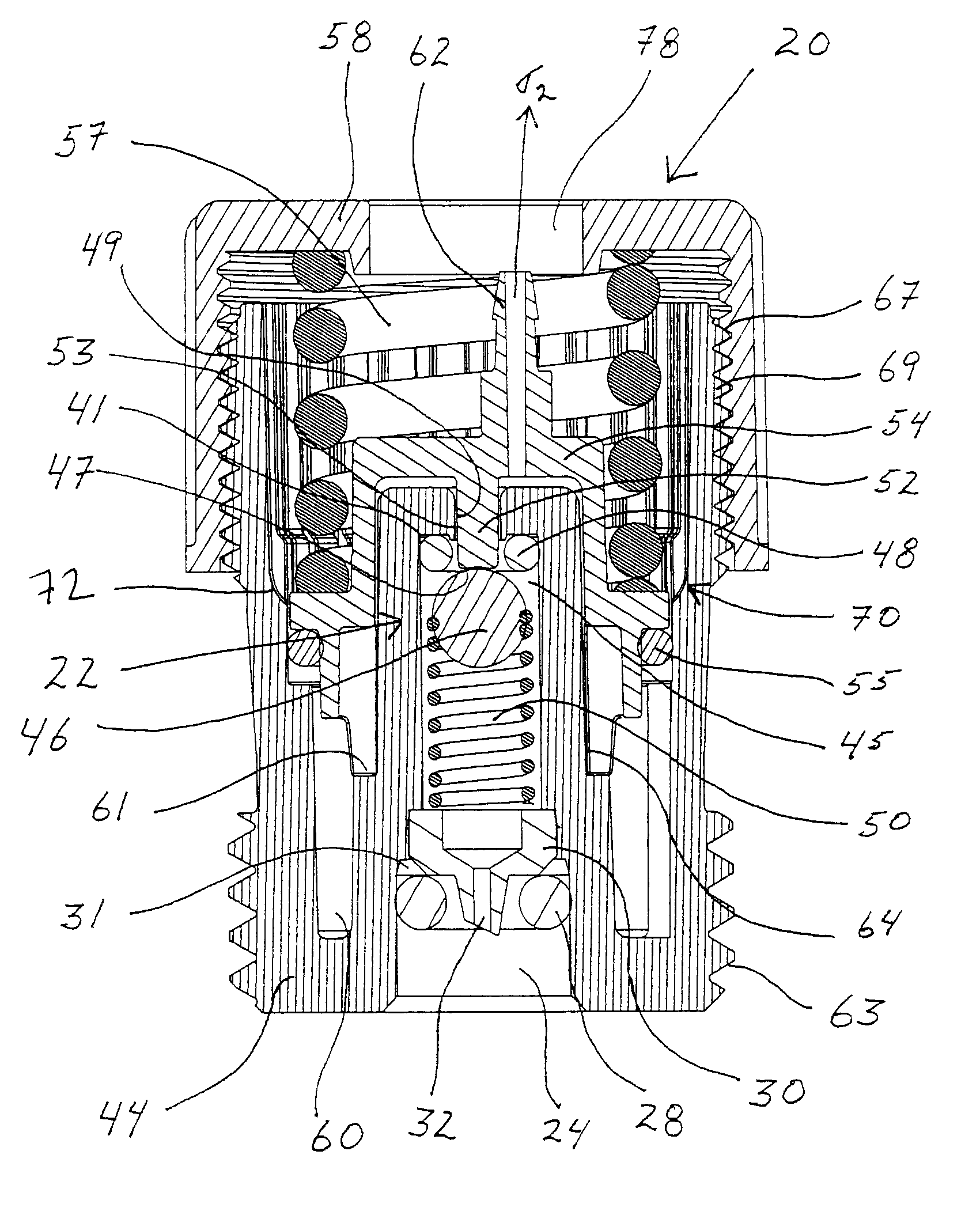

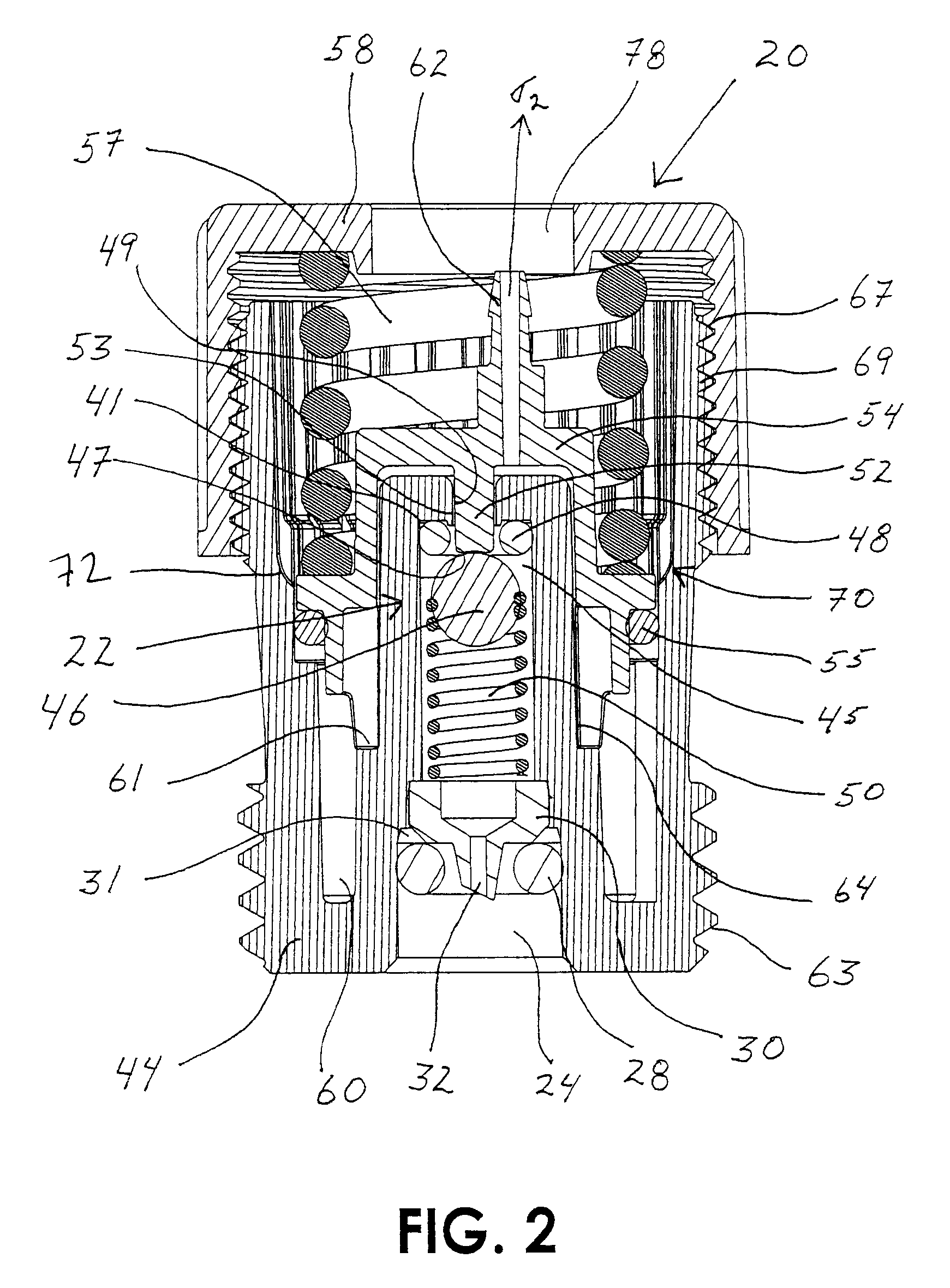

Pressure regulator adaptable to compressed gas cartridge

ActiveUS7334598B1Reduce manufacturing costImprove reliabilityContainer filling methodsGas handling applicationsEngineeringHigh pressure

This pressure regulator is specifically designed to operate with a portable compressed gas cartridge thus reducing the high vapor pressure found in compressed gas cartridges down to a substantially consistent outlet pressure. Due to the nature of the crowded regulator art, the soon to be embodied pressure regulator has been specifically embodied for use in the portable compressed gas cartridge harnessing art and this specific use is carried into the claims. Exemplified in the pressure regulator embodiments is a reduced amount of components over existing designs. Additionally, safety and reliability features have been integrated into the design and will shortly be taught in the following paragraphs. A burp-off feature in all embodiments will be exemplified that vents back-pressure spikes as well as a method of adjusting the burp-off back-pressure spikes independent of regulated pressure in some embodiments.

Owner:HOLLARS ANTHONY SCOTT

Method of preparing a chromatography matrix

ActiveUS7396467B2Increase pressureImprove rendering capabilitiesIon-exchange process apparatusSugar derivativesCross-linkAqueous solution

The present invention relates to a method of preparing a porous cross-linked polysaccharide chromatography matrix, which comprises to provide an aqueous solution of a gellable polysaccharide, wherein part of the hydroxyl groups are substituted with groups which are not susceptible to nucleophilic attack; to provide essentially spherical droplets of the substituted polysaccharide solution; to form a gel of the substituted polysaccharide solution; and to cross-link the gel by adding a cross-linking agent. The invention also encompasses a chromatography column packed with a matrix so produced as well as use thereof in e.g. protein purification.

Owner:CYTIVA BIOPROCESS R&D AB

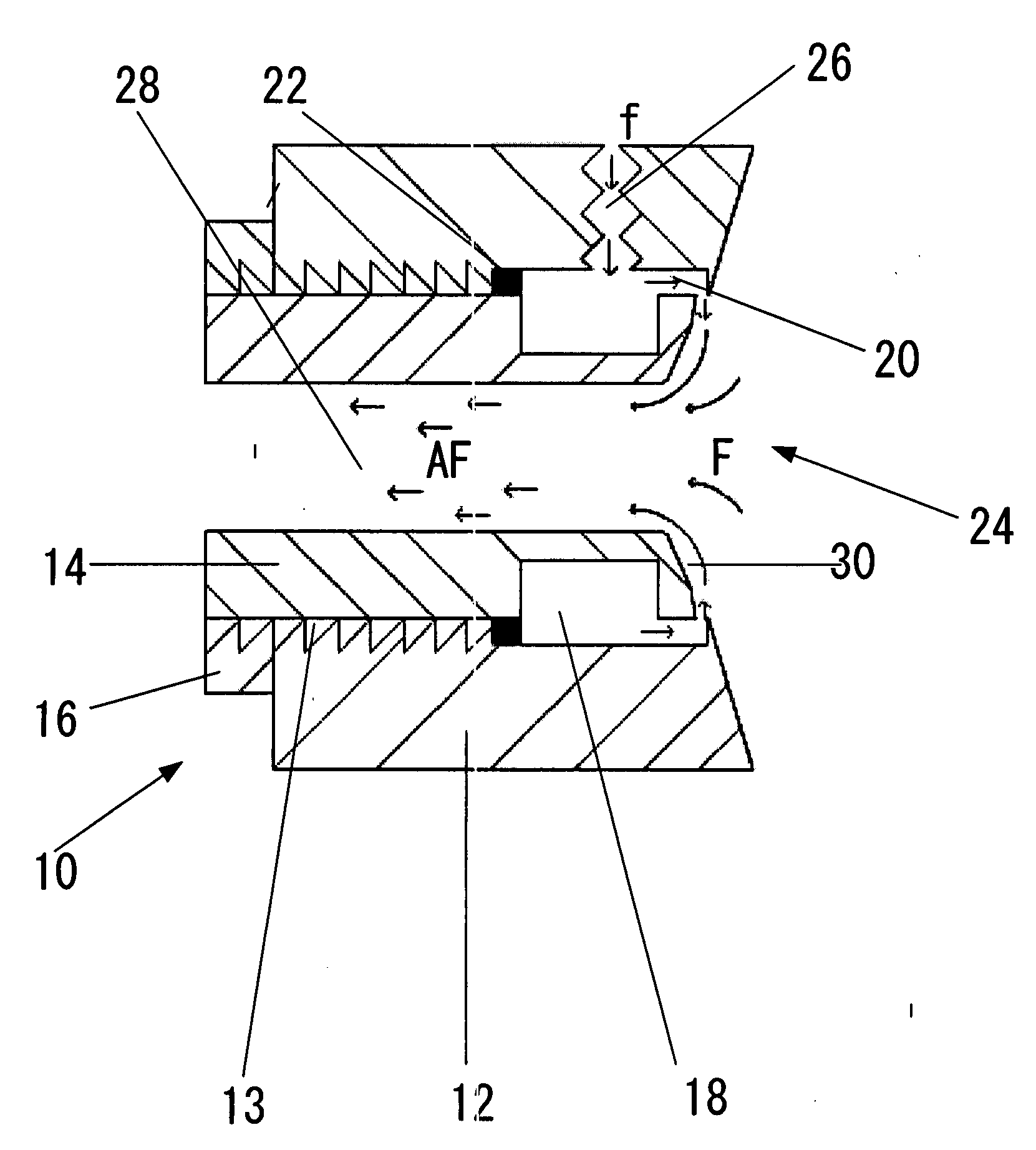

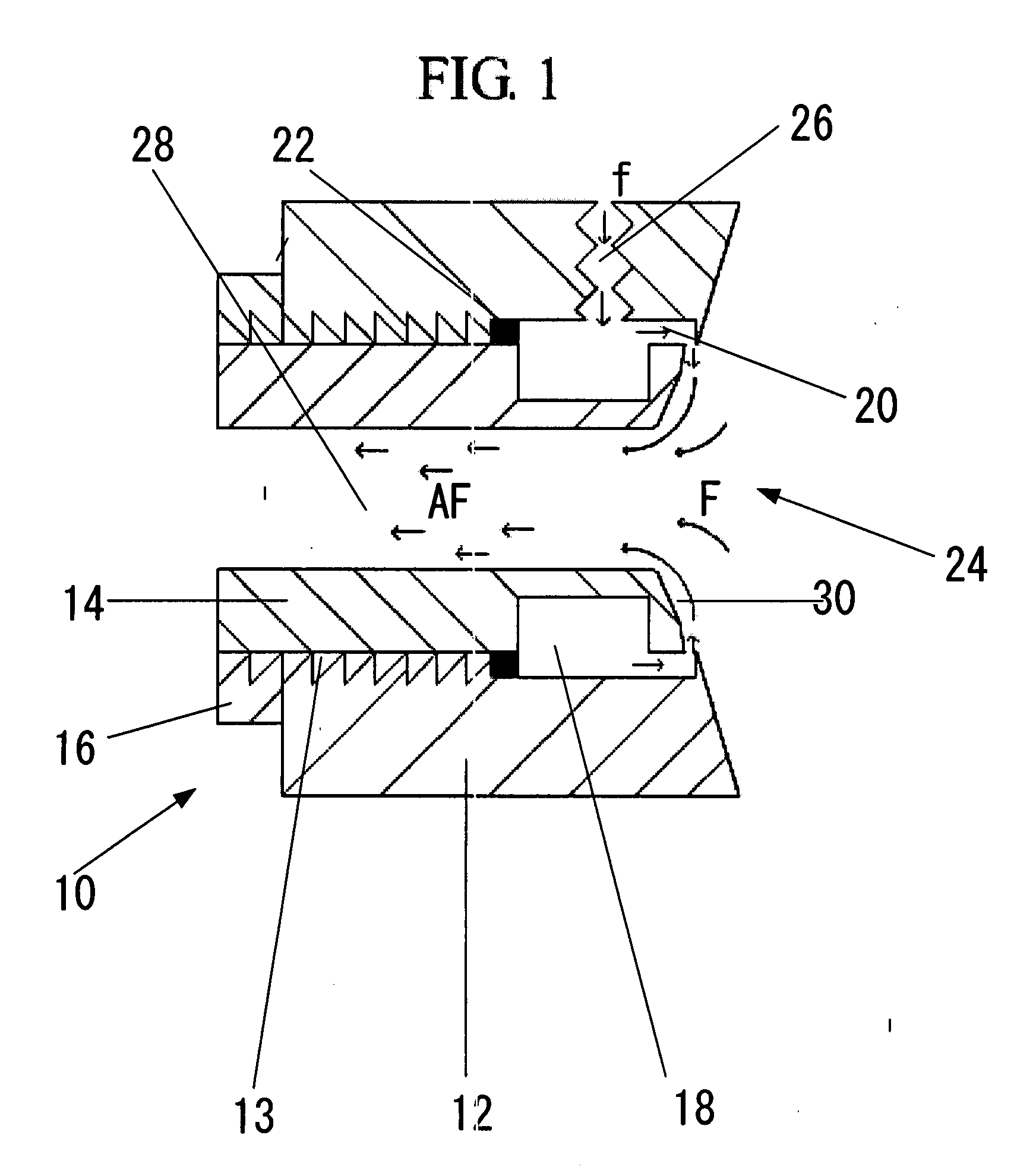

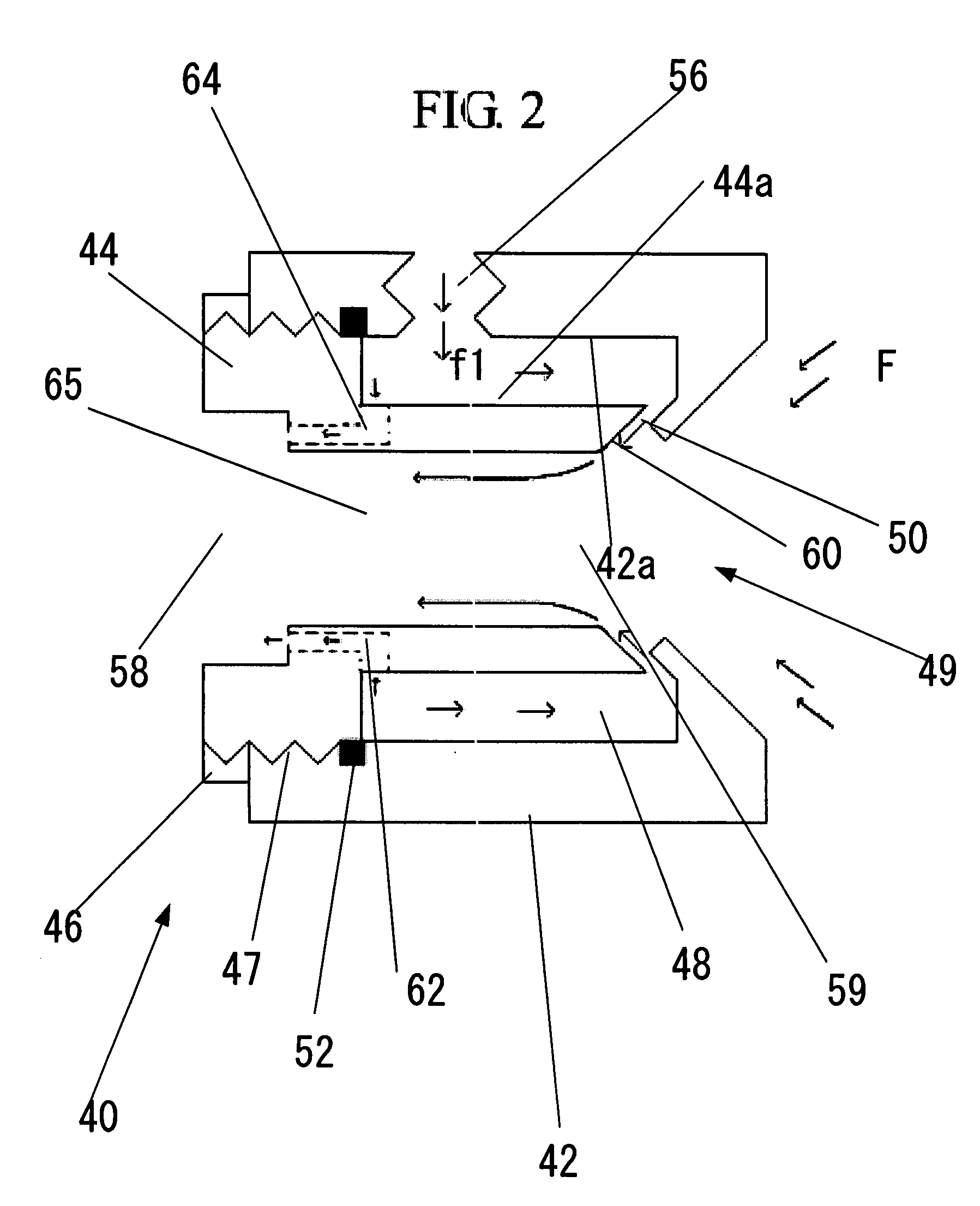

Fluid flow amplifier

ActiveUS20090032130A1Most efficientVelocity becomes largerCircuit elementsJet pumpsAudio power amplifierAir entrainment

A by-pass fluid flow amplifier which contains a primary nozzle and a primary profile for discharging compressed air into a conduit of the air amplifier and entraining ambient air in the process. A secondary nozzle and a secondary profile for discharging compressed air into the conduit of the air amplifier towards the rear that assists the primary nozzle such as to allow consistent fluid wall attachment of the compressed air and the entrained air caused by the primary nozzle and the primary profile. The secondary nozzle increases the total flow of the amplifier and prohibits the total flow from traveling towards the center of the conduit where flow reversal and turbulence are likely to occur.

Owner:DUMAS ELIJAH +2

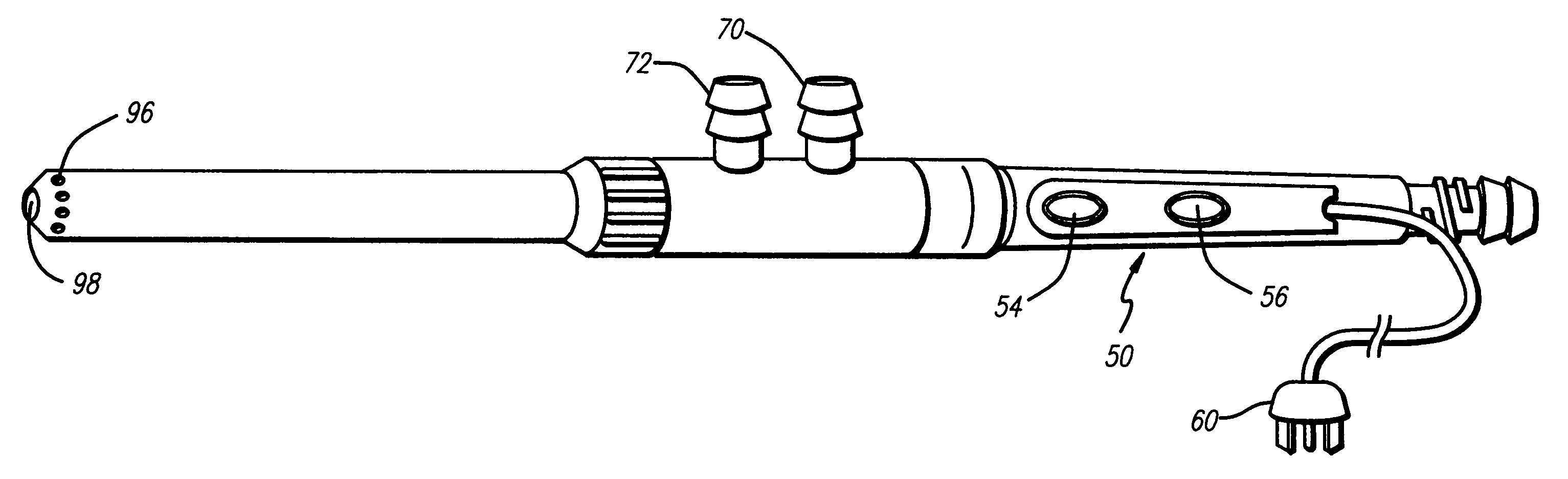

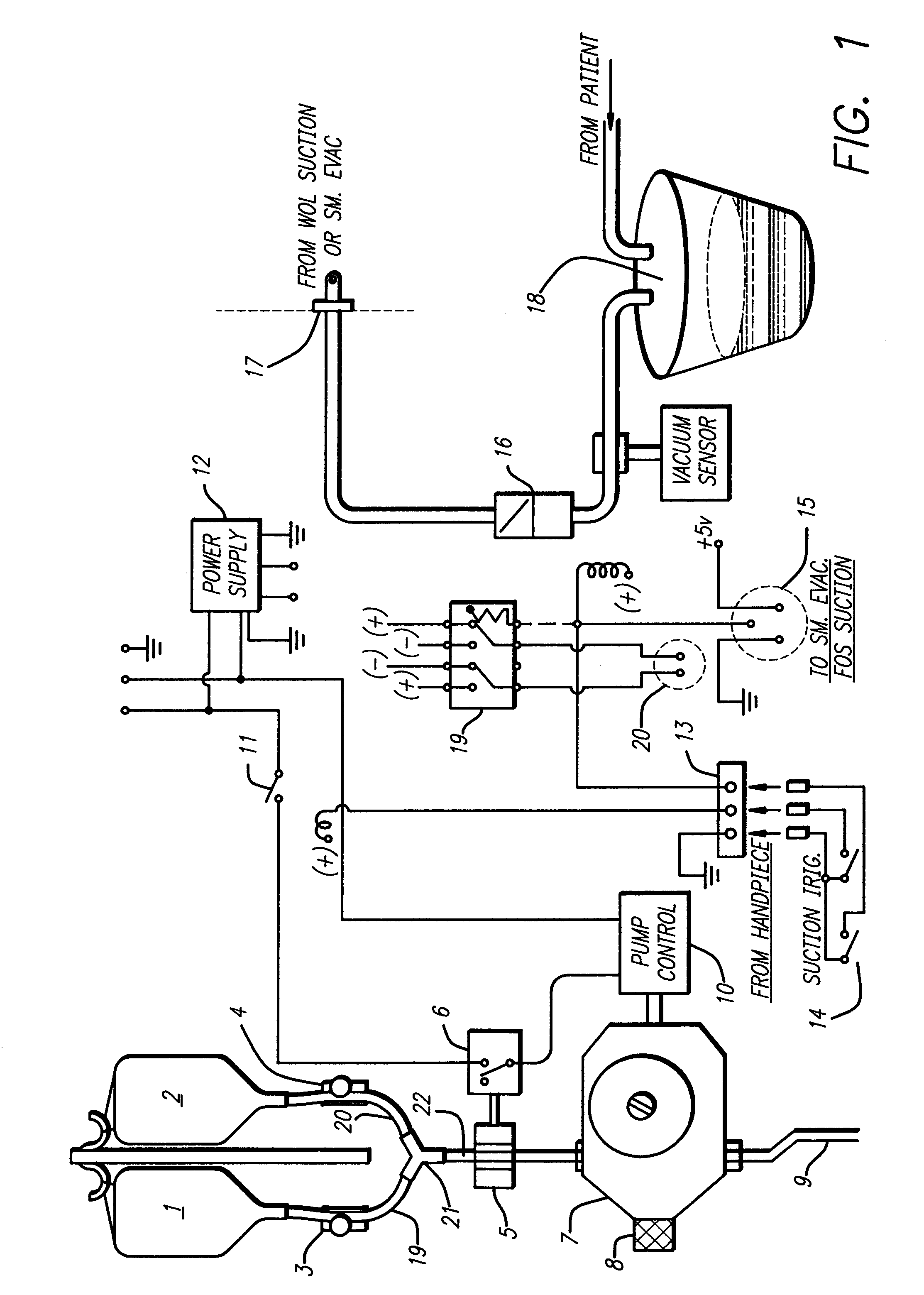

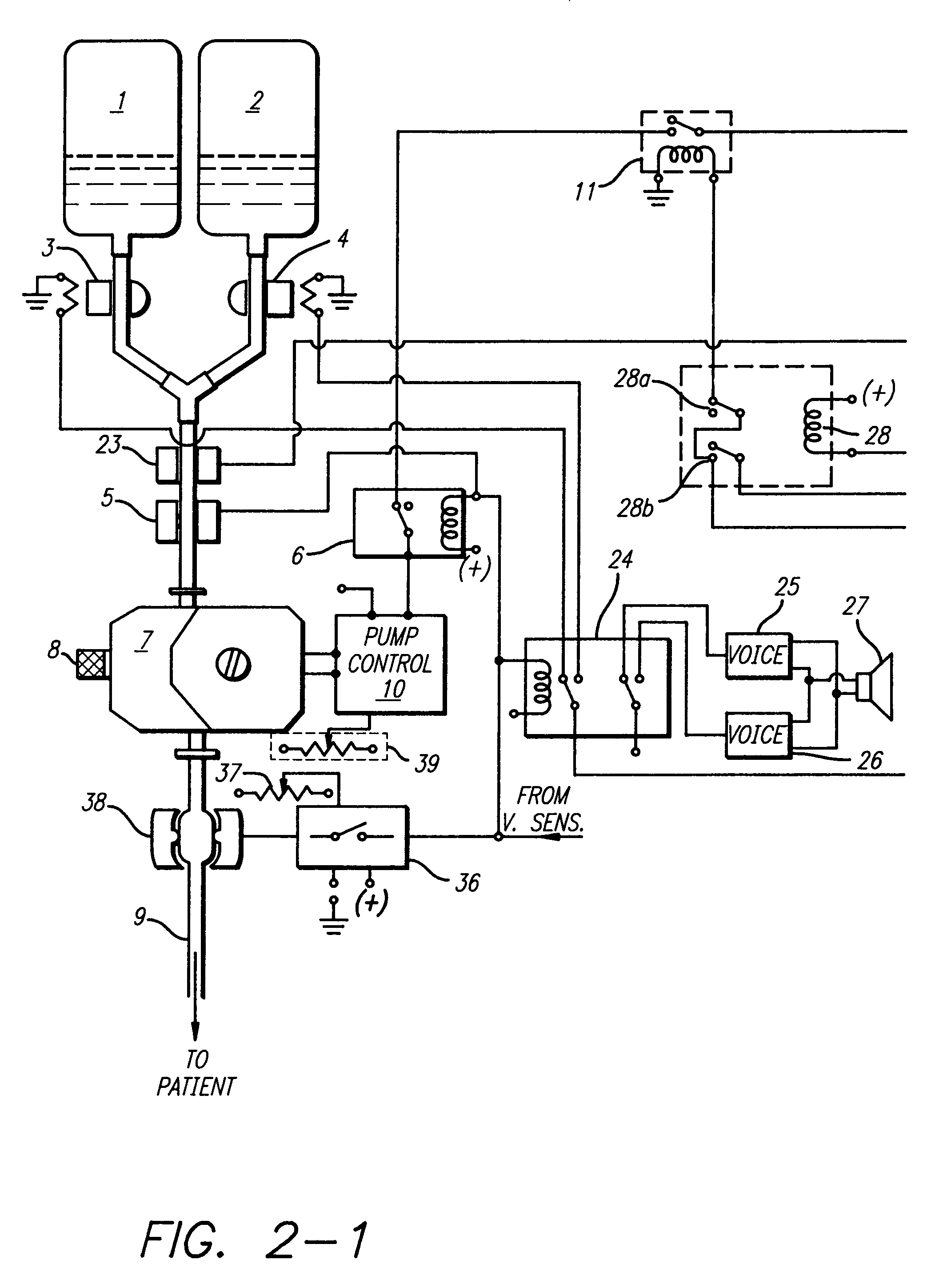

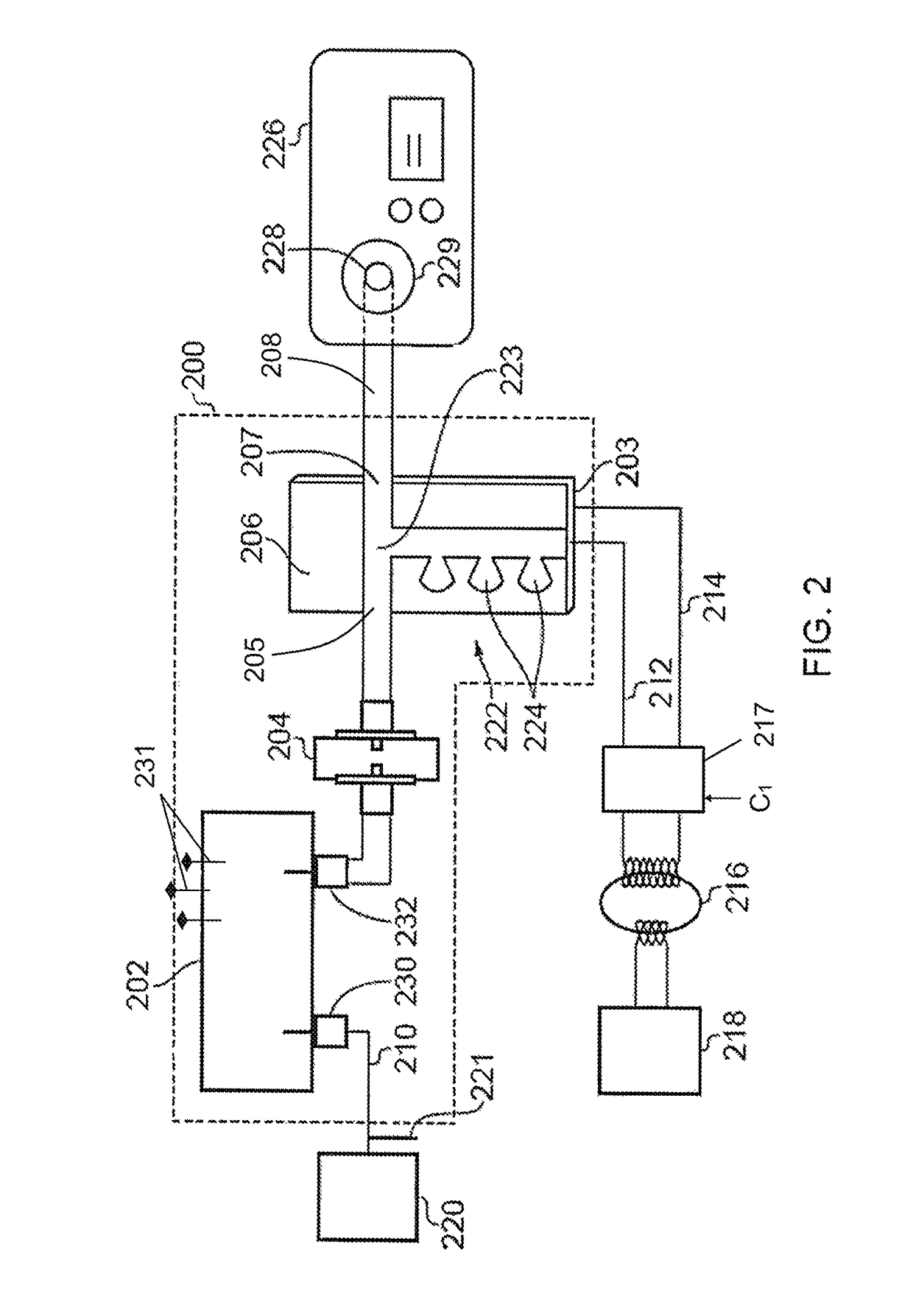

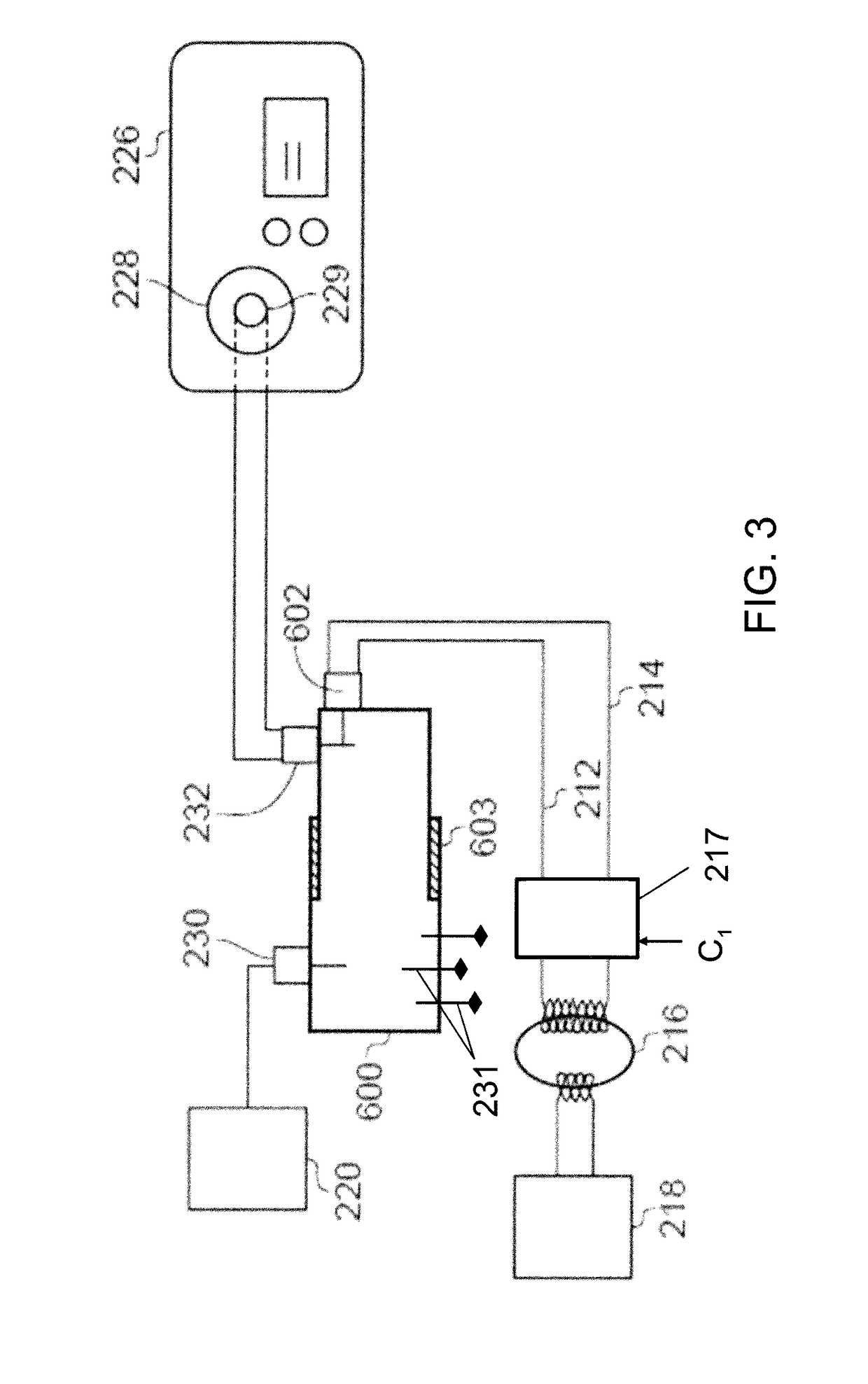

Automatic fluid control system for use in open and laparoscopic laser surgery and electrosurgery and method therefor

InactiveUS7083601B1Increase pressureImprove liquidityEnemata/irrigatorsChiropractic devicesAutomatic controlFluid control

A manual and automatic fluid control system and method for use in open and laparoscopic laser surgery and electrosurgery is disclosed. The system includes a manual mode along with several automatic modes which can effectuate both suction and irrigation, either individually or simultaneously. In the various automatic modes, the suction and / or irrigation is automatically activated during activation of a medical apparatus for laser surgery or electrosurgery without requiring separate activation from the surgeon or operating room staff. Several safety features for monitoring the fluid control system are also incorporated within the system such as fluid sensors for detecting the absence of irrigation fluid, pressure sensors and vacuum systems for monitoring fluid pressure, fluid sensors for monitoring fluid volume, and warning signals for detecting empty containers. All of the safety features are designed to automatically deactivate suction and / or irrigation means contained within the fluid control system upon detection of unsafe levels. Finally, specially designed suction / irrigation hand pieces are disclosed for use in connection with the fluid control system.

Owner:IC MEDICAL

Semiconductor device, substrate for electro-optical device, electro-optical device, electronic device and projection display

InactiveUS6346717B1Potential stabilityImprove pressure resistanceTransistorSolid-state devicesVoltageElectro-optics

The potential at a channel region of a MOSFET on a substrate needs to be stabilized to assure a drain withstand voltage. To this end, a new potential line is additionally required. However, the addition of the potential line causes a drop in the aperture ratio in a transmissive type liquid-crystal display device, in which lightness is particularly important. A light shielding layer overlapping the MOSFET formed on the substrate is electrically connected to the channel region in the MOSFET.

Owner:SEIKO EPSON CORP

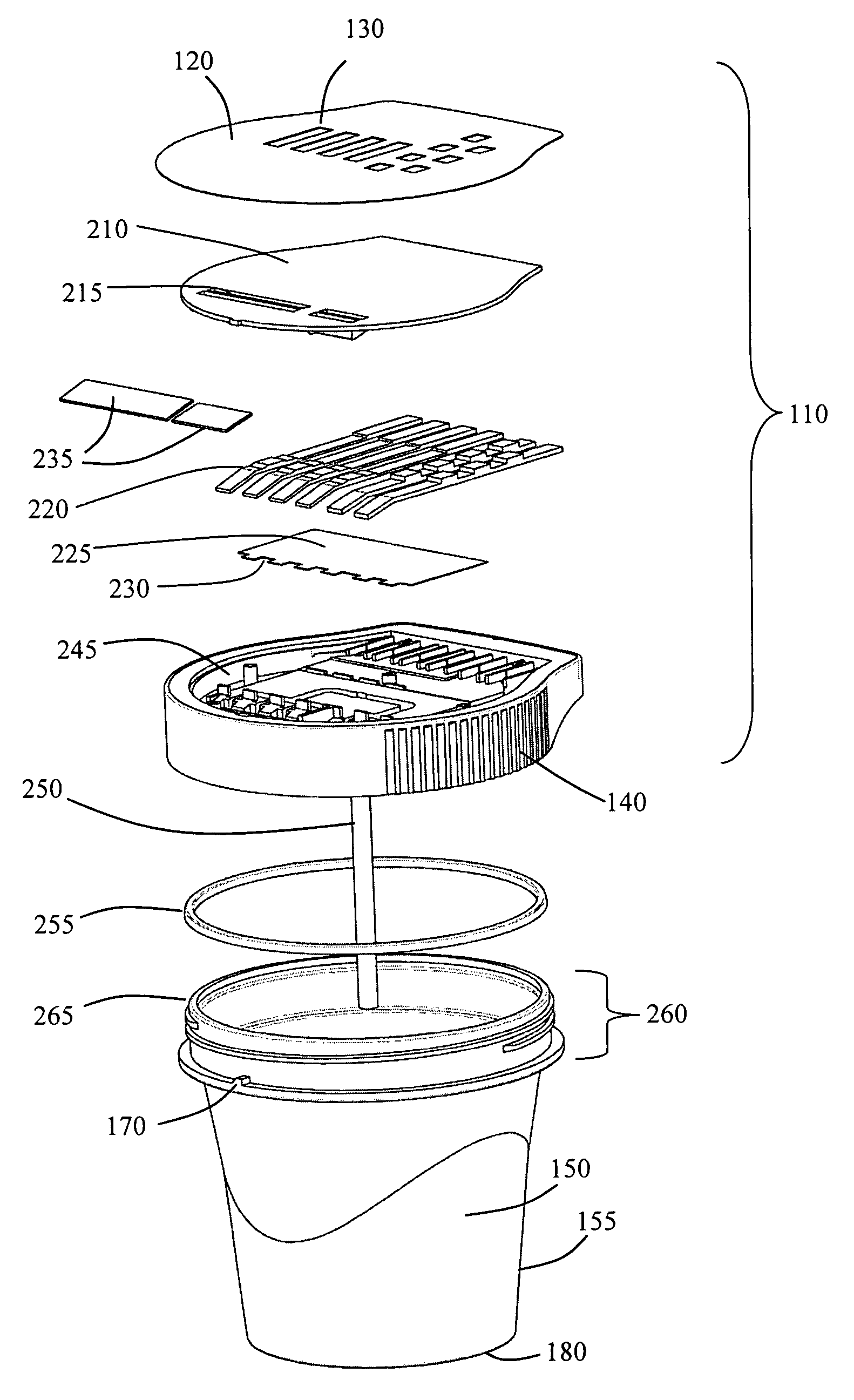

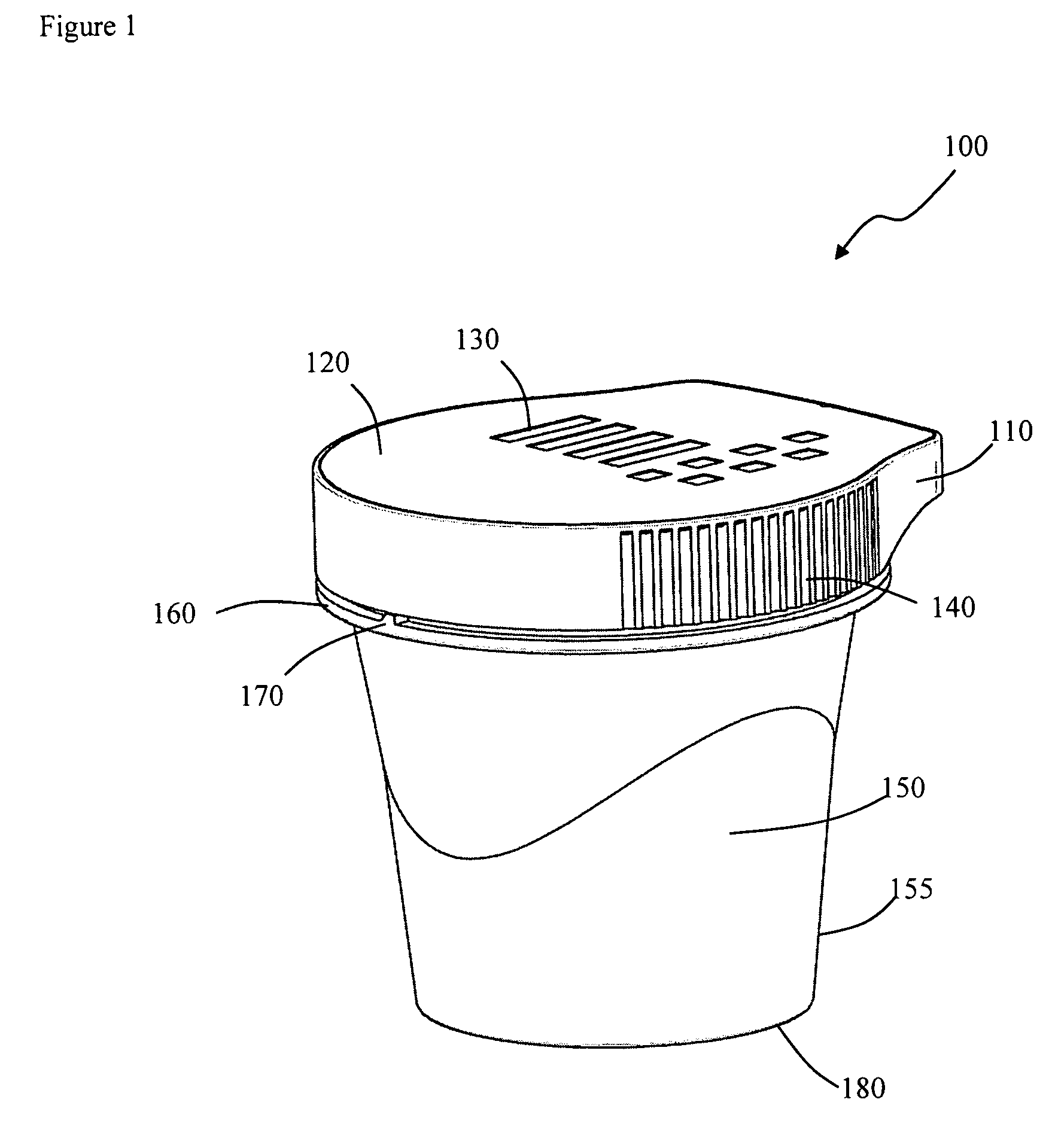

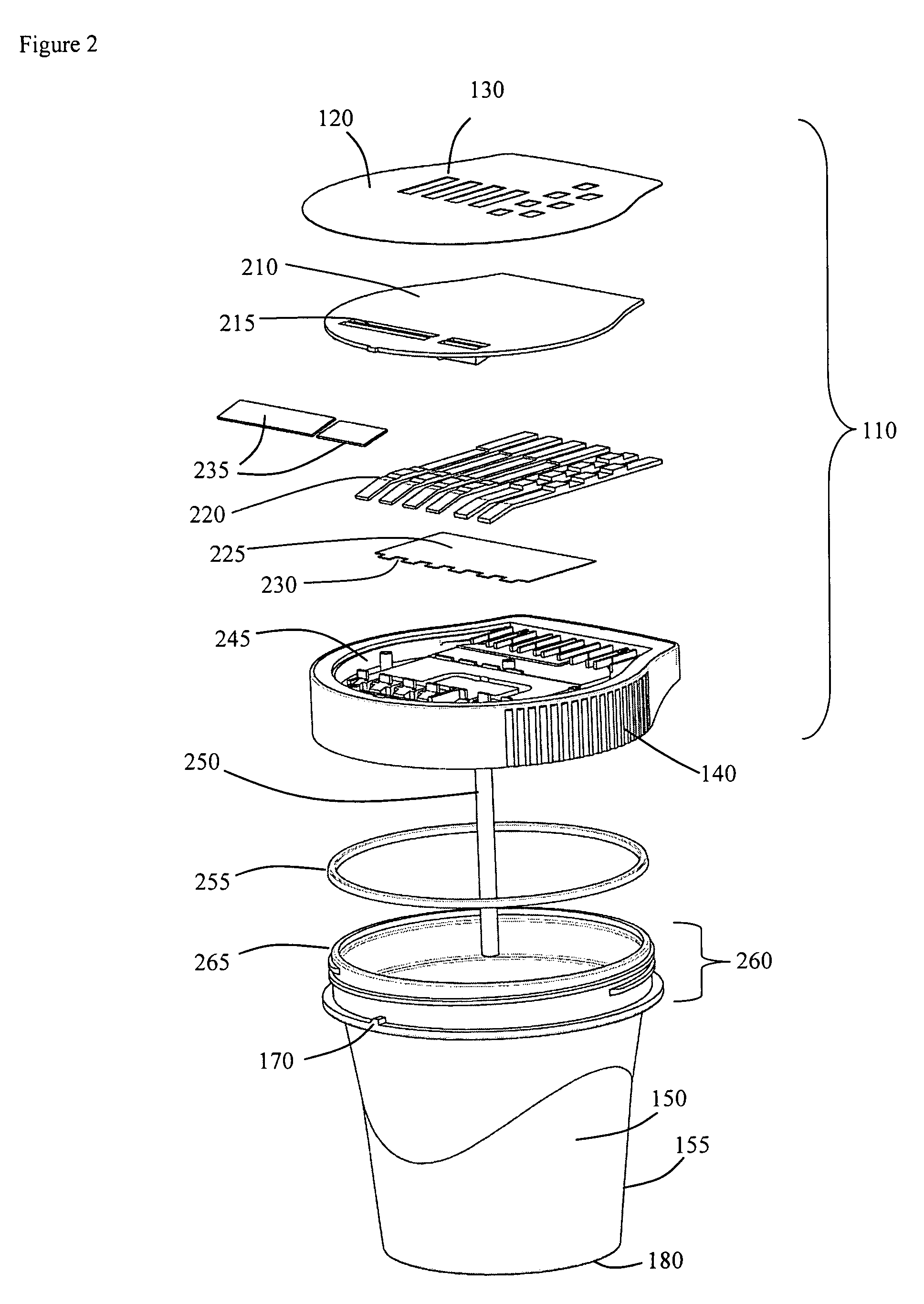

Sample collection cup with integrated sample analysis system

ActiveUS20050106750A1High internal air pressureImprove pressure resistanceMaterial analysis by observing effect on chemical indicatorWithdrawing sample devicesTarget analysisAnalyte

The present invention is directed to devices and methods for collecting liquid samples and of testing the sample for the presence of an analyte of interest and / or a physical property. In one embodiment the device is a urine cup having an interior for containing a liquid sample, a lid, and a chamber for holding liquid. The device contains a test component for determining the presence of an analyte in the liquid sample and / or a physical property. A tube is immersed in liquid sample when the device is filled with liquid sample to be tested. When the lid is applied to the device (e.g., by screwing or snapping on), liquid sample is forced through the tube and into the chamber holding the test component.

Owner:ABBOTT RAPID DIAGNOSTICS INT UNLTD

Electrosurgical apparatus for generating radiofrequency energy and microwave energy for delivery into biological tissue

ActiveUS10188455B2Improve accuracyReduced insertion lossCatheterSurgical instruments for heatingCapacitanceElectrical conductor

An isolating circuit for an electrosurgical generator arranged to produce radiofrequency (RF) energy and microwave energy for treating biological tissues is provided. The generator has an RF channel and a microwave channel which are combined at a signal combiner to enable the RF energy and microwave energy to be delivered into tissues along a common feed path. The isolating circuit includes a tunable wavelength isolator at a junction between the microwave channel and the signal combiner, and can include a capacitive structure between a ground conductor of the signal combiner and a conductive input section of the waveguide isolator to inhibit coupling of the RF energy and leakage of the microwave energy. The isolating circuit can combine into a single tunable unit all the necessary components to isolate the microwave and RF channels from one another while providing a high withstanding voltage.

Owner:CREO MEDICAL LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com