Patents

Literature

38262 results about "Device material" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Semiconductor devices are electronic components that exploit the electronic properties of semiconductor materials, principally silicon, germanium, and gallium arsenide, as well as organic semiconductors. Semiconductor devices have replaced thermionic devices (vacuum tubes) in most applications.

Semiconductor device, manufacturing method, and electronic device

ActiveUS20060244107A1Stabilize element propertyEasy to manufactureTransistorSemiconductor/solid-state device detailsSurface levelIntrinsic resistance

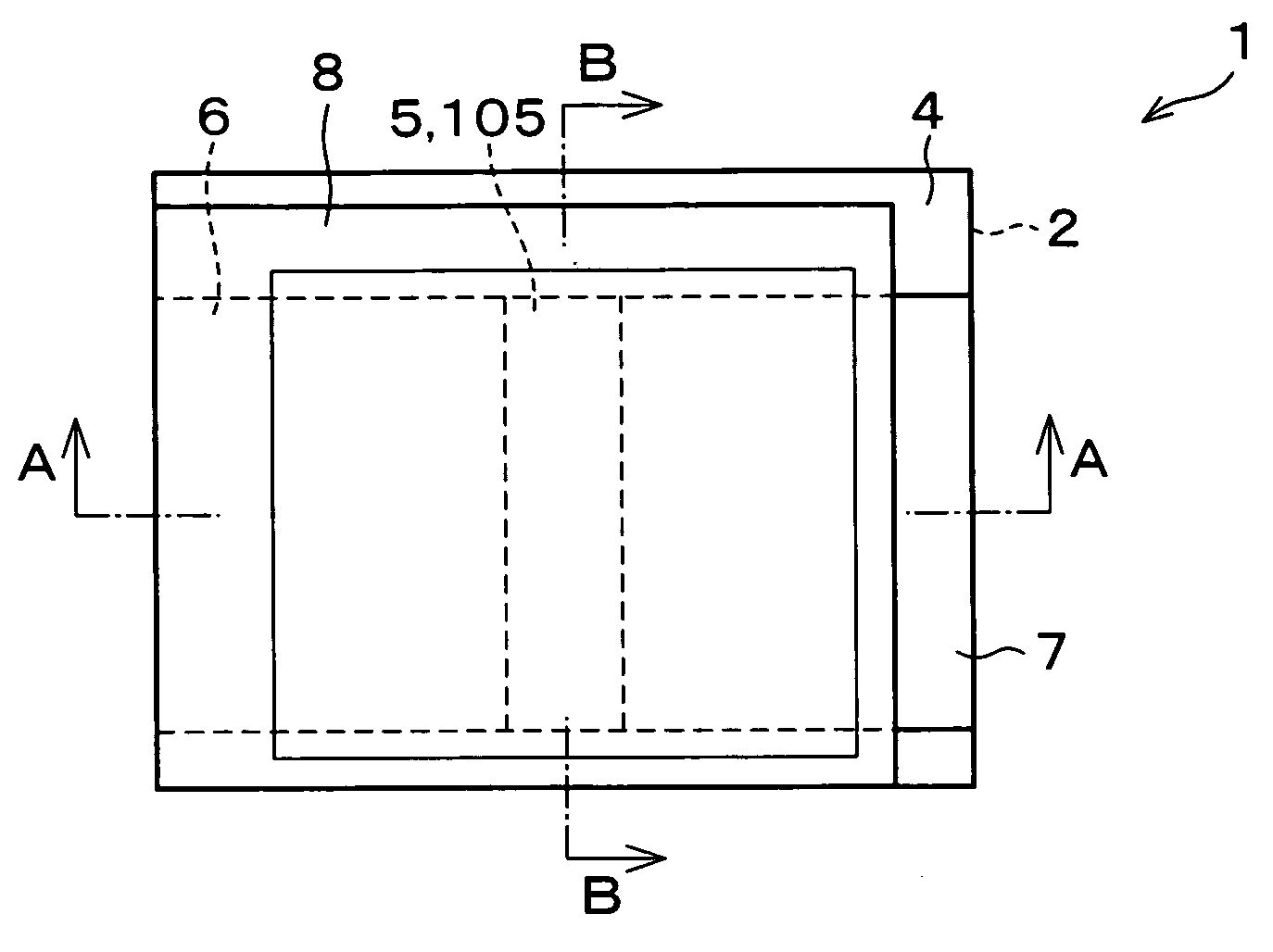

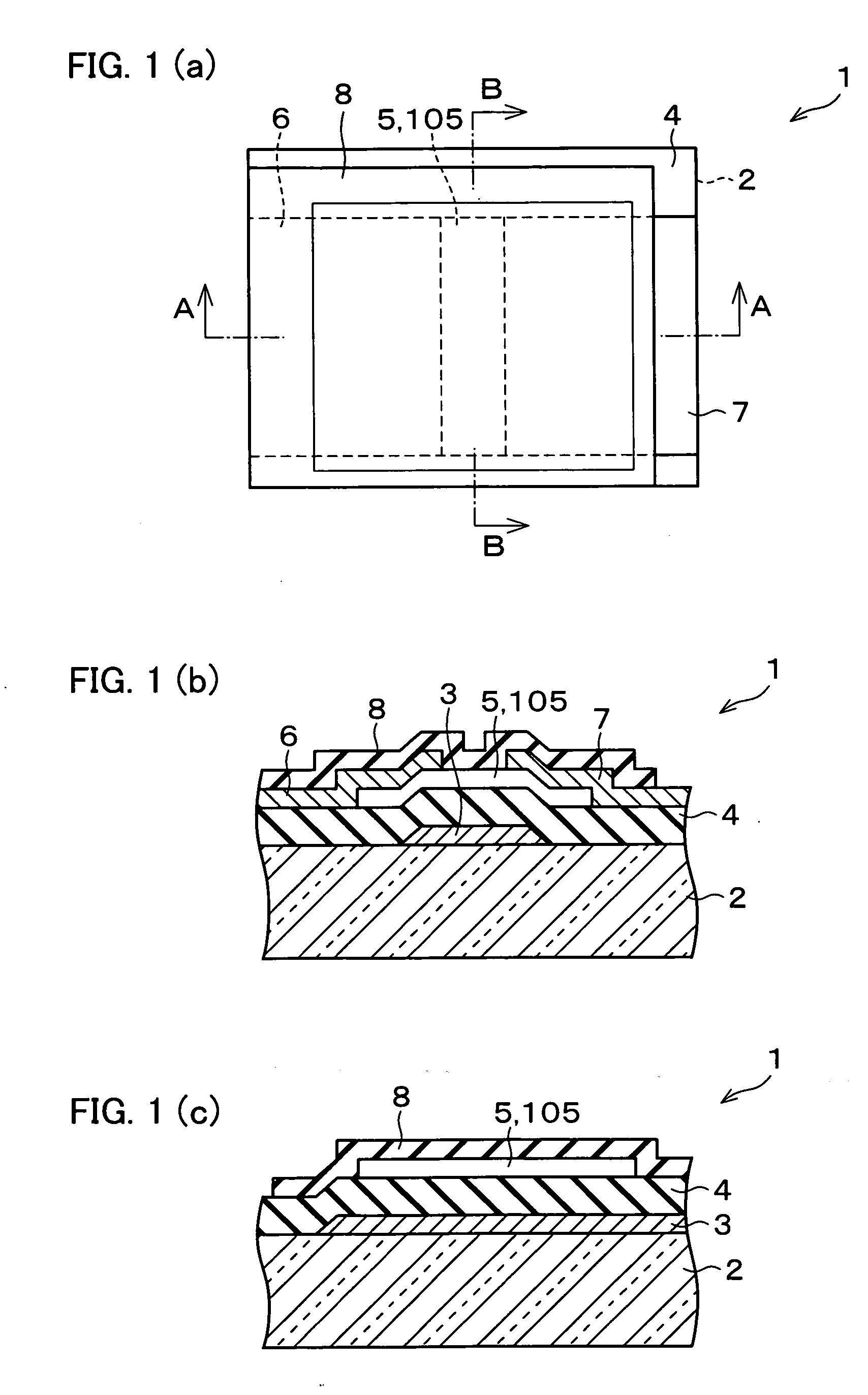

In a thin film transistor (1), a gate insulating layer (4) is formed on a gate electrode (3) formed on an insulating substrate (2). Formed on the gate insulating layer (4) is a semiconductor layer (5). Formed on the semiconductor layer (5) are a source electrode (6) and a drain electrode (7). A protective layer (8) covers them, so that the semiconductor layer (5) is blocked from an atmosphere. The semiconductor layer (5) (active layer) is made of, e.g., a semiconductor containing polycrystalline ZnO to which, e.g., a group V element is added. The protective layer (8) thus formed causes decrease of a surface level of the semiconductor layer (5). This eliminates a depletion layer spreading therewithin. Accordingly, the ZnO becomes an n-type semiconductor indicating an intrinsic resistance, with the result that too many free electrons are generated. However, the added element works on the ZnO as an accepter impurity, so that the free electrons are reduced. This decreases a gate voltage required for removal of the free electrons, so that the threshold voltage of the thin film transistor (1) becomes on the order of 0V. This allows practical use of a semiconductor device which has an active layer made of zinc oxide and which includes an protective layer for blocking the active layer from an atmosphere.

Owner:SHARP KK +2

Transistor and semiconductor device

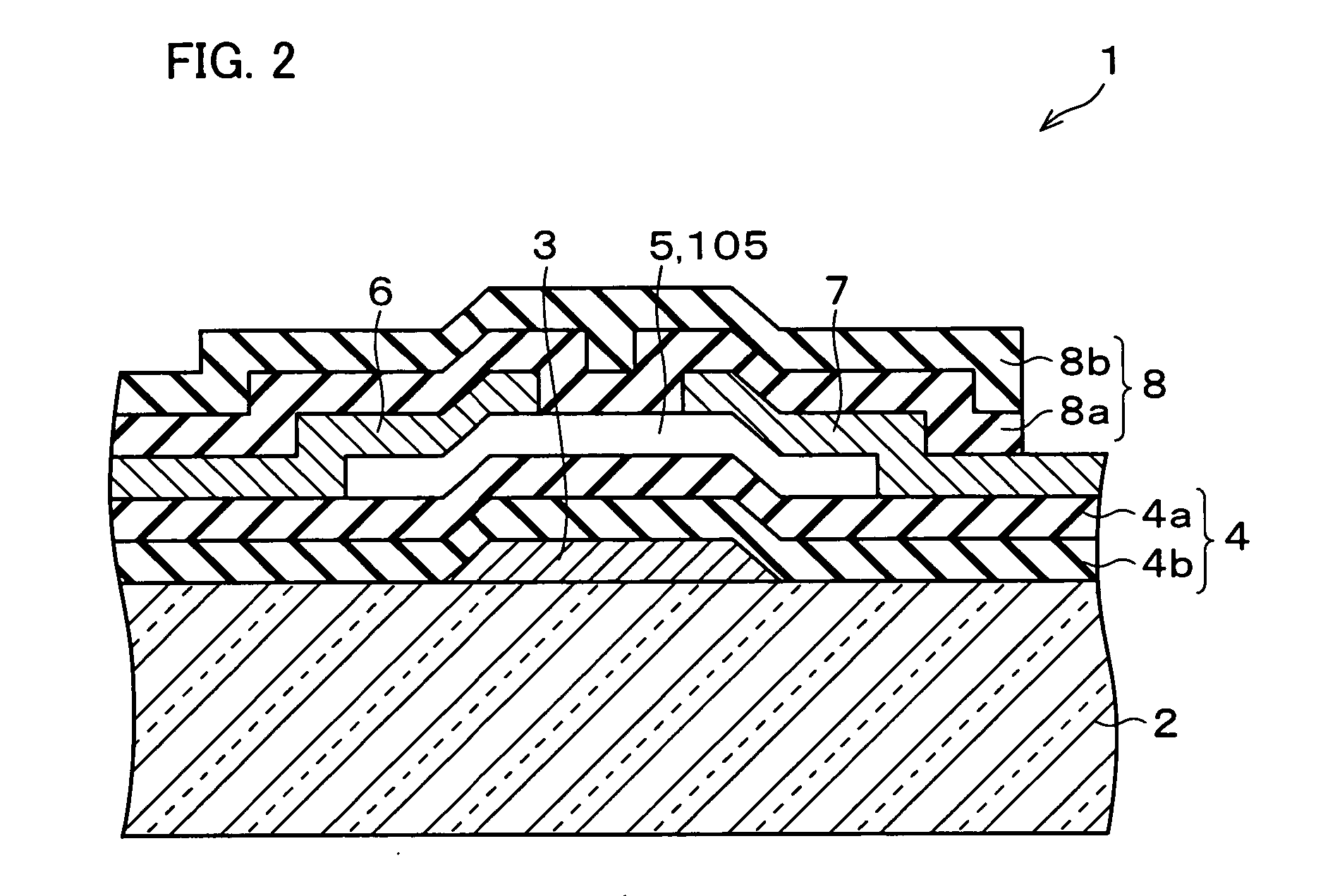

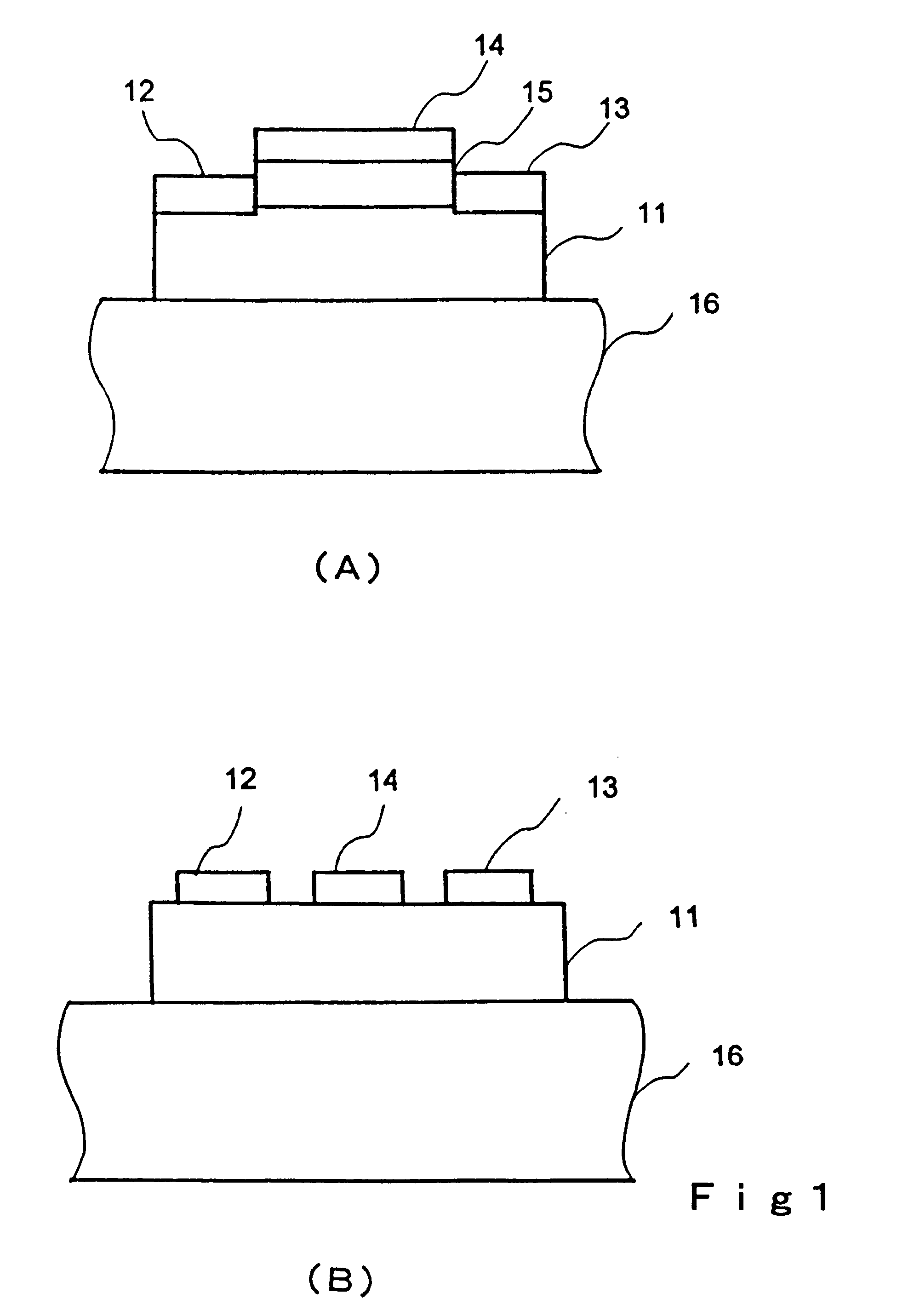

A transistor is provided, which is entirely and partially transparent by the use of a transparent channel layer made of zinc oxide or the like. A channel layer 11 formed of a transparent semiconductor such as zinc oxide ZnO. A transparent electrode is used for all of a source 12, a drain 13 and a gate 14, or a part of them. As the transparent electrode, a transparent conductive material such as conductive ZnO doped with, for example, group III elements is used. As a gate insulating layer 15, a transparent insulative material such as insulative ZnO doped with elements capable of taking a valence of one as a valence number or group V elements is used. If a substrate 16 must be transparent, for example, glass, sapphire, plastic or the like can be used as a transparent material.

Owner:JAPAN SCI & TECH CORP

Electric elements and circuits utilizing amorphous oxides

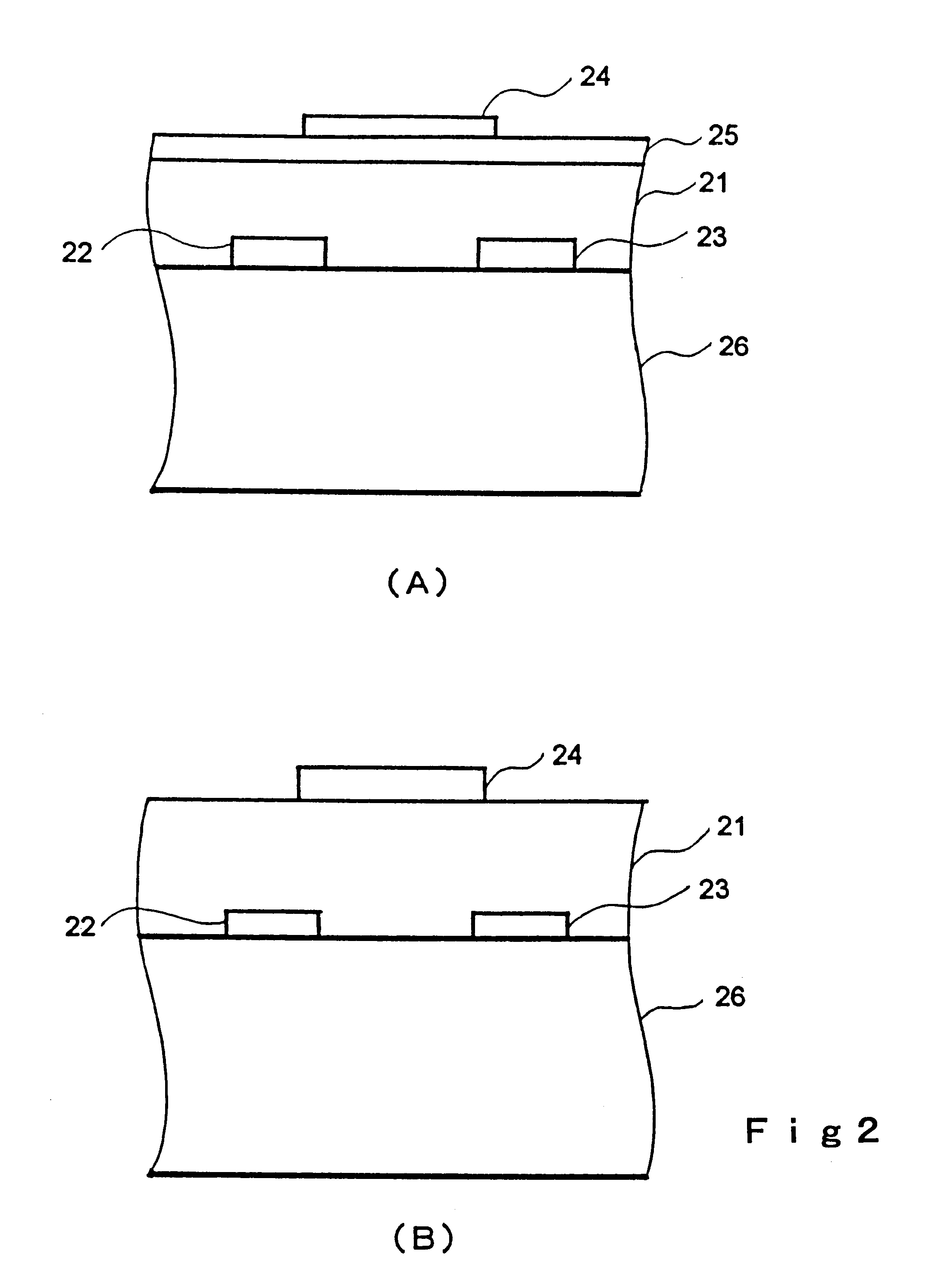

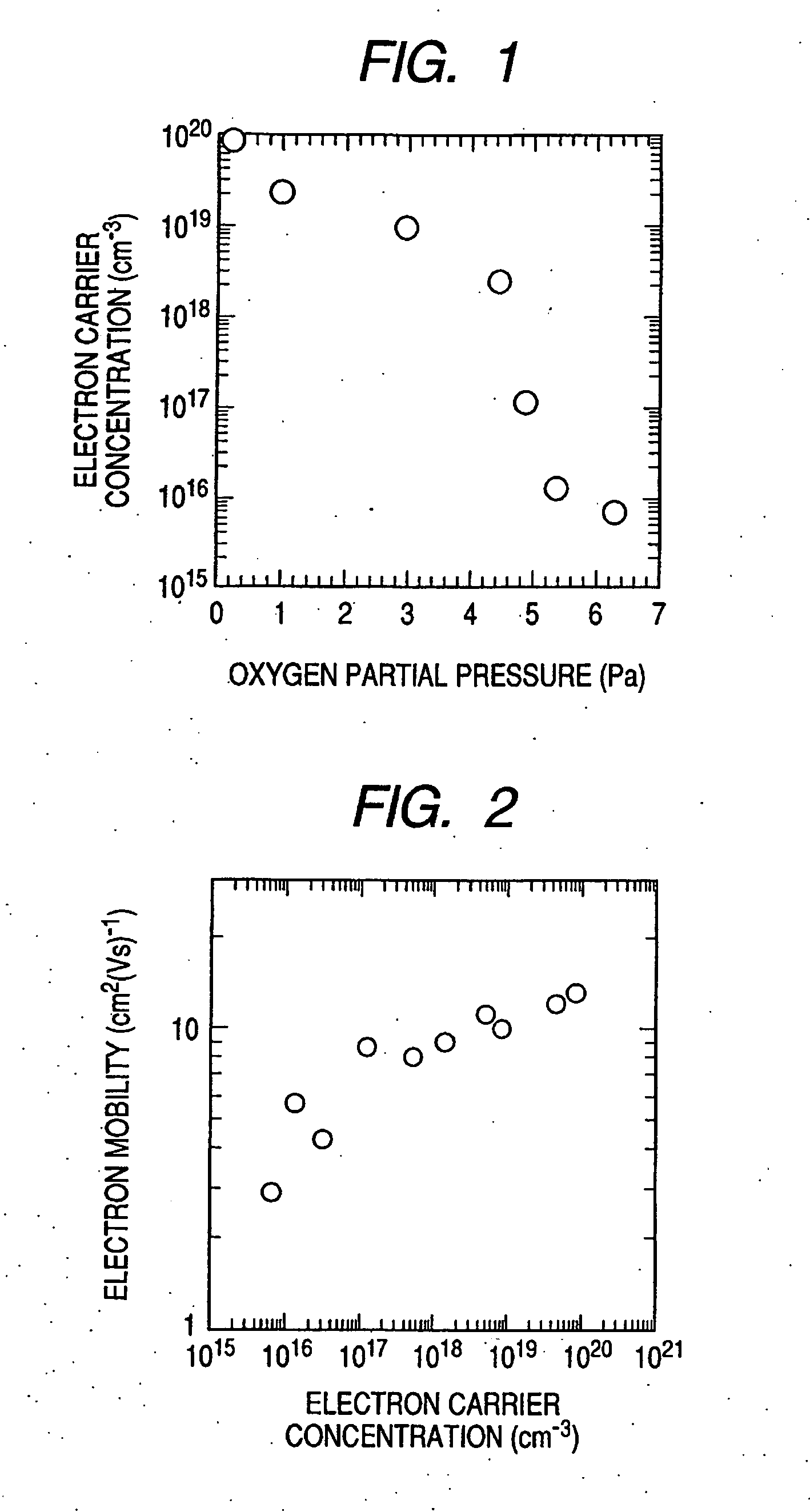

Semiconductor devices and circuits with use of transparent oxide film are provided. The semiconductor device having a P-type region and an N-type region, wherein amorphous oxides with electron carrier concentration less than 1018 / cm3 is used for the N-type region.

Owner:CANON KK +2

Semiconductor device, electronic device, and method of manufacturing semiconductor device

InactiveUS20060170111A1Stable formationImprove performanceSemiconductor/solid-state device detailsSolid-state devicesDevice materialShortest distance

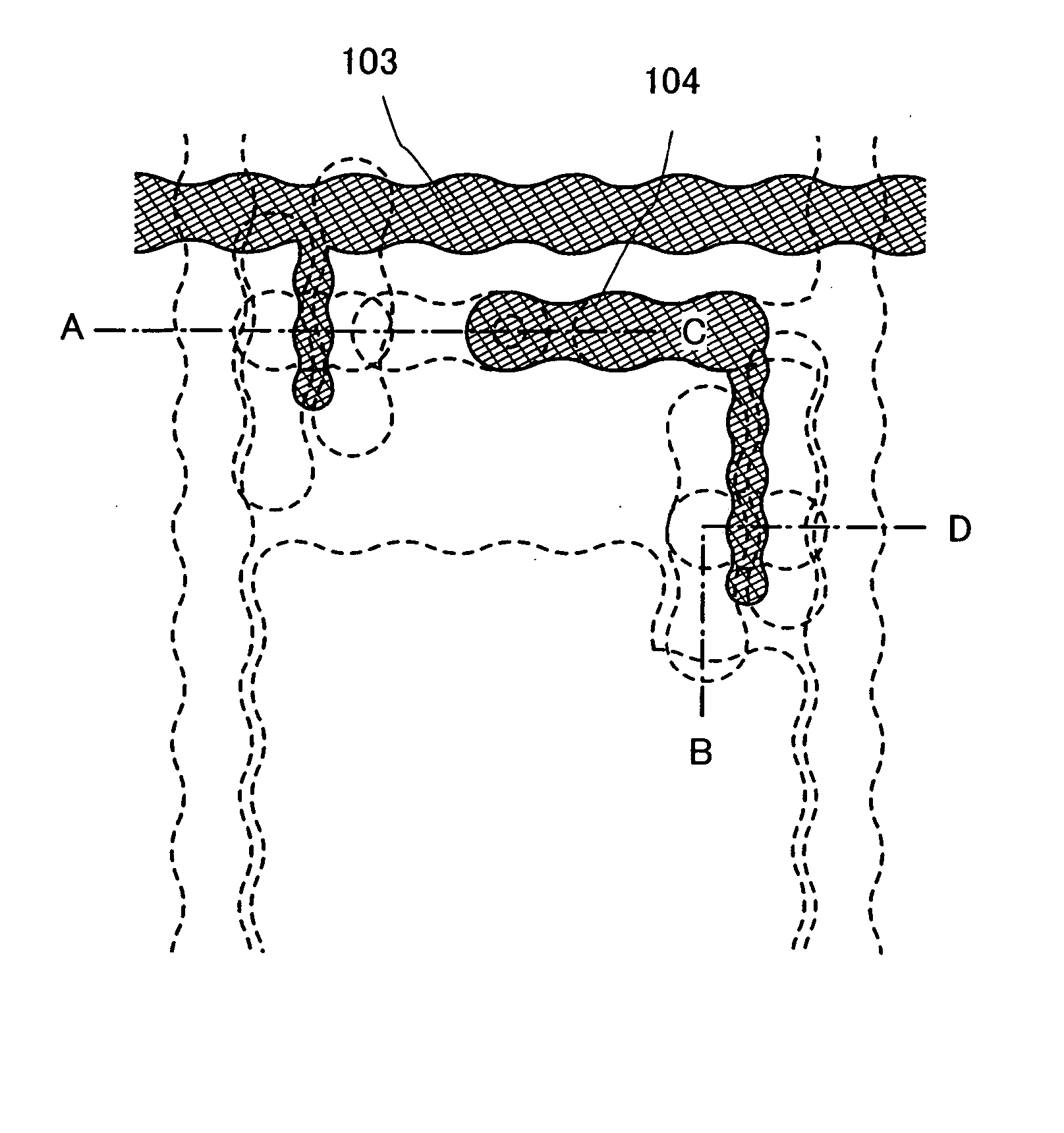

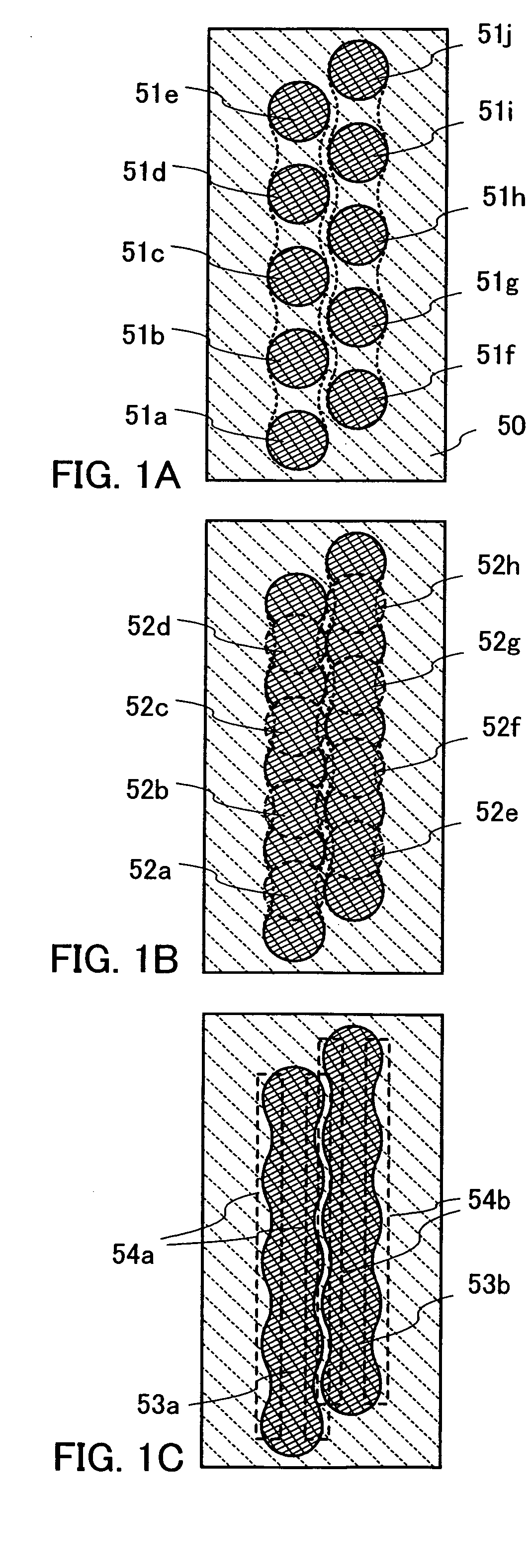

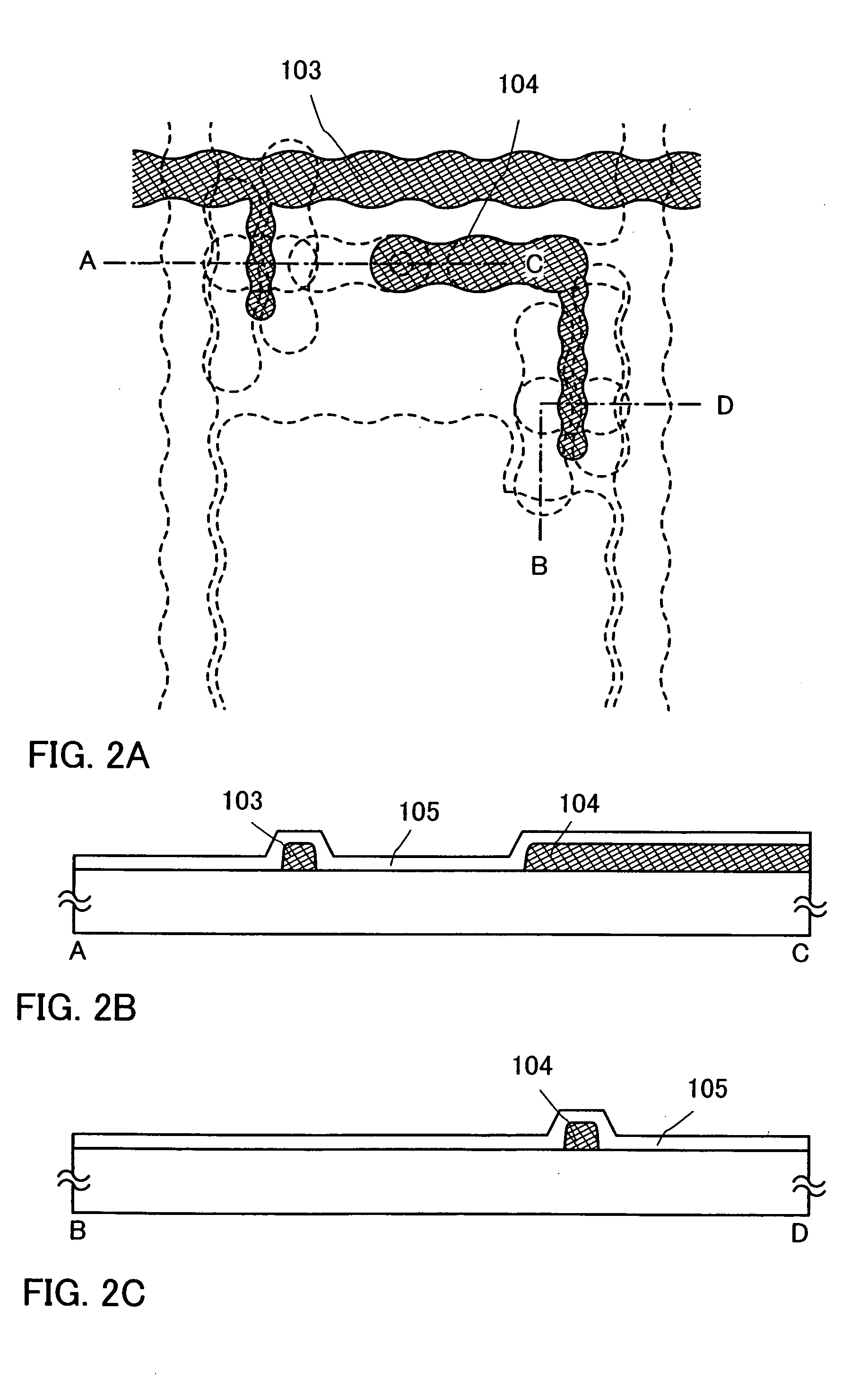

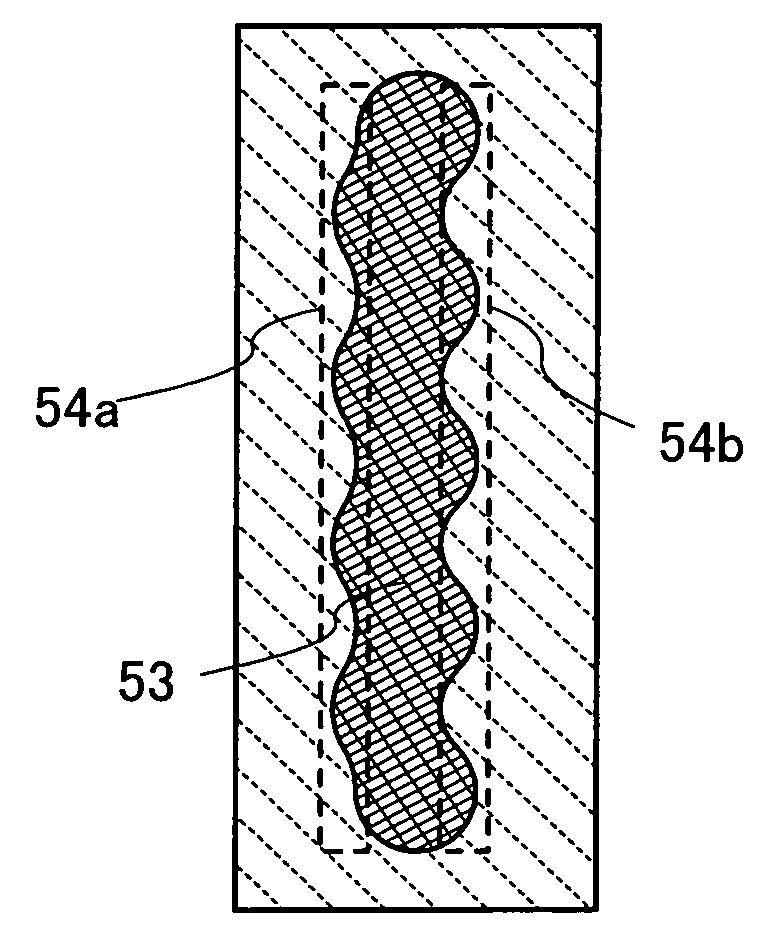

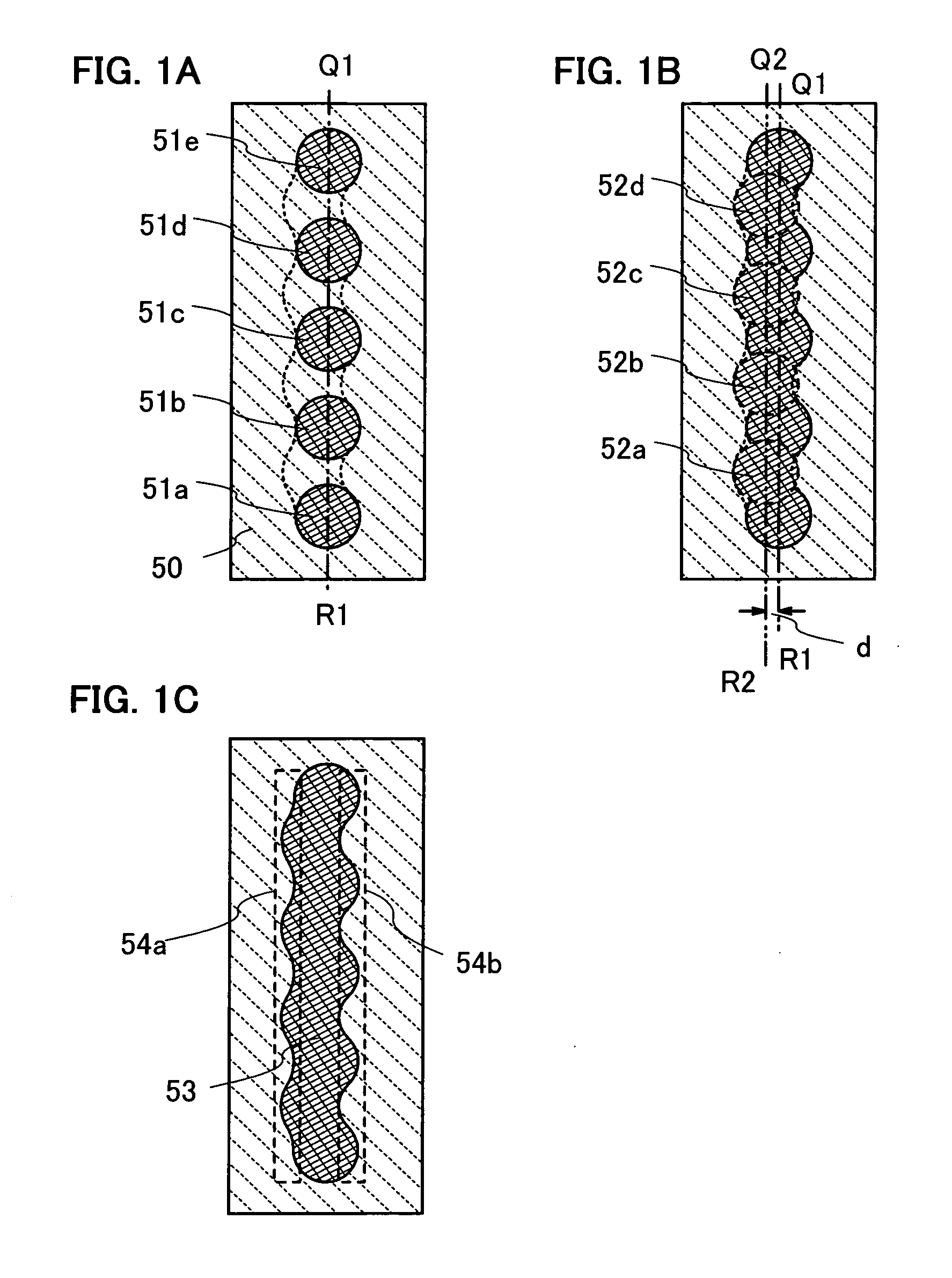

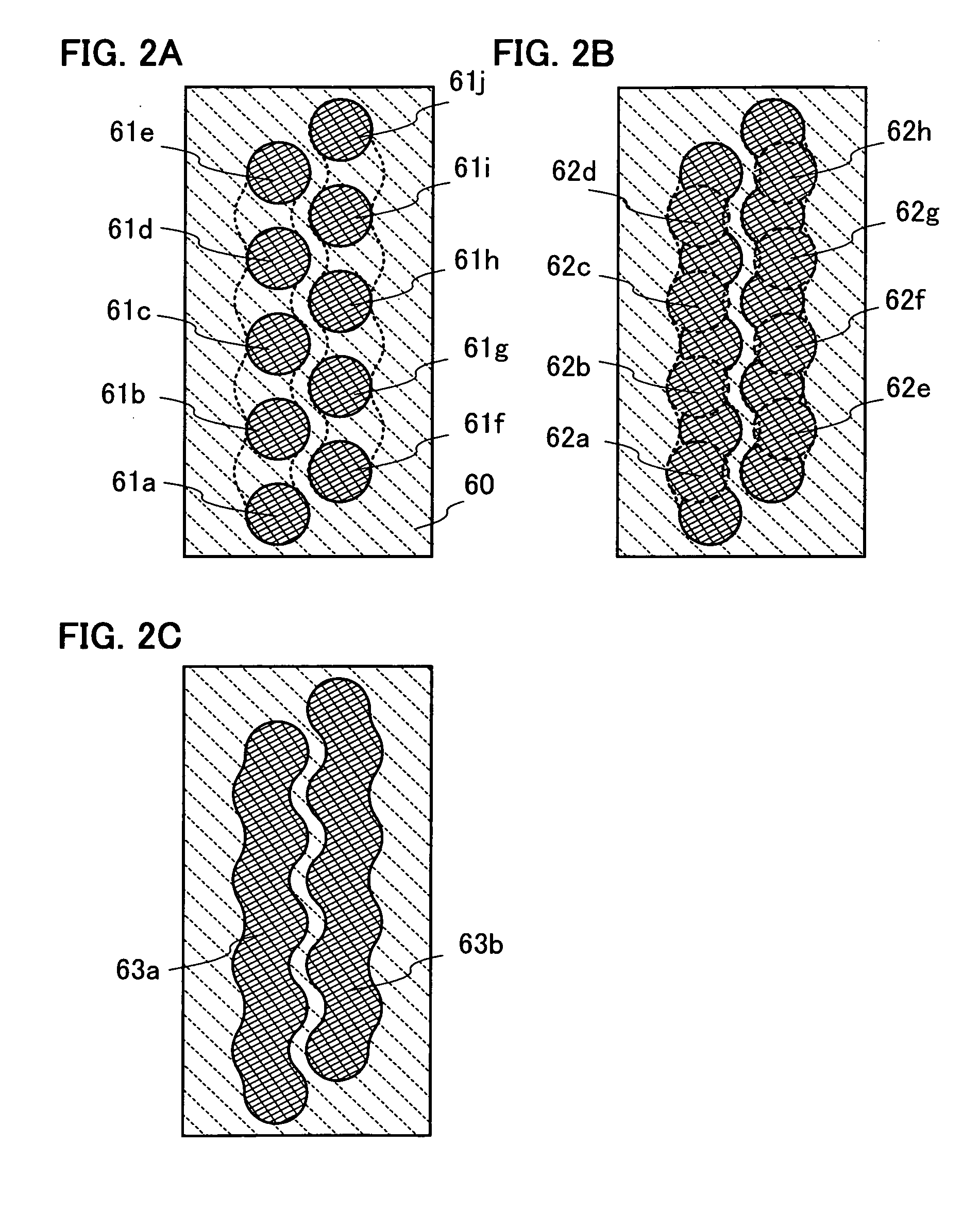

Conductive layers having knots are adjacently formed with uniform distance therebetween. Droplets of the conductive layers are discharged to stagger centers of the droplets in a length direction of wirings so that the centers of the discharged droplets are not on the same line in a line width direction between the adjacent conductive layers. Since the centers of the droplets are staggered, parts of the conductive layers each having a widest line width (the widest width of knot) are not connected to each other, and the conductive layers can be formed adjacently with a shorter distance therebetween.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device in which zinc oxide is used as a semiconductor material and method for manufacturing the semiconductor device

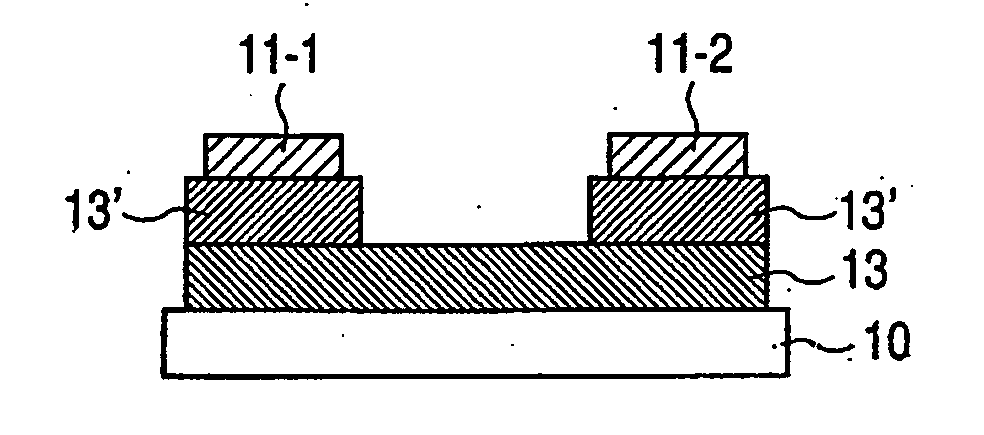

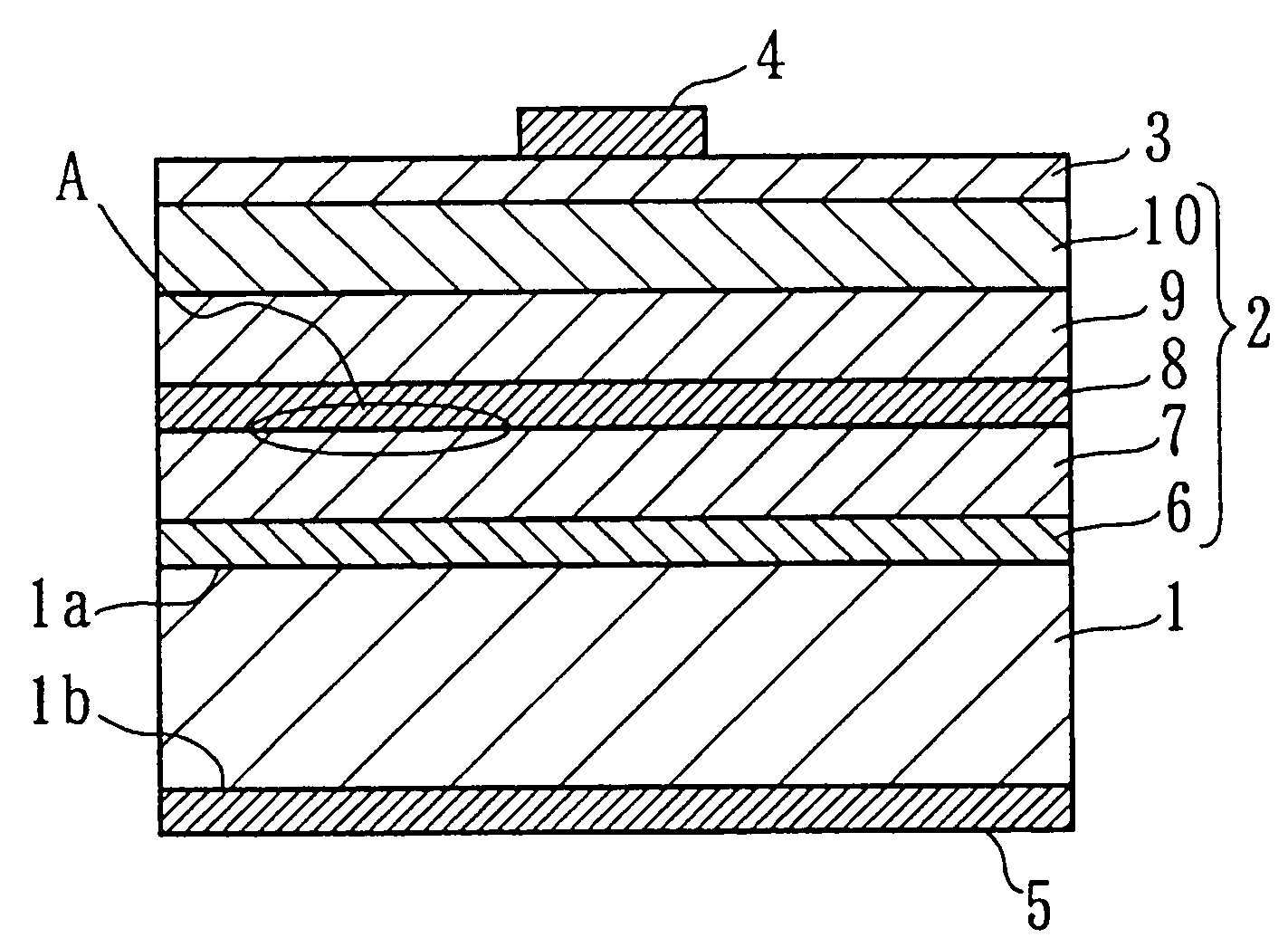

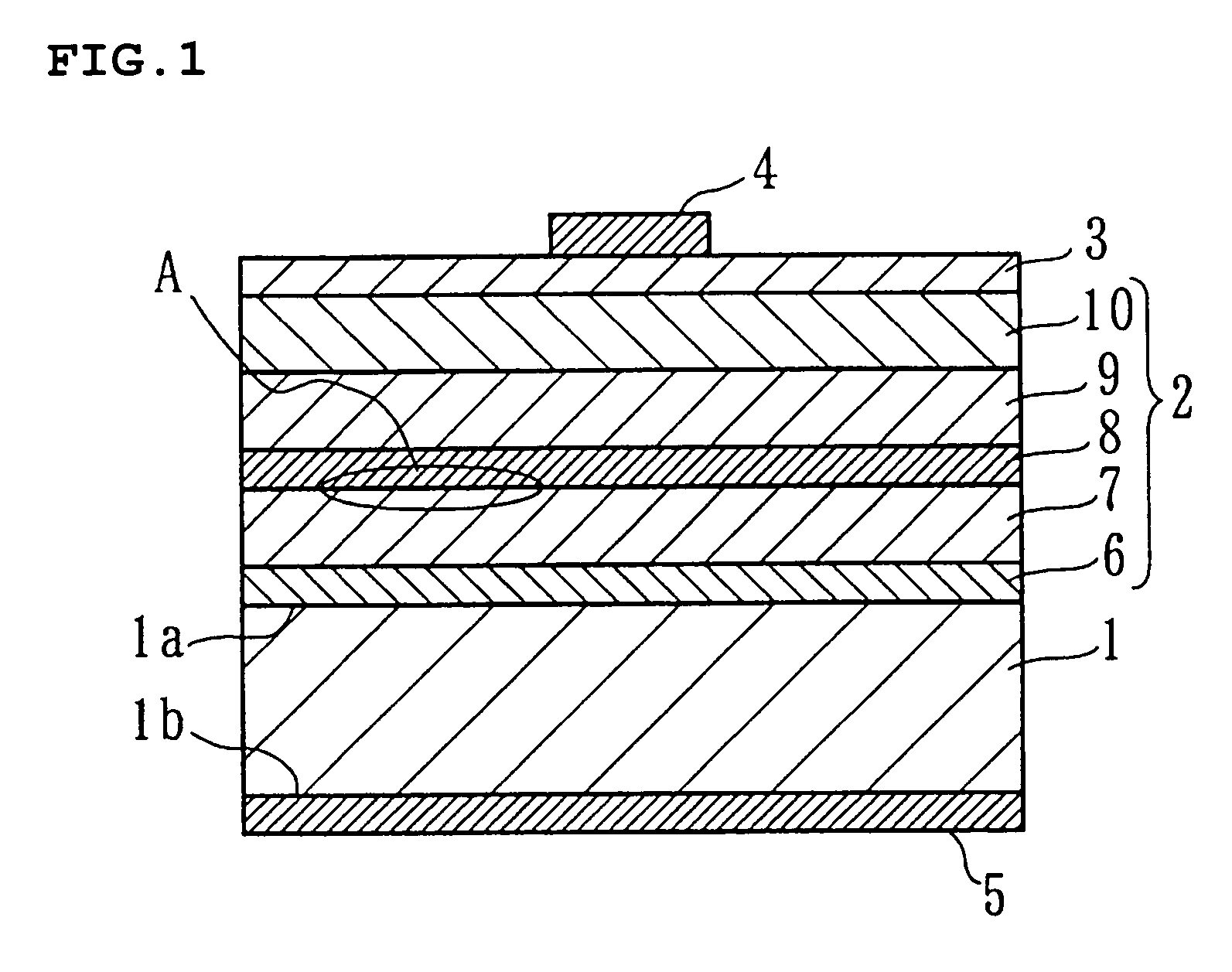

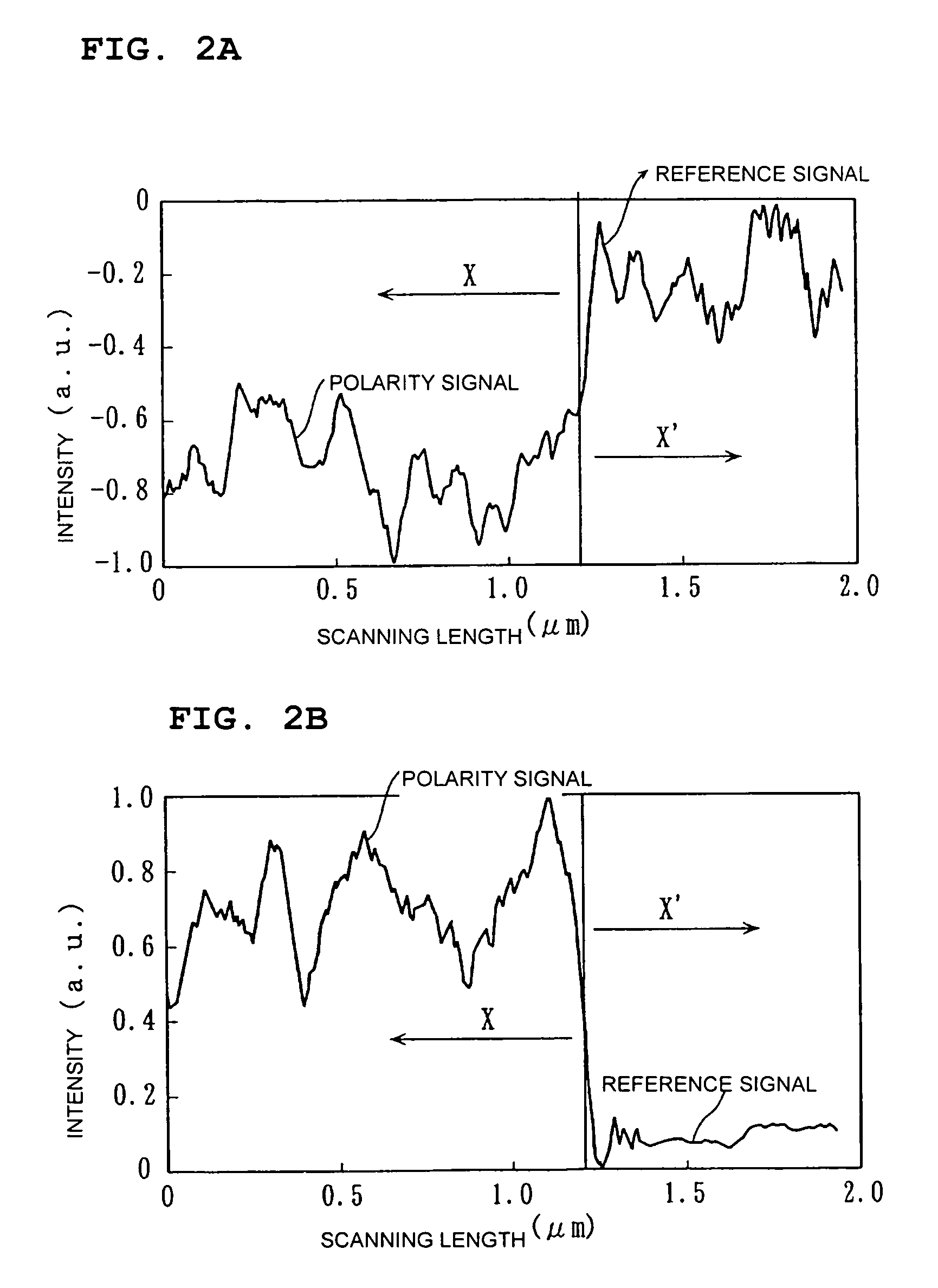

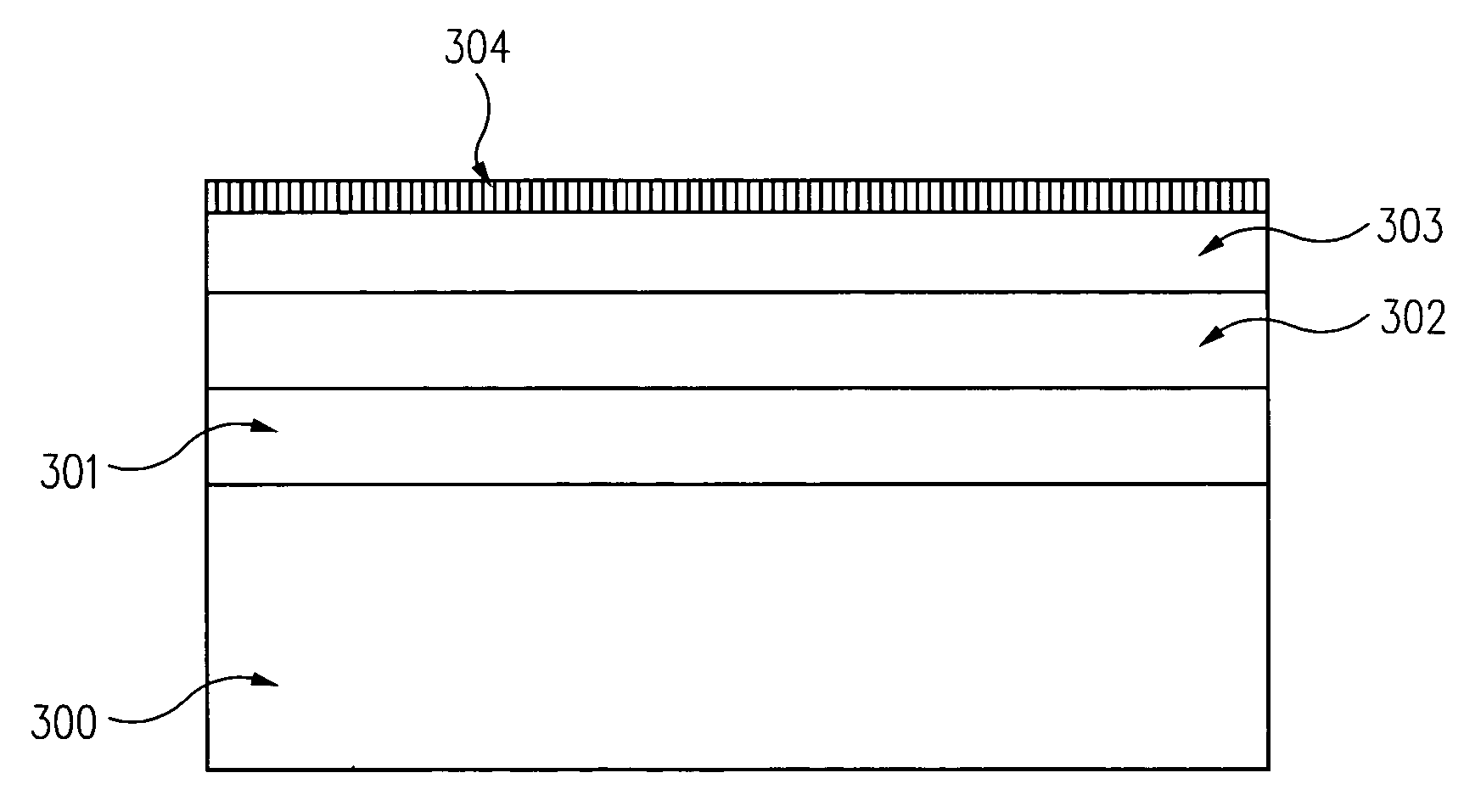

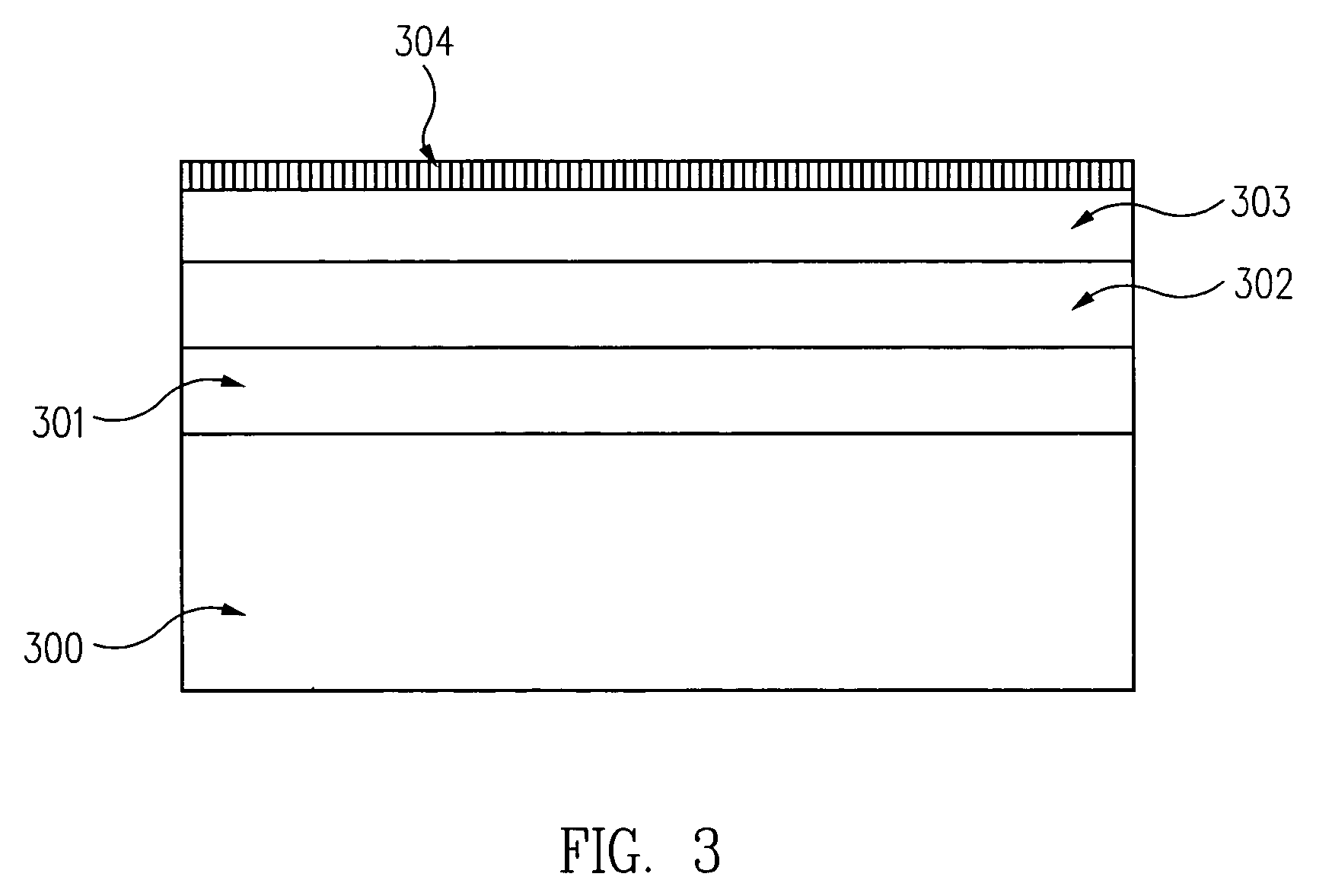

ActiveUS7501293B2Improve surface smoothnessHigh crystallinityTransistorLaser detailsSemiconductor materialsDevice material

A semiconductor device having excellent crystallinity and excellent electric characteristics includes a ZnO thin film having excellent surface smoothness. ZnO-based thin films (an n-type contact layer, an n-type clad layer, an active layer, a p-type clad layer, and a p-type contact layer) primarily including ZnO are formed sequentially by an ECR sputtering method or other suitable method on a zinc-polar surface of a ZnO substrate. A transparent electrode and a p-side electrode are formed by an evaporation method or other suitable method on a surface of the p-type contact layer, and an n-side electrode is formed on an oxygen-polar surface of the ZnO substrate.

Owner:MURATA MFG CO LTD

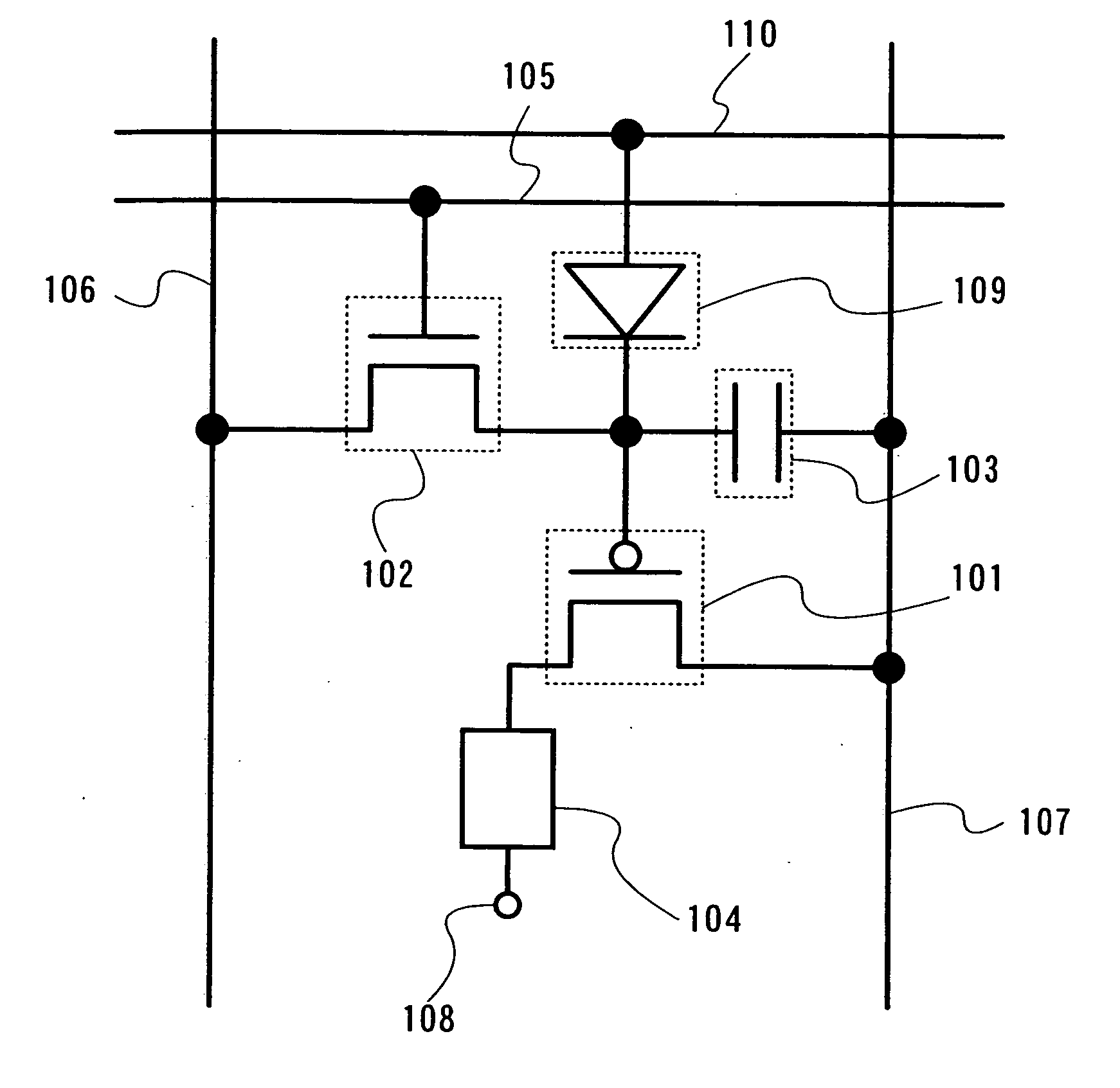

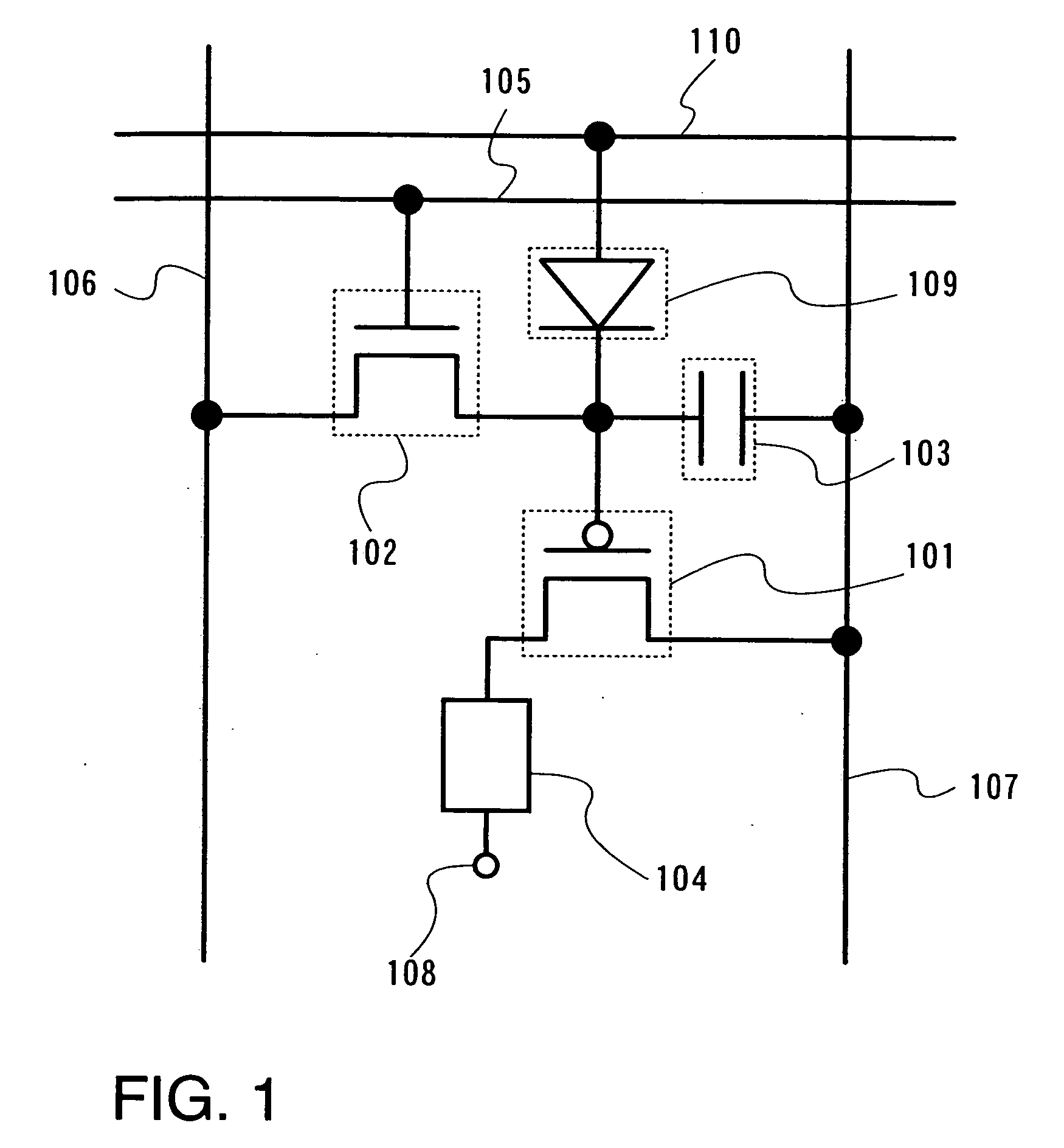

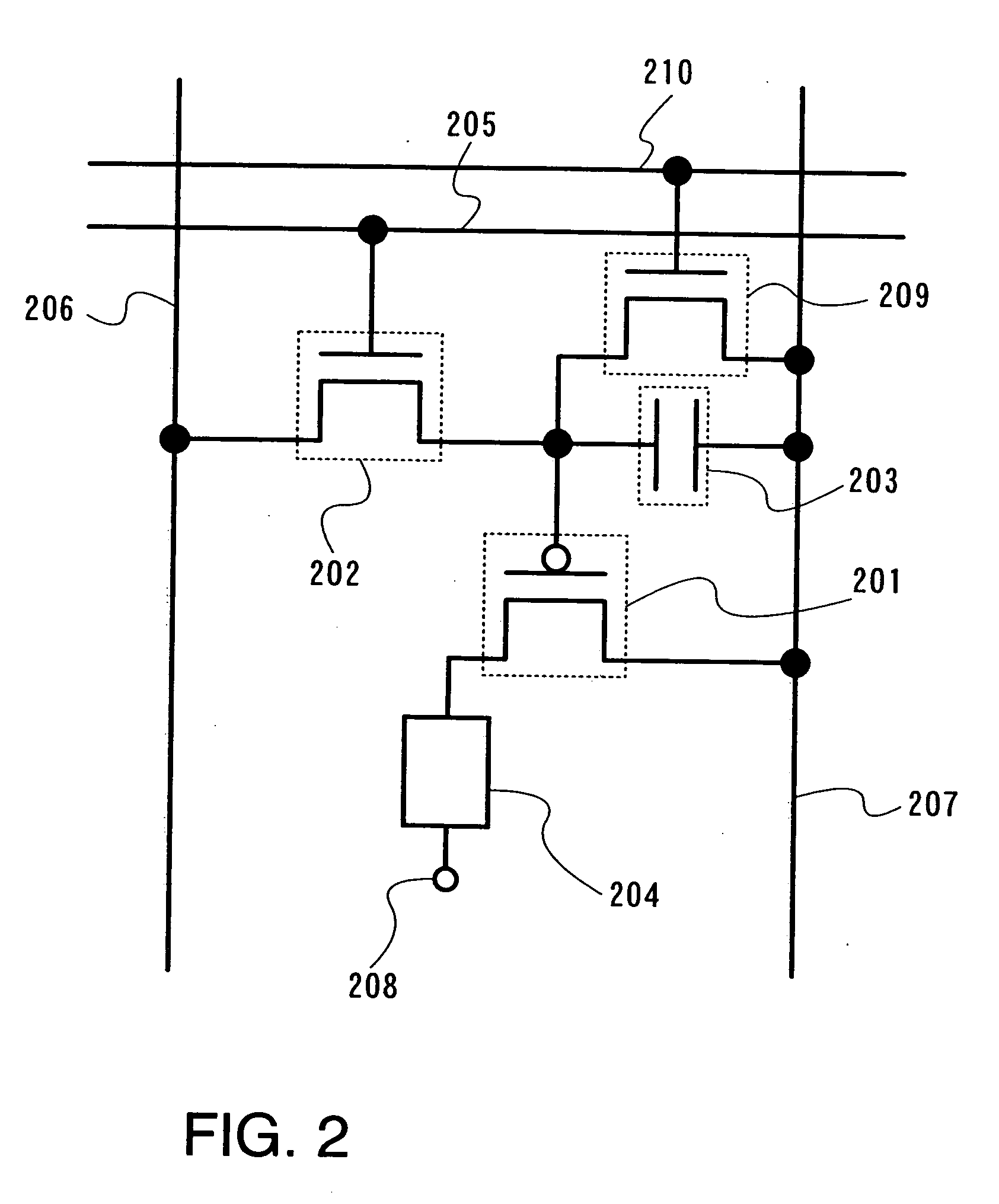

Semiconductor device and display device

InactiveUS20060238135A1Total current dropReduce trafficElectrical apparatusElectroluminescent light sourcesDevice materialScan line

When a signal inputted to a pixel is erased by setting potentials of a gate terminal and a source terminal of a driving transistor to be equal, a current slightly flows through the driving transistor in some cases, which leads to occur a display defect. The invention provides a display device which improves the yield while suppressing the increase in manufacturing cost. When a potential of a scan line for erasure is raised, a potential of the gate terminal of the driving transistor is raised accordingly. For example, the scan line and the gate terminal of the driving transistor are connected through a rectifying element.

Owner:SEMICON ENERGY LAB CO LTD

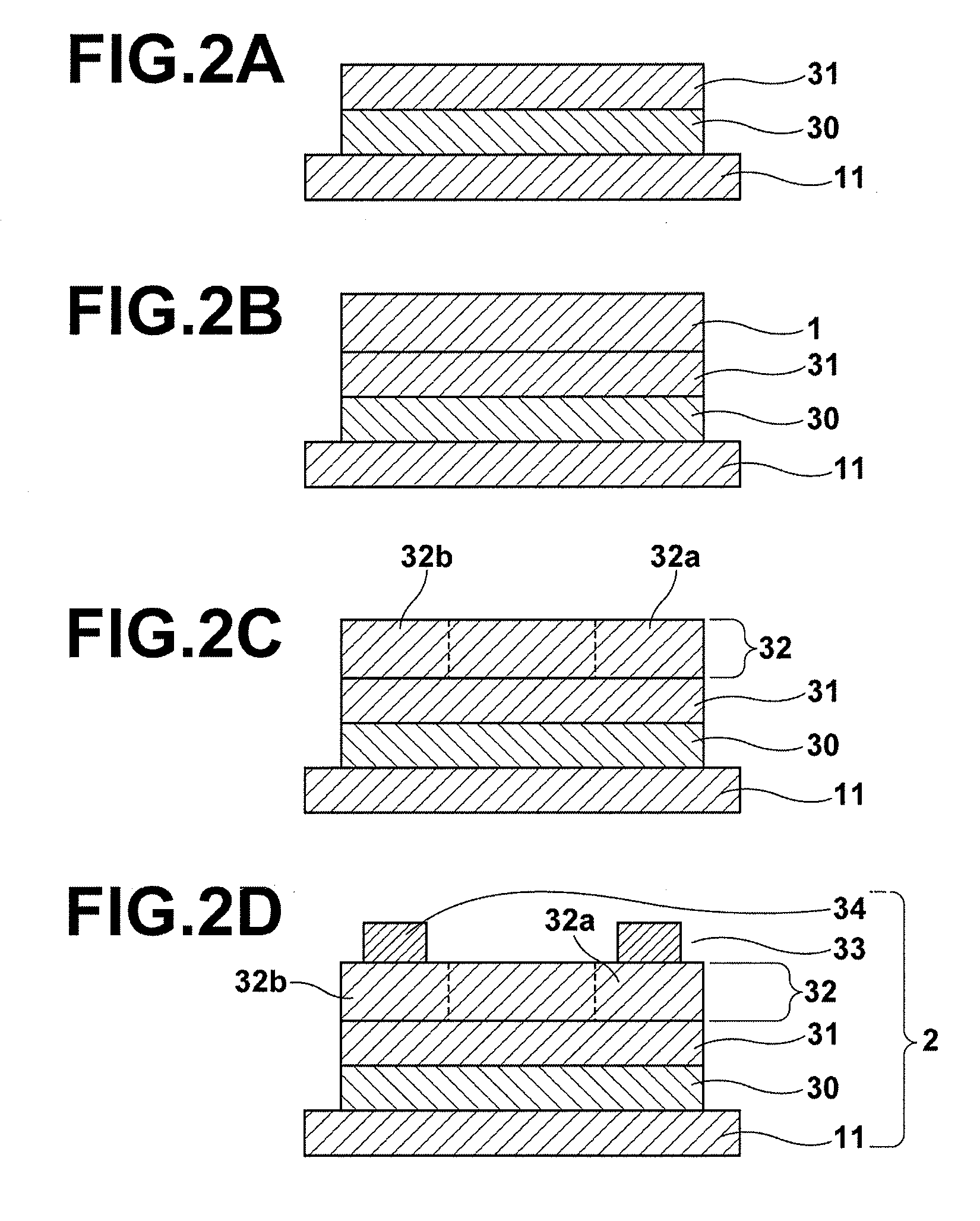

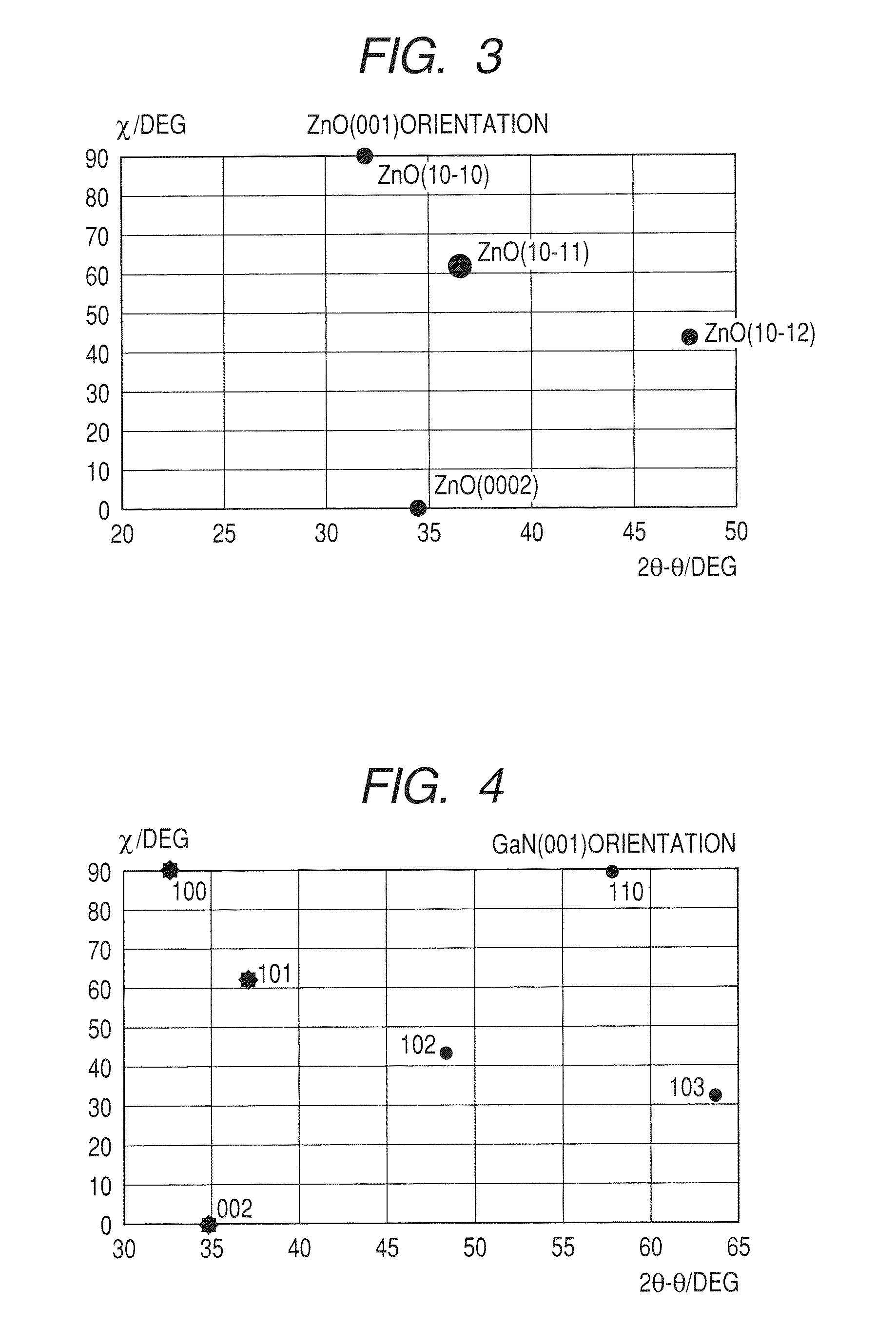

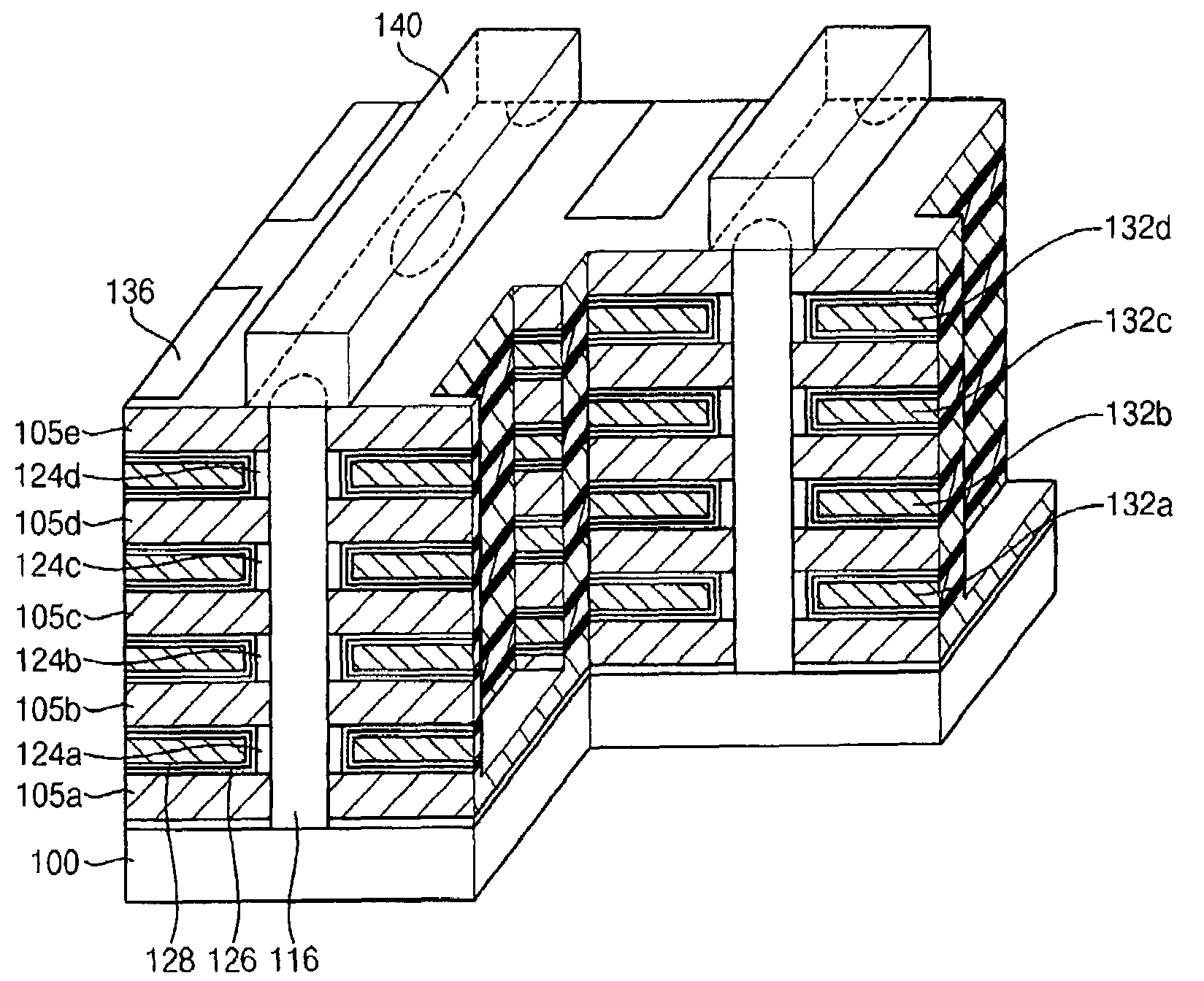

Process for producing oriented inorganic crystalline film, and semiconductor device using the oriented inorganic crystalline film

ActiveUS20090152506A1Orientation can be controlledLow costFrom gel stateFrom solid stateOrganic solventDevice material

In a process for producing an oriented inorganic crystalline film, a non-monocrystalline film containing inorganic crystalline particles is formed on a substrate by a liquid phase technique using a raw-material solution which contains a raw material and an organic solvent, where the inorganic crystalline particles have a layered crystal structure and are contained in the raw material. Then, the non-monocrystalline film is crystallized by heating the non-monocrystalline film to a temperature equal to or higher than the crystallization temperature of the non-monocrystalline film so that part of the inorganic crystalline particles act as crystal nuclei.

Owner:FUJIFILM CORP

Semiconductor device

InactiveUS20090114910A1Uniform and high stabilityIncrease productionTransistorSolid-state devicesIn planeDevice material

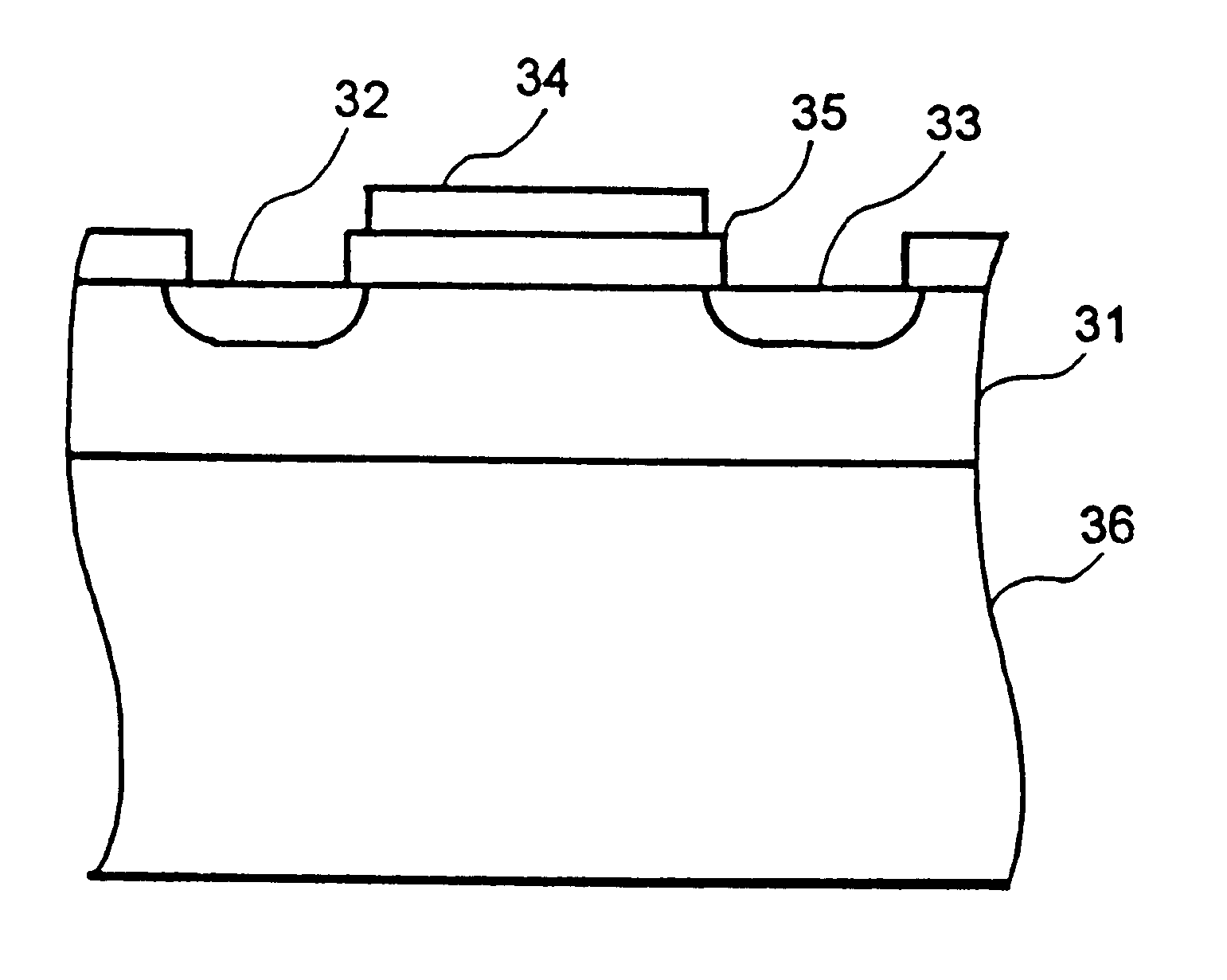

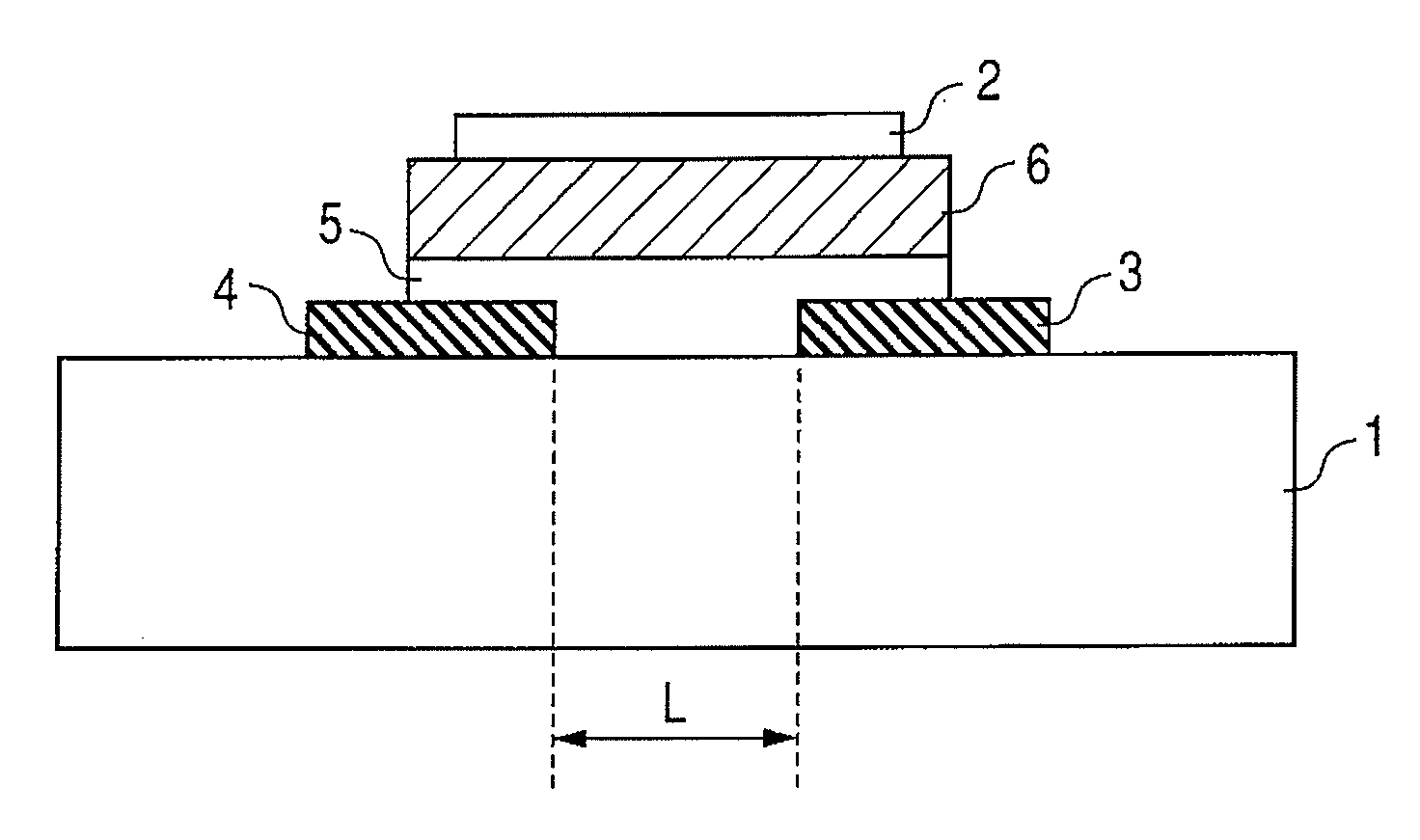

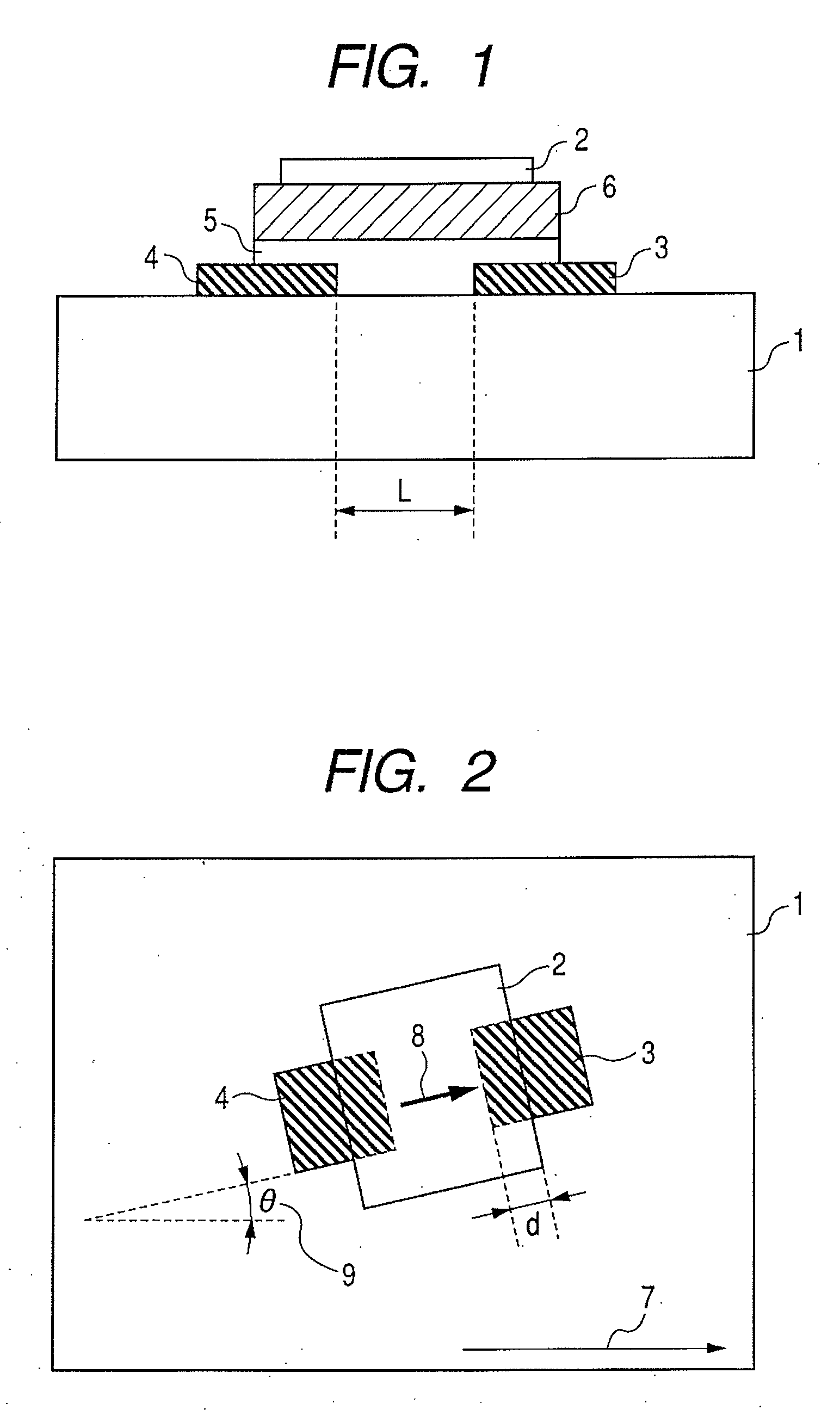

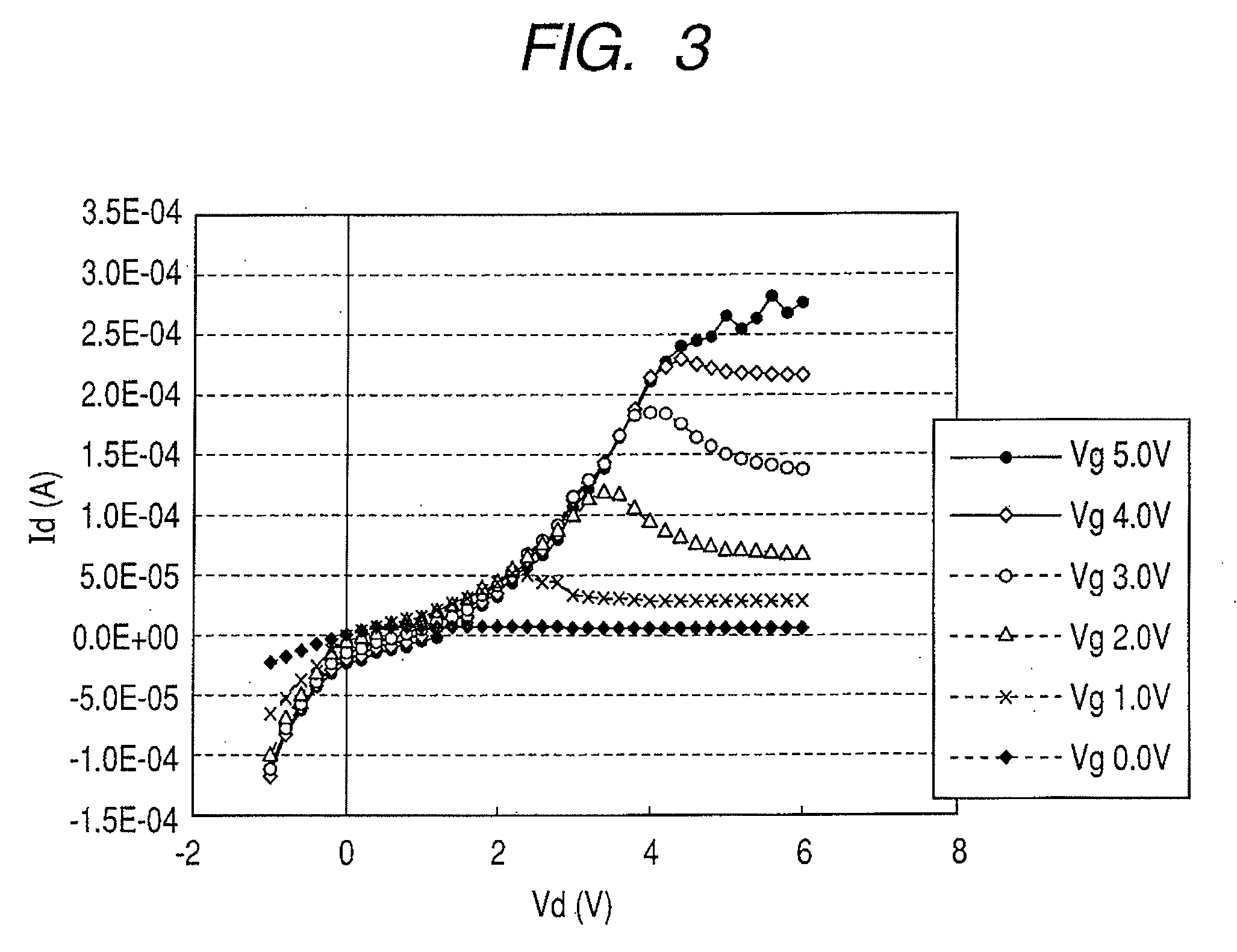

In the present invention, a thin film transistor is formed on a plastic film substrate (1) having anisotropy of thermal shrinkage rate or coefficient of thermal expansion in in-plane directions of the substrate. A channel is formed such thatthe direction (7) in which the thermal shrinkage rate or the coefficient of thermal expansion of the substrate is largest is nonparallel tothe direction (8) of a current flowing through the channel of the thin film transistor. Then, a thin film transistor having stable and uniform electrical characteristics, which is formed on the plastic film substrate, is provided.

Owner:CANON KK

Semiconductor device, electronic device, and method of manufacturing semiconductor device

InactiveUS20060169973A1Stable formationImprove performanceSolid-state devicesSemiconductor/solid-state device manufacturingDevice materialDisplay device

To provide a semiconductor device and a display device which can be manufactured through a simplified process and the manufacturing technique. Another object is to provide a technique by which a pattern of wirings or the like which is partially constitutes a semiconductor device or a display device can be formed with a desired shape with controllability.

Owner:SEMICON ENERGY LAB CO LTD

Substrate for growing wurtzite type crystal and method for manufacturing the same and semiconductor device

ActiveUS20100092800A1Low costHigh crystallinityPolycrystalline material growthVacuum evaporation coatingNitrideSemiconductor

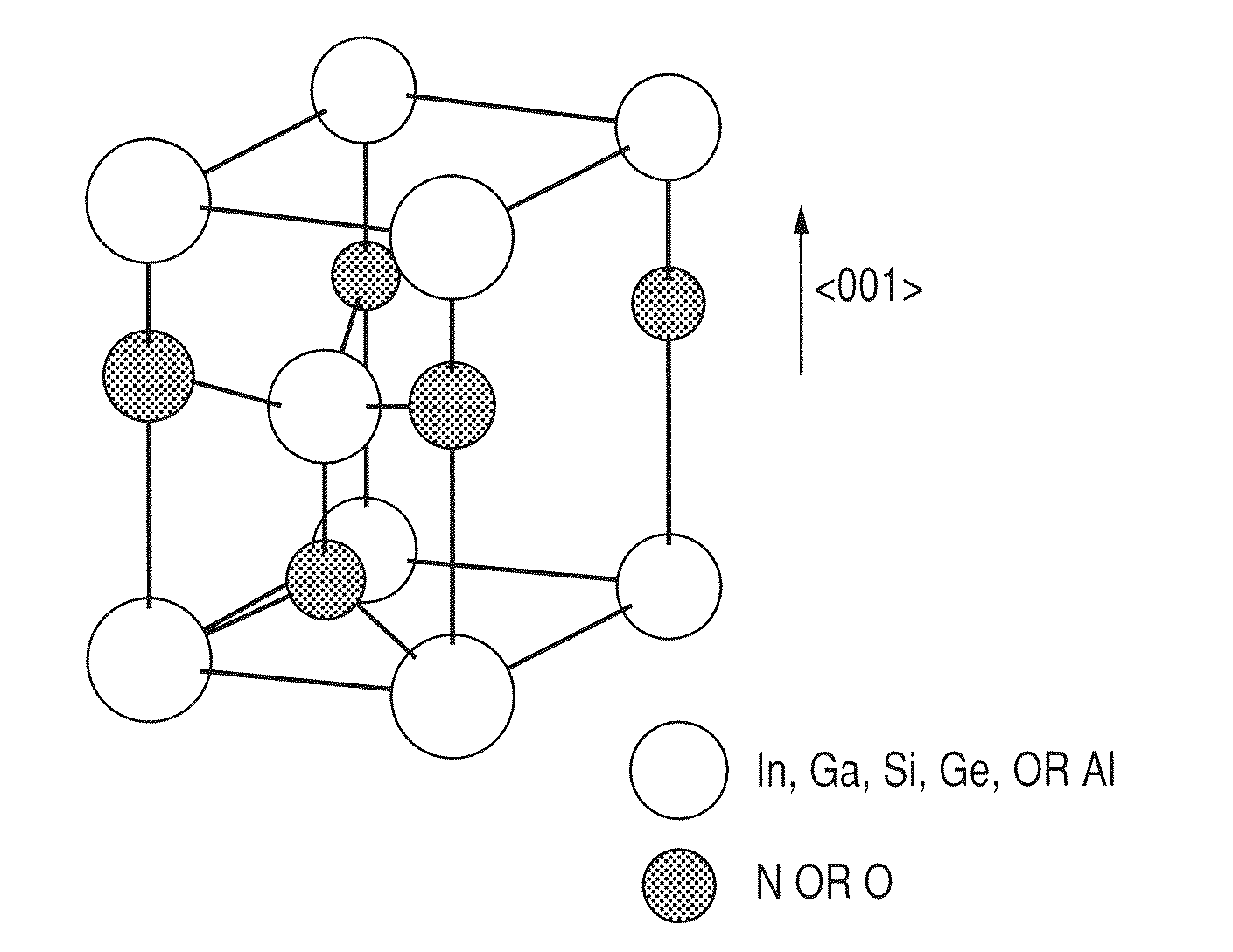

A laminated structure comprises a first layer comprising a crystal with six-fold symmetry, and a second layer comprising a metal oxynitride crystal formed on the first layer, wherein the second layer comprises at least one element selected from the group consisting of In, Ga, Si, Ge and Al, N, O and Zn, as main elements, and wherein the second layer has in-plane orientation.

Owner:CANON KK

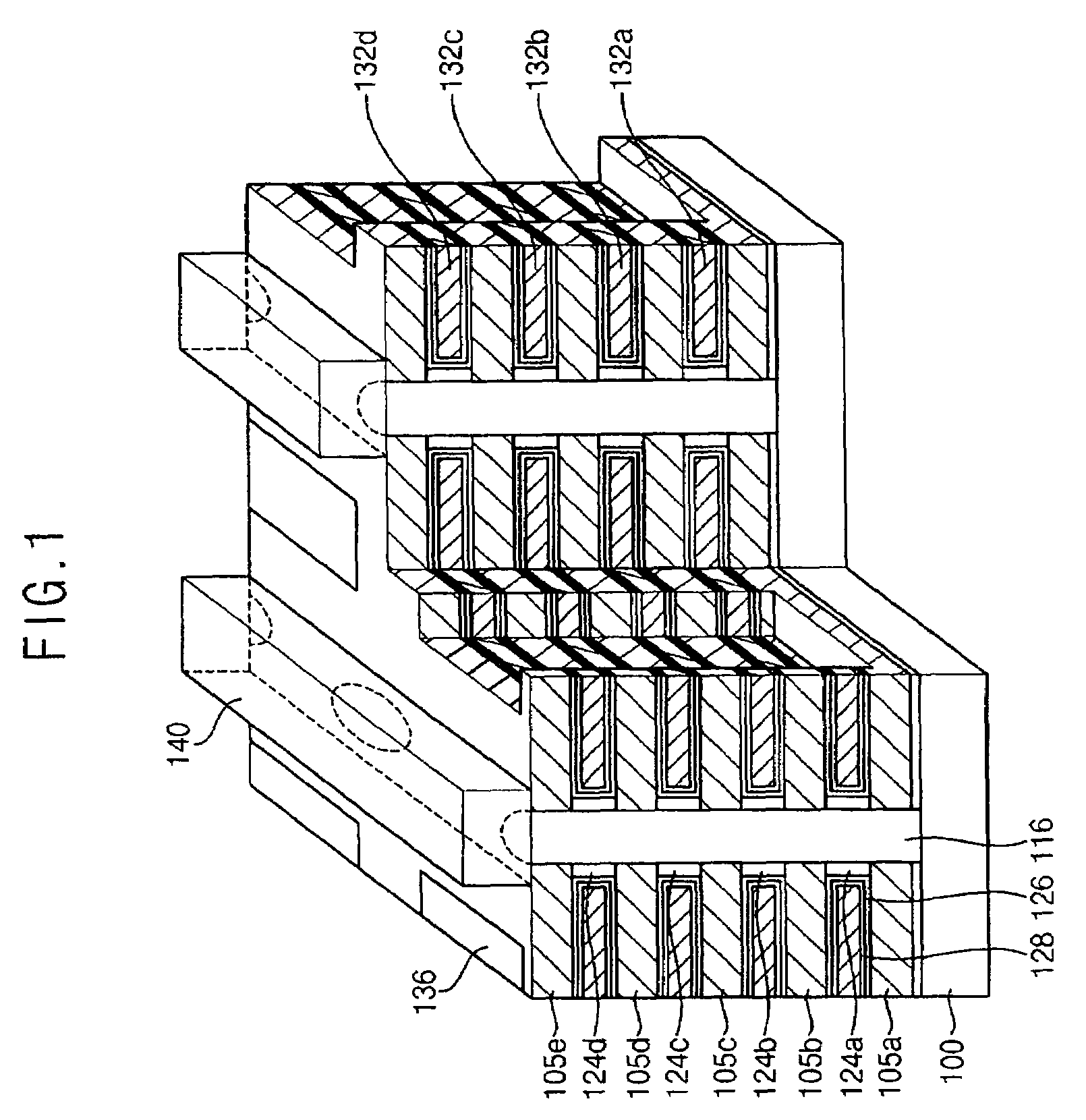

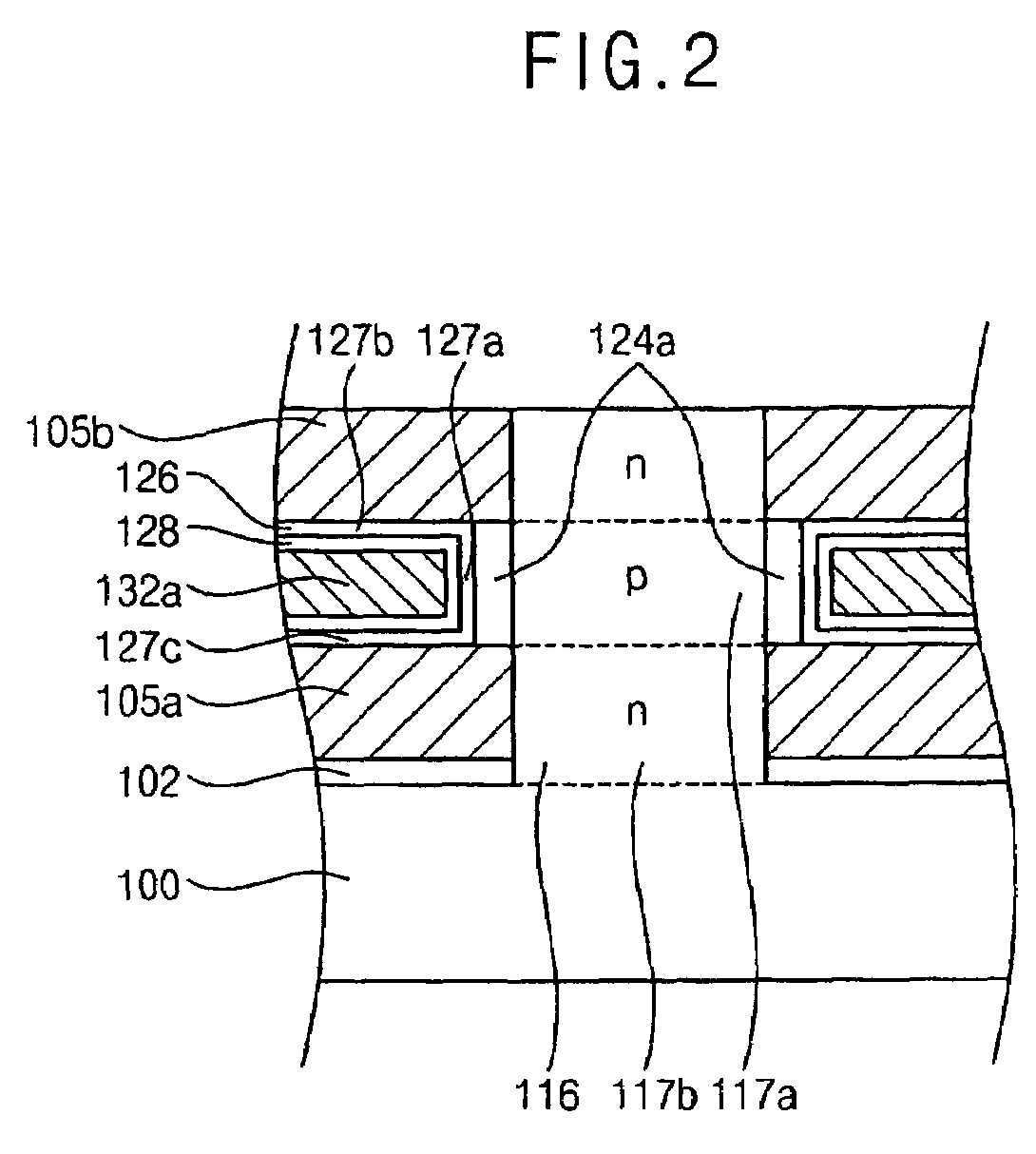

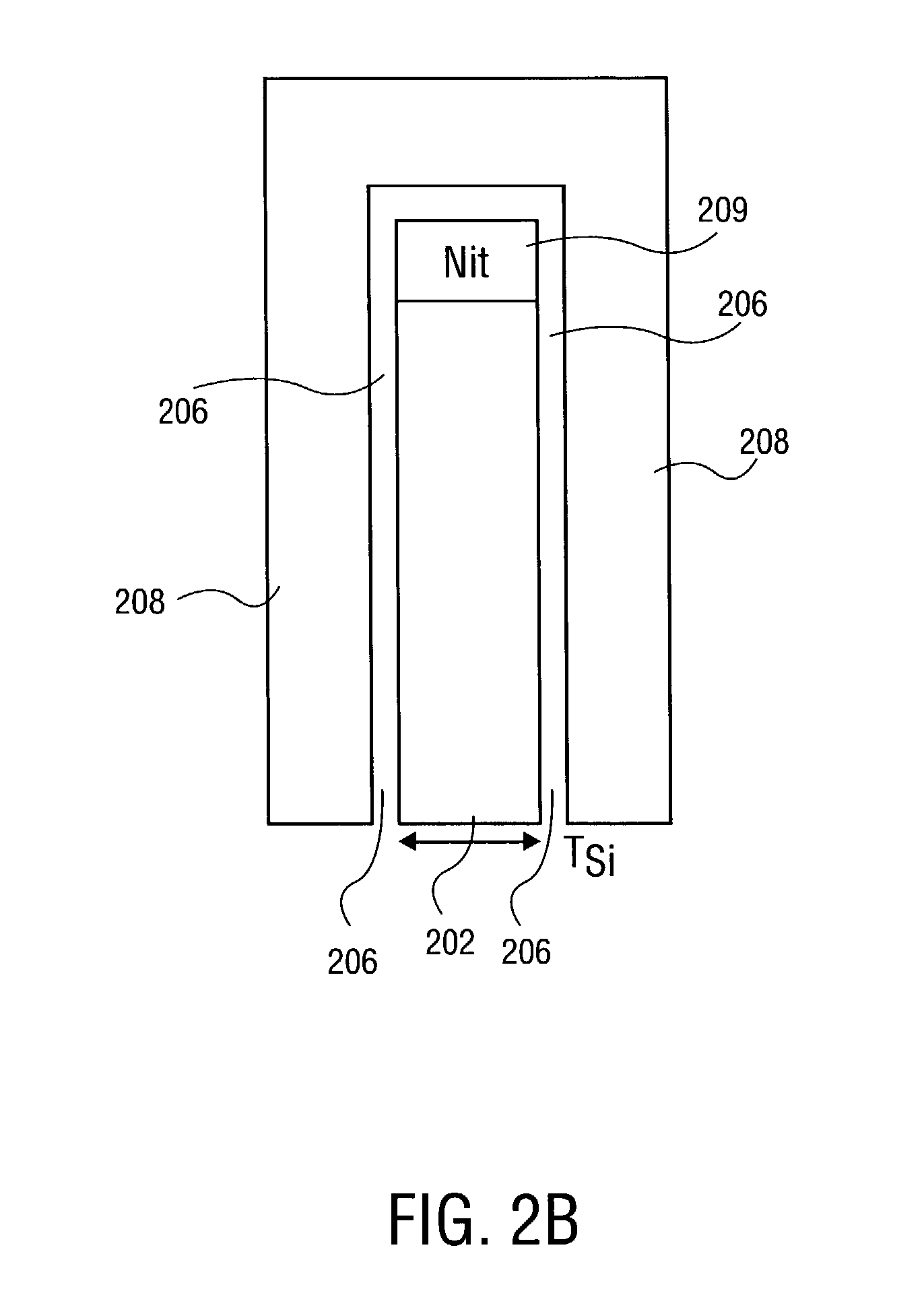

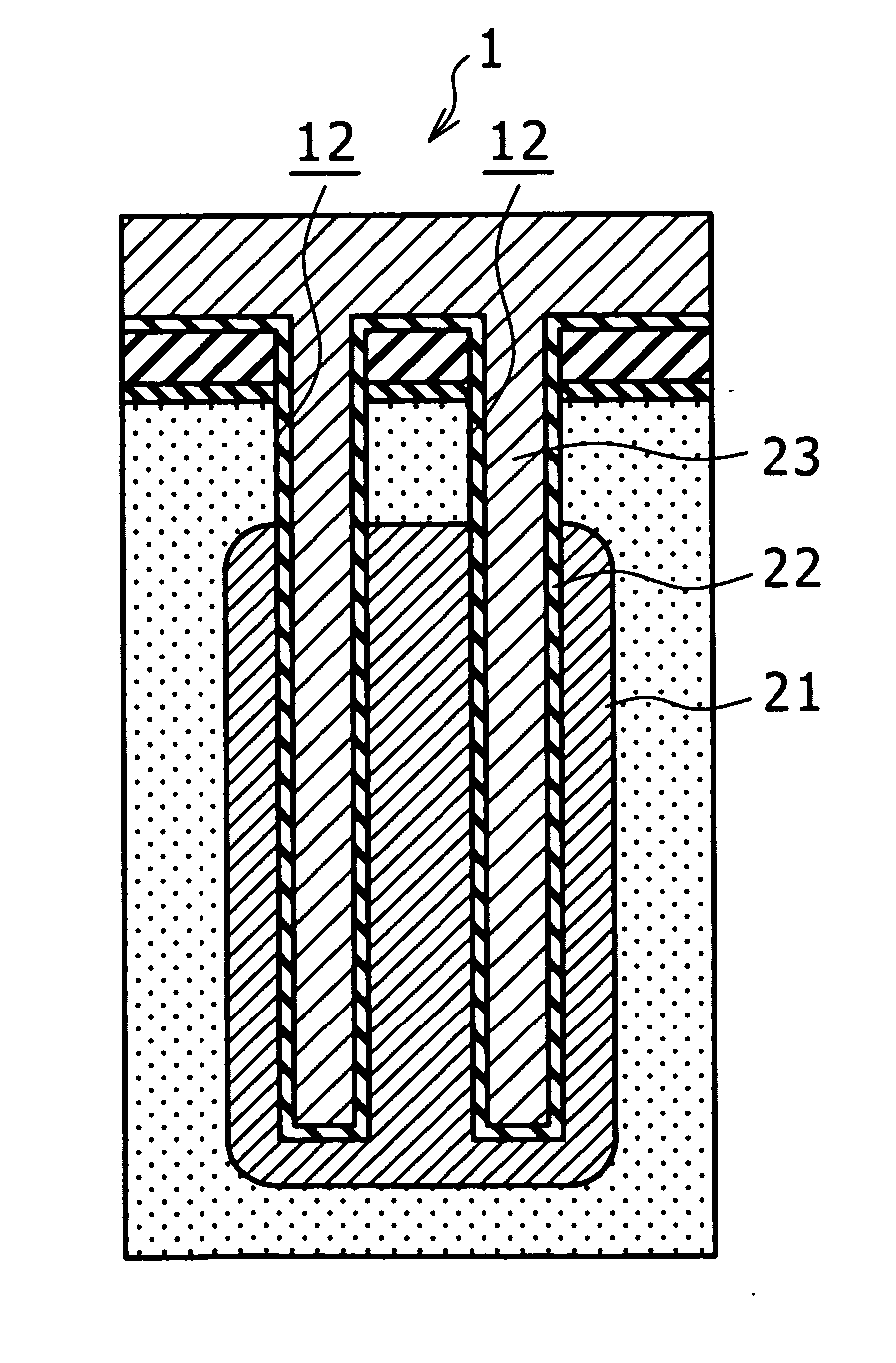

Vertical-type non-volatile memory devices

ActiveUS7679133B2Reduce the possibilityReduce in quantityTransistorSolid-state devicesSemiconductor materialsDevice material

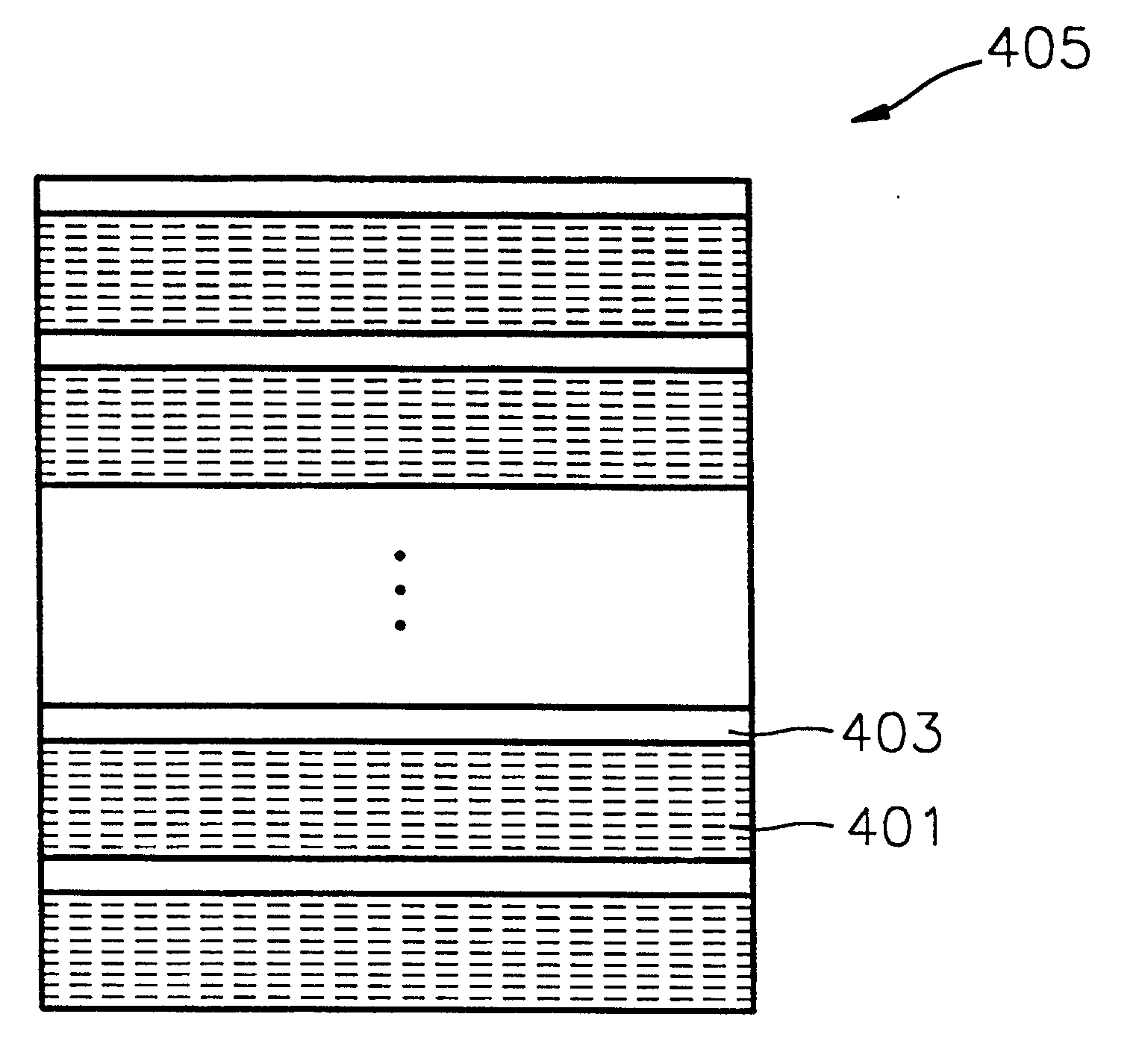

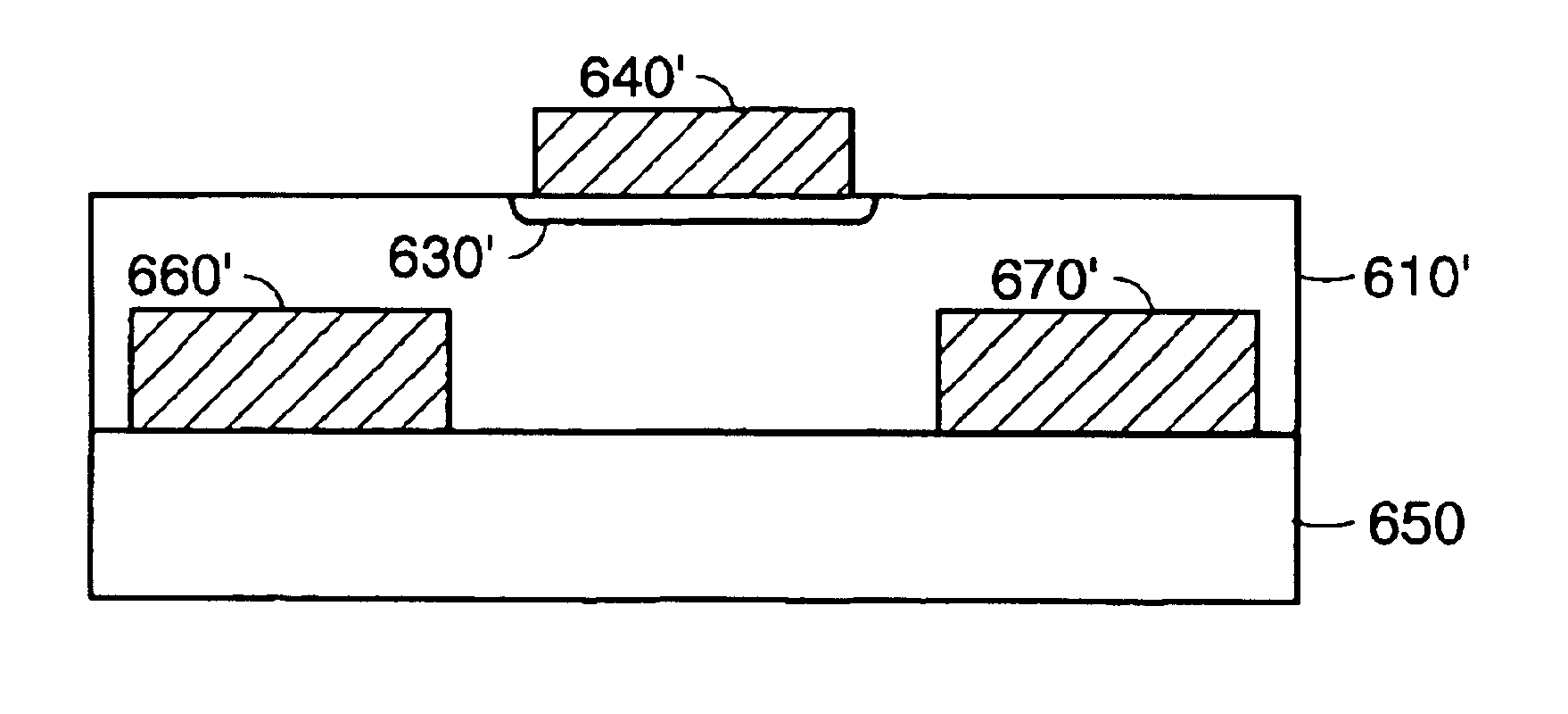

In a semiconductor device, and a method of manufacturing thereof, the device includes a substrate of single-crystal semiconductor material extending in a horizontal direction and a plurality of interlayer dielectric layers on the substrate. A plurality of gate patterns are provided, each gate pattern being between a neighboring lower interlayer dielectric layer and a neighboring upper interlayer dielectric layer. A vertical channel of single-crystal semiconductor material extends in a vertical direction through the plurality of interlayer dielectric layers and the plurality of gate patterns, a gate insulating layer being between each gate pattern and the vertical channel that insulates the gate pattern from the vertical channel.

Owner:SAMSUNG ELECTRONICS CO LTD

Method of forming metal layer using atomic layer deposition and semiconductor device having the metal layer as barrier metal layer or upper or lower electrode of capacitor

InactiveUS6287965B1High thermal resistantEasy to adjustSemiconductor/solid-state device manufacturingCapacitorsNiobiumDevice material

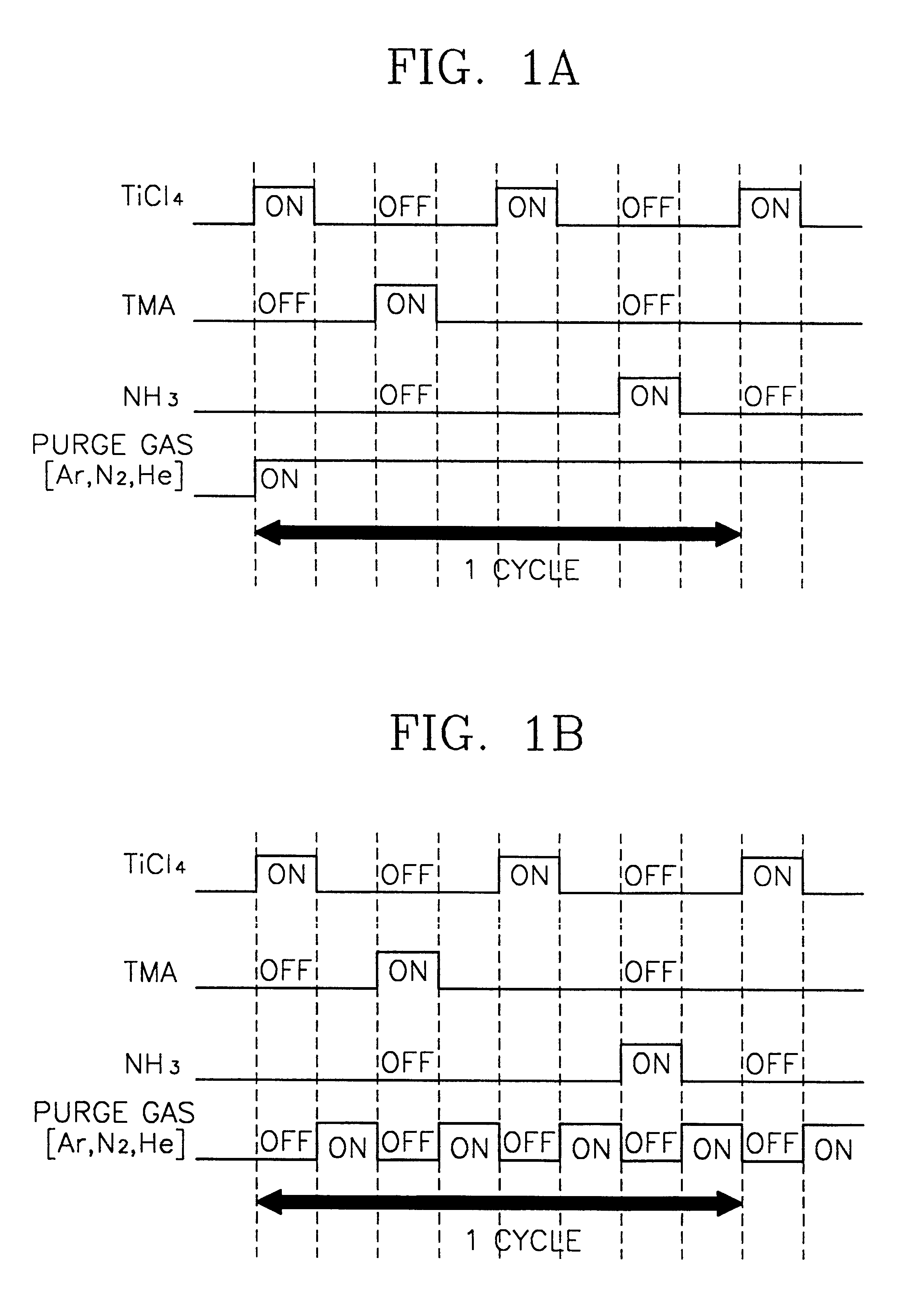

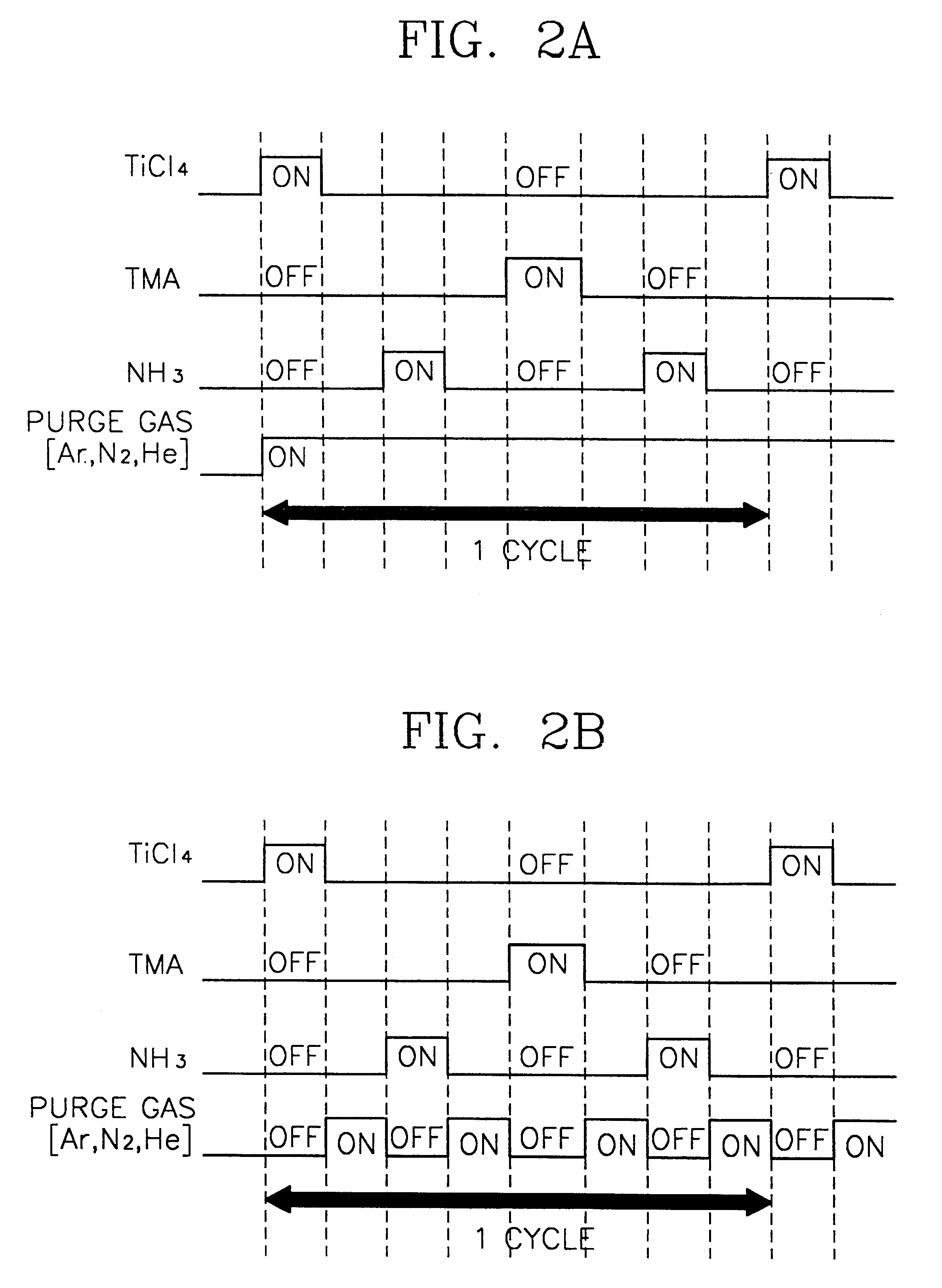

A method of forming a metal layer having excellent thermal and oxidation resistant characteristics using atomic layer deposition is provided. The metal layer includes a reactive metal (A), an element (B) for the amorphous combination between the reactive metal (A) and nitrogen (N), and nitrogen (N). The reactive metal (A) may be titanium (Ti), tantalum (Ta), tungsten (W), zirconium (Zr), hafnium (Hf), molybdenum (Mo) or niobium (Nb). The amorphous combination element (B) may be aluminum (Al), silicon (Si) or boron (B). The metal layer is formed by alternately injecting pulsed source gases for the elements (A, B and N) into a chamber according to atomic layer deposition to thereby alternately stack atomic layers. Accordingly, the composition ratio of a nitrogen compound (A-B-N) of the metal layer can be desirably adjusted just by appropriately determining the number of injection pulses of each source gas. According to the composition ratio, a desirable electrical conductivity and resistance of the metal layer can be accurately obtained. The atomic layers are individually deposited, thereby realizing excellent step coverage even in a complex and compact region. A metal layer formed by atomic layer deposition can be employed as a barrier metal layer, a lower electrode or an upper electrode in a semiconductor device.

Owner:SAMSUNG ELECTRONICS CO LTD

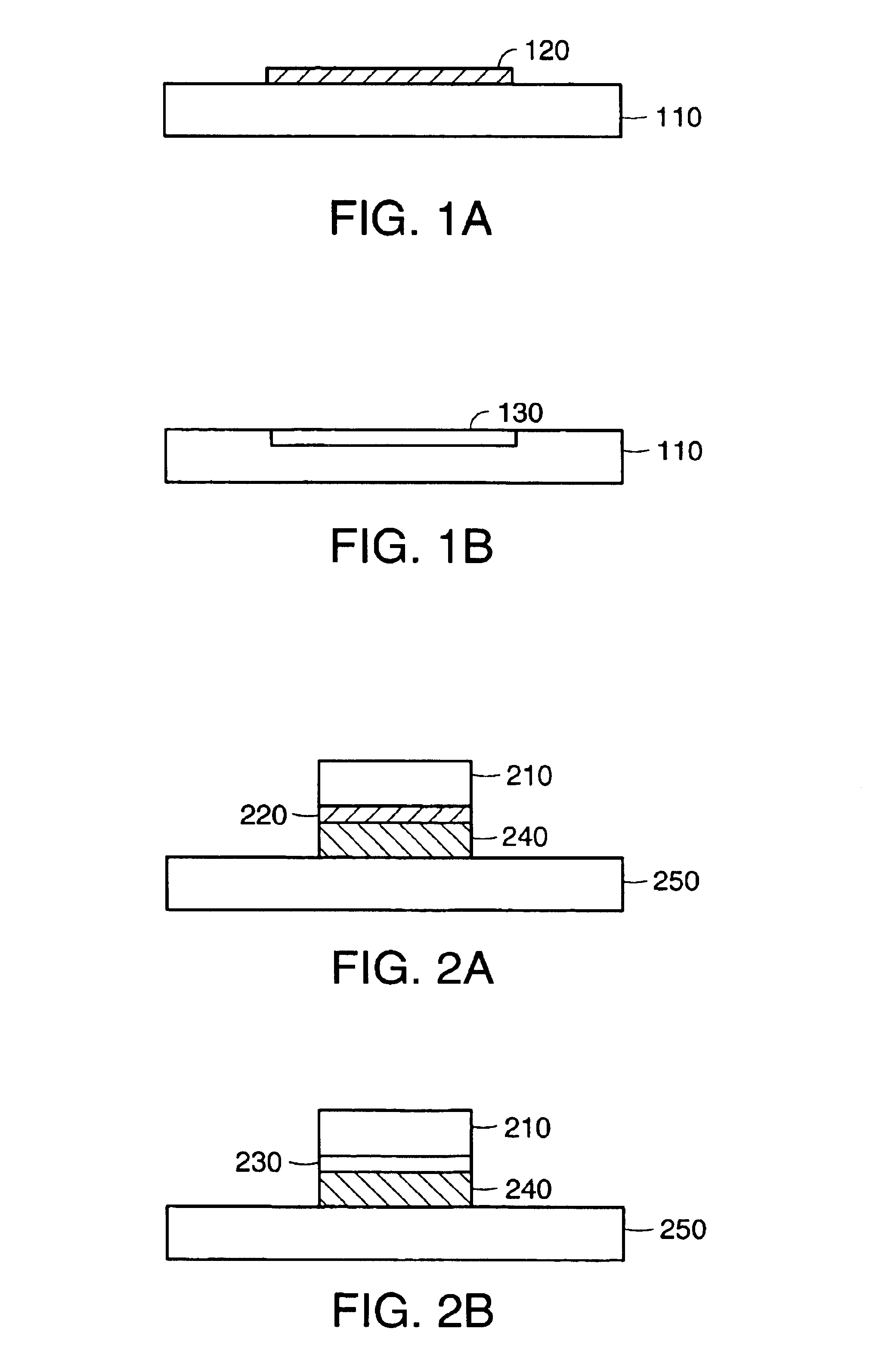

Reactive formation of dielectric layers and protection of organic layers in organic semiconductor device fabrication

InactiveUS6842657B1Use is harmfulDamage is causedSolid-state devicesSemiconductor/solid-state device manufacturingOrganic layerOrganic semiconductor

In one embodiment of the invention, a method of manufacturing a semiconductor device comprises the steps of: a) providing an organic semiconductor layer; b) depositing a reactive species on a portion of the organic semiconductor layer; and c) reacting the reactive species with the portion of the organic layer to form a dielectric layer.

Owner:E INK CORPORATION

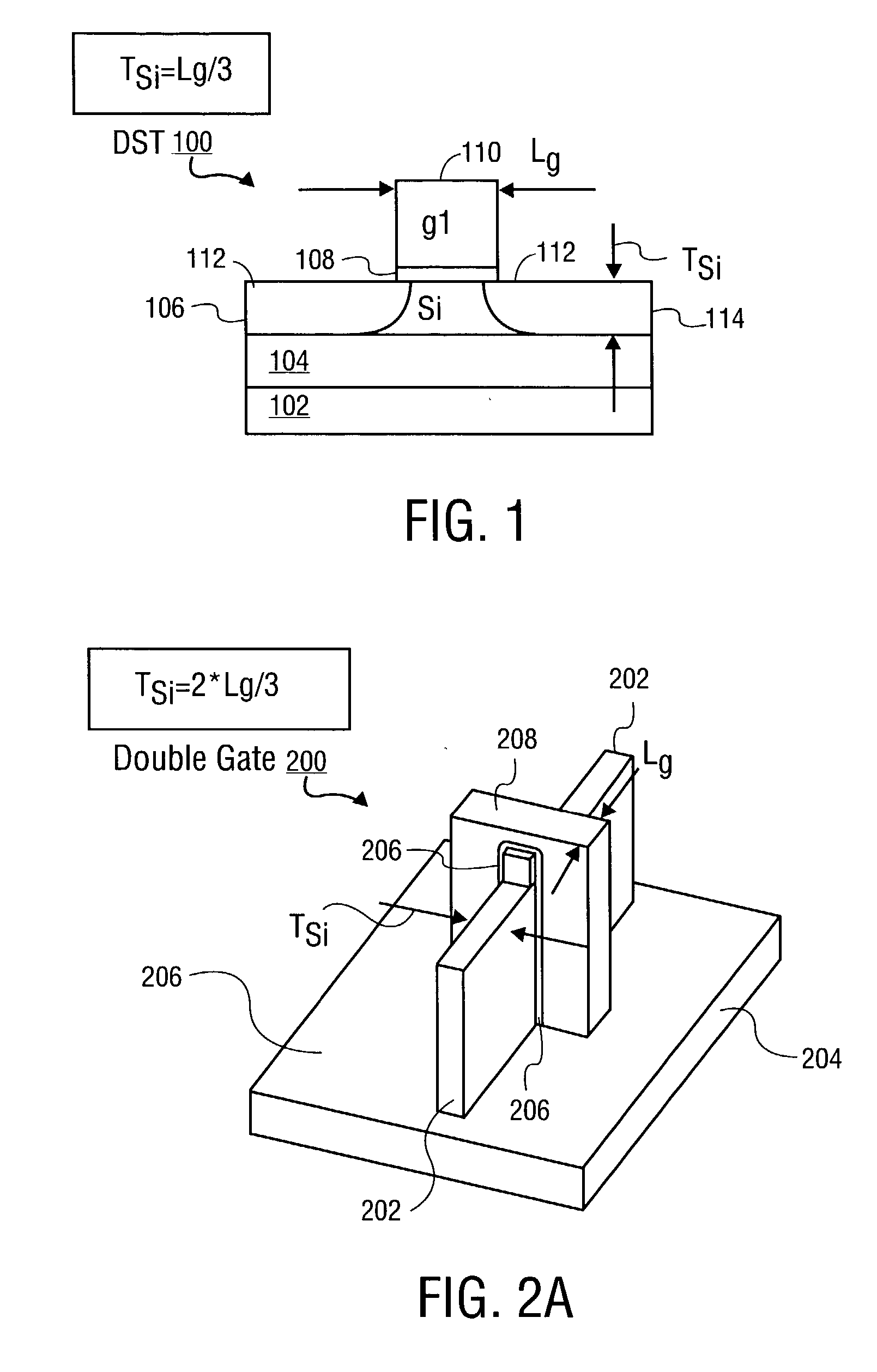

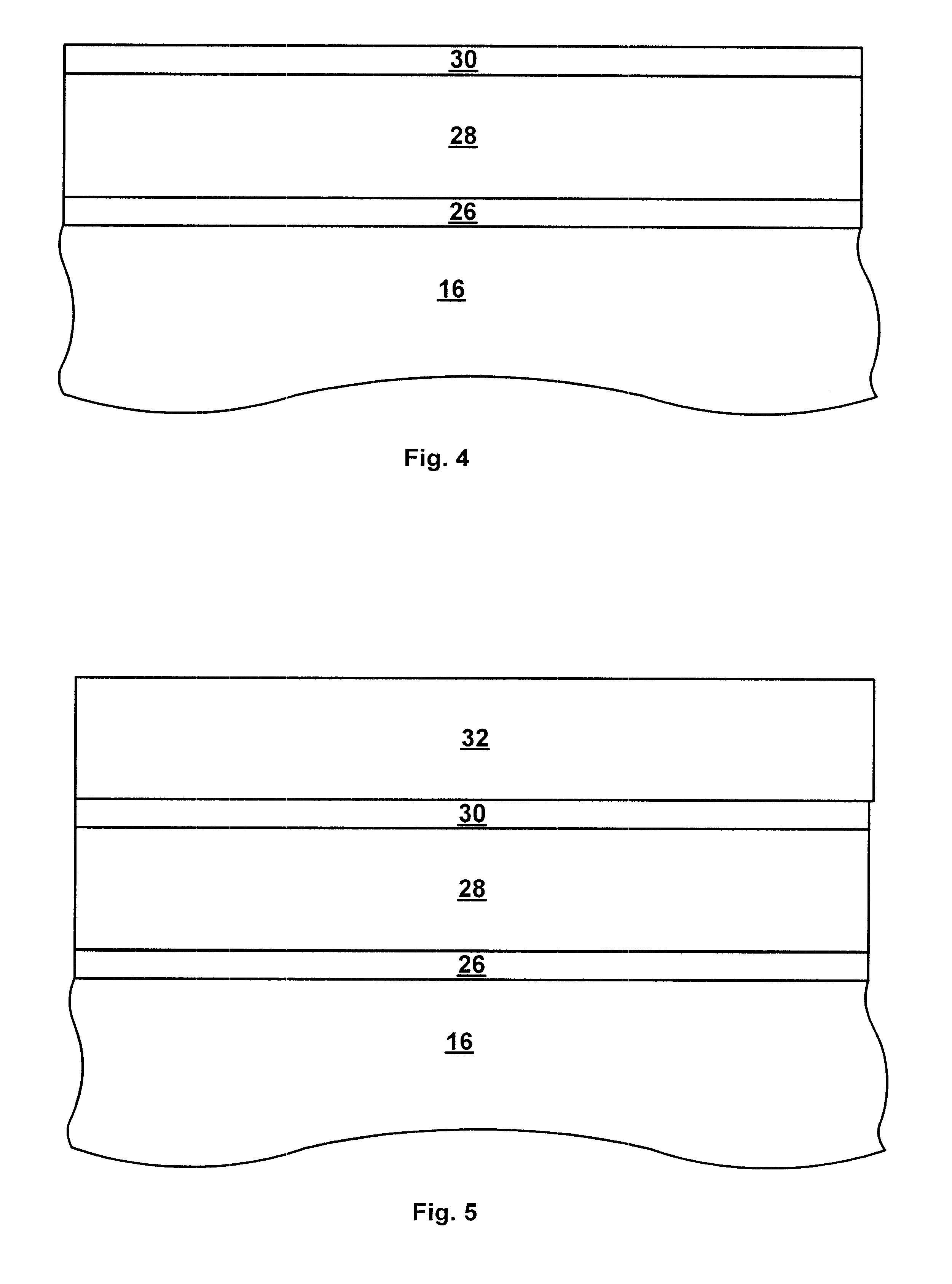

Tri-gate devices and methods of fabrication

The present invention is a semiconductor device comprising a semiconductor body having a top surface and laterally opposite sidewalls formed on a substrate. A gate dielectric layer is formed on the top surface of the semiconductor body and on the laterally opposite sidewalls of the semiconductor body. A gate electrode is formed on the gate dielectric on the top surface of the semiconductor body and adjacent to the gate dielectric on the laterally opposite sidewalls of the semiconductor body.

Owner:INTEL CORP

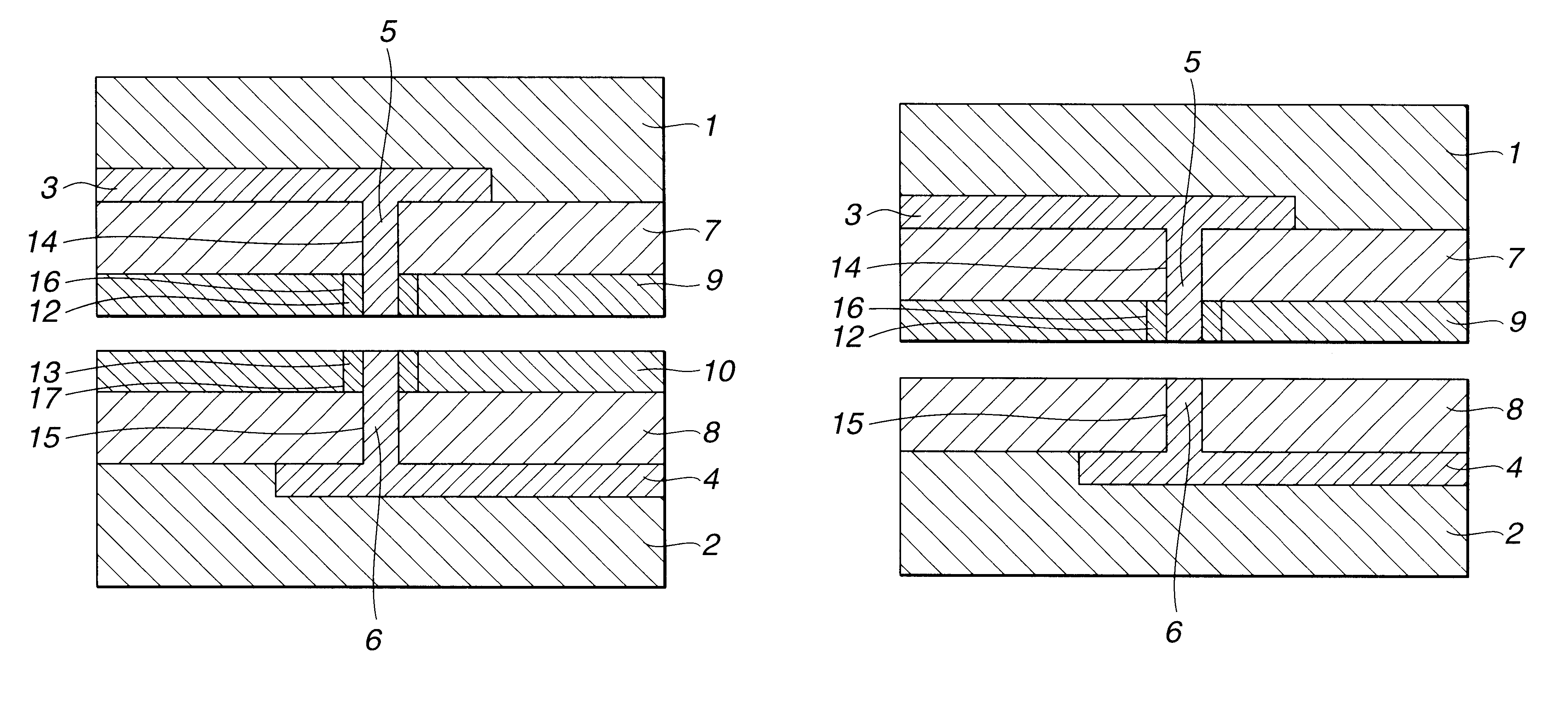

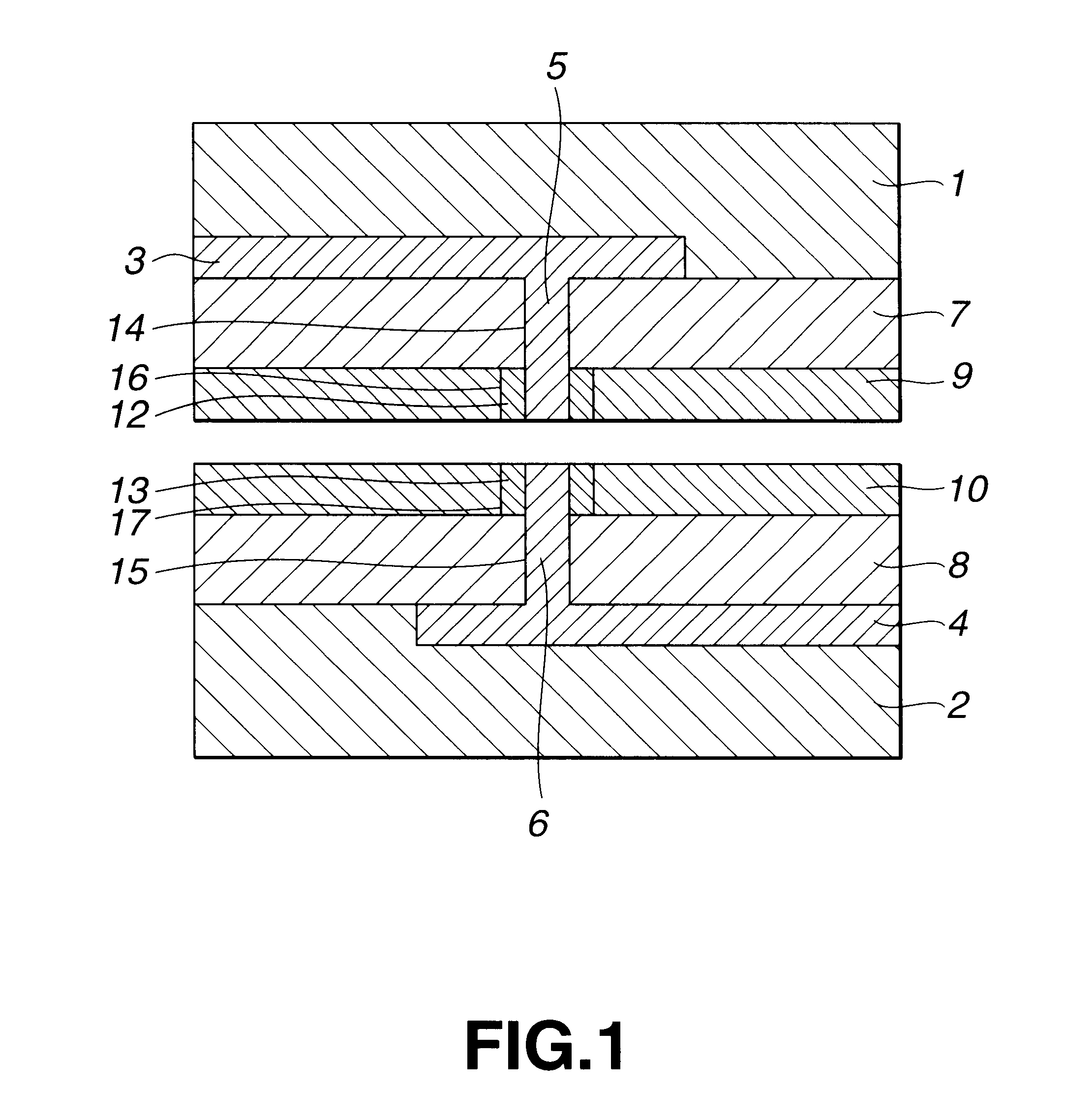

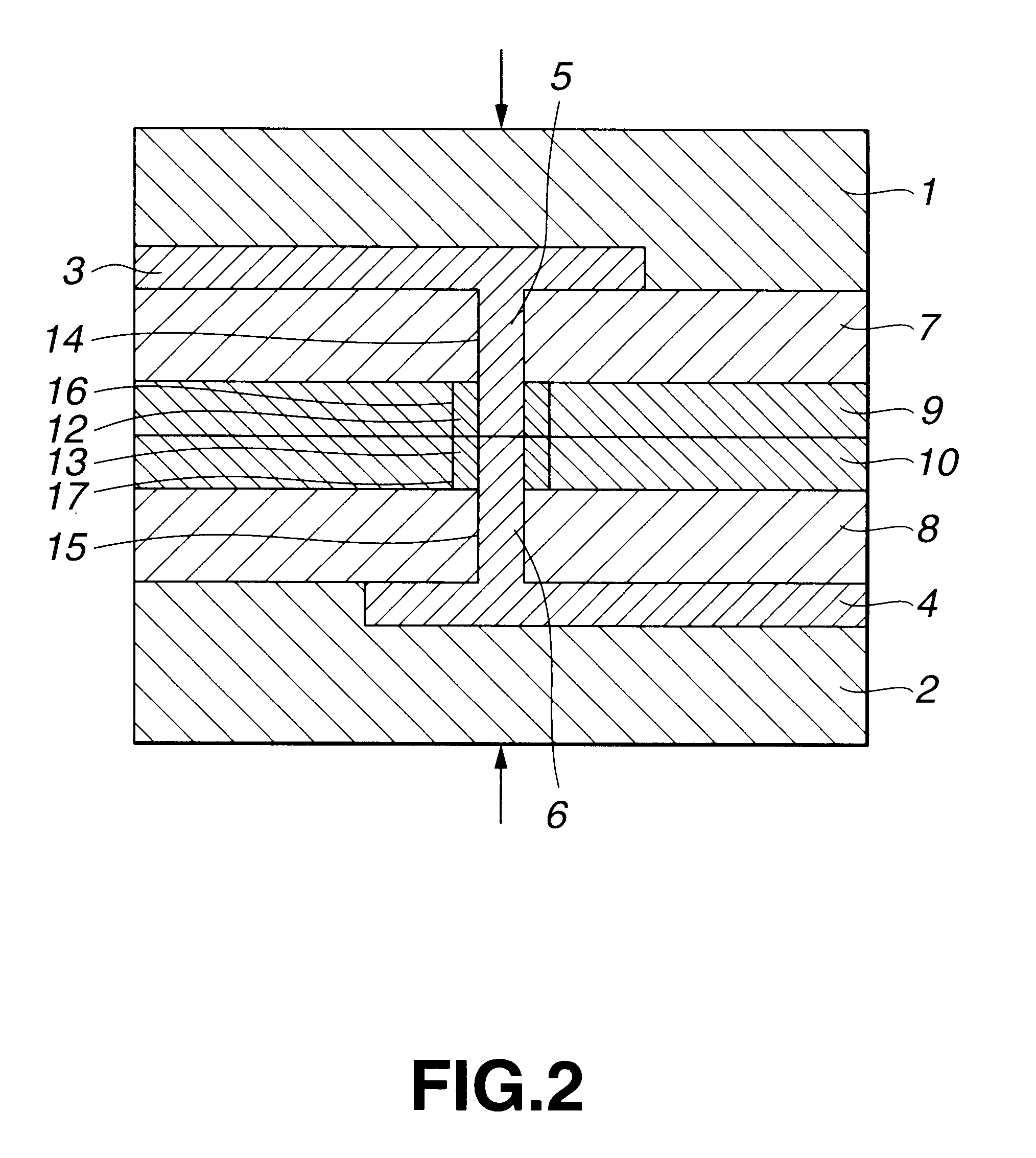

Interconnect structure for stacked semiconductor device

InactiveUS6465892B1Shorten the line lengthEasy to produceSemiconductor/solid-state device detailsSolid-state devicesDevice materialInterconnection

In a multi-layer interconnection structure, the wiring length is to be reduced, and the interconnection is to be straightened, at the same time as measures need to be taken against radiation noise. To this end, there is disclosed a semiconductor device in which plural semiconductor substrates, each carrying semiconductor elements, are bonded together. On each semiconductor substrate is deposited an insulating layer through which is formed a connection wiring passed through the insulating layer so as to be connected to the interconnection layer of the semiconductor element. On a junction surface of at least one of the semiconductor substrates is formed an electrically conductive layer of an electrically conductive material in which an opening is bored in association with the connection wiring. The semiconductor substrates are bonded together by the solid state bonding technique to interconnect the connection wirings formed on each semiconductor substrate.

Owner:LAPIS SEMICON CO LTD +9

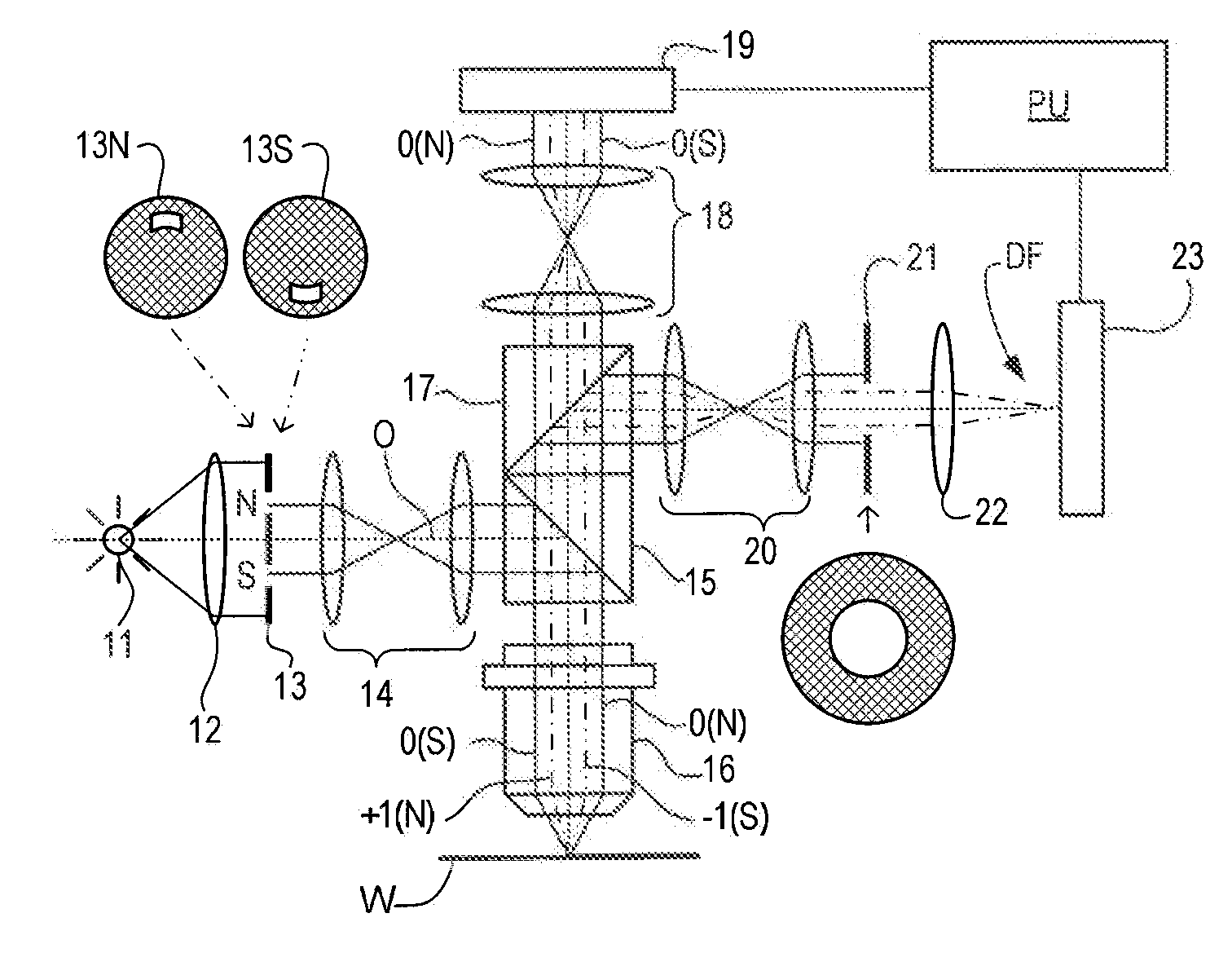

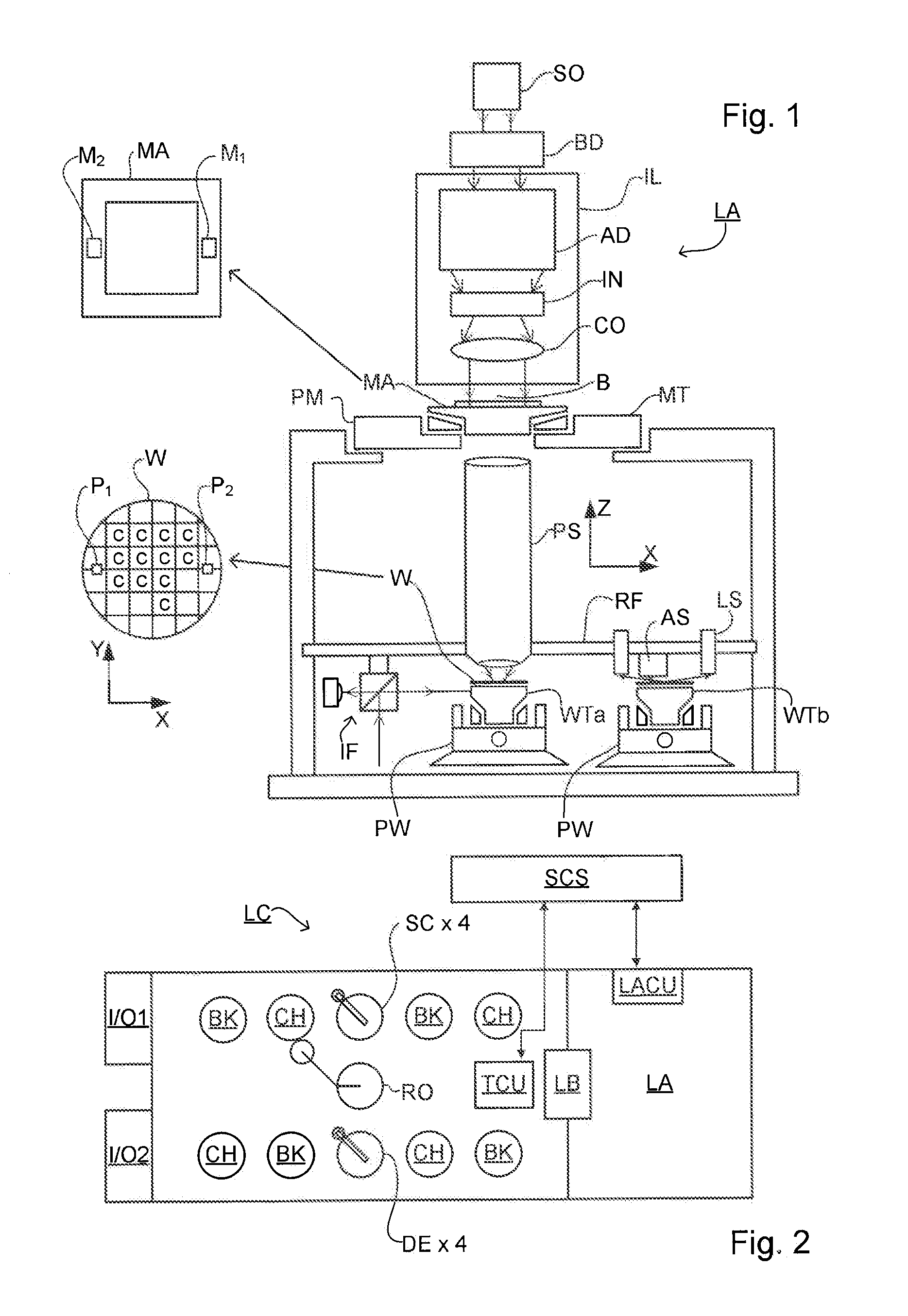

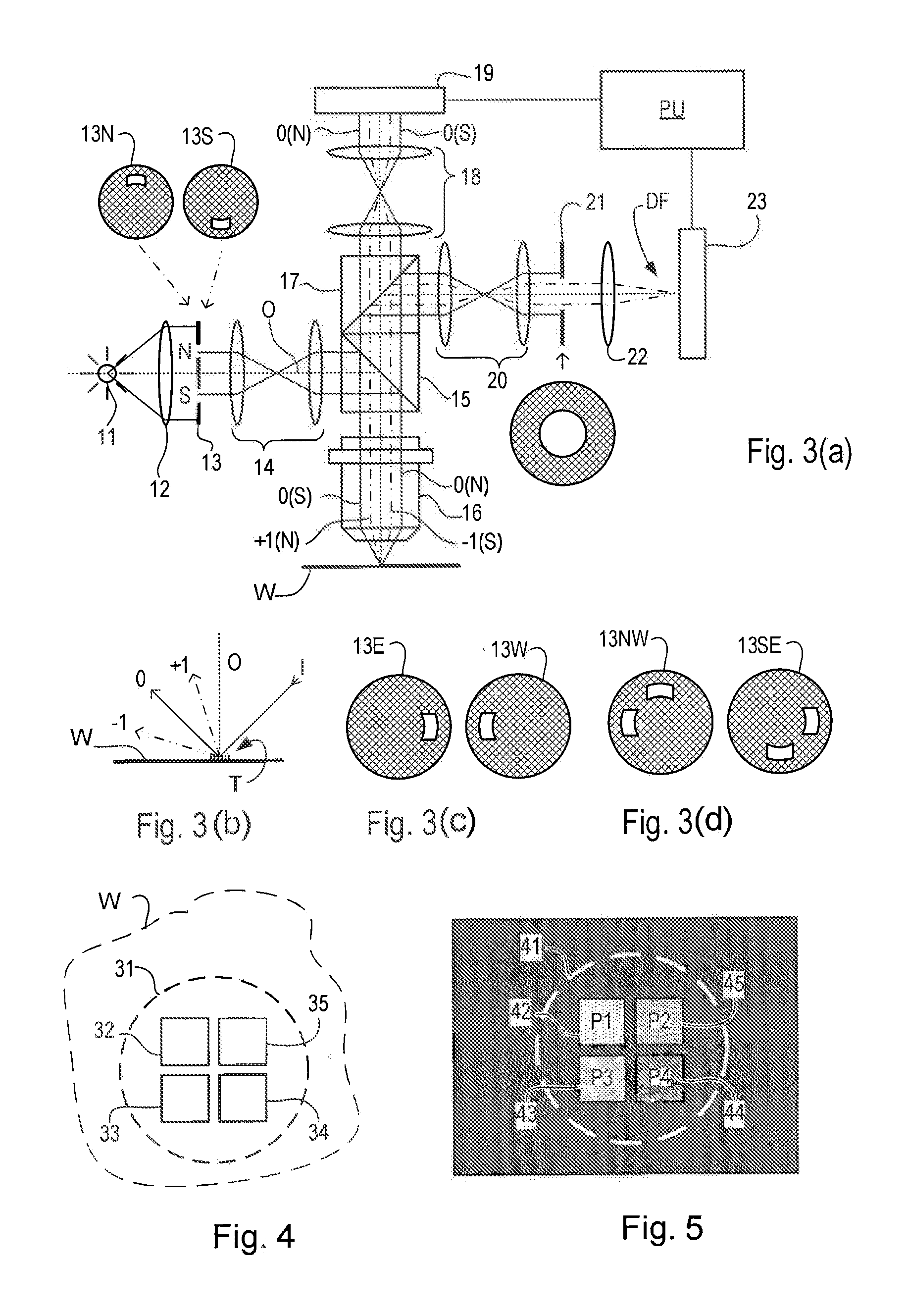

Metrology Method and Apparatus, and Device Manufacturing Method

ActiveUS20120242970A1Improve accuracyImprove throughputPhotomechanical apparatusOptically investigating flaws/contaminationMetrologyGrating

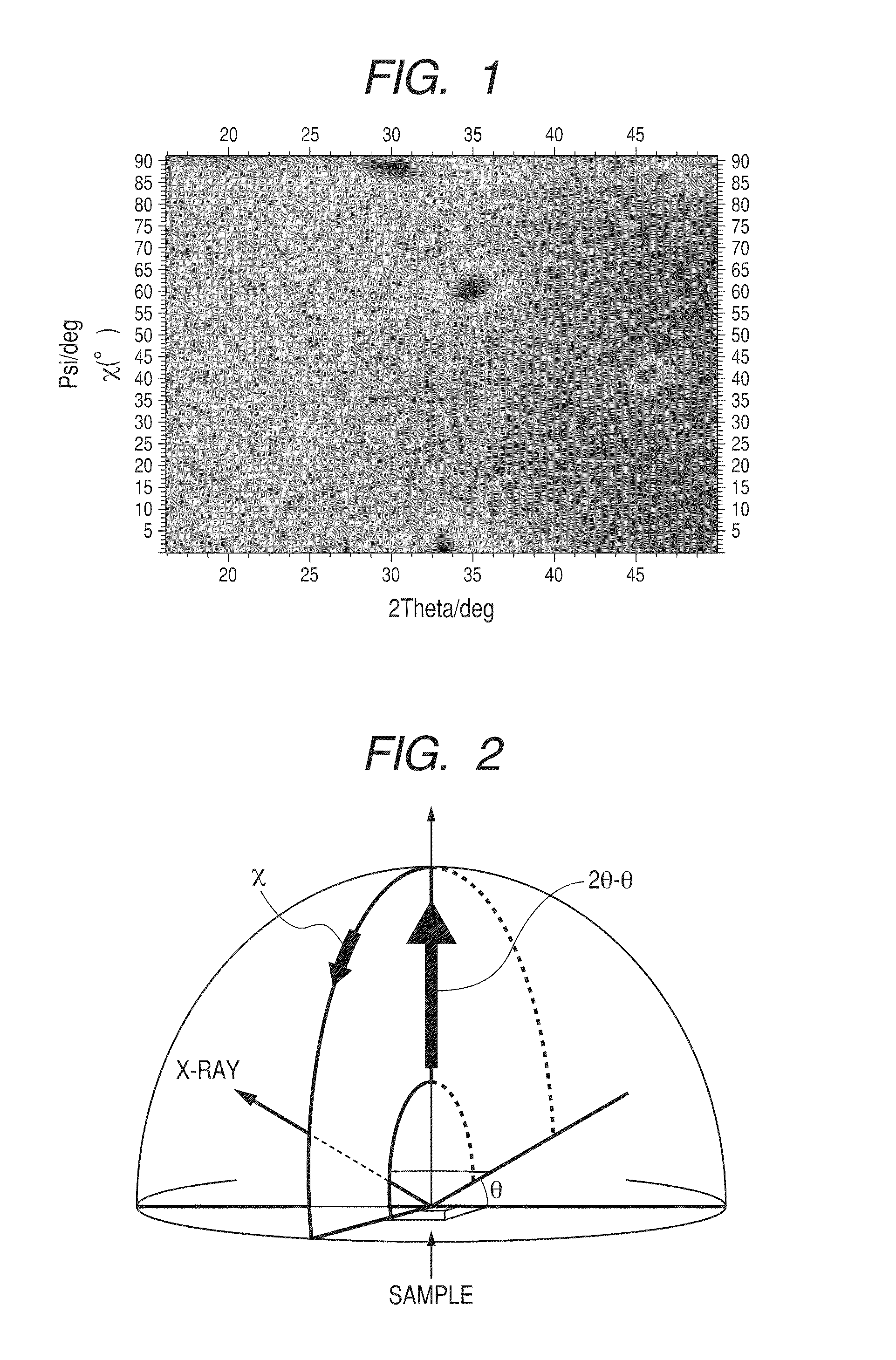

Methods are disclosed for measuring target structures formed by a lithographic process on a substrate. A grating or other structure within the target is smaller than an illumination spot and field of view of a measurement optical system. The position of an image of the component structure varies between measurements, and a first type of correction is applied to reduce the influence on the measured intensities, caused by differences in the optical path to and from different positions. A plurality of structures may be imaged simultaneously within the field of view of the optical system, and each corrected for its respective position. The measurements may comprise first and second images of the same target under different modes of illumination and / or imaging, for example in a dark field metrology application. A second type of correction may be applied to reduce the influence of asymmetry between the first and second modes of illumination or imaging, for example to permit a more accurate overly measurement in a semiconductor device manufacturing process.

Owner:ASML NETHERLANDS BV

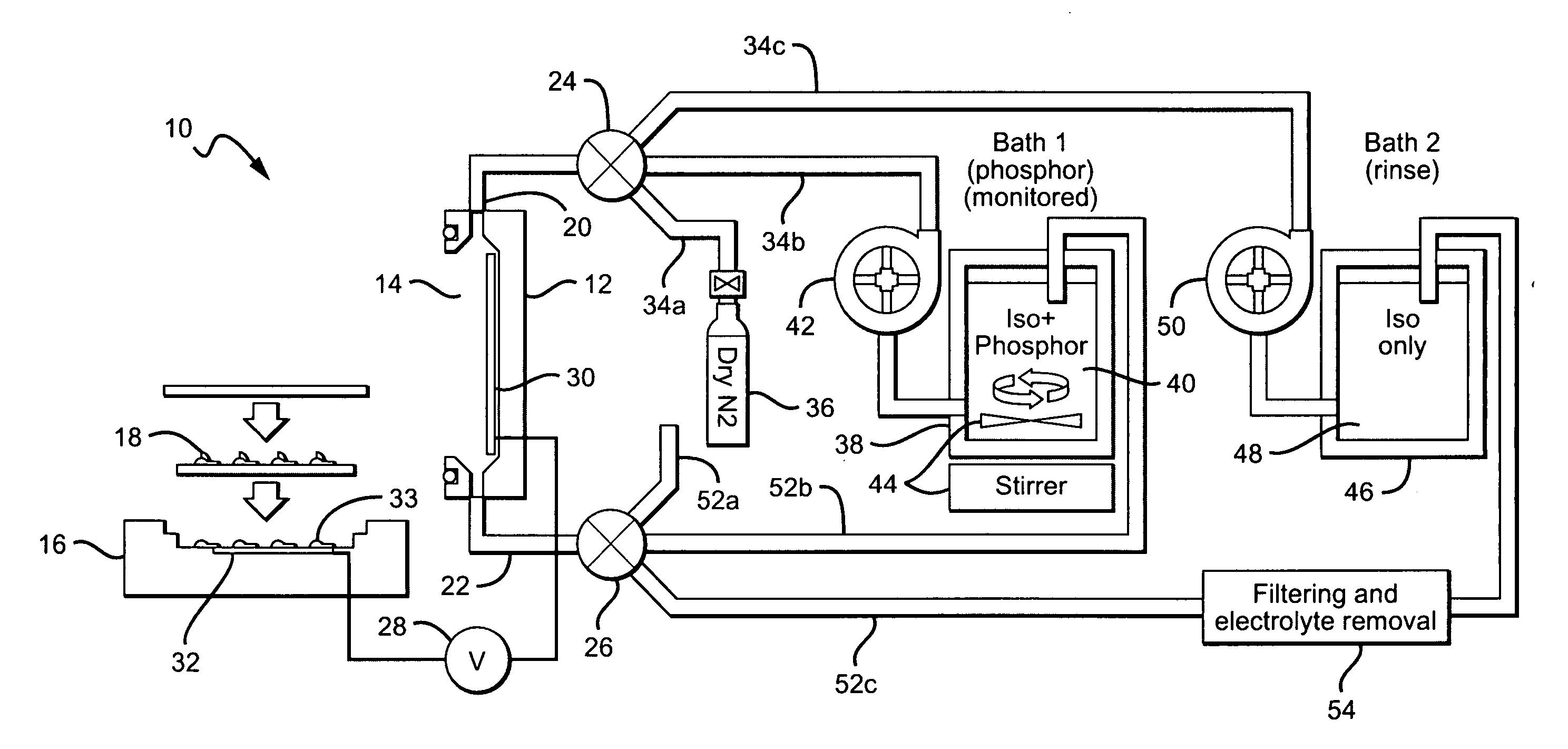

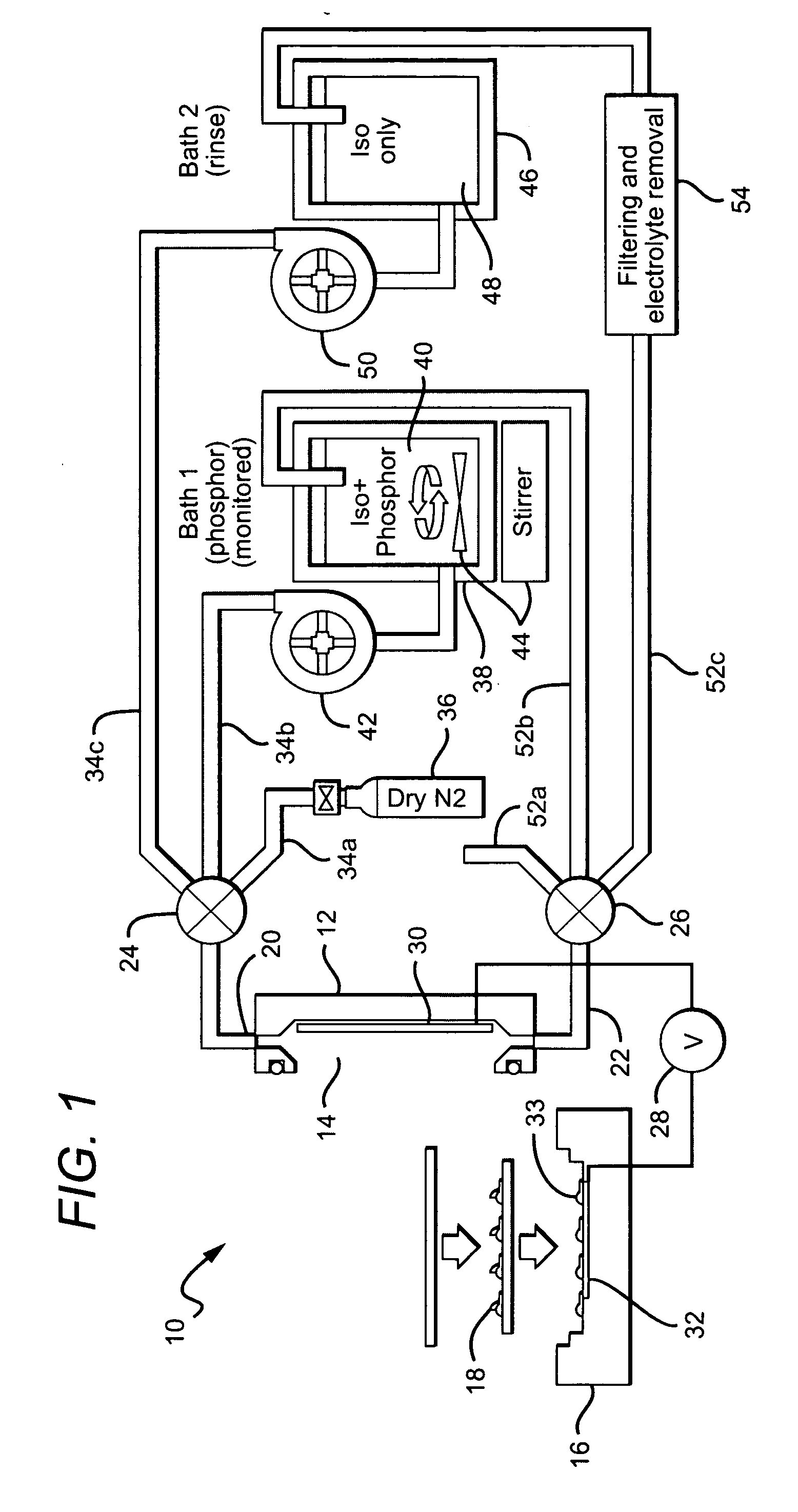

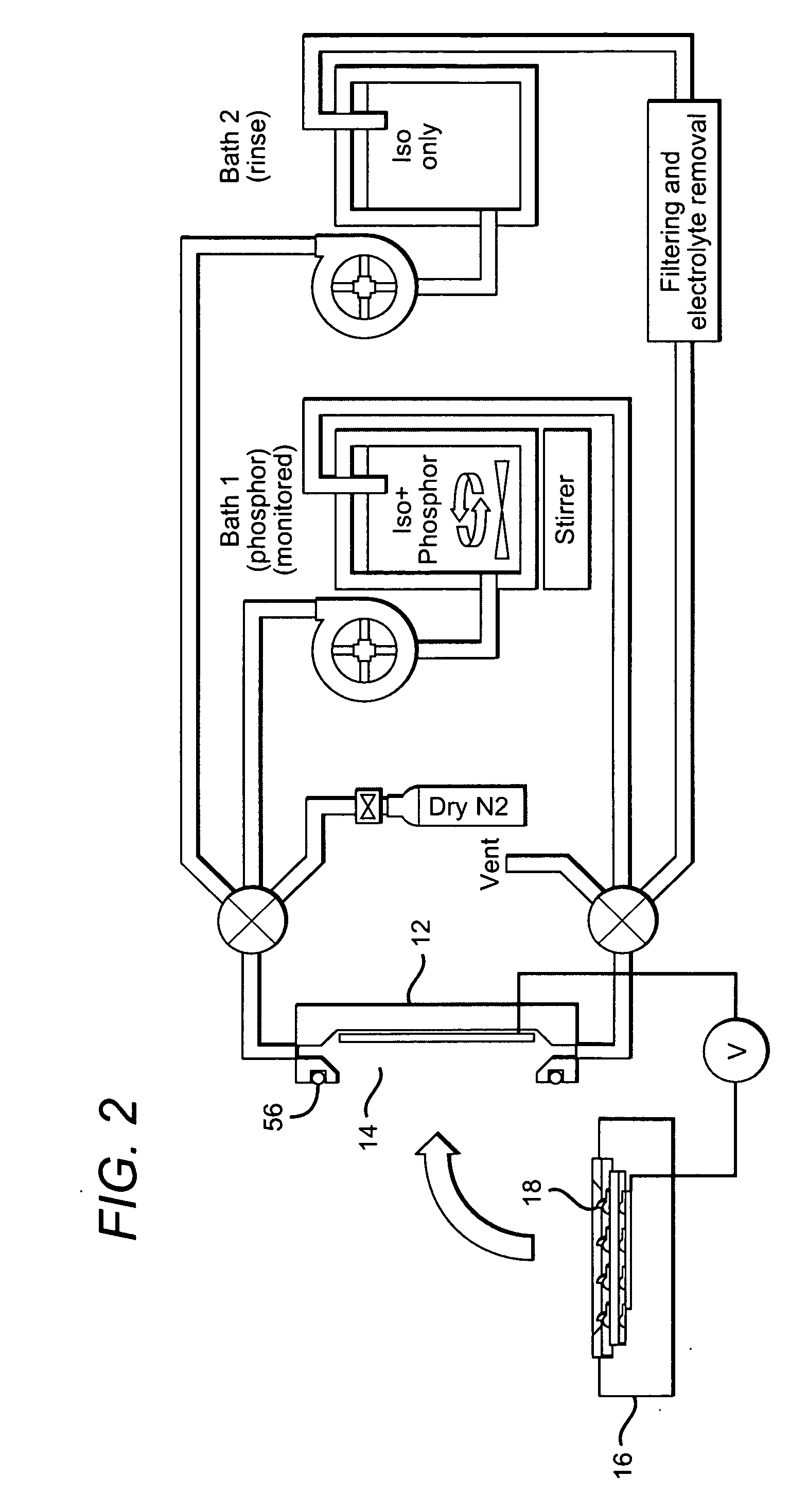

Close loop electrophoretic deposition of semiconductor devices

One close loop system and method for electrophoretic deposition (EPD) of phosphor material on light emitting diodes (LEDs). The system comprises a deposition chamber sealed from ambient air. A mixture of phosphor material and solution is provided to the chamber with the mixture also being sealed from ambient air. A carrier holds a batch of LEDs in the chamber with the mixture contacting the areas of the LEDs for phosphor deposition. A voltage supply applies a voltage to the LEDs and the mixture to cause the phosphor material to deposit on the LEDs at the mixture contacting areas.

Owner:CREELED INC

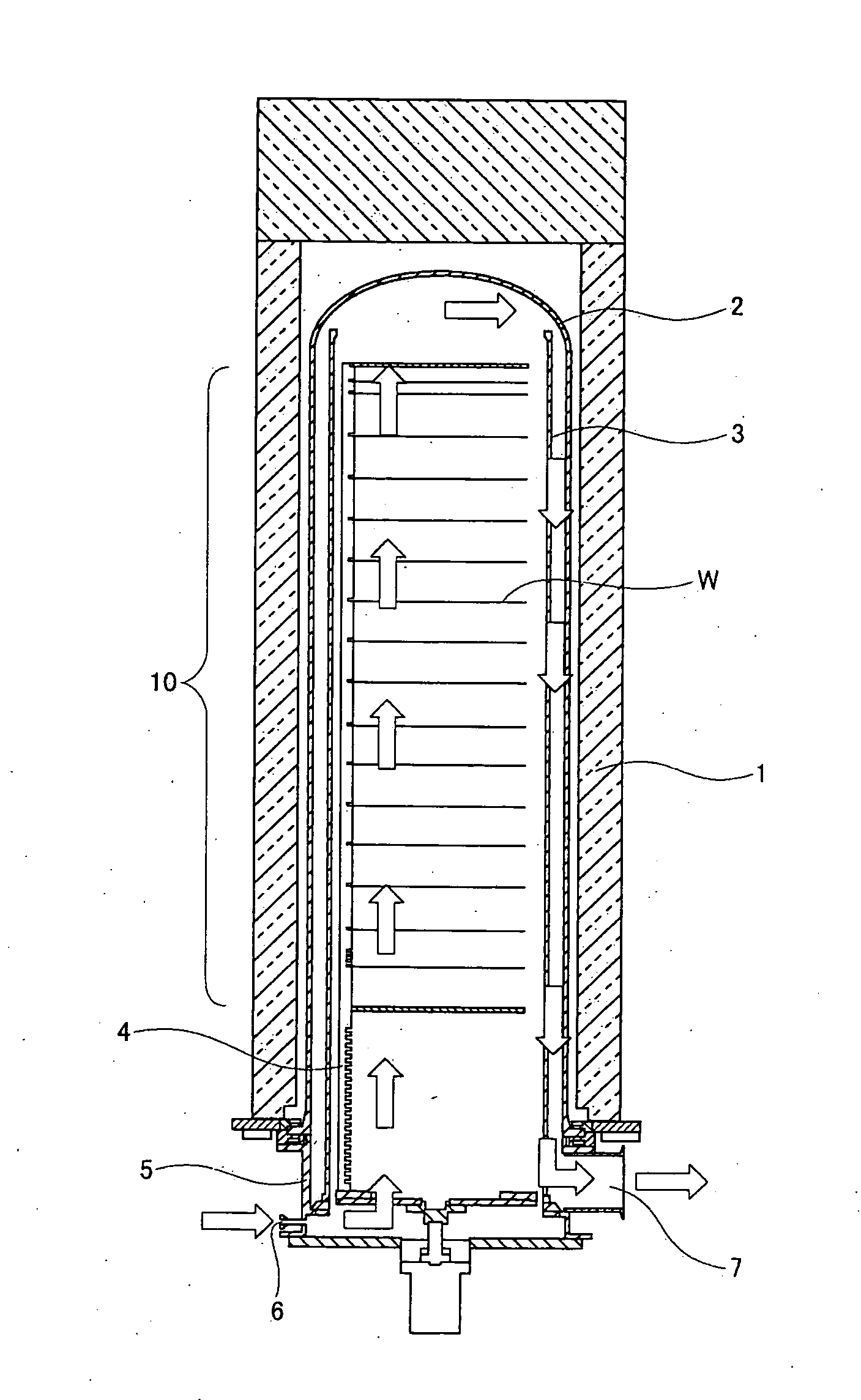

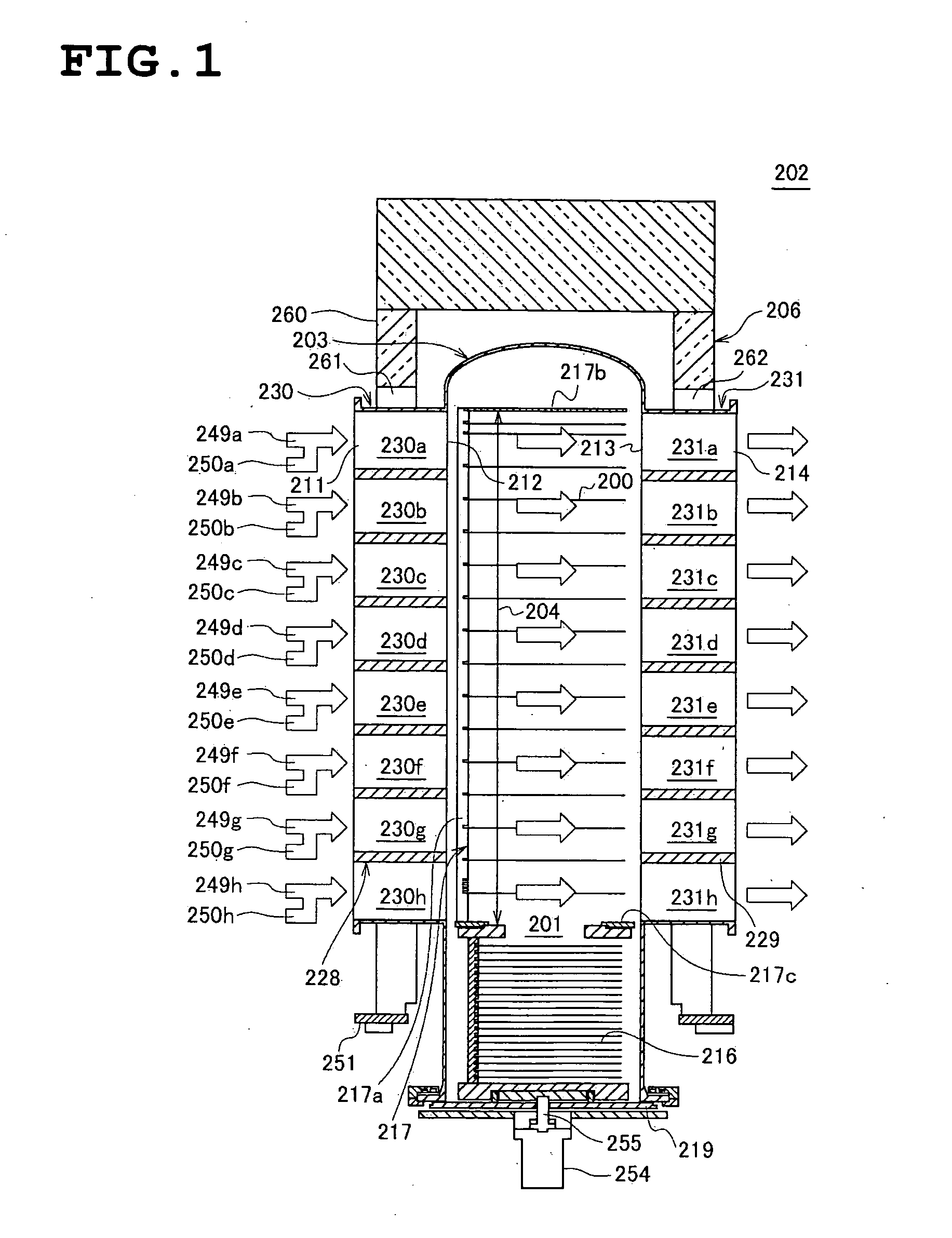

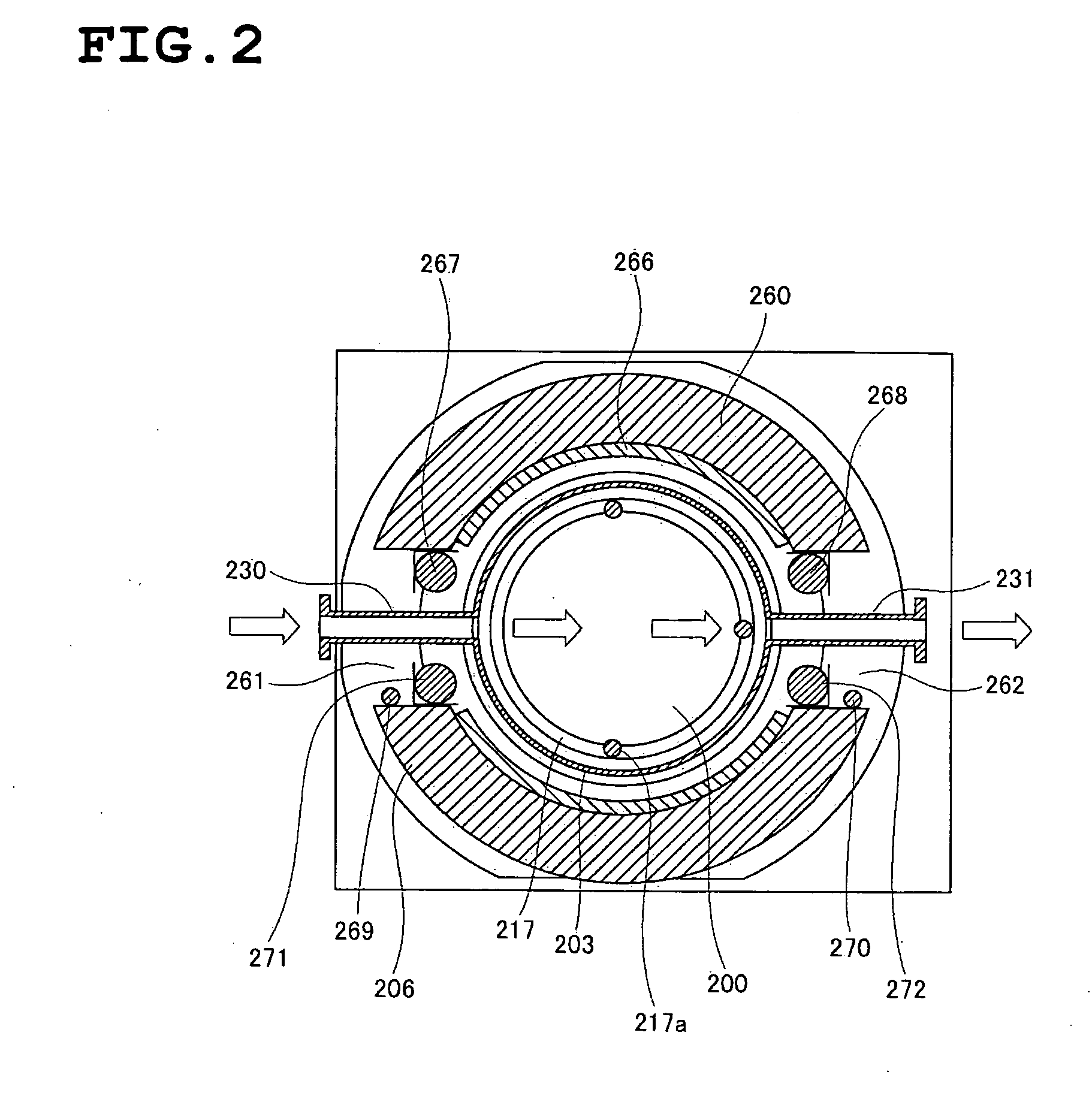

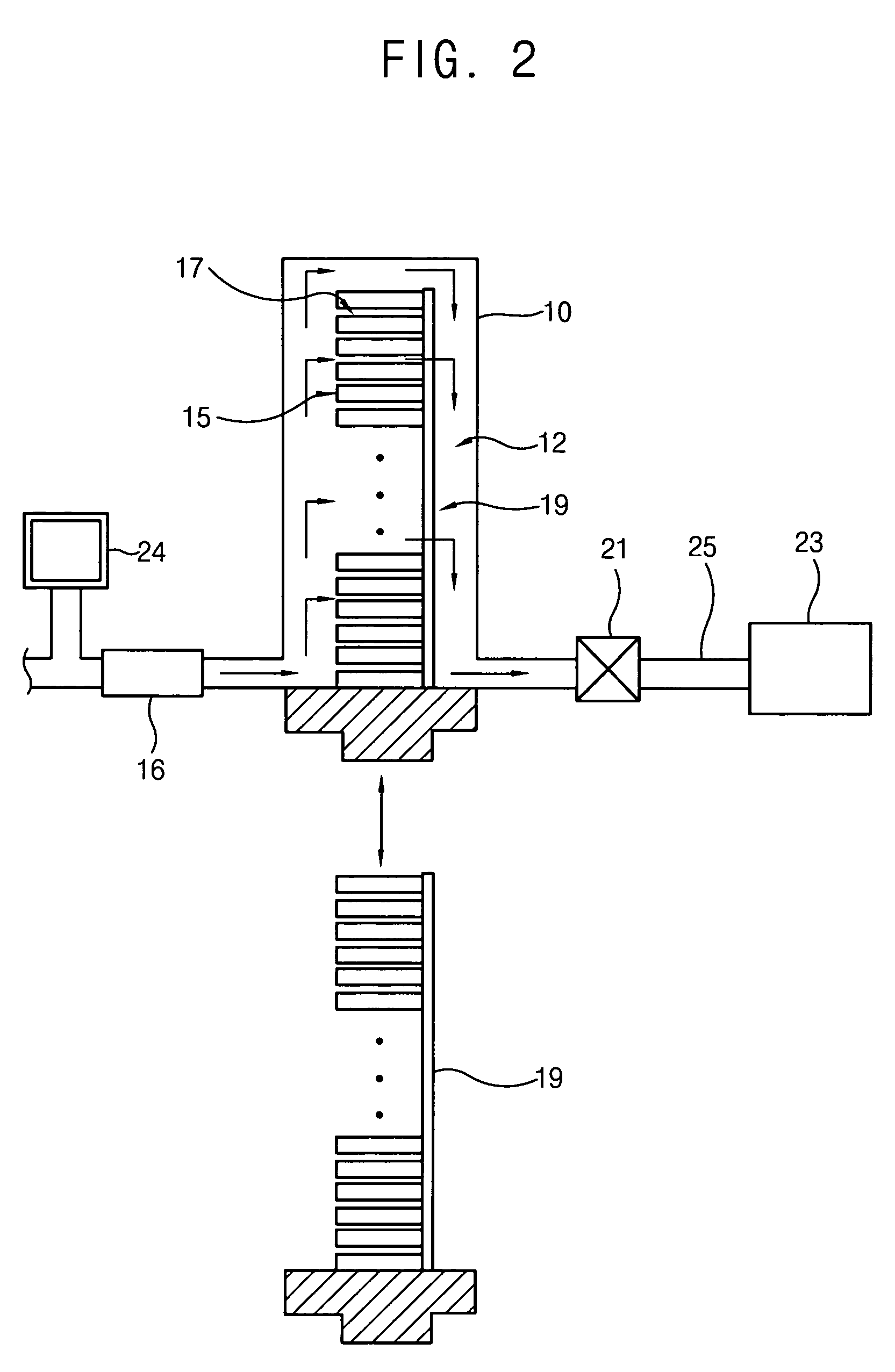

Substrate processing apparatus, method of manufacturing semiconductor device, and reaction vessel

InactiveUS20080173238A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingIn planeProduct gas

A substrate processing apparatus that affords improved uniformity to in-plane wafer and interwafer film thickness of a large number of wafers on which a film is simultaneously formed, having: a reaction tube having in an interior thereof a processing chamber in which a plurality of substrates disposed in a direction perpendicular to a substrate processing surface can be processed; and a heating device provided to surround an outer circumference of the reaction tube, a gas inlet tube being provided on a side face of the reaction tube in a region for processing a substrate inside the reaction tube, so as to reach at least an outside of the heating device; and a gas spouting port being disposed in this gas inlet tube in a slit form so as to straddle at least a plurality of the substrates in a direction perpendicular to the substrate processing surface, for spouting gas from the gas inlet tube into the processing chamber.

Owner:KOKUSA ELECTRIC CO LTD

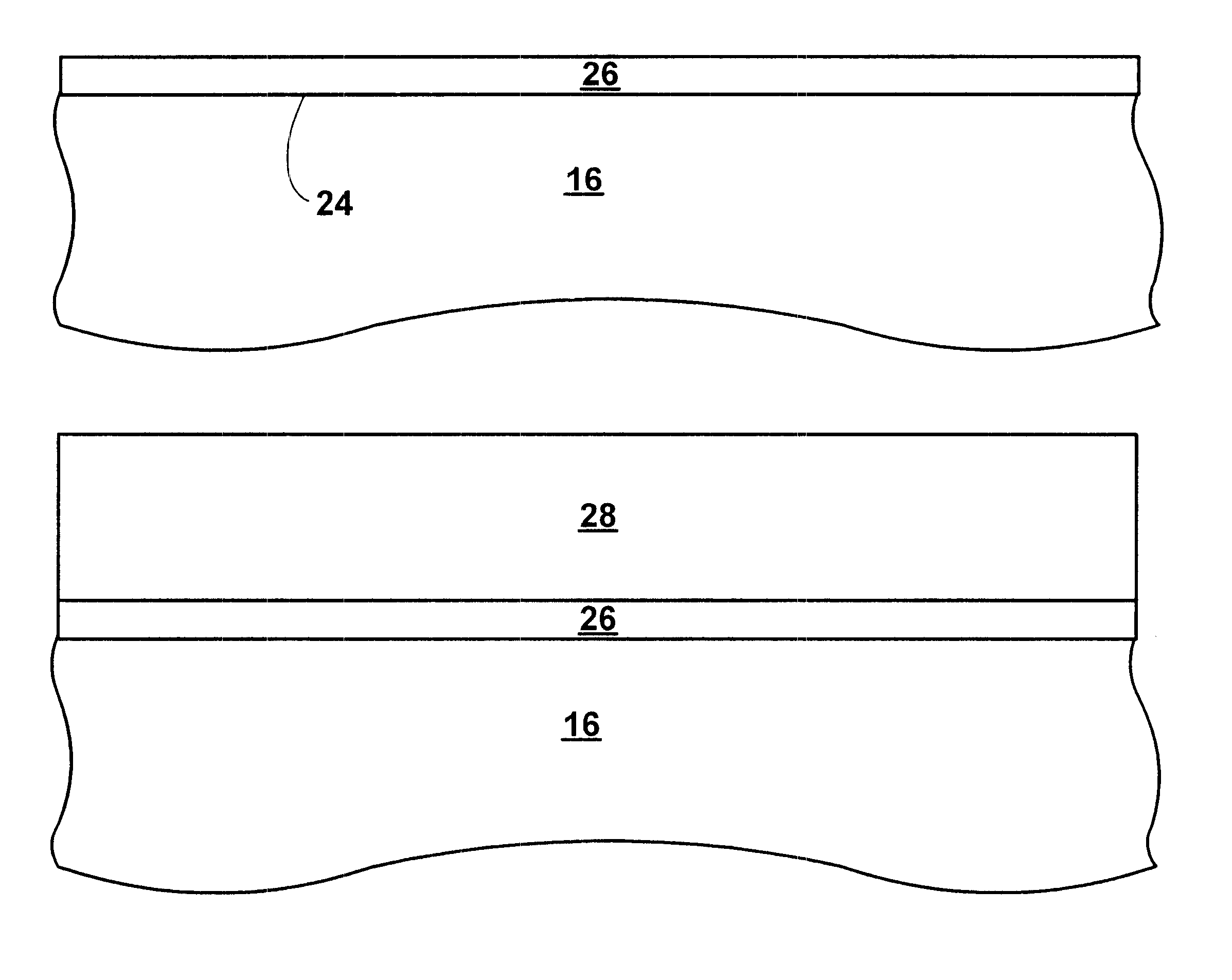

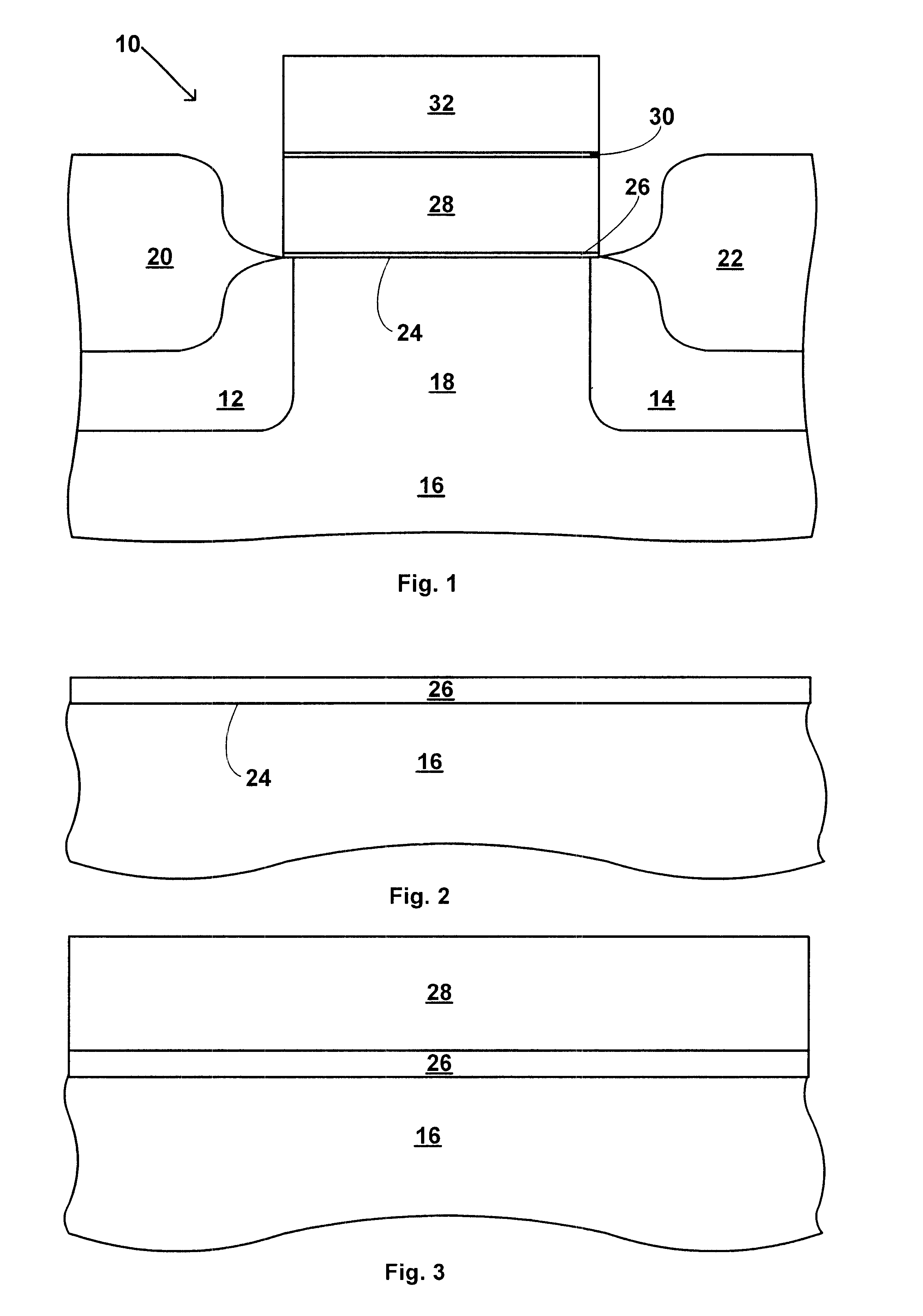

Formation of well-controlled thin SiO, SiN, SiN, SiON layer for multilayer high-K dielectric applications

A process for fabricating a semiconductor device having a high-K dielectric layer over a silicon substrate, including steps of growing on the silicon substrate an interfacial layer of a silicon-containing dielectric material; and depositing on the interfacial layer a layer comprising at least one high-K dielectric material, in which the interfacial layer is grown by laser excitation of the silicon substrate in the presence of oxygen, nitrous oxide, nitric oxide, ammonia or a mixture of two or more thereof. In one embodiment, the silicon-containing material is silicon dioxide, silicon nitride, silicon oxynitride or a mixture thereof.

Owner:ADVANCED MICRO DEVICES INC

Nitridation of high-k dielectric films

InactiveUS20050153571A1Improve mobilityInterface stabilitySemiconductor/solid-state device manufacturingChemical vapor deposition coatingDielectricElectricity

The present invention promotes incorporation of nitrogen (e.g., nitridation) into high-k dielectric films using a low temperature process. Further, the present invention provides an in-situ method; that is formation of the high-k dielectric film and nitridation of the film are carried out in the same process chamber during deposition of the film, as opposed to the conventional post processing techniques. In another aspect, a method for depositing a multi-layer material for use as a gate dielectric layer in semiconductor devices is provided.

Owner:AVIZA TECHNOLOGY INC

Nitride based semiconductor device

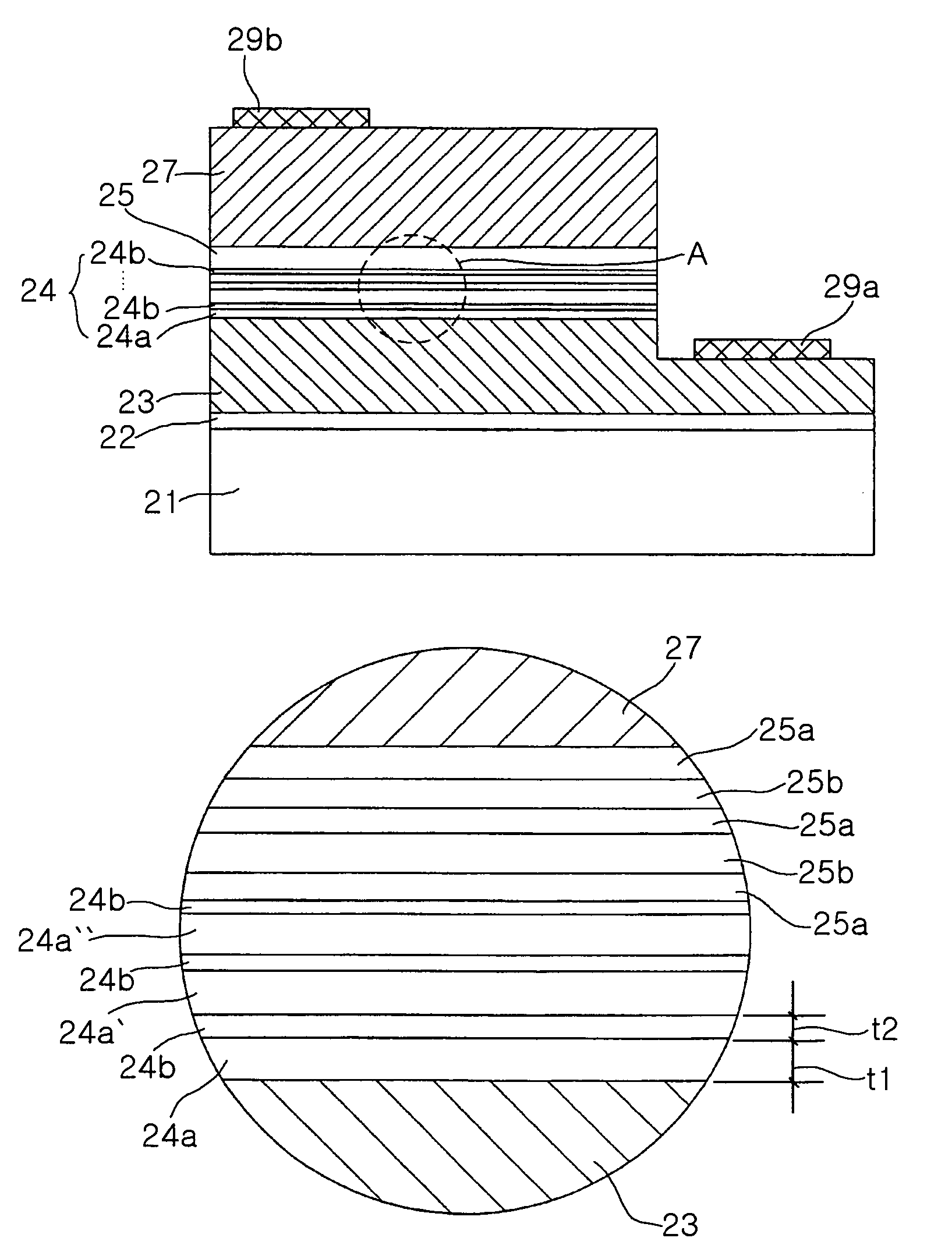

ActiveUS7084420B2Improve efficiencyEliminate the effects ofNanoopticsSemiconductor lasersDevice materialQuantum well

The present invention provides a nitride based semiconductor device comprising an active layer having a quantum well layer and a quantum barrier layer, wherein the device includes an electron emitting layer formed of at least two repeats of a first nitride semiconductor layer and a second nitride semiconductor layer having different compositions between a n-type nitride semiconductor layer and the active layer, the first nitride semiconductor layer has an energy band gap greater than that of the quantum well layer, smaller than that of the quantum barrier layer, and decreasing closer to the active layer, and the second nitride semiconductor layer has an energy band gap at least higher than that of the adjacent first nitride semiconductor layer(s) and has a thickness capable of tunneling electrons.

Owner:SAMSUNG ELECTRONICS CO LTD

Method of forming a layer and forming a capacitor of a semiconductor device having the same layer

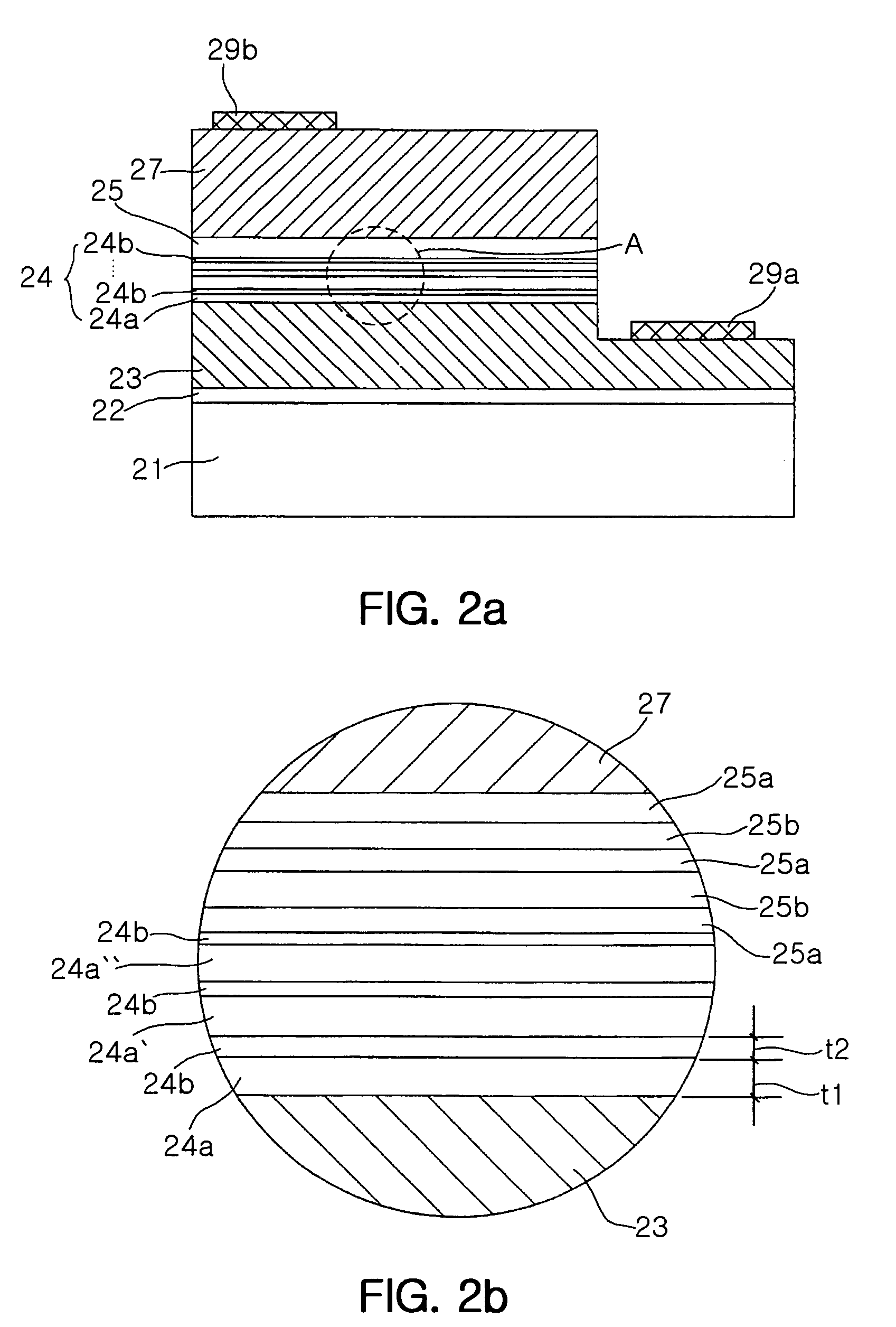

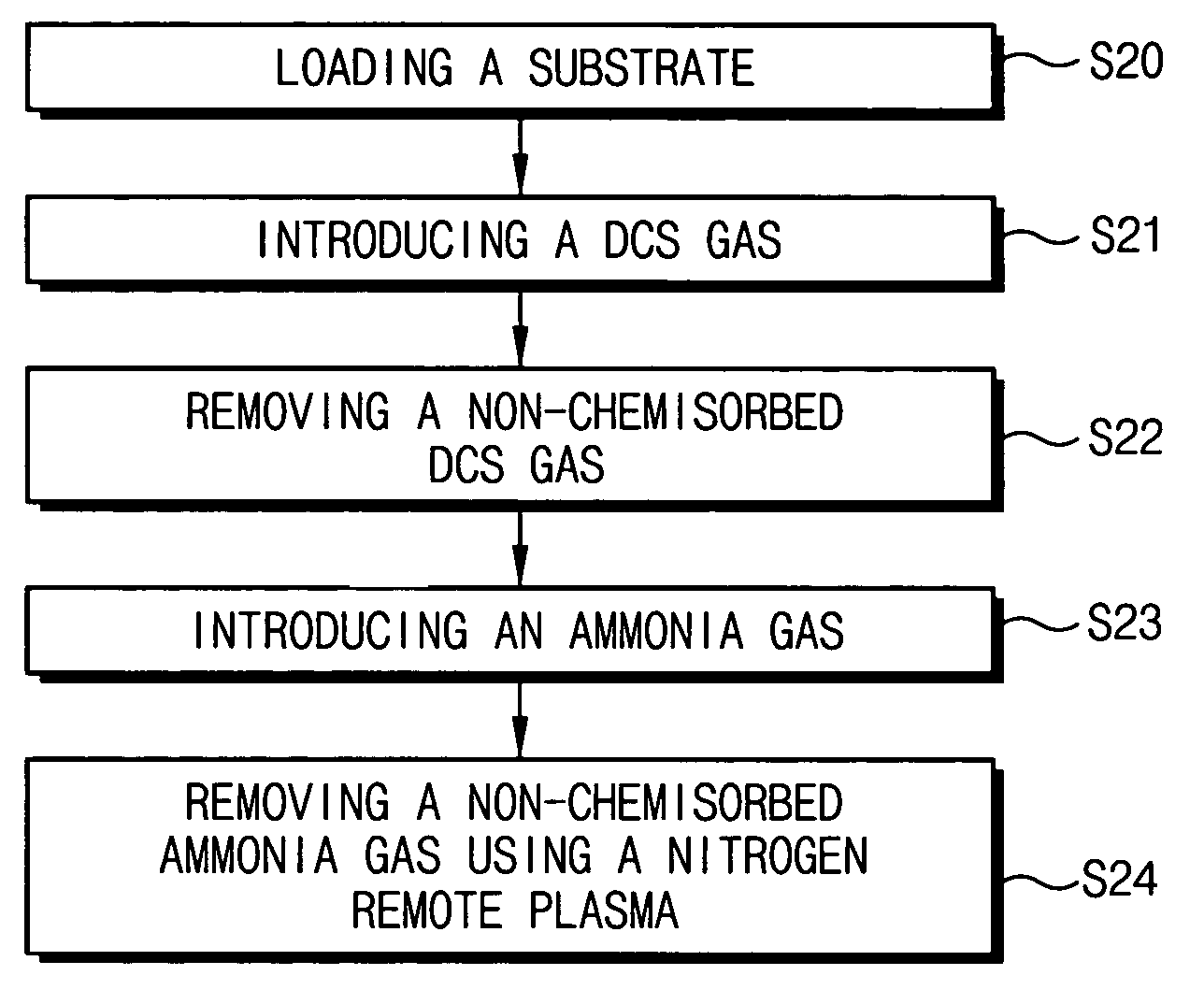

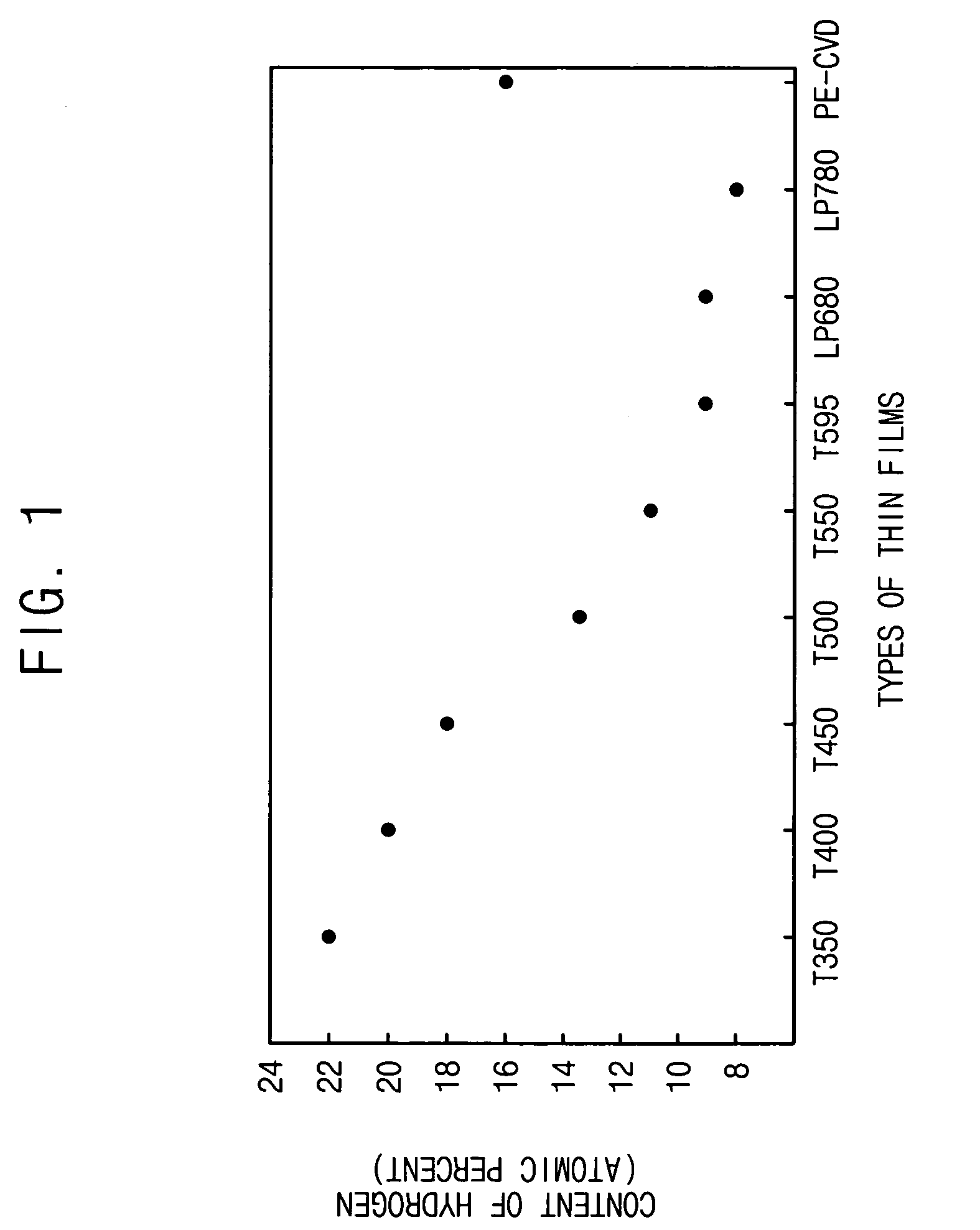

InactiveUS20060014384A1Low hydrogen contentReduce leakage currentSemiconductor/solid-state device manufacturingCapacitorsChemical reactionDevice material

In a method of forming a layer using an atomic layer deposition process, after a substrate is loaded into a chamber, a first reactant is provided onto the substrate. The first reactant is partially chemisorbed on the substrate. A second reactant is introduced into the chamber to form a preliminary layer on the substrate by chemically reacting the second reactant with the chemisorbed first reactant. Impurities in the preliminary layer and unreacted reactants are simultaneously removed using a plasma for removing impurities to thereby form the layer on the substrate. The impurities in the layer may be effectively removed so that the layer may have reduced leakage current.

Owner:SAMSUNG ELECTRONICS CO LTD

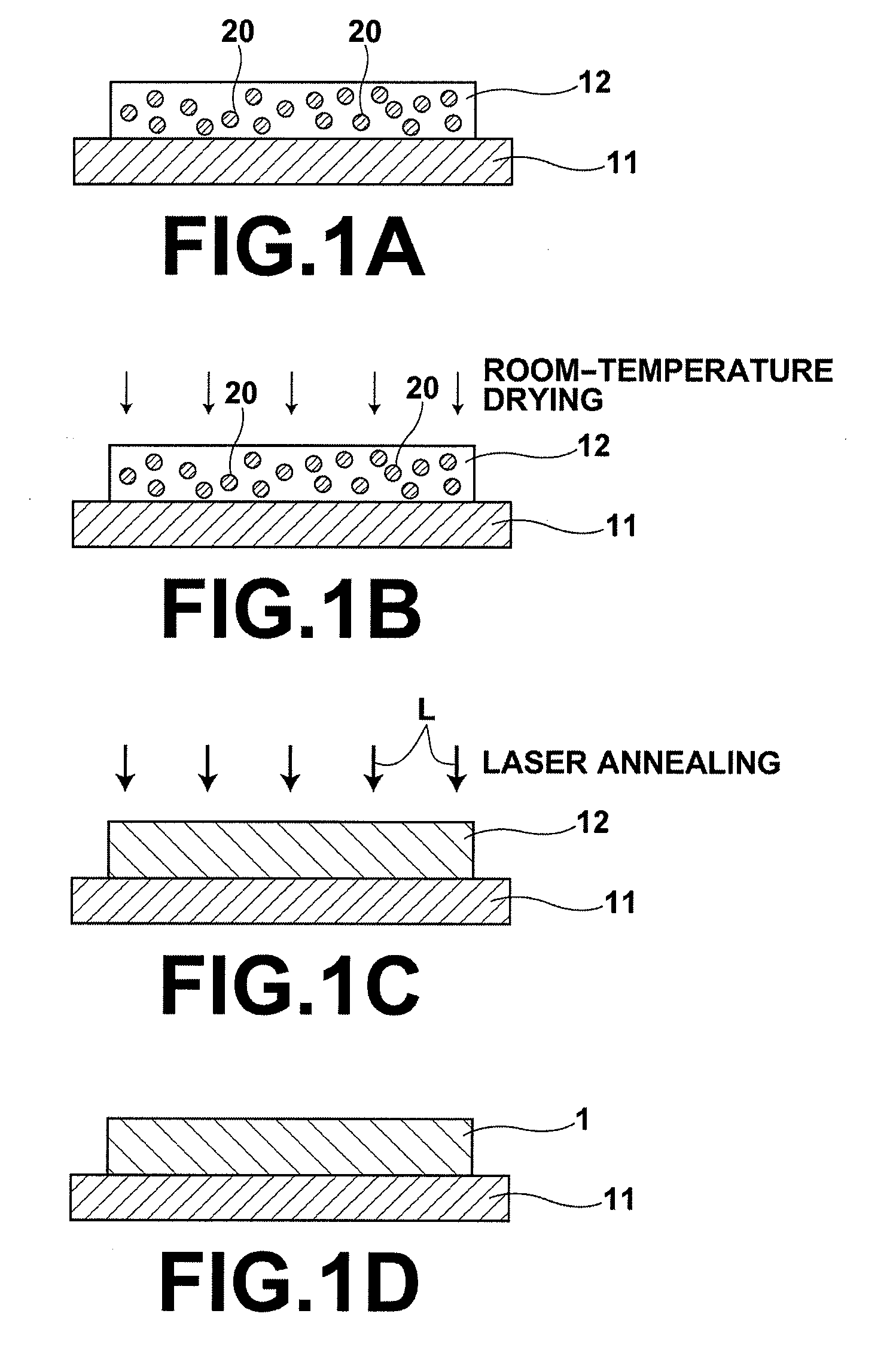

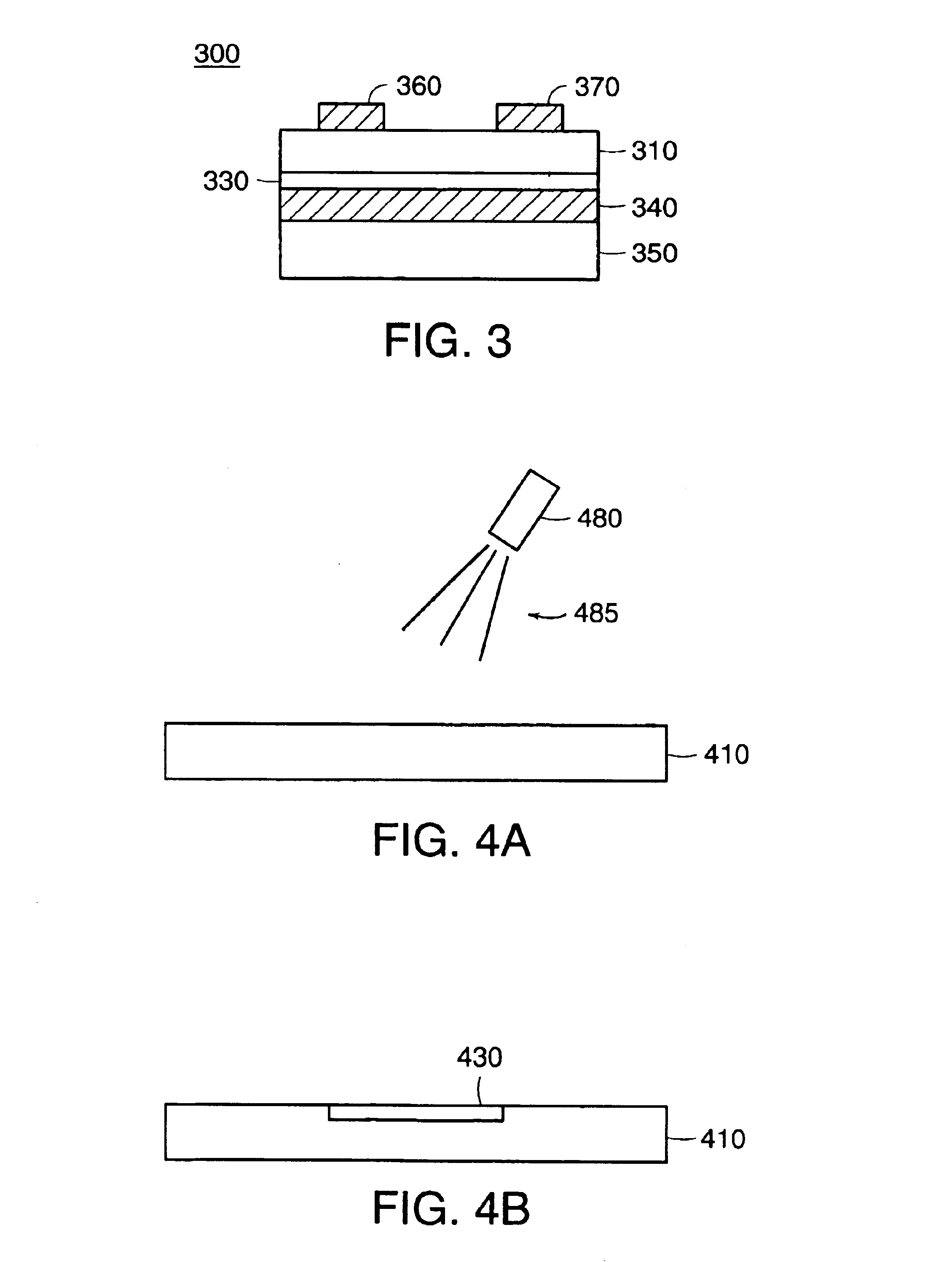

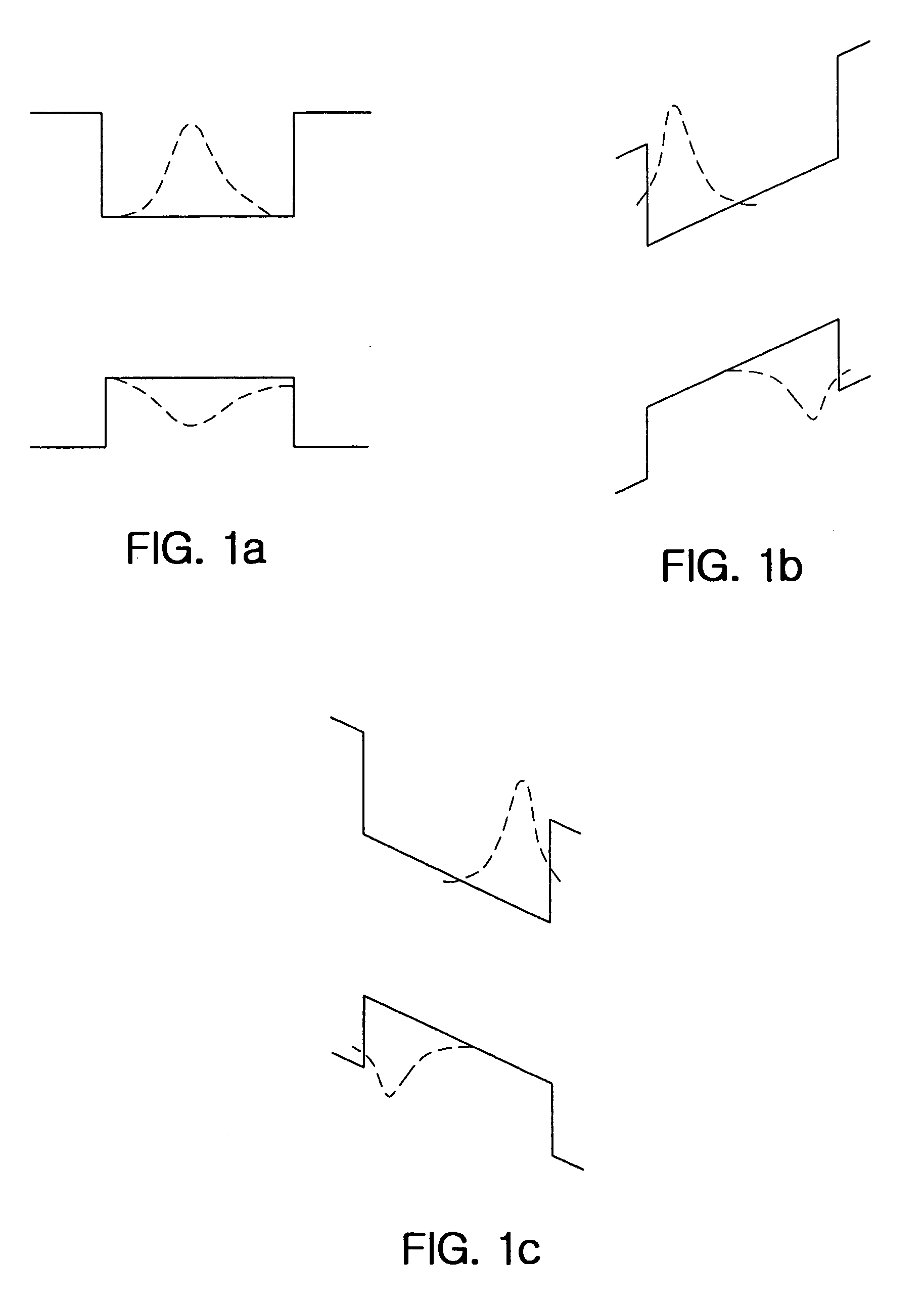

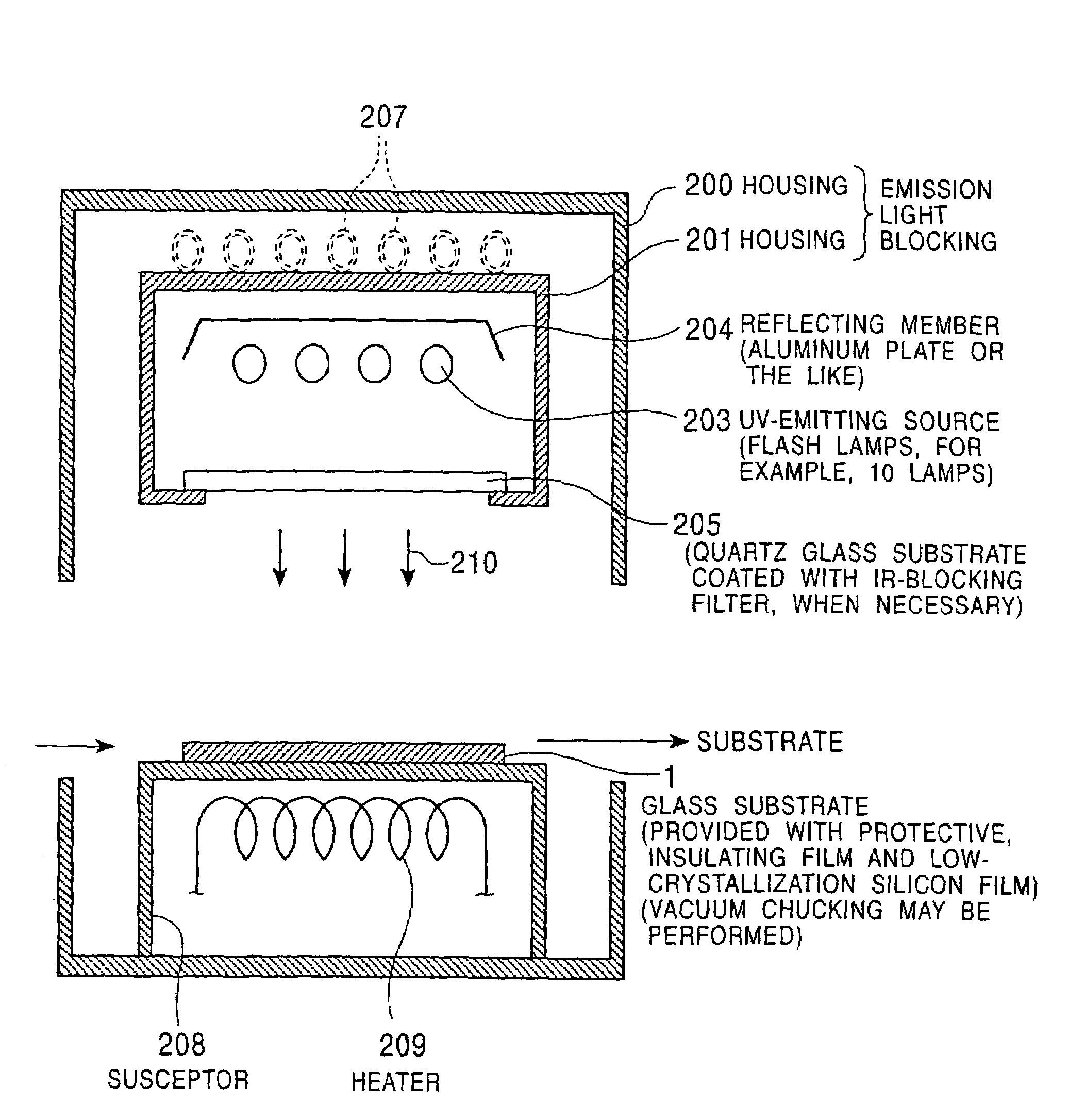

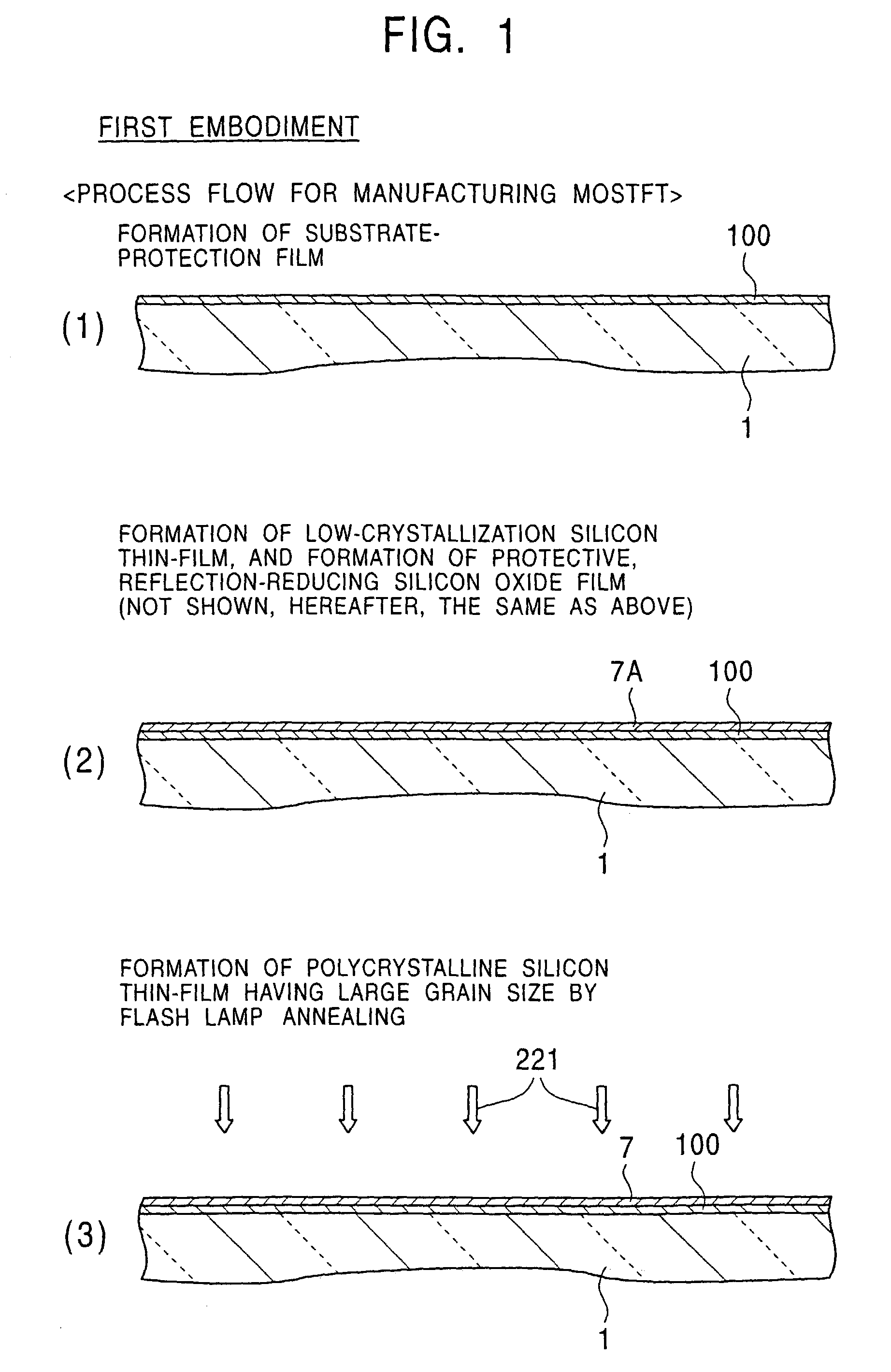

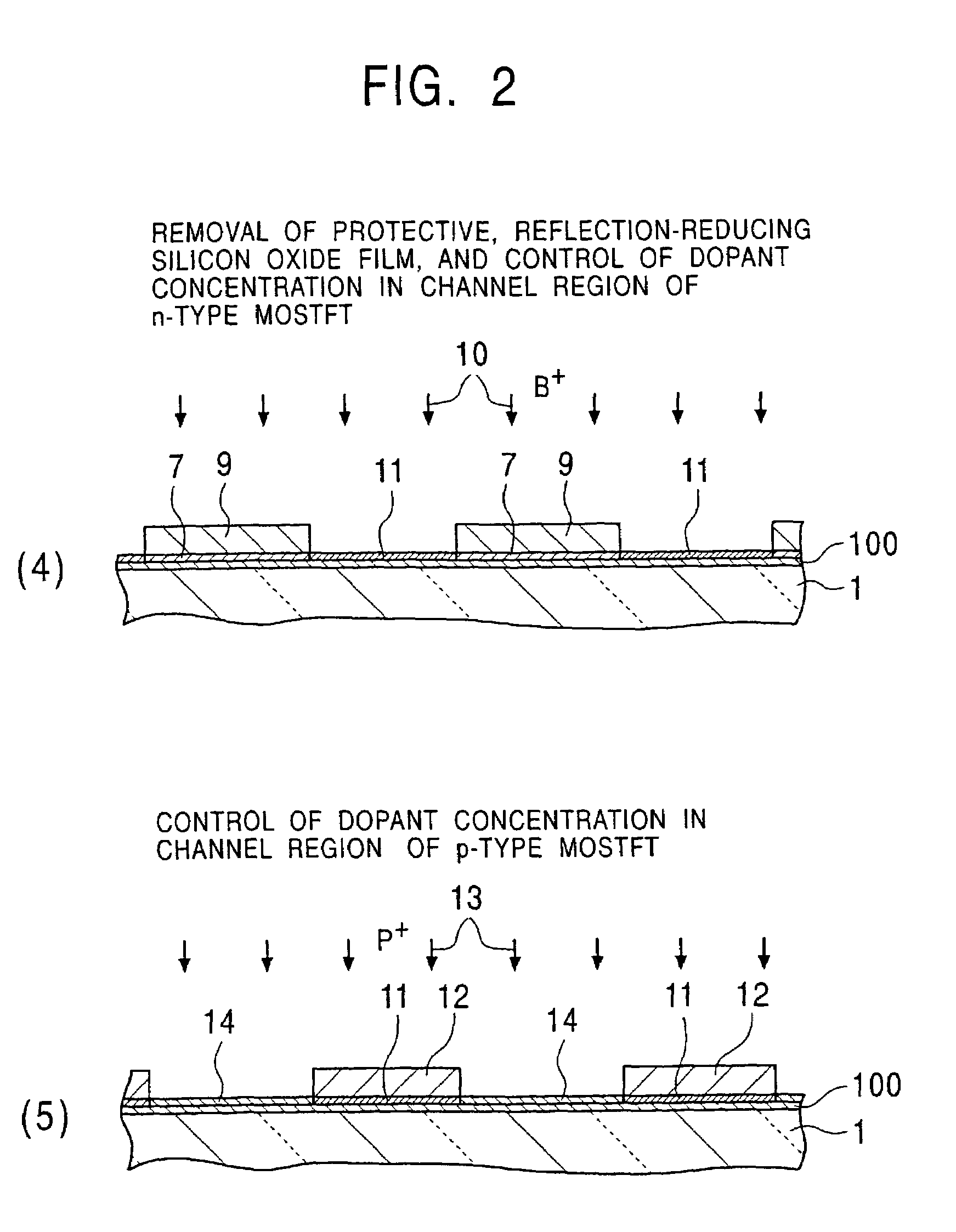

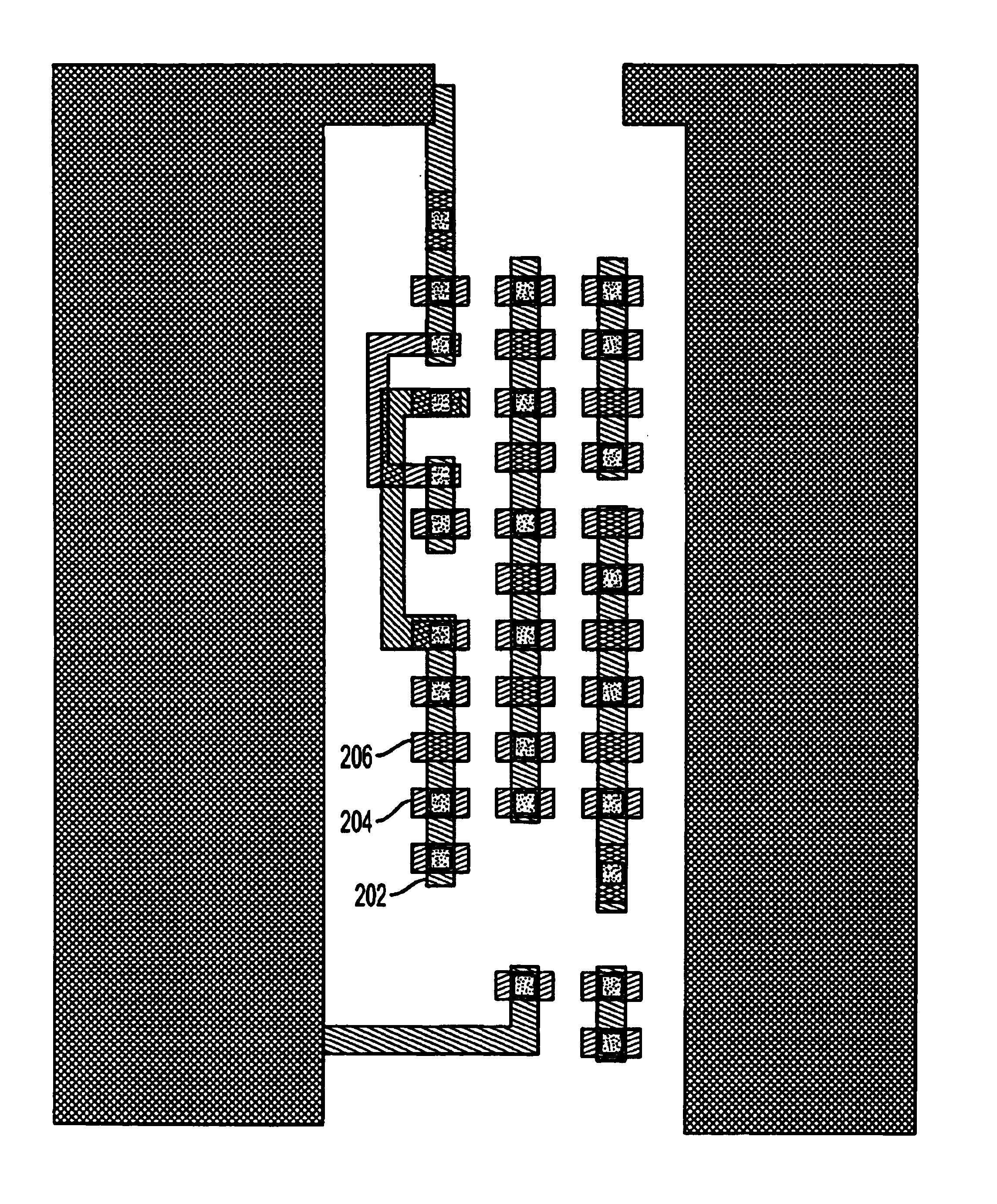

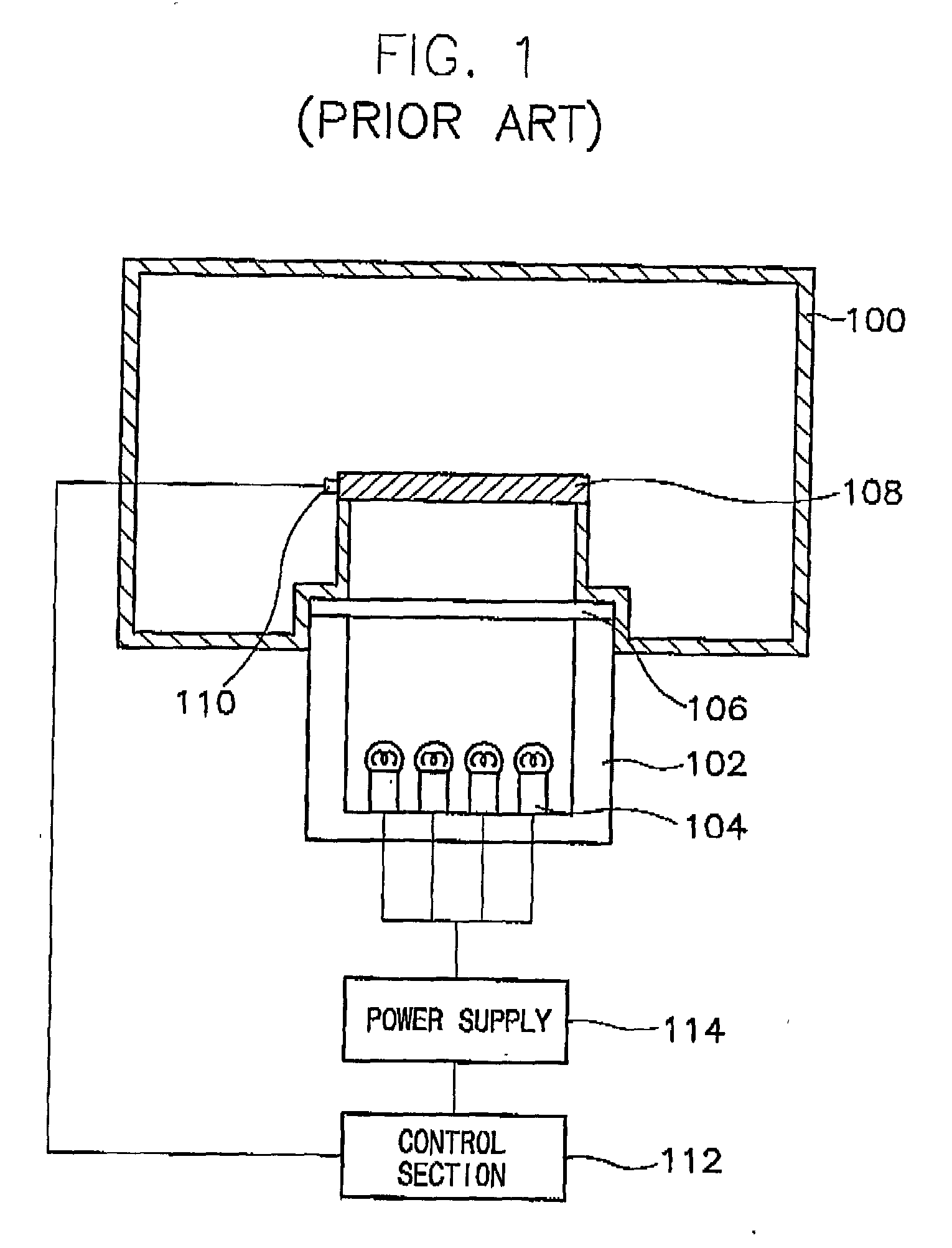

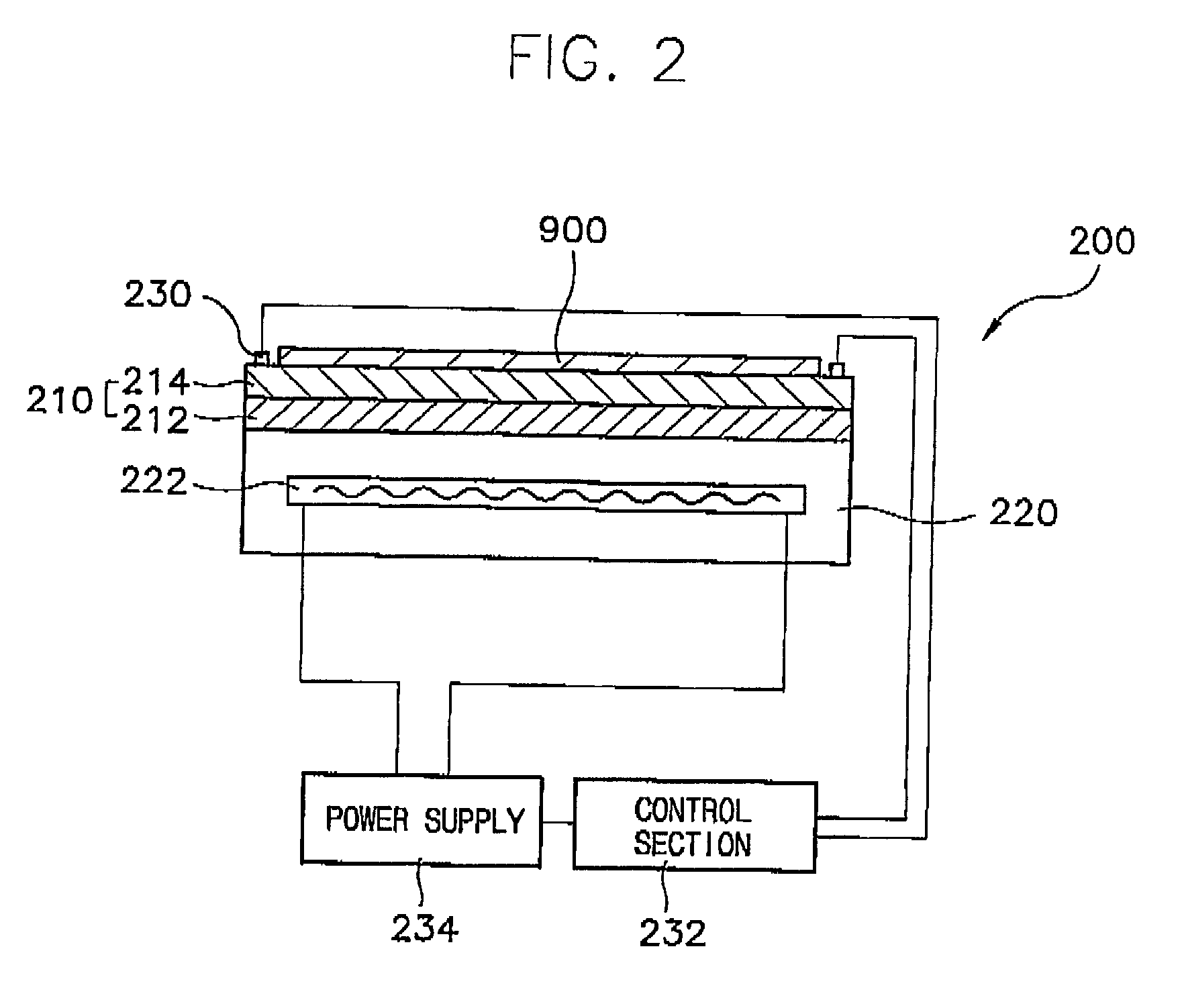

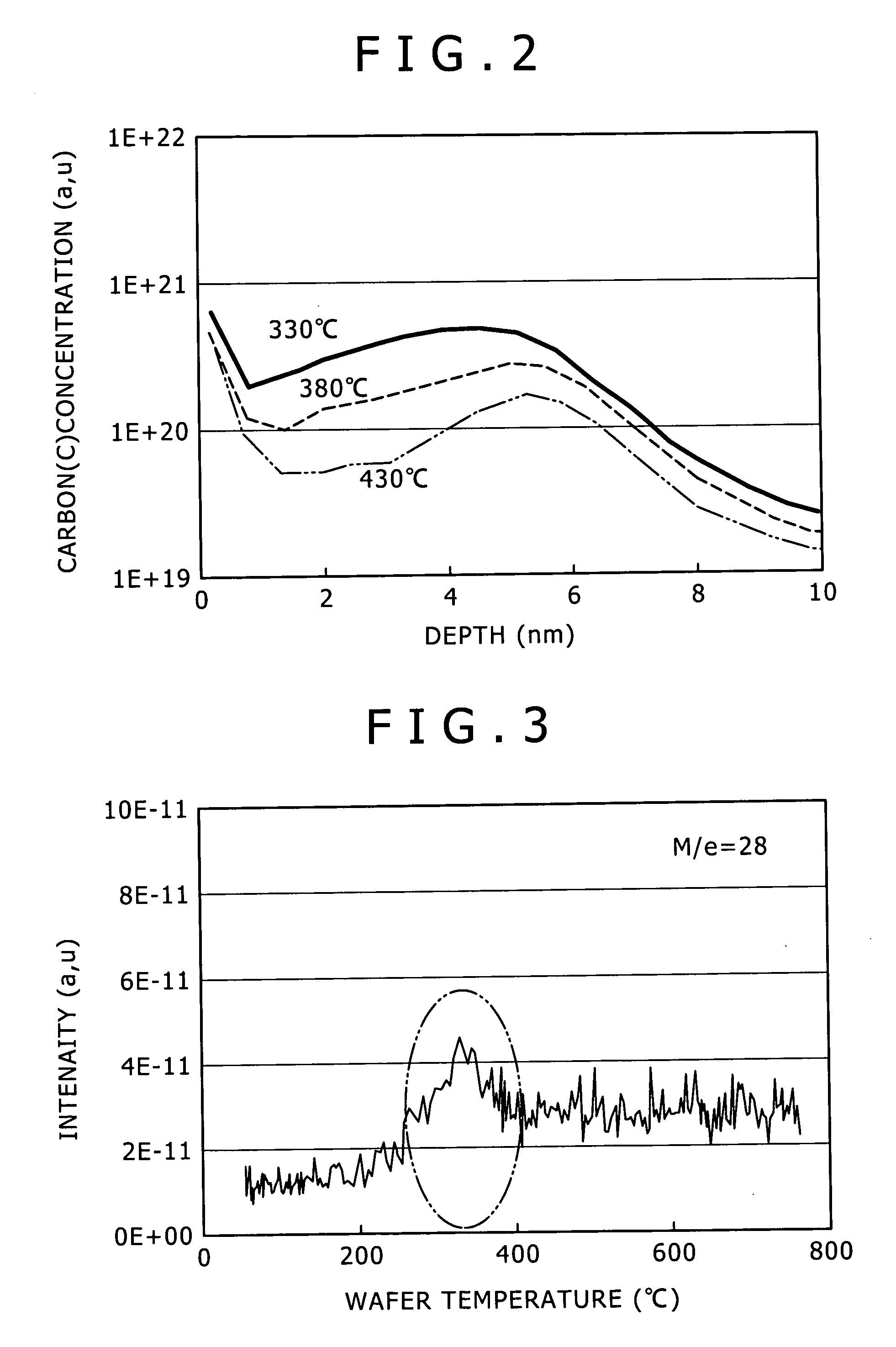

Semiconductor thin film forming method, production methods for semiconductor device and electrooptical device, devices used for these methods, and semiconductor device and electrooptical device

InactiveUS7183229B2Promote crystallizationTransistorDrying solid materials with heatSingle crystalCrystallinity

An object of the present invention is to provide a method for easily forming a polycrystalline semiconductor thin-film, such as polycrystalline silicon having high crystallinity and high quality, or a single crystalline semiconductor thin-film at inexpensive cost, the crystalline semiconductor thin-film having a large area, and to provide an apparatus for processing the method described above. In forming a polycrystalline (or single crystalline) semiconductor thin-film (7), such as a polycrystalline silicon thin-film, having high crystallinity and a large grain size on a substrate (1), or in forming a semiconductor device having the polycrystalline (or single crystalline) semiconductor thin-film (7) on the substrate (1), a method comprises forming a low-crystallization semiconductor thin-film (7A) on the substrate (1), and subsequently heating and cooling this low-crystallization semiconductor thin-film (7A) to a fusion, a semi-fusion, or a non-fusion state by flash lamp annealing to facilitate the crystallization of the low-crystallization semiconductor thin-film, whereby a polycrystalline (single crystalline) semiconductor thin-film (7) is obtained. A method for forming the semiconductor device and an apparatus for processing the methods are also disclosed.

Owner:SONY CORP

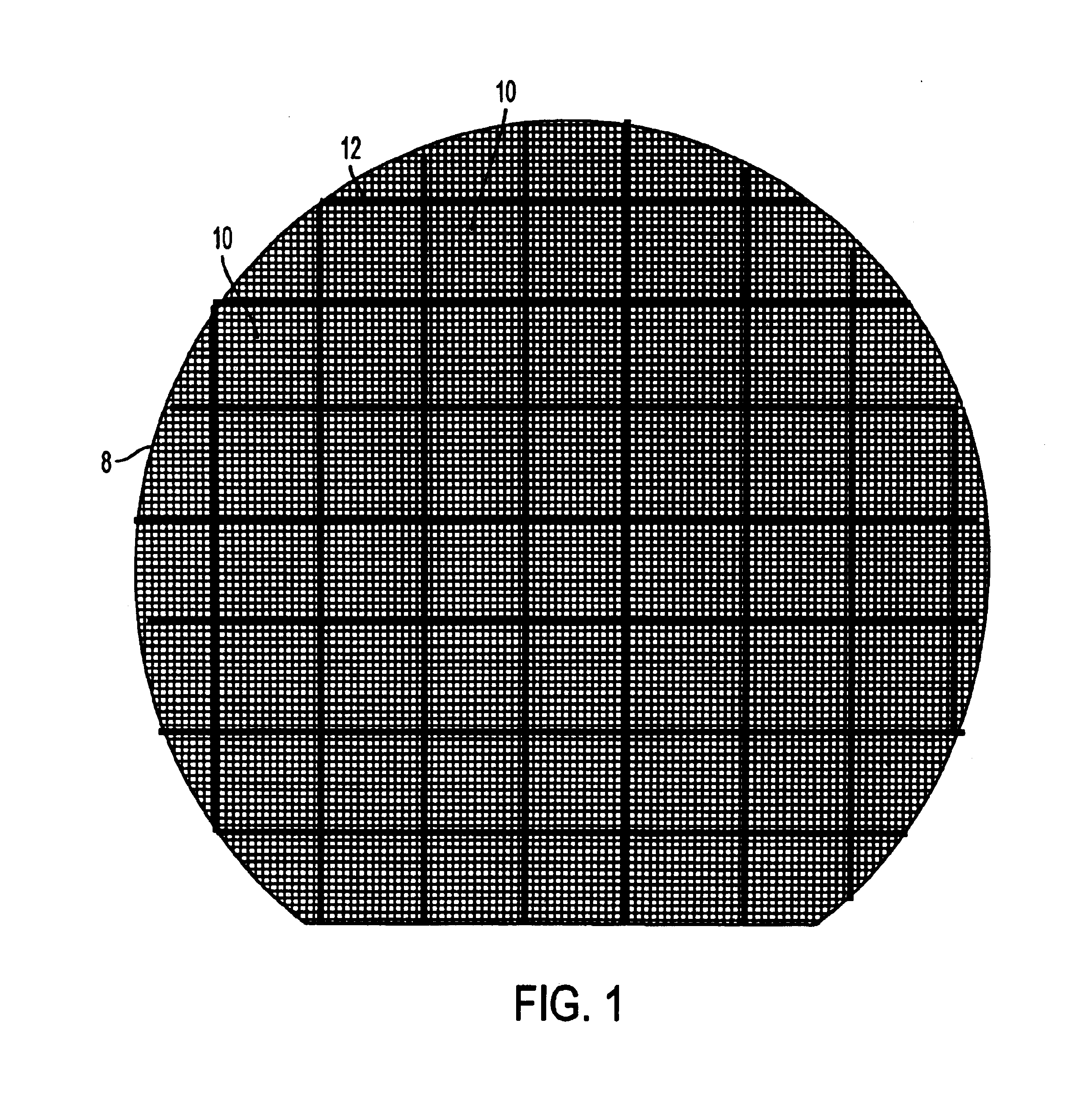

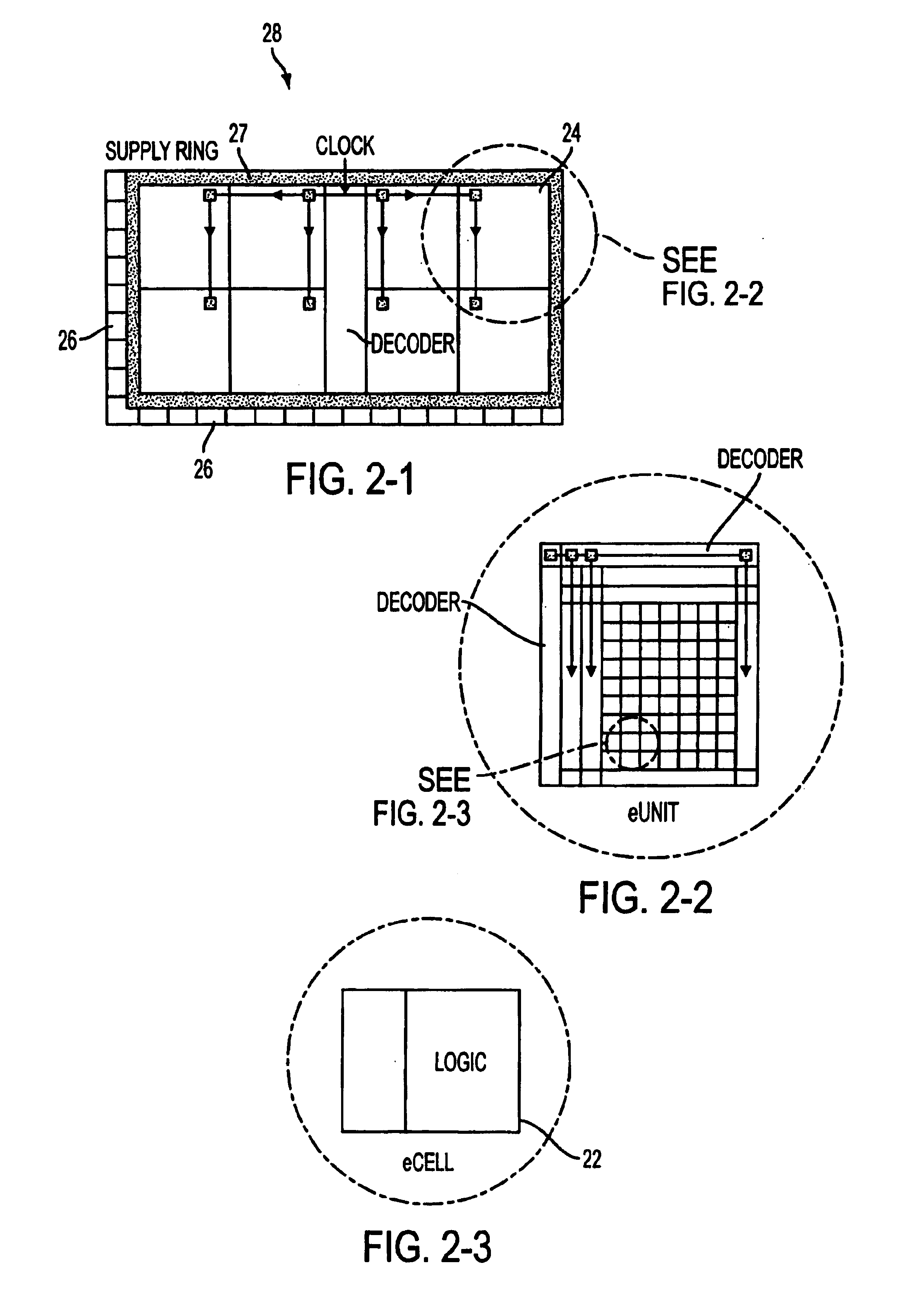

Semiconductor device having borderless logic array and flexible I/O

InactiveUS6953956B2Reduces high cost of manufacturingReduced flexibilitySemiconductor/solid-state device detailsSolid-state devicesRedistribution layerDevice material

Owner:INTEL CORP

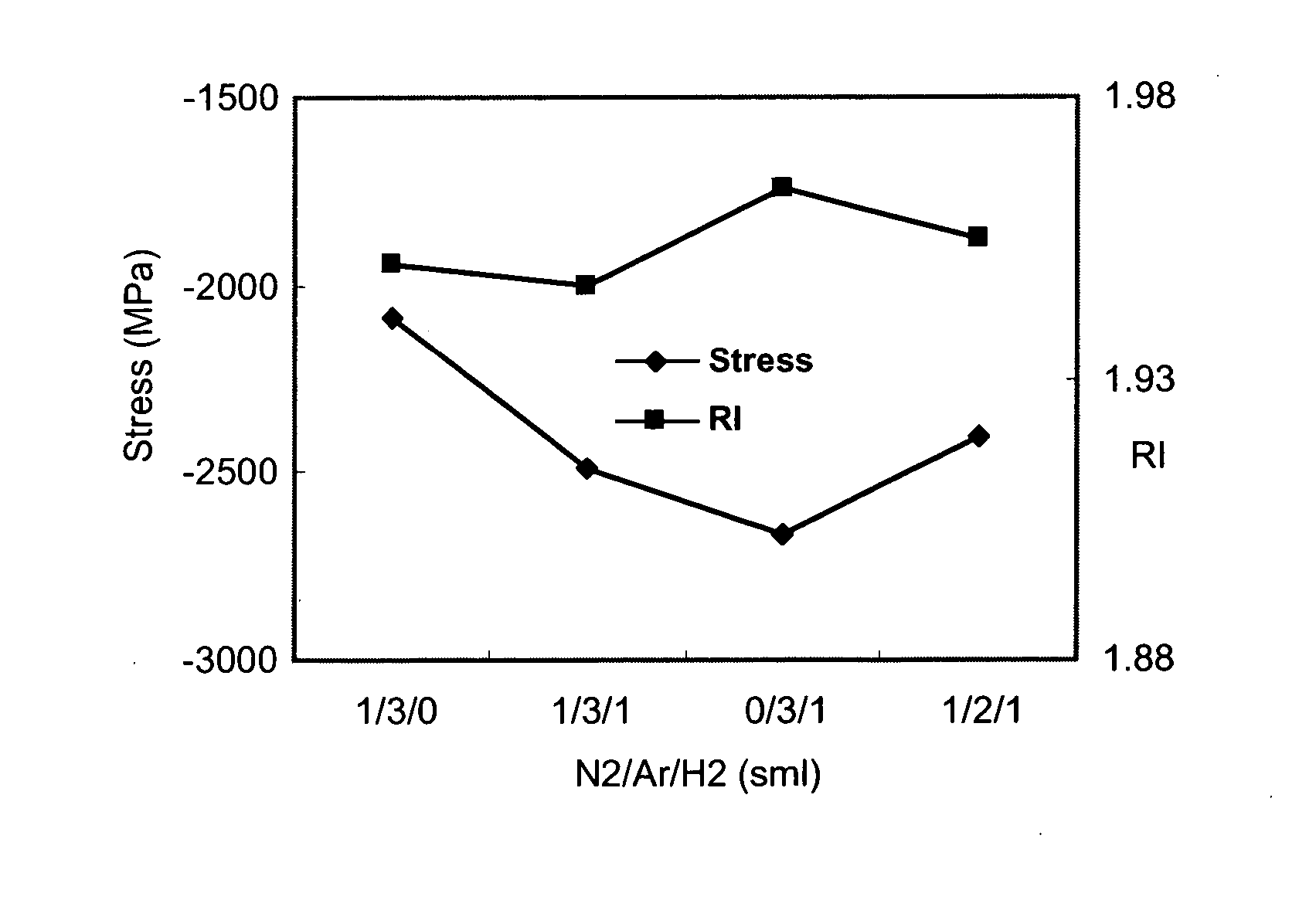

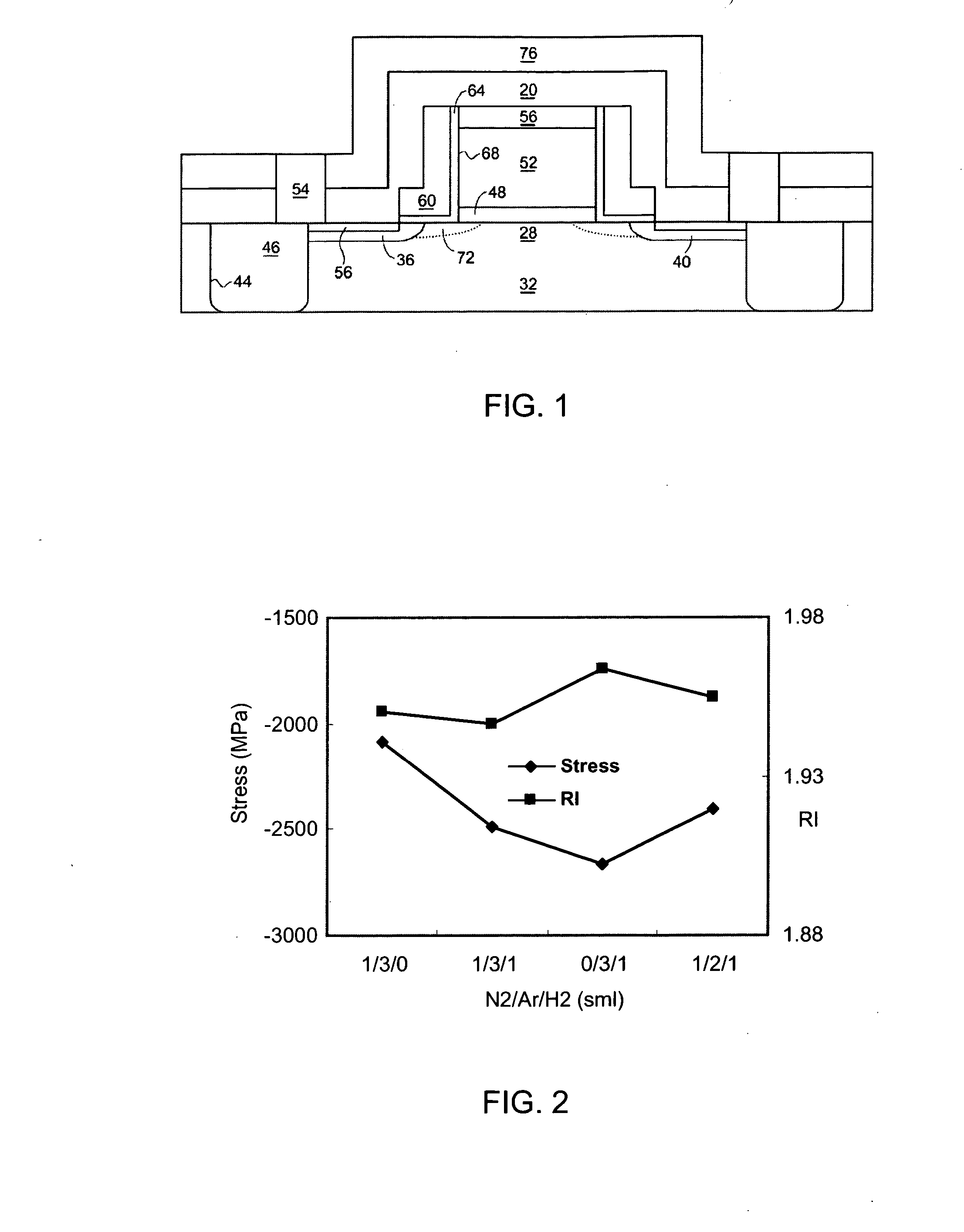

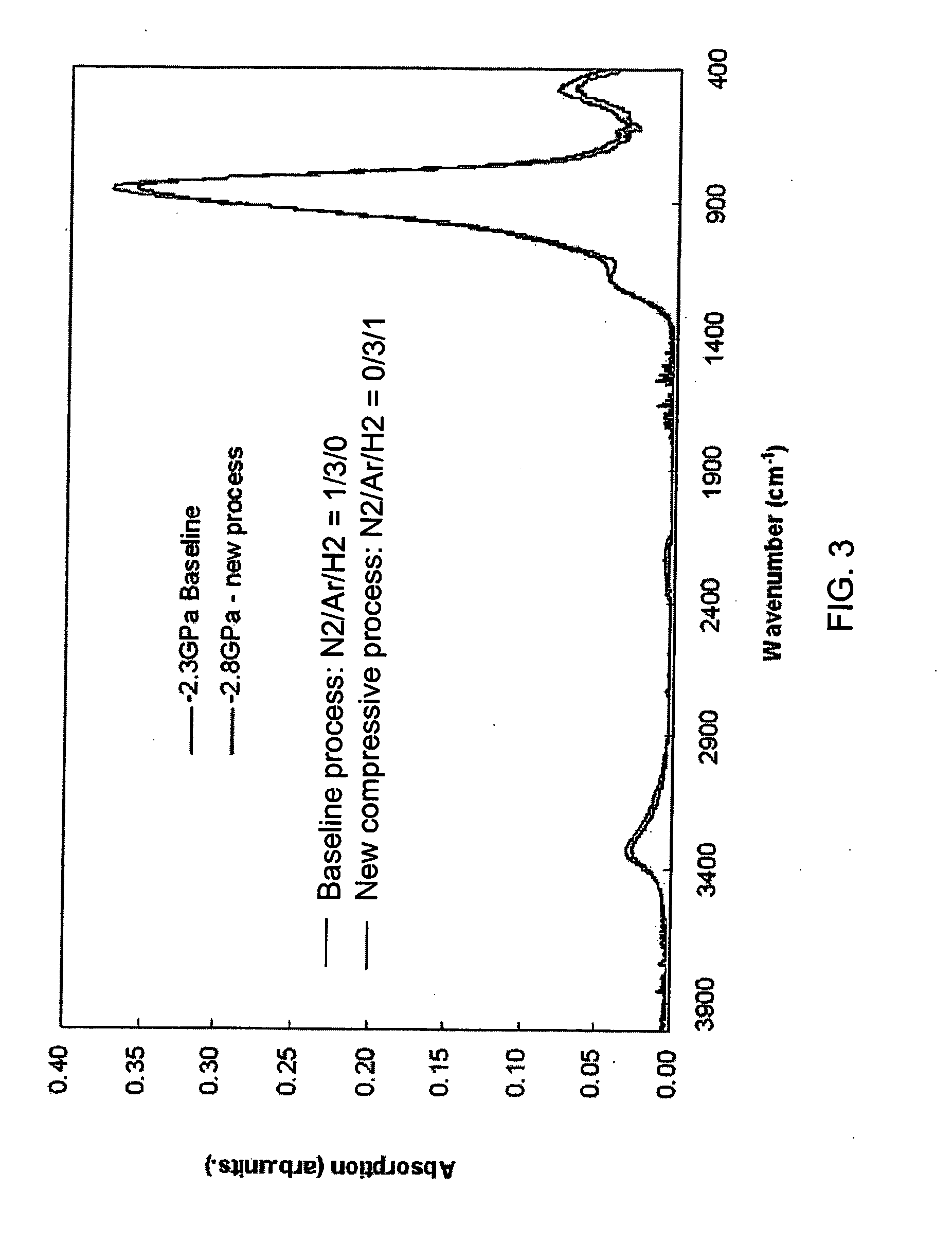

Method to increase the compressive stress of PECVD silicon nitride films

ActiveUS20060269692A1Increase silicon nitride compressive stressReduce defectsSemiconductor/solid-state device manufacturingElectrostatic cleaningHydrogenDevice material

Compressive stress in a film of a semiconductor device may be controlled utilizing one or more techniques, employed alone or in combination. A first set of embodiments increase silicon nitride compressive stress by adding hydrogen to the deposition chemistry, and reduce defects in a device fabricated with a high compressive stress silicon nitride film formed in the presence of hydrogen gas. A silicon nitride film may comprise an initiation layer formed in the absence of a hydrogen gas flow, underlying a high stress nitride layer formed in the presence of a hydrogen gas flow. A silicon nitride film formed in accordance with an embodiment of the present invention may exhibit a compressive stress of 2.8 GPa or higher.

Owner:APPLIED MATERIALS INC

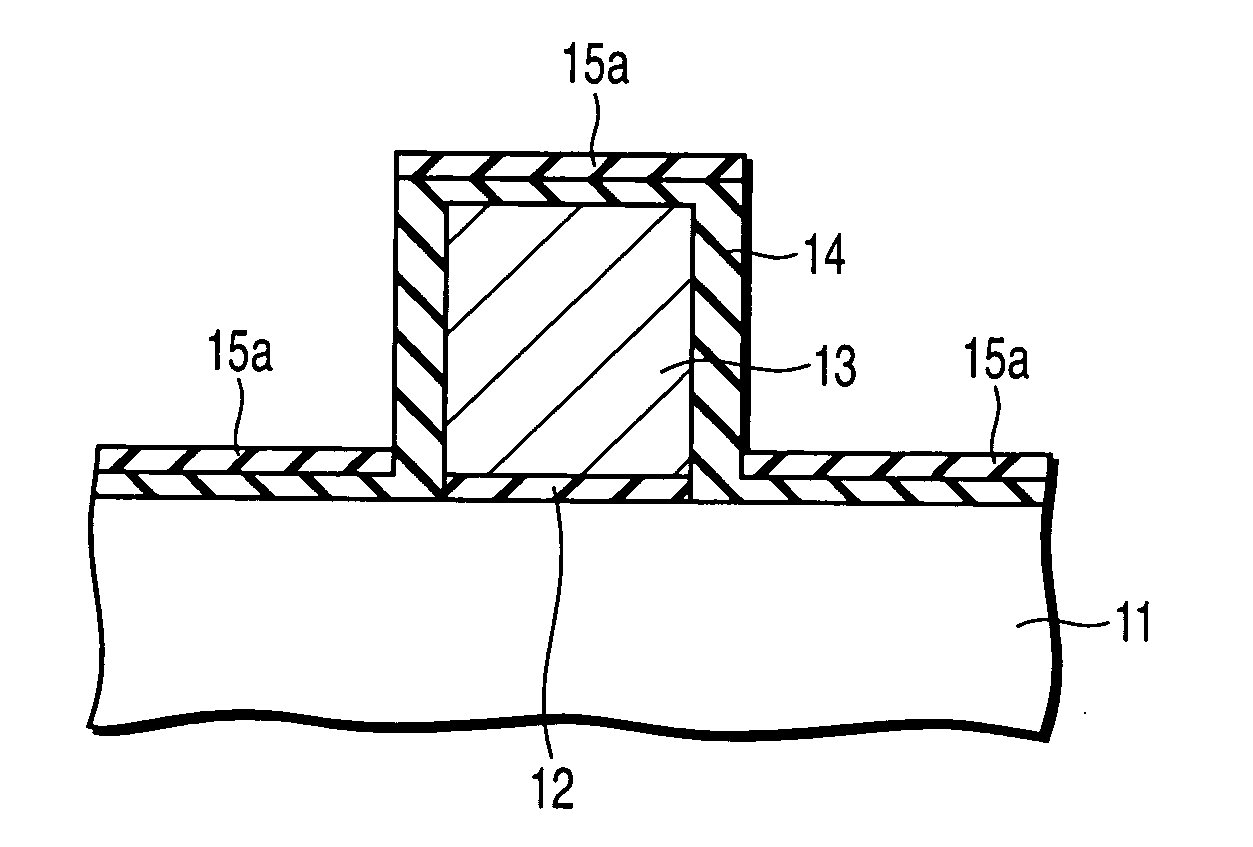

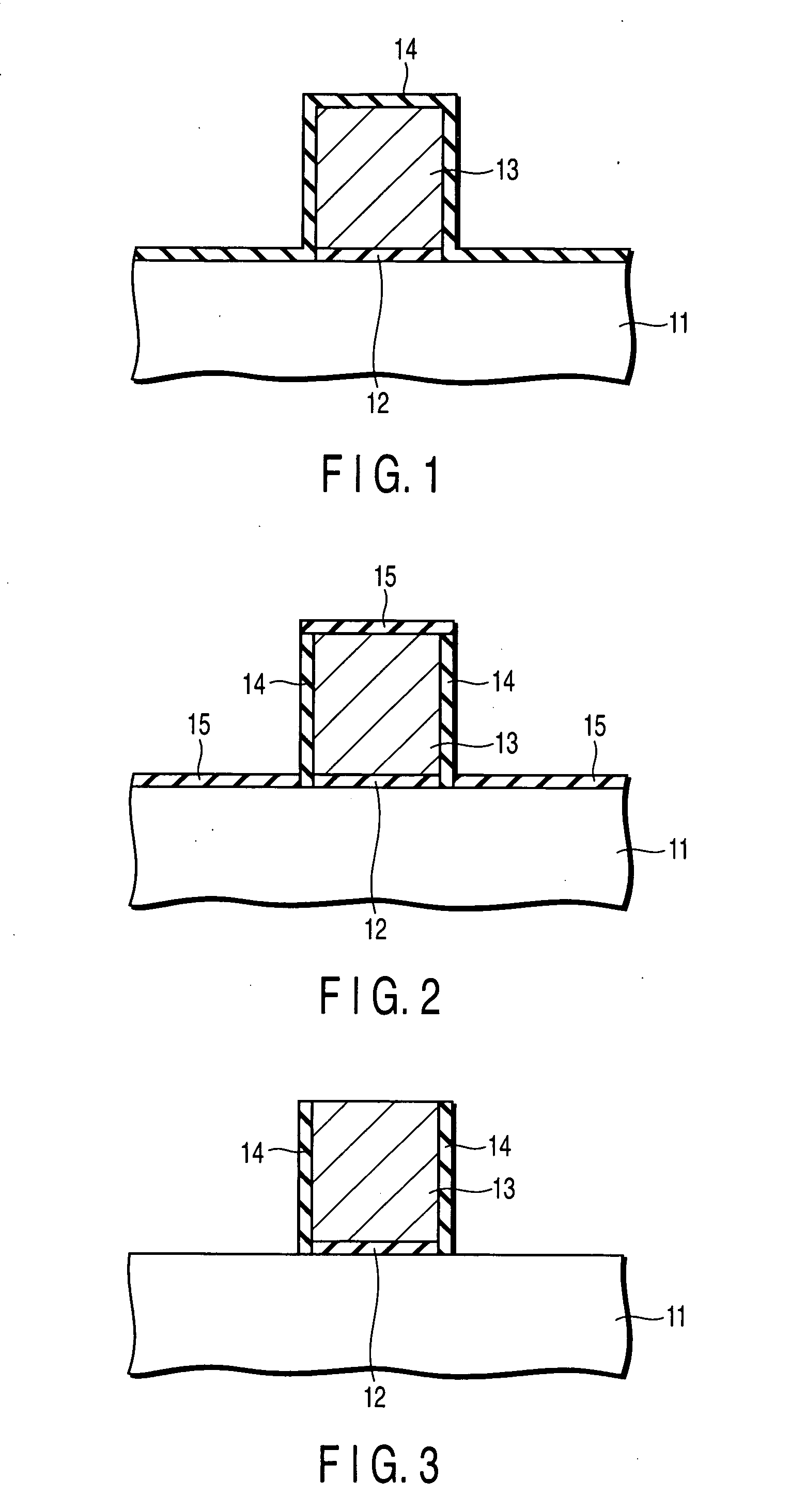

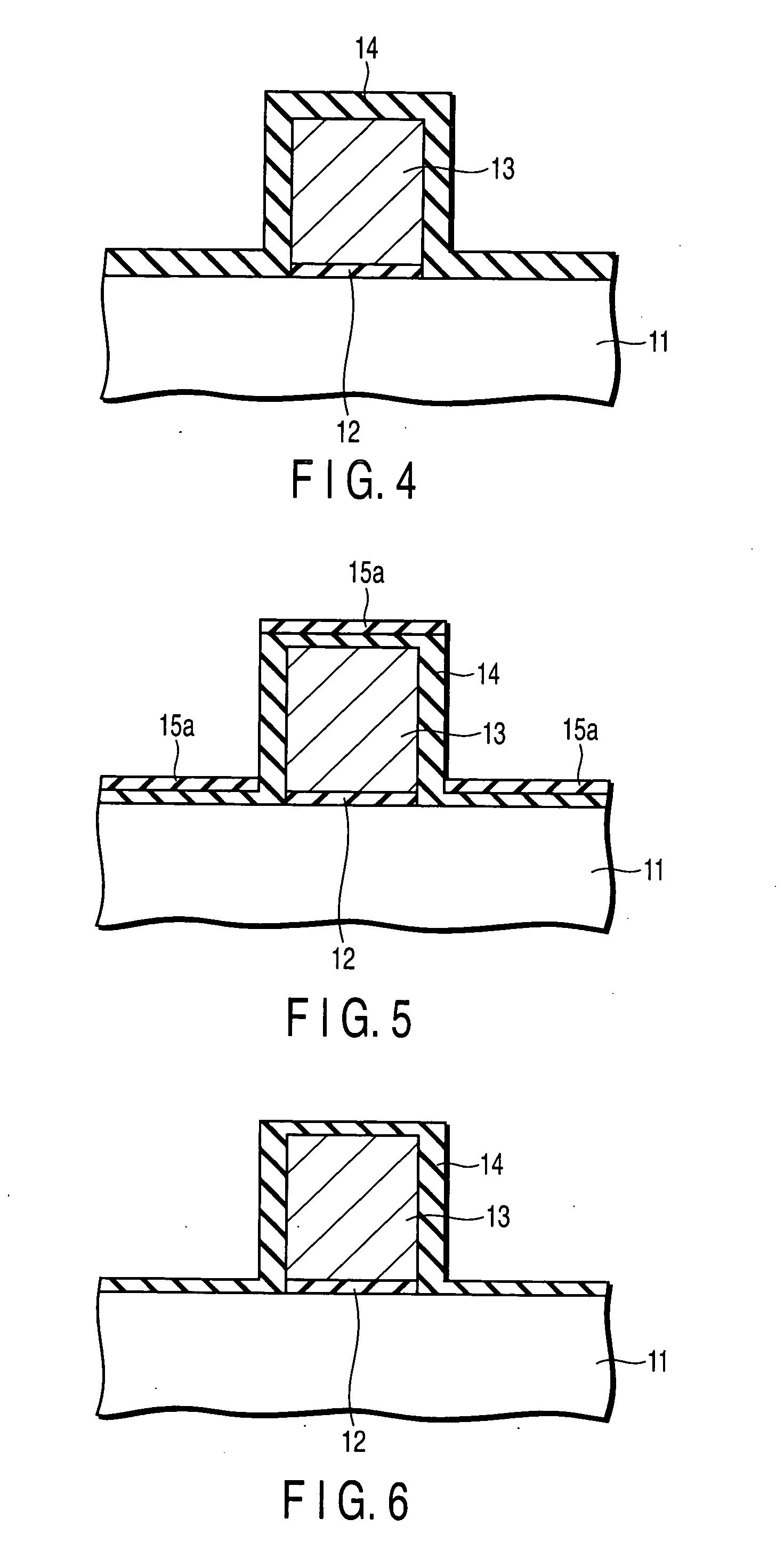

Method of manufacturing semiconductor device

InactiveUS20060057828A1Semiconductor/solid-state device manufacturingSemiconductor devicesDevice materialEngineering

A method of manufacturing a semiconductor device is disclosed which comprises forming a gate structure on a major surface of a semiconductor substrate with a gate insulating film interposed therebetween, forming a first insulating film to cover top and side surfaces of the gate structure and the major surface of the semiconductor substrate, reforming portions of the first insulating film which cover the top surface of the gate structure and the major surface of the semiconductor substrate by an anisotropic plasma process using a gas not containing fluorine, and removing the reformed portions of the first insulating film.

Owner:KK TOSHIBA

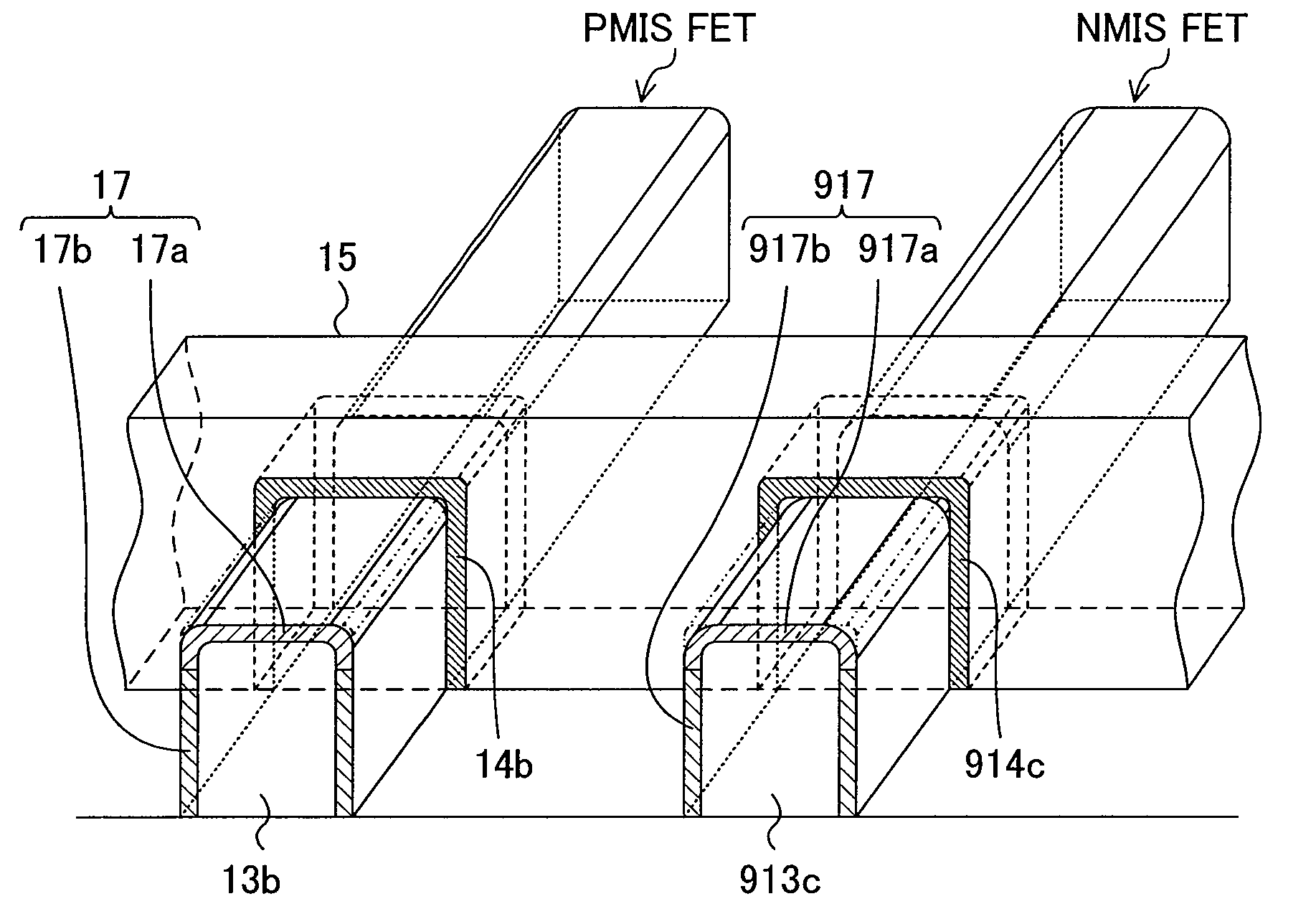

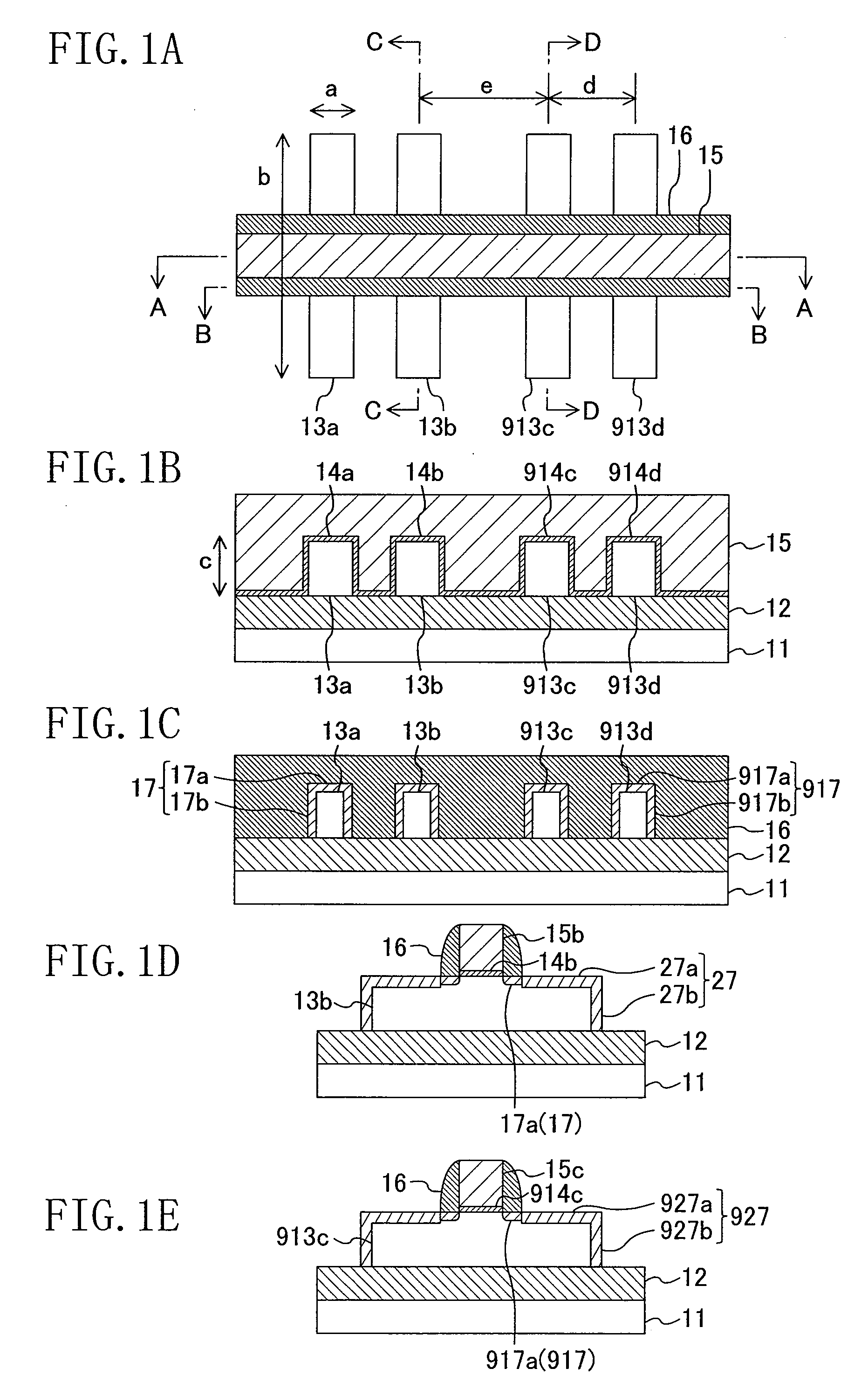

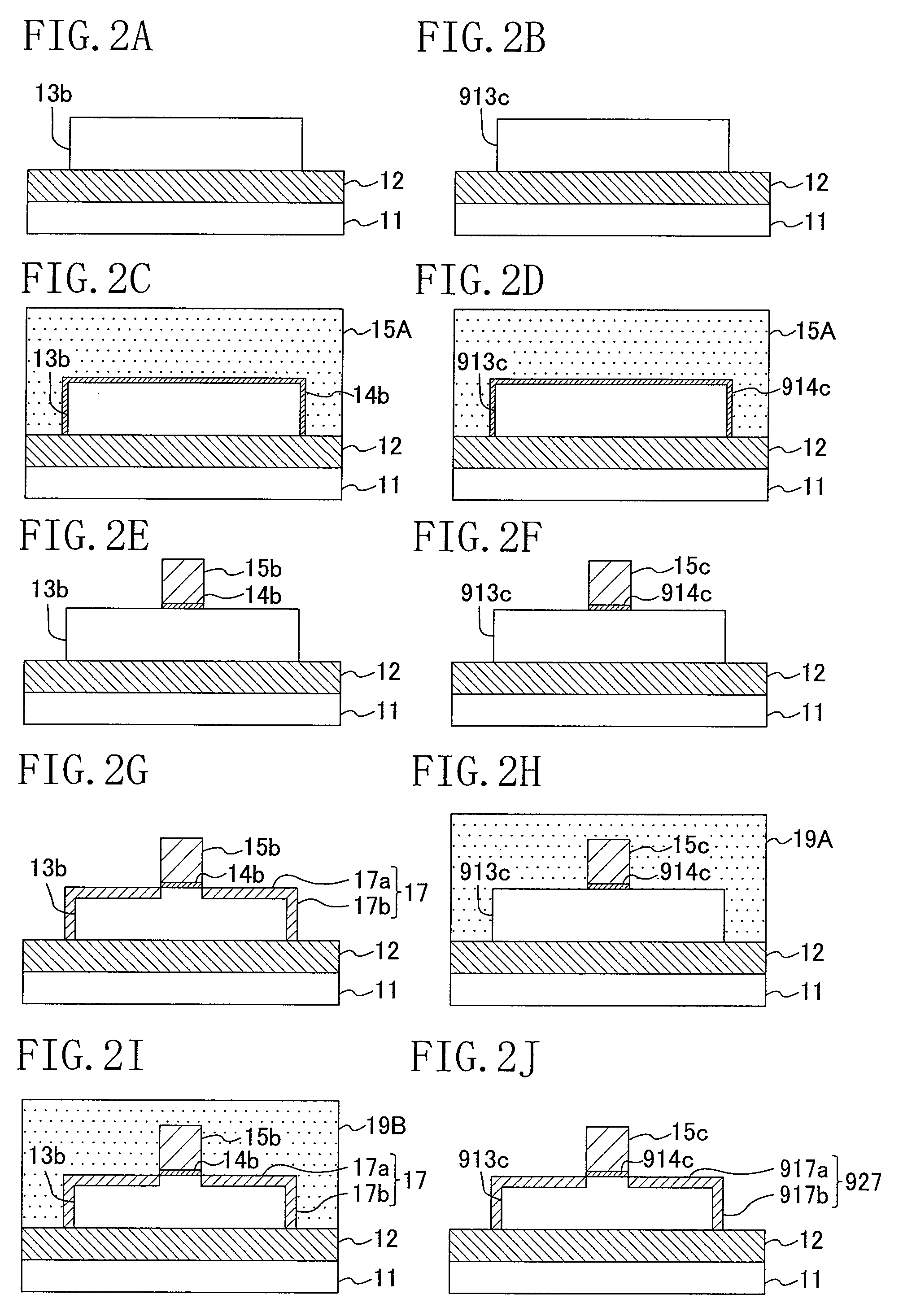

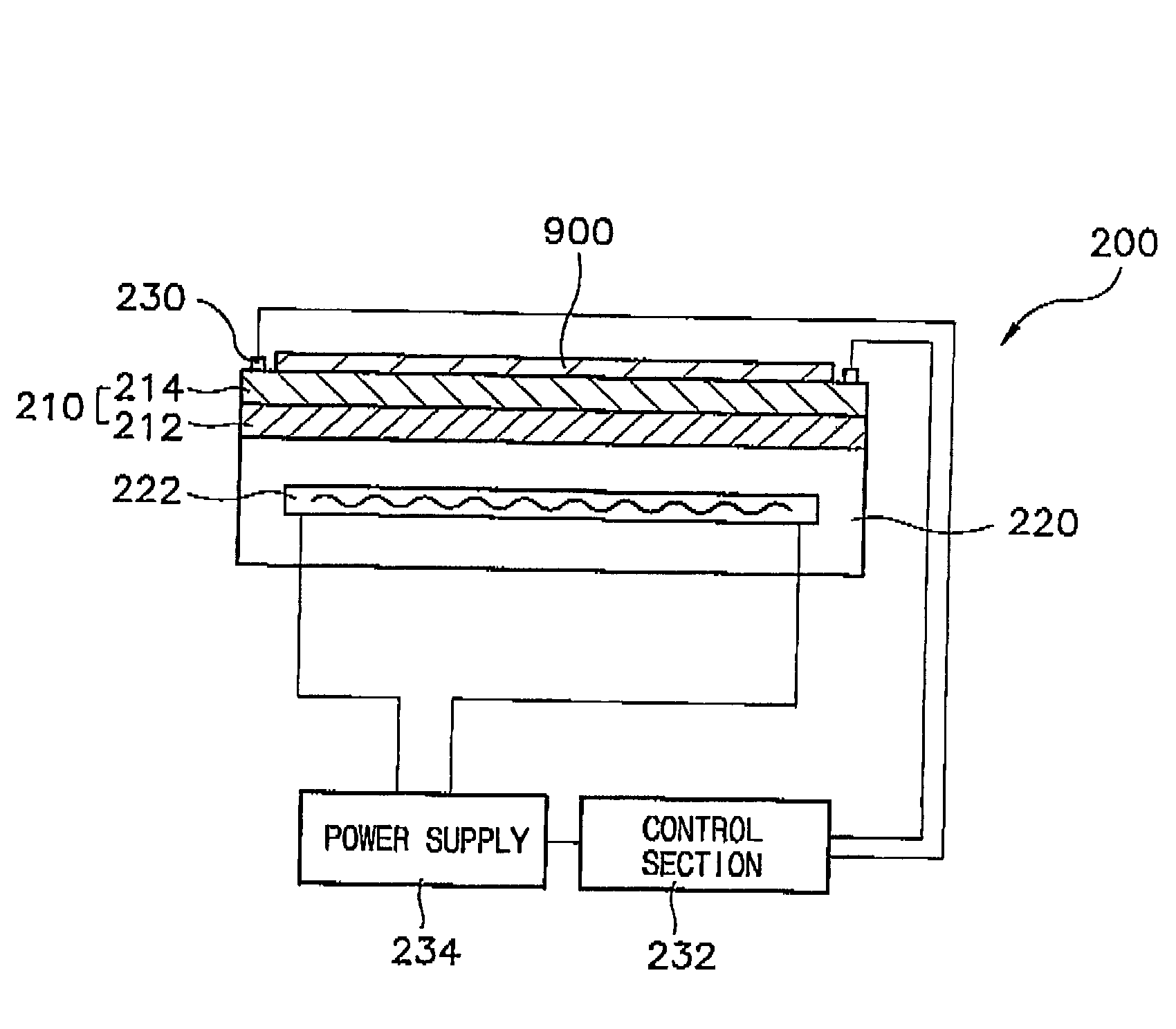

Semiconductor device and method for producing the same

ActiveUS20090289300A1Low ion densityReduce pressureTransistorSolid-state devicesEngineeringSemiconductor

First and second gate insulating films are formed so as to cover at least the upper corner of first and second fin-shaped semiconductor regions. The radius of curvature r1′ of the upper corner of the first fin-shaped semiconductor region located outside the first gate insulating film is greater than the radius of curvature r1 of the upper corner of the first fin-shaped semiconductor region located under the first gate insulating film and is less than or equal to 2×r1. The radius of curvature r2′ of the upper corner of the second fin-shaped semiconductor region located outside the second gate insulating film is greater than the radius of curvature r2 of the upper corner of the second fin-shaped semiconductor region located under the second gate insulating film and is less than or equal to 2×r2.

Owner:GK BRIDGE 1

Apparatus for processing a substrate including a heating apparatus

InactiveUS20030066826A1Drying solid materials with heatMuffle furnacesProduction rateDevice material

An apparatus for heating a substrate of a semiconductor device includes a hot plate, on which a semiconductor substrate is placed, and a heater for heating the hot plate. The hot plate is preferably a composite plate including a plurality of plates having different thermal conductivities from each other. For example, a first plate adjacent to the heater can be made of aluminum, which has a relatively high thermal conductivity. A second plate, laminated on top of the first plate, can be made of titanium or stainless steel, which both have a thermal conductivity lower than aluminum. A composite hot plate as disclosed herein is better able to maintain a constant temperature and a uniform temperature distribution in order to more uniformly heat a substrate and to reduce an amount of energy required for the heating process. In addition, the reliability and productivity of the semiconductor device manufactured by the apparatus can be improved.

Owner:SAMSUNG ELECTRONICS CO LTD

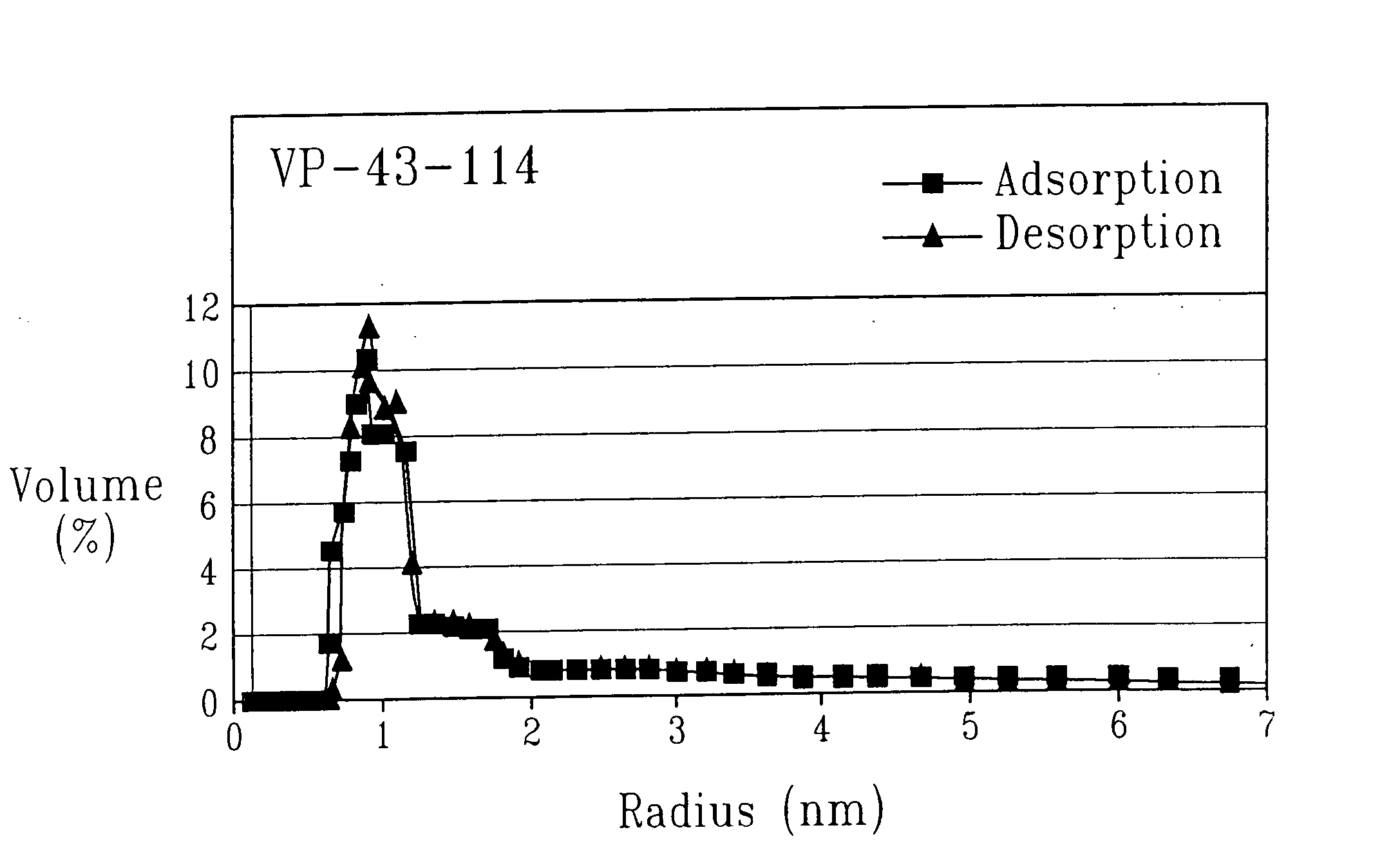

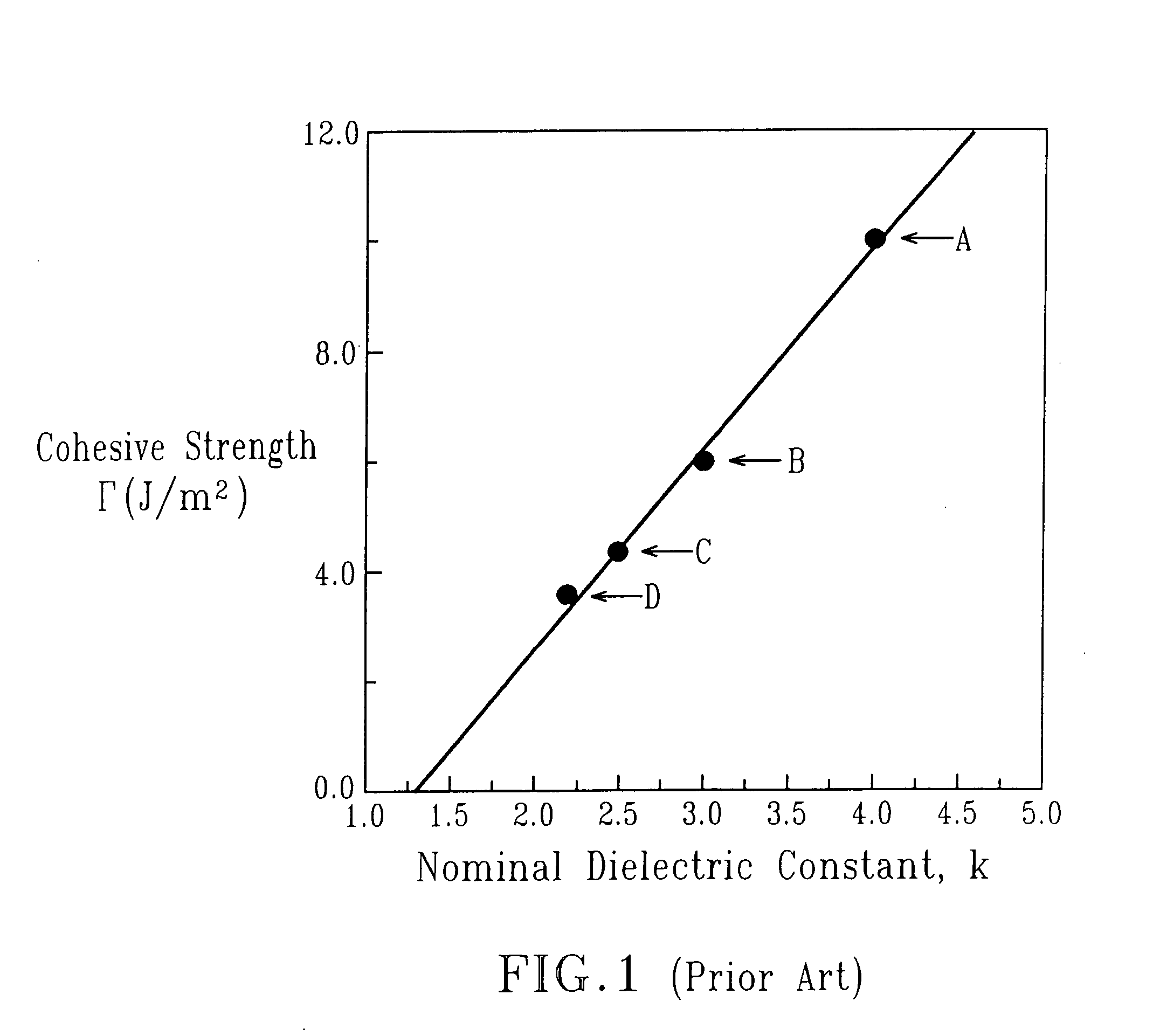

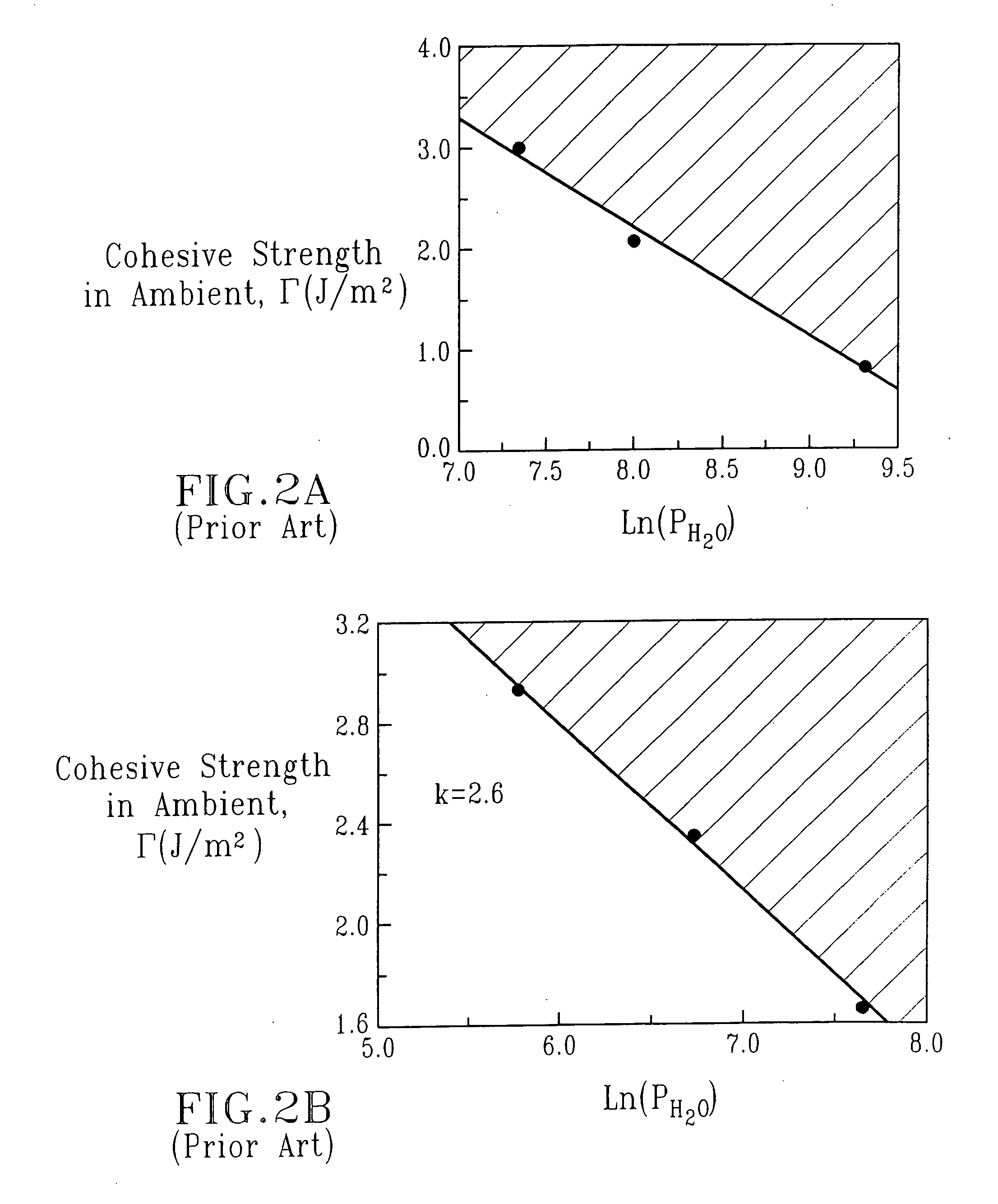

SiCOH dielectric

InactiveUS20070173071A1Improve cohesive strengthReduce brittlenessSemiconductor/solid-state device detailsSolid-state devicesDielectricDevice material

A porous composite material useful in semiconductor device manufacturing, in which the diameter (or characteristic dimension) of the pores and the pore size distribution (PSD) is controlled in a nanoscale manner and which exhibits improved cohesive strength (or equivalently, improved fracture toughness or reduced brittleness), and increased resistance to water degradation of properties such as stress-corrosion cracking, Cu ingress, and other critical properties is provided. The porous composite material is fabricating utilizing at least one bifunctional organic porogen as a precursor compound

Owner:INTEL CORP

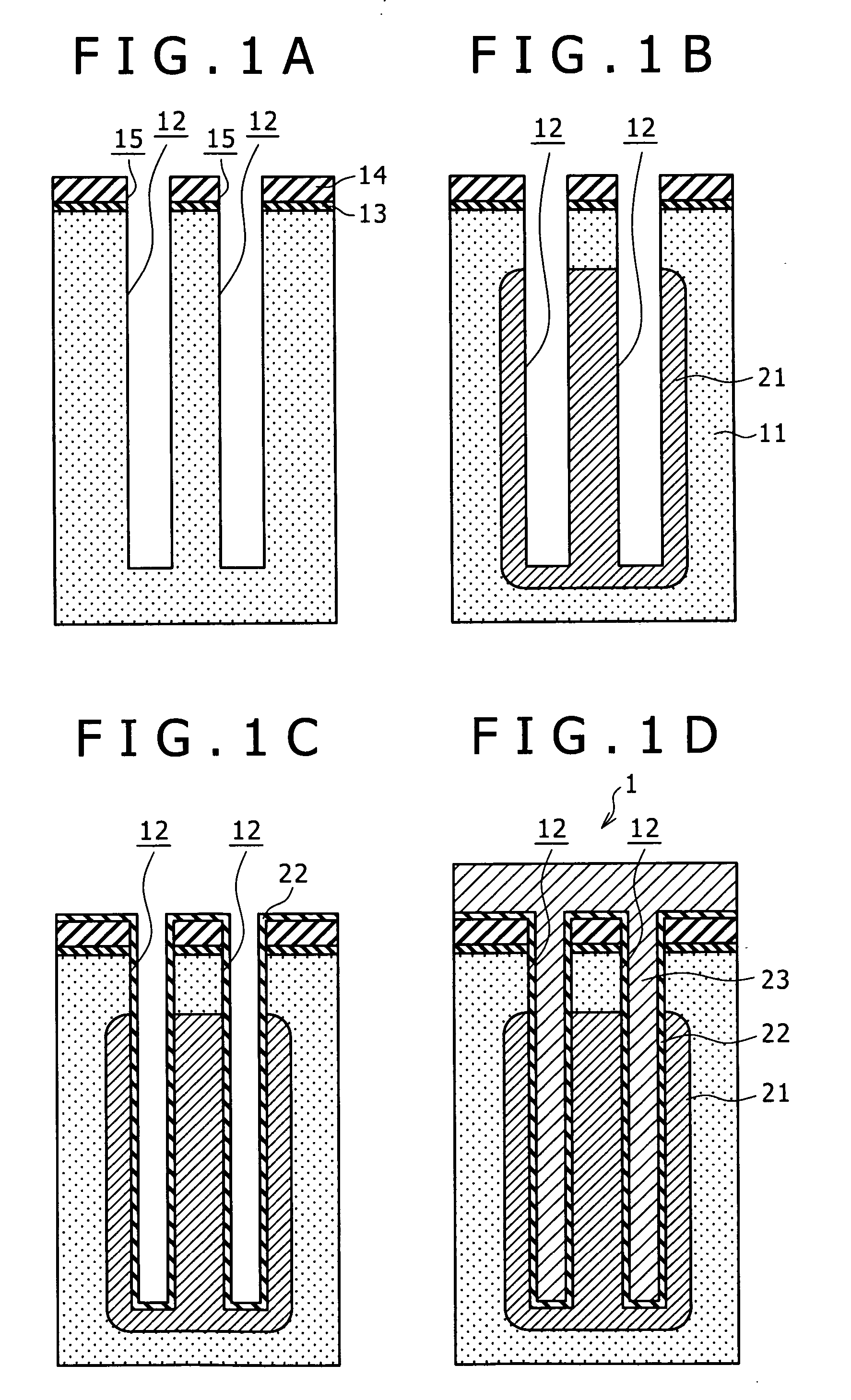

Method of manufacturing semiconductor device

InactiveUS20070066010A1Good step coverageReduce leakage levelTransistorSolid-state devicesDevice materialEvaporation

The invention aims at enabling leakage current characteristics and a step coverage property to be improved by depositing a hafnium silicate film by utilizing an atomic layer evaporation method using a hafnium raw material, a silicon raw material and an oxidizing agent. Disclosed herein is a method of manufacturing a semiconductor device having a trench capacitor including a first electrode formed on an inner surface of a trench, a capacitor insulating film formed on a surface of the first electrode, and a second electrode formed on a surface of the capacitor insulating film. The method includes the step of depositing the capacitor insulating film in a form of a hafnium silicate film by utilizing an atomic layer deposition method using a hafnium raw material, a silicon raw material and an oxidizing agent.

Owner:SONY CORP