Patents

Literature

7928 results about "Gate dielectric" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A gate dielectric is a dielectric used between the gate and substrate of a field-effect transistor. The capacitance and thickness constraints are almost directly opposed to each other. For silicon-substrate FETs, the gate dielectric is almost always silicon dioxide (called "gate oxide"), since thermal oxide has a very clean interface. However, the semiconductor industry is interested in finding alternative materials with higher dielectric constants, which would allow higher capacitance with the same thickness.

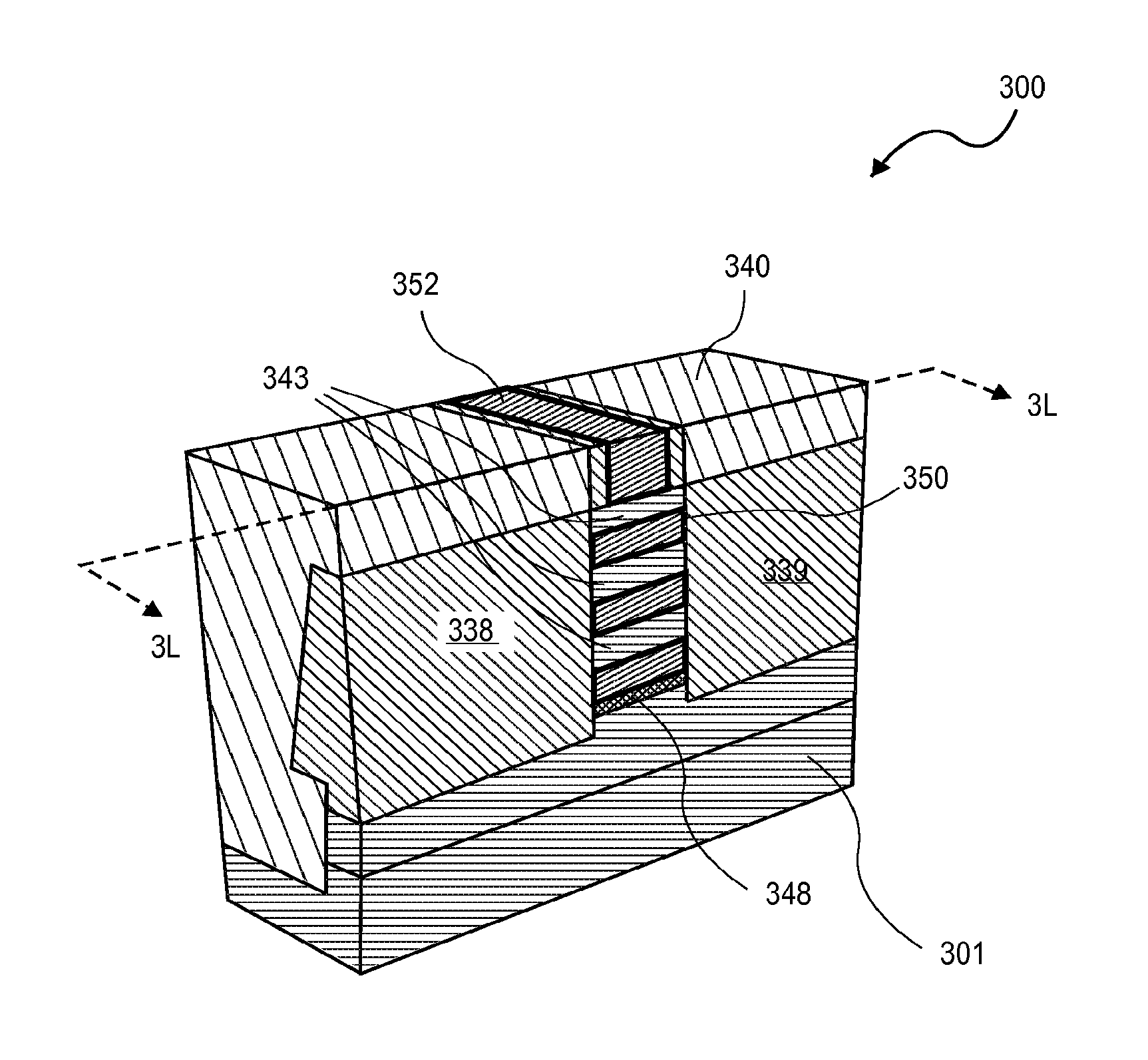

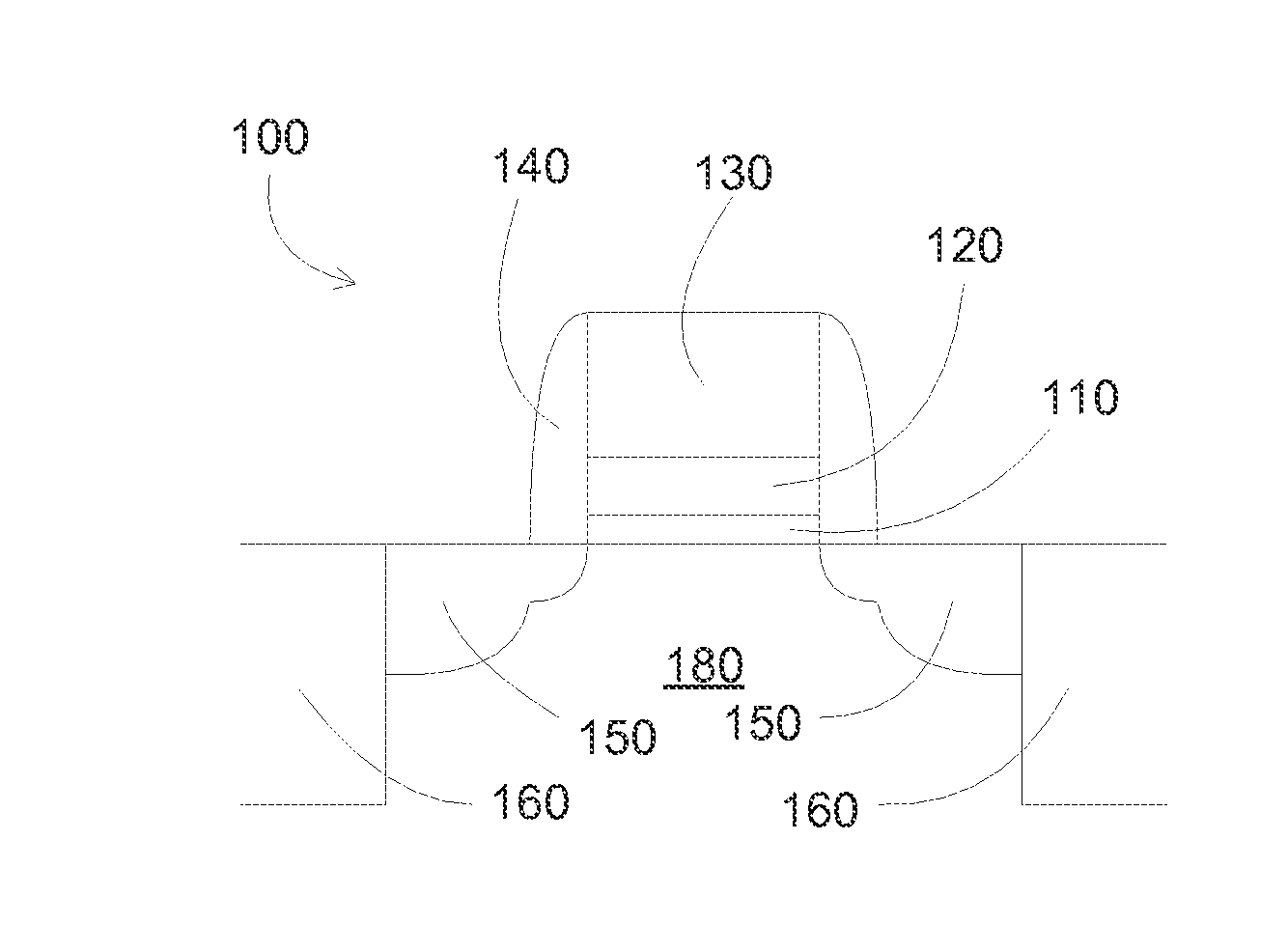

Non-planar gate all-around device and method of fabrication thereof

ActiveUS20140225065A1NanoinformaticsSemiconductor/solid-state device manufacturingNanowireGate dielectric

A non-planar gate all-around device and method of fabrication thereby are described. In one embodiment, the device includes a substrate having a top surface with a first lattice constant. Embedded epi source and drain regions are formed on the top surface of the substrate. The embedded epi source and drain regions have a second lattice constant that is different from the first lattice constant. Channel nanowires having a third lattice are formed between and are coupled to the embedded epi source and drain regions. In an embodiment, the second lattice constant and the third lattice constant are different from the first lattice constant. The channel nanowires include a bottom-most channel nanowire and a bottom gate isolation is formed on the top surface of the substrate under the bottom-most channel nanowire. A gate dielectric layer is formed on and all-around each channel nanowire. A gate electrode is formed on the gate dielectric layer and surrounding each channel nanowire.

Owner:SONY CORP

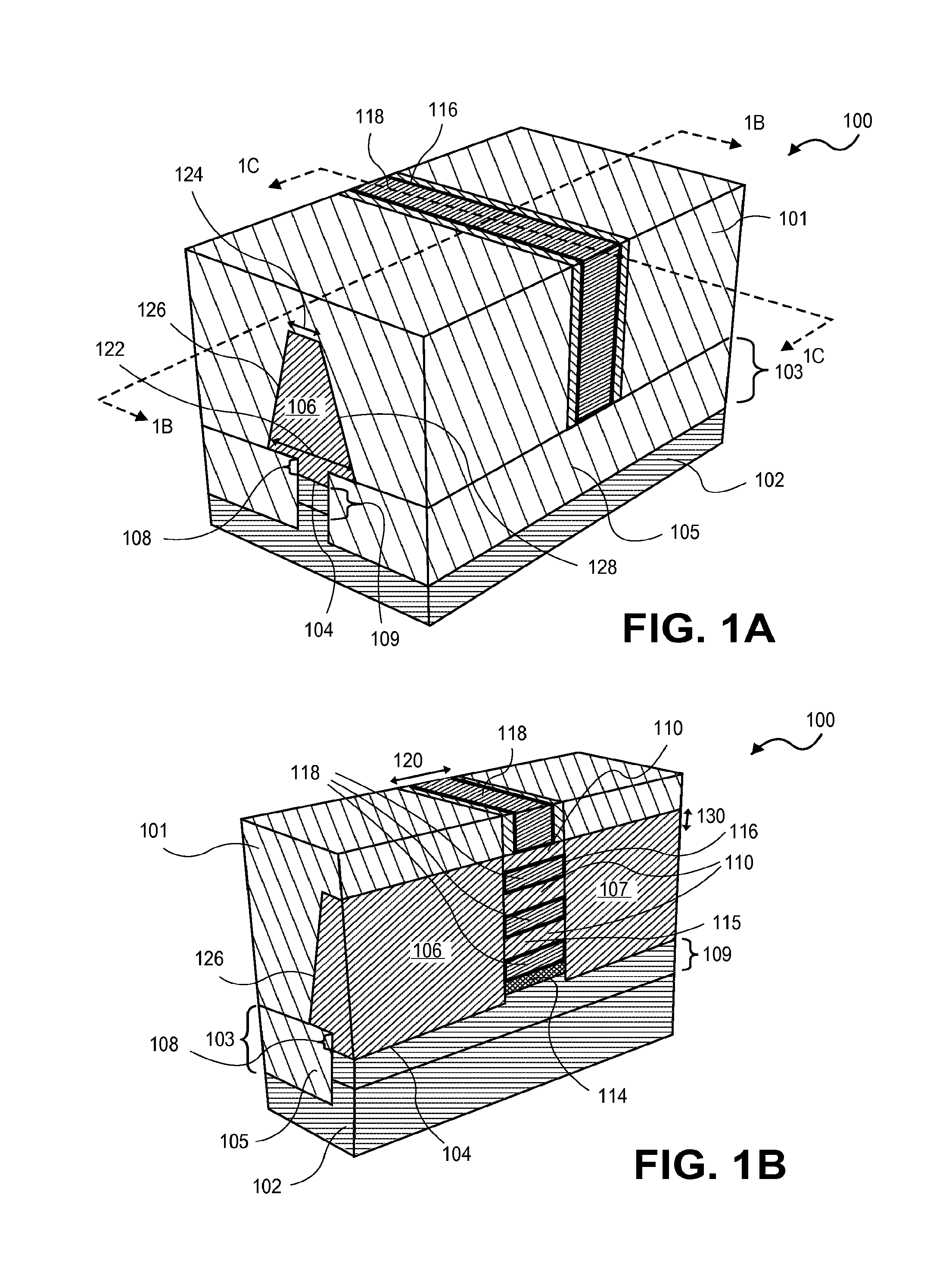

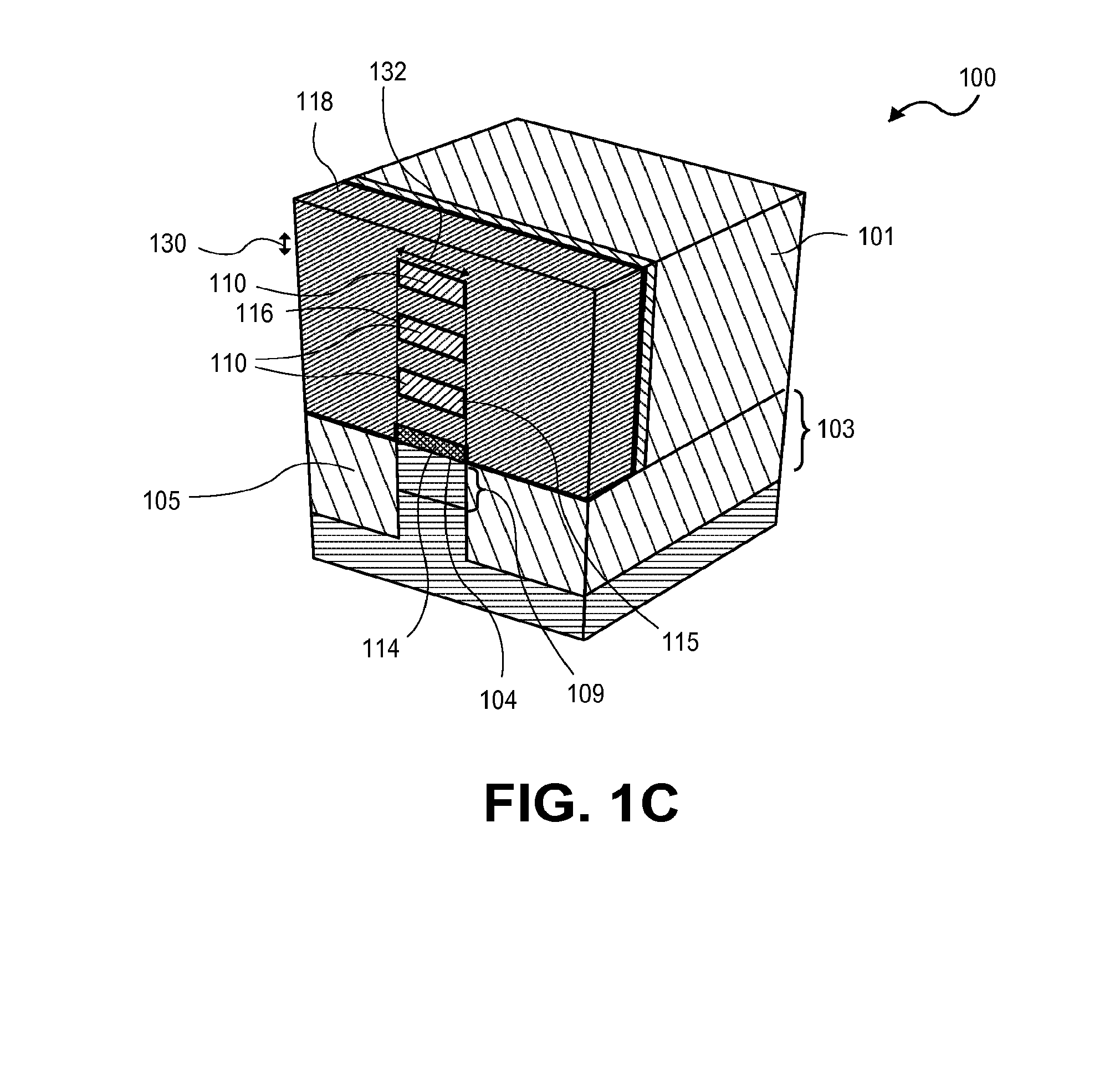

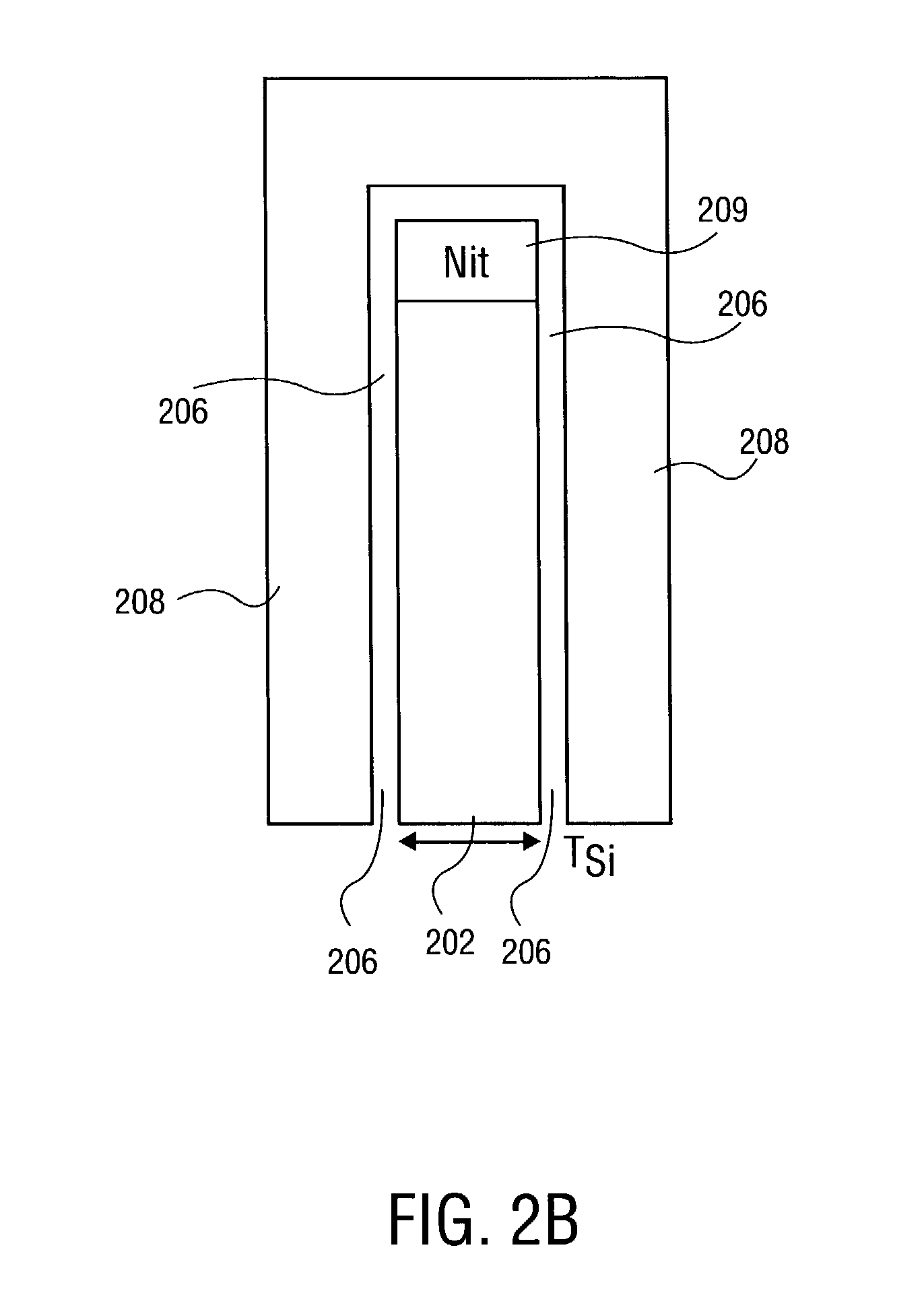

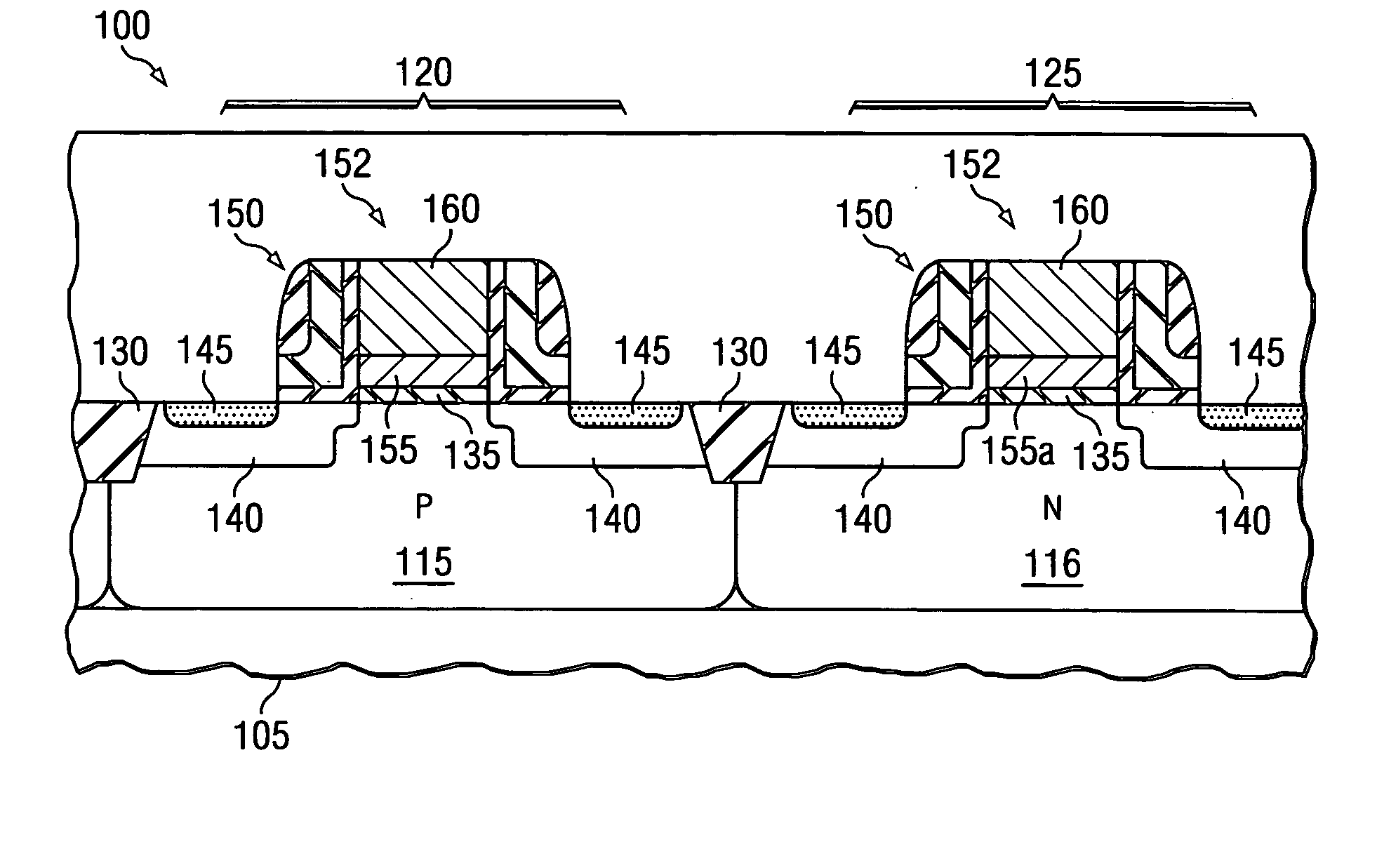

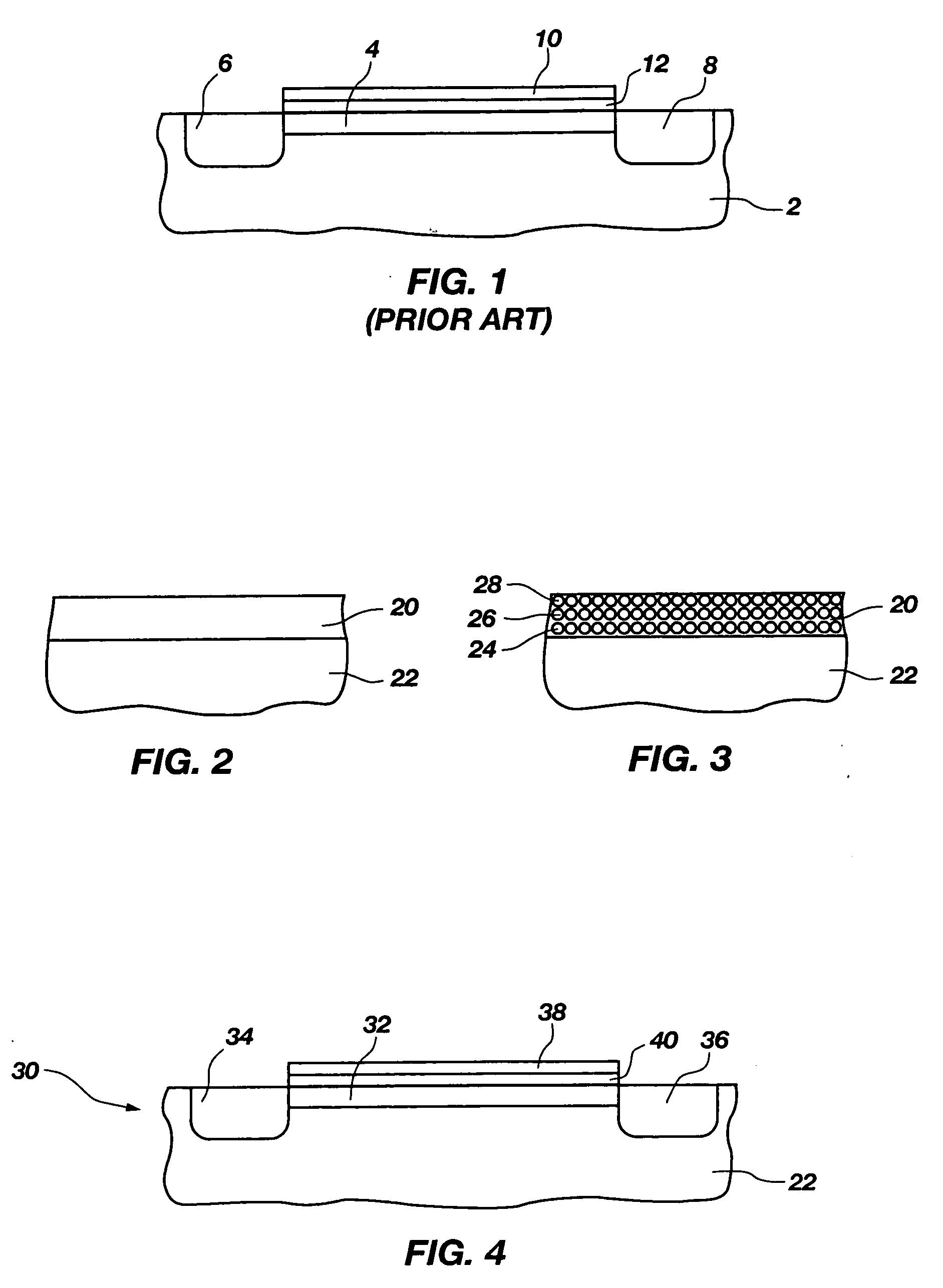

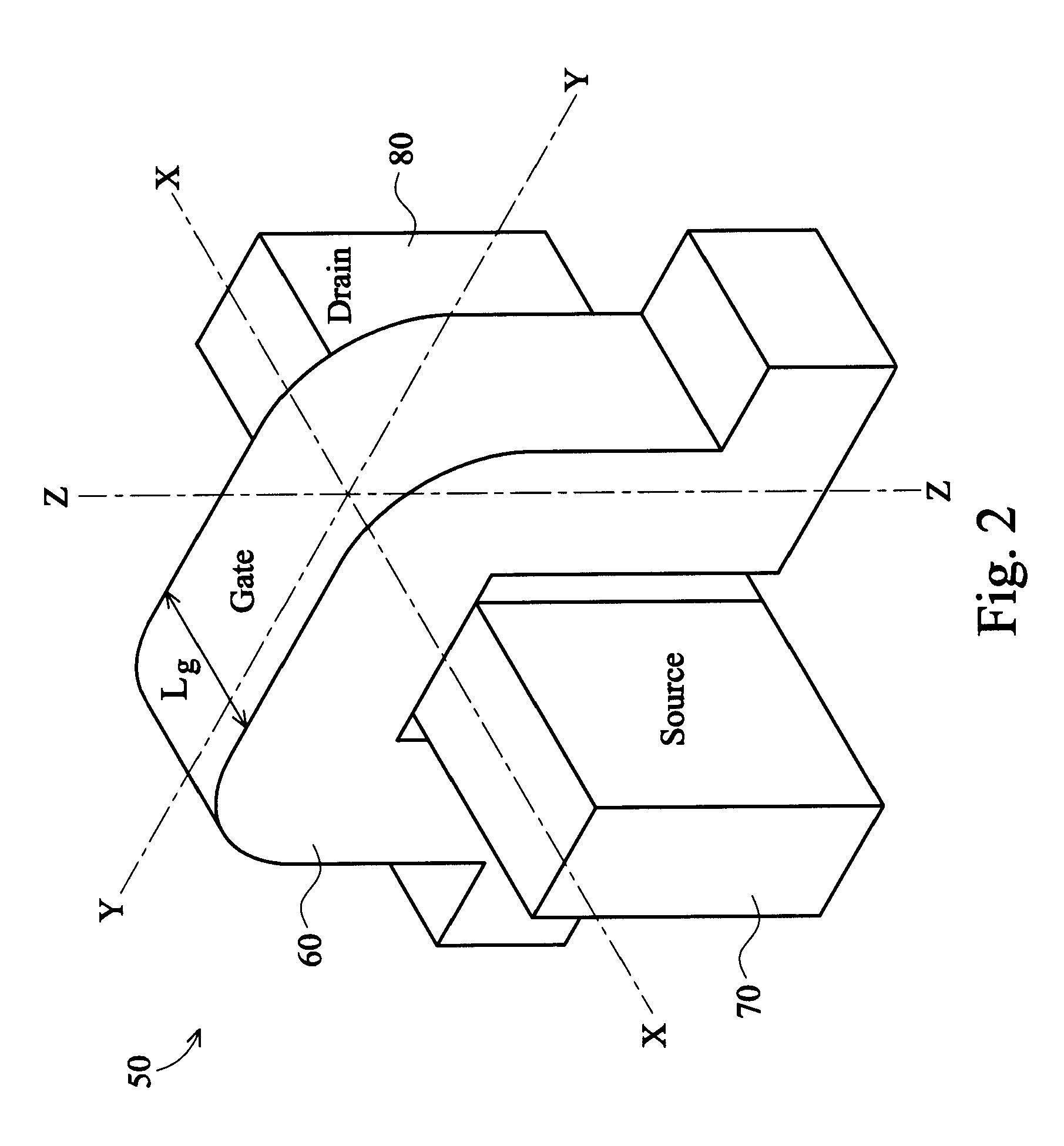

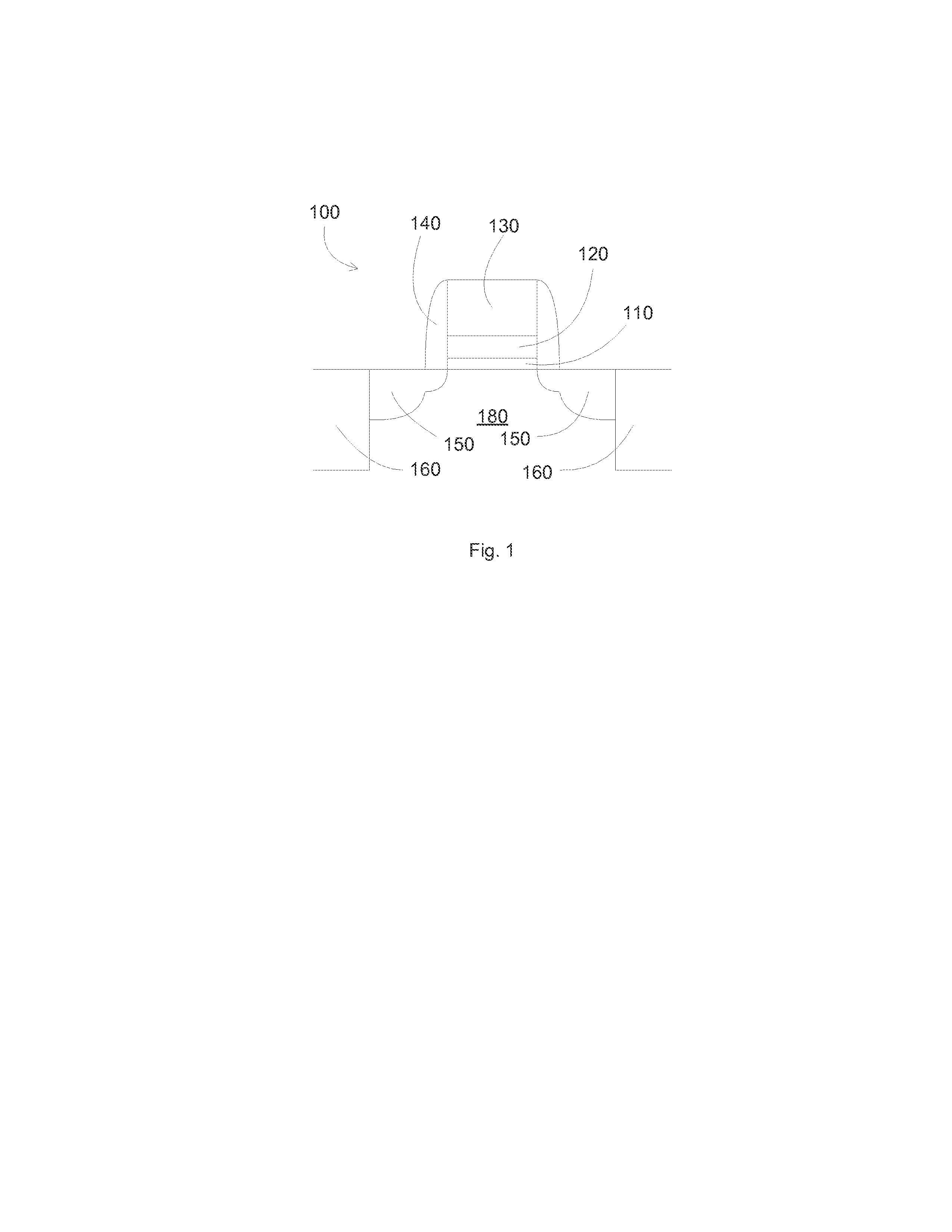

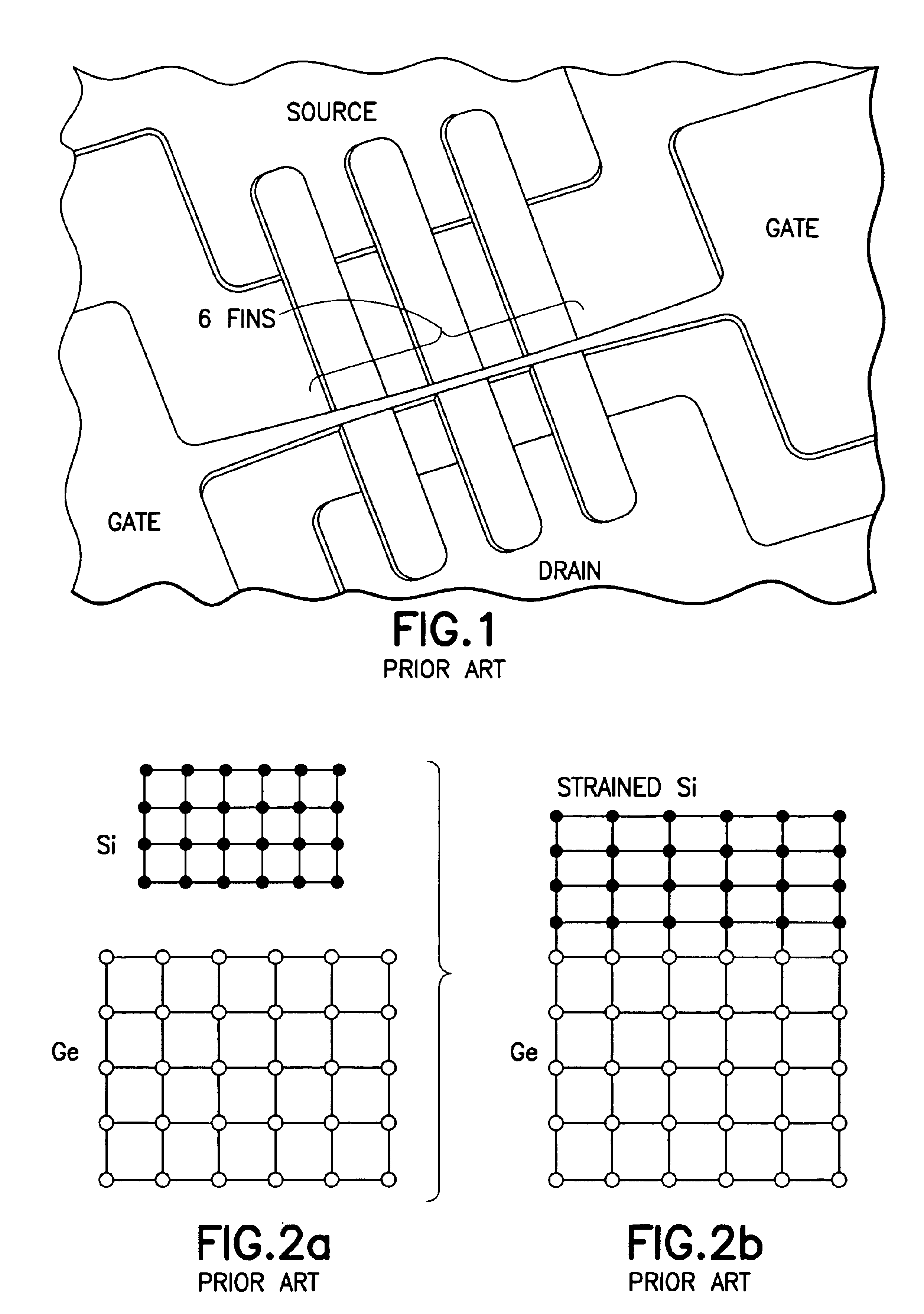

Tri-gate devices and methods of fabrication

The present invention is a semiconductor device comprising a semiconductor body having a top surface and laterally opposite sidewalls formed on a substrate. A gate dielectric layer is formed on the top surface of the semiconductor body and on the laterally opposite sidewalls of the semiconductor body. A gate electrode is formed on the gate dielectric on the top surface of the semiconductor body and adjacent to the gate dielectric on the laterally opposite sidewalls of the semiconductor body.

Owner:INTEL CORP

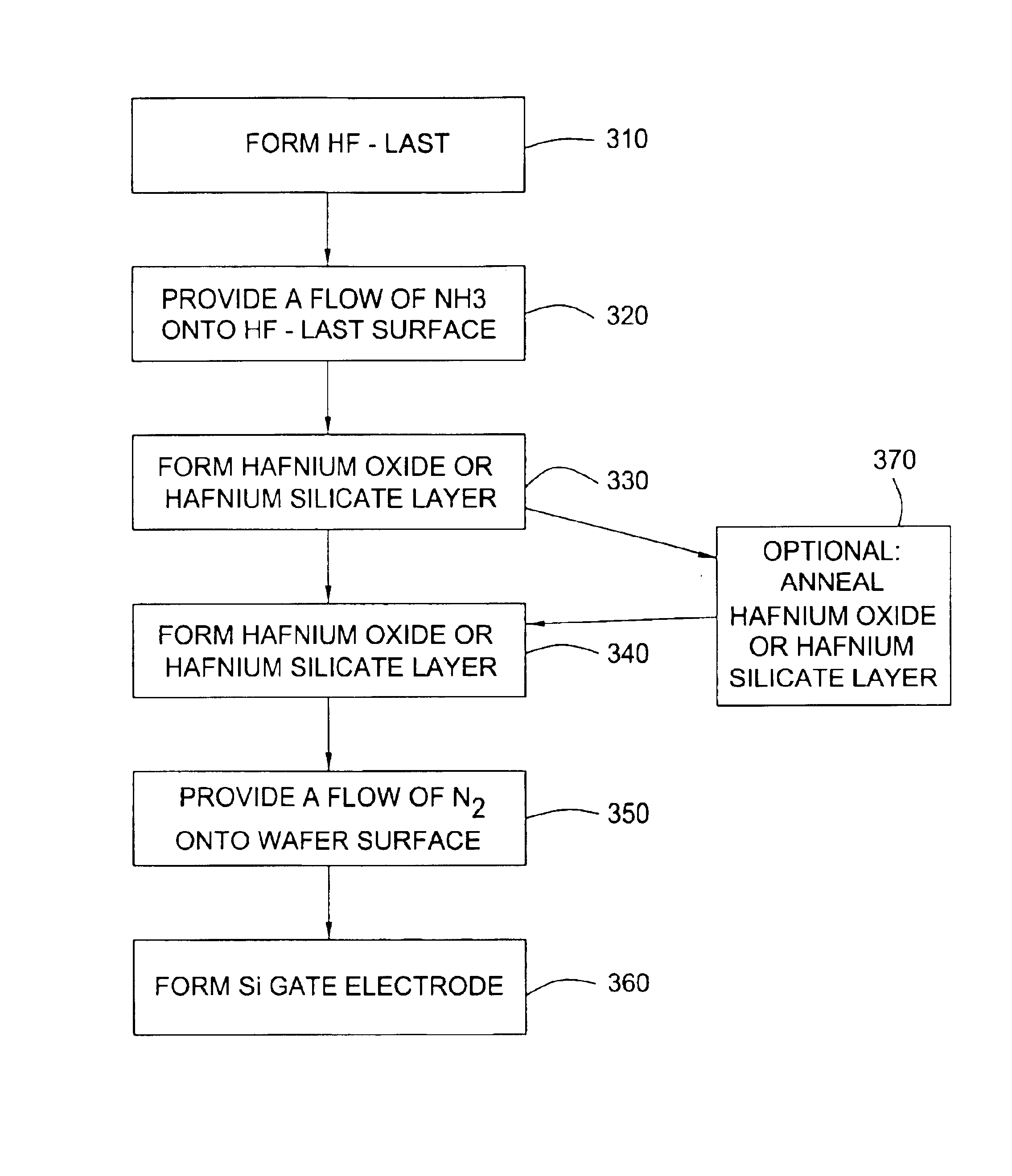

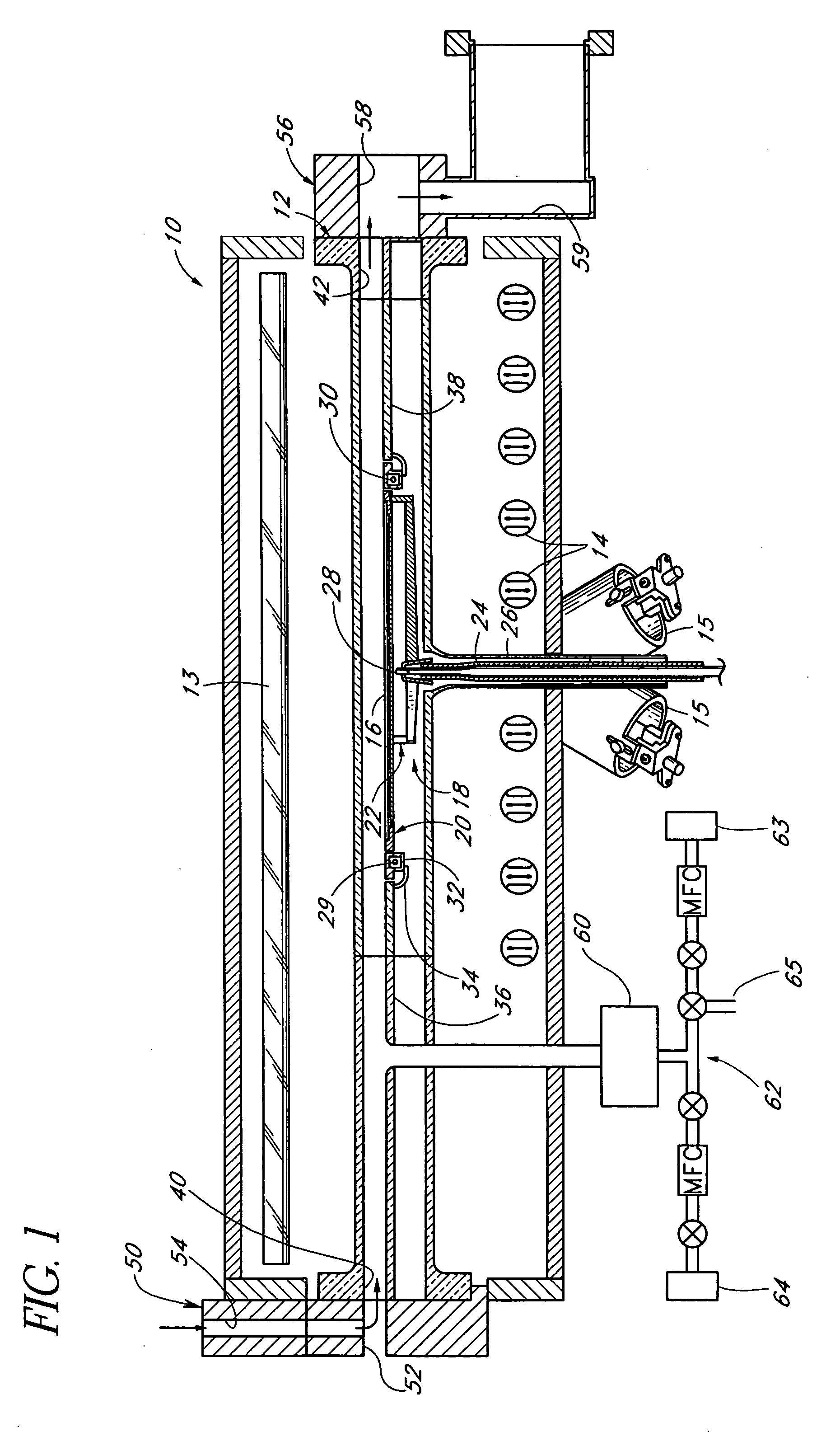

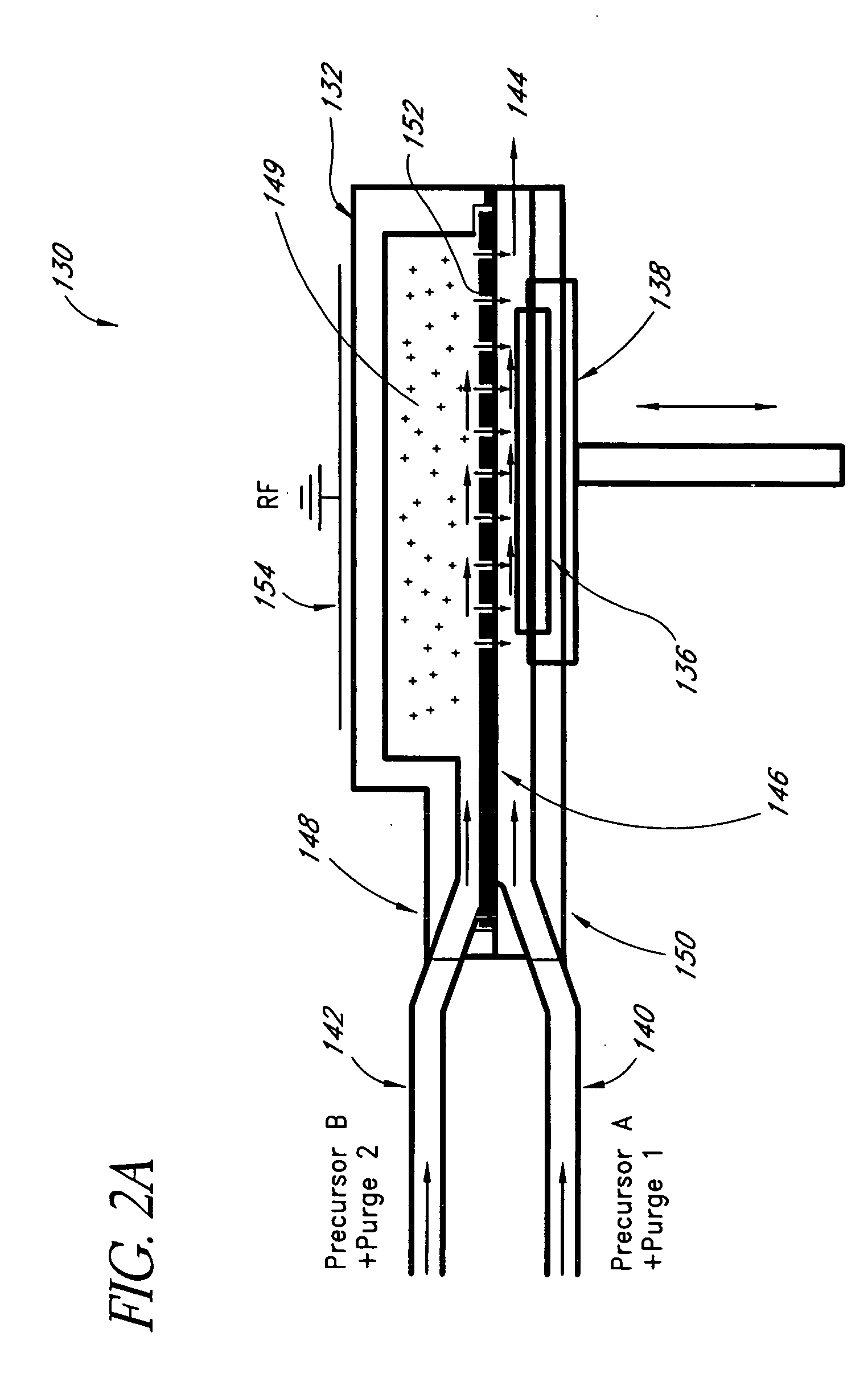

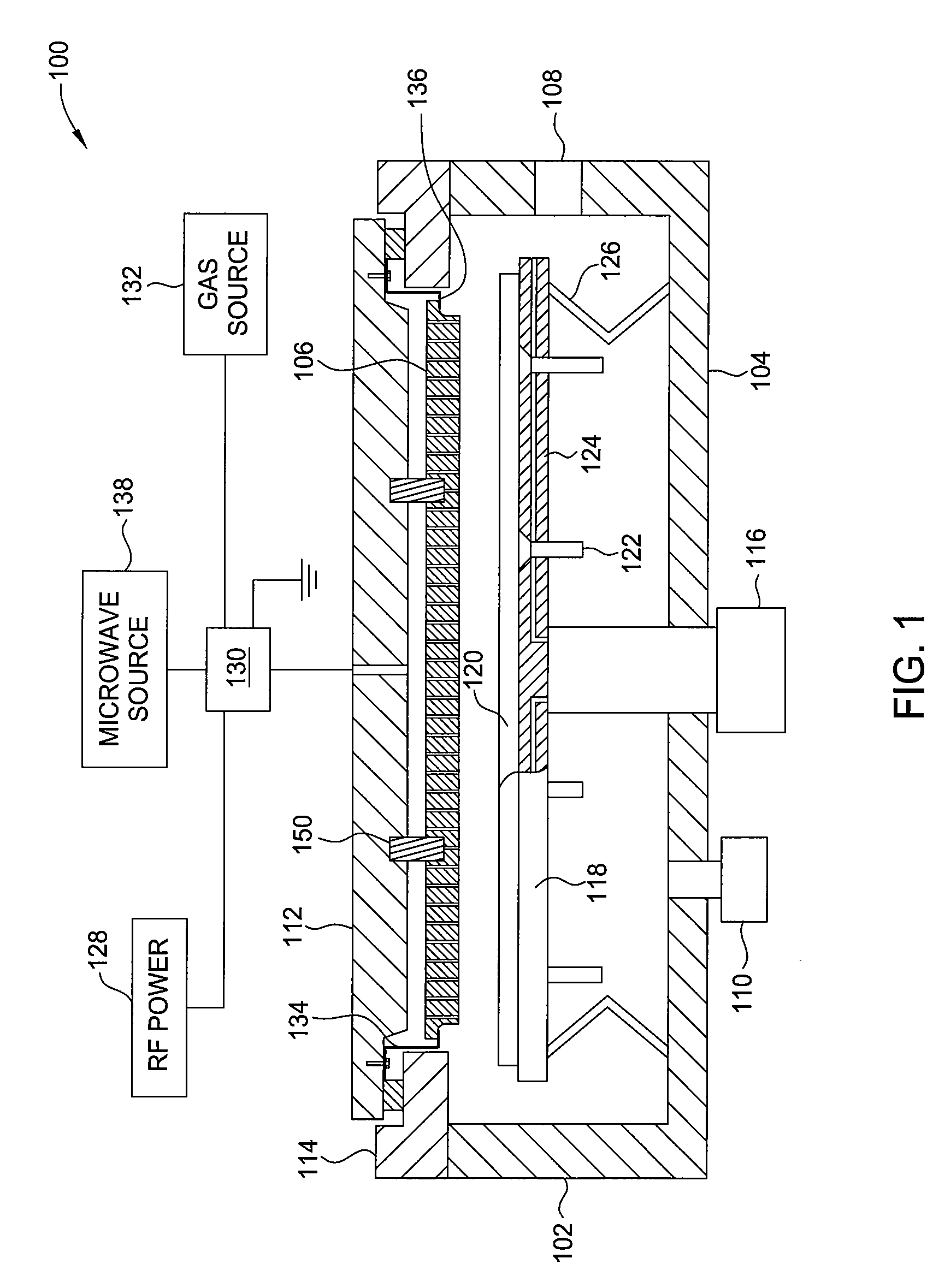

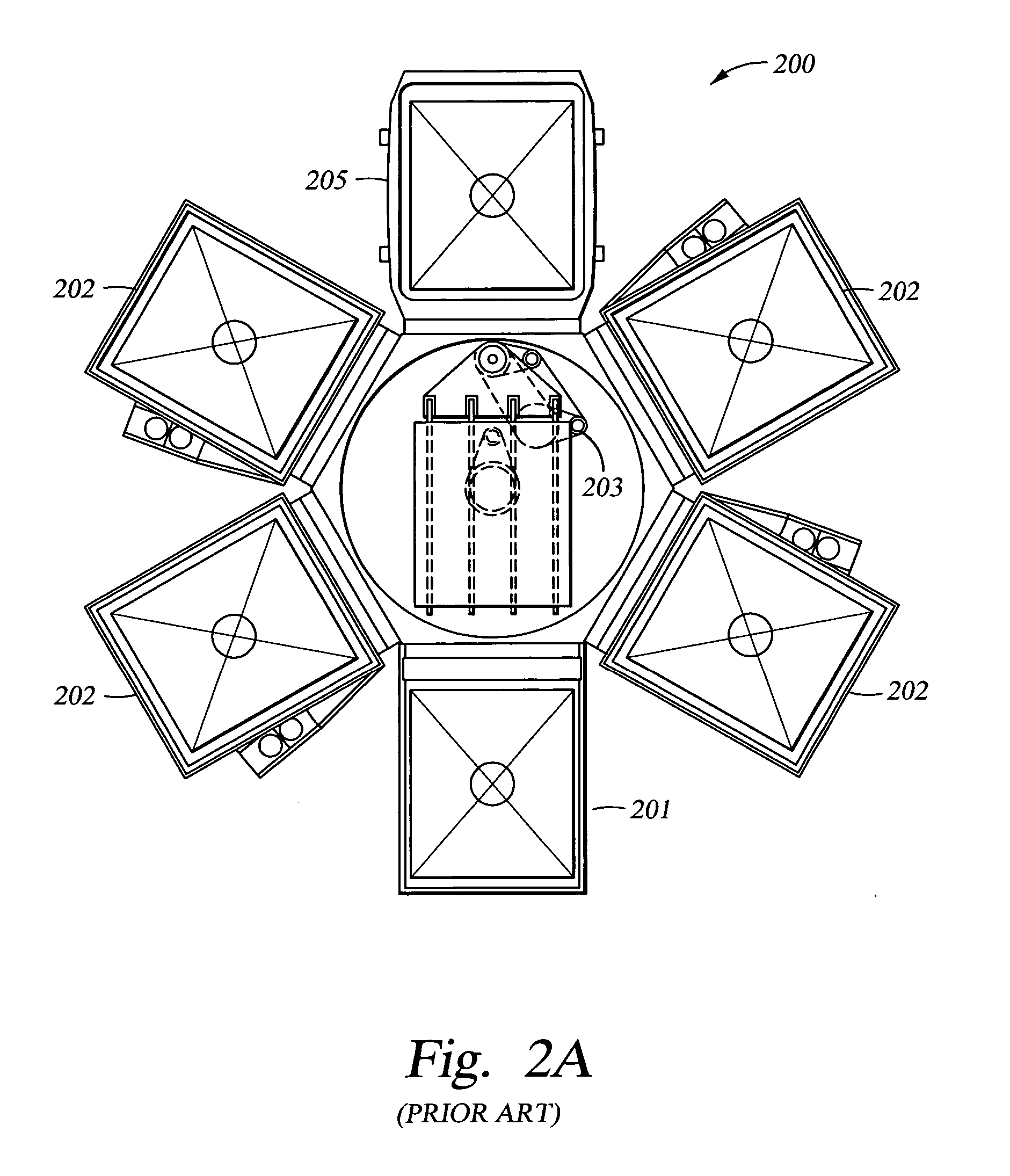

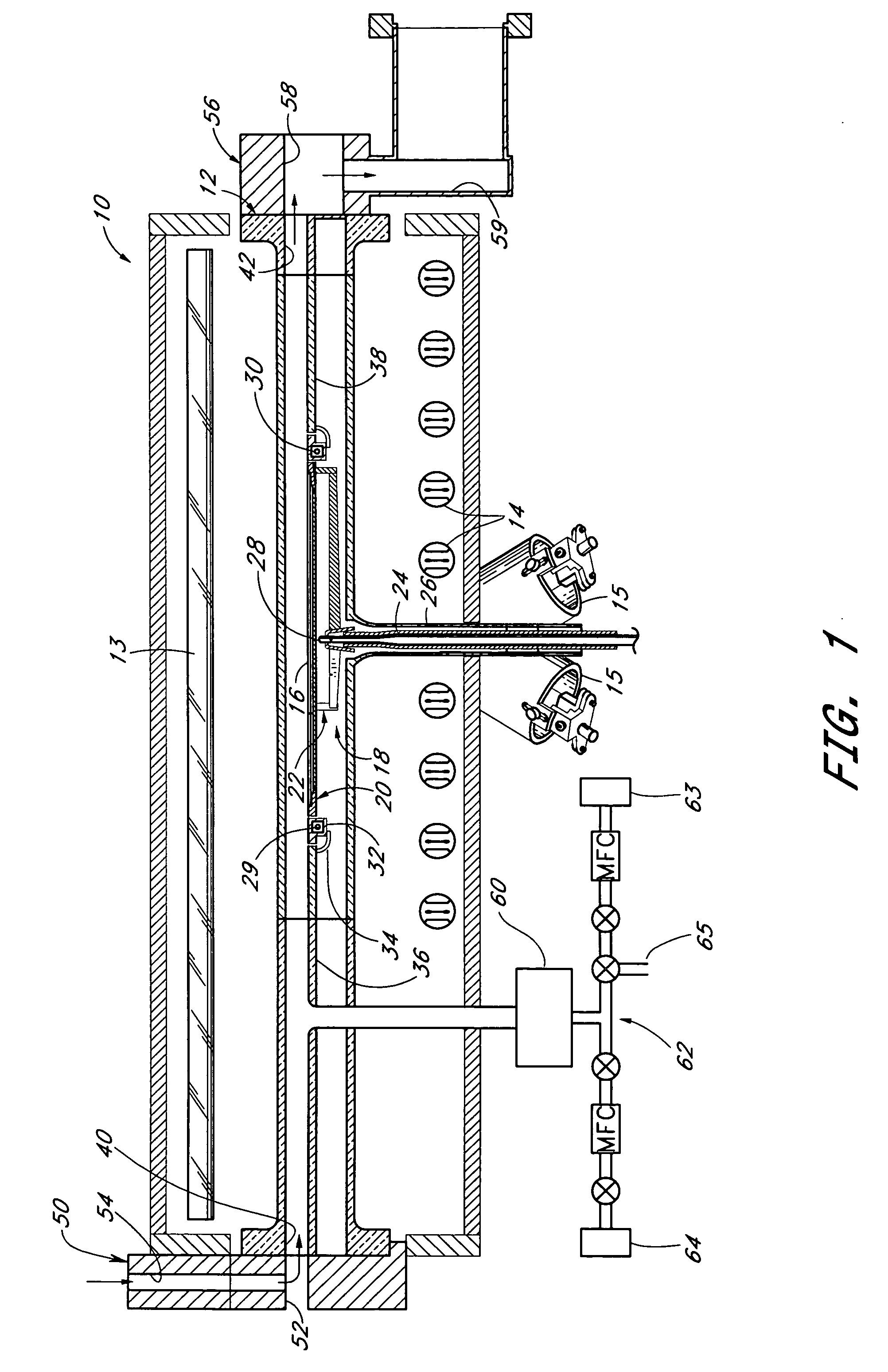

System and method for forming a gate dielectric

InactiveUS6858547B2Vacuum evaporation coatingSemiconductor/solid-state device manufacturingHydrofluoric acidGate dielectric

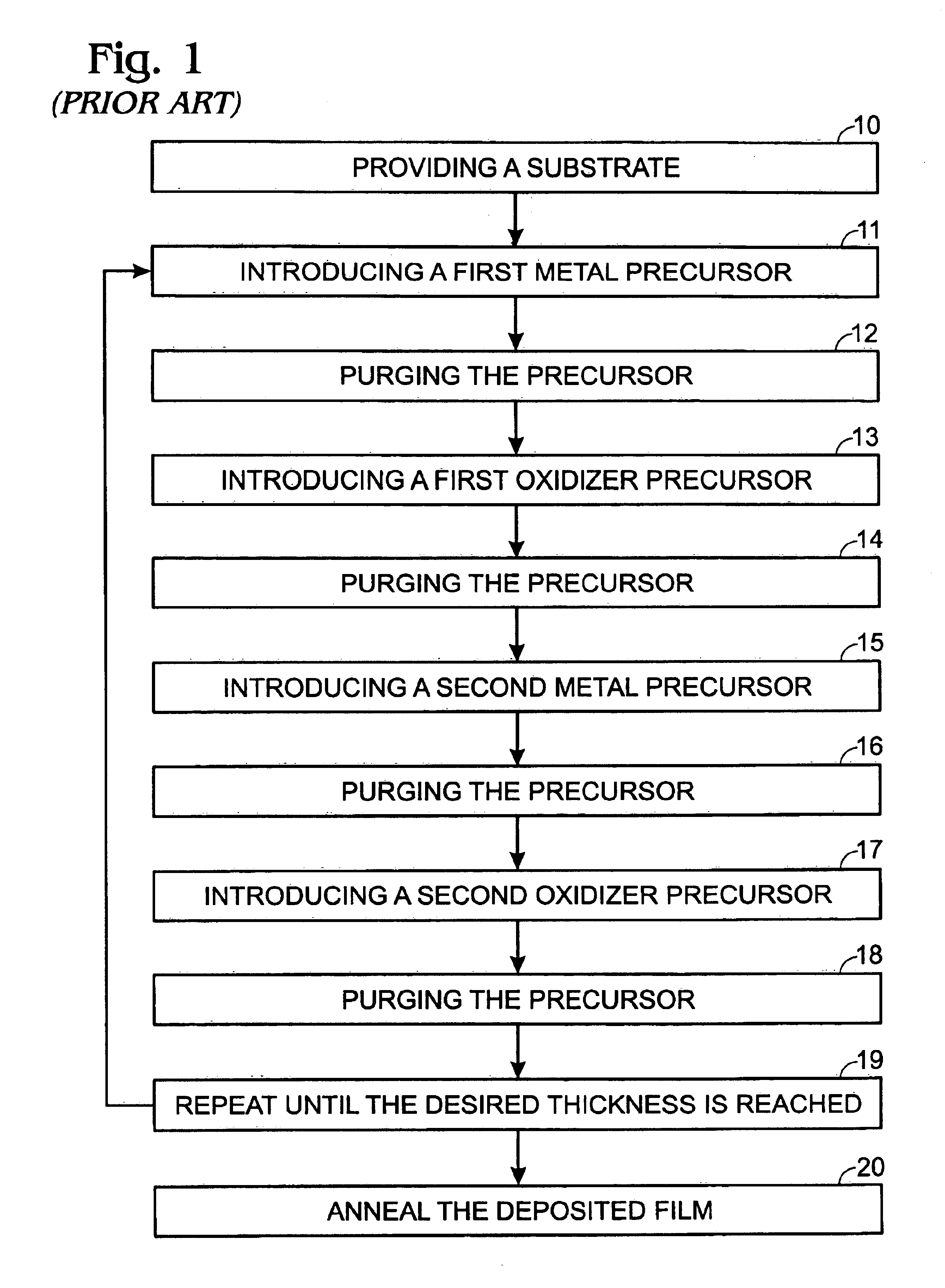

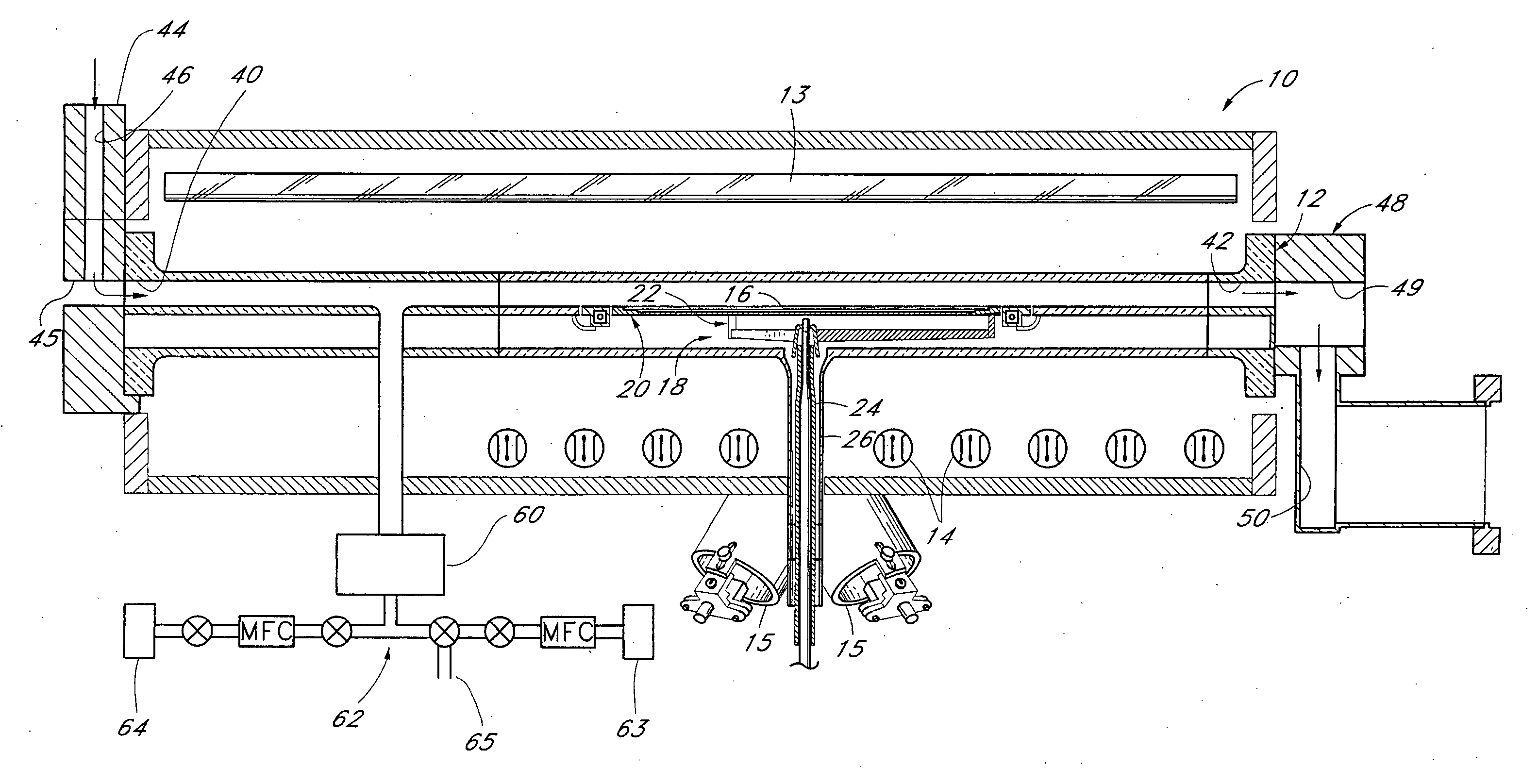

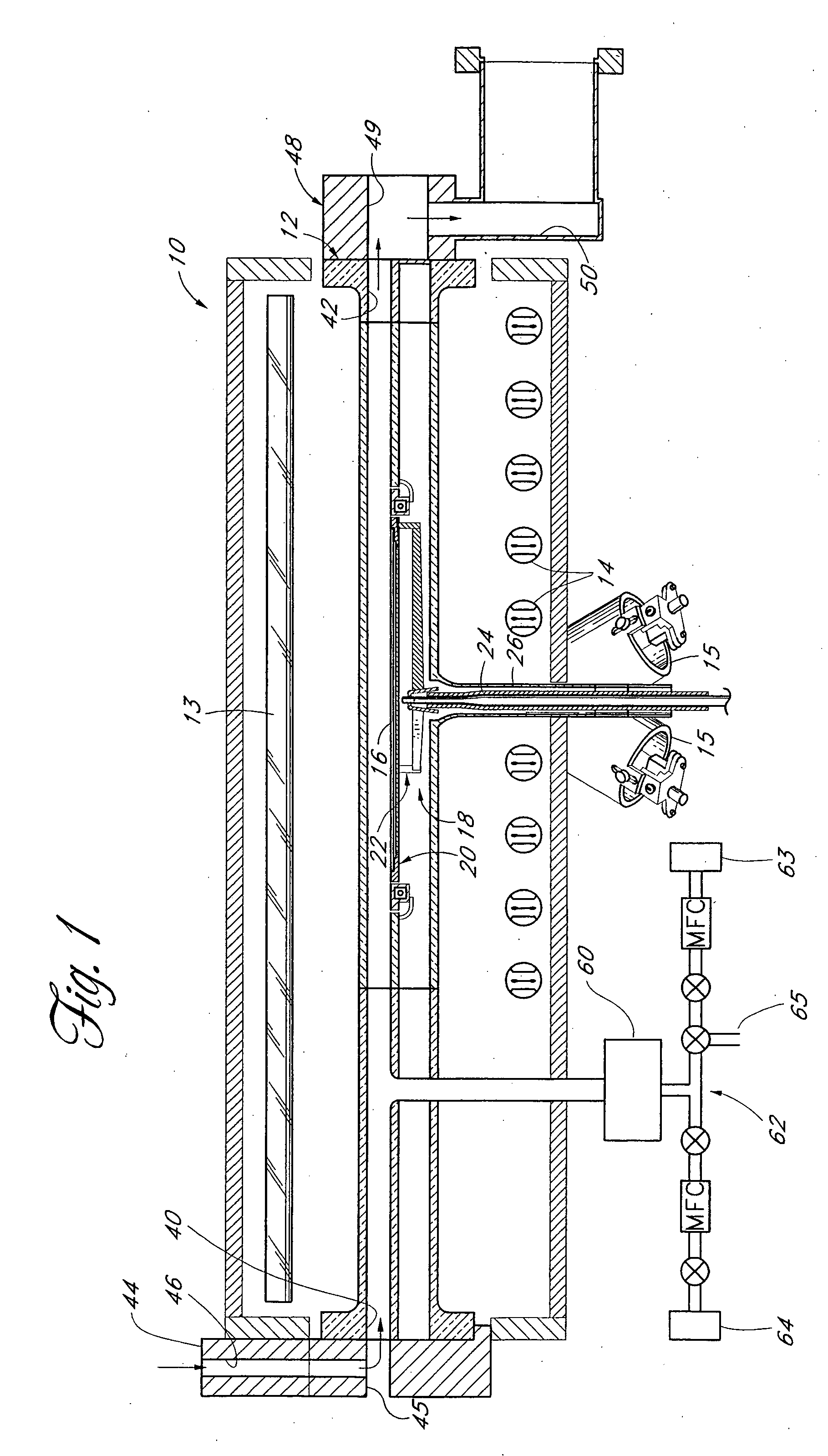

A method of forming a dielectric stack on a pre-treated surface. The method comprises pre-cleaning a semiconductor wafer to remove native oxide, such as by applying hydroflouric acid to form an HF-last surface, pre-treating the HF-last surface with ozonated deionized water, forming a dielectric stack on the pre-treated surface and providing a flow of NH3 in a process zone surrounding the wafer. Alternately, the method includes pre-treating the HF-last surface with NH3, forming the stack after the pre-treating, and providing a flow of N2 in a process zone surrounding the wafer after the forming. The method also includes pre-treating the HF-last surface using an in-situ steam generation process, forming the stack on the pre-treated surface, and annealing the wafer after the forming. The pre-treating includes providing an inert gas flow in a process zone surrounding the HF-last surface, reacting hydrogen with an oxidizer in the process zone for a very short duration, and providing an inert gas flew in the process zone after the reacting.

Owner:APPLIED MATERIALS INC

Method for depositing a nanolaminate film by atomic layer deposition

InactiveUS6930059B2Simple methodQuality improvementTransistorSemiconductor/solid-state device manufacturingGate dielectricHafnium

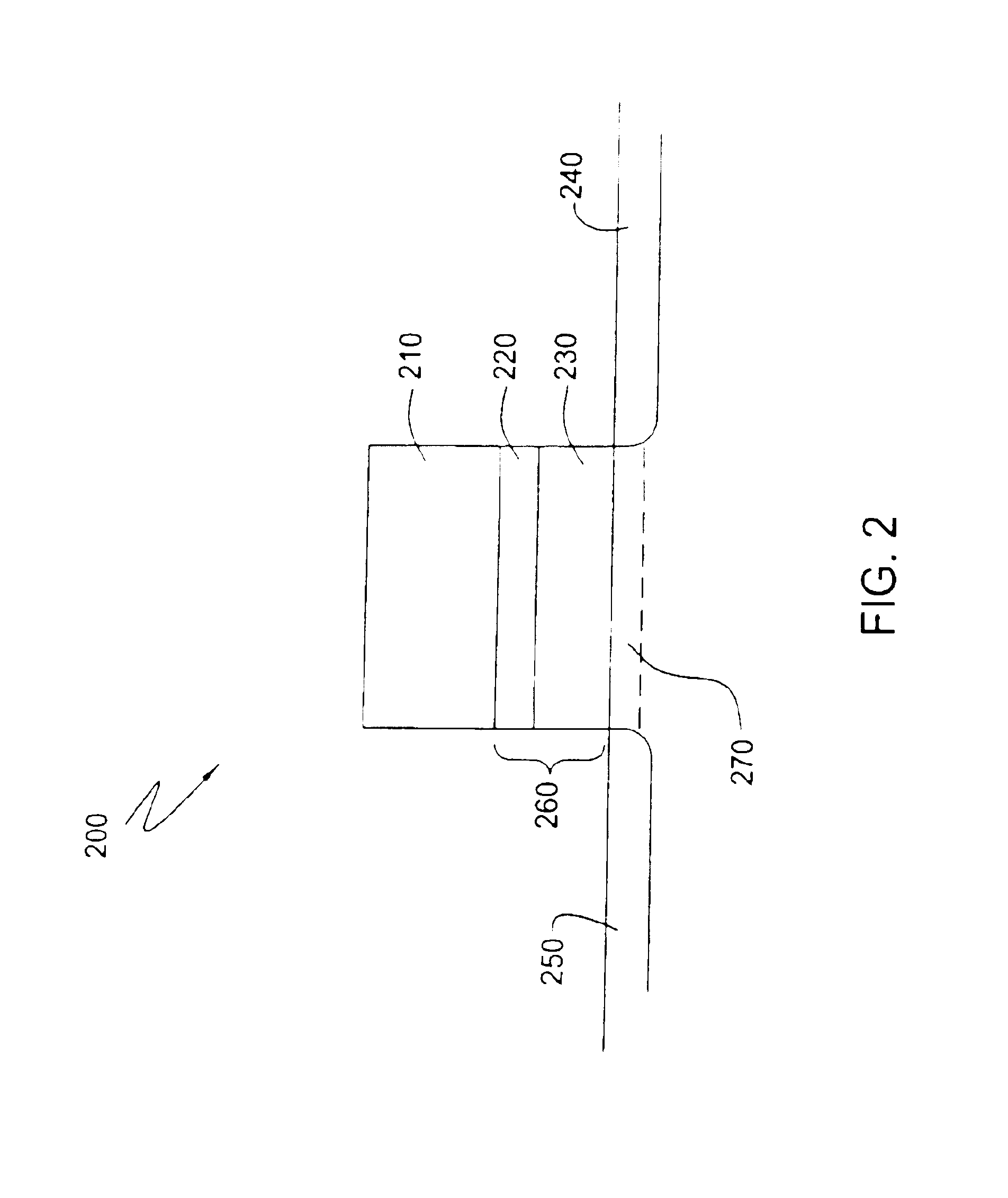

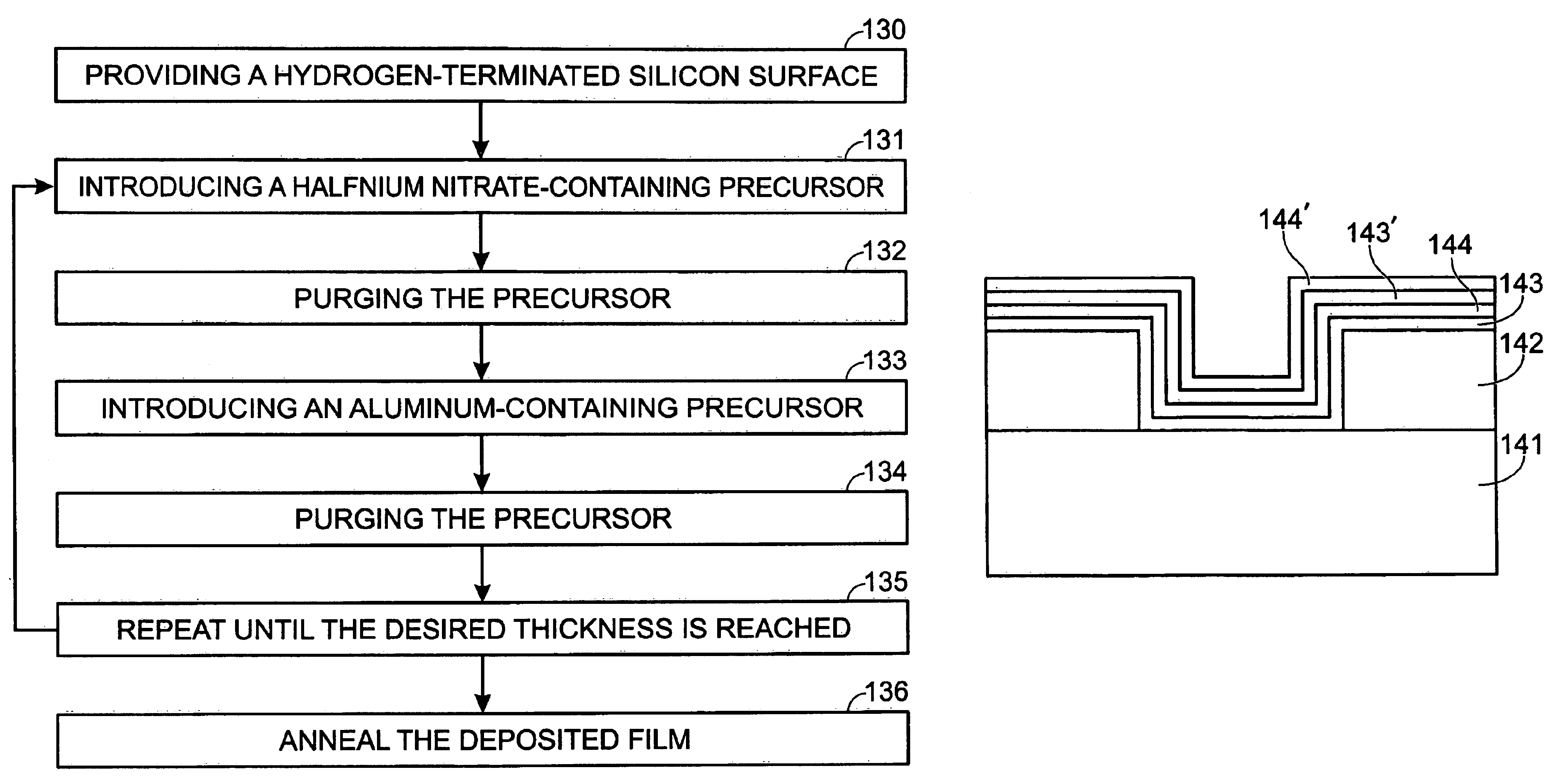

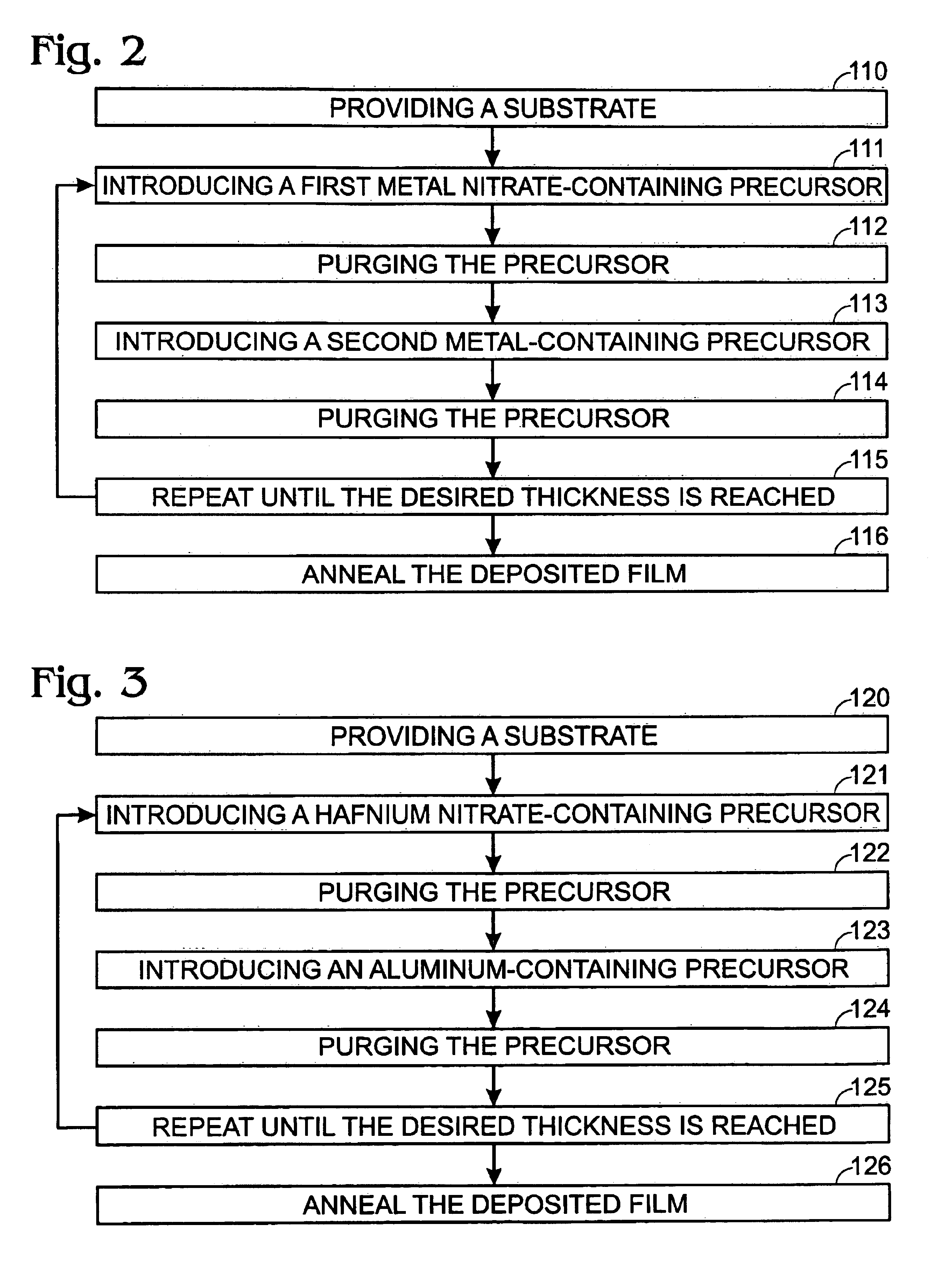

An atomic layer deposition method to deposit an oxide nanolaminate thin film is provided. The method employs a nitrate ligand in a first precursor as an oxidizer for a second precursor to form the oxide nanolaminates. Using a hafnium nitrate precursor and an aluminum precursor, the method is well suited for the deposition of a high k hafnium oxide / aluminum oxide nanolaminate dielectric for gate dielectric or capacitor dielectric applications on a hydrogen-terminated silicon surface.

Owner:SHARP LAB OF AMERICA INC

Method of depositing barrier layer for metal gates

InactiveUS6858524B2Eliminate the problemEasy to controlSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricRemote plasma

A method of manufacturing a high performance MOS device and transistor gate stacks comprises forming a gate dielectric layer over a semiconductor substrate; forming a barrier layer over the gate dielectric layer by an ALD type process; and forming a gate electrode layer over the barrier layer. The method enables the use of hydrogen plasma, high energy hydrogen radicals and ions, other reactive radicals, reactive oxygen and oxygen containing precursors in the processing steps subsequent to the deposition of the gate dielectric layer of the device. The ALD process for forming the barrier layer is performed essentially in the absence of plasma and reactive hydrogen radials and ions. This invention makes it possible to use oxygen as a precursor in the deposition of the metal gates. The barrier film also allows the use of hydrogen plasma in the form of either direct or remote plasma in the deposition of the gate electrode. Furthermore, the barrier film prevents the electrode material from reacting with the gate dielectric material. The barrier layer is ultra thin and, at the same time, it forms a uniform cover over the entire surface of the gate dielectric.

Owner:ASM INTERNATIONAL

Nitridation of high-k dielectric films

InactiveUS20050153571A1Improve mobilityInterface stabilitySemiconductor/solid-state device manufacturingChemical vapor deposition coatingDielectricElectricity

The present invention promotes incorporation of nitrogen (e.g., nitridation) into high-k dielectric films using a low temperature process. Further, the present invention provides an in-situ method; that is formation of the high-k dielectric film and nitridation of the film are carried out in the same process chamber during deposition of the film, as opposed to the conventional post processing techniques. In another aspect, a method for depositing a multi-layer material for use as a gate dielectric layer in semiconductor devices is provided.

Owner:AVIZA TECHNOLOGY INC

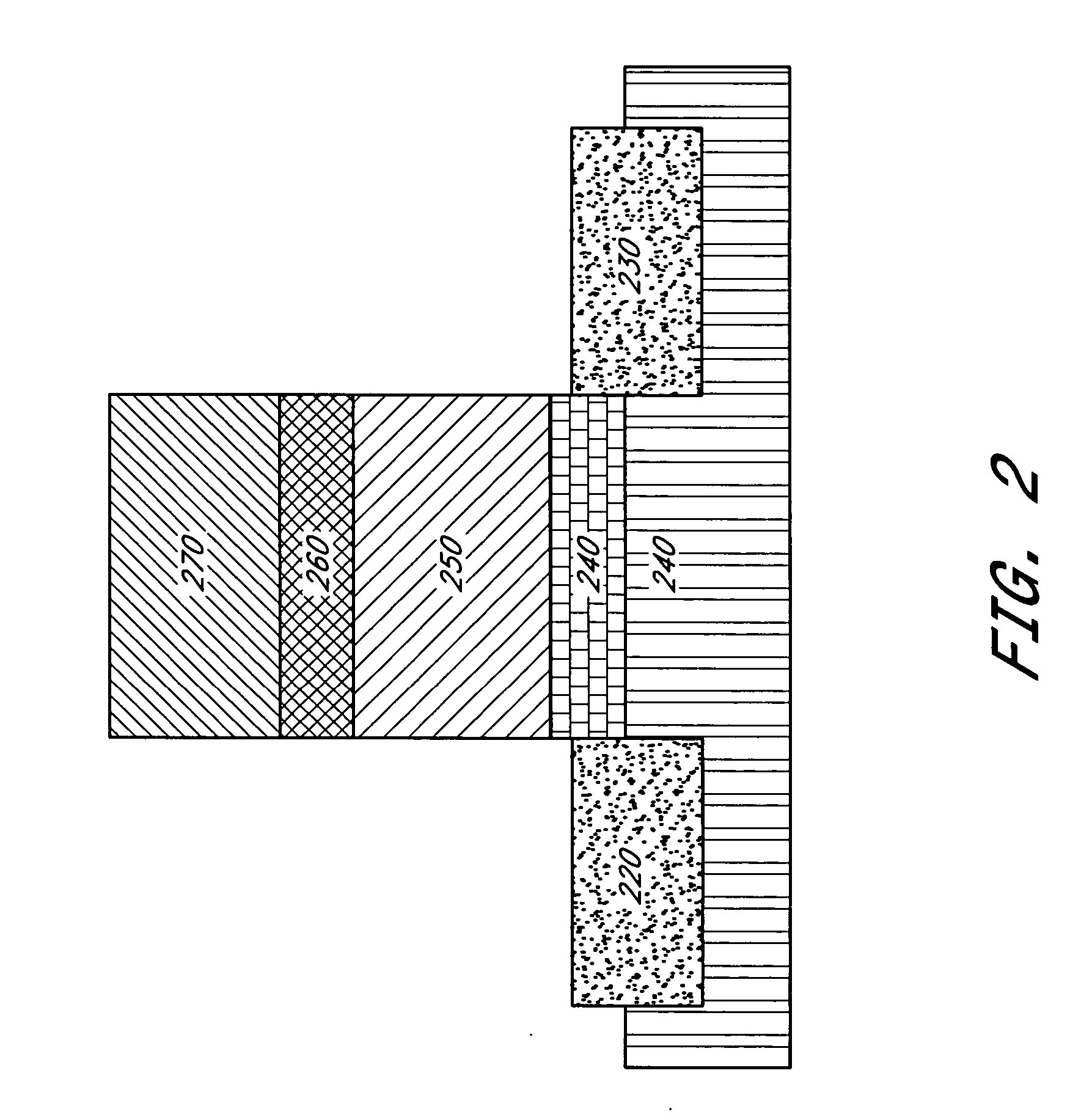

Thin films

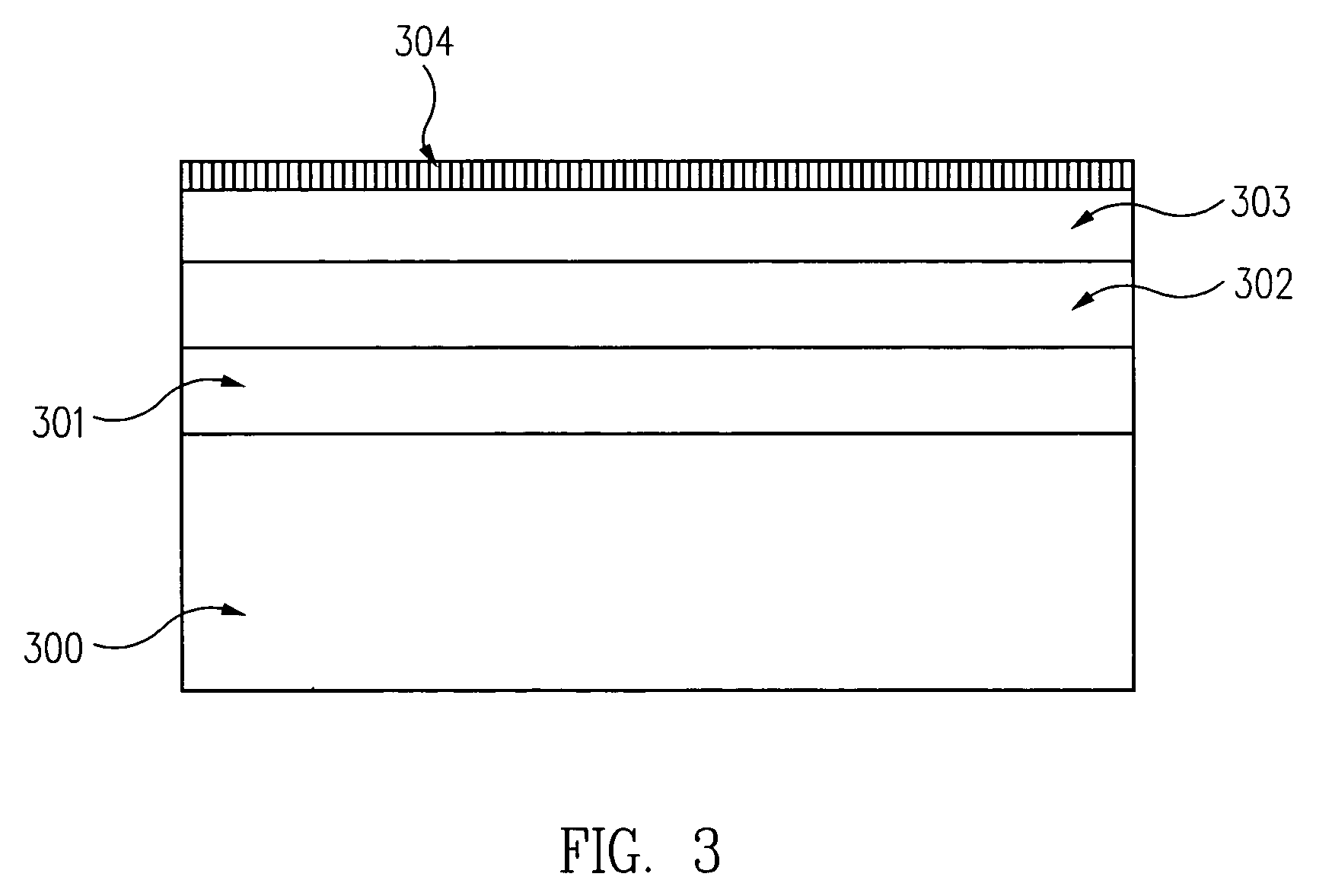

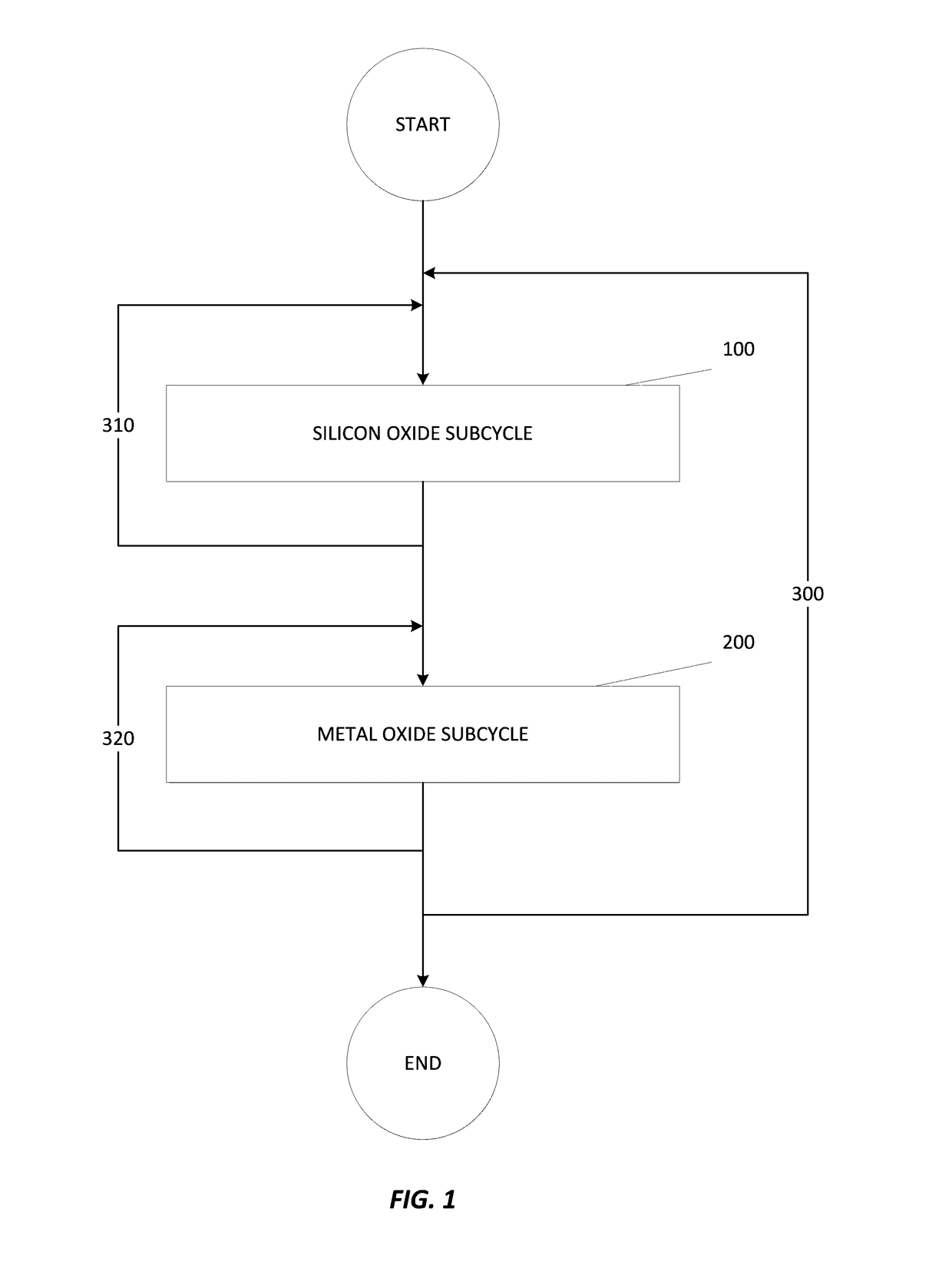

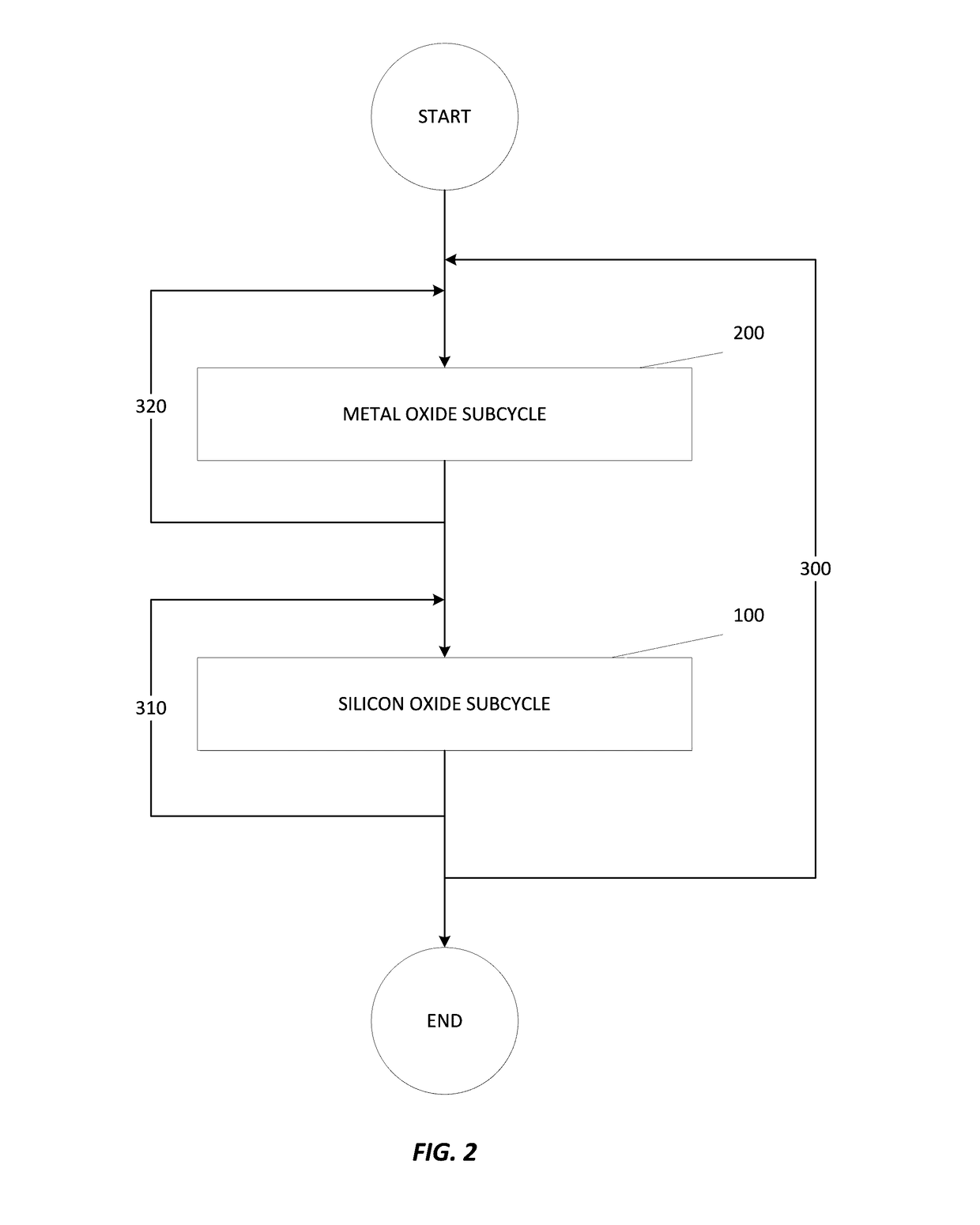

InactiveUS20050181555A1Quality improvementHigh dielectric constantSolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricSilicon oxide

Thin films are formed by formed by atomic layer deposition, whereby the composition of the film can be varied from monolayer to monolayer during cycles including alternating pulses of self-limiting chemistries. In the illustrated embodiments, varying amounts of impurity sources are introduced during the cyclical process. A graded gate dielectric is thereby provided, even for extremely thin layers. The gate dielectric as thin as 2 nm can be varied from pure silicon oxide to oxynitride to silicon nitride. Similarly, the gate dielectric can be varied from aluminum oxide to mixtures of aluminum oxide and a higher dielectric material (e.g., ZrO2) to pure high k material and back to aluminum oxide. In another embodiment, metal nitride (e.g., WN) is first formed as a barrier for lining dual damascene trenches and vias. During the alternating deposition process, copper can be introduced, e.g., in separate pulses, and the copper source pulses can gradually increase in frequency, forming a transition region, until pure copper is formed at the upper surface. Advantageously, graded compositions in these and a variety of other contexts help to avoid such problems as etch rate control, electromigration and non-ohmic electrical contact that can occur at sharp material interfaces. In some embodiments additional seed layers or additional transition layers are provided.

Owner:ASM INTERNATIONAL

Method of Fabricating a Gate Dielectric for High-K Metal Gate Devices

ActiveUS20100075507A1Facilitate formation of the high-k dielectric layerImprove electrical performanceSemiconductor/solid-state device manufacturingChemical vapor deposition coatingGate dielectricSulfur

The present disclosure provides a method of fabricating a semiconductor device. The method includes providing a substrate, forming an interfacial layer on the substrate by treating the substrate with radicals, and forming a high-k dielectric layer on the interfacial layer. The radicals are selected from the group consisting of hydrous radicals, nitrogen / hydrogen radicals, and sulfur / hydrogen radicals.

Owner:TAIWAN SEMICON MFG CO LTD

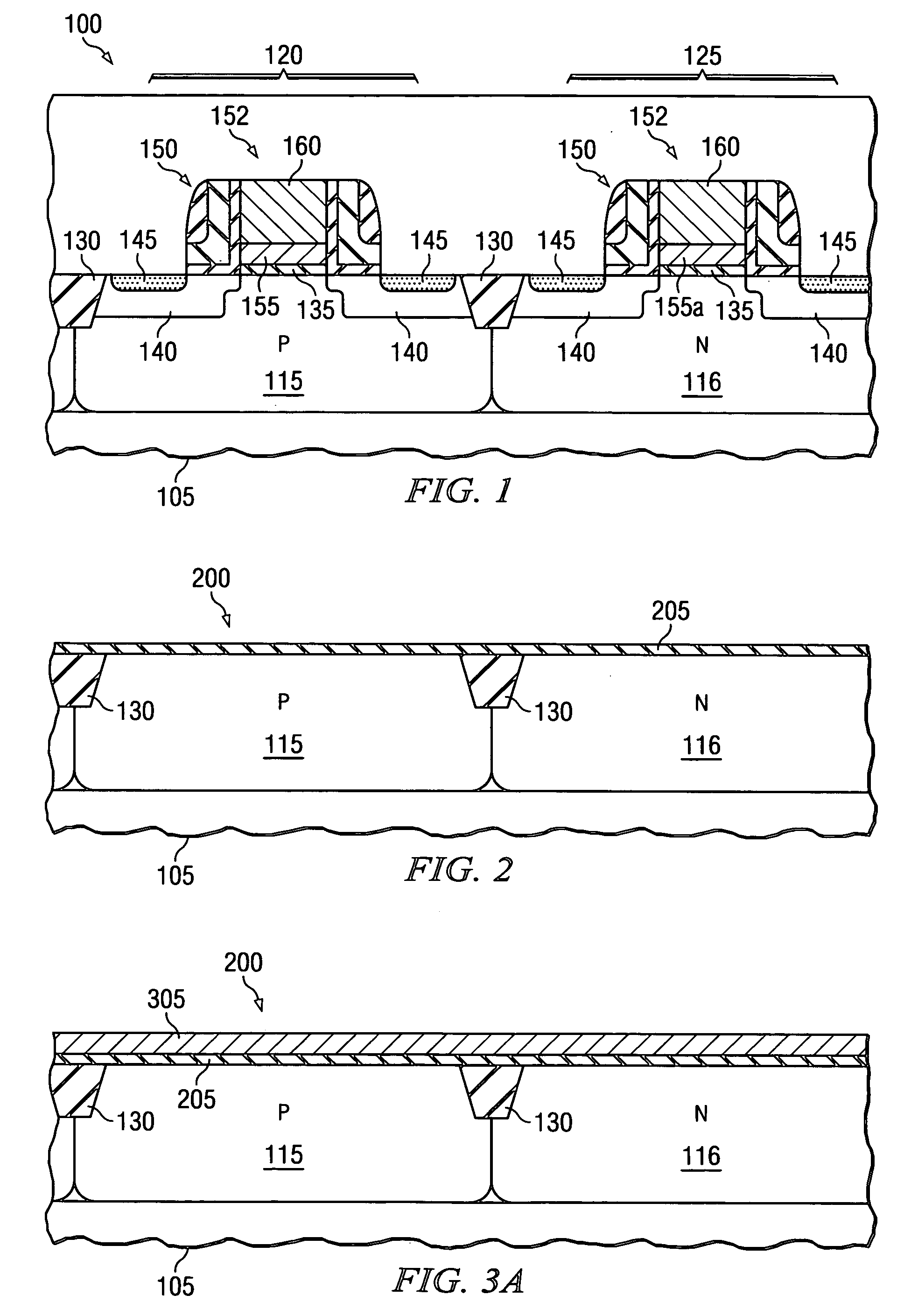

Process for manufacturing dual work function metal gates in a microelectronics device

ActiveUS20070037343A1Semiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricWork function

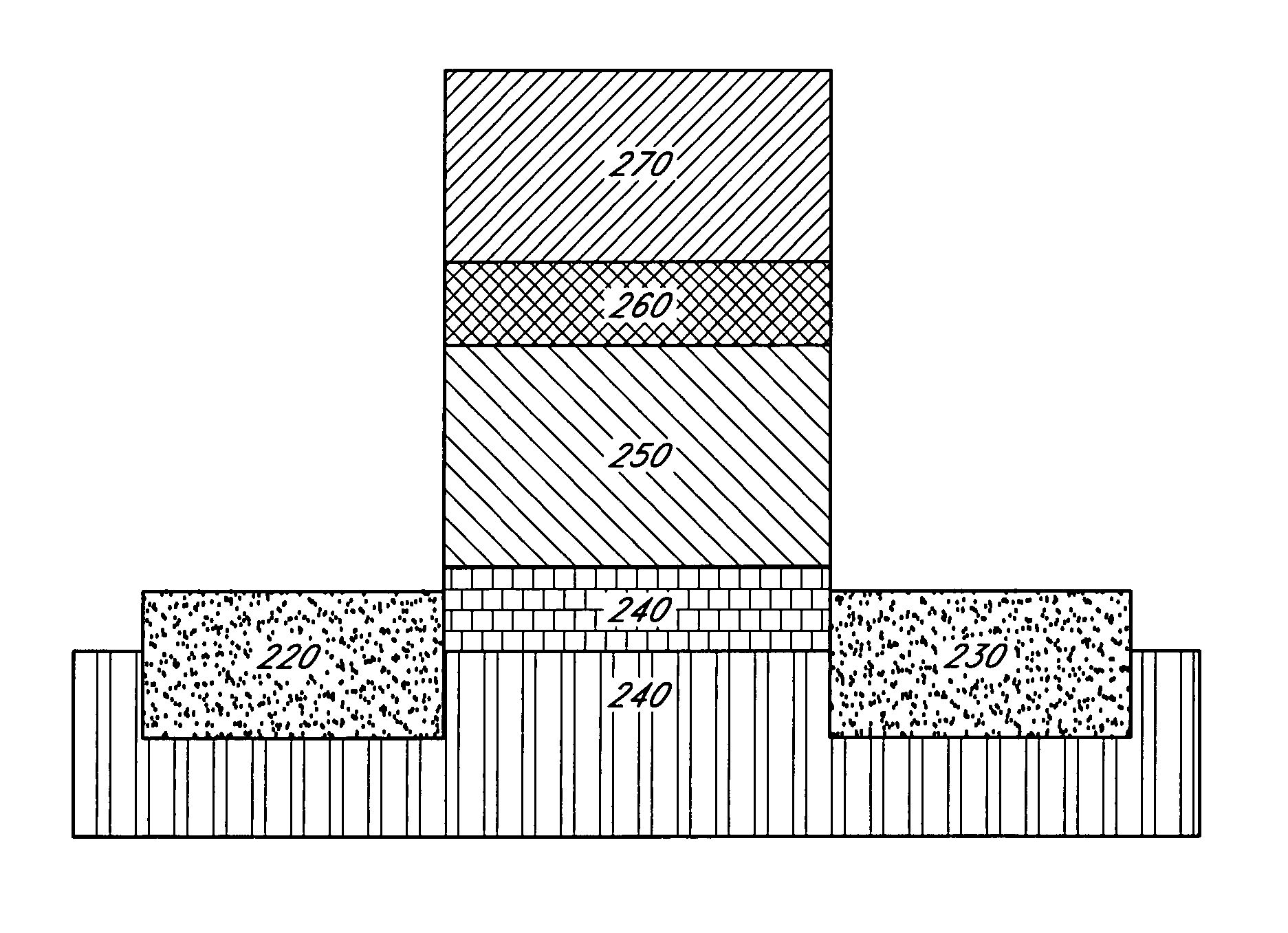

The present invention provides a method of forming a dual work function metal gate microelectronics device 200. In one aspect, the method includes forming nMOS and pMOS stacked gate structures 315a and 315b. The nMOS and pMOS stacked gate structures 315a and 315b each comprise a gate dielectric 205, a first metal layer, 305 located over the gate dielectric 205 and a sacrificial gate layer 310 located over the first metal layer 305. The method further includes removing the sacrificial gate layer 310 in at least one of the nMOS or pMOS stacked gate structures, thereby forming a gate opening 825 and modifying the first metal layer 305 within the gate opening 825 to form a gate electrode with a desired work function.

Owner:TEXAS INSTR INC

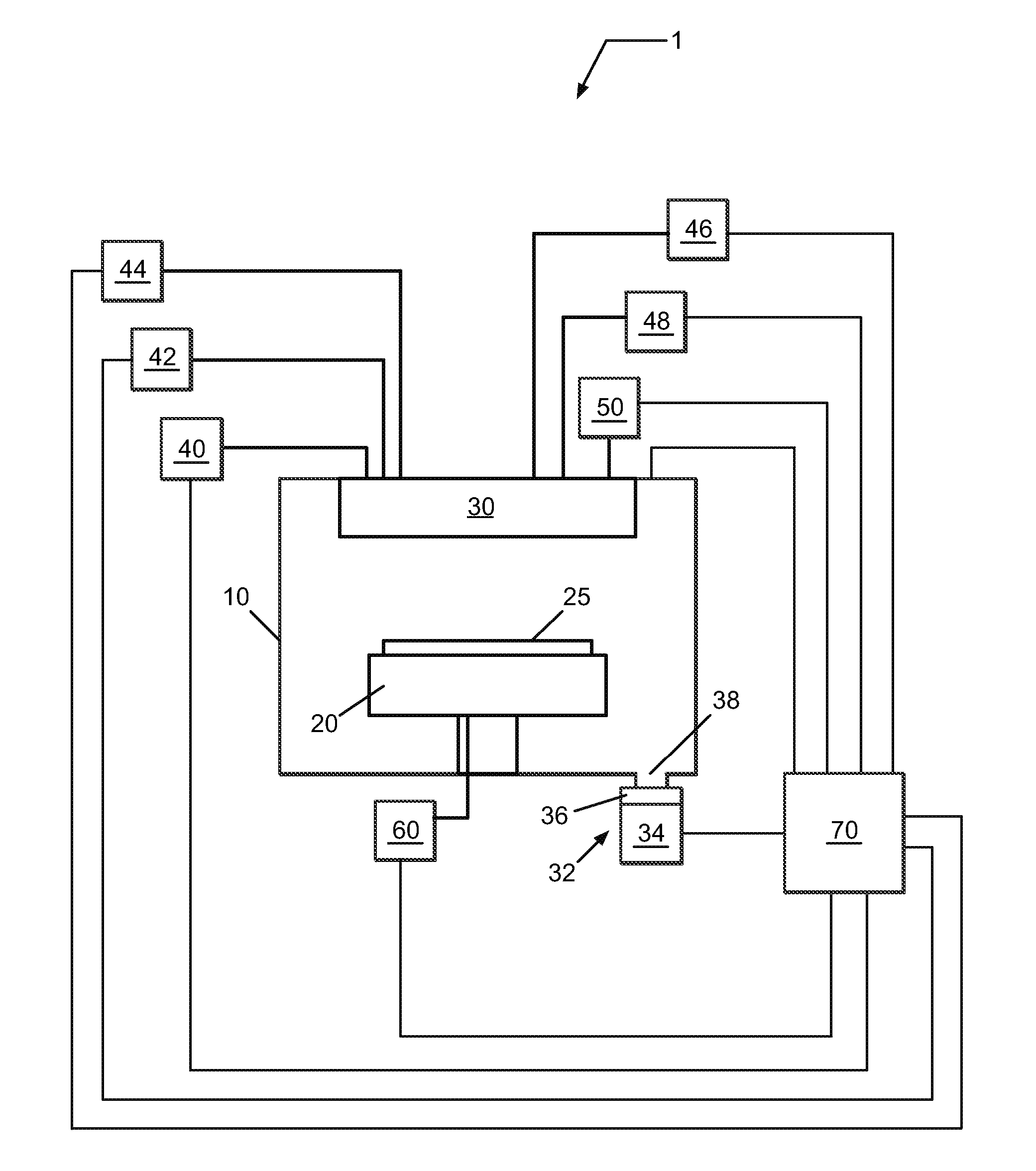

Incorporation of nitrogen into high k dielectric film

InactiveUS20050212119A1Semiconductor/solid-state device detailsSolid-state devicesDielectricCyclic process

A high k dielectric film and methods for forming the same are disclosed. The high k material includes two peaks of impurity concentration, particularly nitrogen, such as at a lower interface and upper interface, making the layer particularly suitable for transistor gate dielectric applications. The methods of formation include low temperature processes, particularly CVD using a remote plasma generator and atomic layer deposition using selective incorporation of nitrogen in the cyclic process. Advantageously, nitrogen levels are tailored during the deposition process and temperatures are low enough to avoid interdiffusion and allow maintenance of the desired impurity profile.

Owner:ASM IP HLDG BV

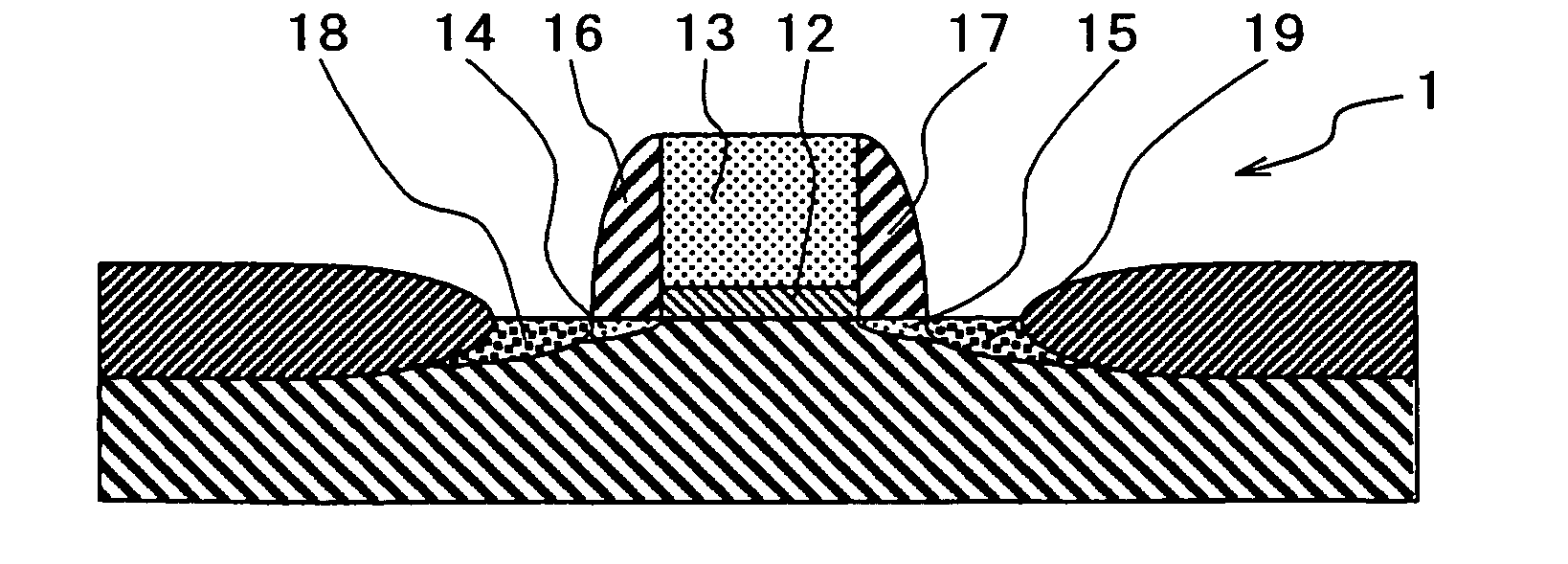

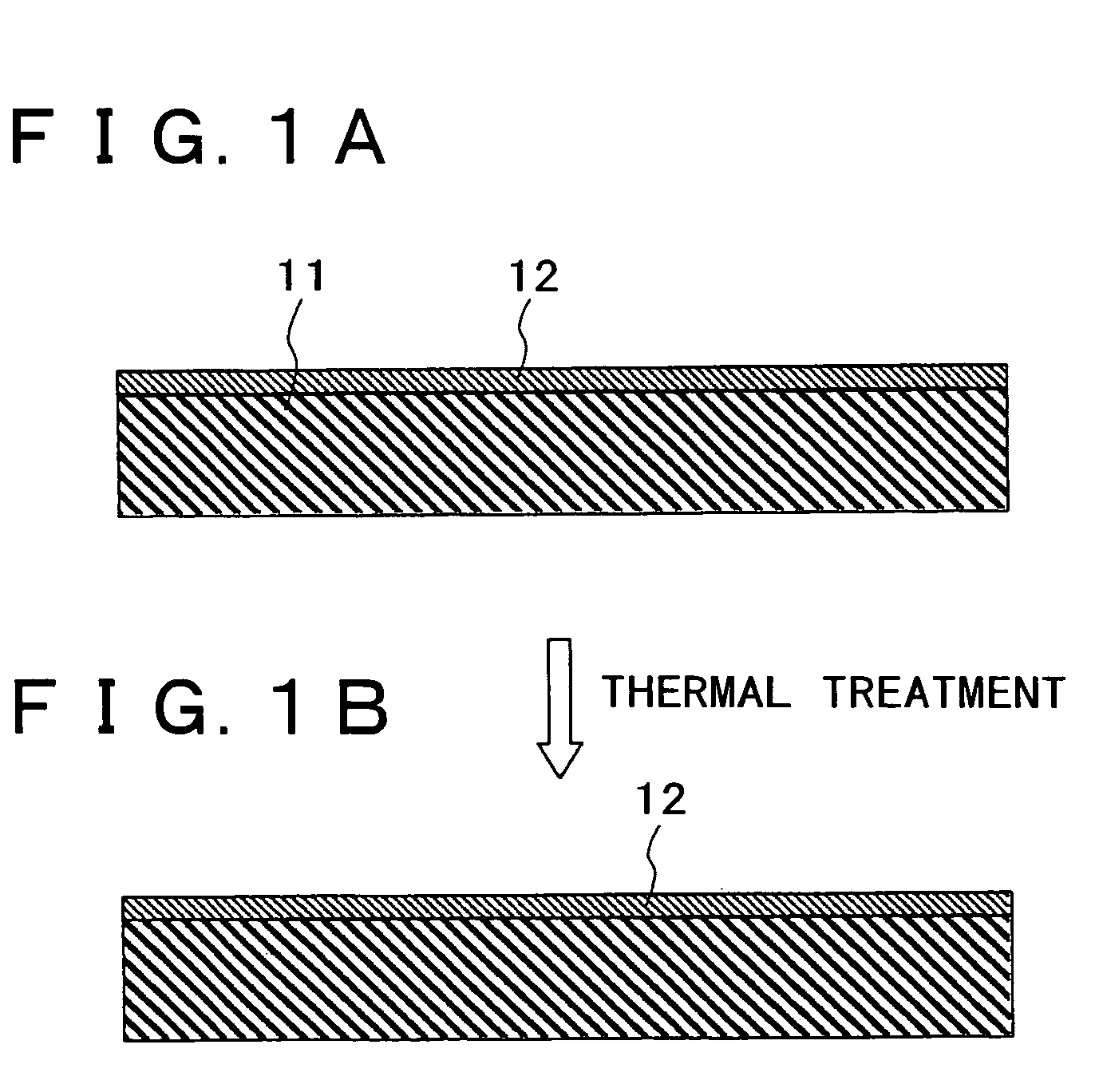

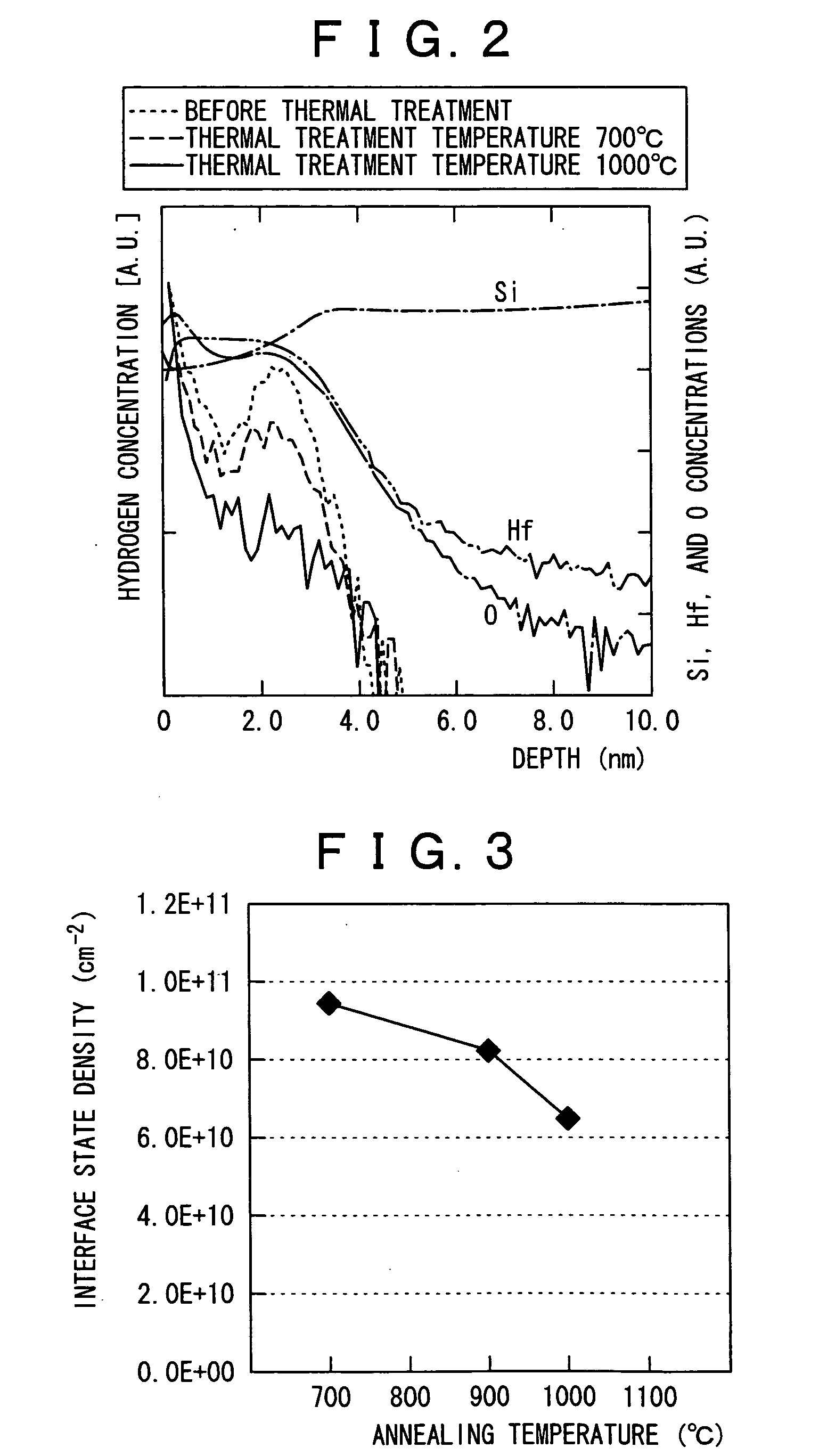

Method for forming a thin film and method for fabricating a semiconductor device

InactiveUS20050070123A1Improve mobility and reliabilitySemiconductor/solid-state device manufacturingChemical vapor deposition coatingGate dielectricHafnium

By conducting a high temperature annealing in a nitrogen atmosphere at a temperature at which a hafnium silicate film undergoes no phase separation, hydrogen contained in the film is removed and prevention of boron penetration is made possible. The present invention provides a method for forming a thin film including a step of forming a hafnium silicate film on a substrate by an atomic layer deposition method and a step of carrying out thermal treatment on the hafnium silicate film at a thermal treatment temperature equal to or higher than a temperature at which hydrogen contained in the hafnium silicate film is removed and lower than a temperature at which the hafnium silicate film undergoes no phase separation, and a method for fabricating a semiconductor device for forming a gate dielectric film using the method for forming a thin film.

Owner:SONY CORP

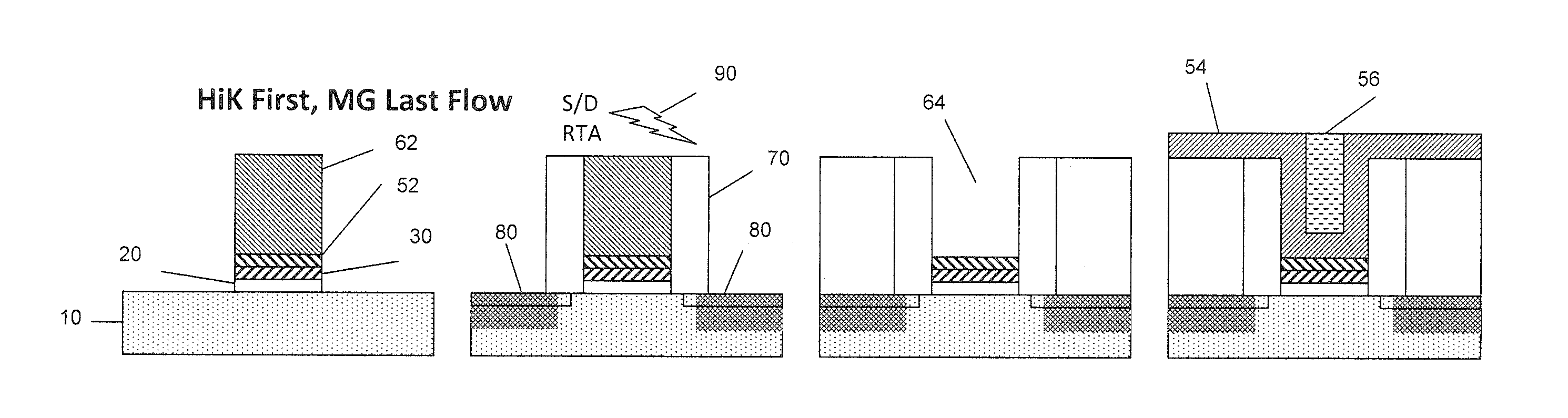

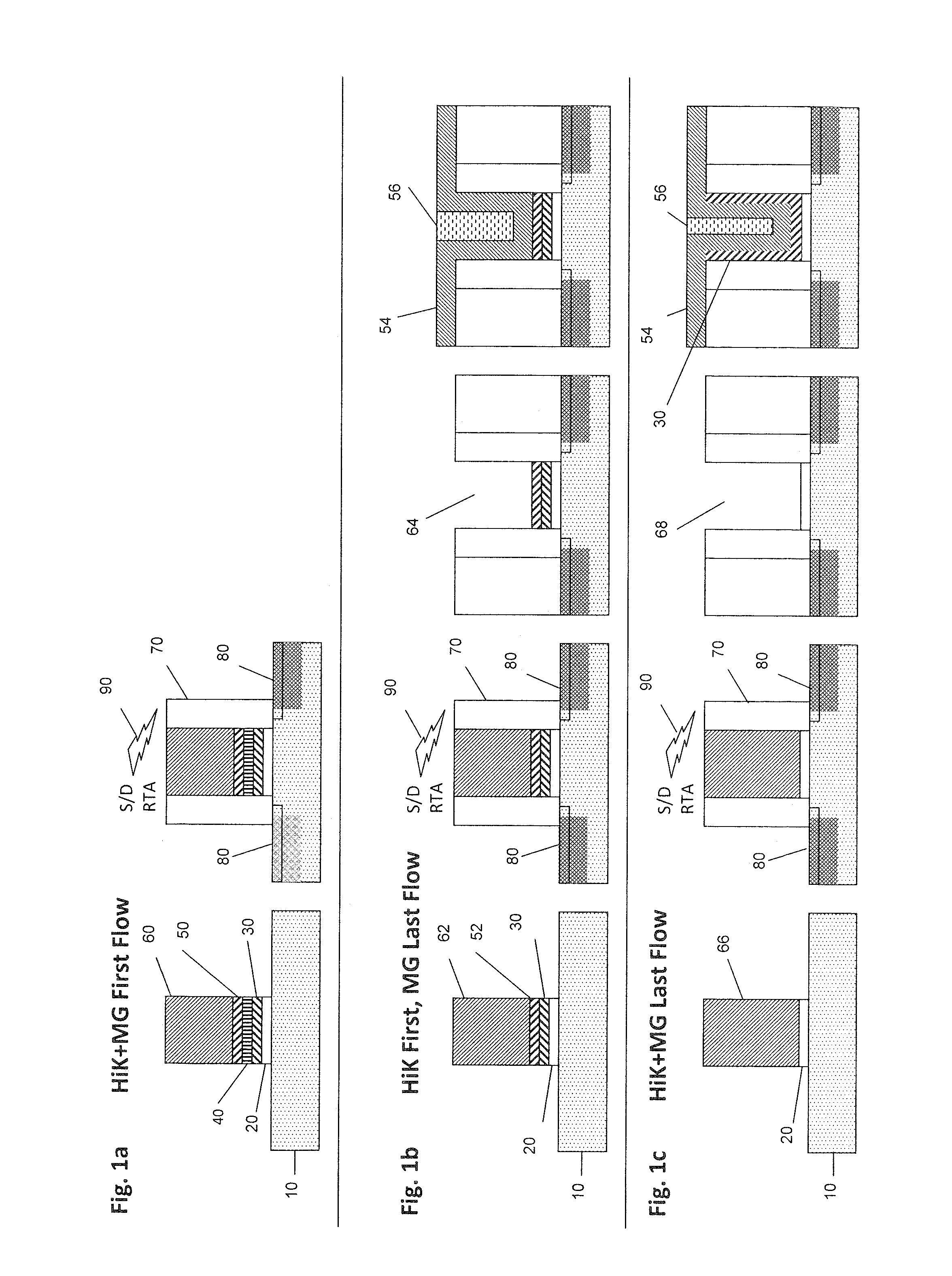

Opto-thermal annealing methods for forming metal gate and fully silicided gate field effect transistors

ActiveUS20070249131A1Avoid opto-thermal annealing damageAvoid damageSemiconductor/solid-state device manufacturingSemiconductor devicesSalicideGate dielectric

An opto-thermal annealing method for forming a field effect transistor uses a reflective metal gate so that electrical properties of the metal gate and also interface between the metal gate and a gate dielectric are not compromised when opto-thermal annealing a source / drain region adjacent the metal gate. Another opto-thermal annealing method may be used for simultaneously opto-thermally annealing: (1) a silicon layer and a silicide forming metal layer to form a fully silicided gate; and (2) a source / drain region to form an annealed source / drain region. An additional opto-thermal annealing method may use a thermal insulator layer in conjunction with a thermal absorber layer to selectively opto-thermally anneal a silicon layer and a silicide forming metal layer to form a fully silicide gate.

Owner:TAIWAN SEMICON MFG CO LTD

Atomic layer deposition of metal oxynitride layers as gate dielectrics

InactiveUS20060051925A1Semiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricHafnium

A metal oxynitride layer formed by atomic layer deposition of a plurality of reacted monolayers, the monolayers comprising at least one each of a metal, an oxide and a nitride. The metal oxynitride layer is formed from zirconium oxynitride, hafnium oxynitride, tantalum oxynitride, or mixtures thereof. The metal oxynitride layer is used in gate dielectrics as a replacement material for silicon dioxide. A semiconductor device structure having a gate dielectric formed from a metal oxynitride layer is also disclosed.

Owner:AHN KIE Y +1

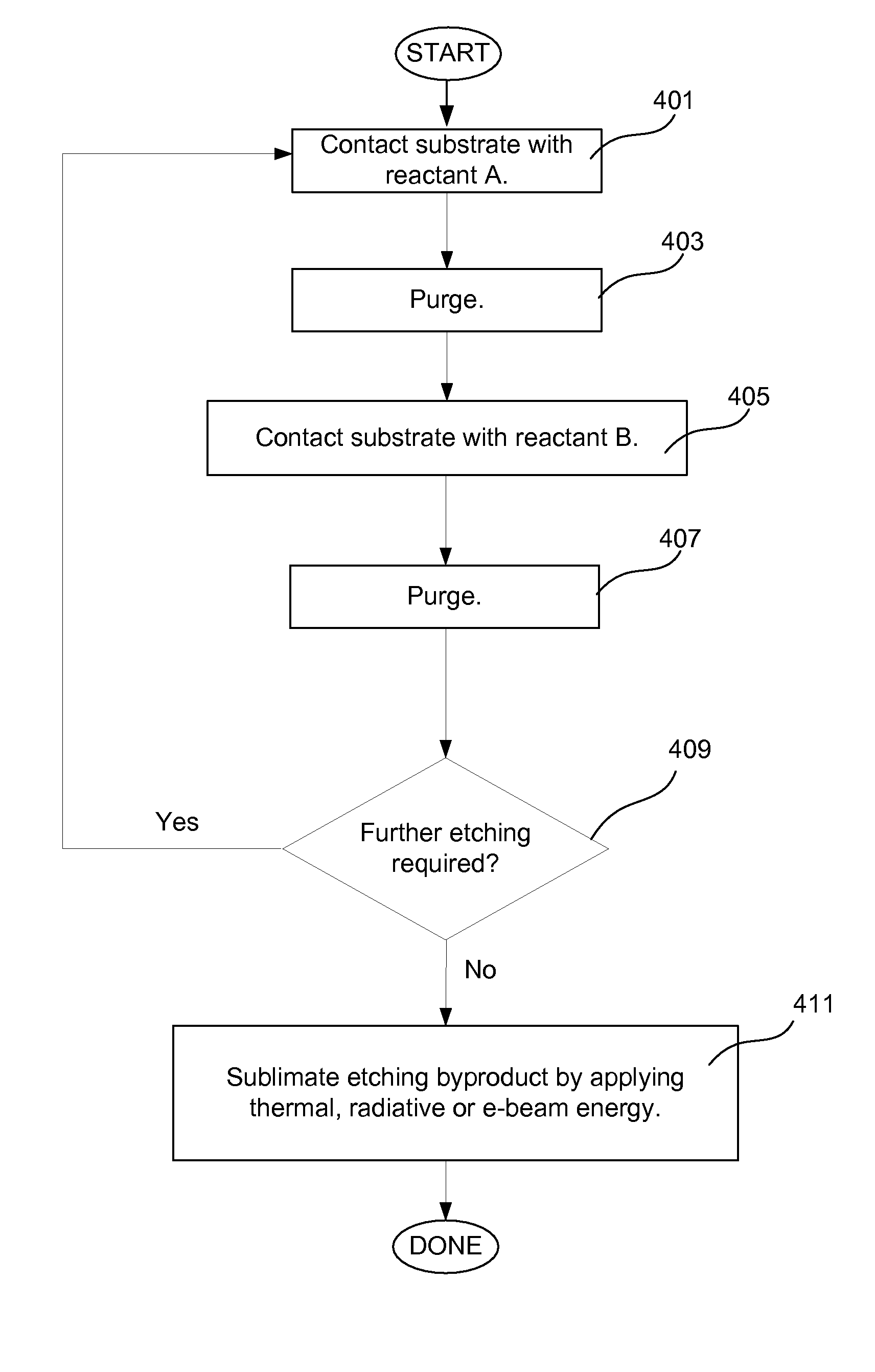

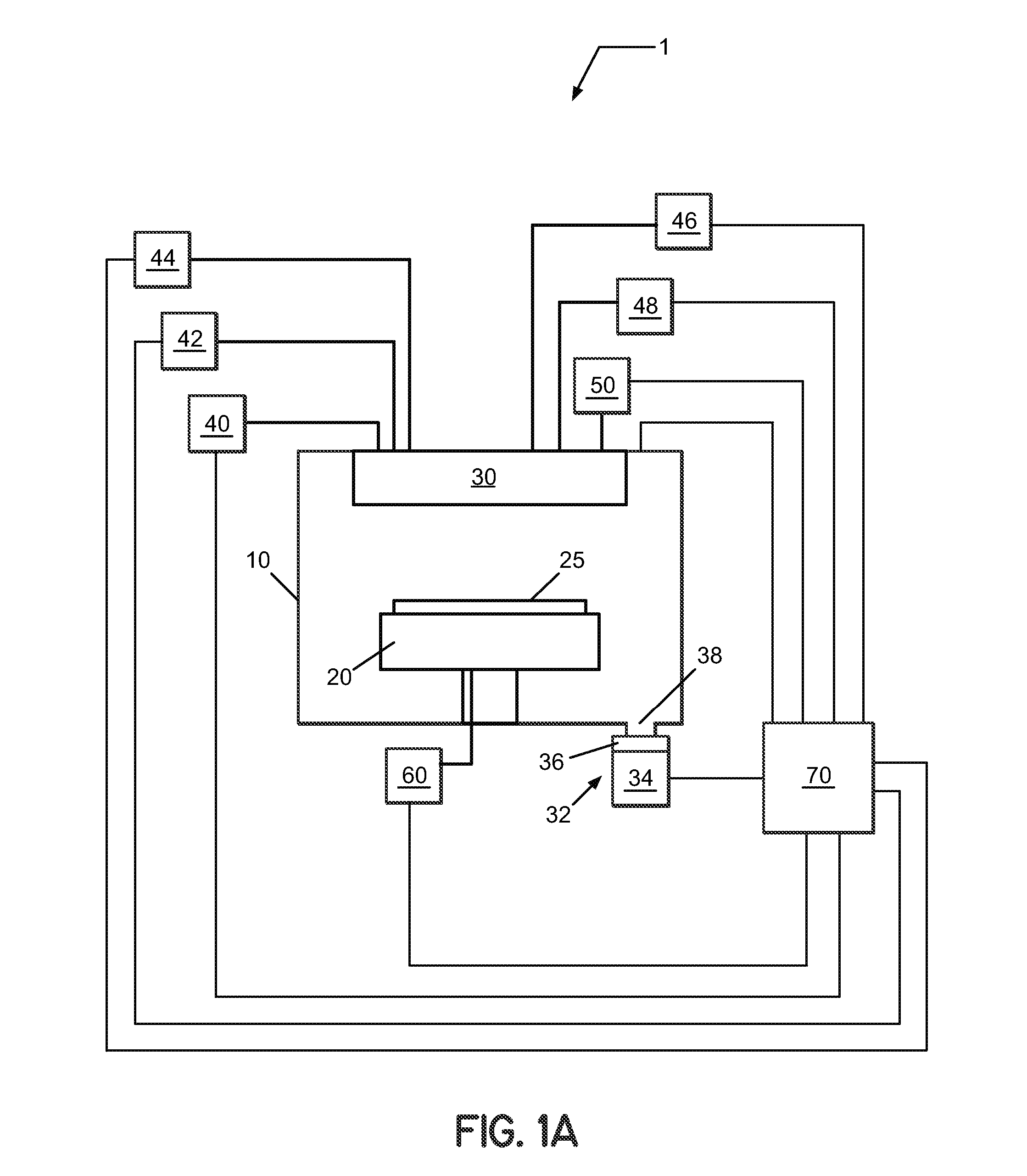

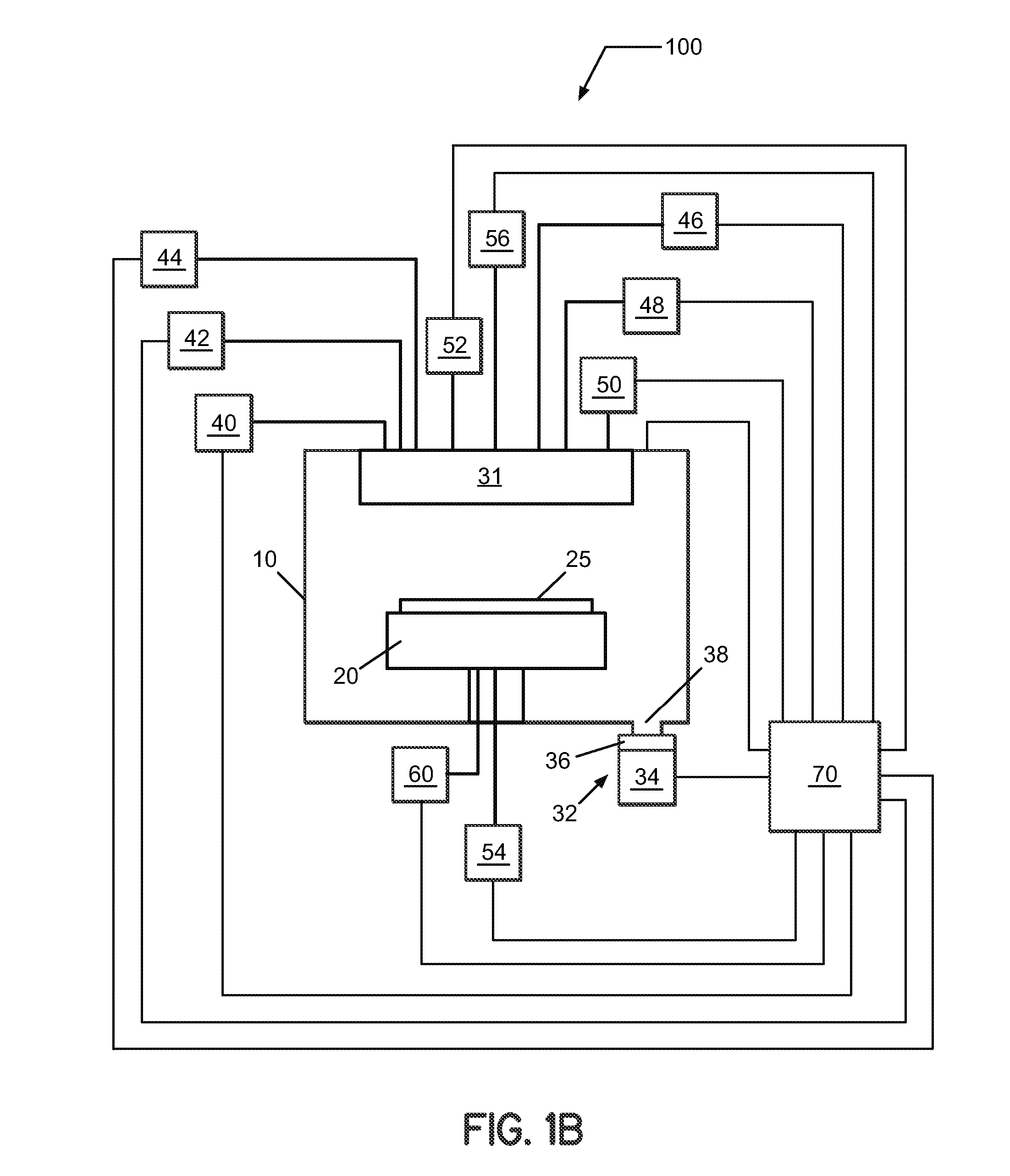

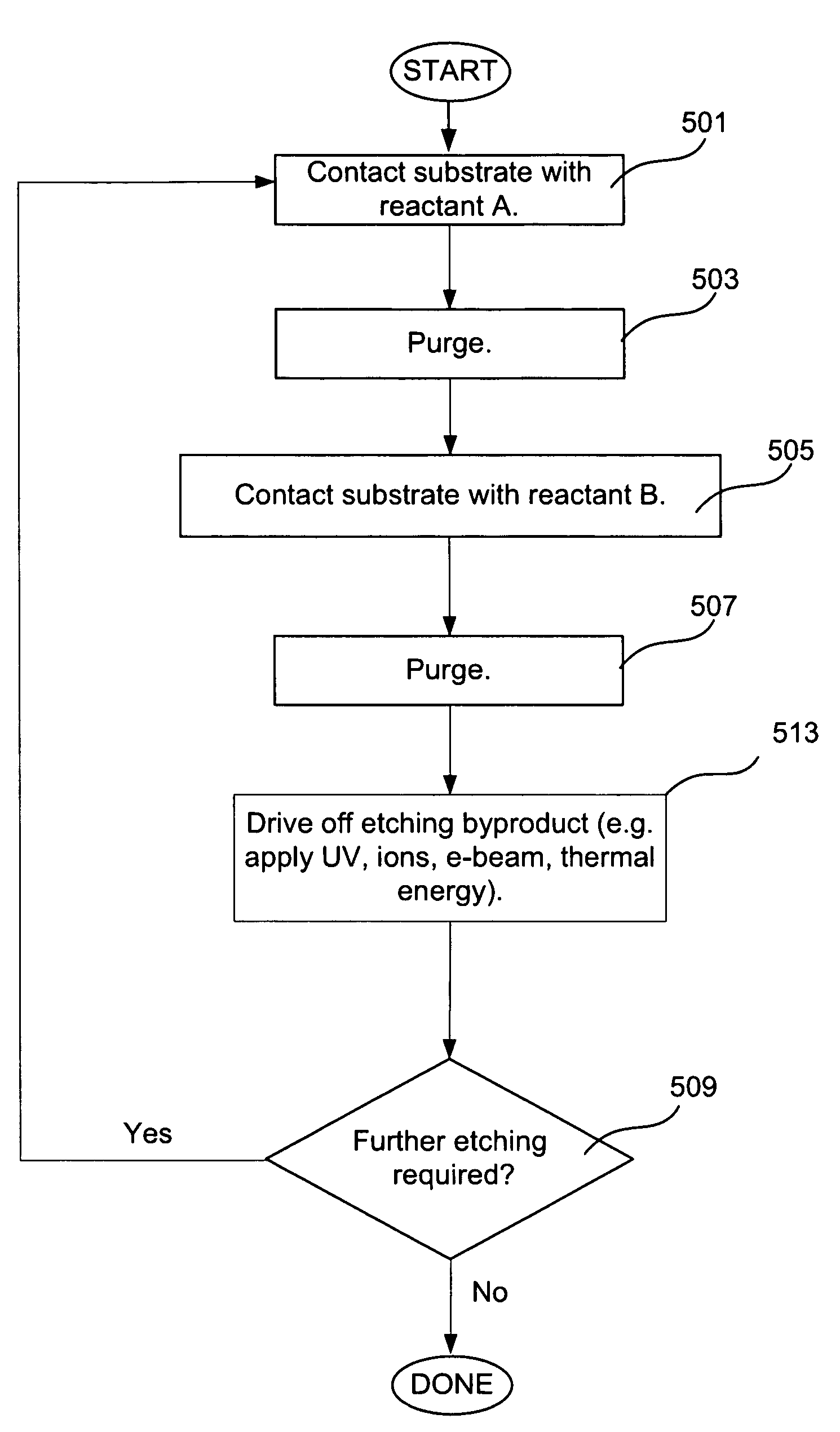

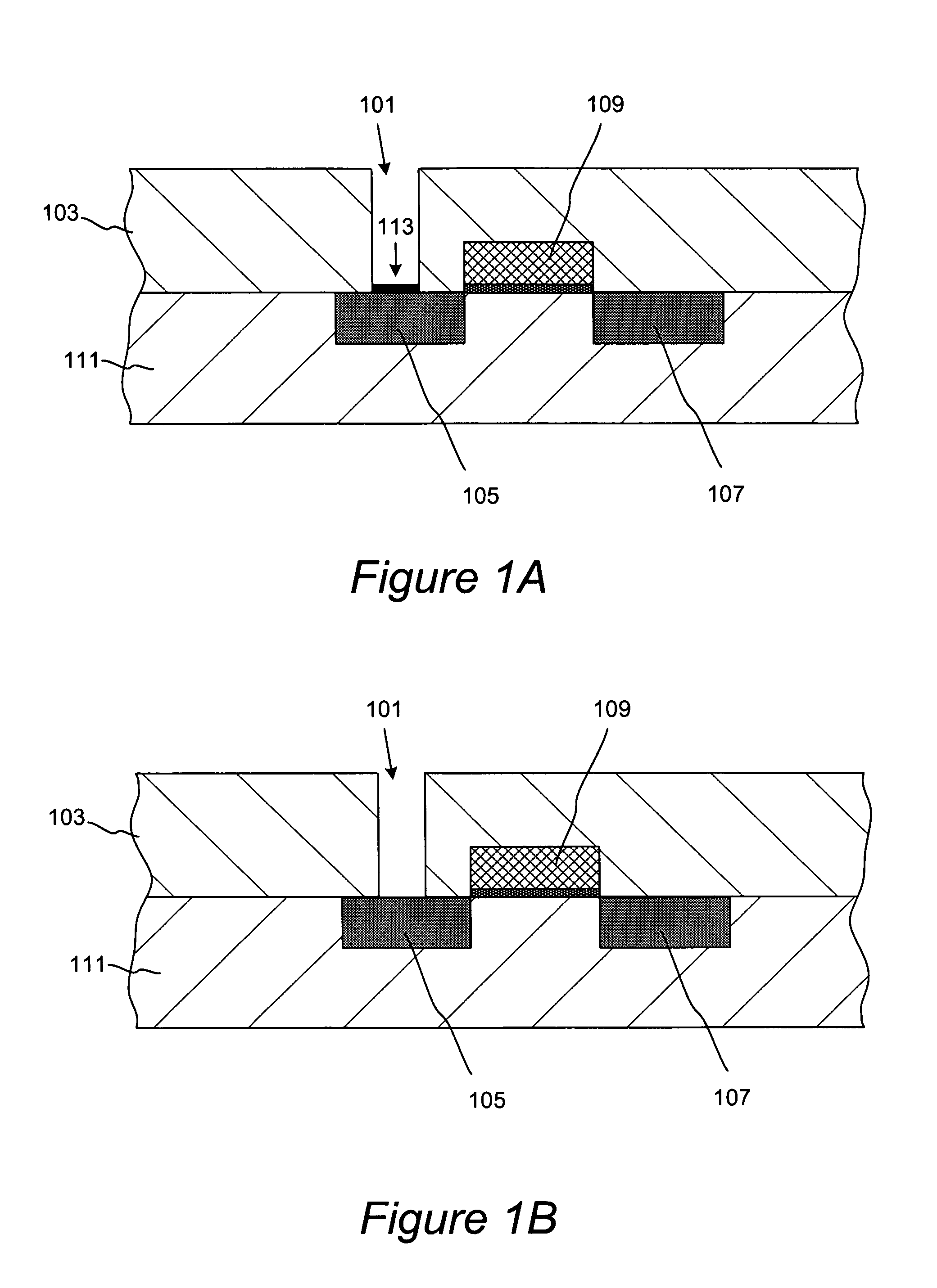

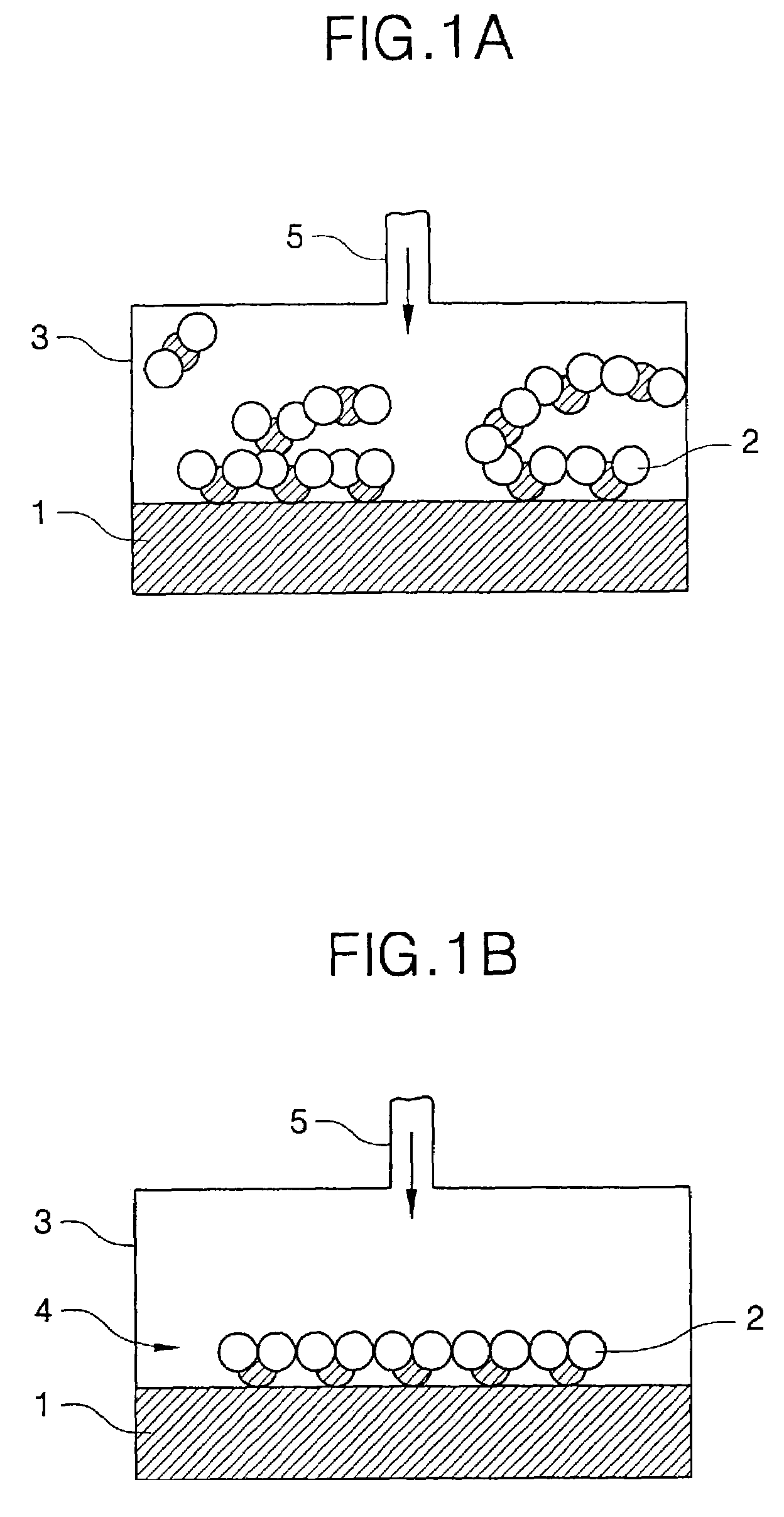

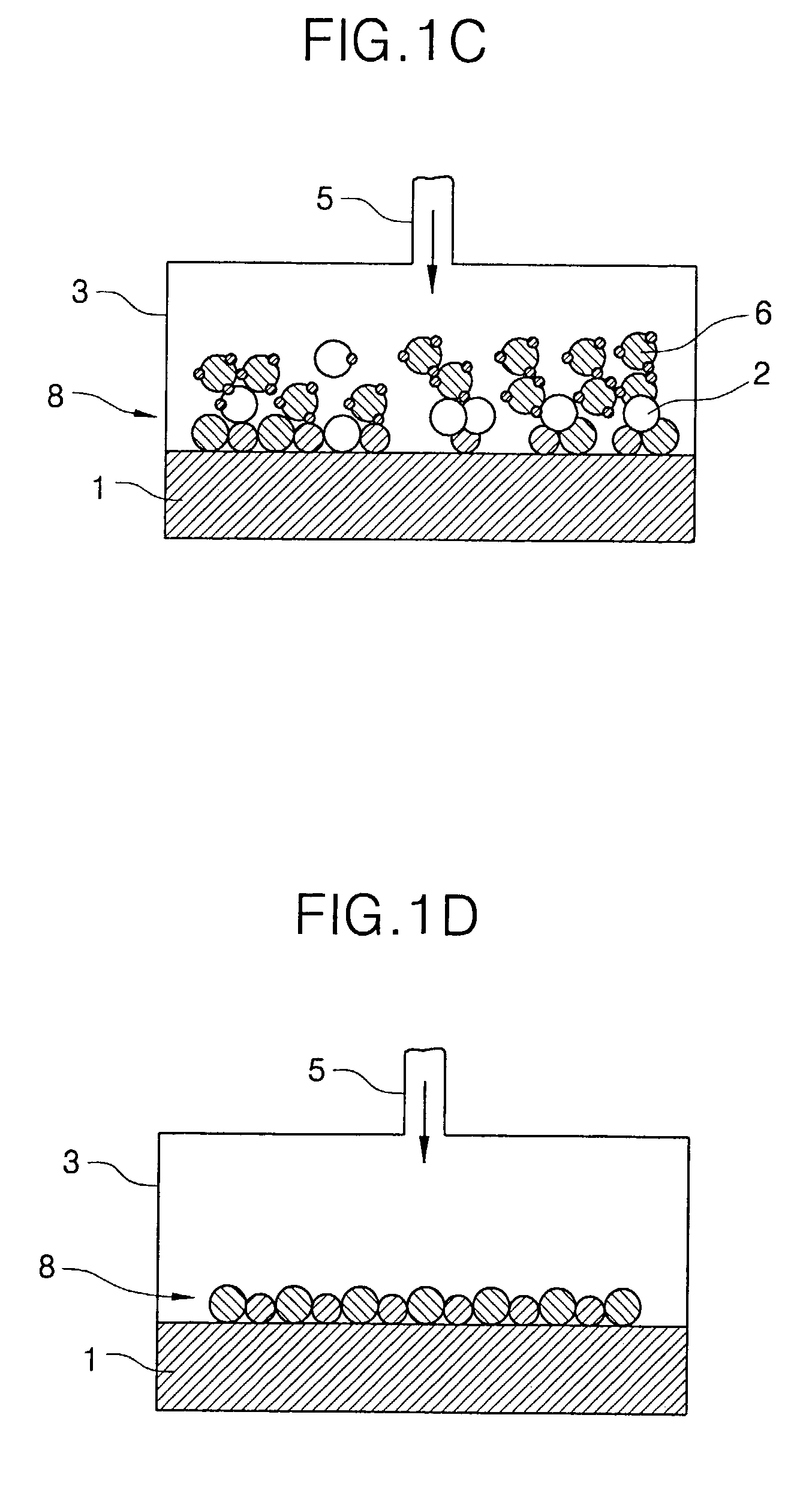

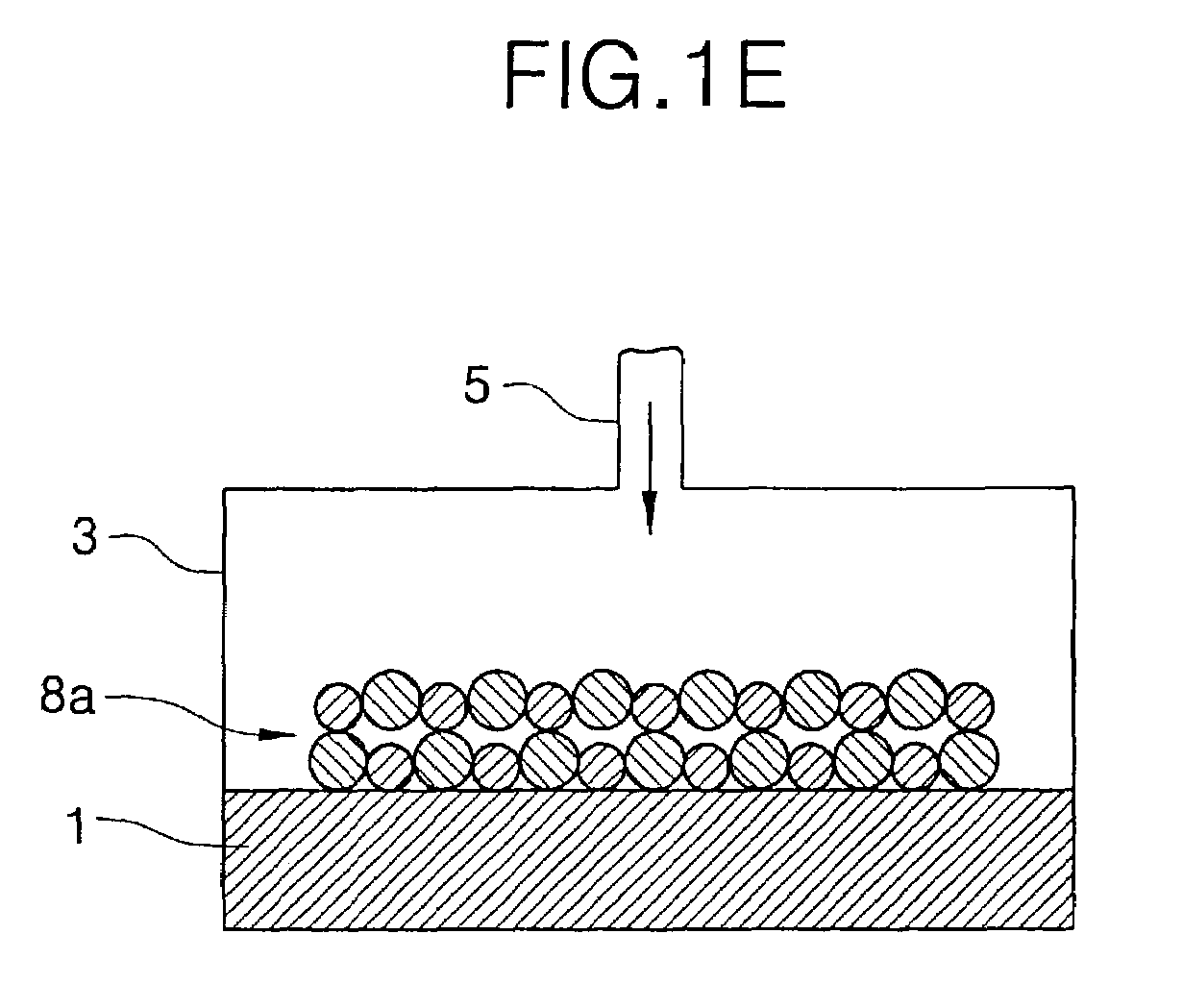

Adsorption based material removal process

InactiveUS8043972B1Decorative surface effectsSemiconductor/solid-state device manufacturingSelf limitingEtching

Methods for accurate and conformal removal of atomic layers of materials make use of the self-limiting nature of adsorption of at least one reactant on the substrate surface. In certain embodiments, a first reactant is introduced to the substrate in step (a) and is adsorbed on the substrate surface until the surface is partially or fully saturated. A second reactant is then added in step (b), reacting with the adsorbed layer of the first reactant to form an etchant. The amount of an etchant, and, consequently, the amount of etched material is limited by the amount of adsorbed first reactant. By repeating steps (a) and (b), controlled atomic-scale etching of material is achieved. These methods may be used in interconnect pre-clean applications, gate dielectric processing, manufacturing of memory devices, or any other applications where removal of one or multiple atomic layers of material is desired.

Owner:NOVELLUS SYSTEMS

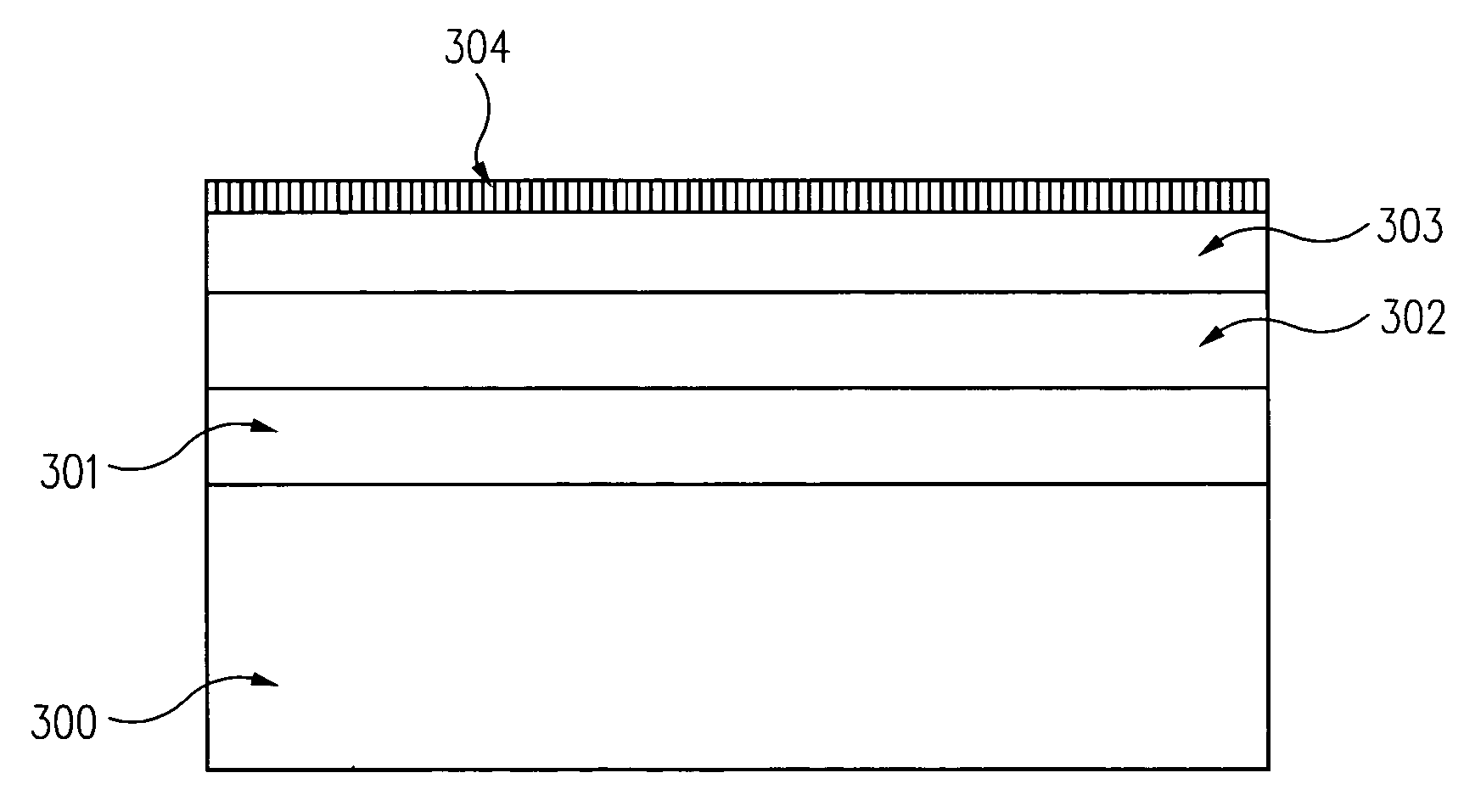

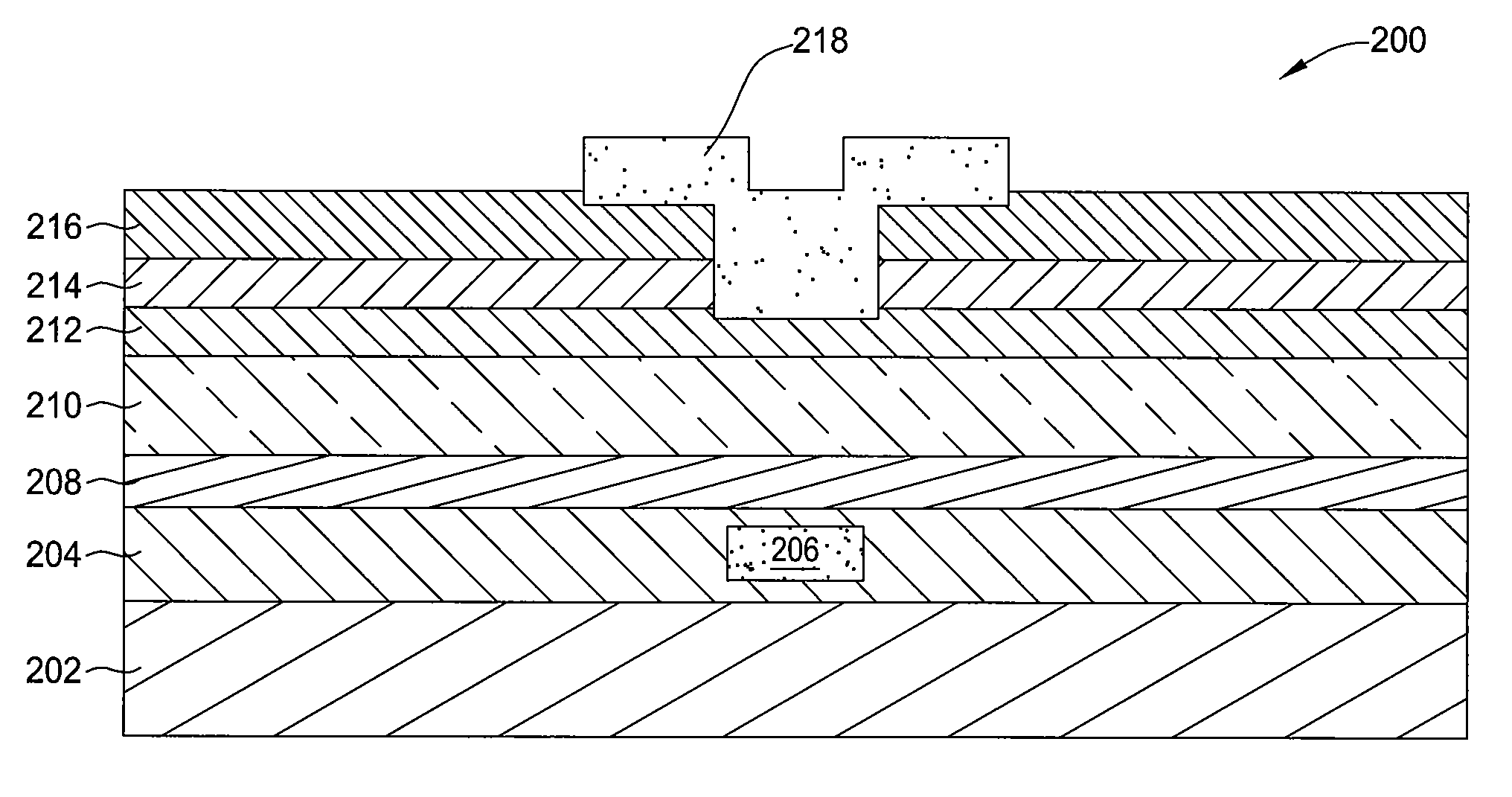

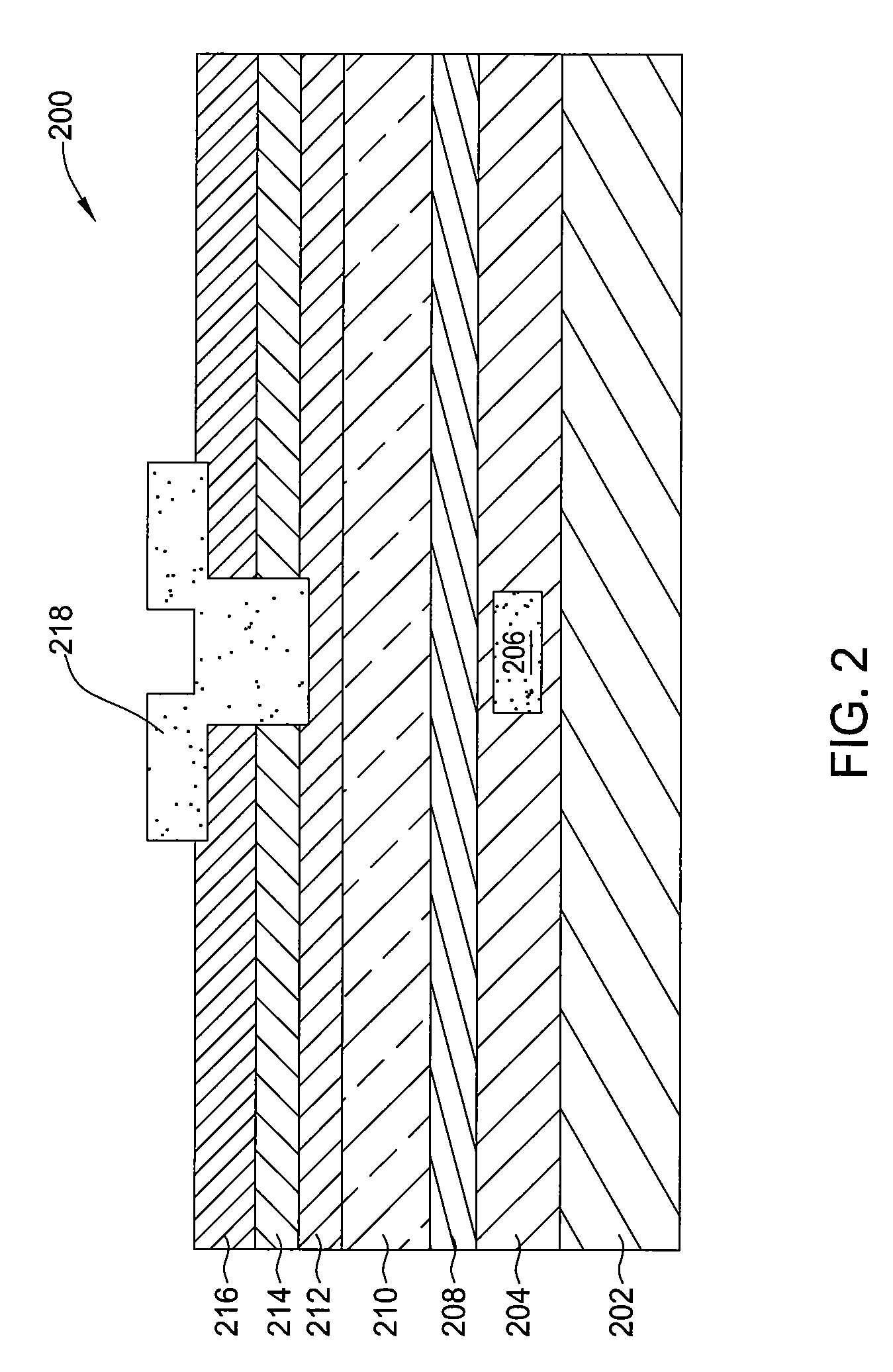

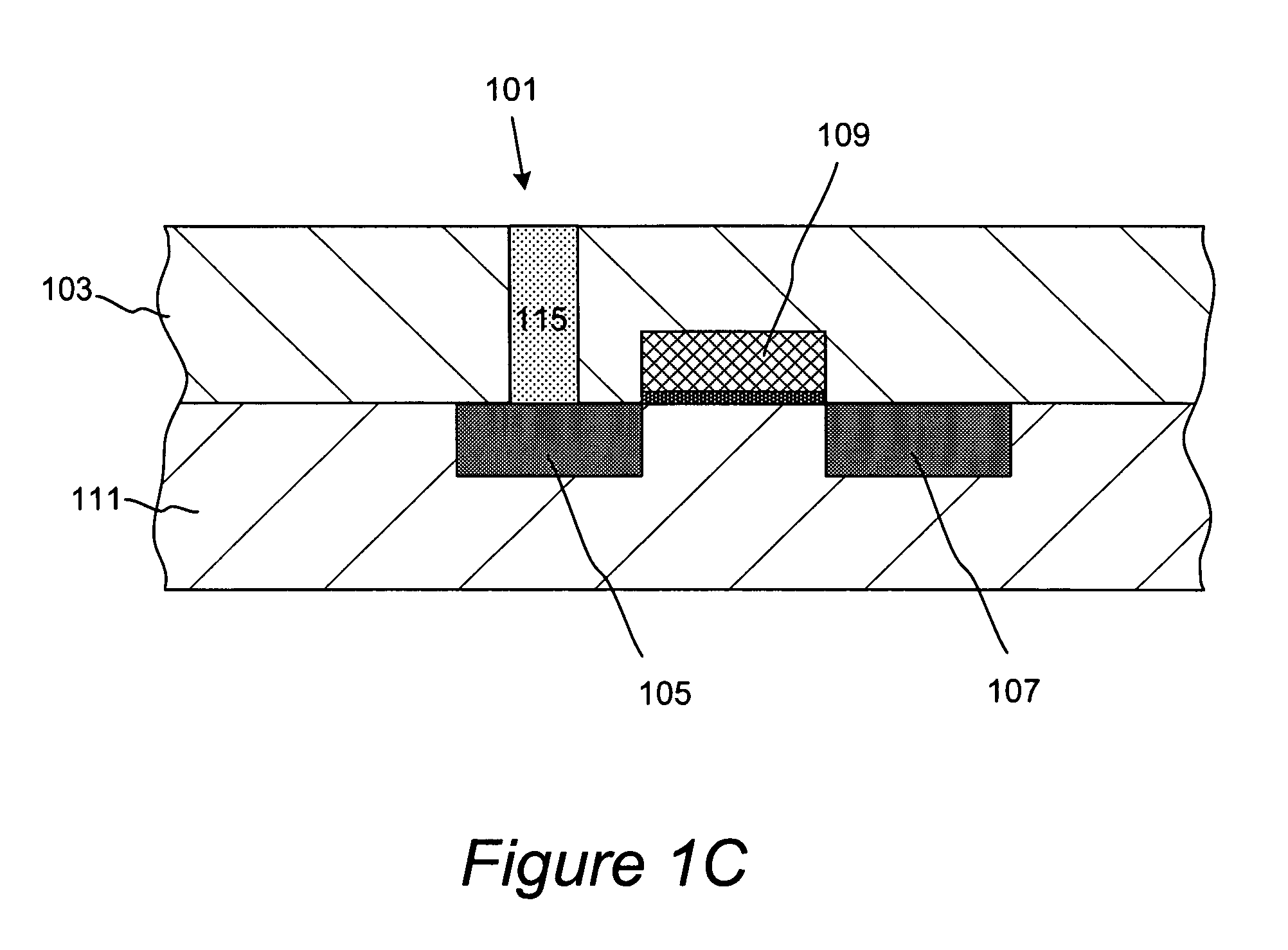

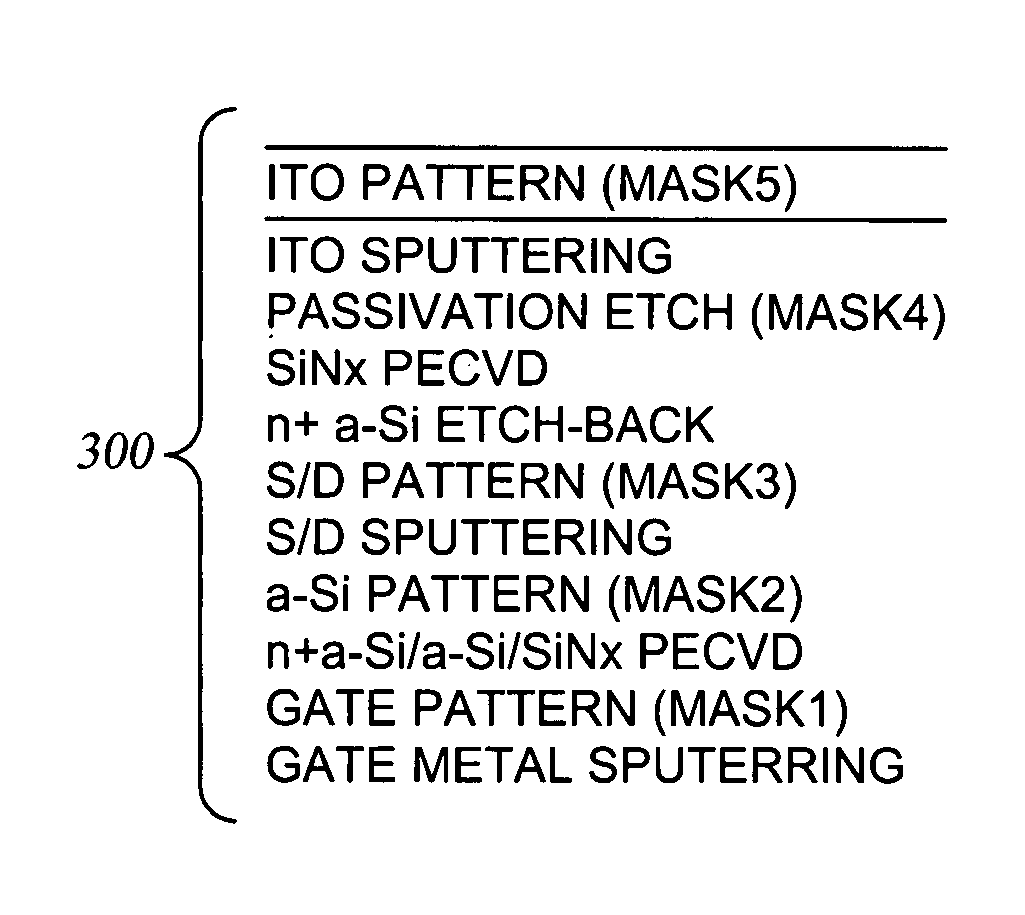

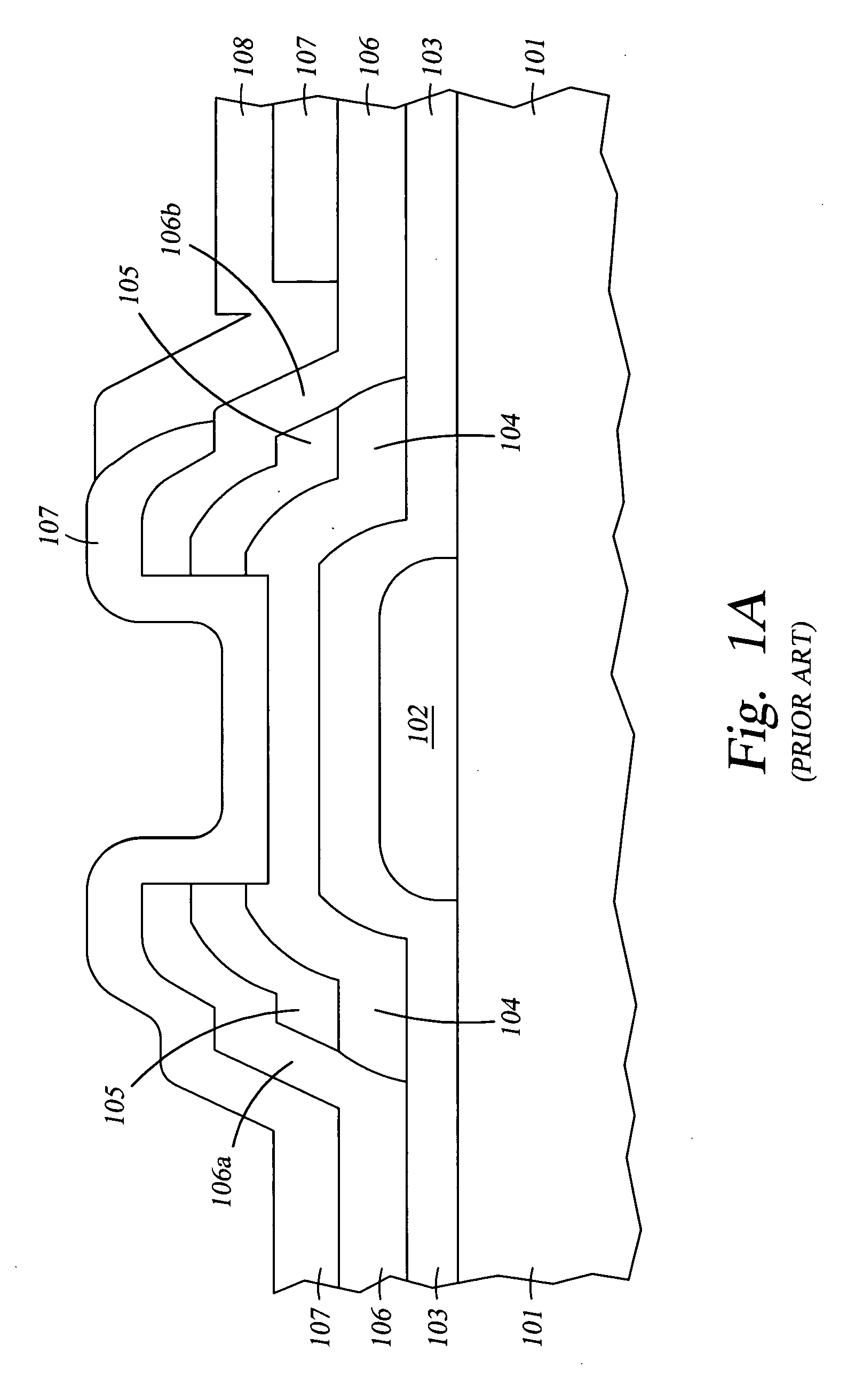

Low temperature thin film transistor process, device property, and device stability improvement

InactiveUS20090261331A1Low deposition rateIncrease deposition rateTransistorSemiconductor/solid-state device manufacturingDevice PropertiesHigh rate

A method and apparatus for forming a thin film transistor is provided. A gate dielectric layer is formed, which may be a bilayer, the first layer deposited at a low rate and the second deposited at a high rate. In some embodiments, the first dielectric layer is a silicon rich silicon nitride layer. An active layer is formed, which may also be a bilayer, the first active layer deposited at a low rate and the second at a high rate. The thin film transistors described herein have superior mobility and stability under stress.

Owner:APPLIED MATERIALS INC

Method of forming mixed rare earth oxynitride and aluminum oxynitride films by atomic layer deposition

InactiveUS20070237699A1Aluminium compoundsSemiconductor/solid-state device manufacturingGate dielectricRare earth

A method is provided for depositing a gate dielectric that includes at least two rare earth metal elements in the form of an oxynitride or an aluminum oxynitride. The method includes disposing a substrate in a process chamber and exposing the substrate to a gas pulse containing a first rare earth precursor and to a gas pulse containing a second rare earth precursor. The substrate may also optionally be exposed to a gas pulse containing an aluminum precursor. Sequentially after each precursor gas pulse, the substrate is exposed to a gas pulse of an oxygen-containing gas, nitrogen-containing gas or an oxygen- and nitrogen-containing gas. In alternative embodiments, the first and second rare earth precursors may be pulsed together, and either or both may be pulsed together with the aluminum precursor. The first and second rare earth precursors comprise a different rare earth metal element. The sequential exposing steps may be repeated to deposit a mixed rare earth oxynitride or aluminum oxynitride layer with a desired thickness. Purge or evacuation steps may also be performed after each gas pulse.

Owner:TOKYO ELECTRON LTD

Adsorption based material removal process

Methods for accurate and conformal removal of atomic layers of materials make use of the self-limiting nature of adsorption of at least one reactant on the substrate surface. In certain embodiments, a first reactant is introduced to the substrate in step (a) and is adsorbed on the substrate surface until the surface is partially or fully saturated. A second reactant is then added in step (b), reacting with the adsorbed layer of the first reactant to form an etchant. The amount of an etchant, and, consequently, the amount of etched material is limited by the amount of adsorbed first reactant. By repeating steps (a) and (b), controlled atomic-scale etching of material is achieved. These methods may be used in interconnect pre-clean applications, gate dielectric processing, manufacturing of memory devices, or any other applications where removal of one or multiple atomic layers of material is desired.

Owner:NOVELLUS SYSTEMS

Method of controlling the film properties of a CVD-deposited silicon nitride film

InactiveUS20060019502A1Increase wet etch rateEasy to controlSemiconductor/solid-state device manufacturingChemical vapor deposition coatingGate dielectricGas composition

We have discovered that adding H2 to a precursor gas composition including SiH4, NH3, and N2 is effective at improving the wet etch rate and the wet etch rate uniformity across the substrate surface of a-SiNx:H films which are deposited on a substrate by PECVD. Wet etch rate is an indication of film density. Typically, the lower the wet etch rate, the denser the film. The addition of H2 to the SiH4 / NH3 / N2 precursor gas composition did not significantly increase the variation in deposited film thickness across the surface of the substrate. The a-SiNx:H films described herein are particularly useful as TFT gate dielectrics in the production of flat panel displays. The uniformity of the film across the substrate enables the production of flat panel displays having surface areas of 25,000 cm2 and larger.

Owner:APPLIED MATERIALS INC

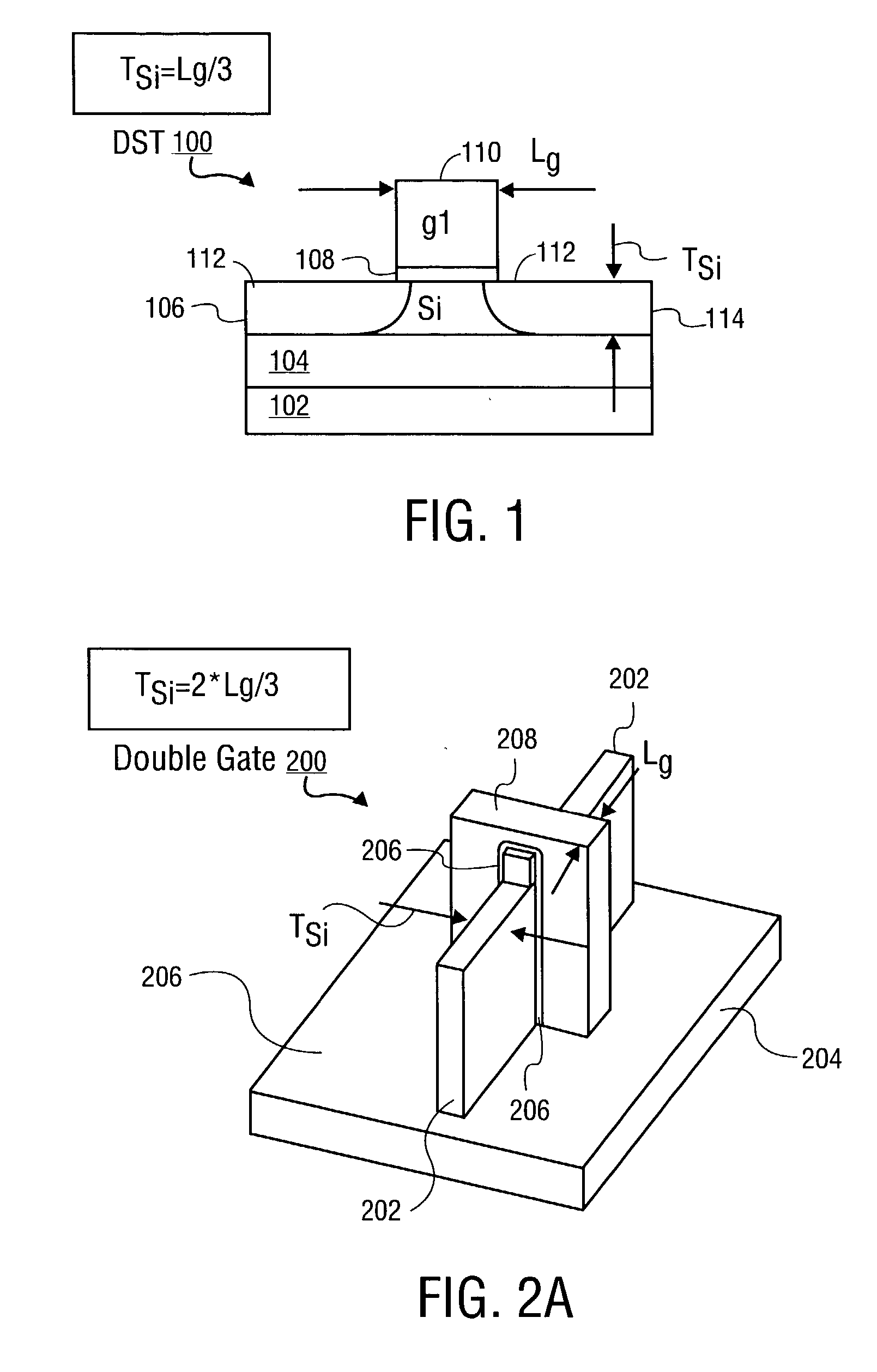

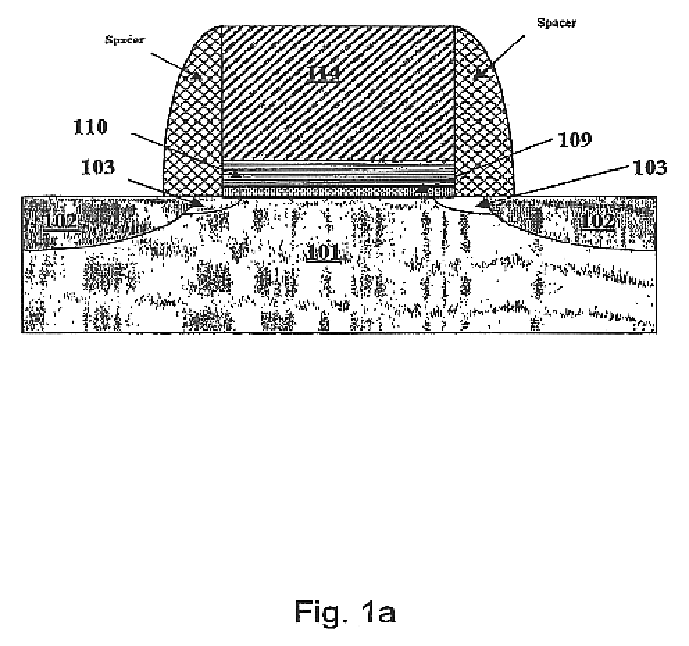

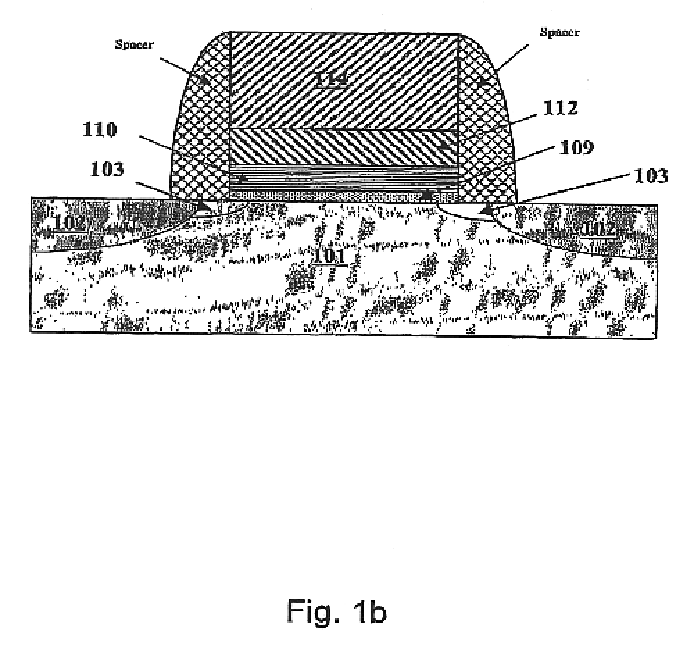

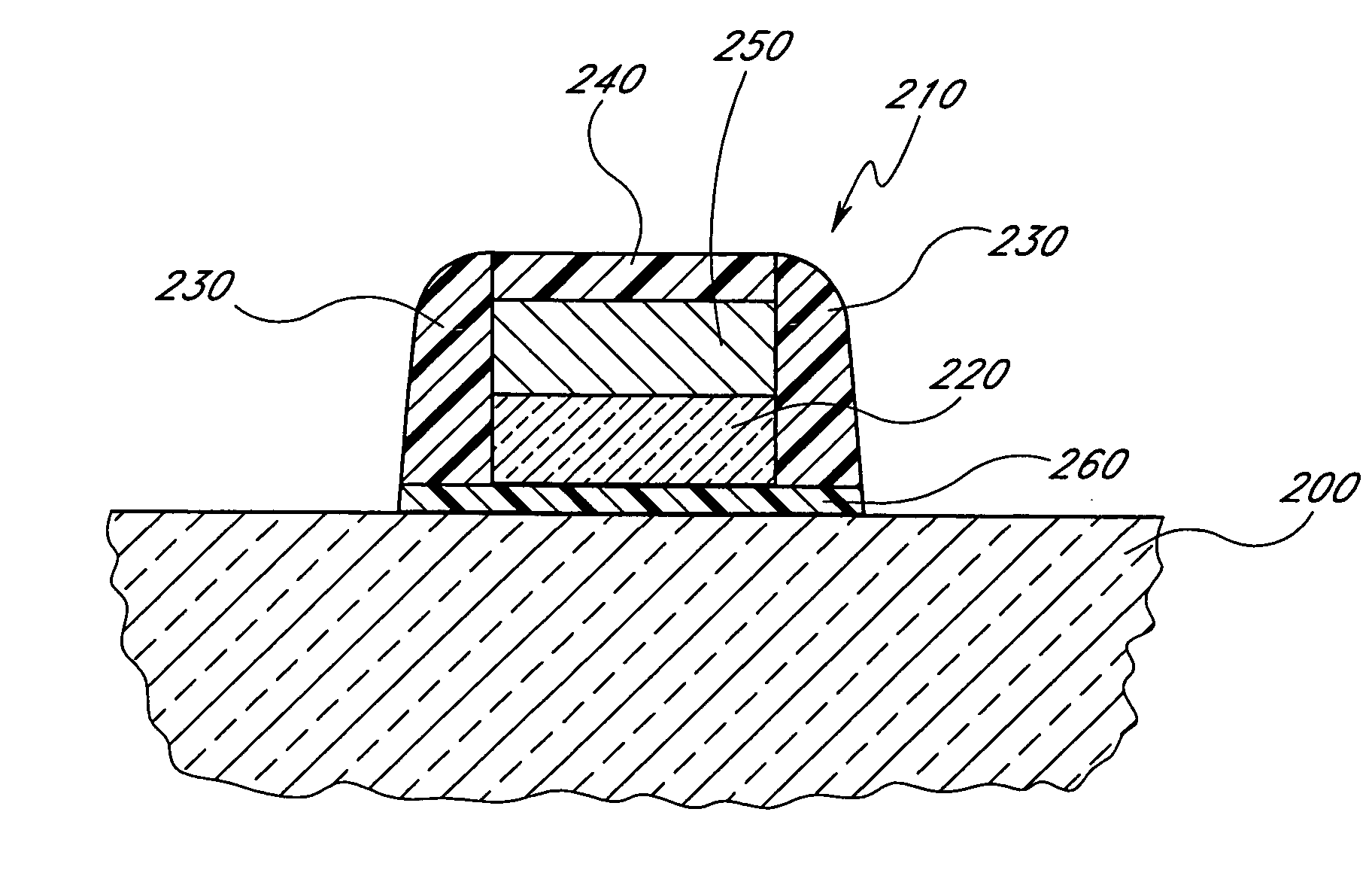

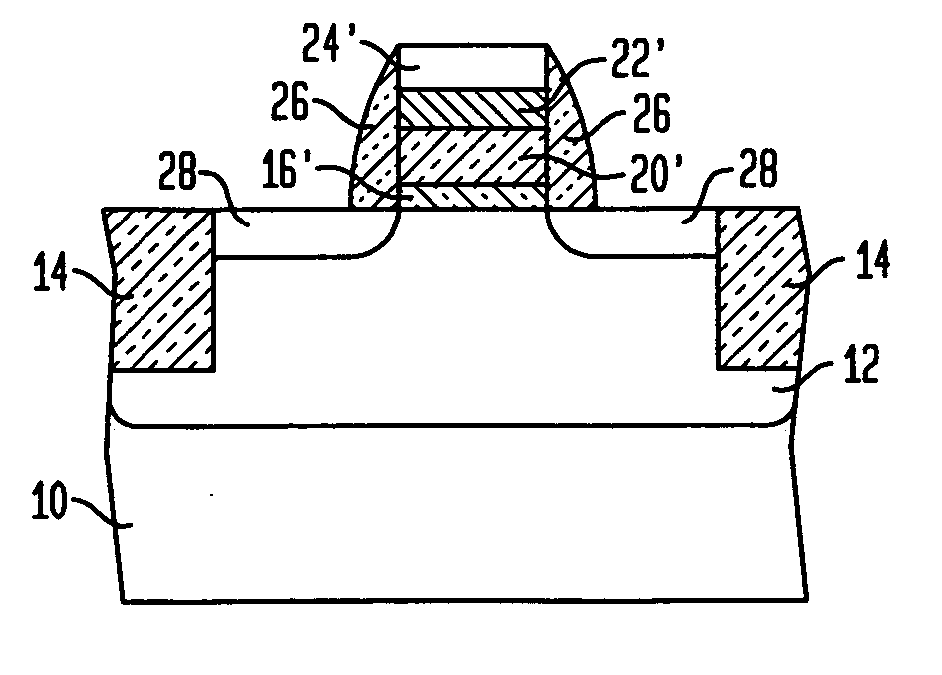

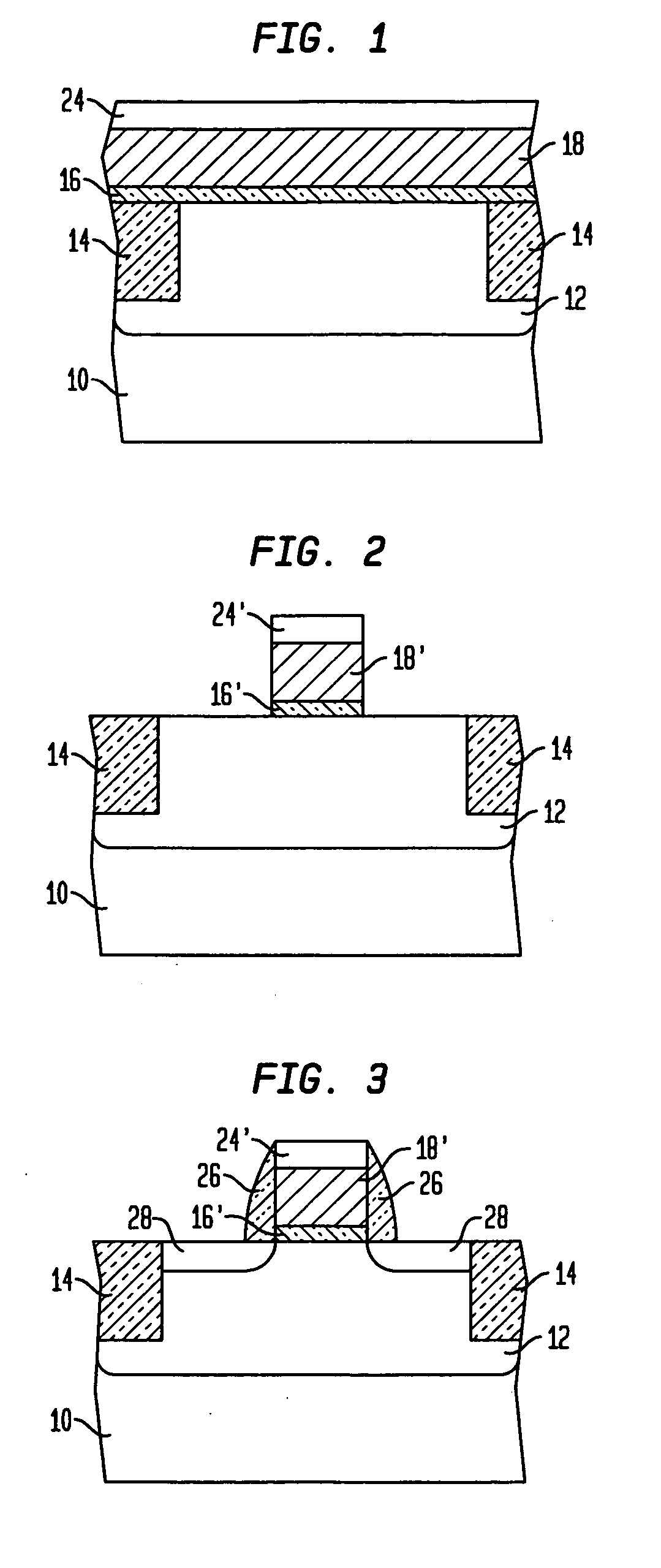

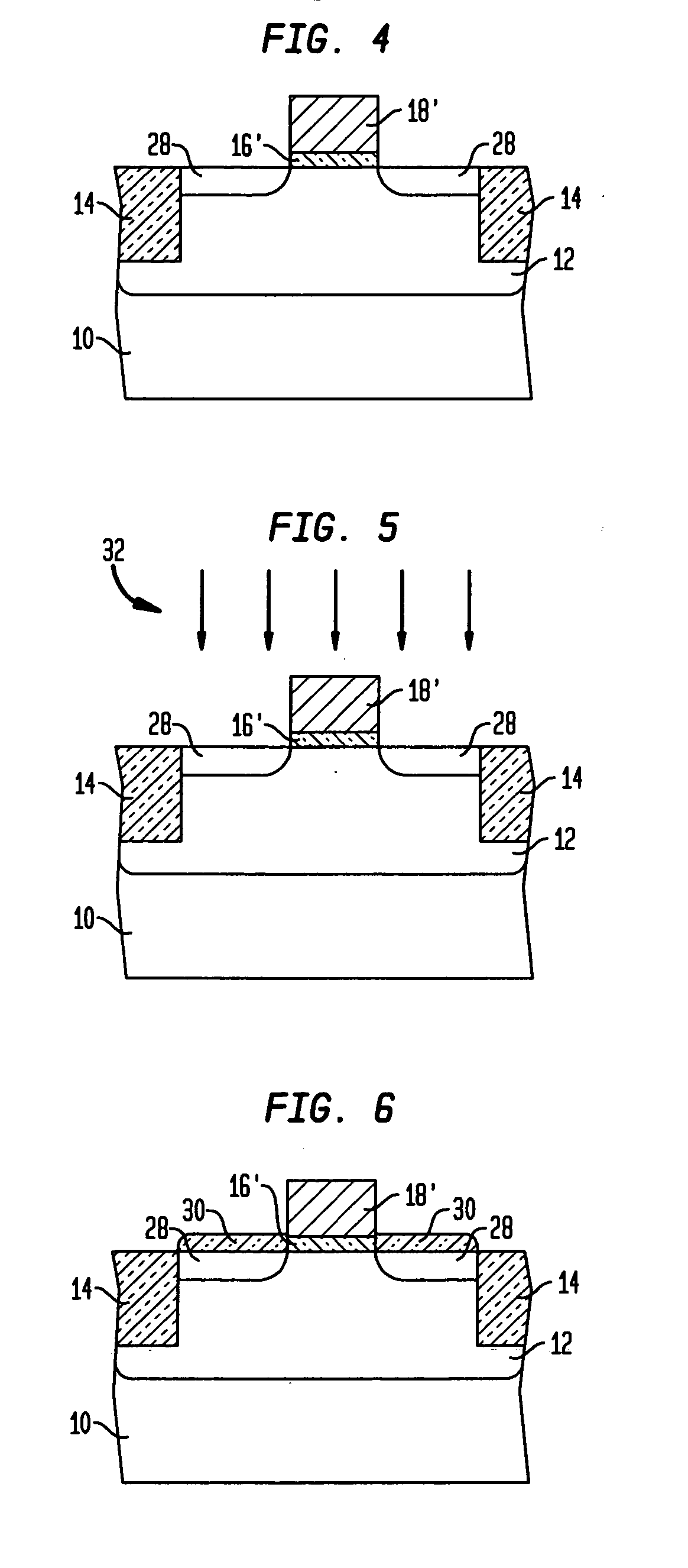

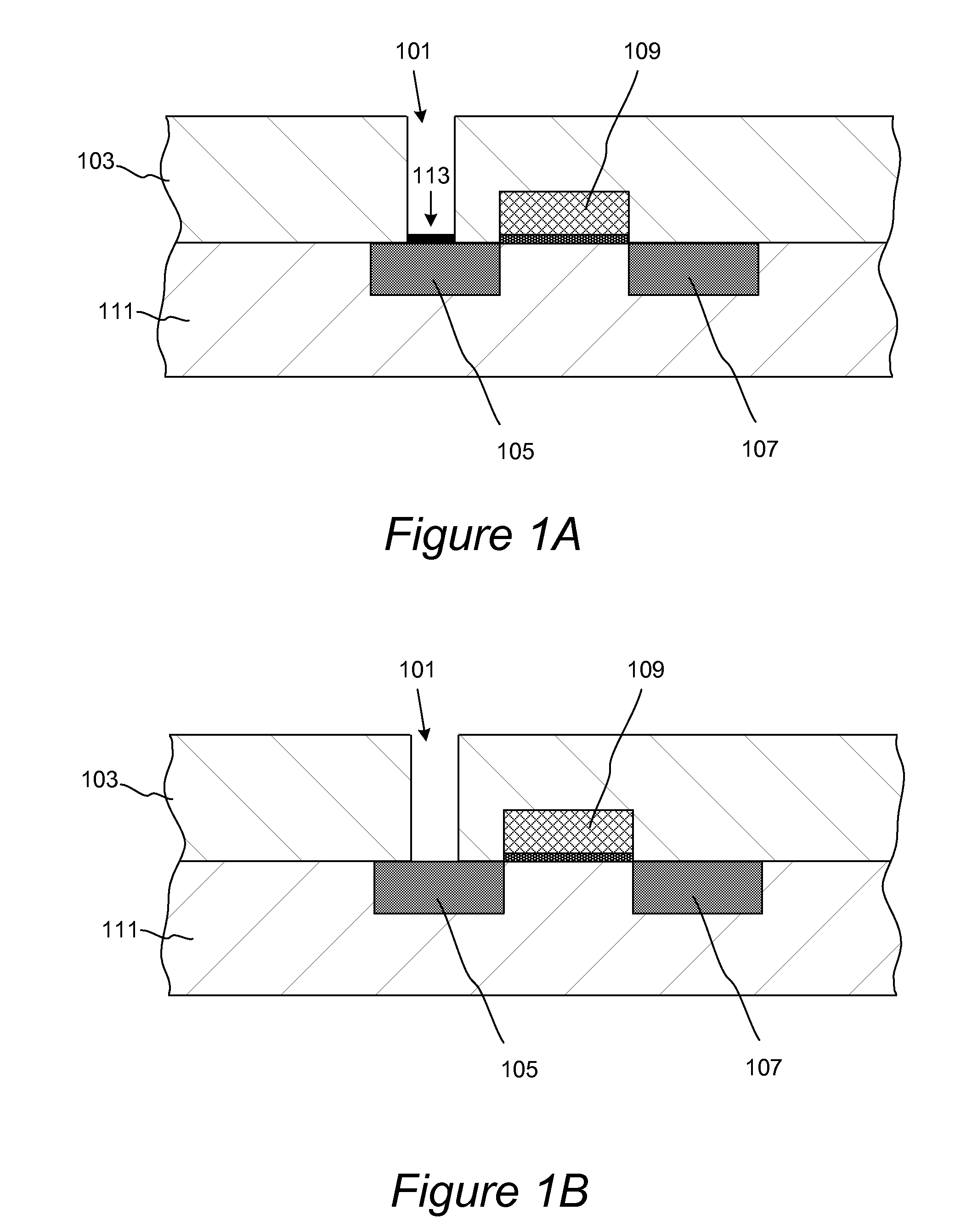

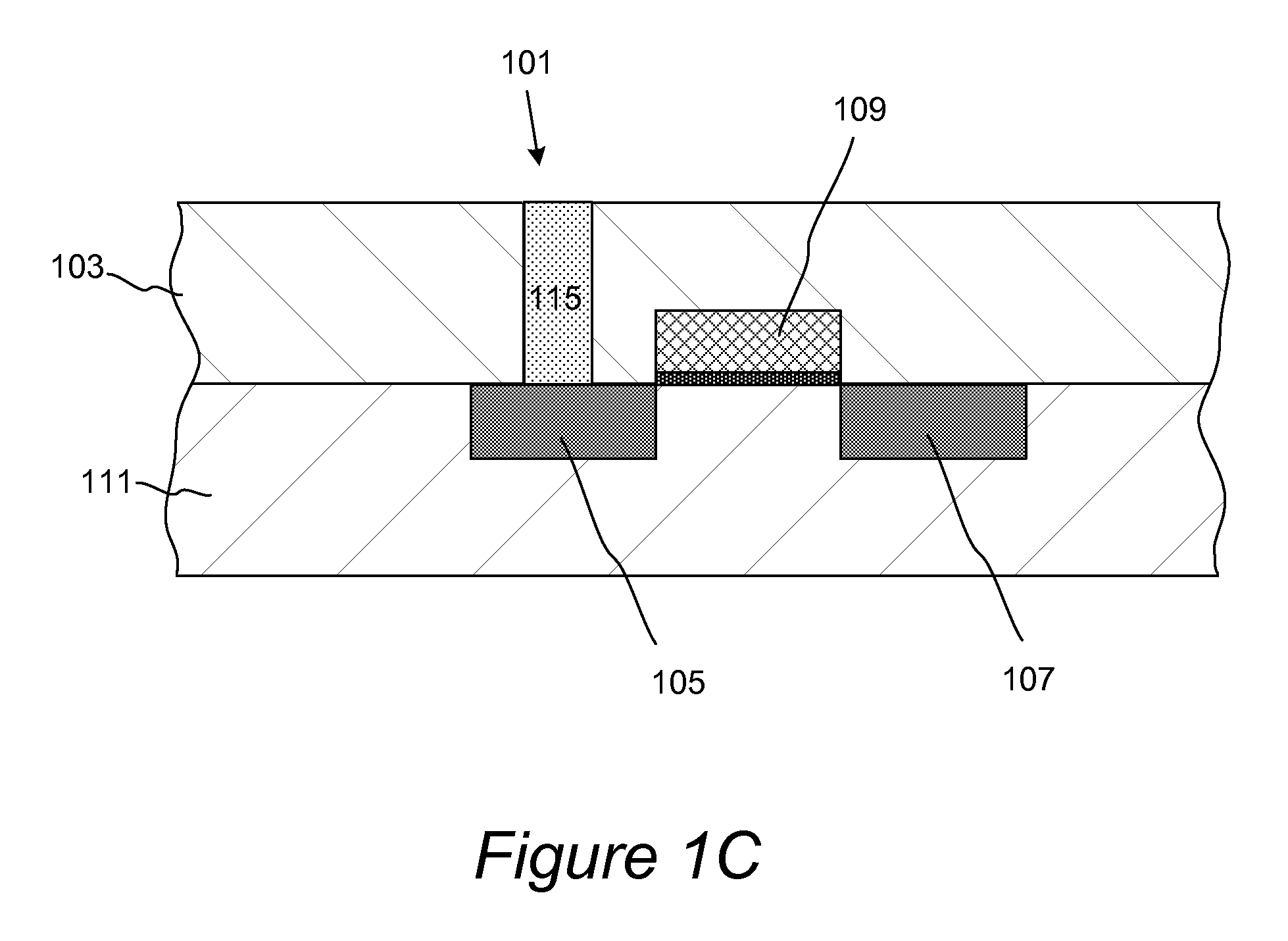

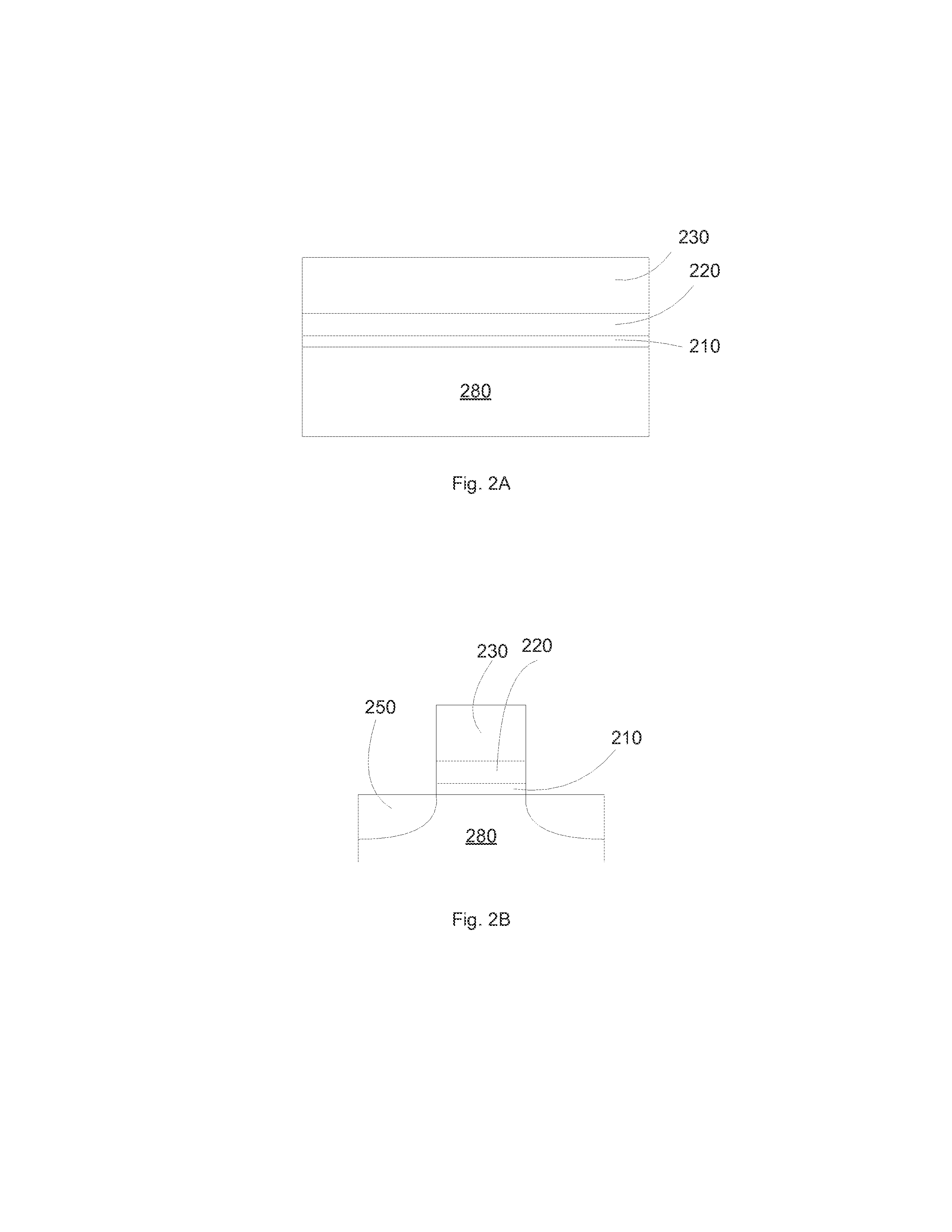

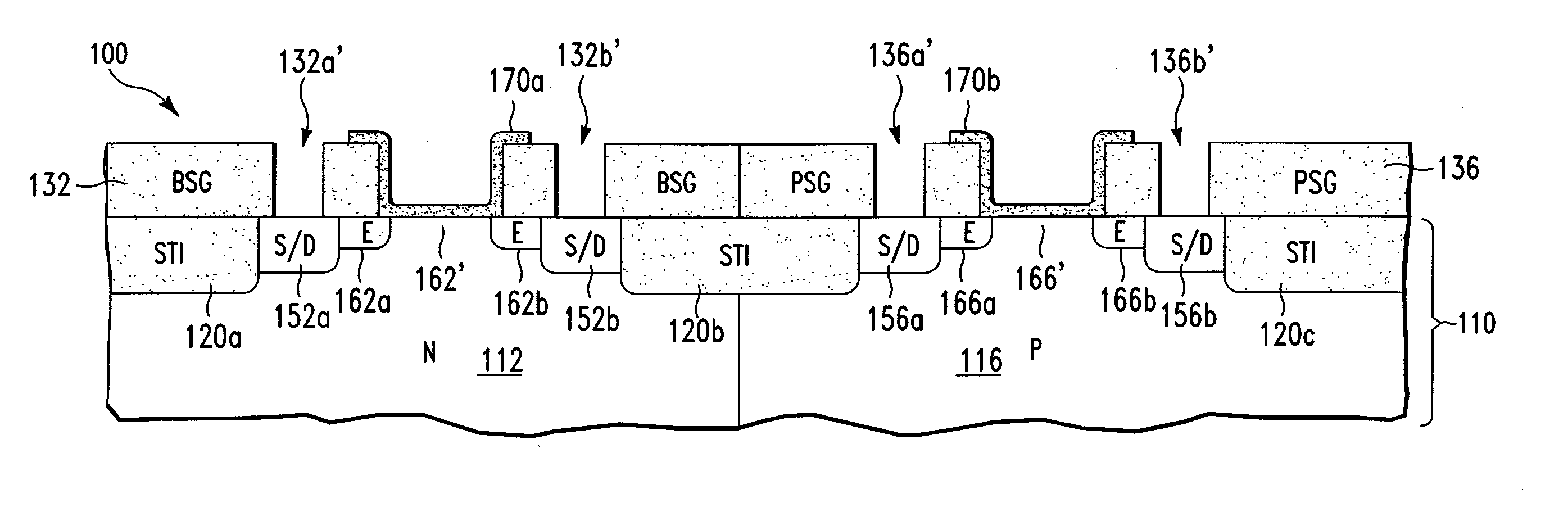

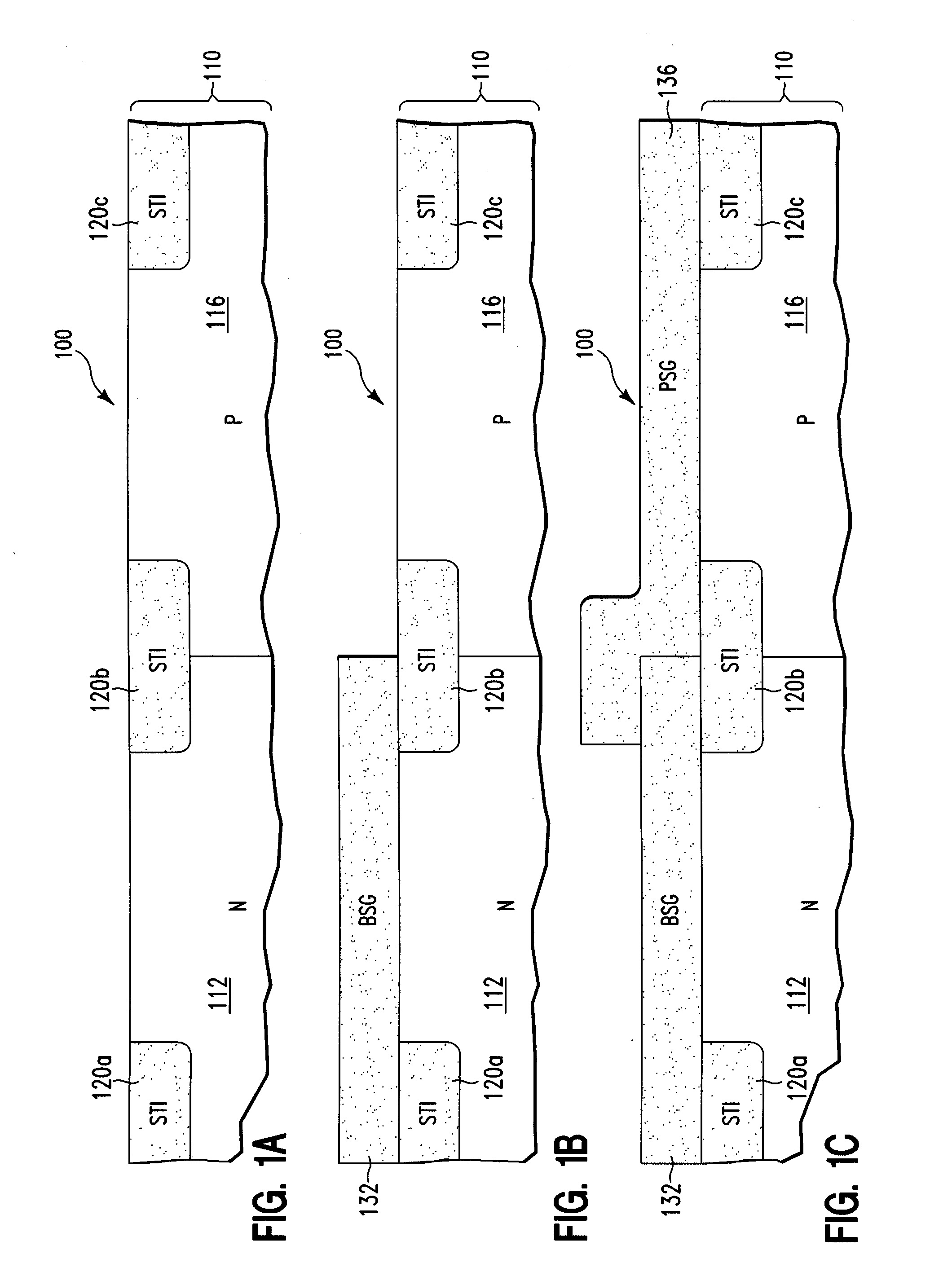

RAISED STI PROCESS FOR MULTIPLE GATE OX AND SIDEWALL PROTECTION ON STRAINED Si/SGOI STRUCTURE WITH ELEVATED SOURCE/DRAIN

InactiveUS20050277271A1Eliminating unnecessary poly over etchingTaller in heightTransistorFrom solid stateGate dielectricActive devices

The present invention provides a strained / SGOI structure that includes an active device region of a relaxed SiGe layer, a strained Si layer located atop the relaxed SiGe layer, a raised source / drain region located atop a portion of the strained Si layer, and a stack comprising at least a gate dielectric and a gate polySi located on another portion of the strained Si layer; and a raised trench oxide region surrounding the active device region. The present invention also provides a method of forming such a structure. In the inventive method, the gate dielectric is formed prior to trench isolation formation thereby avoiding many of the problems associated with prior art processes in which the trench oxide is formed prior to gate dielectric formation.

Owner:GLOBALFOUNDRIES INC

Silicon oxide cap over high dielectric constant films

InactiveUS20060211259A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingGate dielectricThermal chemical vapor deposition

A method for forming an integrated circuit structure on a semiconductor substrate comprises depositing a high k gate dielectric material over the substrate using an atomic layer deposition process. A silicon oxide capping layer is deposited over the gate dielectric material in a rapid thermal chemical vapor deposition process. A gate electrode is formed over the silicon oxide capping layer.

Owner:ASM AMERICA INC

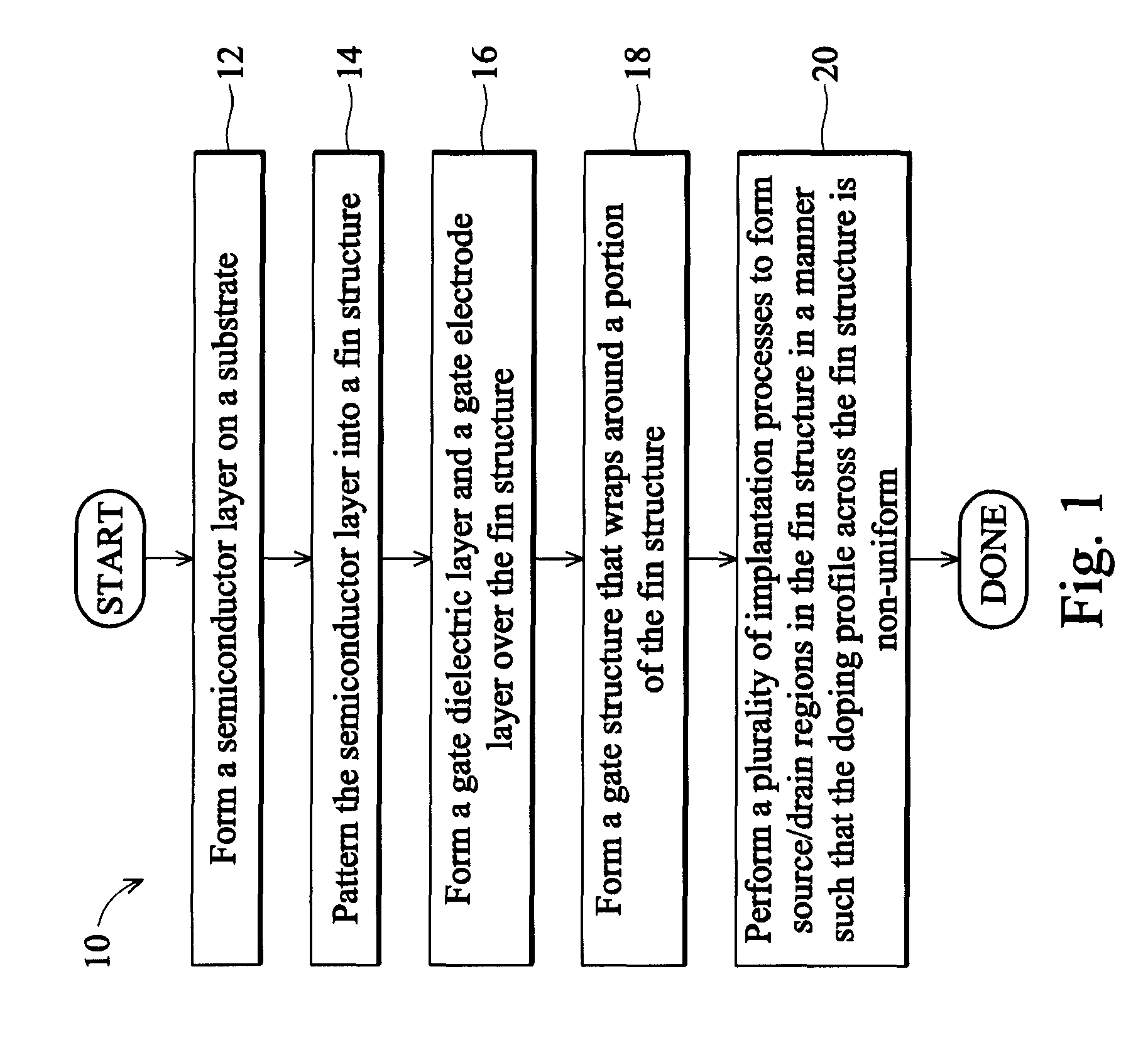

Non-uniform channel junction-less transistor

ActiveUS8487378B2Easy to controlImprove device densitySolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricSemiconductor

Owner:TAIWAN SEMICON MFG CO LTD

Methods of forming atomic layers of a material on a substrate by sequentially introducing precursors of the material

InactiveUS7201943B2Easy to integrateHigh dielectric constantVacuum evaporation coatingSemiconductor/solid-state device manufacturingGate dielectricTitanium

A thin film is formed using an atomic layer deposition process, by introducing a first reacting material including tantalum precursors and titanium precursors onto a substrate. A portion of the first reacting material is chemisorbed onto the substrate. Then, a second reacting material including oxygen is introduced onto the substrate. A portion of the second reacting material is also chemisorbed onto the substrate, to form an atomic layer of a solid material on the substrate. The solid material may be used as a dielectric layer of the capacitor and / or a gate dielectric layer of the transistor.

Owner:SAMSUNG ELECTRONICS CO LTD

Methods of atomic layer deposition of hafnium oxide / erbium oxide bi-layer as advanced gate dielectrics

InactiveUS20130313656A1Improve electrical performanceFew defectSemiconductor/solid-state device manufacturingChemical vapor deposition coatingGate dielectricHafnium

Provided is a two-step ALD deposition process for forming a gate dielectric involving an erbium oxide layer deposition followed by a hafnium oxide layer deposition. Hafnium oxide can provide a high dielectric constant, high density, large bandgap and good thermal stability. Erbium oxide can act as a barrier against oxygen diffusion, which can lead to increasing an effective oxide thickness of the gate dielectric and preventing hafnium-silicon reactions that may lead to higher leakage current.

Owner:INTERMOLECULAR

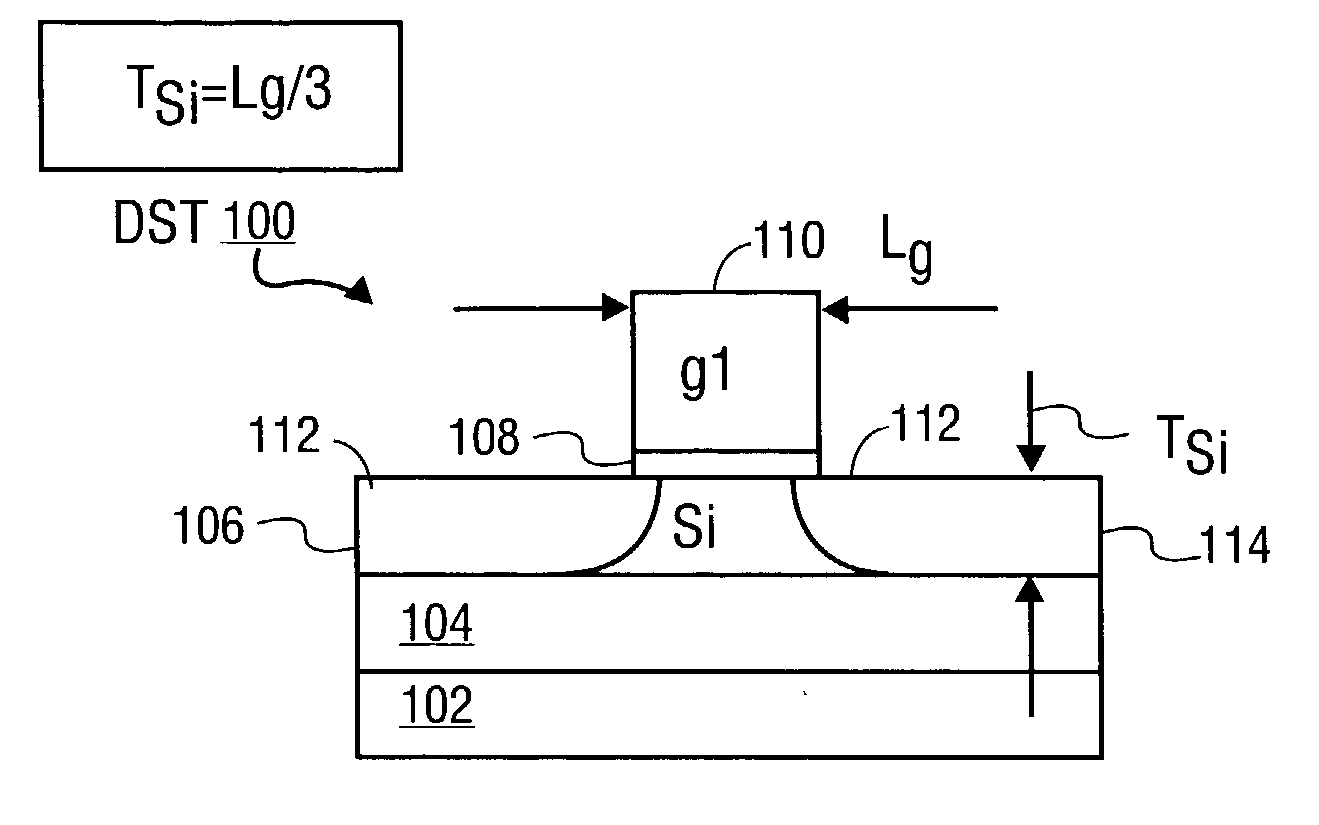

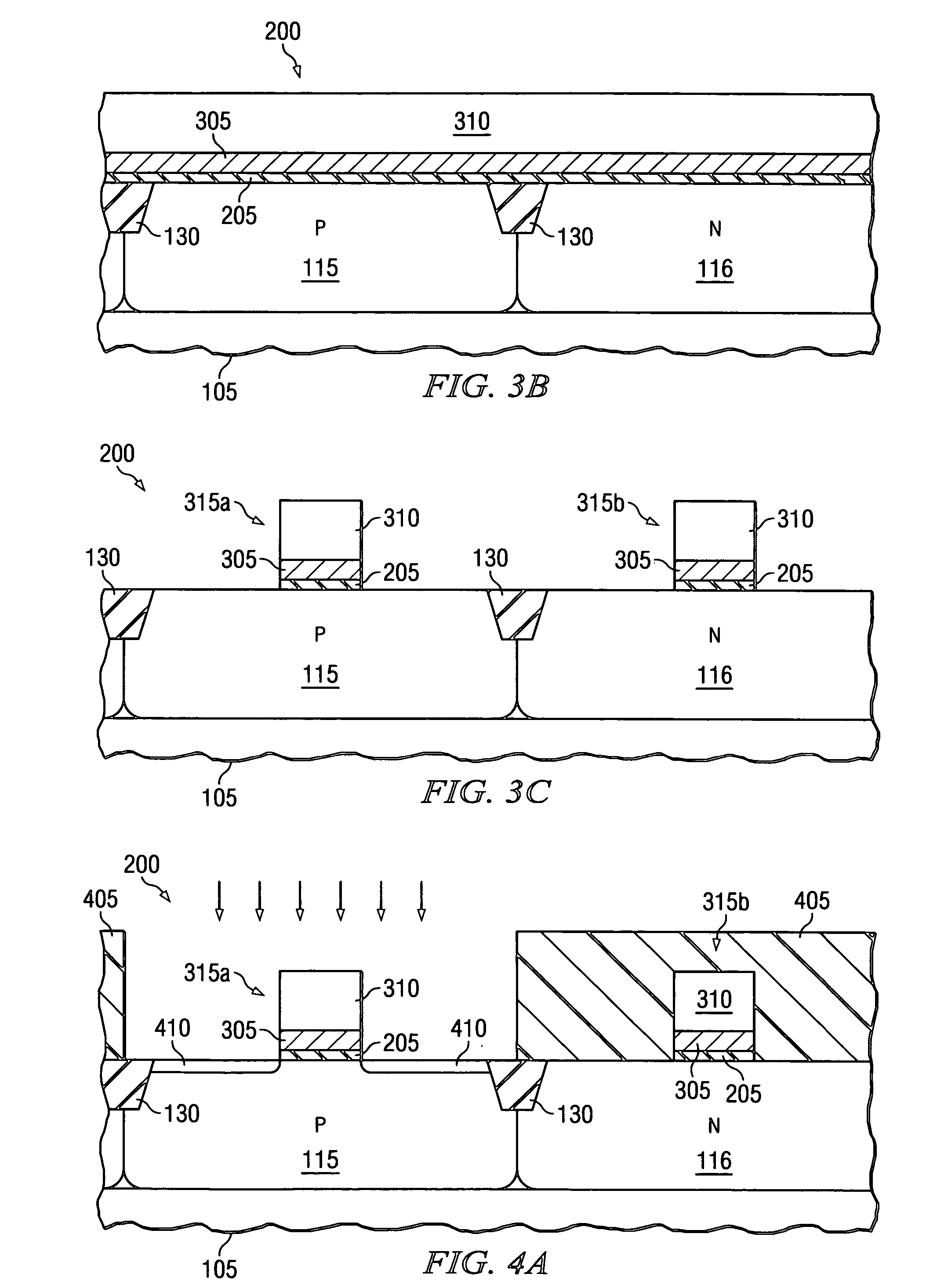

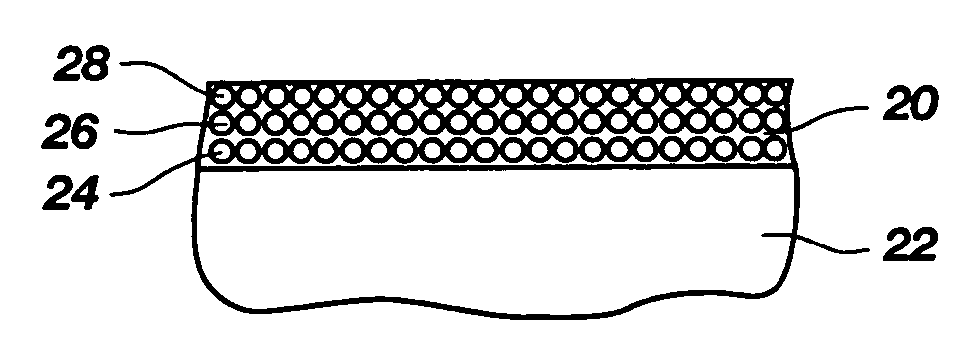

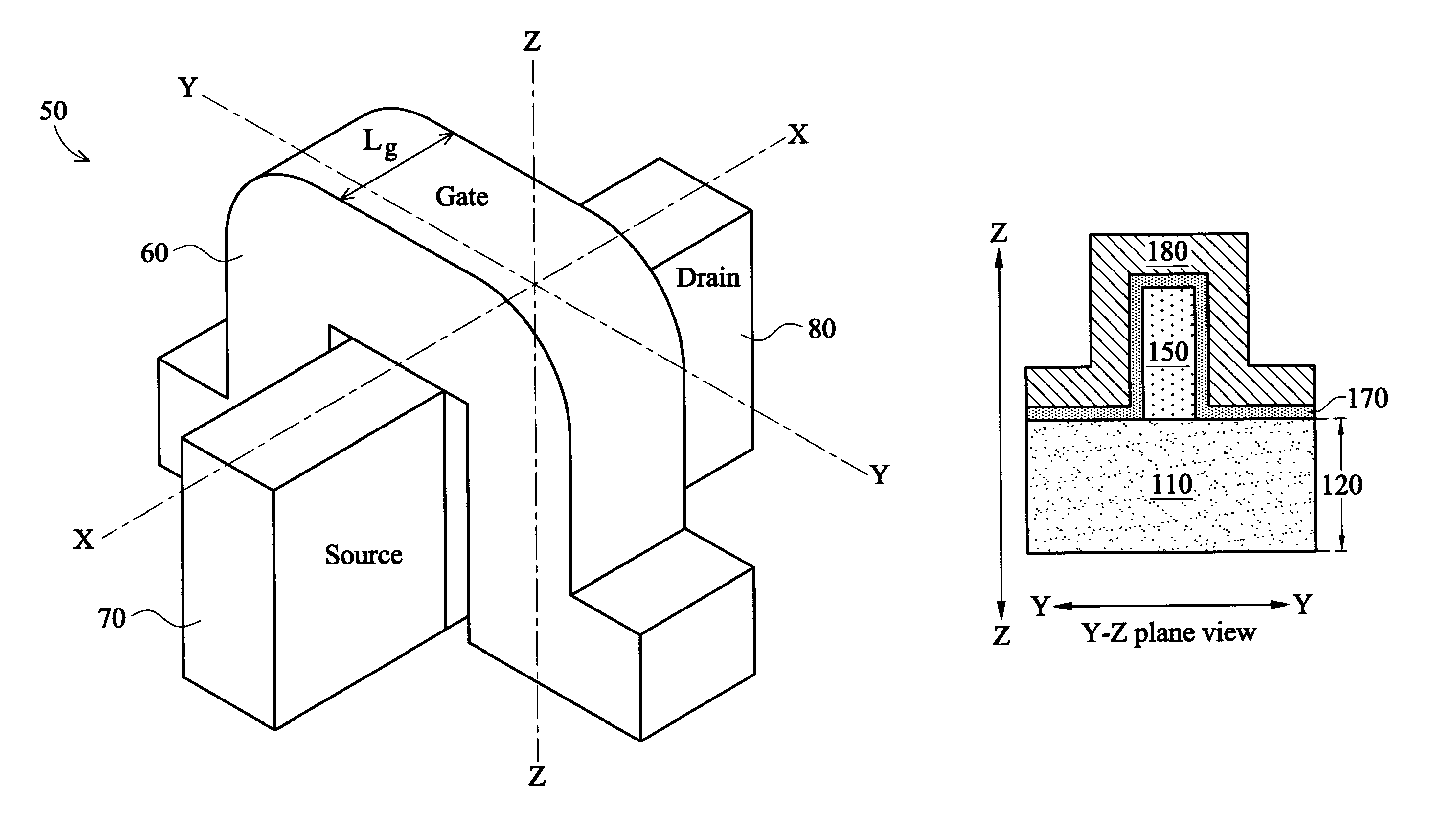

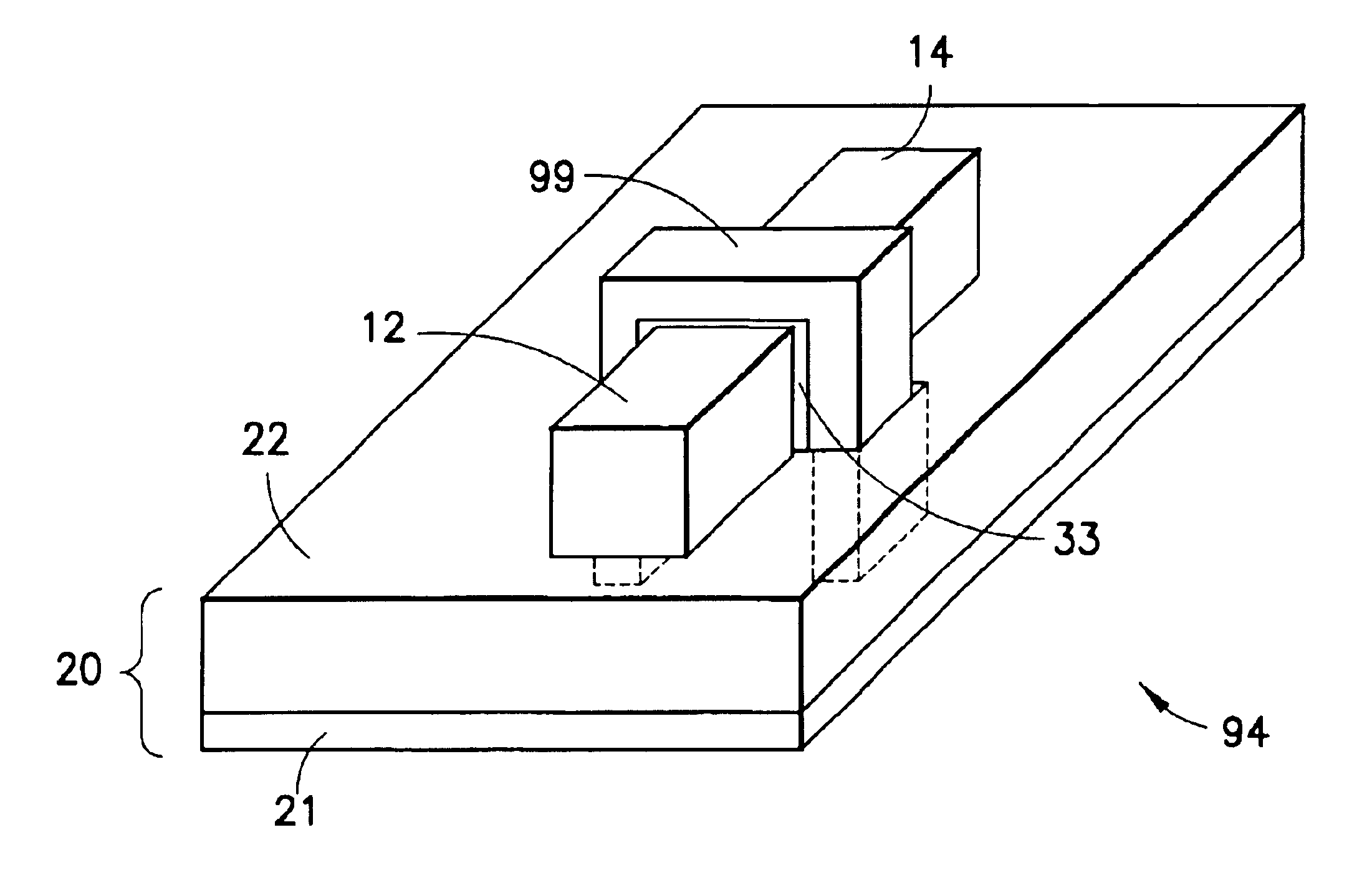

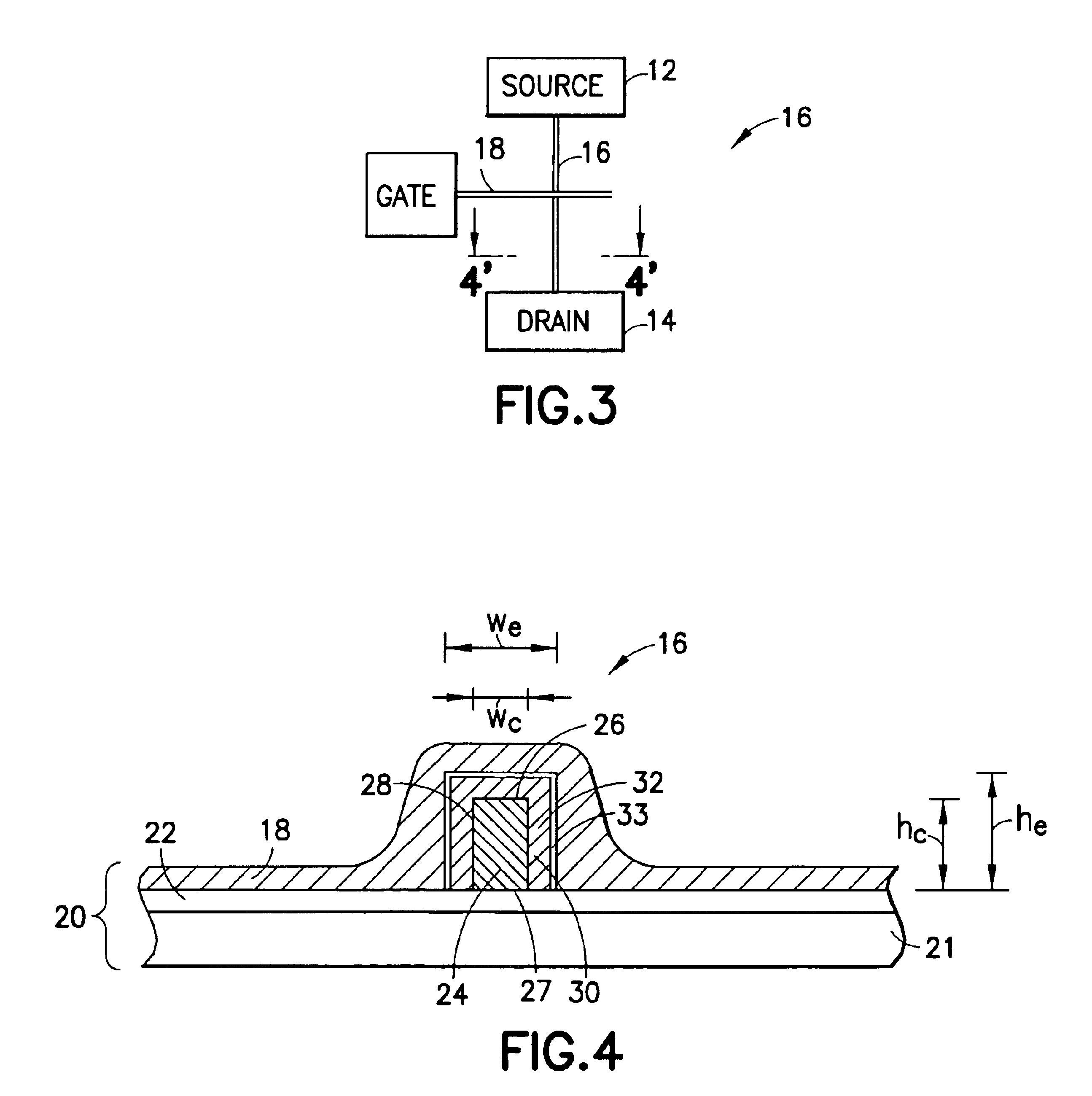

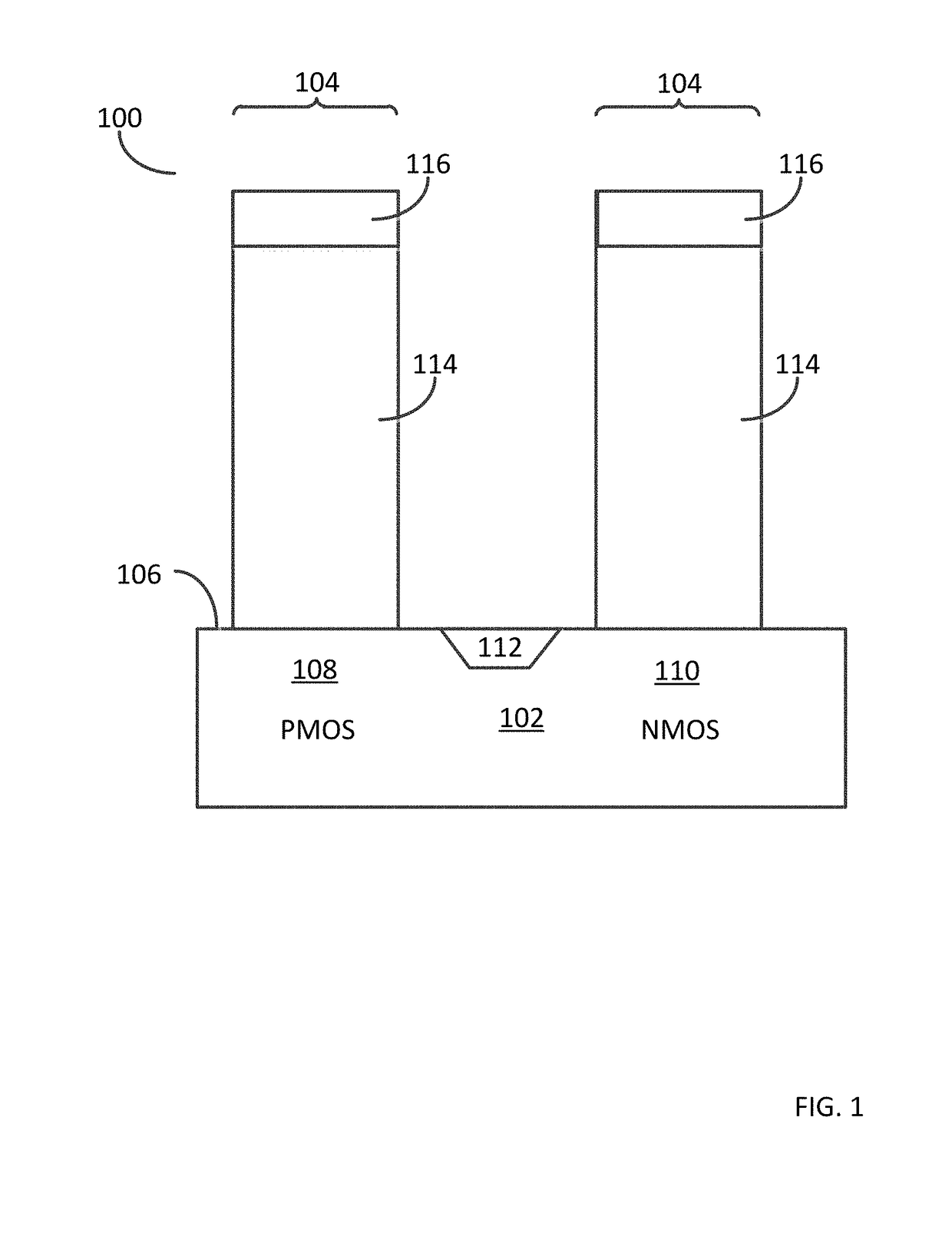

FET channel having a strained lattice structure along multiple surfaces

InactiveUS6921982B2Improve conductivityTransistorSolid-state devicesGate dielectricSemiconductor materials

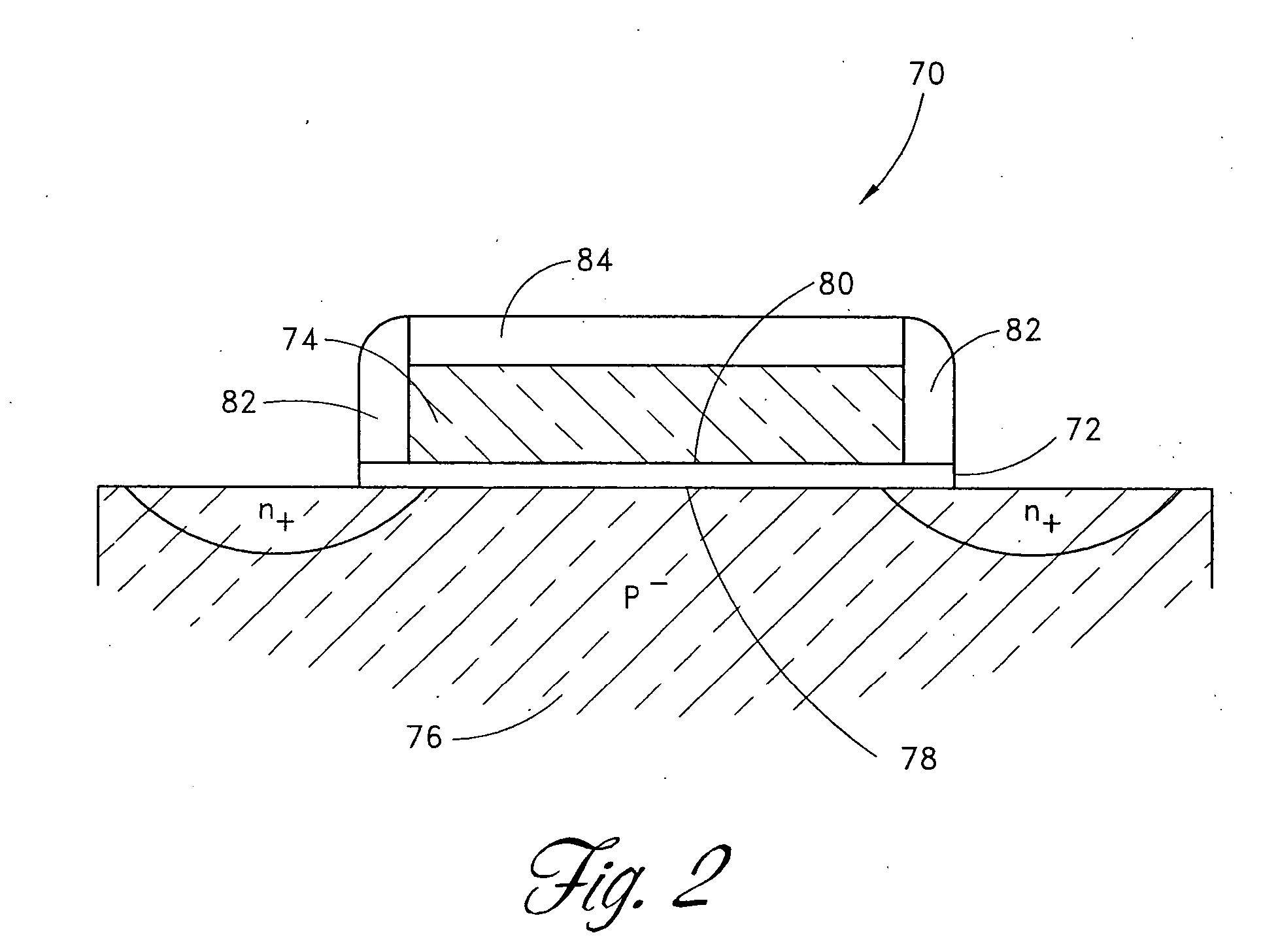

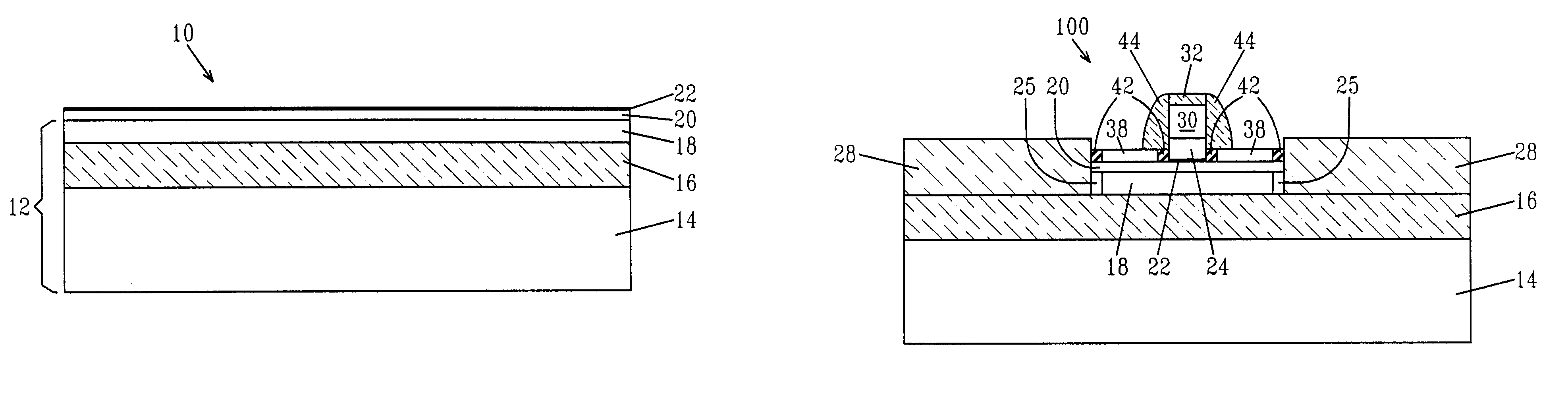

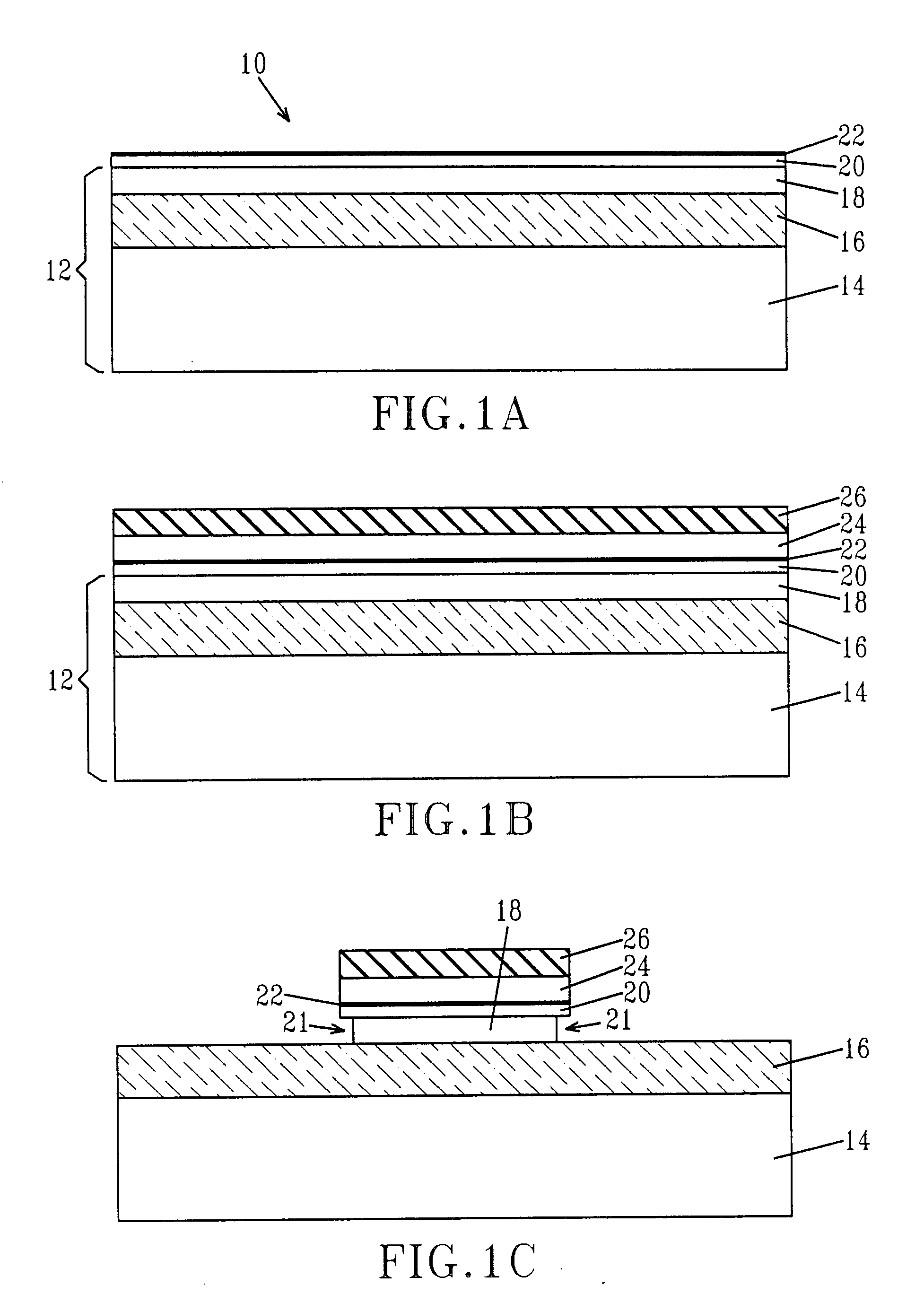

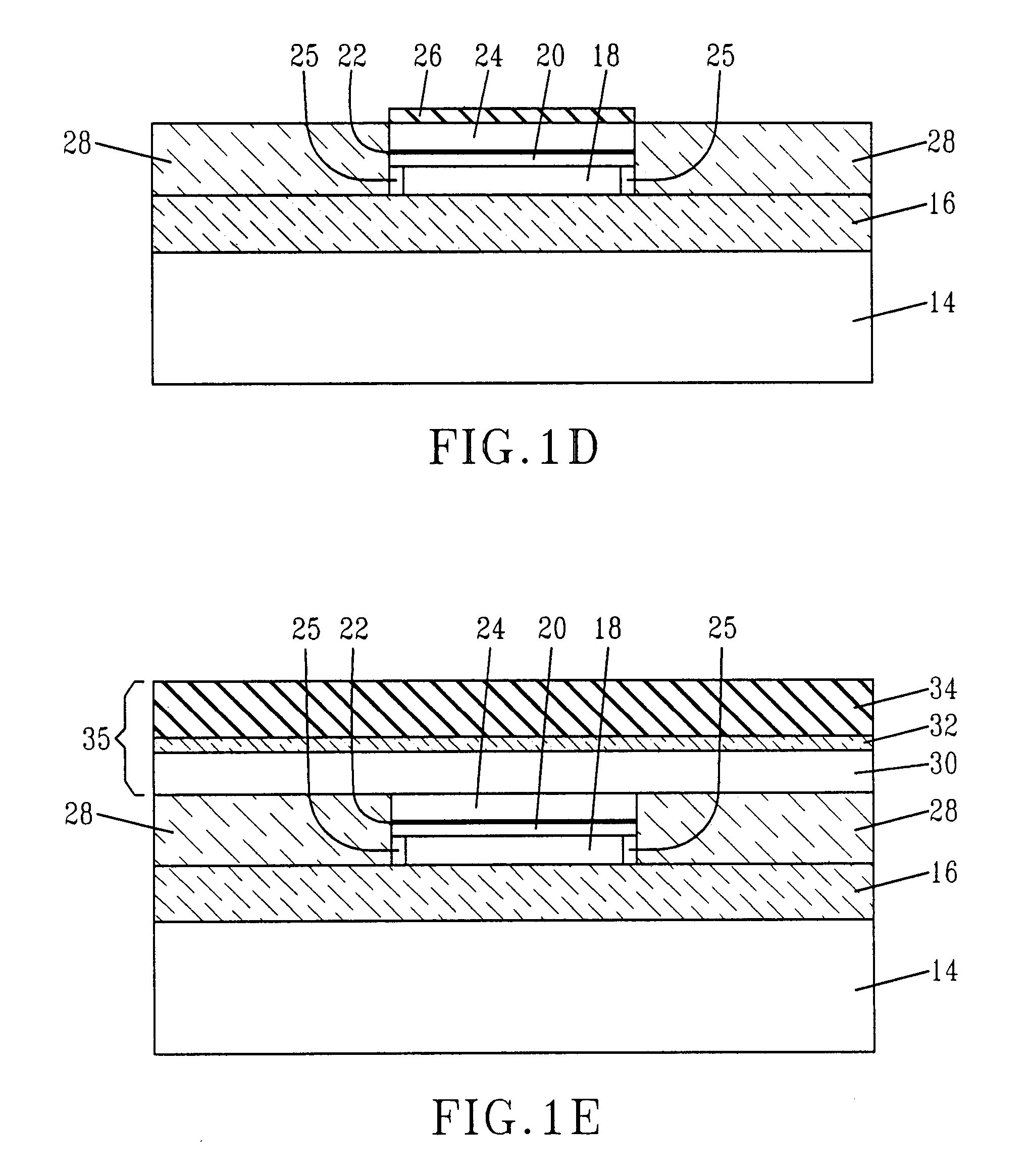

A channel 16 of a FinFET 10 has a channel core 24 and a channel envelope 32, each made from a semiconductor material defining a different lattice structure to exploit strained silicon properties. A gate is coupled to the channel envelope through a gate dielectric. Exemplary materials are Si and SixGe1-x, wherein 78<x<92. The channel core 24 has a top surface 26 of width wc and an upstanding surface 28, 30 of height hc, preferably oriented 90° to one another. The channel envelope 32 is in contact with the top 26 and upstanding surfaces 28, 30 so that the area of interface is increased as compared to contact only along the top surface 26, improving electrical conductivity and gate 18 control over the channel 16. The height hc can be tailored to enable a smaller scale FET 10 within a stabilized SRAM. Various methods of making the channel 16 are disclosed, including a mask and etch method, a handle wafer / carrier wafer method, and a shallow trench method. Embodiments and methods for FinFETs with one to four gates are disclosed.

Owner:MICROSOFT TECH LICENSING LLC

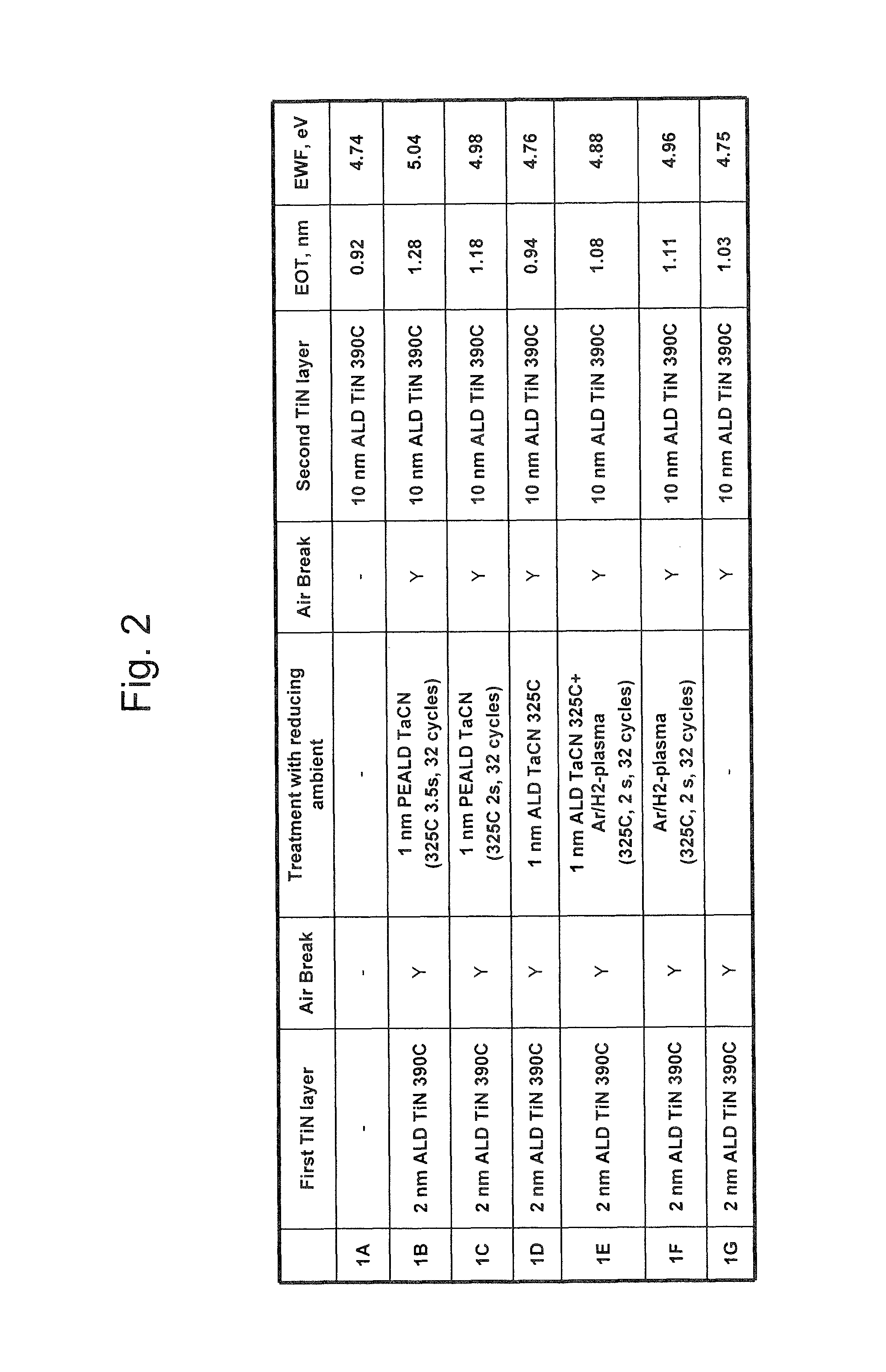

Process for depositing electrode with high effective work function

ActiveUS9136180B2Semiconductor/solid-state device manufacturingSemiconductor devicesHydrogenGate dielectric

Owner:ASM IP HLDG BV

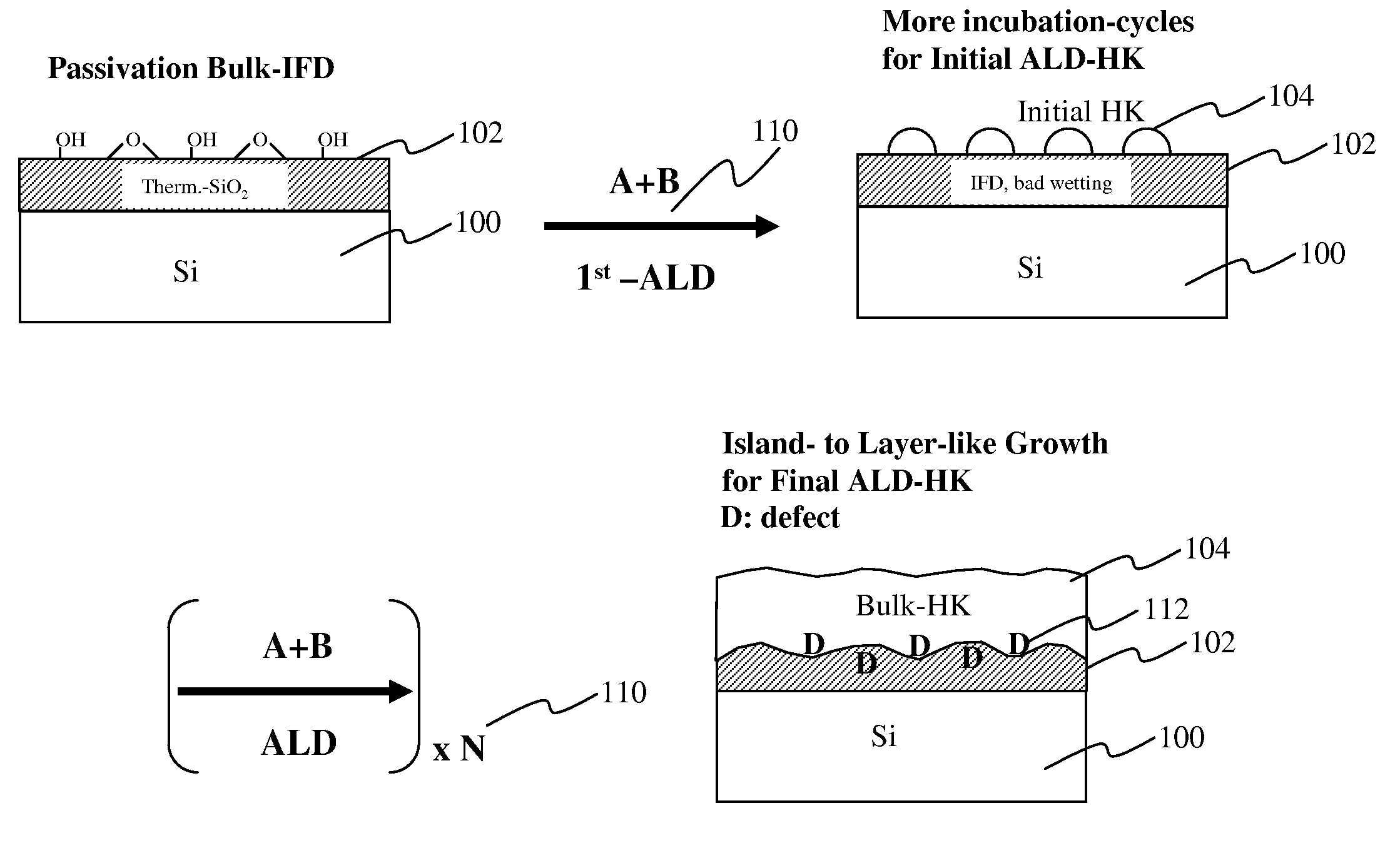

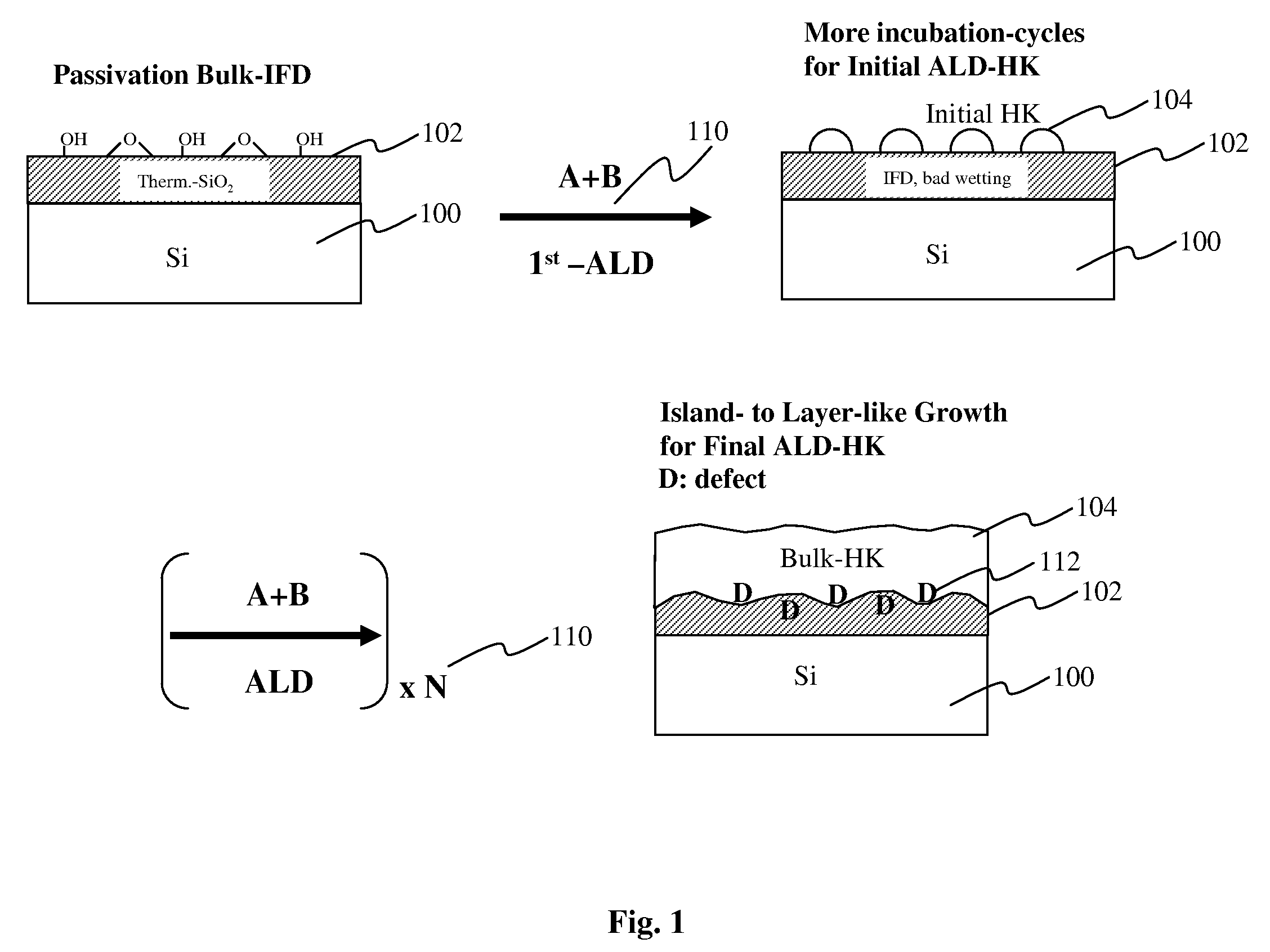

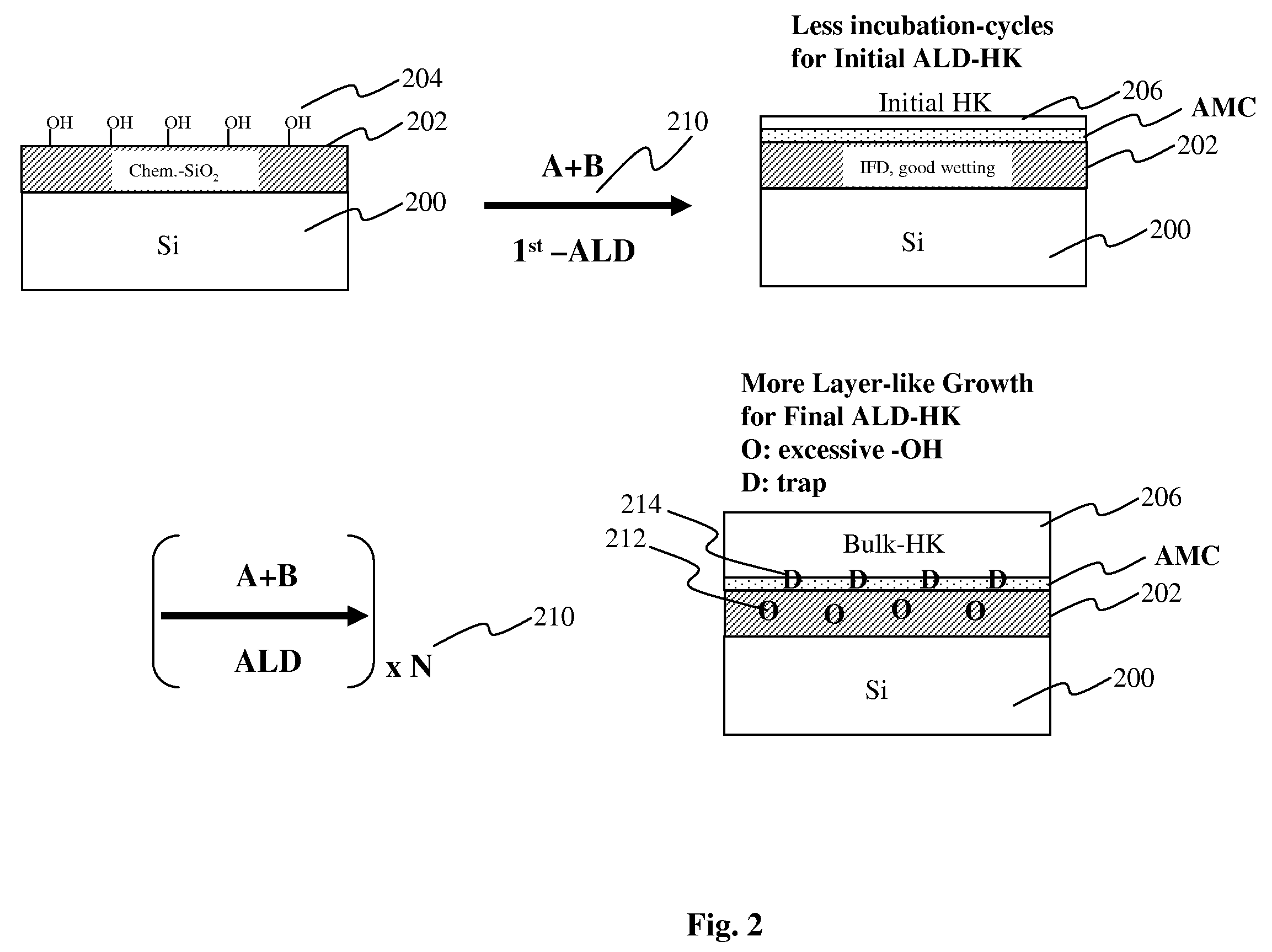

Implementing atomic layer deposition for gate dielectrics

PendingUS20170110313A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingGate dielectricLanthanum

A method for depositing a thin film onto a substrate is disclosed. In particular, the method forms a transitional metal silicate onto the substrate. The transitional metal silicate may comprise a lanthanum silicate or yttrium silicate, for example. The transitional metal silicate indicates reliability as well as good electrical characteristics for use in a gate dielectric material.

Owner:ASM IP HLDG BV

Method of forming mixed rare earth nitride and aluminum nitride films by atomic layer deposition

InactiveUS20070237698A1Semiconductor/solid-state device manufacturingRare earth metal compoundsGate dielectricRare earth

A method is provided for depositing a gate dielectric that includes at least two rare earth metal elements in the form of a nitride or an aluminum nitride. The method includes disposing a substrate in a process chamber and exposing the substrate to a gas pulse containing a first rare earth precursor and to a gas pulse containing a second rare earth precursor. The substrate may also optionally be exposed to a gas pulse containing an aluminum precursor. Sequentially after each precursor gas pulse, the substrate is exposed to a gas pulse of a nitrogen-containing gas. In alternative embodiments, the first and second rare earth precursors may be pulsed together, and either or both may be pulsed together with the aluminum precursor. The first and second rare earth precursors comprise a different rare earth metal element. The sequential exposing steps may be repeated to deposit a mixed rare earth nitride or aluminum nitride layer with a desired thickness. Purge or evacuation steps may also be performed after each gas pulse.

Owner:TOKYO ELECTRON LTD

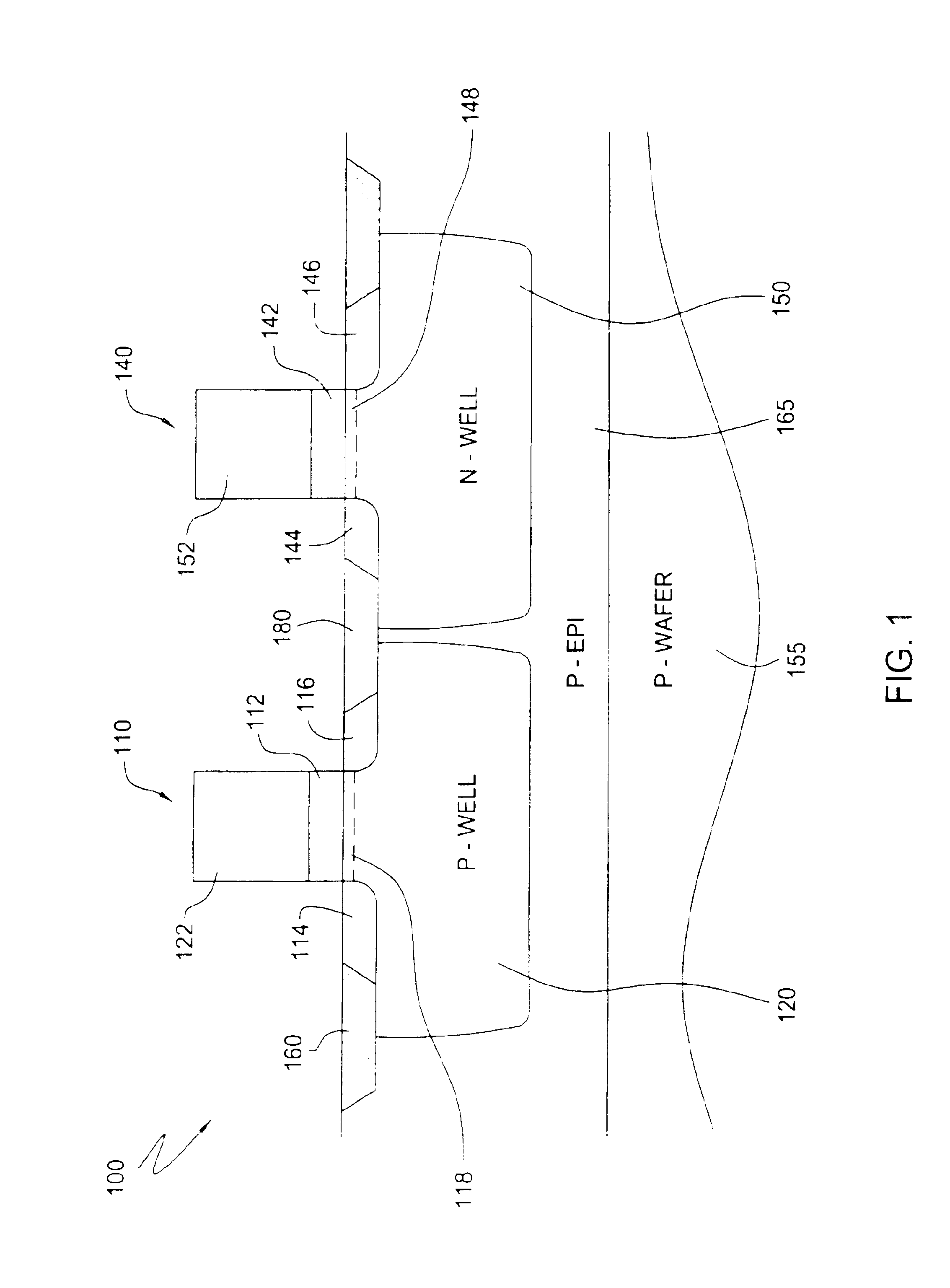

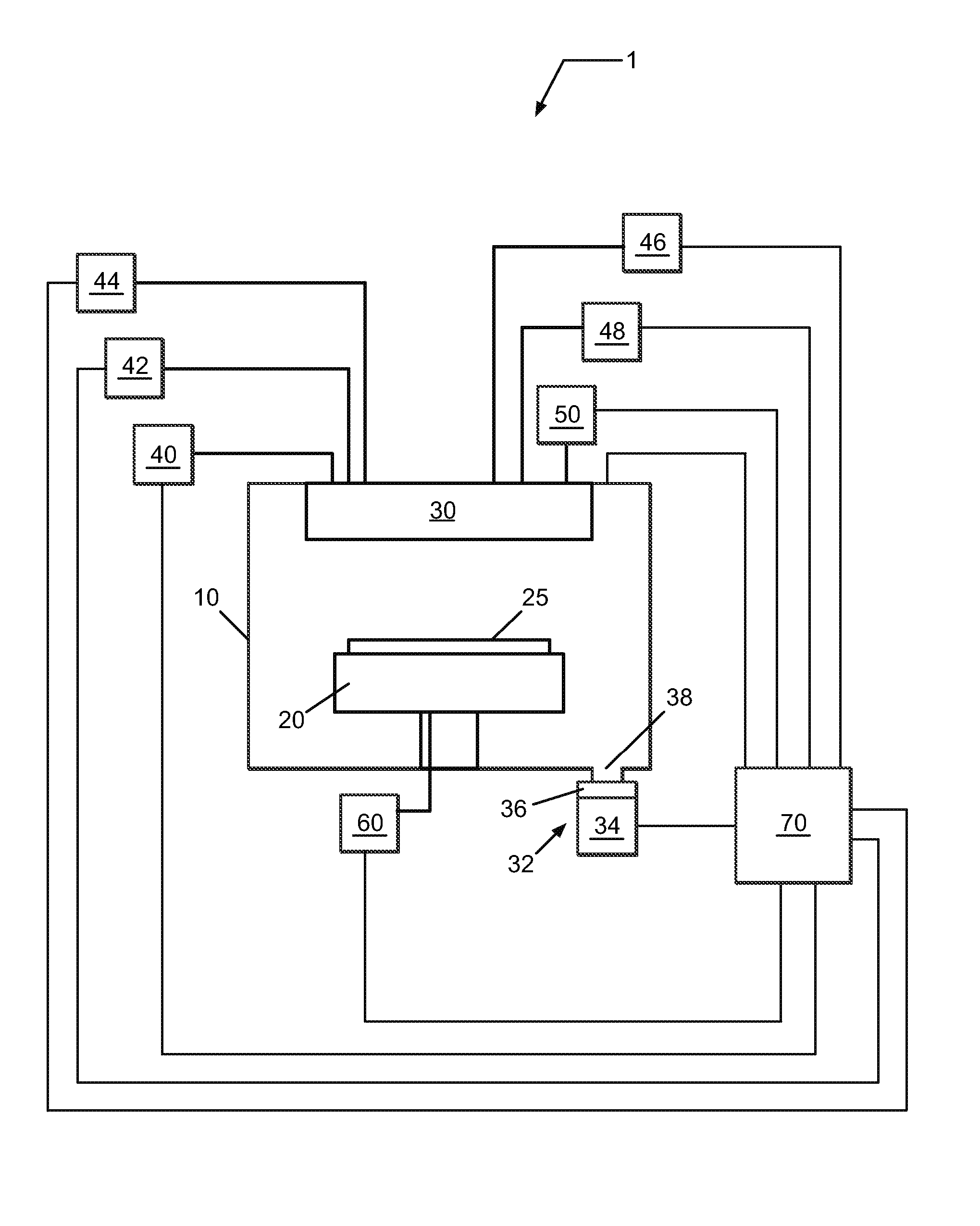

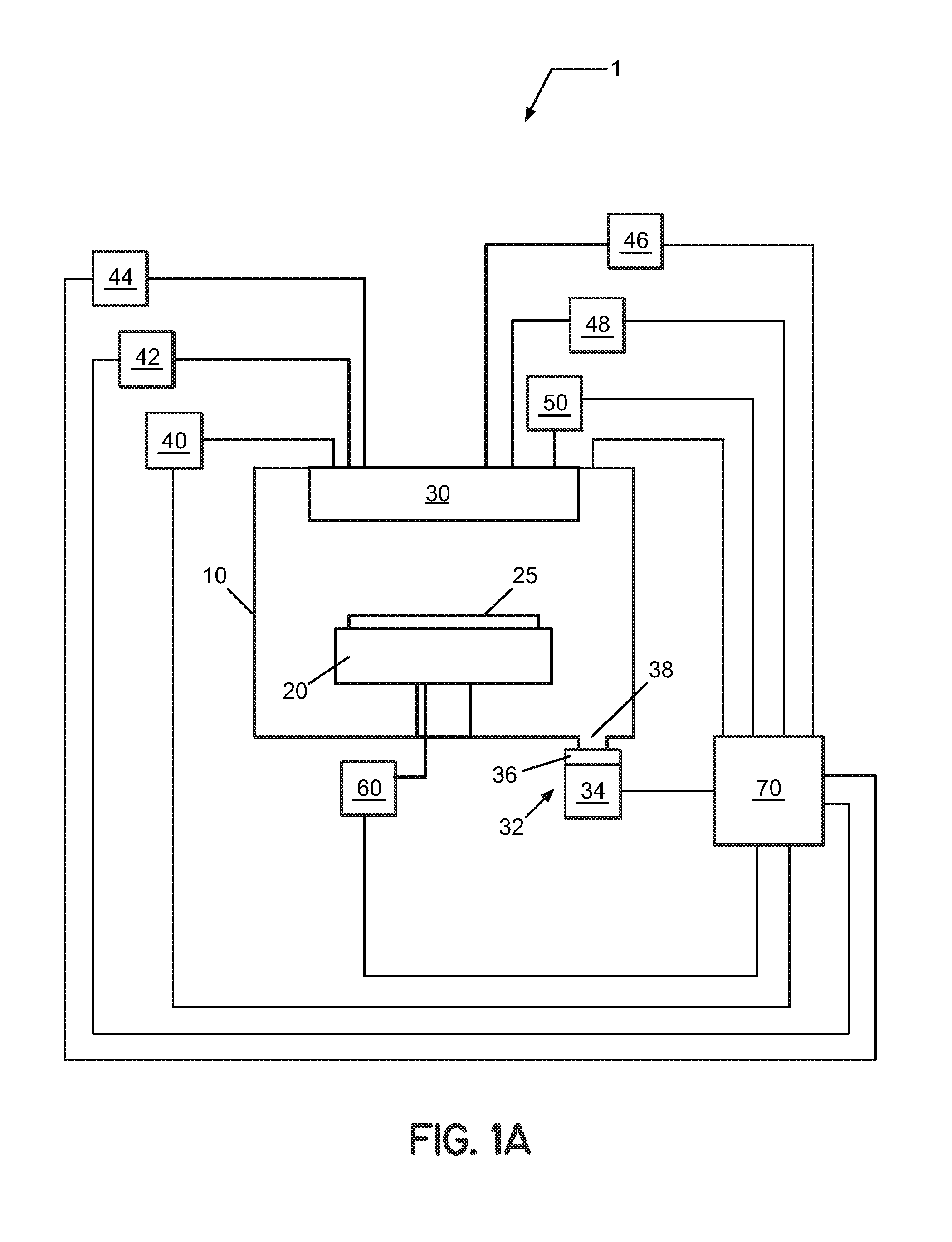

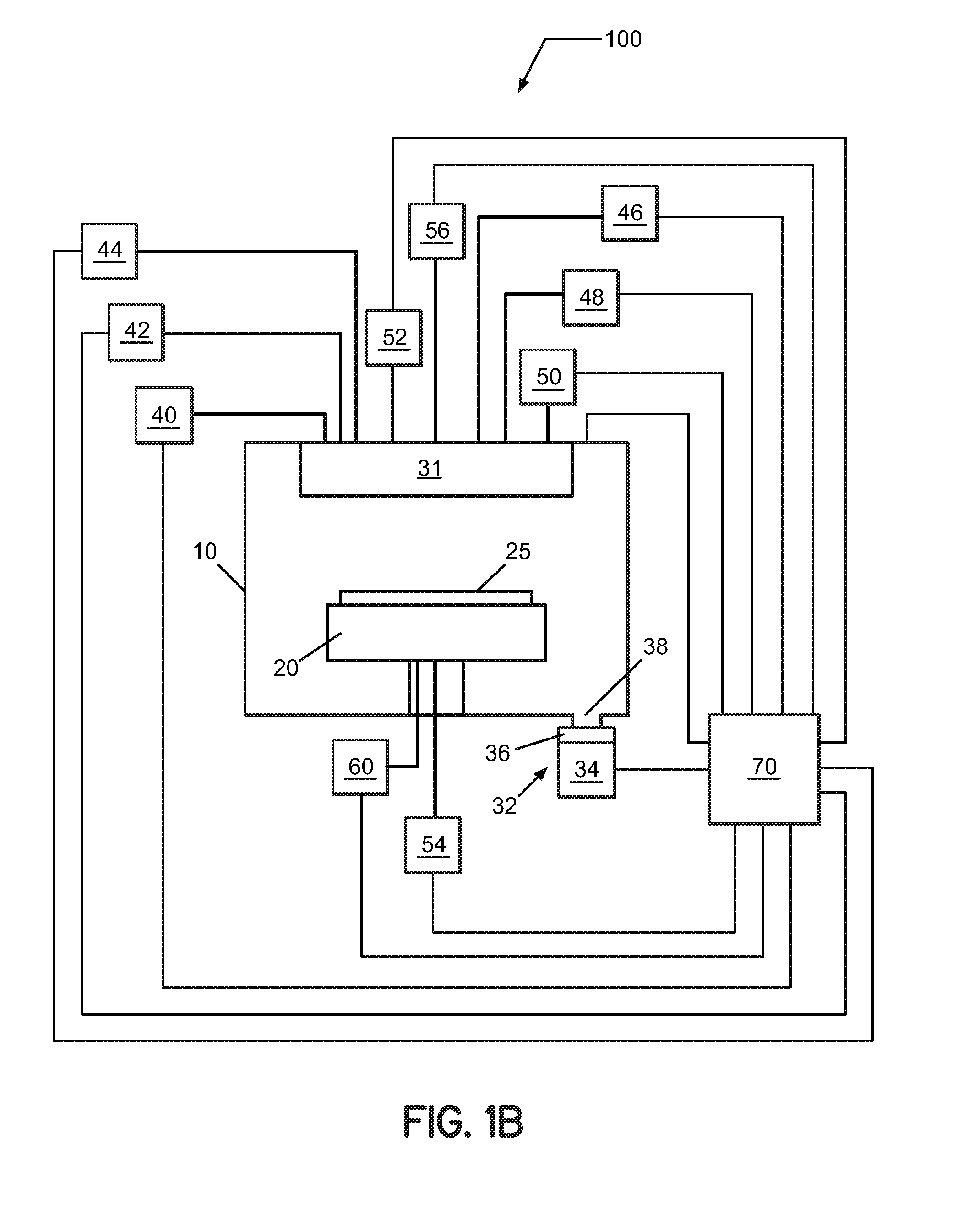

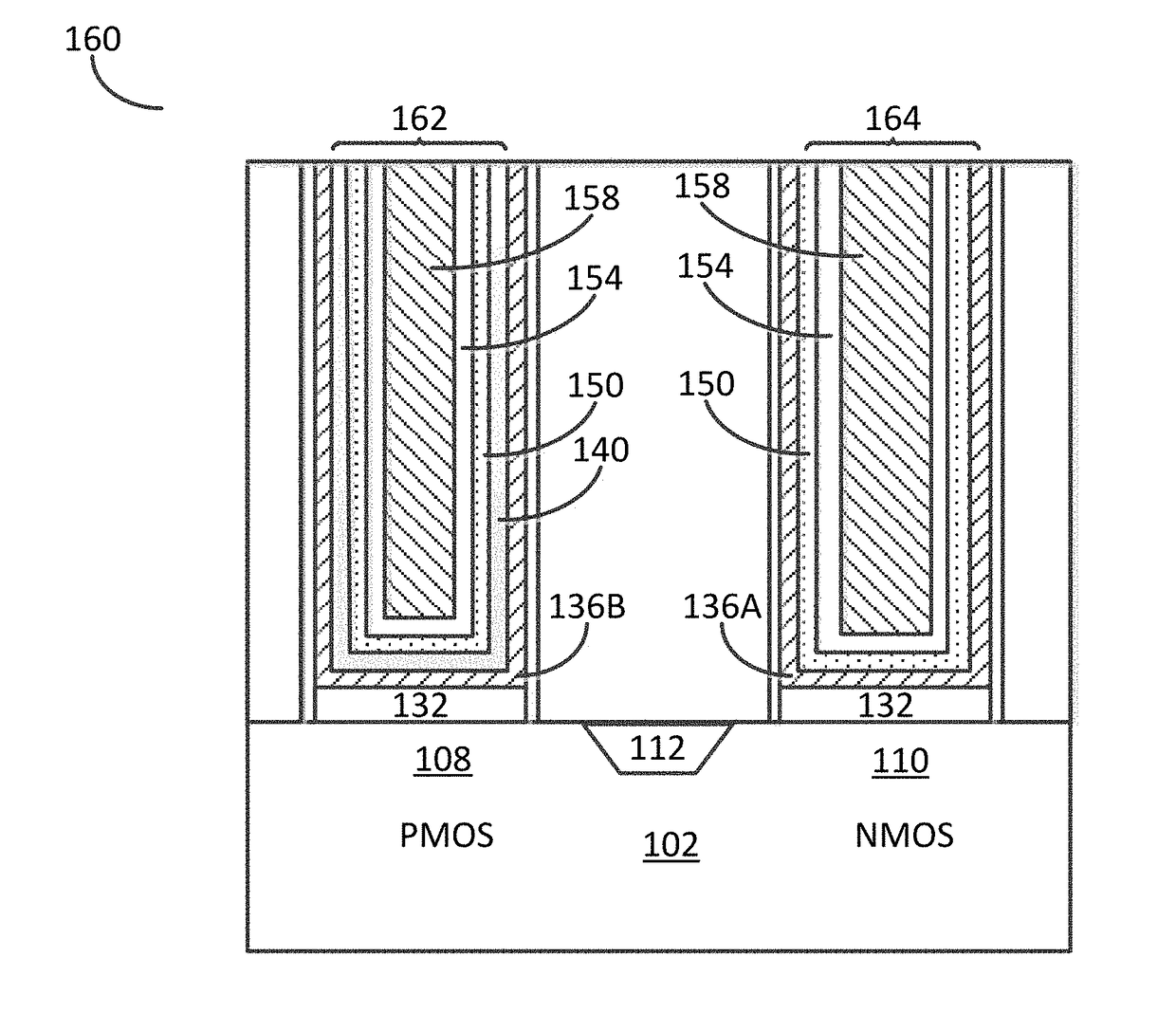

IMPROVED CMOS (Complementary Metal Oxide Semiconductor) TECHNOLOGY

InactiveUS20070020830A1Leakage problemSemiconductor/solid-state device manufacturingSemiconductor devicesDopantCMOS

A method for forming semiconductor transistor. The method comprises providing a structure including (a) a semiconductor region, and (b) first and second dopant source regions on and in direct physical contact with the semiconductor region, wherein each region of the first and second dopant source regions comprises a dielectric material which contains dopants; causing the dopants to diffuse from the first and second dopant source regions into the semiconductor region so as to form first and second source / drain extension regions, respectively, wherein the first and second source / drain extension regions define a channel region disposed between; forming a gate dielectric region on a channel region; and forming a gate region on the gate dielectric region, wherein the gate dielectric region electrically insulates the gate region from the channel region.

Owner:IBM CORP

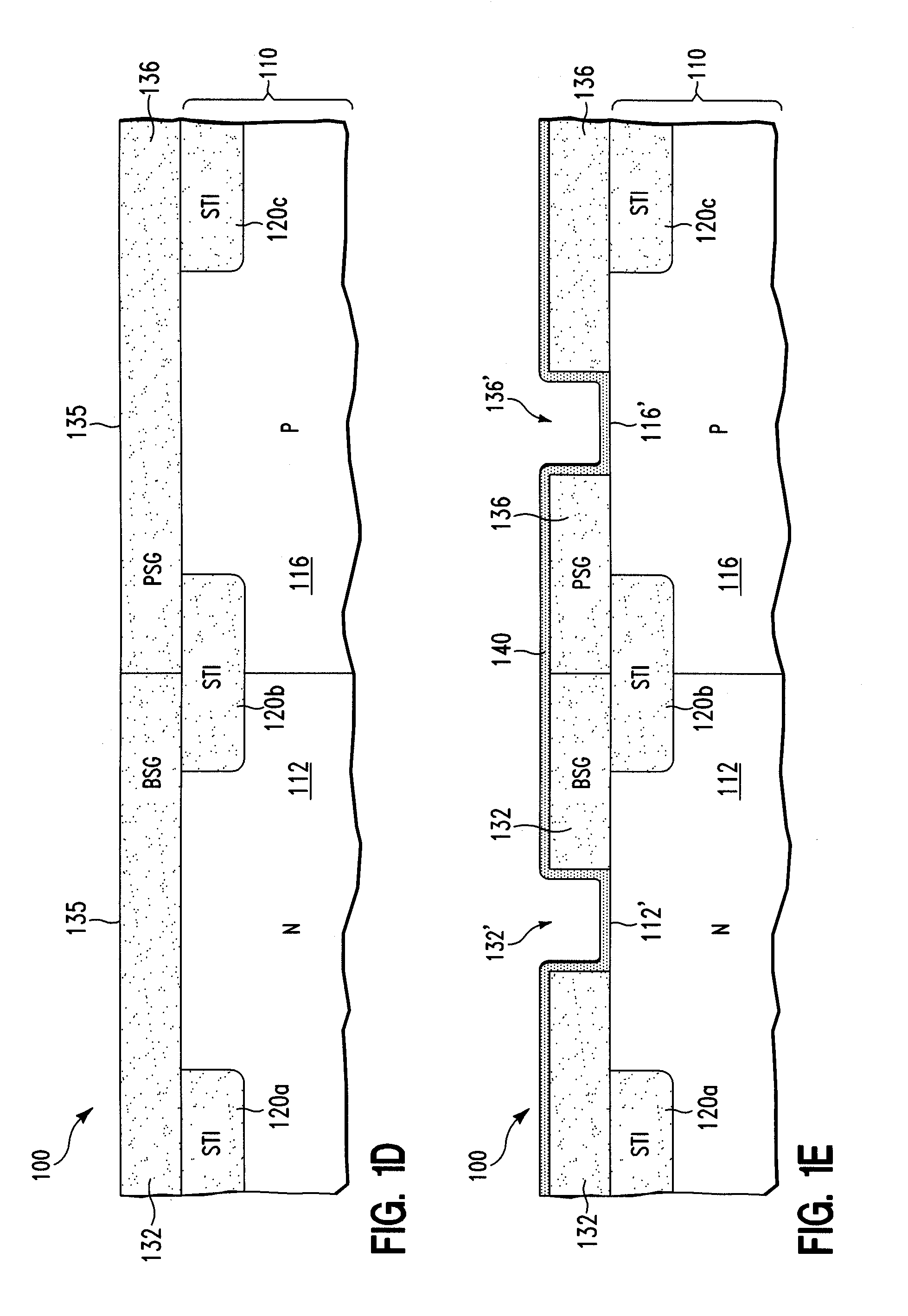

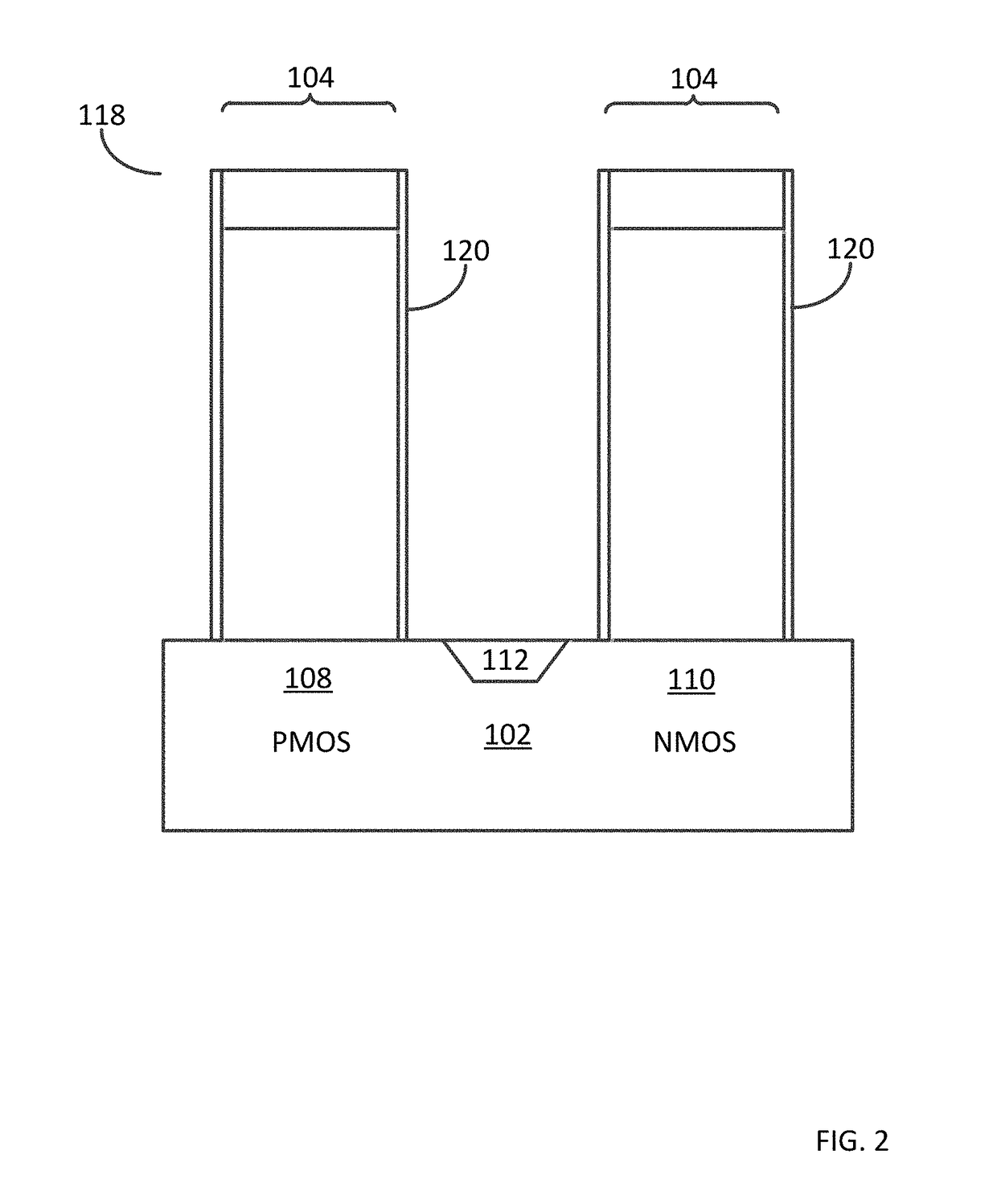

Methods for forming a semiconductor device and related semiconductor device structures

ActiveUS20180122709A1Well formedTransistorSolid-state devicesPower semiconductor deviceGate dielectric

Methods for forming a semiconductor device and related semiconductor device structures are provided. In some embodiments, methods may include forming an NMOS gate dielectric and a PMOS gate dielectric over a substrate and forming a first work function metal over the NMOS gate dielectric and over the PMOS gate dielectric. In some embodiments, methods may also include, removing the first work function metal over the NMOS gate dielectric and forming a second work function metal over the NMOS gate dielectric and over the PMOS gate dielectric. In some embodiments, related semiconductor device structures may include an NMOS gate dielectric and a PMOS gate dielectric disposed over a semiconductor substrate. A PMOS gate electrode may be disposed over the PMOS gate dielectric and the PMOS gate electrode may include a first work function metal disposed over the PMOS gate dielectric and a second work function metal disposed over the first work function metal. A NMOS gate electrode may be disposed over the NMOS gate dielectric and the NMOS gate electrode may include the second work function metal.

Owner:ASM IP HLDG BV

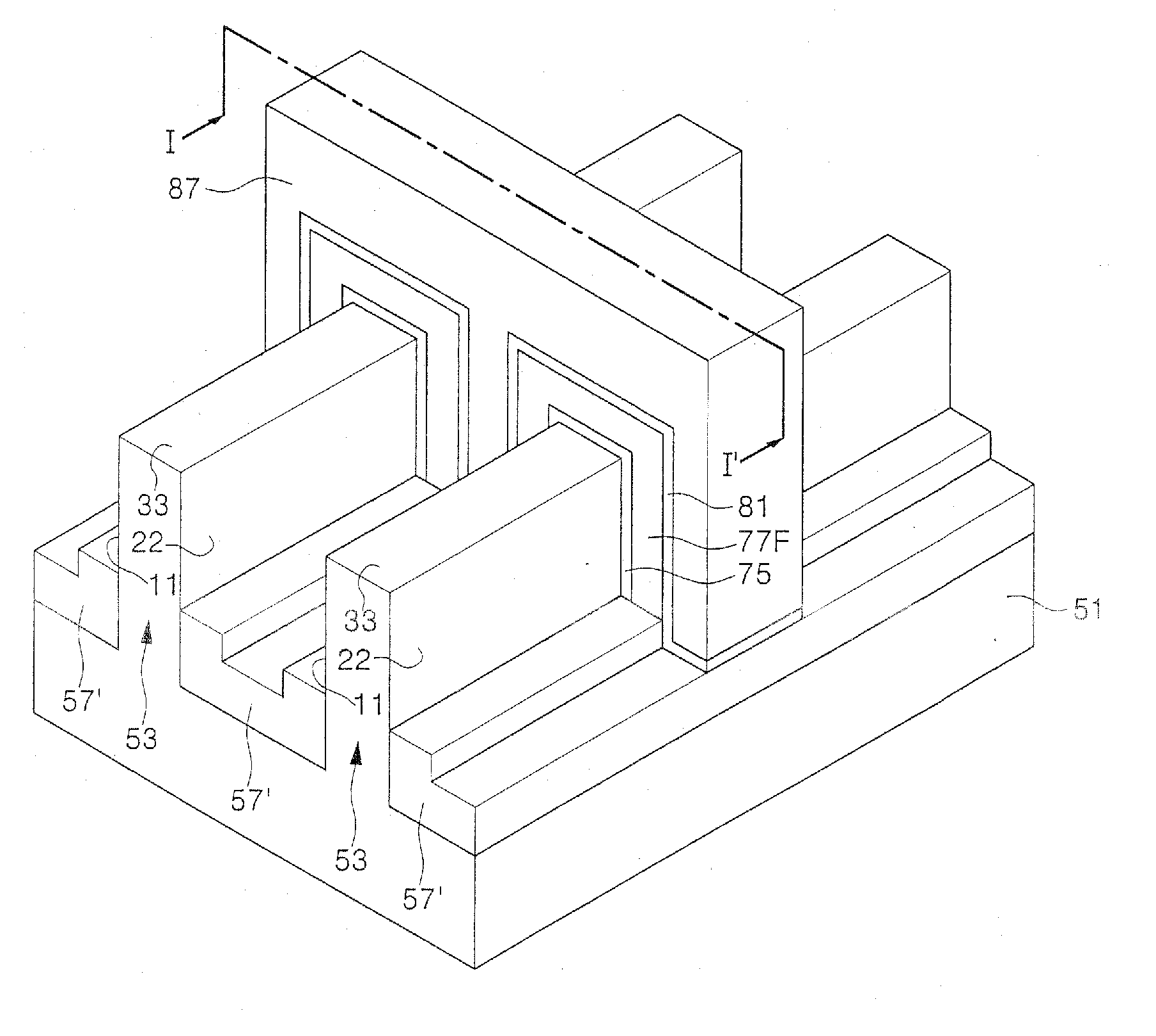

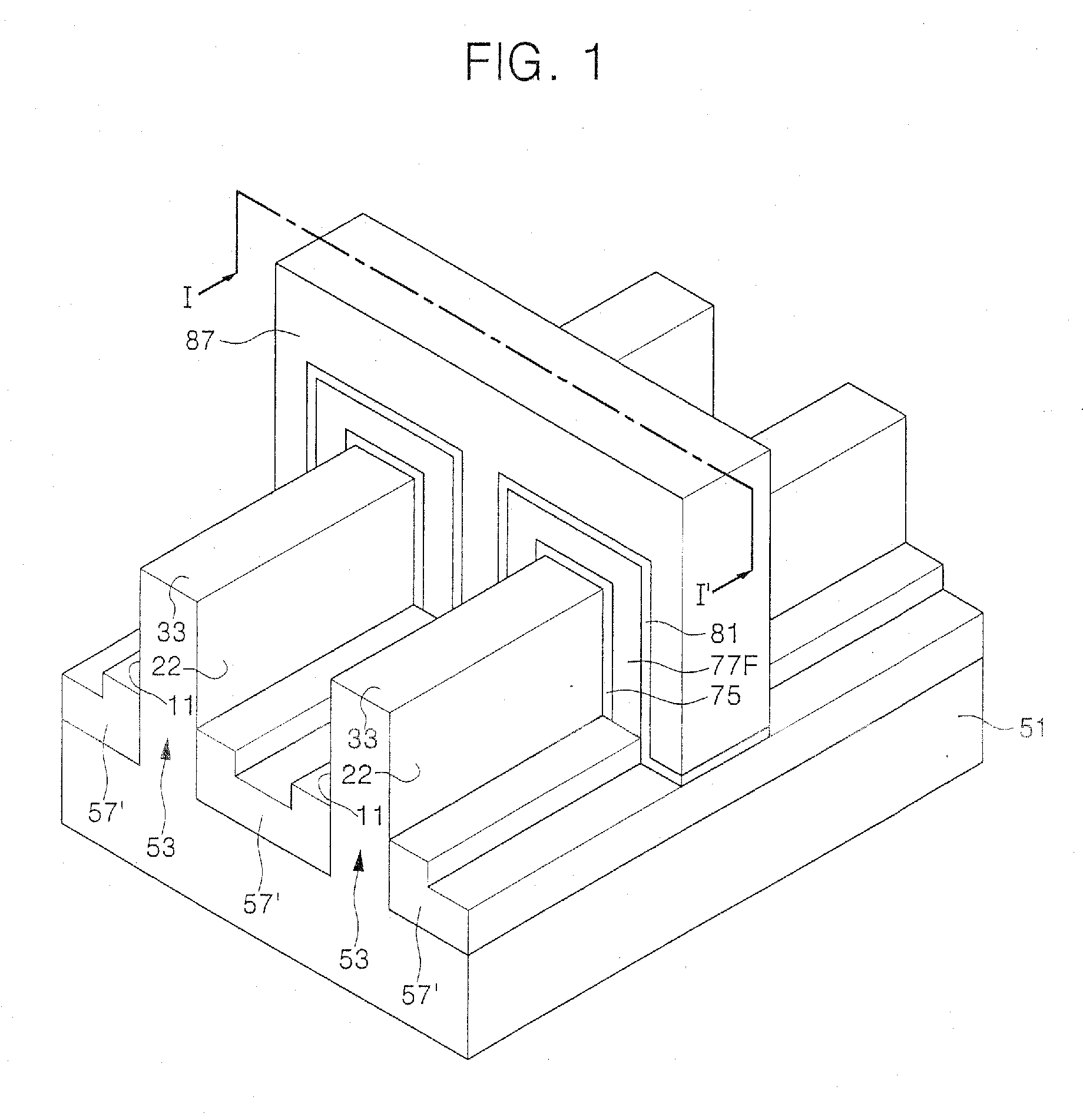

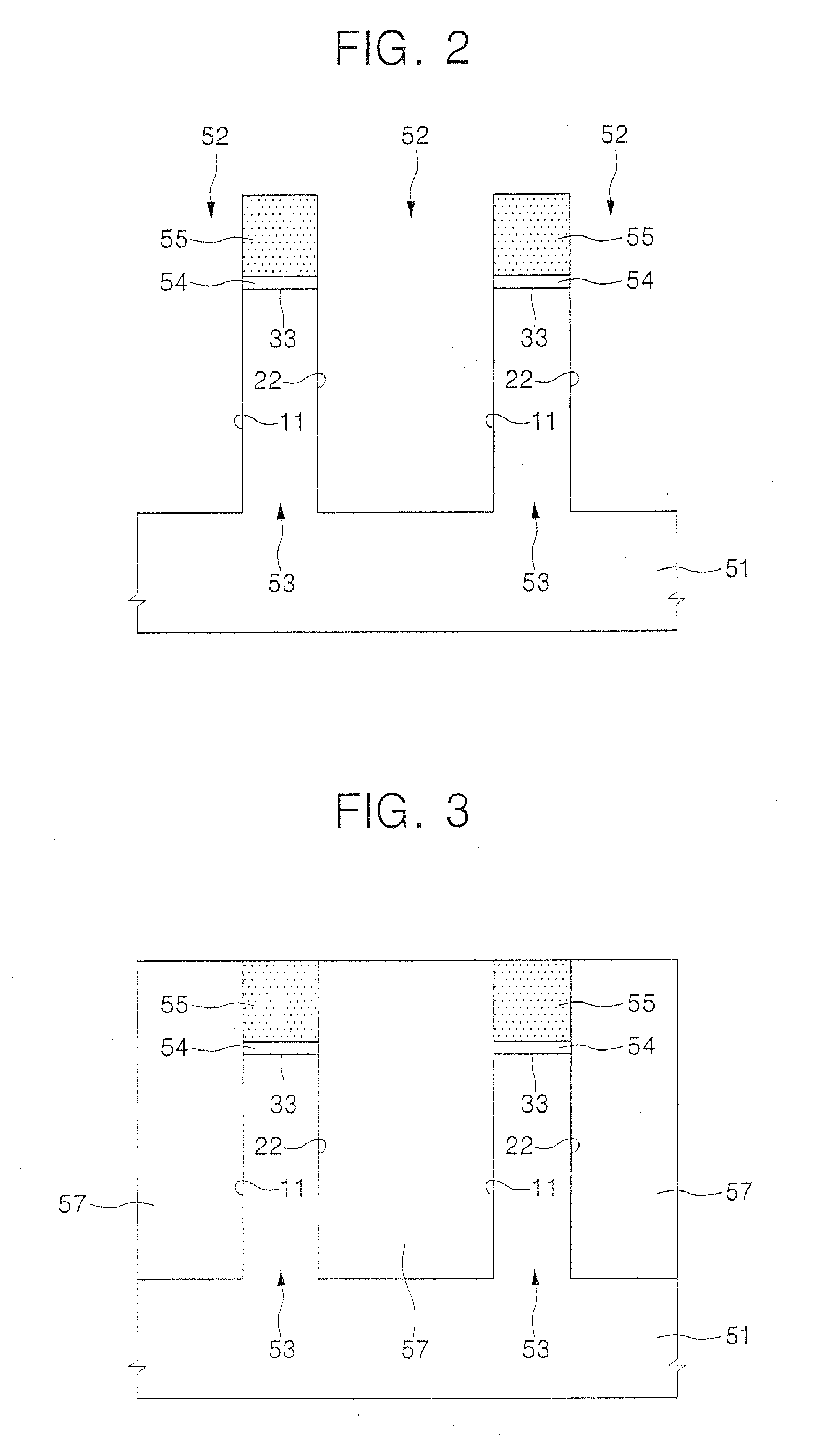

Method of fabricating a semiconductor device having self-aligned floating gate and related device

ActiveUS20070090443A1Solid-state devicesSemiconductor/solid-state device manufacturingGate dielectricIsolation layer

A semiconductor device such as a flash memory device having a self-aligned floating gate and a method of fabricating the same is provided. An embodiment of the device includes an isolation layer defining a fin body is formed in a semiconductor substrate. The fin body has a portion protruding above the isolation layer. A sacrificial pattern is formed on the isolation layer. The sacrificial pattern has an opening self-aligned with the protruding portion of the fin body. The protruding fin body is exposed in the opening. An insulated floating gate pattern is formed to fill the opening. The sacrificial pattern is then removed. An inter-gate dielectric layer covering the floating gate pattern is formed. A control gate conductive layer is formed over the inter-gate dielectric layer. The control gate conductive layer, the inter-gate dielectric layer, and the floating gate pattern are patterned to form a control gate electrode crossing the fin body as well as the insulated floating gate interposed between the control gate electrode and the fin body.

Owner:SAMSUNG ELECTRONICS CO LTD