Patents

Literature

1230 results about "Electromigration" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Electromigration is the transport of material caused by the gradual movement of the ions in a conductor due to the momentum transfer between conducting electrons and diffusing metal atoms. The effect is important in applications where high direct current densities are used, such as in microelectronics and related structures. As the structure size in electronics such as integrated circuits (ICs) decreases, the practical significance of this effect increases.

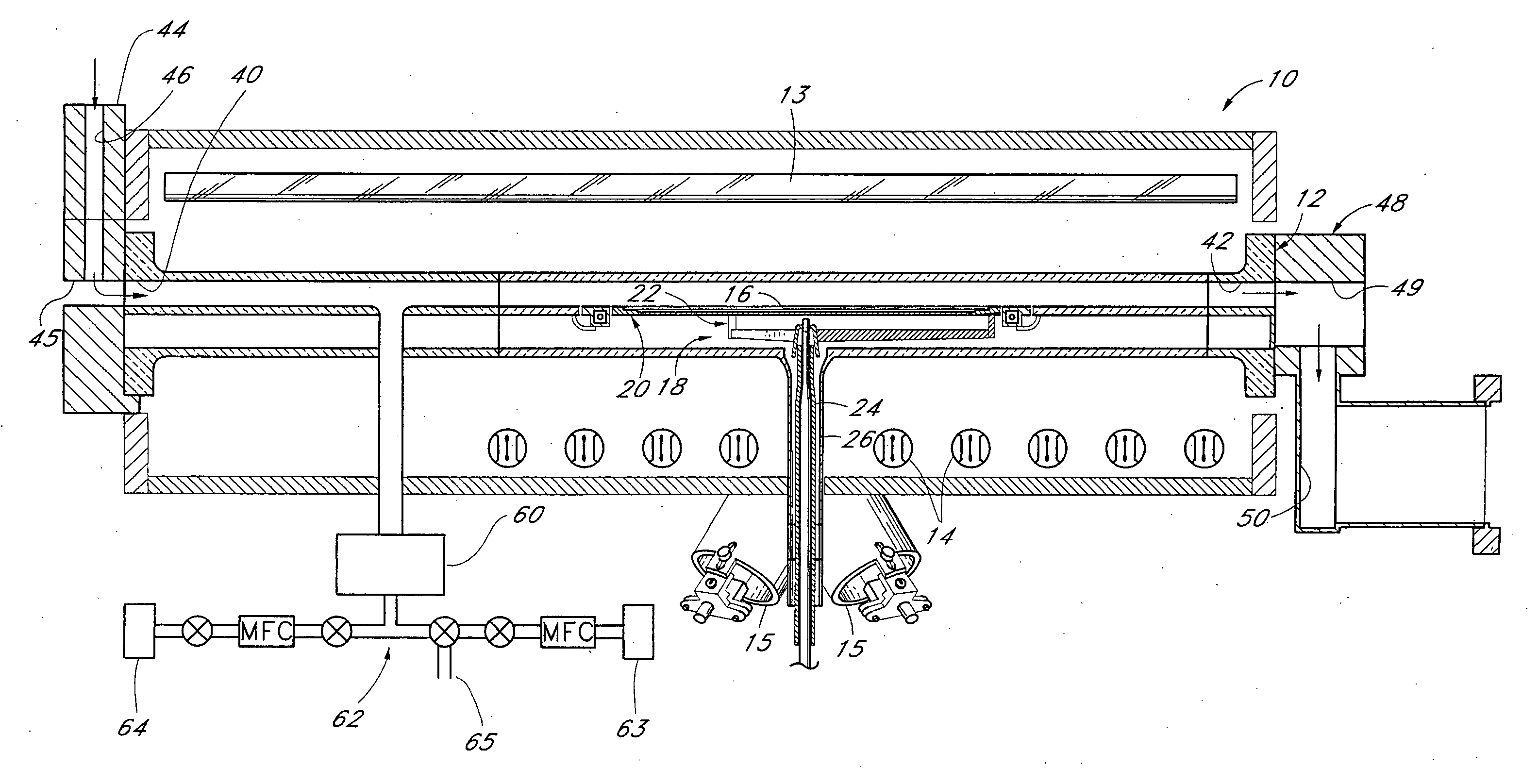

Thin films

InactiveUS20050181555A1Quality improvementHigh dielectric constantSolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricSilicon oxide

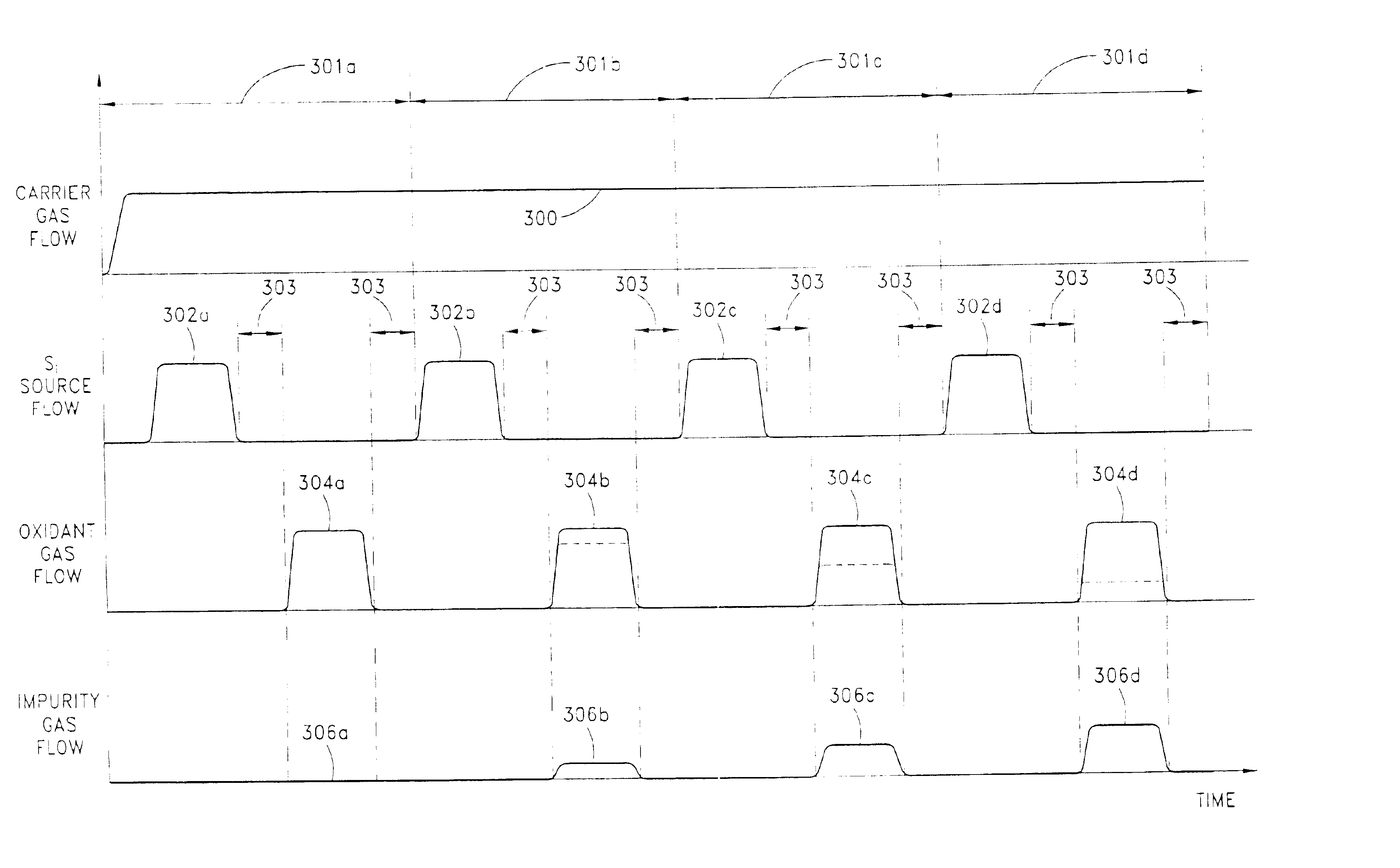

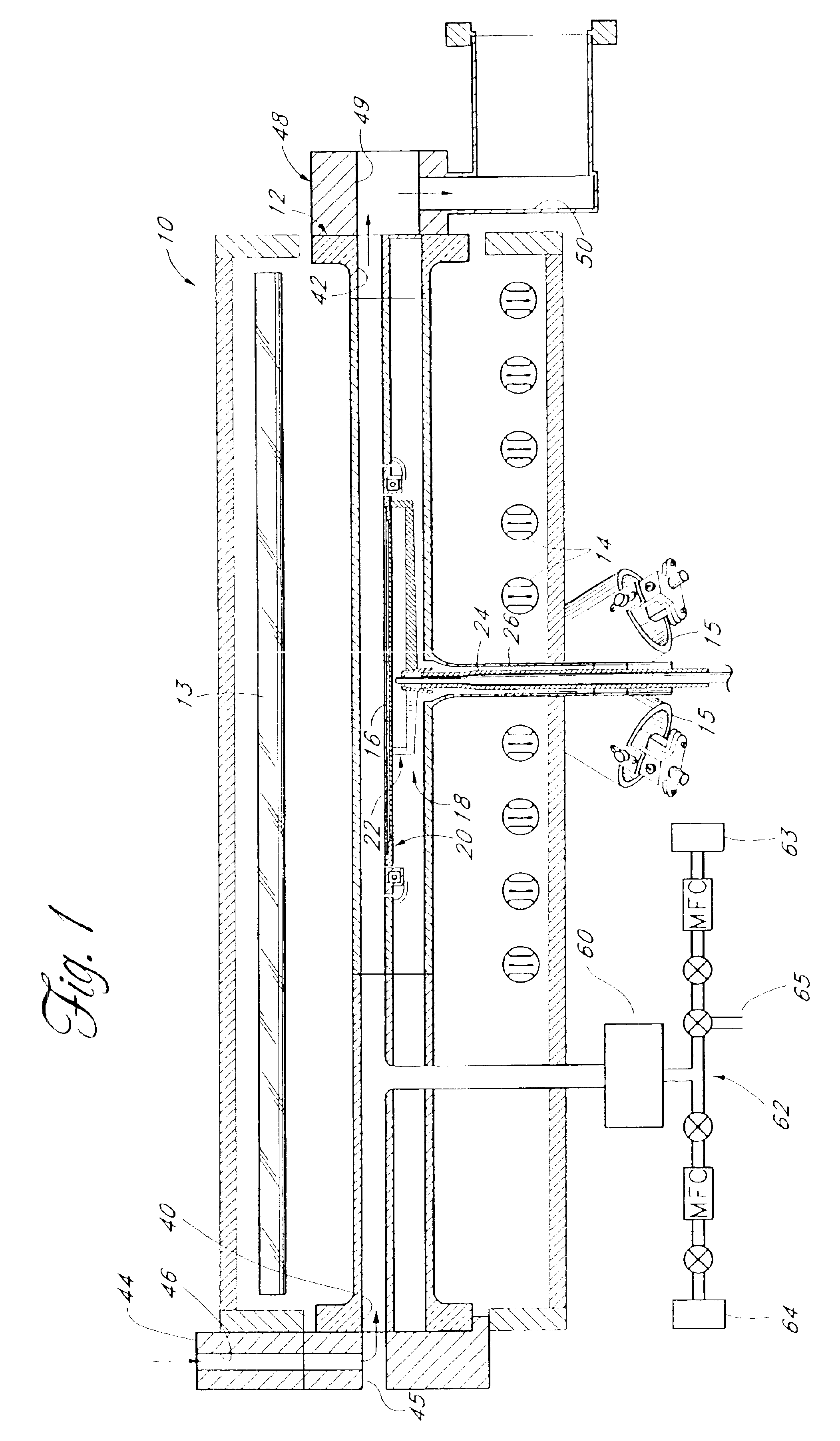

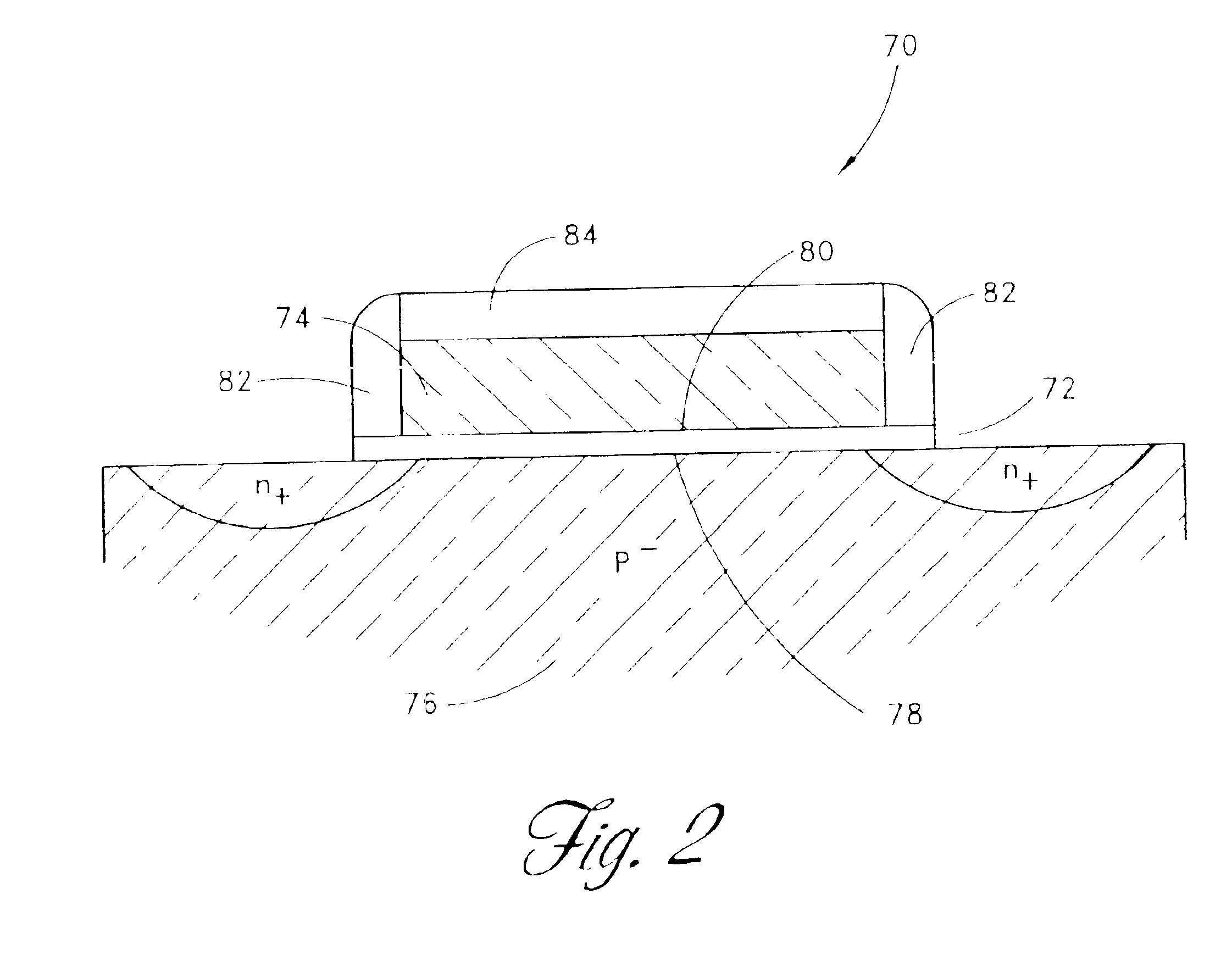

Thin films are formed by formed by atomic layer deposition, whereby the composition of the film can be varied from monolayer to monolayer during cycles including alternating pulses of self-limiting chemistries. In the illustrated embodiments, varying amounts of impurity sources are introduced during the cyclical process. A graded gate dielectric is thereby provided, even for extremely thin layers. The gate dielectric as thin as 2 nm can be varied from pure silicon oxide to oxynitride to silicon nitride. Similarly, the gate dielectric can be varied from aluminum oxide to mixtures of aluminum oxide and a higher dielectric material (e.g., ZrO2) to pure high k material and back to aluminum oxide. In another embodiment, metal nitride (e.g., WN) is first formed as a barrier for lining dual damascene trenches and vias. During the alternating deposition process, copper can be introduced, e.g., in separate pulses, and the copper source pulses can gradually increase in frequency, forming a transition region, until pure copper is formed at the upper surface. Advantageously, graded compositions in these and a variety of other contexts help to avoid such problems as etch rate control, electromigration and non-ohmic electrical contact that can occur at sharp material interfaces. In some embodiments additional seed layers or additional transition layers are provided.

Owner:ASM INTERNATIONAL

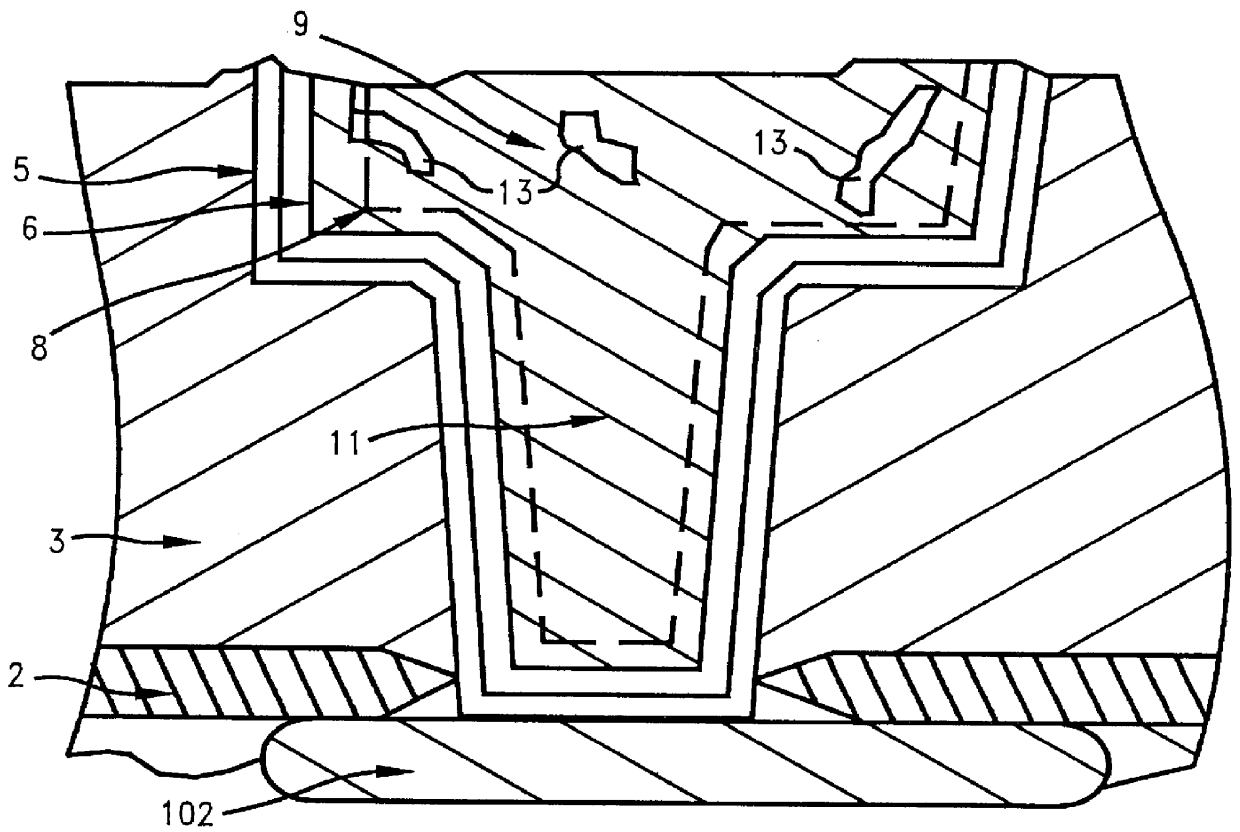

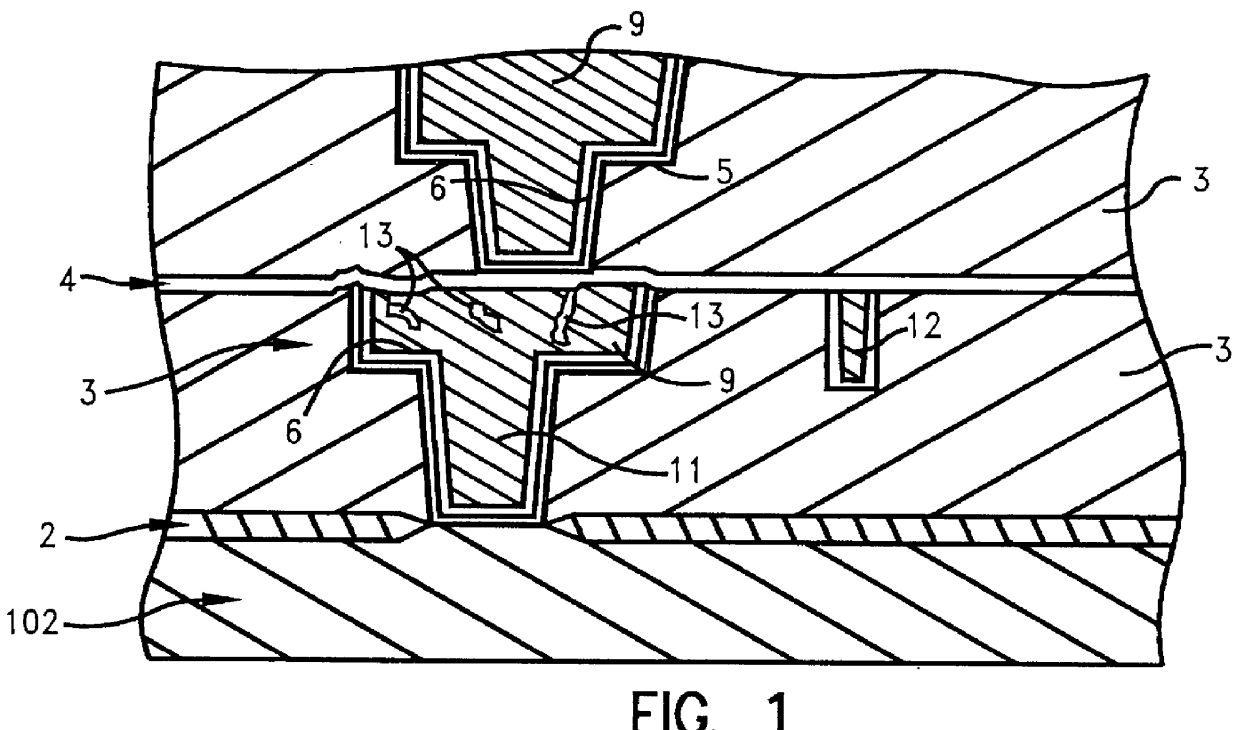

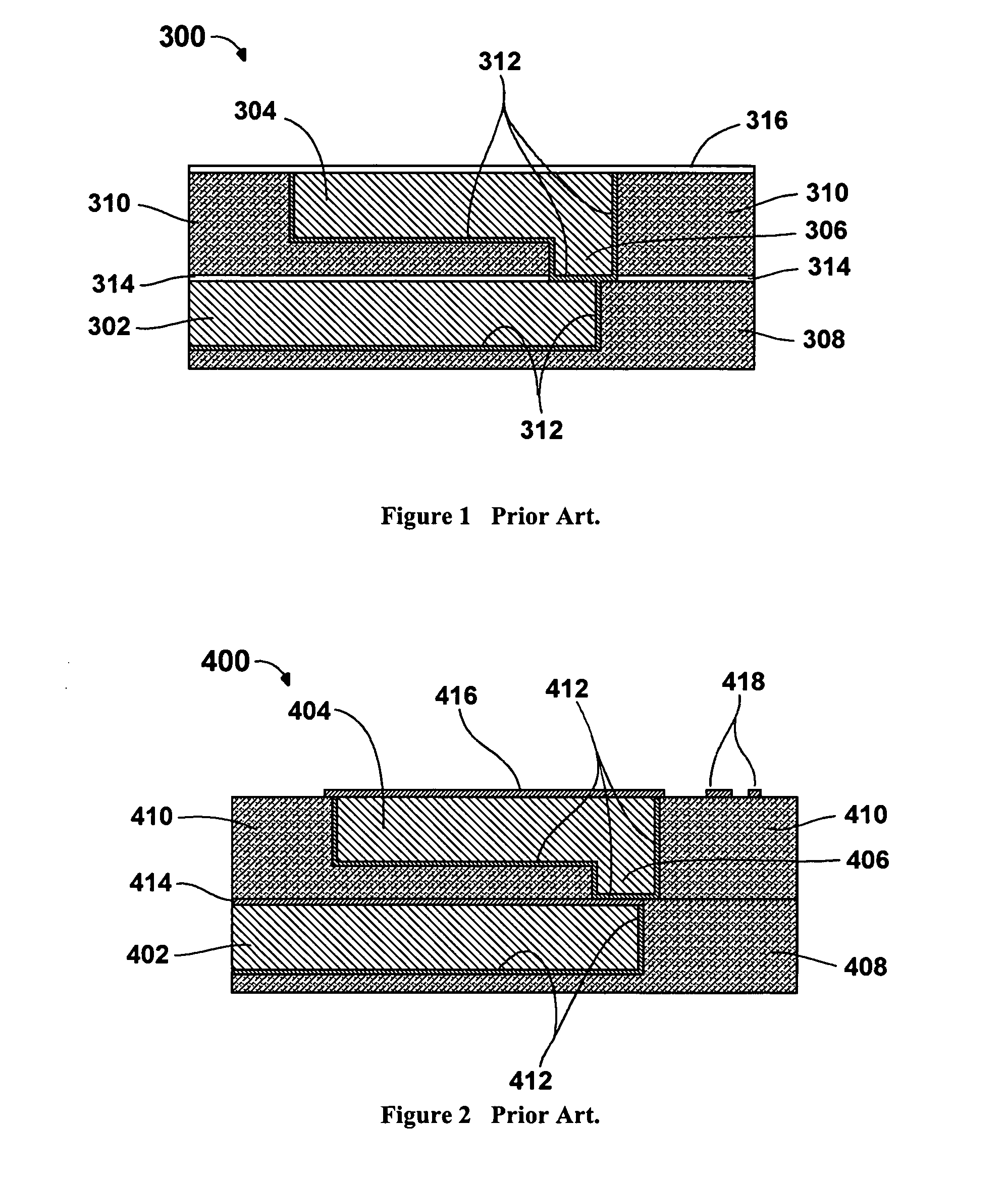

Hard mask arrangement

InactiveUS20060234138A1Reduce spacingIncrease processing costSemiconductor/solid-state device manufacturingOriginals for photomechanical treatmentCarrying capacityLateral region

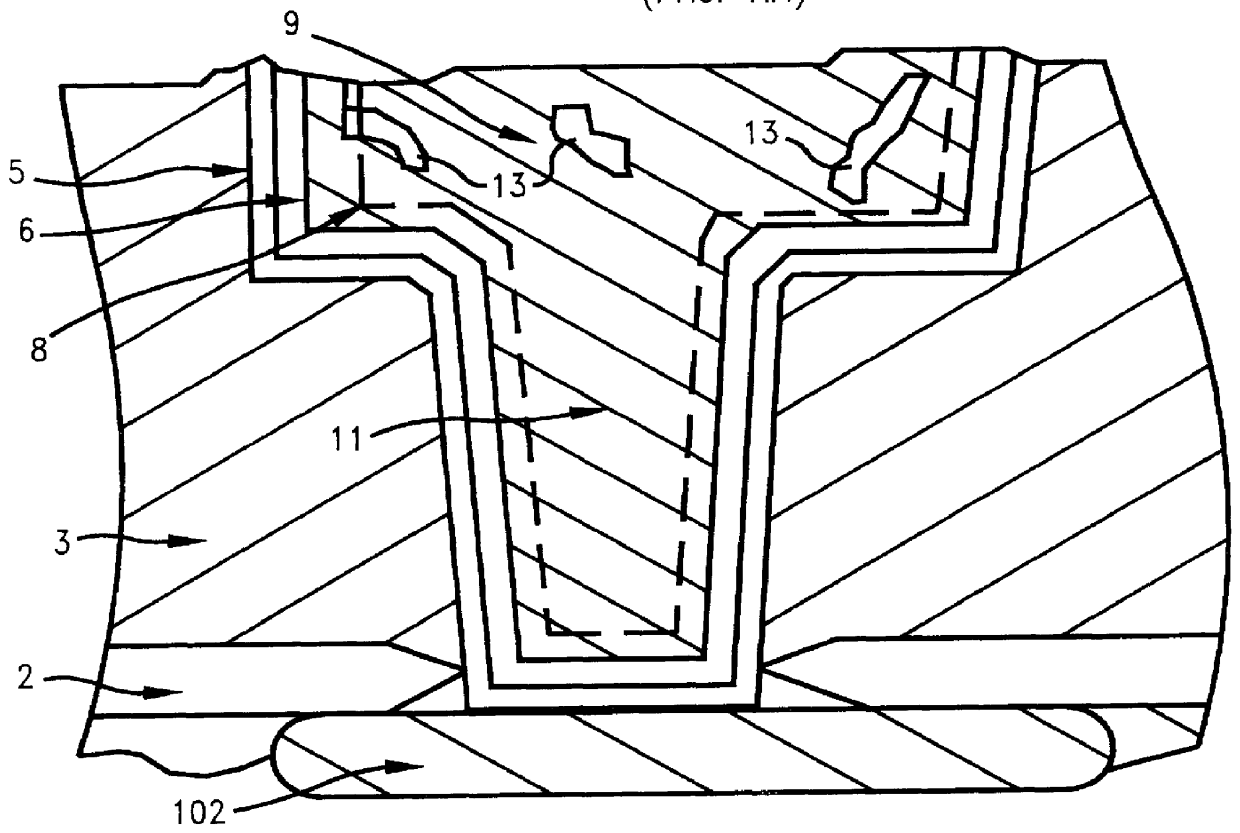

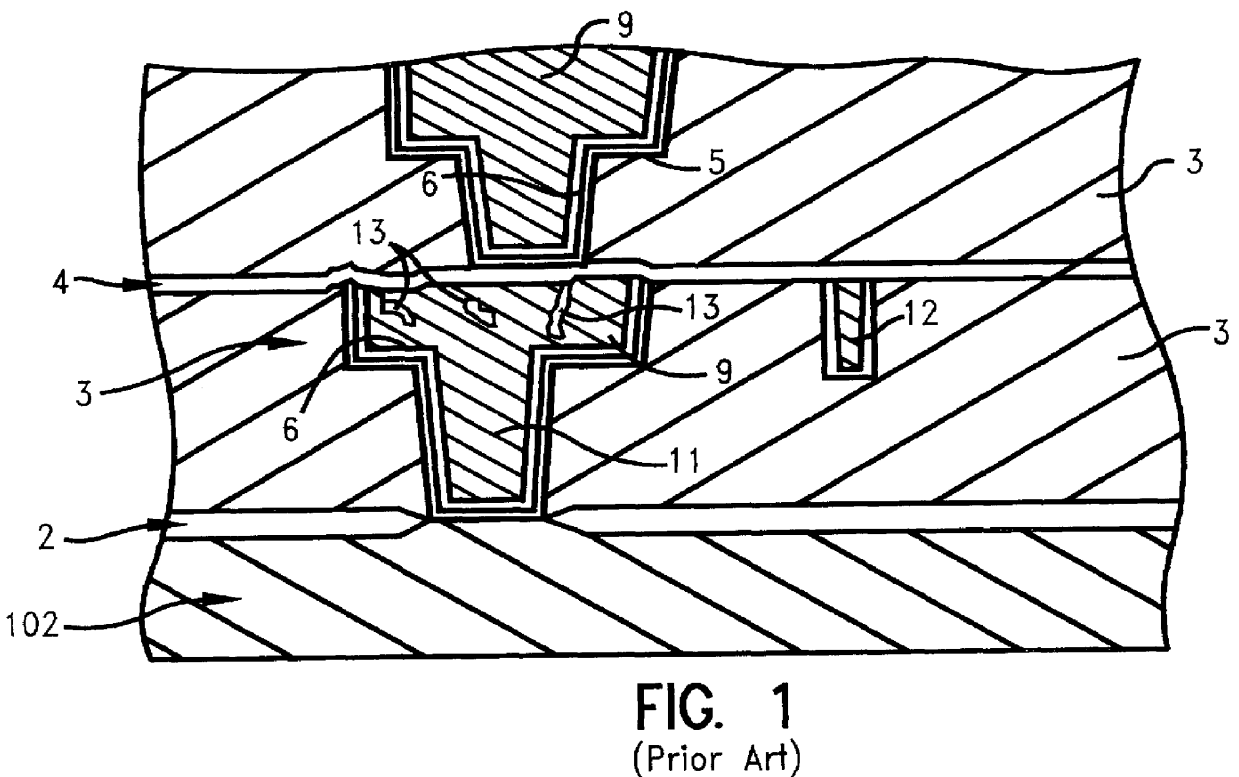

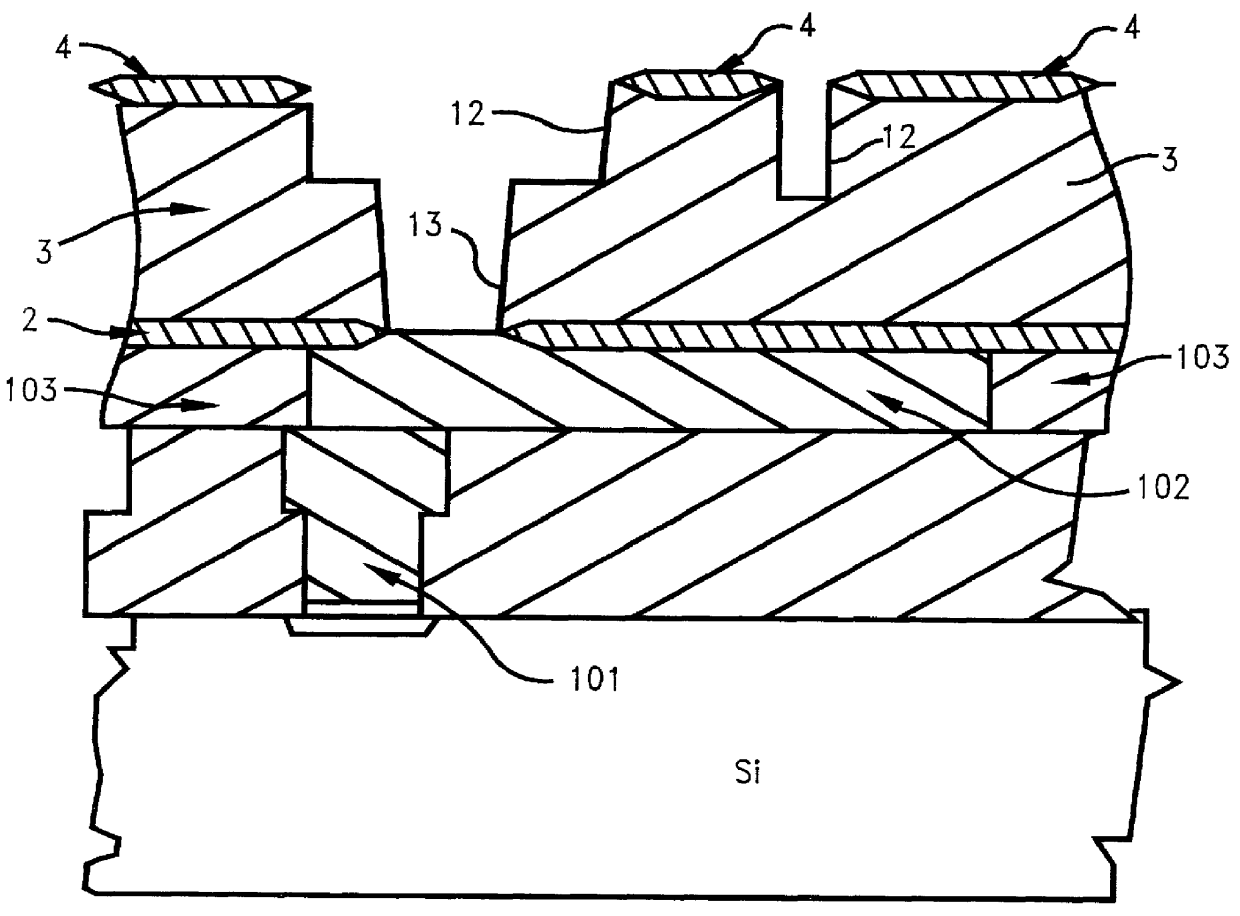

An interconnect connection structure having first and second interconnects and multiple connection elements that electrically connect the first interconnect to the second interconnect is described. The multiple connection elements are formed laterally in a lateral region of the first and second interconnects relative to an overlay orientation of the interconnects. A central region may be free of connection elements so that electro-migration properties of the connection structure are improved and the current-carrying capacity is increased.

Owner:FEHLHABER RODGER +1

Sub-quarter-micron copper interconnections with improved electromigration resistance and reduced defect sensitivity

InactiveUS6069068ASemiconductor/solid-state device detailsVacuum evaporation coatingGas phaseInterconnection

A method of providing sub-half-micron copper interconnections with improved electromigration and corrosion resistance. The method includes double damascene using electroplated copper, where the seed layer is deposited by chemical vapor deposition, or by physical vapor deposition in a layer less than about 800 angstroms.

Owner:GLOBALFOUNDRIES INC

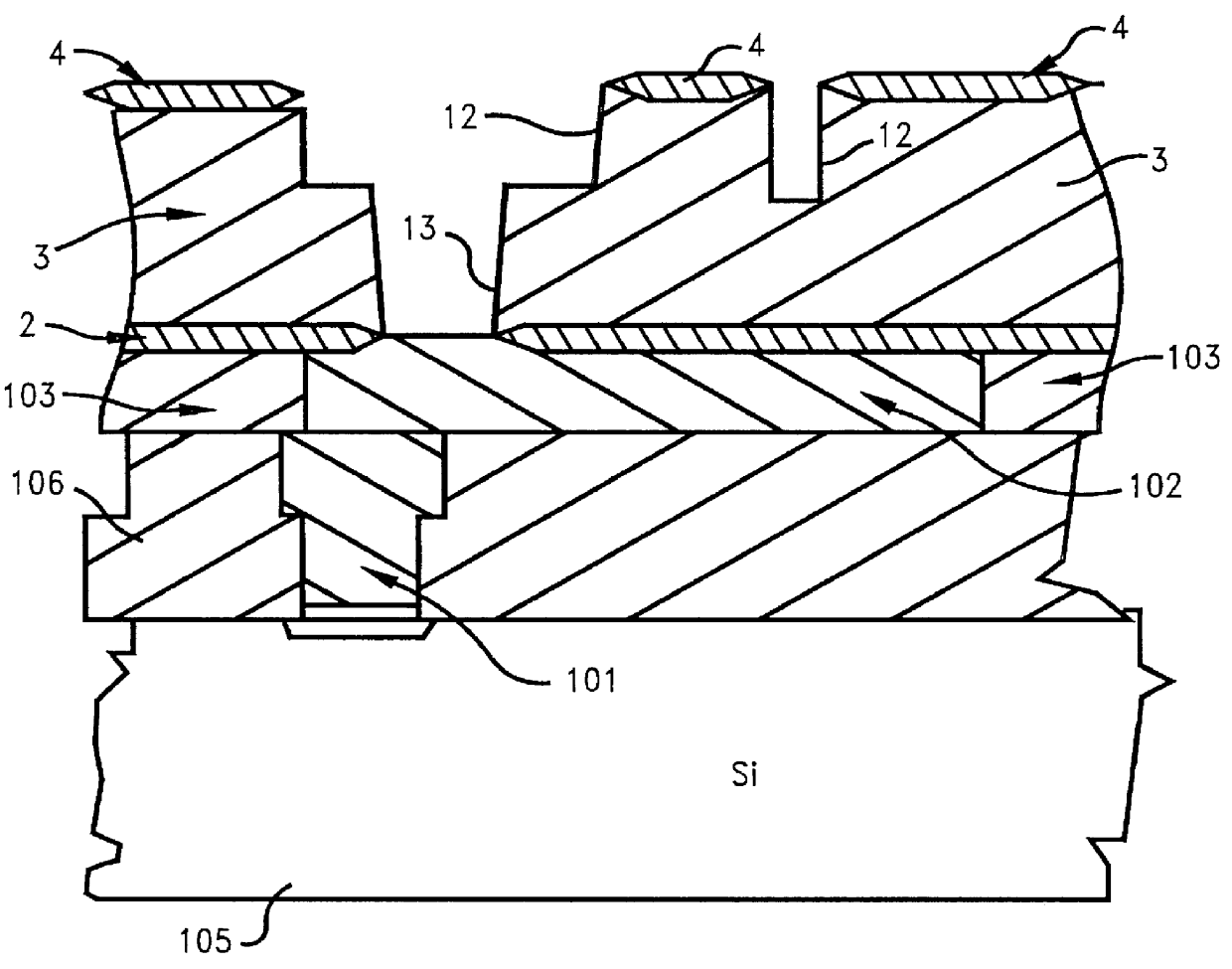

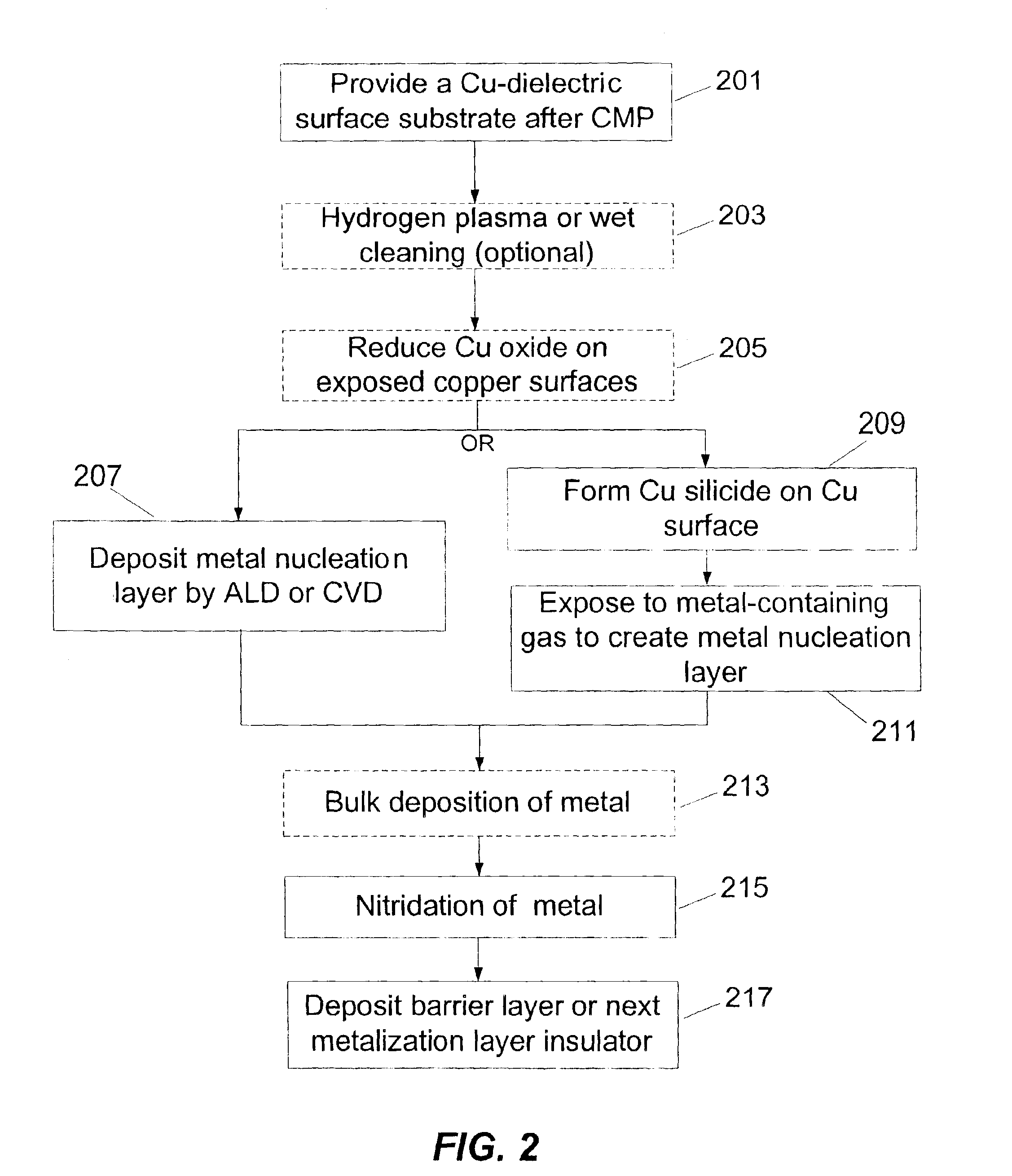

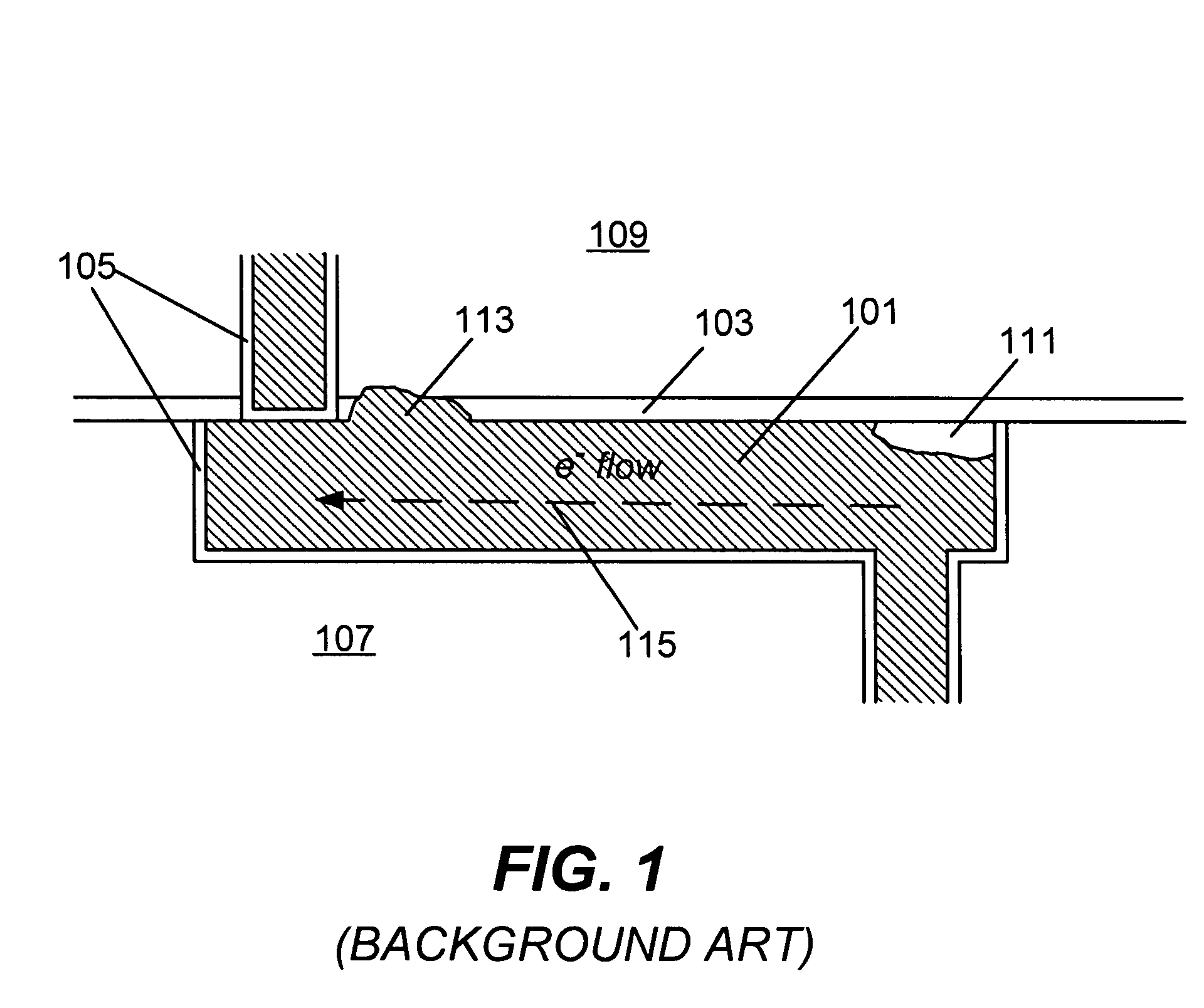

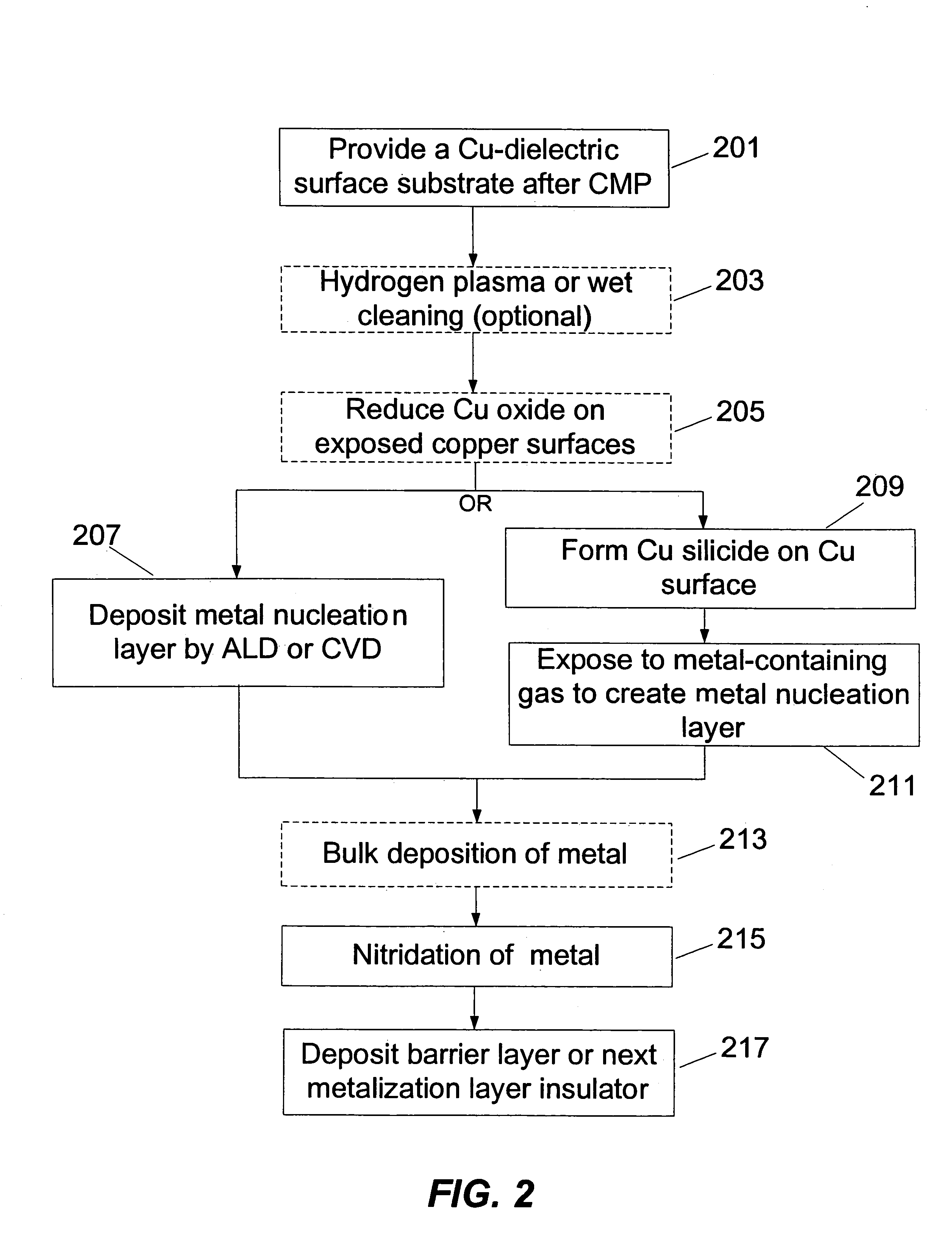

Selective refractory metal and nitride capping

InactiveUS6844258B1Inhibited DiffusionPrevent electromigrationSemiconductor/solid-state device detailsSolid-state devicesCopperNucleation

A method for creating a refractory metal and refractory metal nitride cap effective for reducing copper electromigration and copper diffusion is described. The method includes depositing a refractory metal nucleation layer and nitriding at least the upper portion of the refractory metal layer to form a refractory metal nitride. Methods to reduce and clean the copper lines before refractory metal deposition are also described. Methods to form a thicker refractory metal layer using bulk deposition are also described.

Owner:NOVELLUS SYSTEMS

Graded thin films

InactiveUS6933225B2Reduce the temperatureDesirable interface propertySolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricSilicon oxide

Thin films are formed by atomic layer deposition, whereby the composition of the film can be varied from monolayer to monolayer during cycles including alternating pulses of self-limiting chemistries. In the illustrated embodiments, varying amounts of impurity sources are introduced during the cyclical process. A graded gate dielectric is thereby provided, even for extremely thin layers. The gate dielectric as thin as 2 nm can be varied from pure silicon oxide to oxynitride to silicon nitride. Similarly, the gate dielectric can be varied from aluminum oxide to mixtures of aluminum oxide and a higher dielectric material (e.g., ZrO2) to pure high k material and back to aluminum oxide. In another embodiment, metal nitride (e.g., WN) is first formed as a barrier for lining dual damascene trenches and vias. During the alternating deposition process, copper can be introduced, e.g., in separate pulses, and the copper source pulses can gradually increase in frequency, forming a graded transition region, until pure copper is formed at the upper surface. Advantageously, graded compositions in these and a variety of other contexts help to avoid such problems as etch rate control, electromigration and non-ohmic electrical contact that can occur at sharp material interfaces.

Owner:ASM INTERNATIONAL

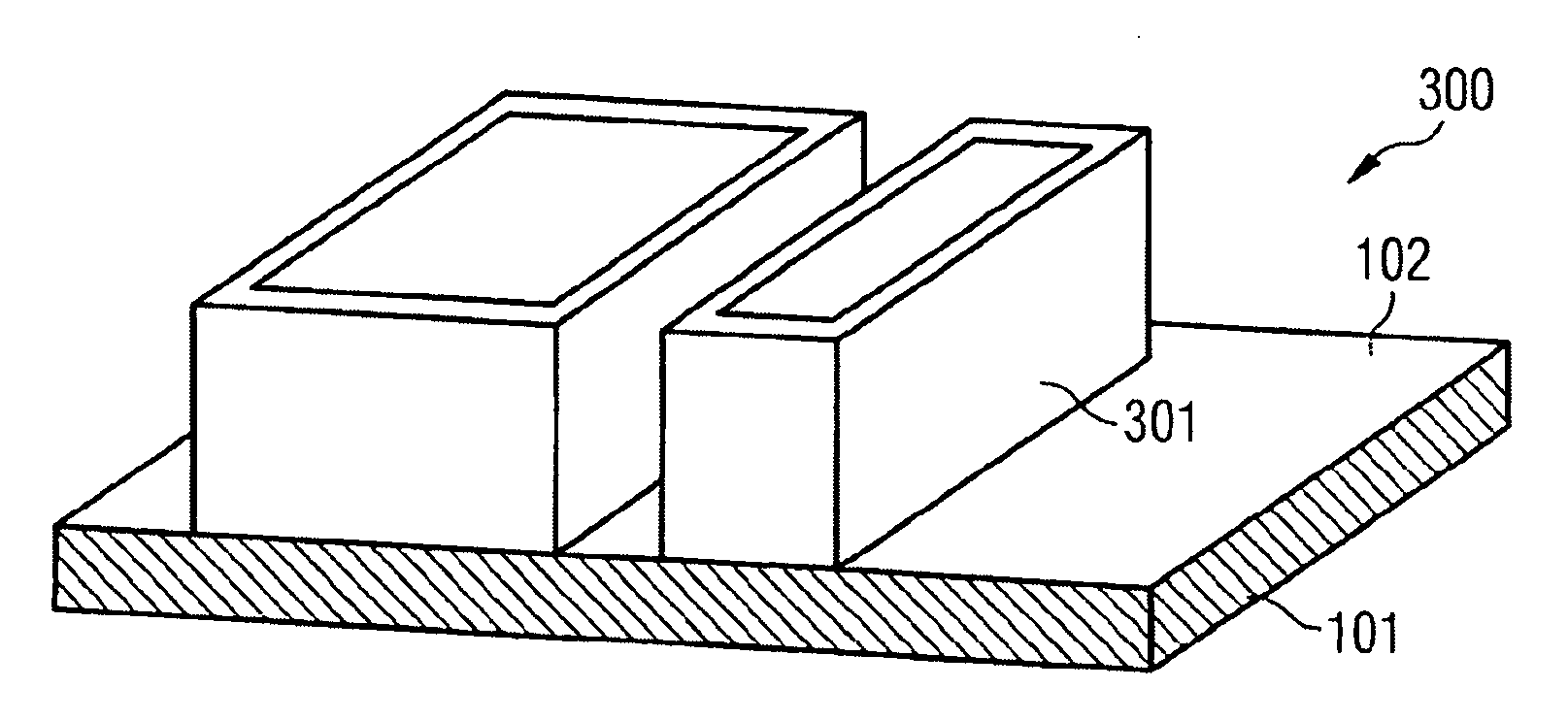

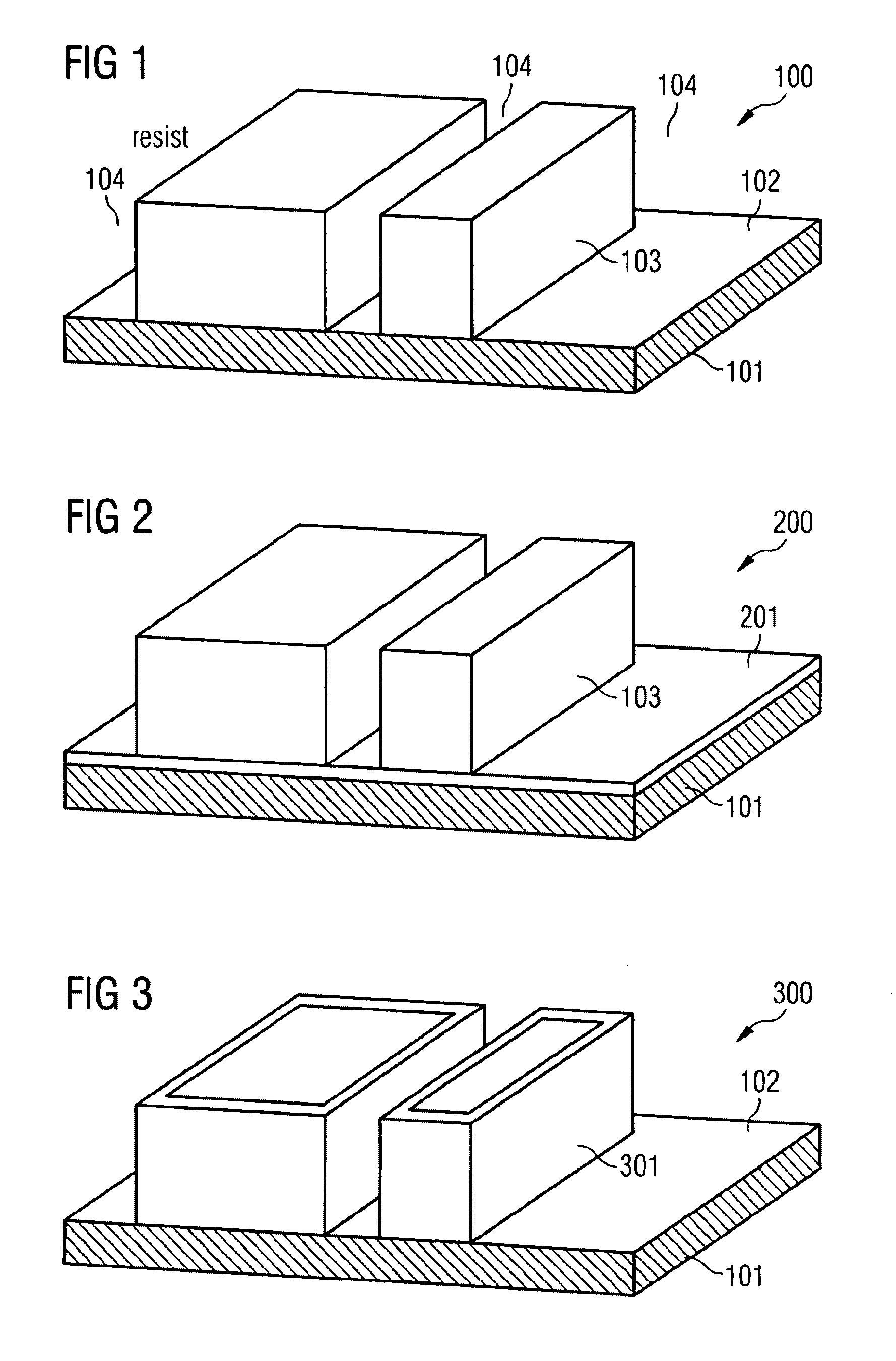

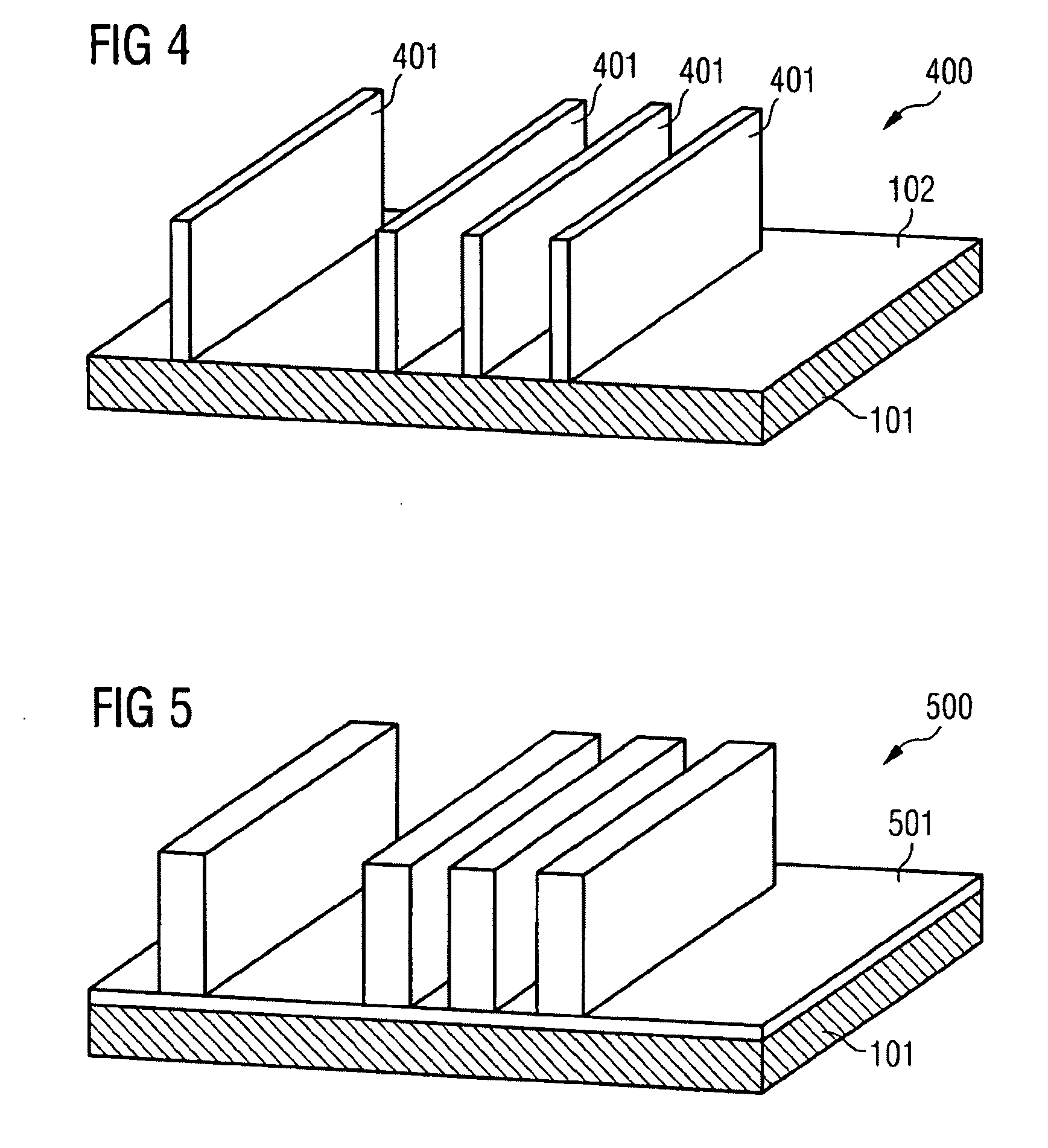

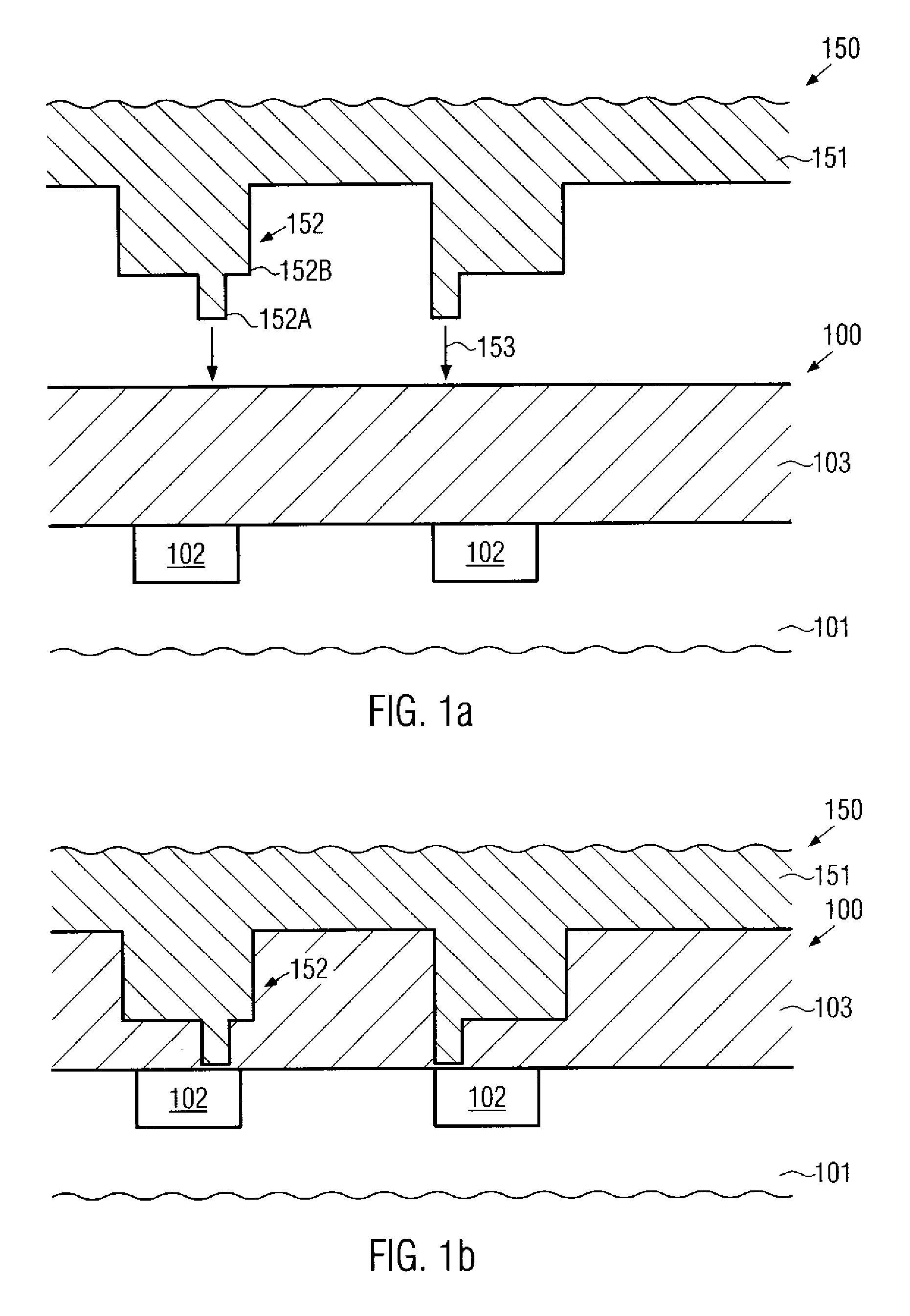

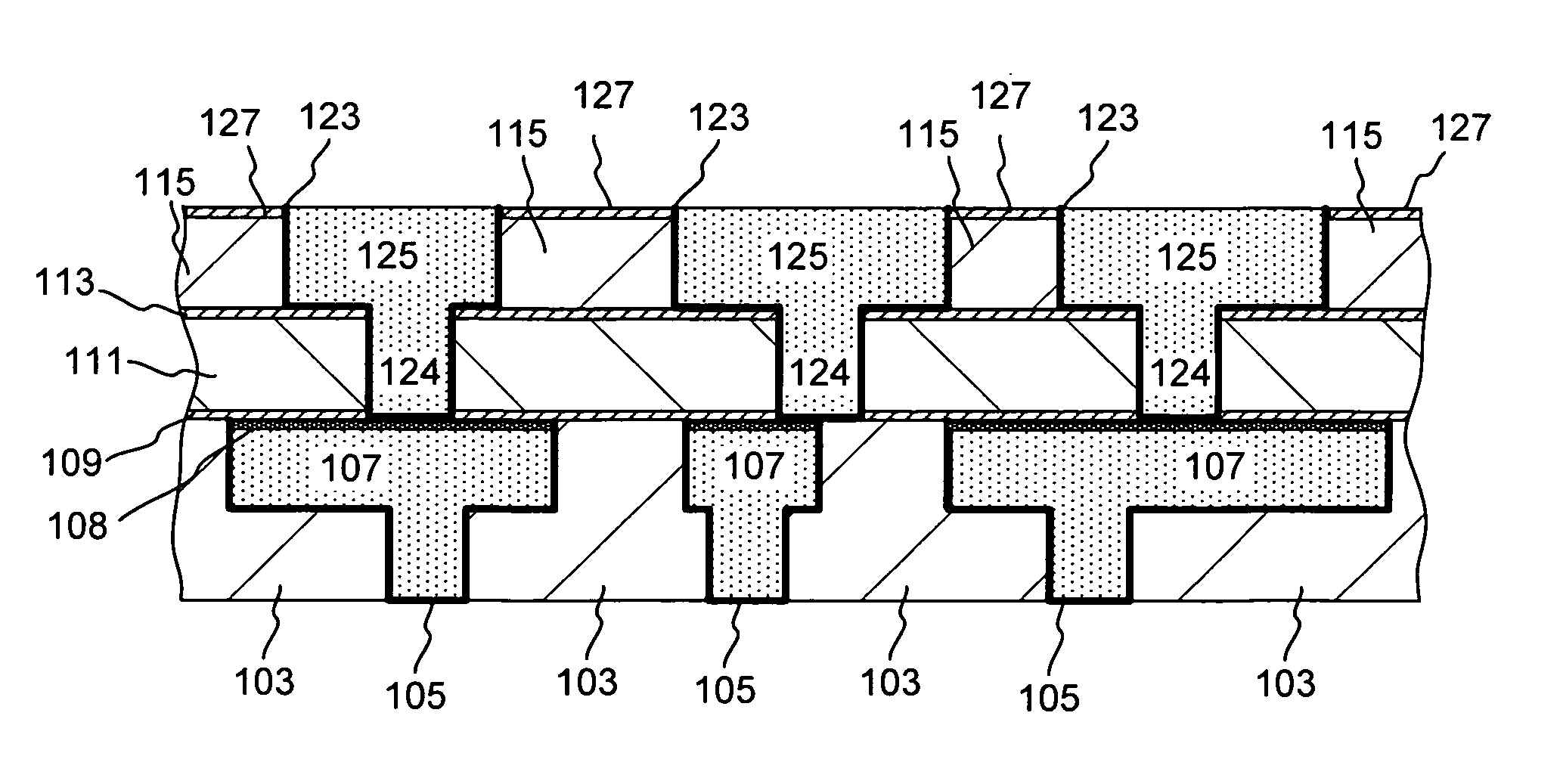

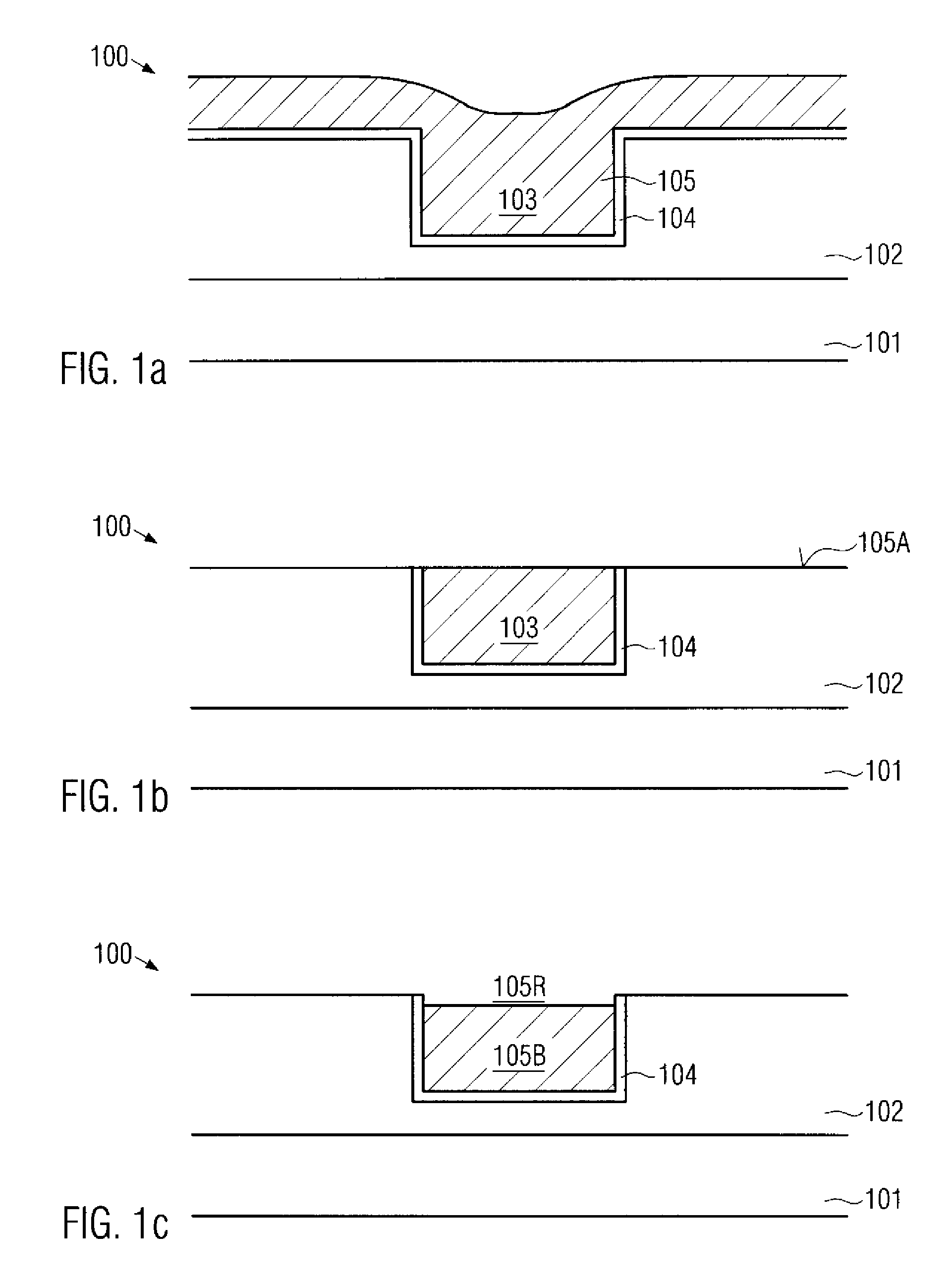

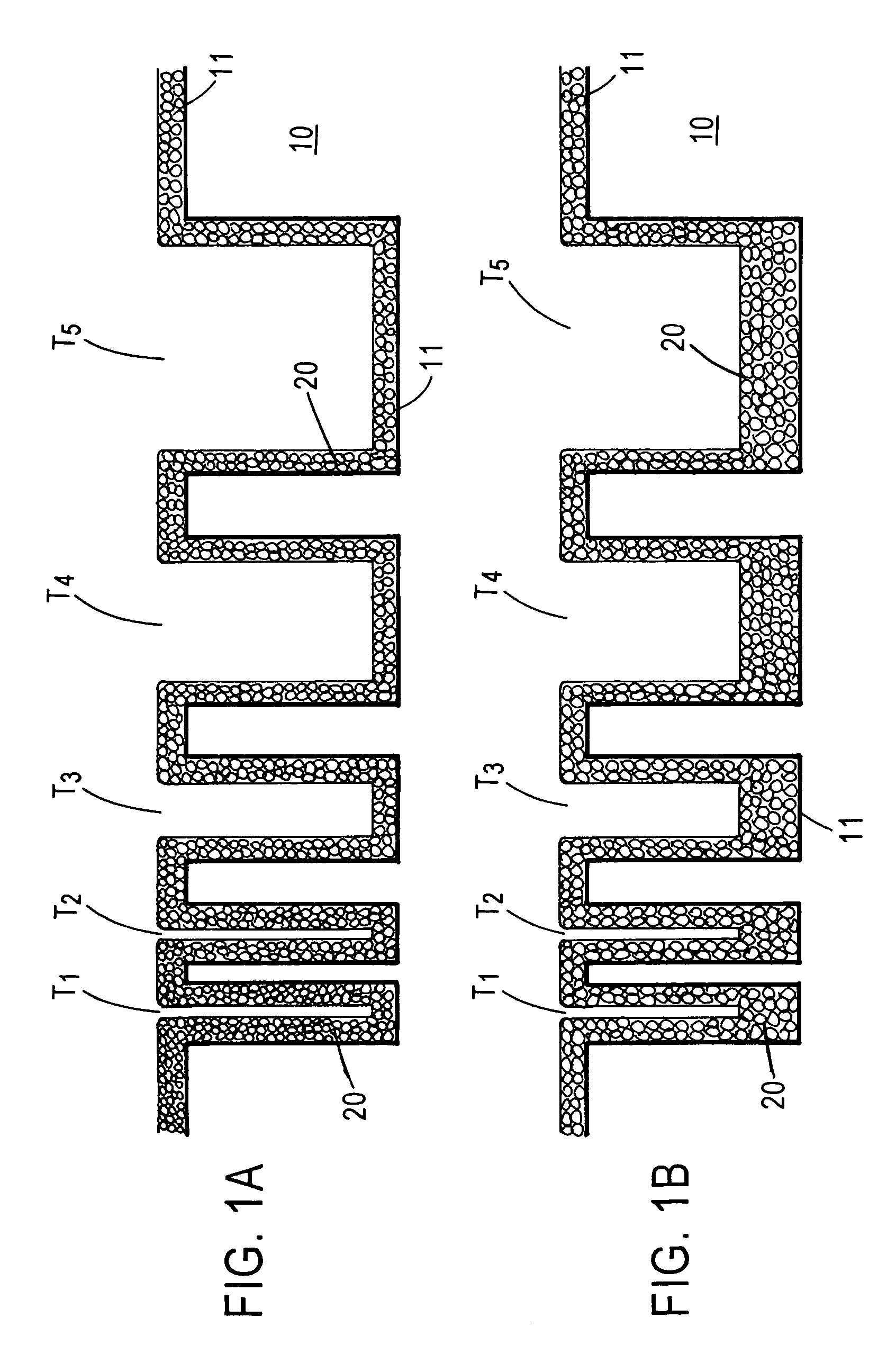

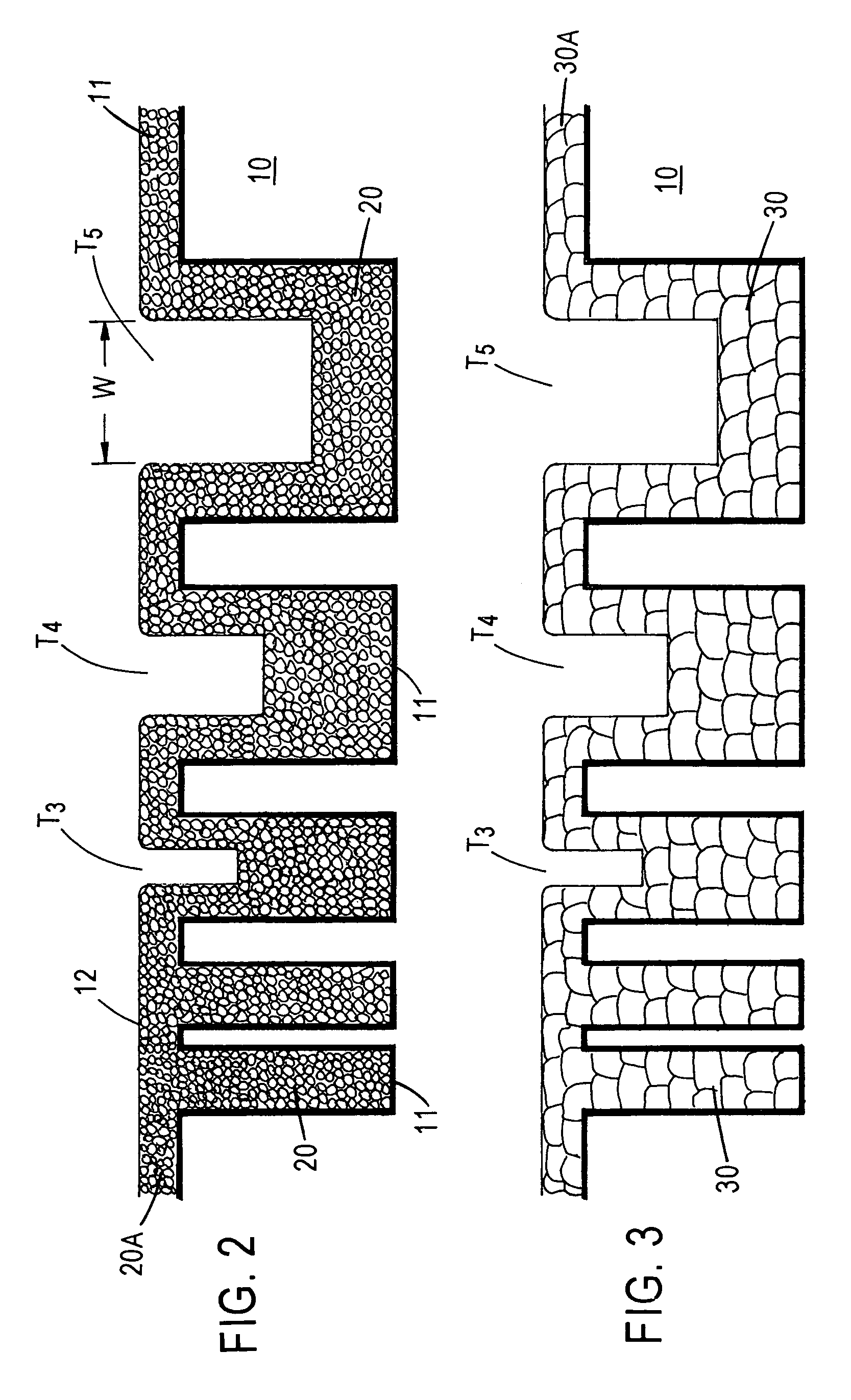

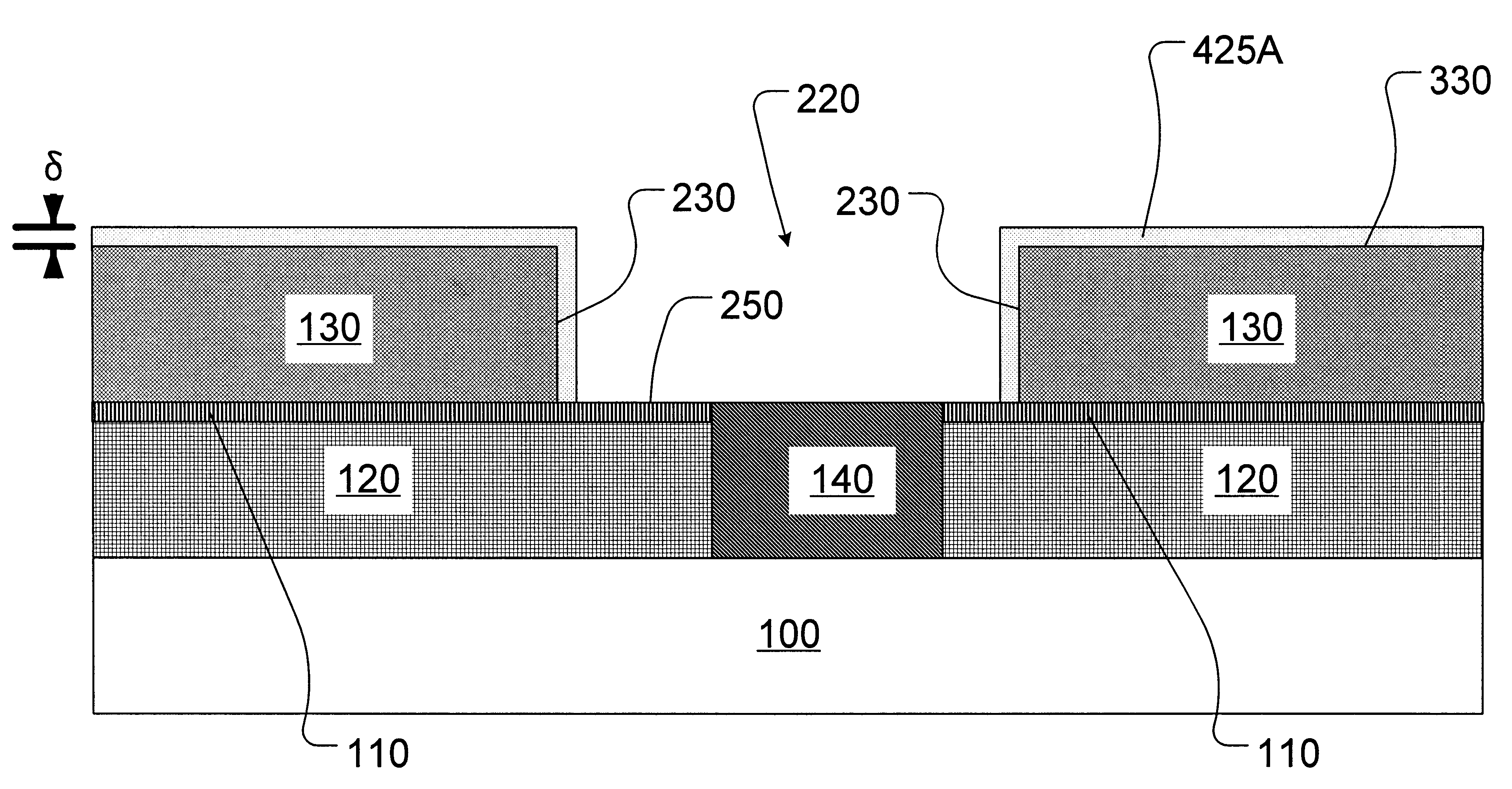

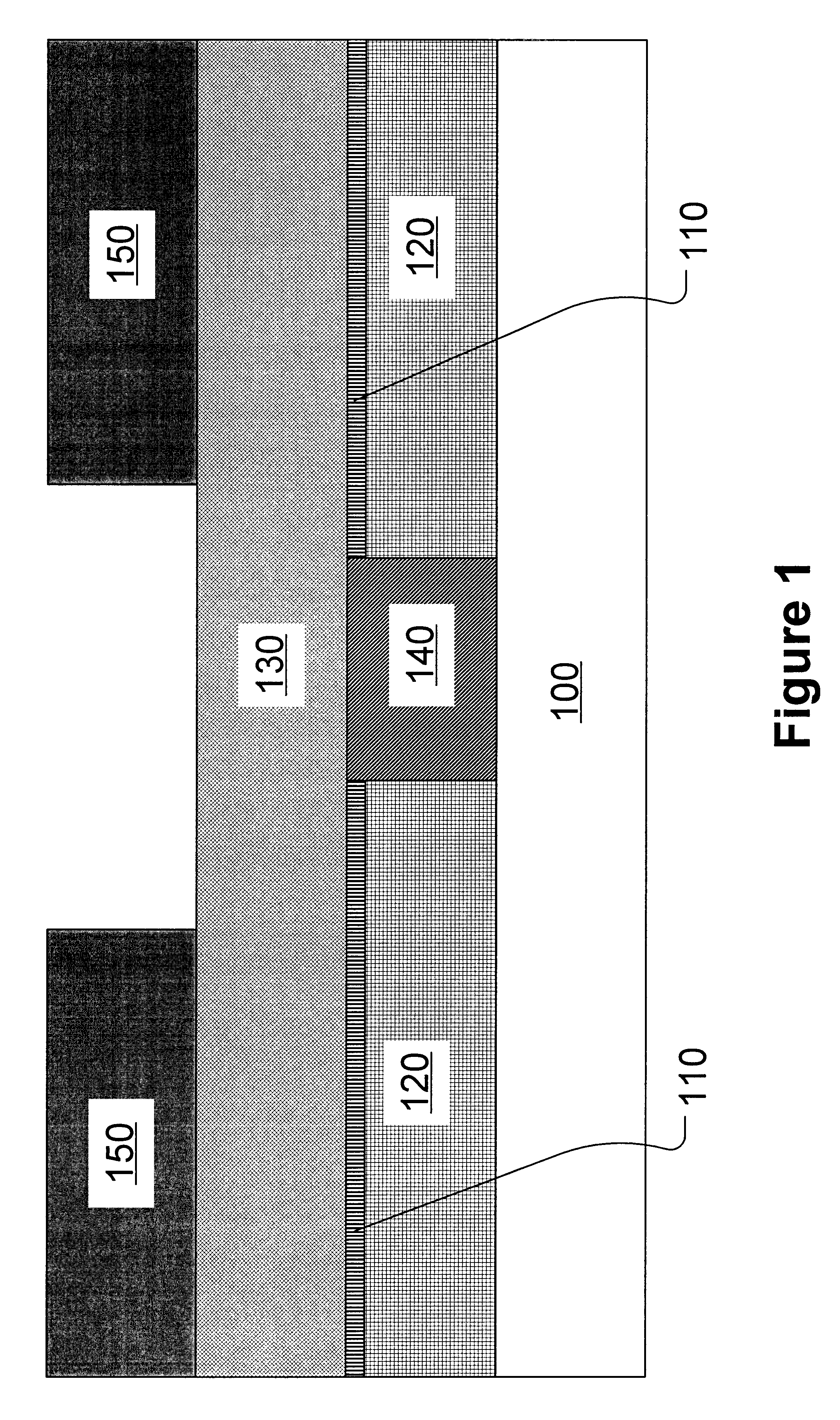

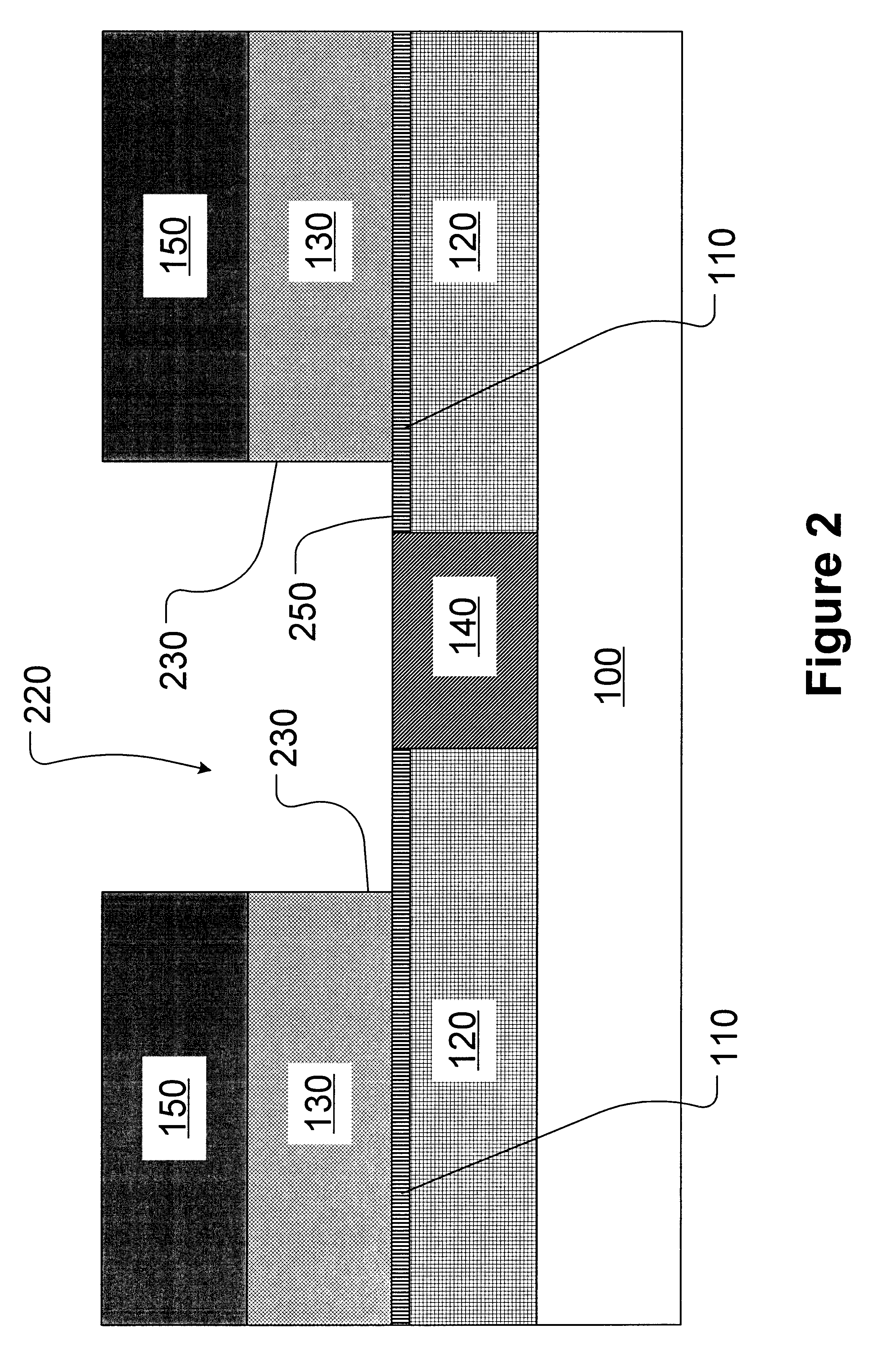

NANO imprint technique with increased flexibility with respect to alignment and feature shaping

ActiveUS20080003818A1Increase flexibilityReduce in quantityNanoinformaticsSolid-state devicesLithographic artistEngineering

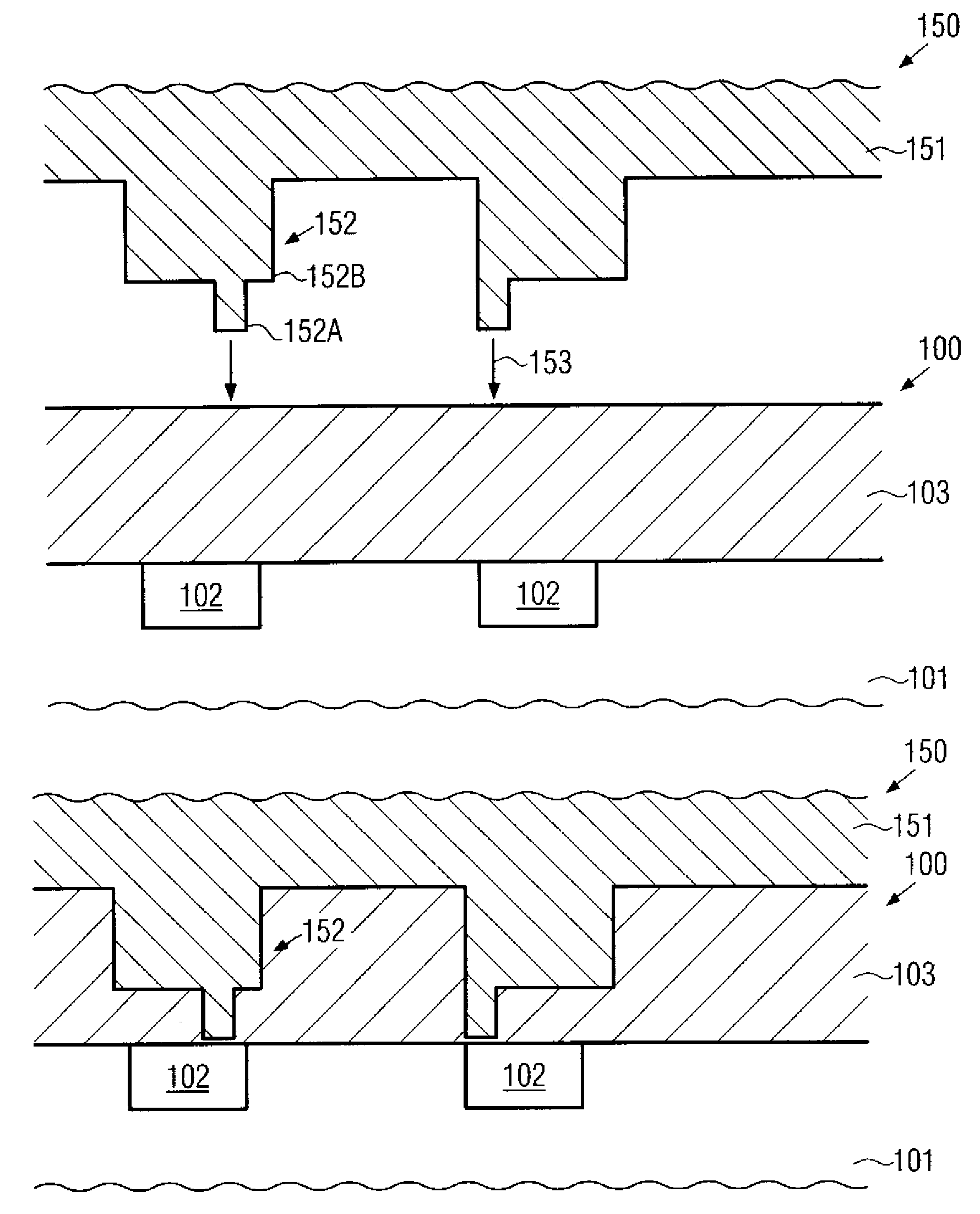

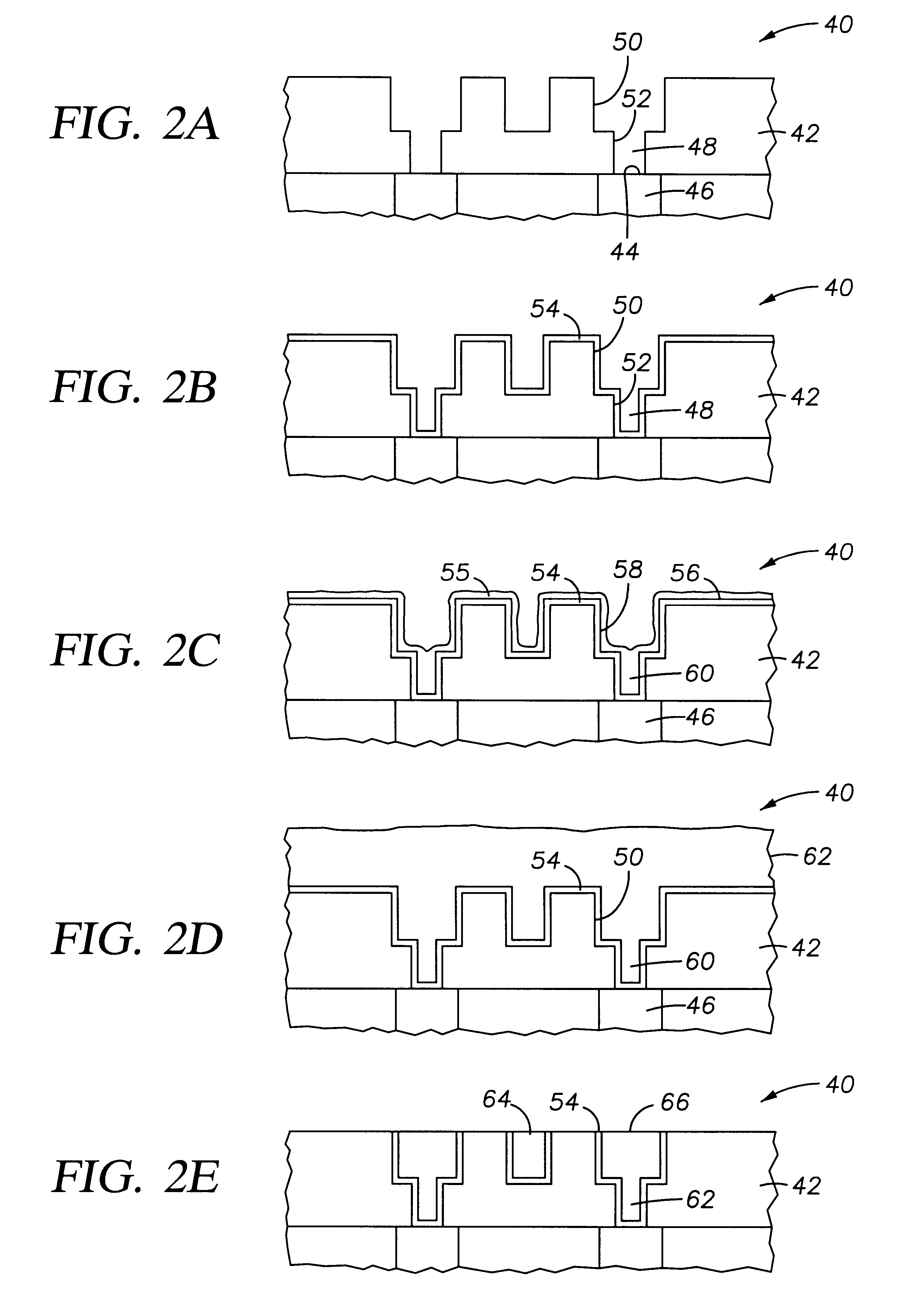

By forming metallization structures on the basis of an imprint technique, in which via openings and trenches may be commonly formed, a significant reduction of process complexity may be achieved due to the omission of at least one further alignment process as required in conventional process techniques. Furthermore, the flexibility and efficiency of imprint lithography may be increased by providing appropriately designed imprint molds in order to provide via openings and trenches exhibiting an increased fill capability, thereby also improving the performance of the finally obtained metallization structures with respect to reliability, resistance against electromigration and the like.

Owner:ADVANCED MICRO DEVICES INC

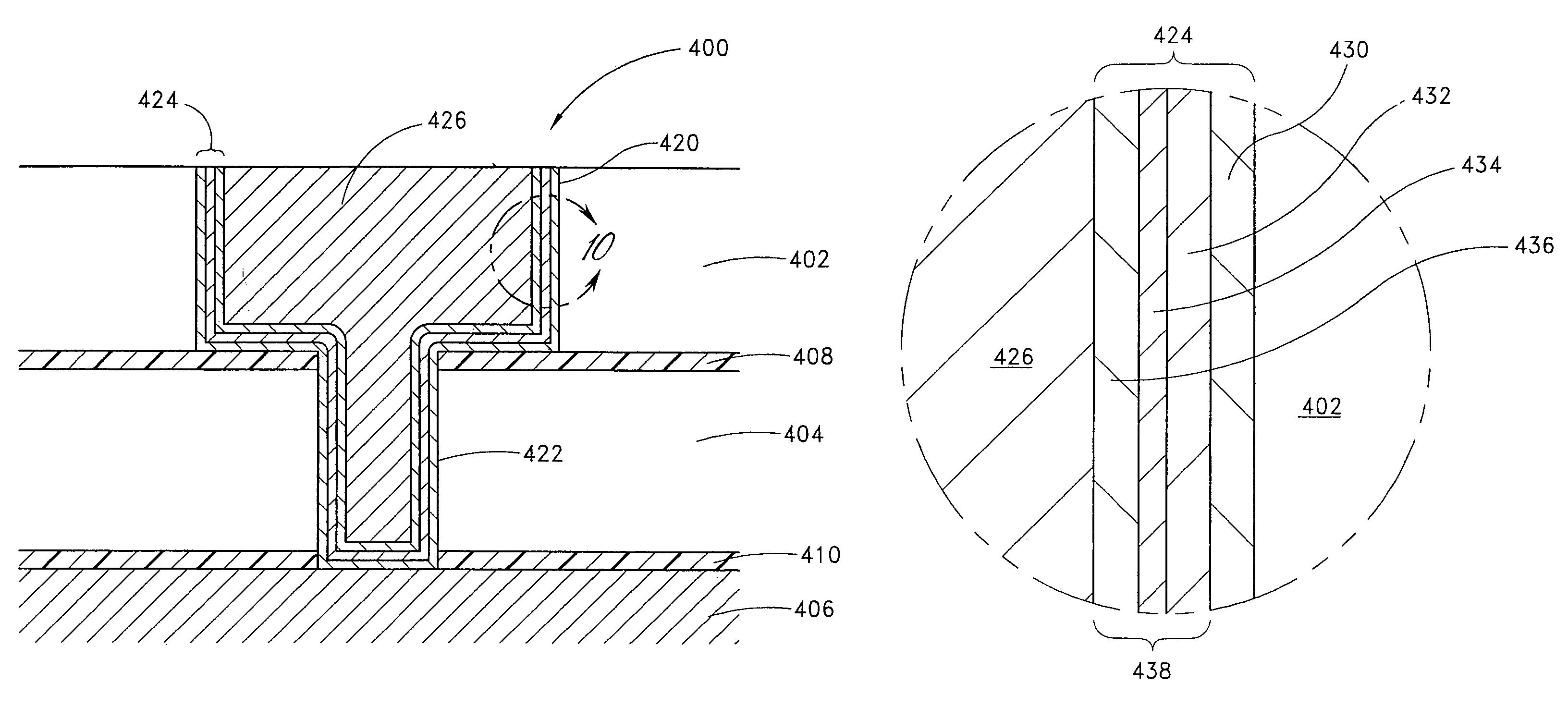

Dual damascene metallization

InactiveUS6207222B1Semiconductor/solid-state device detailsSolid-state devicesCopper wireDielectric layer

The present invention generally provides a metallization process for forming a highly integrated interconnect. More particularly, the present invention provides a dual damascene interconnect module that incorporates a barrier layer deposited on all exposed surface of a dielectric layer which contains a dual damascene via and wire definition. A conductive metal is deposited on the barrier layer using two or more deposition methods to fill the via and wire definition prior to planarization. The invention provides the advantages of having copper wires with lower resistivity (greater conductivity) and greater electromigration resistance than aluminum, a barrier layer between the copper wire and the surrounding dielectric material, void-free, sub-half micron selective CVD Al via plugs, and a reduced number of process steps to achieve such integration.

Owner:APPLIED MATERIALS INC

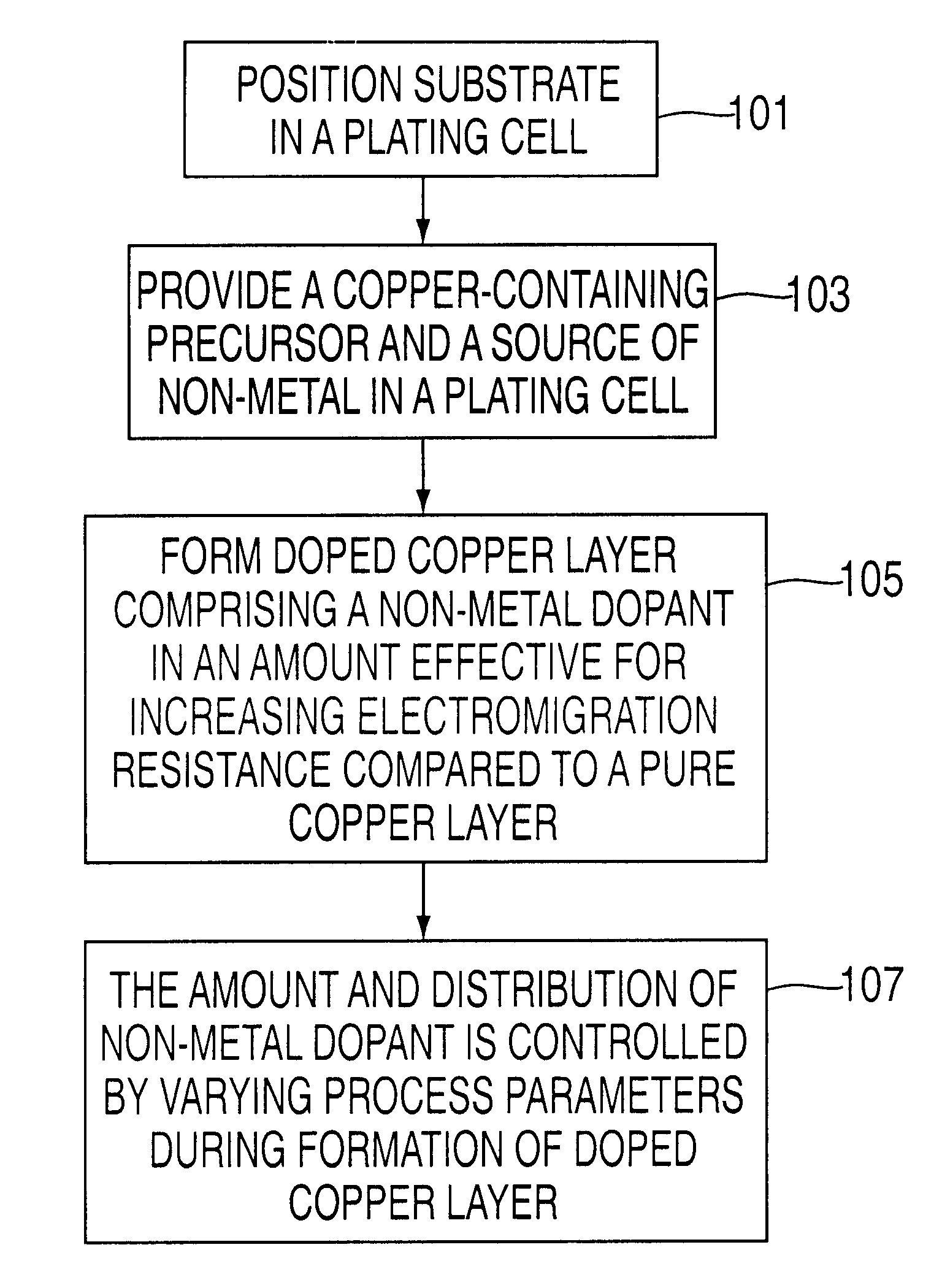

Method of forming copper interconnections with enhanced electromigration resistance and reduced defect sensitivity

A method of providing sub-half-micron copper interconnections with improved electromigration and corrosion resistance. The method includes double damascene using electroplated copper, where the seed layer is converted to an intermetallic layer. A layer of copper intermetallics with halfnium, lanthanum, zirconium or tin, is provided to improve the electromigration resistance and to reduce defect sensitivity. A method is also provided to form a cap atop copper lines, to improve corrosion resistance, which fully covers the surface. Structure and methods are also described to improve the electromigration and corrosion resistance by incorporating carbon atoms in copper intersititial positions.

Owner:GLOBALFOUNDRIES INC

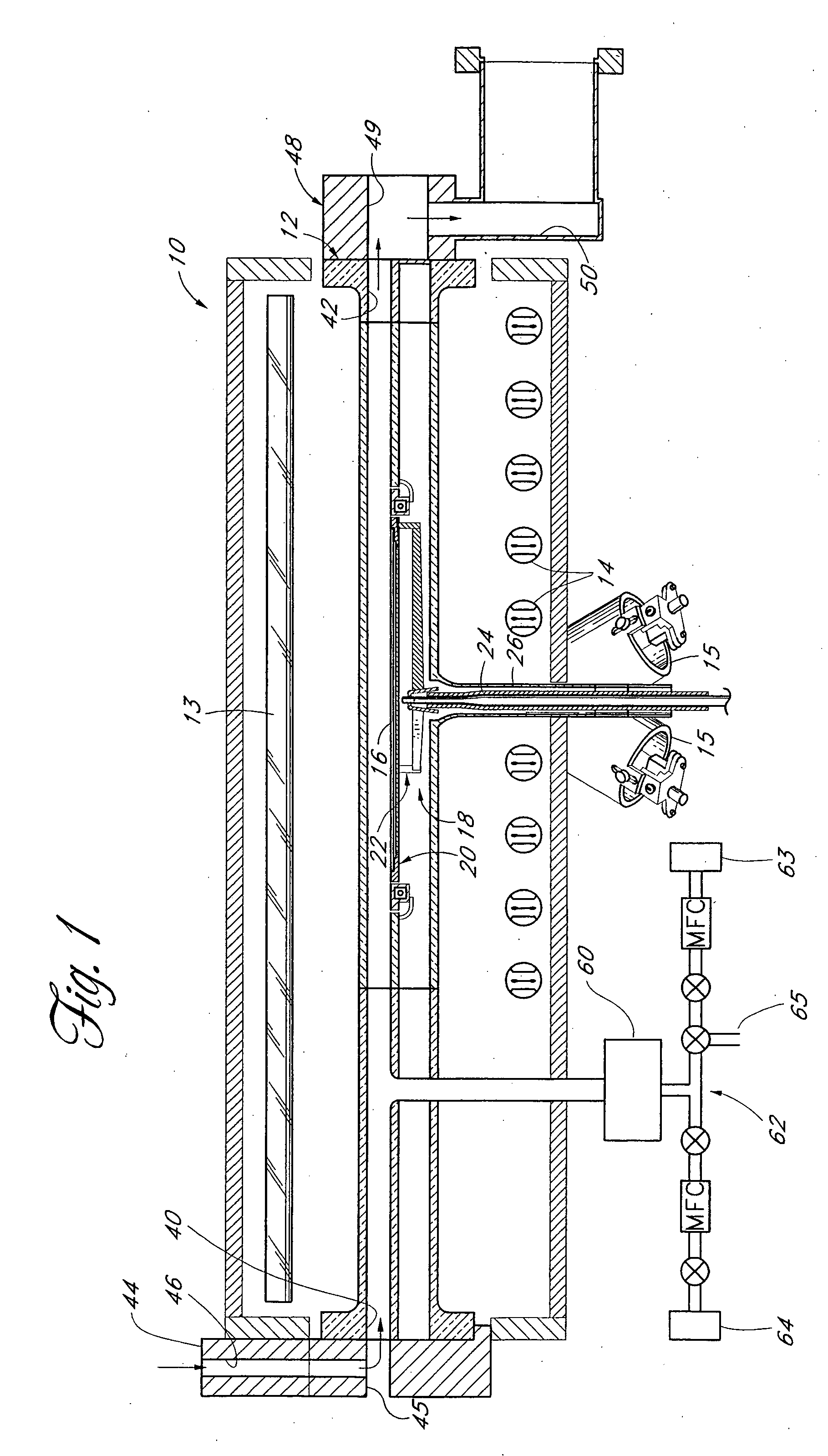

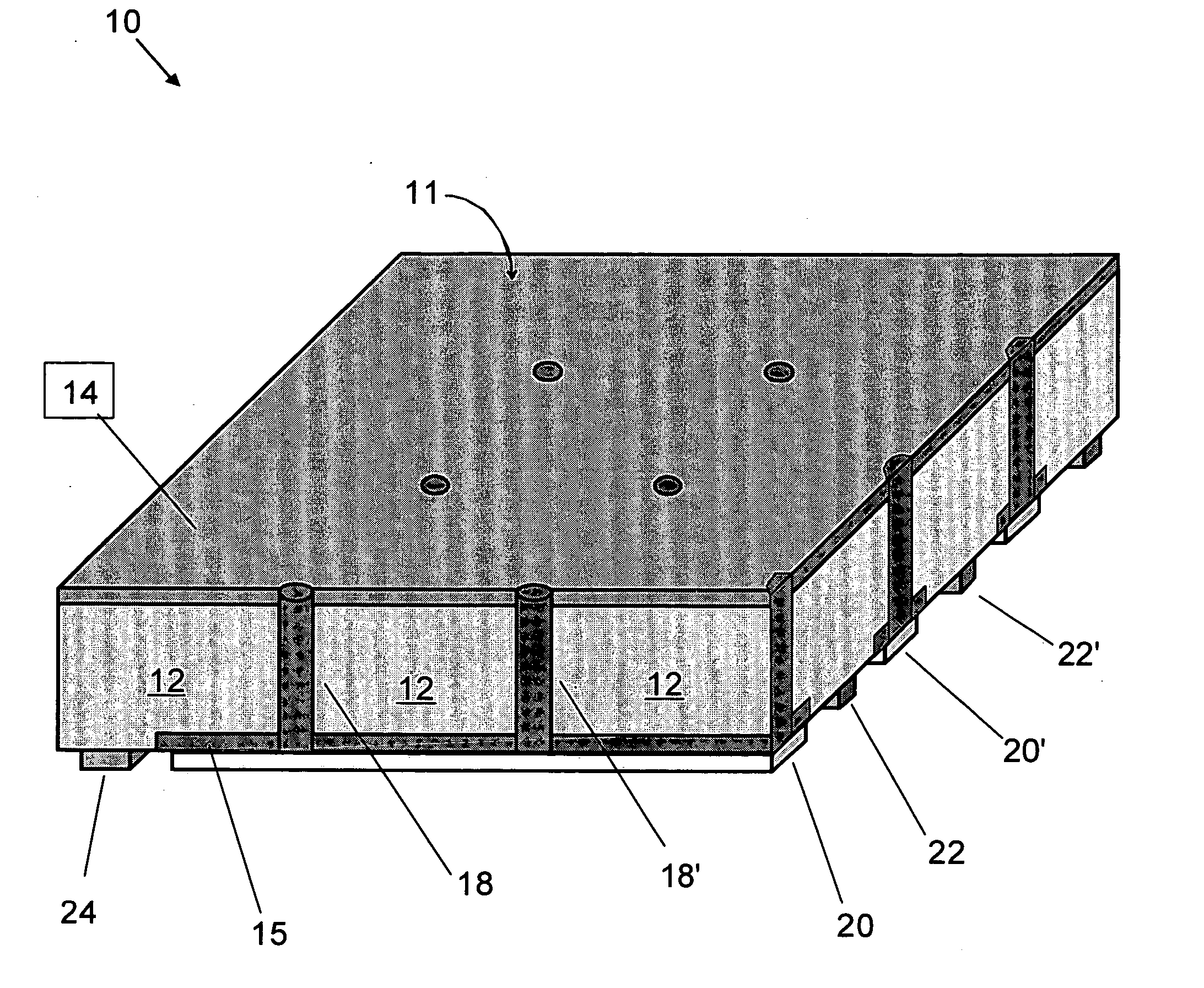

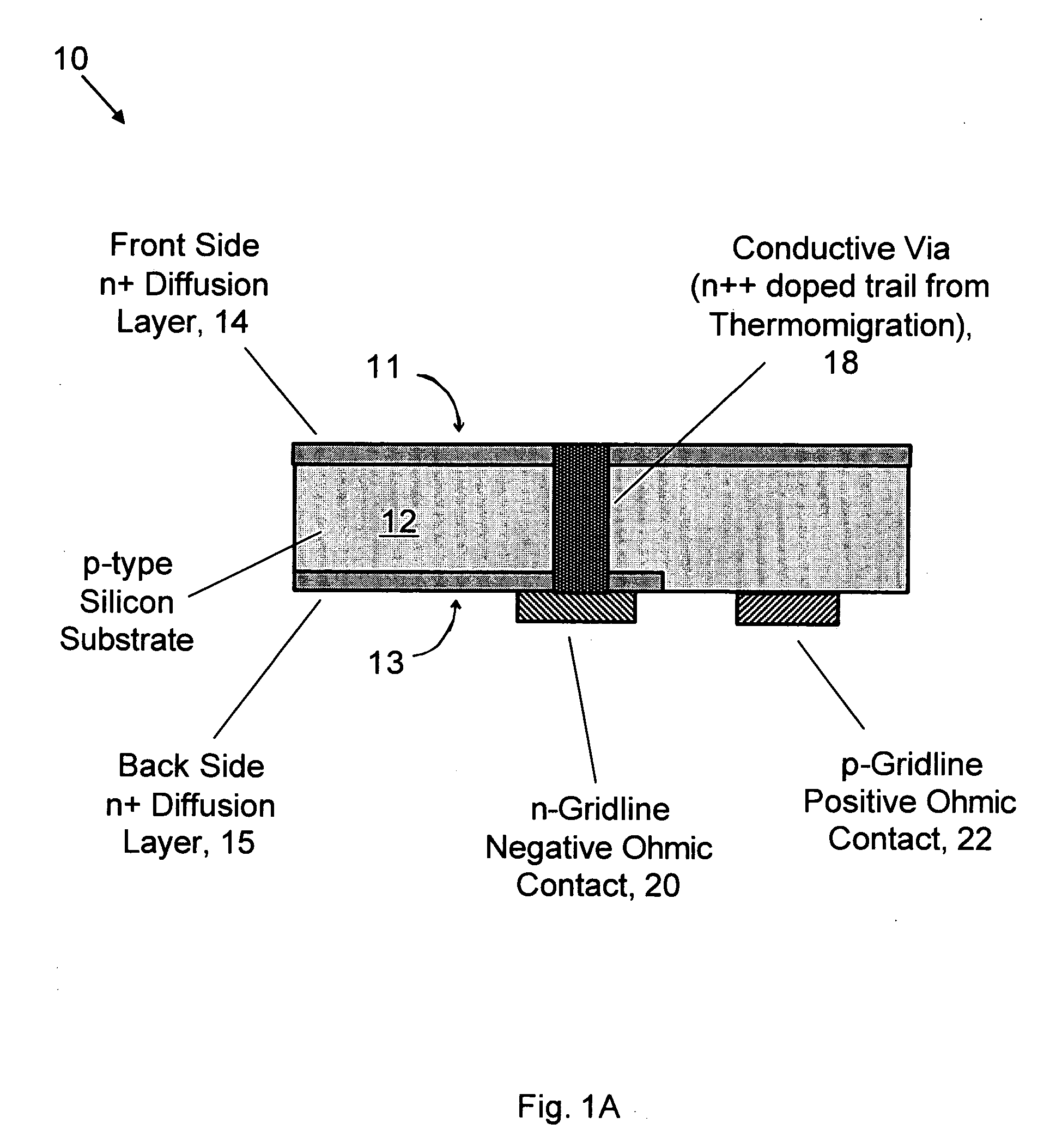

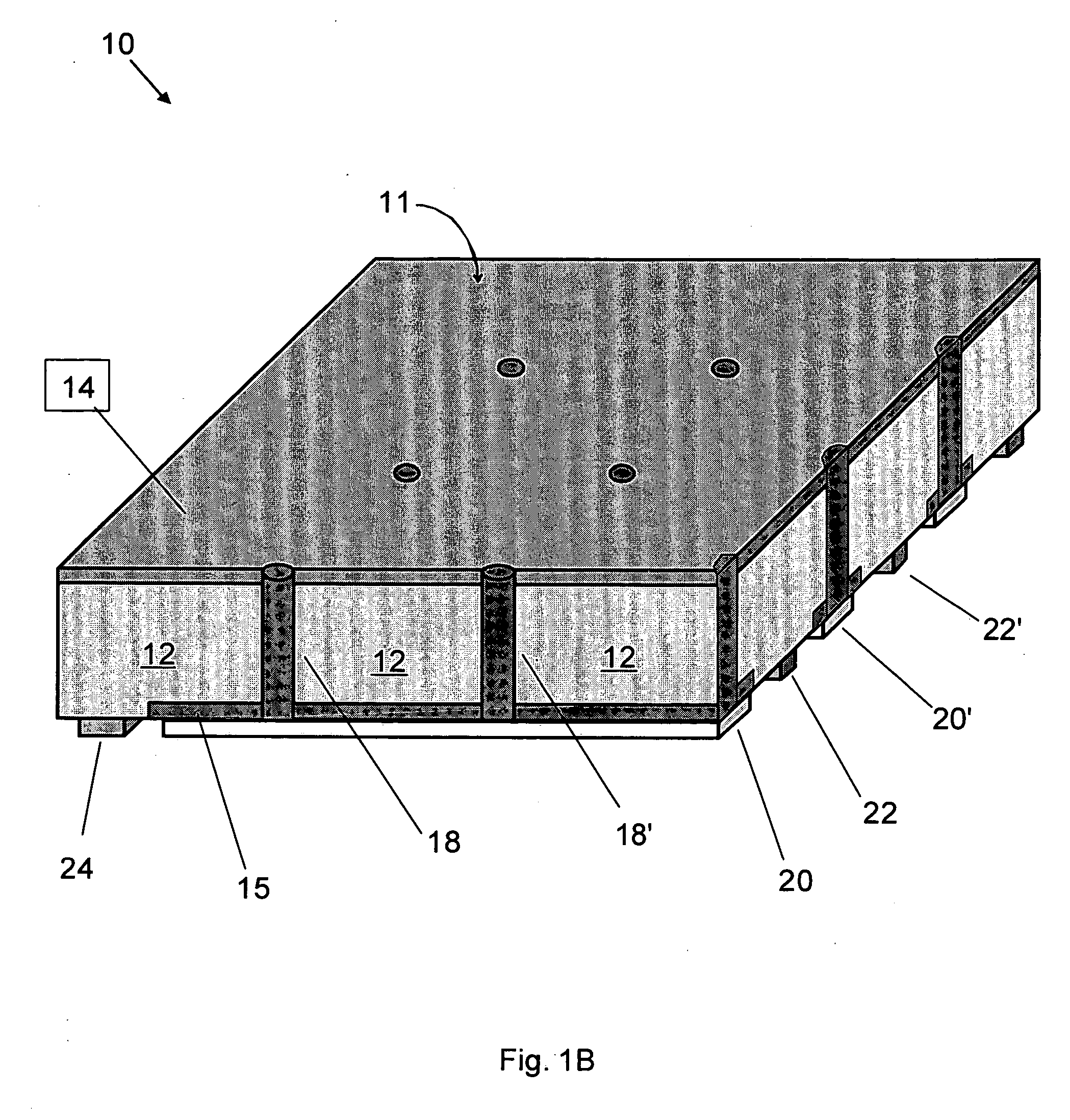

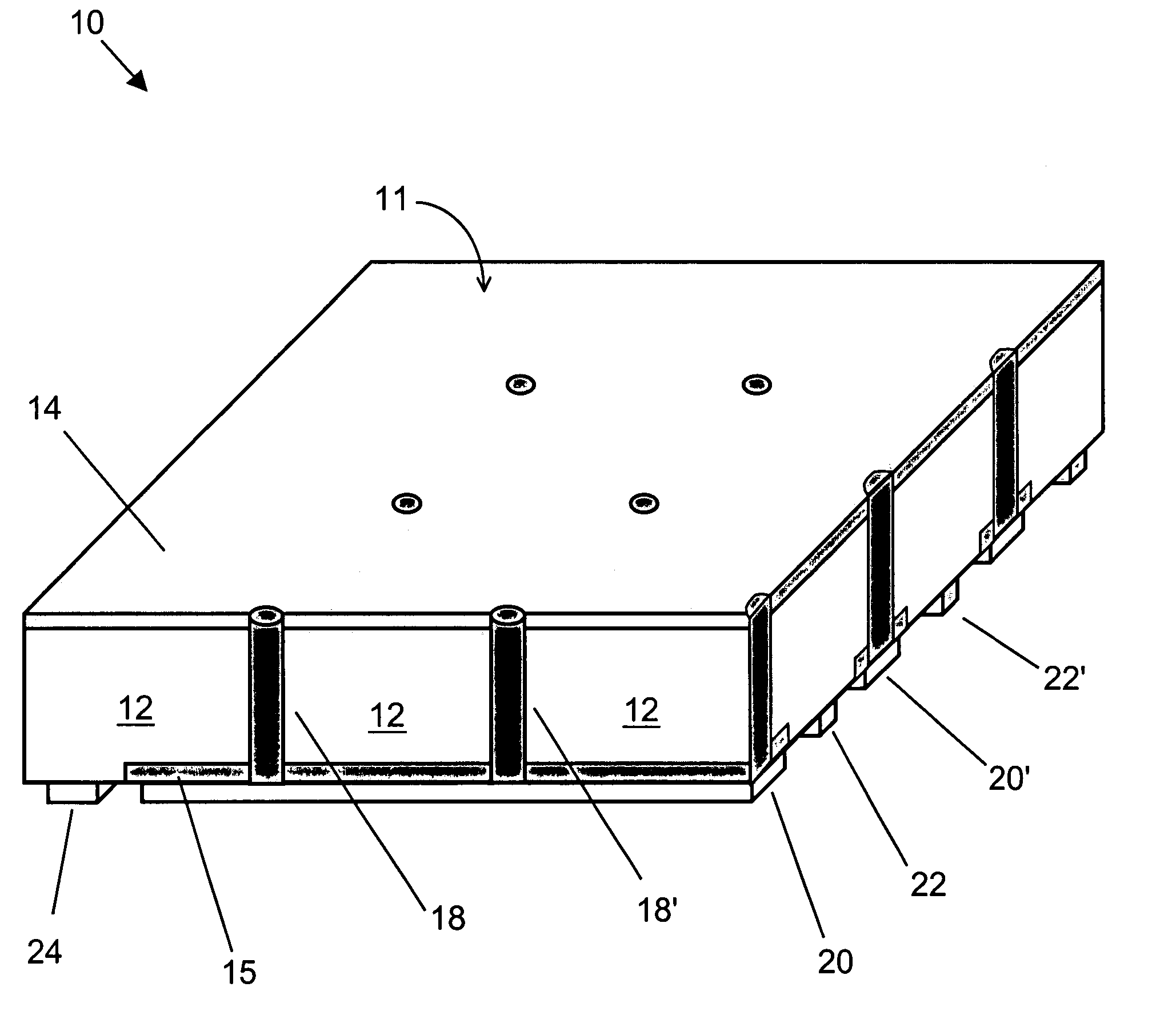

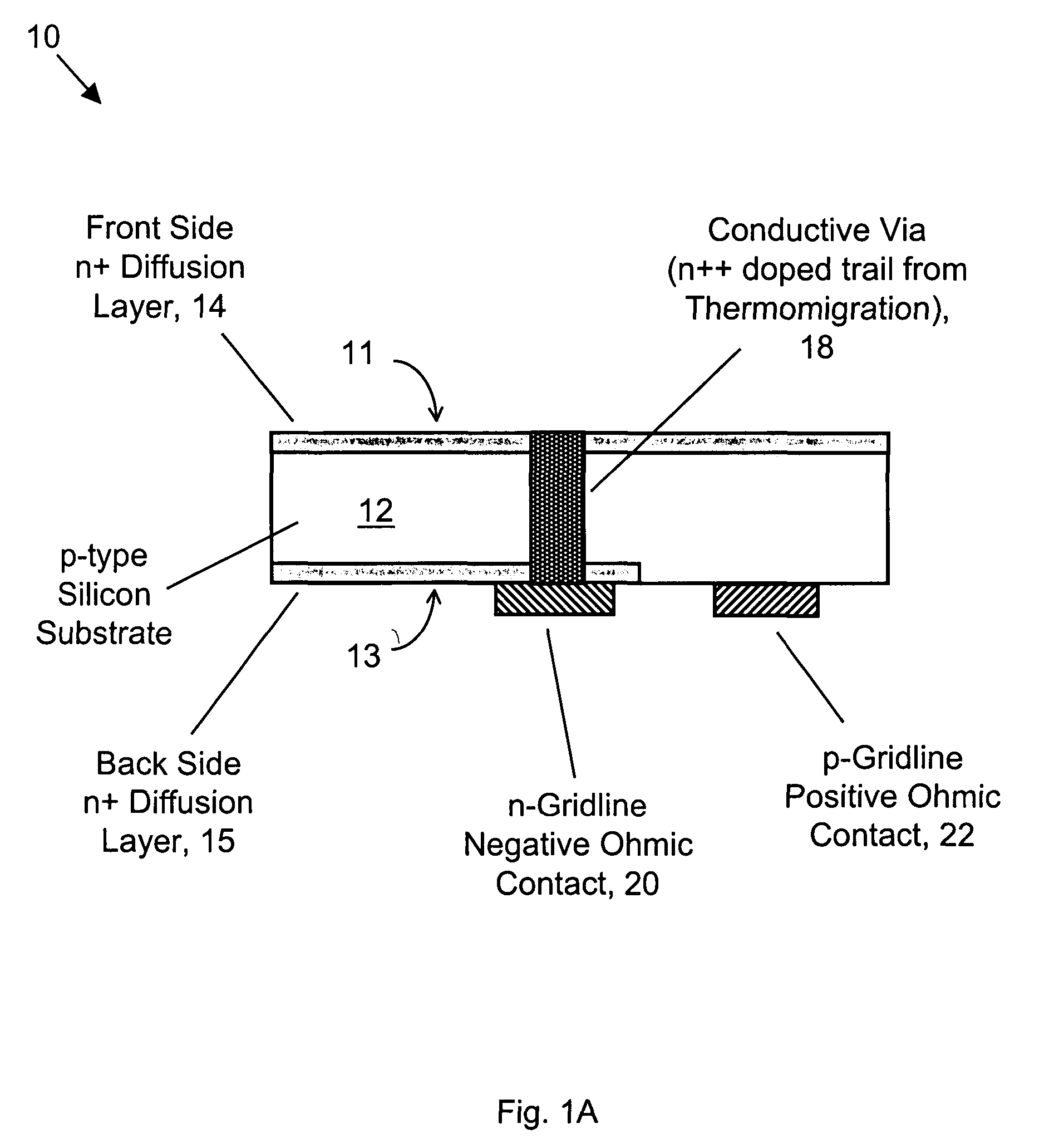

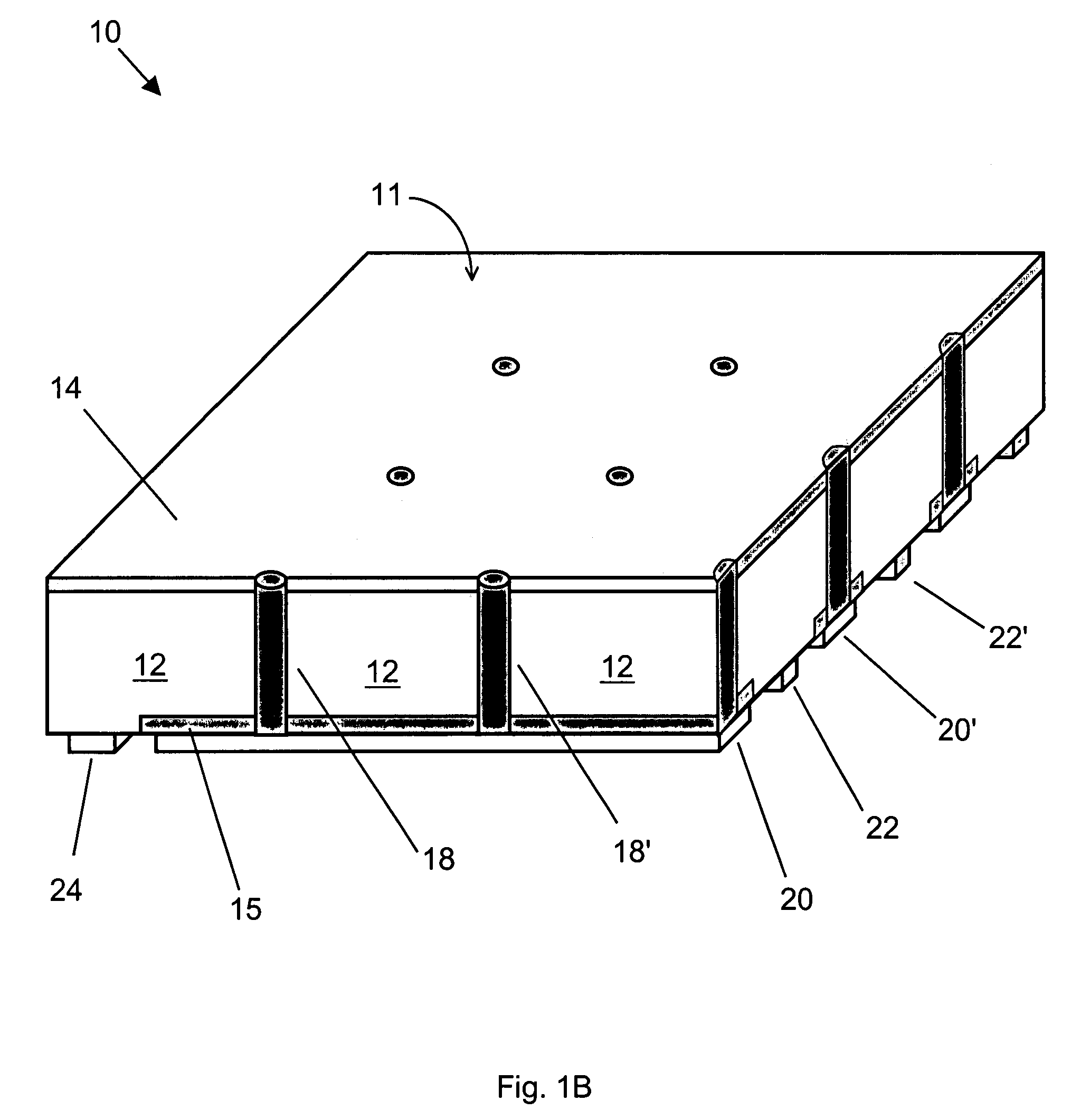

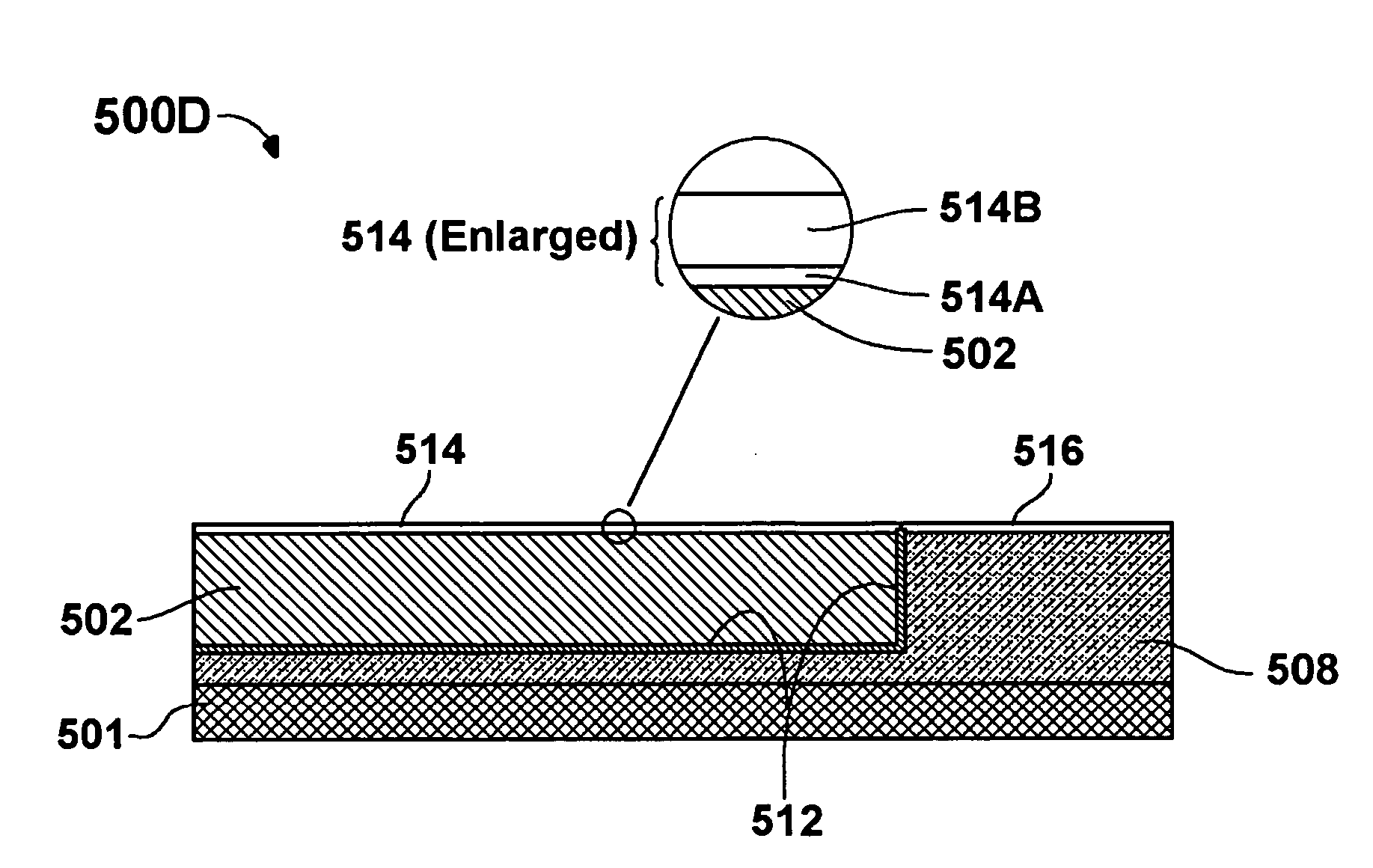

Back-contacted solar cells with integral conductive vias and method of making

Methods of manufacturing back-contacted p-type semiconductor substrate solar cells fabricated using a gradient-driven solute transport process, such as thermomigration or electromigration, to create n-type conductive vias connecting the n-type emitter layer on the front side to n-type ohmic contacts located on the back side, and back-contacted solar cells with integral n-type conductive vias, such as made by a gradient-driven solute transport process.

Owner:ADVENT SOLAR INC

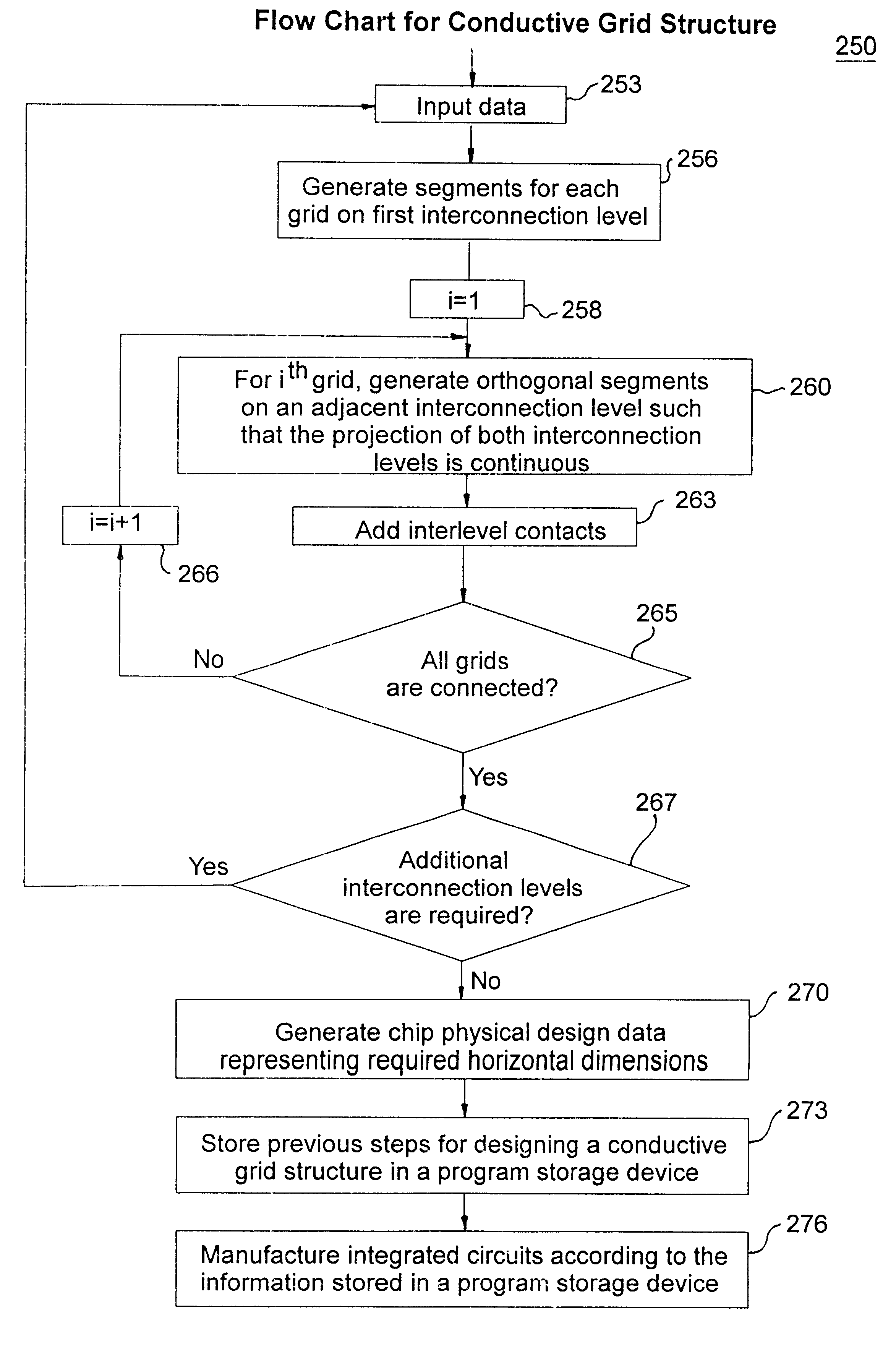

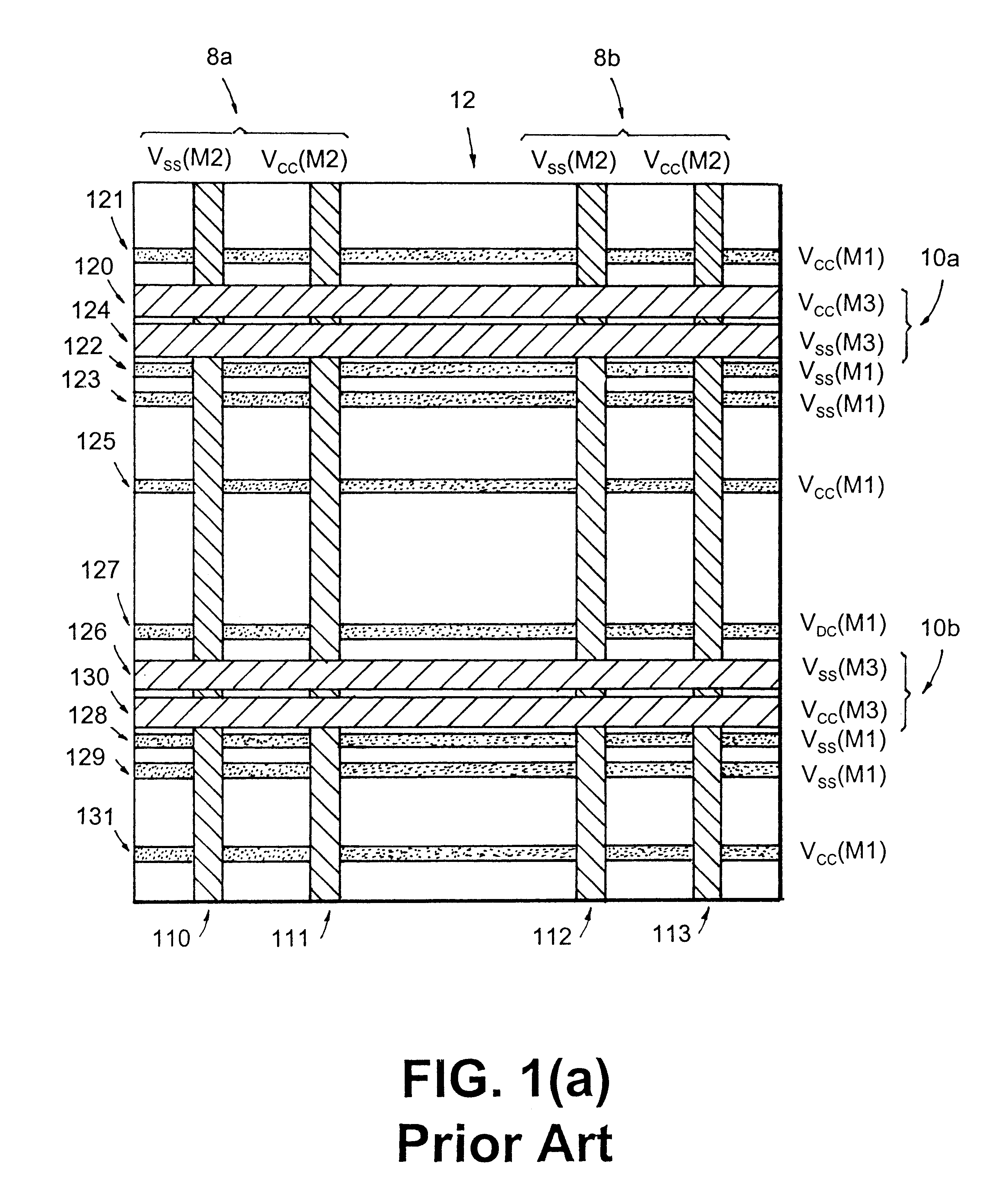

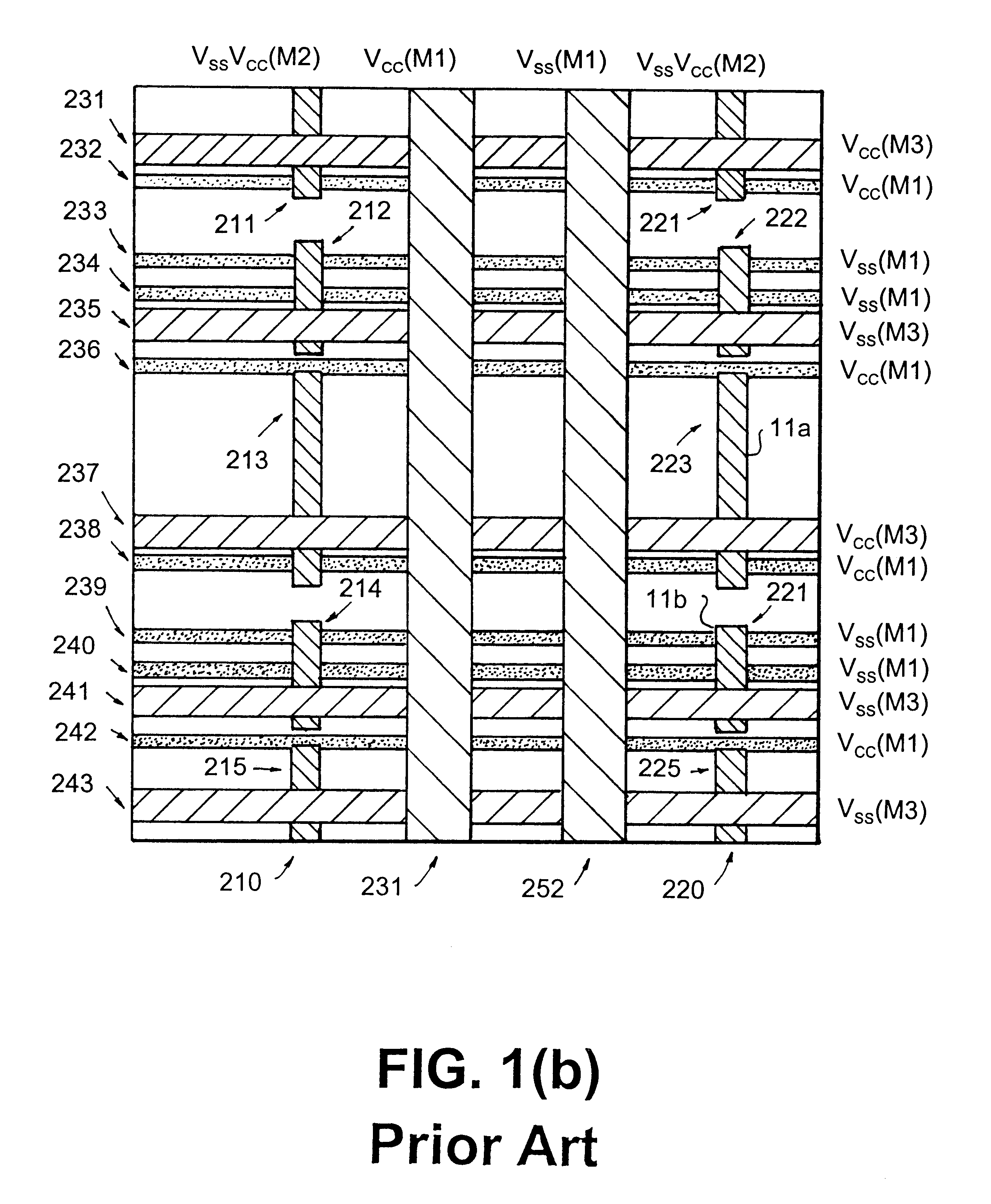

Electromigration resistant power distribution network

InactiveUS6202191B1Semiconductor/solid-state device detailsSolid-state devicesInsulation layerSemiconductor chip

Method for forming a novel power grid structure for integrated circuit semiconductor chip devices that exhibits increased electromigration resistance by including diffusion blocking interlevel contacts and employing a regular array of conducting line elements with "phase shift" between adjacent tracks of segmented power busses. The novel grid structure includes a first metal layer including a first set of conducting line segments that are substantially parallel to one another and run in a first direction; a layer of diffusion blocking dielectric insulation above the first layer; a second metal layer including a second set of conducting line segments substantially parallel to each other and running in a second direction orthogonal to the first direction; and, interlevel contact studs disposed substantially vertically through the diffusion blocking dielectric insulation layer for electrically connecting aligned line segments of the first and second sets, wherein each segment of the first and second sets of line segments is limited to a predetermined length by a diffusion blocking boundary.

Owner:IBM CORP

Thin films

InactiveUS7419903B2Desirable interface propertyQuality improvementSolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricSilicon oxide

Thin films are formed by formed by atomic layer deposition, whereby the composition of the film can be varied from monolayer to monolayer during cycles including alternating pulses of self-limiting chemistries. In the illustrated embodiments, varying amounts of impurity sources are introduced during the cyclical process. A graded gate dielectric is thereby provided, even for extremely thin layers. The gate dielectric as thin as 2 nm can be varied from pure silicon oxide to oxynitride to silicon nitride. Similarly, the gate dielectric can be varied from aluminum oxide to mixtures of aluminum oxide and a higher dielectric material (e.g., ZrO2) to pure high k material and back to aluminum oxide. In another embodiment, metal nitride (e.g., WN) is first formed as a barrier for lining dual damascene trenches and vias. During the alternating deposition process, copper can be introduced, e.g., in separate pulses, and the copper source pulses can gradually increase in frequency, forming a transition region, until pure copper is formed at the upper surface. Advantageously, graded compositions in these and a variety of other contexts help to avoid such problems as etch rate control, electromigration and non-ohmic electrical contact that can occur at sharp material interfaces. In some embodiments additional seed layers or additional transition layers are provided.

Owner:ASM INTERNATIONAL

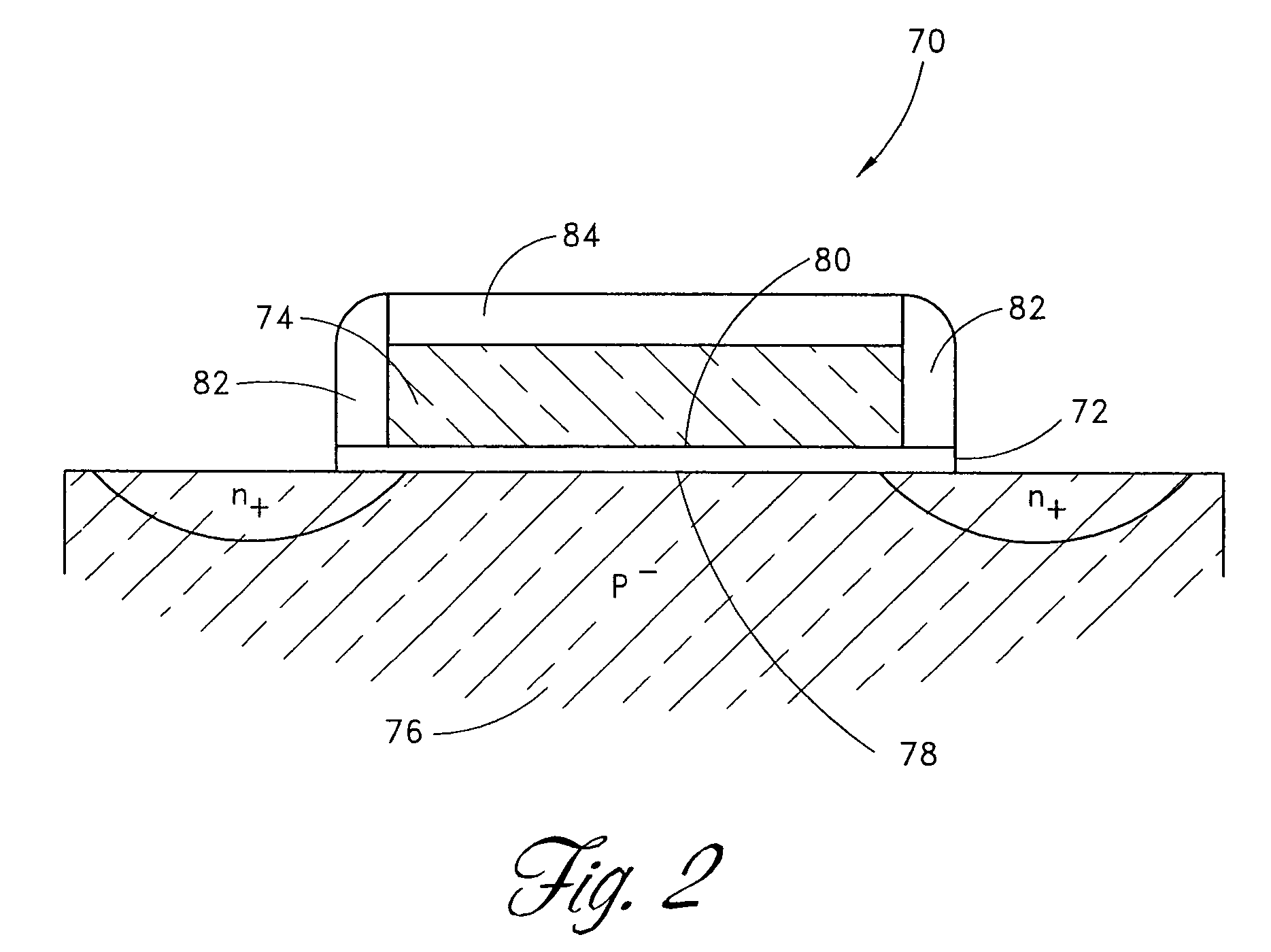

Fabrication of back-contacted silicon solar cells using thermomigration to create conductive vias

InactiveUS7170001B2Improve conversion efficiencyReduce contact resistanceSemiconductor/solid-state device manufacturingPhotovoltaic energy generationOhmic contactEngineering

Methods of manufacturing back-contacted silicon solar cells fabricated using a gradient-driven solute transport process, such as thermomigration or electromigration, to create n-type conductive vias connecting the n-type emitter layer on the front side to n-type ohmic contacts located on the back side.

Owner:ADVENT SOLAR INC +1

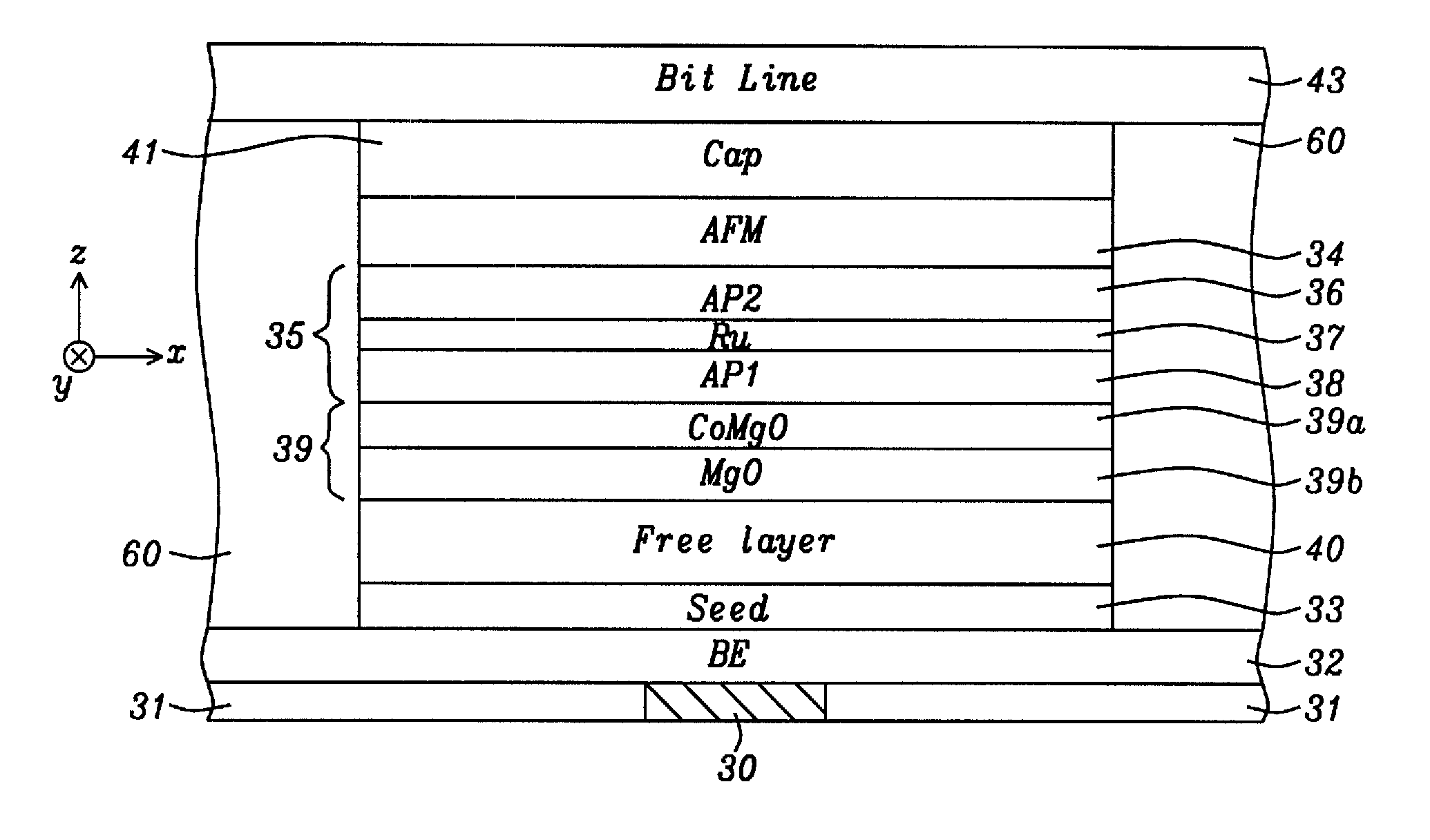

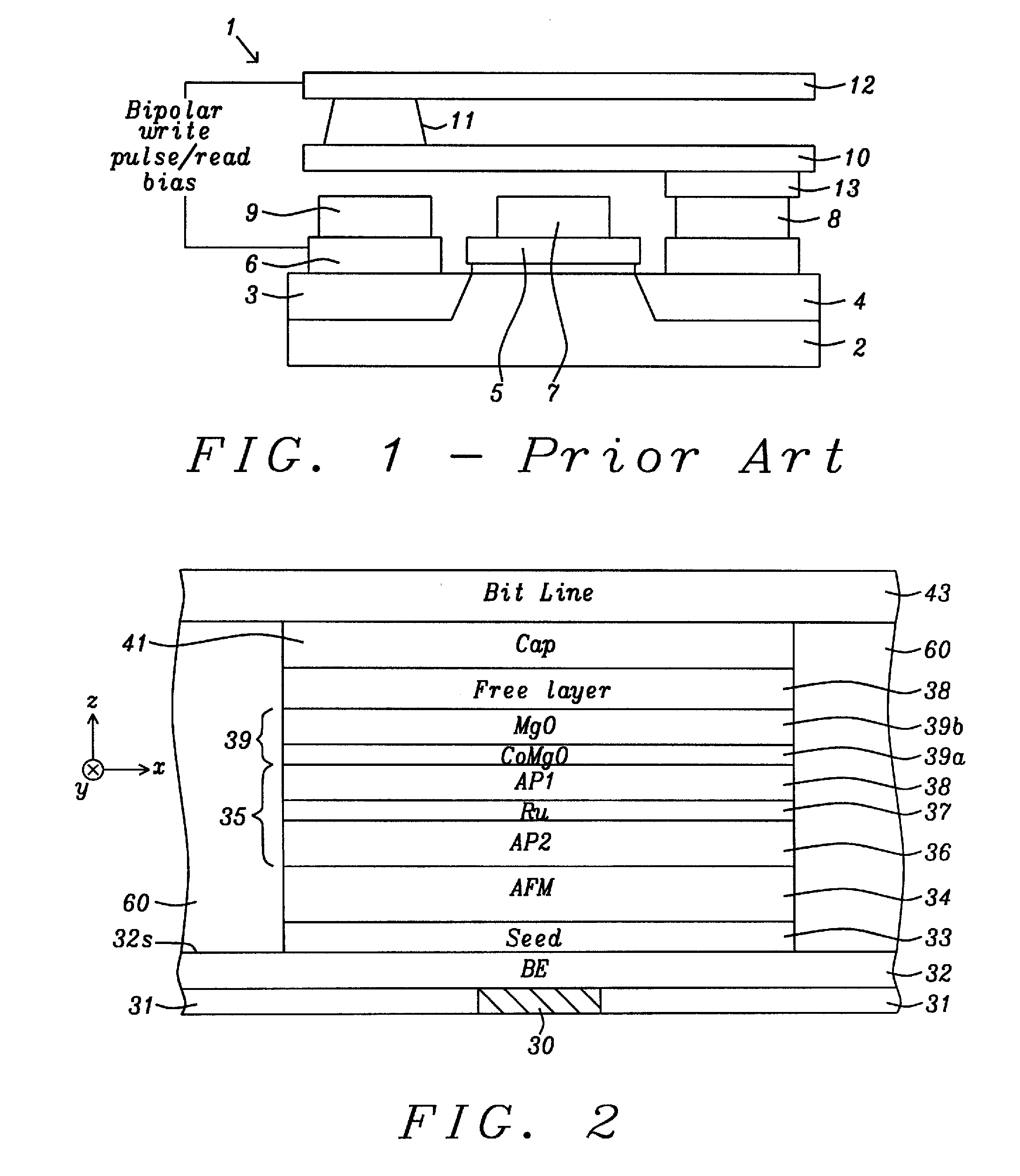

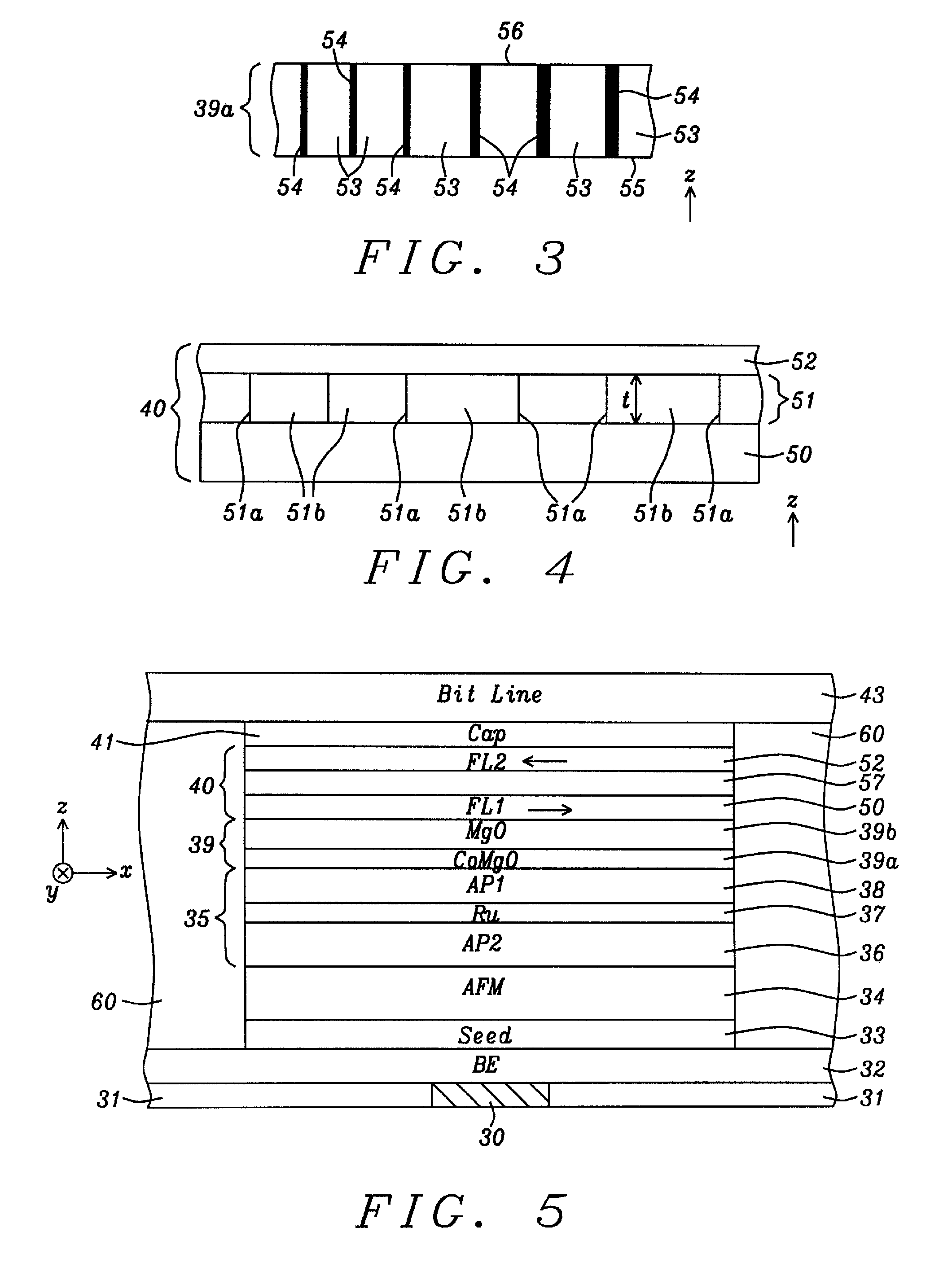

Spin torque transfer magnetic tunnel junction fabricated with a composite tunneling barrier layer

ActiveUS8823118B2Improve performanceHigh densityMagnetic-field-controlled resistorsSolid-state devicesIn planeSpins

A STT-RAM MTJ is disclosed with a composite tunnel barrier comprised of a CoMgO layer that contacts a pinned layer and a MgO layer which contacts a free layer. A CoMg layer with a Co content between 20 and 40 atomic % is deposited on the pinned layer and is then oxidized to produce Co nanoconstrictions within a MgO insulator matrix. The nanoconstrictions control electromigration of Co into an adjoining MgO layer. The free layer may comprise a nanocurrent channel (NCC) layer such as FeSiO or a moment dilution layer such as Ta between two ferromagnetic layers. Furthermore, a second CoMgO layer or a CoMgO / MgO composite may serve as a perpendicular Hk enhancing layer formed between the free layer and a cap layer. One or both of the pinned layer and free layer may exhibit in-plane anisotropy or perpendicular magnetic anisotropy.

Owner:TAIWAN SEMICON MFG CO LTD

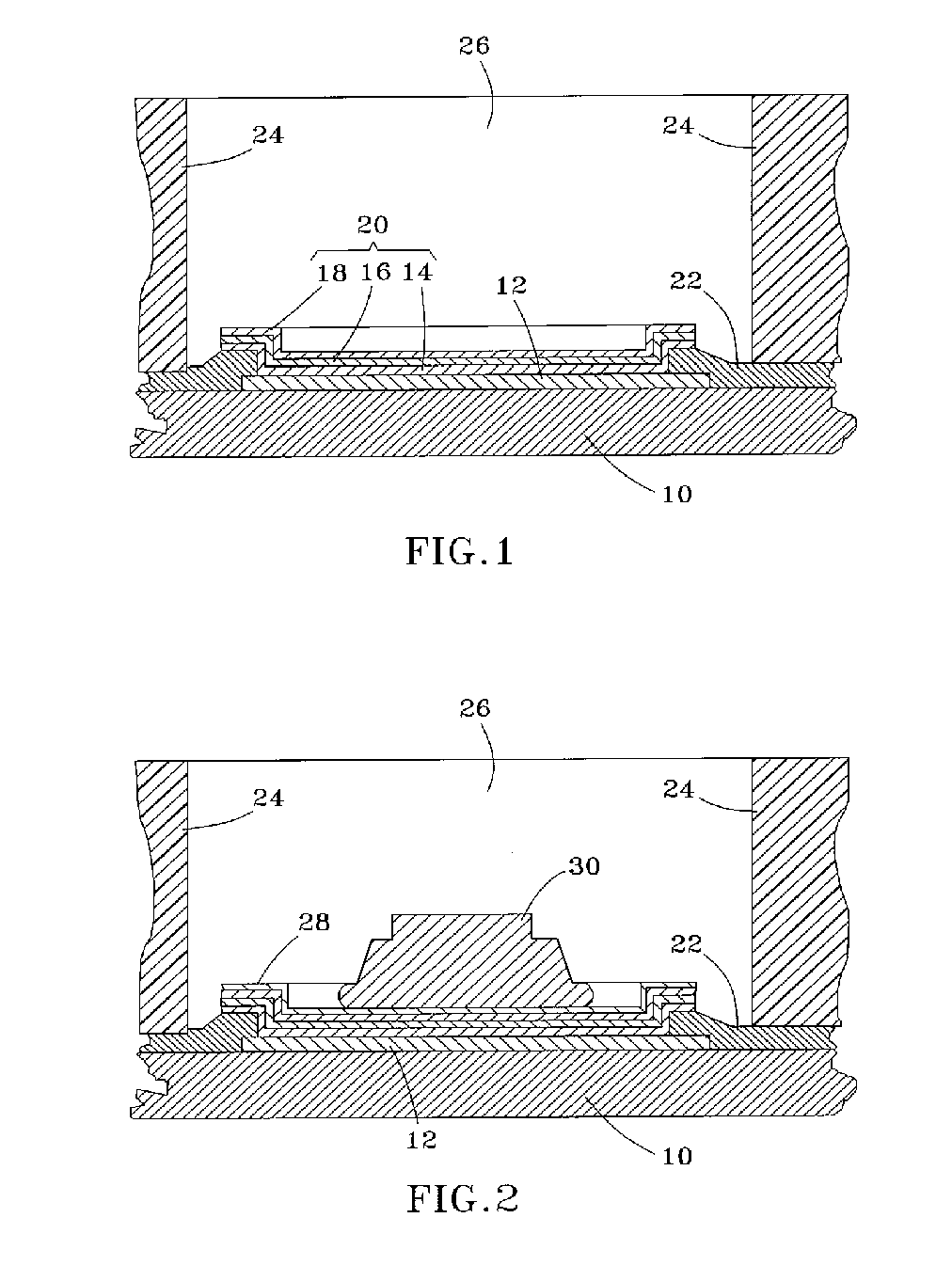

Method of solder bumping a circuit component and circuit component formed thereby

InactiveUS20070045840A1Reduce degradationReducing and eliminating dissolutionSemiconductor/solid-state device detailsSolid-state devicesSurface layerLead bonding

A circuit component and method by which degradation of a solder connection by electromigration can be prevented or reduced. The component generally includes an interconnect pad on a surface of the component, a metallic multilayer structure overlying the interconnect pad and having a solderable surface layer, and a solder material on the multilayer structure. According to a preferred aspect of the component and method, a stud is wire-bonded to the solderable surface layer of the multilayer structure and encased by the solder material to provide a low electrical resistance path through the solder material.

Owner:DELPHI TECH INC

Copper interconnect wiring and method of forming thereof

ActiveUS20060105570A1Electric discharge tubesSemiconductor/solid-state device detailsCopper interconnectIntegrated circuit interconnect

Capping layer or layers on a surface of a copper interconnect wiring layer for use in interconnect structures for integrated circuits and methods of forming improved integration interconnection structures for integrated circuits by the application of gas-cluster ion-beam processing. Reduced copper diffusion and improved electromigration lifetime result and the use of selective metal capping techniques and their attendant yield problems are avoided.

Owner:TEL EPION

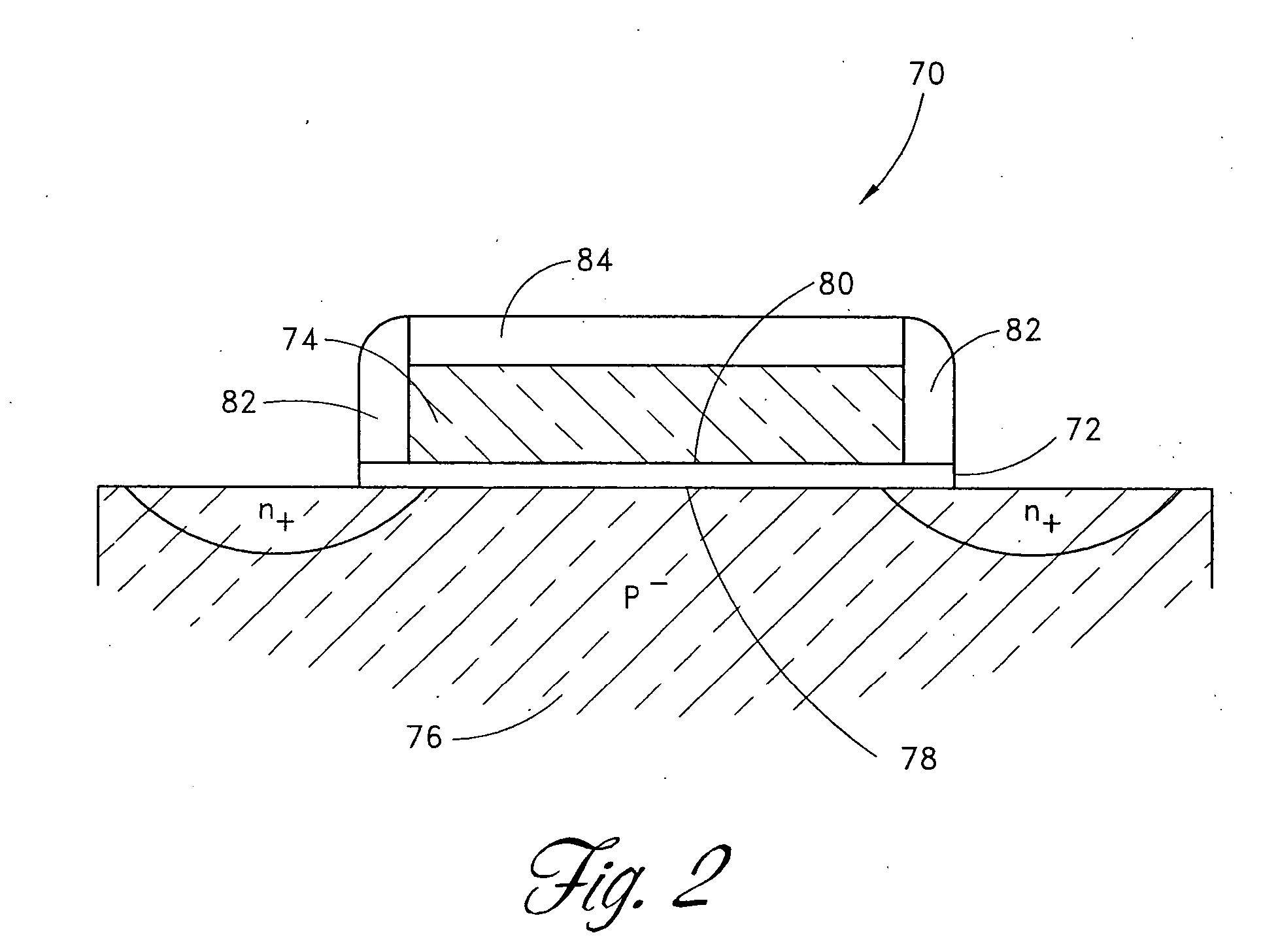

Reversible electric fuse and antifuse structures for semiconductor devices

ActiveUS7557424B2Improve electromigration problemsGood reversibilitySemiconductor/solid-state device detailsSolid-state devicesElectric fusesEngineering

A structure and method of fabricating reversible fuse and antifuse structures for semiconductor devices is provided. In one embodiment, the method includes forming at least one line having a via opening for exposing a portion of a plurality of interconnect features; conformally depositing a first material layer over the via opening; depositing a second material layer over the first material layer, wherein the depositing overhangs a portion of the second material layer on a top portion of the via opening; and depositing a blanket layer of insulating material, where the depositing forms a plurality of fuse elements each having an airgap between the insulating material and the second material layer. The method further includes forming a plurality of electroplates in the insulator material connecting the fuse elements. In another embodiment, the method includes depositing a first and a second material layer on a semiconductor substrate, wherein the second material layer having a higher electrical conductivity than the first material layer; selectively etching the first and second material layer to create at least one constricted region to facilitate electromigration of the second material; wherein the electromigration creates a plurality of micro voids; and forming a plurality of electrical contacts on the second material layer.

Owner:GLOBALFOUNDRIES U S INC

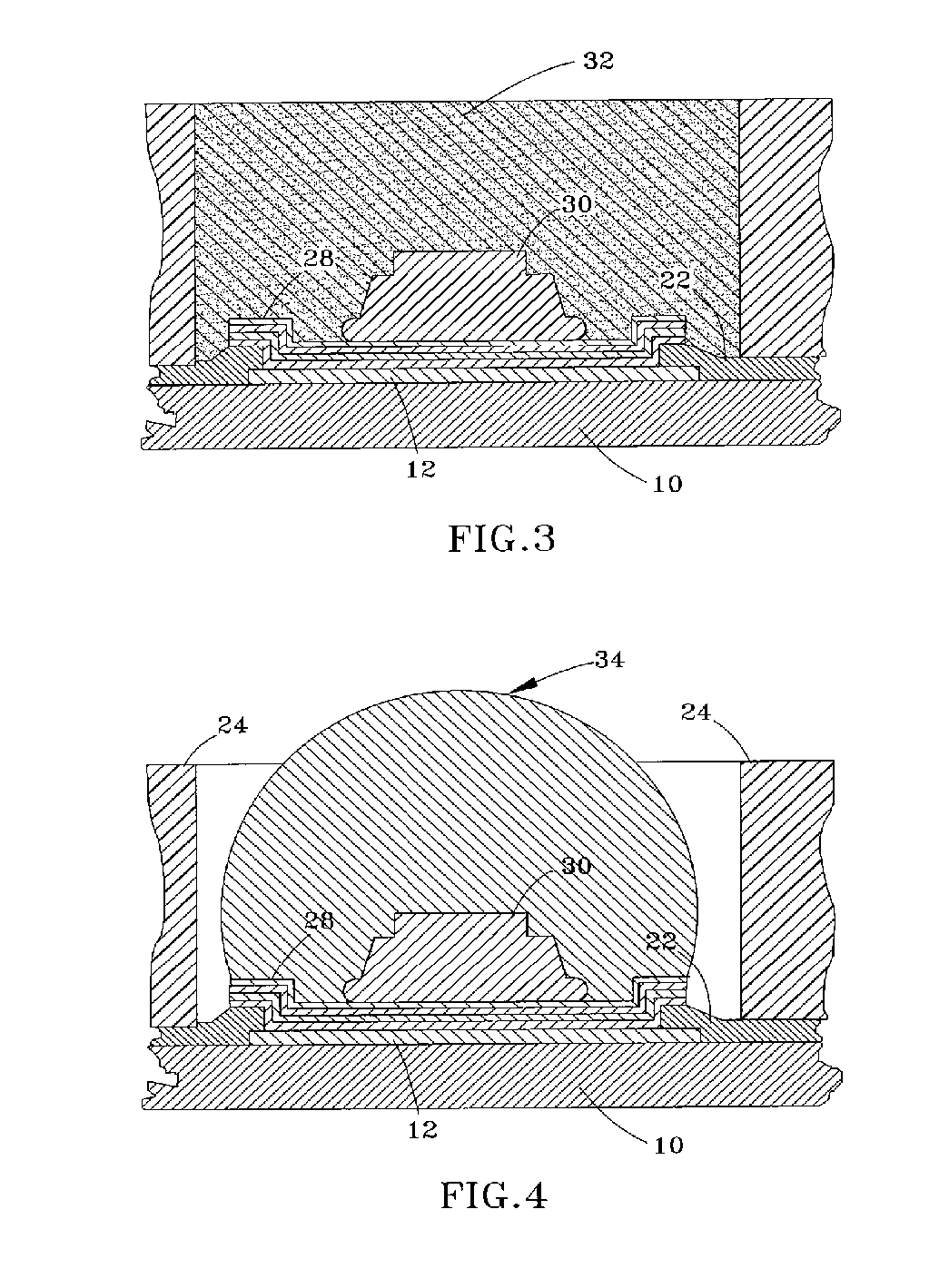

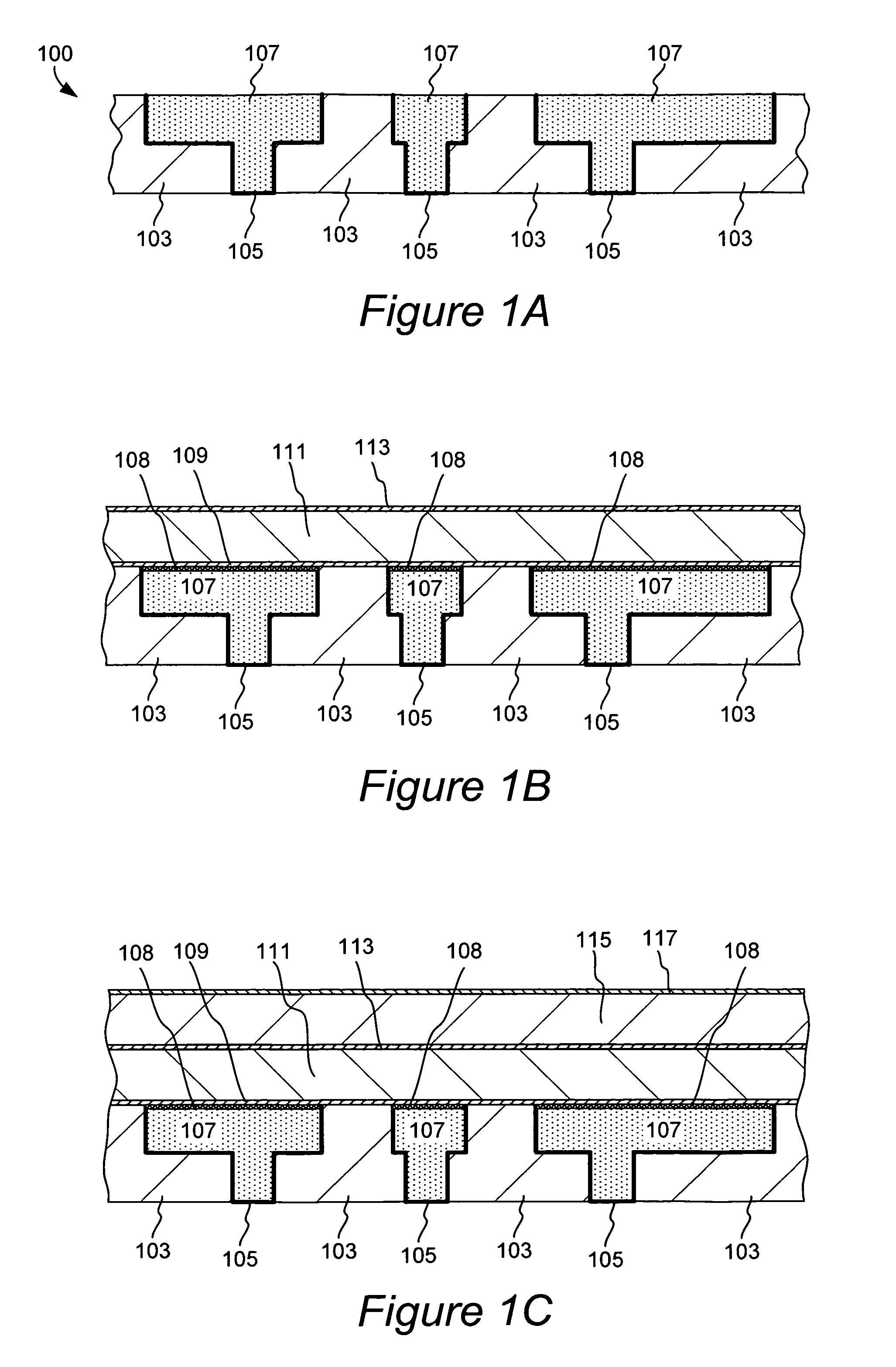

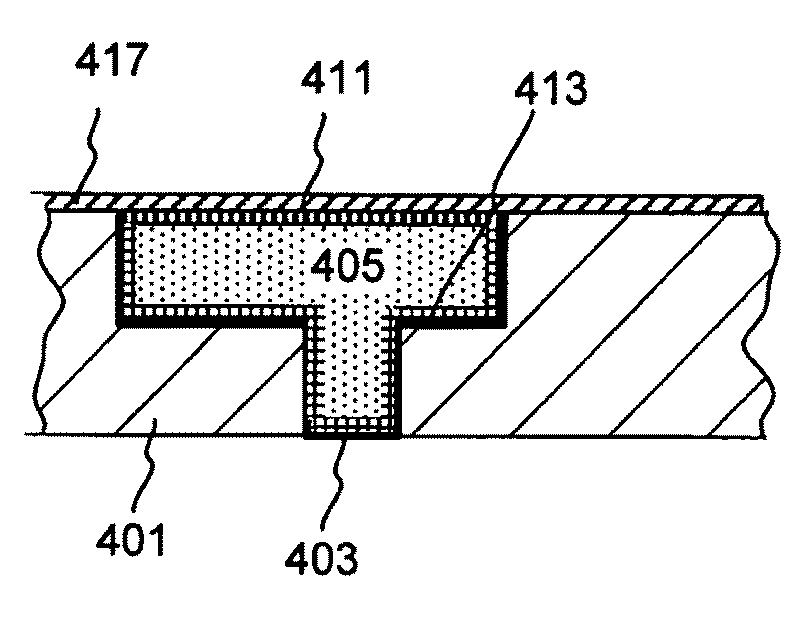

Interfacial layers for electromigration resistance improvement in damascene interconnects

ActiveUS7648899B1Improve performanceIncrease resistanceSemiconductor/solid-state device detailsSolid-state devicesDielectricDopant

Protective caps residing at an interface between metal lines and dielectric diffusion barrier (or etch stop) layers are used to improve electromigration performance of interconnects. Protective caps are formed by depositing a source layer of dopant-generating material (e.g., material generating B, Al, Ti, etc.) over an exposed copper line, converting the upper portion of the source layer to a passivated layer (e.g., nitride or oxide) while allowing an unmodified portion of a dopant-generating source layer to remain in contact with copper, and, subsequently, allowing the dopant from the unmodified portion of source layer to controllably diffuse into and / or react with copper, thereby forming a thin protective cap within copper line. The cap may contain a solid solution or an alloy of copper with the dopant.

Owner:NOVELLUS SYSTEMS

Method of forming copper interconnections with enhanced electromigration resistance and reduced defect sensitivity

A method of providing sub-half-micron copper interconnections with improved electromigration and corrosion resistance. The method includes double damascene using electroplated copper, where the seed layer is converted to an intermetallic layer. A layer of copper intermetallics with hafnium, lanthanum, zirconium or tin, is provided to improve the electromigration resistance and to reduce defect sensitivity. A method is also provided to form a cap atop copper lines, to improve corrosion resistance, which fully covers the surface. Structure and methods are also described to improve the electromigration and corrosion resistance by incorporating carbon atoms in copper interstitial positions.

Owner:GLOBALFOUNDRIES INC

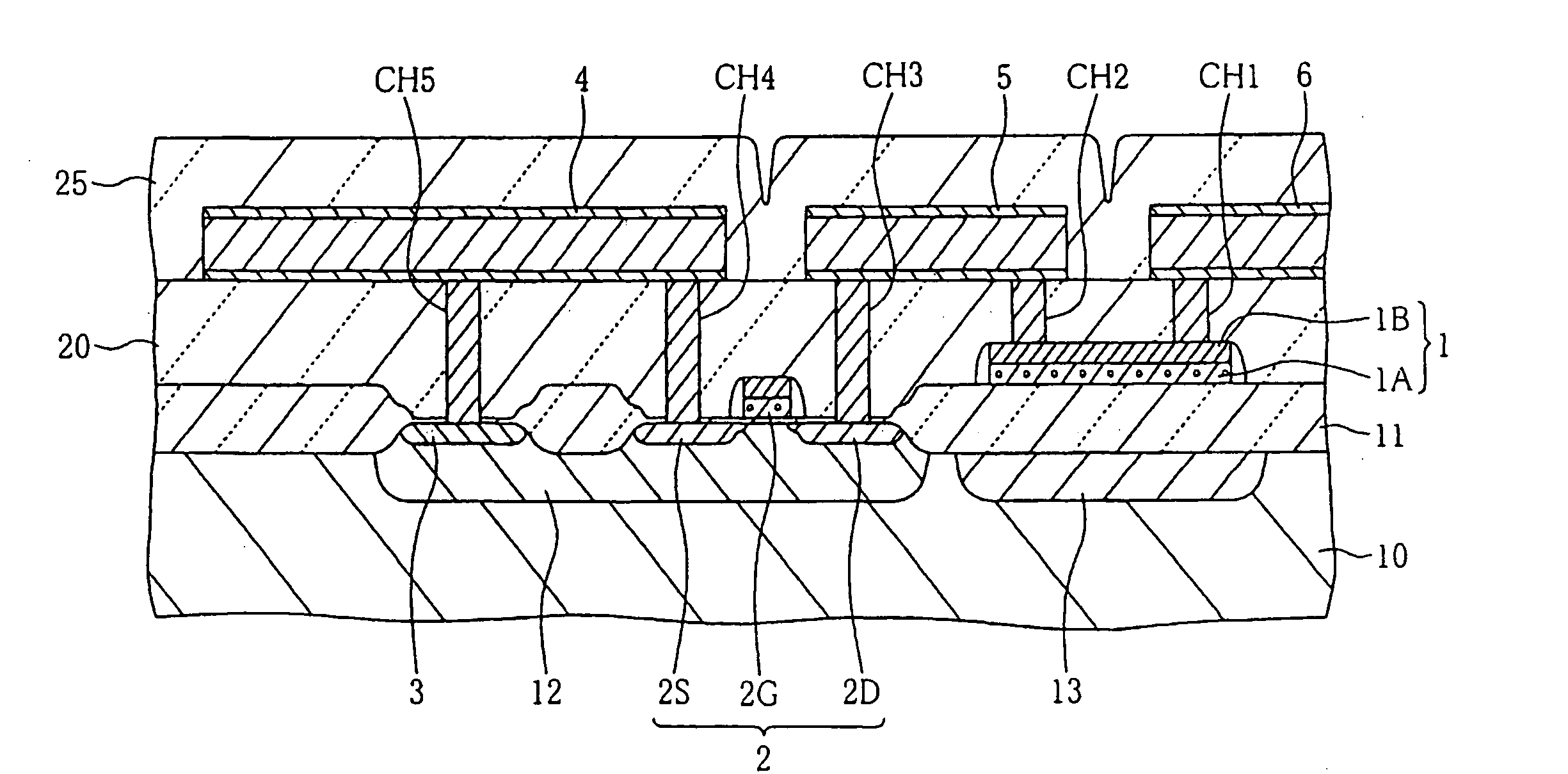

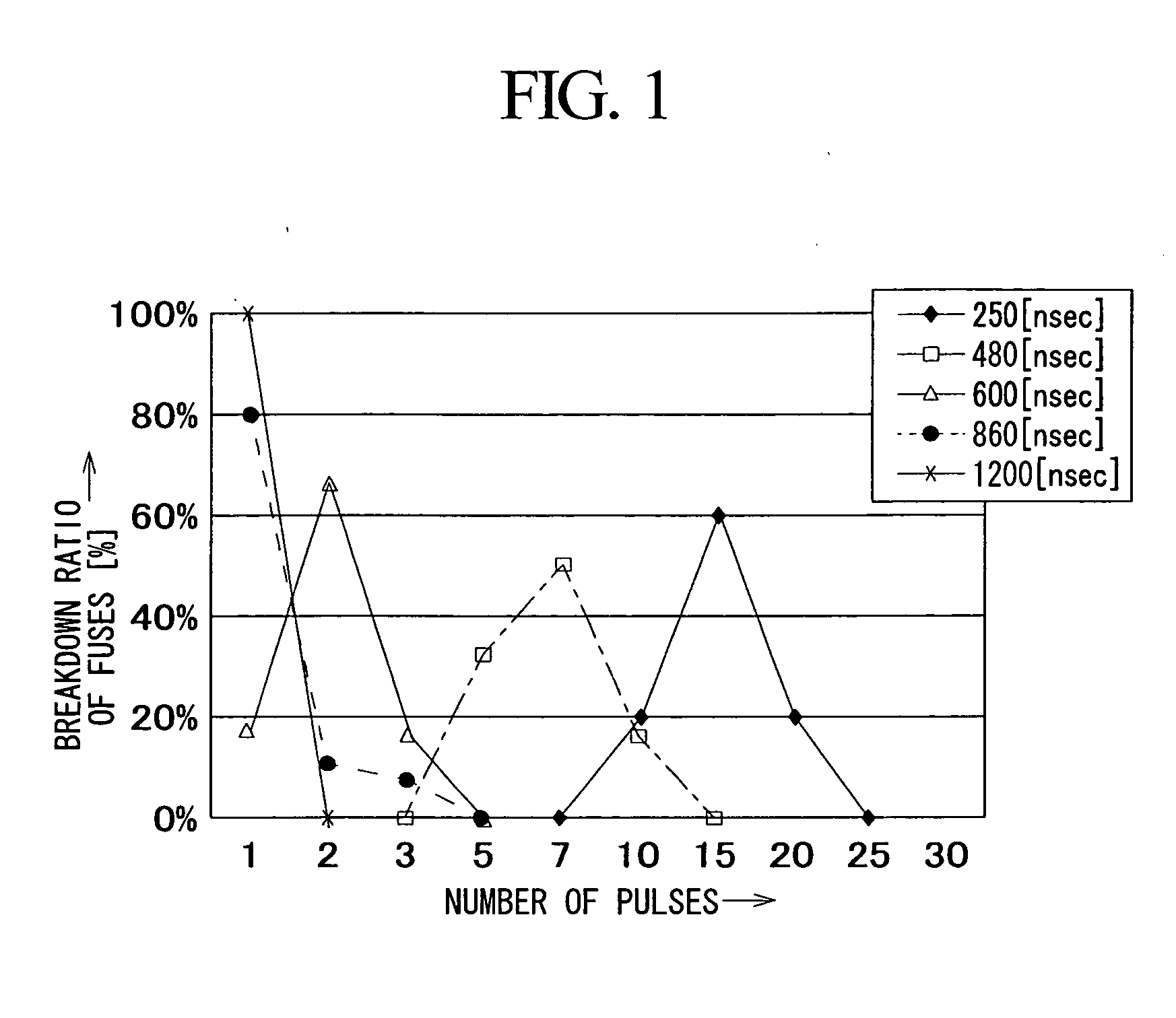

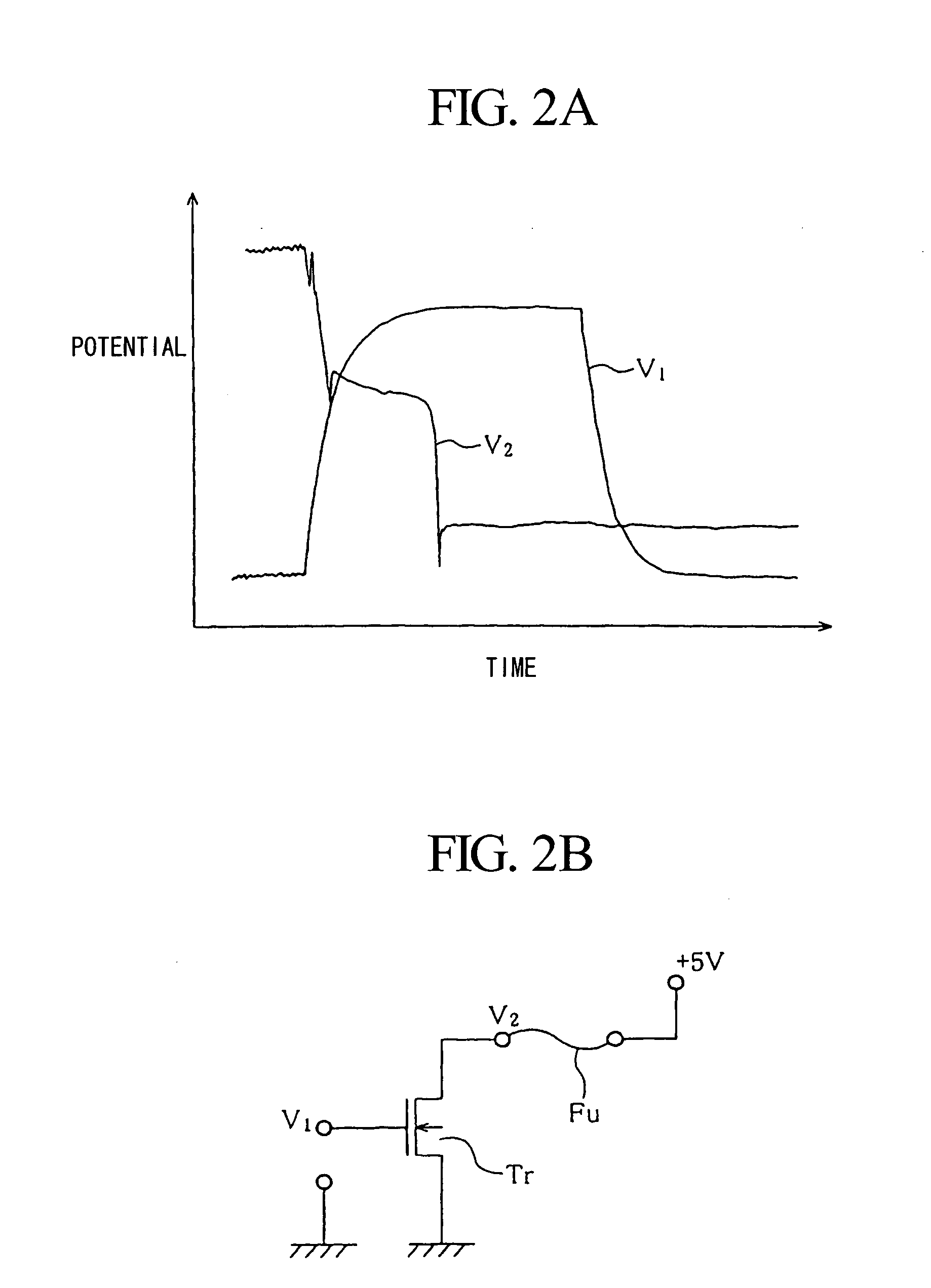

Fuse breakdown method adapted to semiconductor device

InactiveUS20070007621A1Increase distanceInhibit degassingTransistorSemiconductor/solid-state device detailsDevice materialEvaporation

A plurality of pulses each having relatively low energy are consecutively applied to a subject fuse to cause breakdown, wherein the total energy of pulses is set in light of a prescribed breakdown threshold, which is calculated in advance. The subject fuse has a pair of terminals and an interconnection portion that is narrowly constricted in the middle so as to realize fuse breakdown with ease. A pulse generator generates pulses, which are repeatedly applied to the subject fuse by way of a transistor; then, it stops generating pulses upon detection of fuse breakdown. Side wall spacers are formed on side walls of fuses, which are processed in a tapered shape so as to reduce thermal stress applied to coating insulating films. In addition, pulse energy is appropriately determined so as to cause electro-migration in the subject fuse, which is thus increased in resistance without causing instantaneous meltdown or evaporation.

Owner:YAMAHA CORP

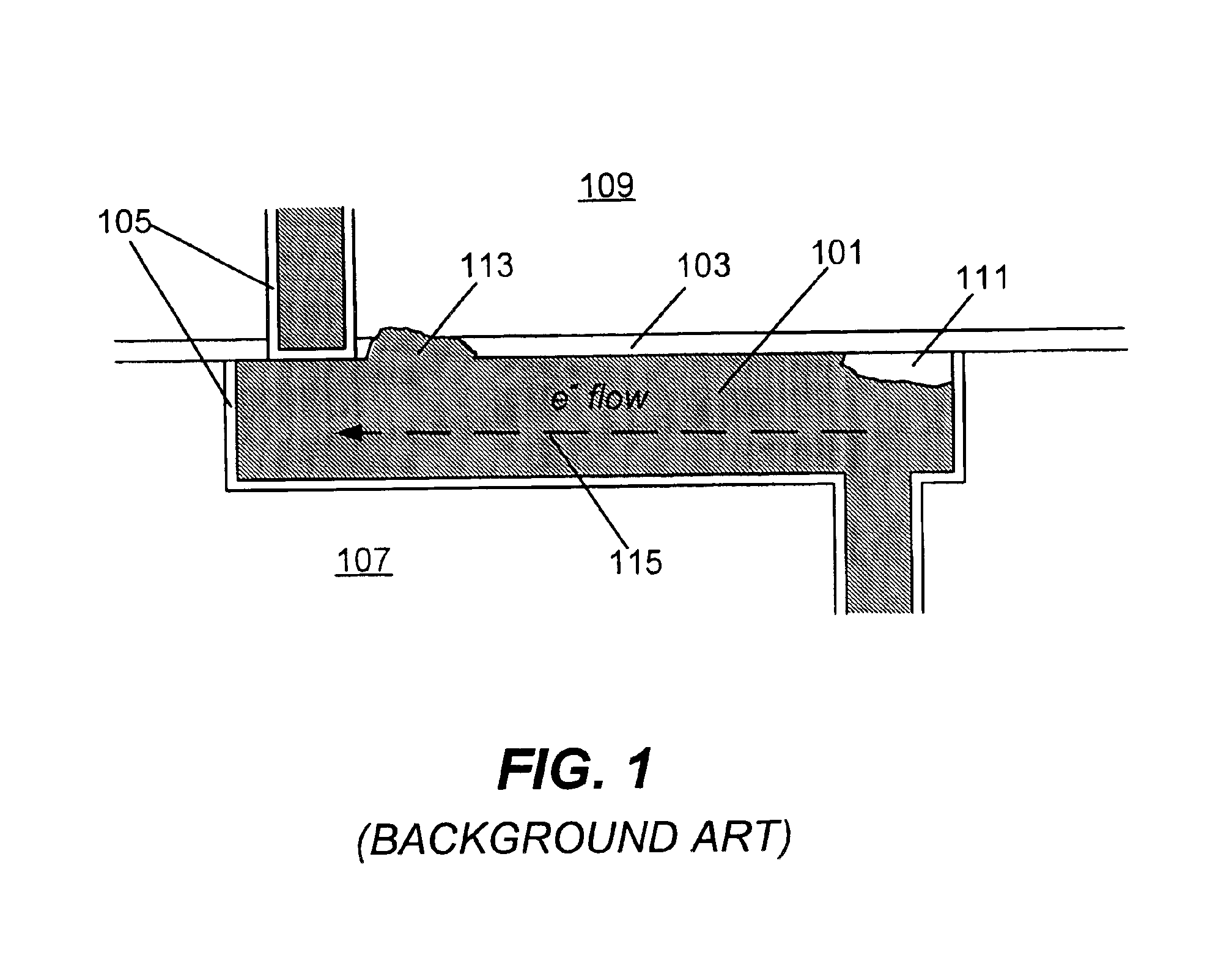

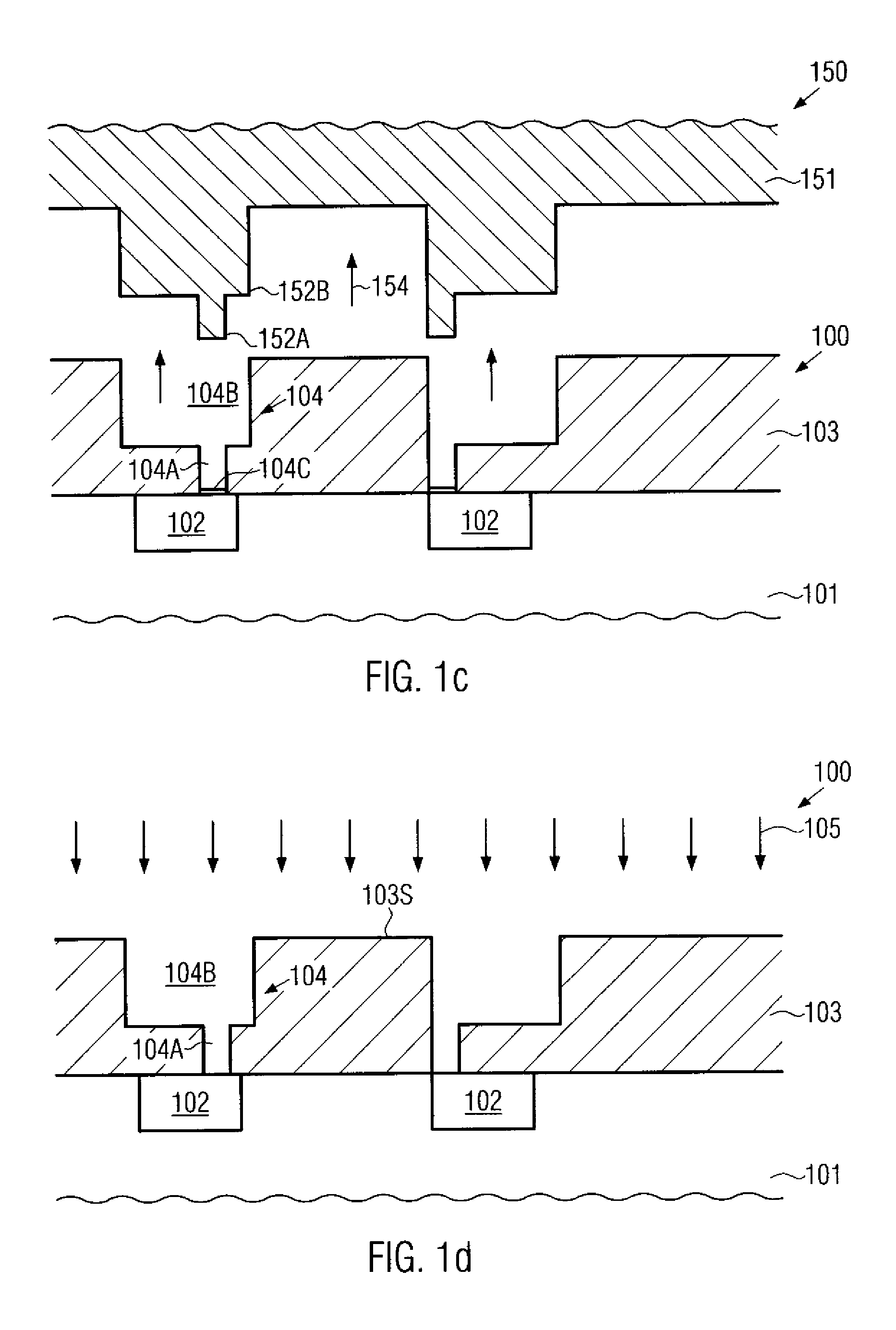

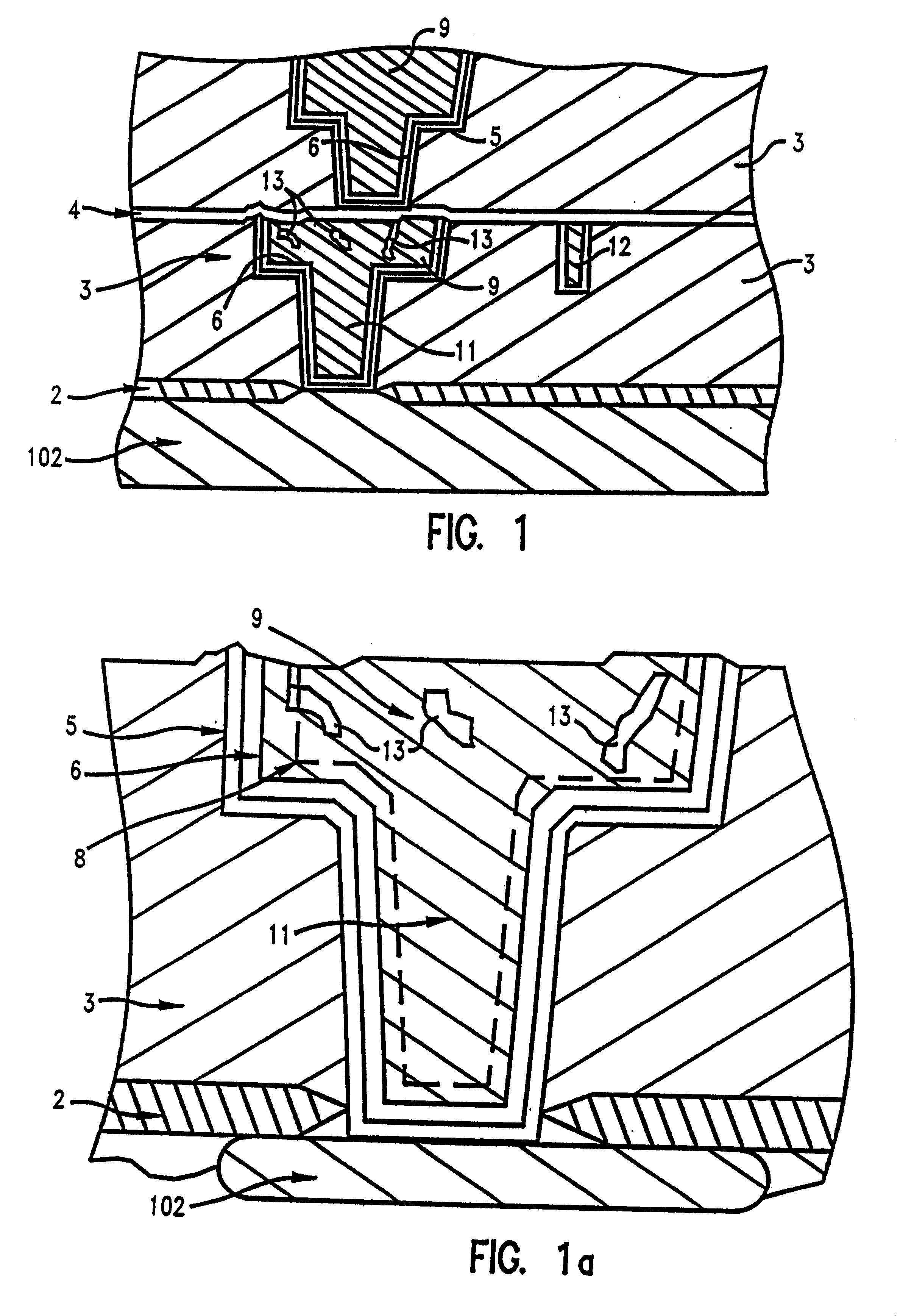

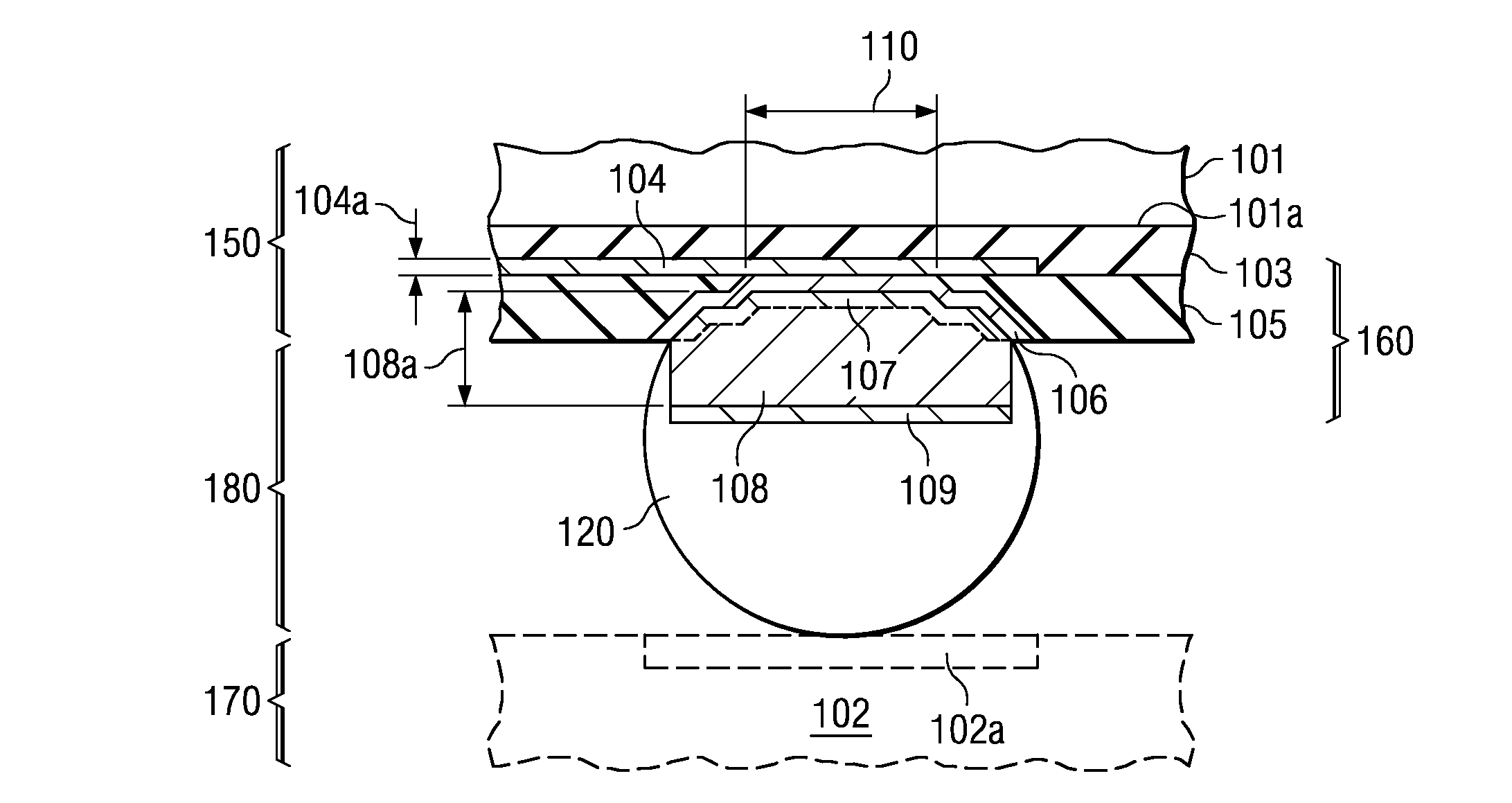

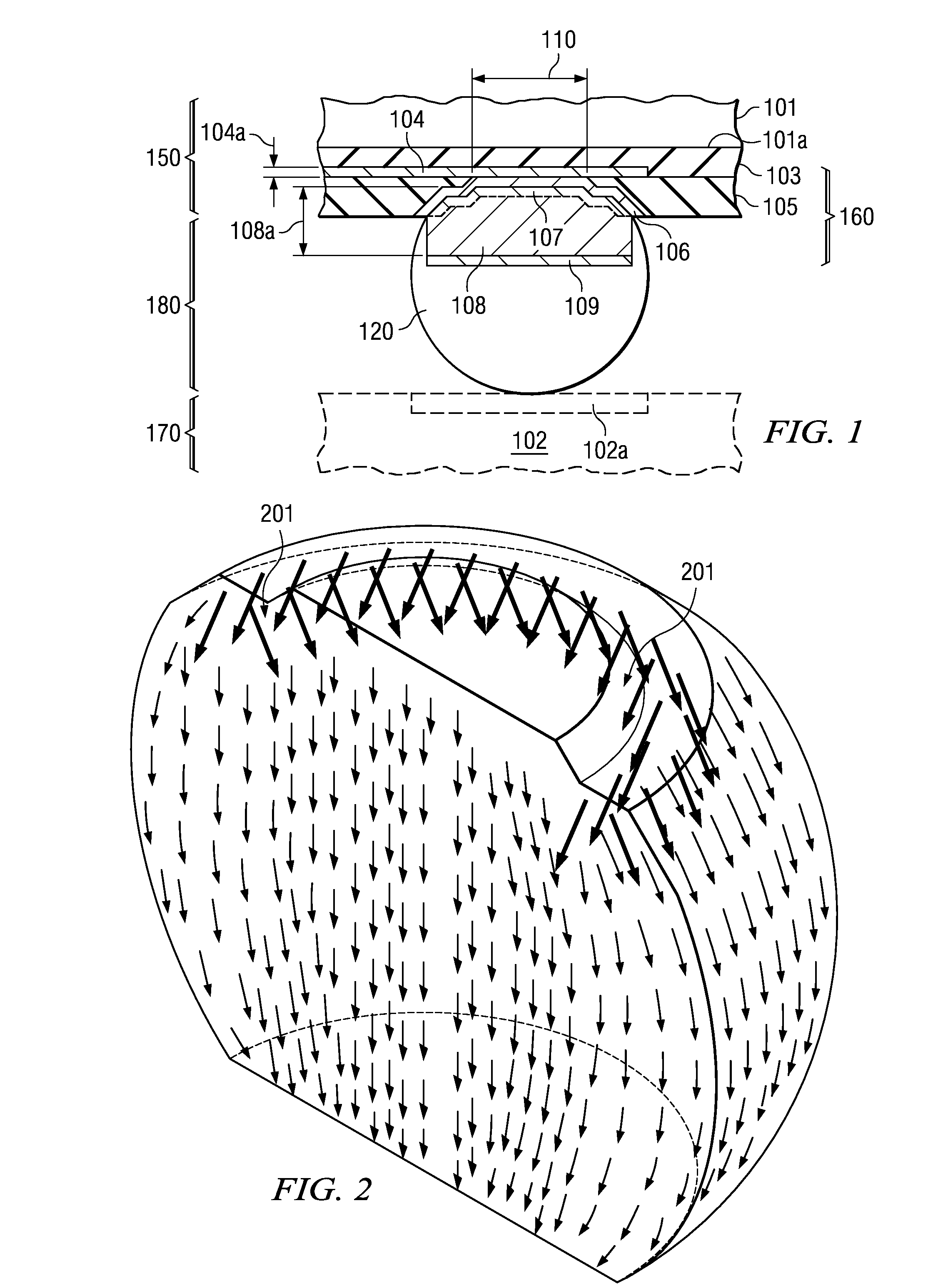

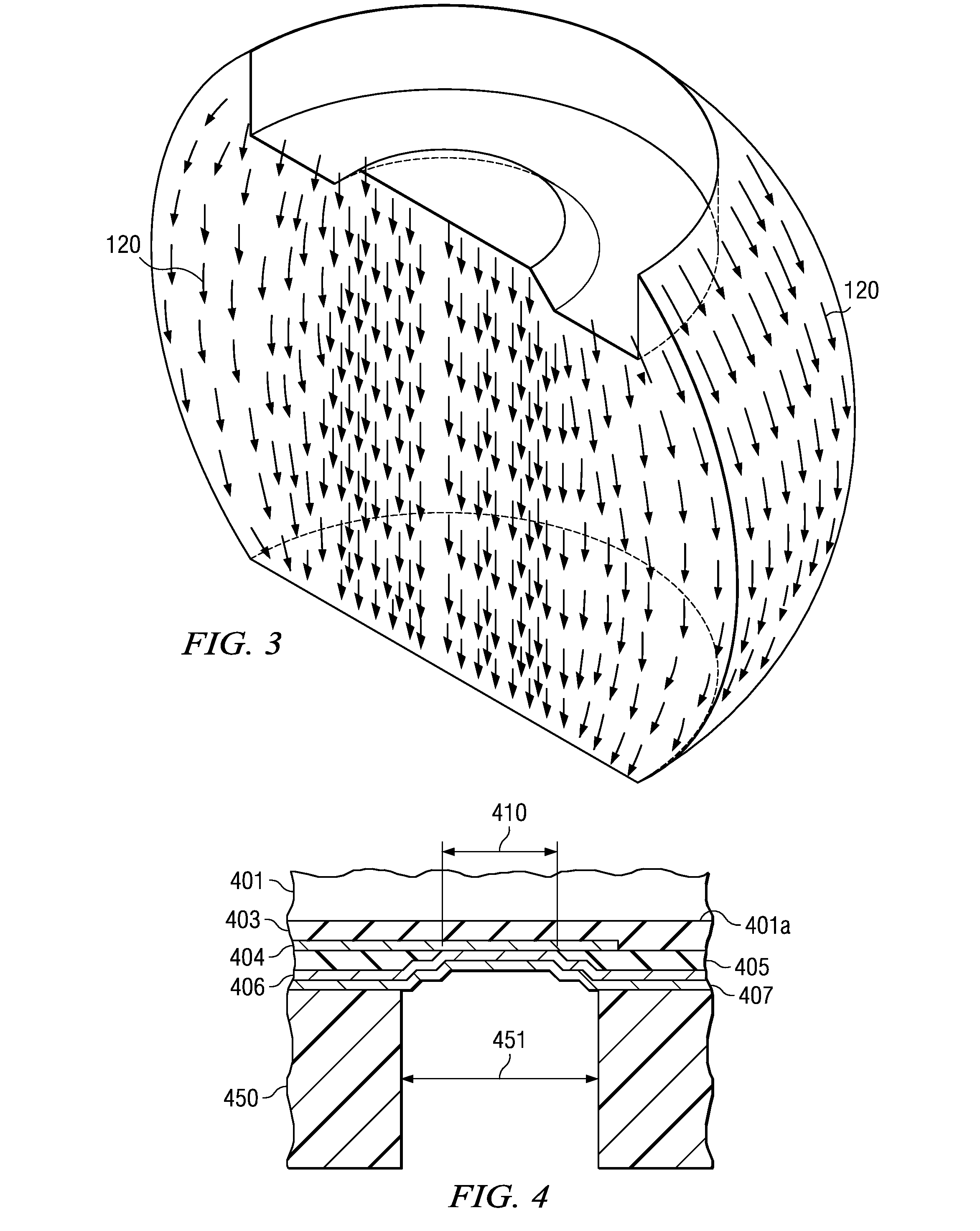

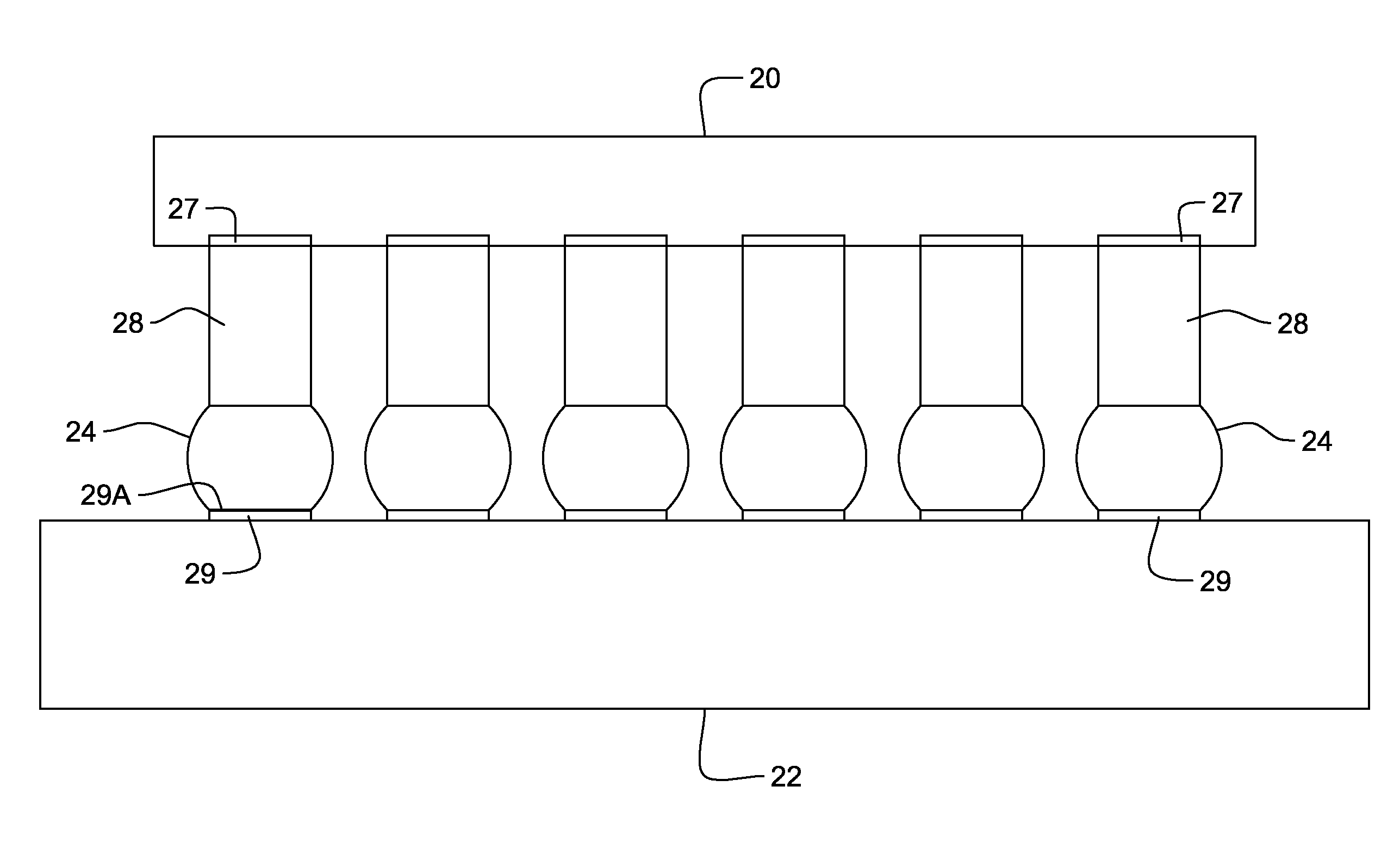

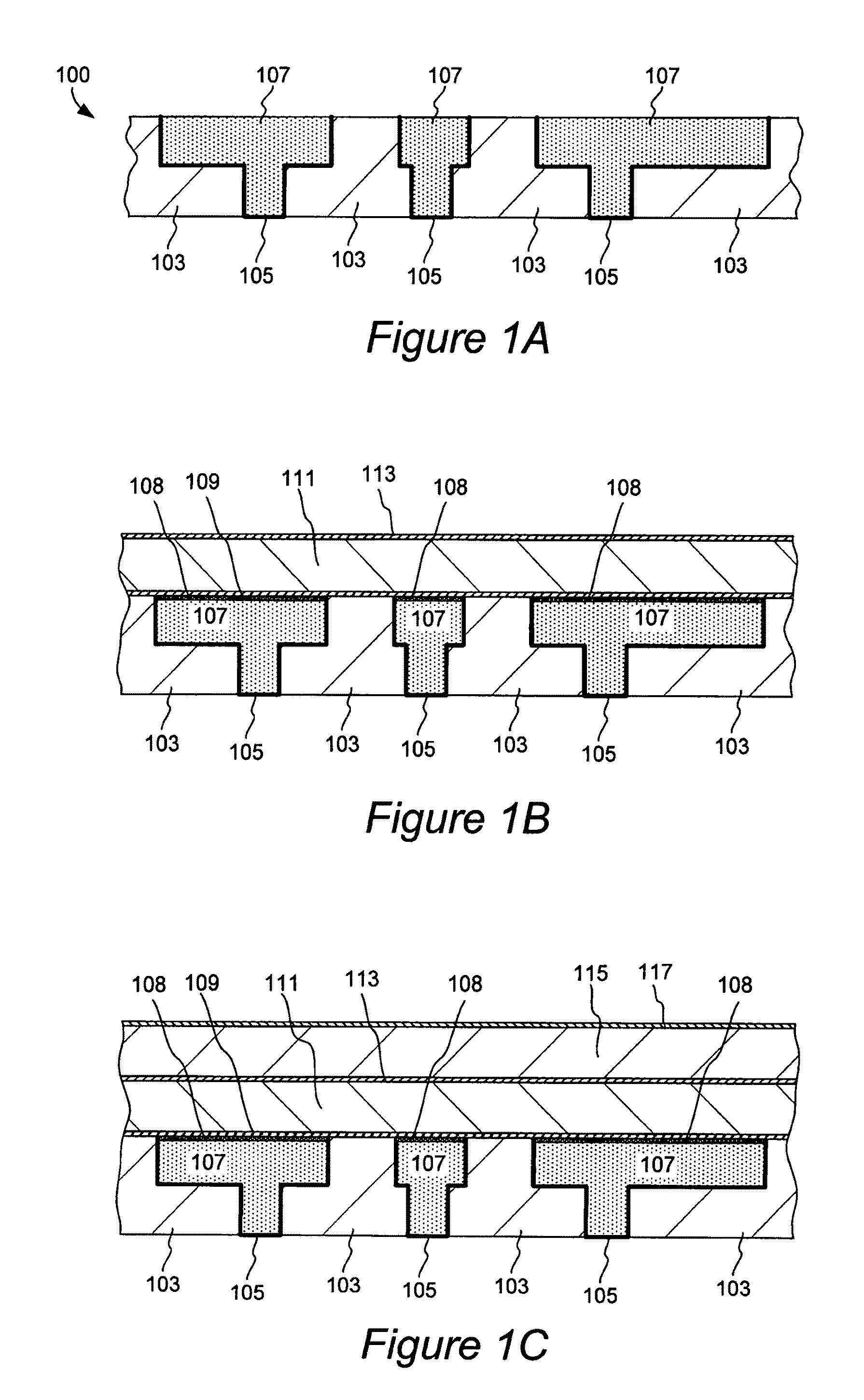

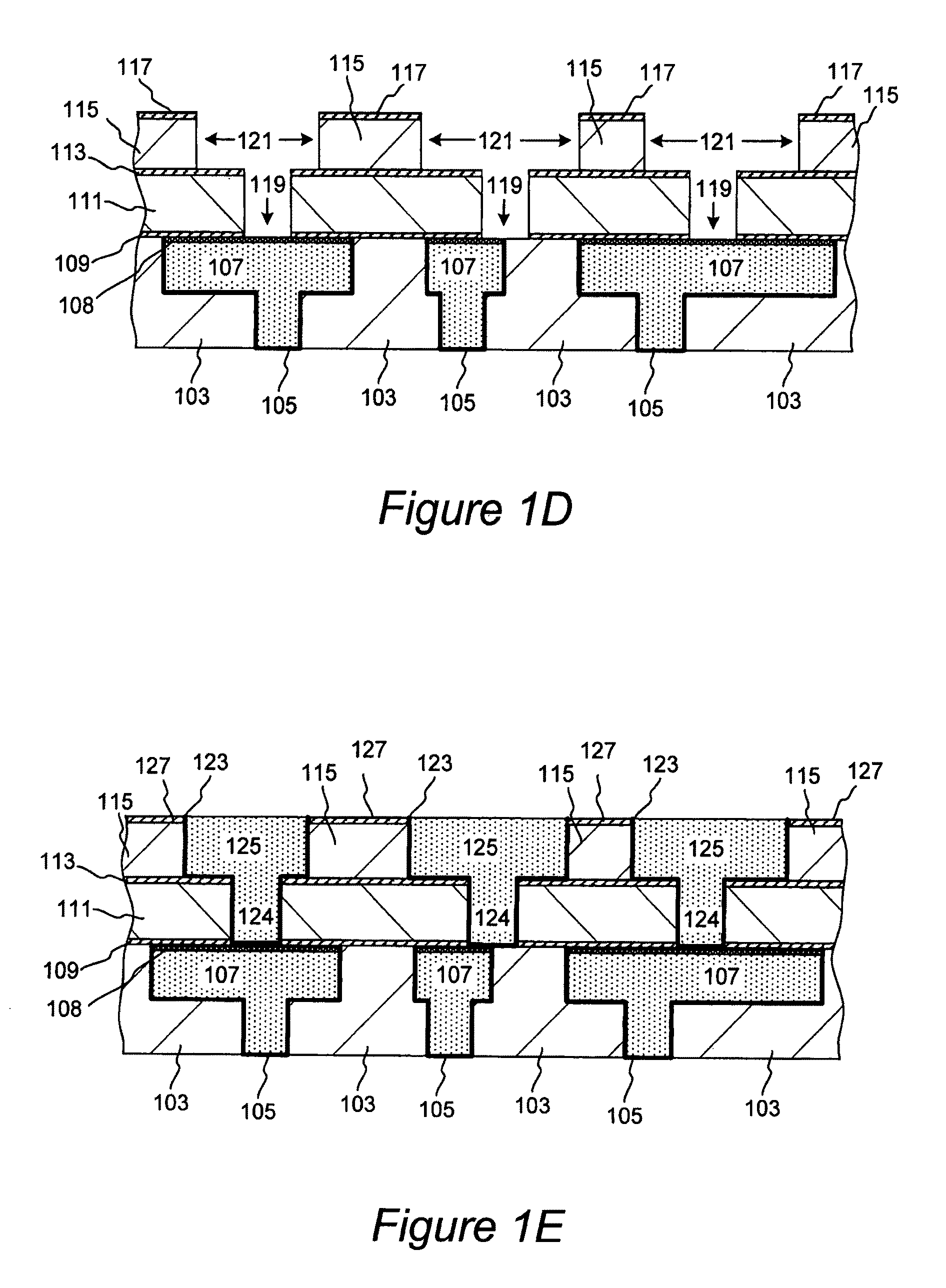

Electromigration-Resistant Flip-Chip Solder Joints

InactiveUS20080251927A1Enhance formation of voidLow reliabilitySemiconductor/solid-state device detailsSolid-state devicesElectrical resistance and conductanceCopper interconnect

A semiconductor device contact structure practically eliminating the copper diffusion into the solder as well as the current crowding at the contact with the subsequent electromigration in the solder. A column-like electroplated copper stud (108) is on each contact pad. The stud is sized to provide low, uniform electrical resistance in order to spread the current from the contact to an approximately uniform, low density. Preferably, the stud height (108a) is at least ten times the thickness of the copper interconnect layer (104). Stud (108) is capped by an electroplated nickel layer (109) thick enough (preferably about 2 μm) to suppress copper diffusion from stud (108) into solder body (120), thus practically inhibiting intermetallic compound formation and Kirkendall voiding.

Owner:TEXAS INSTR INC

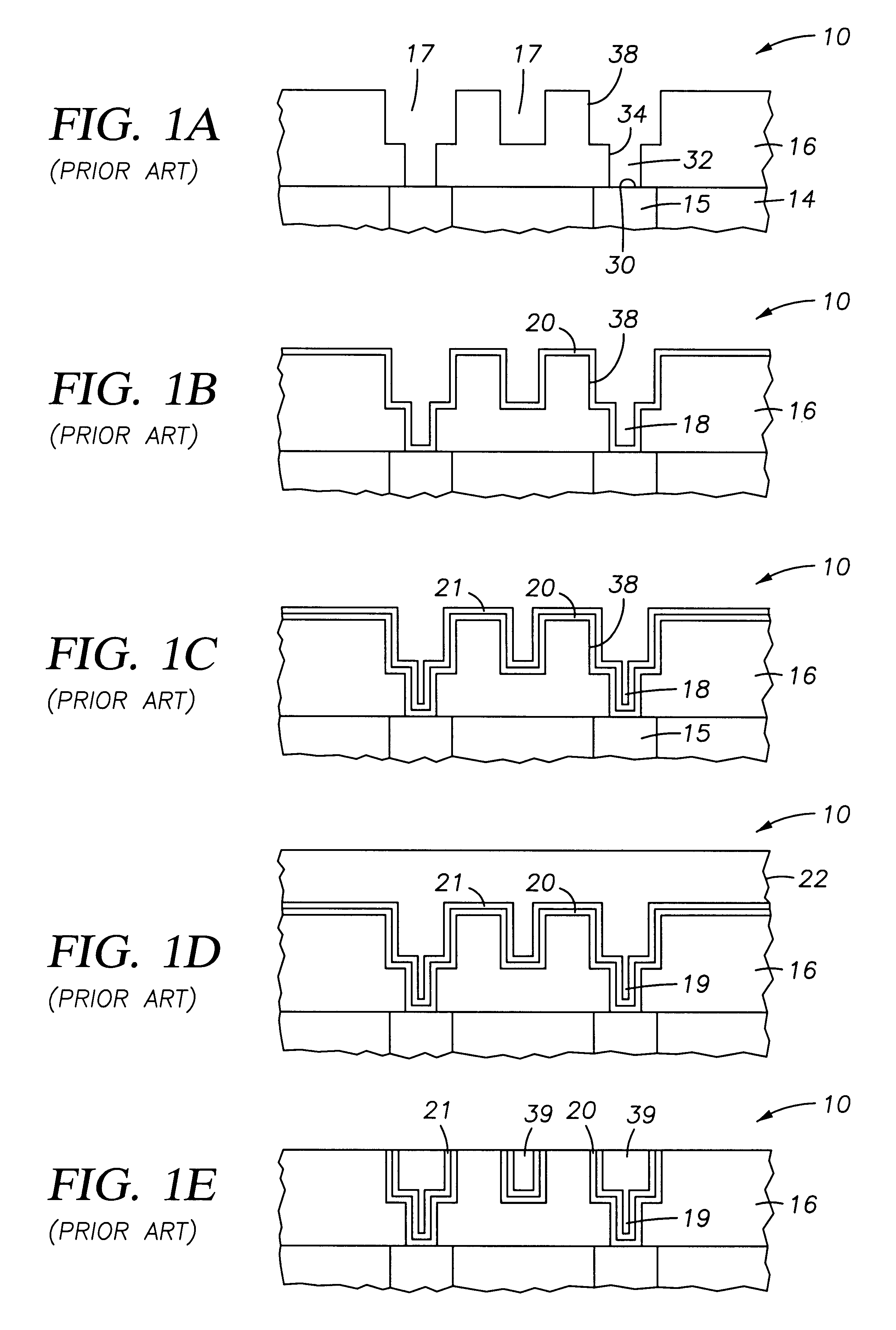

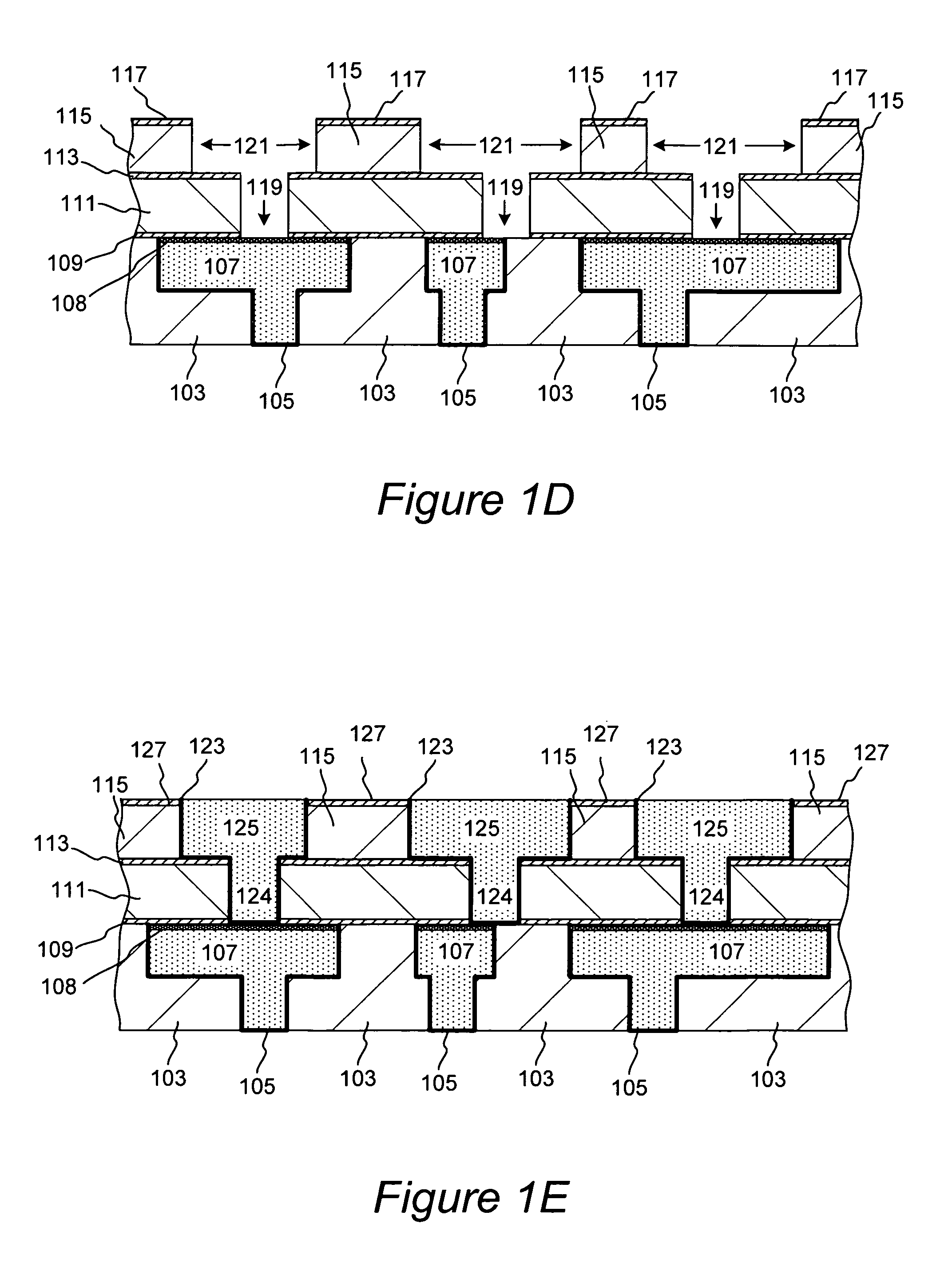

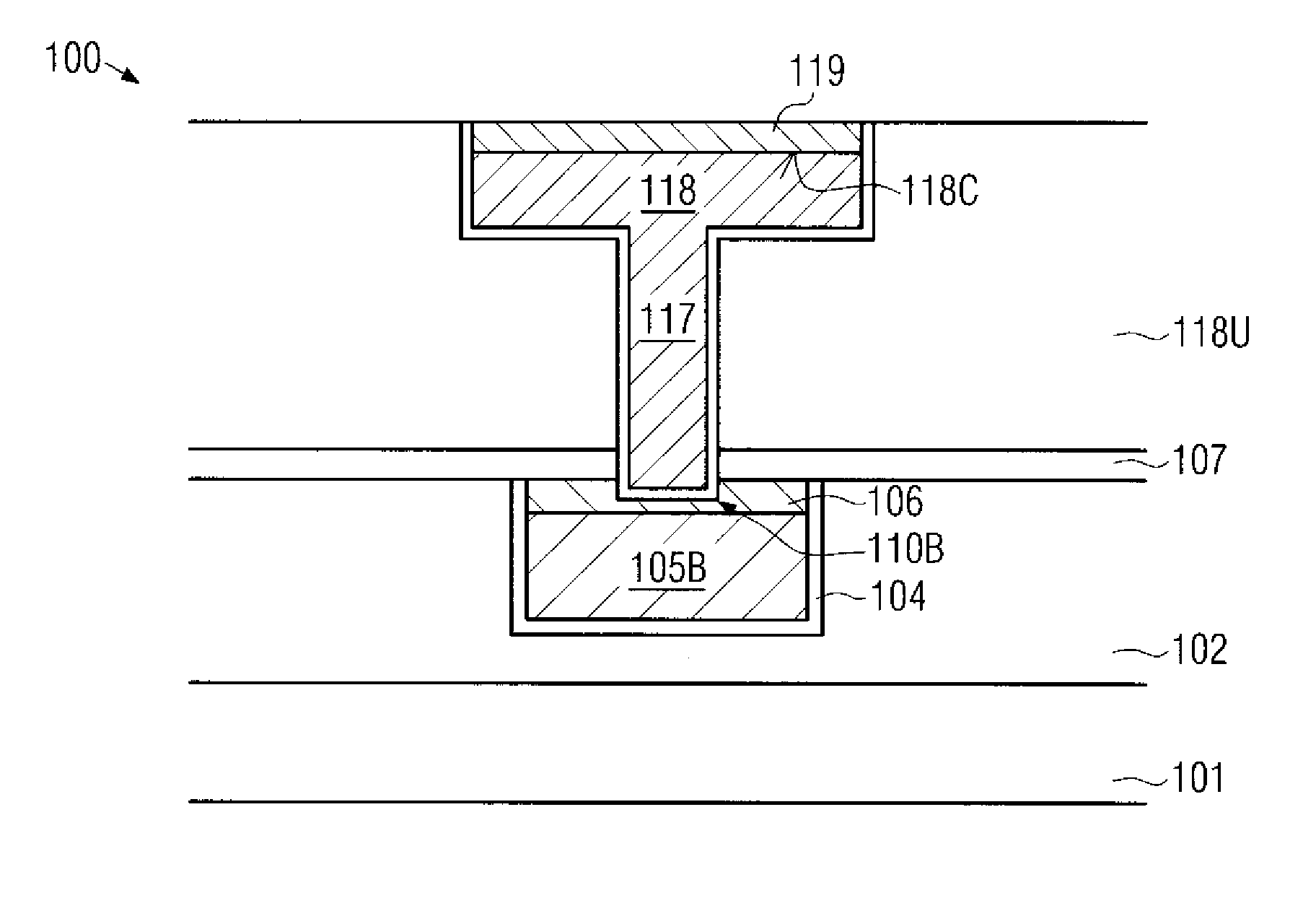

Technique for forming a copper-based metallization layer including a conductive capping layer

InactiveUS20070077761A1Reduce riskSimple materialSemiconductor/solid-state device detailsSolid-state devicesCopperMaterials science

By providing a conductive capping layer for metal-based interconnect lines, an enhanced performance with respect to electromigration may be achieved. Moreover, a corresponding manufacturing technique is provided in which via openings may be reliably etched into the capping layer without exposing the underlying metal, such as copper-based material, thereby also providing enhanced electromigration performance, especially at the transitions between copper lines and vias.

Owner:ADVANCED MICRO DEVICES INC

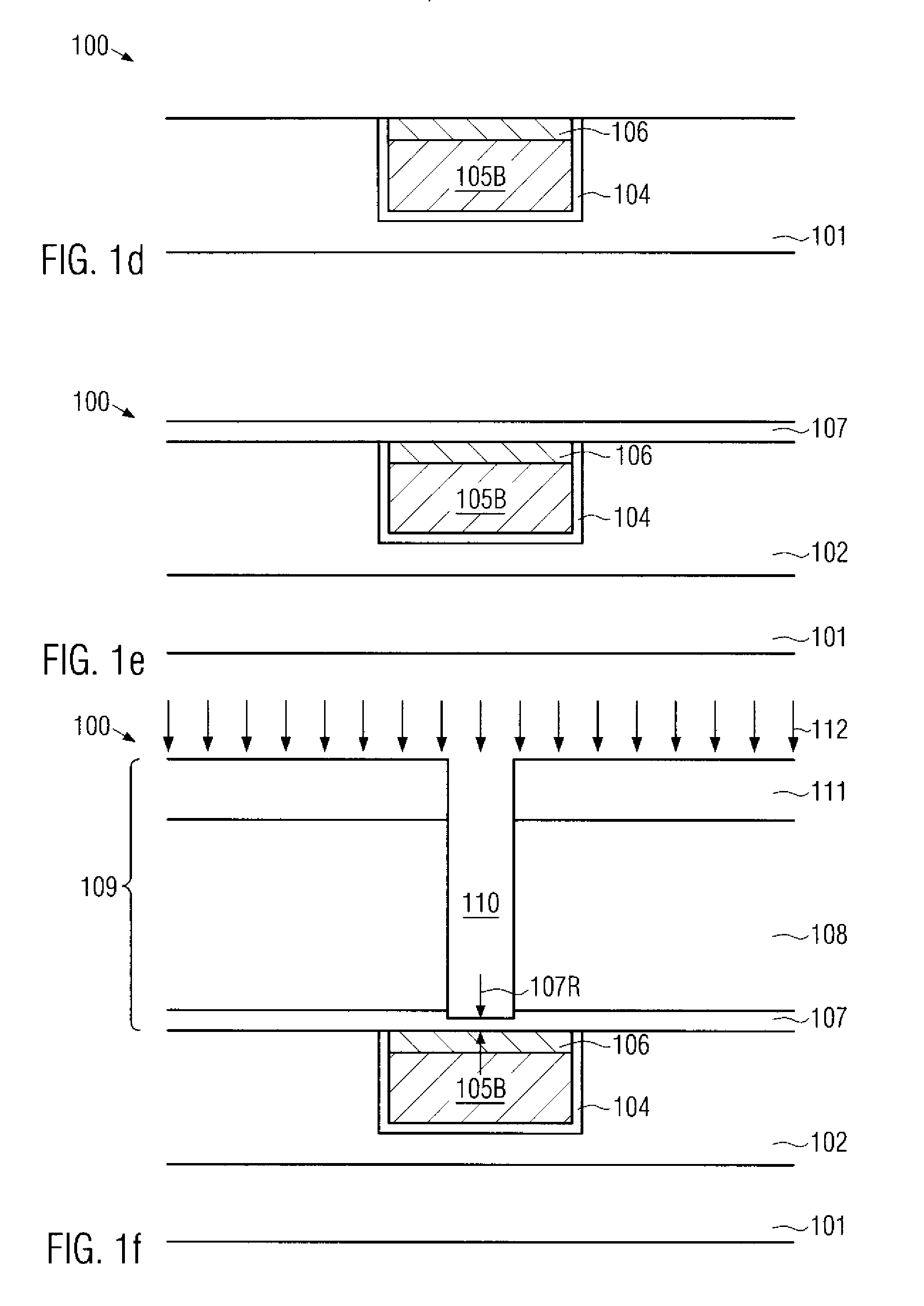

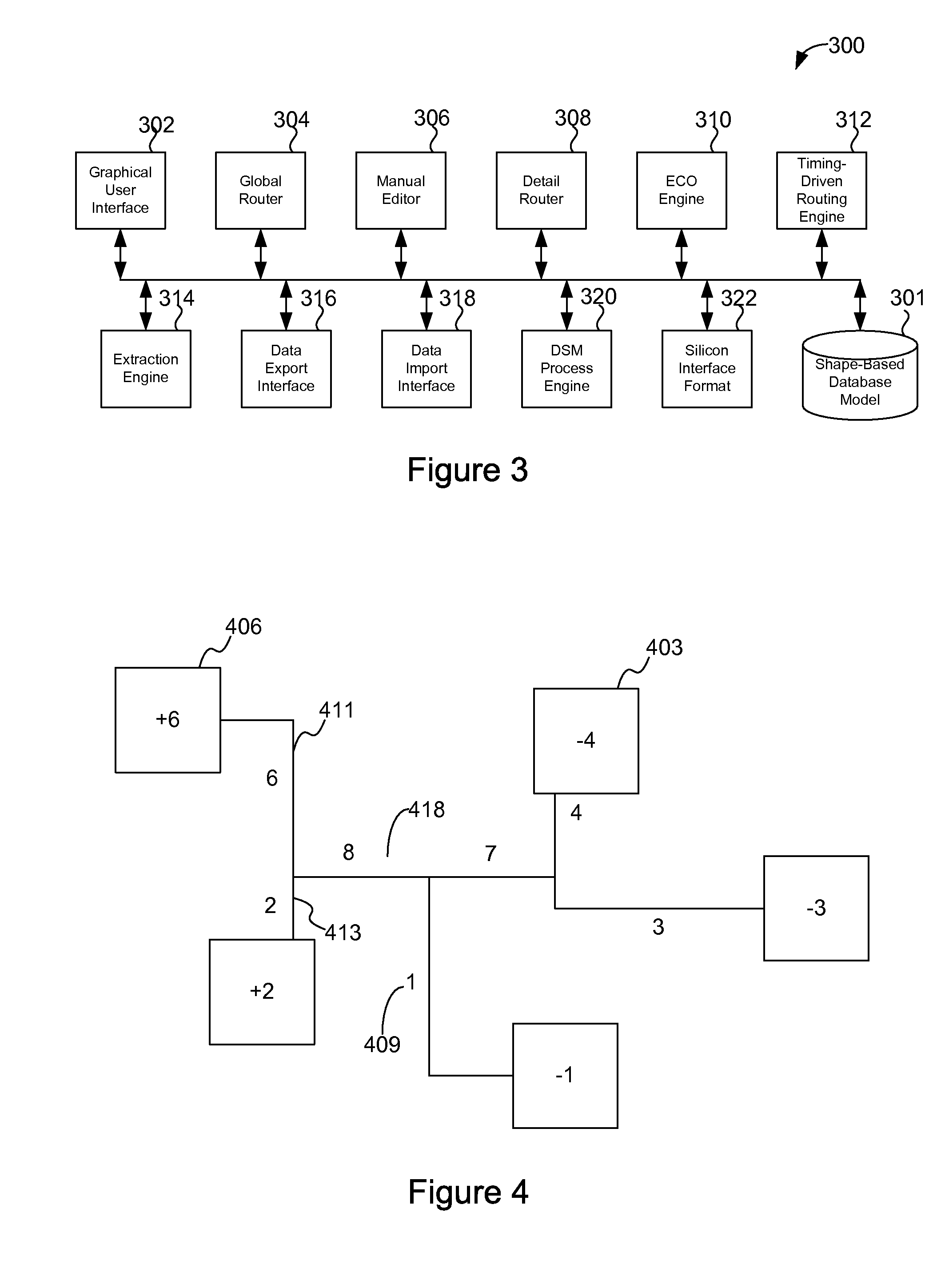

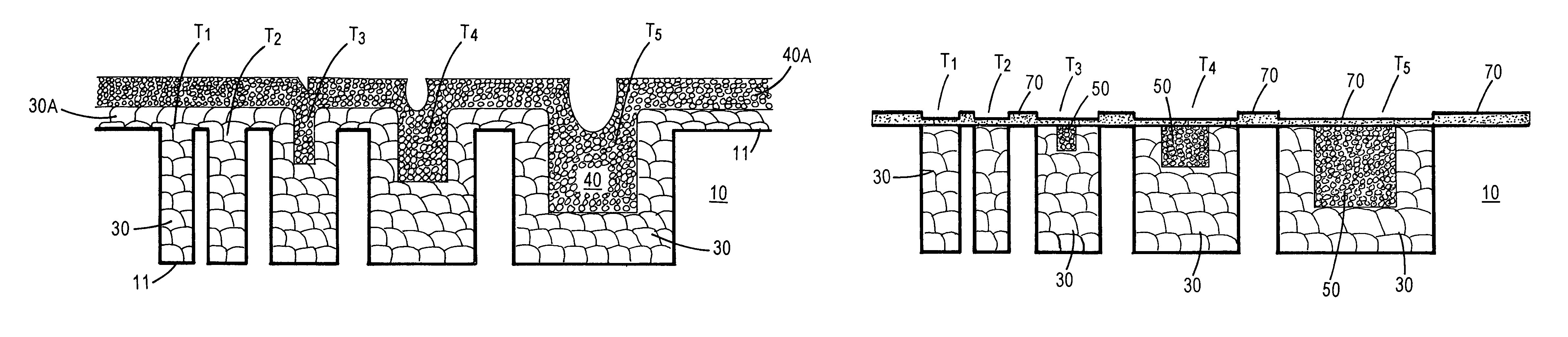

Automatically Routing Nets with Variable Spacing

ActiveUS20080028352A1Improve performanceReduce electromigration effectComputer aided designSoftware simulation/interpretation/emulationCapacitanceAutomatic routing

A technique will automatically route interconnect of an integrated circuit and adjust spacing between tracks or interconnect in order to improve performance or reduce electromigration effects. By increasing spacing between certain tracks or moving tracks, performance can improve because a track will be more noise immunity from nearby tracks on the same layer or on different layers. The automatic router will adjust spacing between tracks depending on one or more factors. These factors may include current associated with a track, width of a track, capacitance, inductance, and electromigration. In a specific implementation, the technique uses a shape-based approach where a grid is not used. The technique may further vary the width of the tracks.

Owner:PULSIC

Copper interconnects with metal capping layer and selective copper alloys

ActiveUS6979625B1Reduce voidsImproved resistance to electromigrationSemiconductor/solid-state device detailsSolid-state devicesCopper interconnectLayer interface

High reliable copper interconnects are formed with copper or a low resistivity copper alloy filling relatively narrow openings and partially filling relatively wider openings and a copper alloy having improved electromigration resistance selectively deposited in the relatively wider openings. The filled openings are recessed and a metal capping layer deposited followed by CMP. The metal capping layer prevents diffusion along the copper-capping layer interface while the copper alloy filling the relatively wider openings impedes electromigration along the grain boundaries.

Owner:ADVANCED MICRO DEVICES INC

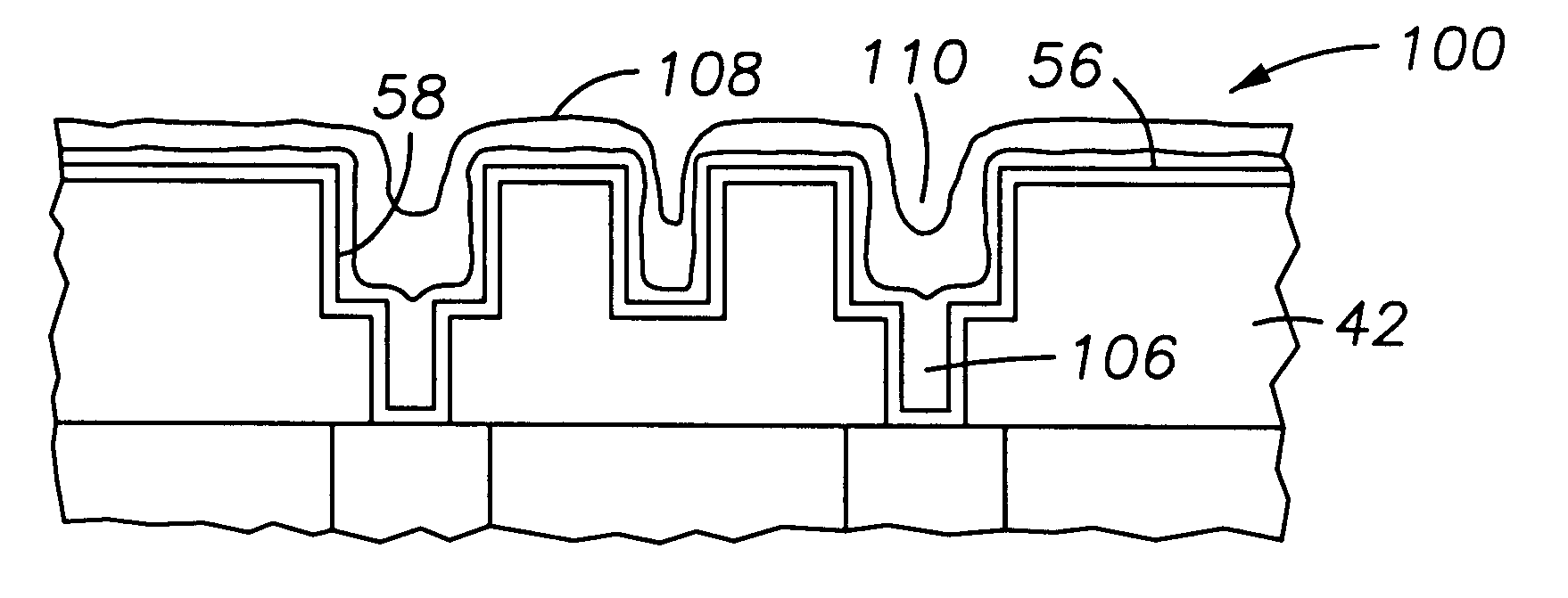

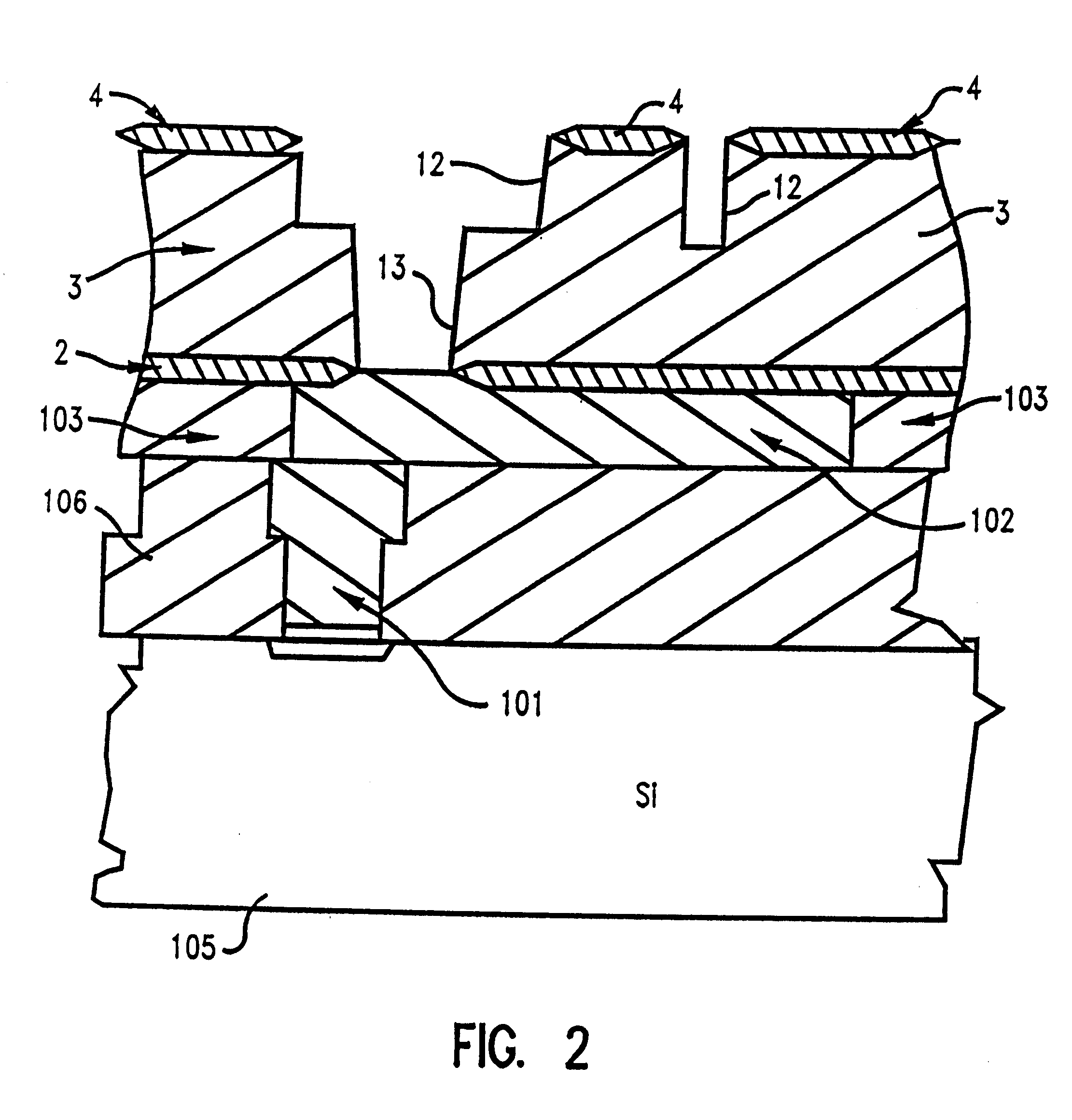

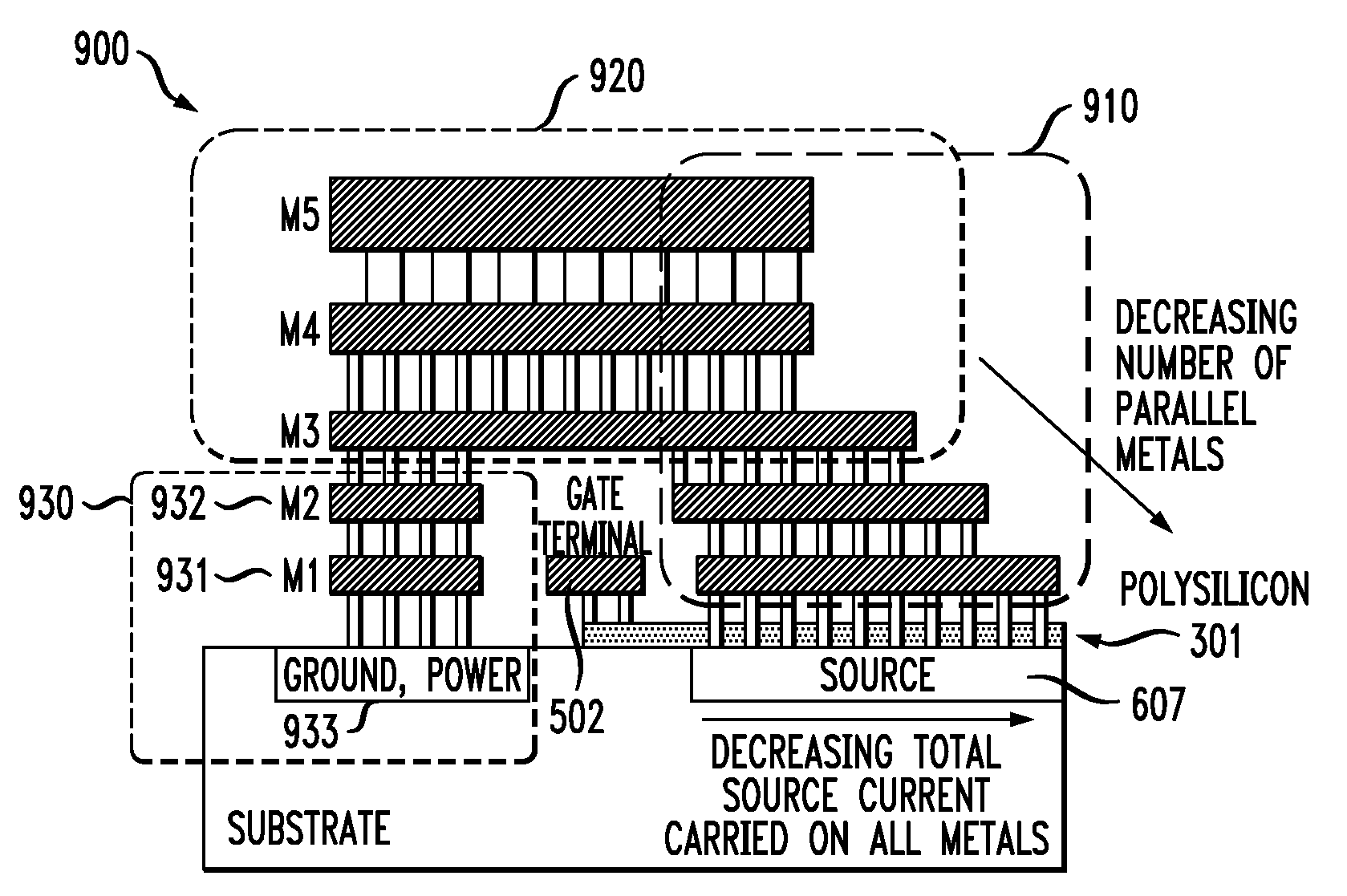

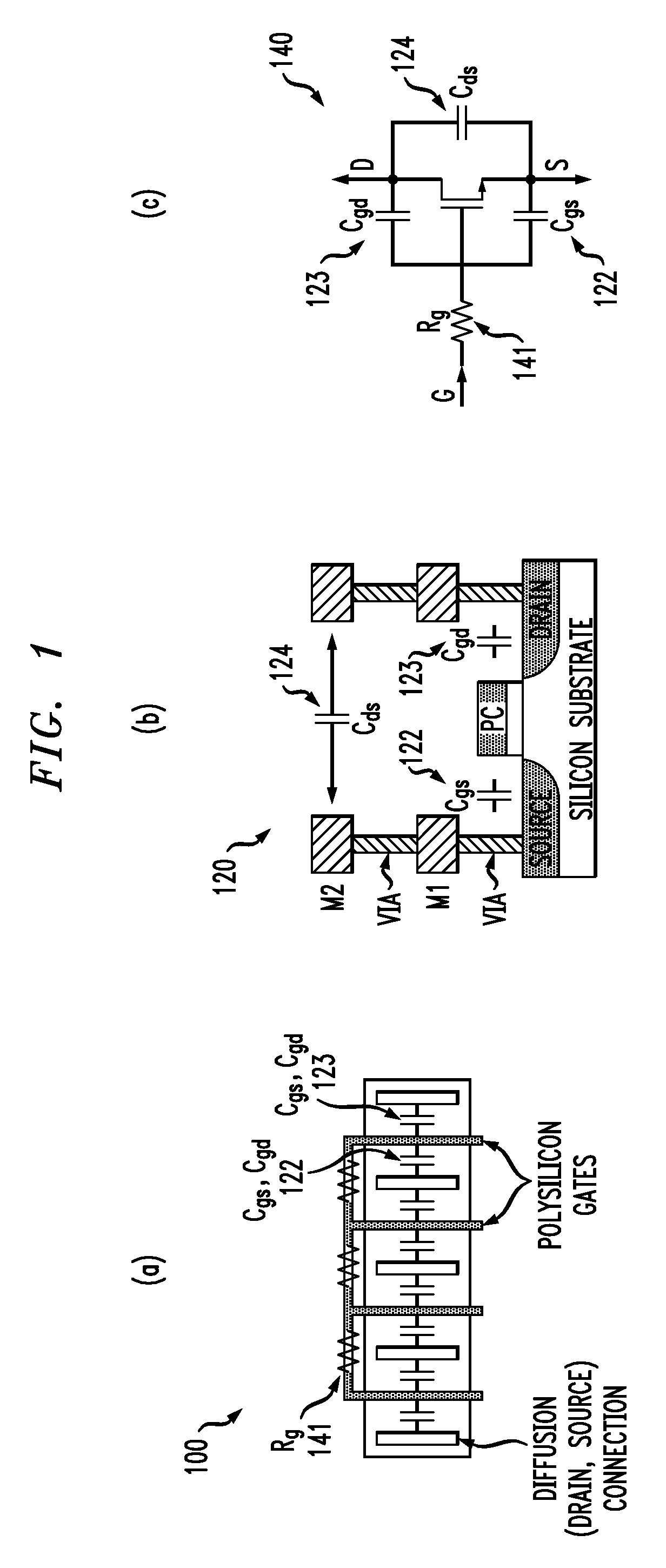

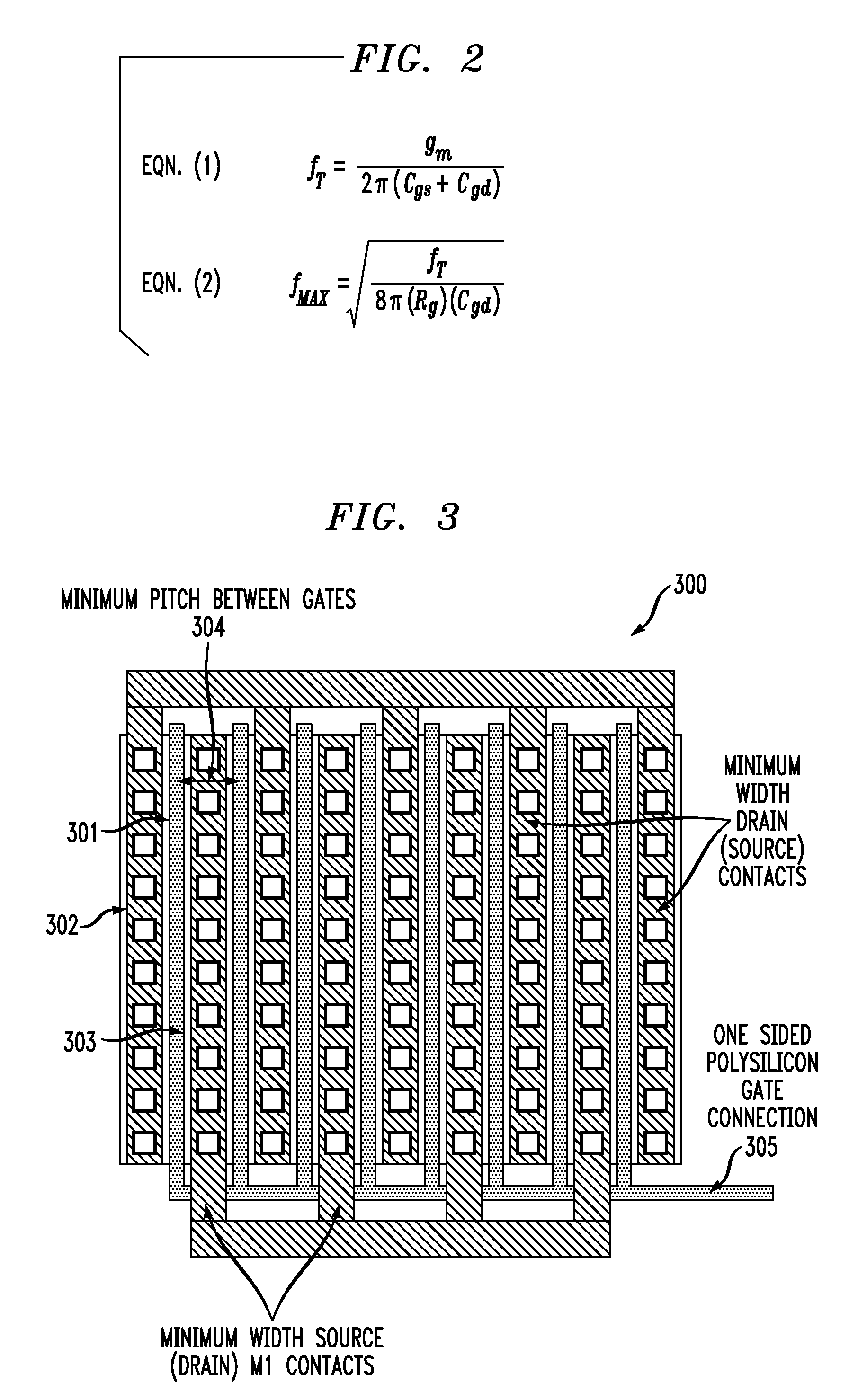

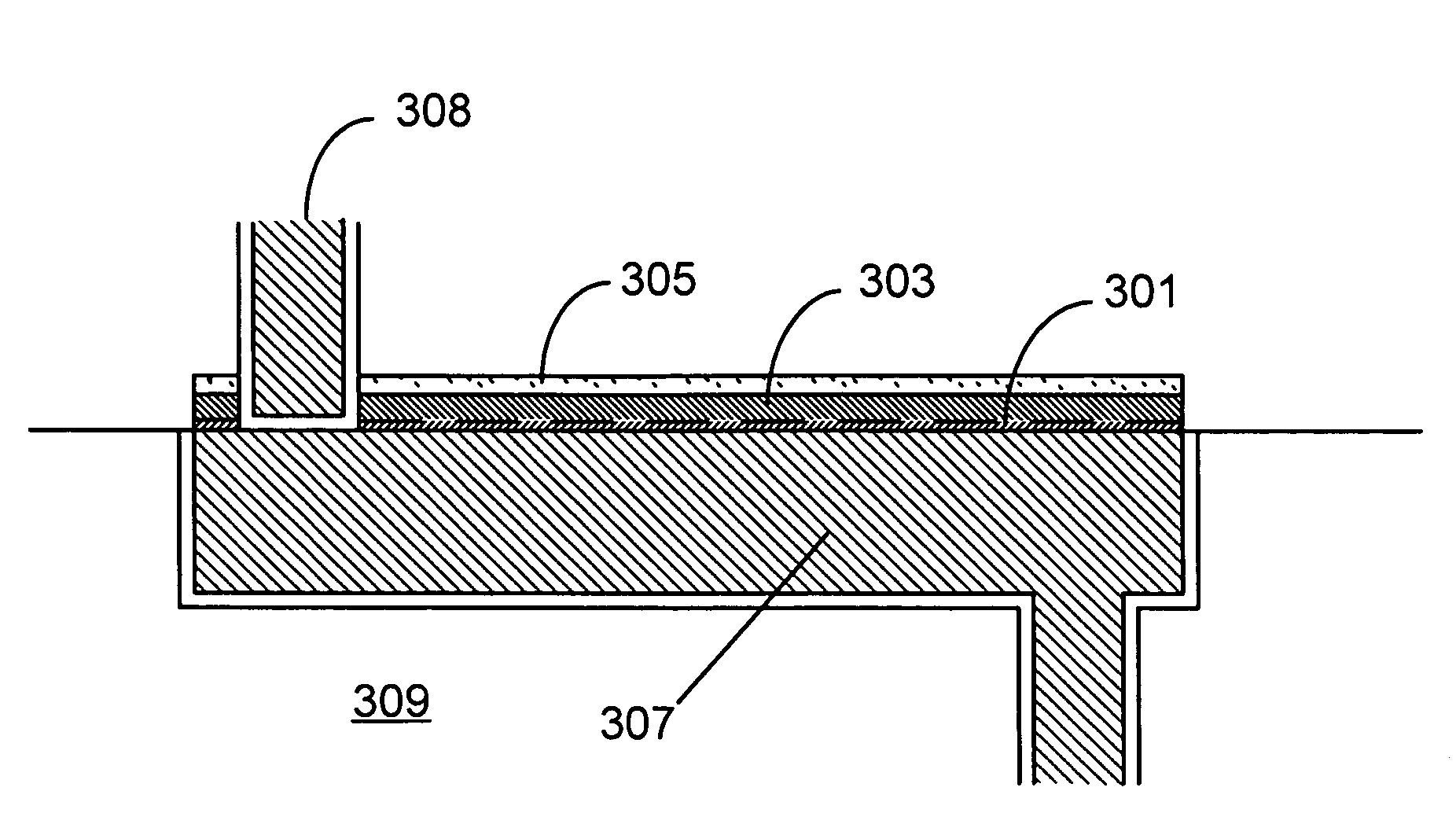

Electromigration-Complaint High Performance FET Layout

An electrical contact structure distributes current along a length thereof. The electrical contact structure includes a plurality of n metal rectangles on n levels of metal. The rectangle on one metal level is at least as wide in width and vertically covers in width the rectangle on the metal level immediately below. The rectangle on one metal level is shorter in length than and substantially aligned at a first end with the rectangle on the metal level immediately below. Rectangle first ends are substantially aligned. Features of an exemplary FET transistor of this invention are a source and drain terminal electrical contact structure, a multi-level metal ring connecting gate rectangles on both ends, and a wider-than-minimum gate-to-gate spacing. The invention is useful, for example, in an electromigration-compliant, high performance transistor.

Owner:GLOBALFOUNDRIES INC

Selective refractory metal and nitride capping

InactiveUS7157798B1Inhibited DiffusionPrevent electromigrationSemiconductor/solid-state device detailsSolid-state devicesNucleationCopper

A method for creating a refractory metal and refractory metal nitride cap effective for reducing copper electromigration and copper diffusion is described. The method includes depositing a refractory metal nucleation layer and nitriding at least the upper portion of the refractory metal layer to form a refractory metal nitride. Methods to reduce and clean the copper lines before refractory metal deposition are also described. Methods to form a thicker refractory metal layer using bulk deposition are also described.

Owner:NOVELLUS SYSTEMS

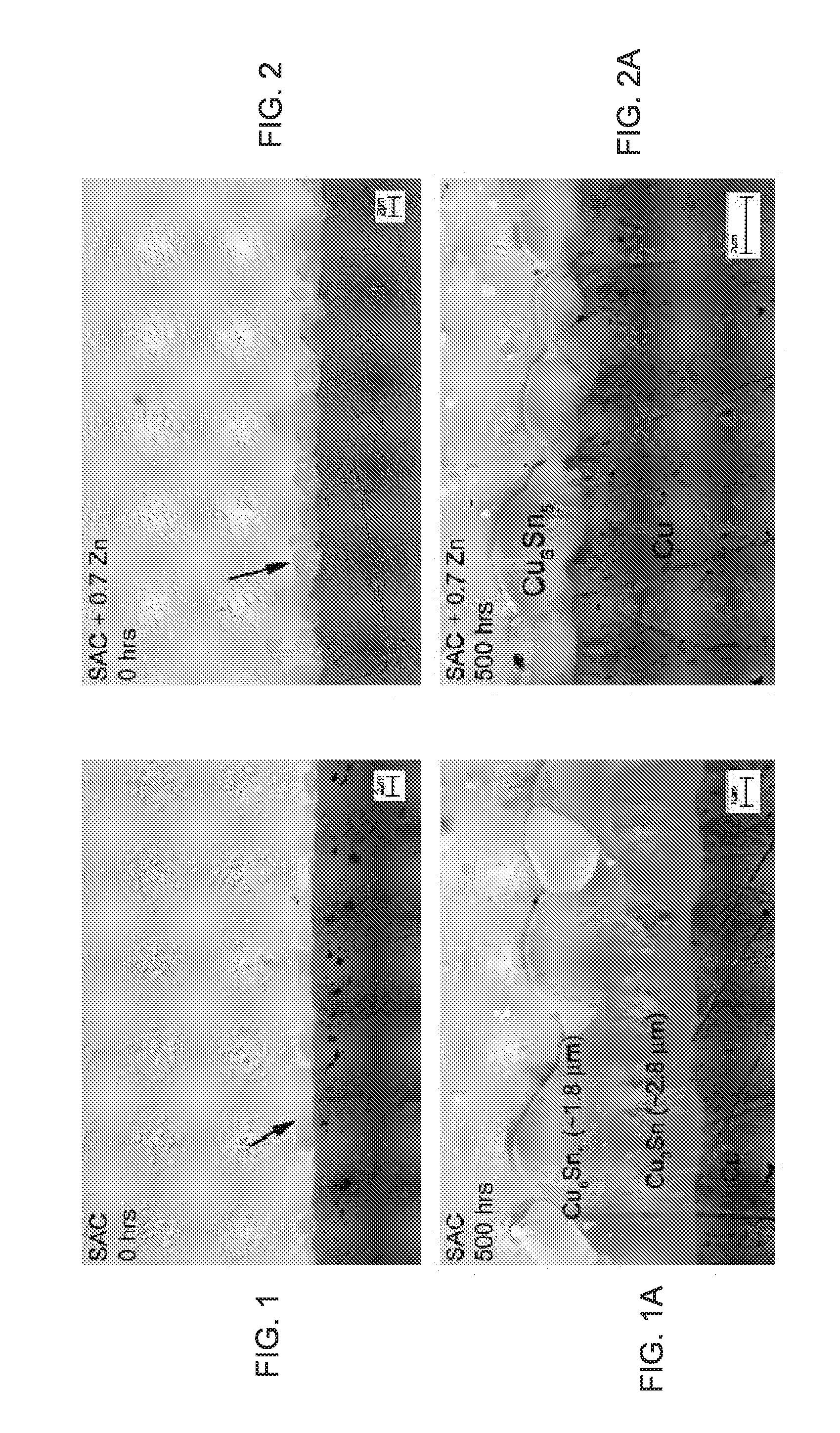

Modification of pb-free solder alloy compositions to improve interlayer dielectric delamination in silicon devices and electromigration resistance in solder joints

InactiveUS20090197114A1Good mechanical integrityImprove reliabilitySolid-state devicesPrinted circuit manufactureDielectricSilicon

A solder joint comprising a solder capture pad on a substrate having a circuit; and a lead free solder selected from the group comprising Sn—Ag—Cu solder and Sn—Ag solder adhered to the solder capture pad; the solder selected from the group comprising between 0.1 to 2.0% by weight Sb or Bi, and 0.5 to 3.0% Ag. Formation of voids at an interface between the solder and the solder capture pad is suppressed, by including Zn. Interlayer dielectric delamination is suppressed, and electromigration characteristics are greatly improved. Methods for forming solder joints using the solders.

Owner:SHIH YUAN +5

Reverse electroplating of barrier metal layer to improve electromigration performance in copper interconnect devices

InactiveUS6261963B1Electrolysis componentsSemiconductor/solid-state device manufacturingCopper interconnectOptoelectronics

A method is provided for forming a conductive interconnect, the method comprising forming a first dielectric layer above a structure layer, forming a first opening in the first dielectric layer, and forming a first conductive structure in the first opening. The method also comprises forming a second dielectric layer above the first dielectric layer and above the first conductive structure, forming a second opening in the second dielectric layer above at least a portion of the first conductive structure, the second opening having a side surface and a bottom surface, and forming at least one barrier metal layer in the second opening on the side surface and on the bottom surface. In addition, the method comprises removing a portion of the at least one barrier metal layer from the bottom surface, and forming a second conductive structure in the second opening, the second conductive structure contacting the at least the portion of the first conductive structure. The method further comprises forming the conductive interconnect by annealing the second conductive structure and the first conductive structure.

Owner:ADVANCED MICRO DEVICES INC

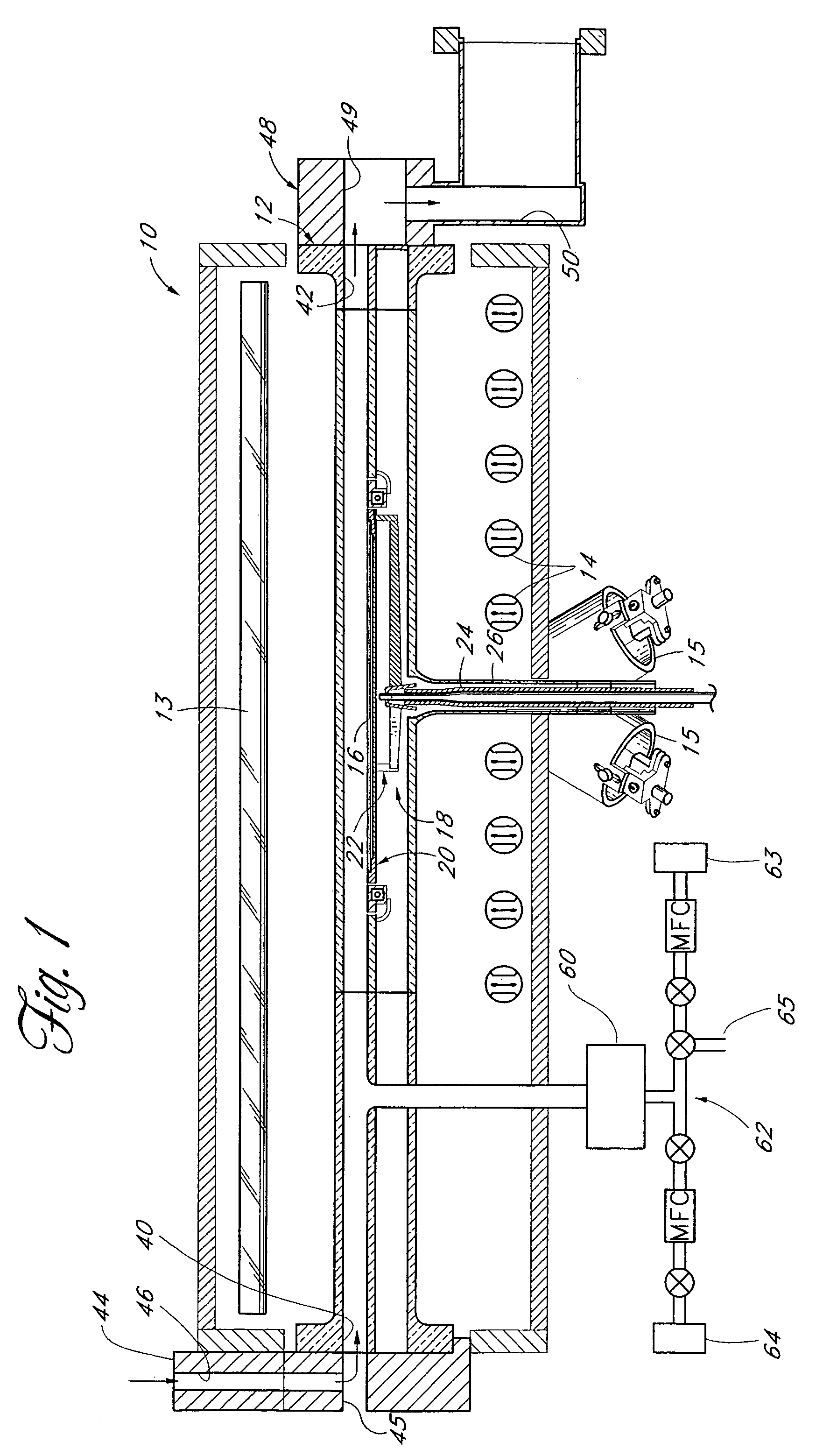

Deposition film orientation and reflectivity improvement using a self-aligning ultra-thin layer

InactiveUS6120844AInhibition formationImprove reflectivityVacuum evaporation coatingSputtering coatingGas phaseCrystal orientation

The present invention relates generally to an improved apparatus and process to provide a thin self-aligning layer prior to forming a conducting film layer thereover to improve the film characteristics and deposition coverage. In one aspect of the invention, a dielectric layer is formed over a conducting or semiconducting layer and etched to form an aperture exposing the underlying conducting or semiconducting layer on the aperture floor. An ultra-thin nucleation layer is then deposited by either vapor deposition or chemical vapor deposition onto the field of the dielectric layer. A CVD metal layer is then deposited onto the structure to achieve selective deposition on the floor of the aperture, while preferably also forming a highly oriented blanket layer on the field. In another aspect of the invention, a thin, self-aligning layer is formed over a barrier layer prior to deposition of a conducting film thereover. It is believed that the self-aligning layer enhances the reflectivity of the films by improving the crystal structure in the resulting film and provides improved electromigration performance by providing <111> crystal orientation. The process is preferably carried out in an integrated processing system that includes both a PVD and CVD processing chamber so that once the substrate is introduced into a vacuum environment, the process occurs without the formation of oxides between the layers.

Owner:APPLIED MATERIALS INC

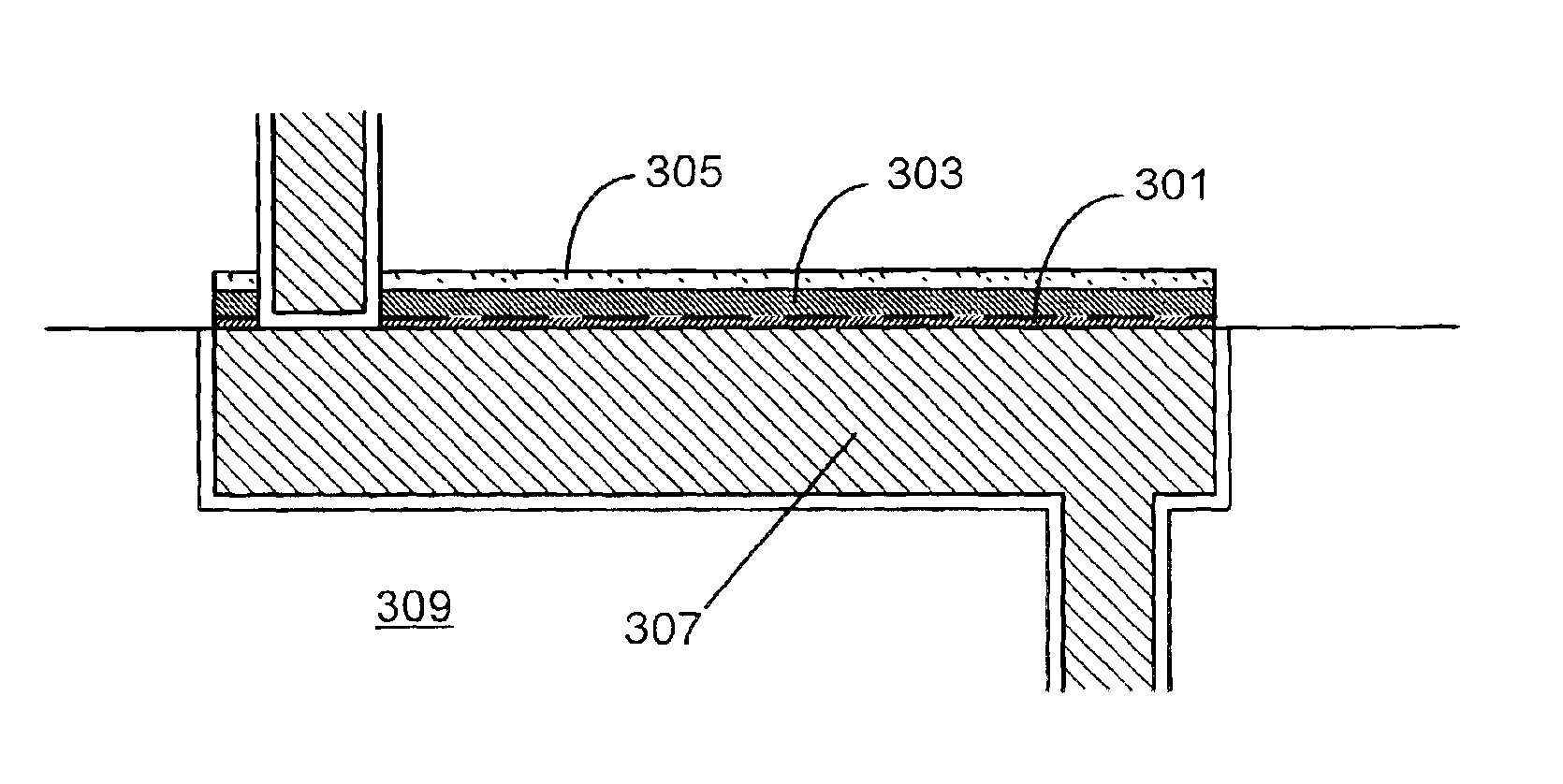

Protective self-aligned buffer layers for damascene interconnects

ActiveUS7576006B1Improve mobilityImproving several propertySemiconductor/solid-state device manufacturingThin material handlingDiffusion barrierSemiconductor

Capping protective self aligned buffer (PSAB) layers are layers of material that are selectively formed at the surface of metal layers in a partially fabricated semiconductor device. Encapsulating PSAB layers are formed not only at the surface of the metal layers, but also within the unexposed portions of the metal lines. Encapsulating PSAB layer, for example, can surround the metal line with the PSAB material, thereby protecting interfaces between the metal line and diffusion barriers. Encapsulating PSAB layers can be formed by treating the exposed surfaces of metal lines with GeH4. Capping PSAB layers can be formed by treating the exposed surfaces of metal lines with SiH4. Interconnects having both a silicon-containing capping PSAB layer and a germanium-containing encapsulating PSAB layer provide good performance in terms of adhesion, resistance shift, and electromigration characteristics.

Owner:NOVELLUS SYSTEMS