Patents

Literature

694 results about "Copper interconnect" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In semiconductor technology, copper interconnects are used in silicon integrated circuits (ICs) to reduce propagation delays and power consumption. Since copper is a better conductor than aluminium, ICs using copper for their interconnects can have interconnects with narrower dimensions, and use less energy to pass electricity through them. Together, these effects lead to ICs with better performance. They were first introduced by IBM, with assistance from Motorola, in 1997.

Selective formation of metal layers in an integrated circuit

ActiveUS20060121733A1Improve reliabilitySemiconductor/solid-state device manufacturingChemical vapor deposition coatingCopper interconnectSelective deposition

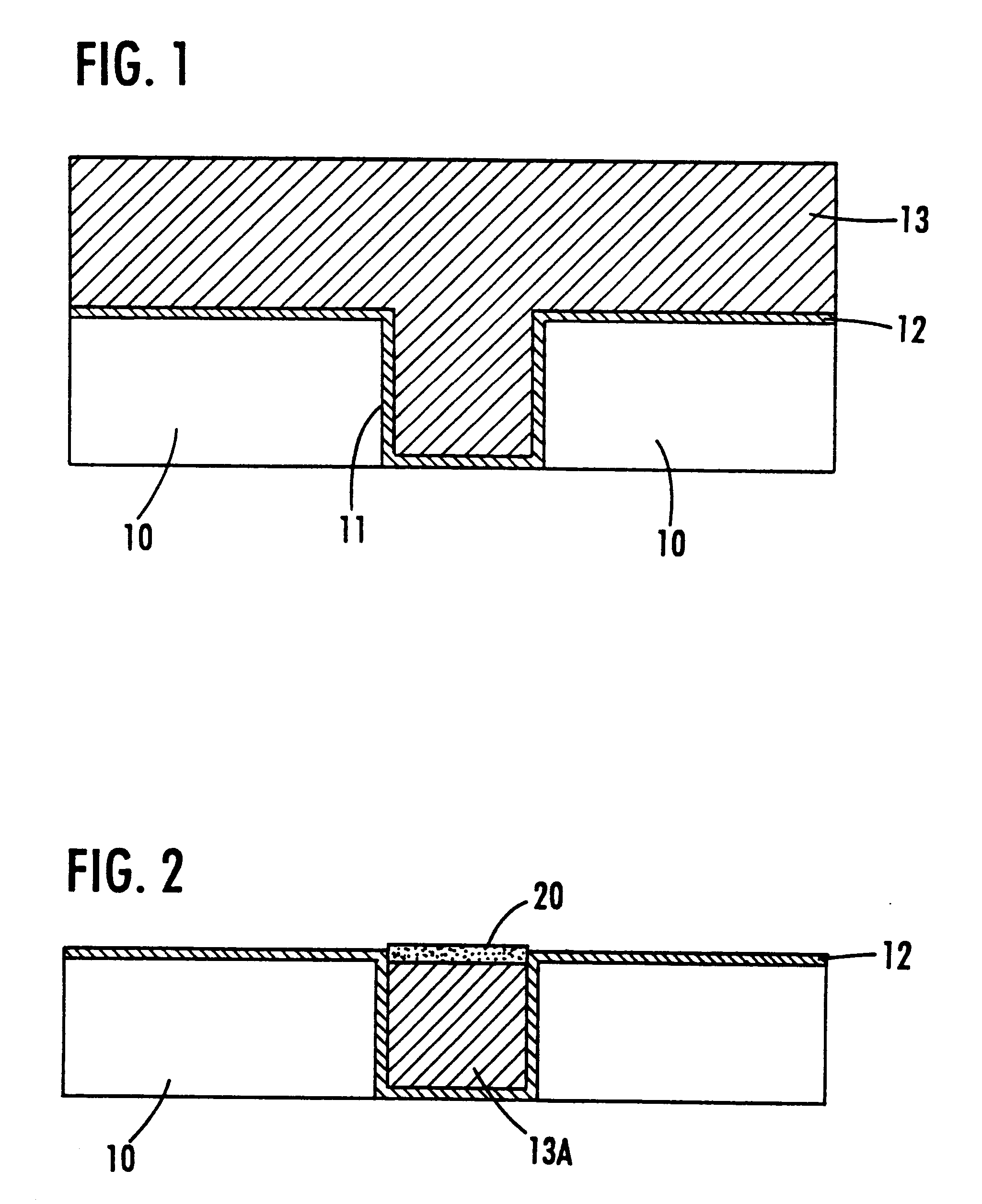

A method for enhancing the reliability of copper interconnects and / or contacts, such as the bottom of vias exposing top surfaces of buried copper, or at the top of copper lines just after CMP. The method comprises contacting the exposed copper surface with a vapor phase compound of a noble metal and selectively forming a layer of the noble metal on the exposed copper surface, either by a copper replacement reaction or selective deposition (e.g., ALD or CVD) of the noble metal.

Owner:ASM JAPAN

Process for reducing copper oxide during integrated circuit fabrication

InactiveUS6033584ADecorative surface effectsSemiconductor/solid-state device manufacturingCopper interconnectCopper oxide

A method of integrated circuit fabrication creating copper interconnect structures wherein the formation of copper oxide is reduced or eliminated by etching away the copper oxide performing an H2 plasma treatment in a plasma enhanced chemical vapor deposition chamber.

Owner:ADVANCED MICRO DEVICES INC

Selective formation of metal layers in an integrated circuit

ActiveUS7476618B2Improve reliabilitySemiconductor/solid-state device manufacturingChemical vapor deposition coatingCopper interconnectSelective deposition

A method for enhancing the reliability of copper interconnects and / or contacts, such as the bottom of vias exposing top surfaces of buried copper, or at the top of copper lines just after CMP. The method comprises contacting the exposed copper surface with a vapor phase compound of a noble metal and selectively forming a layer of the noble metal on the exposed copper surface, either by a copper replacement reaction or selective deposition (e.g., ALD or CVD) of the noble metal.

Owner:ASM JAPAN

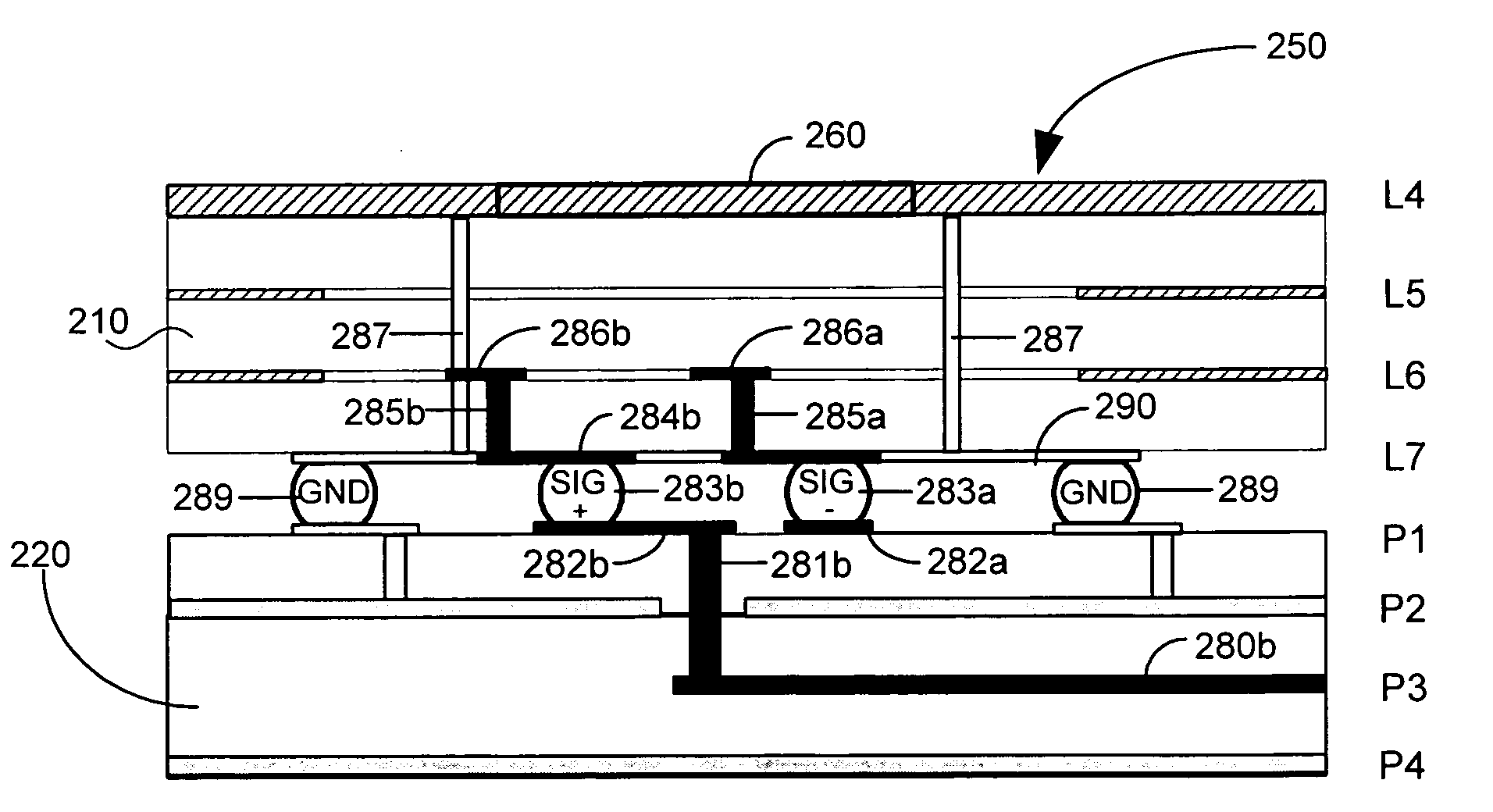

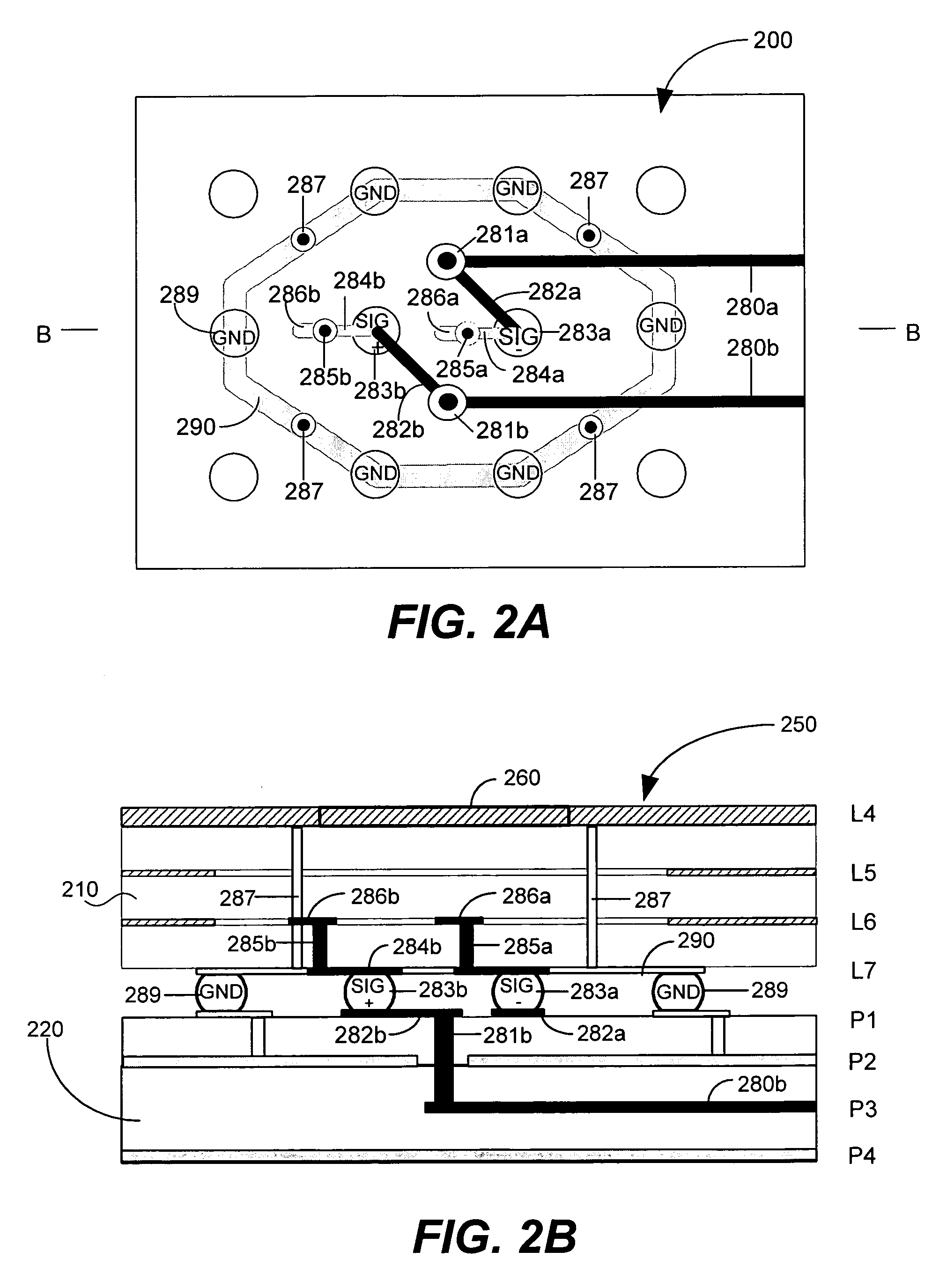

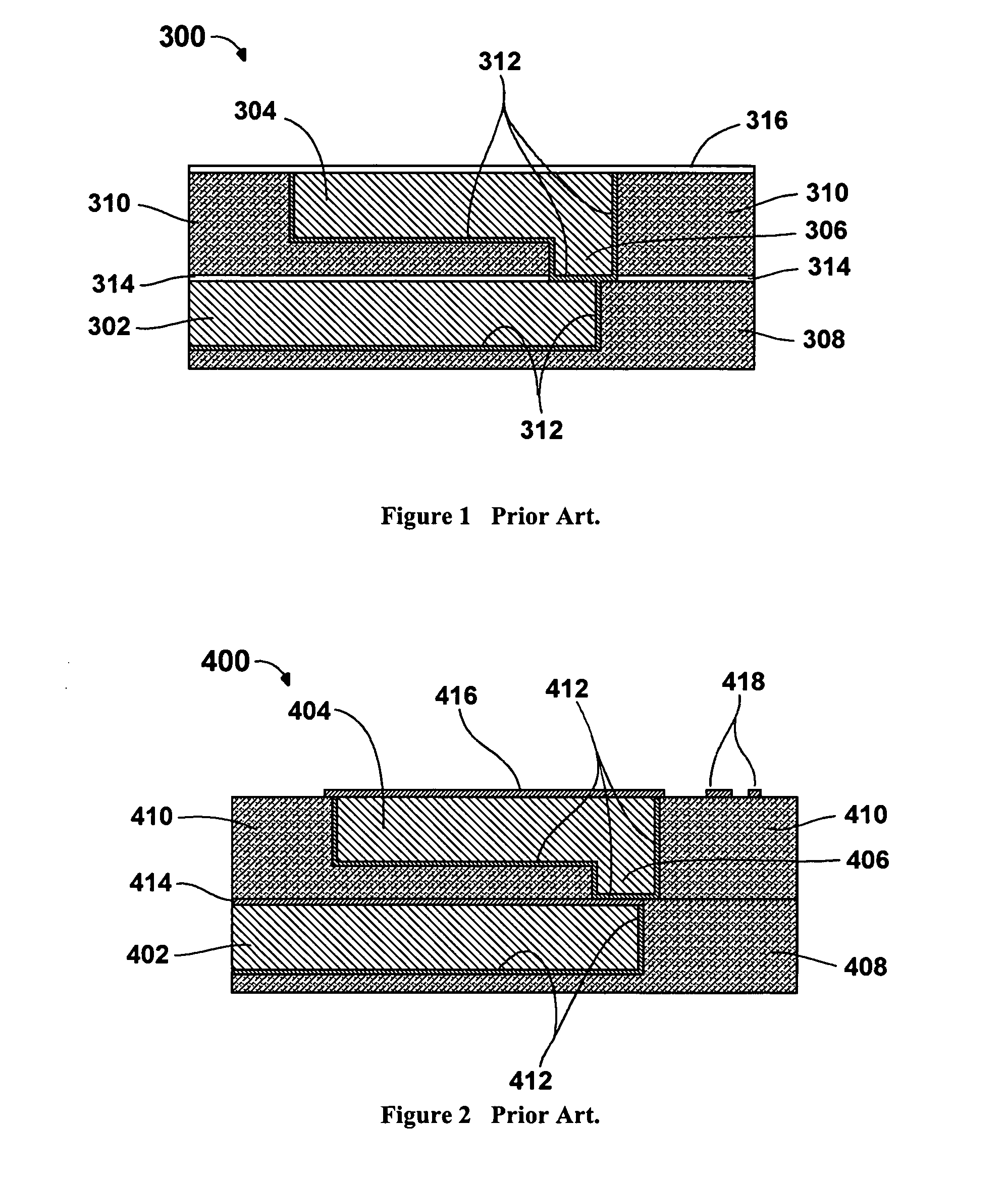

Ball grid array package-to-board interconnect co-design apparatus

InactiveUS7405477B1Signal transmission is convenientAvoid reflectionsSemiconductor/solid-state device detailsPrinted circuit aspectsCopper interconnectData stream

A package-board co-design methodology preserves the signal integrity of high-speed signals passing from semiconductor packages to application PCBs. An optimal architecture of interconnects between package and PCB enhances the signal propagation, minimizes parasitic levels, and decreases electromagnetic interference from adjacent high frequency signals. The invention results in devices with superior signal quality and EMI shielding properties with enhanced capability for carrying data stream at multiple-gigabit per second bit-rates.

Owner:TAHOE RES LTD

Cleaning composition for removing resists and method of manufacturing semiconductor device

InactiveUS20040106531A1Surface-active detergent compositionsNon-surface-active detergent compositionsResistCopper interconnect

The cleaning composition for removing resists includes a salt of hydrofluoric acid and a base not containing a metal (A component), a water-soluble organic solvent (B1 component), at least one acid selected from a group consisting of organic acid and inorganic acid (C component), water (D component), and optionally an ammonium salt (E1 component), and its hydrogen ion concentration (pH) is 4-8. Thus, in the manufacturing process of a semiconductor device such as a copper interconnecting process, removing efficiency of resist residue and other etching residue after etching or ashing improves, and corrosion resistance of copper and insulating film also improves.

Owner:PANASONIC CORP +2

Method to control mechanical stress of copper interconnect line using post-plating copper anneal

A method is provided, the method comprising forming a first dielectric layer above a first structure layer, forming a first opening in the first dielectric layer, and forming a first copper structure above the first dielectric layer and in the first opening. The method also comprises annealing the first copper structure using one of a furnace anneal process performed at a temperature ranging from approximately 100-400° C. for a time ranging from approximately 10-90 minutes and a rapid thermal anneal (RTA) process performed at a temperature ranging from approximately 100-400° C. for a time ranging from approximately 10-180 seconds.

Owner:GLOBALFOUNDRIES INC

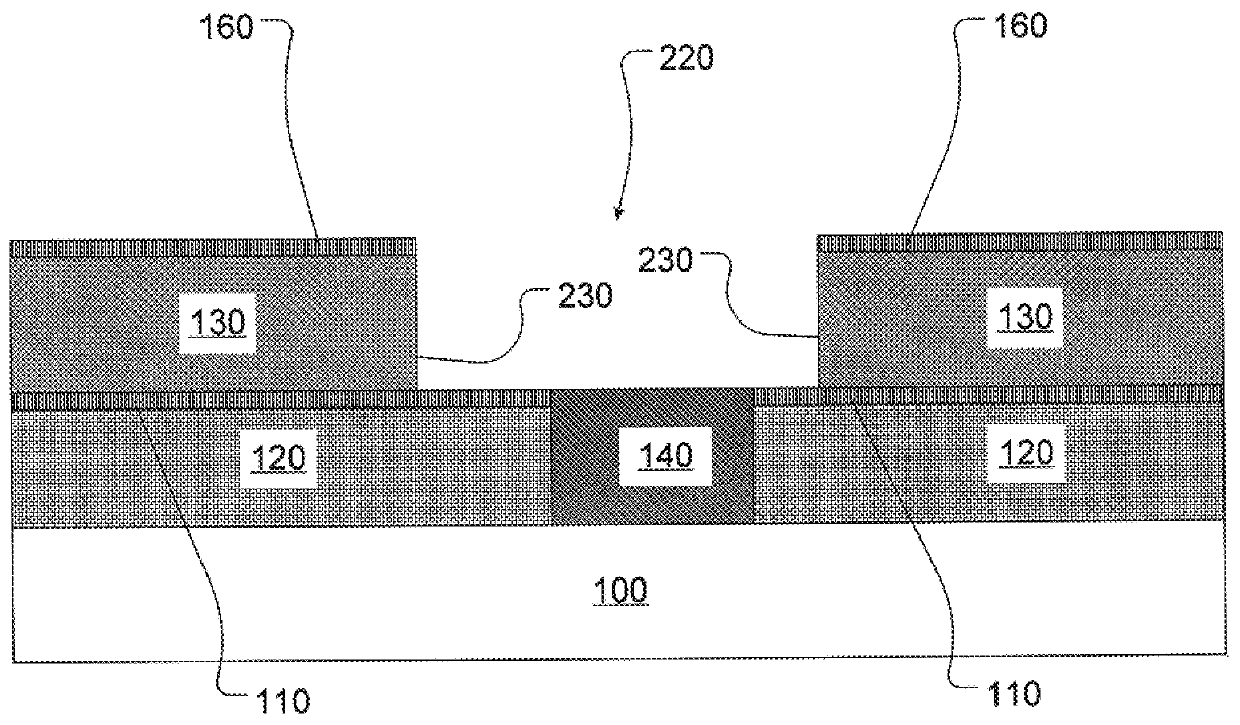

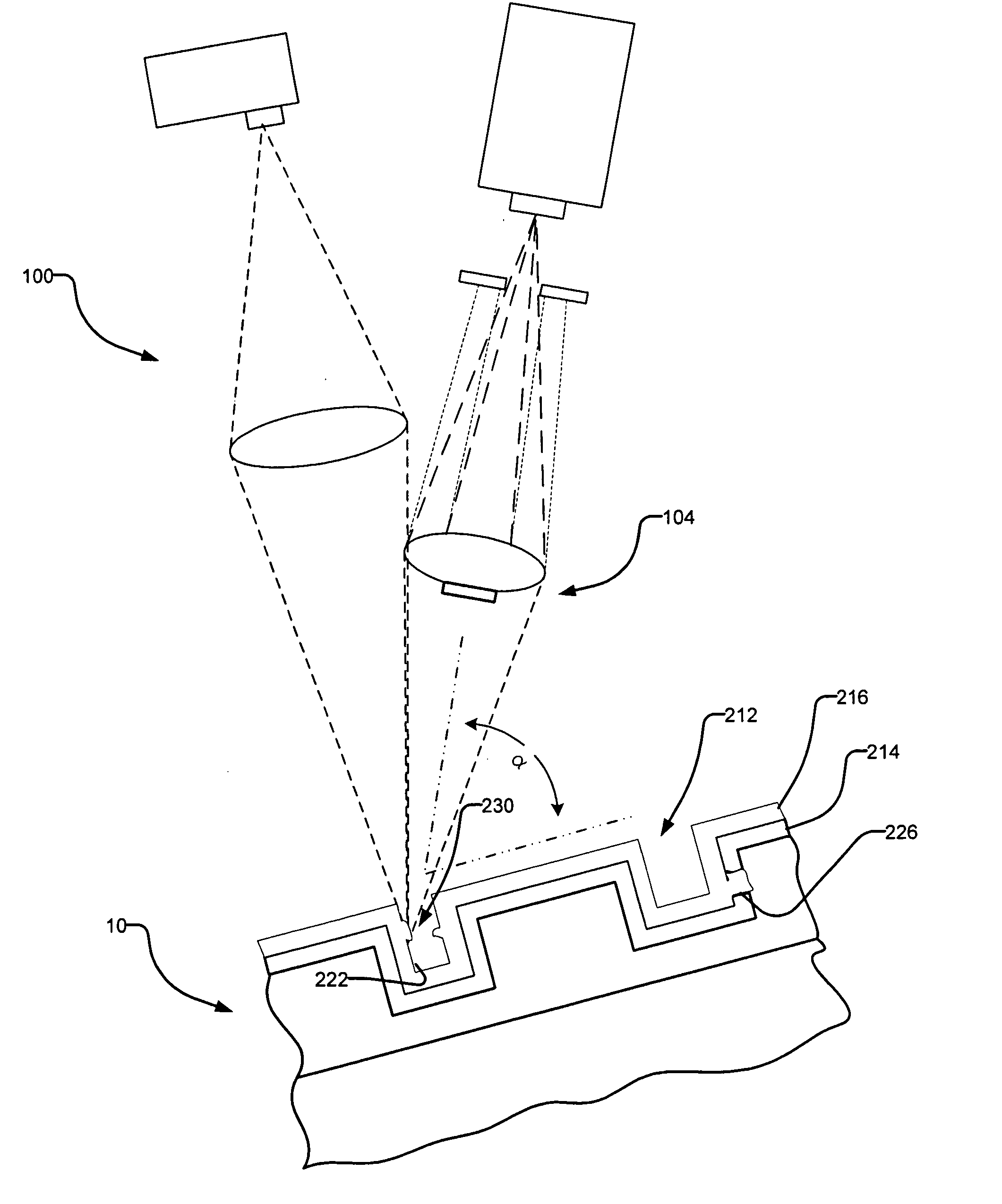

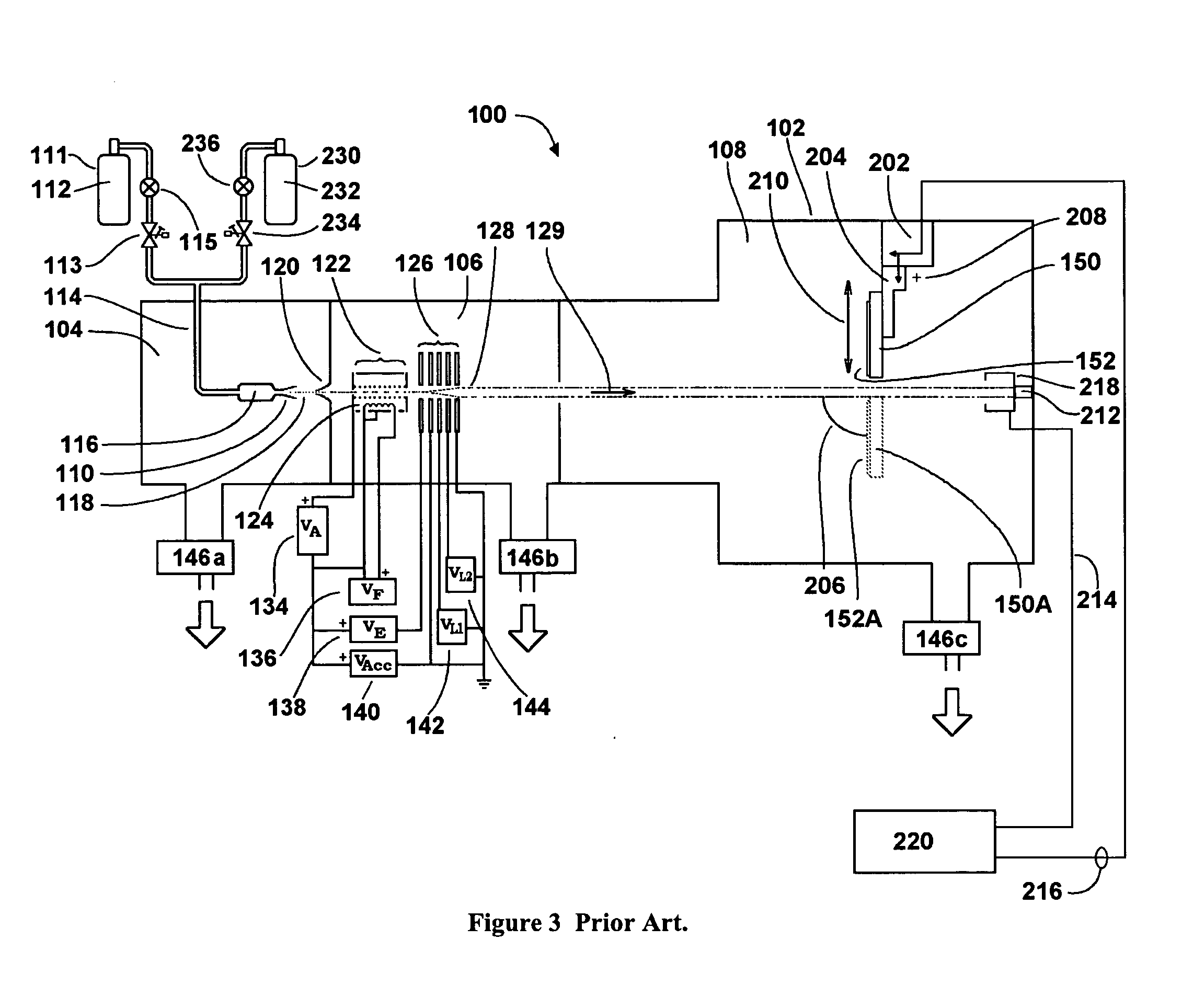

Back-end-of-line metallization inspection and metrology microscopy system and method using x-ray fluorescence

InactiveUS20050282300A1Material analysis using wave/particle radiationSemiconductor/solid-state device testing/measurementCopper interconnectMetrology

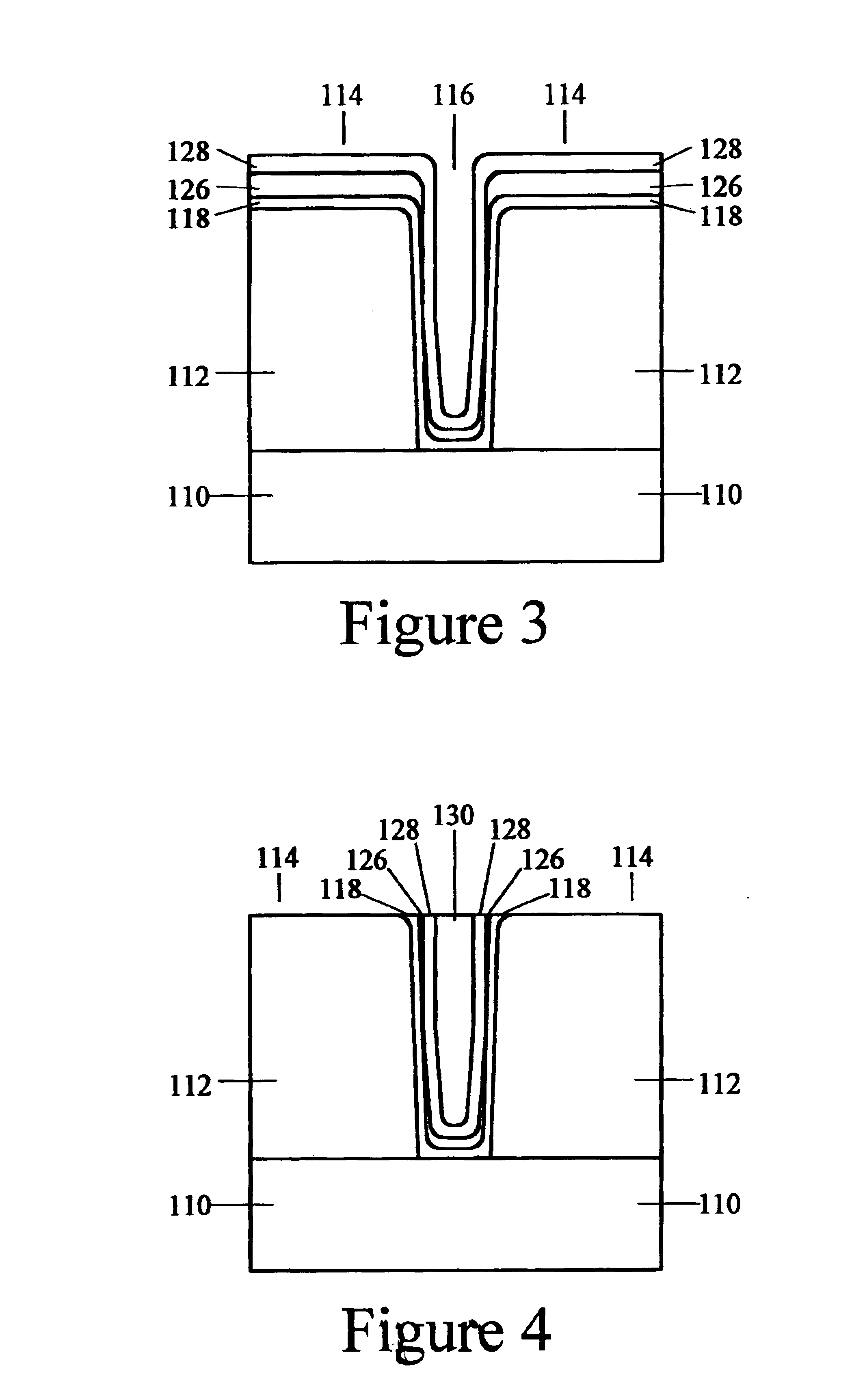

Systems and methods for performing inspection and metrology operations on metallization processes such as on back-end-of-line (BEOL) metallization thickness and step coverage are disclosed. Specific examples include measurements of thickness and uniformity of barrier layers, including tantalum for example, and seed layers, including copper for example, in Damascene, including dual-Damascene, trenches during the interconnect fabrication steps of integrated circuit production. The invention also relates to the detection and measurement of void formation during and after copper electroplating. The invention utilizes x-ray fluorescence to measure the absolute thicknesses and the thickness uniformity of the barrier layers in the trenches, the copper seed layers for electroplating, and the final copper interconnects.

Owner:XRADIA

Cleaning composition for removing resists and method of manufacturing semiconductor device

InactiveUS7250391B2Good removal effectInhibitionSemiconductor/solid-state device manufacturingNon-surface-active detergent solventsResistCopper interconnect

The cleaning composition for removing resists includes a salt of hydrofluoric acid and a base not containing a metal (A component), a water-soluble organic solvent (B1 component), at least one organic acid or inorganic acid (C component), water (D component), and, optionally, an ammonium salt (E1 component), and having a pH 4-8. Thus, in manufacturing a semiconductor device, such as a copper interconnecting process, efficiency of removing resist residue and other etching residue after etching or ashing is improved, and corrosion resistance of a copper and an insulating film is also improved.

Owner:PANASONIC CORP +2

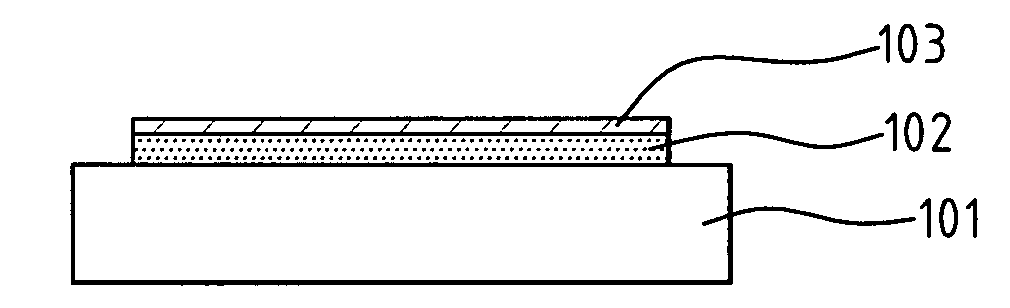

Post-passivation metal scheme on an IC chip with copper interconnection

InactiveUS20050017361A1High performanceSemiconductor/solid-state device detailsSolid-state devicesIntegrated circuitAluminium

In the present invention, copper interconnection with metal caps is extended to the post-passivation interconnection process. Metal caps may be aluminum. A gold pad may be formed on the metal caps to allow wire bonding and testing applications. Various post-passivation passive components may be formed on the integrated circuit and connected via the metal caps.

Owner:QUALCOMM INC

Combined conformal/non-conformal seed layers for metallic interconnects

InactiveUS6903016B2High aspect ratioSemiconductor/solid-state device detailsHeads using thin filmsCopper interconnectGas phase

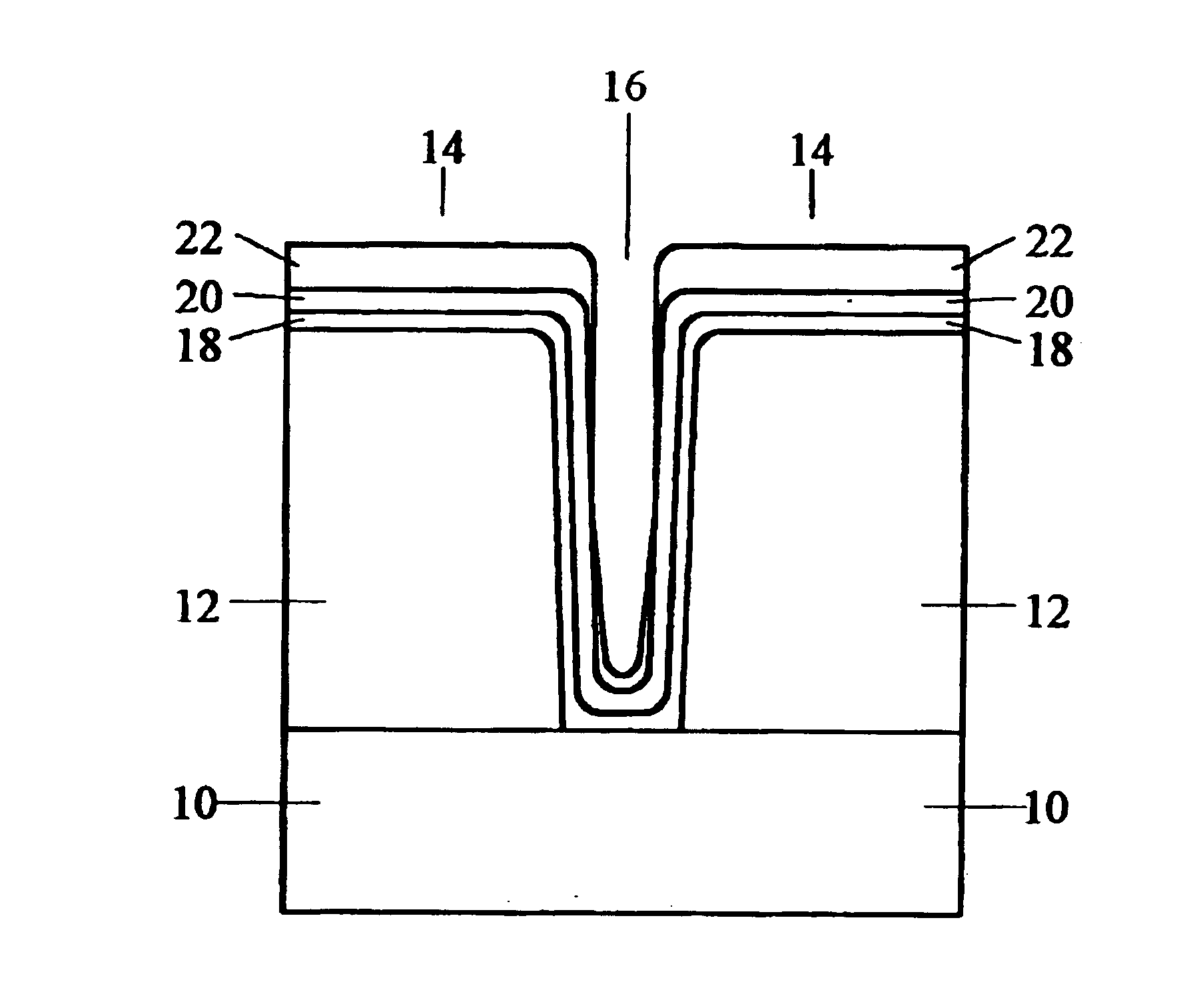

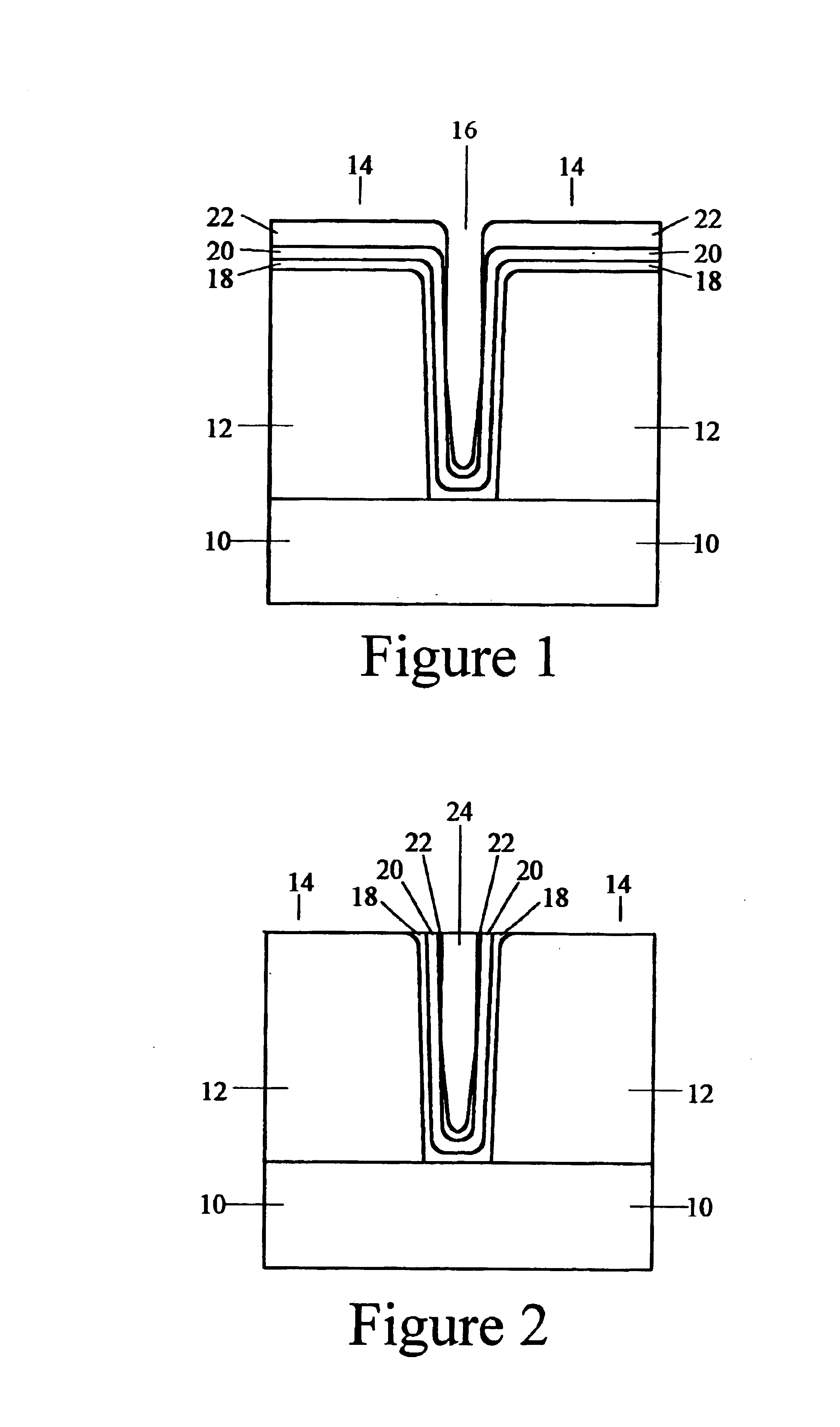

One embodiment of the present invention in a method for making copper interconnects, which method includes: (a) forming a patterned insulating layer on a substrate, the patterned insulating layer including at least one opening and a field surrounding the at least one opening; (b) depositing a barrier layer over the field and inside surfaces of the at least one opening; (c) depositing a non-conformal first copper seed layer over the barrier layer using physical vapor deposition, wherein the first seed layer is thicker than about 500 Å over the field; (d) depositing a conformal second copper seed layer over the first seed layer using chemical vapor deposition; and (e) electroplating a copper layer over the second seed layer.

Owner:COHEN URI DR

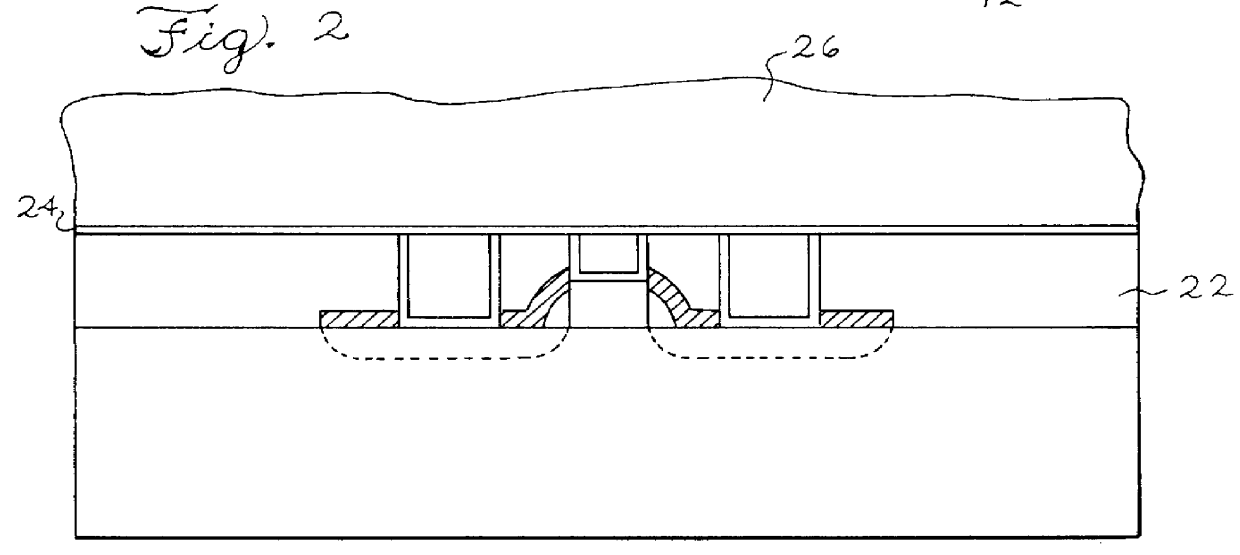

Build-up structures with multi-angle vias for chip to chip interconnects and optical bussing

InactiveUS6919508B2Improve performanceIncrease speedTelevision system detailsPiezoelectric/electrostriction/magnetostriction machinesAnisotropic conductive filmCopper interconnect

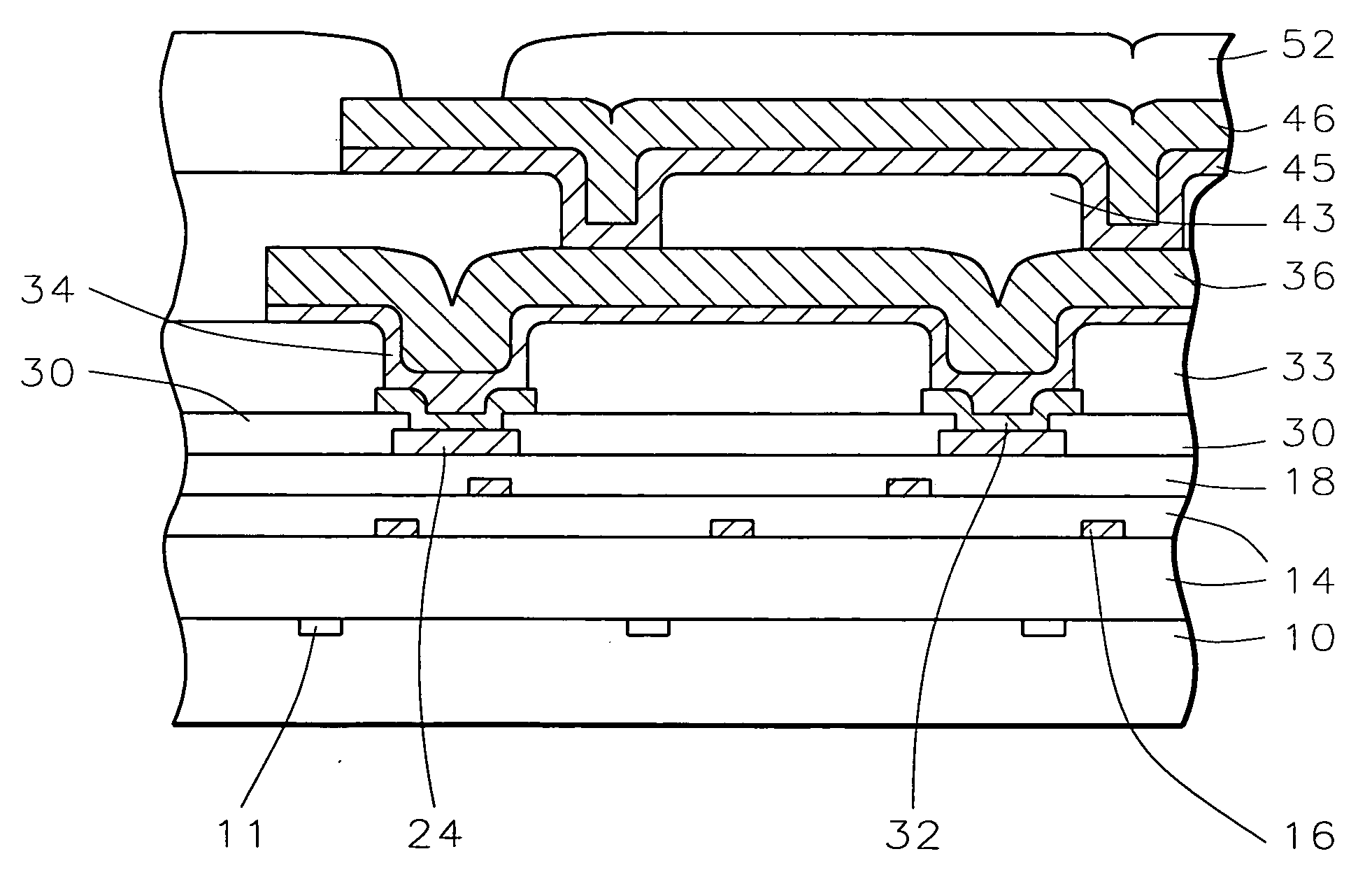

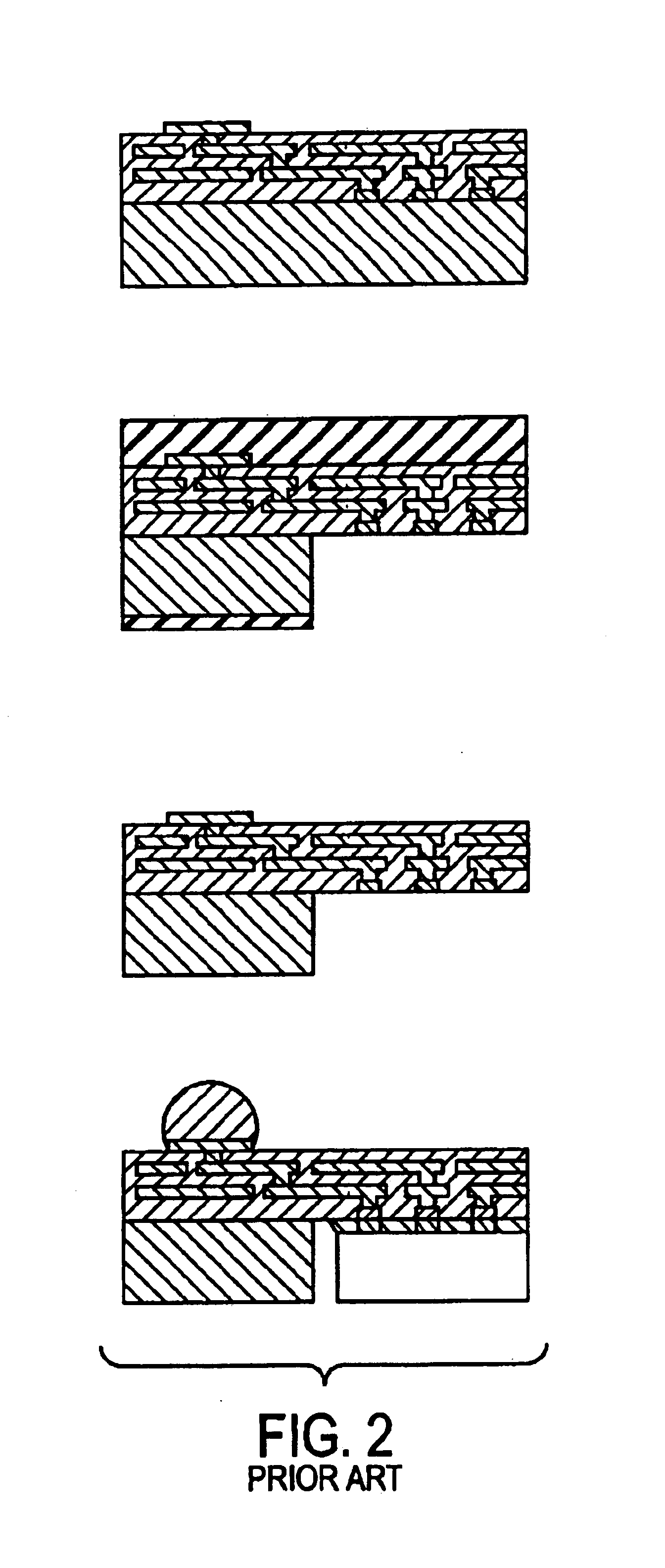

A build-up structure for chip to chip interconnects and System-In-Package utilizing multi-angle vias for electrical and optical routing or bussing of electronic information and controlled CTE dielectrics including mesocomposites to achieve optimum electrical and optical performance of monolithic structures. Die, multiple die, Microelectromechanical Machines (MEMs) and / or other active or passive components such as transducers or capacitors can be accurately positioned on a substrate such as a copper heatsink and multi-angle stud bumps can be placed on the active sites of the components. A first dielectric layer is preferably placed on the components, thereby embedding the components in the structure. Through various processes of photolithography, laser machining, soft lithography or anisotropic conductive film bonding, escape routing and circuitry is formed on the first metal layer. Additional dielectric layers and metal circuitry are formed utilizing multi-angle vias to form escape routing from tight pitch bond pads on the die to other active and passive components. Multi-angle vias can carry electrical or optical information in the form of digital or analog electromagnetic current, or in the form of visible or non-visible optical bussing and interconnections.

Owner:CAPITALSOURCE FINANCE

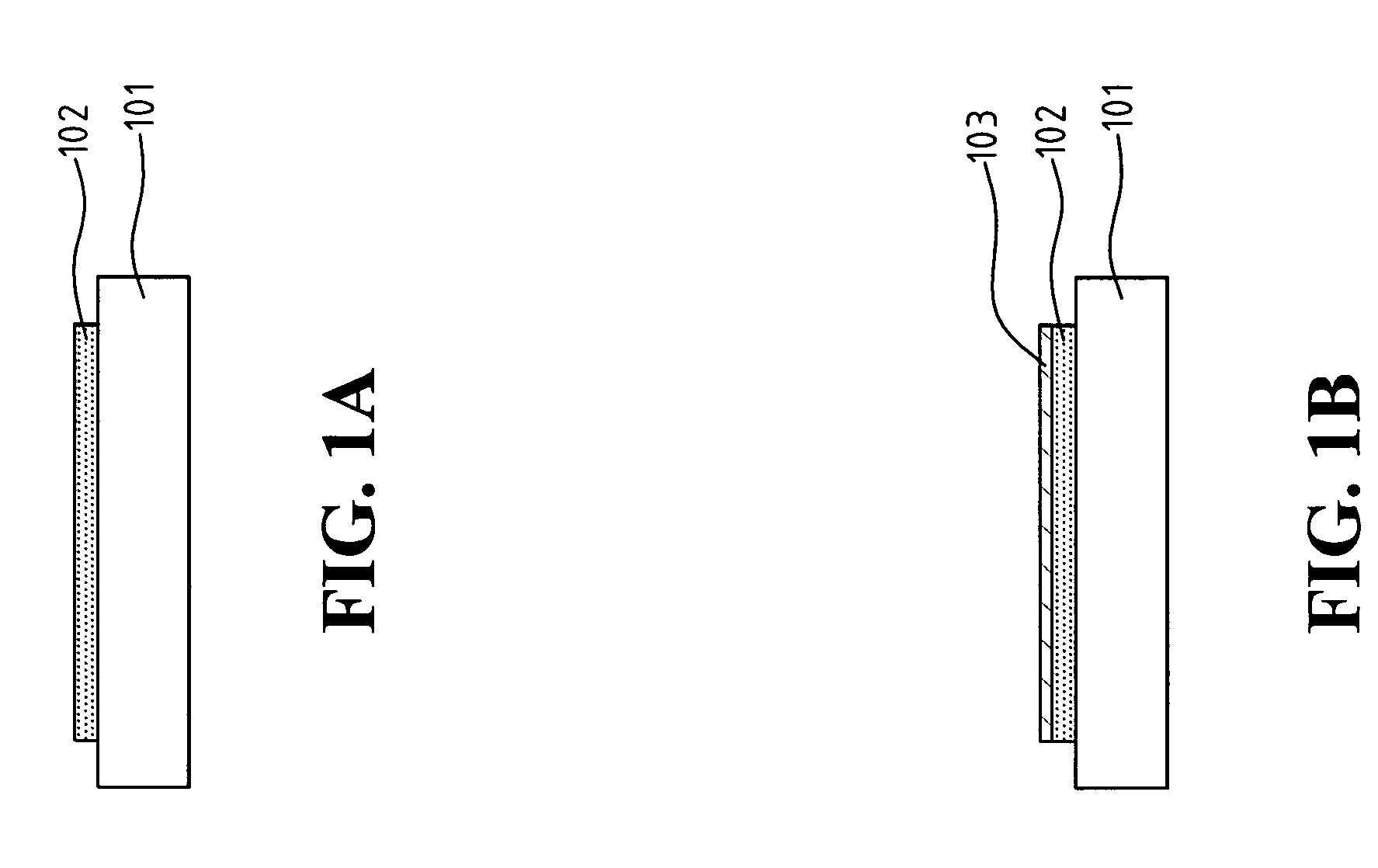

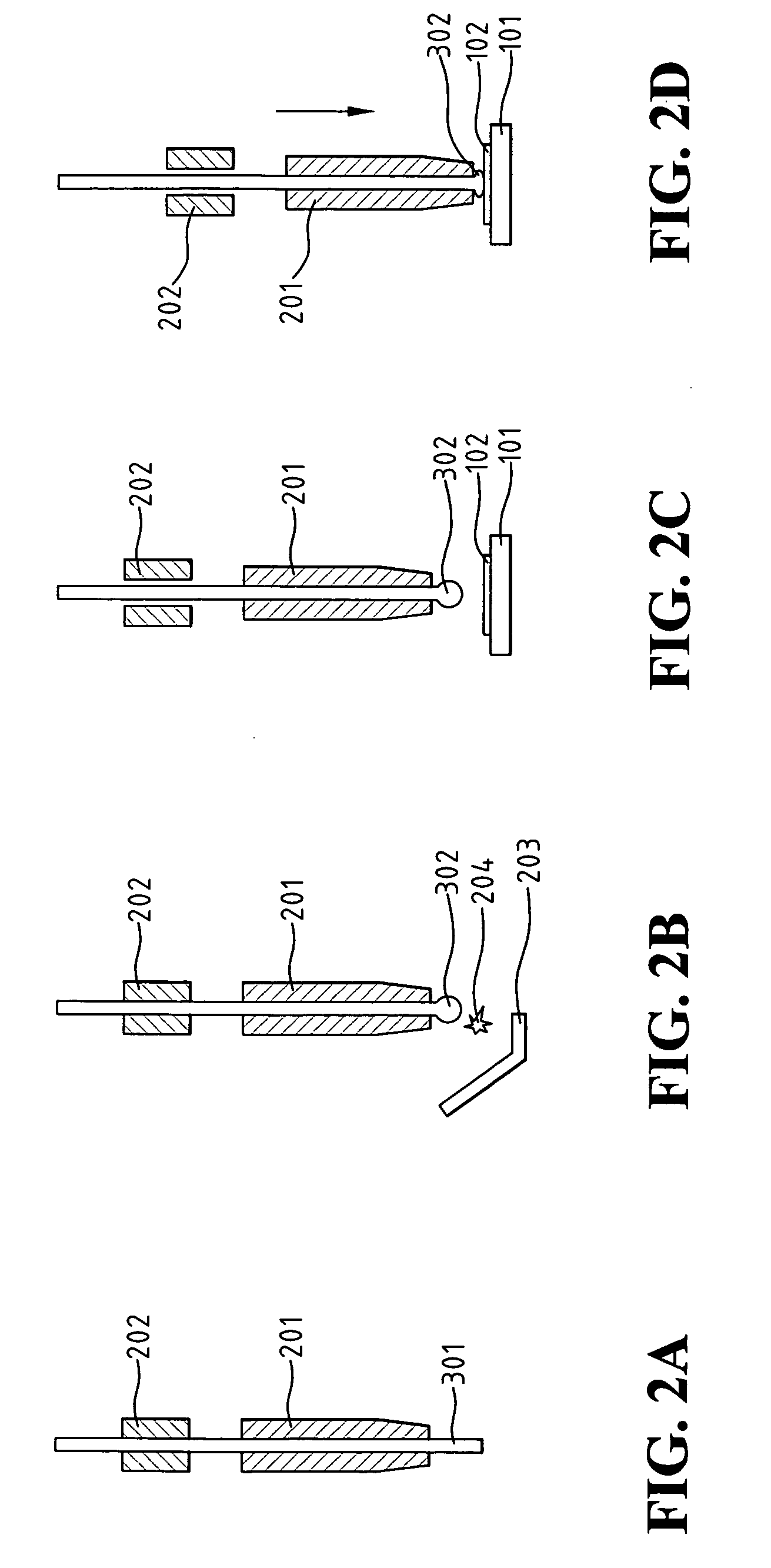

Wire-bonding method for chips with copper interconnects by introducing a thin layer

InactiveUS20050266672A1Prevent oxidationGood adhesionSemiconductor/solid-state device detailsSolid-state devicesCopper interconnectLead bonding

A wire-bonding method for chips with copper interconnects by introducing a thin layer is provided for solving the problem of oxidizing a copper bonding-pad during bonding processing in order not to deteriorate the bonding strength and yield rate thereof. The wire-bonding method of the present invention comprises: a step for providing a chip with a copper bonding-pad; another step for providing an aqueous solution to form a Cuprous oxide thin layer on the copper bonding-pad; and yet another step for setting a plurality of copper interconnects on the copper bonding-pad and providing an ultrasonic power for removing the Cuprous oxide layer to have the interconnects bonded on the copper bonding-pad.

Owner:NATIONAL CHUNG CHENG UNIV

Copper interconnect wiring and method of forming thereof

ActiveUS20060105570A1Electric discharge tubesSemiconductor/solid-state device detailsCopper interconnectIntegrated circuit interconnect

Capping layer or layers on a surface of a copper interconnect wiring layer for use in interconnect structures for integrated circuits and methods of forming improved integration interconnection structures for integrated circuits by the application of gas-cluster ion-beam processing. Reduced copper diffusion and improved electromigration lifetime result and the use of selective metal capping techniques and their attendant yield problems are avoided.

Owner:TEL EPION

Copper interconnect structure having stuffed diffusion barrier

InactiveUS6936535B2Semiconductor/solid-state device detailsSolid-state devicesMetal interconnectCopper interconnect

The present invention provides a method of fabricating a semiconductor device, which could advance the commercialization of semiconductor devices with a copper interconnect. In a process of metal interconnect line fabrication, a TiN thin film combined with an Al intermediate layer is used as a diffusion barrier on trench or via walls. For the formation, Al is deposited on the TiN thin film followed by copper filling the trench. Al diffuses to TiN layer and reacts with oxygen or nitrogen, which will stuff grain boundaries efficiently, thereby blocking the diffusion of copper successfully.

Owner:ASM INTERNATIONAL

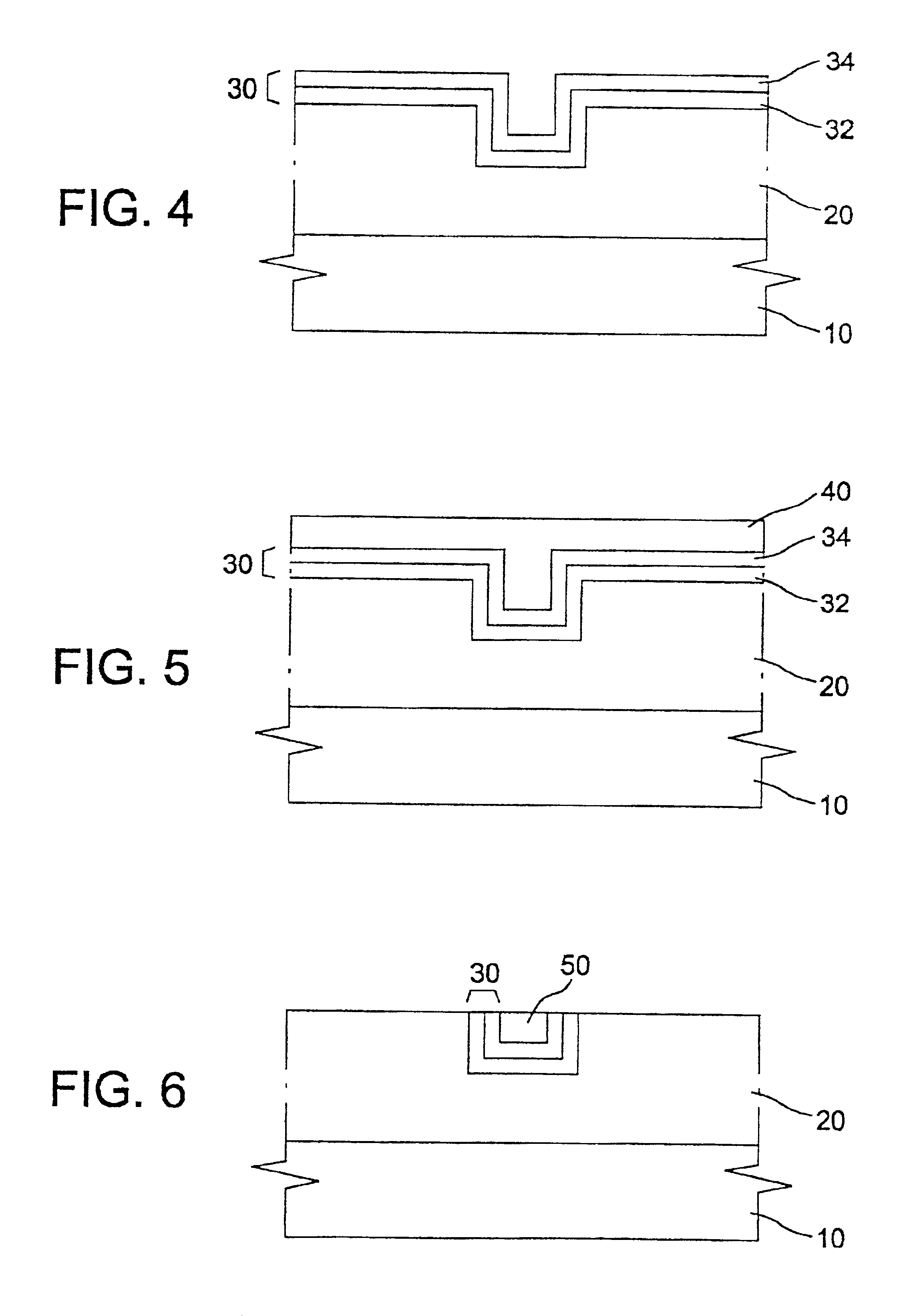

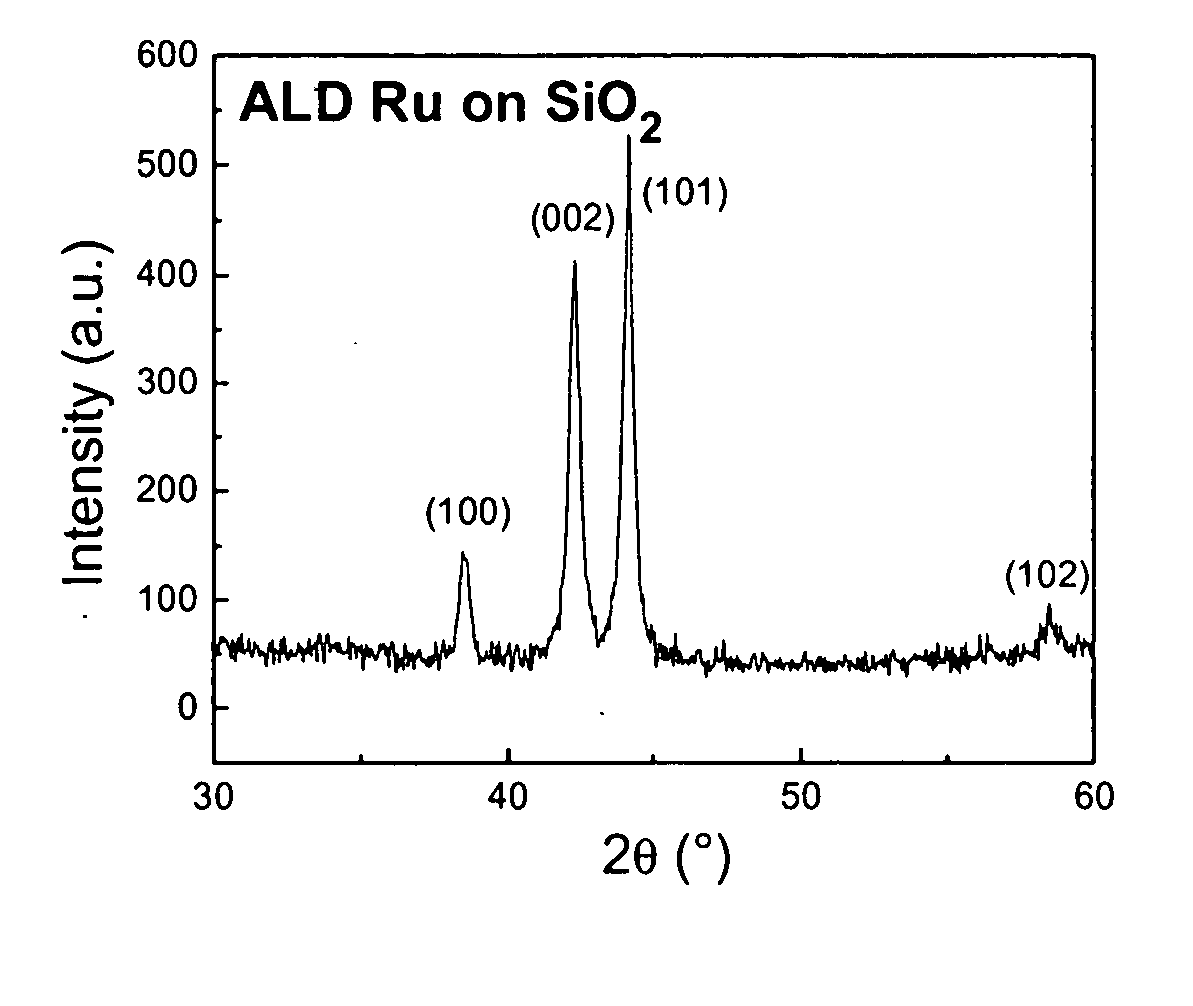

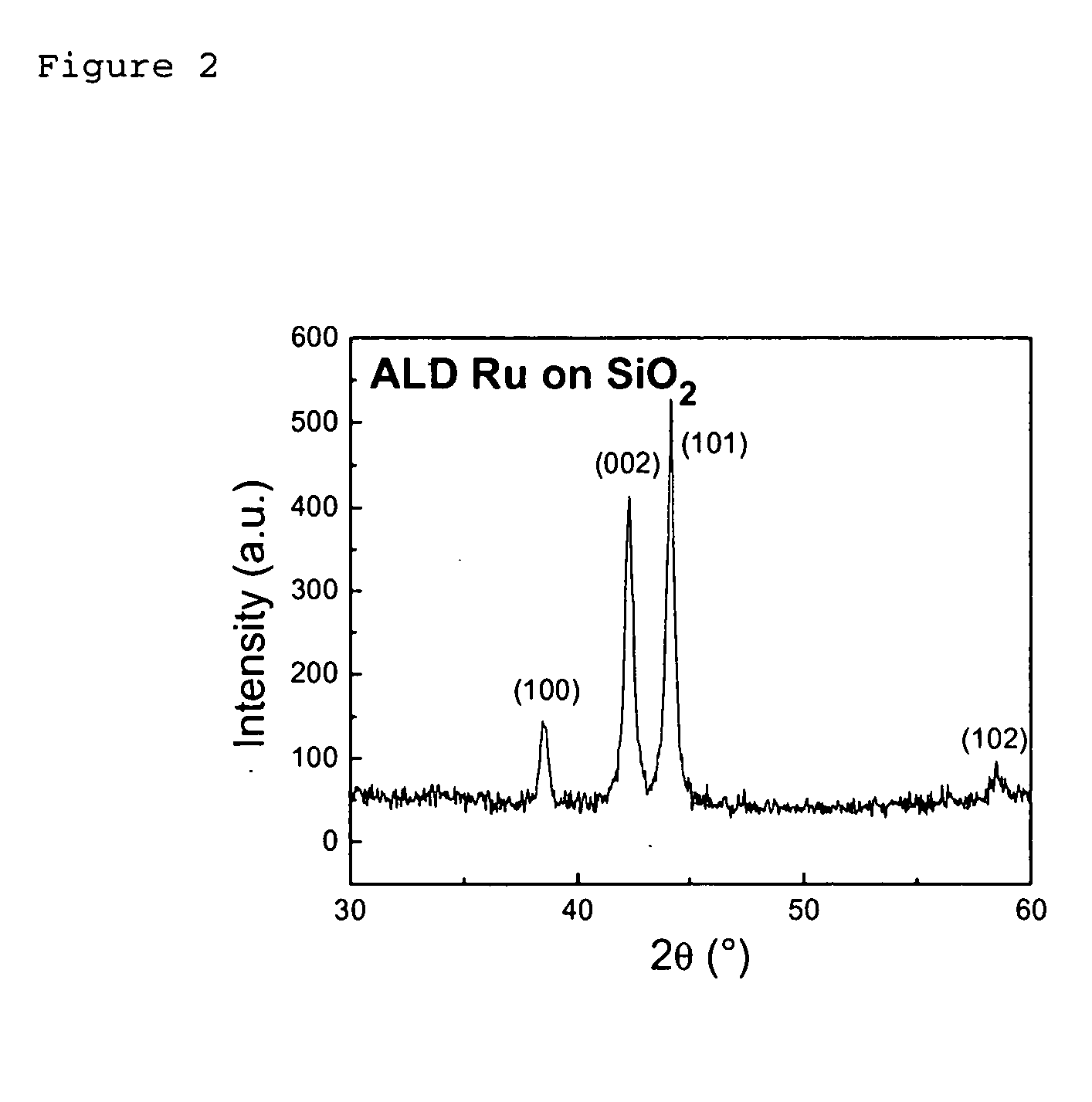

Ald deposition of ruthenium

InactiveUS20050118807A1None be problem freeLow impurity contentSemiconductor/solid-state device detailsSolid-state devicesCMOSCopper interconnect

A method to deposit nucleation problem free ruthenium by ALD. The nucleation problem free, relatively smooth ruthenium ALD film is deposited by the use of plasma-enhanced ALD of ruthenium underlay for consequent thermal ruthenium ALD layer. In addition, oxygen or nitrogen plasma treatments of SiO2 or other dielectrics leads to uniform ALD ruthenium deposition. The method has application as a direct plating layer for a copper interconnect or metal gate structure for advanced CMOS devices.

Owner:IBM CORP

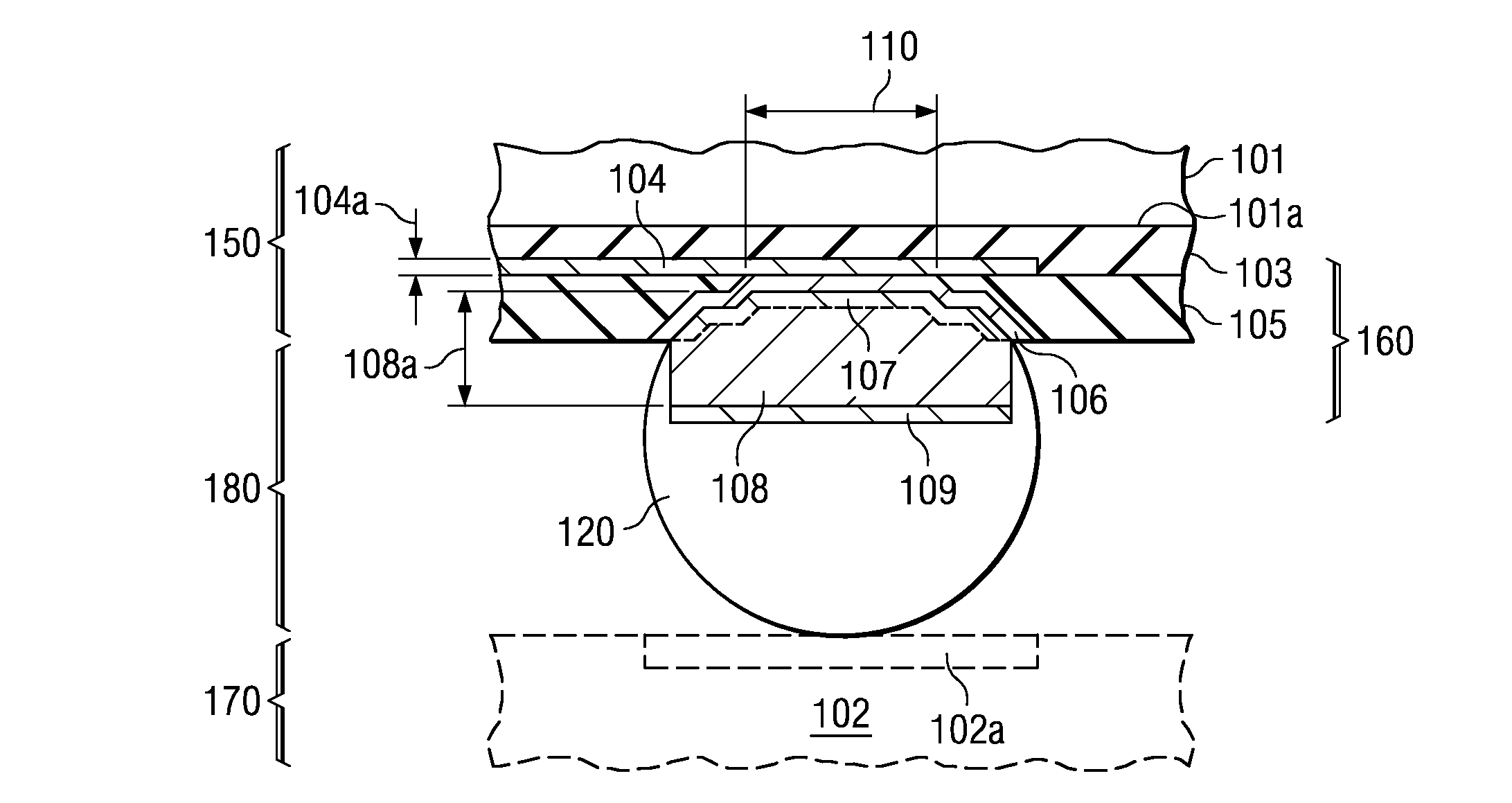

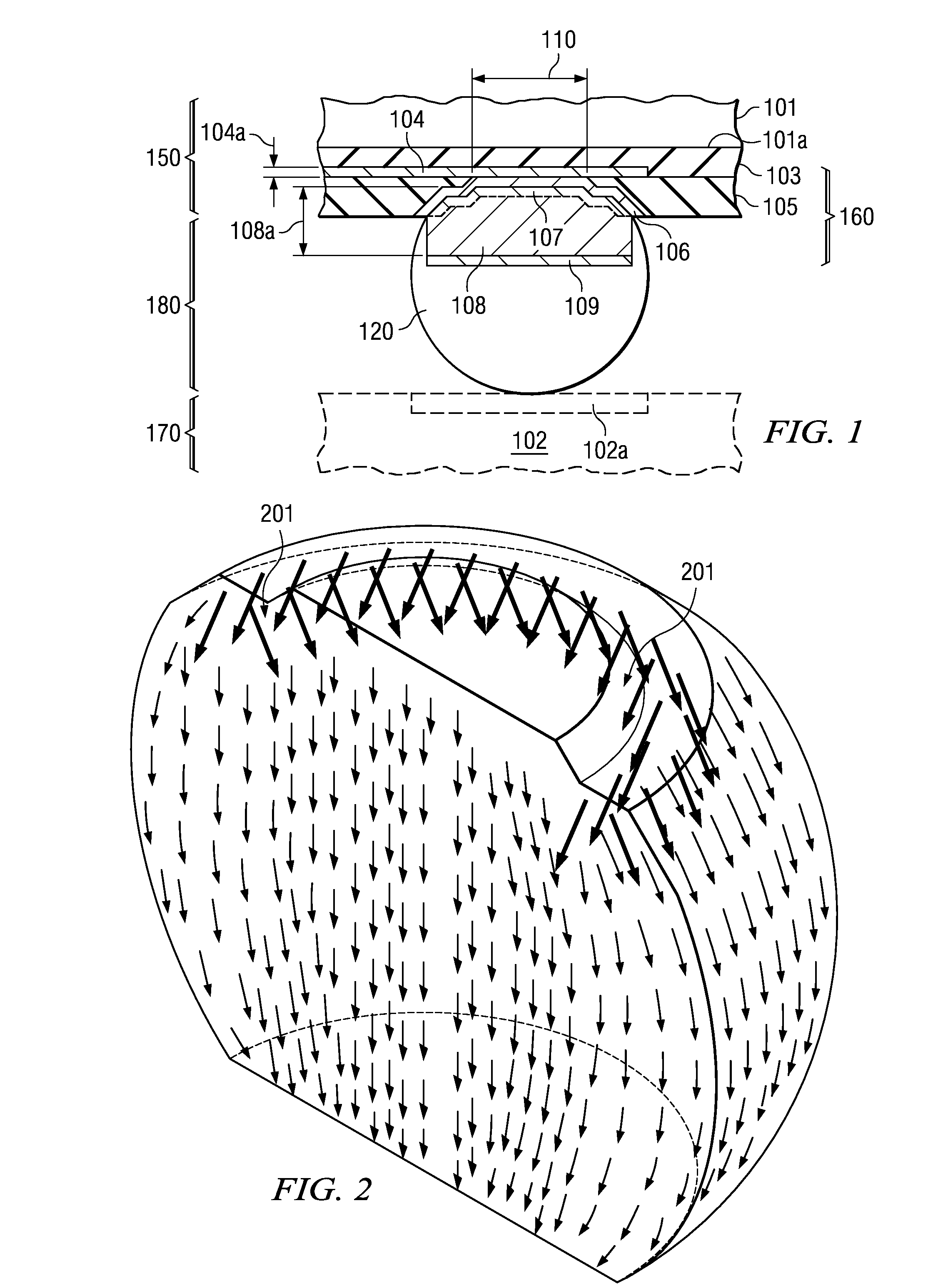

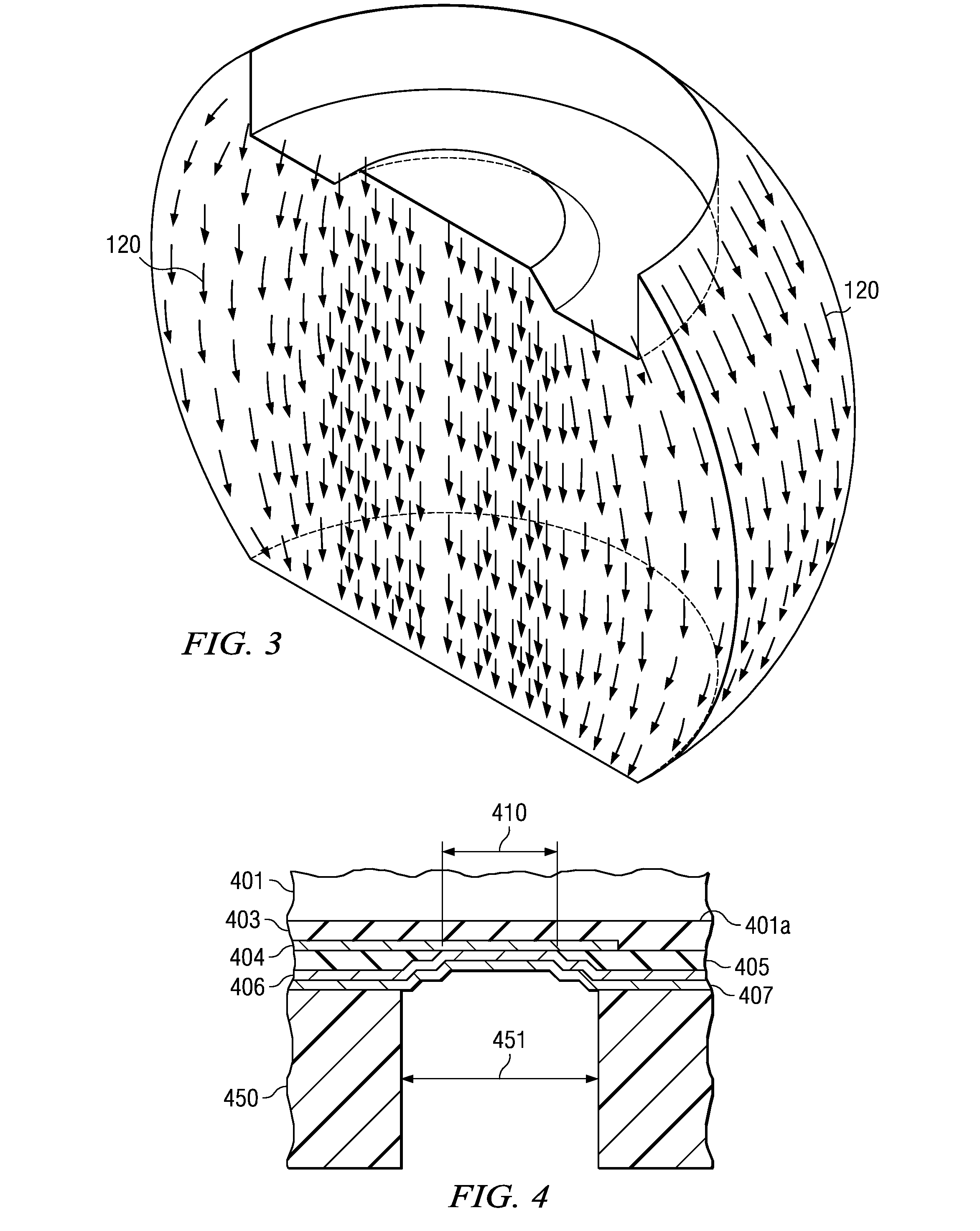

Electromigration-Resistant Flip-Chip Solder Joints

InactiveUS20080251927A1Enhance formation of voidLow reliabilitySemiconductor/solid-state device detailsSolid-state devicesElectrical resistance and conductanceCopper interconnect

A semiconductor device contact structure practically eliminating the copper diffusion into the solder as well as the current crowding at the contact with the subsequent electromigration in the solder. A column-like electroplated copper stud (108) is on each contact pad. The stud is sized to provide low, uniform electrical resistance in order to spread the current from the contact to an approximately uniform, low density. Preferably, the stud height (108a) is at least ten times the thickness of the copper interconnect layer (104). Stud (108) is capped by an electroplated nickel layer (109) thick enough (preferably about 2 μm) to suppress copper diffusion from stud (108) into solder body (120), thus practically inhibiting intermetallic compound formation and Kirkendall voiding.

Owner:TEXAS INSTR INC

Copper interconnects with metal capping layer and selective copper alloys

ActiveUS6979625B1Reduce voidsImproved resistance to electromigrationSemiconductor/solid-state device detailsSolid-state devicesCopper interconnectLayer interface

High reliable copper interconnects are formed with copper or a low resistivity copper alloy filling relatively narrow openings and partially filling relatively wider openings and a copper alloy having improved electromigration resistance selectively deposited in the relatively wider openings. The filled openings are recessed and a metal capping layer deposited followed by CMP. The metal capping layer prevents diffusion along the copper-capping layer interface while the copper alloy filling the relatively wider openings impedes electromigration along the grain boundaries.

Owner:ADVANCED MICRO DEVICES INC

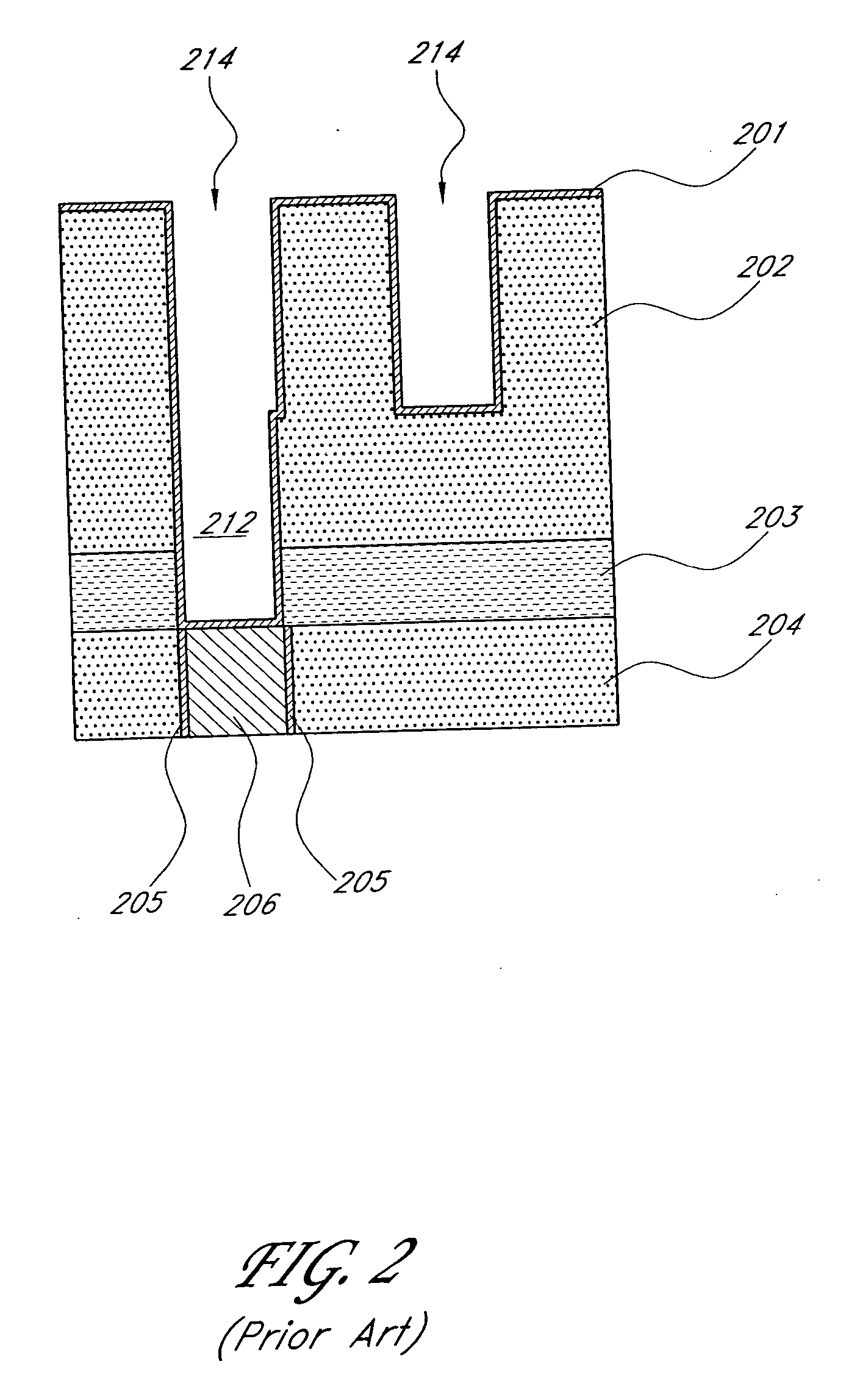

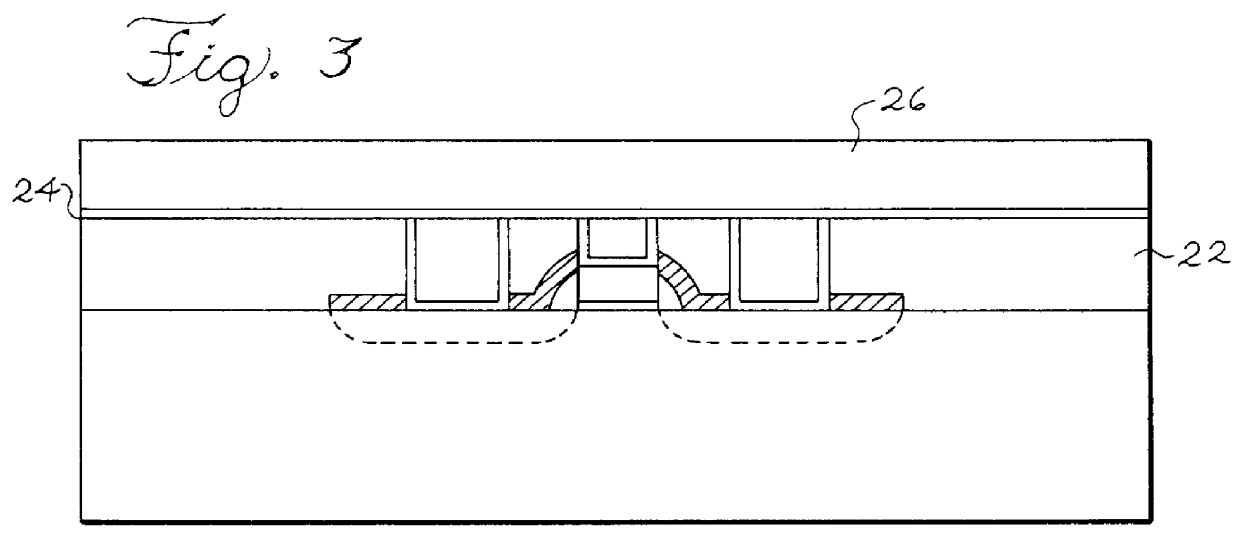

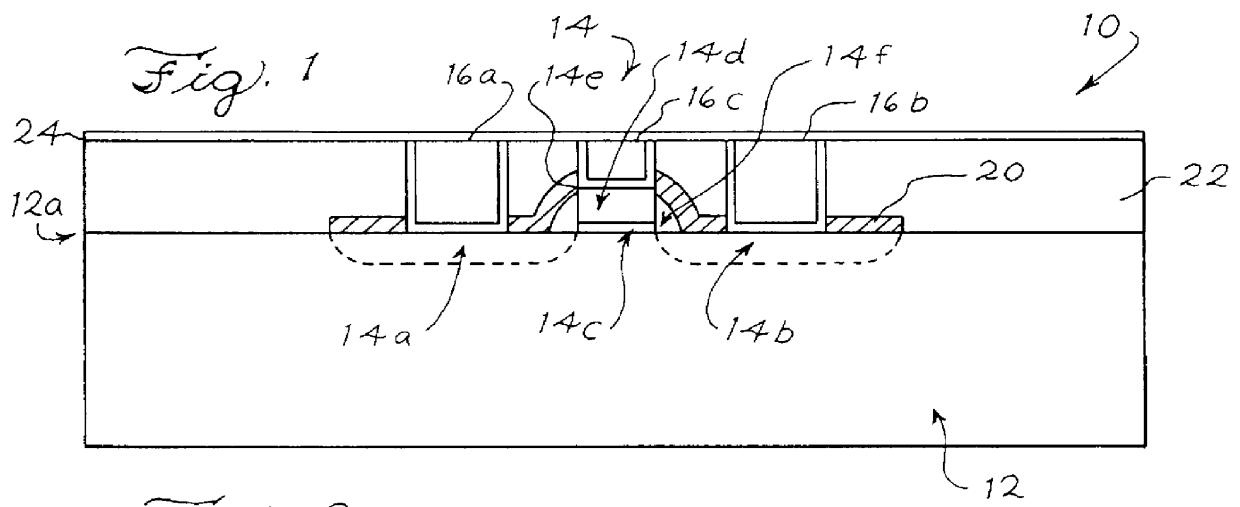

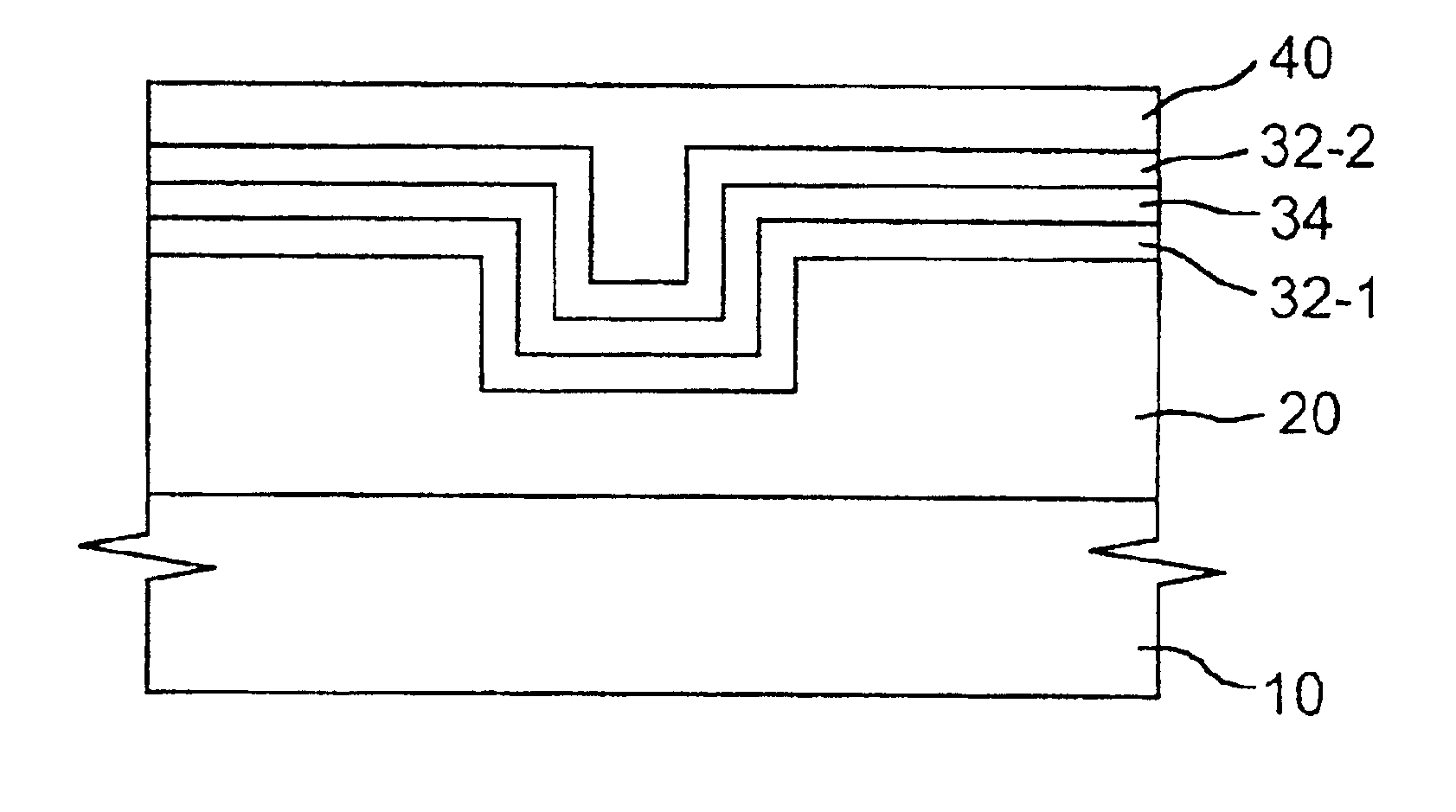

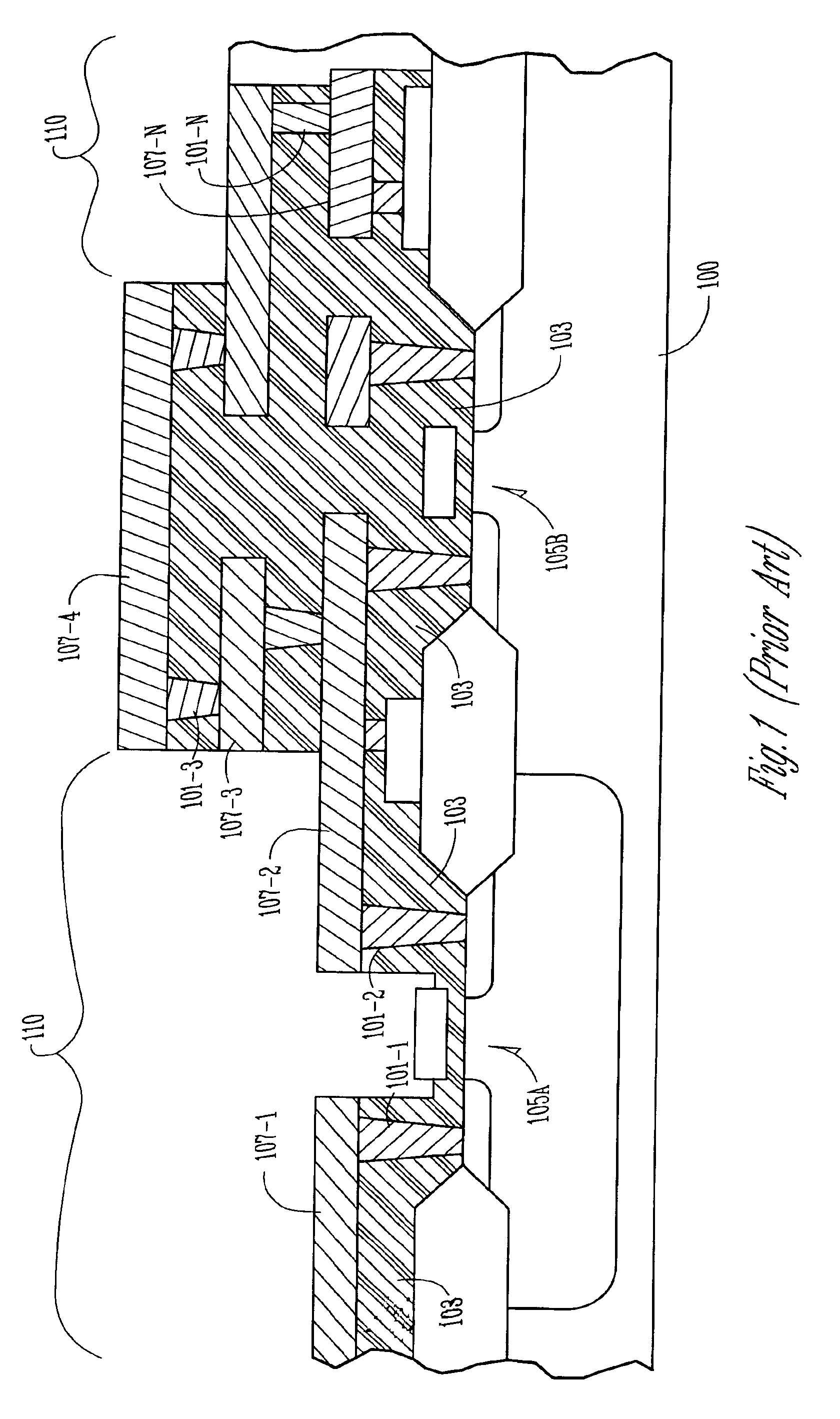

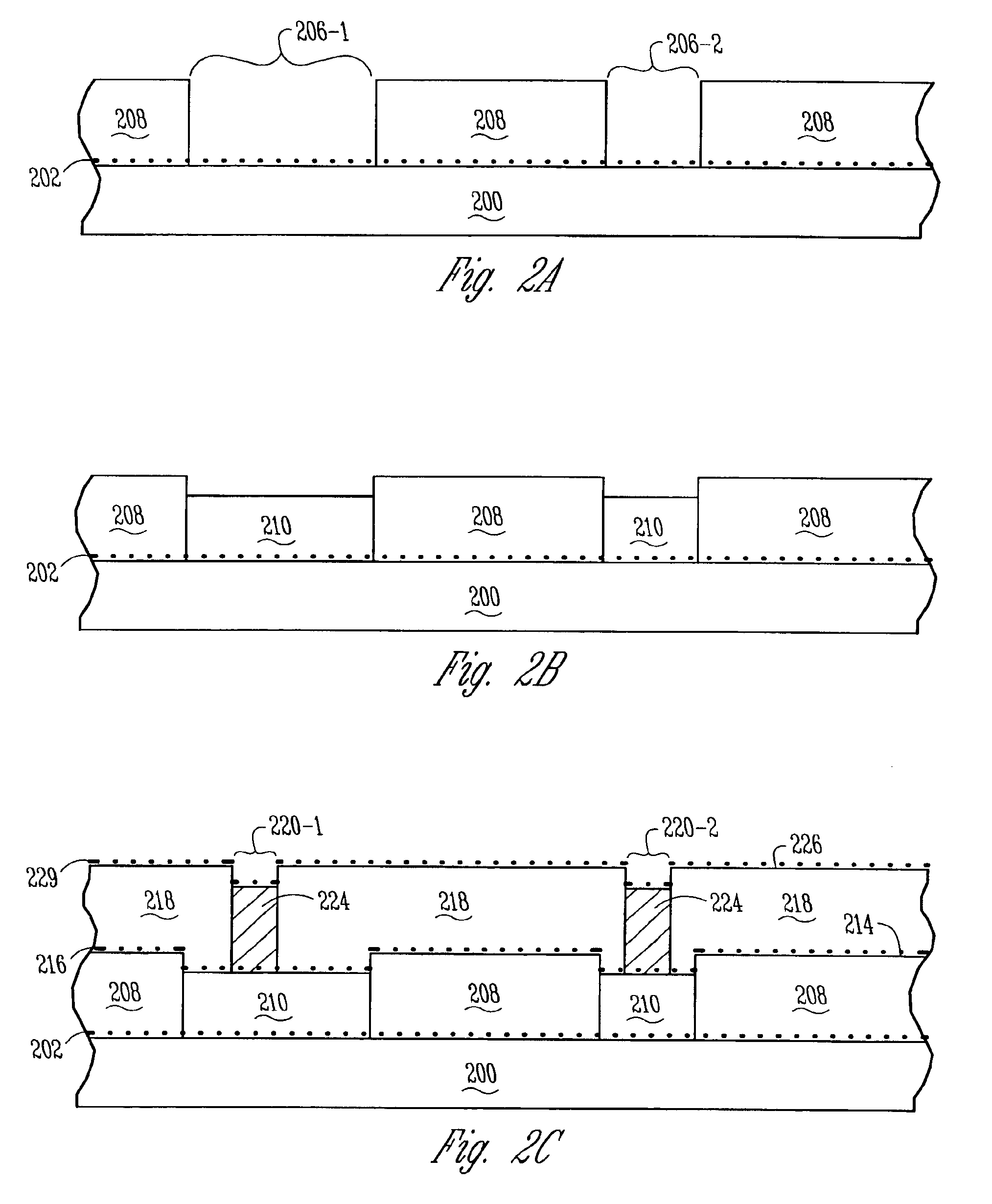

Method of fabricating copper-based semiconductor devices using a sacrificial dielectric layer and an unconstrained copper anneal

InactiveUS6303486B1TransistorSemiconductor/solid-state device detailsCopper interconnectDielectric layer

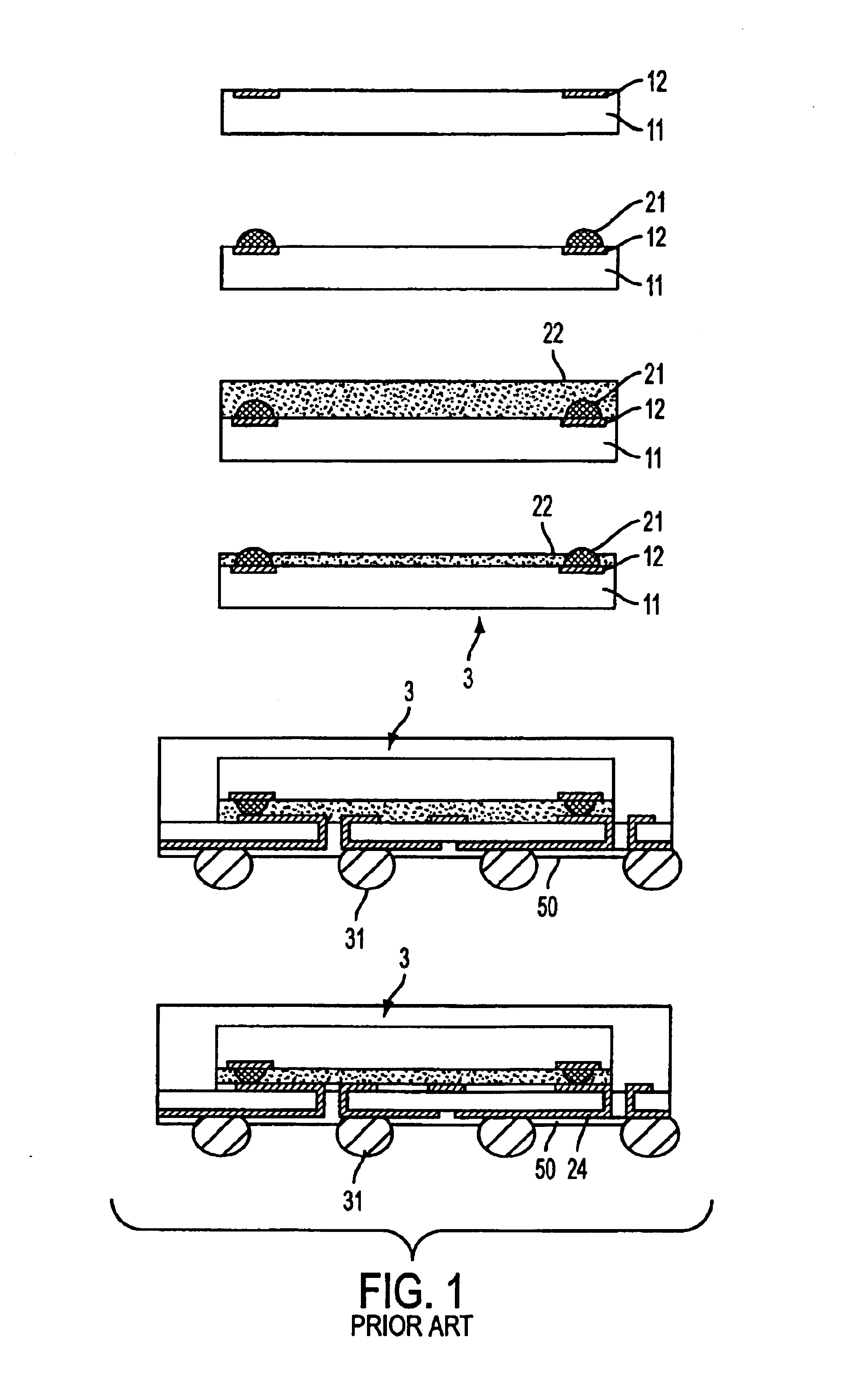

A method is provided for forming a copper interconnect, the method including forming a first dielectric layer above a structure layer, forming a first opening in the first dielectric layer, and forming a first copper structure in the first opening. The method also includes forming a sacrificial dielectric layer above the first dielectric layer and above the first copper structure, forming a second opening in the sacrificial dielectric layer above at least a portion of the first copper structure, and forming a second copper structure in the second opening, the second copper structure contacting the at least the portion of the first copper structure. The method further includes removing the sacrificial dielectric layer above the first dielectric layer and adjacent the second copper structure, and forming the copper interconnect by annealing the second copper structure and the first copper structure.

Owner:GLOBALFOUNDRIES INC

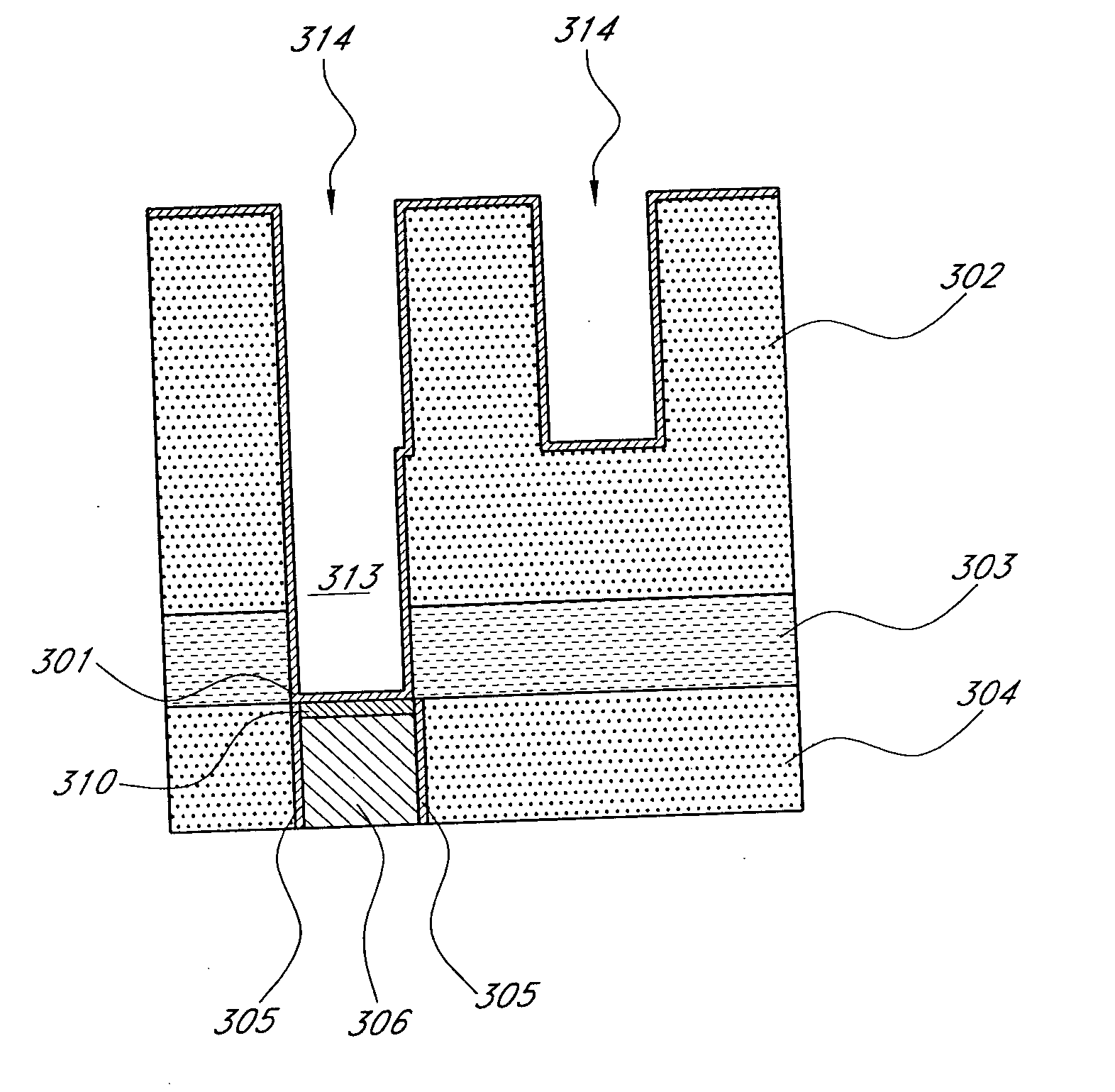

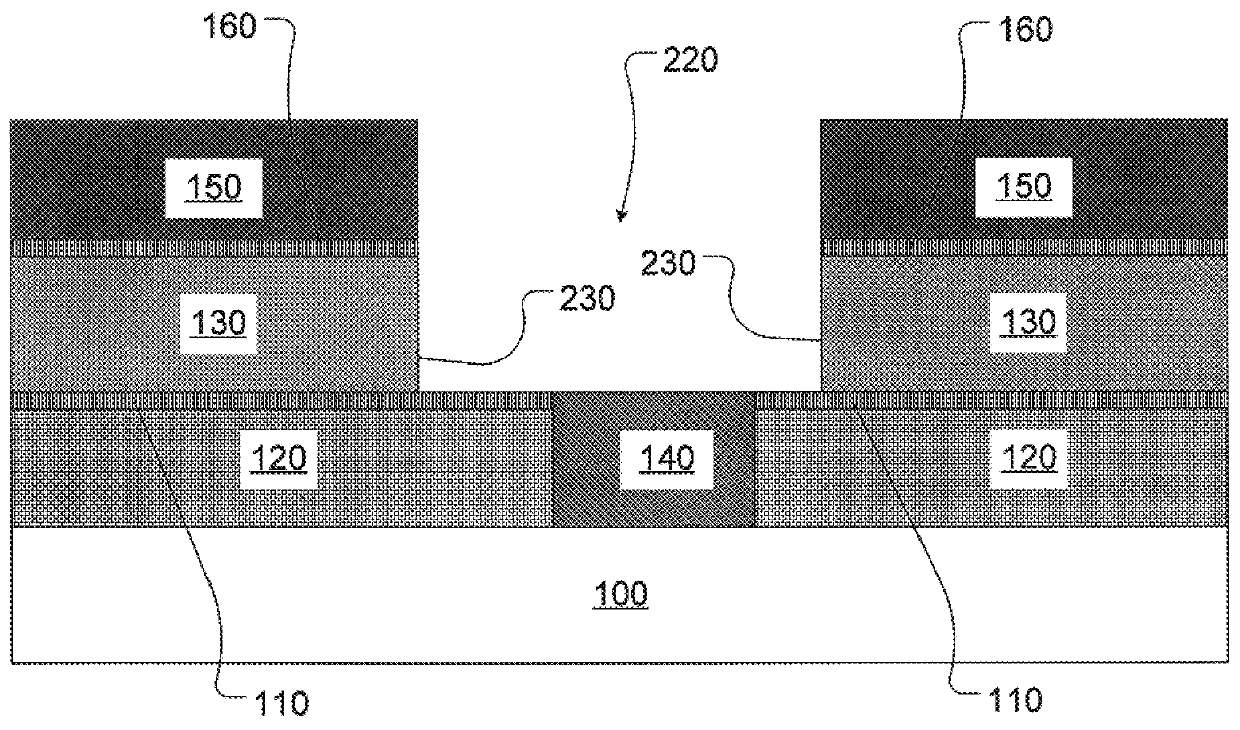

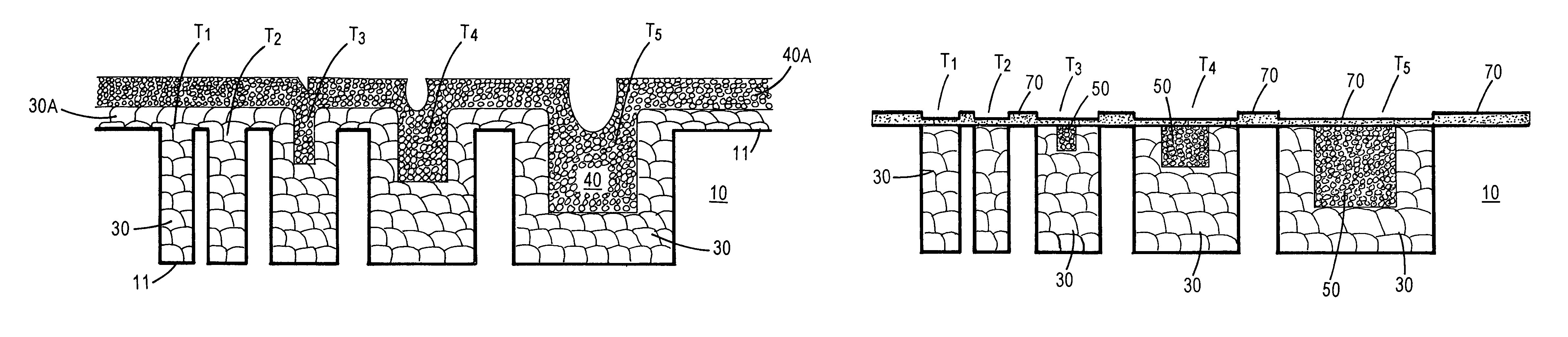

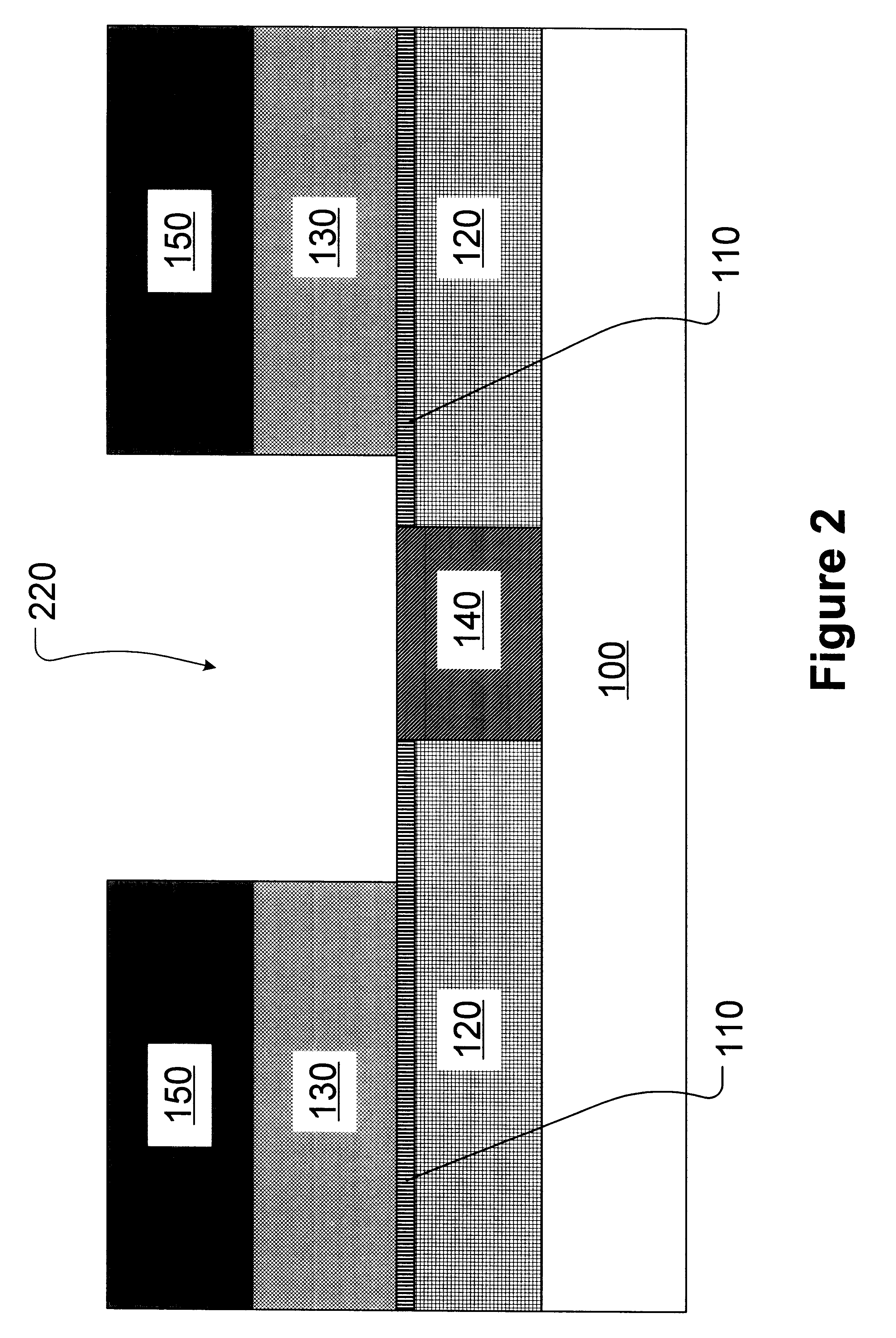

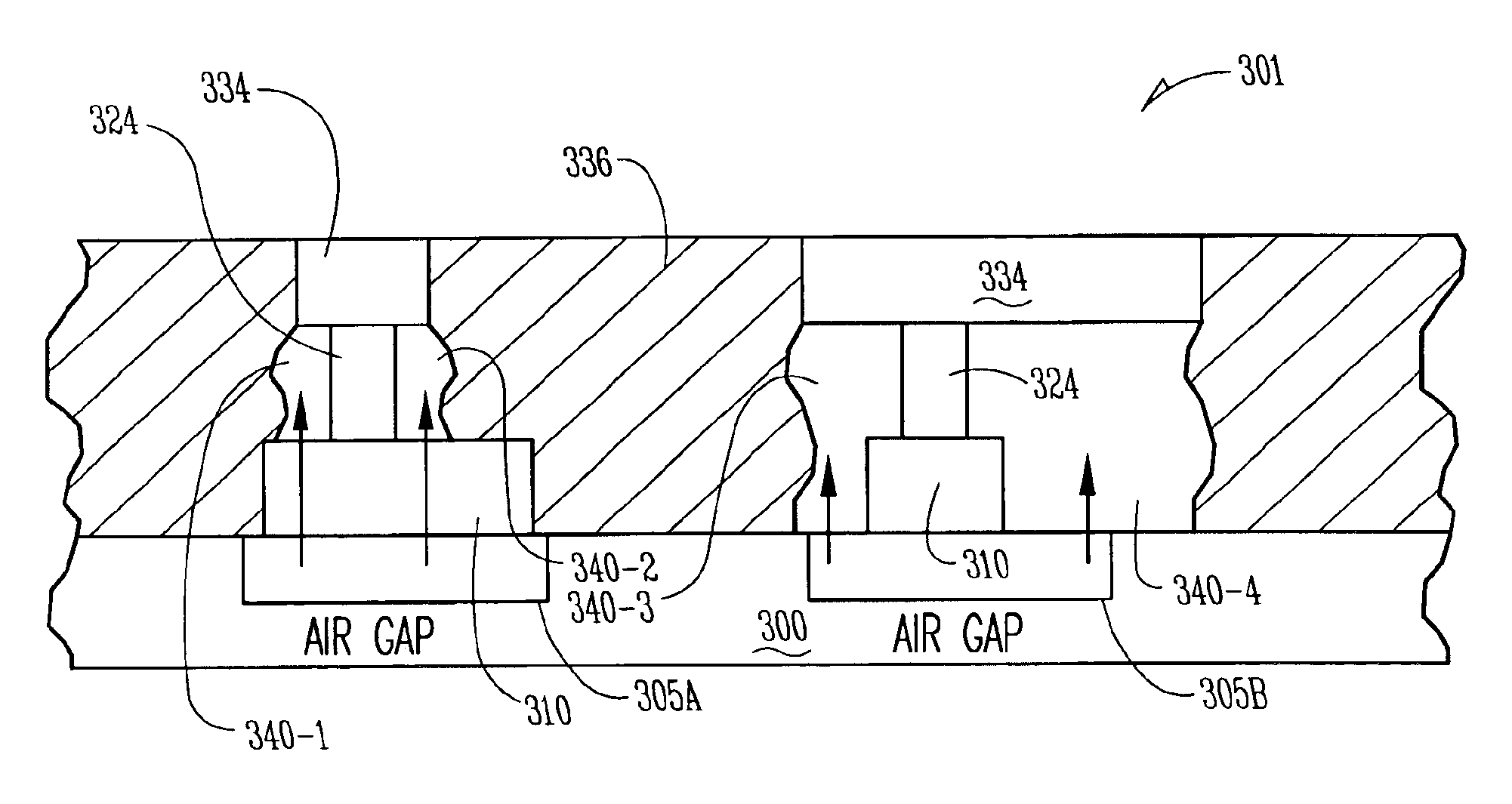

Multilevel copper interconnects with low-k dielectrics and air gaps

InactiveUS7091611B2Semiconductor/solid-state device detailsSolid-state devicesCapacitanceCopper interconnect

Structures and methods are provided for an improved multilevel wiring interconnect in an integrated circuit assembly. The present invention provides for a multilayer copper wiring structure by electroless, selectively deposited copper in a streamlined process which further reduces both intra-level line to line capacitance and the inter-level capacitance.In particular, an illustrative embodiment of the present invention includes a novel methodology for forming multilevel wiring interconnects in an integrated circuit assembly. The method includes forming a number of multilayer metal lines, e.g. copper lines formed by selective electroless plating, separated by air gaps above a substrate. A low dielectric constant material is deposited between the number of metal lines and the substrate using a directional process. According to the teachings of the present invention, using a directional process includes maintaining a number of air gaps in the low dielectric constant material. Structures and systems are similarly included in the present invention.

Owner:ROUND ROCK RES LLC

Antioxidants for post-cmp cleaning formulations

ActiveUS20090239777A1Maximum cleaningLens cleaning compositionsNon-surface-active detergent compositionsCopper interconnectAntioxidant

An cleaning composition and process for cleaning post-chemical mechanical polishing (CMP) residue and contaminants from a microelectronic device having said residue and contaminants thereon. The cleaning compositions include novel corrosion inhibitors. The composition achieves highly efficacious cleaning of the post-CMP residue and contaminant material from the surface of the microelectronic device without compromising the low-k dielectric material or the copper interconnect material.

Owner:ENTEGRIS INC

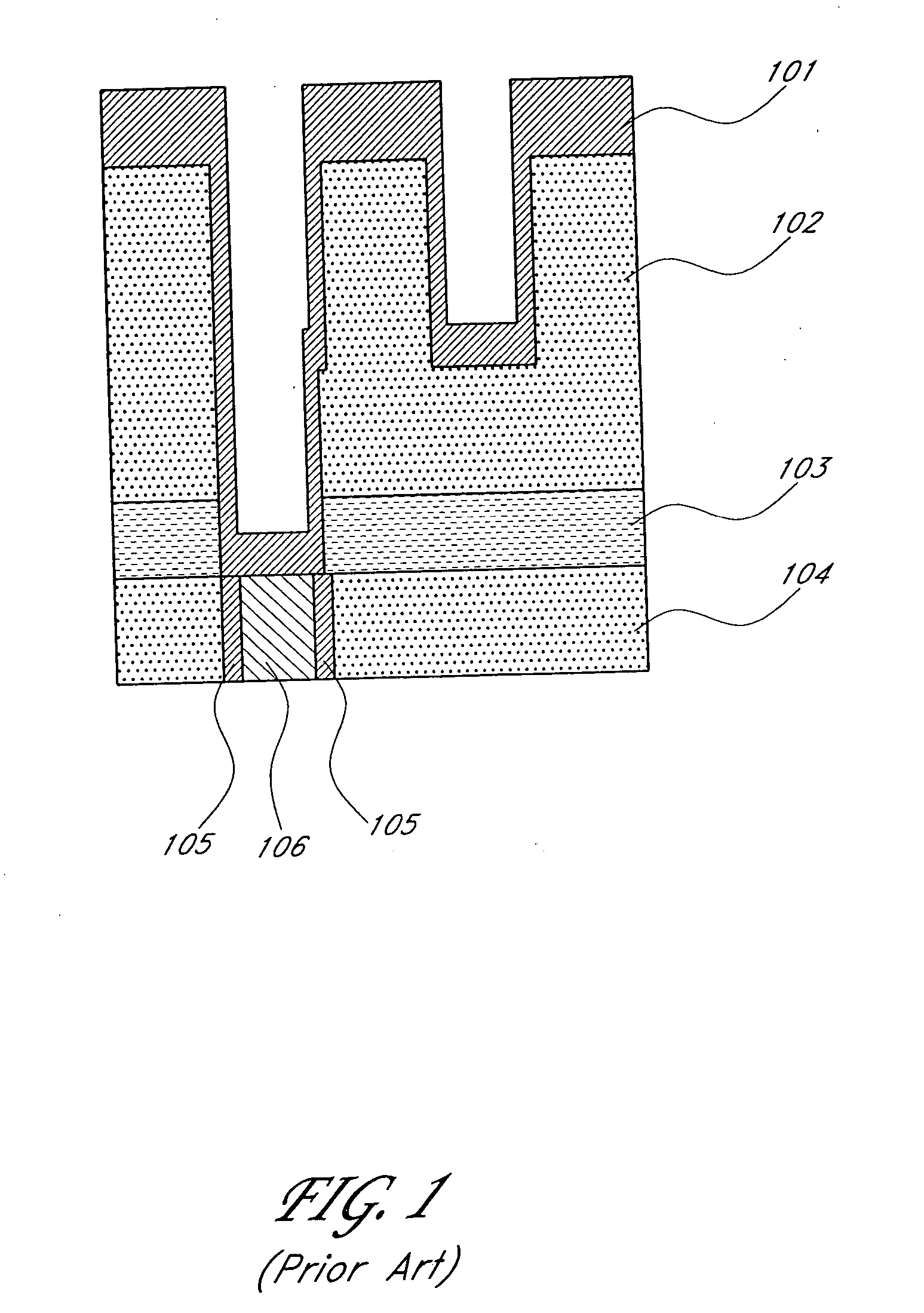

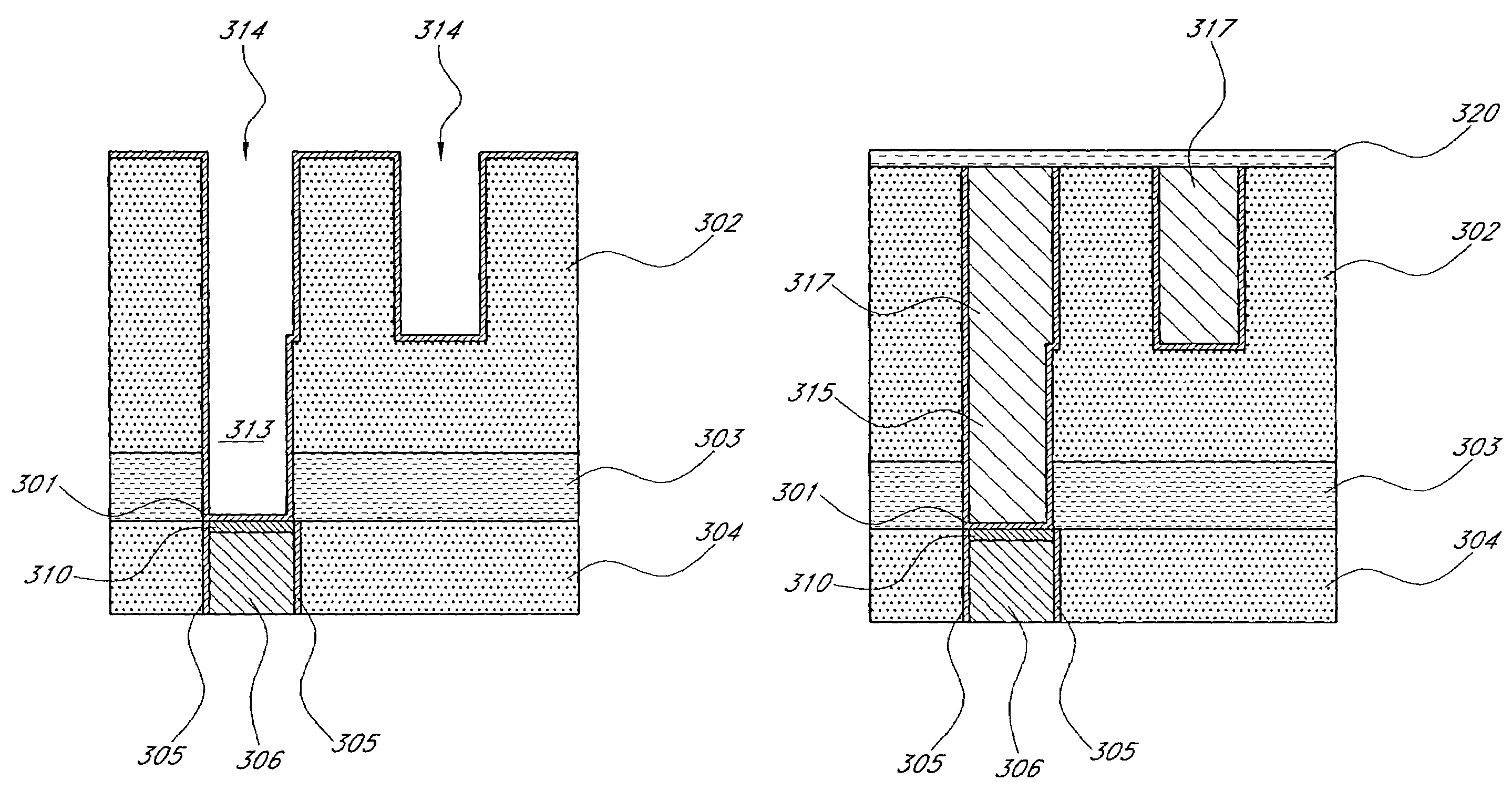

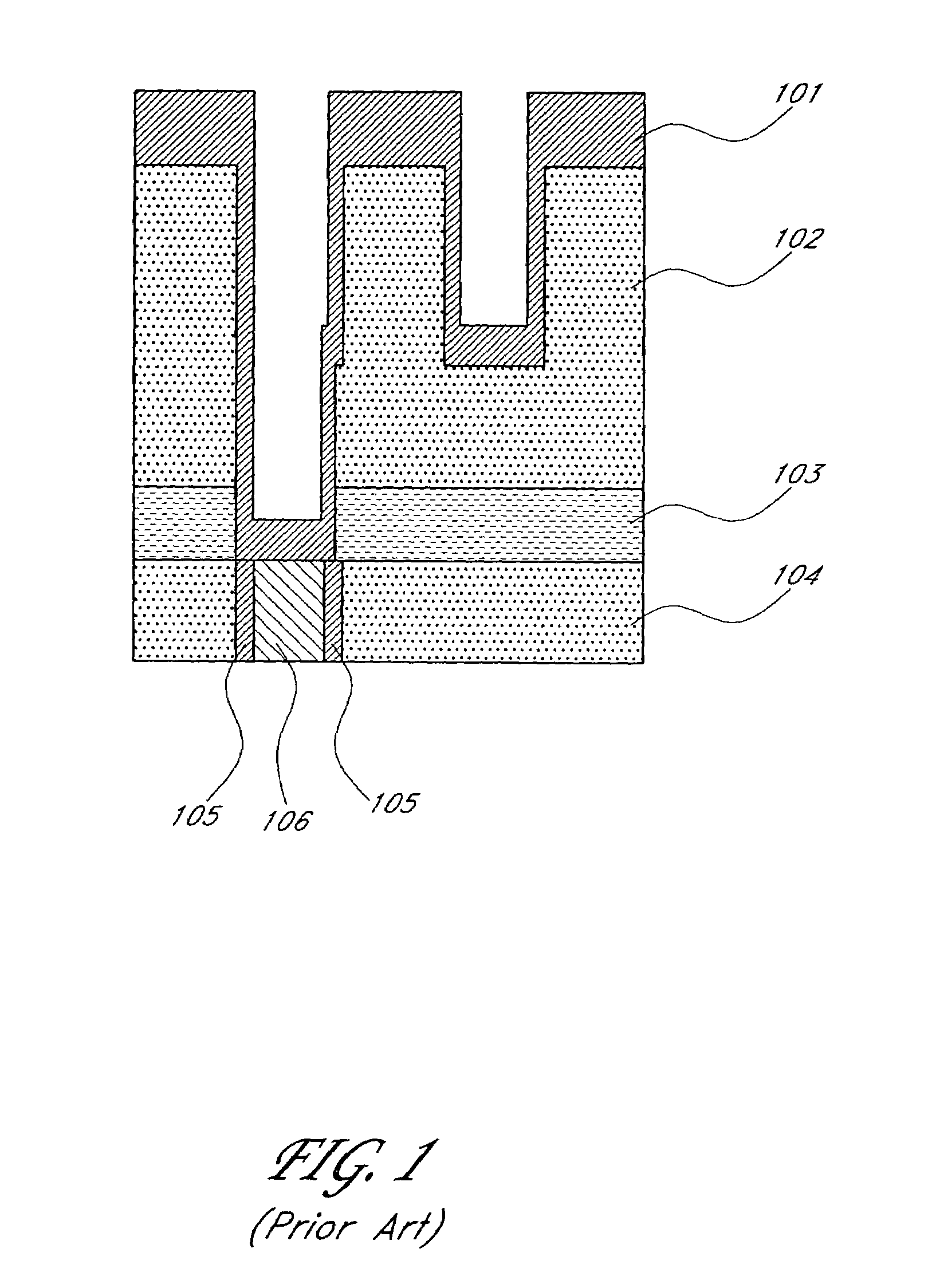

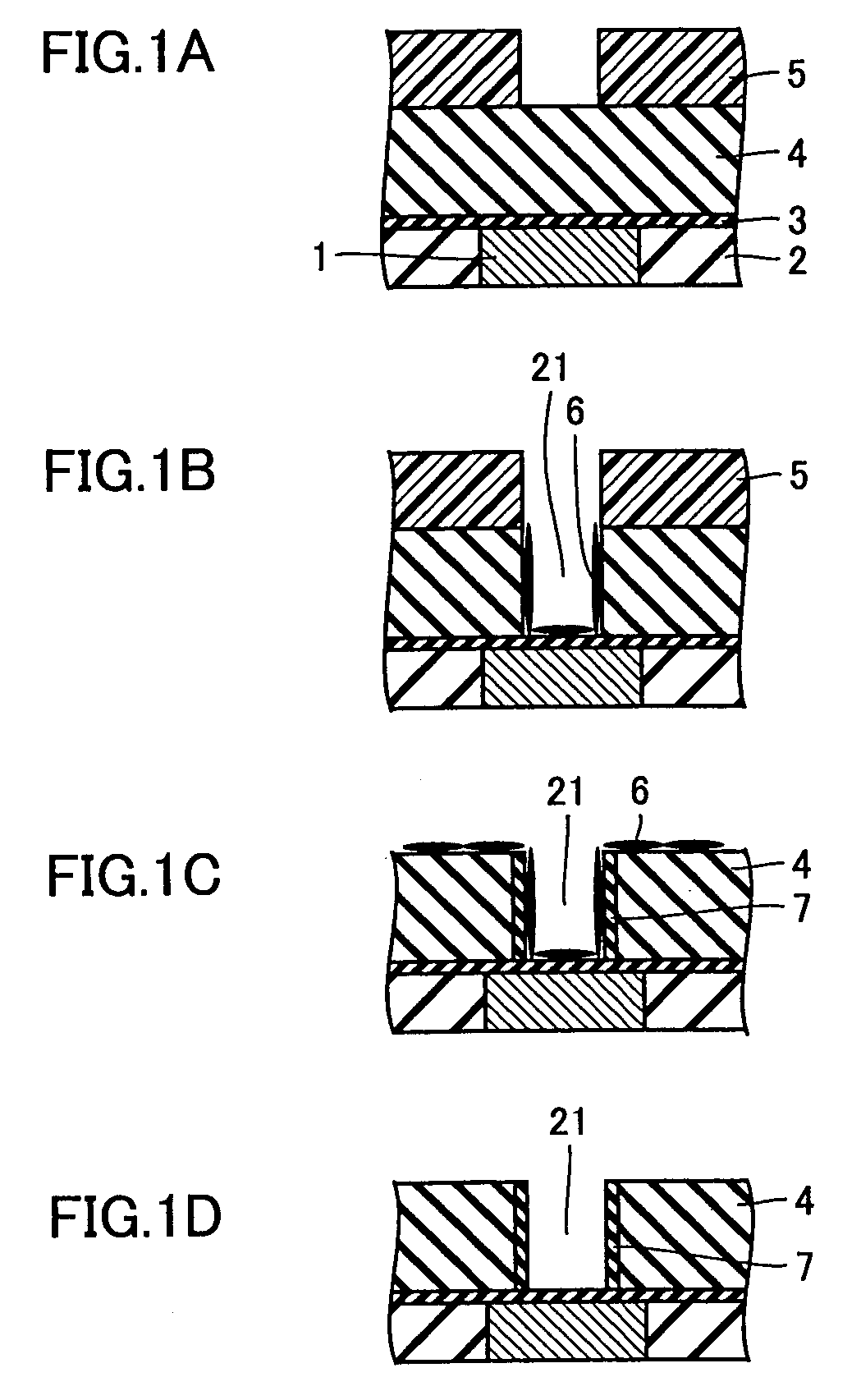

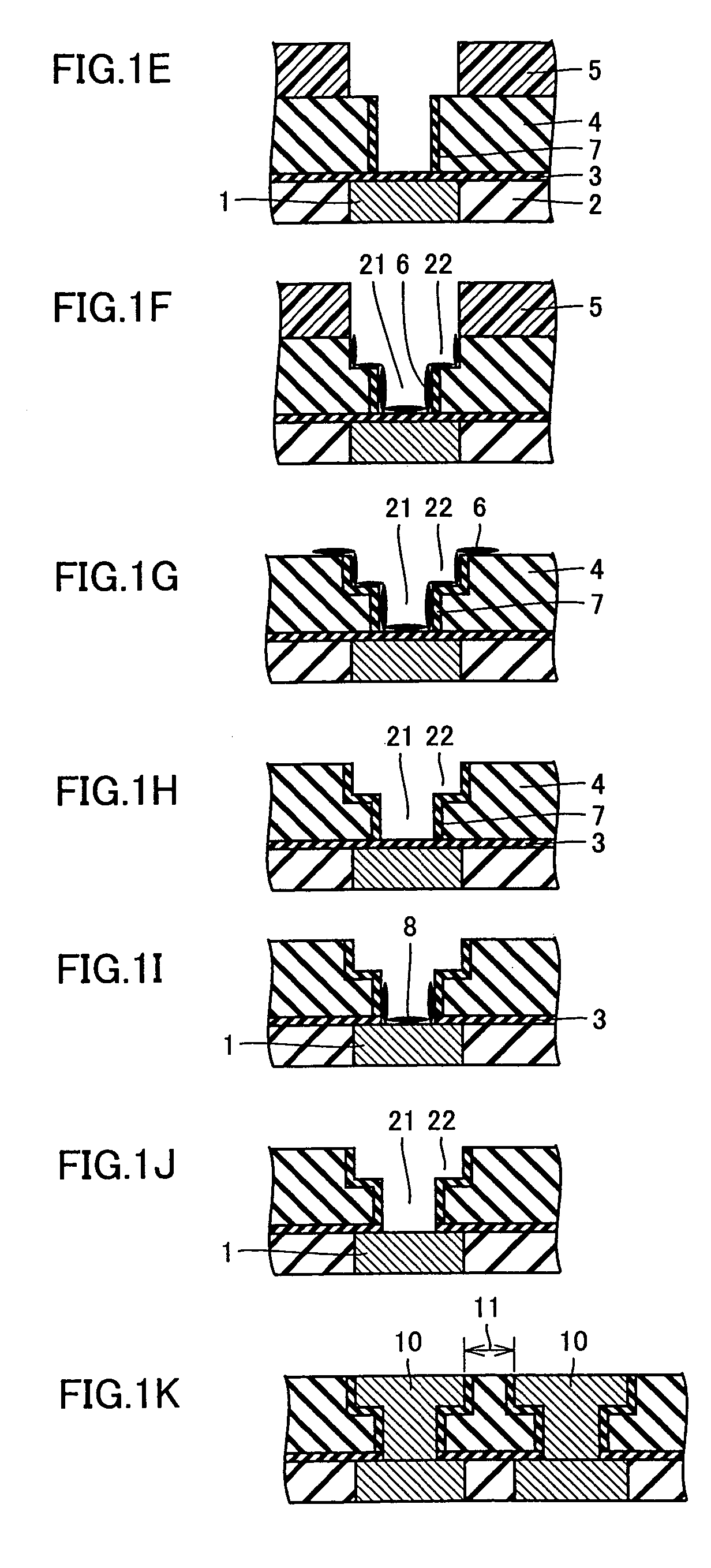

Reverse electroplating of barrier metal layer to improve electromigration performance in copper interconnect devices

InactiveUS6261963B1Electrolysis componentsSemiconductor/solid-state device manufacturingCopper interconnectOptoelectronics

A method is provided for forming a conductive interconnect, the method comprising forming a first dielectric layer above a structure layer, forming a first opening in the first dielectric layer, and forming a first conductive structure in the first opening. The method also comprises forming a second dielectric layer above the first dielectric layer and above the first conductive structure, forming a second opening in the second dielectric layer above at least a portion of the first conductive structure, the second opening having a side surface and a bottom surface, and forming at least one barrier metal layer in the second opening on the side surface and on the bottom surface. In addition, the method comprises removing a portion of the at least one barrier metal layer from the bottom surface, and forming a second conductive structure in the second opening, the second conductive structure contacting the at least the portion of the first conductive structure. The method further comprises forming the conductive interconnect by annealing the second conductive structure and the first conductive structure.

Owner:ADVANCED MICRO DEVICES INC

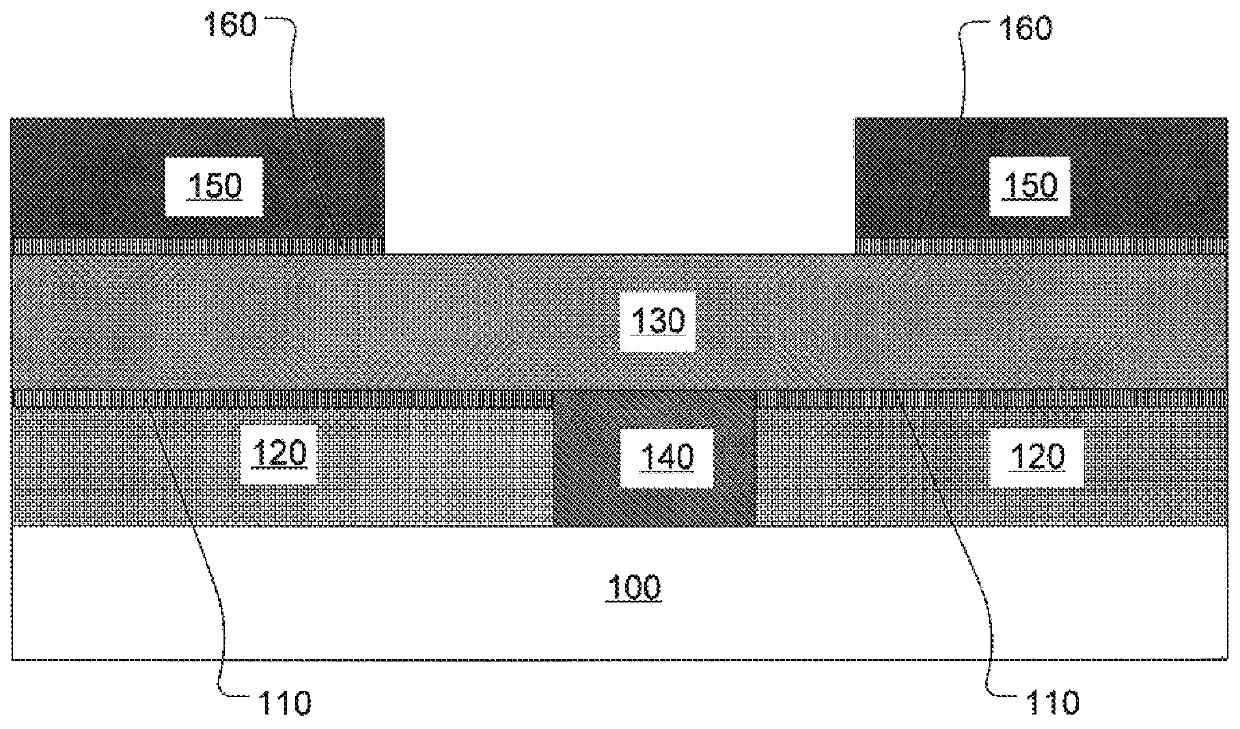

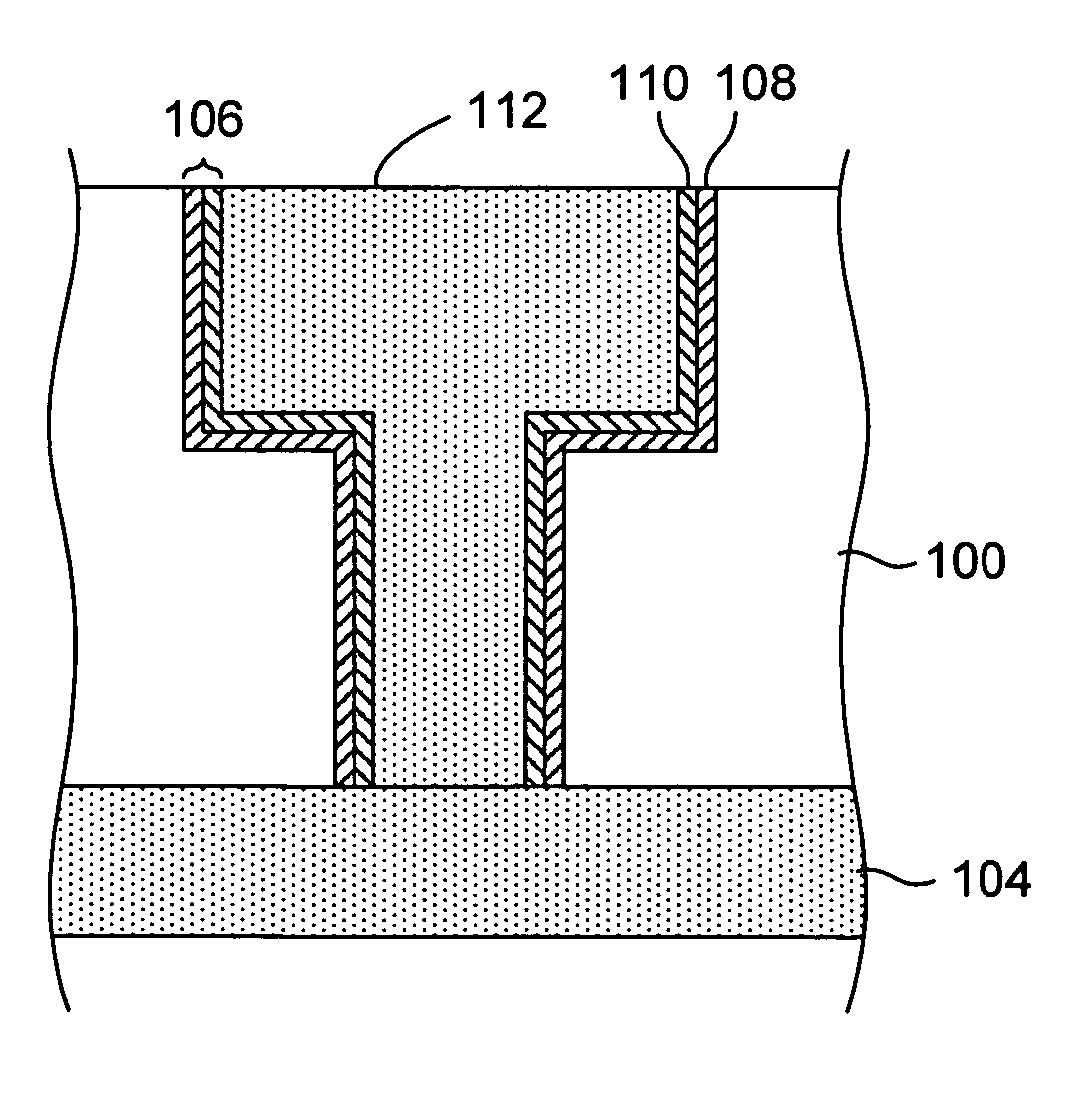

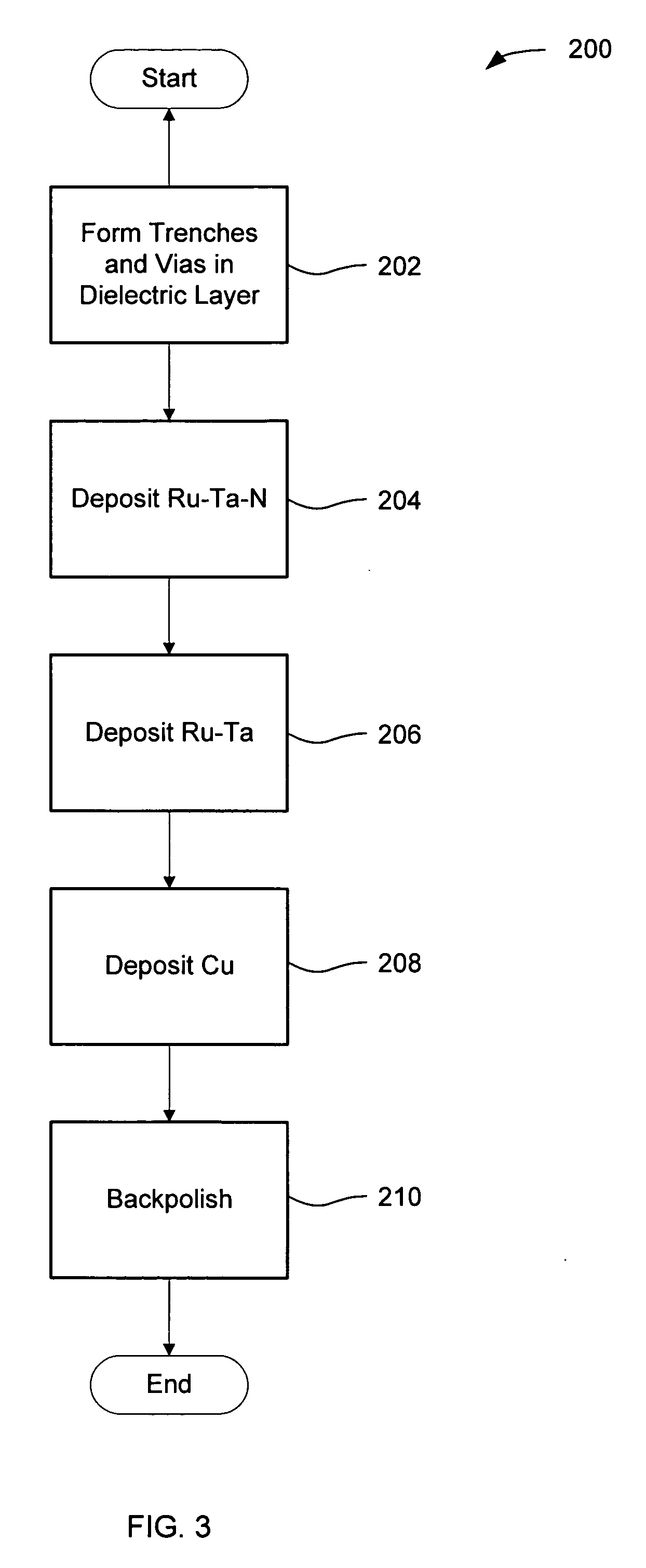

Integrated barrier and seed layer for copper interconnect technology

ActiveUS20060063375A1Low stress levelInhibited DiffusionSemiconductor/solid-state device detailsSolid-state devicesCopper interconnectDevice material

An integrated barrier and seed layer that is useful for creating conductive pathways in semiconductor devices. The barrier portion of the integrated layer prevents diffusion of the conductive material into the underlying dielectric substrate while the seed portion provides an appropriate foundation upon which to deposit the conductive material. The barrier portion of the integrated layer is formed of a metal nitride, while the seed portion is formed of ruthenium or a ruthenium alloy. The metal nitride forms an effective barrier layer while the ruthenium or ruthenium alloy forms an effective seed layer for a metal such as copper. In some embodiments, the integrated layer is formed in a way so that its composition changes gradually from one region to the next.

Owner:BELL SEMICON LLC

Low ph post-cmp residue removal composition and method of use

InactiveUS20100286014A1Transportation and packagingNon-surface-active detergent compositionsCopper interconnectNuclear chemistry

An acidic composition and process for cleaning post-chemical mechanical polishing (CMP) residue and contaminants from a microelectronic device having said residue and contaminants thereon. The acidic composition includes surfactant, dispersing agent, sulfonic acid-containing hydrocarbon, and water. The composition achieves highly efficacious cleaning of the post-CMP residue and contaminant material from the surface of the microelectronic device without compromising the low-k dielectric material or the copper interconnect material.

Owner:ADVANCED TECH MATERIALS INC

Method of forming reliable copper interconnects

InactiveUS6211084B1Semiconductor/solid-state device detailsSolid-state devicesCopper interconnectSilanes

The adhesion of a diffusion barrier or capping layer to Cu and / or Cu alloy interconnect members is significantly enhanced by treating the exposed surface of the Cu and / or Cu alloy interconnect members with a silane or dichlorosilane plasma to form a layer of copper silicide thereon prior to depositing the capping layer. Embodiments include electroplating or electroless plating Cu or a Cu alloy to fill a damascene opening in a dielectric interlayer, chemical mechanical polishing, treating the exposed surface of the Cu or Cu alloy interconnect member in a silane or dichlorosilane plasma to form the copper silicide layer and depositing a capping layer of silicon nitride thereon.

Owner:GLOBALFOUNDRIES INC

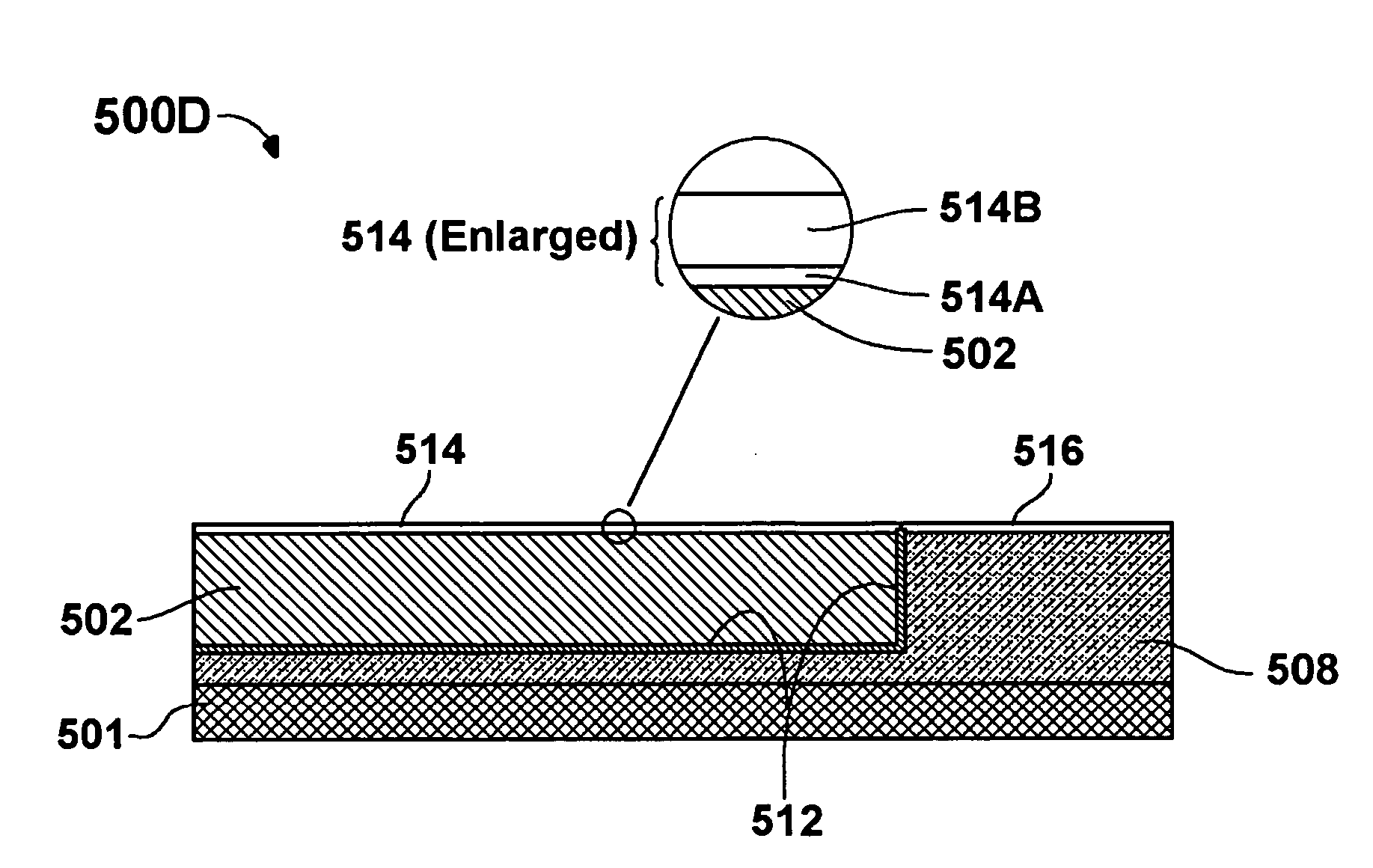

Polymer encapsulated dicing lane (PEDL) technology for Cu/low/ultra-low k devices

InactiveUS20060079025A1Semiconductor/solid-state device detailsSolid-state devicesCopper interconnectLead bonding

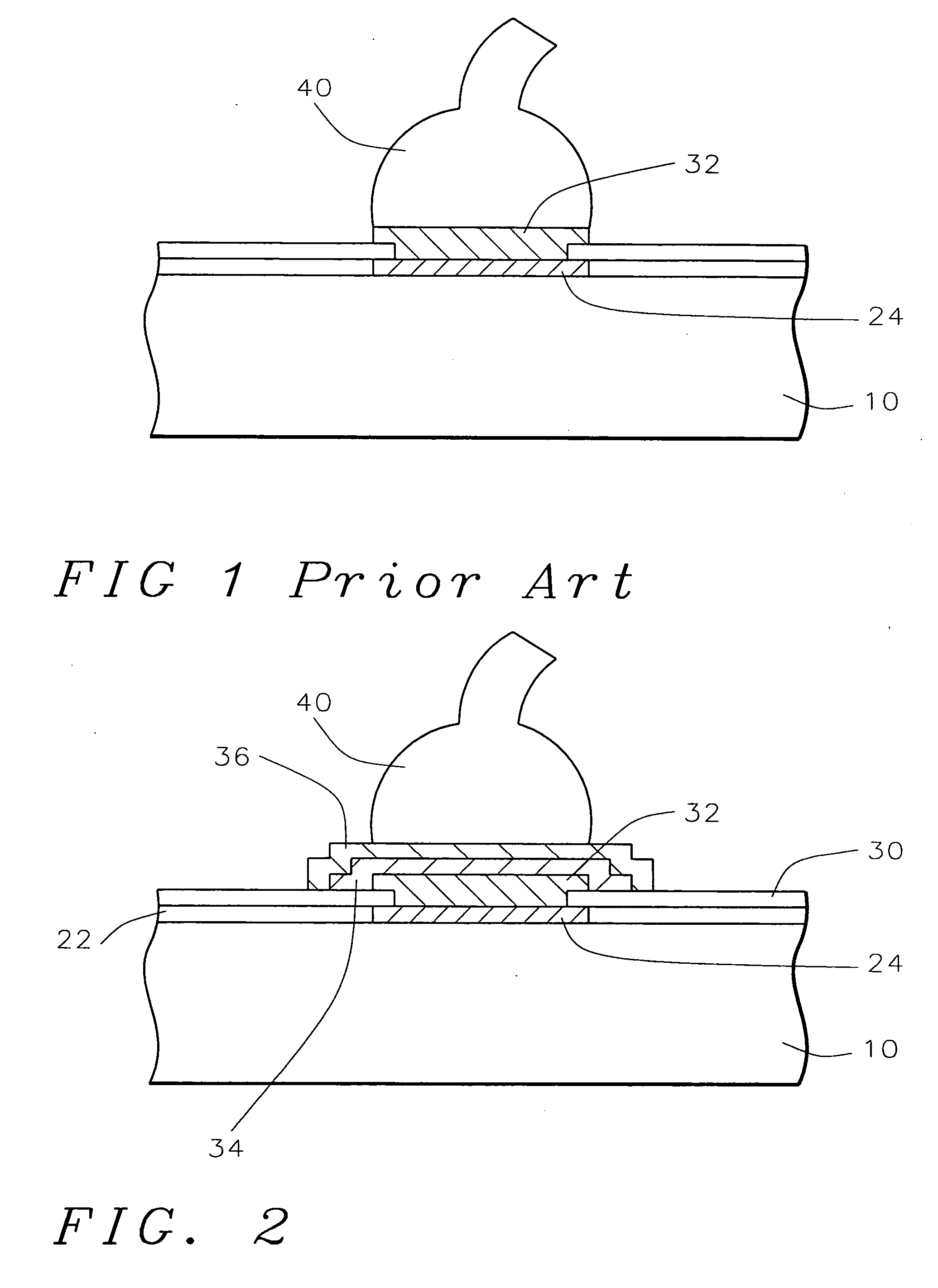

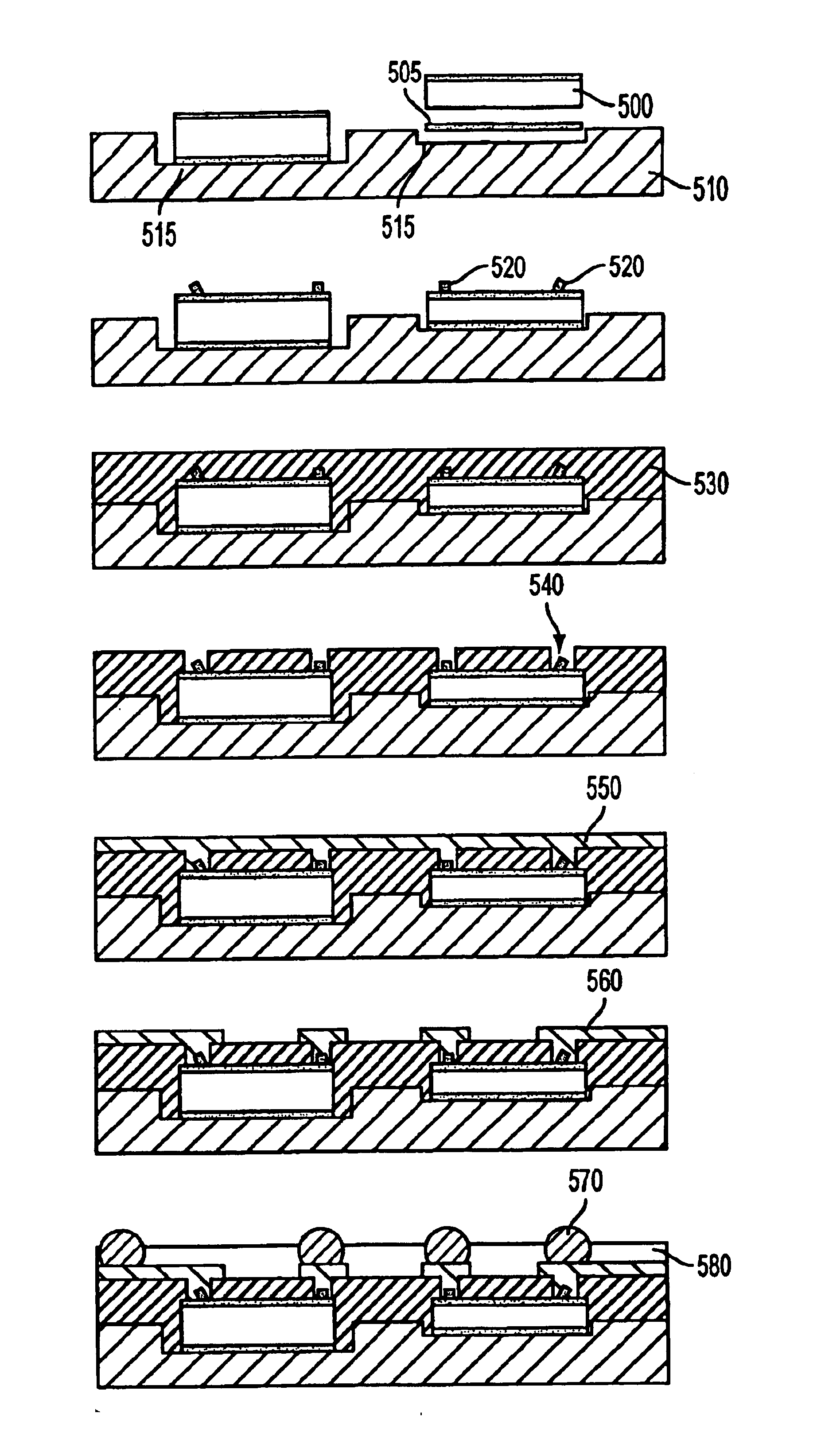

A process for packaging semiconductor devices for flip chip and wire bond applications, wherein specific materials of the semiconductor devices are protected during device processing sequences and dicing procedures, has been developed. After definition of copper interconnect structures surrounded by a low k insulator layer, a protective, first photosensitive polymer layer comprised with a low dielectric constant is applied. After definition of openings in the first photosensitive polymer layer exposing portions of the top surface of the copper interconnect structures, a dicing lane opening is defined in materials located between copper interconnect structures. Conductive redistribution shapes are formed on the copper interconnect structures exposed in the openings in the first photosensitive polymer layer, followed by application of a protective, second photosensitive polymer layer. An opening is defined in the second photosensitive polymer layer exposing a portion of the top surface of a redistribution shape followed by placement of a solder ball in this opening. A reflow anneal procedure results in the solder ball wetting and overlying only the portion of the redistribution shape exposed in the opening in the second photosensitive polymer layer. Separation of the solder ball, flip chip regions from the non-solder ball, wire bond regions is accomplished via a dicing procedure performed in the dicing lane.

Owner:AGENCY FOR SCI TECH & RES

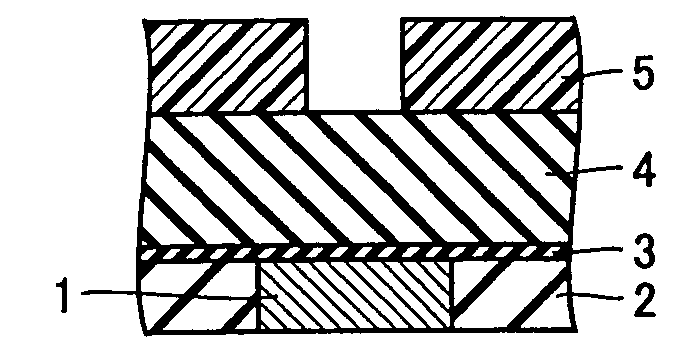

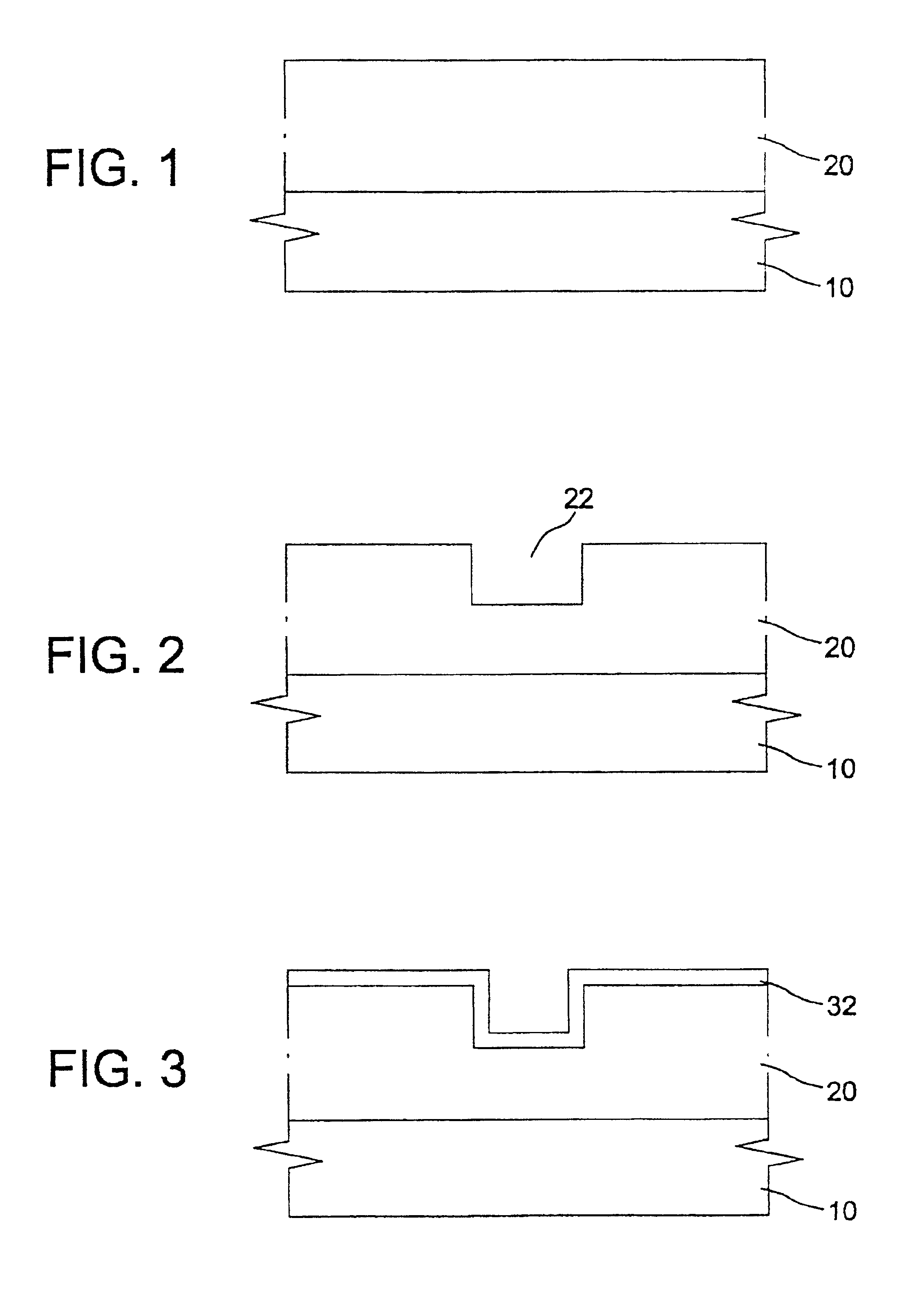

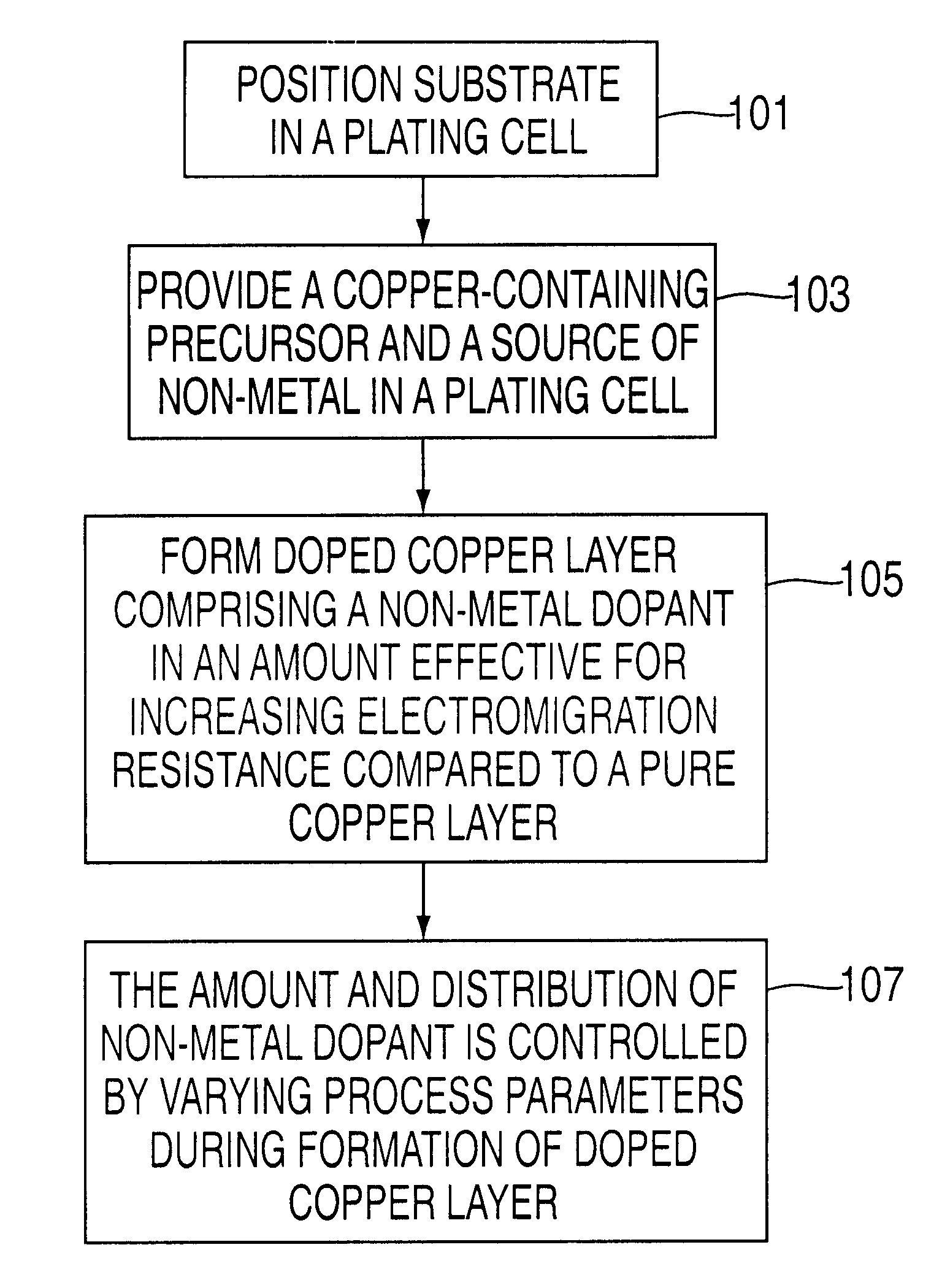

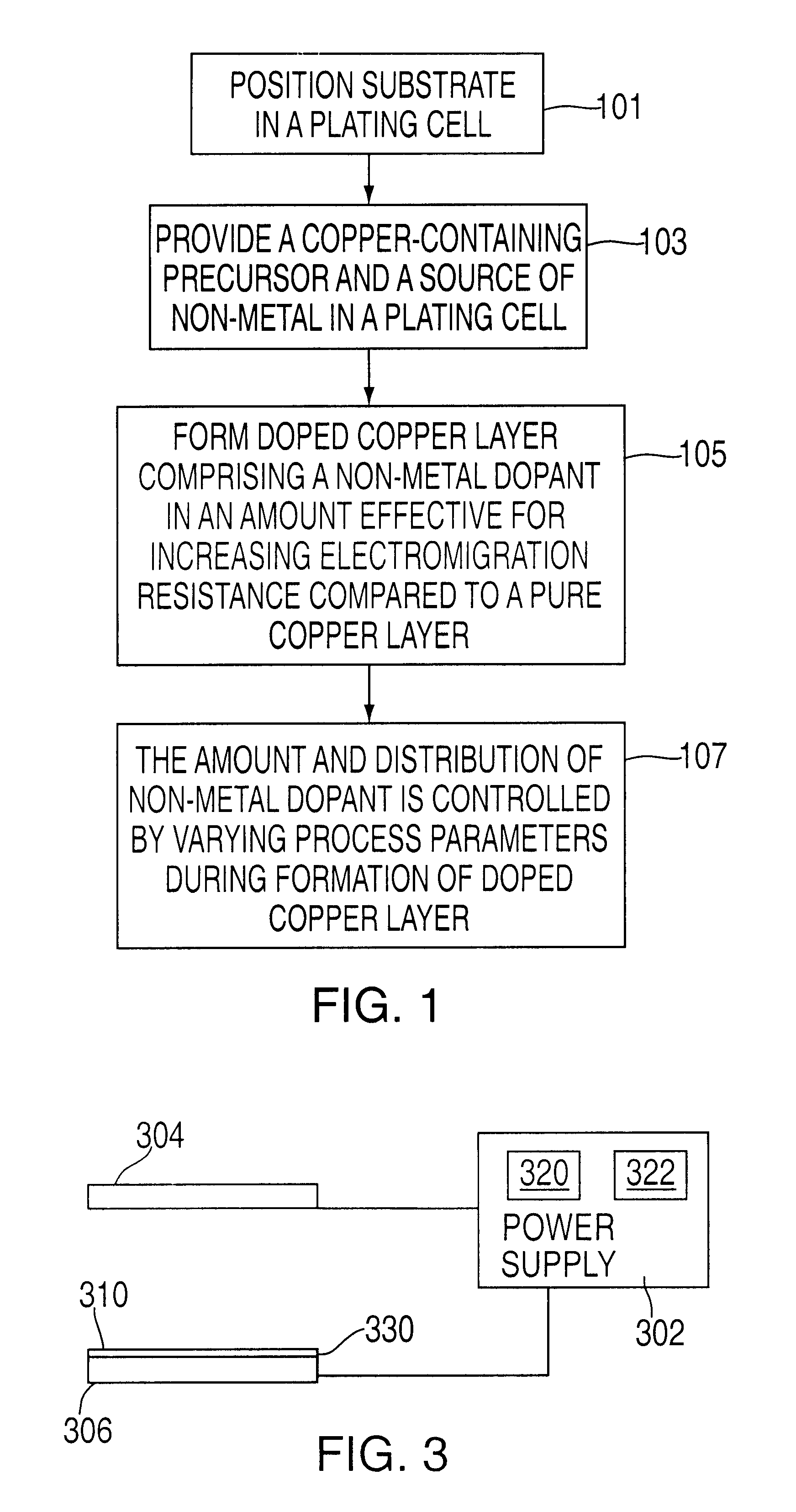

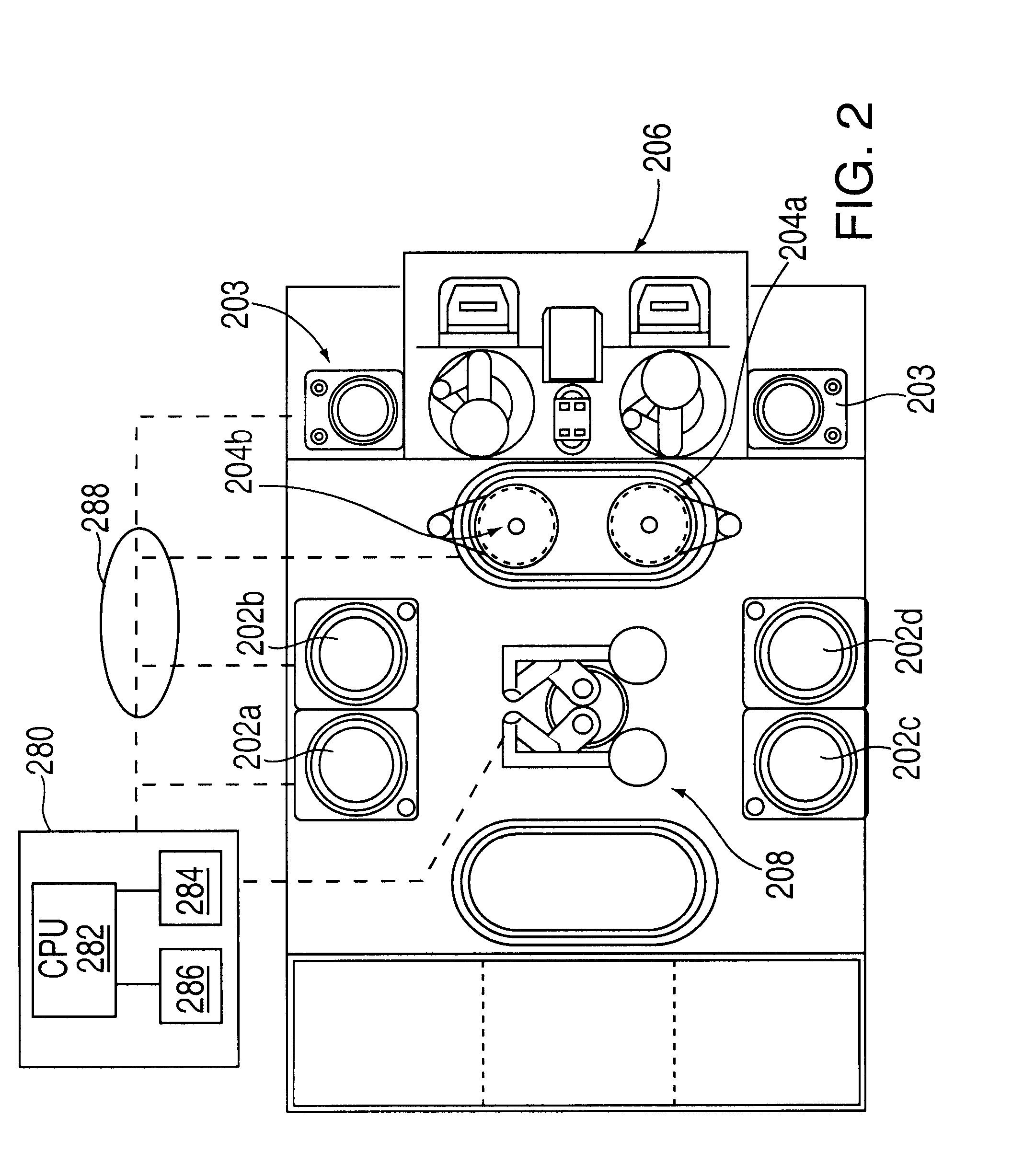

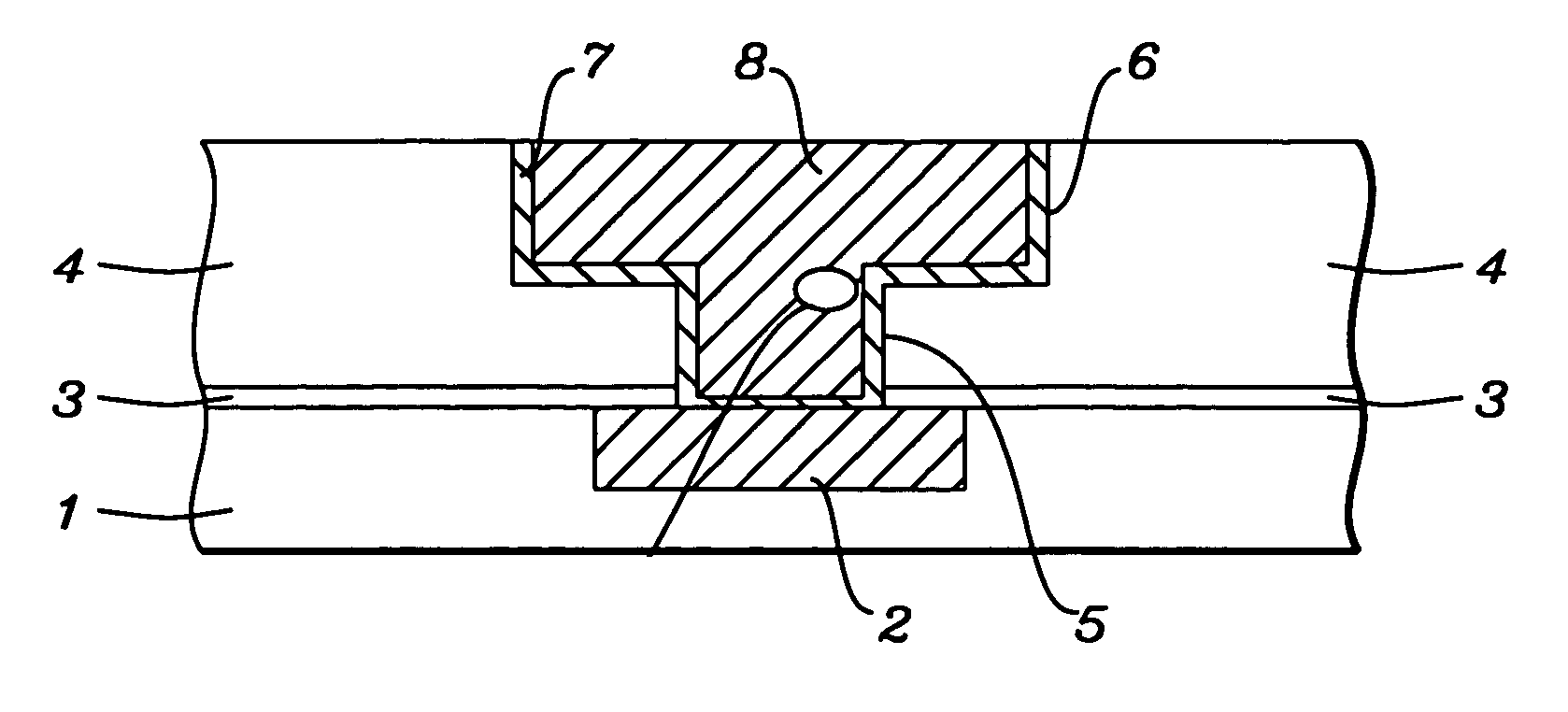

Method of forming copper interconnects

A method of forming a copper layer with increased electromigration resistance. A doped copper layer is formed by controlling the incorporation of a non-metallic dopant during copper electroplating.

Owner:APPLIED MATERIALS INC

Post ECP multi-step anneal/H2 treatment to reduce film impurity

InactiveUS20050227479A1Improve reliabilityReduce defect densitySemiconductor/solid-state device manufacturingCopper interconnectCarbon impurities

A method of forming a copper interconnect in a dual damascene scheme is described. After a diffusion barrier layer and seed layer are sequentially formed on the sidewalls and bottoms of a trench and via in a dielectric layer, a first copper layer is deposited by a first ECP process at a 10 mA / cm2 current density to fill the via and part of the trench. A first anneal step is performed to remove carbon impurities and optionally includes a H2 plasma treatment. A second ECP process with a first deposition step at a 40 mA / cm2 current density and second deposition step at a 60 mA / cm2 current density is used to deposit a second copper layer-that overfills the trench. After a second anneal step, a CMP process planarizes the copper layers. Fewer copper defects, reduced S, Cl, and C impurities, and improved Rc performance are achieved by this method.

Owner:TAIWAN SEMICON MFG CO LTD

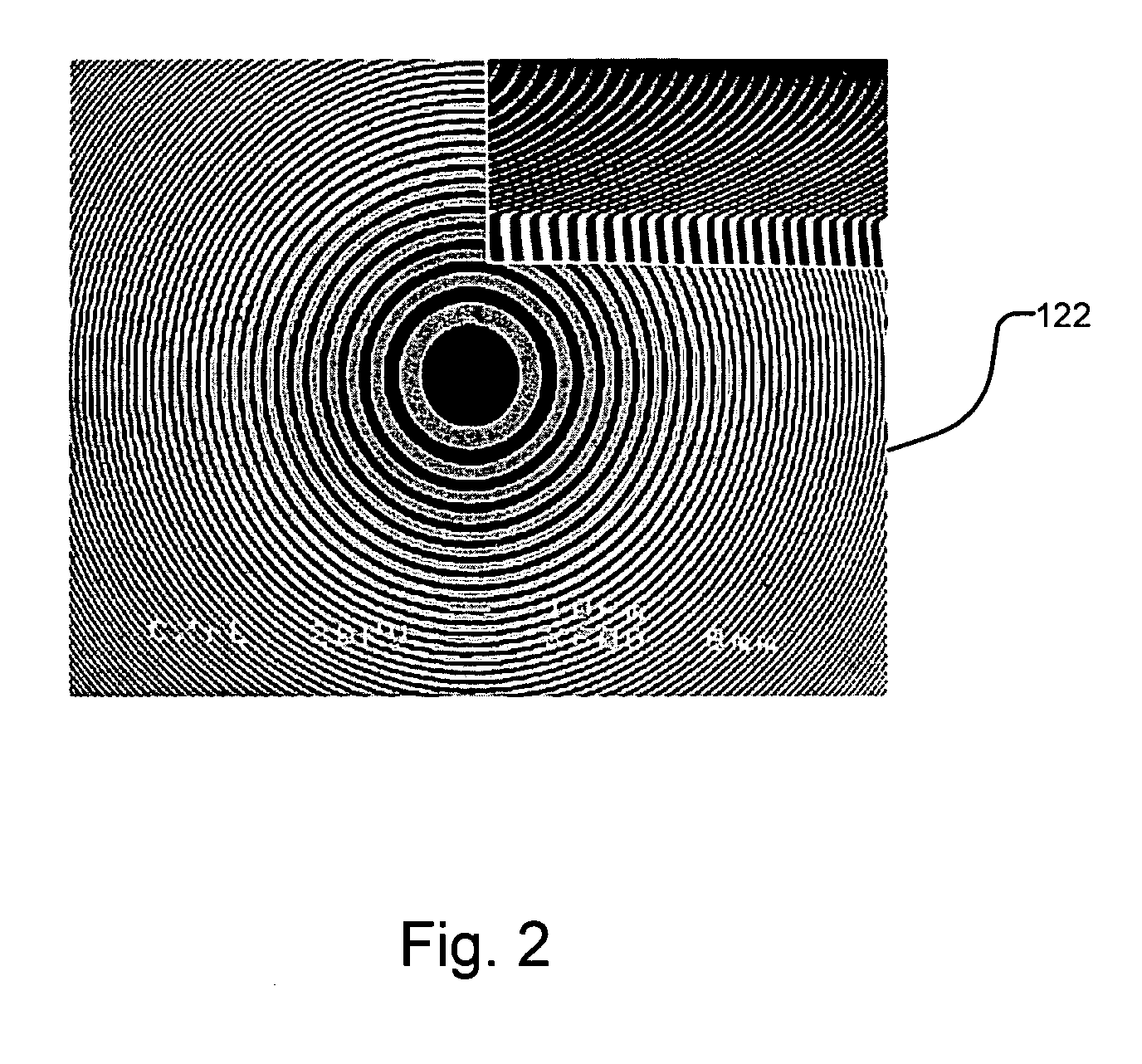

Copper interconnect systems which use conductive, metal-based cap layers

ActiveUS7026714B2Improve adhesionImprove interfacial adhesionSemiconductor/solid-state device detailsSolid-state devicesCopper interconnectDiffusion barrier

An integrated circuit (IC) may include a substrate, a first dielectric layer adjacent the substrate, and at least one trench in the first dielectric layer. The IC may also include a metal liner within the at least one trench, and a first conductive region including copper within the at least one trench. A cap layer including metal may be provided on the first conductive region. A second dielectric layer may be over the first conductive region and the cap layer. A dielectric etch stop and diffusion barrier layer may be over the second dielectric layer, and a via may be over the first conductive region and through the second dielectric layer and the cap layer. A diffusion barrier layer may be on sidewalls of the via, and an alloy seed layer including copper and at least one of tantalum, molybdenum, chromium, and tungsten may be over the diffusion barrier. The alloy seed layer may also be over the dielectric etch stop and diffusion barrier layer, and the alloy seed layer may be in contact with the first conductive region.

Owner:INTELLECTUAL VENTURES ASSETS 185

Two step copper electroplating process with anneal for uniform across wafer deposition and void free filling on ruthenium coated wafers

ActiveUS7964506B1Reduce the possibilityLow resistivityElectrolysis componentsSolid-state devicesCopper interconnectHigh density

A two-step semiconductor electroplating process deposits copper onto wafers coated with a semi-noble metal in manner that is uniform across the wafer and free of voids after a post electrofill anneal. A seed-layer plating bath nucleates copper uniformly and conformably at a high density in a very thin film using a unique pulsed waveform. The wafer is then annealed before a second bath fills the features. The seed-layer anneal improves adhesion and stability of the semi-noble to copper interface, and the resulting copper interconnect stays void-free after a post electrofill anneal.

Owner:NOVELLUS SYSTEMS

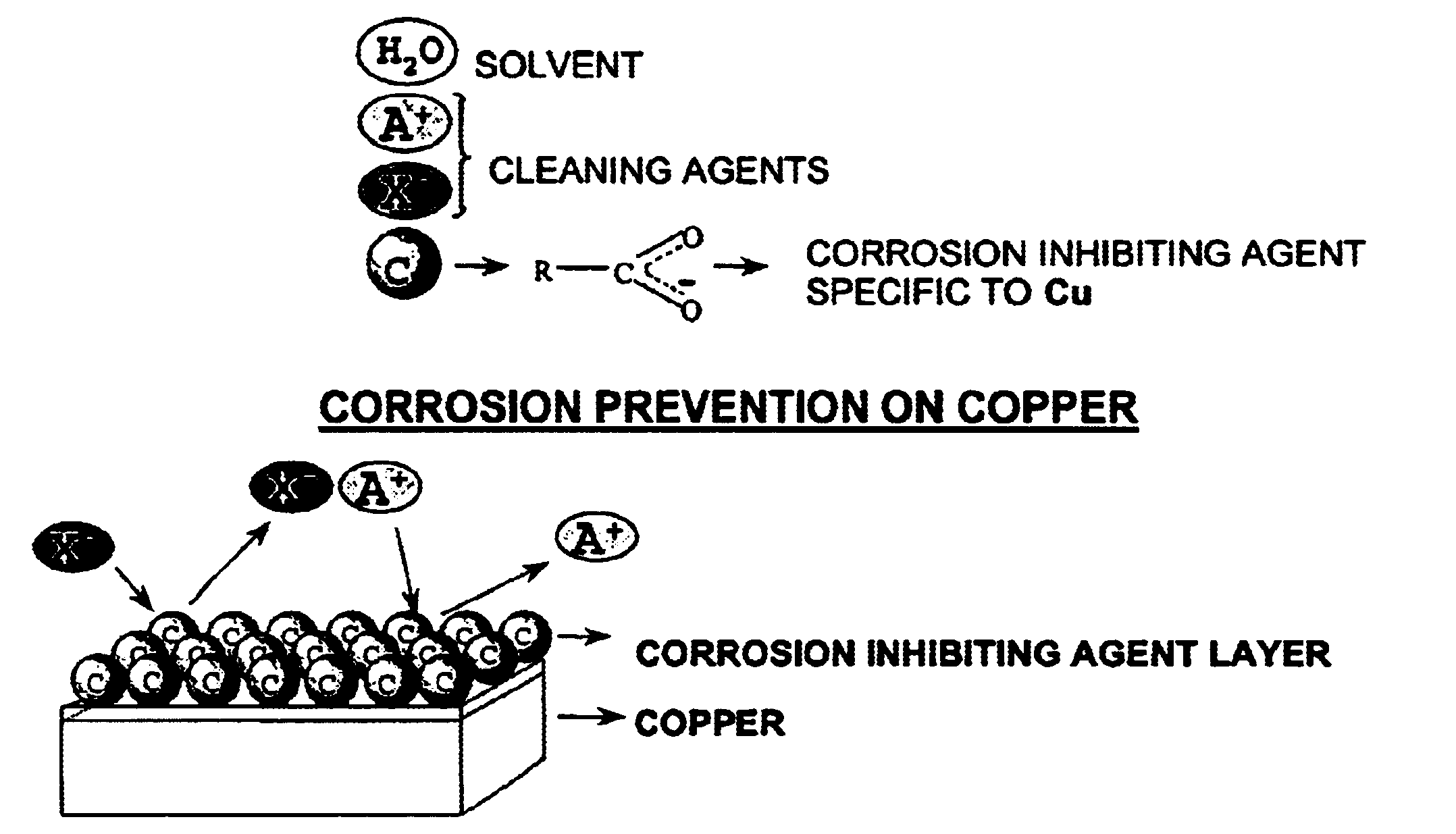

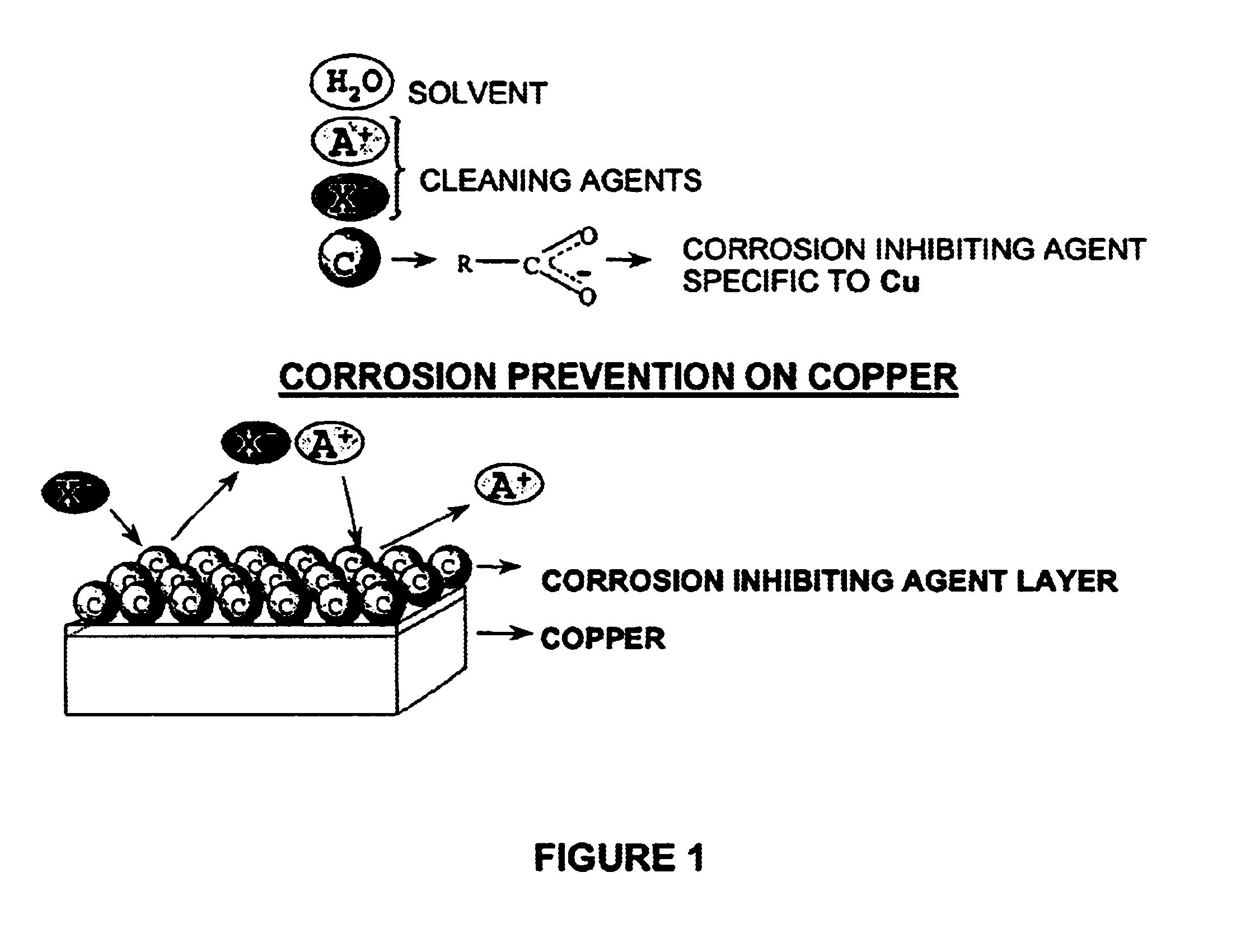

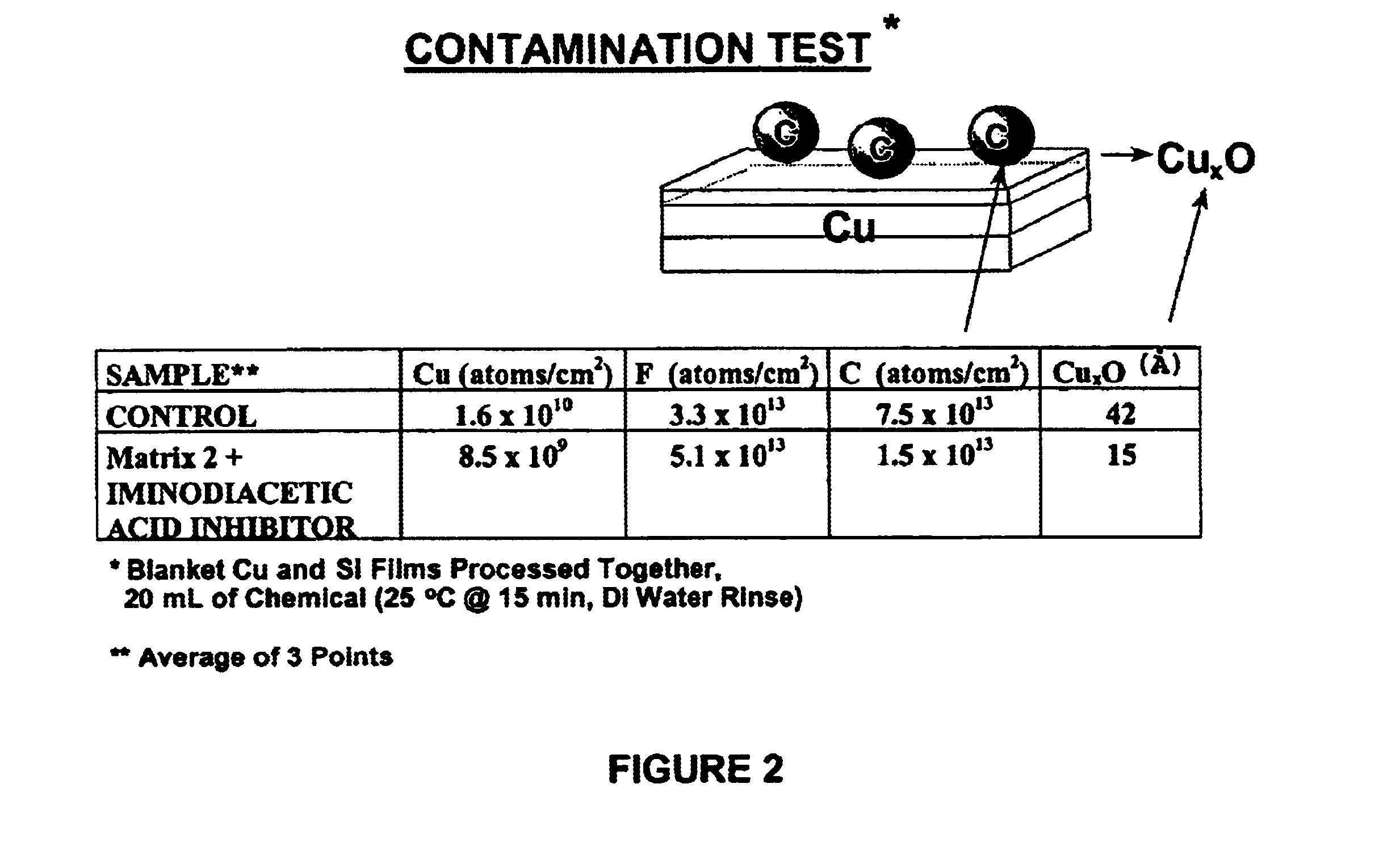

Aqueous cleaning composition containing copper-specific corrosion inhibitor for cleaning inorganic residues on semiconductor substrate

InactiveUS6755989B2Inorganic/elemental detergent compounding agentsOrganic detergent compounding agentsCopper interconnectCarboxylic acid

A semiconductor wafer cleaning formulation, including 1-21% wt. fluoride source, 20-55% wt. organic amine(s), 0.5-40% wt. nitrogenous component, e.g., a nitrogen-containing carboxylic acid or an imine, 23-50% wt. water, and 0-21% wt. metal chelating agent(s). The formulations are useful to remove residue from wafers following a resist plasma ashing step, such as inorganic residue from semiconductor wafers containing delicate copper interconnecting structures.

Owner:ENTEGRIS INC