Patents

Literature

1010 results about "Anisotropic conductive film" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

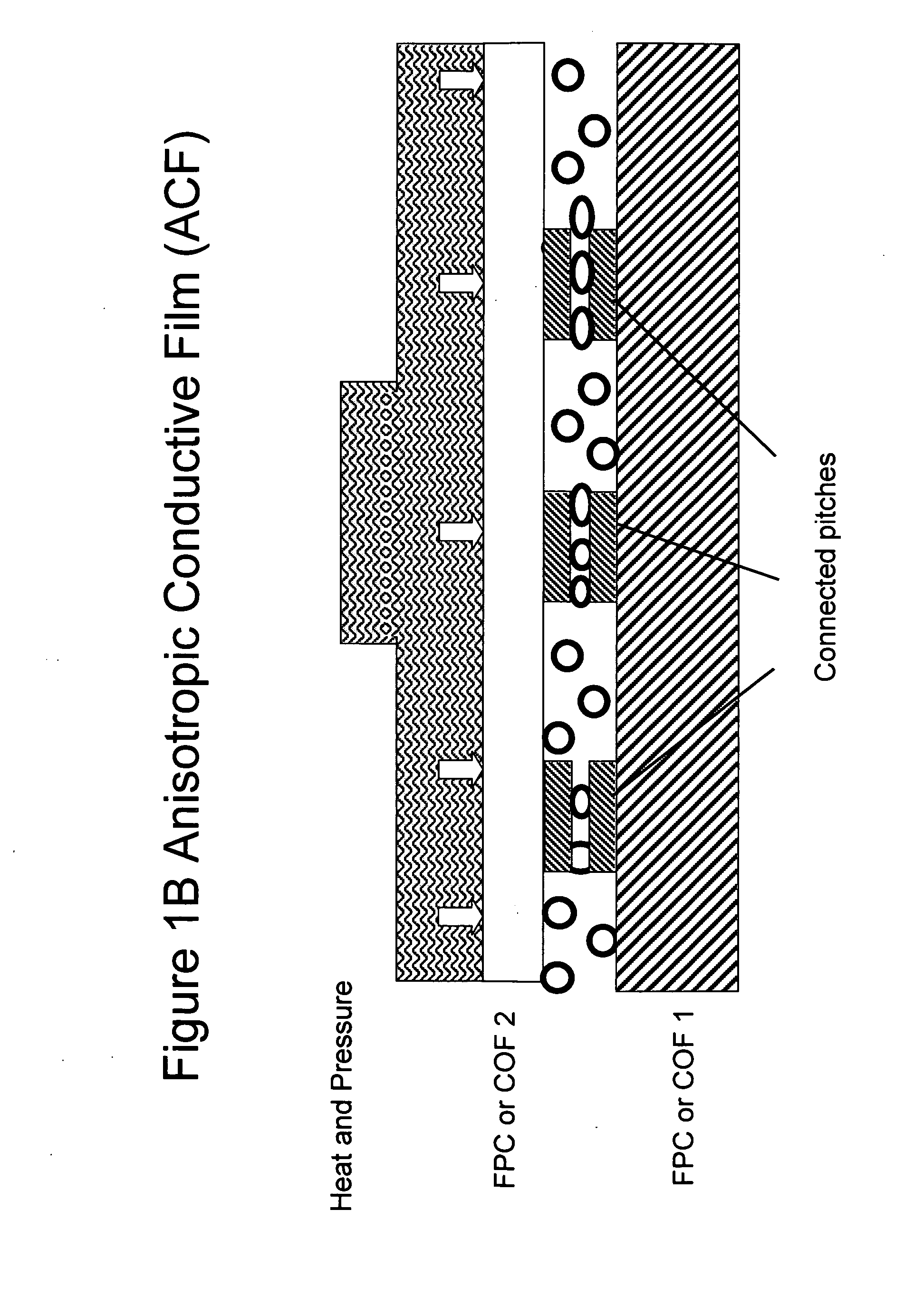

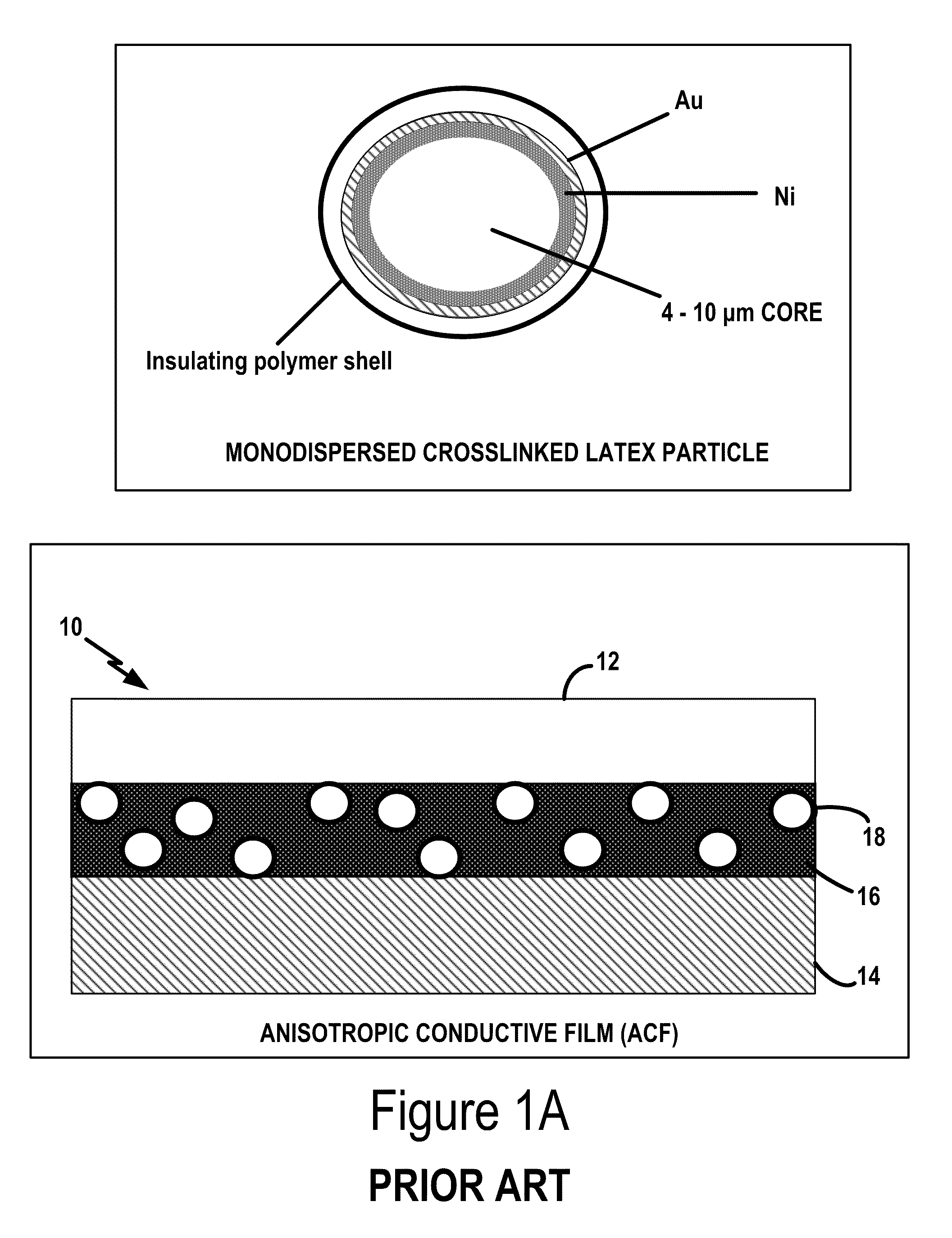

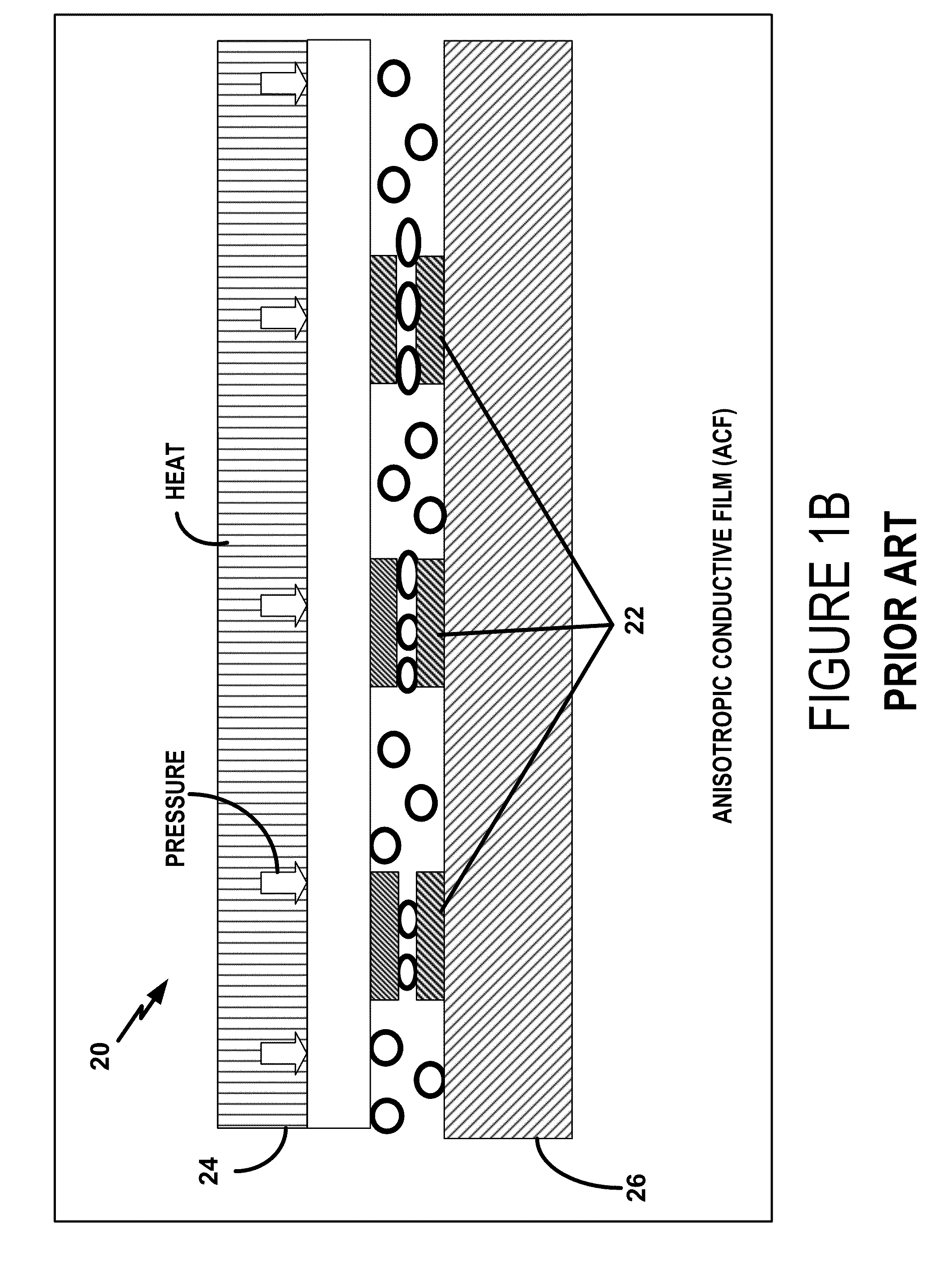

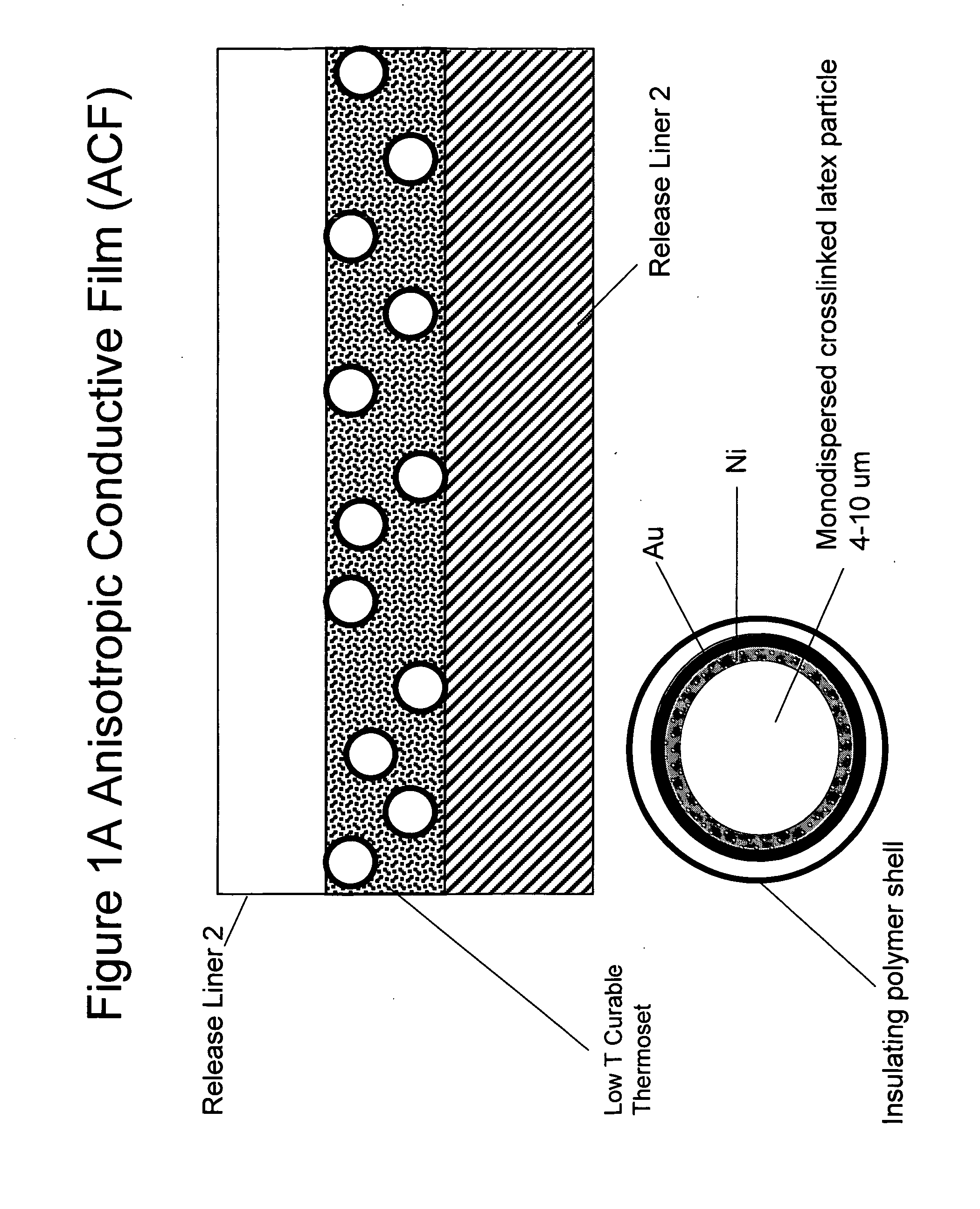

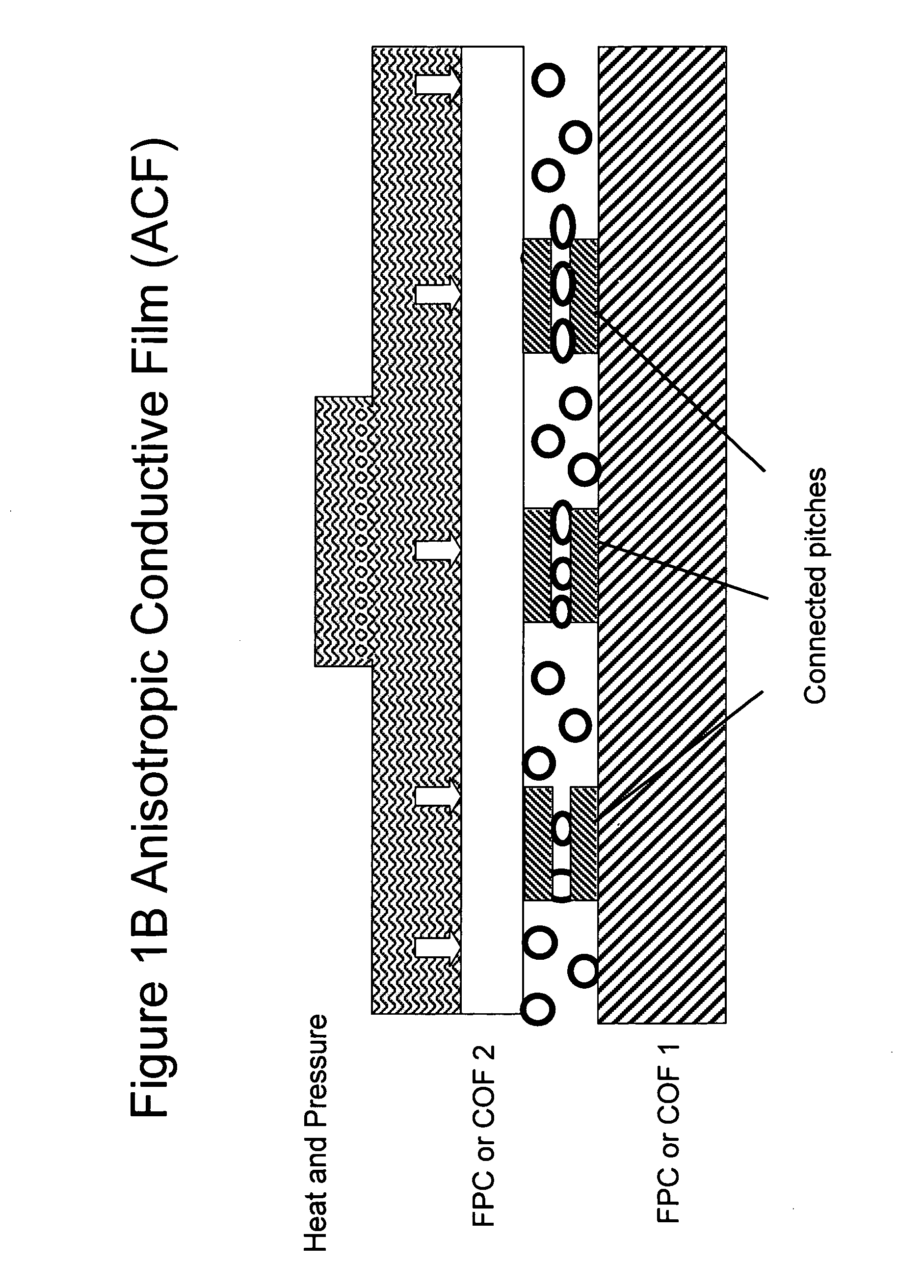

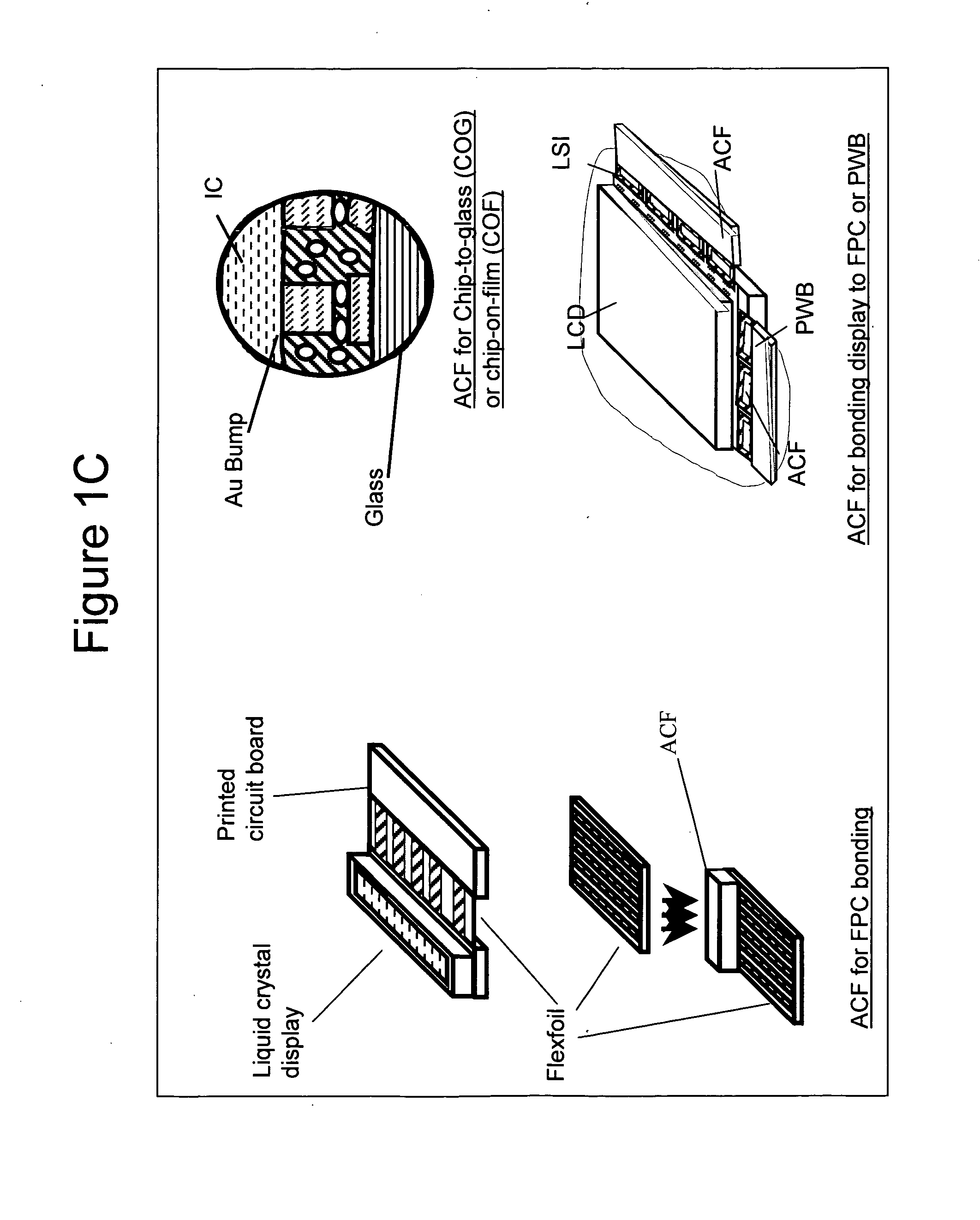

Anisotropic conductive film (ACF), is a lead-free and environmentally friendly adhesive interconnect system that is commonly used in liquid crystal display manufacturing to make the electrical and mechanical connections from the driver electronics to the glass substrates of the LCD. The material is also available in a paste form referred to as anisotropic conductive paste (ACP), and both are grouped together as anisotropic conductive adhesives (ACAs). ACAs have more recently been used to perform the flex-to-board or flex-to-flex connections used in handheld electronic devices such as mobile phones, MP3 players, or in the assembly of CMOS camera modules.

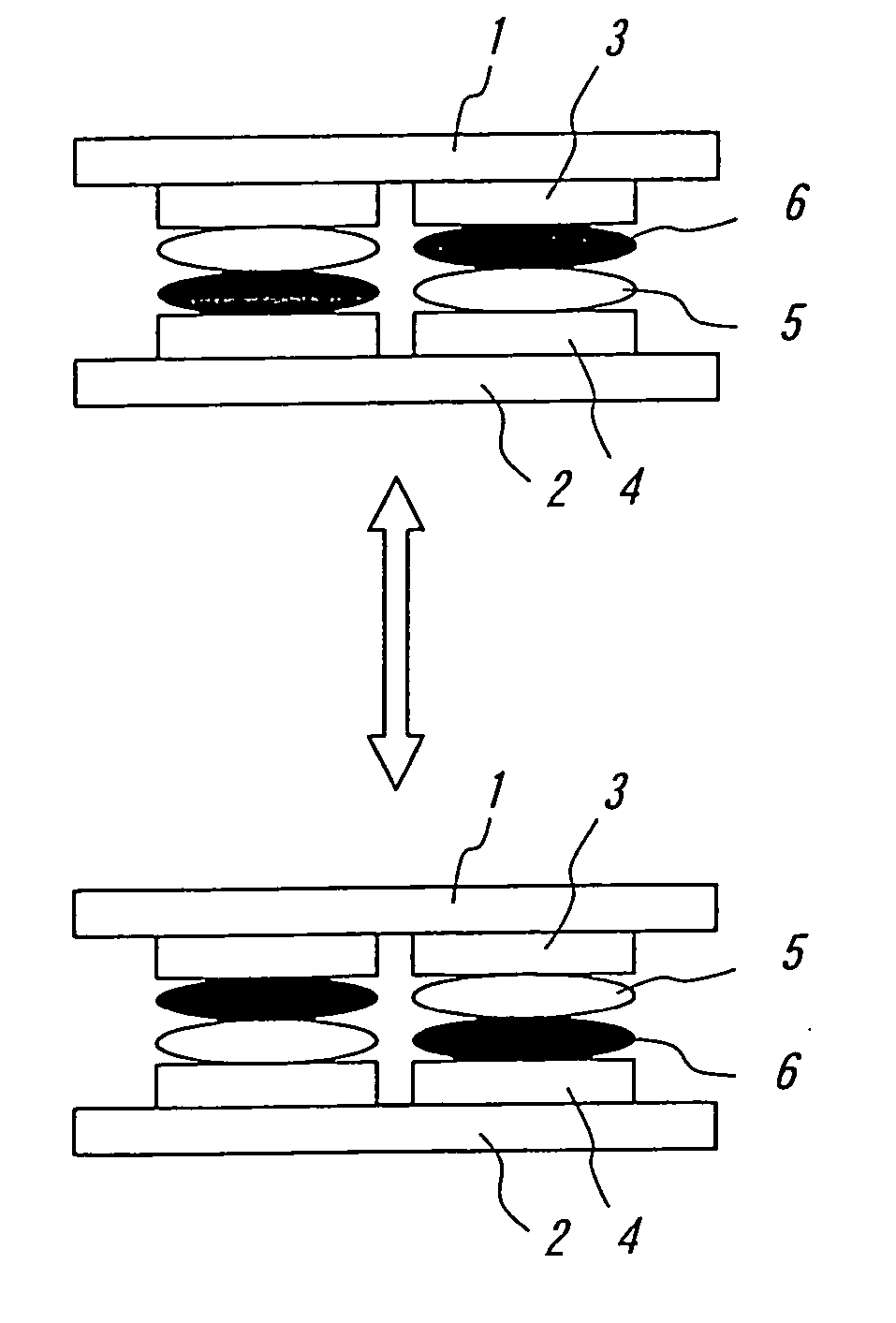

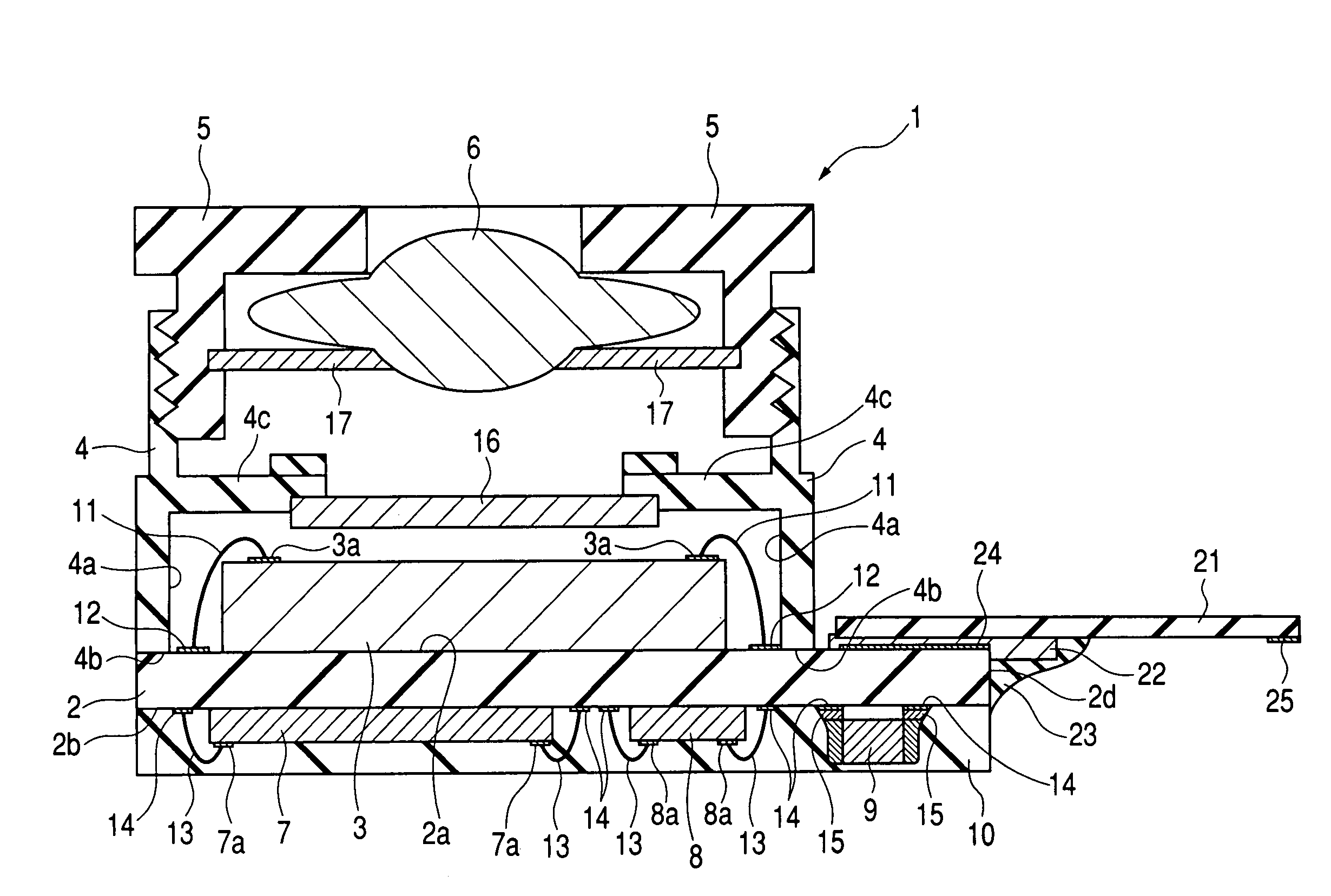

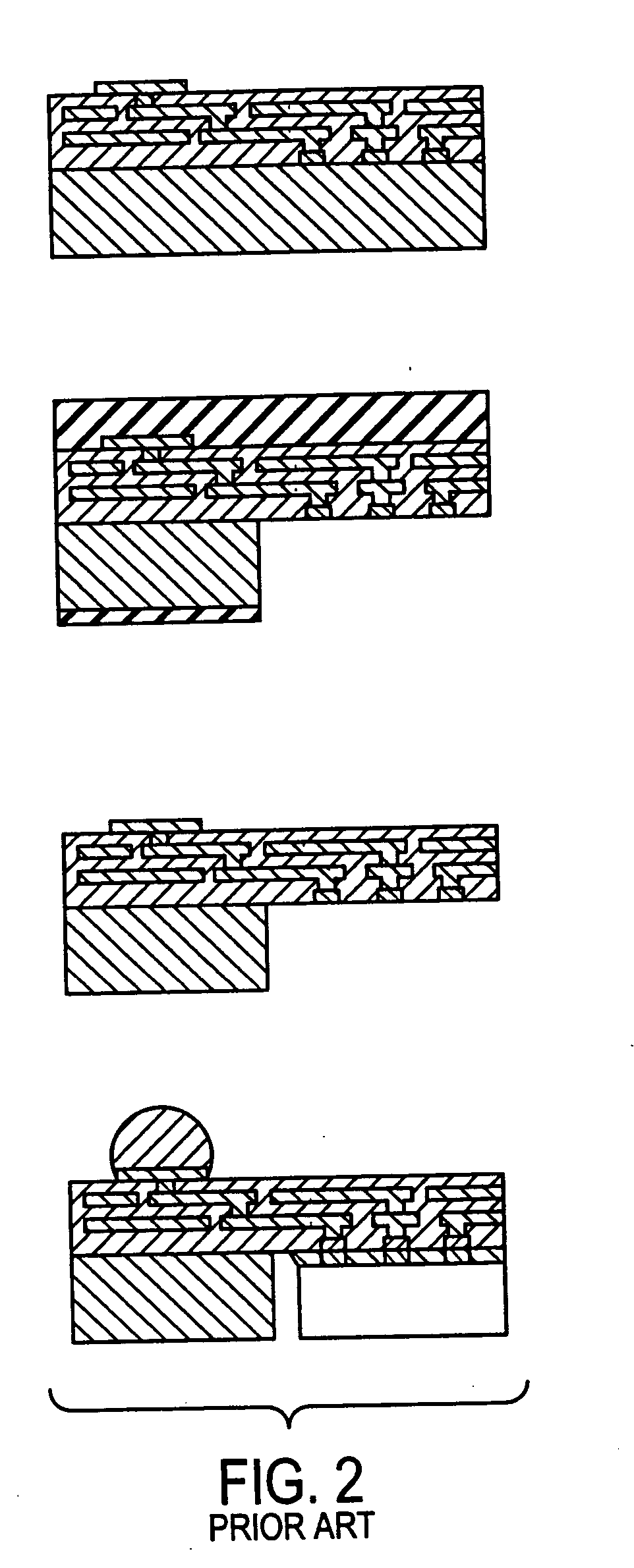

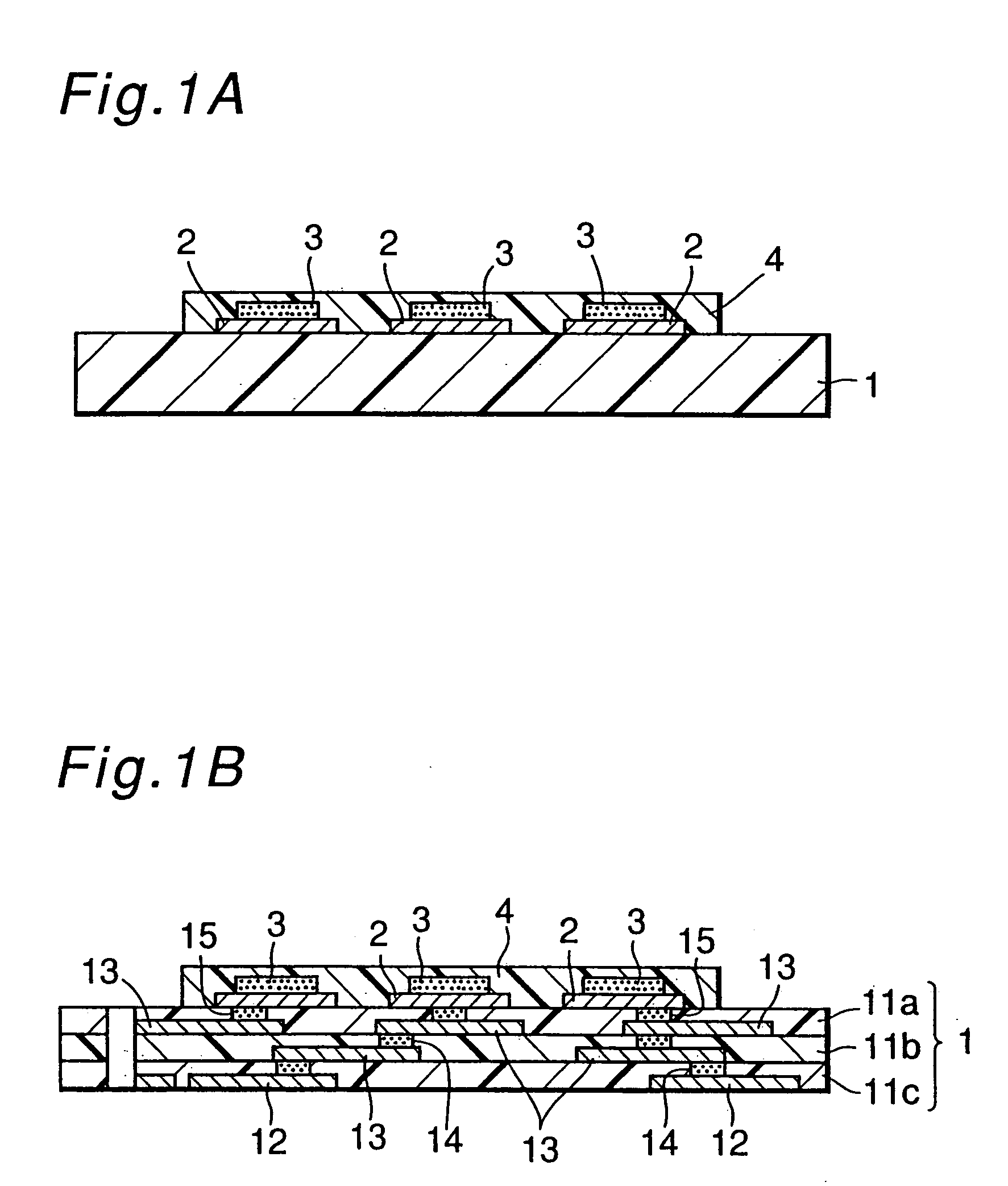

Image display and method for manufacturing image display

InactiveUS20060087479A1Improve performanceRapid responseStatic indicating devicesNon-linear opticsAnisotropic conductive filmDisplay device

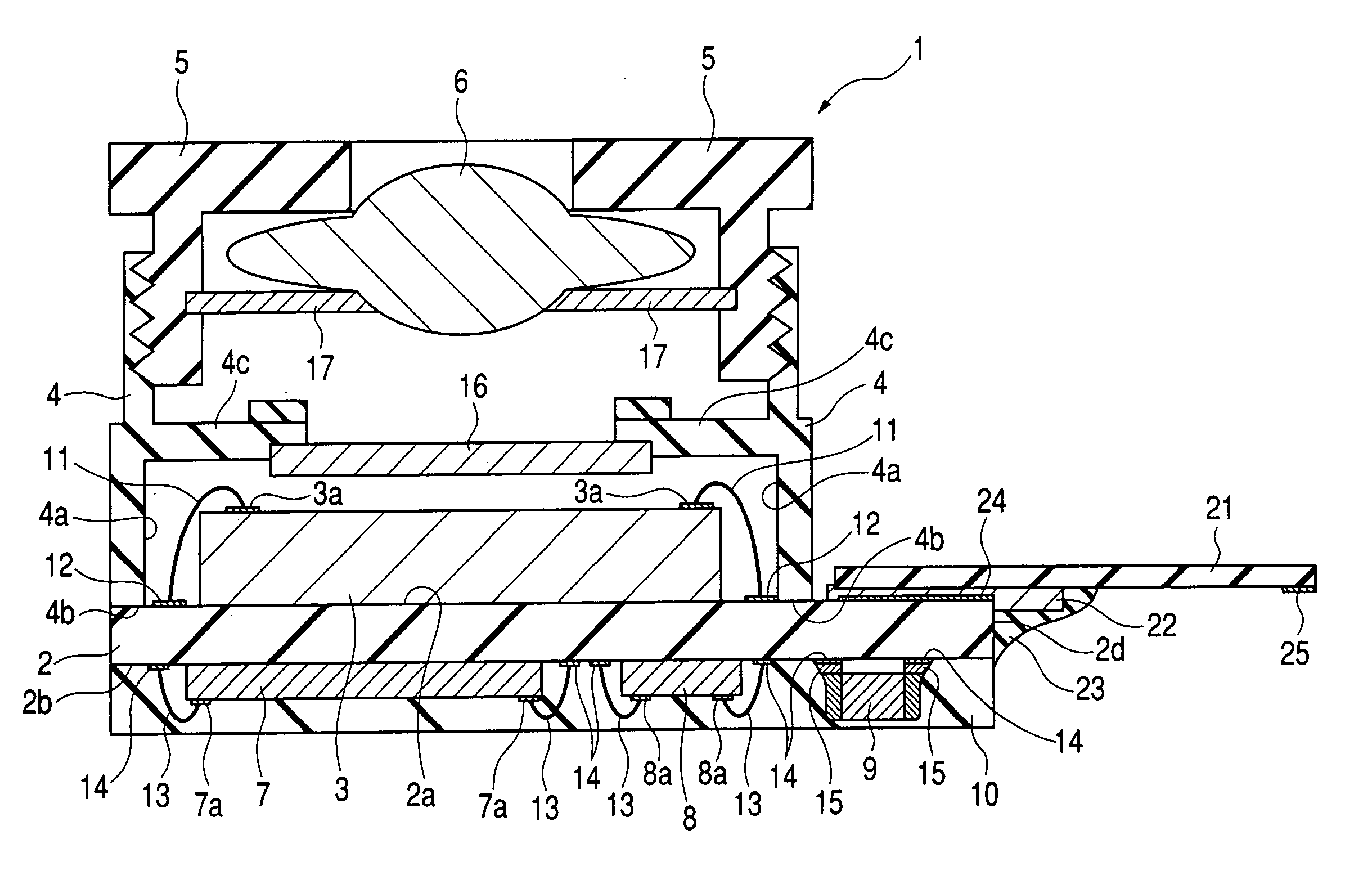

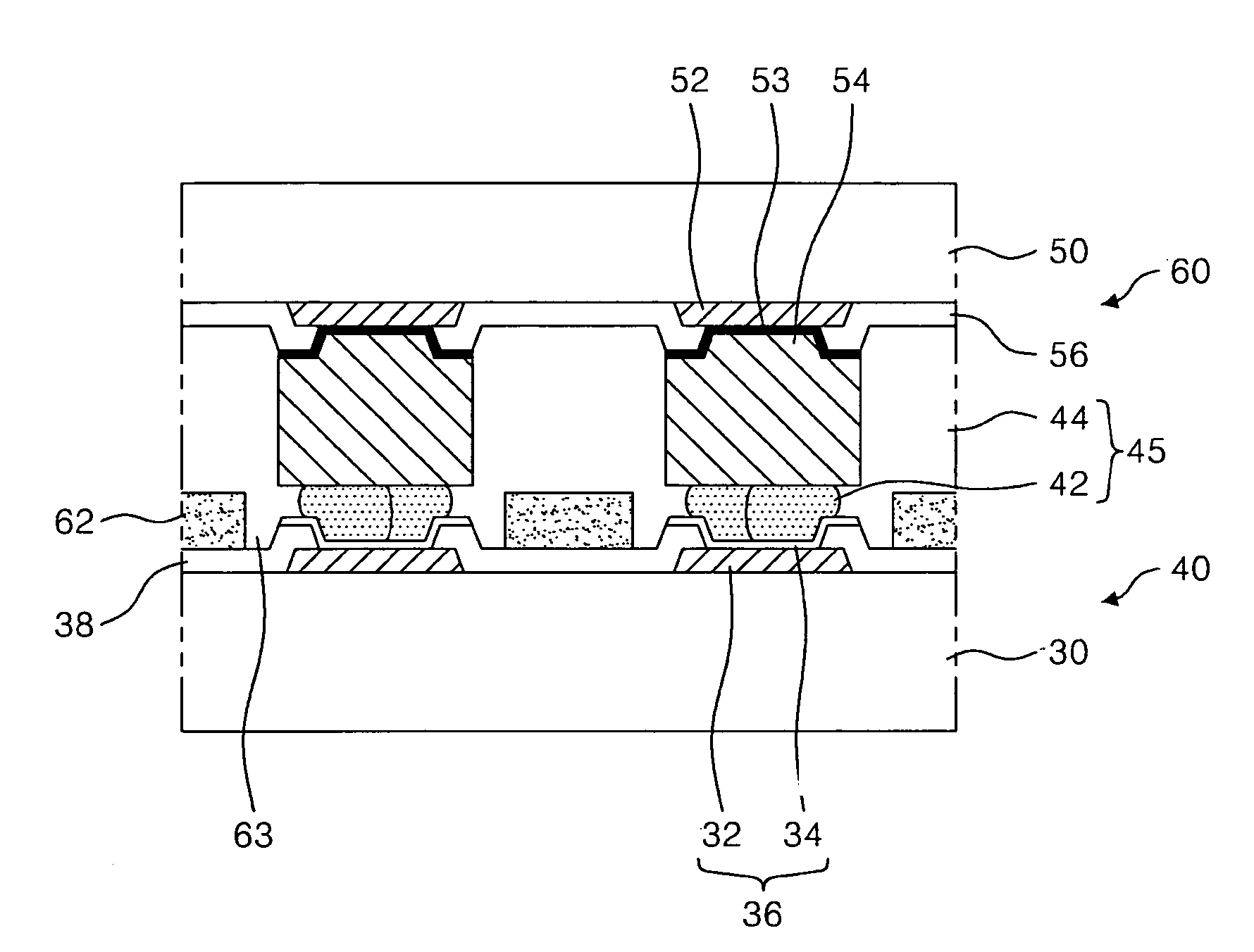

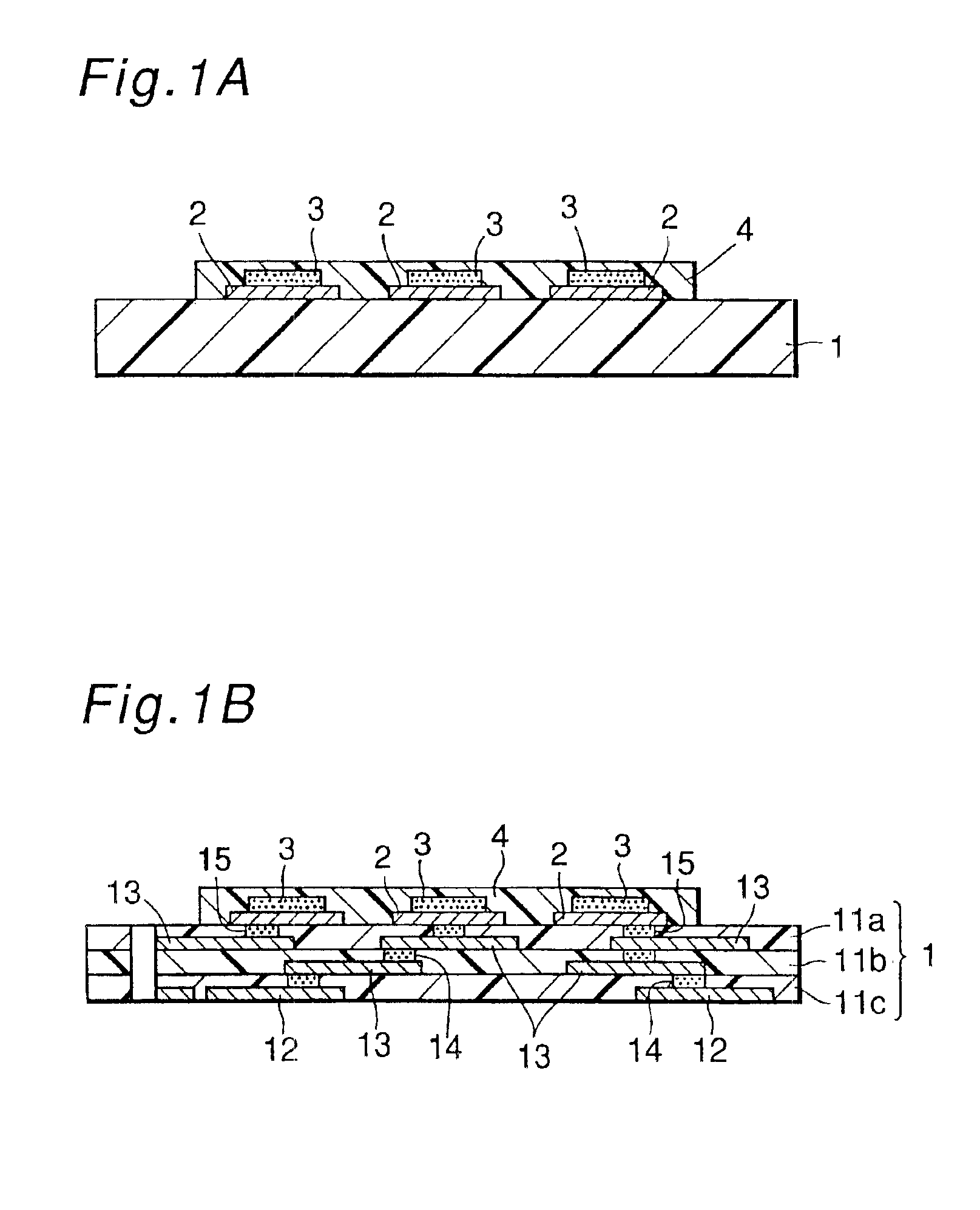

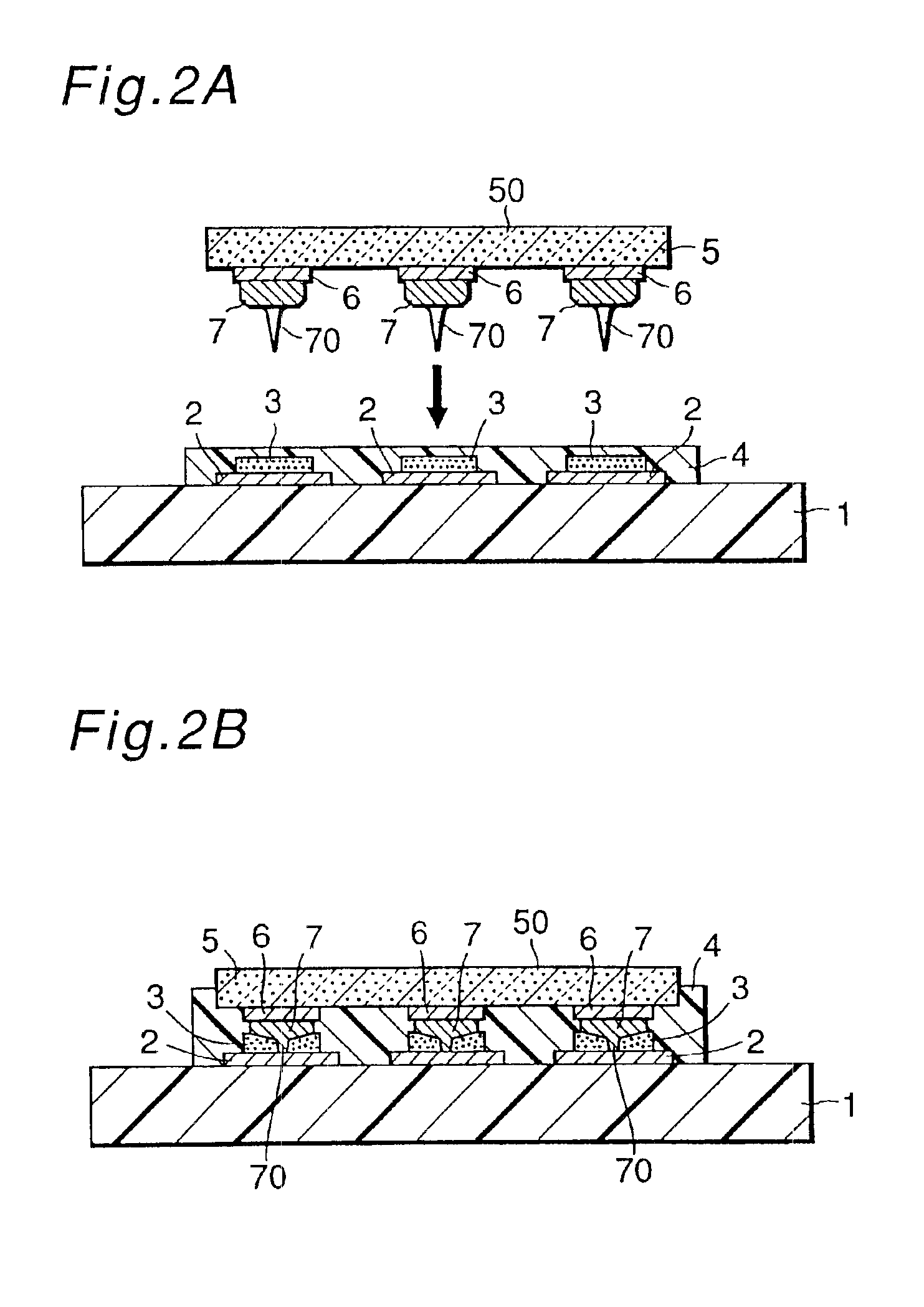

In a first aspect of the invention, an image display device, in which one or more groups of particles or liquid powders are sealed between opposed two substrates, at least one of two substrates being transparent, and, in which the particles or the liquid powders, to which an electrostatic field produced by two groups of electrodes having different potentials is applied, are made to move so as to display an image, has a construction such that a member for transmitting a signal, which is applied to circuits for an image display, is provided to the substrate by means of an anisotropic conductive film and members such as the electrode are provided to a substrate opposed to a transparent substrate. In second to sixth aspects of the invention, an image display device has a construction such that the electrode is arranged to a surface of the substrate through a transparent elastic member, or, an anti-reflection layer is arranged, or, a connection operation between two substrates through a partition wall is optimized.

Owner:BRIDGESTONE CORP

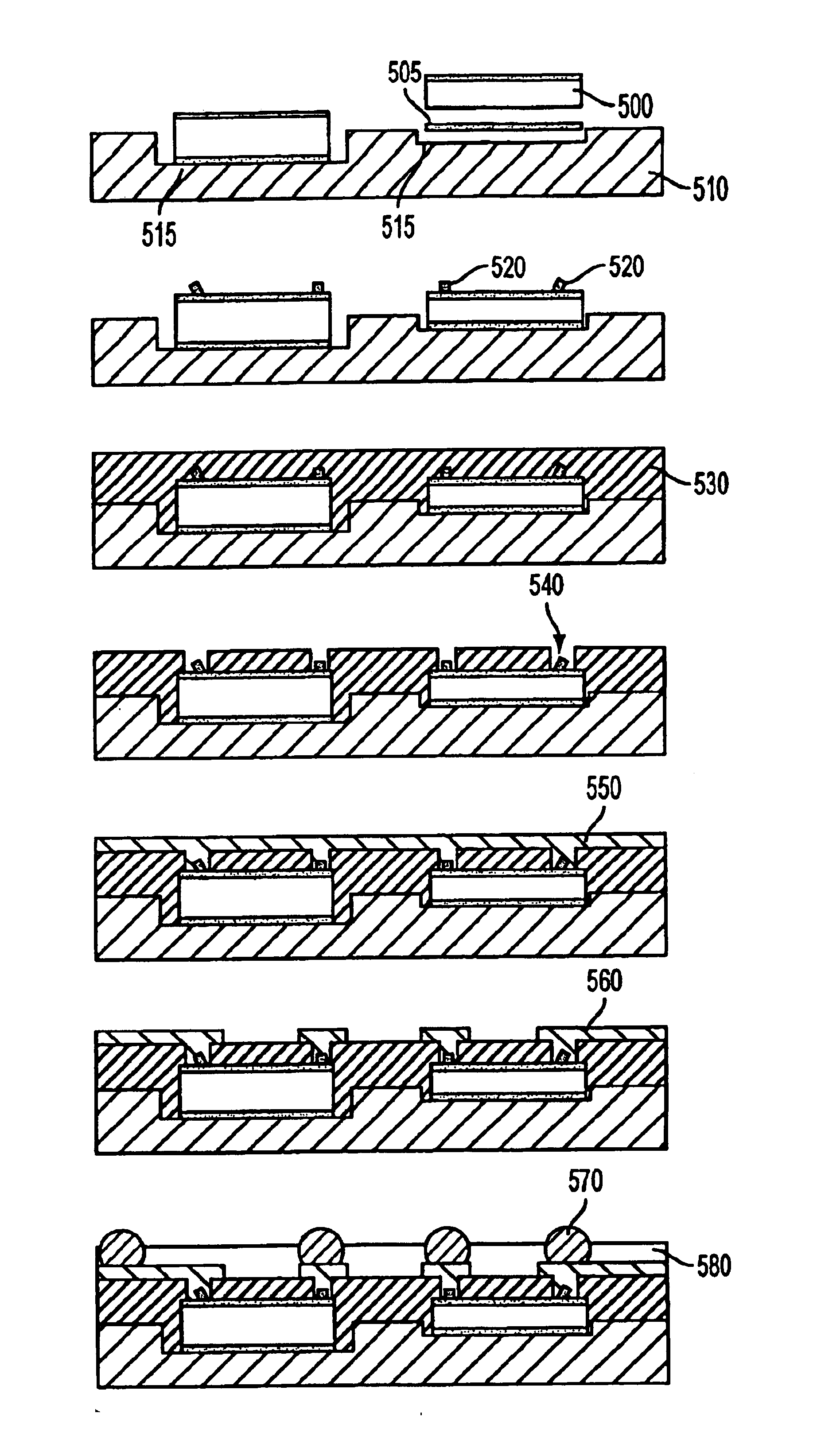

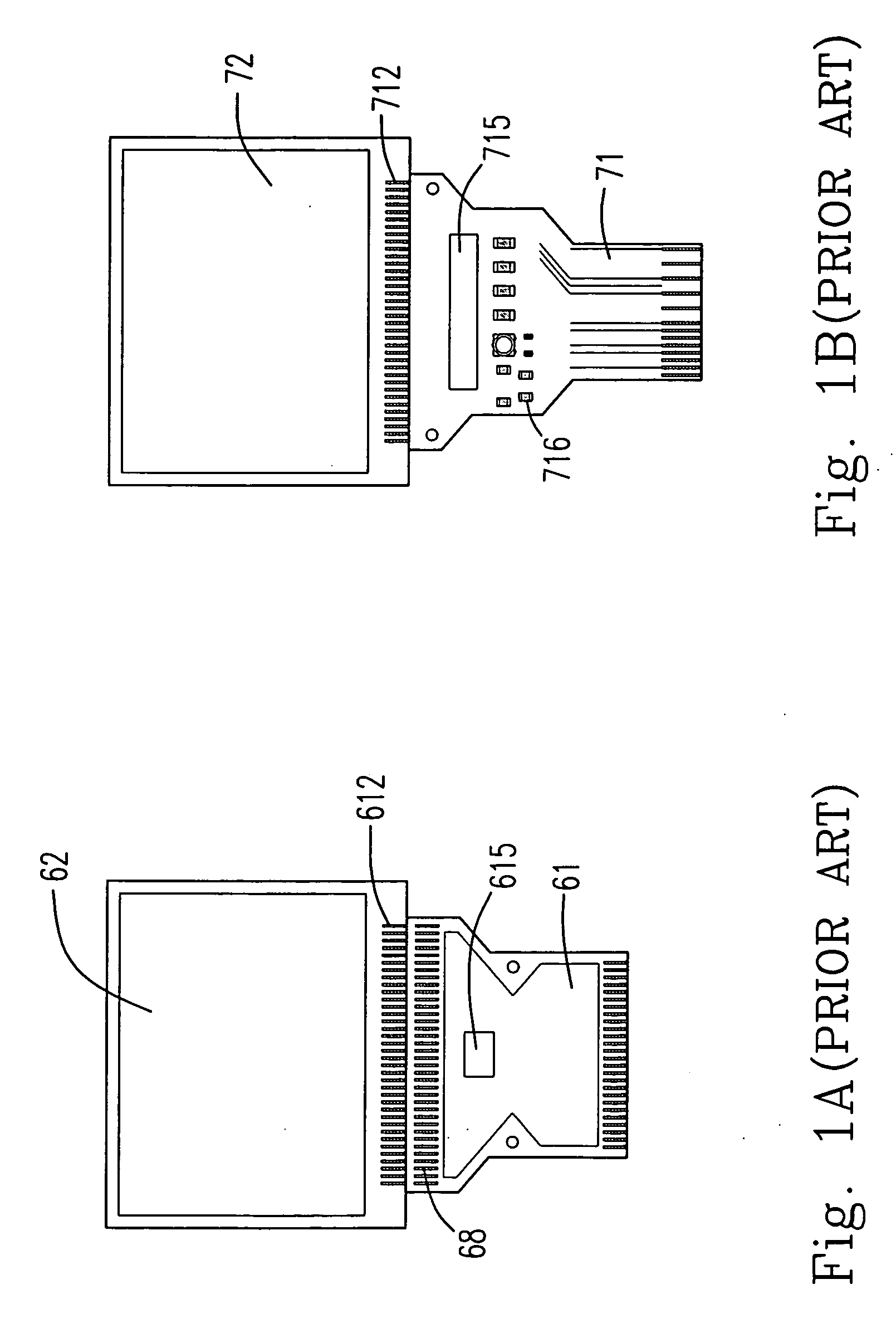

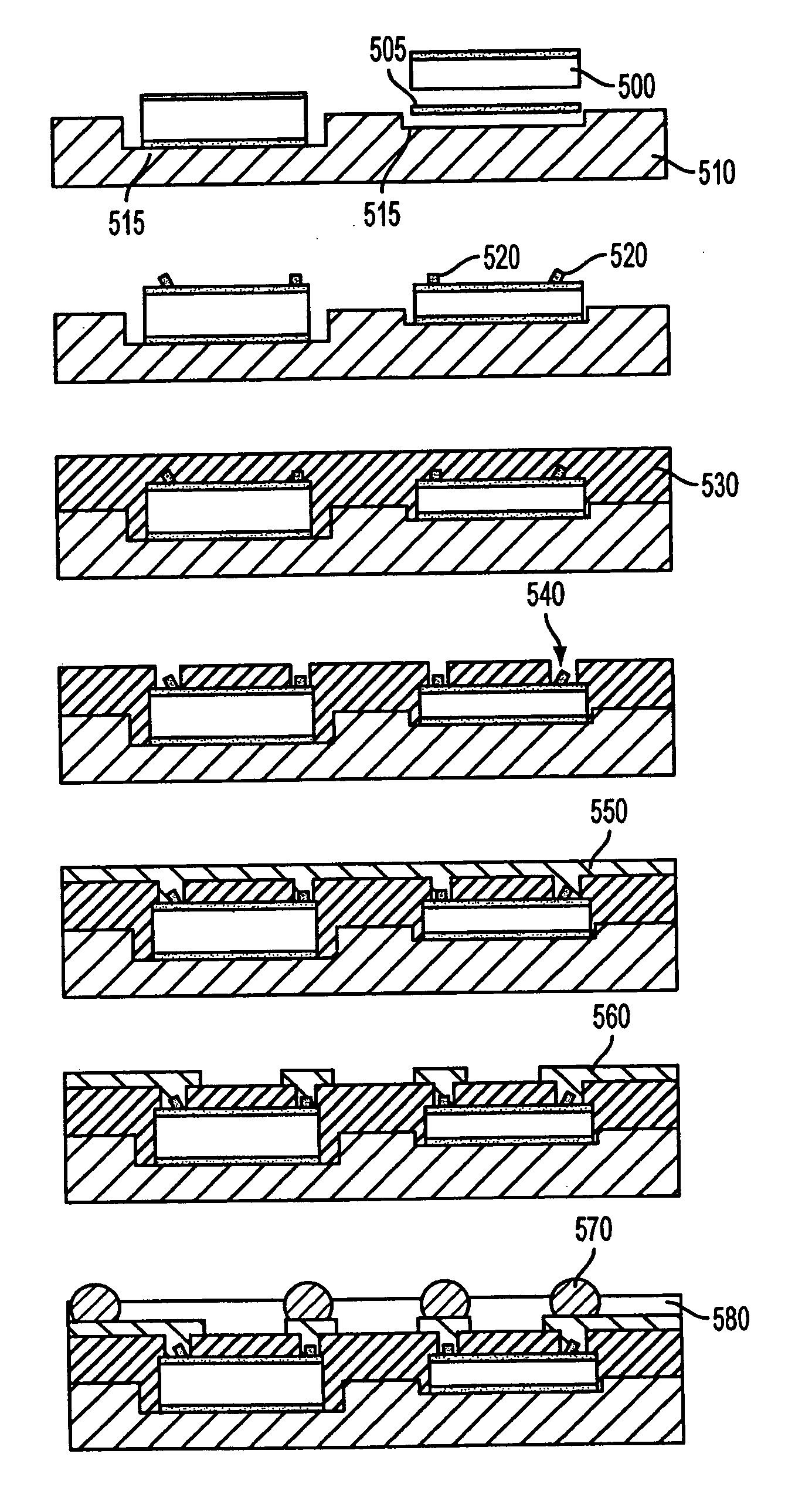

Chip package and method for fabricating the same

ActiveUS20070205520A1Semiconductor/solid-state device detailsSolid-state devicesAnisotropic conductive filmLead bonding

A chip package includes a semiconductor substrate, a first metal pad over the semiconductor substrate, and a second metal pad over the semiconductor substrate. In a case, the first metal pad is tape automated bonded thereto, and the second metal pad is solder bonded thereto. In another case, the first metal pad is tape automated bonded thereto, and the second metal pad is wirebonded thereto. In another case, the first metal pad is solder bonded thereto, and the second metal pad is wirebonded thereto. In another case, the first metal pad is bonded to an external circuitry using an anisotropic conductive film, and the second metal pad is solder bonded thereto. In another case, the first metal pad is bonded to an external circuitry using an anisotropic conductive film, and the second metal pad is wirebonded thereto.

Owner:SUMITOMO ELECTRIC IND LTD +1

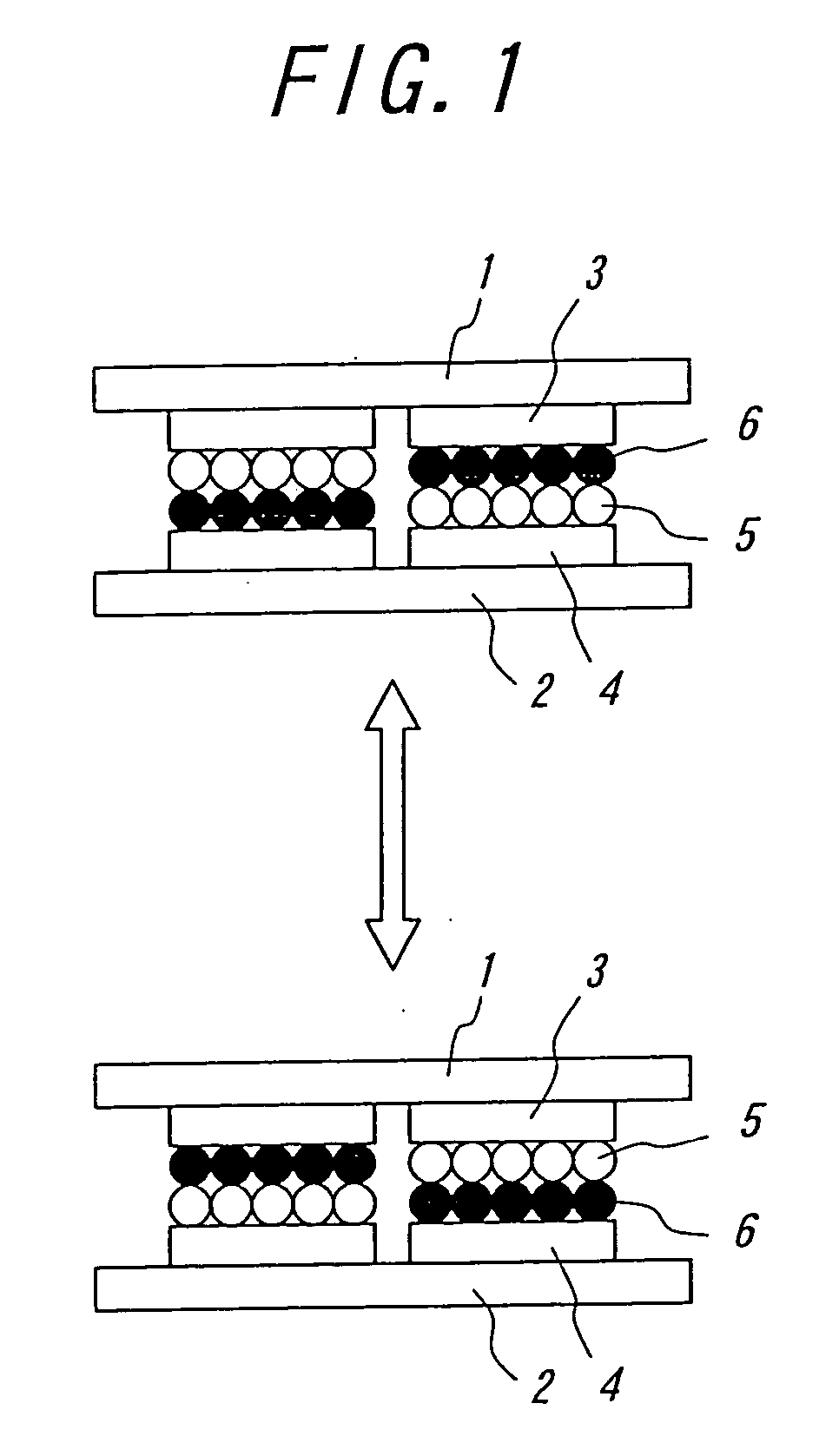

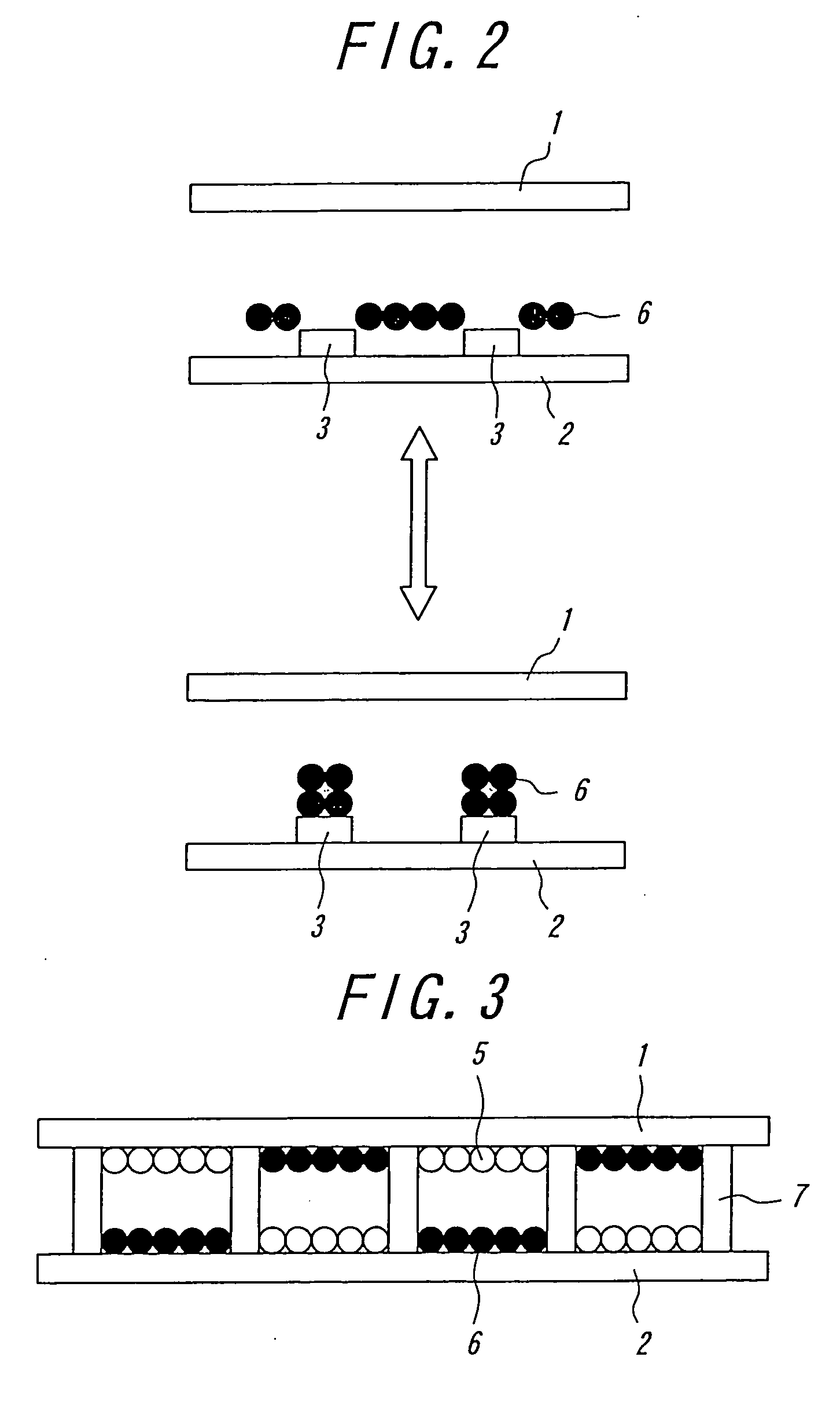

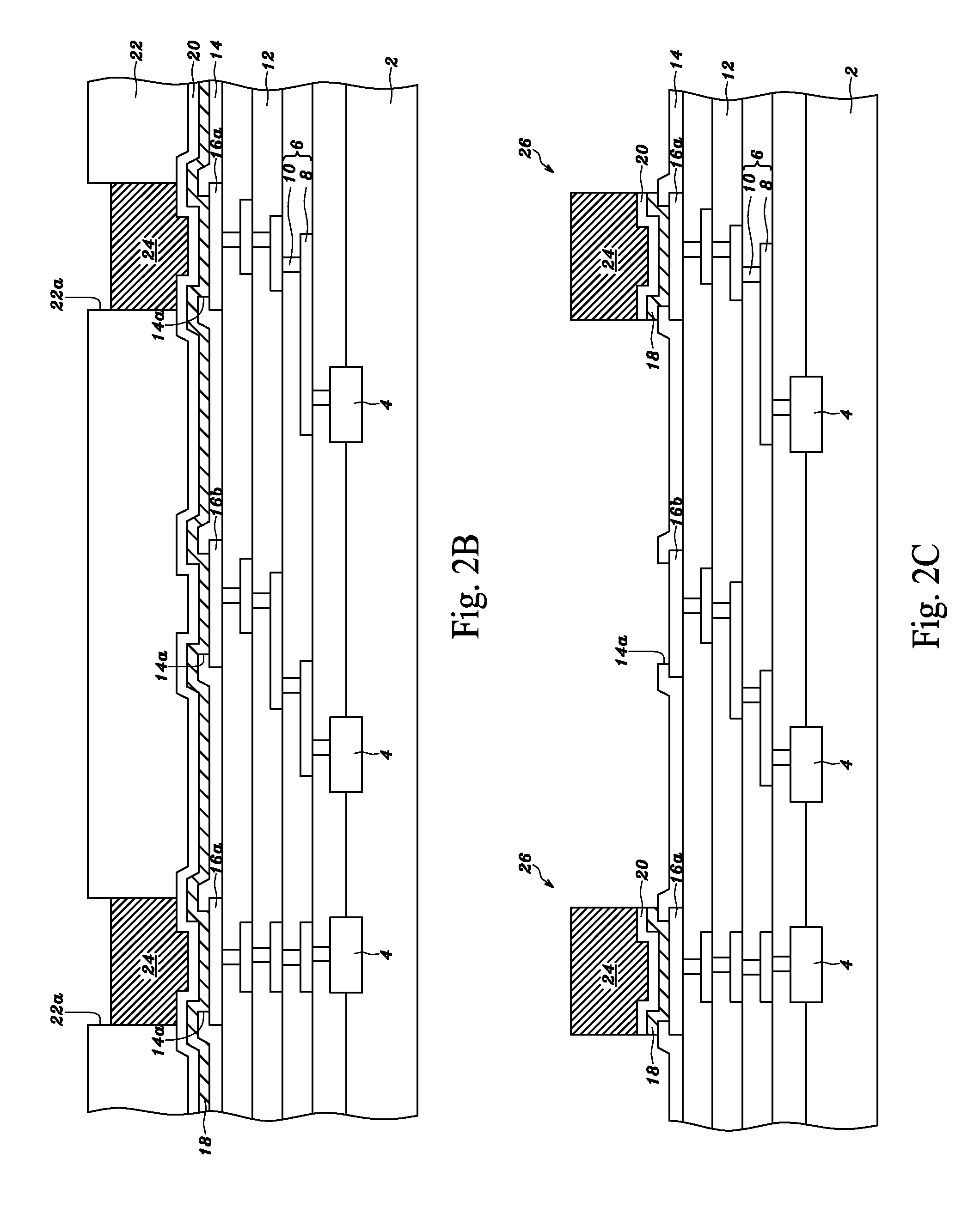

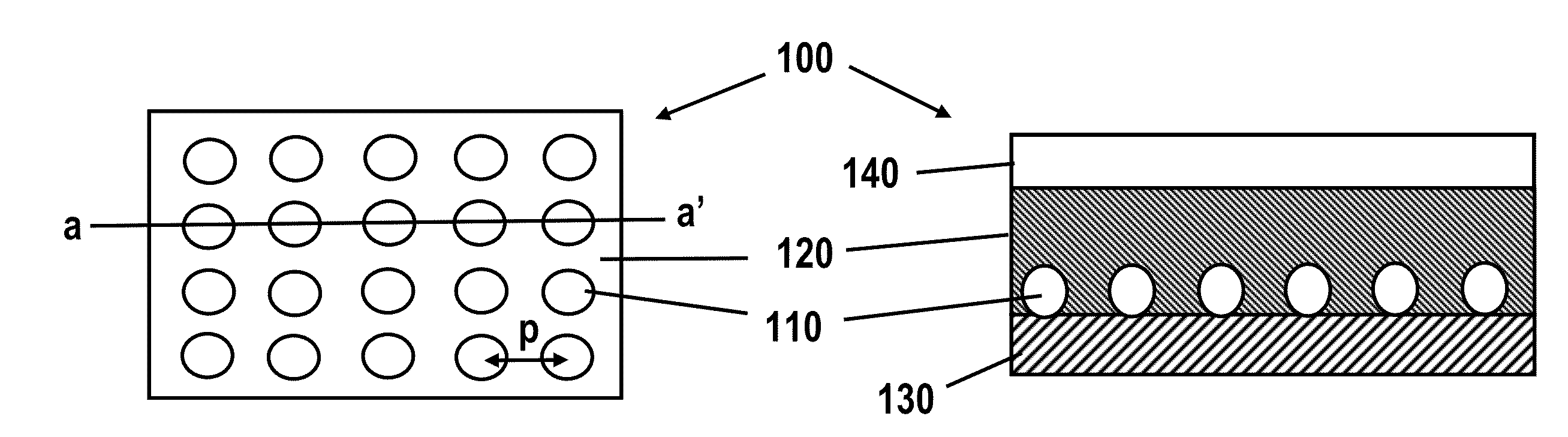

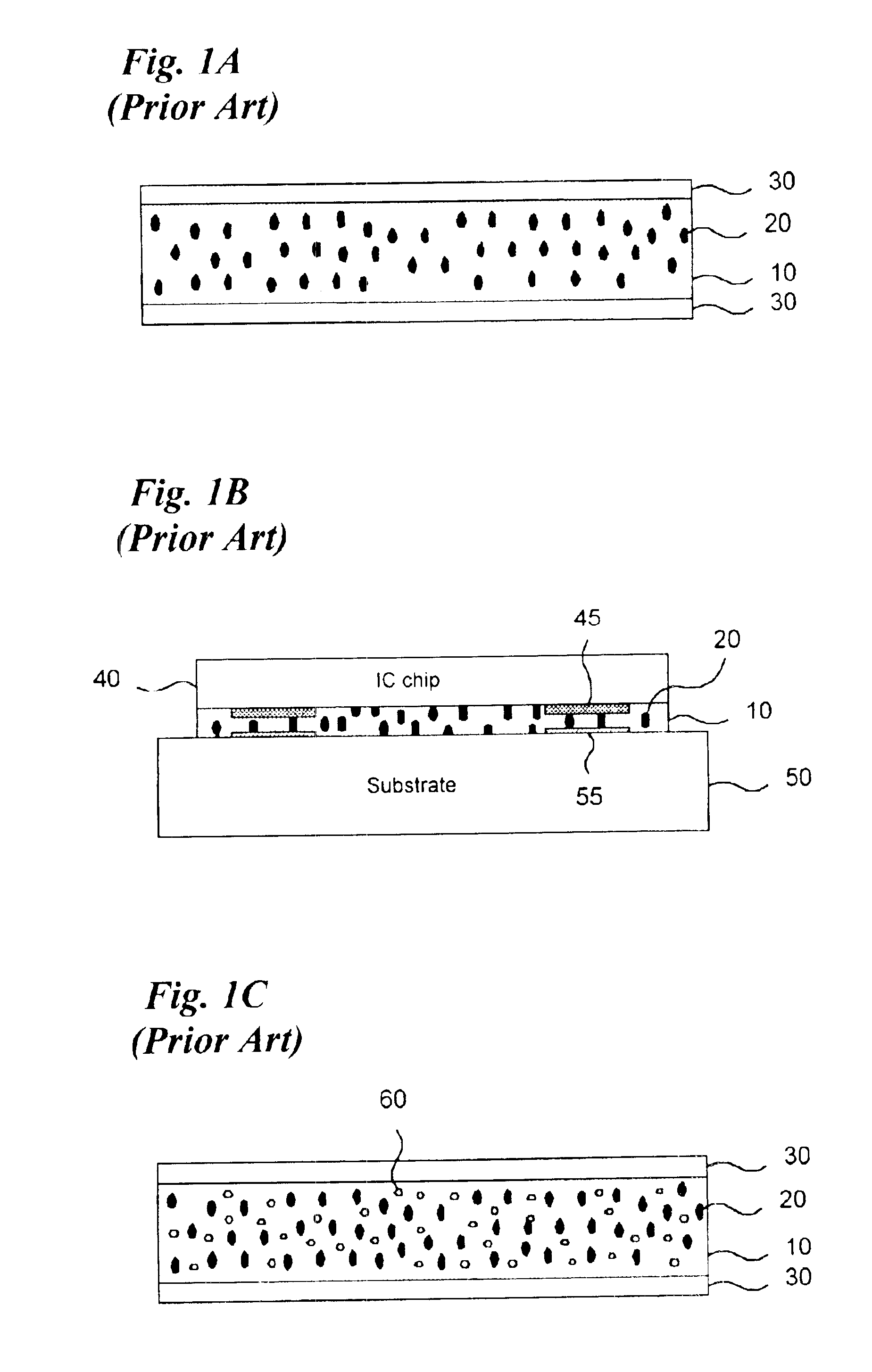

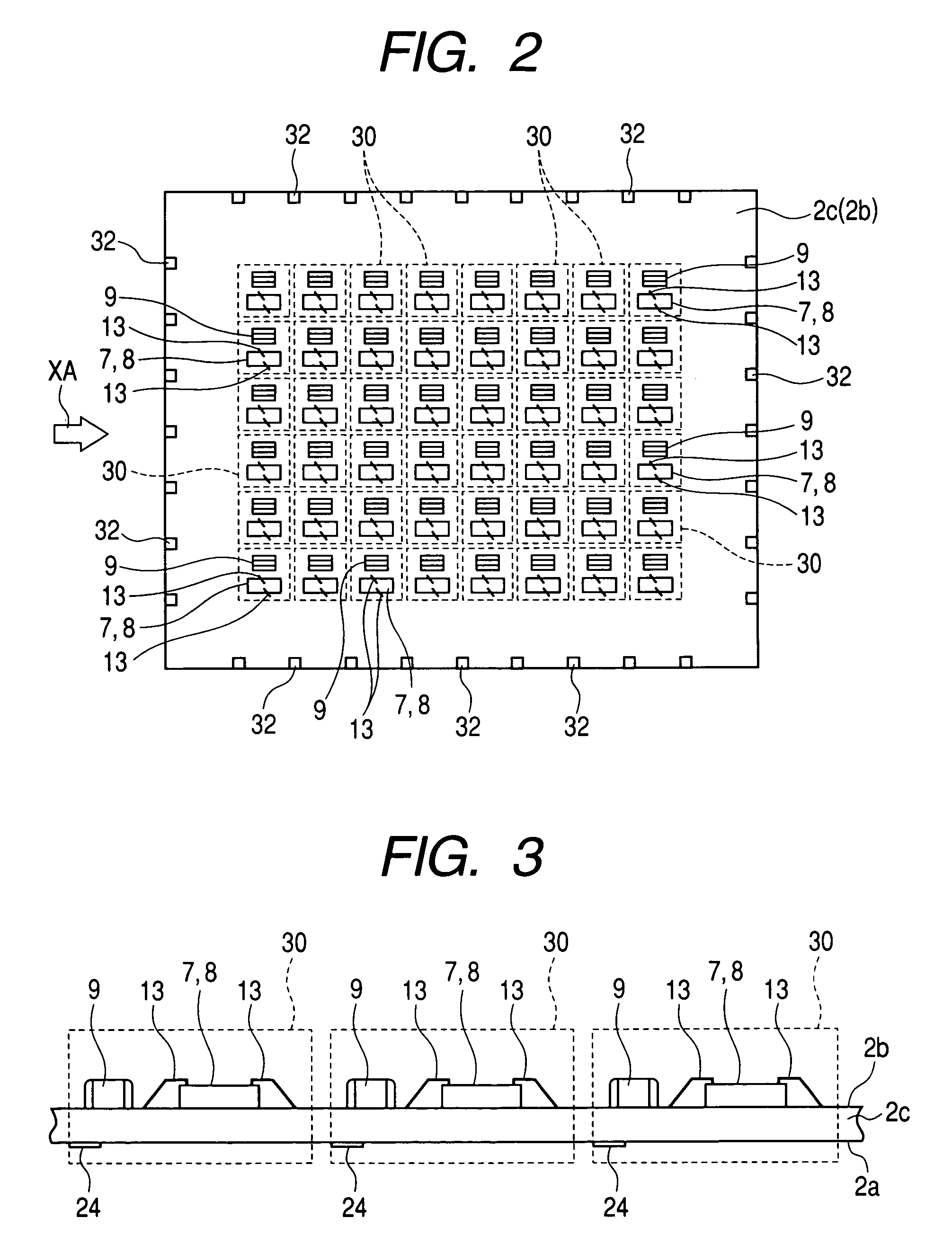

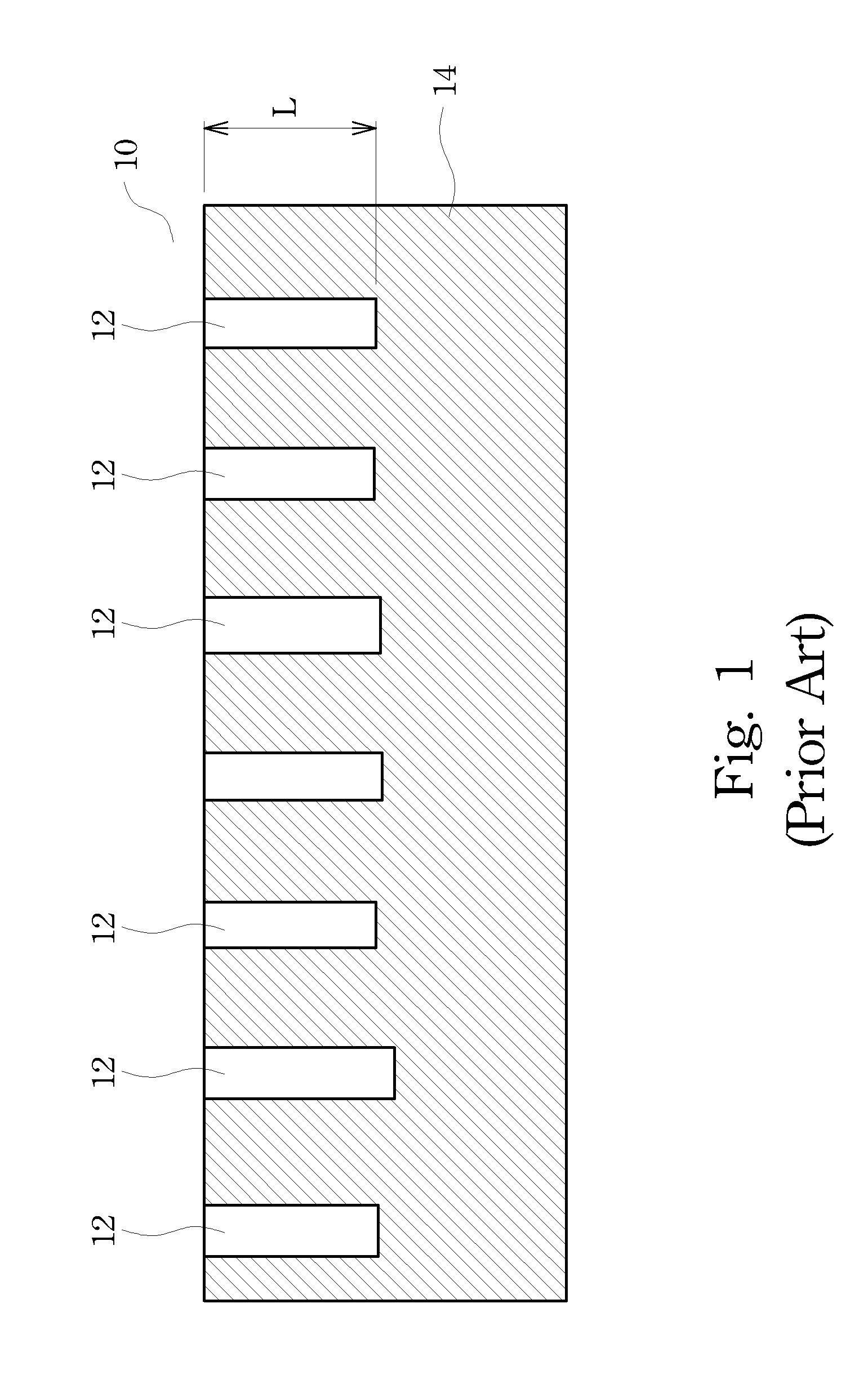

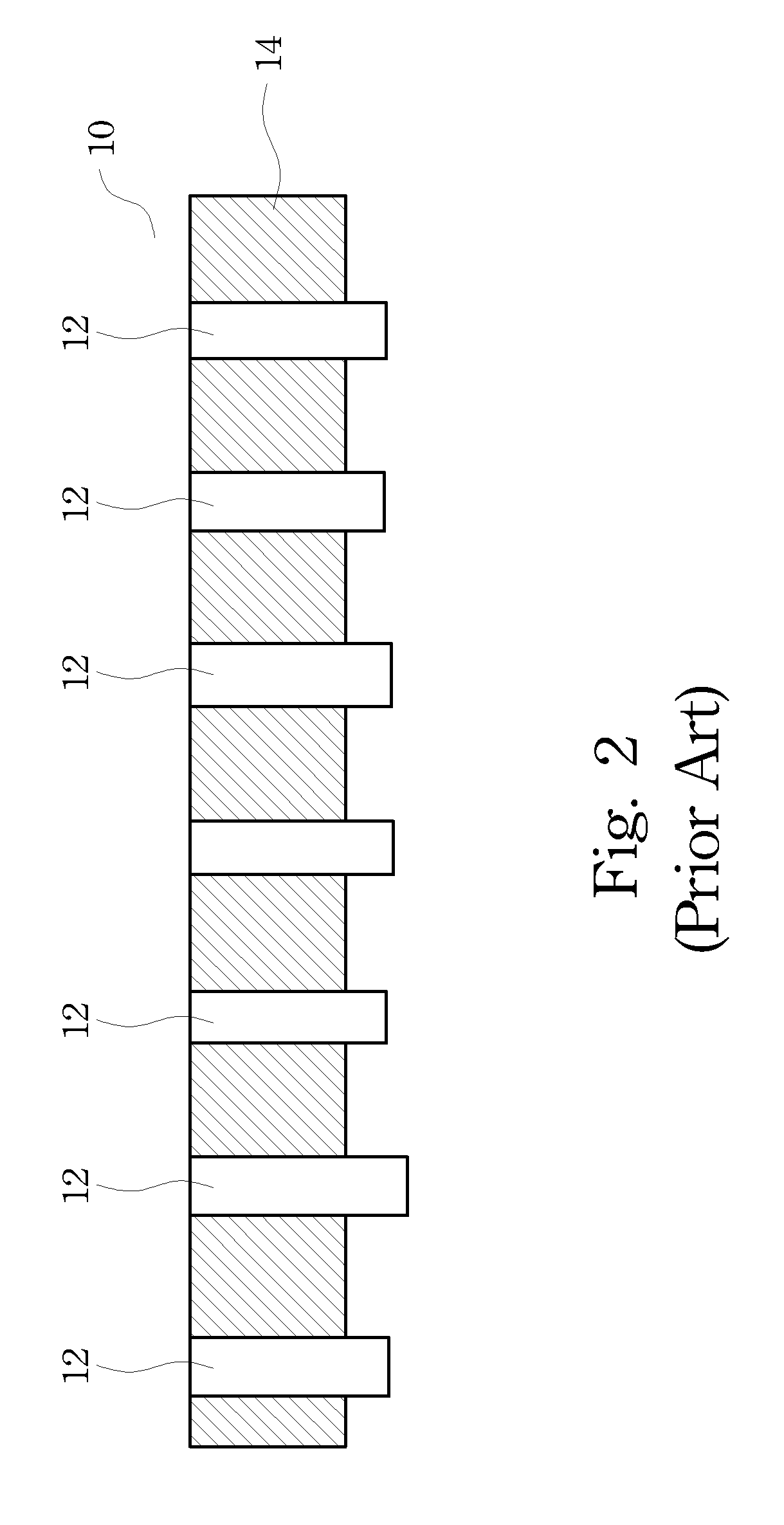

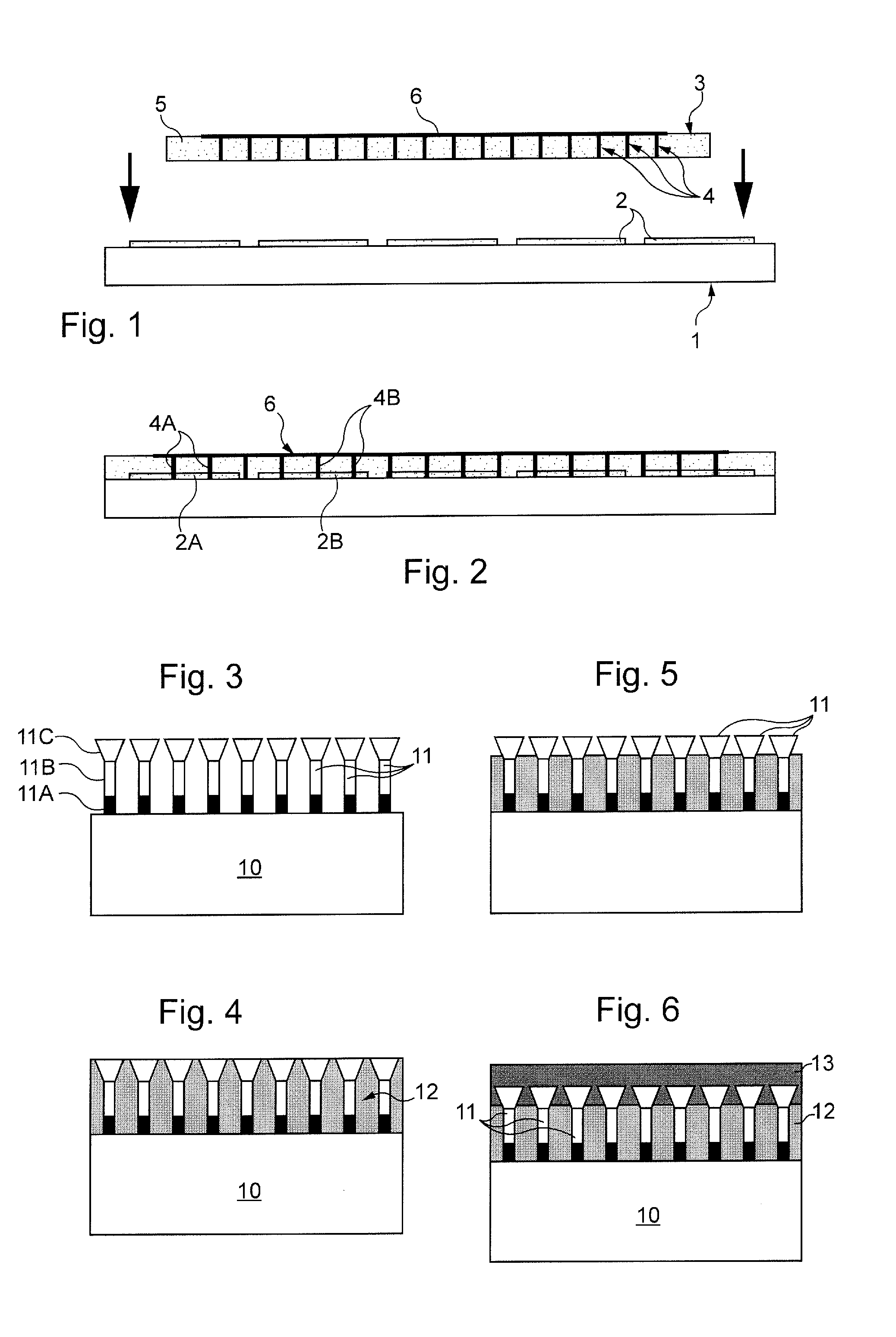

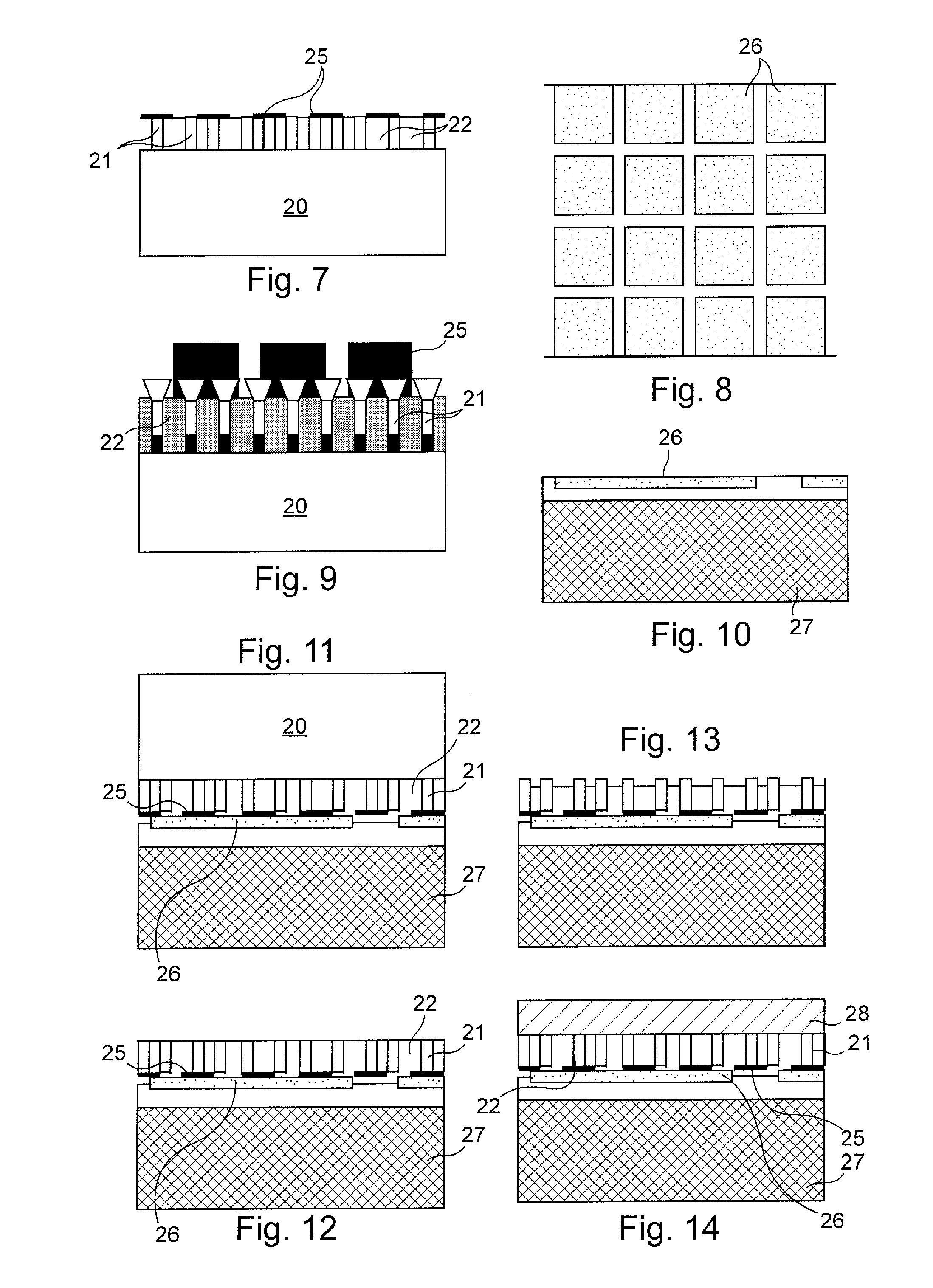

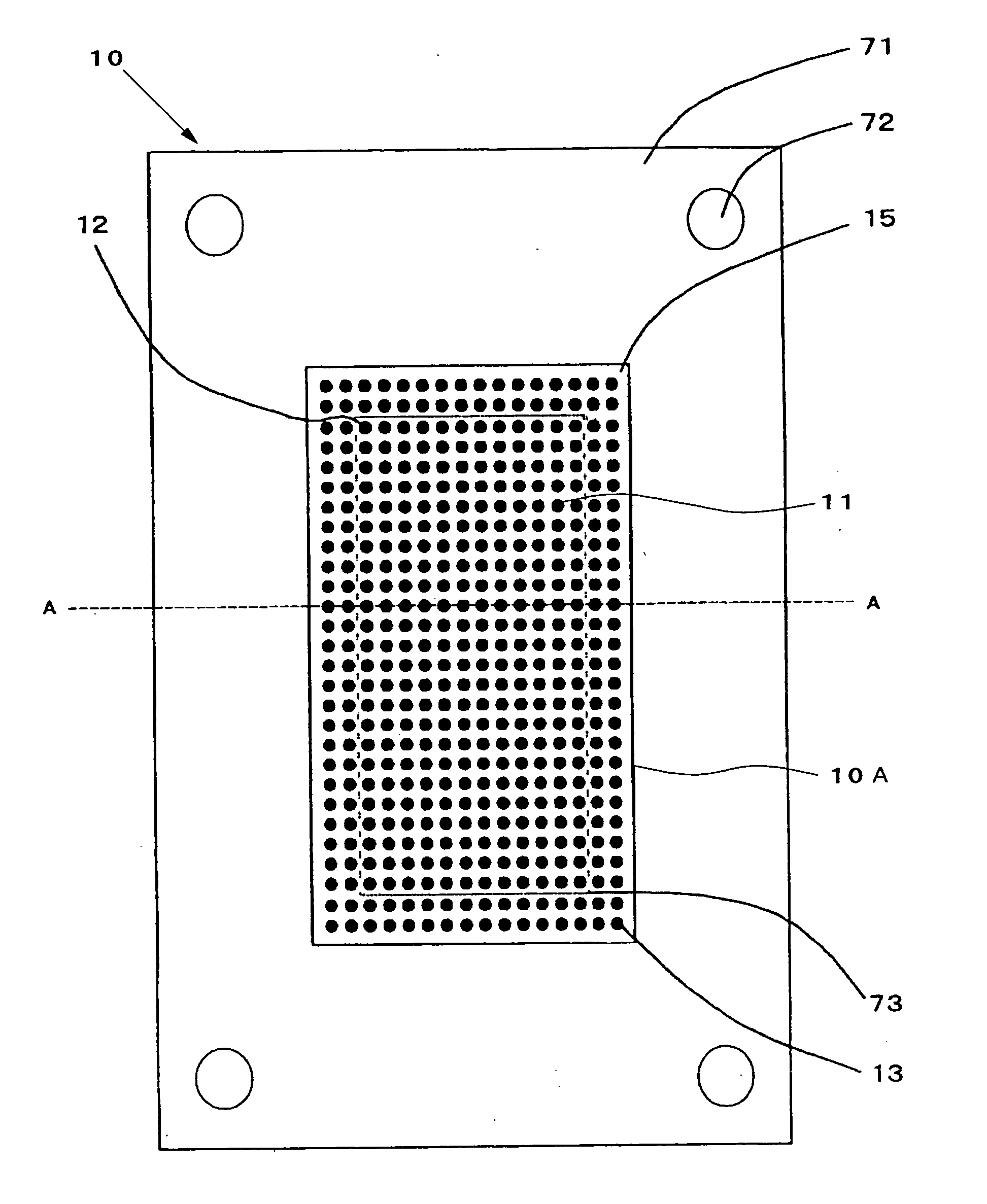

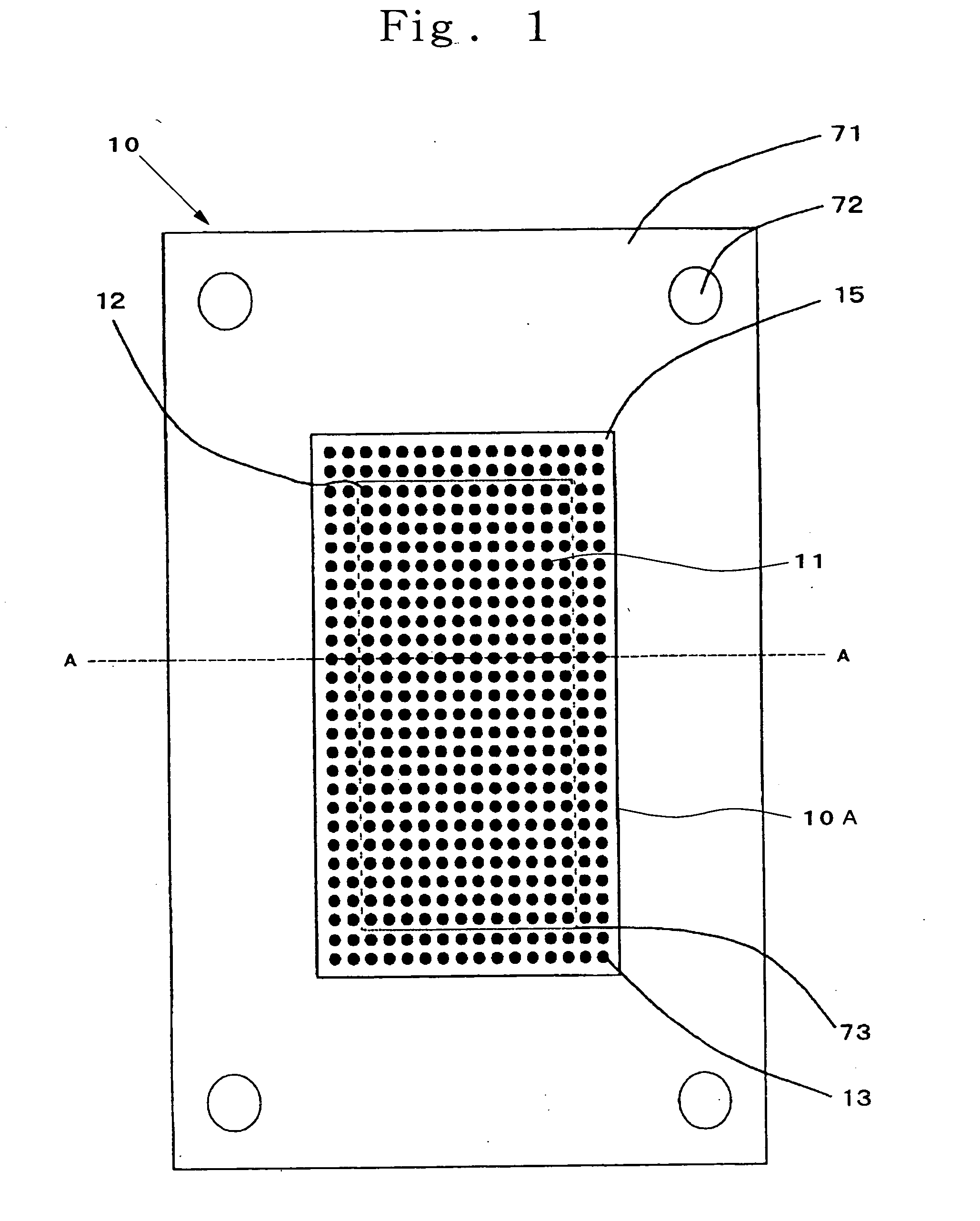

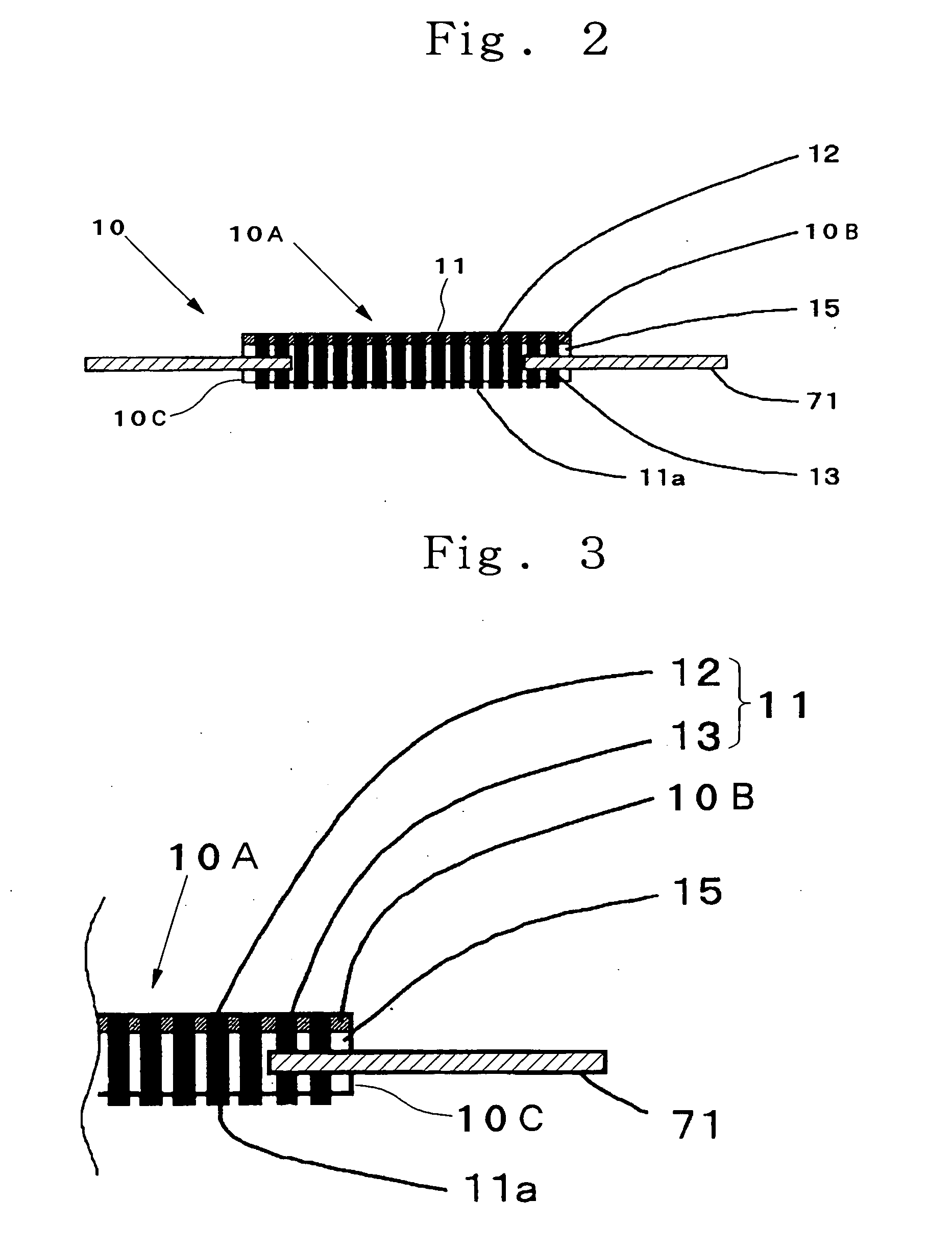

Non-random array anisotropic conductive film (ACF) and manufacturing processes

InactiveUS20060280912A1High resolutionReduce manufacturing costLayered productsCoupling device detailsAnisotropic conductive filmManufacturing technology

The present invention discloses structures and manufacturing processes of an ACF of improved resolution and reliability of electrical connection using a non-random array of microcavities of predetermined configuration, shape and dimension. The manufacturing process includes the steps of (i) fluidic filling of conductive particles onto a substrate or carrier web comprising a predetermined array of microcavities, or (ii) selective metallization of the array followed by filling the array with a filler material and a second selective metallization on the filled microcavity array. The thus prepared filled conductive microcavity array is then over-coated or laminated with an adhesive film.

Owner:TRILLION SCI INC

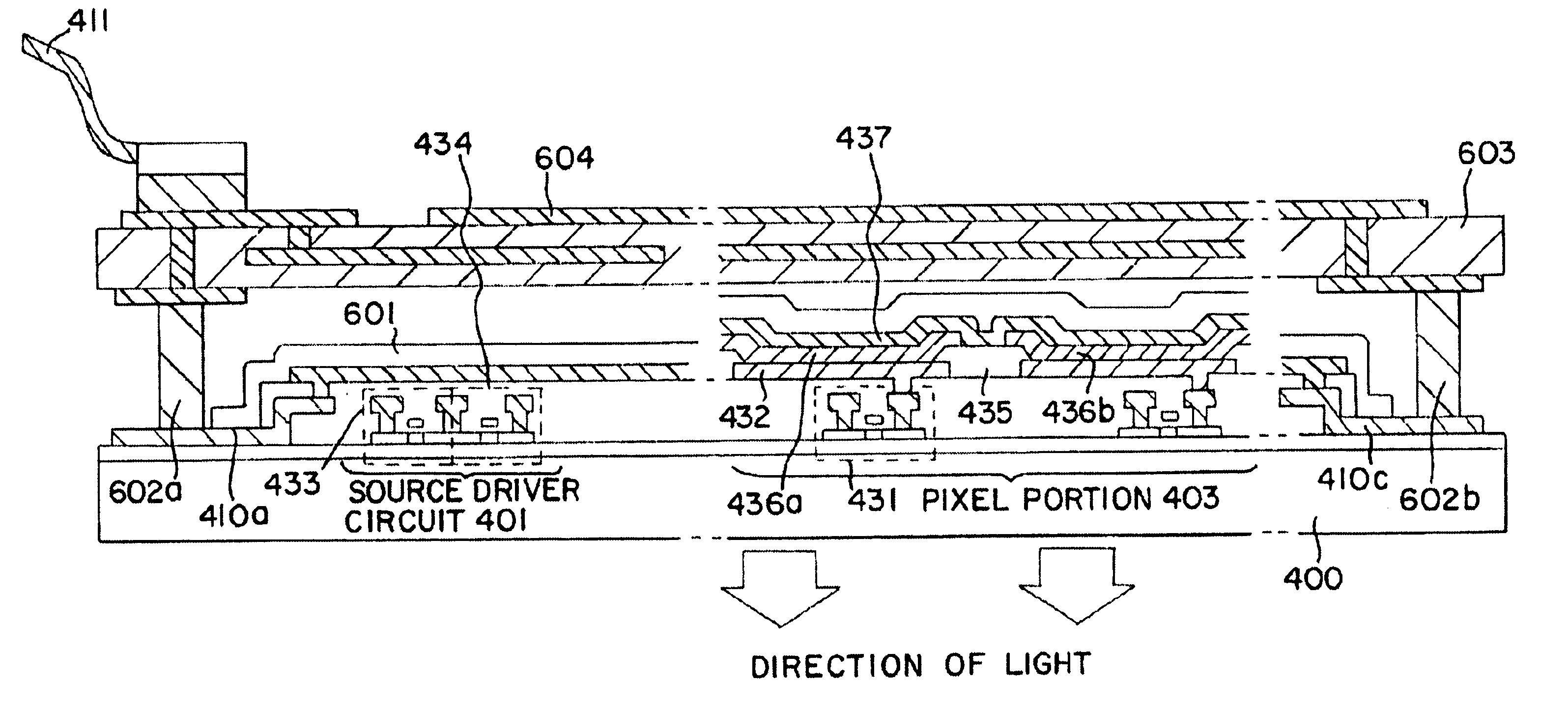

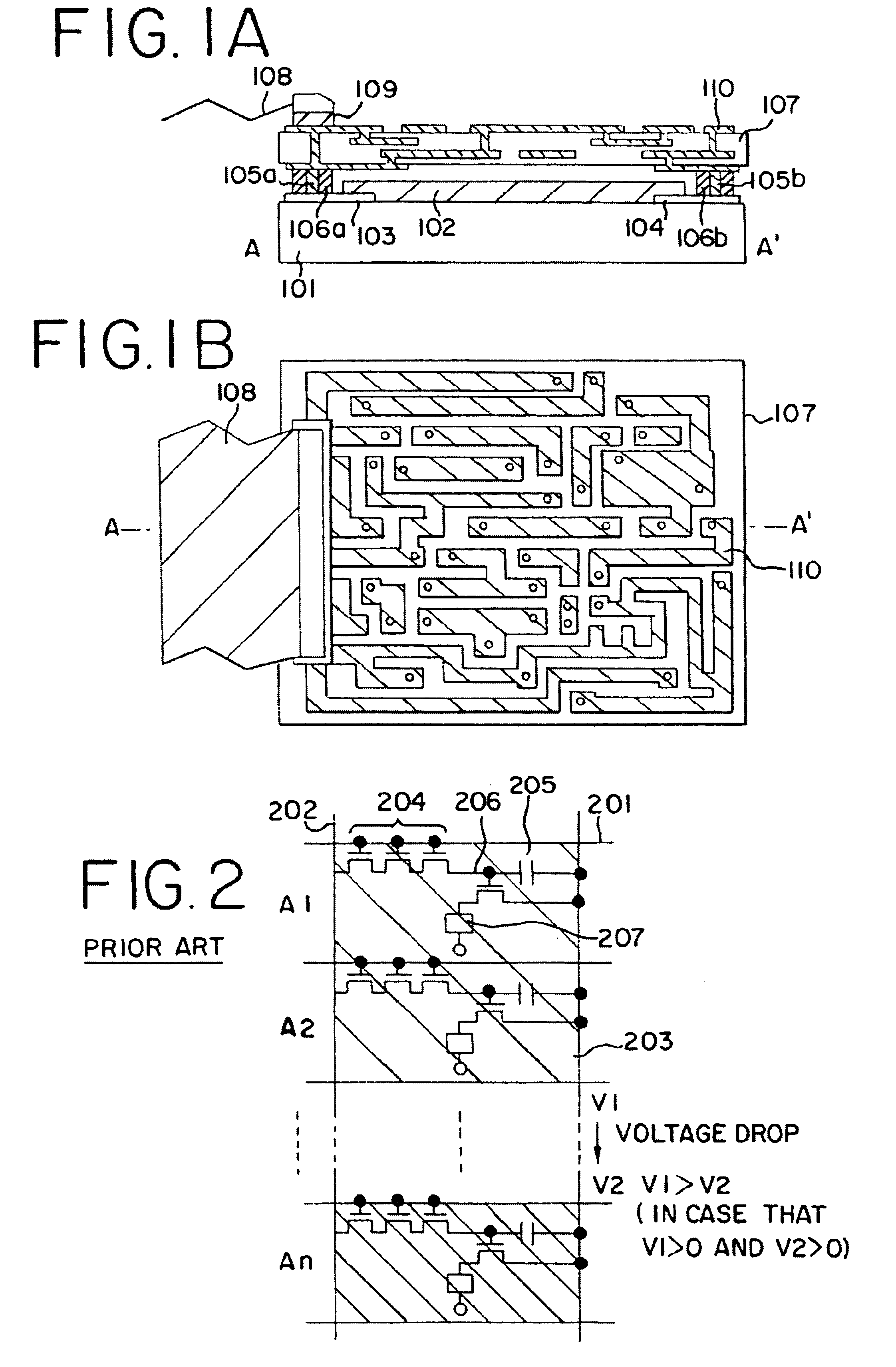

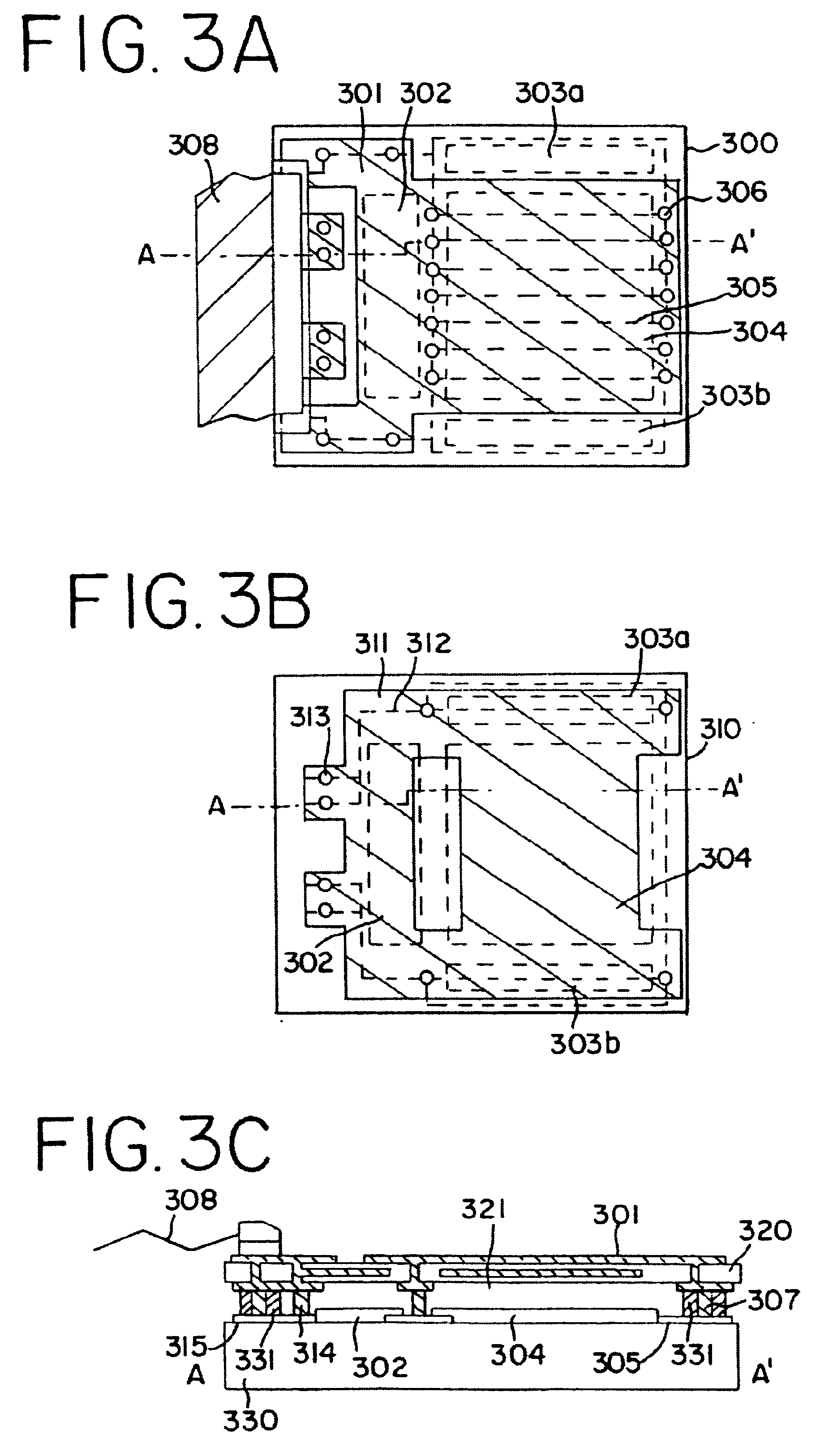

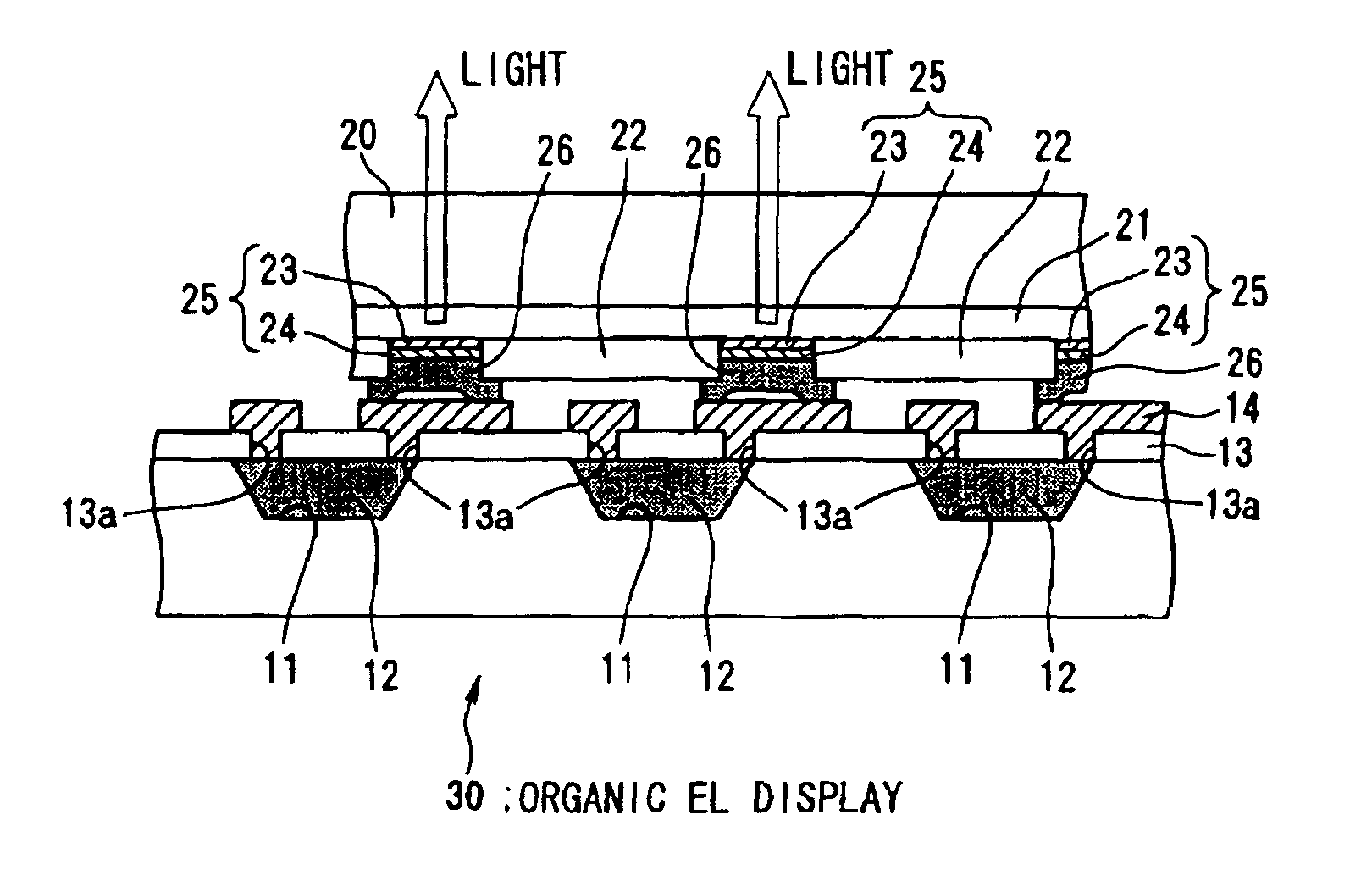

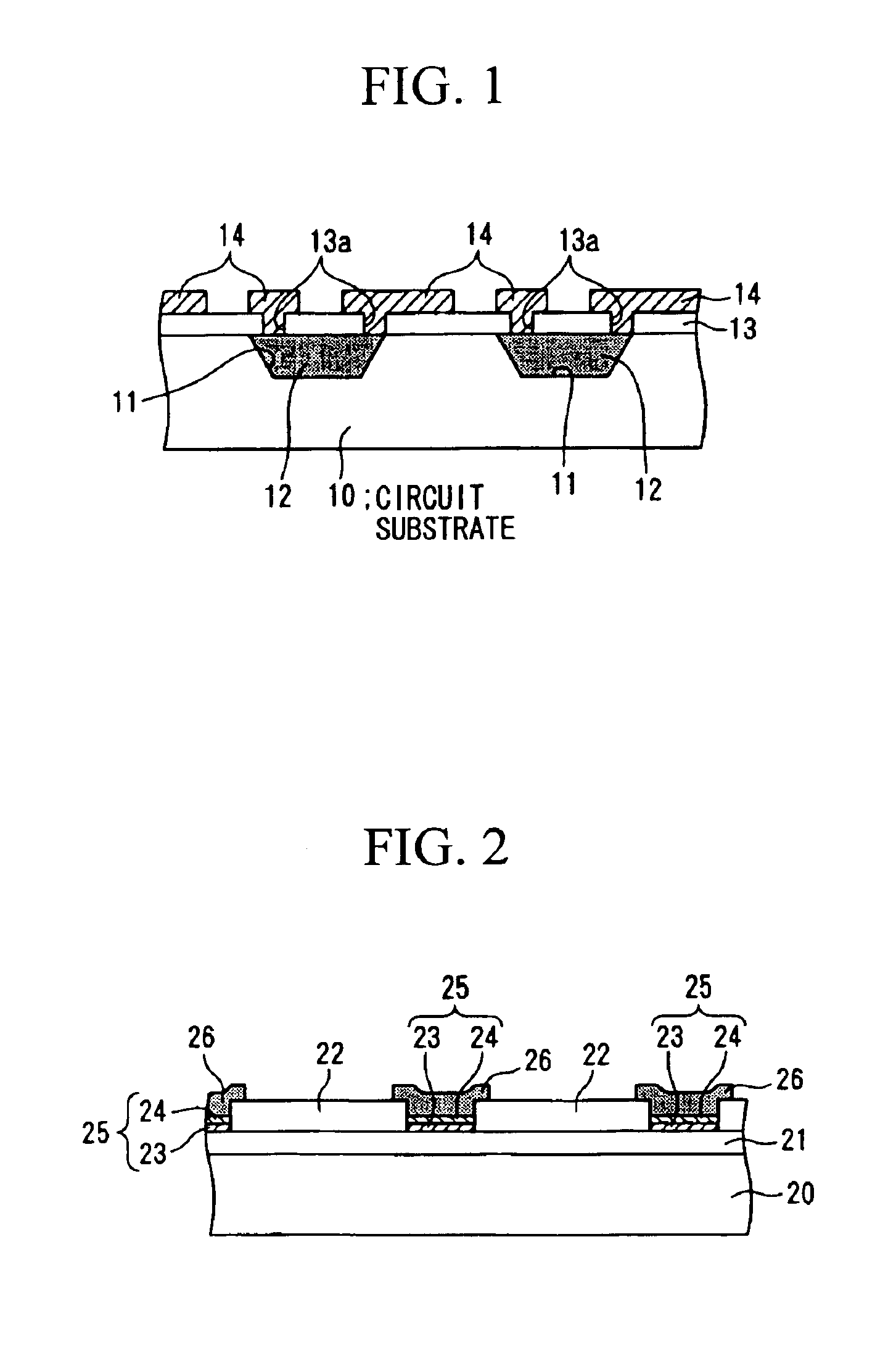

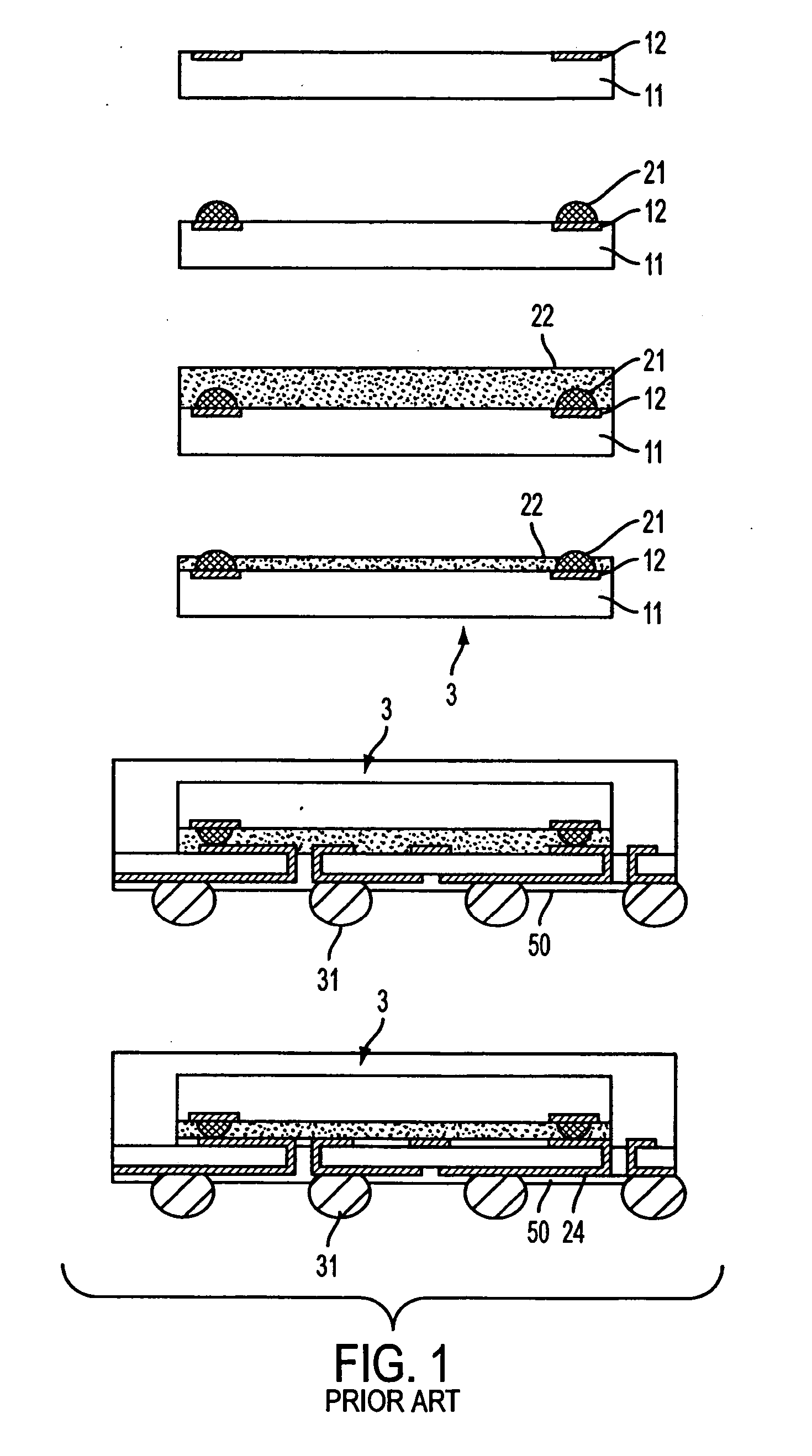

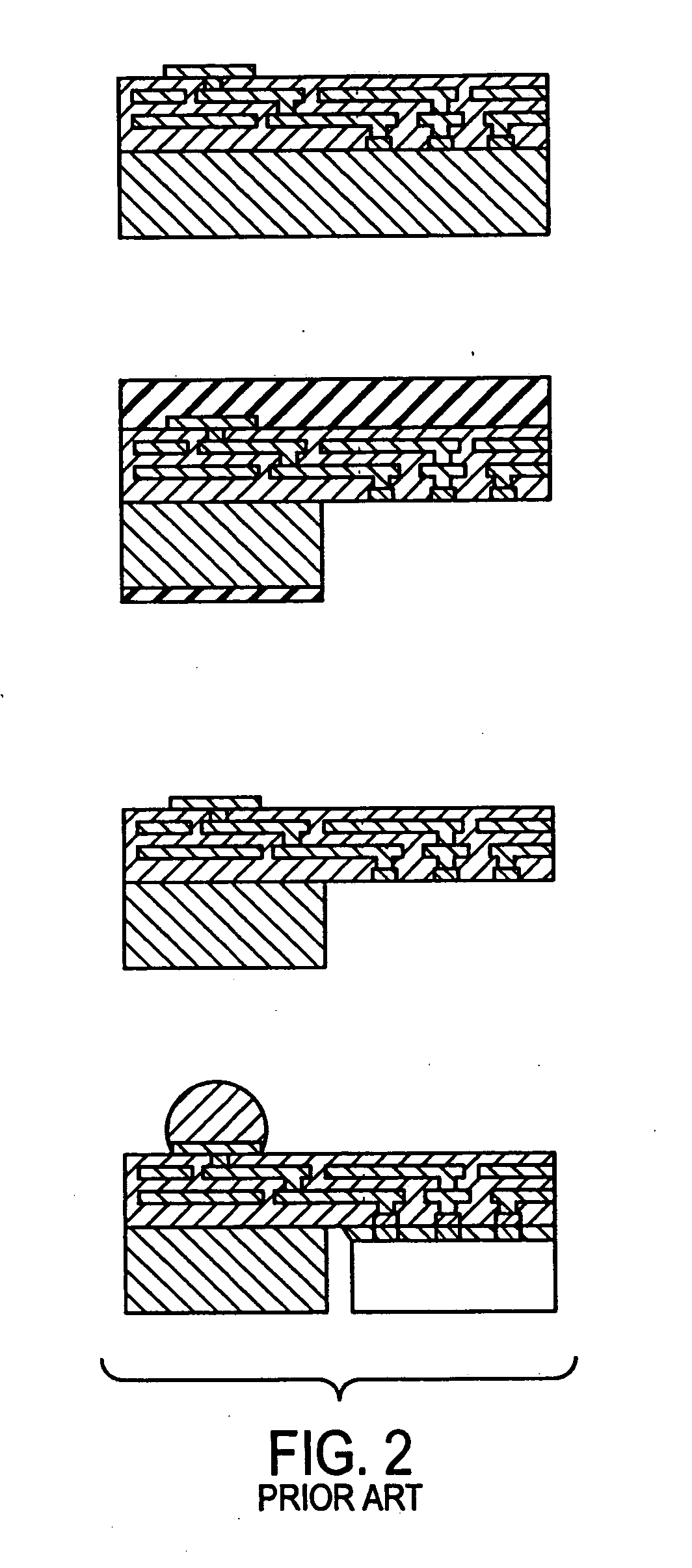

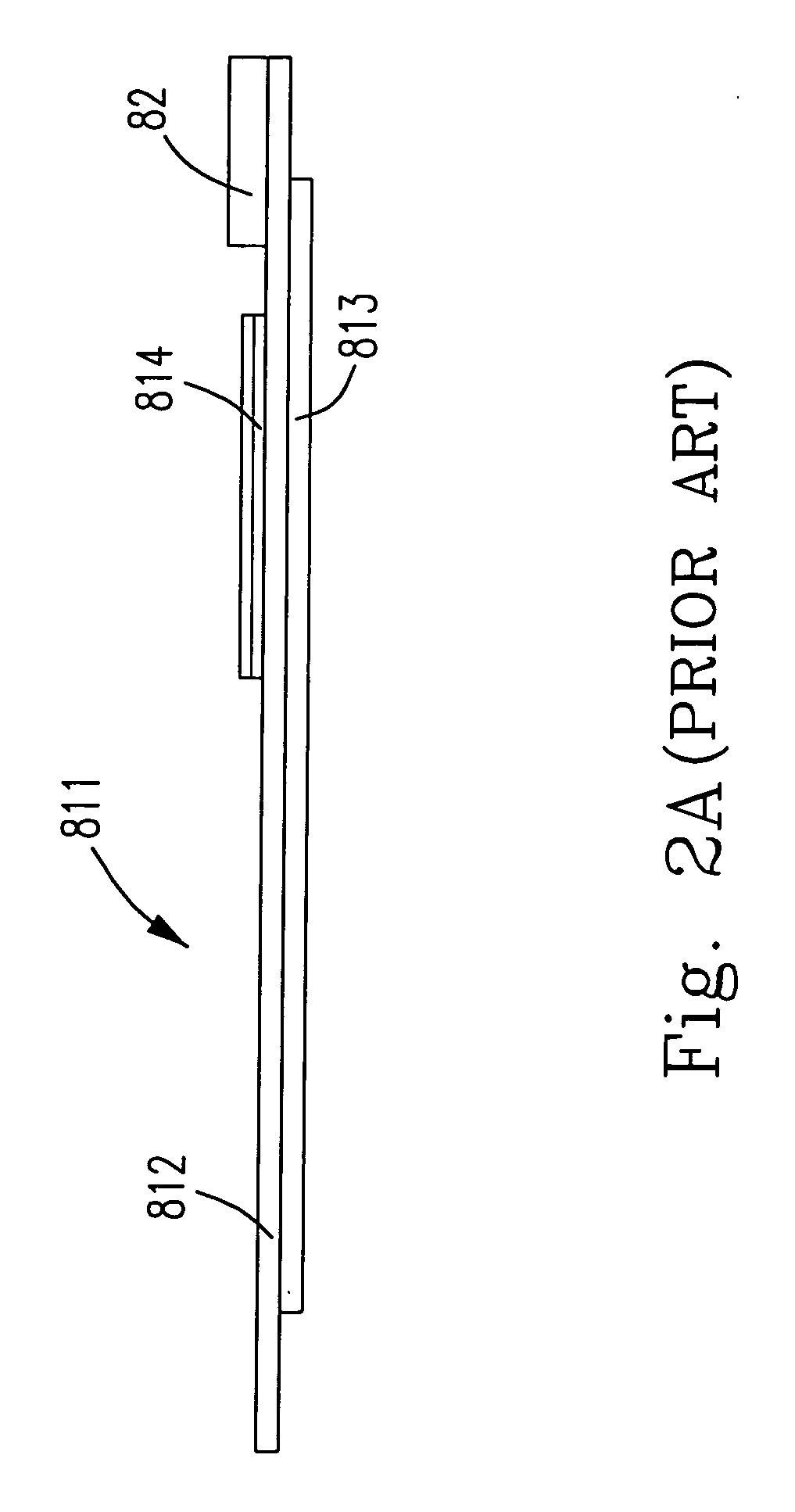

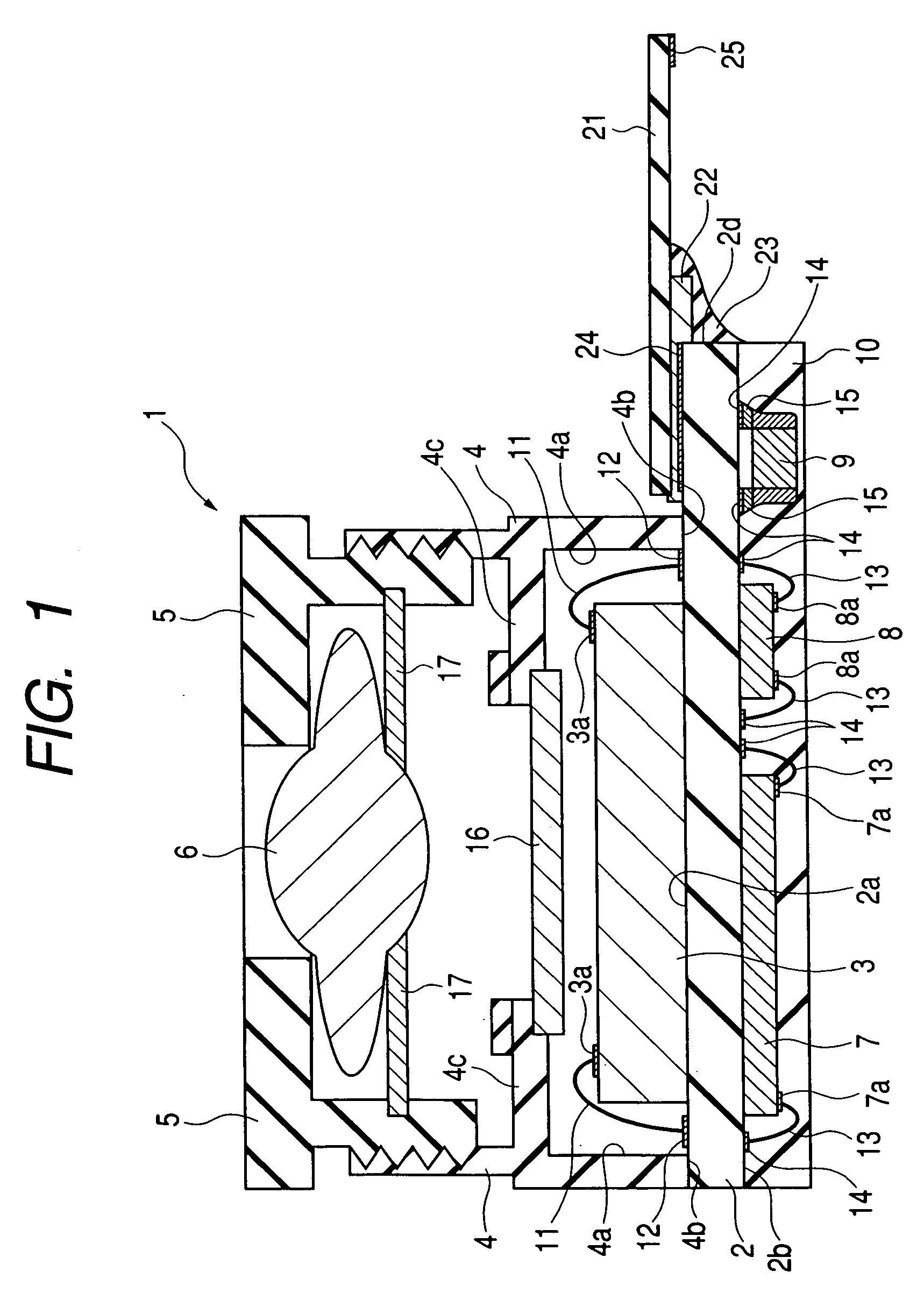

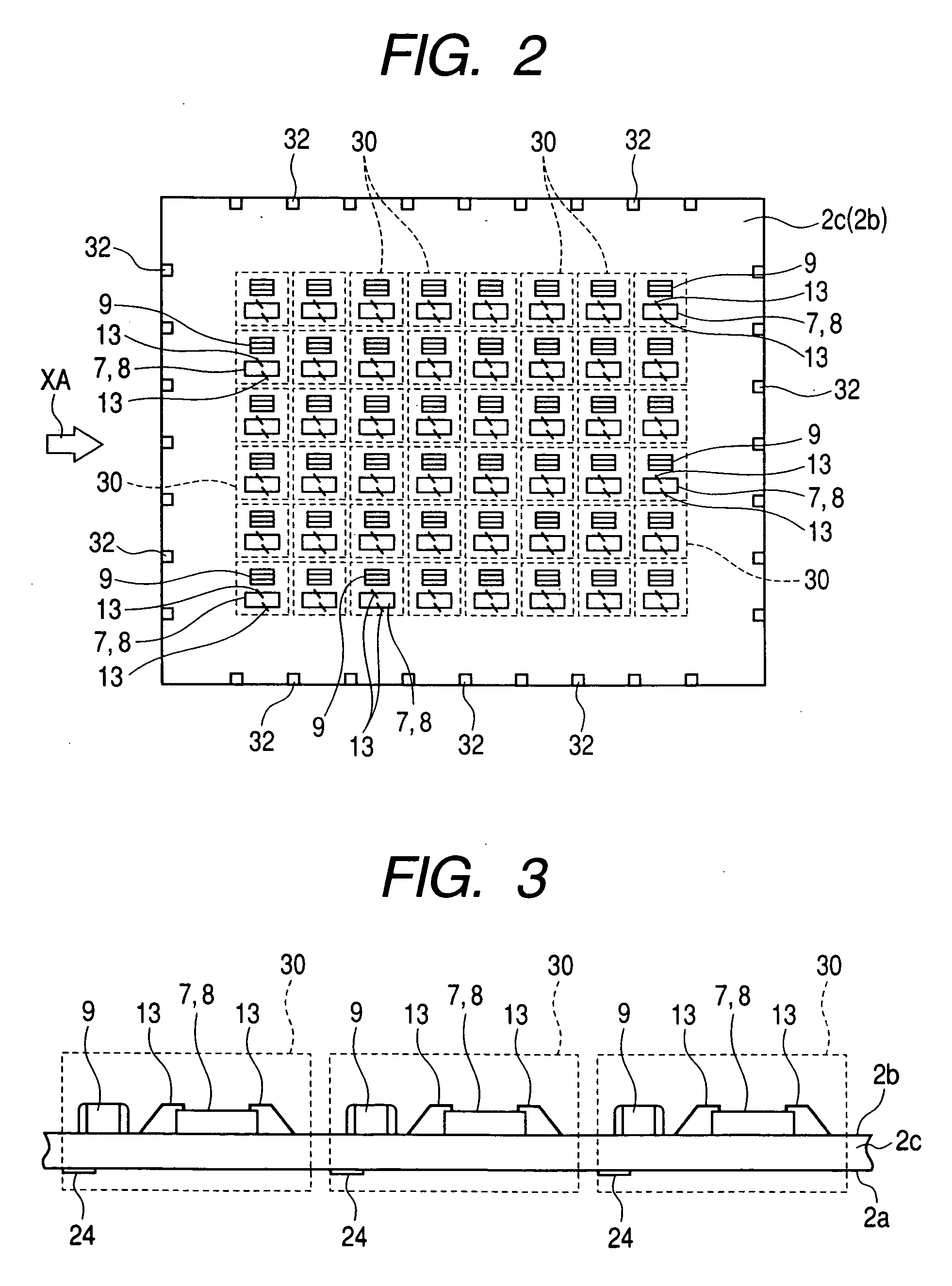

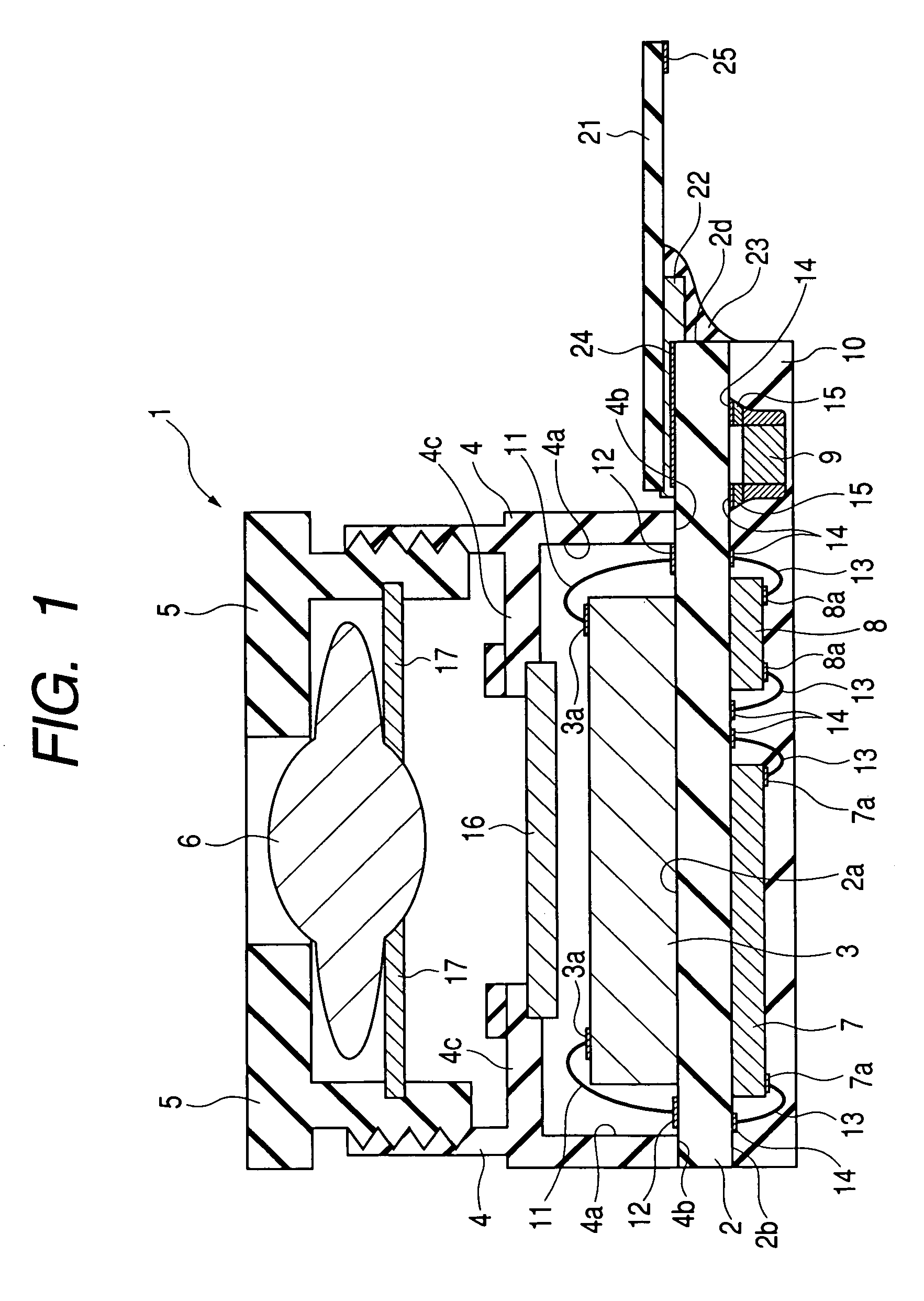

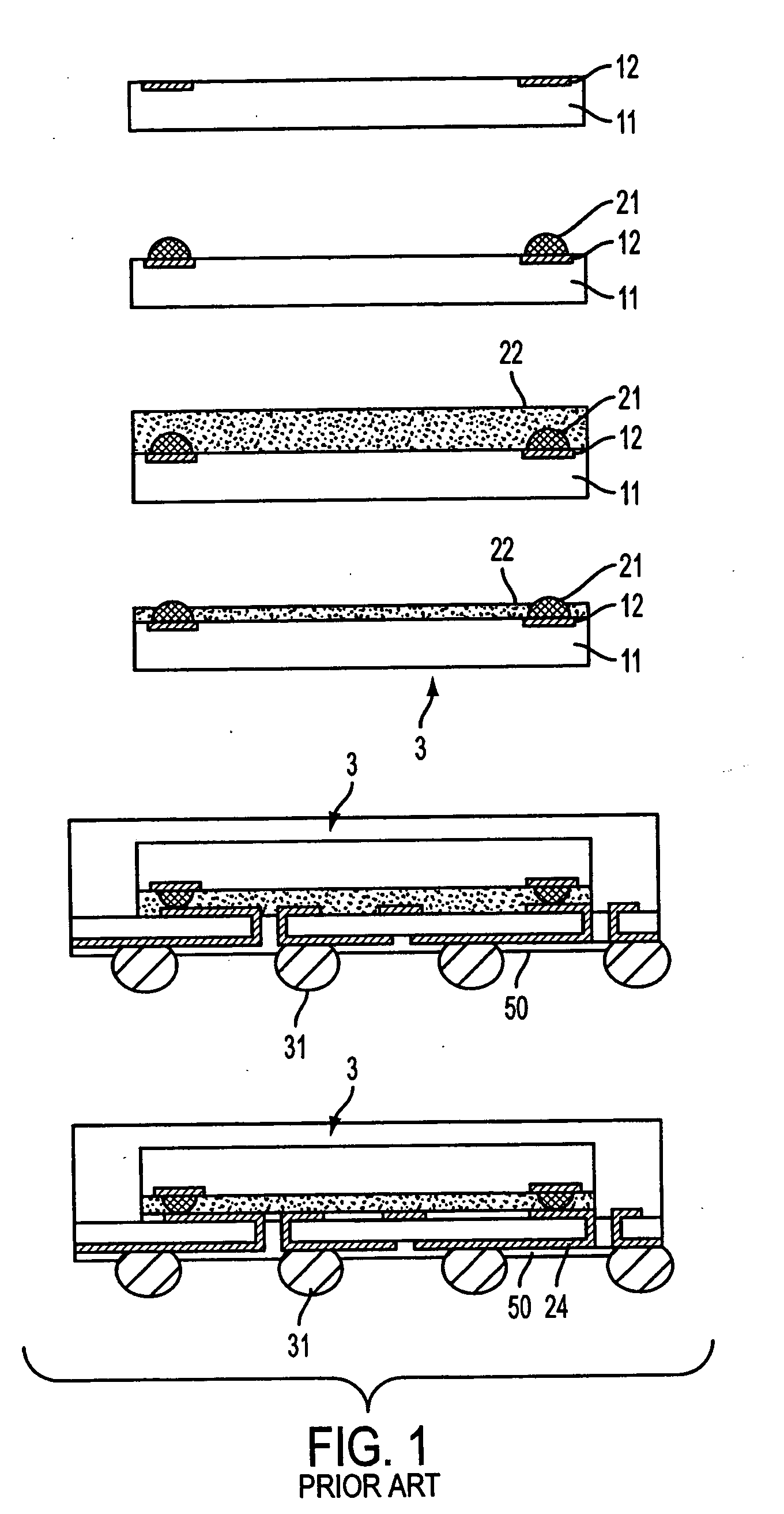

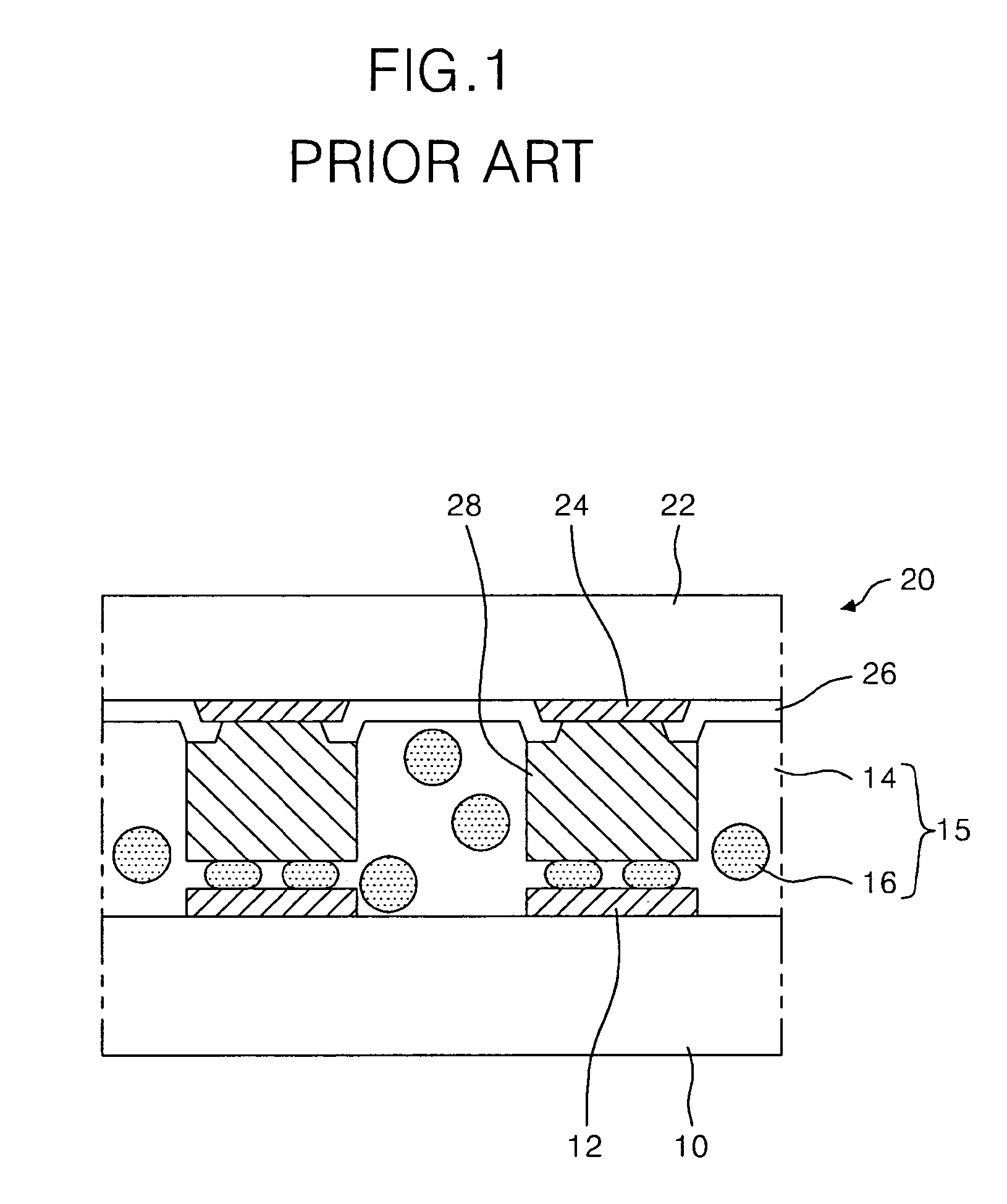

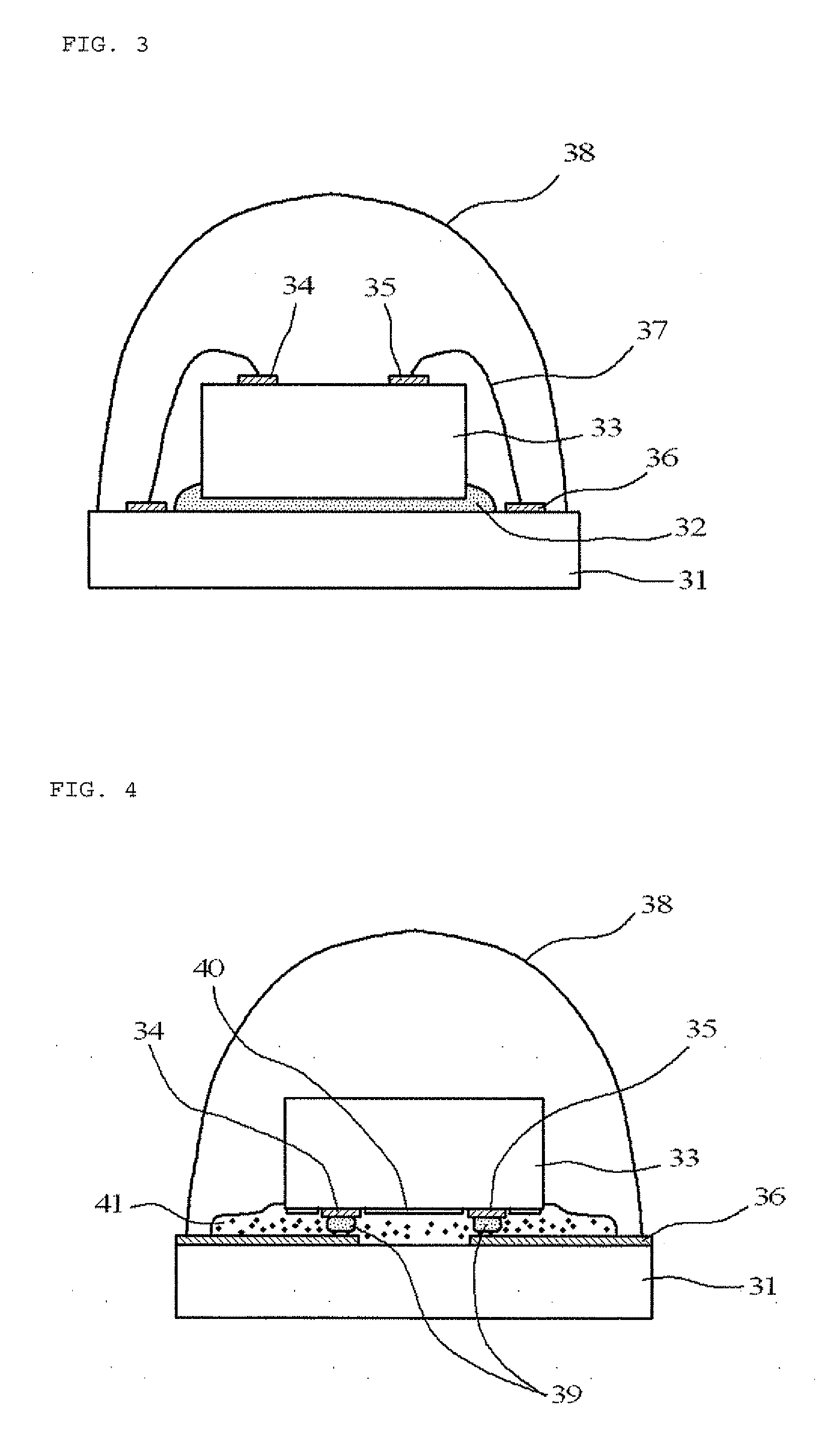

Light-emitting device

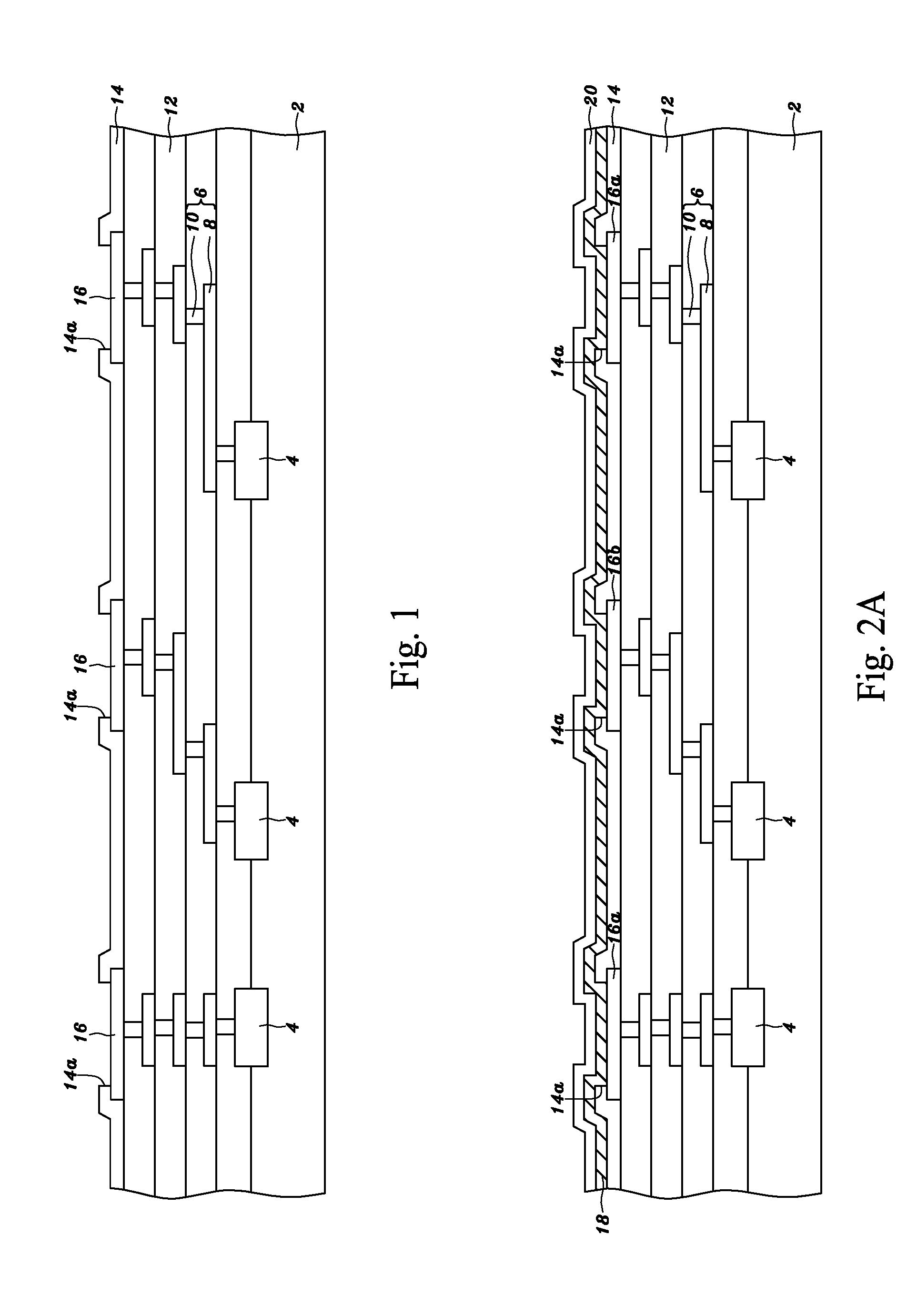

InactiveUS6894431B2High speedSuppress delay of wiringTelevision system detailsStatic indicating devicesDriver circuitElectricity

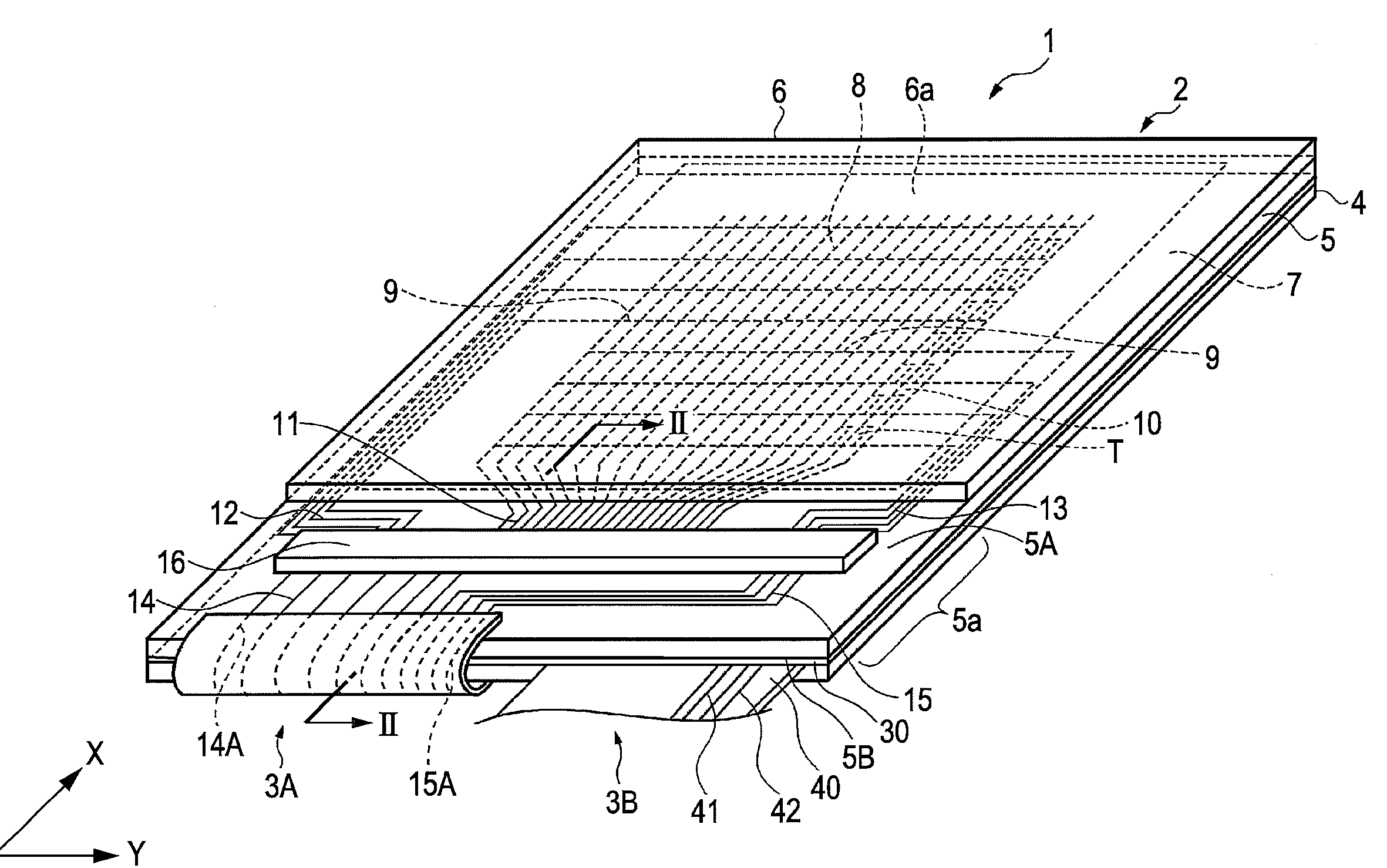

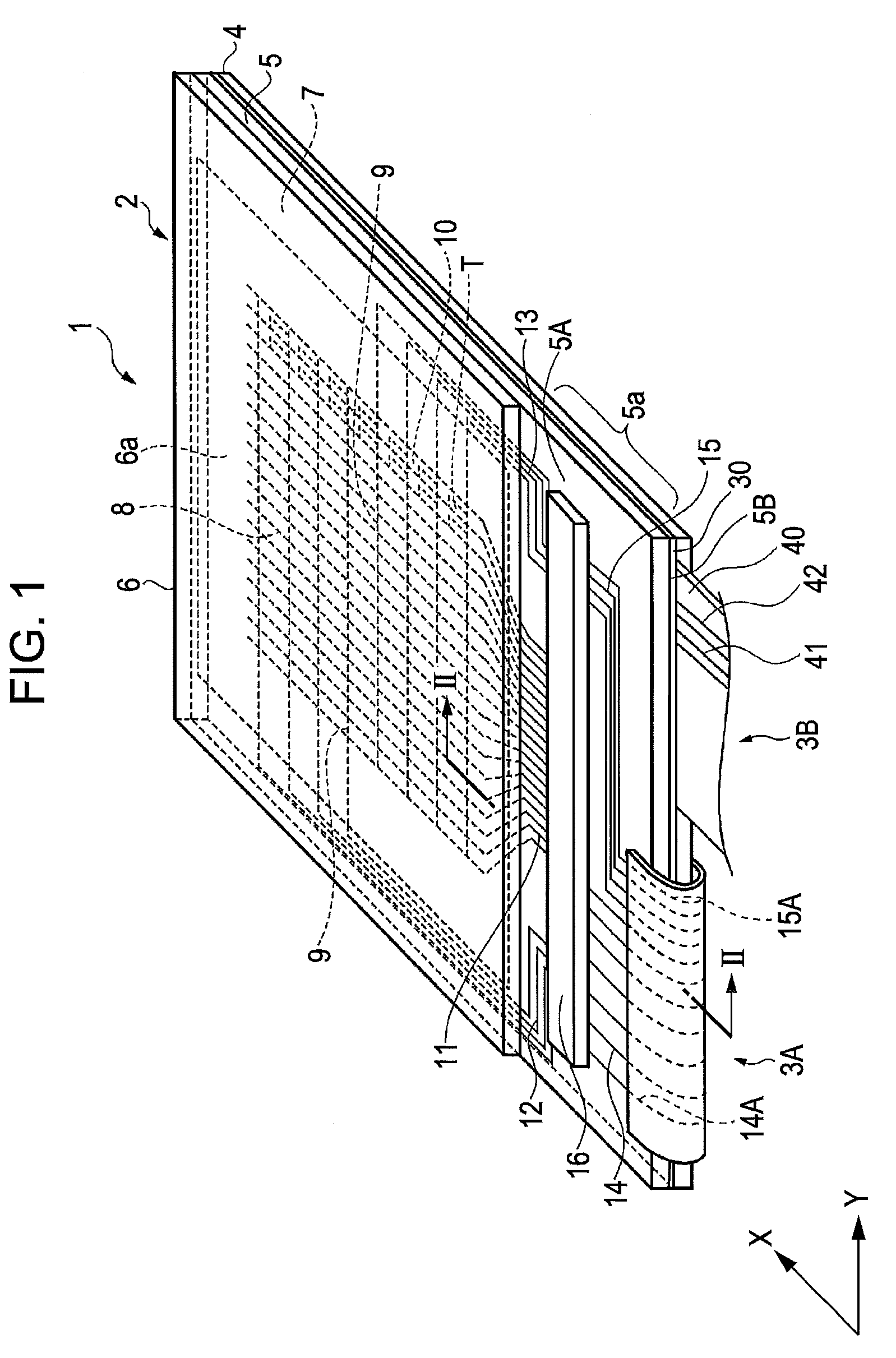

A light-emitting device having the quality of an image high in homogeneity is provided. A printed wiring board (second substrate) (107) is provided facing a substrate (first substrate) (101) that has a luminous element (102) formed thereon. A PWB side wiring (second group of wirings) (110) on the printed wiring board (107) is electrically connected to element side wirings (first group of wirings) (103, 104) by anisotropic conductive films (105a, 105b). At this point, because a low resistant copper foil is used to form the PWB side wiring (110), a voltage drop of the element side wirings (103, 104) and a delay of a signal can be reduced. Accordingly, the homogeneity of the quality of an image is improved, and the operating speed of a driver circuit portion is enhanced.

Owner:SEMICON ENERGY LAB CO LTD

Non-random array anisotropic conductive film (ACF) and manufacturing processes

ActiveUS20100101700A1High resolutionReduce manufacturing costSemiconductor/solid-state device detailsSolid-state devicesAnisotropic conductive filmRandom array

Structures and manufacturing processes of an ACF array using a non-random array of microcavities of predetermined configuration, shape and dimension. The manufacturing process includes fluidic filling of conductive particles onto a substrate or carrier web comprising a predetermined array of microcavities, or selective metallization of the array followed by filling the array with a filler material and a second selective metallization on the filled microcavity array. The thus prepared filled conductive microcavity array is then over-coated or laminated with an adhesive film. Cavities in the array, and particles filling the cavities, can have a unimodal, bimodal, or multimodal distribution.

Owner:POLAROID IP BV

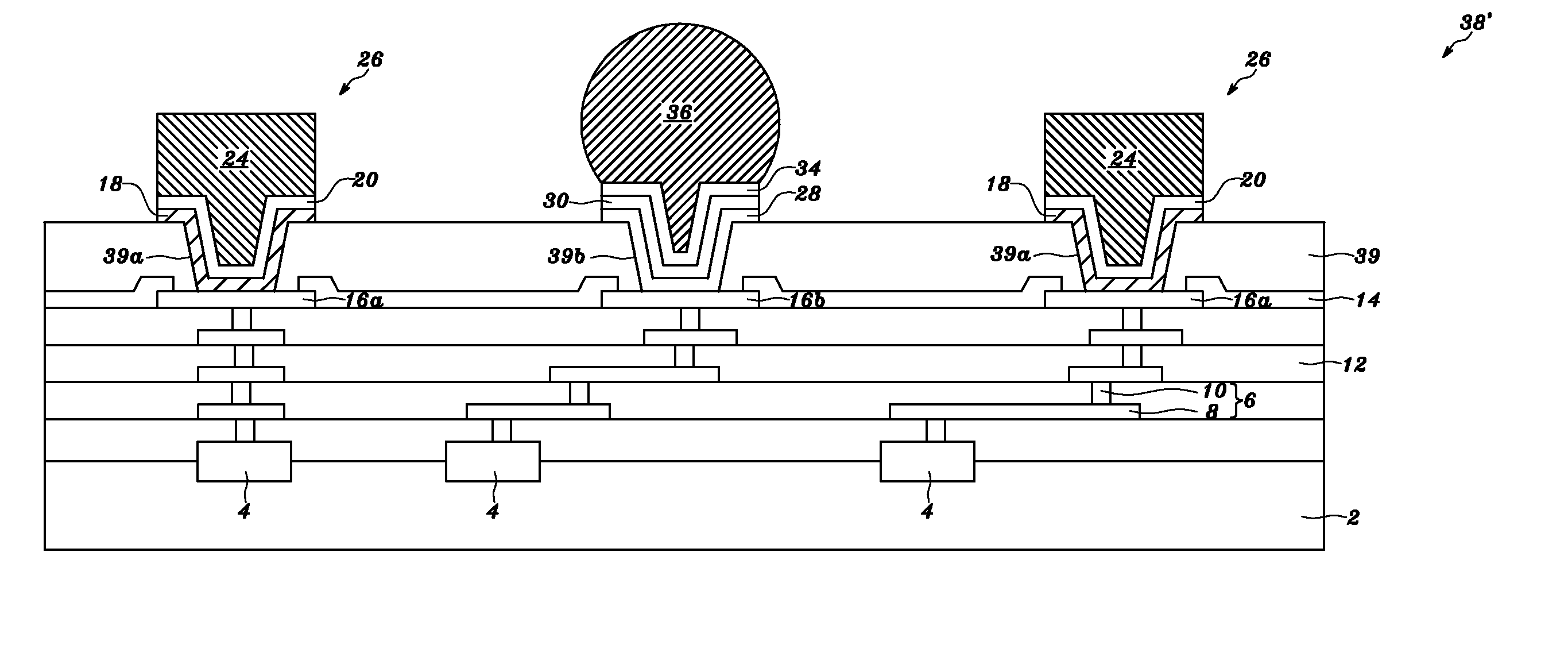

Build-up structures with multi-angle vias for chip to chip interconnects and optical bussing

InactiveUS6919508B2Improve performanceIncrease speedTelevision system detailsPiezoelectric/electrostriction/magnetostriction machinesAnisotropic conductive filmCopper interconnect

A build-up structure for chip to chip interconnects and System-In-Package utilizing multi-angle vias for electrical and optical routing or bussing of electronic information and controlled CTE dielectrics including mesocomposites to achieve optimum electrical and optical performance of monolithic structures. Die, multiple die, Microelectromechanical Machines (MEMs) and / or other active or passive components such as transducers or capacitors can be accurately positioned on a substrate such as a copper heatsink and multi-angle stud bumps can be placed on the active sites of the components. A first dielectric layer is preferably placed on the components, thereby embedding the components in the structure. Through various processes of photolithography, laser machining, soft lithography or anisotropic conductive film bonding, escape routing and circuitry is formed on the first metal layer. Additional dielectric layers and metal circuitry are formed utilizing multi-angle vias to form escape routing from tight pitch bond pads on the die to other active and passive components. Multi-angle vias can carry electrical or optical information in the form of digital or analog electromagnetic current, or in the form of visible or non-visible optical bussing and interconnections.

Owner:CAPITALSOURCE FINANCE

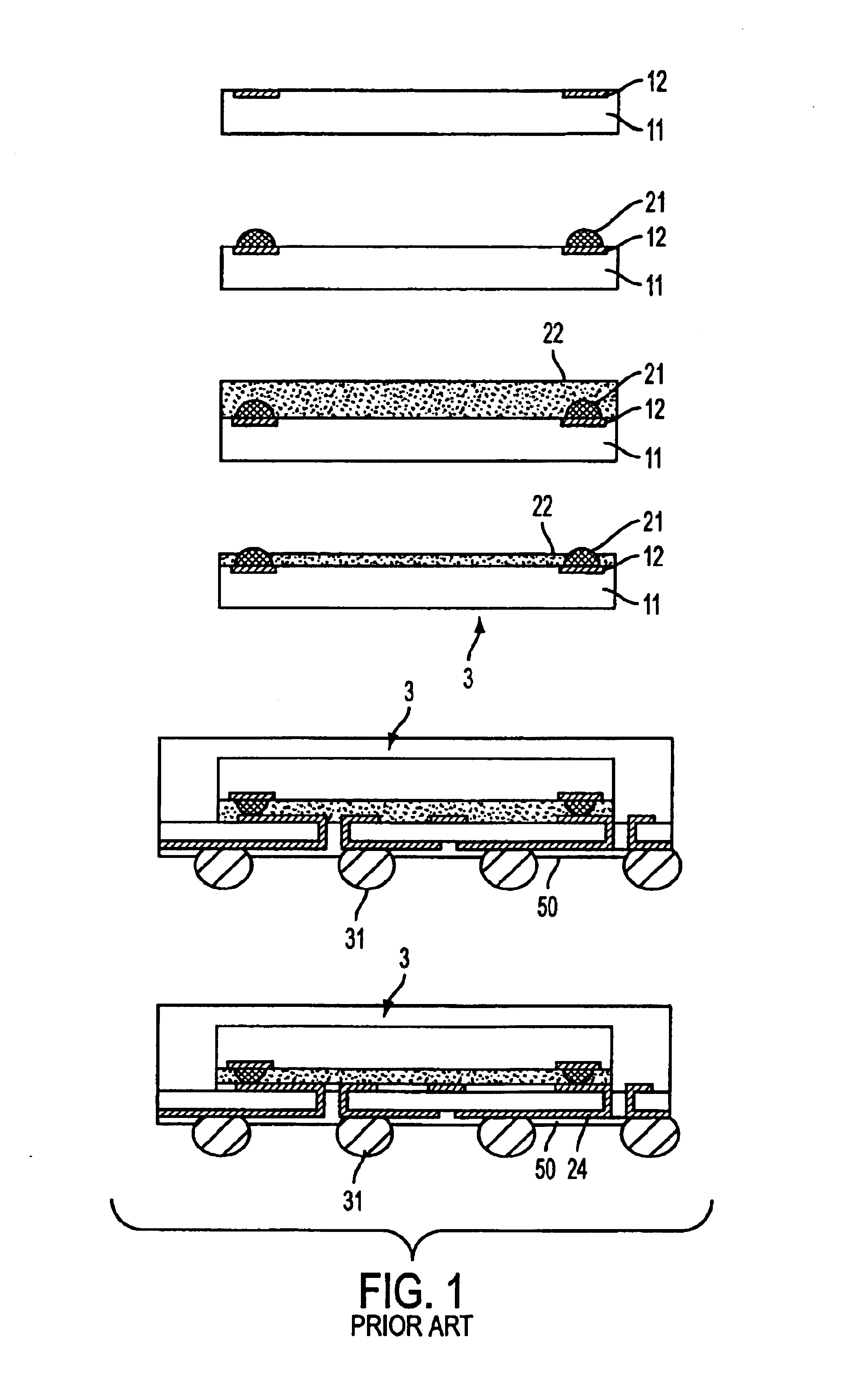

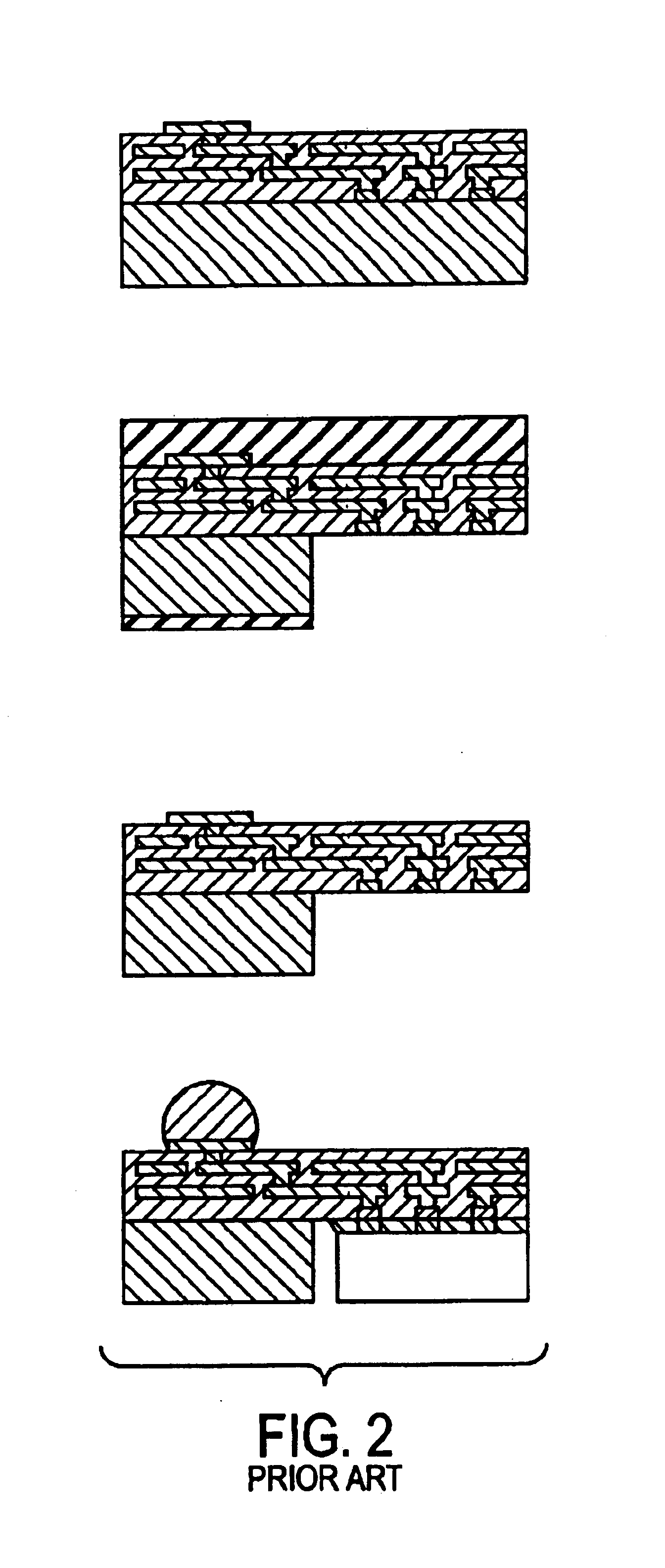

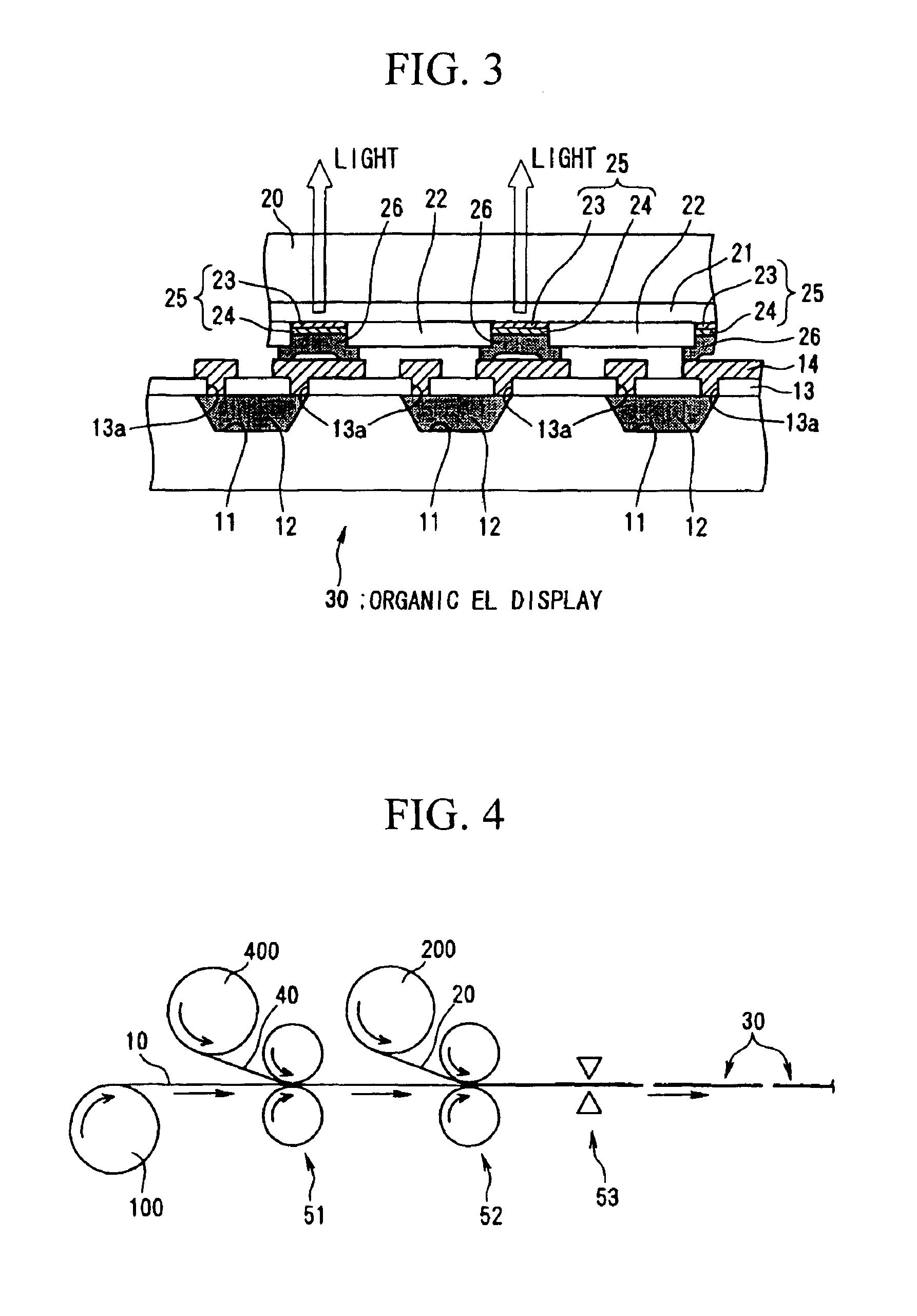

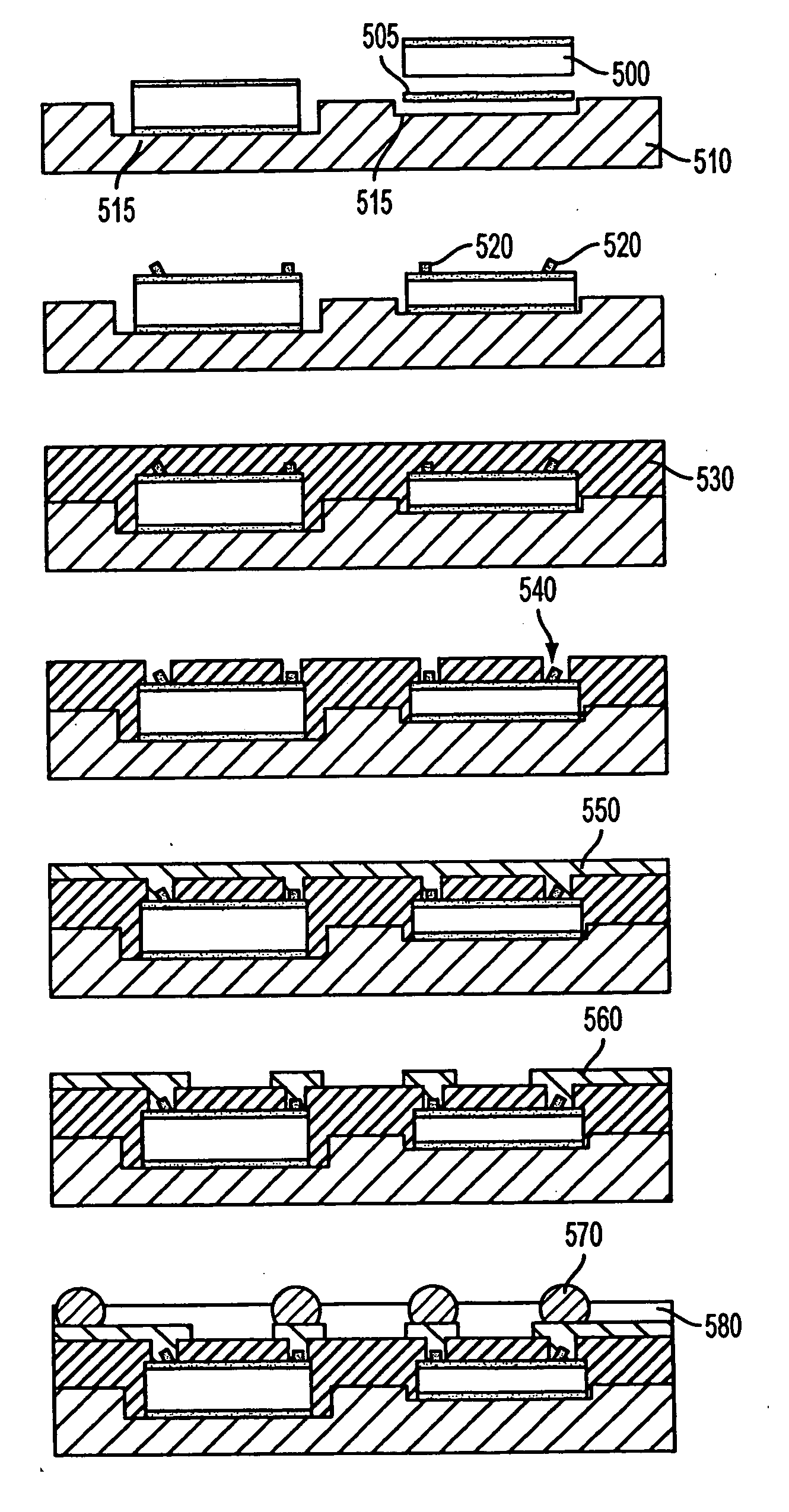

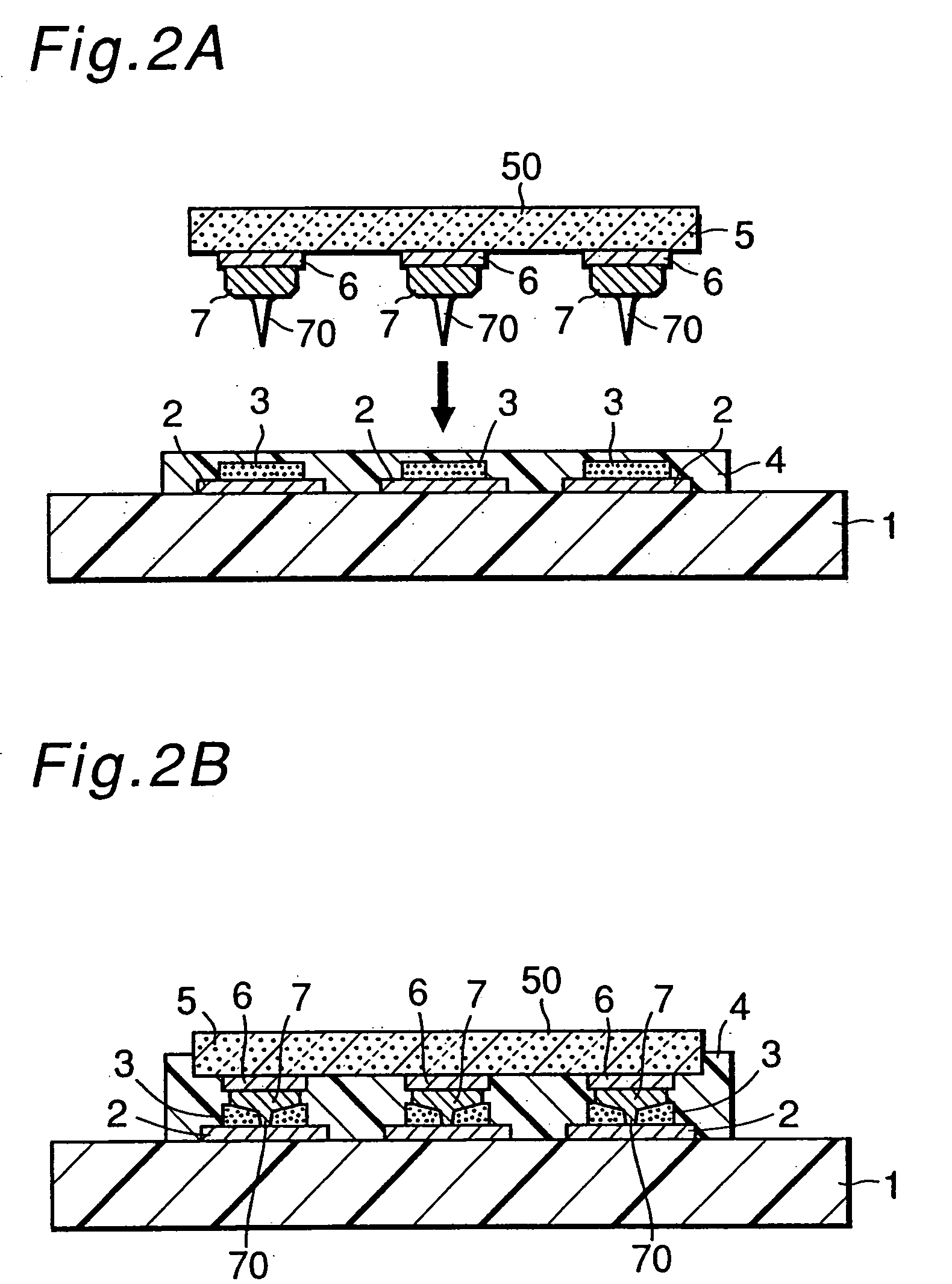

Organic electroluminescent display and manufacturing method thereof, electro-optic device and manufacturing method thereof, and electronic device

InactiveUS6919680B2Efficient preparationDischarge tube luminescnet screensElectroluminescent light sourcesAnisotropic conductive filmConductive paste

Owner:ELEMENT CAPITAL COMMERCIAL CO PTE LTD

Build-up structures with multi-angle vias for chip to chip interconnects and optical bussing

InactiveUS20050087356A1Enhanced signalReduce in quantityTelevision system detailsPiezoelectric/electrostriction/magnetostriction machinesAnisotropic conductive filmEngineering

A build-up structure for chip to chip interconnects and System-In-Package utilizing multi-angle vias for electrical and optical routing or bussing of electronic information and controlled CTE dielectrics including mesocomposites to achieve optimum electrical and optical performance of monolithic structures. Die, multiple die, Microelectromechanical Machines (MEMs) and / or other active or passive components such as transducers or capacitors can be accurately positioned on a substrate such as a copper heatsink and multi-angle stud bumps can be placed on the active sites of the components. A first dielectric layer is preferably placed on the components, thereby embedding the components in the structure. Through various processes of photolithography, laser machining, soft lithography or anisotropic conductive film bonding, escape routing and circuitry is formed on the first metal layer. Additional dielectric layers and metal circuitry are formed utilizing multi-angle vias to form escape routing from tight pitch bond pads on the die to other active and passive components. Multi-angle vias can carry electrical or optical information in the form of digital or analog electromagnetic current, or in the form of visible or non-visible optical bussing and interconnections.

Owner:CAPITALSOURCE FINANCE

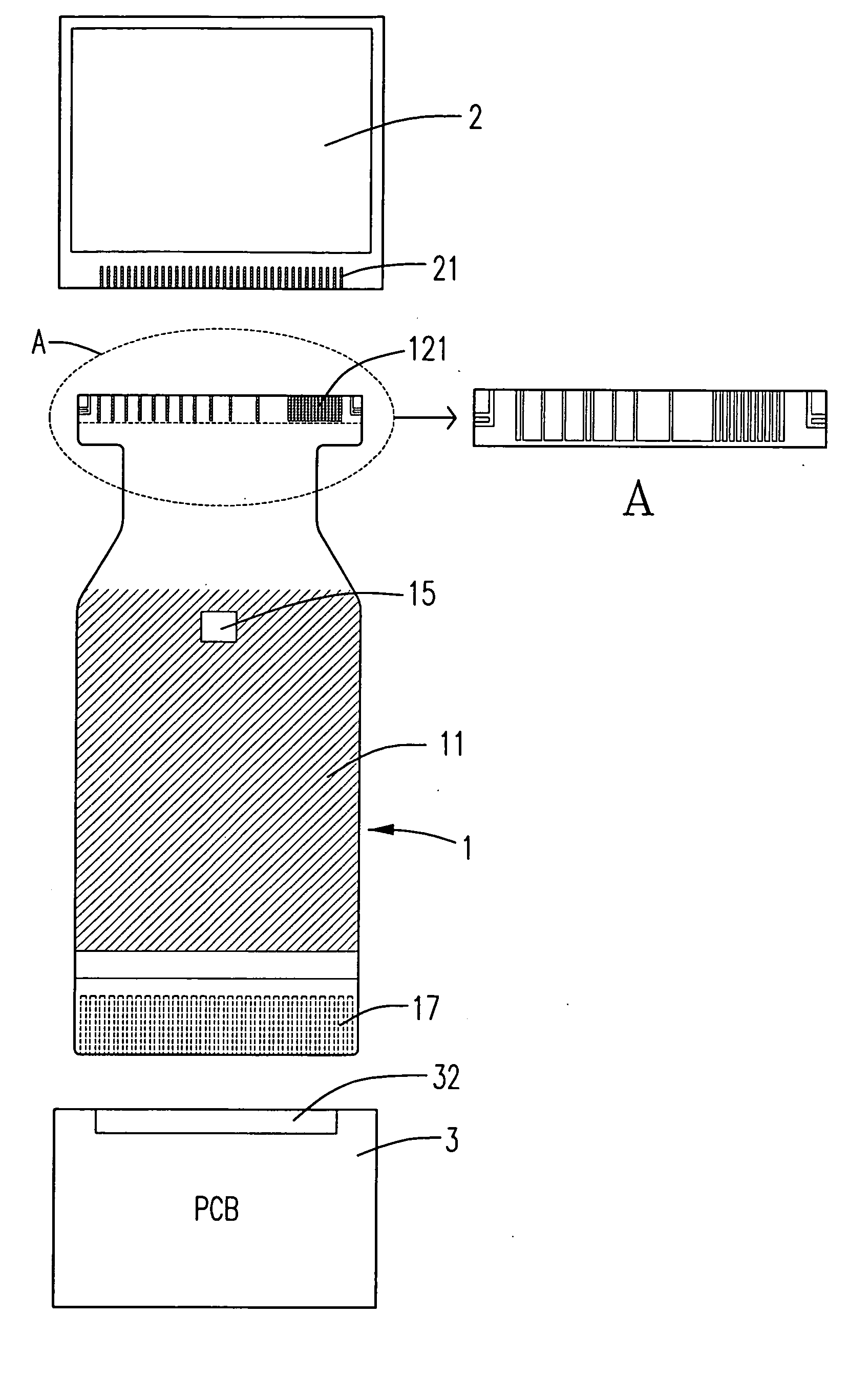

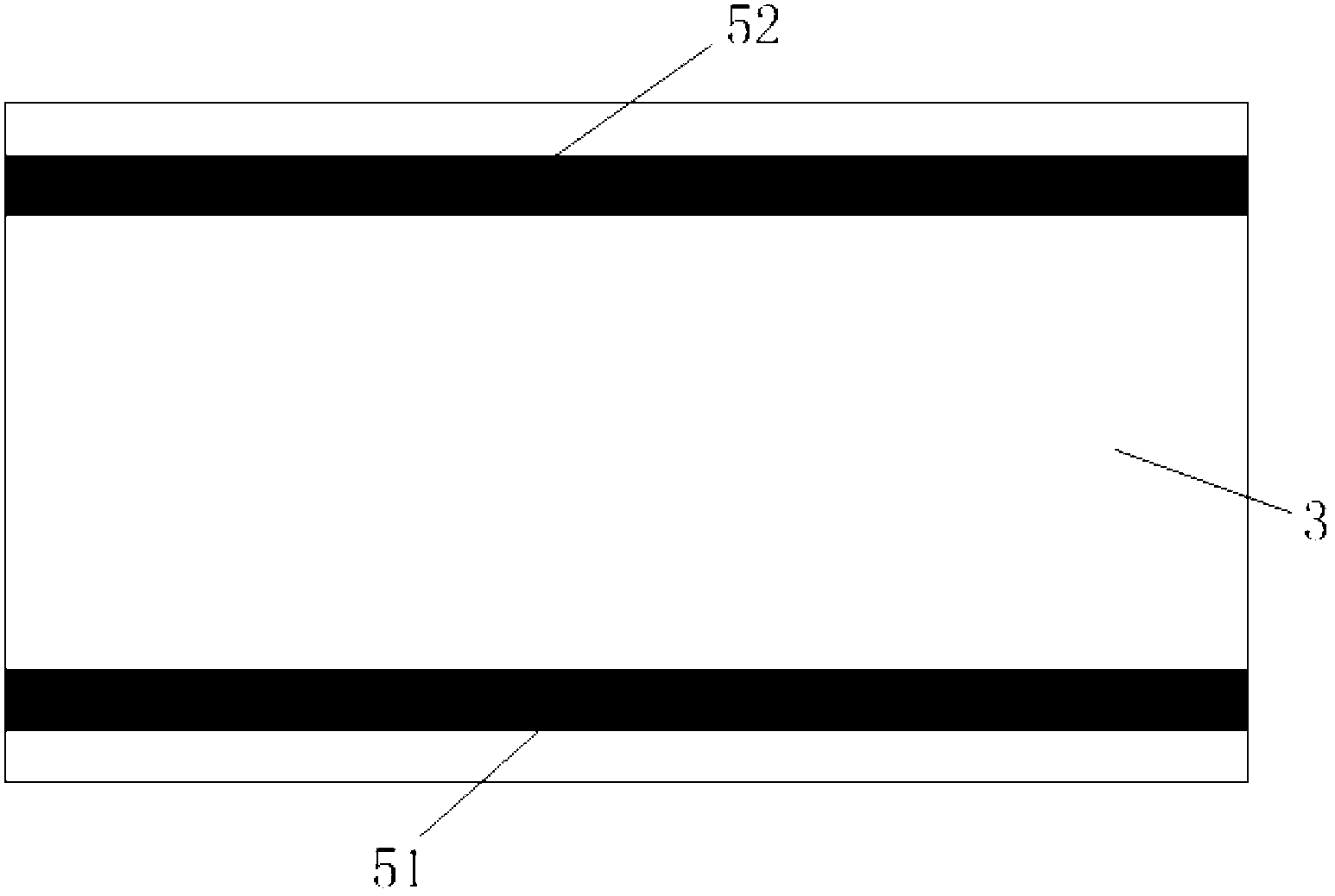

Flexible printed circuit board

InactiveUS20050183884A1Improve reliabilityPrinted circuit assemblingPrinted circuit aspectsAnisotropic conductive filmEngineering

A flexible printed circuit with a broadened anisotropic conductive film is provided. The flexible printed circuit includes a substrate layer and a circuit layer, characterized in that a pitch of the anisotropic conductive film is broadened to be ranged from 0.5 mm to 3.0 mm. It has even and low impedance, even breakage of conductive particles, even pressure, and thus has good reliability of the anisotropic conductive film for use in handheld electronic devices.

Owner:ARIMA DISPLAY

Manufacturing method of solid-state image sensing device

InactiveUS20060091487A1Improve manufacturing yieldYield easilyTelevision system detailsSolid-state devicesMemory chipAnisotropic conductive film

A sensor chip and a lens mount accommodating therein the sensor chip are mounted on a surface of a wiring substrate and a lens holder accommodating a lens therein is coupled with the lens mount. On a rear surface of the wiring substrate, a logic chip, a memory chip and a passive component are mounted and they are sealed with a seal resin. An electrode pad of the sensor chip is electrically connected to an electrode on the surface of the wiring substrate via a bonding wire but a stud bump is also formed on the electrode at the surface of the wiring substrate and this stud bump is connected with the bonding wire. On the surface of the wiring substrate, a flexible substrate is bonded with an anisotropic conductive film and a bonding material. When a camera module is to be manufactured, the surface side of the wiring substrate is assembled after the rear surface side of the wiring substrate is assembled.

Owner:RENESAS TECH CORP +1

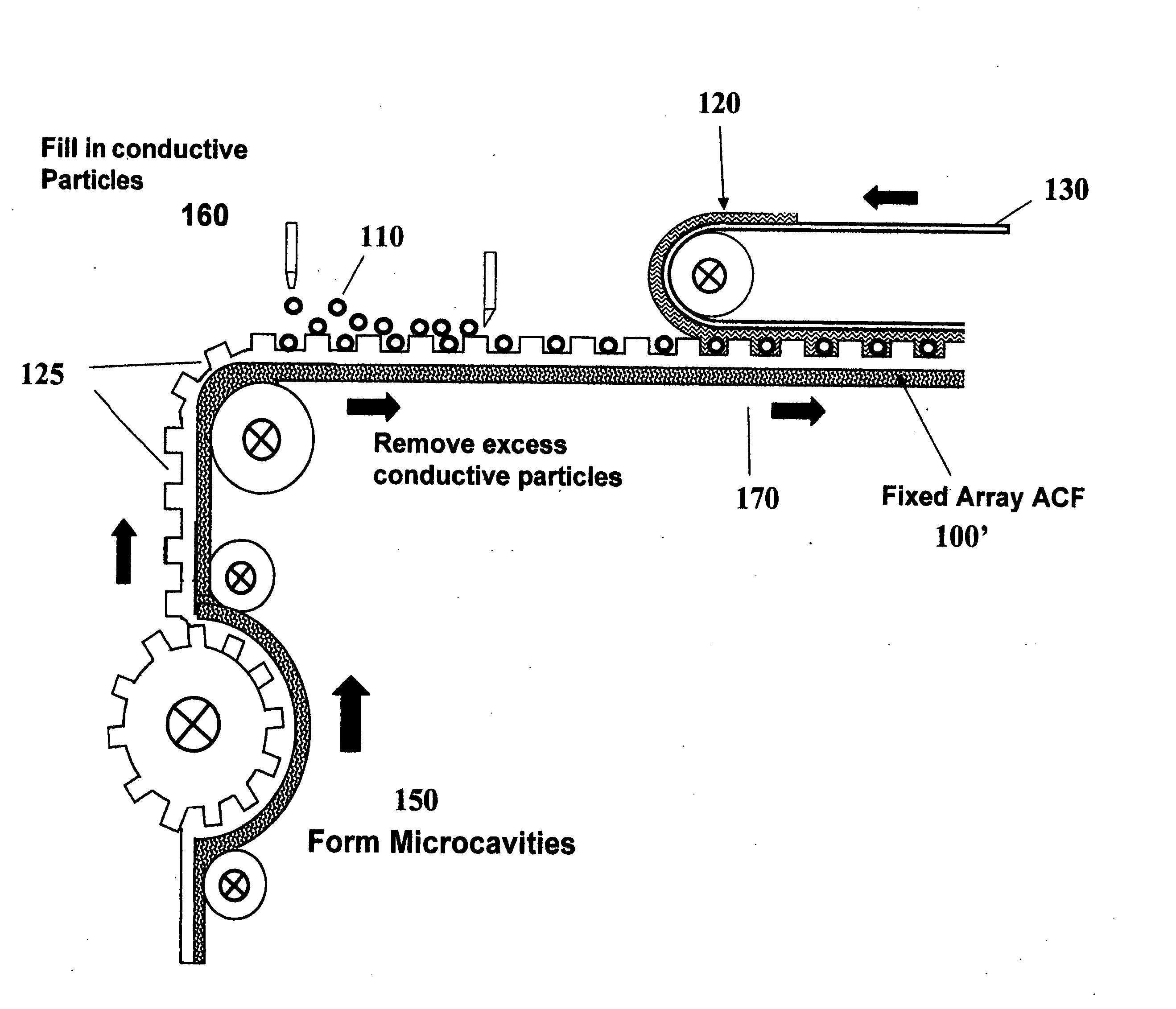

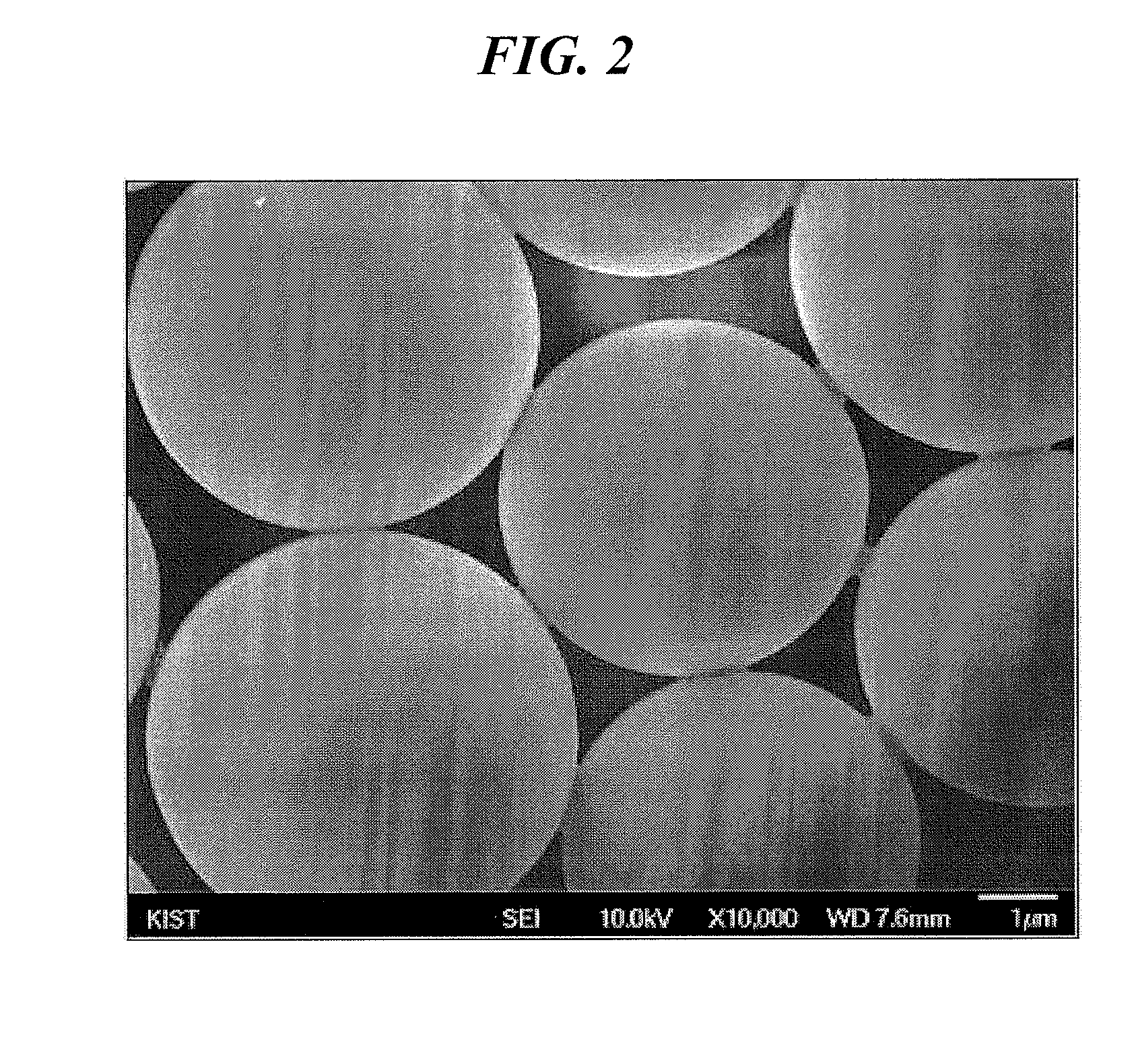

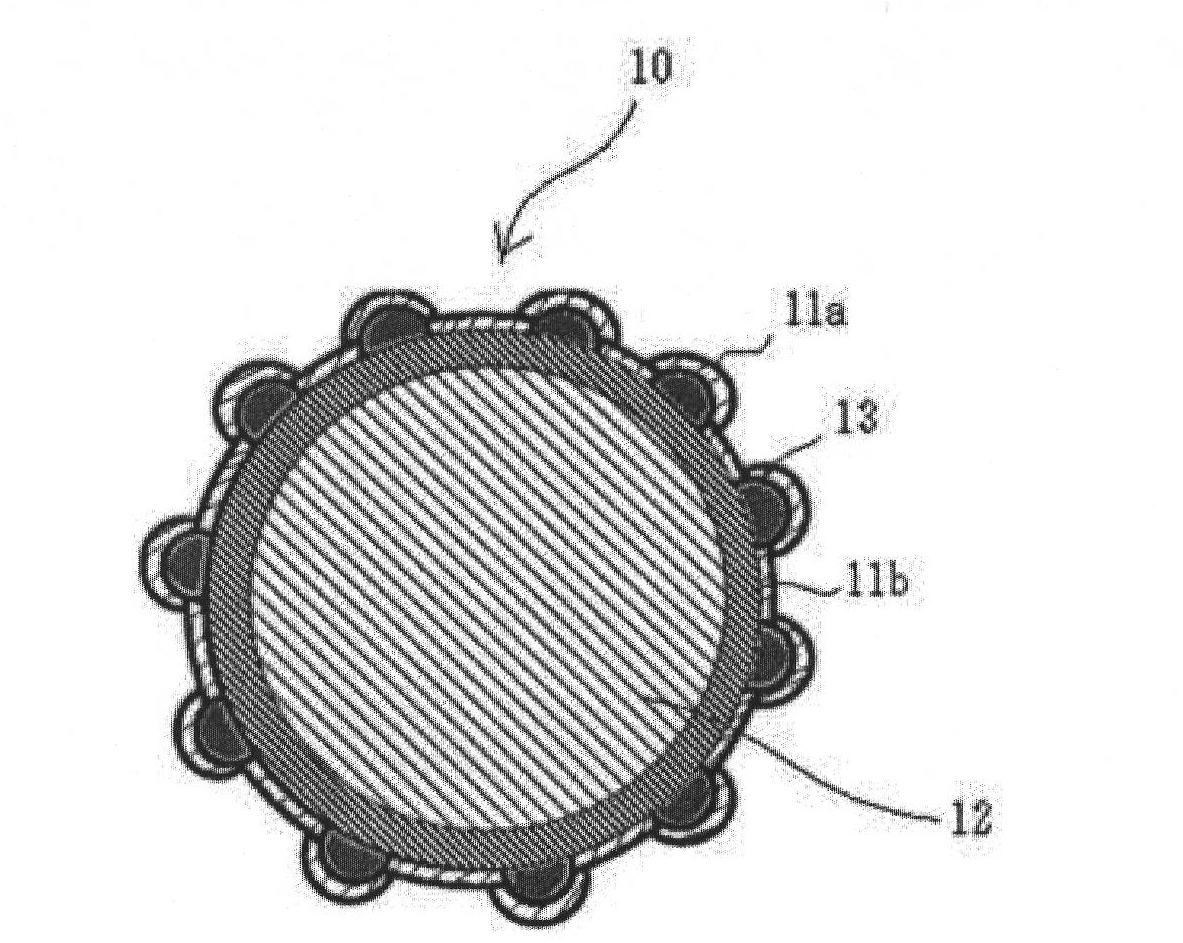

Electroconductive particle and anisotropic conductive film comprising same

InactiveUS20100247892A1Performance in of long-termLong-term of resistanceLiquid surface applicatorsConductive materialAnisotropic conductive filmGraphene coating

The present invention discloses an electroconductive particle comprising (a) a polymer microparticle, and (b) a graphene coating layer grafted on the polymer microparticle, which has improved long-term stability of the conductivity, surface conductivity, durability, and thermal resistance, and is applicable for producing an anisotropic conductive film used for packaging electronic devices.

Owner:KOREA INST OF SCI & TECH

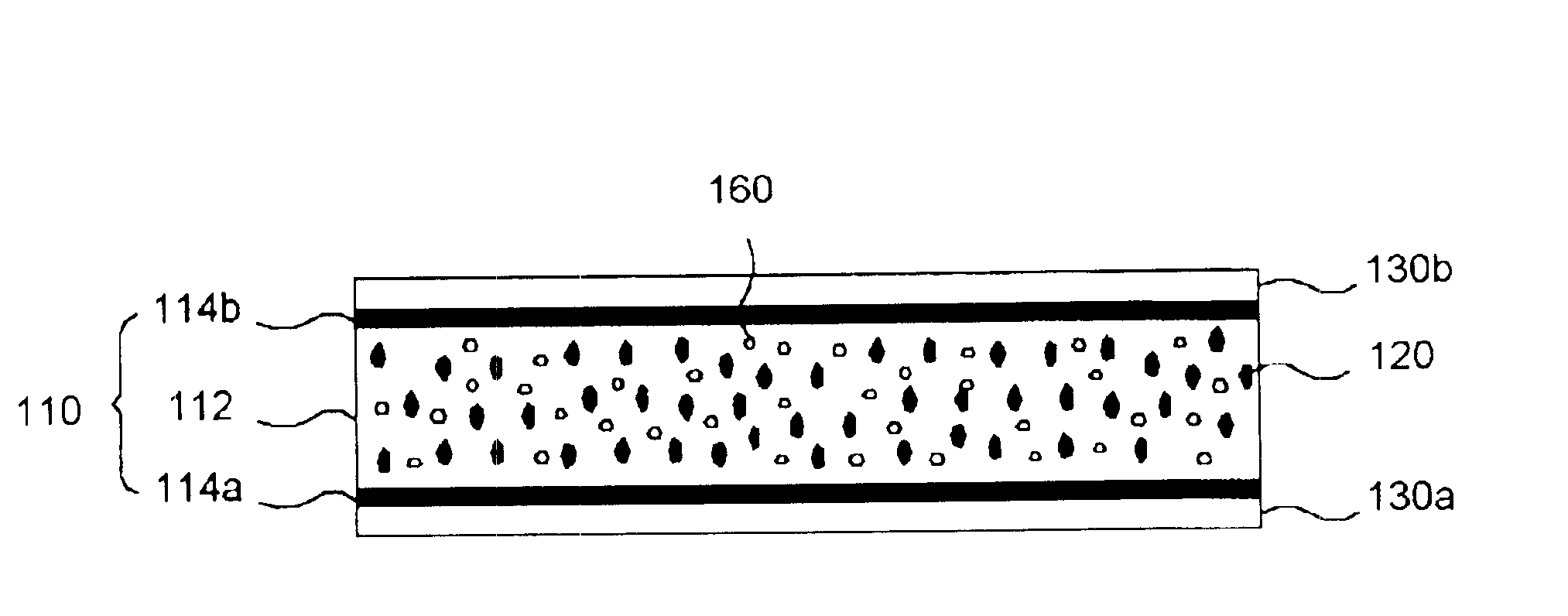

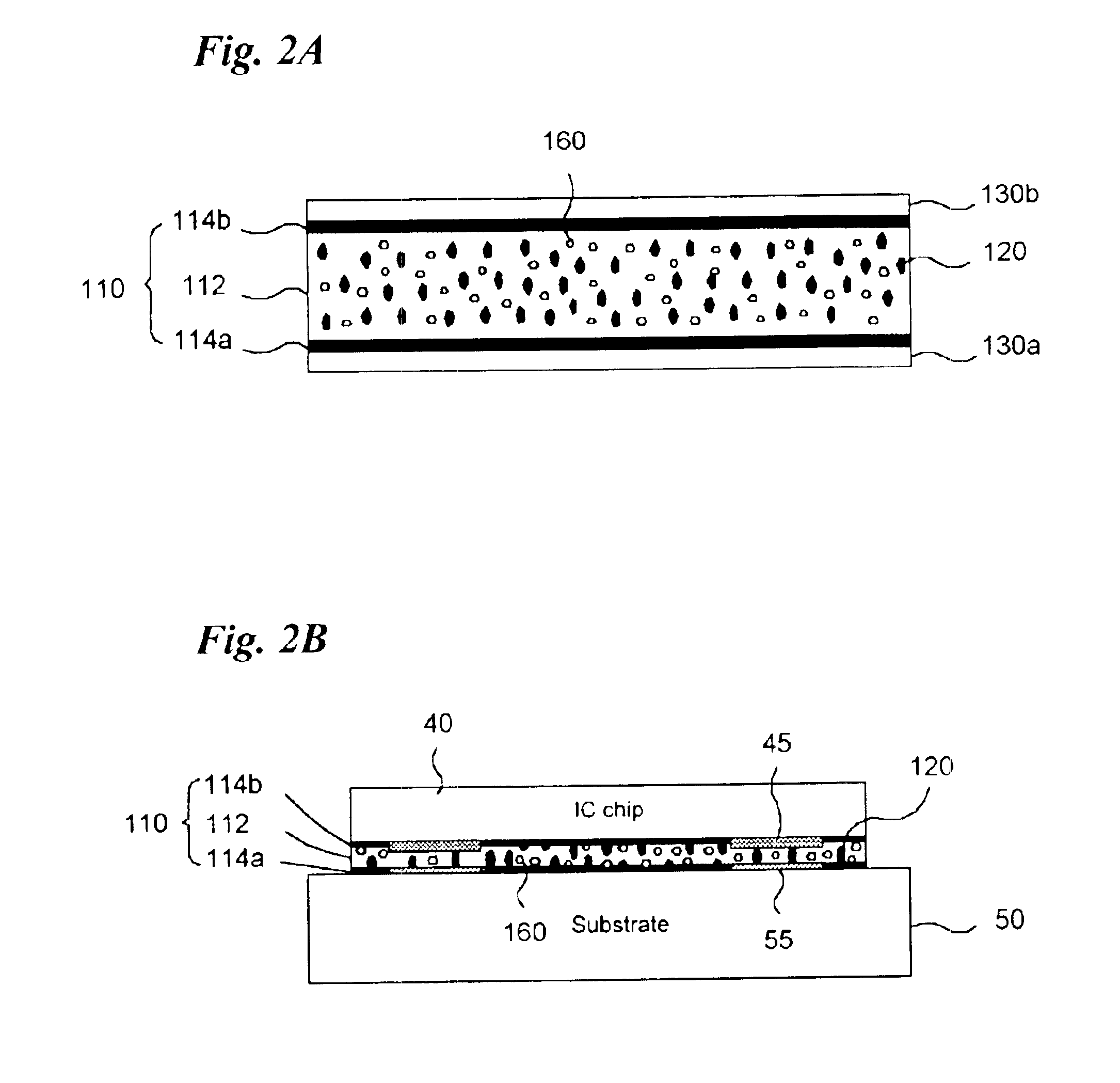

High adhesion triple layered anisotropic conductive adhesive film

InactiveUS6878435B2High bonding strengthImprove adhesionNon-insulated conductorsSolid-state devicesEpoxyAnisotropic conductive film

Disclosed is a triple layered ACA film adapted for enhancing the adhesion strength of a typical single layer Anisotropic Conductive Film or for enhancing the adhesion strength of the ACA film in flip chip bonding. The triple layered ACA film of the invention comprises: a main ACA film based upon epoxy resin and containing conductive particles having a particle size of 3 to 10 μm and optionally non-conductive particles having a particle size of 0.1 to 1 μm; and adhesion reinforcing layers based upon epoxy resin and formed at both sides of the main ACA film.

Owner:KOREA ADVANCED INST OF SCI & TECH

Manufacturing method of solid-state image sensing device

InactiveUS7005310B2Improve manufacturing yieldYield easilyPrinted circuit assemblingTelevision system detailsMemory chipAnisotropic conductive film

A sensor chip and a lens mount accommodating therein the sensor chip are mounted on a surface of a wiring substrate and a lens holder accommodating a lens therein is coupled with the lens mount. On a rear surface of the wiring substrate, a logic chip, a memory chip and a passive component are mounted and they are sealed with a seal resin. An electrode pad of the sensor chip is electrically connected to an electrode on the surface of the wiring substrate via a bonding wire but a stud bump is also formed on the electrode at the surface of the wiring substrate and this stud bump is connected with the bonding wire. On the surface of the wiring substrate, a flexible substrate is bonded with an anisotropic conductive film and a bonding material. When a camera module is to be manufactured, the surface side of the wiring substrate is assembled after the rear surface side of the wiring substrate is assembled.

Owner:RENESAS ELECTRONICS CORP

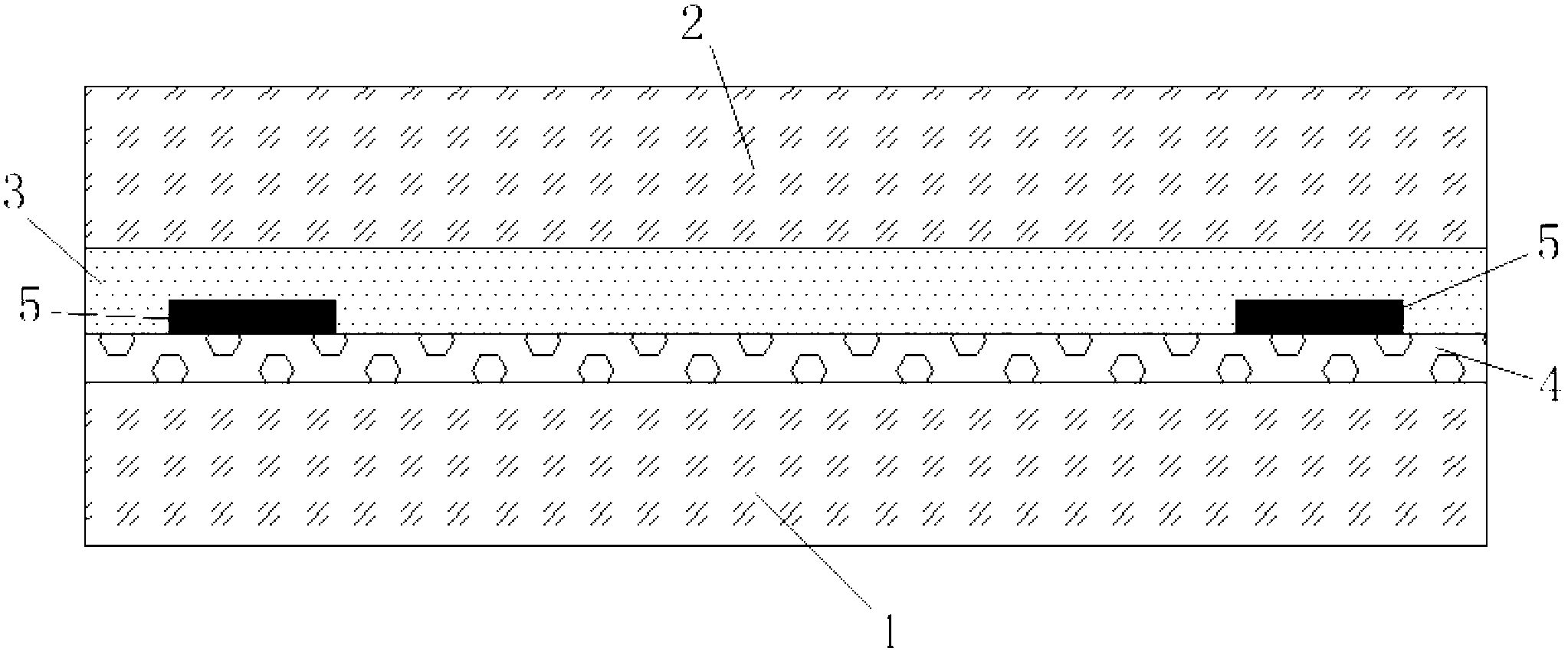

Electrically-heatable low-emissivity coated laminated glass

ActiveCN102795793ALow costSave hot pressing processAnisotropic conductive filmAnisotropic conductive adhesive

The invention relates to the field of laminated glass, particularly a laminated glass with high heat reflectivity and electric heating function applicable to the field of vehicles or construction, more particularly an automobile windshield glass installed on a vehicle. The electrically-heatable low-emissivity coated laminated glass comprises two glass substrates, a middle polymer sandwiched between the two glass substrates, low-emissivity film and a bus, wherein the low-emissivity film is arranged on at least one glass substrate surface in contact with the middle polymer; the bus is distributed on the low-emissivity film; and the bus is a pressure-sensitive adhesive or anisotropic conductive adhesive. According to the electrically-heatable low-emissivity coated laminated glass provided by the invention, the ACF (anisotropic conductive film) or PSA (pressure-sensitive adhesive) is used as the bus in combination with the low-emissivity film to heat the laminated glass, thereby removing frost and melting ice; and thus, compared with the adoption of other buses, the invention simplifies the production technique, is convenient to operate, lowers the material cost and enhances the production efficiency and process yield.

Owner:FUYAO GLASS IND GROUP CO LTD

Build-up structures with multi-angle vias for chip to chip interconnects and optical bussing

InactiveUS20050269687A1Improve performanceIncrease speedTelevision system detailsPiezoelectric/electrostriction/magnetostriction machinesAnisotropic conductive filmEngineering

A build-up structure for chip to chip interconnects and System-In-Package utilizing multi-angle vias for electrical and optical routing or bussing of electronic information and controlled CTE dielectrics including mesocomposites to achieve optimum electrical and optical performance of monolithic structures. Die, multiple die, Microelectromechanical Machines (MEMs) and / or other active or passive components such as transducers or capacitors can be accurately positioned on a substrate such as a copper heatsink and multi-angle stud bumps can be placed on the active sites of the components. A first dielectric layer is preferably placed on the components, thereby embedding the components in the structure. Through various processes of photolithography, laser machining, soft lithography or anisotropic conductive film bonding, escape routing and circuitry is formed on the first metal layer. Additional dielectric layers and metal circuitry are formed utilizing multi-angle vias to form escape routing from tight pitch bond pads on the die to other active and passive components. Multi-angle vias can carry electrical or optical information in the form of digital or analog electromagnetic current, or in the form of visible or non-visible optical bussing and interconnections.

Owner:CAPITALSOURCE FINANCE

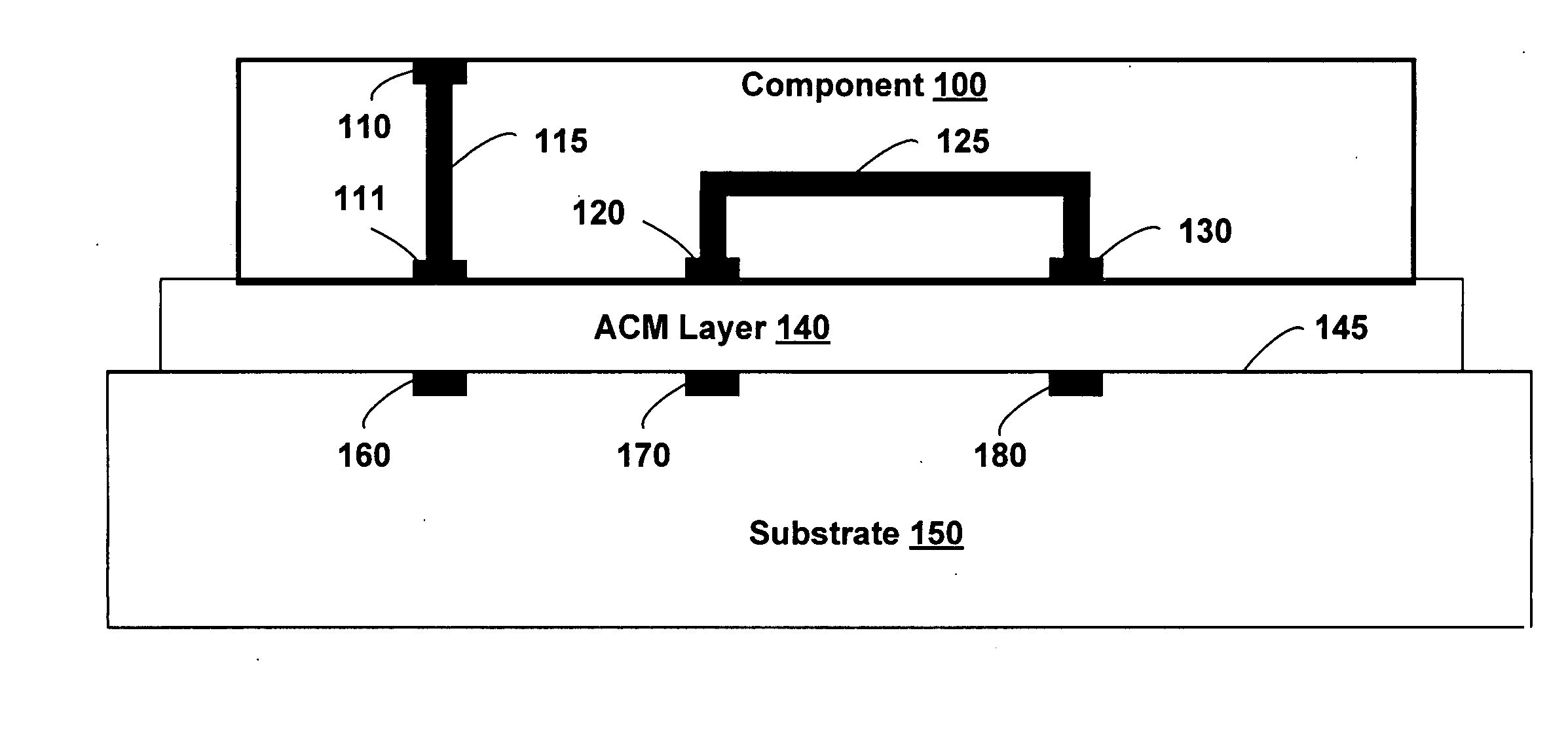

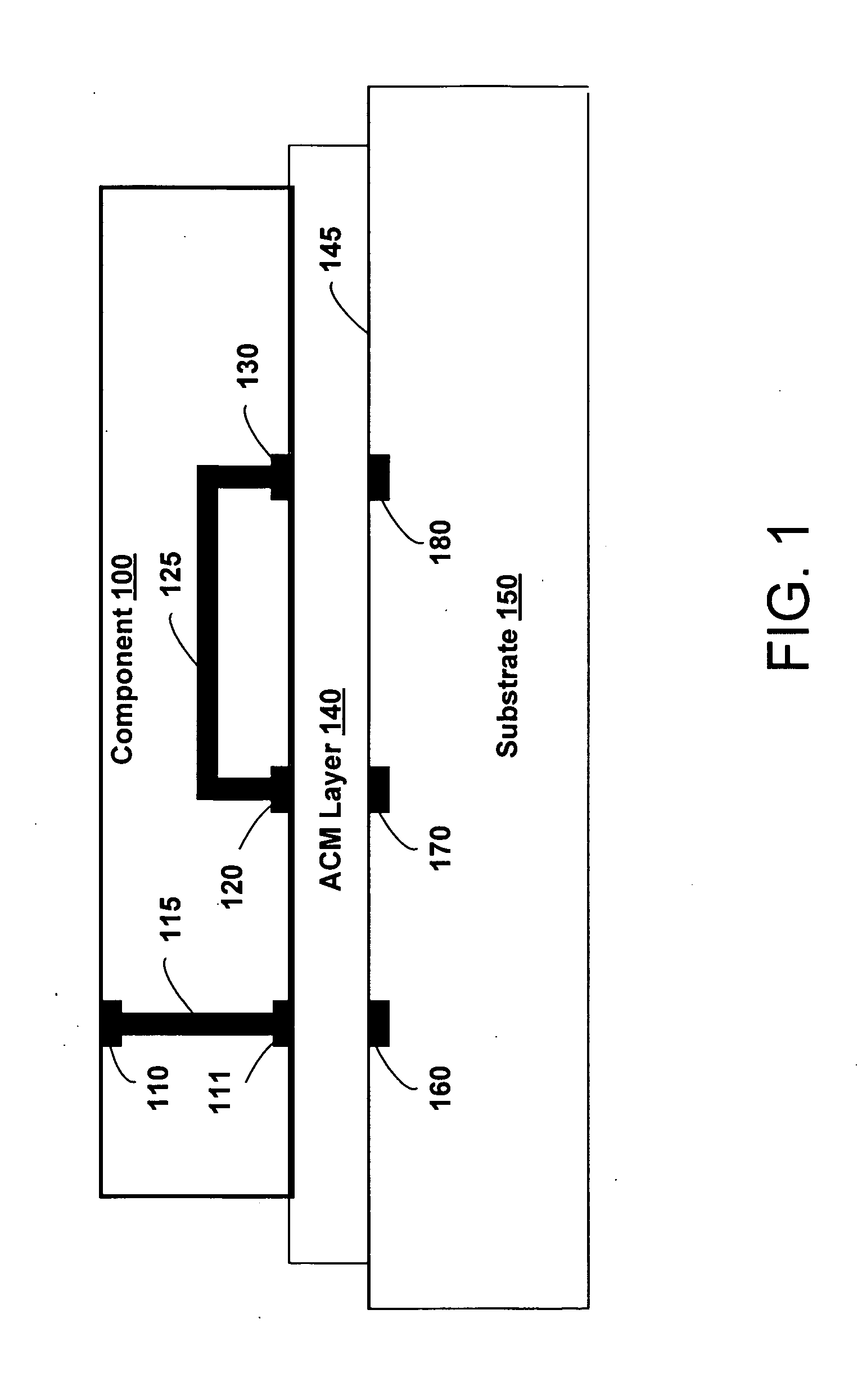

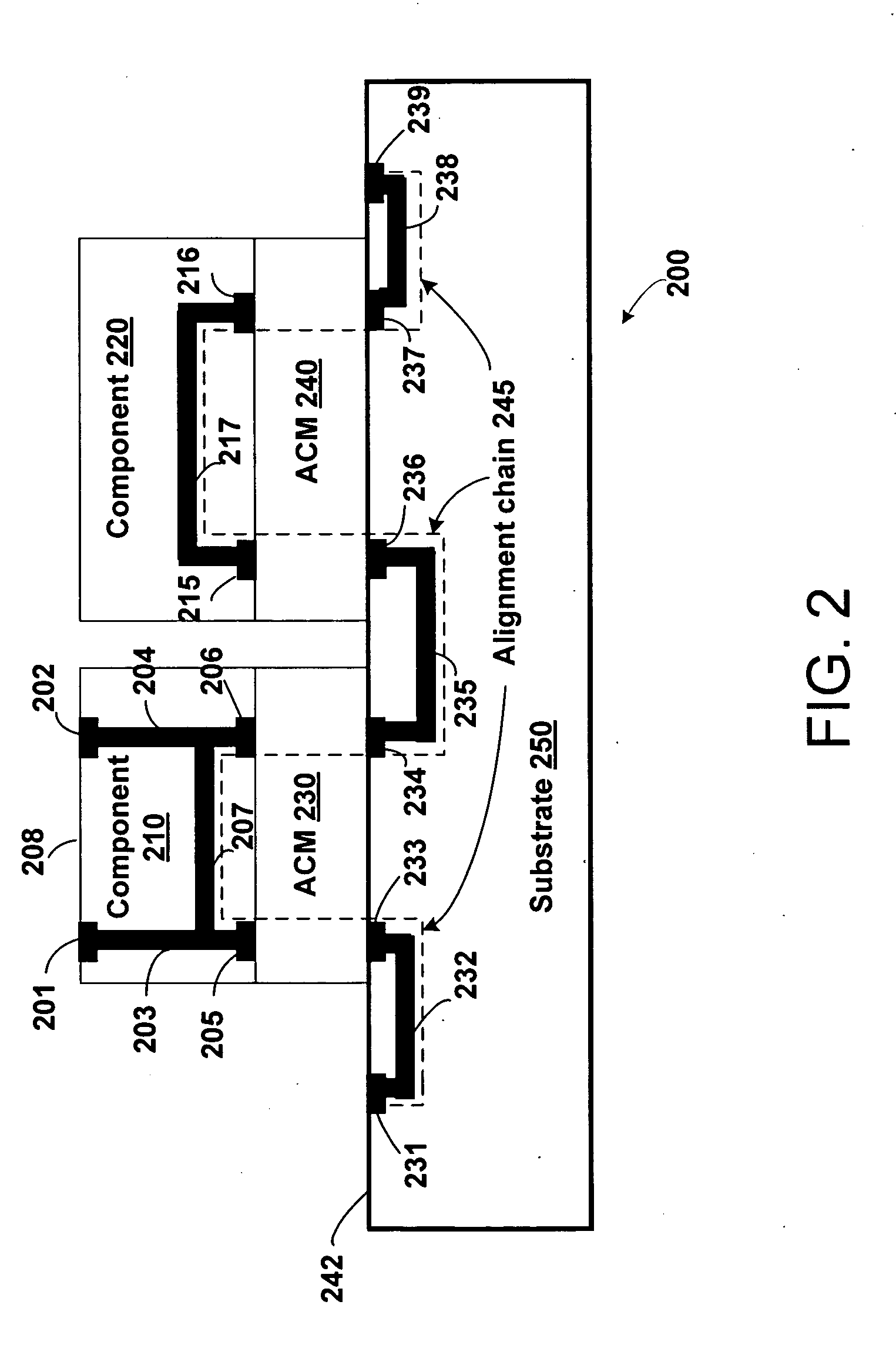

Electronic assembly with detachable components

InactiveUS20070187844A1Improve connectivitySimple designSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsAnisotropic conductive filmConduction pathway

The present invention provides systems and methods for assembling an electronic assembly using an anisotropic conducting membrane (ACM) as a component interconnect and a substrate embossed with placement cavities or a positional fixture to facilitate component placement on the substrate in the electronic assembly. The fixture may comprise multiple layers of interconnects to improve routing density for the electronic assembly enclosed in a housing. An alignment chain may be used to monitor positional and contact integrity of the ACM interfaced components in a complex assembly. The systems and methods allow components to be detached for reuse. Interconnection elements or conduction pathways at the components can be used to interconnect a plurality of neighboring substrates over the ACM layers into a stacked electronic assembly.

Owner:WINTEC IND INC

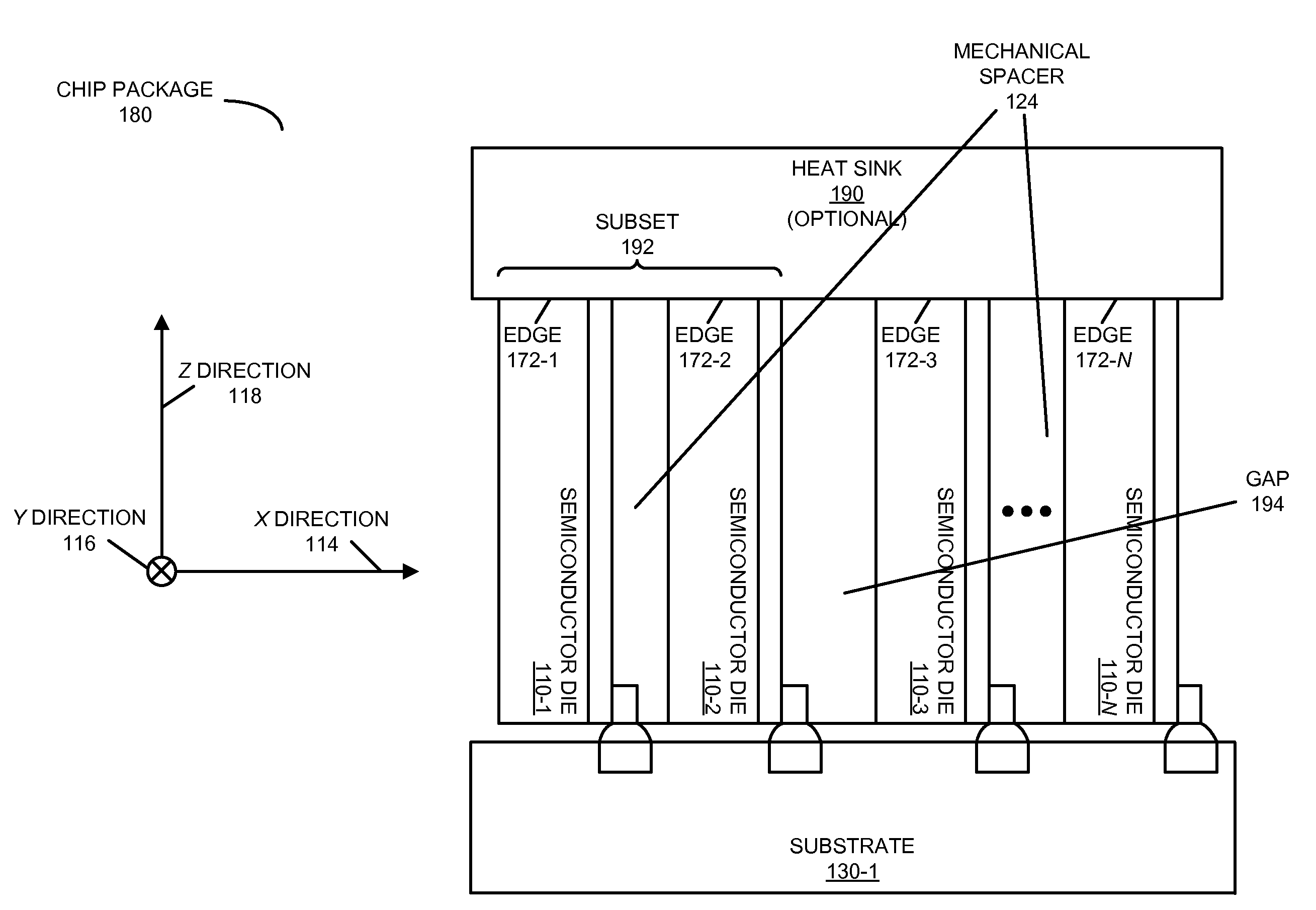

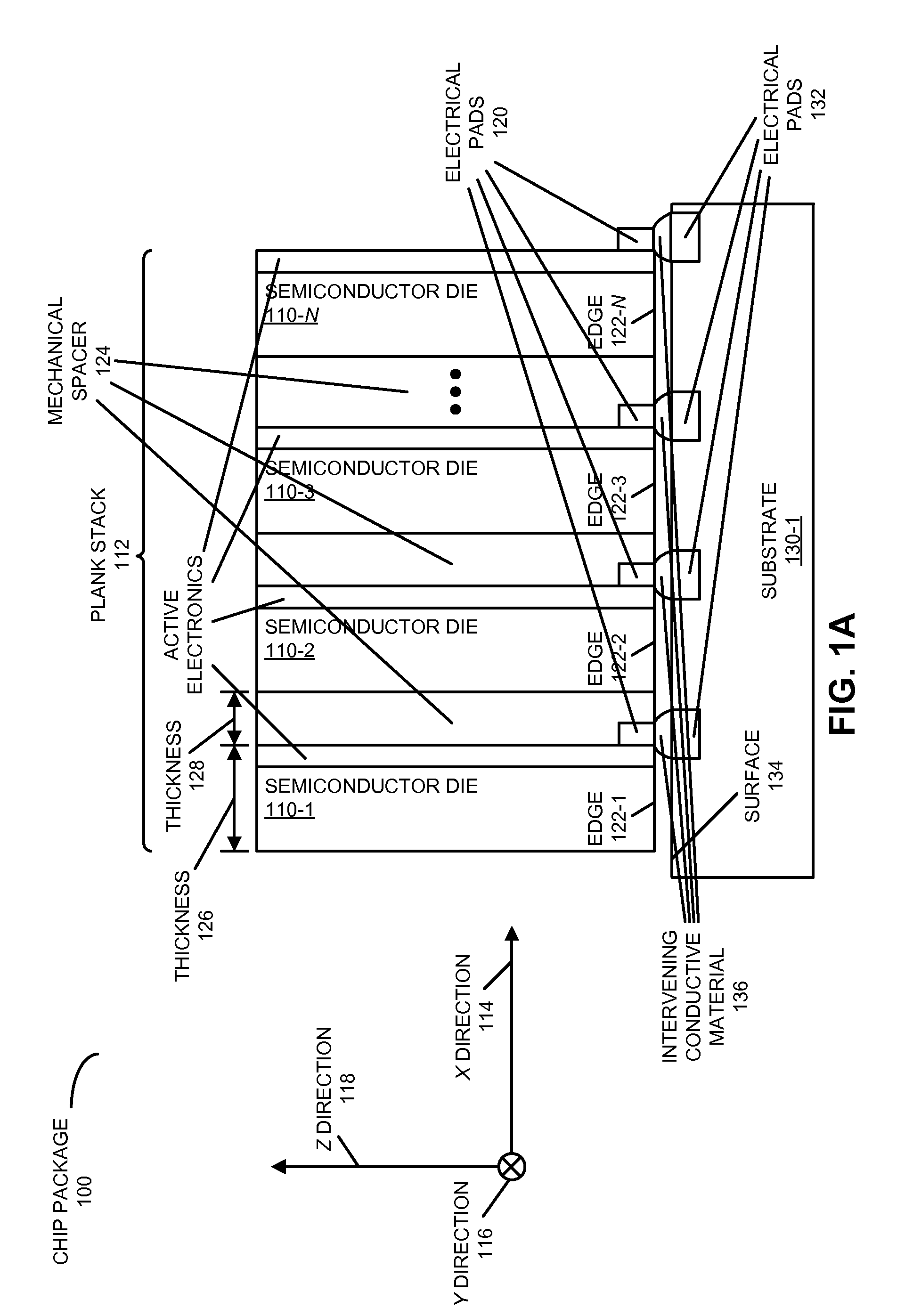

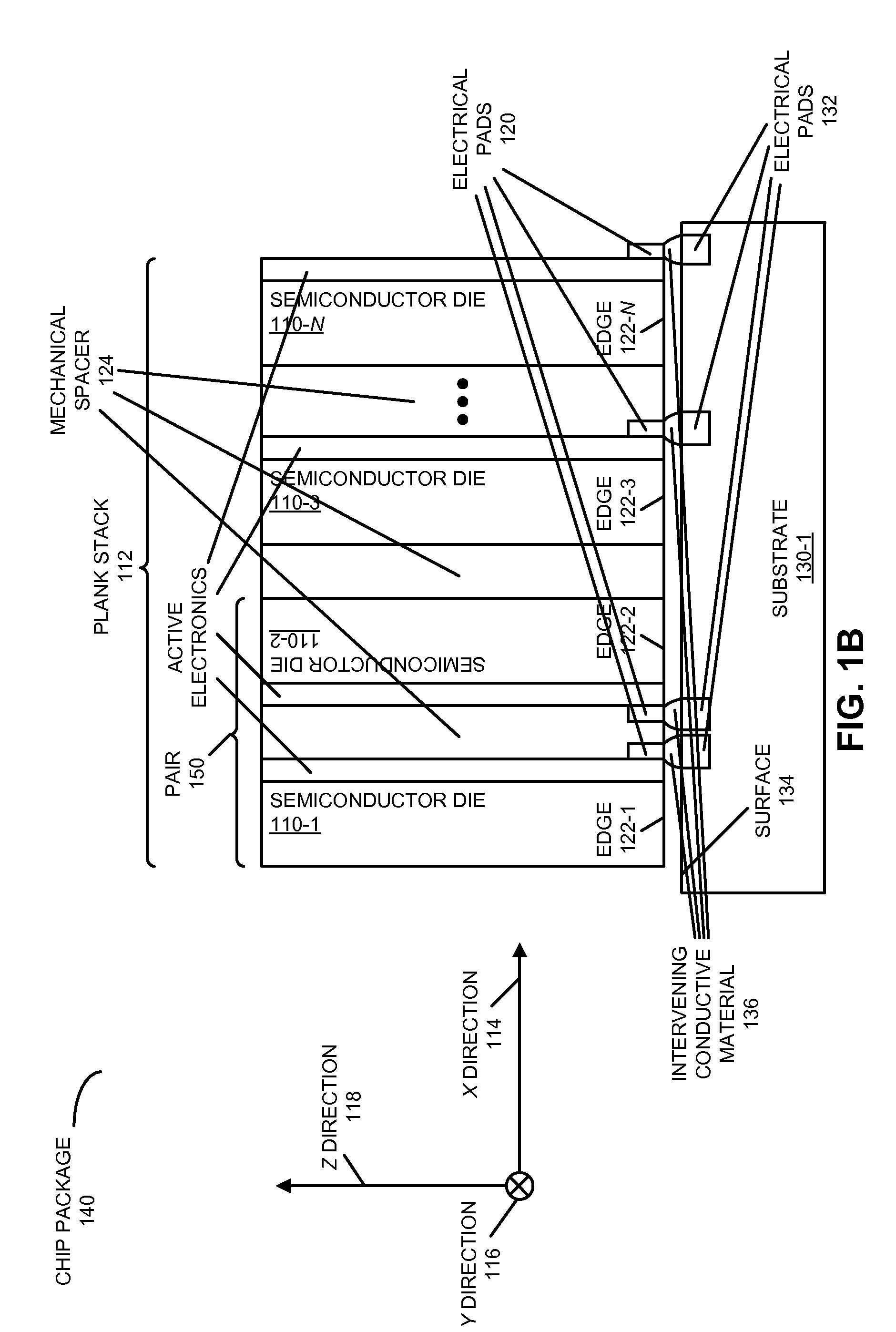

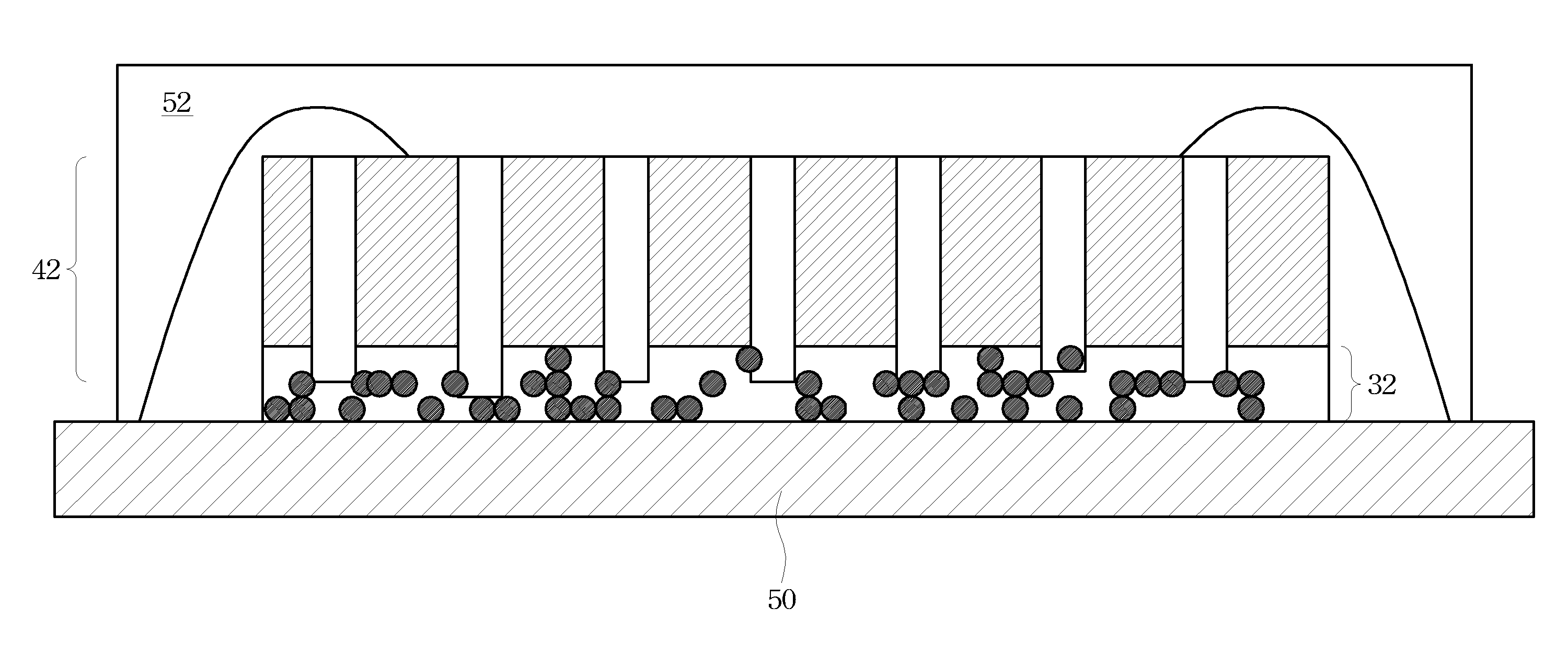

Chip package with plank stack of semiconductor dies

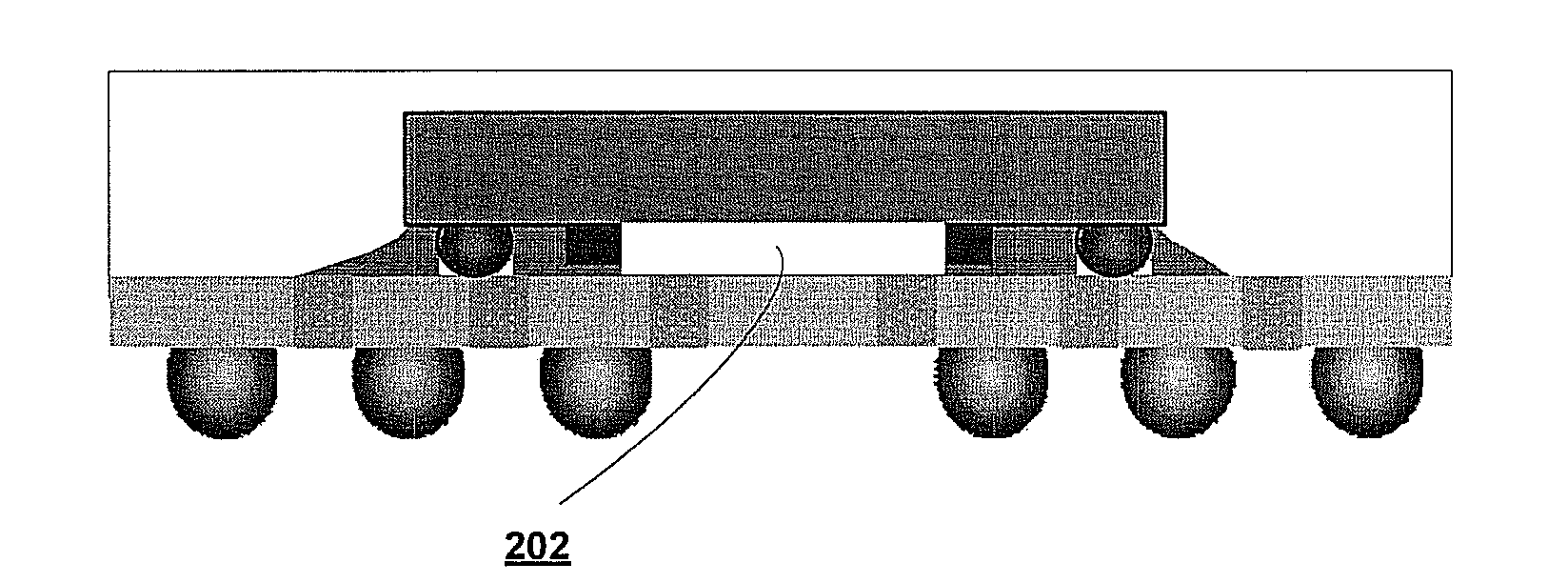

ActiveUS20120211878A1Increase heatImprove flowSemiconductor/solid-state device detailsSolid-state devicesAnisotropic conductive filmHigh bandwidth

In a chip package, semiconductor dies in a vertical stack of semiconductor dies or chips (which is referred to as a ‘plank stack’) are separated by a mechanical spacer (such as a filler material or an adhesive). Moreover, the chip package includes a substrate at a right angle to the plank stack, which is electrically coupled to the semiconductor dies along an edge of the plank stack. In particular, electrical pads proximate to a surface of the substrate (which are along a stacking direction of the plank stack) are electrically coupled to pads that are proximate to edges of the semiconductor dies by an intervening conductive material, such as: solder, stud bumps, plated traces, wire bonds, spring connectors, a conductive adhesive and / or an anisotropic conducting film. Note that the chip package may facilitate high-bandwidth communication of signals between the semiconductor dies and the substrate.

Owner:ORACLE INT CORP

Circuit substrate for packaging semiconductor device, method for producing the same, and method for producing semiconductor device package structure using the same

InactiveUS20050163982A1Reduced characteristicsAvoid damagePrinted circuit assemblingSemiconductor/solid-state device detailsAnisotropic conductive filmDevice material

The invention is intended for providing a semiconductor package structure which prevents degradation in characteristics of a semiconductor device, and breakage of interconnections, when the semiconductor device is packaged on a circuit substrate. In the package structure having the semiconductor device mounted on the circuit substrate, bump electrodes of the semiconductor device are placed on input / output terminal electrodes of the circuit substrate and are electrically and mechanically connected thereto by bonding with a conductive adhesive, and the semiconductor device is bonded and fixed to the circuit substrate by a resin film formed previously on a surface of a main body of the circuit substrate. The structure does no damage to a semiconductor functional part and to interconnections, and allows mounting with a lower load as compared to structures using conventional anisotropic conductive films and the like.

Owner:ONO MASAHIRO +1

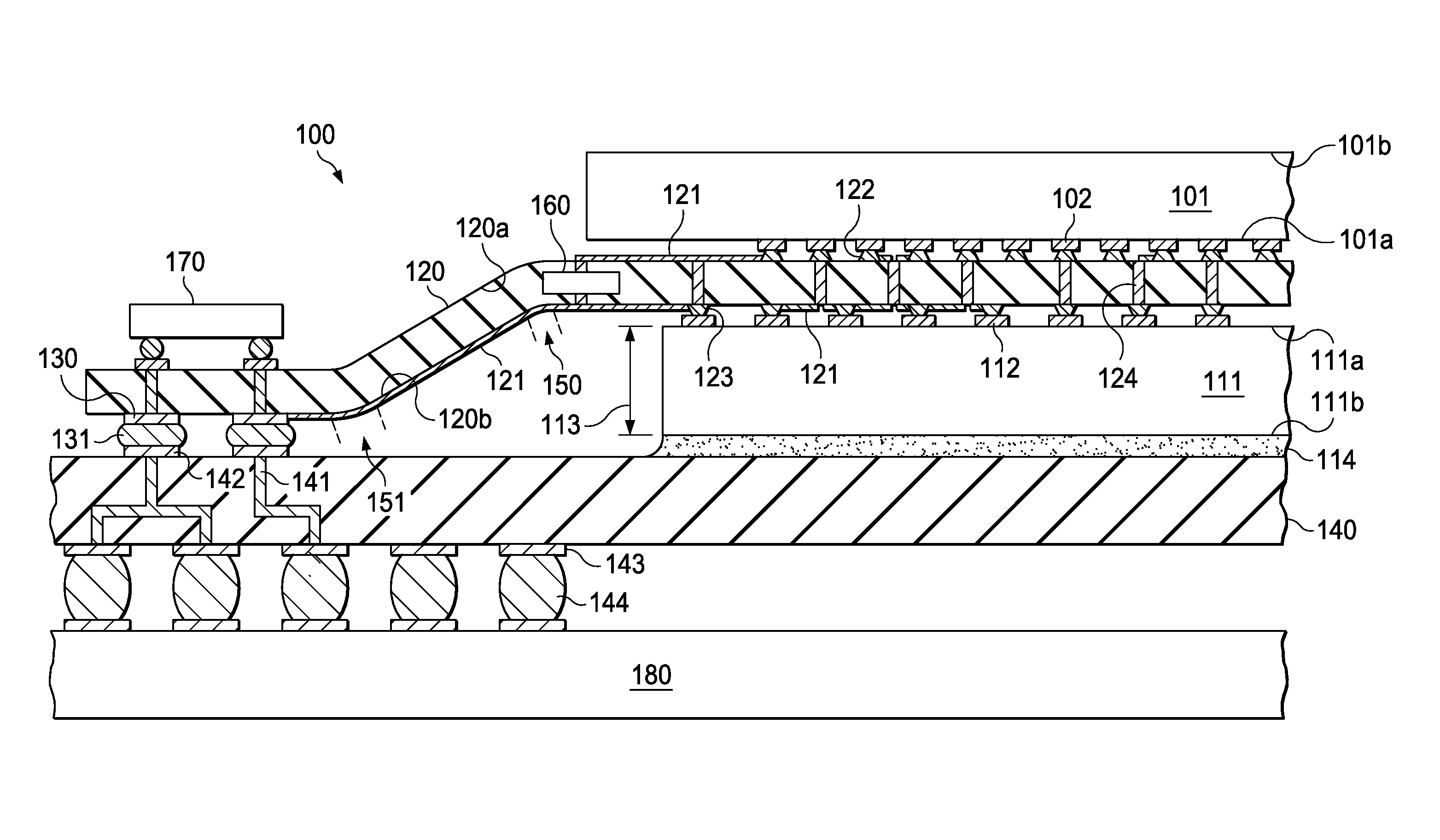

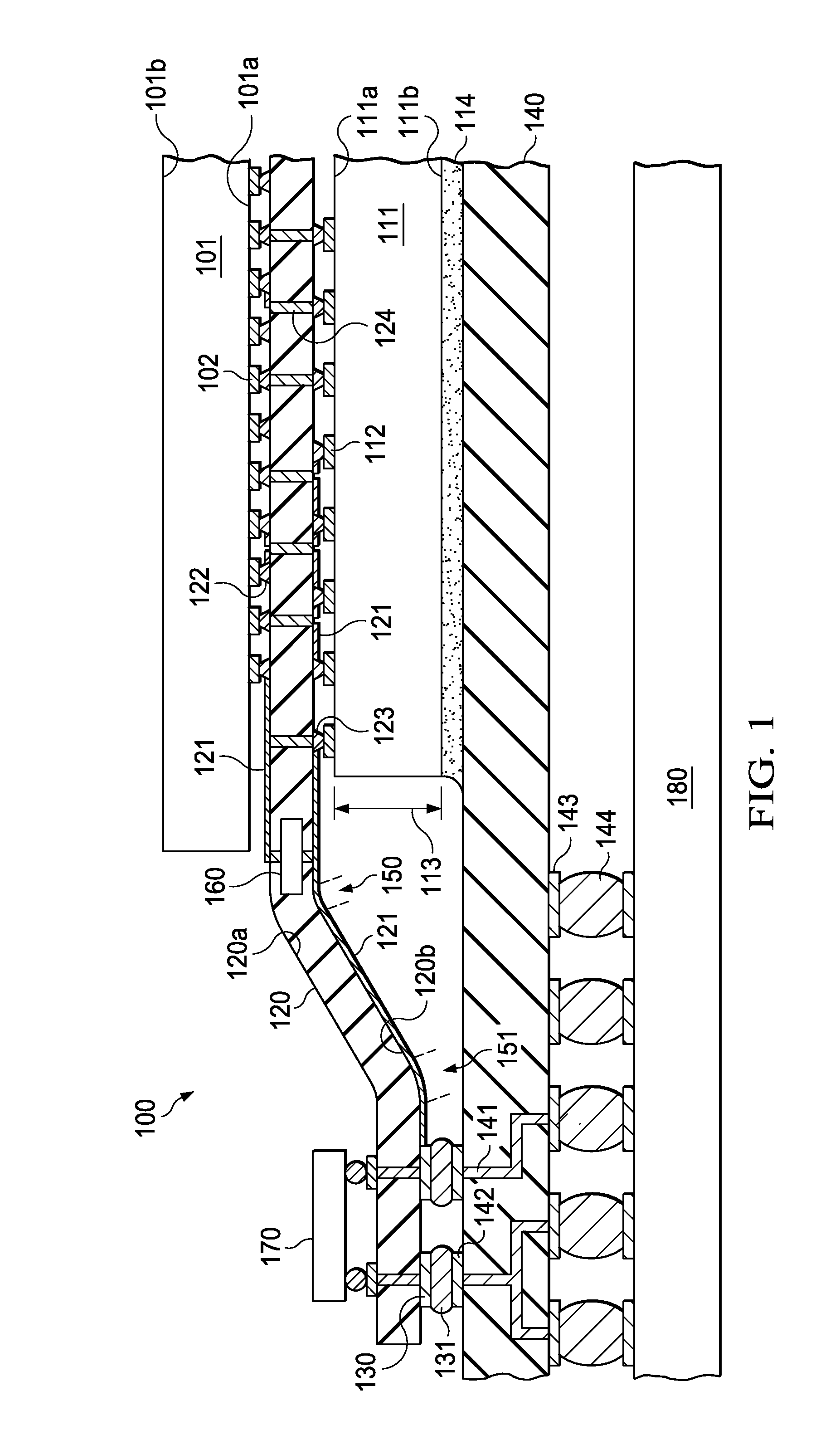

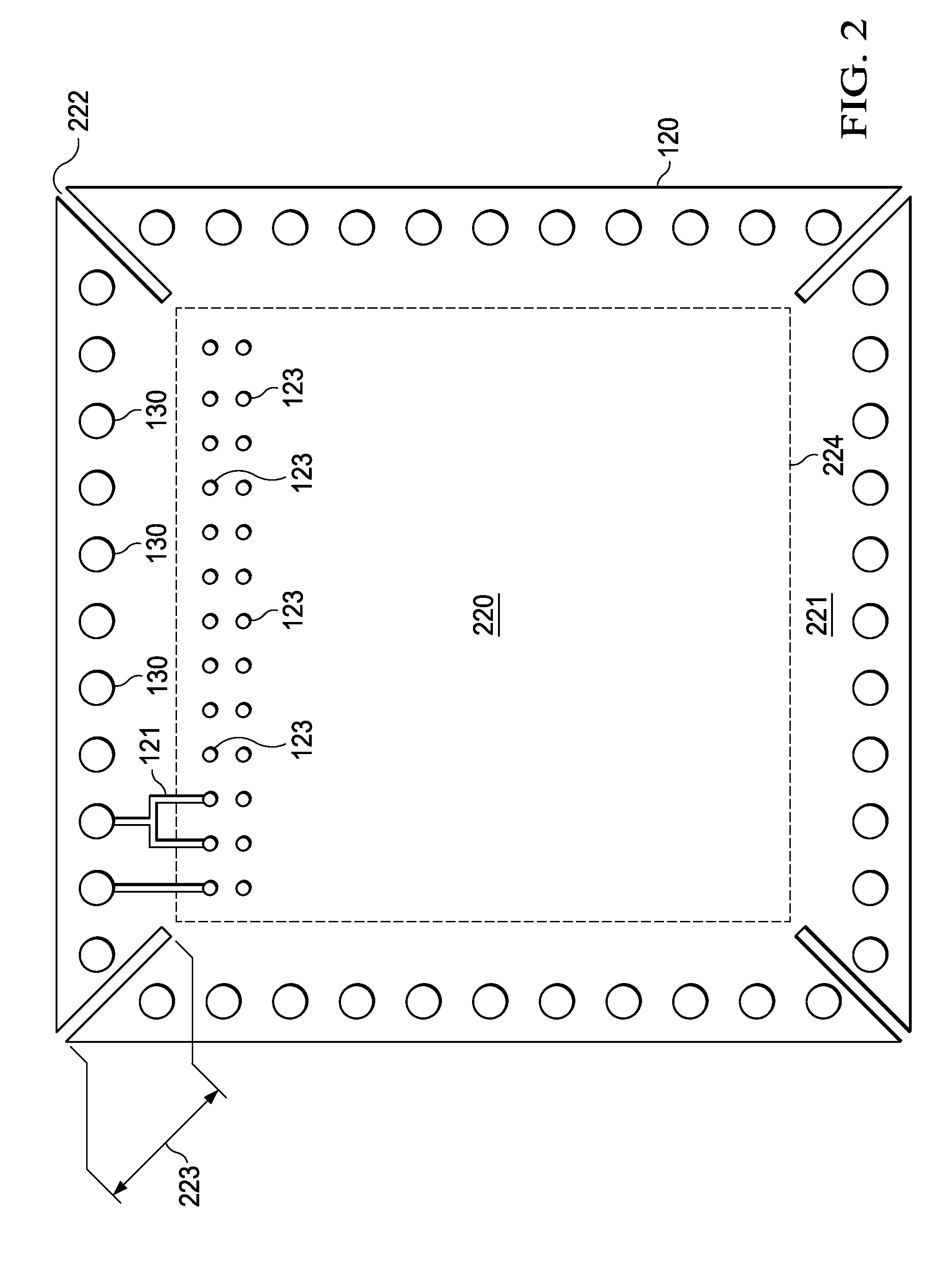

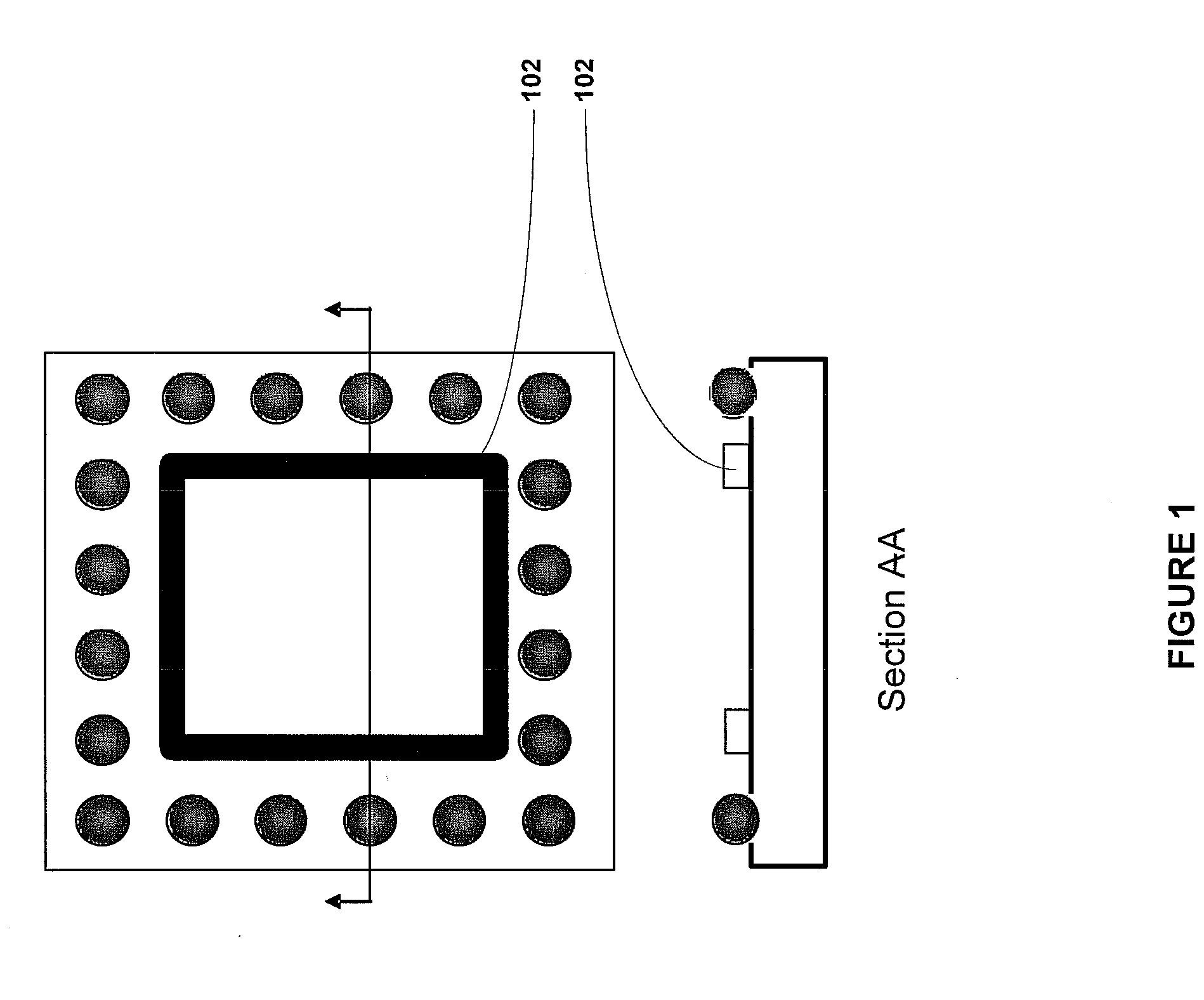

Flexible Interposer for Stacking Semiconductor Chips and Connecting Same to Substrate

ActiveUS20090121346A1Increase the number ofReduce exposureSemiconductor/solid-state device detailsSolid-state devicesAnisotropic conductive filmContact pad

A semiconductor device with a first (101) and a second (111) semiconductor chip assembled on an insulating flexible interposer (120). The interposer, preferably about 25 to 50μm thick, has conductive traces (121), a central planar rectangular area and on each side of the rectangle a wing bent at an angle from the central plane. The central area has metal studs (122, 123) on the top and the bottom surface, which match the terminals of the chips, further conductive vias of a pitch center-to-center about 50 μm or less. The side wings have contact pads (130) with metallic connectors (131) on the bottom surface; the connectors may be solder balls, metal studs, or anisotropic conductive films. The second chip is adhesively attached to a substrate, whereby the interposer faces away from the substrate. The interposer side wings have a convex bending (150) downwardly along the second chip and a concave bending (151) over the substrate; the side wing connectors are attached to the matching substrate sites.

Owner:TEXAS INSTR INC

Method for Packaging Semiconductor Dies Having Through-Silicon Vias

InactiveUS20090020865A1Semiconductor/solid-state device detailsSolid-state devicesAnisotropic conductive filmEngineering

An integrated circuit structure is provided. The integrated circuit structure includes a die and an anisotropic conducing film (ACF) adjoining the back surface of the die. The die includes a front surface; a back surface on an opposite side of the die than the front surface; and a through-silicon via (TSV) exposed through the back surface of the die.

Owner:TAIWAN SEMICON MFG CO LTD

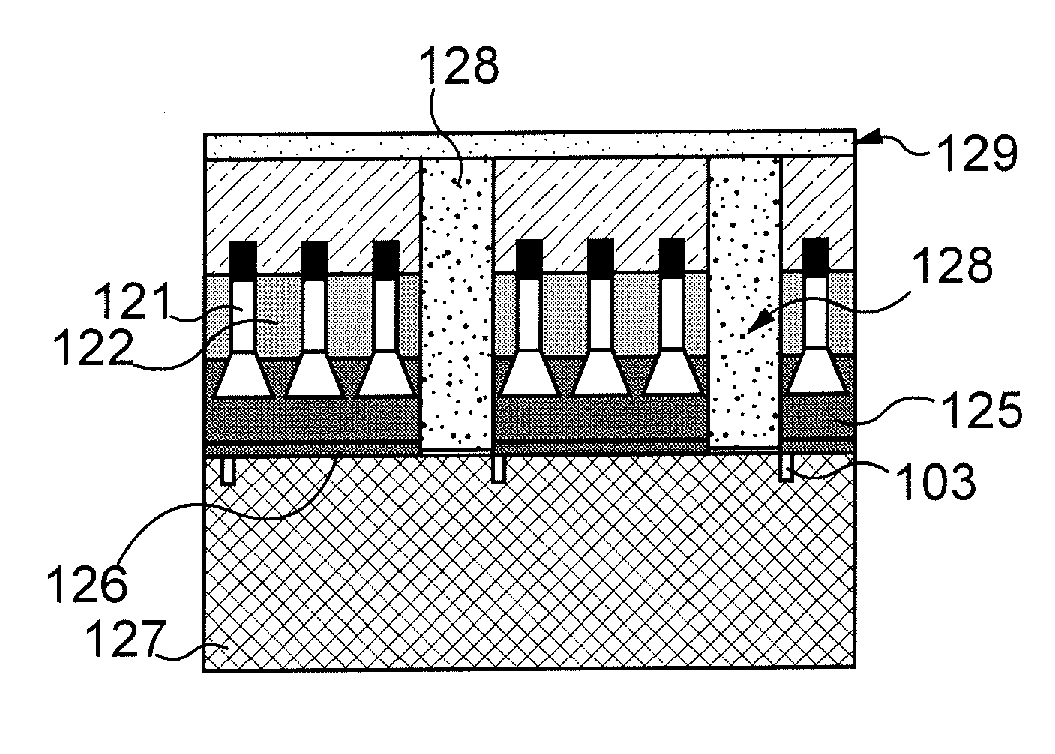

Method for manufacturing a very-high-resolution screen using a nanowire-based emitting anisotropic conductive film

ActiveUS20120205614A1Solid-state devicesSemiconductor/solid-state device manufacturingAnisotropic conductive filmNanowire

A method for producing an emissive pixel screen includes forming an active pixel matrix along which an electrode forming layer runs and having pixels arranged according to a distribution, forming an anisotropic substrate that includes a set of light emitting diodes constituted by parallel nanowires and arranged in an insulating matrix transversely with respect to a substrate thickness and having a density higher than a density of the pixels irrespective of the pixel distribution, connecting the substrate to the active pixel matrix by connecting only sub-groups of the parallel nanowires by a first end to separate pixel electrodes defined in the electrode forming layer according to the distribution of the pixels in the matrix, and connecting the sub-groups, by another end, to a common electrode, and delimiting the sub-groups by rendering the nanowires of the substrate that are arranged between the sub-groups emissively inactive.

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES

Epoxy compositions

InactiveUS20080090943A1Improve thermomechanical propertyImprove heat managementSynthetic resin layered productsSolid-state devicesEpoxyAnisotropic conductive film

An epoxy composition for applications such as one-part adhesives, coatings, prepreg and molding compounds that includes leuco dyes, particularly those comprising a N,N-dialkylamino-, N,N-diarylamino-, or cycloalkylamino-functional group on one of the aromatic rings, as a co-catalyst or co-curing agent. The use of the leuco dye co-catalyst provides improved curing speed of the epoxy composition comprising a latent curing agent / catalyst such as Novacure imidazole microcapsules while maintaining the shelf-life stability. The epoxy may also include a secondary co-catalyst that includes amides and lactams, particularly those comprising a N,N-dialkylamino-, N,N-diarylamino-, or dicycloalkylamino-functional group. Secondary cocatalysts of low mobility at the storage conditions, such as those with a long chain substitutent, dimeric or oligomeric amides or lactams, are particularly preferred. The improved epoxy composition is implemented as adhesives for manufacturing an anisotropic conductive film (ACF) and also for connecting, encapsulating, or packaging of electronic devices.

Owner:TRILLION +1

Insulating layer between bumps of semiconductor chip, and display panel using the same with anisotropic conductive film between semiconductor chip and substrate

ActiveUS7750469B2Raise the ratioSemiconductor/solid-state device detailsSolid-state devicesAnisotropic conductive filmSemiconductor chip

A semiconductor chip and manufacturing method thereof, the semiconductor chip including a plurality of bumps connected to a driving circuit integrated on a semiconductor substrate and an organic insulating layer disposed on the driving circuit. The organic insulating layer extends from the semiconductor substrate less than the plurality of bumps such that a lower edge of the plurality of bumps protrudes further than a lower edge of the organic insulating layer.

Owner:SAMSUNG DISPLAY CO LTD

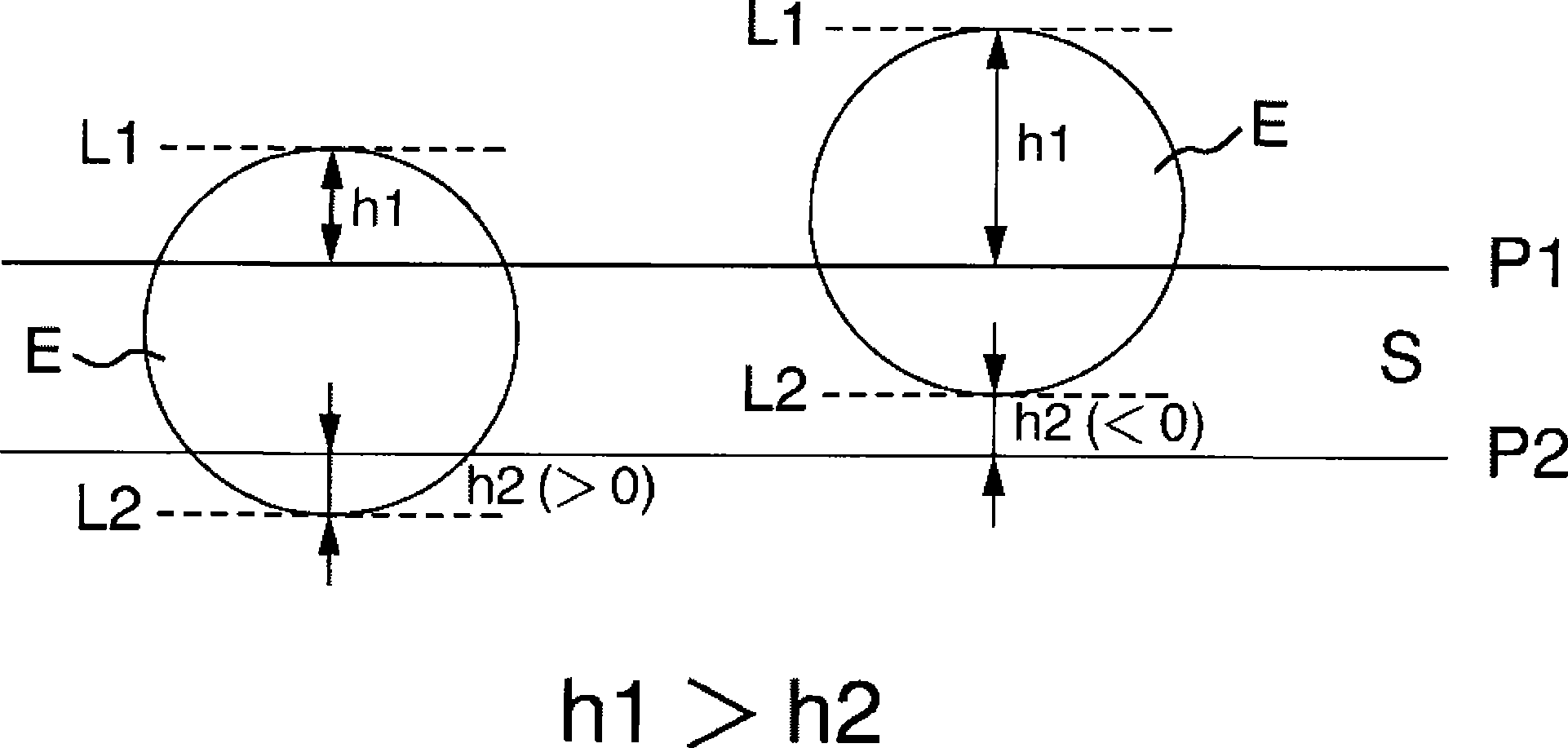

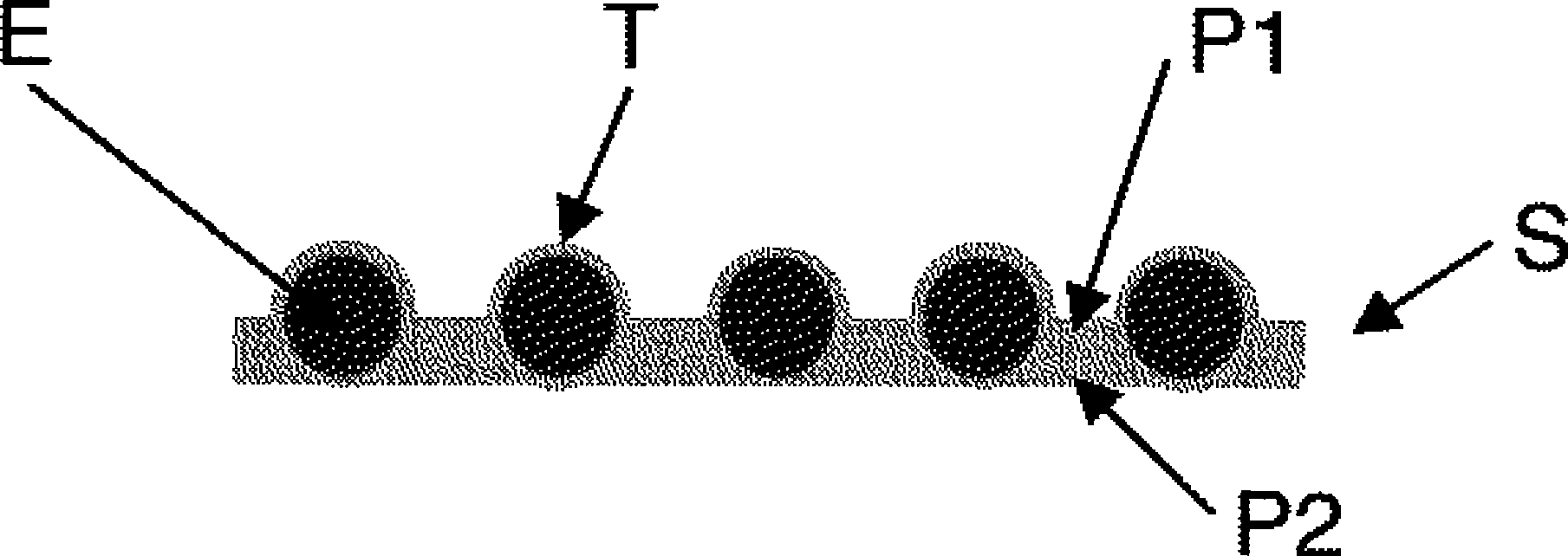

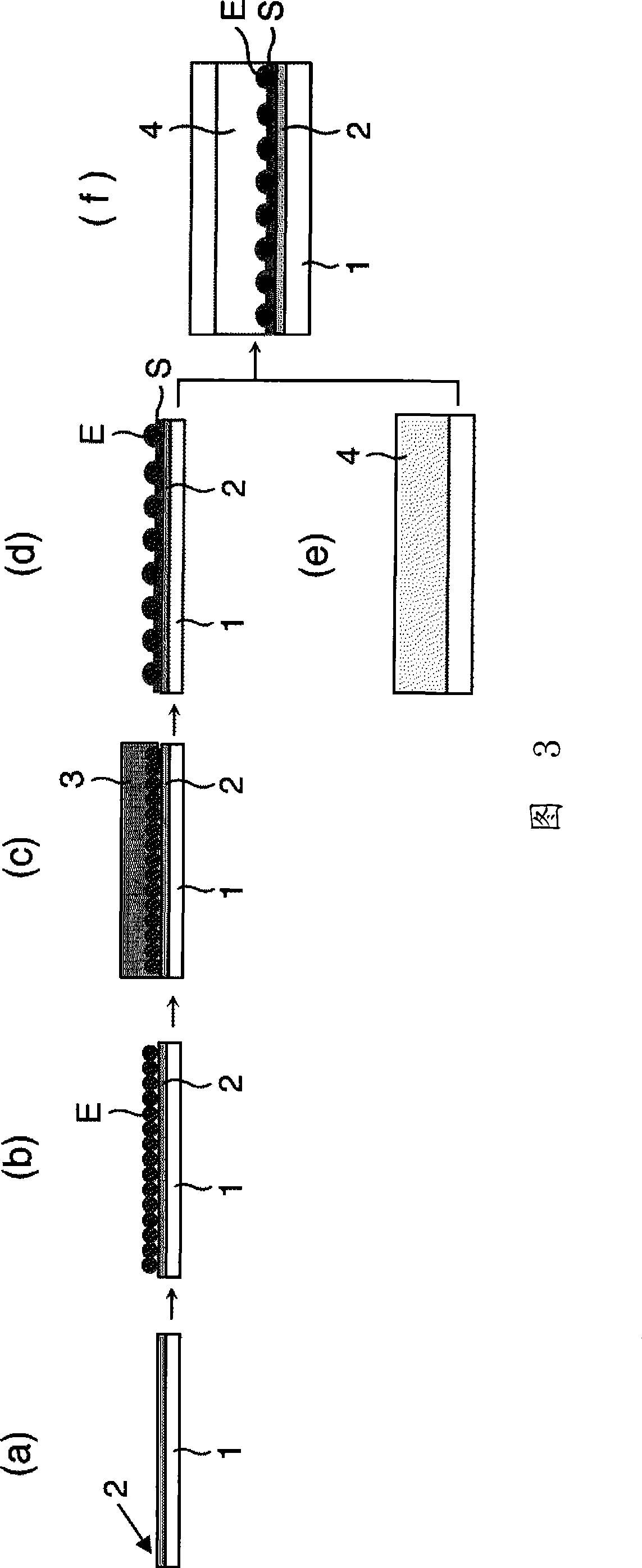

Electroconductive particle placement sheet and anisotropic elctroconductive film

ActiveCN101432931AImprove connection reliabilityImprove insulation performancePrinted circuit assemblingNon-macromolecular adhesive additivesAnisotropic conductive filmMaterials science

This invention provides an electroconductive particle placement sheet comprising electroconductive particles and an insulating resin sheet. The thickness of the insulating resin sheet is smaller than the average particle diameter of the electroconductive particles. Electroconductive particles are protruded from the reference plane (P1) on at least one side of the insulating resin sheet. The electroconductive particle in is part protruded from the reference plane (P1) is covered with a layer formed of the same resin as in the insulating resin sheet. The electroconductive particle placement sheet is characterized by satisfying a relationship of h1 > h2 wherein h1 represents an average protrusion height, which is the average of distance between the reference plane (P1) and a tangential line (L1), which is a tangential line parallel to the reference plane (P1) of the electroconductive particle and is in contact with the part protruded from the reference plane (P1), and h2 represents an average protrusion height which is the average of distance between the reference plane (P2) and a tangential line (L2), which is a tangential line parallel to the reference plane (P2) of the electroconductive particle and is on the side opposite to the tangential line (L1), provided that, when the tangential line (L2) is within the insulating resin sheet, h2 < 0; when the tangential line (L2) is on the reference plane (P2), h2 = 0; and when the tangential line (L2) is outside the insulating resin sheet, h2 > 0.

Owner:DEXERIALS CORP

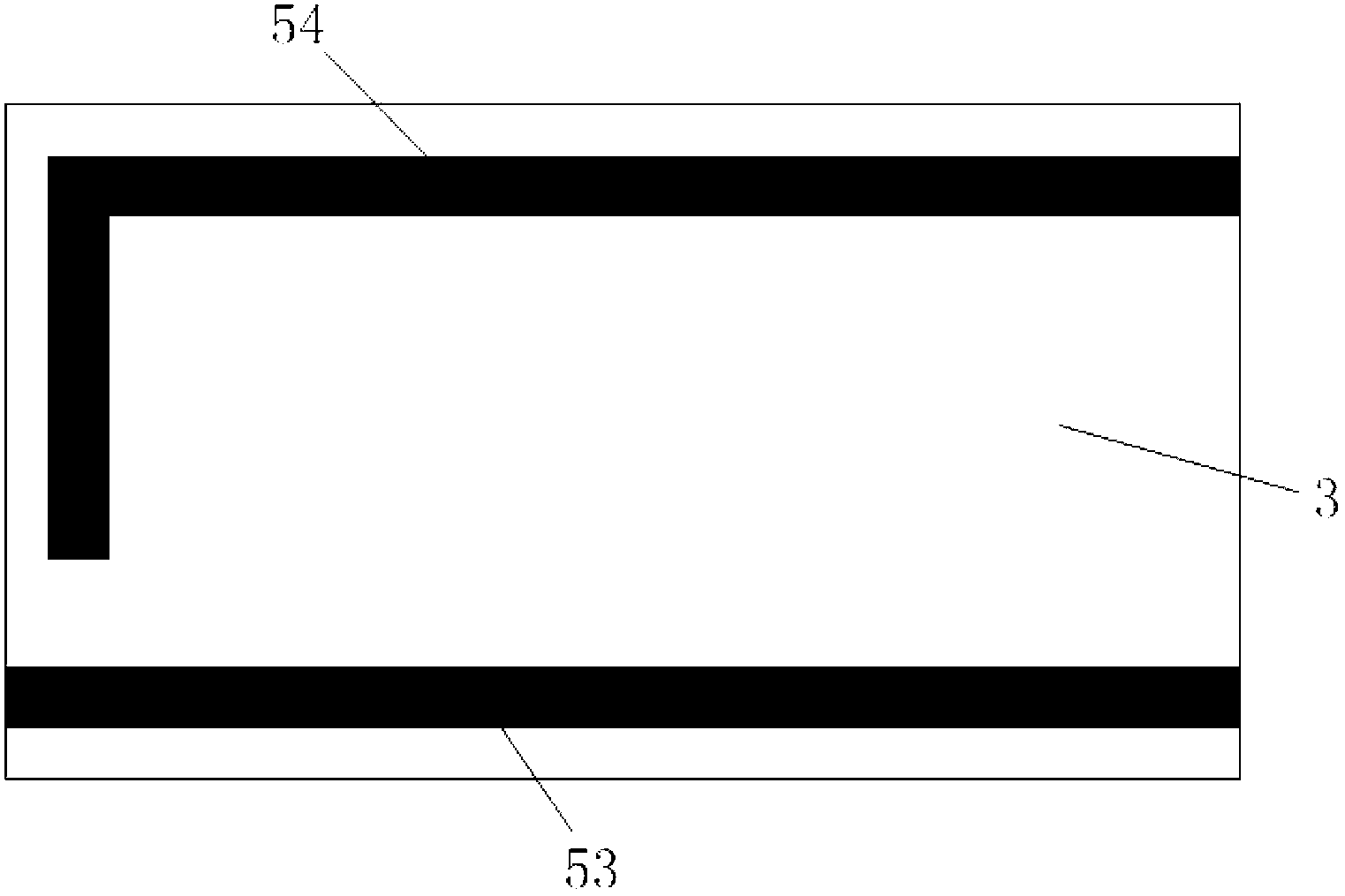

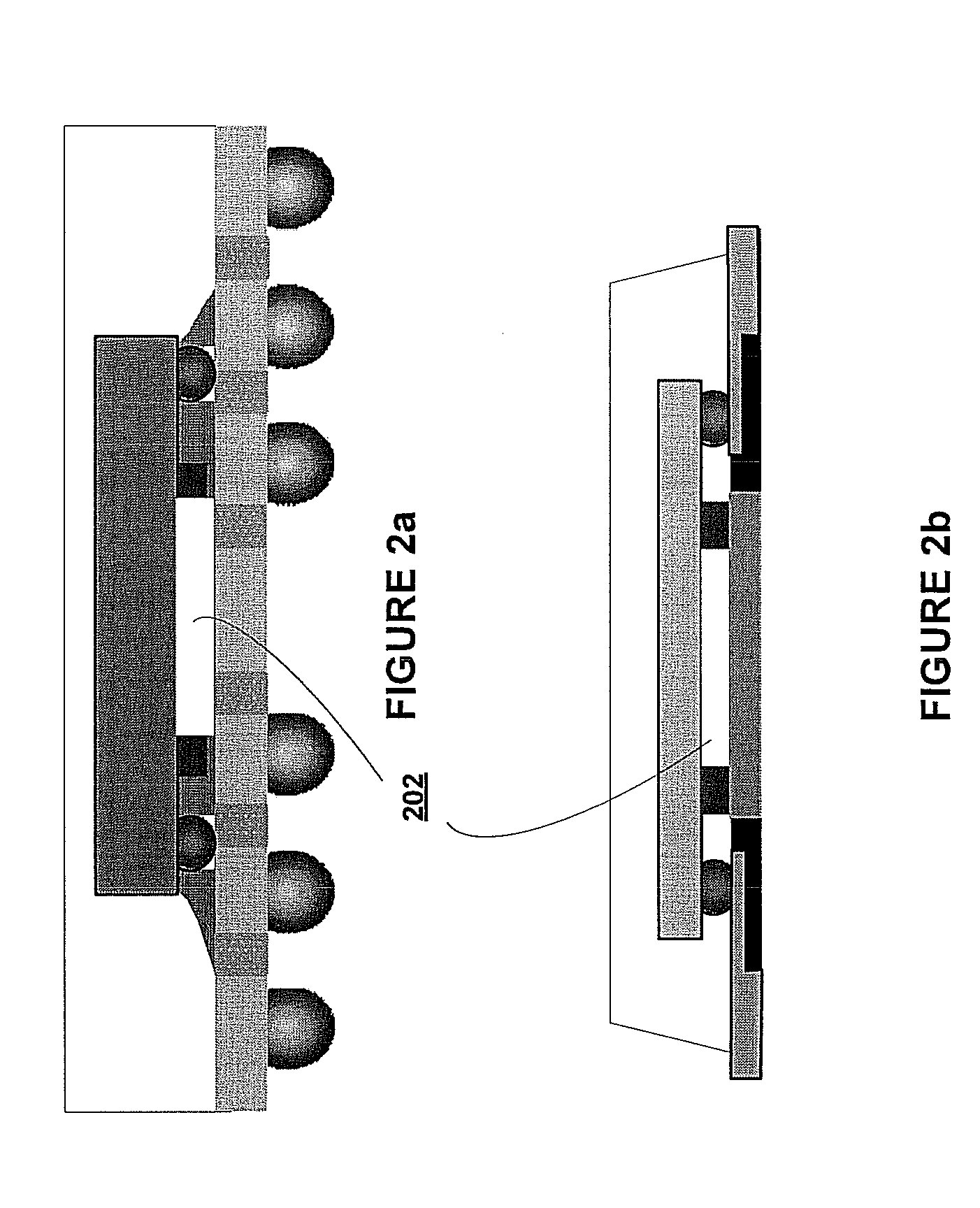

Stress free package and laminate-based isolator package

InactiveUS20080176362A1Relieve pressureSemiconductor/solid-state device detailsSolid-state devicesAnisotropic conductive filmCoupling

Various methods are described where the semiconductor die and the lead frame (or the BGA or LGA substrate) are spaced apart to reduce stress. In one scenario, an air gap is formed between the semiconductor die and the lead frame by depositing a perimeter (made, for example, using polymer) either on the semiconductor die or the lead frame. In another scenario, an anisotropic conducting film (ACF) is formed with an air gap between the semiconductor die and the lead frame (or the BGA or LGA substrate). The air gap relieves stress on the semiconductor die. Further, a lead frame-based isolator package and a BGA (or LGA) isolator package are described. A window-frame ACF-based isolation method for magnetic coupling in a lead-frame package and BGA (or LGA) package is also described.

Owner:ANALOG DEVICES INC

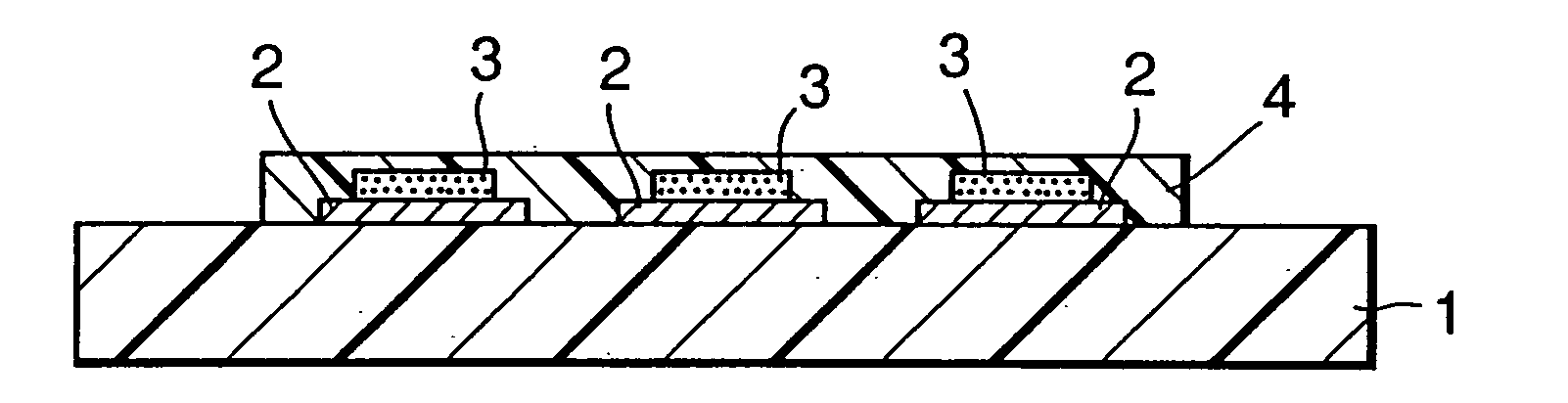

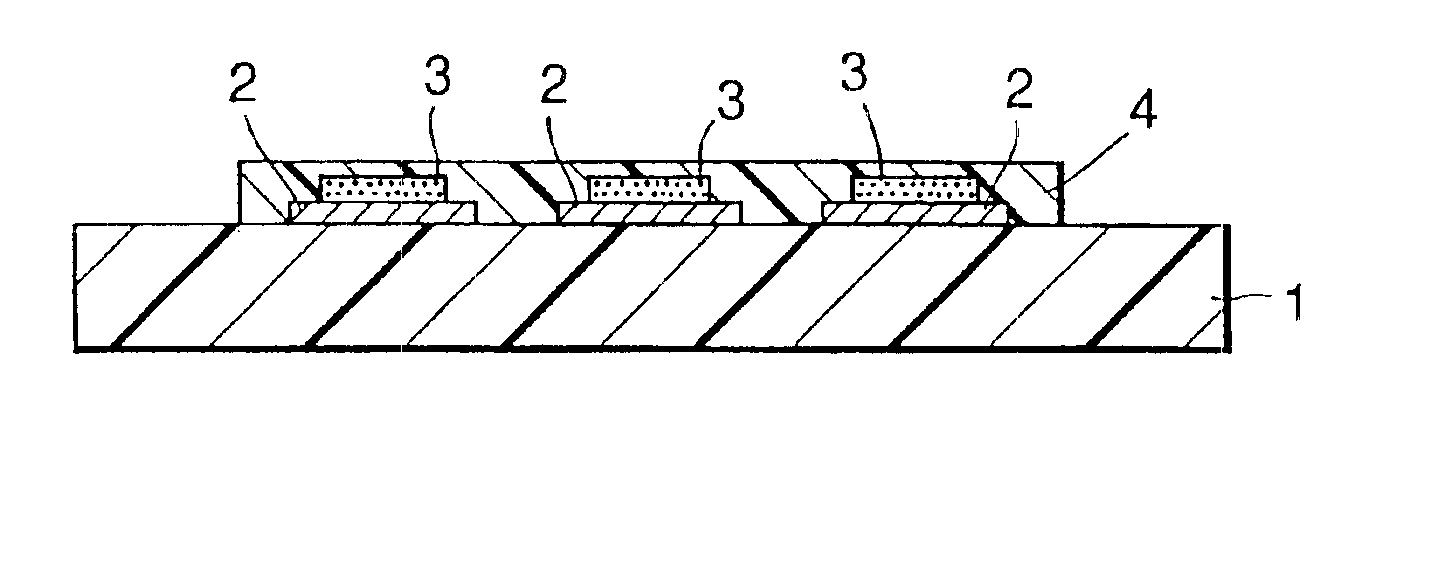

Semiconductor device, mounting circuit board, method of producing the same, and method of producing mounting structure using the same

InactiveUS6909180B2Avoid damageImprove productivityPrinted circuit assemblingLamination ancillary operationsAnisotropic conductive filmAdhesive

The invention is intended for providing a semiconductor package structure which prevents degradation in characteristics of a semiconductor device, and breakage of interconnections, when the semiconductor device is packaged on a circuit substrate. In the package structure having the semiconductor device mounted on the circuit substrate, bump electrodes of the semiconductor device are placed on input / output terminal electrodes of the circuit substrate and are electrically and mechanically connected thereto by bonding with a conductive adhesive, and the semiconductor device is bonded and fixed to the circuit substrate by a resin film formed previously on a surface of a main body of the circuit substrate. The structure does no damage to a semiconductor functional part and to interconnections, and allows mounting with a lower load as compared to structures using conventional anisotropic conductive films and the like.

Owner:PANASONIC CORP

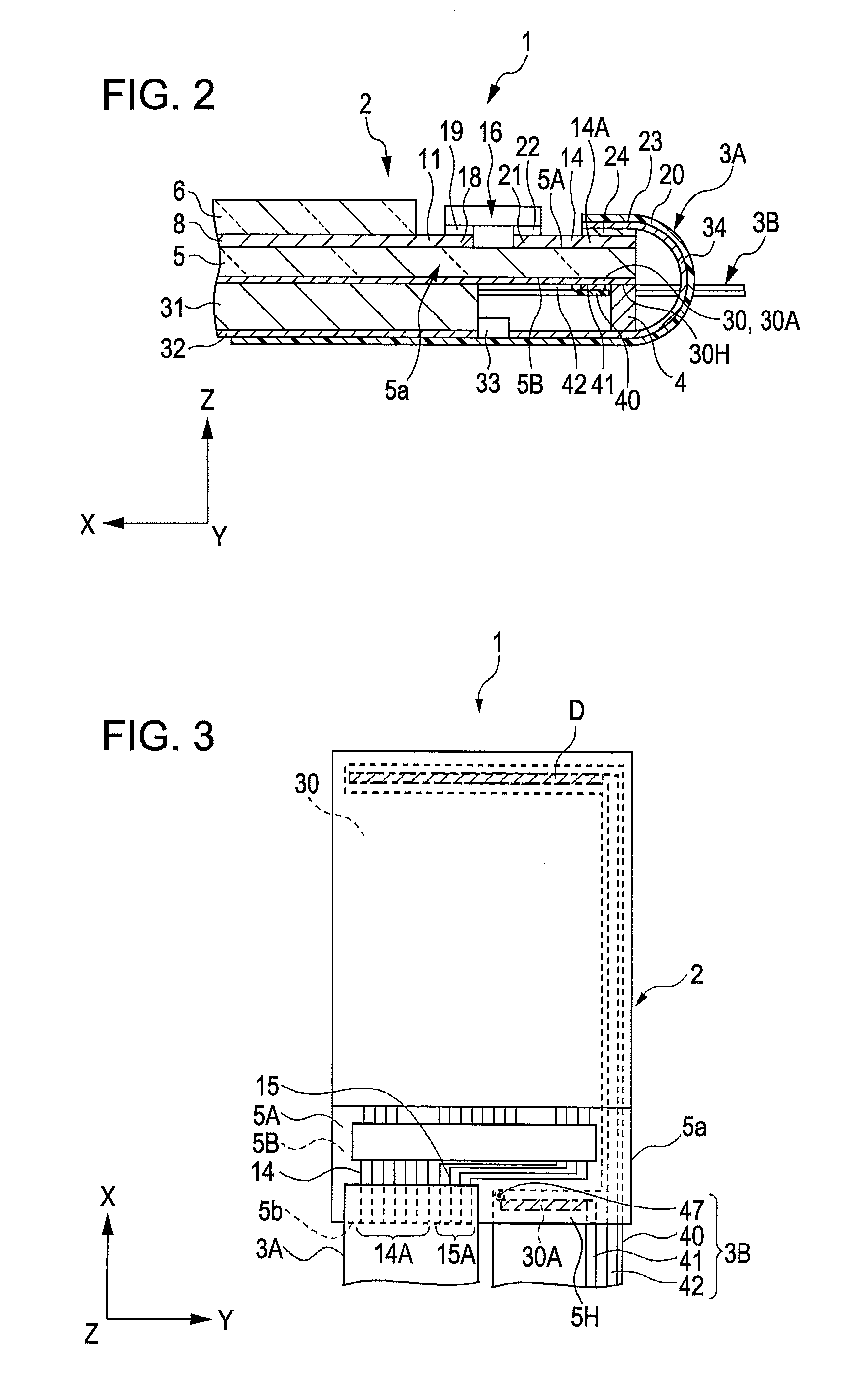

Mounting structure, electro-optical device, input device, method of manufacturing mounting structure, and electronic apparatus

ActiveUS20080232047A1Improve connection reliabilityEven by forceDigital data processing detailsPrinted circuit aspectsAnisotropic conductive filmFlexible circuits

A mounting structure includes a substrate, a first terminal, a first flexible circuit board, and a second terminal. The first terminal is arranged in a first region of a first face of the substrate. The first flexible circuit board is connected to the first terminal through an anisotropic conductive film. The second terminal is arranged in a second region of a second face, which is a rear face relative to the first face of the substrate, wherein the second region does not overlap the first region in plan view. A region of the second face of the substrate, which overlaps the first region in plan view, is formed to be a smooth face.

Owner:JAPAN DISPLAY WEST

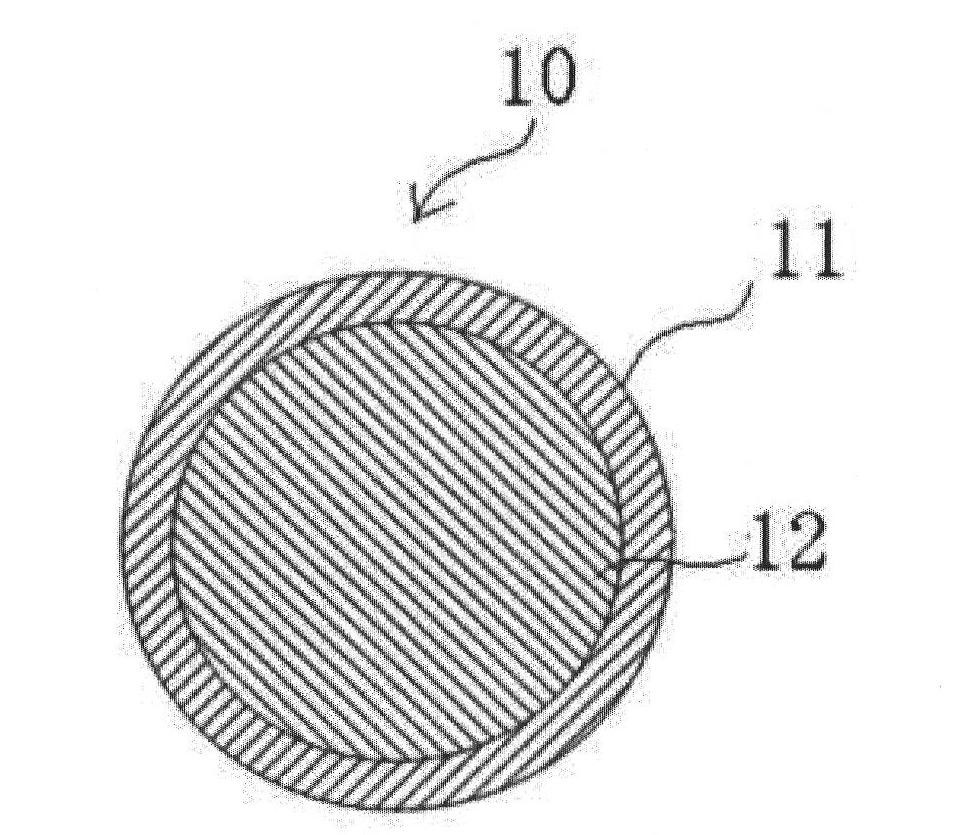

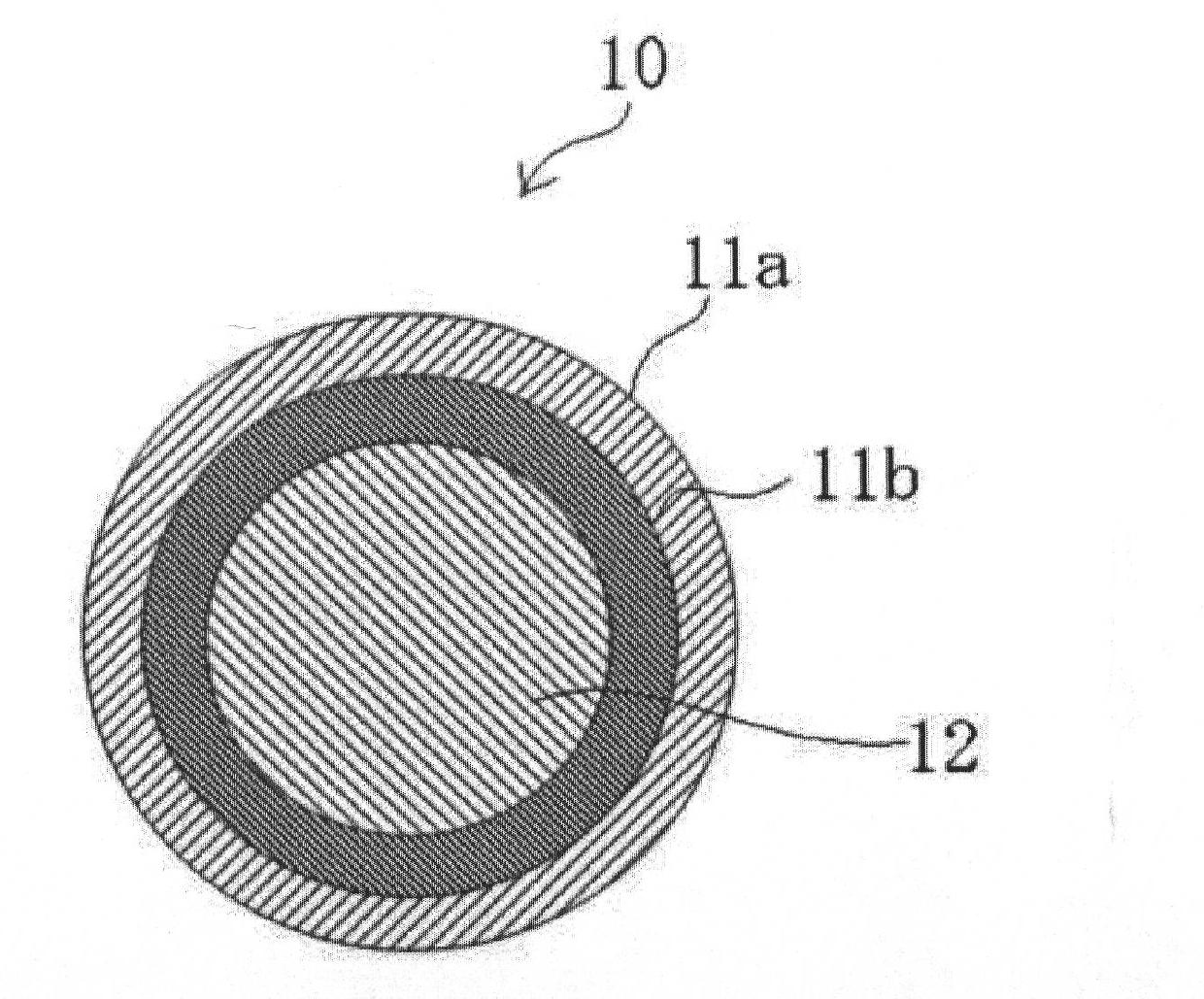

Conductive particle, anisotropic conductive film, joined body, and connecting method

ActiveCN102089832AGood spreadabilitySuppress stressPrinted circuit assemblingNon-insulated conductorsAnisotropic conductive filmElectrical connection

Disclosed are conductive particles wherein stress can be suppressed by improving spreadability while maintaining high hardness (cracks hardly occur even when the particles are crushed during the connection). The conductive particles assure sufficient electrical connection reliability not only for ITO substrates but also for IZO substrates. An anisotropic conductive film comprising the conductive particles, a joined body comprising the anisotropic conductive film, and a connecting method using the anisotropic conductive film are also disclosed. Each of the conductive particles comprises a polymer fine particle and a conductive layer formed on the surface of the polymer fine particle, and is characterized in that the outermost shell of the conductive layer is composed of a nickel-palladium alloy layer.

Owner:DEXERIALS CORP

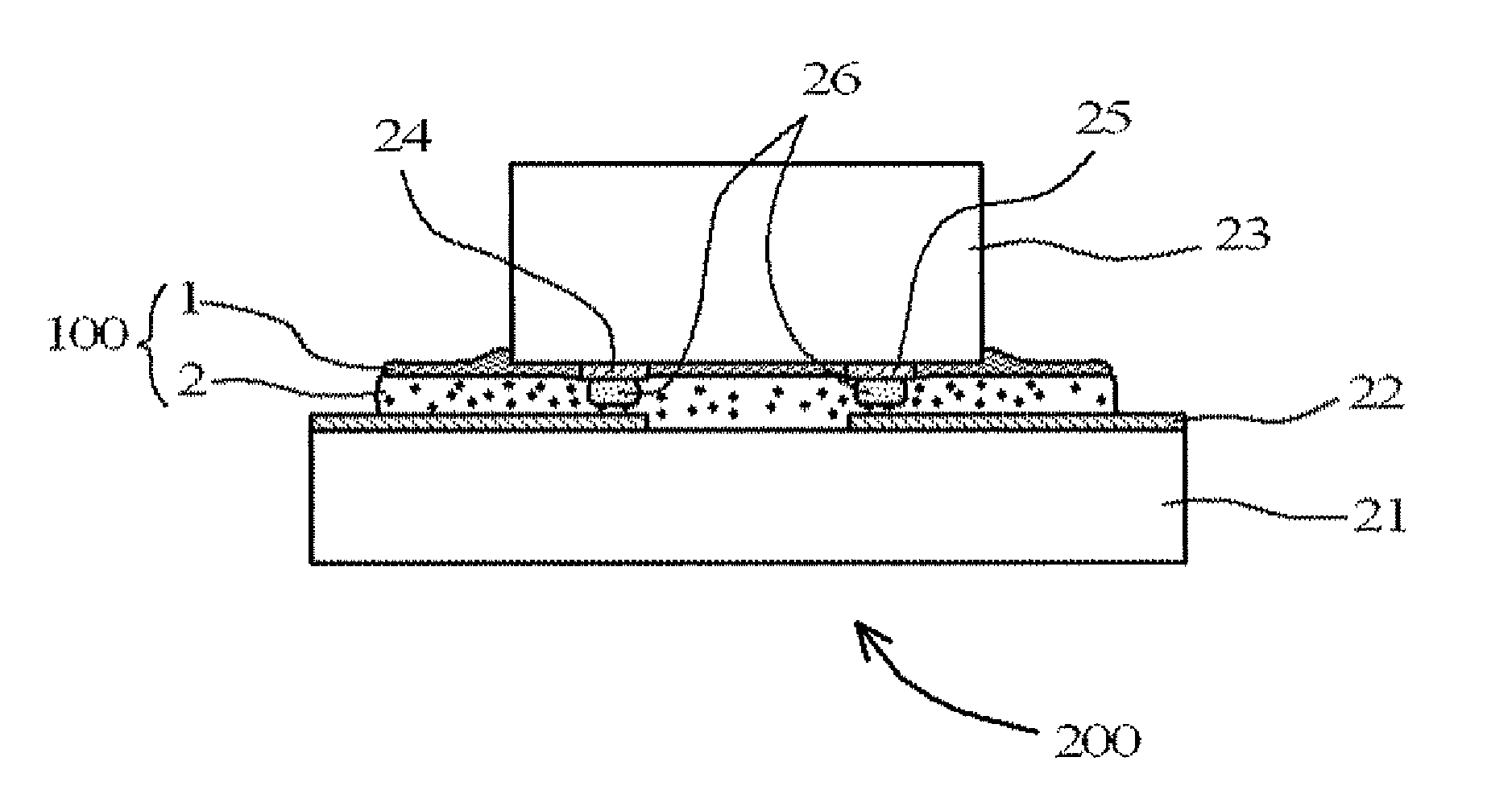

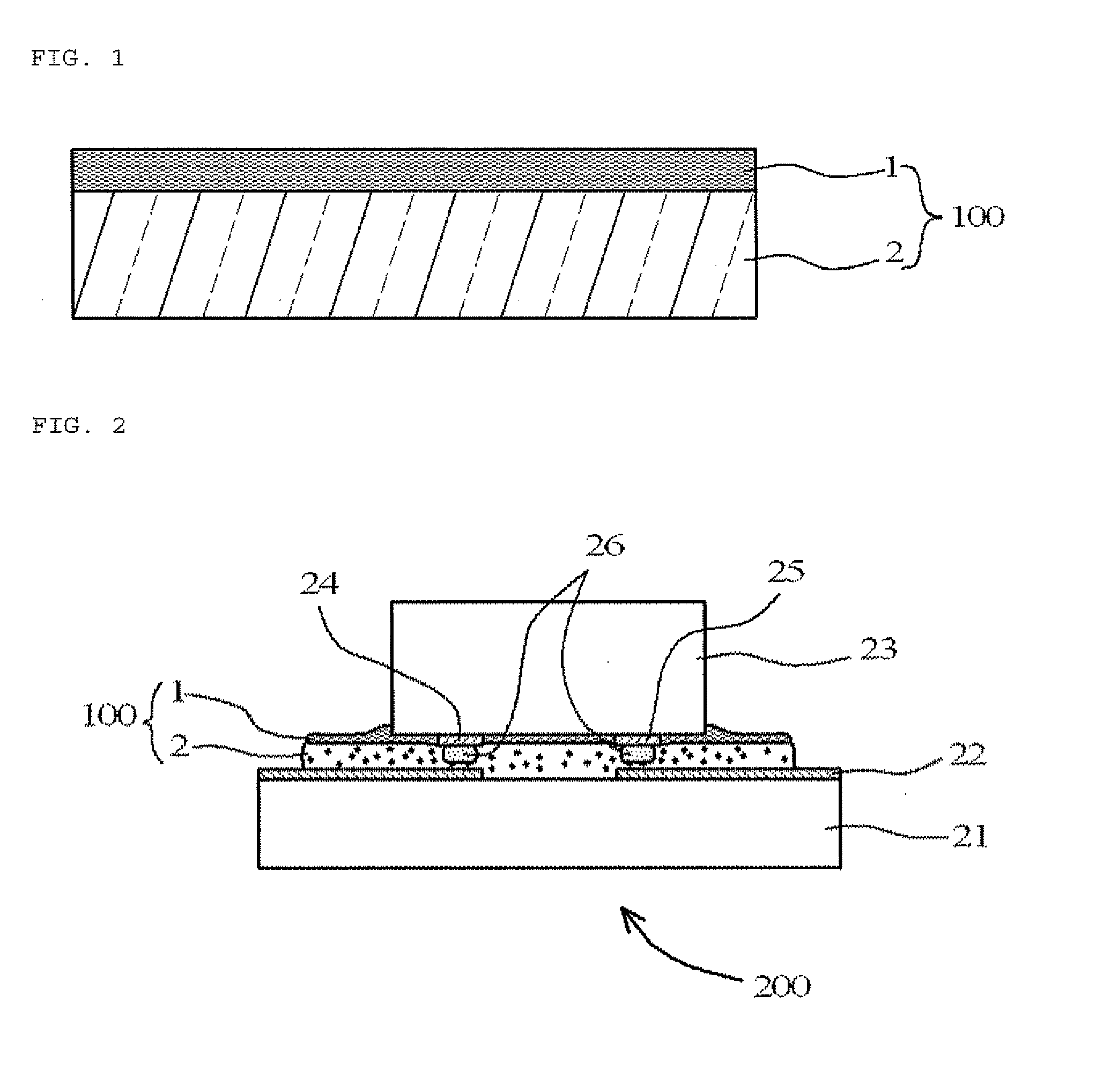

Anisotropic conductive film and light emitting device

InactiveUS20110266578A1Emission efficiency of the light emitting device does not deteriorateNon-macromolecular adhesive additivesPrinted circuit aspectsAnisotropic conductive filmAnisotropic conductive adhesive

An anisotropic conductive film is provided that does not have a light-reflecting layer on a light emitting diode element which causes costs to increase when a light emitting device that uses an LED element is flip-chip mounted, and that does not cause emission efficiency to deteriorate. Further, a light emitting device that uses such an anisotropic conductive film is provided. This anisotropic conductive film has a structure in which a light-reflecting insulating adhesive layer and an anisotropic conductive adhesive layer are laminated, wherein the light-reflecting insulating adhesive layer has a structure in which light-reflecting particles are dispersed in an insulating adhesive. The light emitting device has a structure in which a light emitting diode element is flip-chip-mounted on a substrate, with this anisotropic conductive film provided between a connection terminal on the substrate and a bump for connection of the light emitting diode element.

Owner:DEXERIALS CORP

Anisotropic conductive connector and its production method, and circuit device test instrument

InactiveUS20050106907A1Improve conductivityPrevent permanent deformationElectrically conductive adhesive connectionsElectrical testingAnisotropic conductive filmEngineering

An anisotropically conductive connector, not causing permanent deformation by contact of target electrodes to be connected with pressure and deformation by abrasion even if the target electrodes are projected, and achieving stable conductivity over a long time period even when pressed repeatedly, a production process thereof, and an inspection circuit board equipped with the connector. The connector includes (1) anisotropically conductive film, with plural conductive path-forming parts each extending in a thickness-wise direction of the film arranged insulated by insulating parts and including at least 2 elastic layers, which are each formed by an insulating elastic polymeric substance, and (2) conductive particles exhibiting magnetism in portions of the respective elastic layers, at which conductive path-forming parts are formed. The connector satisfies H1≧30, and H1 / H2≧1.1, H1, H2 being durometer hardnesses of the elastic polymeric substance of one of elastic layers forming surfaces of the film, and of the elastic polymeric substance of the other, respectively.

Owner:ISC CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com