Patents

Literature

8192 results about "Lead frame" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

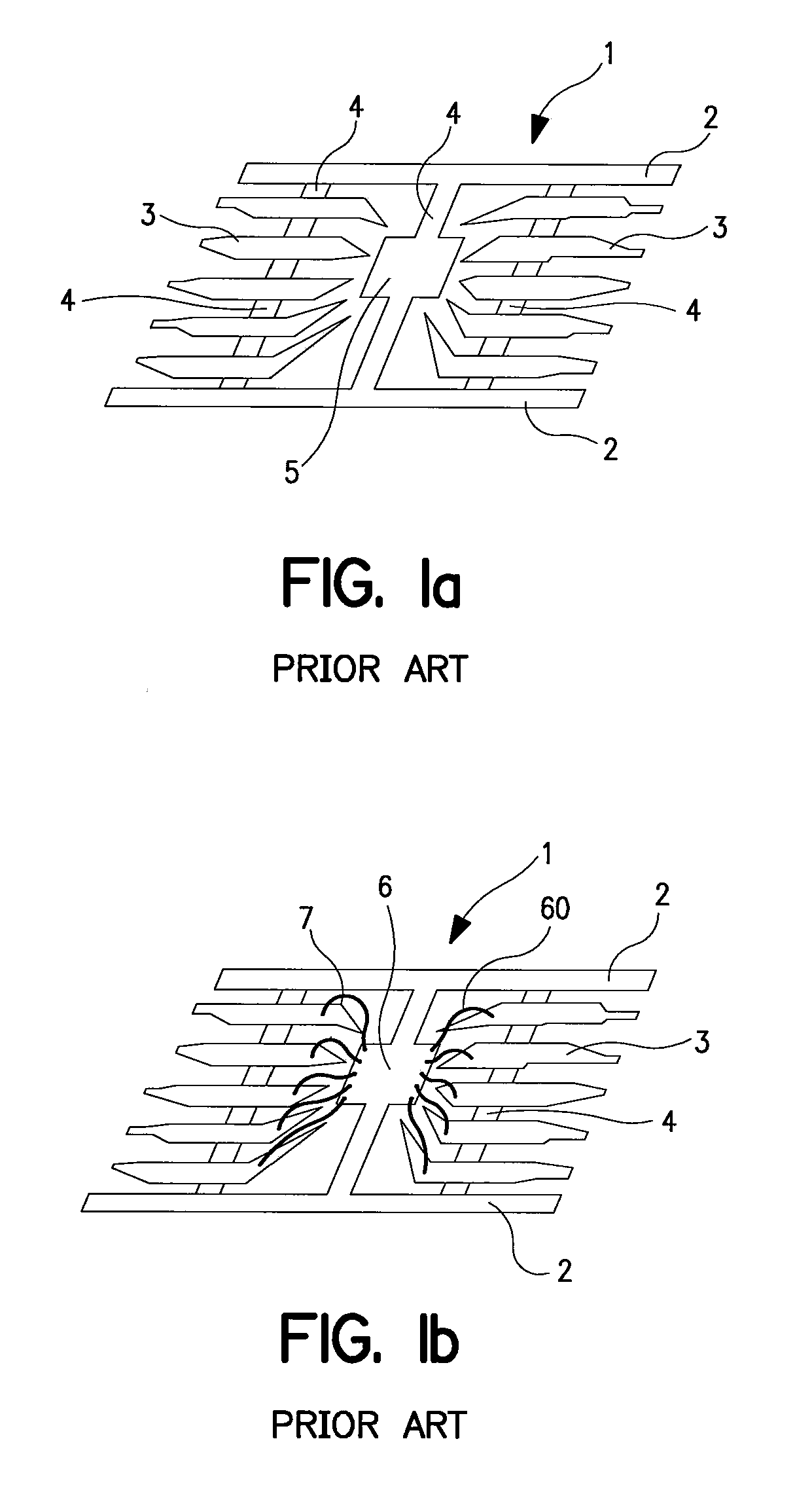

Lead frames are the metal structures inside a chip package that carry signals from the die to the outside. The die inside the package is typically glued to the lead frame, and then bond wires attach the die pads to the leads. In the last stage of the manufacturing process, the lead frame is moulded in a plastic case, and outside of the lead frame is cut-off, separating all leads.

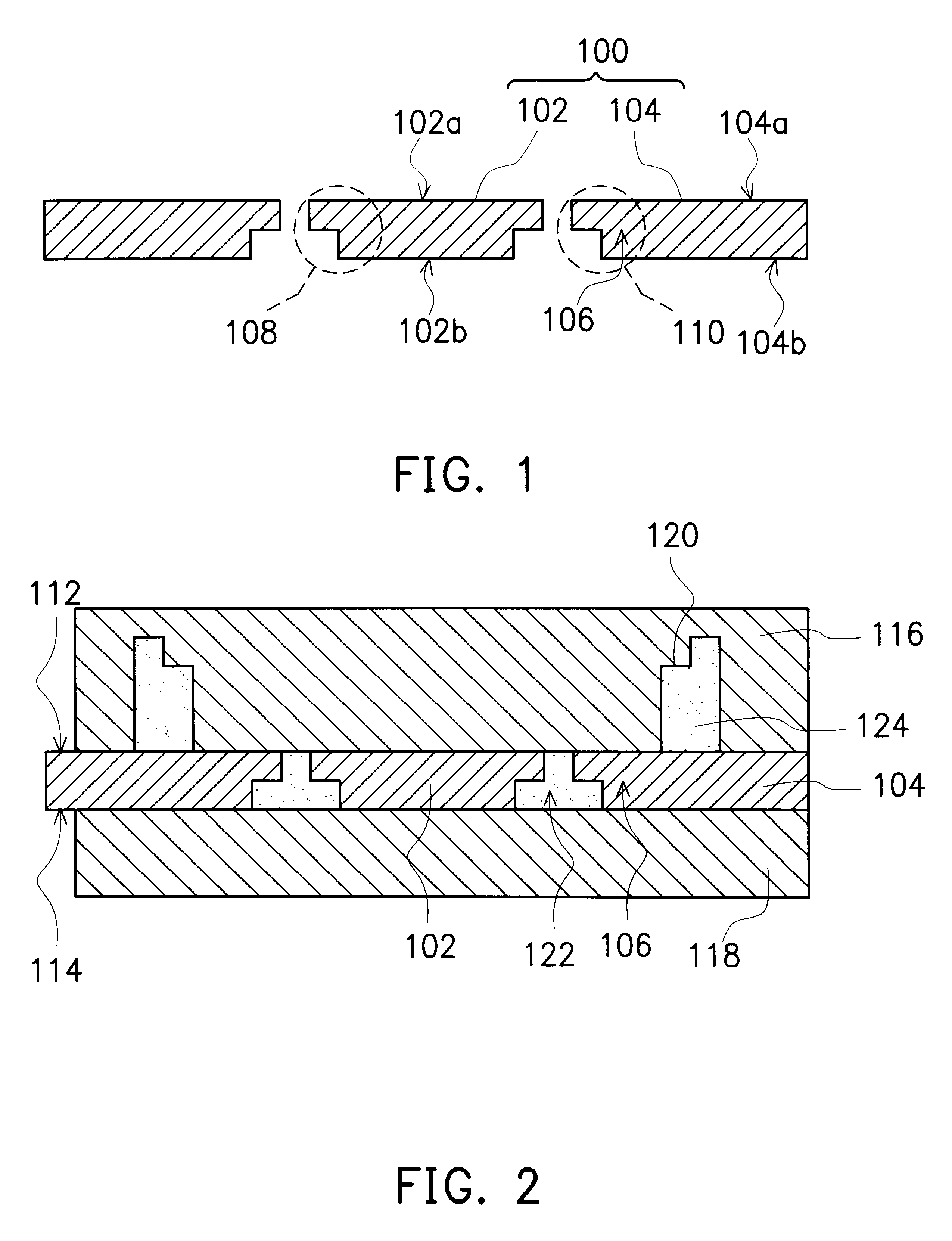

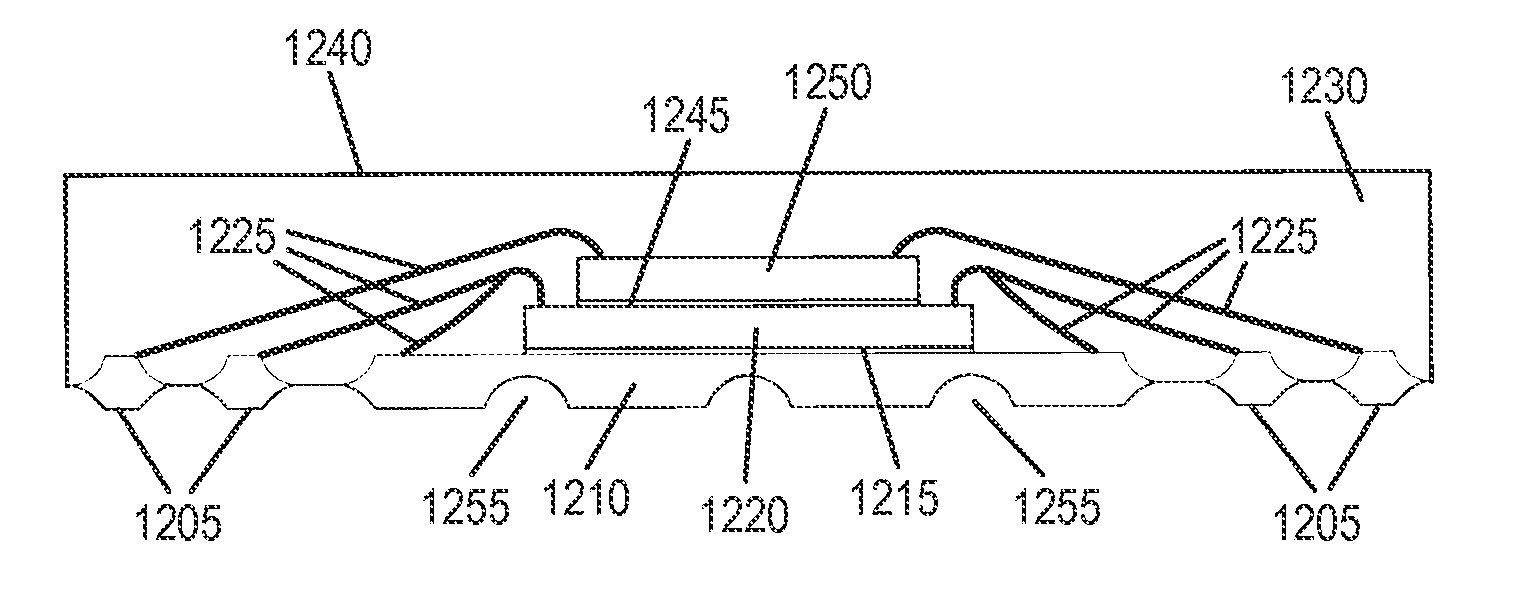

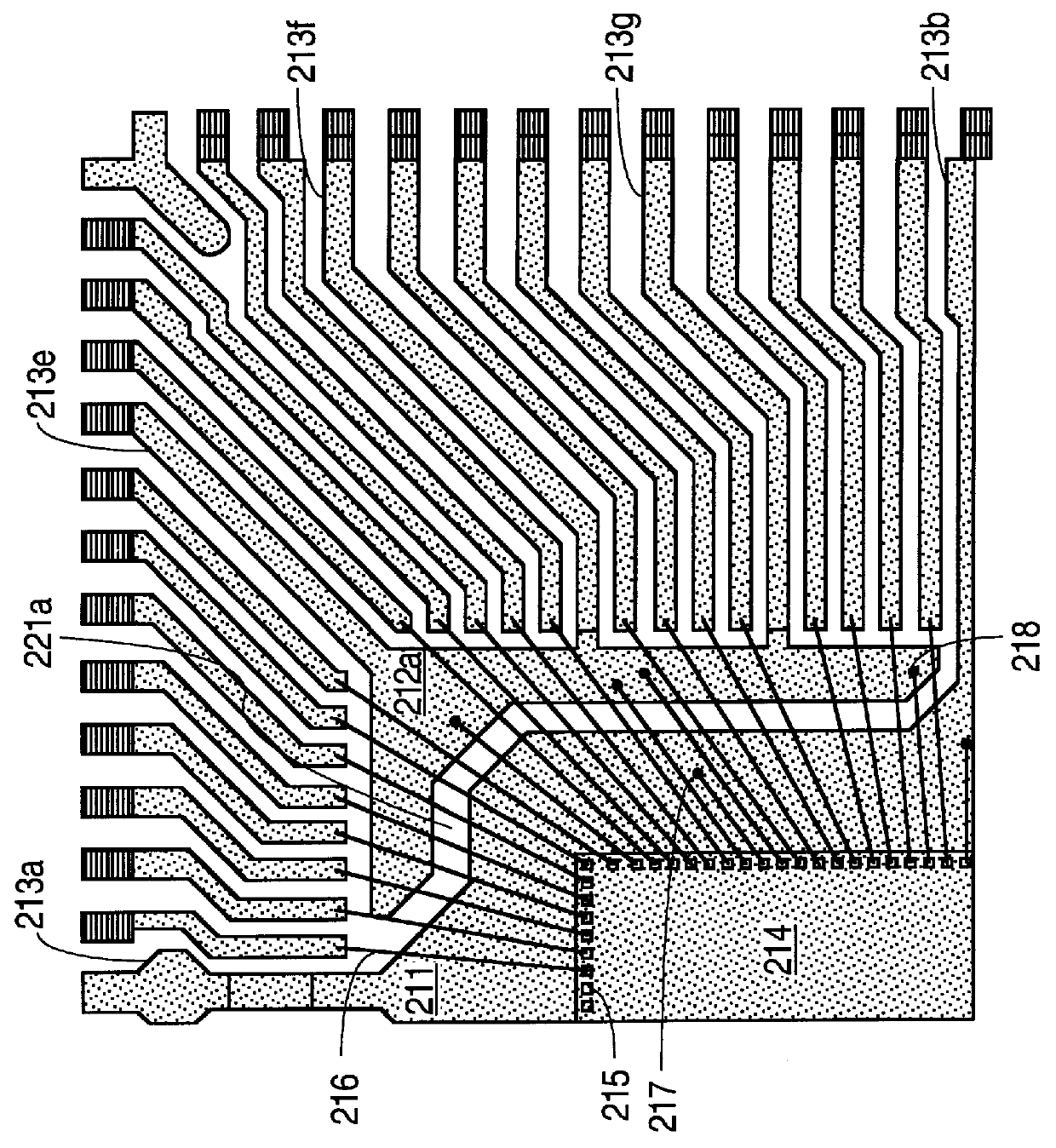

Bendable high flux LED array

ActiveUS6936855B1Easily variableWell formedSolid-state devicesSemiconductor devices for light sourcesLed arrayHigh flux

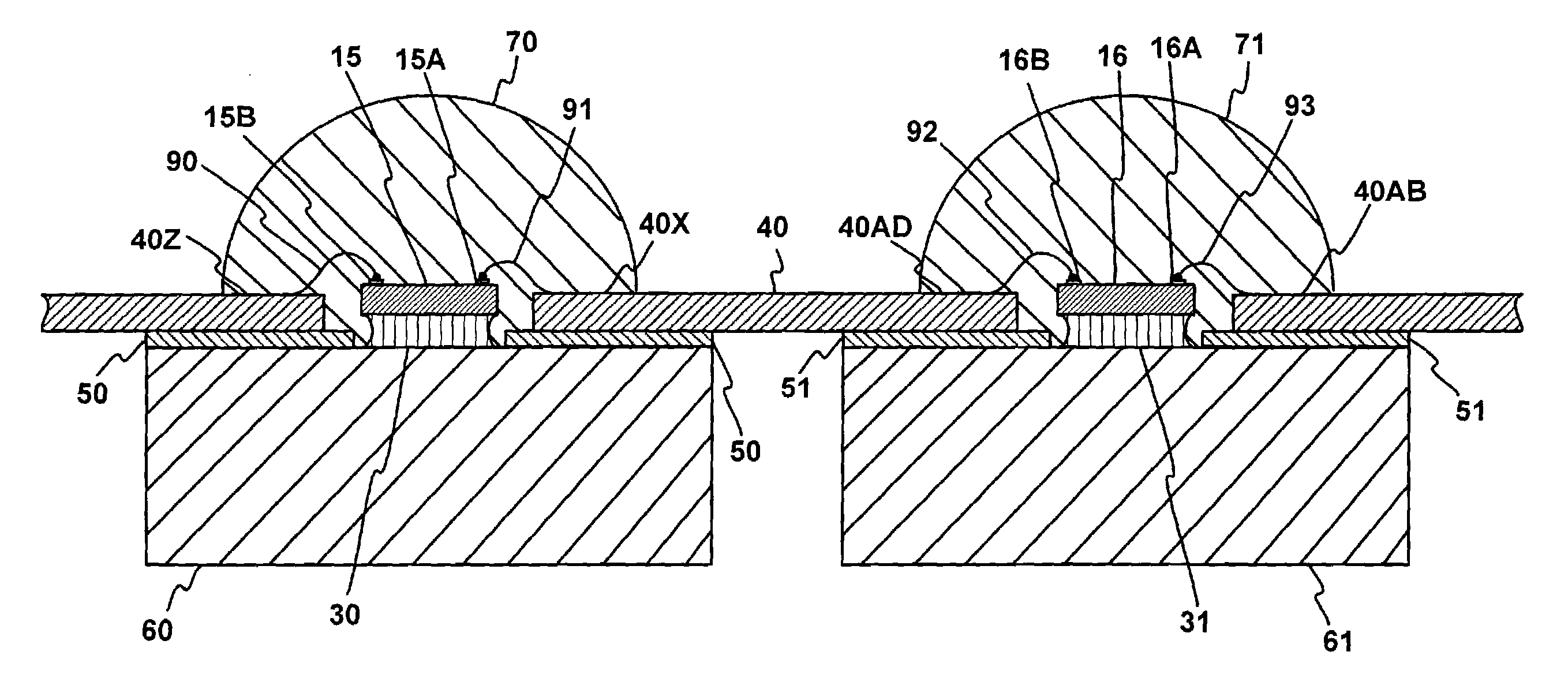

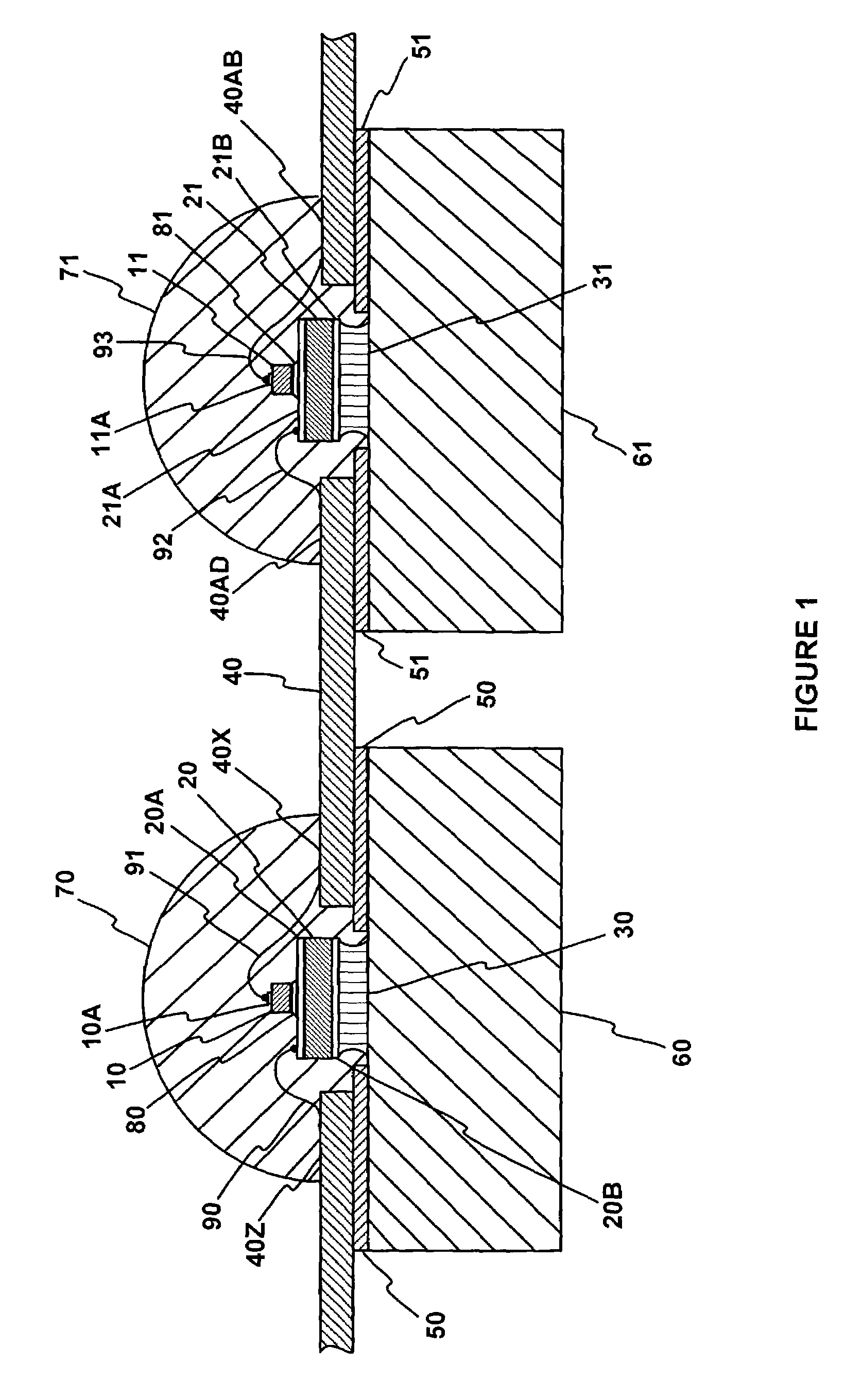

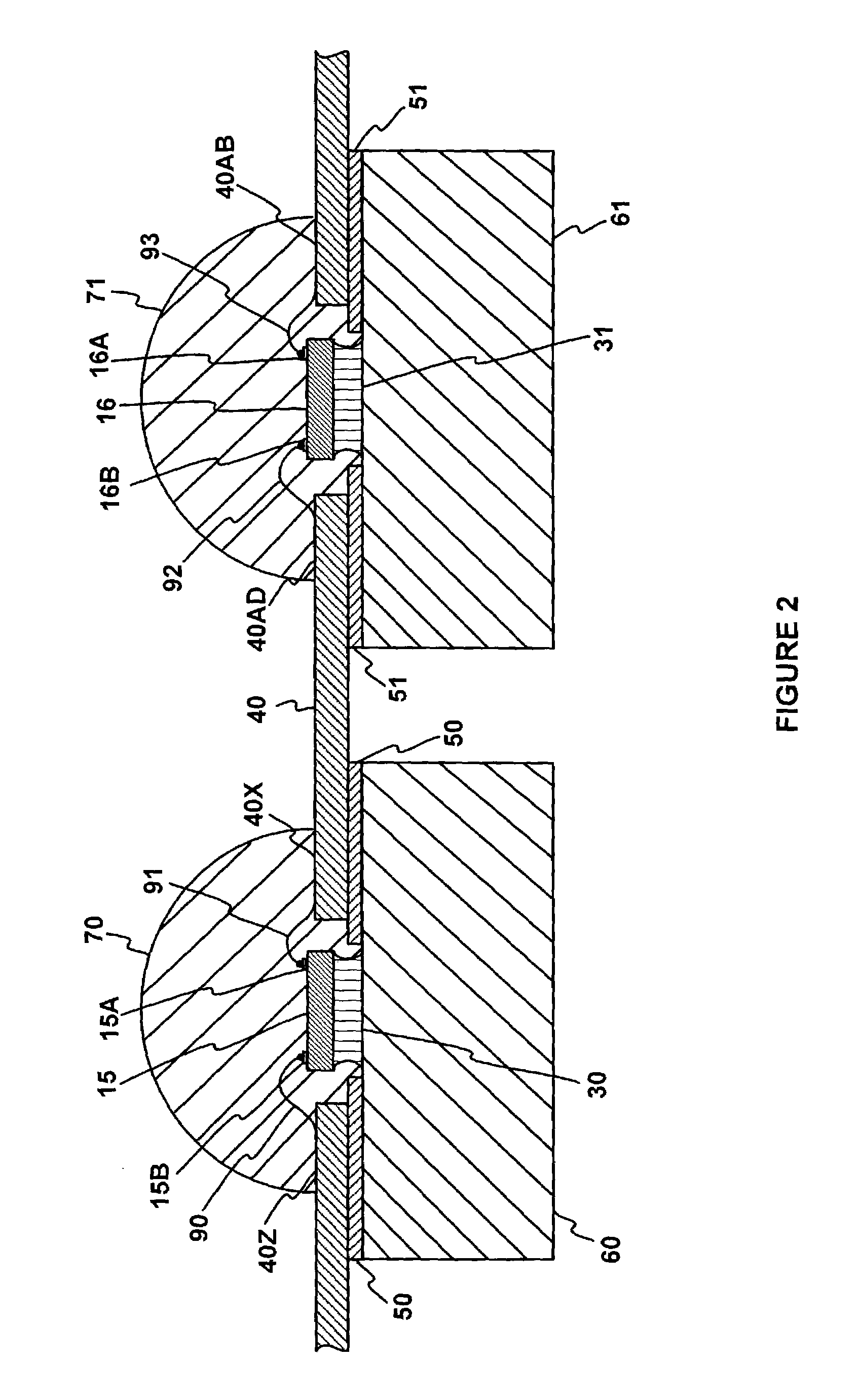

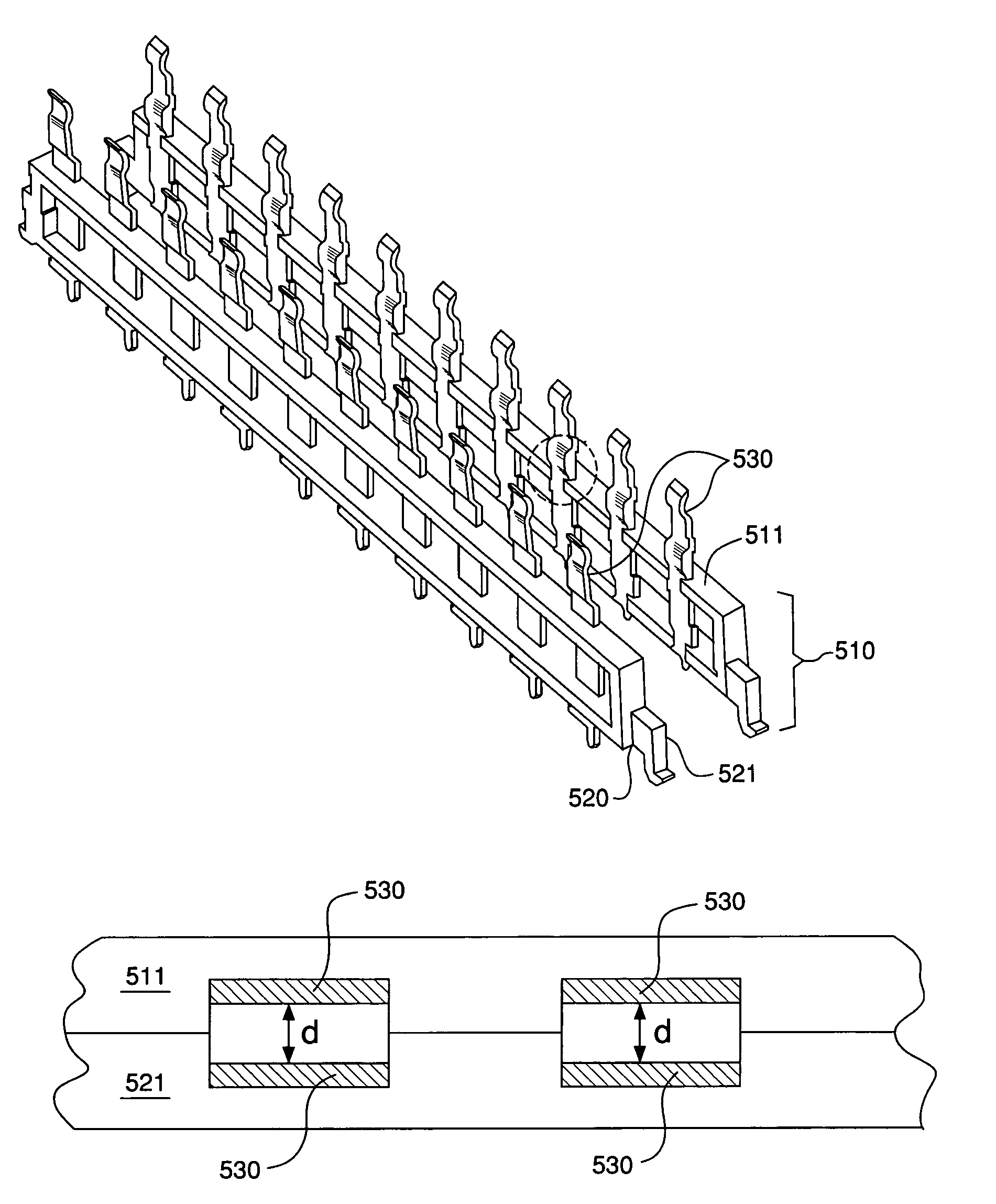

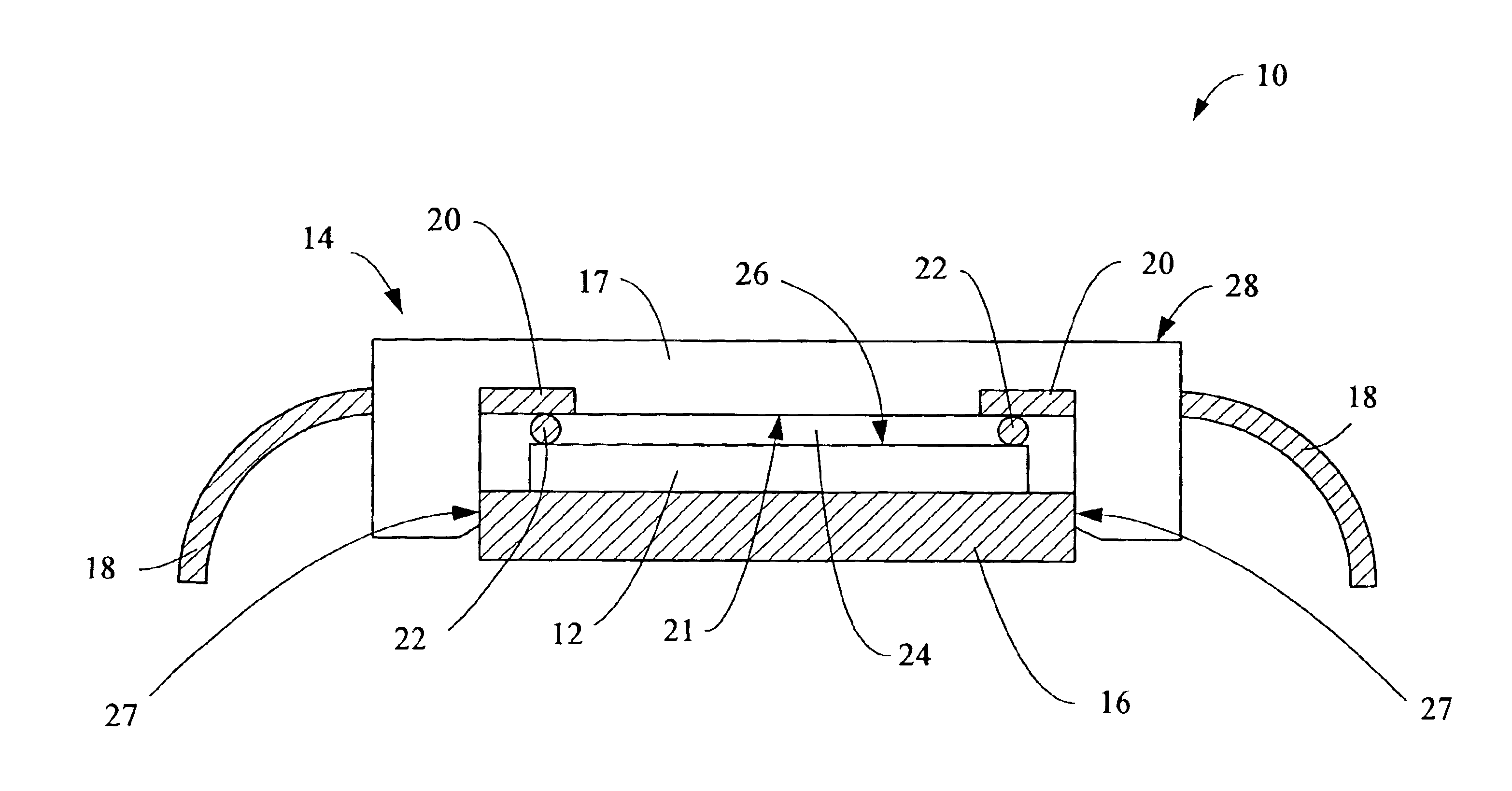

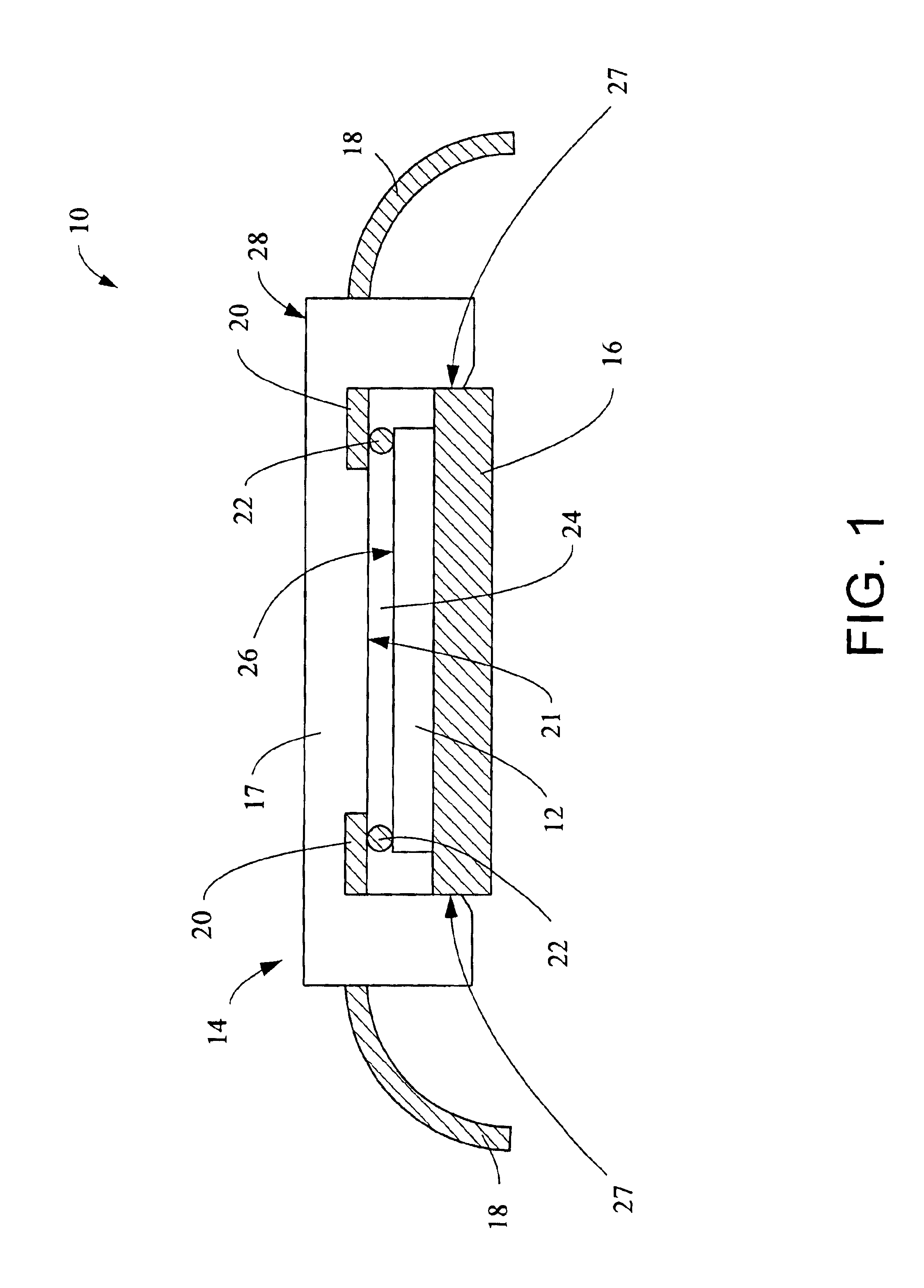

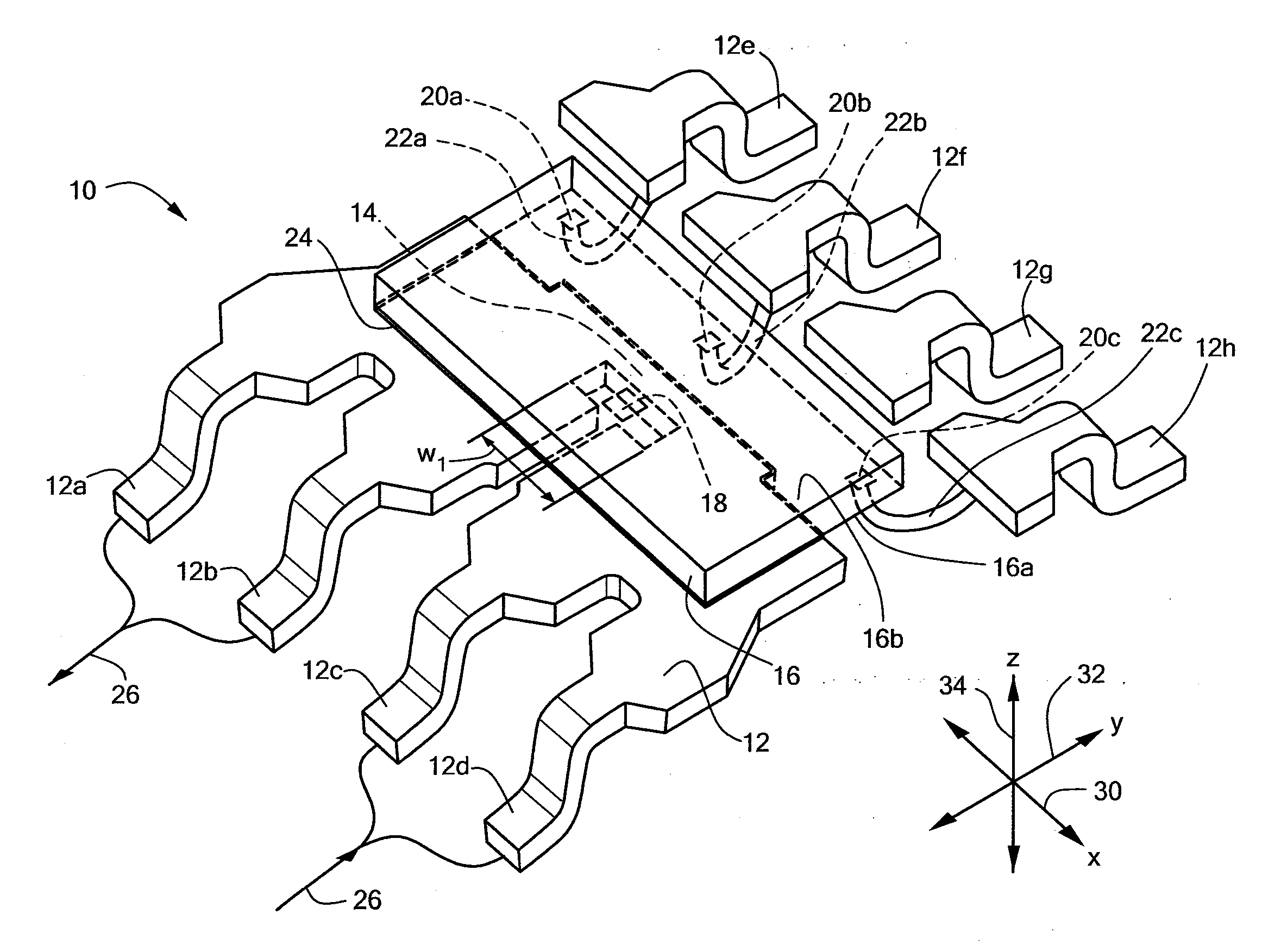

A bendable light emitting diode (LED) array in accordance with the present invention includes heat spreaders, dielectric material disposed above each heat spreader, and a bendable electrical interconnection layer disposed above these heat spreaders and electrically insulated from these heat spreaders by the dielectric material. At least one via passes through the dielectric material above each heat spreader, and at least one LED die is disposed above each via. The bendable electrical interconnection layer may be a lead frame comprising metal pathways that electrically interconnect some or all LED dice in series, in parallel, in anti-parallel, or in some combination of these configurations. Each via contains a thermally conductive material in thermal contact with the corresponding heat spreader below it and in thermal contact with the corresponding LED die above it. The LED dice may be thermally and electrically coupled to submounts disposed above corresponding heat spreaders in some embodiments.

Owner:EPISTAR CORP

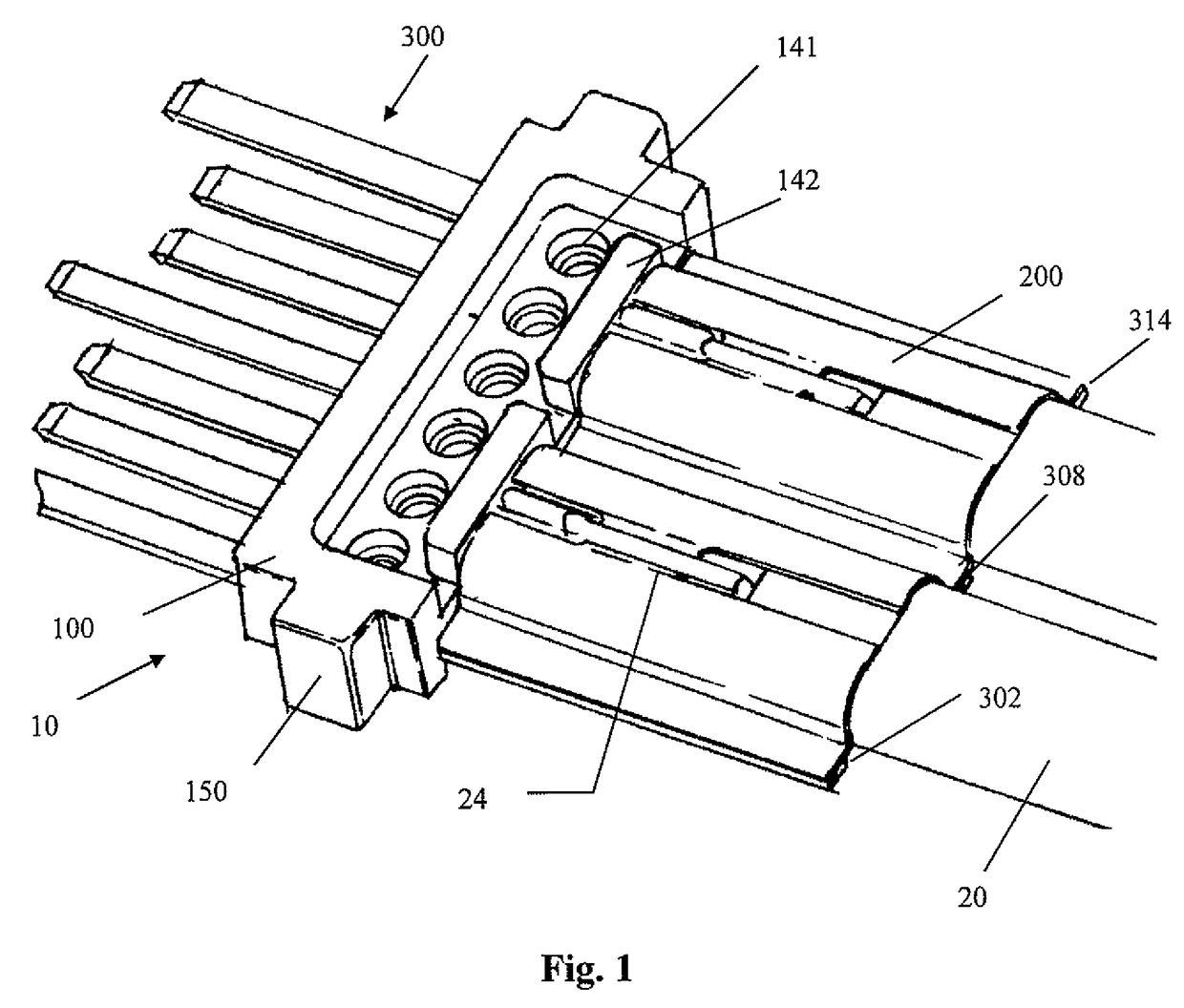

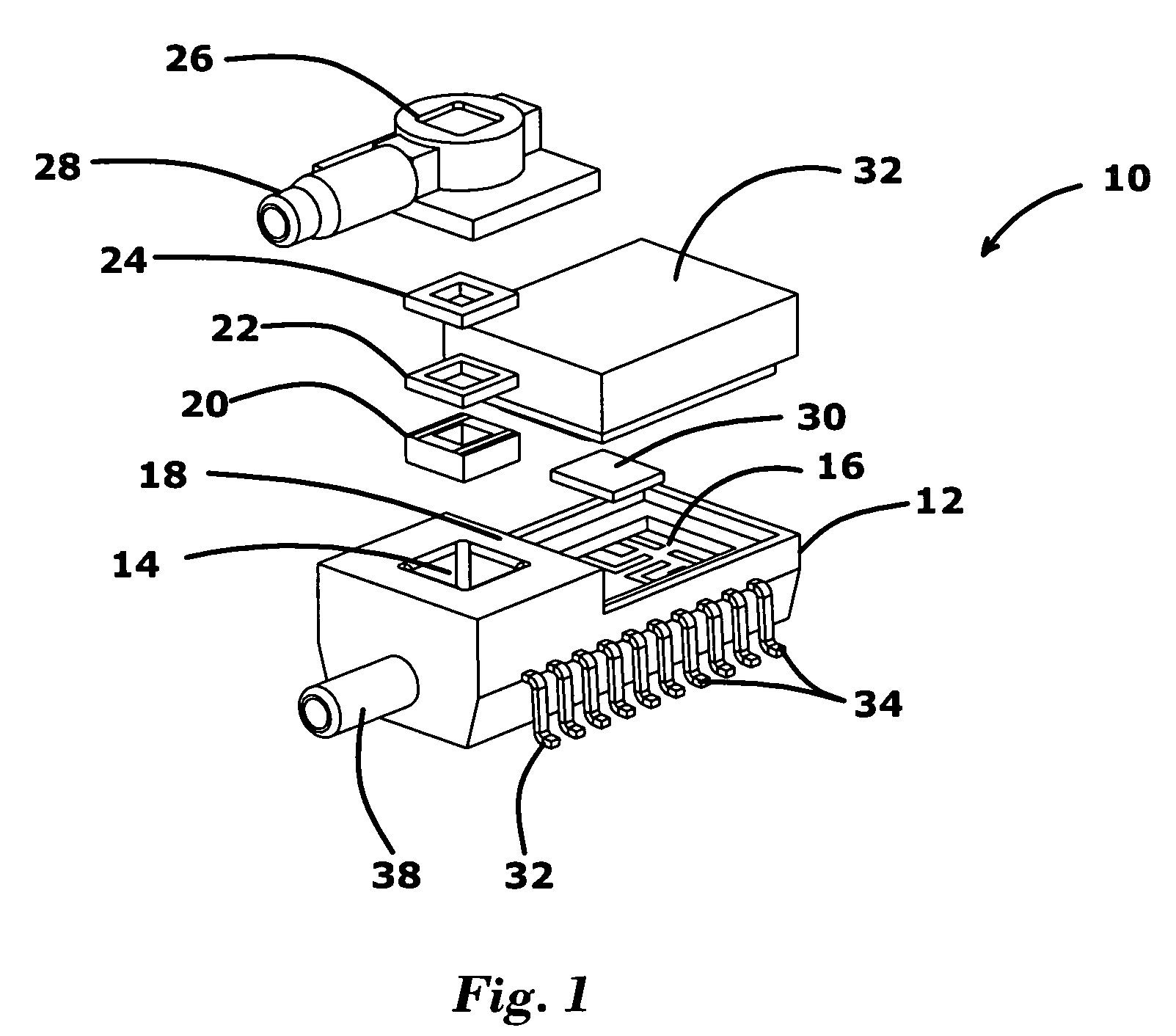

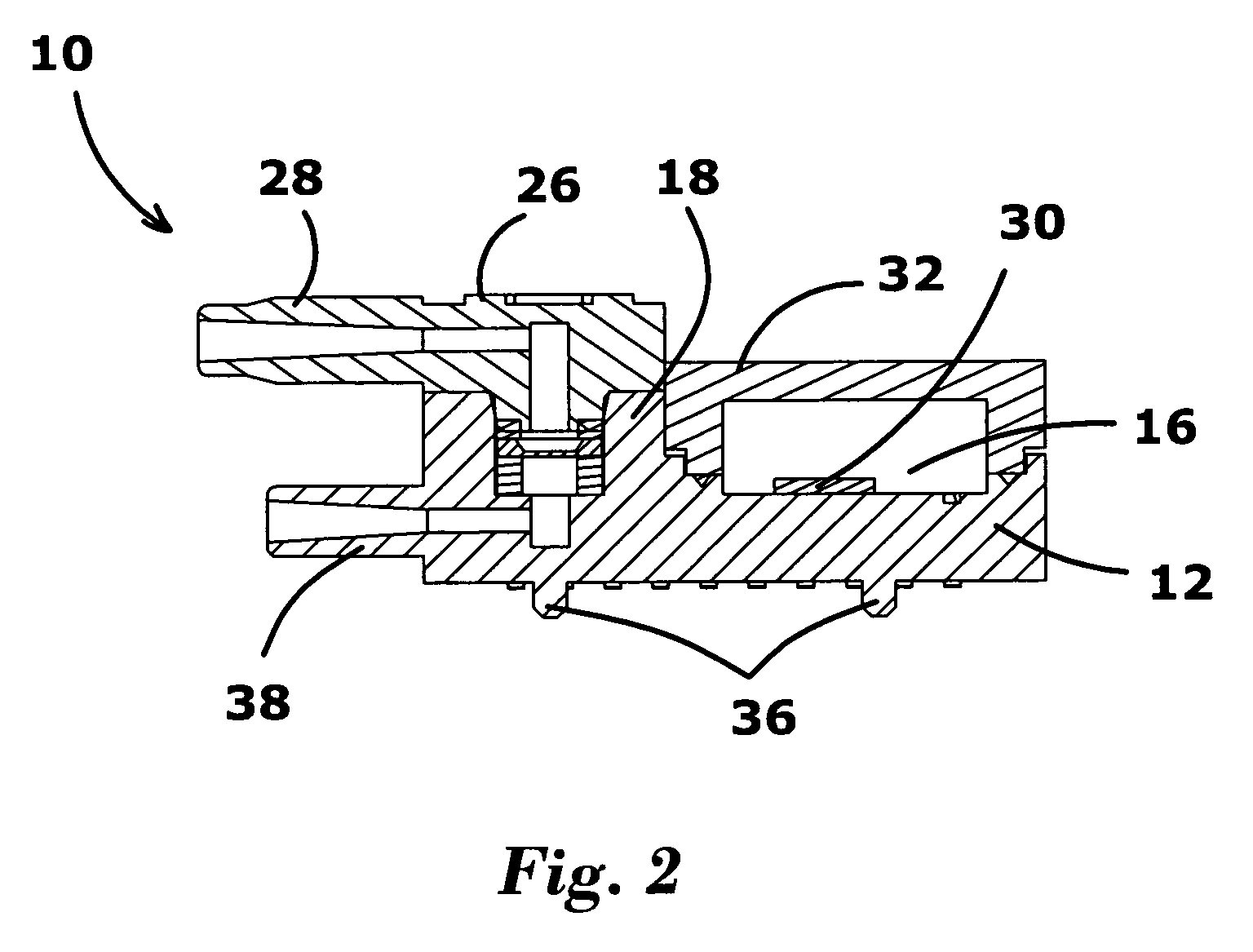

Imaging module having lead frame supported light source or sources

ActiveUS8915444B2Easy to disassembleImprove rigiditySensing by electromagnetic radiationBarcodeEngineering

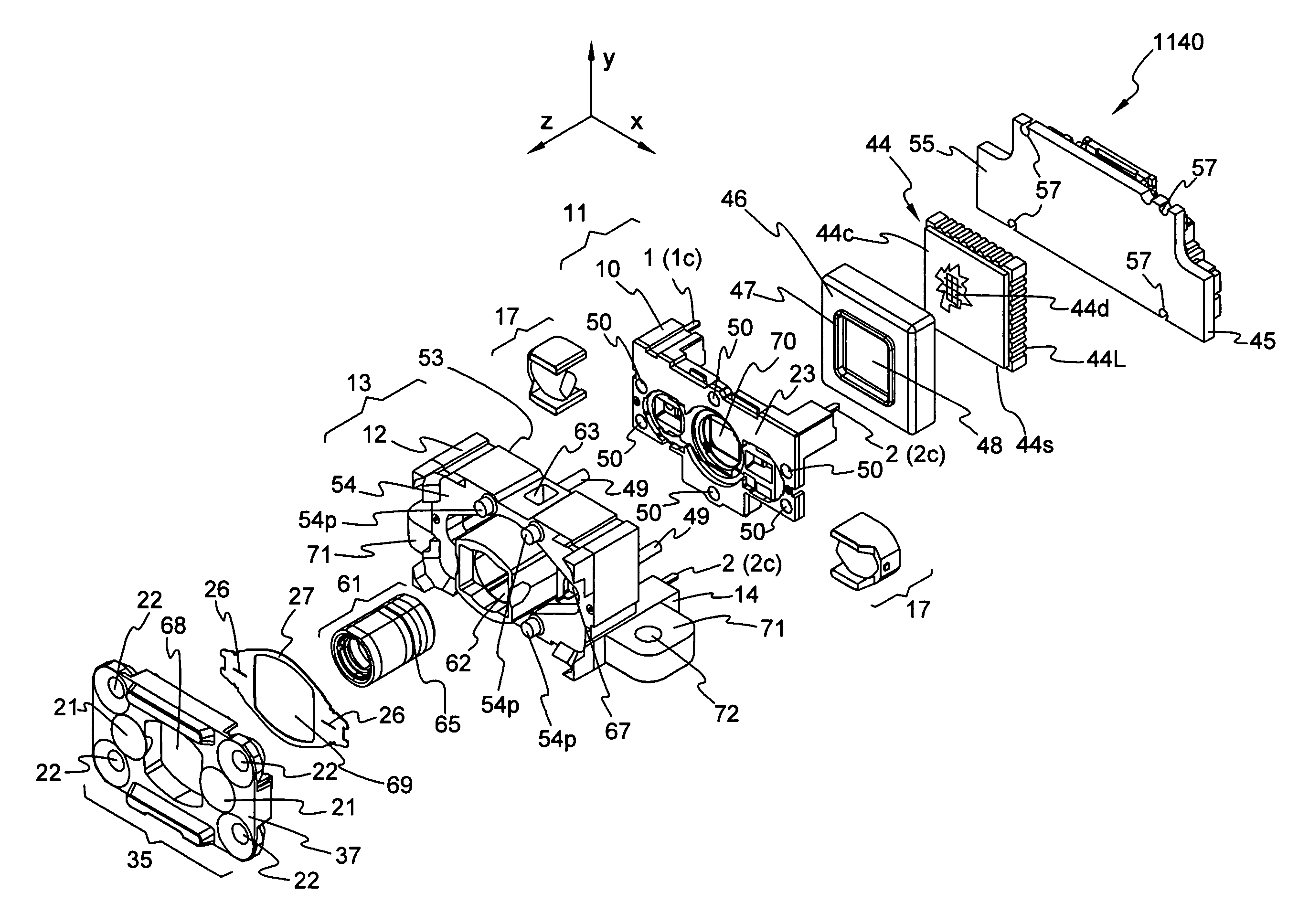

An imaging module for data collection devices, such as bar code scanners. The module includes an aiming or illumination light source or sources, seated on a support is mounted in a housing. The support is fixed in the housing to provide for its precise placement therein, in a predetermined position.

Owner:HAND HELD PRODS

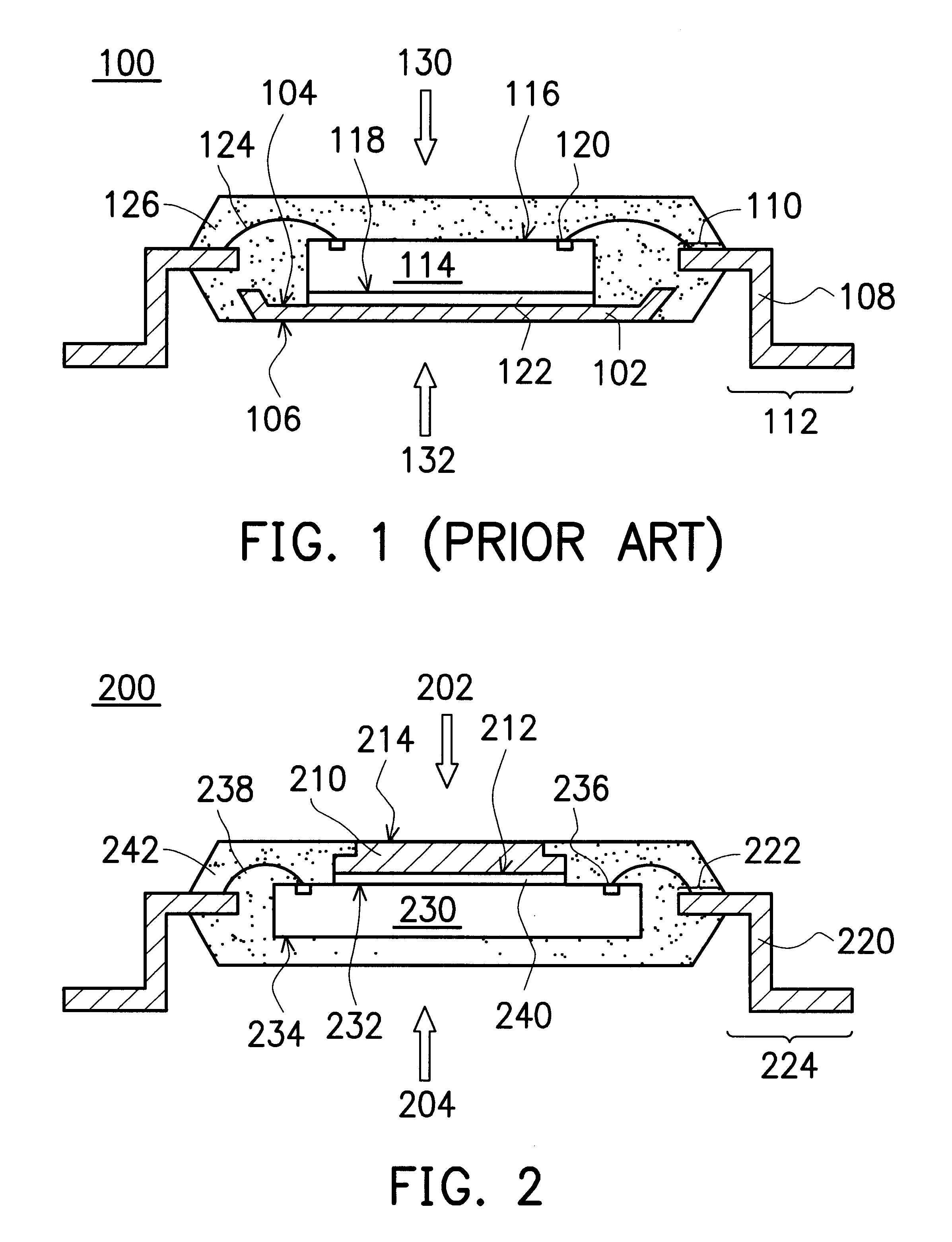

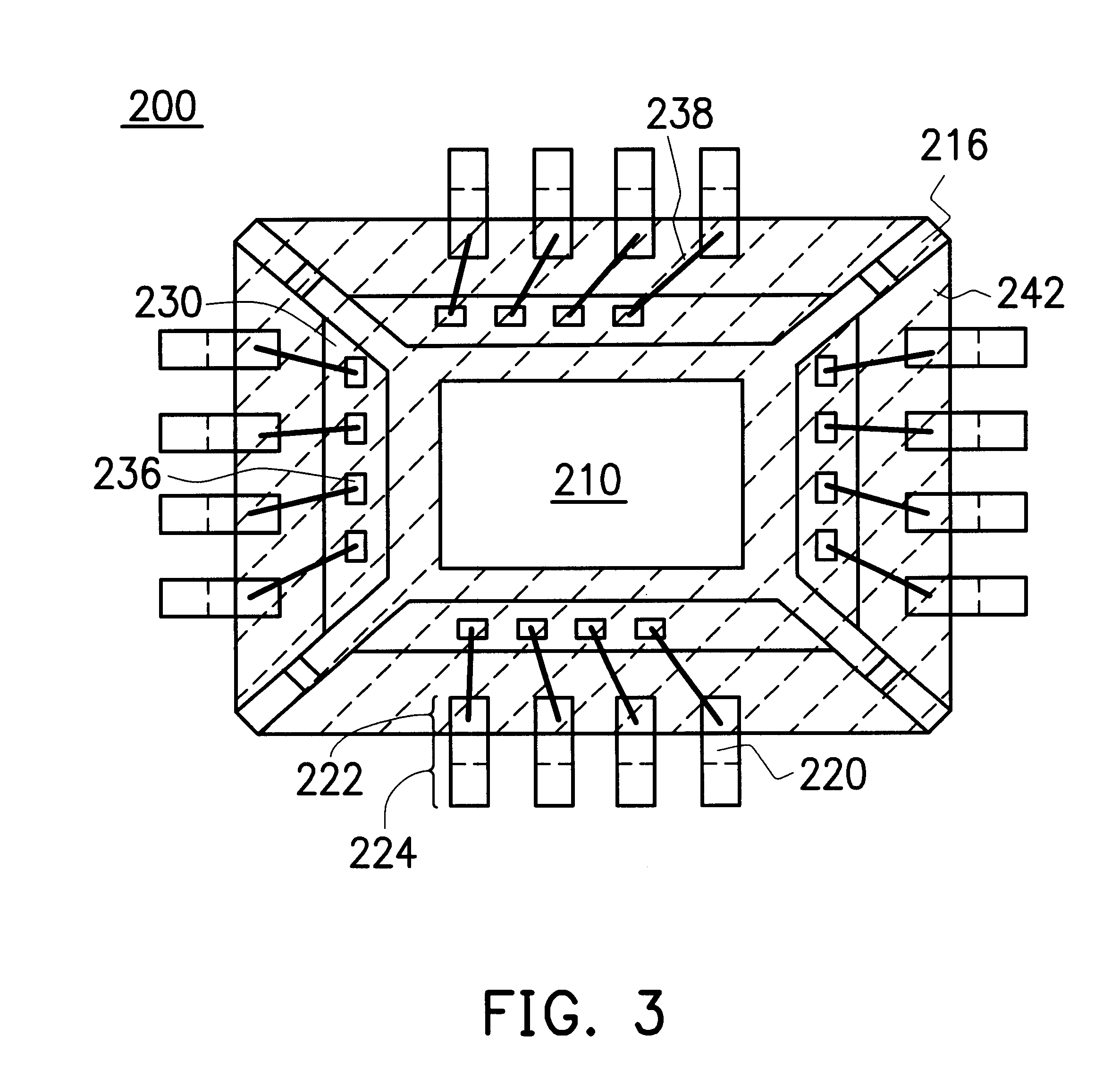

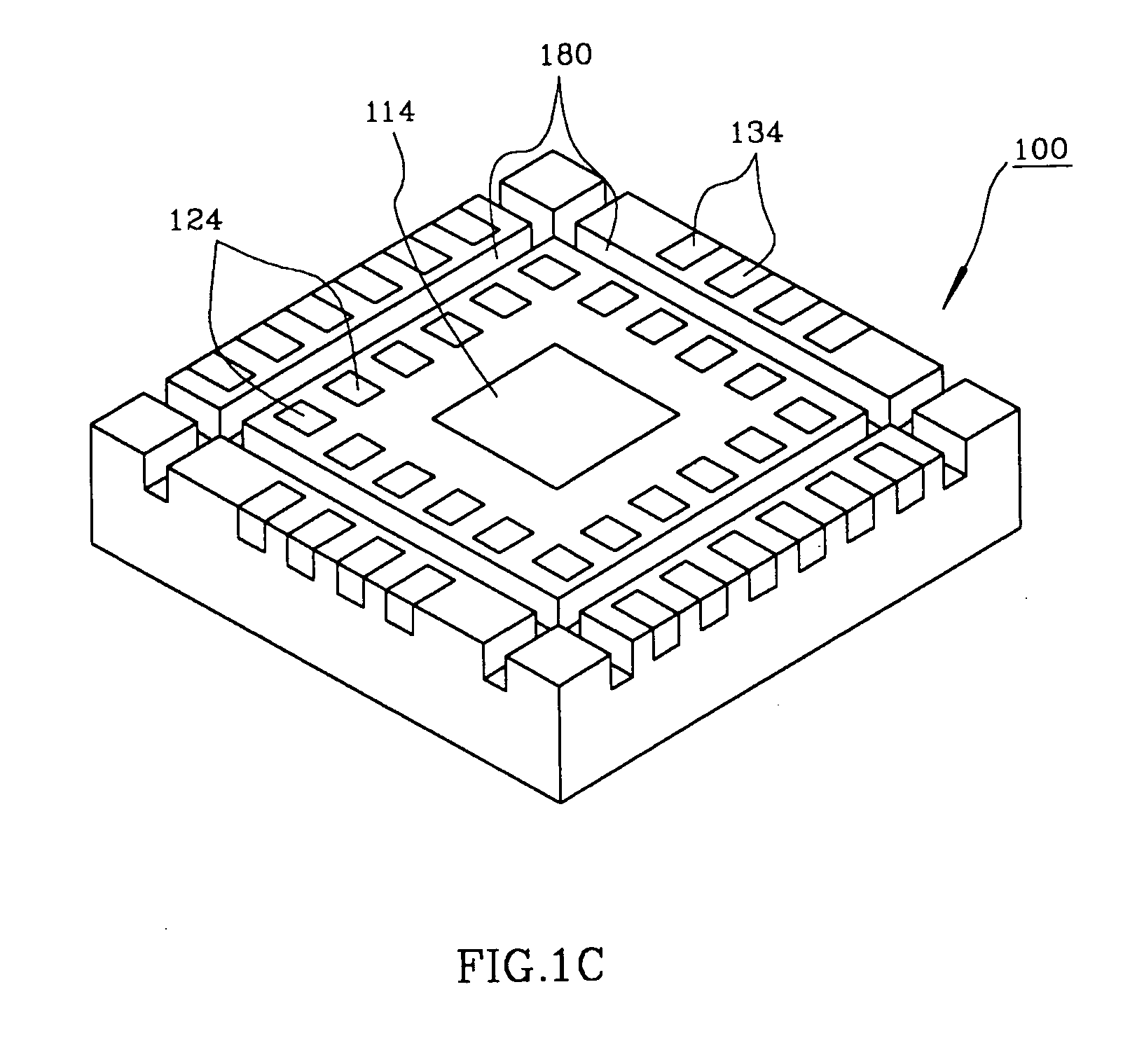

Leadless image sensor package structure and method for making the same

InactiveUS6384472B1Semiconductor/solid-state device detailsSolid-state devicesLead bondingEngineering

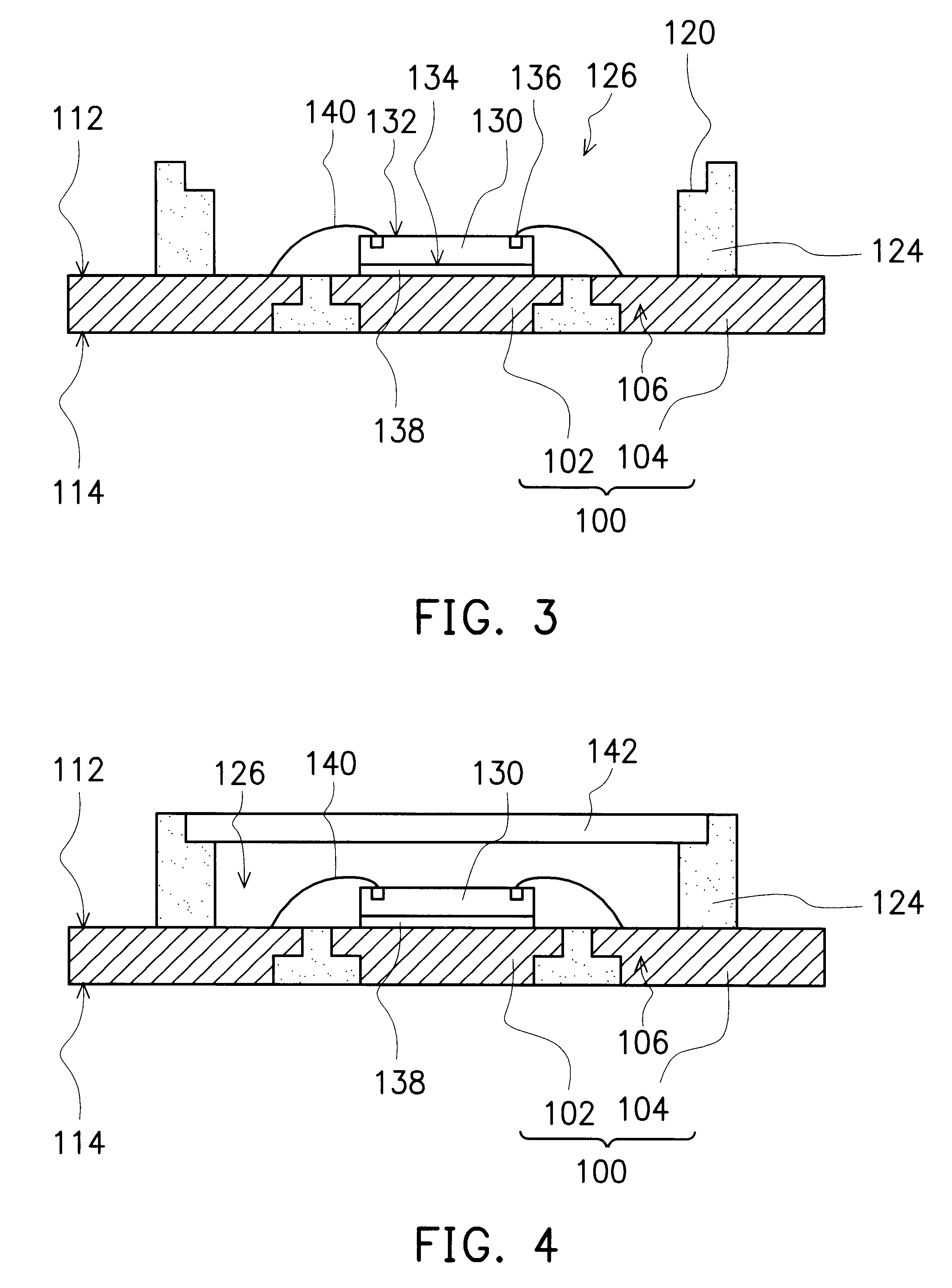

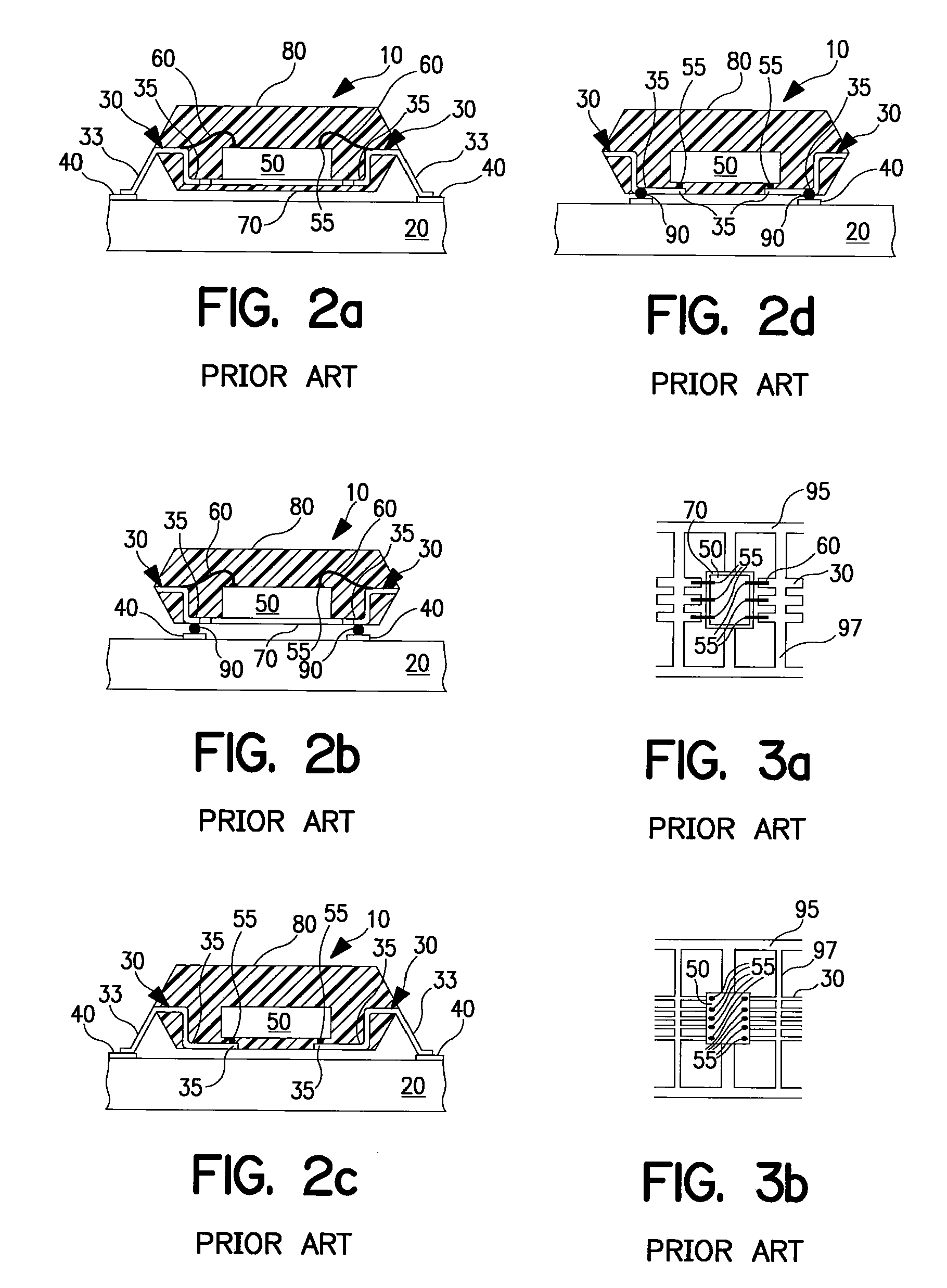

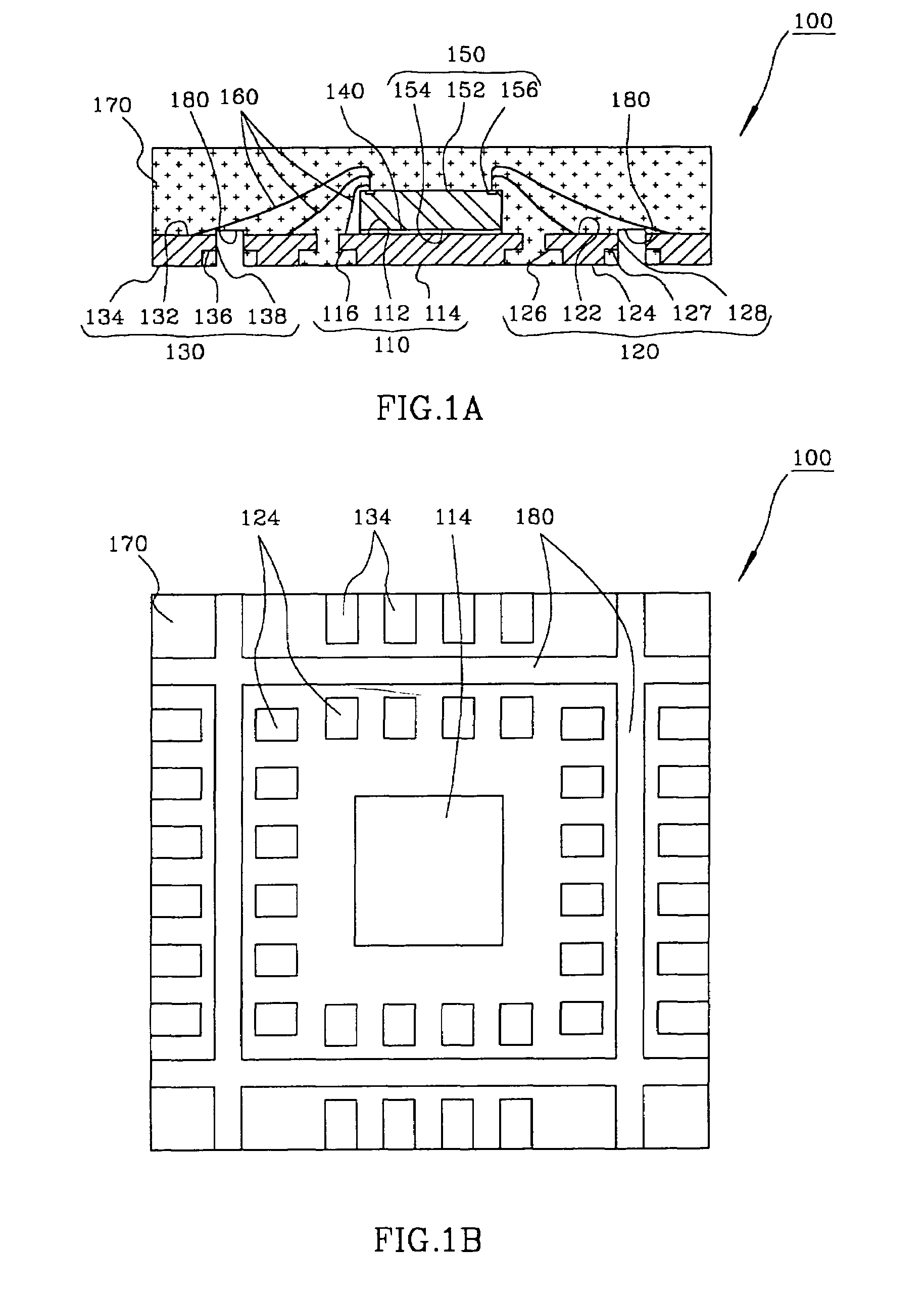

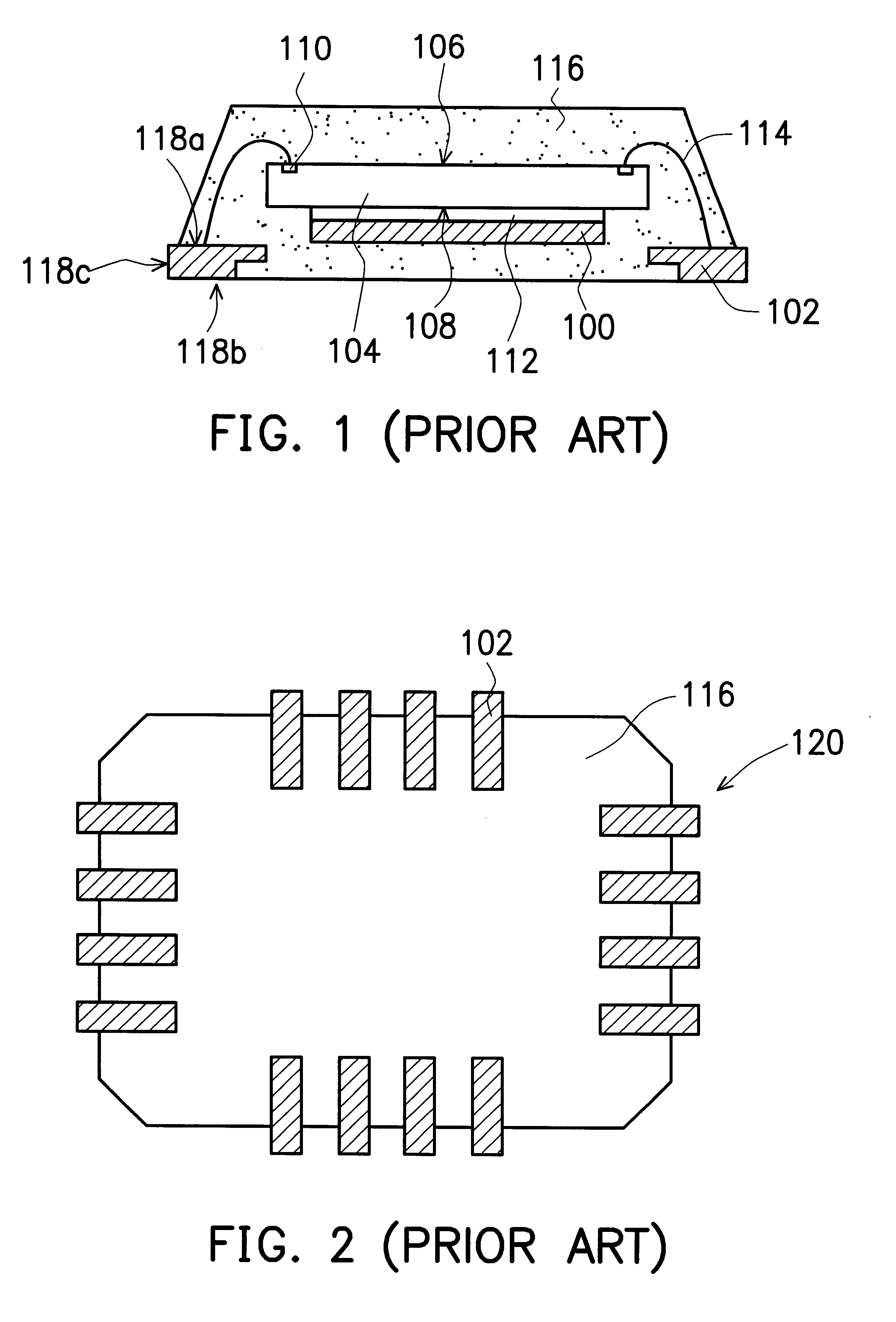

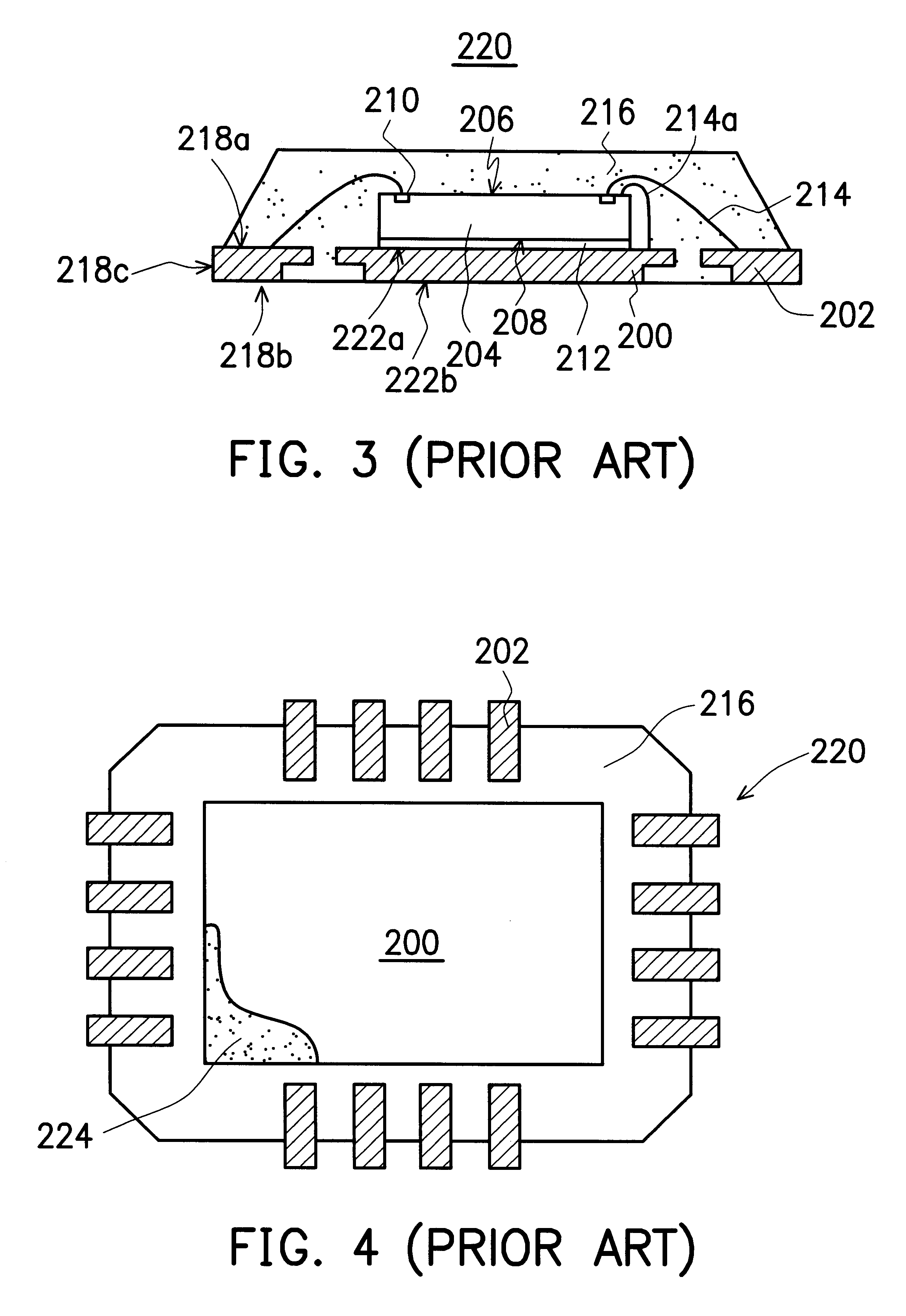

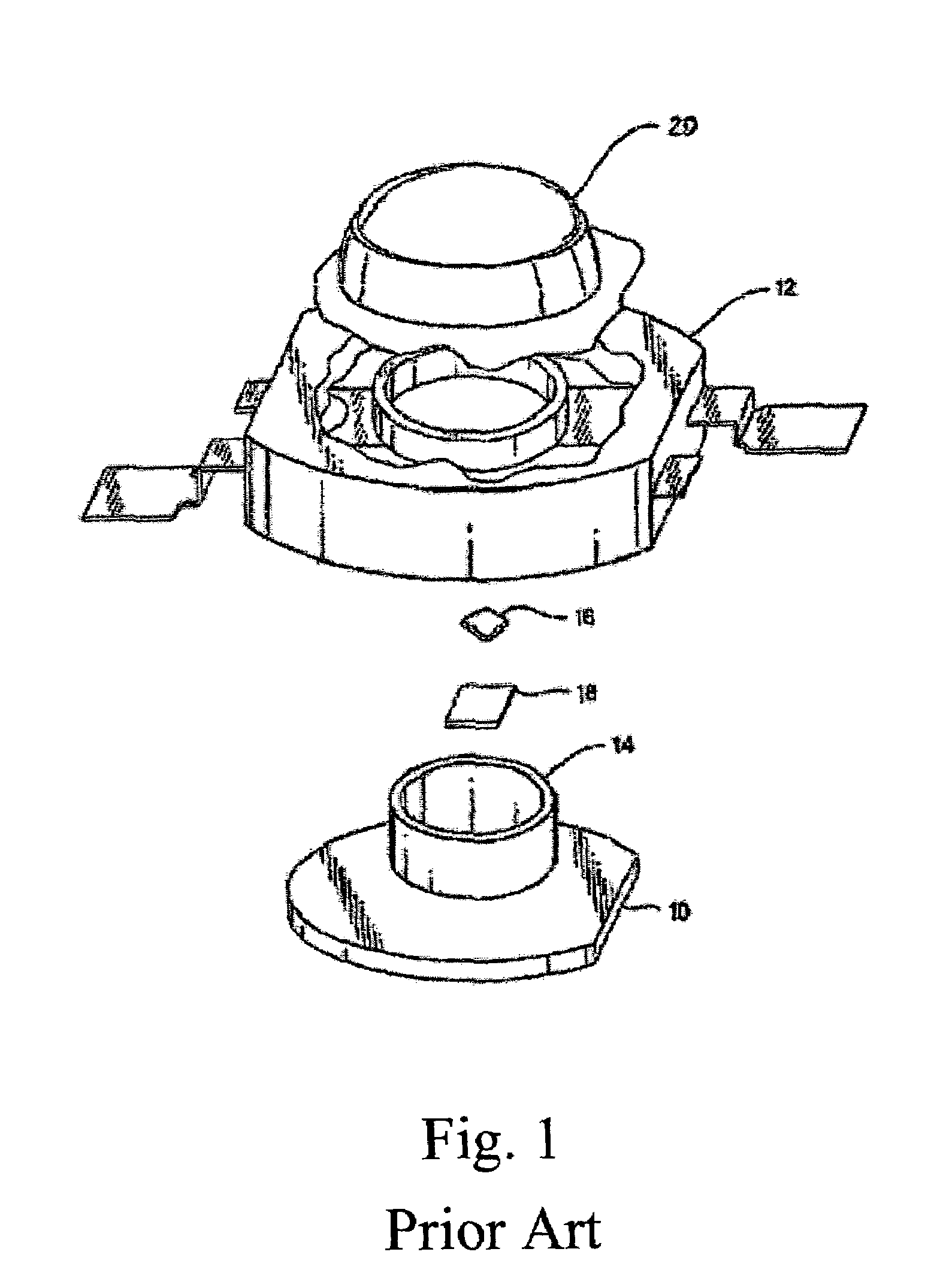

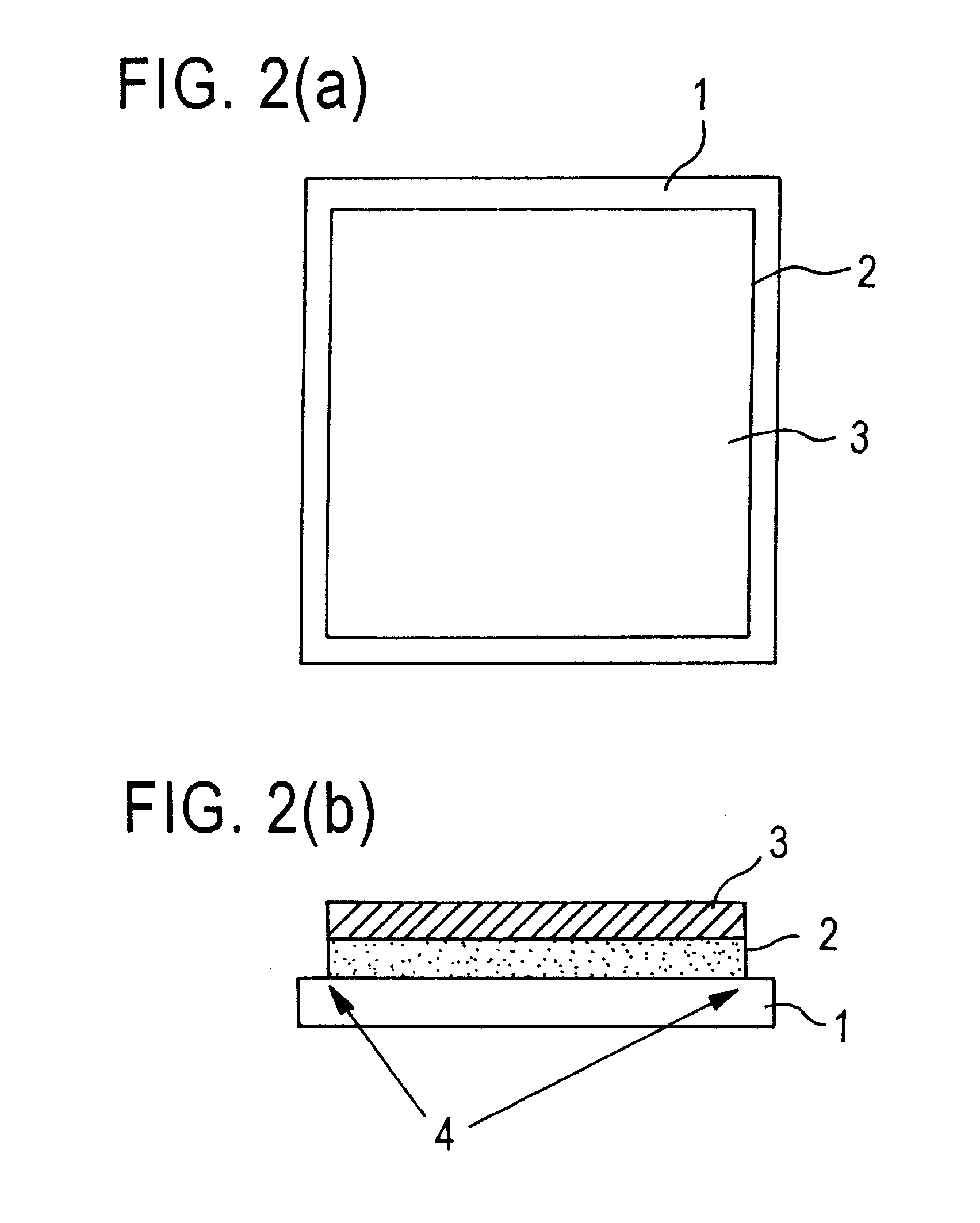

A leadless image sensor package constructed on a lead frame includes a die pad and a plurality of leads disposed at the periphery of the die pad. A molding compound, disposed on the top surface of the lead frame and being surrounding the die pad on the periphery of the lead frame, fills the clearance between the die pad and the leads and exposes, on the top surface, the die pad and the wire-bonding portion of the leads. Moreover, the lead frame and the molding compound constitute a "chip containing space" with chip set therein. Further, the chip with its back surface attached to the top surface of the die pad makes use of the wires to electrically connect to the bonding pad and the top surface of the wire-bonding portion, thereafter, a transparent lid is used to cap and seal the "chip containing space".

Owner:SILICONWARE PRECISION IND CO LTD

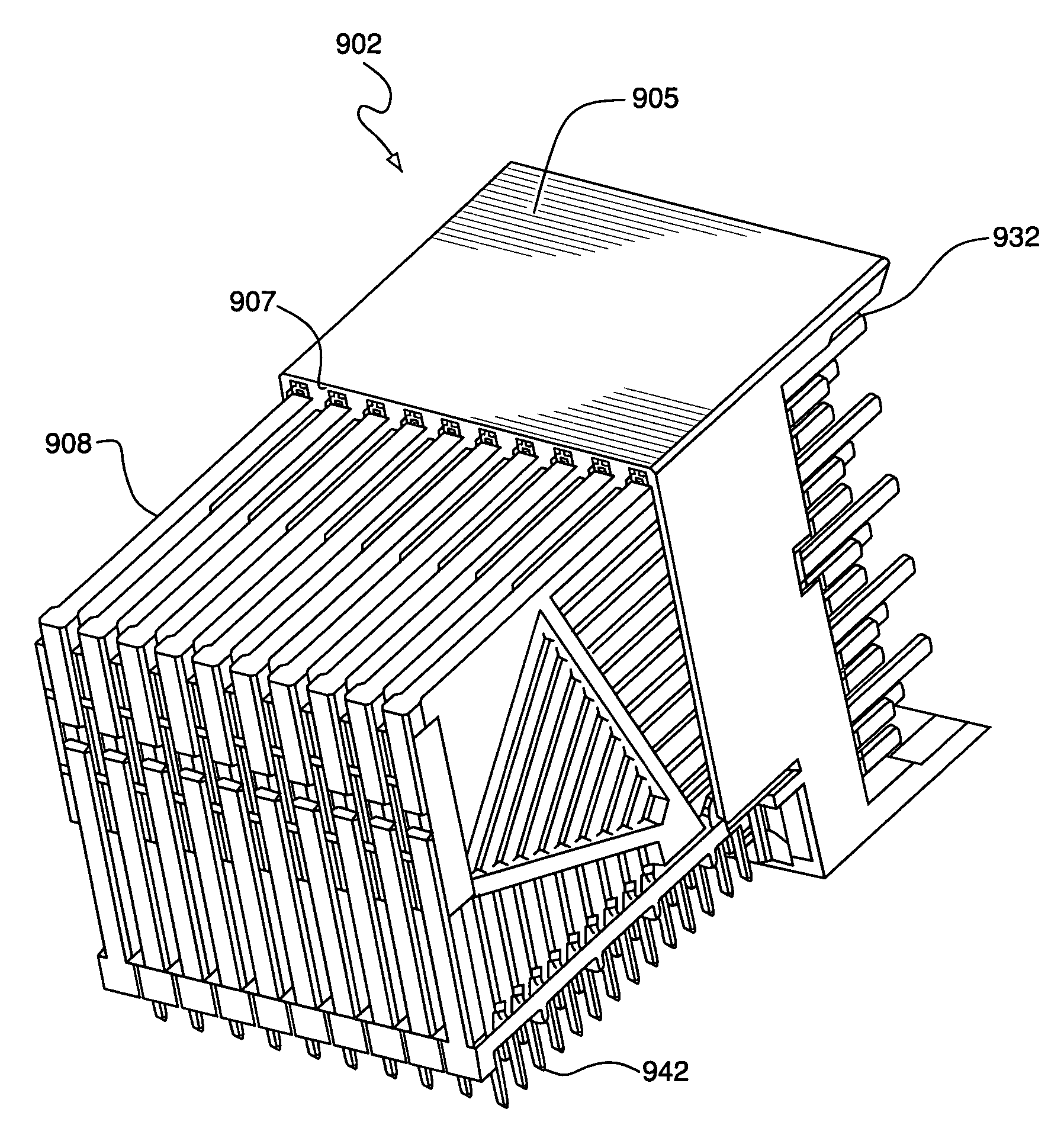

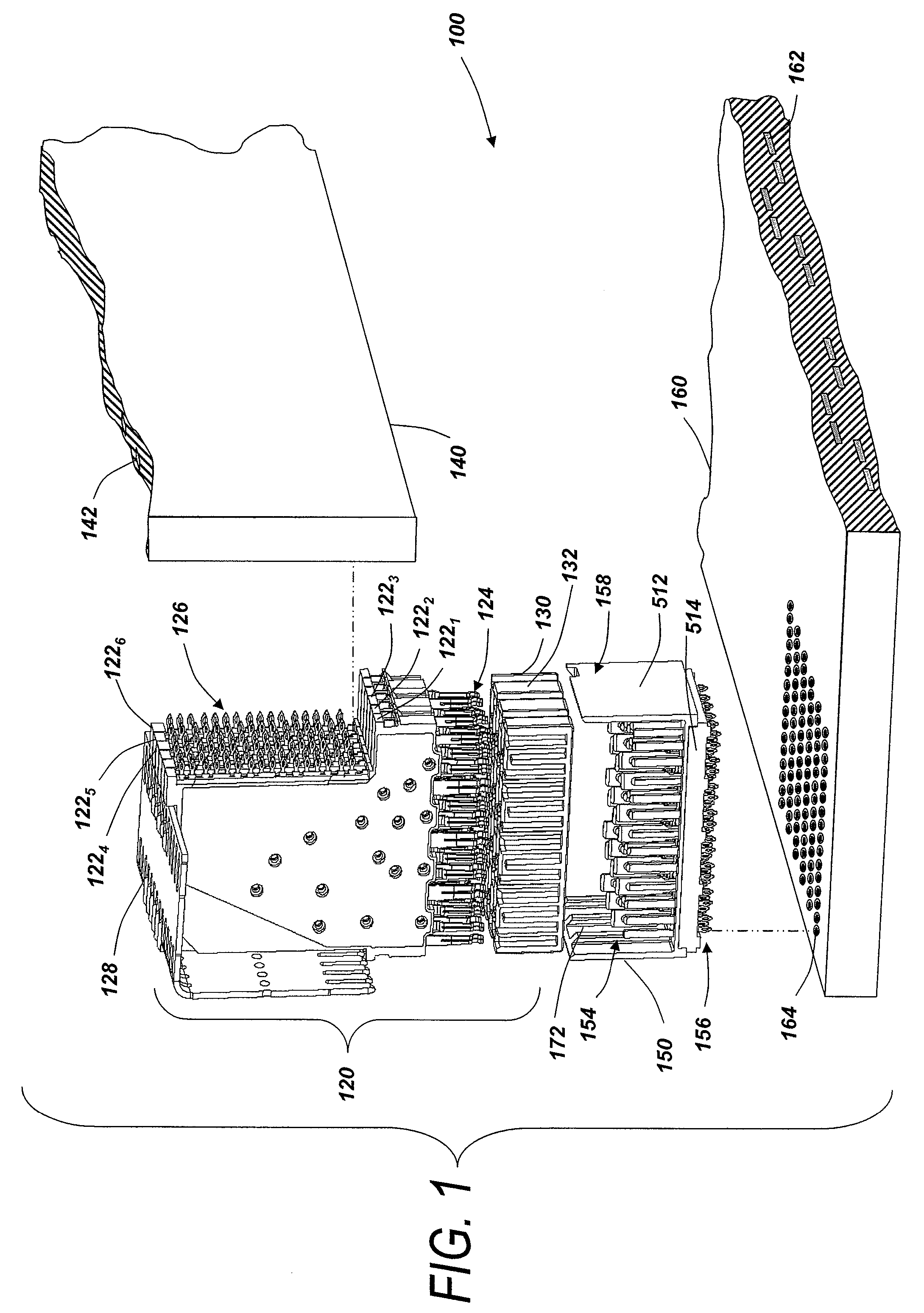

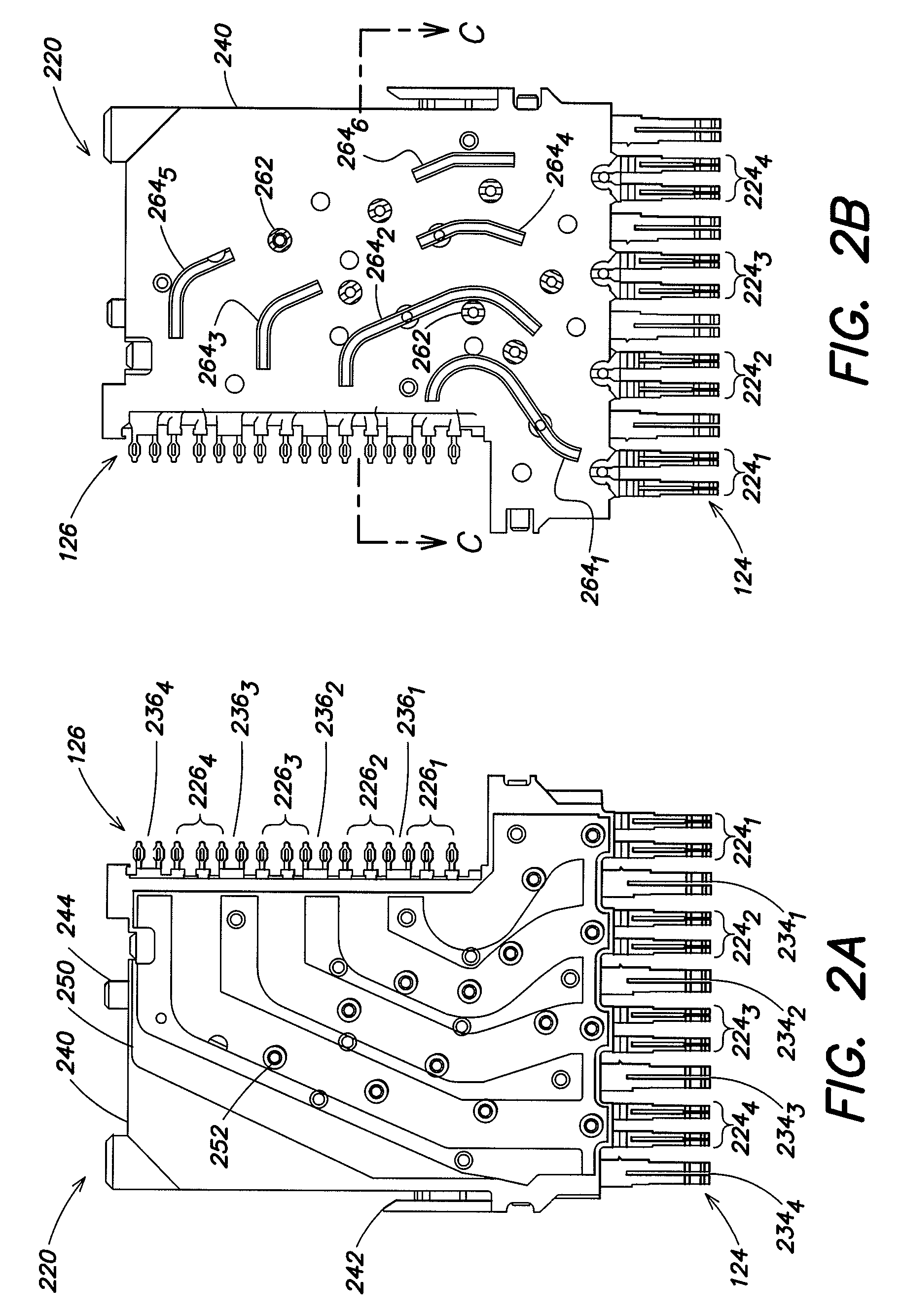

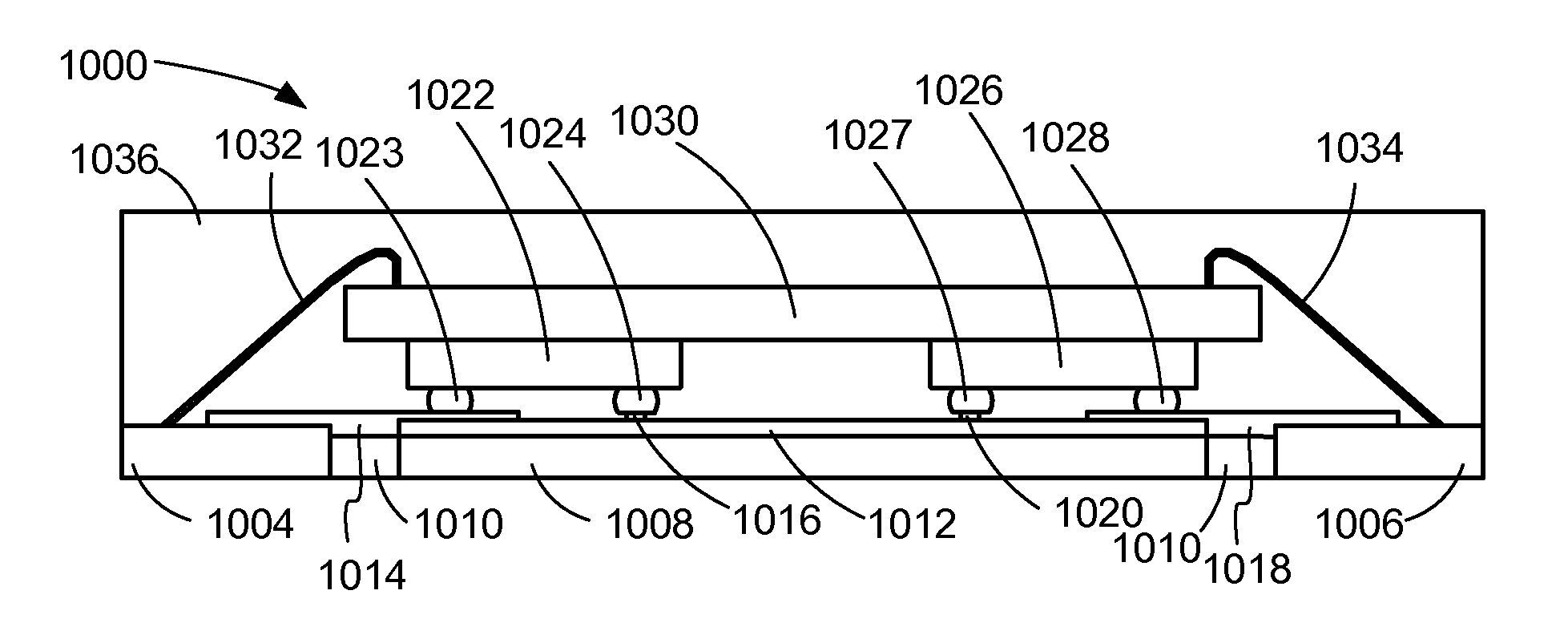

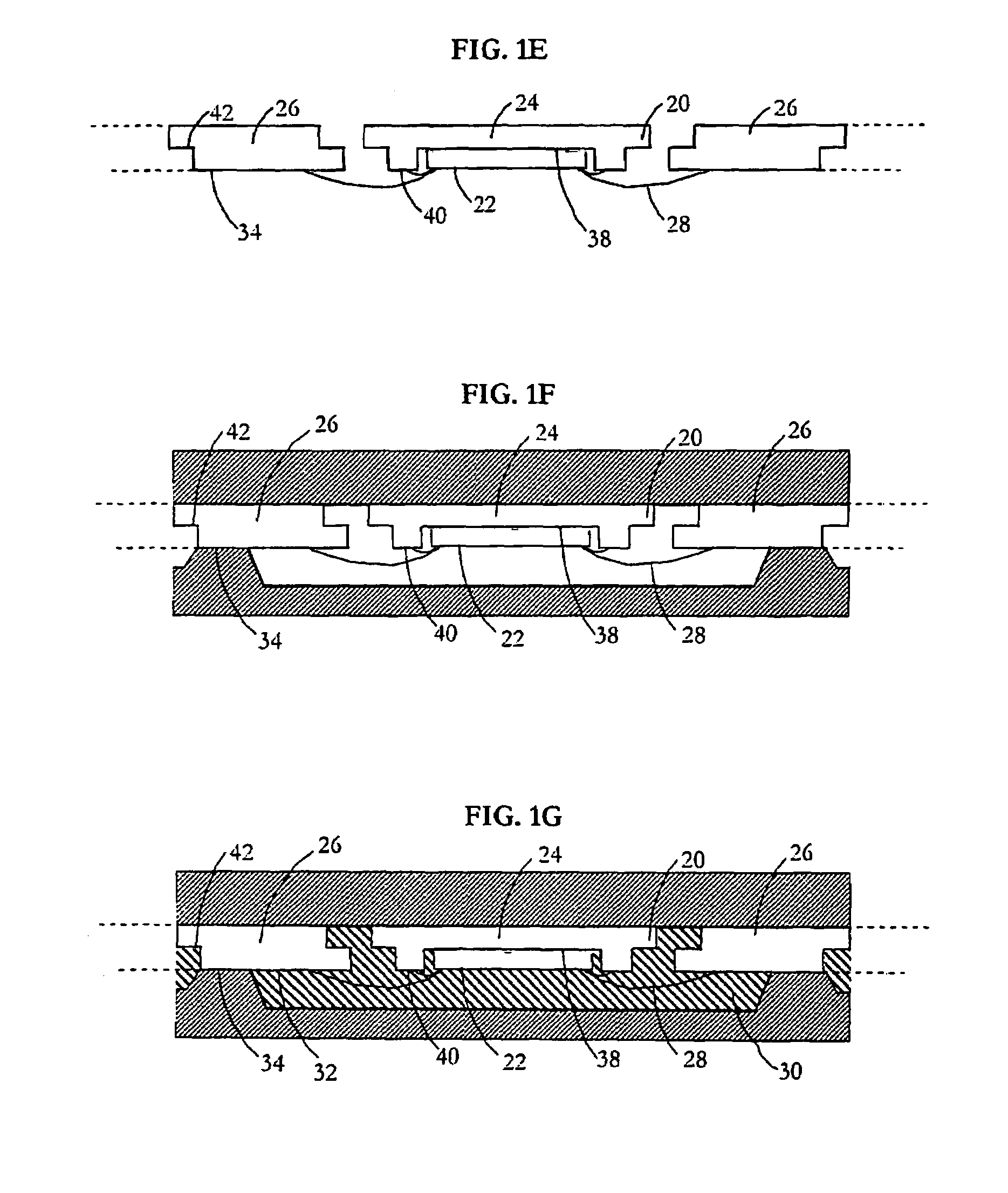

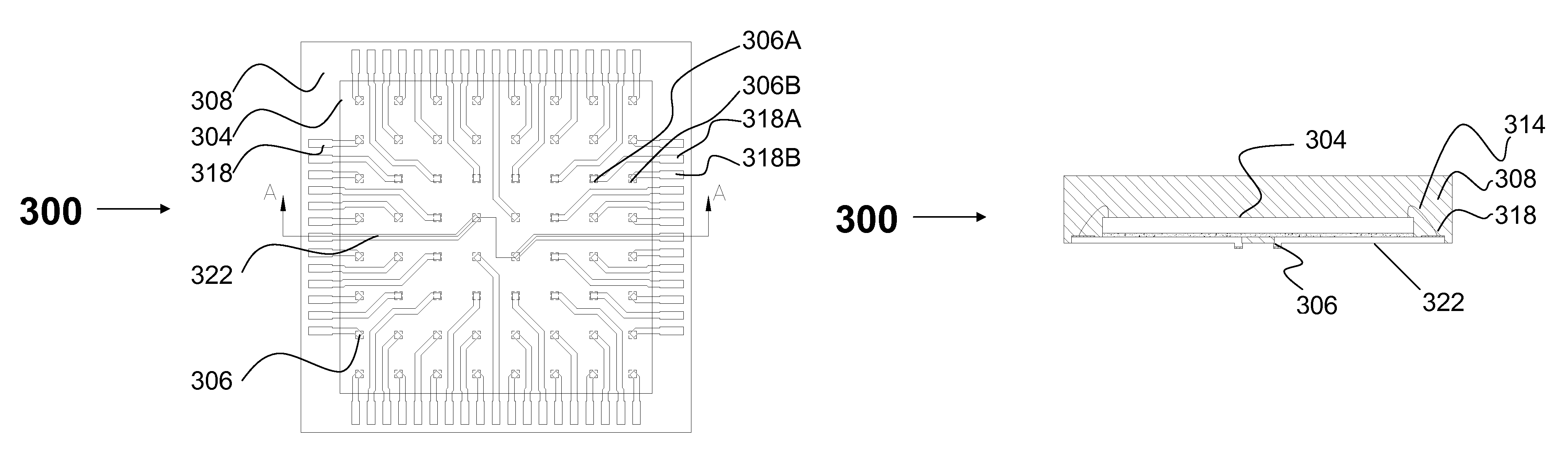

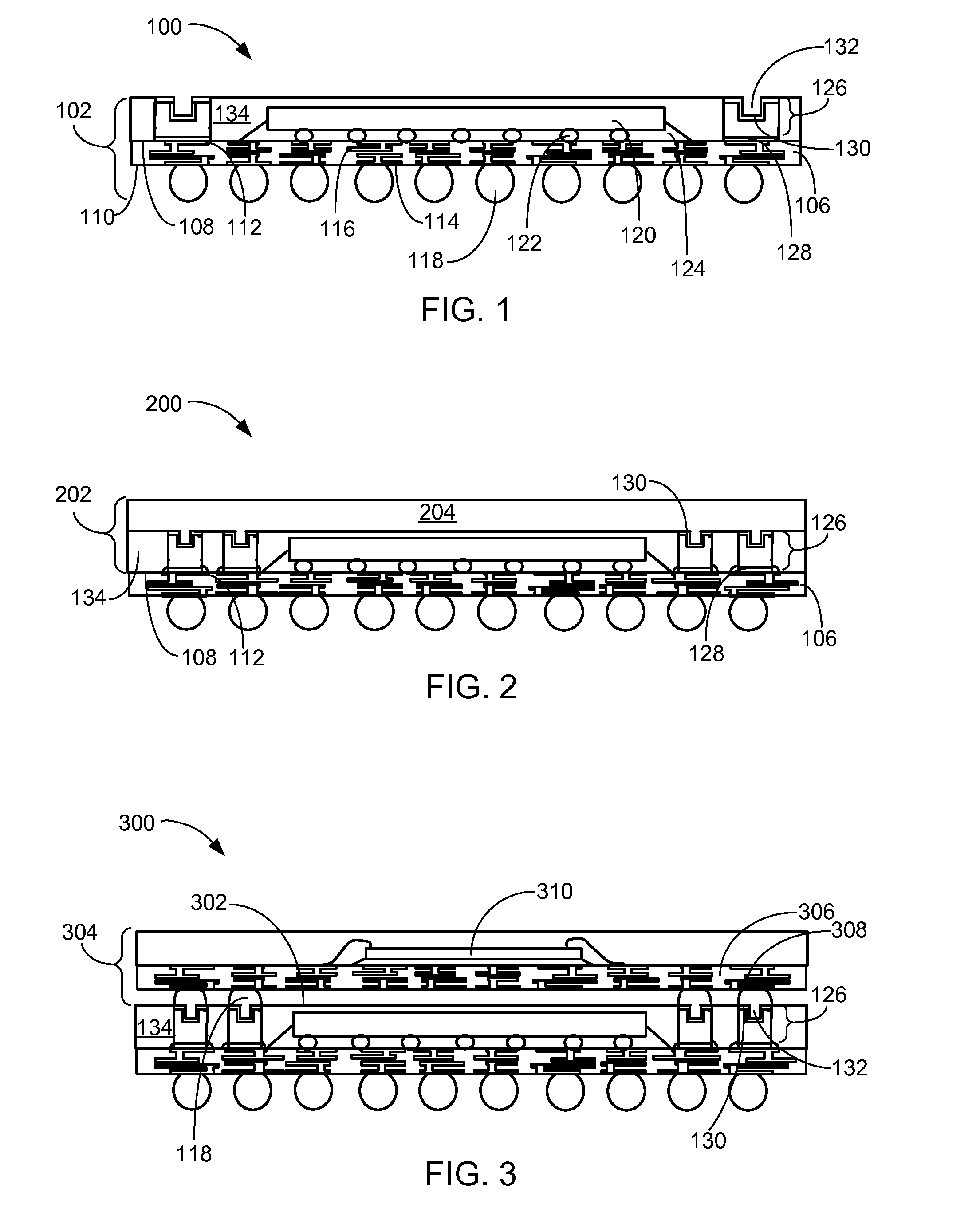

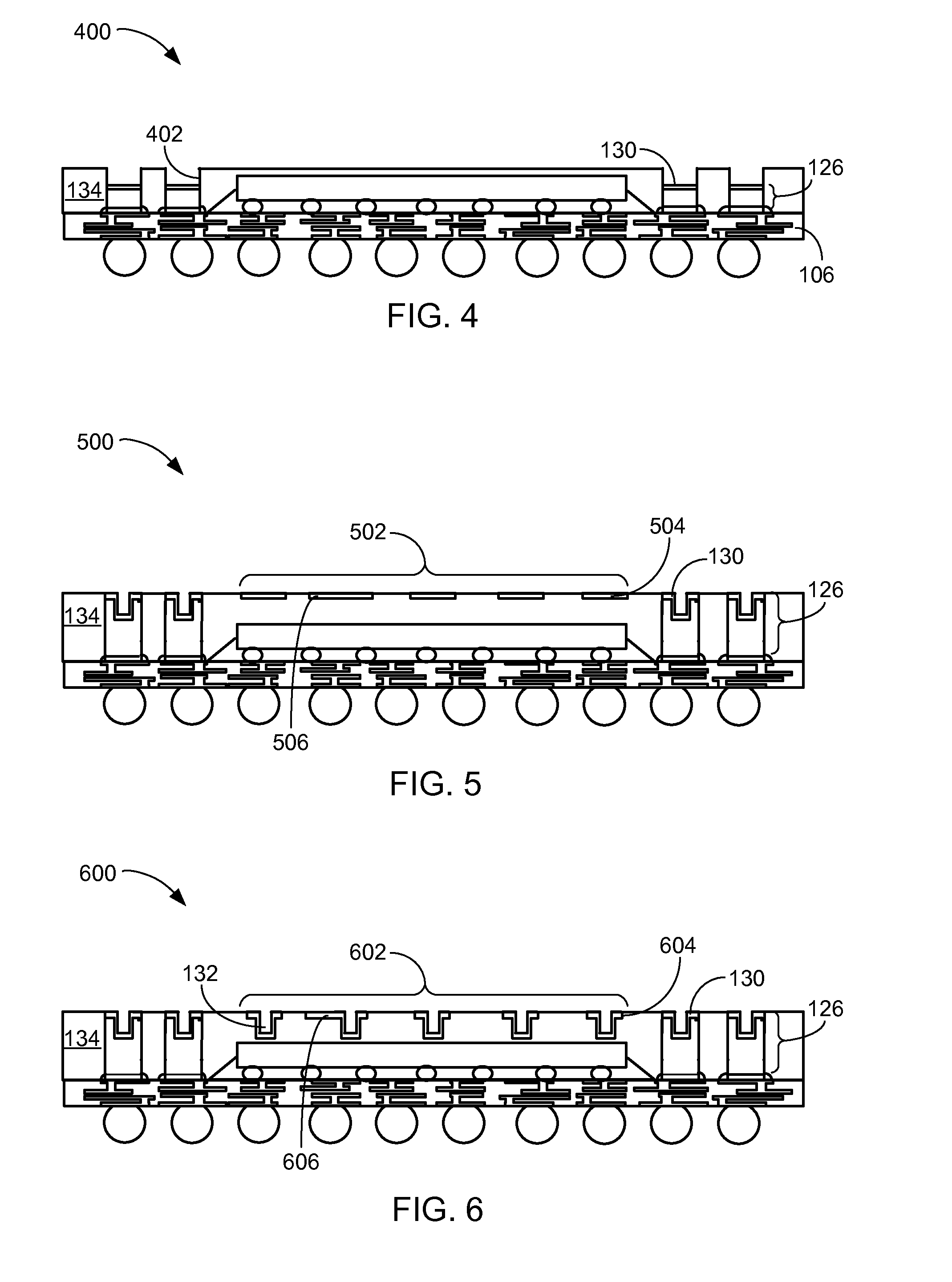

High frequency chip packages with connecting elements

InactiveUS7176506B2Reduce packaging costsLow impedance connectionImpedence networksSemiconductor/solid-state device detailsFlexible circuitsSurface mounting

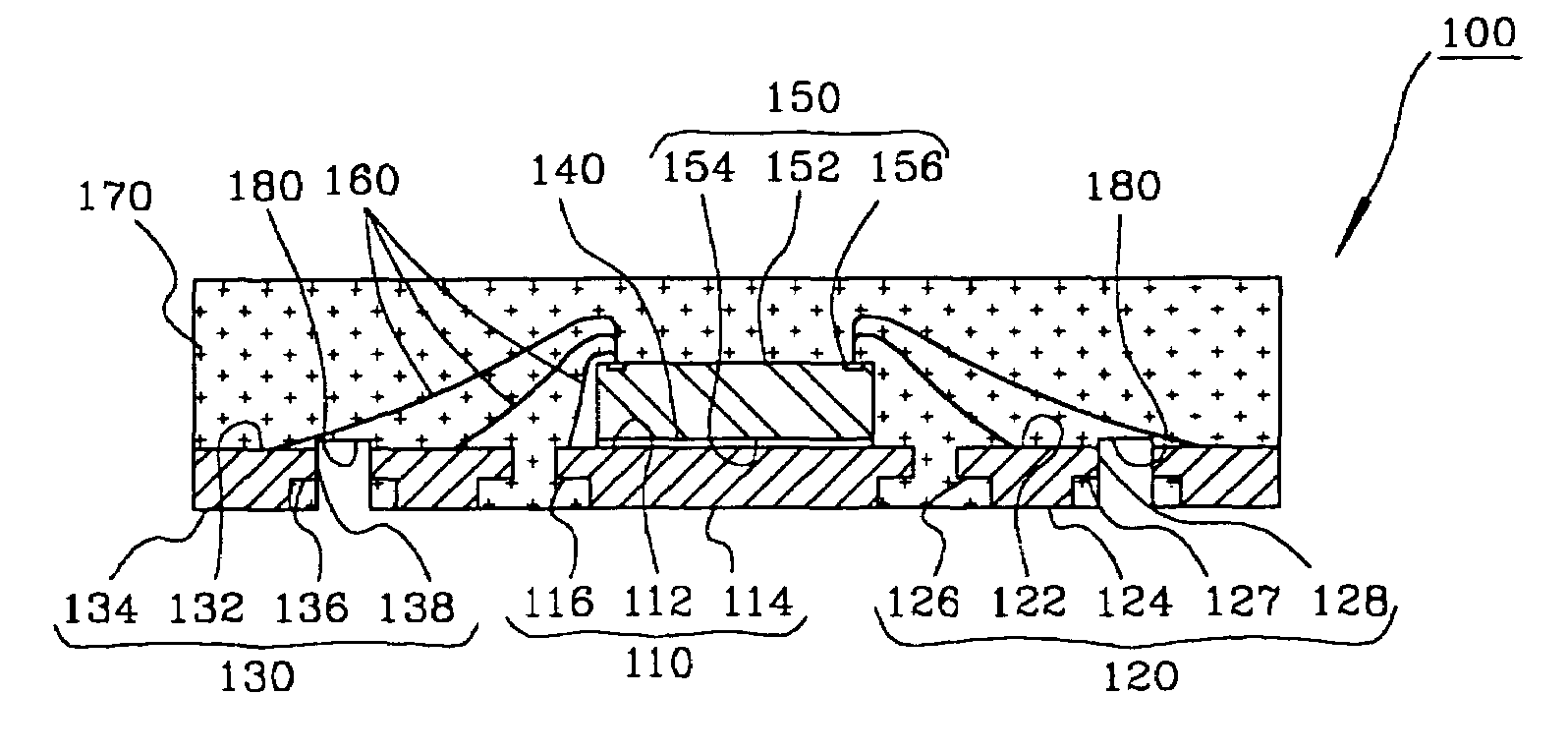

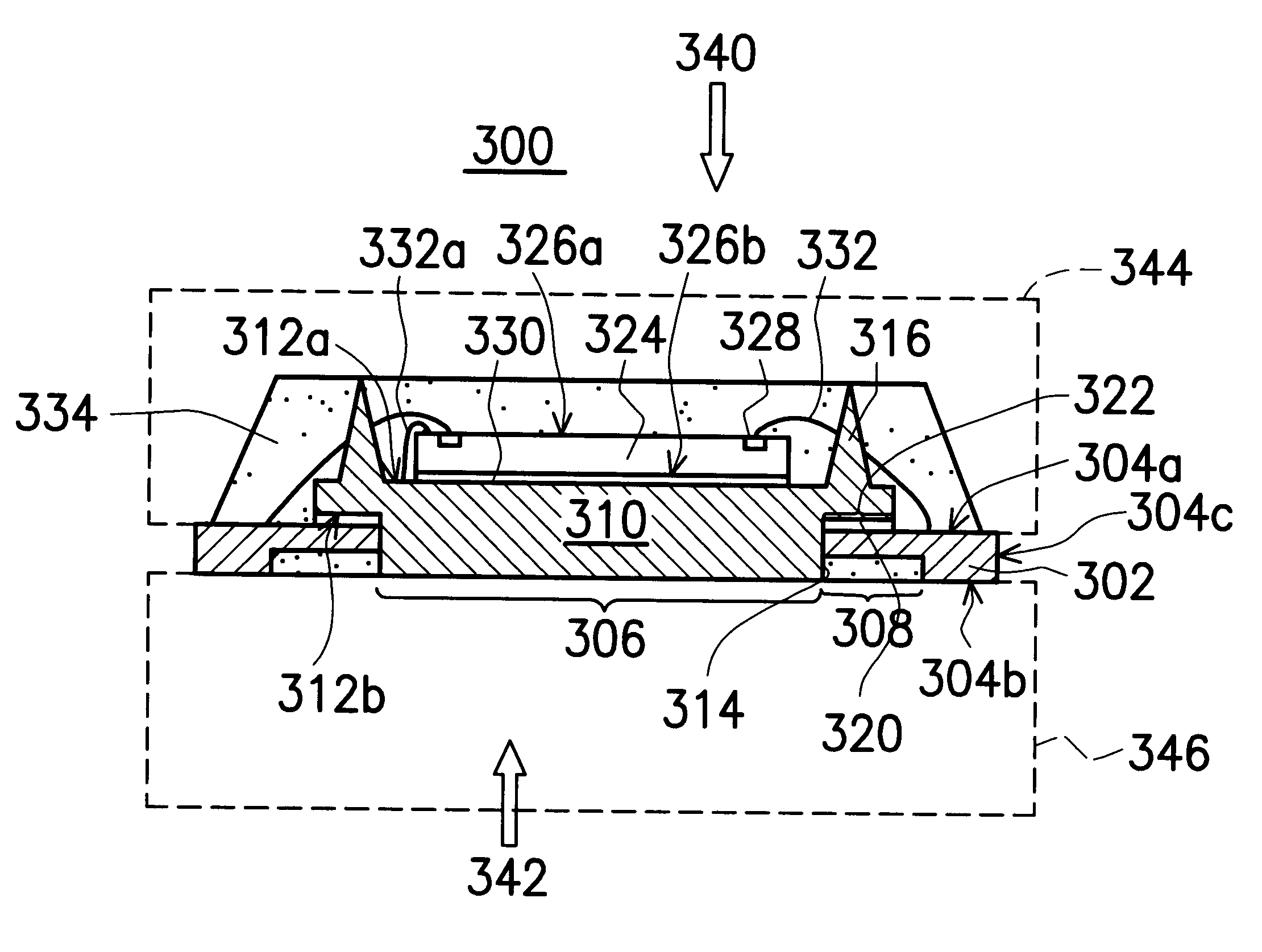

A radio frequency chip package is formed by assembling a connecting element such as a circuit board or flexible circuit tape having chips thereon with a bottom plane element such as a lead frame incorporating a large thermally-conductive plate and leads projecting upwardly from the plane of the plate. The assembly step places the rear surfaces of the chips on the bottom side of the connecting element into proximity with the thermal conductor and joins the conductive traces on the connecting element with the leads. The resulting assembly is encapsulated, leaving terminals at the bottom ends of the leads exposed. The encapsulated assembly may be surface-mounted to a circuit board. The leads provide robust electrical connections between the connecting element and the circuit board.

Owner:TESSERA INC

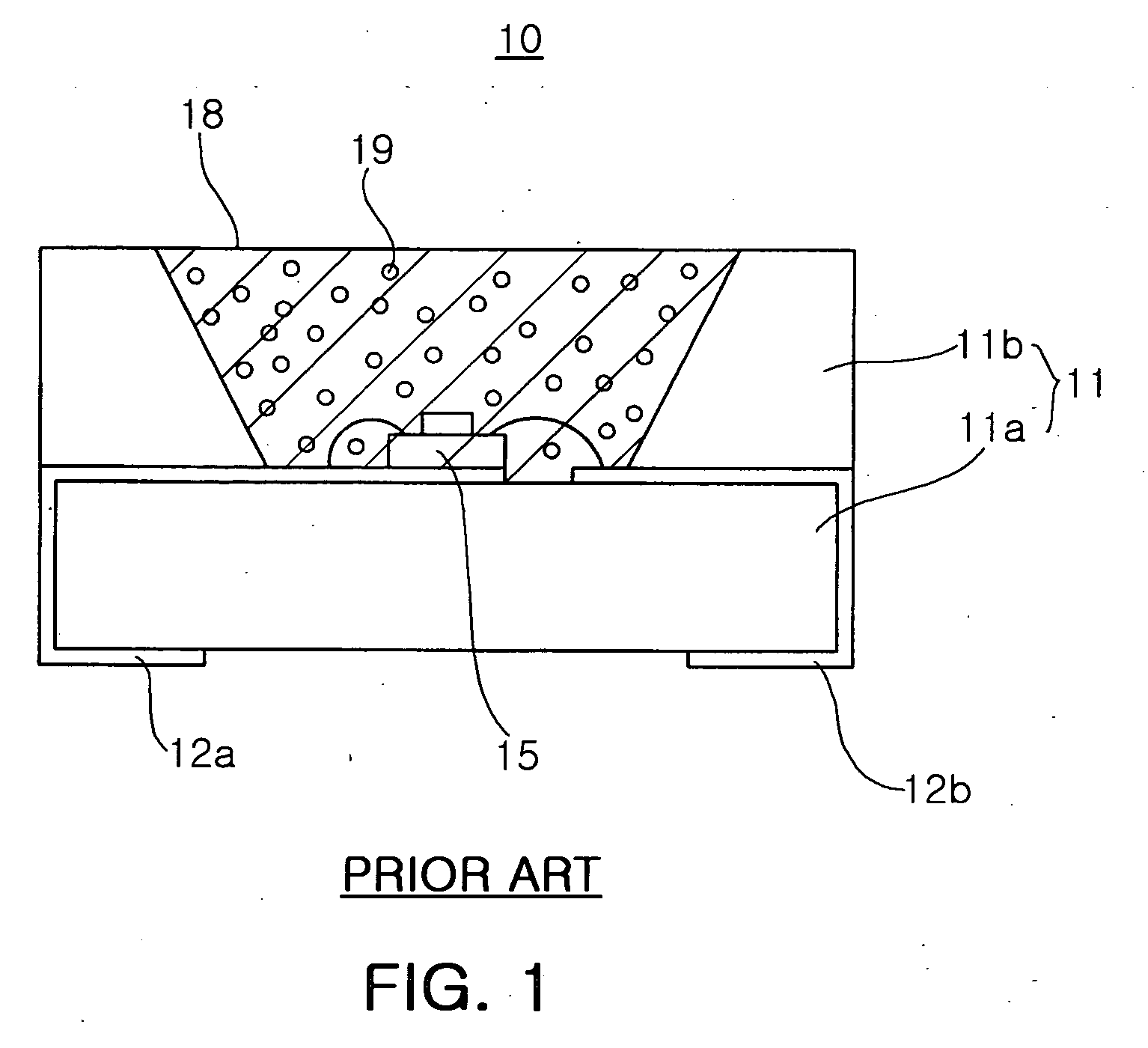

Semiconductor package having heat sink at the outer surface

InactiveUS6559525B2Easy to addImprove packaging efficiencySemiconductor/solid-state device detailsSolid-state devicesSemiconductor packageLead frame

A semiconductor package having heat sink at the outer surface is constructed on a lead frame. The package comprises a chip, a die pad, a plurality of leads, a plurality of bonding wires, and a molding compound. The die pad has a first surface and a second surface, and the chip has its active surface bonded to the first surface of the die pad. The area of the die pad is smaller than the area of the chip in order to expose the bonding pads on the active surface of the chip. The leads having an inner lead portions and an outer lead portions are disposed at the periphery of the die pad, and the inner lead portions are electrically connected to the bonding pads by a plurality of bonding wires. The molding compound encapsulates the chip, the die pad, the inner lead portions of the leads, and the bonding wires. The second surface of the die pad is exposed on the top surface of the package structure while the outer lead portion of the leads is exposed at the side edge of the package structure.

Owner:SILICONWARE PRECISION IND CO LTD

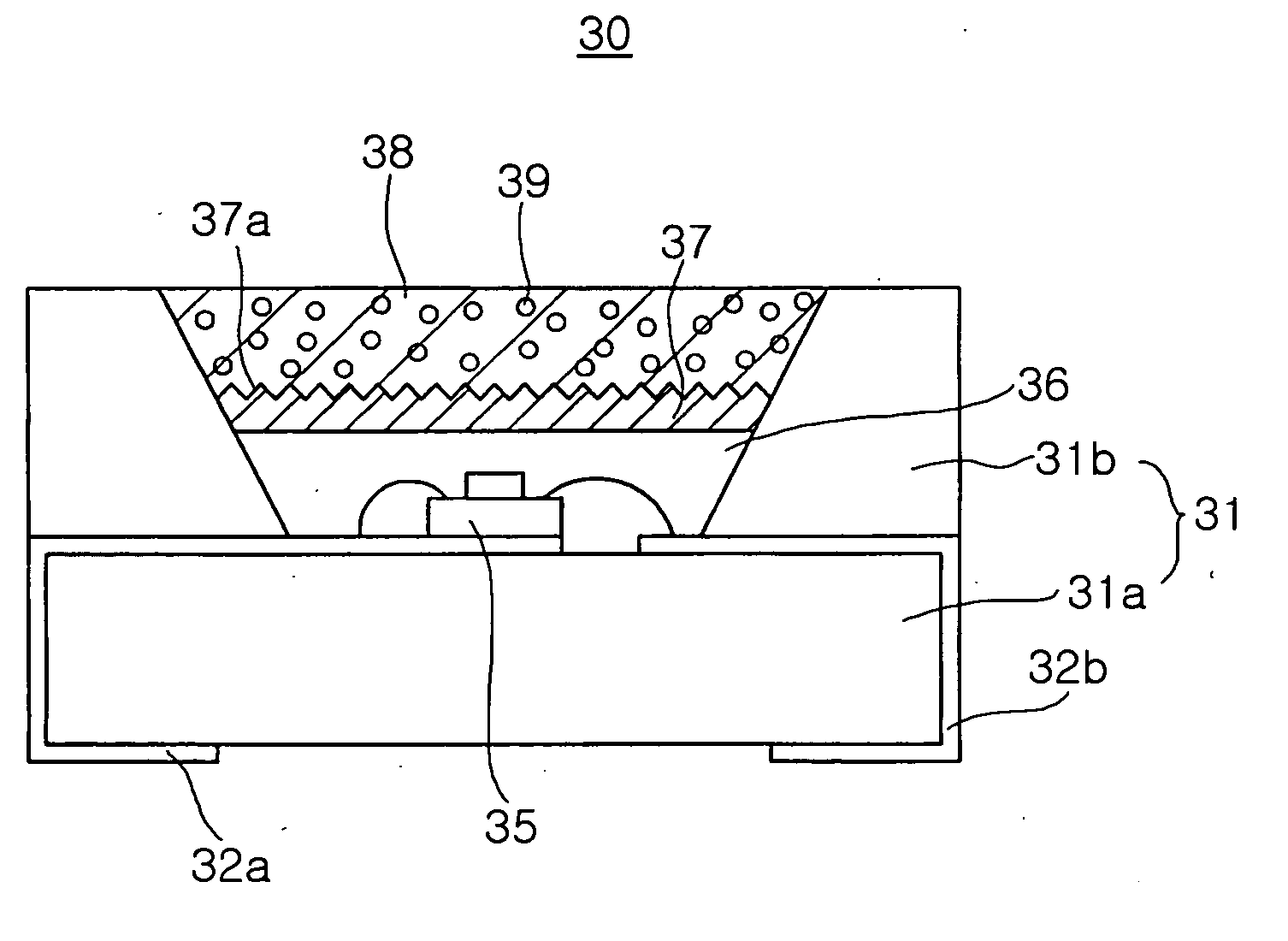

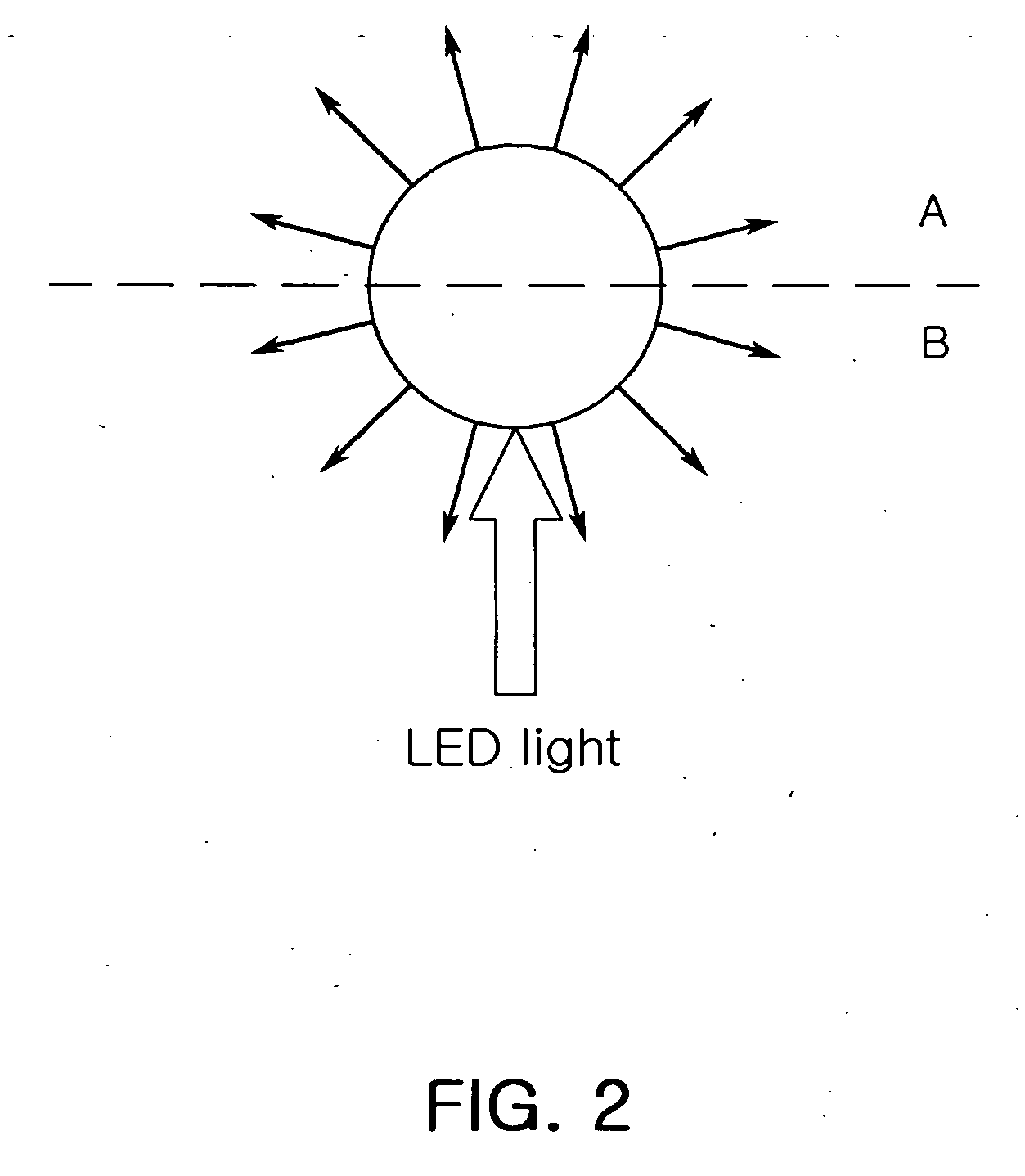

Wavelength-convertible light emitting diode package

InactiveUS20070012940A1Efficient extractionSolid-state devicesSemiconductor devicesPhosphorRefractive index

The invention relates to a wavelength-convertible LED package including a package substrate having a lead frame, and an LED mounted on the package substrate and electrically connected to the lead frame. The wavelength-convertible LED package also includes a low refractive index region surrounding the LED, having a first refractive index, and a high refractive index layer formed on the low refractive index region, having a rough pattern on an upper surface thereof and a second refractive index higher than the first refractive index. The wavelength-convertible LED package further includes a resin part containing phosphor for converting the wavelength of light emitted from the LED, having a third refractive index lower than the second refractive index.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

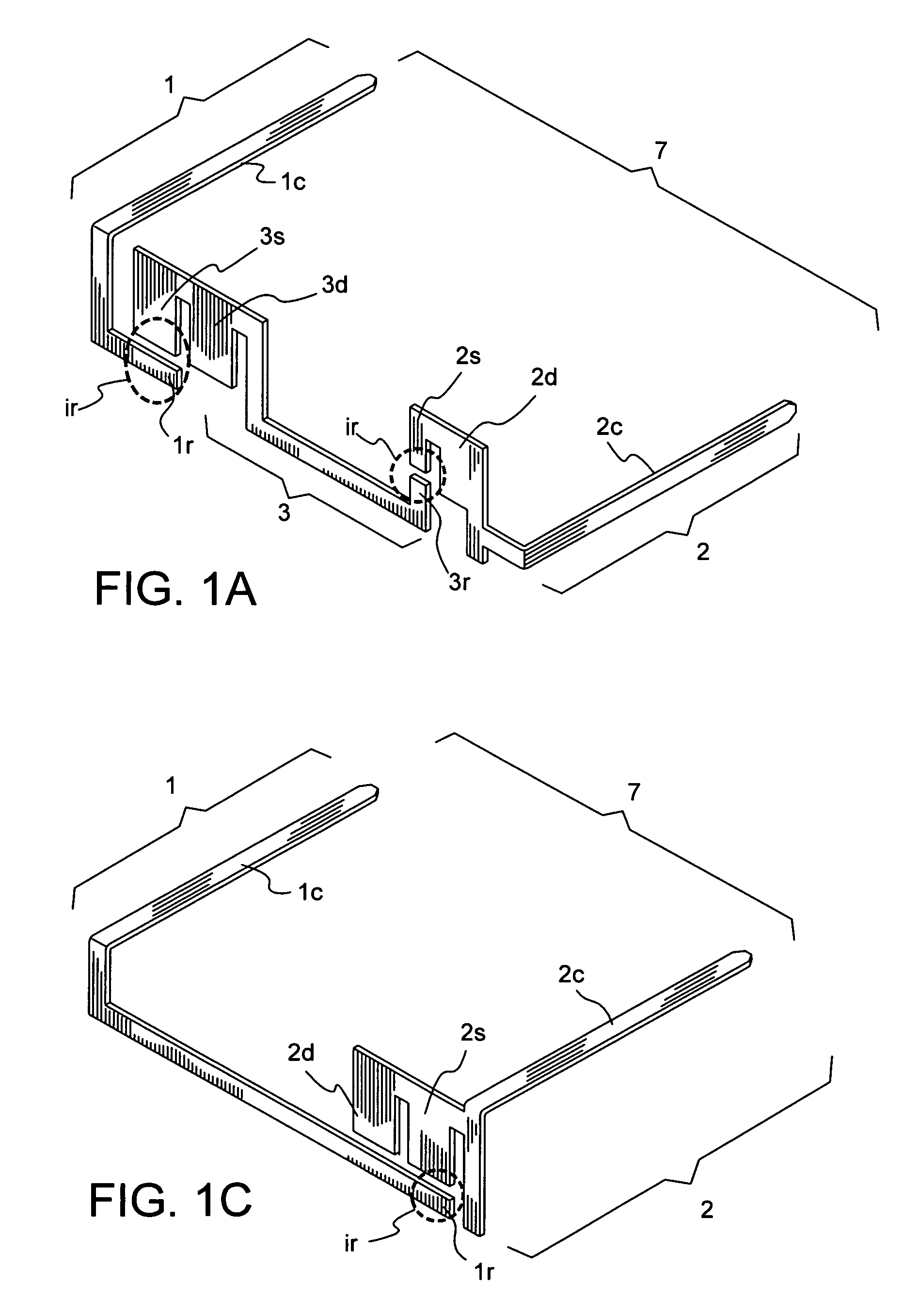

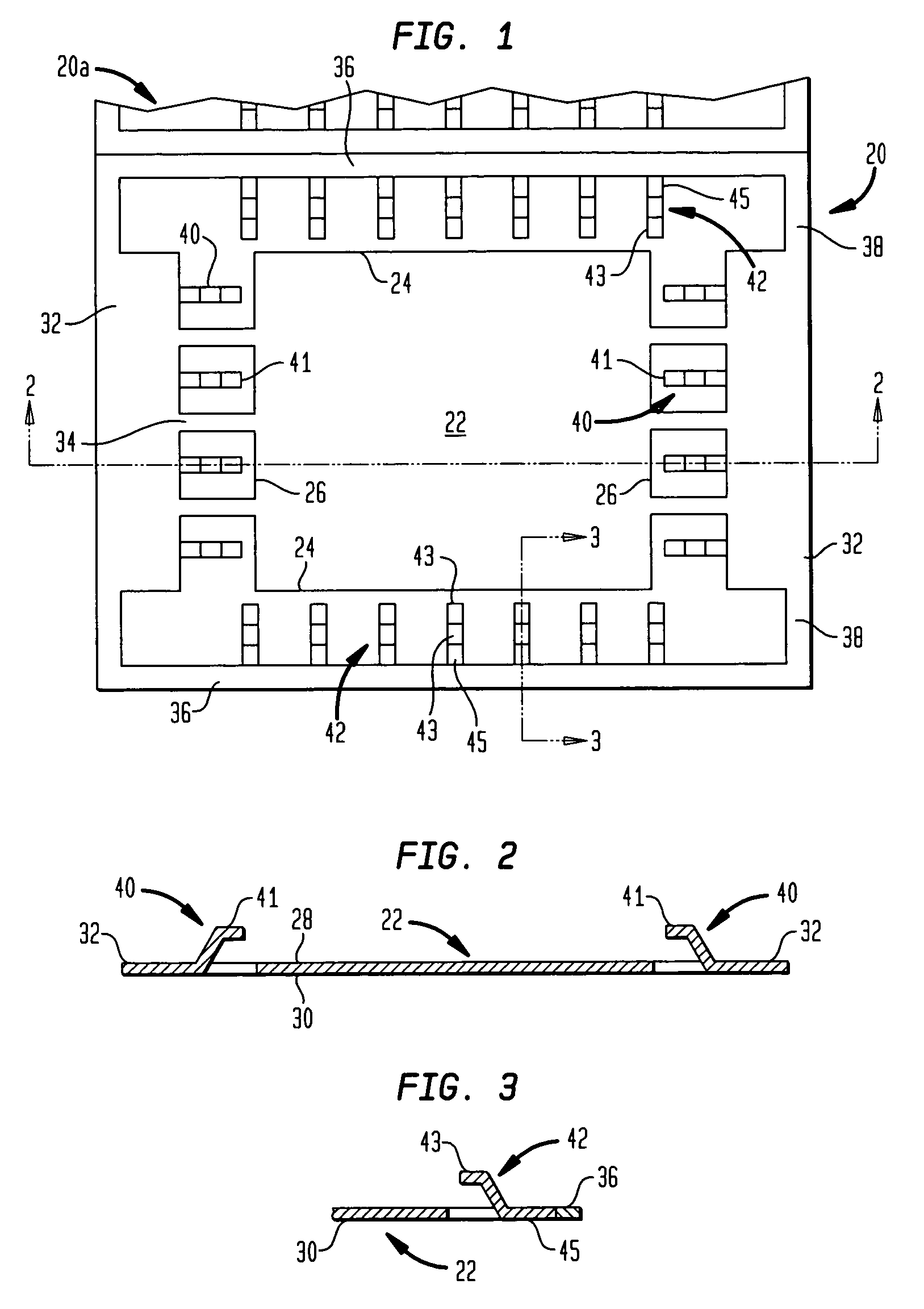

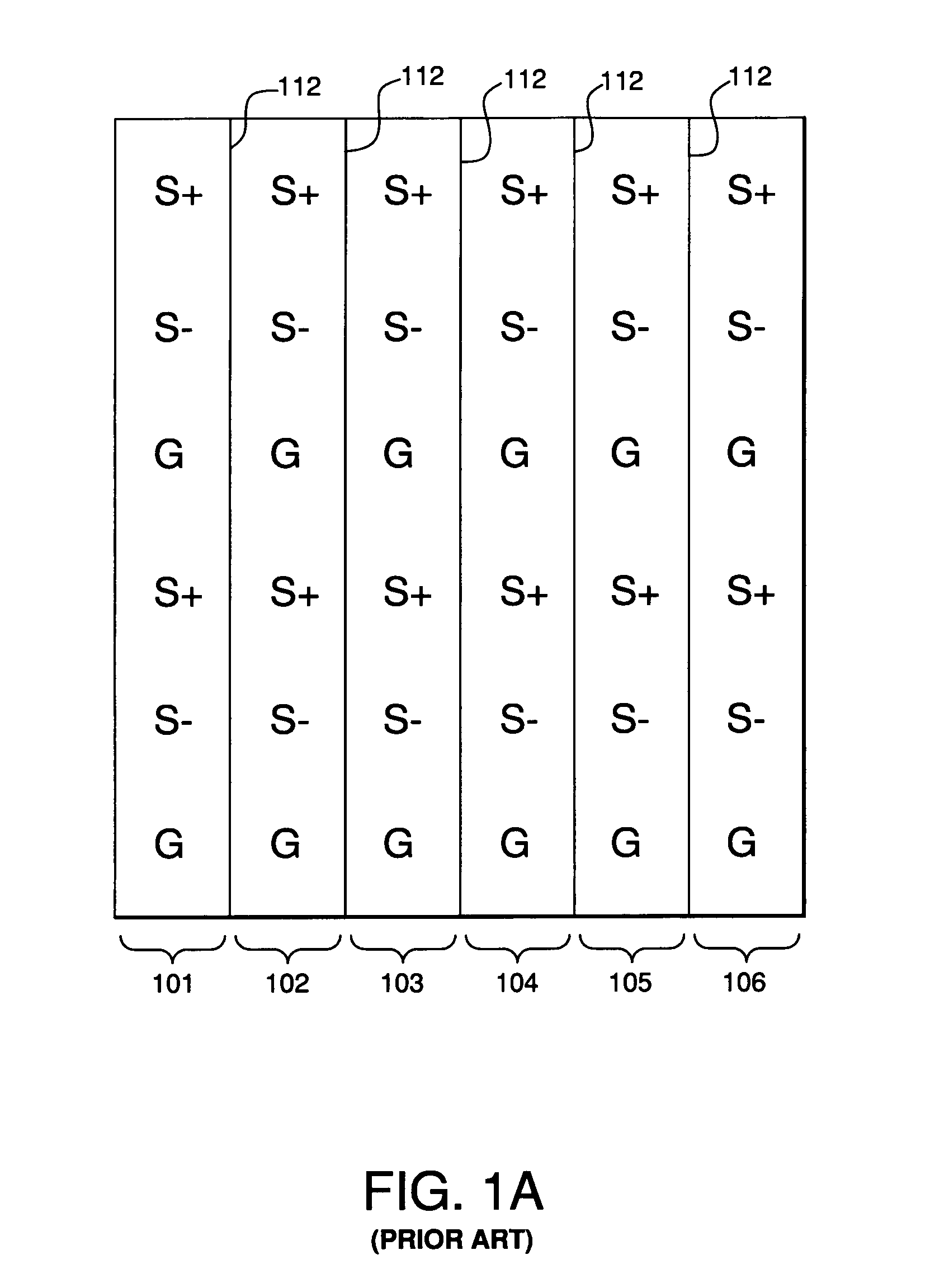

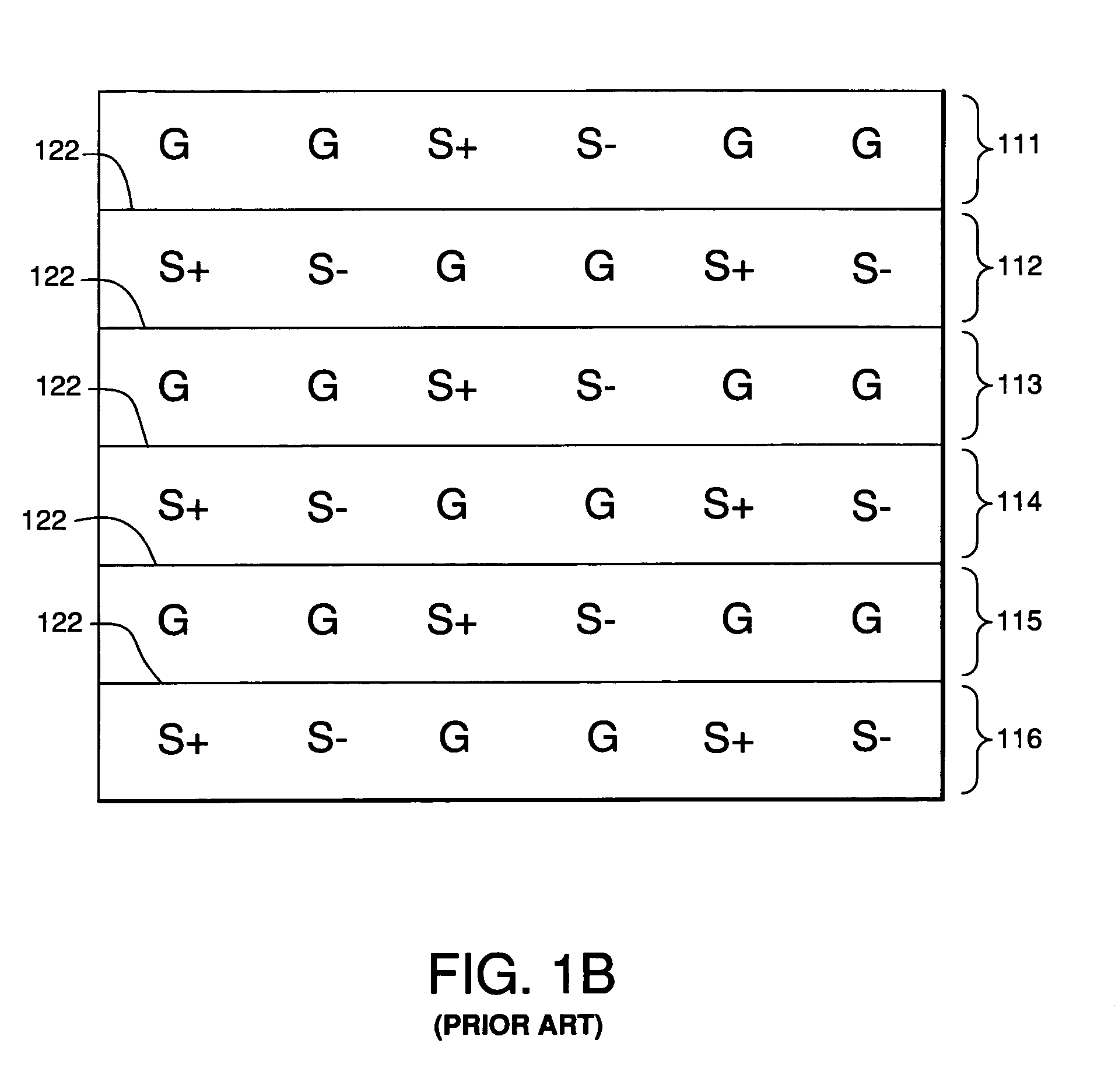

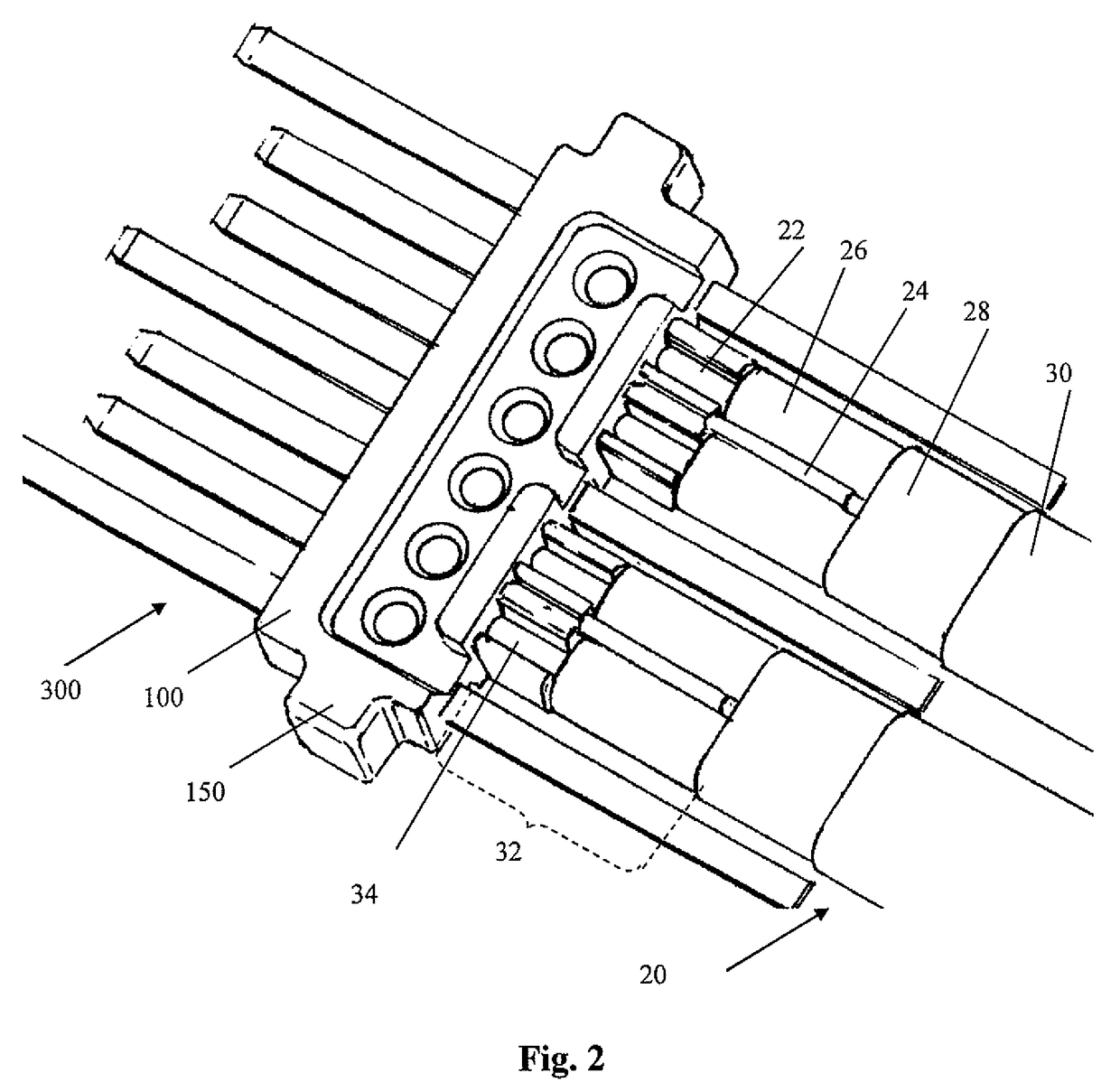

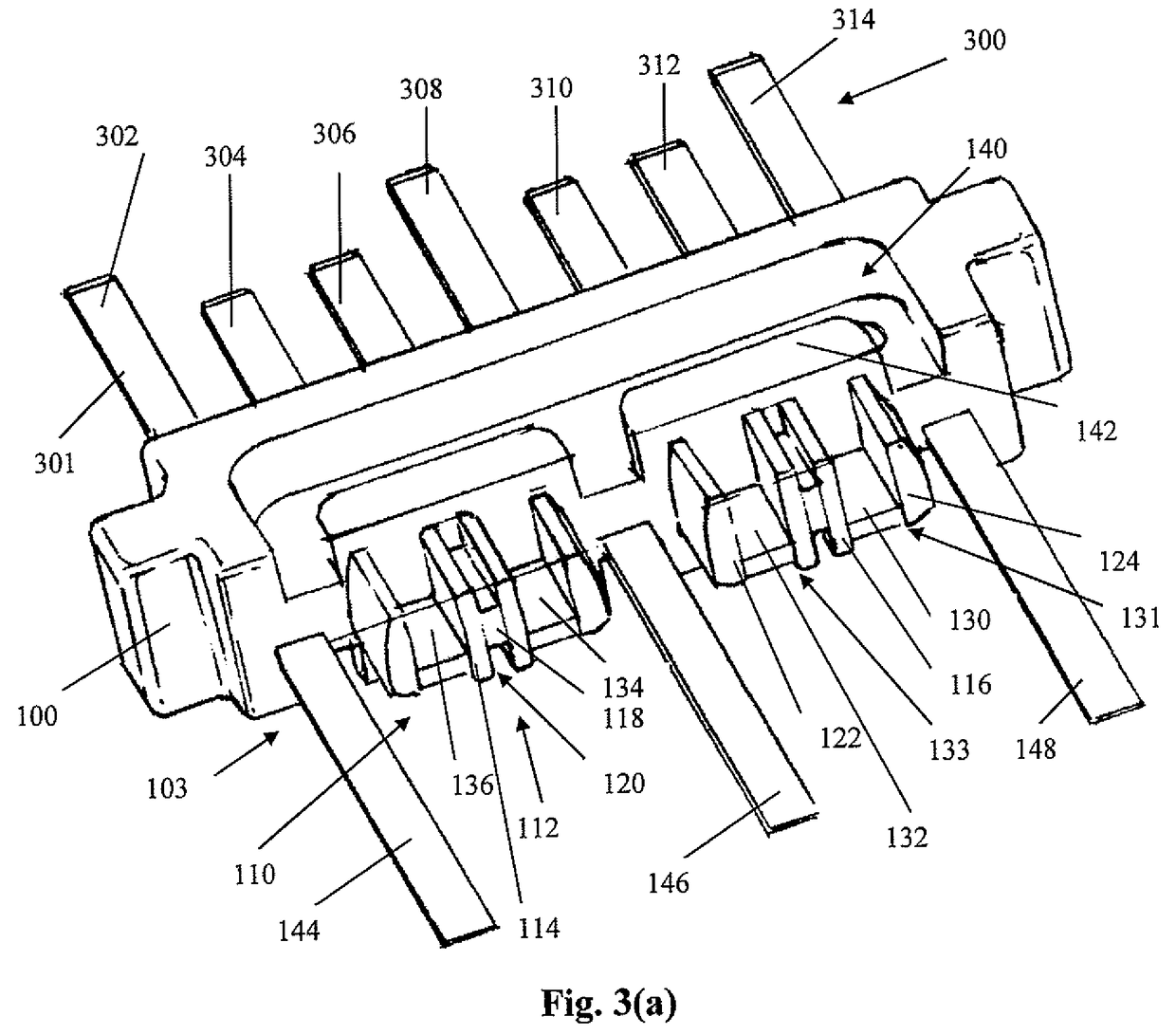

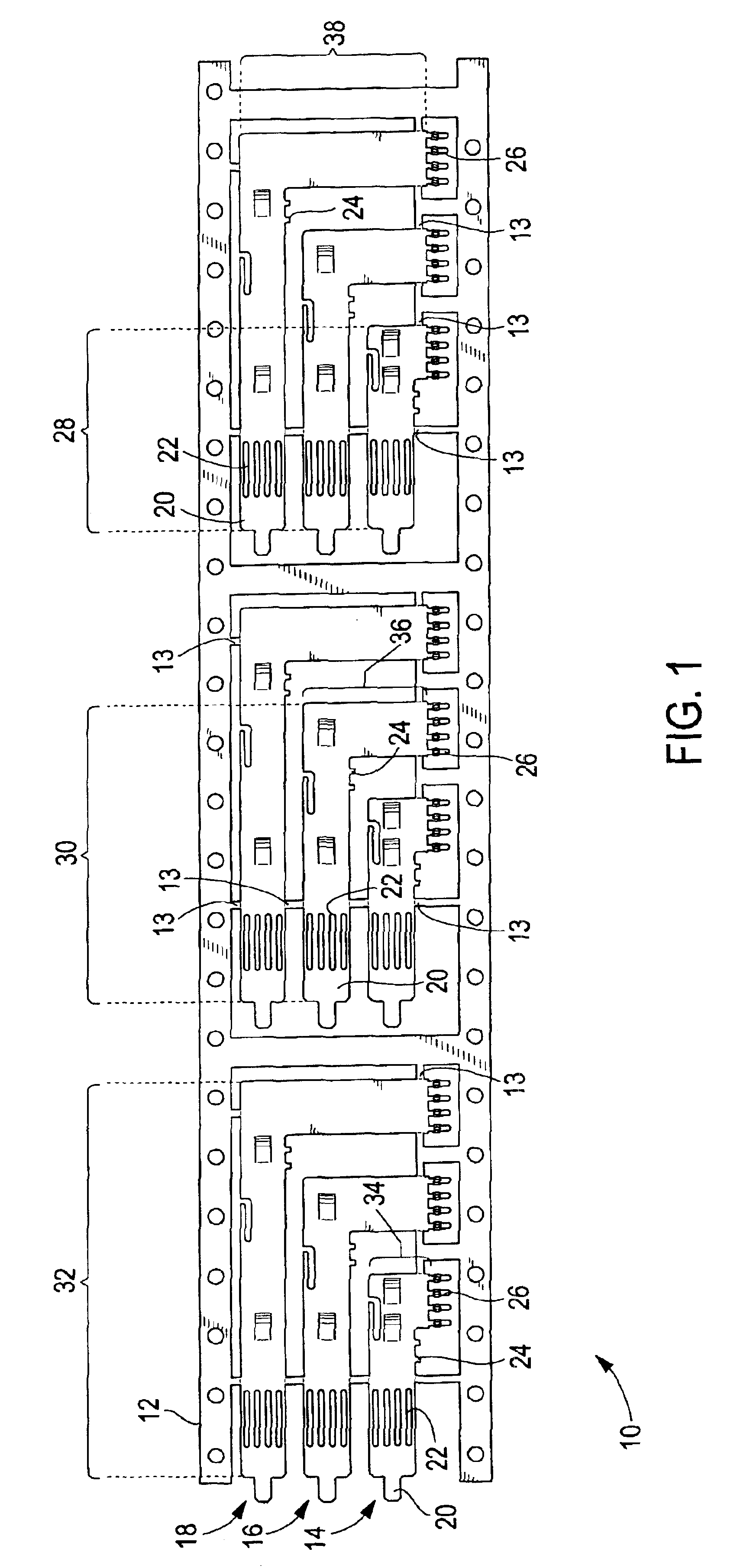

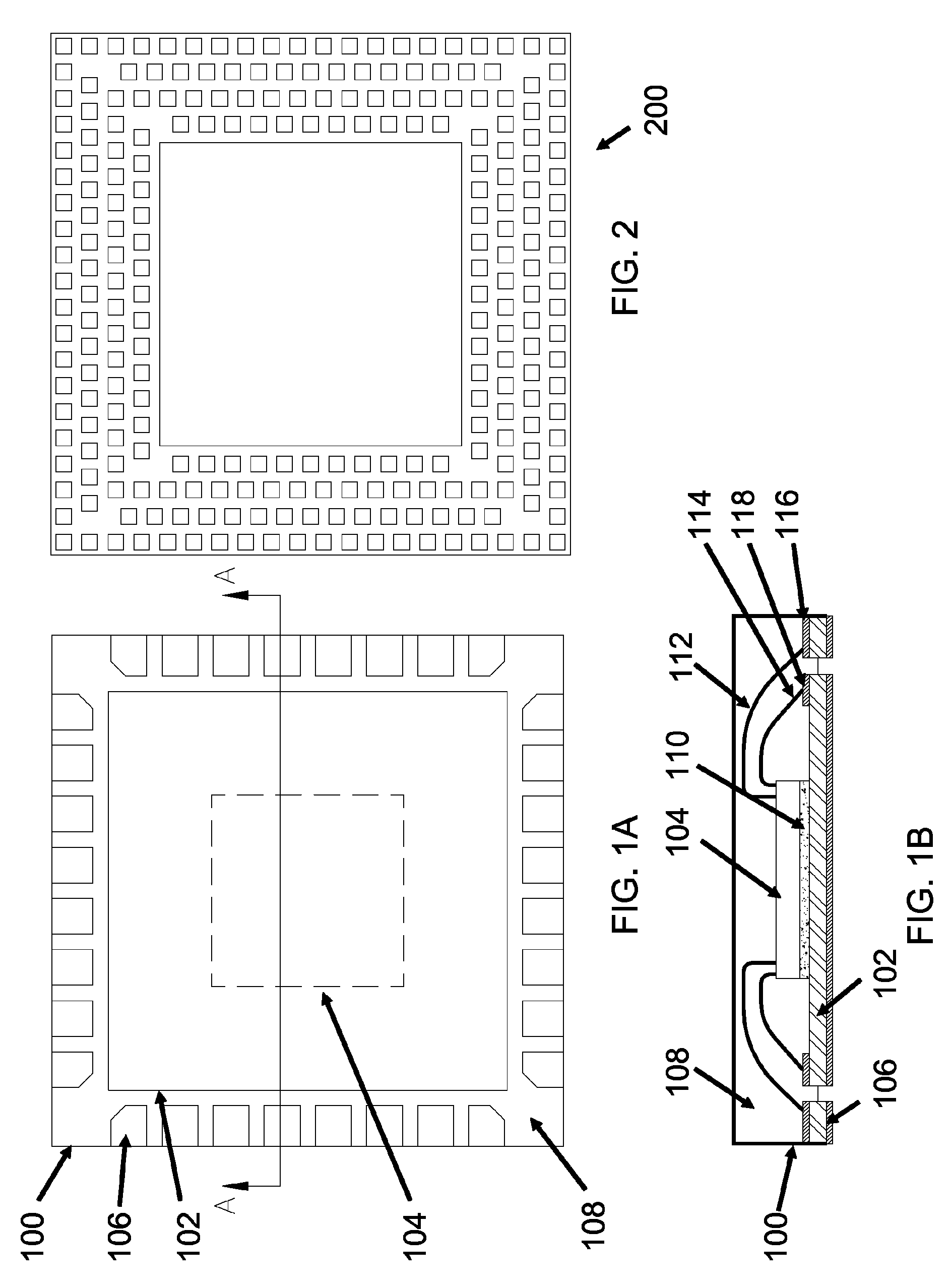

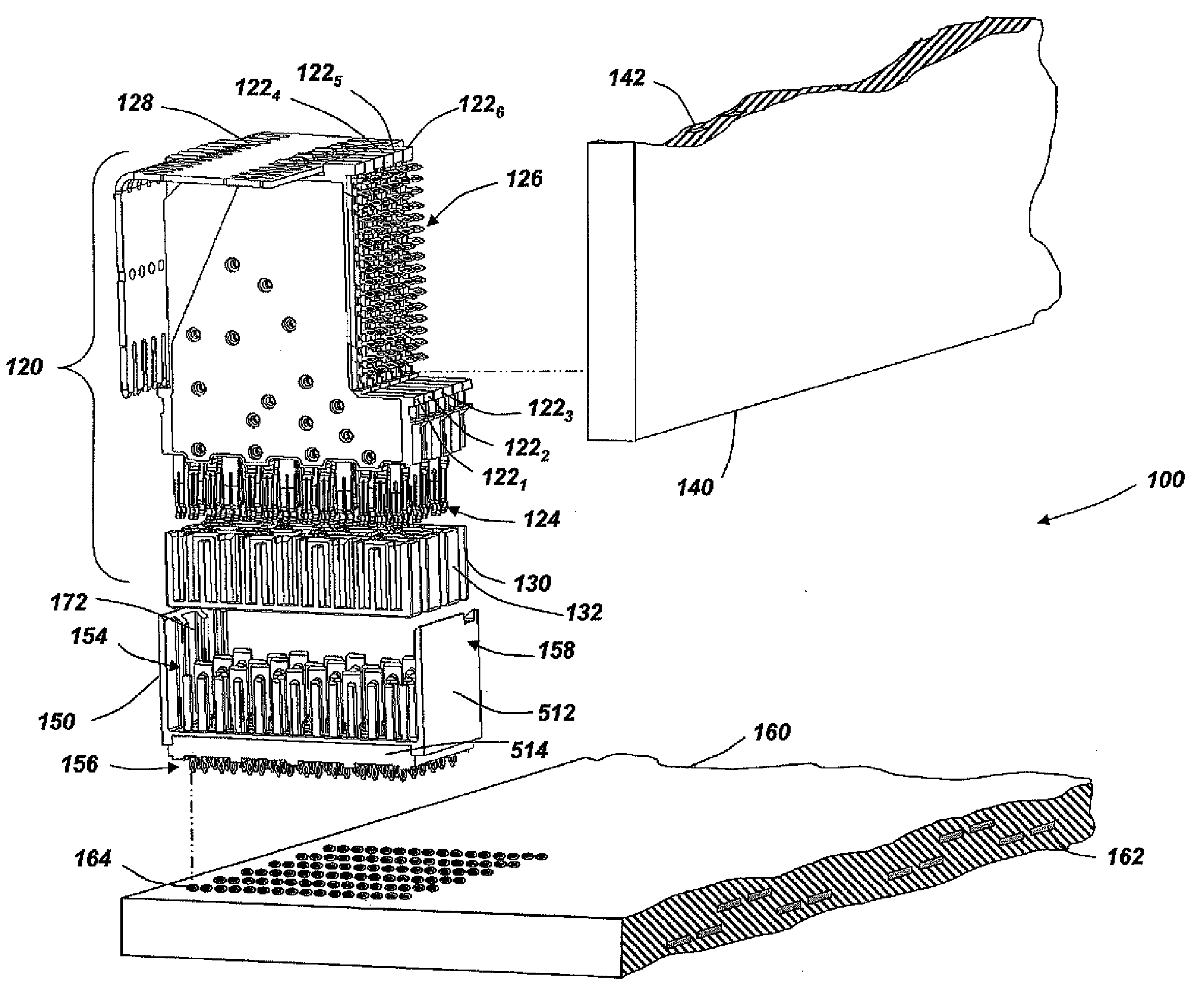

Electrical connectors having contacts that may be selectively designated as either signal or ground contacts

An electrical connector according to the invention includes a linear contact array of electrically conductive contacts and a lead frame into which the contacts at least partially extend. The contacts may be selectively designated as either ground or signal contacts such that, in a first designation, the contacts form at least one differential signal pair comprising a pair of signal contacts, and, in a second designation, the contacts form at least one single-ended signal conductor.

Owner:FCI AMERICAS TECH LLC

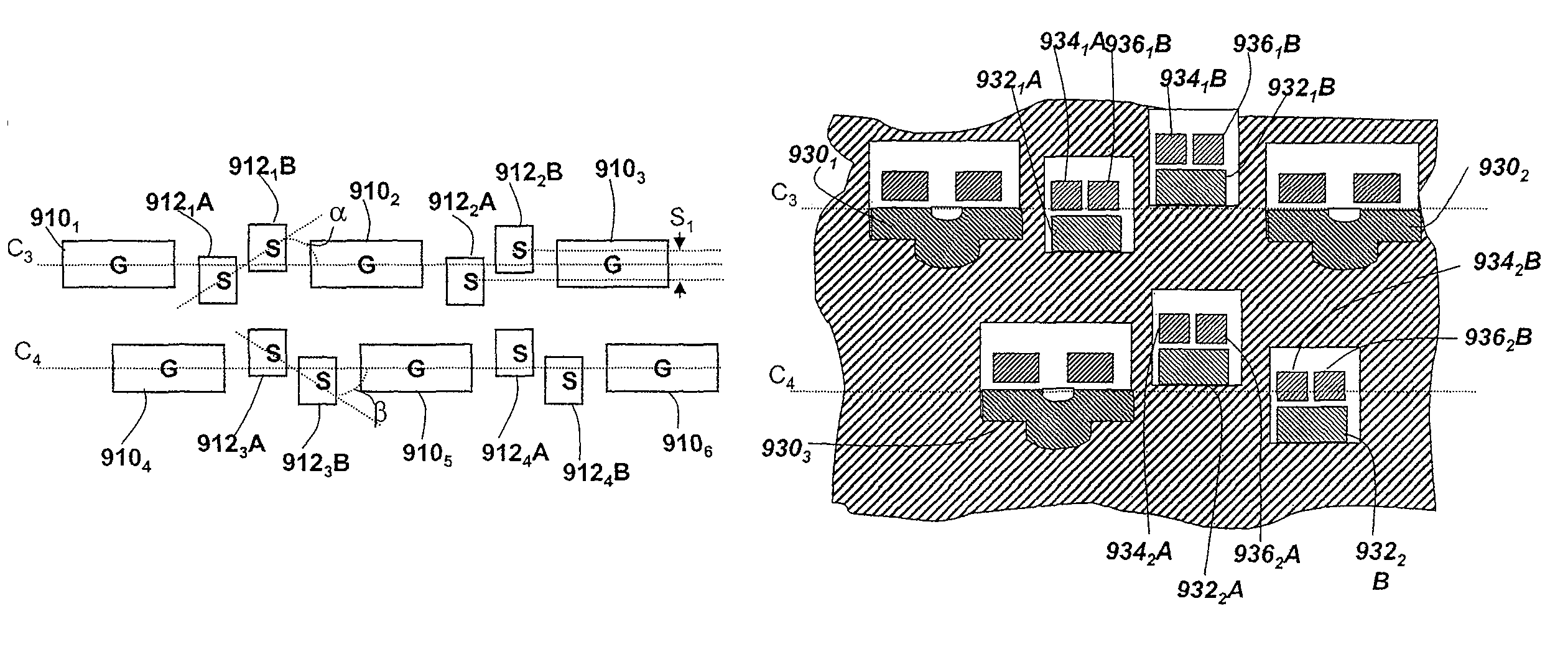

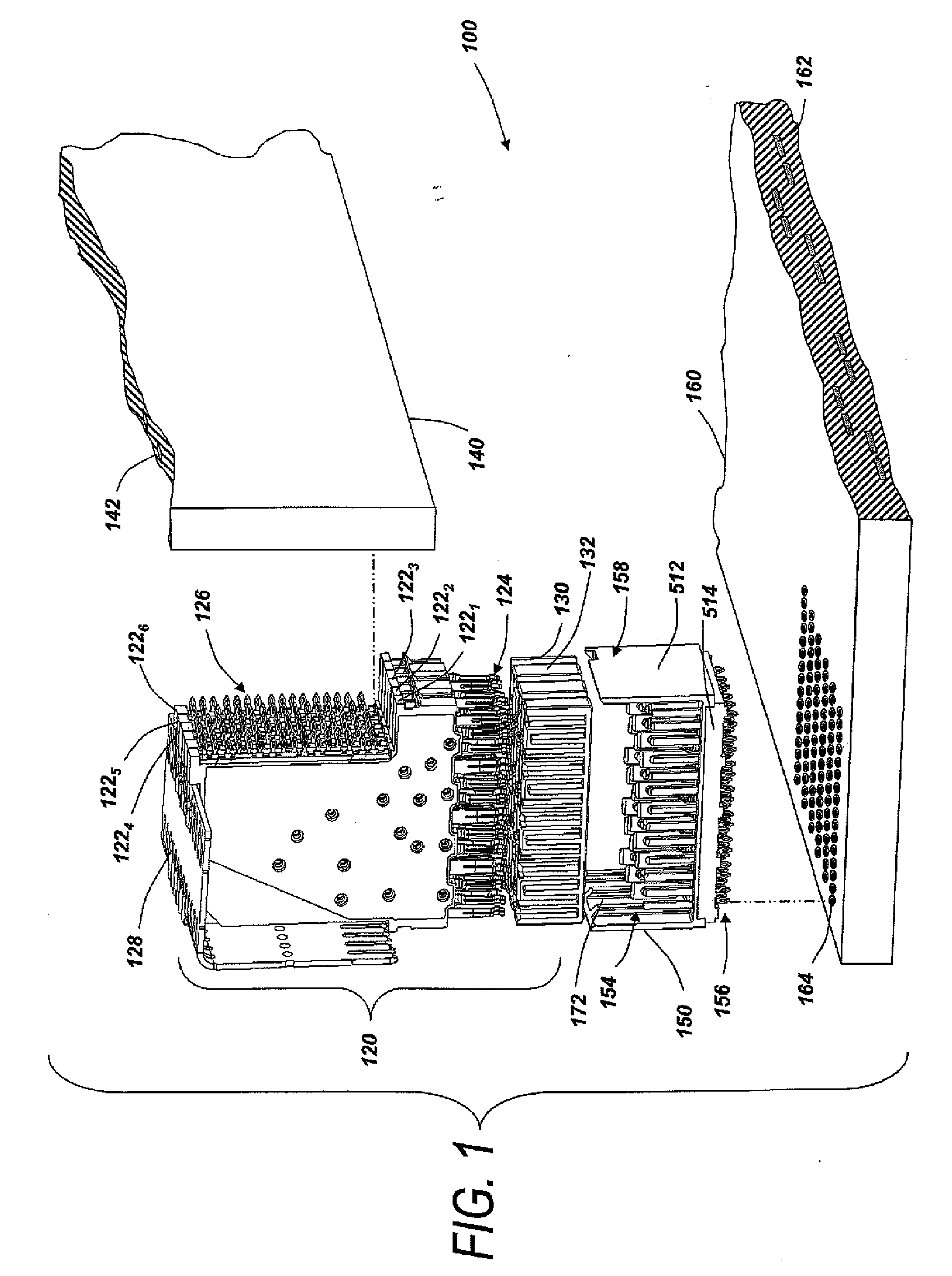

Electrical connector lead frame

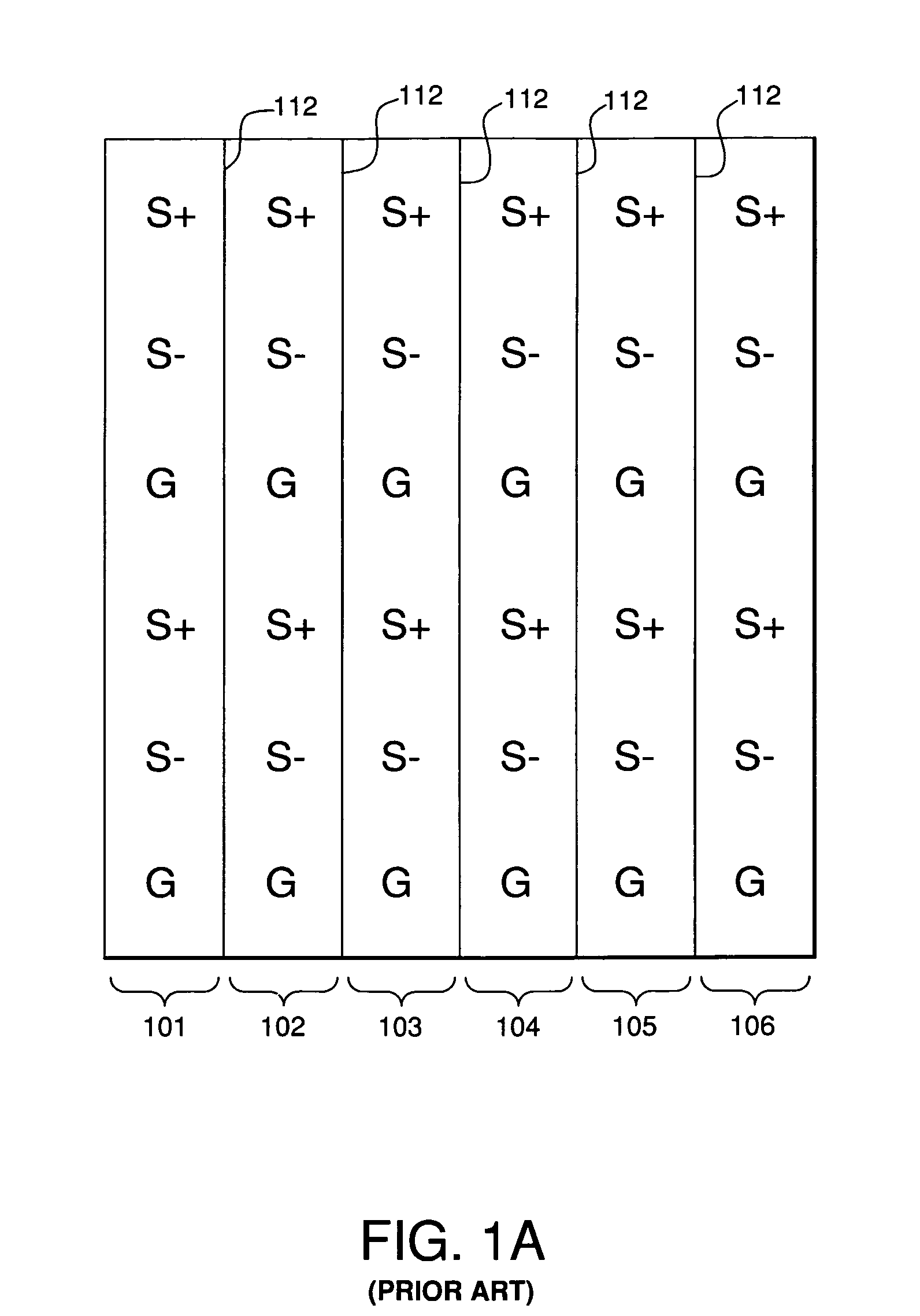

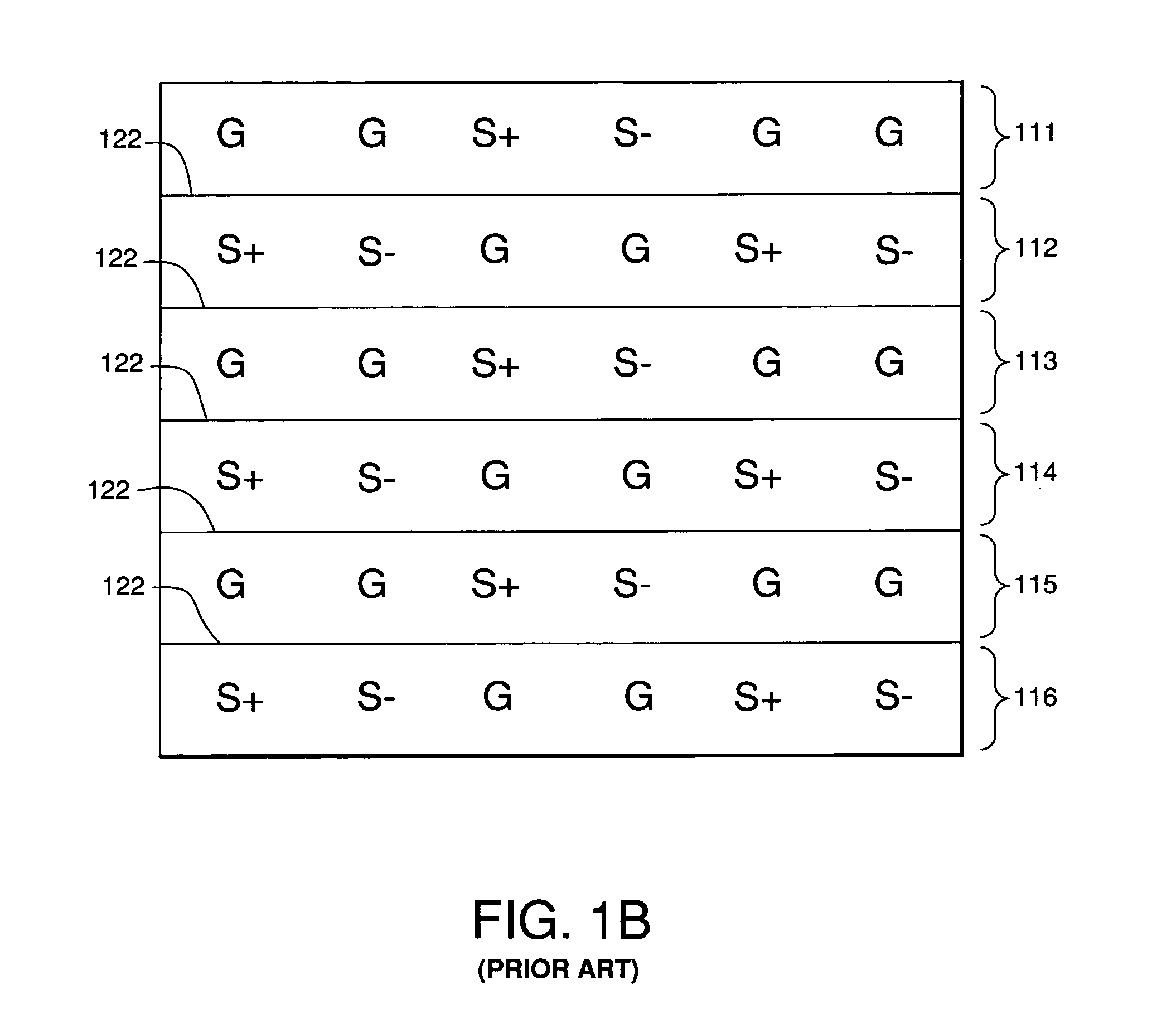

An electrical interconnection system with high speed, differential electrical connectors. The connector is assembled from wafers containing columns of conductive elements, some of which form differential pairs. Each column may include ground conductors adjacent pairs of signal conductors. The ground conductors may be wider than the signal conductors, with ground conductors between adjacent pairs of signal conductors being wider than ground conductors positioned at an end of at least some of the columns. Each of the conductive elements may end in a mating contact portion positioned to engage a complementary contact element in a mating connector. The mating contact portions of the signal conductors in some of the pairs may be rotated relative to the columns. The printed circuit board to which the differential signal connector is mounted may be constructed with elongated antipads around pairs of signal conductors.

Owner:AMPHENOL CORP

Integrated circuit packaging system with flipchip leadframe and method of manufacture thereof

An integrated circuit packaging system and method of manufacture thereof includes: leads and a paddle; a first encapsulant molded between the leads and the paddle, the first encapsulant thinner than the leads; a non-conductive layer over the paddle; and conductive traces directly on the leads, the first encapsulant, and the non-conductive layer.

Owner:STATS CHIPPAC LTD

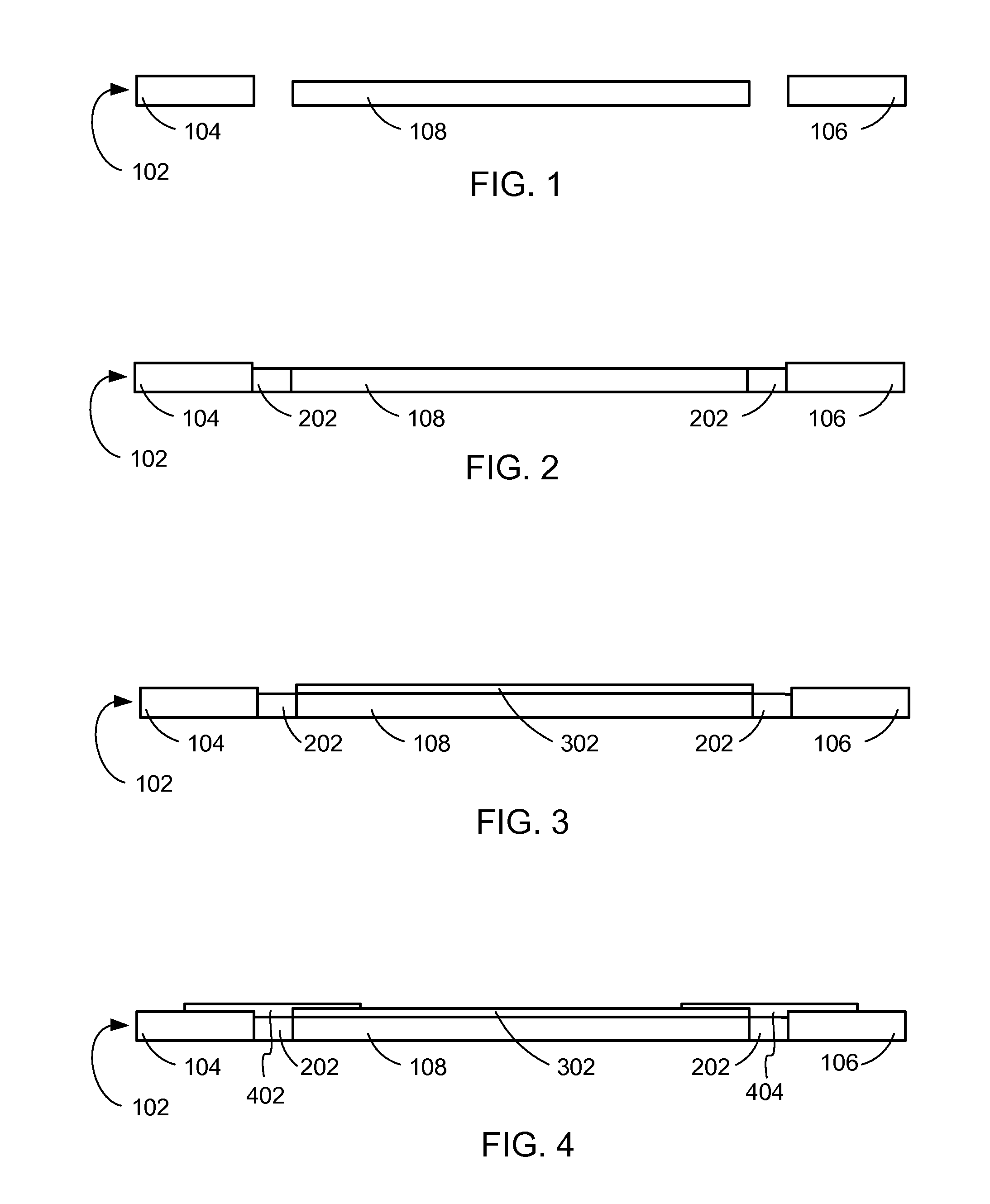

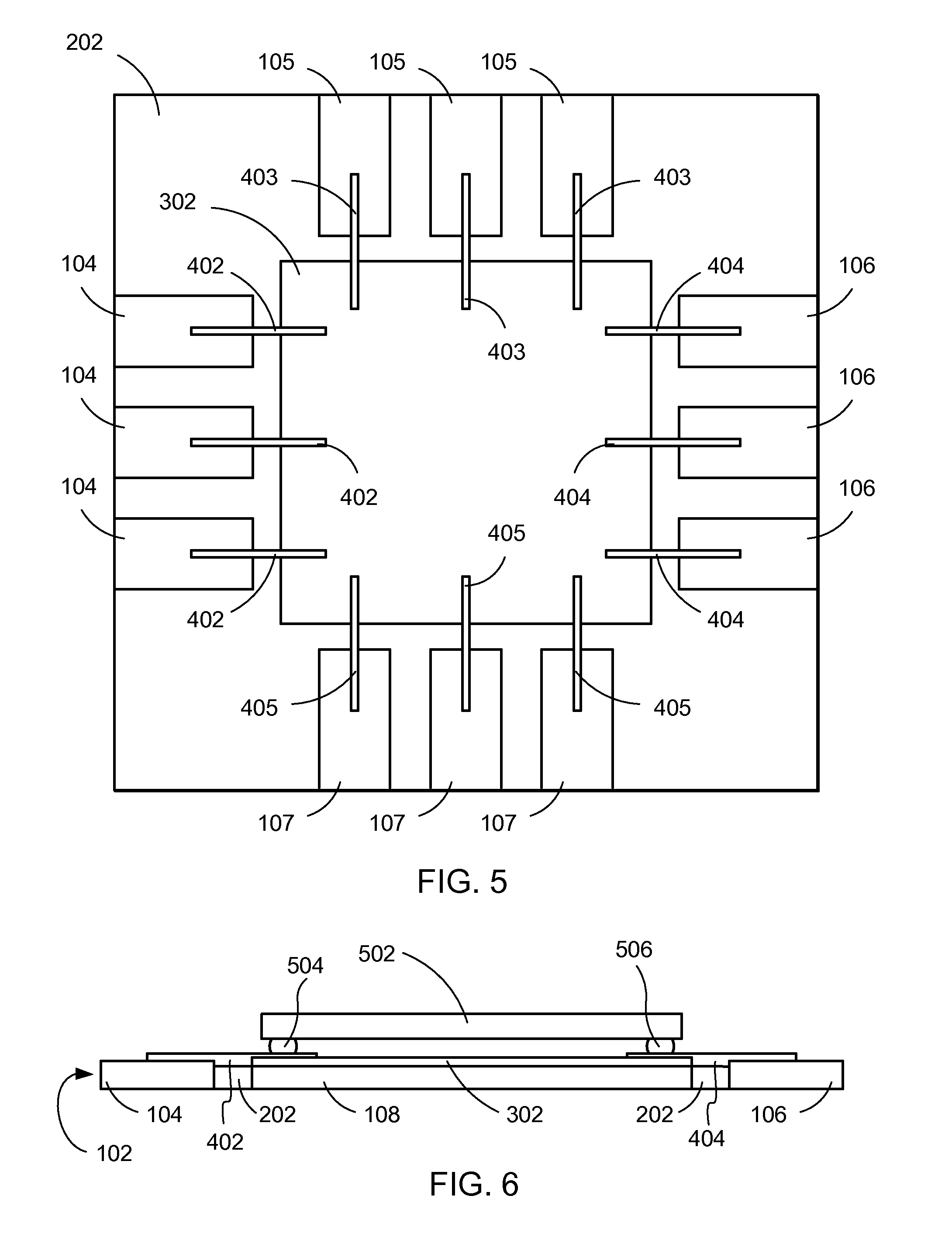

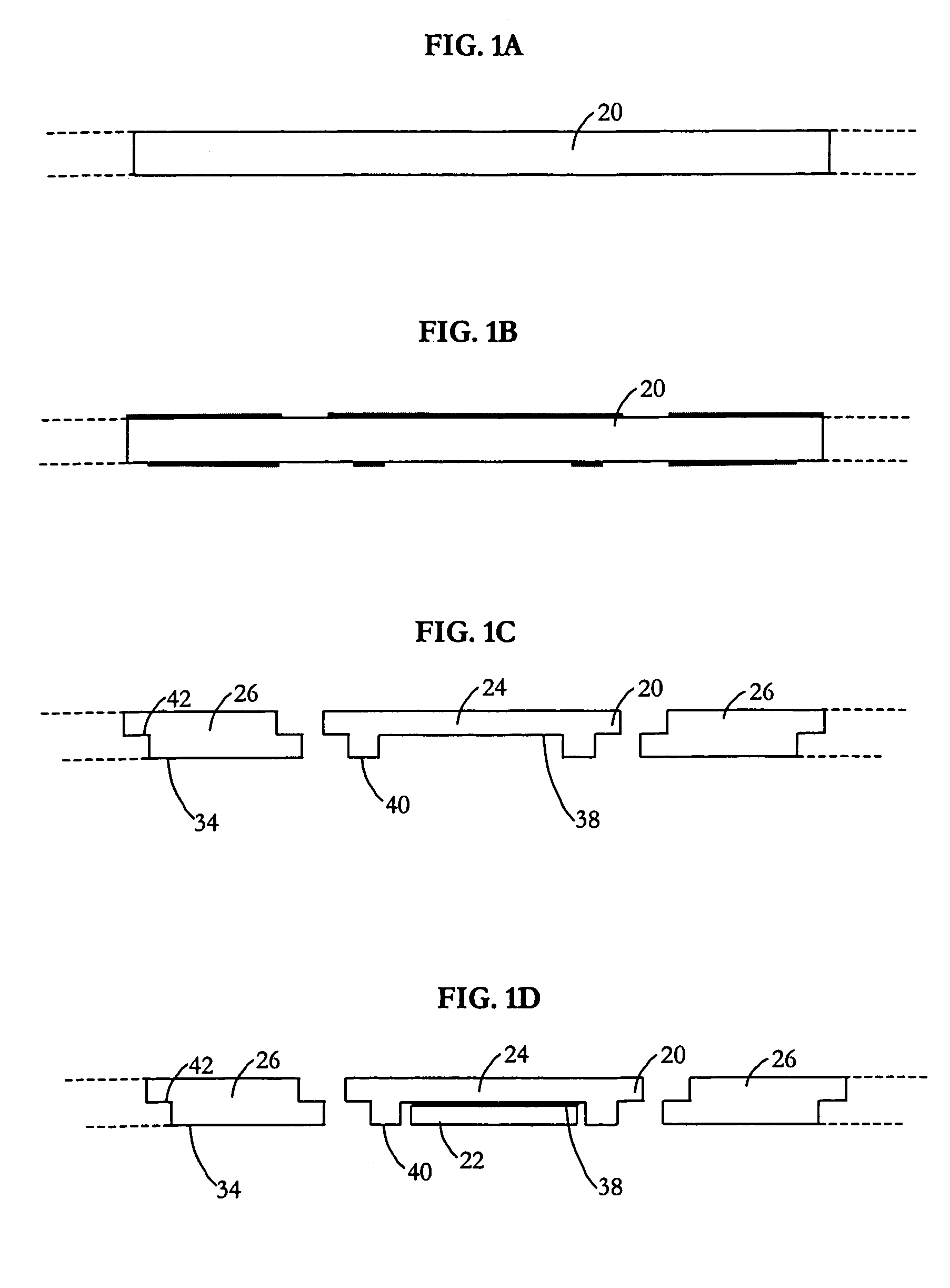

Partially patterned lead frames and methods of making and using the same in semiconductor packaging

InactiveUS20080258278A1Reduce thicknessImprove structural rigiditySemiconductor/solid-state device detailsSolid-state devicesLead bondingBonding process

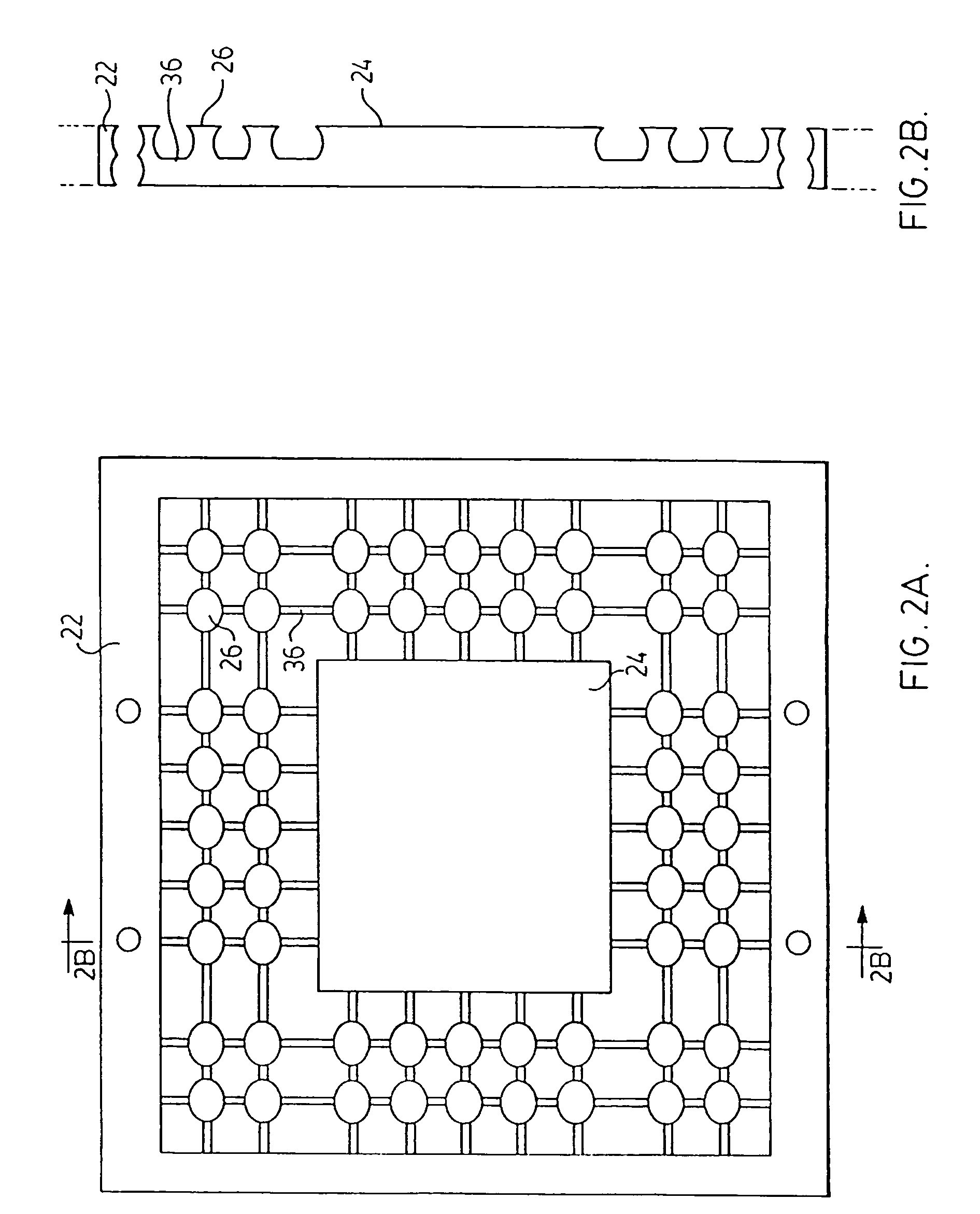

A method of making a lead frame and a partially patterned lead frame package with near-chip scale packaging lead-count, wherein the method lends itself to better automation of the manufacturing line and improved quality and reliability of the packages produced therefrom. A major portion of the manufacturing process steps is performed with a partially patterned strip of metal formed into a web-like lead frame on one side so that the web-like lead frame is also rigid mechanically and robust thermally to perform without distortion or deformation during the chip-attach and wire bond processes, both at the chip level and the package level. The bottom side of the metal lead frame is patterned to isolate the chip-pad and the wire bond contacts only after the front side, including the chip and wires, is hermetically sealed with an encapsulant. The resultant package being electrically isolated enables strip testing and reliable singulation.

Owner:UNISEM M BERHAD

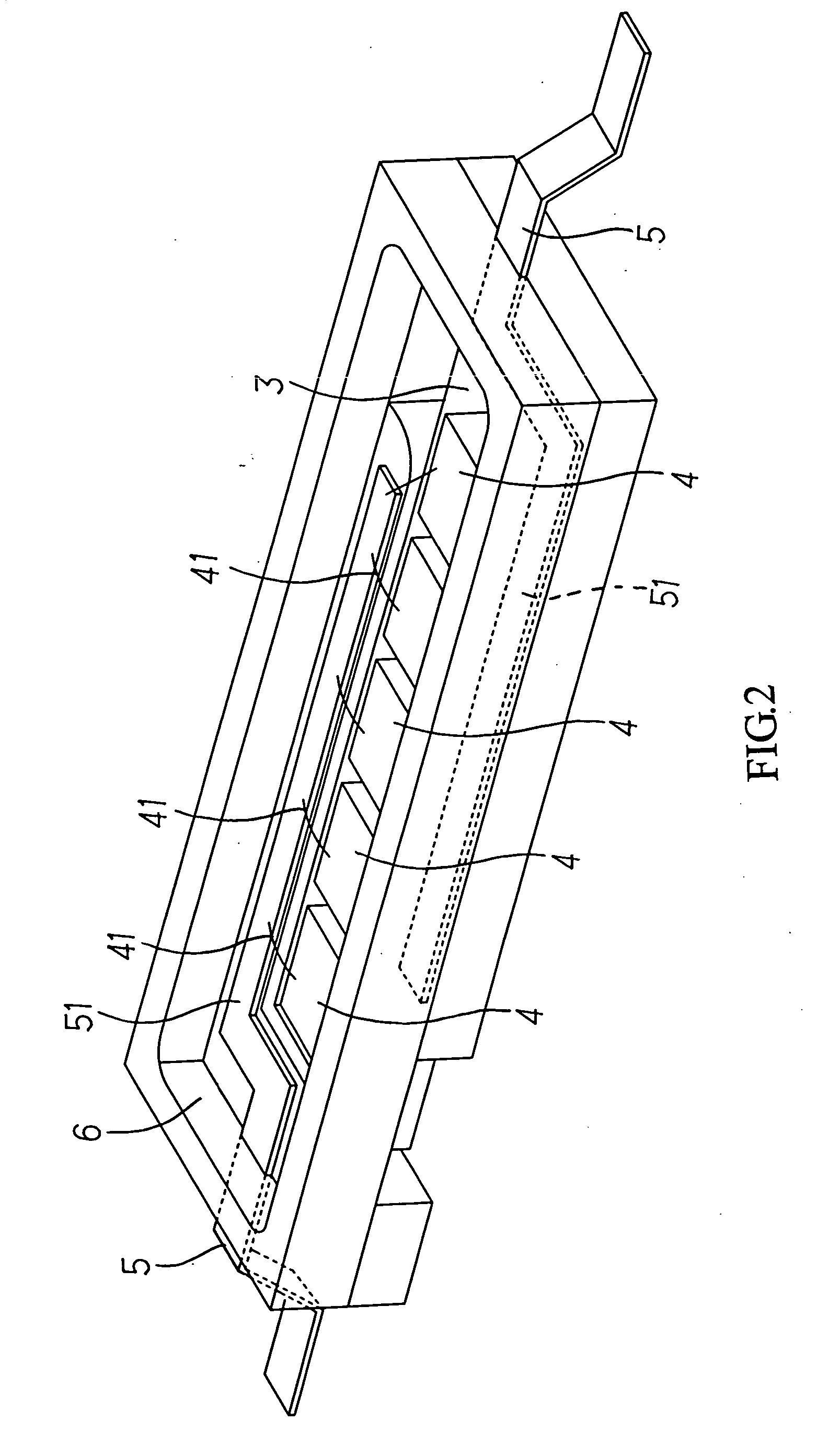

LED package

InactiveUS20070063213A1Effective heat dissipation purposeSimple structureSolid-state devicesSemiconductor devicesEngineeringConductive materials

A package allowing agile deployment of the location of each LED chip includes a heat slug to secure multiple LED chips, two lead frames, a conducting area extending along the edge of the heat slug, and a non-conductive material that connects the heat slug and the lead frame for those multiple LED chips to connect to the conducting area by means of a gold wire without being subject to the presence of the lead frame.

Owner:LEXTAR ELECTRONICS CORP

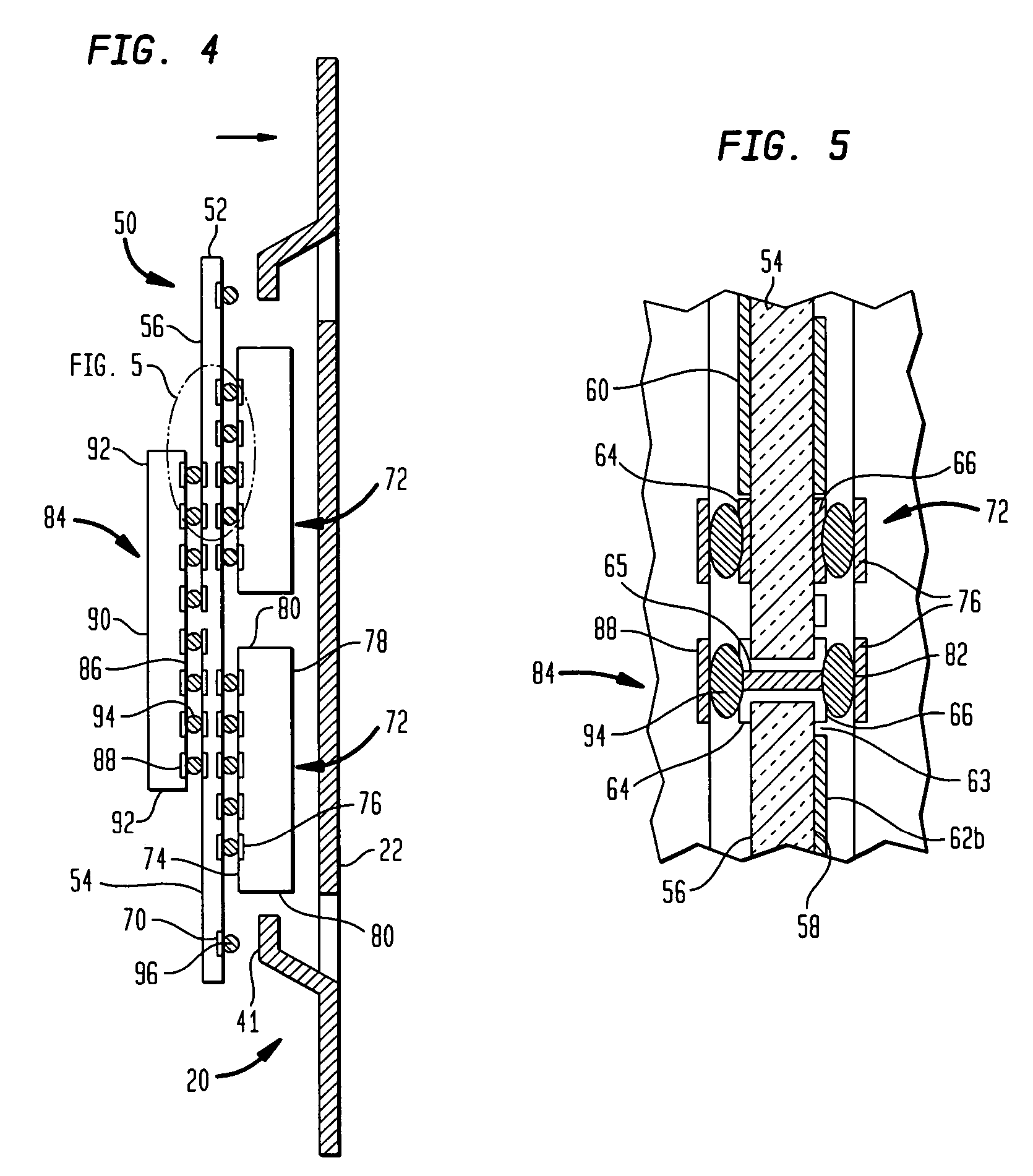

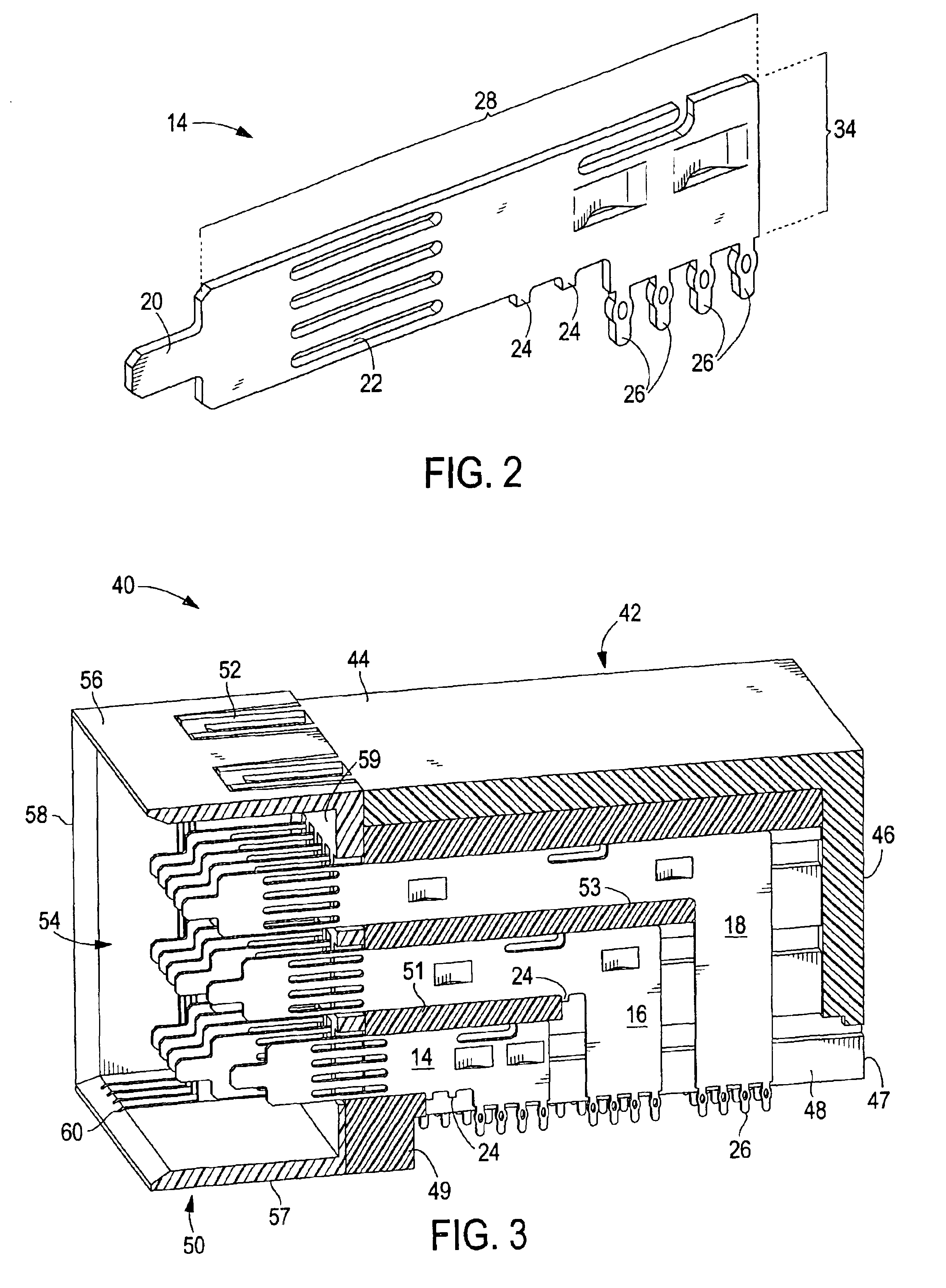

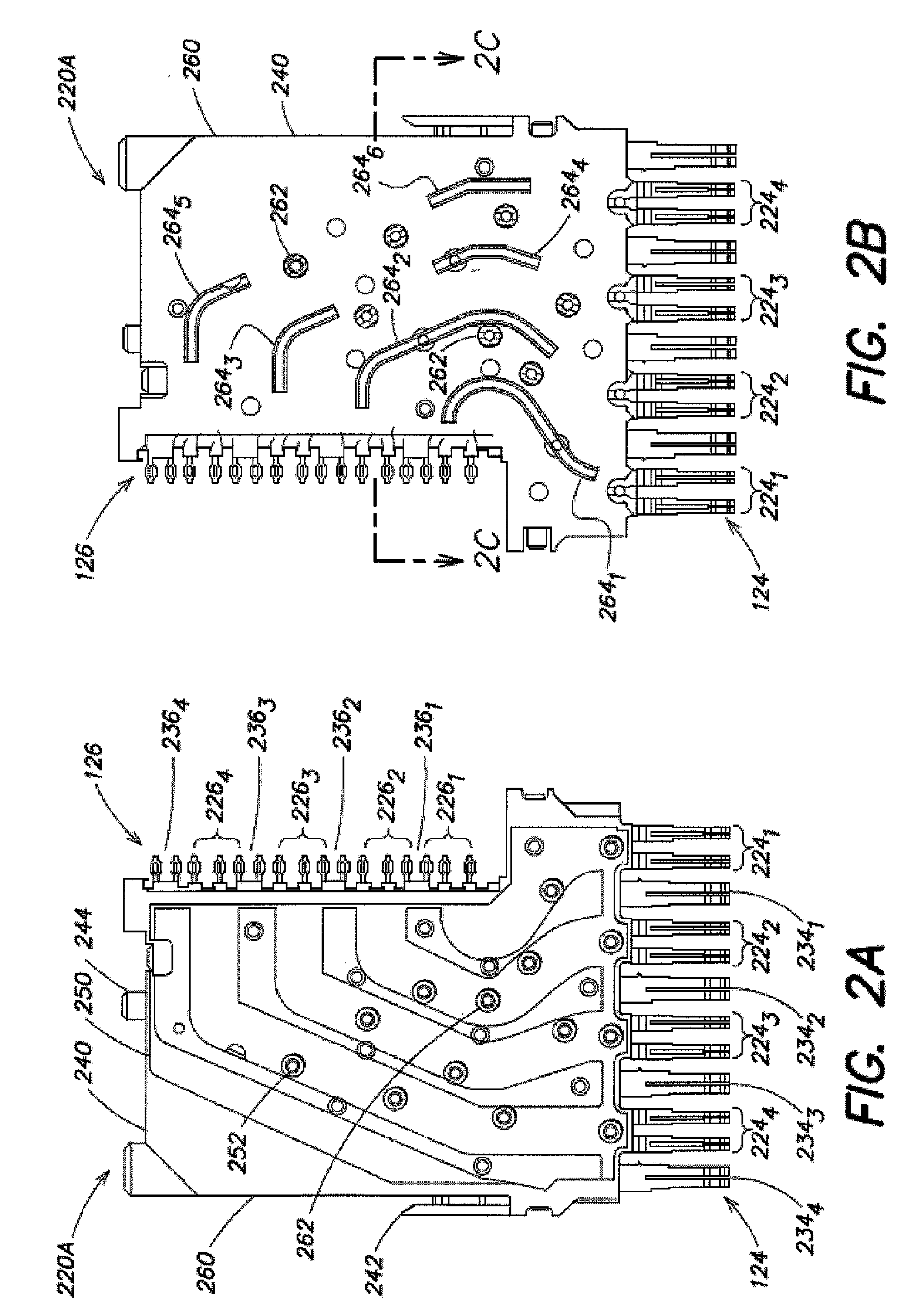

Ground sleeve having improved impedance control and high frequency performance

A waferized connector connects to two twinax cables. The connector includes a molded lead frame, ground sleeve, twinax cable, and overmolded strain relief. The lead frame is molded to retain a lead frame containing both differential signal pins and ground pins. Termination sections are provided at the rear of the lead frame to terminate each of the signal wires of the cables to respective signal lands. The ground sleeve has two general H-shape structures connected together by a center cross-support member. Each of the H-shaped structures having curved legs, each of which fits over the signal wires of one of the twinax cables. The wings of the ground sleeve are terminated to the ground lands of the lead frame and the drain wire of the cable is terminated to the ground sleeve to terminate the drain wire to a ground reference. The ground sleeve controls the impedance in the termination area of the cables, where the twinax foil is removed to expose the wires for termination to the lands. The ground sleeve also shields the cables to reduce crosstalk between themselves and adjacent wafers when arranged in a connector housing. A conductive slab member is formed over the sleeve to provide a capacitive coupling with the conductive foil of the signal cable.

Owner:AMPHENOL CORP

Impedance control in electrical connectors

InactiveUS6981883B2Coupling contact membersTwo-part coupling devicesDifferential signalingElectrical connector

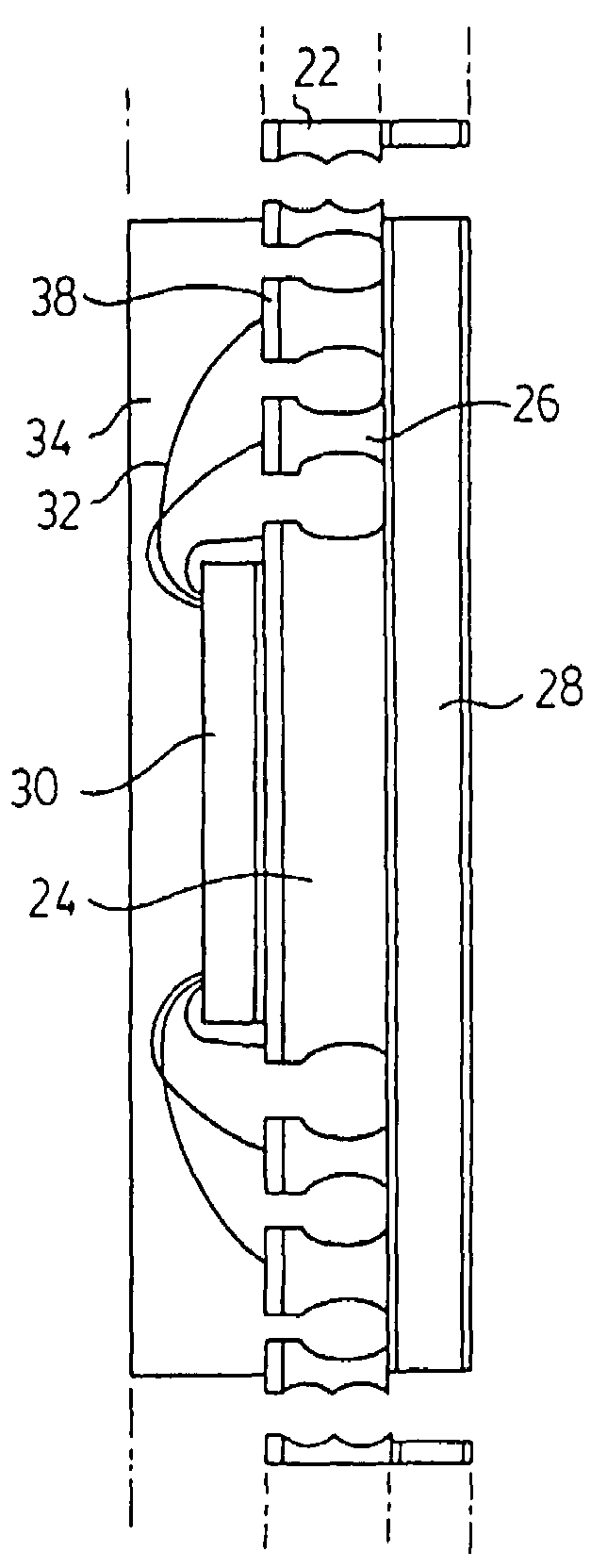

The invention provides a high speed connector wherein differential signal pairs are arranged so as to limit the level of cross talk between adjacent differential signal pairs. The connector comprises lead frame assembly having a pair of overmolded lead frame housings. Each lead frame housing has a respective signal contact extending therethrough. The lead frame housings may be operatively coupled such that the signal contacts form a broadside-coupled differential signal pair. The contacts may be separated by a gap having a gap width that enables insertion loss and cross talk between signal pairs to be limited.

Owner:FCI AMERICAS TECH LLC

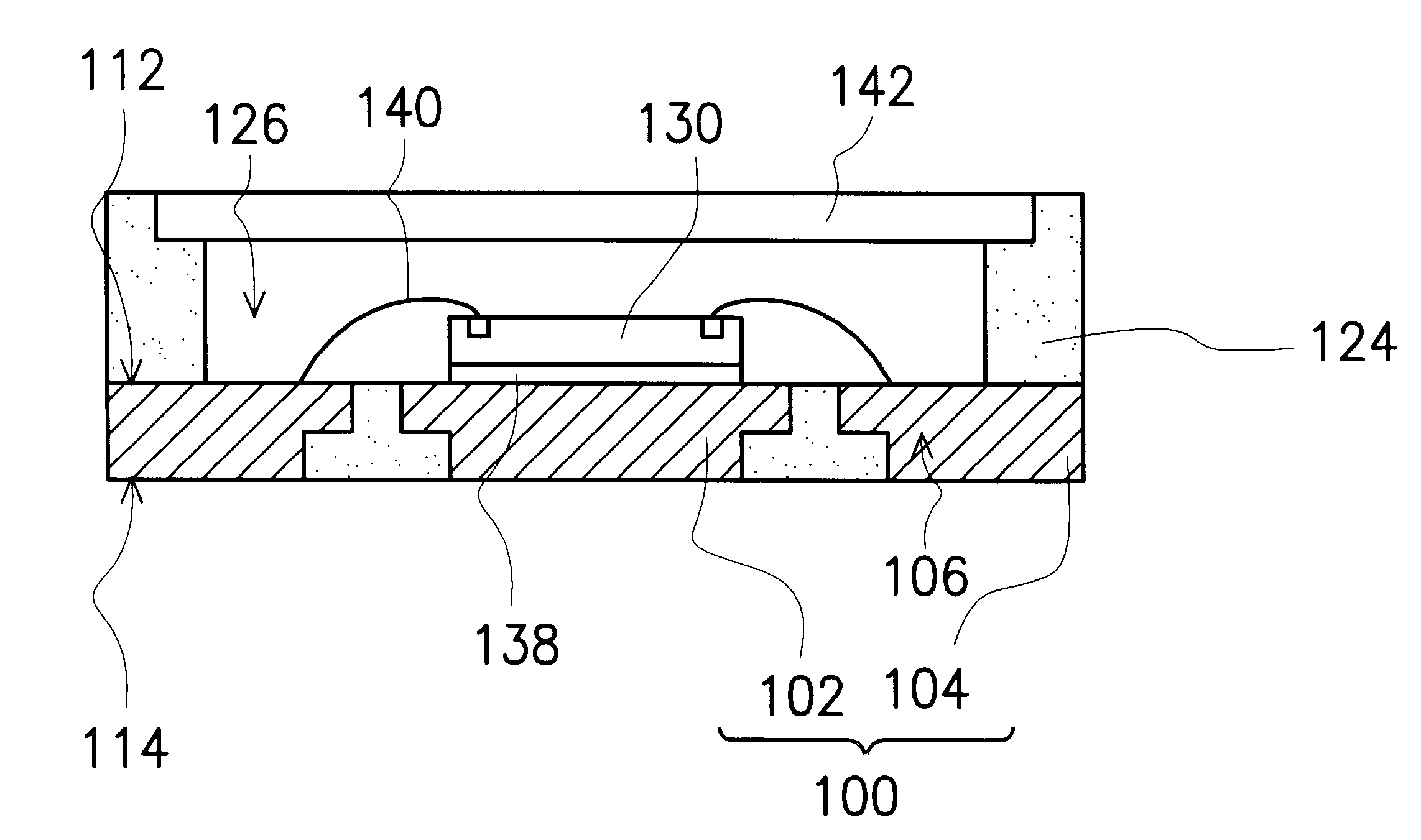

Process for fabricating an integrated circuit package

InactiveUS7247526B1Board mount reliabilityReduce manufacturing costSemiconductor/solid-state device detailsSolid-state devicesLead frameSemiconductor

A process for fabricating an integrated circuit package. At least a first side of a leadframe strip is selectively etched to define portions of a die attach pad and at least one row of contacts adjacent the die attach pad. A carrier strip is laminated to the first side of the leadframe strip and a second side of the leadframe strip is selectively etched to thereby define a remainder of the die attach pad and the at least one row of contacts. A semiconductor die is mounted to the die attach pad, on the second side of the leadframe strip and the semiconductor die is wire bonded to ones of the contacts. The second side of the leadframe strip is encapsulating, including the semiconductor die and wire bonds, in a molding material. The carrier strip is removed from the leadframe strip and the integrated circuit package is singulated from a remainder of the leadframe strip.

Owner:UTAC HEADQUARTERS PTE LTD

Semiconductor package exhibiting efficient lead placement

InactiveUS6927483B1Effective placementSemiconductor/solid-state device detailsSolid-state devicesSemiconductor packageLead frame

A semiconductor package exhibiting efficient placement of semiconductor leads in a micro lead frame design is provided. An integrated circuit die is bonded to the top surfaces of leads, thereby allowing the leads to partially reside under the die. As a result, surface area on the bottom surface of the semiconductor package is recaptured. The die can be further bonded a die paddle if so desired. One or more channels can be cut into the bottom surface of the package in order to separate first and second leads. Such channels allow separate leads to be fabricated from a single lead member which is subsequently cut.

Owner:AMKOR TECH SINGAPORE HLDG PTE LTD

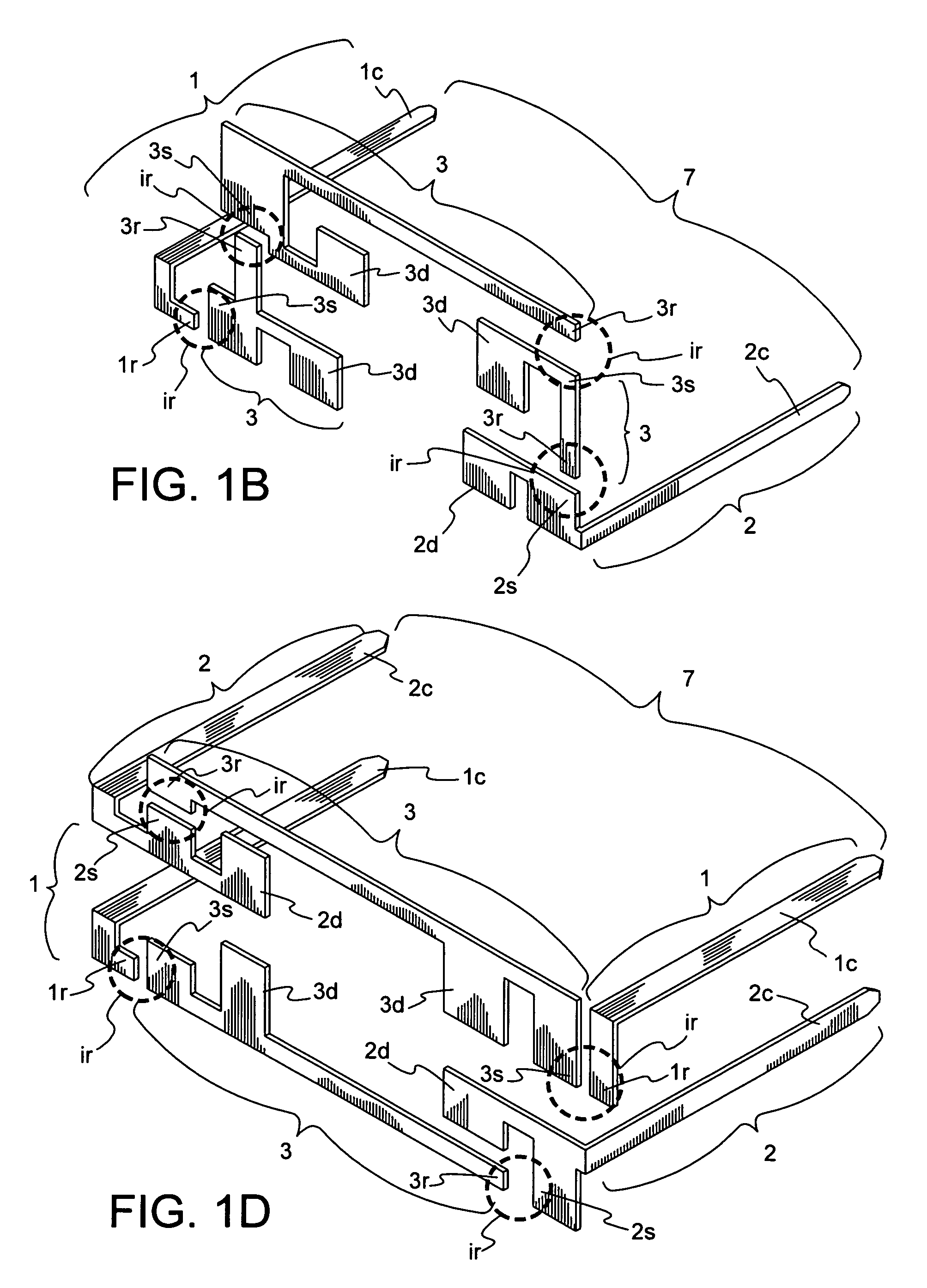

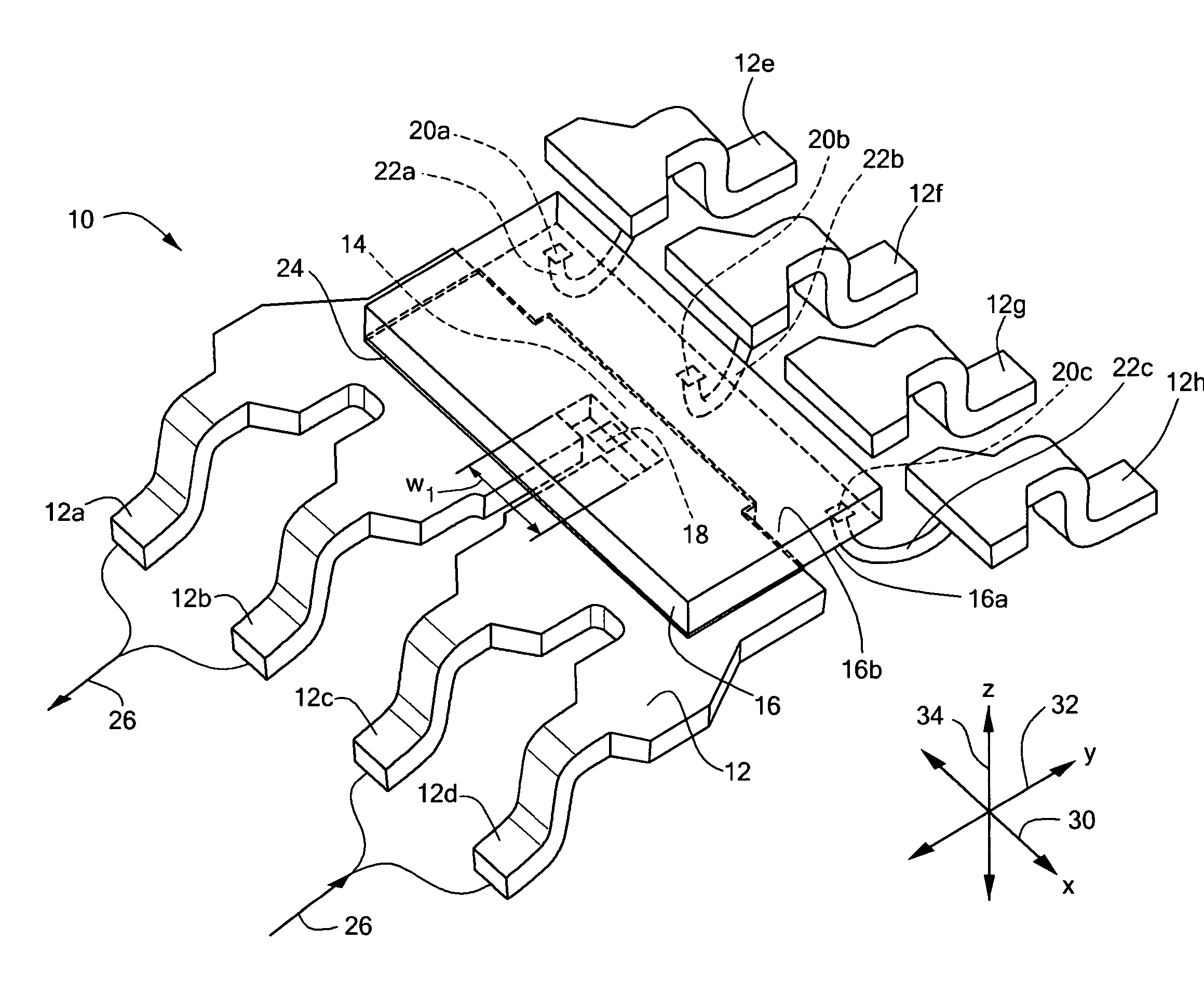

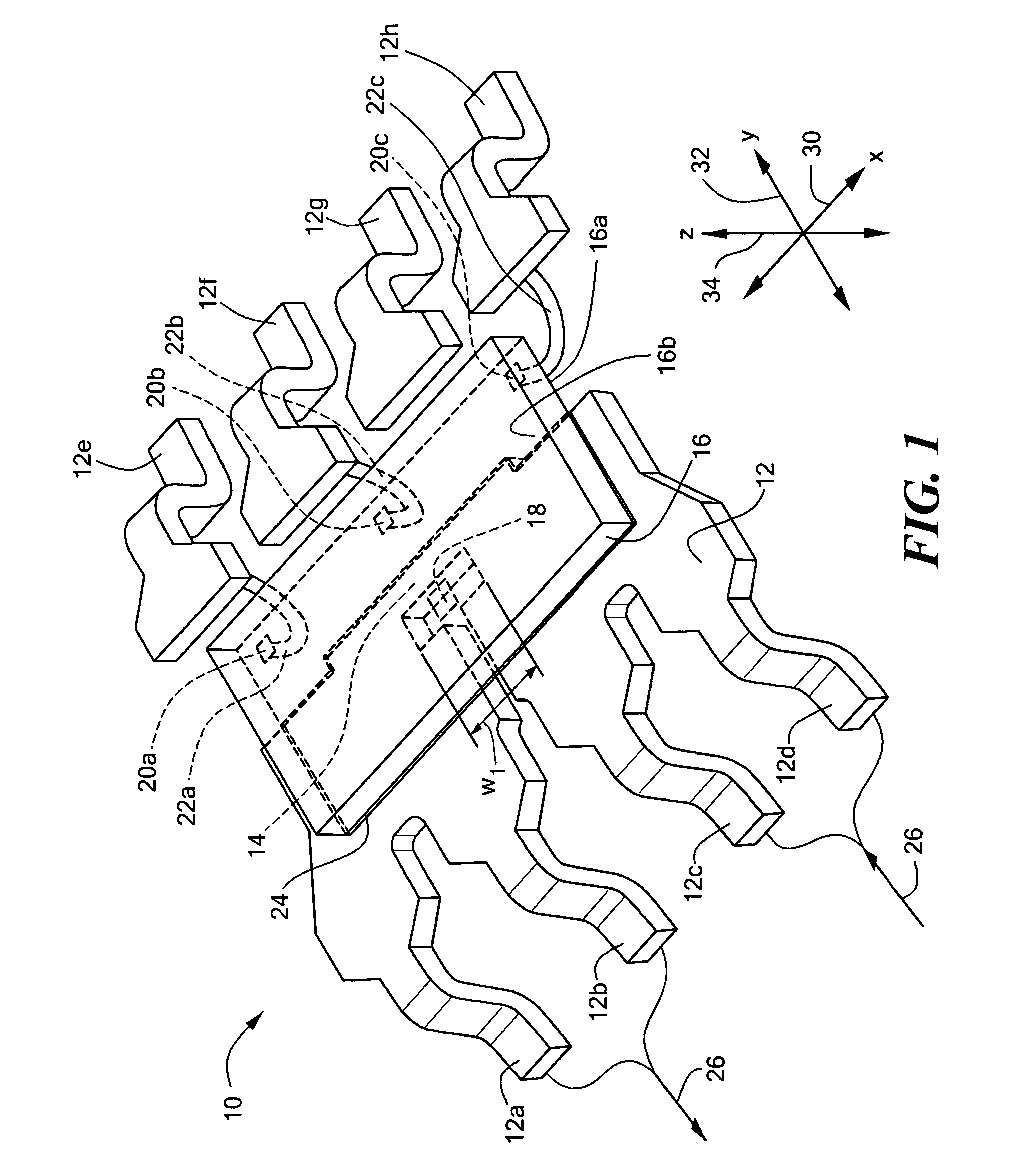

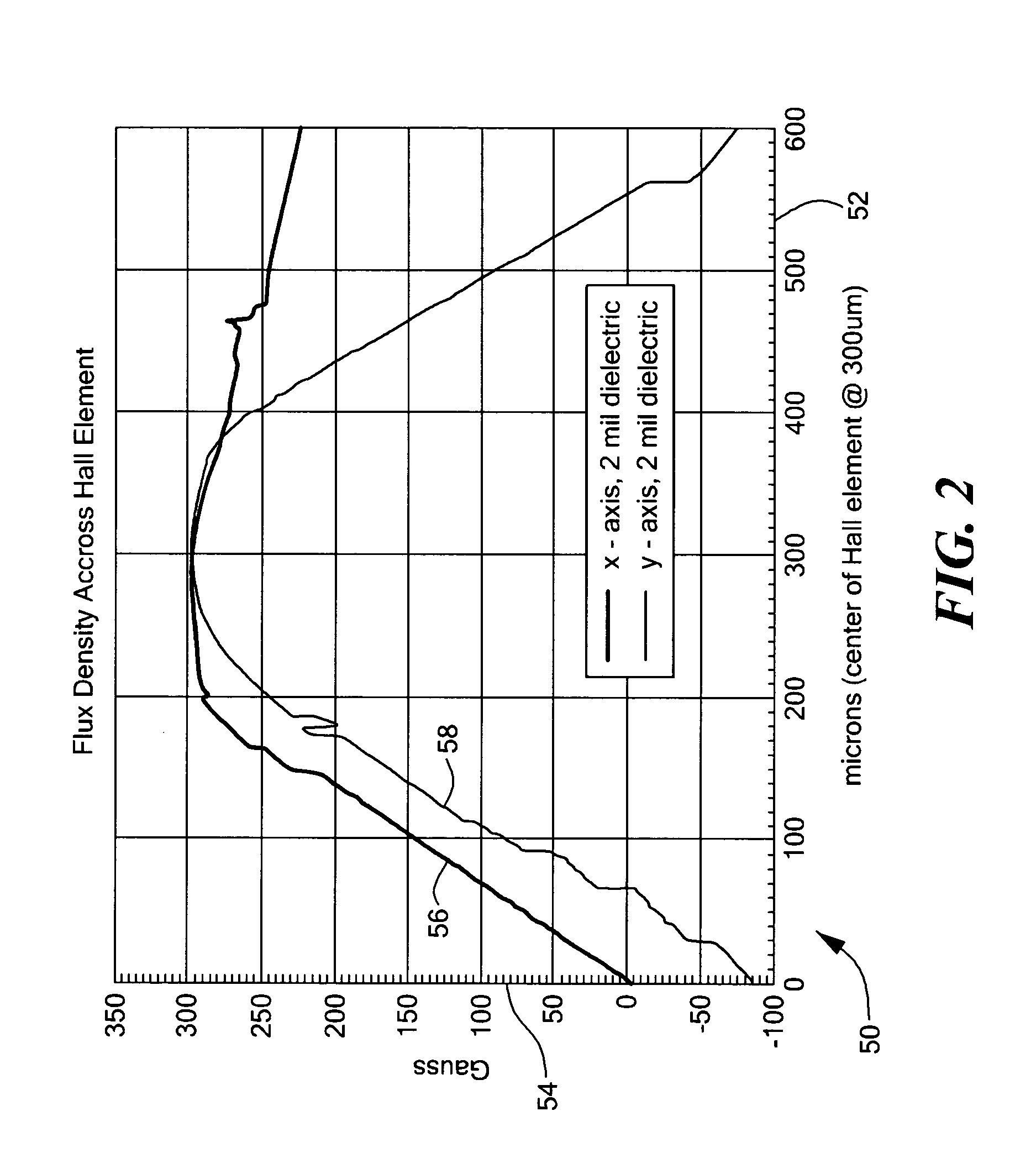

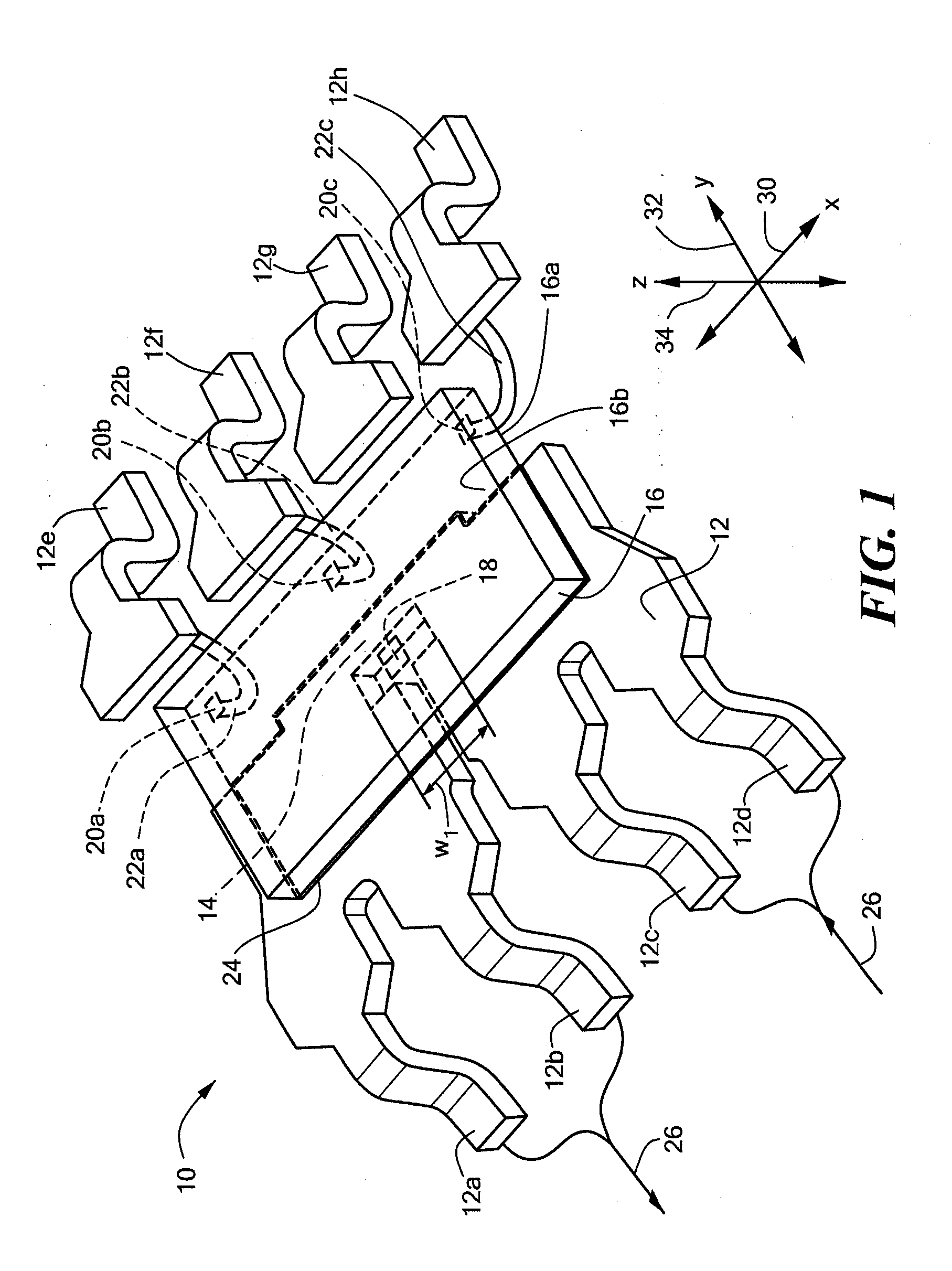

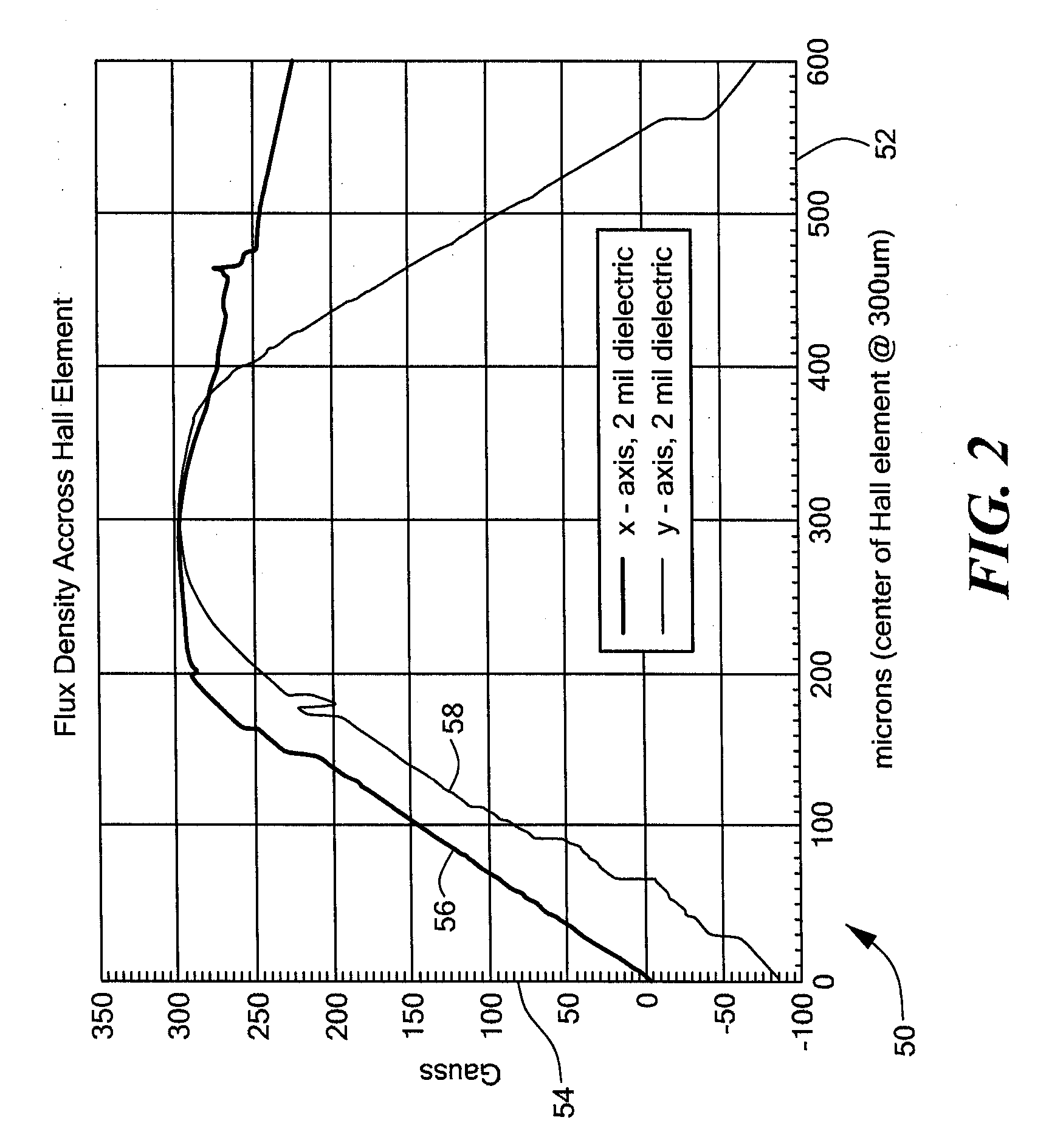

Current sensor

ActiveUS20050045359A1High sensitivitySemiconductor/solid-state device detailsSolid-state devicesElectrical conductorCurrent sensor

An integrated circuit current sensor includes a lead frame having at least two leads coupled to provide a current conductor portion, and substrate having a first surface in which is disposed one or more magnetic field transducers, with the first surface being proximate the current conductor portion and a second surface distal from the current conductor portion. In one particular embodiment, the substrate is disposed having the first surface of the substrate above the current conductor portion and the second surface of the substrate above the first surface. In this particular embodiment, the substrate is oriented upside-down in the integrated circuit relative to a conventional orientation. With this arrangement, a current sensor is provided for which the one or more magnetic field transducers are very close to the current conductor portion, resulting in a current sensor having improved sensitivity.

Owner:ALLEGRO MICROSYSTEMS INC

Universal lead frame type of quad flat non-lead package of semiconductor

InactiveUS6246111B1Semiconductor/solid-state device detailsSolid-state devicesSemiconductor packageLead frame

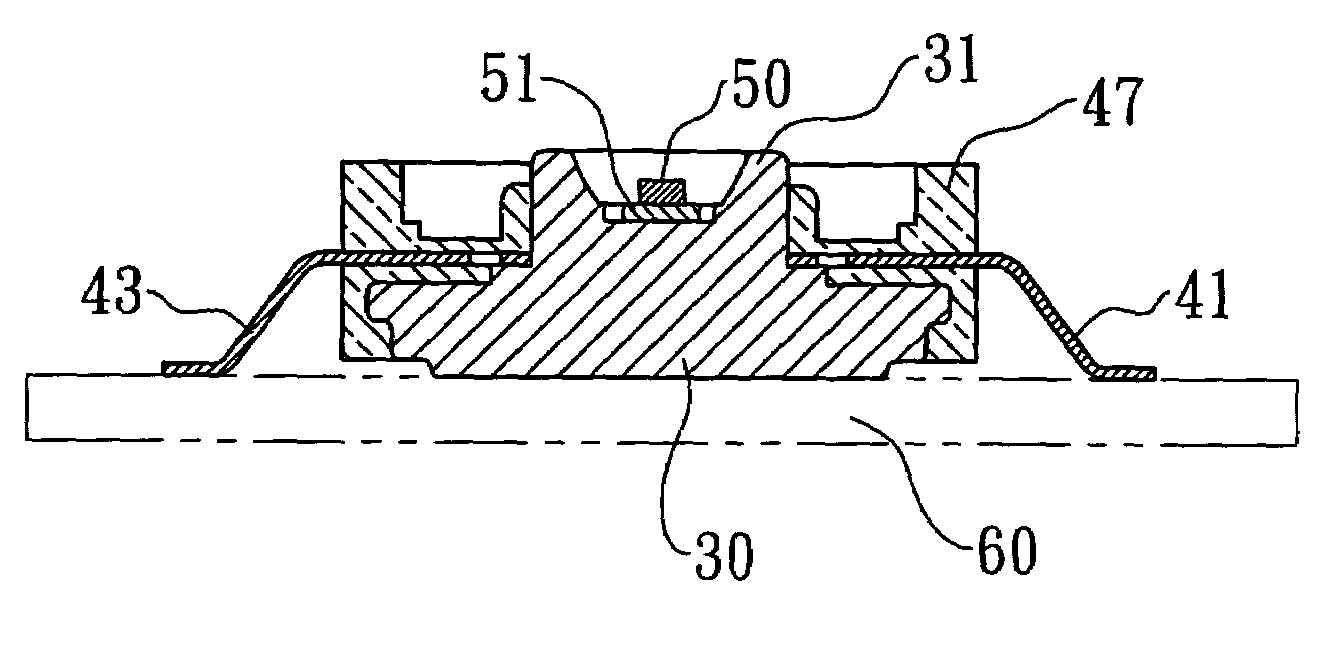

An universal lead frame type of Quad Flat Non-Lead package of semiconductor comprises a chip, a plurality of leads, a heat sink, and a molding compound. The leads are disposed at the periphery of the chip. The chip has its back surface bonded to the top surface of the heat sink, and the periphery of the top surface of the heat sink has a plurality of projections. The bonding portion at the periphery on the bottom surface of the heat sink is bonded to the top surface of the leads. The protruded portion at the center of the bottom surface of the heat sink is disposed in the opening region such that the bottom surface of the heat sink and the bottom surface of the leads are coplaner. The bonding pads of the chip are electrically connected to the top surface of the leads by a plurality of bonding wires. The molding compound encapsulates the chip, the heat sink, the top surface of the leads, and the bonding wires while exposes the protruded portion of the heat sink.

Owner:SILICONWARE PRECISION IND CO LTD

Solid-state semiconductor light emitting device

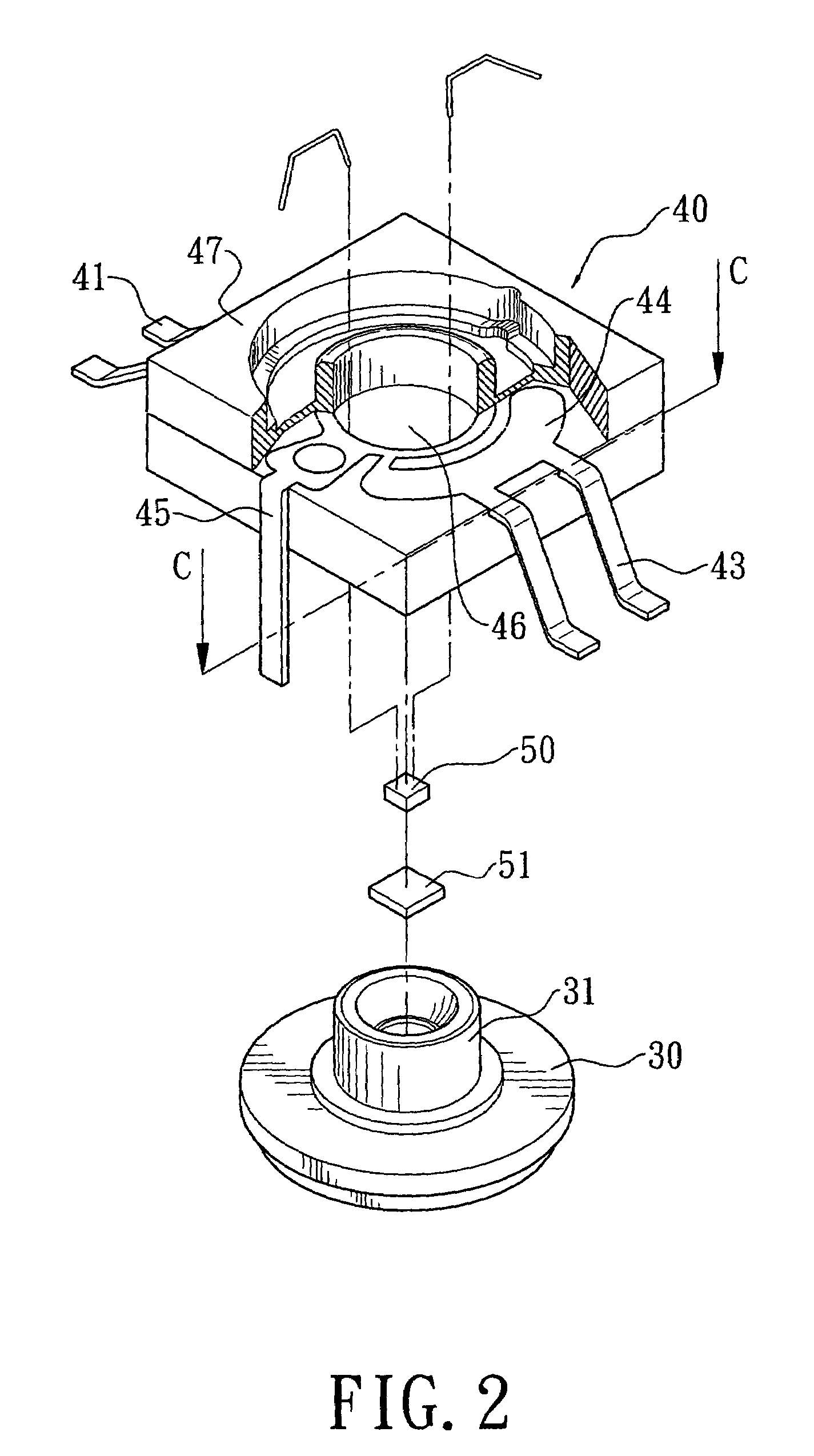

ActiveUS7119422B2Increase cooling areaImprove connection stabilitySemiconductor/solid-state device detailsLighting heating/cooling arrangementsPlastic materialsLead frame

Owner:EPISTAR CORP

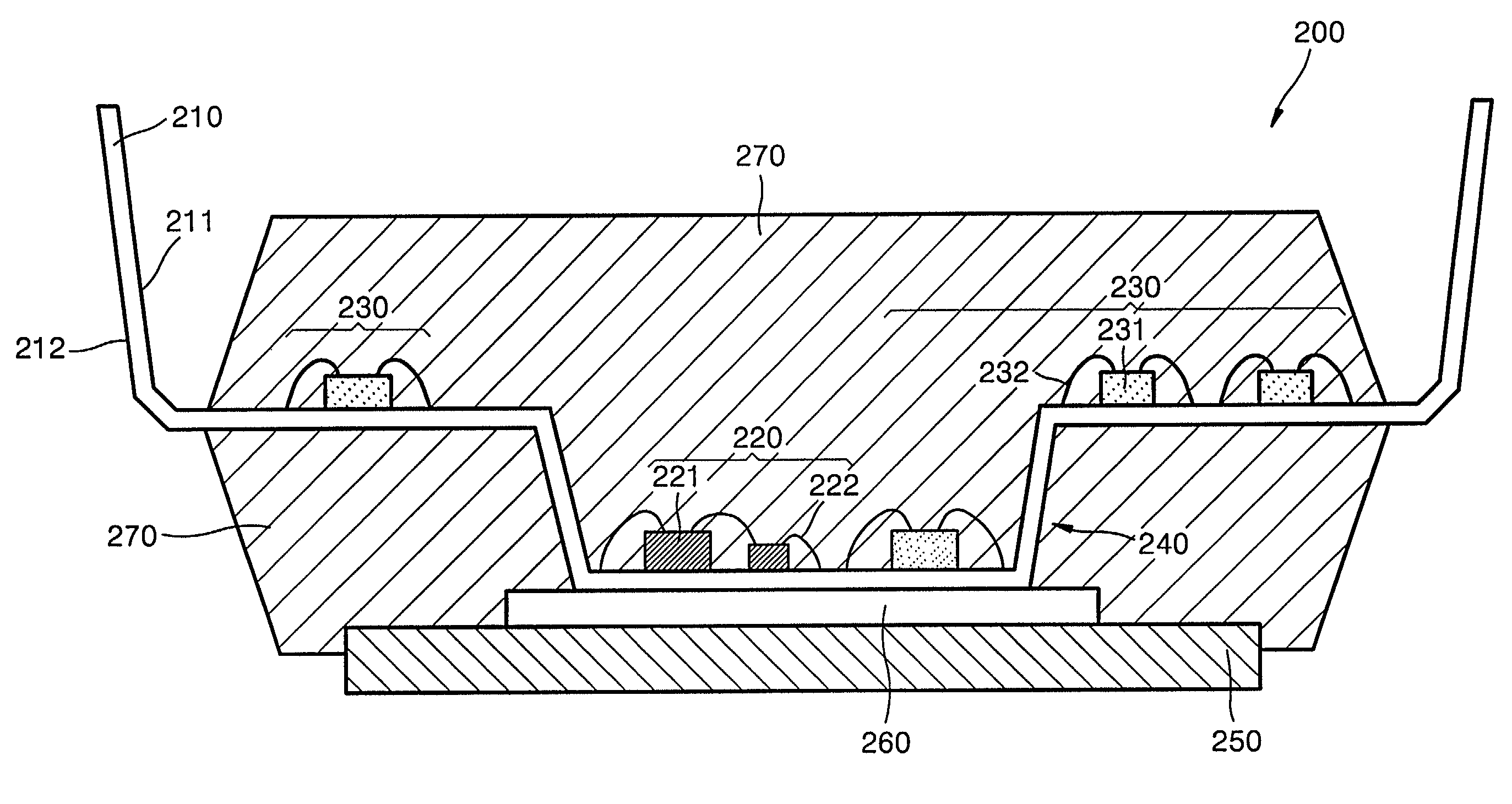

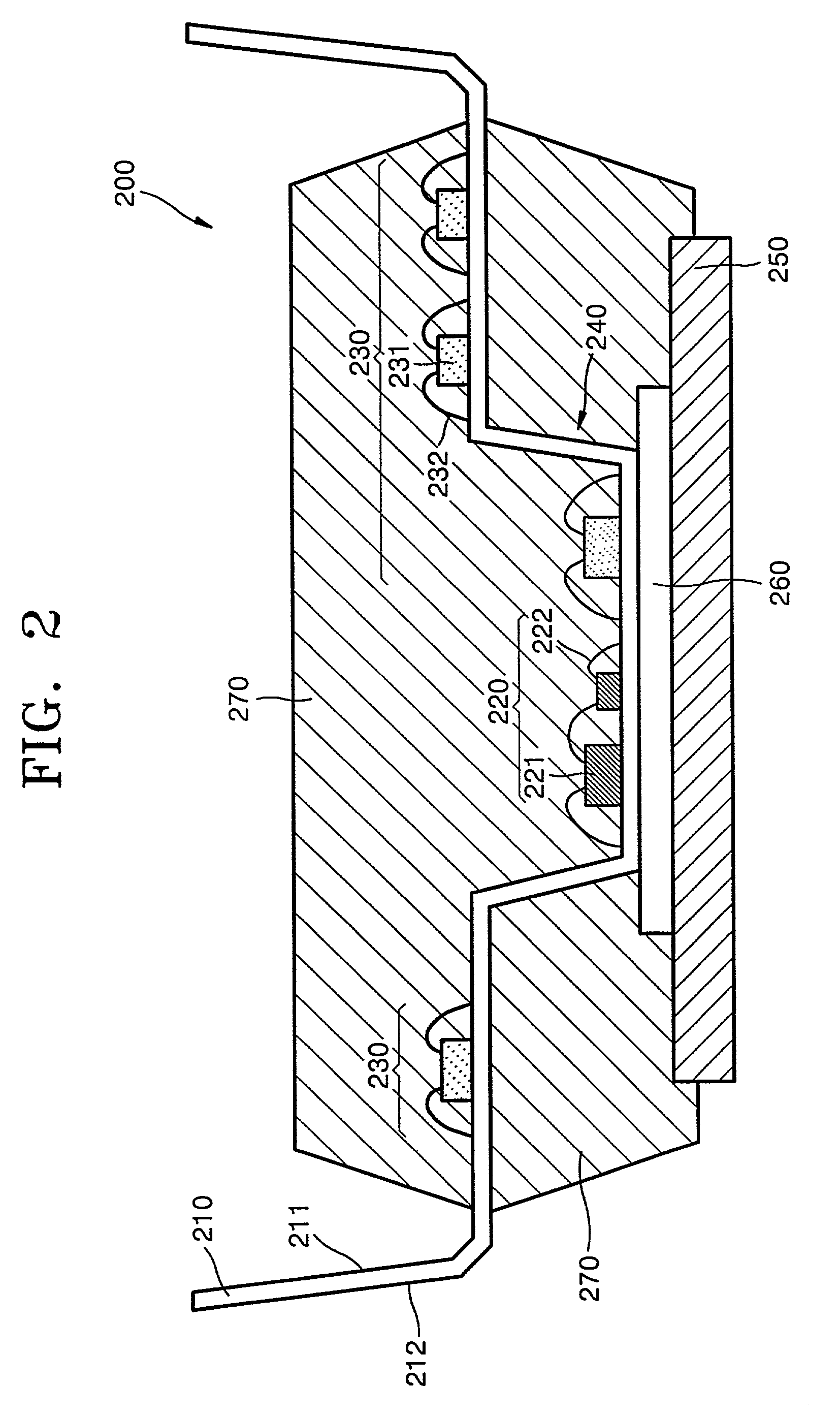

Method of packaging a device with a lead frame, and an apparatus formed therefrom

InactiveUS6828663B2Semiconductor/solid-state device detailsSolid-state devicesLead frameBiomedical engineering

A method of packaging a device and an apparatus formed by the method. According to one embodiment, the apparatus includes a base connected to the device, and a cover. The cover includes an injection molded plastic body and at least one electrically conductive lead. The body of the cover is connected to the base such that the device is enclosed by the cover, and the electrically conductive lead includes an exposed portion that is electrically connected to the device.

Owner:TELEDYNE DEFENSE ELECTRONICS LLC

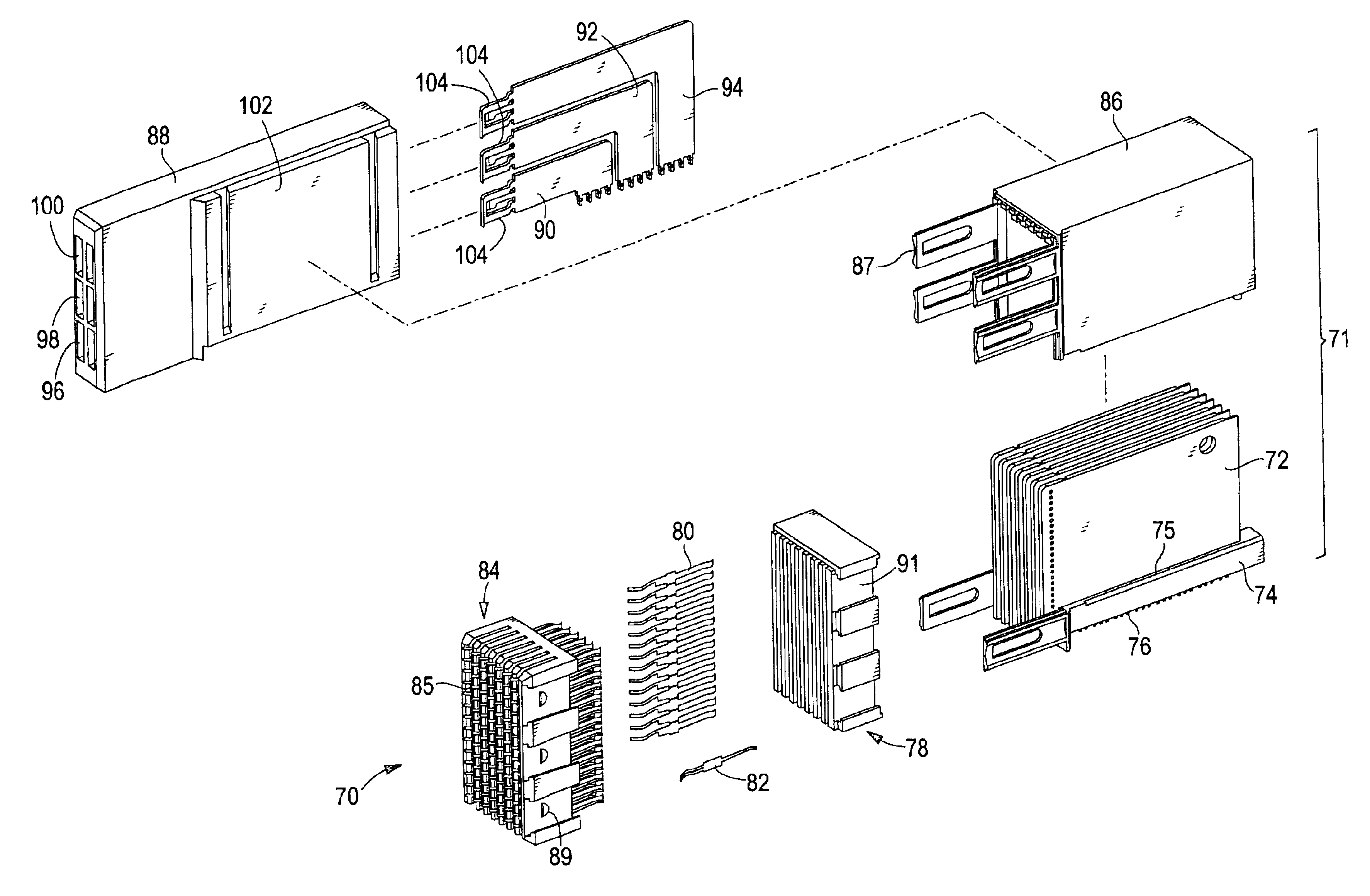

Power module package having improved heat dissipating capability

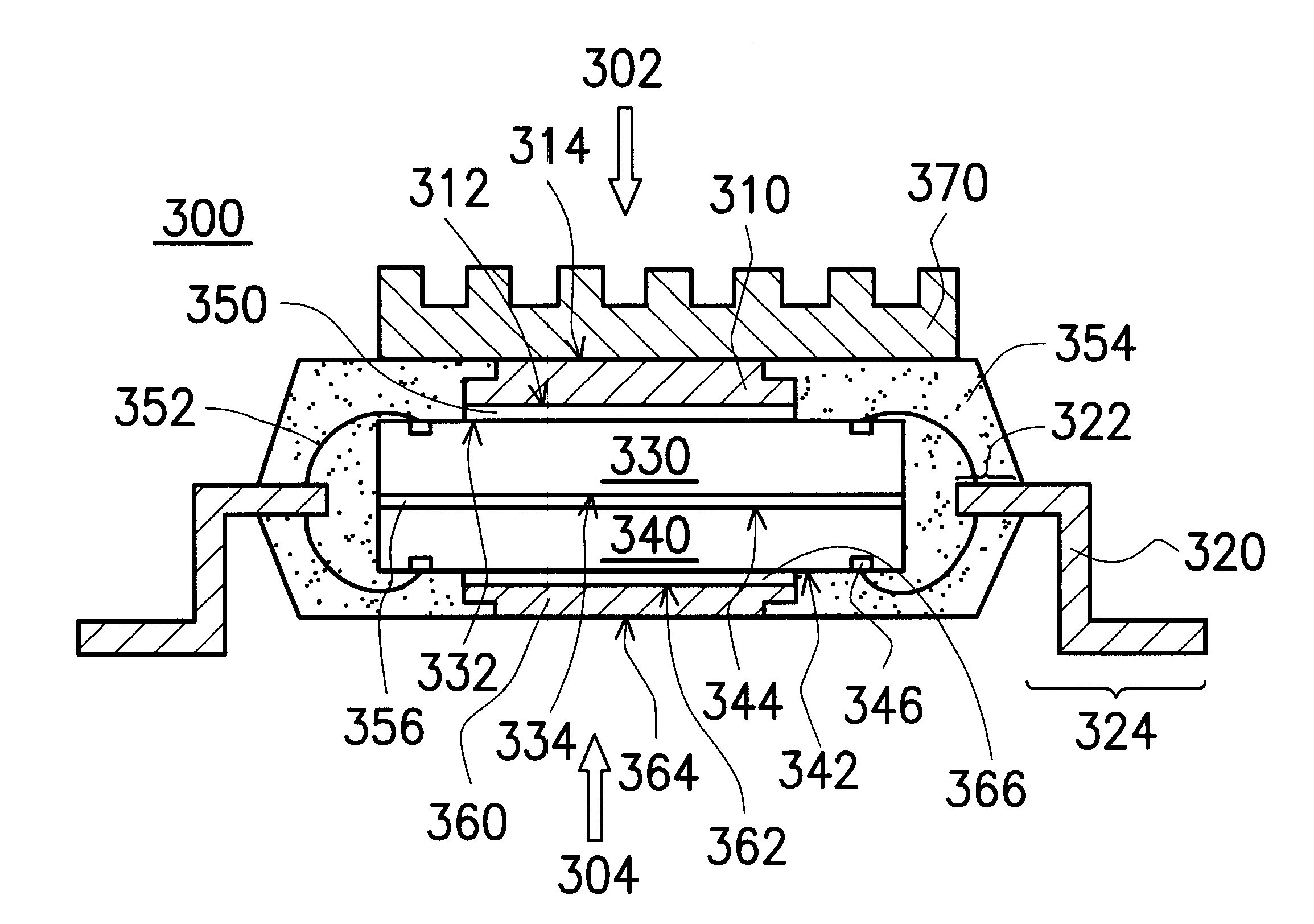

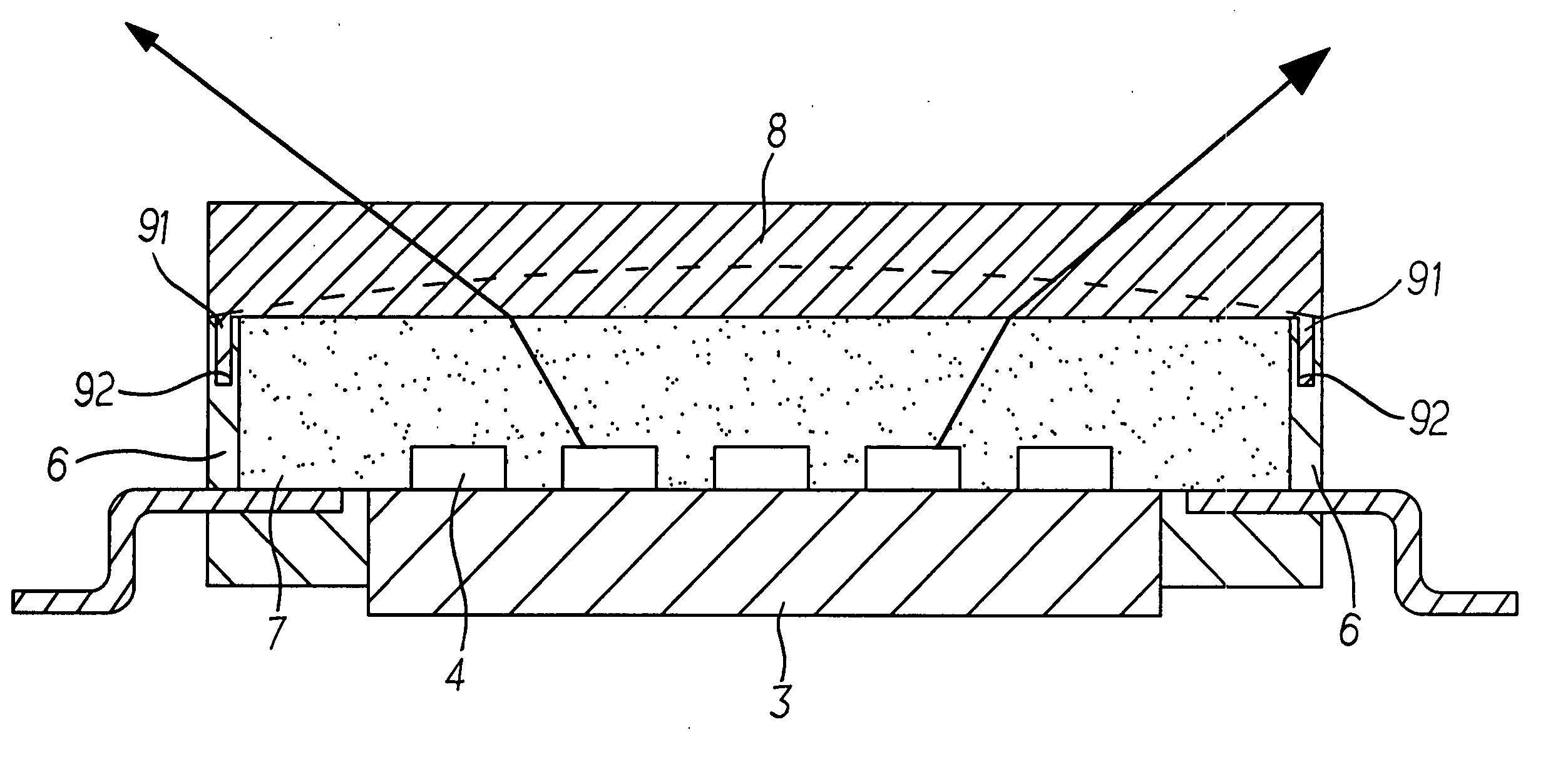

InactiveUS7061080B2Efficiently dissipatedSimpler and cheap to manufactureSemiconductor/solid-state device detailsSolid-state devicesAdhesiveEngineering

A power module package is provided. The power module package includes a power circuit element, a control circuit element, a lead frame, a heat sink, and an epoxy molding compound (EMC). The control circuit element is connected to the power circuit and controls chips in the power circuit. The lead frame has external connecting means formed at the edges thereof, and a down set part, namely, formed between the external connecting means. The lead frame has a first surface to which the power circuit and the control circuit are attached, and a second surface used as a heat dissipating path, in particular, the power circuit is attached to the down set part. The heat sink which is closely attached to the down set part of the second surface of the lead frame by an adhesive. The EMC surrounds the power circuit, the control circuit, the lead frame and the heat sink, and exposes the external connecting means of the lead frame and a side of the heat sink.

Owner:SEMICON COMPONENTS IND LLC

Multi-sequenced contacts from single lead frame

InactiveUS6890214B2Electrically conductive connectionsContact member assembly/disassemblyEngineeringLead frame

An electrical connector assembly comprising a housing having an interior chamber defining at least one lead frame plane, and identical sets of non-identical lead frame elements. The lead frame plane has a reference point. The lead frame elements are mounted in the interior chamber and aligned within at least one lead frame plane. The lead frame elements are adjustable along the lead frame plane between multiple levels with respect to the reference point. The multiple mating levels of the lead frame elements are created from only one lead frame. The mating levels are selected by the individual lead frame elements being positioned with respect to the reference point. The electrical connector also comprises N lead frame elements, each of which is adjustable between M mating levels to form X lead frame configurations, wherein X=MN.

Owner:TYCO ELECTRONICS LOGISTICS AG (CH)

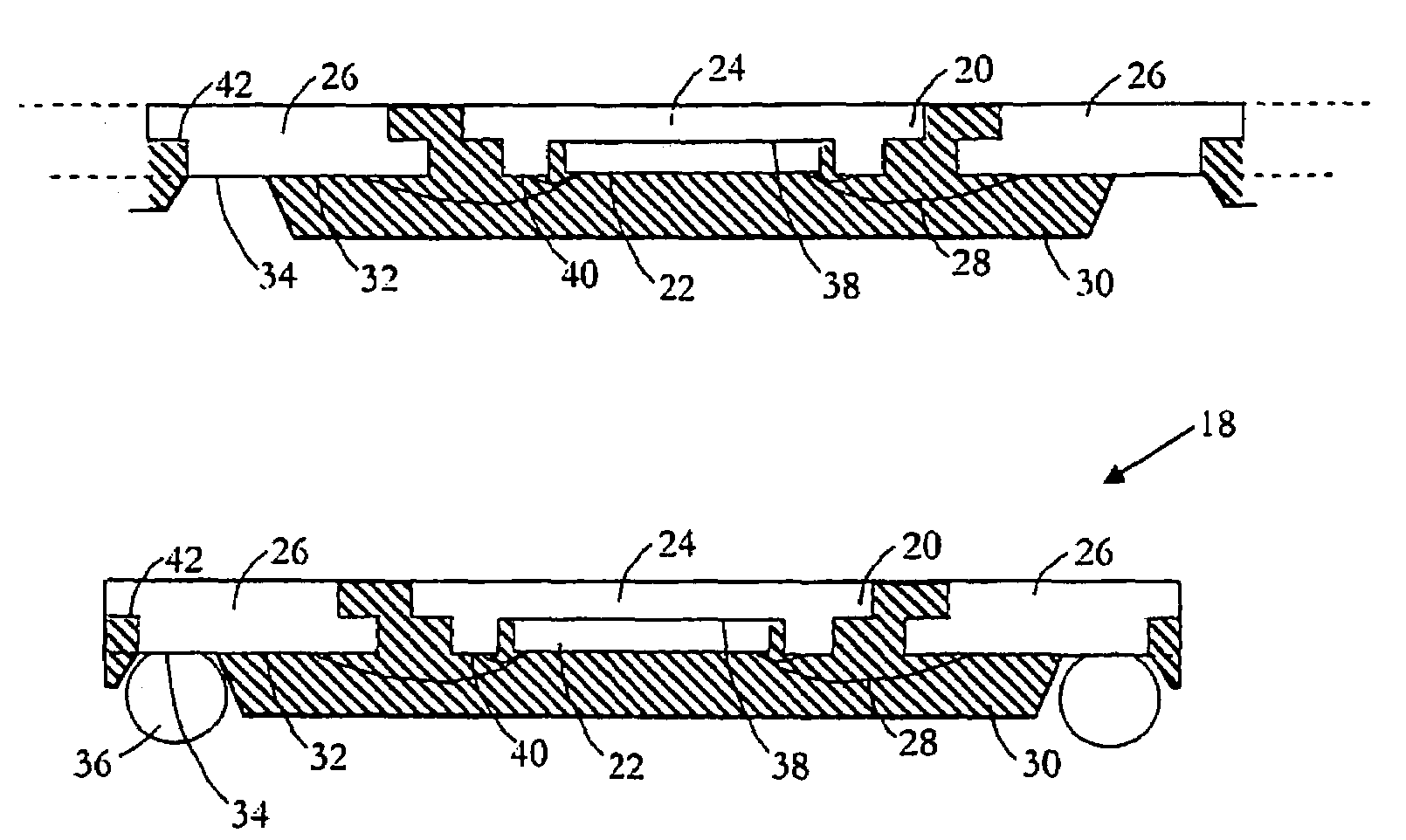

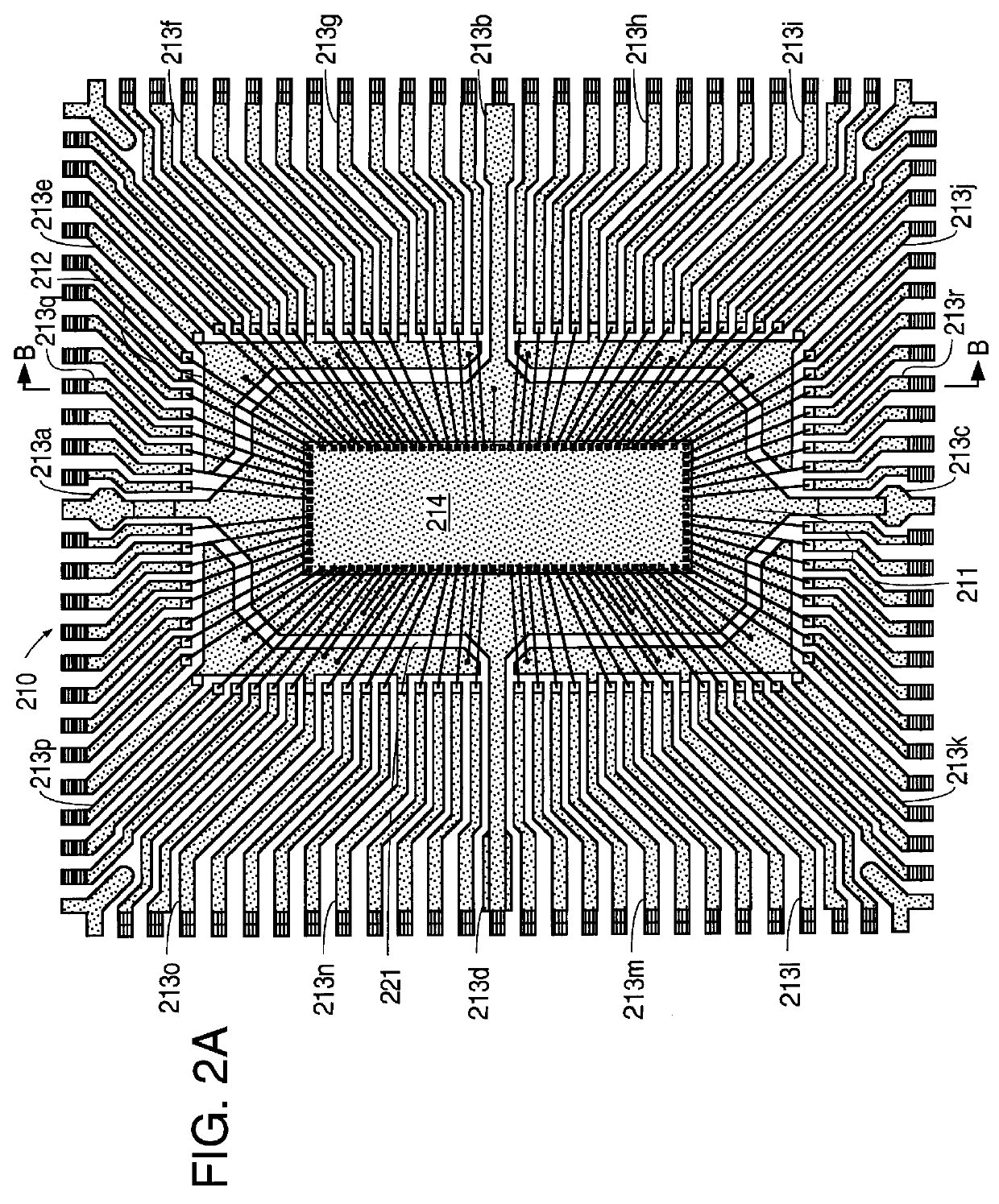

Integrated circuit package and process for fabricating the same

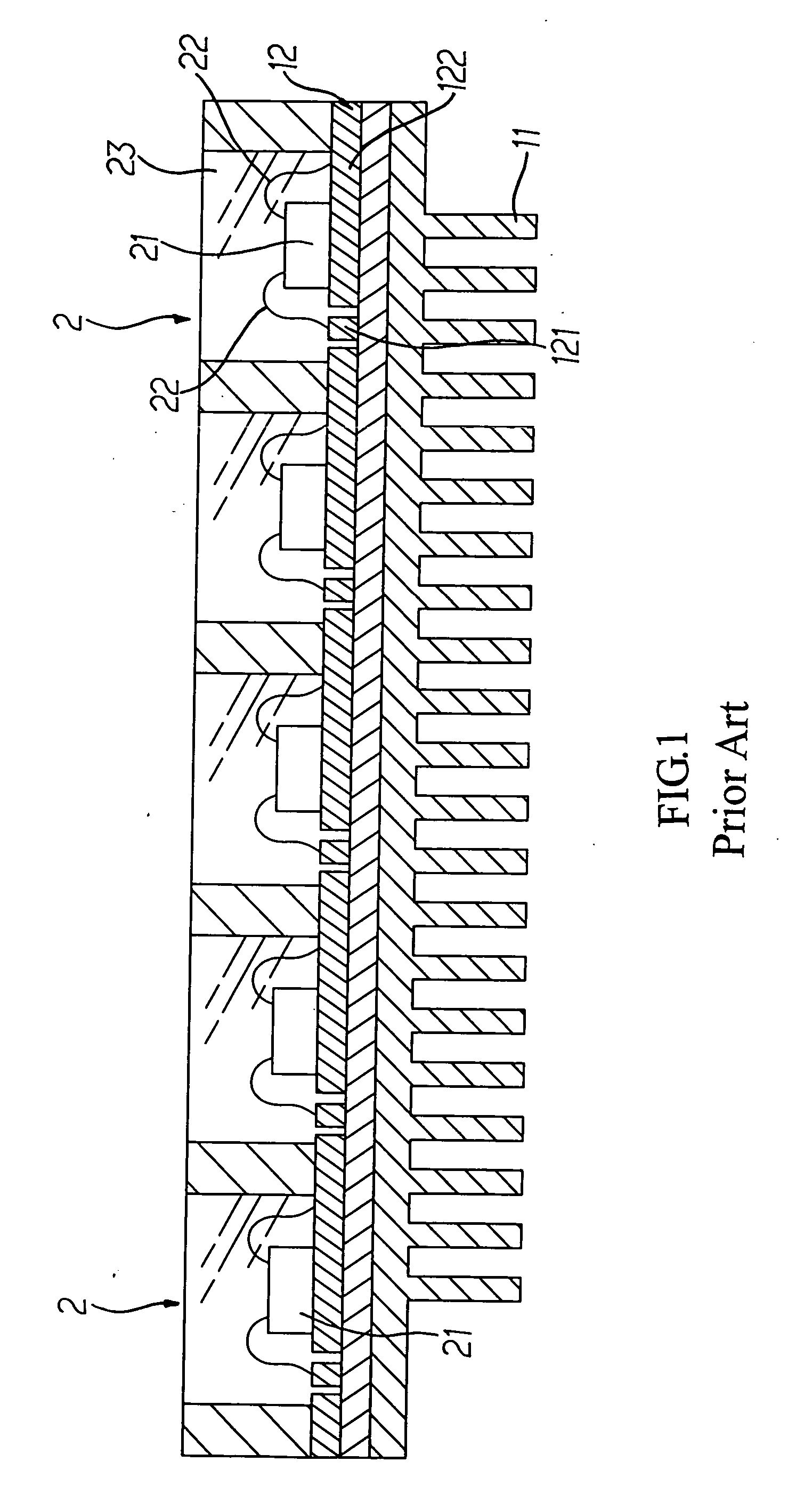

ActiveUS7091581B1Improve thermal characteristicsReduce generationSemiconductor/solid-state device detailsSolid-state devicesContact padLead bonding

A process for fabricating an integrated circuit package includes: selectively etching a leadframe strip to define a die attach pad and at least one row of contact pads; mounting a semiconductor die to one side of the leadframe strip, on the die attach pad; wire bonding the semiconductor die to ones of the contact pads; releasably clamping the leadframe strip in a mold by releasably clamping the contact pads; molding in a molding compound to cover the semiconductor die, the wire bonds and a portion of the contact pads not covered by the clamping; releasing the leadframe strip from the mold; depositing a plurality of external contacts on the one side of the leadframe strip, on the contact pads, such that the external contacts protrude from the molding compound; and singulating to provide the integrated circuit package.

Owner:UTAC HEADQUARTERS PTE LTD

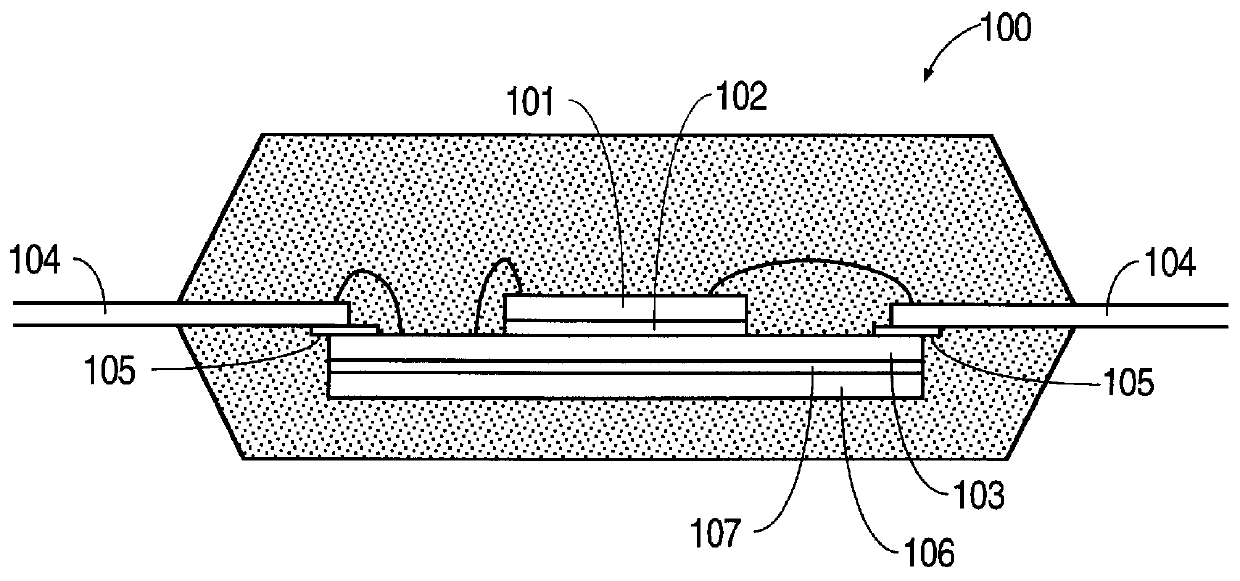

Leadframe with power and ground planes

InactiveUSRE36907E1Reduced effective inductanceReduce crosstalkSemiconductor/solid-state device detailsSolid-state devicesVoltage sourceLead frame

A leadframe for use in an integrated circuit package is described. The leadframe comprises a plurality of electrically conductive leads, a die attach pad, and an electrically conductive ring or rings formed generally around the circumference of the die attach pad and between the die attach pad and leads. In one embodiment, at least one of the leads is formed integrally with each ring. The die attach pad may also be formed integrally with one or more leads. In another embodiment, the ring or rings are formed so that they are electrically isolated from the die attach pad, and the die attach pad, leads, and ring or rings are all formed in substantially the same plane. In some embodiments, the ring or rings are broken into electrically isolated sections. Each of the ring sections (and die attach pad, if appropriate) may be electrically connected to a voltage source outside the integrated circuit package (e.g., a power supply or ground). The leadframe is formed from a single sheet of material by, for instance, stamping or etching. The leadframe may be used in either ceramic or plastic packages. The leadframe reduces switching noise and crosstalk, allows more flexibility in placement of power and / or ground bond pads on the die, and allows provision of ground and power planes in an integrated circuit package that is thinner than previous integrated circuit packages containing both ground and power planes.

Owner:INTEGRATED DEVICE TECH INC

Leadless integrated circuit package having electrically routed contacts

A leadless integrated circuit (IC) package comprising an IC chip mounted on a metal leadframe and a plurality of electrical contacts electrically coupled to the IC chip. The IC chip, the electrical contacts, and a portion of the metal leadframe are covered with an encapsulation compound, with portions of the electrical contacts exposed on a bottom surface of the encapsulation compound. The electrical contacts of the IC package having metal traces connecting bonding areas on a top surface thereof and contact areas on a bottom surface thereof, wherein at least some of the bonding areas are laterally disposed from the contact areas connected thereto.

Owner:KAIXIN INC

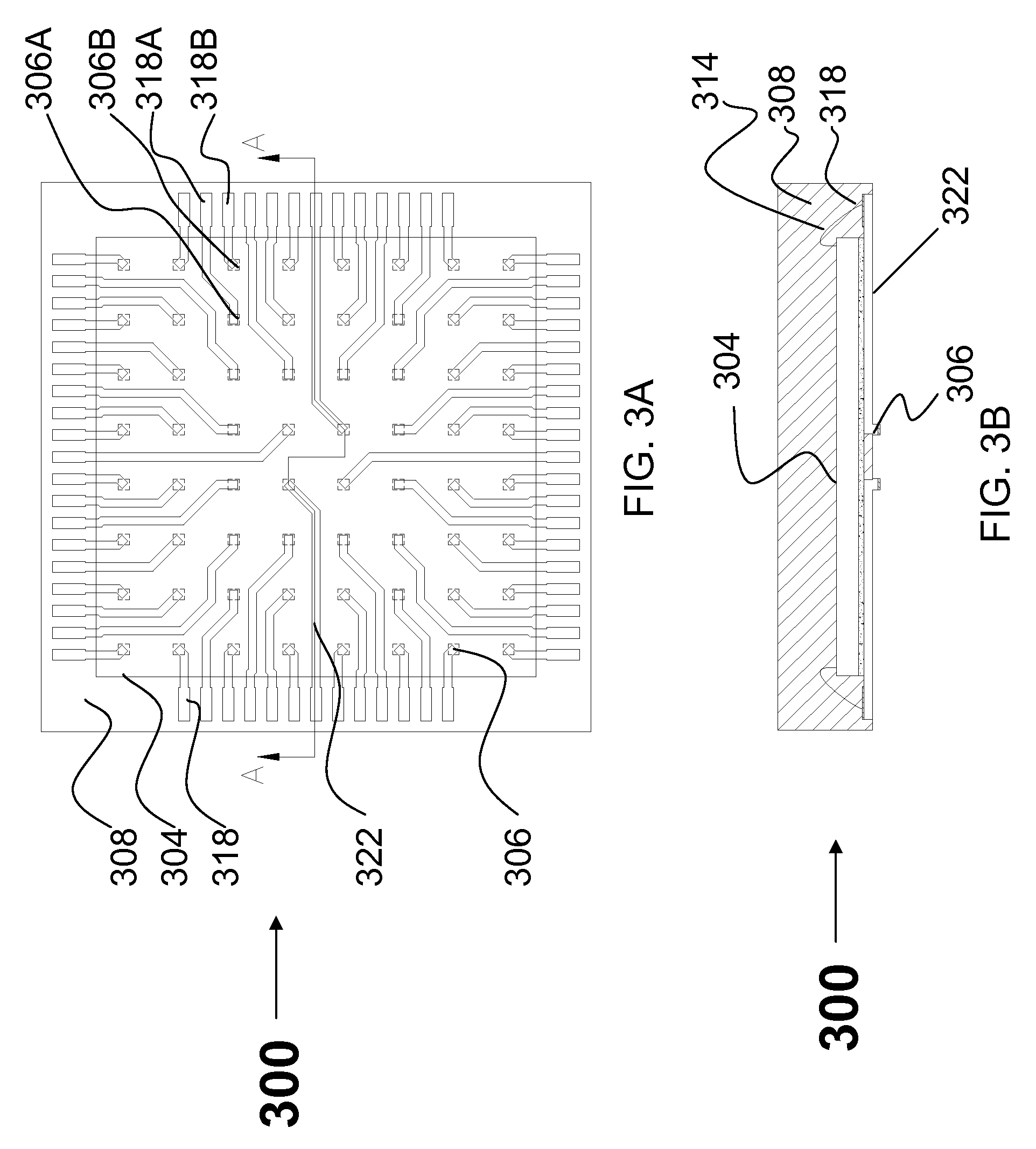

Electrical connector lead frame

InactiveUS20090239395A1Printed circuitsCoupling protective earth/shielding arrangementsHigh densityLight beam

An electrical interconnection system with high speed, high density electrical connectors. The connector is assembled from wafers containing columns of conductive elements, held in an insulative housing. The conductive elements may each have a plurality of beams of different lengths such that the mating contact surfaces of the first beam are offset, in a direction perpendicular with the columns, from the mating contact surfaces of the second beam. The mating contact surface of the shorter beam of each conductive element may be behind the mating contact of the longer beam such that the width of the conductive element is reduced while still protecting the shorter beam from stubbing upon connector mating. The multi-beam conductive elements may be used as signal or ground conductors.

Owner:AMPHENOL CORP

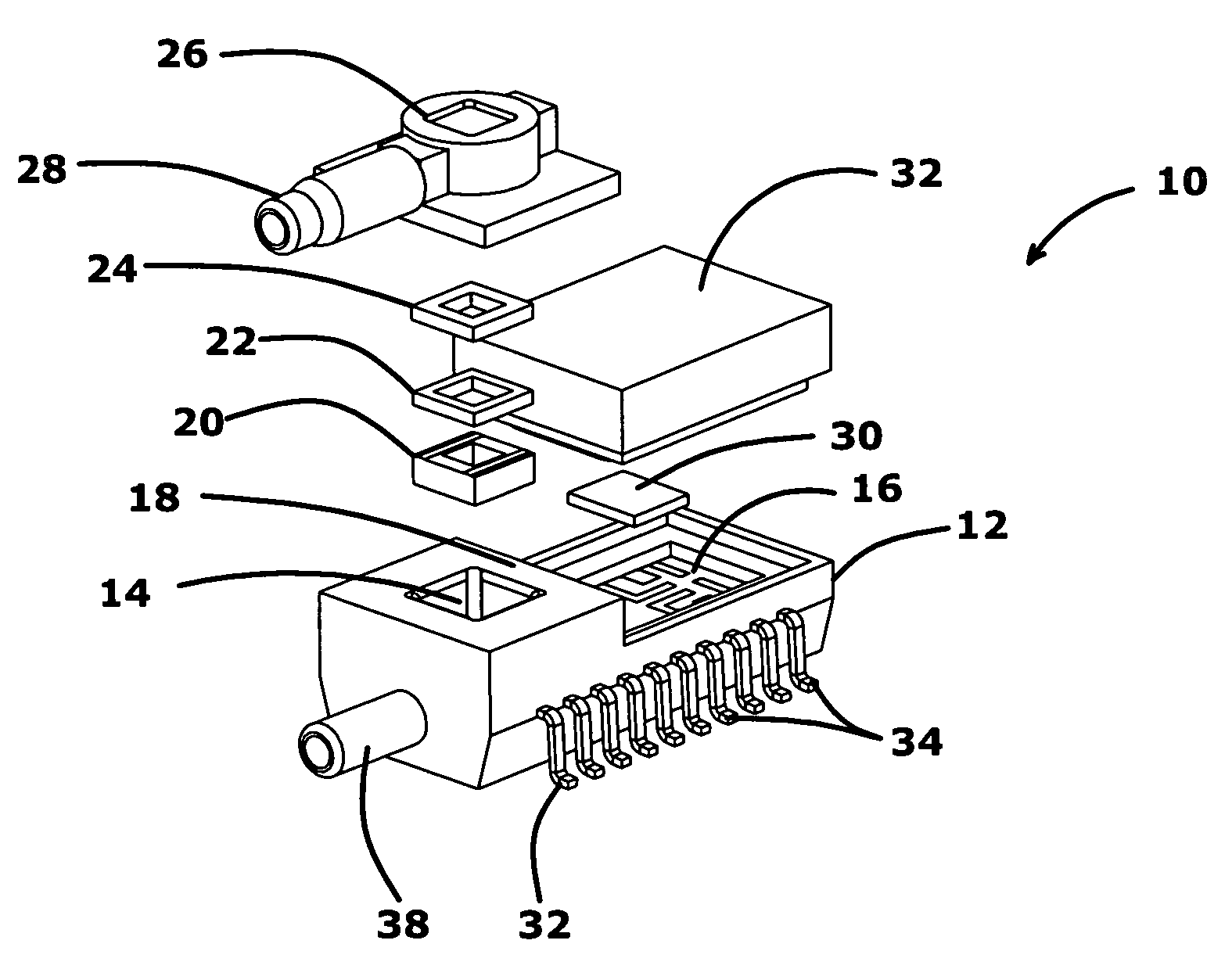

Design of a wet/wet amplified differential pressure sensor based on silicon piezoresistive technology

InactiveUS7162927B1Fluid pressure measurement by electric/magnetic elementsFluid pressure measurement by mechanical elementsAudio power amplifierHermetic seal

The invention provides pressure sensors for use in wet environments. A pressure sensor package according to the invention has a housing having a pair of cavities separated by a wall member. Sequentially contained within one cavity is a conductive elastomeric seal pad, a pressure sensor and an elastomeric media seal. A pressure cap is attached to the housing such that the pressure cap and the housing together form a hermetic seal. The pressure cap has a port for admitting a gas under pressure into the first cavity. A signal amplifier is positioned within the second cavity and a cover encloses the signal amplifier within the second cavity. An electrical connector through the wall member forms an electrical connection between the pressure sensor and the signal amplifier. A lead frame extends through the housing and forms electrical connections with the pressure sensor and the signal amplifier.

Owner:HONEYWELL INT INC

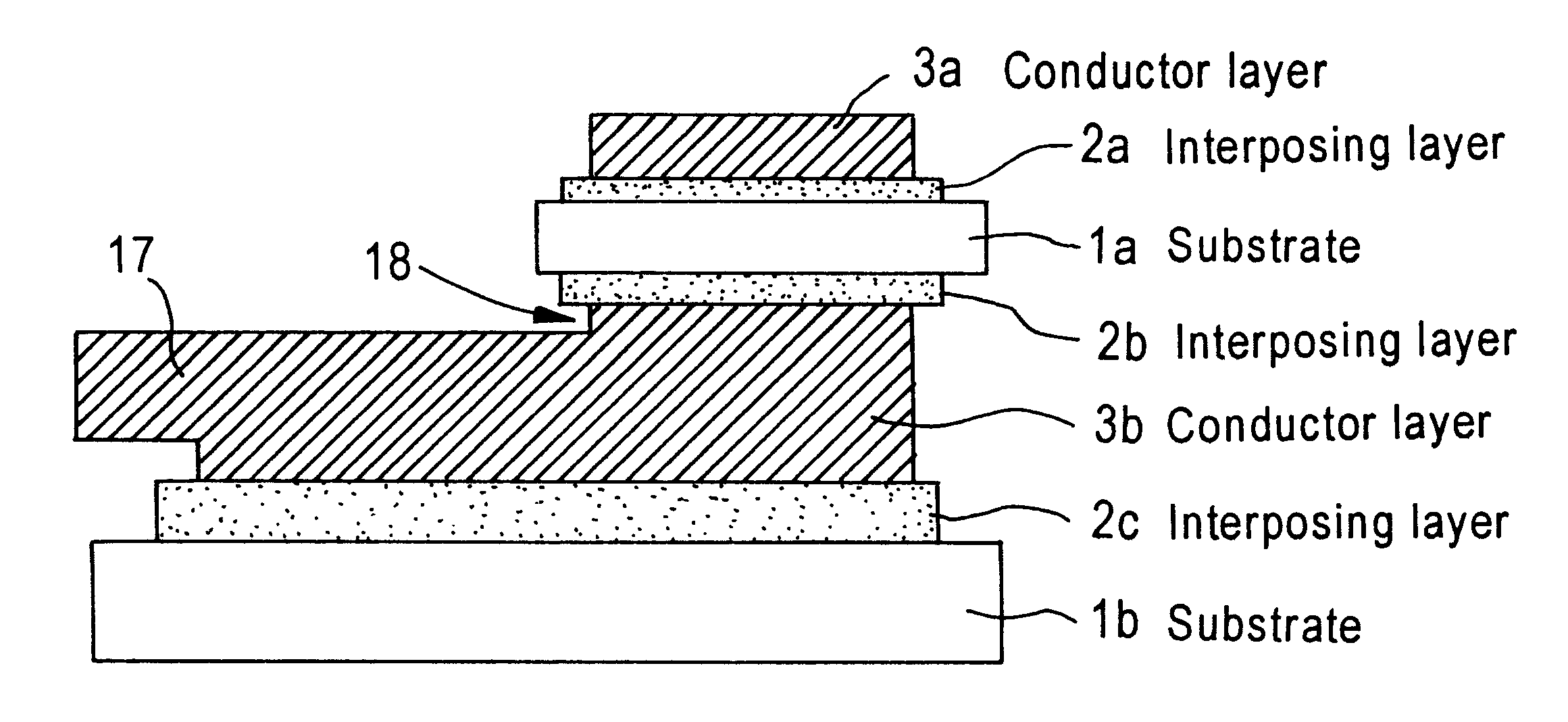

Copper circuit junction substrate and method of producing the same

InactiveUS6261703B1Avoid discharge phenomenonHigh concentration of thermal stressInsulating substrate metal adhesion improvementSemiconductor/solid-state device detailsElectrical conductorCopper oxide

A highly reliable copper circuit-joined board that, in mounting a semiconductor element, a lead frame or the like on a ceramic substrate, enables the semiconductor element, the lead frame or the like to be strongly joined to the substrate without breaking or deformation of the substrate found in conventional joining methods, such as brazing and joining using a copper / copper oxide eutectic crystal. Any one of an interposing layer comprising a brazing material layer comprising silver and / or copper as a main component and an active metal or an interposing layer having a two-layer structure comprising a first interposing layer comprising the brazing material layer or a high-melting metallizing layer and a second interposing layer, having a melting point of 1000.degree. C. or below, comprising Ni, Fe, Cu as a main component in that order from the substrate side, is formed on a ceramic substrate, and a conductor layer, comprising copper as a main component, which, in both the lengthwise and widthwise directions, is at least 0.05 mm shorter than the interposing layer, is formed on the interposing layer to prepare a copper circuit-joined board. The copper circuit-joined board may comprise the base board having thereon an outer layer comprising Ni as a main component. A semiconductor element is mounted on the copper circuit-joined board to prepare a semiconductor device.

Owner:SUMITOMO ELECTRIC IND LTD

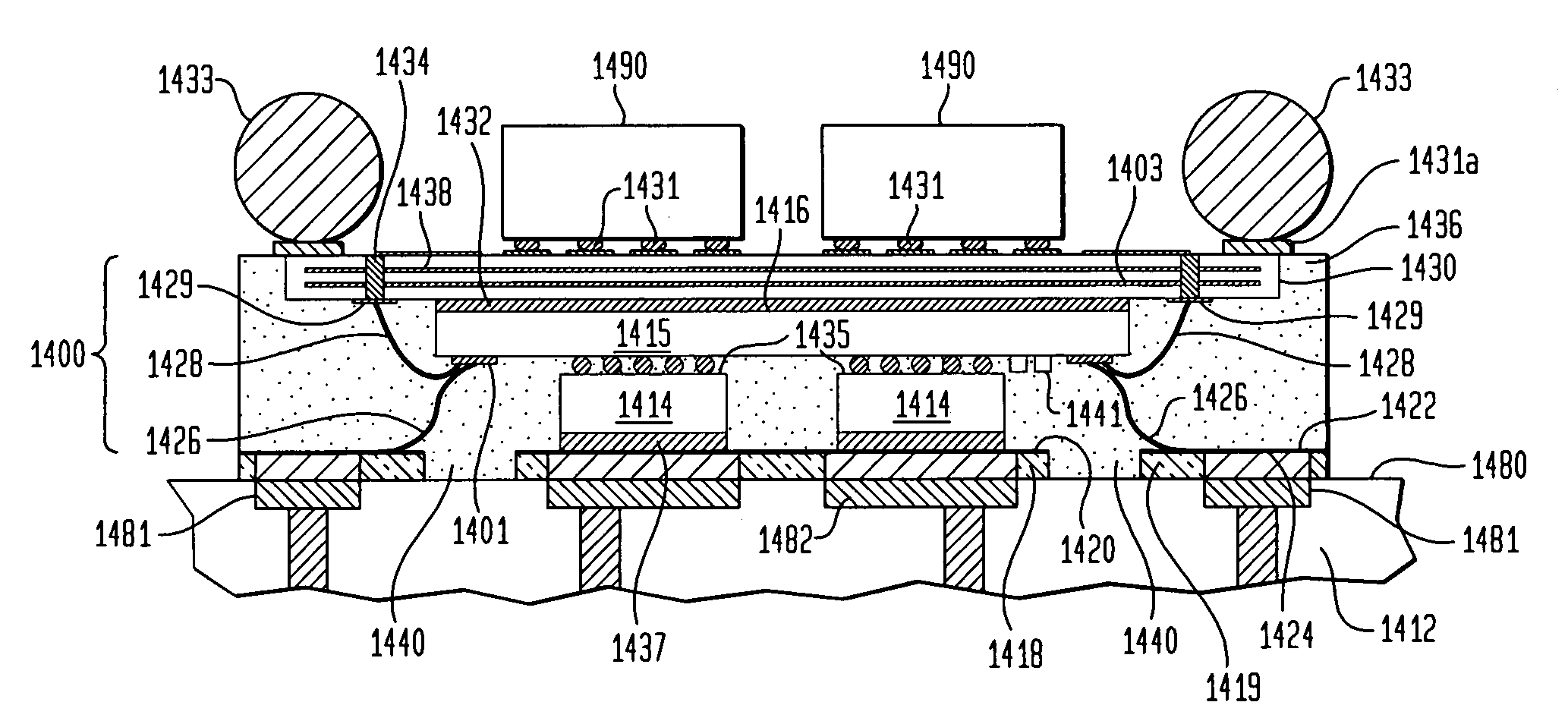

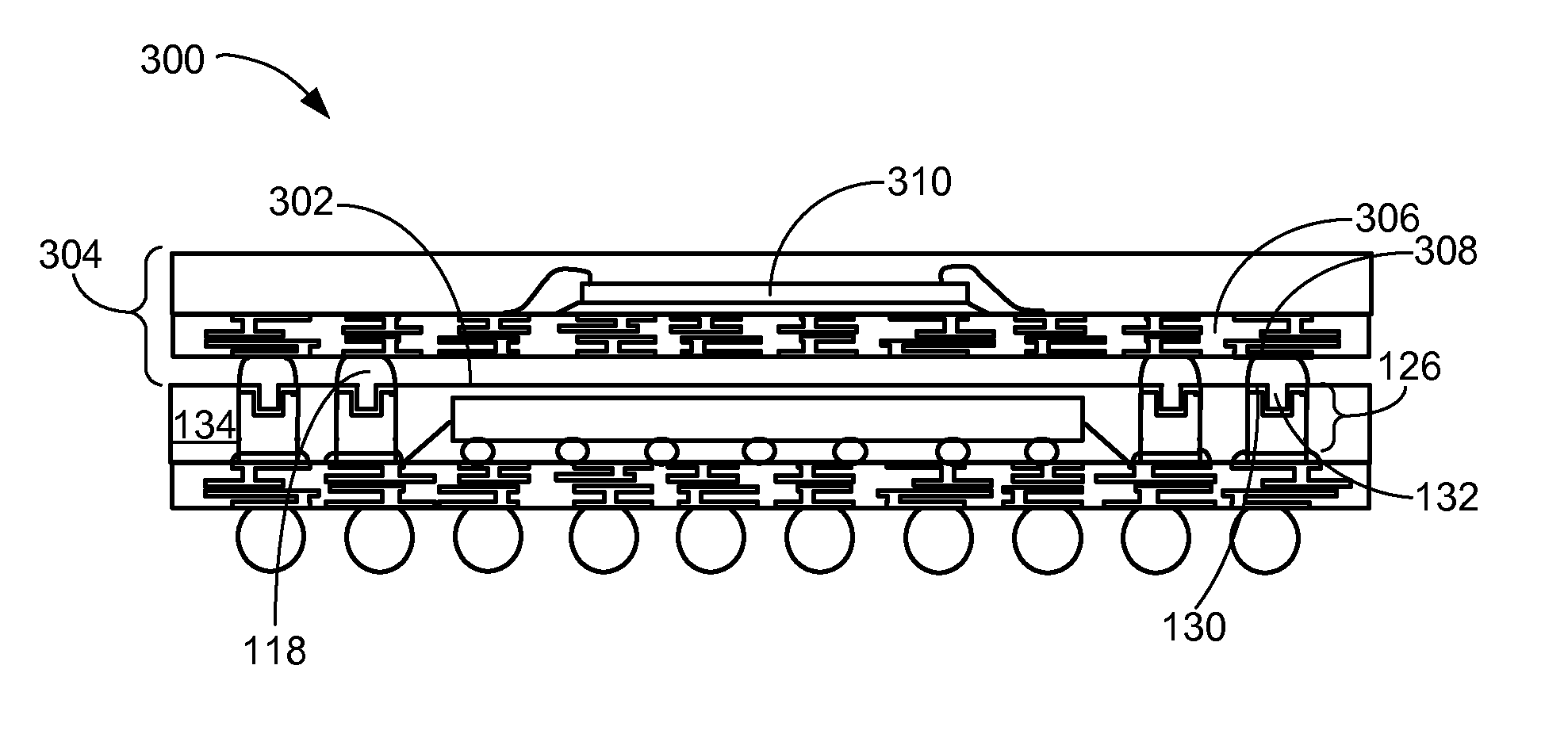

Integrated circuit packaging system with stacking interconnect and method of manufacture thereof

ActiveUS20110140259A1Semiconductor/solid-state device detailsSolid-state devicesConductive materialsLead frame

A method of manufacture of an integrated circuit packaging system includes: fabricating a base package substrate; coupling a conductive column lead frame to the base package substrate by: providing a lead frame support, patterning a conductive material on the lead frame support including forming an interconnect securing structure, and coupling the conductive material to the base package substrate; forming a base package body between the base package substrate and the conductive column lead frame; and removing the lead frame support from the conductive column lead frame for exposing the interconnect securing structure from the base package body.

Owner:STATS CHIPPAC LTD

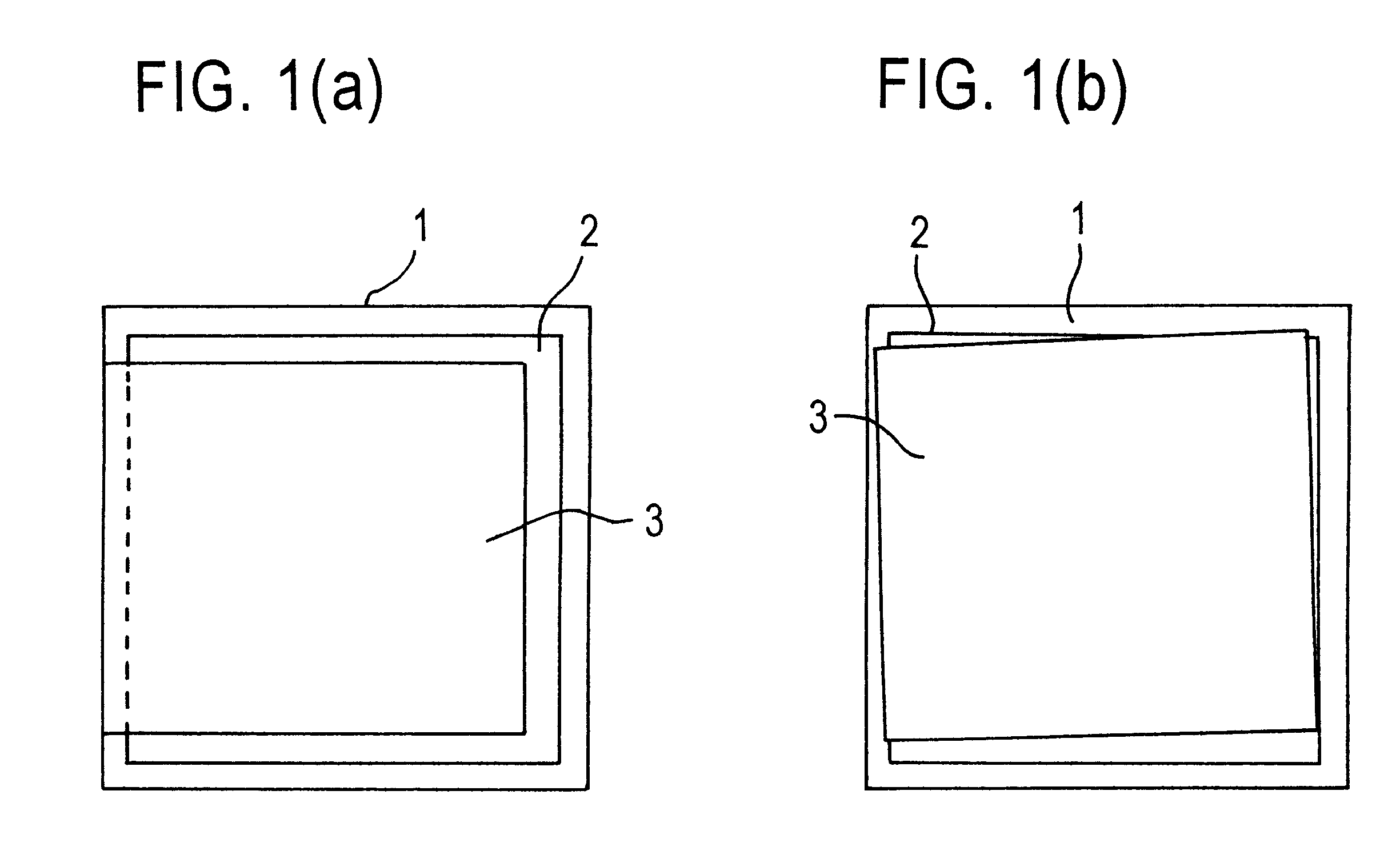

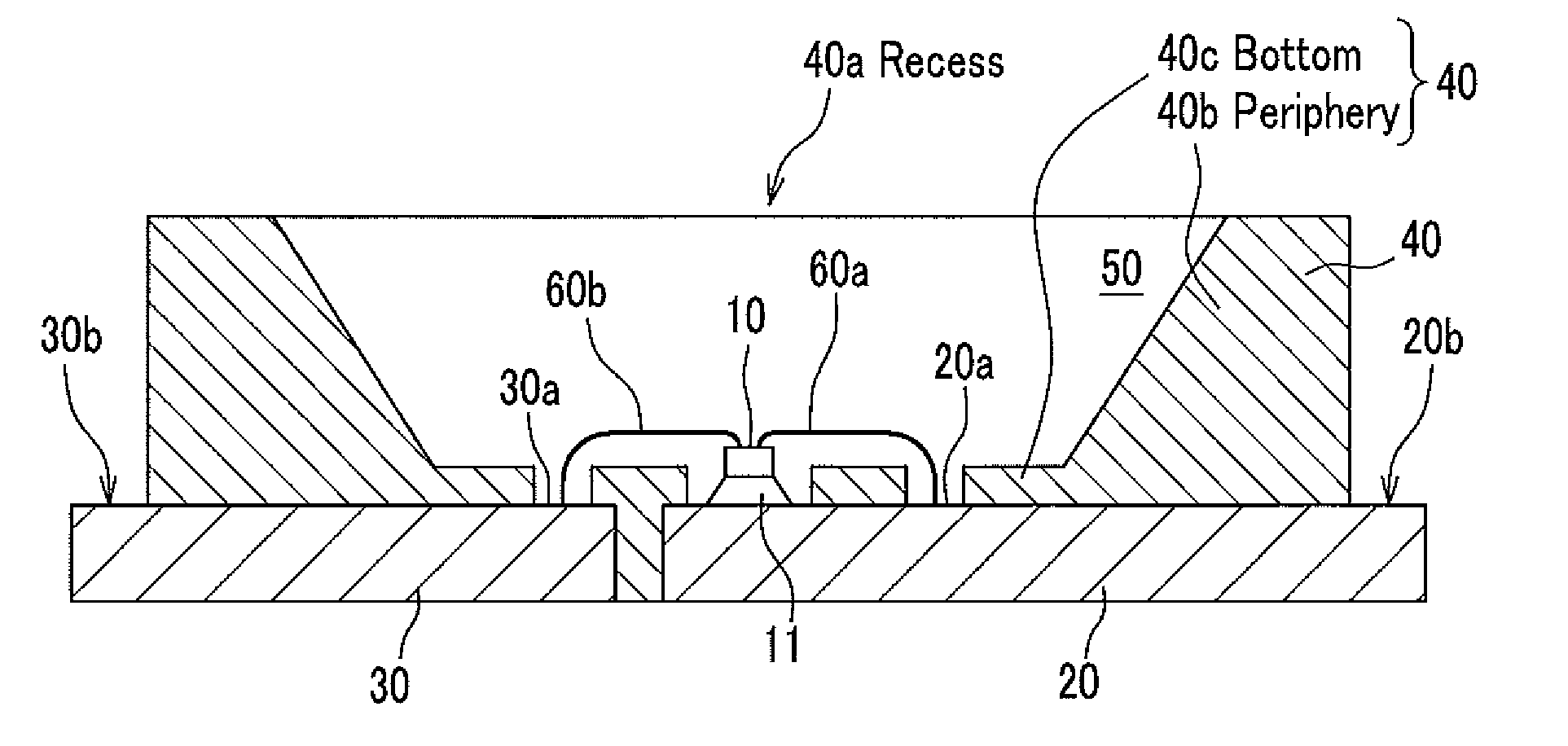

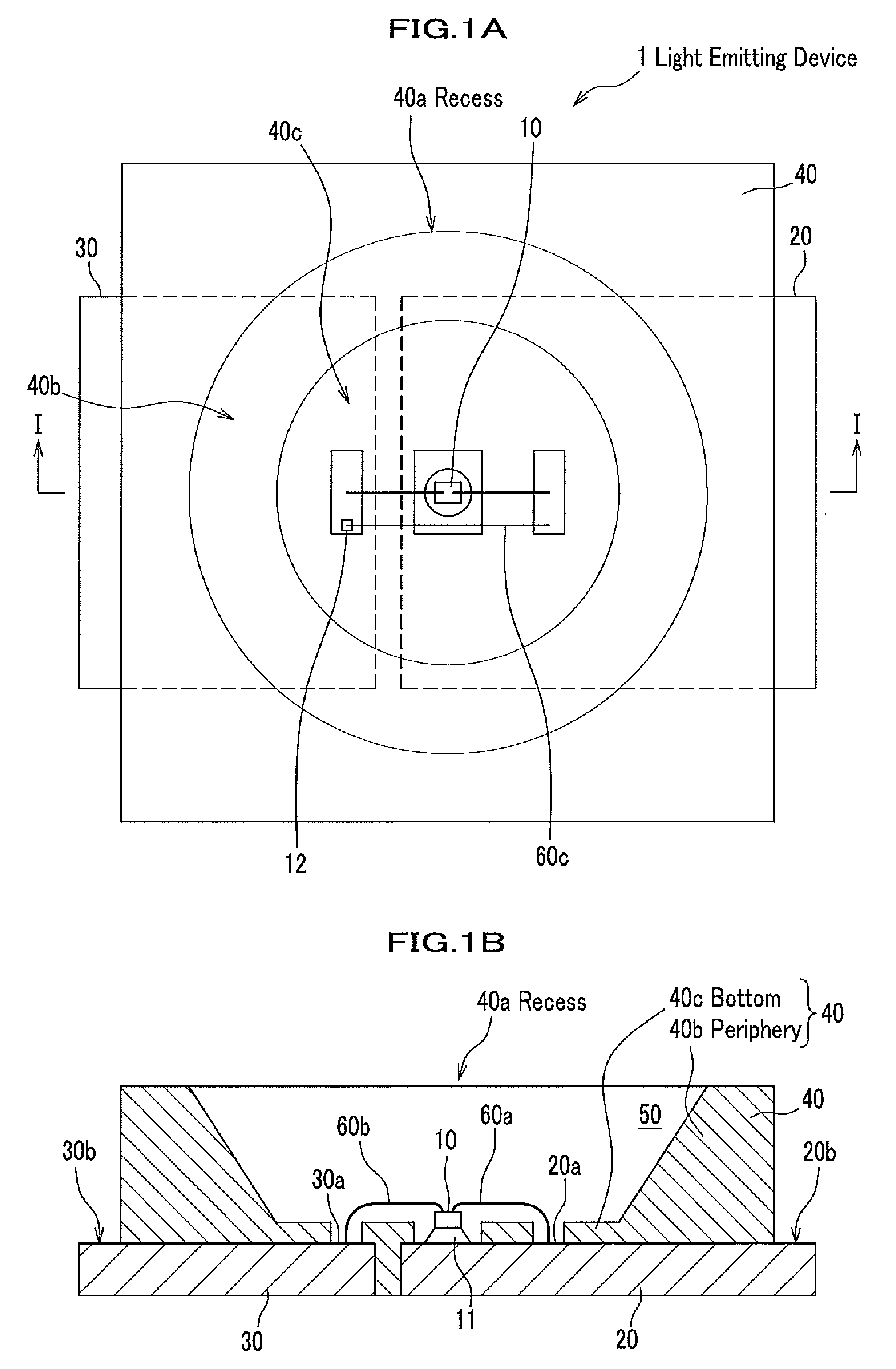

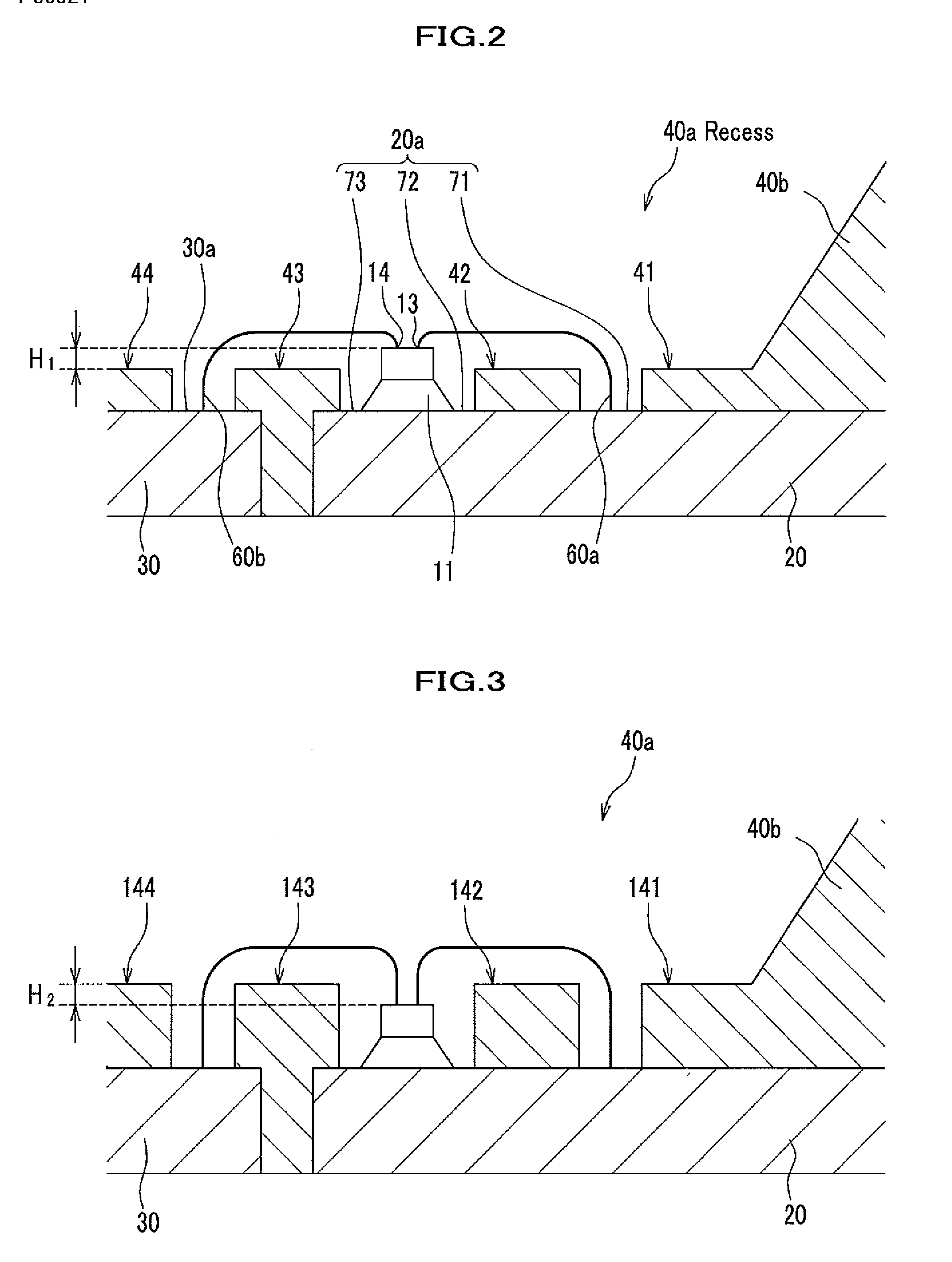

Light emitting device and method for manufacturing the same

ActiveUS20100314654A1Improve luminous performanceEfficient productionSolid-state devicesSemiconductor/solid-state device manufacturingEpoxyEpoxy resin composite

A light emitting device, which can be efficiently manufactured and maintain a stable light emitting property for a long period, is provided. The light emitting device comprises a first resin forming body including a periphery that forms a recess to house a light emitting element and a bottom that forms a bottom portion of the recess, and a second resin forming body which covers the light emitting element. The first resin forming body is composed of a thermosetting epoxy resin composite whose essential component is an epoxy resin. The bottom covers surfaces of lead frames excluding mounting regions of the light emitting element and wires. A thickness of the bottom is formed thinner than a thickness from the surface of the lead frames to a leading end of the light emitting element.

Owner:NICHIA CORP

Current sensor

InactiveUS20060219436A1Reduce eddy currentSemiconductor/solid-state device detailsInstrument screening arrangementsElectrical conductorCurrent sensor

An integrated circuit current sensor includes a lead frame having at least two leads coupled to provide a current conductor portion, and a substrate having a first surface in which is disposed one or more magnetic field sensing elements, with the first surface being proximate to the current conductor portion and a second surface distal from the current conductor portion. In one particular embodiment, the substrate is disposed having the first surface of the substrate above the current conductor portion and the second surface of the substrate above the first surface. In this particular embodiment, the substrate is oriented upside-down in the integrated circuit in a flip-chap arrangement. The current sensor can also include an electromagnetic shield disposed between the current conductor portion and the magnetic field sensing elements.

Owner:ALLEGRO MICROSYSTEMS INC