Patents

Literature

101139 results about "Crystal" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A crystal or crystalline solid is a solid material whose constituents (such as atoms, molecules, or ions) are arranged in a highly ordered microscopic structure, forming a crystal lattice that extends in all directions. In addition, macroscopic single crystals are usually identifiable by their geometrical shape, consisting of flat faces with specific, characteristic orientations. The scientific study of crystals and crystal formation is known as crystallography. The process of crystal formation via mechanisms of crystal growth is called crystallization or solidification.

Oxide semiconductor thin film transistor and method of manufacturing the same

InactiveUS20070052025A1Improve reliabilityUnstability of may lessenSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringSemiconductor

Provided is a thin film transistor comprising a channel layer comprised of an oxide semiconductor containing In, M, Zn, and O, M including at least one selected from the group consisting of Ga, Al, and Fe. The channel layer is covered with a protective film.

Owner:CANON KK

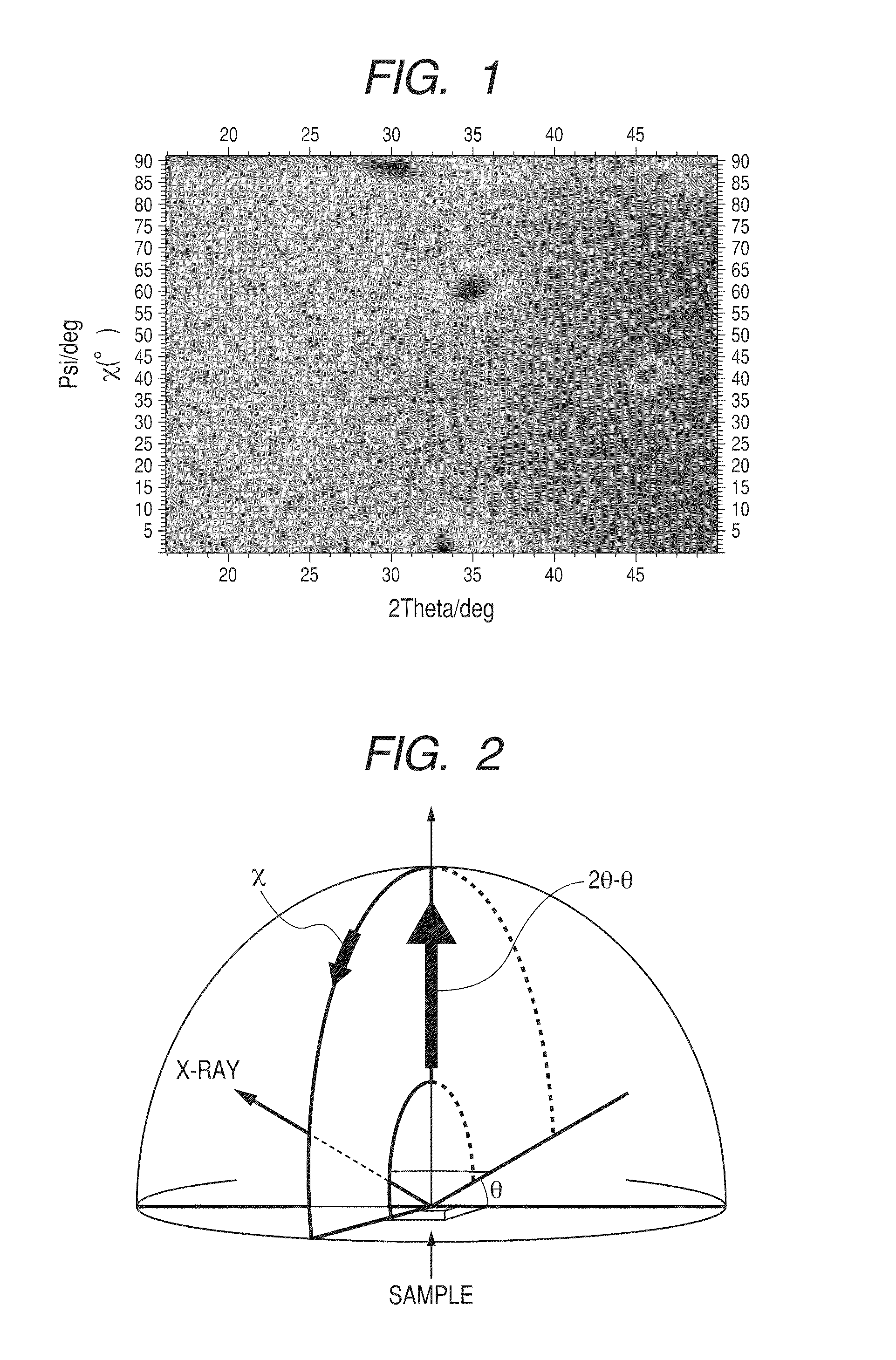

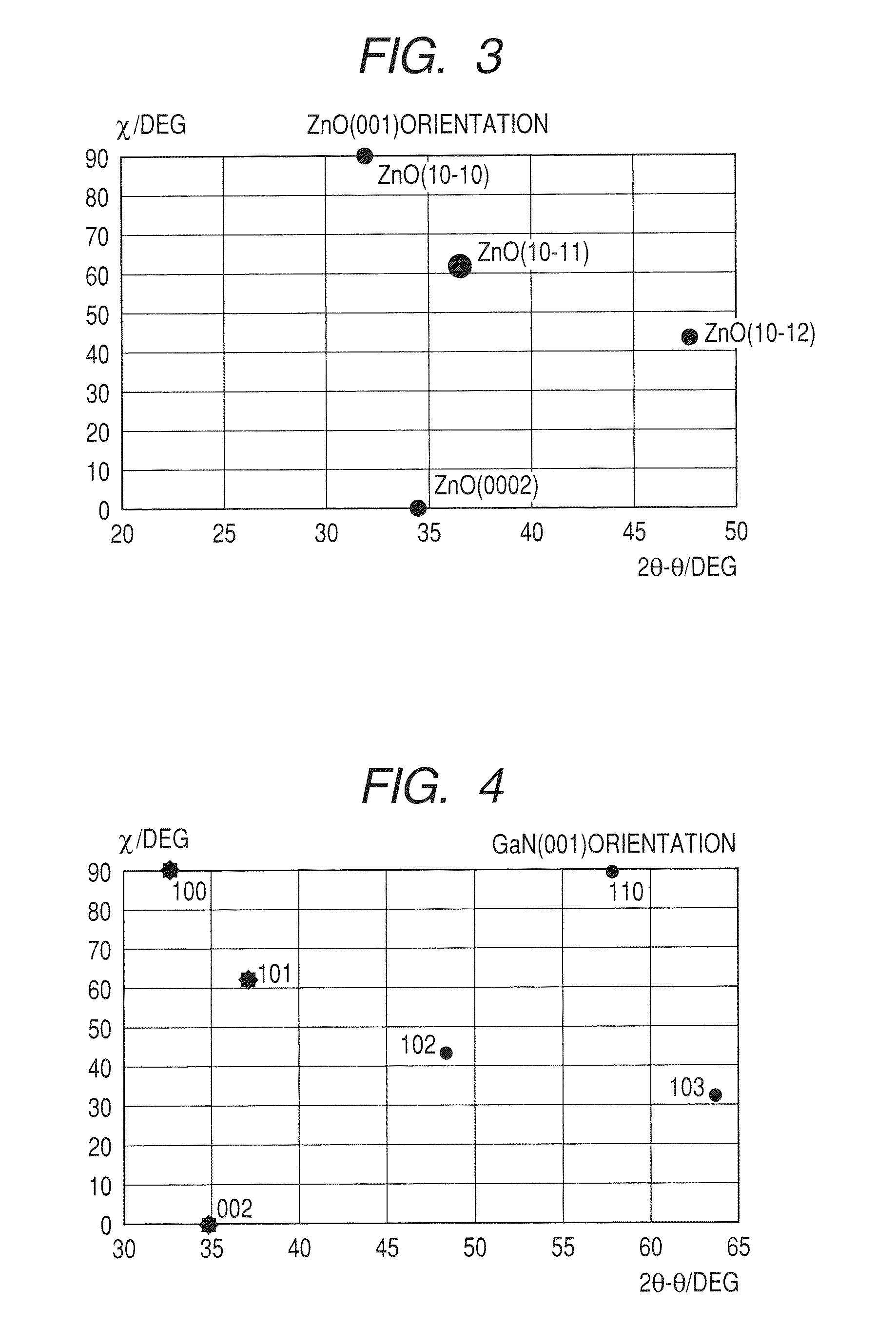

Method for forming ZnO film, method for forming ZnO semiconductor layer, method for fabricating semiconductor device, and semiconductor device

InactiveUS7049190B2High crystallinityLow costTransistorPolycrystalline material growthX-rayElectrical resistivity and conductivity

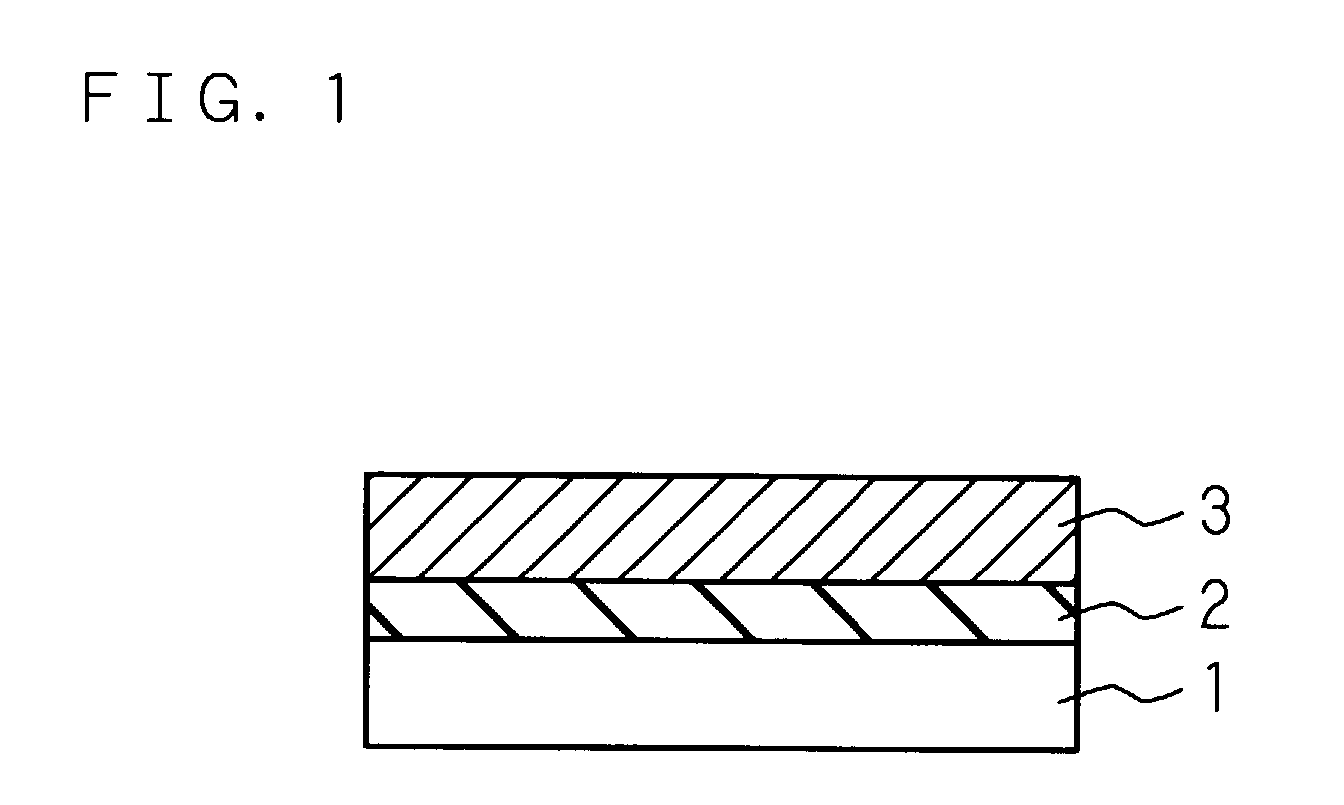

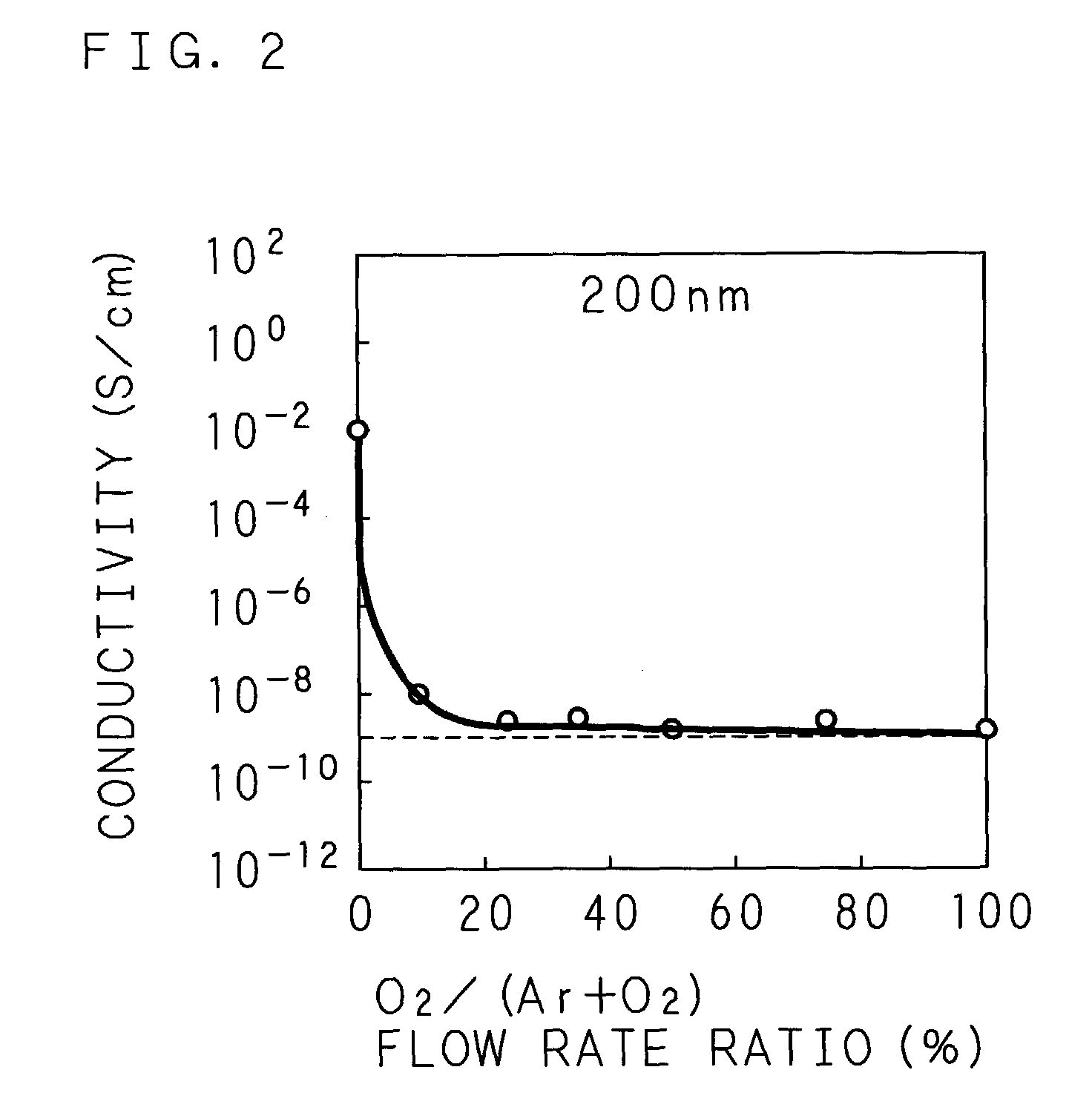

A ZnO buffer layer having an electric conductivity of 1×10−9 S / cm or lower or alternatively a ZnO buffer layer having a diffraction peak of a crystal face other than (002) and (004) in X-ray diffraction is formed on a substrate by sputtering. A ZnO semiconductor layer is formed on the ZnO buffer layer. The ZnO semiconductor layer is formed under the condition that the flow rate ratio of an oxygen gas in a sputtering gas is lower than that in the formation of the ZnO buffer layer.

Owner:SANYO ELECTRIC CO LTD

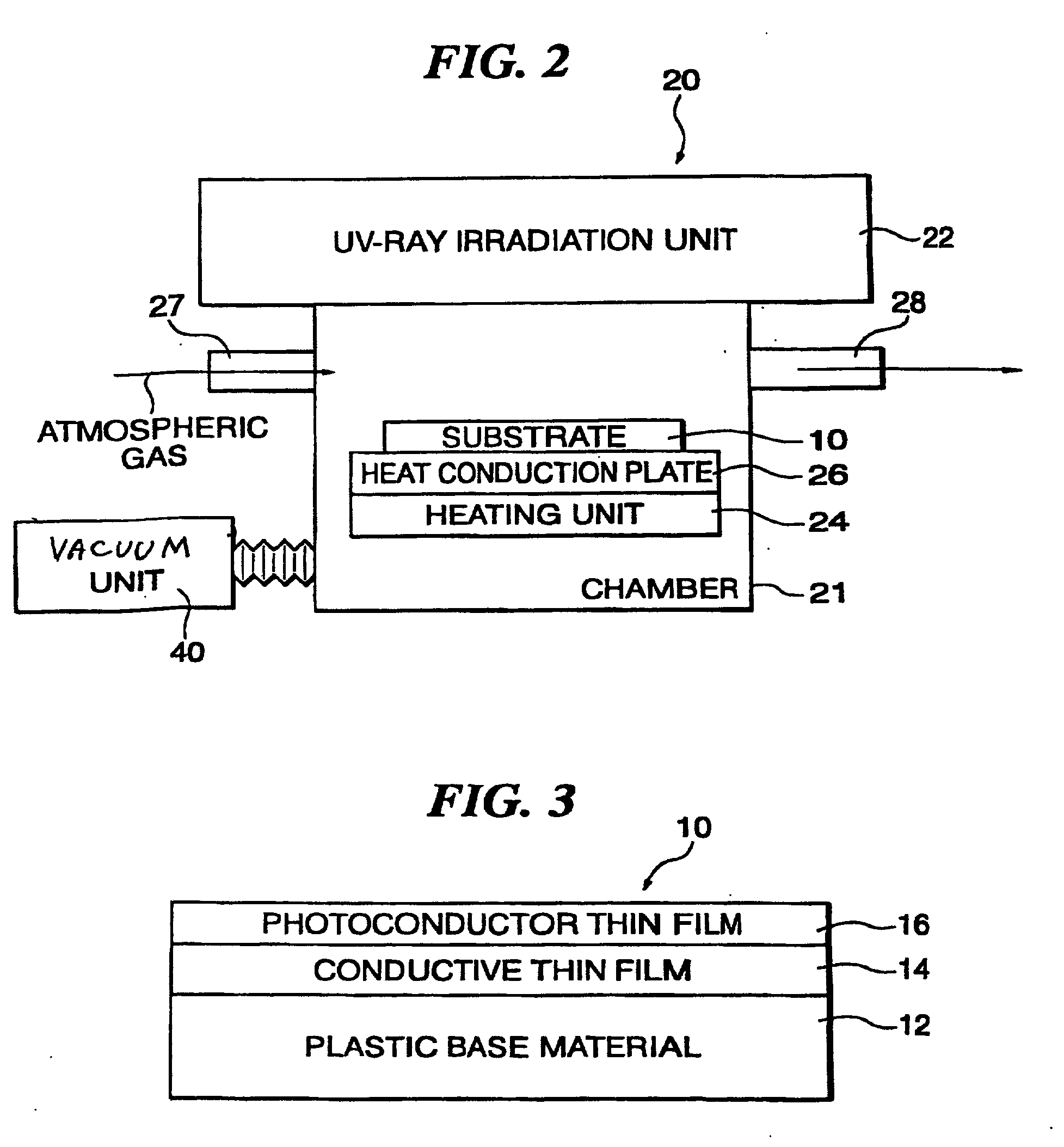

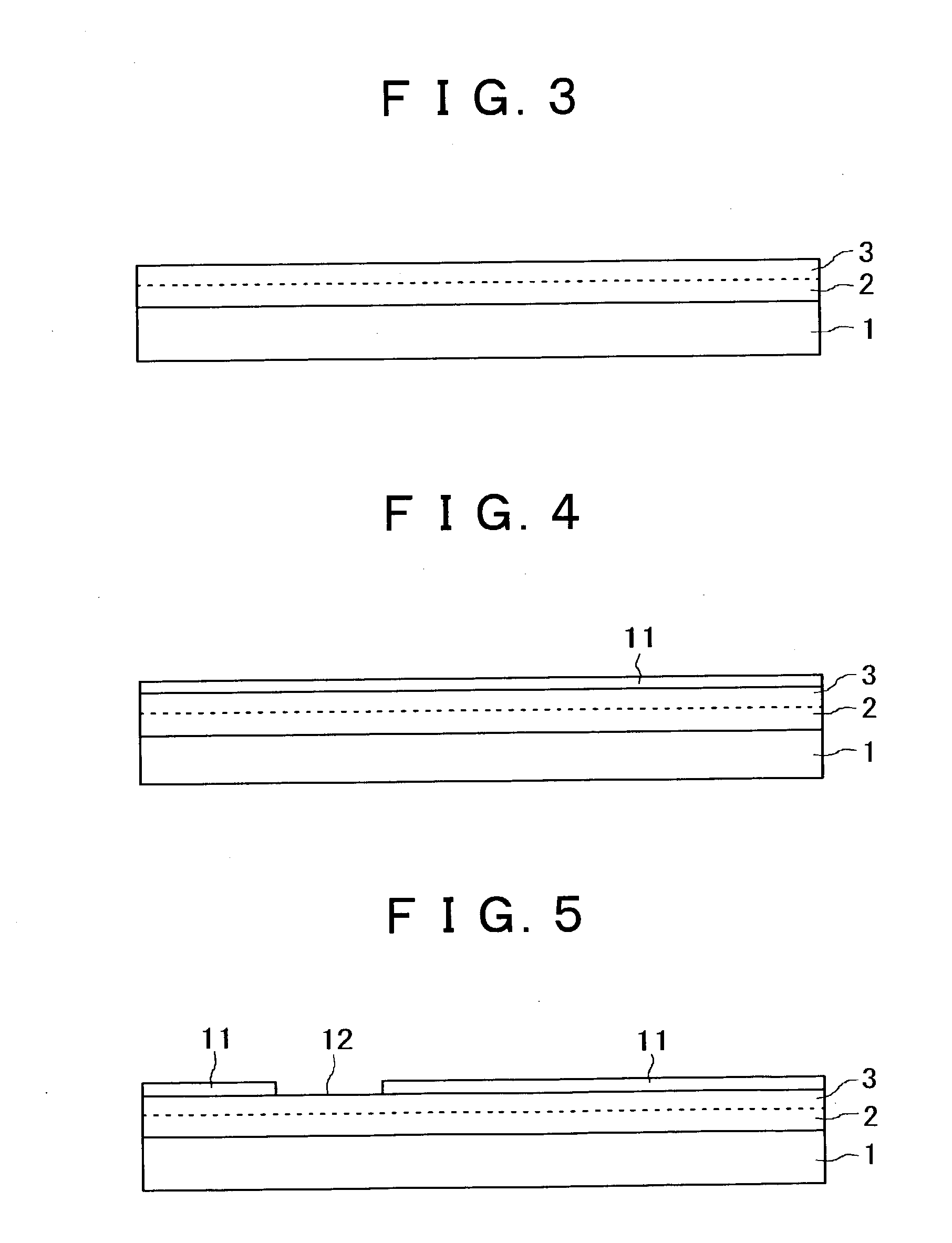

Method of forming crystalline semiconductor thin film on base substrate, lamination formed with crystalline semiconductor thin film and color filter

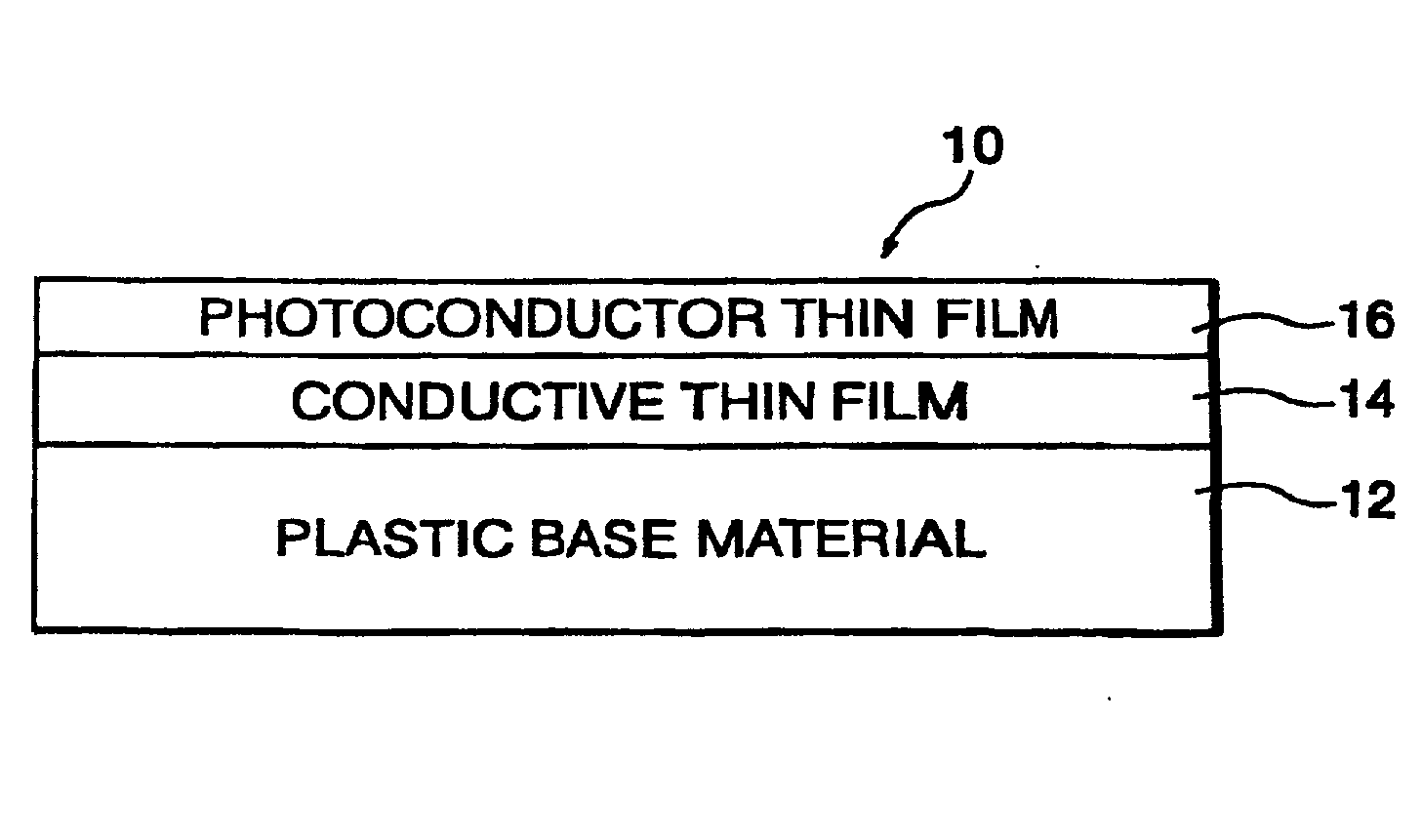

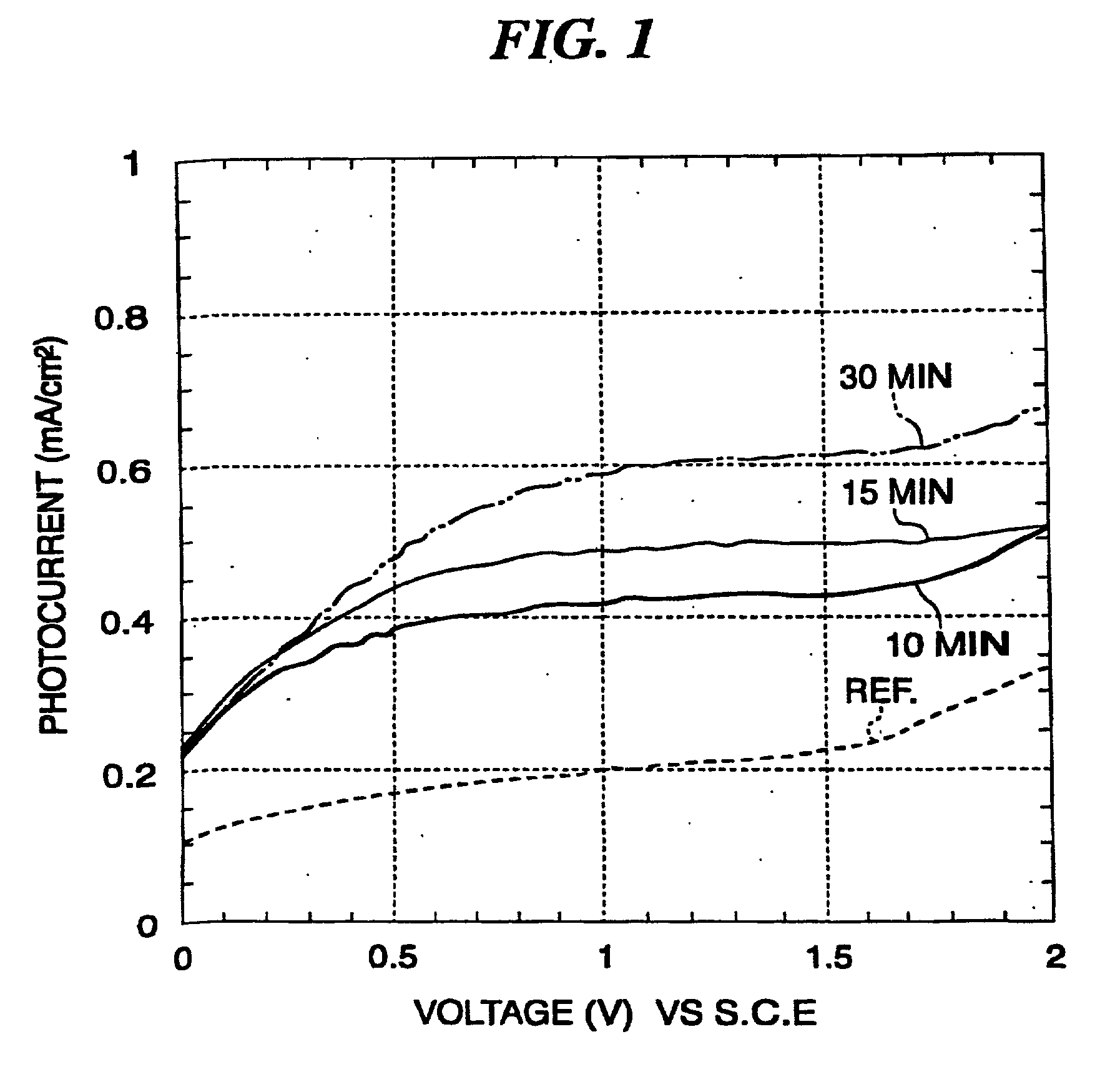

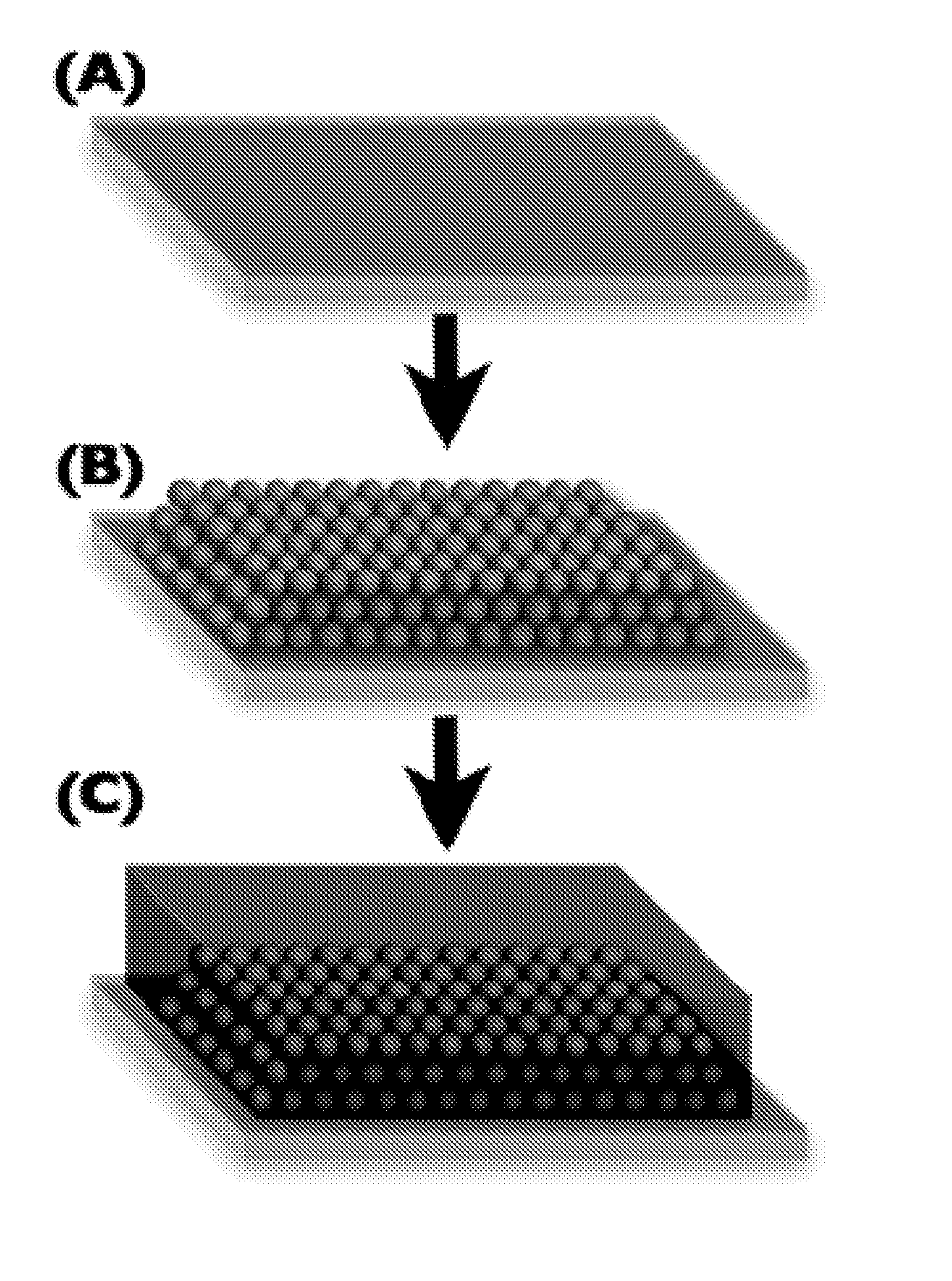

A method of forming a crystalline semiconductor thin film on a base material which can be prepared at a low temperature by simple step and device, the method including a processing step of applying UV-rays to an amorphous semiconductor thin film provided on a base material while keeping a temperature at not less than 25° C. and not more than 300° C. in a vacuum or a reducing gas atmosphere, as well as a substrate having the semiconductor thin film provided on the base material, a substrate for forming a color filter and a color filter using the substrate.

Owner:FUJIFILM BUSINESS INNOVATION CORP

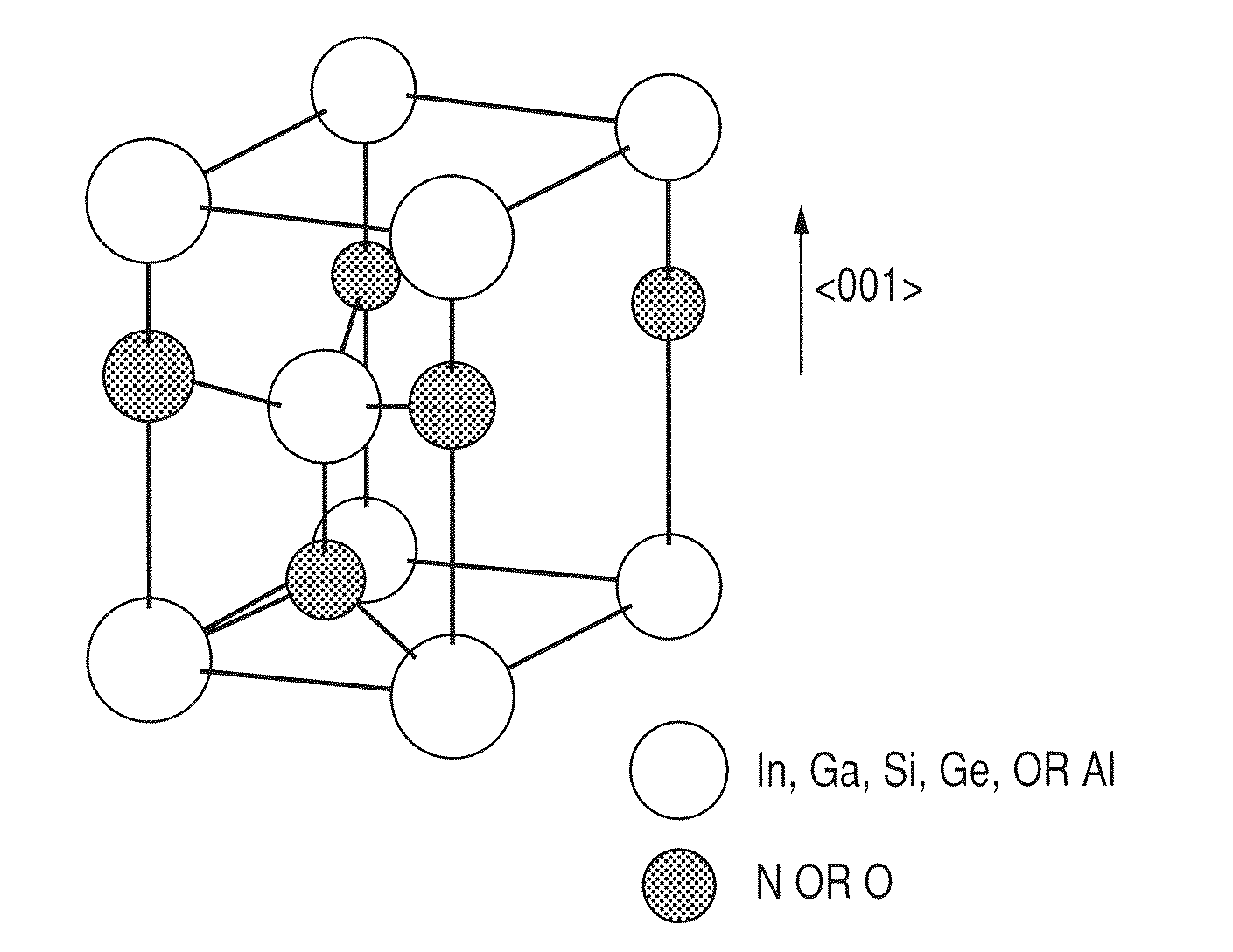

Substrate for growing wurtzite type crystal and method for manufacturing the same and semiconductor device

ActiveUS20100092800A1Low costHigh crystallinityPolycrystalline material growthVacuum evaporation coatingNitrideSemiconductor

A laminated structure comprises a first layer comprising a crystal with six-fold symmetry, and a second layer comprising a metal oxynitride crystal formed on the first layer, wherein the second layer comprises at least one element selected from the group consisting of In, Ga, Si, Ge and Al, N, O and Zn, as main elements, and wherein the second layer has in-plane orientation.

Owner:CANON KK

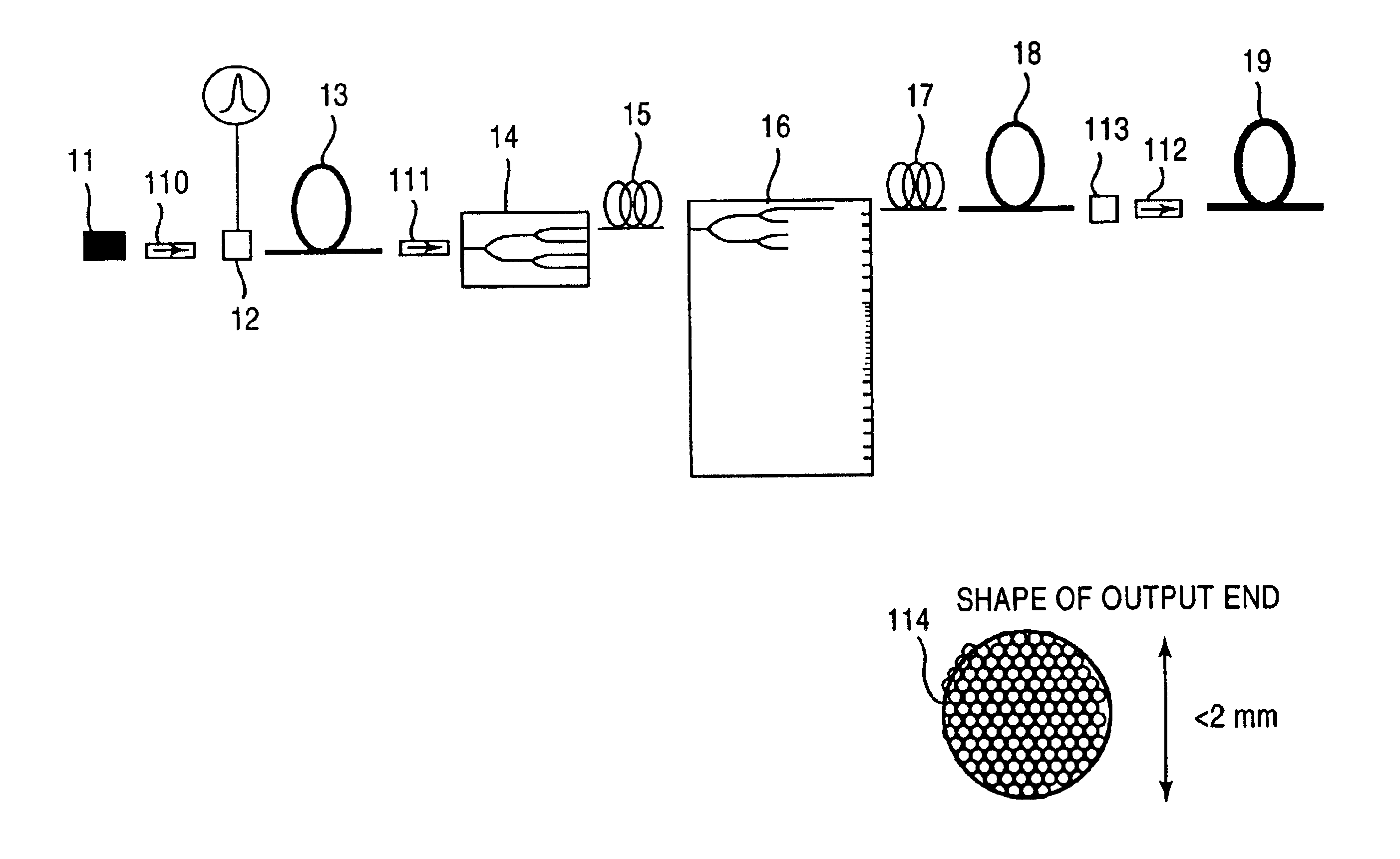

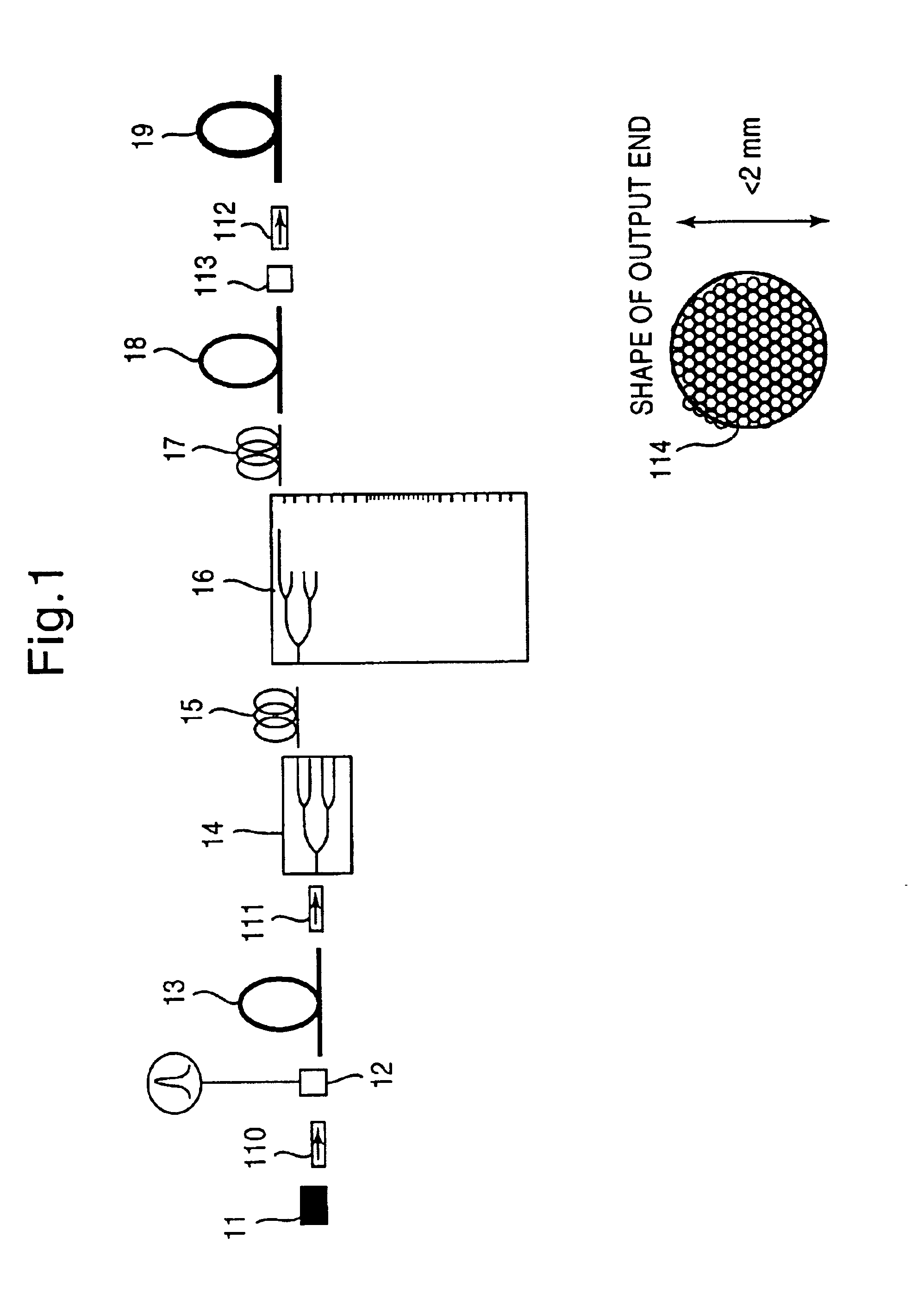

Ultraviolet laser apparatus and exposure apparatus using same

InactiveUS7023610B2Easy to getReduce spatial coherenceLaser using scattering effectsLaser arrangementsFiberUltraviolet lights

An ultraviolet laser apparatus having a single-wavelength oscillating laser generating laser light between an infrared band and a visible band, an optical amplifier for amplifying the laser light, and a wavelength converting portion converting the amplified laser light into ultraviolet light using a non-linear optical crystal. An exposure apparatus transfers a pattern image of a mask onto a substrate and includes a light source having a laser apparatus emitting laser light having a single wavelength, a first fiber optical amplifier for amplifying the laser light, a light dividing device for dividing or branching the amplified laser light into plural lights, and second fiber optical amplifiers for amplifying the plural divided or branched lights, respectively, and a transmission optical system for transmitting the laser light emitted from the light source to the exposure apparatus.

Owner:NIKON CORP

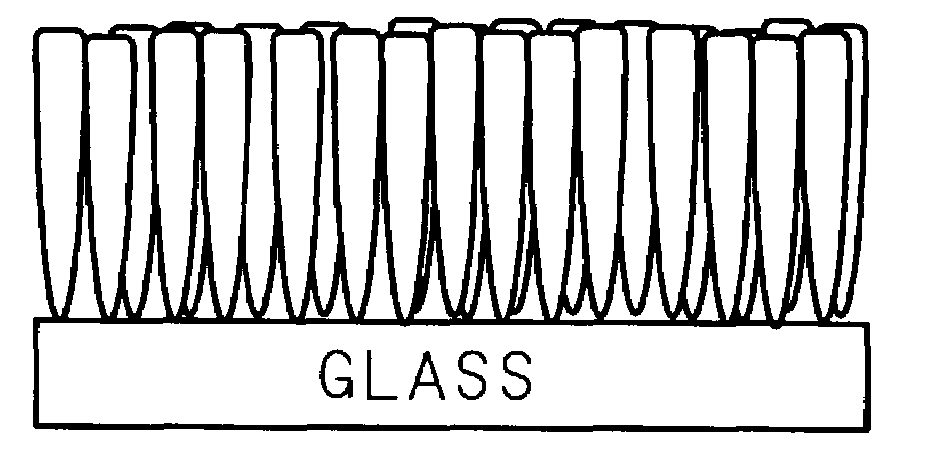

Method of growing nitride semiconductors, nitride semiconductor substrate and nitride semiconductor device

InactiveUS6153010APolycrystalline material growthLaser detailsNitrogen sourceCrystallographic defect

PCT No. PCT / JP98 / 01640 Sec. 371 Date Dec. 9, 1998 Sec. 102(e) Date Dec. 9, 1998 PCT Filed Apr. 9, 1998 PCT Pub. No. WO98 / 47170 PCT Pub. Date Oct. 22, 1998A method of growing a nitride semiconductor crystal which has very few crystal defects and can be used as a substrate is disclosed. This invention includes the step of forming a first selective growth mask on a support member including a dissimilar substrate having a major surface and made of a material different from a nitride semiconductor, the first selective growth mask having a plurality of first windows for selectively exposing the upper surface of the support member, and the step of growing nitride semiconductor portions from the upper surface, of the support member, which is exposed from the windows, by using a gaseous Group 3 element source and a gaseous nitrogen source, until the nitride semiconductor portions grown in the adjacent windows combine with each other on the upper surface of the selective growth mask.

Owner:NICHIA CORP

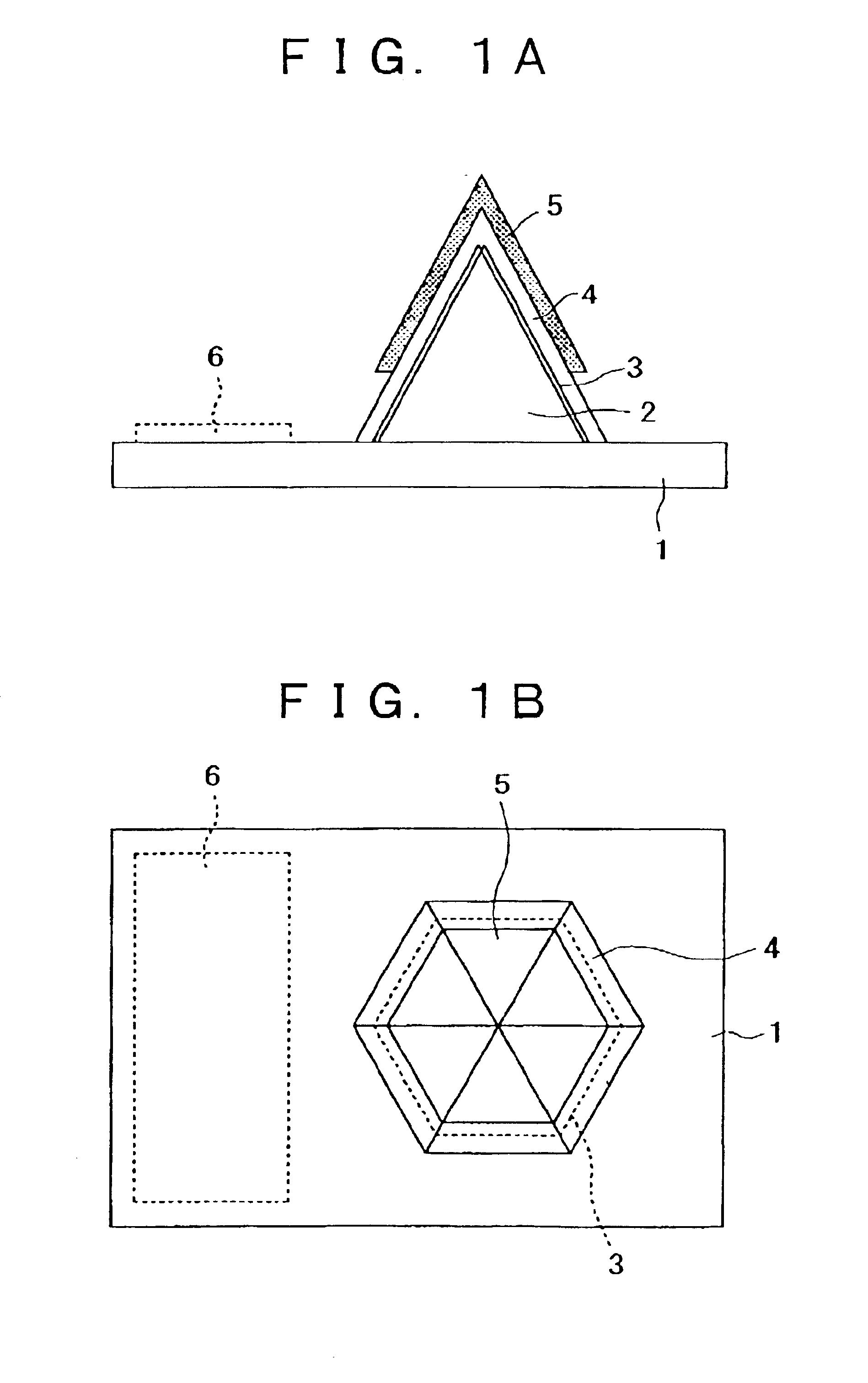

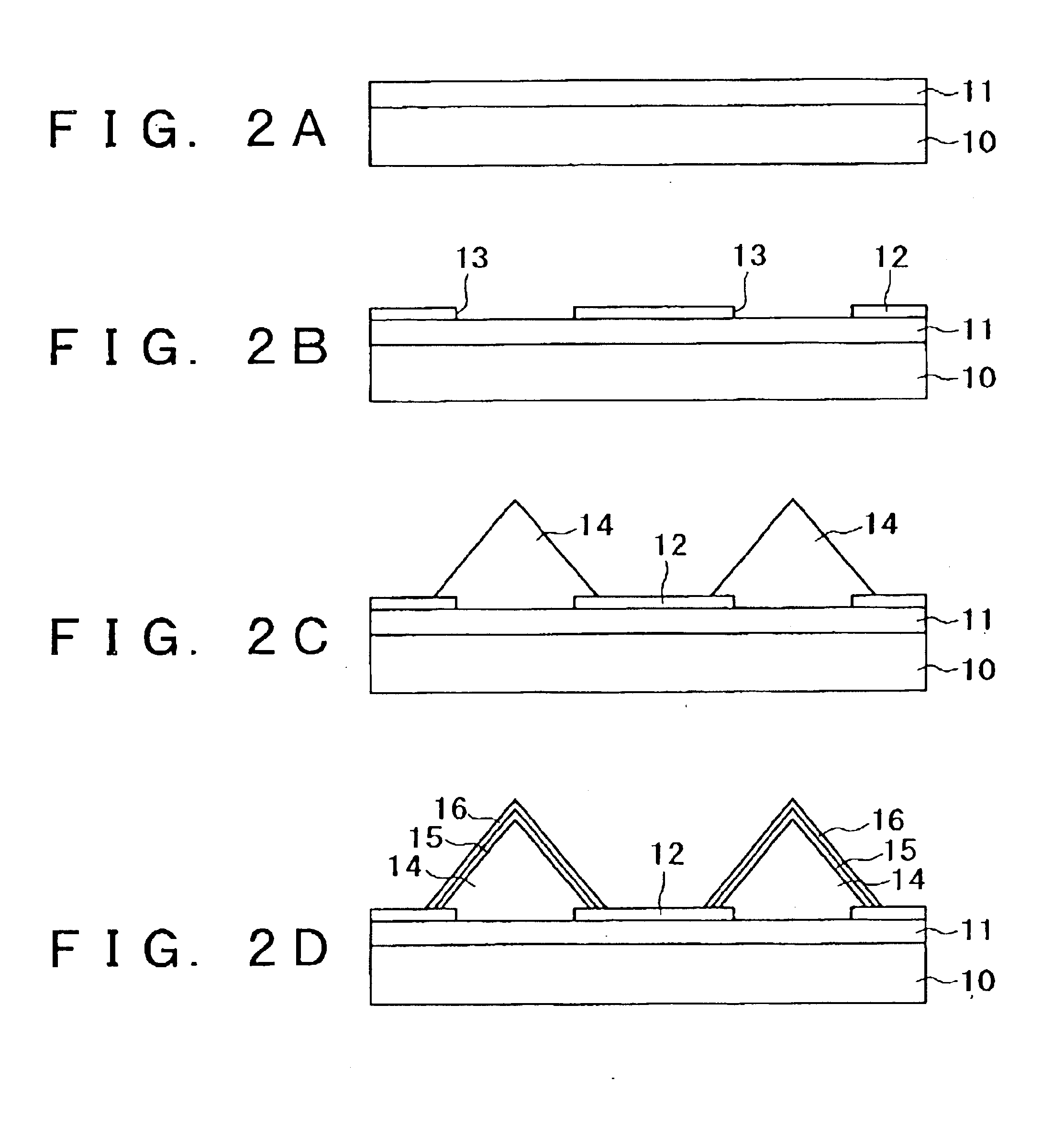

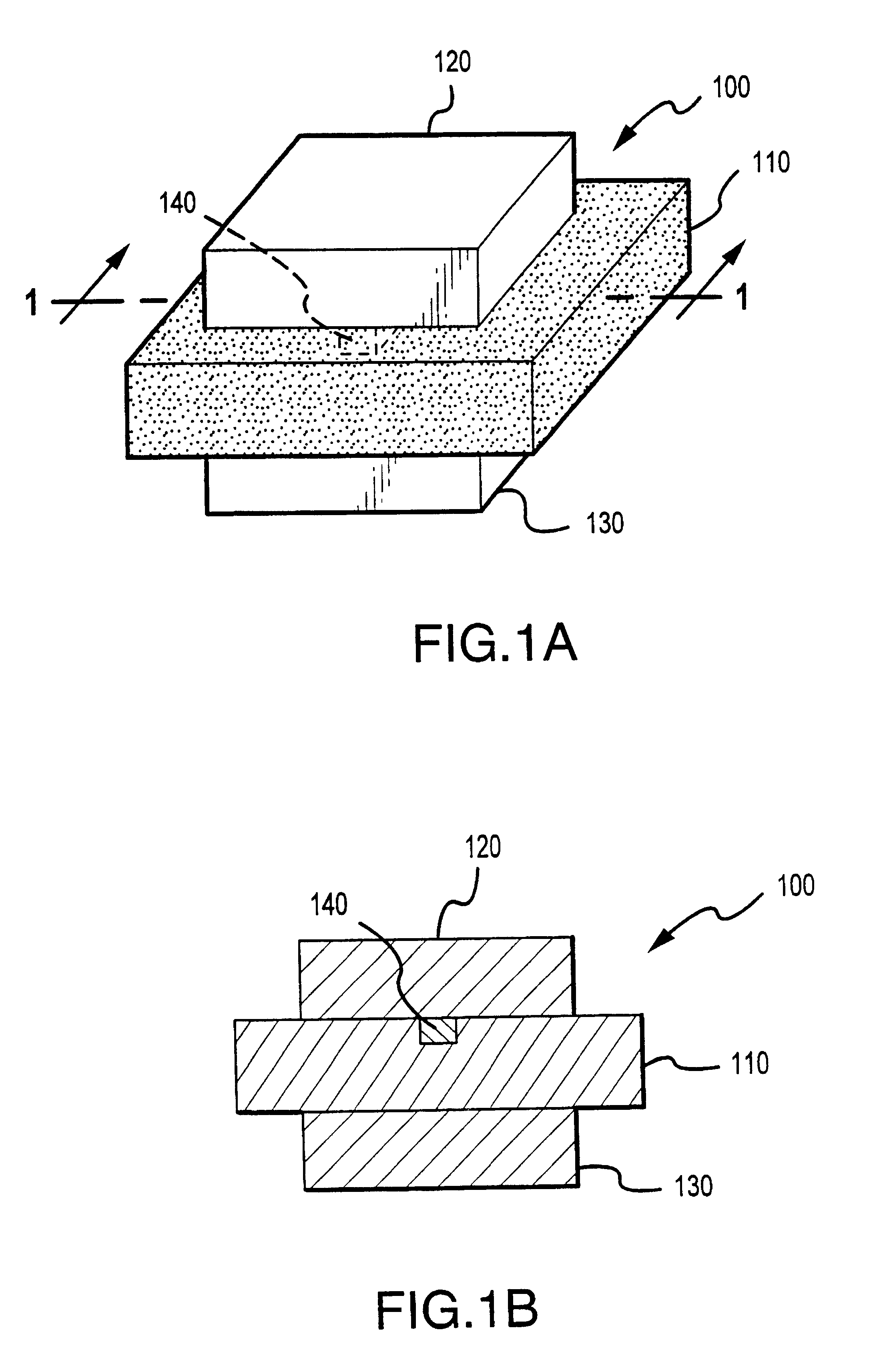

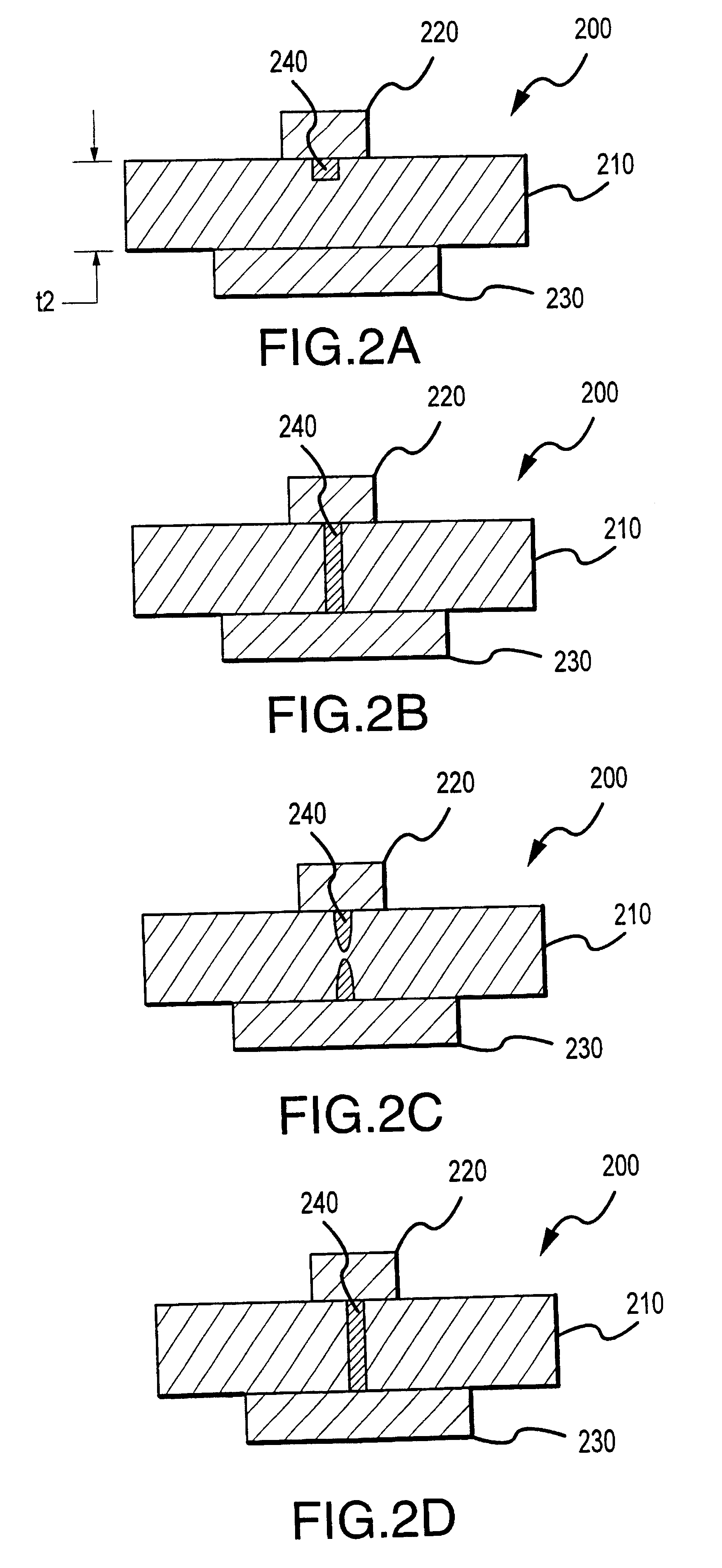

Selective growth method, and semiconductor light emitting device and fabrication method thereof

InactiveUS6858081B2Improve featuresReduce widthPolycrystalline material growthSemiconductor/solid-state device manufacturingThree dimensional shapeActive layer

In a selective growth method, growth interruption is performed at the time of selective growth of a crystal layer on a substrate. Even if the thickness distribution of the crystal layer becomes non-uniform at the time of growth of the crystal layer, the non-uniformity of the thickness distribution of the crystal layer can be corrected by inserting the growth interruption. As a result of growth interruption, an etching rate at a thick portion becomes higher than that at a thin portion, to eliminate the difference in thickness between the thick portion and the thin portion, thereby solving the problem associated with degradation of characteristics due to a variation in thickness of the crystal layer, for example, an active layer. The selective growth method is applied to fabrication of a semiconductor light emitting device including an active layer as a crystal layer formed on a crystal layer having a three-dimensional shape by selective growth.

Owner:SAMSUNG ELECTRONICS CO LTD

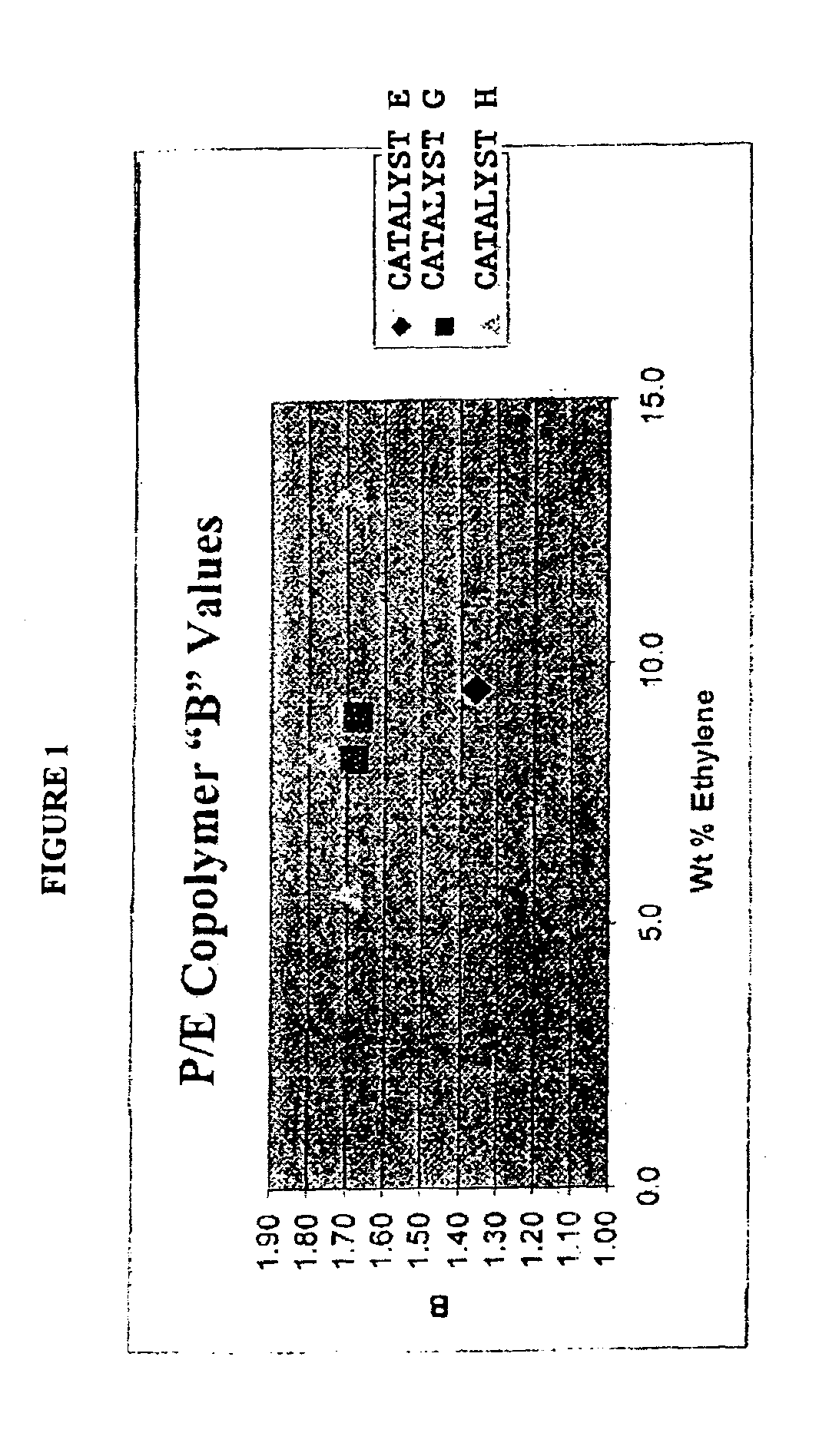

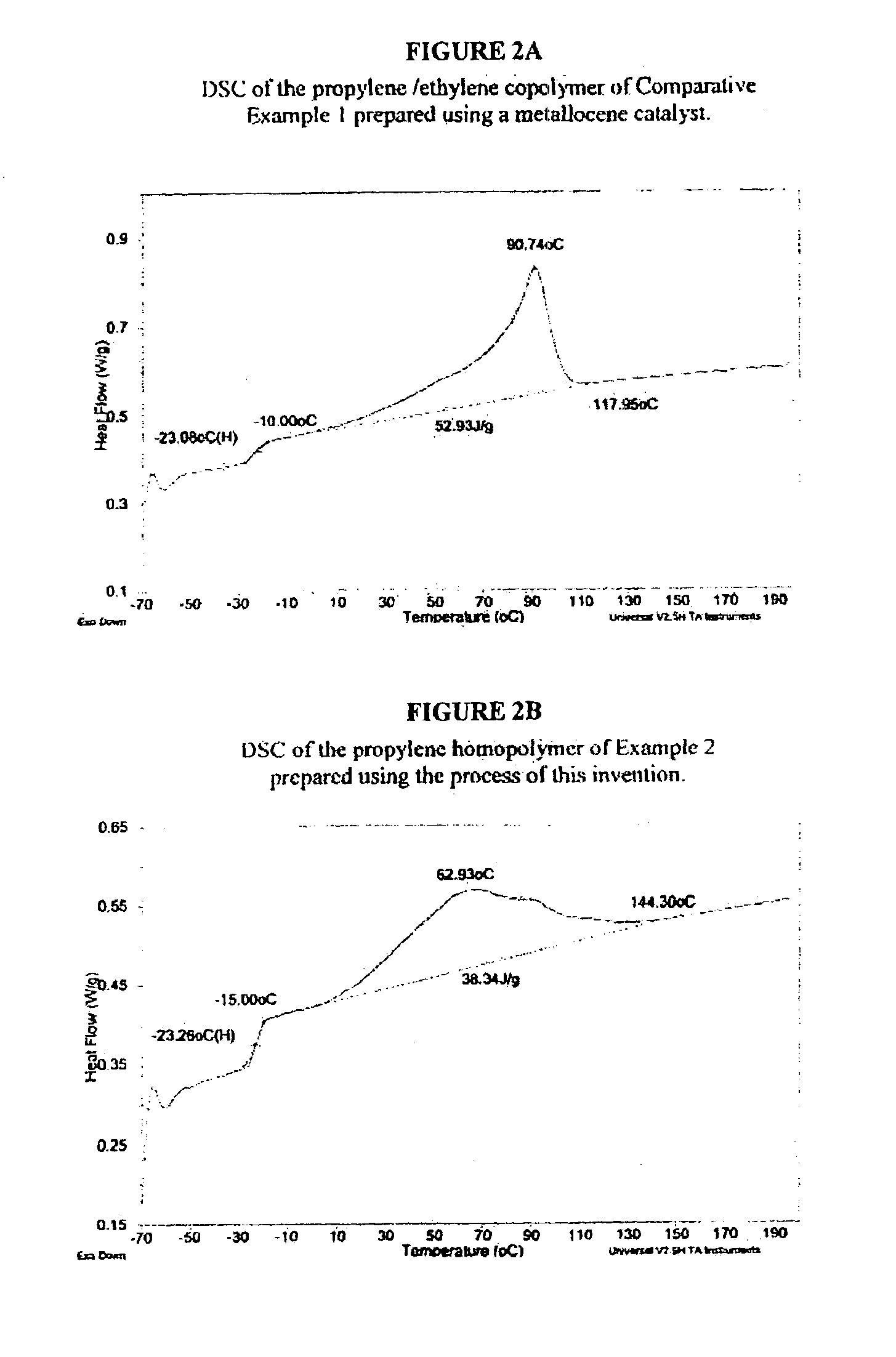

Isotactic propylene copolymers, their preparation and use

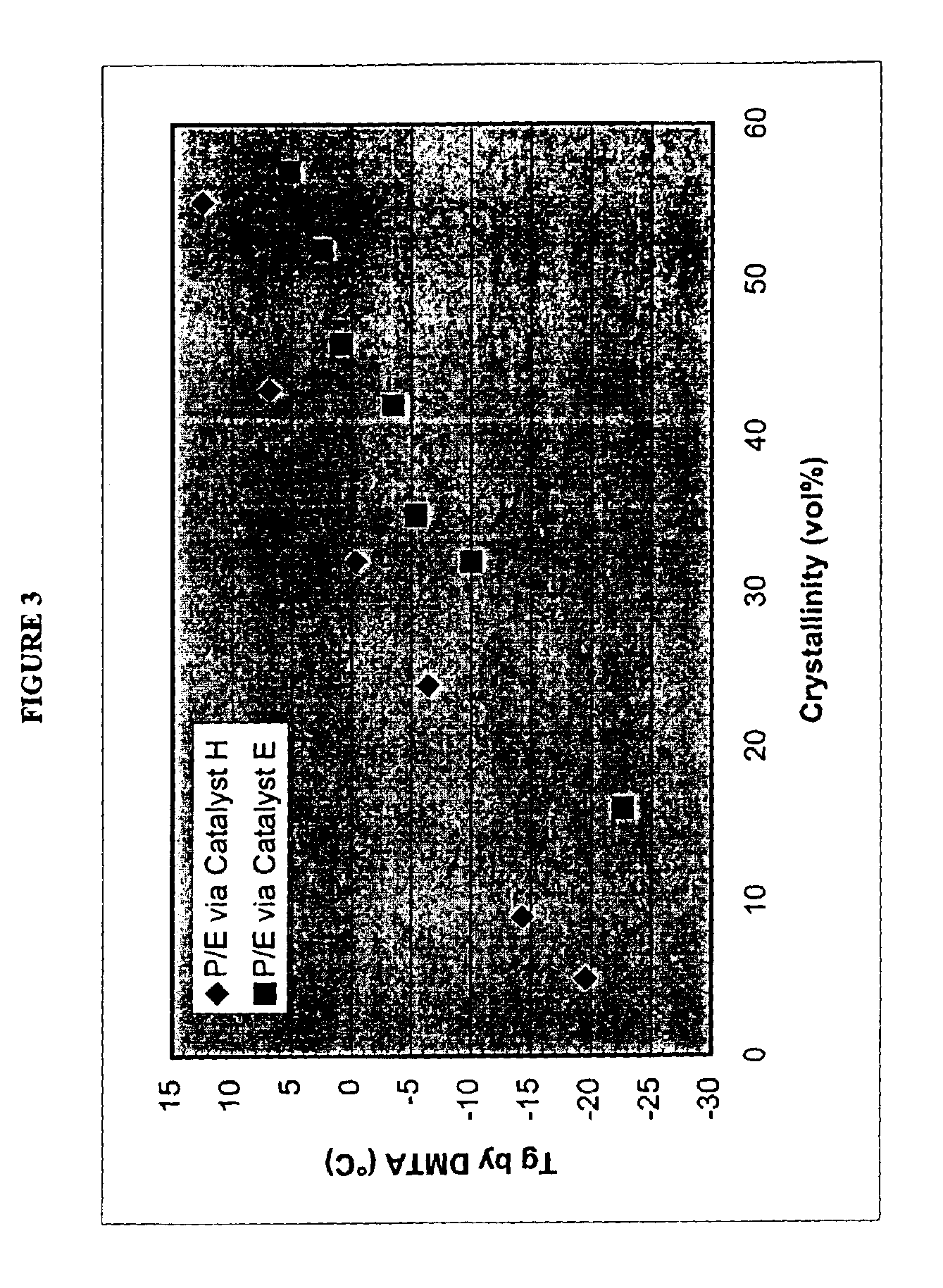

InactiveUS6960635B2Group 4/14 element organic compoundsOther chemical processesFiberZiegler–Natta catalyst

Unique copolymers comprising propylene, ethylene and / or one or more unsaturated comonomers are characterized as having: at least one, preferably more than one, of the following properties: (i) 13C NMR peaks corresponding to a regio-error at about 14.6 and about 15.7 ppm, the peaks of about equal intensity, (ii) a B-value greater than about 1.4 when the comonomer content of the copolymer is at least about 3 wt %, (iii) a skewness index, Six, greater than about −1.20, (iv) a DSC curve with a Tme that remains essentially the same and a Tmax that decreases as the amount of comonomer in the copolymer is increased, and (v) an X-ray diffraction pattern that reports more gamma-form crystals than a comparable copolymer prepared with a Ziegler-Natta catalyst. These polypropylene polymers are made using a nonmetallocene, metal-centered, heteroaryl ligand catalyst. These polymers can be blended with other polymers, and are useful in the manufacture of films, sheets, foams, fibers and molded articles.

Owner:DOW GLOBAL TECH LLC

Organo luminescent semiconductor nanocrystal probes for biological applications and process for making and using such probes

A semiconductor nanocrystal compound is described capable of linking to an affinity molecule. The compound comprises (1) a semiconductor nanocrystal capable of emitting electromagnetic radiation and / or absorbing energy, and / or scattering or diffracting electromagnetic radiation-when excited by an electromagnetic radiation source or a particle beam; and (2) at least one linking agent, having a first portion linked to the semiconductor nanocrystal and a second portion capable of linking to an affity molecule. The compound is linked to an affinity molecule to form a semiconductor nanocrystal probe capable of bonding with a detectable substance. Subsequent exposure to excitation energy will excite the semiconductor nanocrystal in he probe, causing the emission of electromagnetic radiation. Further described are processes for respectively: making the semiconductor nanocrystal compound; making the semiconductor nanocrystal probe; and using the probe to determine the presence of a detectable substance in a material.

Owner:RGT UNIV OF CALIFORNIA

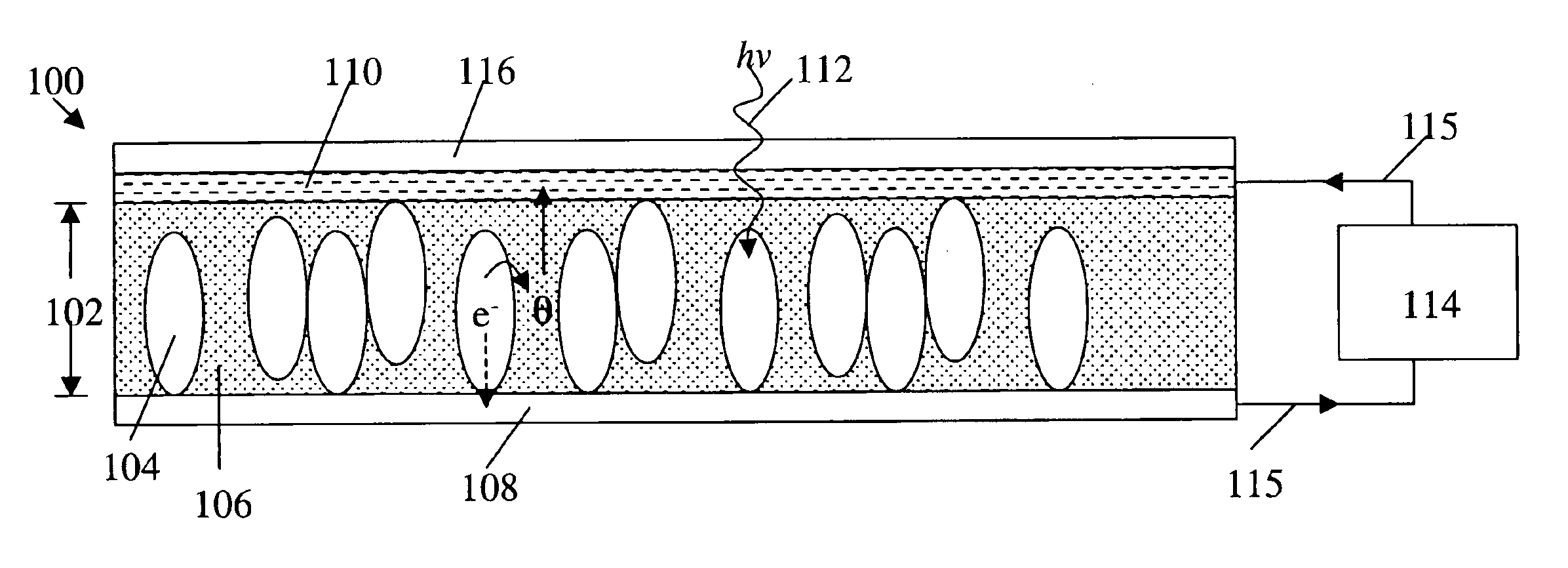

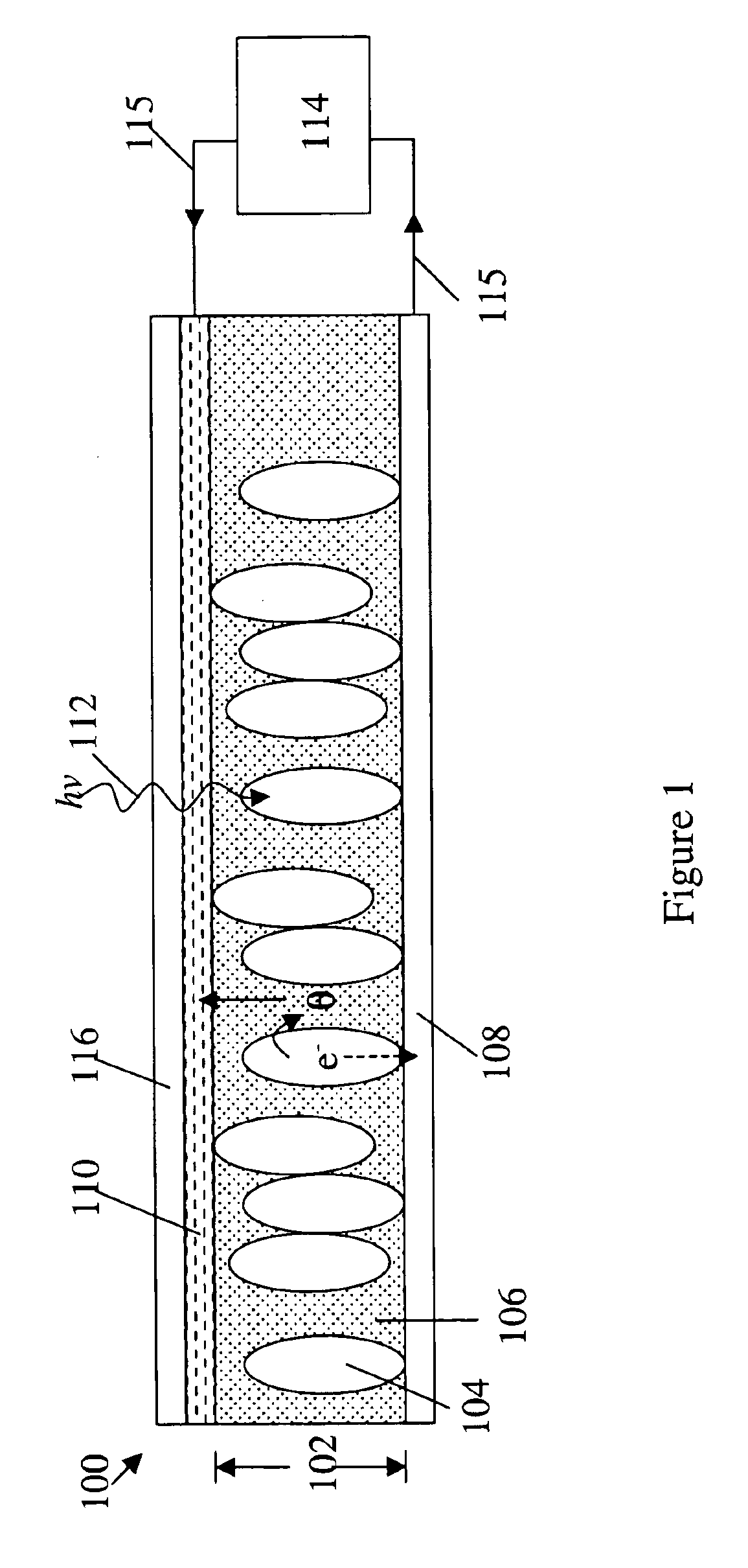

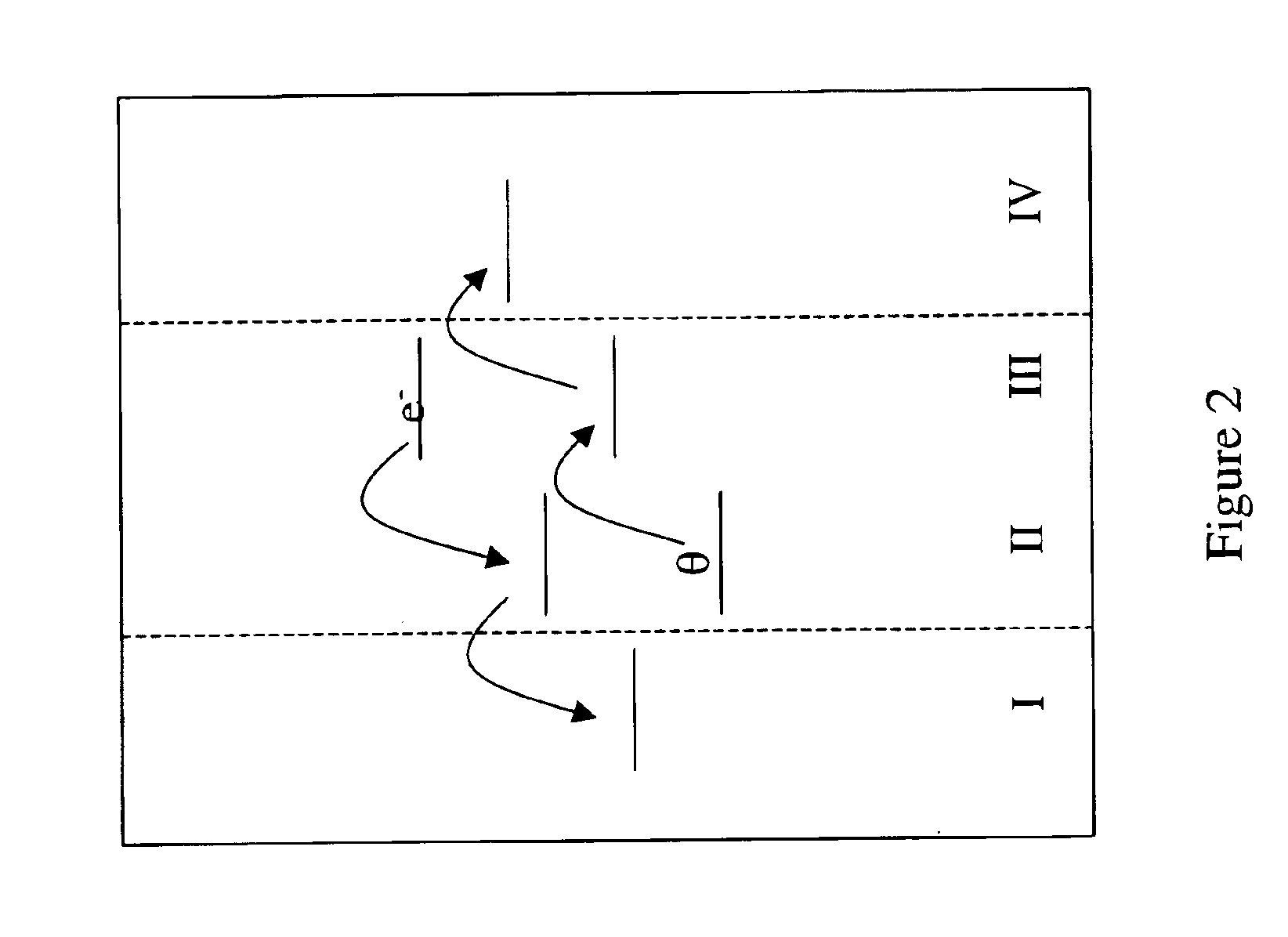

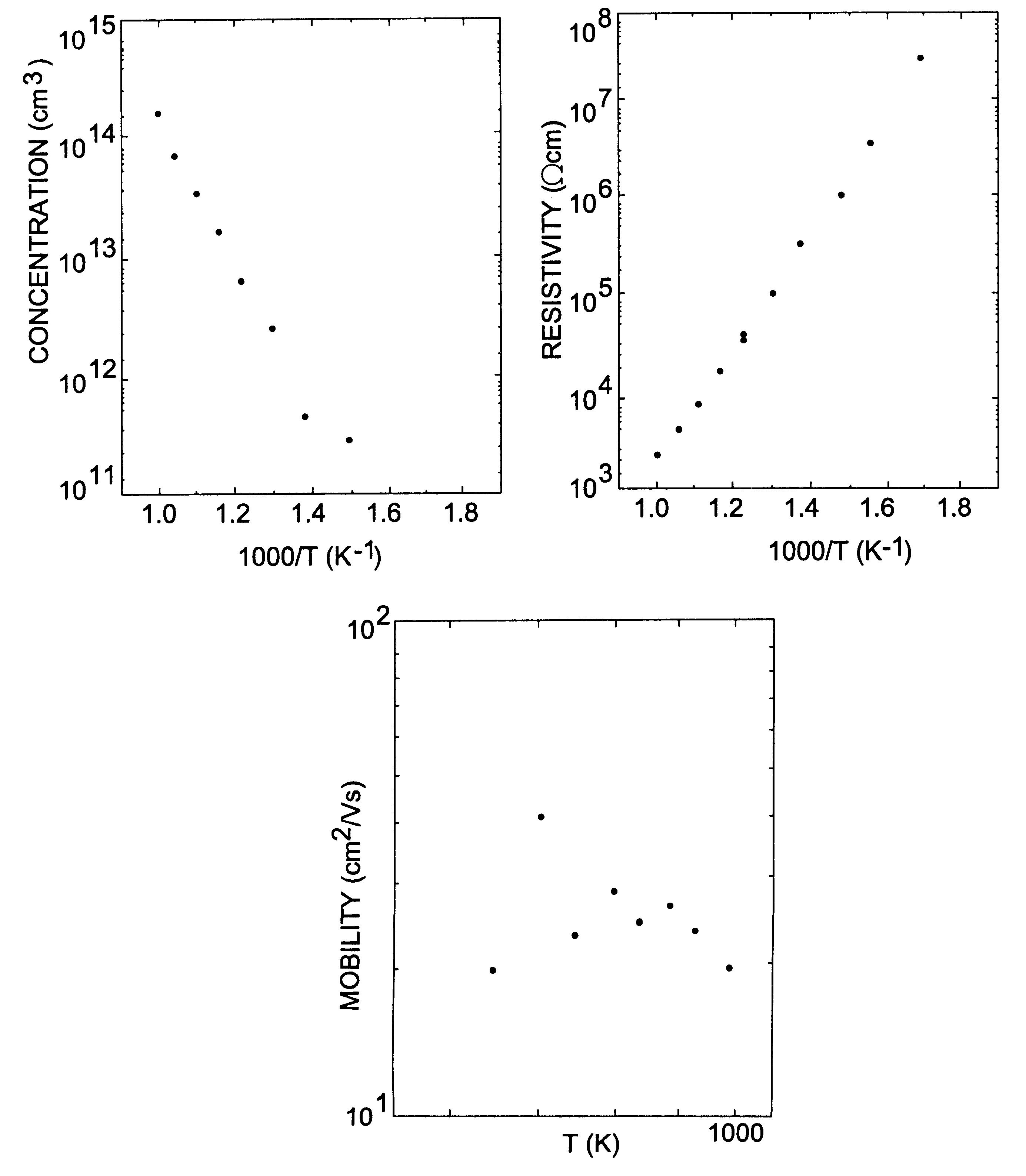

Nanostructure and nanocomposite based compositions and photovoltaic devices

InactiveUS6878871B2Improve equipment efficiencyMaterial nanotechnologyFinal product manufactureSemiconductor nanocrystalsNanostructure

Nanocomposite photovoltaic devices are provided that generally include semiconductor nanocrystals as at least a portion of a photoactive layer. Photovoltaic devices and other layered devices that comprise core-shell nanostructures and / or two populations of nanostructures, where the nanostructures are not necessarily part of a nanocomposite, are also features of the invention. Varied architectures for such devices are also provided including flexible and rigid architectures, planar and non-planar architectures and the like, as are systems incorporating such devices, and methods and systems for fabricating such devices. Compositions comprising two populations of nanostructures of different materials are also a feature of the invention.

Owner:NANOSYS INC

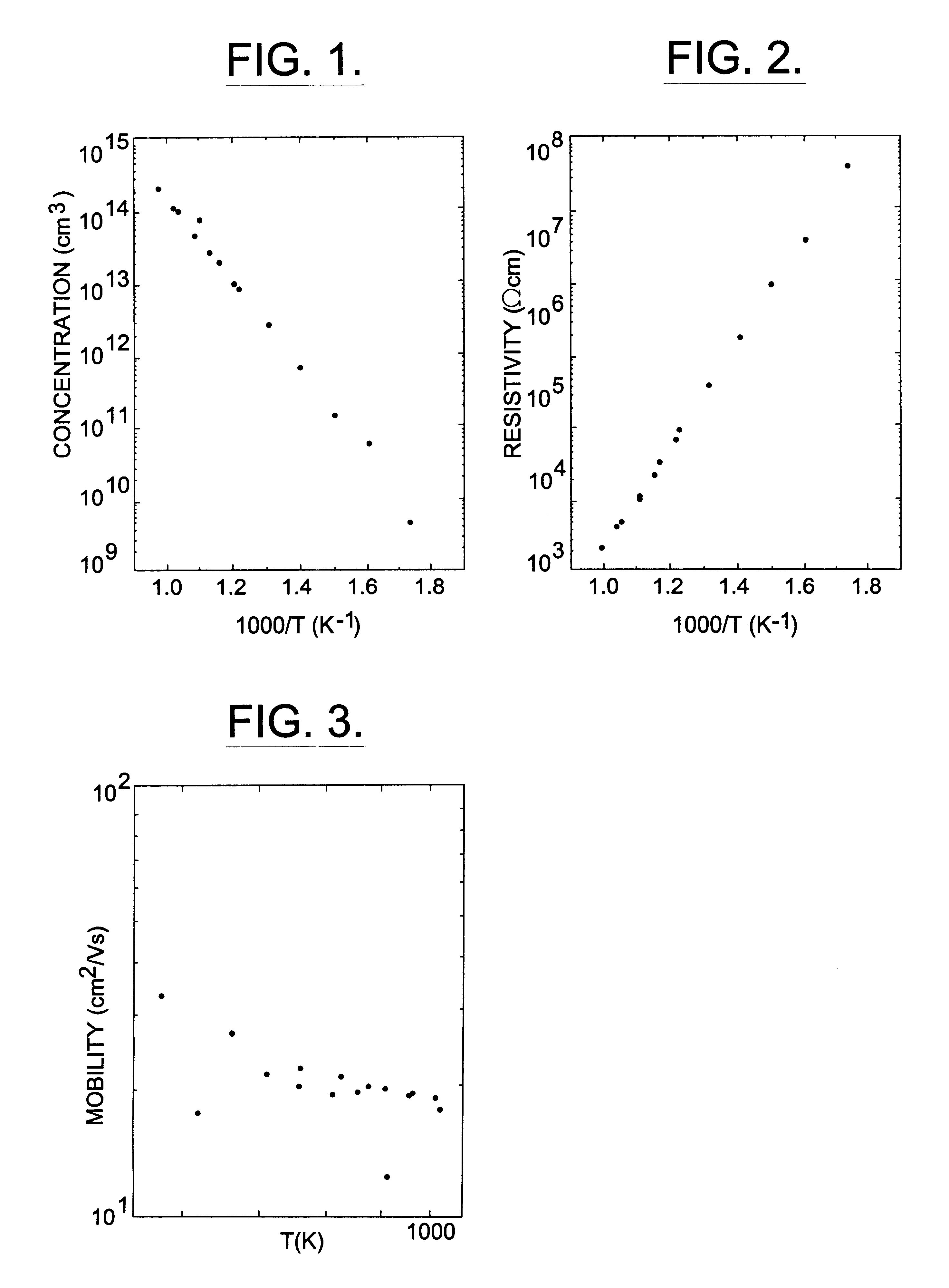

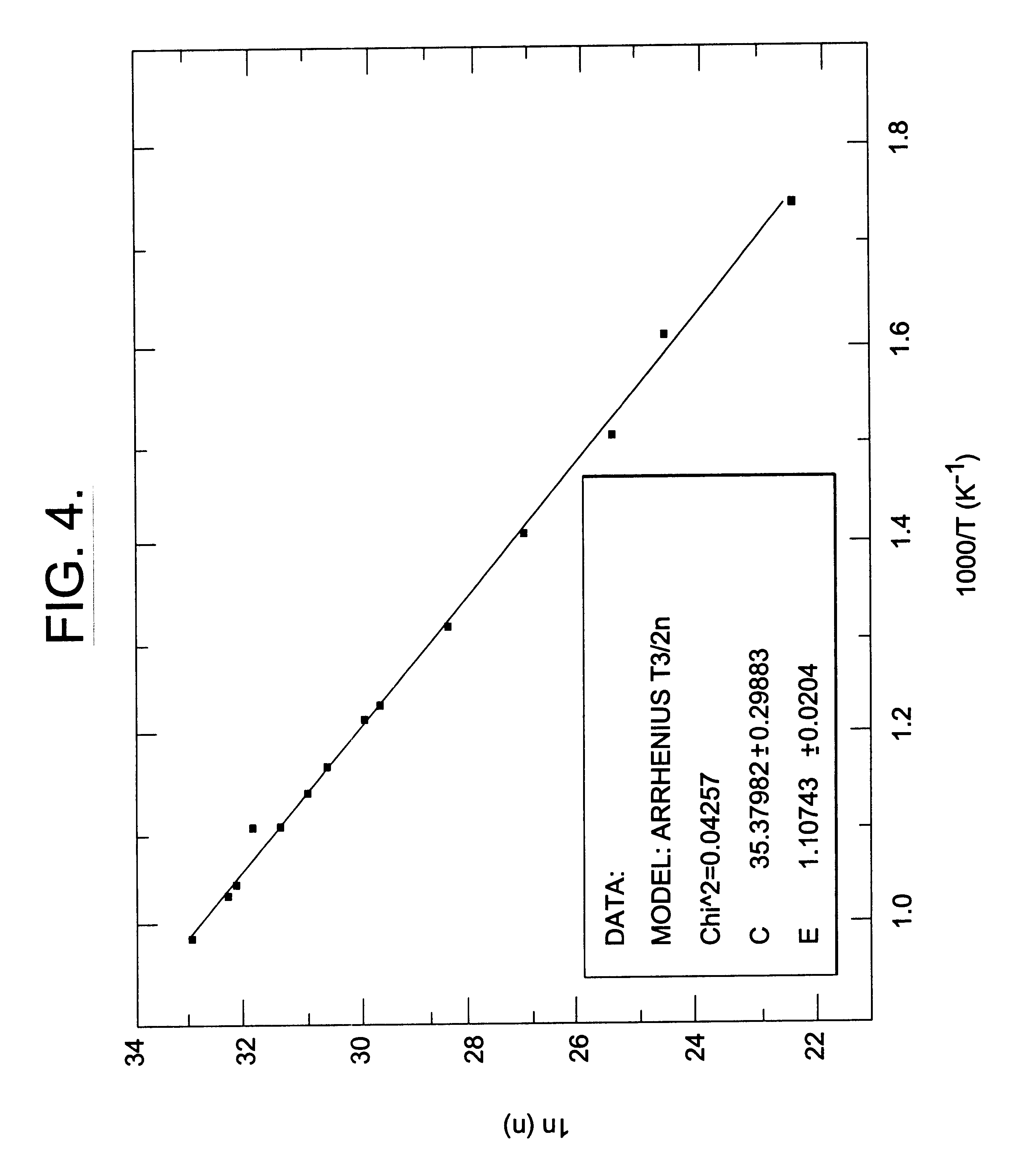

Semi-insulating silicon carbide without vanadium domination

InactiveUS6218680B1Reduce the amount requiredIncrease the number ofPolycrystalline material growthAfter-treatment detailsDevice formTrapping

Owner:CREE INC

Programmable metallization cell structure and method of making same

InactiveUS6084796ASolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceElectrical conductor

A programmable metallization cell ("PMC") comprises a fast ion conductor such as a chalcogenide-metal ion and a plurality of electrodes (e.g., an anode and a cathode) disposed at the surface of the fast ion conductor and spaced a set distance apart from each other. Preferably, the fast ion conductor comprises a chalcogenide with Group IB or Group IIB metals, the anode comprises silver, and the cathode comprises aluminum or other conductor. When a voltage is applied to the anode and the cathode, a non-volatile metal dendrite grows from the cathode along the surface of the fast ion conductor towards the anode. The growth rate of the dendrite is a function of the applied voltage and time. The growth of the dendrite may be stopped by removing the voltage and the dendrite may be retracted by reversing the voltage polarity at the anode and cathode. Changes in the length of the dendrite affect the resistance and capacitance of the PMC. The PMC may be incorporated into a variety of technologies such as memory devices, programmable resistor / capacitor devices, optical devices, sensors, and the like. Electrodes additional to the cathode and anode can be provided to serve as outputs or additional outputs of the devices in sensing electrical characteristics which are dependent upon the extent of the dendrite.

Owner:AXON TECH +1

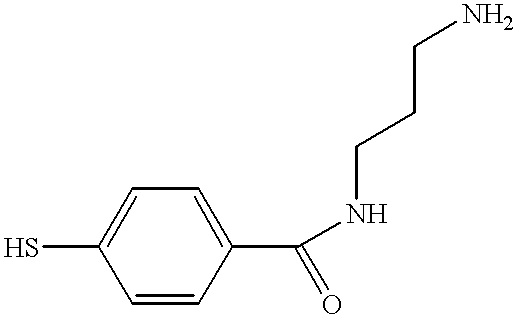

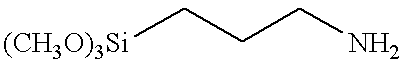

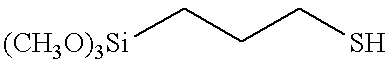

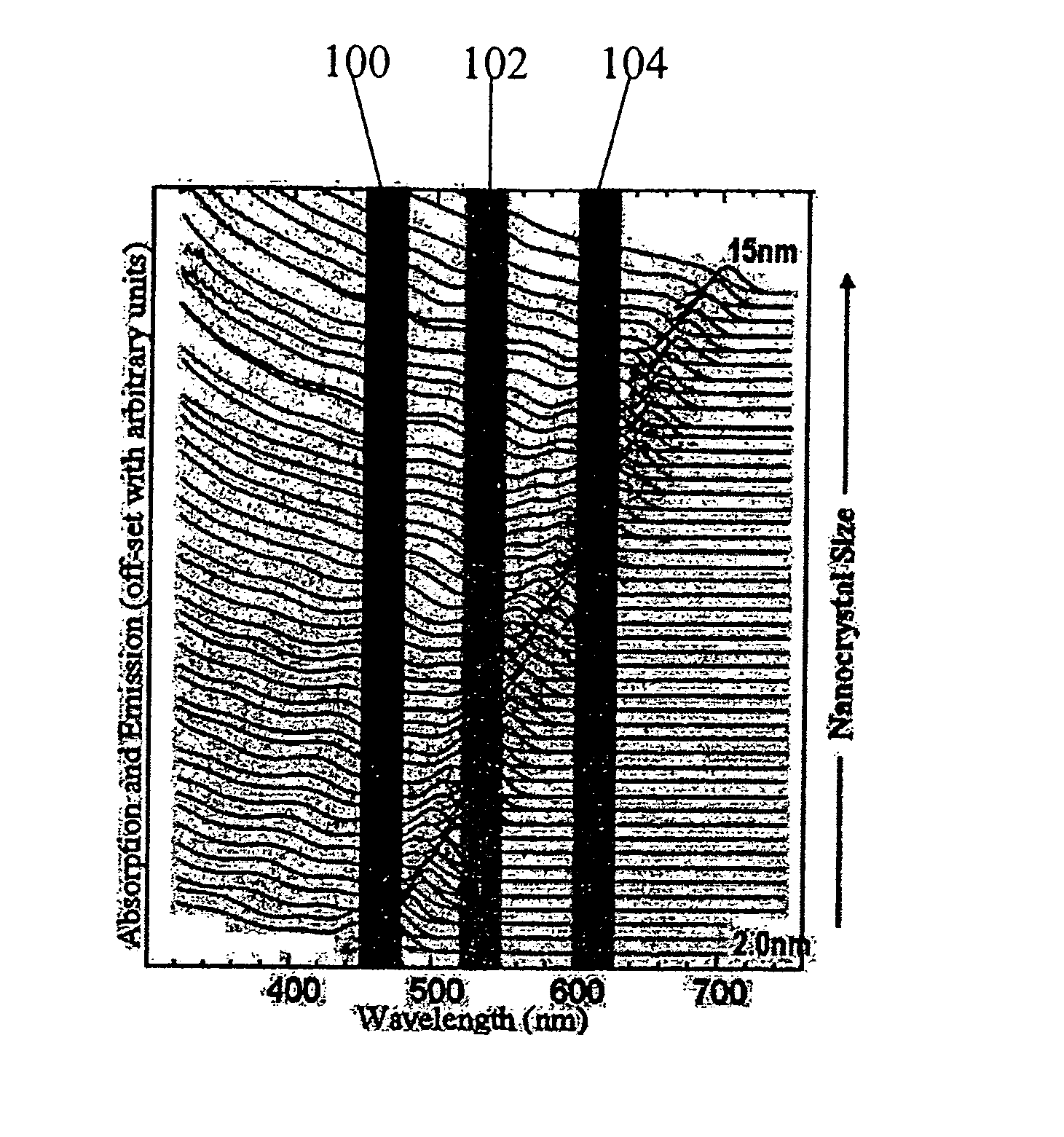

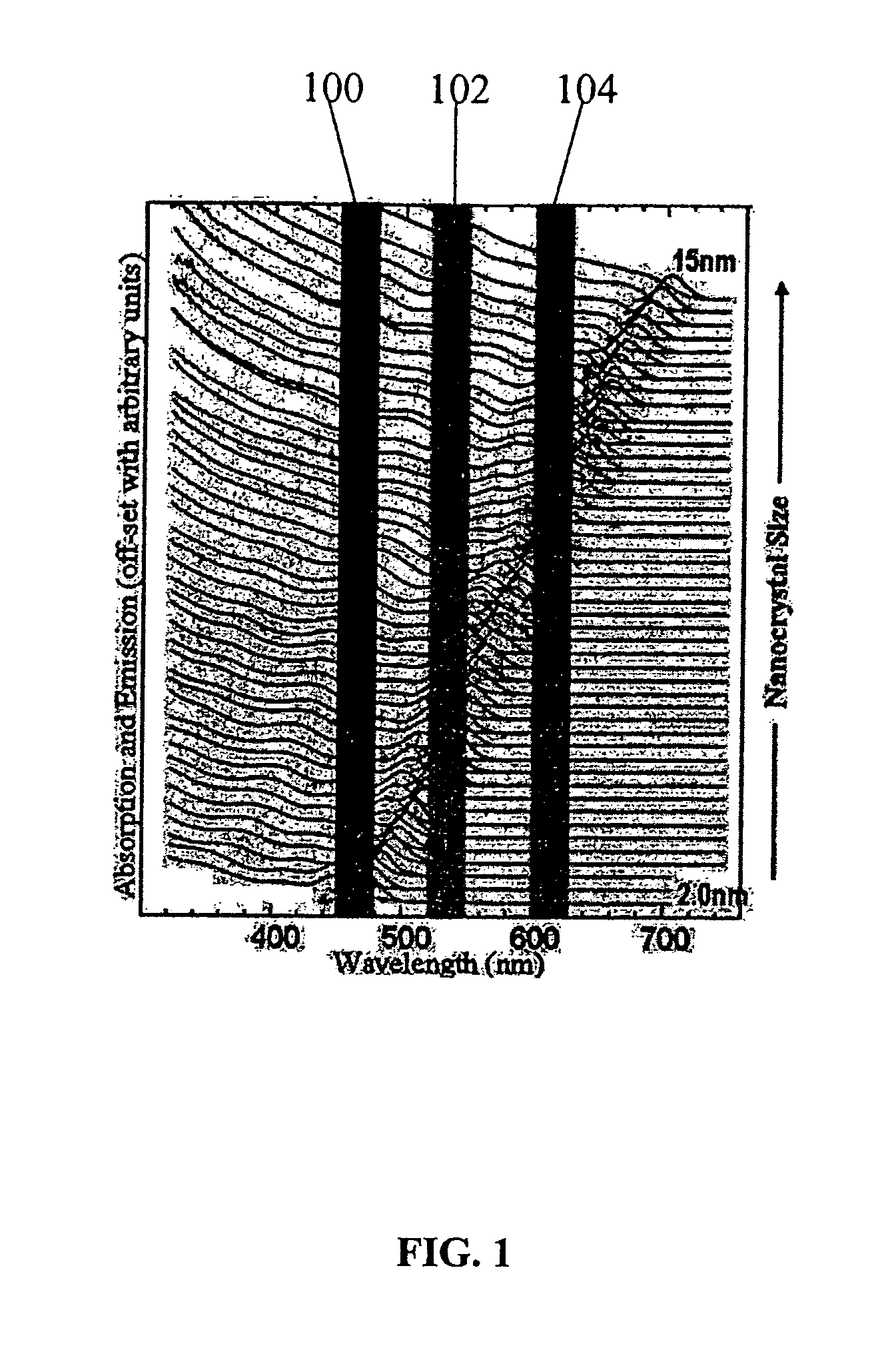

Water-soluble fluorescent nanocrystals

InactiveUS6444143B2High quantum yieldHigh spectral purityMaterial nanotechnologyNanosensorsQuantum yieldOrganic layer

A water soluble semiconductor nanocrystal capable of light emission is provided, including a quantum dot having a selected band gap energy, a layer overcoating the quantum dot, the overcoating layer comprised of a material having a band gap energy greater than that of the quantum dot, and an organic outer layer, the organic layer comprising a compound having a least one linking group for attachment of the compound to the overcoating layer and at least one hydrophilic group space apart from the linking group by a hydrophobic region sufficient to prevent electron charge transfer across the hydrophobic region. The particle size of the nanocrystal core is in the range of about 12.ANG. to about 150.ANG., with a deviation of less than 10% in the core. The coated nanocrystal exhibits photoluminescende having quantum yield of greater than 10% in water.

Owner:MASSACHUSETTS INST OF TECH

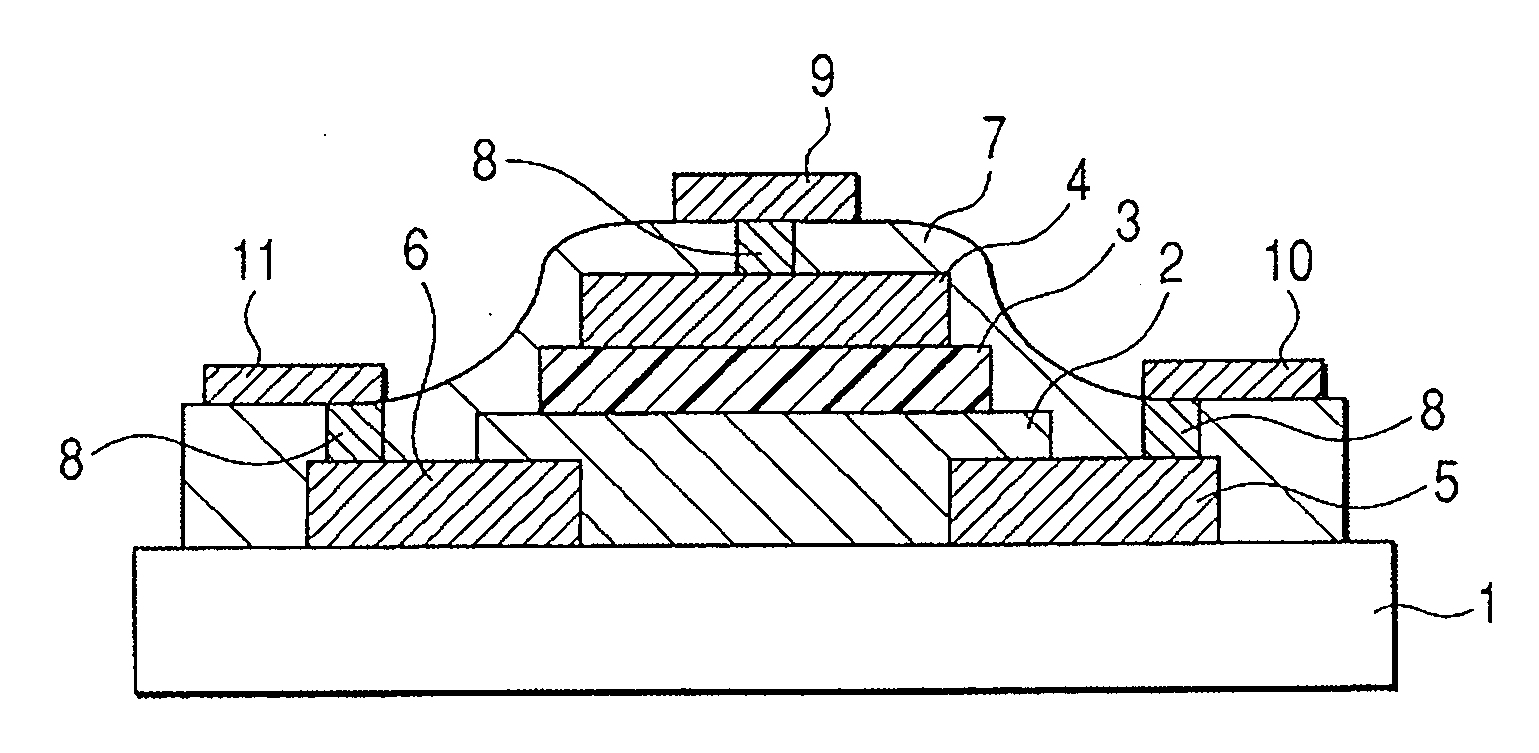

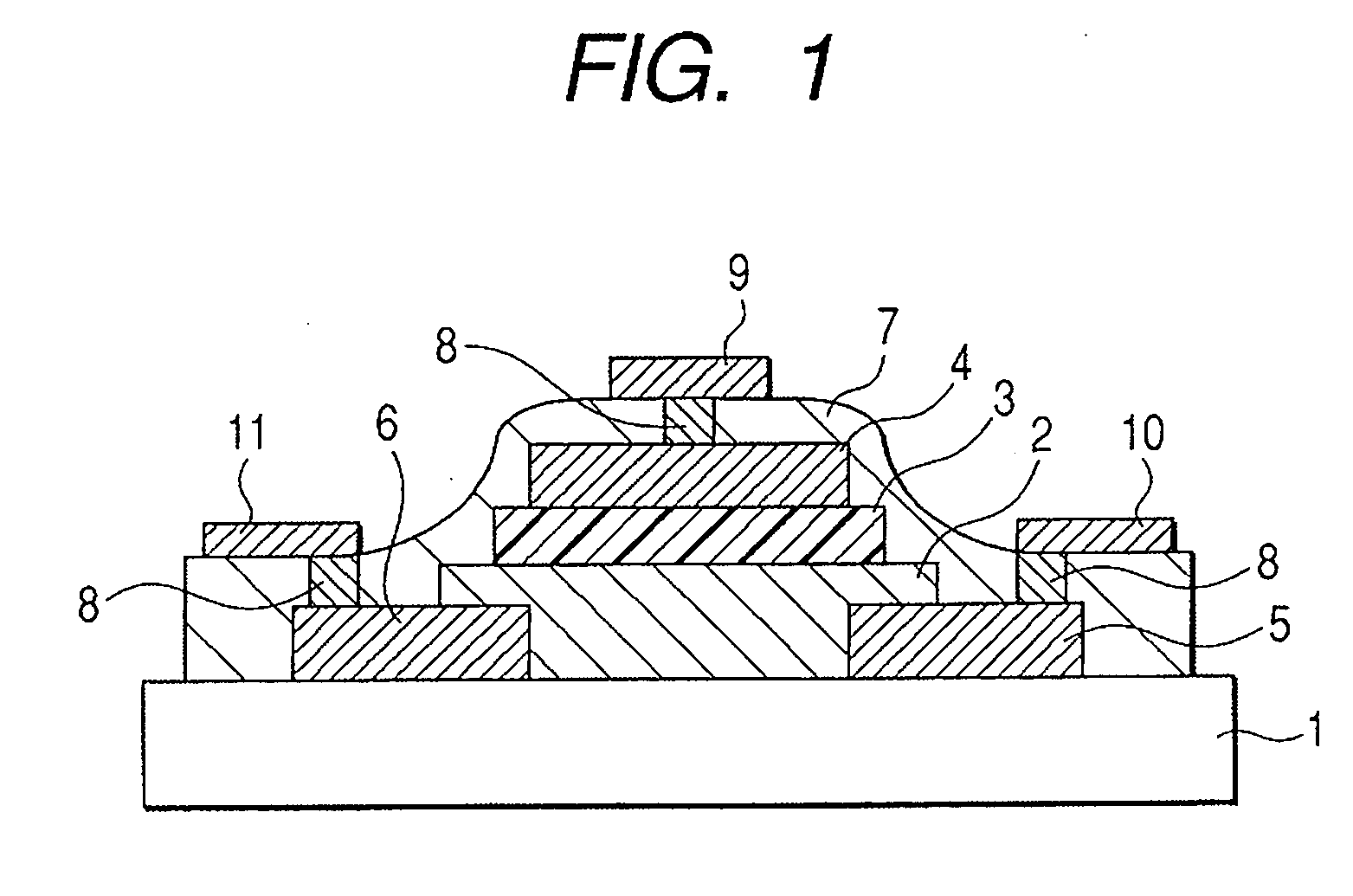

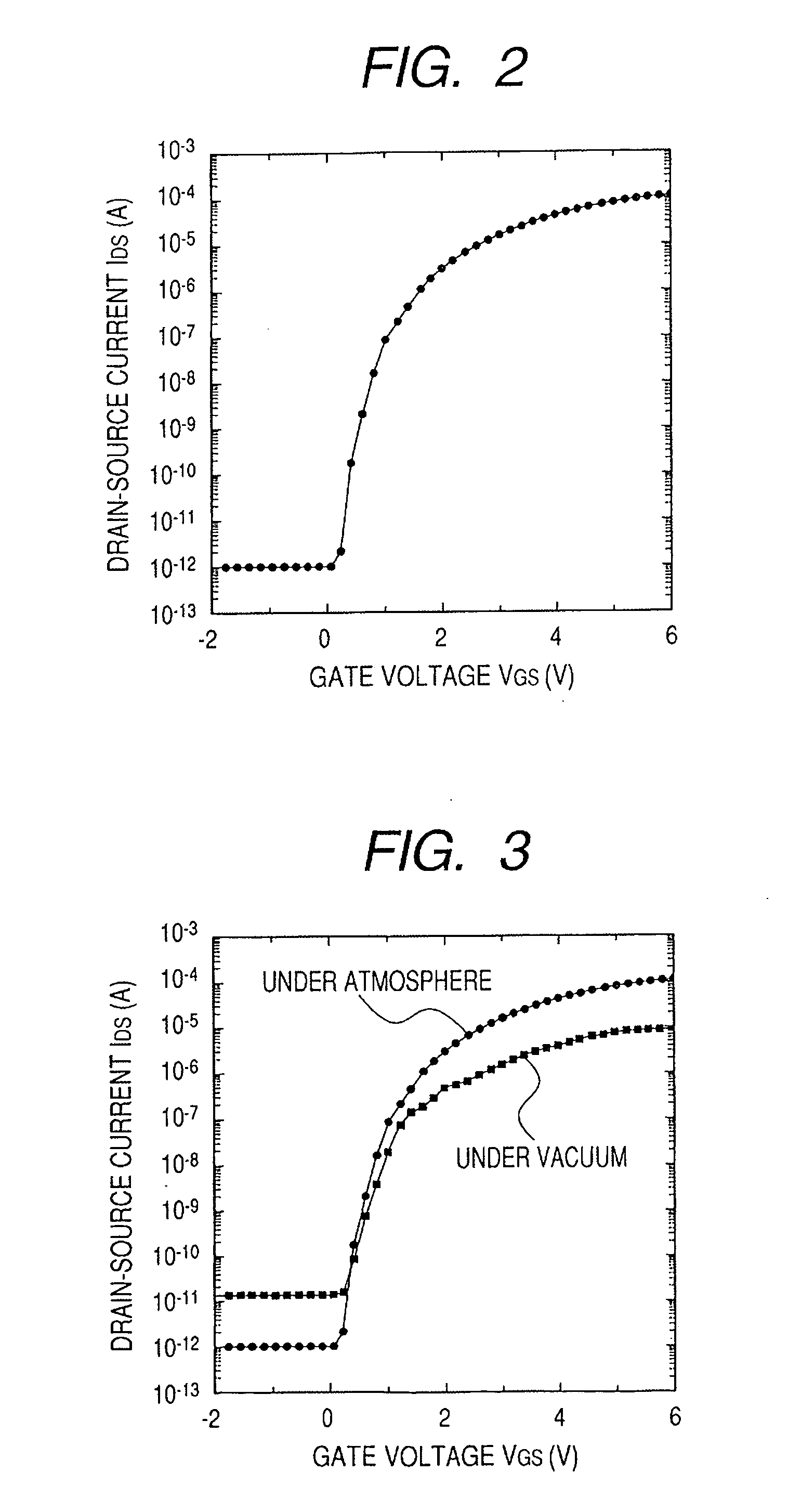

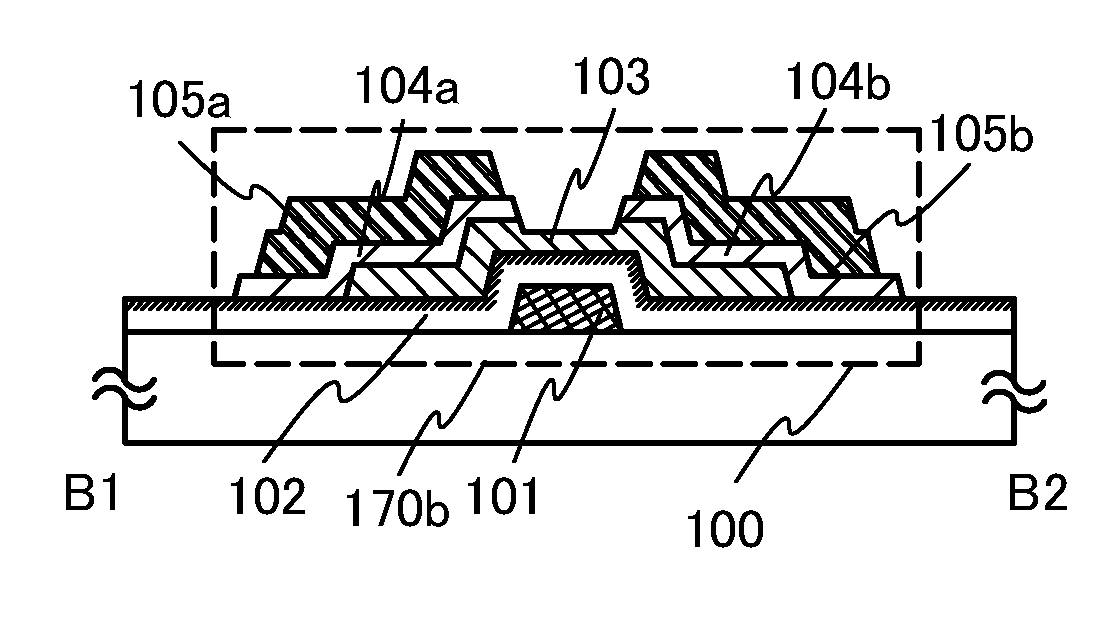

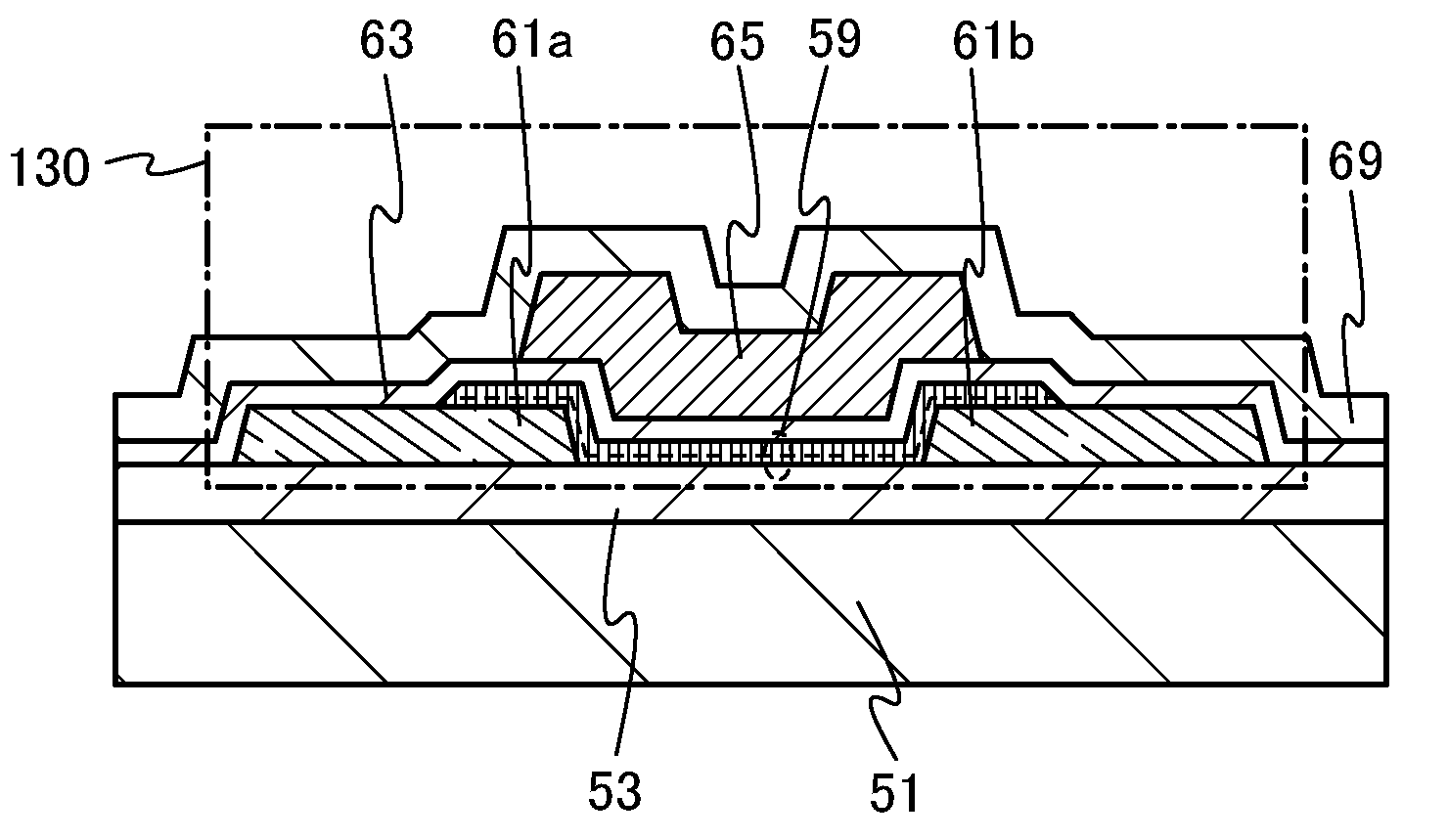

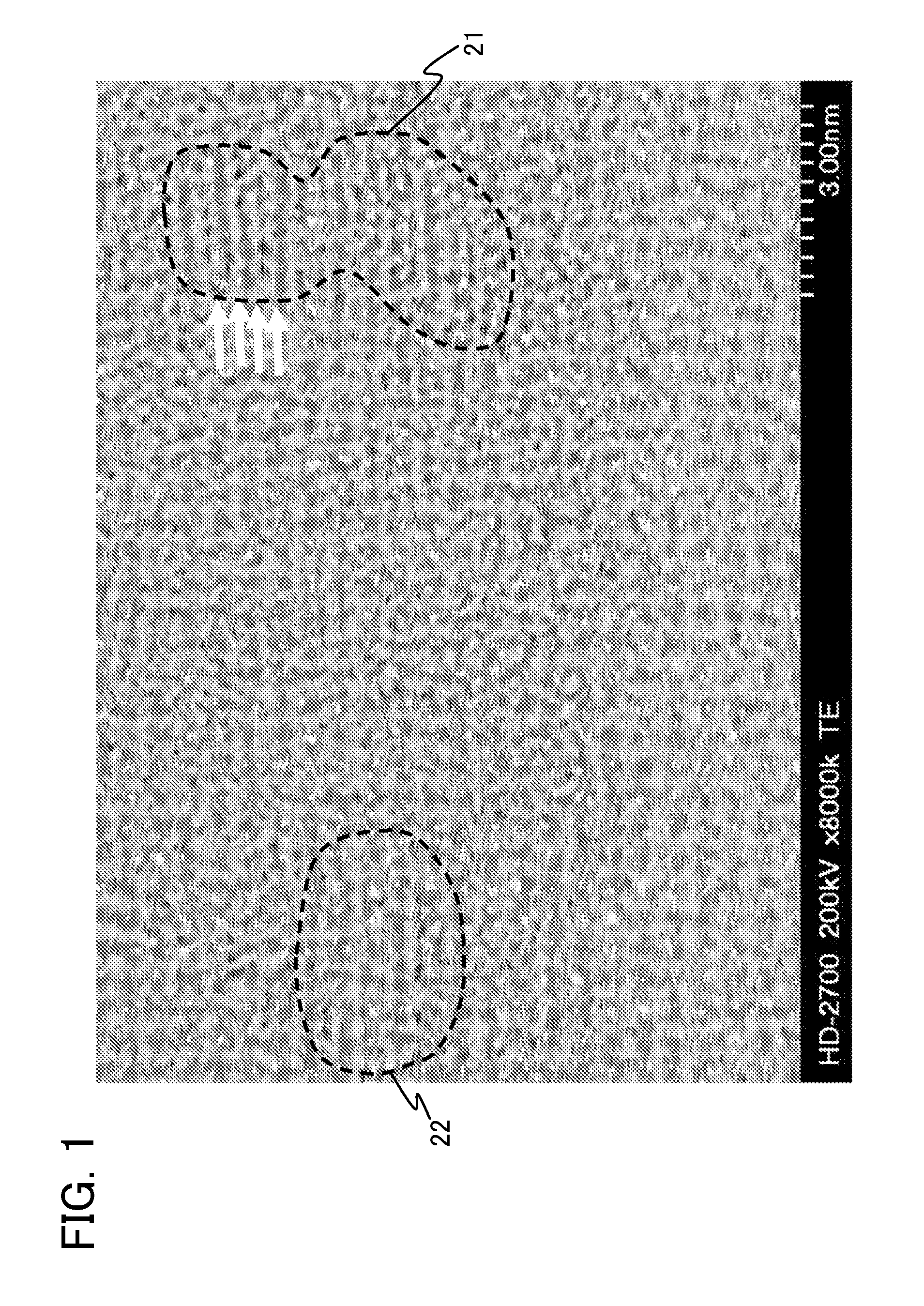

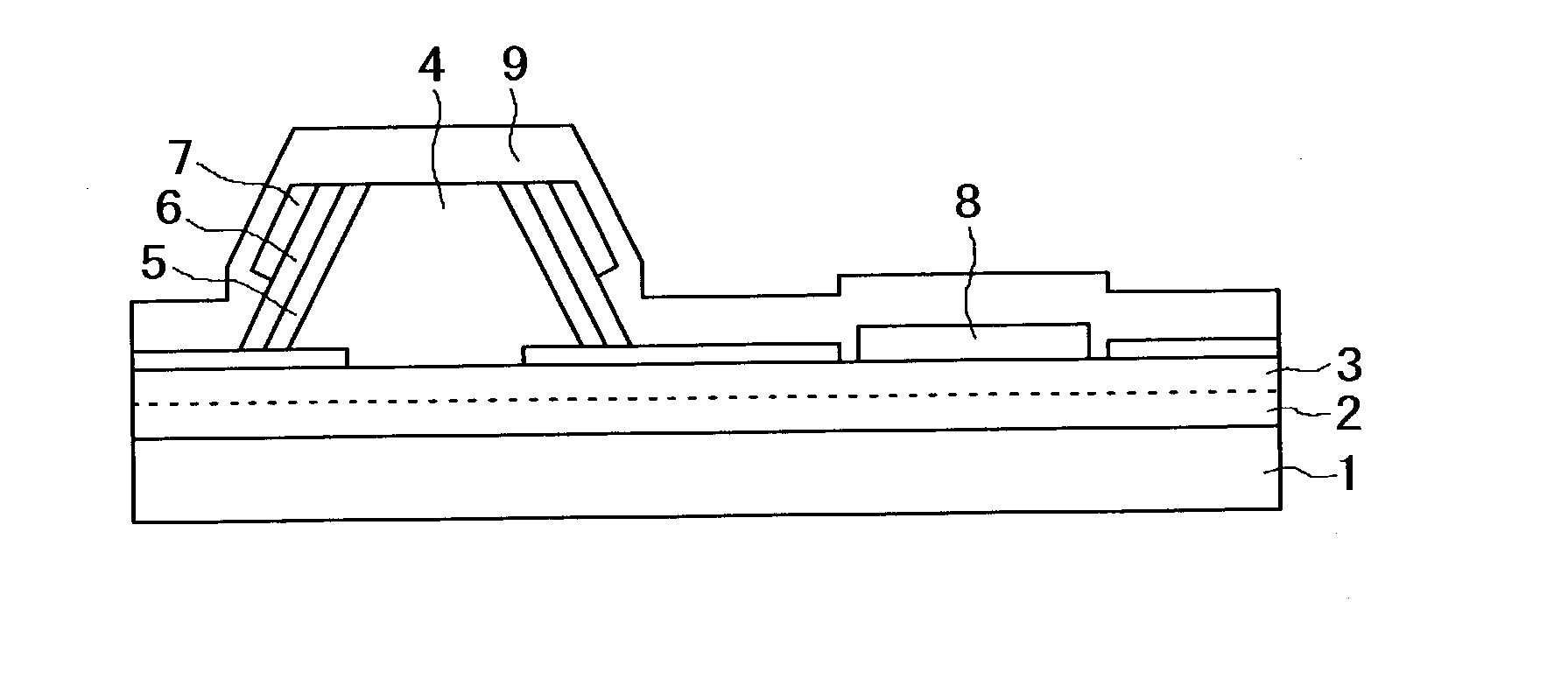

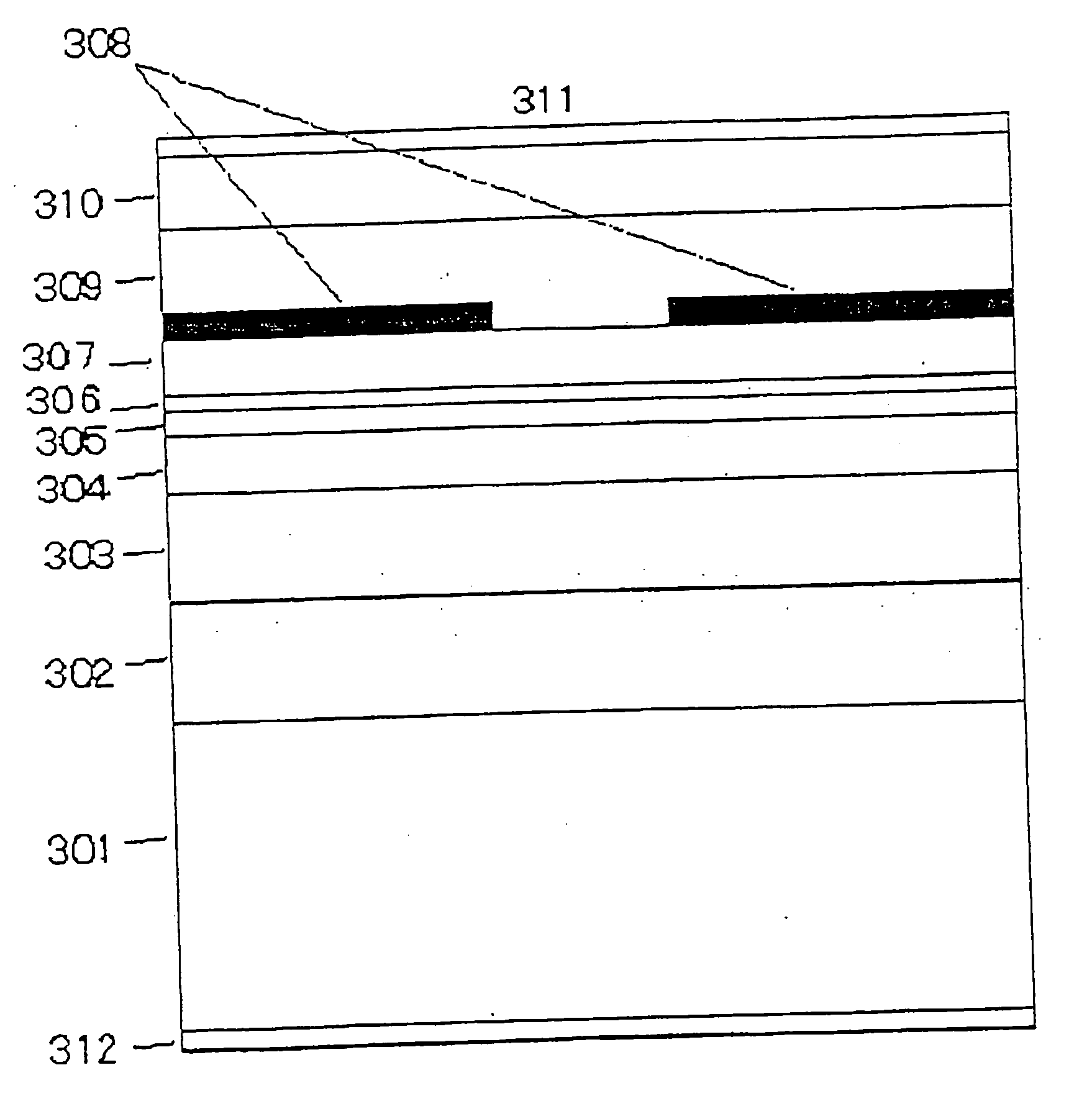

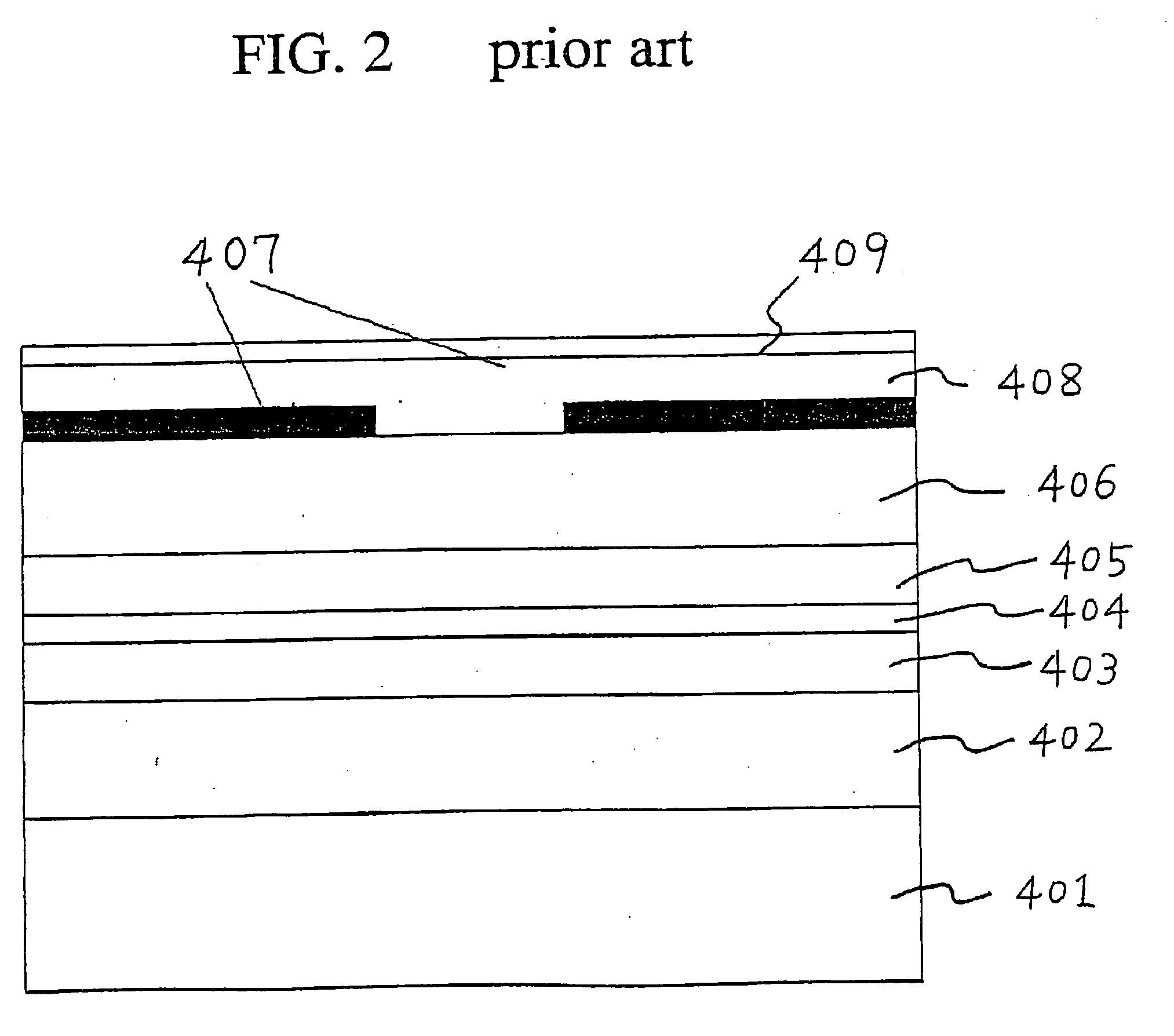

Semiconductor device and method for manufacturing the same

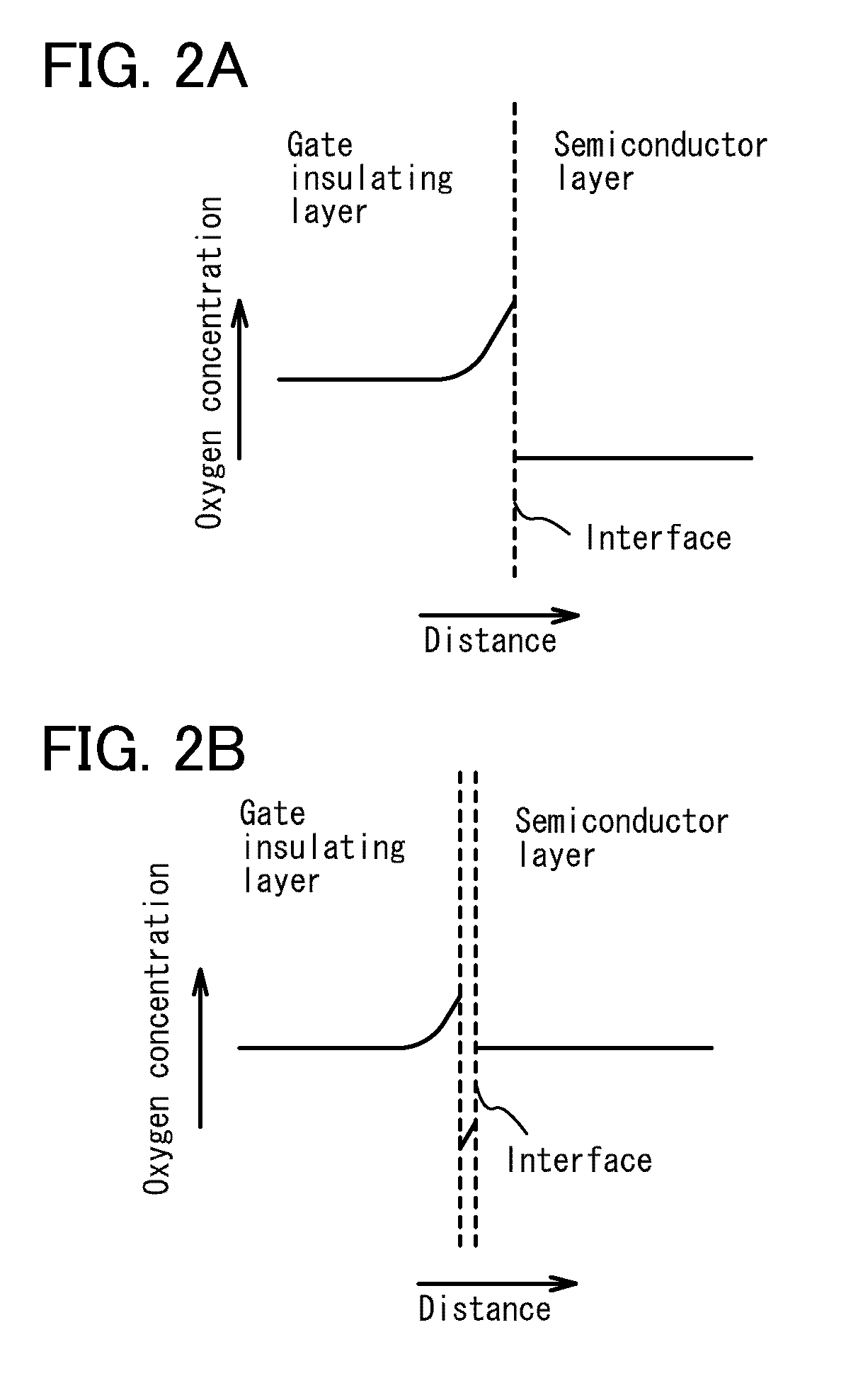

ActiveUS20100051949A1Small currentHigh on-off ratioTransistorStatic indicating devicesMetallic materialsOxygen deficient

A thin film transistor structure in which a source electrode and a drain electrode formed from a metal material are in direct contact with an oxide semiconductor film may lead to high contact resistance. One cause of high contact resistance is that a Schottky junction is formed at a contact plane between the source and drain electrodes and the oxide semiconductor film. An oxygen-deficient oxide semiconductor layer which includes crystal grains with a size of 1 nm to 10 nm and has a higher carrier concentration than the oxide semiconductor film serving as a channel formation region is provided between the oxide semiconductor film and the source and drain electrodes.

Owner:SEMICON ENERGY LAB CO LTD

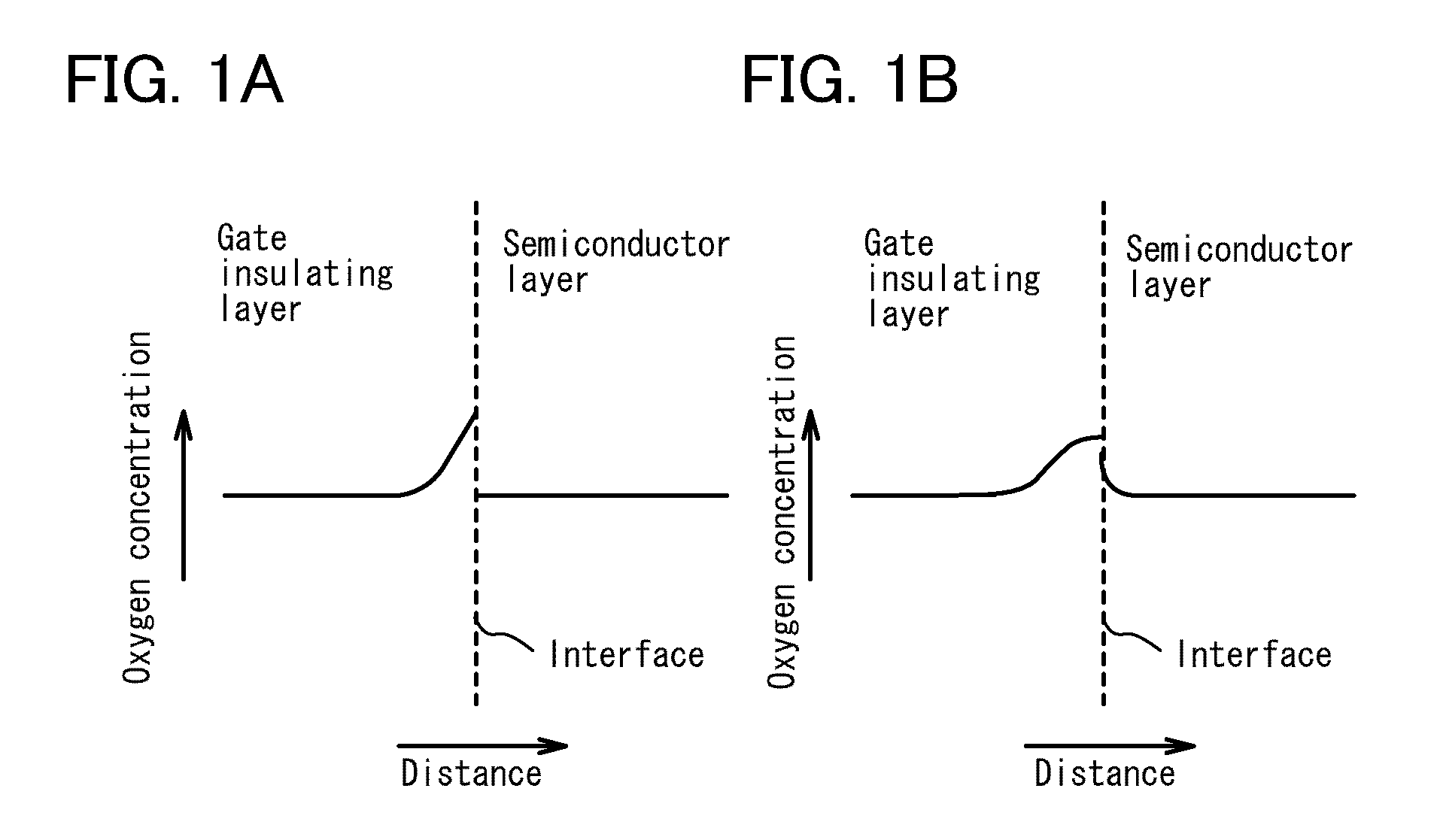

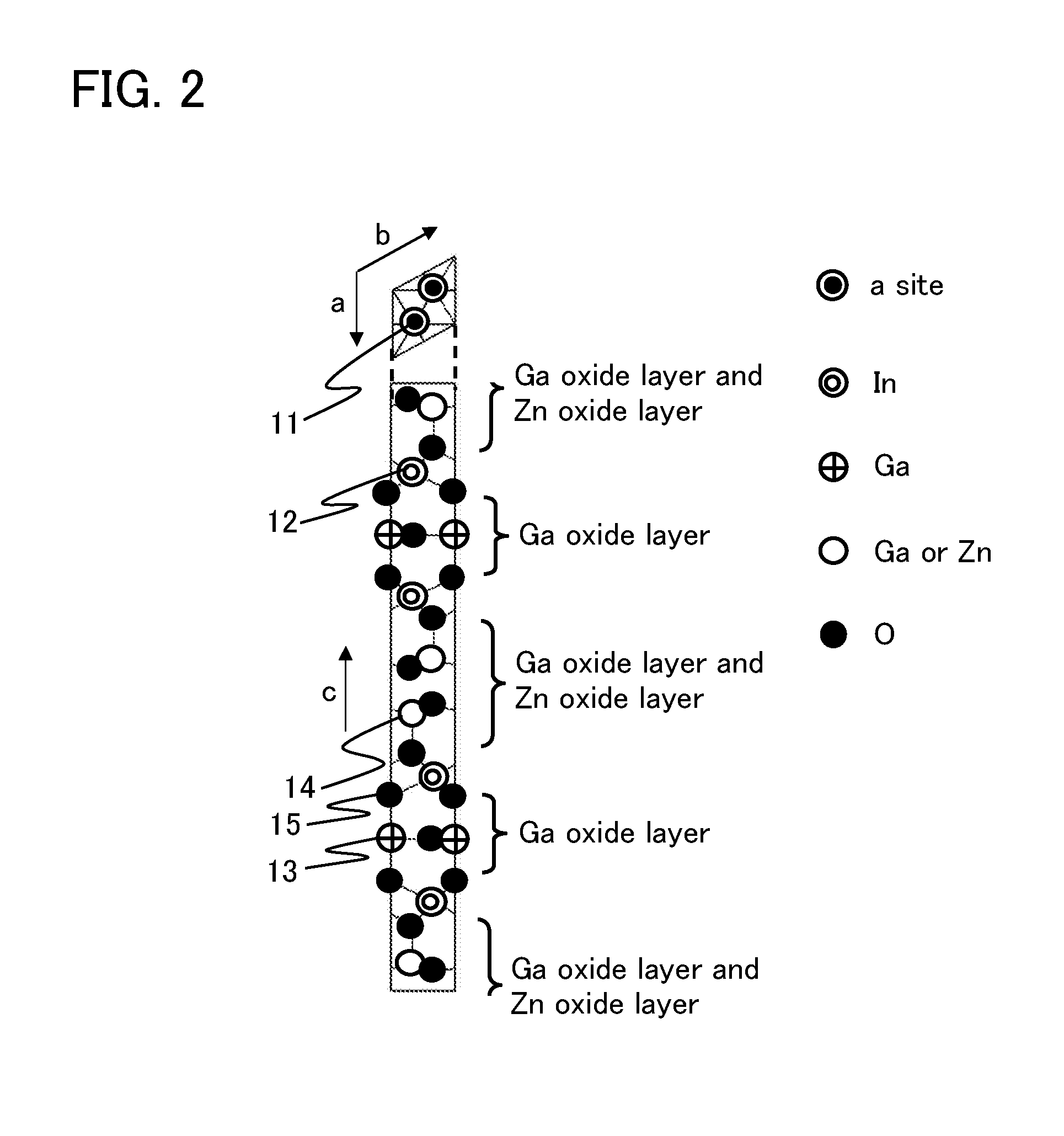

Oxide semiconductor film and semiconductor device

ActiveUS20120138922A1Improve conductivityMore electrically stableElectroluminescent light sourcesSemiconductor devicesUltraviolet lightsIrradiation

An oxide semiconductor film which has more stable electric conductivity is provided. Further, a semiconductor device which has stable electric characteristics and high reliability is provided by using the oxide semiconductor film. An oxide semiconductor film includes a crystalline region, and the crystalline region includes a crystal in which an a-b plane is substantially parallel with a surface of the film and a c-axis is substantially perpendicular to the surface of the film; the oxide semiconductor film has stable electric conductivity and is more electrically stable with respect to irradiation with visible light, ultraviolet light, and the like. By using such an oxide semiconductor film for a transistor, a highly reliable semiconductor device having stable electric characteristics can be provided.

Owner:SEMICON ENERGY LAB CO LTD

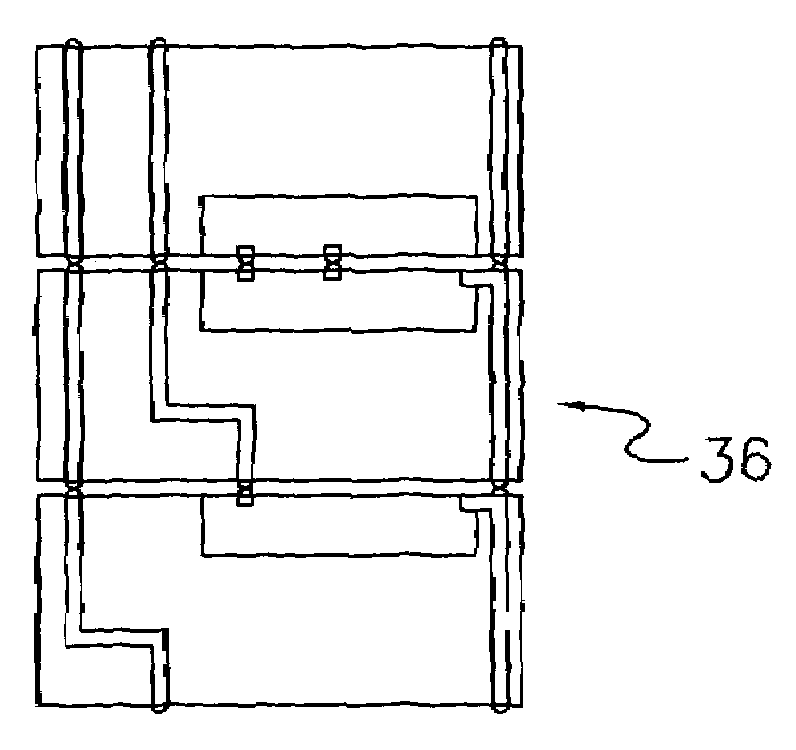

Programmable sub-surface aggregating metallization structure and method of making same

InactiveUS6418049B1Low costHighly manufacturableNanoinformaticsSolid-state devicesCapacitanceElectrical conductor

A programmable sub-surface aggregating metallization sructure ("PSAM") includes an ion conductor such as a chalcogenide-glass which includes metal ions and at least two electrodes disposed at opposing surfaces of the ion conductor. Preferably, the ion conductor includes a chalcogenide material with Group IB or Group IIB metals. One of the two electrodes is preferably configured as a cathode and the other as an anode. When a voltage is applied between the anode and cathode, a metal dendrite grows from the cathode through the ion conductor towards the anode. The growth rate of the dendrite may be stopped by removing the voltage or the dendrite may be retracted back towards the cathode by reversing the voltage polarity at the anode and cathode. When a voltage is applied for a sufficient length of time, a continuous metal dendrite grows through the ion conductor and connects the electrodes, thereby shorting the device. The continuous metal dendrite then can be broken by applying another voltage. The break in the metal dendrite can be reclosed by applying yet another voltage. Changes in the length of the dendrite or the presence of a break in the dendrite affect the resistance, capacitance, and impedance of the PSAM.

Owner:THE ARIZONA BOARD OF REGENTS ON BEHALF OF THE UNIV OF ARIZONA +1

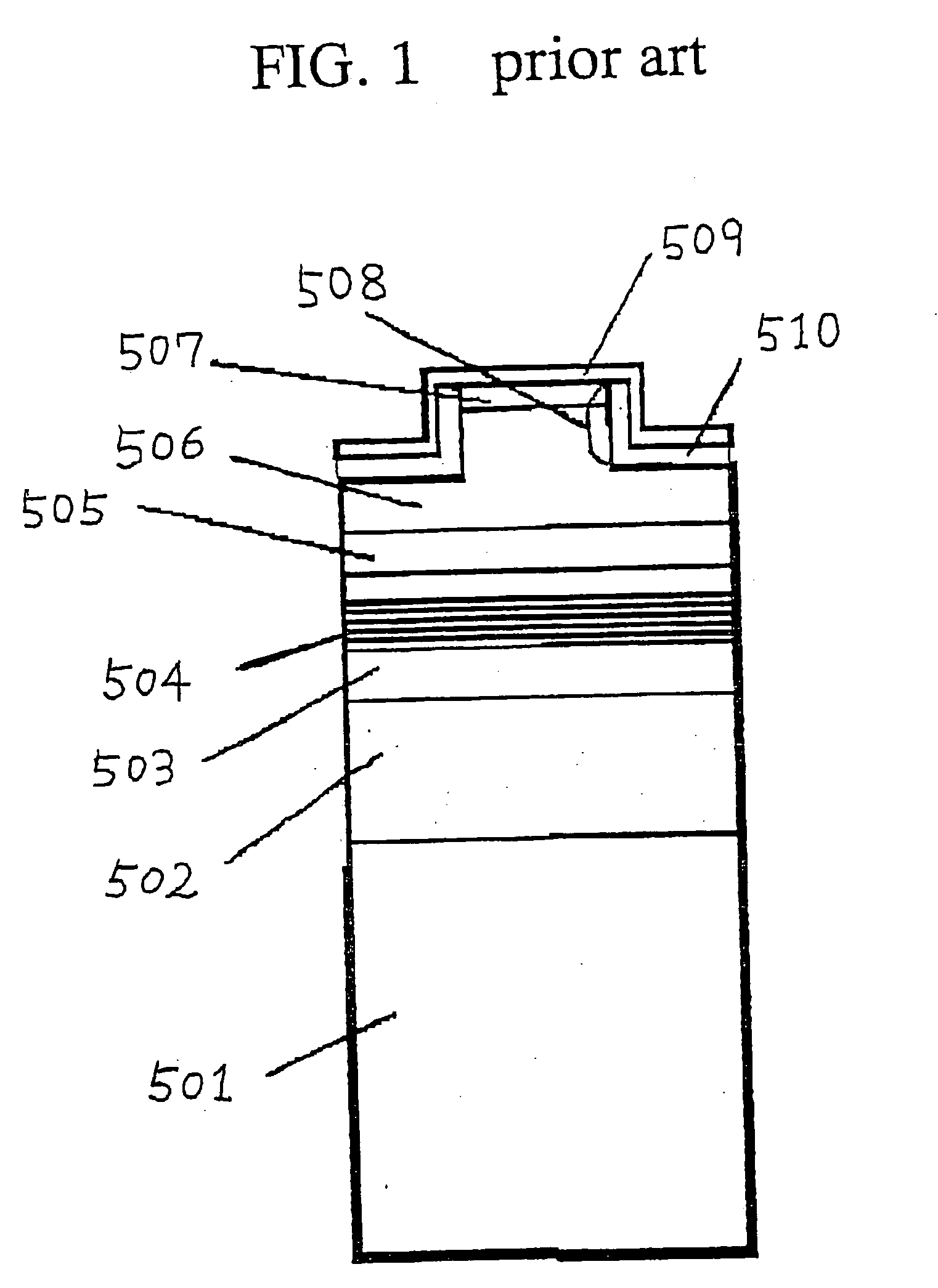

Semiconductor light emitting device and fabrication method thereof

InactiveUS6967353B2Improve luminous efficiencyIncrease brightnessSolid-state devicesSemiconductor/solid-state device manufacturingCrystal planeActive layer

A semiconductor light emitting device includes a crystal layer formed on a substrate, the crystal layer having a tilt crystal plane tilted from the principal plane of the substrate, and a first conductive type layer, an active layer, and a second conductive type layer, which are formed on the crystal layer in such a manner as to extend within planes parallel to the tilt crystal plane, wherein the device has a shape formed by removing the apex and its vicinity of the stacked layer structure formed on the substrate. Such a semiconductor light emitting device is excellent in luminous efficiency even if the device has a three-dimensional device structure. The present invention also provides a method of fabricating the above semiconductor light emitting device.

Owner:SAMSUNG ELECTRONICS CO LTD

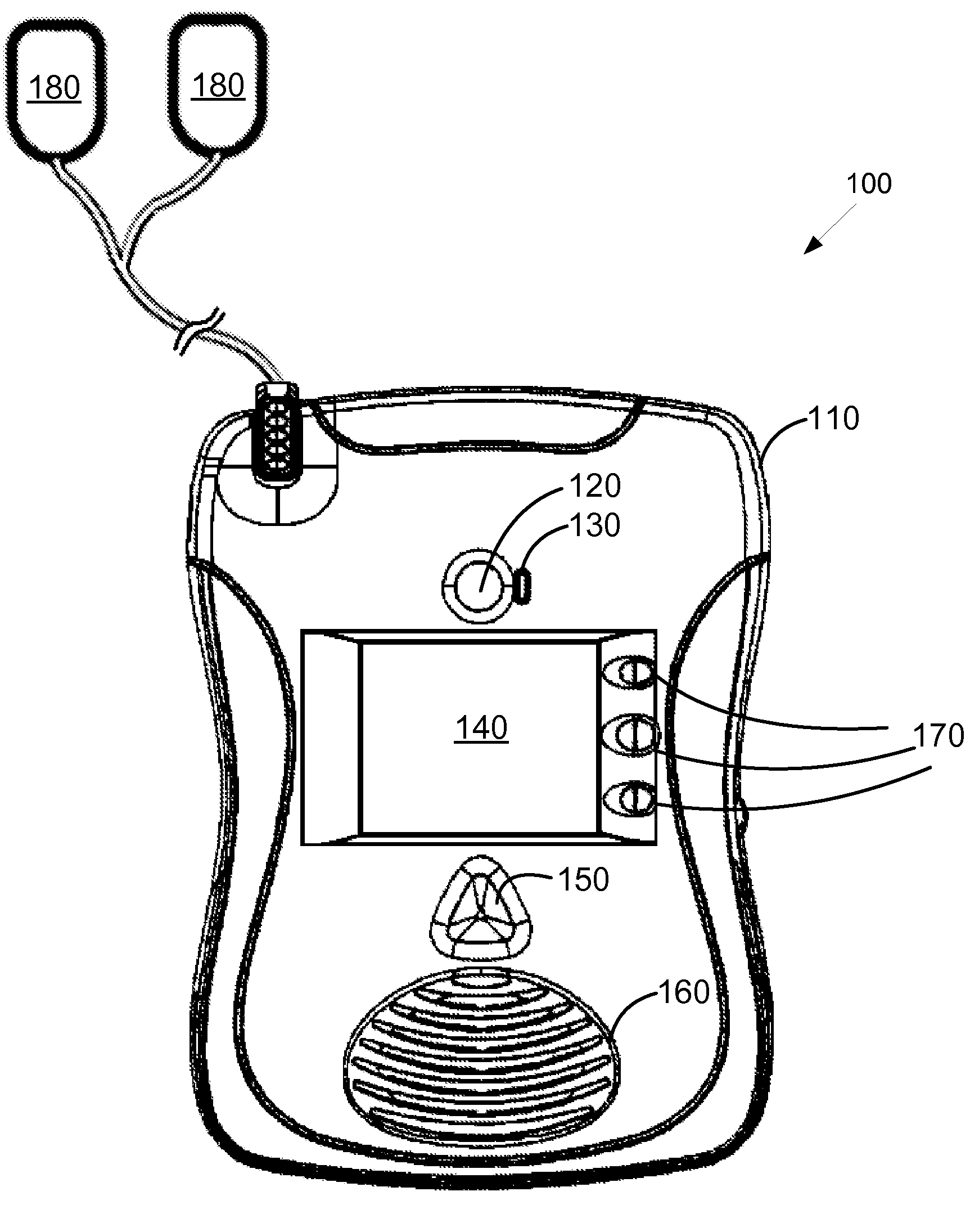

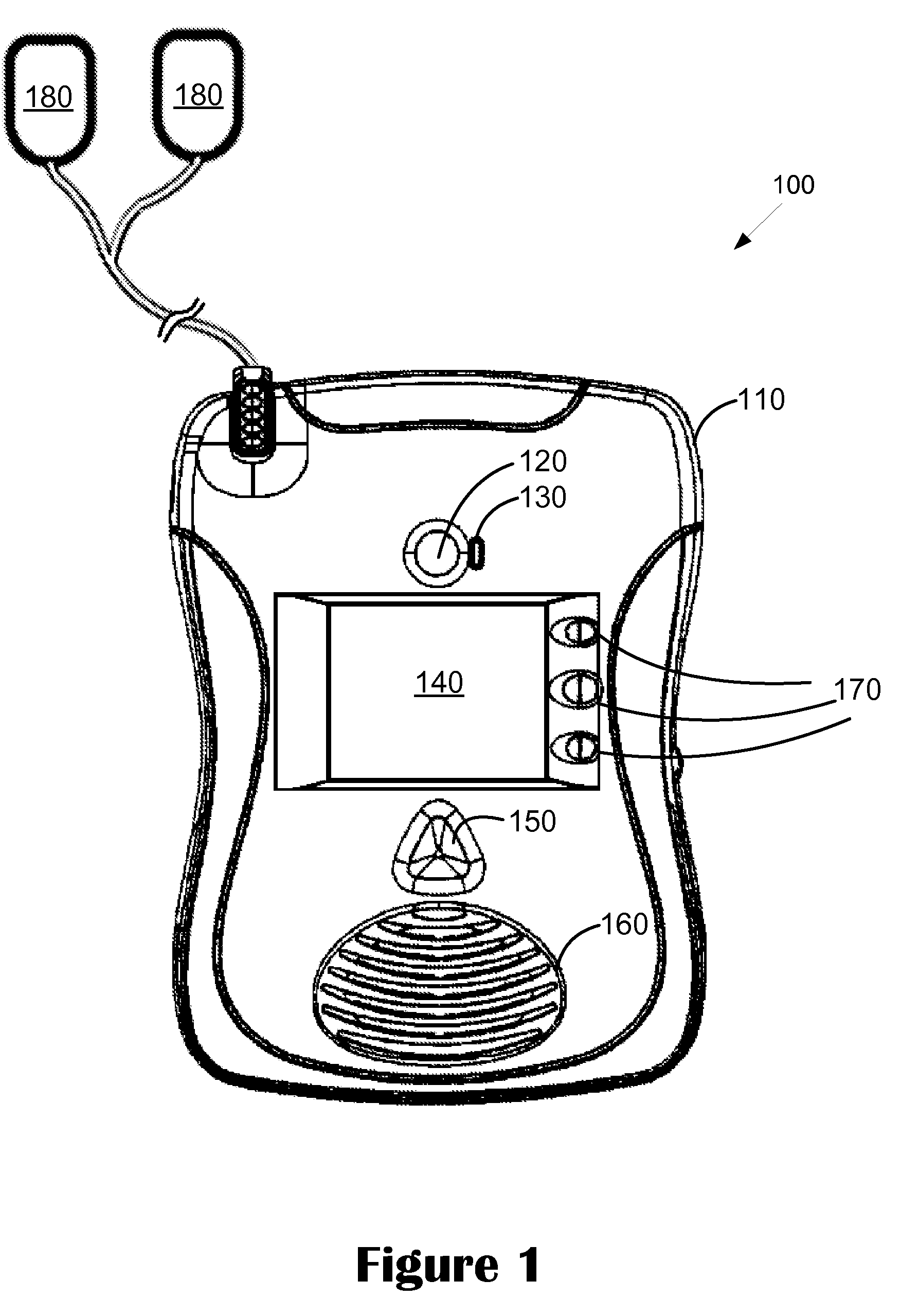

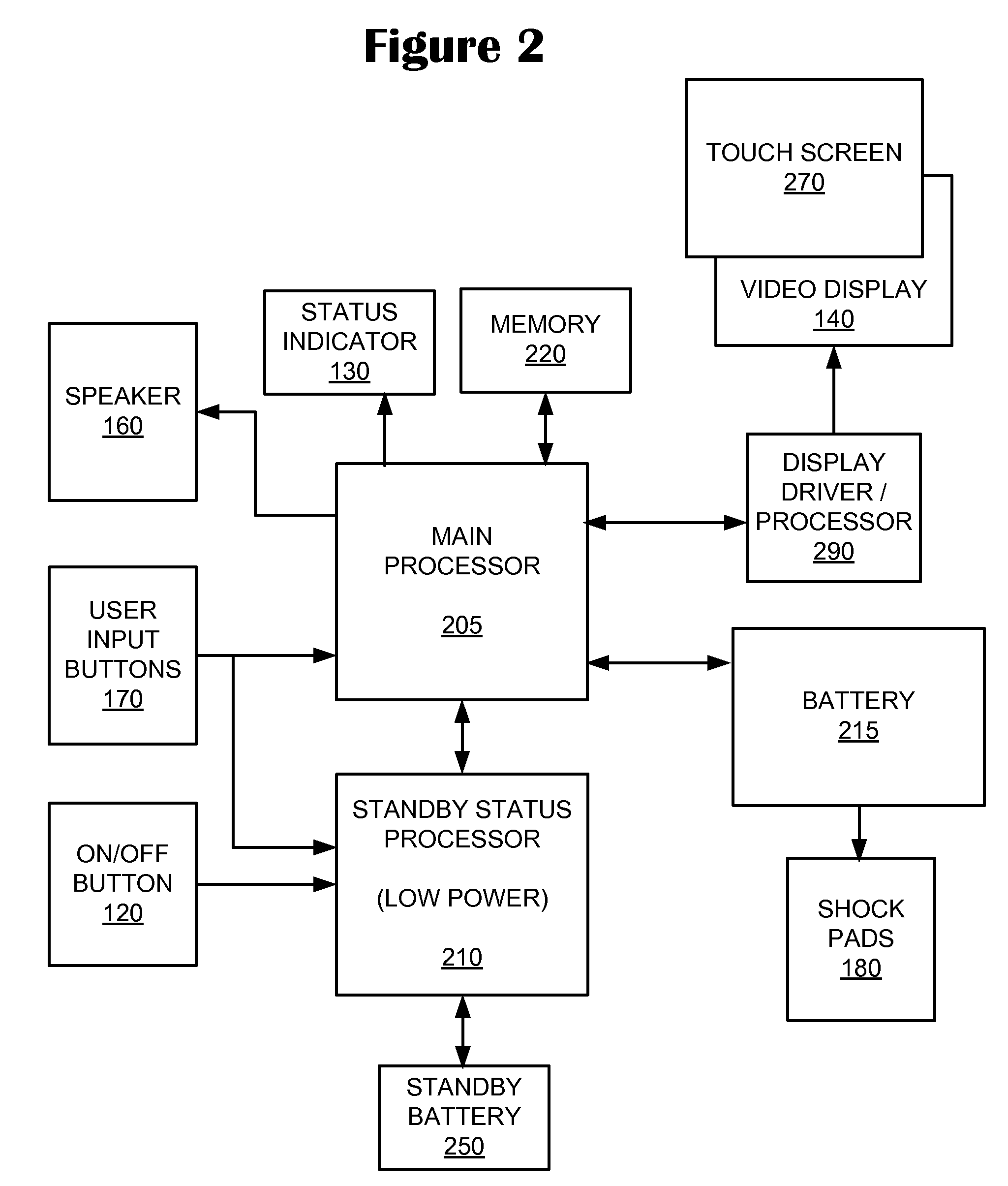

System and Method for Conditioning a Lithium Battery in an Automatic External Defibrillator

An inventive system and method de-passivates a direct current (DC) power source of an Automatic External Defibrillator (AED), such as an AED lithium battery. The system includes a main processor and standby processor. The standby processor monitors the age and usage of the battery. Based on the status of the monitored parameters, the system executes a conditioning discharge to remove a layer of salt crystals on the DC power source.

Owner:DEFIBTECH

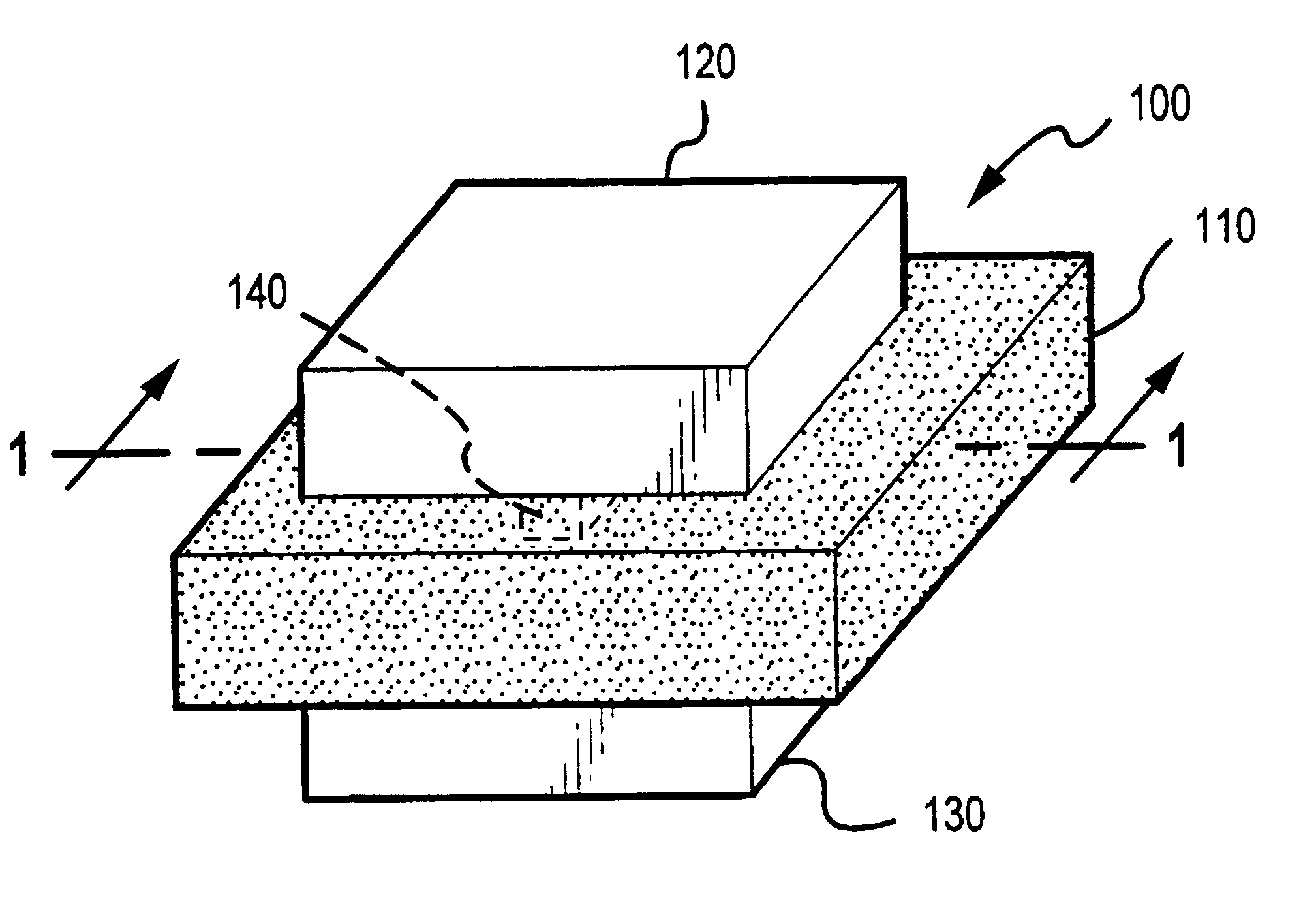

Space-saving packaging of electronic circuits

InactiveUS7071546B2Simplifies electrical connectionsMinimized volumeSemiconductor/solid-state device detailsSolid-state devicesInterior spaceSurface mounting

An apparatus and packaging method for stacking a plurality of integrated circuit substrates, i.e., substrates having integrated circuits formed as integral portions of the substrates, which provides interconnection paths through the substrates to simplify electrical connections between the integrated circuits while facilitating minimization of the volume and customization of the three dimensional package size to conform to the available internal space within a housing, e.g., one used in an implantabie device where package volume is at a premium. Furthermore, an internal cavity can be created by the stacked formation that is suitable for mounting of a surface mount device, e.g., a crystal or the like.

Owner:ALFRED E MANN FOUND FOR SCI RES

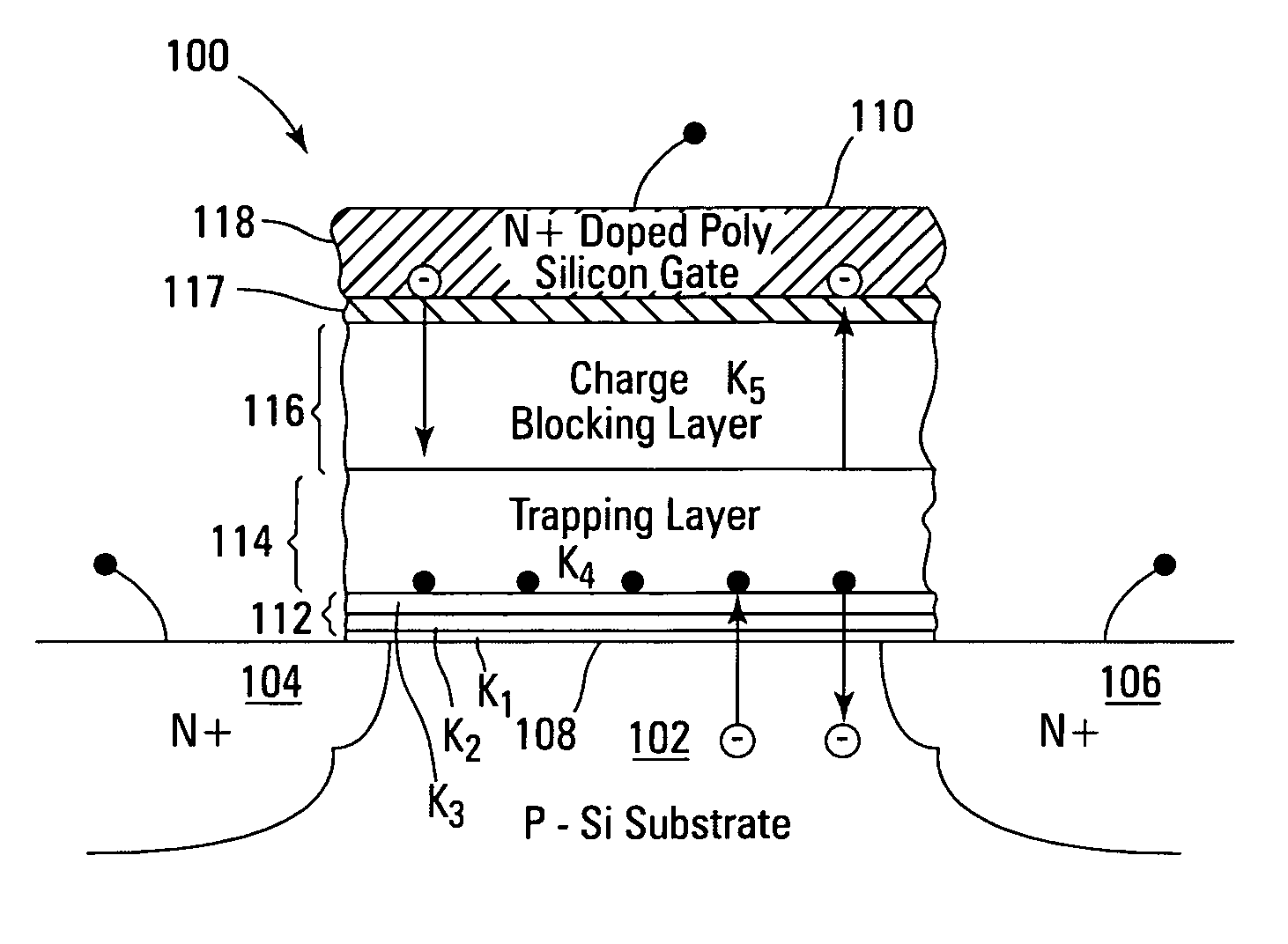

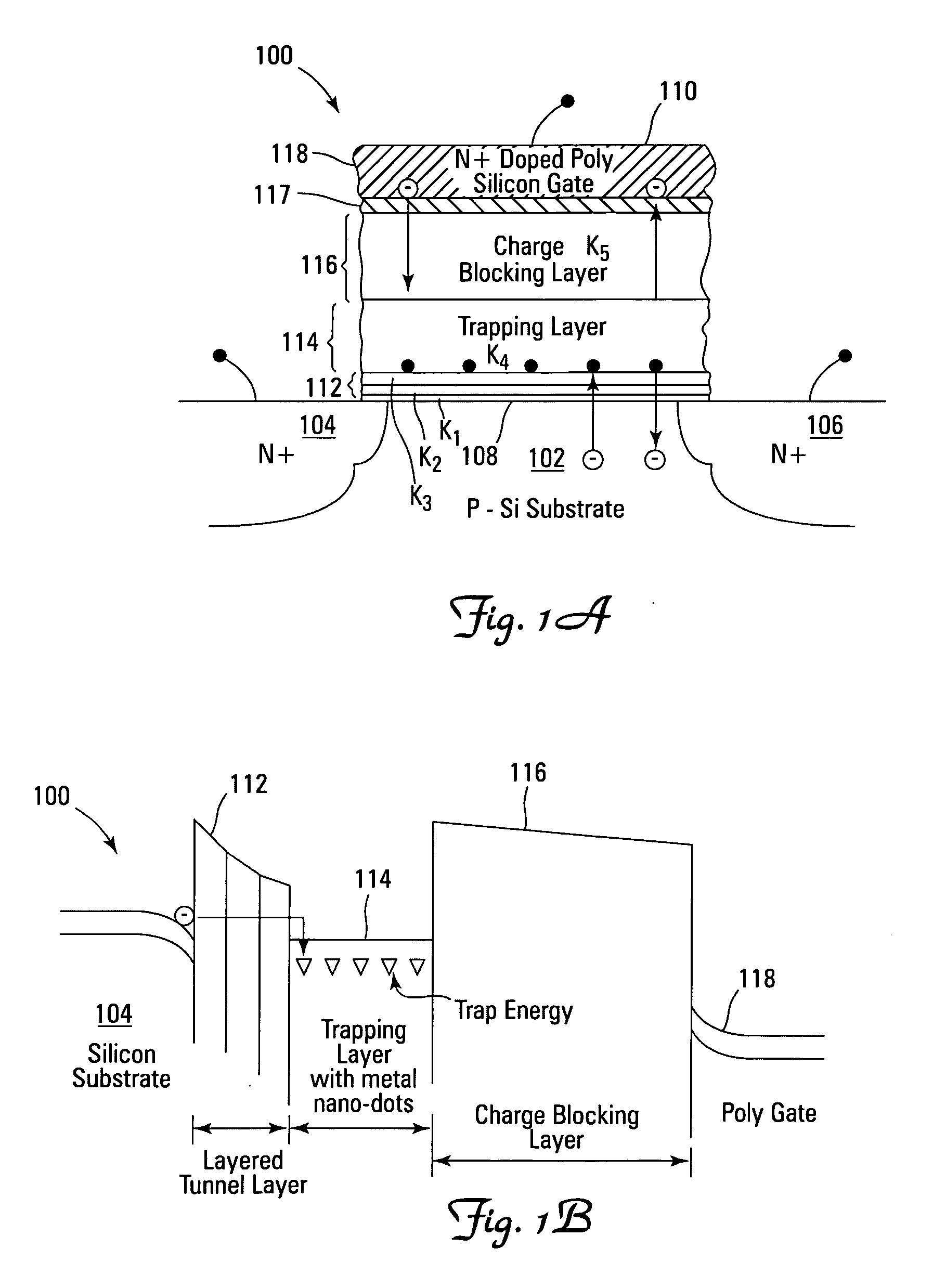

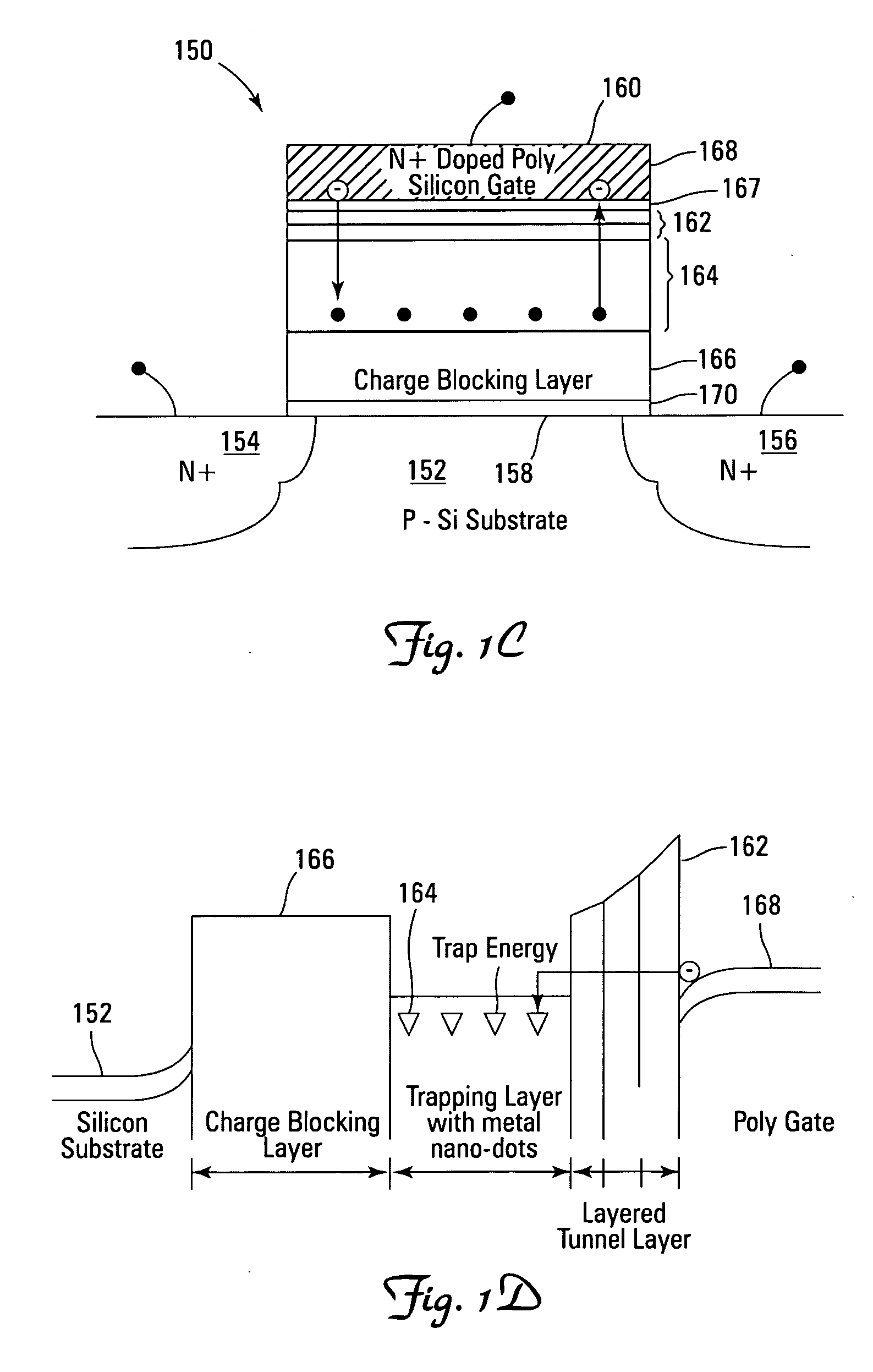

Novel low power non-volatile memory and gate stack

ActiveUS20060261401A1High charge blocking barrierExcellent charge retentionTransistorNanoinformaticsCharge retentionLow voltage

Non-volatile memory devices and arrays are described that facilitate the use of band-gap engineered gate stacks with asymmetric tunnel barriers in reverse and normal mode floating node memory cells in NOR or NAND memory architectures that allow for direct tunnel programming and erase, while maintaining high charge blocking barriers and deep carrier trapping sites for good charge retention. The low voltage direct tunneling program and erase capability reduces damage to the gate stack and the crystal lattice from high energy carriers, reducing write fatigue and enhancing device lifespan. The low voltage direct tunnel program and erase capability also enables size reduction through low voltage design and further device feature scaling. Memory cells of the present invention also allow multiple bit storage. These characteristics allow memory device embodiments of the present invention to operate within the definition of a universal memory, capable of replacing both DRAM and ROM in a system.

Owner:MICRON TECH INC

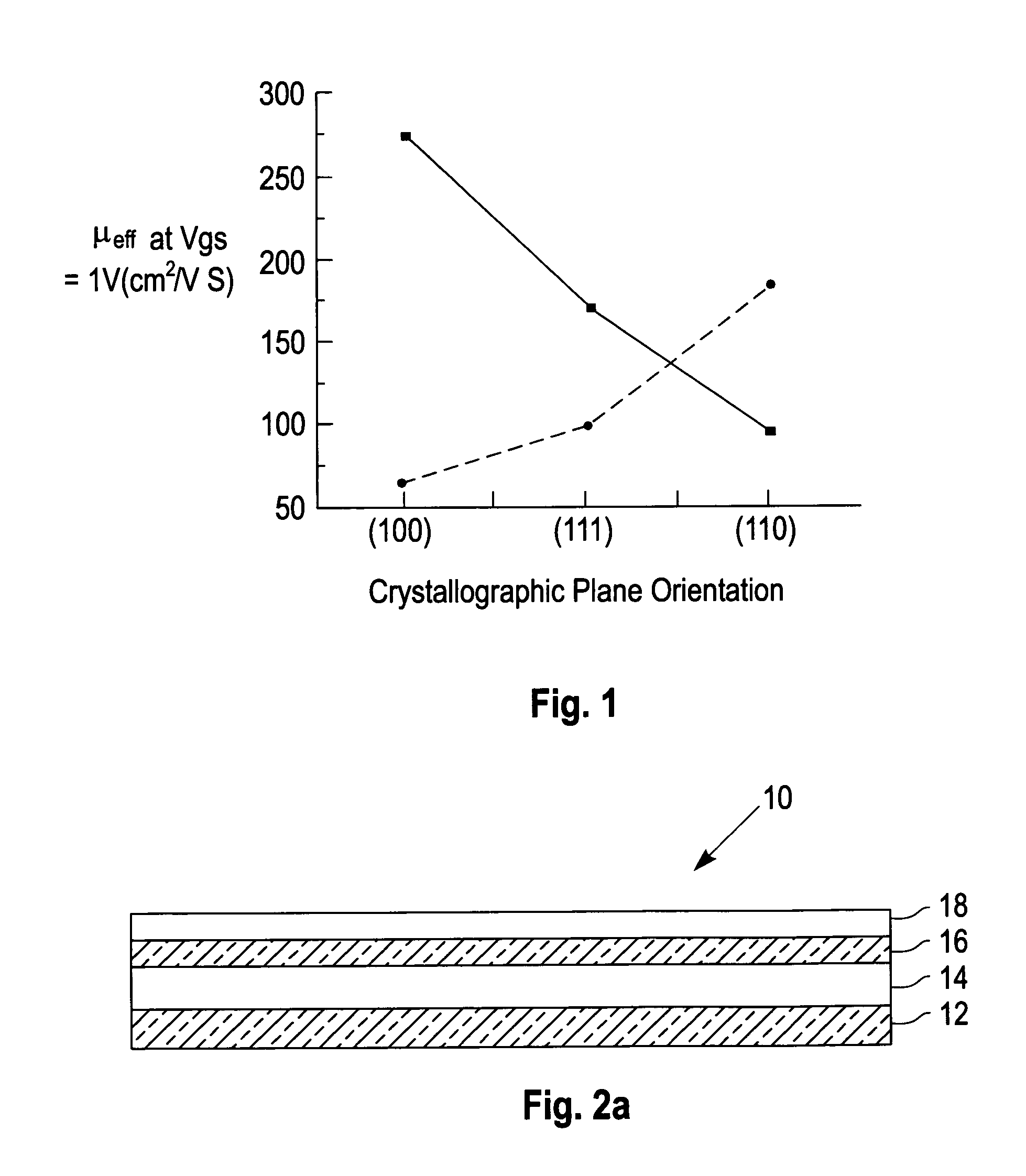

High-performance CMOS SOI devices on hybrid crystal-oriented substrates

InactiveUS6995456B2Type of goodDifferent typeTransistorSolid-state devicesEngineeringIntegrated circuit

Disclosed is an integrated circuit structure that has a substrate having at least two types of crystalline orientations. The first-type transistors are on first portions of the substrate that have a first type of crystalline orientation and second-type transistors are on second portions of the substrate that have a second type of crystalline orientation. The straining layer is above the first-type transistors and the second-type transistors. Further, the straining layer can be strained above the first-type transistors and relaxed above the second-type transistors.

Owner:INT BUSINESS MASCH CORP

Inorganic Bulk Multijunction Materials and Processes for Preparing the Same

InactiveUS20110220874A1Material nanotechnologyFinal product manufactureAlloySemiconductor nanocrystals

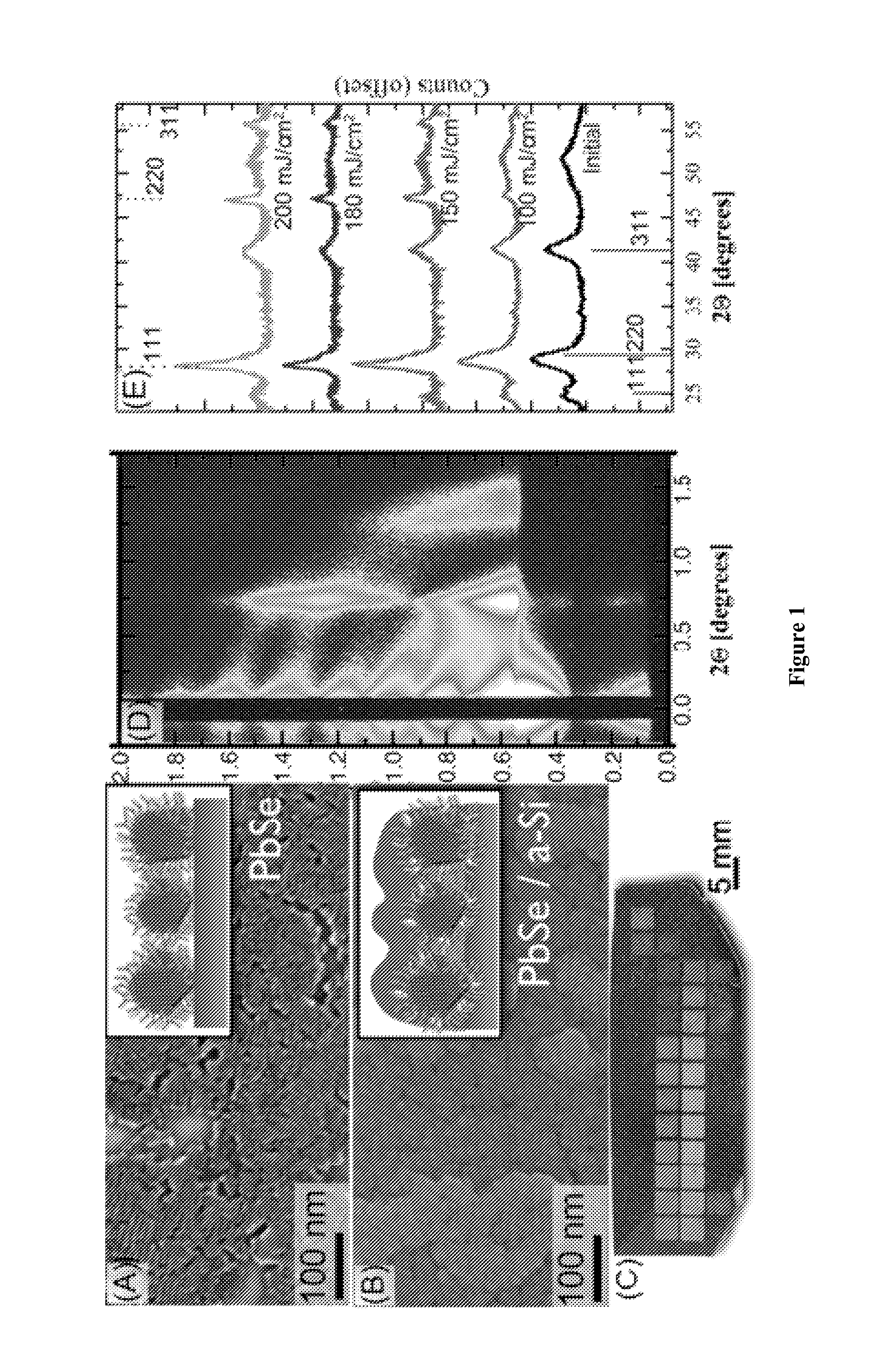

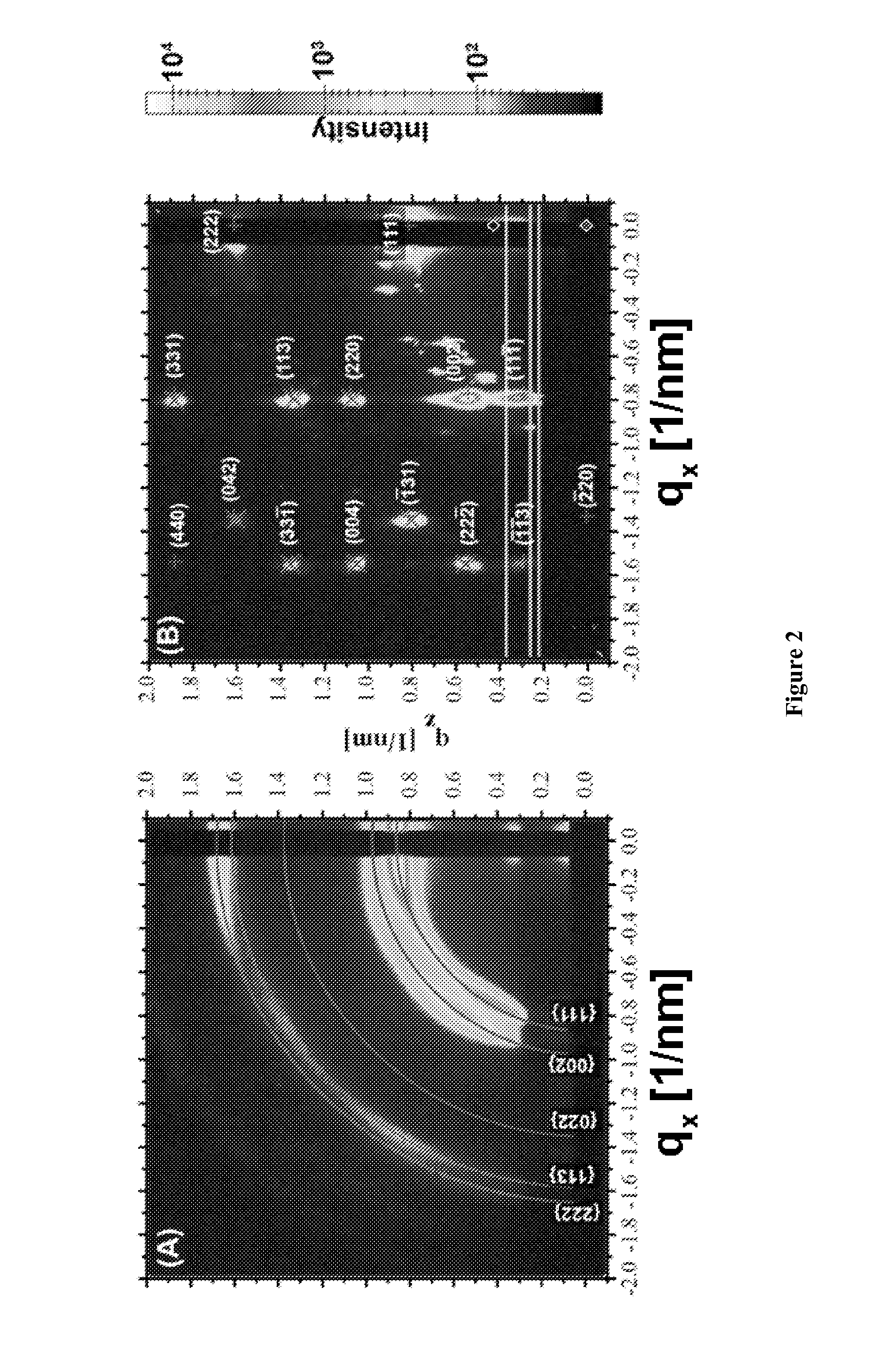

A nanostructured composite material comprising semiconductor nanocrystals in a crystalline semiconductor matrix. Suitable nanocrystals include silicon, germanium, and silicon-germanium alloys, and lead salts such as PbS, PbSe, and PbTe. Suitable crystalline semiconductor matrix materials include Si and silicon-germanium alloys. A process for making the nanostructured composite materials. Devices comprising nanostructured composite materials.

Owner:CORNELL UNIVERSITY

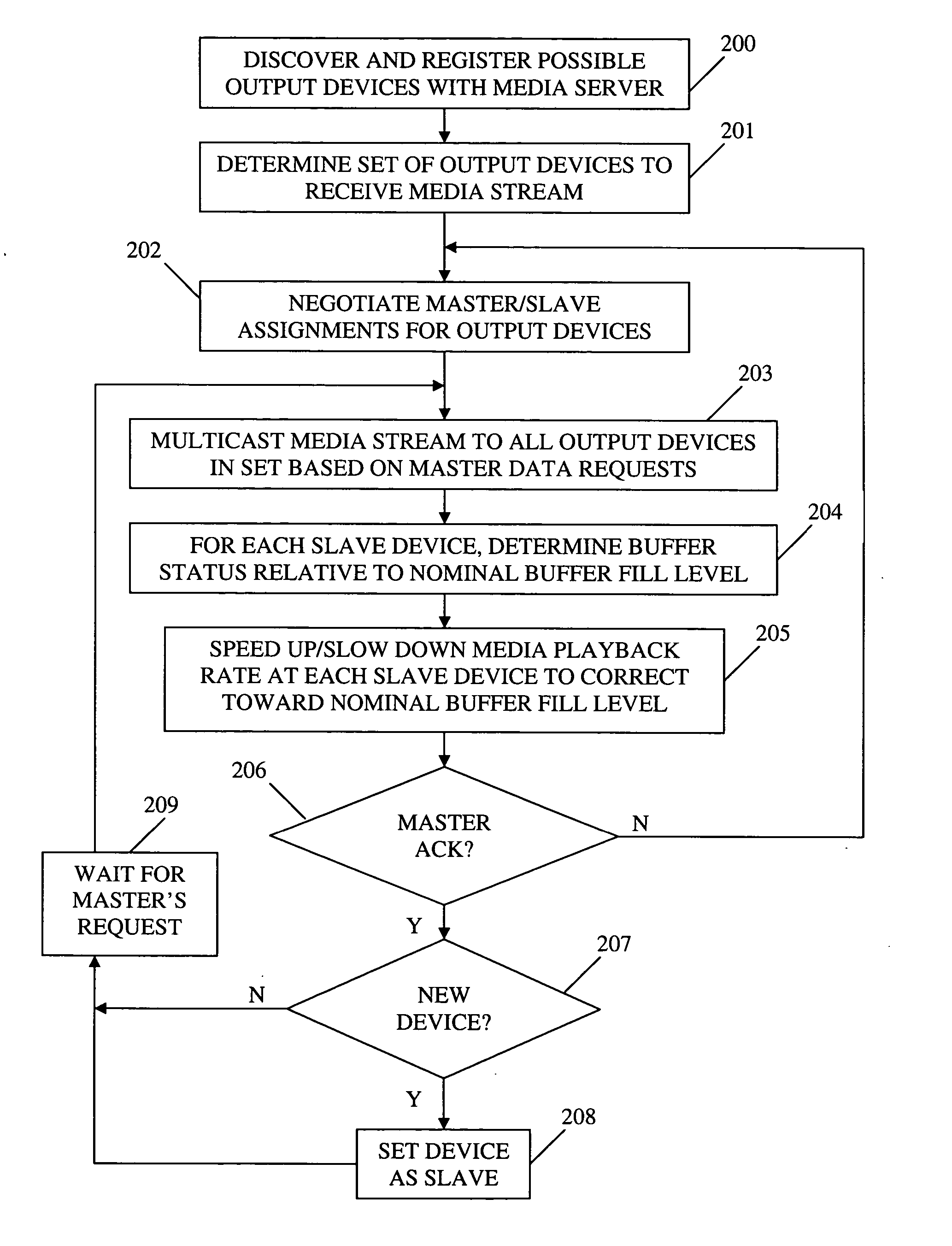

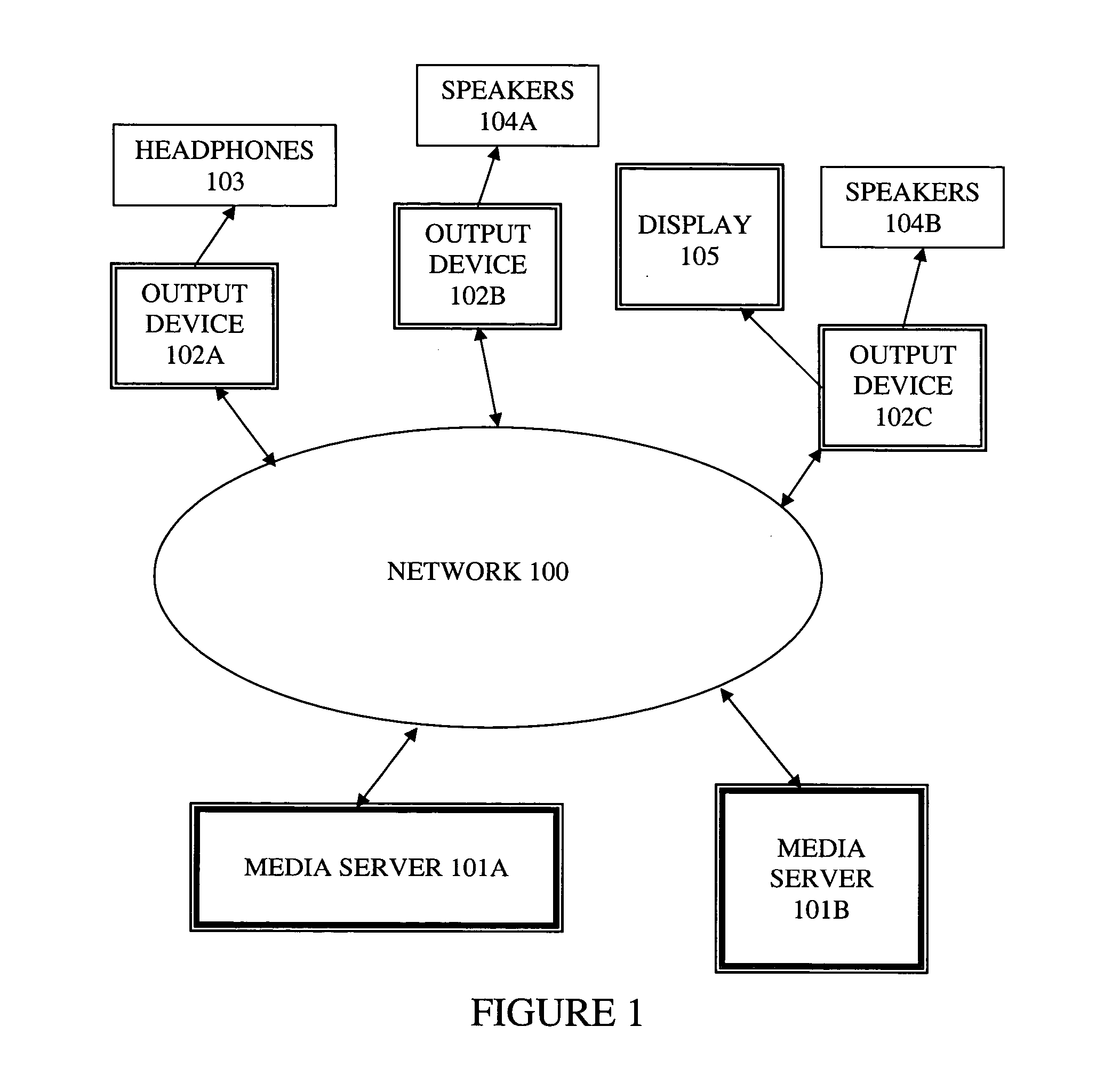

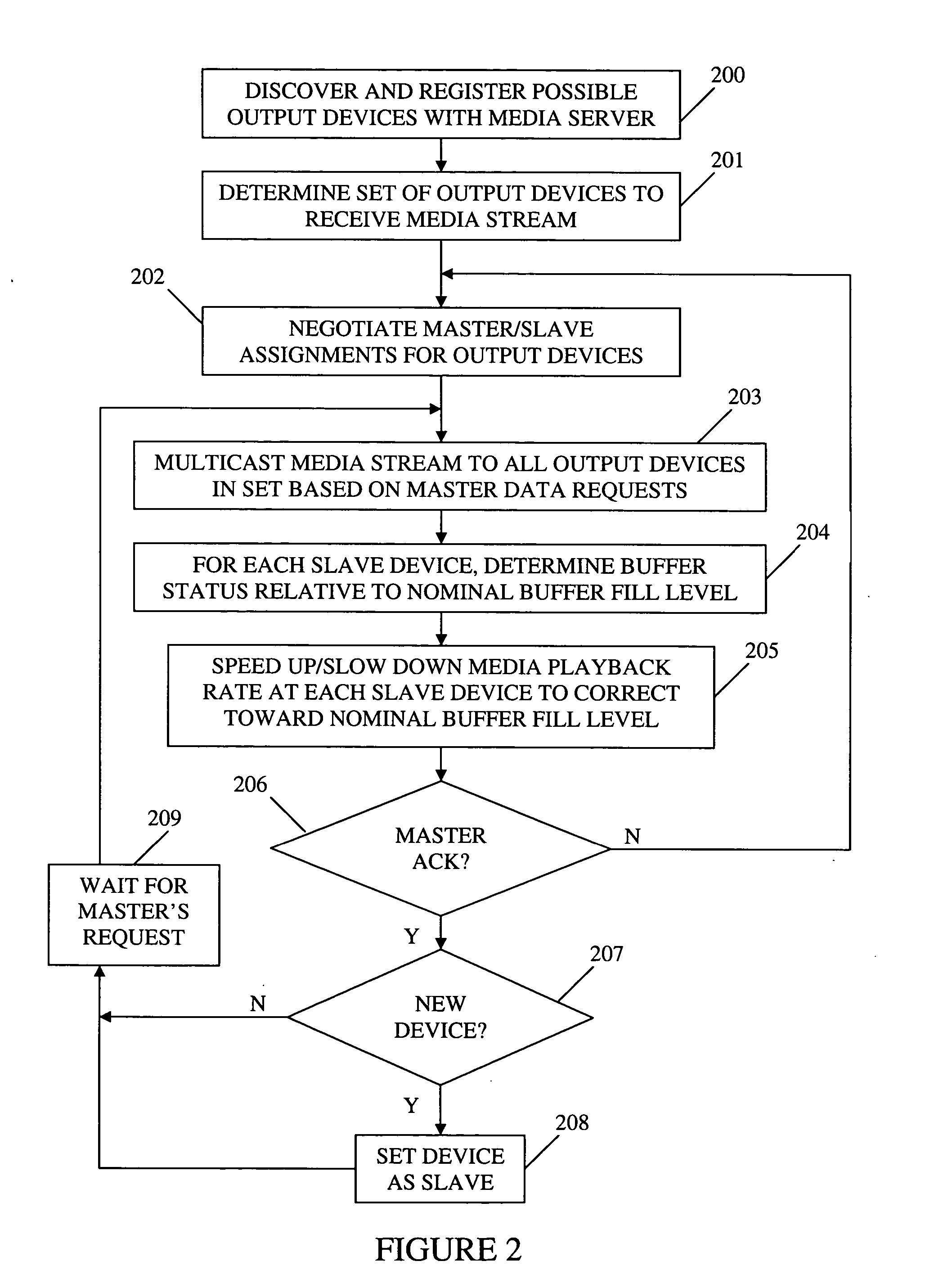

Method and apparatus for synchronizing playback of streaming media in multiple output devices

ActiveUS20060149850A1Maintaining average timing synchronizationError preventionTransmission systemsStreaming dataTimestamp

A method and apparatus for synchronizing streaming media with multiple output devices. One or more media servers serve media streams to one or more output devices (i.e., players). For playback synchronization, one output device is the “master”, whereas the remaining output devices are “slaves”. More data is requested from the media server by the “master” device to maintain a nominal buffer fill level over time. The “slave” devices receive streamed data from the media server at the rate determined by the master device's data requests, and the average rate of data flow over the streaming network is thus controlled by the frequency of the single “master” device's crystal. “Slave” devices make playback rate corrections to maintain respective buffer fill levels within upper and lower threshold levels. For slow networks, each media data packet timestamp is calculated from the time the master's buffer reaches nominal level.

Owner:SNAP ONE LLC

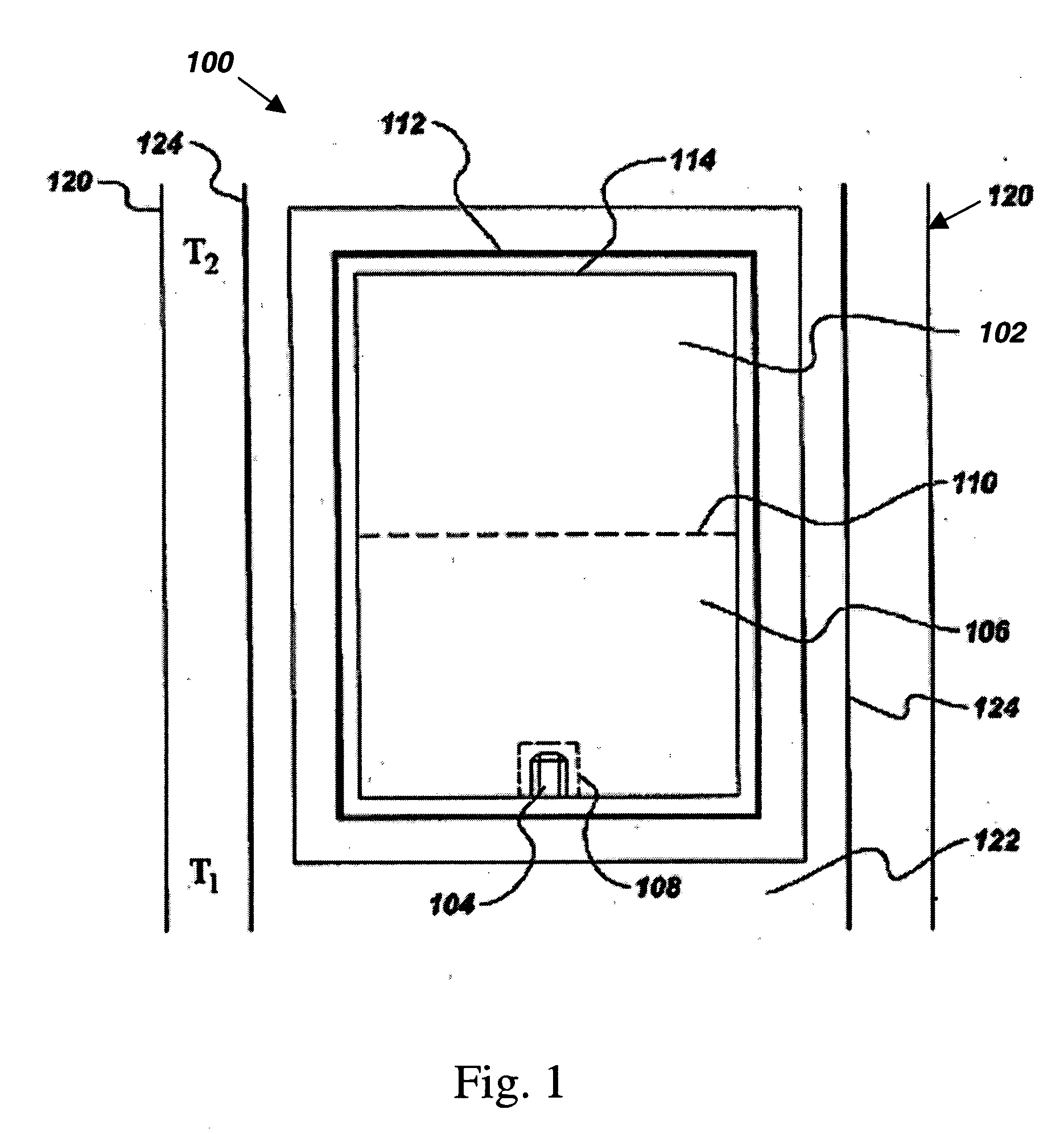

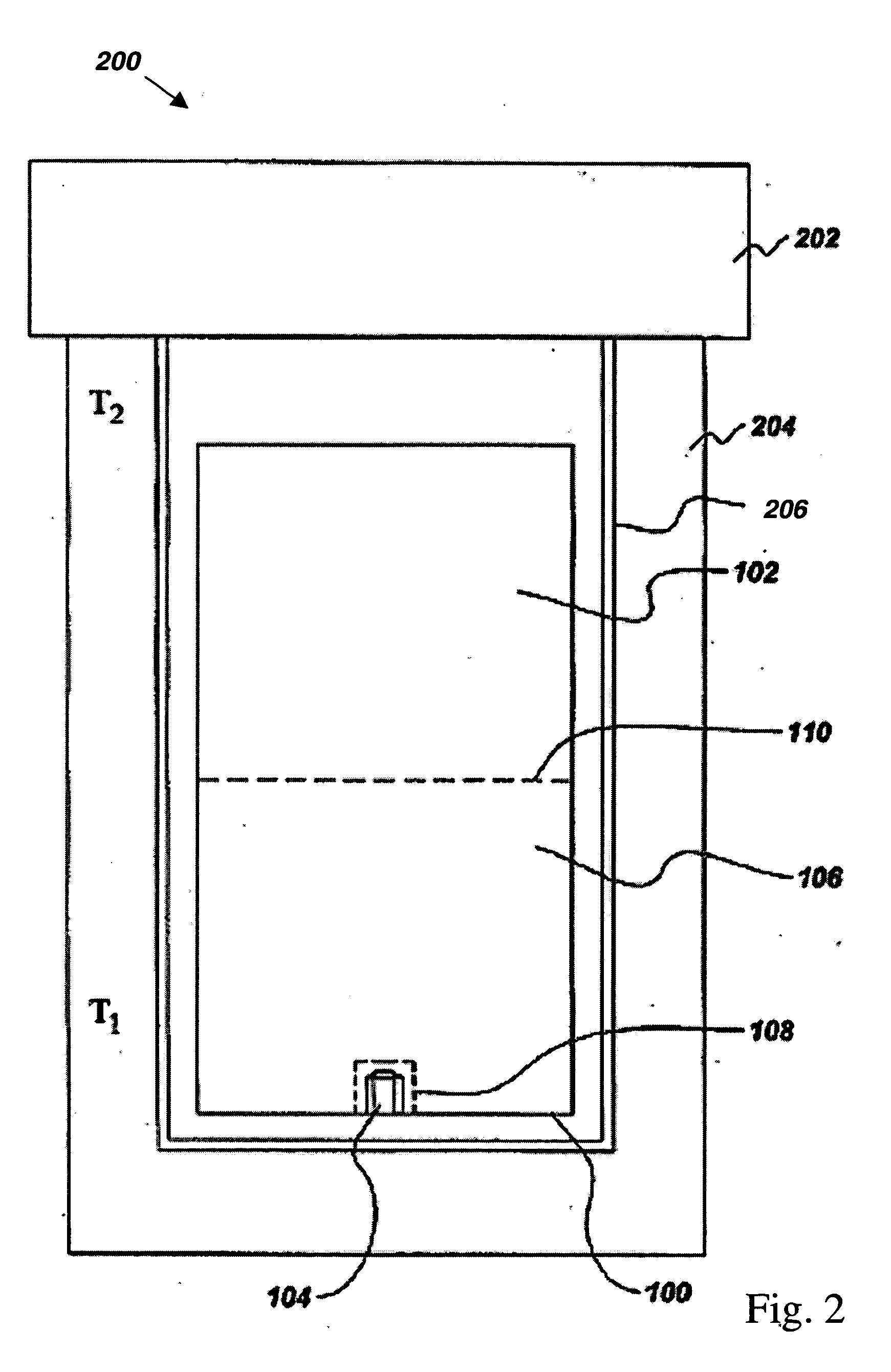

Single crystal and quasi-single crystal, composition, apparatus, and associated method

InactiveUS20060037529A1Material nanotechnologyPolycrystalline material growthMischmetalSource material

Owner:SORAA

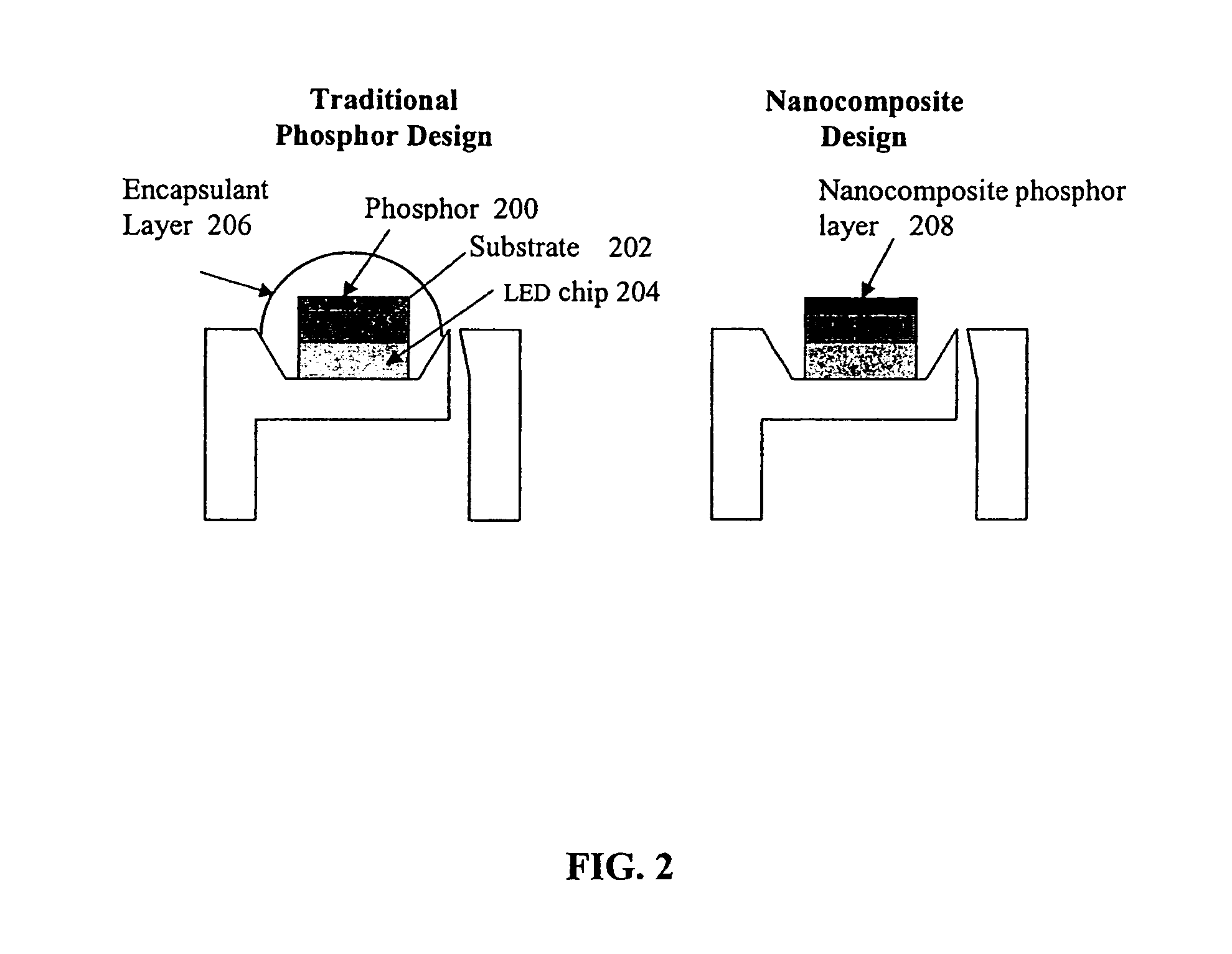

Nanocrystal doped matrixes

ActiveUS20070034833A1Good miscibilityInhibit aggregationMaterial nanotechnologyIndividual molecule manipulationAnti-reflective coatingSemiconductor nanocrystals

Matrixes doped with semiconductor nanocrystals are provided. In certain embodiments, the semiconductor nanocrystals have a size and composition such that they absorb or emit light at particular wavelengths. The nanocrystals can comprise ligands that allow for mixing with various matrix materials, including polymers, such that a minimal portion of light is scattered by the matrixes. The matrixes of the present invention can also be utilized in refractive index matching applications. In other embodiments, semiconductor nanocrystals are embedded within matrixes to form a nanocrystal density gradient, thereby creating an effective refractive index gradient. The matrixes of the present invention can also be used as filters and antireflective coatings on optical devices and as down-converting layers. Processes for producing matrixes comprising semiconductor nanocrystals are also provided. Nanostructures having high quantum efficiency, small size, and / or a narrow size distribution are also described, as are methods of producing indium phosphide nanostructures and core-shell nanostructures with Group II-VI shells.

Owner:SAMSUNG ELECTRONICS CO LTD

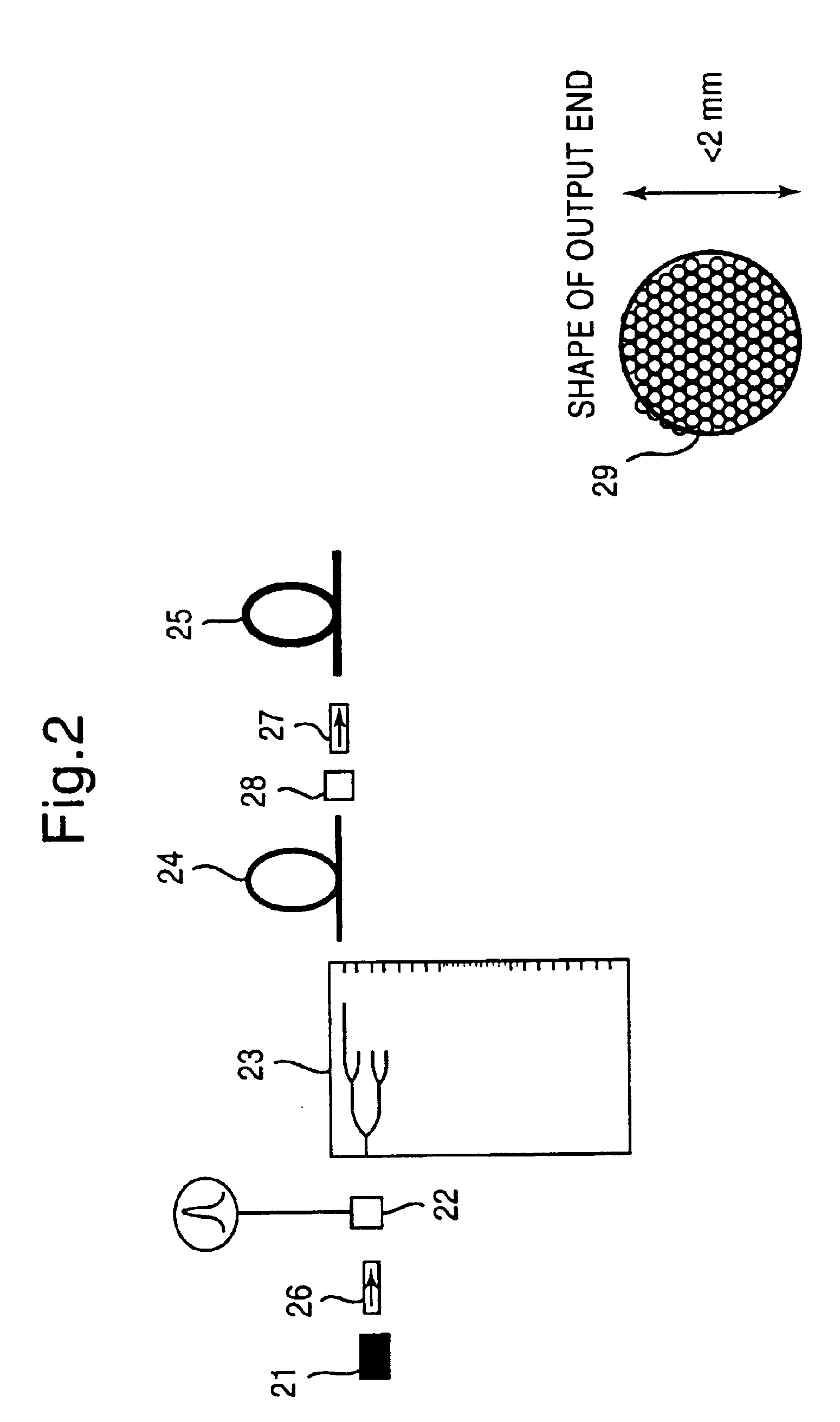

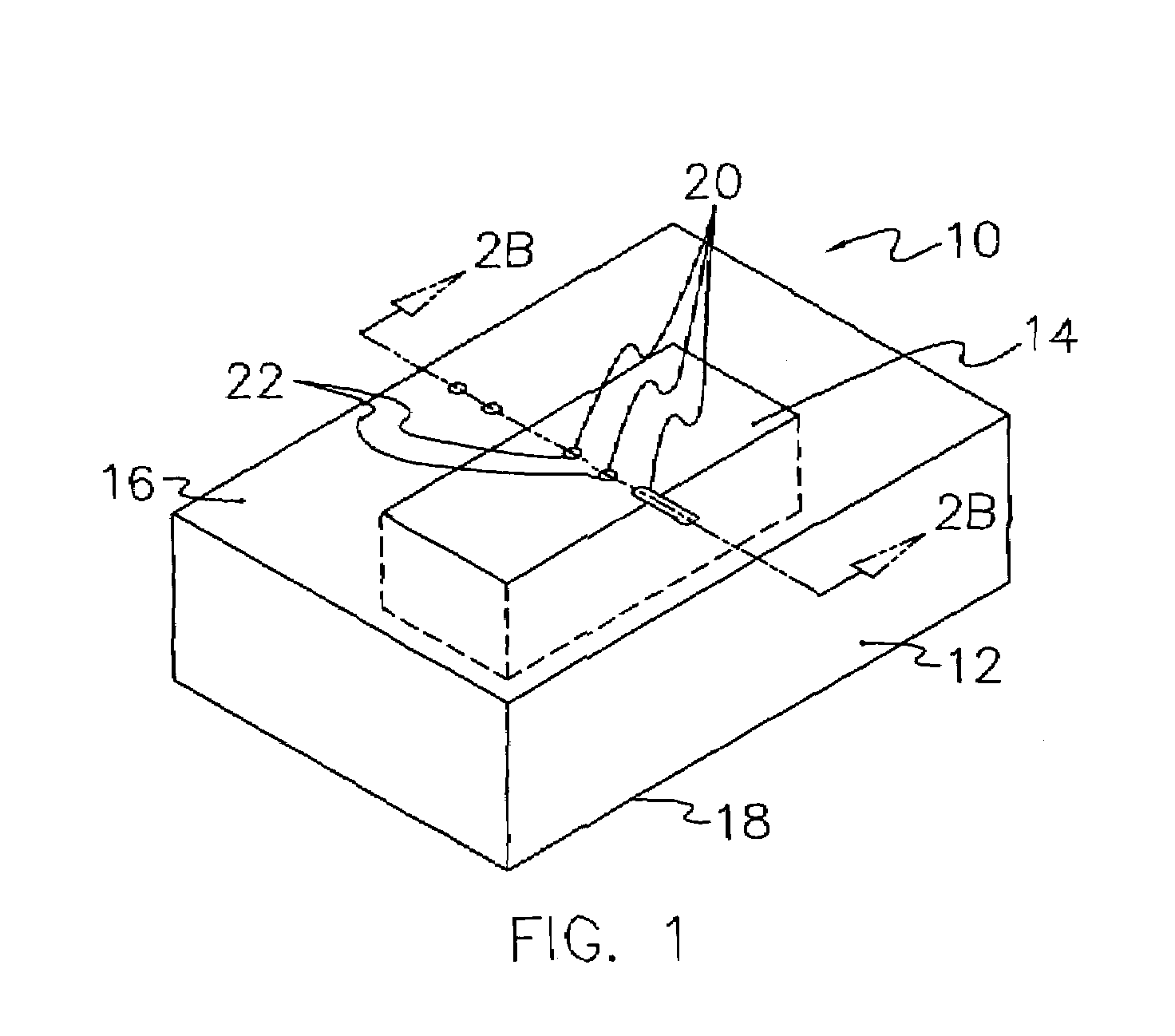

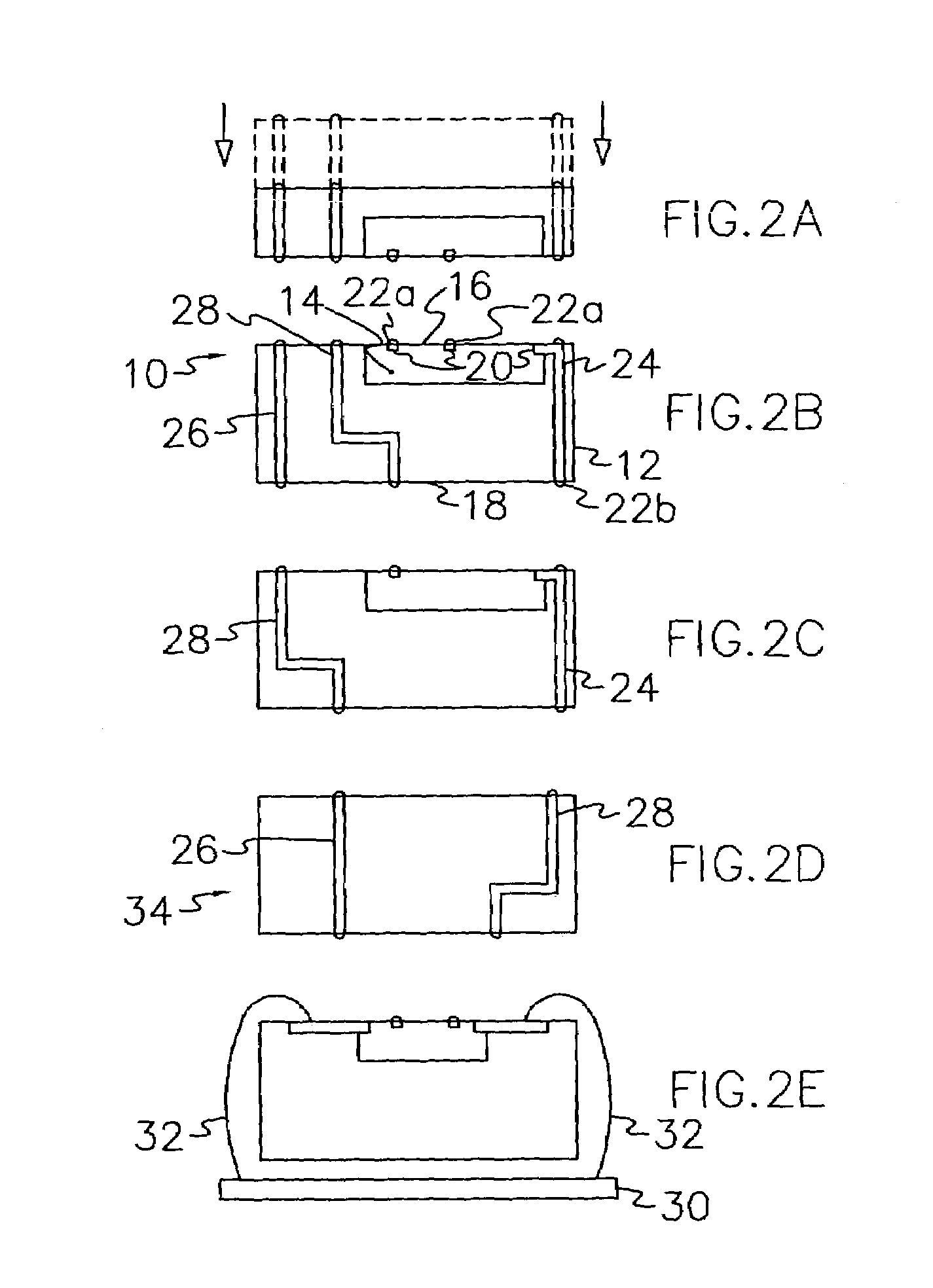

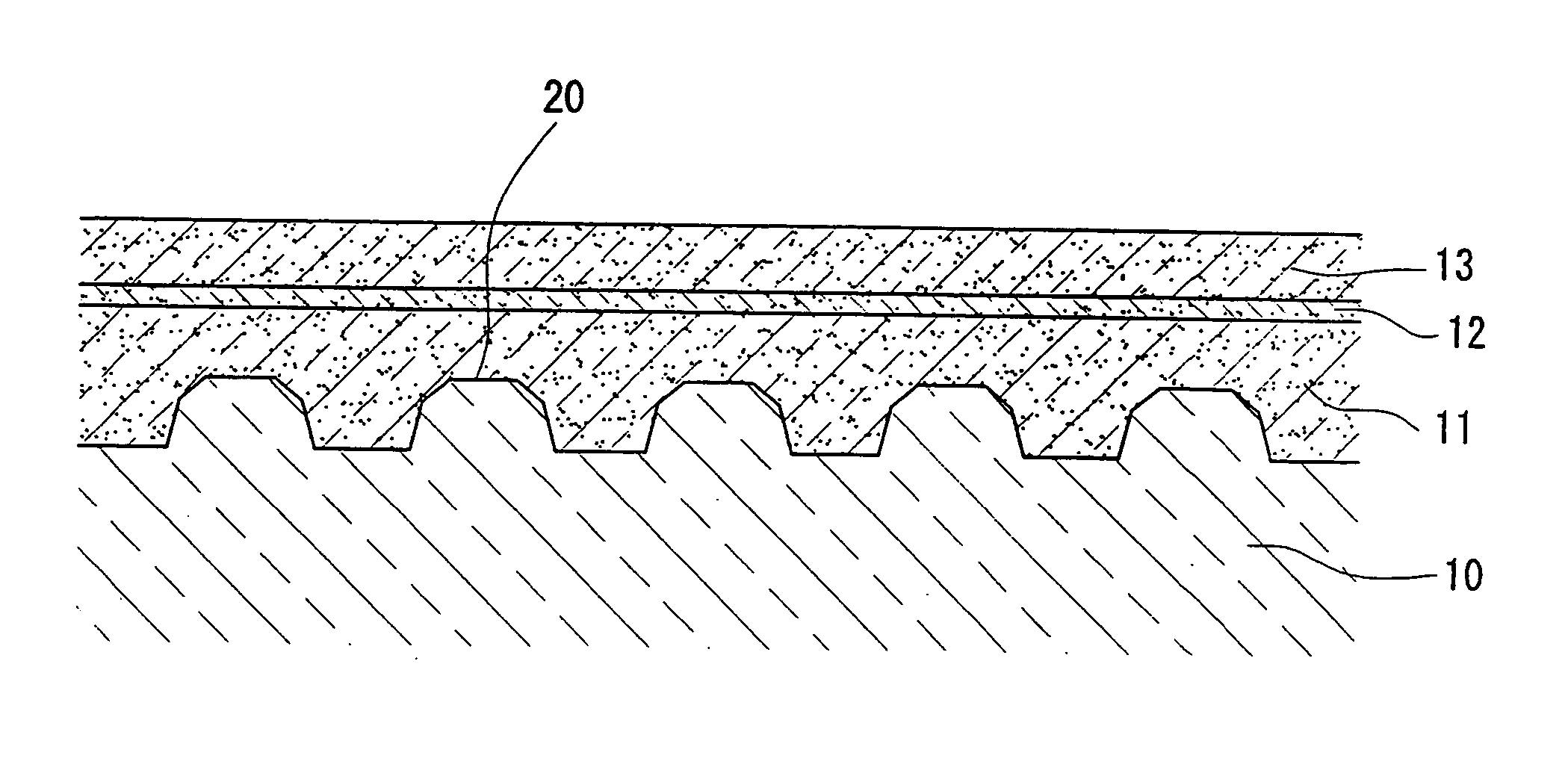

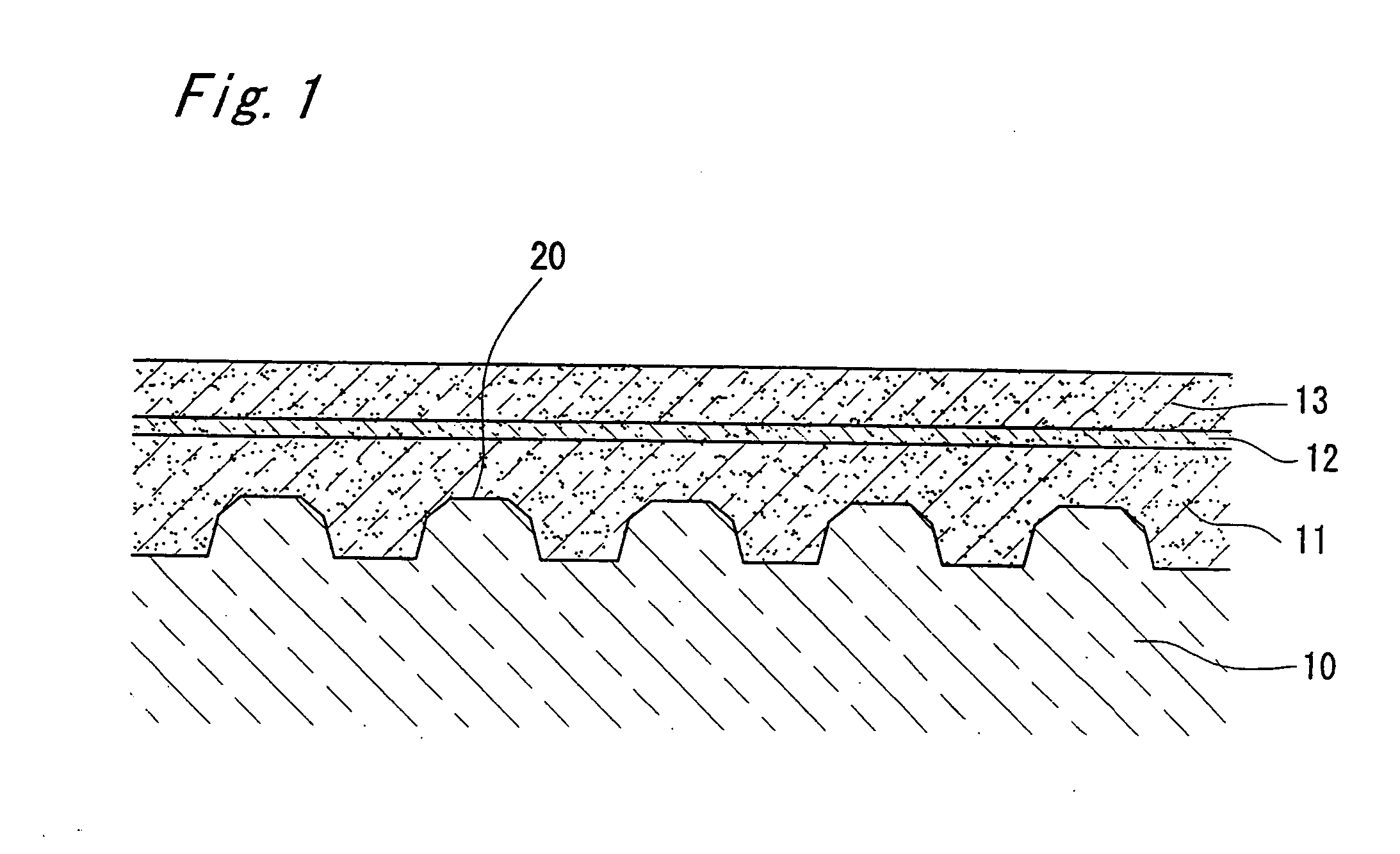

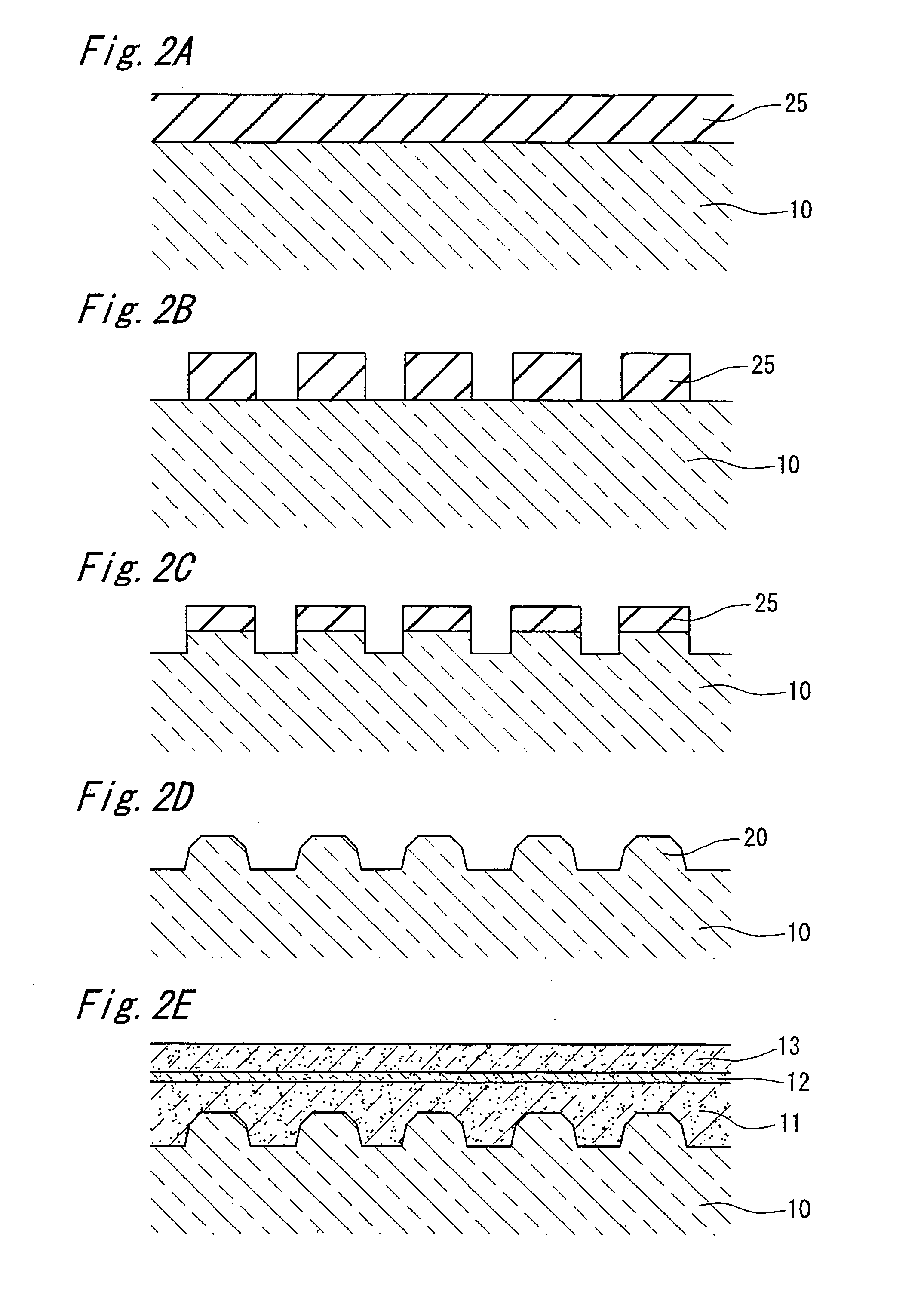

Semiconductor device

ActiveUS20050179130A1Easy to produceReduce crystallinitySemiconductor/solid-state device detailsSolid-state devicesDevice materialEngineering

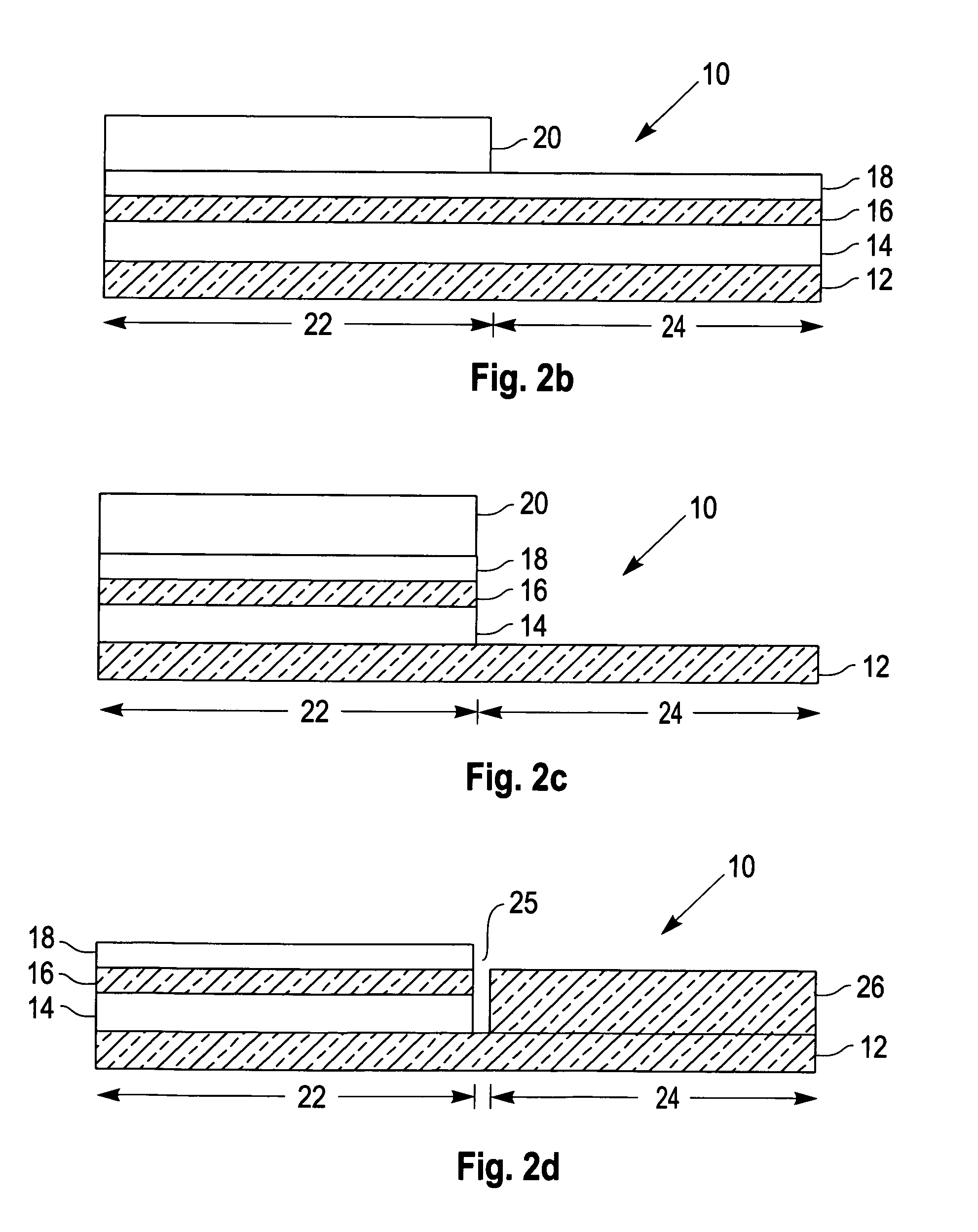

A substrate (10) has at least one recess (20) and / or protrusion (21) formed on the surface thereof so as to scatter or diffract the light generated in an active layer (12). The recess and / or protrusion is formed in such a shape that can reduce crystalline defect in semiconductor layers (11, 13).

Owner:NICHIA CORP

Bacillus thuringiensis cryET33 and cryET34 compositions and uses therefor

Disclosed are Bacillus thuringiensis strains comprising novel crystal proteins which exhibit insecticidal activity against coleopteran insects including red flour beetle larvae (Tribolium castaneum) and Japanese beetle larvae (Popillia japonica). Also disclosed are novel B. thuringiensis crystal toxin genes, designated cryET33 and cryET34, which encode the colepteran-toxic crystal proteins, CryET33 (29-kDa) crystal protein, and the cryET34 gene encodes the 14-kDa CryET34 crystal protein. The CryET33 and CryET34 crystal proteins are toxic to red flour beetle larvae and Japanese beetle larvae. Also disclosed are methods of making and using transgenic cells comprising the novel nucleic acid sequences of the invention.

Owner:MONSANTO TECH LLC

Group-III nitride semiconductor device

InactiveUS20050072986A1Suppress an undesired mass-transportPrevent surfaceOptical wave guidanceLaser detailsNitride semiconductorsCompound semiconductor

A method of forming a partially etched nitride-based compound semiconductor crystal layer includes the following steps. A non-crystal layer of a nitride-based compound semiconductor is formed. At least a part of the non-crystal layer is then etched to form a partially etched non-crystal layer before the partially etched non-crystal layer is crystallized to form a partially etched nitride-based compound semiconductor crystal layer.

Owner:RENESAS ELECTRONICS CORP

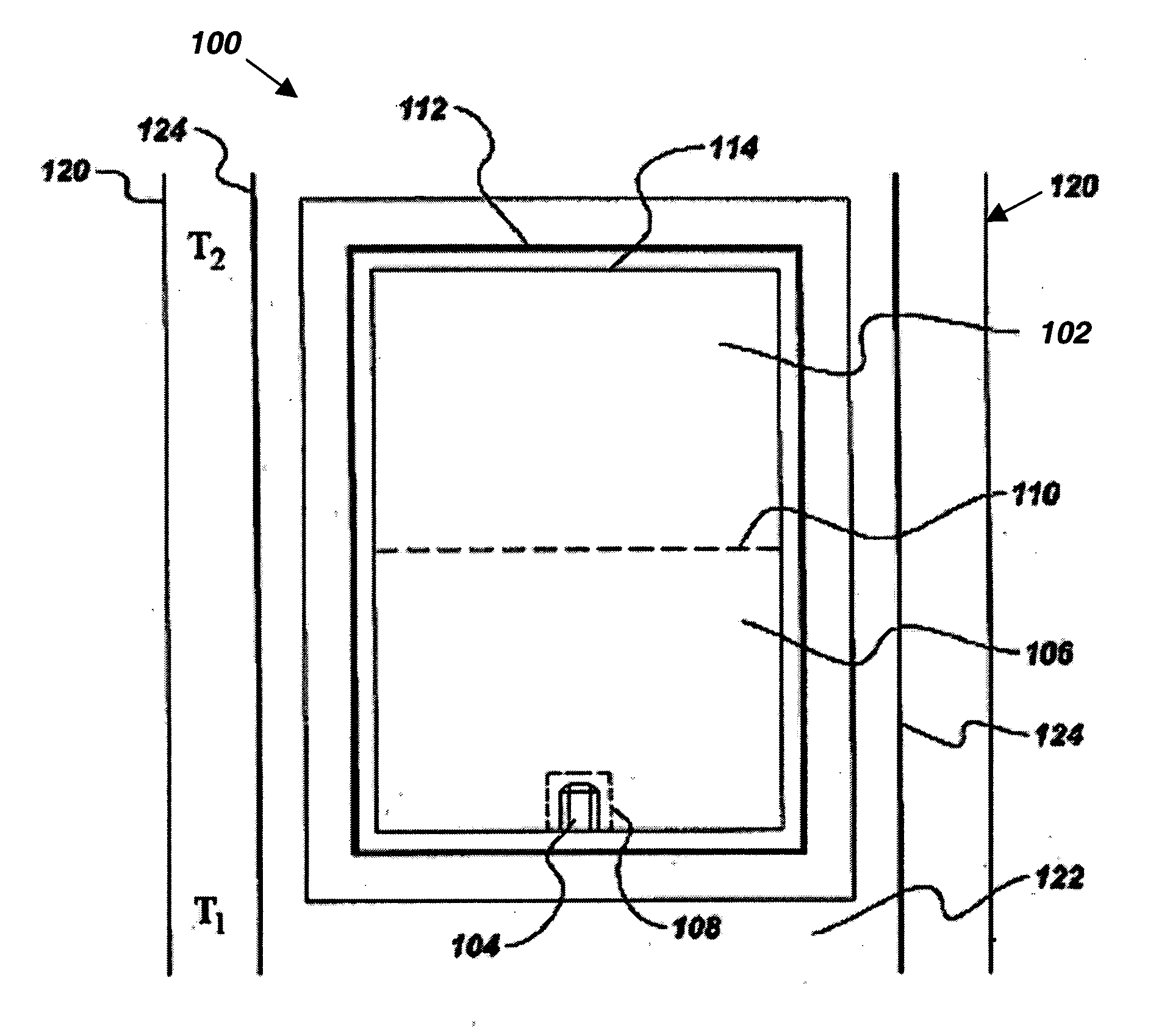

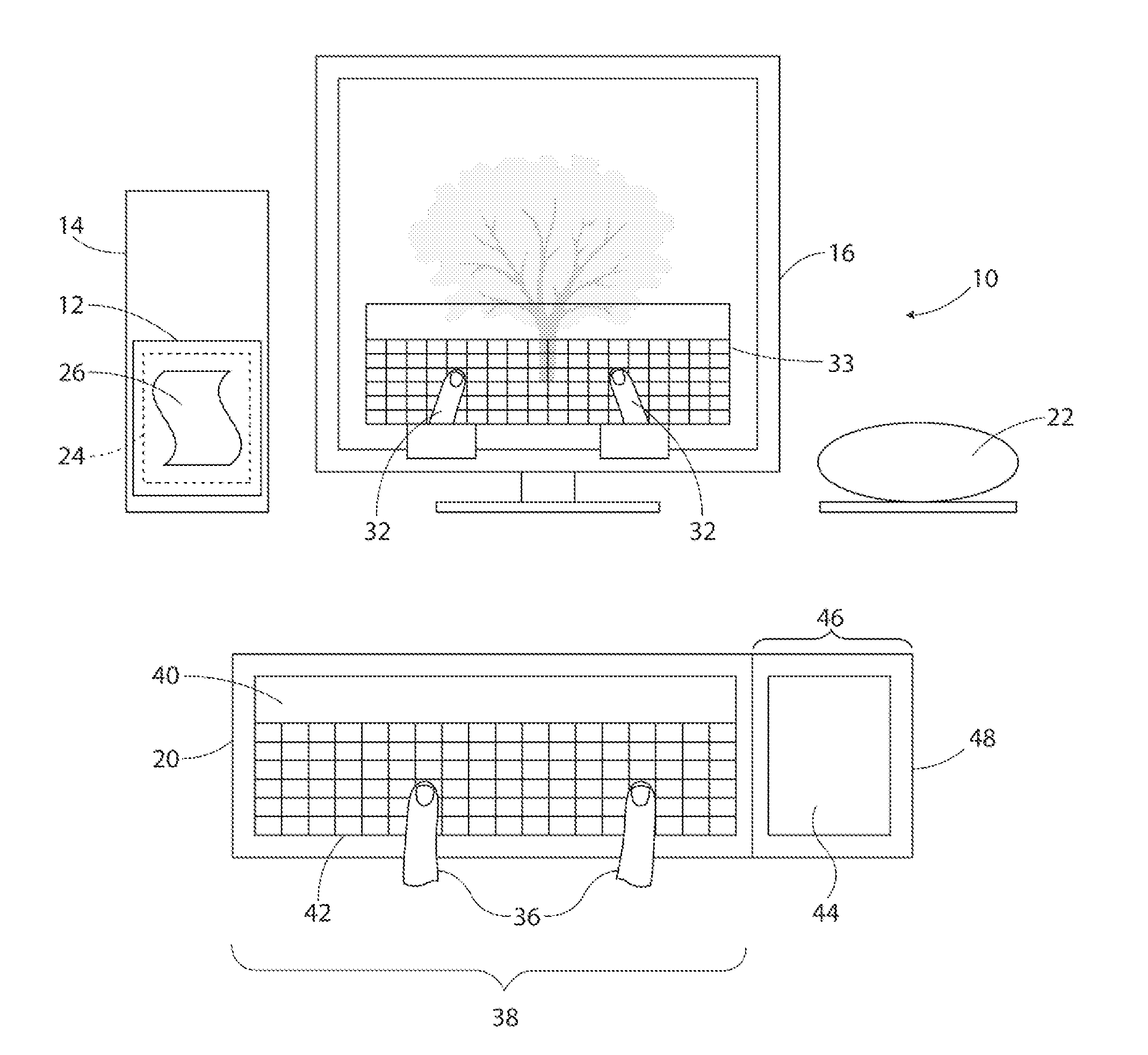

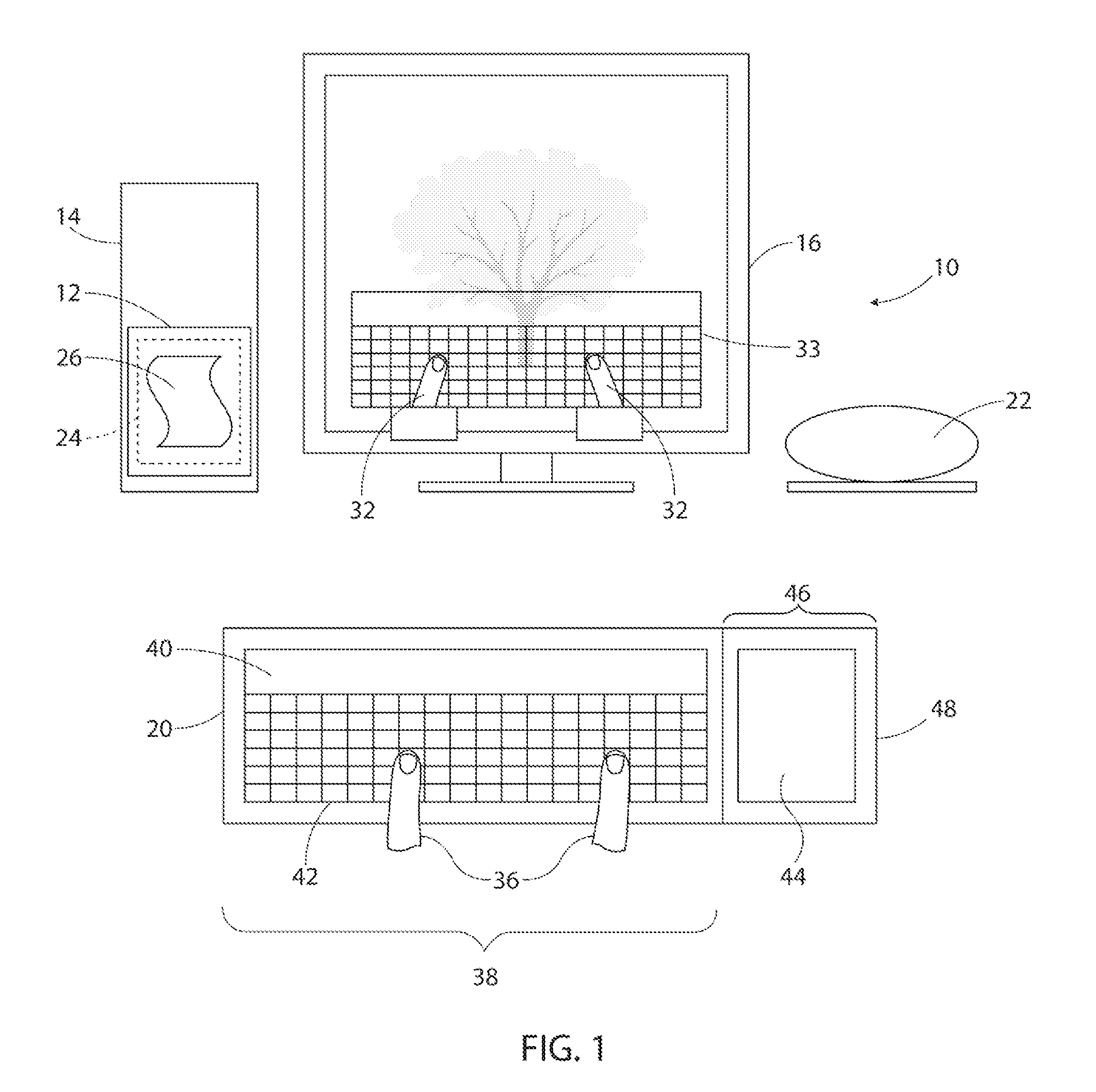

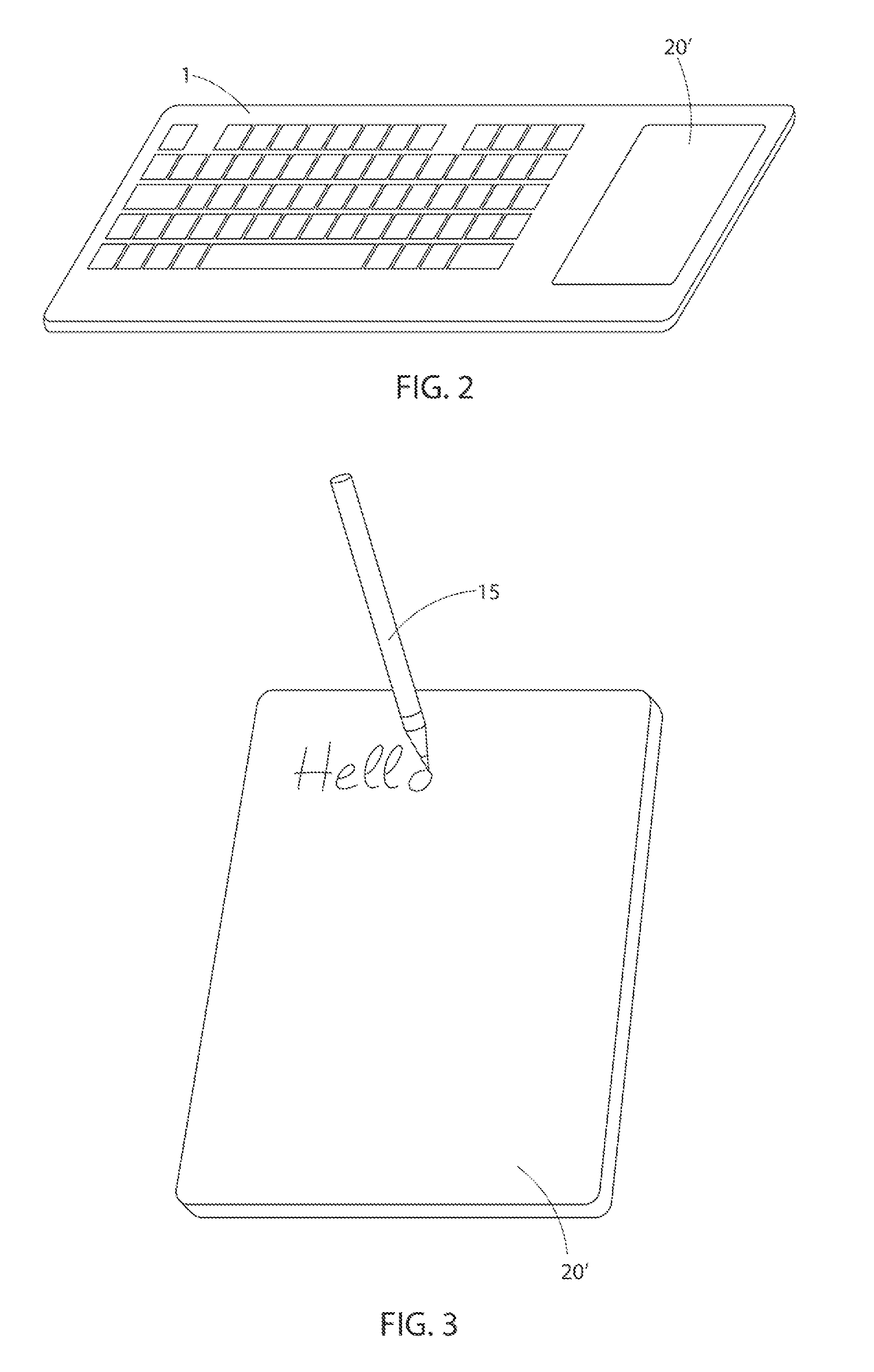

System and method for capturing hand annotations

ActiveUS20110248941A1Simplified entryLow costInput/output processes for data processingGraphicsJava annotation

A capture device for remote, virtual on screen data input by hand annotation comprises at least three functional layers including a bottom rigid layer, a middle pressure sensor layer and a top flexible layer. The bottom rigid layer has a surface that provides a mechanical support for writing. The middle pressure sensor layer is adapted to measuring a pressure array or map on the capture active area and to send data representing the measured pressure to a personal computer. The top flexible touch-sensitive passive LCD display layer includes an LCD surface by which whatever is written down on the LCD is impressed graphically due to its liquid crystal physical properties wherein applied pressure changes the crystal particles orientation and light properties, such that when a stylus presses against a writing surface thereof, it leaves a visible trace allowing the user to produce a drawing though no real ink has flown.

Owner:LOGITECH EURO SA

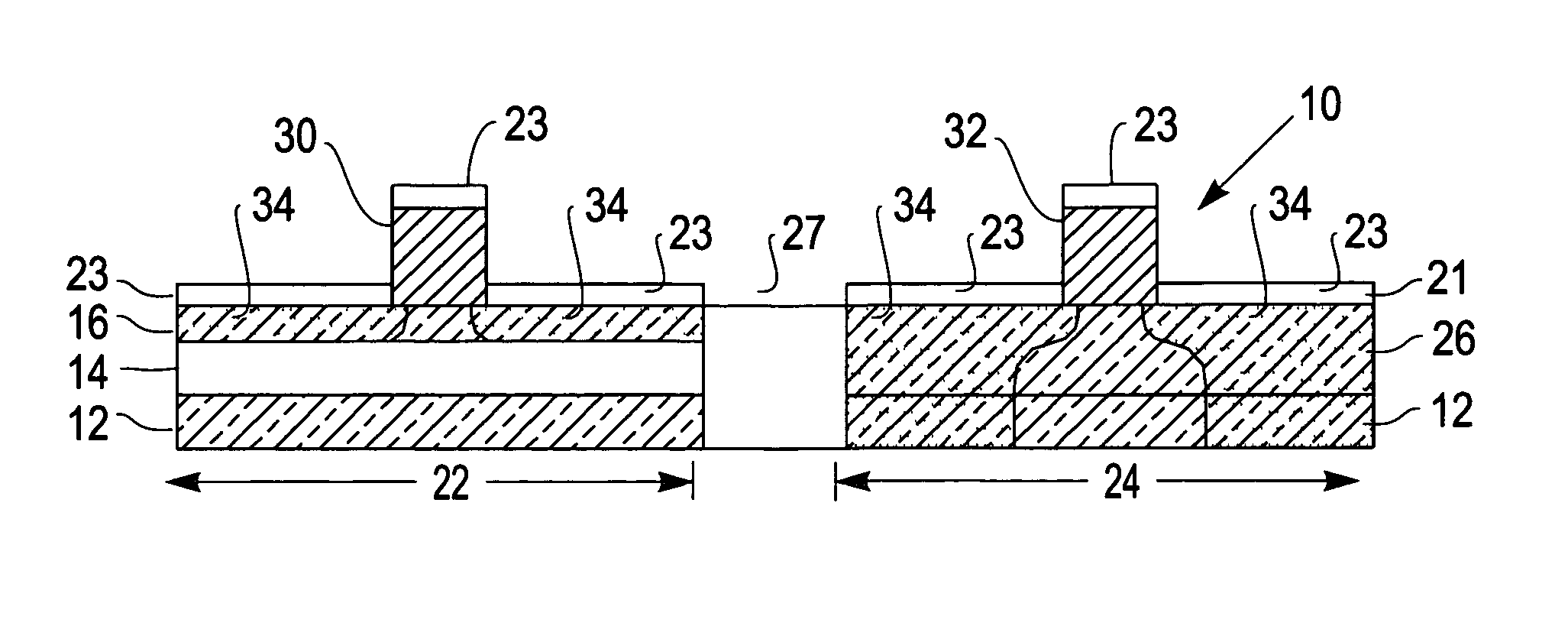

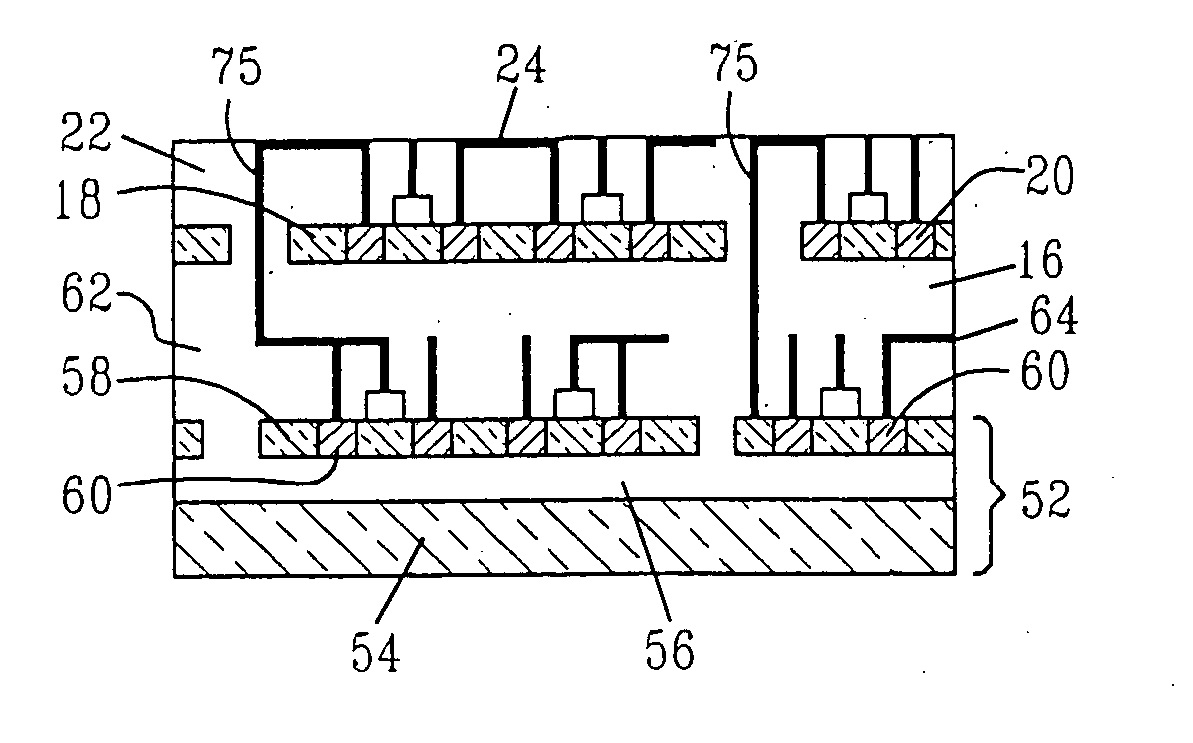

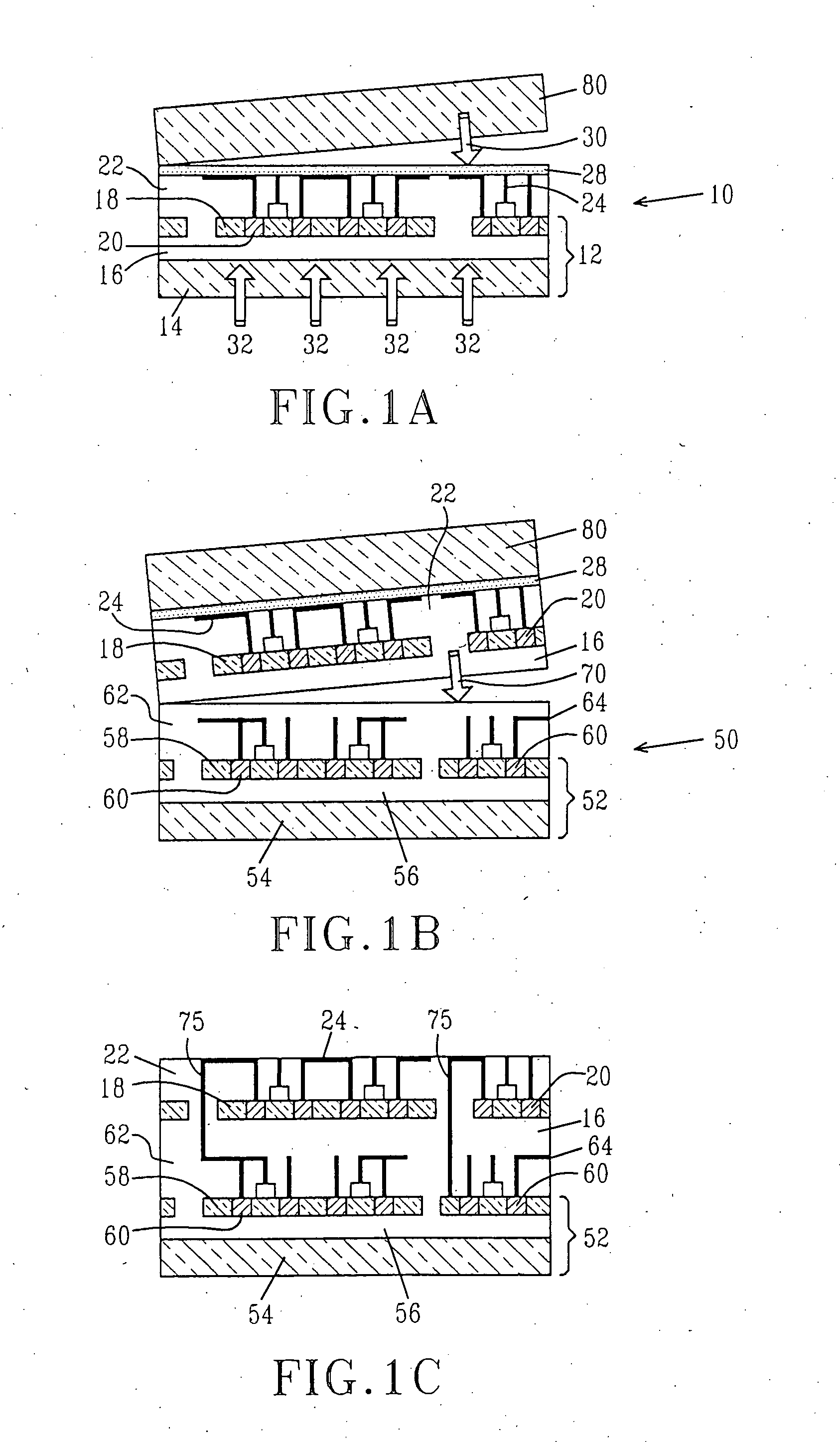

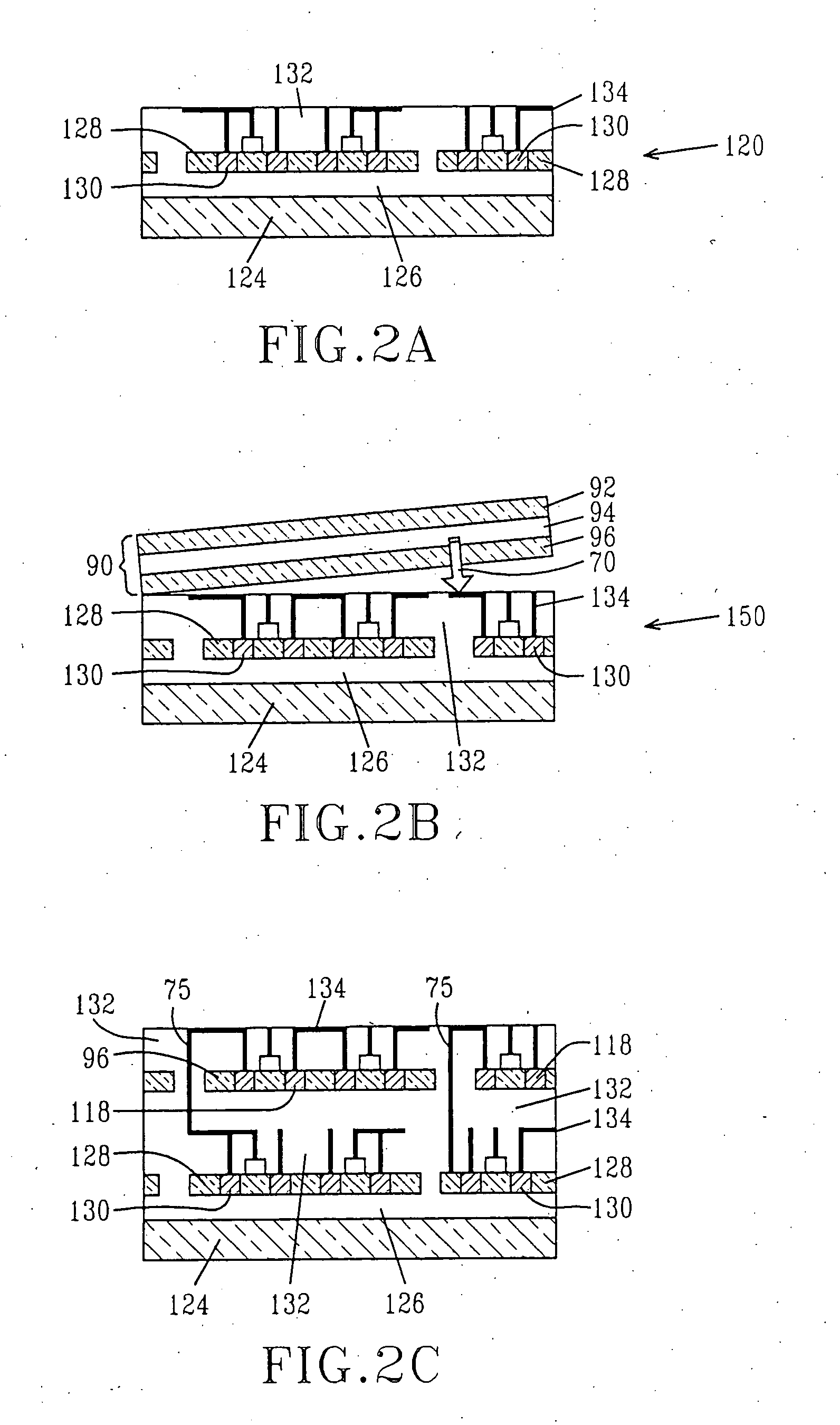

Three dimensional CMOS integrated circuits having device layers built on different crystal oriented wafers

InactiveUS20050067620A1High bulk densityReduce chip footprintTransistorSemiconductor/solid-state device details3d integrated circuitCMOS

Three-dimensional (3D) integration schemes of fabricating a 3D integrated circuit in which the pFETs are located on an optimal crystallographic surface for that device and the nFETs are located on a optimal crystallographic surface for that type of device are provided. In accordance with a first 3D integration scheme of the present invention, first semiconductor devices are pre-built on a semiconductor surface of a first silicon-on-insulator (SOI) substrate and second semiconductor devices are pre-built on a semiconductor surface of a second SOI substrate. After pre-building those two structures, the structure are bonded together and interconnect through wafer-via through vias. In a second 3D integration scheme, a blanket silicon-on-insulator (SOI) substrate having a first SOI layer of a first crystallographic orientation is bonded to a surface of a pre-fabricating wafer having second semiconductor devices on a second SOI layer that has a different crystallographic orientation than the first SOI layer; and forming first semiconductor device on the first SOI layer.

Owner:GLOBALFOUNDRIES INC