Patents

Literature

54results about How to "Excellent charge retention" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

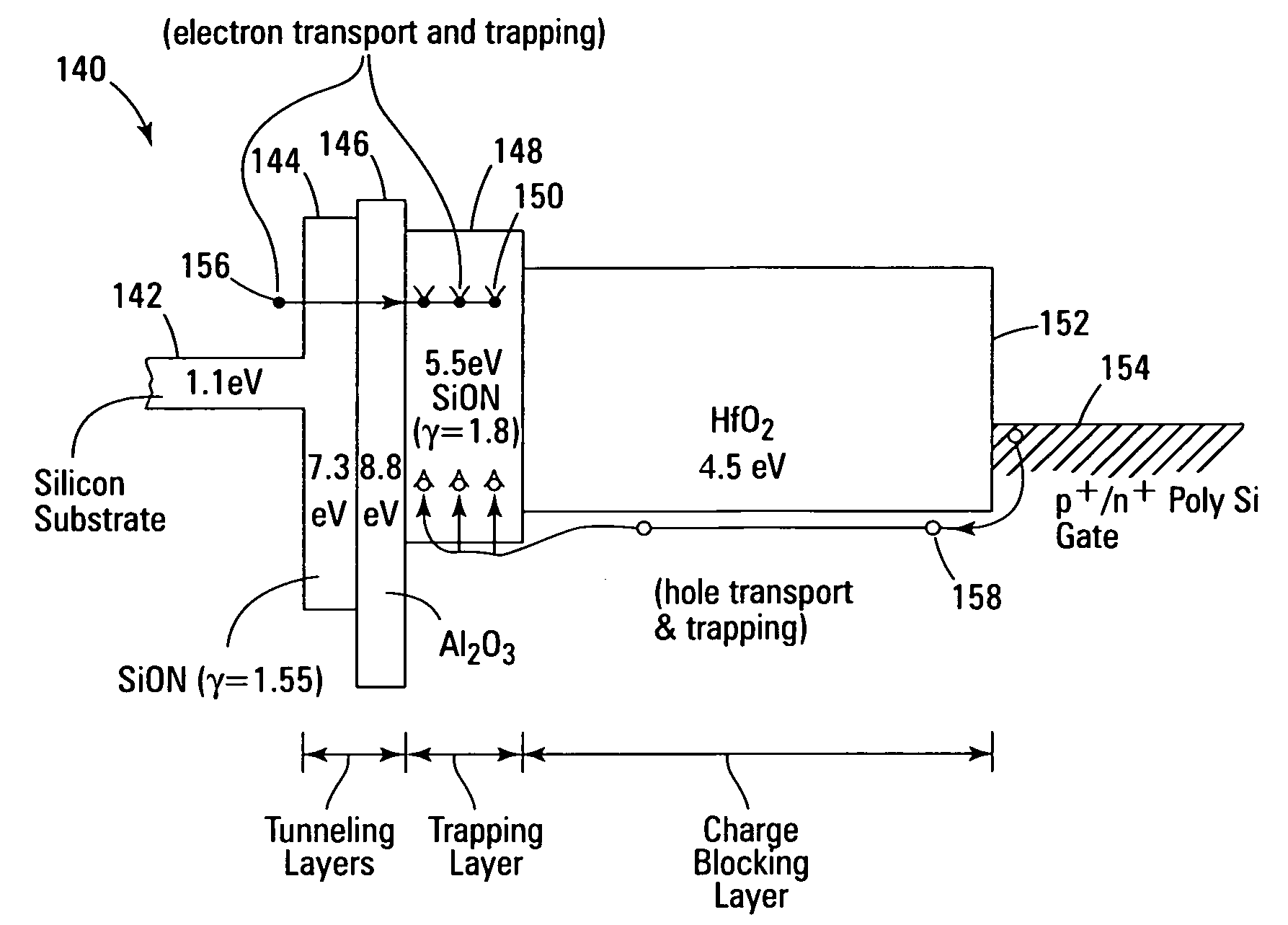

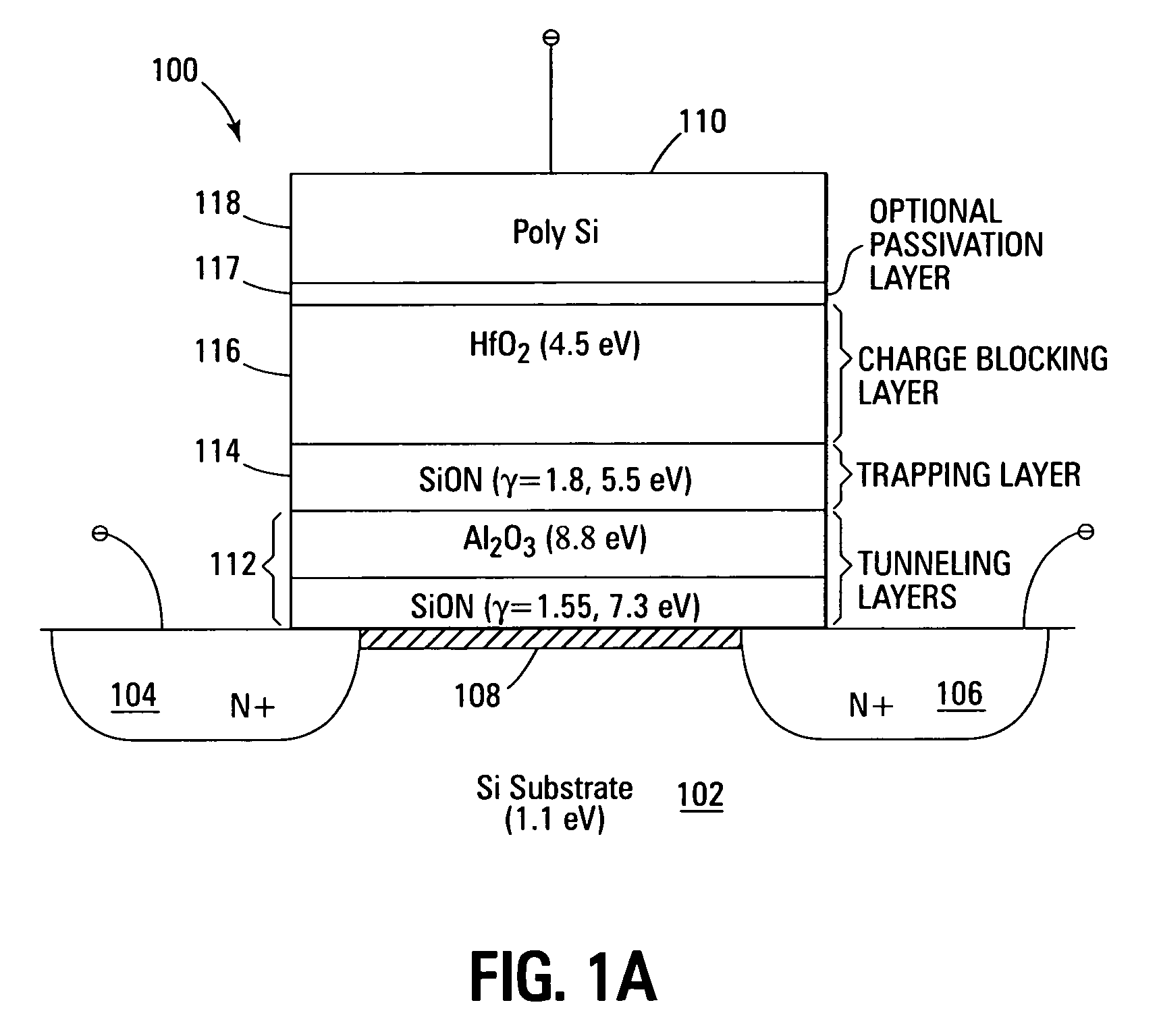

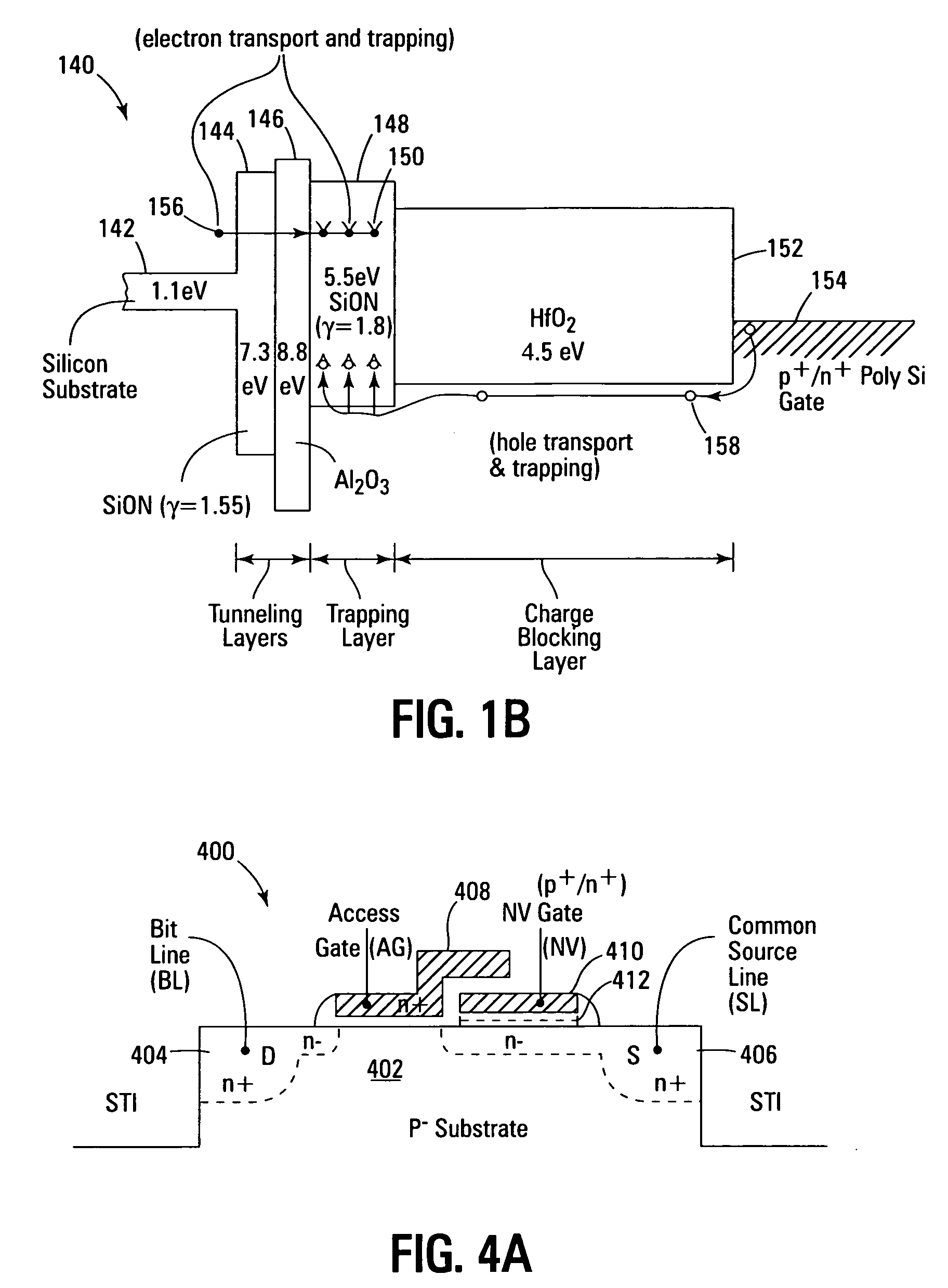

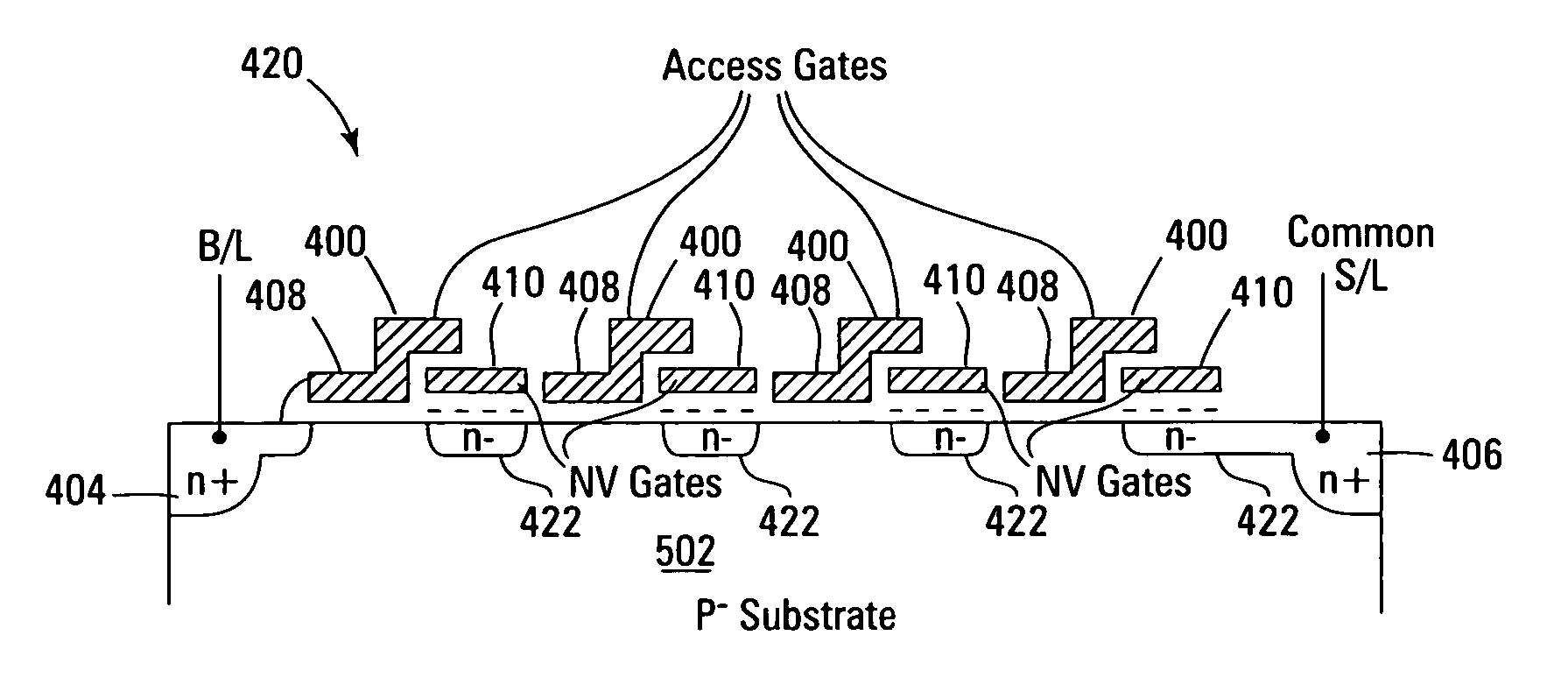

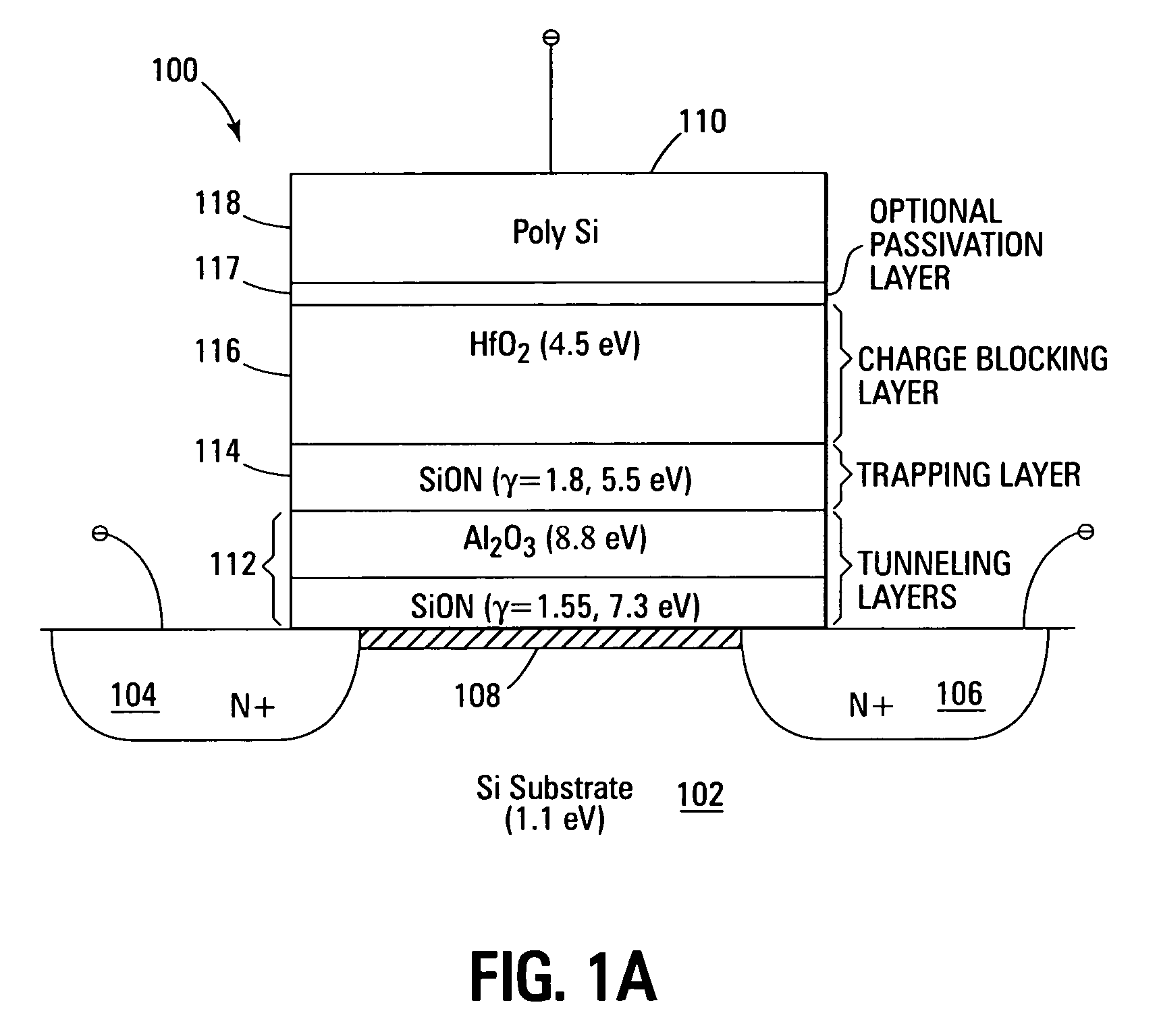

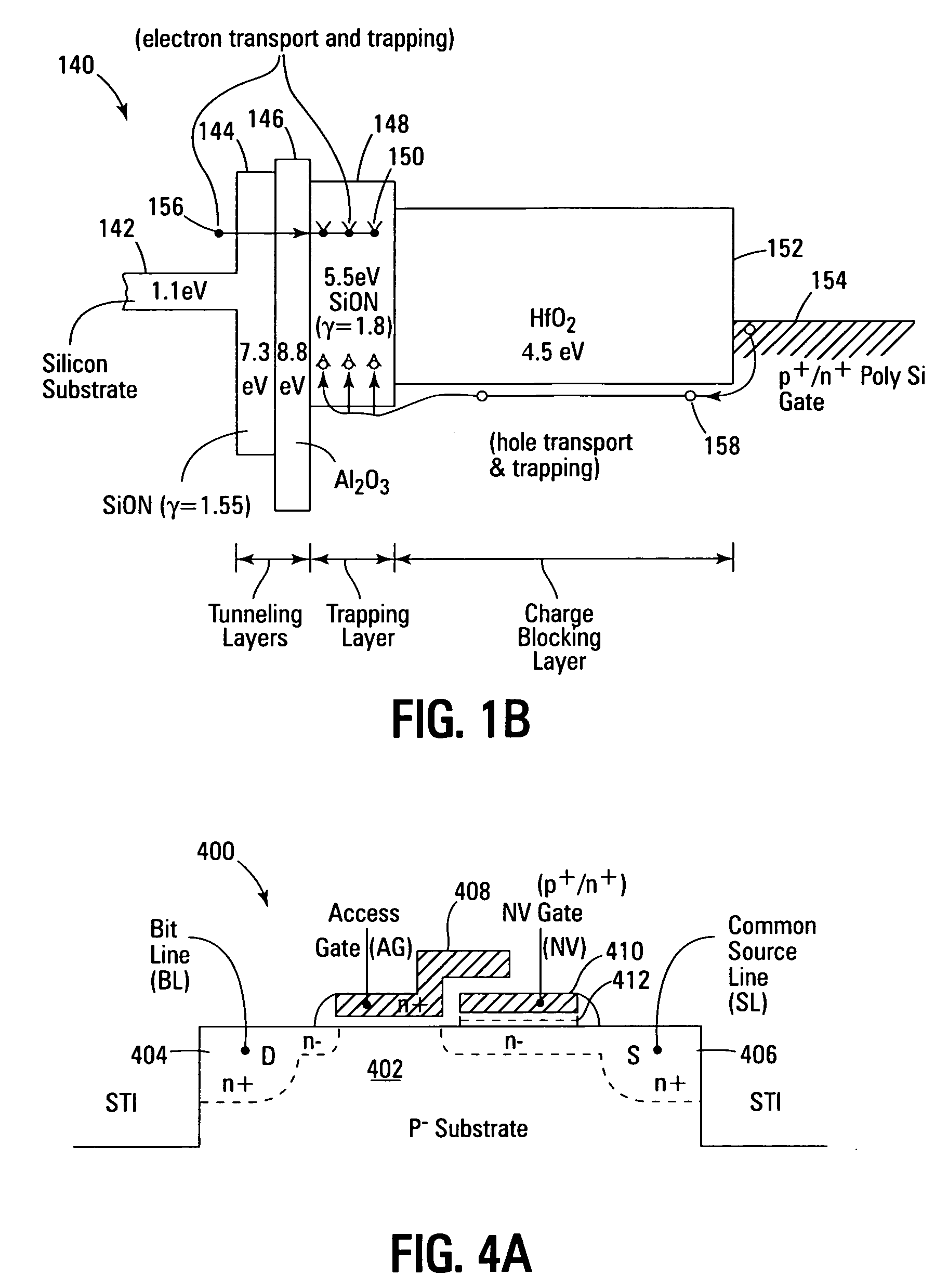

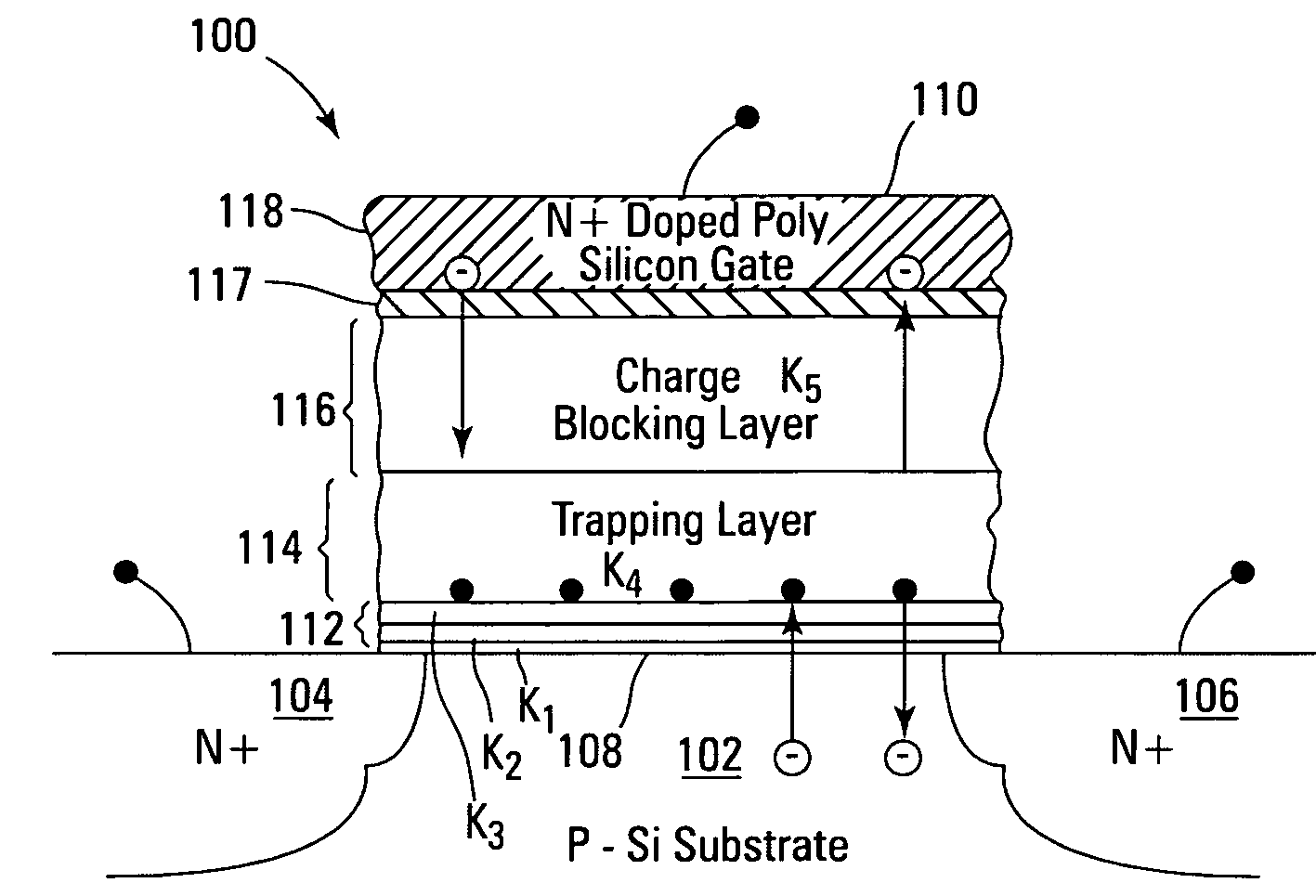

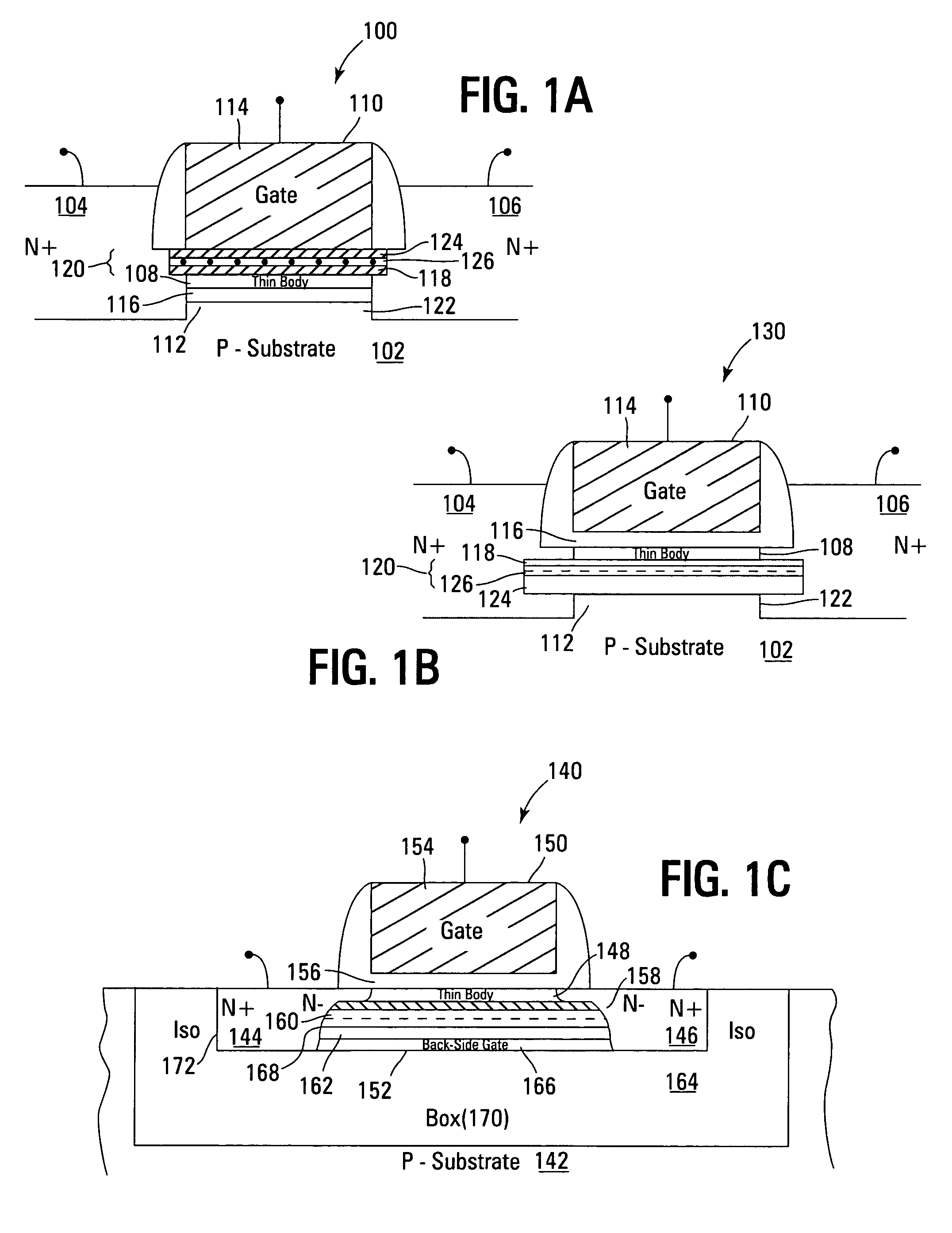

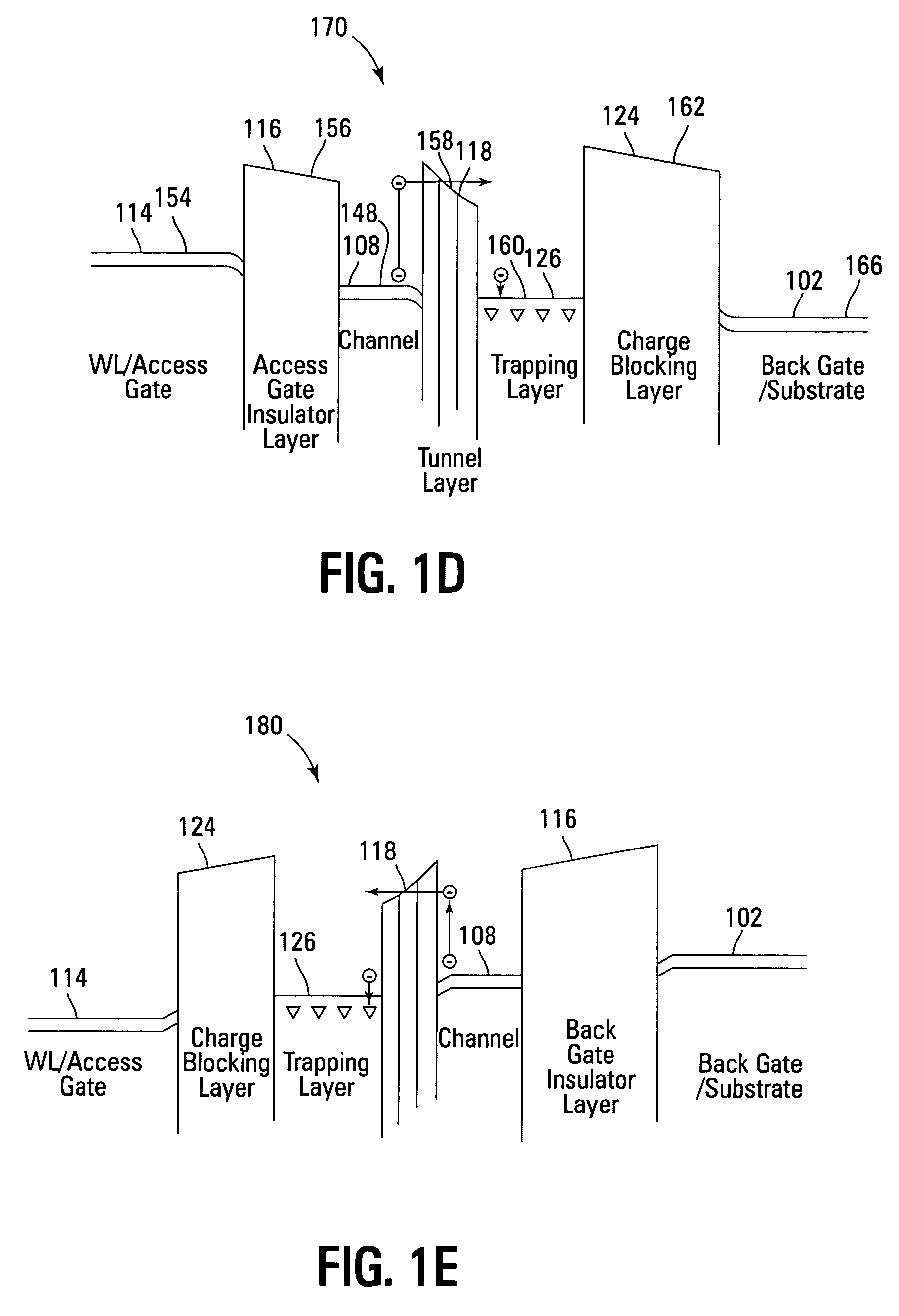

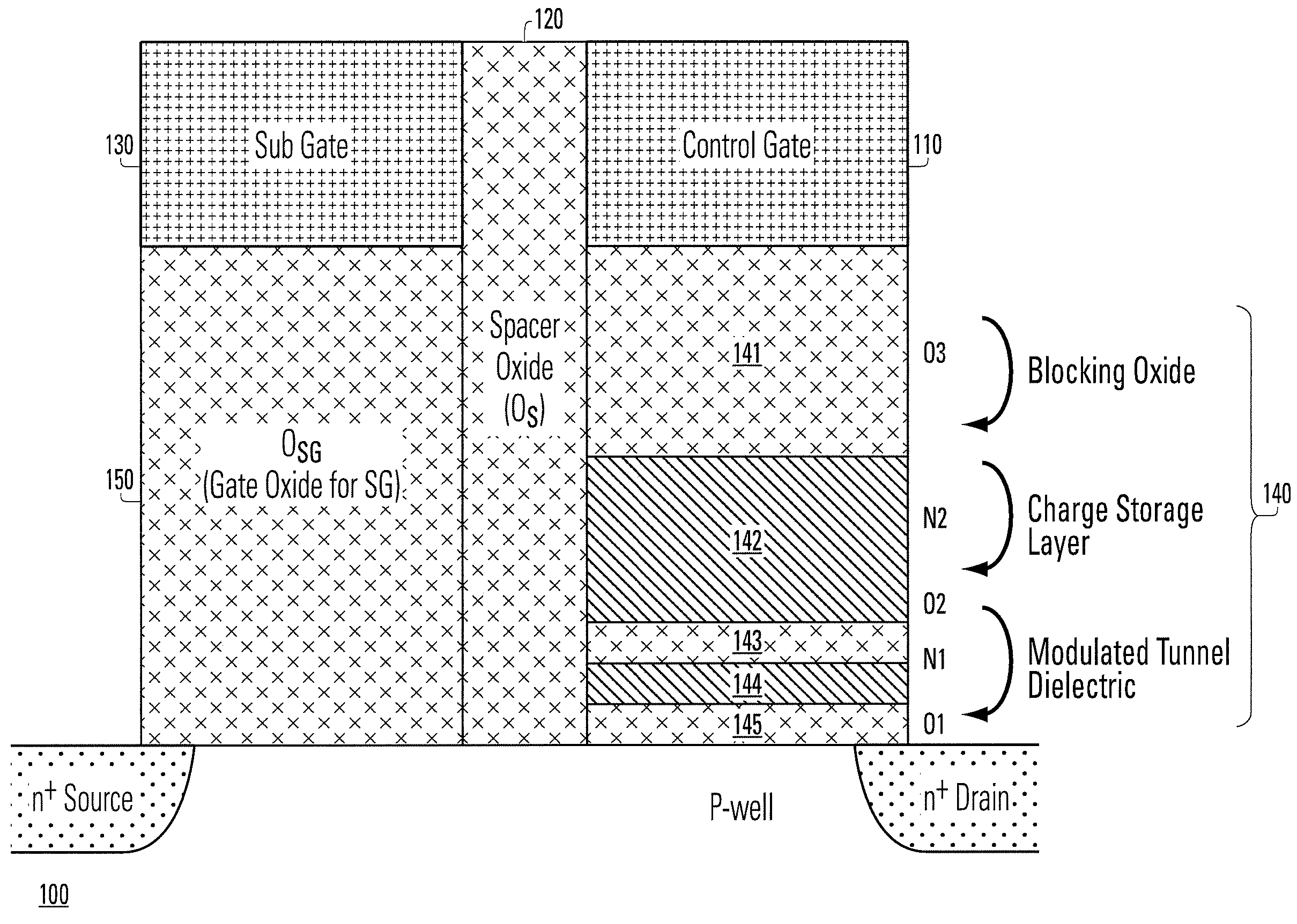

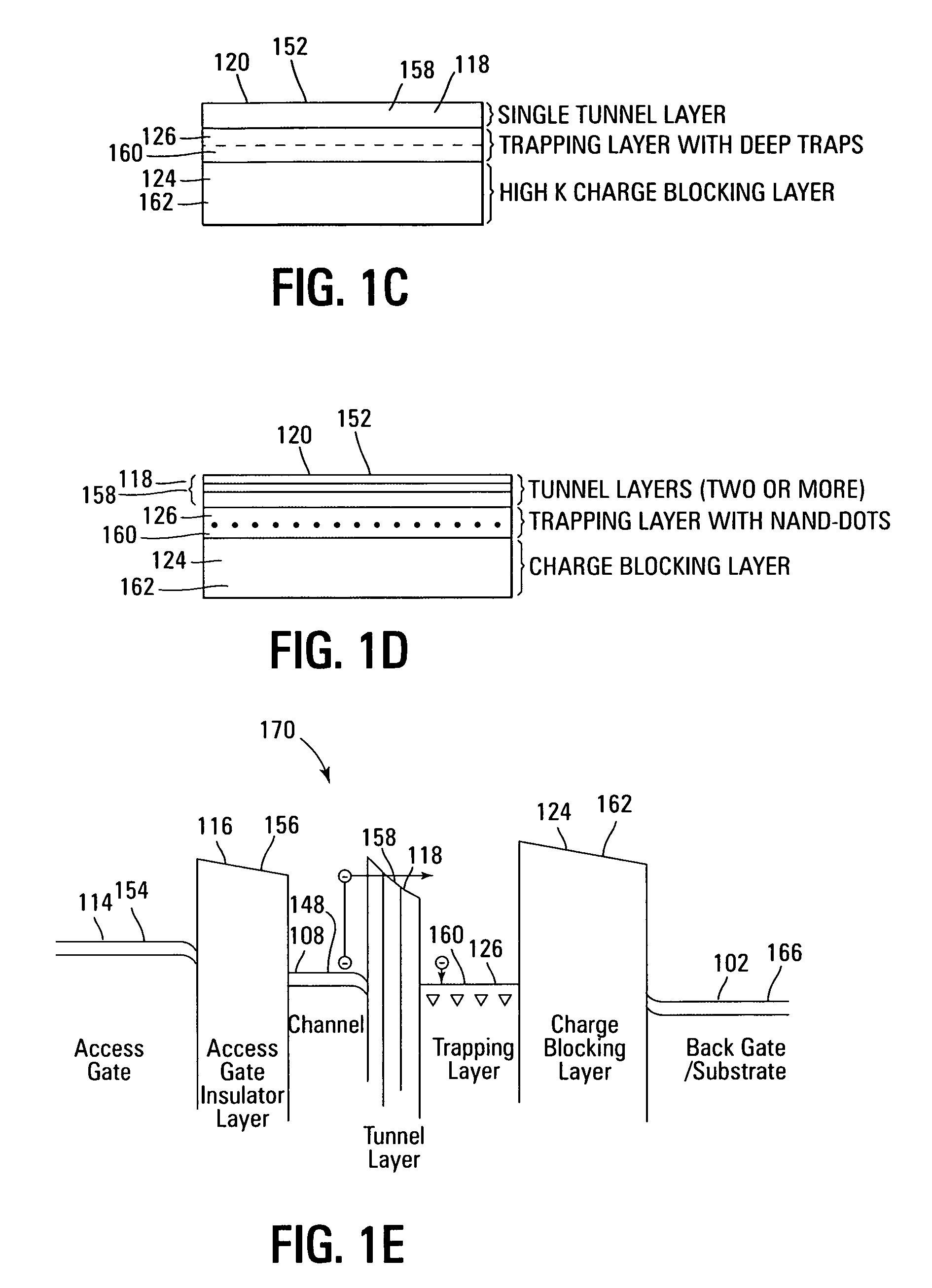

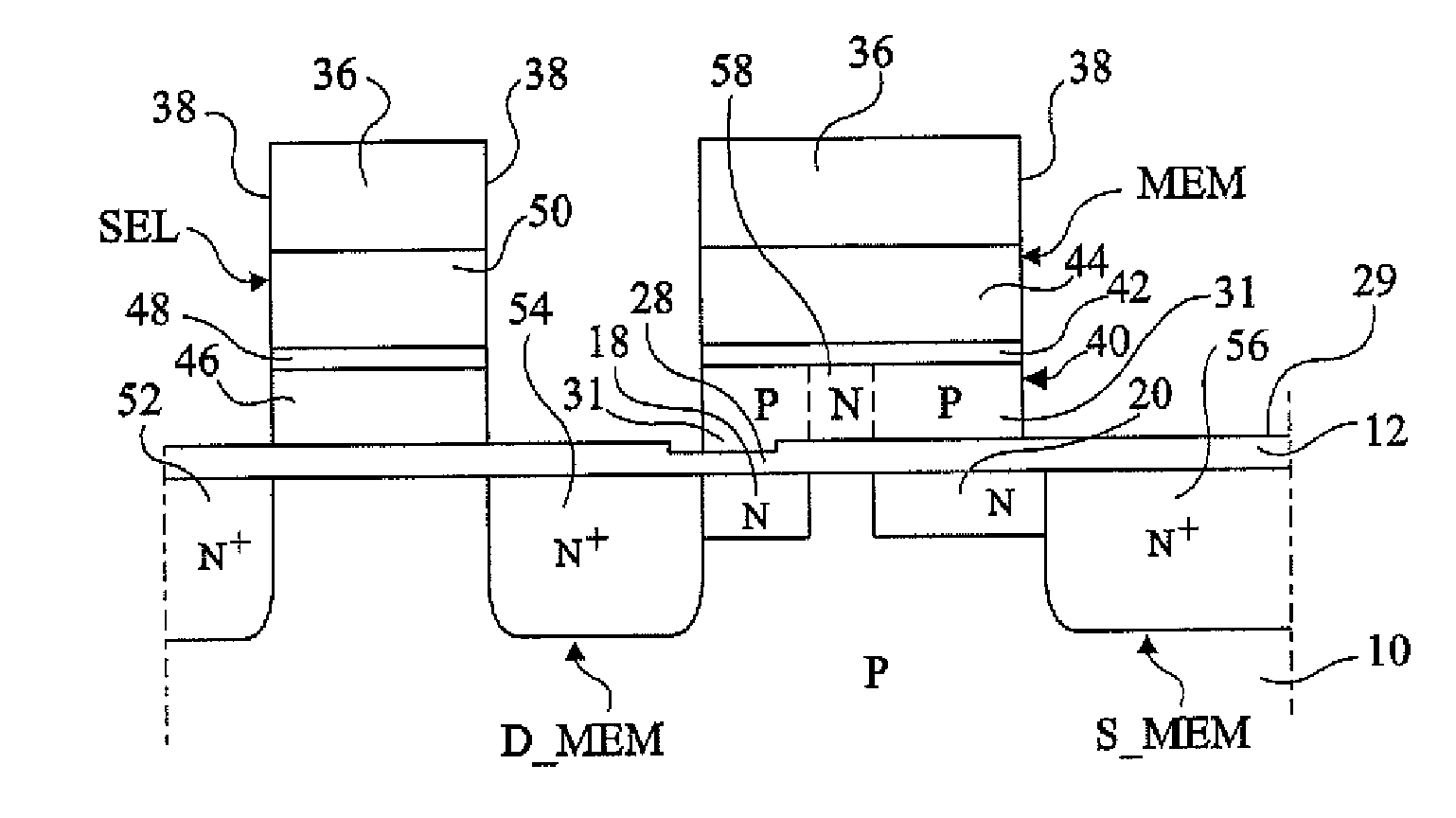

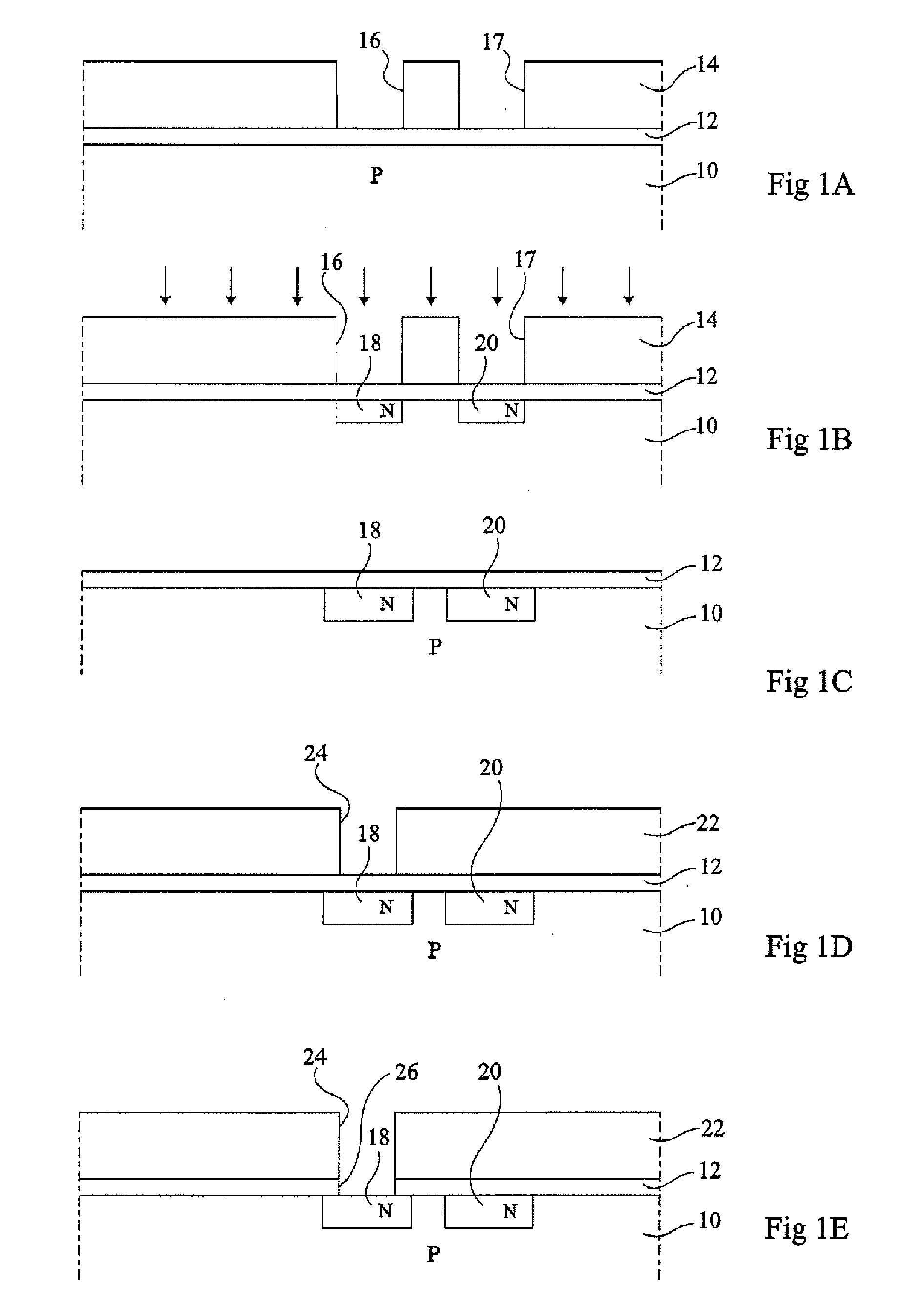

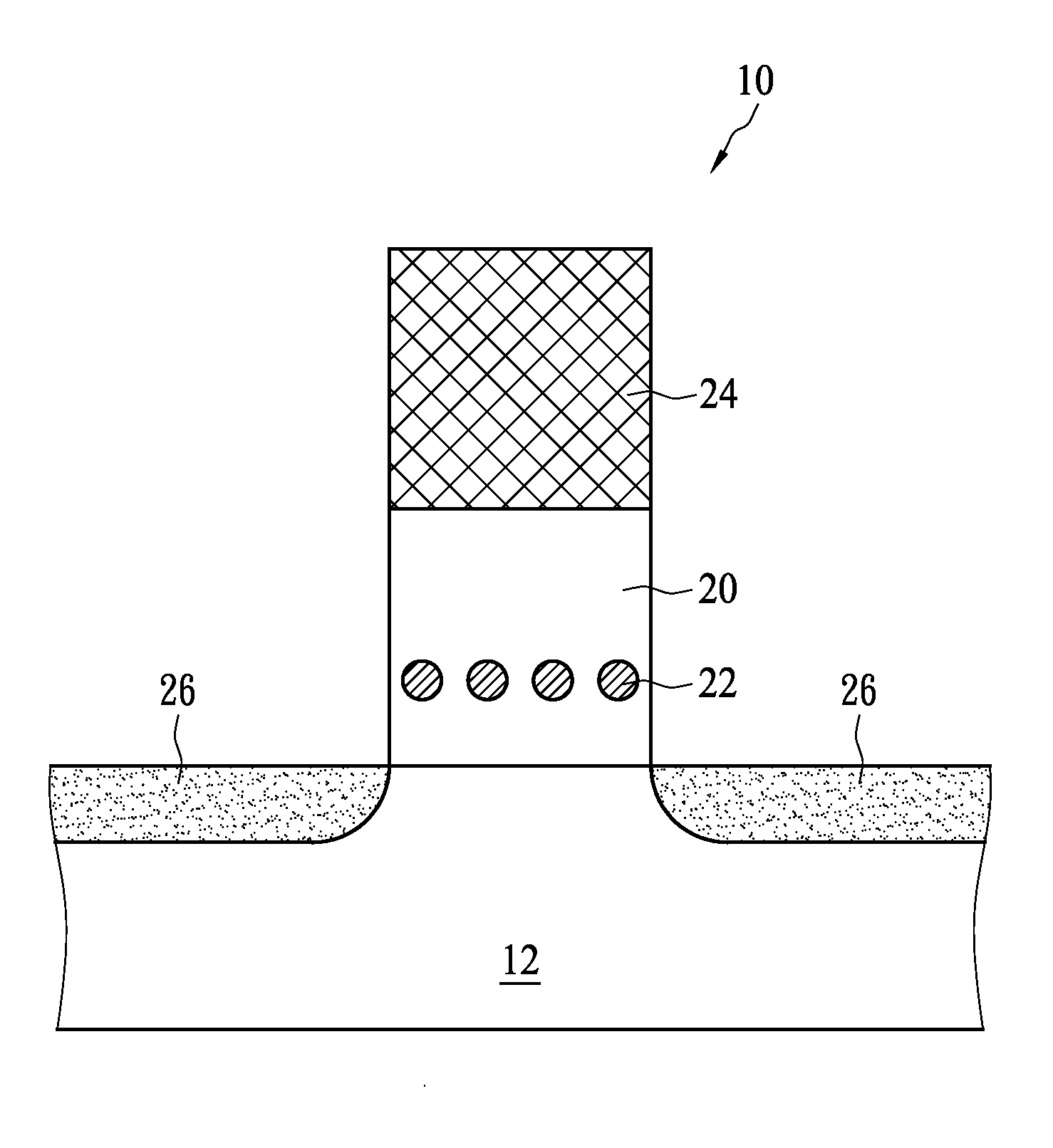

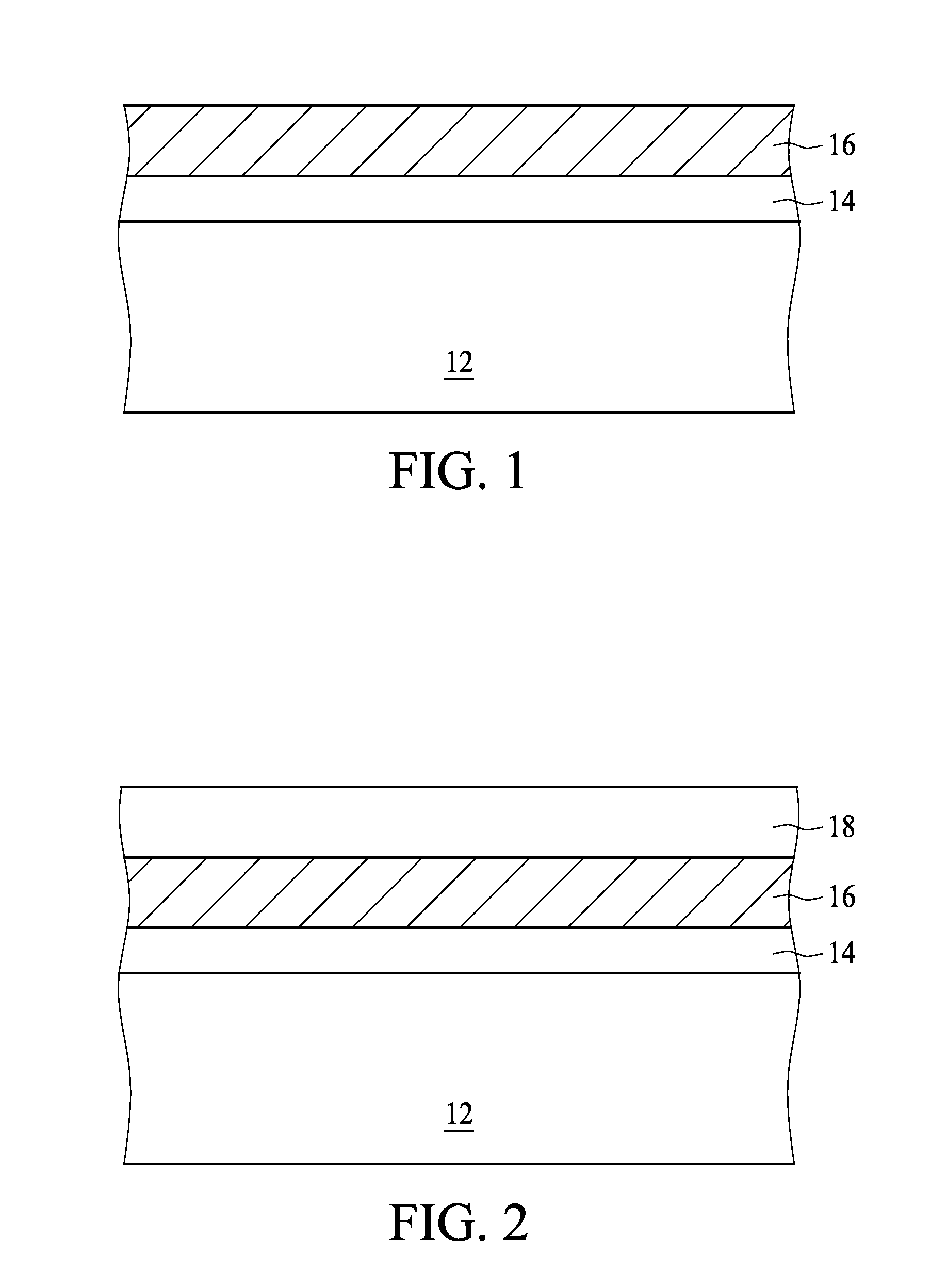

Band-engineered multi-gated non-volatile memory device with enhanced attributes

ActiveUS7279740B2Reduce harmExcellent charge retentionSolid-state devicesRead-only memoriesCharge retentionHigh energy

Non-volatile memory devices and arrays are described that facilitate the use of band-gap engineered gate stacks with asymmetric tunnel barriers in floating gate memory cells in NOR or NAND memory architectures that allow for direct tunneling programming and erase with electrons and holes, while maintaining high charge blocking barriers and deep carrier trapping sites for good charge retention. The direct tunneling program and erase capability reduces damage to the gate stack and the crystal lattice from high energy carriers, reducing write fatigue and leakage issues and enhancing device lifespan. Memory cells of the present invention also allow multiple bit storage in a single memory cell, and allow for programming and erase with reduced voltages. A positive voltage erase process via hole tunneling is also provided.

Owner:MICRON TECH INC

Band-engineered multi-gated non-volatile memory device with enhanced attributes

ActiveUS20060258090A1Reduce harmExcellent charge retentionSolid-state devicesRead-only memoriesCharge retentionHigh energy

Non-volatile memory devices and arrays are described that facilitate the use of band-gap engineered gate stacks with asymmetric tunnel barriers in floating gate memory cells in NOR or NAND memory architectures that allow for direct tunneling programming and erase with electrons and holes, while maintaining high charge blocking barriers and deep carrier trapping sites for good charge retention. The direct tunneling program and erase capability reduces damage to the gate stack and the crystal lattice from high energy carriers, reducing write fatigue and leakage issues and enhancing device lifespan. Memory cells of the present invention also allow multiple bit storage in a single memory cell, and allow for programming and erase with reduced voltages. A positive voltage erase process via hole tunneling is also provided.

Owner:MICRON TECH INC

Non-volatile memory device

InactiveUS7012298B1Small design featureExcellent charge retentionTransistorSemiconductor/solid-state device detailsSiliconNon-volatile memory

Owner:MONTEREY RES LLC

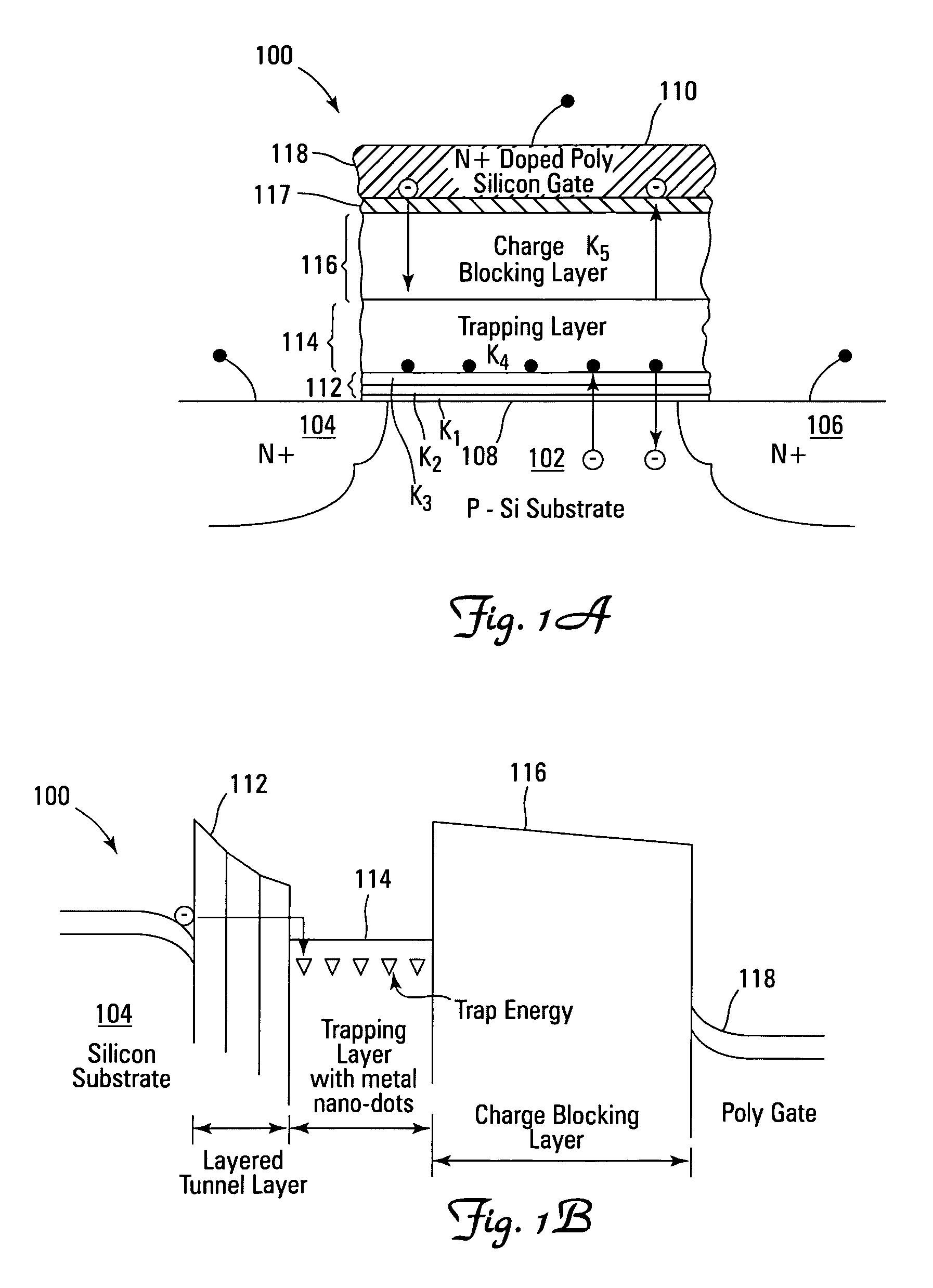

Low power non-volatile memory and gate stack

Non-volatile memory devices and arrays are described that facilitate the use of band-gap engineered gate stacks with asymmetric tunnel barriers in reverse and normal mode floating node memory cells in NOR or NAND memory architectures that allow for direct tunnel programming and erase, while maintaining high charge blocking barriers and deep carrier trapping sites for good charge retention. The low voltage direct tunneling program and erase capability reduces damage to the gate stack and the crystal lattice from high energy carriers, reducing write fatigue and enhancing device lifespan. The low voltage direct tunnel program and erase capability also enables size reduction through low voltage design and further device feature scaling. Memory cells of the present invention also allow multiple bit storage. These characteristics allow memory device embodiments of the present invention to operate within the definition of a universal memory, capable of replacing both DRAM and ROM in a system.

Owner:MICRON TECH INC

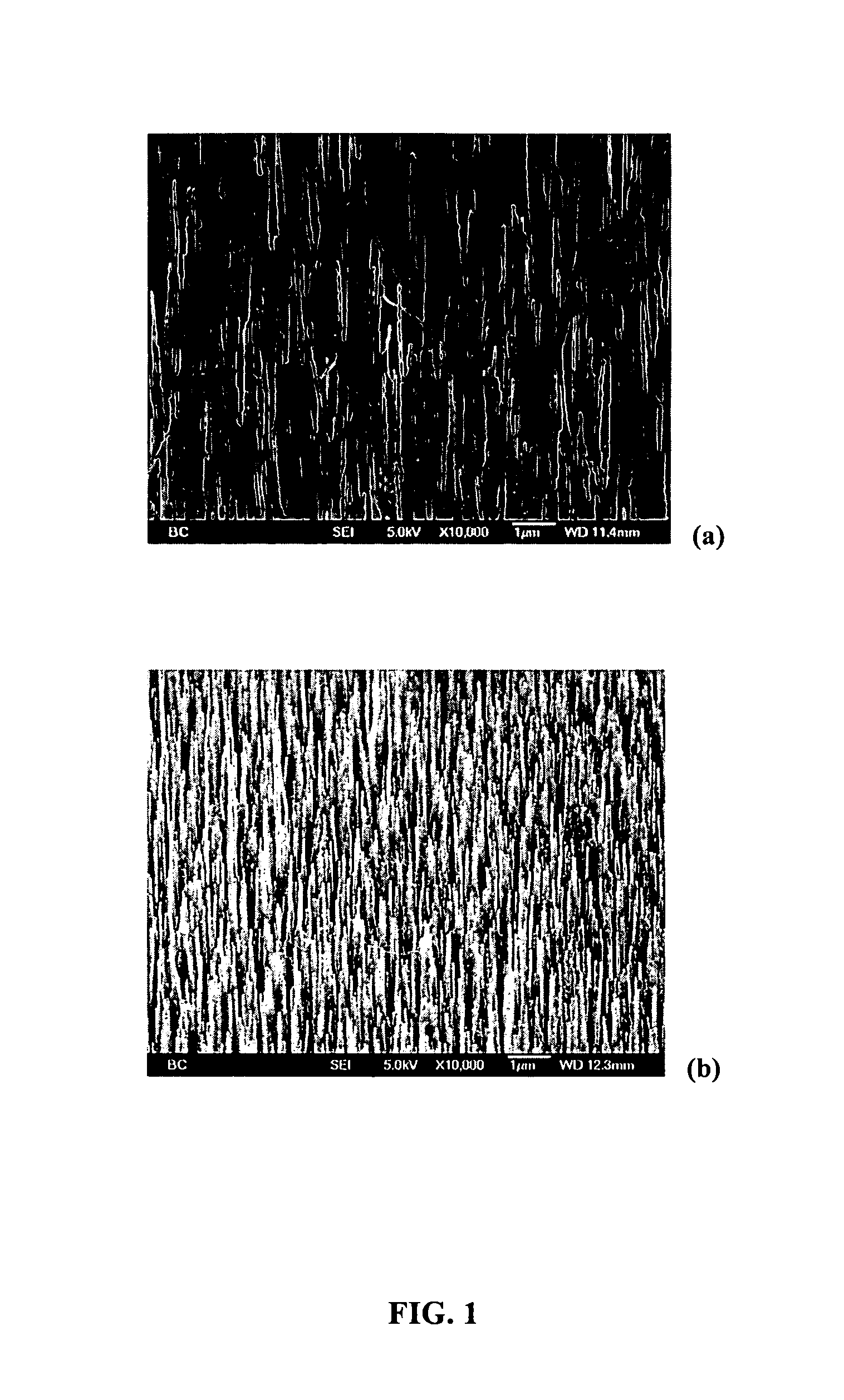

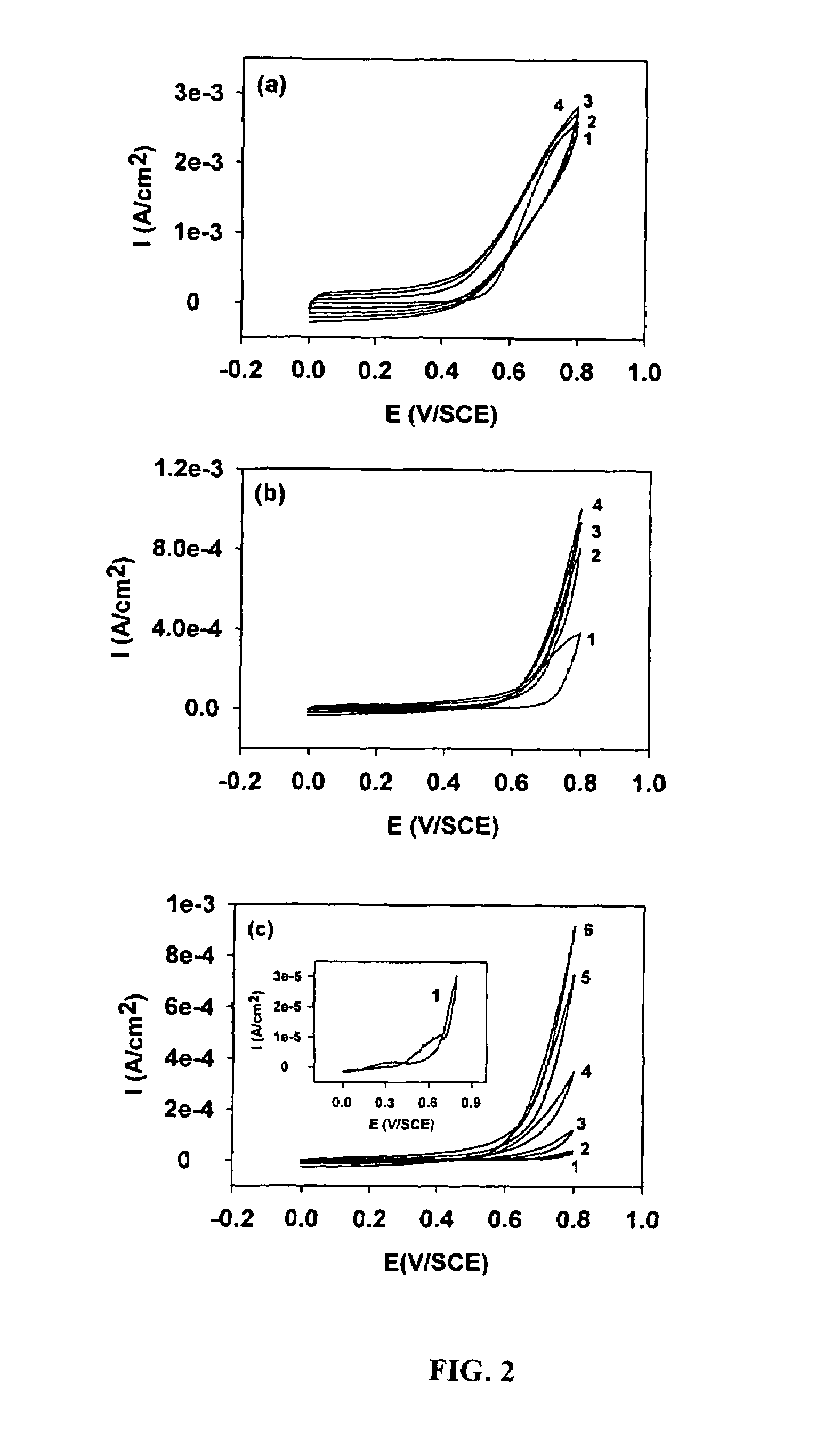

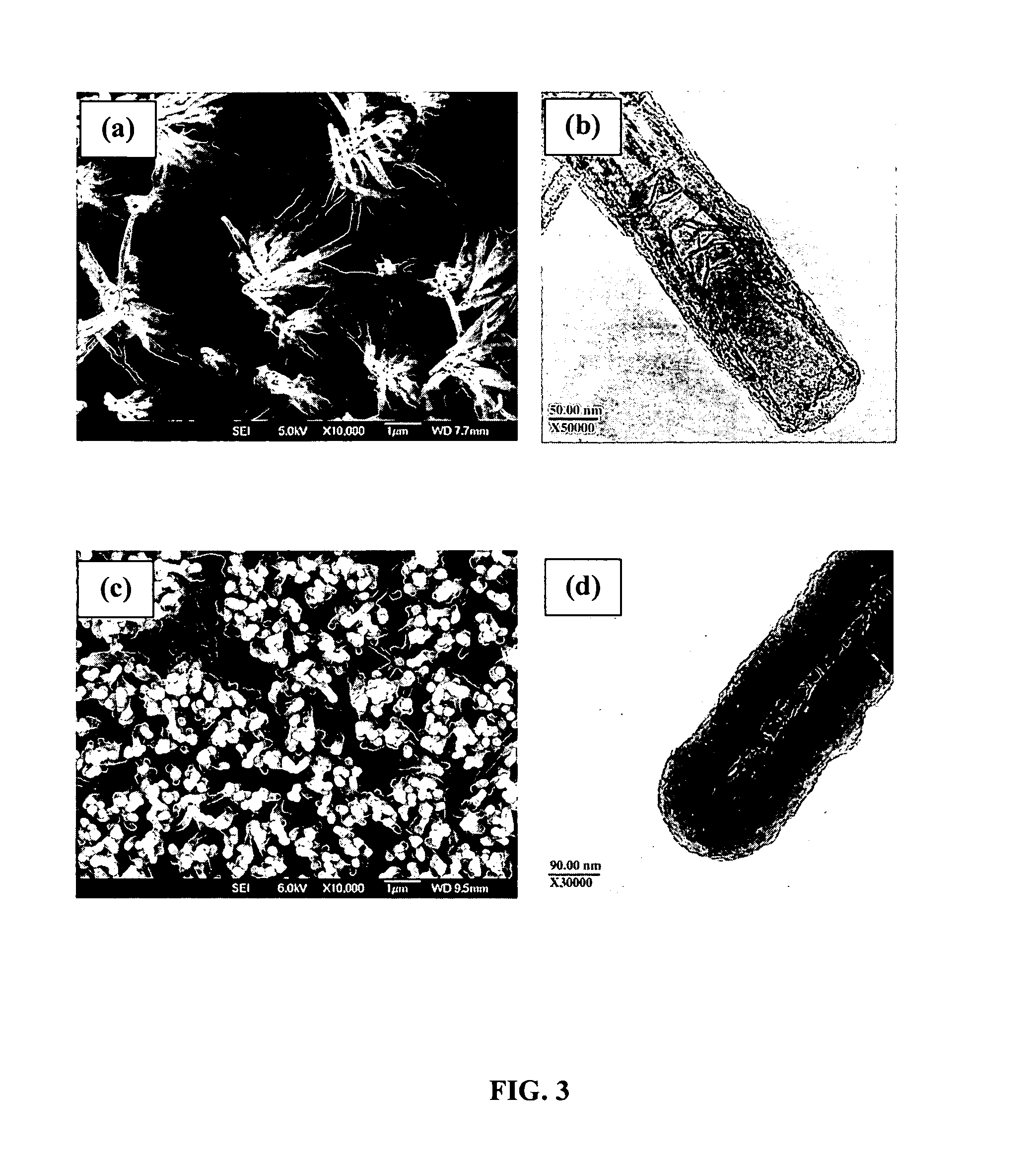

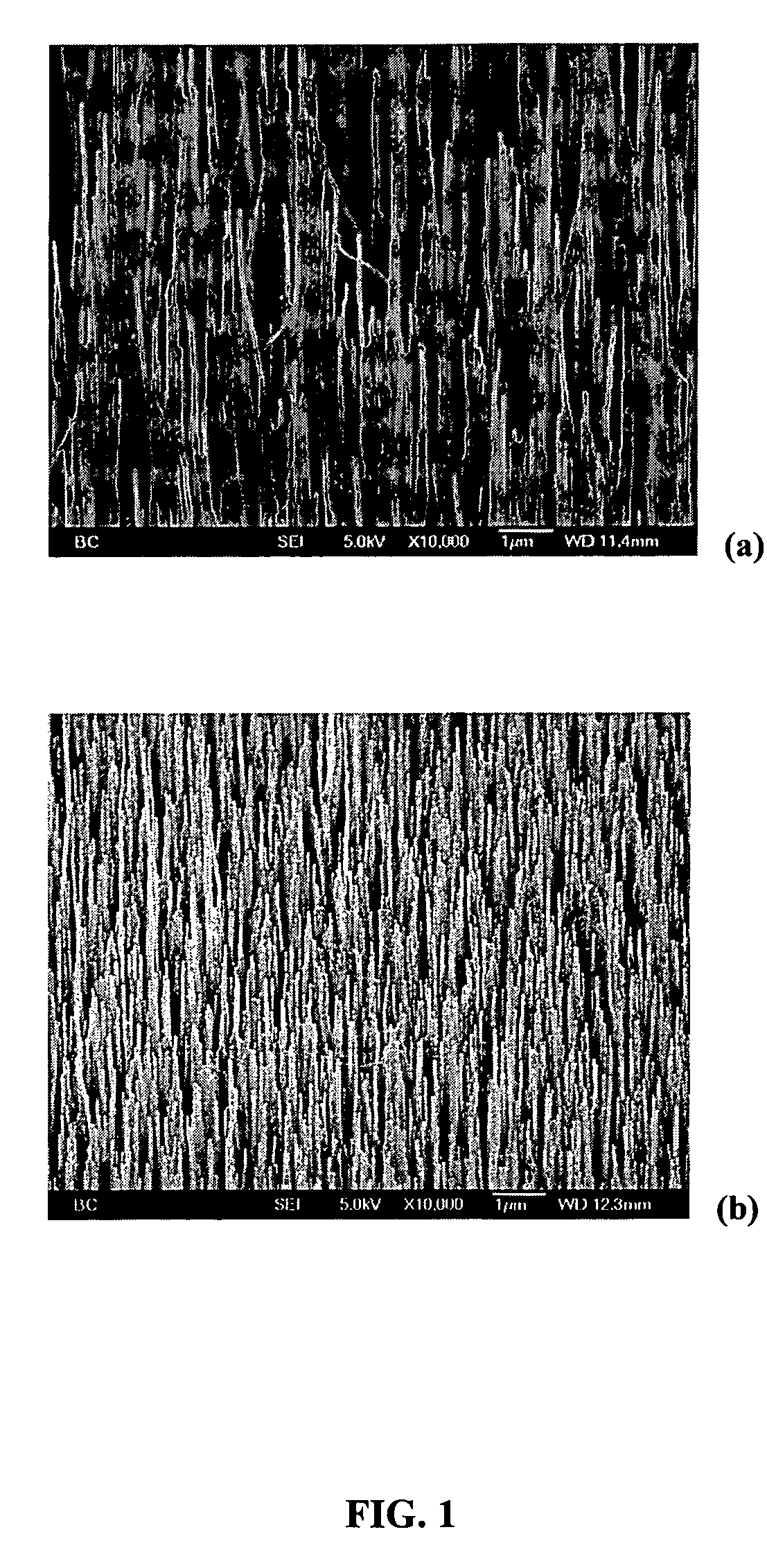

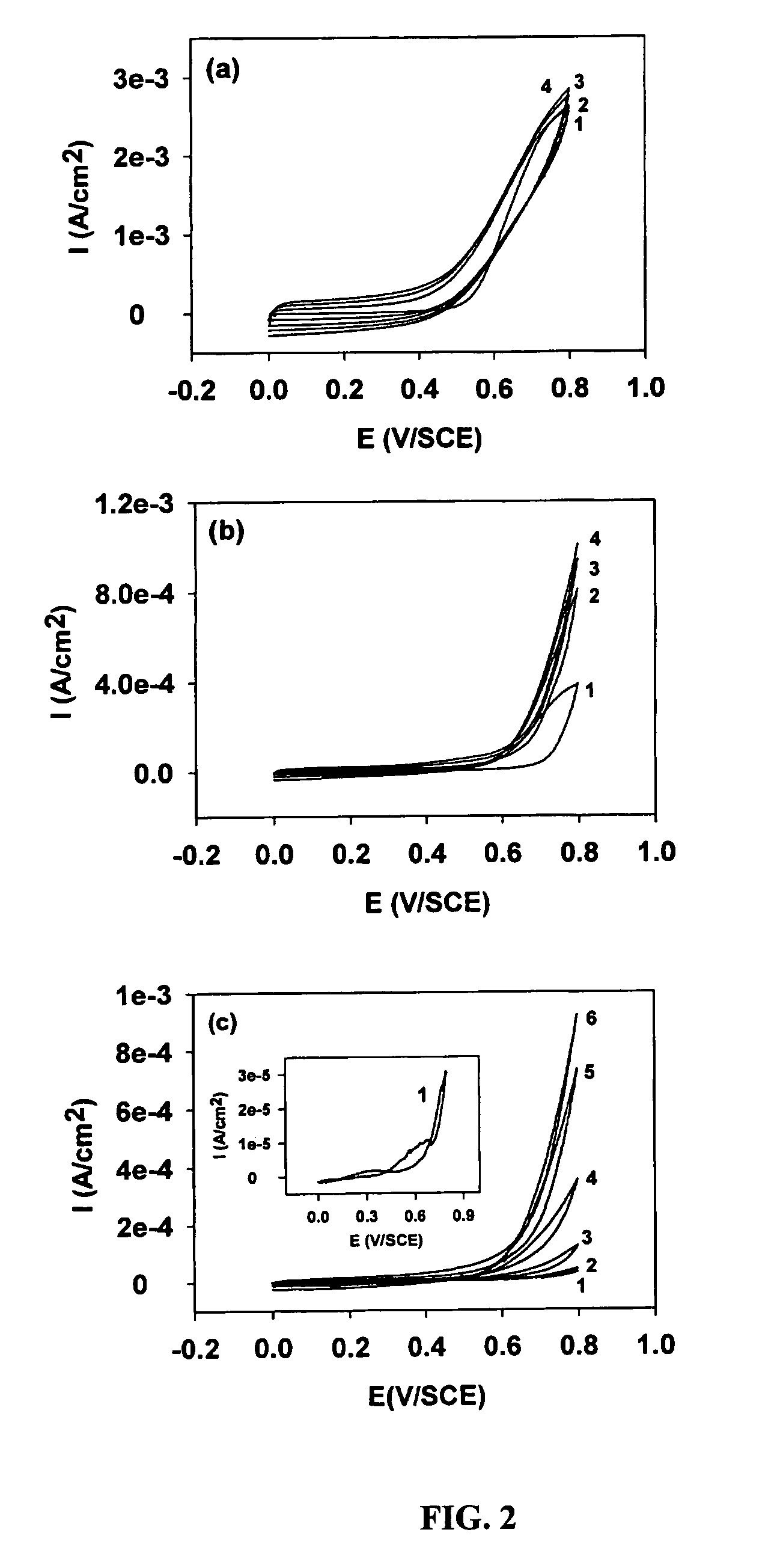

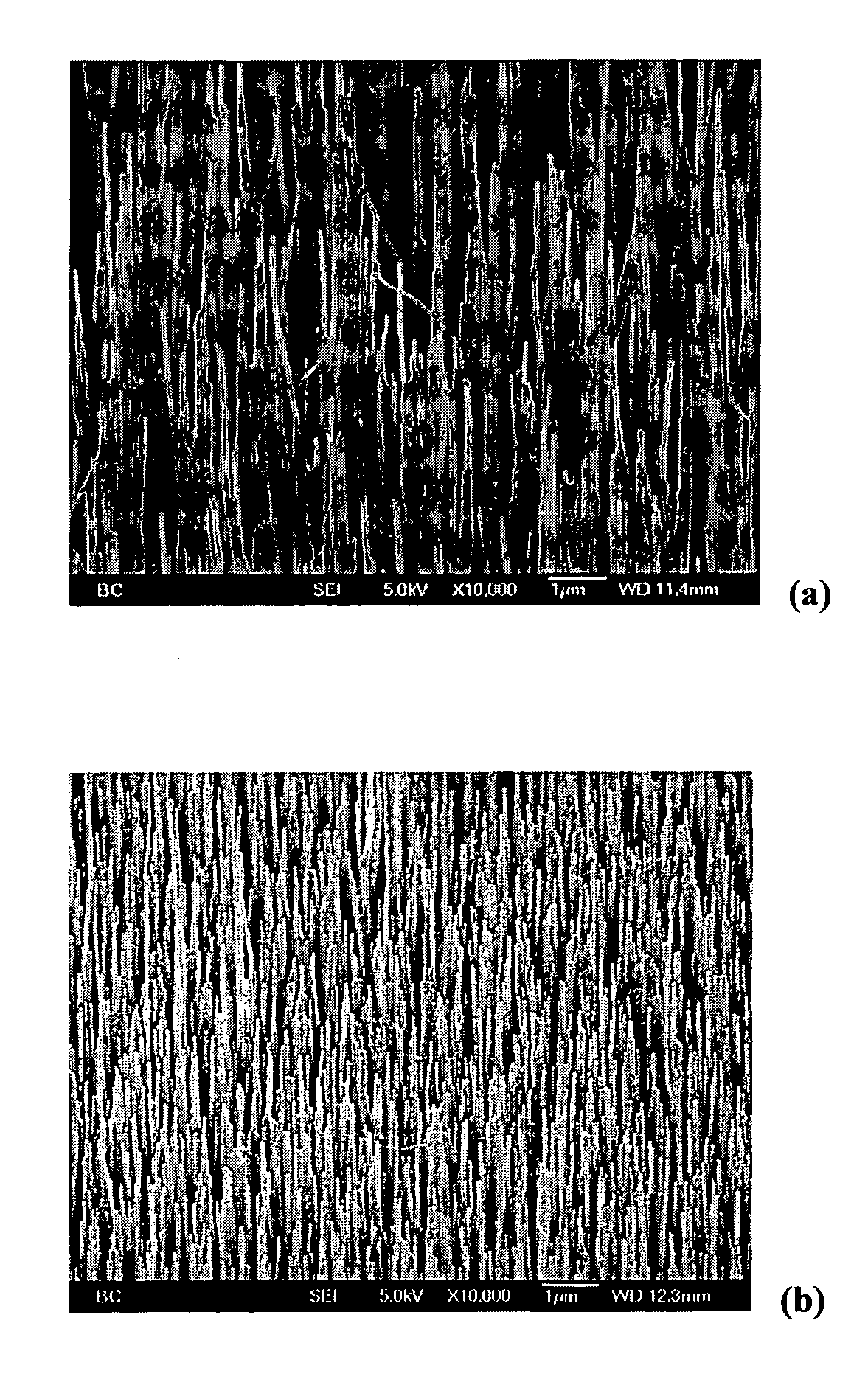

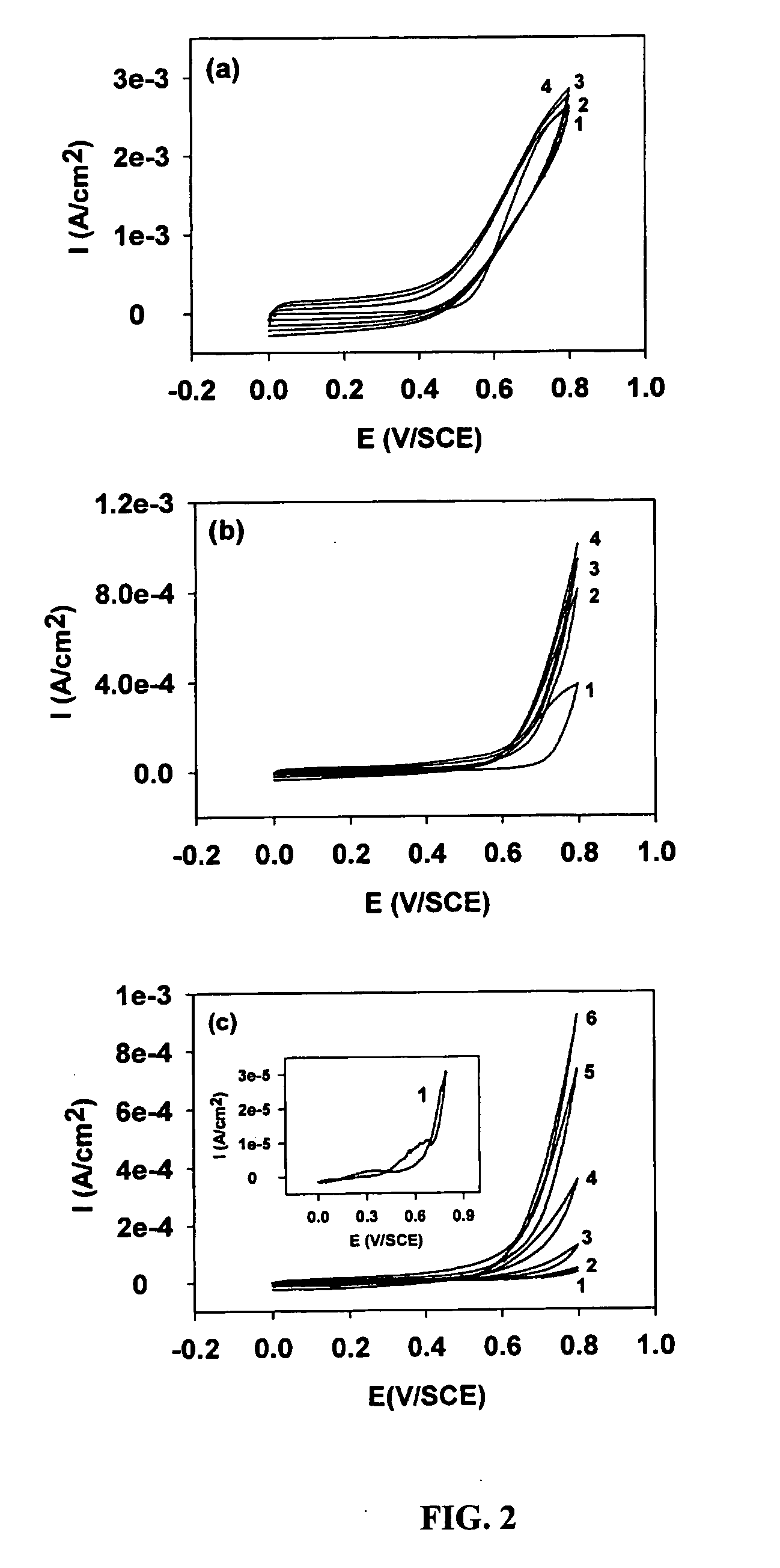

Coated carbon nanotube array electrodes

InactiveUS7147966B2Improve conductivityImprove conductive polymer film adhesionMaterial nanotechnologyNanoinformaticsPolypyrroleConductive polymer

The present invention provides conductive carbon nanotube (CNT) electrode materials comprising aligned CNT substrates coated with an electrically conducting polymer, and the fabrication of electrodes for use in high performance electrical energy storage devices. In particular, the present invention provides conductive CNTs electrode material whose electrical properties render them especially suitable for use in high efficiency rechargeable batteries. The present invention also provides methods for obtaining surface modified conductive CNT electrode materials comprising an array of individual linear, aligned CNTs having a uniform surface coating of an electrically conductive polymer such as polypyrrole, and their use in electrical energy storage devices.

Owner:BOSTON COLLEGE

Coated carbon nanotube array electrodes

InactiveUS7442284B2Improve conductive polymer film adhesionExcellent charge retentionMaterial nanotechnologyHybrid capacitor electrodesPolypyrroleConductive polymer

The present invention provides conductive carbon nanotube (CNT) electrode materials comprising aligned CNT substrates coated with an electrically conducting polymer, and the fabrication of electrodes for use in high performance electrical energy storage devices. In particular, the present invention provides conductive CNTs electrode material whose electrical properties render them especially suitable for use in high efficiency rechargeable batteries. The present invention also provides methods for obtaining surface modified conductive CNT electrode materials comprising an array of individual linear, aligned CNTs having a uniform surface coating of an electrically conductive polymer such as polypyrrole, and their use in electrical energy storage devices.

Owner:TRUSTEES OF BOSTON COLLEGE THE

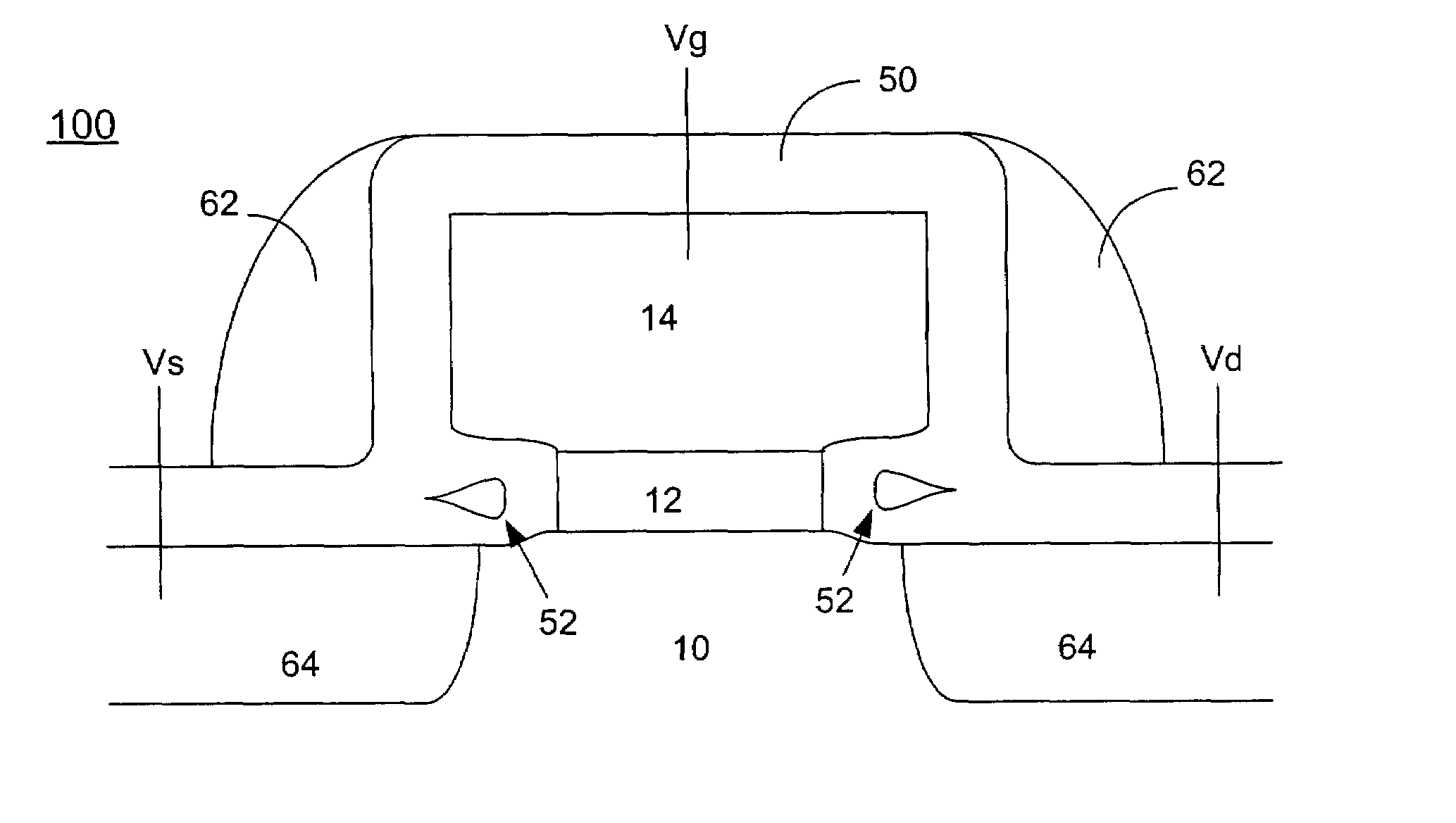

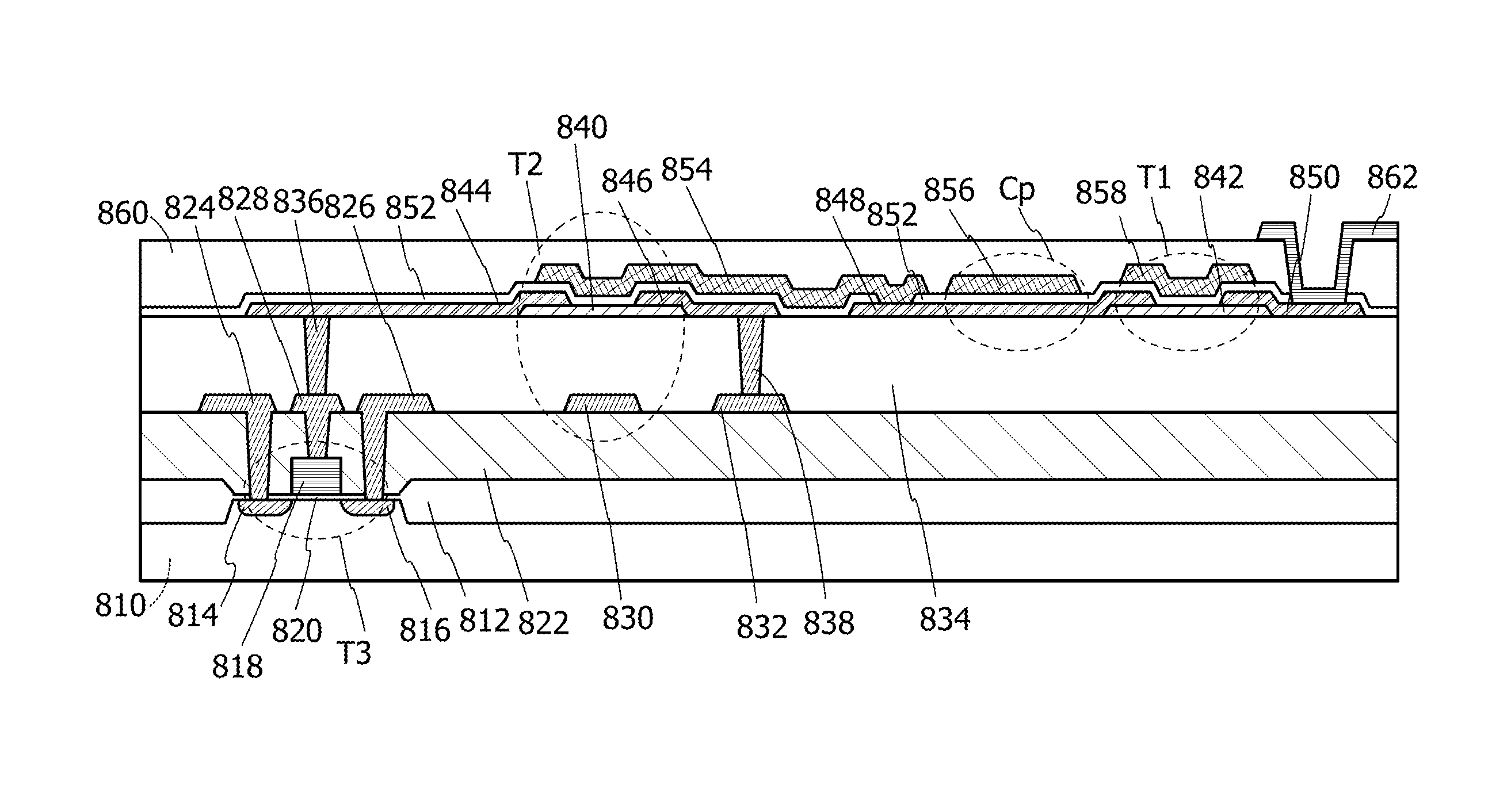

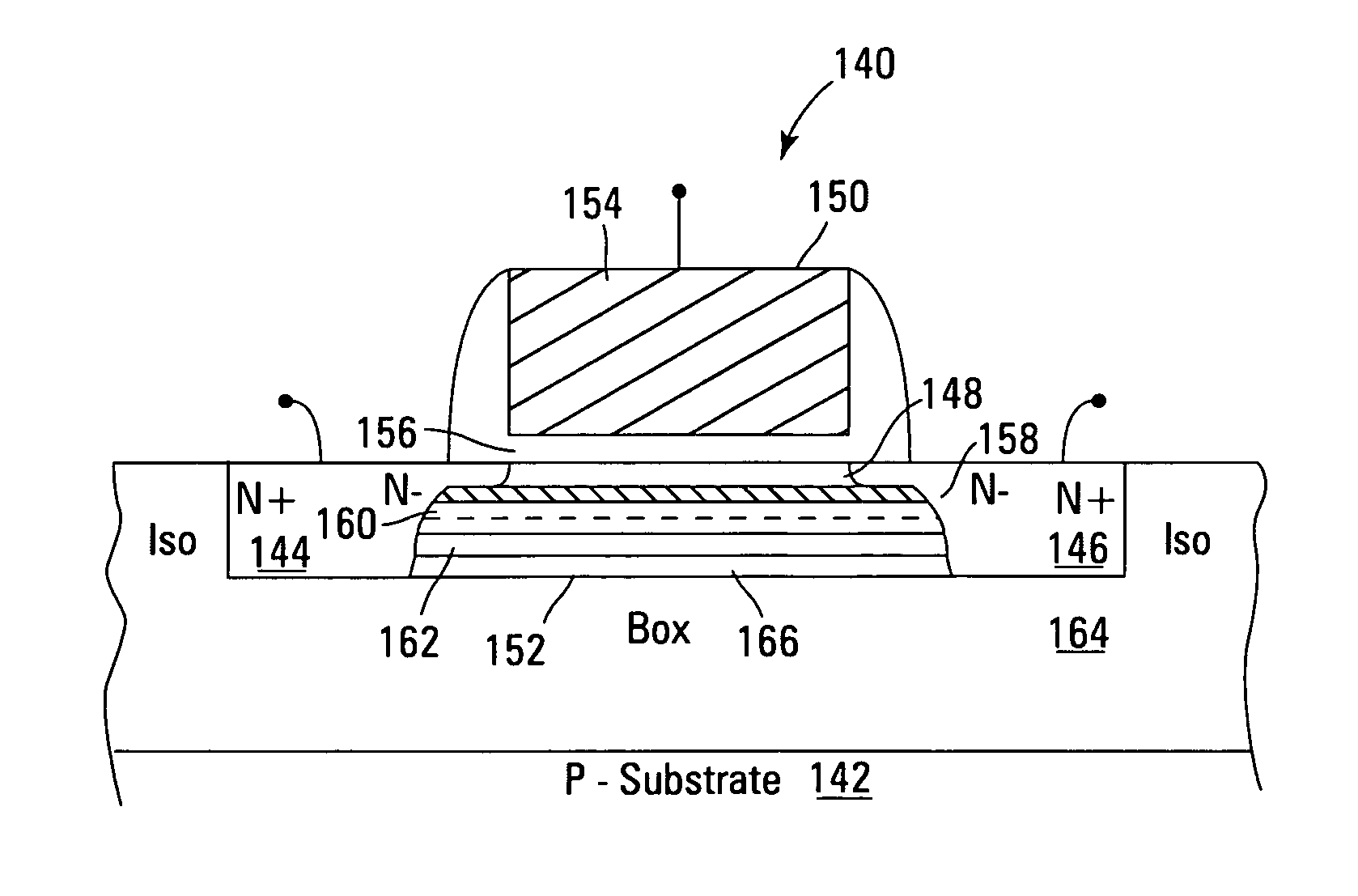

High density NAND non-volatile memory device

ActiveUS7829938B2Reduce harmImproved high density memory device and arraySolid-state devicesRead-only memoriesCharge retentionTrapping

Non-volatile memory devices and arrays are described that utilize dual gate (or back-side gate) non-volatile memory cells with band engineered gate-stacks that are placed above or below the channel region in front-side or back-side charge trapping gate-stack configurations in NAND memory array architectures. The band-gap engineered gate-stacks with asymmetric or direct tunnel barriers of the floating node memory cells of embodiments of the present invention allow for low voltage tunneling programming and efficient erase with electrons and holes, while maintaining high charge blocking barriers and deep carrier trapping sites for good charge retention. The memory cell architecture also allows for improved high density memory devices or arrays with the utilization of reduced feature word lines and vertical select gates.

Owner:MICRON TECH INC

Coated carbon nanotube array electrodes

InactiveUS20070134555A1Improve conductive polymer film adhesionExcellent charge retentionMaterial nanotechnologyElectrode manufacturing processesPolypyrroleConductive polymer

The present invention provides conductive carbon nanotube (CNT) electrode materials comprising aligned CNT substrates coated with an electrically conducting polymer, and the fabrication of electrodes for use in high performance electrical energy storage devices. In particular, the present invention provides conductive CNTs electrode material whose electrical properties render them especially suitable for use in high efficiency rechargeable batteries. The present invention also provides methods for obtaining surface modified conductive CNT electrode materials comprising an array of individual linear, aligned CNTs having a uniform surface coating of an electrically conductive polymer such as polypyrrole, and their use in electrical energy storage devices.

Owner:TRUSTEES OF BOSTON COLLEGE THE

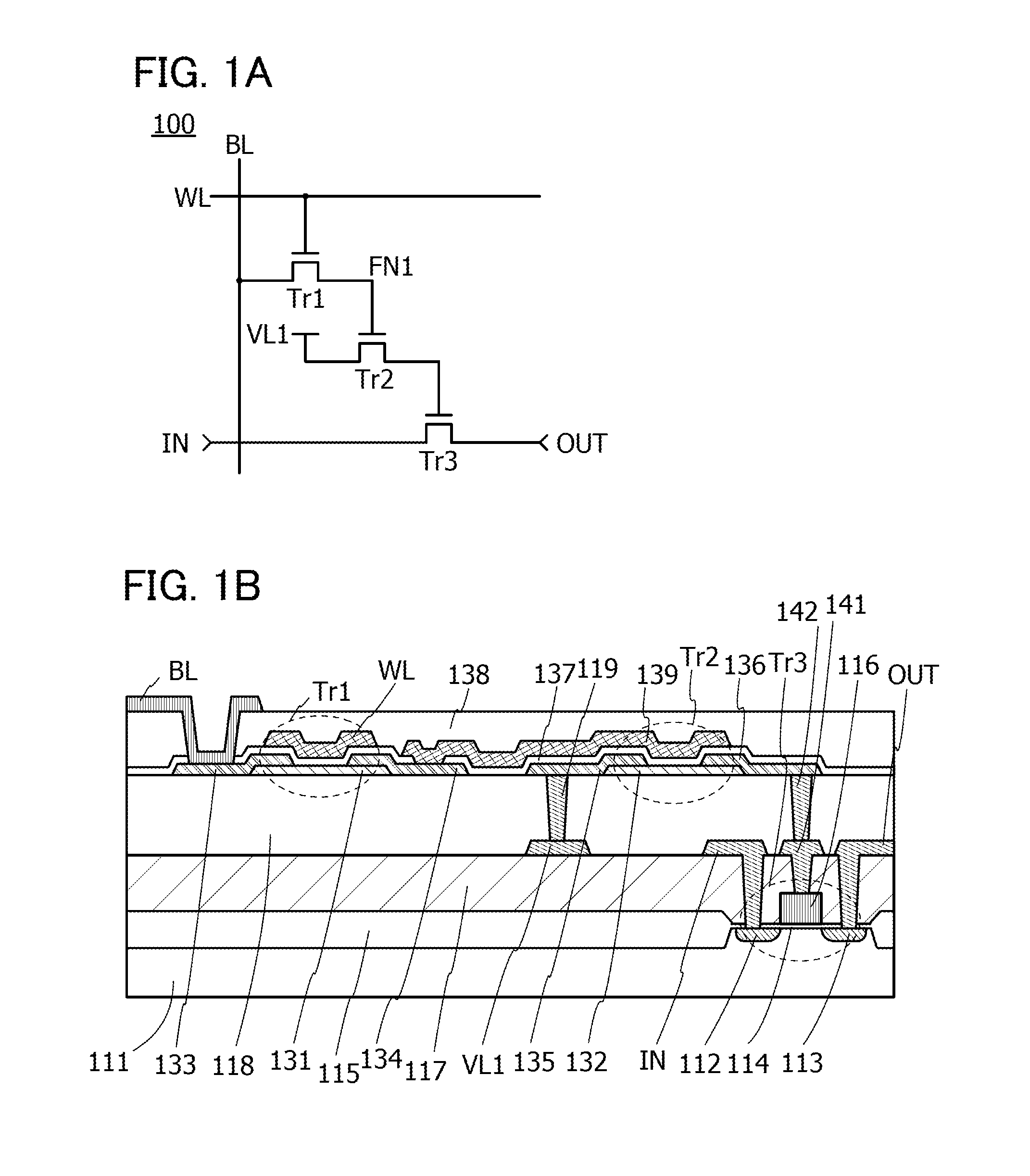

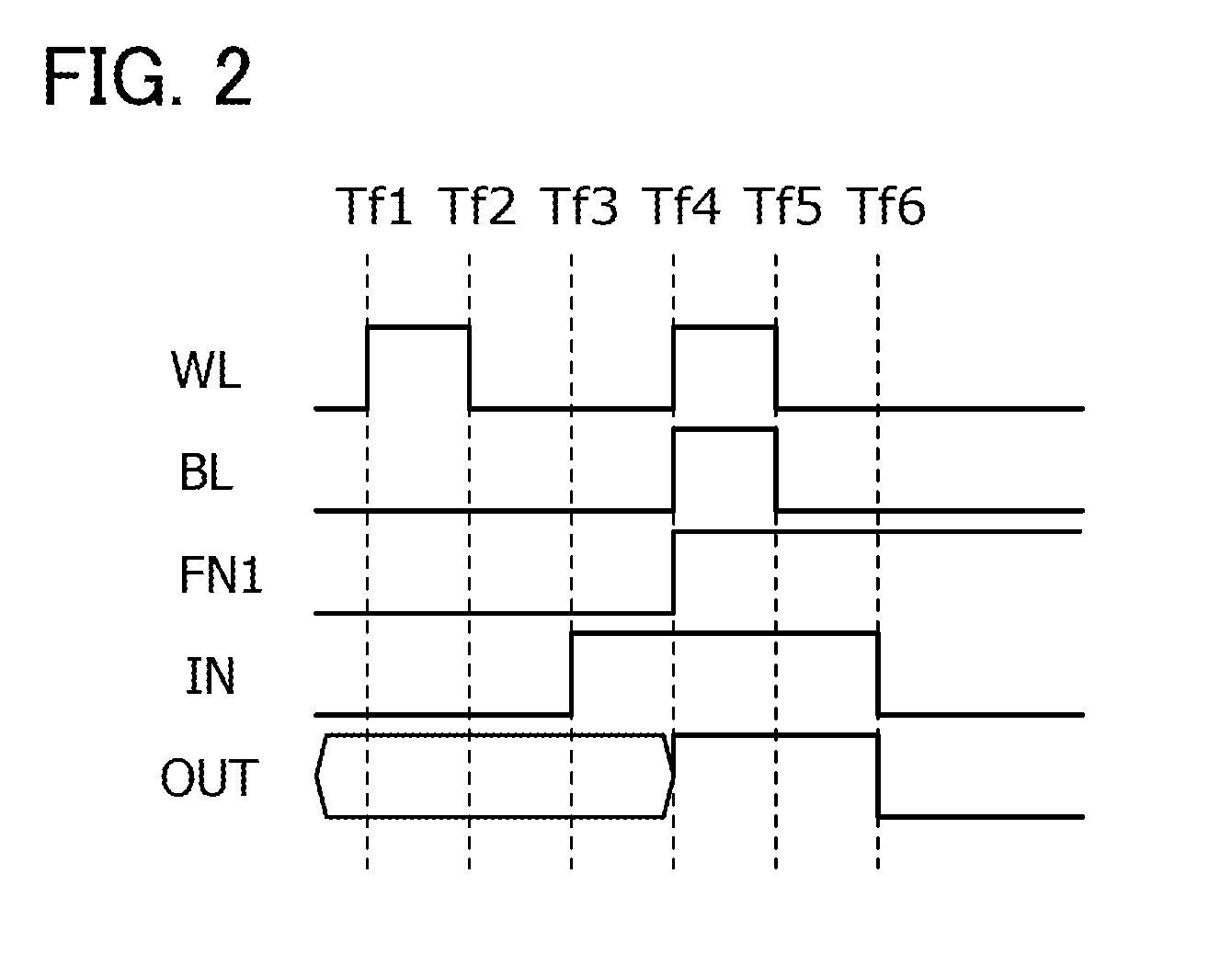

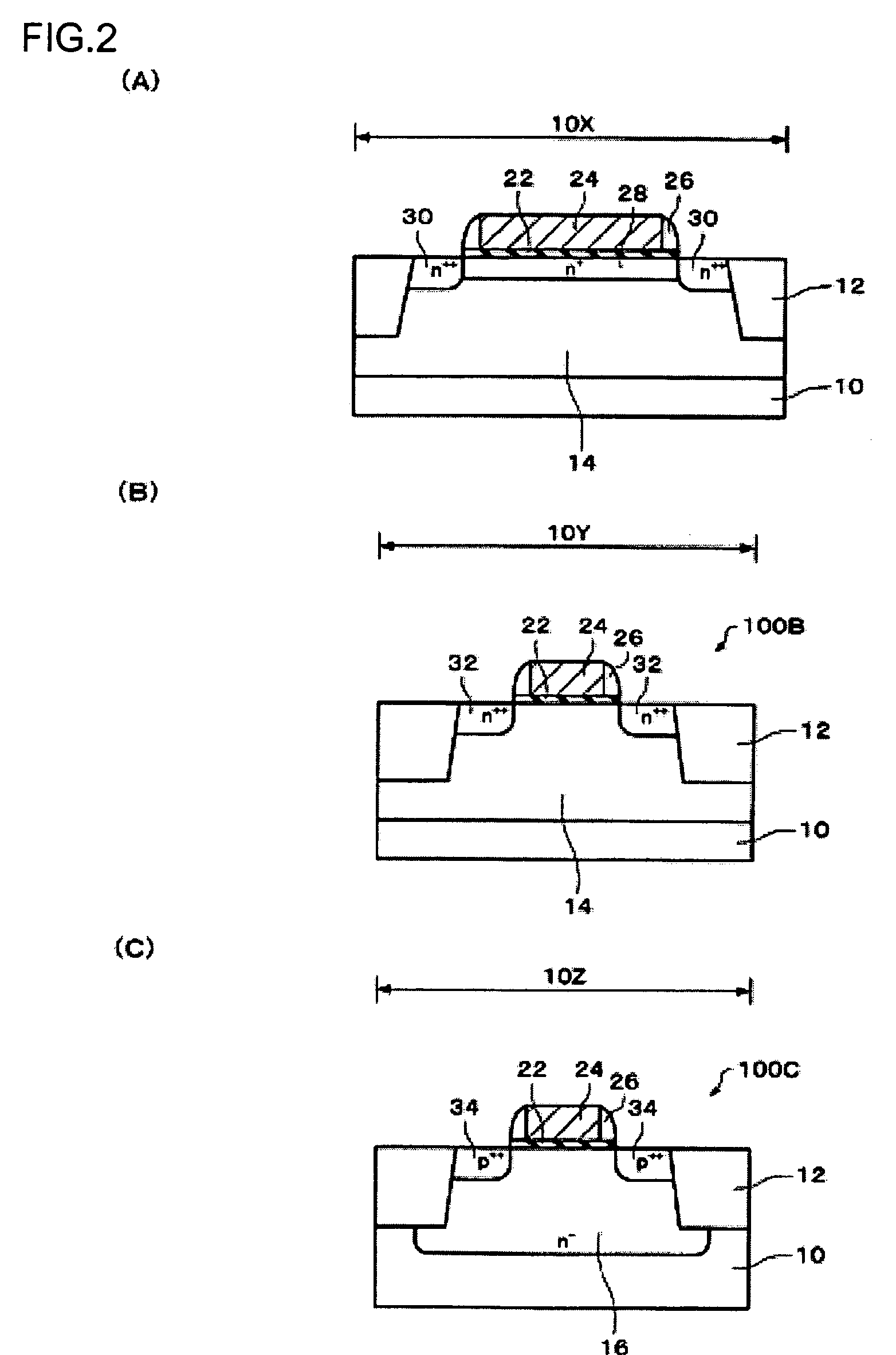

Semiconductor device

InactiveUS20140374747A1Small sizeImprove charge retention characteristicsTransistorSolid-state devicesGate leakage currentCharge retention

To provide a semiconductor device with excellent charge retention characteristics, a transistor including a thick gate insulating film to achieve low leakage current is additionally provided such that its gate is connected to a node for holding charge. The node is composed of this additional transistor and a transistor using an oxide semiconductor in its semiconductor layer including a channel formation region. Charge corresponding to data is held at the node.

Owner:SEMICON ENERGY LAB CO LTD

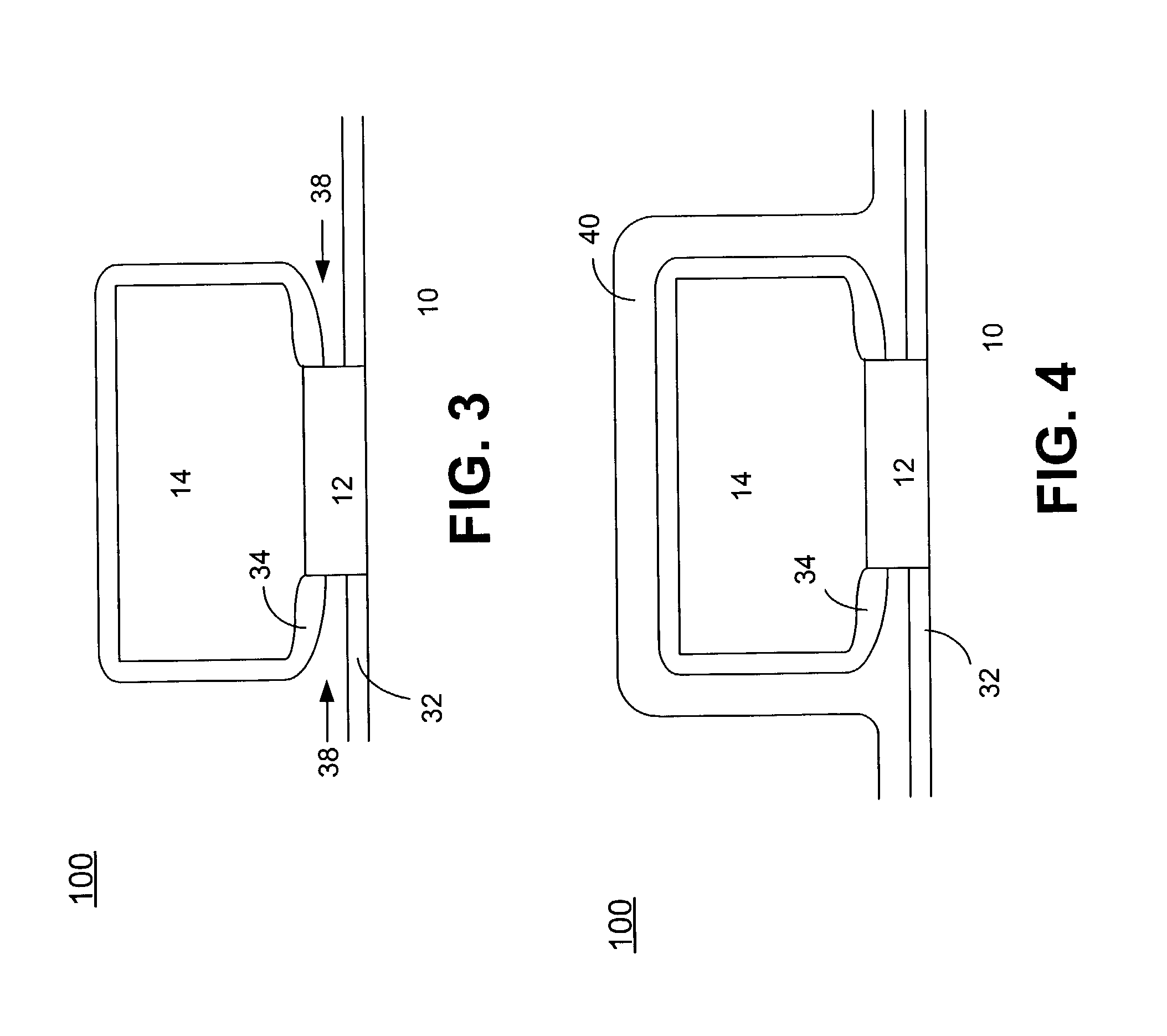

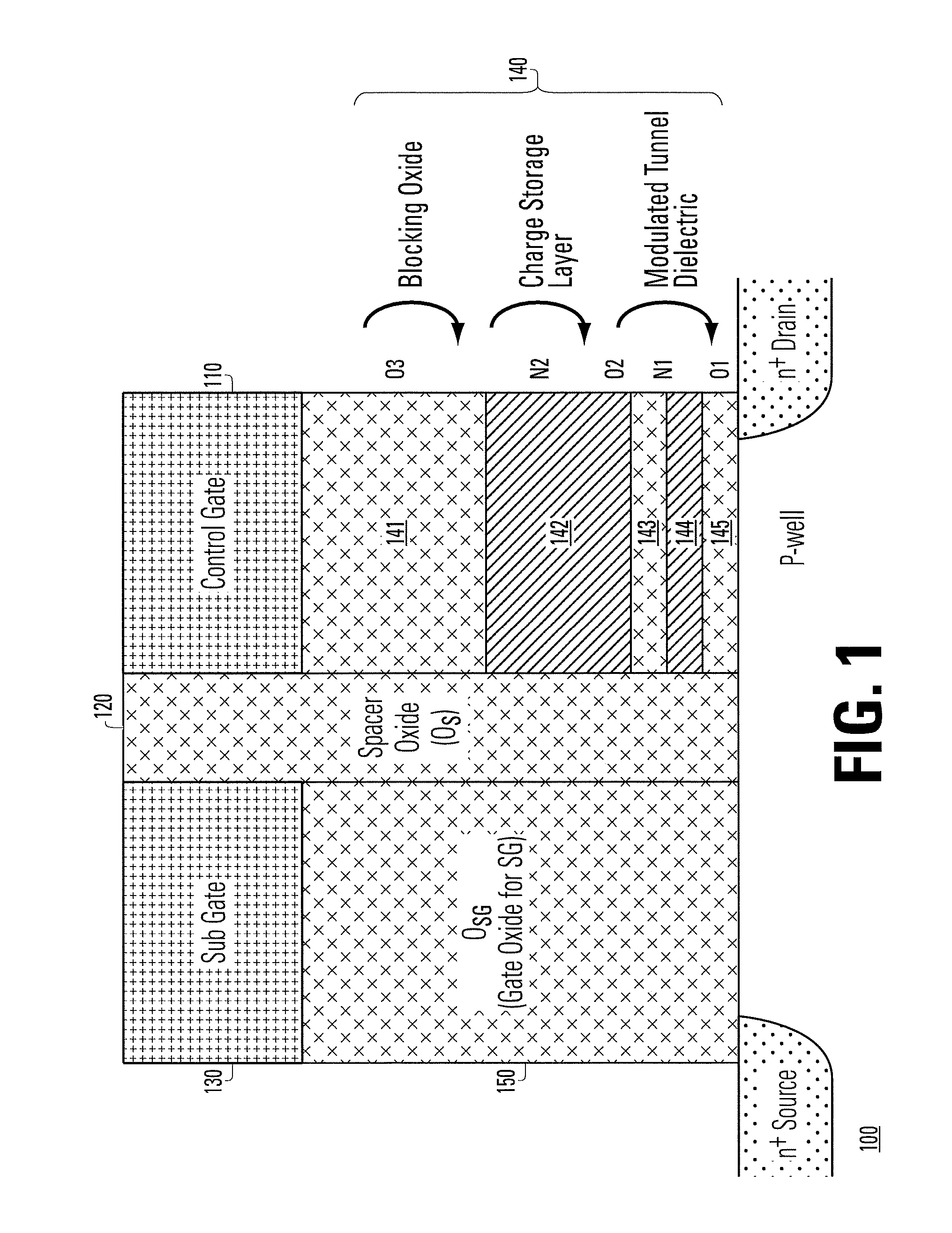

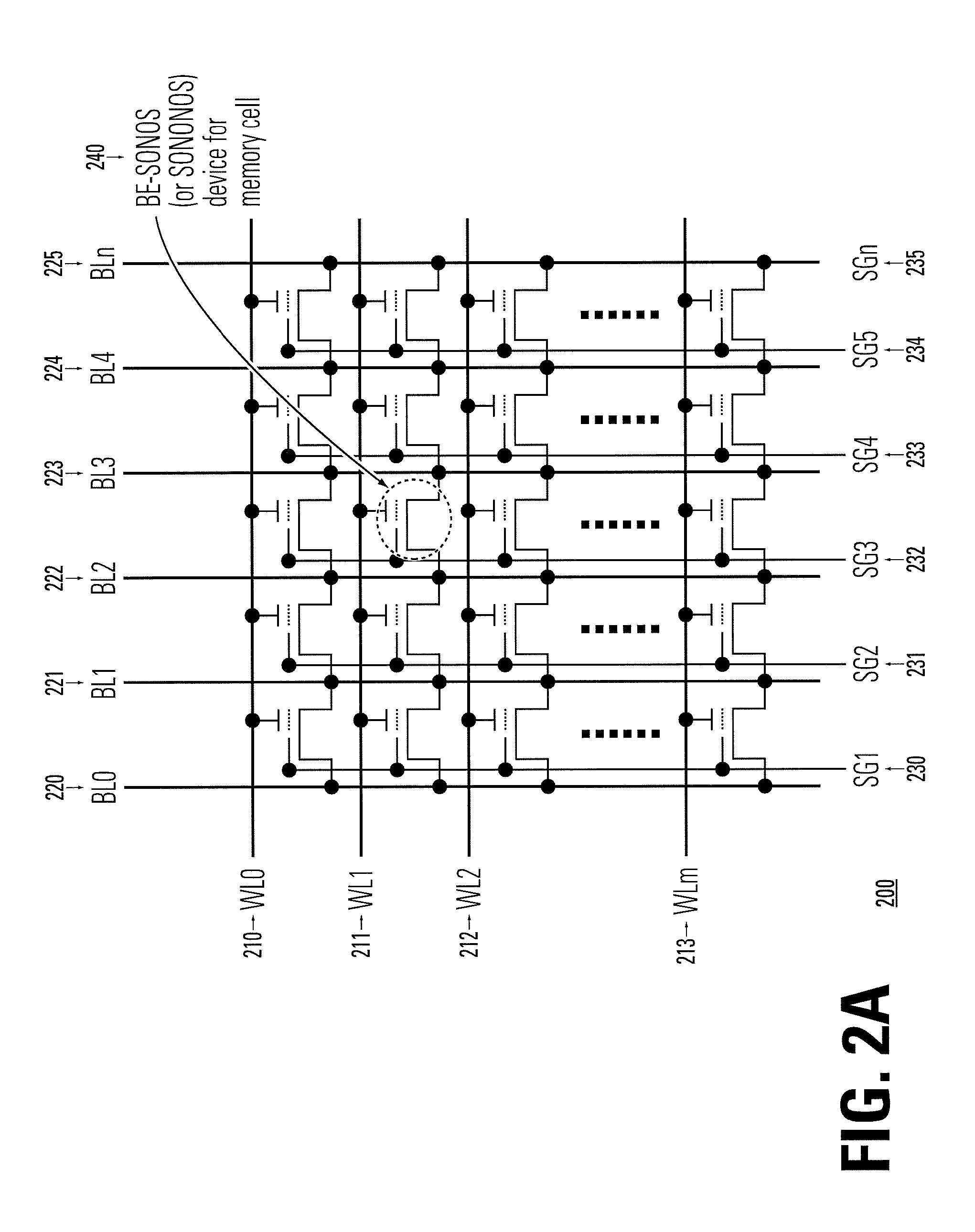

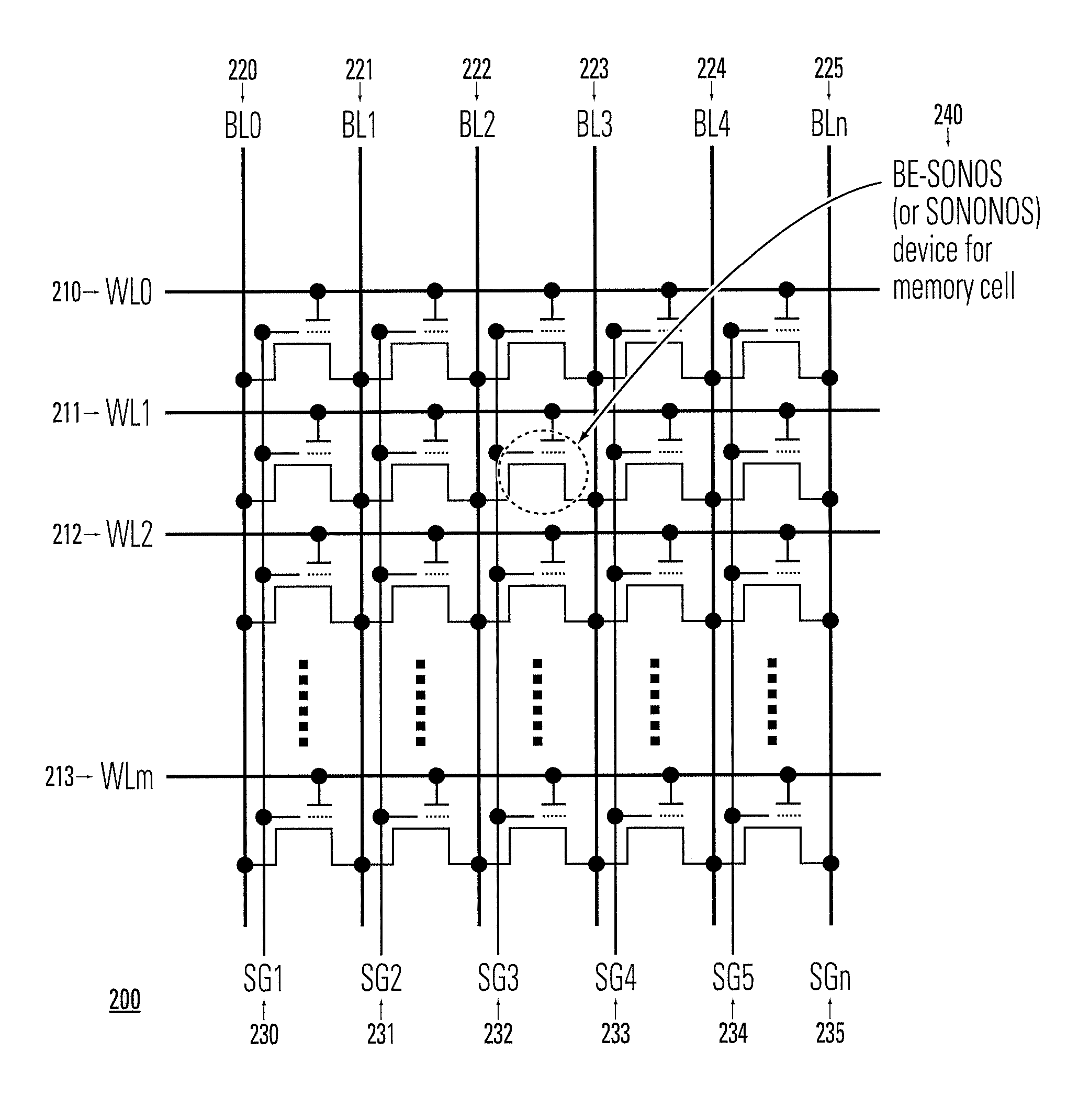

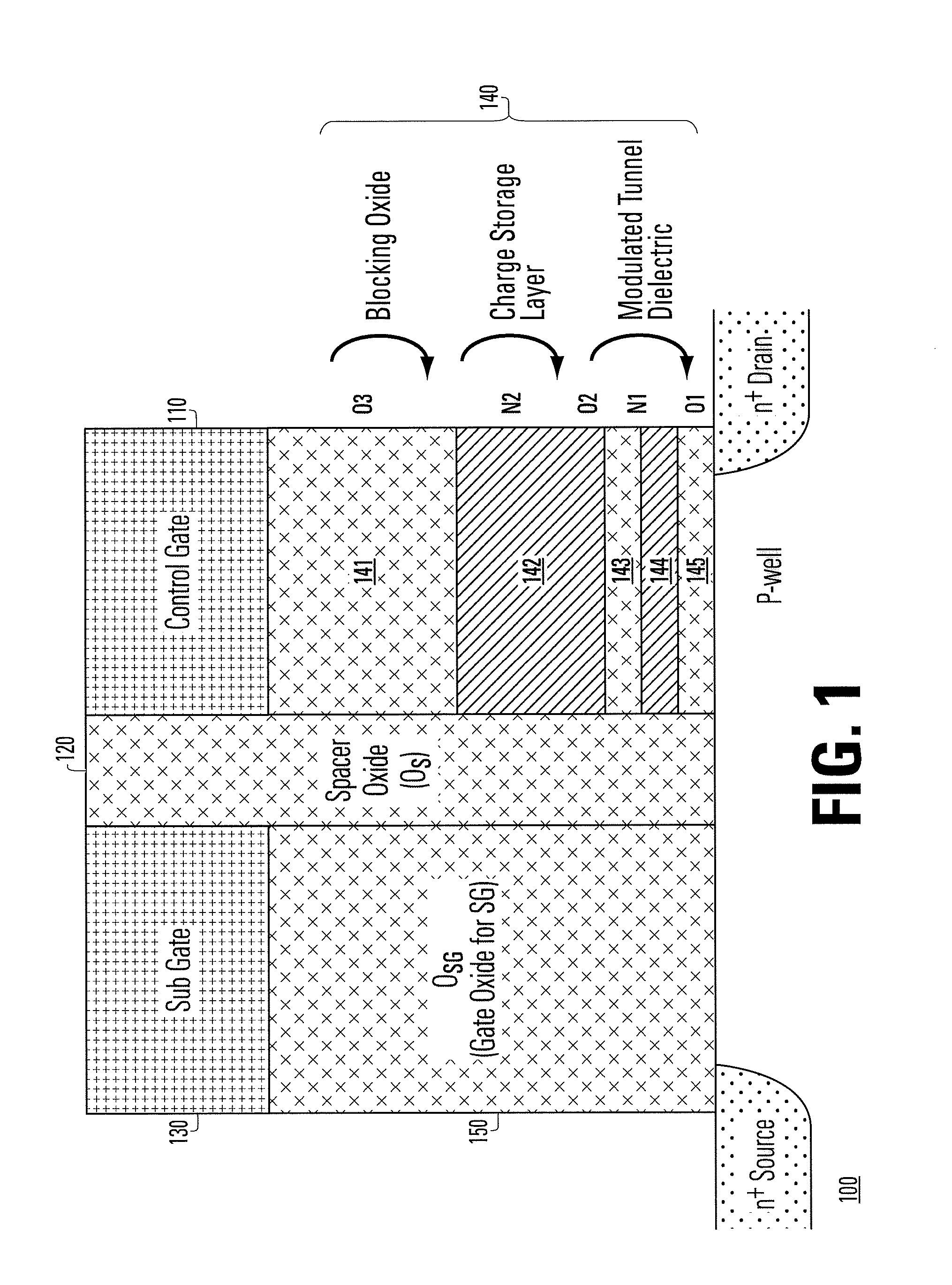

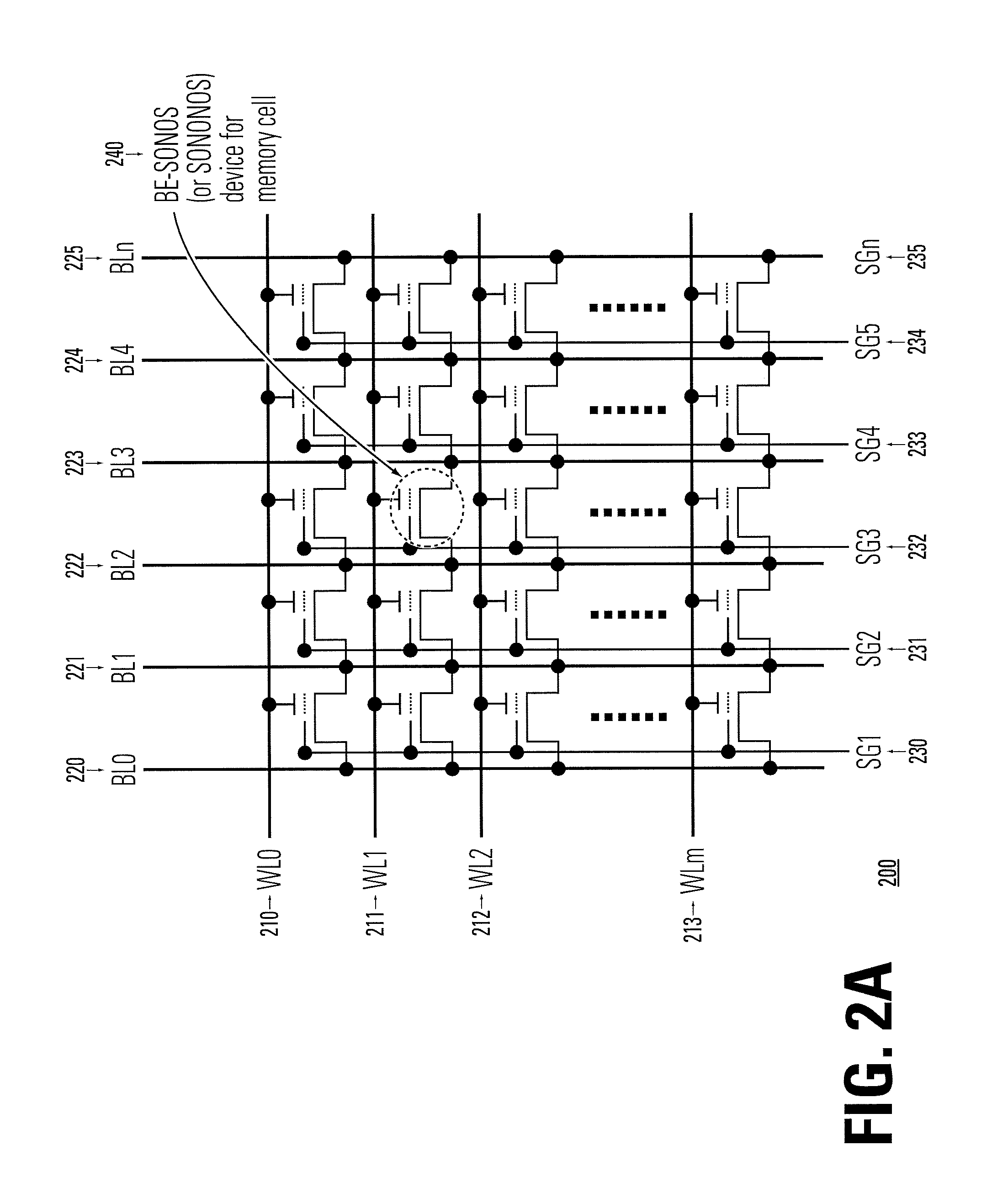

Structure and method of sub-gate NAND memory with bandgap engineered SONOS devices

ActiveUS7948799B2Improve good performanceReduce coupling effectTransistorSolid-state devicesBit lineEngineering

A bandgap engineered SONOS device structure for design with various AND architectures. The BE-SONOS device structure comprises a spacer oxide disposed between a control gate overlaying an oxide-nitride-oxide-nitride-oxide stack and a sub-gate overlaying a gate oxide. In one example, a BE-SONOS sub-gate-AND array architecture has multiple strings of SONONOS devices with sub-gate lines and diffusion bit lines. In another example, a BE-SONOS sub-gate-AND architecture has multiple strings of SONONOS devices with sub-gate lines, relying on the sub-gate lines that create inversions to substitute for the diffusion bit lines.

Owner:MACRONIX INT CO LTD

Structure and method of sub-gate and architectures employing bandgap engineered SONOS devices

ActiveUS7414889B2Improve scalabilityGreater typeSolid-state devicesRead-only memoriesBit lineDiffusion

Owner:MACRONIX INT CO LTD

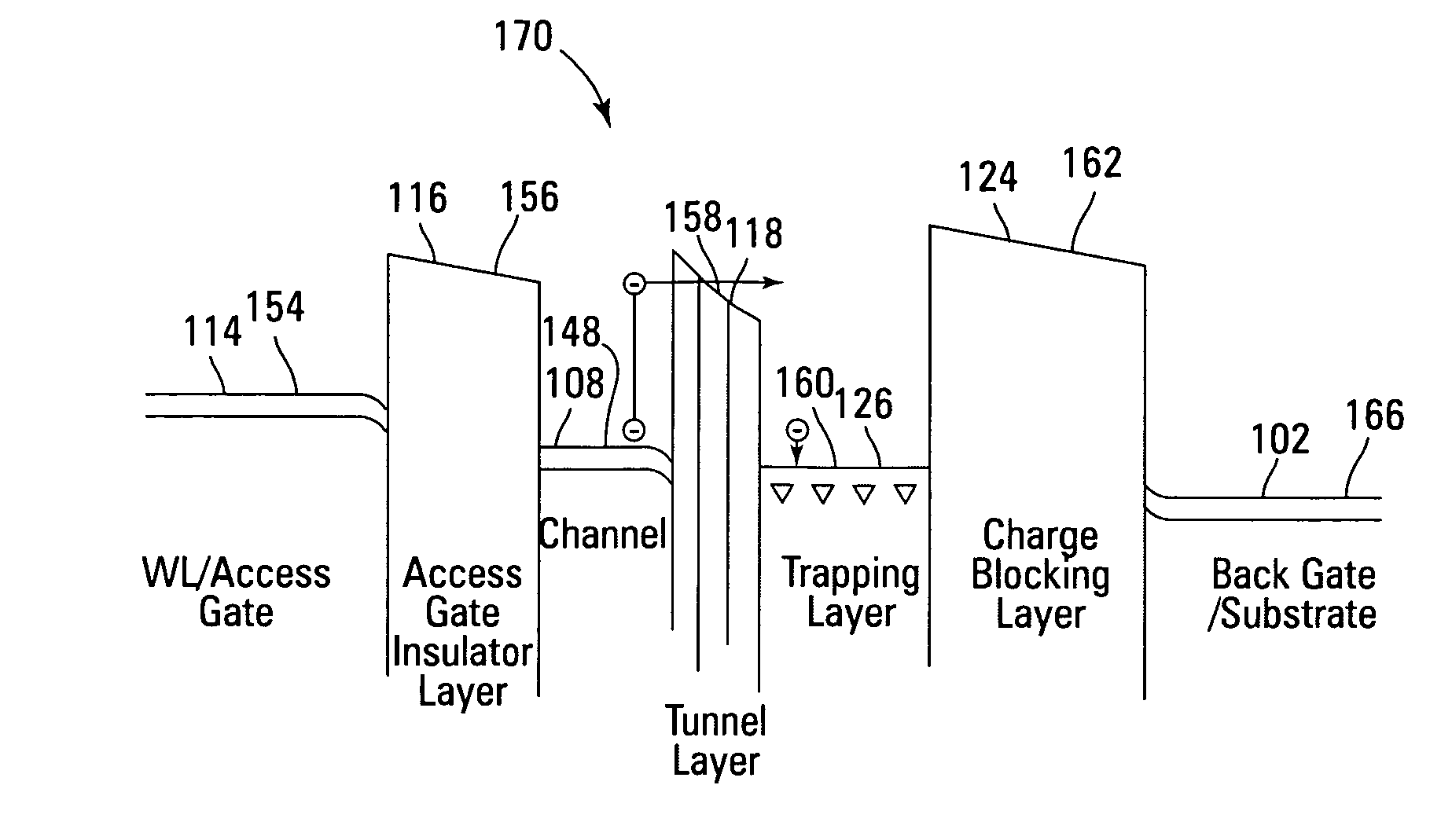

Back-side trapped non-volatile memory device

ActiveUS7402850B2Excellent charge retentionReduce voltageThyristorNanoinformaticsCharge retentionHigh energy

Non-volatile memory devices and arrays are described that utilize back-side trapped floating node memory cells with band-gap engineered gate stacks with asymmetric tunnel barriers. Embodiments of the present invention allow for direct tunneling programming and efficient erase with electrons and holes, while maintaining high charge blocking barriers and deep carrier trapping sites for good charge retention and reduces the possibility of damage to the channel / insulator interface. The direct tunneling program and efficient erase capability reduces damage to the gate stack and the crystal lattice from high energy carriers, reducing write fatigue and leakage issues and enhancing device lifespan. Memory device embodiments of the present invention are presented that are arranged in NOR or NAND memory architecture arrays. Memory cell embodiments of the present invention also allow multiple levels of bit storage in a single memory cell, and allow for programming and erase with reduced voltages.

Owner:MICRON TECH INC

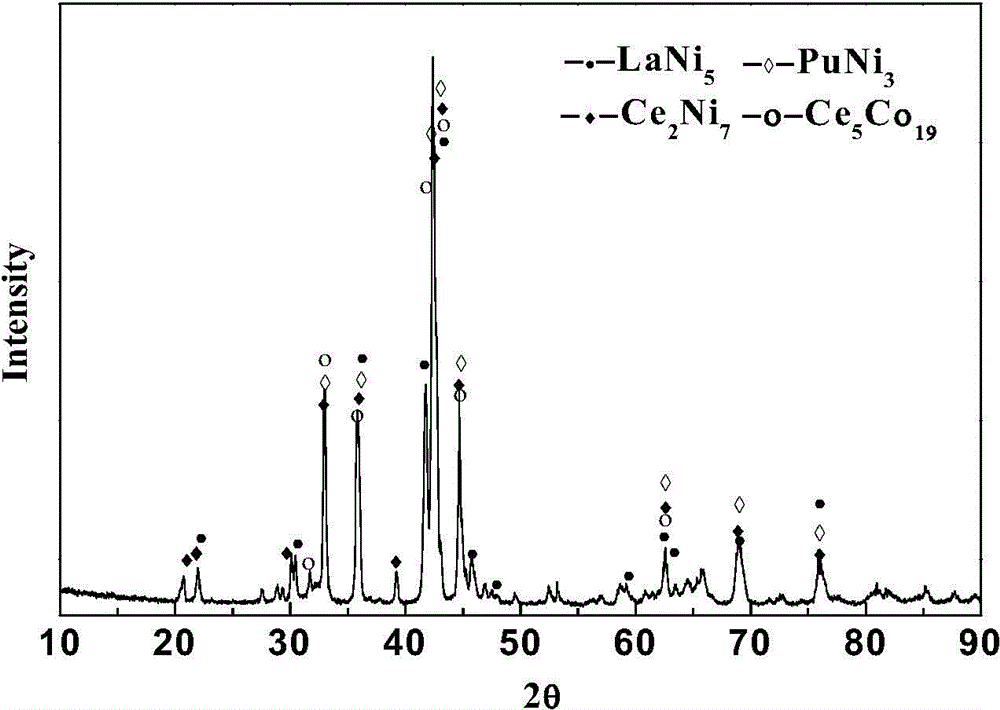

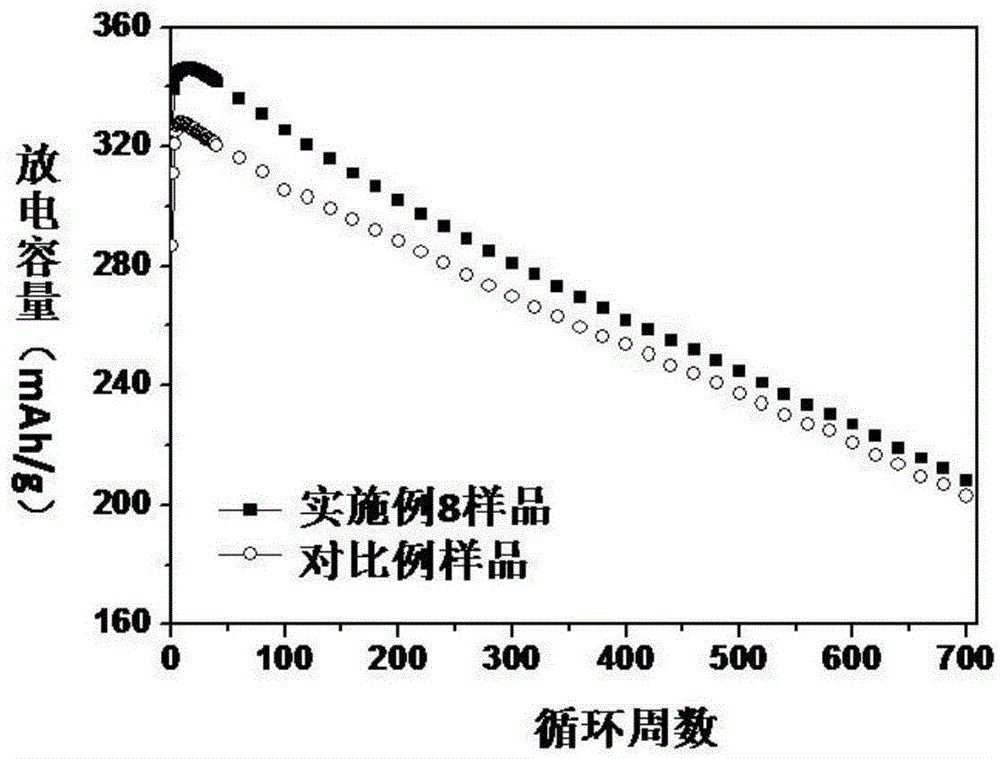

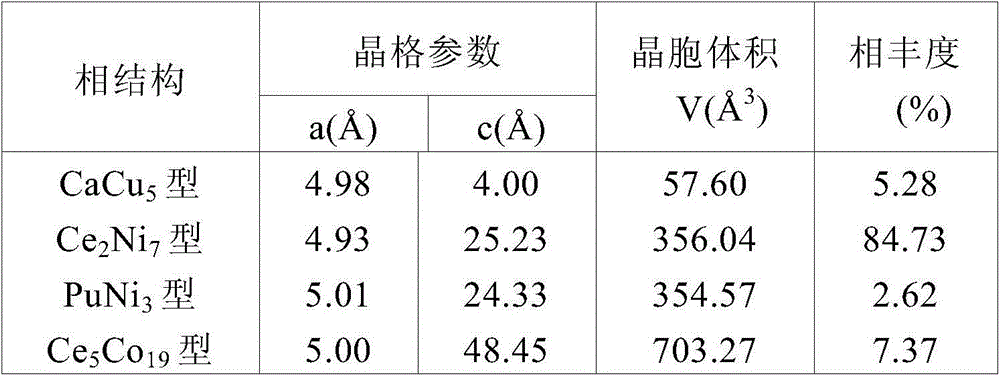

La-Mg-Ni hydrogen storage material

ActiveCN105274395AExcellent rate performanceImprove cycle stabilityCell electrodesPower performanceMetal

The invention discloses a La-Mg-Ni hydrogen storage material with high multiplying power performance and long cycling life. The chemical formula is La1-a-b-c-dSmaYbAcMgaNixA1yRz, wherein A is one or more of Gd, Pr and Nd, R comprises one or more of Co, Mn, Fe, Zn, Sn, Si, Cu, V, Nb, Mo, P, B, Ta, Cr, Ga and In, and the requirements that a>0, b>0, 0<a+b<=0.5, 0<c<=0.2, 0.05<=d<=0.3, 3.2<=x+y+z<=3.8, 0.05<=y<=0.3 and 0<=z<=1.0 are met. The hydrogen storage material is the La-Mg-Ni hydrogen storage material with Ce2Ni7 type phase as a main phase and has good high multiplying power performance and good cycling stability; in addition, the hydrogen storage material is low in cost and can be applied to the cathode of a nickel-metal hydride secondary battery.

Owner:GRIMAT ENG INST CO LTD

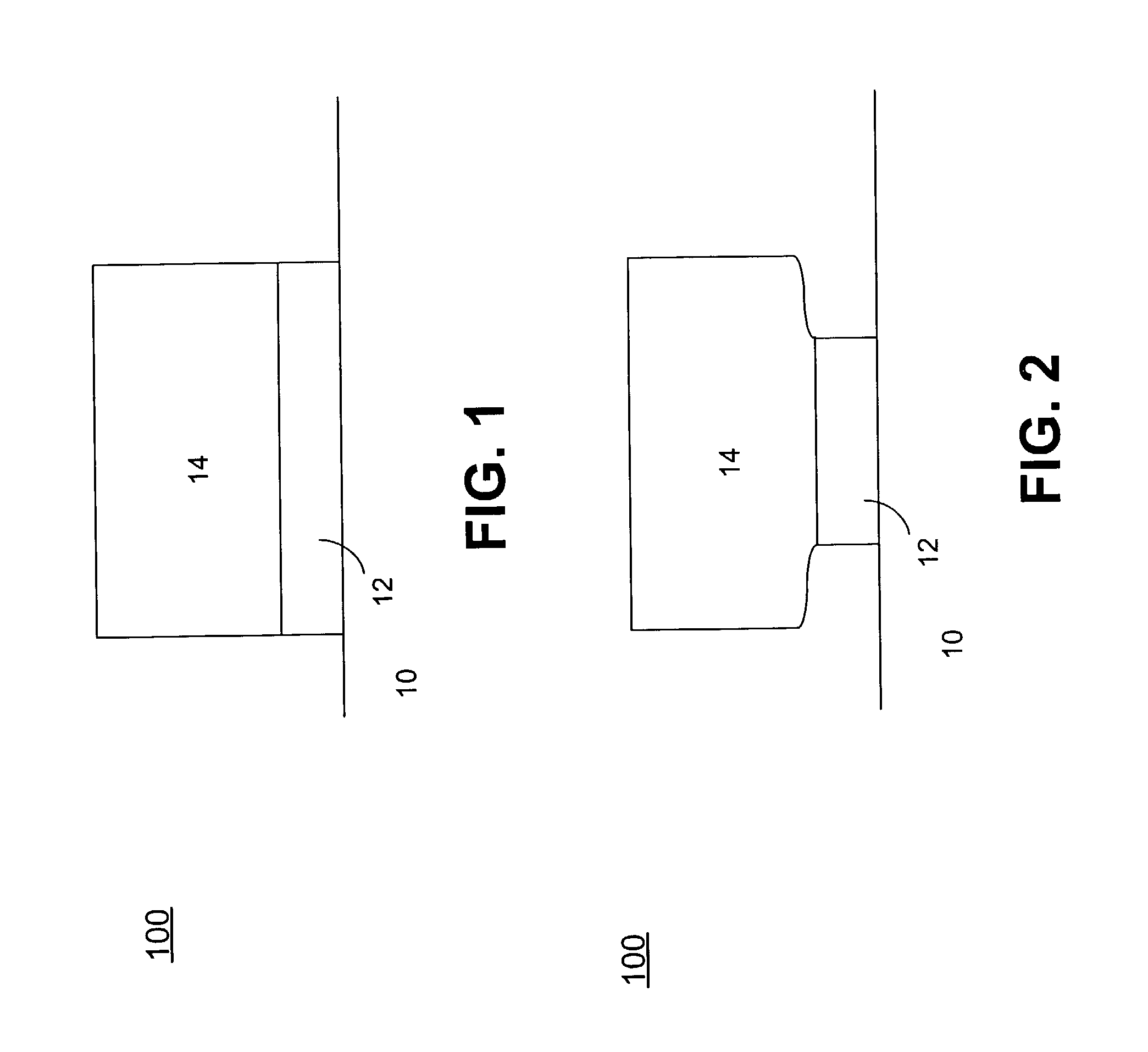

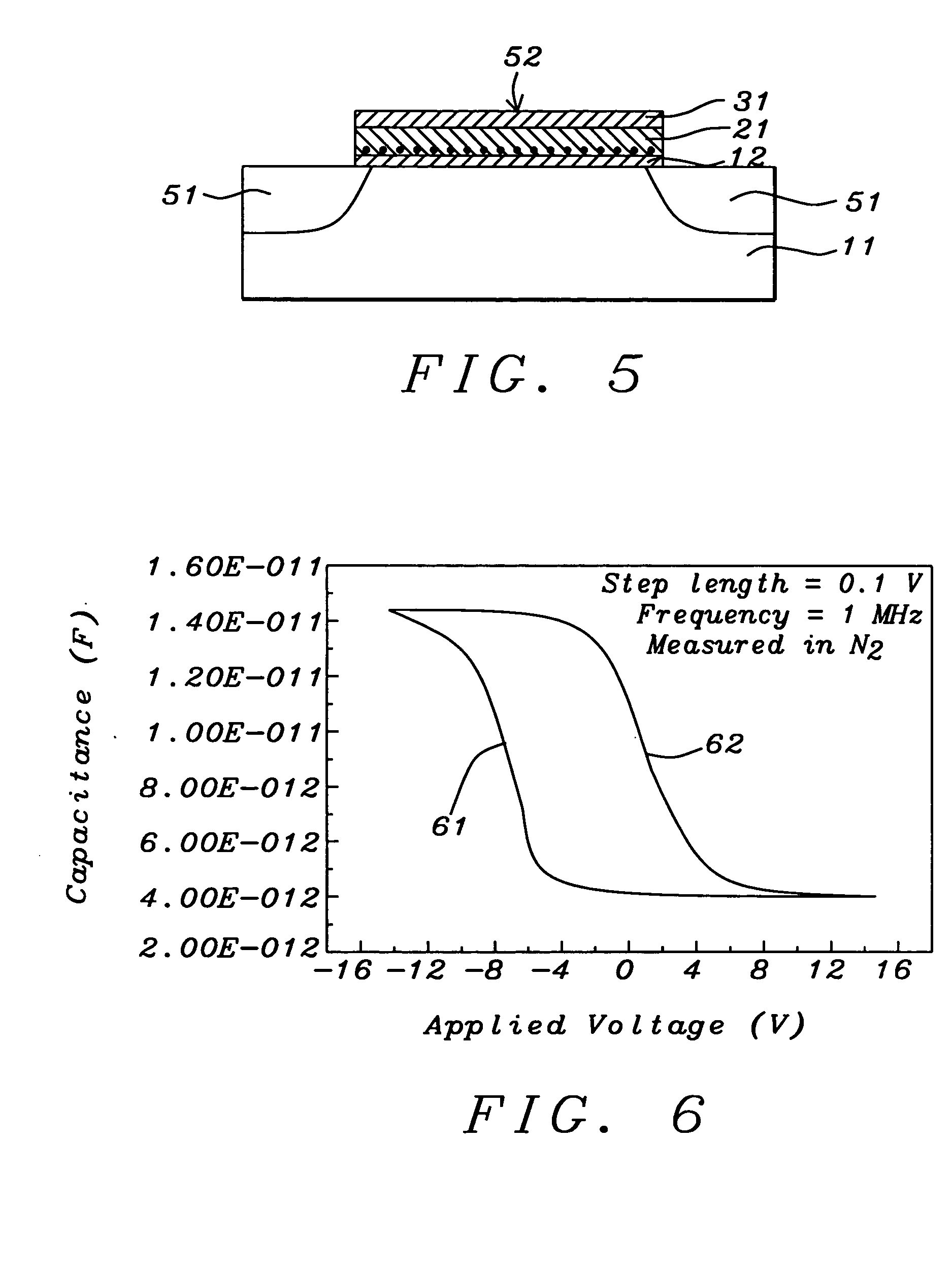

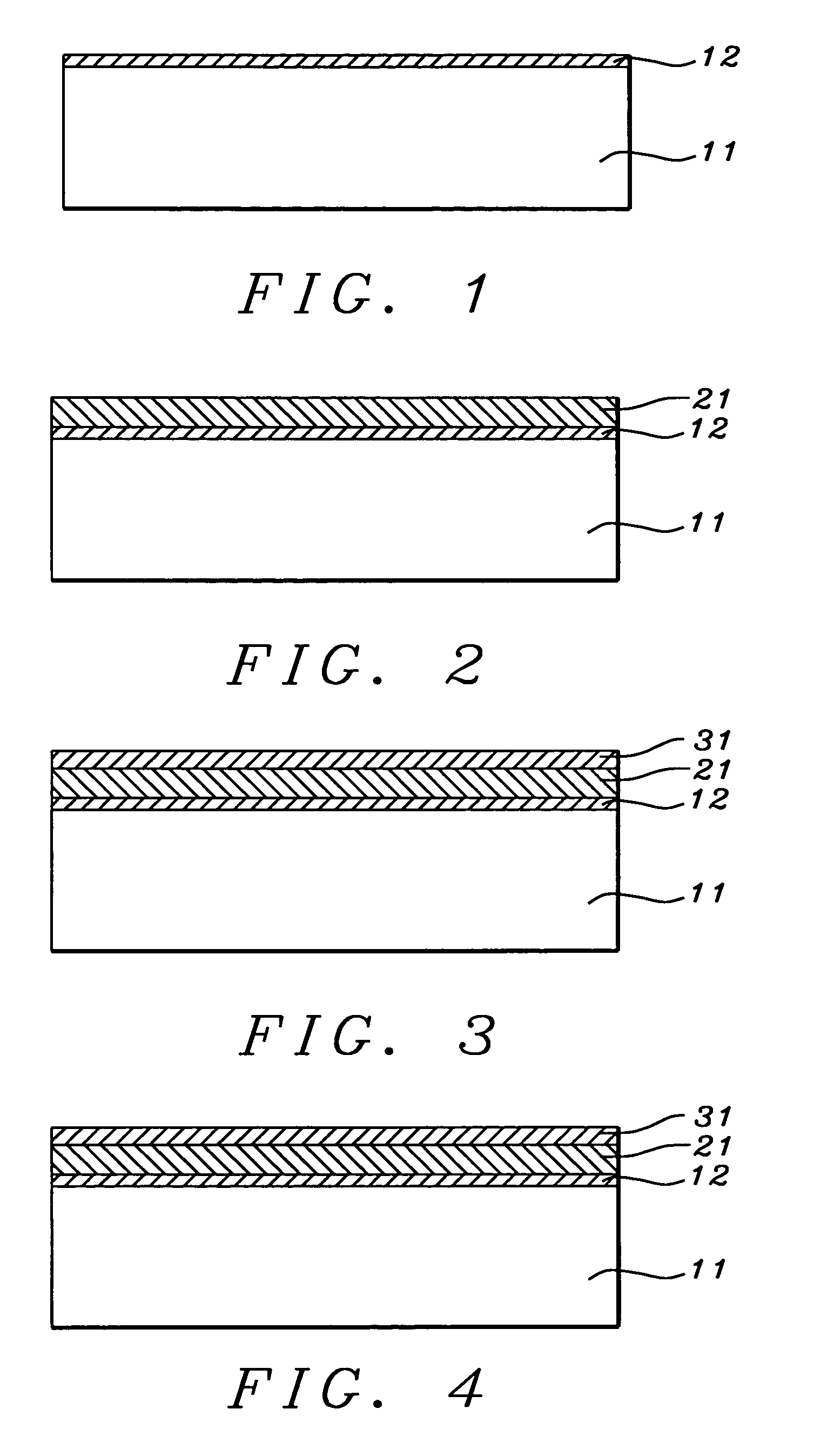

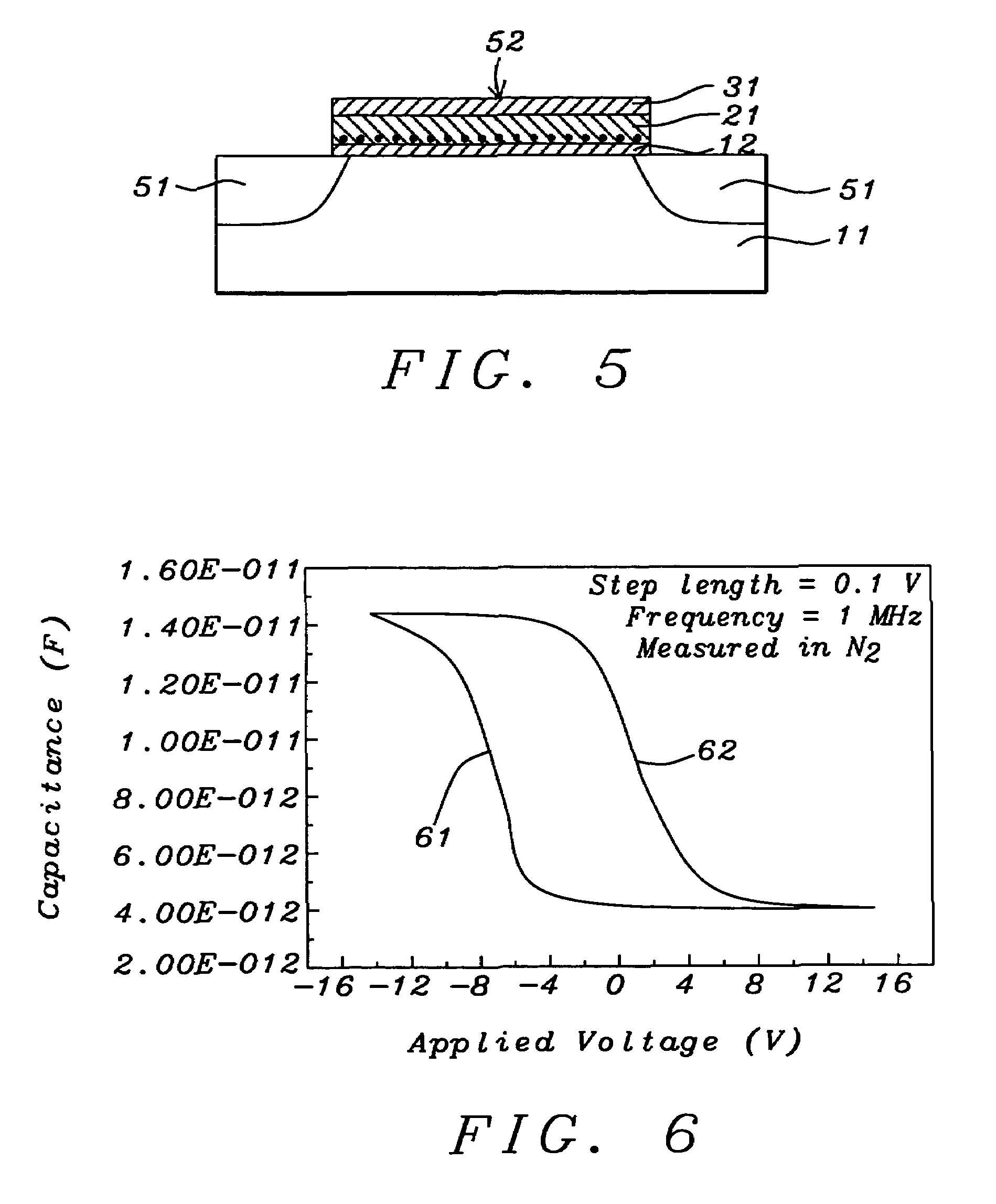

Process to manufacture nonvolatile MOS memory device

InactiveUS20050074939A1Improve interface qualityExcellent charge retentionTransistorNanoinformaticsGas phaseDoped oxide

Devices with embedded silicon or germanium nanocrystals, fabricated using ion implantation, exhibit superior data-retention characteristics relative to conventional floating-gate devices. However, the prior art use of ion implantation for their manufacture introduces several problems. These have been overcome by initial use of rapid thermal oxidation to grow a high quality layer of thin tunnel oxide. Chemical vapor deposition is then used to deposit a germanium doped oxide layer. A capping oxide is then deposited following which the structure is rapid thermally annealed to synthesize the germanium nanocrystals.

Owner:CHARTERED SEMICONDUCTOR MANUFACTURING

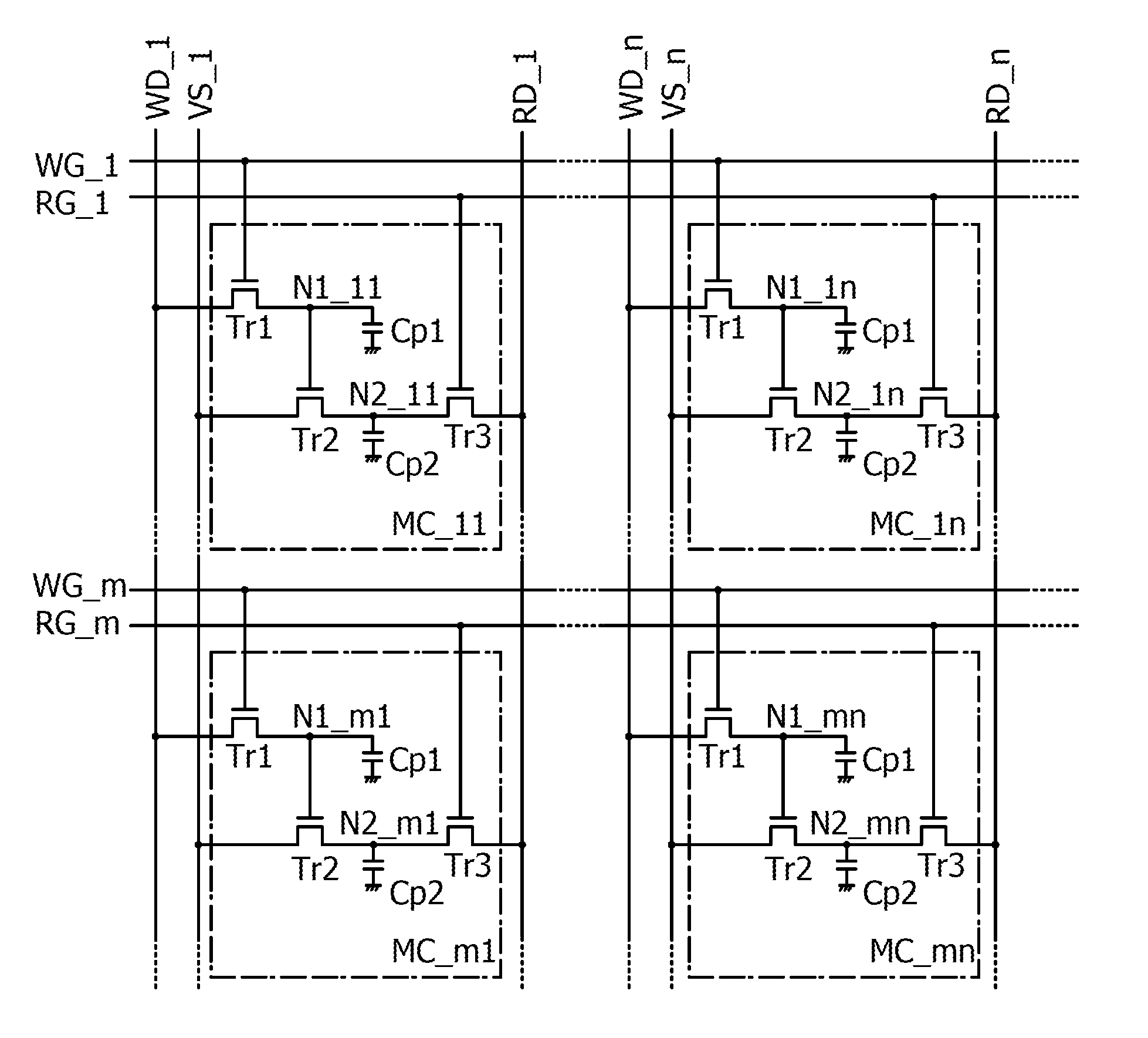

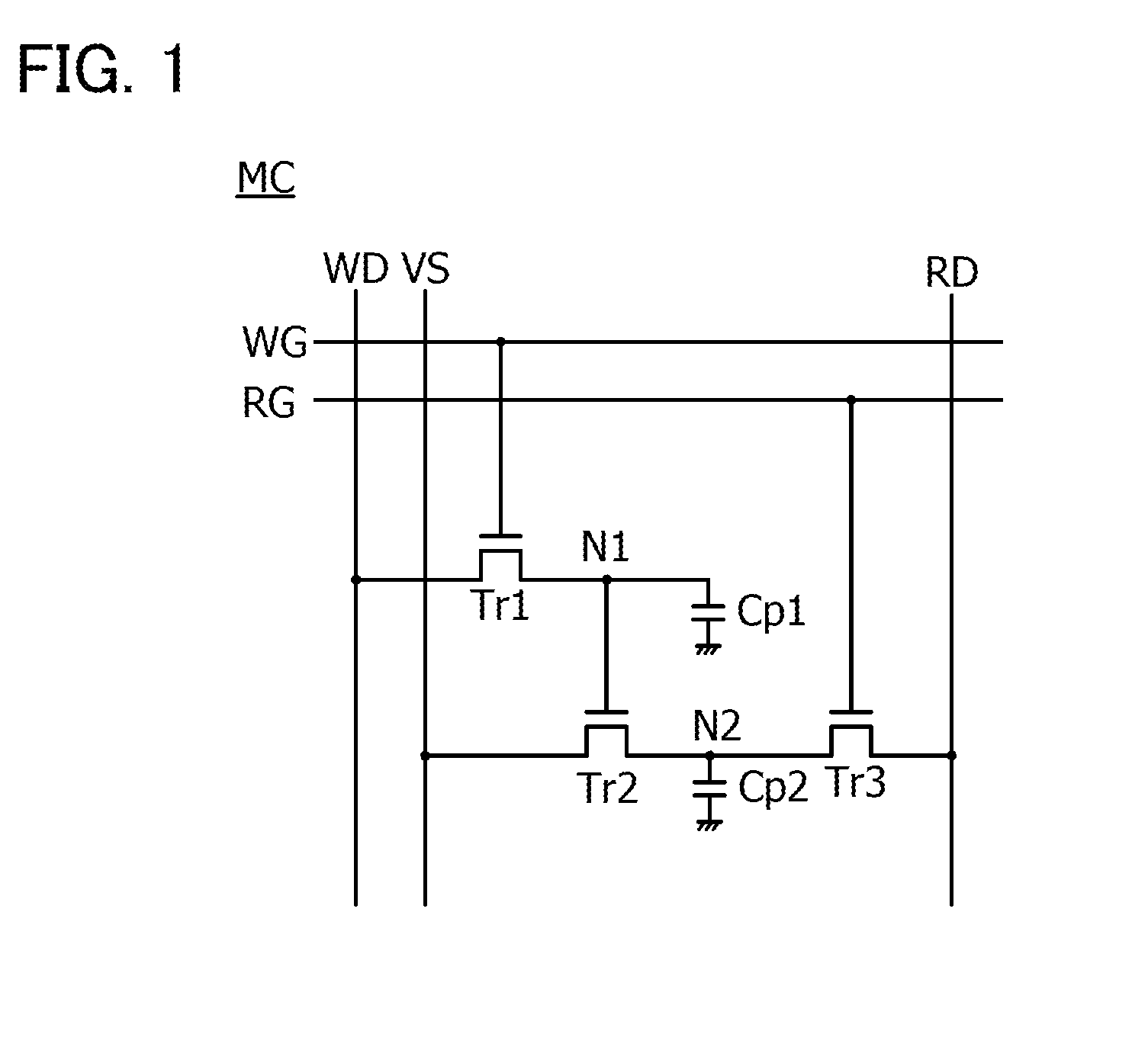

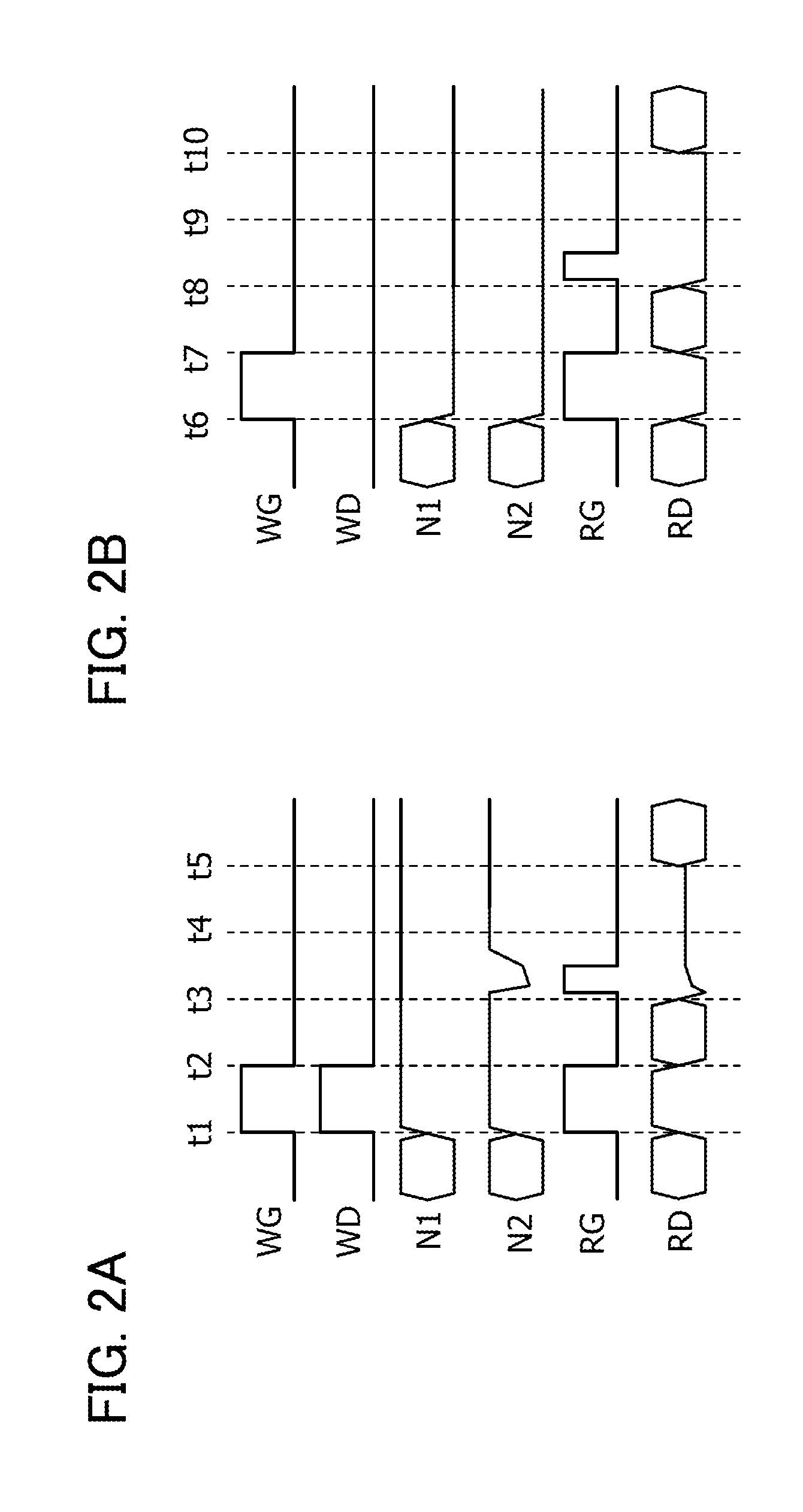

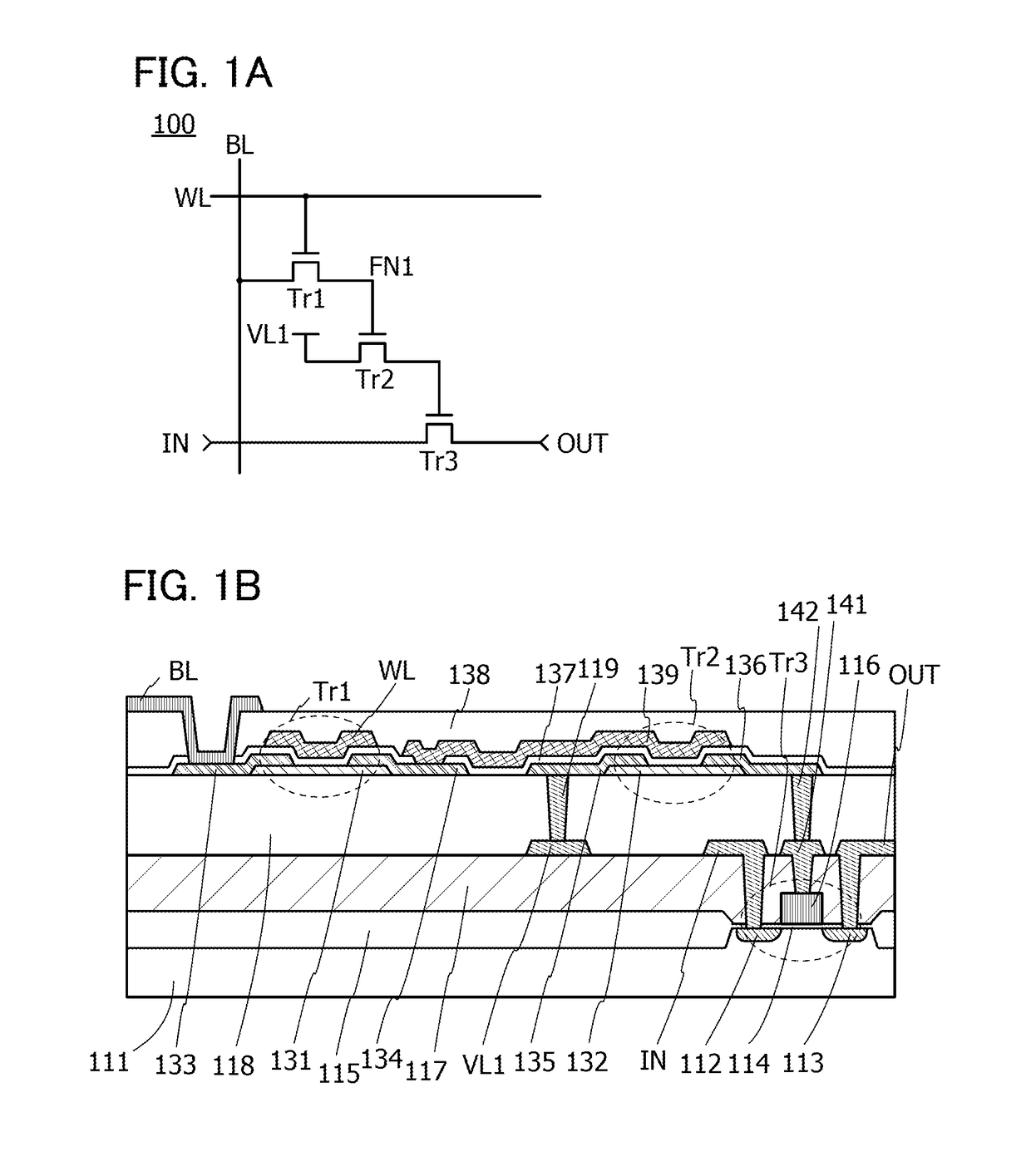

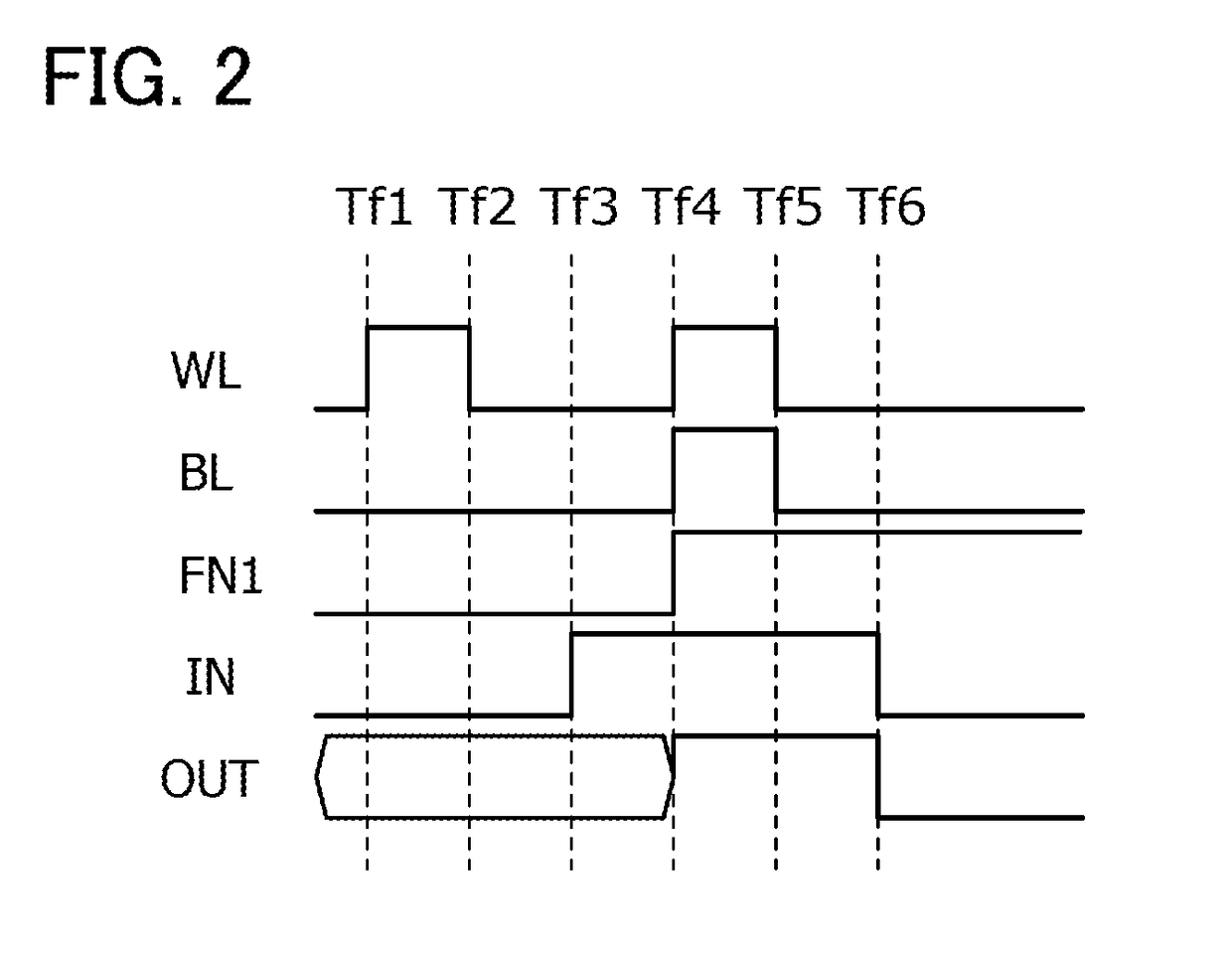

Semiconductor device and method for driving the same

ActiveUS20150023114A1Improve semiconductor device performanceDownsizing of Si transistorsTransistorSolid-state devicesCharge injectionCharge retention

One of a source and a drain of a first oxide semiconductor (OS) transistor is connected to a gate of a second OS transistor and one electrode of a first capacitor. One of a source and a drain of the second OS transistor is connected to one electrode of a second capacitor and one of a source and a drain of a Si transistor. The gate of the second OS transistor serves as a charge retention node. Charge injection and retention at this node is controlled by the first OS transistor. The other of the source and the drain of the second OS transistor is connected to a wiring applying a high potential, and a potential of the second capacitor that corresponds to the write data is maintained. A signal corresponding to the write data is read by the Si transistor.

Owner:SEMICON ENERGY LAB CO LTD

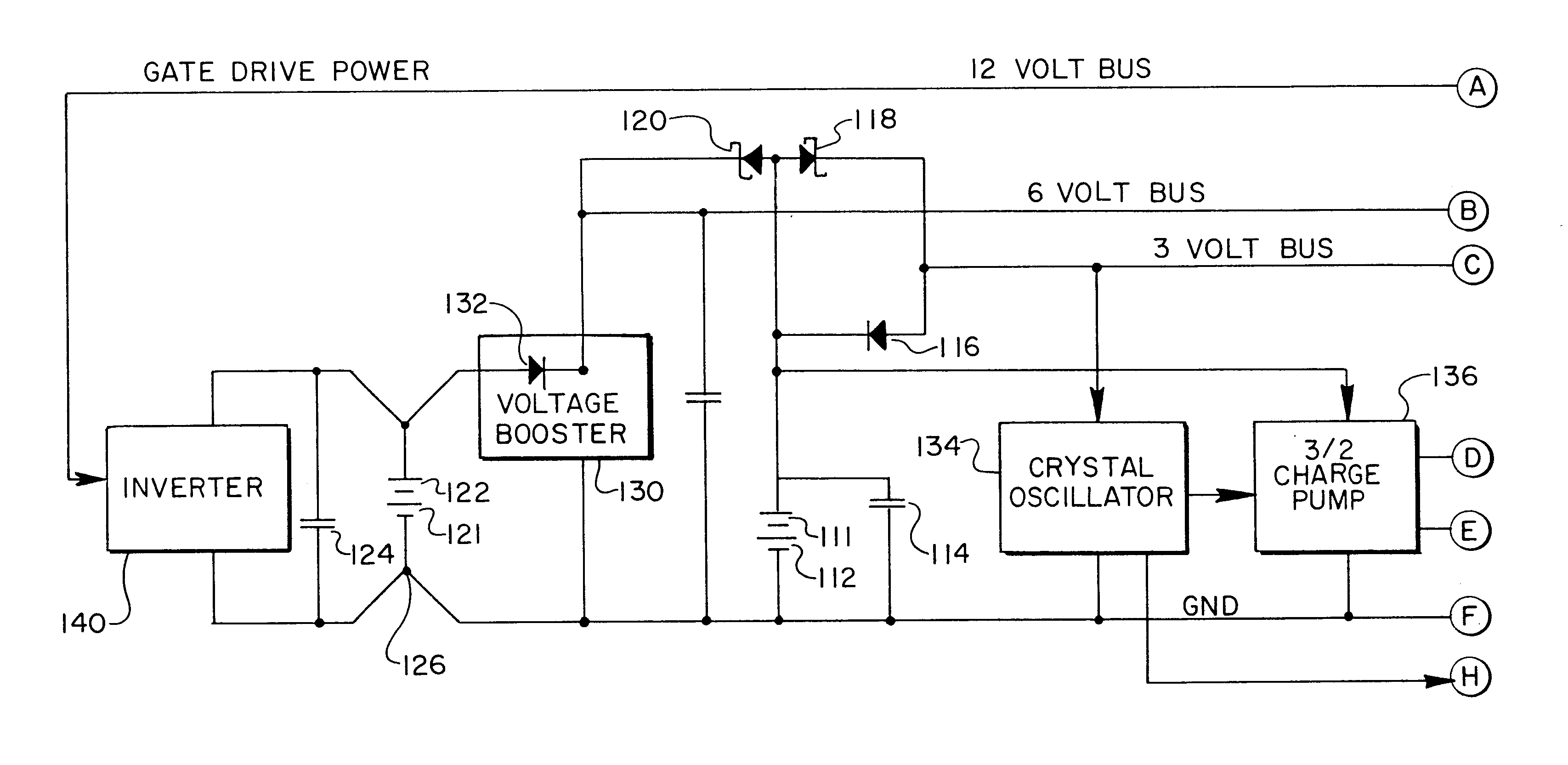

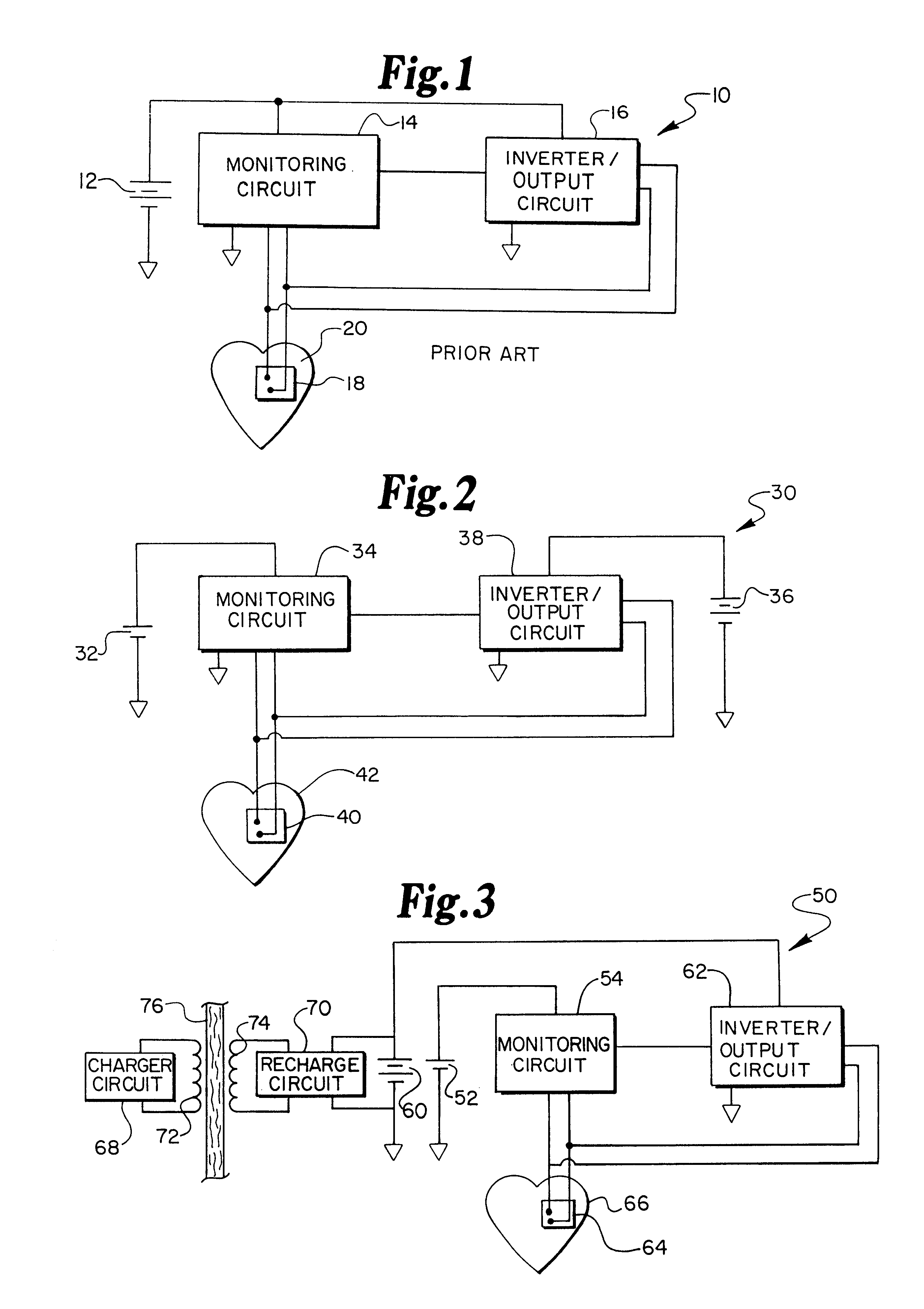

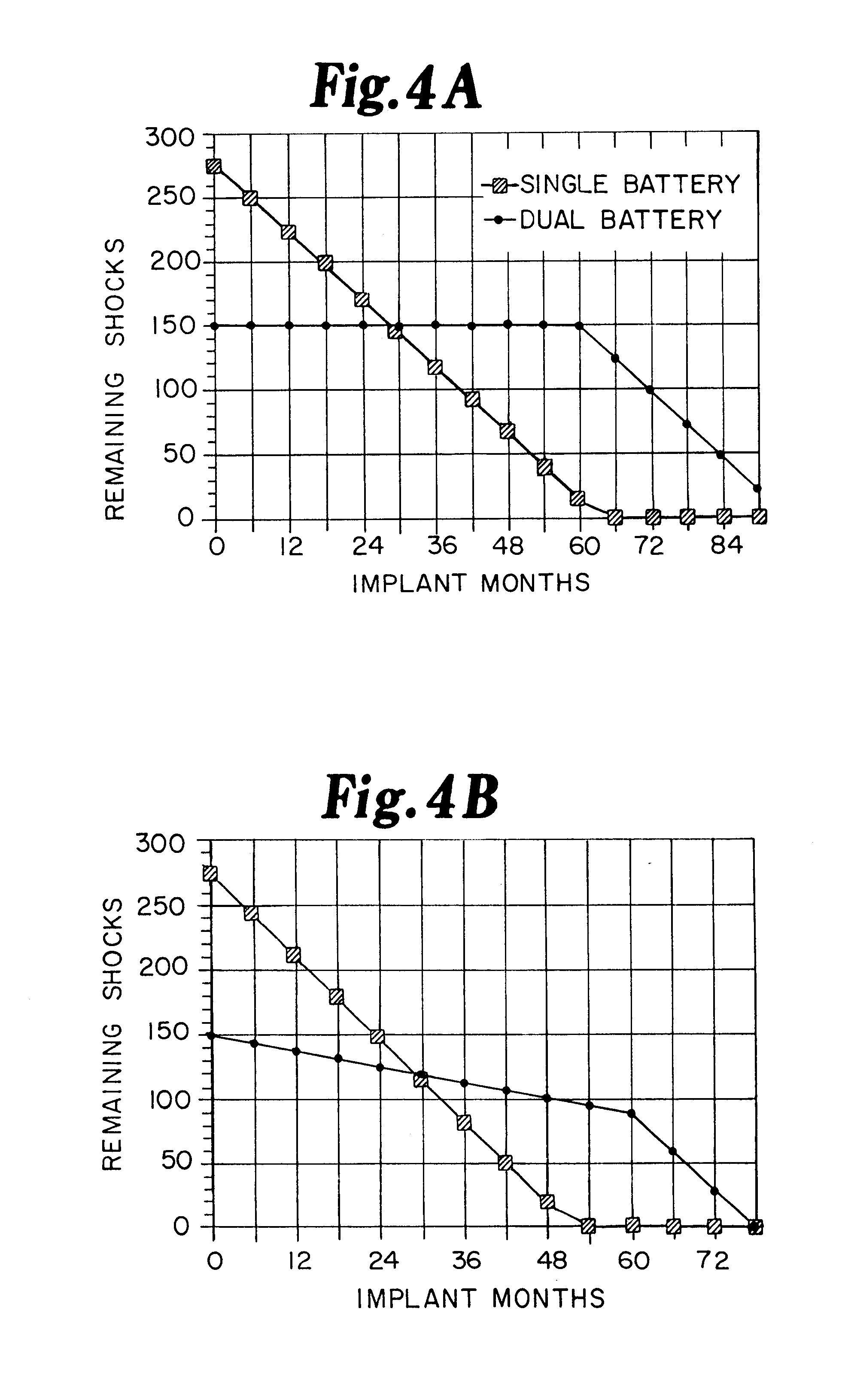

Dual battery power system for an implantable cardioverter defibrillator with voltage booster

InactiveUSRE38777E1Reduce in sizeDecrease riskSeveral cell simultaneous arrangementsHeart defibrillatorsLithium Iodide BatteryCardiac pacemaker electrode

An improved dual battery power system uses two separate battery power sources for an implantable cardioverter defibrillator, each having optimized characteristics for monitoring functions and for output energy delivery functions, respectively. The monitoring functions are supplied electrical power by a first battery source, such as a conventional pacemaker power source in the form of a lithium iodide battery which is optimized for long life at very low current levels. The output energy delivery functions are supplied by a separate second battery source, such as a pair of lithium vanadium pentoxide batteries, which is optimized for high current drain capability and low self-discharge for long shelf life. The first battery source provides electrical power only to the monitoring functions of the implantable cardioverter defibrillator, and the second battery source provides all of the electrical power for the output energy delivery functions.

Owner:ANGEION

Process to manufacture nonvolatile MOS memory device

Devices with embedded silicon or germanium nanocrystals, fabricated using ion implantation, exhibit superior data-retention characteristics relative to conventional floating-gate devices. However, the prior art use of ion implantation for their manufacture introduces several problems. These have been overcome by initial use of rapid thermal oxidation to grow a high quality layer of thin tunnel oxide. Chemical vapor deposition is then used to deposit a germanium doped oxide layer. A capping oxide is then deposited following which the structure is rapid thermally annealed to synthesize the germanium nanocrystals.

Owner:CHARTERED SEMICONDUCTOR MANUFACTURING

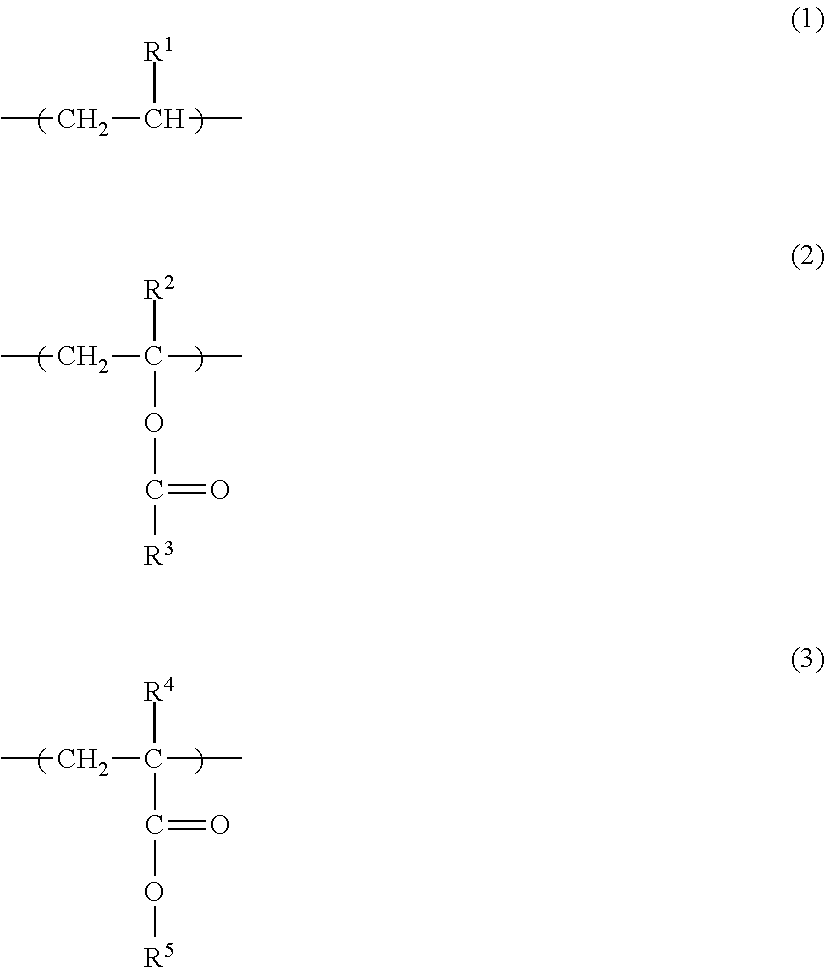

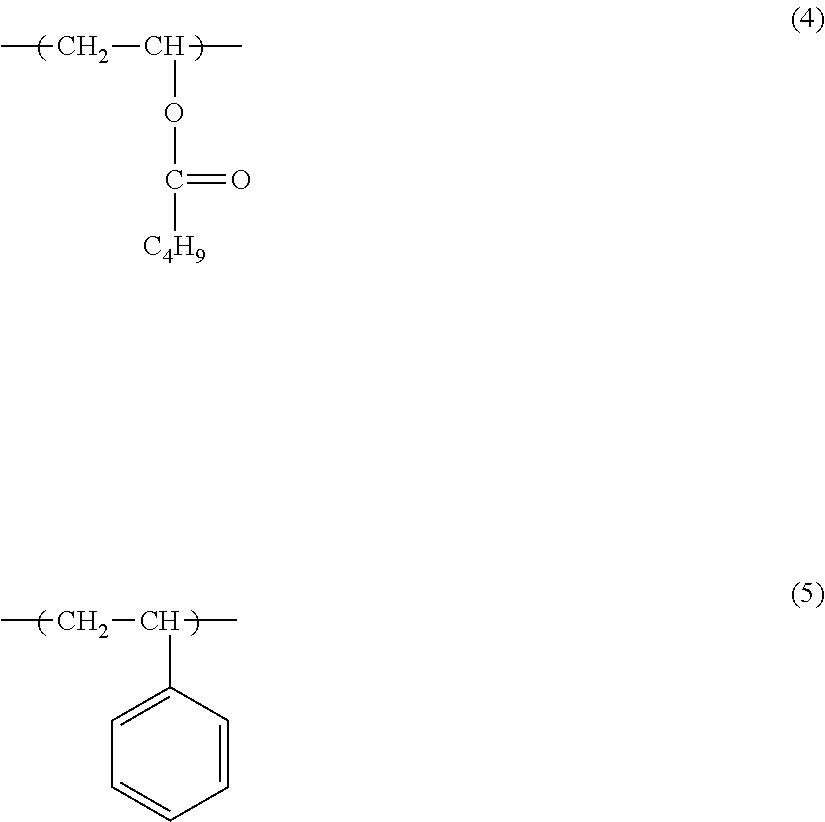

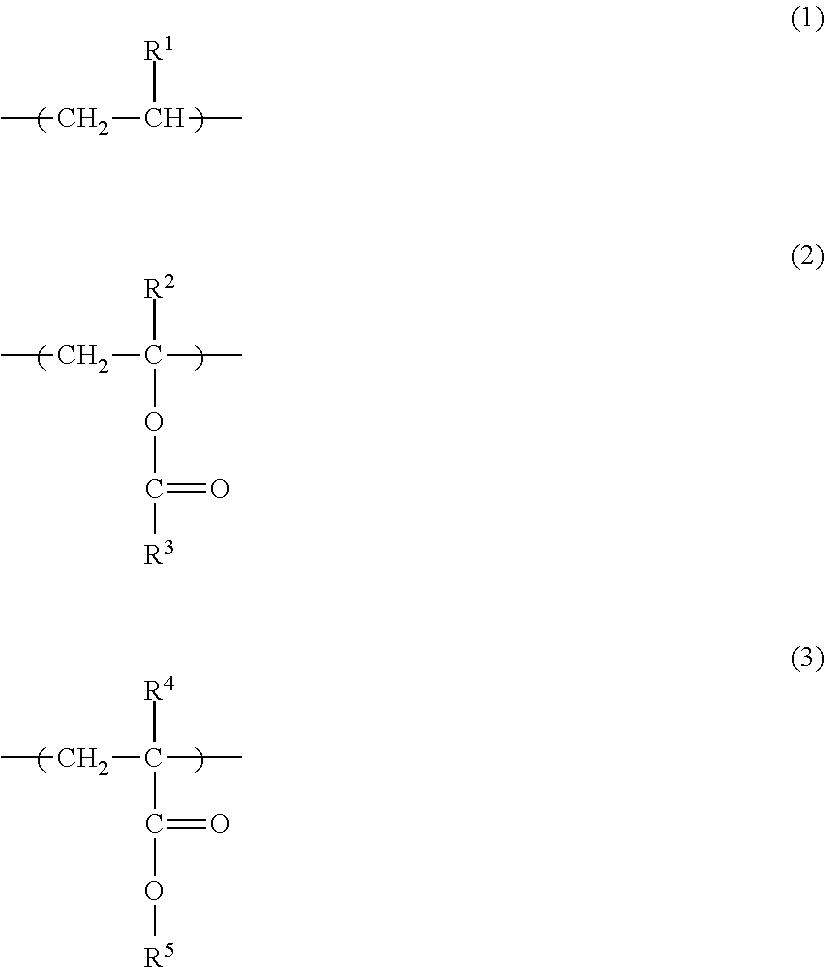

Toner

ActiveUS10514624B2Excellent low temperature fixabilityIncrease resistanceDevelopersPolymer scienceAlkene

A toner comprising: a toner particle that contains a resin component and a silicone compound, wherein the resin component contains at least 50 mass % of olefin resin; a content of the silicone compound is from 1 mass part to 42 mass parts per 100 mass parts of the resin component; a weight-average molecular weight of the silicone compound as measured by GPC is from 1,000 to 25,000; and a content, in a molecular weight distribution of the silicone compound as measured by GPC, of a component having a weight-average molecular weight of not more than 500 is not more than 0.05 mass % of the silicone compound.

Owner:CANON KK

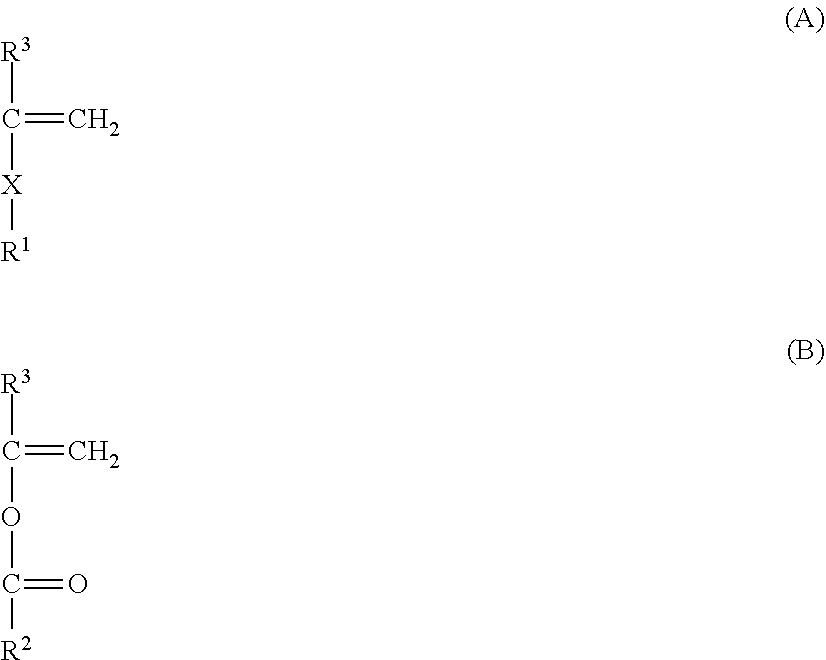

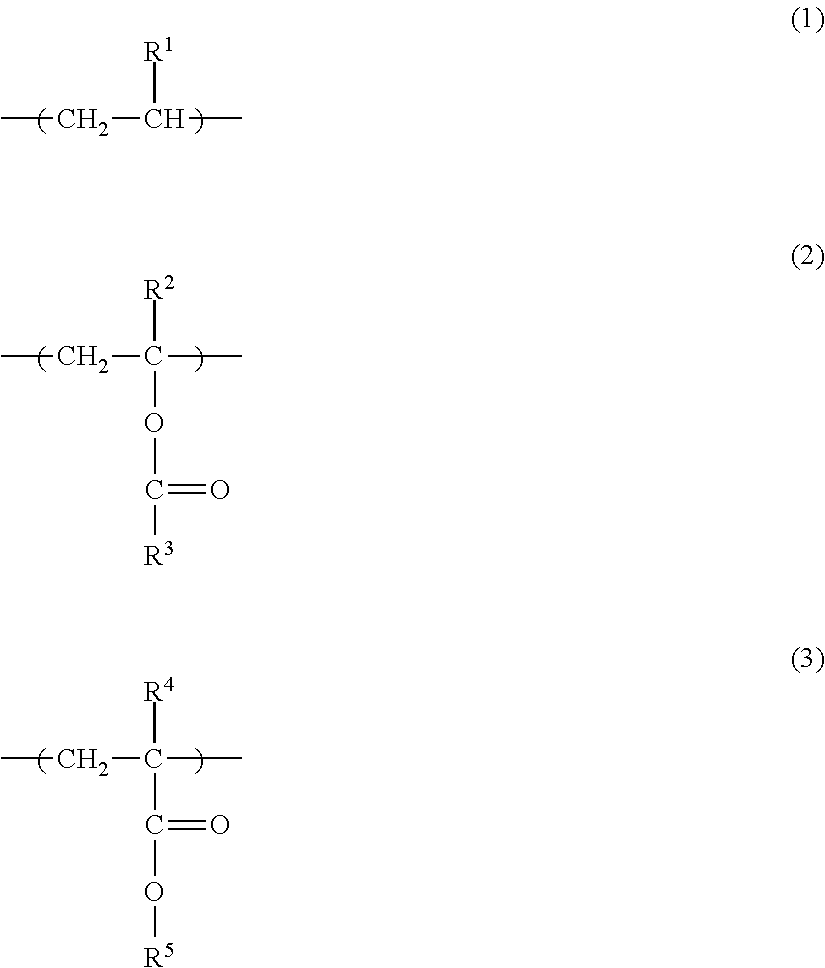

Toner and method for producing toner

ActiveUS10656545B2Excellent low temperature fixabilityPromote generationDevelopersPolymer scienceMeth-

A toner has a toner particle including a binder resin, the binder resin includes a polymer A, the polymer A contains a first monomer unit derived from a first polymerizable monomer and a second monomer unit derived from a second polymerizable monomer, the first polymerizable monomer is selected from (meth)acrylic acid esters having an alkyl group having 18 to 36 carbon atoms, the content of the first monomer unit in the polymer A is 5.0 mol % to 60.0 mol %, the content of the second monomer unit in the polymer A is 20.0 mol % to 95.0 mol %, the SP value of the first monomer unit and the SP value of the second monomer unit satisfy a predetermined relationship, the polymer A includes a predetermined polyvalent metal, and the content of the polyvalent metal is 25 ppm to 500 ppm.

Owner:CANON KK

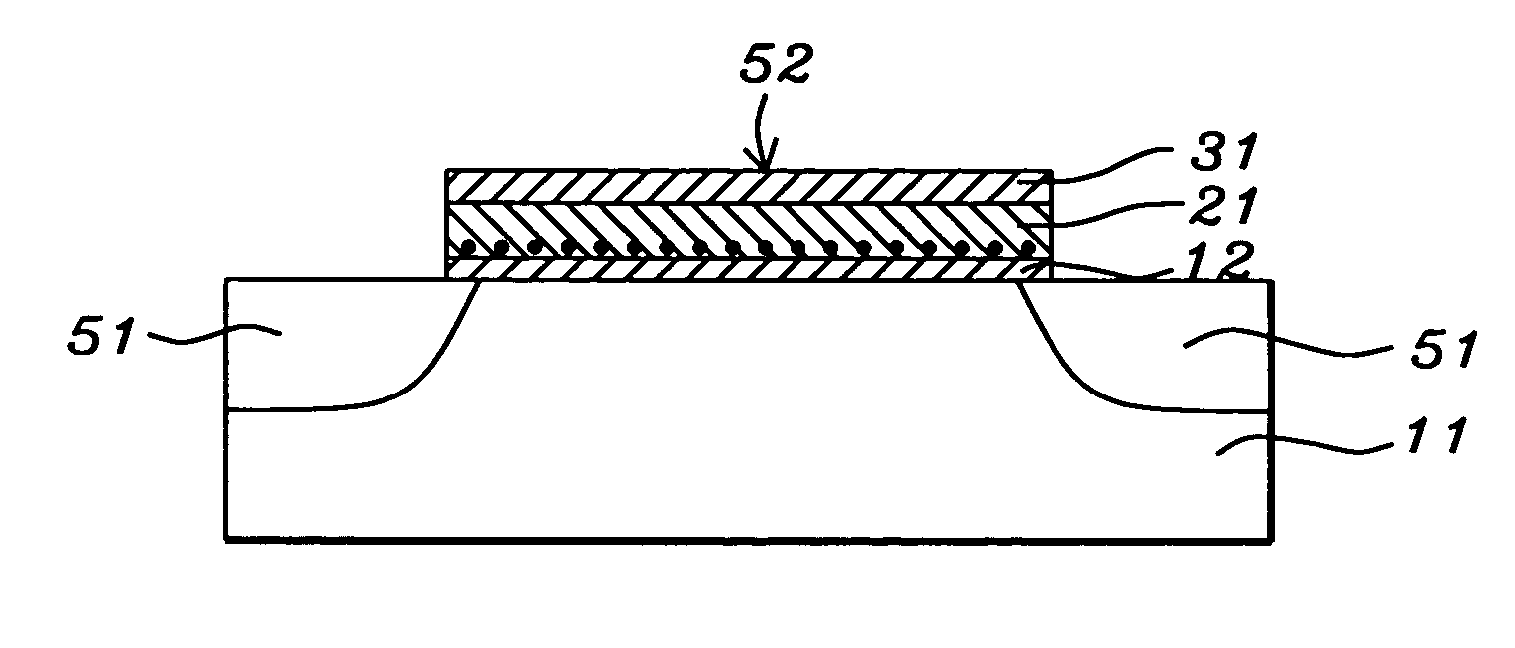

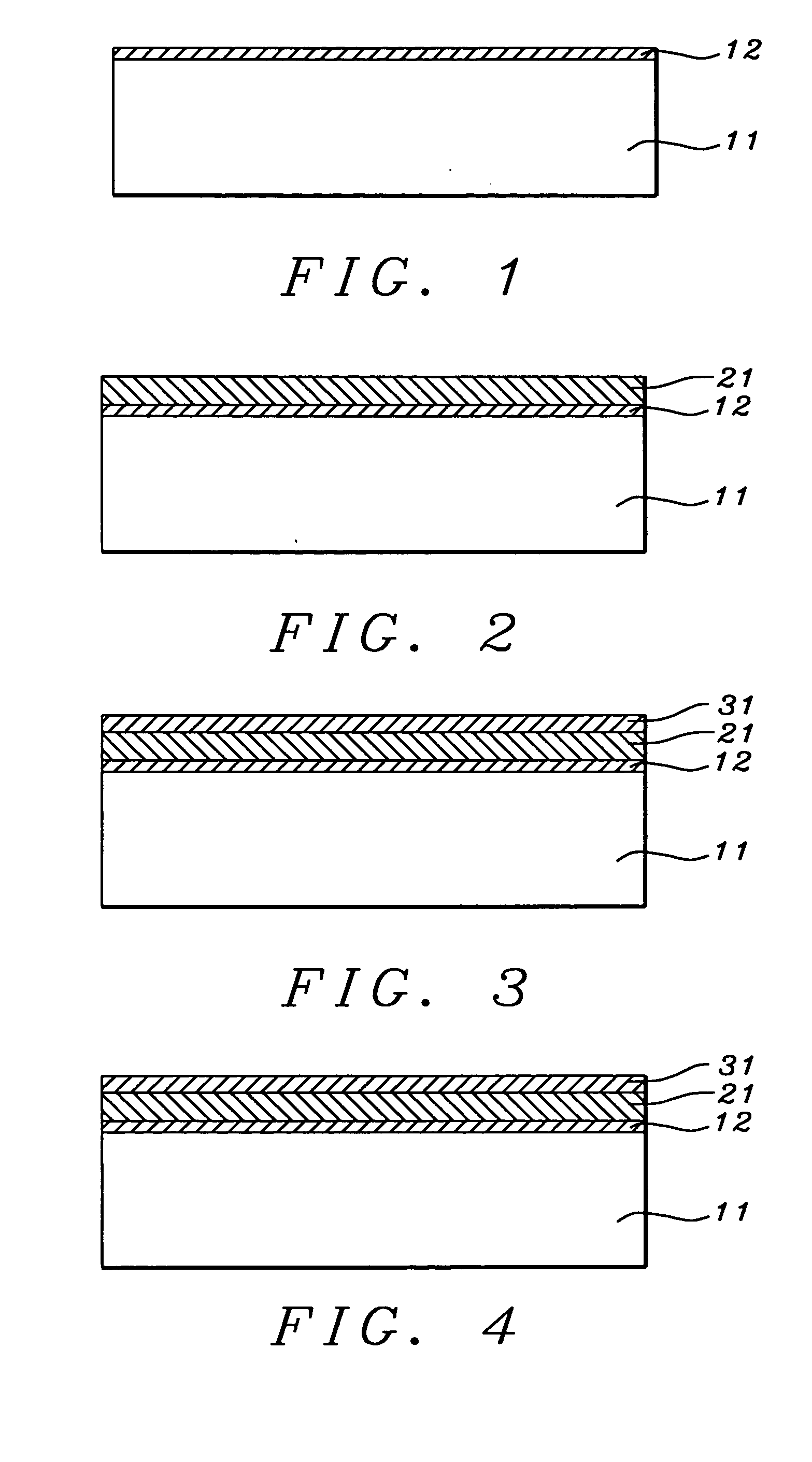

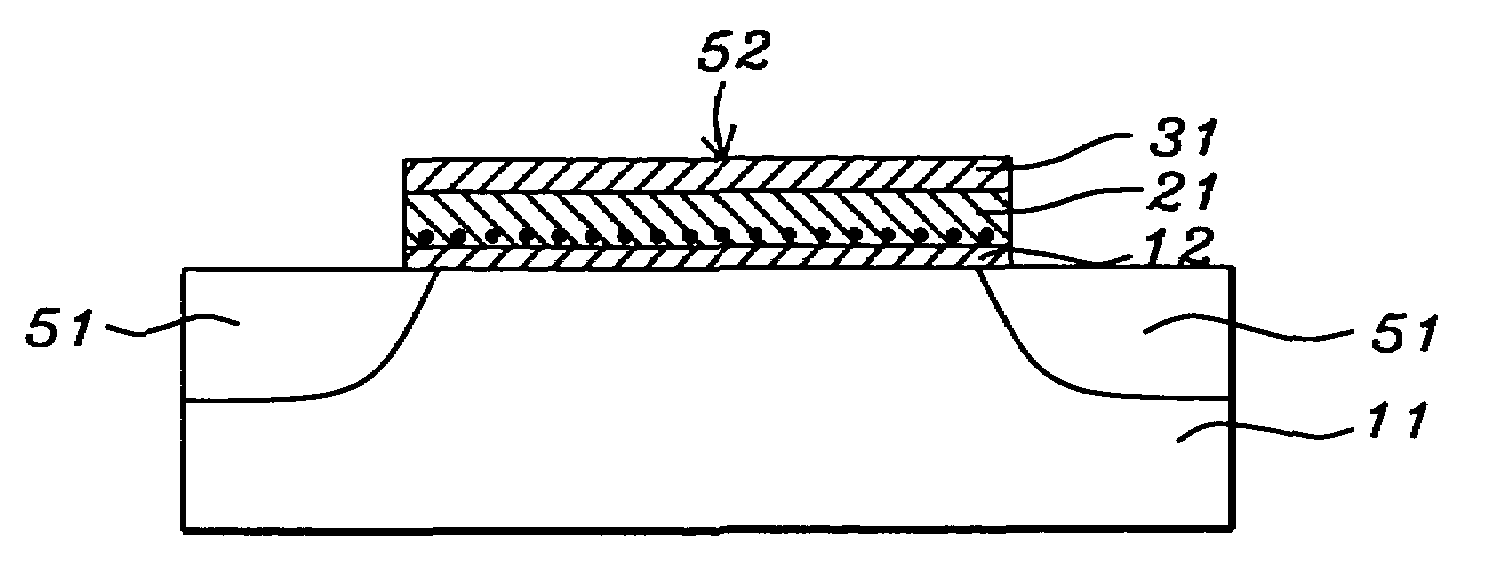

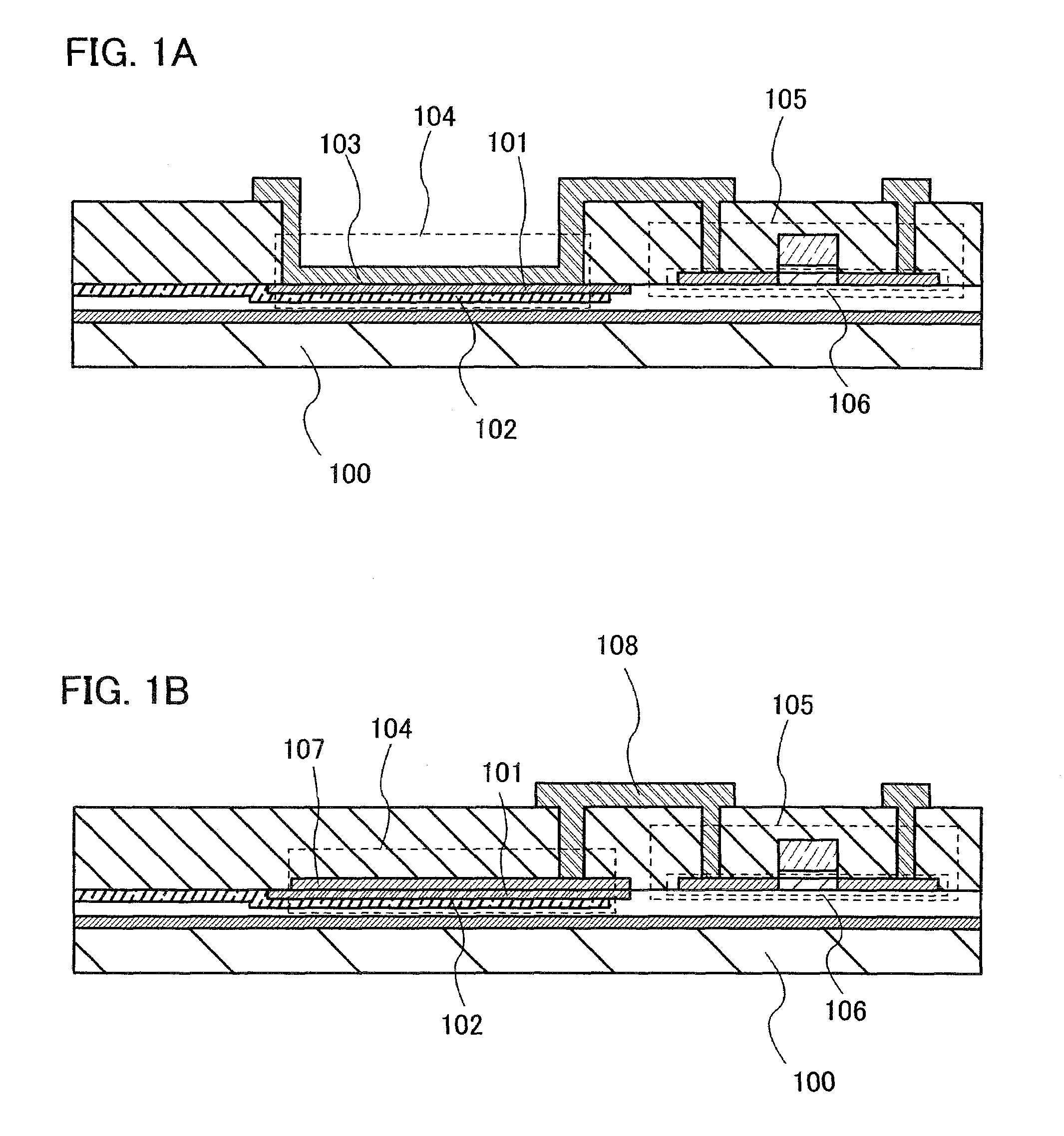

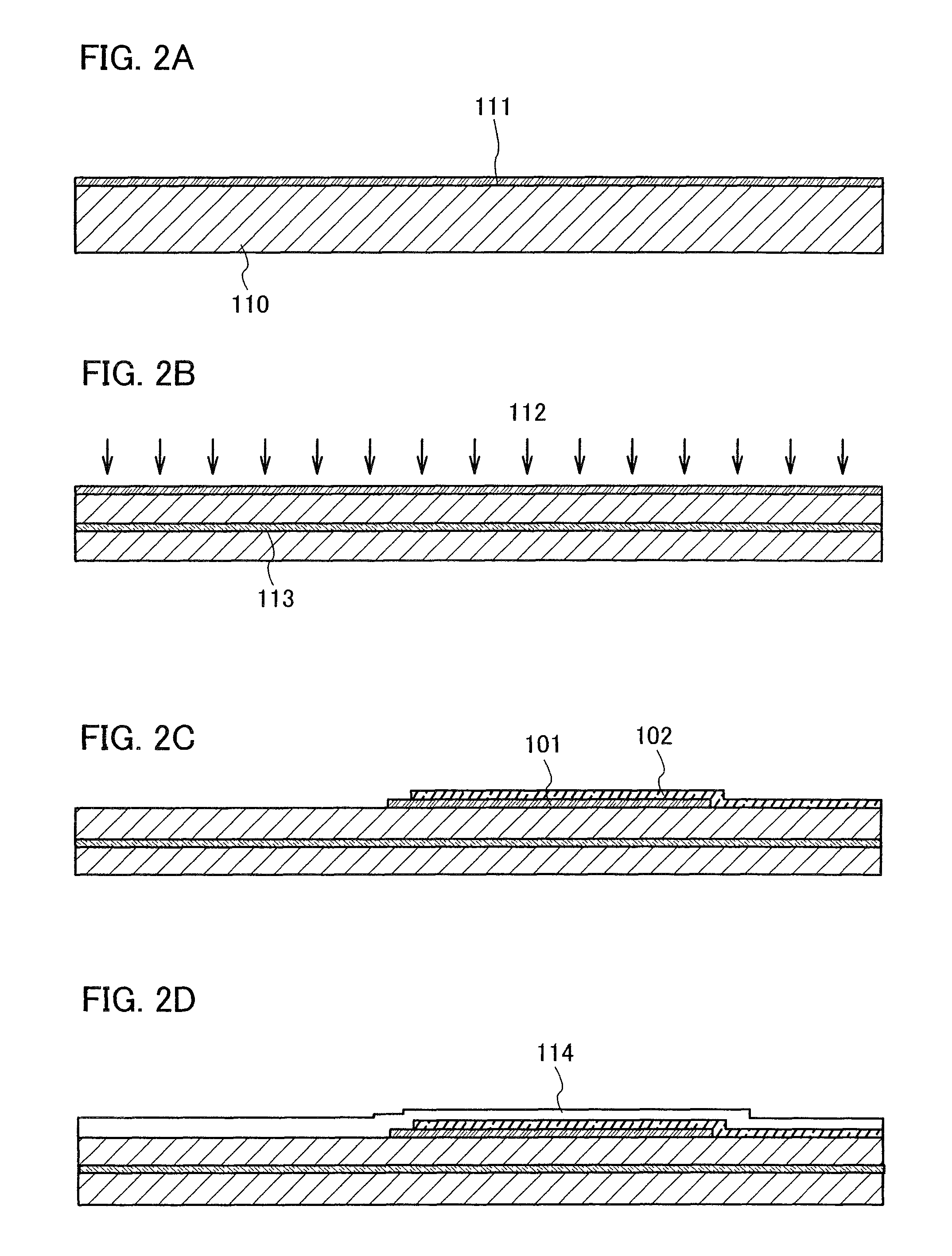

Semiconductor device including storage capacitor with yttrium oxide capacitor dielectric

InactiveUS8067793B2Reduce areaDeterioration of characteristicTransistorSolid-state devicesCapacitanceEngineering

A method for manufacturing a semiconductor device with high response speed and high reliability. In the method for manufacturing a semiconductor device of the invention, a bonding layer is formed over a substrate, an insulating film and a storage capacitor portion lower electrode are formed over the bonding layer, a single crystal silicon layer is formed over the insulating film, a storage capacitor portion insulating film is formed over the storage capacitor portion lower electrode, a wiring is formed over the storage capacitor portion insulating film, a channel forming region and a low concentration impurity region are formed over the single crystal silicon layer, and a gate insulating film and a gate electrode are formed over the single crystal silicon layer. The storage capacitor portion insulating film is formed by depositing a YSZ film with a single crystal silicon layer used as a base film, whereby the permittivity increases and thus the leakage current from the storage capacitor portion is suppressed.

Owner:SEMICON ENERGY LAB CO LTD

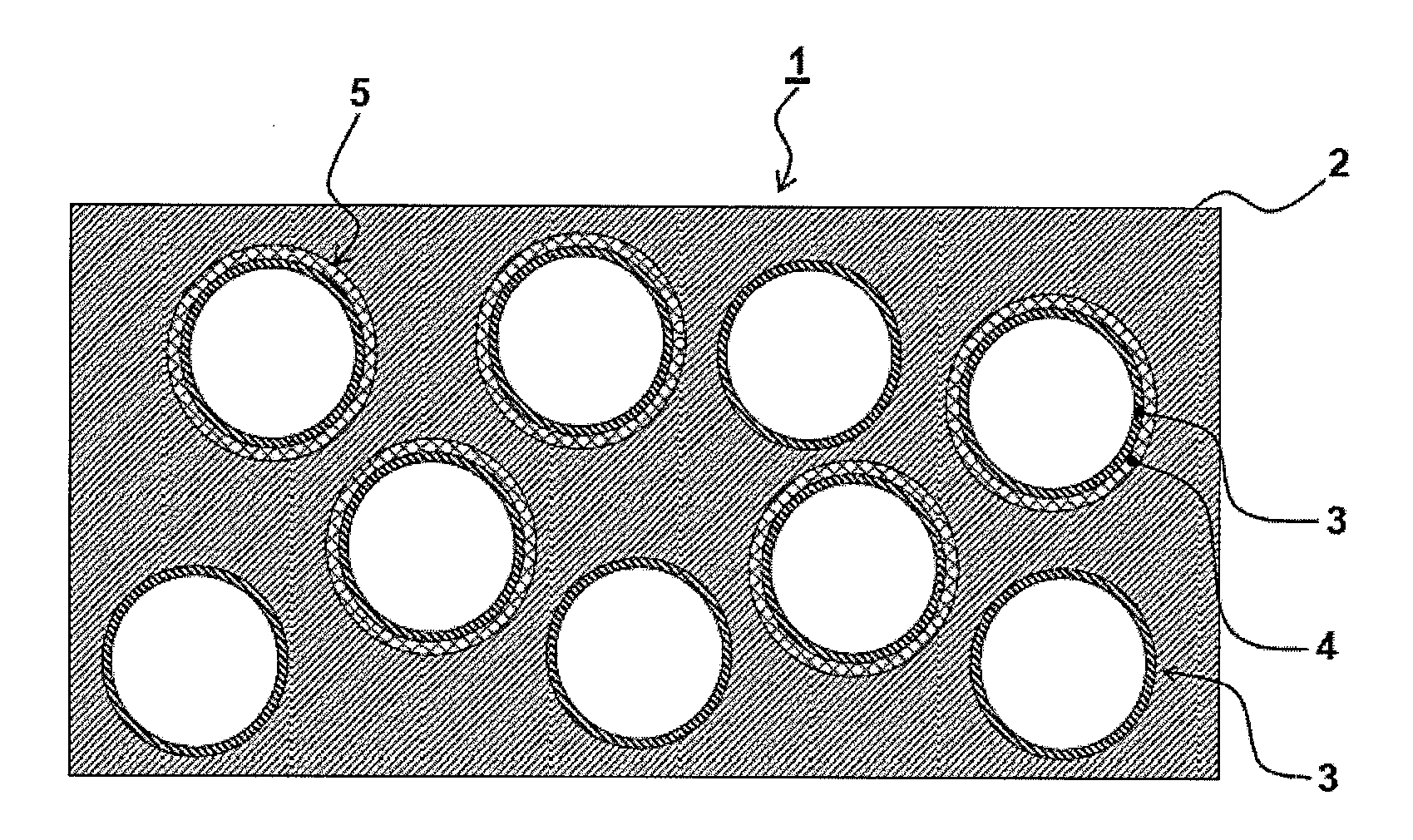

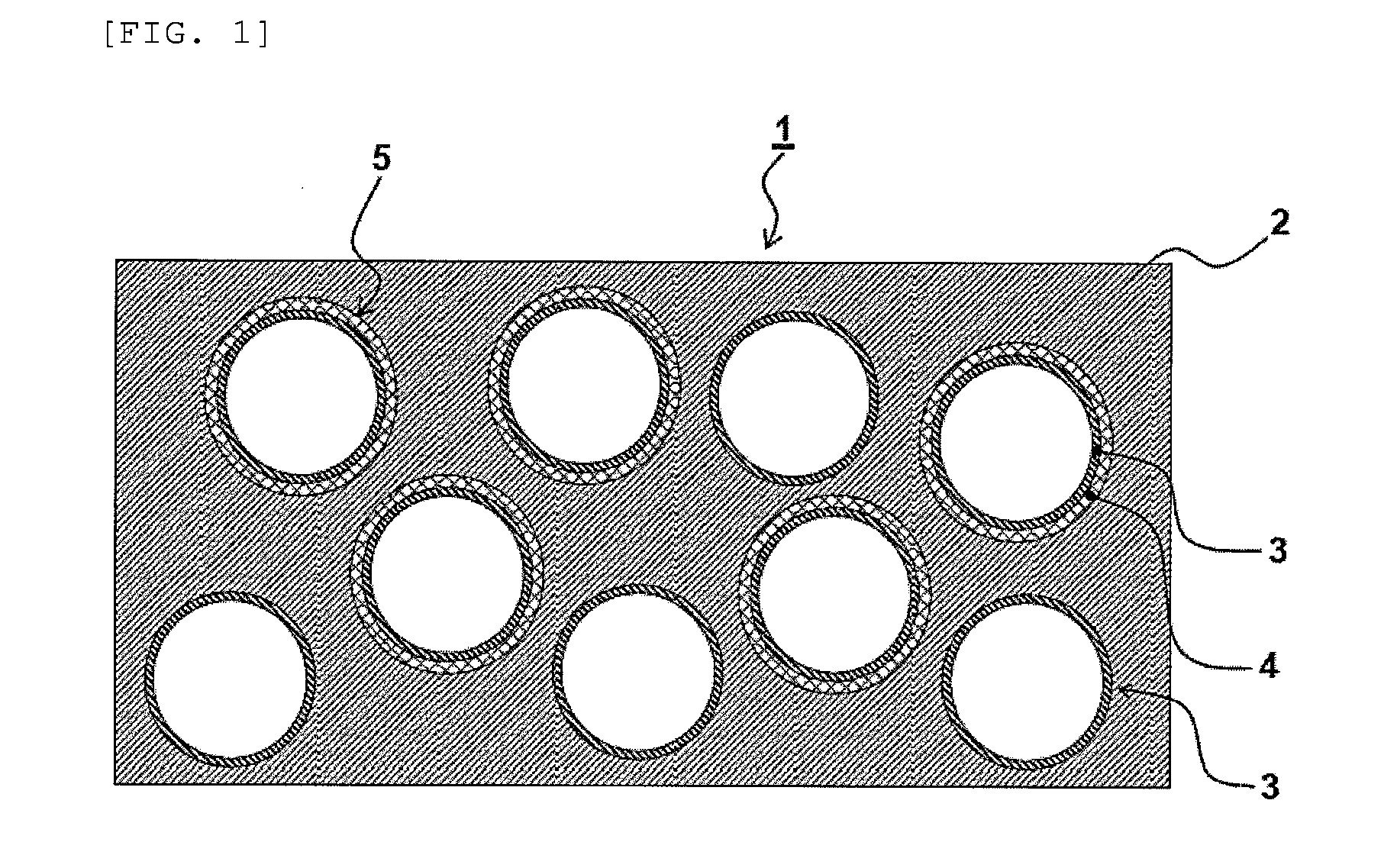

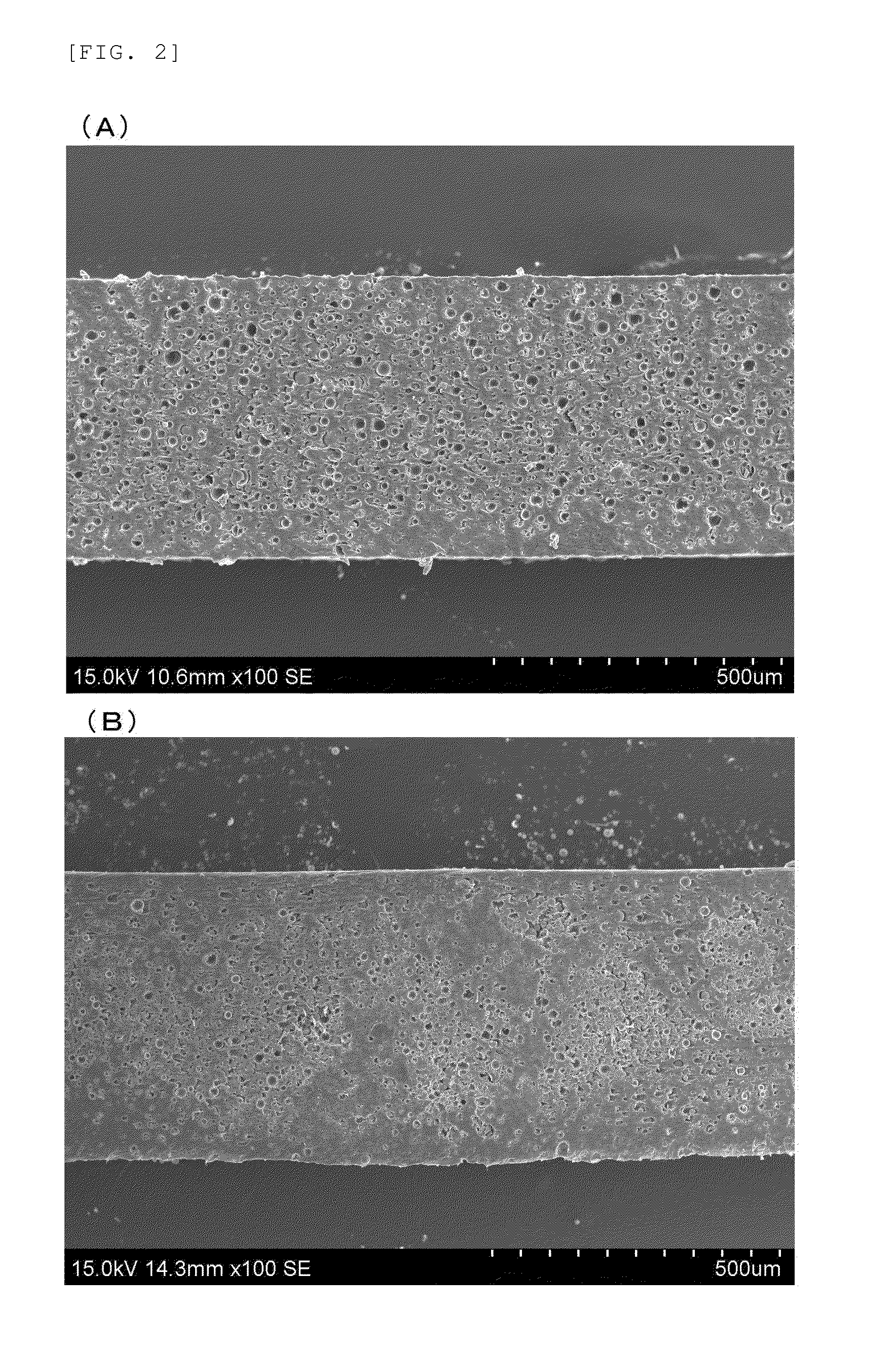

Piezoelectric Stack

ActiveUS20150295163A1High piezoelectric coefficientRetention of coefficientLayered productsElectretsElastic modulusSurface coating

A piezoelectric stack includes a porous resin sheet, and a surface coating layer disposed on an exterior surface of the porous resin sheet, the exterior surface including at least one of a front surface and a back surface of the porous resin sheet, the surface coating layer having a volume resistivity of not less than 1×1013 Ω·cm, the porous resin sheet and the surface coating layer having different elastic moduli.

Owner:KANSAI UNIVERSITY +1

Semiconductor device and method for manufacturing the same

InactiveUS20090085081A1Reduce areaHigh dielectric constantTransistorSolid-state devicesEngineeringPermittivity

A method for manufacturing a semiconductor device with high response speed and high reliability. In the method for manufacturing a semiconductor device of the invention, a bonding layer is formed over a substrate, an insulating film and a storage capacitor portion lower electrode are formed over the bonding layer, a single crystal silicon layer is formed over the insulating film, a storage capacitor portion insulating film is formed over the storage capacitor portion lower electrode, a wiring is formed over the storage capacitor portion insulating film, a channel forming region and a low concentration impurity region are formed over the single crystal silicon layer, and a gate insulating film and a gate electrode are formed over the single crystal silicon layer. The storage capacitor portion insulating film is formed by depositing a YSZ film with a single crystal silicon layer used as a base film, whereby the permittivity increases and thus the leakage current from the storage capacitor portion is suppressed.

Owner:SEMICON ENERGY LAB CO LTD

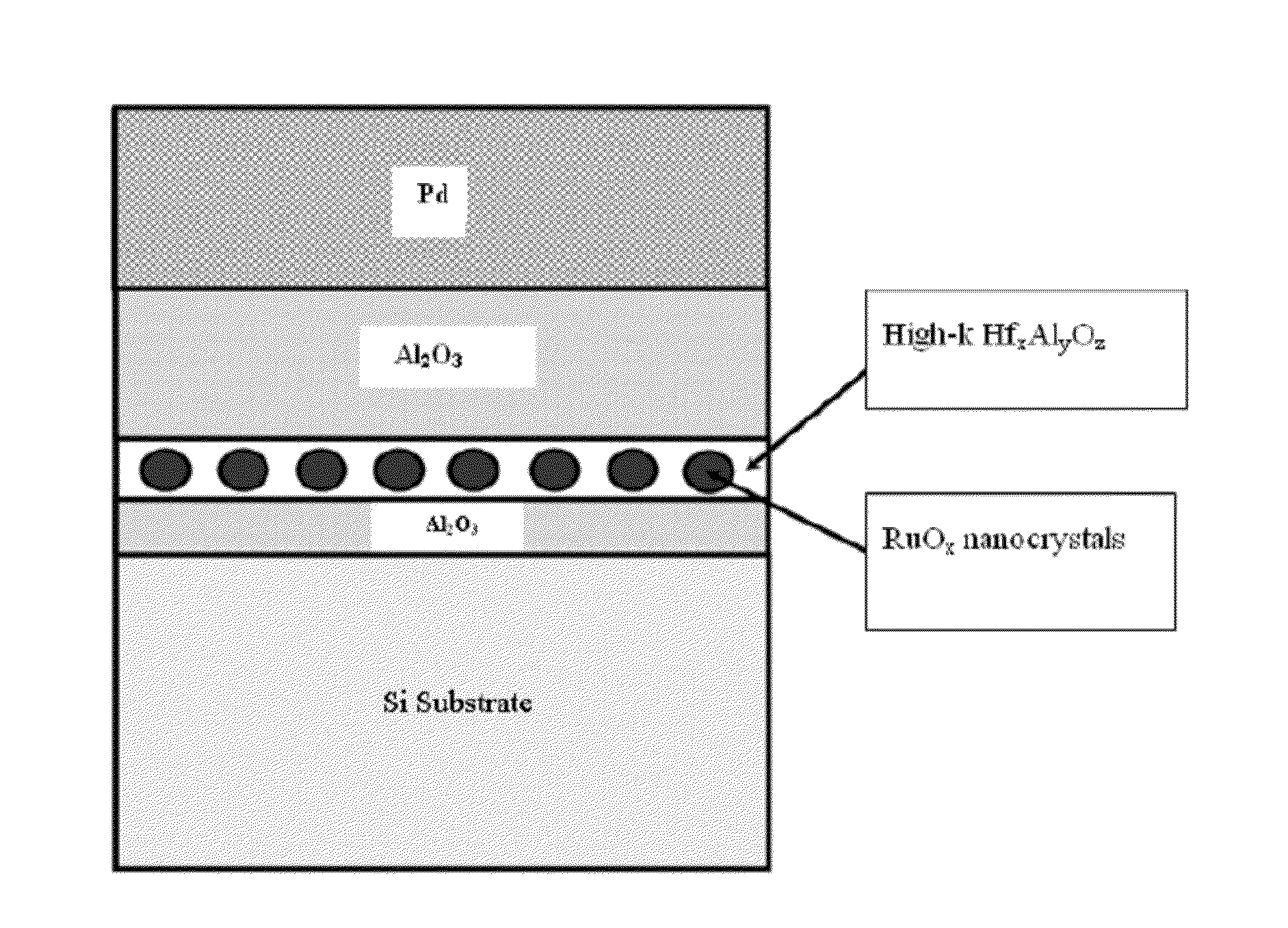

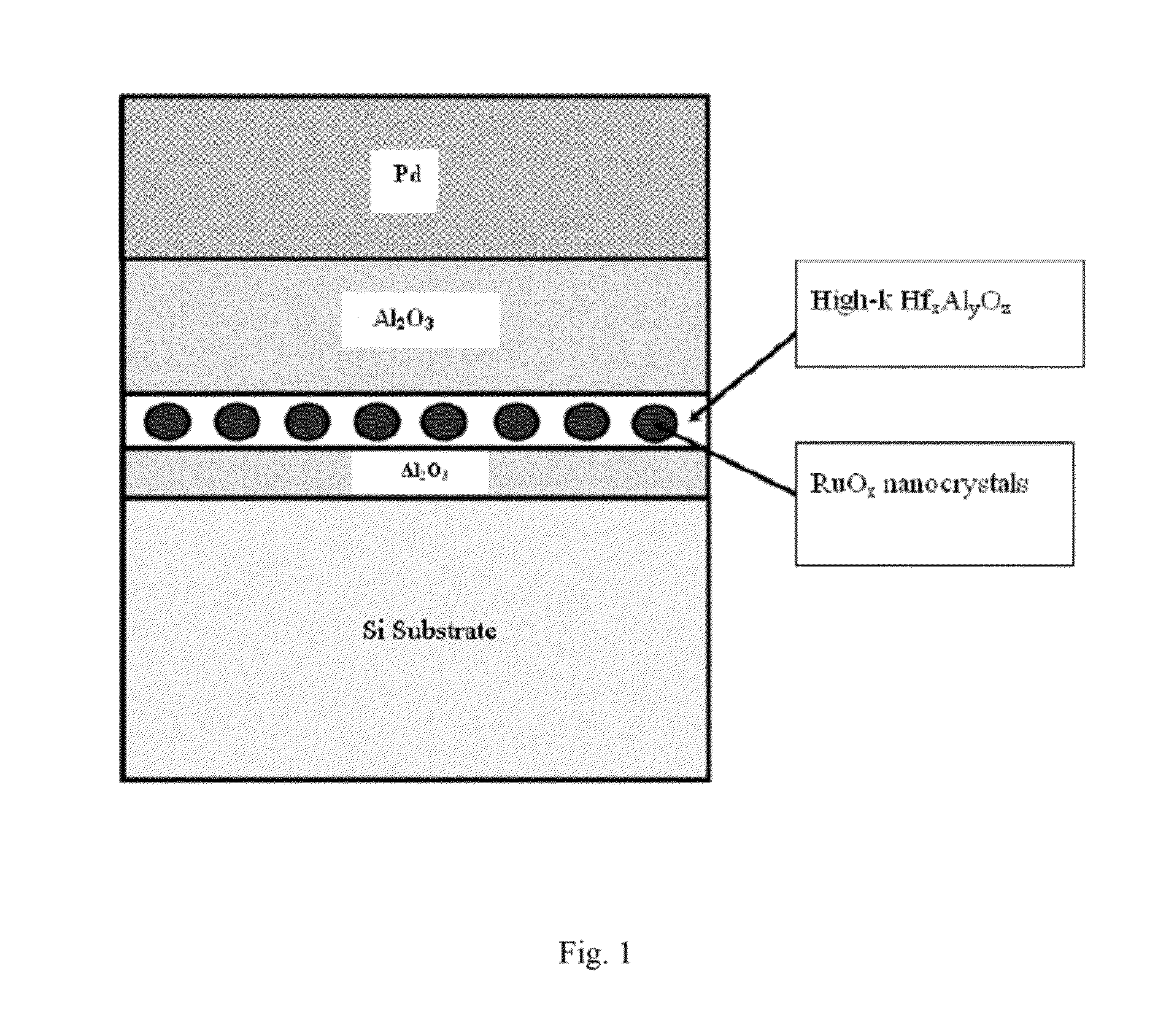

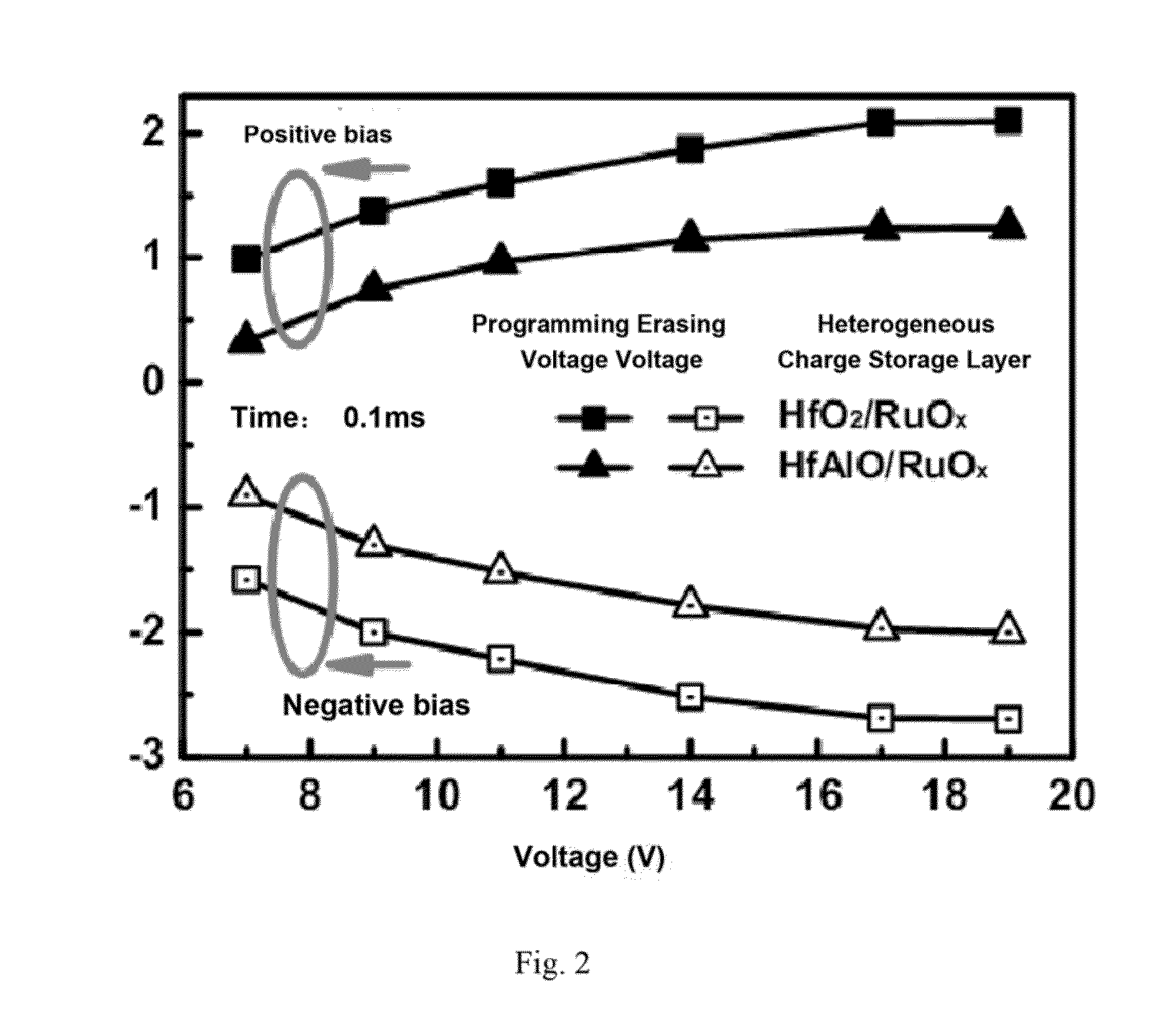

Gate stack structure and fabricating method used for semiconductor flash memory device

InactiveUS20130062684A1High stored-charge densityLow working voltageNanoinformaticsSemiconductor/solid-state device manufacturingTrappingGate stack

The invention relates to a gate stack structure suitable for use in a semiconductor flash memory device and its fabricating method. The gate stack structure is fabricated on a p-type 100 silicon substrate, which also includes the following components in sequence from bottom to top: a charge tunnel layer of Al2O3 film, the first charge trapping layer of RuOx nanocrystals; the second charge trapping layer of high-k HxAlyOz film, a charge blocking layer of Al2O3 film, and a top electrode. In this invention, the RuOx nanocrystals have excellent thermal stability, and do not diffuse easily at high temperatures. The high-k HfxAlyOz film has high density charge traps.Pd with a high work function is used as the top electrode. Therefore, the present gate stack structure has vast practical prospects for nanocrystal memory devices.

Owner:FUDAN UNIV

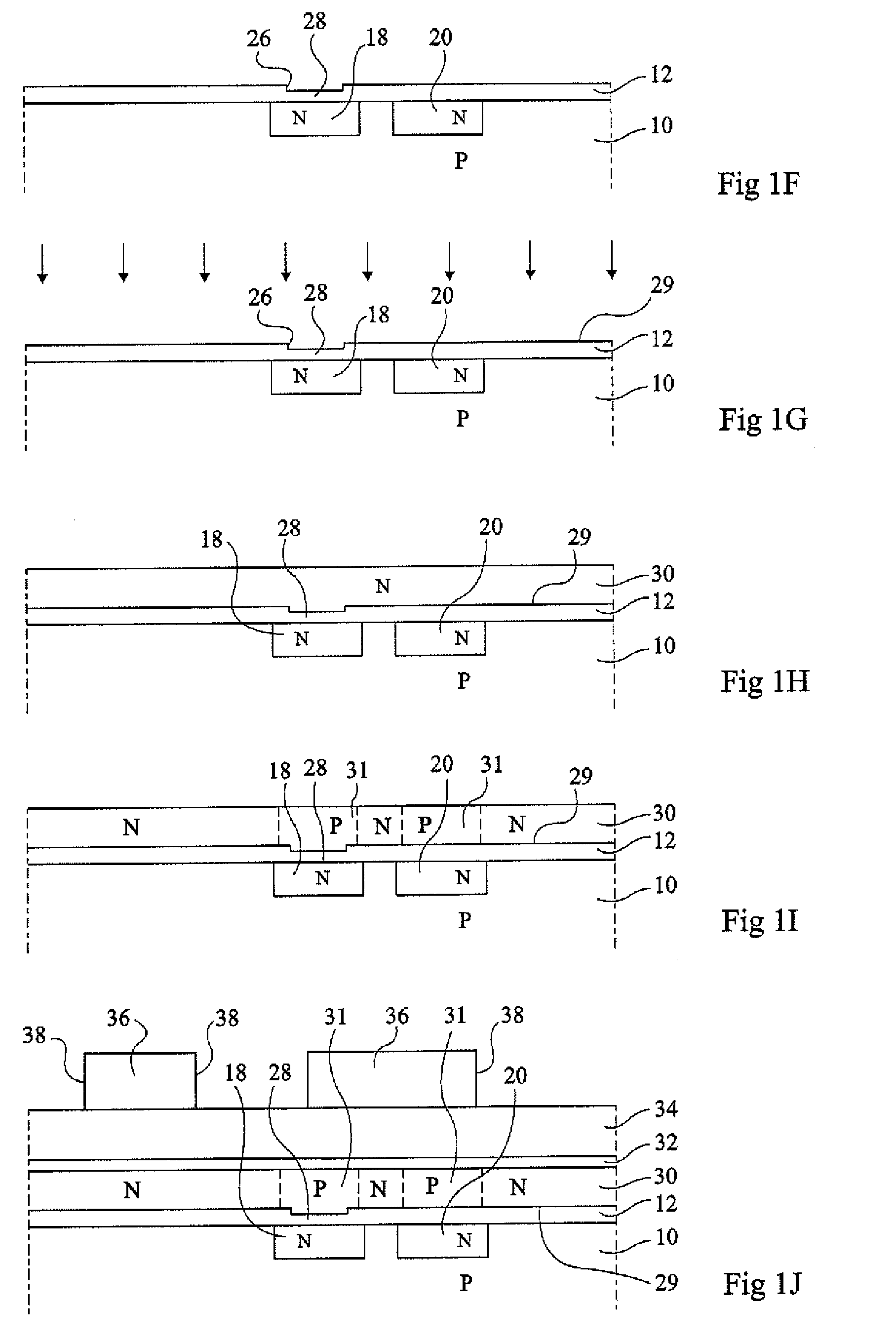

Method for manufacturing an eeprom cell

ActiveUS20090146214A1Improve charge retentionExcellent charge retentionSolid-state devicesRead-only memoriesEngineeringSemiconductor

A method for manufacturing a cell of a non-volatile electrically erasable and programmable memory including a dual-gate MOS transistor. The method includes the steps of providing a semiconductor substrate covered with an insulating layer including a thinned down portion and having a first surface common with the substrate and a second surface opposite to the first surface; and incorporating nitrogen at the level of the second surface, whereby the maximum nitrogen concentration is closer to the second surface than to the first surface.

Owner:STMICROELECTRONICS (ROUSSET) SAS

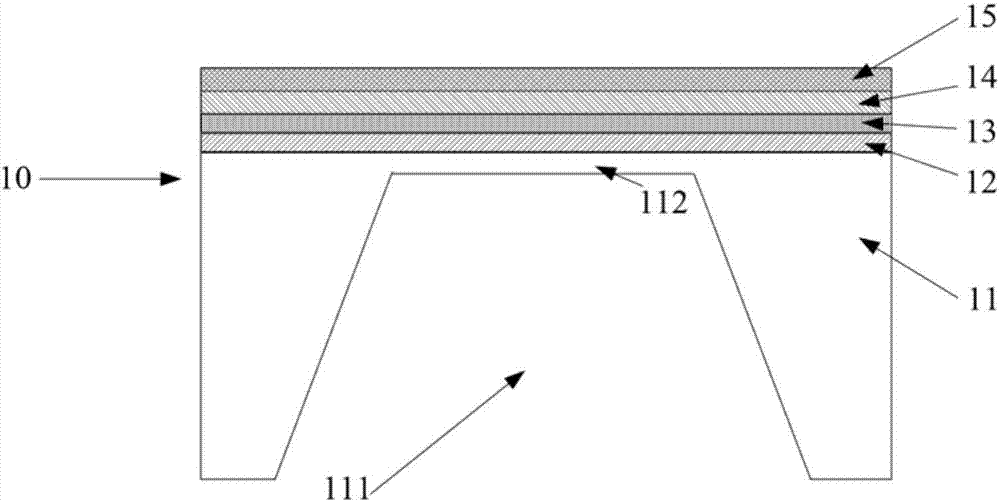

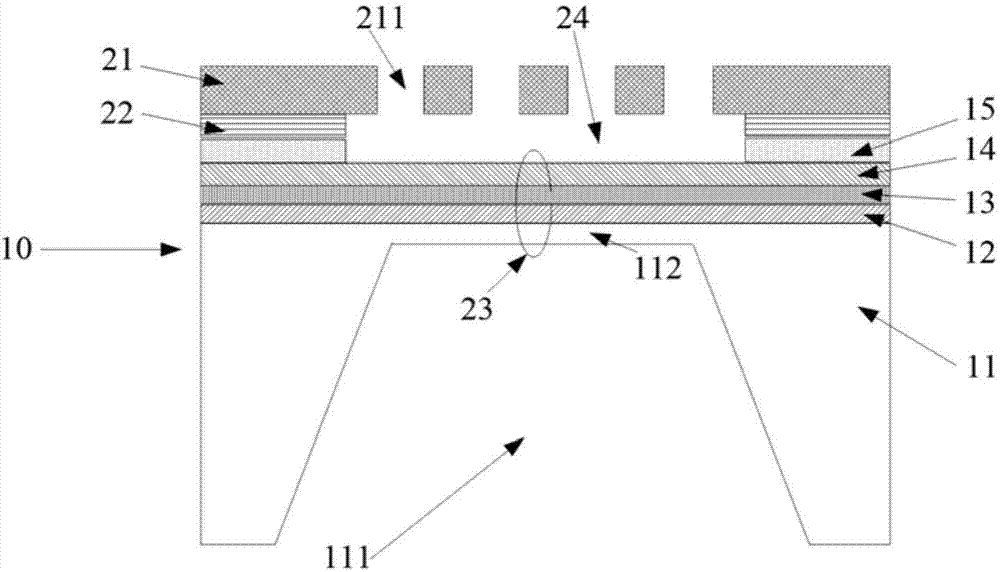

Capacitive silicon miniature microphone and manufacturing method thereof

ActiveCN103888888AExcellent charge retentionImprove reliabilityElectrets selectrostatic transducerHigh humidityEngineering

The invention provides a capacitive silicon miniature microphone and a manufacturing method thereof. The capacitive silicon miniature microphone comprises a substrate, a backing plate and a supporting structure. A tunneling layer is arranged on the substrate, a dielectric layer is arranged on the tunneling layer and serves as a storage layer, a barrier layer is arranged on the storage layer, a cavity is formed in the position under the substrate, the substrate, the tunneling layer, the storage layer and the barrier layer, located over the cavity, form a vibrating diaphragm together, the backing plate is arranged above the substrate, through holes are formed in the backing plate, the backing plate is connected with the vibrating diaphragm through the supporting structure, and a gap is formed over the vibrating diaphragm. An additional power supply is not needed by the capacitive silicon miniature microphone, and the capacitive silicon miniature microphone is compatible with a CMOS process, has the advantages of being easy to microminiaturize, low in cost, high in precision and high in reliability and can be applied to severe environments such as a high-temperature environment and a high-humidity environment.

Owner:SOUTHEAST UNIV

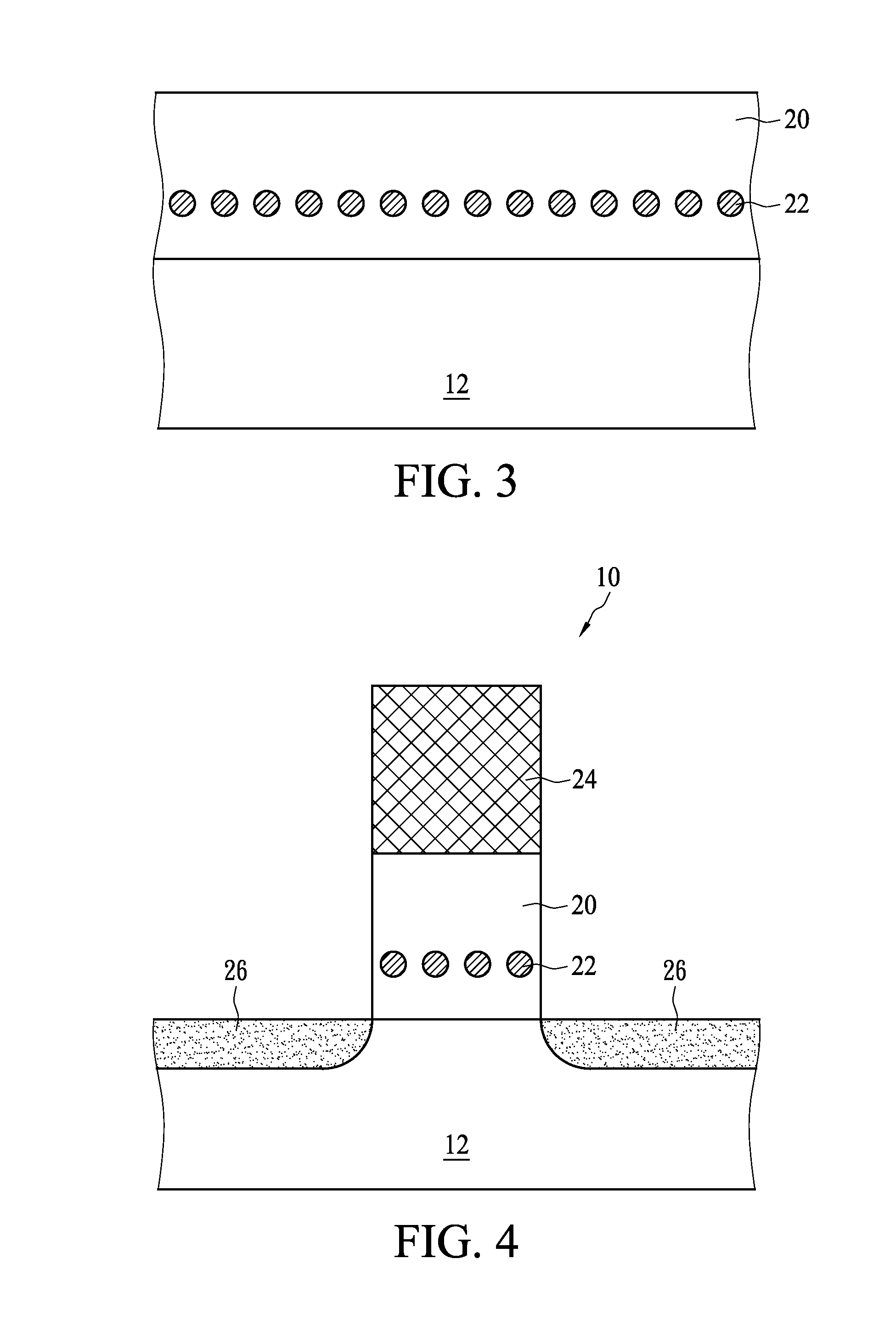

Non-volatile memory structure and method for preparing the same

InactiveUS20090283822A1Charge retention enduranceExcellent charge retentionSemiconductor/solid-state device manufacturingSemiconductor devicesTrappingNitrogen

A non-volatile memory structure includes a substrate having two doped regions, a charge-trapping structure positioned substantially between the two doped regions, and a conductive structure positioned on the charge-trapping structure, wherein the charge-trapping structure includes a silicon-oxy-nitride layer and metallic nano-dots embedded in the silicon-oxy-nitride layer. The non-volatile memory structure formed by performing a first thermal oxidation process to form a high-k dielectric layer on a substrate, forming a metal-containing semiconductor layer including silicon or germanium on the high-k dielectric layer, forming a silicon layer on the metal-containing semiconductor layer, and performing a second thermal oxidation process to convert the metal-containing semiconductor layer to a silicon-oxy-nitride layer with embedded metallic nano-dots, wherein at least one of the first thermal oxidation process and the second thermal oxidation process is performed in a nitrogen-containing atmosphere.

Owner:PROMOS TECH INC

Toner

ActiveUS20190107793A1Excellent low temperature fixabilityIncrease resistanceDevelopersPolymer chemistryWeight distribution

A toner comprising: a toner particle that contains a resin component and a silicone compound, wherein the resin component contains at least 50 mass % of olefin resin; a content of the silicone compound is from 1 mass part to 42 mass parts per 100 mass parts of the resin component; a weight-average molecular weight of the silicone compound as measured by GPC is from 1,000 to 25,000; and a content, in a molecular weight distribution of the silicone compound as measured by GPC, of a component having a weight-average molecular weight of not more than 500 is not more than 0.05 mass % of the silicone compound.

Owner:CANON KK

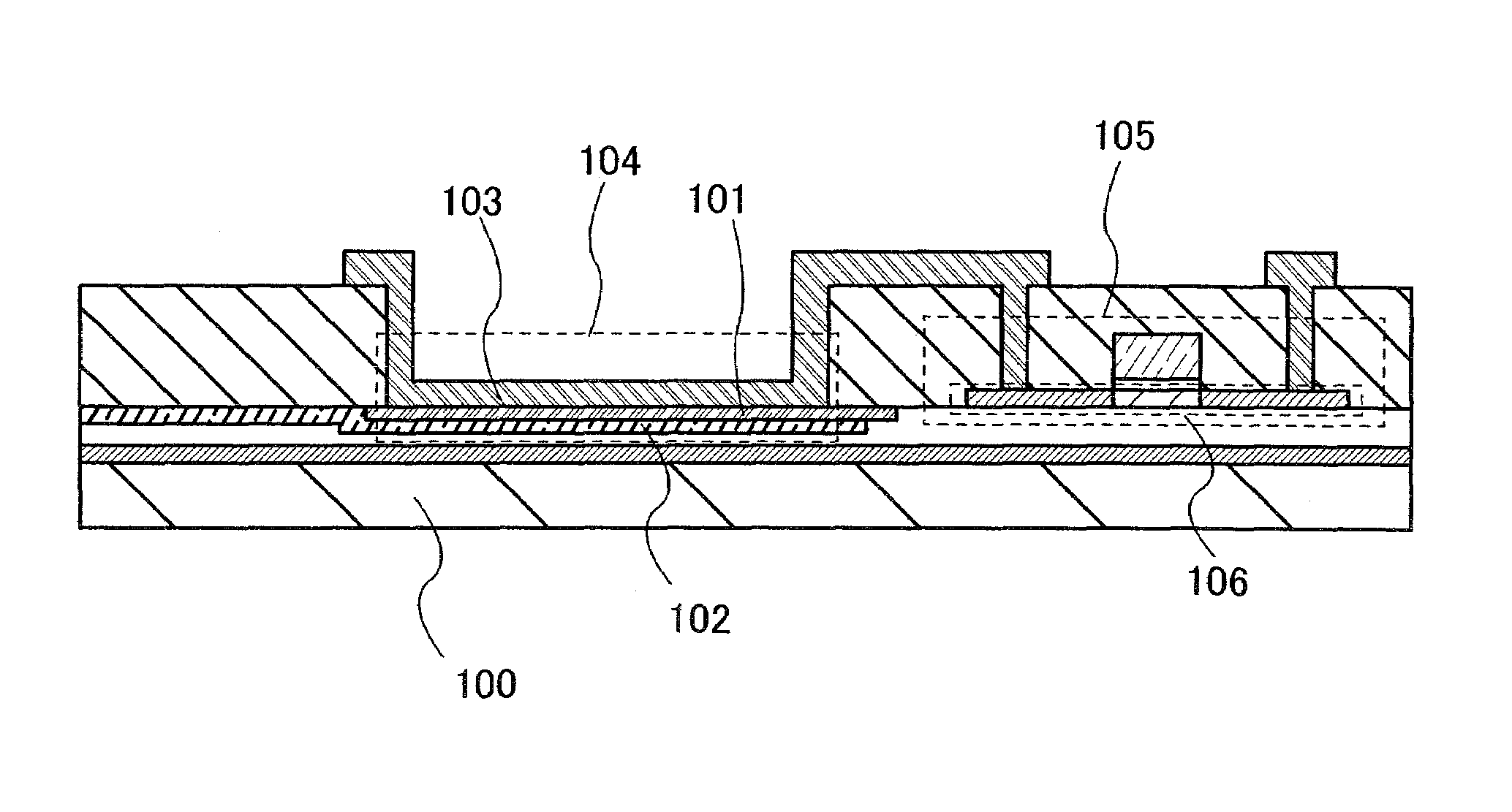

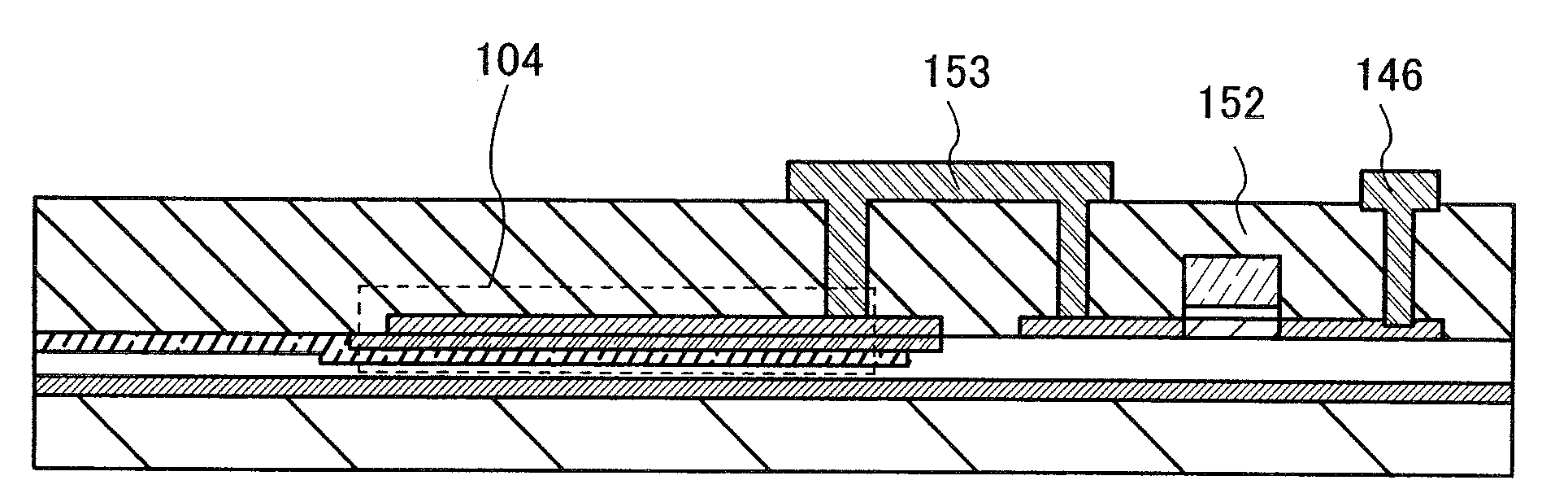

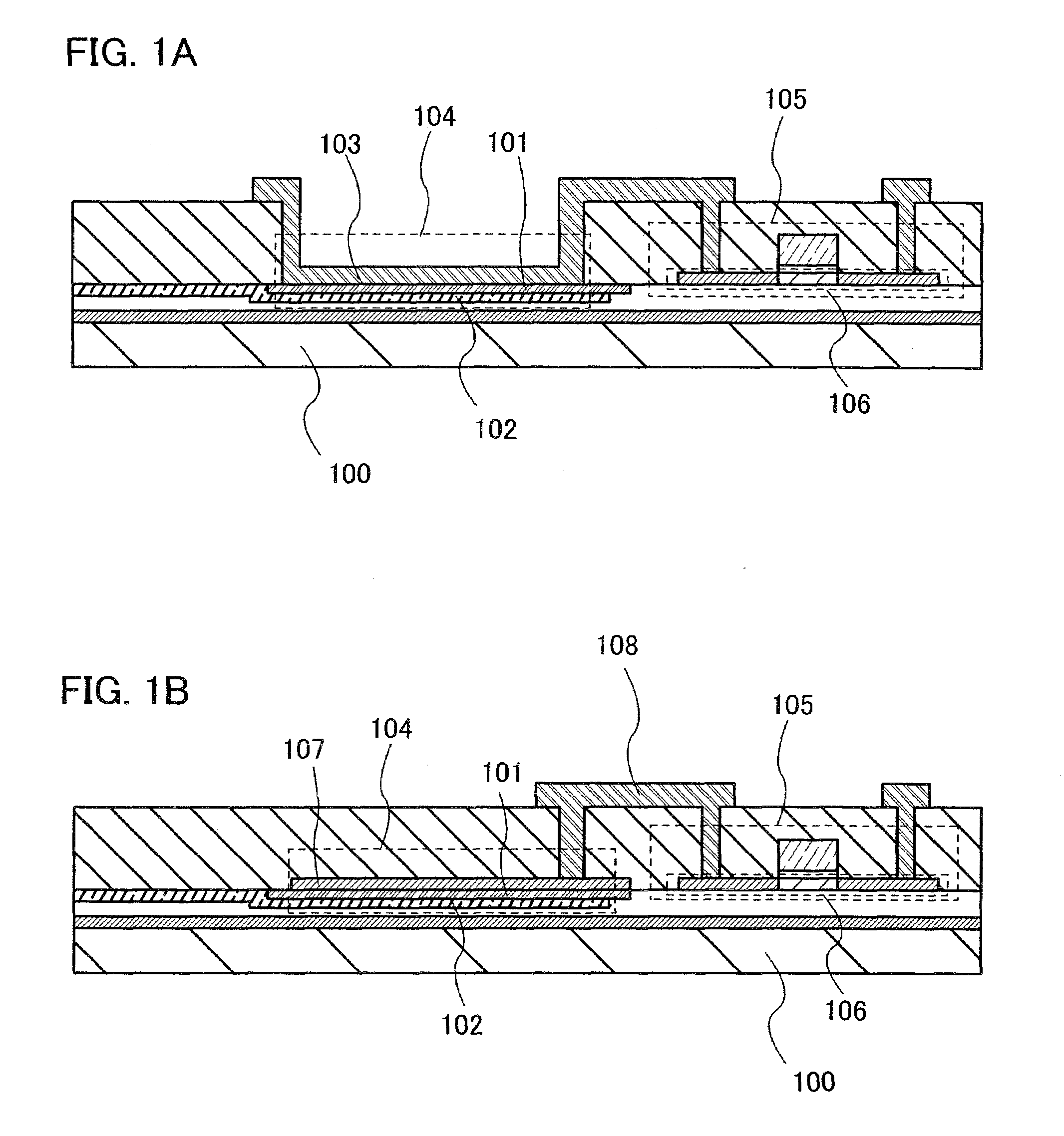

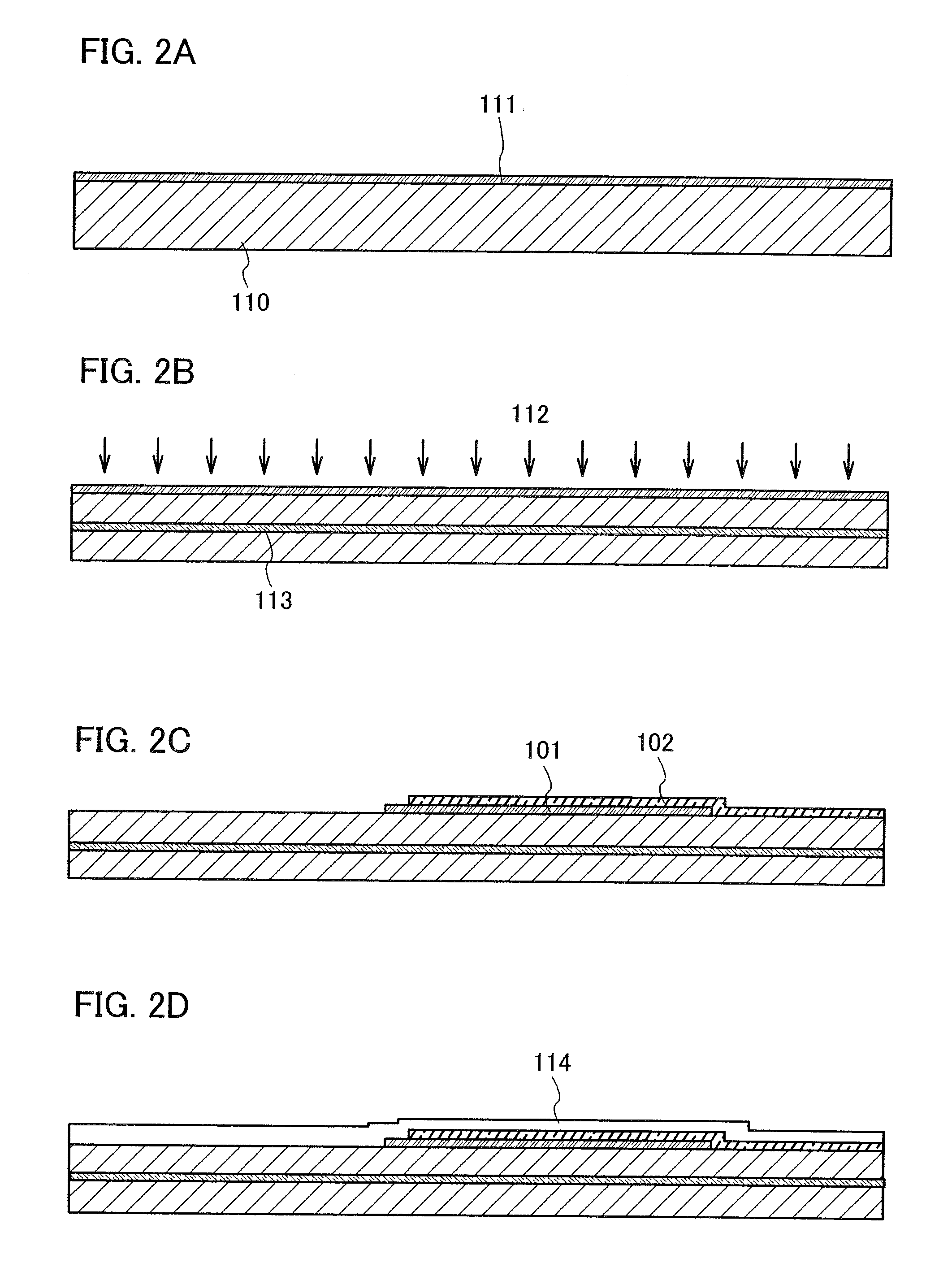

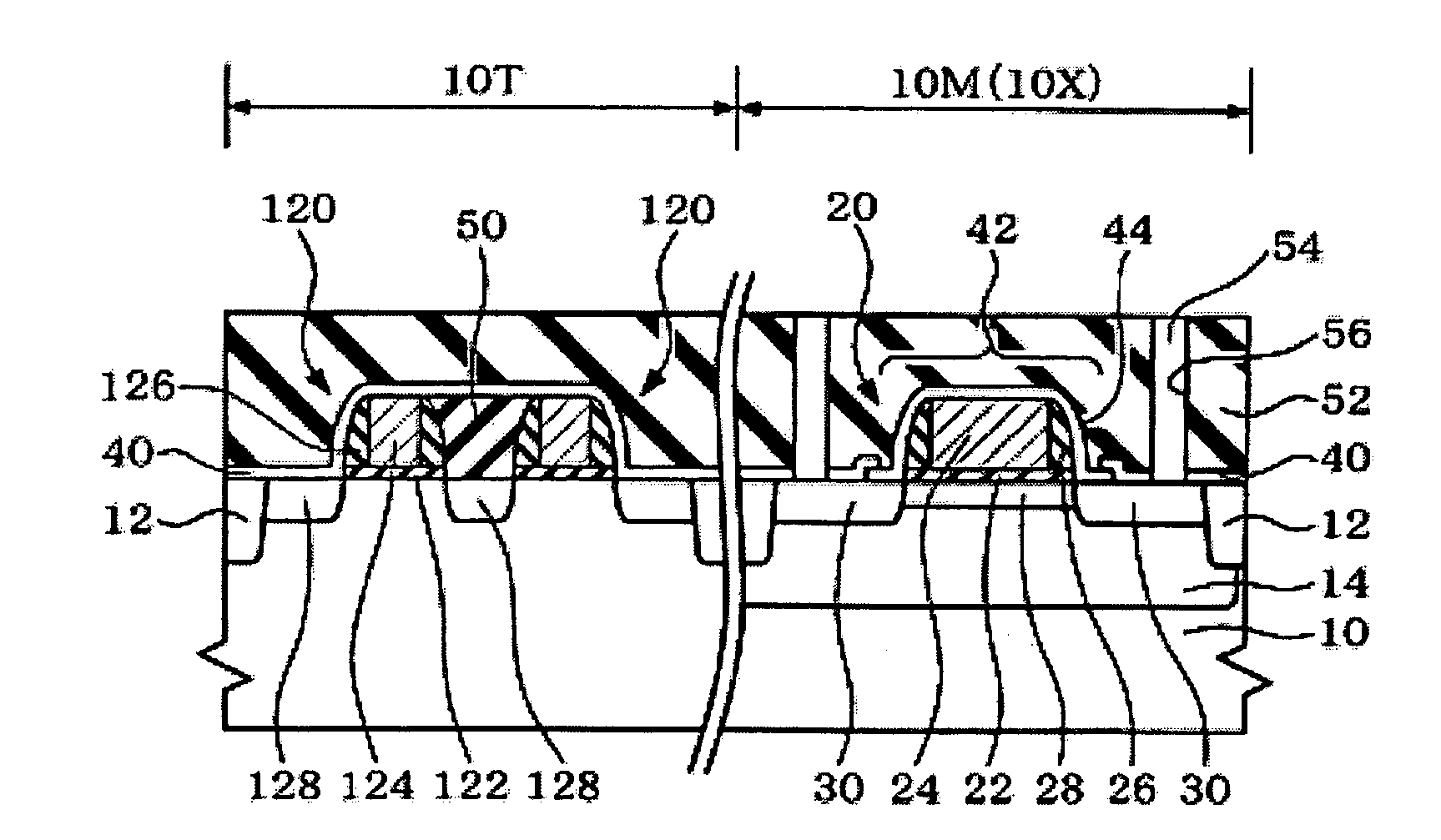

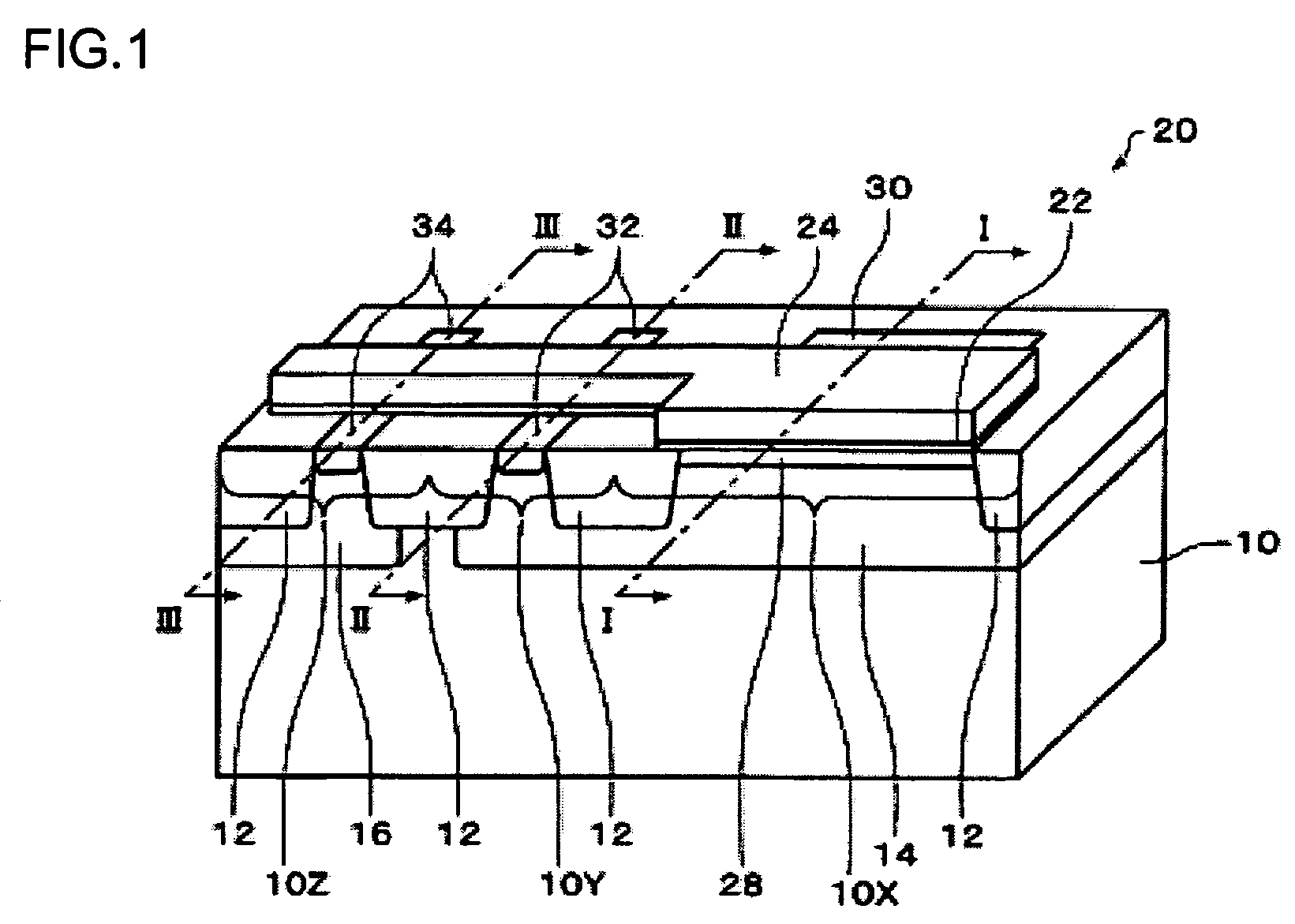

Semiconductor device having nonvolatile memory device with improved charge holding property

InactiveUS7473962B2Excellent charge retentionTransistorSolid-state devicesCharge retentionSemiconductor

A semiconductor device includes: a semiconductor layer; a first area and a second area which are demarcated by a separation insulating layer provided on the semiconductor layer; a nonvolatile memory provided on the first area; a plurality of MOS transistors provided on the second area; a first interlayer insulating layer embedded between the plurality of MOS transistors on the second area; and a second interlayer insulating layer provided above the first area and the second area. The second interlayer insulating layer is provided as if covering the nonvolatile memory on the first area and, on the second area, provided, being above the first interlayer insulating layer, as if covering the MOS transistor.

Owner:SEIKO EPSON CORP

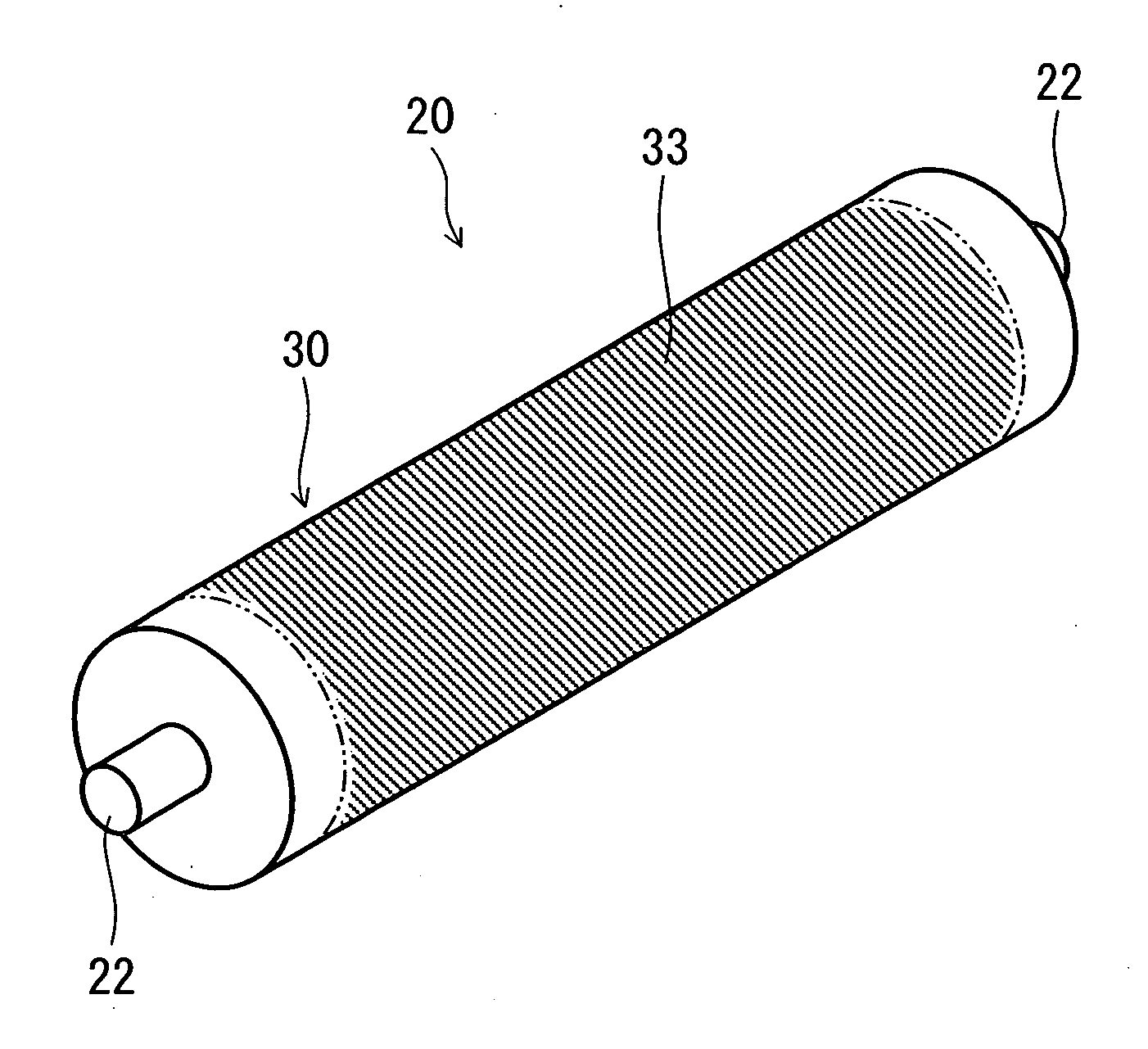

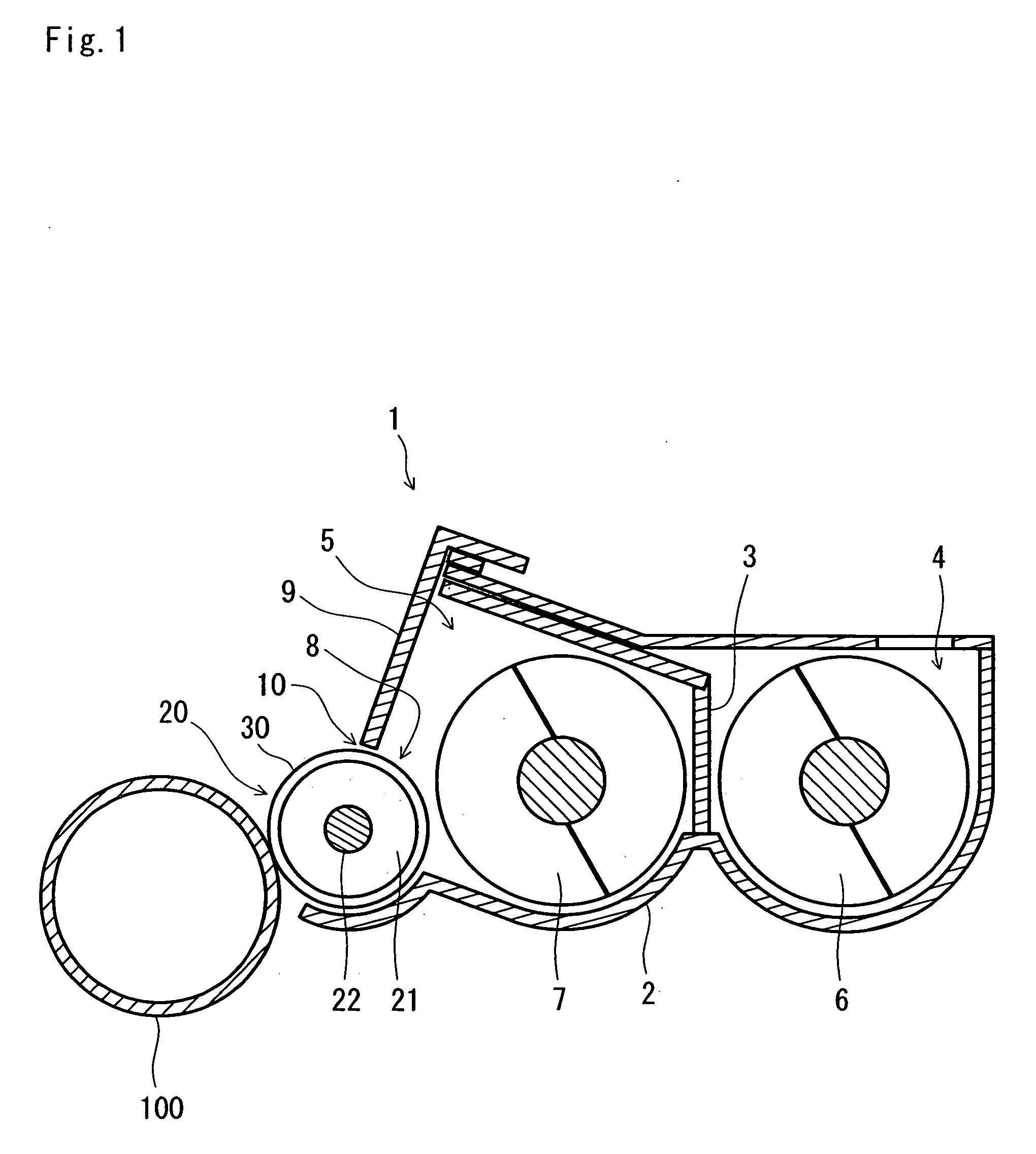

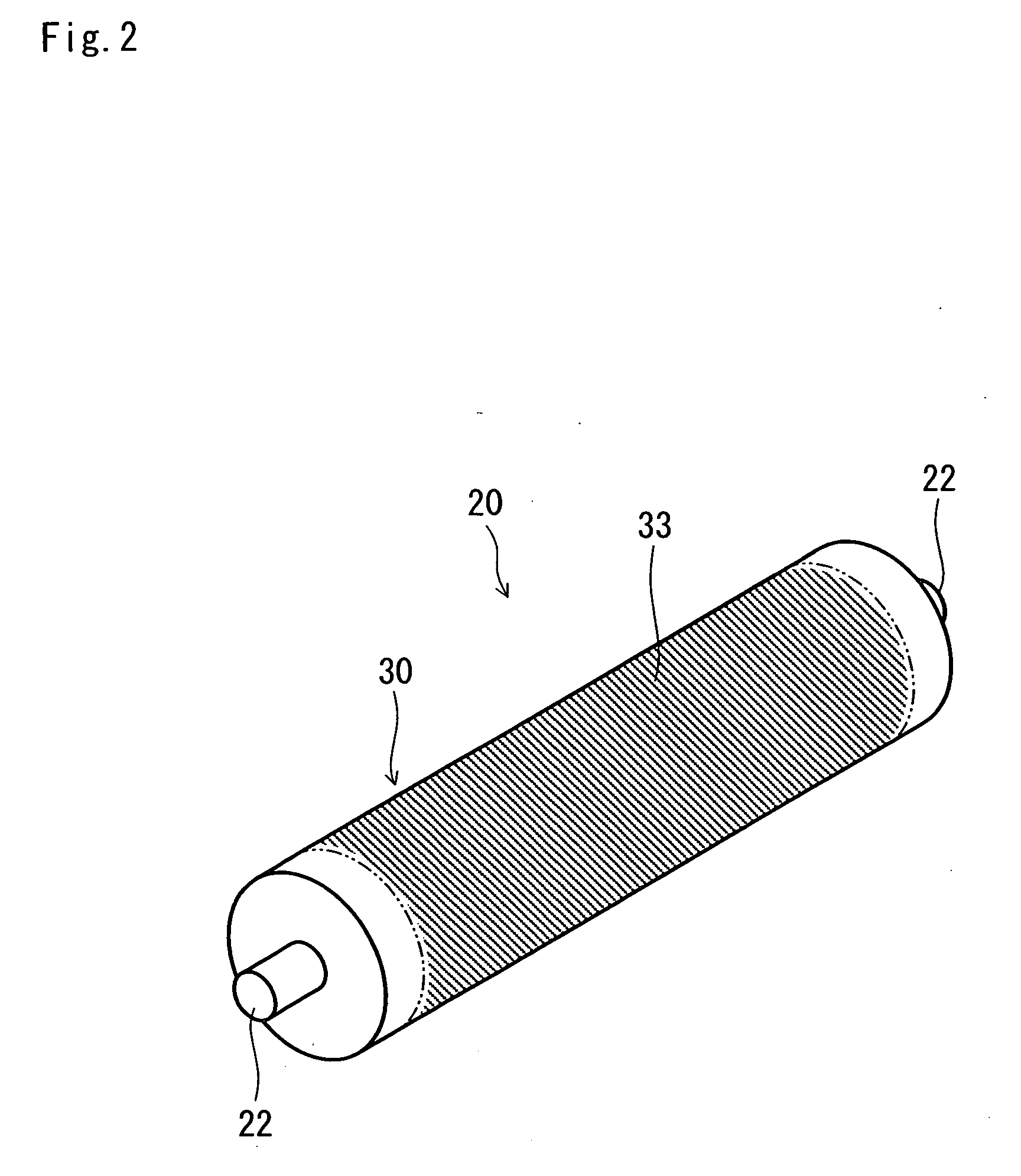

Developing roller and manufacturing method thereof

InactiveUS20060191139A1Avoid failureImprove concentrationMetal-working apparatusElectrographic process apparatusLatent imageEngineering

A developing roller 20 included in a developing device 1 and a photoconductor drum 100 are located adjacently to or in contact with each other. A toner absorbed on the surface of the developing roller 20 moves to the photoconductor drum 100 by an electrostatic force, whereby an electrostatic latent image is formed. The developing roller 20 has on the surface thereof a developing sleeve 30. On the surface of a base 31 of the developing sleeve 30, an electroless nickel plating layer 32 is formed. Further, on the surface of the nickel plating layer 32, a nickel oxide coating 33 is formed. The nickel oxide coating 33 passivates the surface of the developing sleeve 30 to thereby suppress the tendency of the toner charge to dissipate as a result of nickel plating treatment, thus permitting the toner charge holding property to be maintained in a favorable state.

Owner:KYOCERA DOCUMENT SOLUTIONS INC

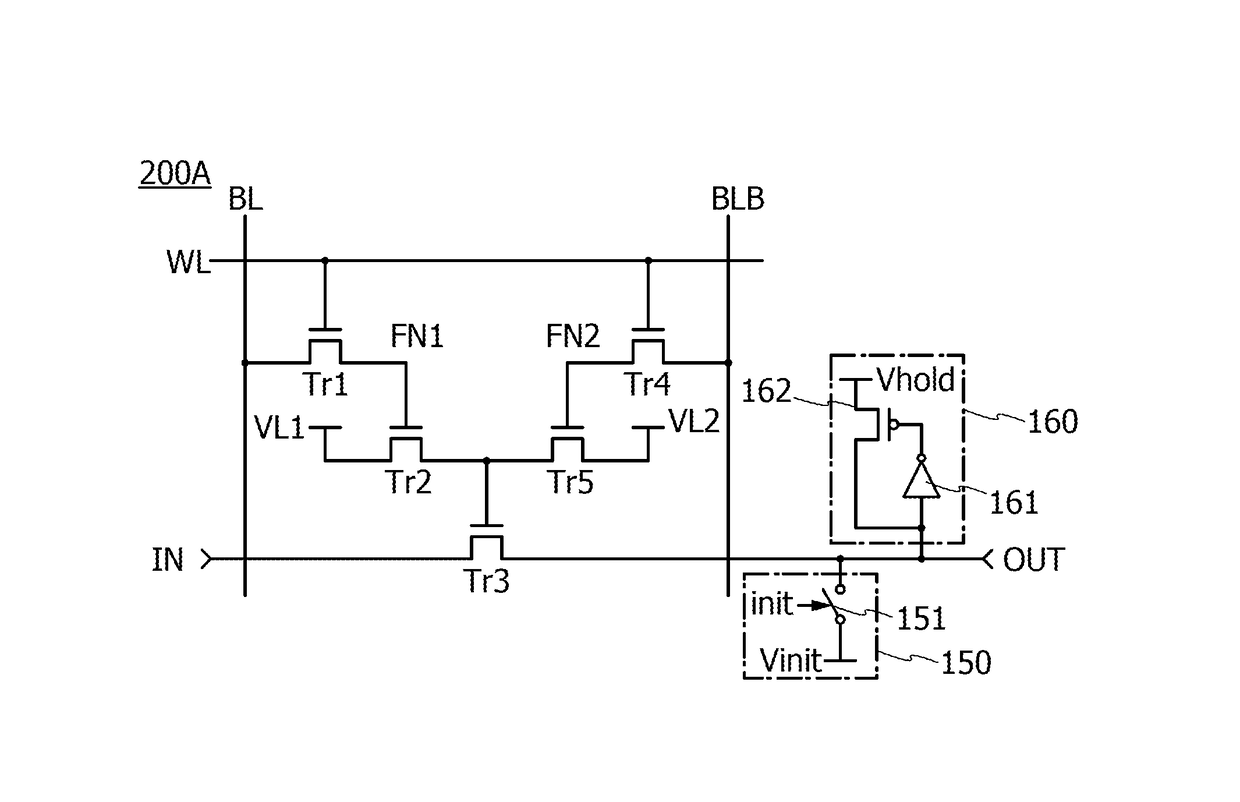

Programmable logic device (PLD)

InactiveUS9761598B2Small sizeImprove charge retention characteristicsTransistorSolid-state devicesCharge retentionProgrammable logic device

Owner:SEMICON ENERGY LAB CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com