Patents

Literature

3263 results about "Gate stack" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

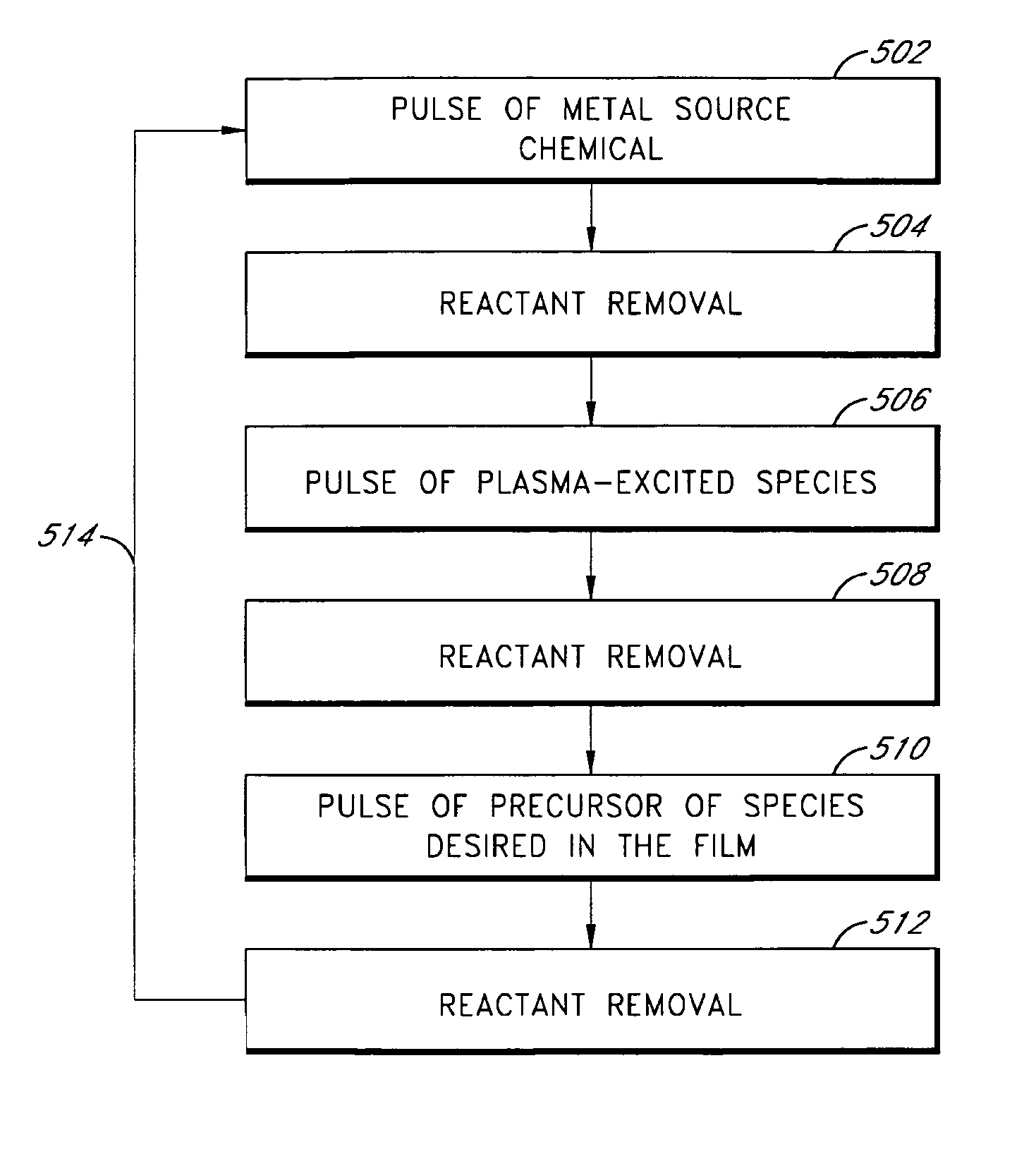

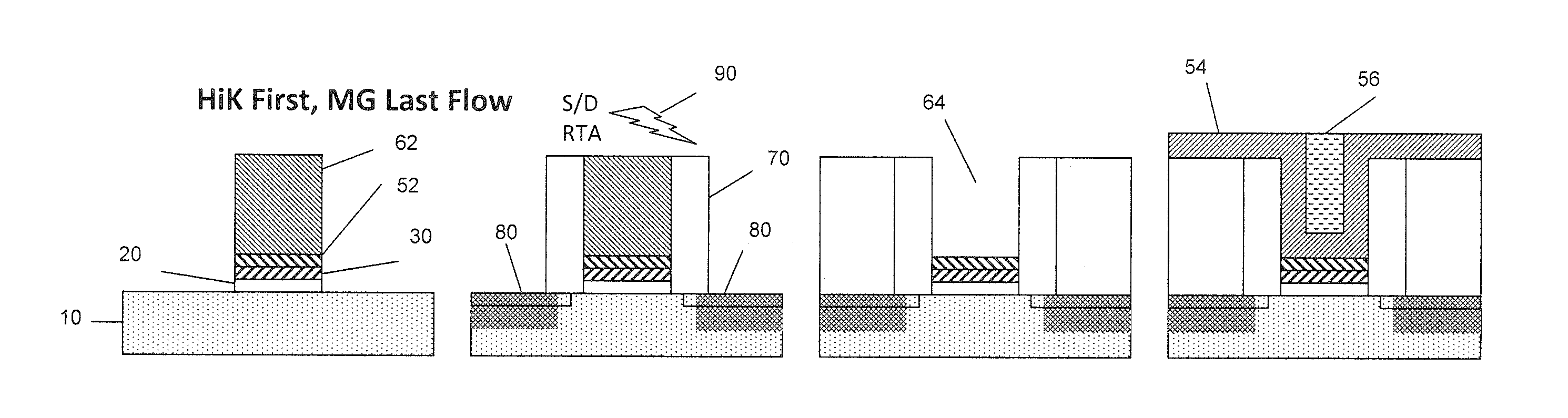

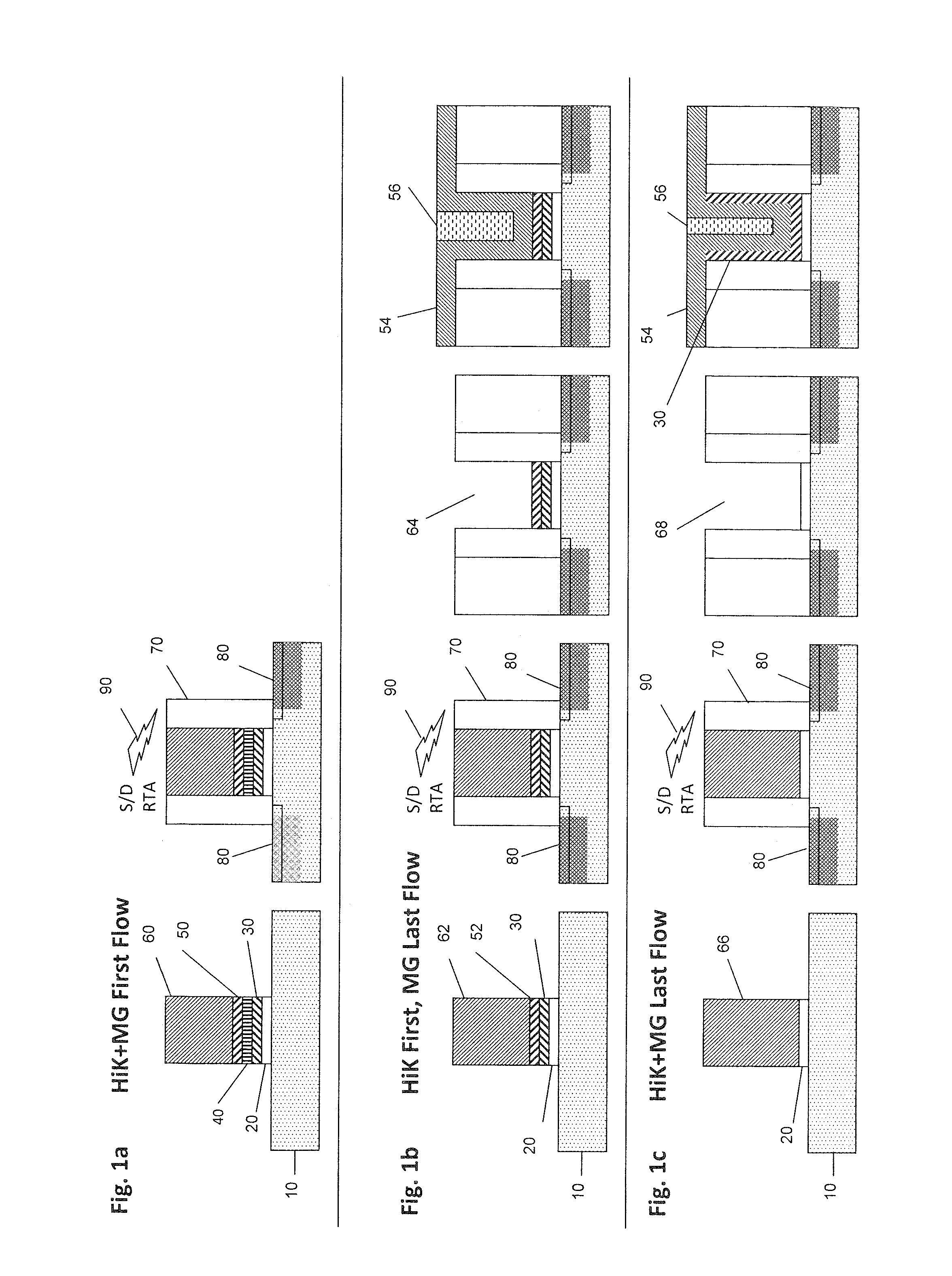

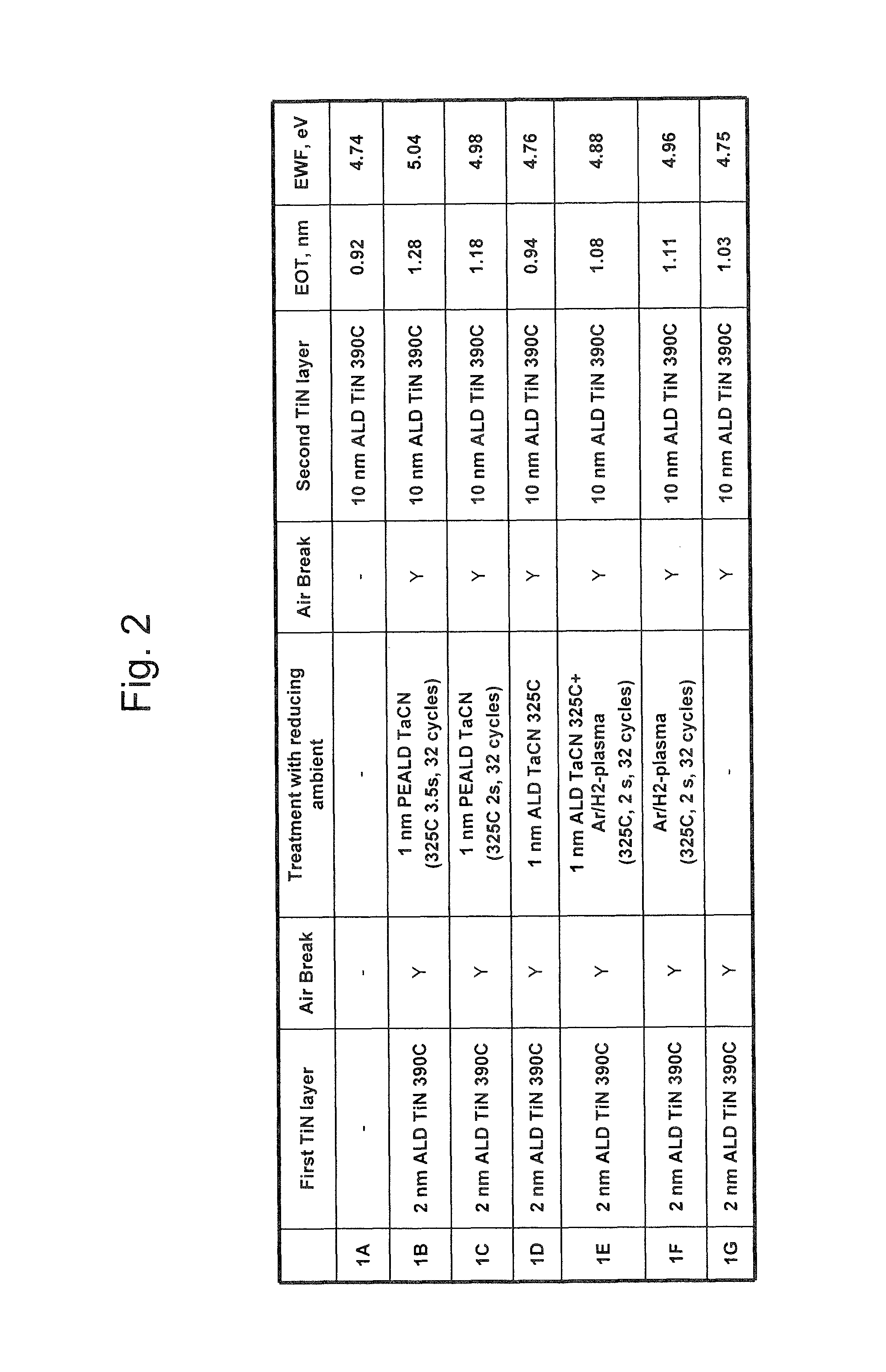

Controlled composition using plasma-enhanced atomic layer deposition

ActiveUS7727864B2Easily and accurately adjusted to a desired valueSemiconductor/solid-state device manufacturingChemical vapor deposition coatingOxidation stateWork function

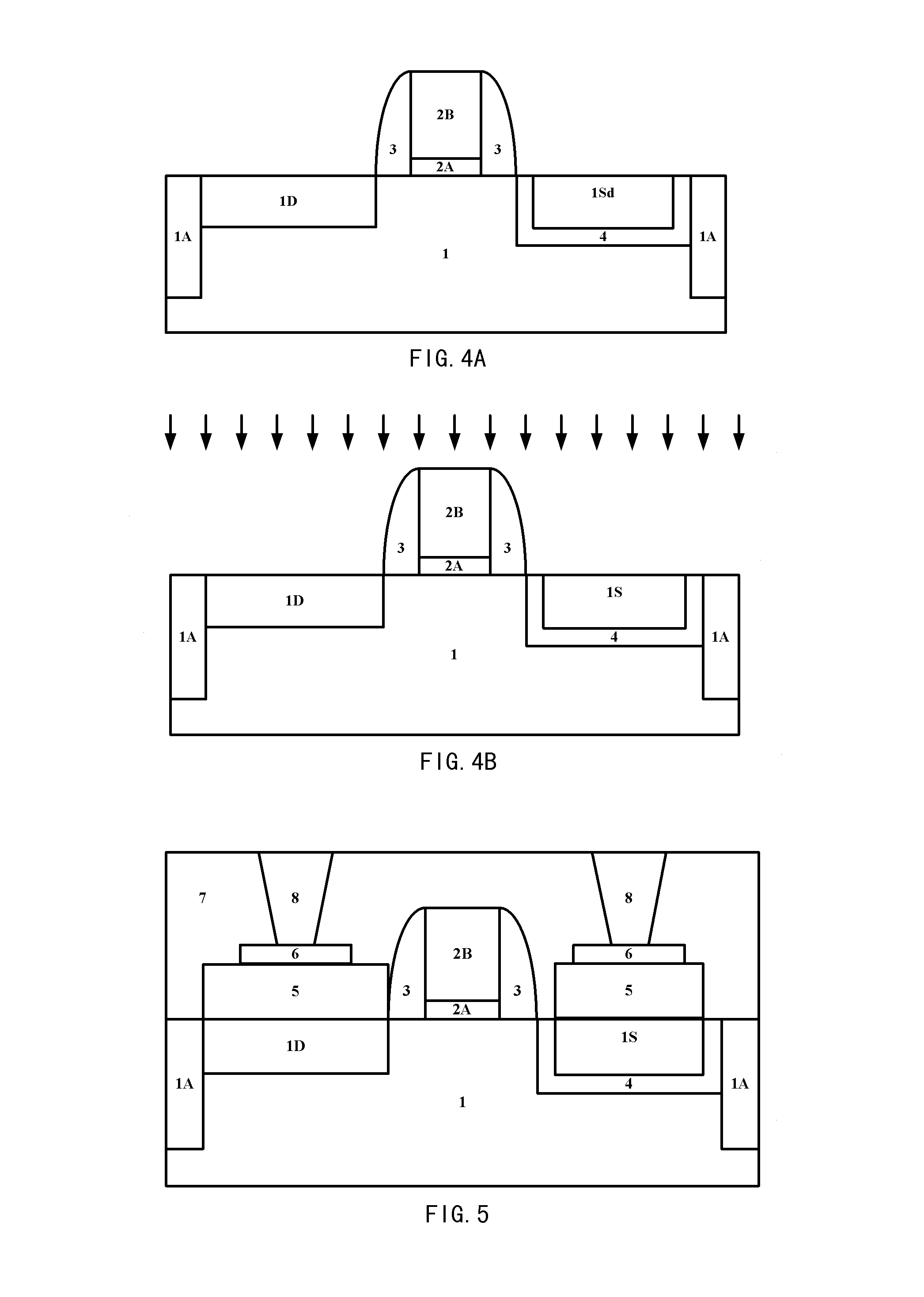

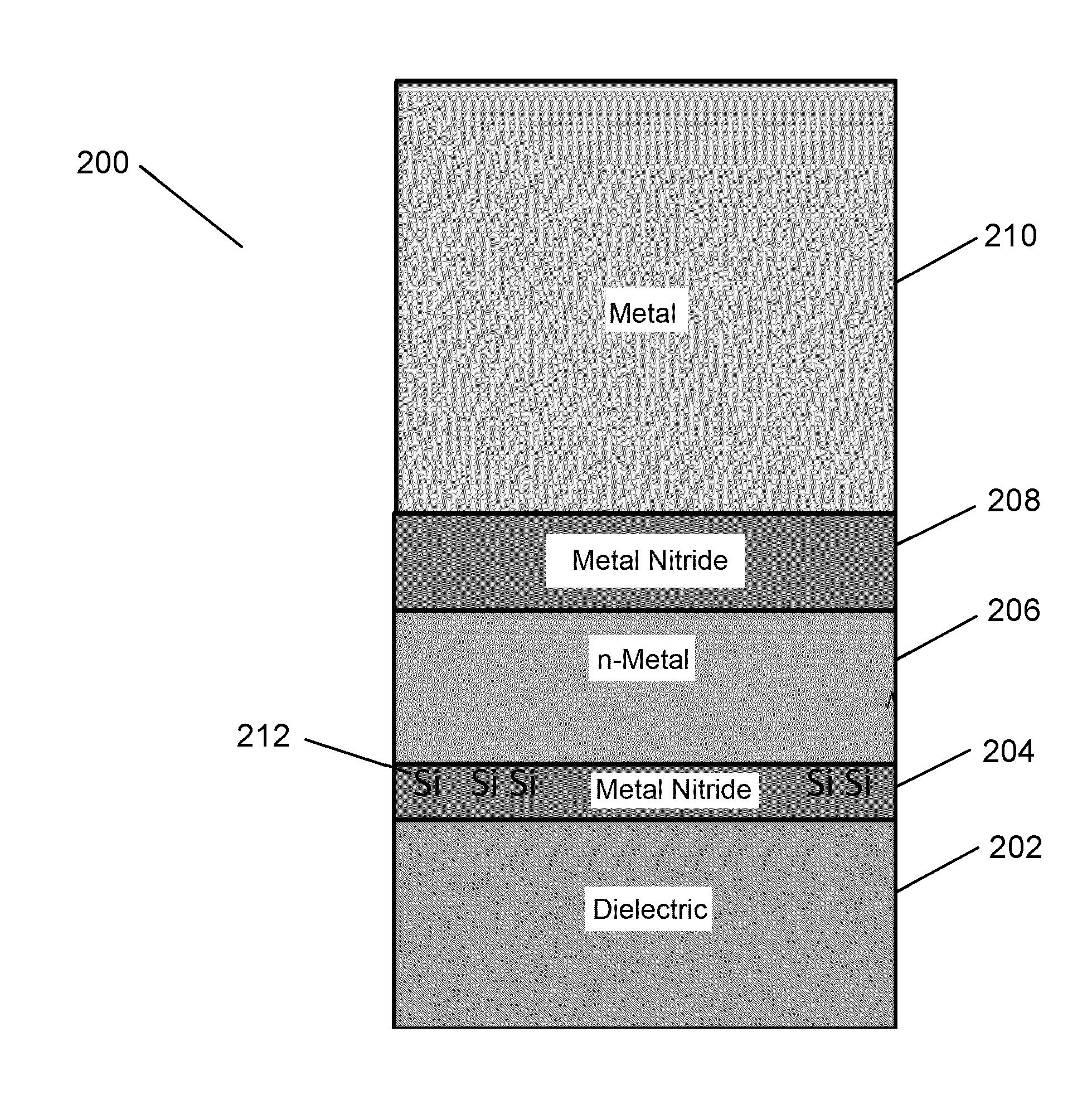

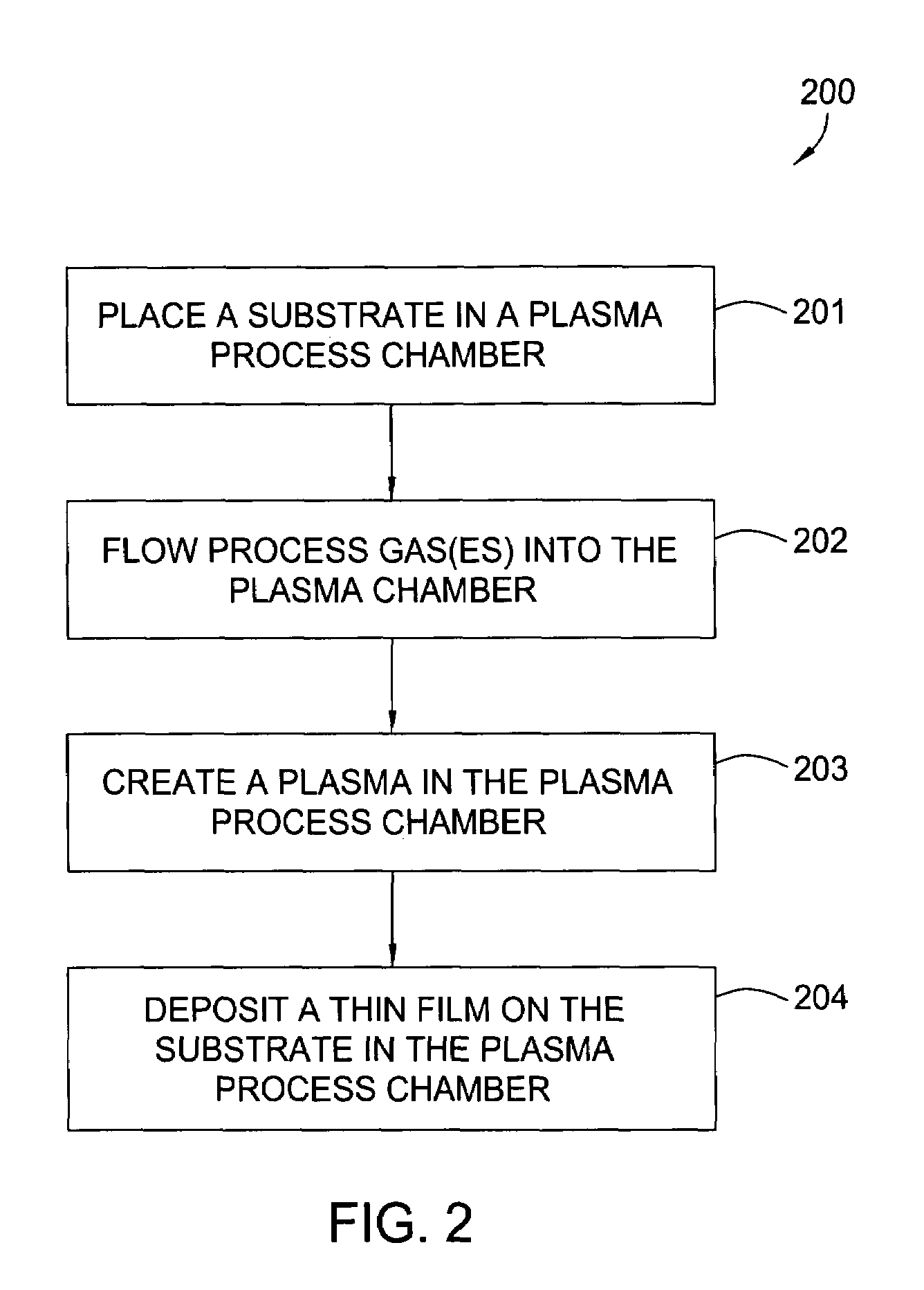

Metallic-compound films are formed by plasma-enhanced atomic layer deposition (PEALD). According to preferred methods, film or thin film composition is controlled by selecting plasma parameters to tune the oxidation state of a metal (or plurality of metals) in the film. In some embodiments, plasma parameters are selected to achieve metal-rich metallic-compound films. The metallic-compound films can be components of gate stacks, such as gate electrodes. Plasma parameters can be selected to achieve a gate stack with a predetermined work function.

Owner:ASM IP HLDG BV

Semiconductor device and method for manufacturing the same

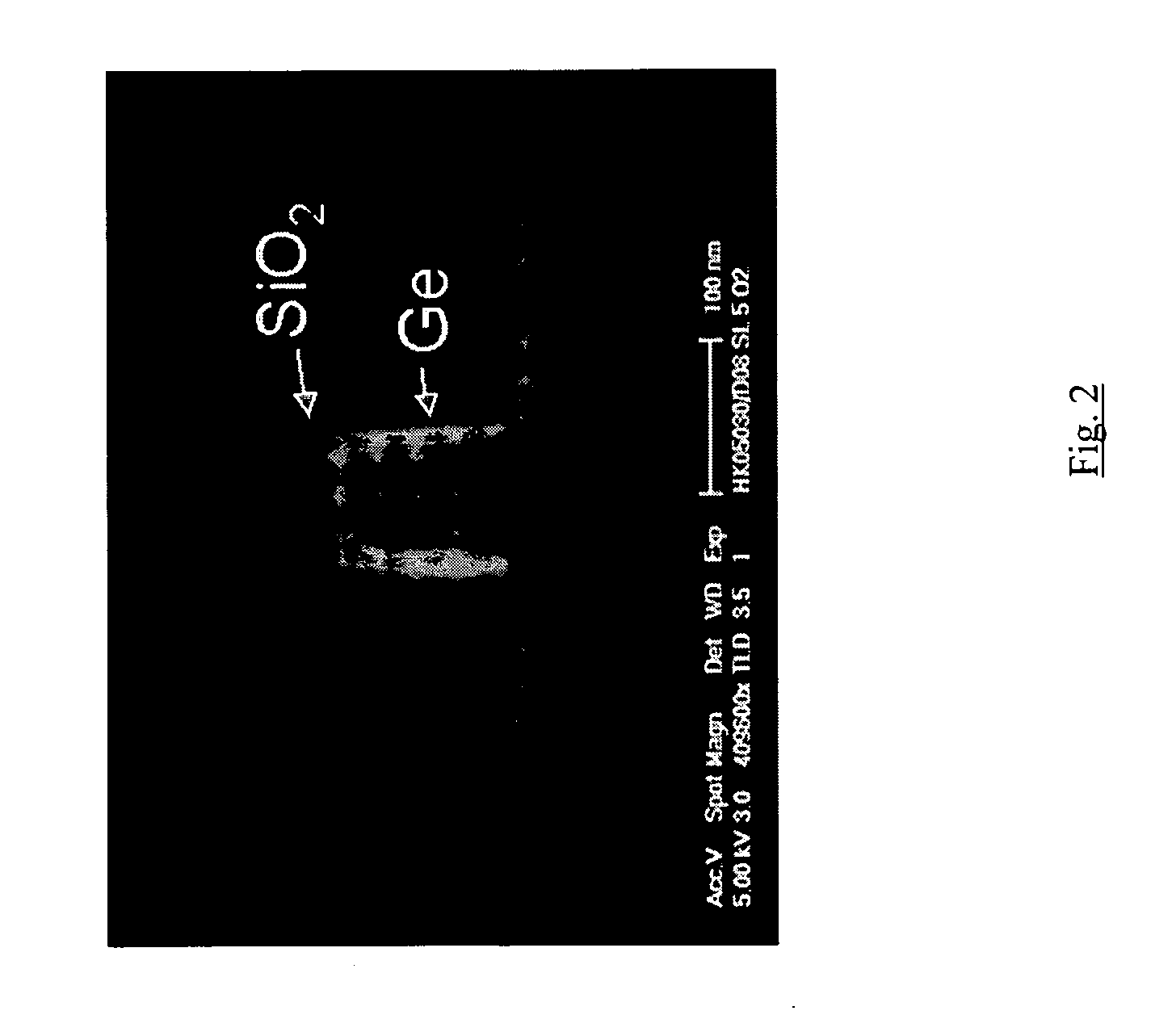

ActiveUS20140048765A1Increase currentReduce power consumptionSemiconductor/solid-state device manufacturingDiodeAlloyGate stack

The present invention discloses a semiconductor device, comprising: a substrate, a gate stack structure on the substrate, source and drain regions in the substrate on both sides of the gate stack structure, and a channel region between the source and drain regions in the substrate, characterized in that the source region in the source and drain regions comprises GeSn alloy, and a tunnel dielectric layer is optionally comprised between the GeSn alloy of the source region and the channel region. In accordance with the semiconductor device and method for manufacturing the same of the present invention, GeSn alloy having a narrow band gap is formed by implanting precursors and performing a laser rapid annealing, the on-state current of TFET is effectively enhanced, accordingly it has an important application prospect in a high performance low power consumption application.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

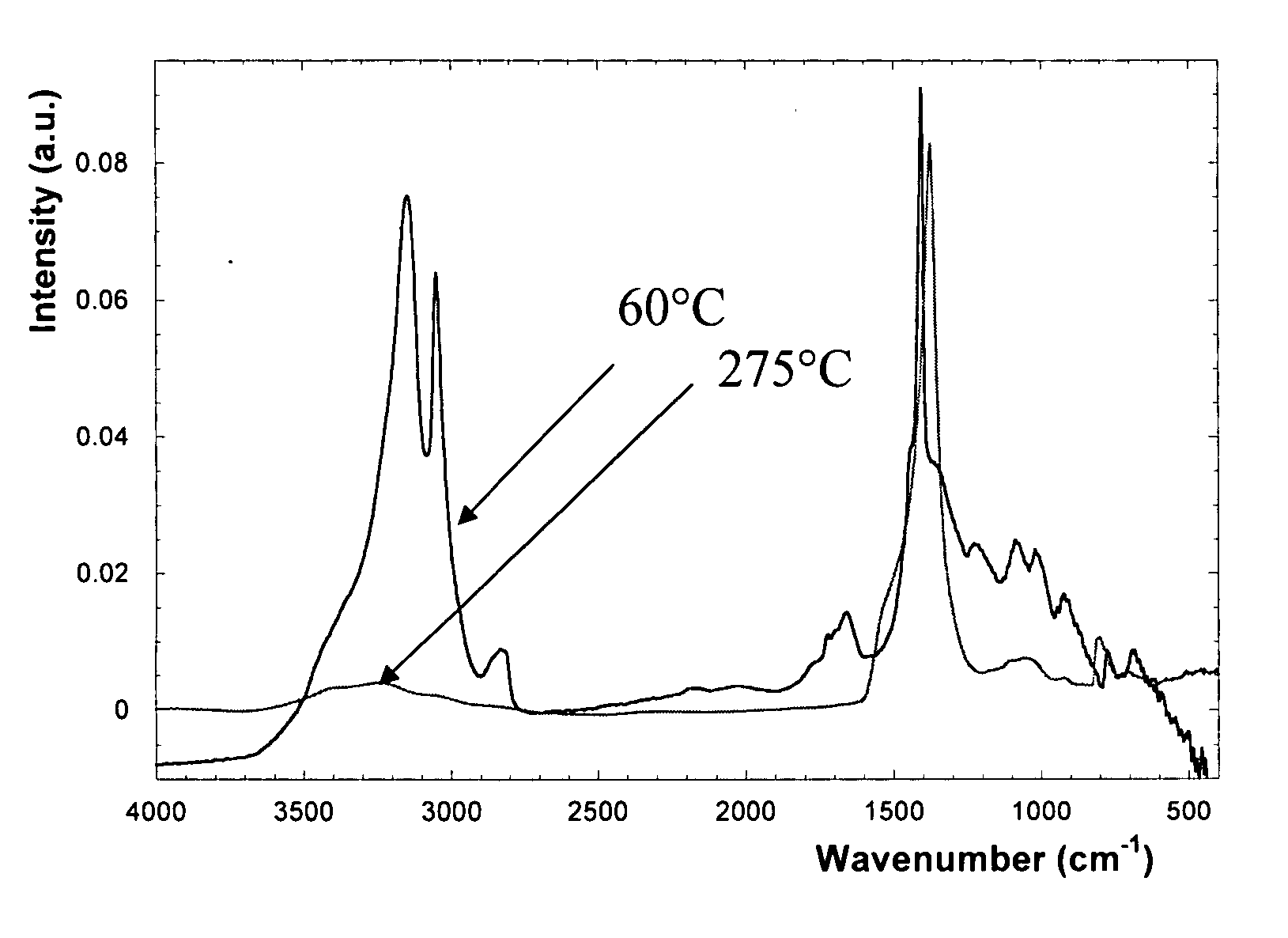

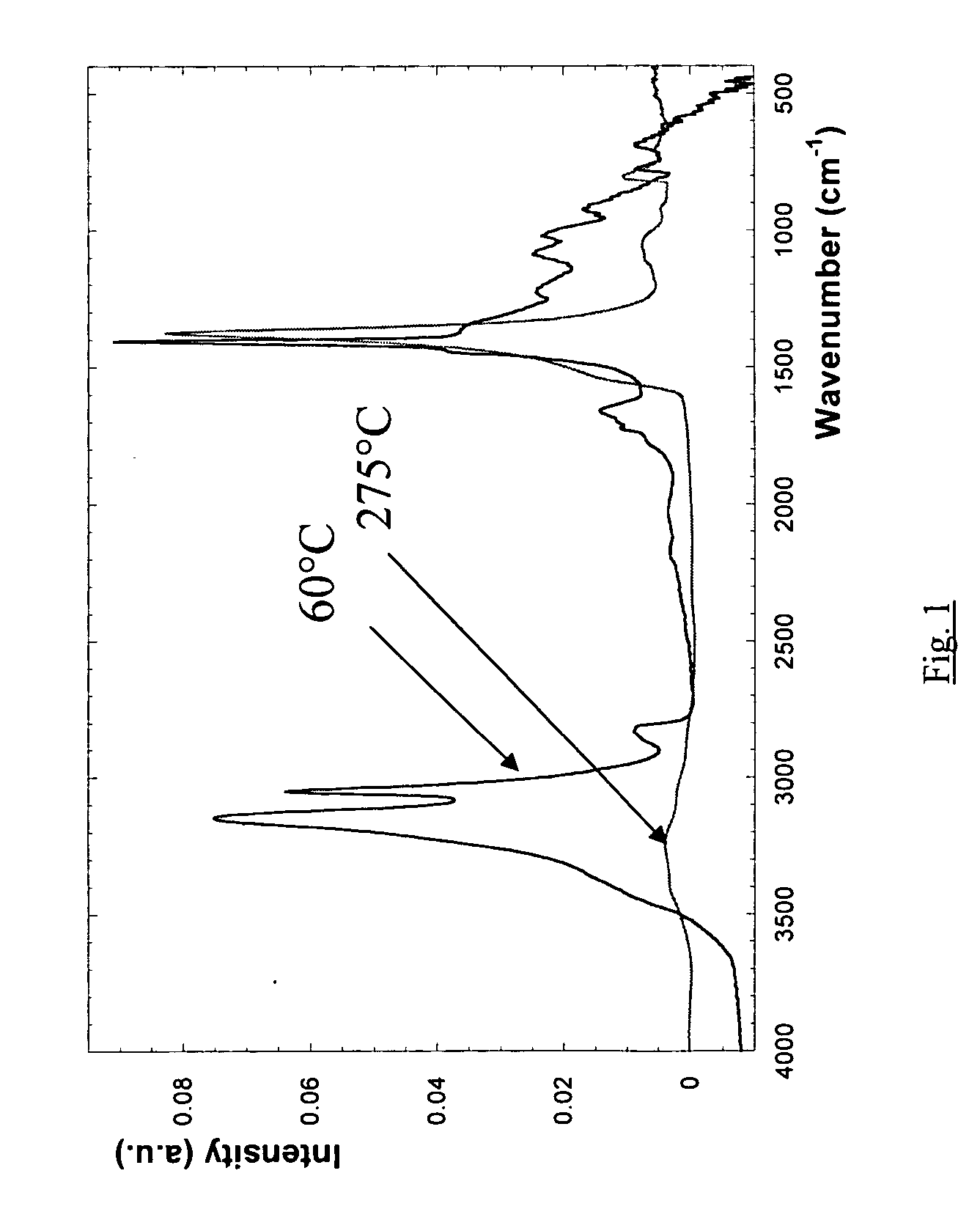

Silane or borane treatment of metal thin films

ActiveUS20140273428A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingSilanesGate stack

The negative effect of oxygen on some metal films can be reduced or prevented by contacting the films with a treatment agent comprising silane or borane. In some embodiments, one or more films in an NMOS gate stack are contacted with a treatment agent comprising silane or borane during or after deposition.

Owner:ASM IP HLDG BV

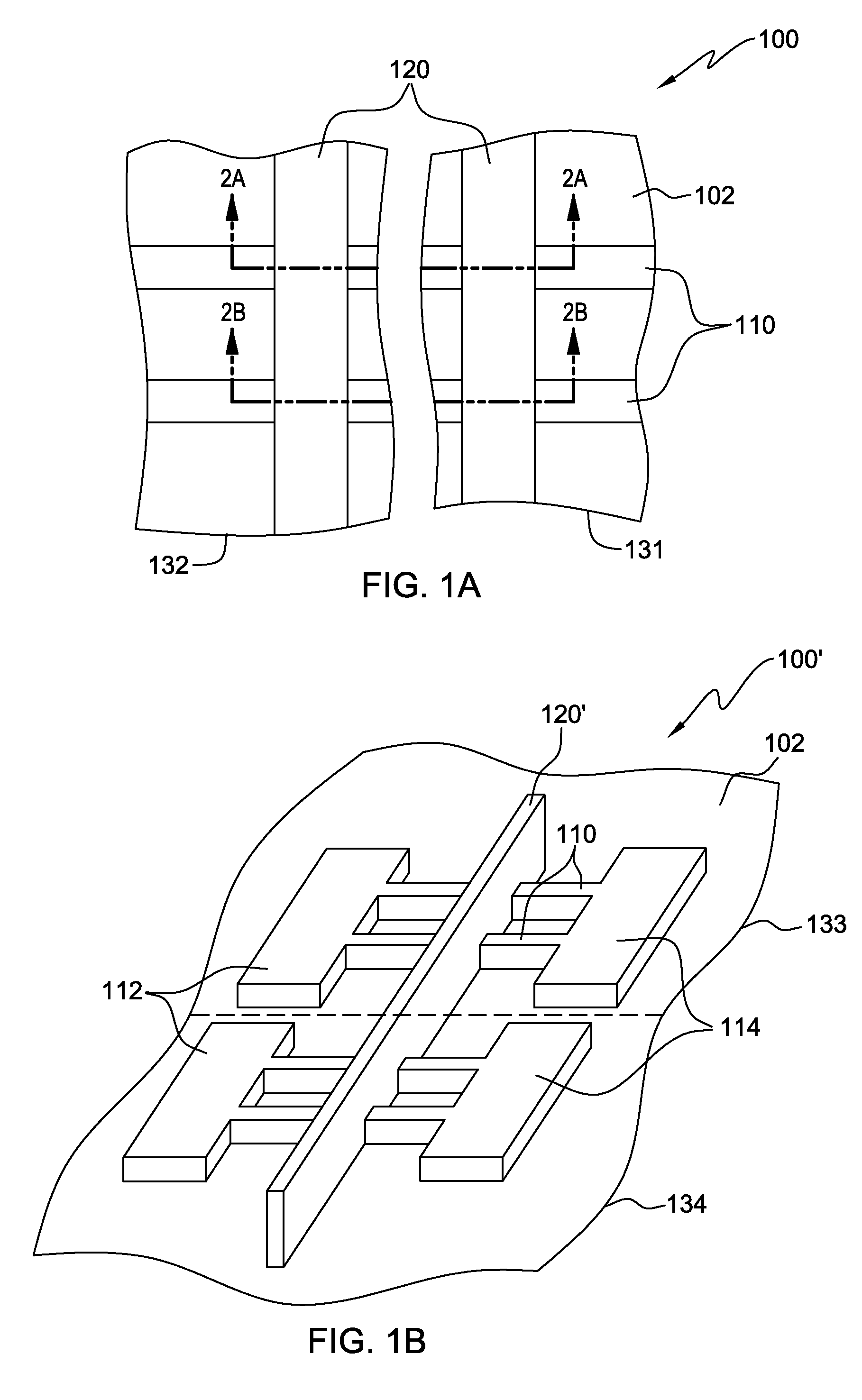

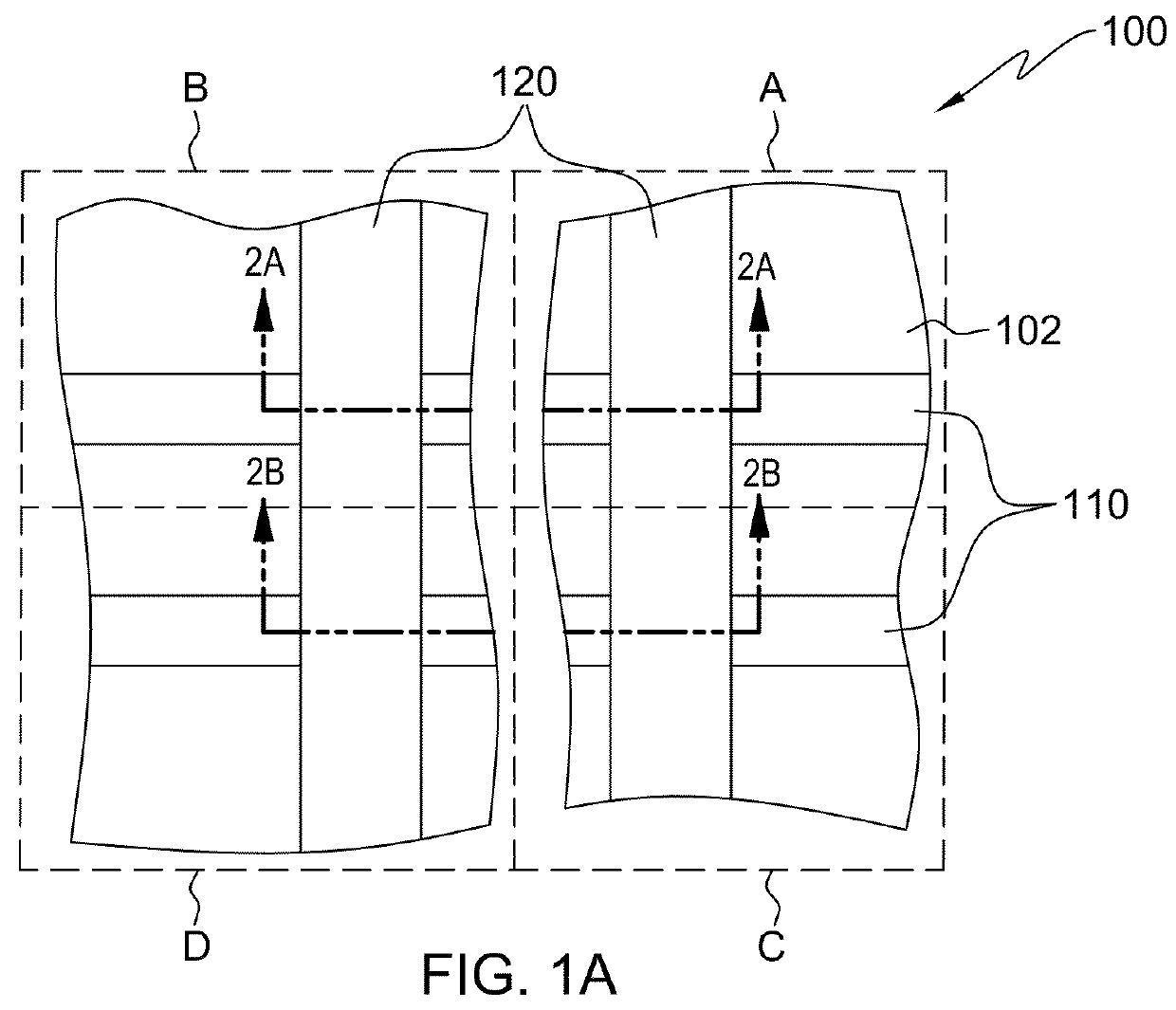

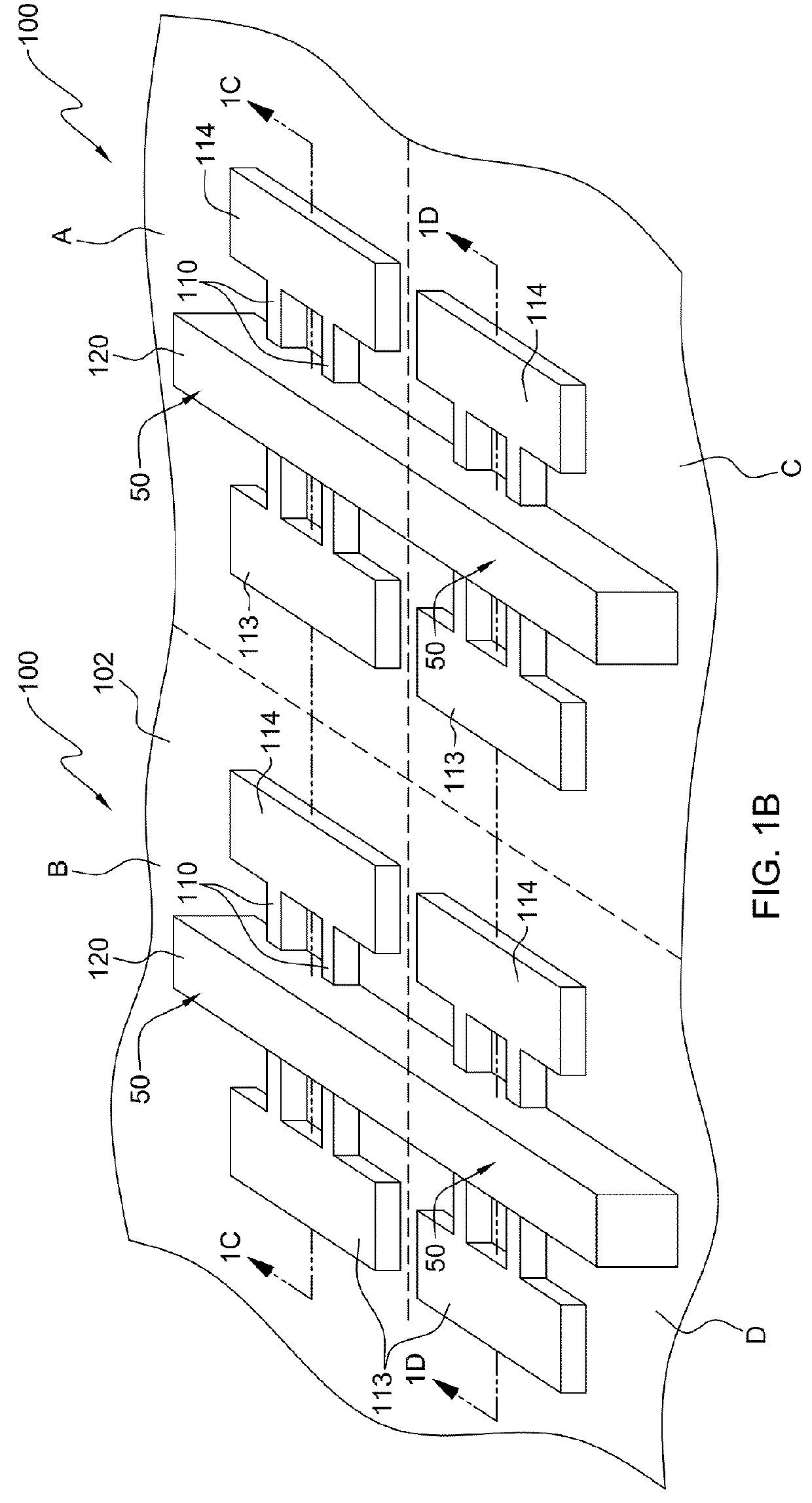

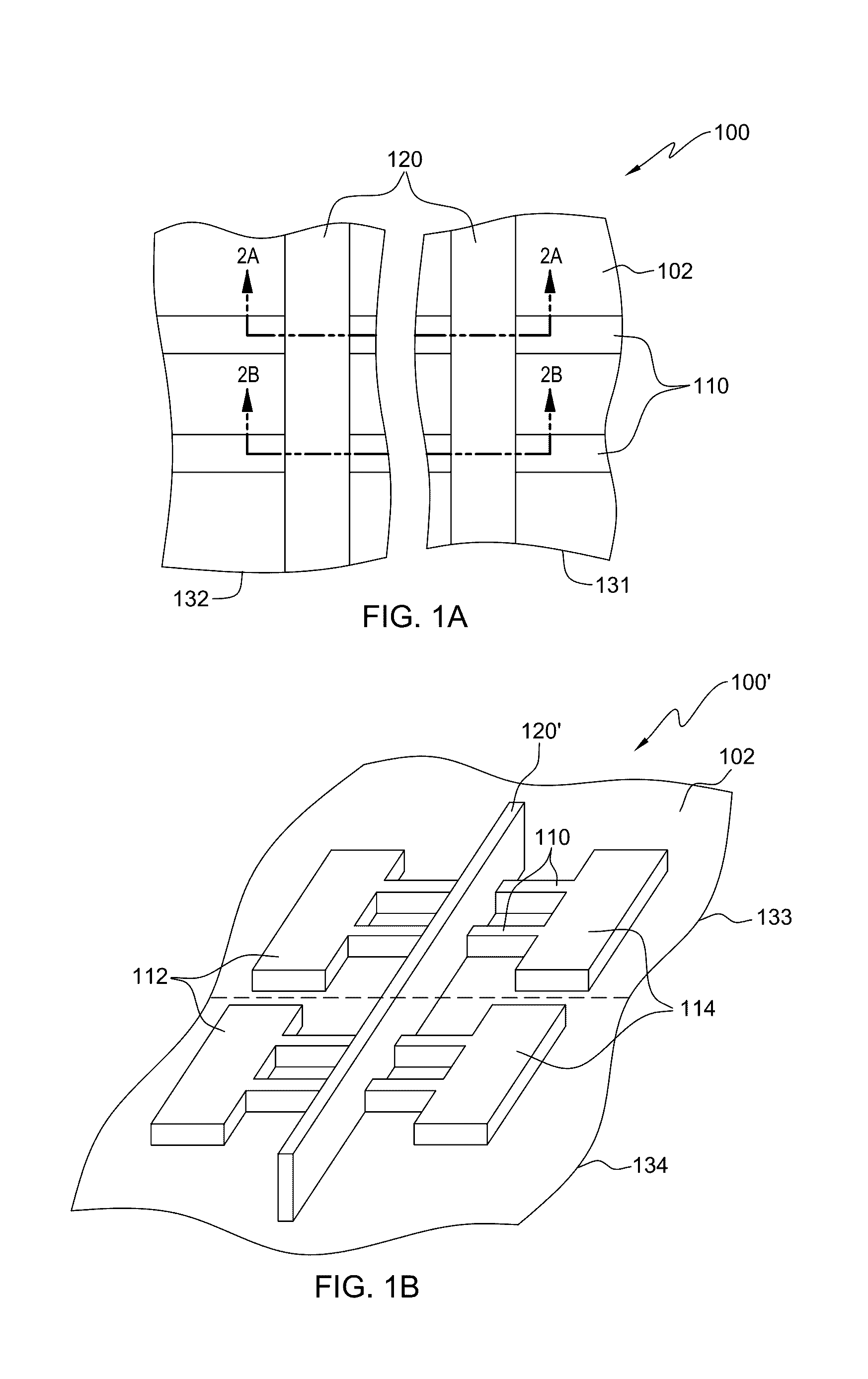

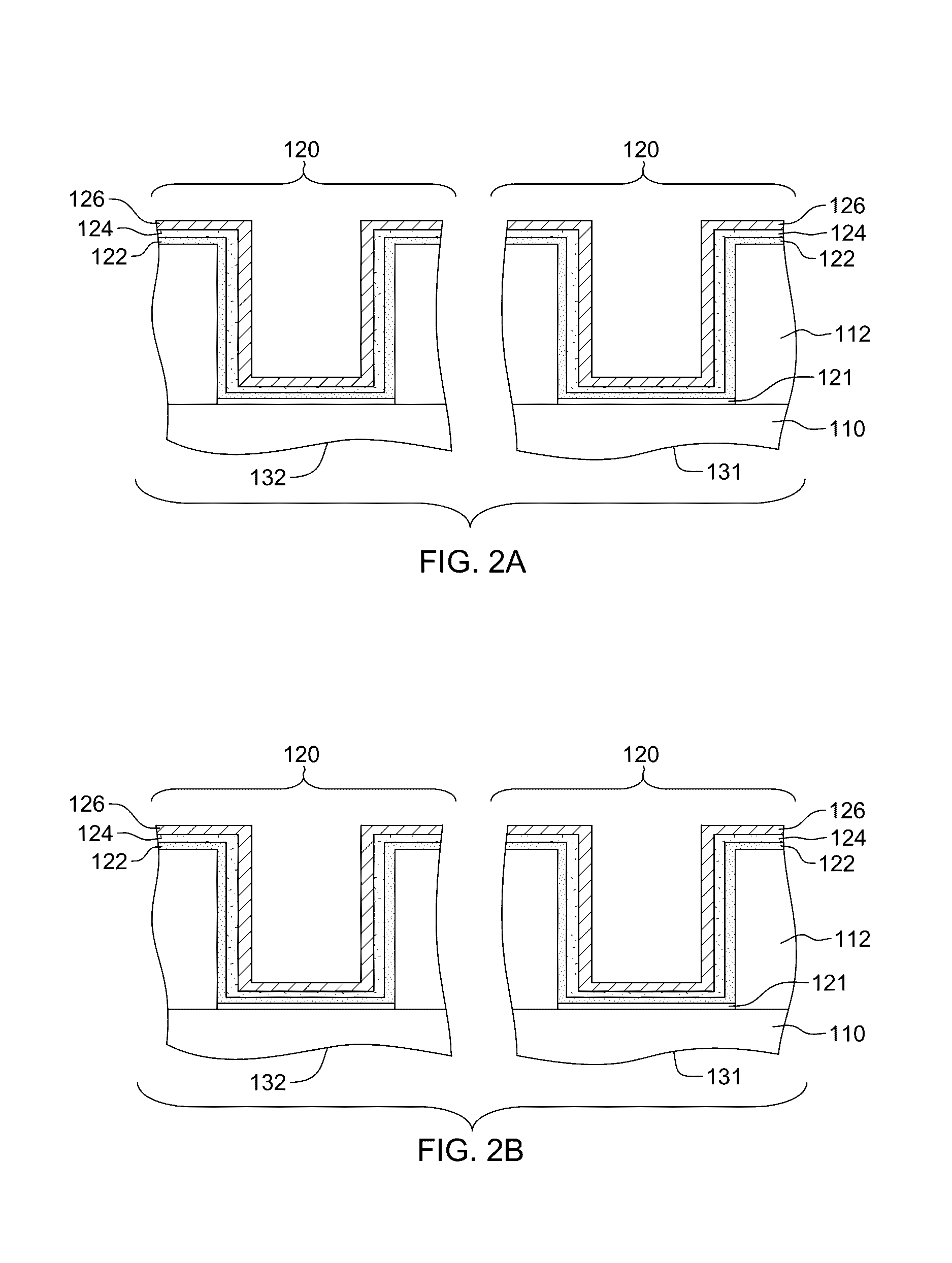

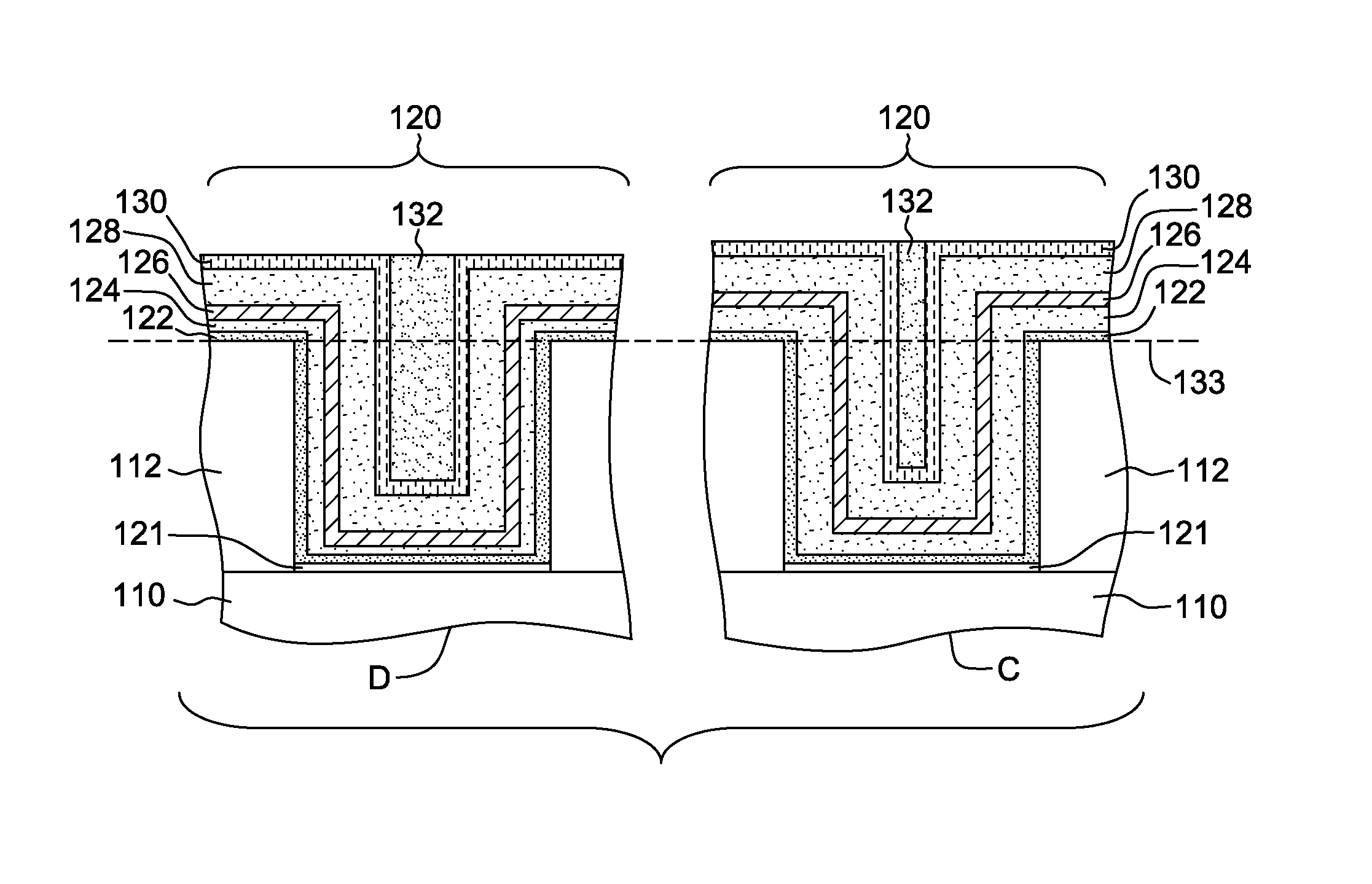

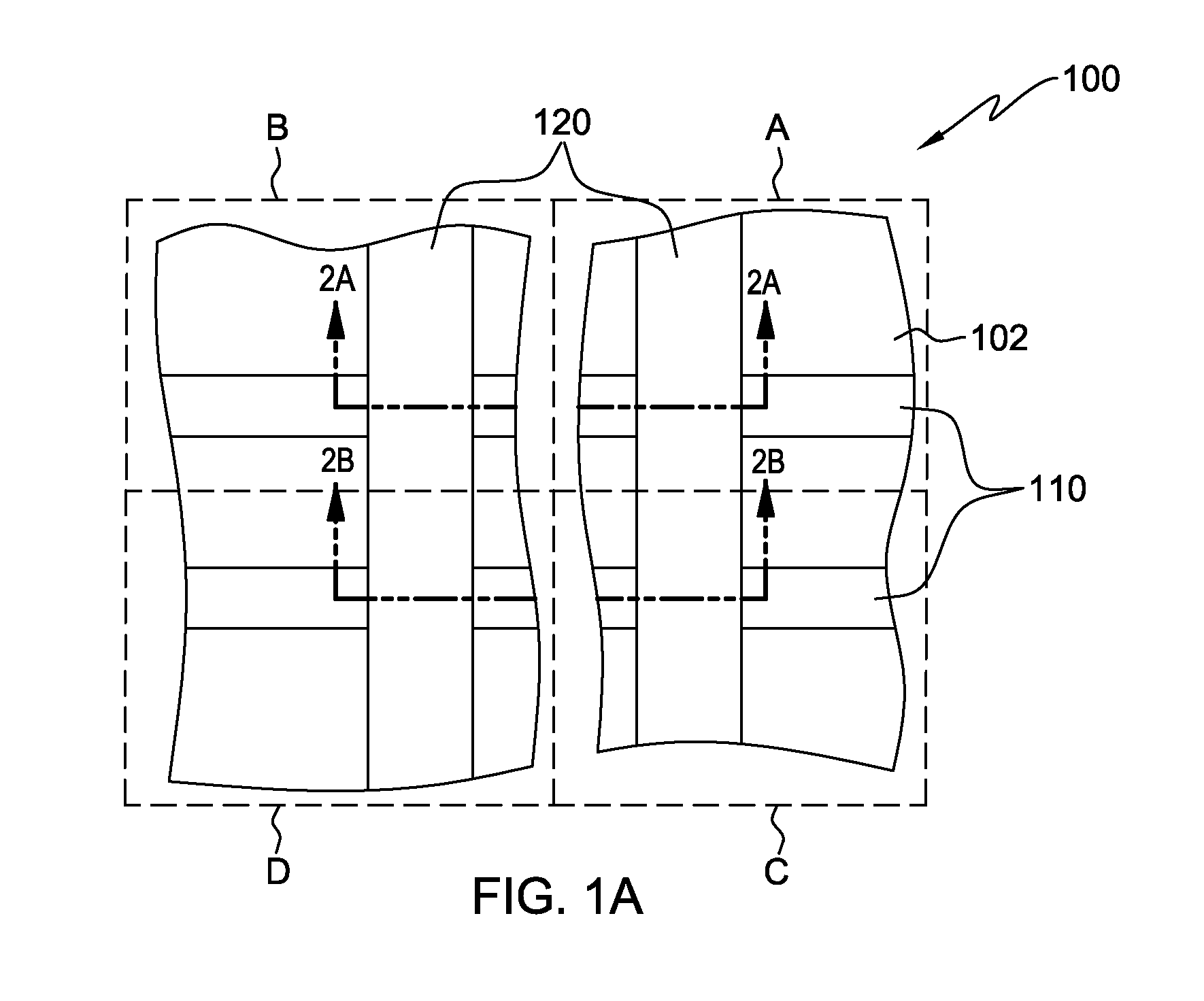

Integrated circuits with varying gate structures and fabrication methods

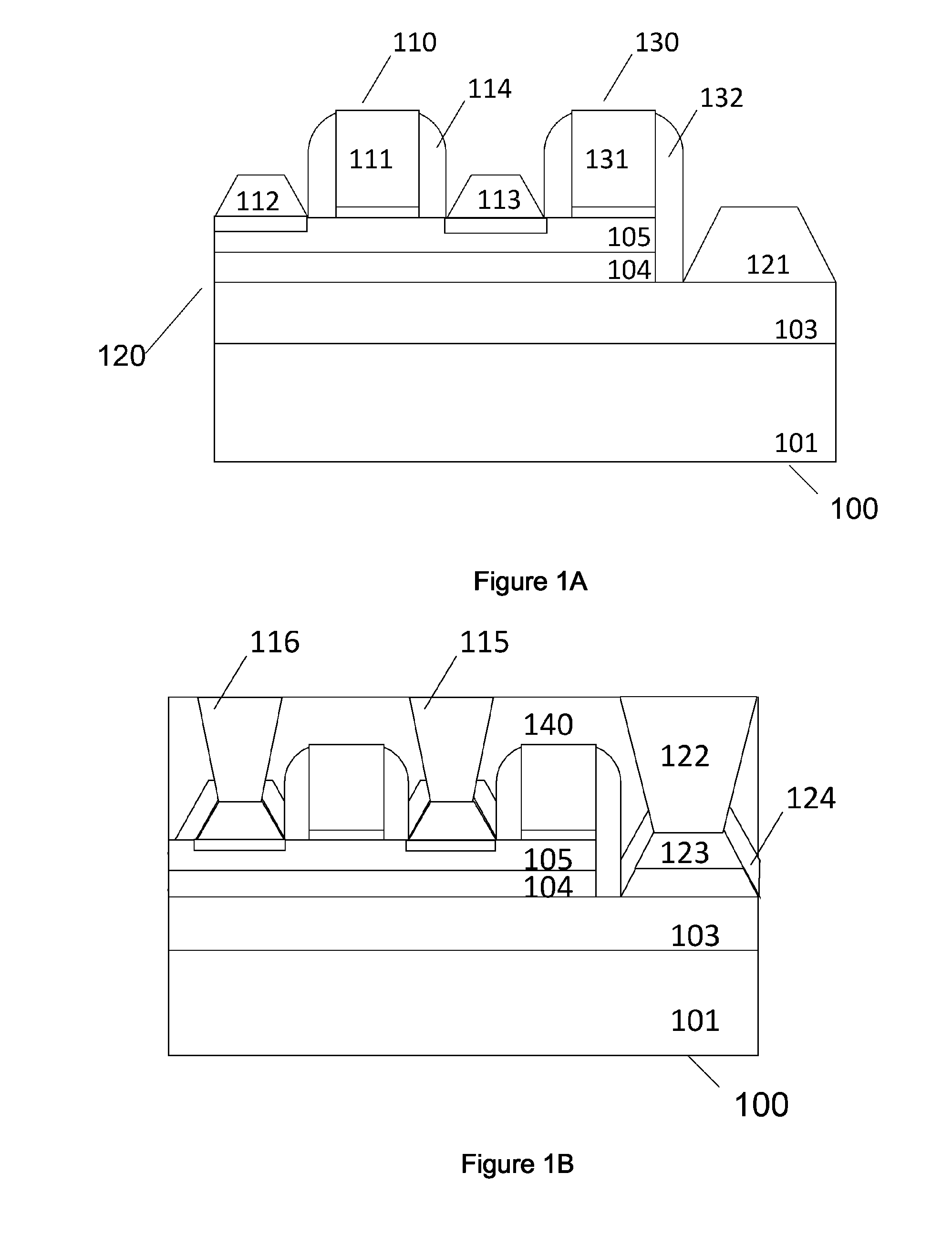

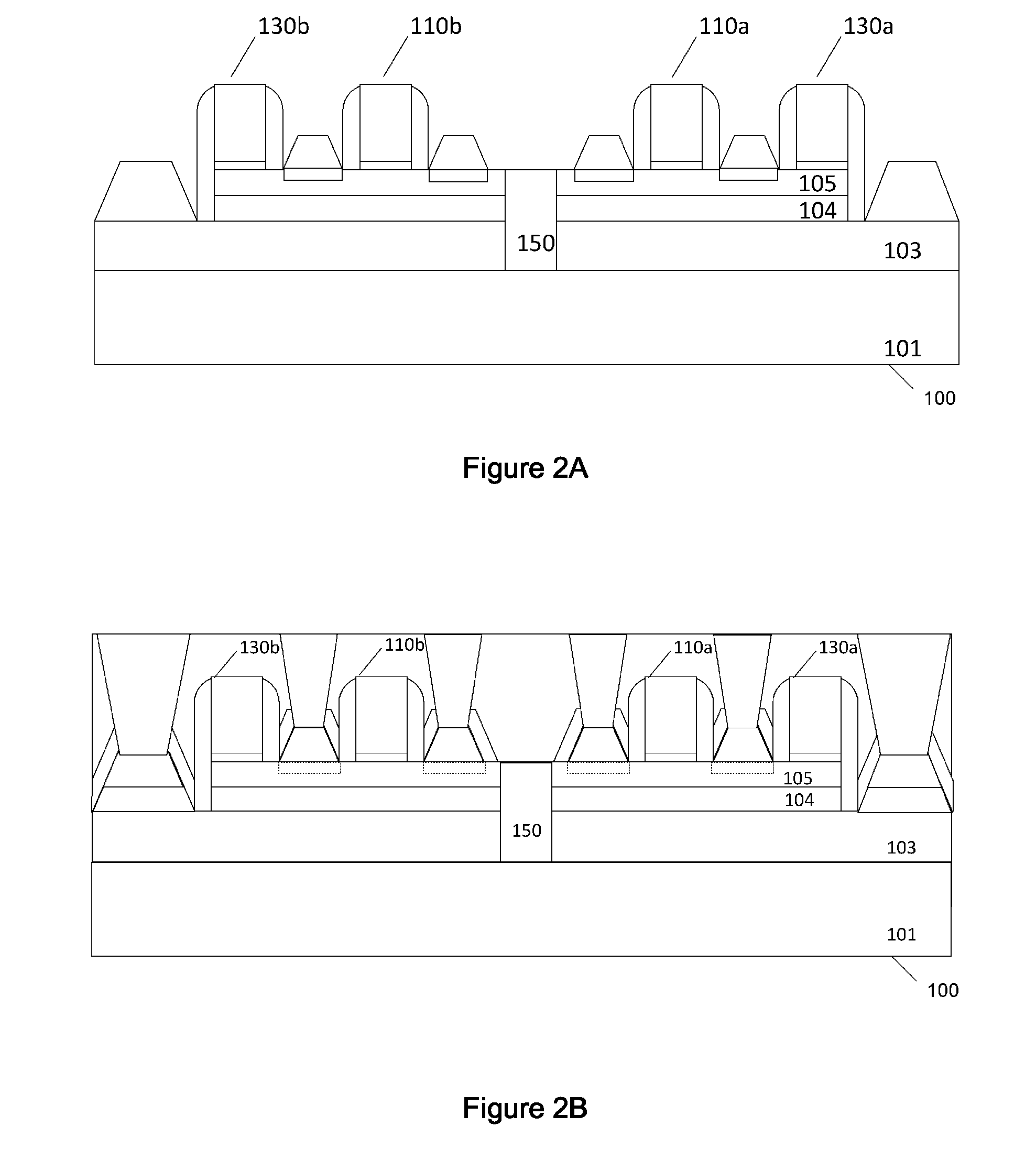

ActiveUS20150243658A1Overcomes shortcomingEnhanced advantageTransistorSolid-state devicesGate stackField-effect transistor

Integrated circuits and fabrication methods are provided. The integrated circuit includes: a varying gate structure disposed over a substrate structure, the varying gate structure including a first gate stack in a first region of the substrate structure, and a second gate stack in a second region of the substrate structure; a first field-effect transistor in the first region, the first field-effect transistor including the first gate stack and having a first threshold voltage; and a second field-effect transistor in the second region, the second field-effect transistor including the second gate stack and having a second threshold voltage, where the first threshold voltage is different from the second threshold voltage. The methods include providing the varying gate structure, the providing including: sizing layer(s) of the varying gate structure with different thickness(es) in different region(s).

Owner:GLOBALFOUNDRIES US INC

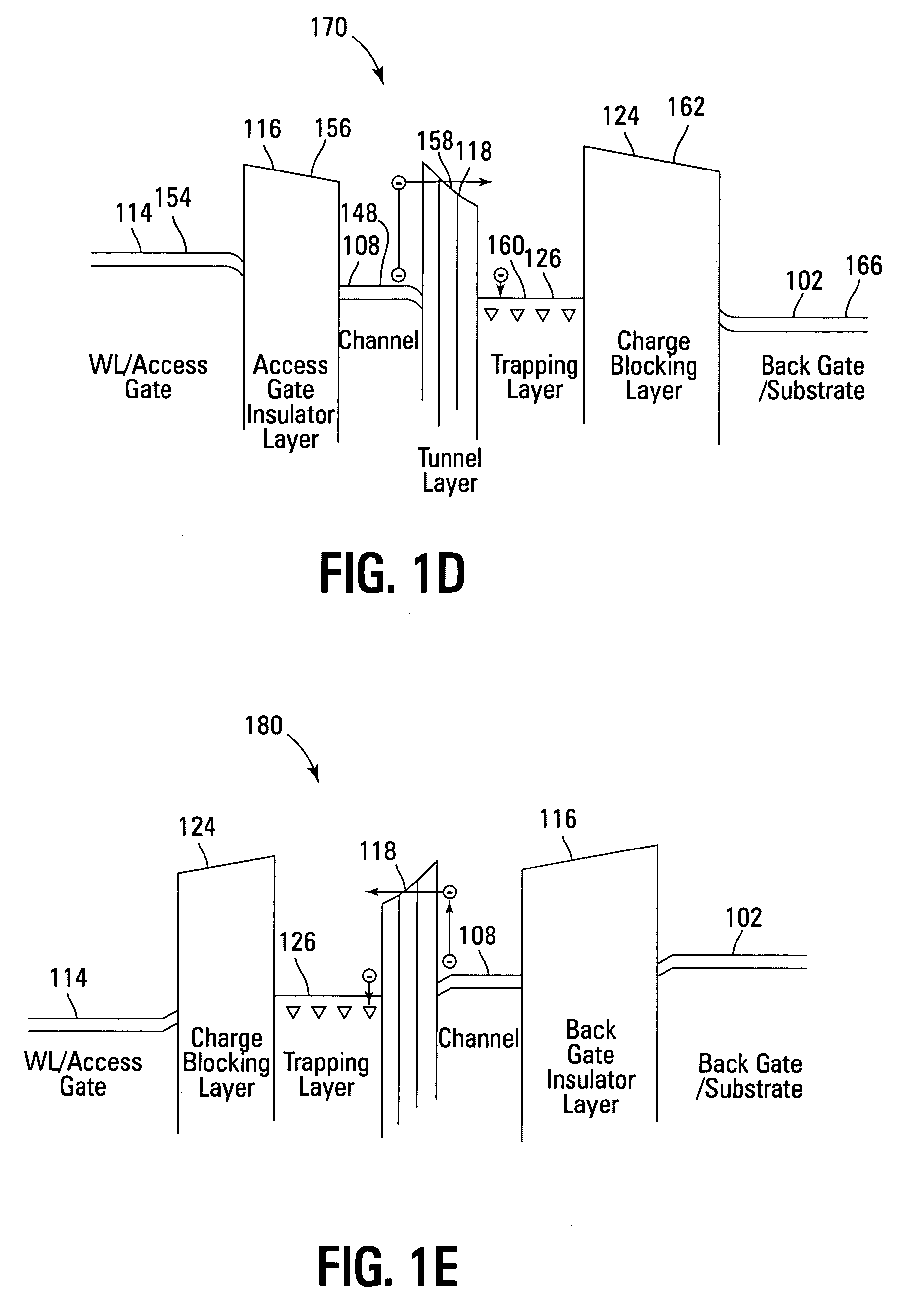

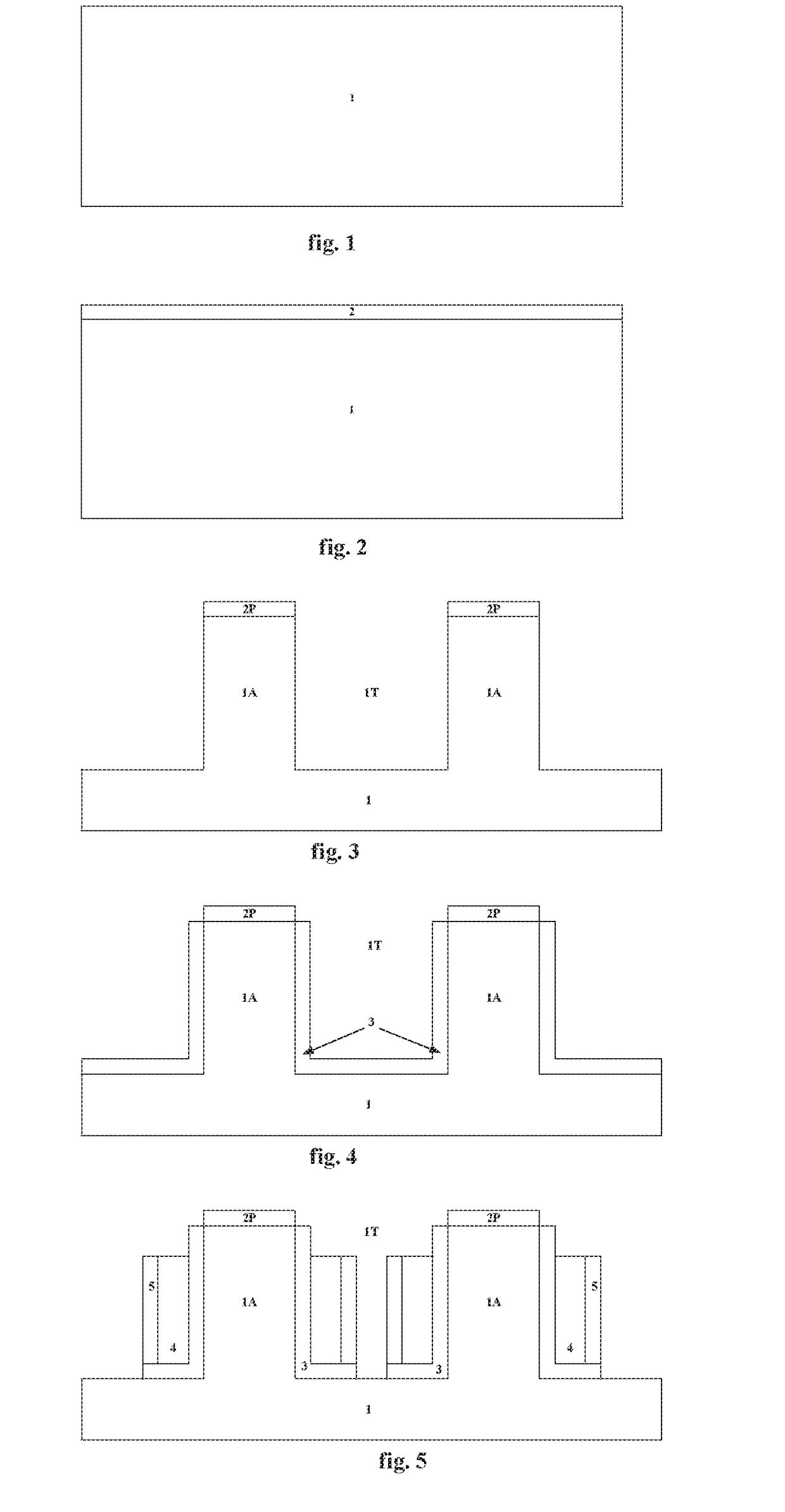

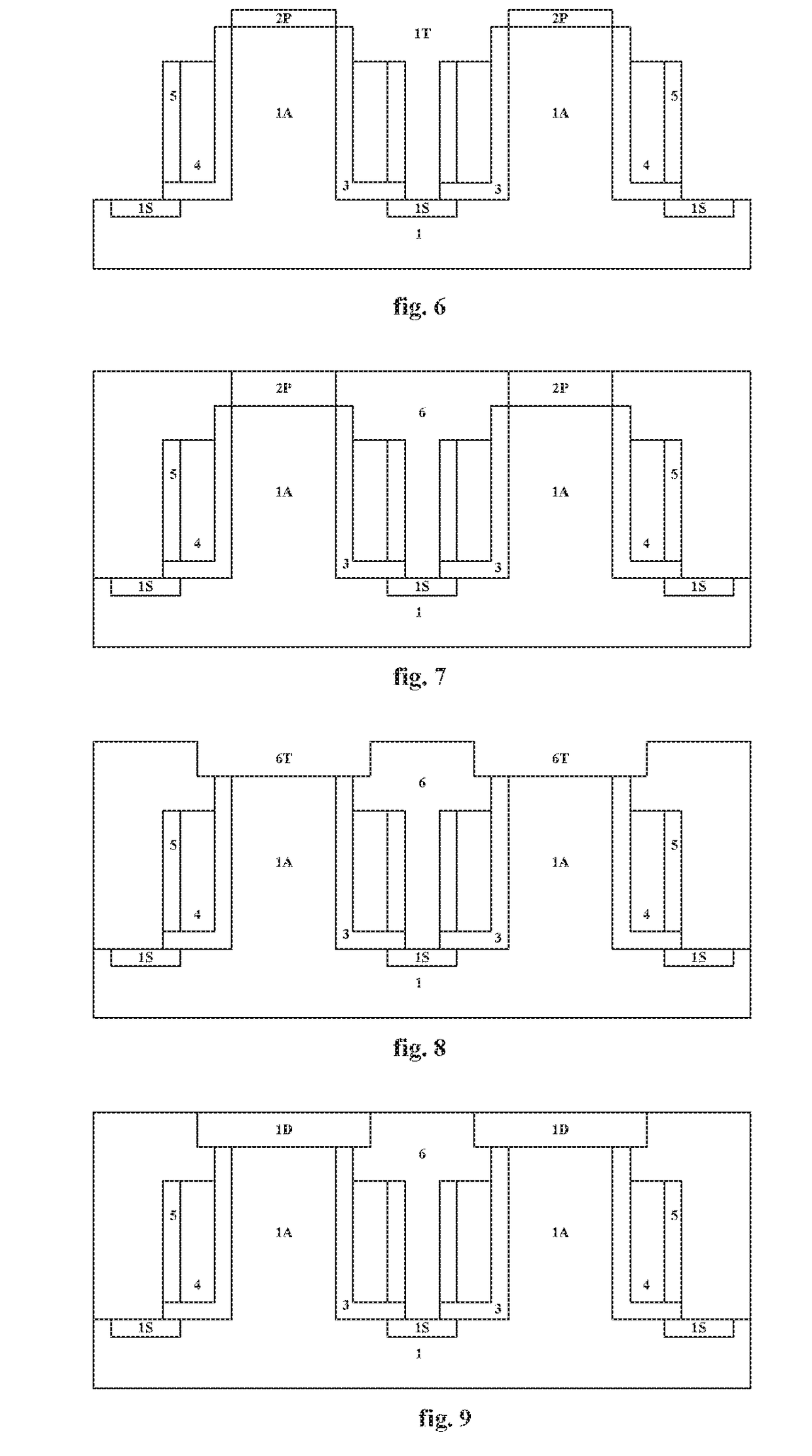

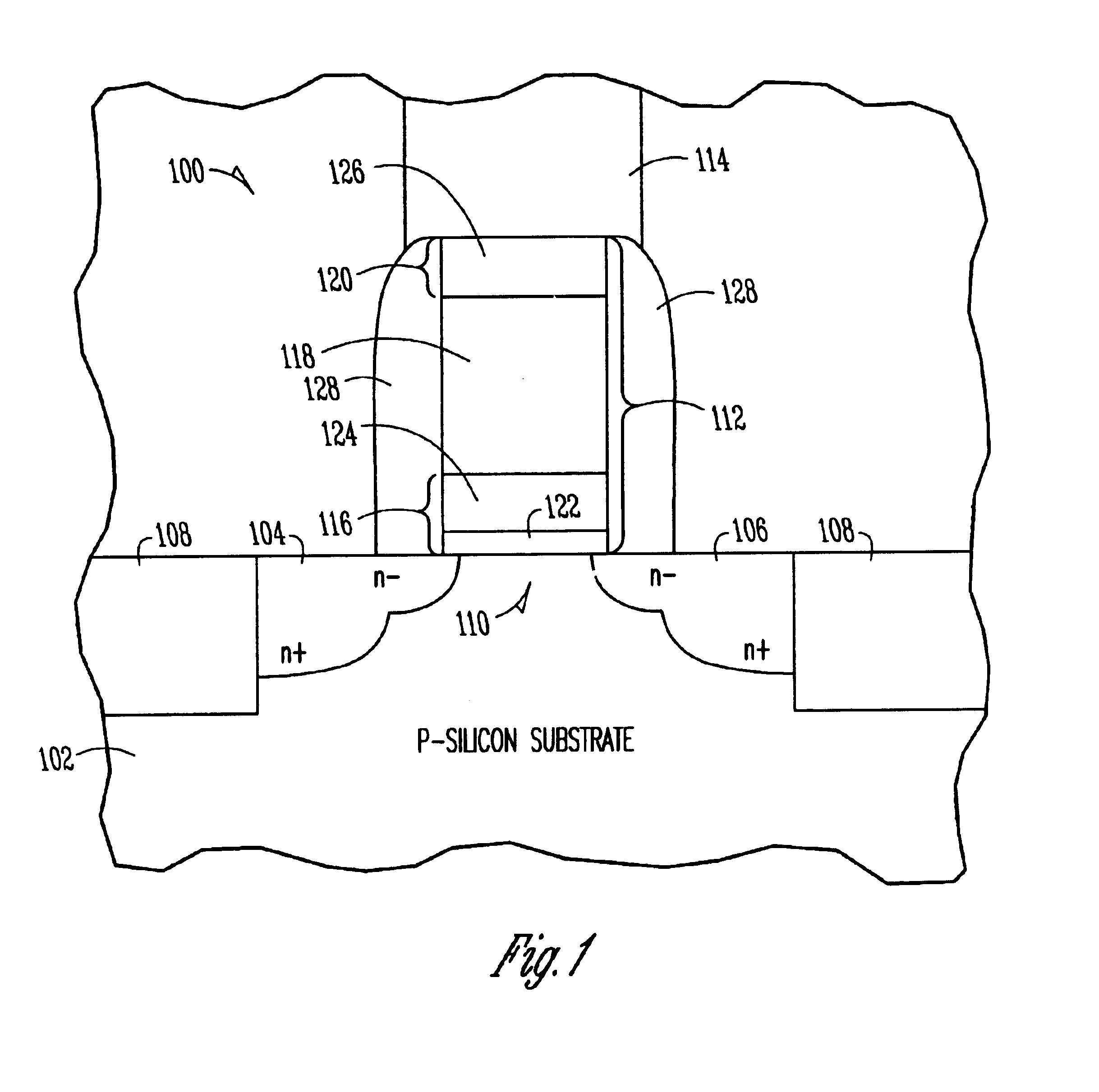

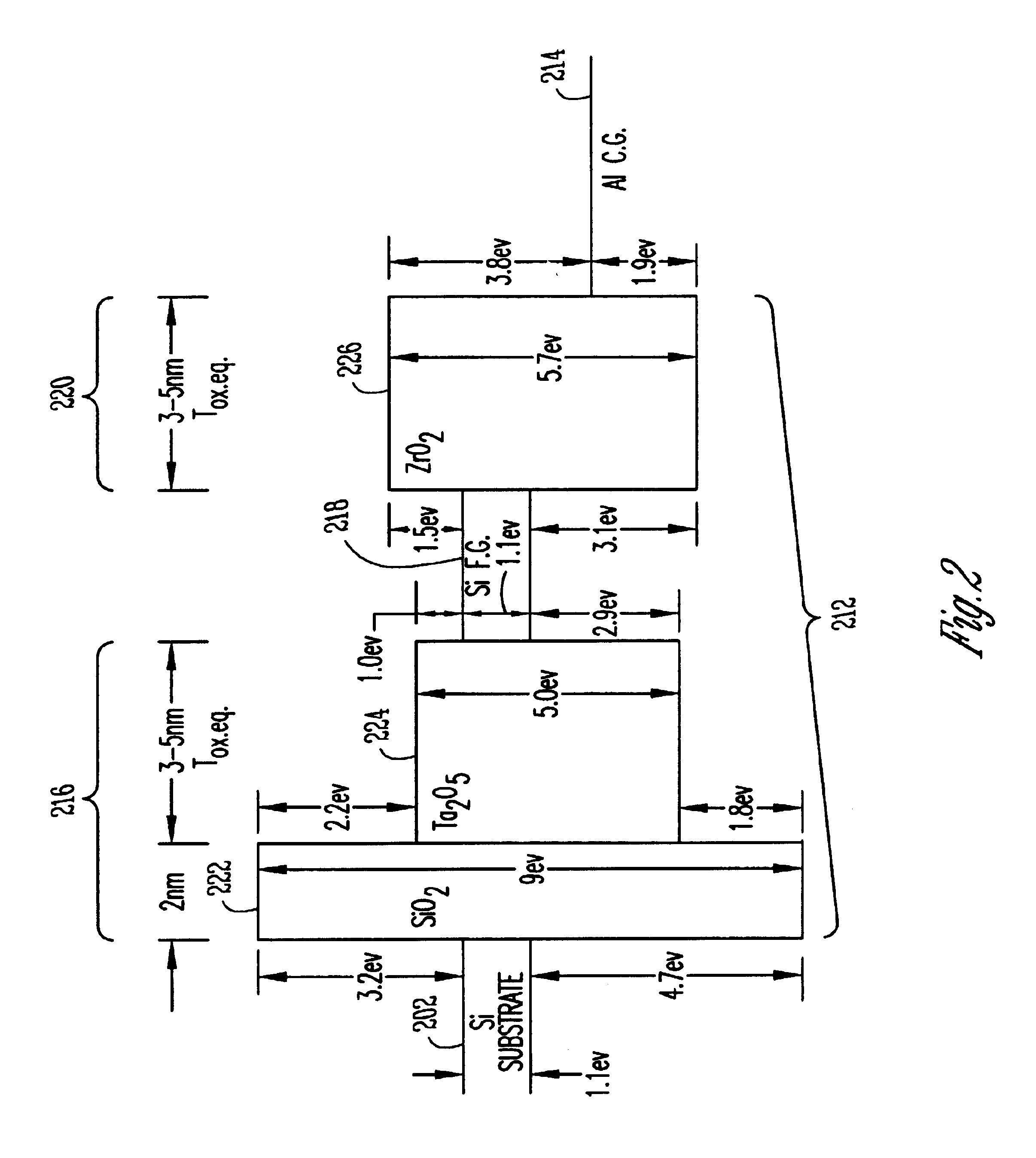

Novel low power non-volatile memory and gate stack

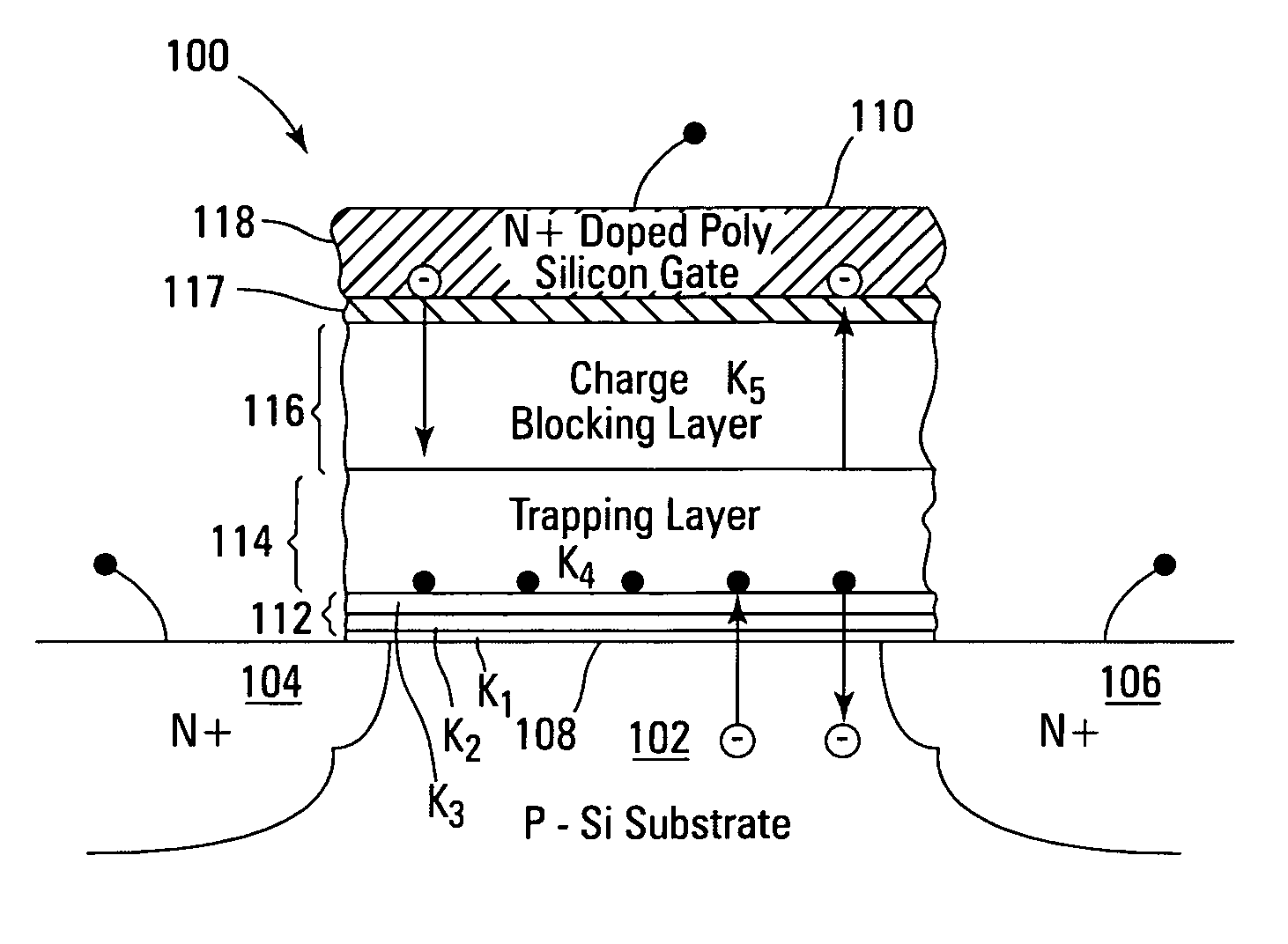

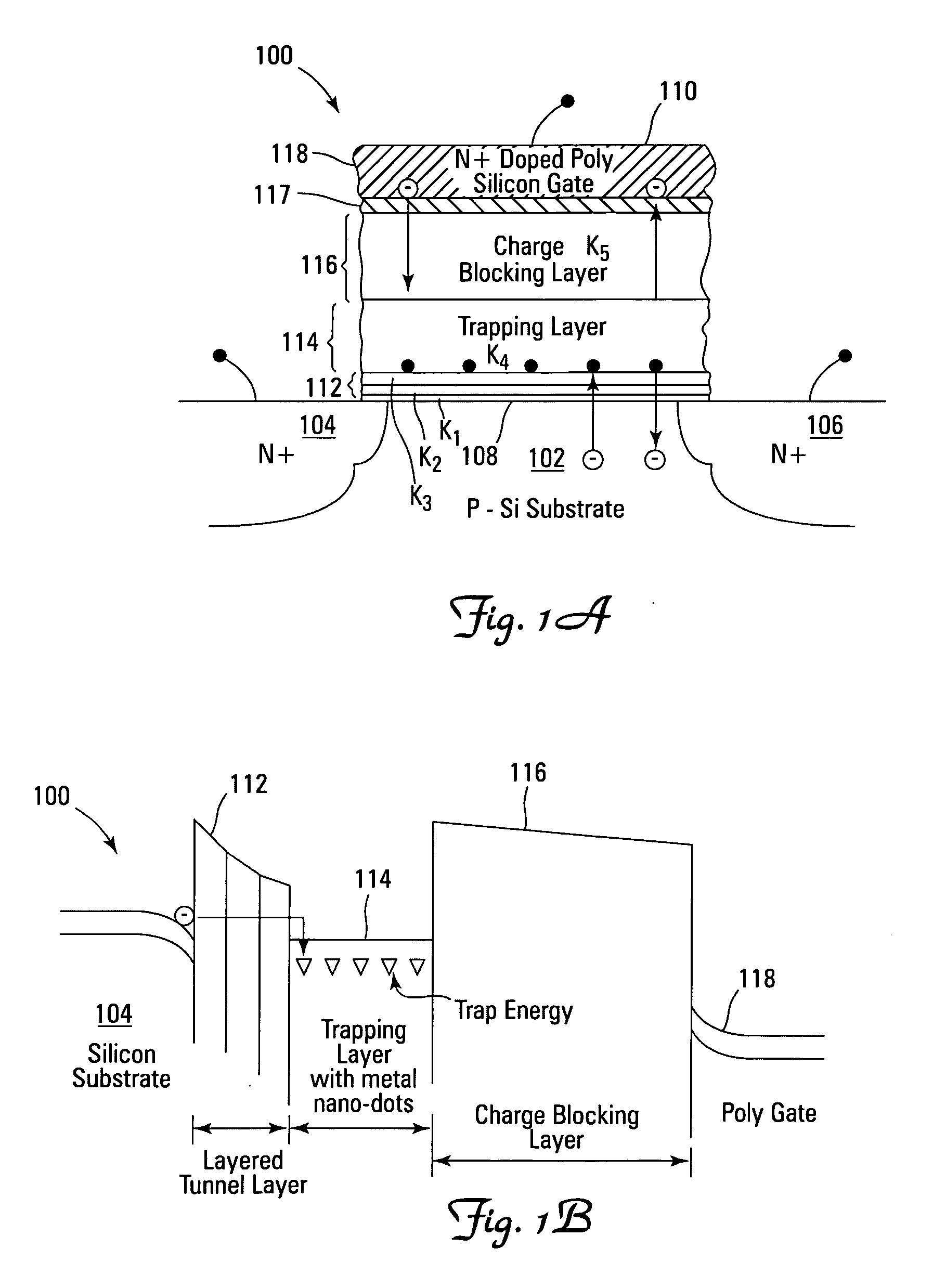

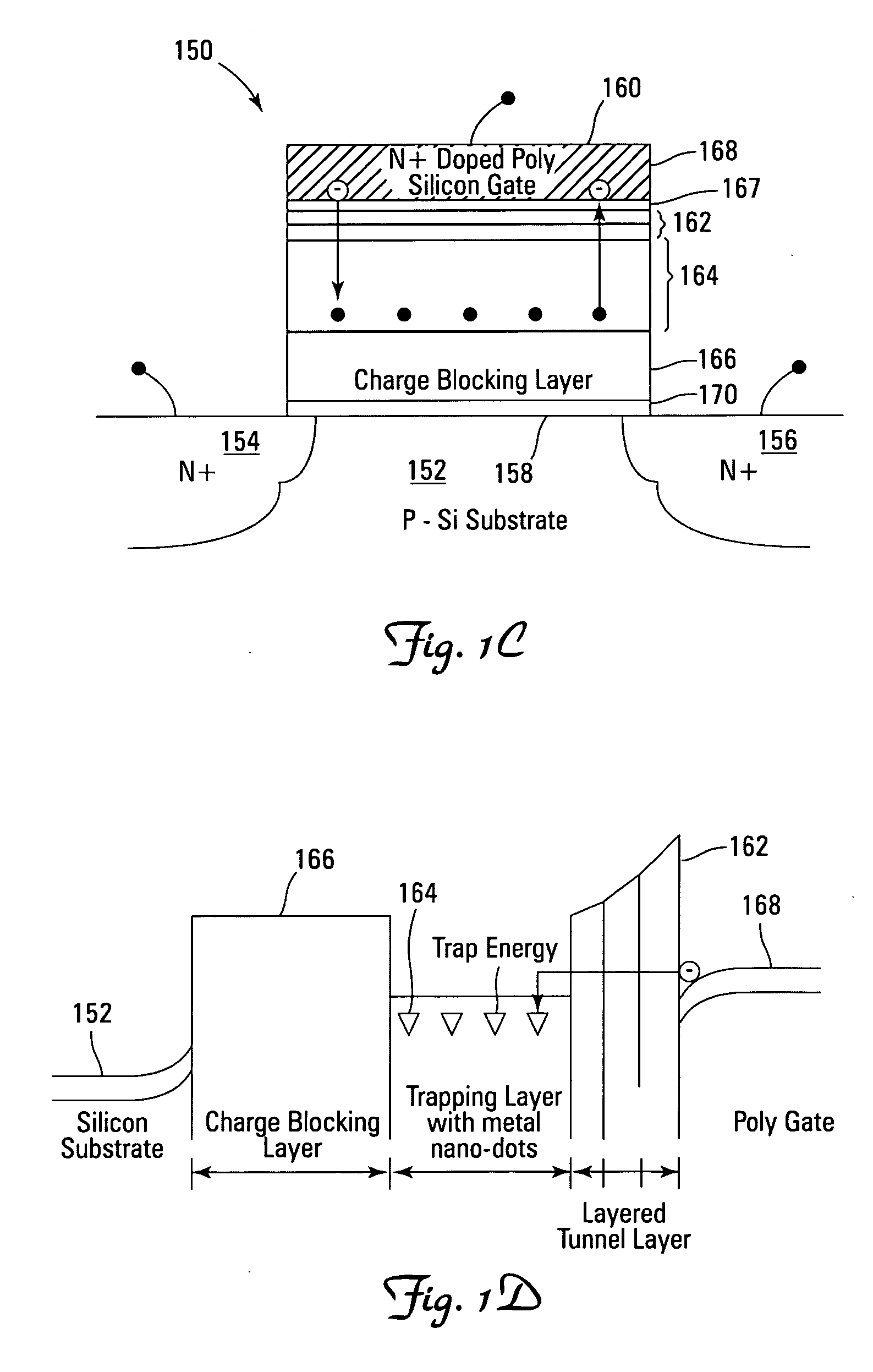

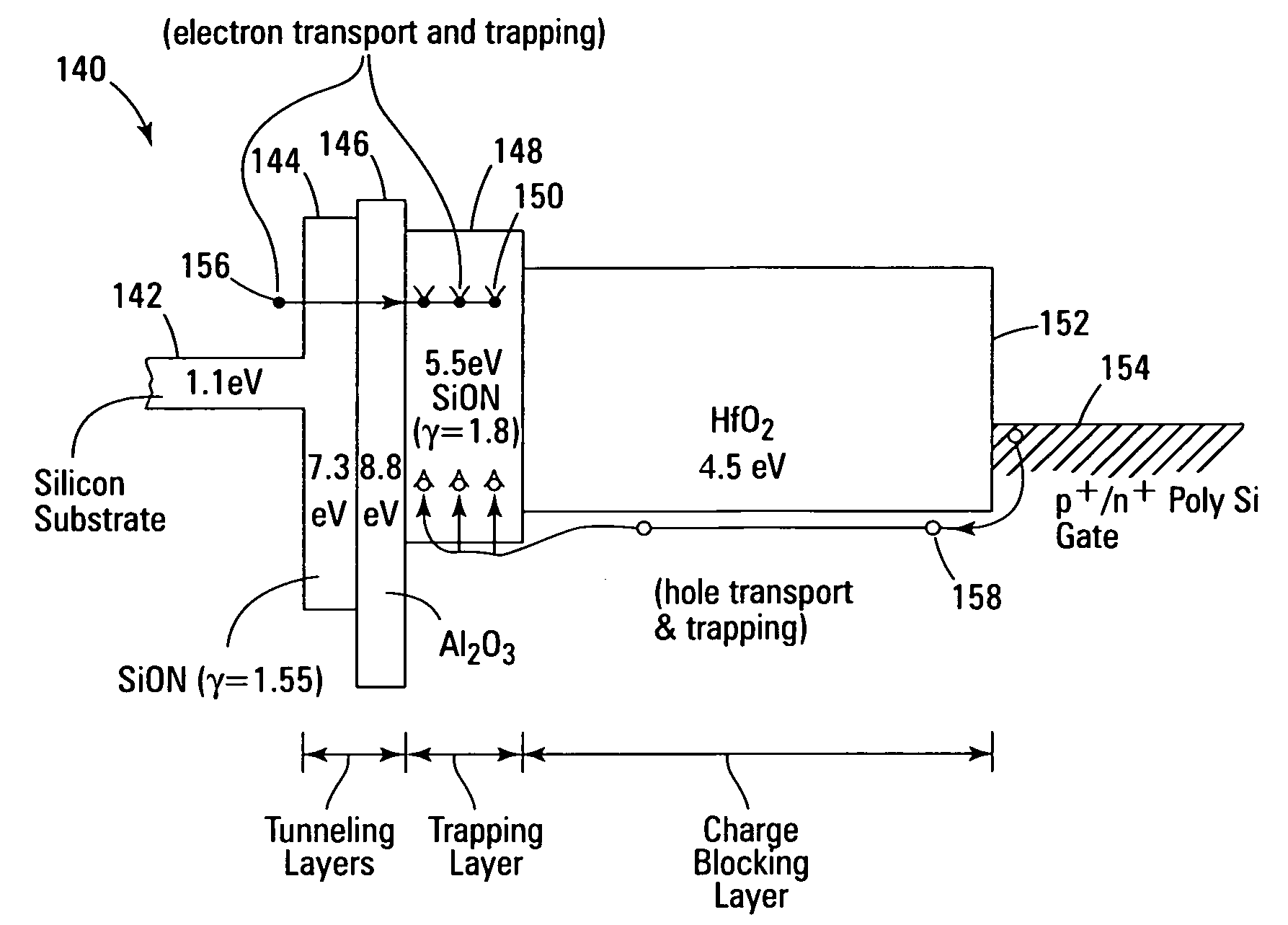

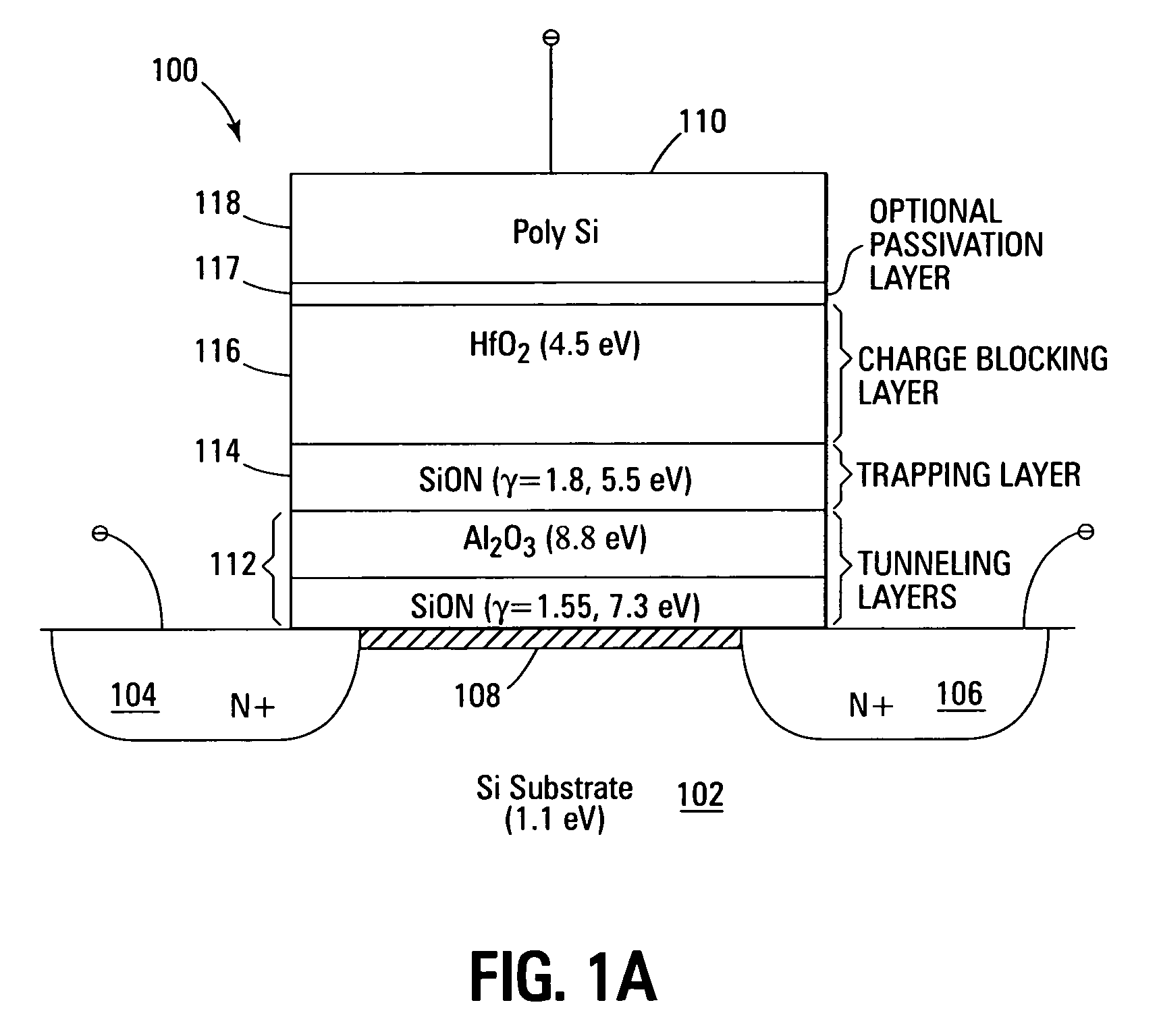

ActiveUS20060261401A1High charge blocking barrierExcellent charge retentionTransistorNanoinformaticsCharge retentionLow voltage

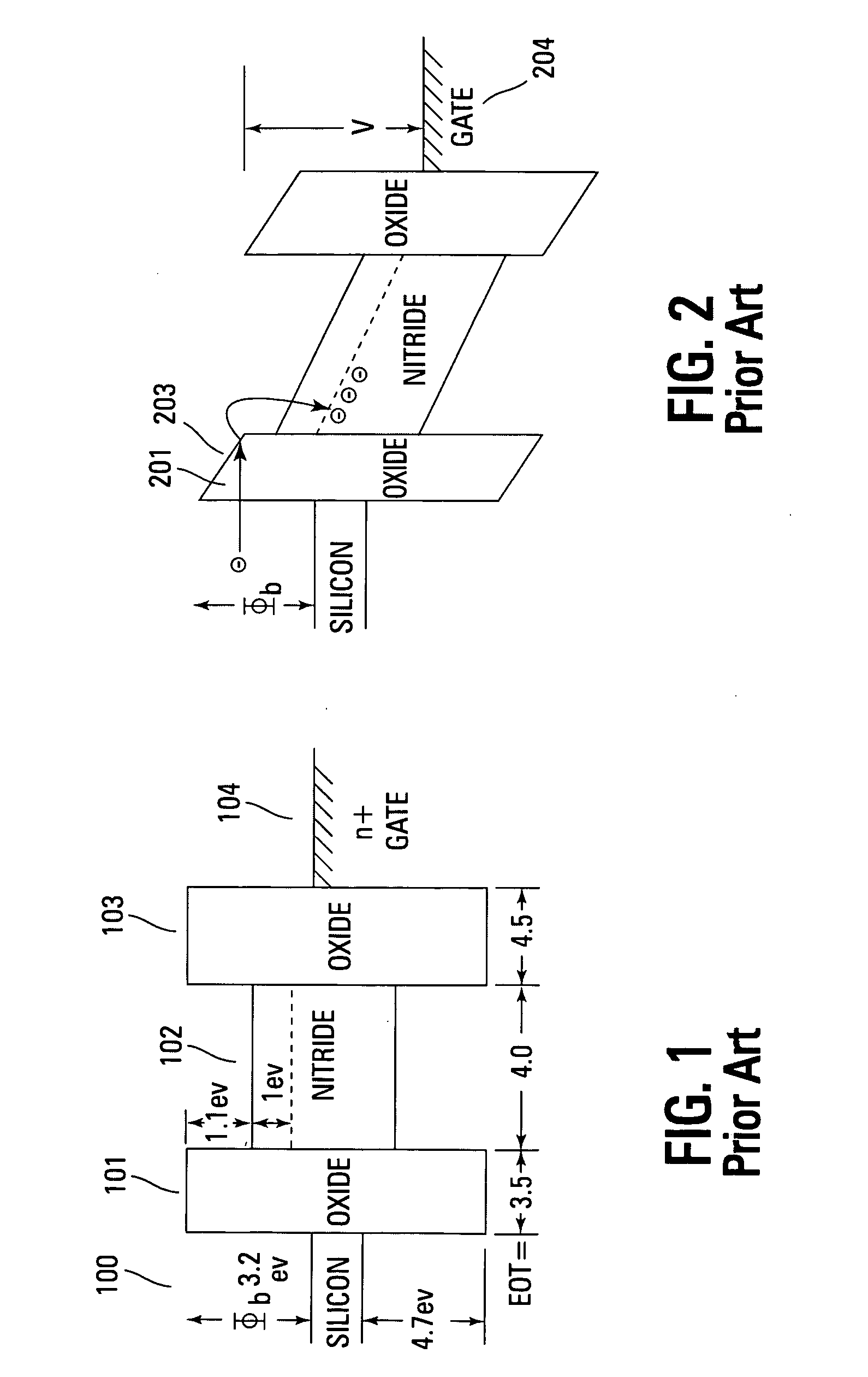

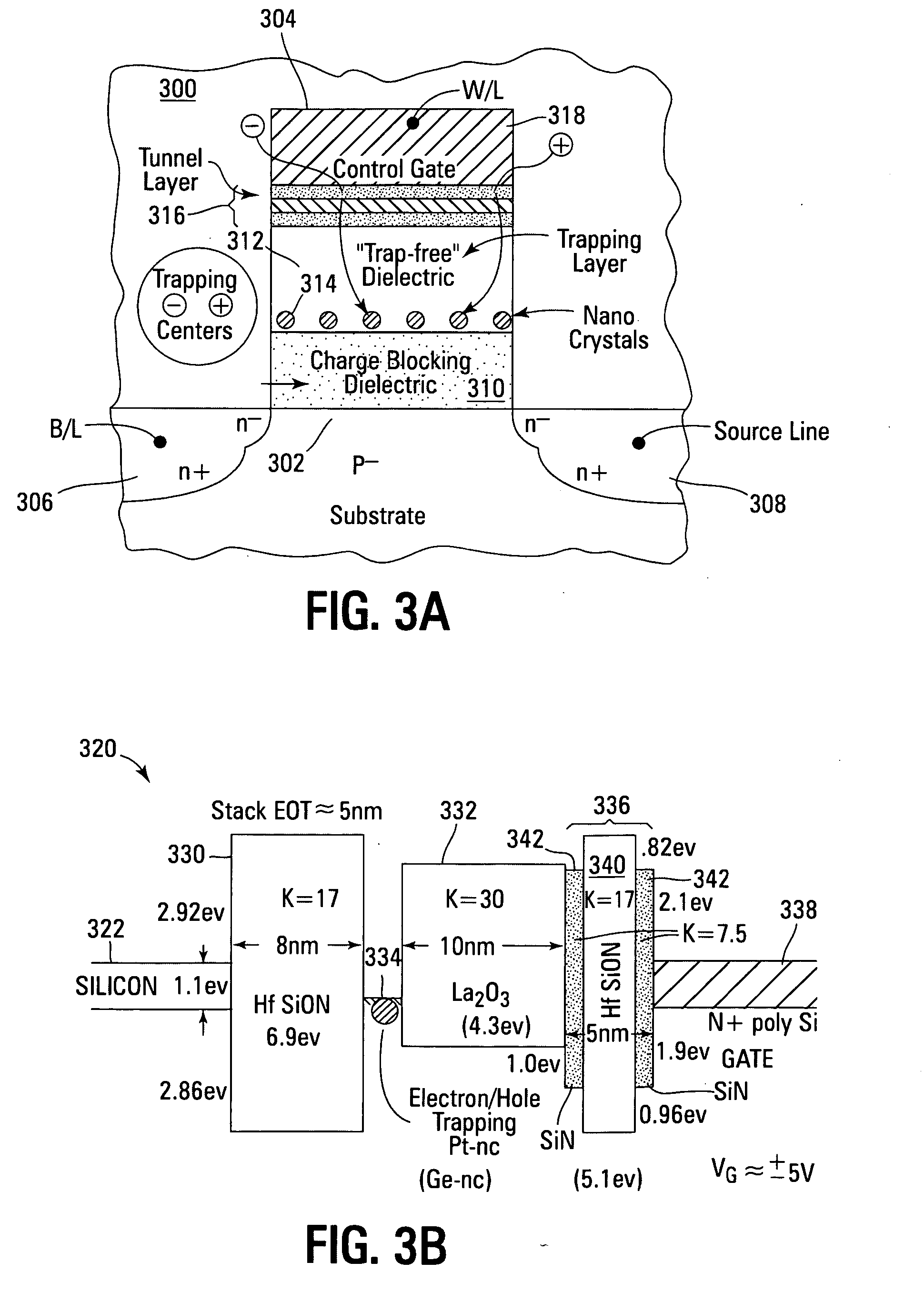

Non-volatile memory devices and arrays are described that facilitate the use of band-gap engineered gate stacks with asymmetric tunnel barriers in reverse and normal mode floating node memory cells in NOR or NAND memory architectures that allow for direct tunnel programming and erase, while maintaining high charge blocking barriers and deep carrier trapping sites for good charge retention. The low voltage direct tunneling program and erase capability reduces damage to the gate stack and the crystal lattice from high energy carriers, reducing write fatigue and enhancing device lifespan. The low voltage direct tunnel program and erase capability also enables size reduction through low voltage design and further device feature scaling. Memory cells of the present invention also allow multiple bit storage. These characteristics allow memory device embodiments of the present invention to operate within the definition of a universal memory, capable of replacing both DRAM and ROM in a system.

Owner:MICRON TECH INC

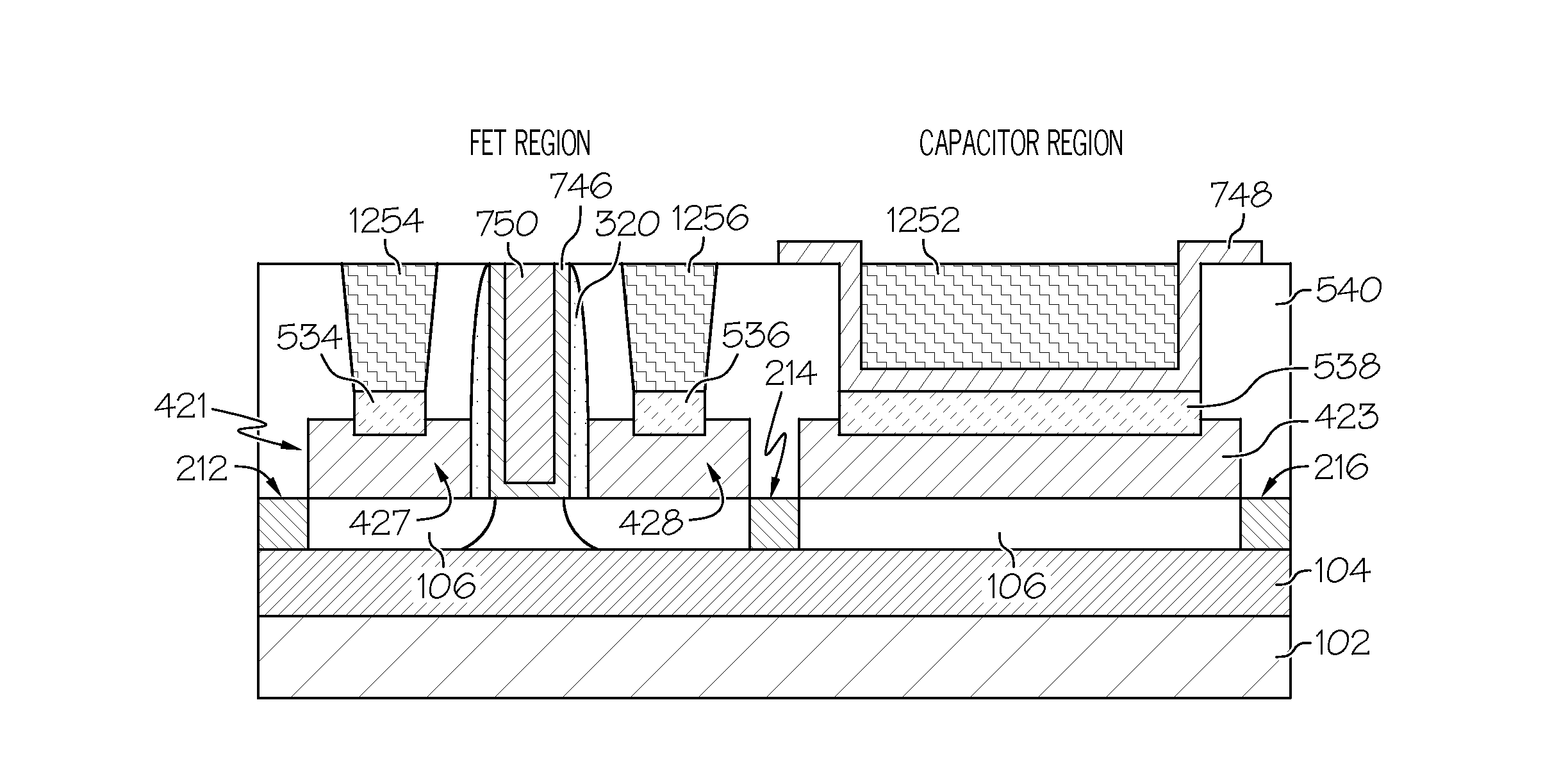

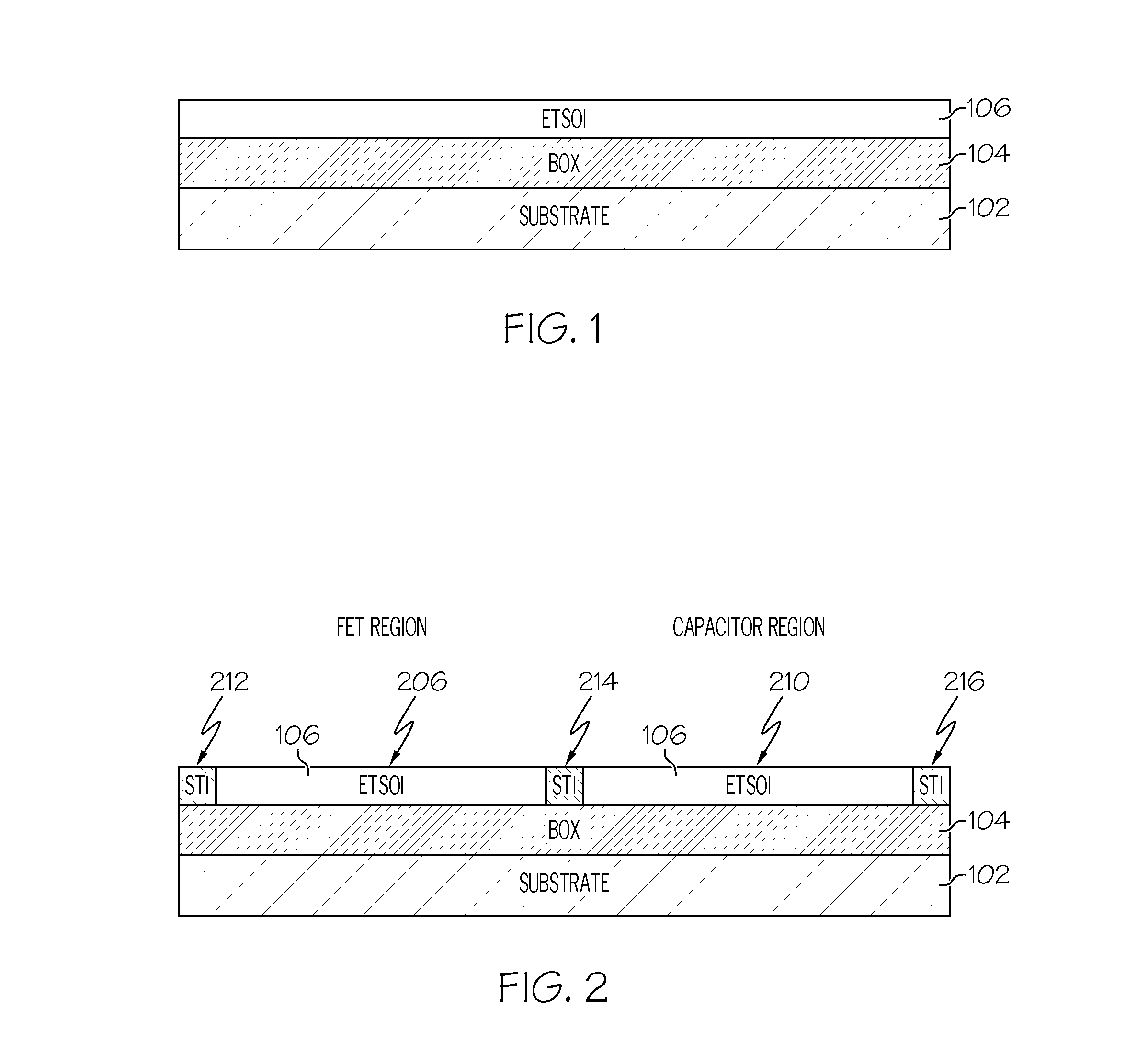

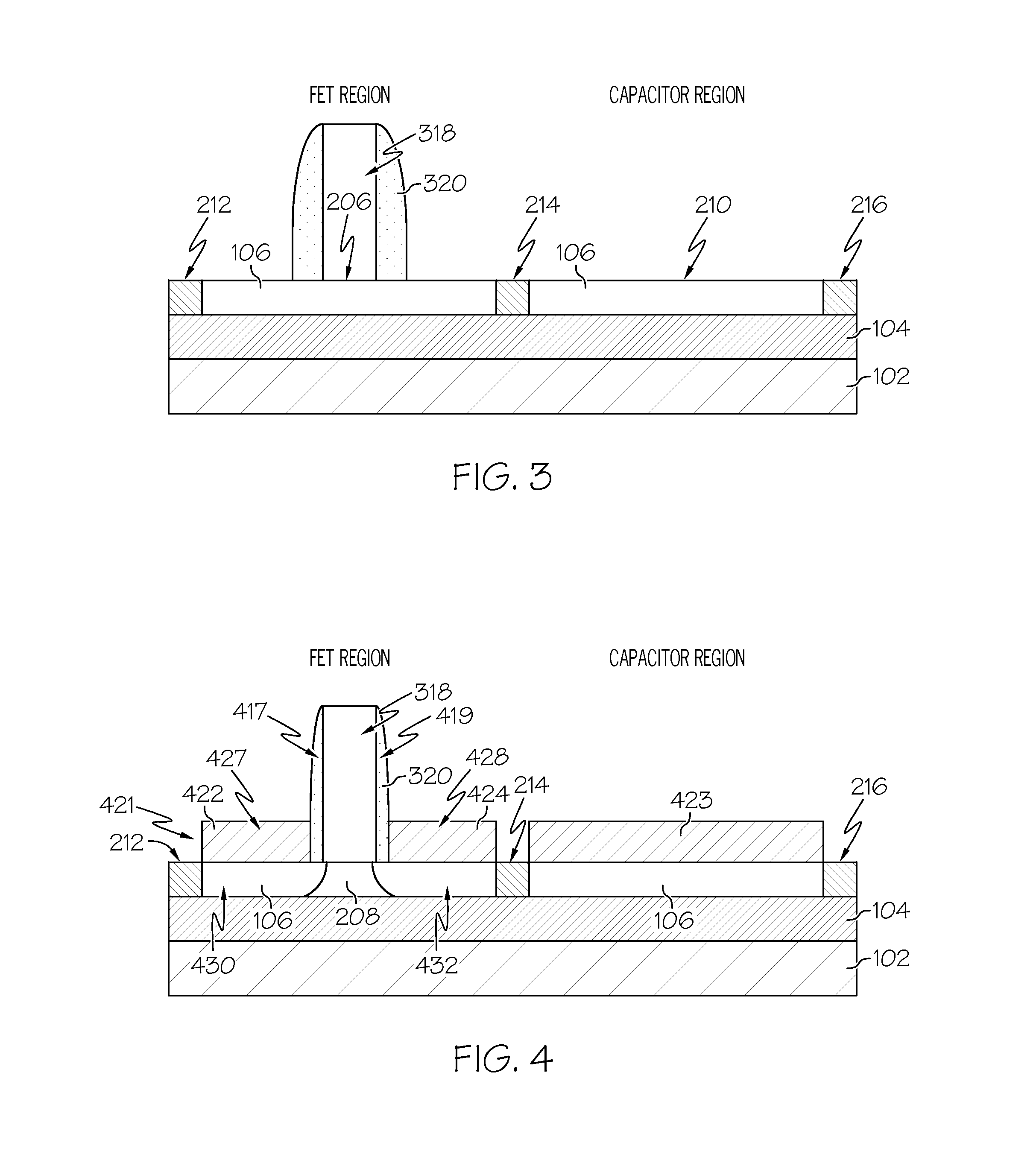

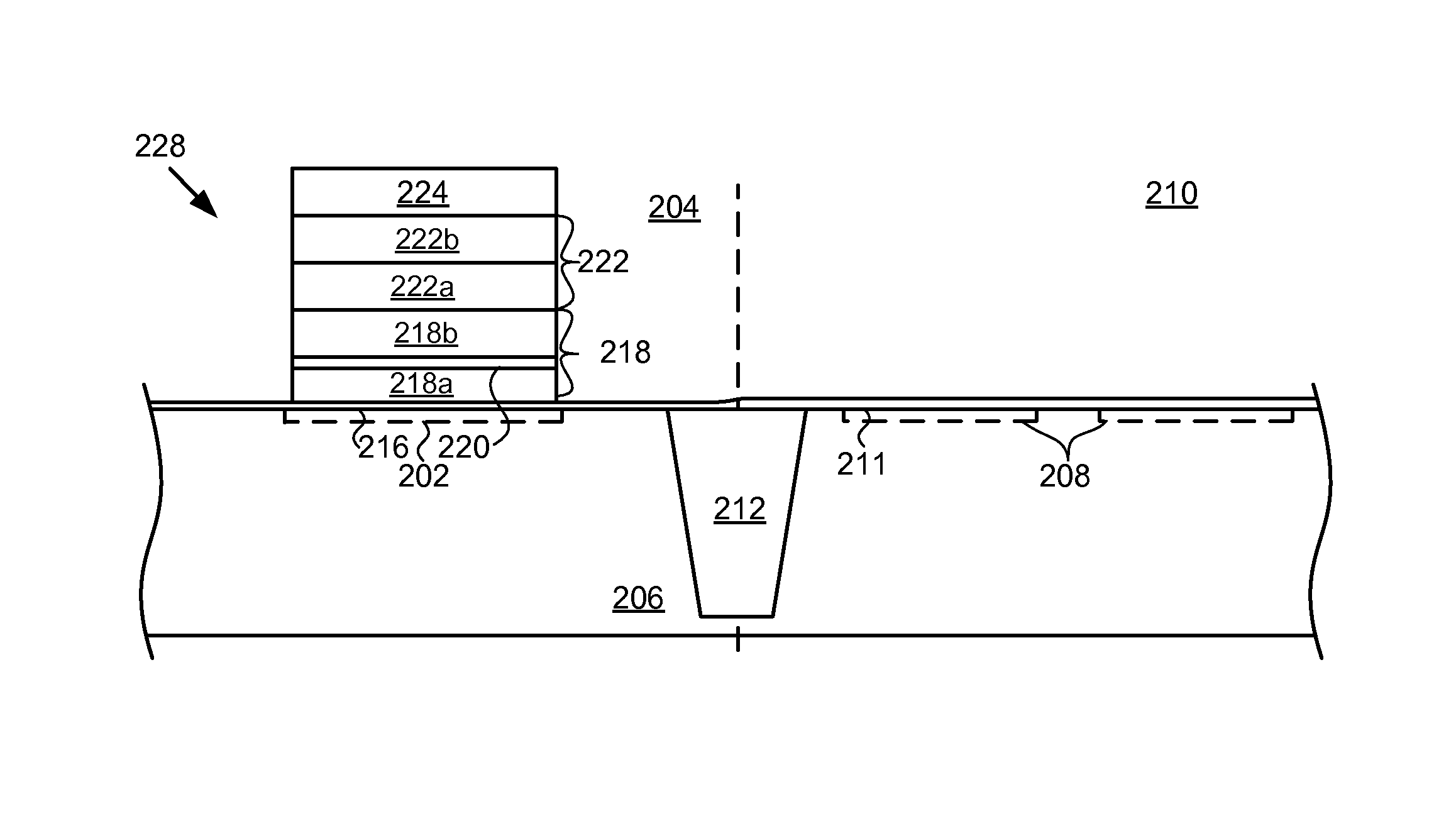

Integrated circuit with a thin body field effect transistor and capacitor

An integrated circuit includes a transistor and a capacitor. The transistor includes a first semiconductor layer and a gate stack located on the first semiconductor layer. The gate stack includes a metal layer and a first high-k dielectric layer. A gate spacer is located on sidewalls of the gate stack. The first high-k dielectric layer is located between the first semiconductor layer and the metal layer and between the gate spacer and sidewalls of the metal layer. A first silicide region is located on a first source / drain region. A second silicide region is located on a second source / drain region. The capacitor includes a first terminal that comprises a third silicide region located on a portion of the second semiconductor. A second high-k dielectric layer is located on the silicide region. A second terminal comprises a metal layer that is located on the second high-k dielectric layer.

Owner:GLOBALFOUNDRIES US INC

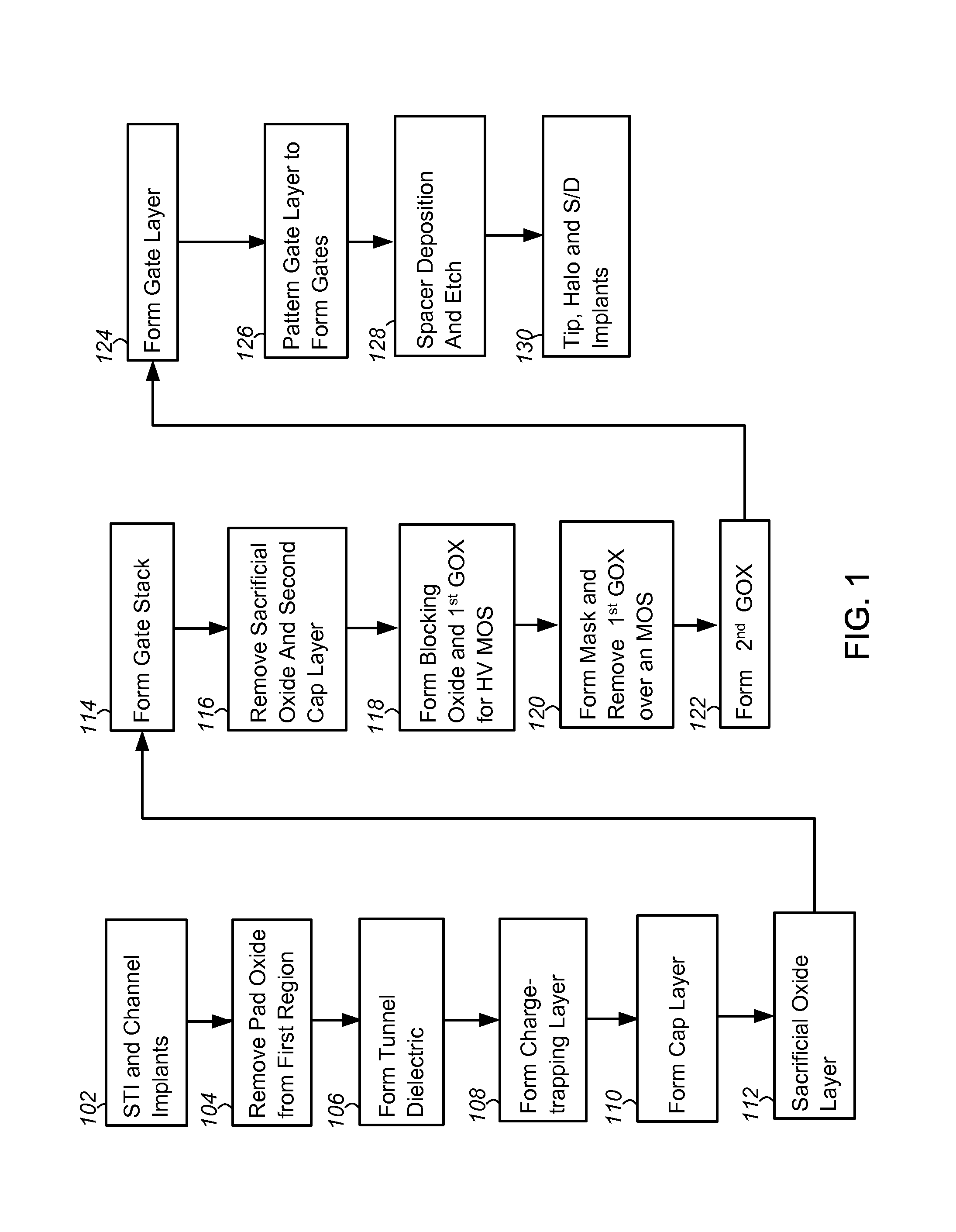

Method of fabricating a charge-trapping gate stack using a CMOS process flow

ActiveUS8993457B1Semiconductor/solid-state device manufacturingSemiconductor devicesDielectricTrapping

A method of fabricating a memory device is described. Generally, the method includes: forming on a surface of a substrate a dielectric stack including a tunneling dielectric and a charge-trapping layer overlying the tunneling dielectric; depositing a first cap layer comprising an oxide over the dielectric stack; forming a second cap layer comprising a nitride over the first cap layer; patterning the first and second cap layers and the dielectric stack to form a gate stack of a memory device; removing the second cap layer; and performing an oxidation process to form a blocking oxide over the charge-trapping layer, wherein the oxidation process consumes the first cap layer. Other embodiments are also described.

Owner:LONGITUDE FLASH MEMORY SOLUTIONS LTD

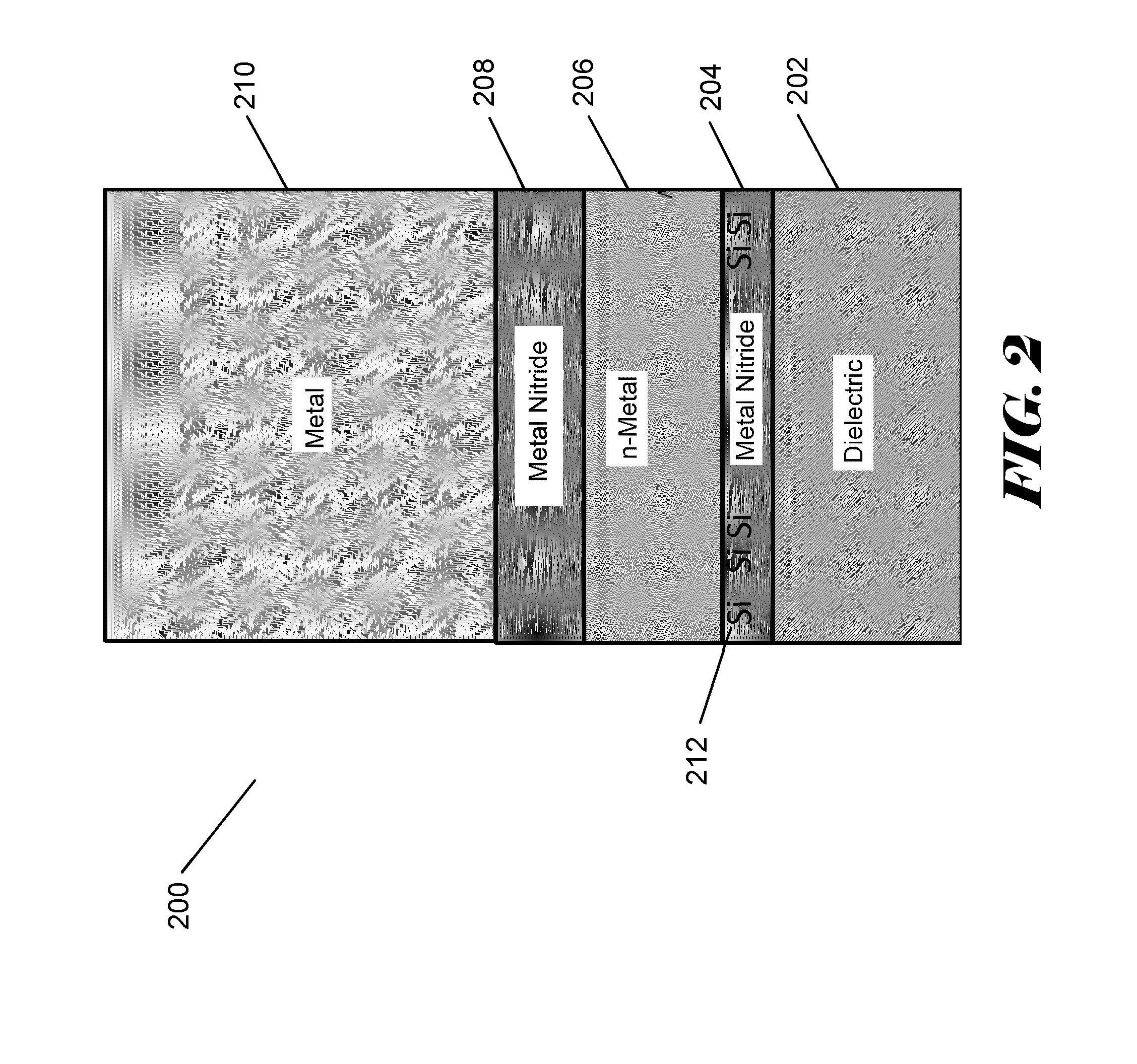

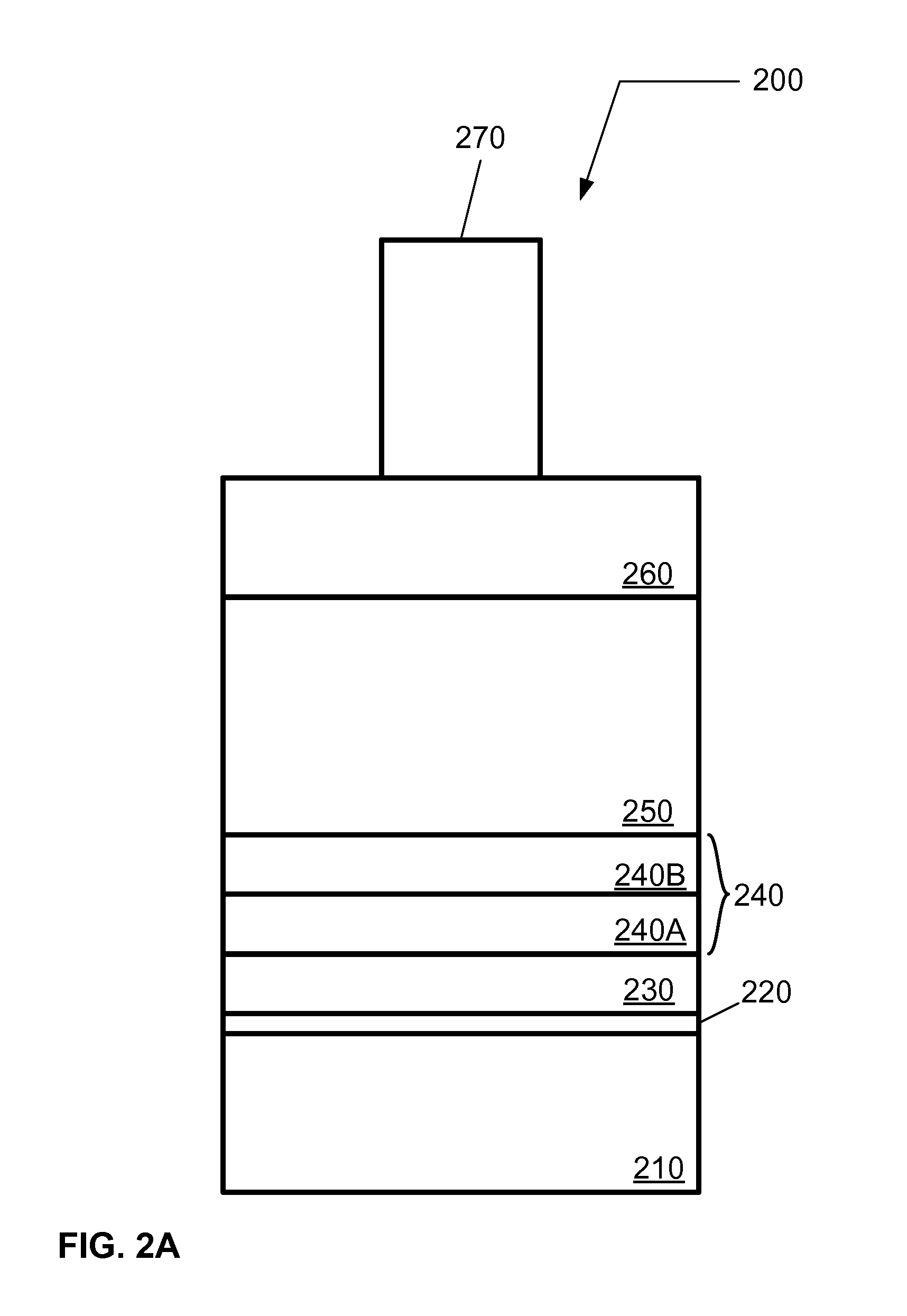

Process for depositing electrode with high effective work function

ActiveUS9136180B2Semiconductor/solid-state device manufacturingSemiconductor devicesHydrogenGate dielectric

Owner:ASM IP HLDG BV

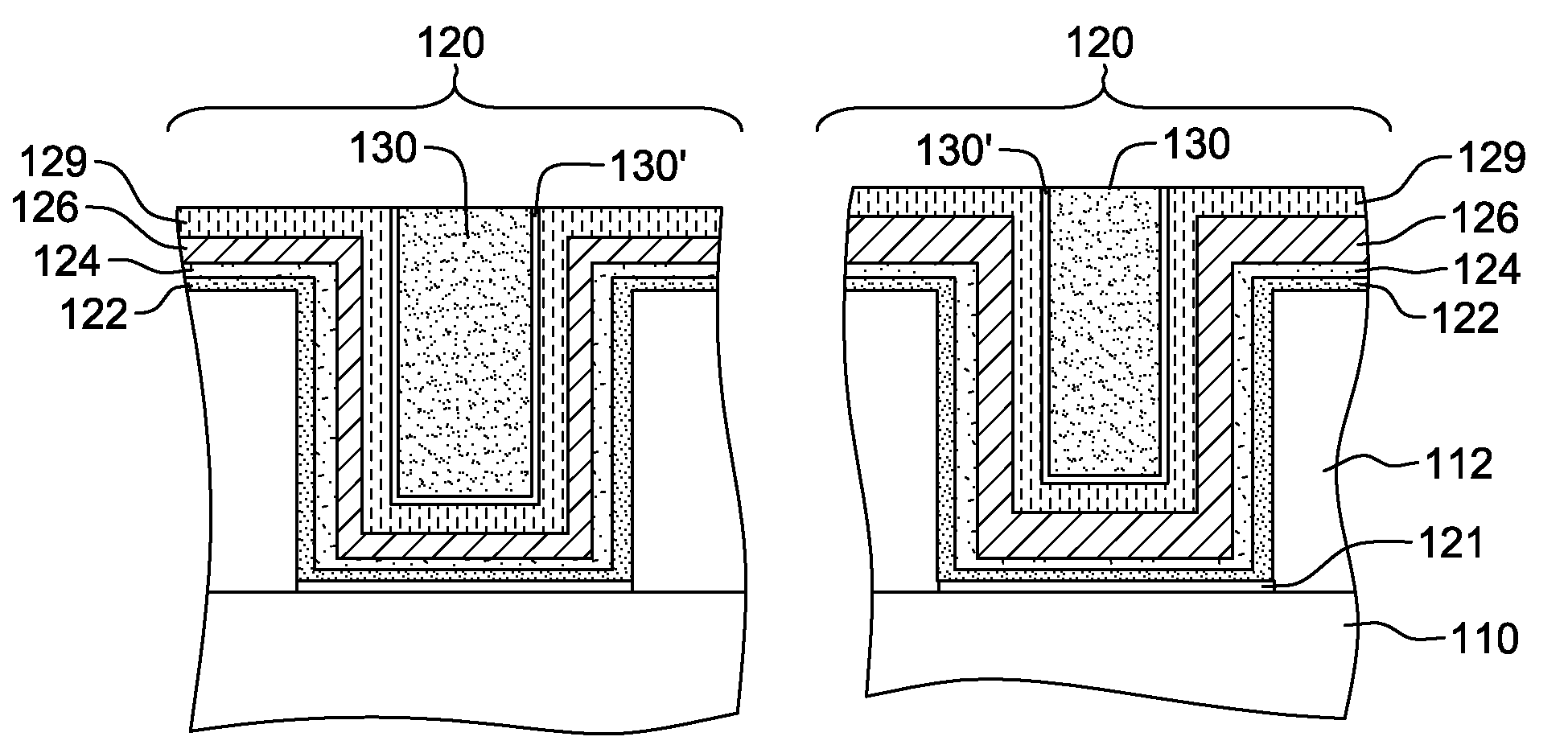

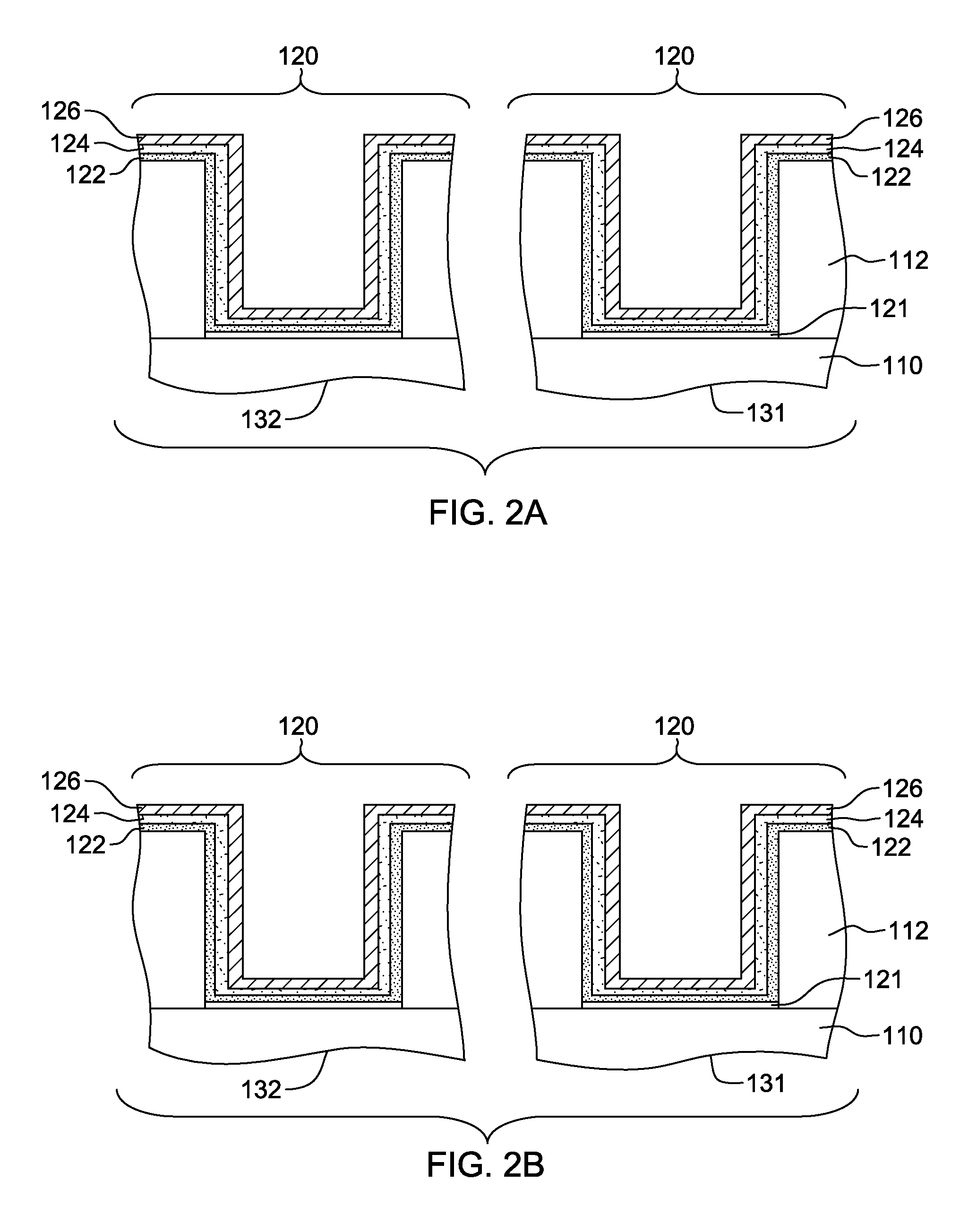

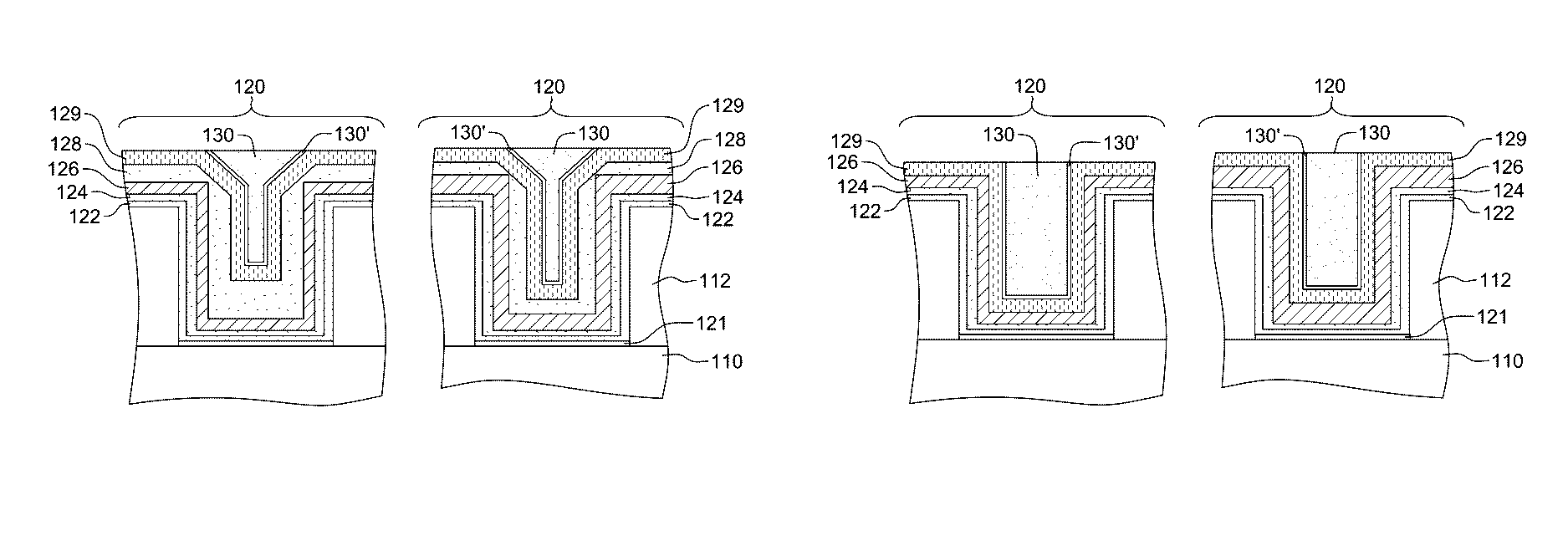

Integrated circuit having multiple threshold voltages

In one aspect there is set forth herein an integrated circuit having a first plurality of field effect transistors and a second plurality of field effect transistor, wherein field effect transistors of the first plurality of field effect transistors each have a first gate stack and wherein field effect transistors of the second plurality of field effect transistors each have a second gate stack, the second gate stack being different from the first gate stack by having a metal layer common to the first gate stack and the second gate stack that includes a first thickness at the first gate stack and a second thickness at the second gate stack.

Owner:GLOBALFOUNDRIES U S INC

Integrated circuits with varying gate structures and fabrication methods

Integrated circuits and fabrication methods are provided. The integrated circuit includes: a varying gate structure disposed over a substrate structure, the varying gate structure including a first gate stack in a first region of the substrate structure, and a second gate stack in a second region of the substrate structure; a first field-effect transistor in the first region, the first field-effect transistor including the first gate stack and having a first threshold voltage; and a second field-effect transistor in the second region, the second field-effect transistor including the second gate stack and having a second threshold voltage, where the first threshold voltage is different from the second threshold voltage. The methods include providing the varying gate structure, the providing including: sizing layer(s) of the varying gate structure with different thickness(es) in different region(s).

Owner:GLOBALFOUNDRIES U S INC

Integrated circuit having multiple threshold voltages

In one aspect there is set forth herein an integrated circuit having a first plurality of field effect transistors and a second plurality of field effect transistor, wherein field effect transistors of the first plurality of field effect transistors each have a first gate stack and wherein field effect transistors of the second plurality of field effect transistors each have a second gate stack, the second gate stack being different from the first gate stack by having a metal layer common to the first gate stack and the second gate stack that includes a first thickness at the first gate stack and a second thickness at the second gate stack.

Owner:GLOBALFOUNDRIES US INC

Semiconductor device incorporating a multi-function layer into gate stacks

InactiveUS8859368B2Reduce in quantityReduce complexityTransistorSolid-state devicesWork functionGate stack

Approaches are provided for forming a semiconductor device (e.g., a FET) having a multi-function layer (e.g., niobium carbide (NbC)) that serves as a work function layer and a gate metal layer in gate stacks of solid state applications. By introducing a single layer with multiple functions, total number of layers that needs processing (e.g., recessing) may be decreased. As such, the complexity of device integration and resulting complications may be reduced.

Owner:GLOBALFOUNDRIES INC

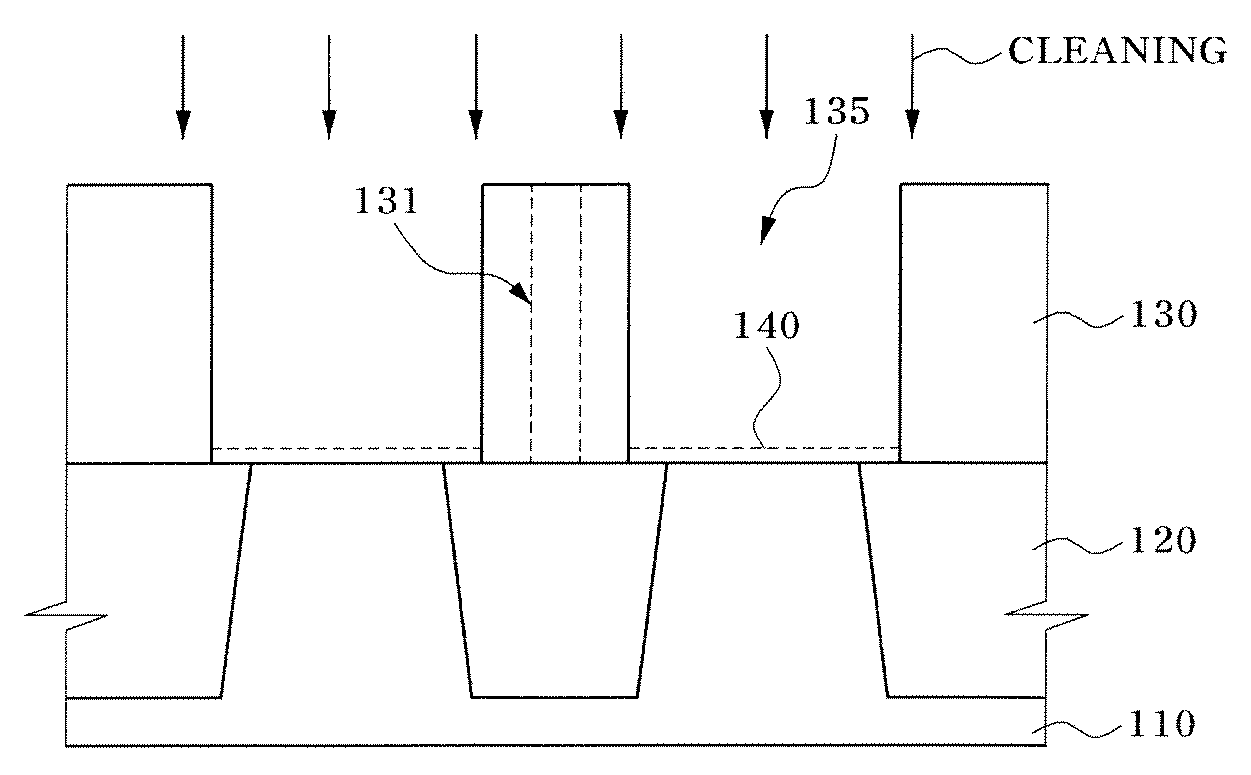

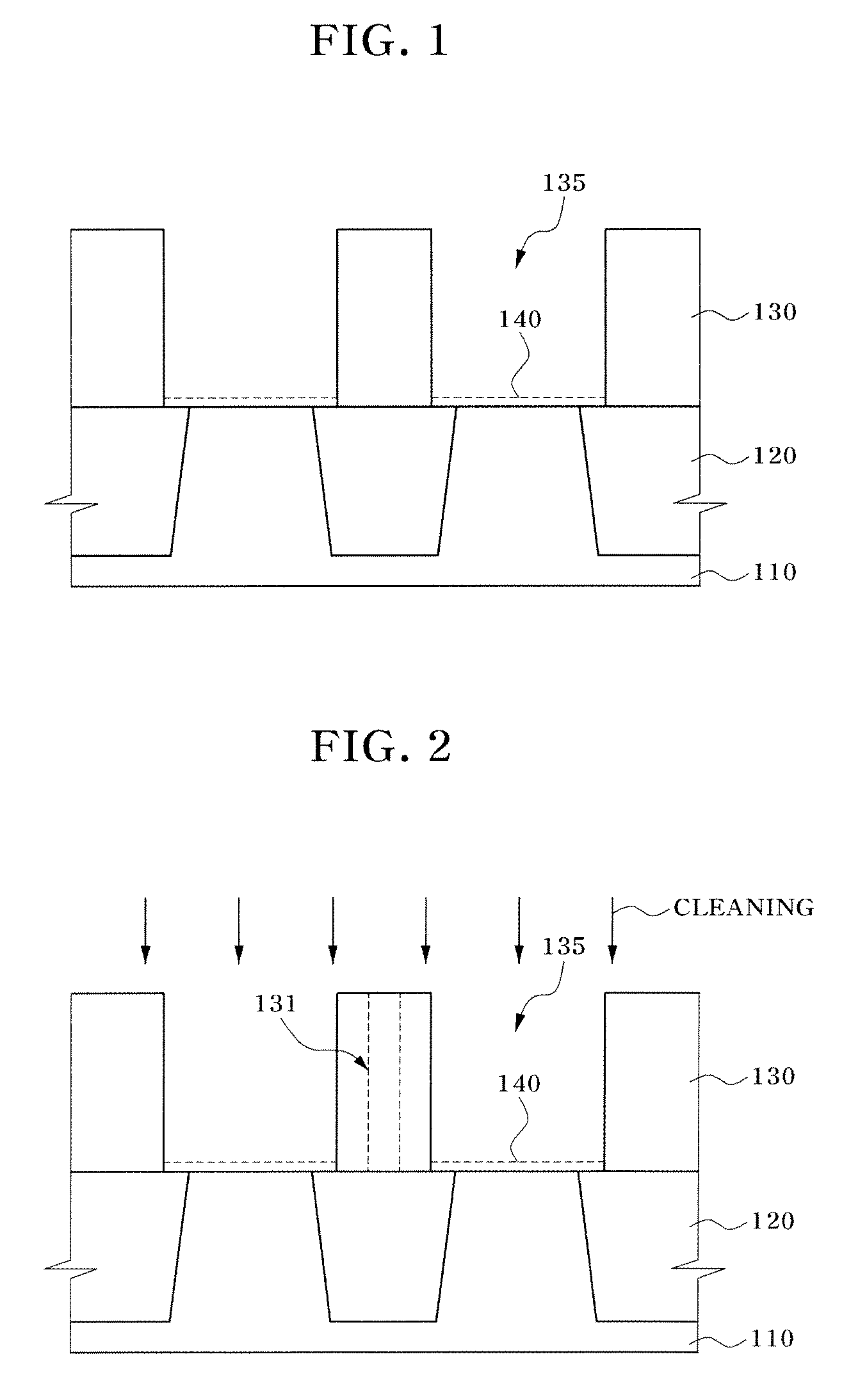

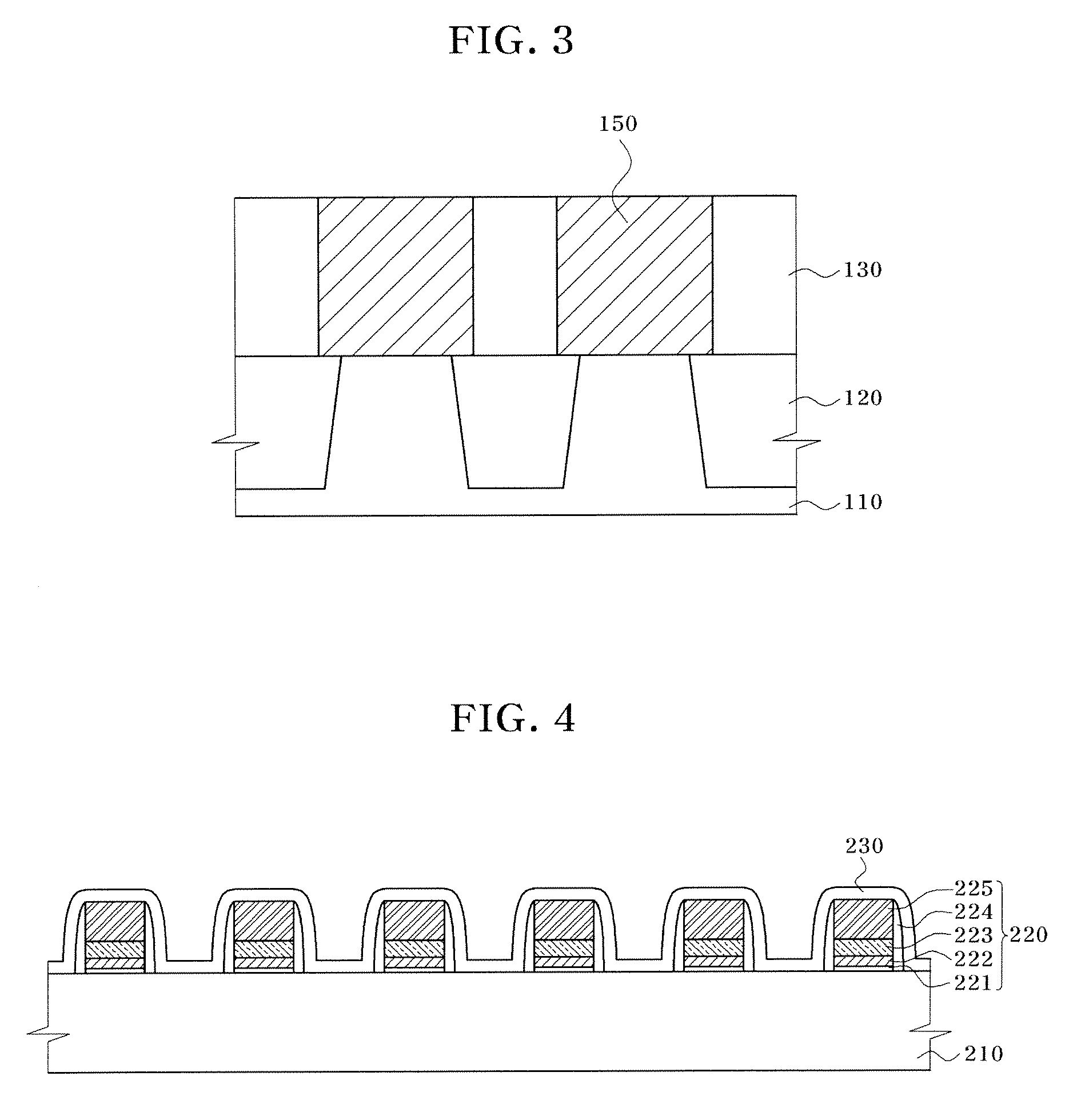

Method for Fabricating A Semiconductor Device Comprising Surface Cleaning

InactiveUS20080044990A1Efficient removalPreventing corrosion lossSemiconductor/solid-state device manufacturingAlcoholSurface cleaning

A method for fabricating a semiconductor device including surface cleaning includes forming a gate stack on a semiconductor substrate, cleaning contaminants present on the surface of the semiconductor substrate exposed through a contact hole using an etchant including a fluorine (F)-containing species dispersed in an alcohol, and filling a contact hole with a conductive layer to form a connection contact. The etchant preferably has a low selectivity of 1 or less.

Owner:SK HYNIX INC

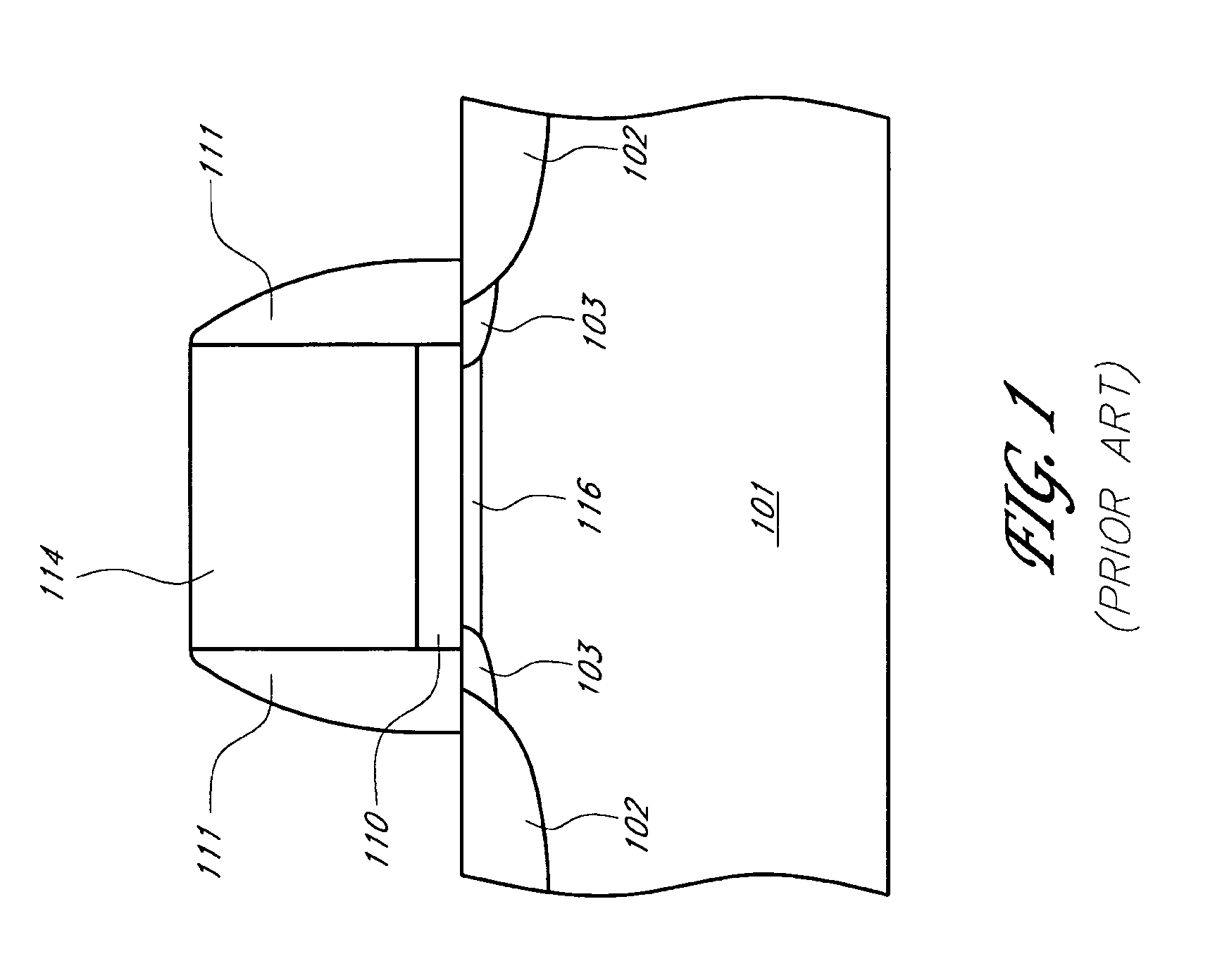

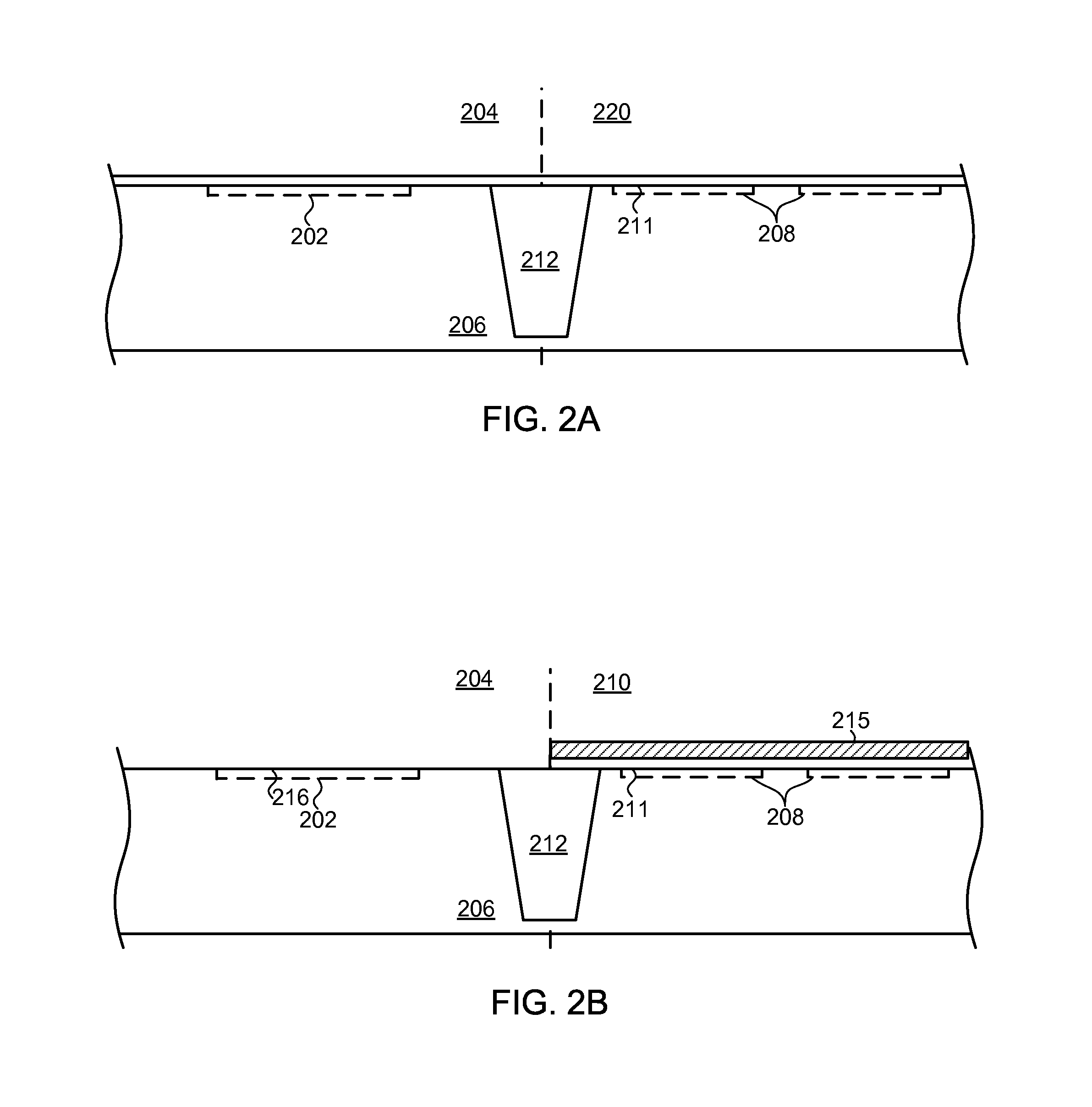

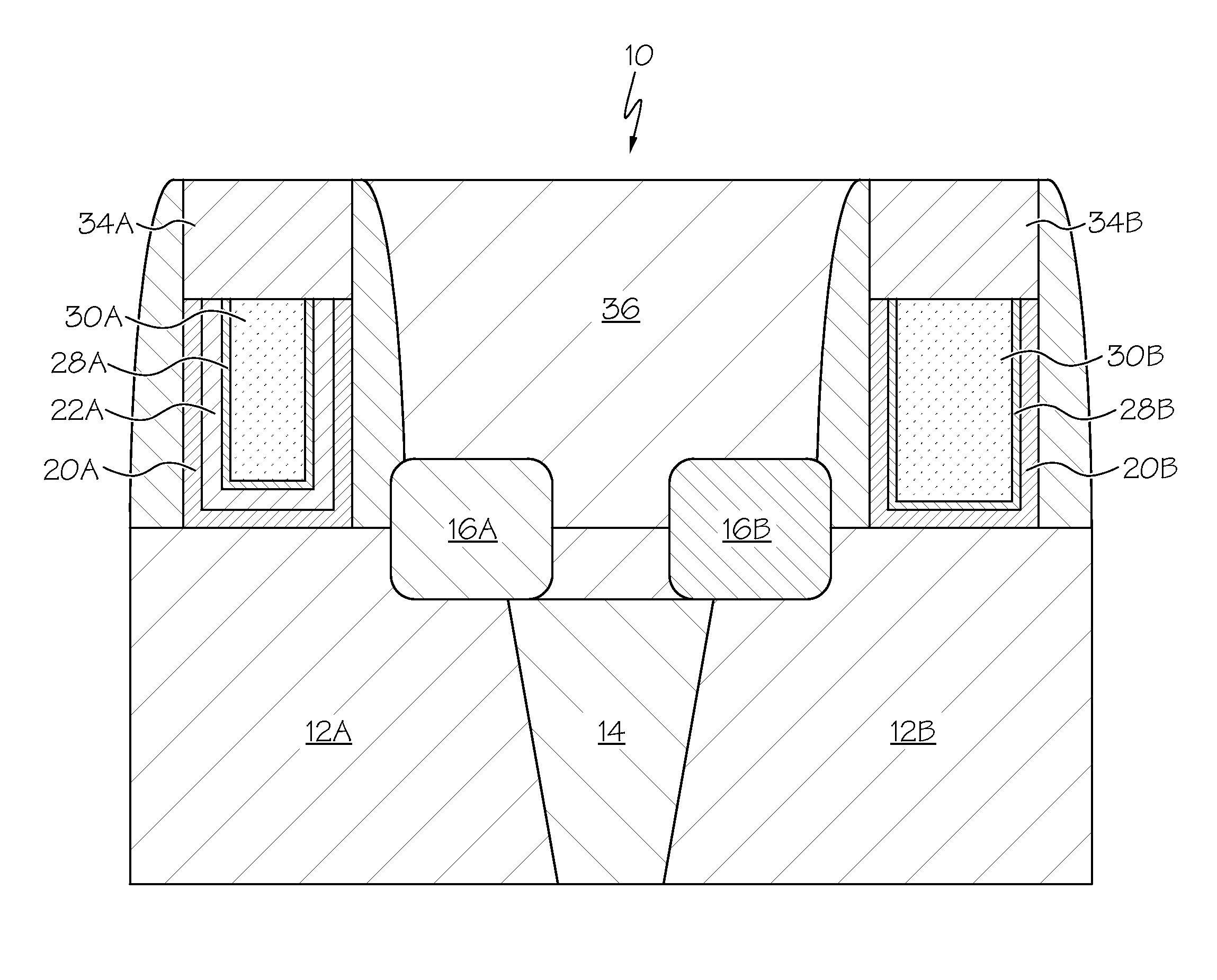

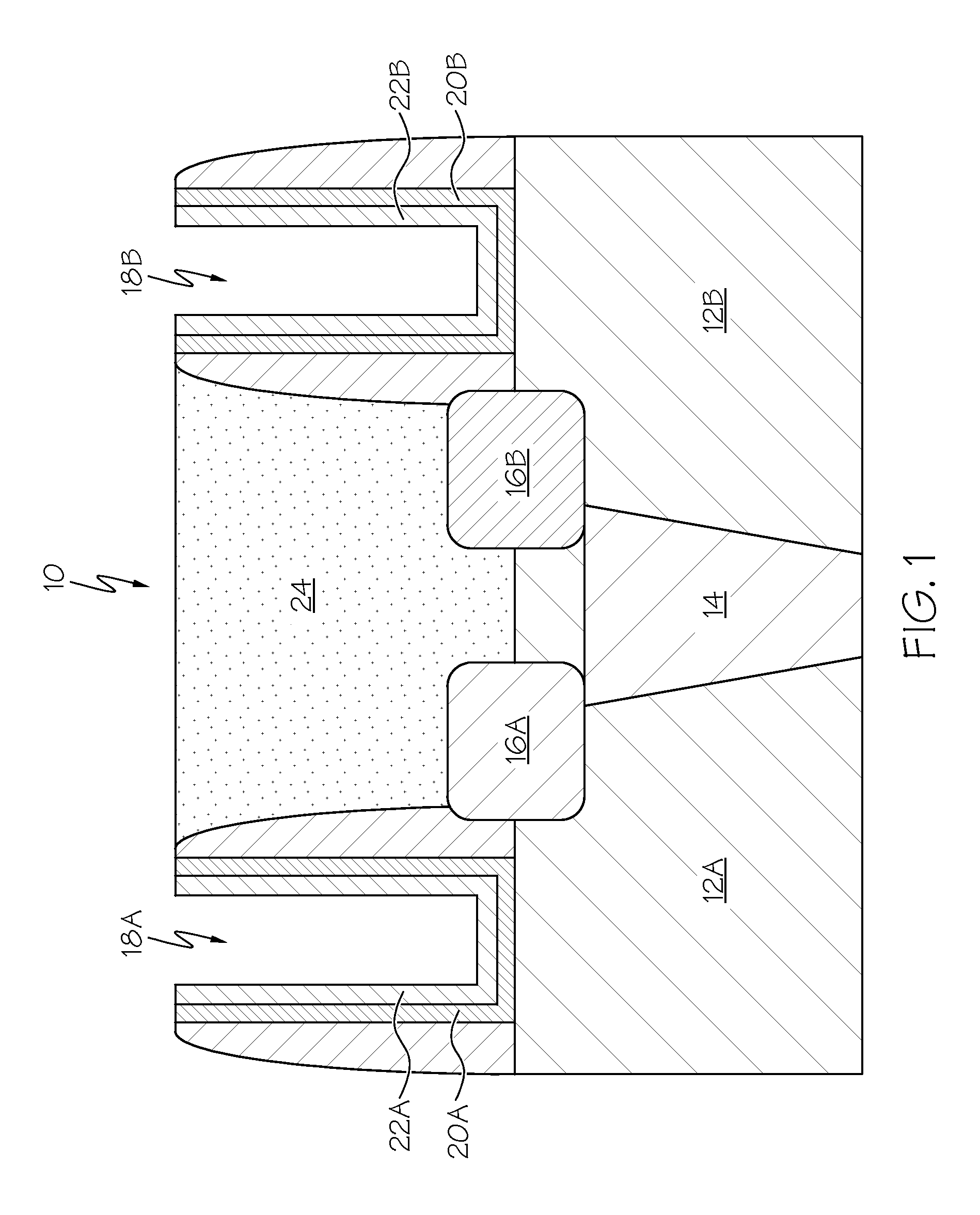

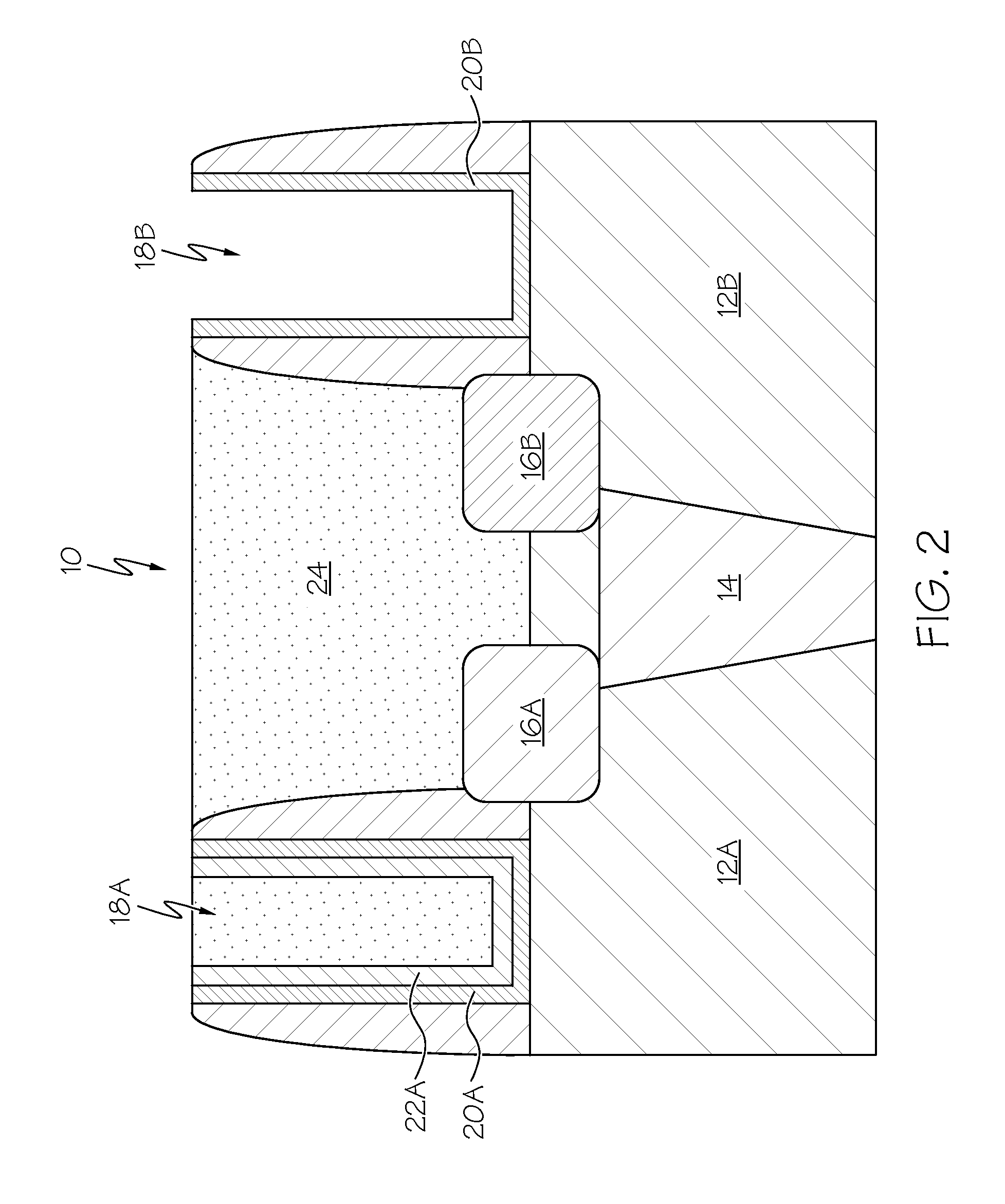

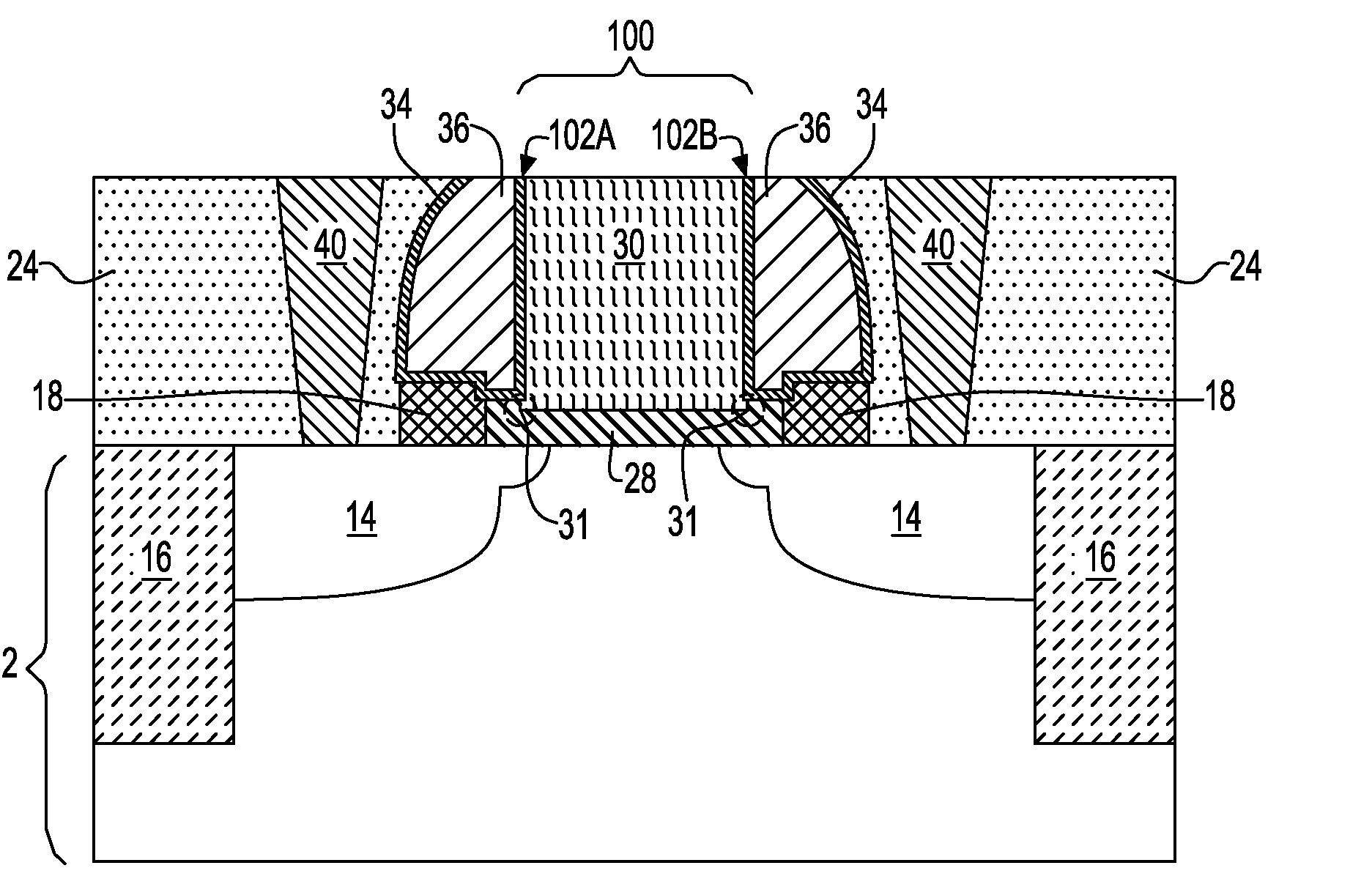

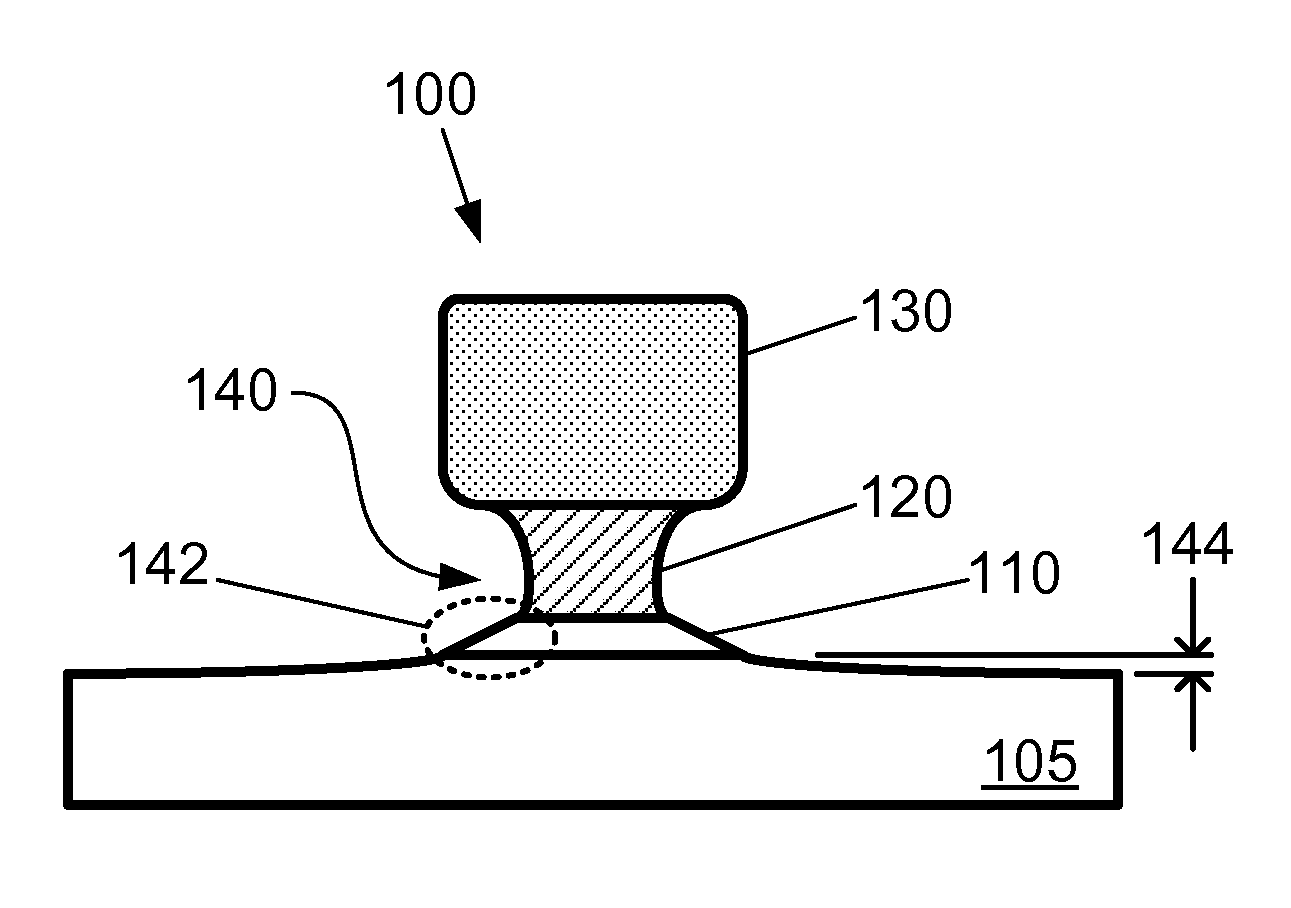

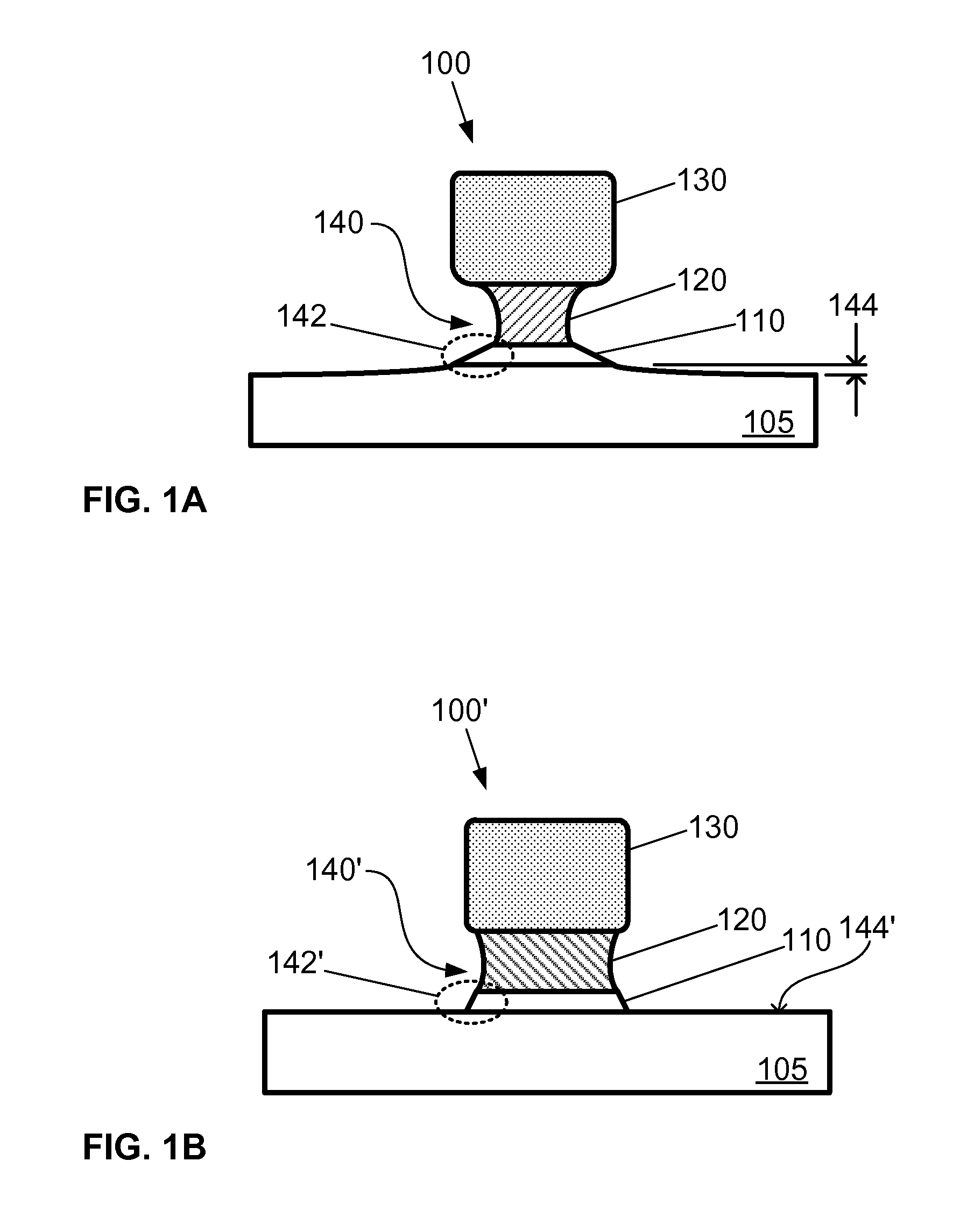

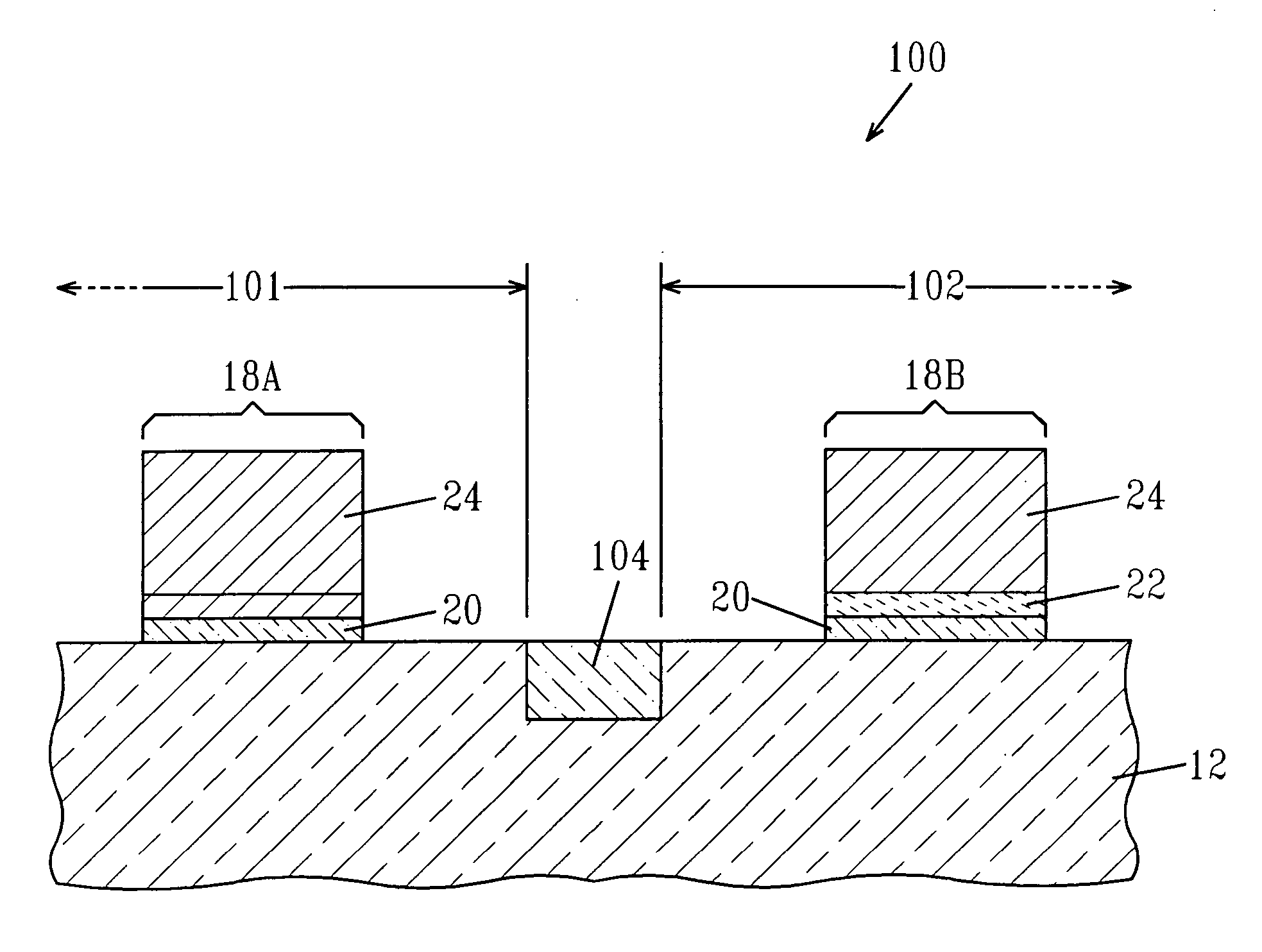

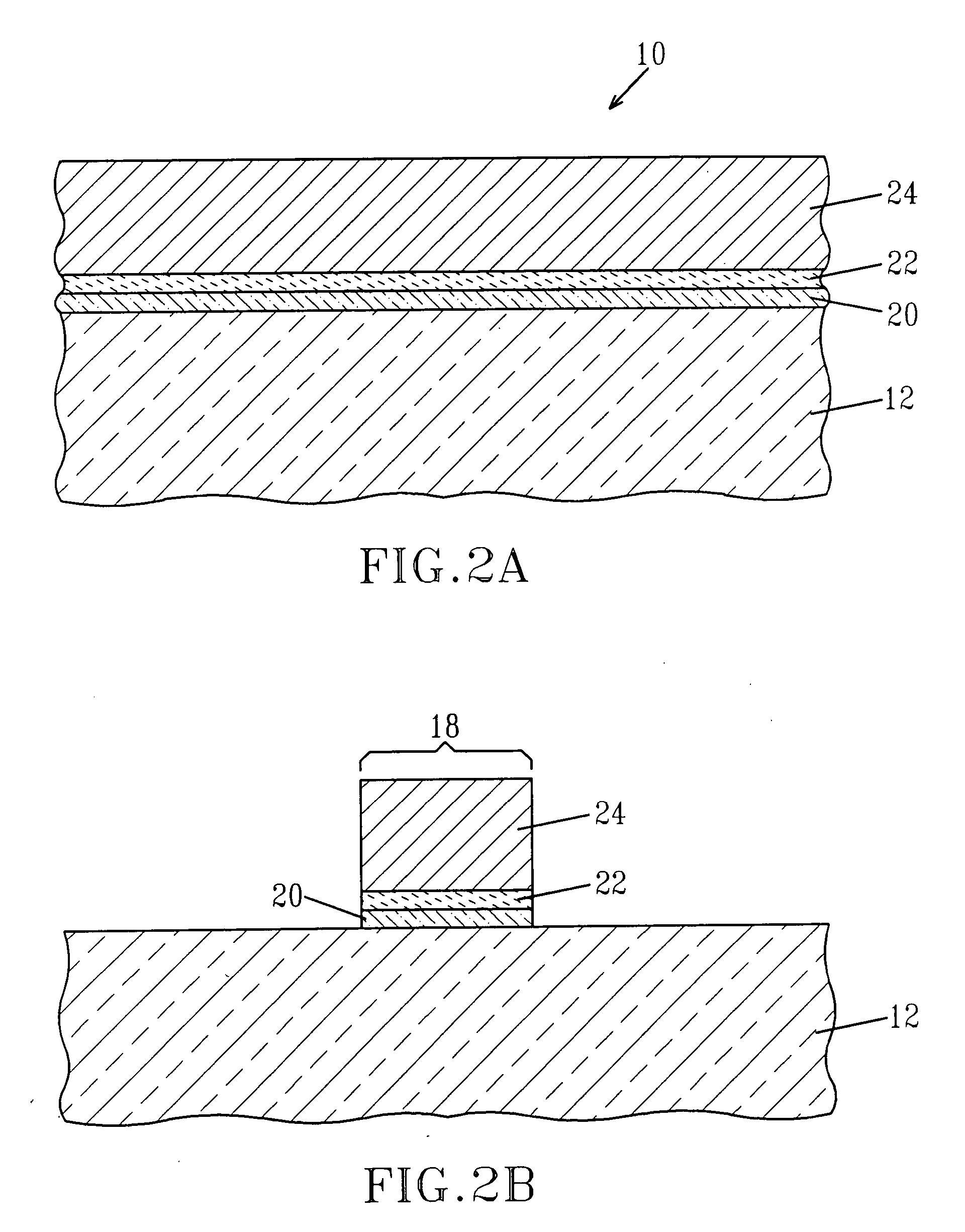

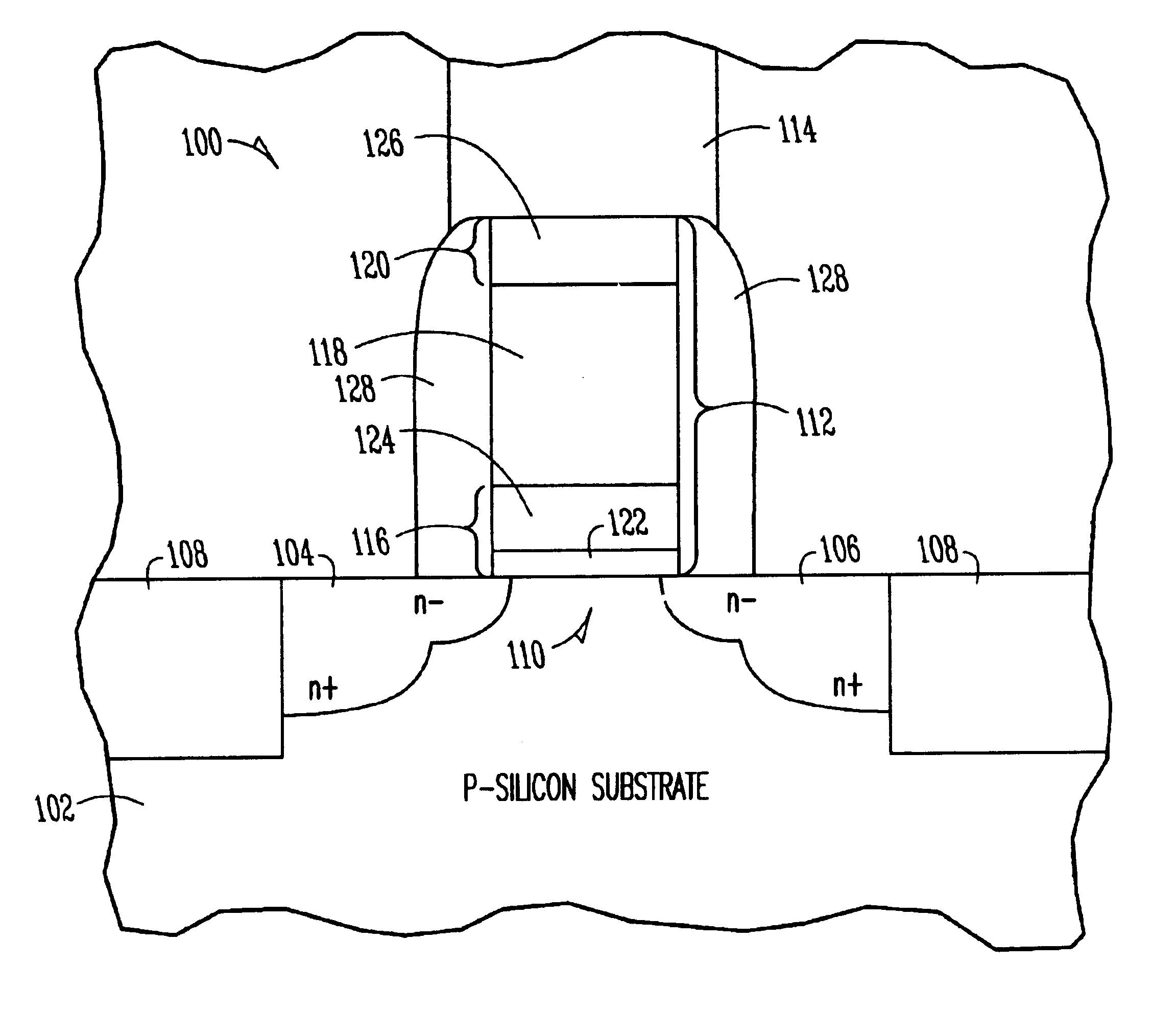

HIGH-k/METAL GATE MOSFET WITH REDUCED PARASITIC CAPACITANCE

InactiveUS20090001480A1Reduce parasitic capacitanceSolid-state devicesSemiconductor/solid-state device manufacturingMOSFETElectrical conductor

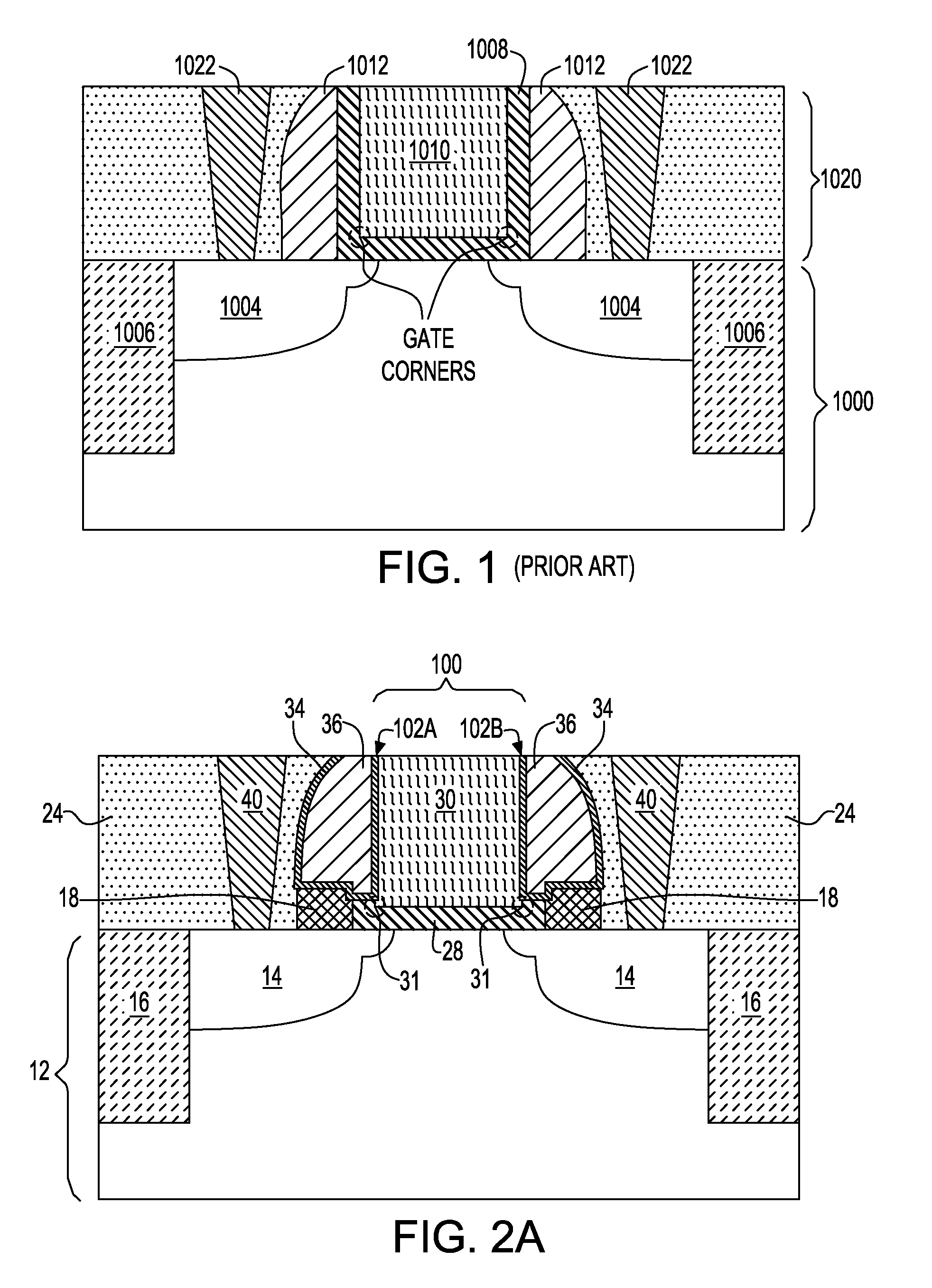

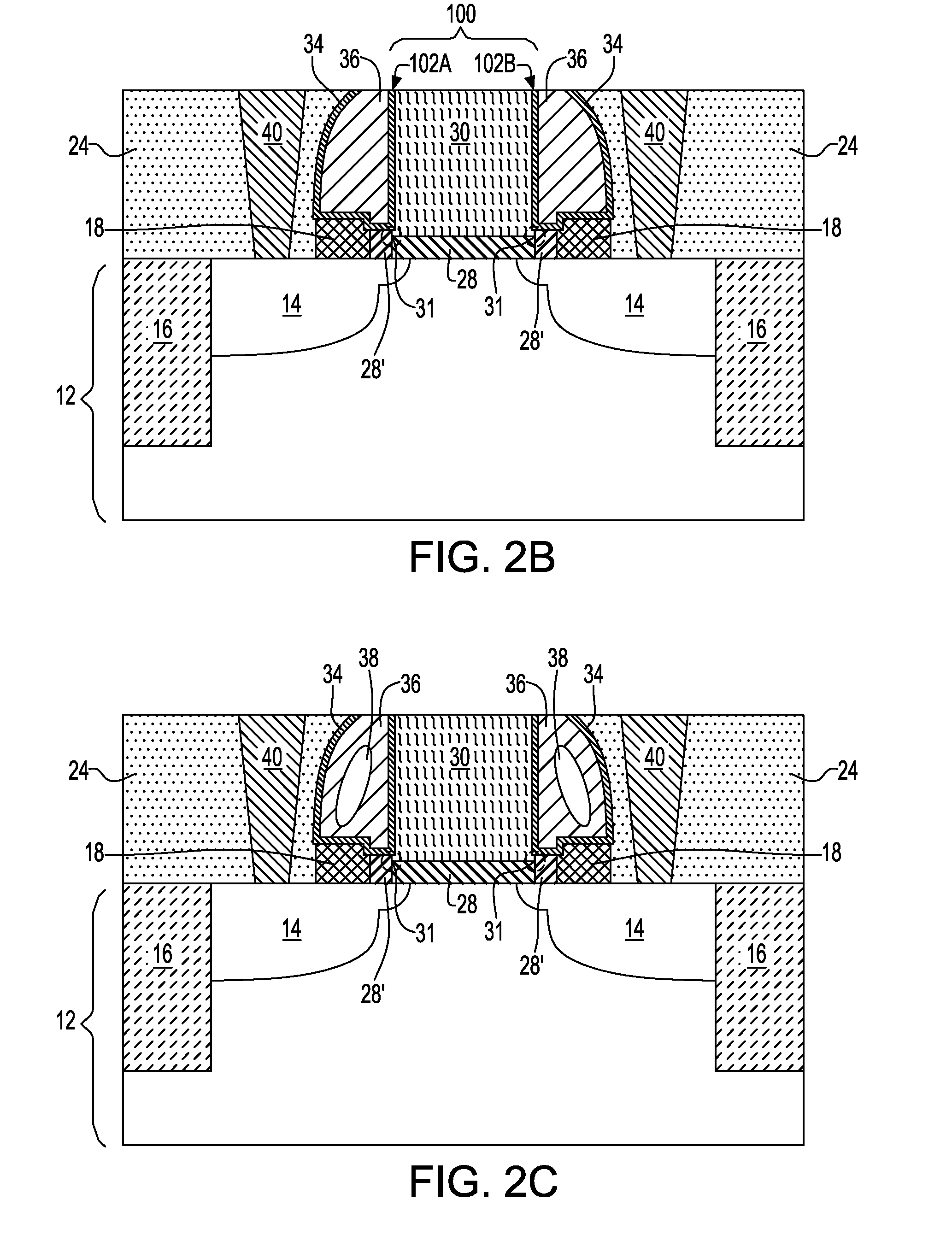

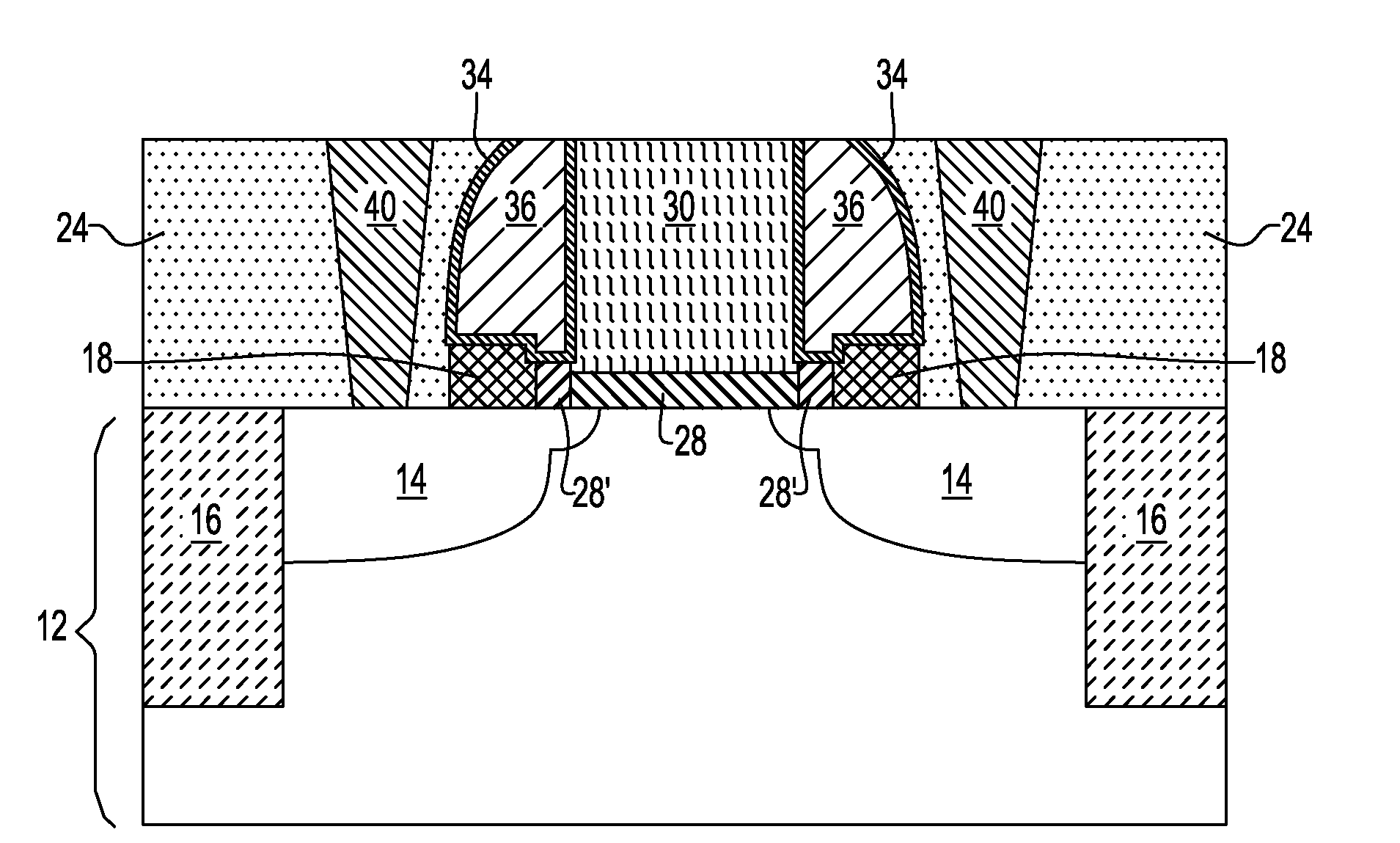

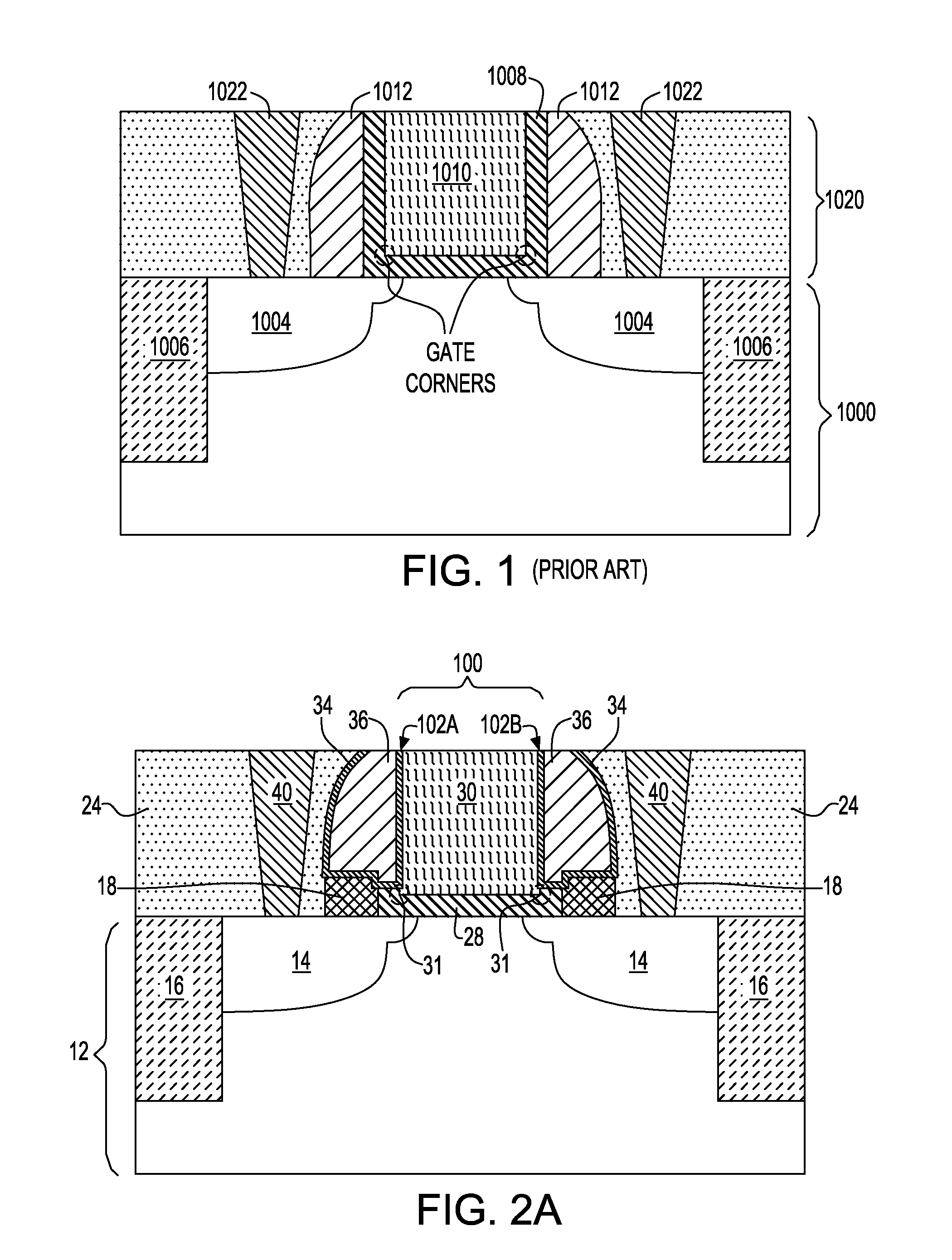

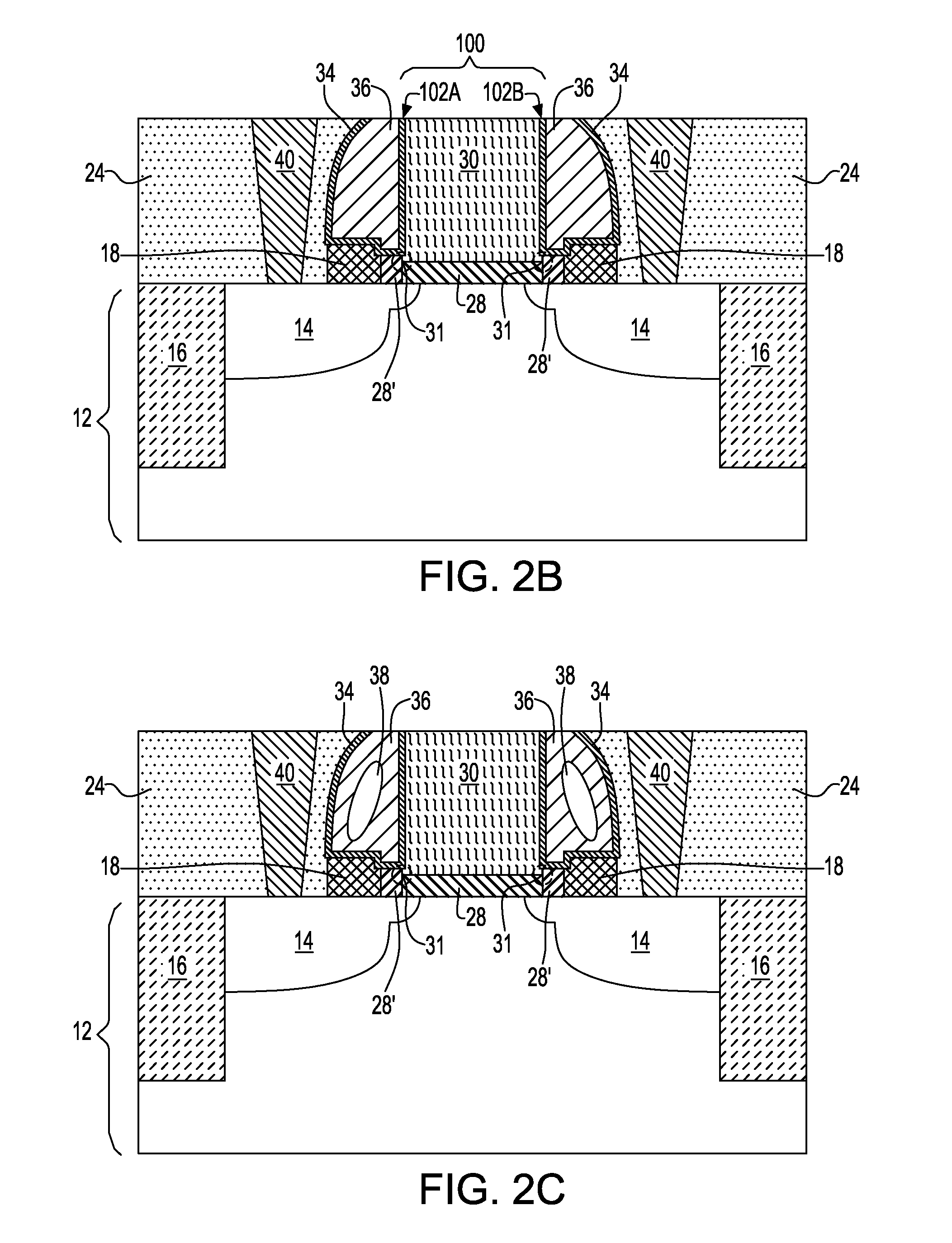

The present invention provides a high-k gate dielectric / metal gate MOSFET that has a reduced parasitic capacitance. The inventive structure includes at least one metal oxide semiconductor field effect transistor (MOSFET) 100 located on a surface of a semiconductor substrate 12. The least one MOSFET 100 includes a gate stack including, from bottom to top, a high-k gate dielectric 28 and a metal-containing gate conductor 30. The metal-containing gate conductor 30 has gate corners 31 located at a base segment of the metal-containing gate conductor. Moreover, the metal-containing gate conductor 30 has vertically sidewalls 102A and 102B devoid of the high-k gate dielectric 28 except at the gate corners 31. A gate dielectric 18 laterally abuts the high-k gate dielectric 28 present at the gate corners 31 and a gate spacer 36 laterally abuts the metal-containing gate conductor 30. The gate spacer 36 is located upon an upper surface of both the gate dielectric 18 and the high-k gate dielectric that is present at the gate corners 31.

Owner:TESSERA INC

Method for producing gate stack sidewall spacers

A method for forming sidewall spacers on a gate stack by depositing one or more layers of silicon containing materials using PECVD process(es) on a gate structure to produce a spacer having an overall k value of about 3.0 to about 5.0. The silicon containing materials may be silicon carbide, oxygen doped silicon carbide, nitrogen doped silicon carbide, carbon doped silicon nitride, nitrogen doped silicon oxycarbide, or combinations thereof. The deposition is performed in a plasma enhanced chemical vapor deposition chamber and the deposition temperature is less than 450° C. The sidewall spacers so produced provide good capacity resistance, as well as excellent structural stability and hermeticity.

Owner:APPLIED MATERIALS INC

HIGH-k/METAL GATE MOSFET WITH REDUCED PARASITIC CAPACITANCE

ActiveUS20090321853A1Reduce parasitic capacitanceSolid-state devicesSemiconductor/solid-state device manufacturingMOSFETGate dielectric

The present invention provides a high-k gate dielectric / metal gate MOSFET that has a reduced parasitic capacitance. The inventive structure includes at least one metal oxide semiconductor field effect transistor (MOSFET) 100 located on a surface of a semiconductor substrate 12. The least one MOSFET 100 includes a gate stack including, from bottom to top, a high-k gate dielectric 28 and a metal-containing gate conductor 30. The metal-containing gate conductor 30 has gate corners 31 located at a base segment of the metal-containing gate conductor. Moreover, the metal-containing gate conductor 30 has vertically sidewalls 102A and 102B devoid of the high-k gate dielectric 28 except at the gate corners 31. A gate dielectric 18 laterally abuts the high-k gate dielectric 28 present at the gate corners 31 and a gate spacer 36 laterally abuts the metal-containing gate conductor 30. The gate spacer 36 is located upon an upper surface of both the gate dielectric 18 and the high-k gate dielectric that is present at the gate corners 31.

Owner:TESSERA INC

Method of fabricating an ultra-narrow channel semiconductor device

A method of forming a nanowire is disclosed. A nanowire having a first dimension is deposited on a first dielectric layer that is formed on a substrate. A sacrificial gate stack having a sacrificial dielectric layer and a sacrificial gate electrode layer is deposited over a first region of the nanowire leaving exposed a second region and a third region of the nanowire. A first spacer is deposited on each side of the sacrificial gate stack. A second dielectric layer is deposited over the first dielectric layer to cover the second region and third region. The sacrificial gate stack is removed. The first region of the nanowire is thinned by at least one thermal oxidation process and oxide removal process to thin said first region from said first dimension to a second dimension.

Owner:TAHOE RES LTD

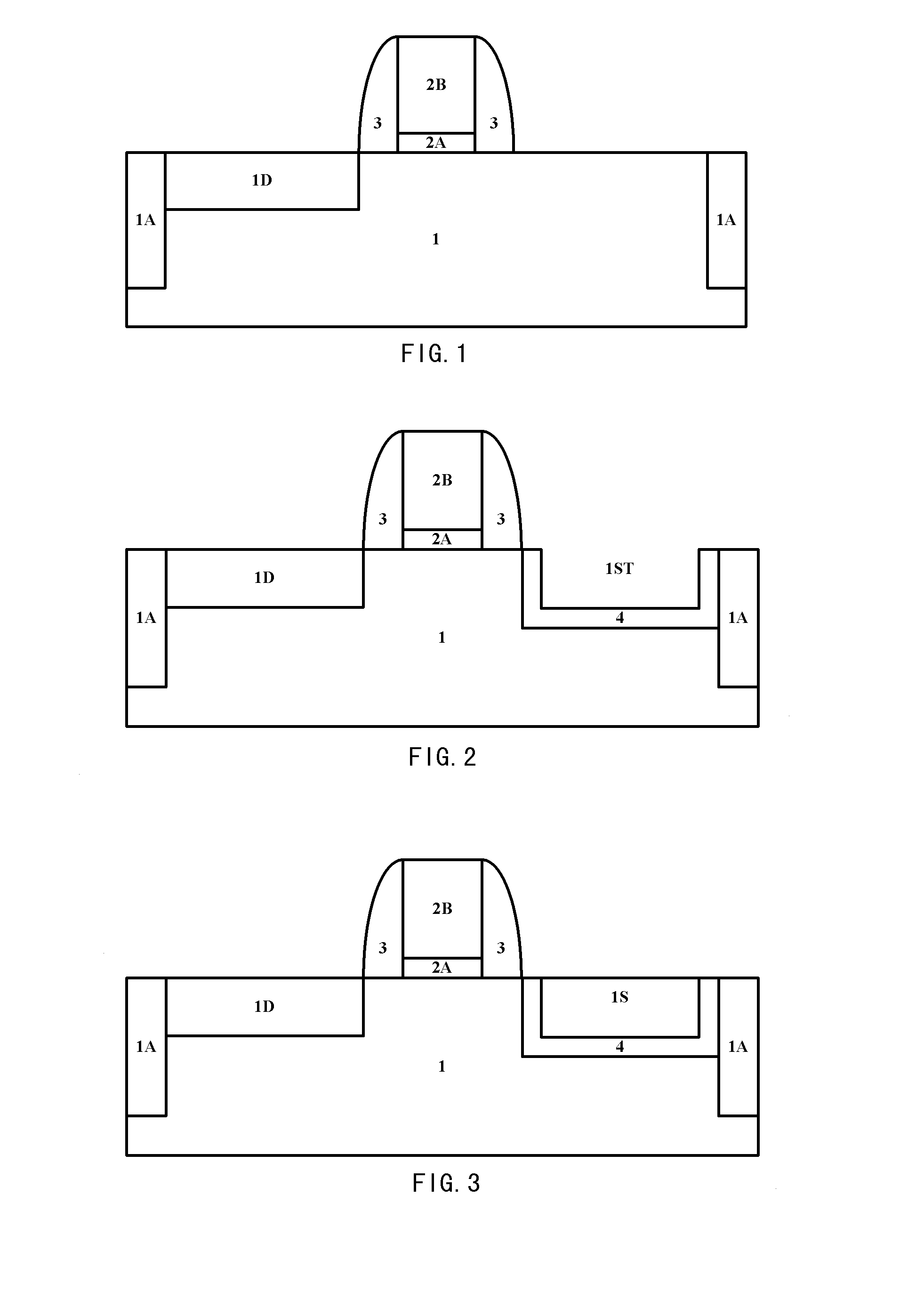

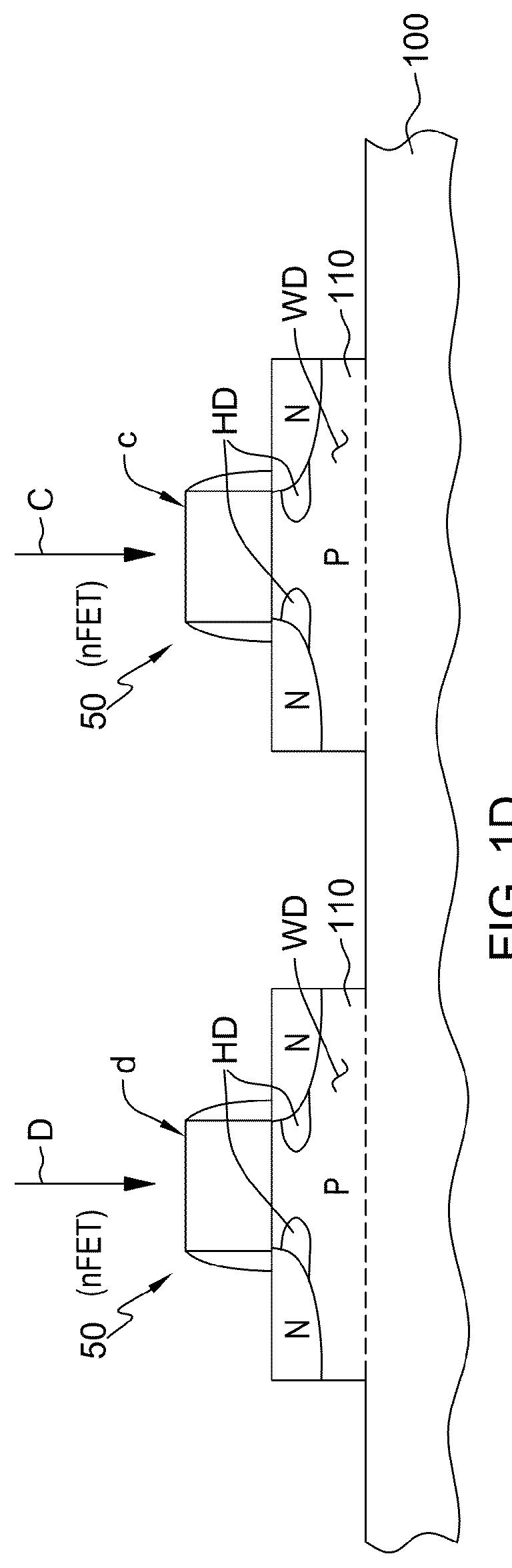

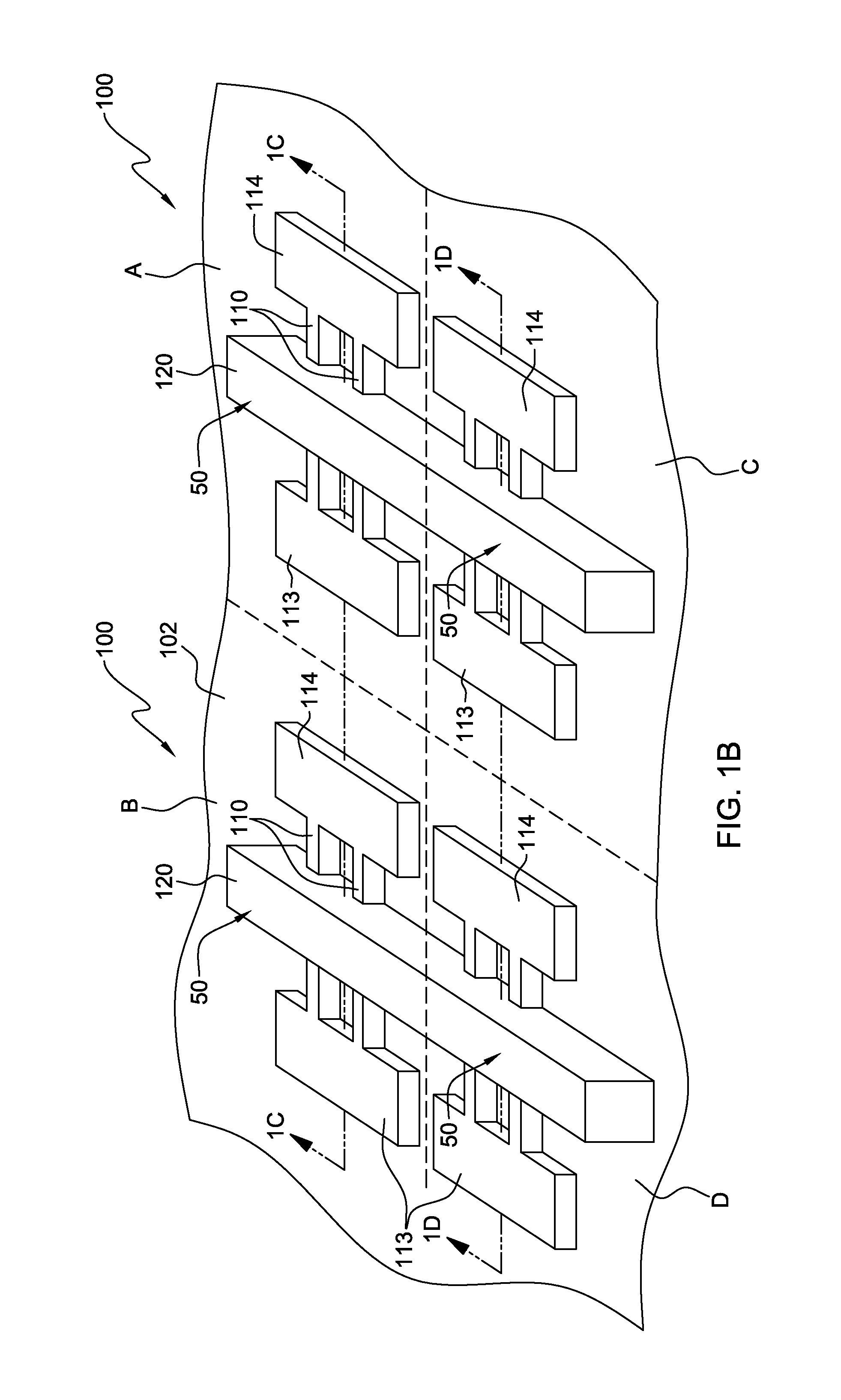

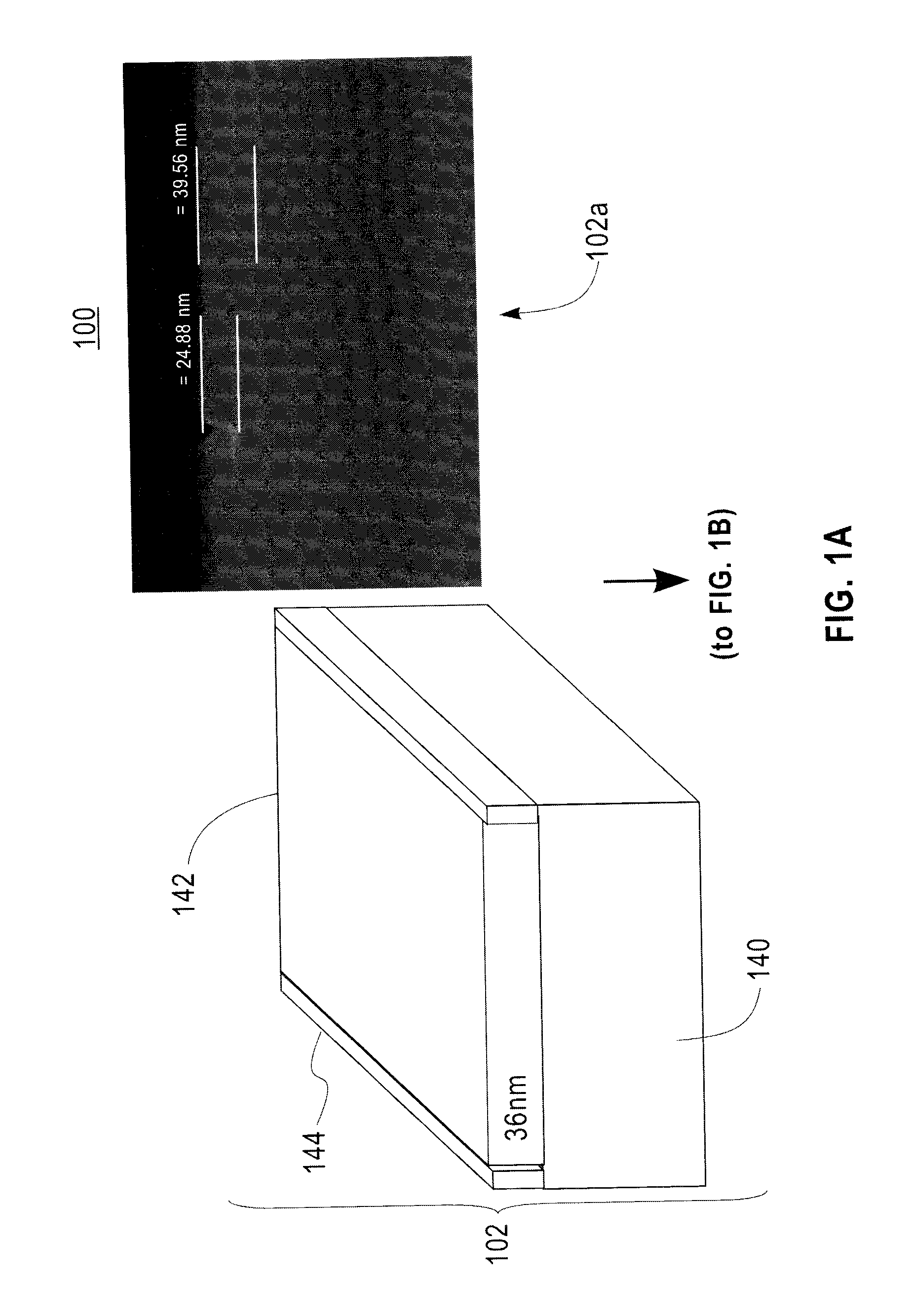

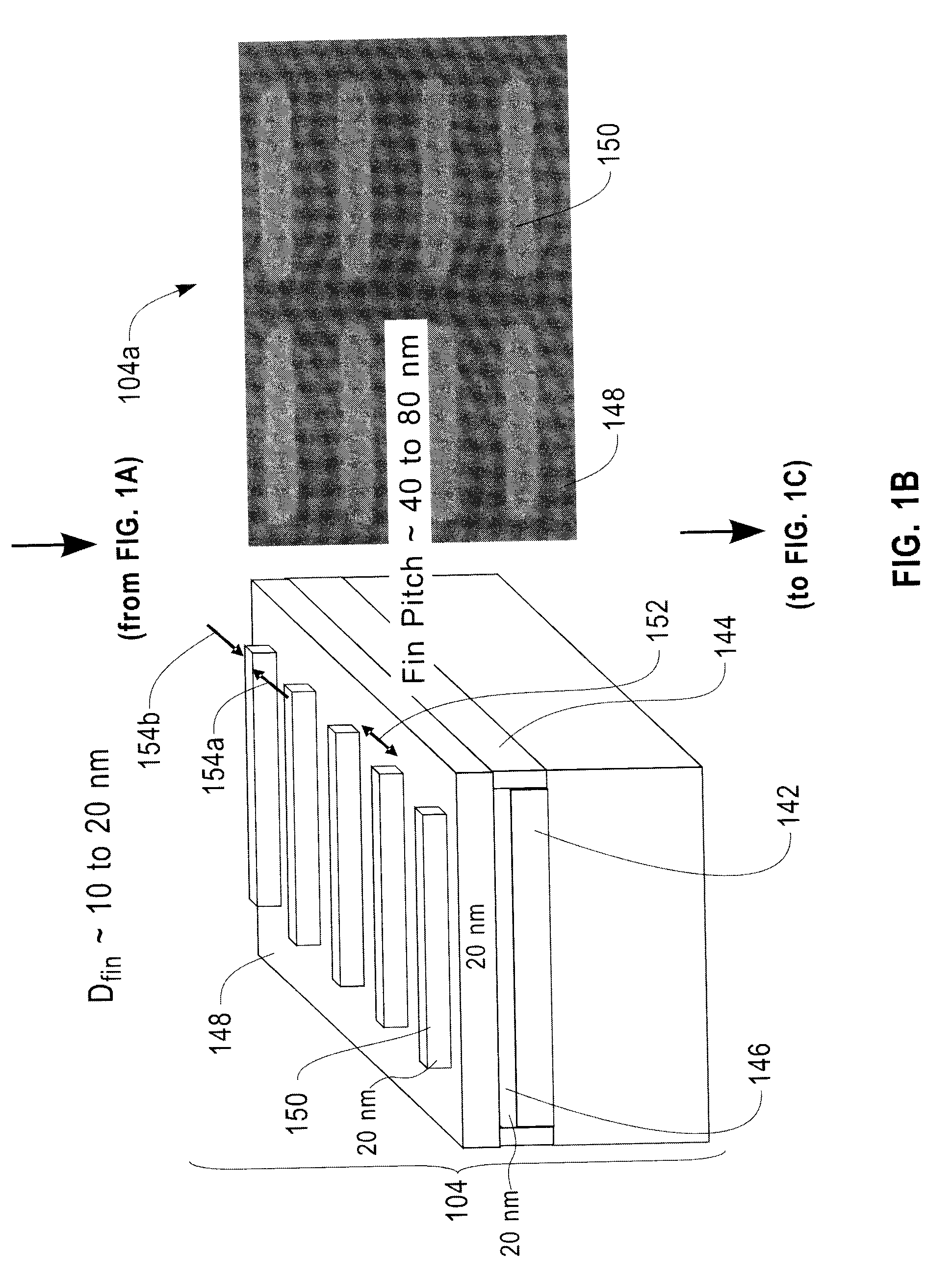

Fin Field Effect Transistor Devices with Self-Aligned Source and Drain Regions

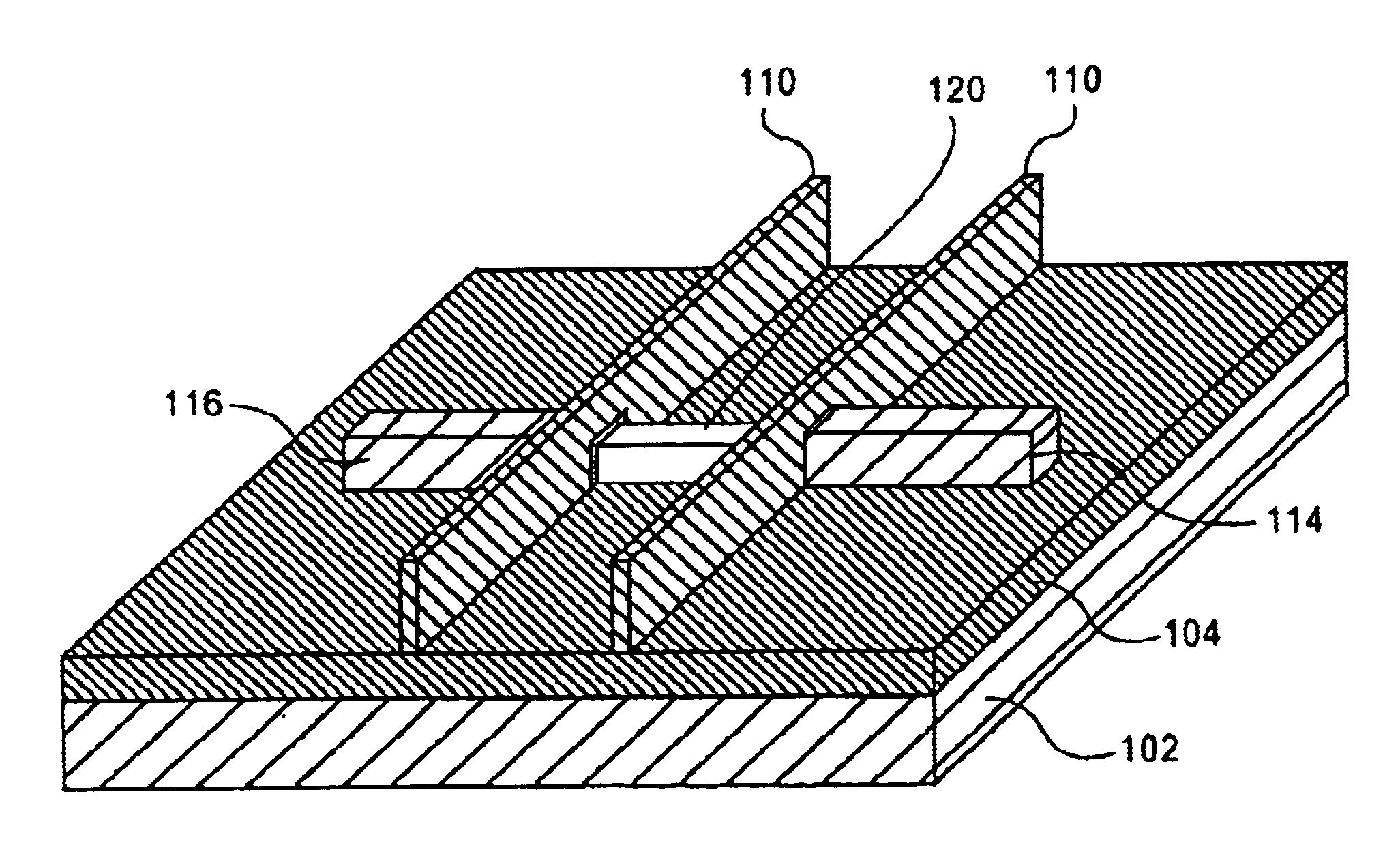

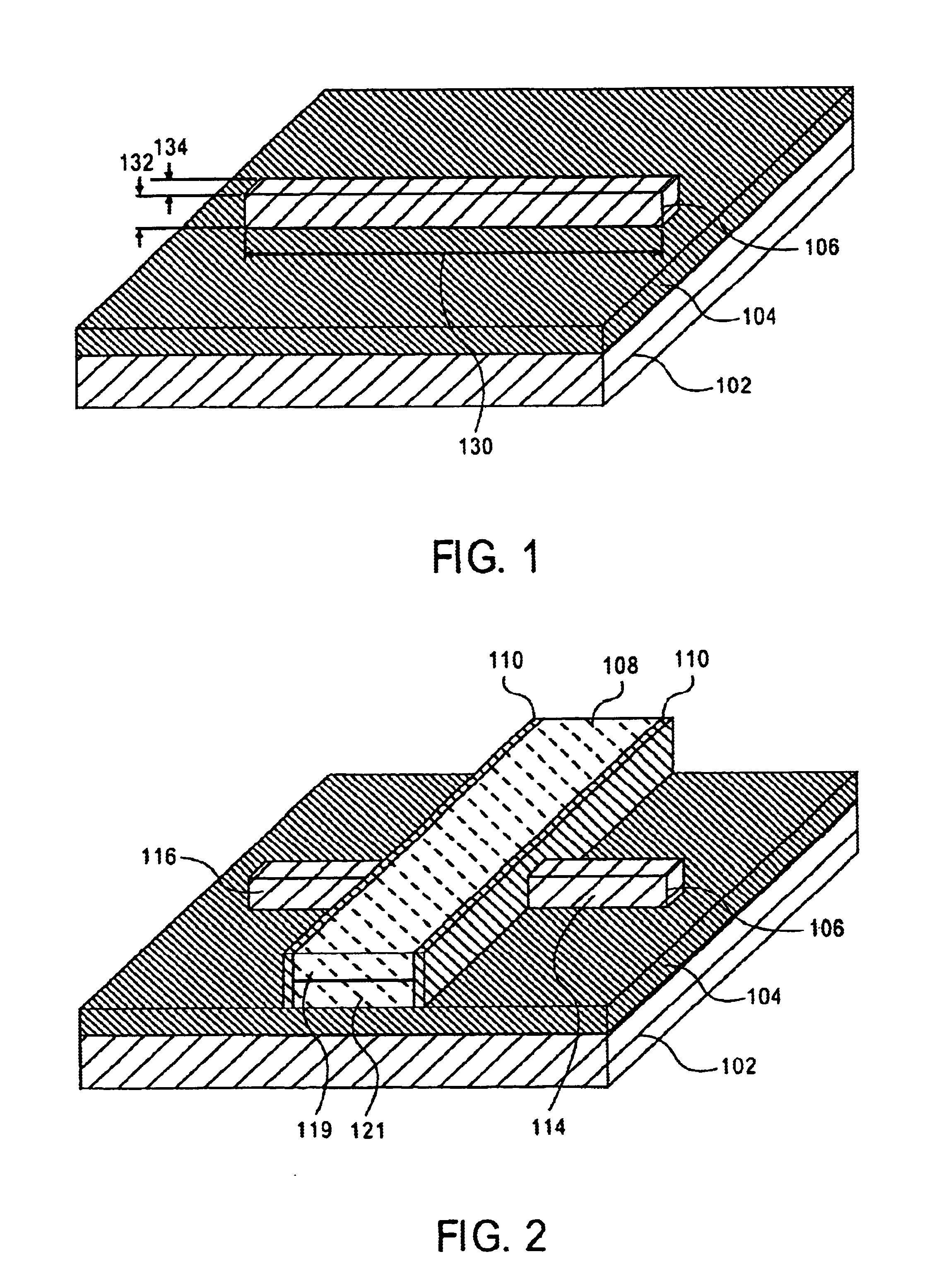

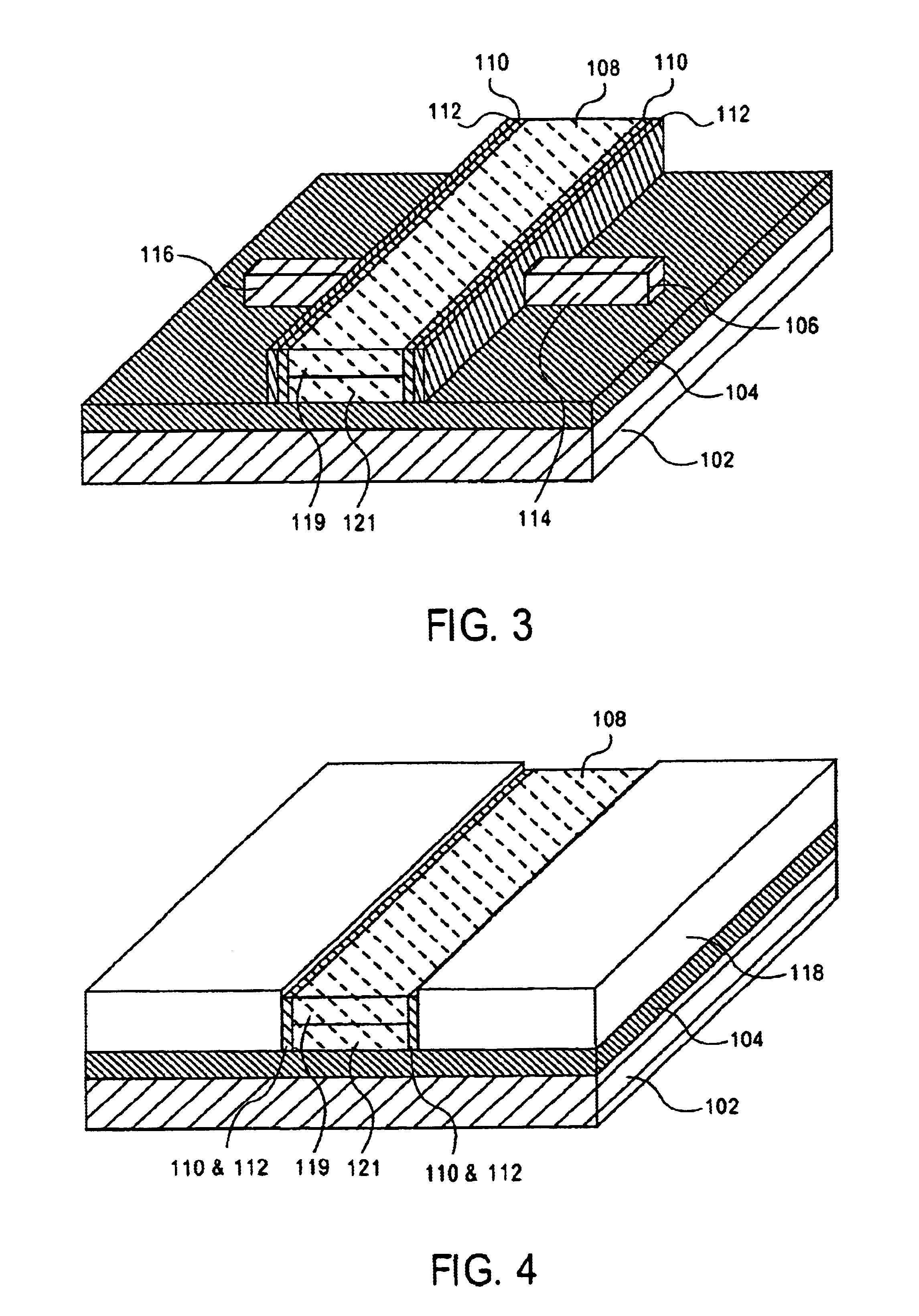

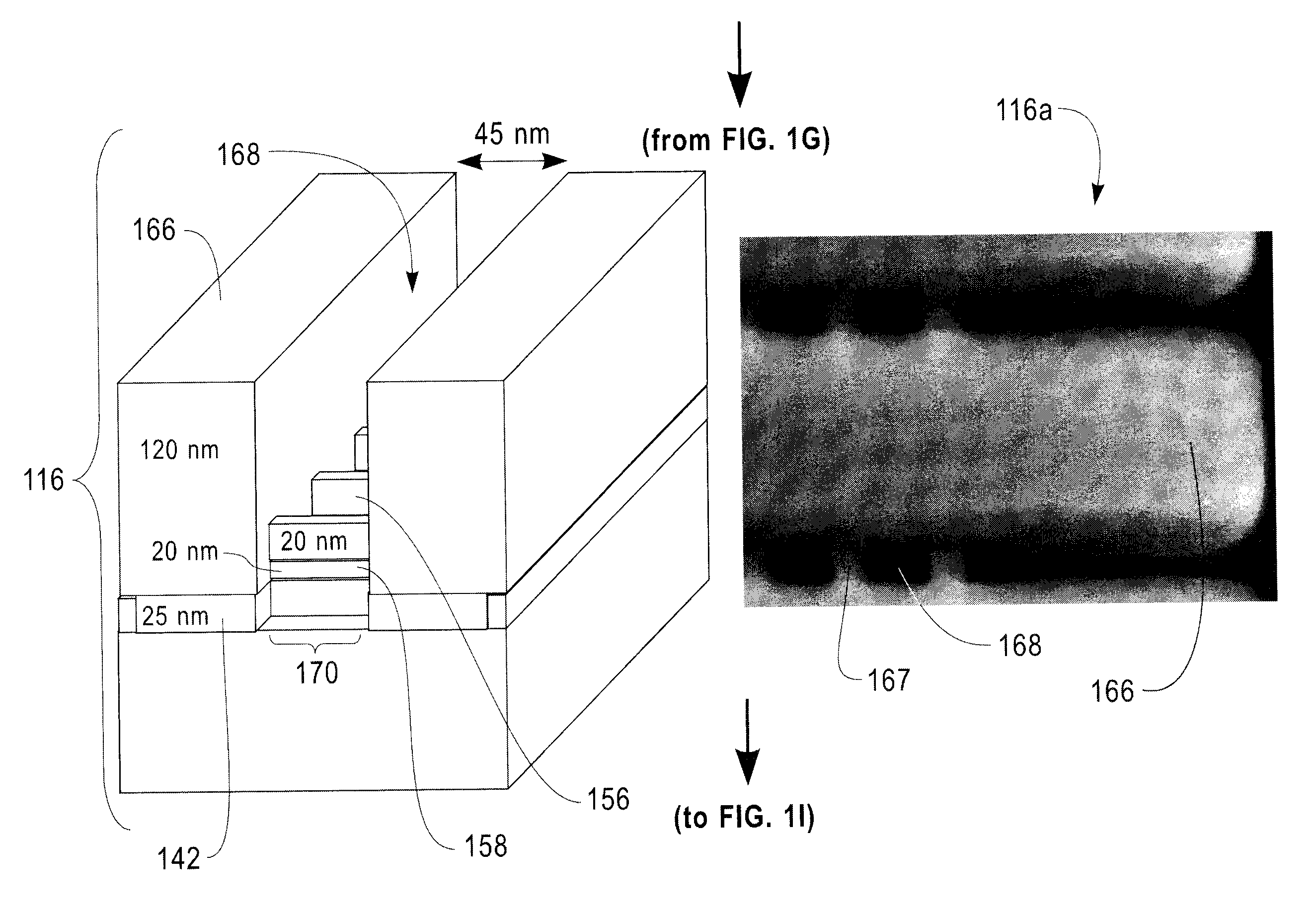

Improved fin field effect transistor (FinFET) devices and methods for the fabrication thereof are provided. In one aspect, a method for fabricating a field effect transistor device comprises the following steps. A substrate is provided having a silicon layer thereon. A fin lithography hardmask is patterned on the silicon layer. A dummy gate structure is placed over a central portion of the fin lithography hardmask. A filler layer is deposited around the dummy gate structure. The dummy gate structure is removed to reveal a trench in the filler layer, centered over the central portion of the fin lithography hardmask, that distinguishes a fin region of the device from source and drain regions of the device. The fin lithography hardmask in the fin region is used to etch a plurality of fins in the silicon layer. The trench is filled with a gate material to form a gate stack over the fins. The filler layer is removed to reveal the source and drain regions of the device, wherein the source and drain regions are intact and self-aligned with the gate stack.

Owner:GLOBALFOUNDRIES US INC

Method for etching high-k dielectric using pulsed bias power

InactiveUS20130052833A1Electric discharge tubesSemiconductor/solid-state device manufacturingDielectricPhysical chemistry

A method of patterning a gate stack on a substrate is described. The method includes preparing a gate stack on a substrate, wherein the gate stack includes a high-k layer and a gate layer formed on the high-k layer. The method further includes transferring a pattern formed in the gate layer to the high-k layer using a pulsed bias plasma etching process, and selecting a process condition for the pulsed bias plasma etching process to achieve a silicon recess formed in the substrate having a depth less than 2 nanometer (nm).

Owner:TOKYO ELECTRON LTD

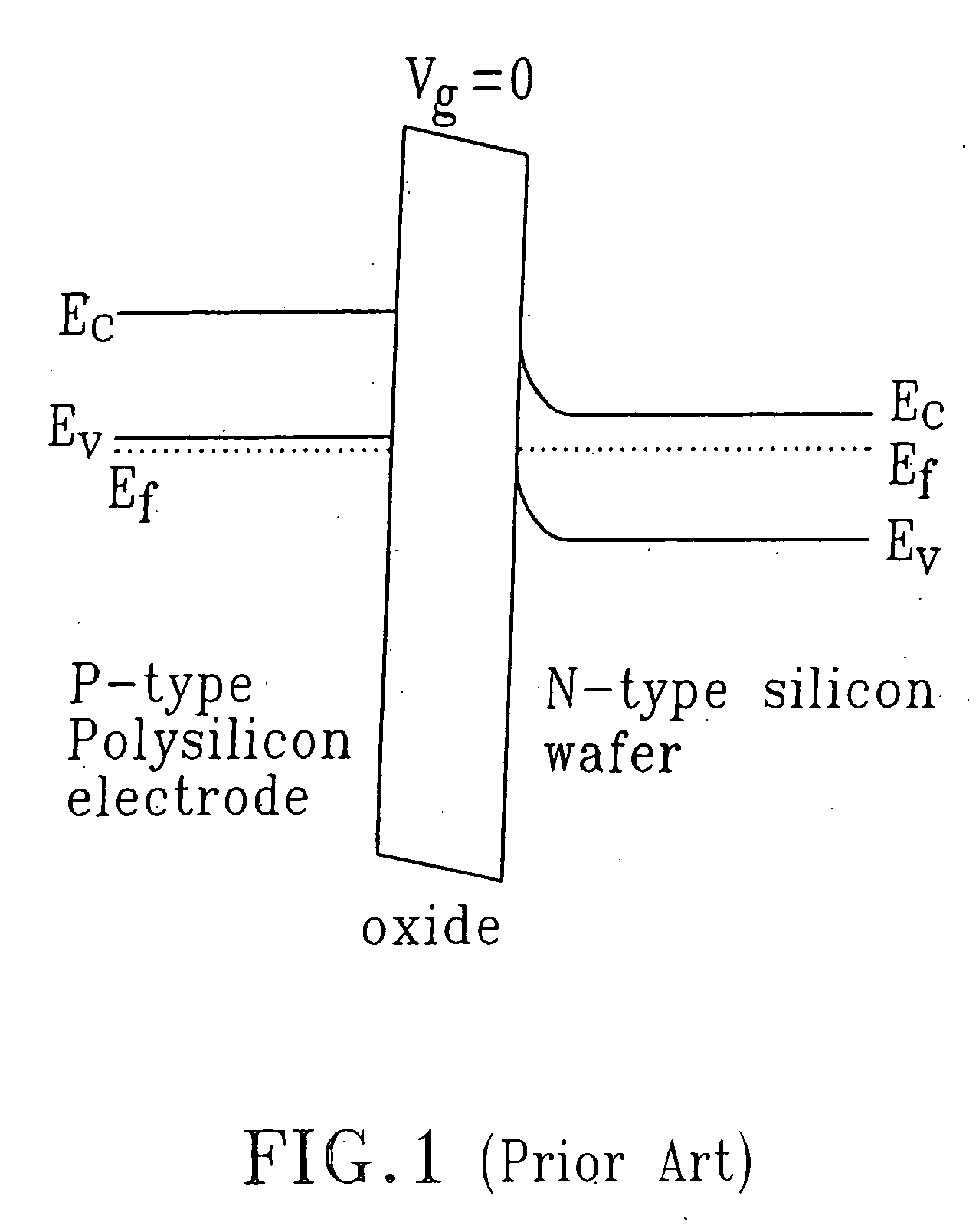

Nitrogen-containing field effect transistor gate stack containing a threshold voltage control layer formed via deposition of a metal oxide

InactiveUS20060102968A1Raise the threshold voltageImprove voltage stabilityTransistorSemiconductor/solid-state device detailsGate dielectricControl layer

A semiconductor structure is provided that includes a Vt stabilization layer between a gate dielectric and a gate electrode. The Vt stabilization layer is capable of stabilizing the structure's threshold voltage and flatband voltage to a targeted value and comprises a nitrided metal oxide, or a nitrogen-free metal oxide, with the proviso that when the Vt stabilization layer comprises a nitrogen-free metal oxide, at least one of the semiconductor substrate or the gate dielectric includes nitrogen. The present invention also provides a method of fabricating such a structure.

Owner:GLOBALFOUNDRIES INC

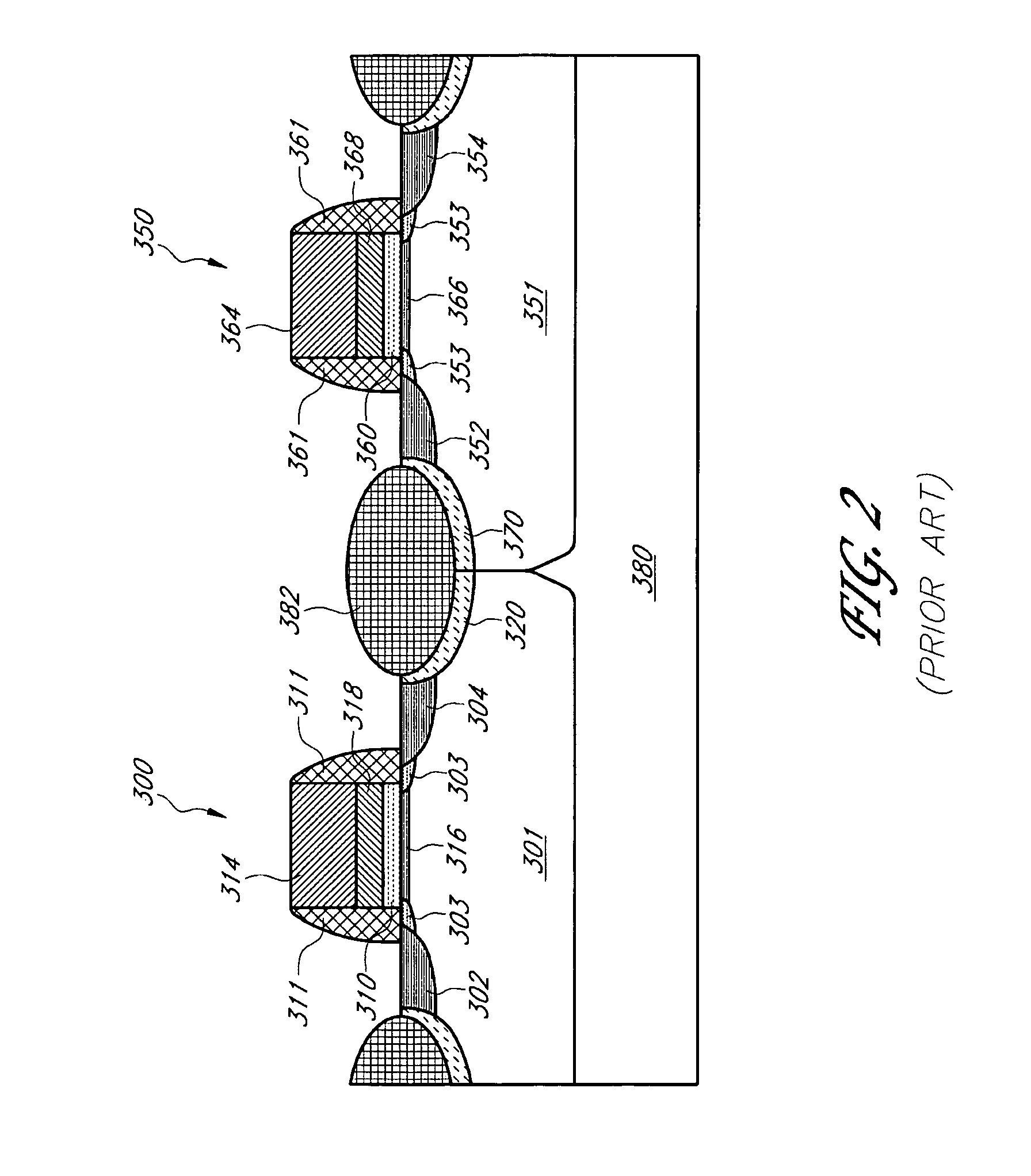

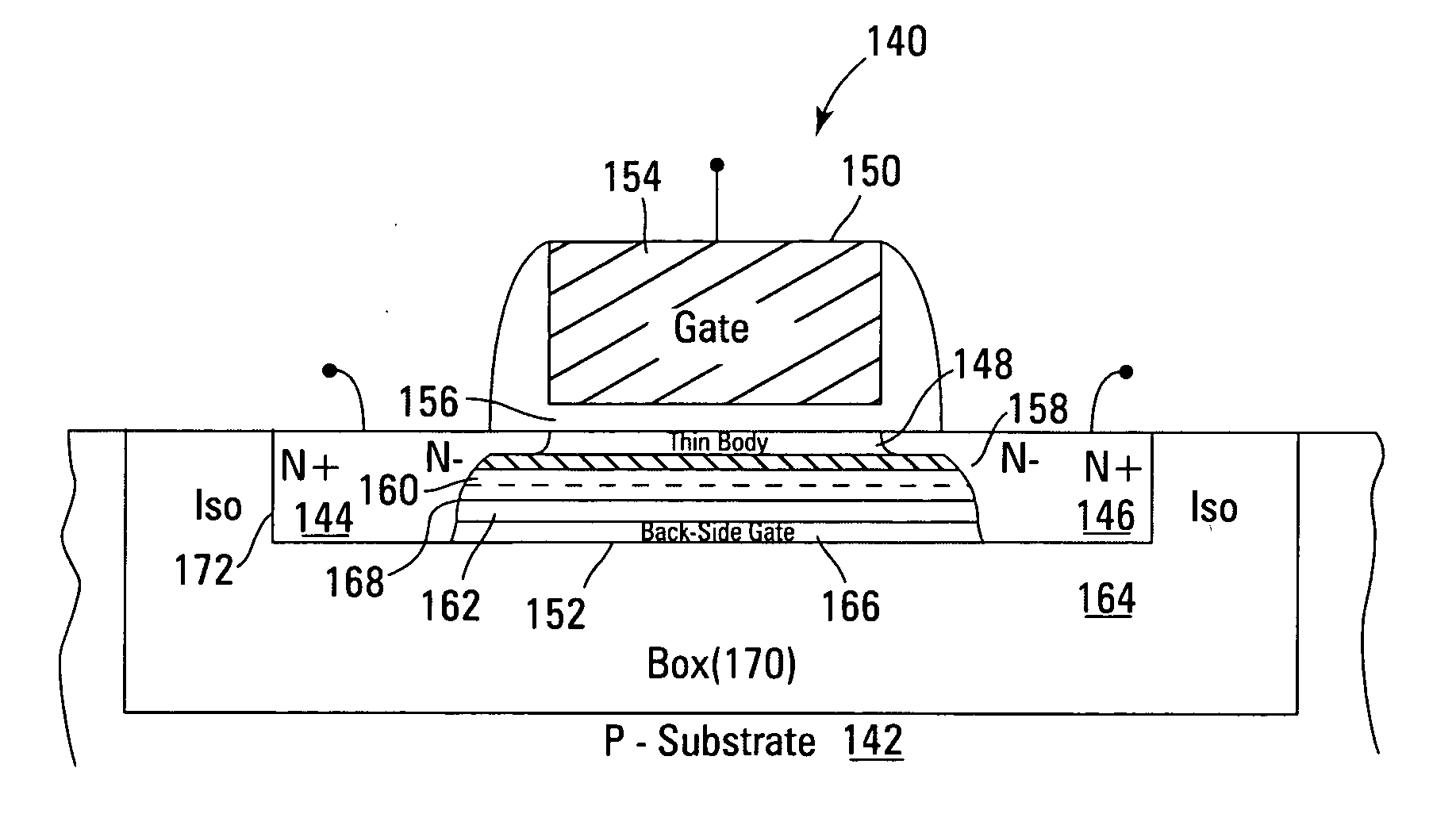

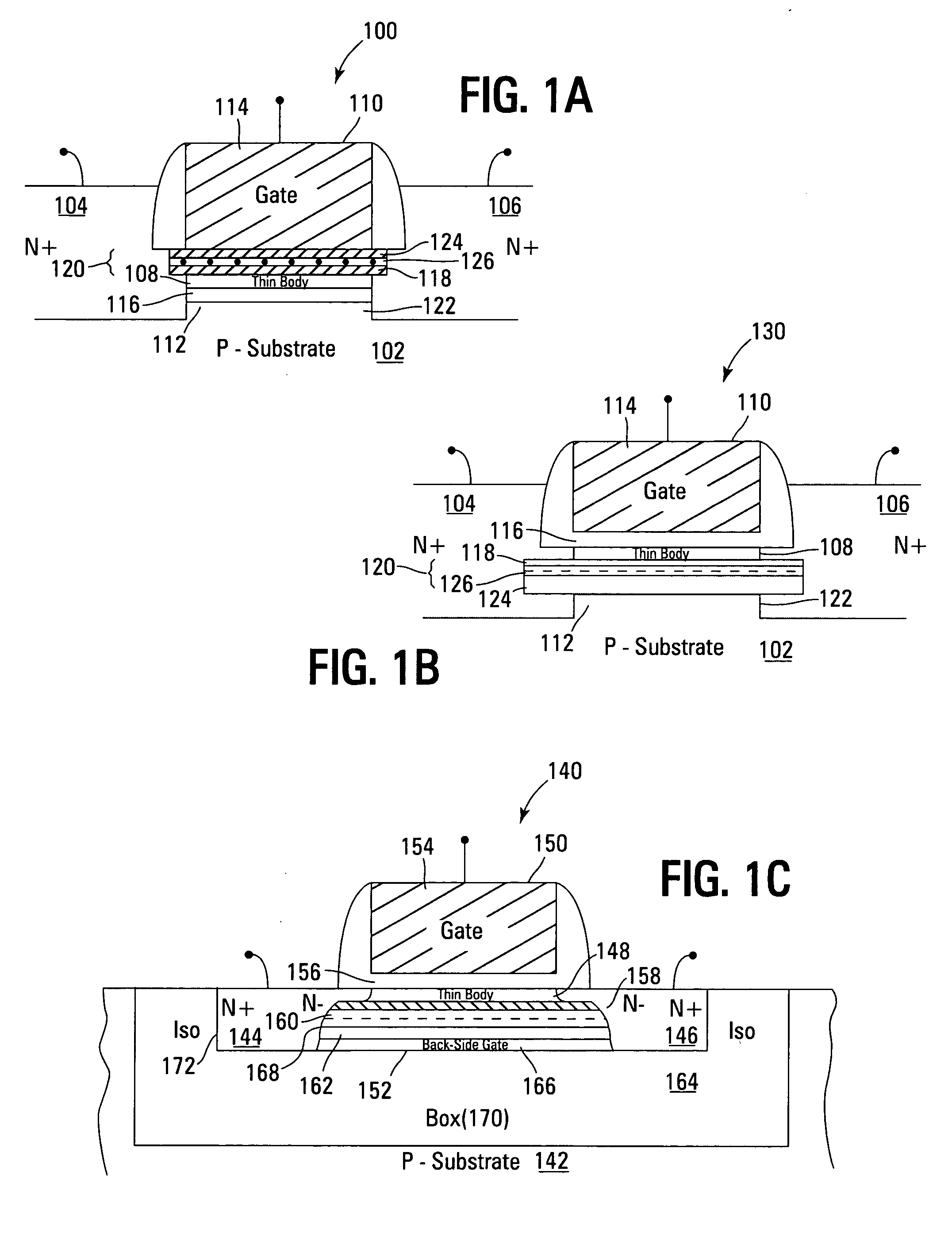

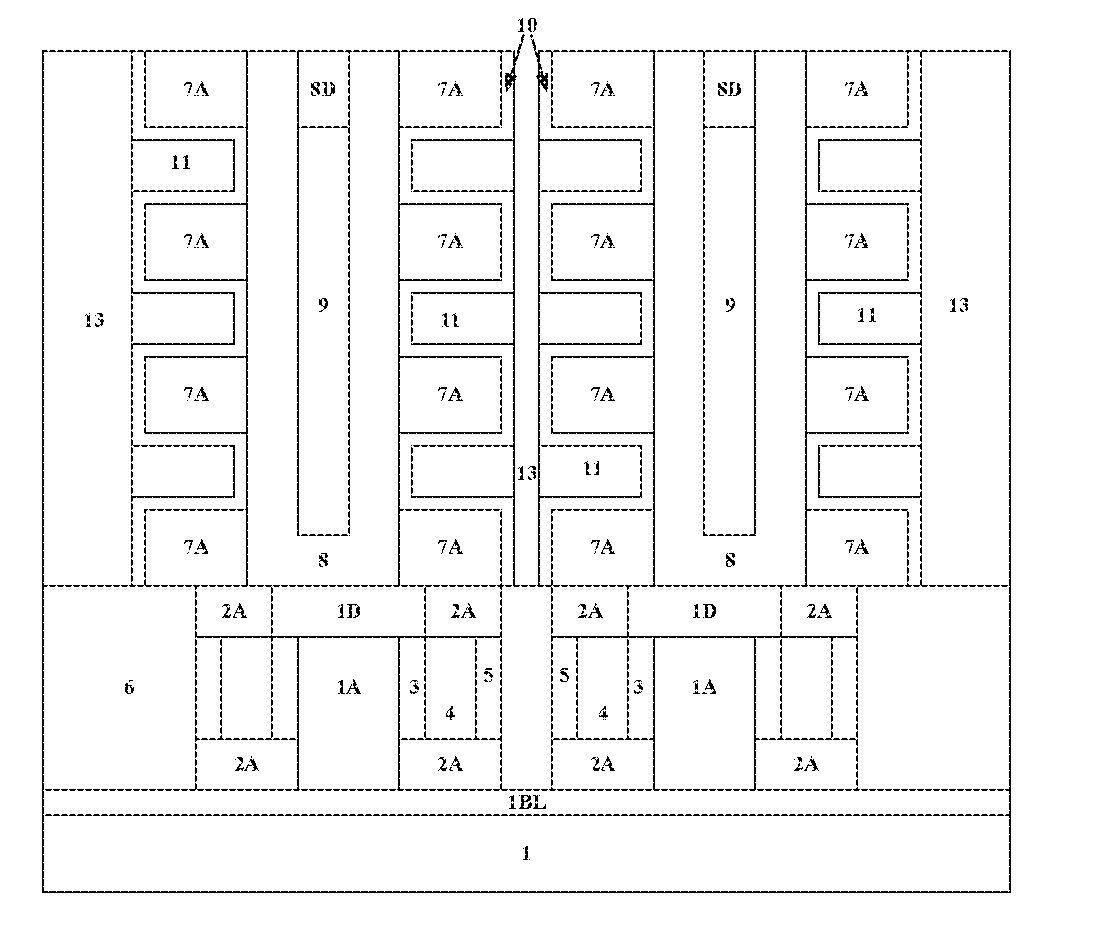

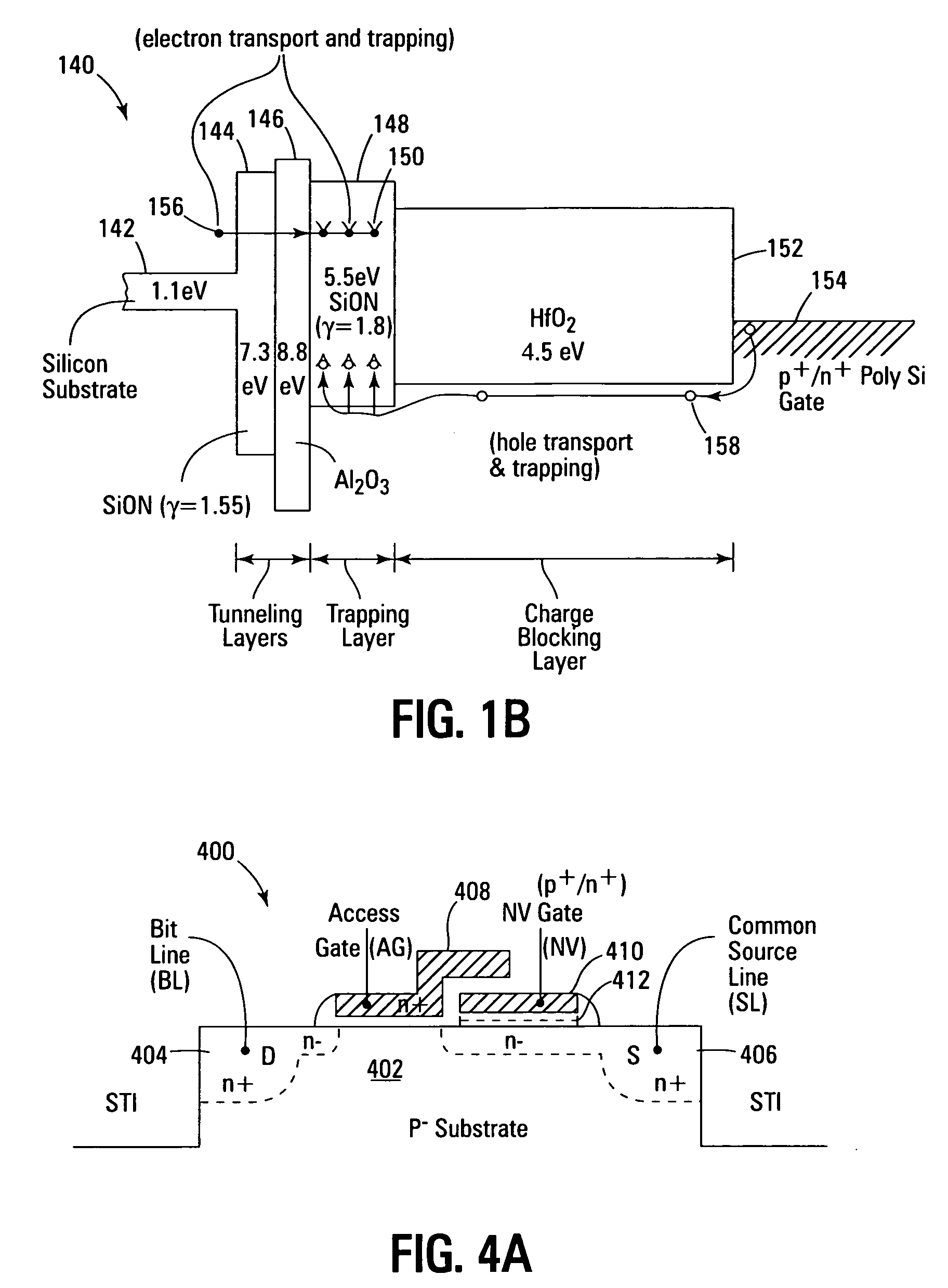

High density NAND non-volatile memory device

ActiveUS20070012988A1Efficient eraseReduce harmSolid-state devicesRead-only memoriesCharge retentionLow voltage

Non-volatile memory devices and arrays are described that utilize dual gate (or back-side gate) non-volatile memory cells with band engineered gate-stacks that are placed above or below the channel region in front-side or back-side charge trapping gate-stack configurations in NAND memory array architectures. The band-gap engineered gate-stacks with asymmetric or direct tunnel barriers of the floating node memory cells of embodiments of the present invention allow for low voltage tunneling programming and efficient erase with electrons and holes, while maintaining high charge blocking barriers and deep carrier trapping sites for good charge retention. The memory cell architecture also allows for improved high density memory devices or arrays with the utilization of reduced feature word lines and vertical select gates.

Owner:MICRON TECH INC

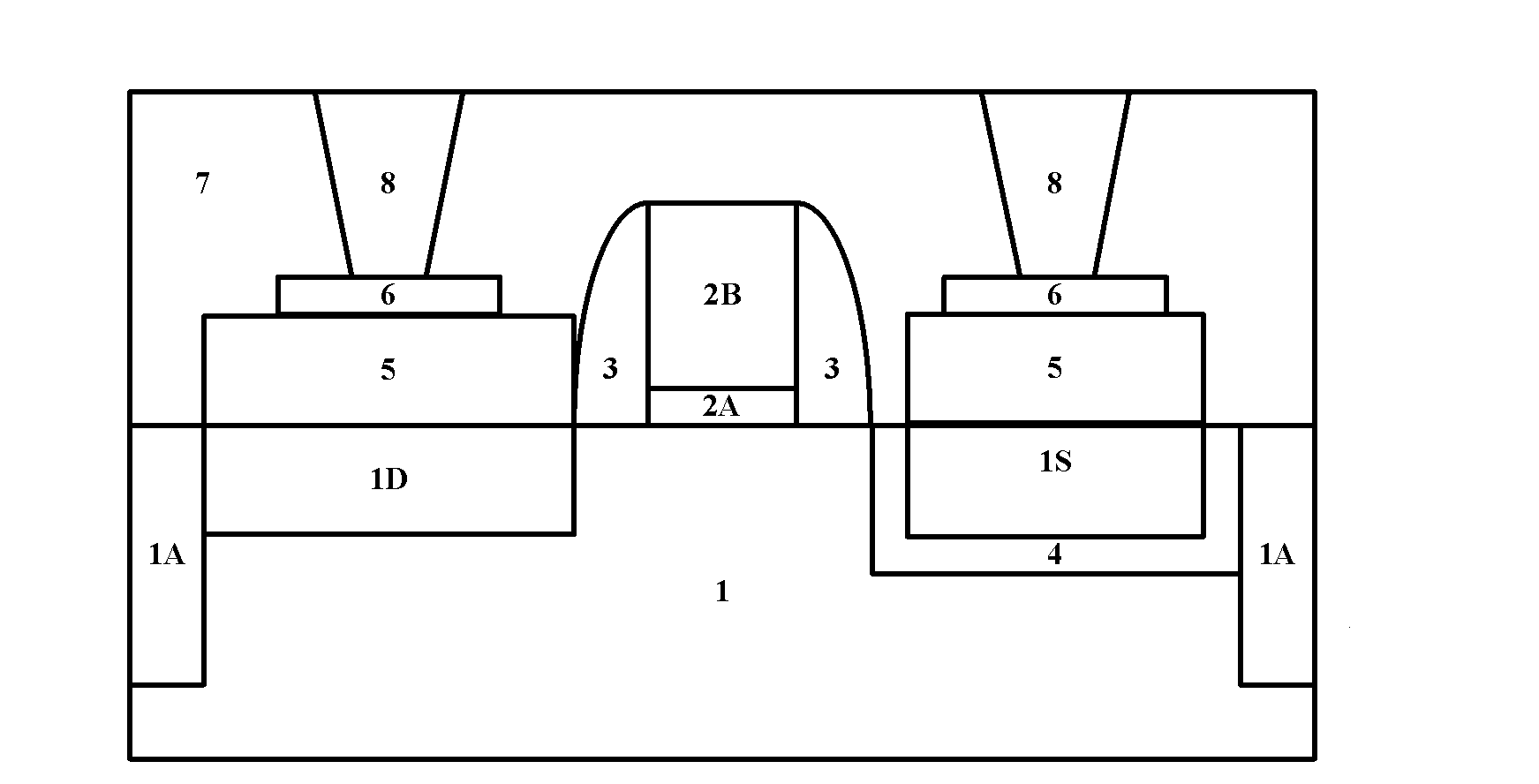

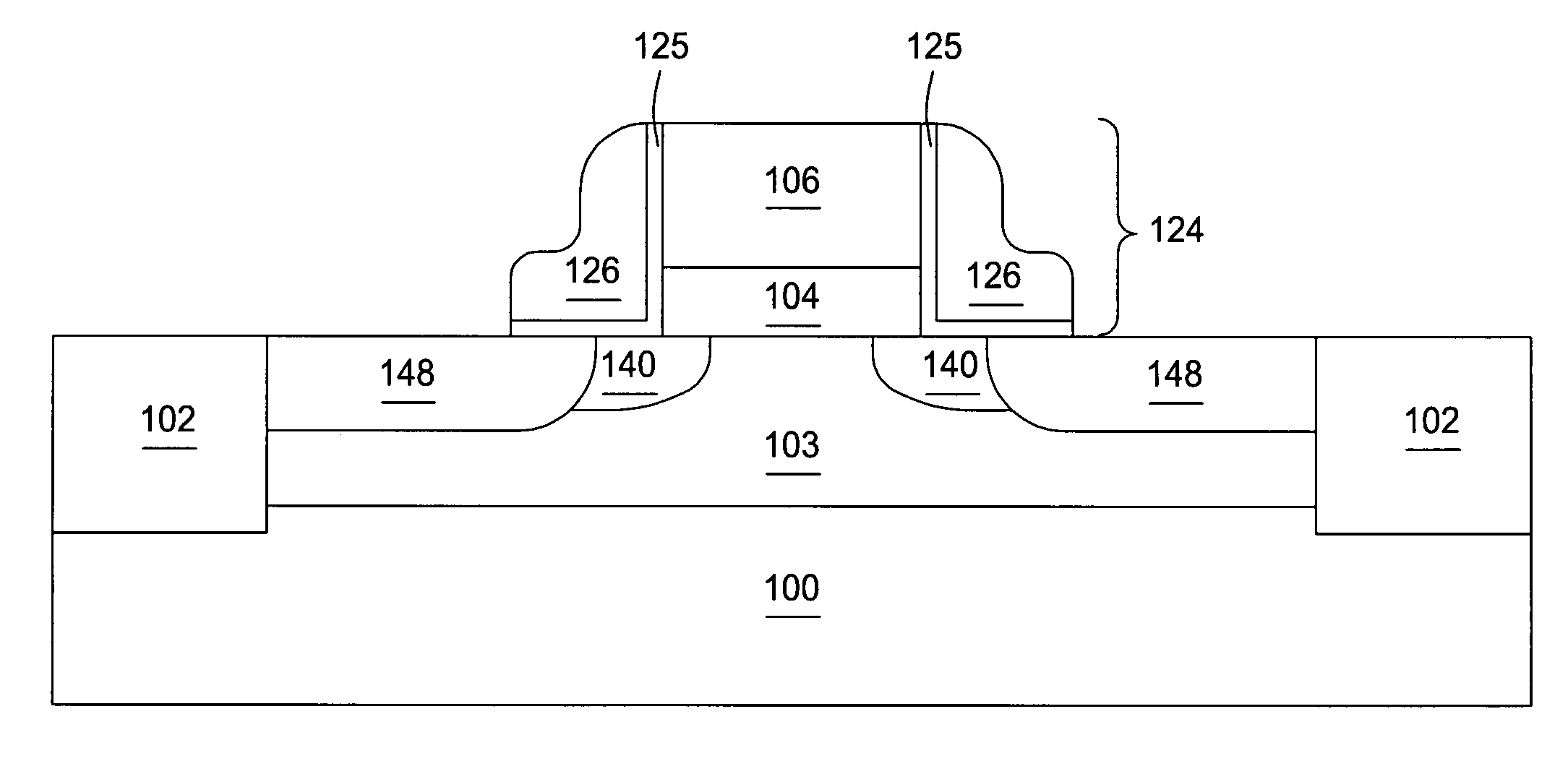

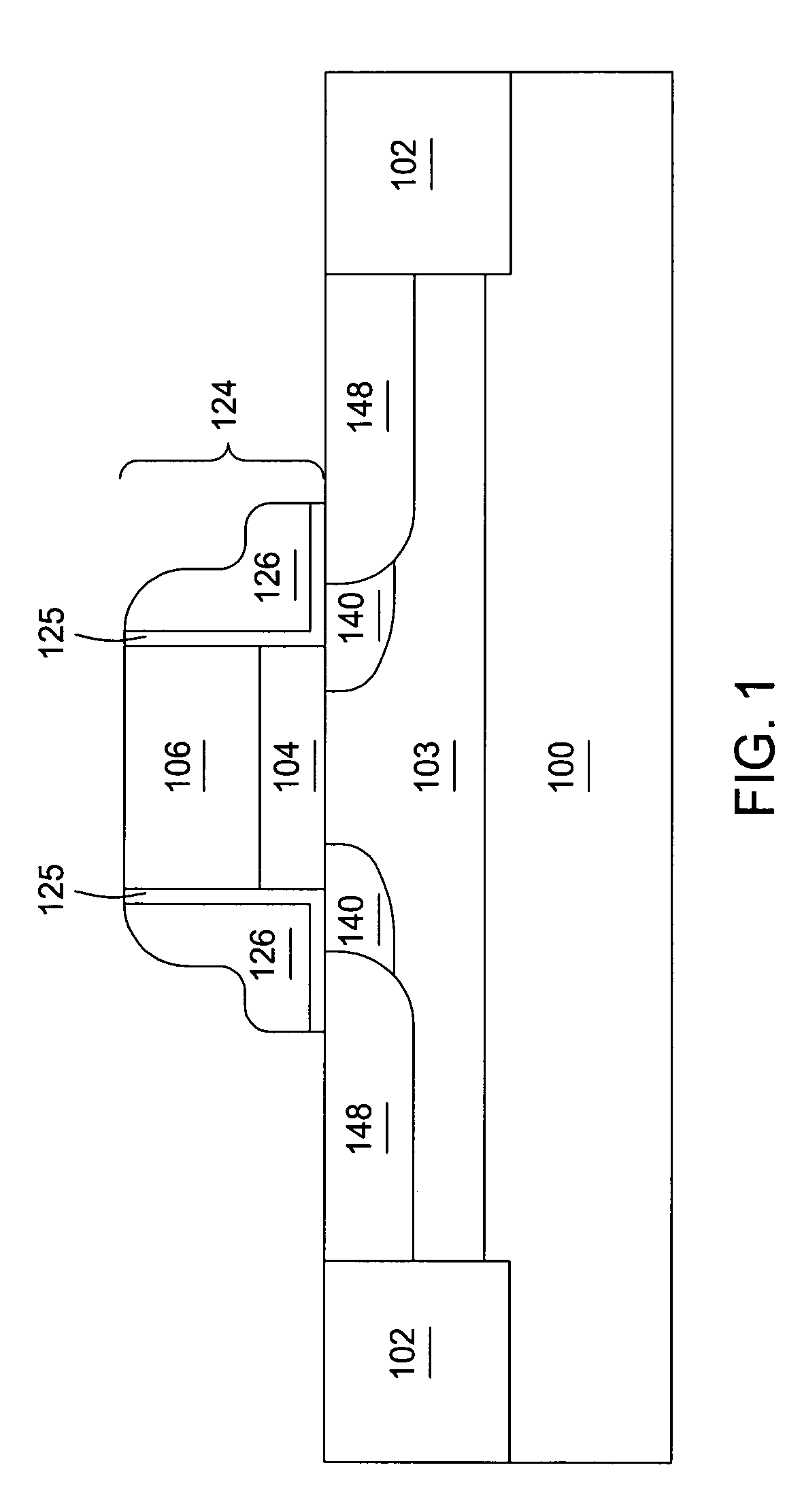

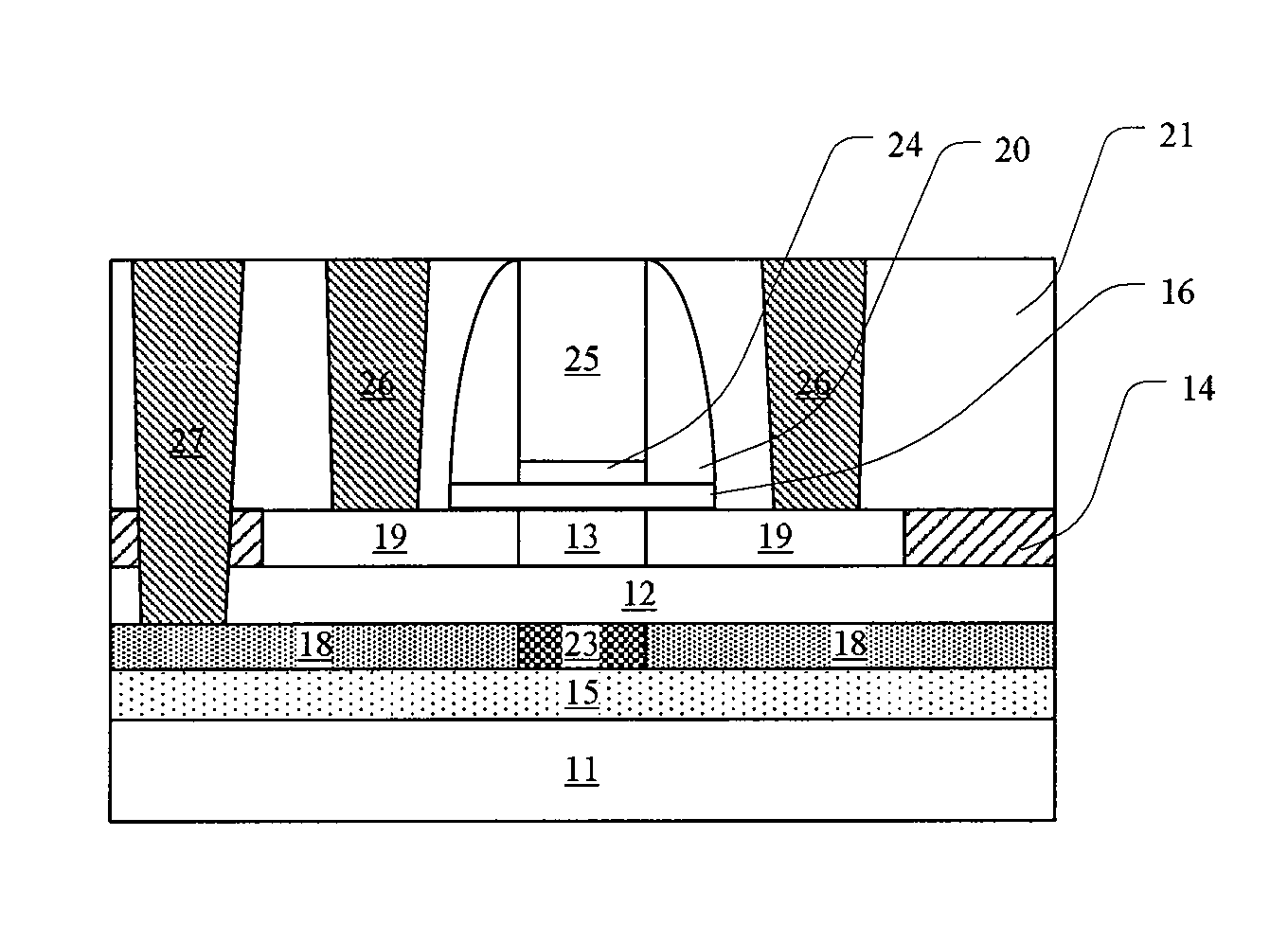

Transistor, Semiconductor Device Comprising the Transistor and Method for Manufacturing the Same

ActiveUS20120153393A1Simple manufacturing processReduce manufacturing costSolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricElectrical conductor

The invention relates to a transistor, a semiconductor device comprising the transistor and manufacturing methods for the transistor and the semiconductor device. The transistor according to the invention comprises: a substrate comprising at least a base layer, a first semiconductor layer, an insulating layer and a second semiconductor layer stacked sequentially; a gate stack formed on the second semiconductor layer; a source region and a drain region located on both sides of the gate stack respectively; a back gate comprising a back gate dielectric and a back gate electrode formed by the insulating layer and the first semiconductor layer, respectively; and a back gate contact formed on a portion of the back gate electrode. The back gate contact comprises an epitaxial part raised from the surface of the back gate electrode, and each of the source region and the drain region comprises an epitaxial part raised from the surface of the second semiconductor layer. As compared to a conventional transistor, the manufacturing process of the transistor of the invention is simplified and the cost of manufacture is reduced.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Plasma for patterning advanced gate stacks

InactiveUS20070099428A1Avoid attackSemiconductor/solid-state device manufacturingSemiconductor devicesPlasma compositionNitrogen

A plasma composition and its use in a method for the dry etching of a stack of at least one material chemically too reactive towards the use of a Cl-based plasma are provided. Small amounts of nitrogen (5% up to 10%) can be added to a BCl3 comprising plasma and used in an anisotropical dry etching method whereby a passivation film is deposited onto the vertical sidewalls of stack etched for protecting the vertical sidewalls from lateral attack such that straight profiles can be obtained.

Owner:INTERUNIVERSITAIR MICRO ELECTRONICS CENT (IMEC VZW)

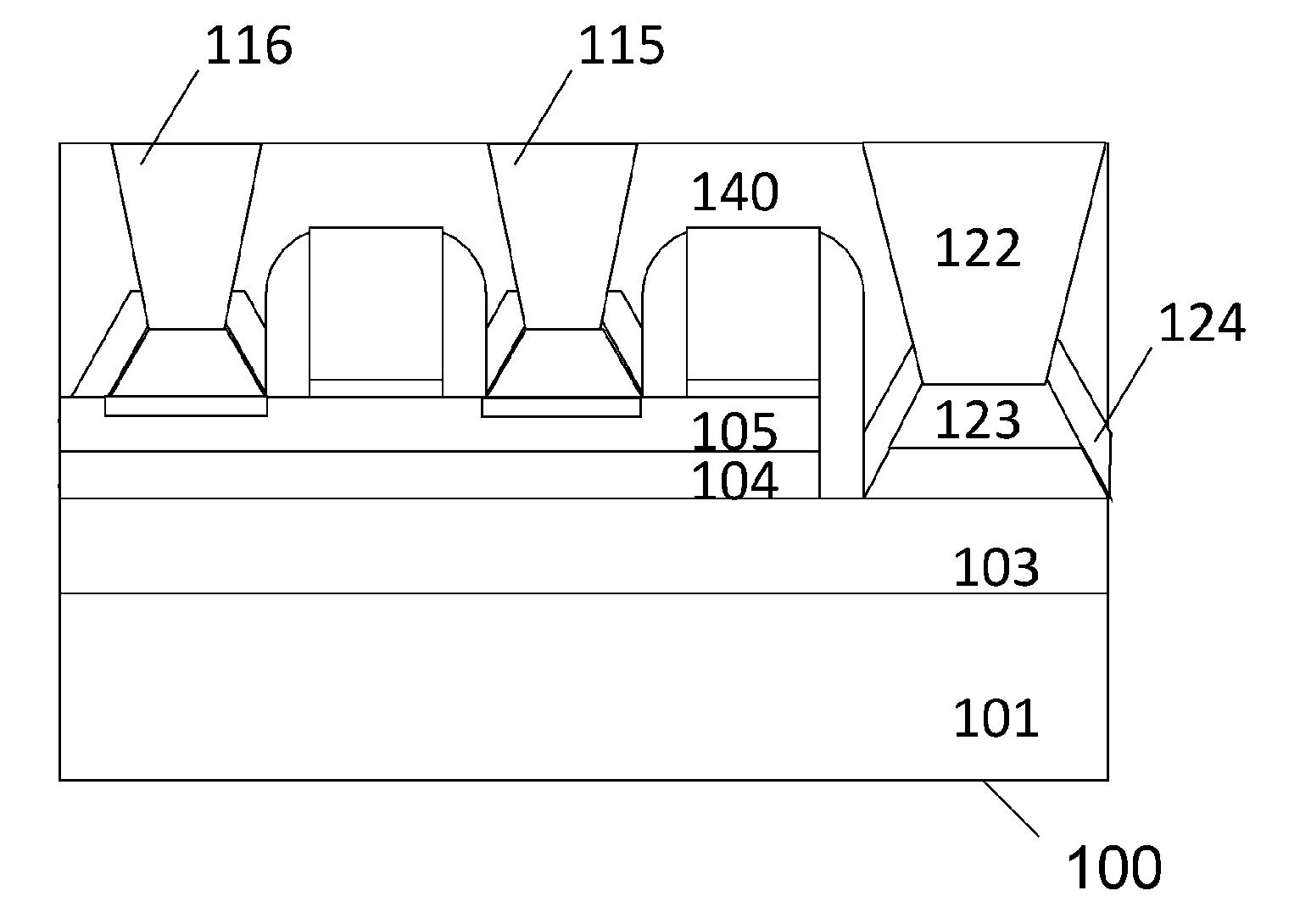

Three-Dimensional Semiconductor Device and Manufacturing Method Therefor

InactiveUS20170154895A1Improve control characteristicsReduce off-state leakage currentSolid-state devicesSemiconductor/solid-state device manufacturingMOSFETEtching

A three-dimensional semiconductor device, comprising a plurality of memory cell transistors and a plurality of select transistors at least partially overlapped in the vertical direction, wherein each select transistor comprises a first drain, an active region and a common source formed in the substrate, distributed along the vertical direction, as well as a metal gate distributed around the active region; wherein each memory cell transistor comprises a channel layer distributed perpendicularly to the substrate surface, a plurality of inter-layer insulating layers and a plurality of gate stack structures alternately stacked along the sidewalls of said channel layer, a second drain located on top of said channel layer; wherein said channel layer and said the first drain are electrically connected. In accordance with the three-dimensional semiconductor memory device and manufacturing method of the present invention, the multi-gate MOSFET is formed beneath the stack structure of the memory cell string including vertical channel to serve as the select transistor, this can improve the control characteristics of the gate threshold voltage, reduce the off-state leakage current, prevent the substrate from over-etching, and effectively improve the reliability of the device.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

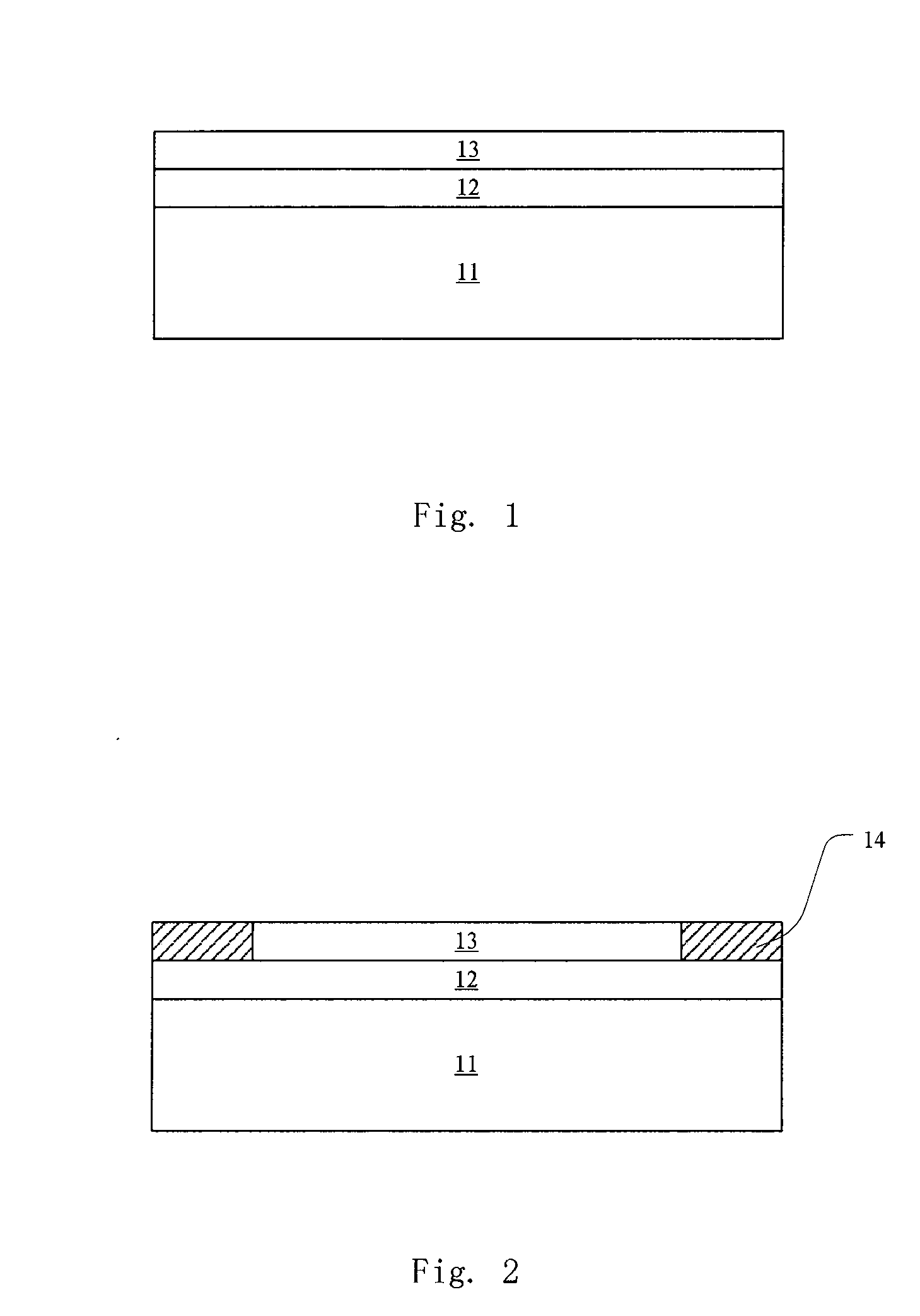

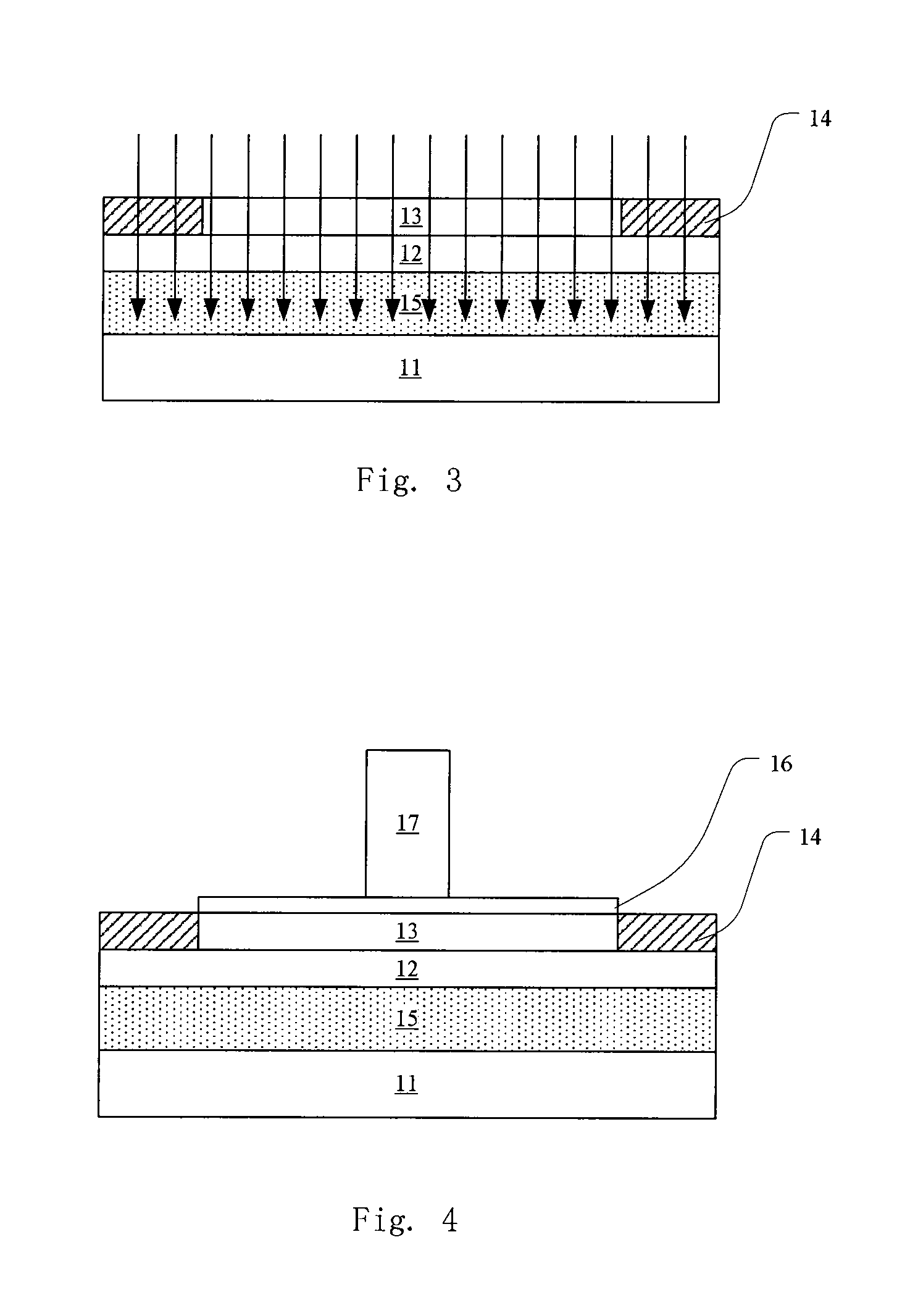

Mosfet and method for manufacturing the same

ActiveUS20130099315A1Adjustment of threshold voltageRaise the threshold voltageTransistorSolid-state devicesMOSFETWafering

The present disclosure discloses a MOSFET and a method for manufacturing the same, wherein the MOSFET comprises: an SOI wafer which comprises a semiconductor substrate, a buried insulating layer, and a semiconductor layer, the buried insulating layer being on the semiconductor substrate, and the semiconductor layer being on the buried insulating layer; a gate stack on the semiconductor layer; a source region and a drain region, which are in the semiconductor layer and on opposite sides of the gate stack; and a channel region, which is in the semiconductor layer and sandwiched by the source region and the drain region, wherein the MOSFET further comprises a back gate, the back gate being located in the semiconductor substrate and having a first doped region in a lower portion of the back gate and a second doped region in an upper portion of the back gate. The MOSFET can adjust the threshold voltage by changing the doping type and doping concentration of the anti-doped region.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Asymmetric band-gap engineered nonvolatile memory device

Owner:MICRON TECH INC

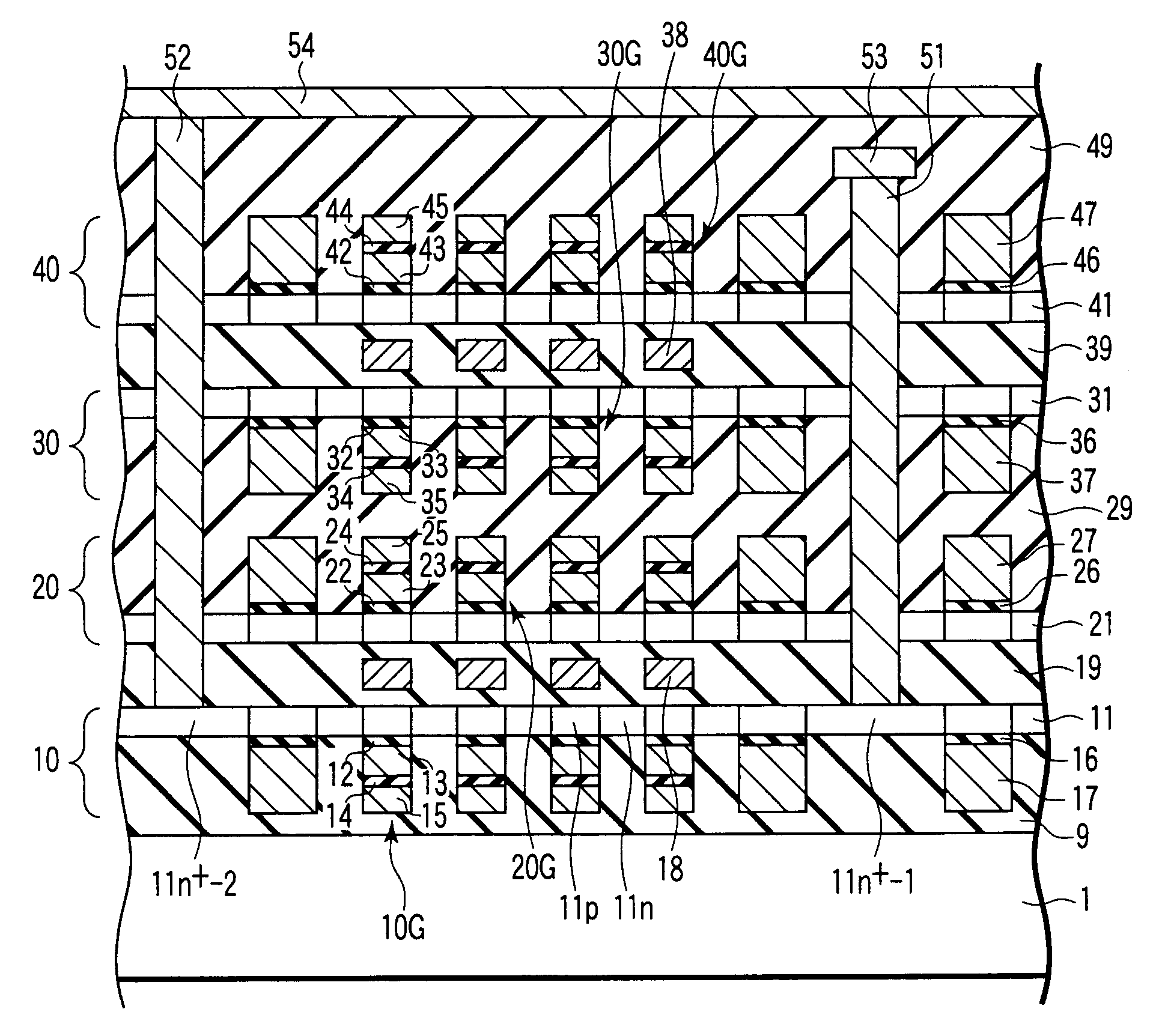

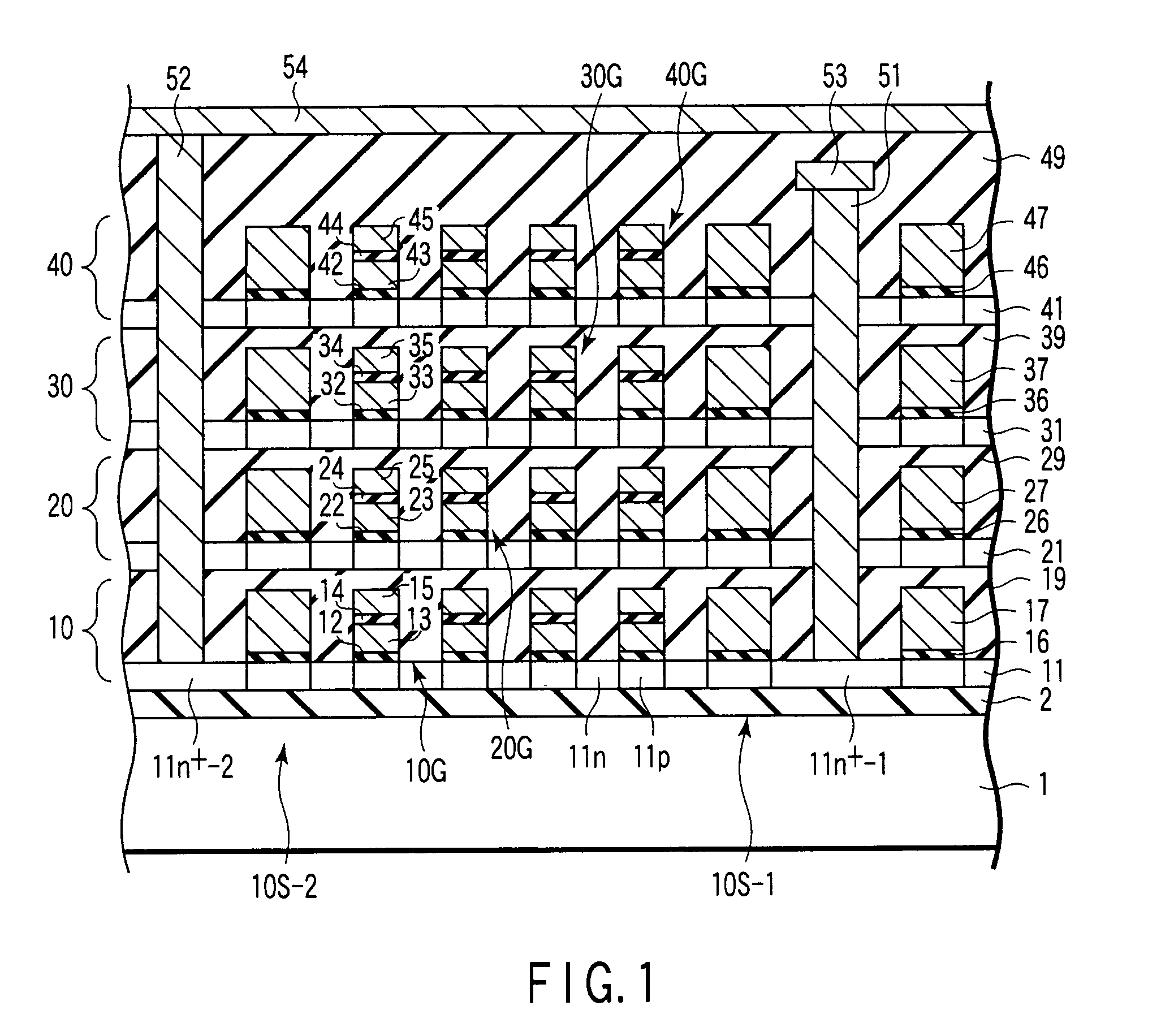

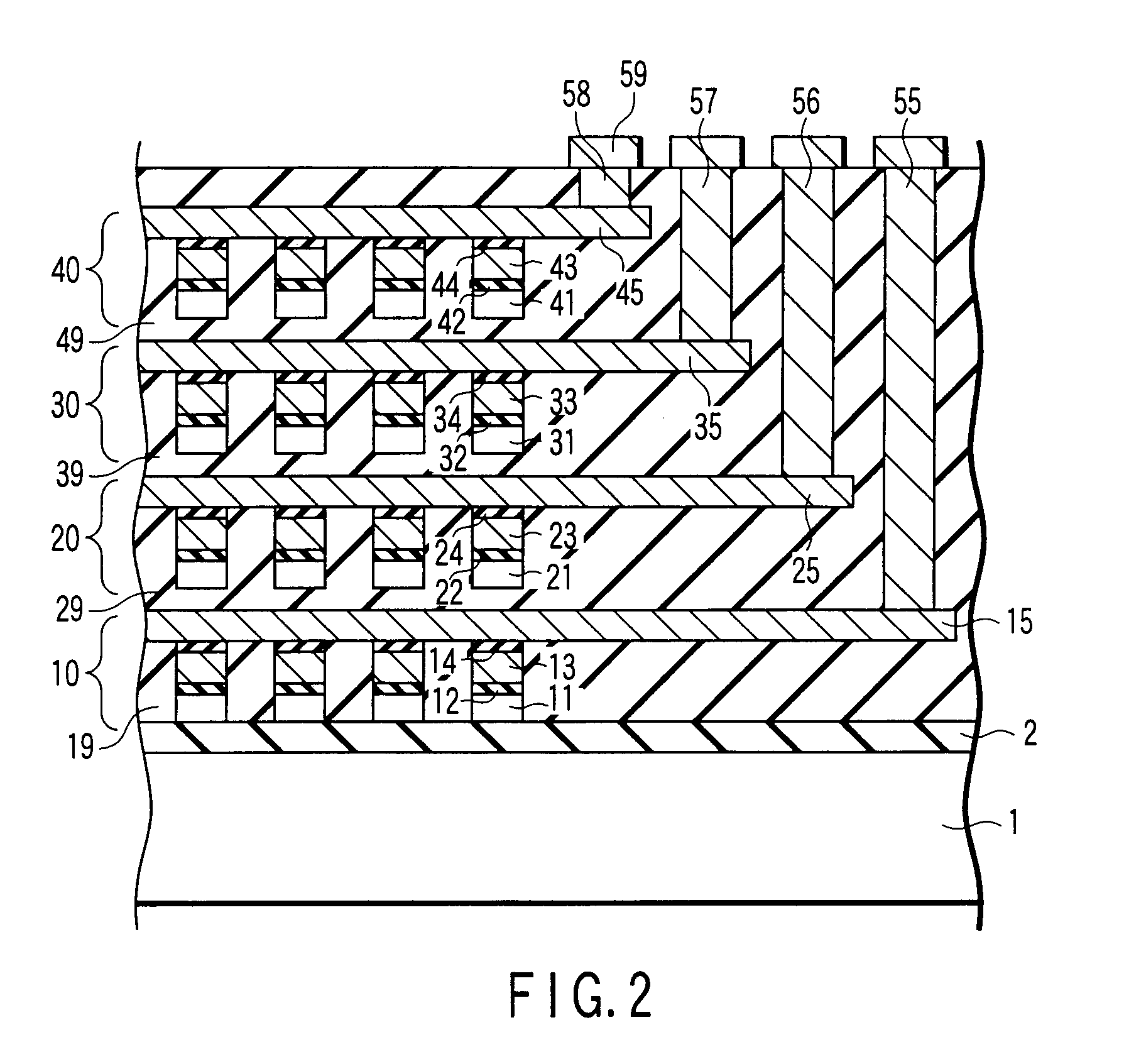

Non-volatile semiconductor storage device

InactiveUS20080128780A1TransistorSolid-state devicesElectrical conductorSemiconductor storage devices

A three-dimensional non-volatile semiconductor storage device which realizes both increased packing density and improved performance is disclosed. According to one aspect, there is provided a non-volatile semiconductor storage device comprising a first non-volatile memory cell provided on a first insulator, which includes a first semiconductor layer, and a first gate stack provided above the first semiconductor layer and including a first charge storage layer and a first control gate electrode, and a second non-volatile memory cell provided above the first non-volatile memory cell, which includes a second semiconductor layer, and a second gate stack provided above the second semiconductor layer and including a second charge storage layer and a second control gate electrode, the second gate stack being positioned to be aligned with the first gate stack, and wherein the first control gate electrode functions as a back gate electrode to the second non-volatile memory cell.

Owner:KK TOSHIBA

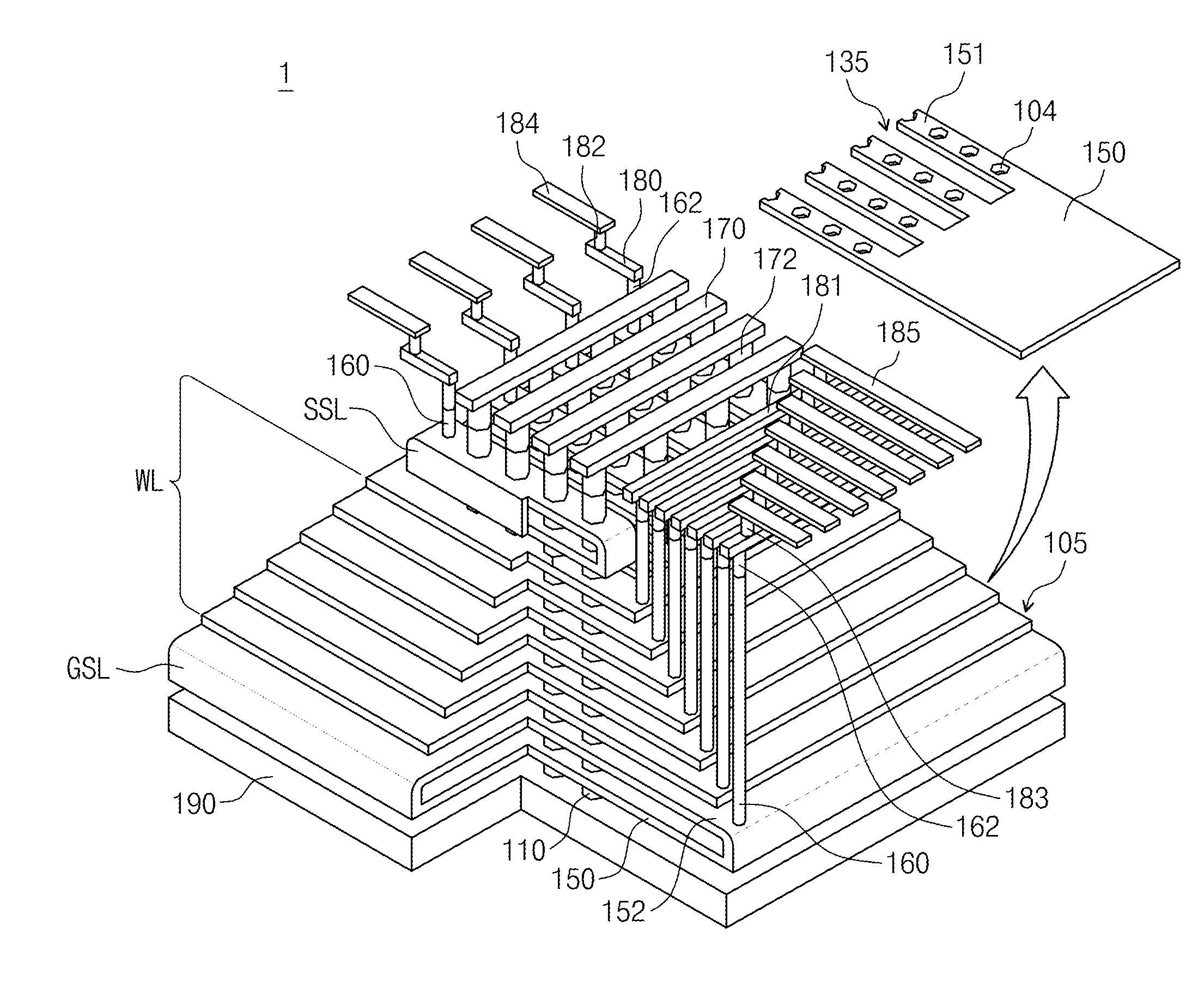

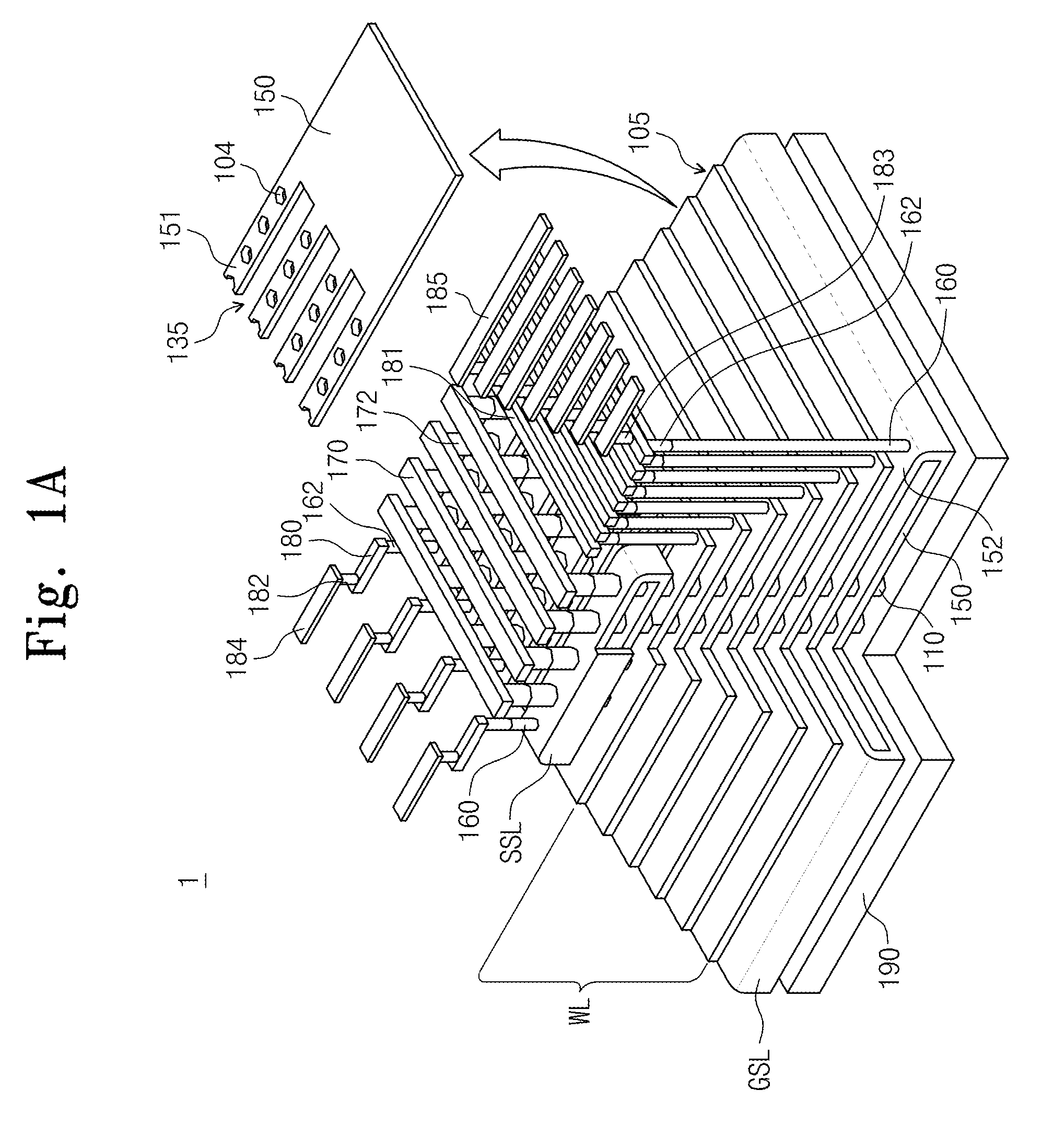

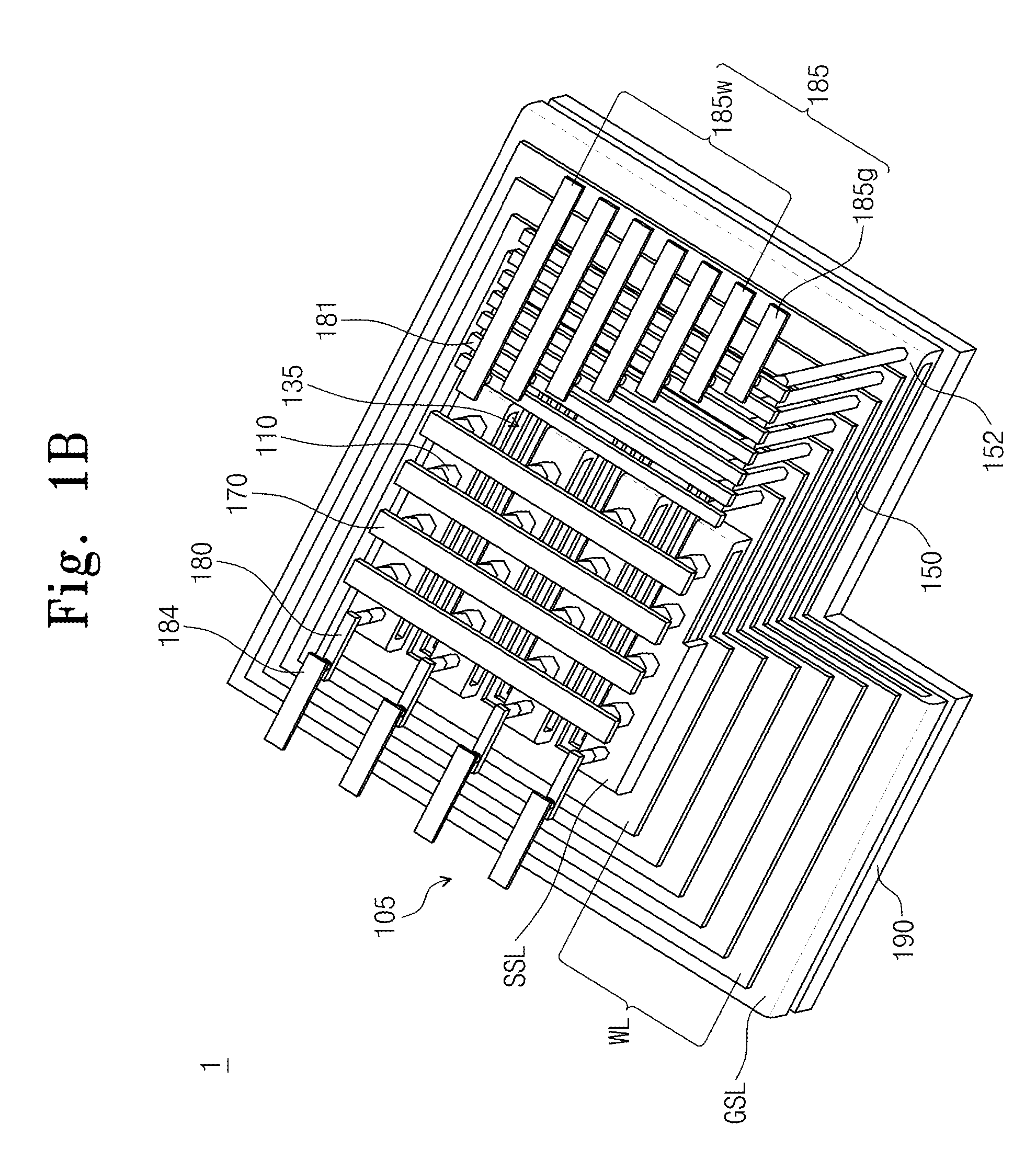

3D semiconductor devices and methods of fabricating same

ActiveUS20120119287A1Fabrication yield can be improvedPrevent and minimize process errorSolid-state devicesSemiconductor/solid-state device manufacturingMemory cellDevice material

A three dimensional (3D) semiconductor device includes; a vertical channel extending from a lower end proximate a substrate to an upper end and connecting a plurality of memory cells, and a cell array comprising the plurality of cells, wherein the cell array is arranged in a gate stack of layers having a stair-stepped structure disposed on the substrate. The gate stack includes a lower layer including a lower select line coupled to a lower non-memory transistor proximate the lower end, upper layers including conductive lines respectively coupled to an upper non-memory transistor proximate the upper end and connected as a single conductive piece to form an upper select line, and intermediate layers respectively including a word line and coupled to a cell transistor, wherein the intermediate layers are disposed between the lower select line and the upper select line.

Owner:SAMSUNG ELECTRONICS CO LTD

Band-engineered multi-gated non-volatile memory device with enhanced attributes

ActiveUS7279740B2Reduce harmExcellent charge retentionSolid-state devicesRead-only memoriesCharge retentionHigh energy

Non-volatile memory devices and arrays are described that facilitate the use of band-gap engineered gate stacks with asymmetric tunnel barriers in floating gate memory cells in NOR or NAND memory architectures that allow for direct tunneling programming and erase with electrons and holes, while maintaining high charge blocking barriers and deep carrier trapping sites for good charge retention. The direct tunneling program and erase capability reduces damage to the gate stack and the crystal lattice from high energy carriers, reducing write fatigue and leakage issues and enhancing device lifespan. Memory cells of the present invention also allow multiple bit storage in a single memory cell, and allow for programming and erase with reduced voltages. A positive voltage erase process via hole tunneling is also provided.

Owner:MICRON TECH INC

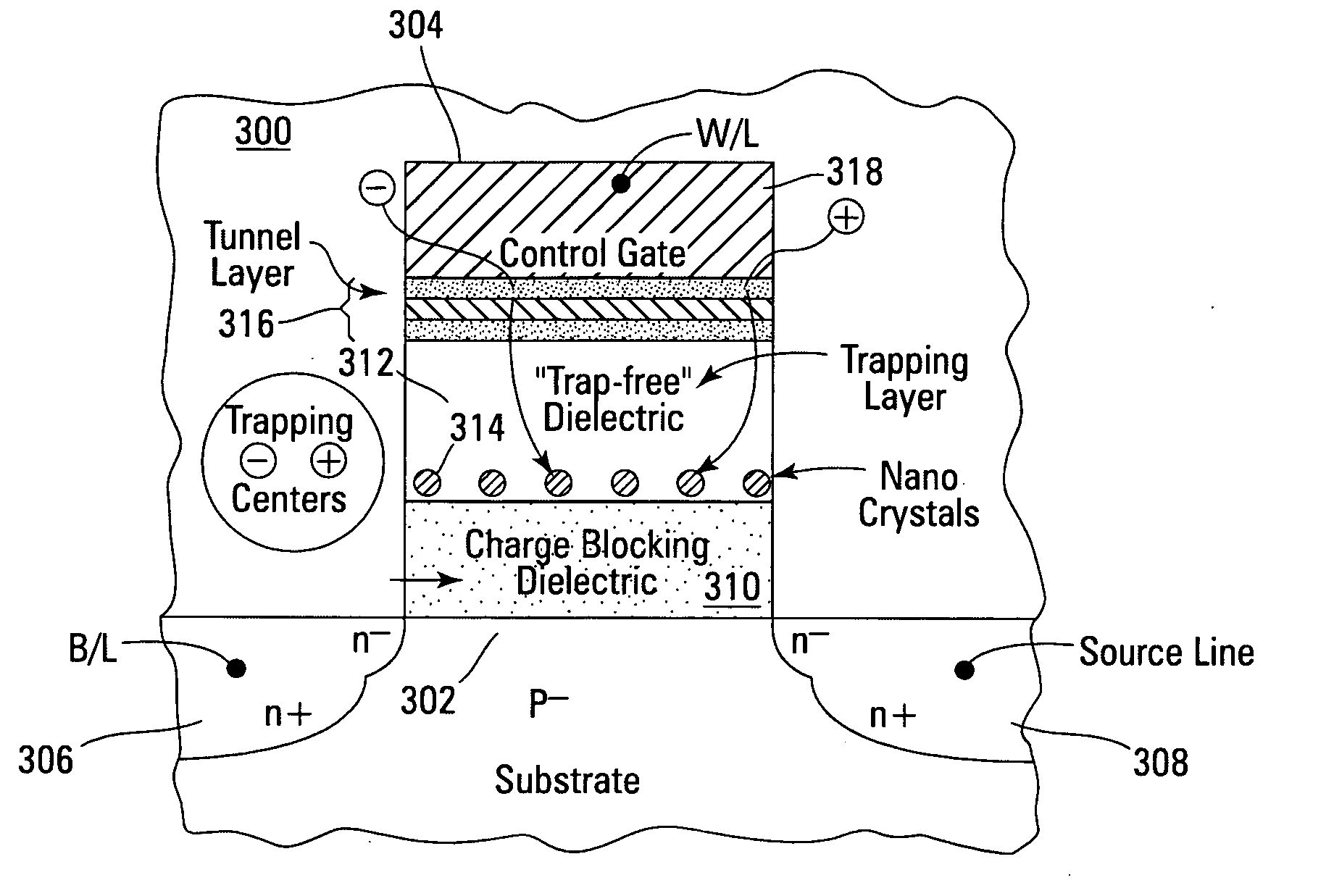

Band engineered nano-crystal non-volatile memory device utilizing enhanced gate injection

ActiveUS20070045718A1Increased device feature scalingEfficient erasureTransistorNanoinformaticsCharge retentionNon symmetric

Non-volatile memory devices and arrays are described that utilize reverse mode non-volatile memory cells that have band engineered gate-stacks and nano-crystal charge trapping in EEPROM and block erasable memory devices, such as Flash memory devices. Embodiments of the present invention allow a reverse mode gate-insulator stack memory cell that utilizes the control gate for programming and erasure through a band engineered crested tunnel barrier. Charge retention is enhanced by utilization of high work function nano-crystals in a non-conductive trapping layer and a high K dielectric charge blocking layer. The band-gap engineered gate-stack with symmetric or asymmetric crested barrier tunnel layers of the non-volatile memory cells of embodiments of the present invention allow for low voltage tunneling programming and erase with electrons and holes, while maintaining high charge blocking barriers and deep carrier trapping sites for good charge retention.

Owner:MICRON TECH INC